Patents

Literature

1518 results about "Non symmetric" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

So a non symmetric matrix is one which when transposed gives a different matrix than the one you started with. The identity matrix is symmetric whereas if you add just one more 1 to any one of its non diagonal elements then it becomes non symmetric.

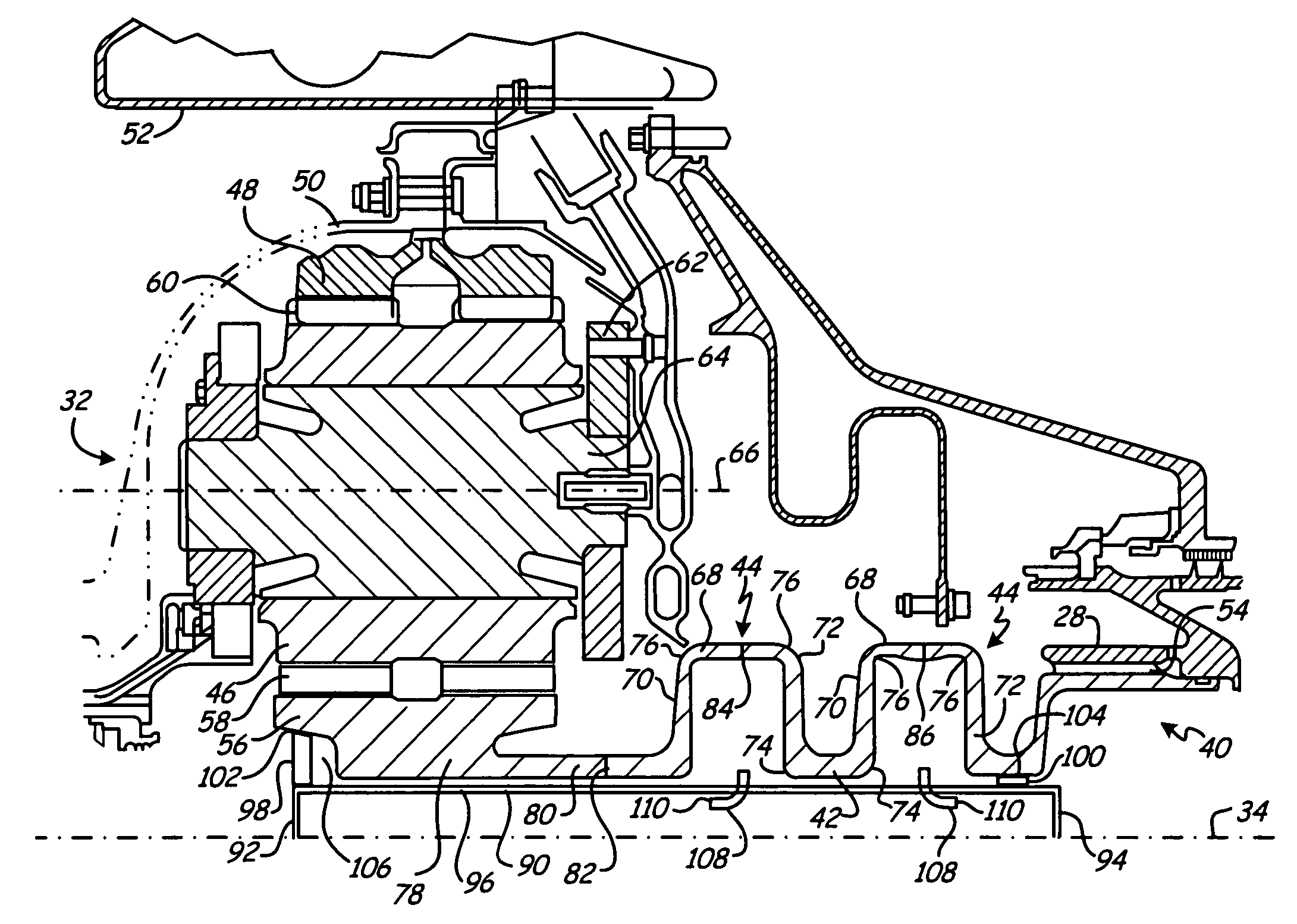

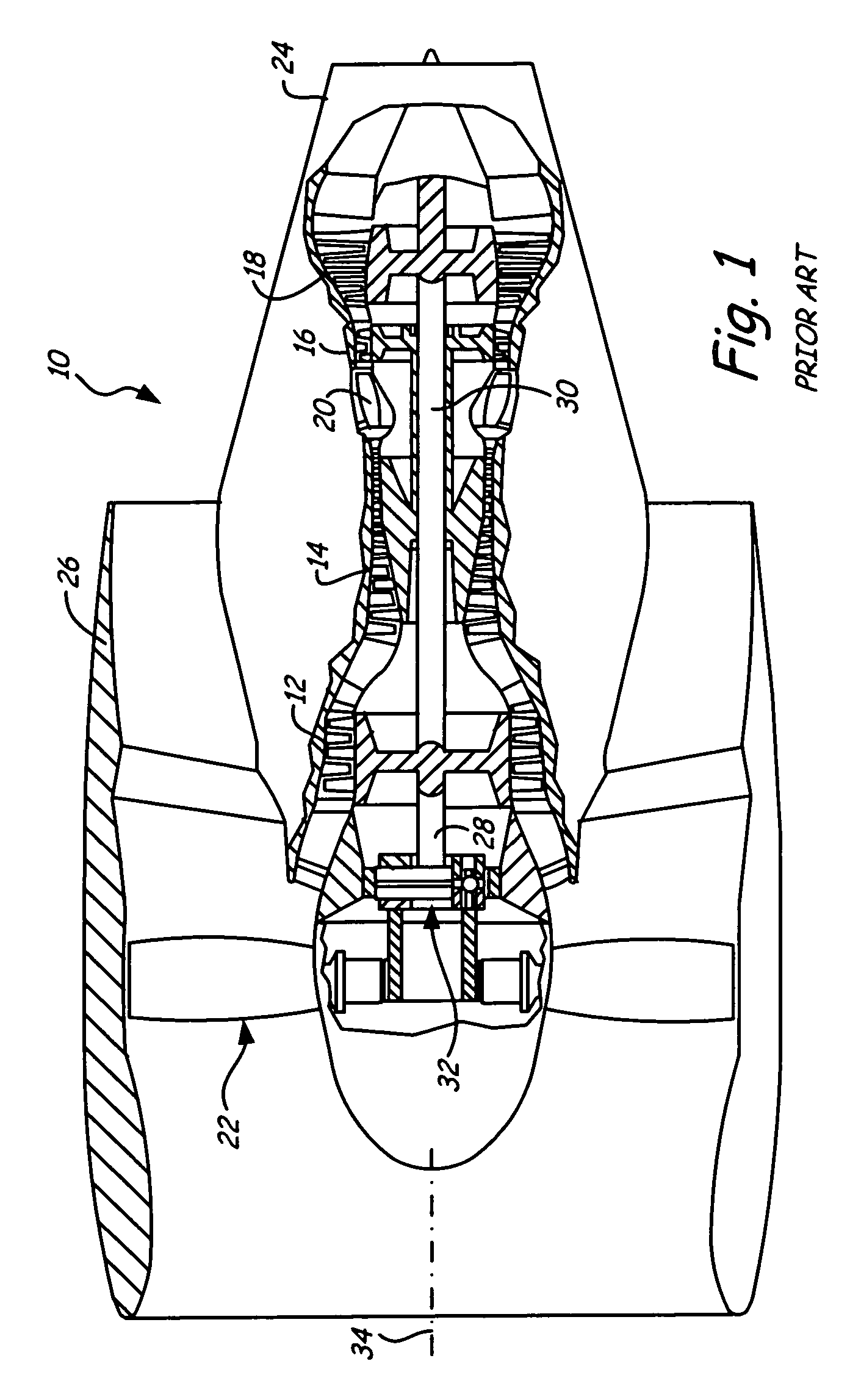

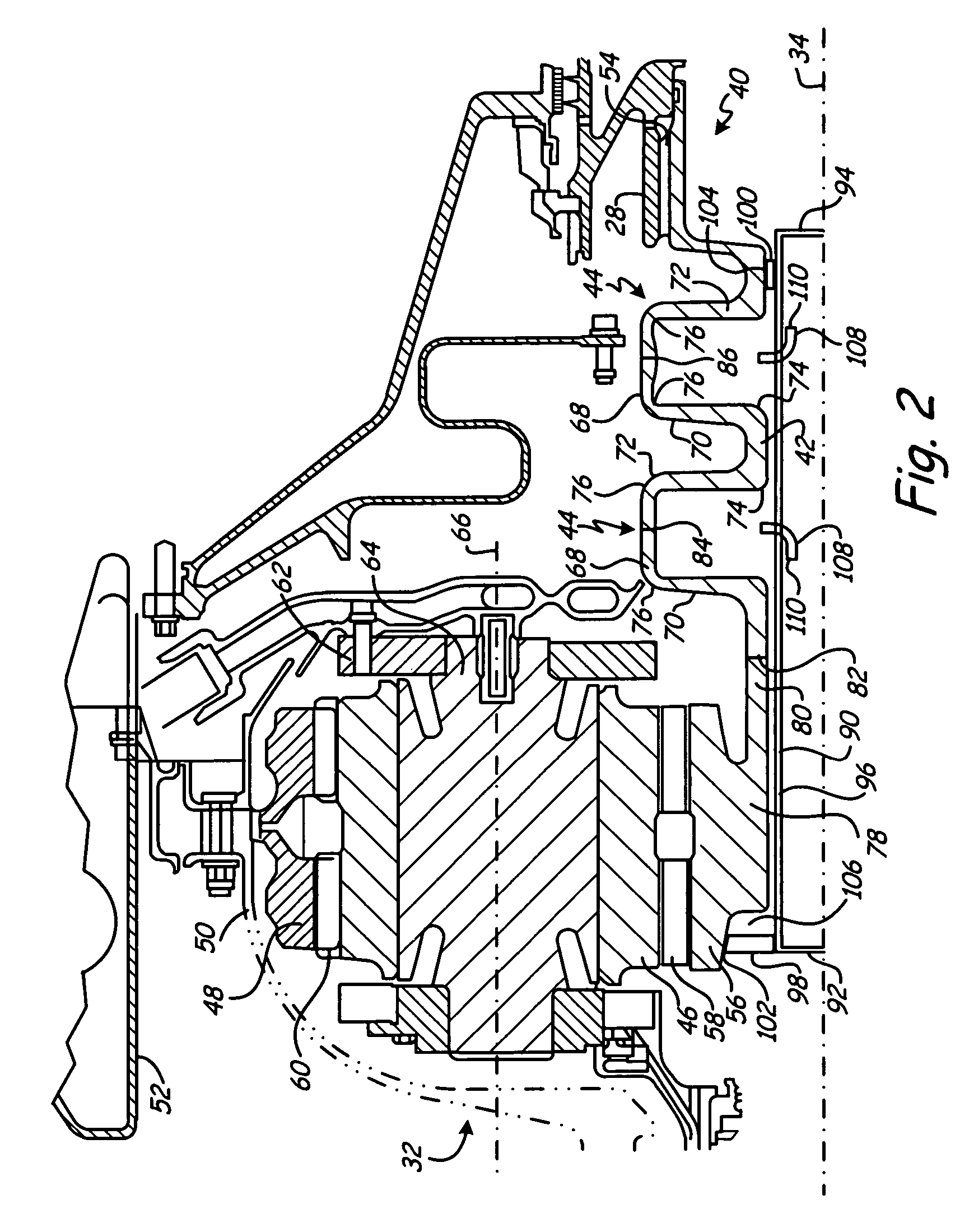

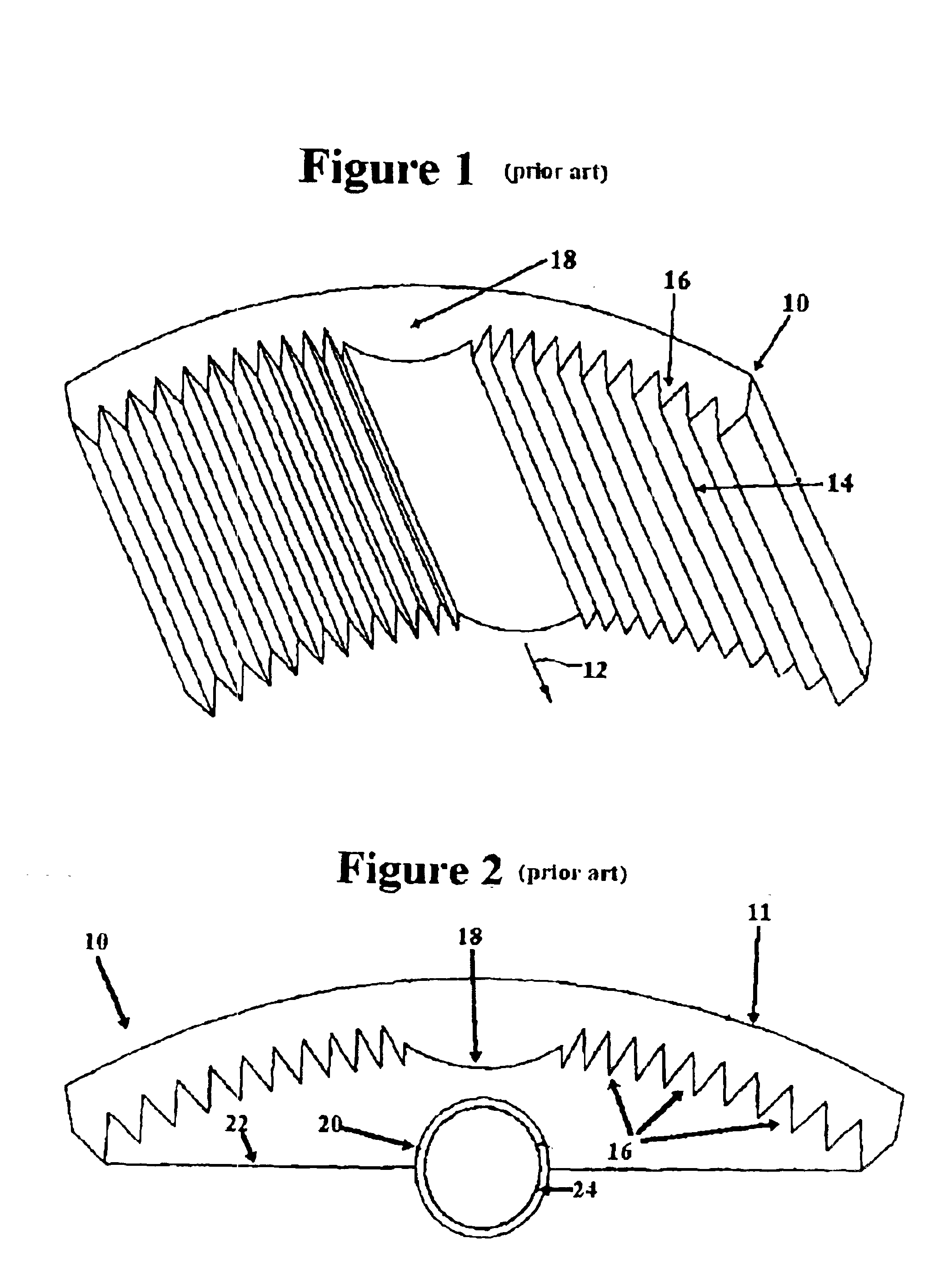

Epicyclic gear train integral sun gear coupling design

A coupling system for connecting a sun gear to a shaft within a planetary gear train, includes a sun gear coupling connecting the sun gear to the shaft. The sun gear coupling has at least one undulant flexible section joined to an inflexible spindle for accommodating misalignment between the sun gear and the shaft. The flexible section comprises a cylindrical ring having a diameter greater than the diameter of the spindle, and joined to the spindle by two longitudinally spaced apart diaphragms. The juncture between the diaphragms, the ring, and the spindle is curved in cross section on an outer side to improve flexibility and minimize stress concentrations, and the inner sides of the diaphragms are straight edges which result in a non-symmetric contour of the diaphragm walls.

Owner:RTX CORP

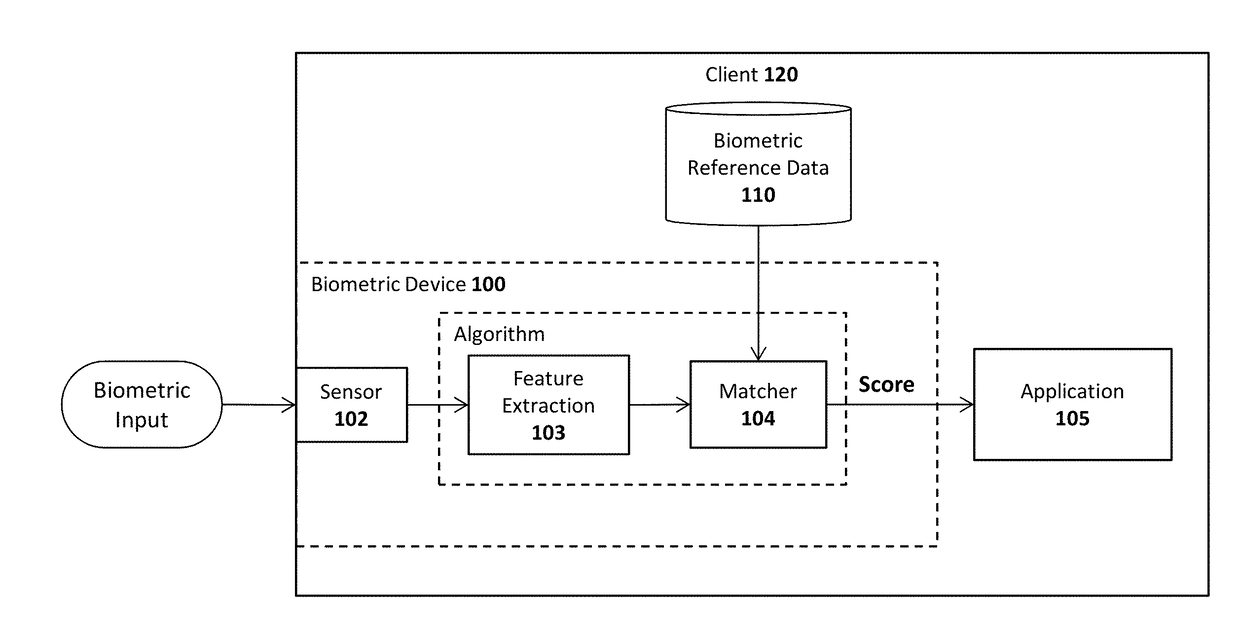

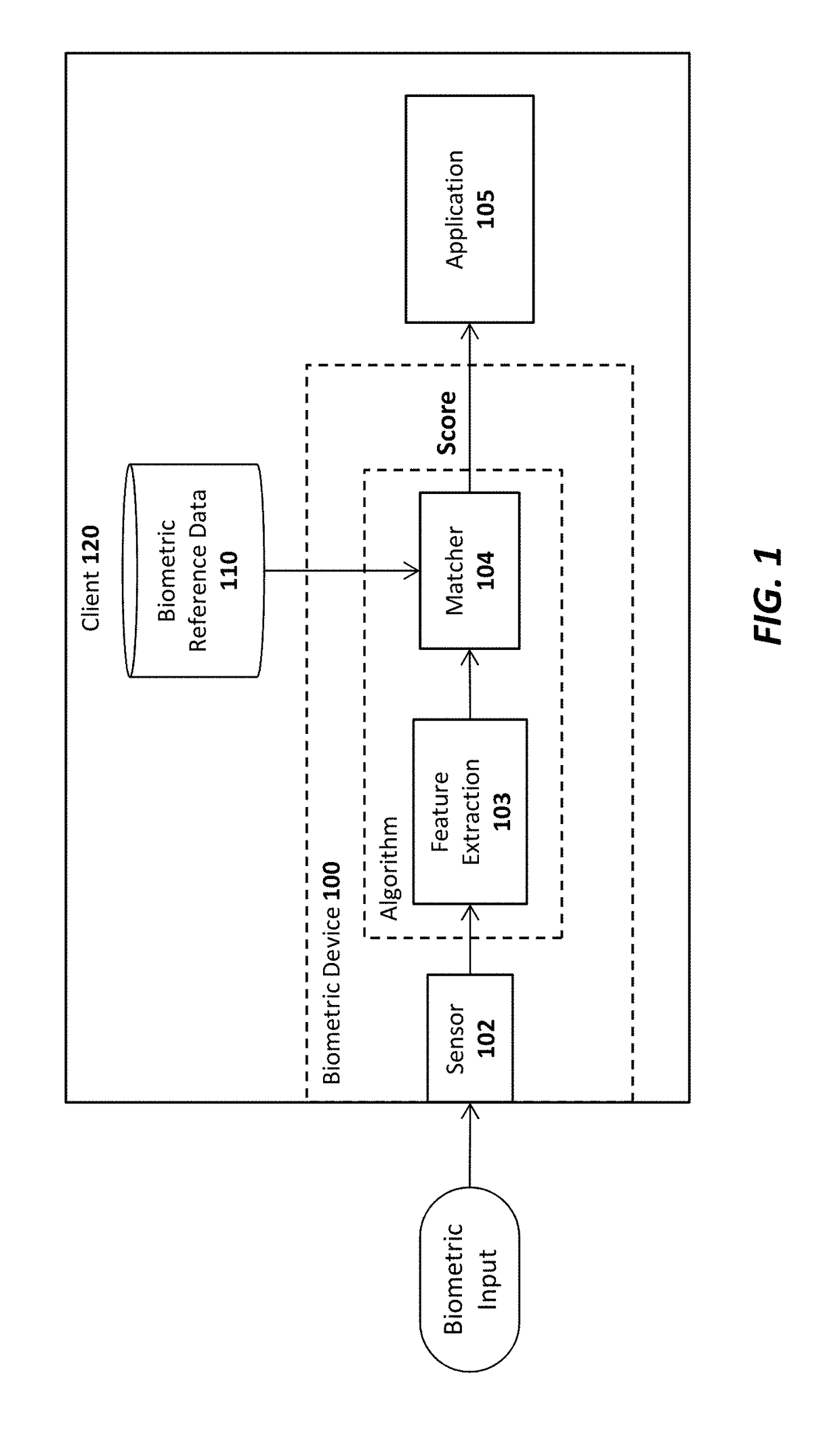

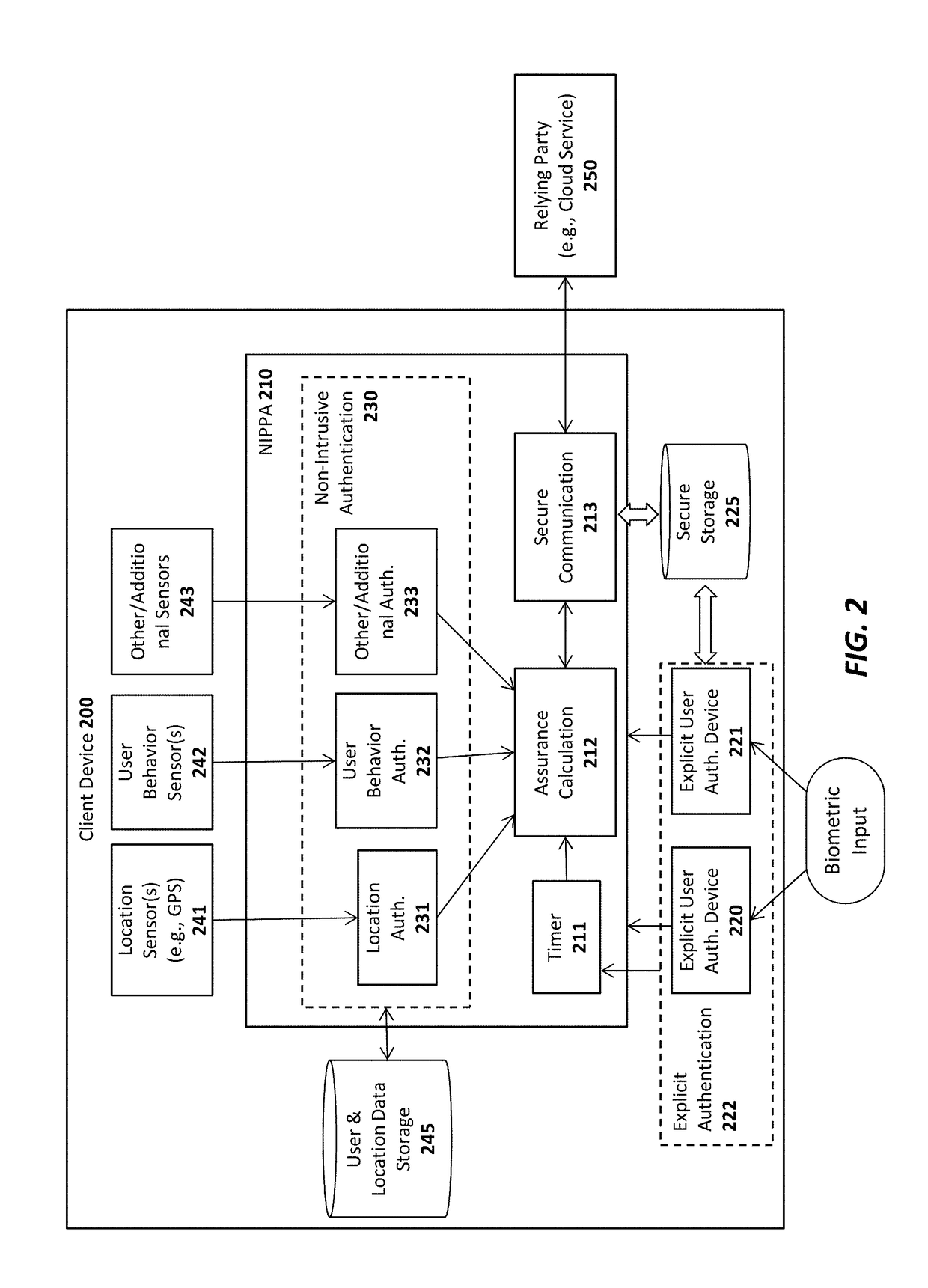

System and method for sharing keys across authenticators

ActiveUS20180191501A1Key distribution for secure communicationInput/output to record carriersNon symmetricAuthorization

A system, apparatus, method, and machine readable medium are described for sharing authentication data. For example, one embodiment of a method comprises: generating and storing a persistent group identification code (Group-ID) for a group of authenticators sharing a common set of authorization (Uauth) keys, an initial Group-ID to be generated on a first use of a first authenticator and / or following a factory reset of the first authenticator generating and storing an individual asymmetric wrapping key encryption key (WKEK) on a first use of the first authenticator and / or following each factory reset of the first authenticator; generating and storing a symmetric wrapping key (WK), the wrapping key to be generated on a first use of the first authenticator and / or following each factory reset of the first authenticator; generating a join-block using an authenticator identification code for the first authenticator and the WKEK, the join-block usable to join an existing authenticator group, the join block to be sent to a second authenticator; verifying the join-block at the second authenticator and generating a join response block responsive to user approval, the join response block generated by encrypting the WK and Group-ID using the WKEK, the join response block to be transmitted to the first authenticator; and decrypting the join response block and storing the WK and Group-ID.

Owner:NOK NOK LABS

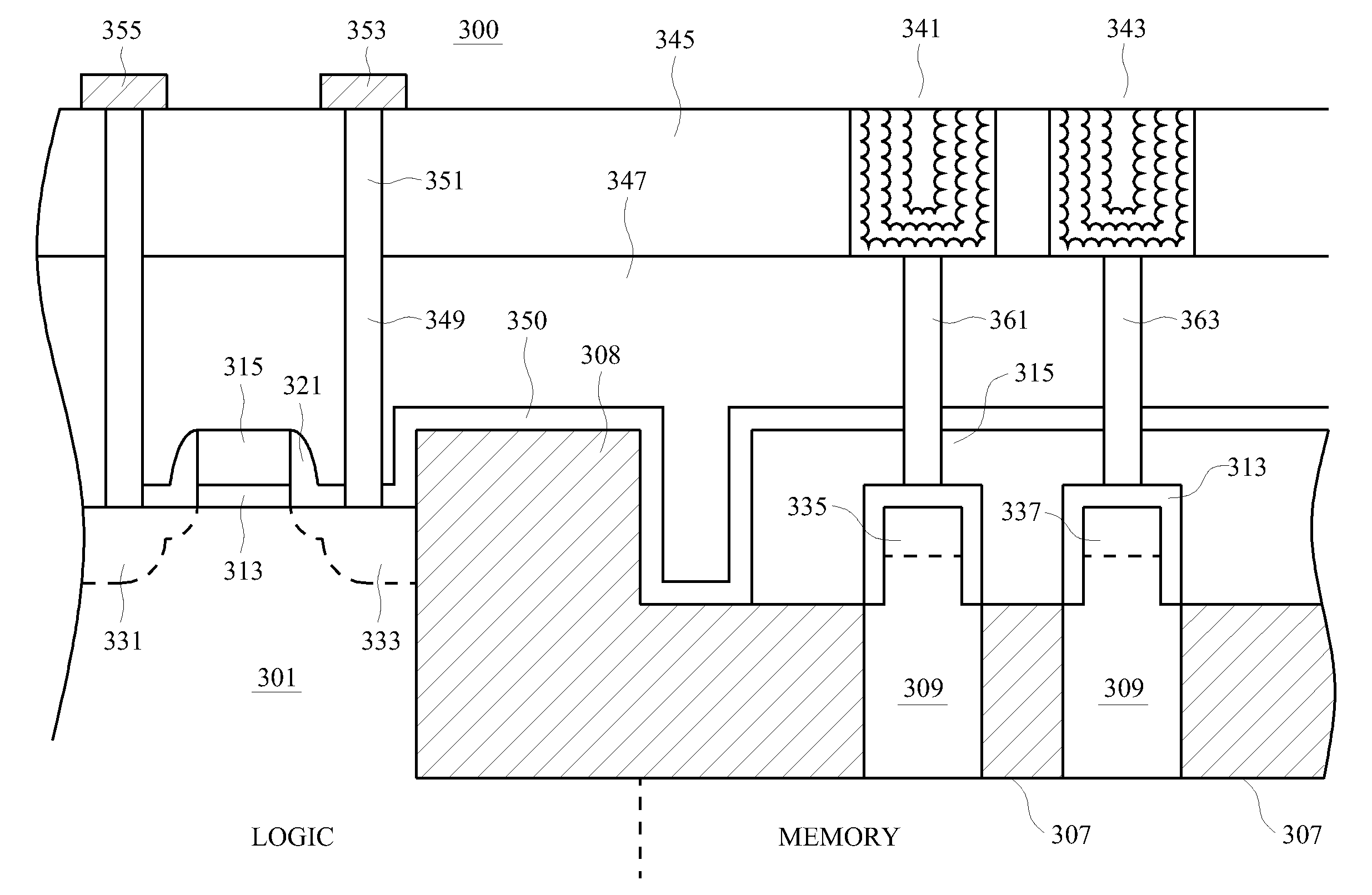

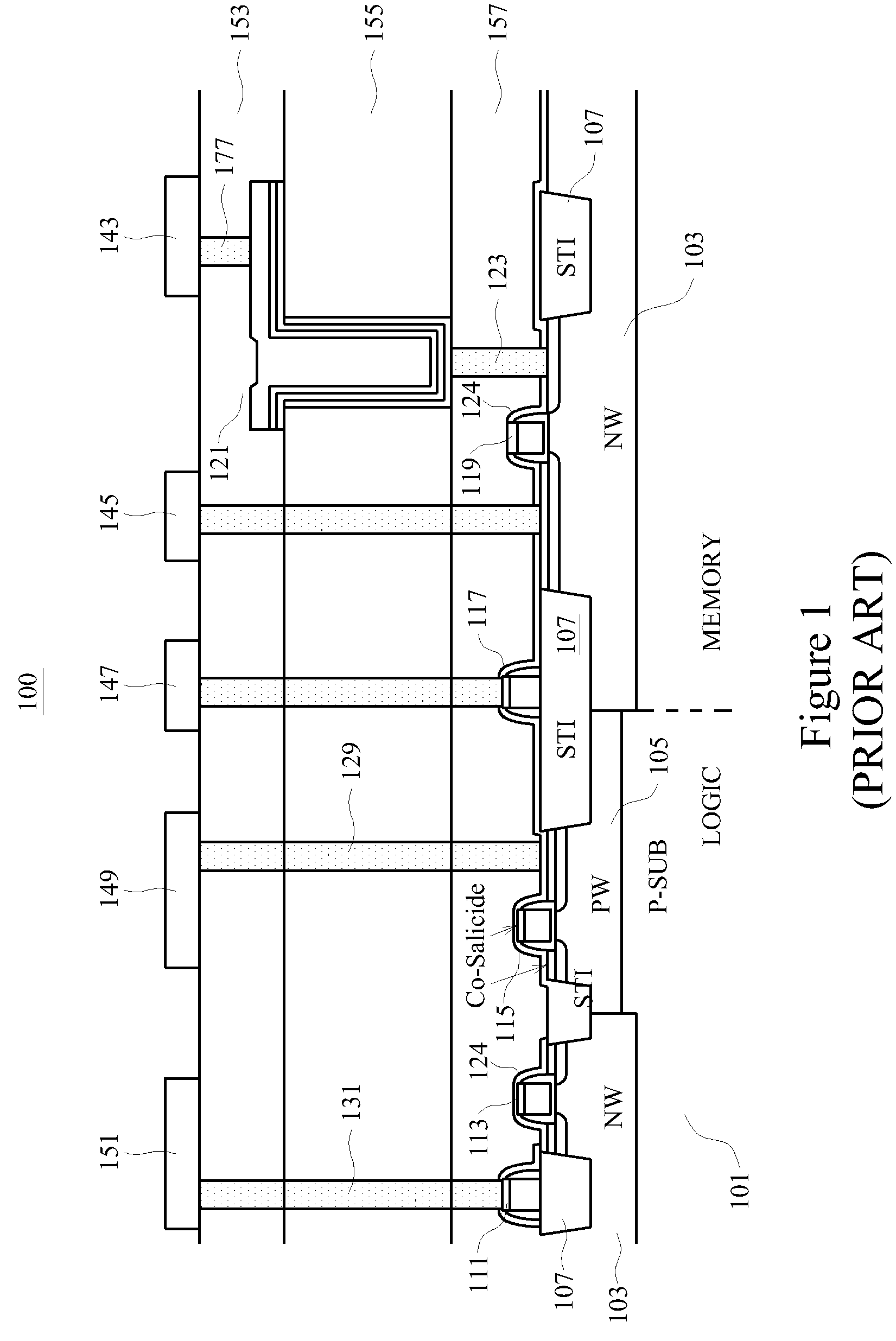

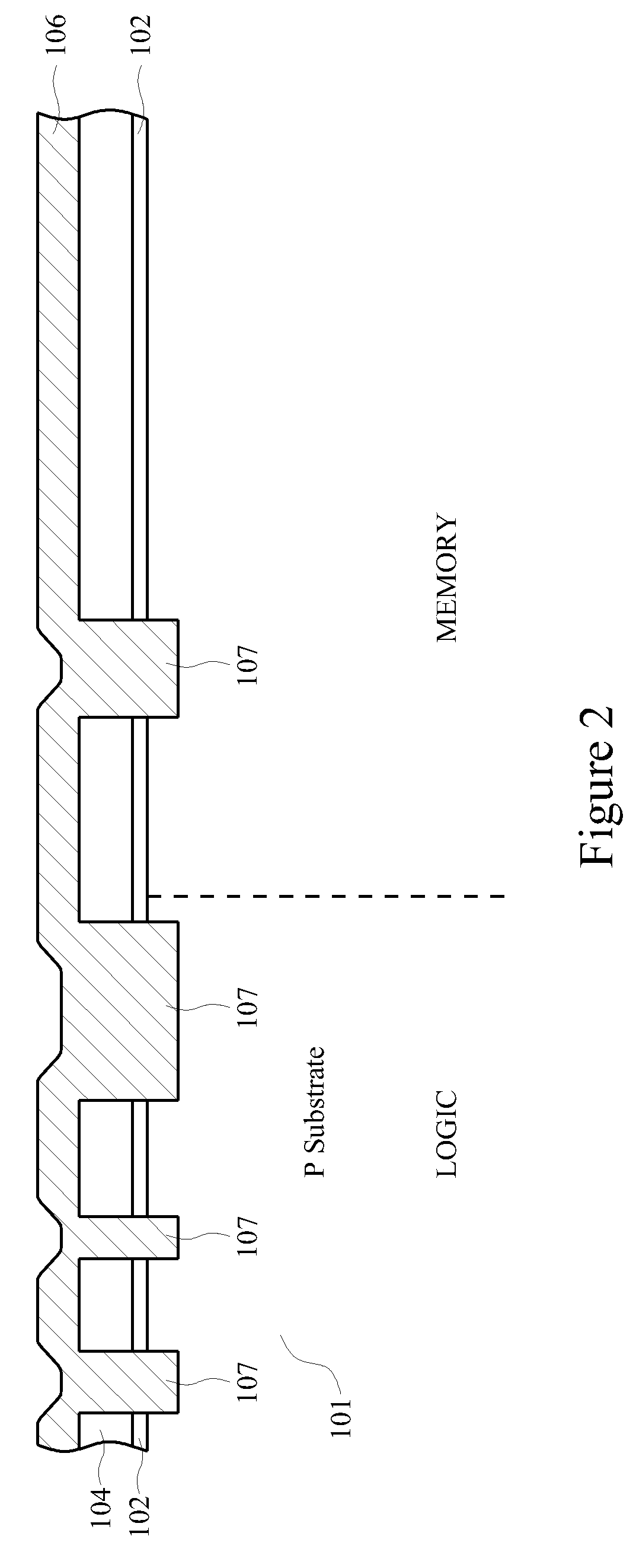

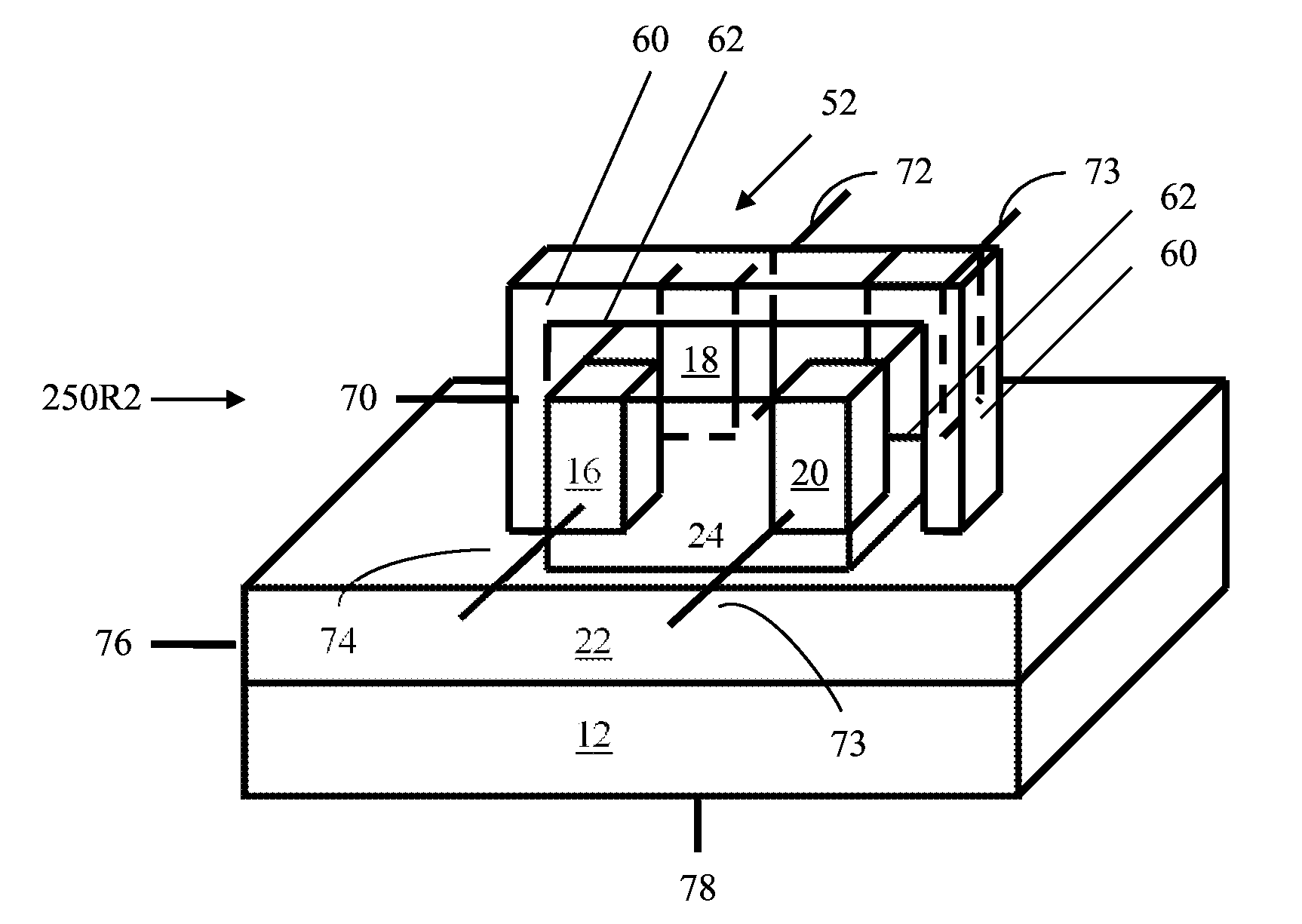

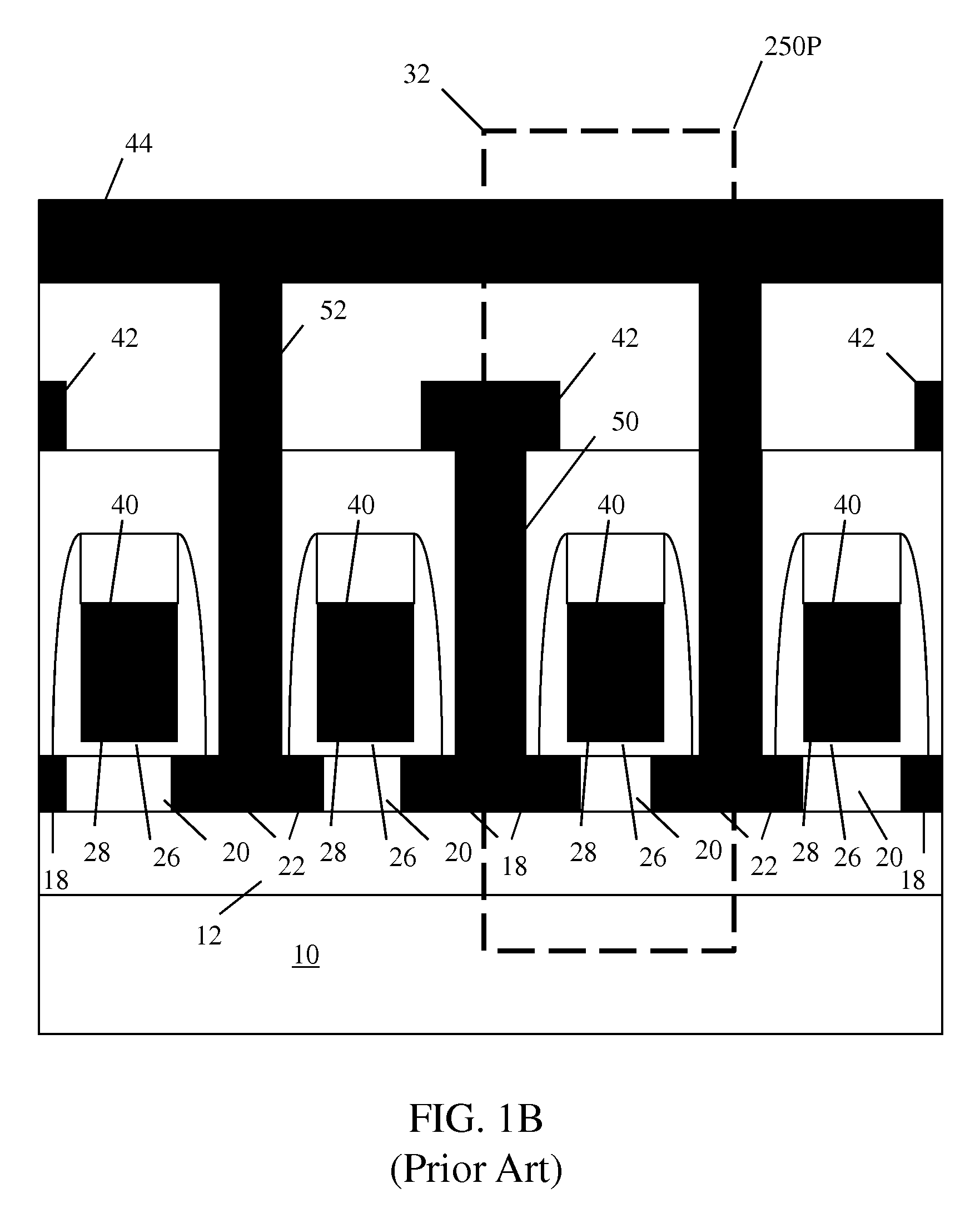

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

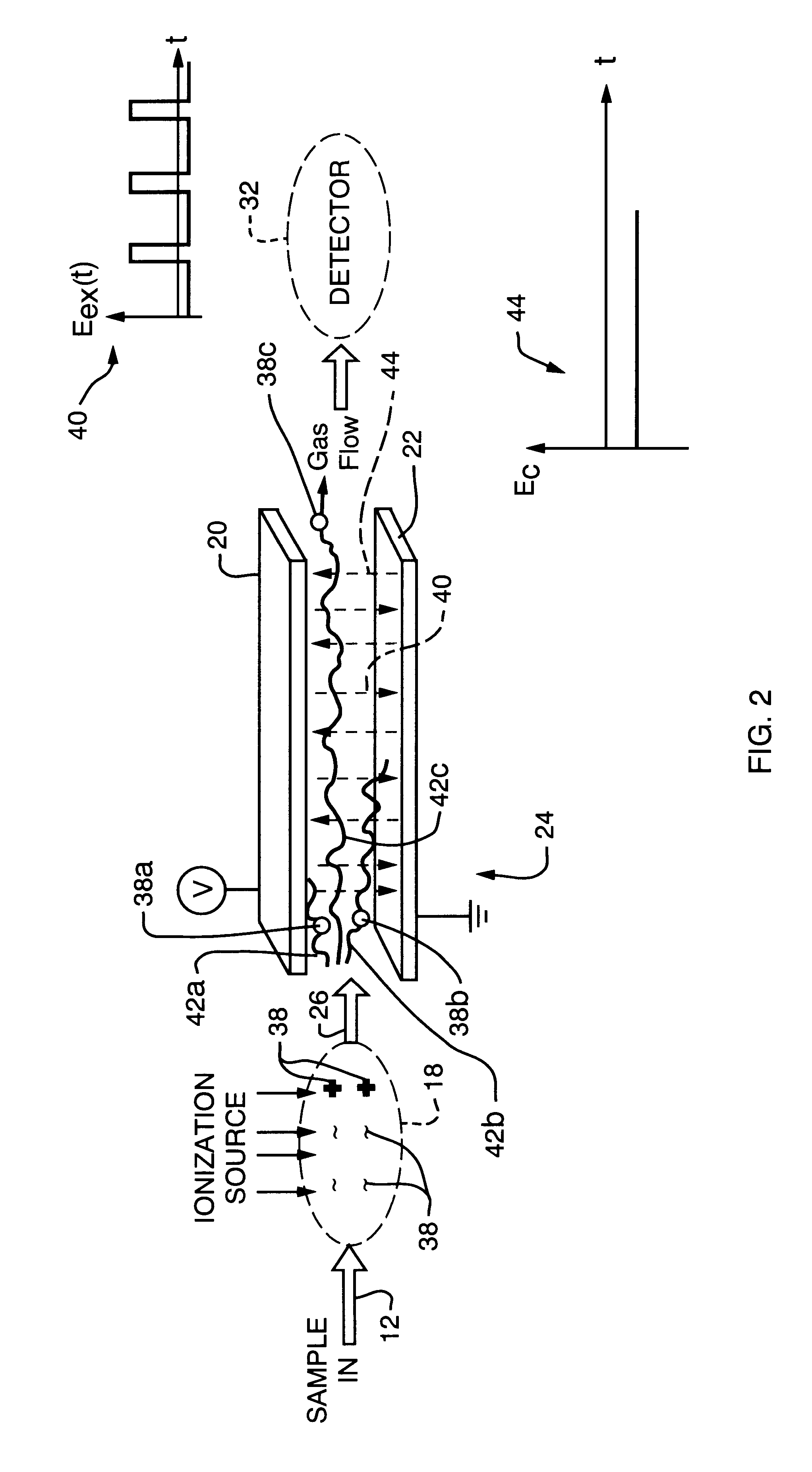

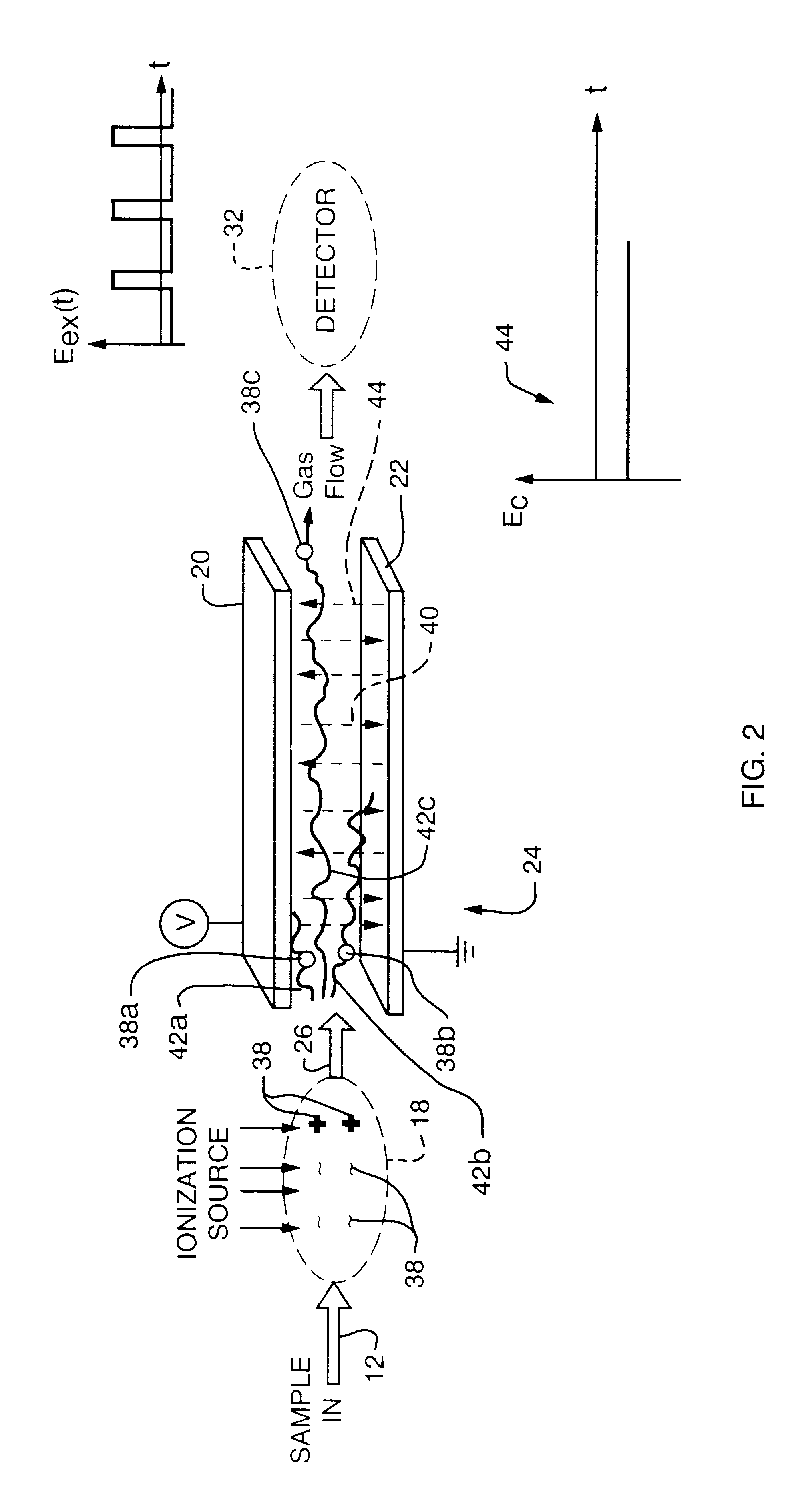

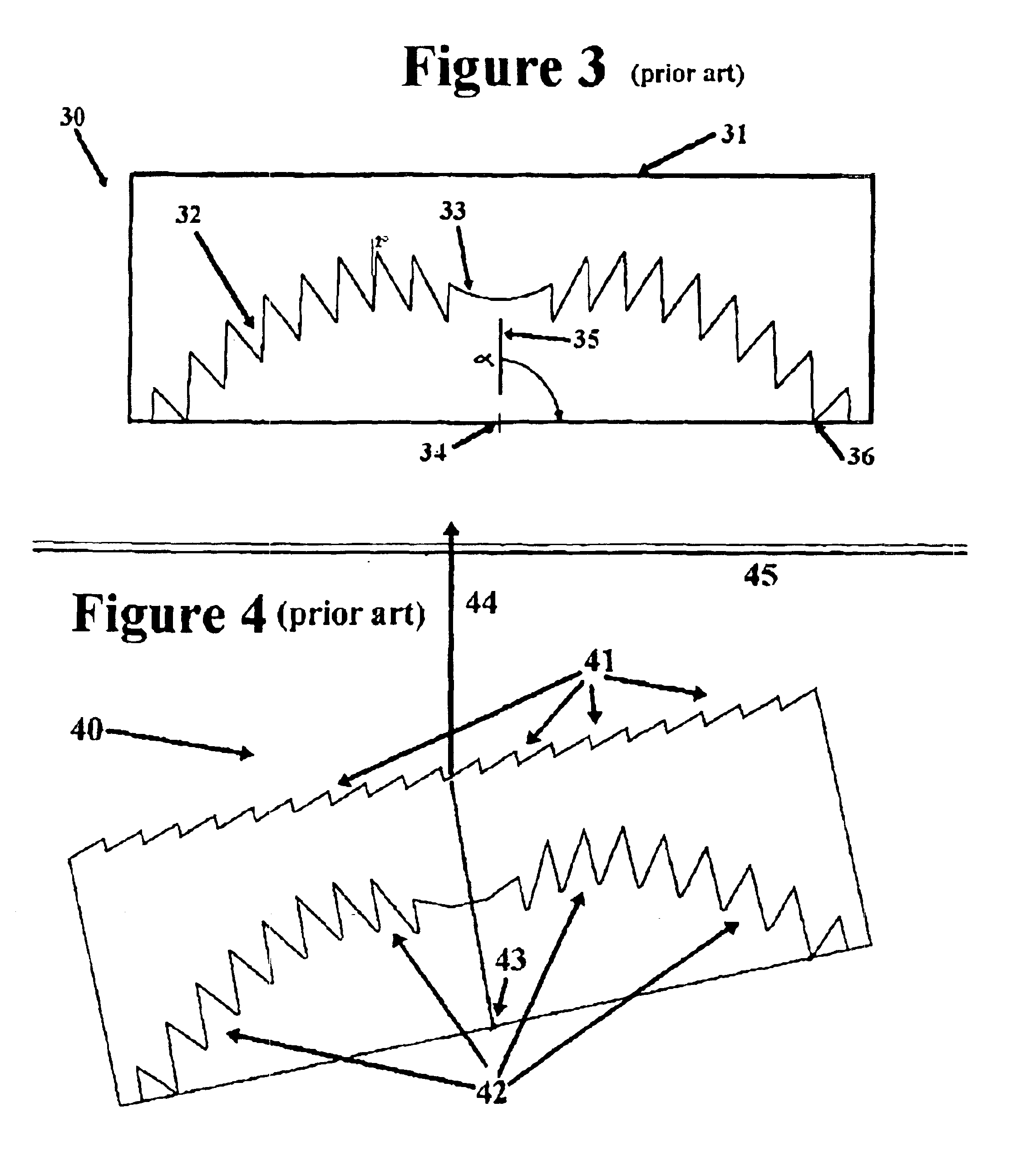

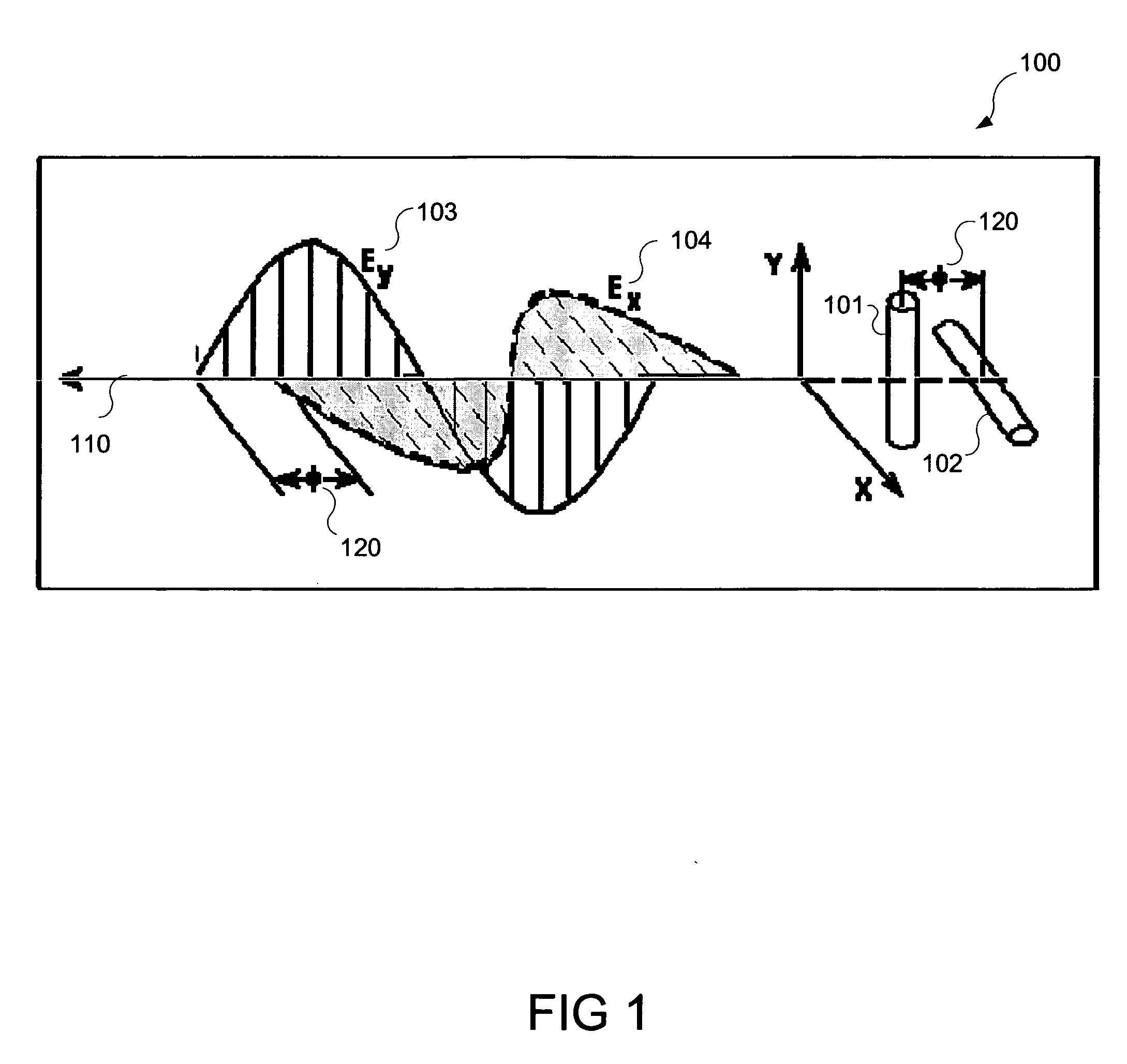

Micromachined field asymmetric ion mobility filter and detection system

InactiveUS6495823B1High resolutionQuick checkStability-of-path spectrometersTime-of-flight spectrometersNon symmetricAsymmetry

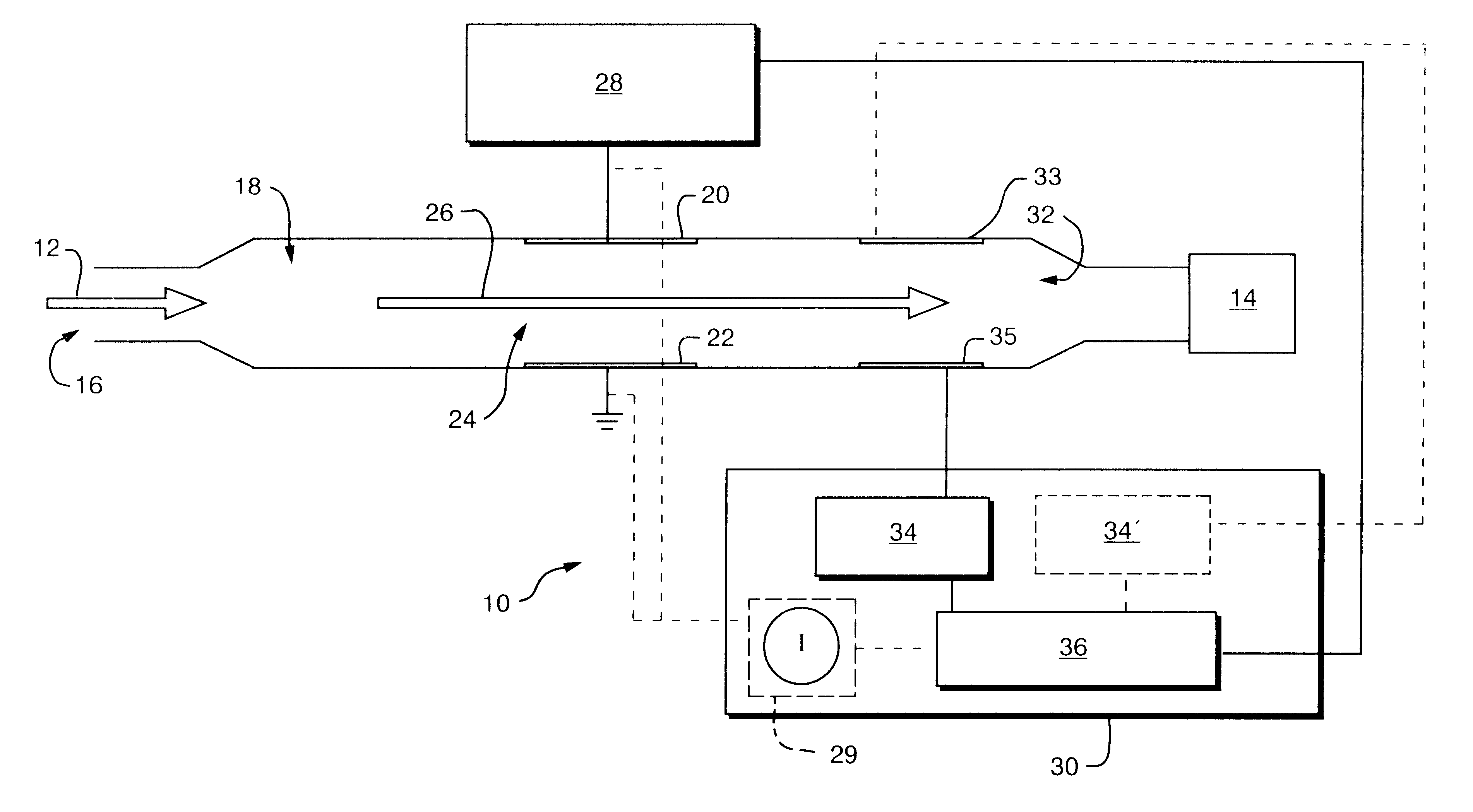

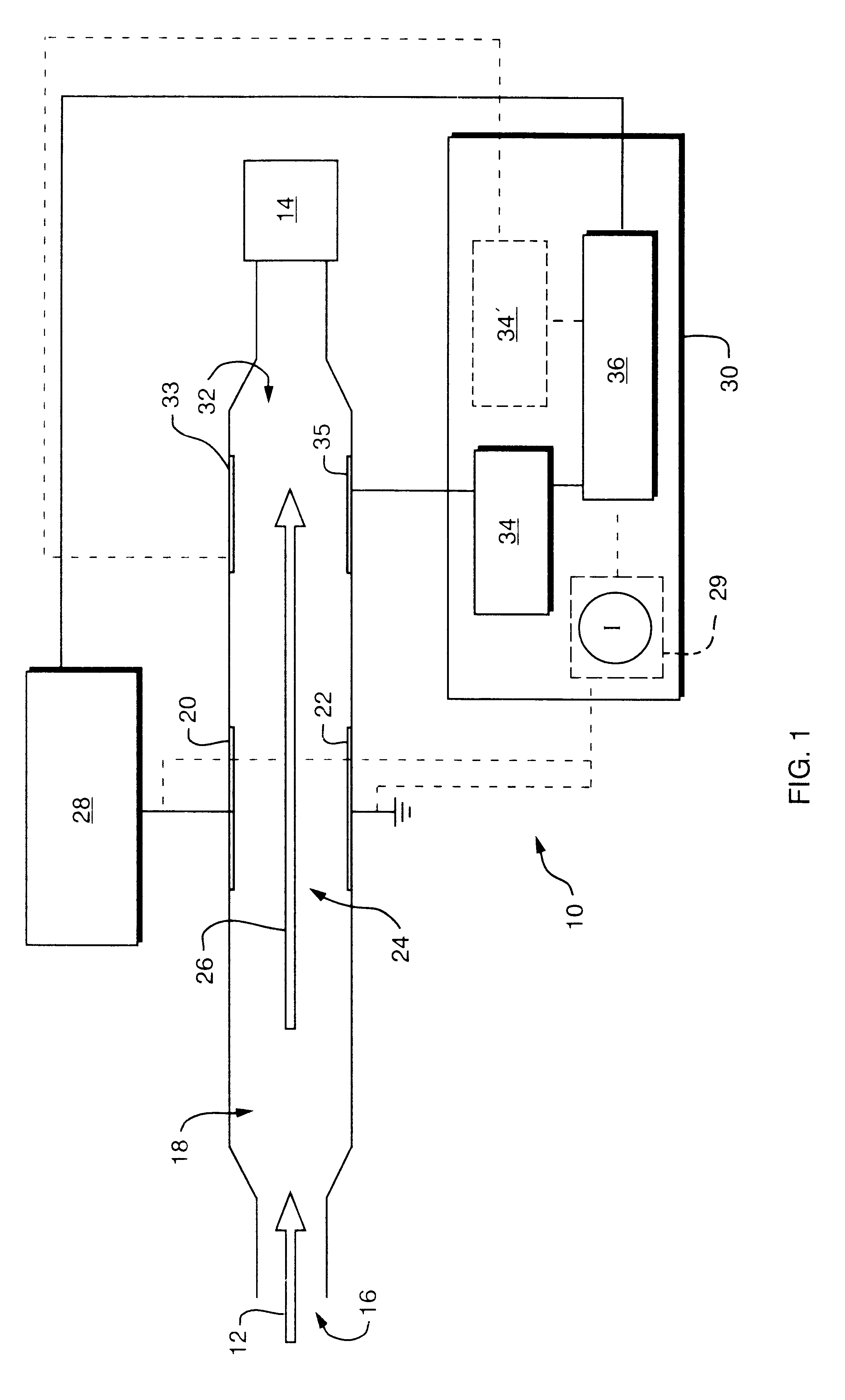

A micromechanical field asymmetric ion mobility filter for a detection system includes a pair of spaced substrates defining between them a flow path between a sample inlet and an outlet; an ion filter disposed in the path and including a pair of spaced filter electrodes, one electrode associated with each substrate; and an electrical controller for applying a bias voltage and an asymmetric periodic voltage across the ion filter electrodes for controlling the paths of ions through the filter.

Owner:CHARLES STARK DRAPER LABORATORY

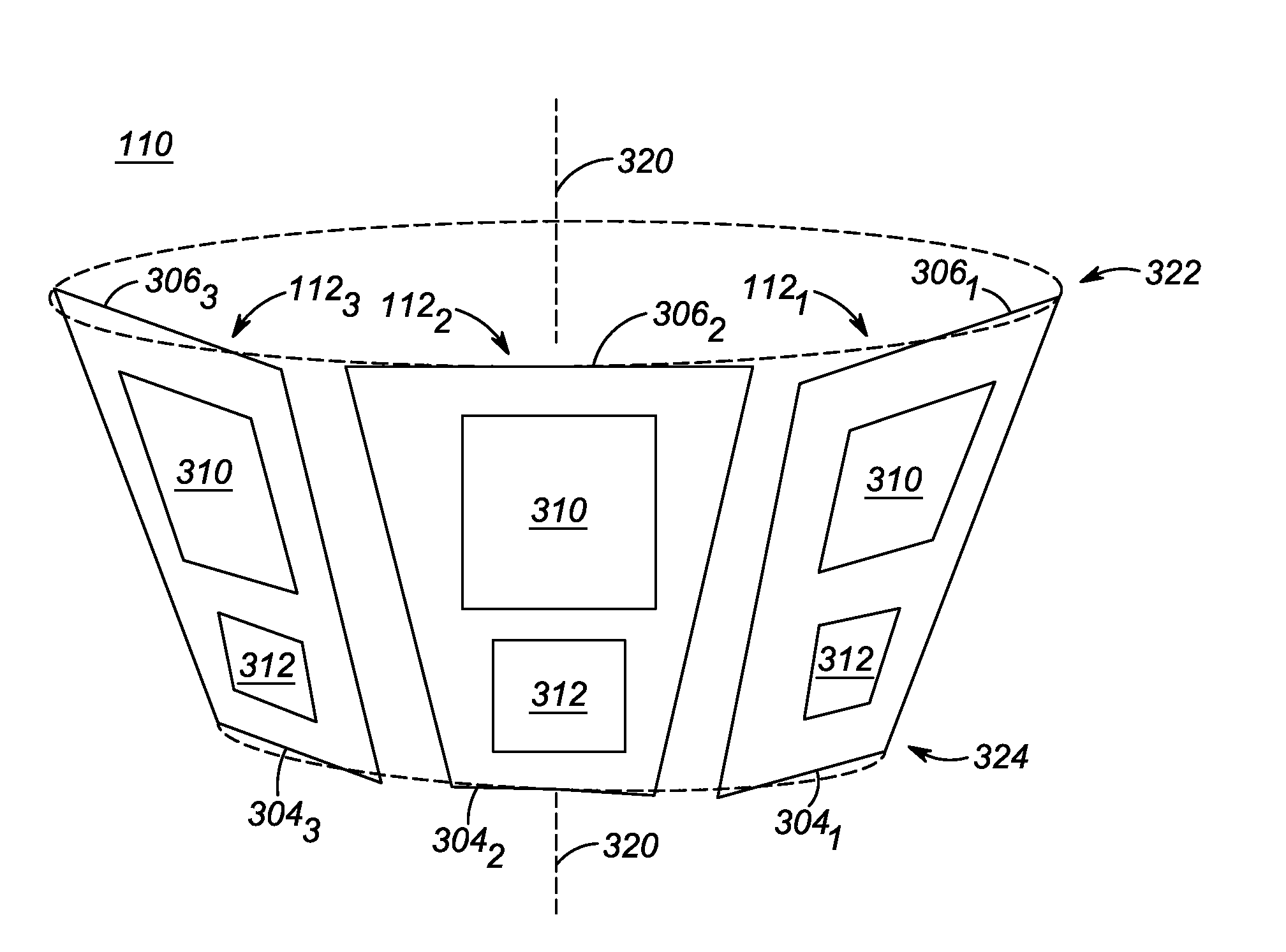

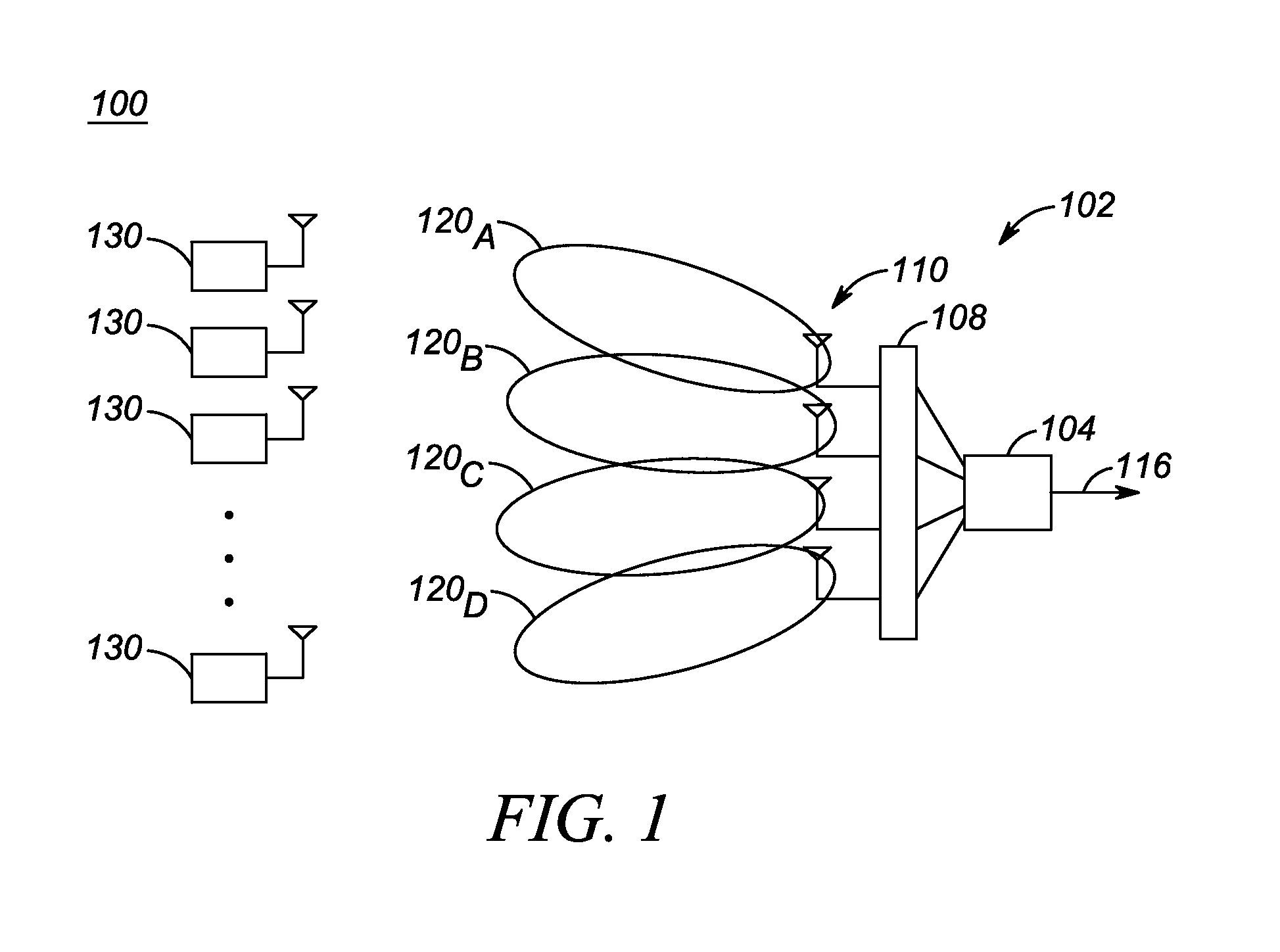

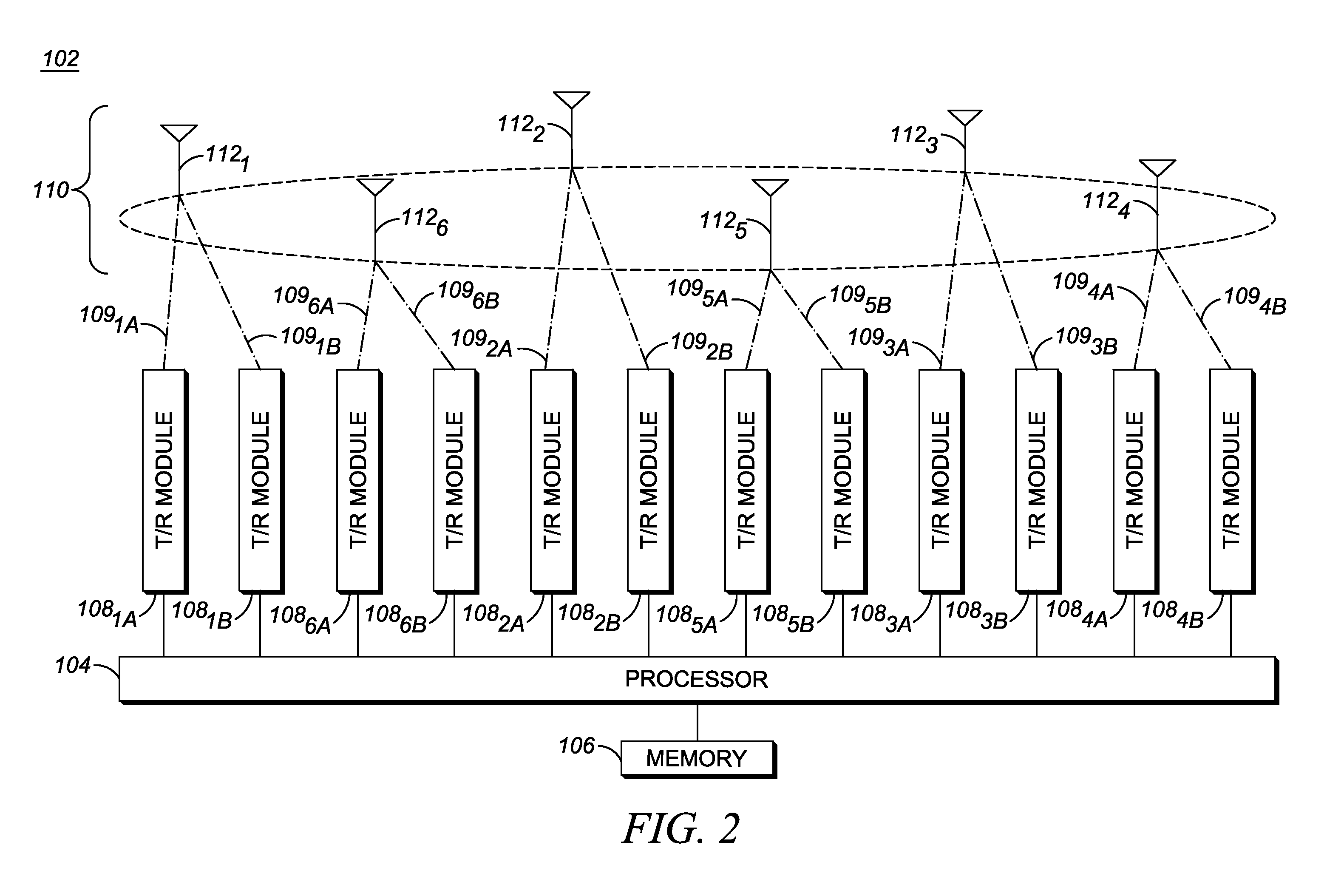

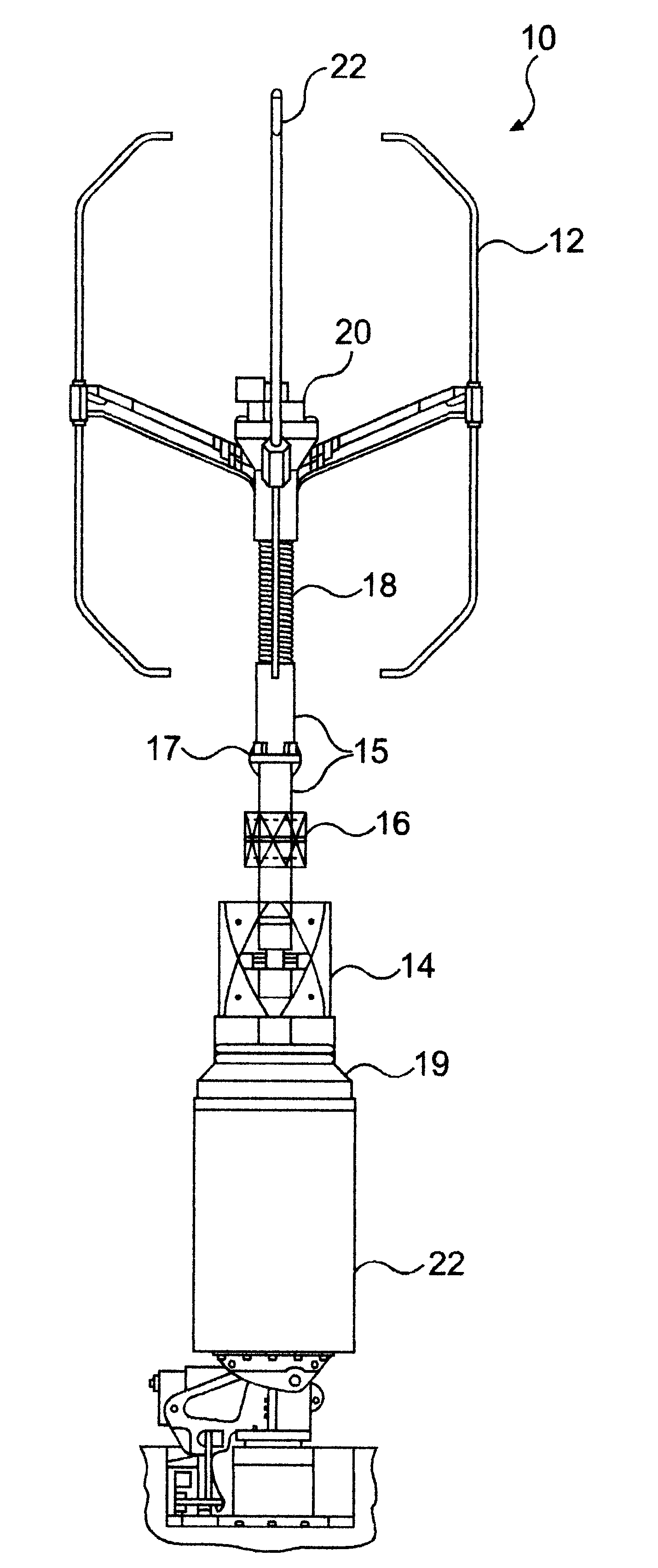

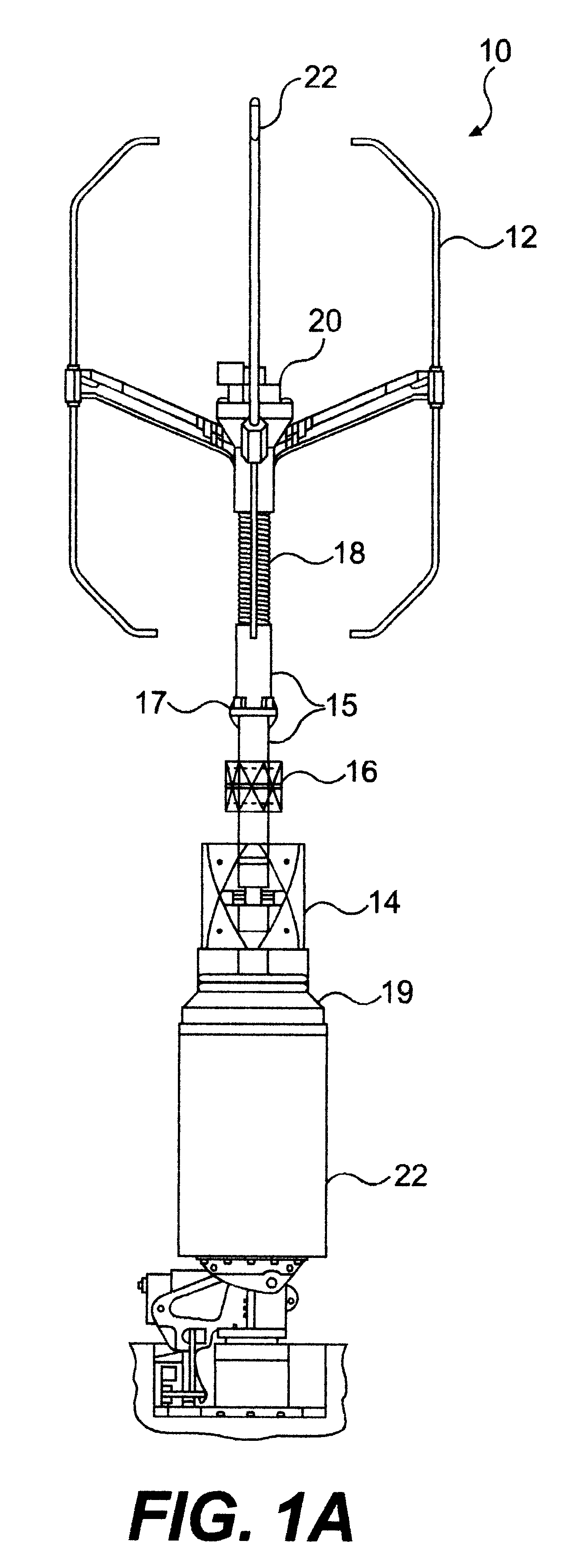

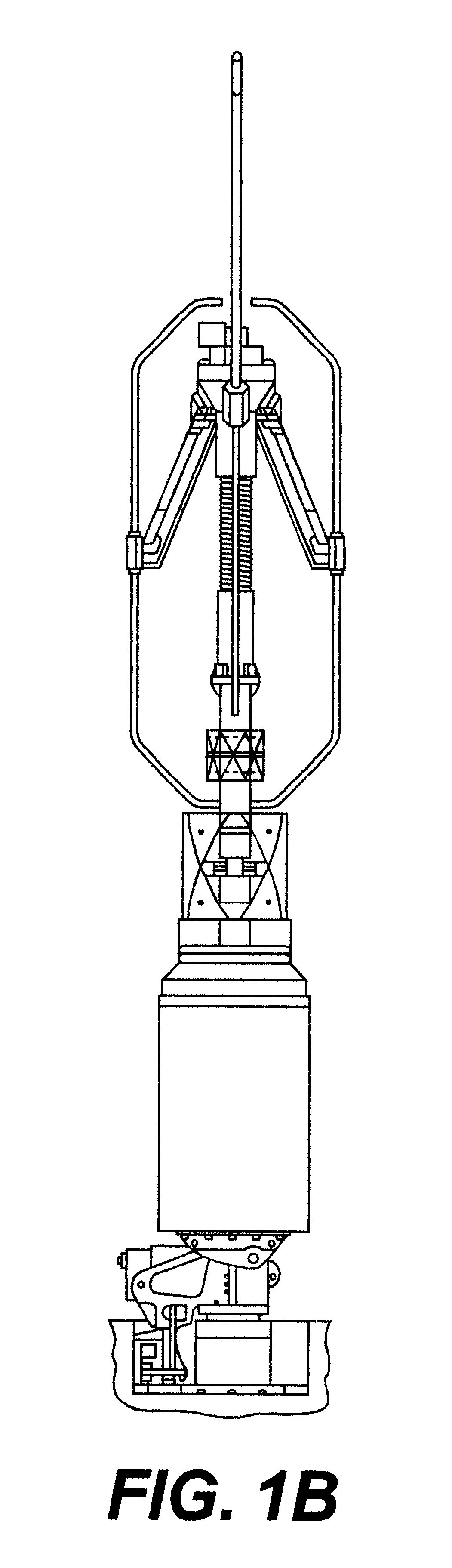

Antenna array with asymmetric elements

ActiveUS20150122886A1Particular array feeding systemsIndividually energised antenna arraysNon symmetricAntenna element

An RFID reader is provided that includes an antenna array comprising multiple antenna elements circumferentially distributed around a longitudinal axis of the antenna array. Each antenna element includes multiple patch elements disposed above one or more underlying substrates, wherein the patch elements of each antenna element are disposed on an outer side of the antenna element. Further, one or more of the antenna elements is an asymmetric antenna element, wherein a first end of the asymmetric antenna element is wider than a second, opposite end of the asymmetric antenna element, wherein a first patch element disposed proximate to the first end of the asymmetric antenna element is larger than a second patch element disposed proximate to the second end of the asymmetric antenna element, and wherein a resonant frequency associated with the first patch element is approximately the same as a resonant frequency associated with the second patch element.

Owner:SYMBOL TECH LLC

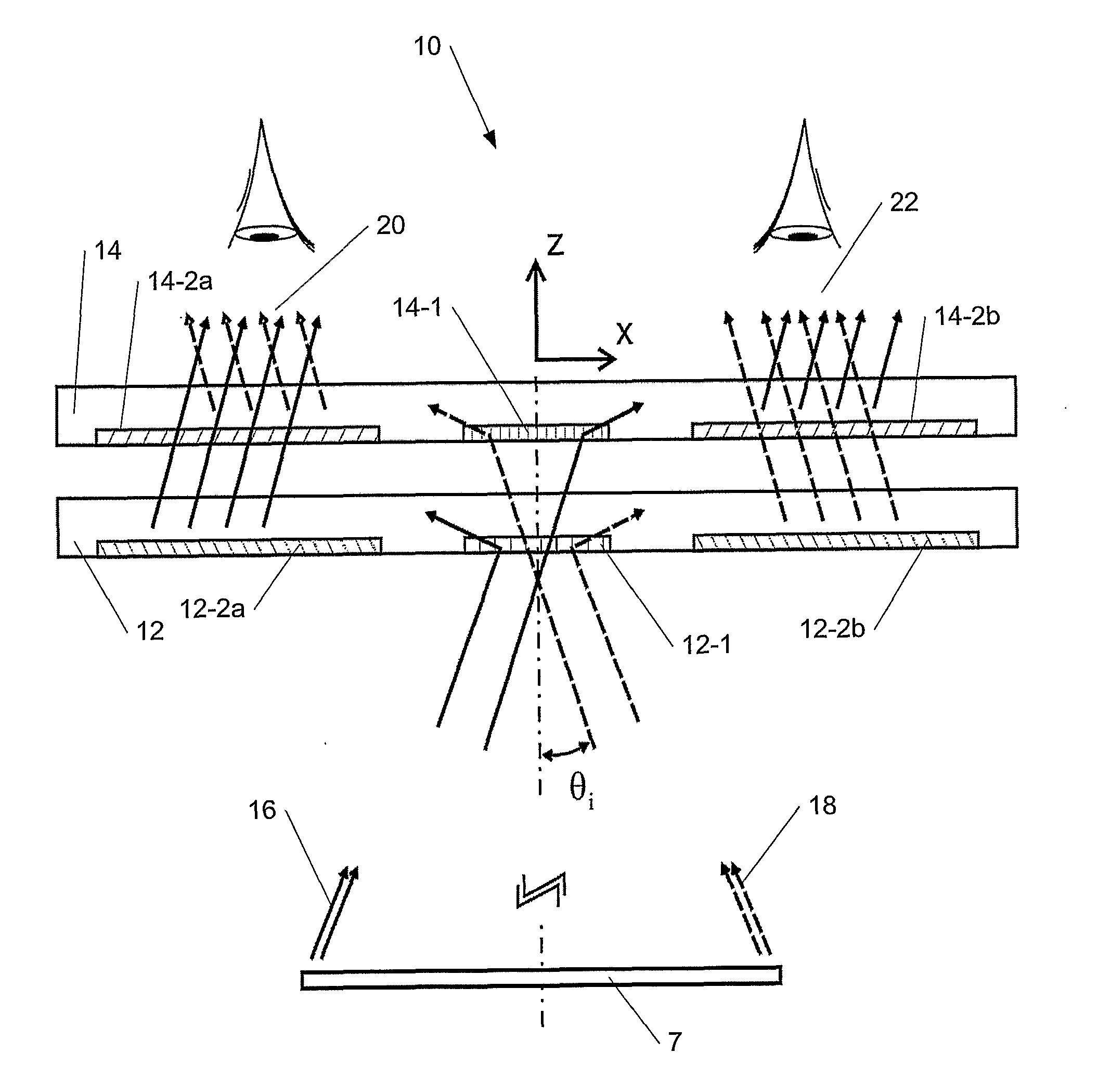

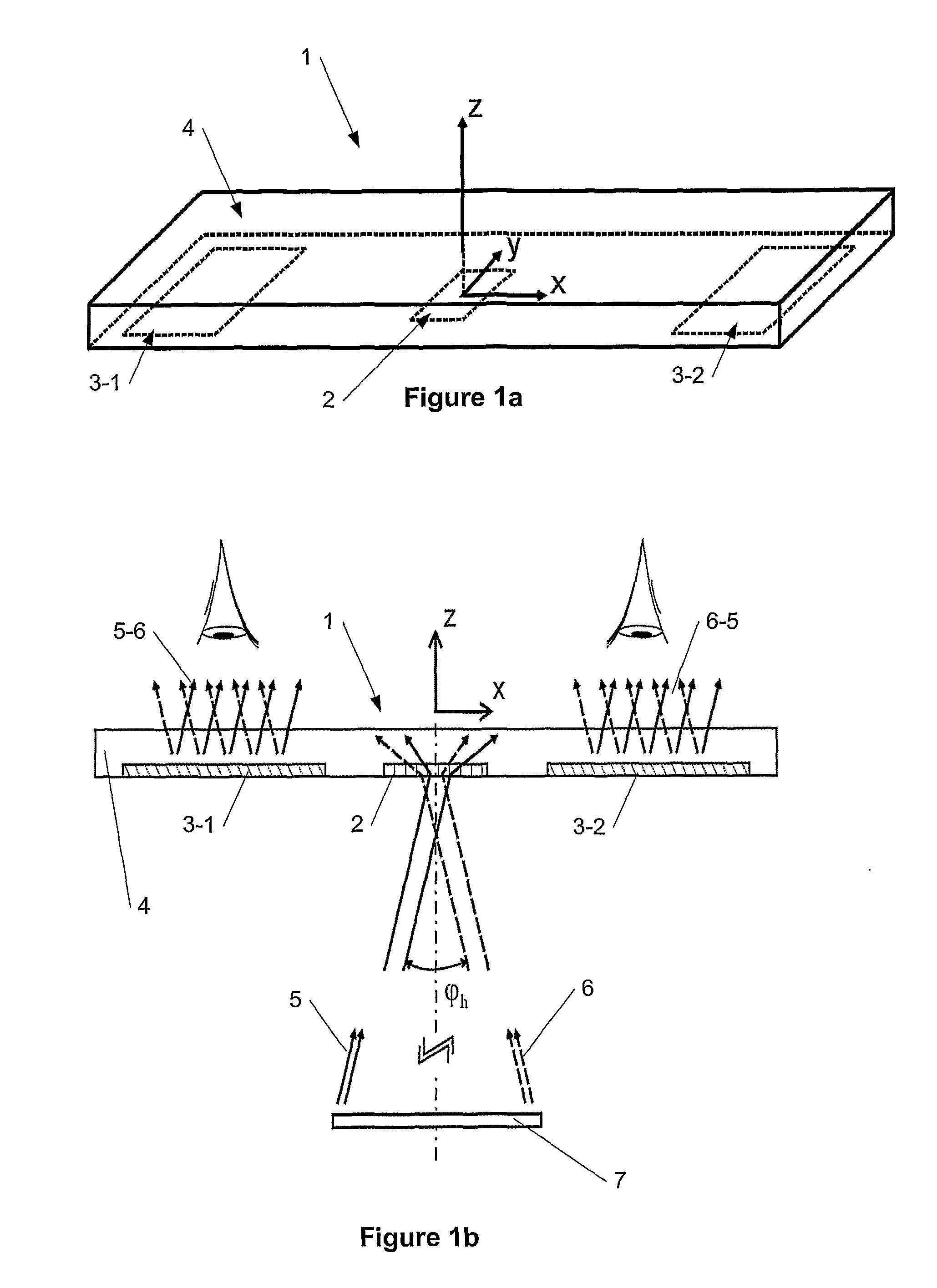

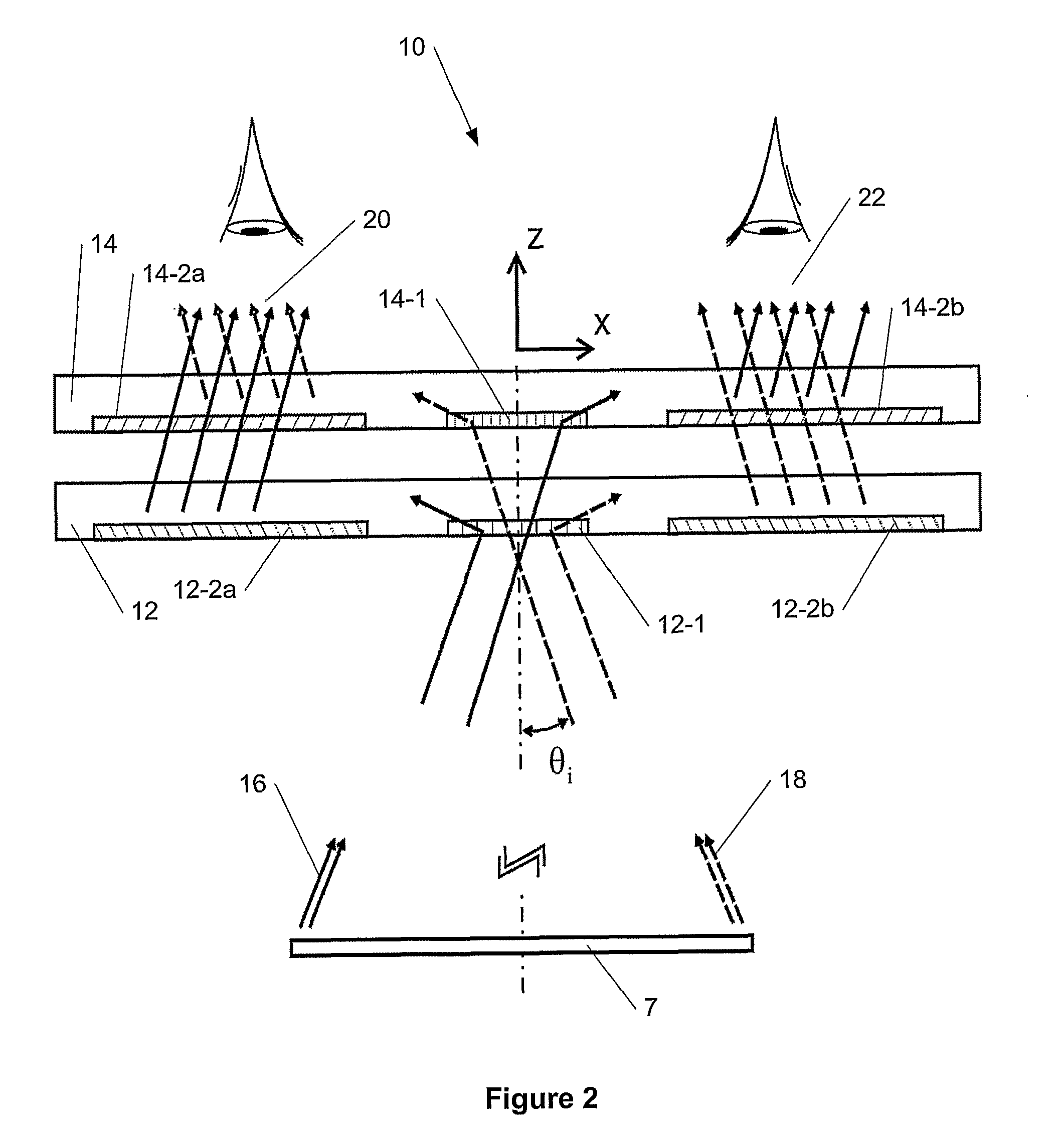

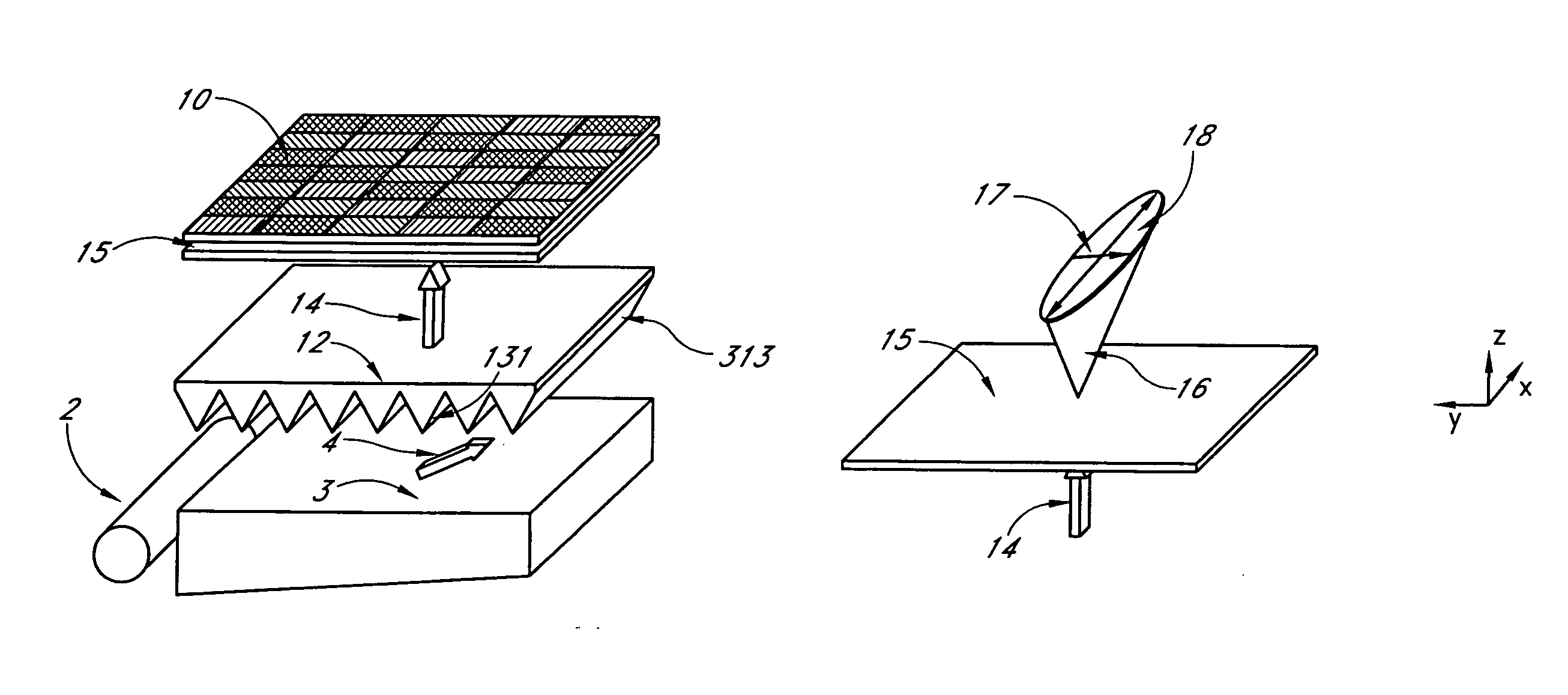

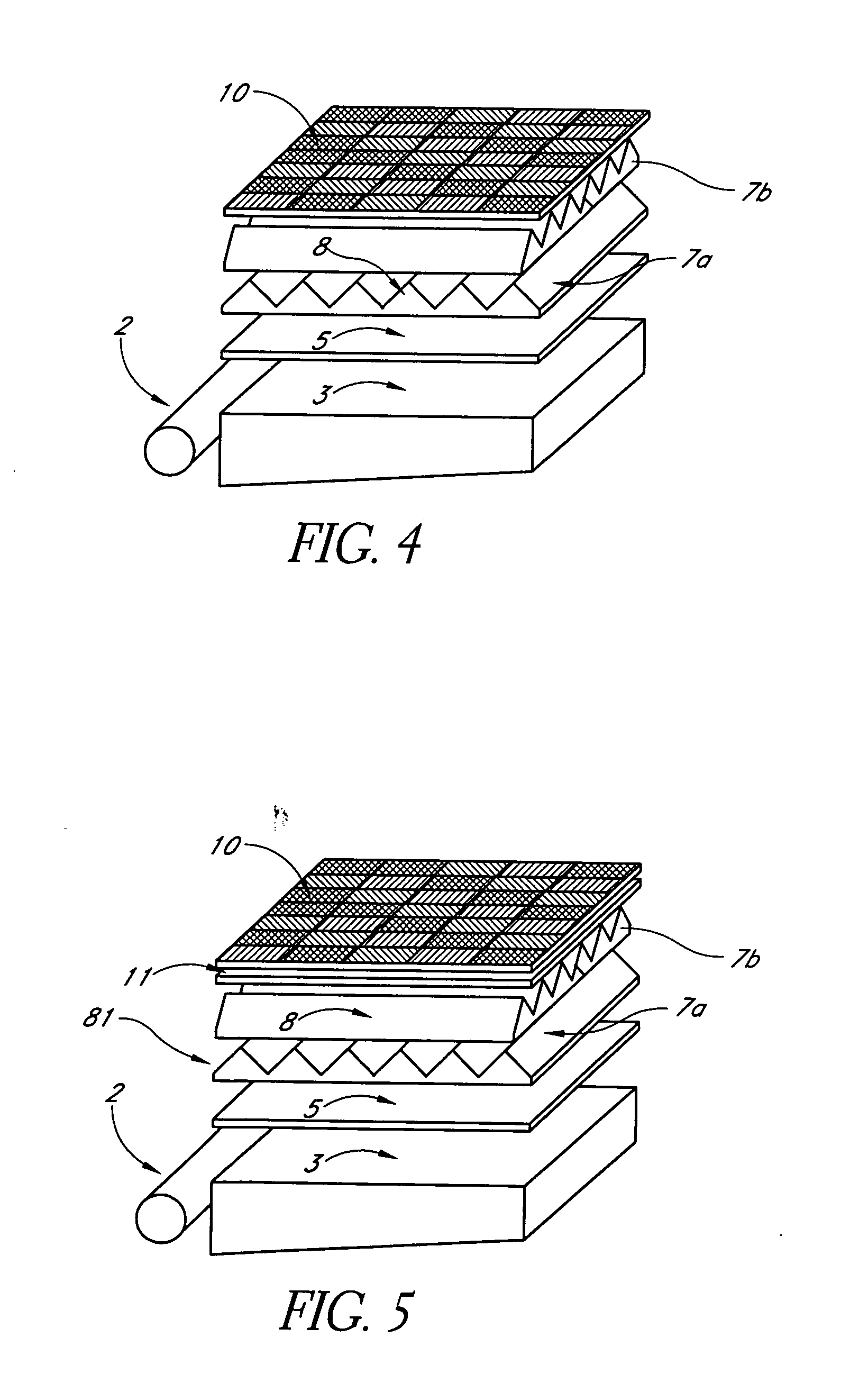

Exit Pupil Expanders with Wide Field-of-View

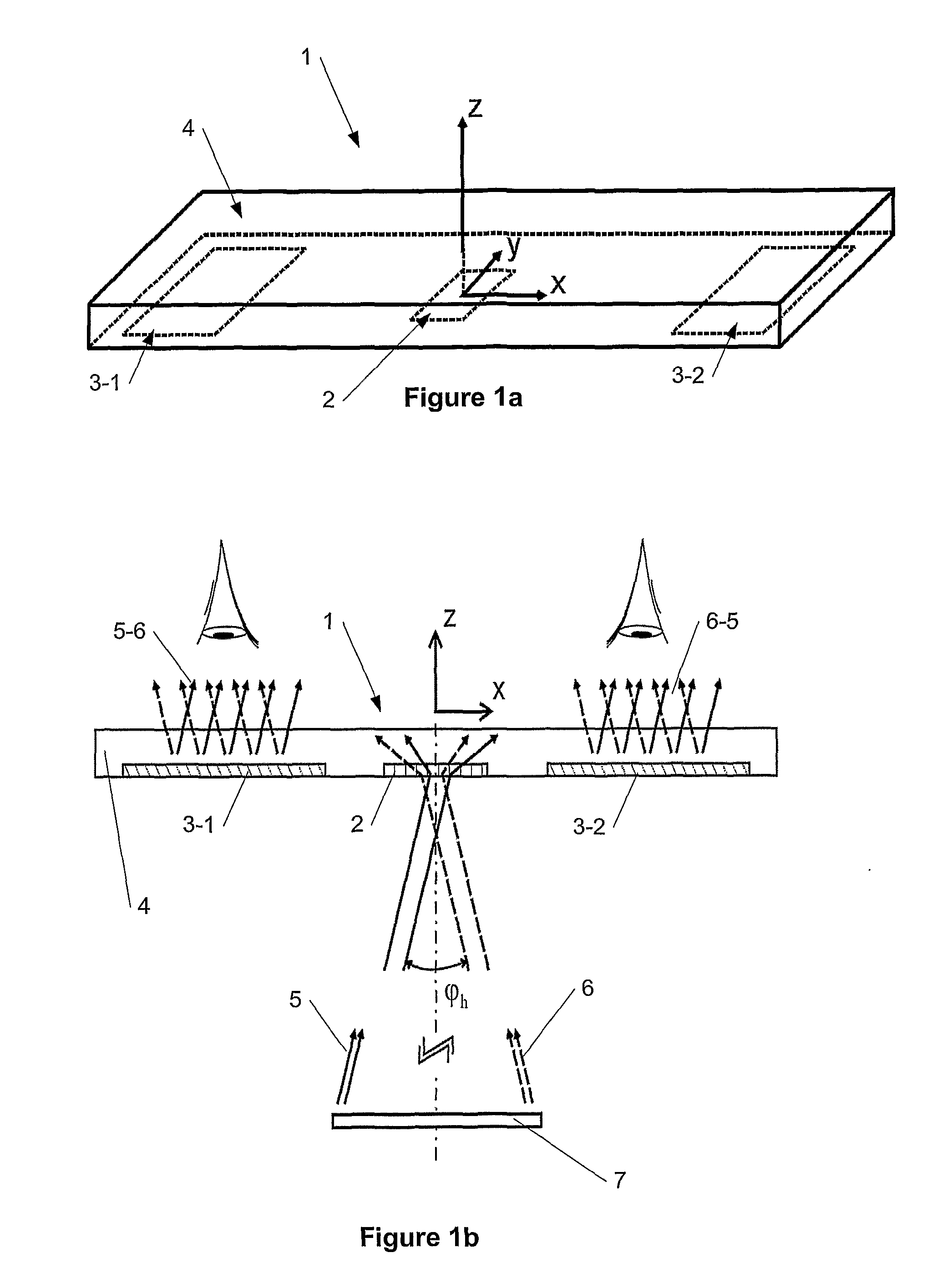

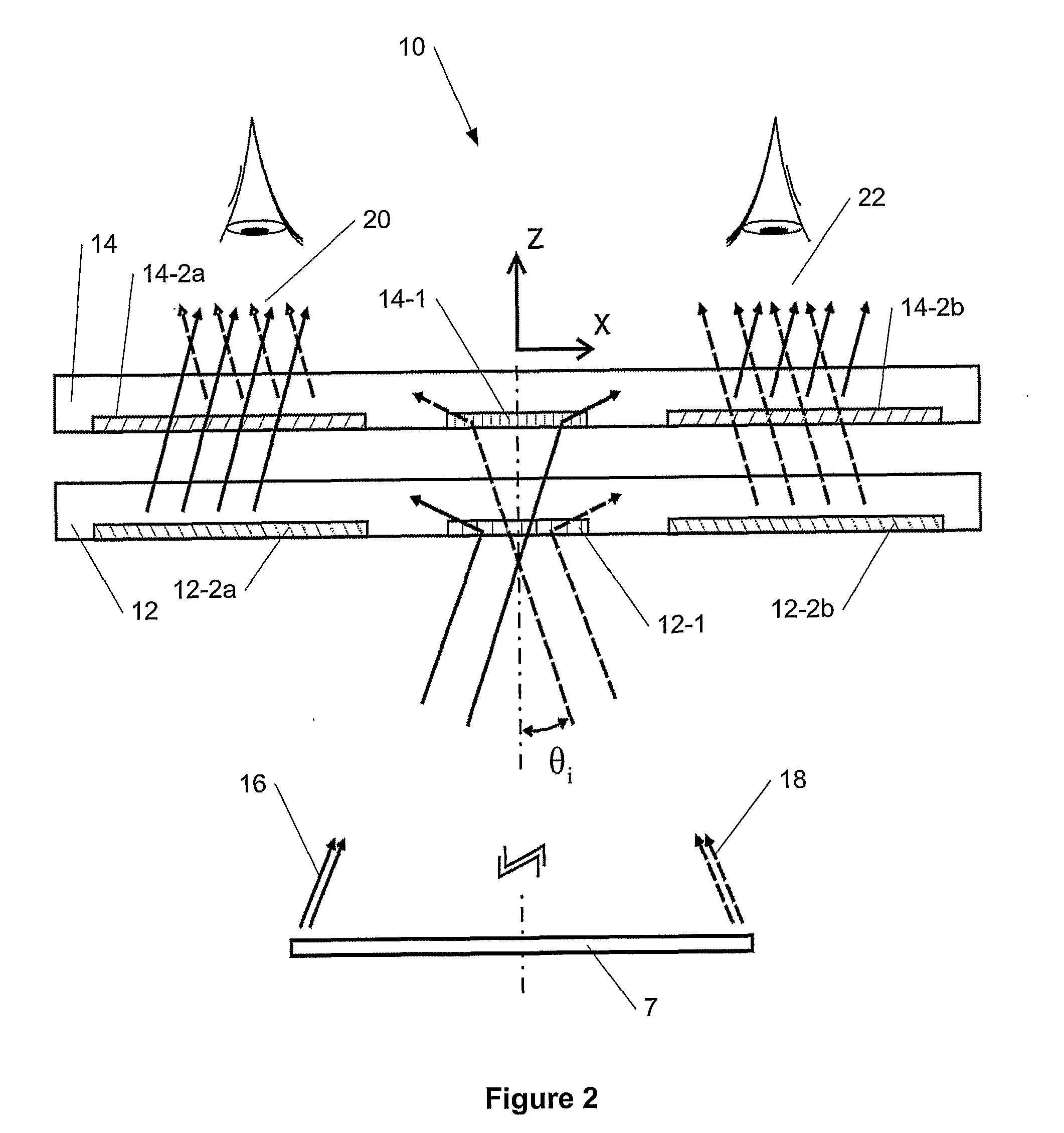

The specification and drawings present a new apparatus and method for providing a wide field-of-view as well as illumination uniformity in exit pupil expanders (EPE) using stacked EPE substrates (or plates) with non-symmetric exit pupil expansion that use a plurality of diffractive elements for expanding the exit pupil of a display for viewing.

Owner:MAGIC LEAP

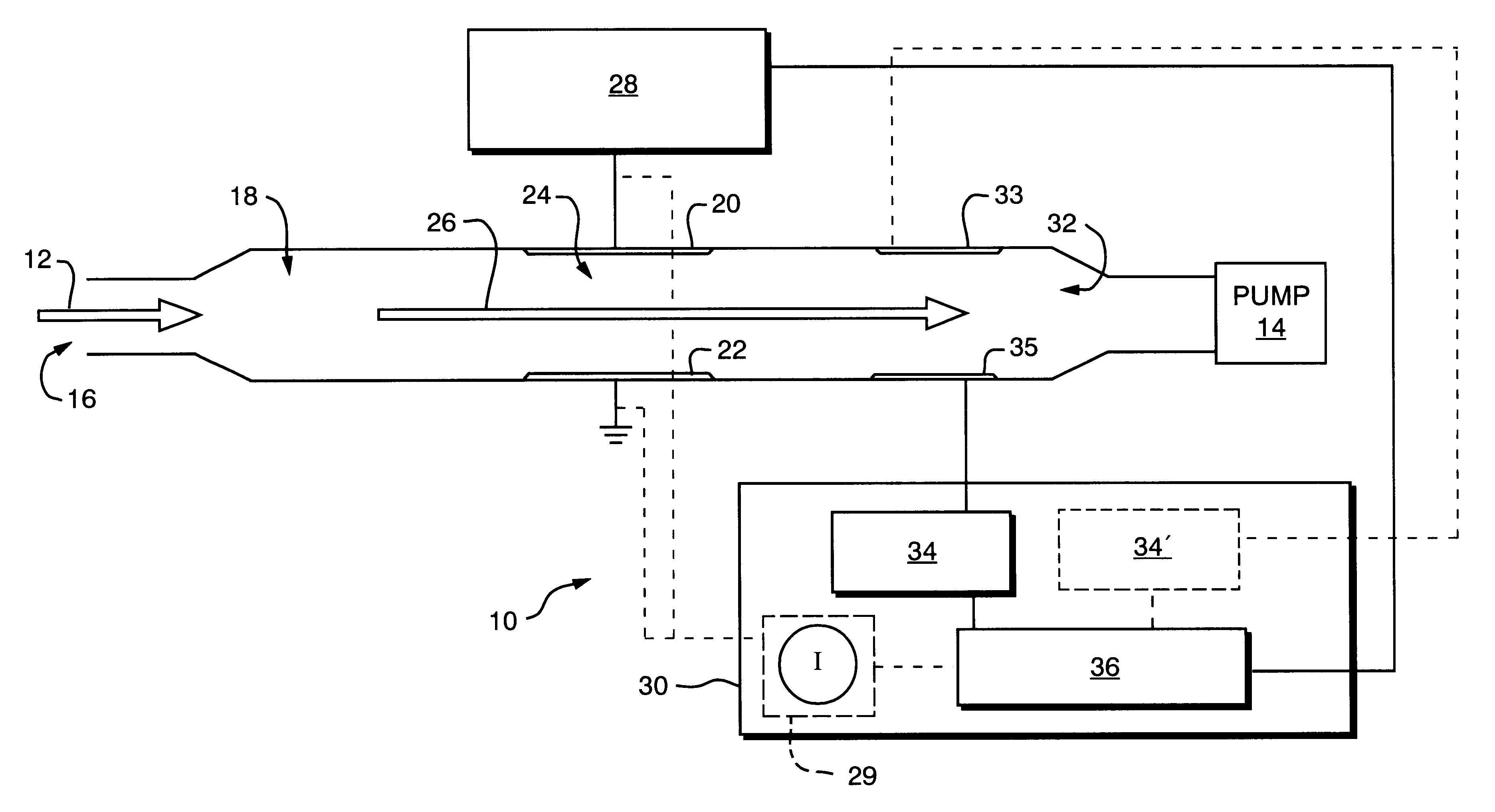

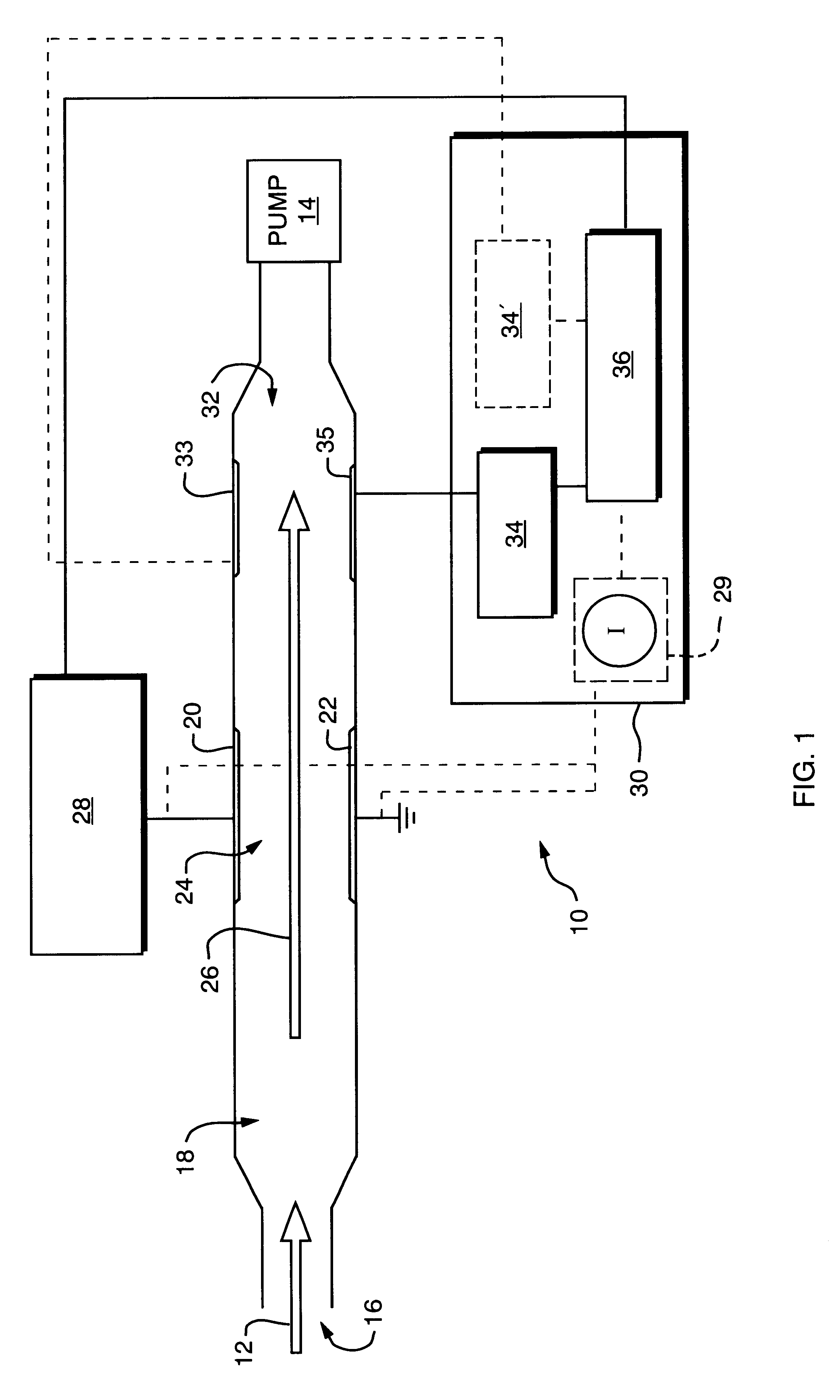

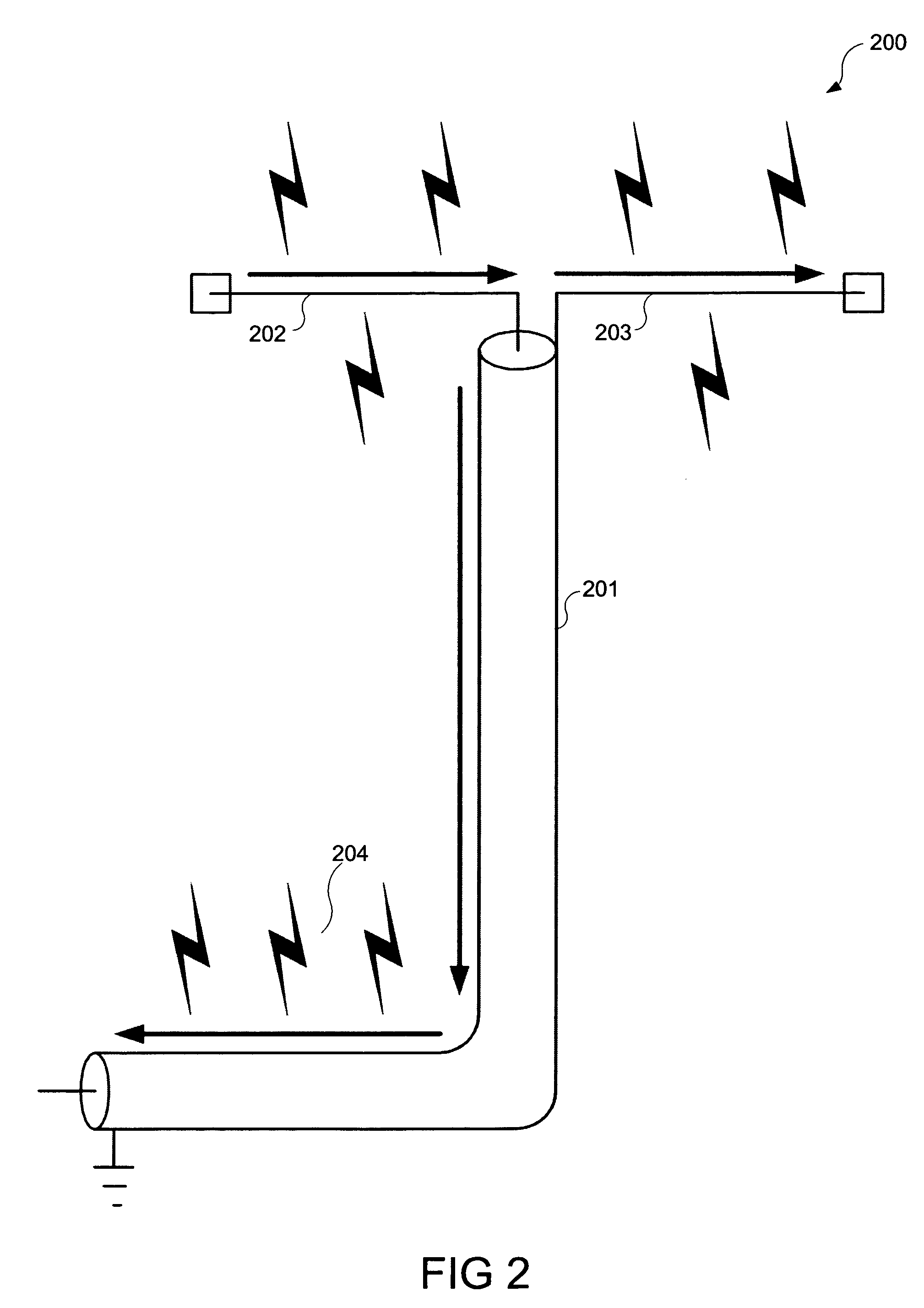

Longitudinal field driven field asymmetric ion mobility filter and detection system

InactiveUS6512224B1Improve accuracyHigh resolutionStability-of-path spectrometersTime-of-flight spectrometersNon symmetricIon-mobility spectrometry

An asymmetric field ion mobility spectrometer with an ionization source for ionizing a sample media and creating ions. An ion filter is disposed in the analytical gap downstream from the ionization source for creating an asymmetric electric field to filter the ions. An ion flow generator for creating an electric field in a direction transverse to the asymmetric electric field and which propels the ions through the asymmetric electric field towards a detector.

Owner:CHARLES STARK DRAPER LABORATORY

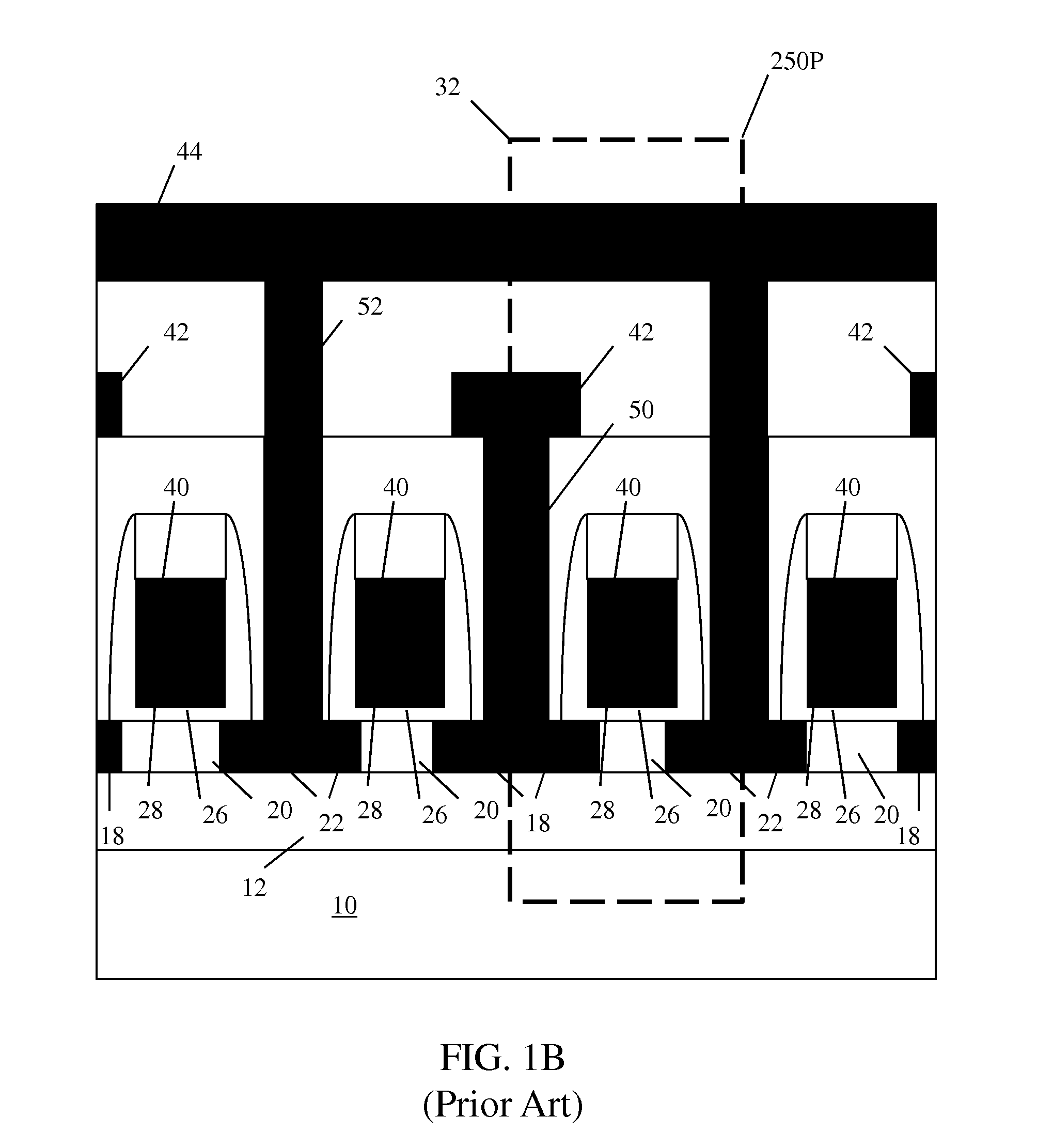

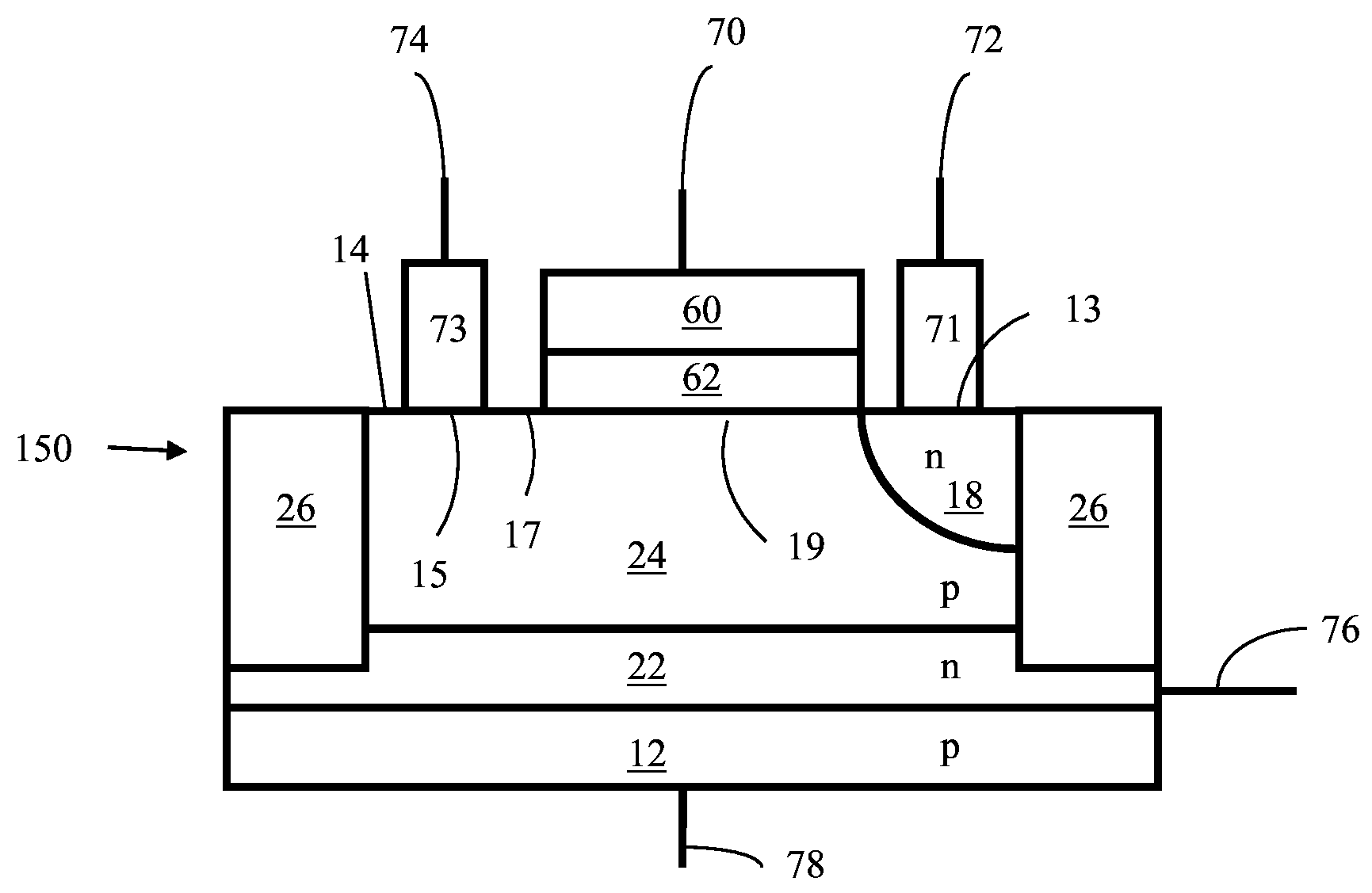

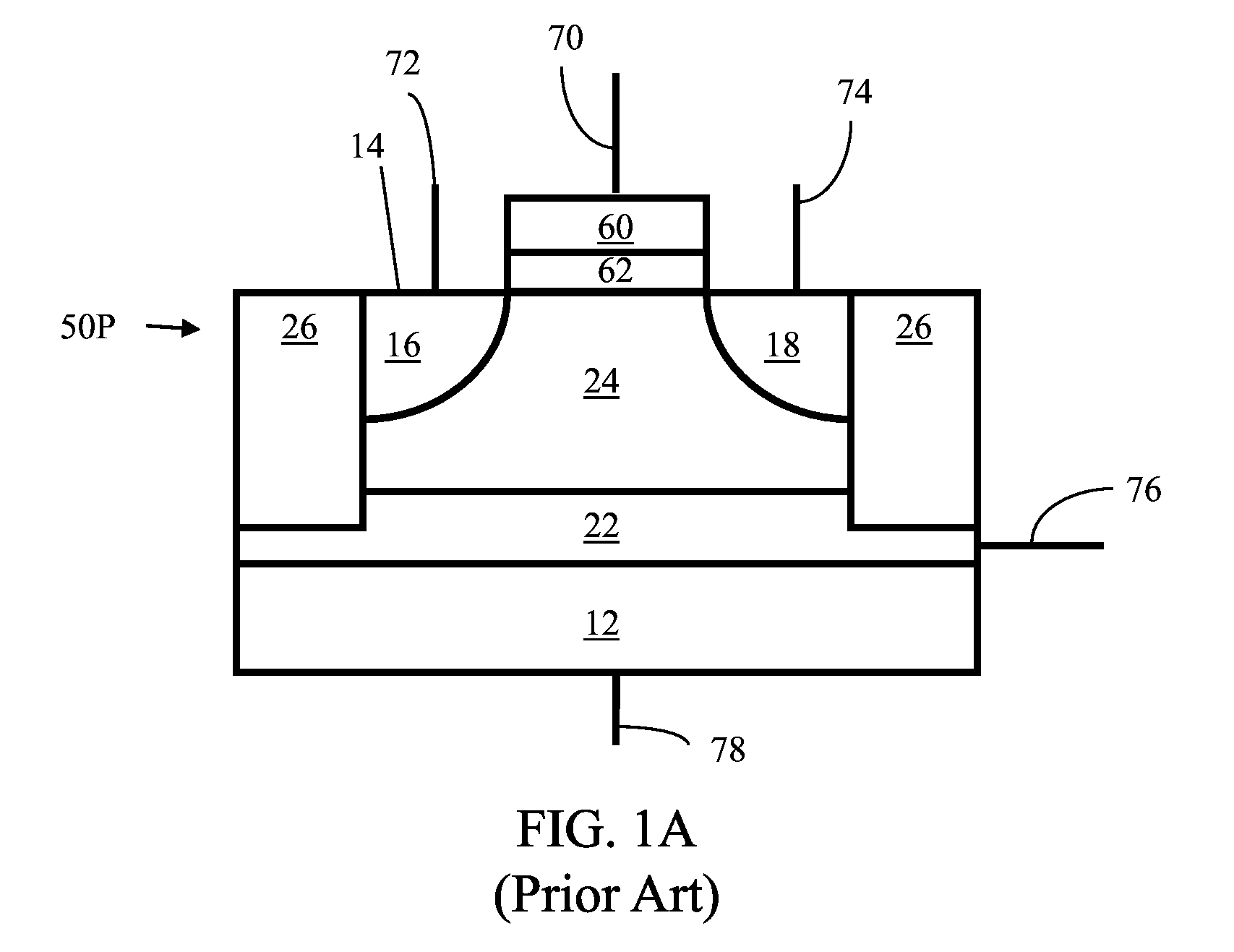

Asymmetric semiconductor memory device having electrically floating body transistor

Asymmetric, semiconductor memory cells, arrays, devices and methods are described. Among these, an asymmetric, bi-stable semiconductor memory cell is described that includes: a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with the floating body region; a second region in electrical contact with the floating body region and spaced apart from the first region; and a gate positioned between the first and second regions, such that the first region is on a first side of the memory cell relative to the gate and the second region is on a second side of the memory cell relative to the gate; wherein performance characteristics of the first side are different from performance characteristics of the second side.

Owner:ZENO SEMICON

Exit pupil expanders with wide field-of-view

Owner:MAGIC LEAP INC

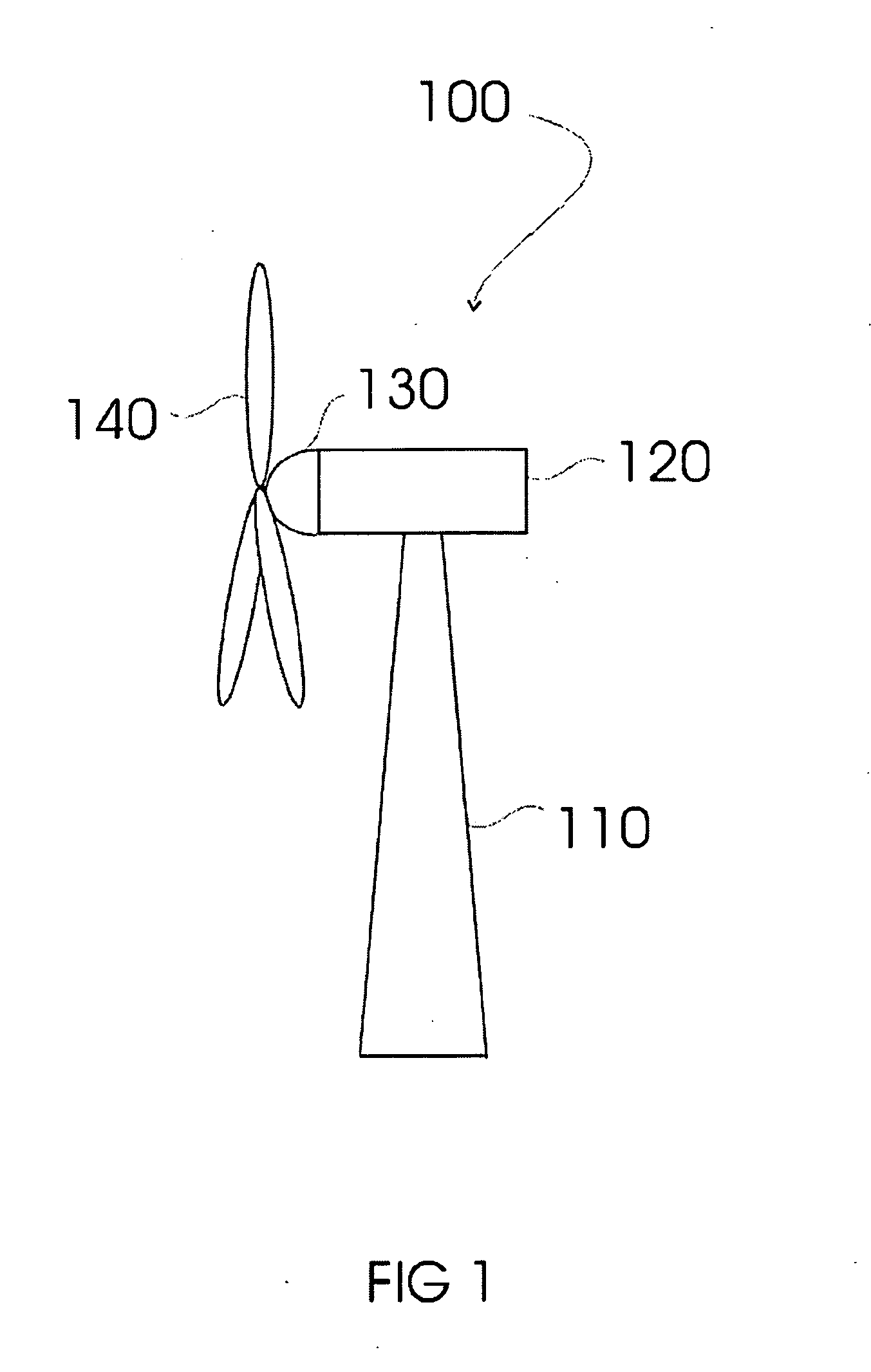

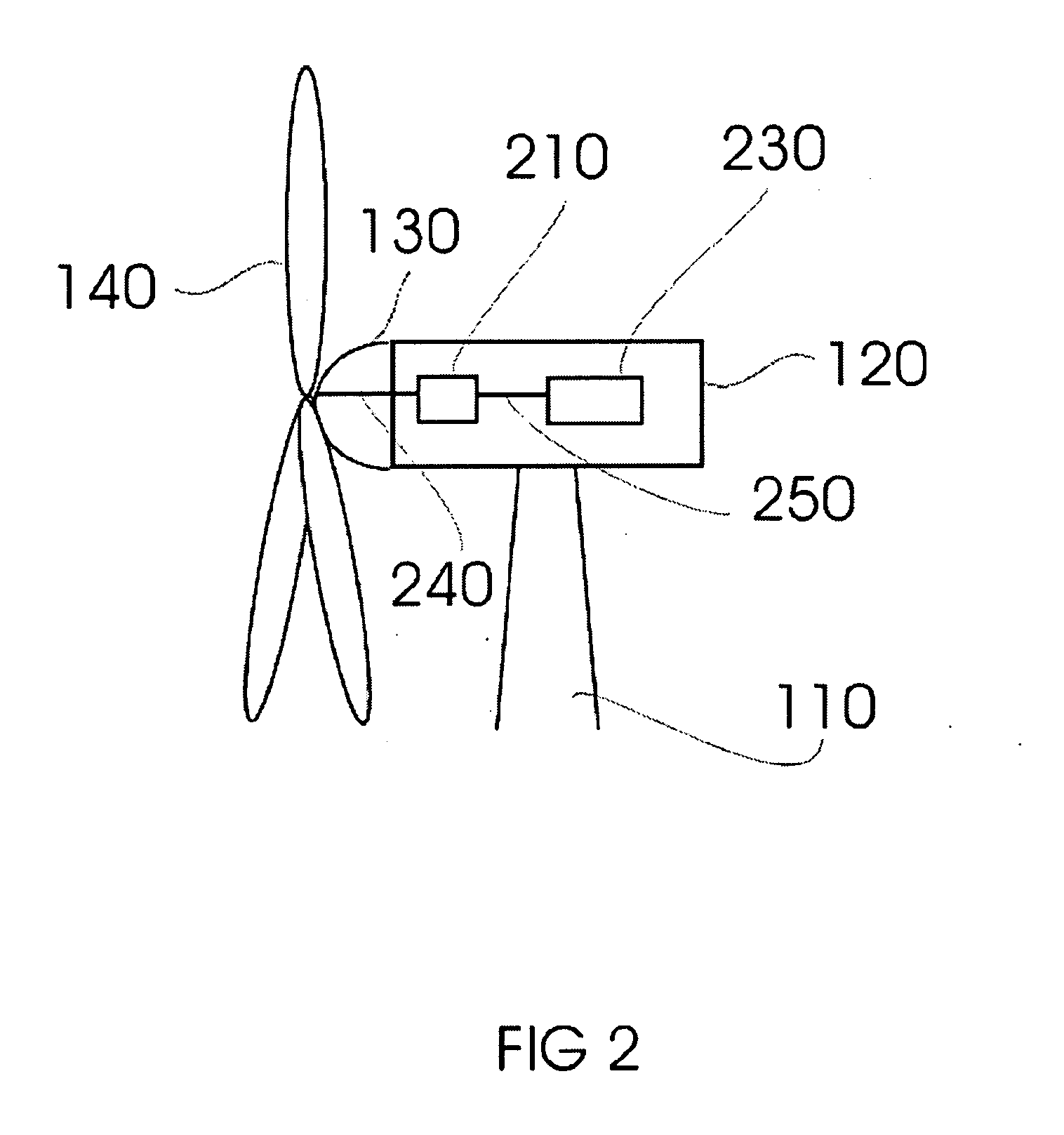

Wind energy system with fluid-working machine with non-symmetric actuation

The invention relates to a wind energy system with hydraulic energy transmission with non-symmetric actuation. The non-symmetric actuation is caused by valve control and mechanical means for controlling the actuation of the pistons. A cylinder unit is provided comprising a drive unit and an output unit associated with two hydraulic connections. The drive and the output unit comprise a minimum of two cylinders, in which pistons are reciprocating. Some of the cylinders can be switched off during low wind speeds. The cylinders communicate with a low pressure manifold and a high pressure manifold. These manifolds are part of the hydraulic connections. Use of the fluid-working machine as transmission in wind energy systems increases the overall economical efficiency.

Owner:GENERAL ELECTRIC CO

Compact multi-band direction-finding antenna system

InactiveUS6480168B1Easy to transportEconomically manufacturedAntenna supports/mountingsAntenna adaptation in movable bodiesMulti bandNon symmetric

An compact and rugged antenna system particularly suited to direction finding includes a plurality of antenna arrays for receiving respective frequency bands and colocated on a mast with separation between antenna arrays along the mast. The mast includes a coil wound of an insulator and functioning as a loaded inductor to shift the mast resonance out of the frequency band of the antenna system. A VHF dipole array having elements shaped to reduce scattering to UHF and SHF arrays is supported on movable arms which allow retraction that reduces height and provides mechanical protection to one or more other arrays as well as damping against vibration by contacting the mast with shaped portions of the dipole elements. The bowtie elements of the UHF array are angled at a central region to optimize array diameter at low UHF frequencies. A finned RF electronics housing is preferably provided which reduces solar loading and dissipates heat from antenna electronics. Asymmetrically keyed fittings are provided to permit accurate antenna system, array and element positioning and replaceable components and wiring, both internally and externally of the housing, is held in position to allow field repairs without recalibration.

Owner:LOCKHEED MARTIN CORP

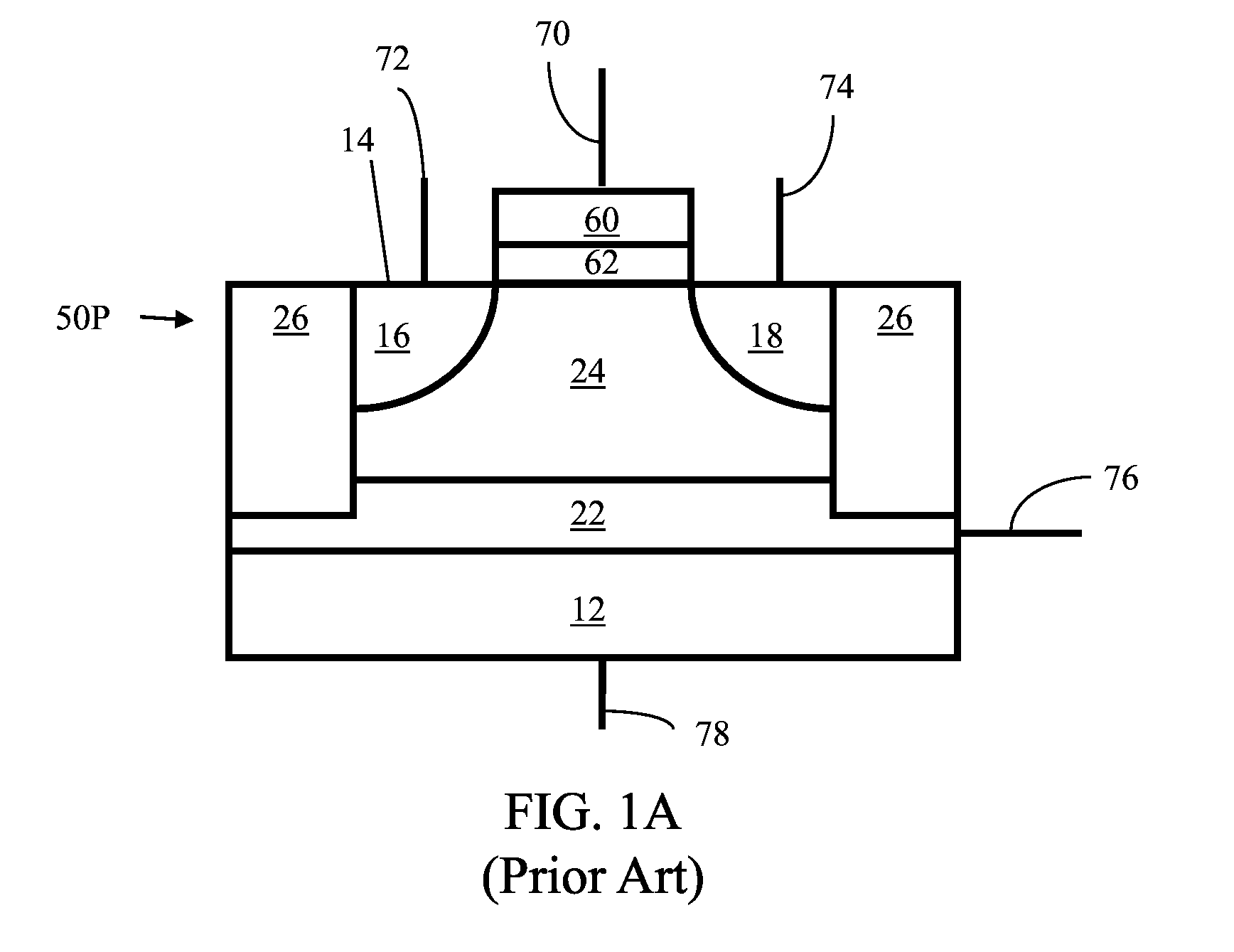

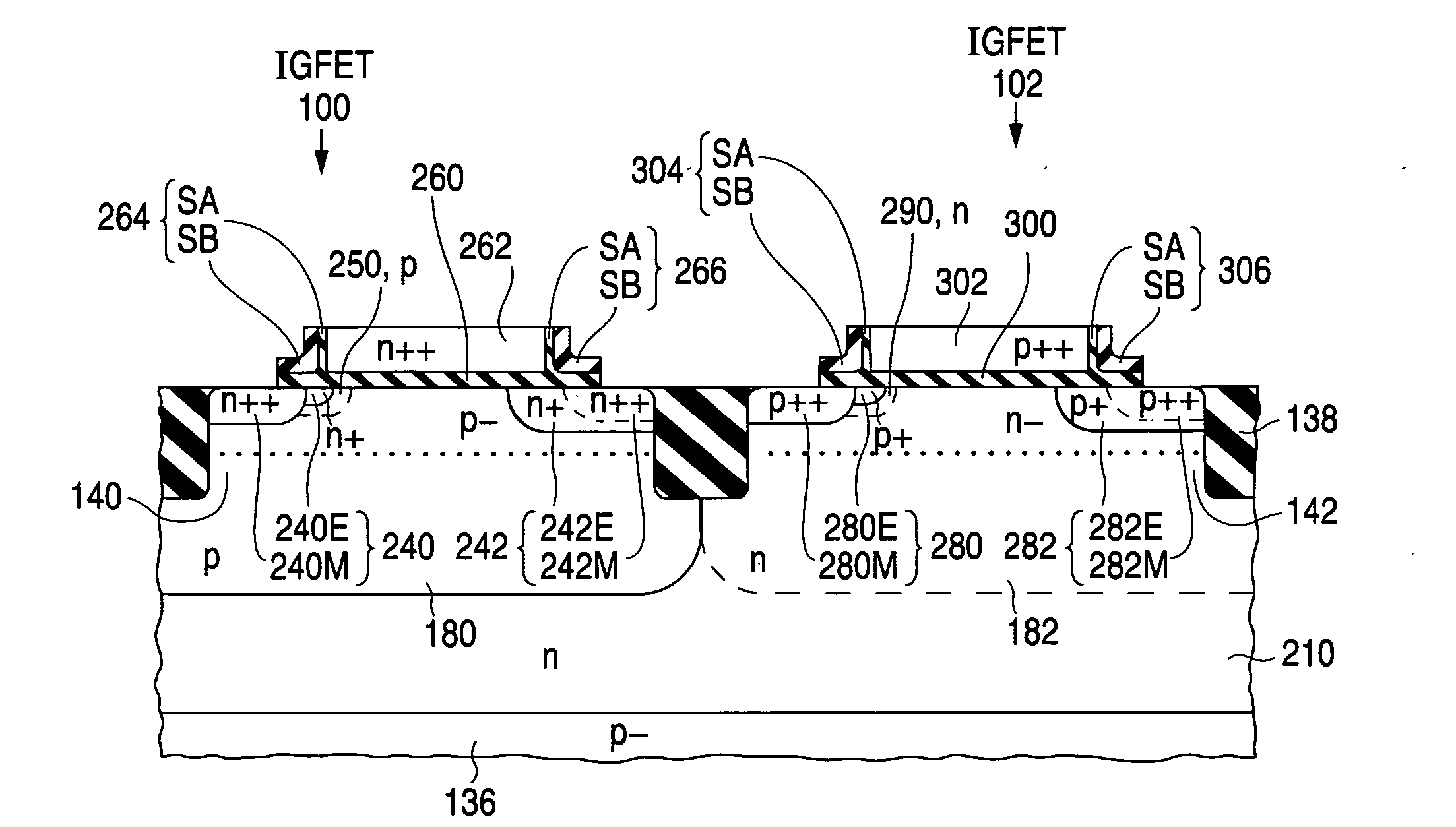

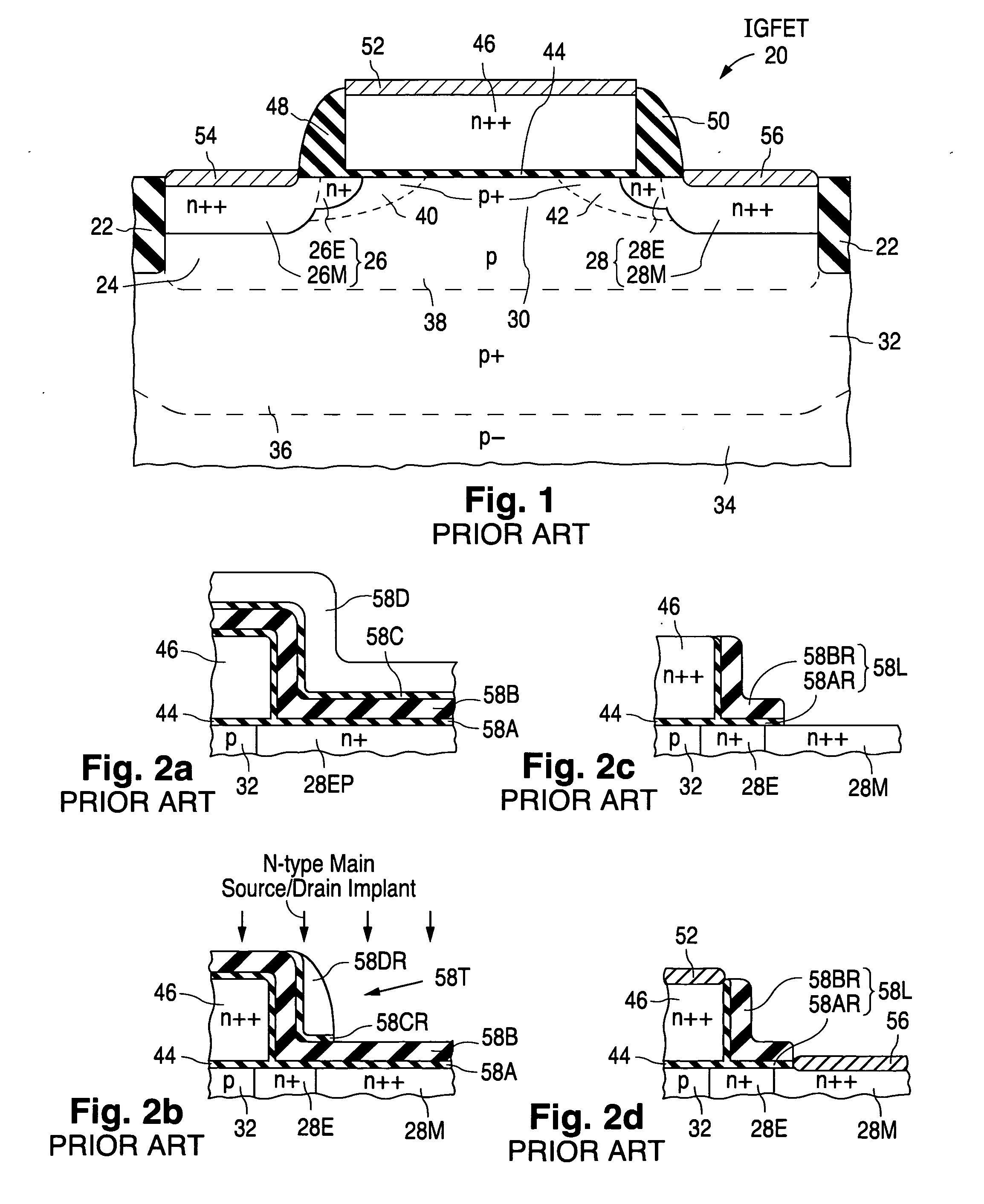

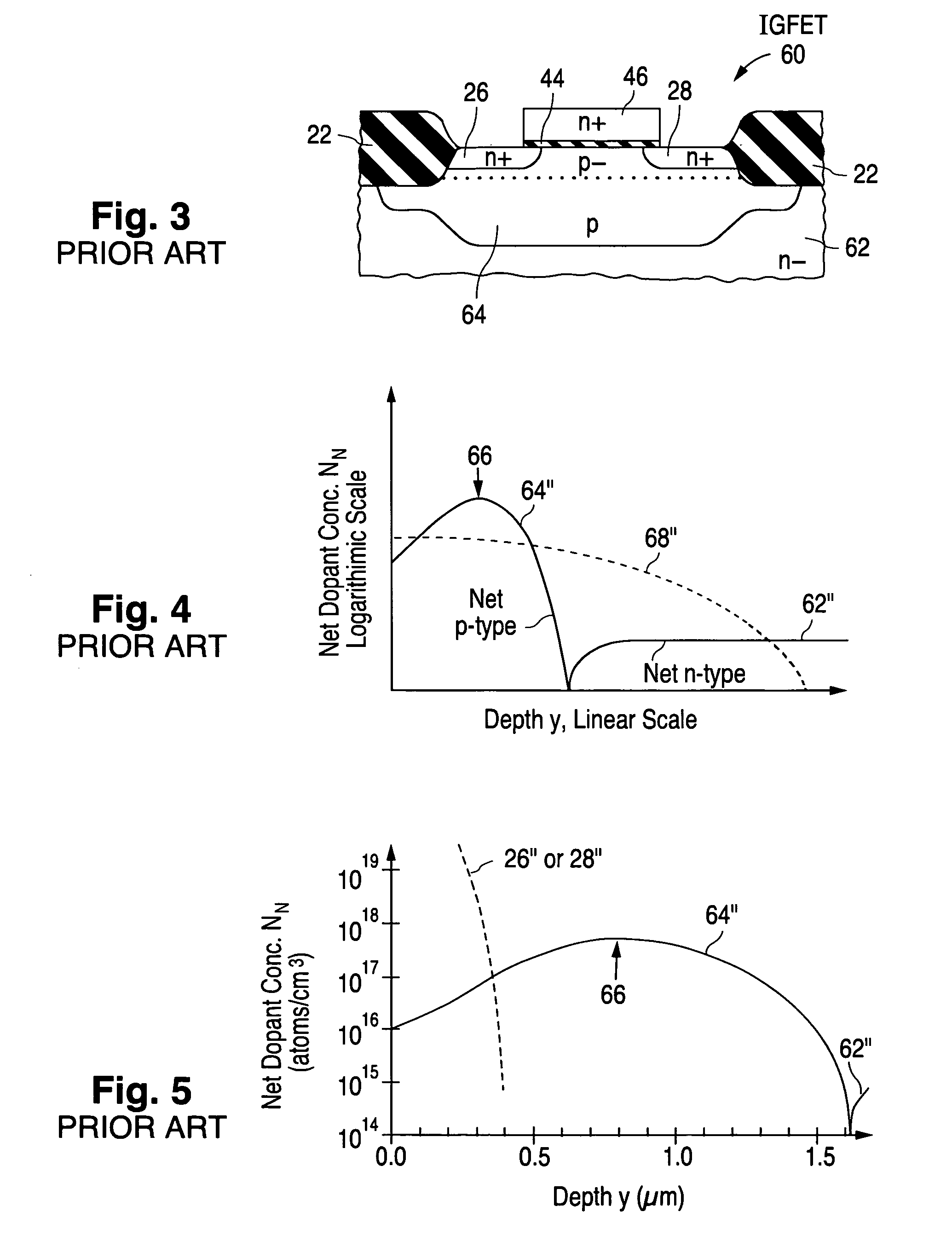

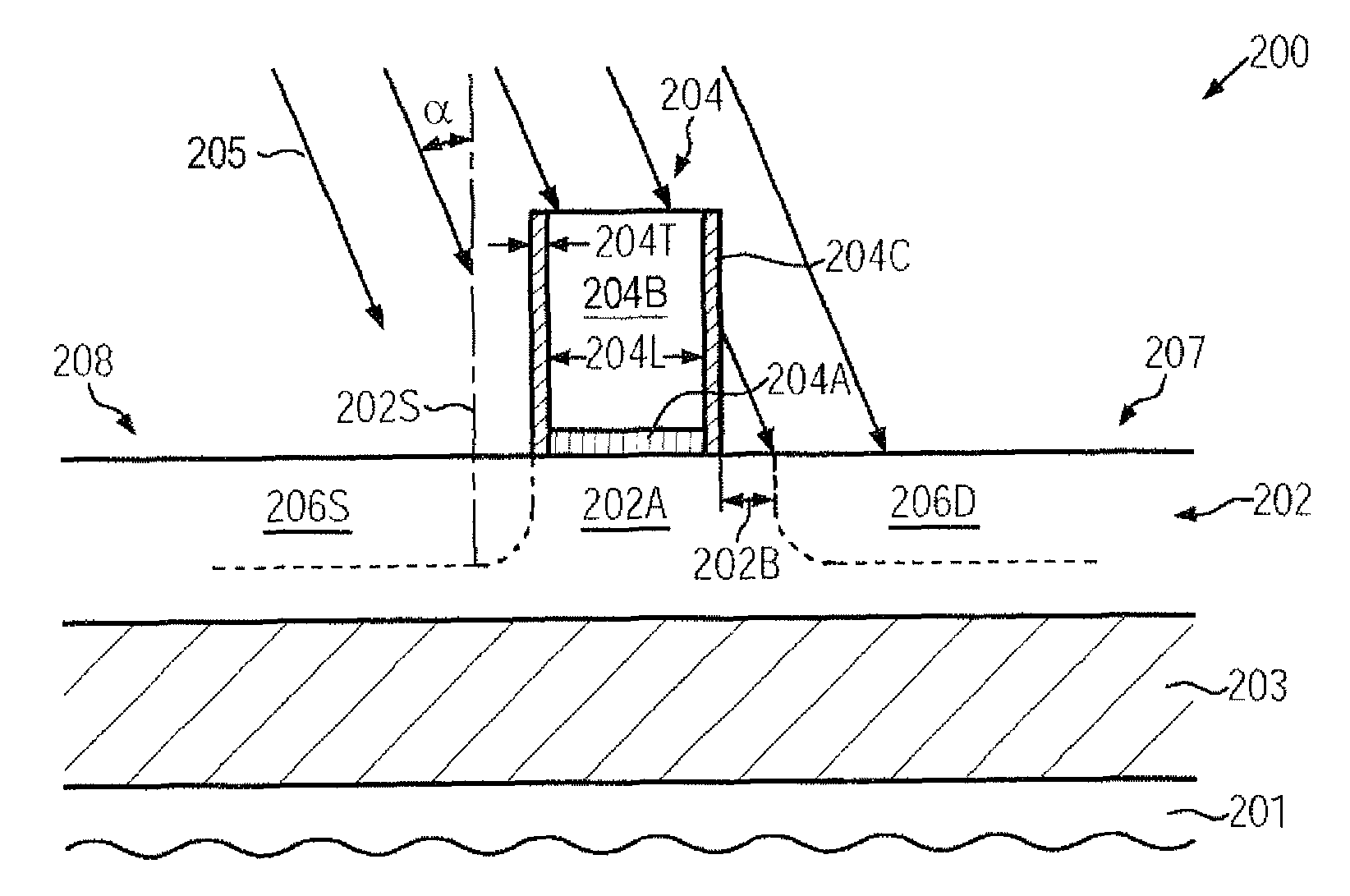

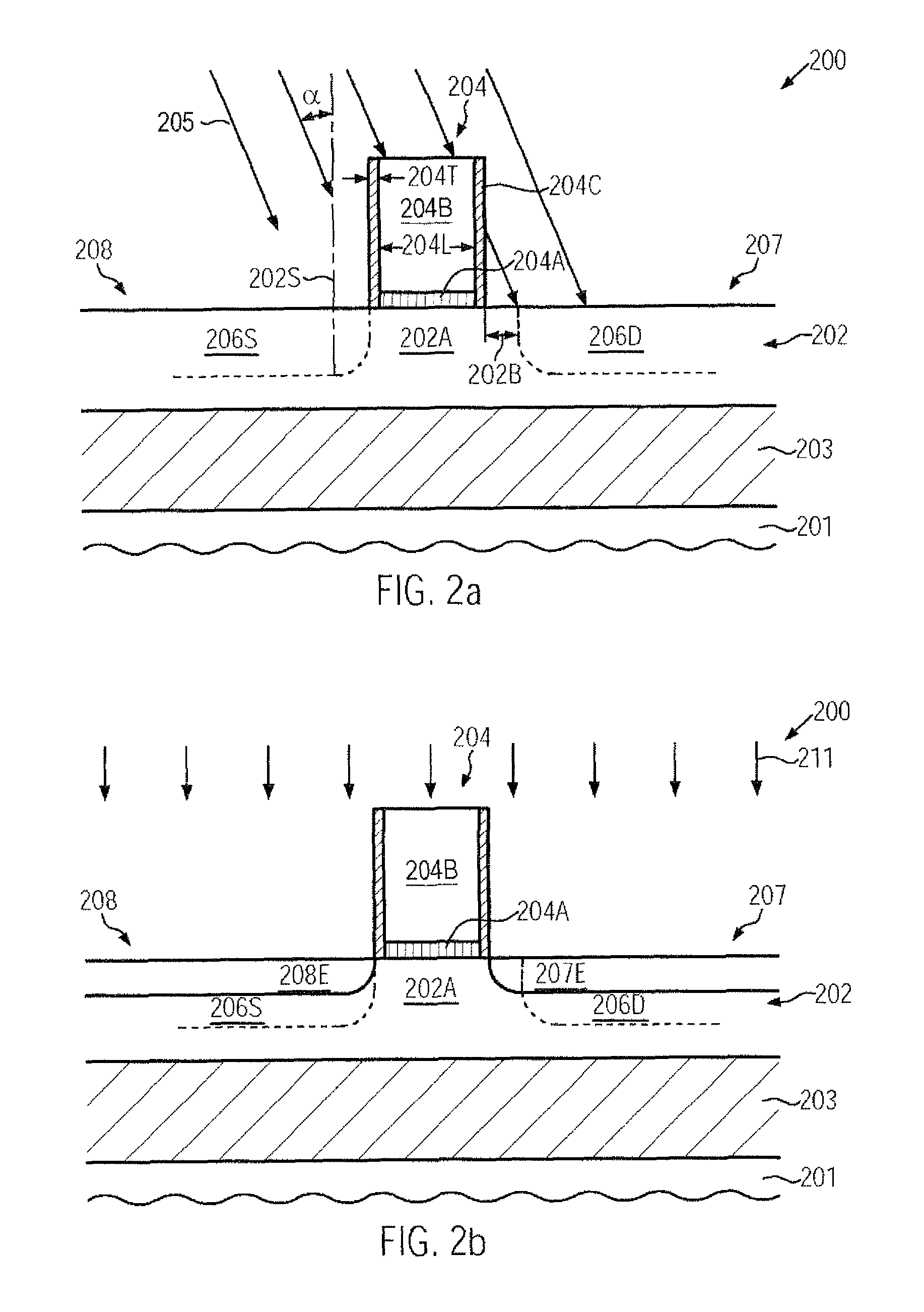

Fabrication and structure of asymmetric field-effect transistors using L-shaped spacers

ActiveUS20100244106A1Improve transconductanceLightly dopedSolid-state devicesSemiconductor/solid-state device manufacturingDopantNon symmetric

Fabrication of an asymmetric field-effect transistor (100) entails defining a gate electrode (262) above, and vertically separated by a gate dielectric layer (260) from, a channel-zone portion (244) of body material of a semiconductor body. Semiconductor dopant is introduced into the body material to define a more heavily doped pocket portion (250) using the gate electrode as a dopant-blocking shield. A spacer (264T) is provided along the gate electrode. The spacer includes (i) a dielectric portion situated along the gate electrode, (ii) a dielectric portion situated along the semiconductor body, and (iii) a filler portion (SC) largely occupying the space between the other two spacer portions. Semiconductor dopant is introduced into the semiconductor body to define a pair of main source / drain portions (240M and 240E) using the gate electrode and the spacer as a dopant-blocking shield. The filler spacer portion is removed to convert the spacer to an L shape (264). A pair of electrical contacts are formed respectively to the main S / D portions.

Owner:NAT SEMICON CORP

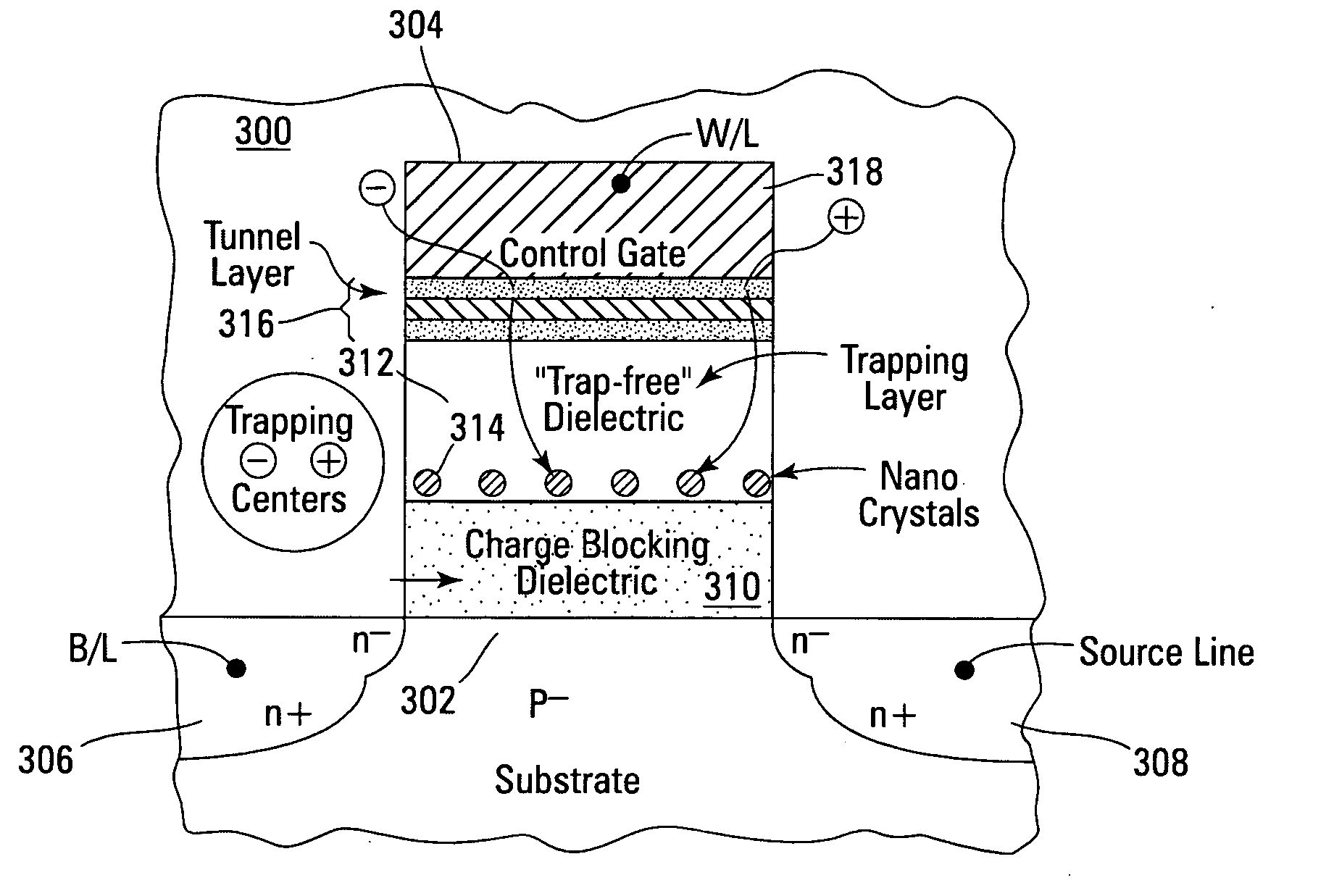

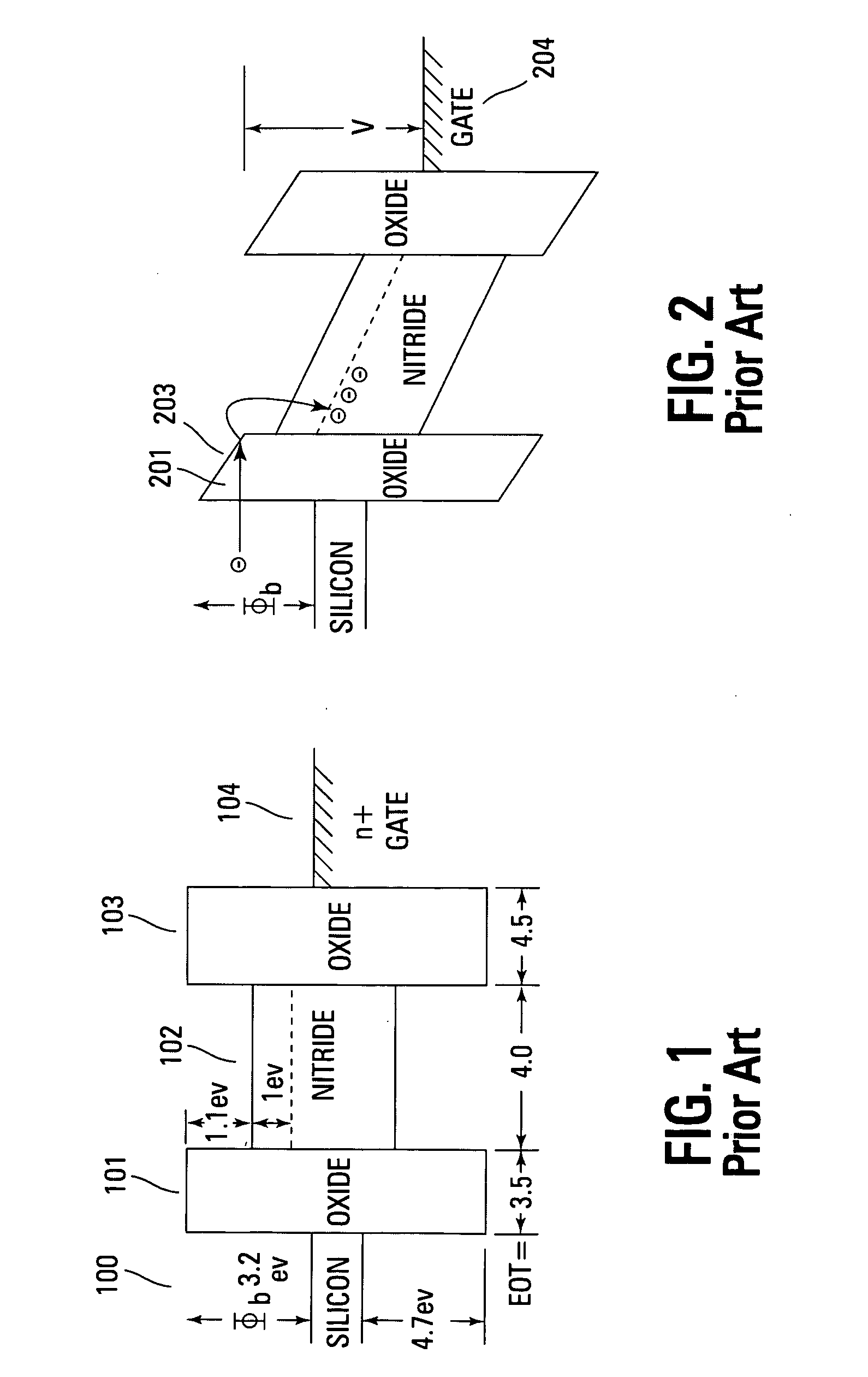

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

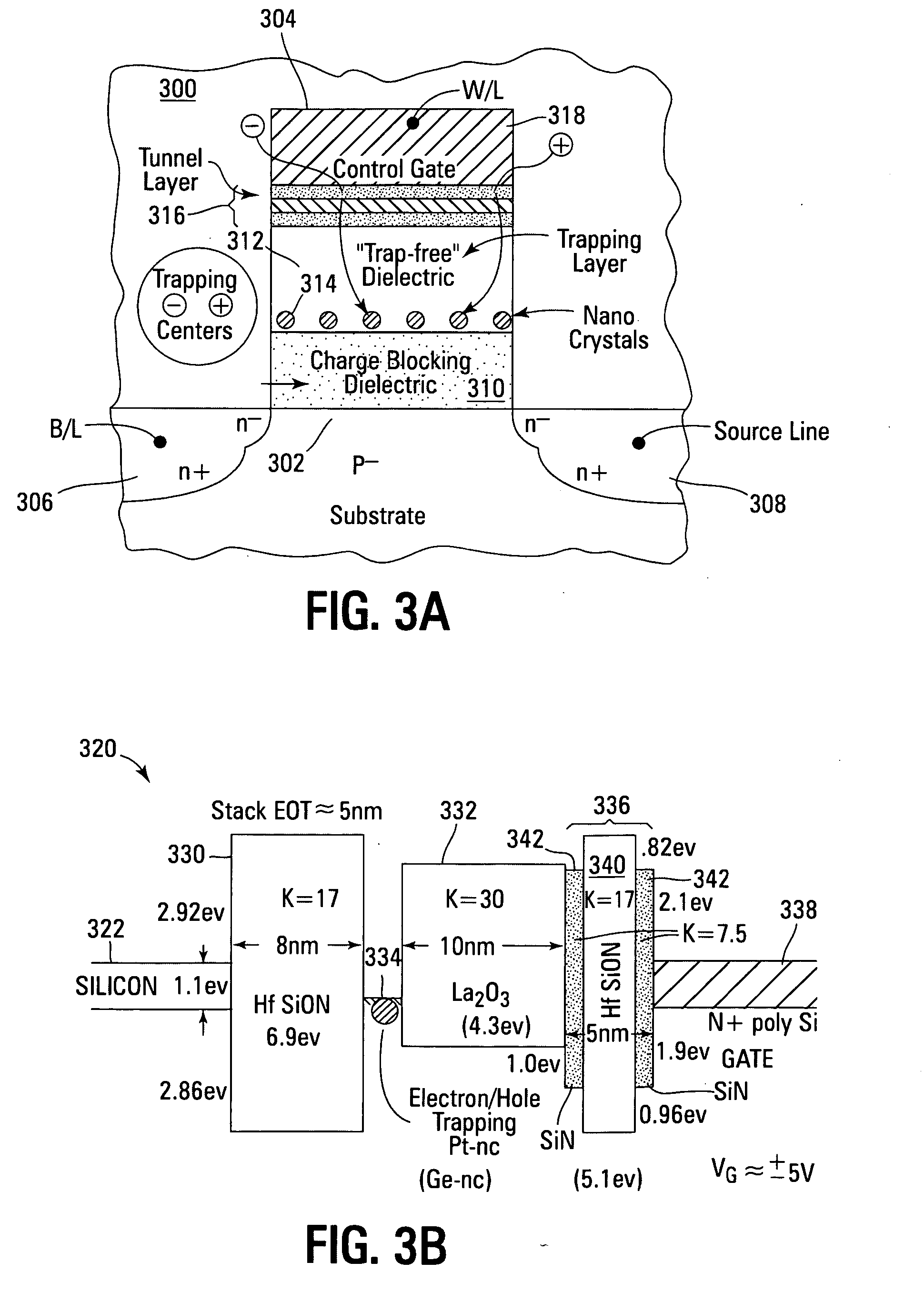

Elliptical diffusers used in displays

A backlit light display comprises a light guide panel, a prismatic film, an asymmetric top diffuser and an LCD. A linear light source is disposed along a side face of the light guide panel. Light from the linear light source is transmitted though the light guide panel where it is spread and uniformly output through a front face to the prismatic film. Light incident on the prismatic film is redirected more along a first direction than along a second direction. This light is directed more normal to the LCD. An asymmetric diffuser is applied between the prismatic film and the LCD panel to smear the periodic information from the prismatic film and eliminate the Moiré fringe pattern resulting from interference between the periodic structure of the prismatic film and the periodic arrangement of pixels in the LCD. The asymmetric diffuser is aligned with respect to the prismatic film such that it scatters and spreads light more in a second direction than the first direction.

Owner:WAVEFRONT TECH INC

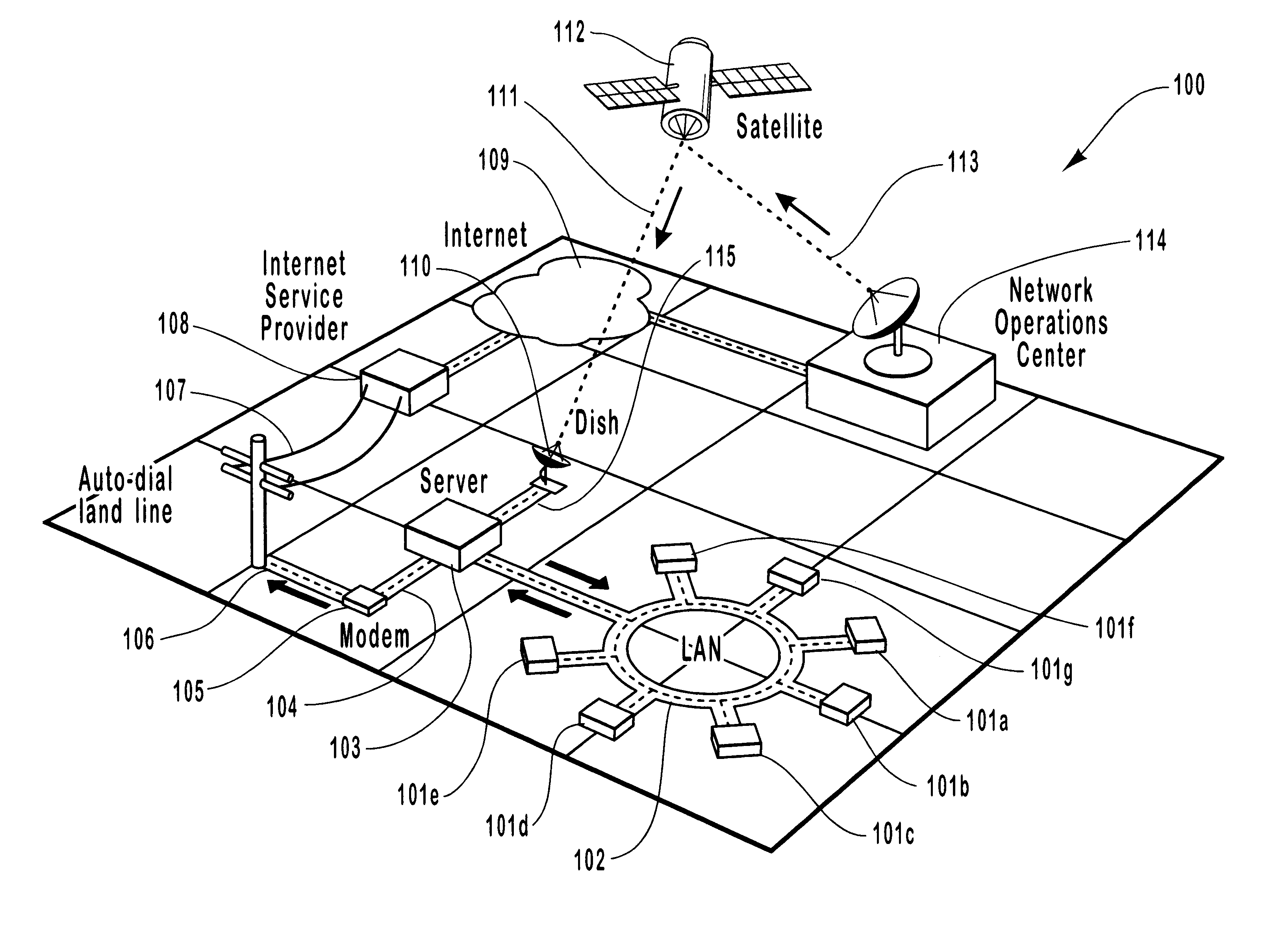

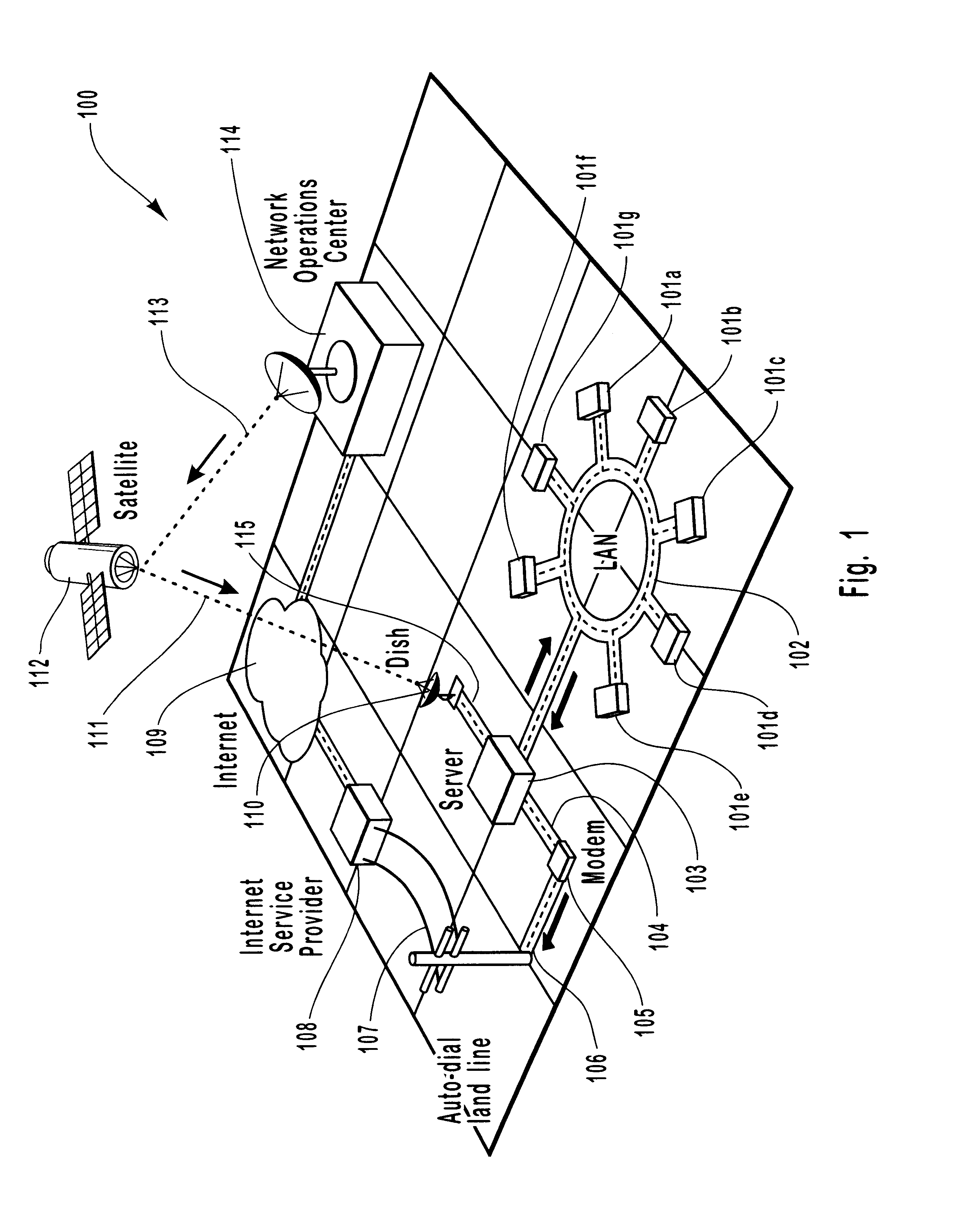

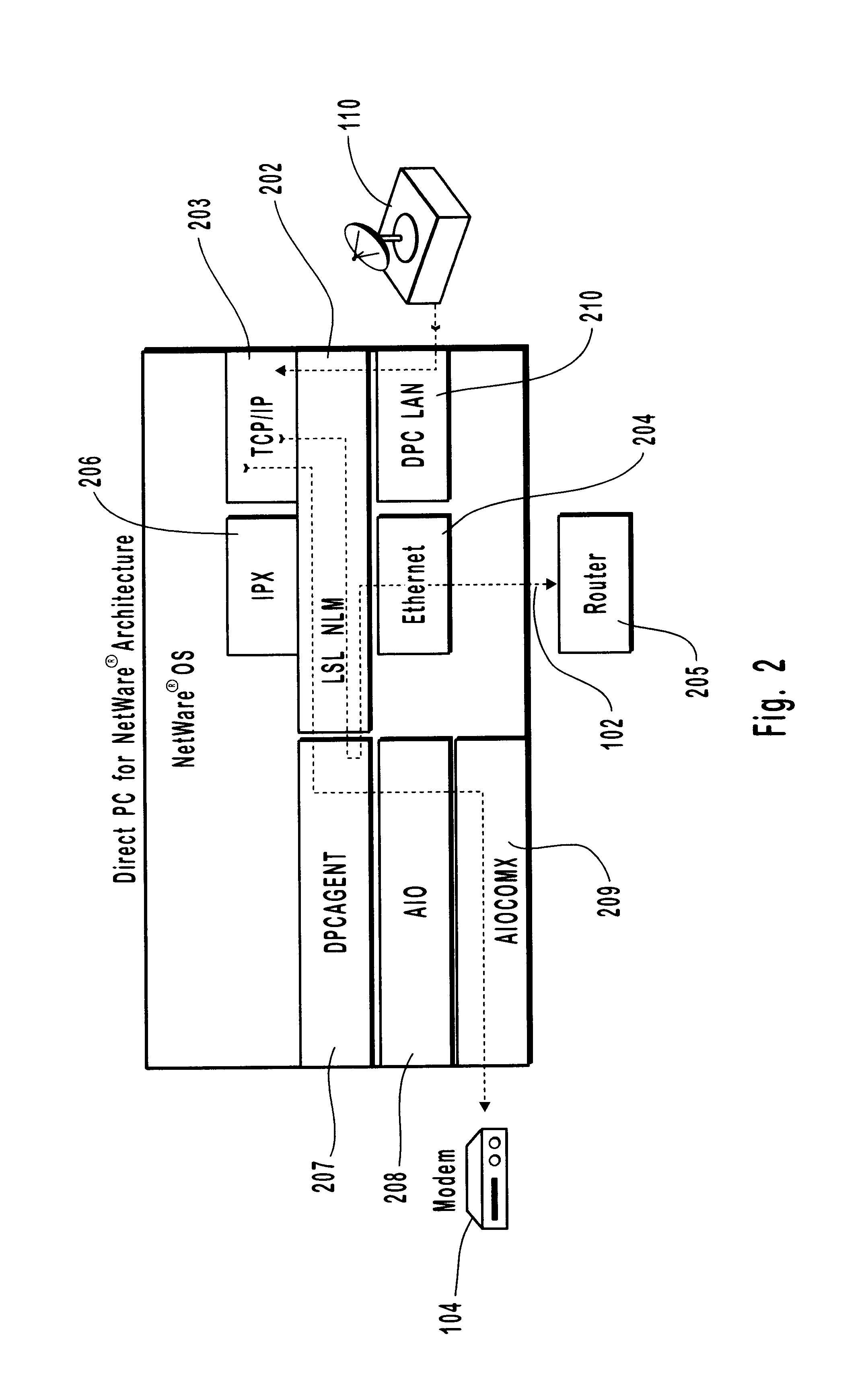

Method and system for asymmetric satellite communications for local area networks

InactiveUS6205473B1Efficient communicationIncrease speedError preventionTransmission systemsNon symmetricLow speed

A method and system for providing high-speed, satellite-based information delivery is described. Improved communication channel efficiency is accomplished by employing an asymmetric data flow. The high bandwidth channel capacity of digital satellite systems is used for the download of large volumes of data. While relatively low speed communication channels are used for upstream data requests. The use of separate channels for upstream data and downloaded data provides an increased efficiency of use for typical internet and other electronic information service subscribers. A typical user in such systems generally makes relatively short information requests. These requests are then followed by large amounts of information being transferred to the user's computer in response to the request. The volume of data being downloaded often causes a capacity overload of typically used land lines. This invention solves this problem, without becoming prohibitively expensive, by employing digital satellite dish receivers to receive the high volume of downloaded data and using the relatively low speed communication channels low volume upstream requests. Moreover, this invention is designed to interface with all common communication devices as well as being designed to operate on and with all common computing platforms.

Owner:HUGHES NETWORK SYST

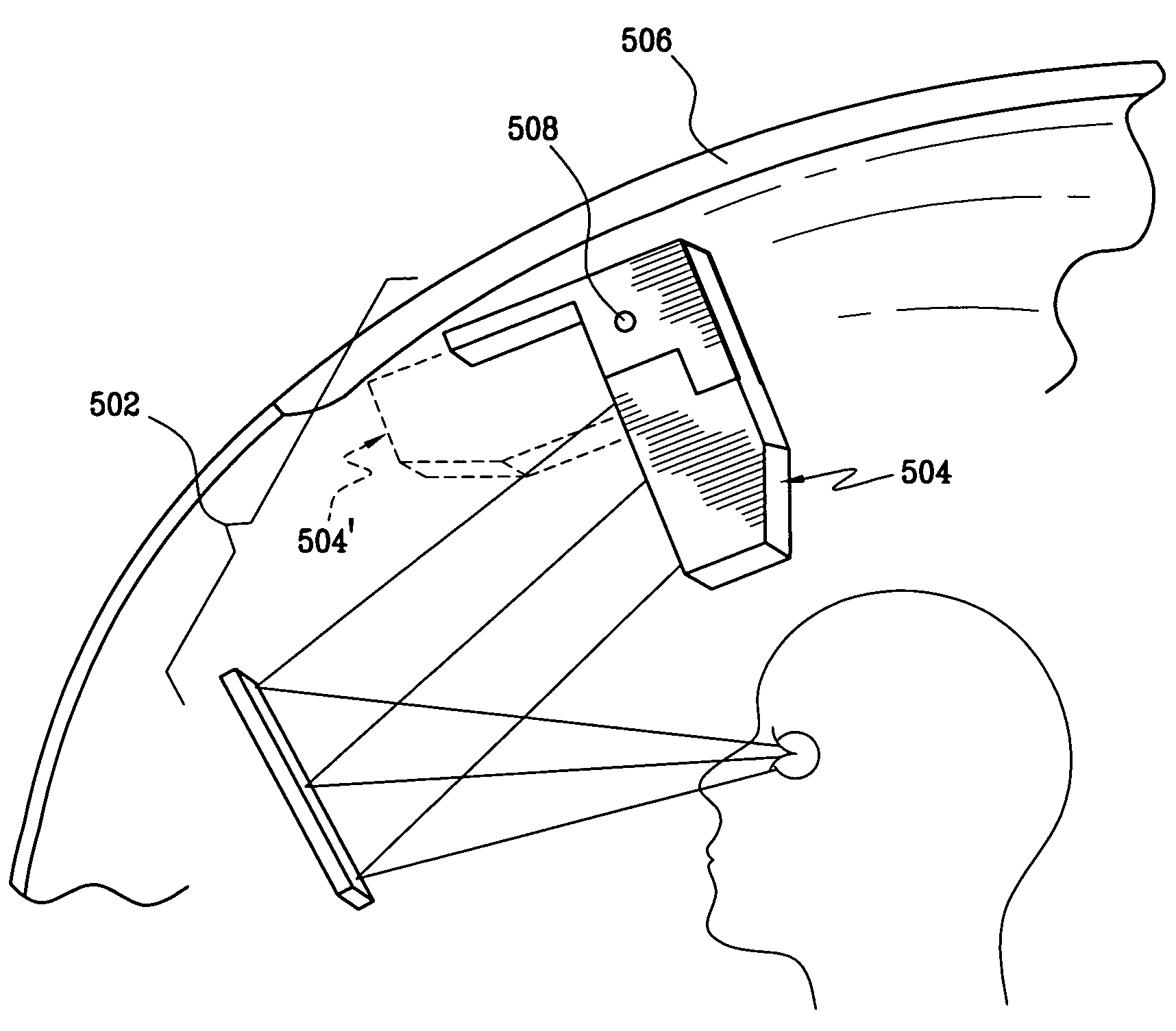

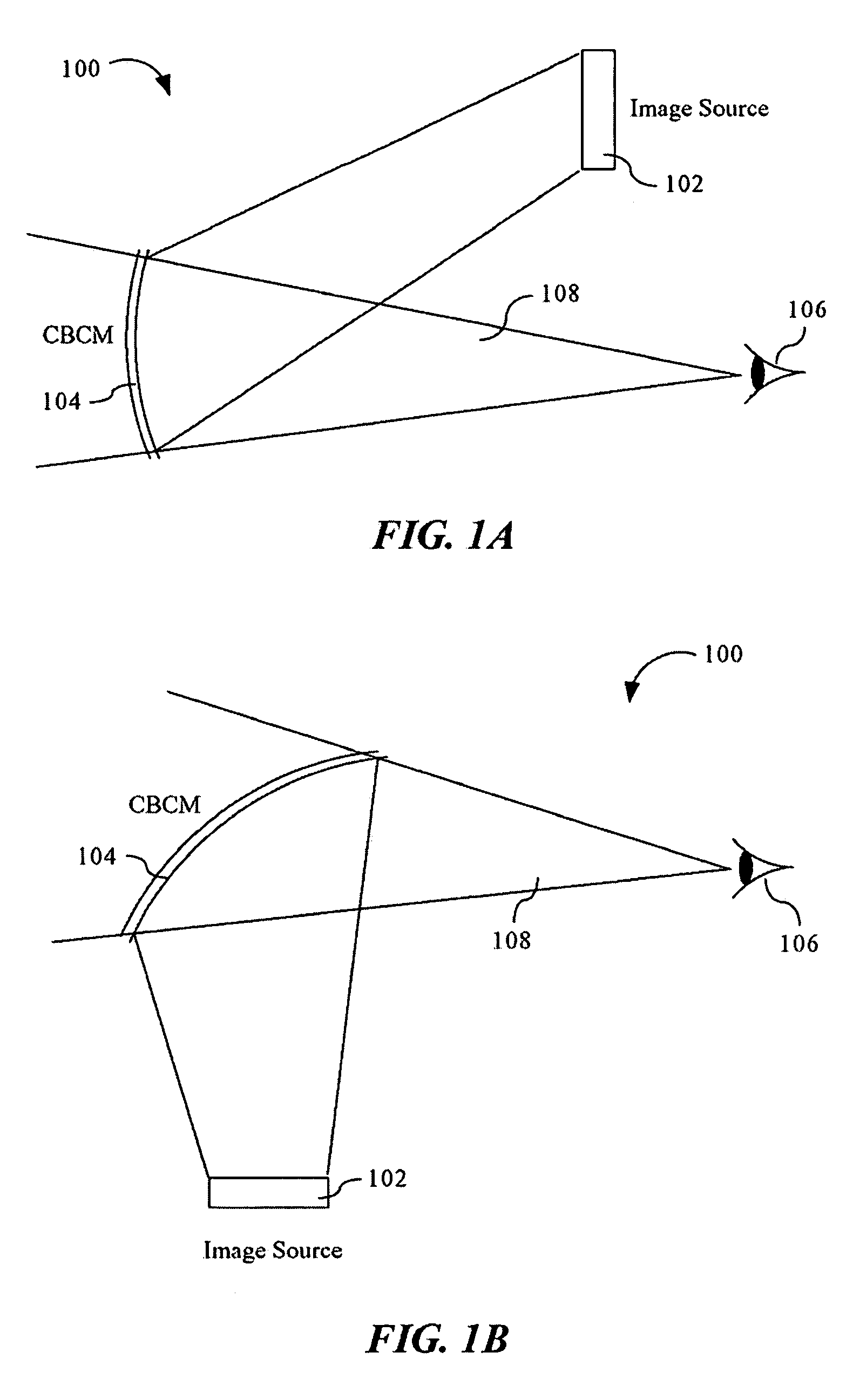

Advanced compact head up display

ActiveUS7095562B1Simplifies optical systemMinimize aberrationLighting support devicesCathode-ray tube indicatorsHead-up displayDashboard

A head up display system for a vehicle that includes a compact image source for projecting an image. The compact image source may be foldable up toward or into a cockpit ceiling of the vehicle, be positioned within a dashboard of the vehicle, or located at another suitable position. A combiner reflects the projected image with optical power toward an observer for observation. The combiner is positioned so that the observer, in a line of sight, may see a visual exterior view of an outside scene through the combiner and the projected image in the combiner. In a preferred embodiment, the image source includes an illumination system that includes a high power light emitting diode (LED) array assembly. A Fresnel lens array is operatively associated with the LED array assembly for receiving light produced by the LED and providing a nearly collimated light output. A spatial light modulator receives the nearly collimated light output. The preferred combiner is a meniscus combiner that includes a meniscus lens; a multi-layer dichroic coating formed on a first surface of the meniscus lens; and, an anti-reflection coating formed on a second, opposite surface of the meniscus lens. The meniscus combiner preferably utilizes a non-symmetric aspheric meniscus lens.

Owner:ROCKWELL COLLINS INC

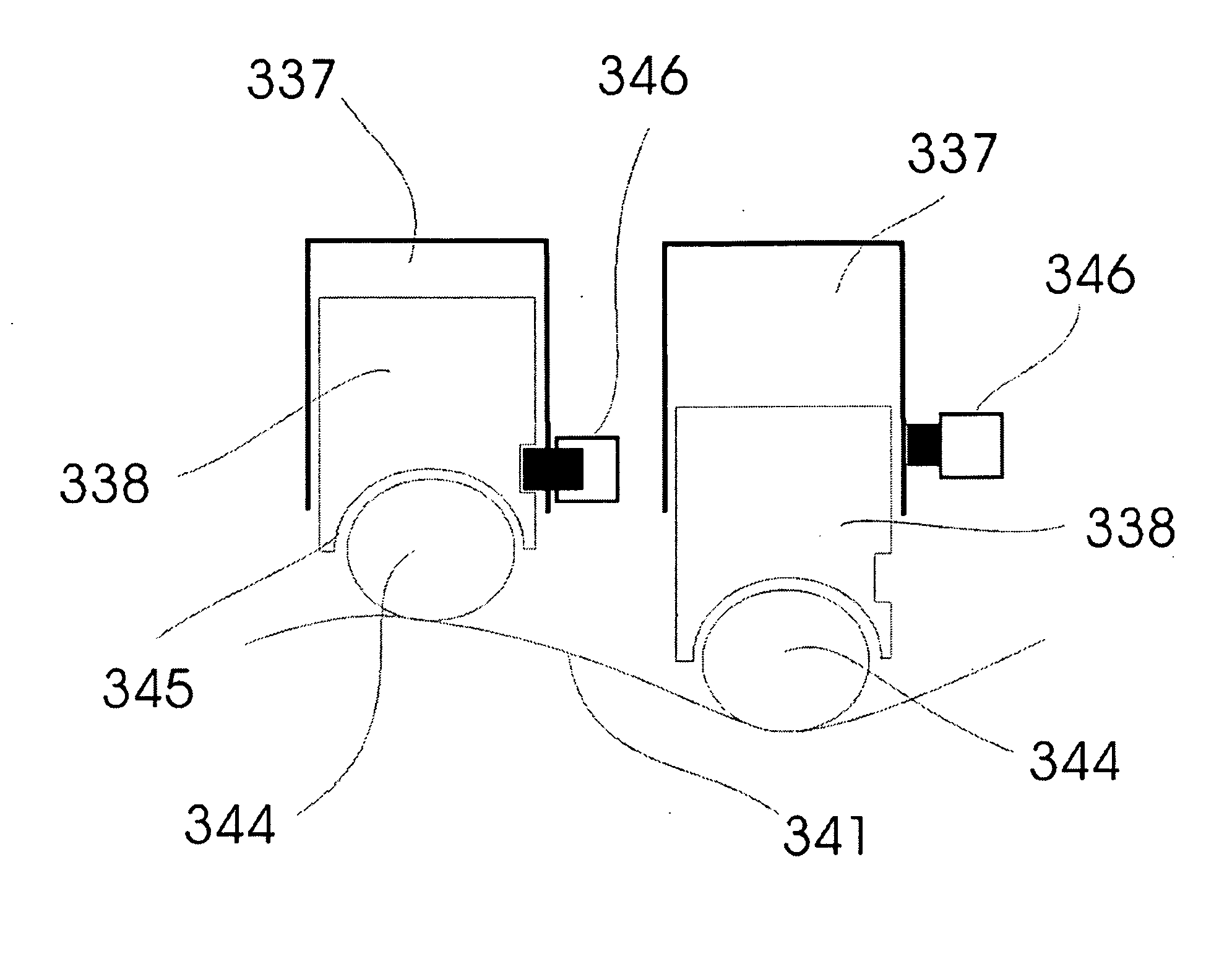

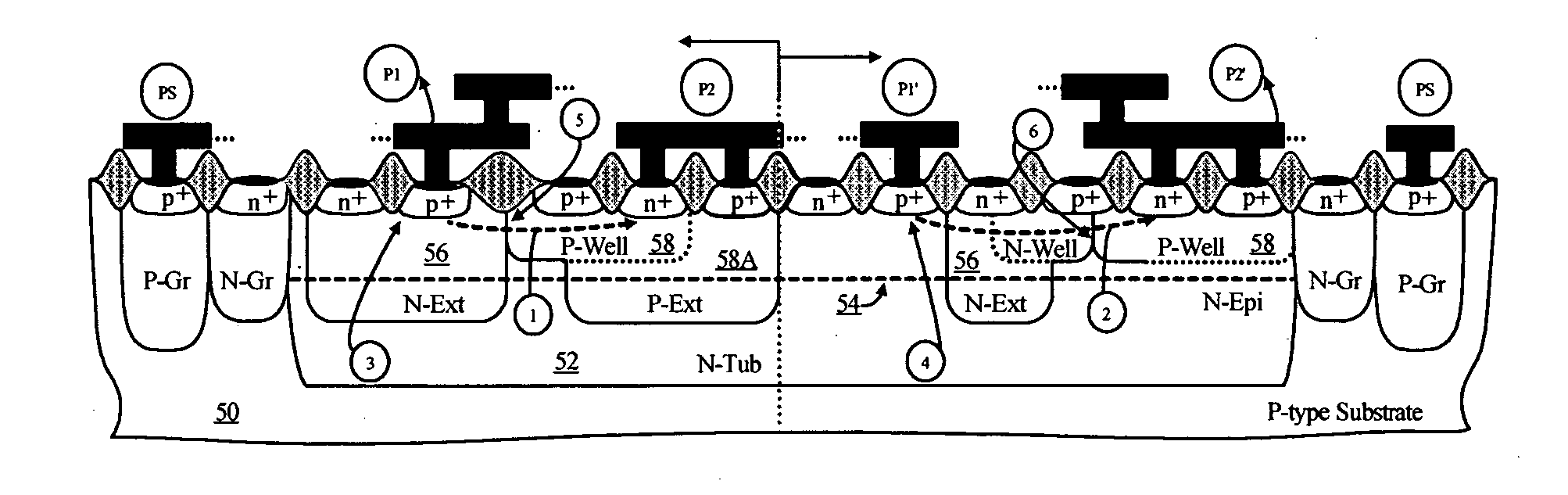

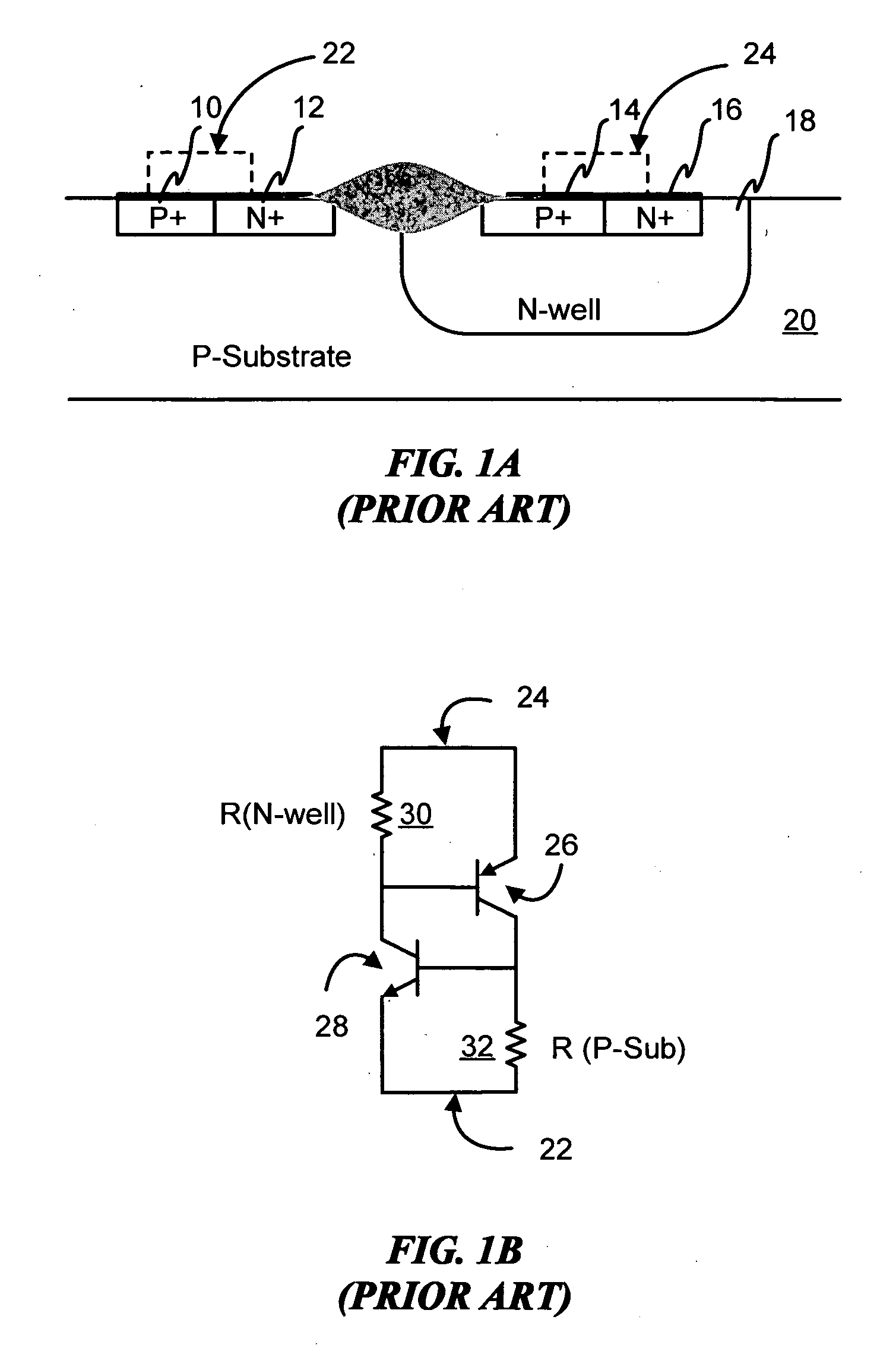

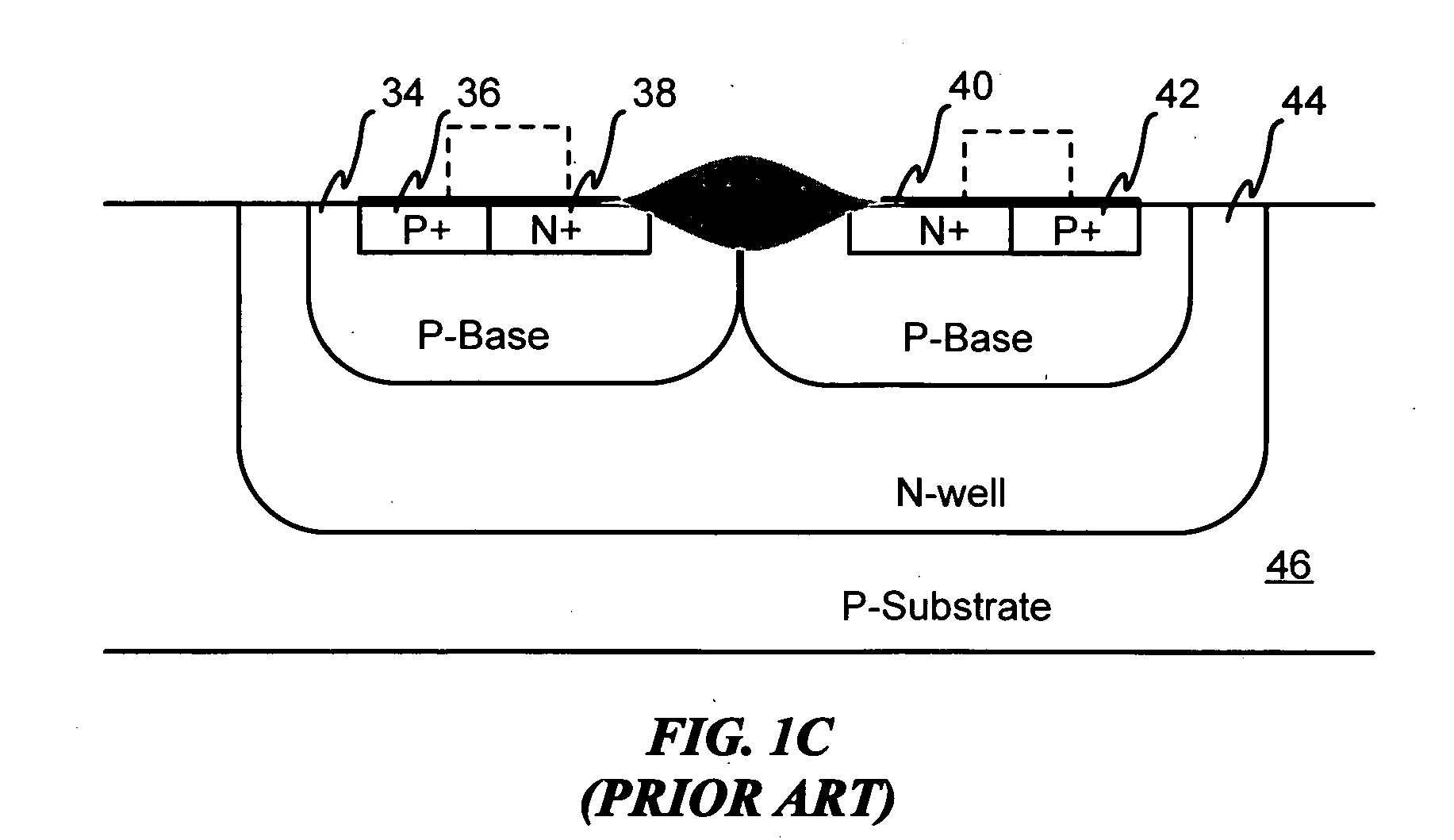

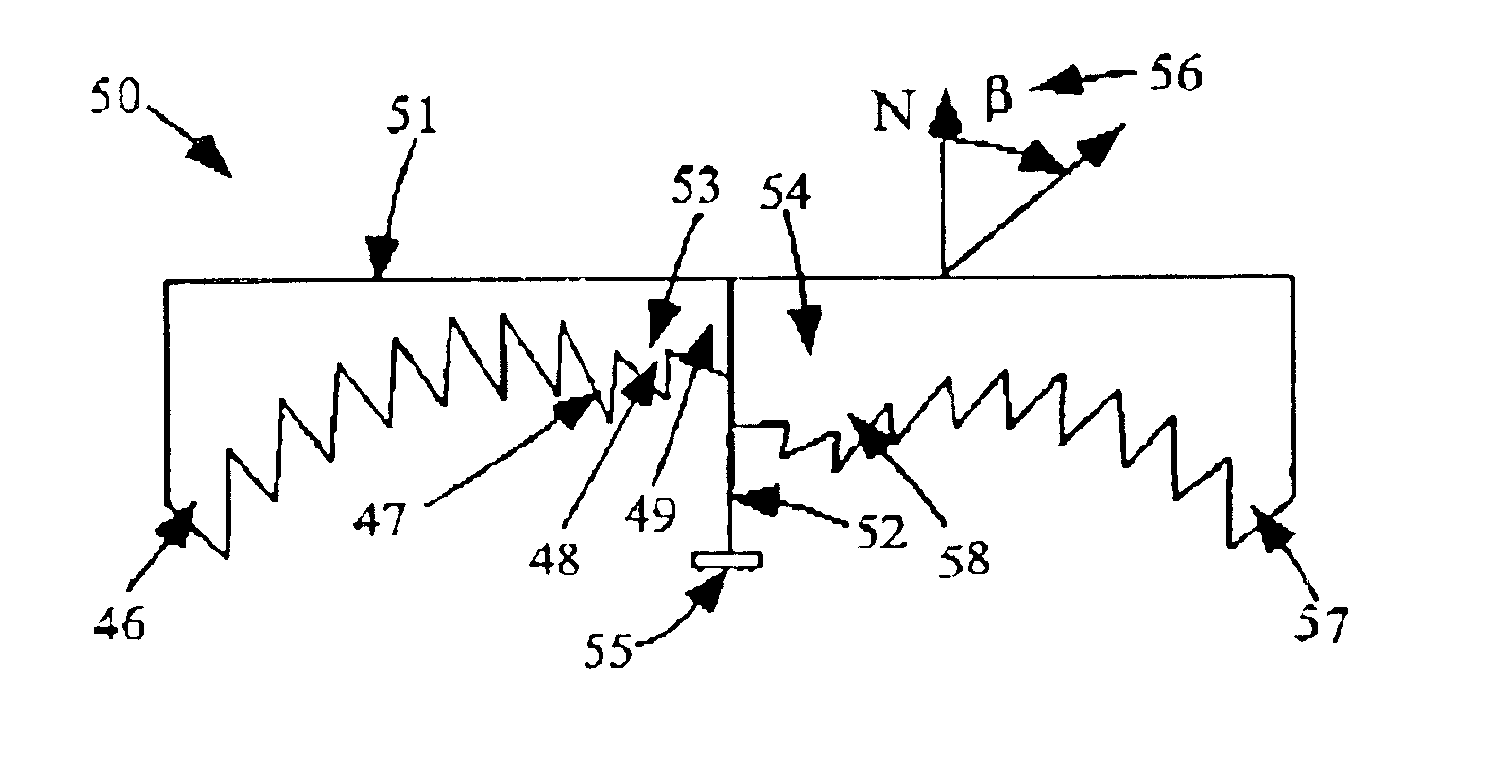

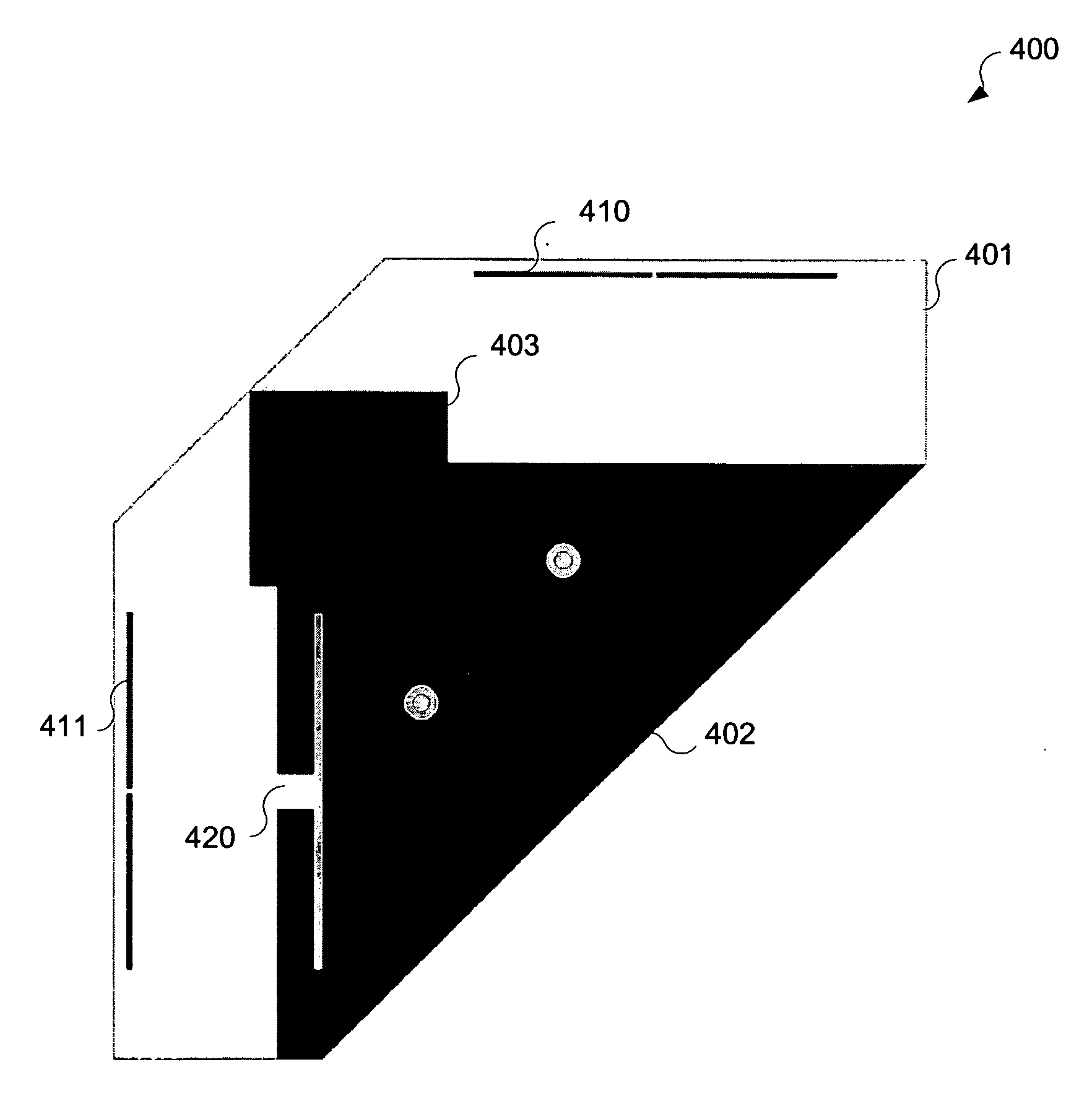

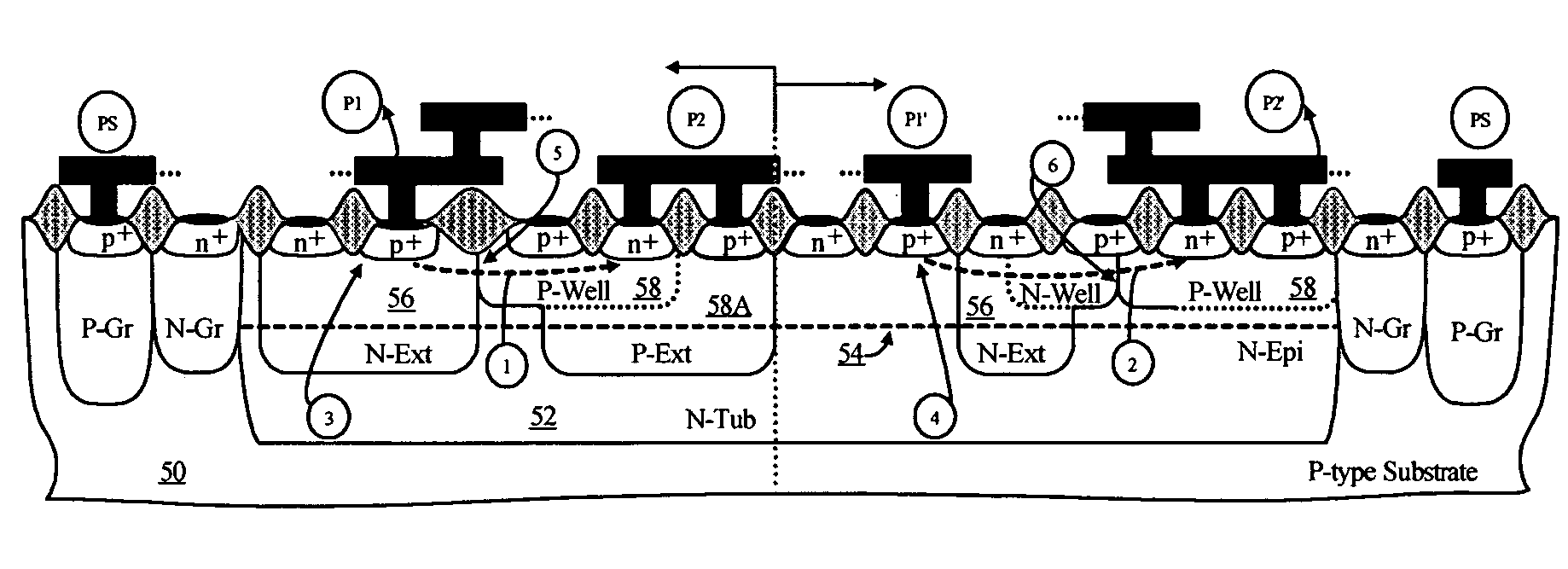

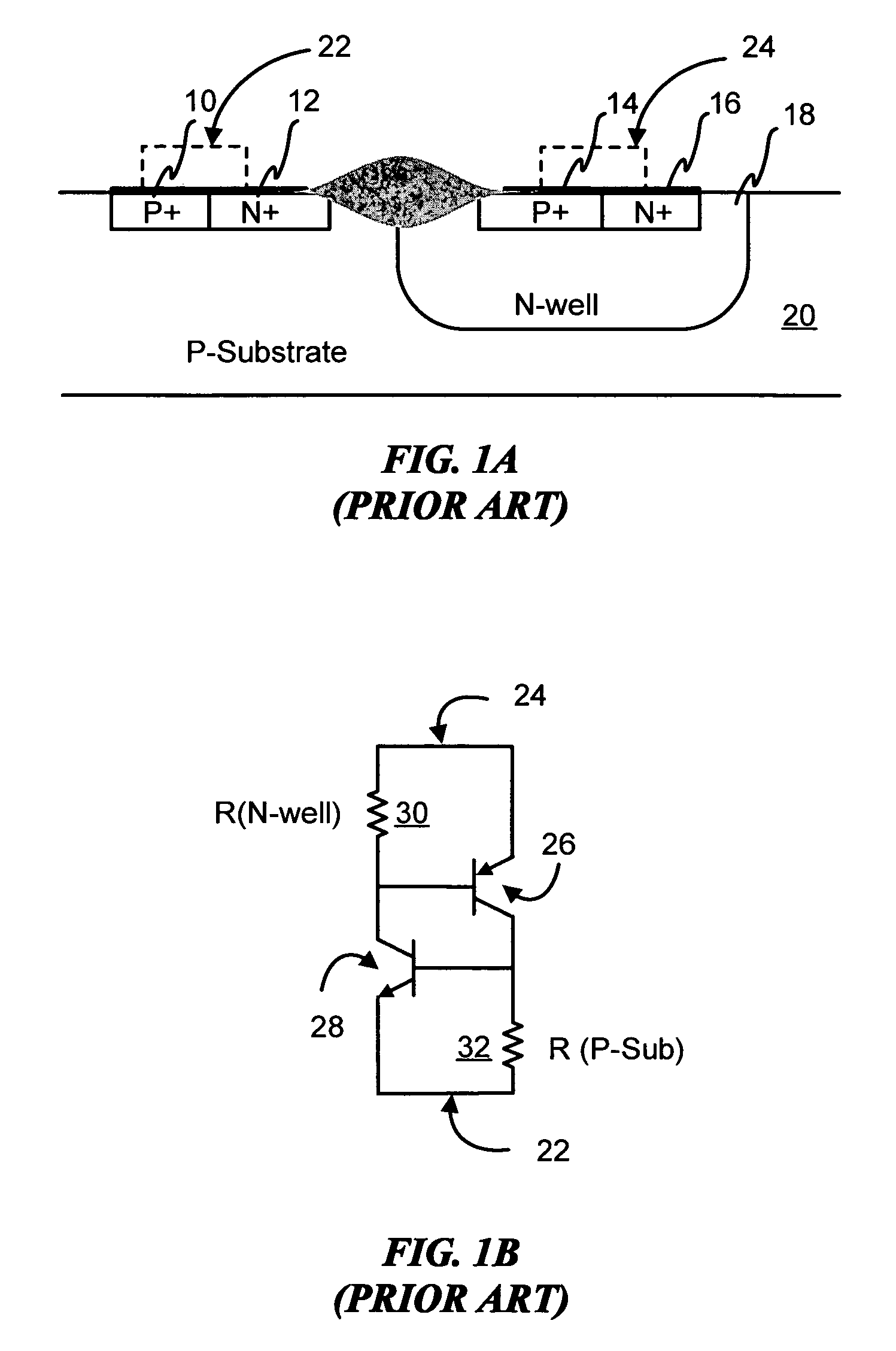

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

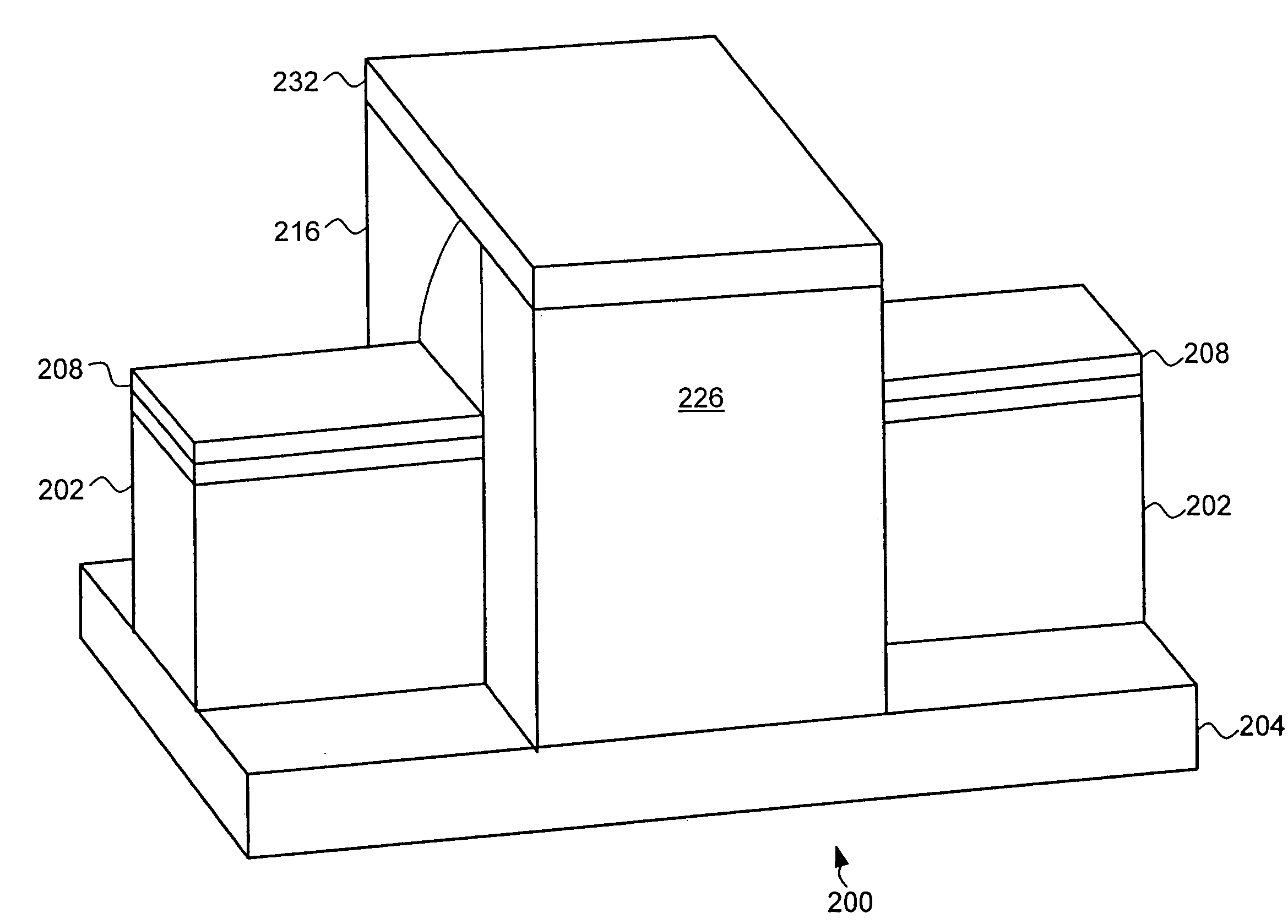

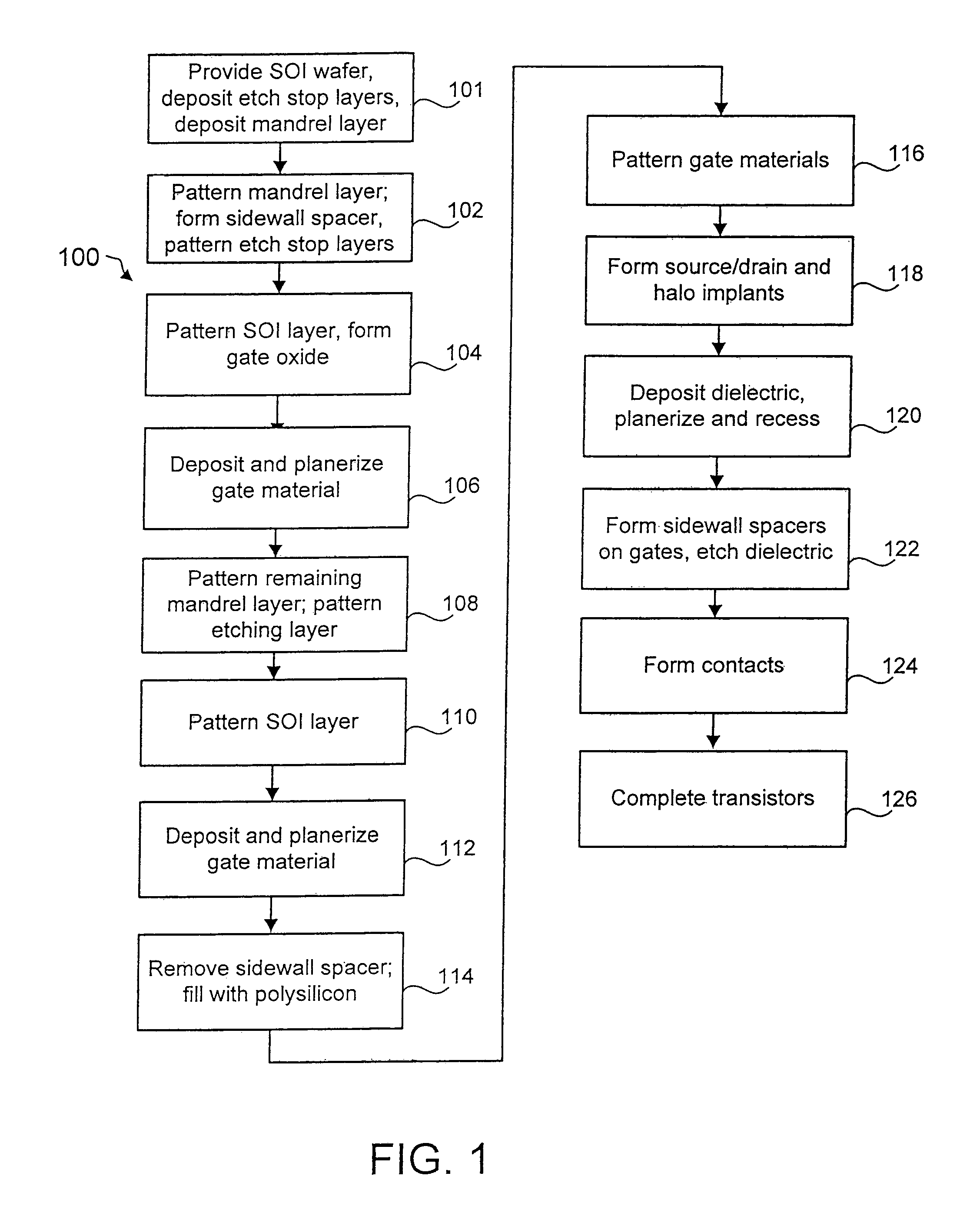

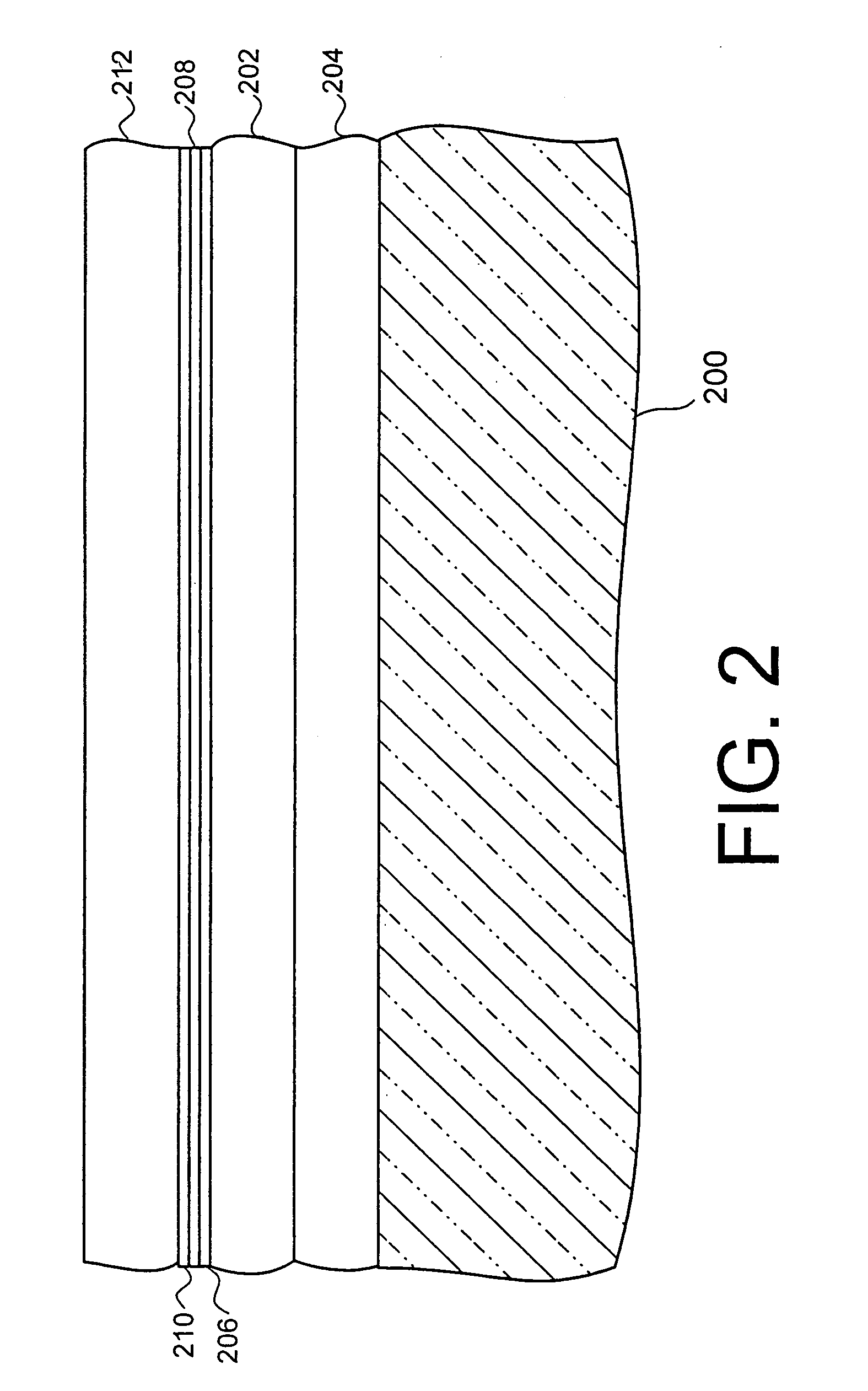

Double gated transistor and method of fabrication

InactiveUS7288445B2High densityImprove performanceTransistorSemiconductor/solid-state device manufacturingNon symmetricLow voltage cmos

Owner:GLOBALFOUNDRIES INC

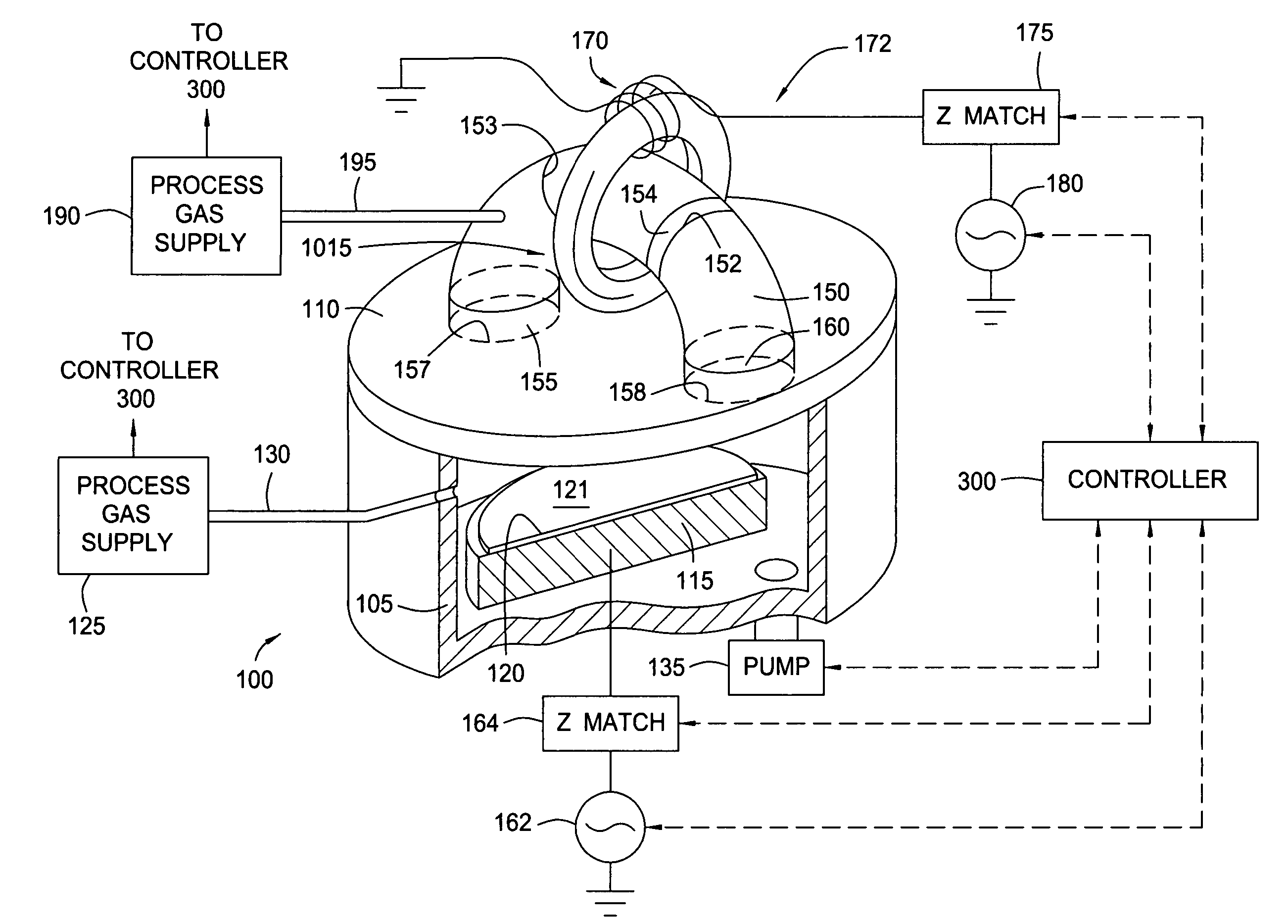

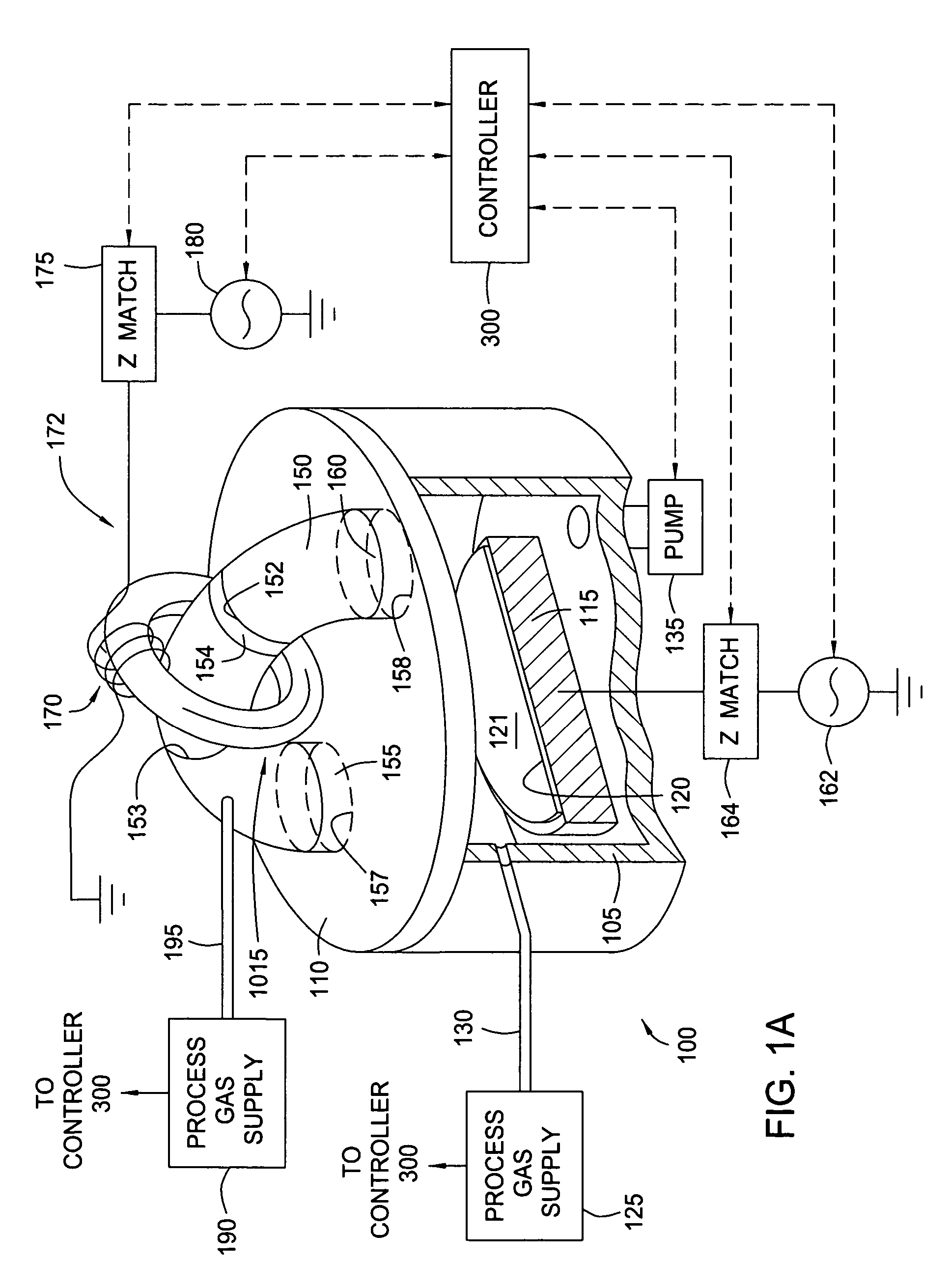

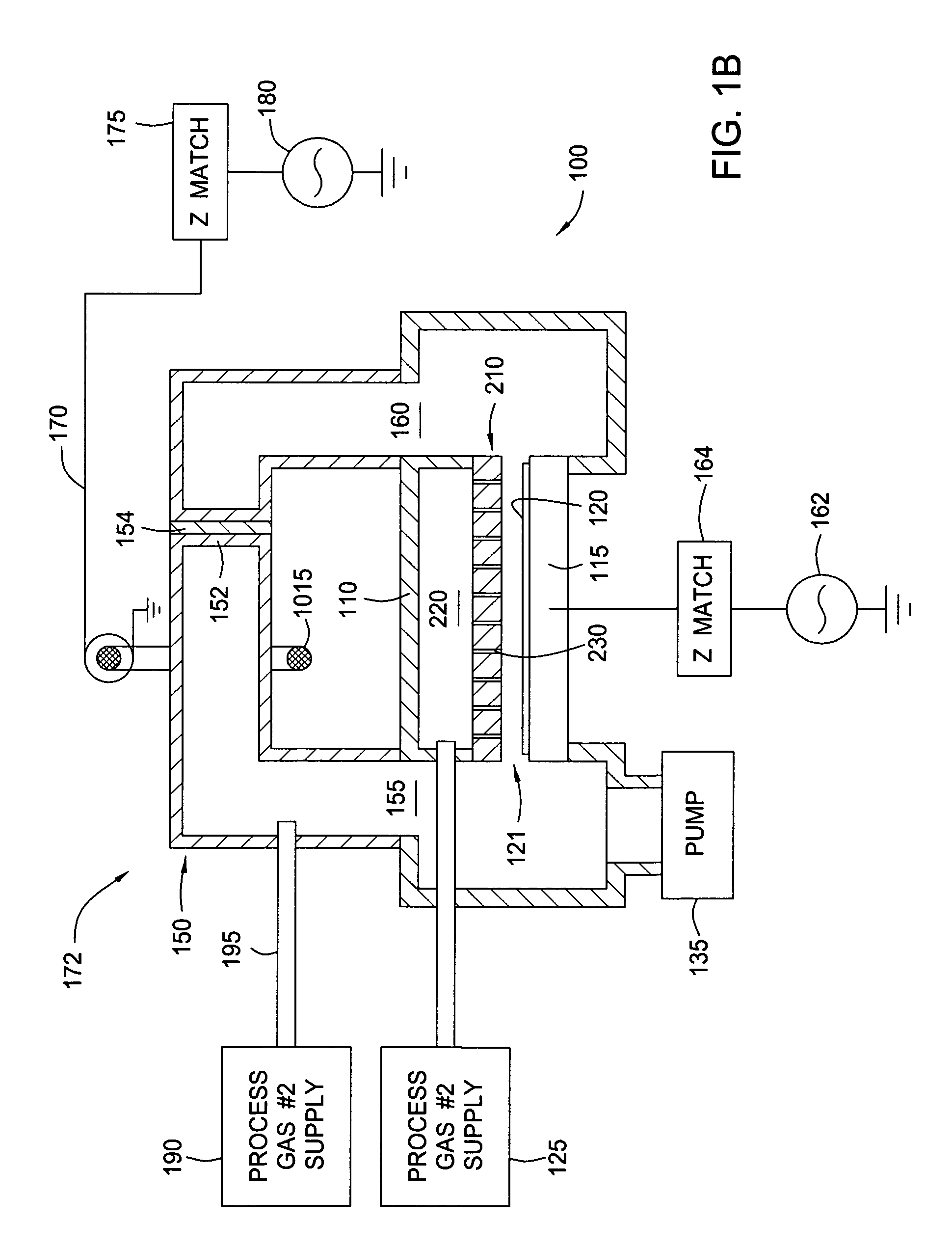

Alternating asymmetrical plasma generation in a process chamber

InactiveUS20050241762A1Improving uniformity of plasma processImprove uniformityElectric discharge tubesDecorative surface effectsCapacitanceNon symmetric

Embodiments of the invention generally provide etch or CVD plasma processing methods and apparatus used to generate a uniform plasma across the surface of a substrate by modulation pulsing the power delivered to a plurality of plasma controlling devices found in a plasma processing chamber. The plasma generated and / or sustained in the plasma processing chamber is created by the one or more plasma controlling devices that are used to control, generate, enhance, and / or shape the plasma during the plasma processing steps by use of energy delivered from a RF power source. Plasma controlling devices may include, for example, one or more coils (inductively coupled plasma), one or more electrodes (capacitively coupled plasma), and / or any other energy inputting device such as a microwave source.

Owner:APPLIED MATERIALS INC

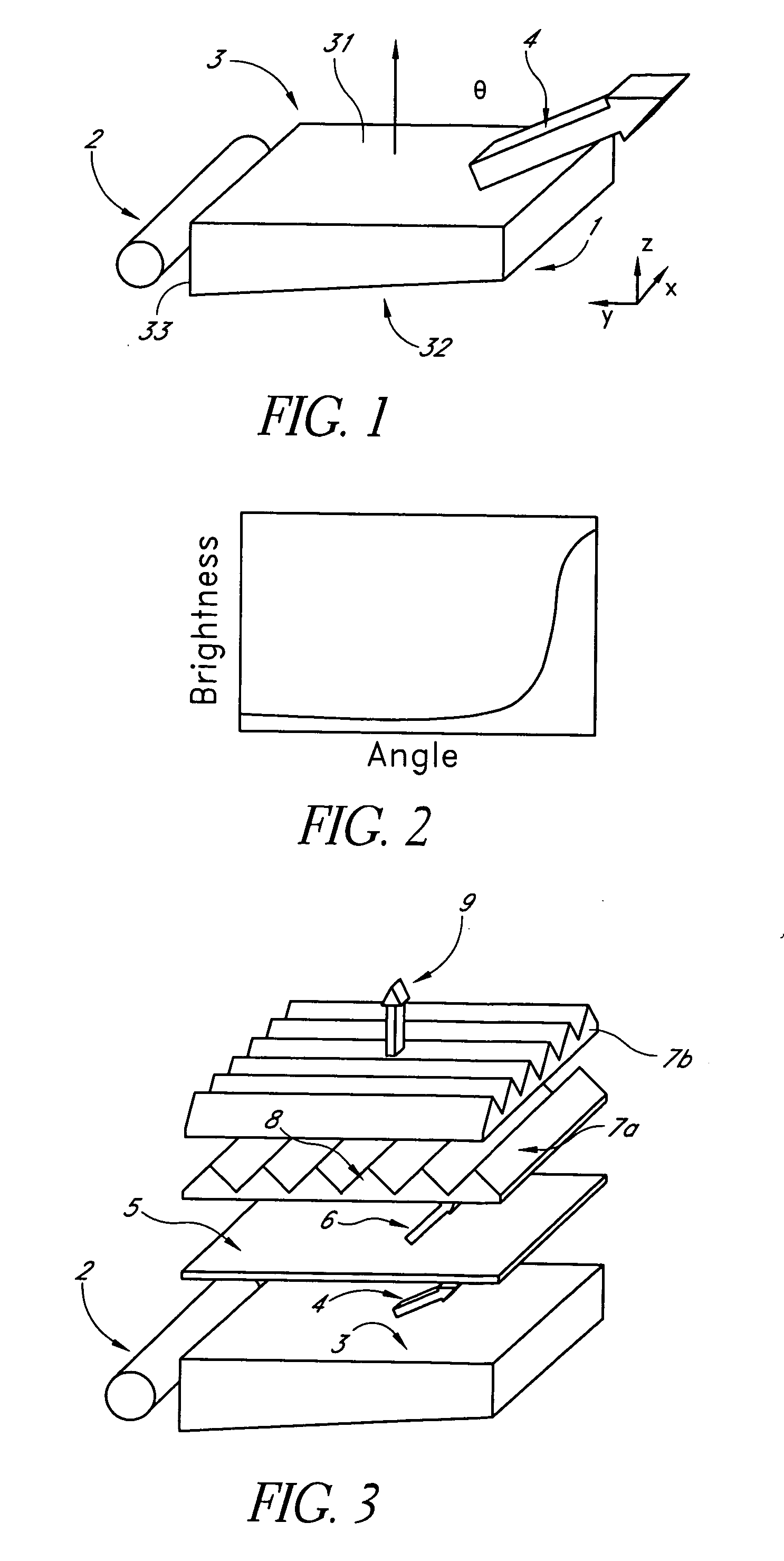

Asymmetric TIR lenses producing off-axis beams

The present invention relates to an improvement of a total internal reflection lens whereby a tilted symmetry axis leads to a net deflection of the output beam away from the surface normal of the exit surface. Linear TIR lenses have a net deflection transverse to their focal strip. Circular TIR lens profiles going beyond 90° are tilted to bring the rim level with the source, the deflected rays exiting the lens to form an off-axis beam.

Owner:LIGHT ENGINE

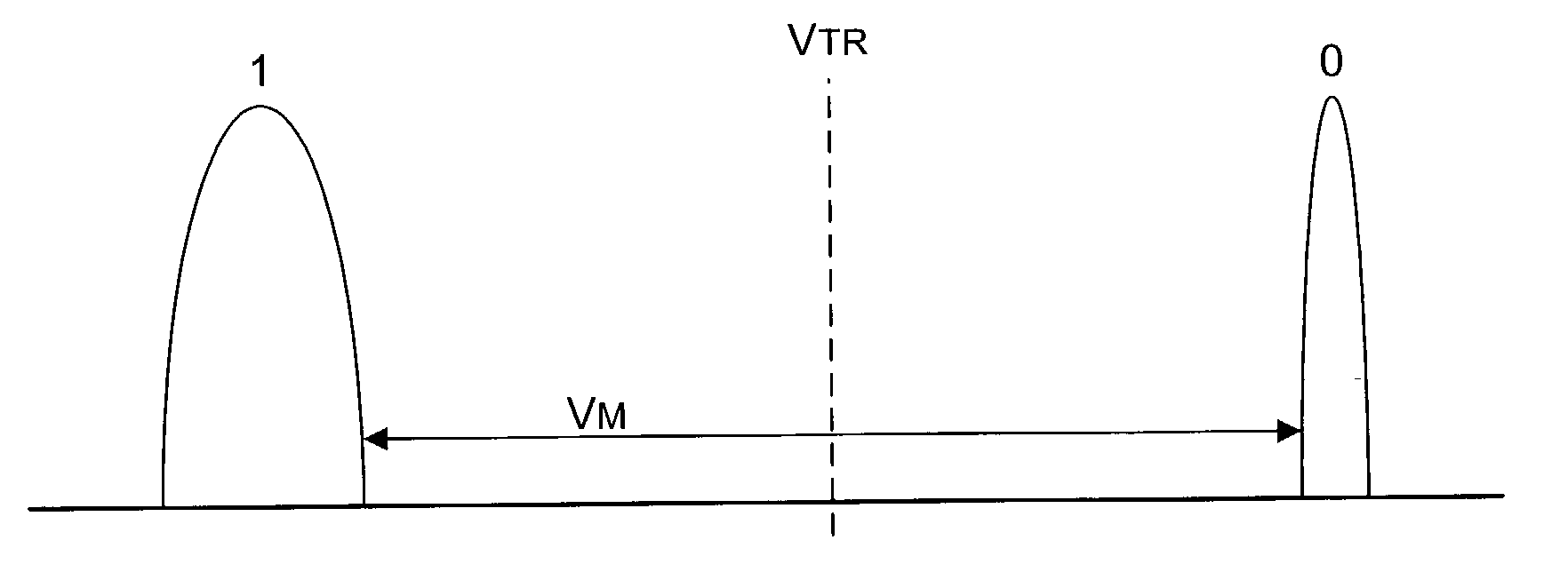

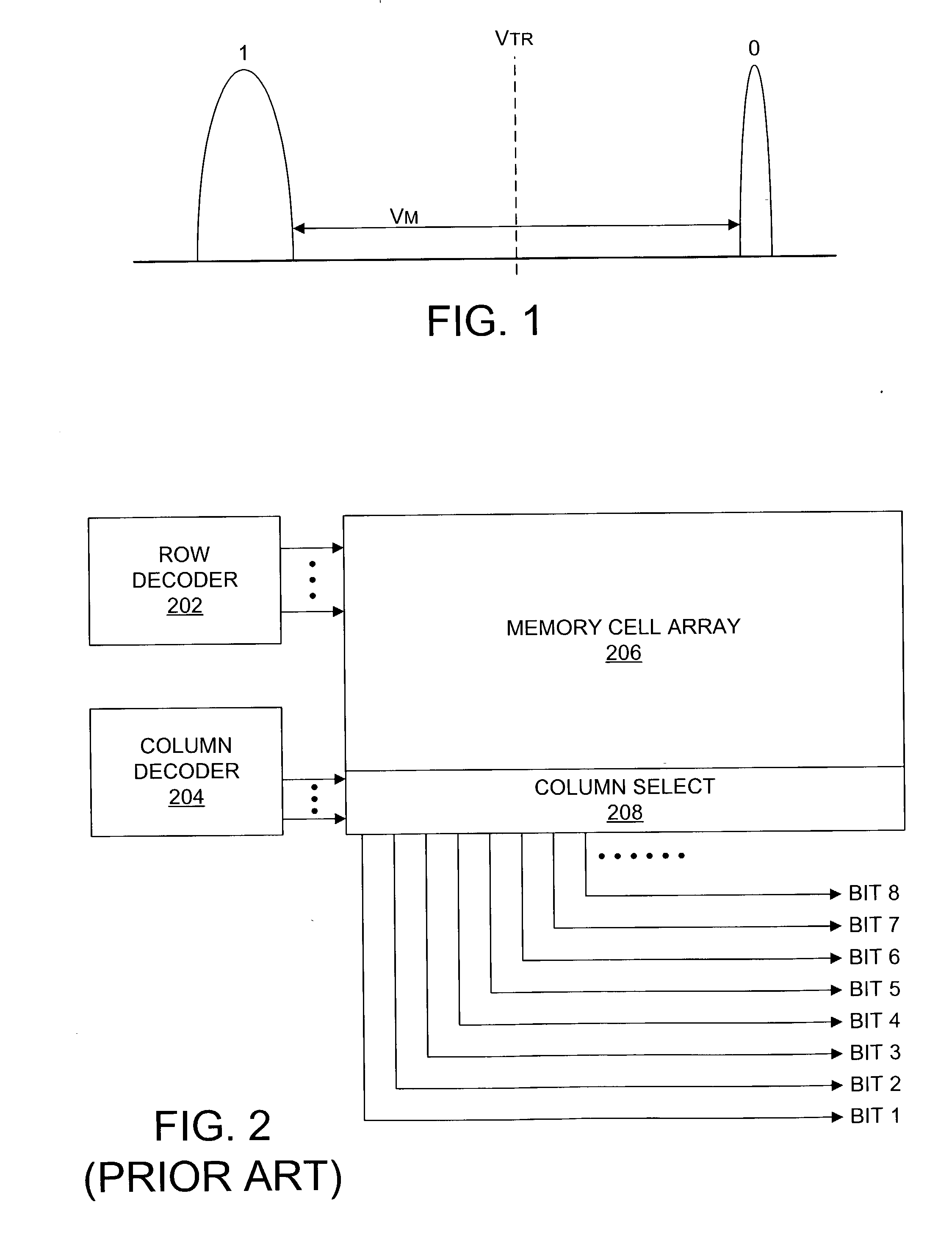

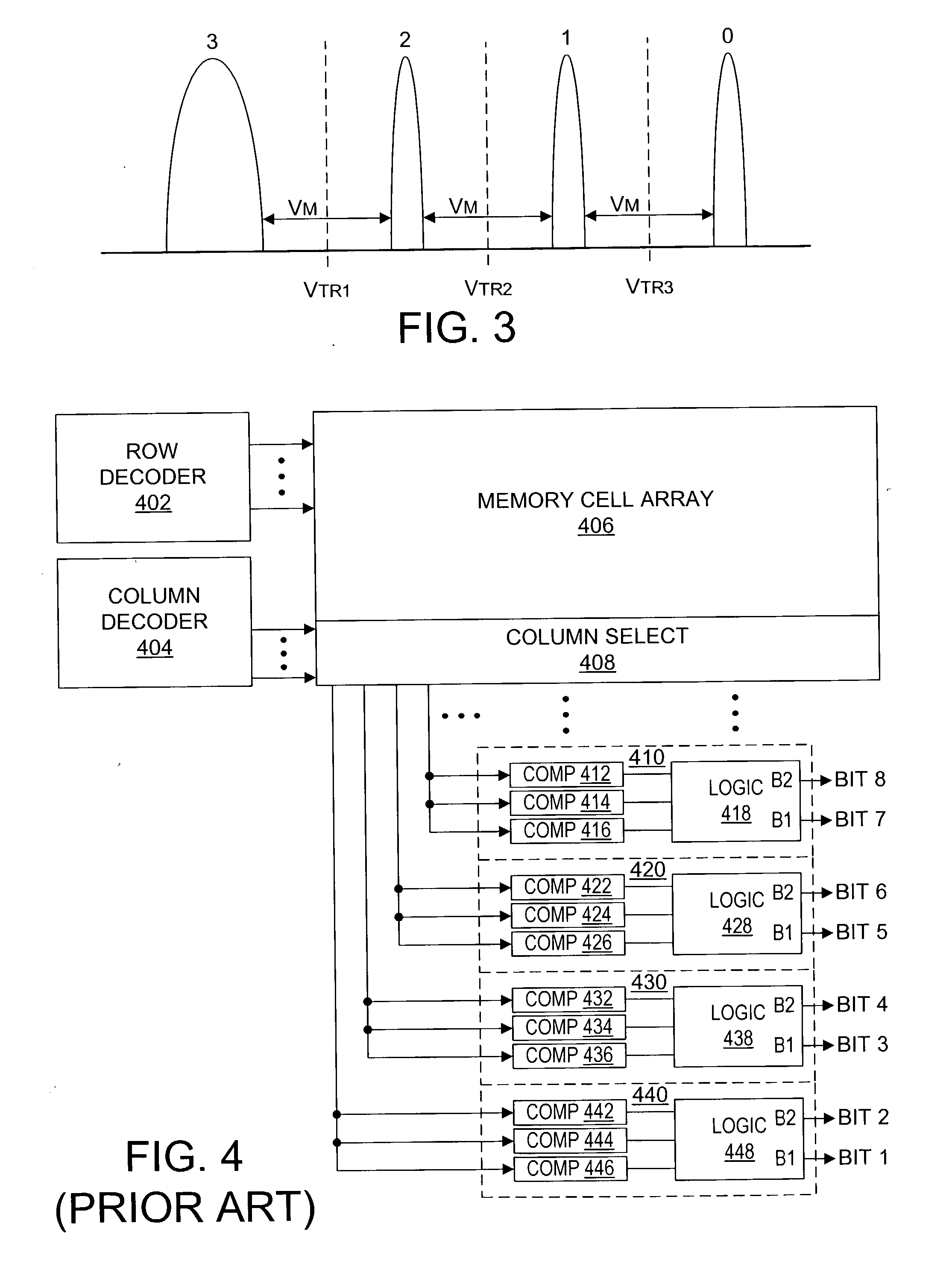

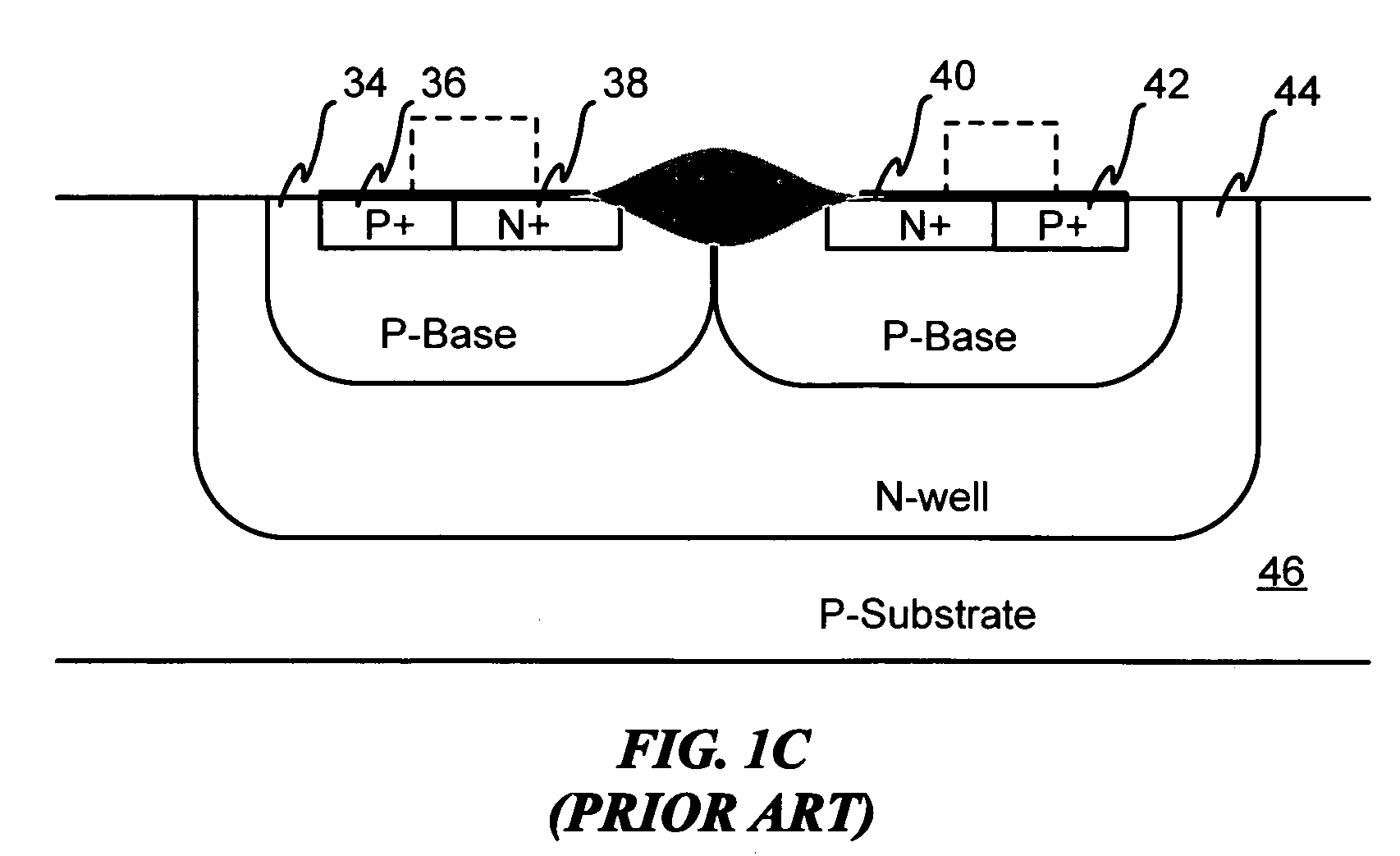

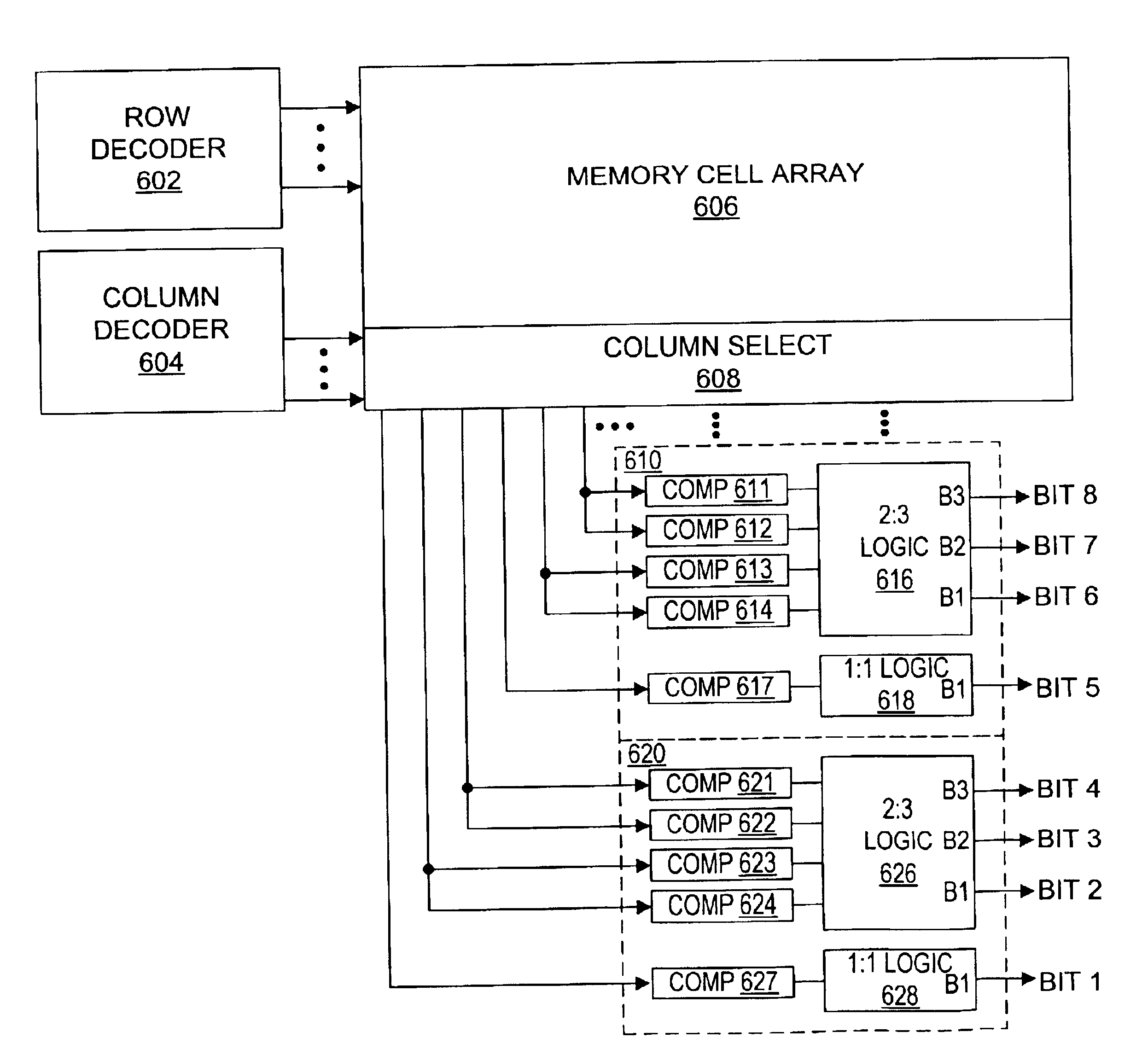

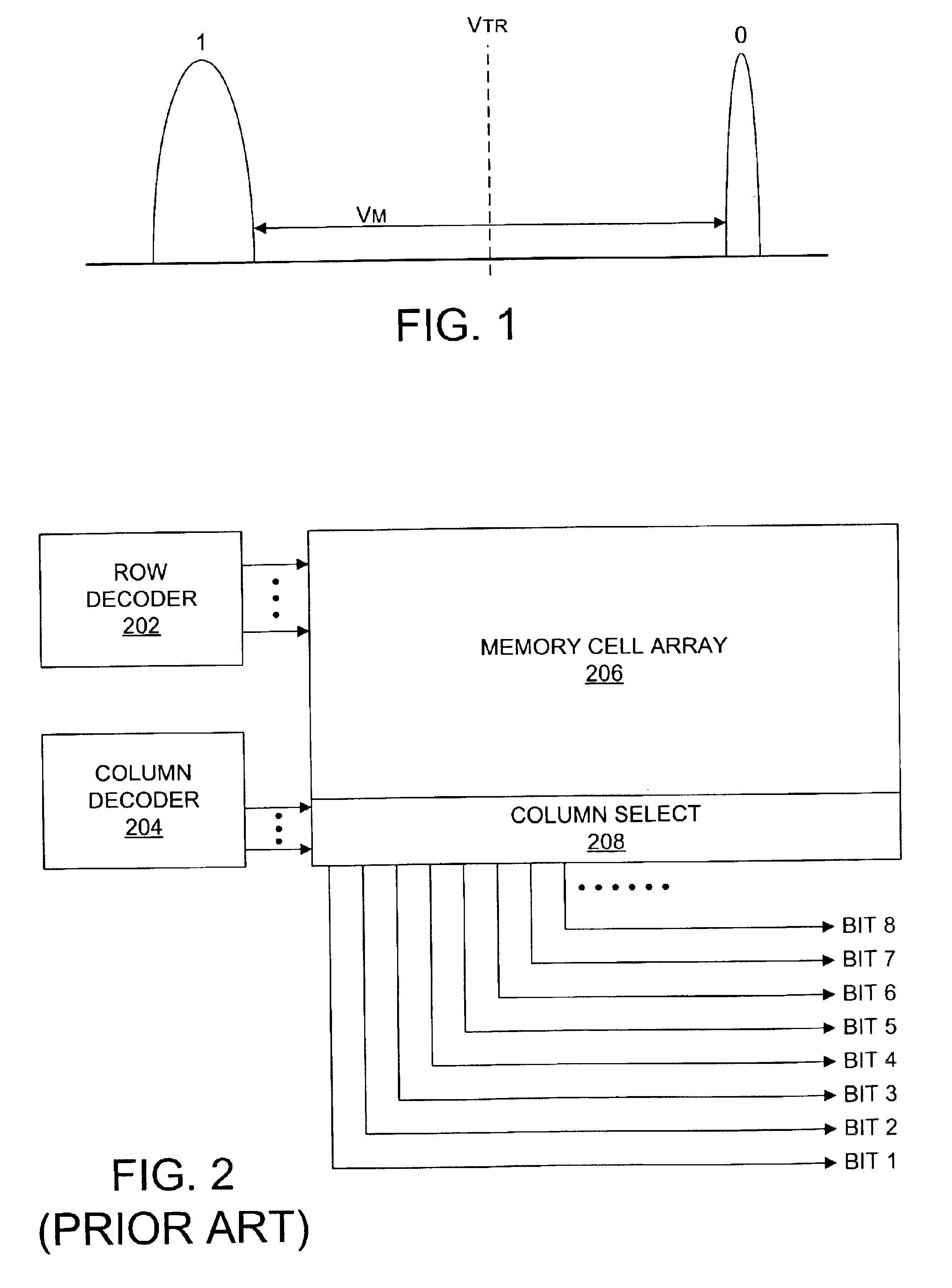

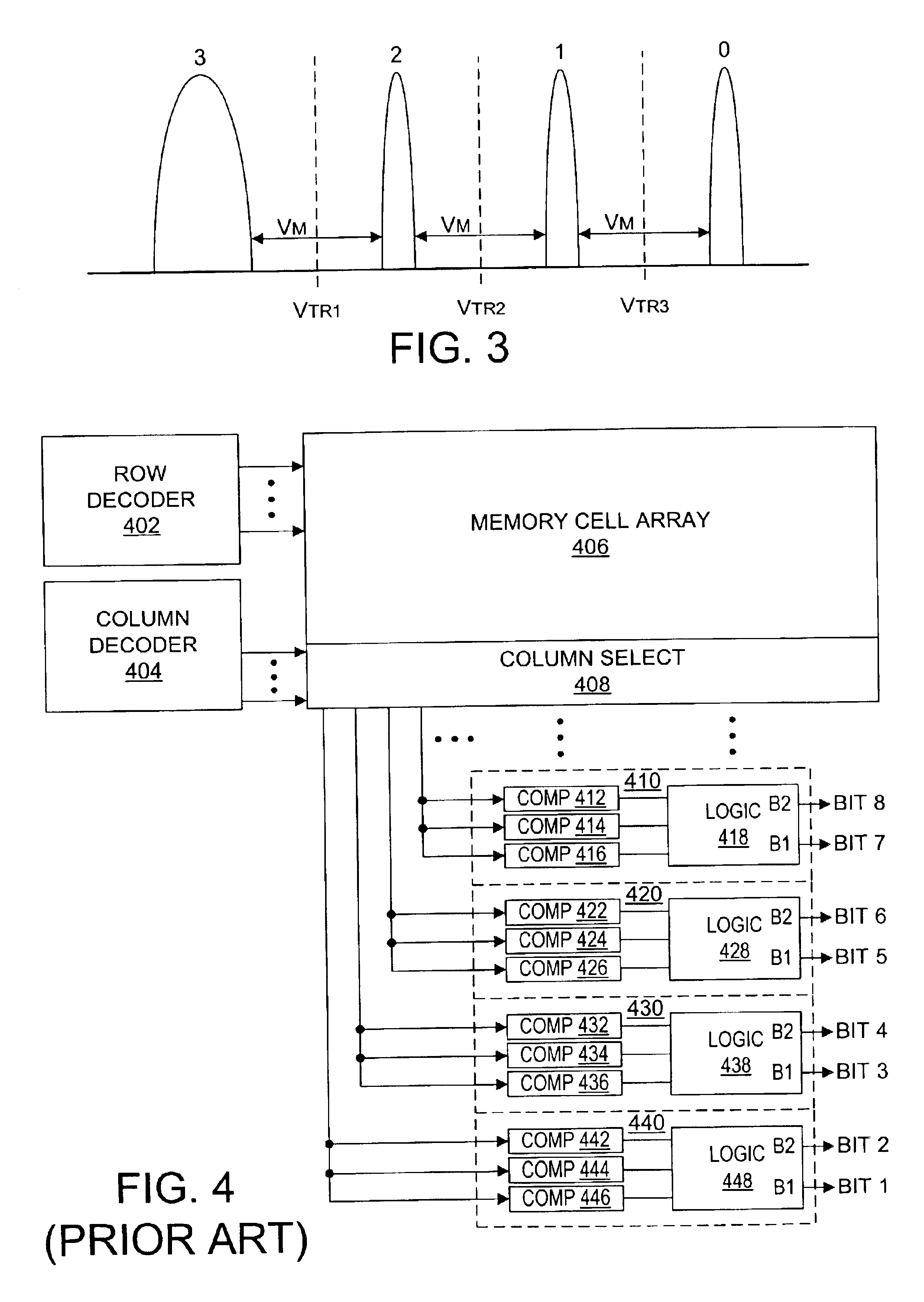

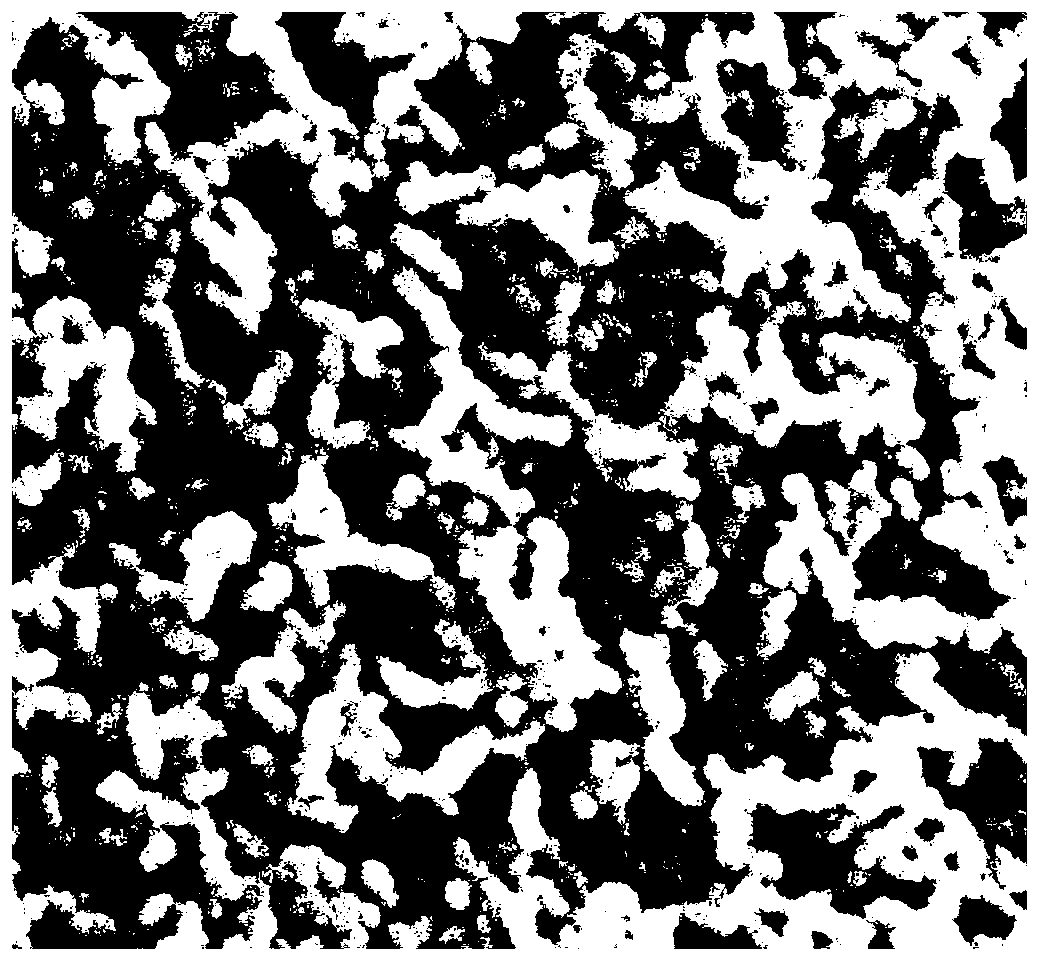

Nonvolatile semiconductor memory having three-level memory cells and program and read mapping circuits therefor

A memory uses multiple threshold levels in a memory cell that are not a power of two, and further uses a cell mapping technique wherein the read mapping is only a partial function The domain of read states for a single three-level memory cell, for example, has three states, but only two of them can be uniquely mapped to a bit. The domain of read states for two three-level memory cell, for example, has nine states, but only eight of them can be uniquely mapped to three bits. Although the read mapping is only partial, the voltage margin for the three-level memory cells is larger that the voltage margin available in the commonly used four-level memory cells. This increased voltage margin facilitates memory cell threshold voltage sensing, thereby increasing the reliability of the memory. Memory reliability may be further improved by increasing the voltage margin between the memory cell 0 state and the 1 state relative to the voltage margin between the 1 state and the 2 state, which more effectively accommodates charge loss from the 0 state through electron leakage. Asymmetrical read and program mapping may also be used to improve read reliability in the presence of ground noise or VCC noise.

Owner:WINBOND ELECTRONICS CORP

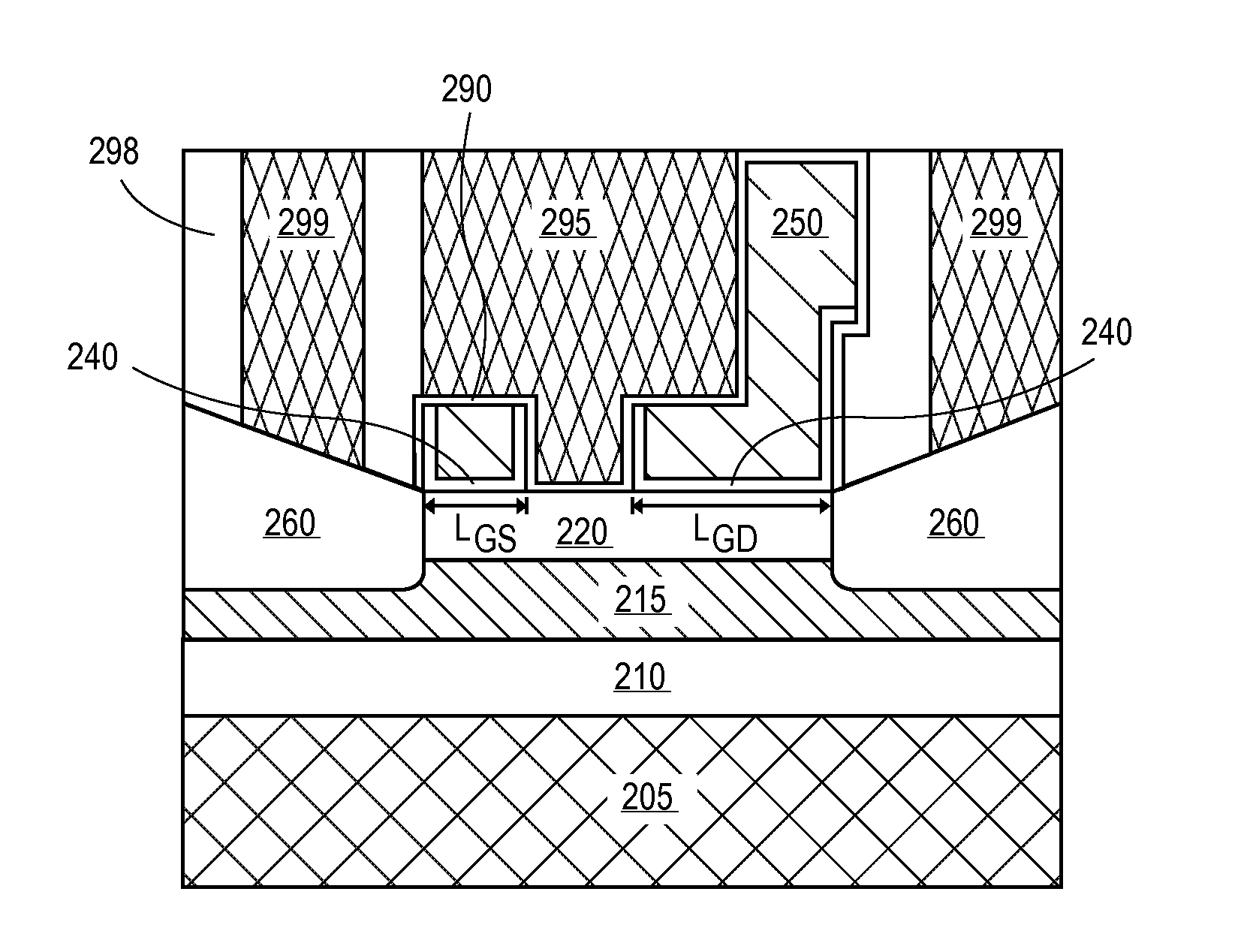

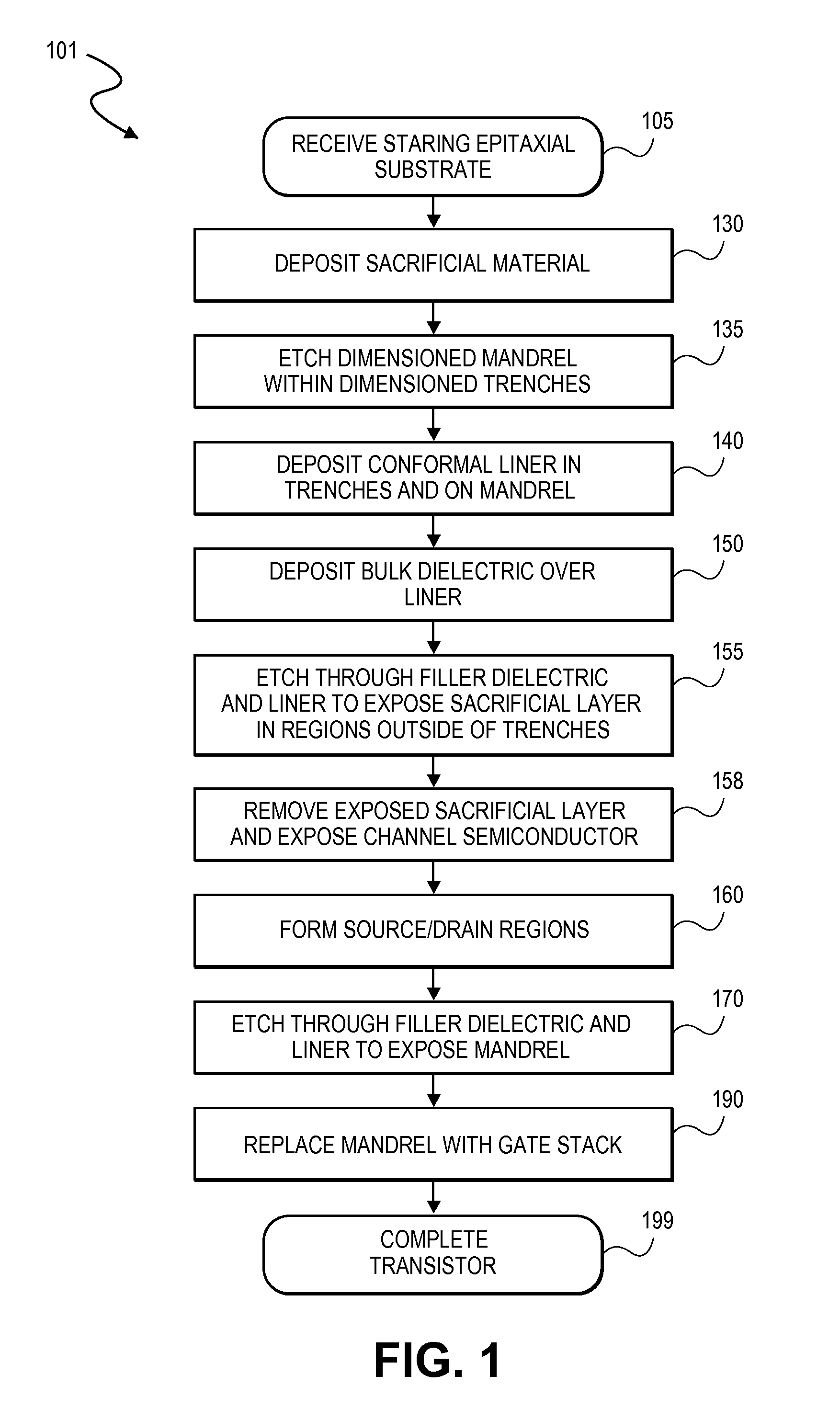

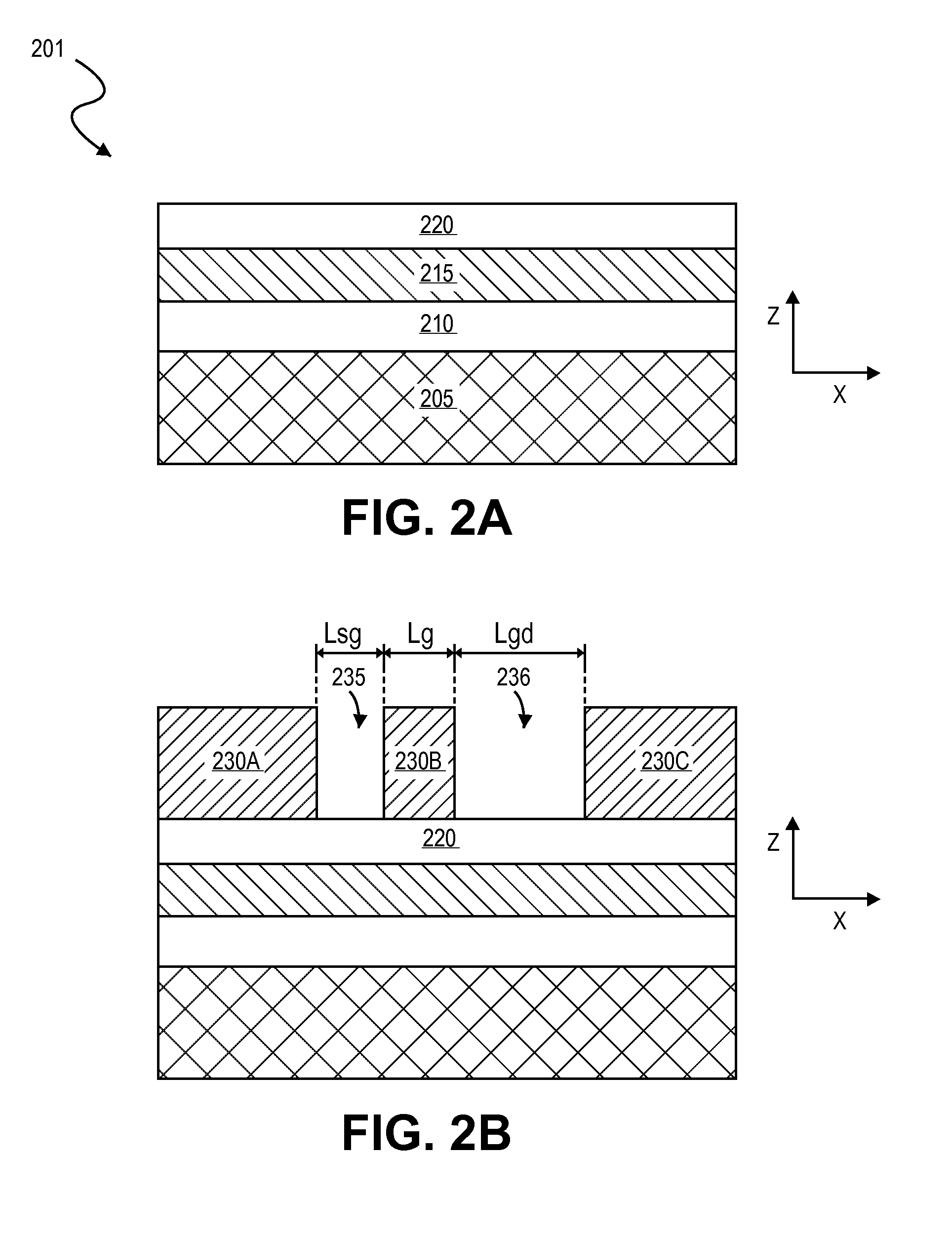

Self-aligned structures and methods for asymmetric GAN transistors & enhancement mode operation

ActiveUS20140091308A1Semiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricEngineering

Embodiments include high electron mobility transistors (HEMT). In embodiments, a gate electrode is spaced apart by different distances from a source and drain semiconductor region to provide high breakdown voltage and low on-state resistance. In embodiments, self-alignment techniques are applied to form a dielectric liner in trenches and over an intervening mandrel to independently define a gate length, gate-source length, and gate-drain length with a single masking operation. In embodiments, III-N HEMTs include fluorine doped semiconductor barrier layers for threshold voltage tuning and / or enhancement mode operation.

Owner:INTEL CORP

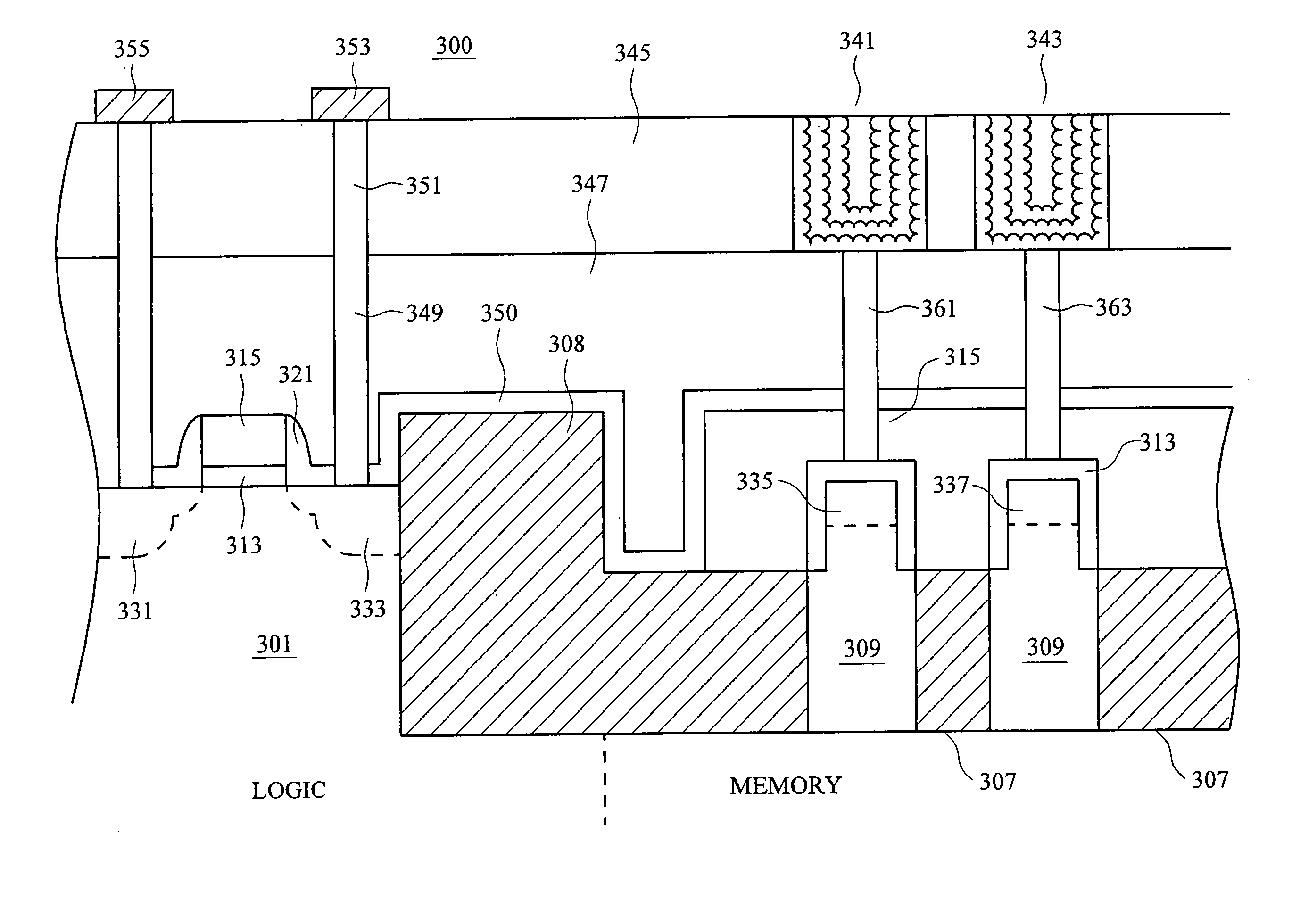

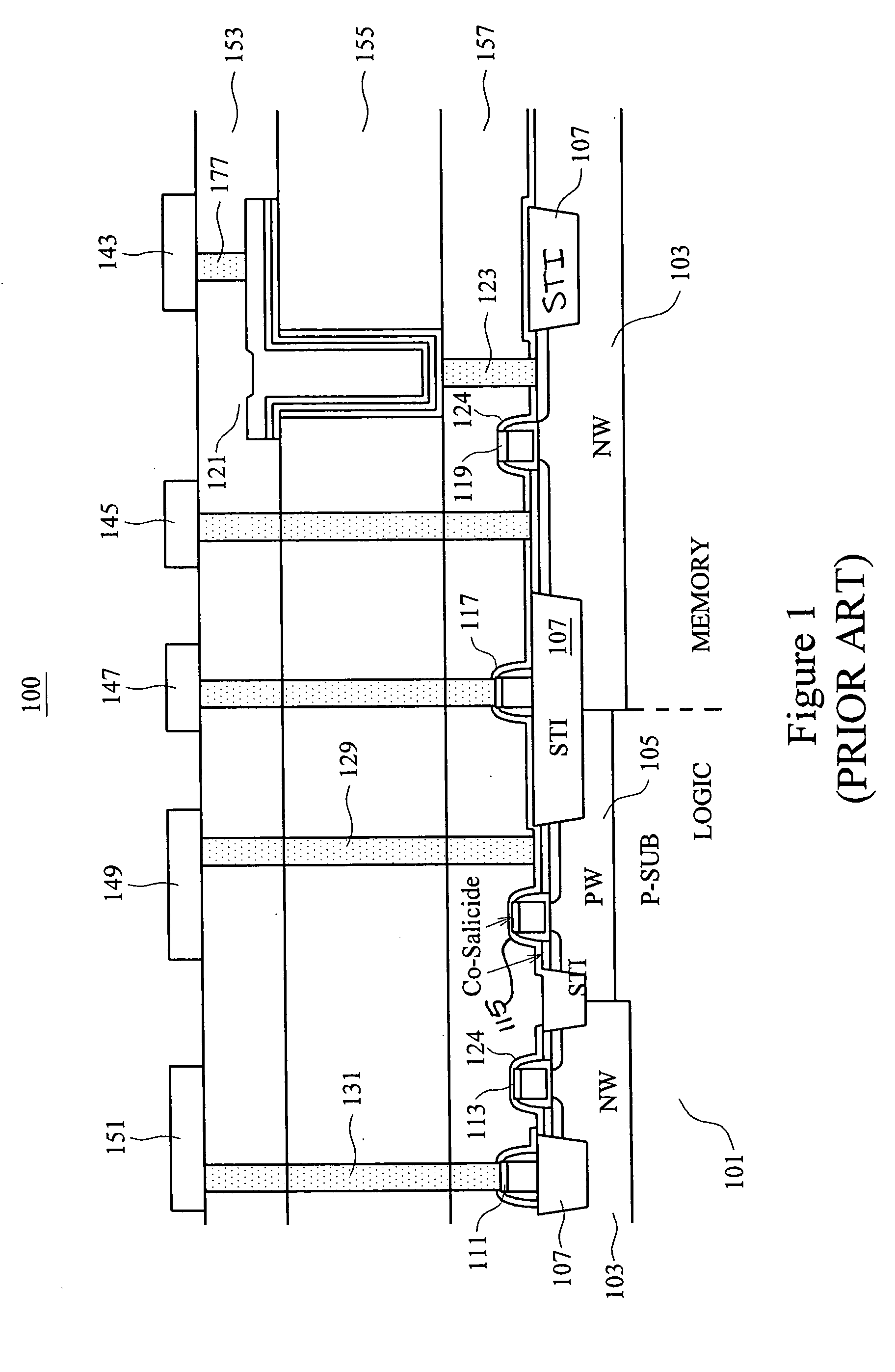

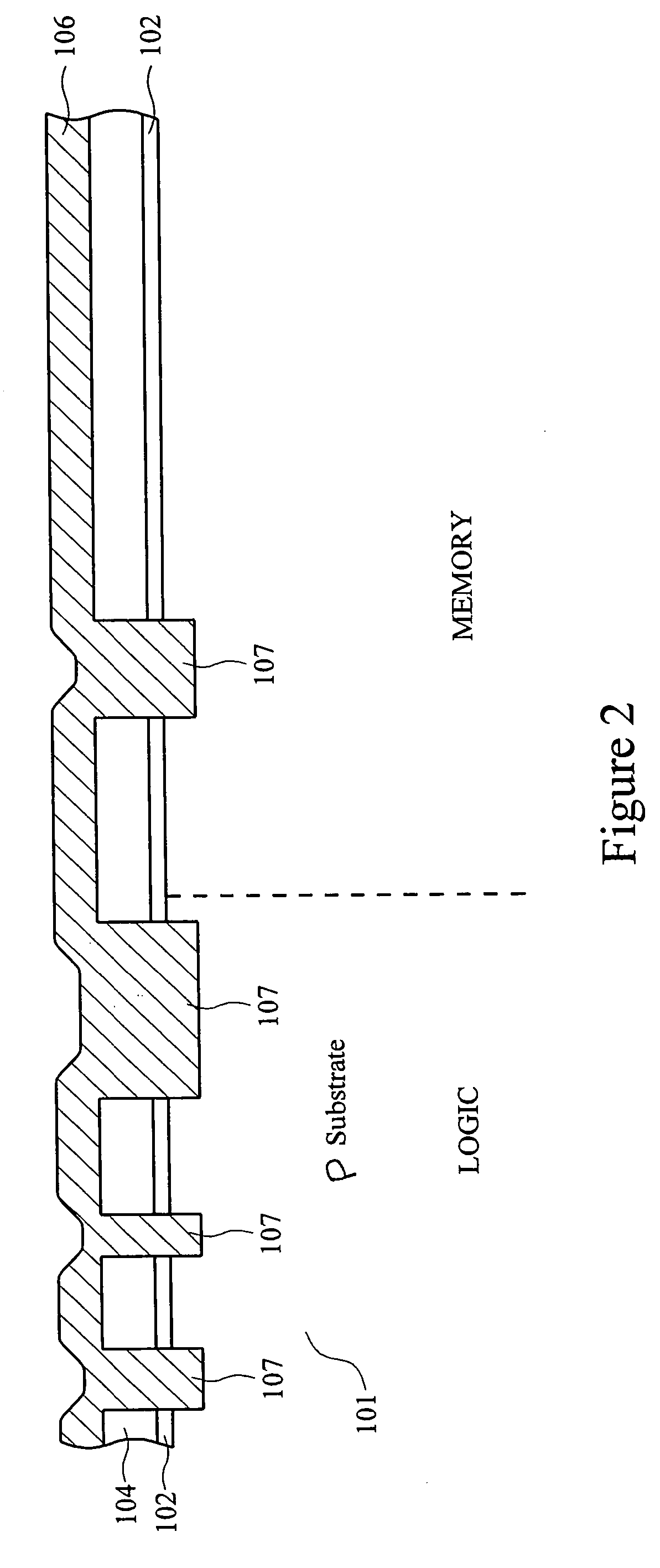

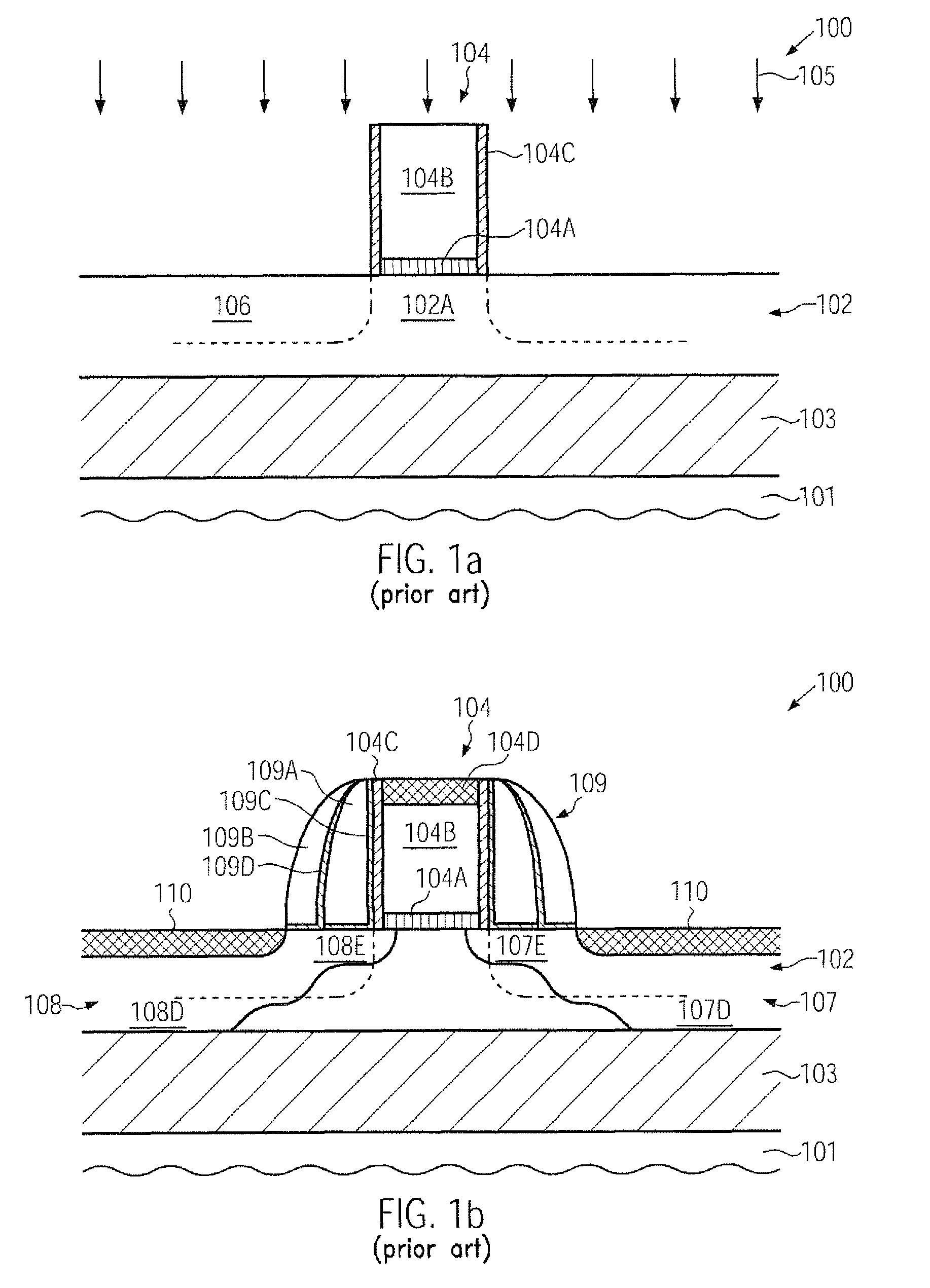

Method and structure for a 1T-RAM bit cell and macro

InactiveUS20070080387A1Function increaseIncrease capacitanceTransistorSolid-state devicesMetal-insulator-metalMOSFET

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

Integrated, closely spaced, high isolation, printed dipoles

ActiveUS20060262026A1Improve antenna isolationReduce electromagnetic couplingSimultaneous aerial operationsRadiating elements structural formsTransceiverNon symmetric

An antenna configuration includes two closely spaced antennas each positioned so as to be orthogonally polarized with respect to the other. The antenna configuration increases antenna isolation and reduces electromagnetic coupling between donor side antenna and repeat side antenna. The antennas include printed dipoles connected to respective transceivers through respective baluns to balance the non-symmetrical portions of the antenna feed paths to reduce unwanted radiation therein. Printed features such as chokes and non-symmetrical and non-parallel structures are preferably included in the ground plane of a multi-layer circuit board to reduce or eliminate circulating ground currents.

Owner:QUALCOMM INC

Drive current increase in transistors by asymmetric amorphization implantation

ActiveUS7855118B2Increased complexityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentNon symmetric

By providing a substantially non-damaged semiconductor region between a pre-amorphization region and the gate electrode structure, an increase of series resistance at the drain side during the re-crystallization may be reduced, thereby contributing to overall transistor performance, in particular in the linear operating mode. Thus, symmetric and asymmetric transistor architectures may be achieved with enhanced performance without unduly adding to overall process complexity.

Owner:ADVANCED MICRO DEVICES INC

Asymmetric semiconductor memory device having electrically floating body transistor

Asymmetric, semiconductor memory cells, arrays, devices and methods are described. Among these, an asymmetric, bi-stable semiconductor memory cell is described that includes: a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with the floating body region; a second region in electrical contact with the floating body region and spaced apart from the first region; and a gate positioned between the first and second regions, such that the first region is on a first side of the memory cell relative to the gate and the second region is on a second side of the memory cell relative to the gate; wherein performance characteristics of the first side are different from performance characteristics of the second side.

Owner:ZENO SEMICON

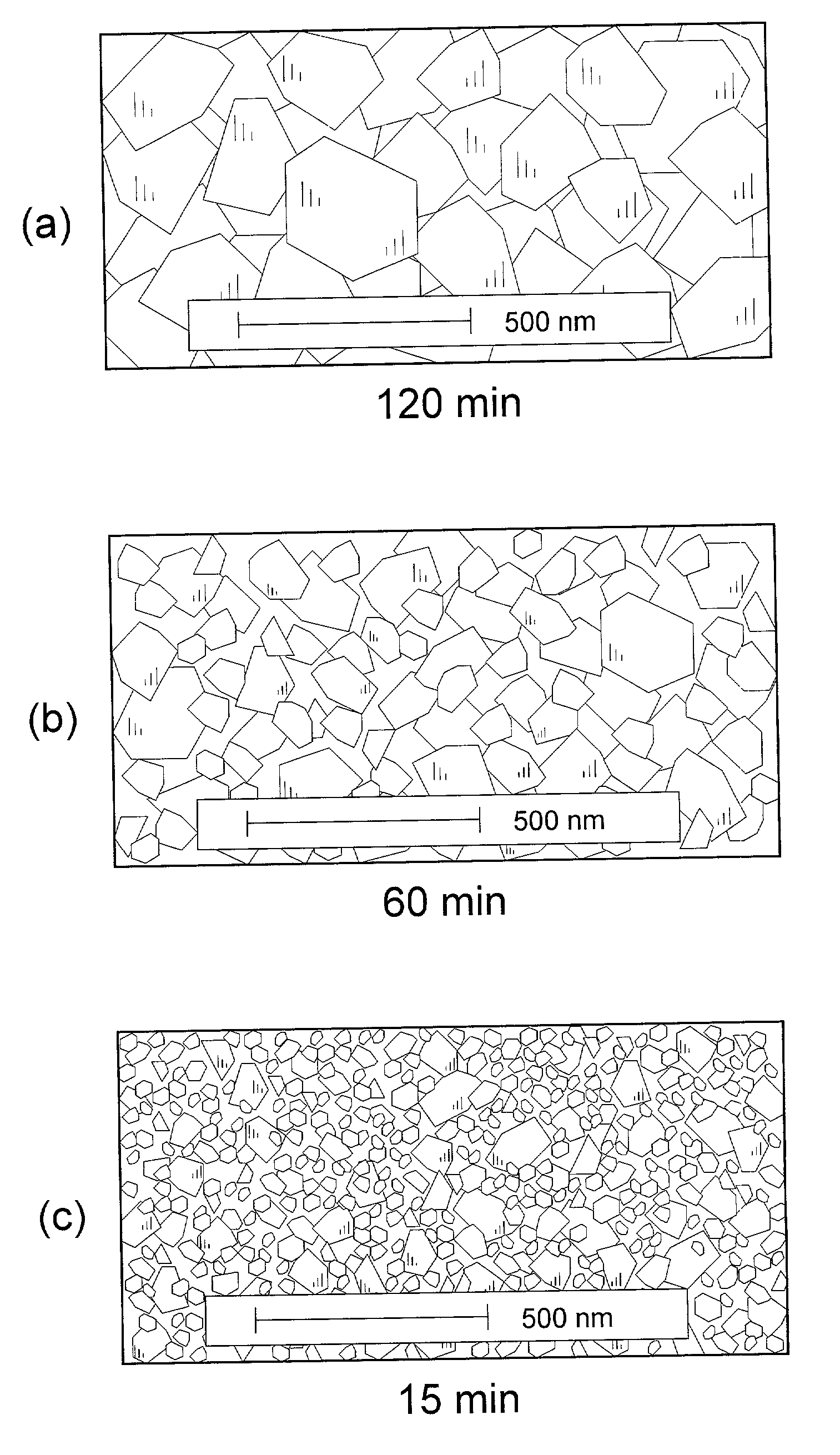

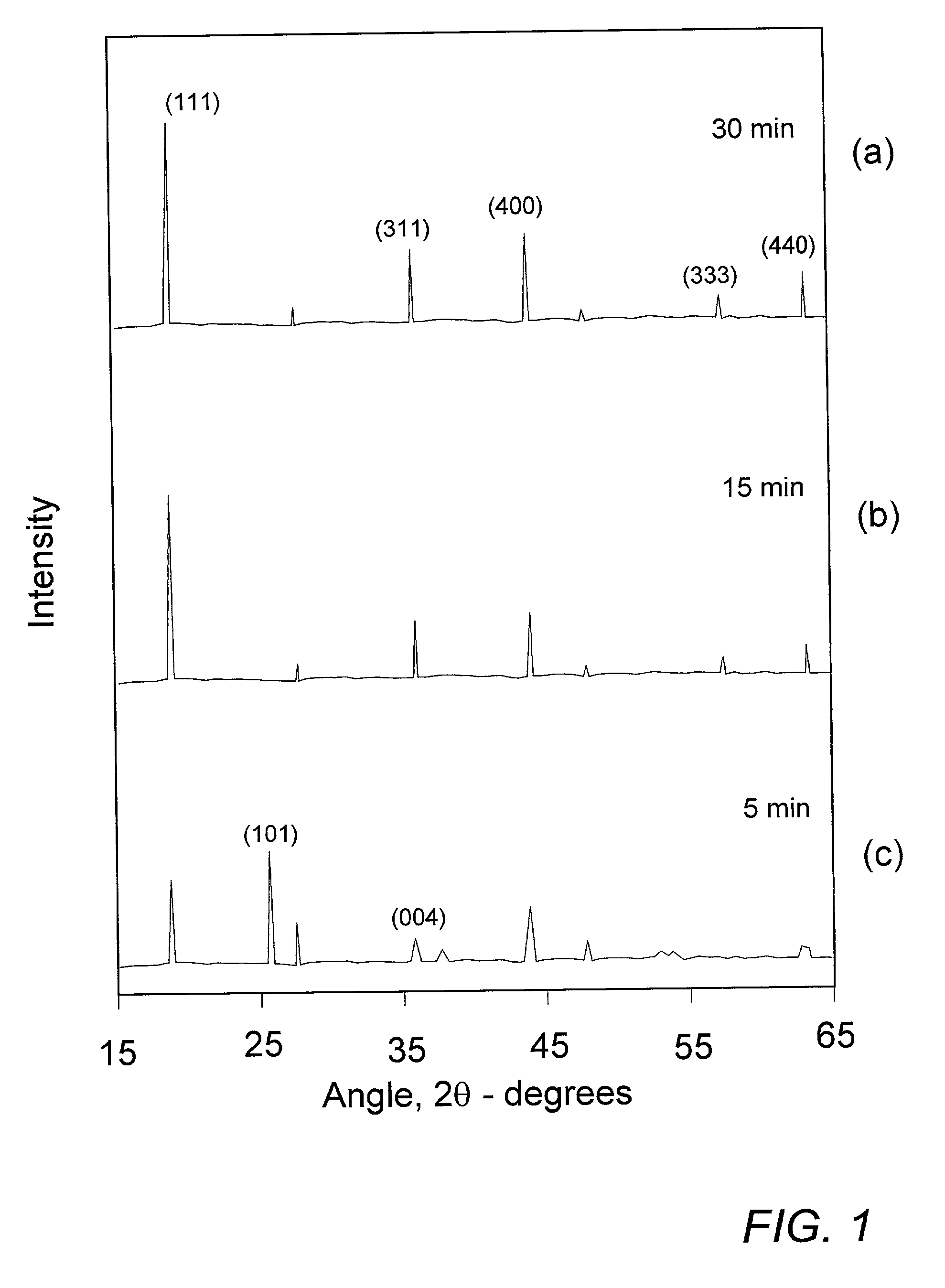

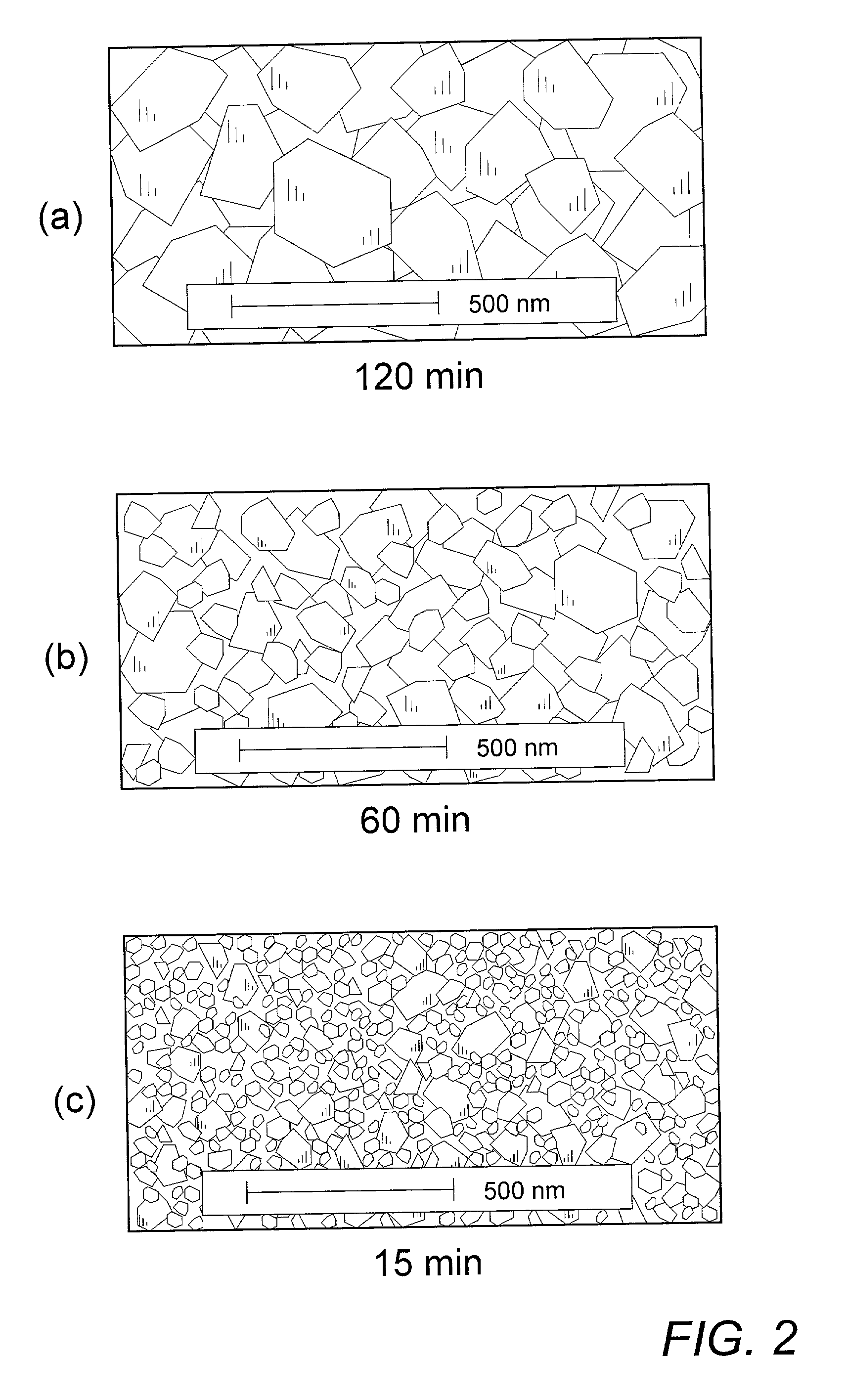

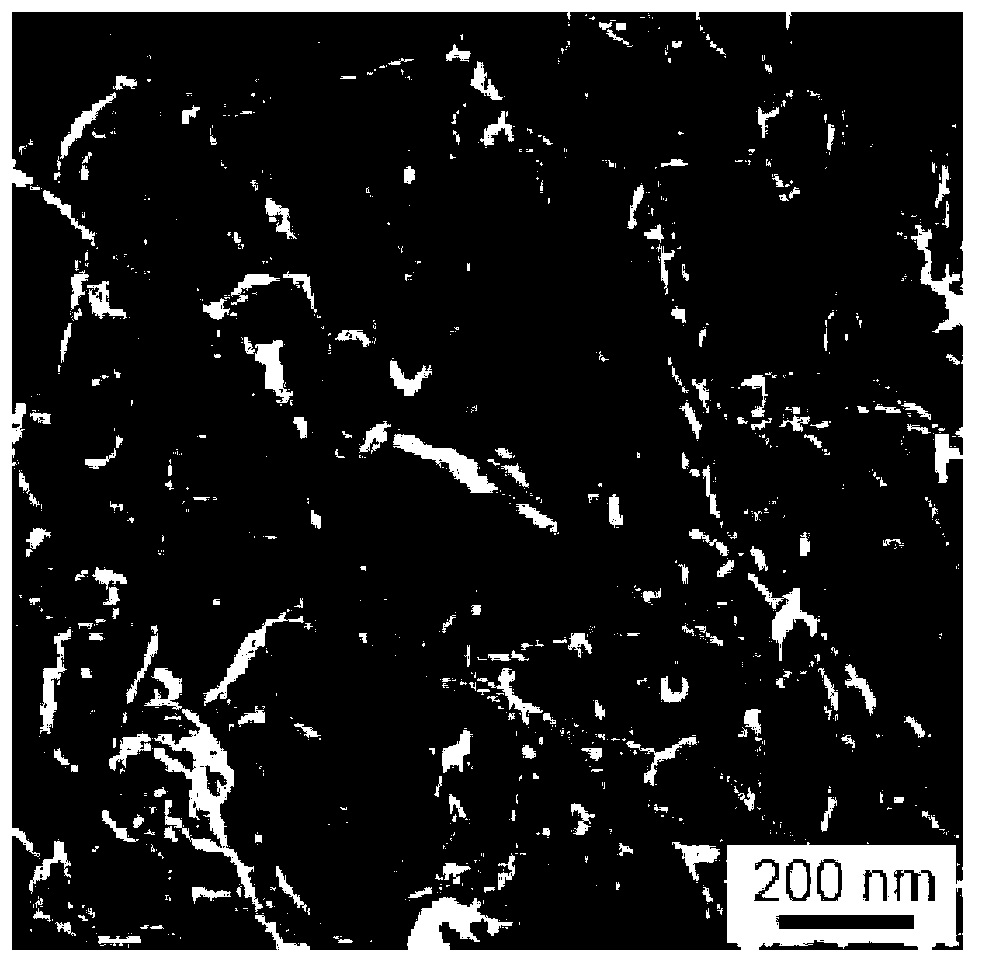

Nanostructure lithium titanate electrode for high cycle rate rechargeable electrochemical cell

Rechargeable electrochemical cells, such as lithium batteries and asymmetric hybrid battery / supercapacitor systems, exhibiting exceptional specific capacity levels and stability over extended high-rate recharge cycling comprise nanostructure zero strain Li4Ti5O12 intercalation electrode material synthesized in a short duration process of annealing mixed TiO2 and Li-source precursor compounds at about 800° C. for a time of about 15–30 min which is not substantially longer than that required to effect maximum available reaction between the precursors, thereby substantially eliminating the growth of synthesized Li4Ti5O12 particles beyond nanostructure size. The process reduces by order of magnitude the time and energy required for synthesis of the active electrode material and fabrication of utilizing cell devices, and provides such nanostructure material which enables repeated, high-rate recharge cycling without loss of cell capacity or efficiency.

Owner:RUTGERS THE STATE UNIV

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

Nonvolatile semiconductor memory having three-level memory cells and program and read mapping circuits therefor

InactiveUS6847550B2Improve reliabilityHigh voltageRead-only memoriesDigital storageThree levelNon symmetric

A memory uses multiple threshold levels in a memory cell that are not a power of two, and further uses a cell mapping technique wherein the read mapping is only a partial function The domain of read states for a single three-level memory cell, for example, has three states, but only two of them can be uniquely mapped to a bit. The domain of read states for two three-level memory cell, for example, has nine states, but only eight of them can be uniquely mapped to three bits. Although the read mapping is only partial, the voltage margin for the three-level memory cells is larger that the voltage margin available in the commonly used four-level memory cells. This increased voltage margin facilitates memory cell threshold voltage sensing, thereby increasing the reliability of the memory. Memory reliability may be further improved by increasing the voltage margin between the memory cell 0 state and the 1 state relative to the voltage margin between the 1 state and the 2 state, which more effectively accommodates charge loss from the 0 state through electron leakage. Asymmetrical read and program mapping may also be used to improve read reliability in the presence of ground noise or VCC noise.

Owner:WINBOND ELECTRONICS CORP

Method for preparing electrodes of super capacitor based on nickel foam and products thereof

InactiveCN103258656AHigh specific capacitanceIncrease energy densityHybrid capacitor electrolytesHybrid capacitor electrodesCapacitanceNon symmetric

The invention discloses a method for preparing electrodes of a dissymmetric super capacitor based on nickel foam. The method comprises the steps: washing the nickel foam, soaking the nickel foam into a graphene oxide aqueous solution to obtain nickel foam in which graphene oxide deposits, serving the nickel foam in which the graphene oxide deposits as precursor materials, and respectively adopting a three-electrode method for preparaing a positive electrode and a negative electrode of the dissymmetric super capacitor, wherein the positive electrode is composed of composite materials of graphene, a carbon nanometer tube and the nickel foam, and the negative electrode is composed of composite materials of graphene, manganese dioxide and the nickel foam. The invention further discloses some other methods for preparing the electrodes of the super capacitor based on the similar principle, and products which correspond to the methods. By means of the methods and the products, respective high-ratio capacitance characteristics of the composite materials are fully played, and energy density of the super capacitor is improved. In addition, usage of various combined reagents can be avoided, and accordingly large-batch industrial production is conducted in a mode of convenient control, low cost and low energy consumption.

Owner:HUAZHONG UNIV OF SCI & TECH