Patents

Literature

4073results about How to "Increase capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

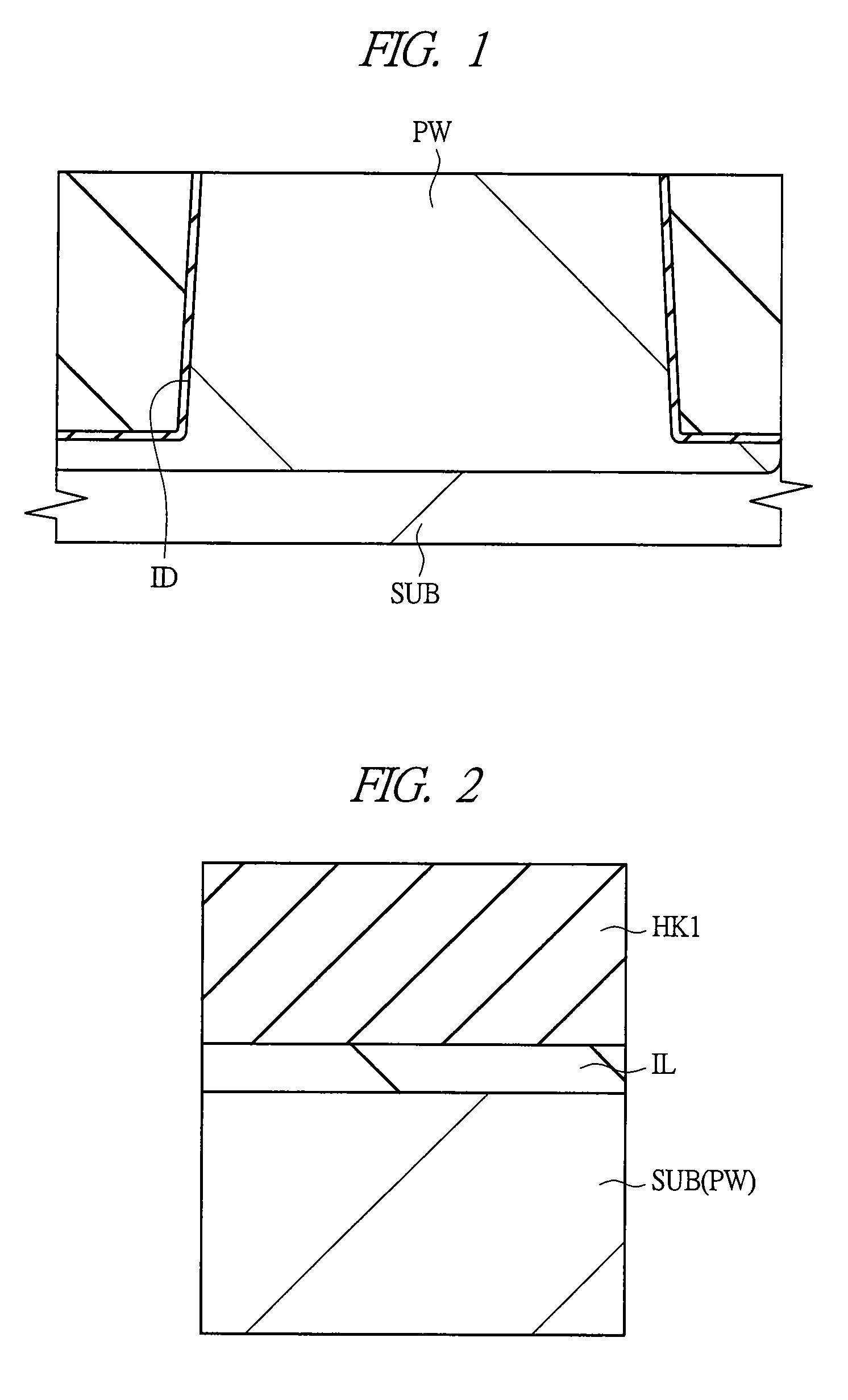

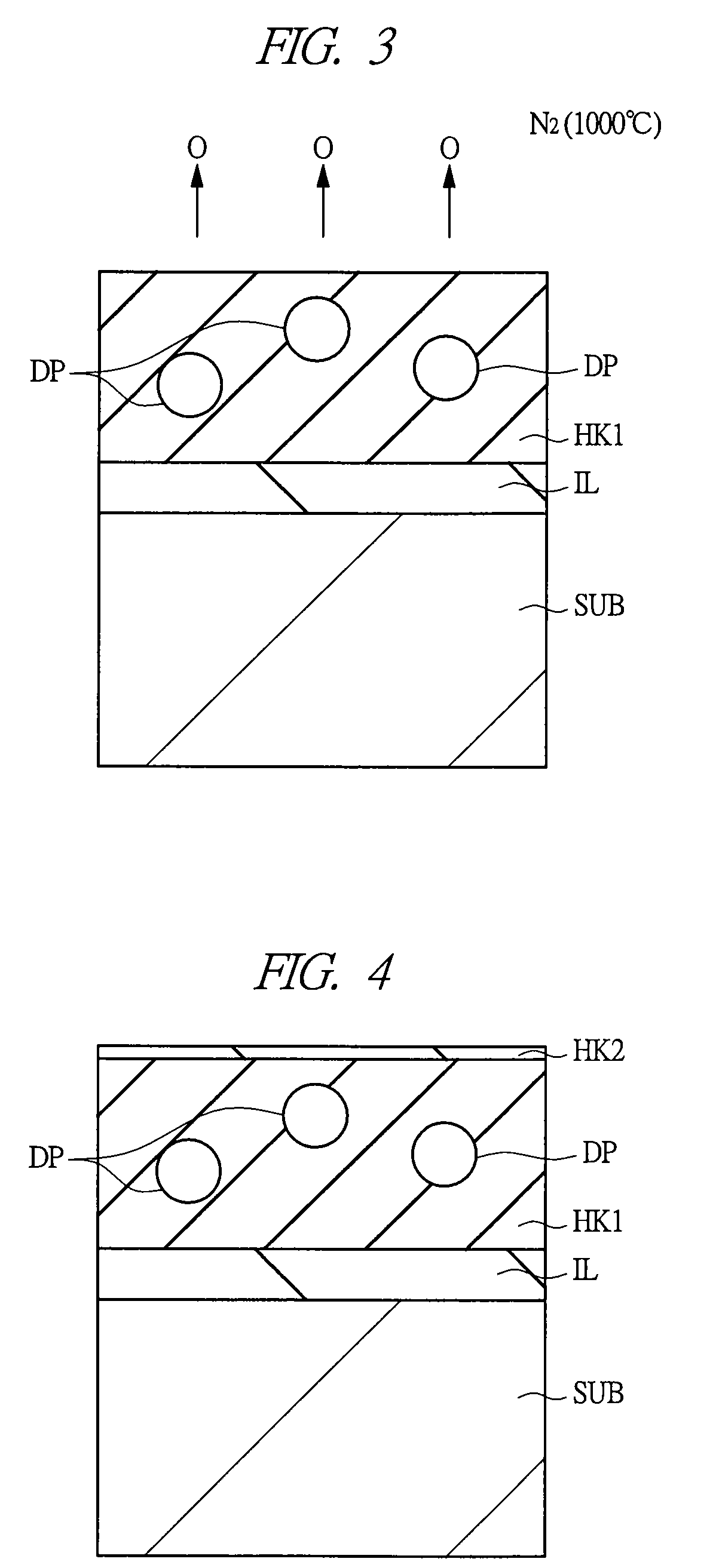

Manufacturing method of semiconductor device

InactiveUS20090011608A1Reduce hypoxiaSuppression of interface silicon oxide growthSemiconductor/solid-state device manufacturingSemiconductor devicesTantalum nitrideSilicon oxide

The transistor characteristics of a MIS transistor provided with a gate insulating film formed to contain oxide with a relative dielectric constant higher than that of silicon oxide are improved. After a high dielectric layer made of hafnium oxide is formed on a main surface of a semiconductor substrate, the main surface of the semiconductor substrate is heat-treated in a non-oxidation atmosphere. Next, an oxygen supplying layer made of hafnium oxide deposited by ALD and having a thickness smaller than that of the high dielectric layer is formed on the high dielectric layer, and a cap layer made of tantalum nitride is formed. Thereafter, the main surface of the semiconductor substrate is heat-treated.

Owner:RENESAS TECH CORP

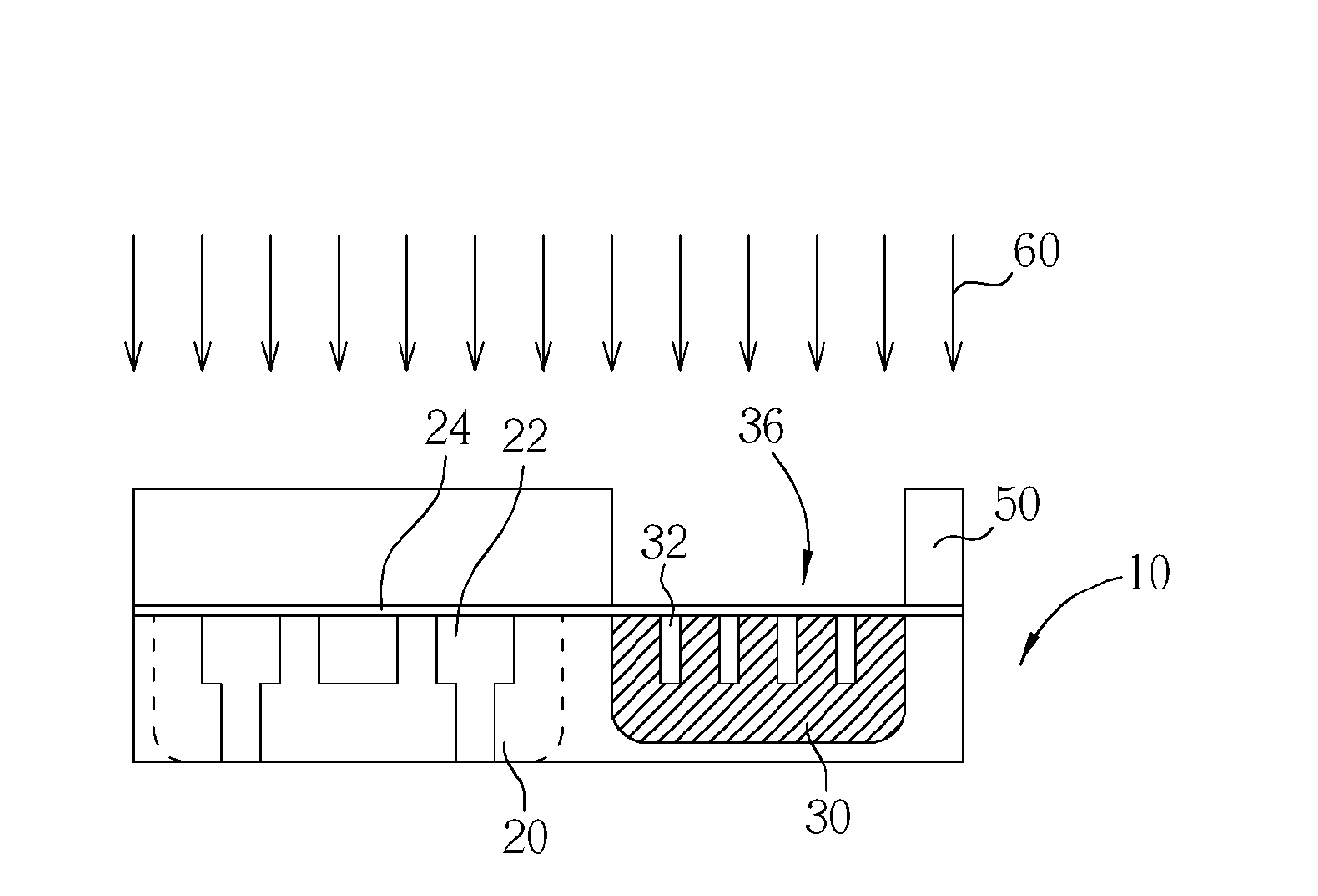

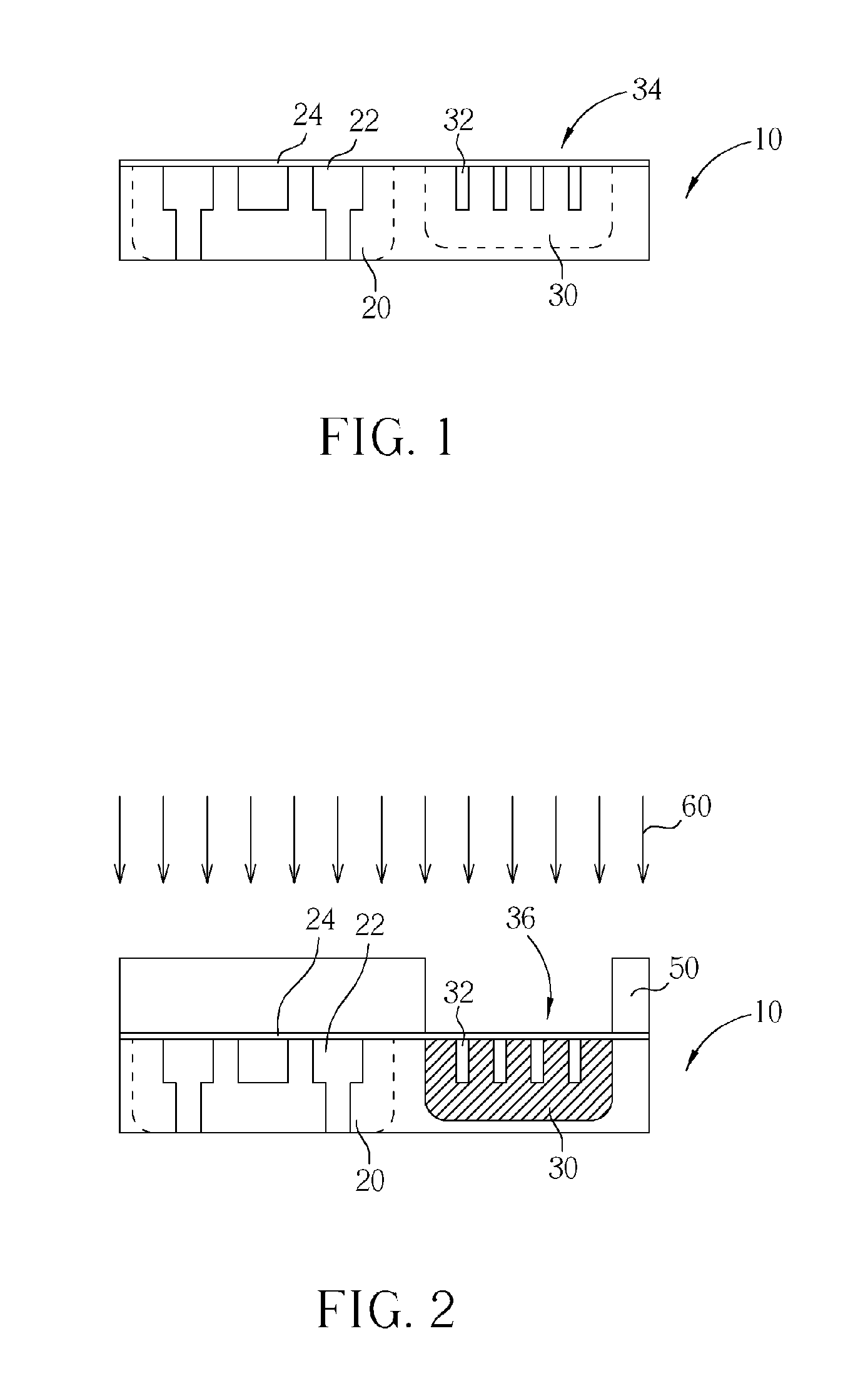

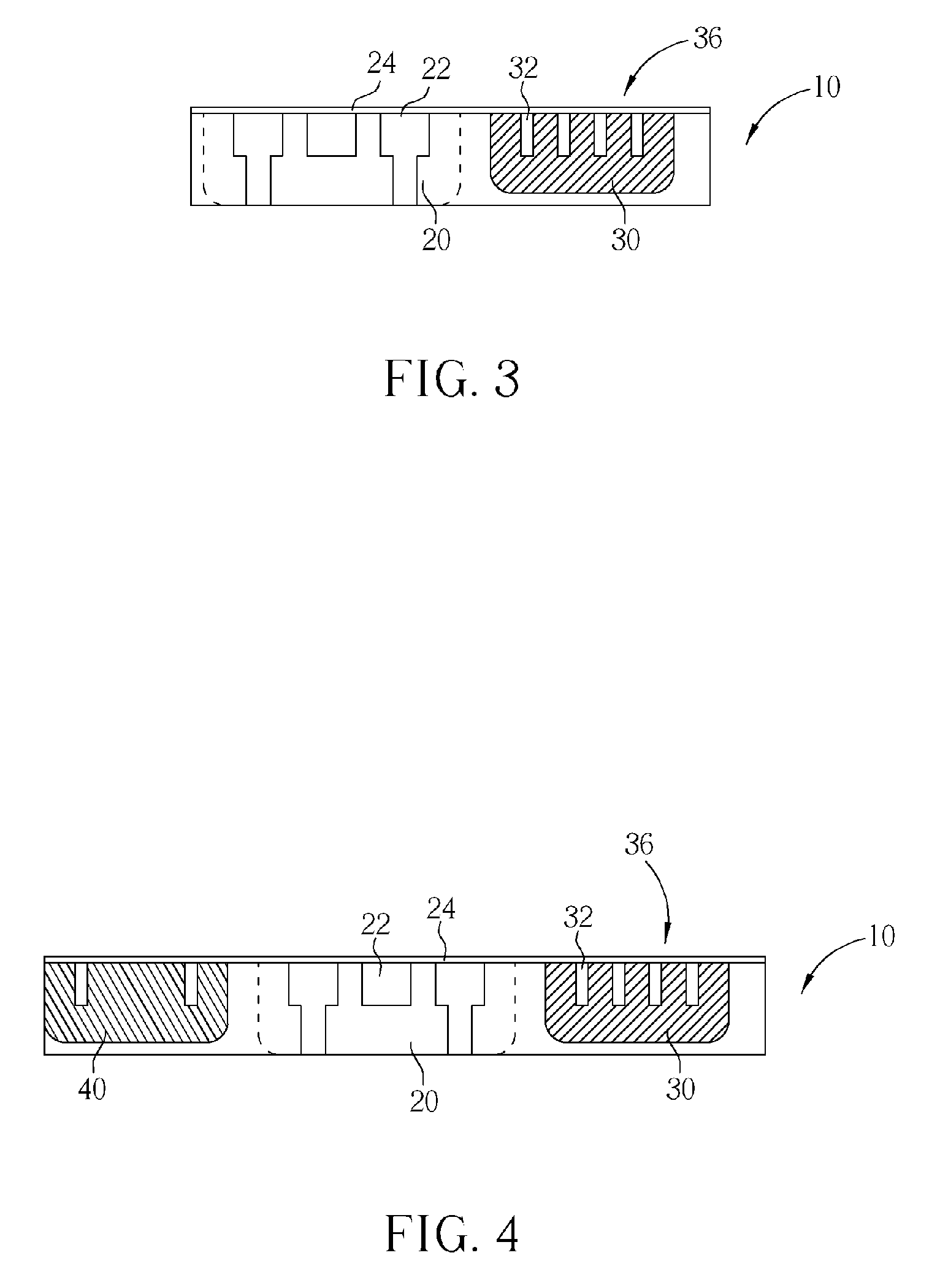

Metal capacitor and method of making the same

ActiveUS8114734B2Increase capacitanceAvoid delaySemiconductor/solid-state device detailsSolid-state devicesCapacitanceInterconnection

A method of making a metal capacitor includes the following steps. A dielectric layer having a metal interconnection and a capacitor electrode is provided. Then, a treatment is performed to increase the dielectric constant of the dielectric layer surrounding the capacitor electrode. The treatment can be UV radiation, a plasma treatment or an ion implantation. Accordingly, the metal capacitor will have a higher capacitance and RC delay between the metal interconnection and the dielectric layer can be prevented.

Owner:MARLIN SEMICON LTD

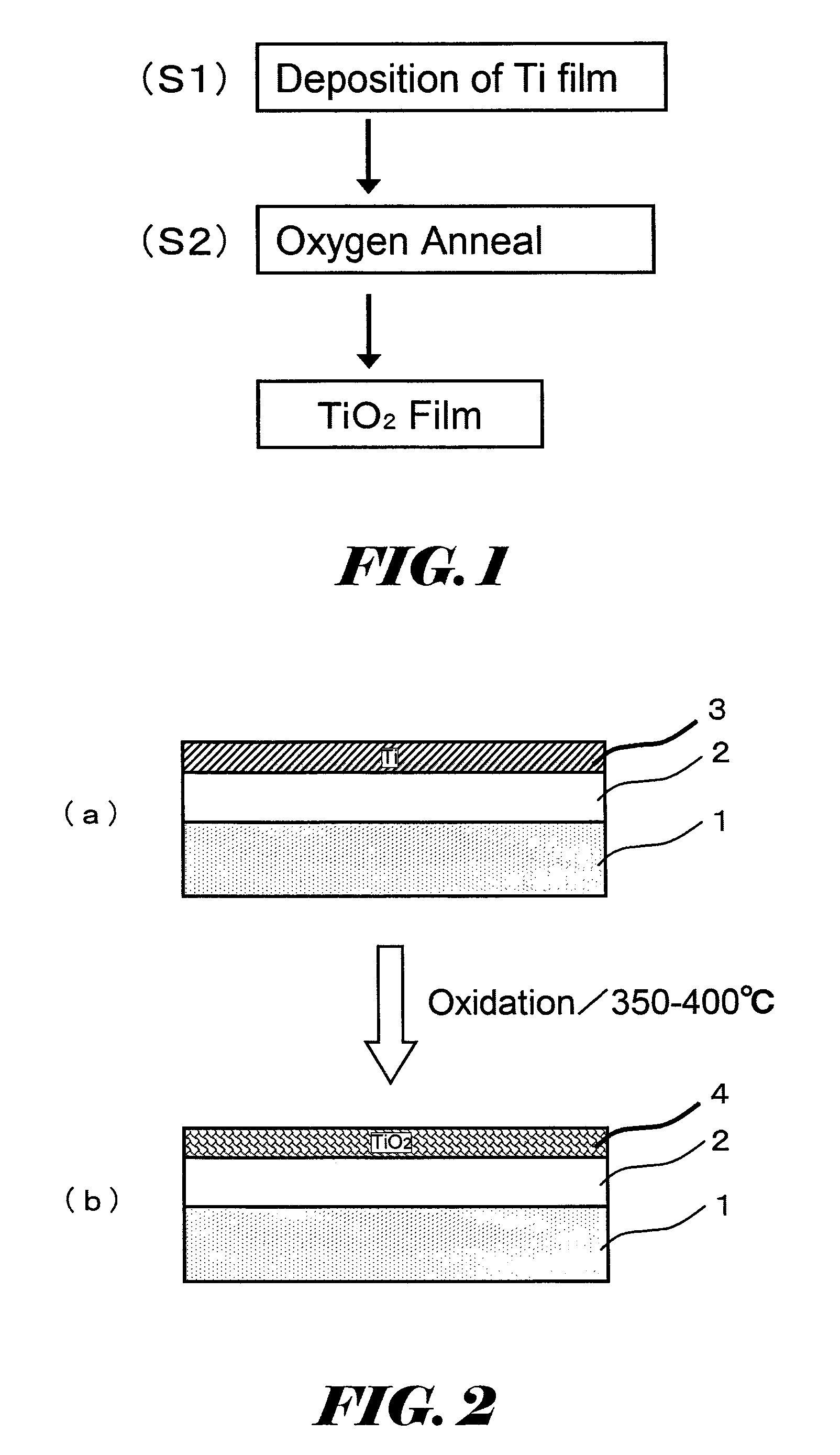

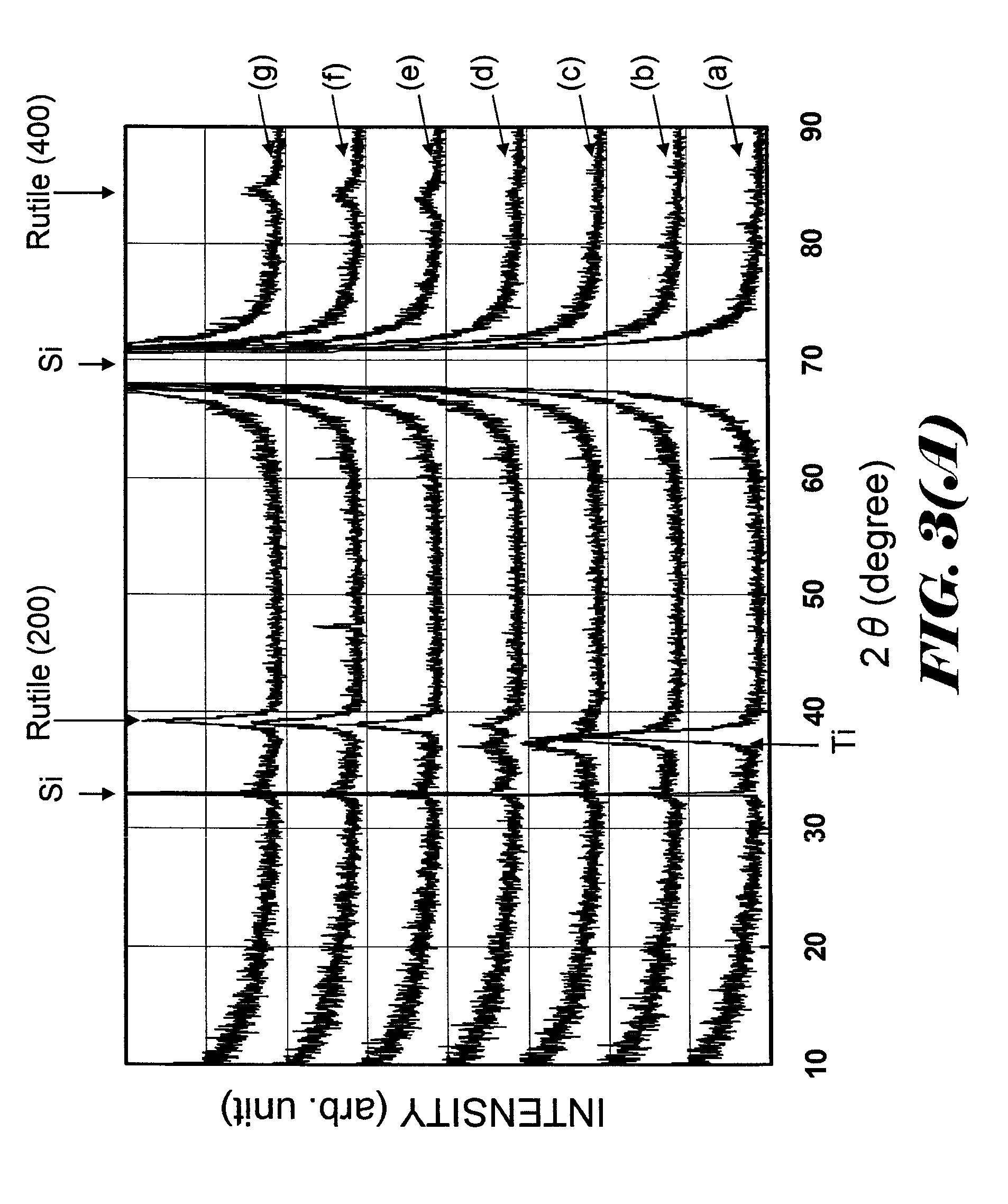

Method of manufacturing capacitive insulating film for capacitor

InactiveUS8198168B2Increase capacitanceReduce adverse effectsThin/thick film capacitorSemiconductor/solid-state device manufacturingCapacitanceCrystal structure

According to the invention, a Ti film is formed on a substrate and is annealed at the temperatures of 350° C.-400° C. under oxidative environment, so that a TiO2 film having a rutile crystal structure is formed. Since the TiO2 film having a rutile crystal structure has a high dielectric constant, it is useful for a capacitive insulating film for a capacitor.

Owner:PS4 LUXCO SARL

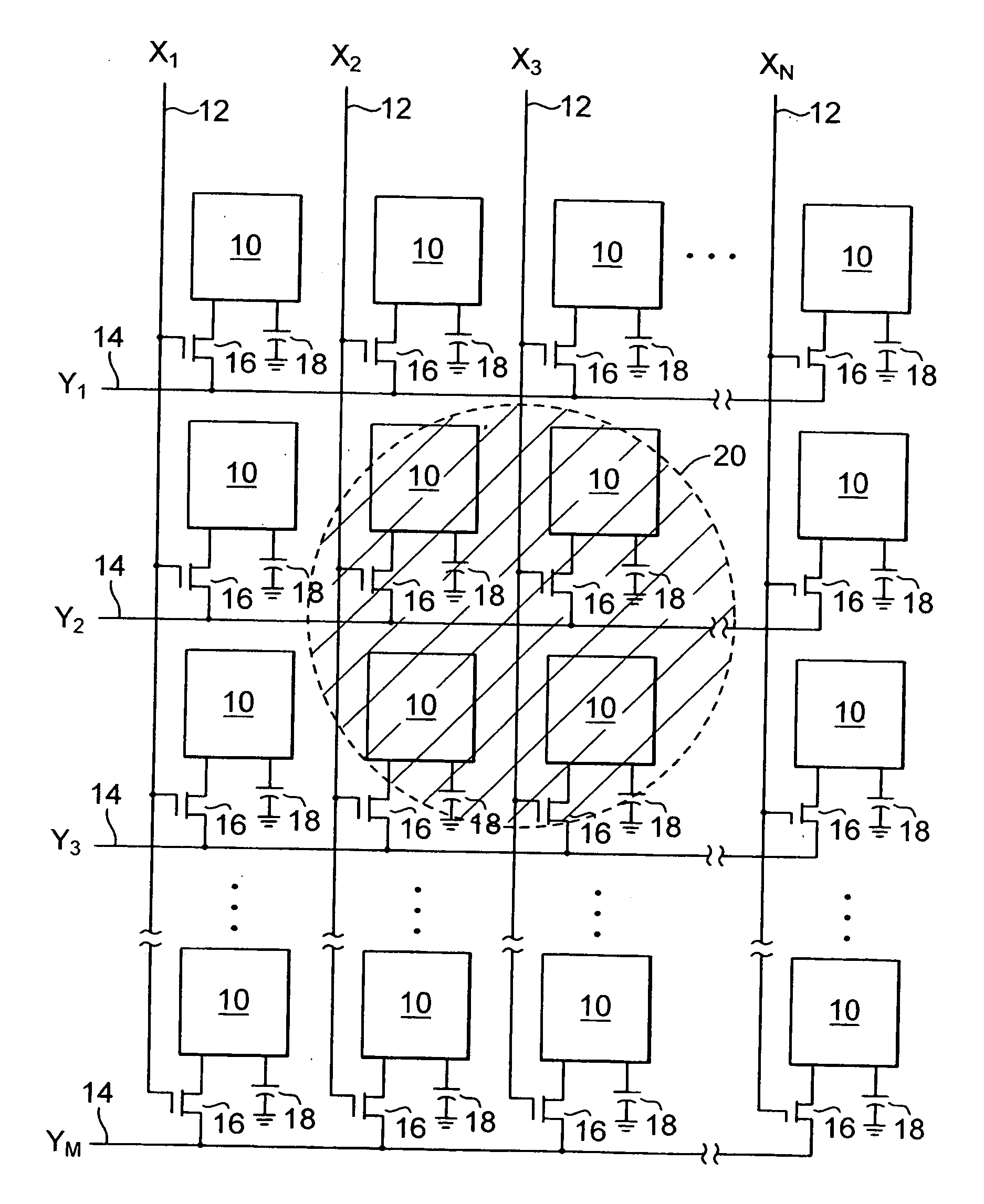

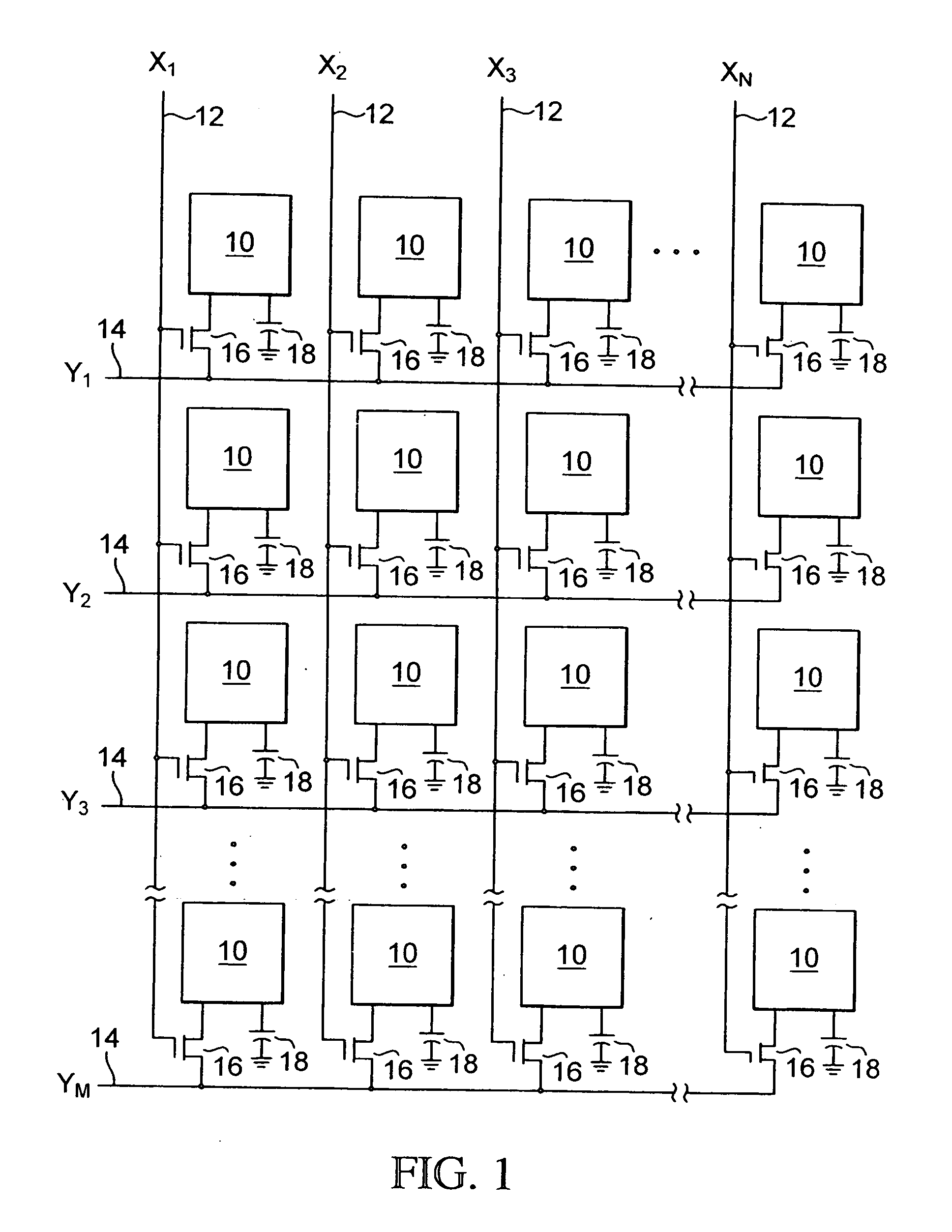

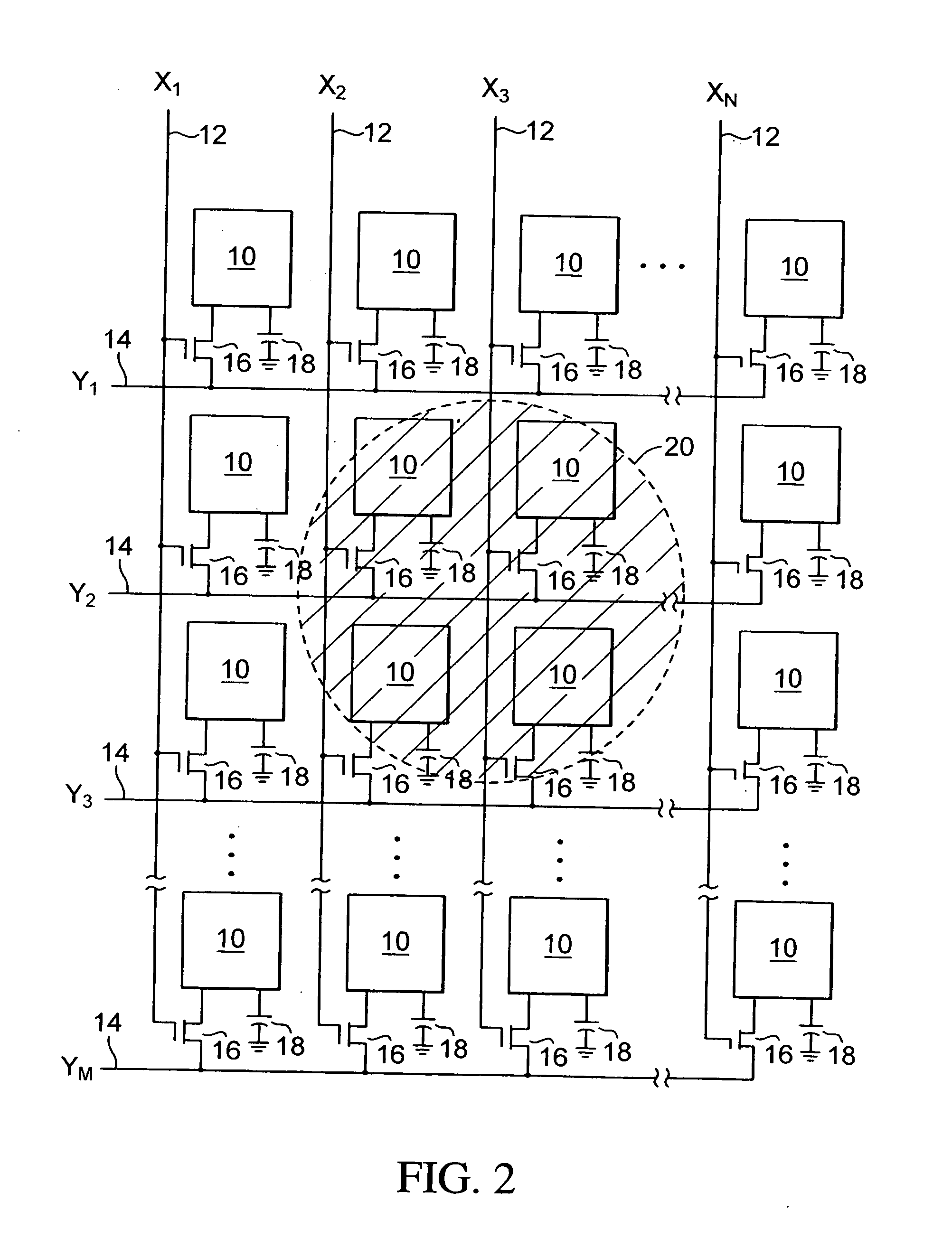

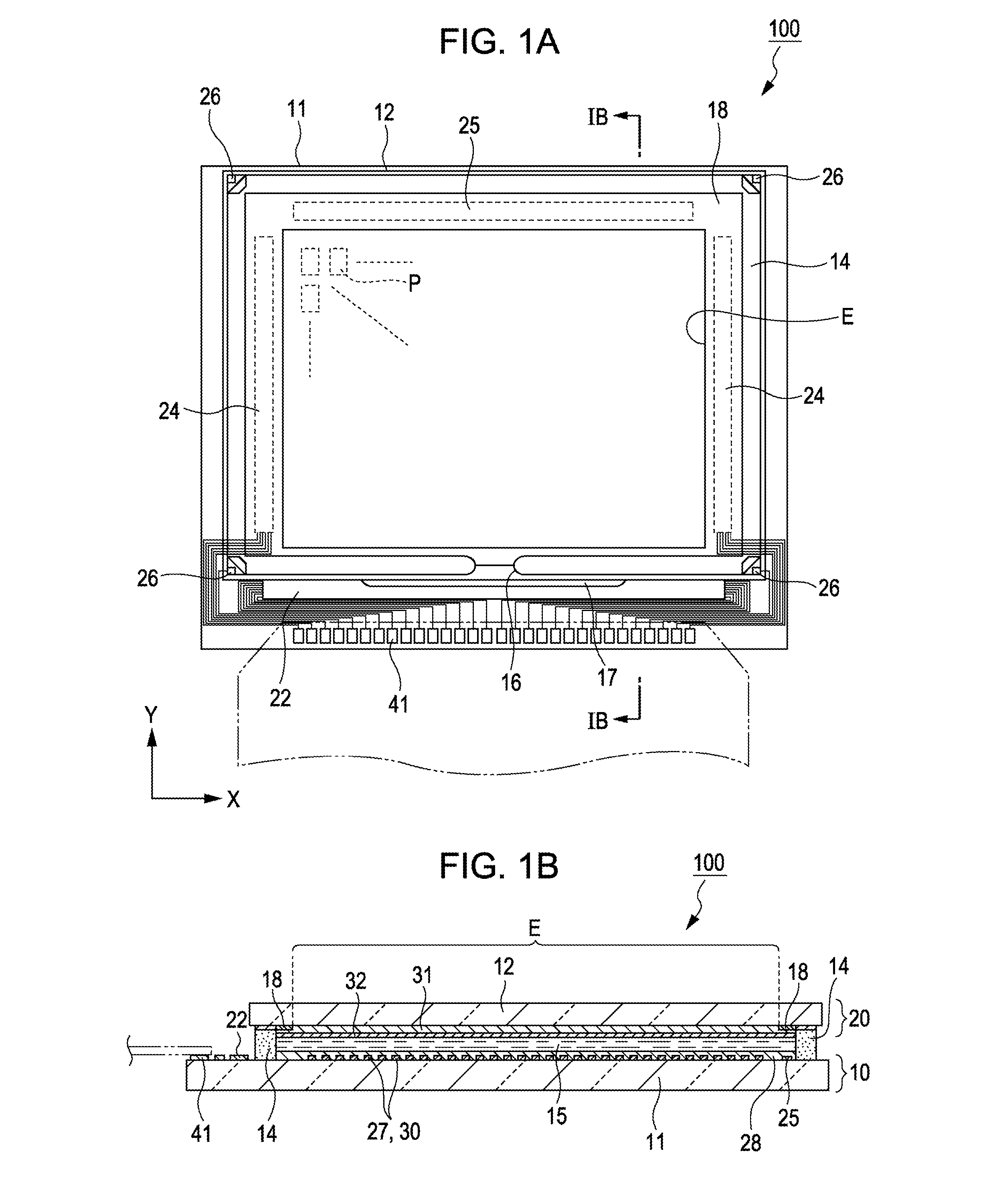

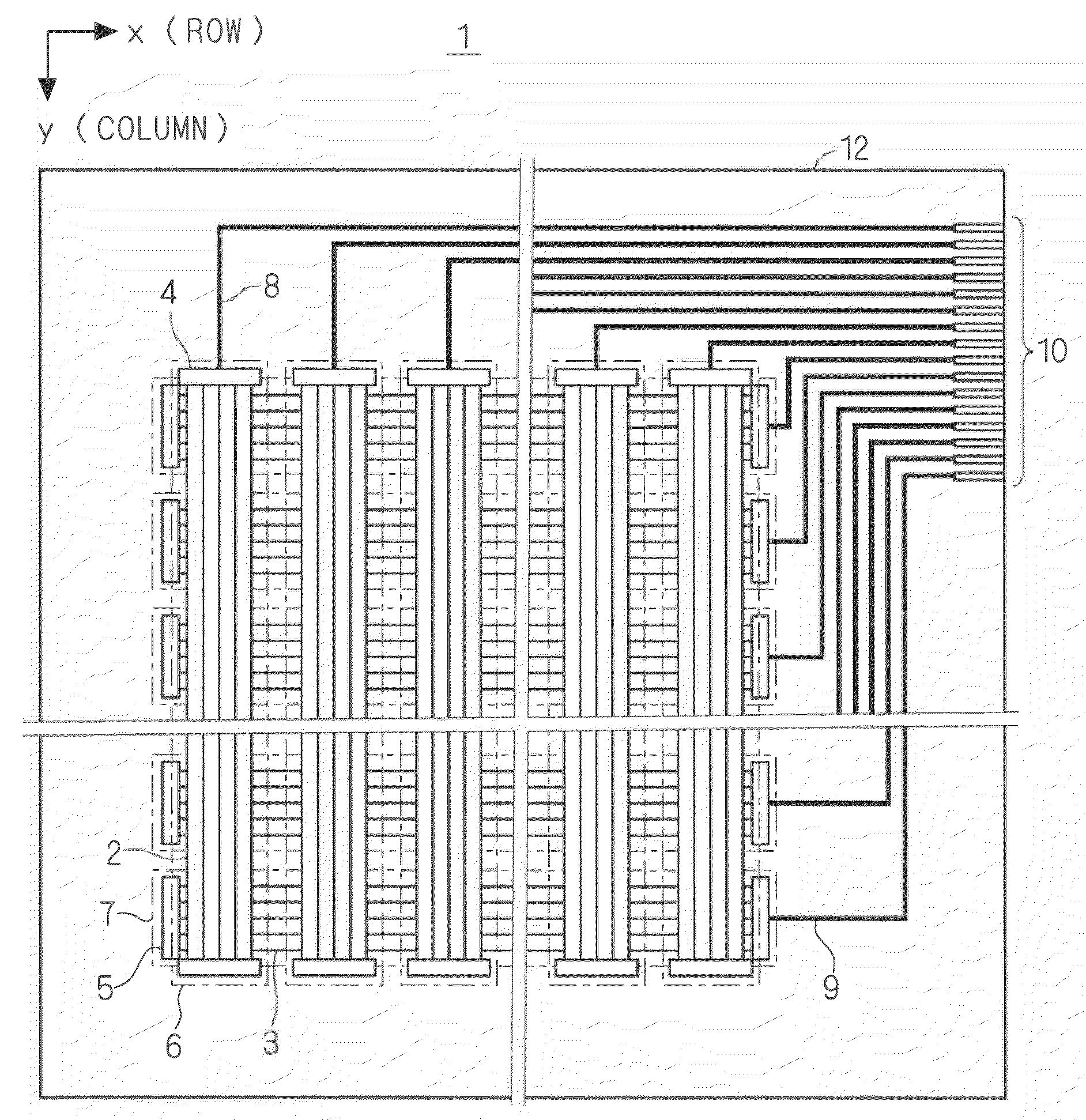

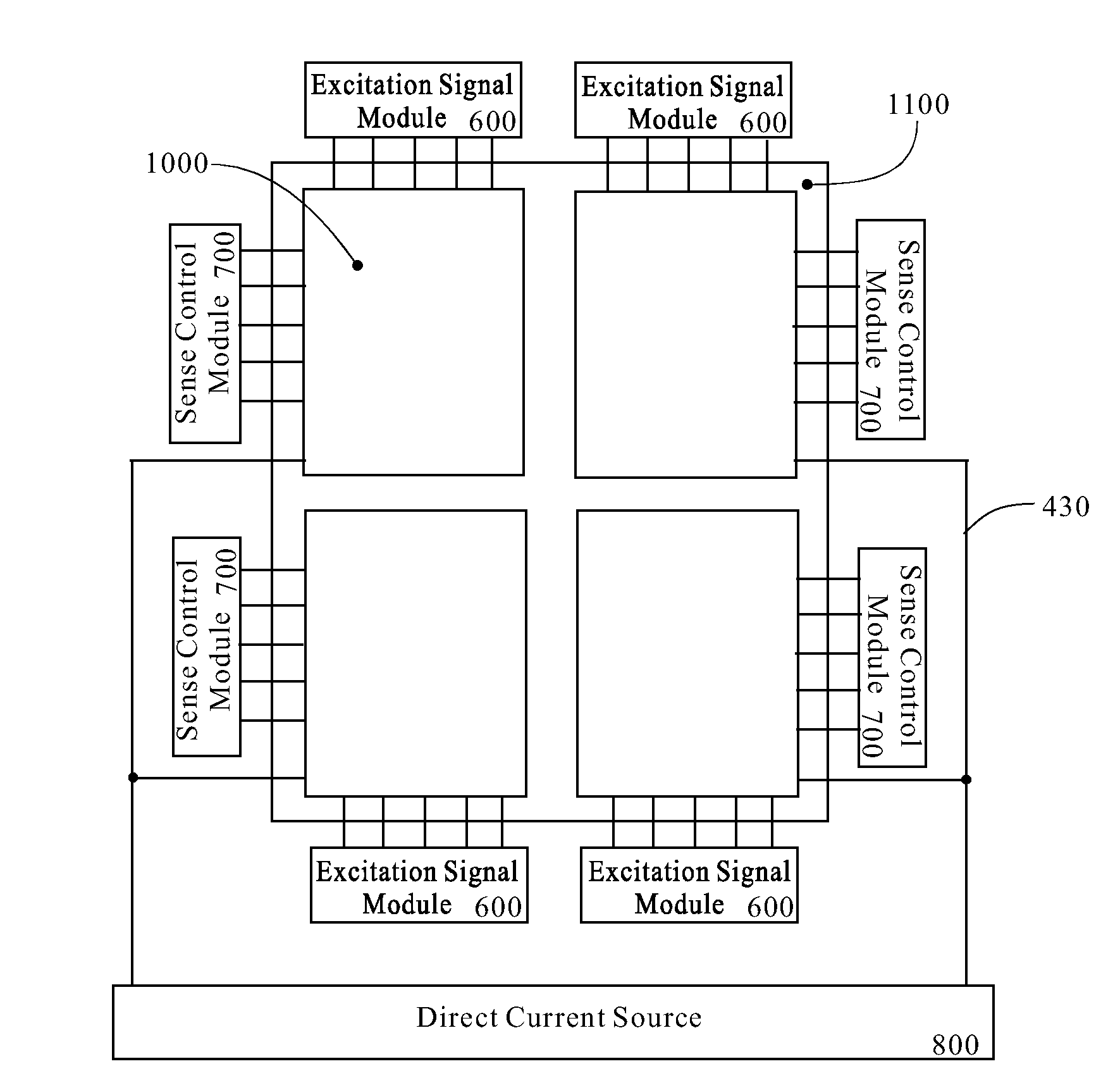

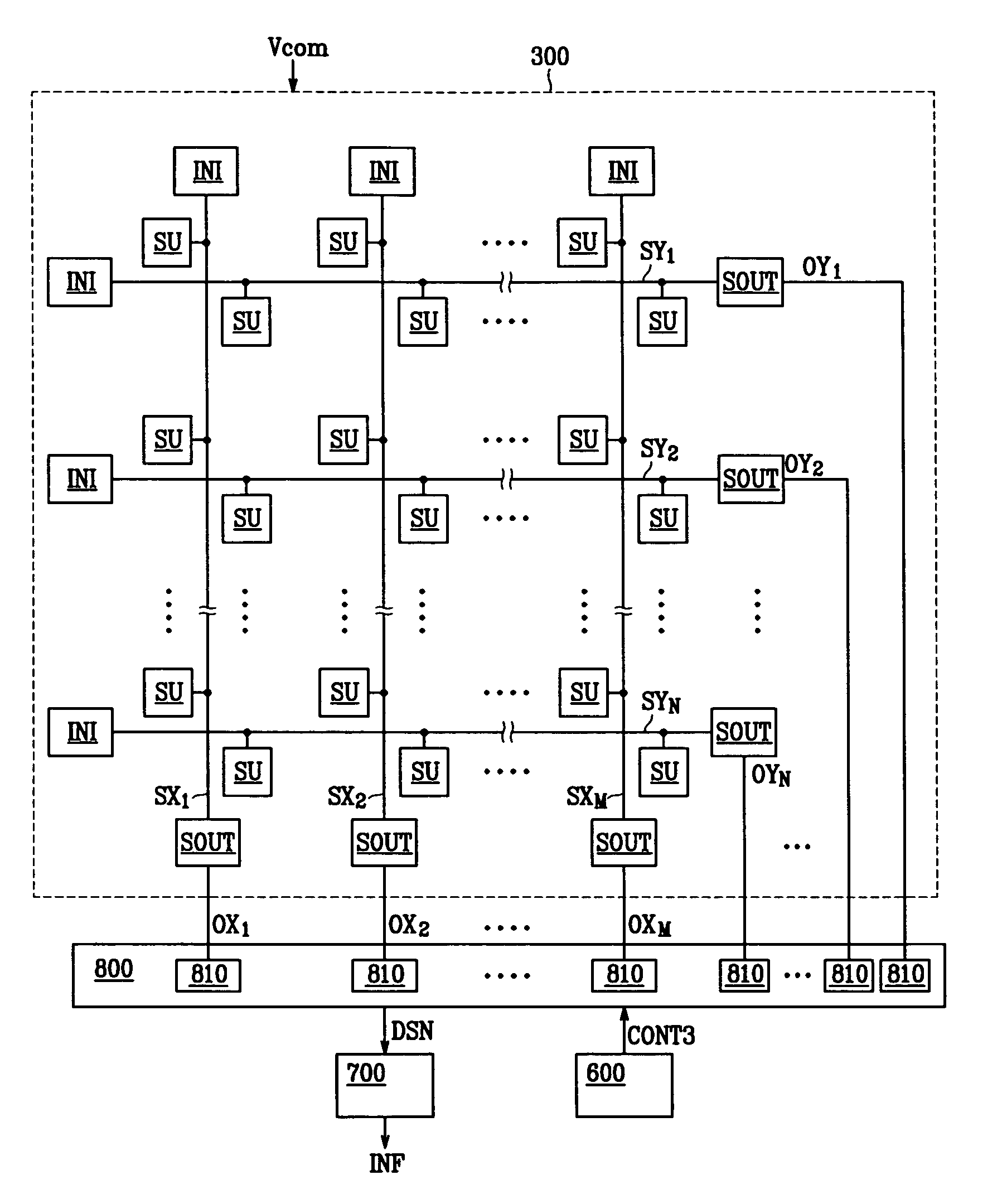

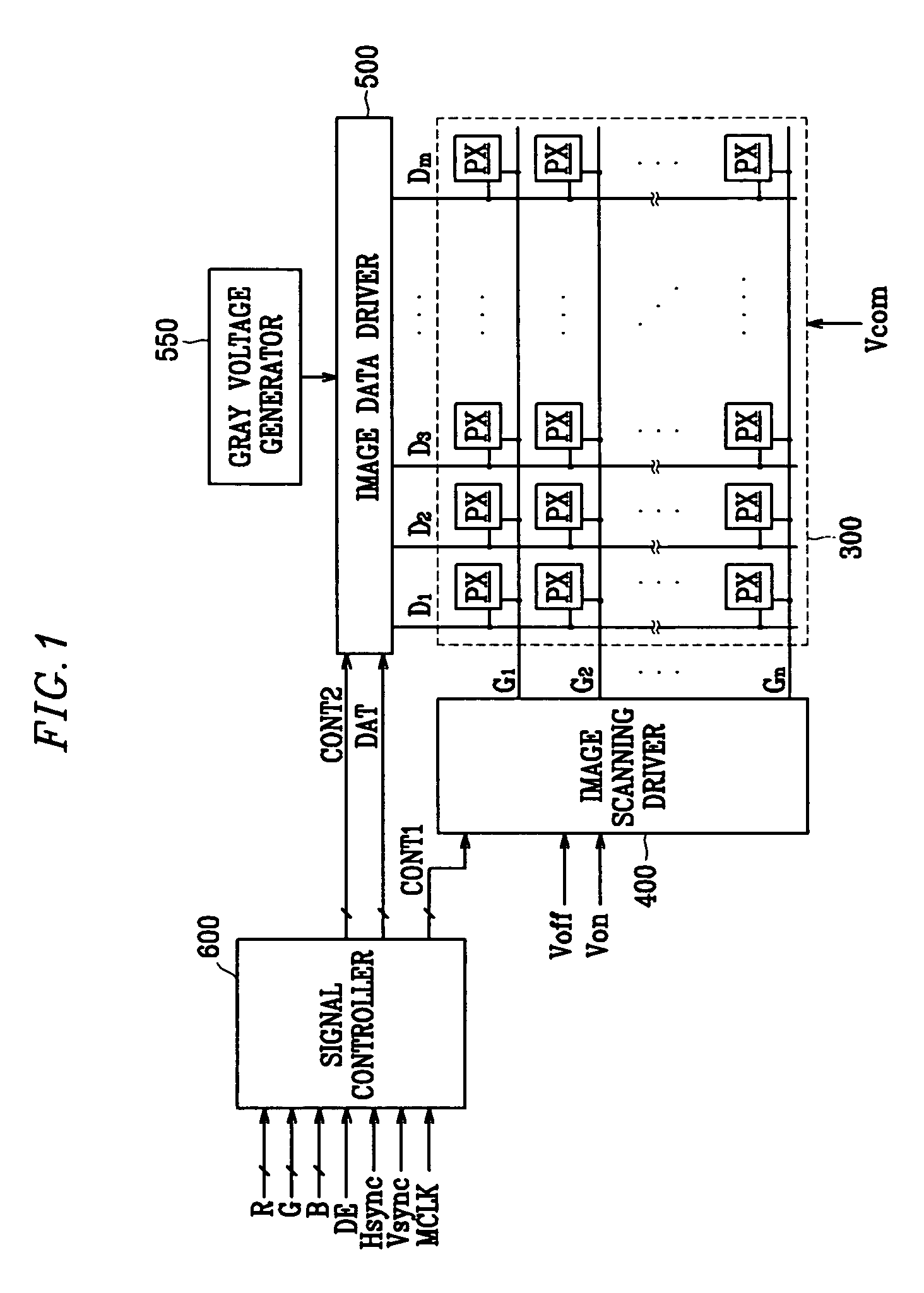

Flat panel display screen operable for touch position determination system and methods

InactiveUS20070216657A1Raising pixel capacitanceQuickly and easily determineStatic indicating devicesAcquiring/reconising fingerprints/palmprintsDisplay deviceQuantum dot display

A system and method are disclosed that determines the location of an object touching a display screen. The system and method modifies already existing display technology, including using the underlying structure of many types of existing displays as the touch detecting structure. The systems and methods are applicable to virtually all LCD and LCD-like displays, including emissive displays (OLED, PLED, quantum dot displays, etc.), electronic paper, and others.

Owner:KONICEK JEFFREY C

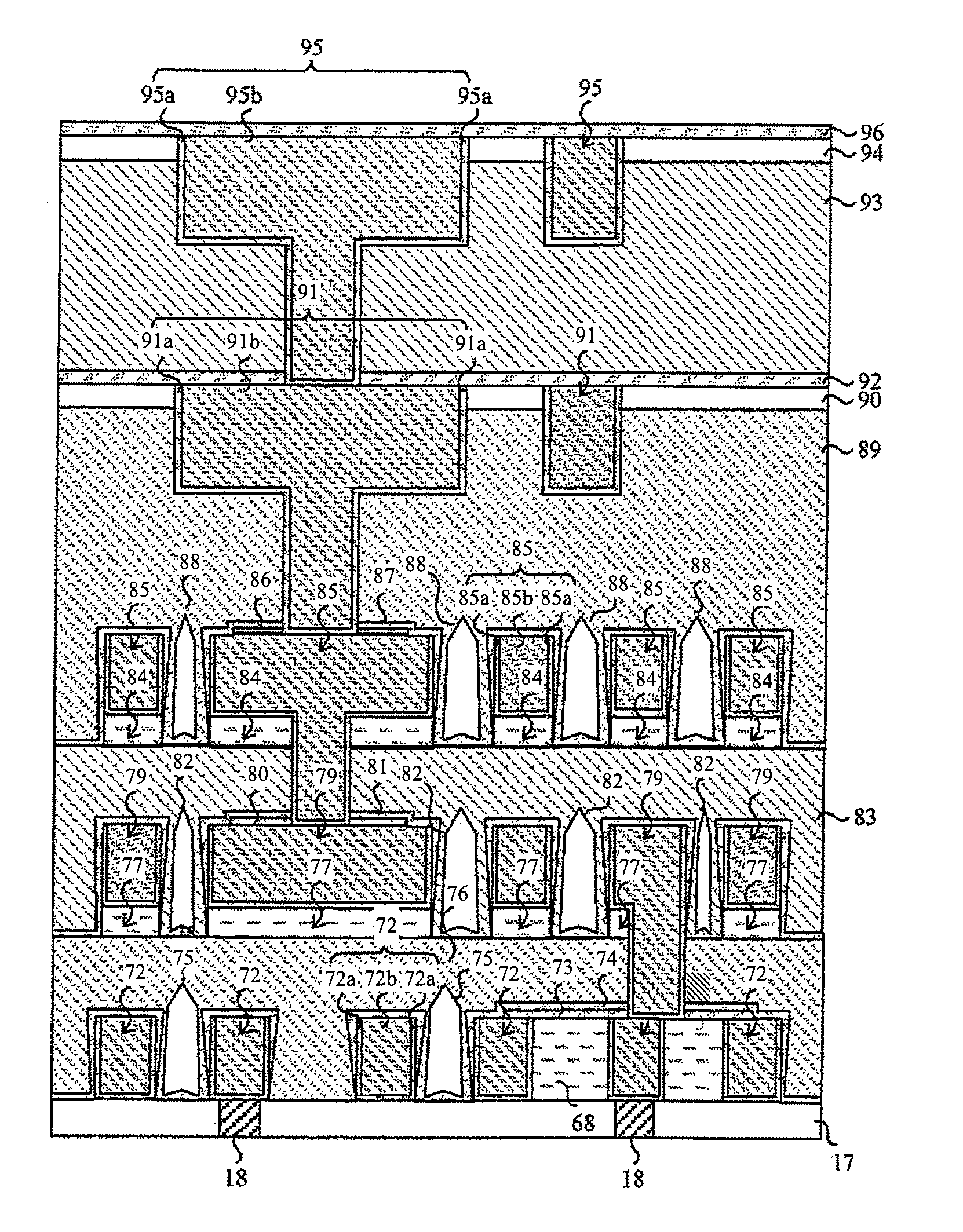

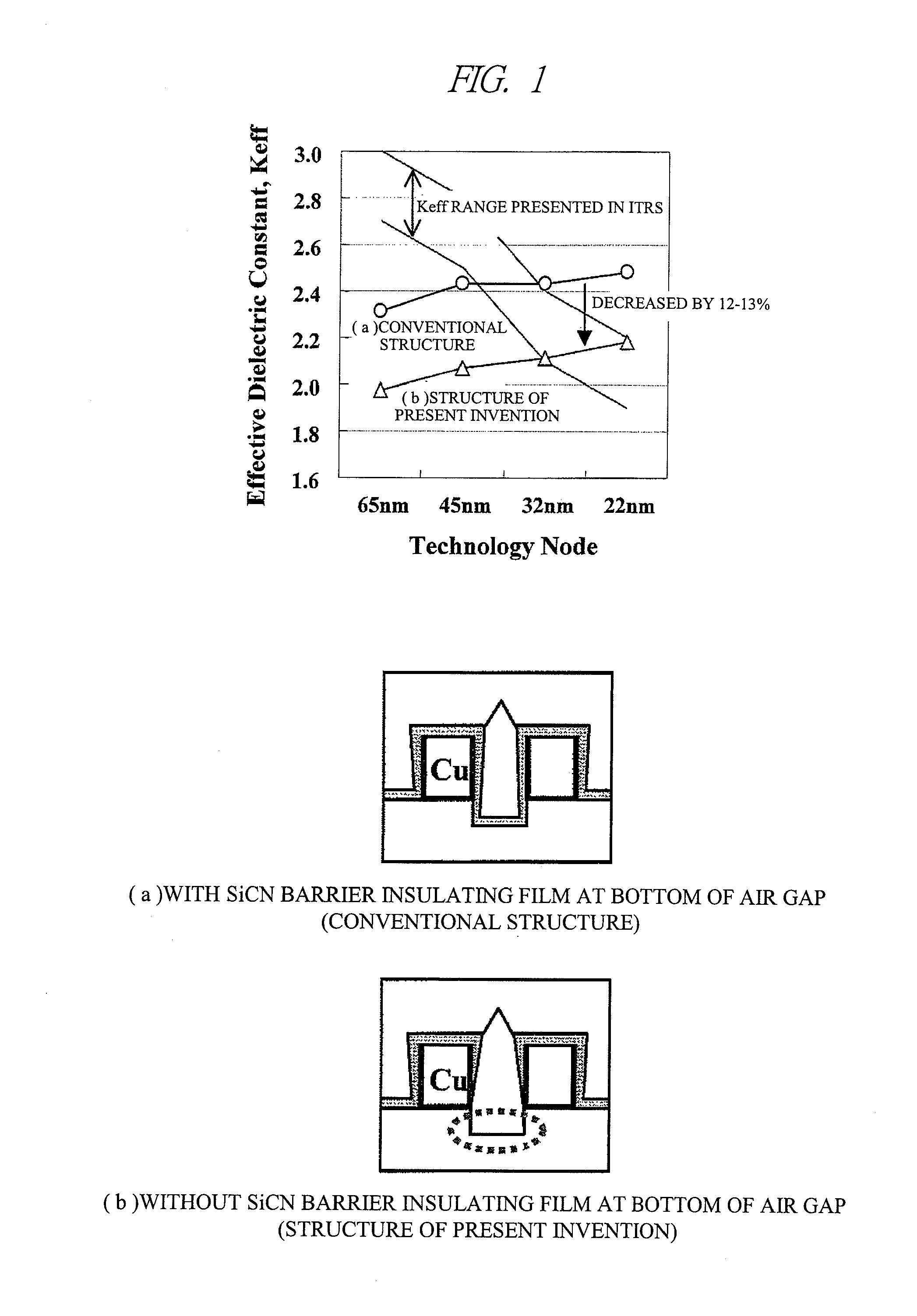

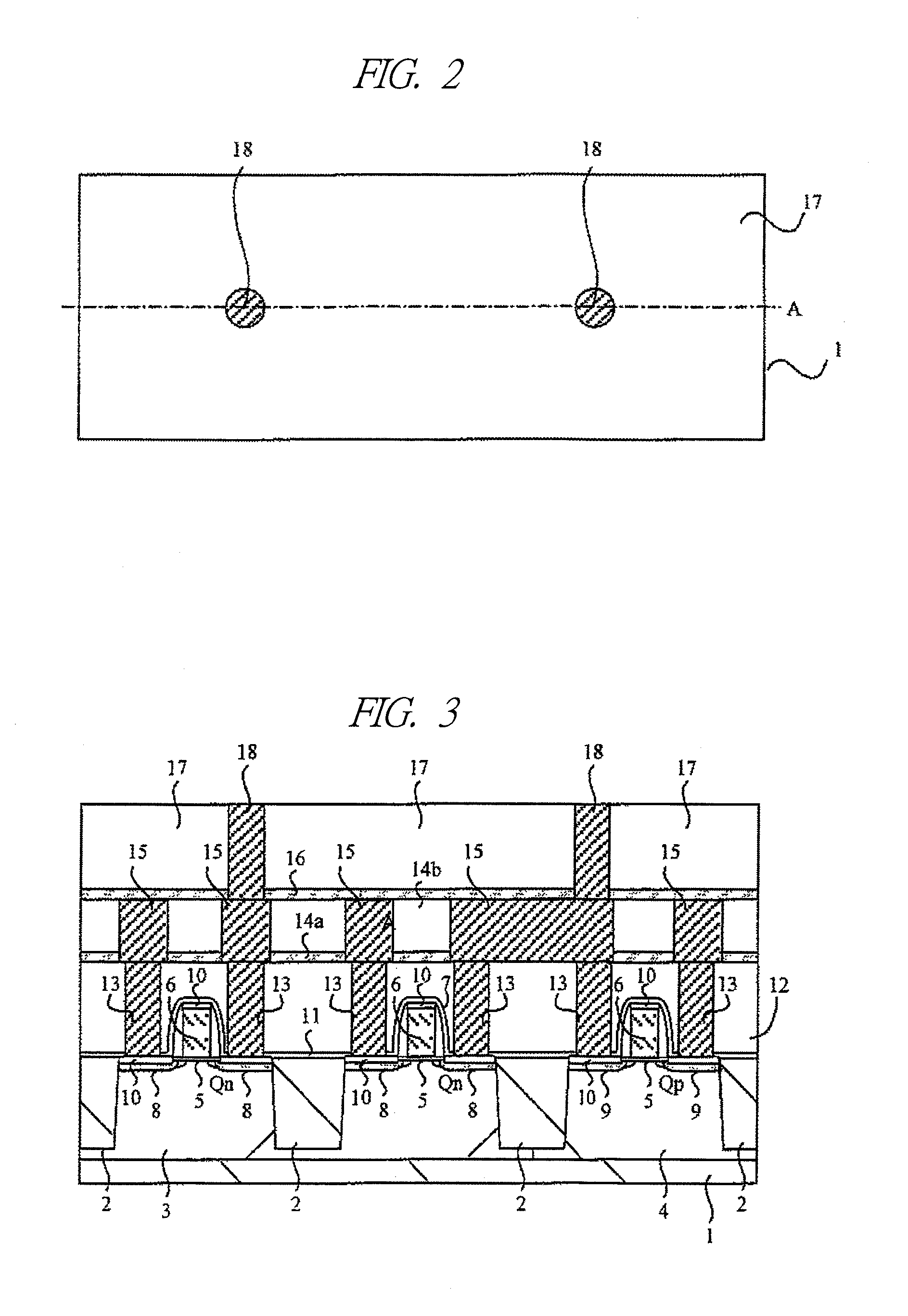

Semiconductor device and manufacturing method thereof

ActiveUS20100130001A1Reduce capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesCapacitanceCopper

Wirings mainly containing copper are formed on an insulating film on a substrate. Then, after forming insulating films for reservoir pattern and a barrier insulating film, an insulating film for suppressing or preventing diffusion of copper is formed on upper and side surfaces of the wirings, the insulating film on the substrate, and the barrier insulating film. Here, thickness of the insulating film for suppressing or preventing diffusion of copper at the bottom of a narrow inter-wiring space is made smaller than that on the wirings, thereby efficiently reducing wiring capacitance of narrow-line pitches. Then, first and second low dielectric constant insulating films are formed. Here, a deposition rate of the first insulating film at an upper portion of the side surfaces of facing wirings is made higher than that at a lower portion thereof, thereby forming air gaps. Finally, the second insulating film is planarized by interlayer CMP.

Owner:KOKUSA ELECTRIC CO LTD

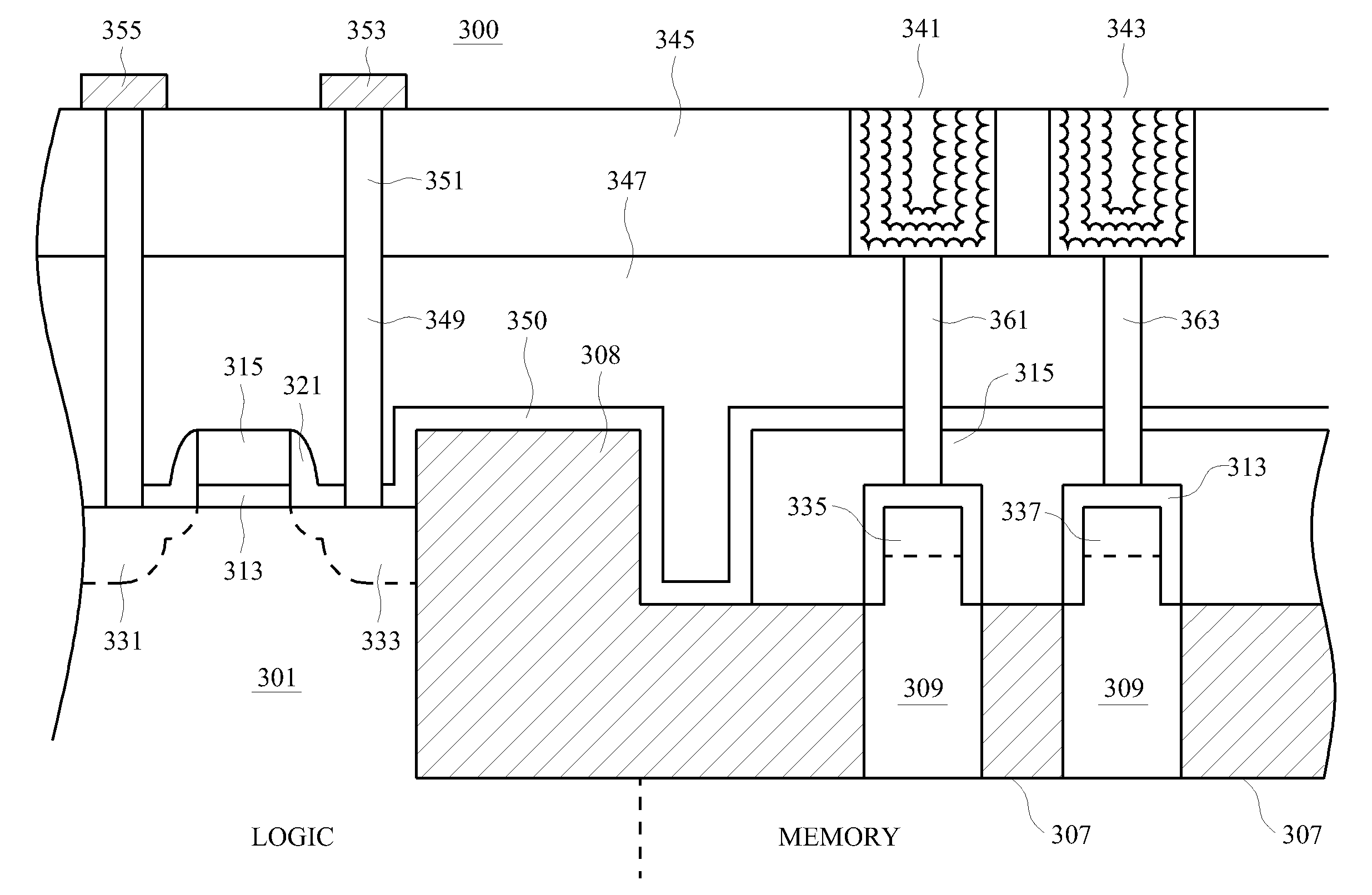

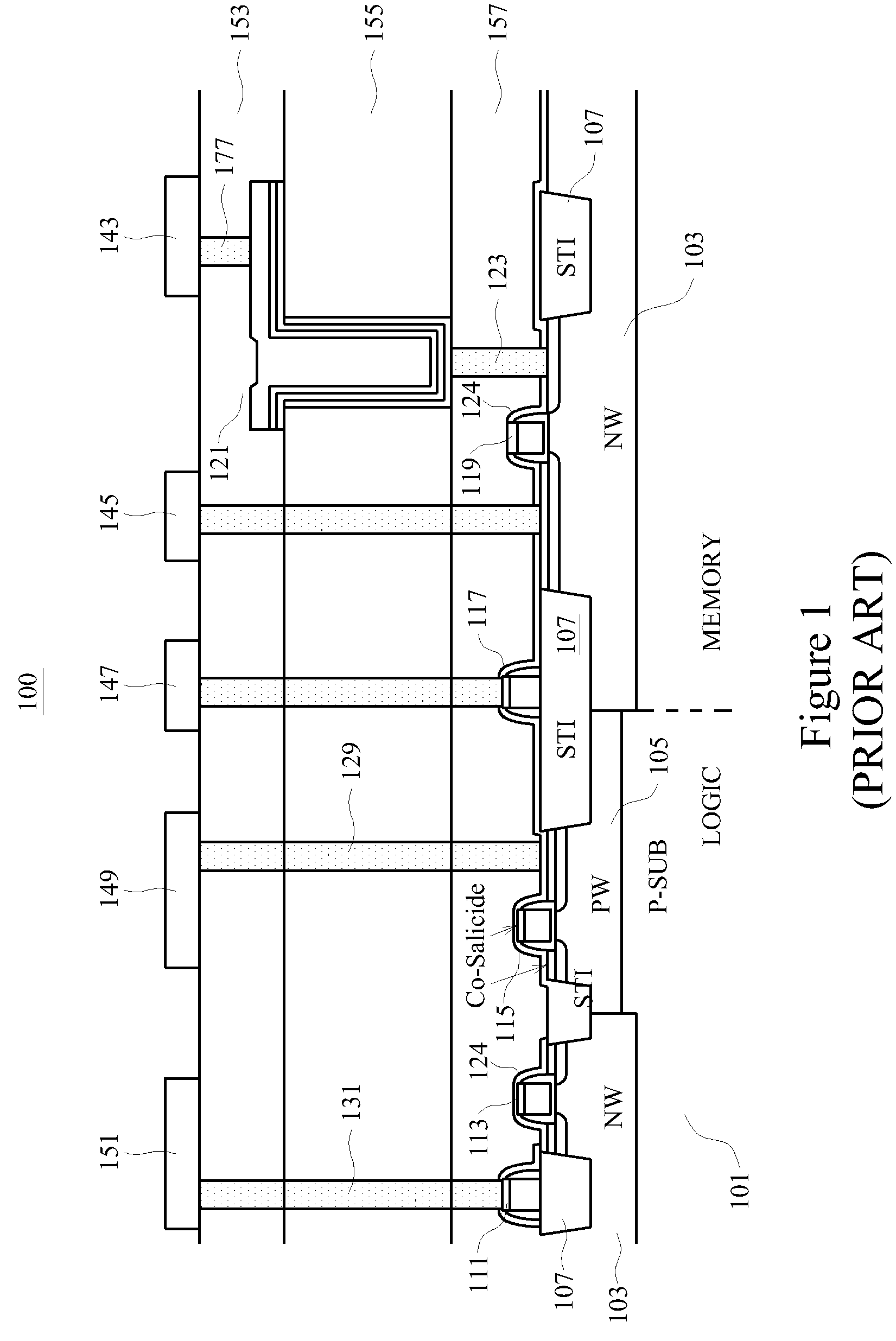

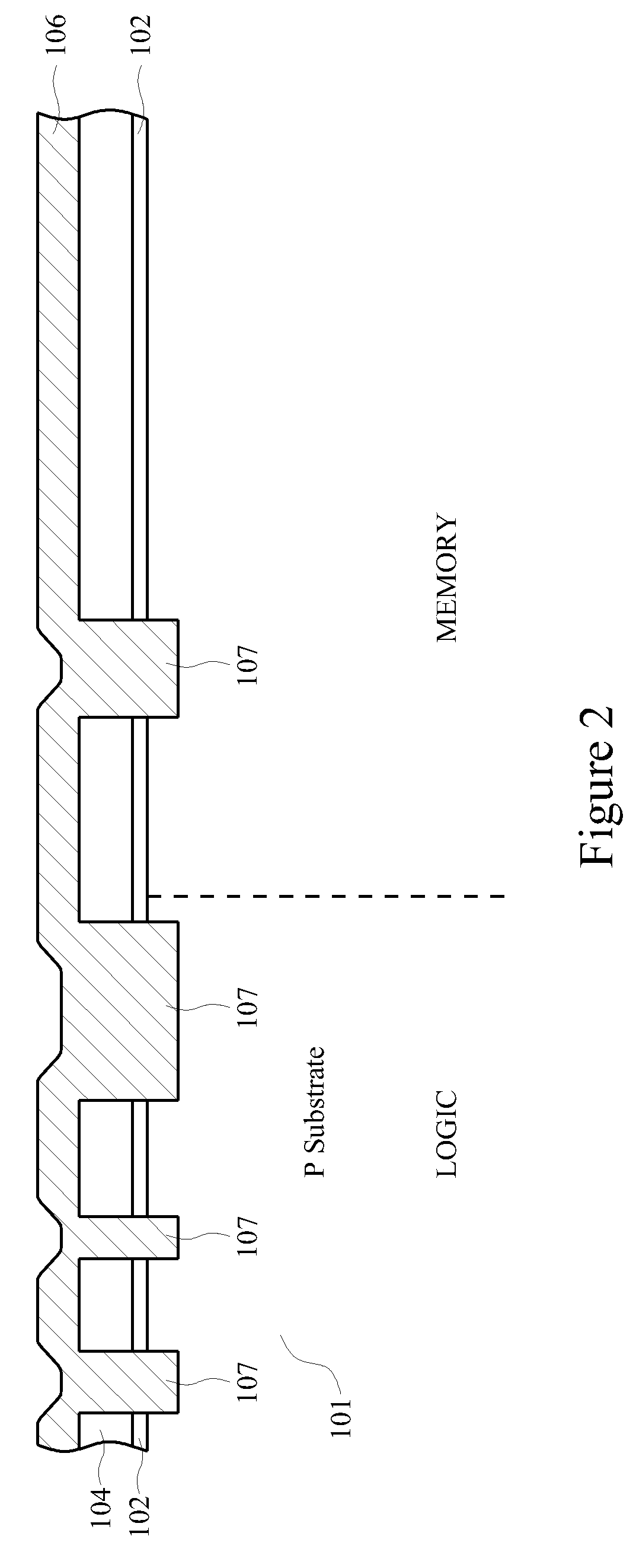

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

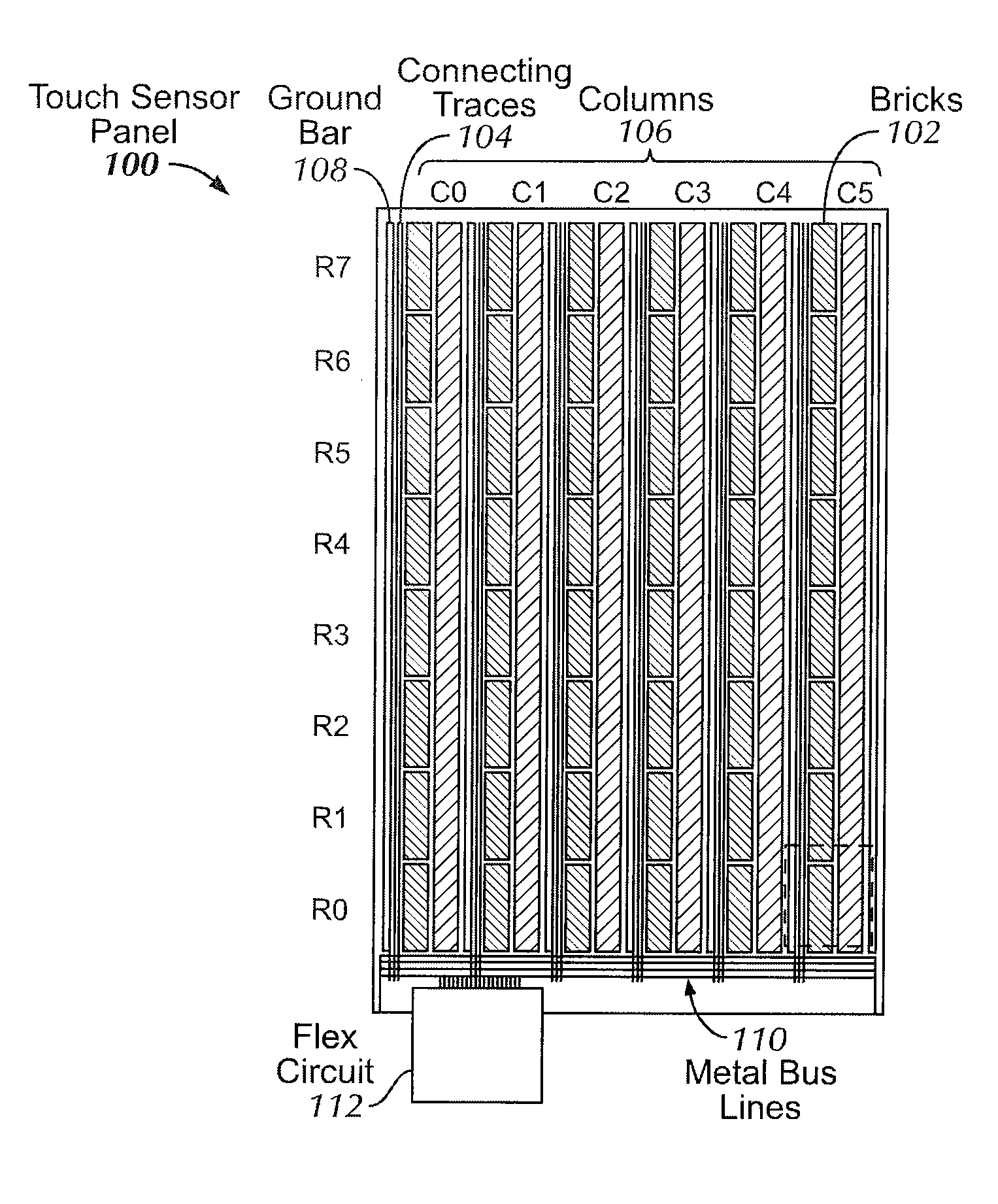

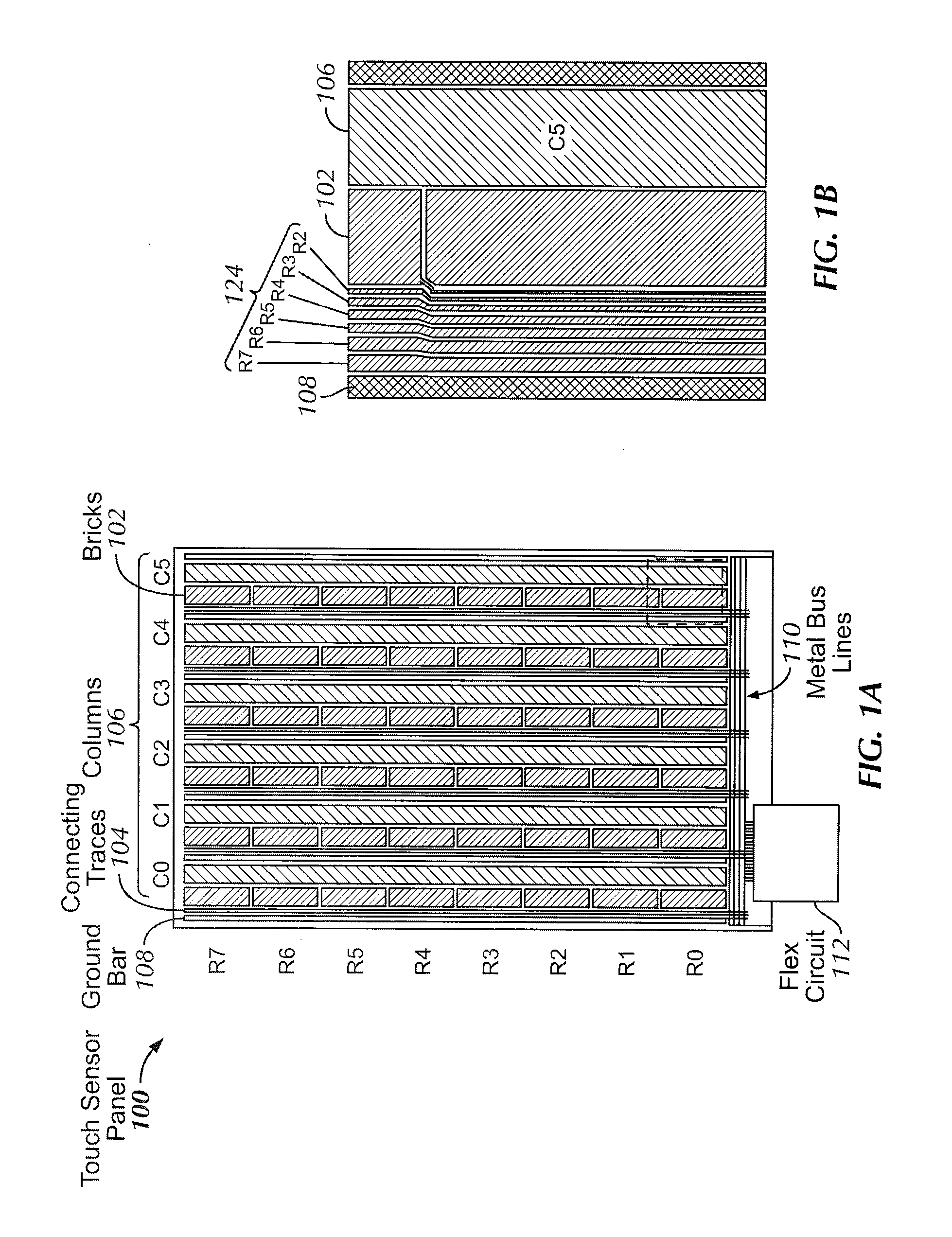

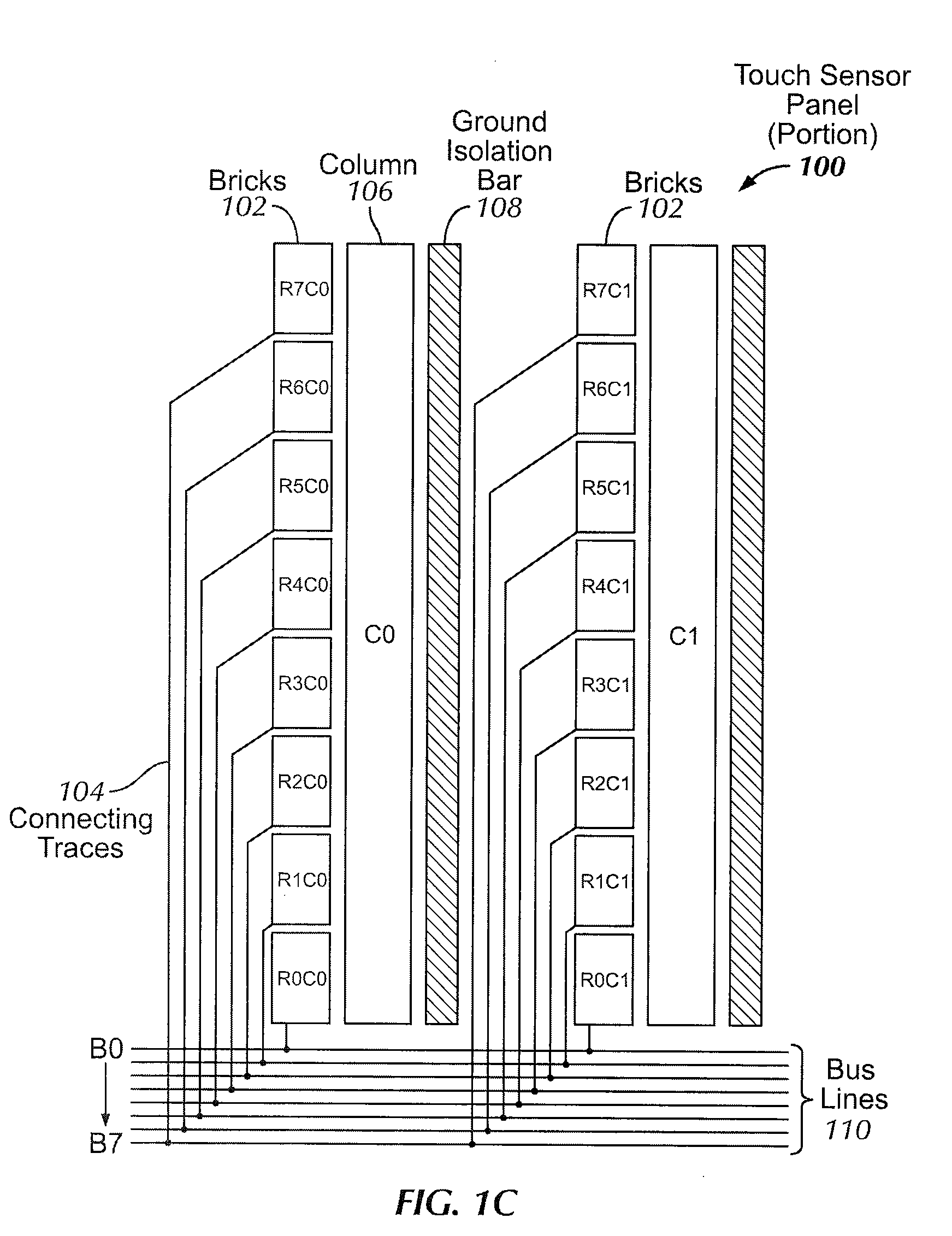

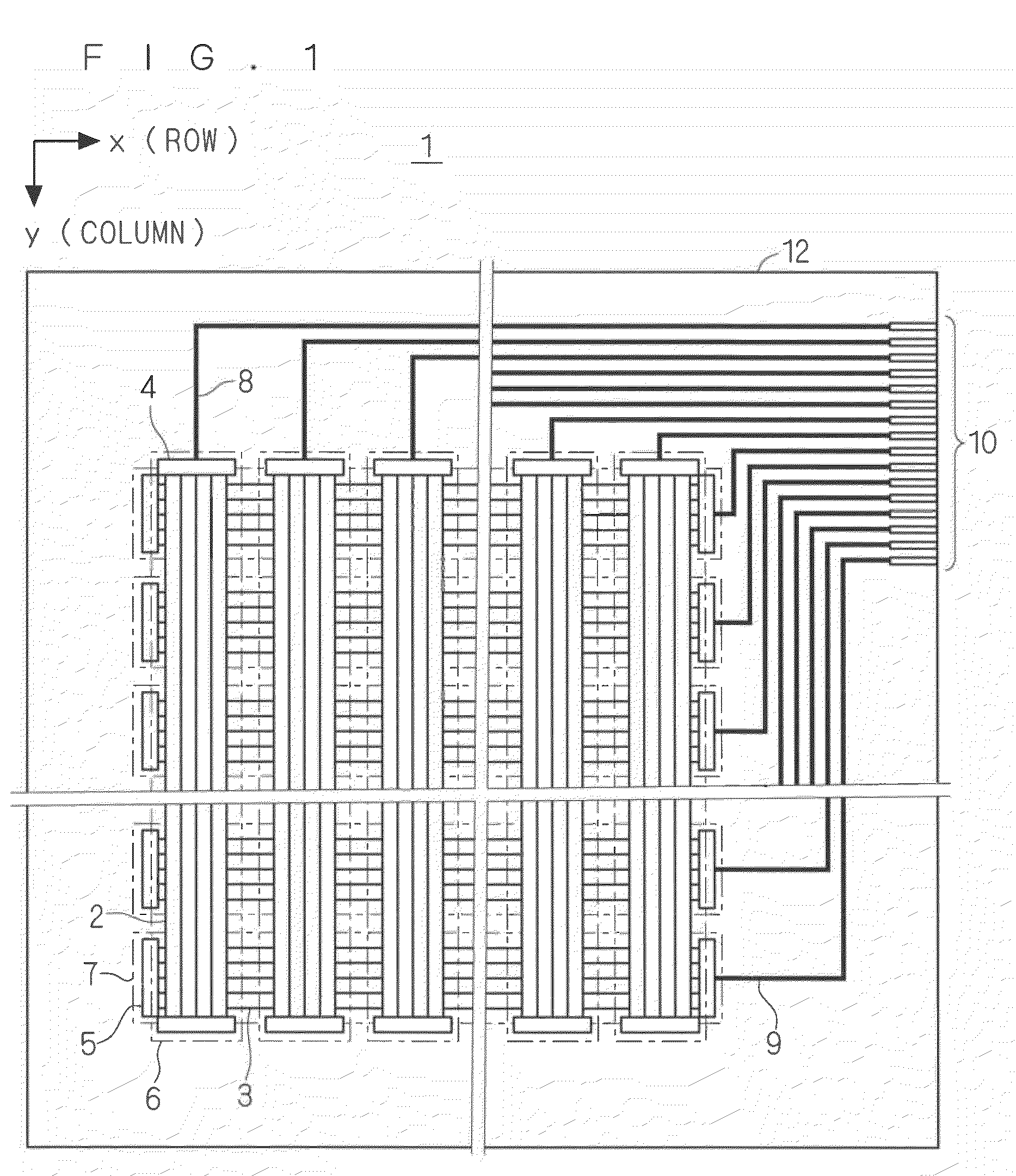

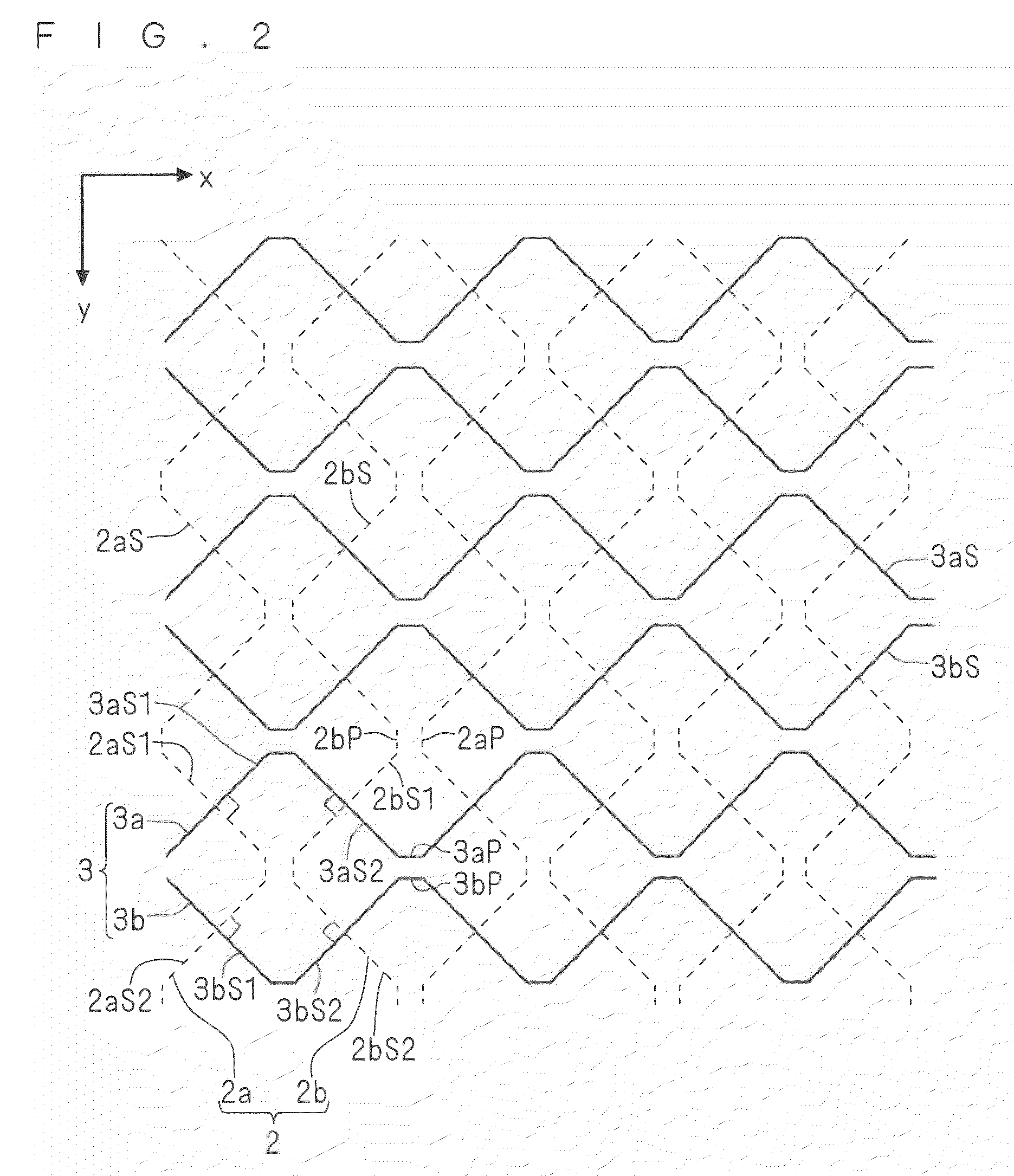

Brick Layout and Stackup for a Touch Screen

ActiveUS20090314621A1Reduce dynamic range budgetDifficult to makeElectronic switchingInput/output processes for data processingSensor arrayBrick

A touch sensor panel is disclosed having an array of co-planar single-layer touch sensors fabricated on a single side of a substrate. The sense (or drive) lines can be fabricated in a single strip as columnar or zig-zag patterns in a first orientation, and the drive (or sense) lines can be fabricated as rows of polygonal (e.g. brick-shaped or pentagonal) conductive areas in a second orientation. Each sense (or drive) line in the first orientation can be coupled to a separate metal trace in the border area of the touch sensor panel, and each polygonal area in the second orientation can also be coupled to a metal trace in the border area of the touch sensor panel. The metal traces can allow both the row and column lines to be routed to the same edge of the substrate for flex circuit attachment.

Owner:APPLE INC

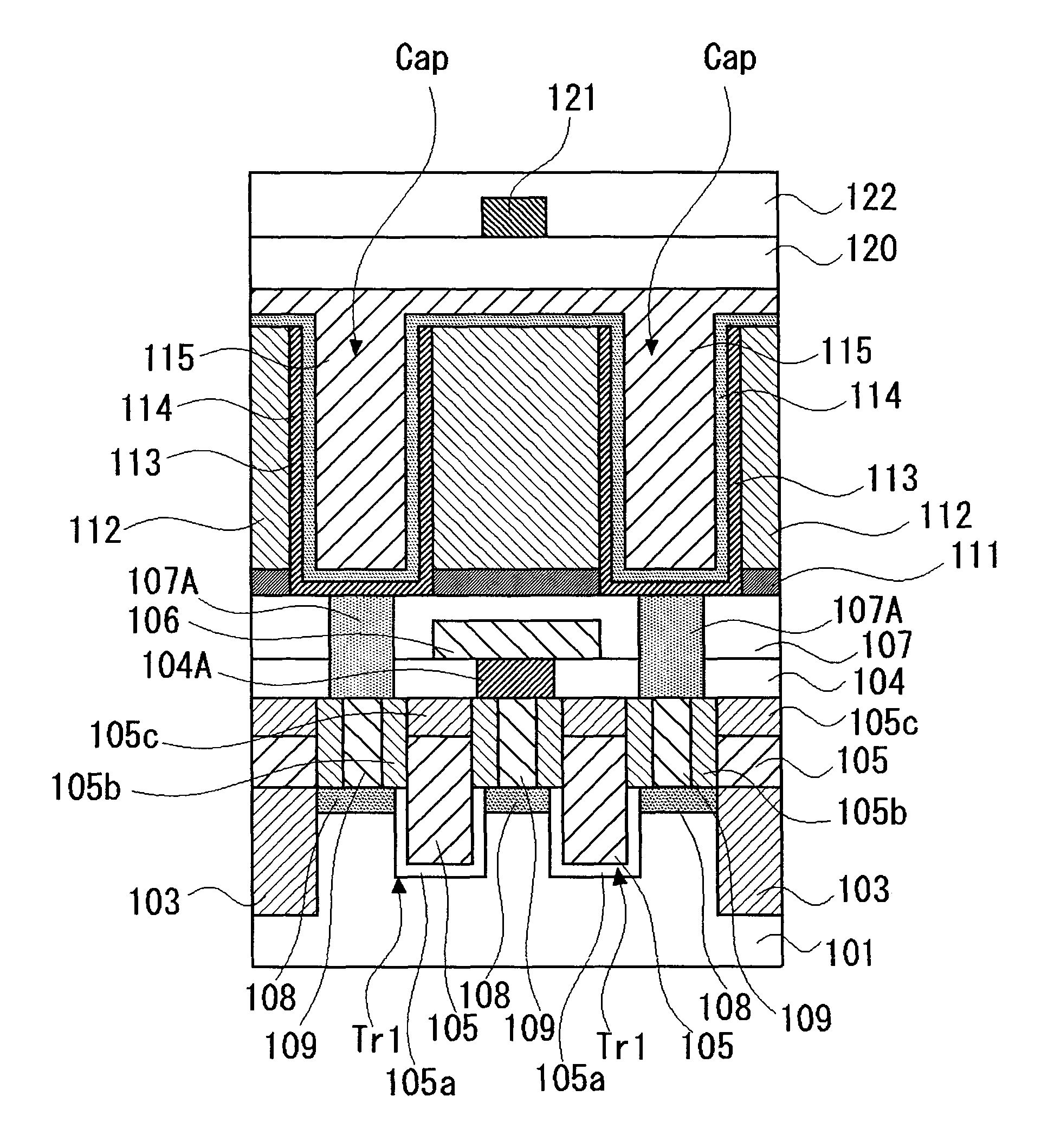

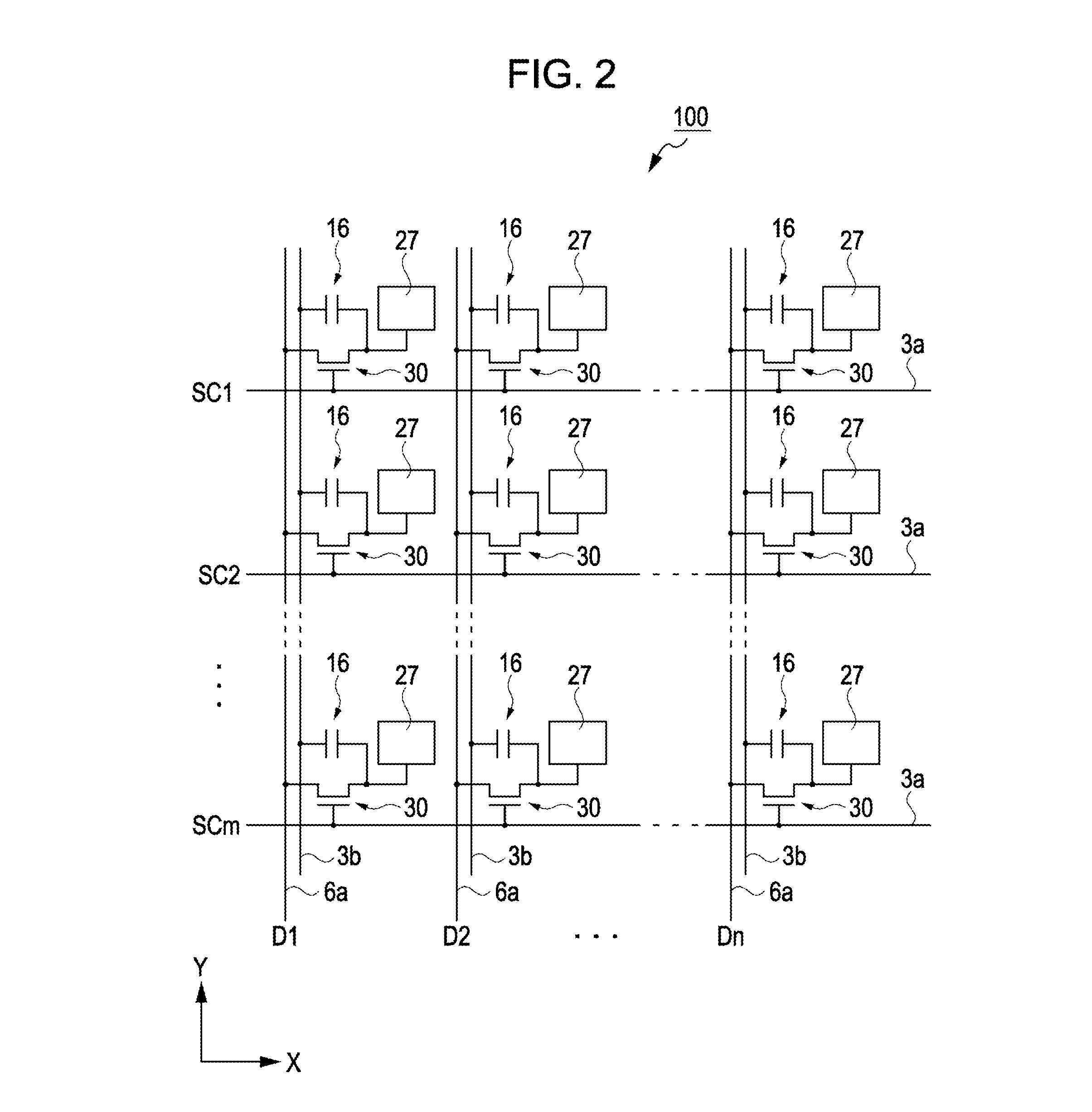

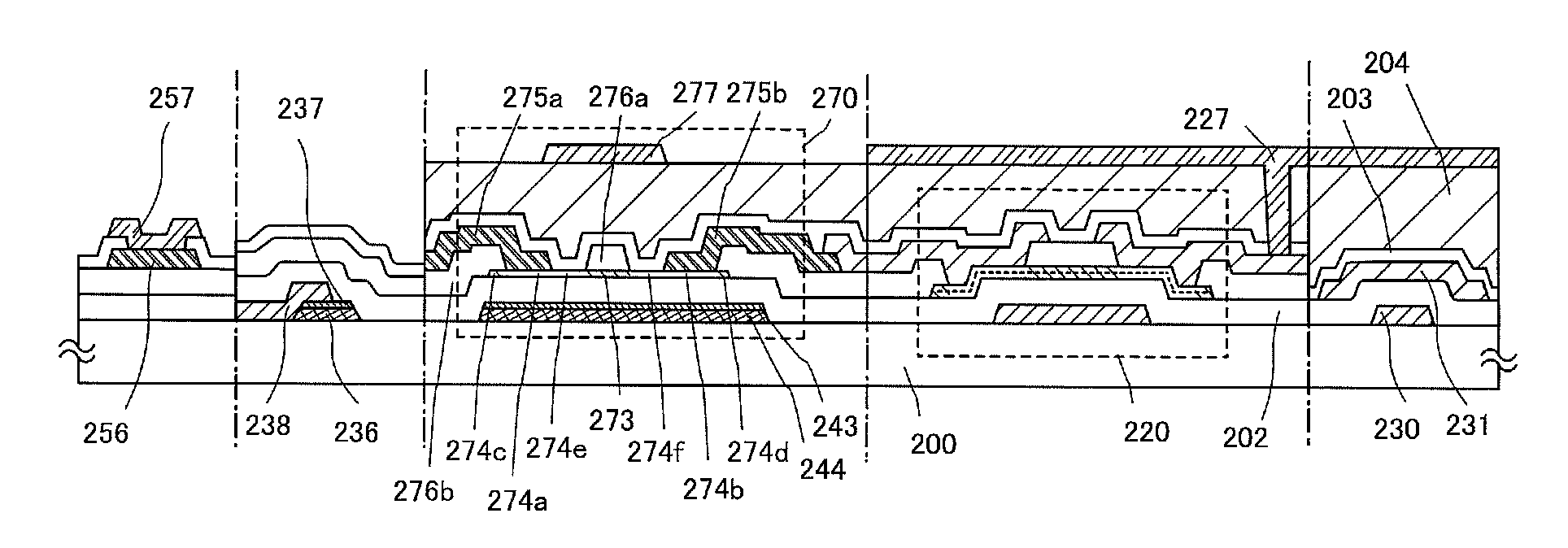

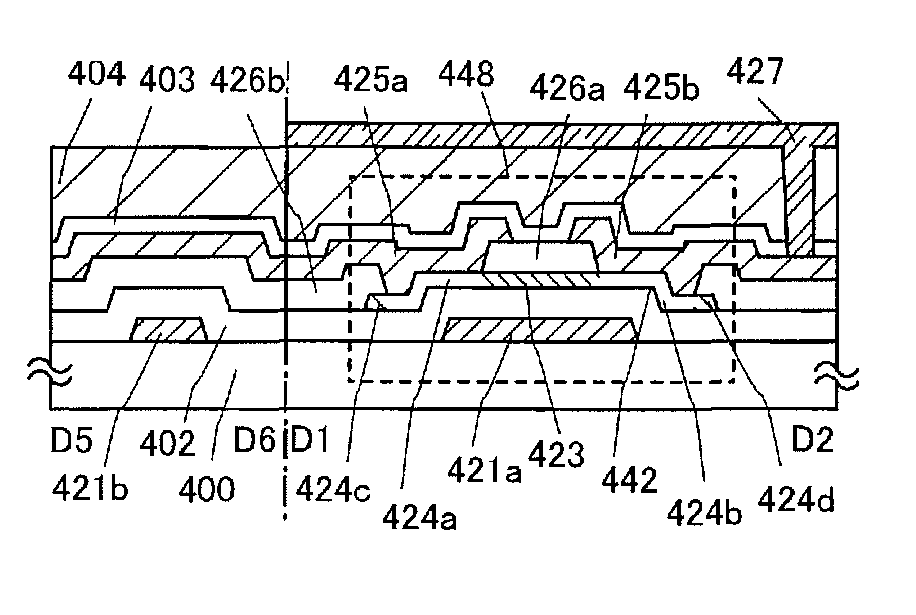

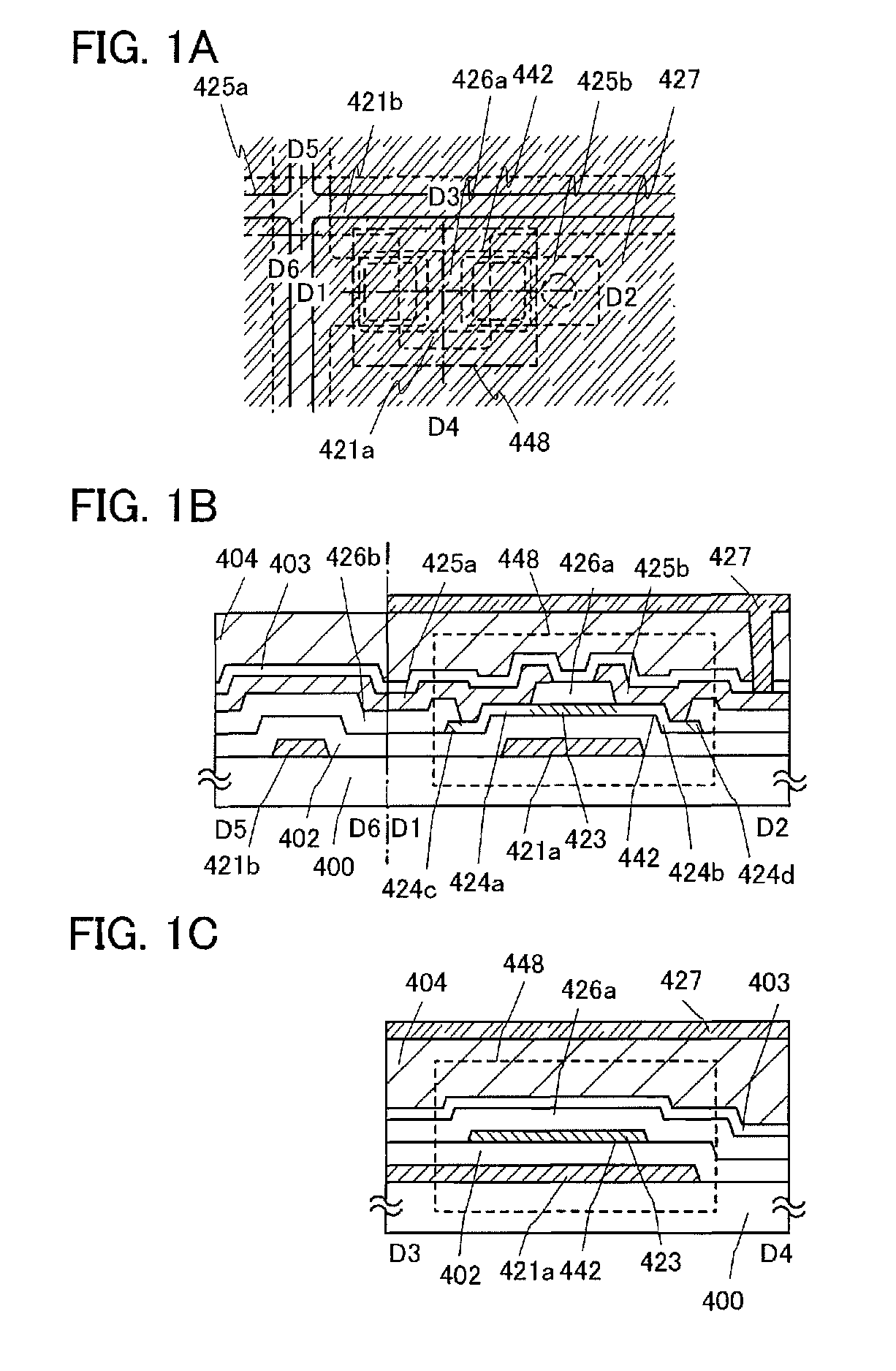

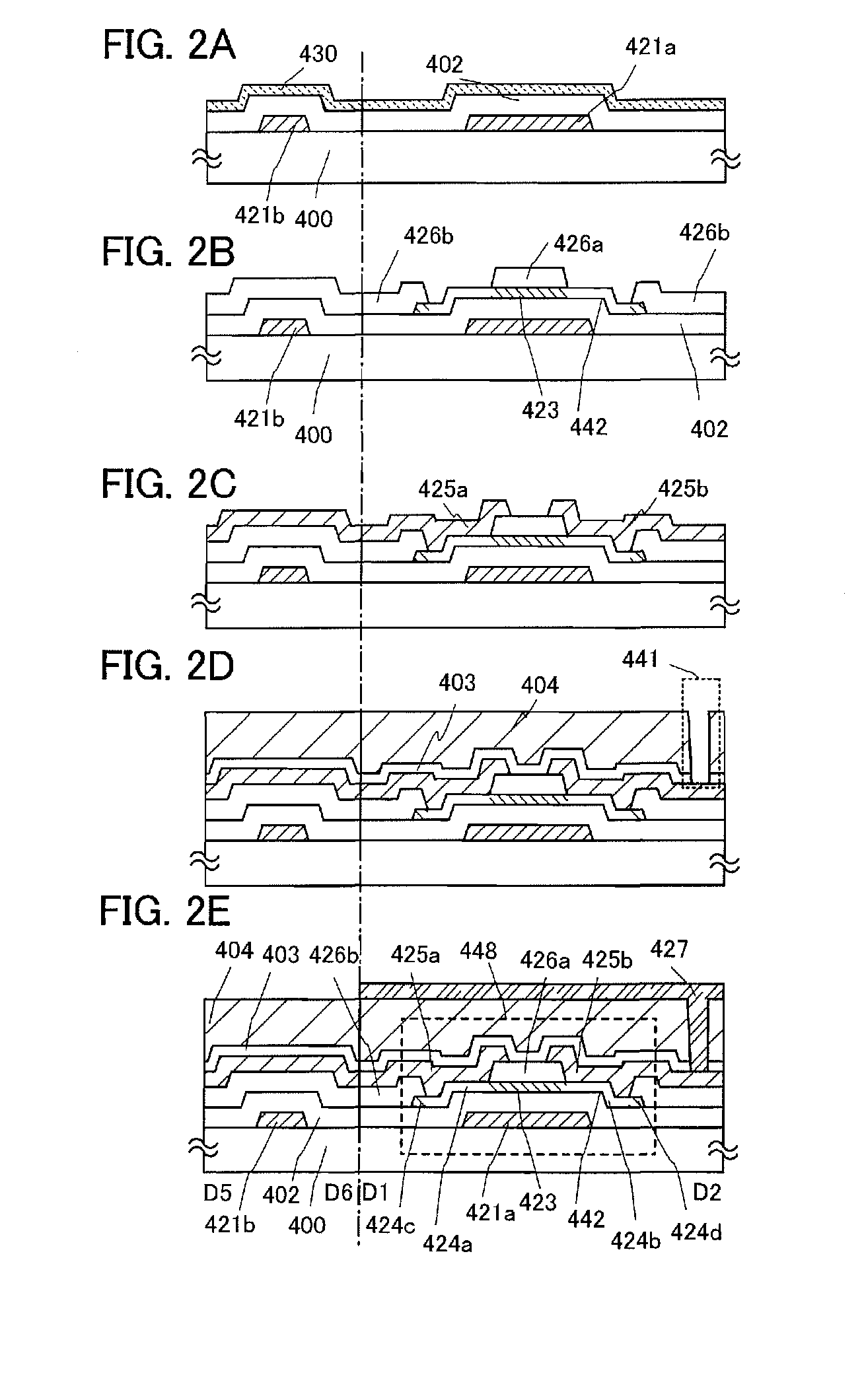

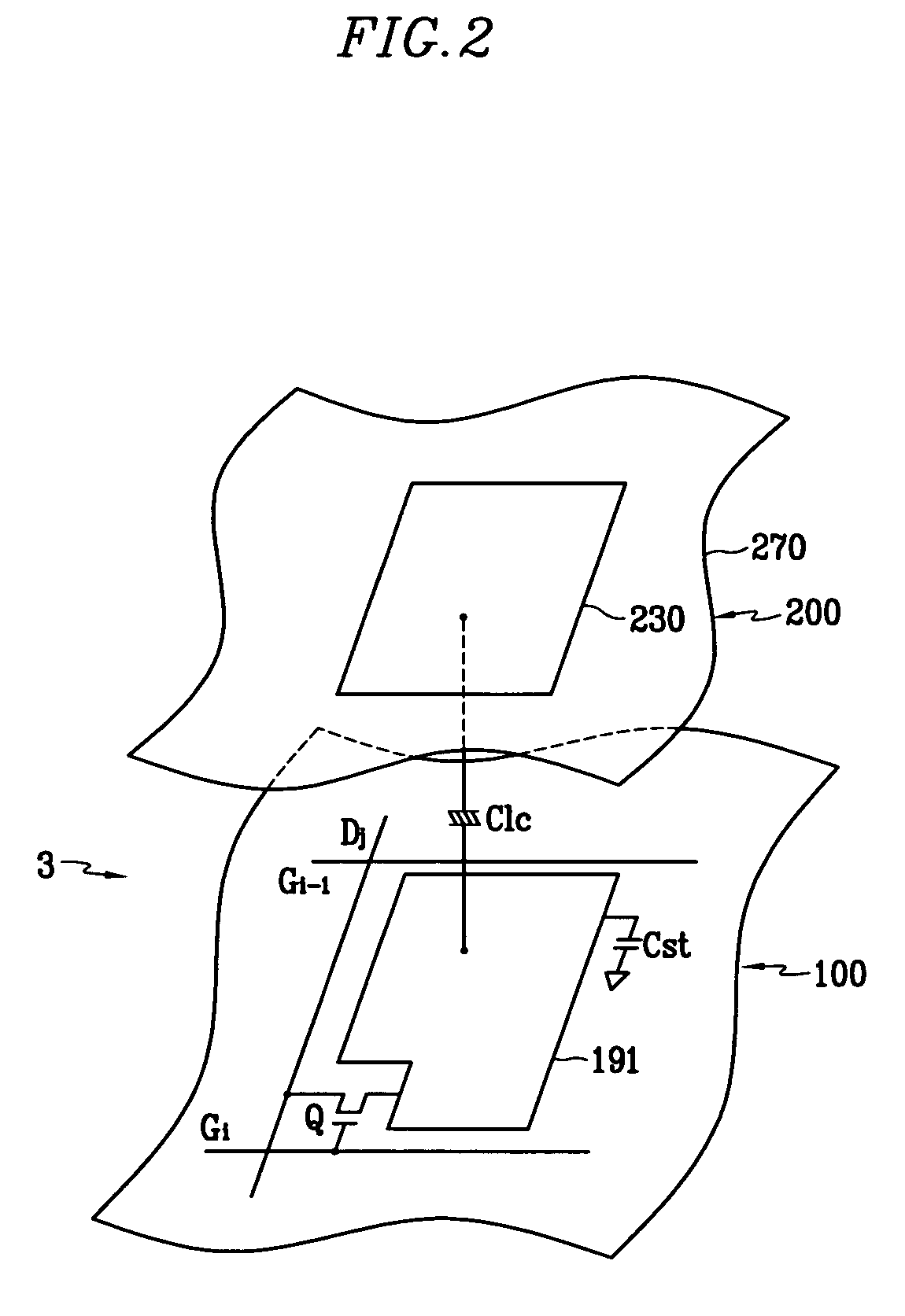

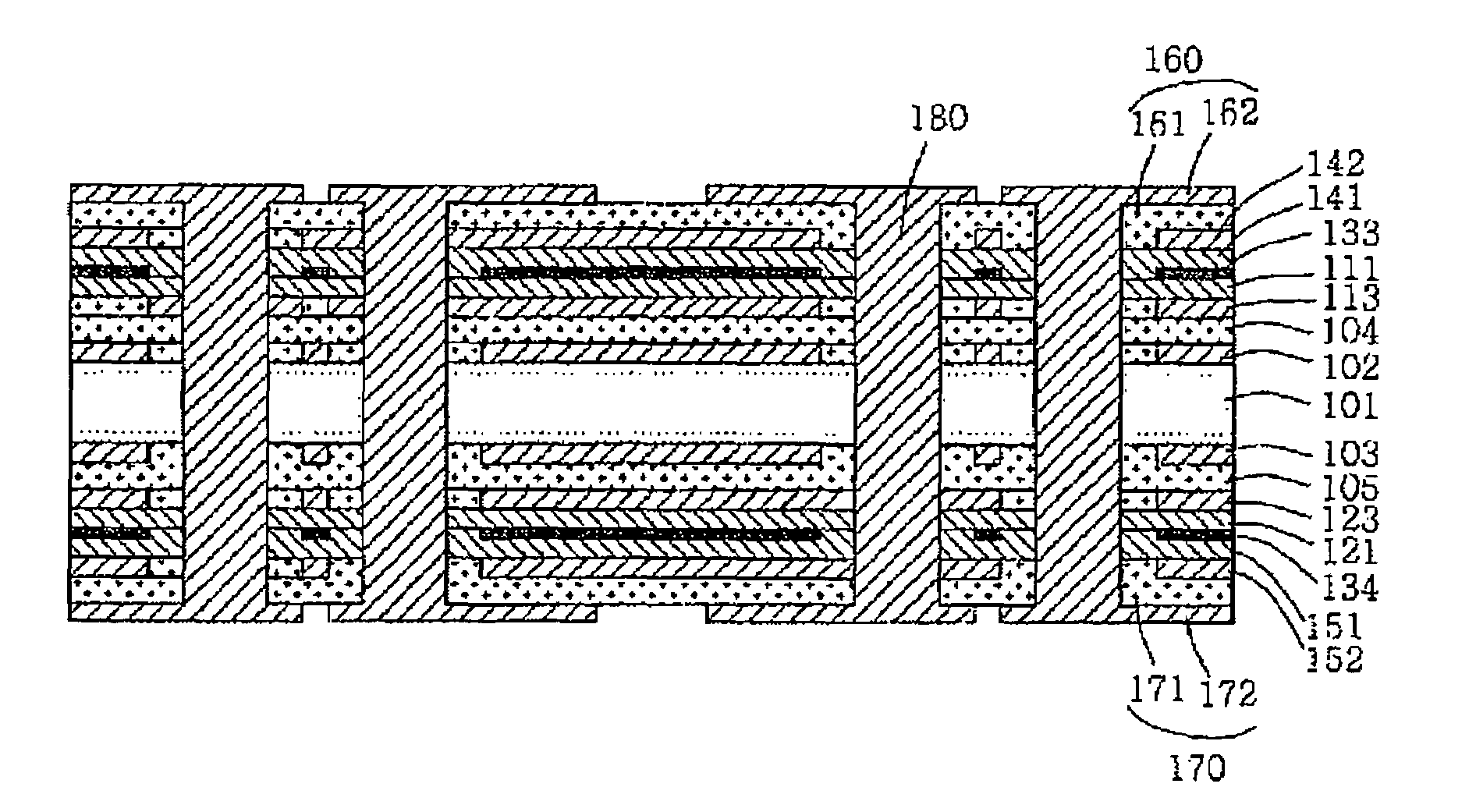

Electro-optical device and electronic apparatus

Disclosed is a pixel electrode which is electrically connected to a scanning line electrically connected to a gate electrode, a data line electrically connected to a data line side source and drain region, and a pixel electrode side source and drain region; and a capacitance element which has a first capacitance electrode which is electrically connected to a capacitance line, a second capacitance electrode which is provided to oppose the first capacitance electrode, and a dielectric layer which is interposed between the first capacitance electrode and the second capacitance electrode, where the first capacitance electrode is arranged to be covered with the dielectric layer and the second capacitance electrode between a layer where the transistor, the scanning line, and the data line are provided and a layer where the pixel electrode is provided.

Owner:138 EAST LCD ADVANCEMENTS LTD

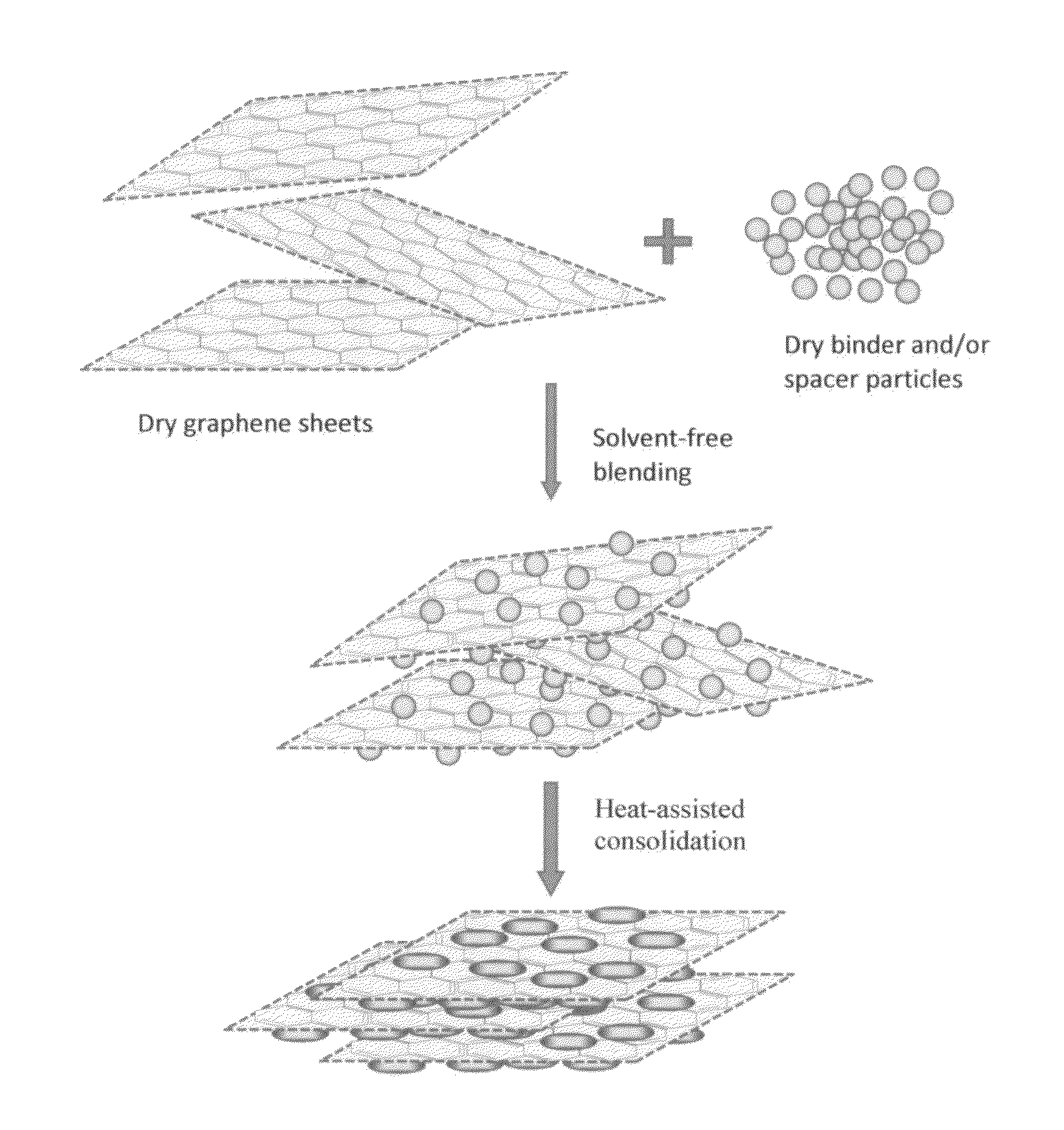

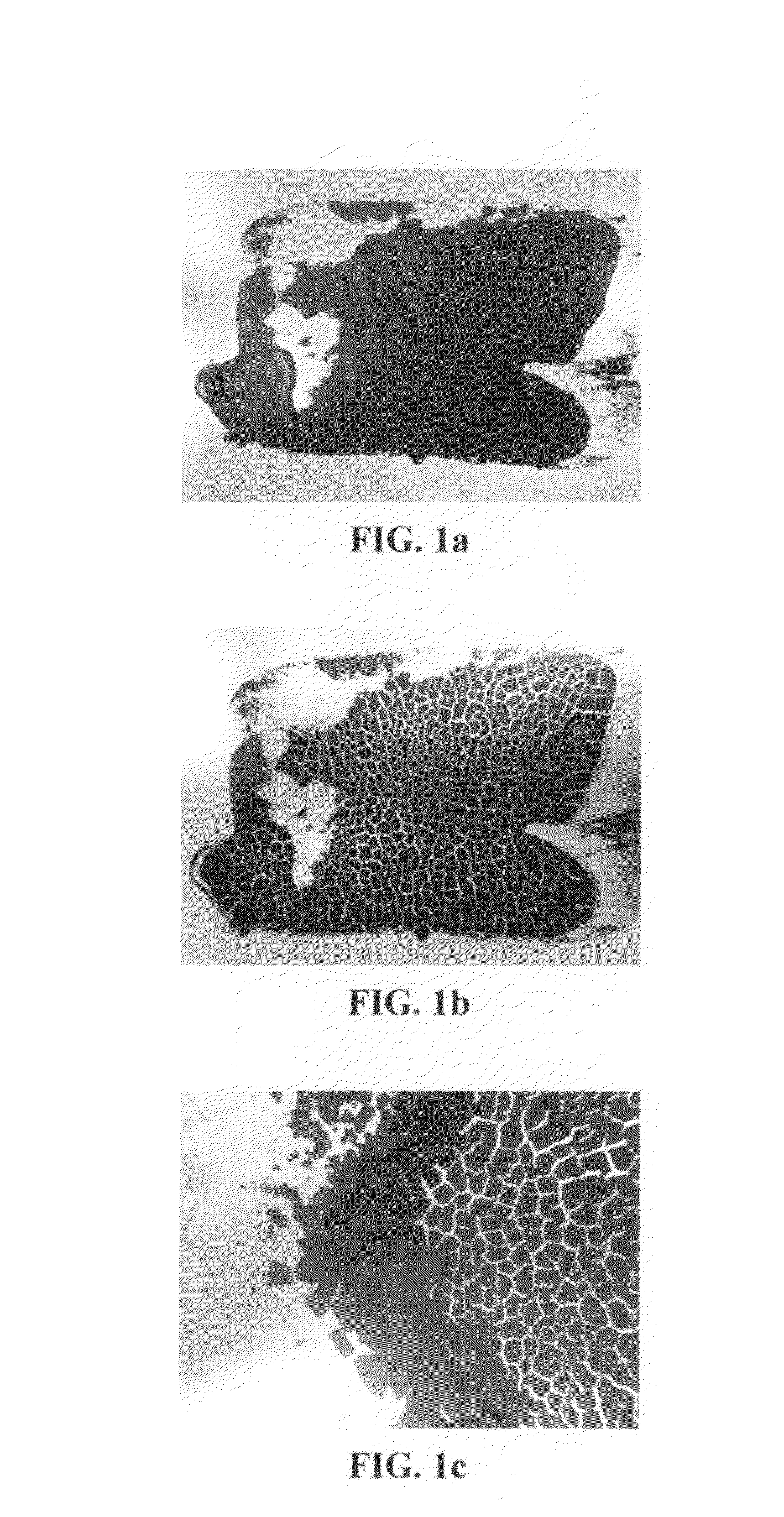

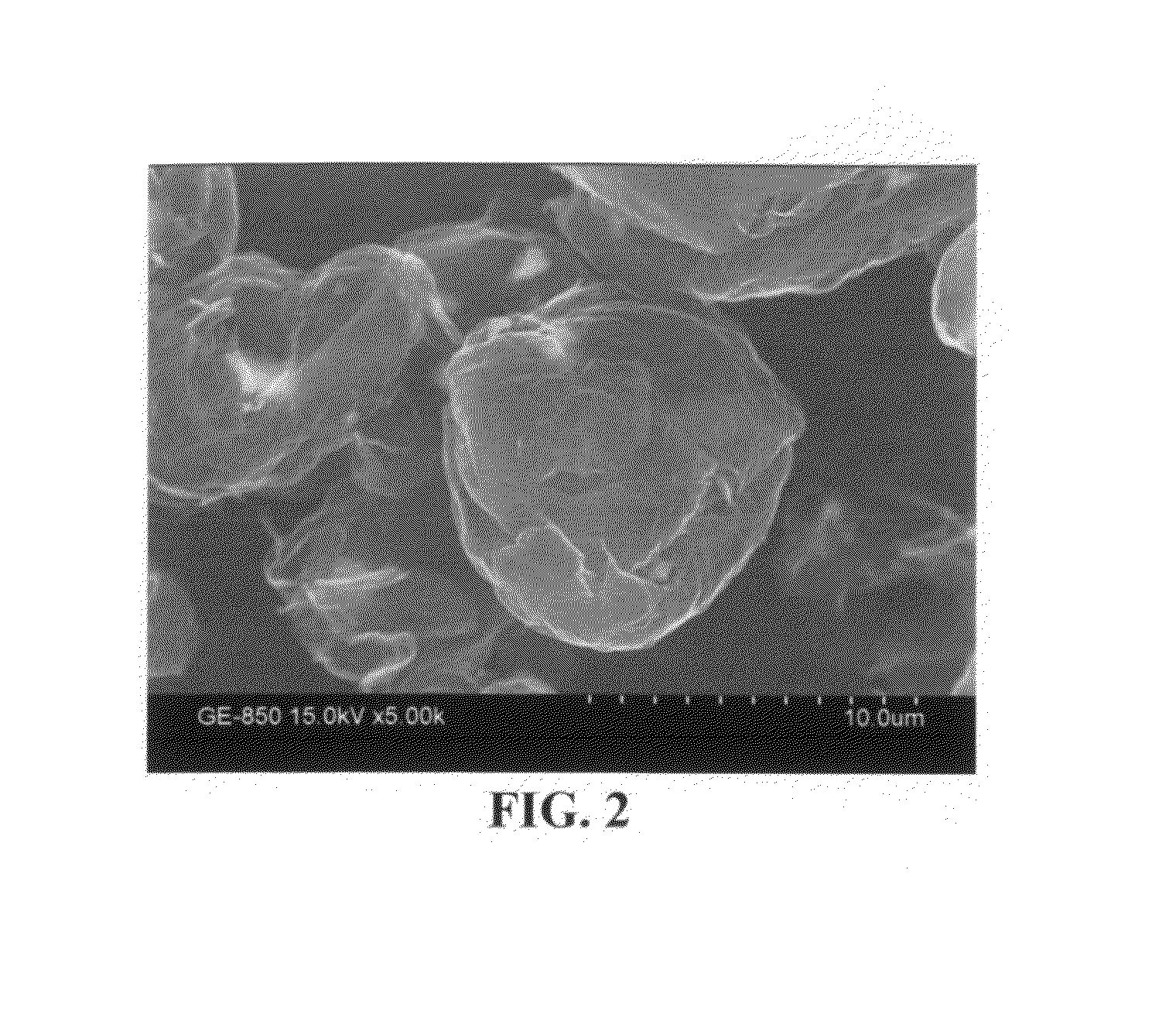

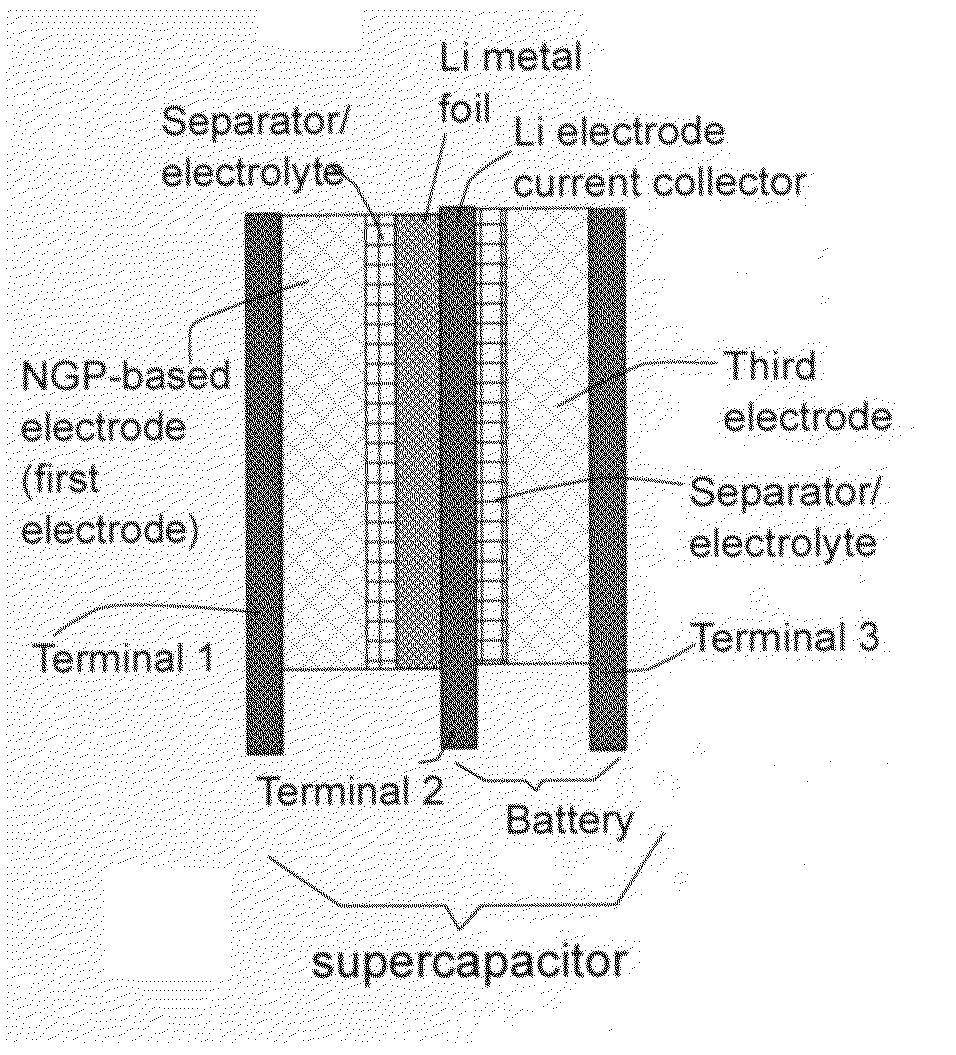

Solvent-free process based graphene electrode for energy storage devices

PendingUS20140030590A1Inexpensive and durable and highly reliableHigh capacitanceMaterial nanotechnologyHybrid capacitor electrodesGraphene flakeSolvent free

Disclosed is an electrode for an electrochemical energy storage device, the electrode comprising a self-supporting layer of a mixture of graphene sheets and spacer particles and / or binder particles, wherein the electrode is prepared without using water, solvent, or liquid chemical. The graphene electrode prepared by the solvent-free process exhibits many desirable features and advantages as compared to the corresponding electrode prepared by a known wet process. These advantages include a higher electrode specific surface area, higher energy storage capacity, improved or higher packing density or tap density, lower amount of binder required, lower internal electrode resistance, more consistent and uniform dispersion of graphene sheets and binder, reduction or elimination of undesirable effect of electrolyte oxidation or decomposition due to the presence of water, solvent, or chemical, etc.

Owner:GLOBAL GRAPHENE GRP INC

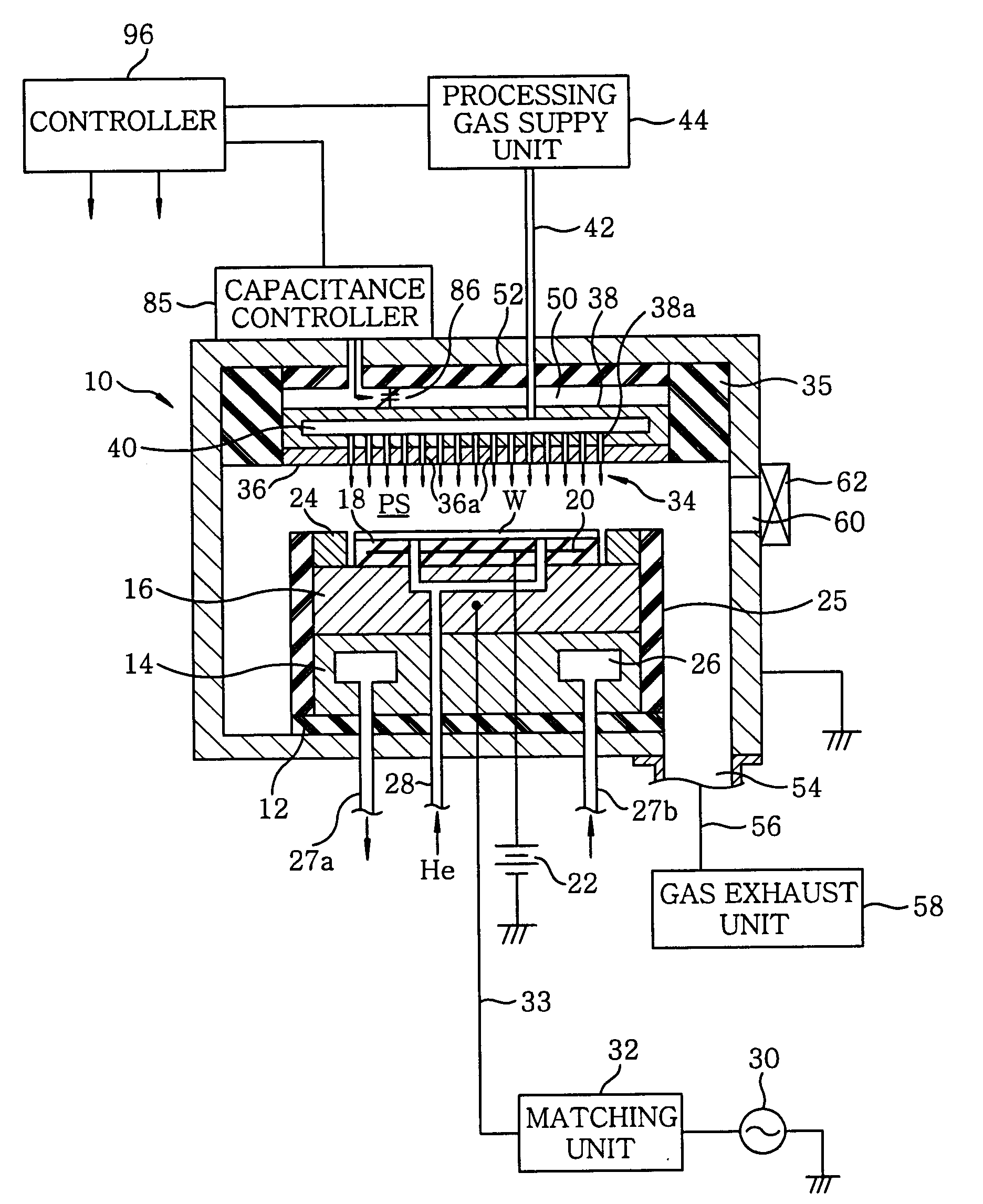

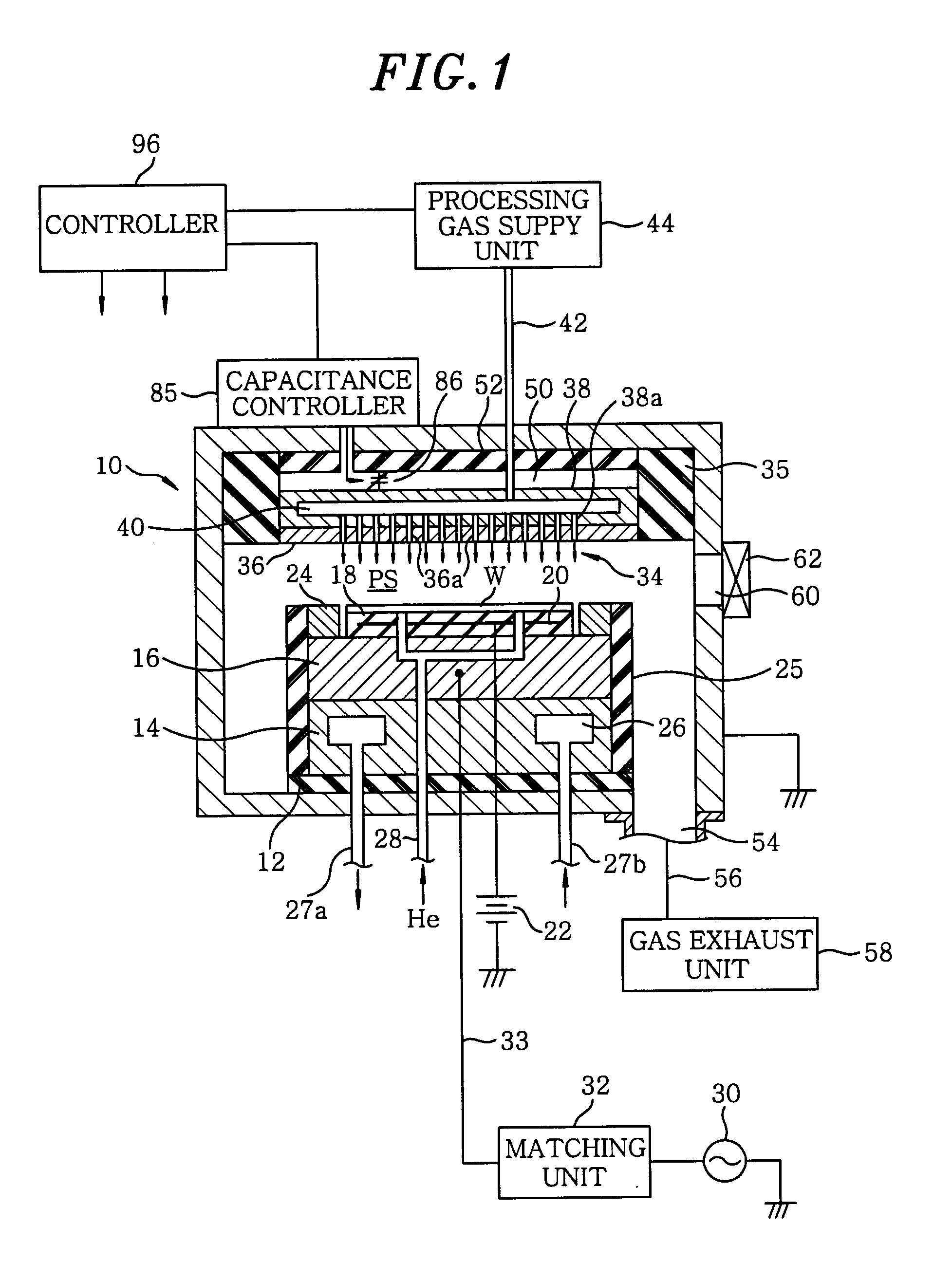

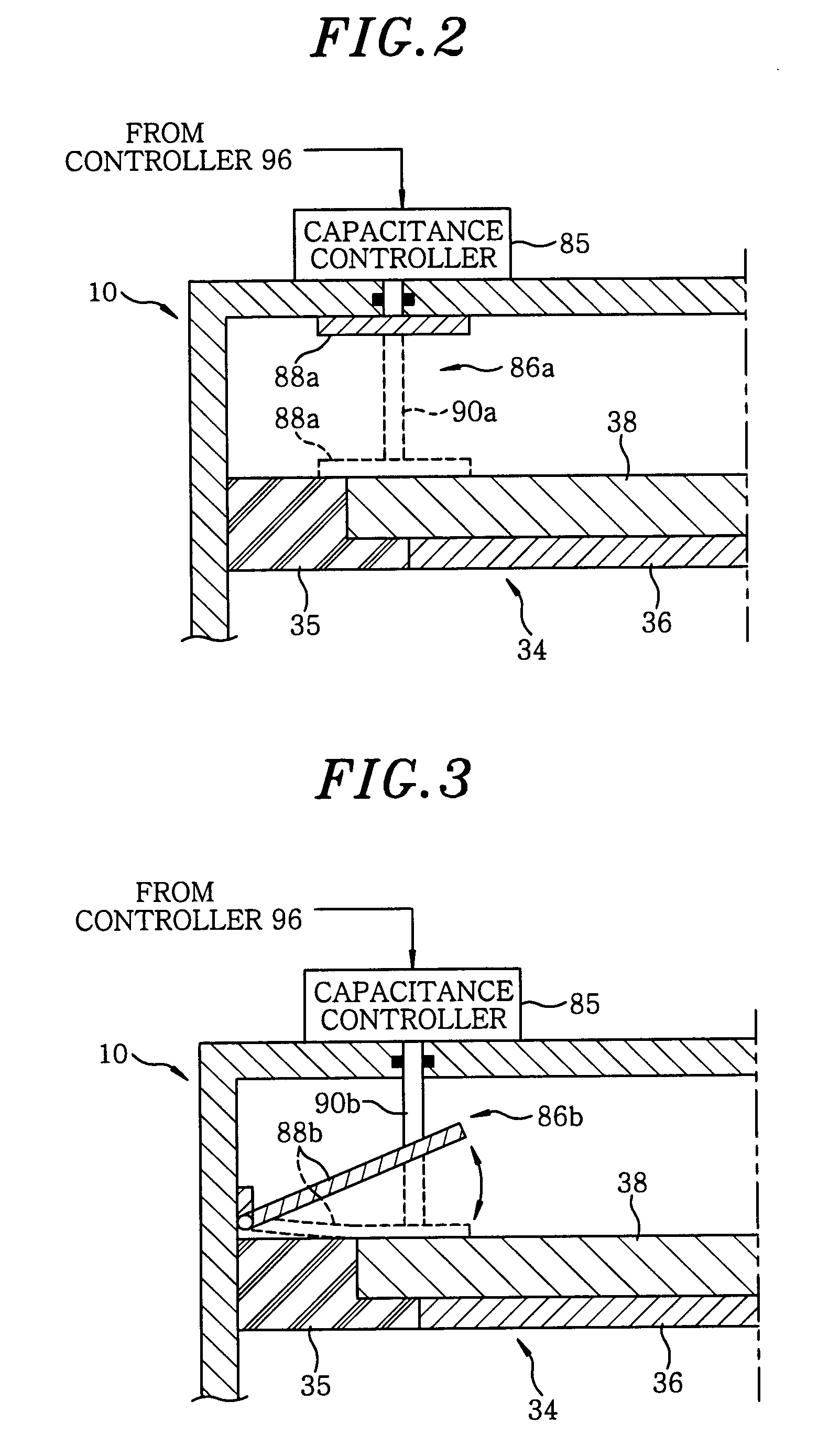

Plasma processing method and plasma processing apparatus

ActiveUS20070227665A1Uniform processingSecuring uniformityLiquid surface applicatorsElectric discharge tubesCapacitanceEngineering

A plasma processing method performs a desired plasma process on substrates by using a plasma generated in a processing space. A first and a second electrode are disposed in parallel in a processing vessel that is grounded, the substrate is supported on the second electrode to face the first electrode, the processing vessel is vacuum evacuated, a desired processing gas is supplied into the processing space formed between the first electrode, the second electrode and a sidewall of the processing vessel, and a first radio frequency power is supplied to the second electrode. The first electrode is connected to the processing vessel via an insulator or a space, and is electrically coupled to a ground potential via a capacitance varying unit whose electrostatic capacitance is varied based on a process condition of the plasma process performed on the substrate.

Owner:TOKYO ELECTRON LTD

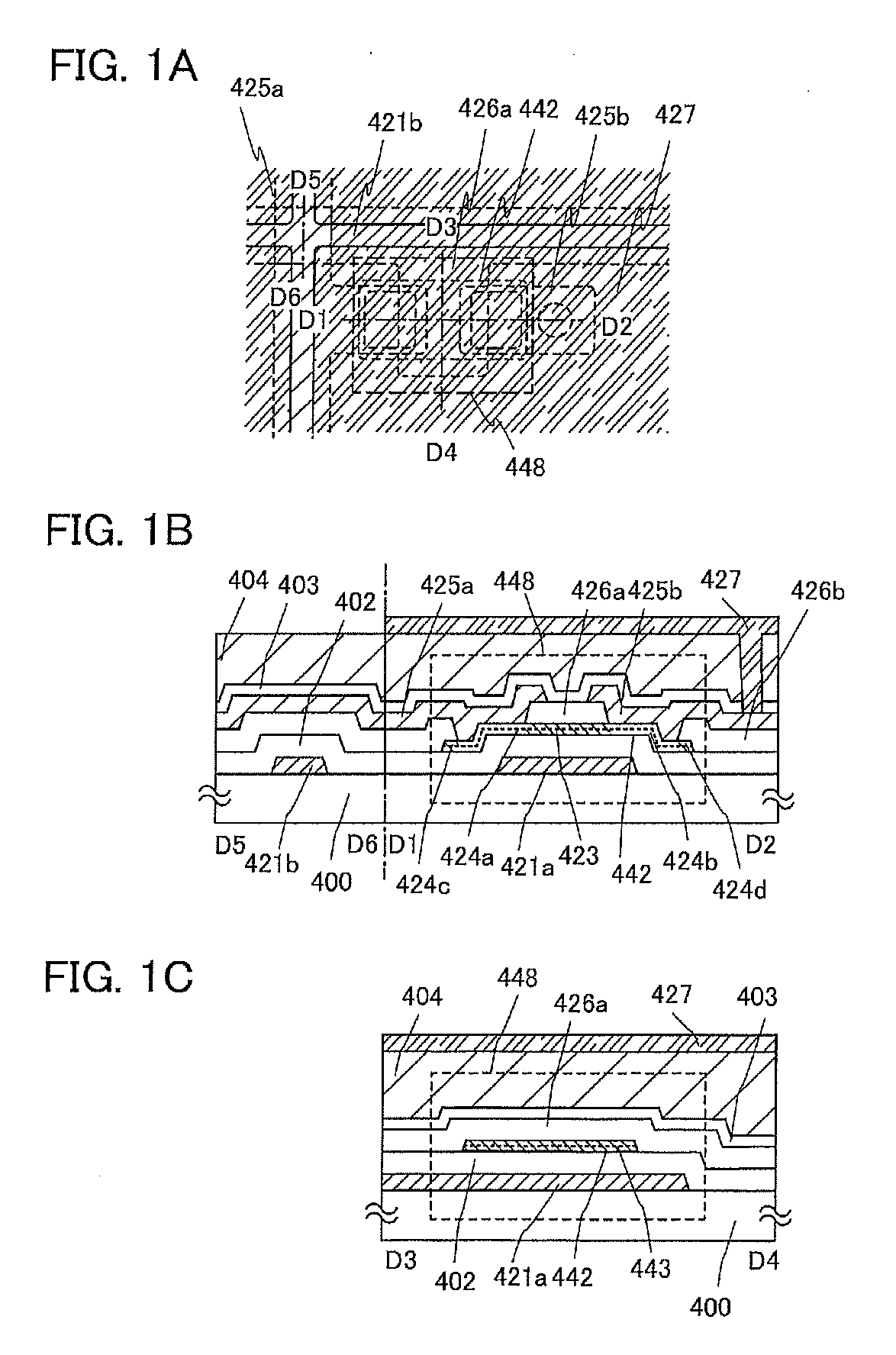

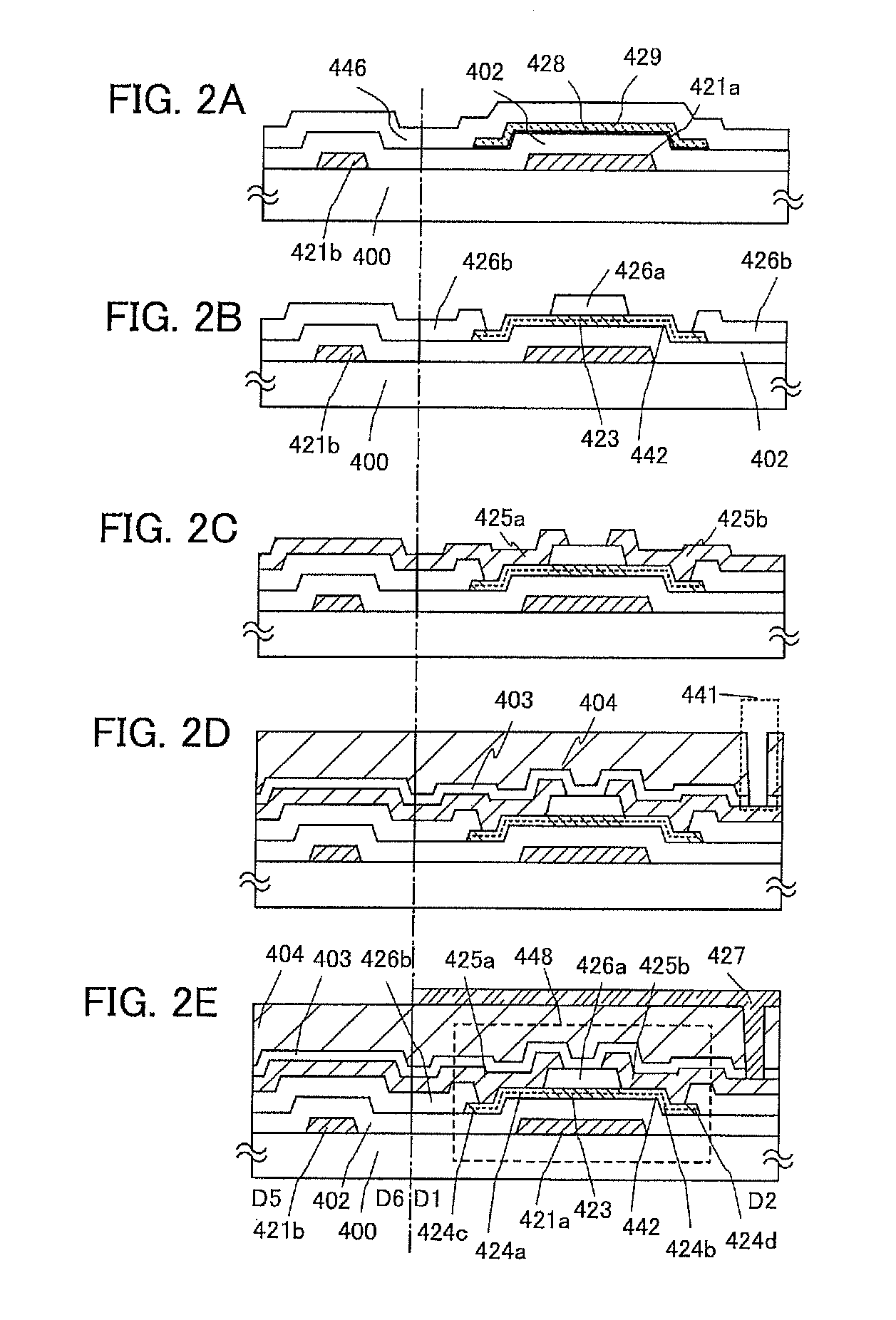

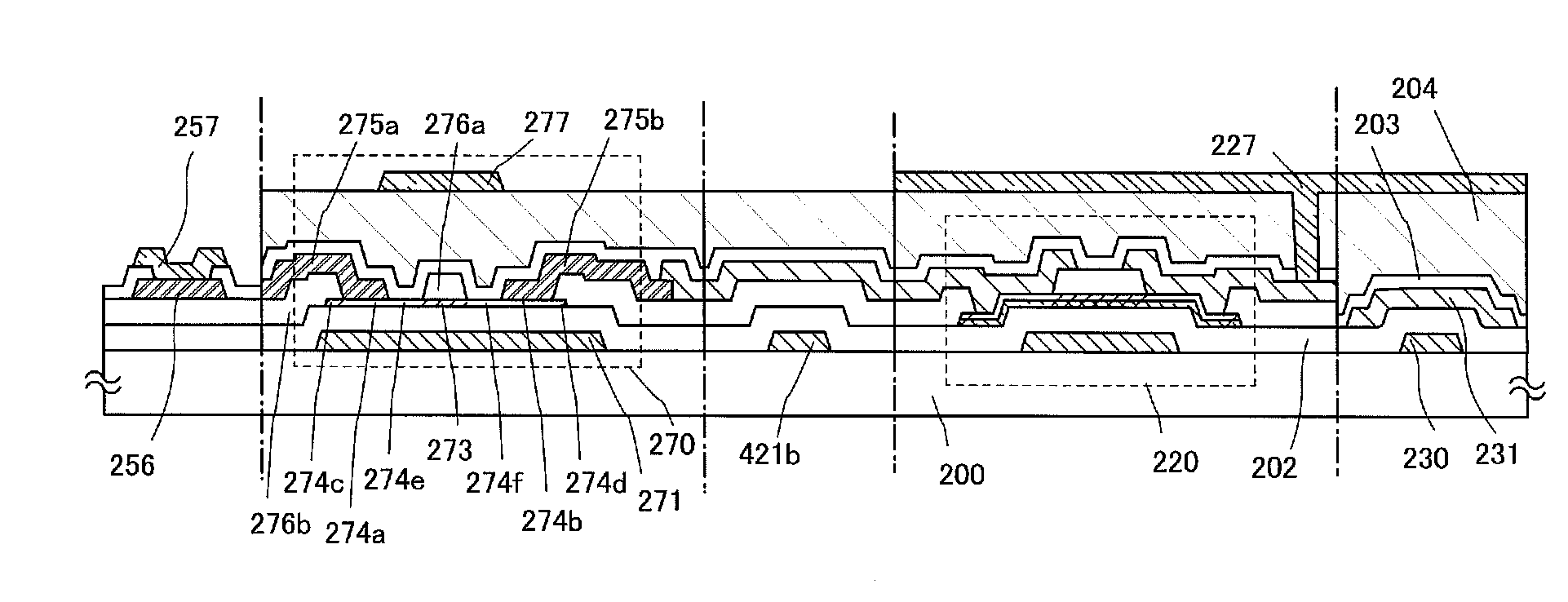

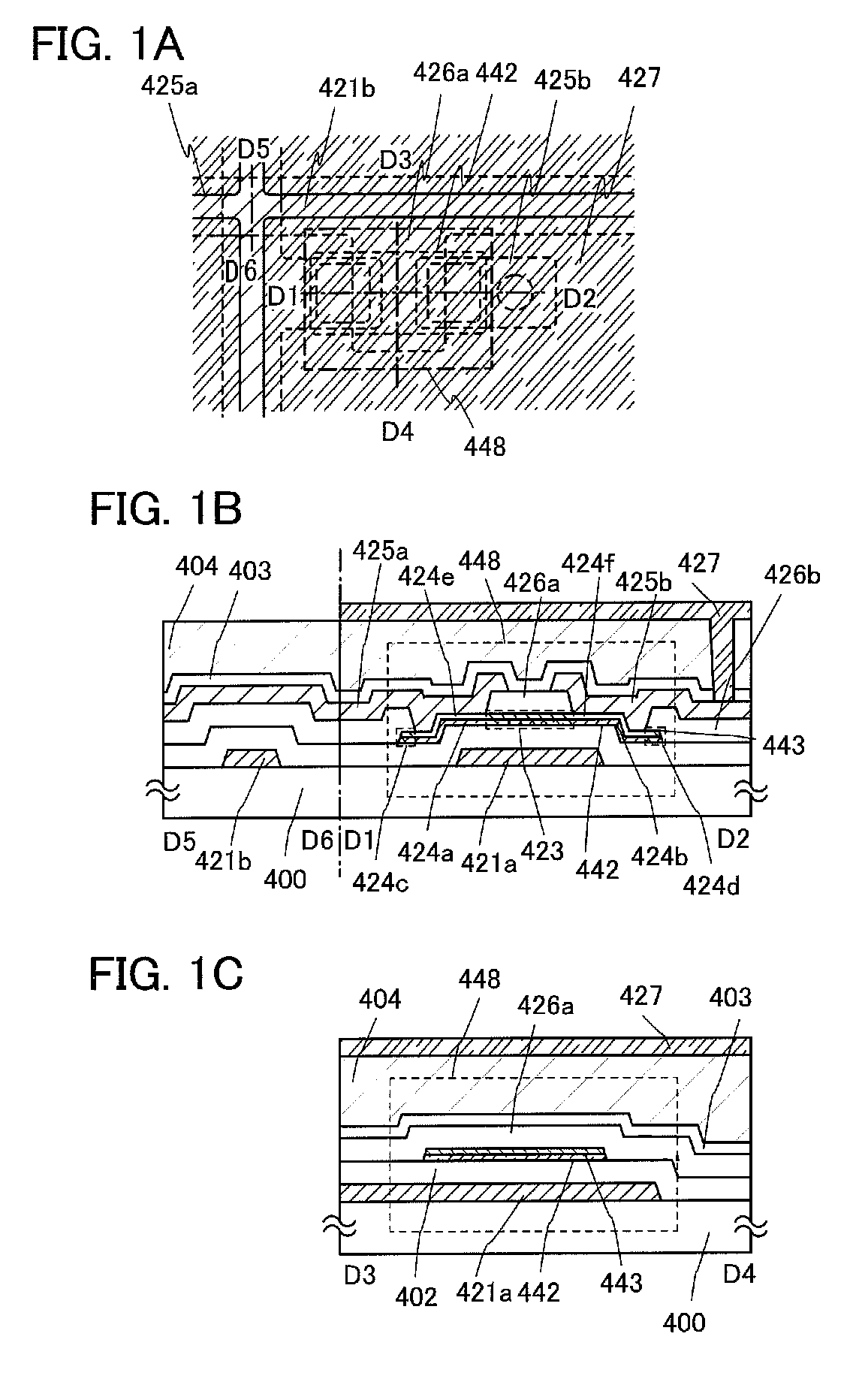

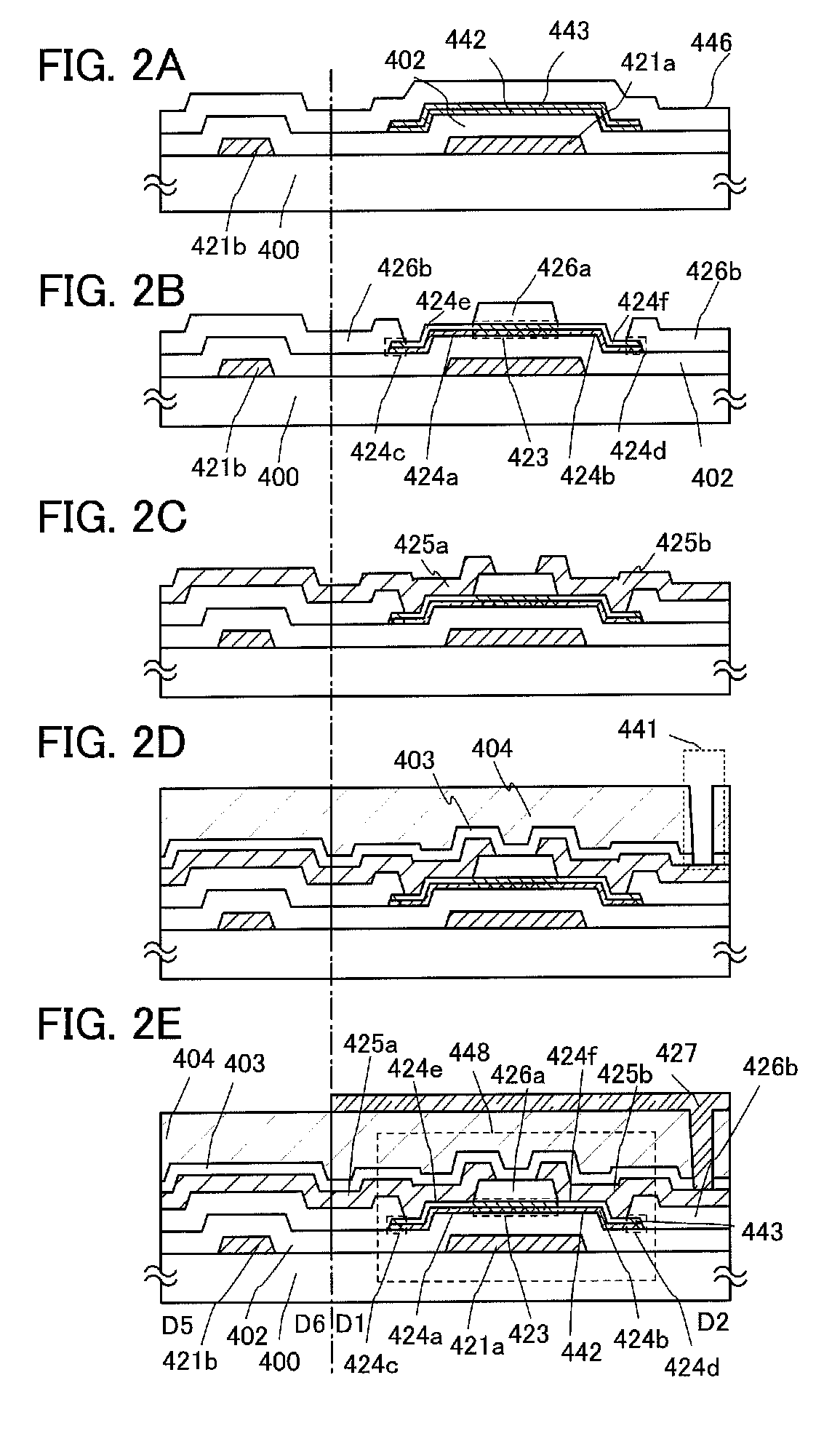

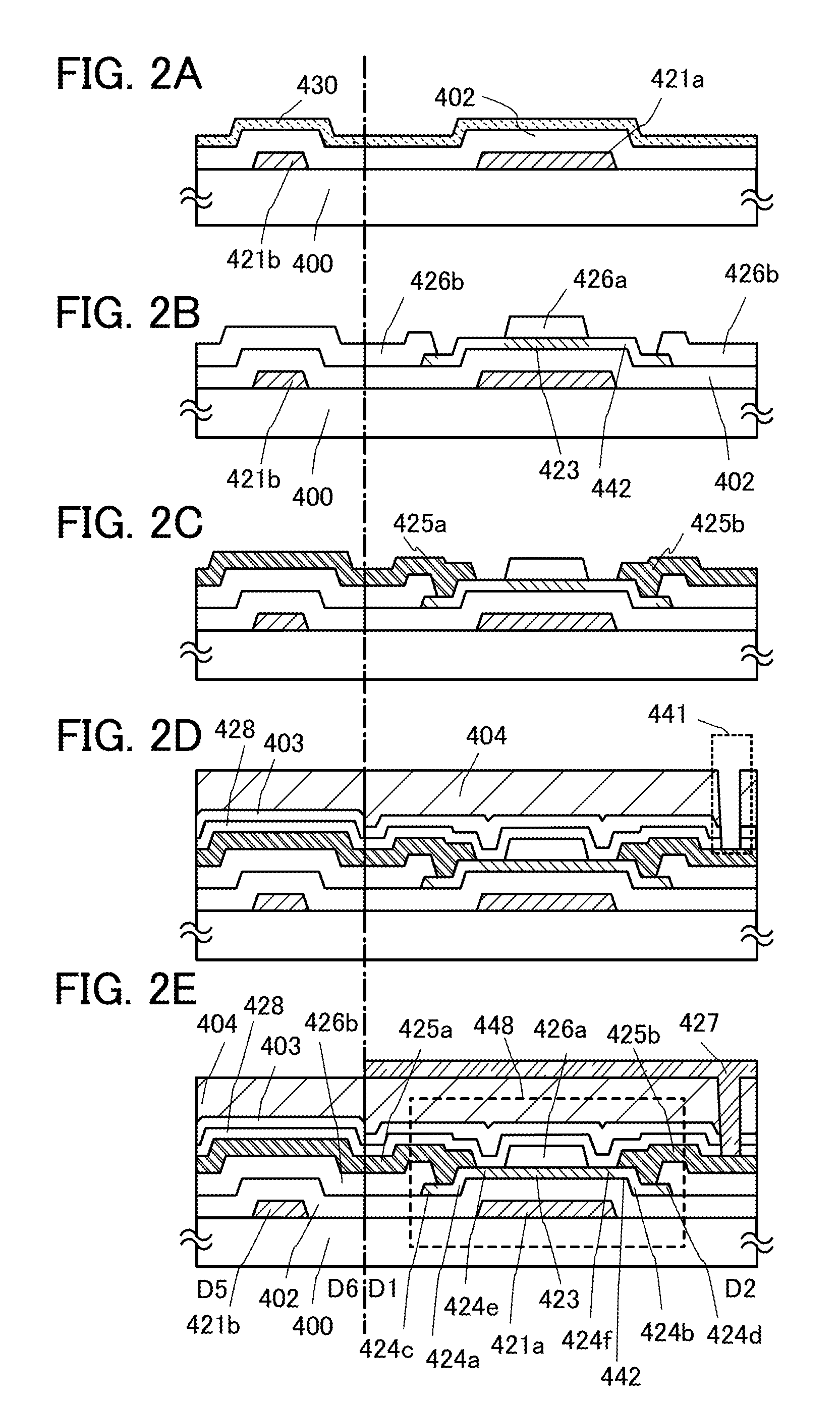

Semiconductor device and method for manufacturing the same

ActiveUS20110037068A1Manufacturing cost be reduceEasily breakTransistorSolid-state devicesOxide semiconductorOxide

One object is to provide a semiconductor device with a structure which enables reduction in parasitic capacitance sufficiently between wirings. In a bottom-gate type thin film transistor including a stacked layer of a first layer which is a metal thin film oxidized partly or entirely and an oxide semiconductor layer, the following oxide insulating layers are formed together: an oxide insulating layer serving as a channel protective layer which is over and in contact with a part of the oxide semiconductor layer overlapping with a gate electrode layer; and an oxide insulating layer which covers a peripheral portion and a side surface of the stacked oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

ActiveUS20110024751A1Reduce manufacturing costEasily brokenTransistorSolid-state devicesBottom gateSemiconductor

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

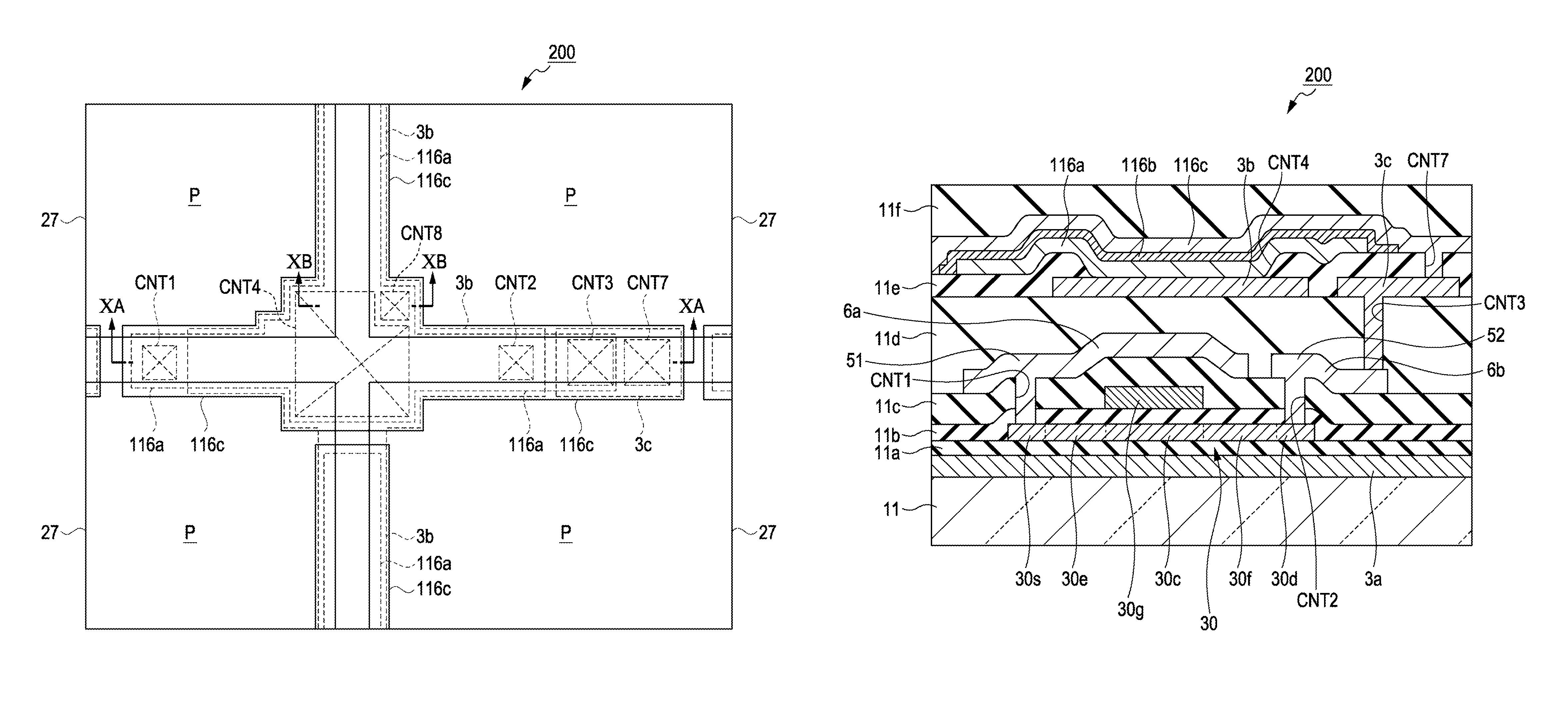

Touch screen, touch panel and display device

ActiveUS20100060602A1Reduce decreaseHigh sensitivityInput/output processes for data processingDisplay deviceEngineering

Each detection column wiring is constituted by a set of a first metal wiring having a zigzag pattern and a second metal wiring having a structure axisymmetric with the first metal wiring about a column direction as an axis, wherein the first metal wiring is constituted by first sloped portions which are obliquely sloped by an inclination angle of 45 degrees with respect to the column direction, and first parallel portions which are parallel with the column direction and are continuous with the first sloped portions, such that the first sloped portions and the first parallel portions are repeatedly placed in a zigzag shape along the column direction. Each detection row wiring also has the same structure. A sloped portion out of the first sloped portions of the first metal wiring is always orthogonally and spatially intersected, at its middle point, with a sloped portion out of the second sloped portions of the third metal wiring at its middle point. There is also the same orthogonal relationship among the other portions.

Owner:MITSUBISHI ELECTRIC CORP

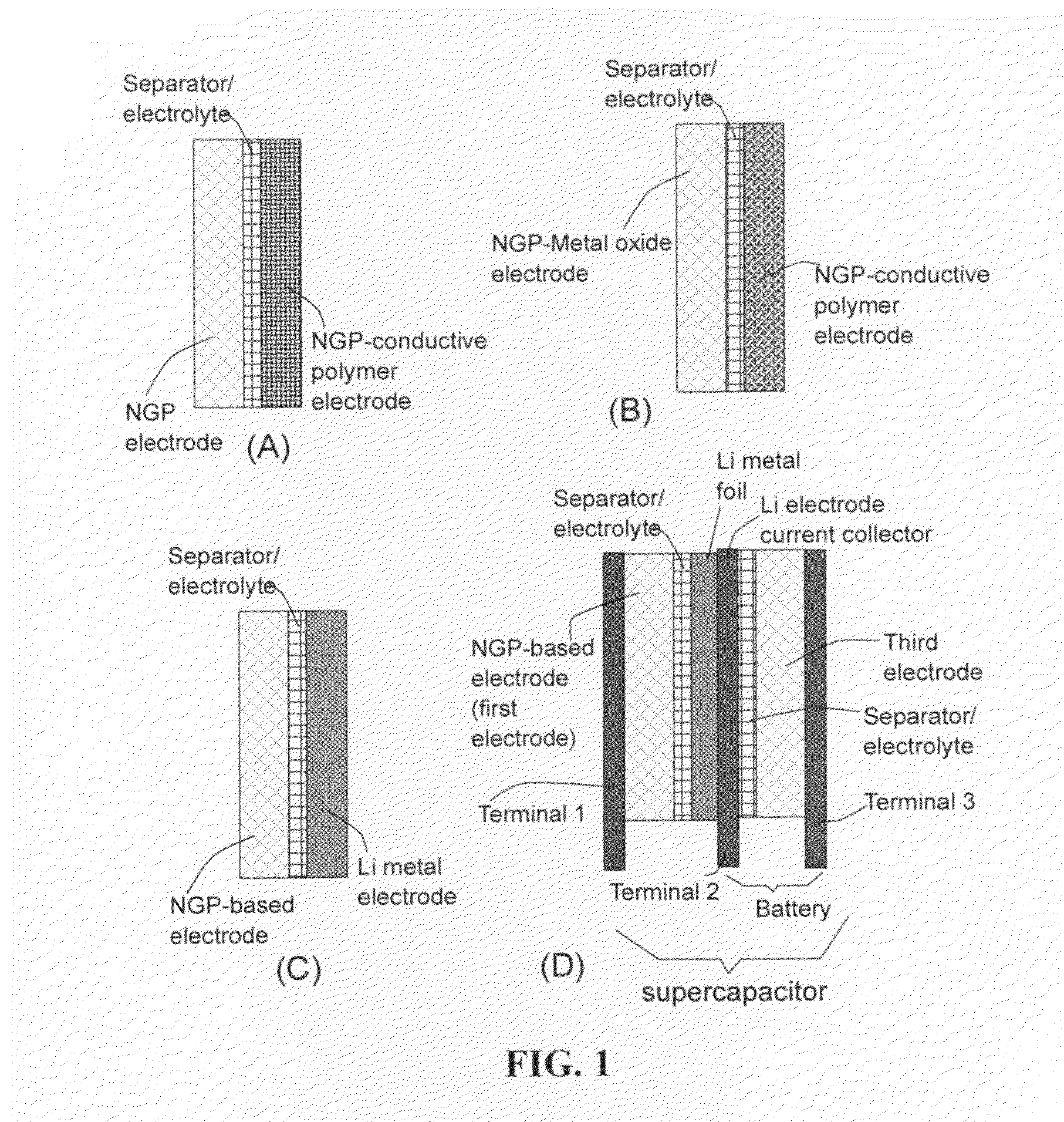

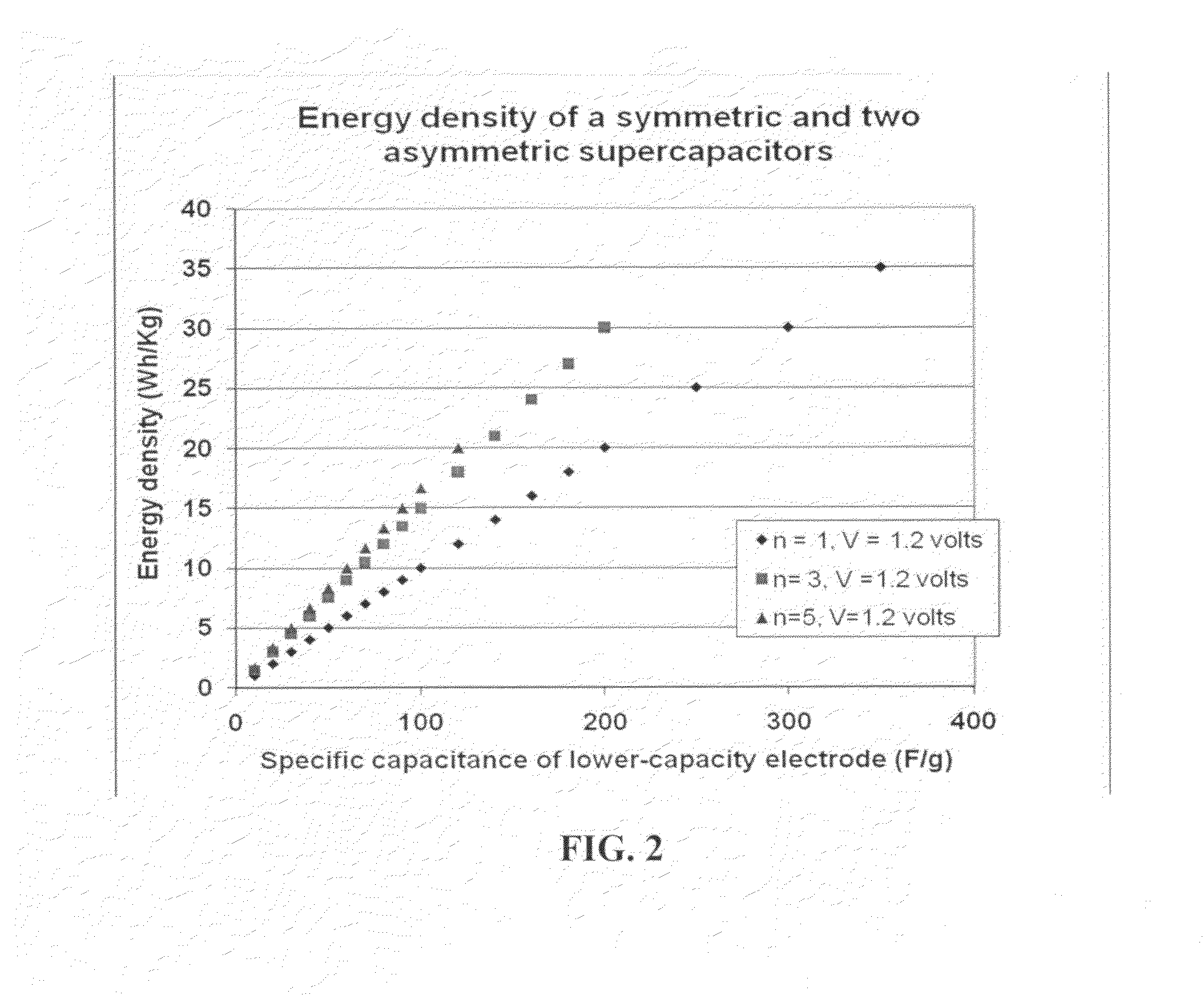

Flexible asymmetric electrochemical cells using nano graphene platelet as an electrode material

InactiveUS20110183180A1Excellent specific capacitanceLarge specific surface areaElectrochemical generatorsHybrid capacitor separatorsPlateletGraphene

A flexible, asymmetric electrochemical cell comprising: (A) A sheet of graphene paper as first electrode comprising nano graphene platelets having a platelet thickness less than 1 nm, wherein the first electrode has electrolyte-accessible pores; (B) A thin-film or paper-like first separator and electrolyte; and (C) A thin-film or paper-like second electrode which is different in composition than the first electrode; wherein the separator is sandwiched between the first and second electrode to form a flexible laminate configuration. The asymmetric supercapacitor cells with different NGP-based electrodes exhibit an exceptionally high capacitance, specific energy, and stable and long cycle life.

Owner:NANOTEK INSTR GRP LLC

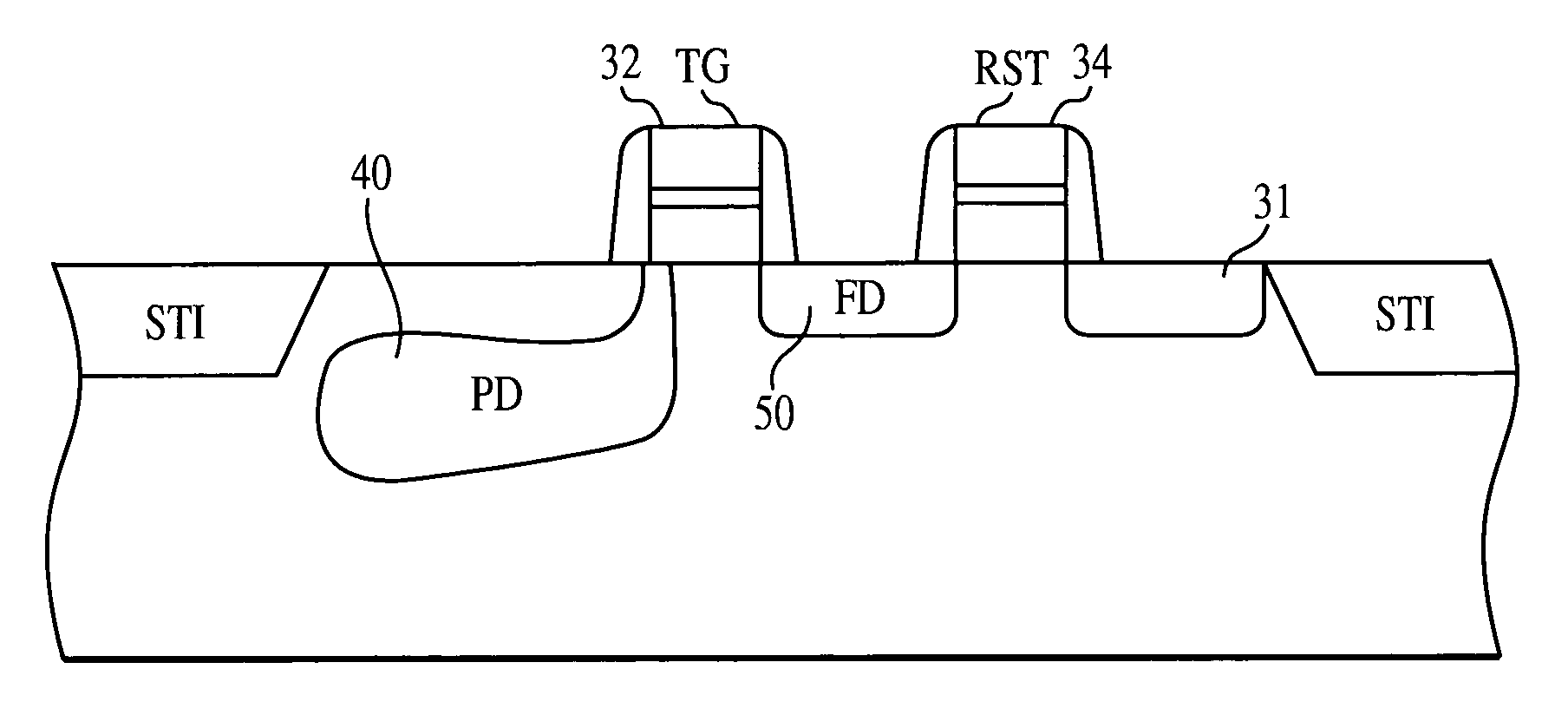

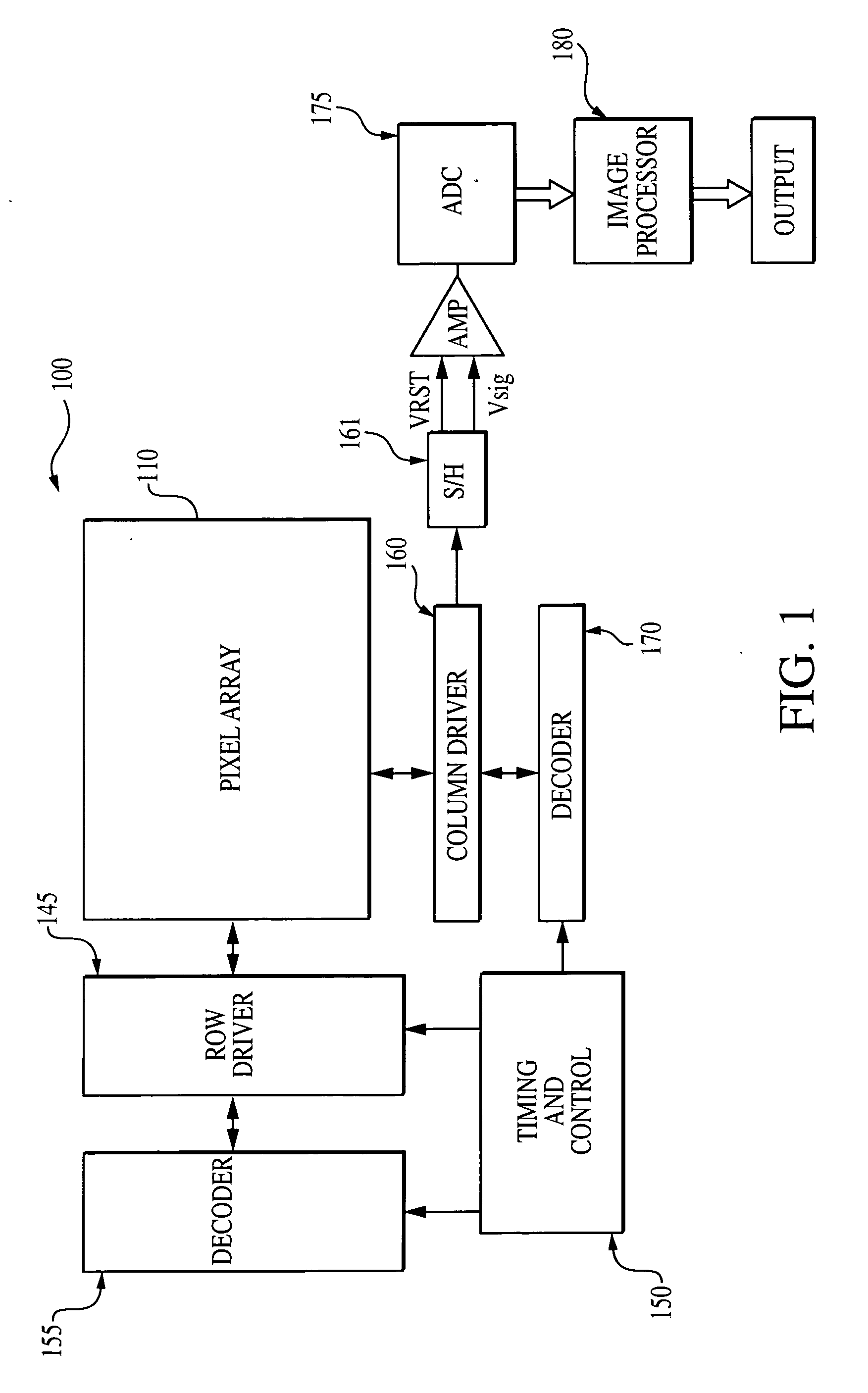

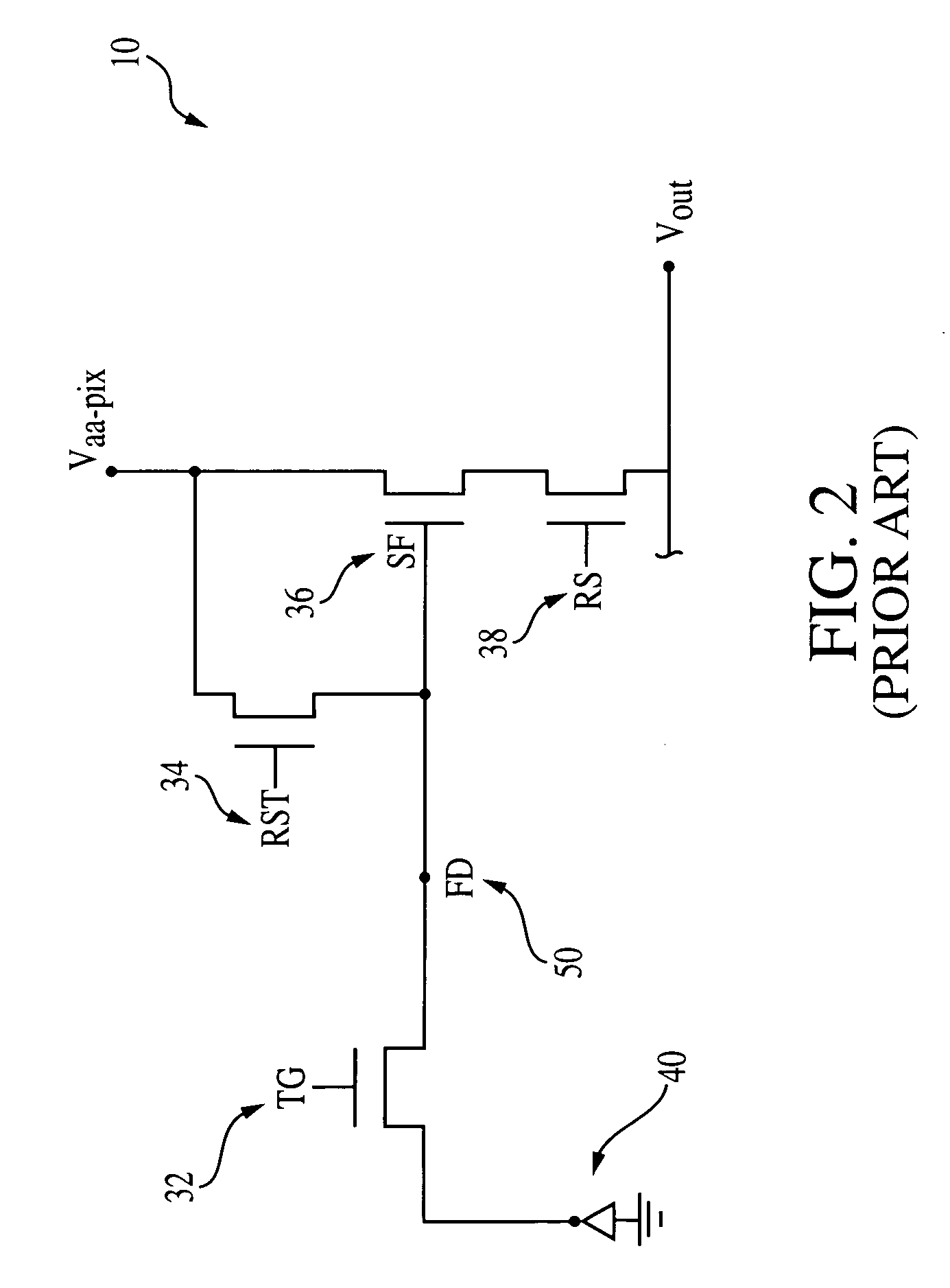

High dynamic range pixel amplifier

ActiveUS20050224843A1Increase capacitanceReduce capacitanceTelevision system detailsTelevision system scanning detailsCapacitanceEngineering

A pixel cell with increased dynamic range is formed by providing a floating diffusion region having a variable capacitance, controlled by at least one gate having source and drain regions commonly connected to the floating diffusion region. The gate has an intrinsic capacitance which, when the gate is activated, is added to the capacitance of the floating diffusion region, providing a low conversion gain readout. When the gate is off, the floating diffusion region capacitance is minimized, providing a high conversion gain readout. The gate may also be selectively switched to mid-level. At mid-level, a mid-level conversion gain, which is between the high and low conversion gains, readout is provided, but the gate still provides some capacitance to prevent the floating diffusion region from saturating.

Owner:APTINA IMAGING CORP

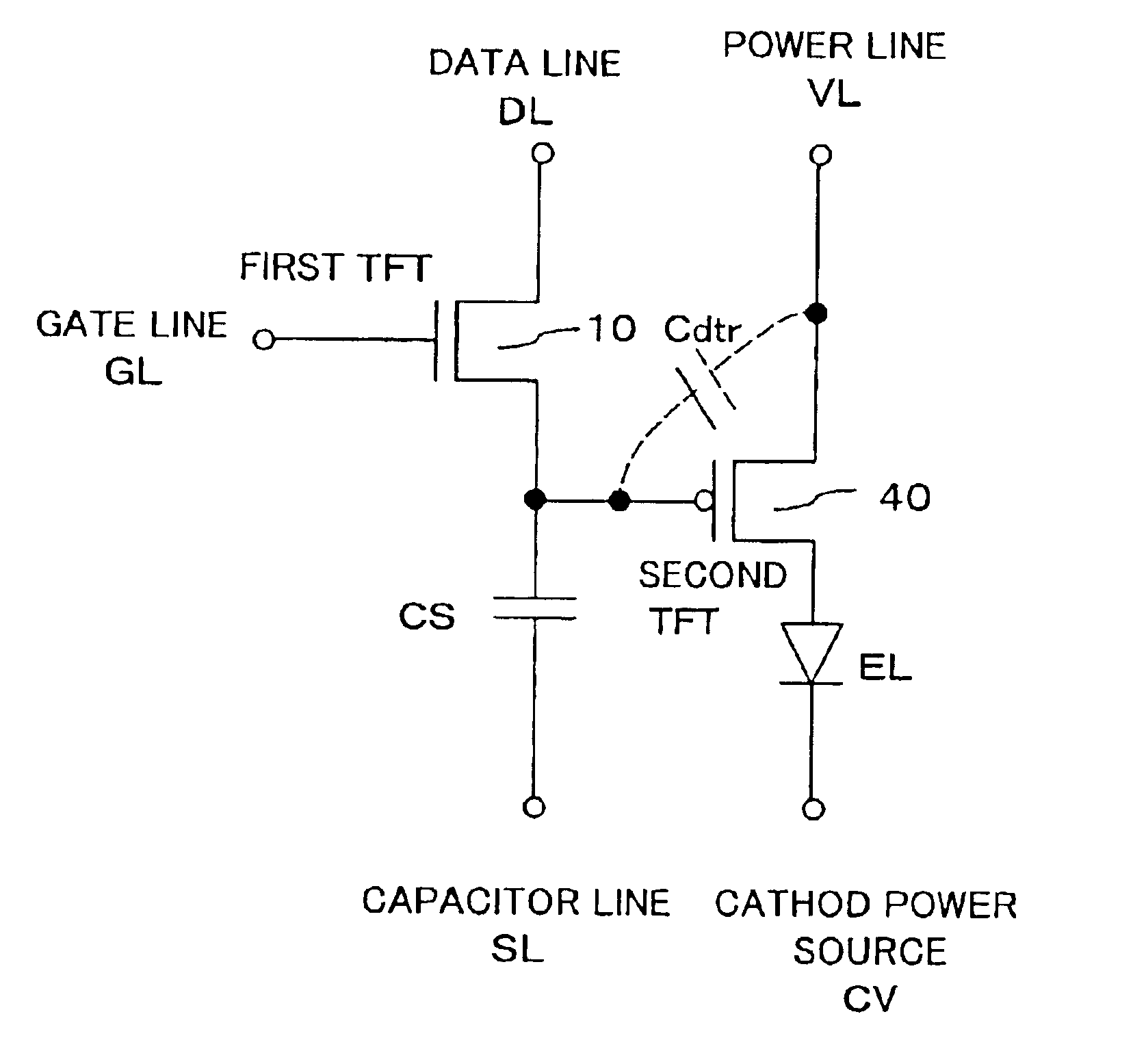

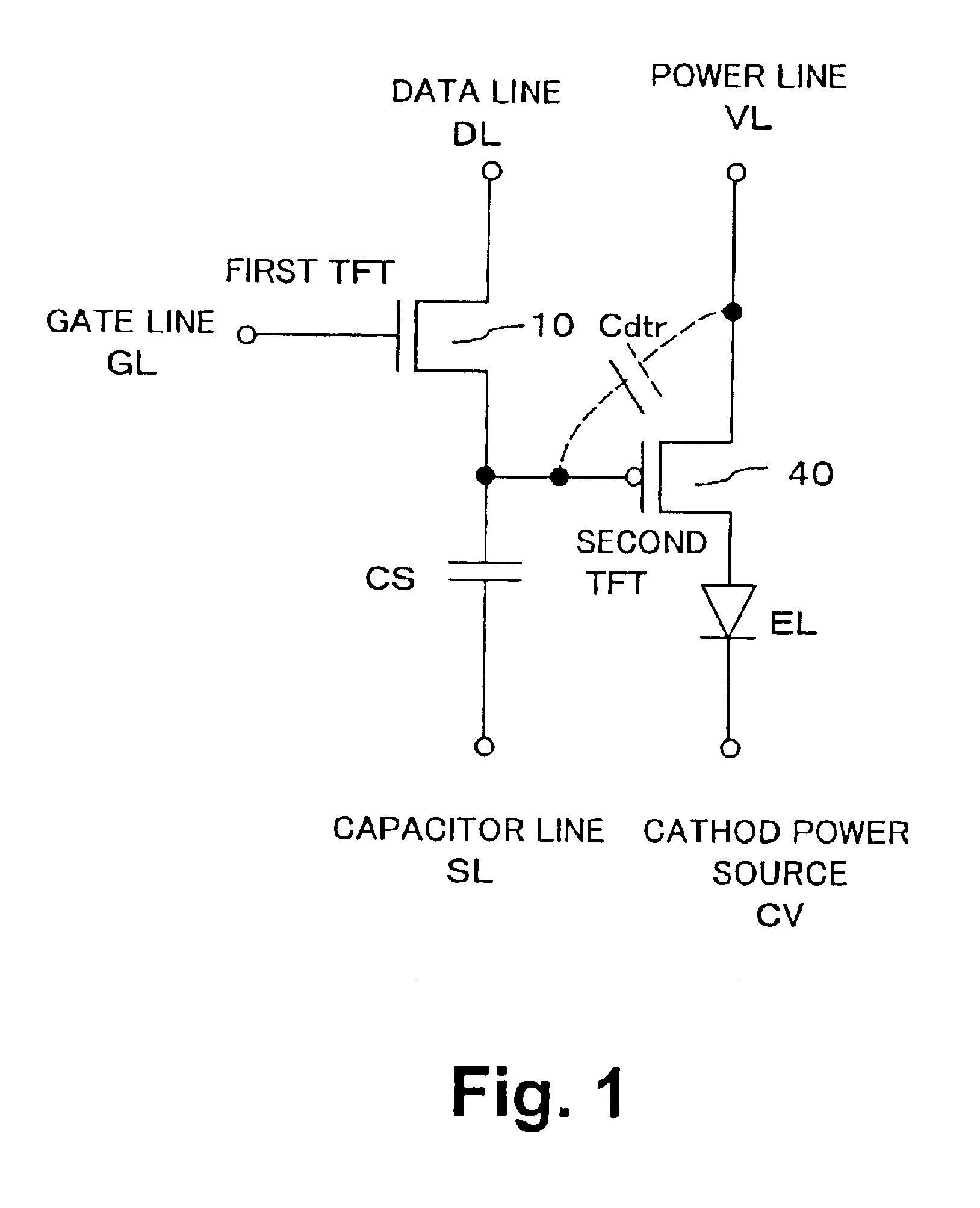

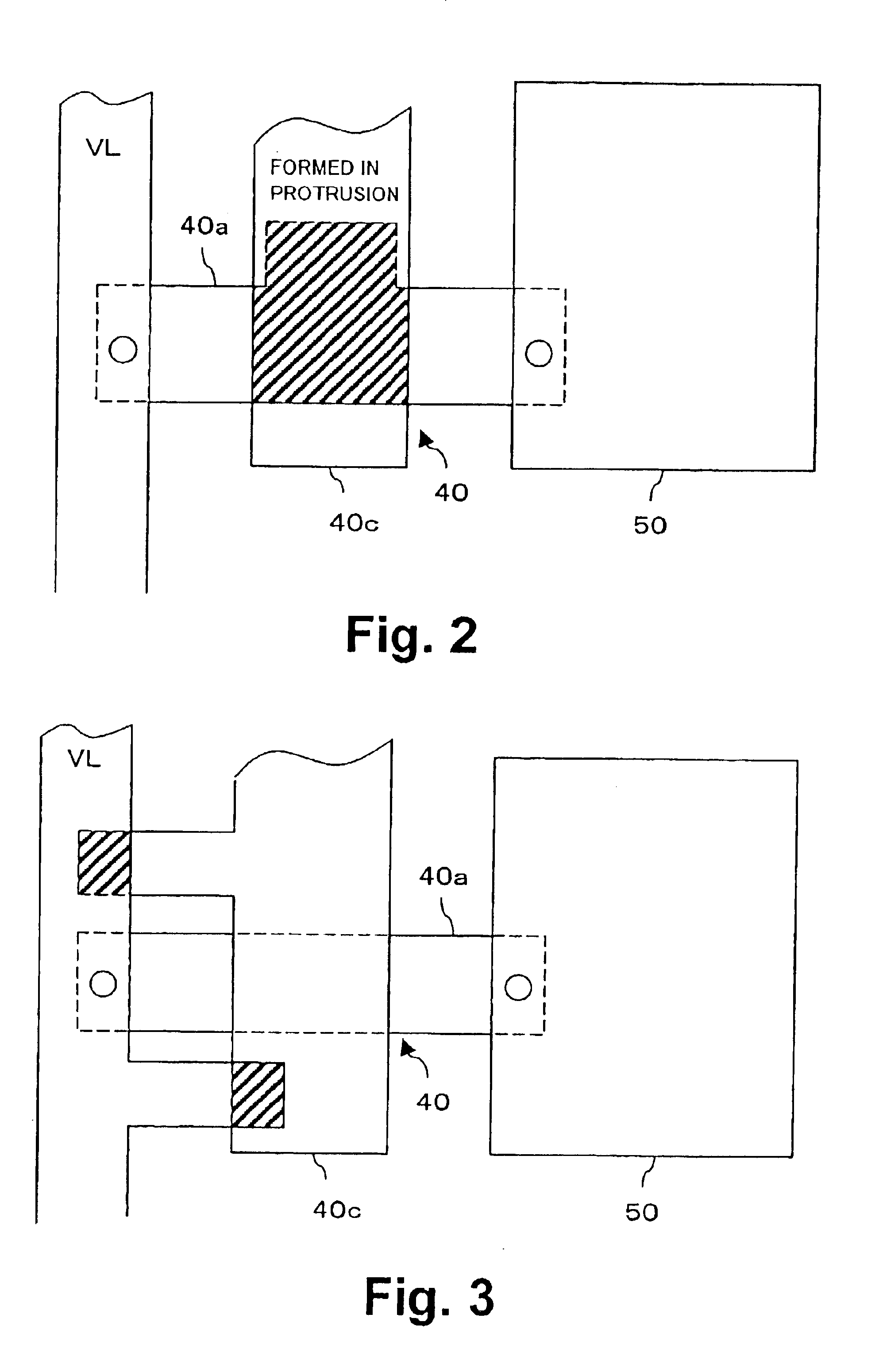

Transistor circuit

InactiveUS6914448B2Increase capacitanceTransistorStatic indicating devicesCapacitanceTransistor circuits

Transistor capacitance Cdtr inevitably generated between the gate and the drain of a second TFT is increased. Accordingly, an operation test of a first TFT and the second TFT can be conducted by turning on the first TFT to charge the transistor capacitance Cdtr and detecting the stored charges.

Owner:SANYO ELECTRIC CO LTD

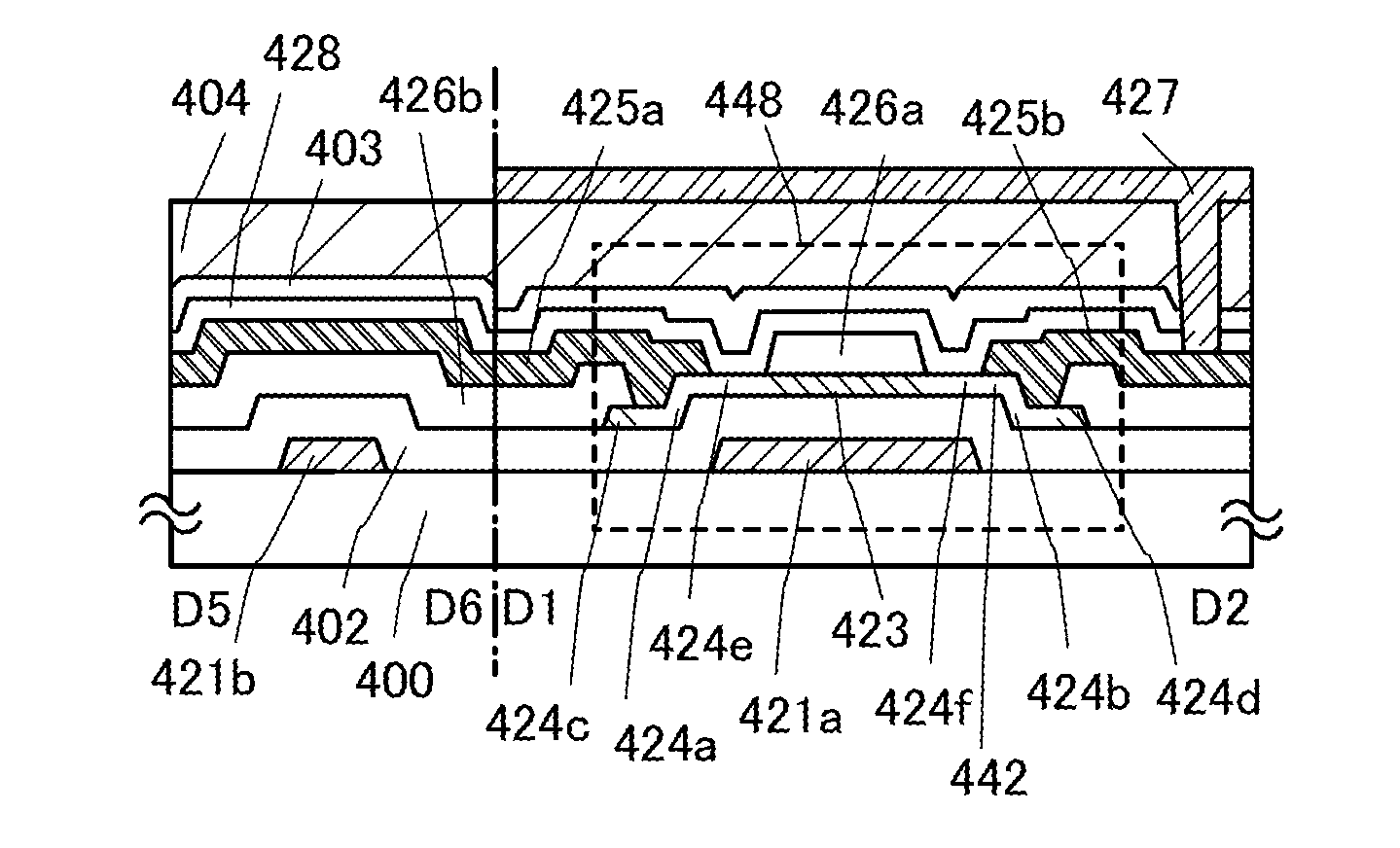

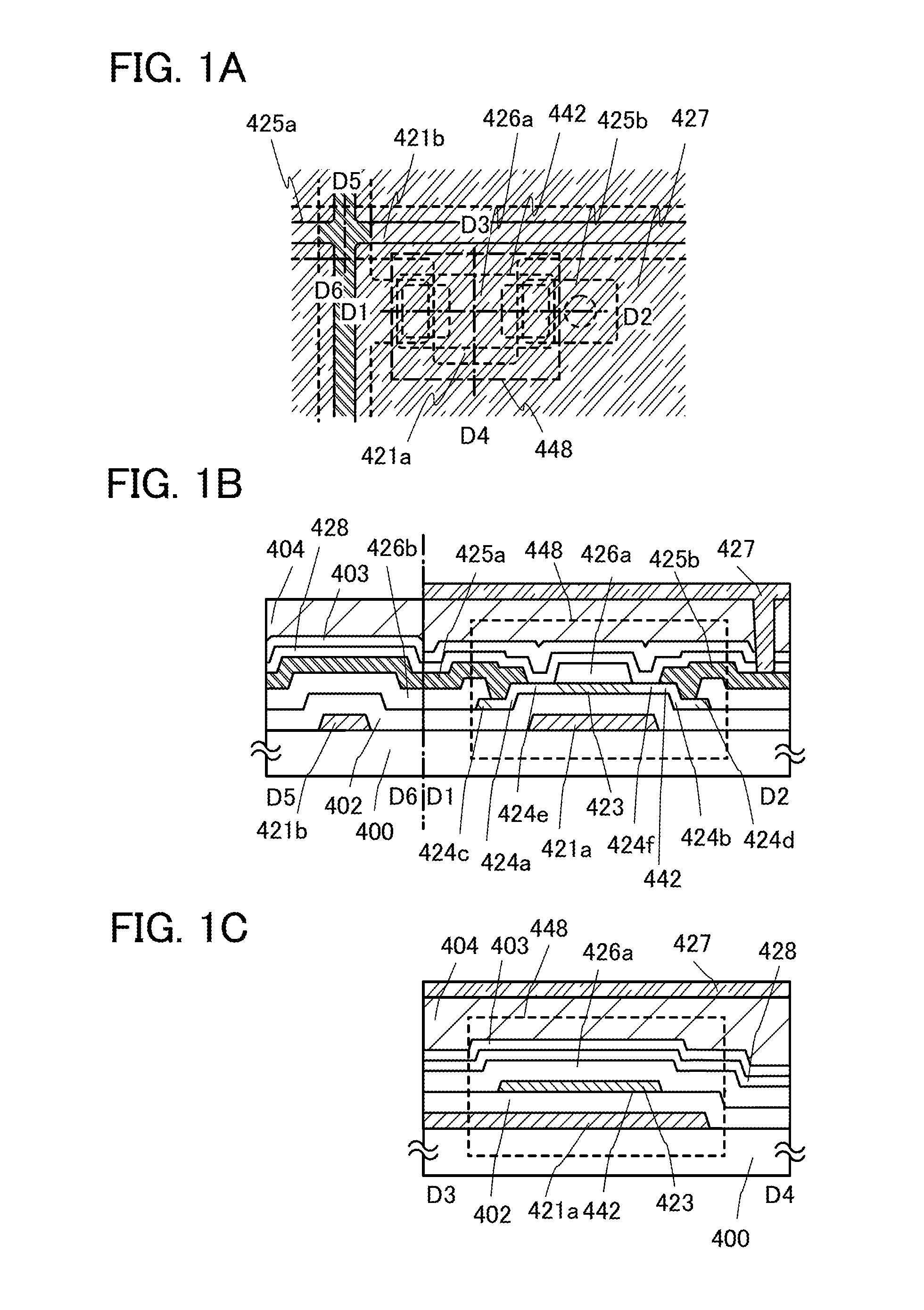

Semiconductor device and manufacturing method thereof

ActiveUS20110031491A1Reduce parasitic capacitanceOff-current can be reducedTransistorStatic indicating devicesBottom gateParasitic capacitance

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

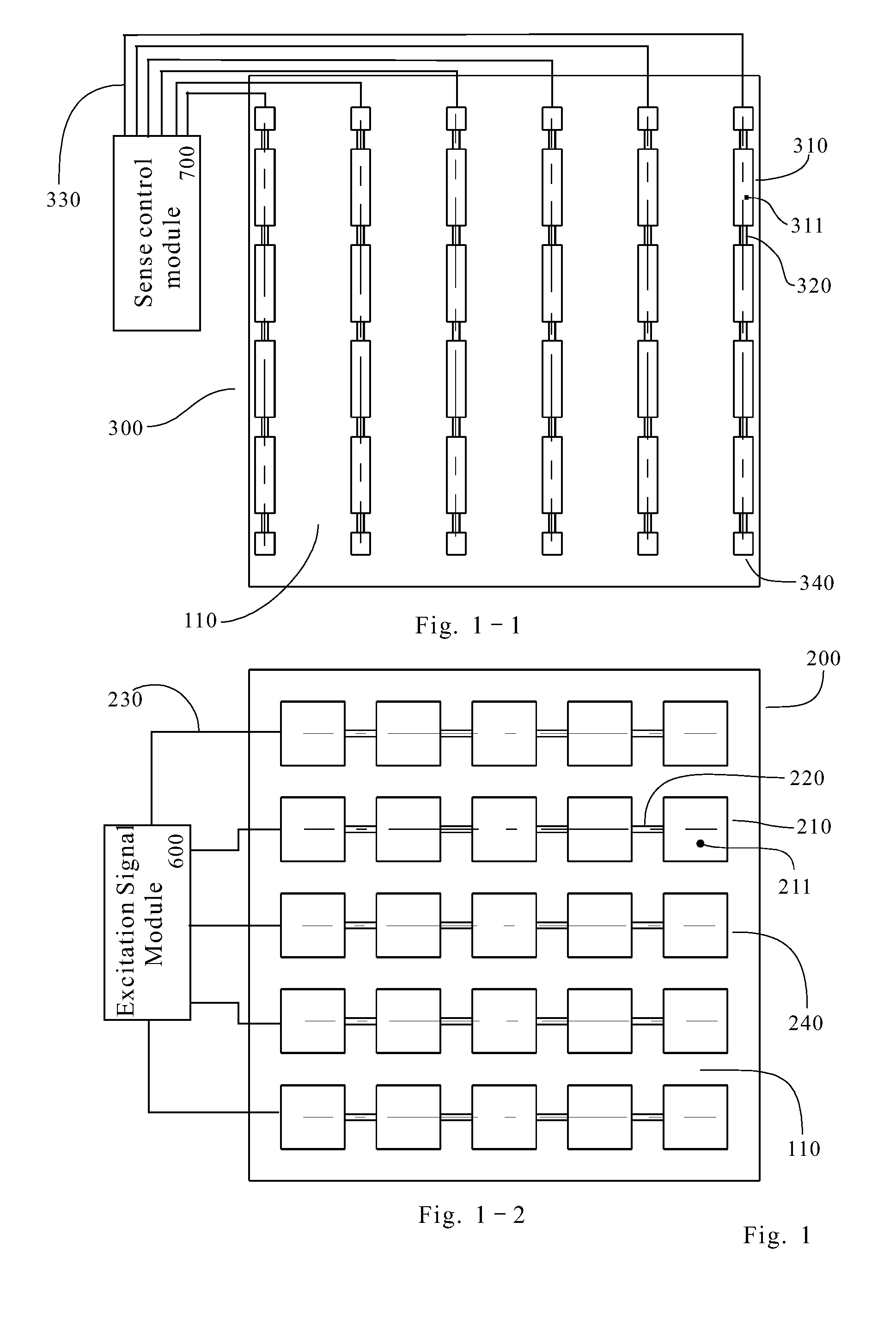

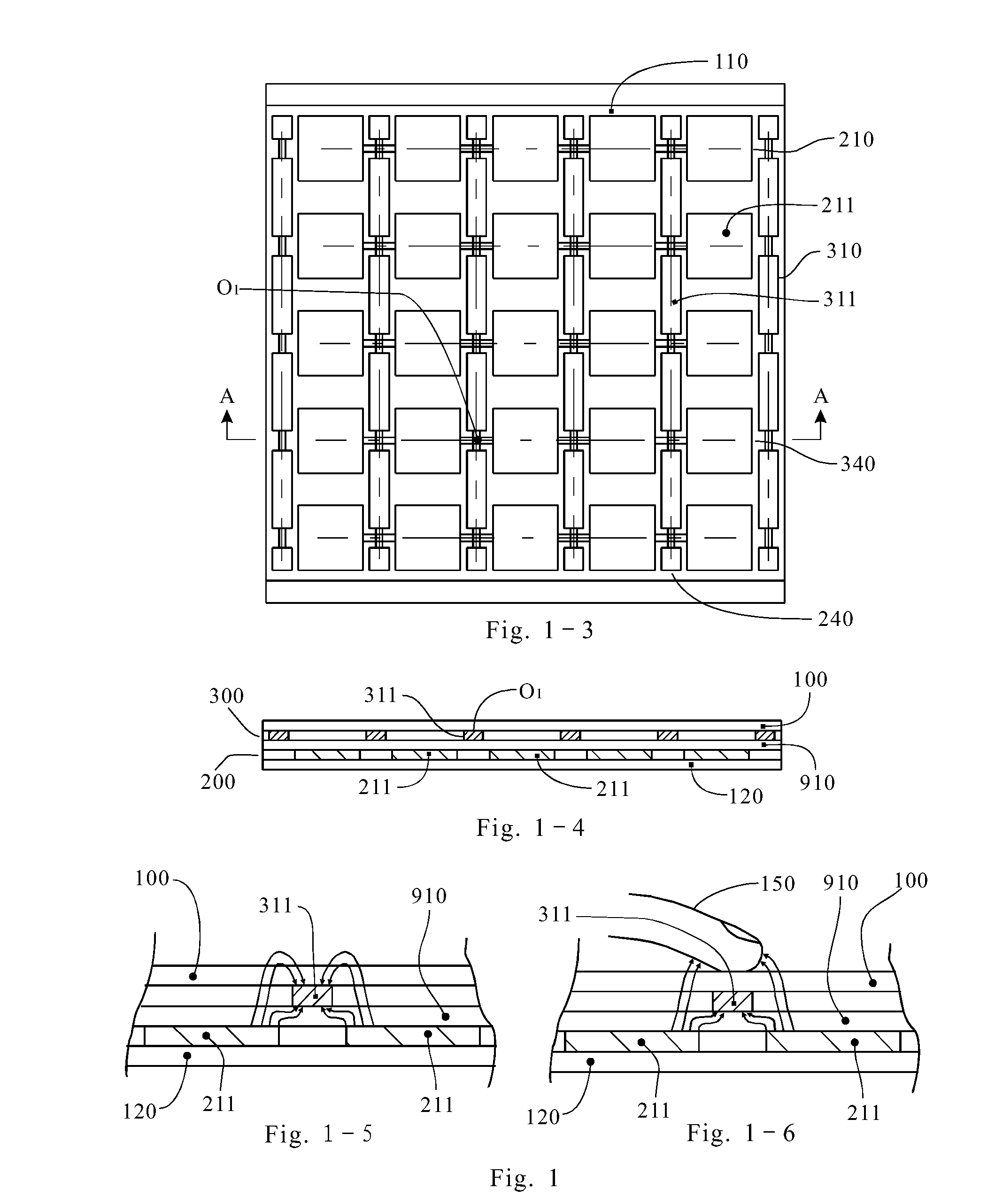

Mutual capacitance touch screen and combined mutual capacitance touch screen

InactiveUS20100110038A1Increase capacitanceReduce capacitanceInput/output processes for data processingEngineeringComputational physics

A mutual capacitance touch screen and a combined mutual capacitance touch screen formed by the combination of mutual capacitance touch screens. A driving layer and a sensor layer are included, wherein the driving layer comprises driving electrodes distributed at intervals in the same plane; the sensor layer comprises sense electrodes distributed at intervals in the same plane; and the places where the sense electrodes are distributed in the sensor layer are just over against the intervals between the driving electrodes in the driving layer so that the driving electrodes and the sense electrodes together fill the touch area of the touch screen. The driving electrodes are not over against the sense electrodes in terms of space positions to increase the proportion of capacitance CT to mutual capacitance C, wherein the capacitance CT is formed between the driving electrodes and the top of the sense electrodes; consequently, the effective capacitivity of the mutual capacitance touch screen is effectively increased.

Owner:FOCALTECH SYST LTD

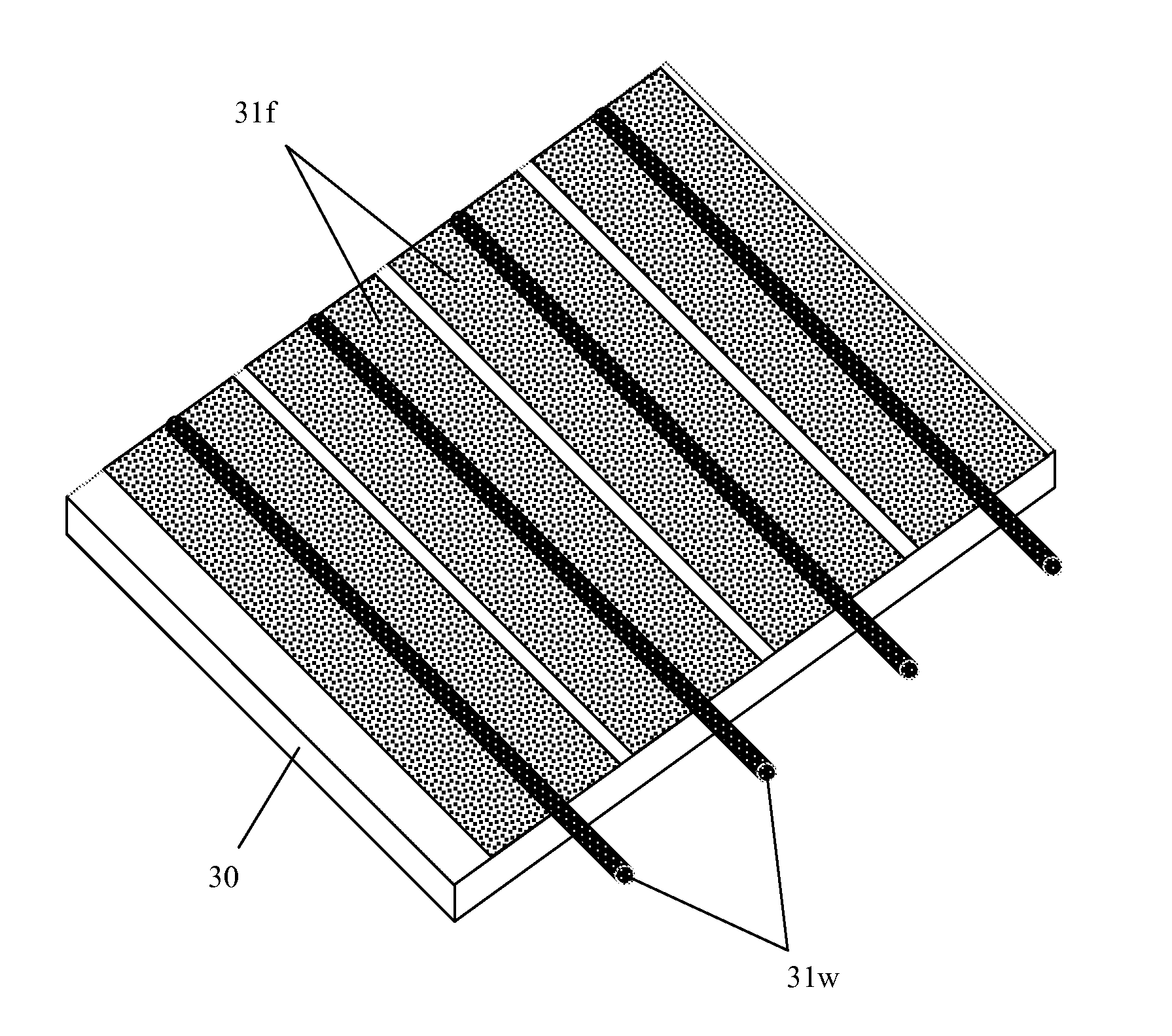

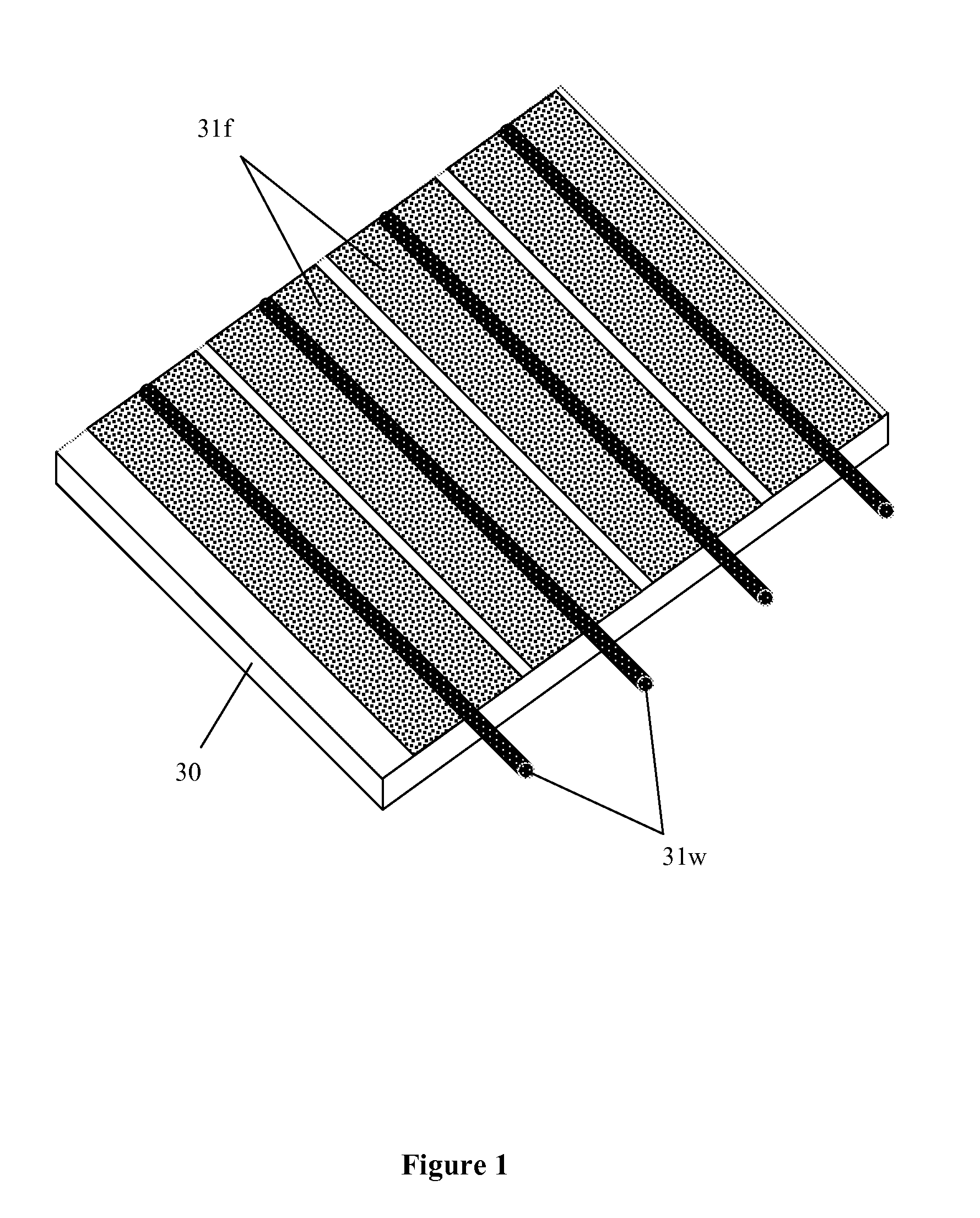

Electroded Sheet for a Multitude of Products

InactiveUS20120105370A1Increase capacitanceLarge displayLight-sensitive devicesSolid-state devicesCapacitanceElectronic form

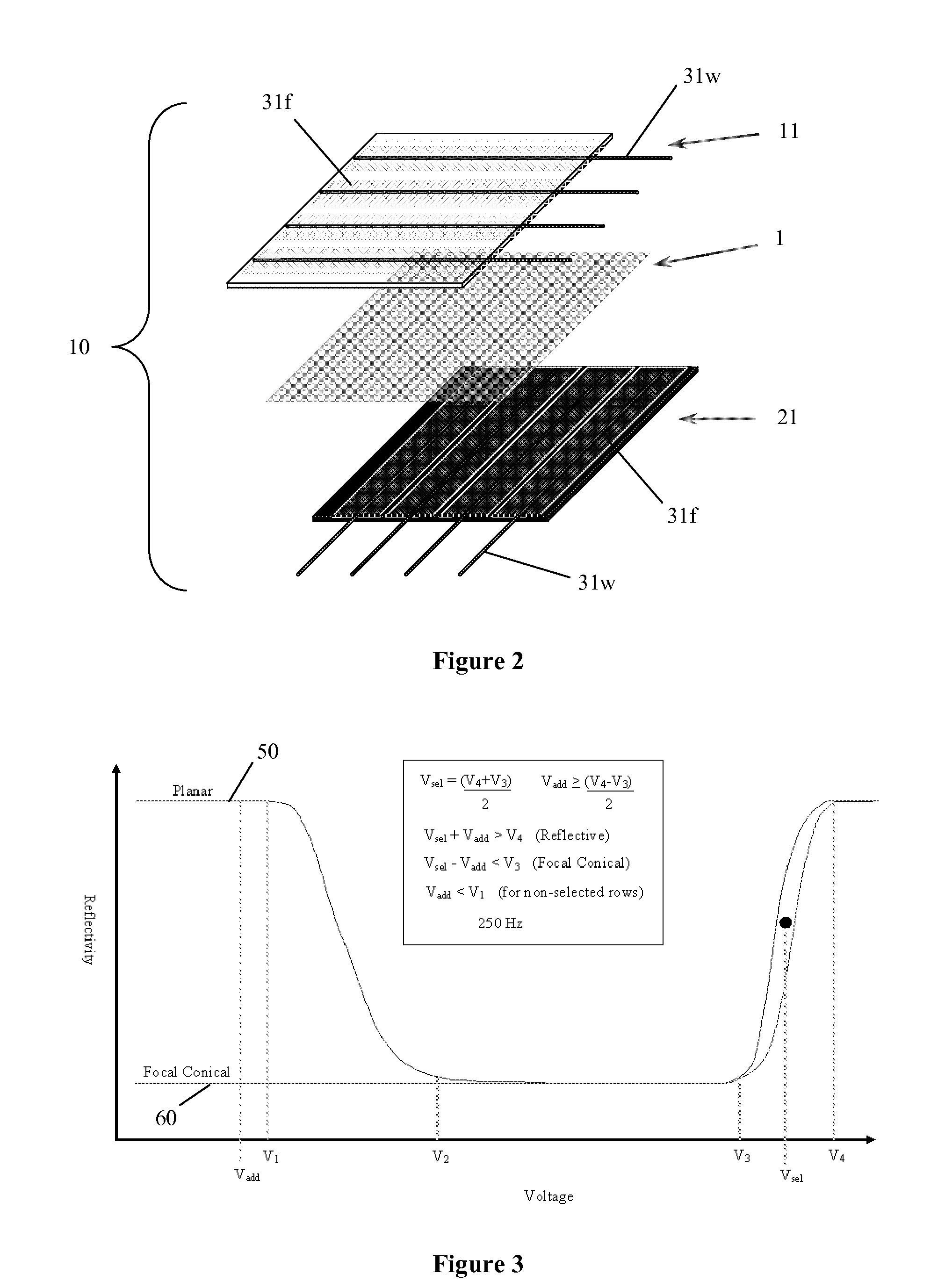

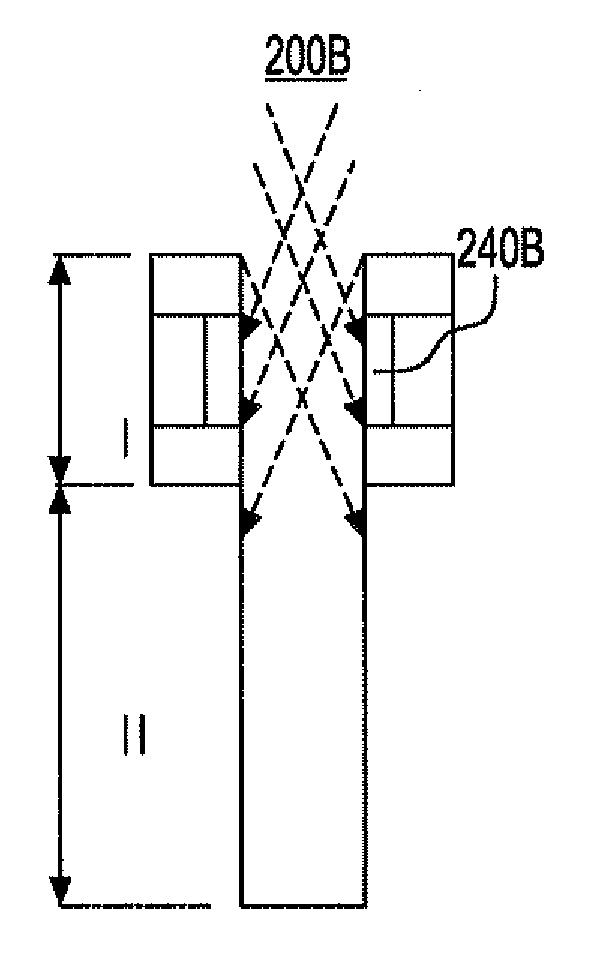

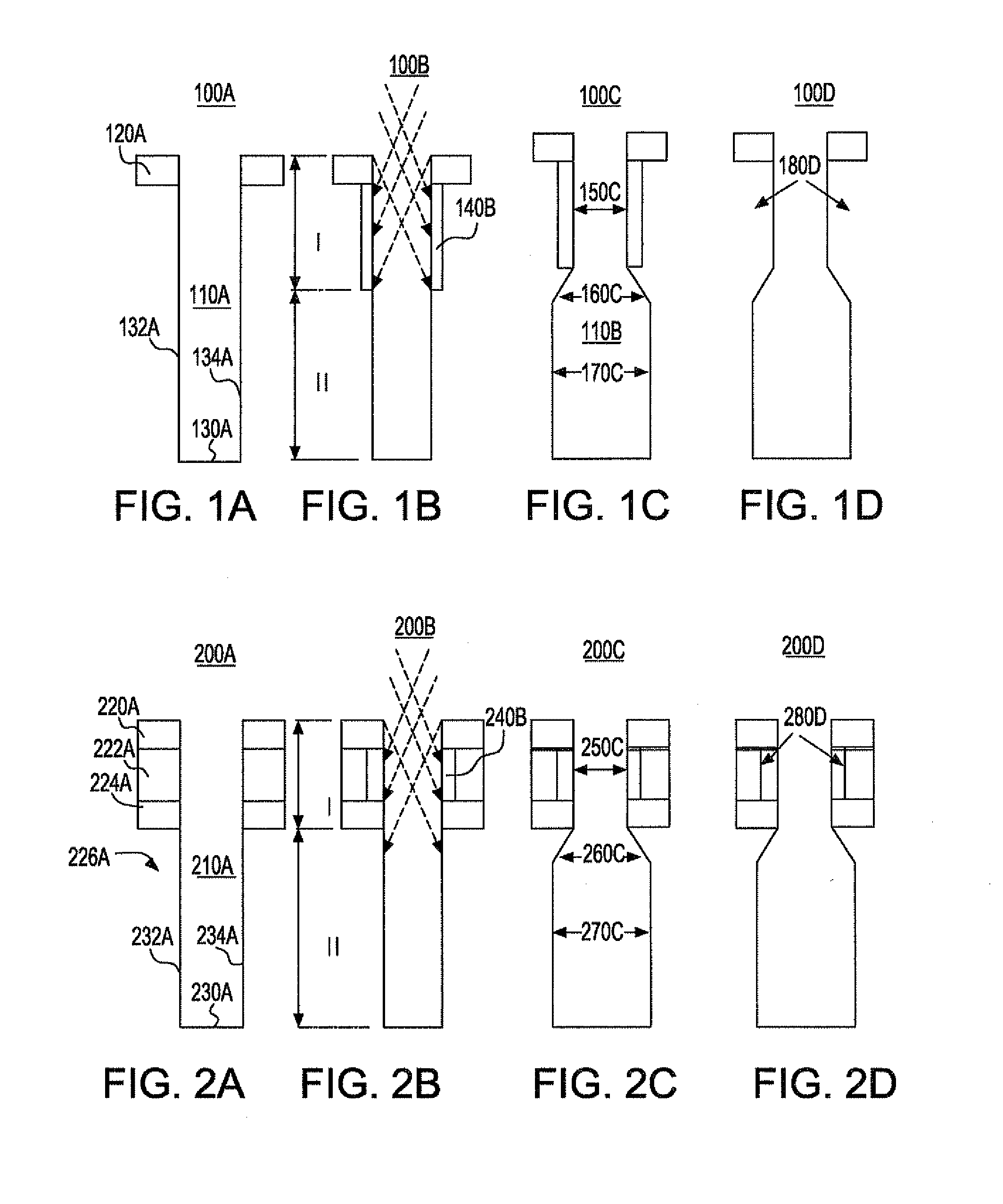

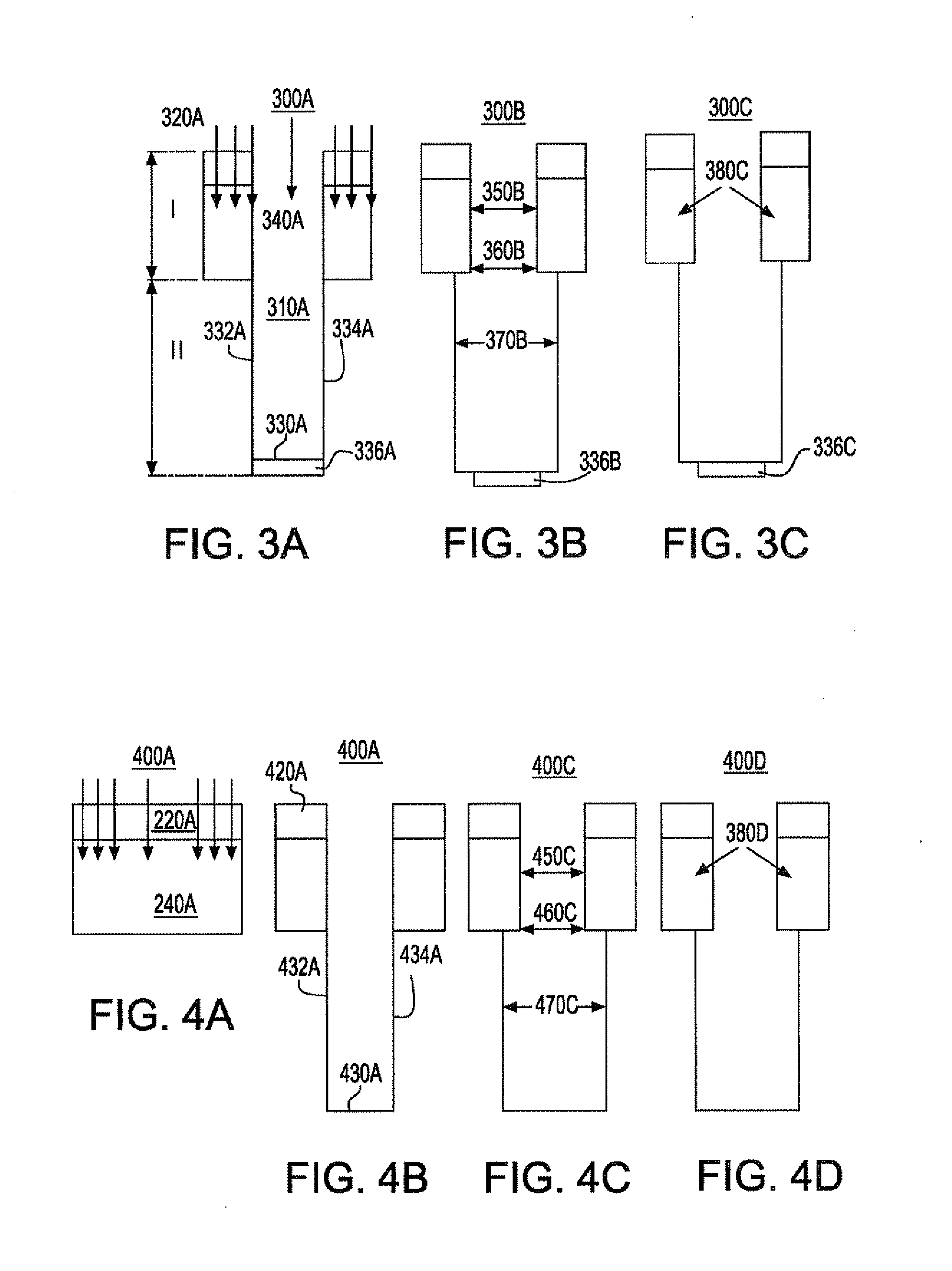

eSheets create a multitude of different products. One embodiment is a projected capacitive touch sensor created by embedding orthogonal arrays of coated metal wires into the surface of a polymer sheet or onto the back of a projector screen. To increase the capacitance of the electrodes or pixels in the sensor, transparent conductive electrodes can be electrically connected to the wire electrodes. Another embodiment is a reflective, energy-efficient display formed by sandwiching a reflective cholesteric liquid crystal (Ch. LC) material between electroded sheet substrates. The eSheet Ch. LCD is pressure sensitive and can be written on using a finger or stylus. The eSheet Ch. LCD can then be read using the wire electrodes in the eSheet LCD.

Owner:NUPIX

Method of forming a bottle-shaped trench by ion implantation

InactiveUS20090170331A1Increase capacitanceSemiconductor/solid-state device manufacturingSemiconductorRegioselectivity

Disclosed is a method of forming a bottle shaped trench in a substrate which includes forming at least one trench having an upper portion and a lower portion into a semiconductor substrate, the at least one trench having vertical sidewalls that extend to a common bottom wall; implanting ions into the semiconductor substrate abutting the upper portion of the at least one trench to form an amorphous region in the semiconductor substrate abutting the upper portion of the at least one trench; and etching the lower portion of the at least one trench selective to the amorphous region to provide an elongated bottom portion which extends laterally beyond the upper portion.

Owner:GLOBALFOUNDRIES INC

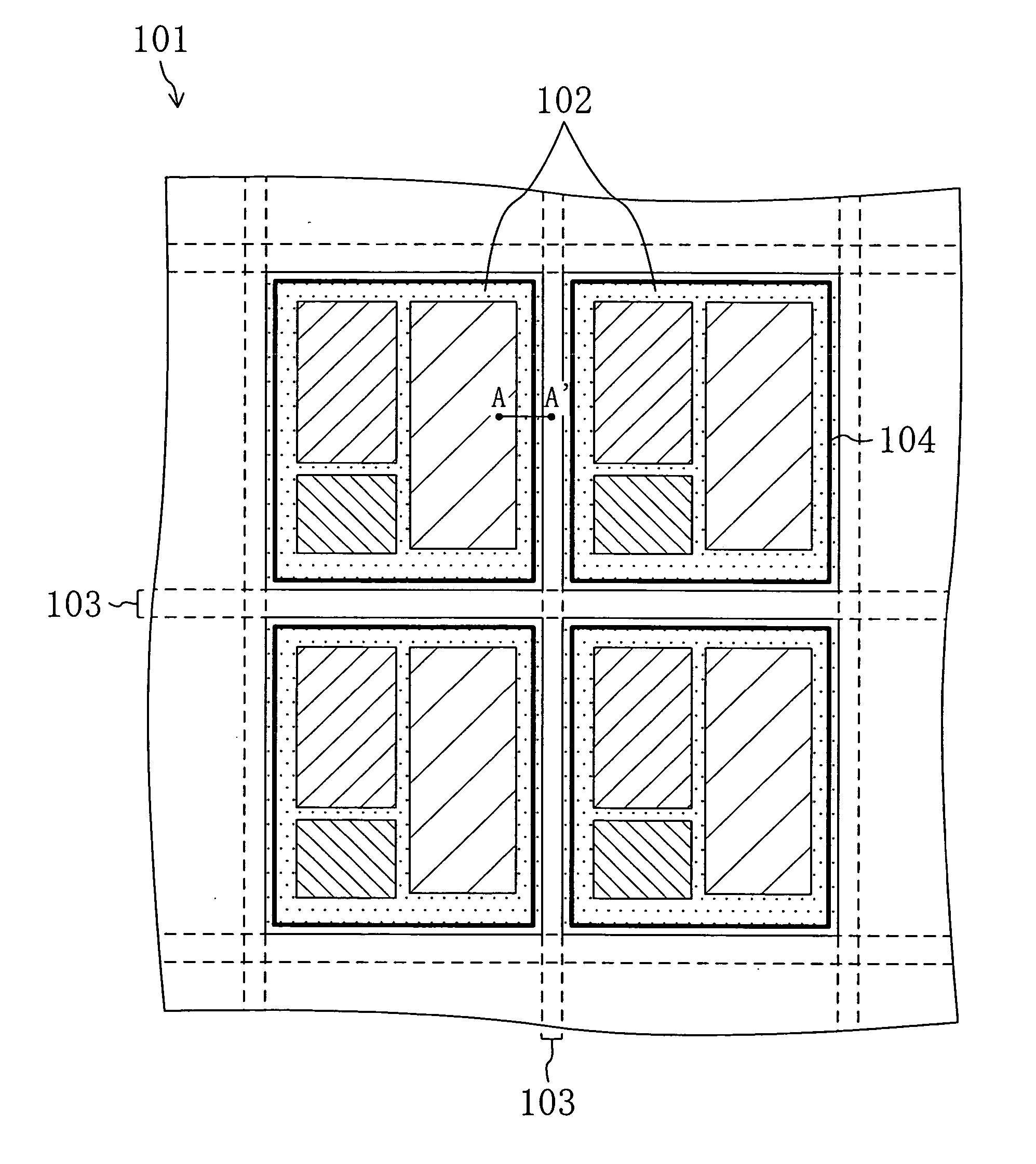

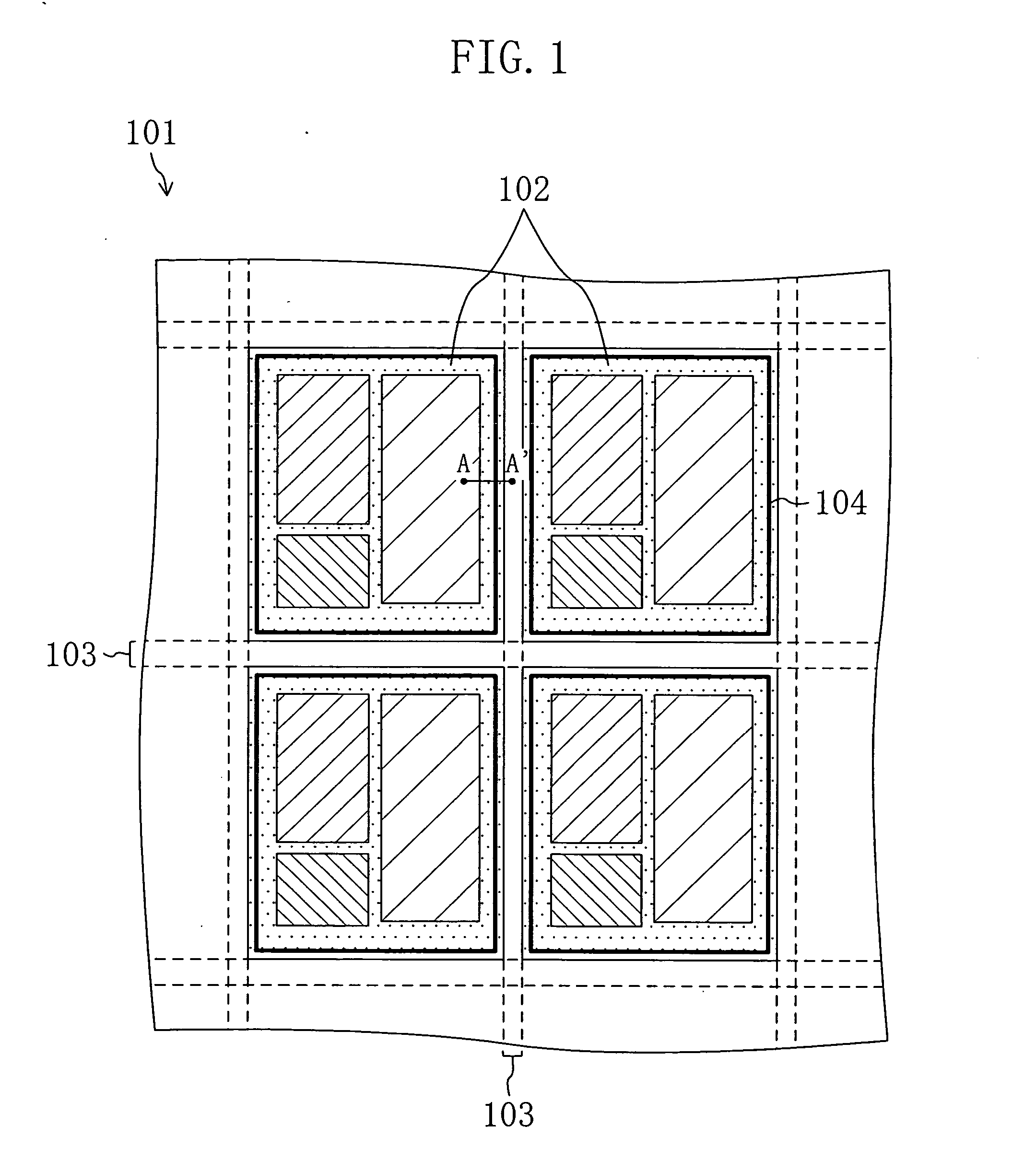

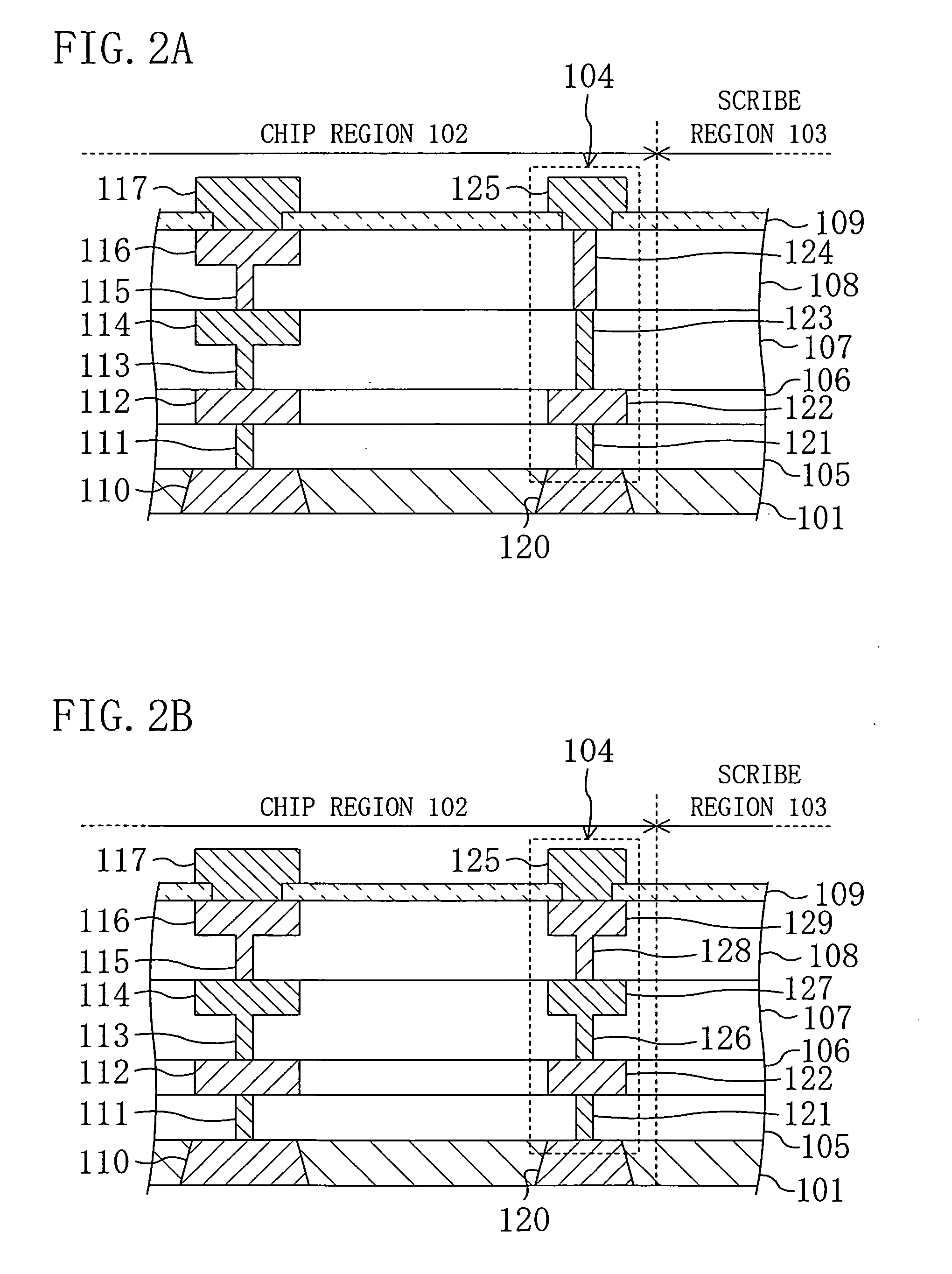

Semiconductor device and method for fabricating the same

ActiveUS20050098893A1Prevent chipping and breakingDegradation of moisture resistanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

A seal ring structure is formed through a multilayer structure of a plurality of dielectric films in a peripheral part of a chip region to surround the chip region. A dual damascene interconnect in which an interconnect and a plug connected to the interconnect are integrated is formed in at least one of the dielectric films in the chip region. Part of the seal ring structure formed in the dielectric film in which the dual damascene interconnect is formed is continuous. A protection film formed on the multilayer structure has an opening on the seal ring. A cap layer connected to the seal ring is formed in the opening.

Owner:PANASONIC CORP

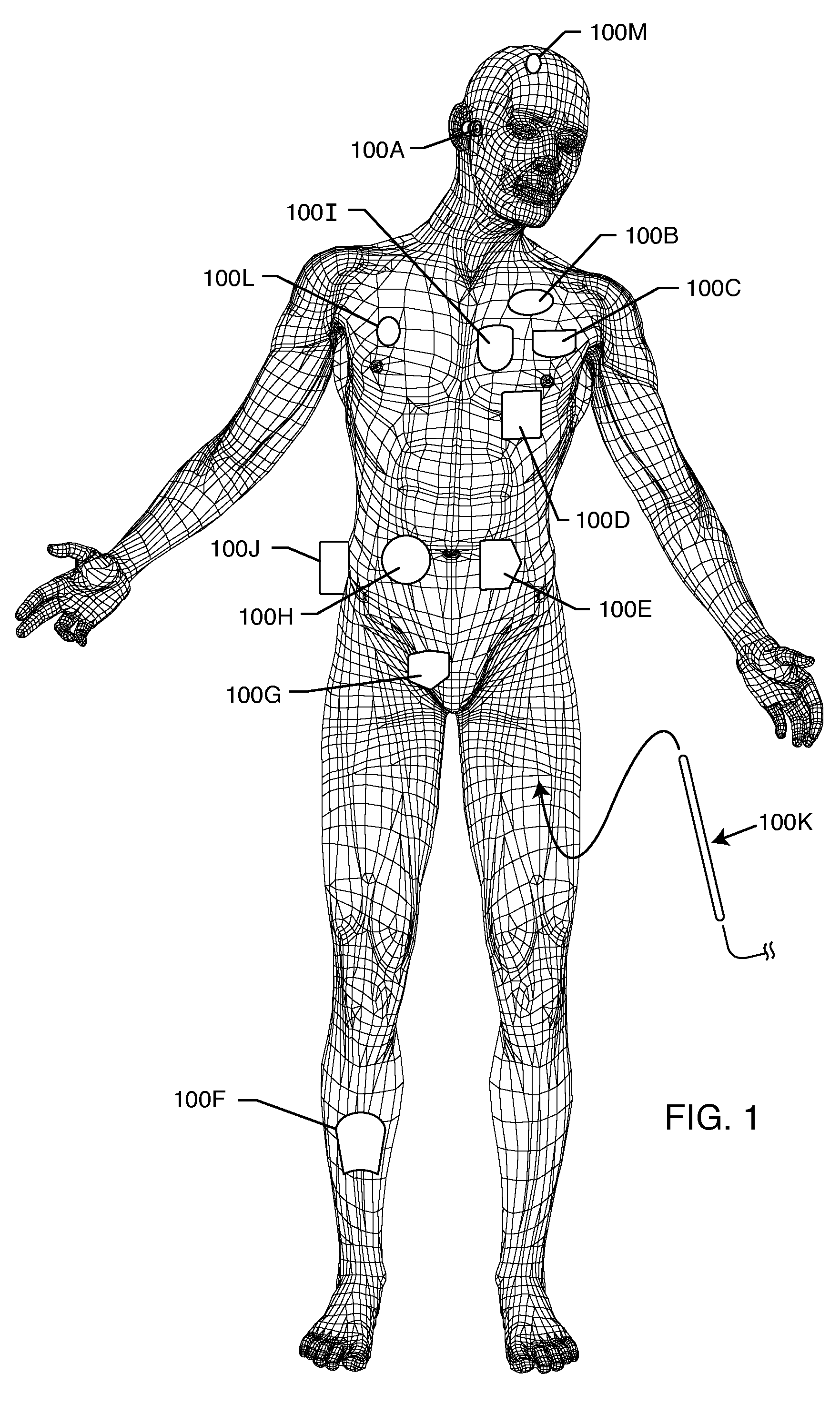

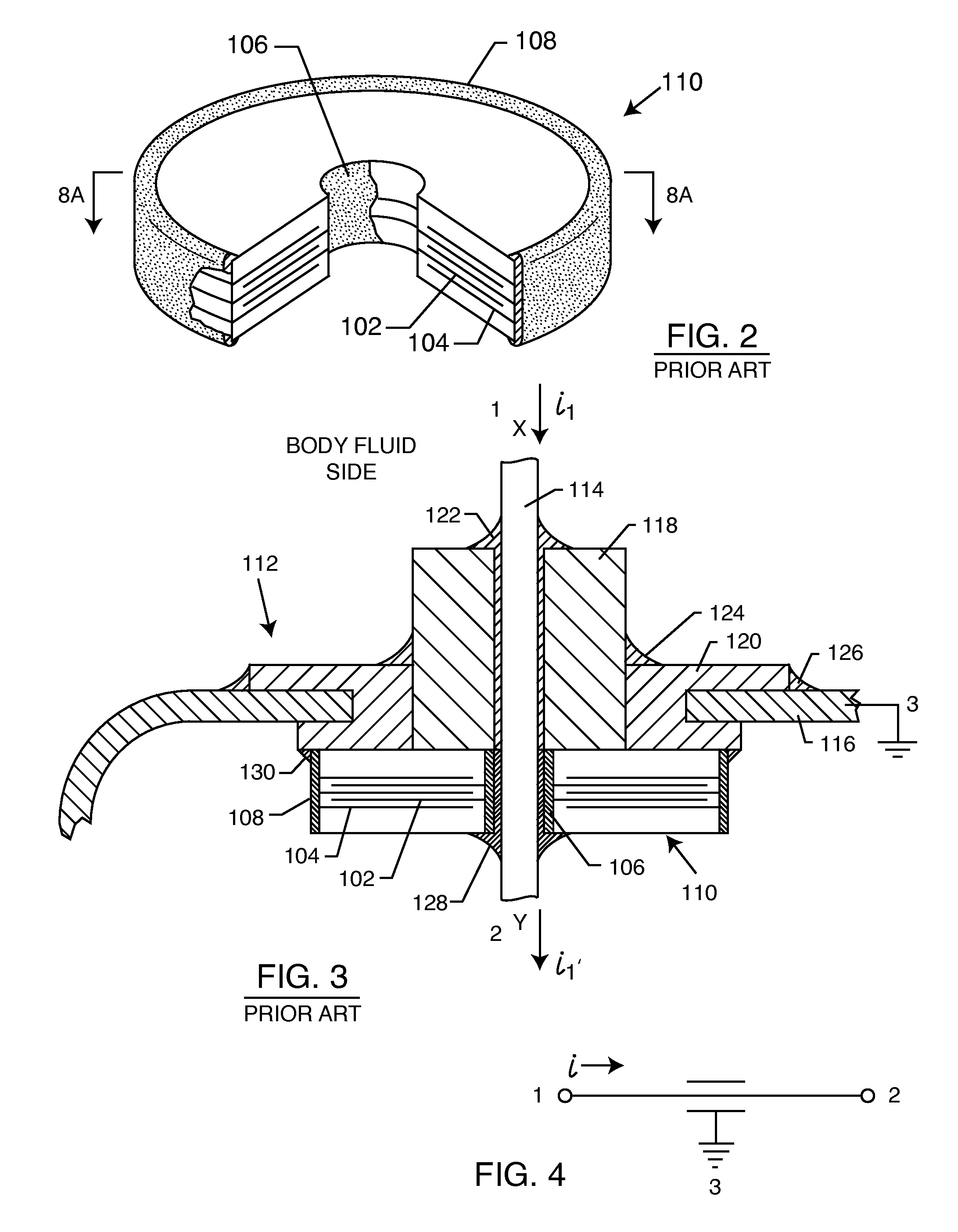

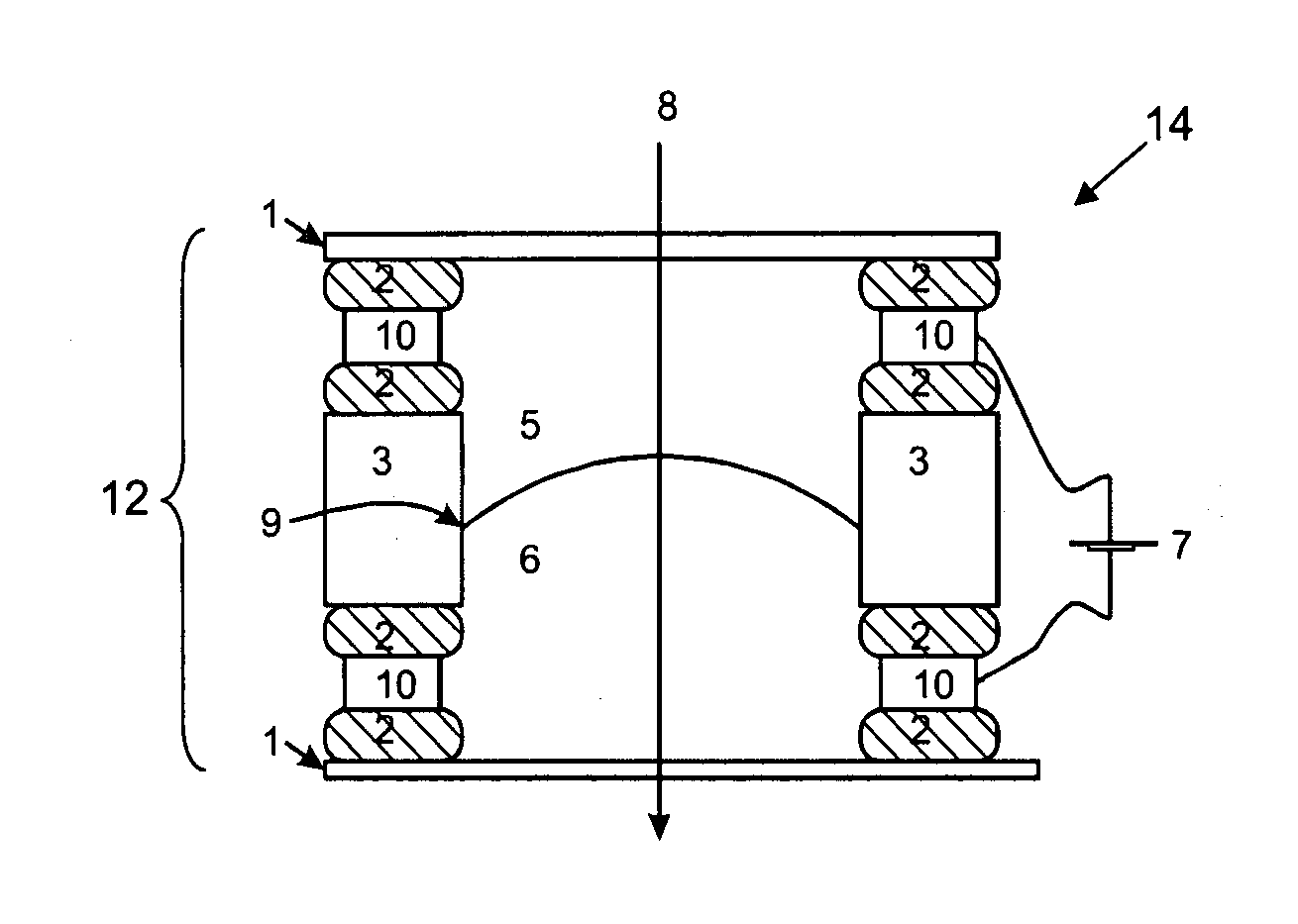

Shielded three-terminal flat-through emi/energy dissipating filter

ActiveUS20090243756A1Maximize valueHigh surface areaMultiple-port networksAnti-noise capacitorsEngineeringFlexible cable

A shielded three-terminal flat-through EMI / energy dissipating filter includes an active electrode plate through which a circuit current passes between a first terminal and a second terminal, a first shield plate on a first side of the active electrode plate, and a second shield plate on a second side of the active electrode plate opposite the first shield plate. The first and second shield plates are conductively coupled to a grounded third terminal. In preferred embodiments, the active electrode plate and the shield plates are at least partially disposed with a hybrid flat-through substrate that may include a flex cable section, a rigid cable section, or both.

Owner:WILSON GREATBATCH LTD

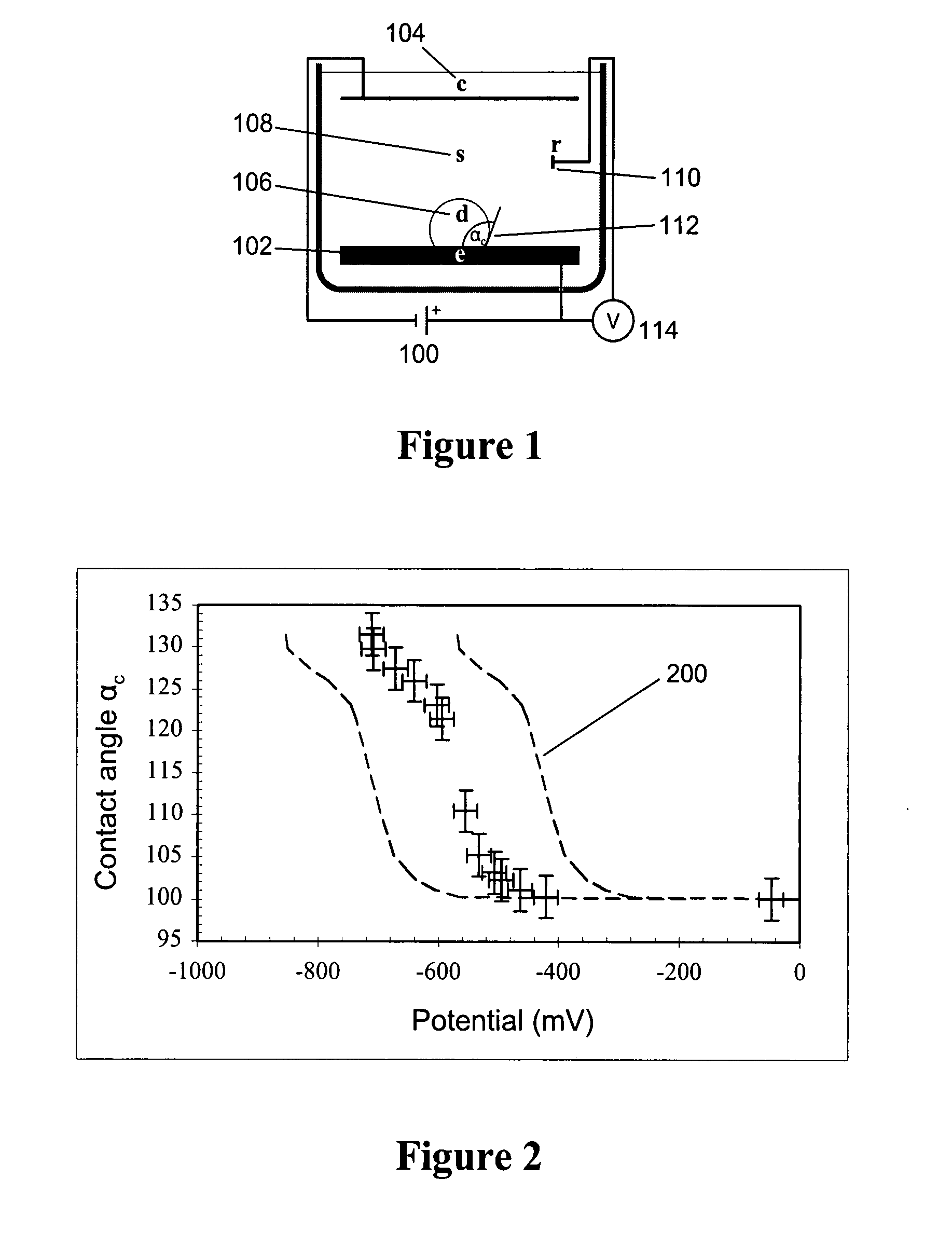

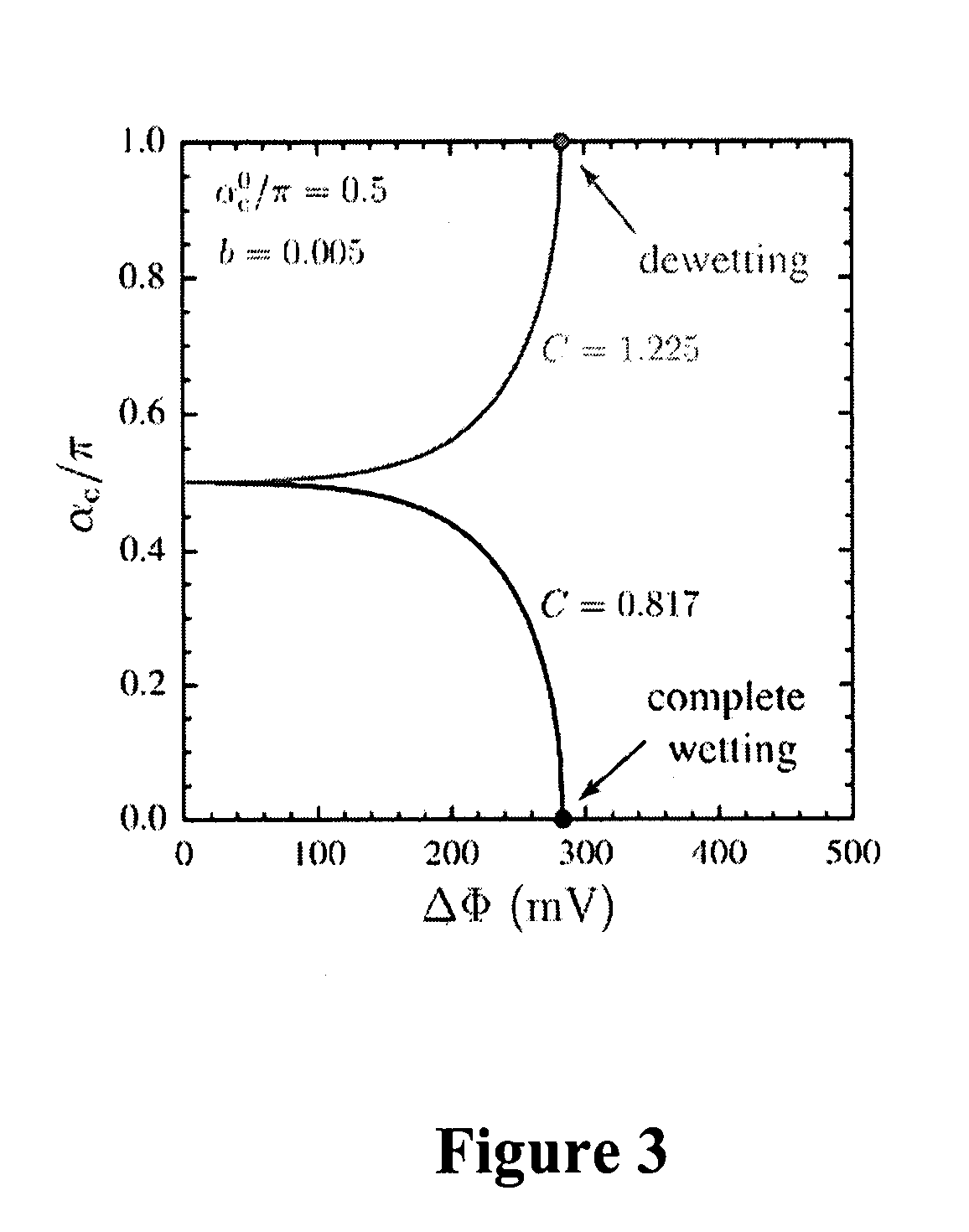

Electrowetting devices

InactiveUS20080283414A1Reduce hysteresisShort response timeCellsPolycrystalline material growthEngineeringVoltage

A device comprising: a chamber containing two immiscible conductive liquids, the liquids having an interface therebetween; and electrodes arranged to apply a voltage across the interface between the said liquids such as to control the shape of the interface.

Owner:IMPERIAL INNOVATIONS LTD +1

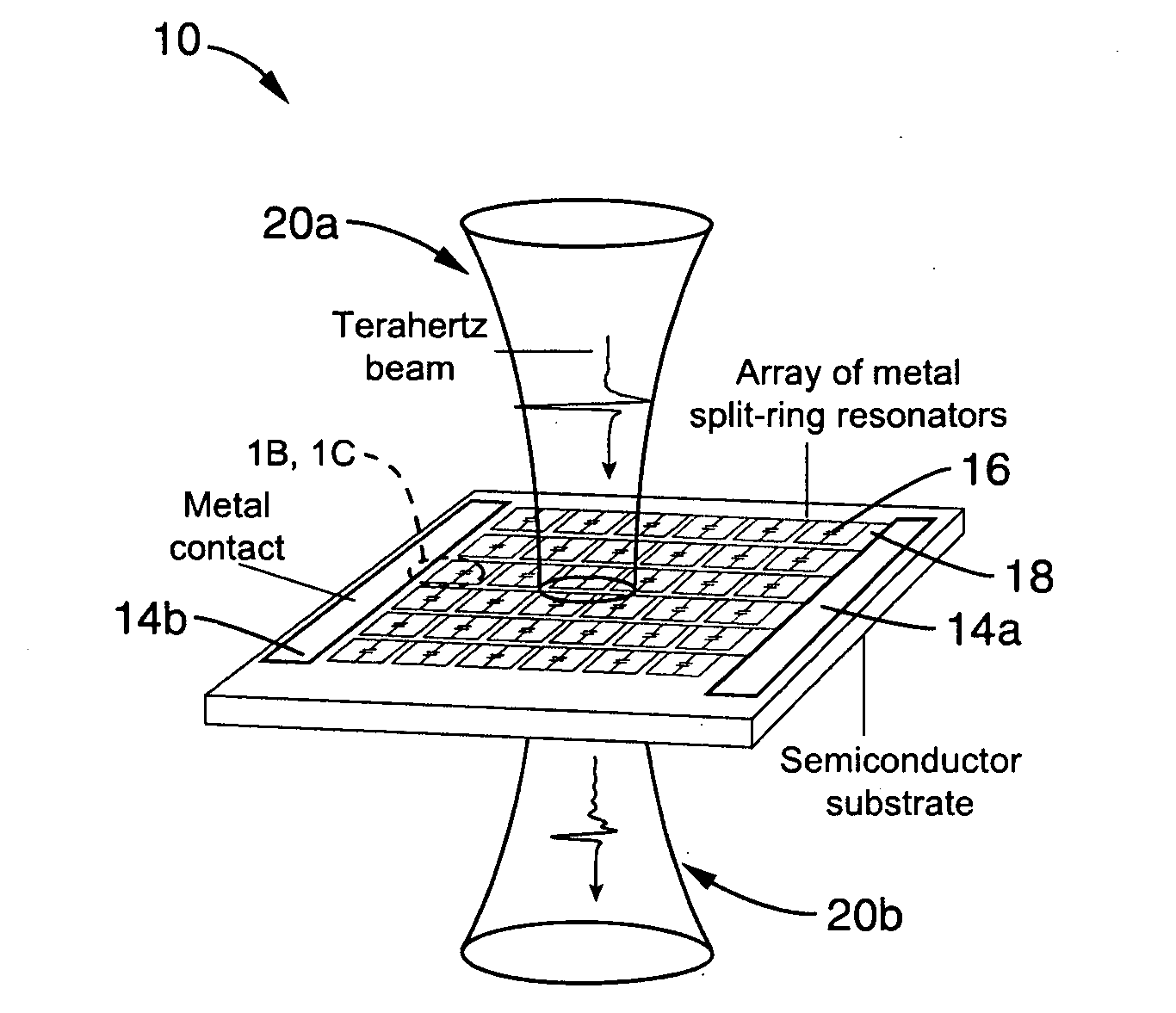

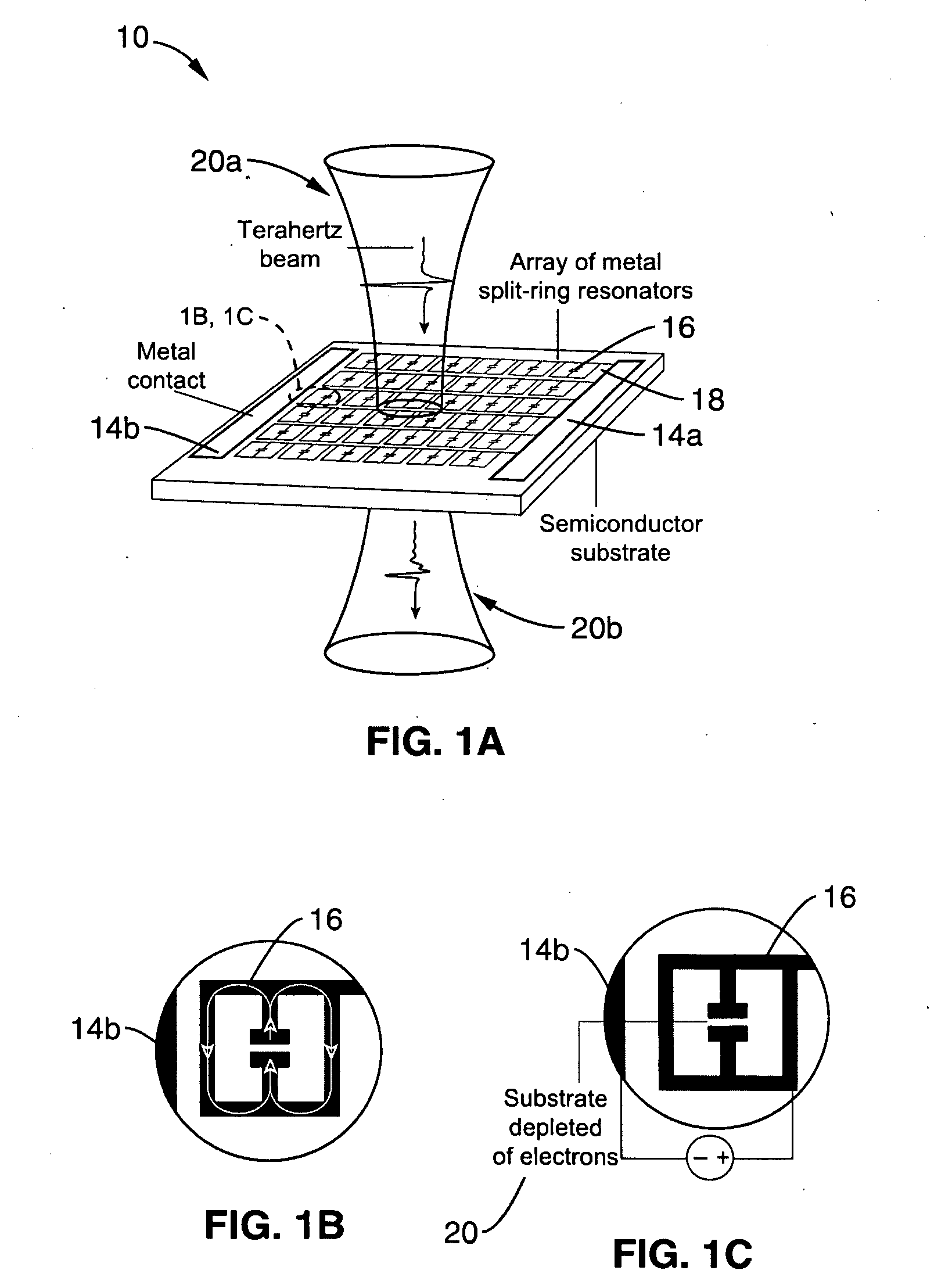

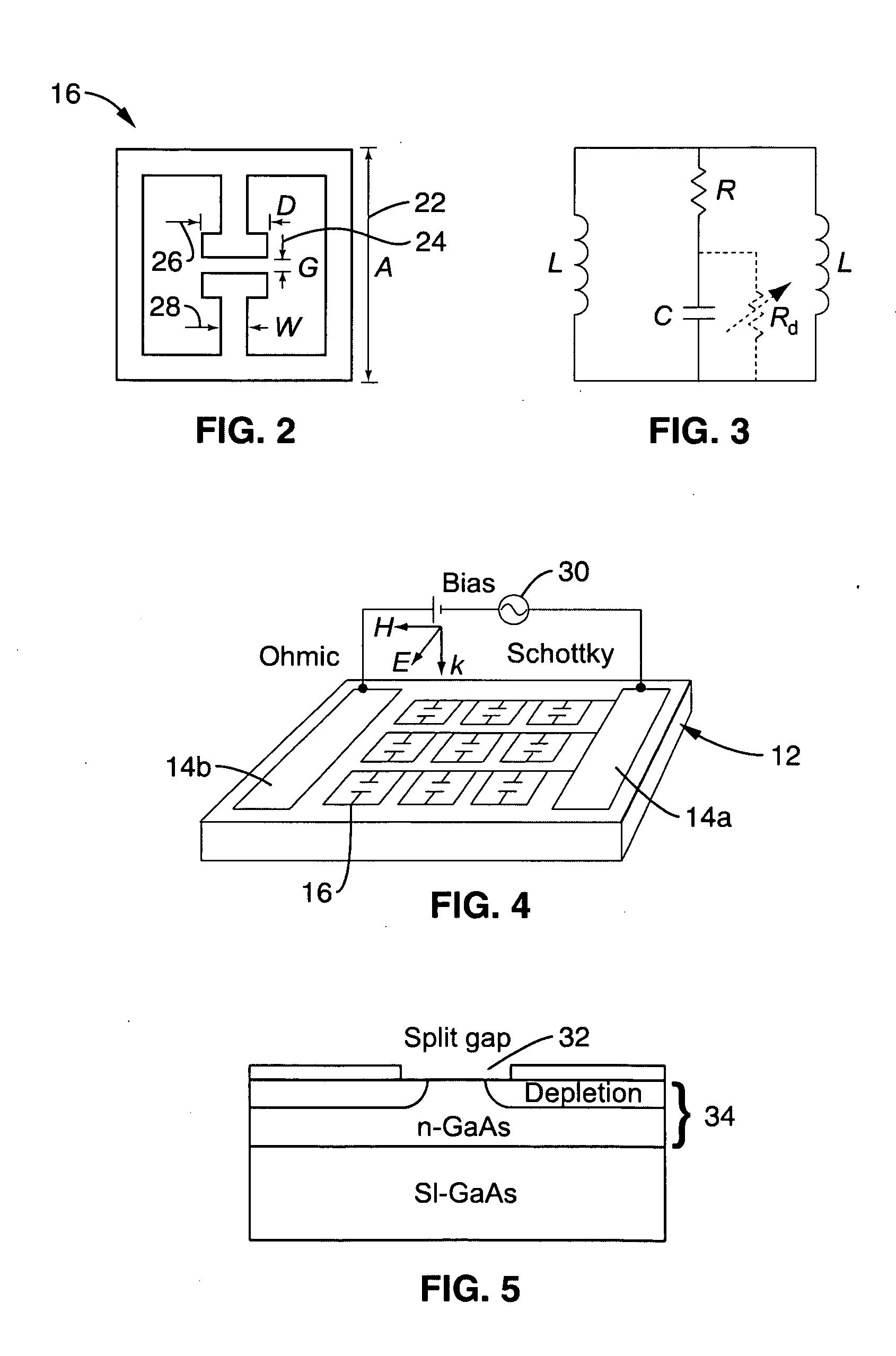

Active terahertz metamaterial devices

ActiveUS20090262766A1Dampens resonant responseIncrease capacitanceResonant long antennasLaser detailsTerahertz metamaterialsTransmittance

Metamaterial structures are taught which provide for the modulation of terahertz frequency signals. Each element within an array of metamaterial (MM) elements comprises multiple loops and at least one gap. The MM elements may comprise resonators with conductive loops and insulated gaps, or the inverse in which insulated loops are present with conductive gaps; each providing useful transmissive control properties. The metamaterial elements are fabricated on a semiconducting substrate configured with a means of enhancing or depleting electrons from near the gaps of the MM elements. An on to off transmissivity ratio of about 0.5 is achieved with this approach. Embodiments are described in which the MM elements incorporated within a Quantum Cascade Laser (QCL) to provide surface emitting (SE) properties.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

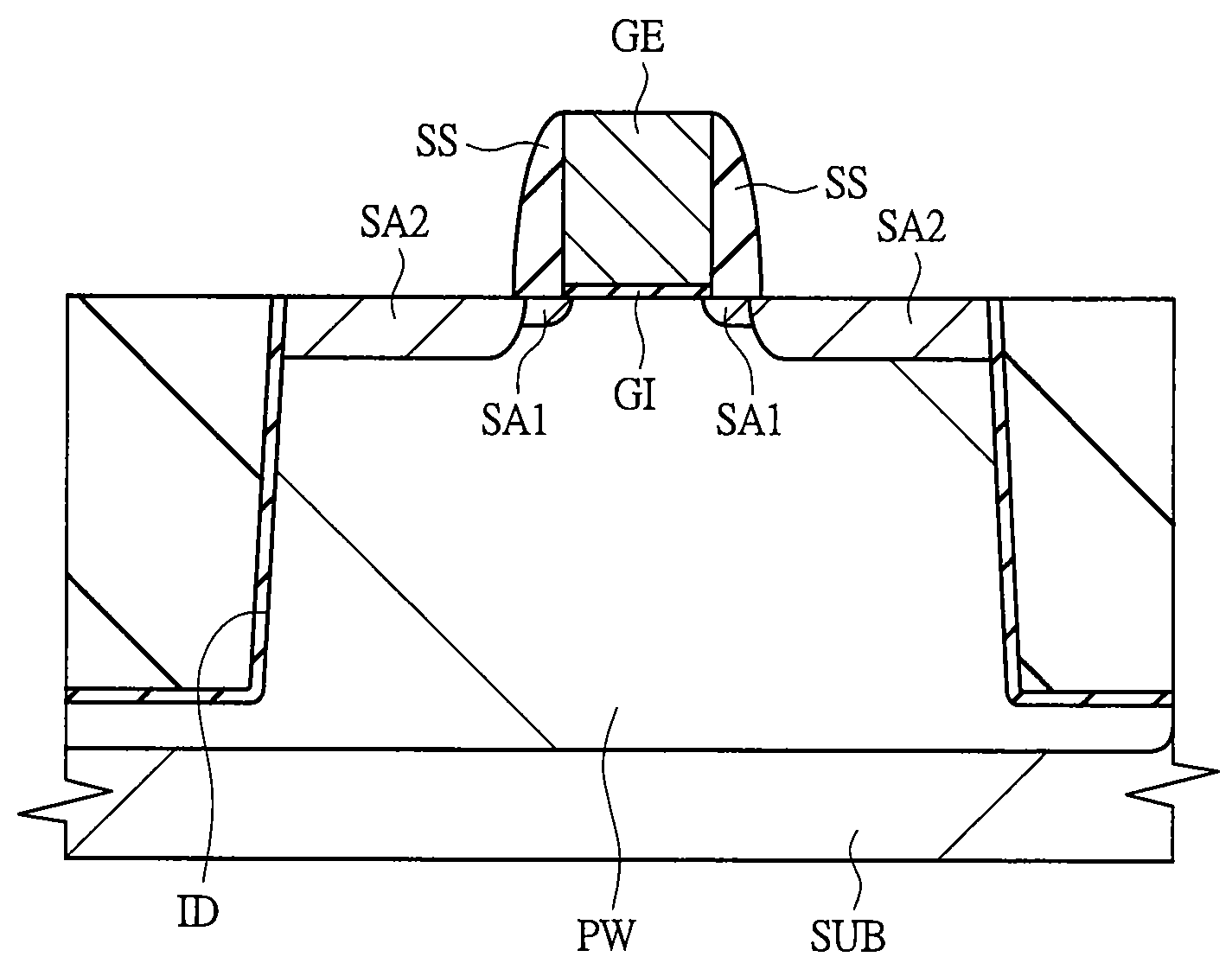

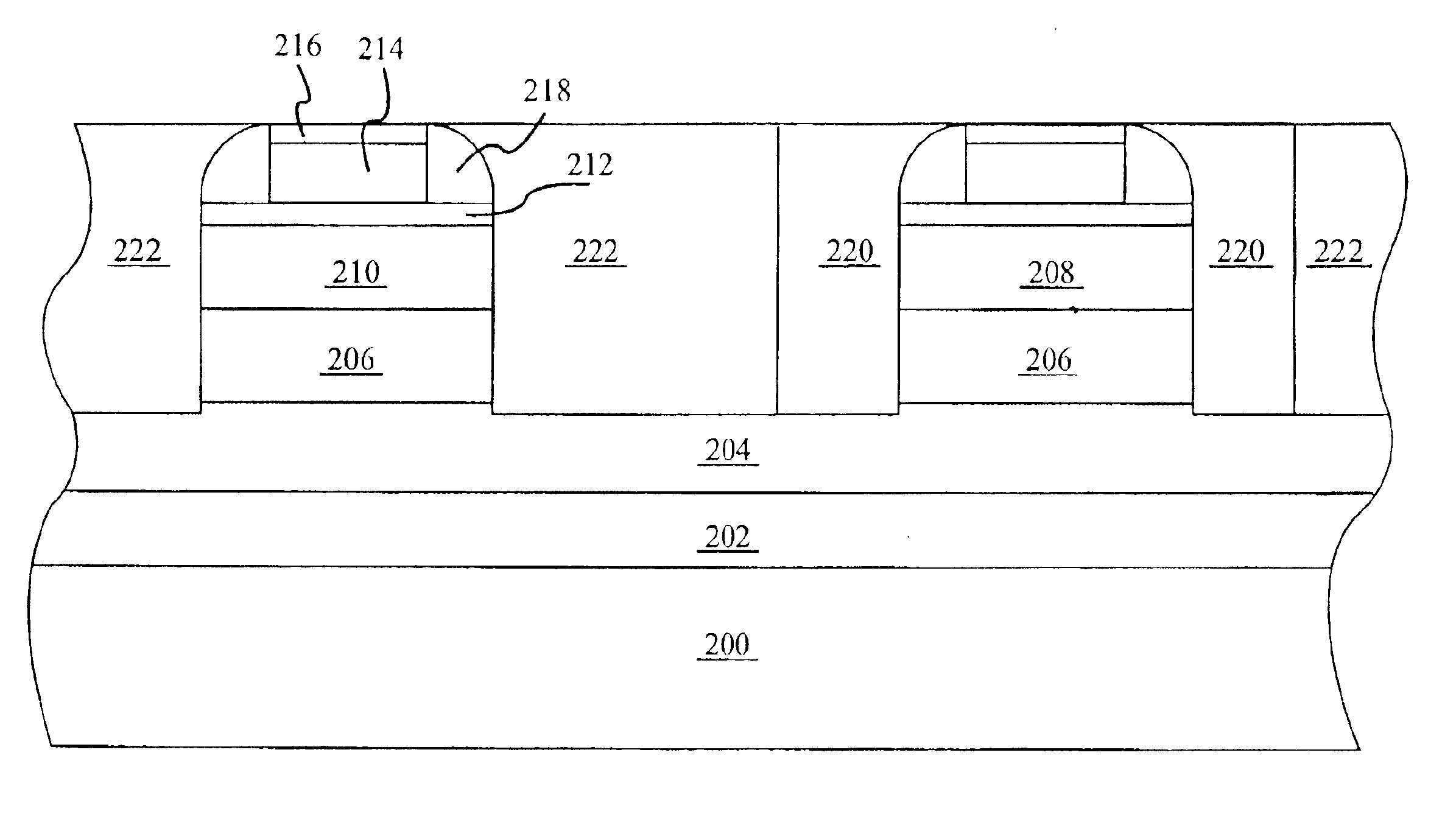

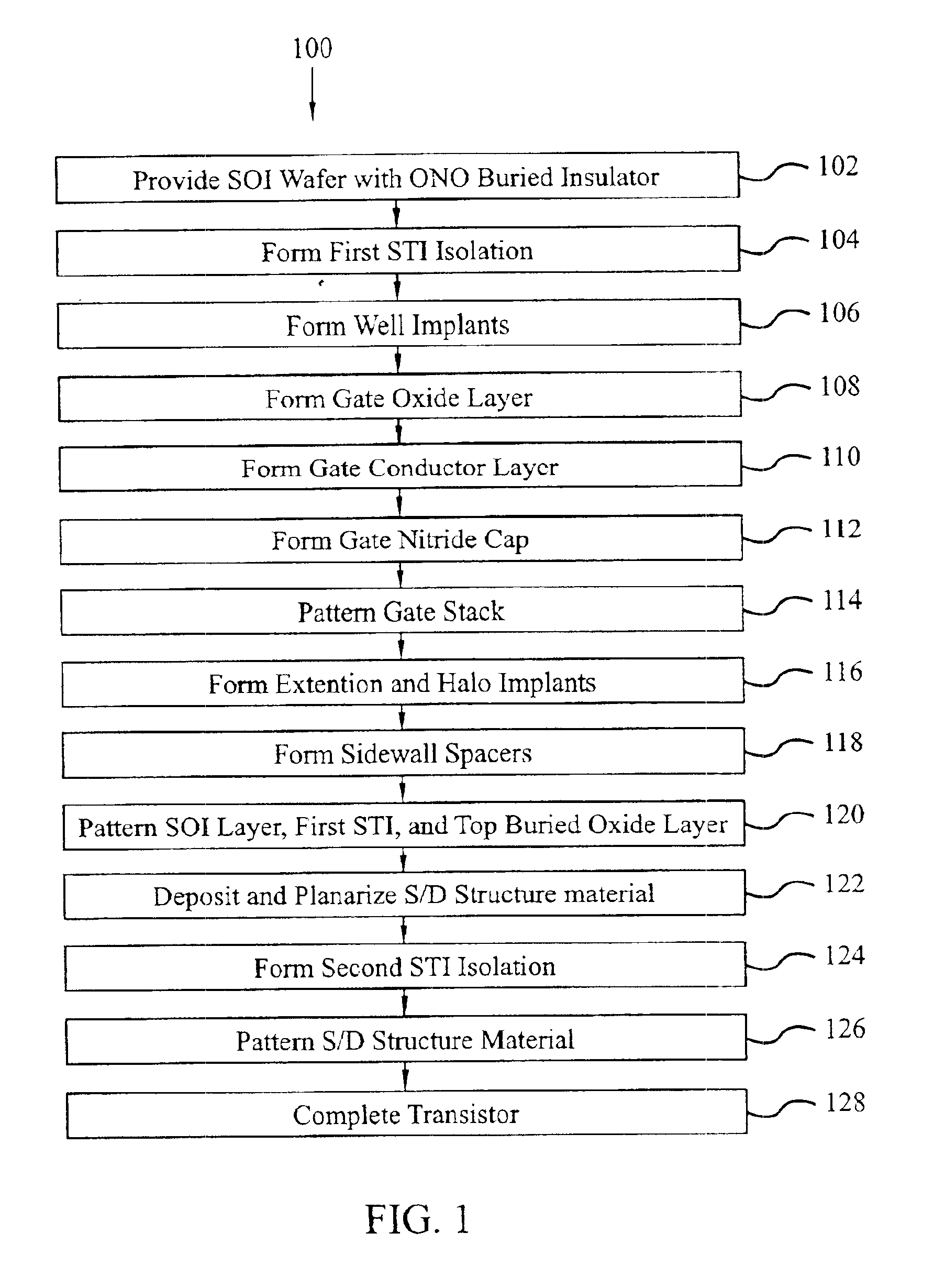

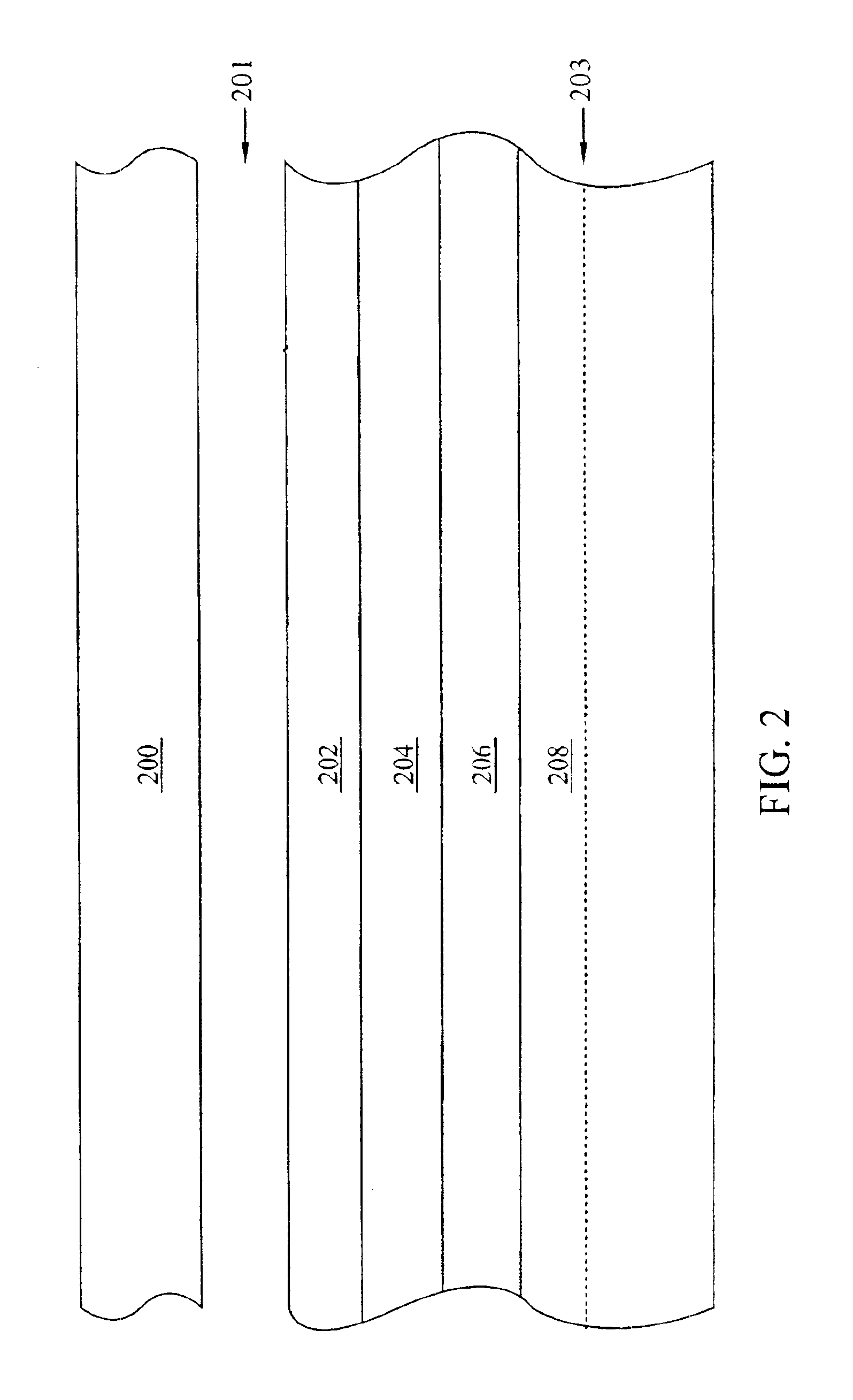

Transistor structure with thick recessed source/drain structures and fabrication process of same

InactiveUS6870225B2Decrease S/D resistanceIncrease capacitanceTransistorSemiconductor/solid-state device detailsCapacitanceEngineering

An improved transistor structure that decreases source / drain (S / D) resistance without increasing gate-to-S / D capacitance, thereby increasing device operation. S / D structures are formed into recesses formed on a semiconductor wafer through a semiconductor layer and a first layer of a buried insulator having at least two layers. A body is formed from the semiconductor layer situated between the recesses, and the body comprises a top body surface and a bottom body surface that define a body thickness. Top portions of the S / D structures are within and abut the body thickness. An improved method for forming the improved transistor structure is also described and comprises: forming recesses through a semiconductor layer and a first layer of a buried insulator so that a body is situated between the recesses; and forming S / D structures into the recesses so that top portions of the S / D structures are within and abut a body thickness.

Owner:IBM CORP

Semiconductor device and method for manufacturing the same

ActiveUS20110024750A1Excellent electrical propertiesImprove reliabilityTransistorSolid-state devicesDevice materialParasitic capacitance

An object is to provide a semiconductor device having a structure with which parasitic capacitance between wirings can be sufficiently reduced. An oxide insulating layer serving as a channel protective layer is formed over part of an oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the oxide insulating layer, an oxide insulating layer covering a peripheral portion of the oxide semiconductor layer is formed. The oxide insulating layer which covers the peripheral portion of the oxide semiconductor layer is provided to increase the distance between the gate electrode layer and a wiring layer formed above or in the periphery of the gate electrode layer, whereby parasitic capacitance is reduced.

Owner:SEMICON ENERGY LAB CO LTD

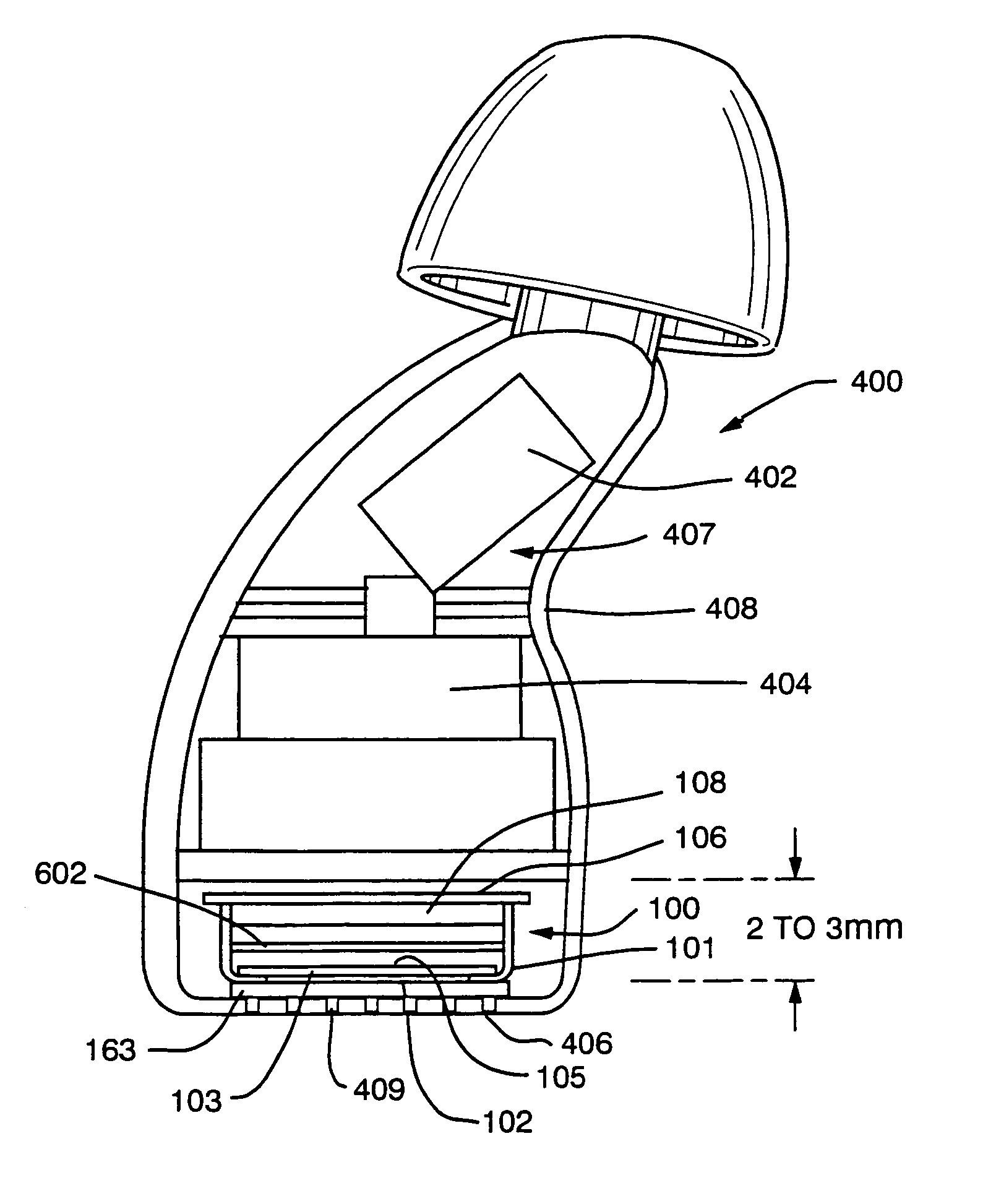

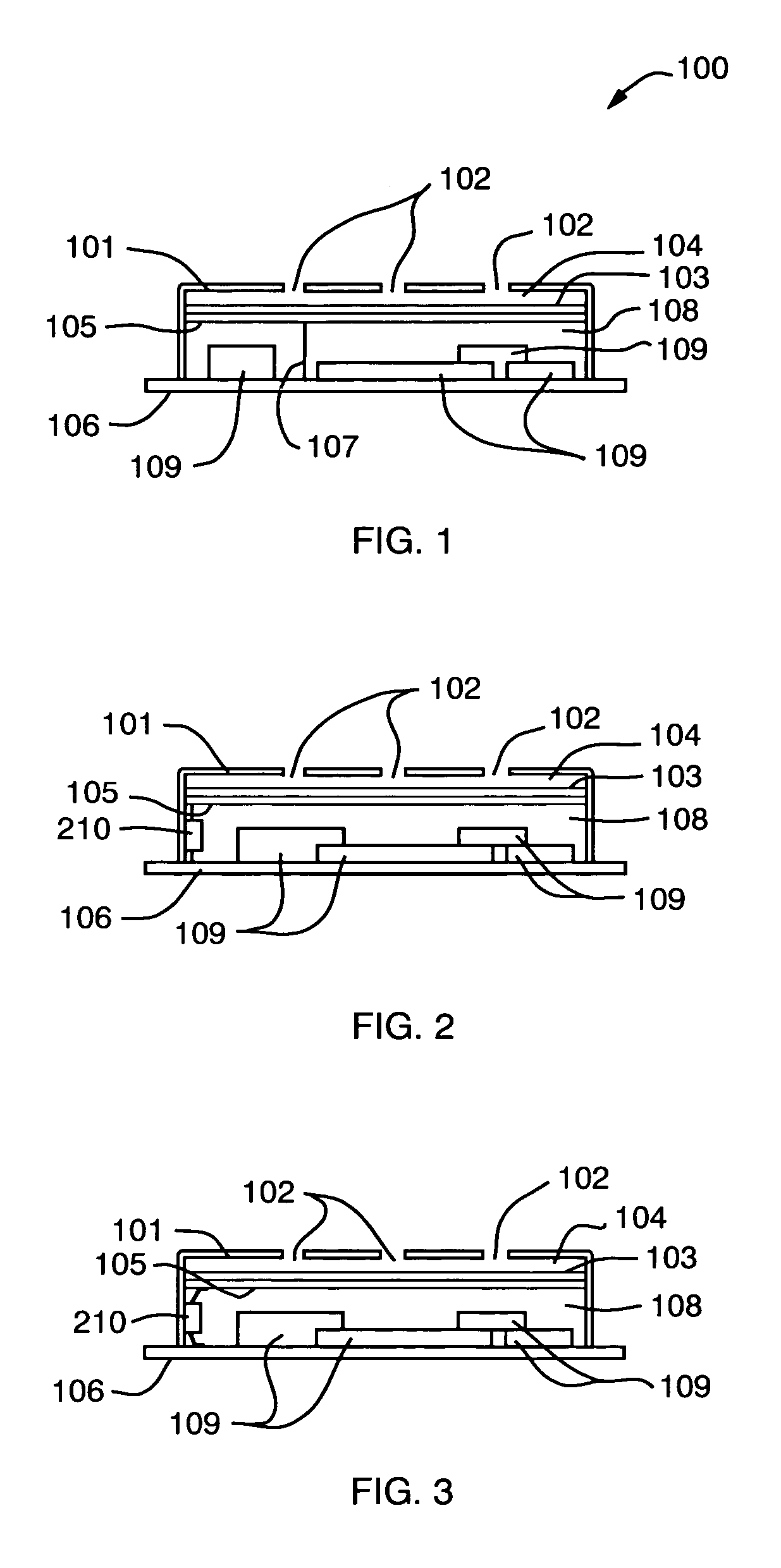

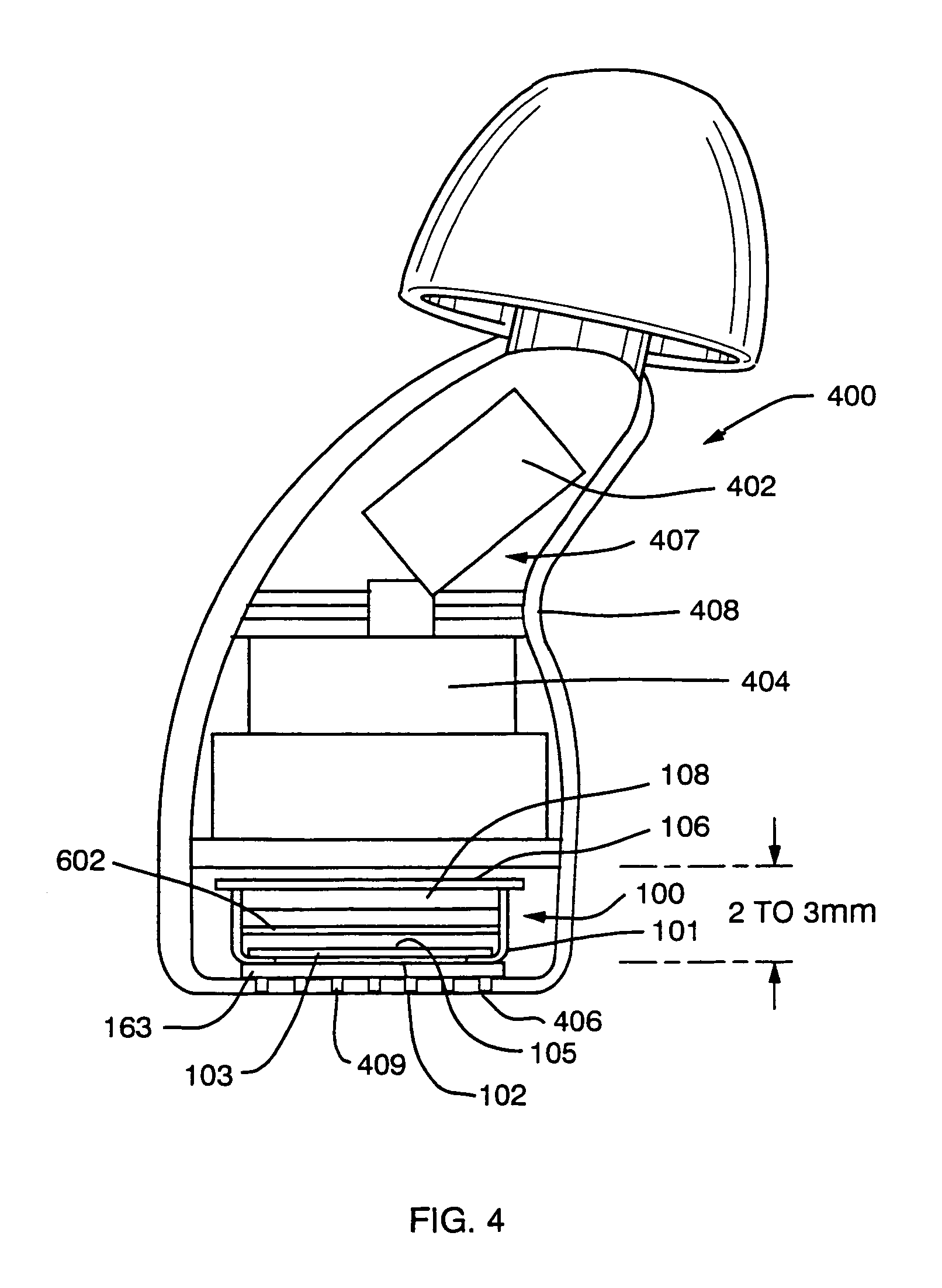

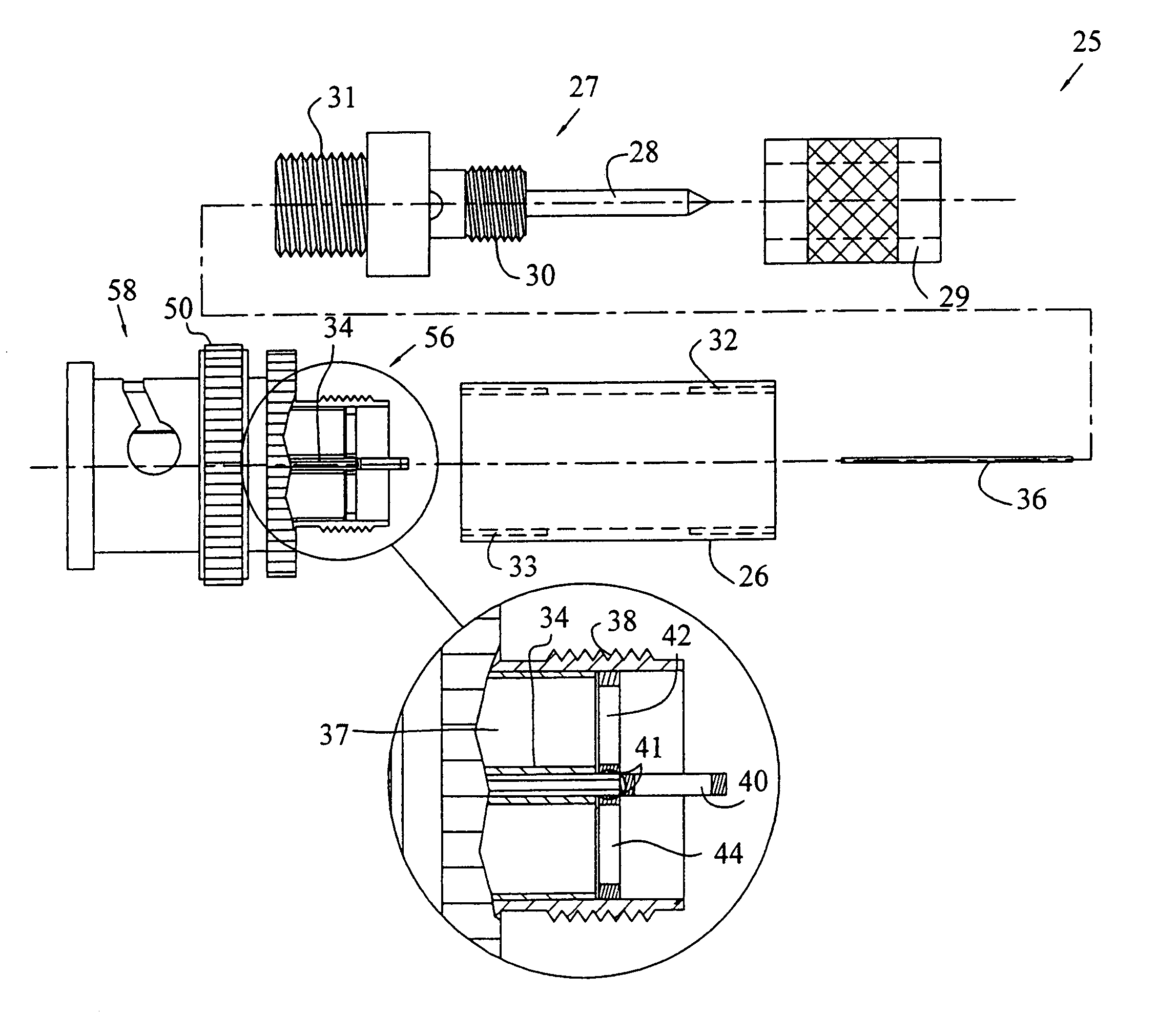

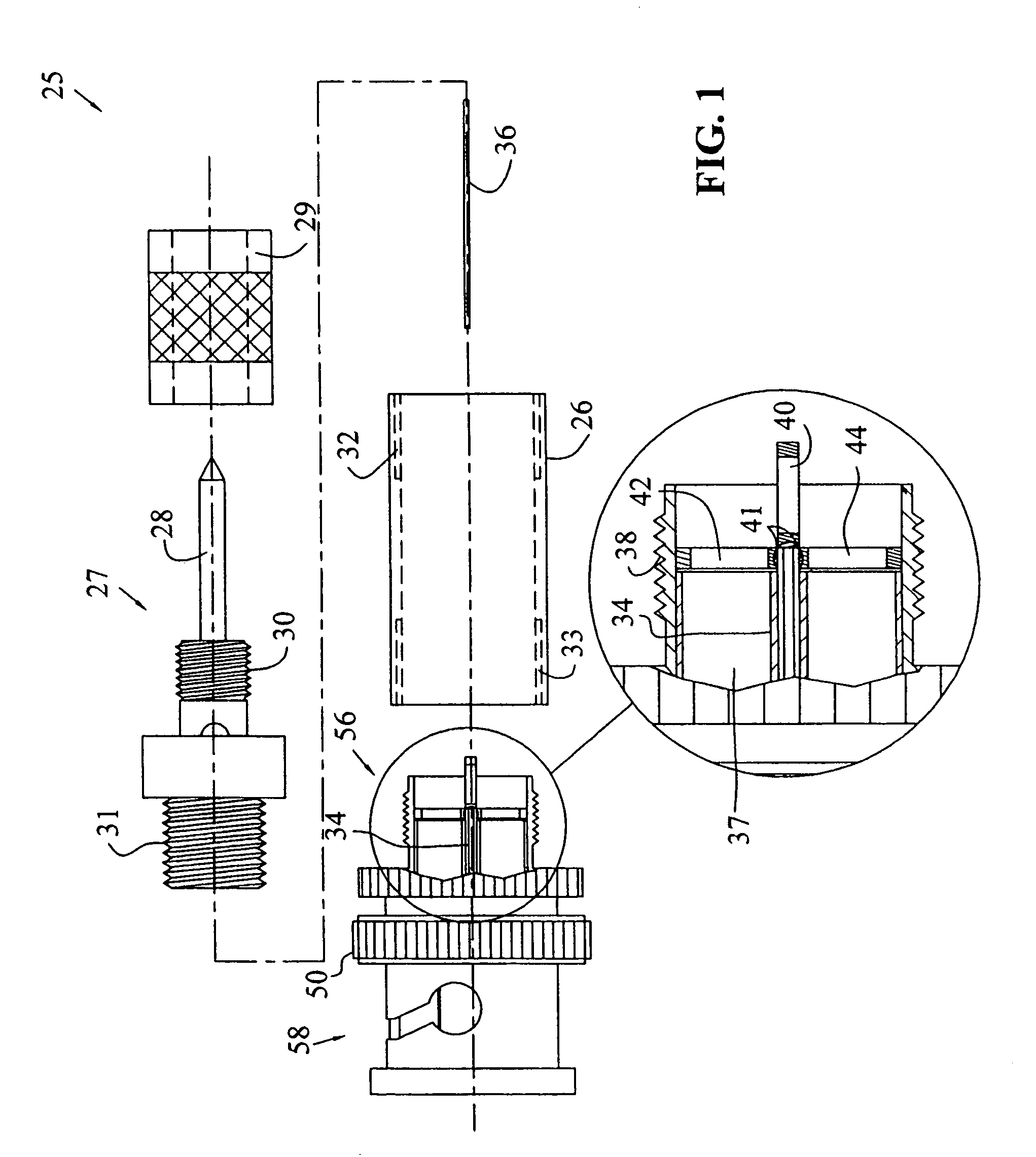

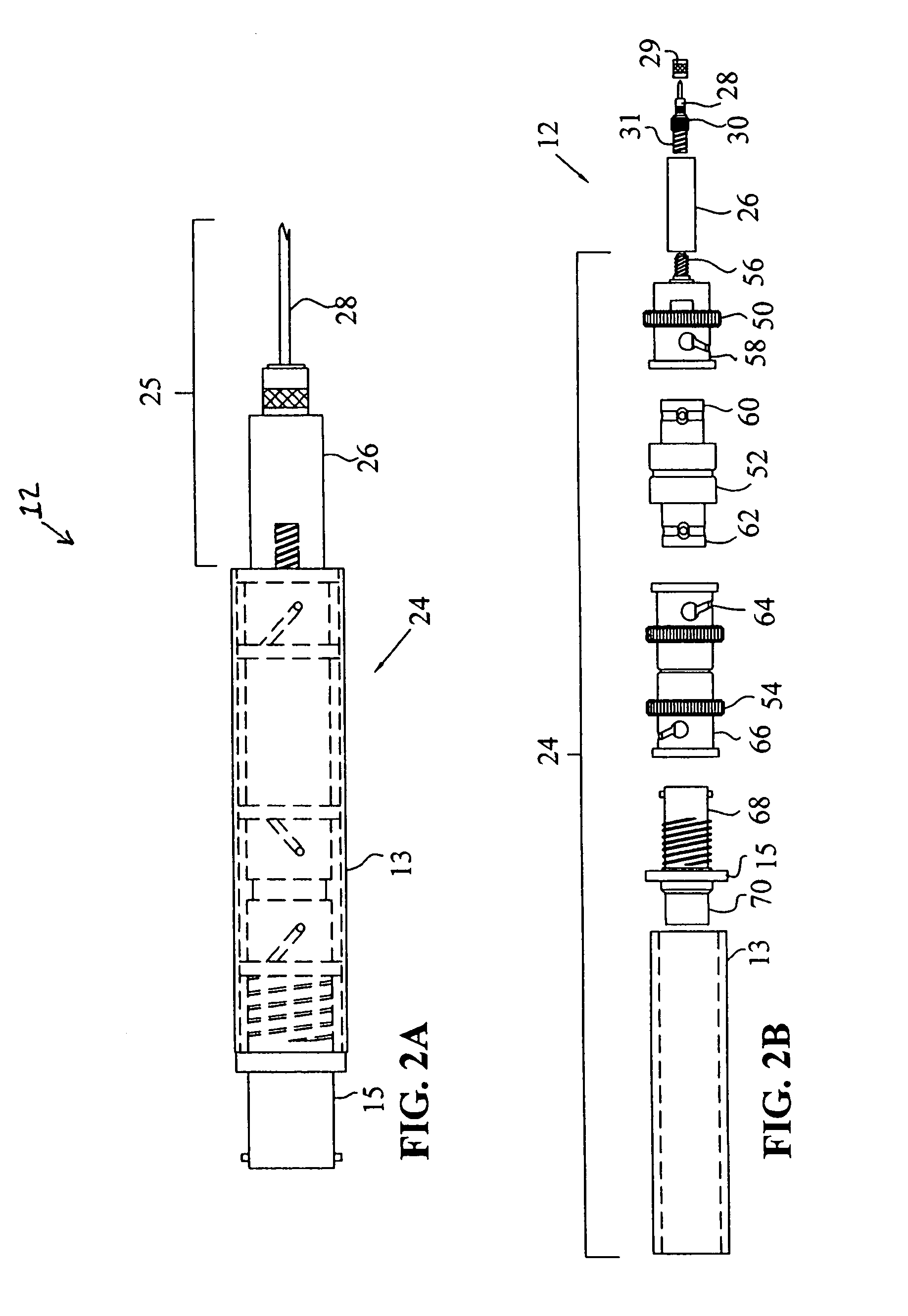

Hearing aid with large diaphragm microphone element including a printed circuit board

InactiveUS7003127B1Low costImprove performanceElectrostatic transducersHearing aids housingLow noiseElectrical connection

A disposable-type hearing aid uses a relatively large single diaphragm or a large single diaphragm subdivided into a plurality of smaller active diaphragm areas obtained using a grate-like back support plate with ridges which contact and divide the diaphragm into the several smaller active diaphragm areas. The diaphragm and a backplate are enclosed in a metal housing and are disposed proximal and parallel to a shell-like hearing aid enclosure having sound inlets. The metal housing is closed at an end opposite the sound inlets by a printed circuit board (PCB) forming an acoustical seal for a back volume of the microphone. The PCB also carries substantially all the electronic components for the hearing aid thereon. The PCB has a ground plane in contact with the housing whereby the PCB also acts as an EMI shield. An electrical connection is formed in various ways between the back support plate and the PCB during assembly of the metal housing and components with the PCB. Mass production of disposable hearing aids with large diaphragms and relatively low noise levels is thus possible using this invention.

Owner:HIMPP

Ultra-broadband differential voltage probes

ActiveUS7015709B2Reduce parasitic inductanceError minimizationElectrical testingMeasurement leads/probesElectricityElectrical conductor

Passive balanced probes are disclosed for use with a signal analysis device. The probes are very low cost relative to typical commercially available probes and provide an extremely flat response over a frequency range of approximately 0 to at least 1.5 gigahertz. The probes include a probe body constructed primarily from conventional components, a first surface mount resistor electrically connected between a probe tip and a center conductor, and two surface mount resistors electrically connected and parallel between the center conductor and a conductive shield. The probes further include a coaxial cable for connection to an instrument combiner or other instrument connection device.

Owner:APTIV TECH LTD

Liquid crystal display device having improved touch screen

InactiveUS20070040814A1Increase capacitanceReduce the amount requiredCathode-ray tube indicatorsNon-linear opticsSignal onVariable capacitor

A liquid crystal display having a touch screen includes a plurality of sensing data lines formed on a display panel, a plurality of variable capacitors connected to the sensing data lines and having capacitance that varies with a pressure, a plurality of reference capacitors connected to the sensing data lines, and a plurality of sensing signal output units each connected to the sensing data lines for generating output signals on the basis of sensing data signals that flow through the sensing data lines. The sensing signal output units change the amount of current based on the sensing data signals to reduce current corresponding to the output signals.

Owner:SAMSUNG ELECTRONICS CO LTD

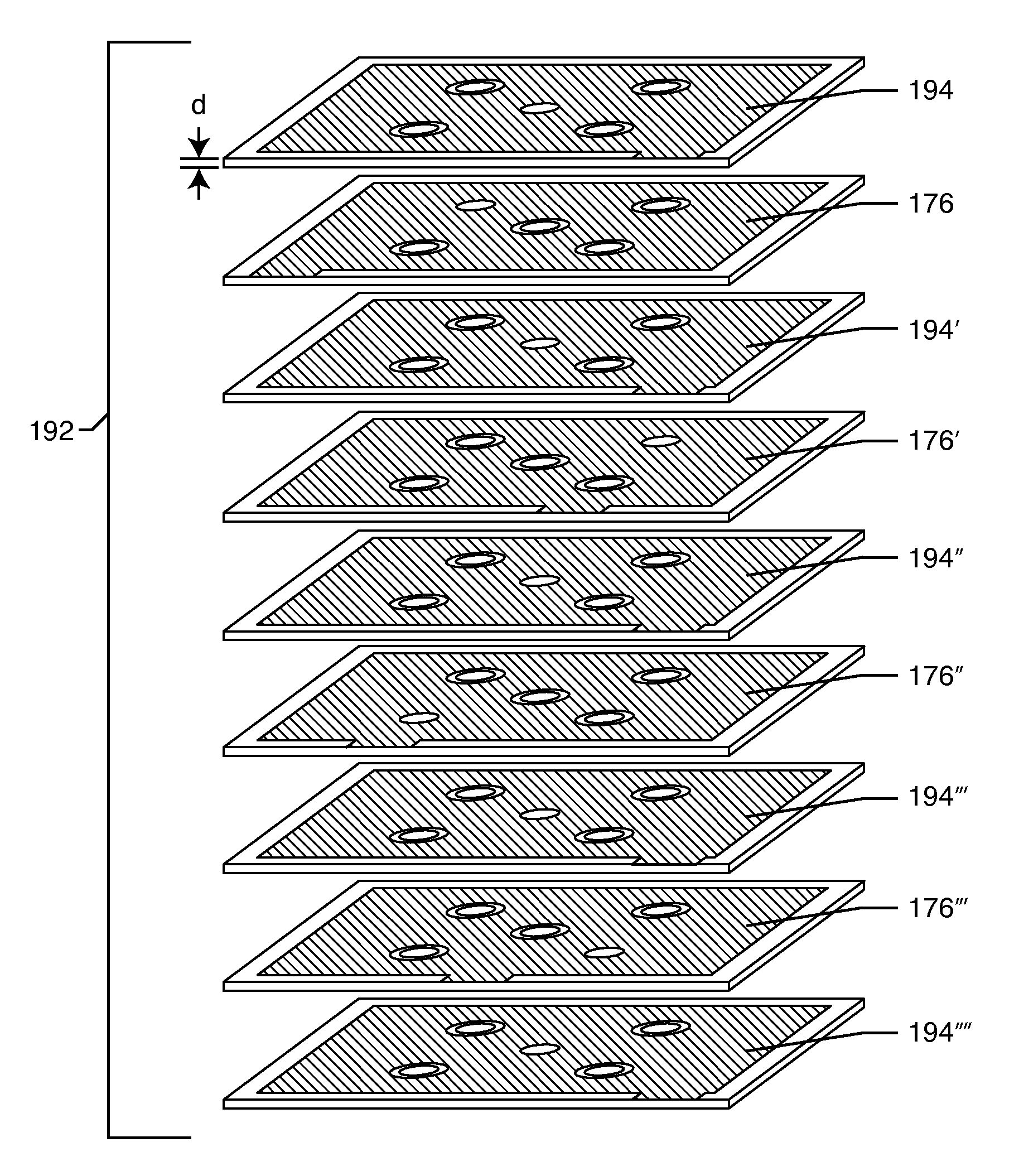

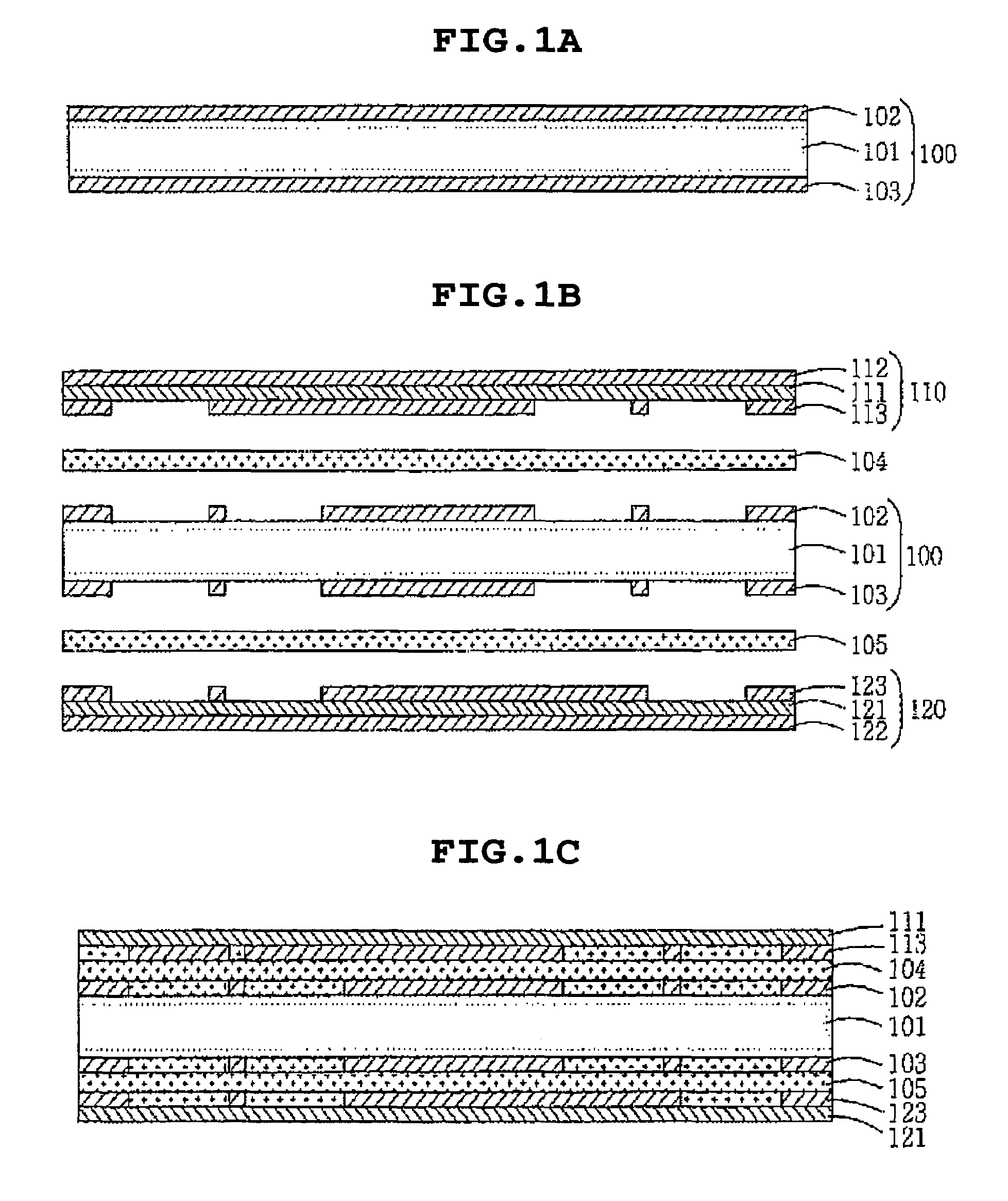

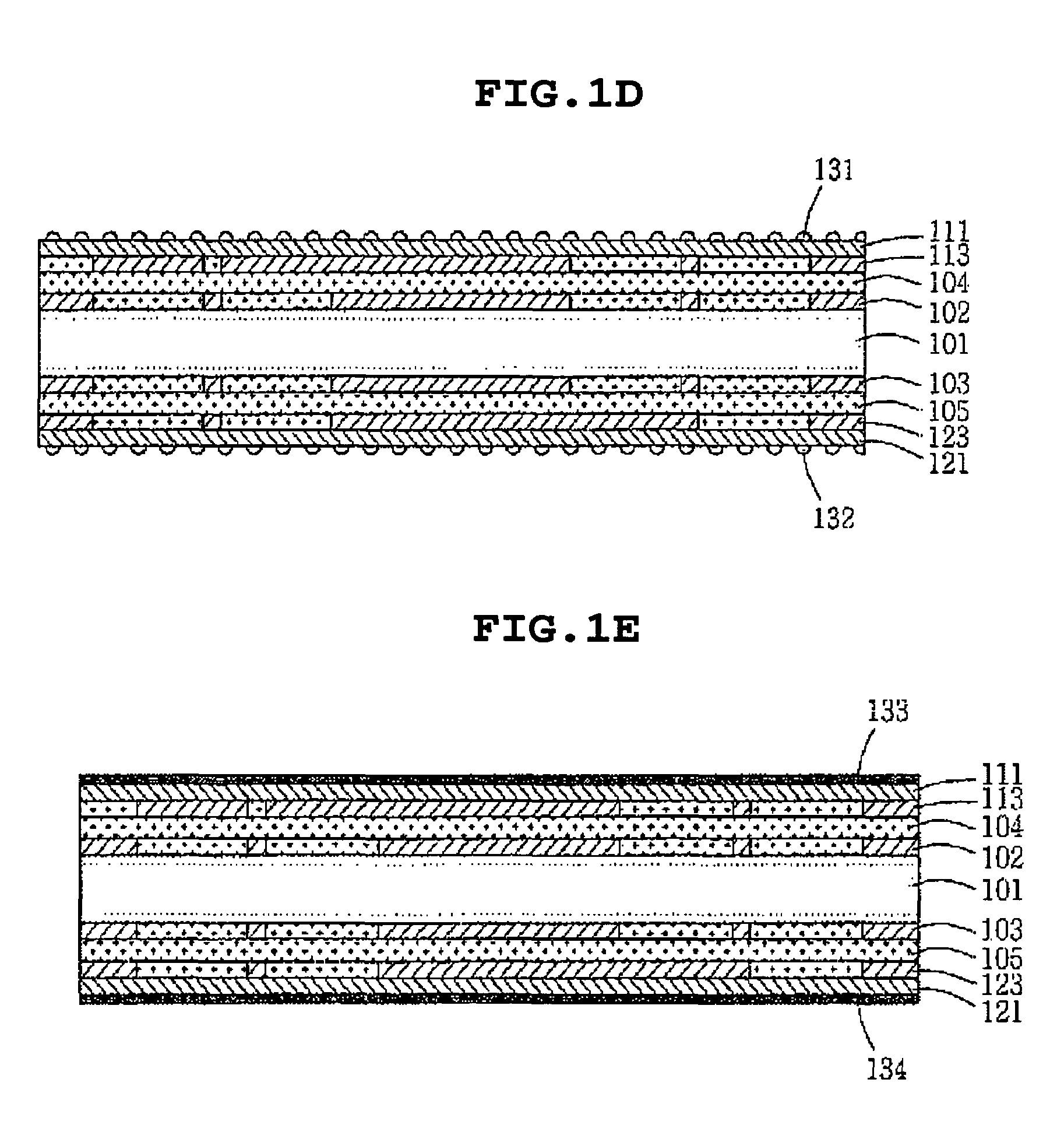

Method of fabricating printed circuit board having embedded multi-layer passive devices

InactiveUS7293356B2Increase capacitancePrinted circuit assemblingPrinted circuit aspectsCapacitancePrinted circuit board

The present invention relates to a method of fabricating a printed circuit board having embedded multi-layer passive devices, and particularly, to a method of fabricating a printed circuit board having an embedded multi-layer capacitor, in which a capacitor is formed to have multiple layers in the PCB to increase capacitance.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD