Patents

Literature

38337results about How to "Improve features" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

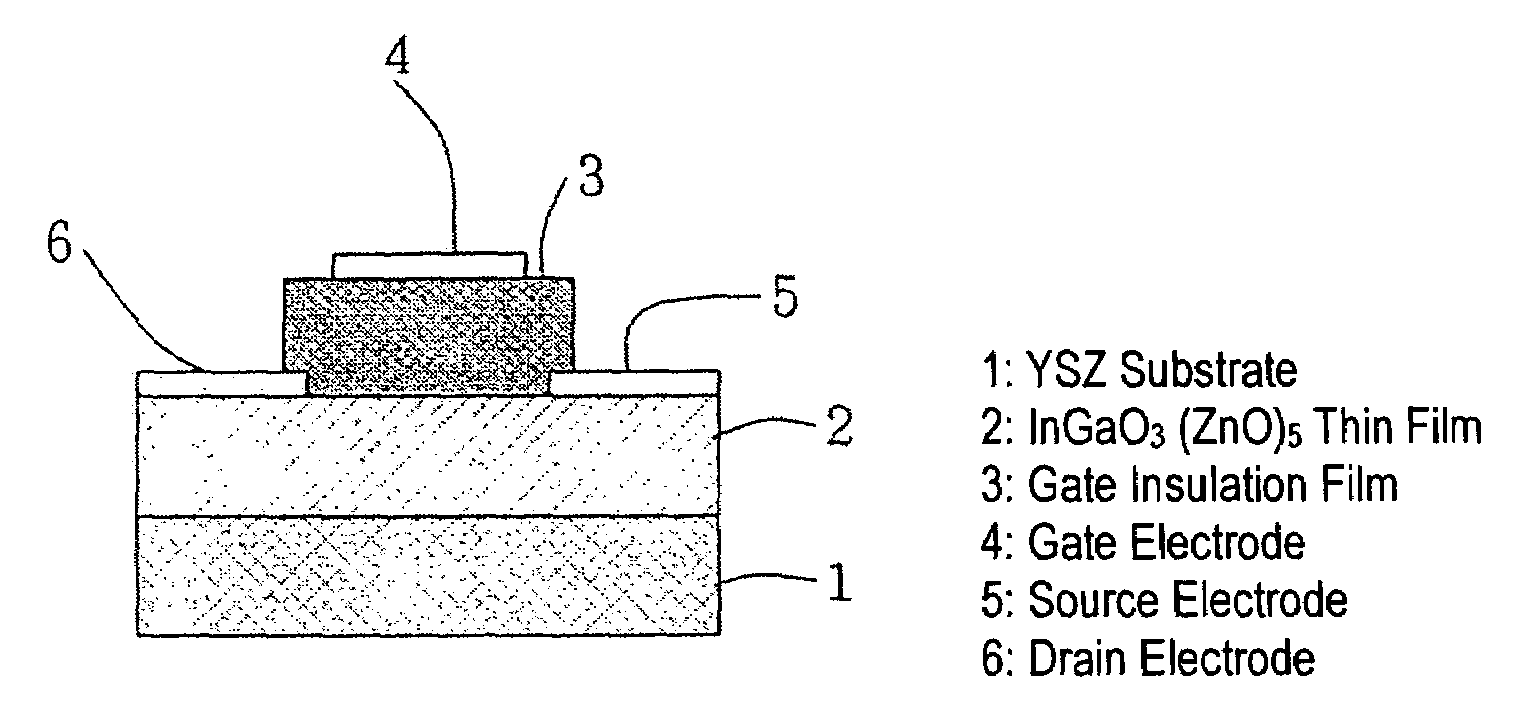

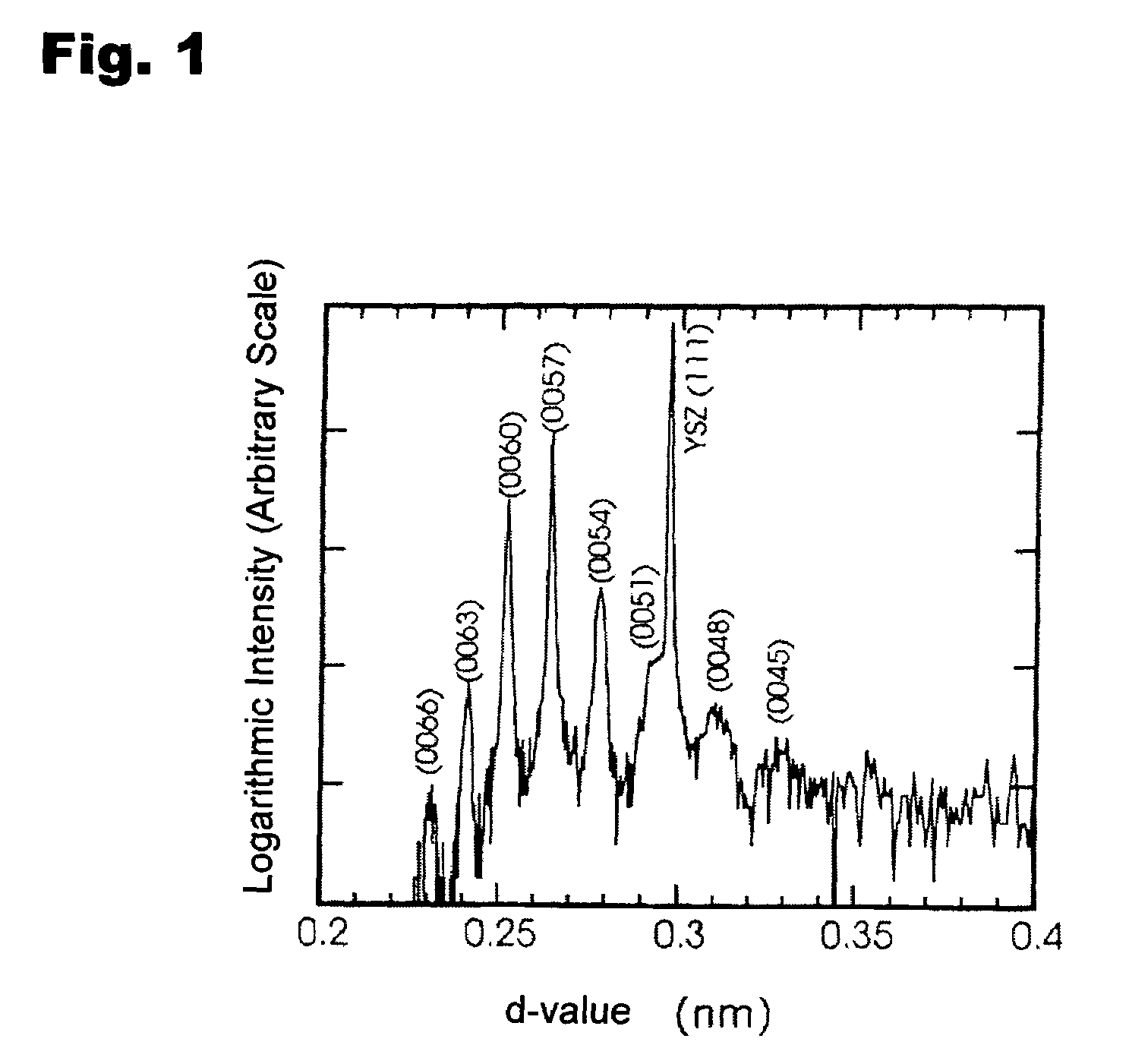

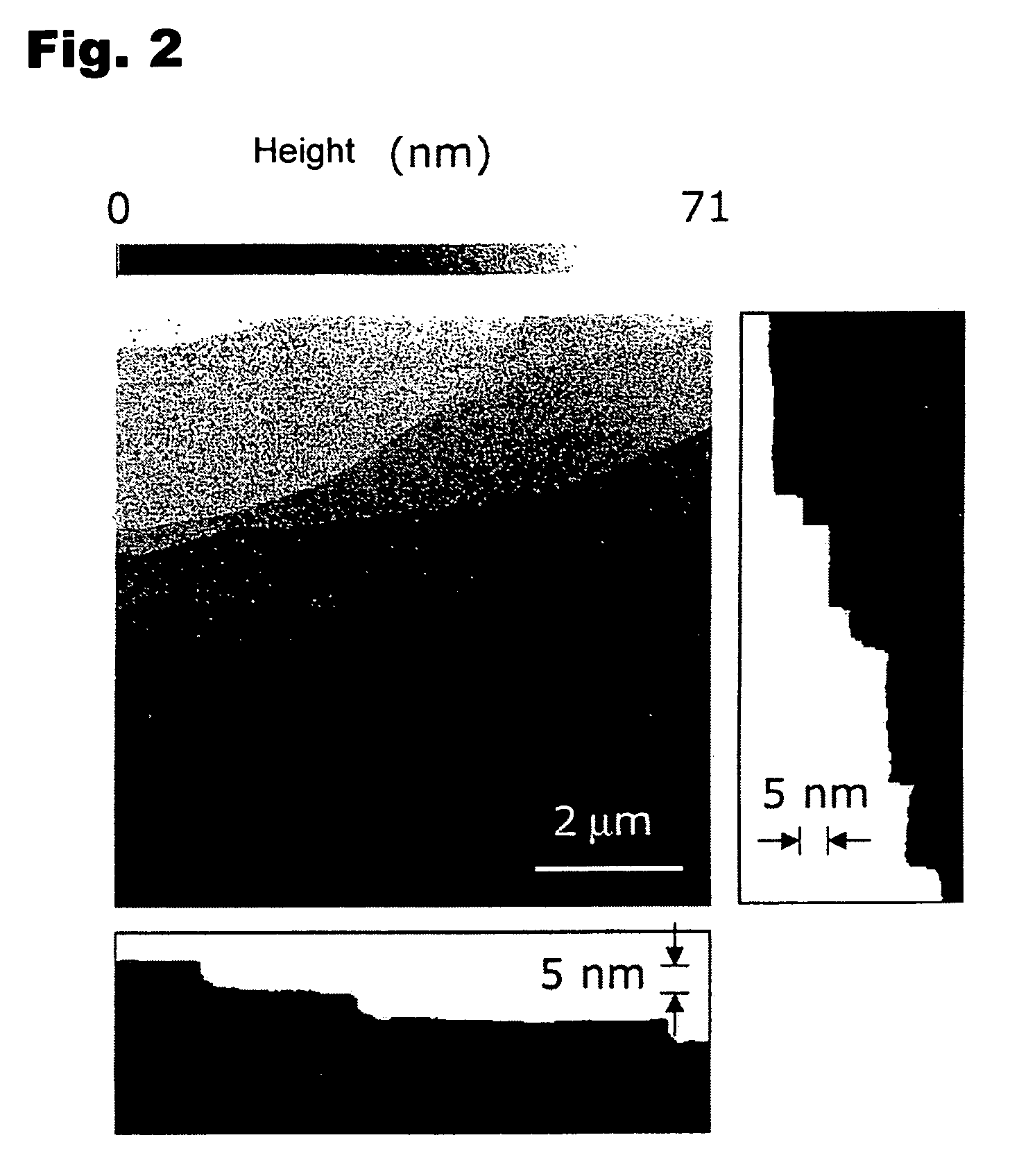

Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film

InactiveUS7061014B2Easy to controlSimple processTransistorPolycrystalline material growthSingle crystal substrateSingle crystal

Disclosed is a natural-superlattice homologous single-crystal thin film, which includes a complex oxide which is epitaxially grown on either one of a ZnO epitaxial thin film formed on a single-crystal substrate, the single-crystal substrate after disappearance of the ZnO epitaxial thin film and a ZnO single crystal. The complex oxide is expressed by the formula: M1M2O3 (ZnO)m, wherein M1 is at least one selected from the group consisting of Ga, Fe, Sc, In, Lu, Yb, Tm, Er, Ho and Y, M2 is at least one selected from the group consisting of Mn, Fe, Ga, In and Al, and m is a natural number of 1 or more. A natural-superlattice homologous single-crystal thin film formed by depositing the complex oxide and subjecting the obtained layered film to a thermal anneal treatment can be used in optimal devices, electronic devices and X-ray optical devices.

Owner:HOYA CORP +1

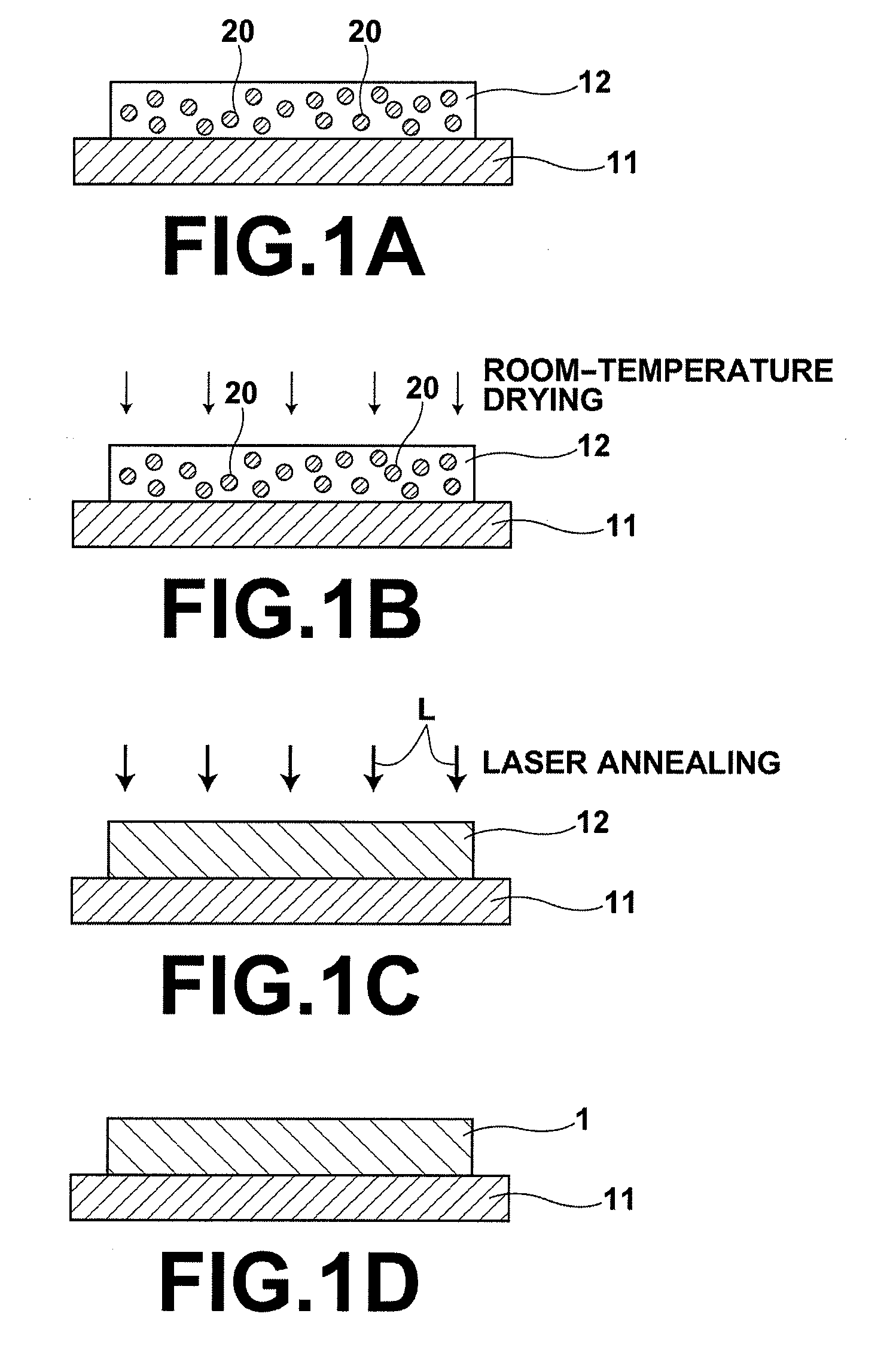

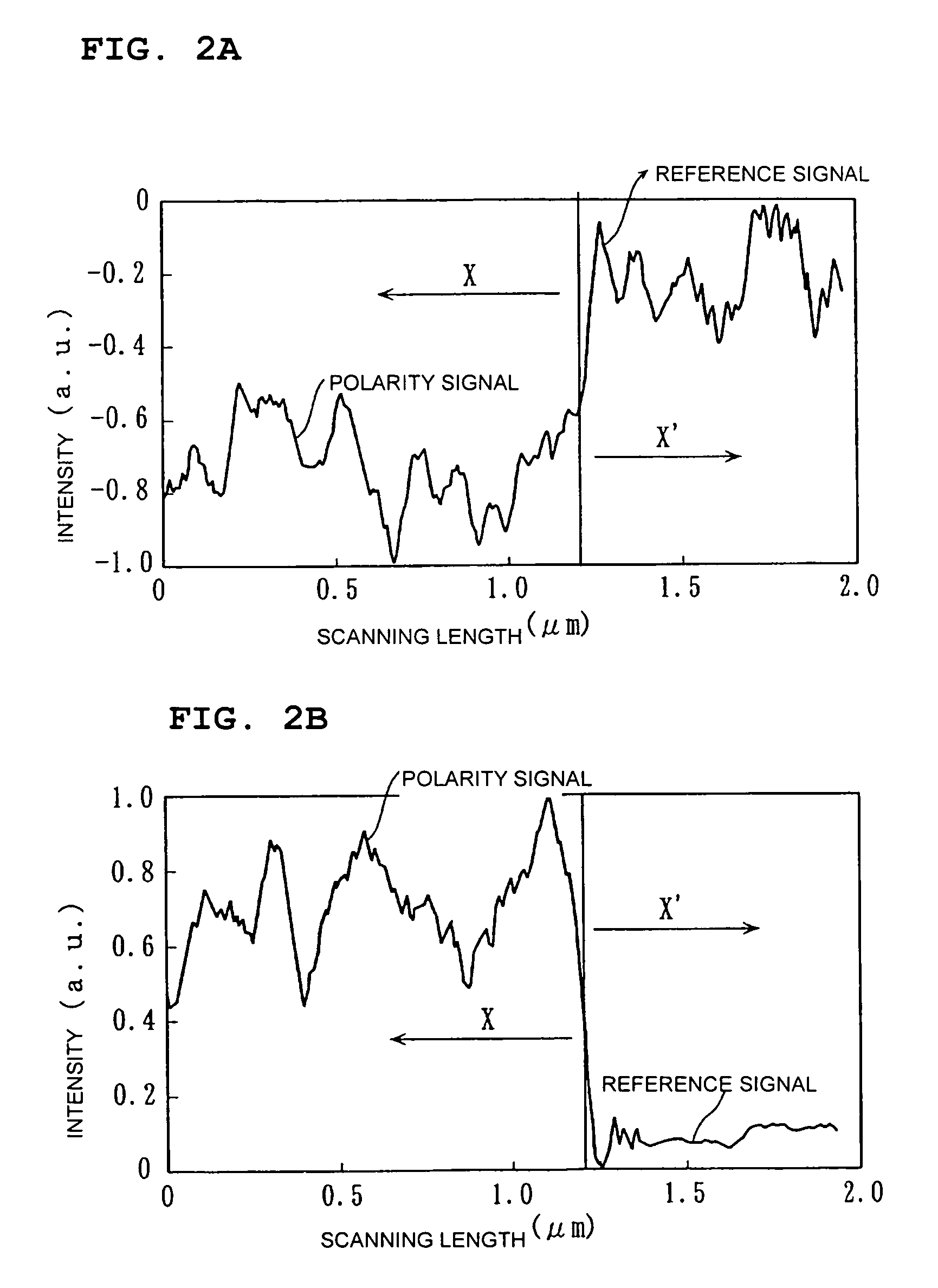

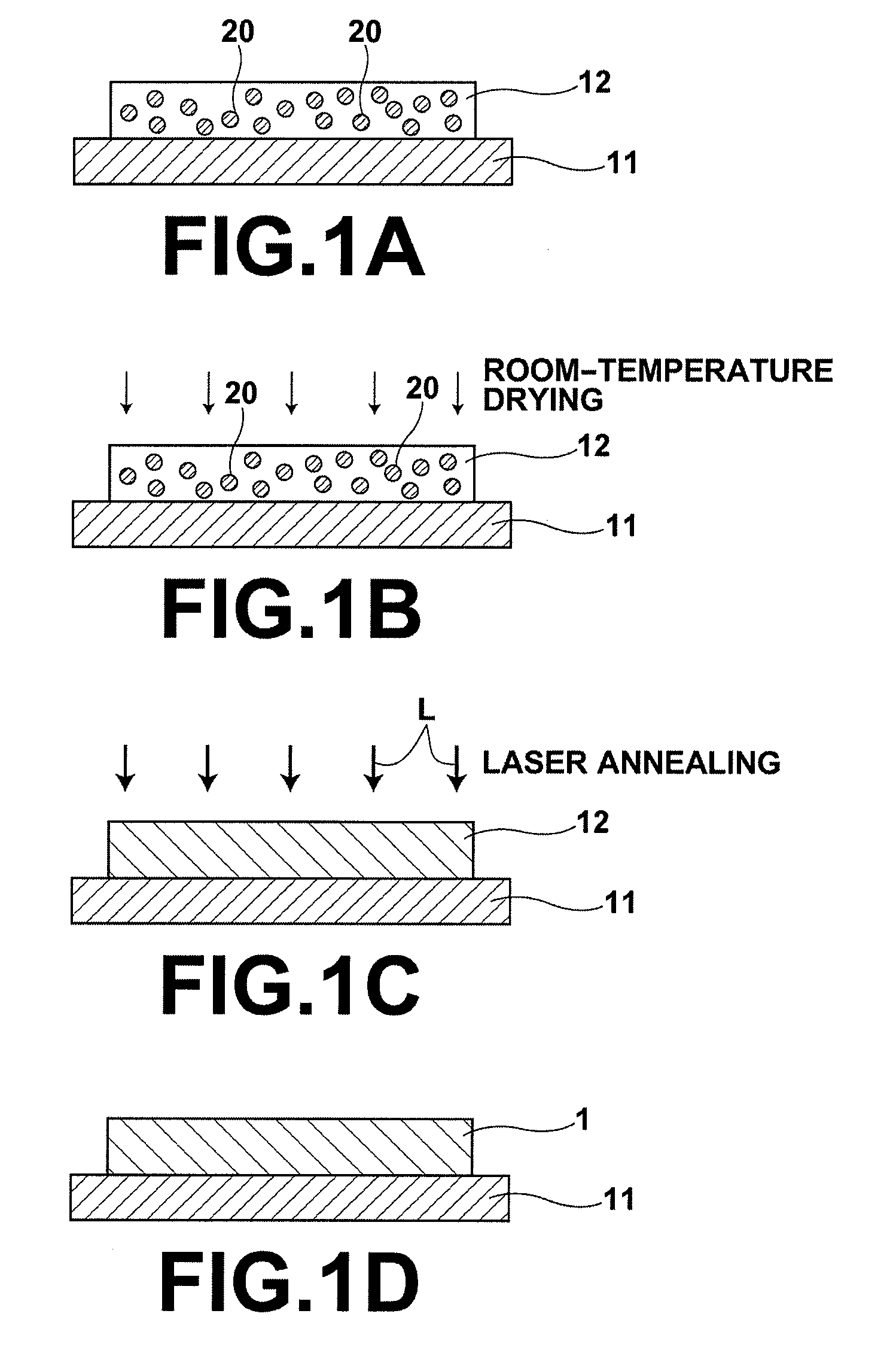

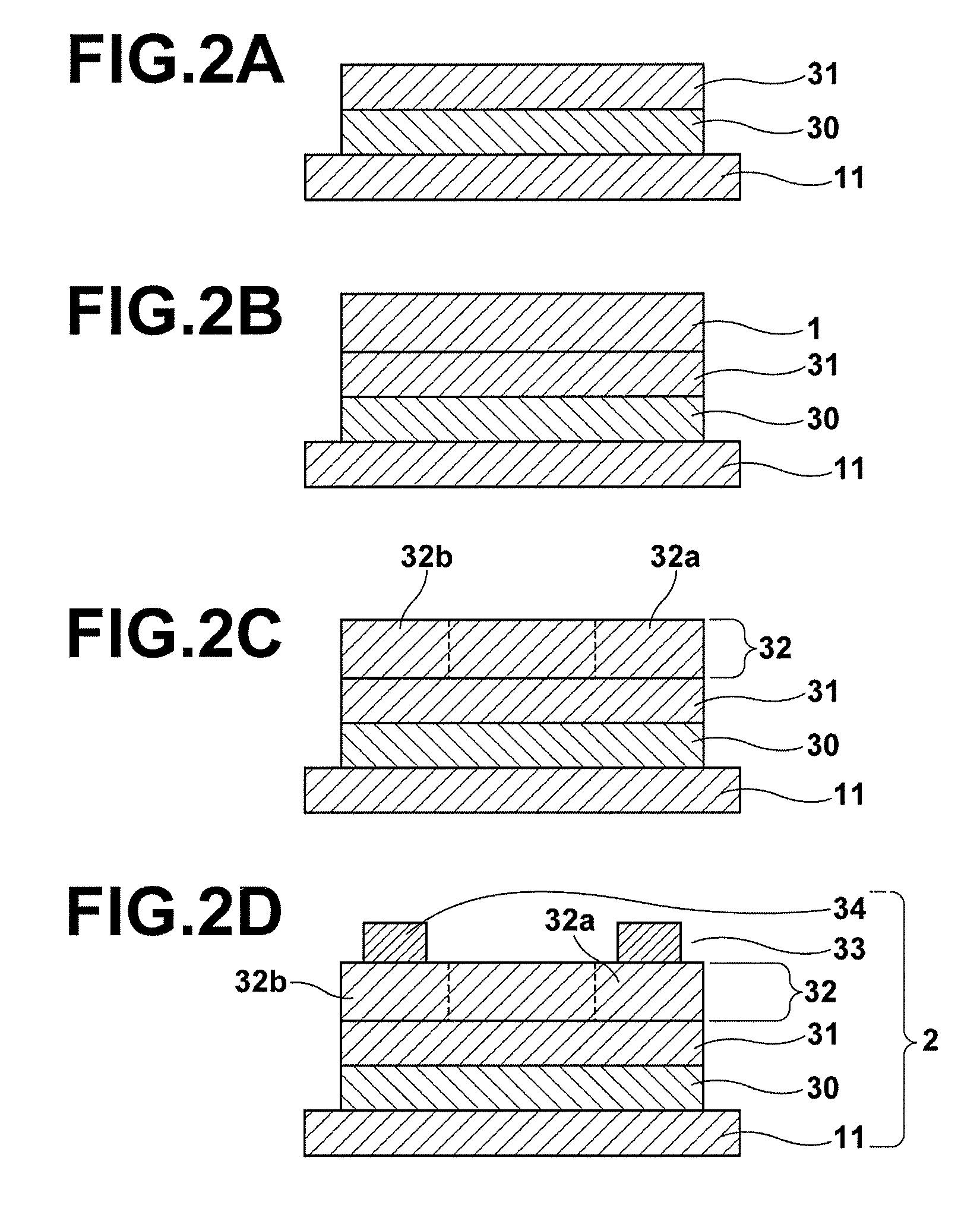

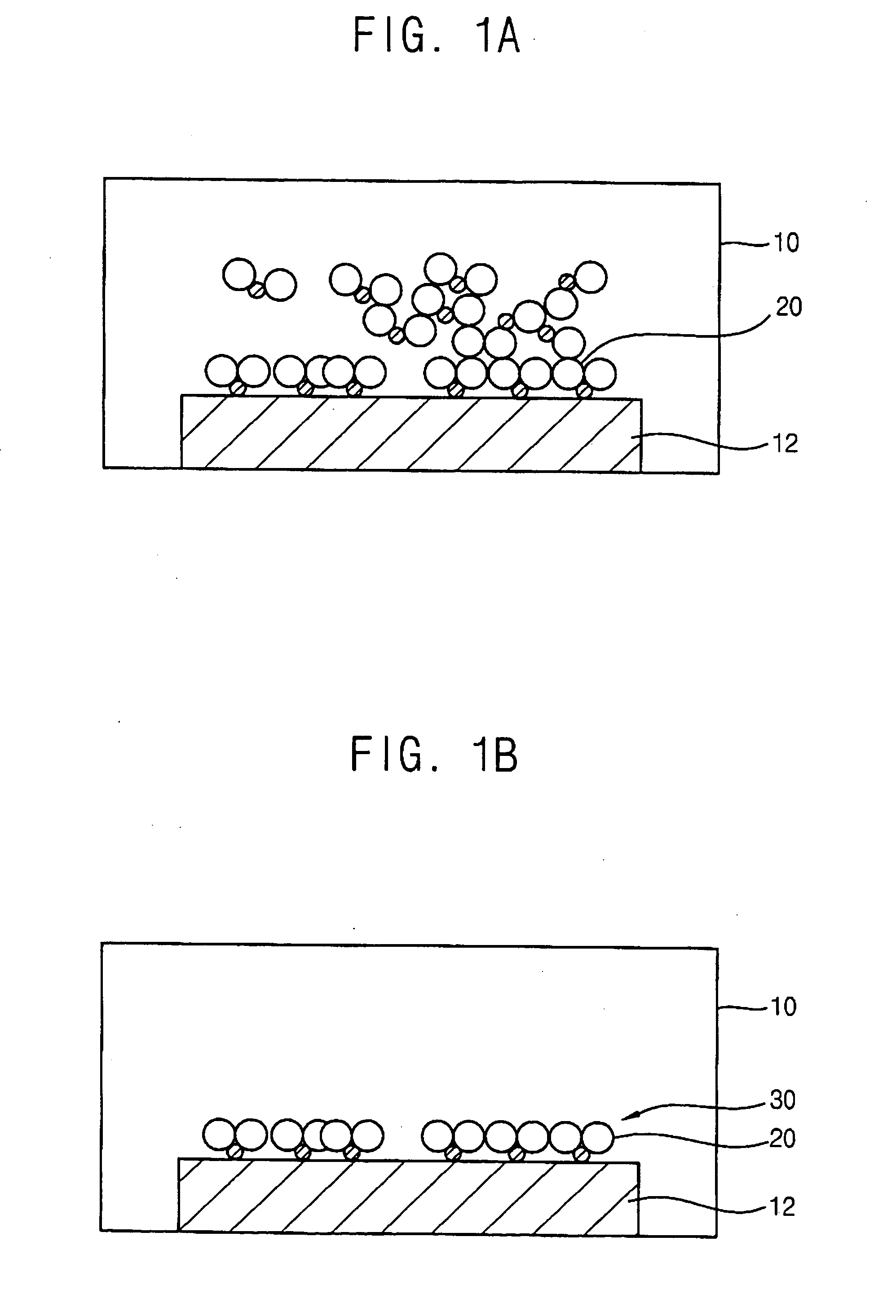

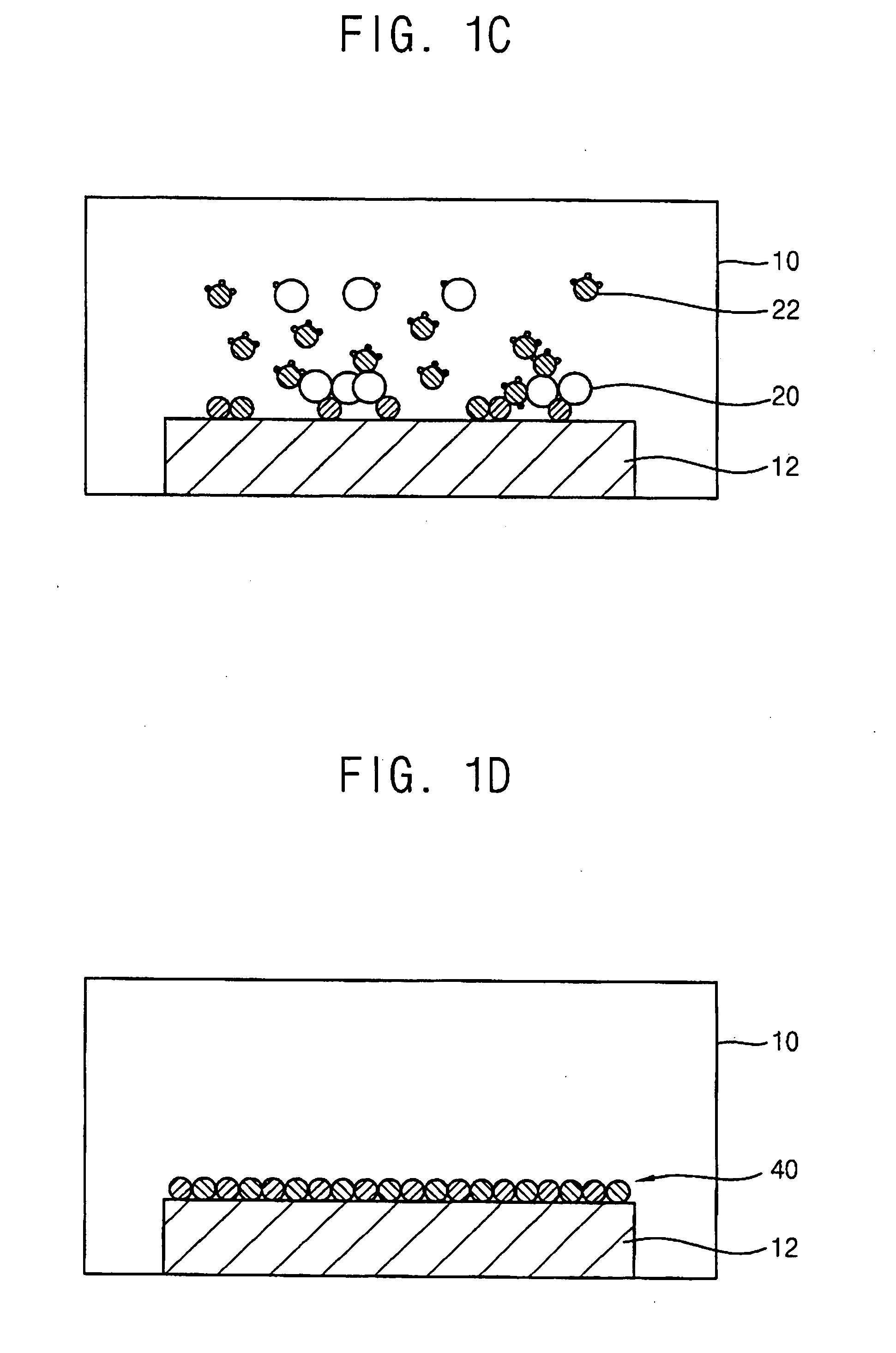

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

ActiveUS20090152506A1Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventDevice material

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

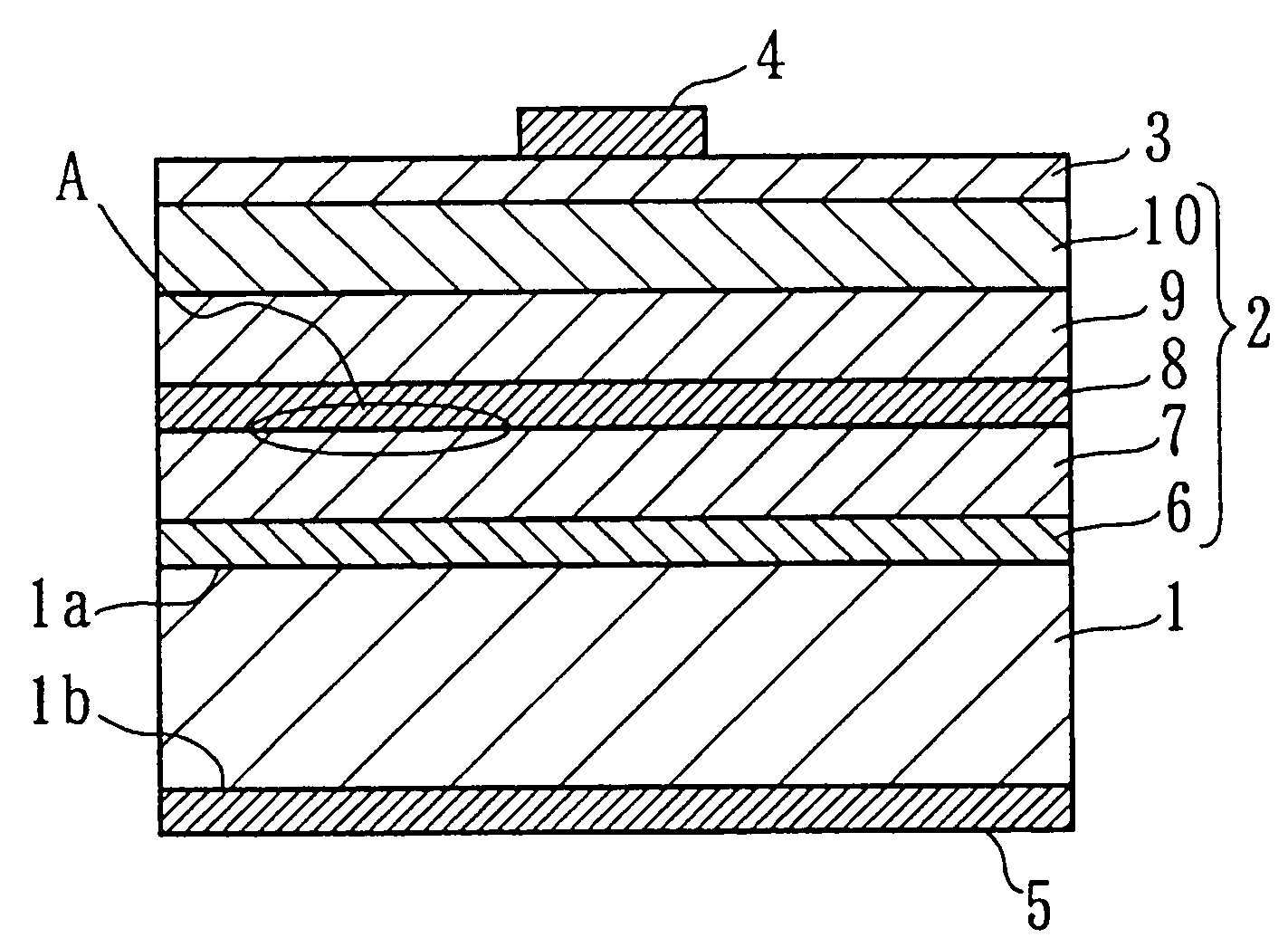

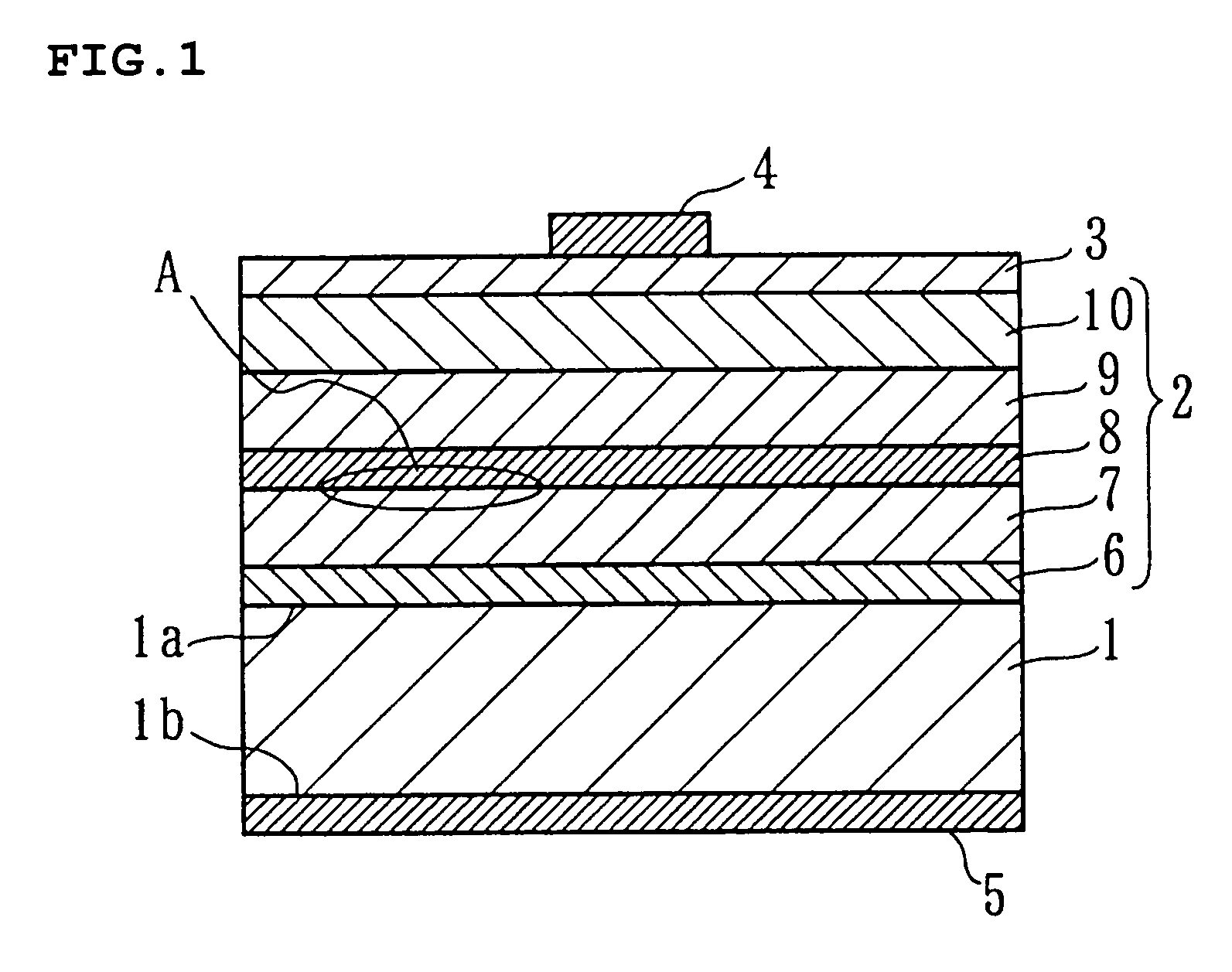

Semiconductor device in which zinc oxide is used as a semiconductor material and method for manufacturing the semiconductor device

ActiveUS7501293B2Improve surface smoothnessHigh crystallinityTransistorLaser detailsSemiconductor materialsDevice material

A semiconductor device having excellent crystallinity and excellent electric characteristics includes a ZnO thin film having excellent surface smoothness. ZnO-based thin films (an n-type contact layer, an n-type clad layer, an active layer, a p-type clad layer, and a p-type contact layer) primarily including ZnO are formed sequentially by an ECR sputtering method or other suitable method on a zinc-polar surface of a ZnO substrate. A transparent electrode and a p-side electrode are formed by an evaporation method or other suitable method on a surface of the p-type contact layer, and an n-side electrode is formed on an oxygen-polar surface of the ZnO substrate.

Owner:MURATA MFG CO LTD

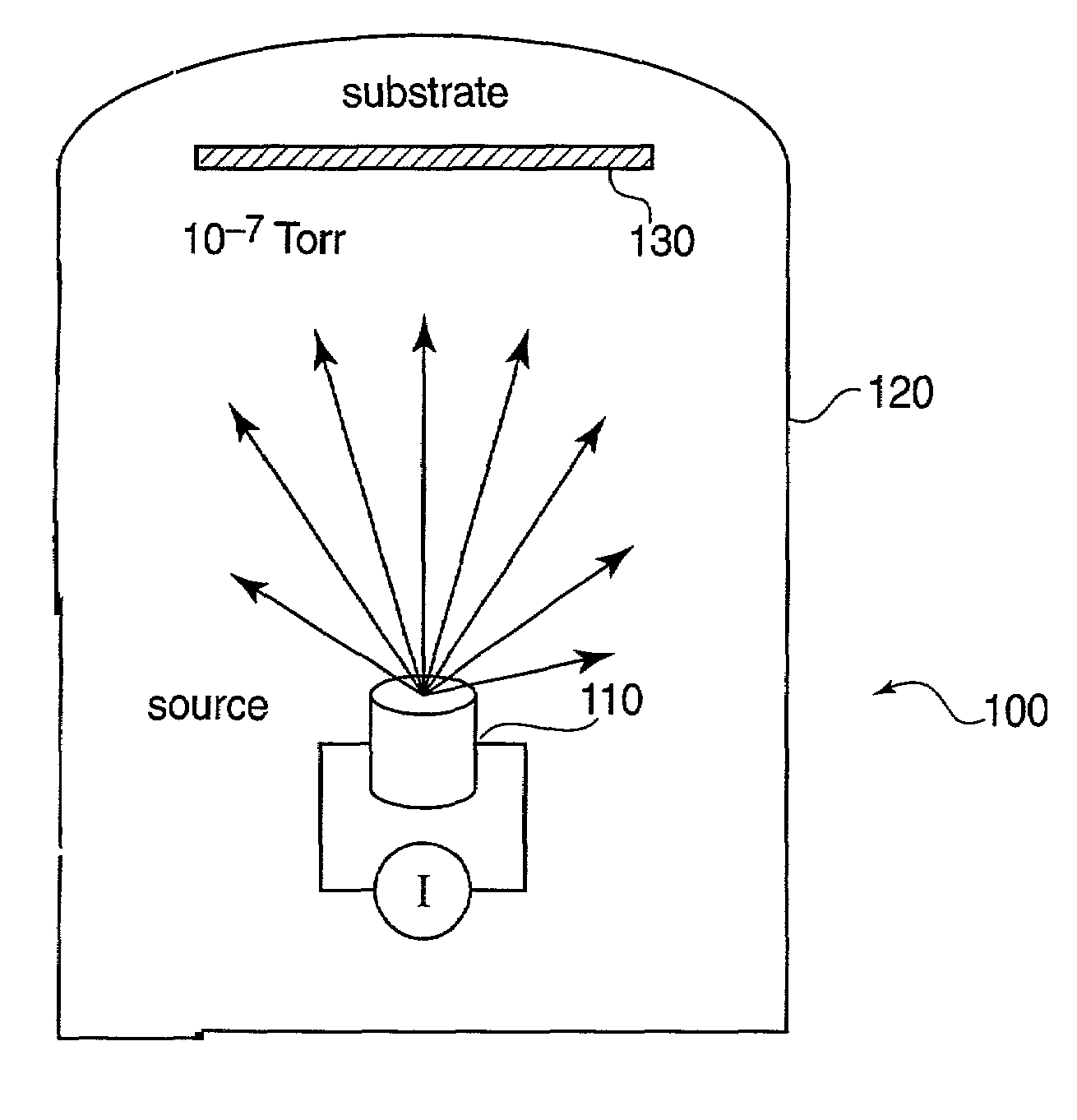

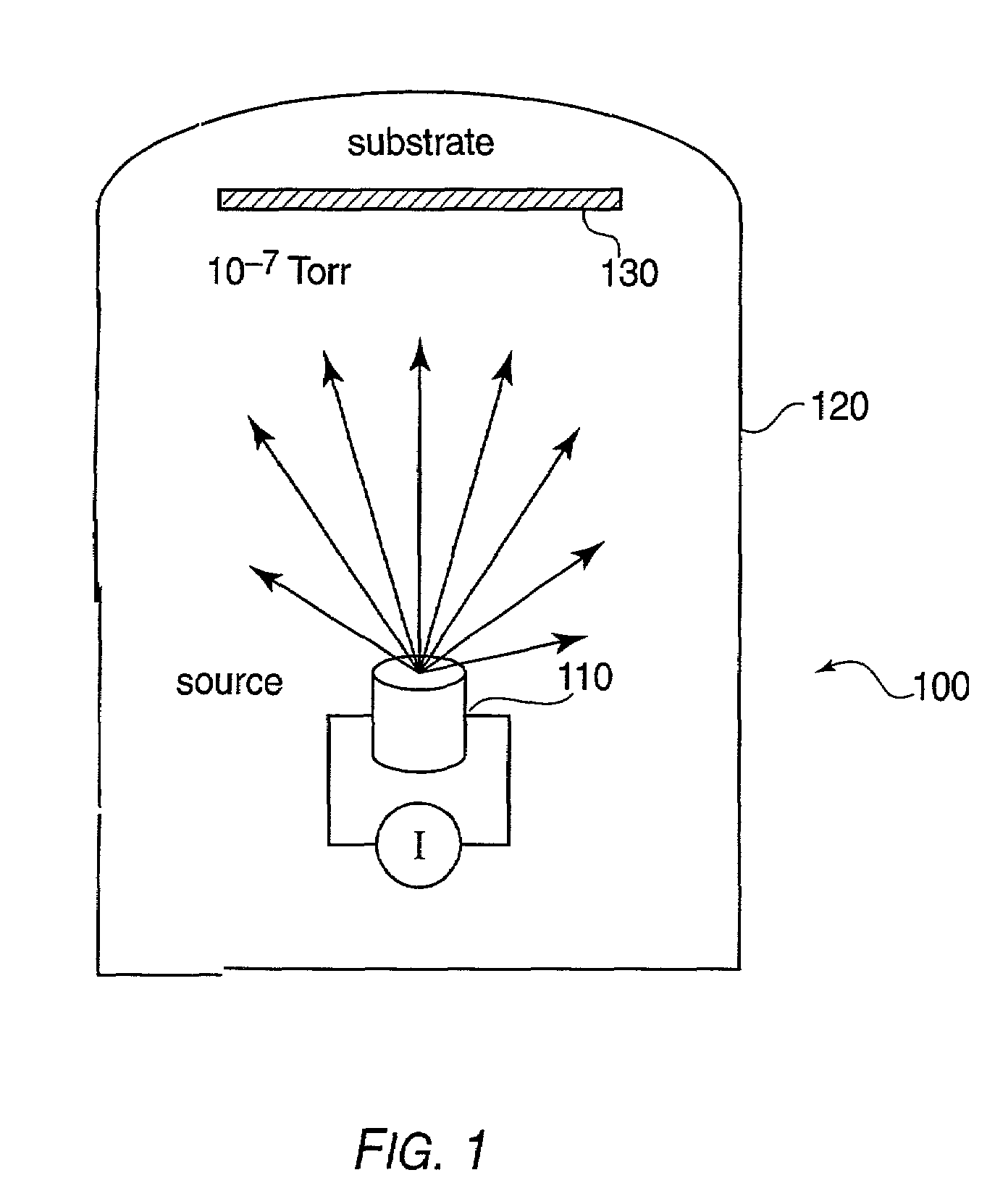

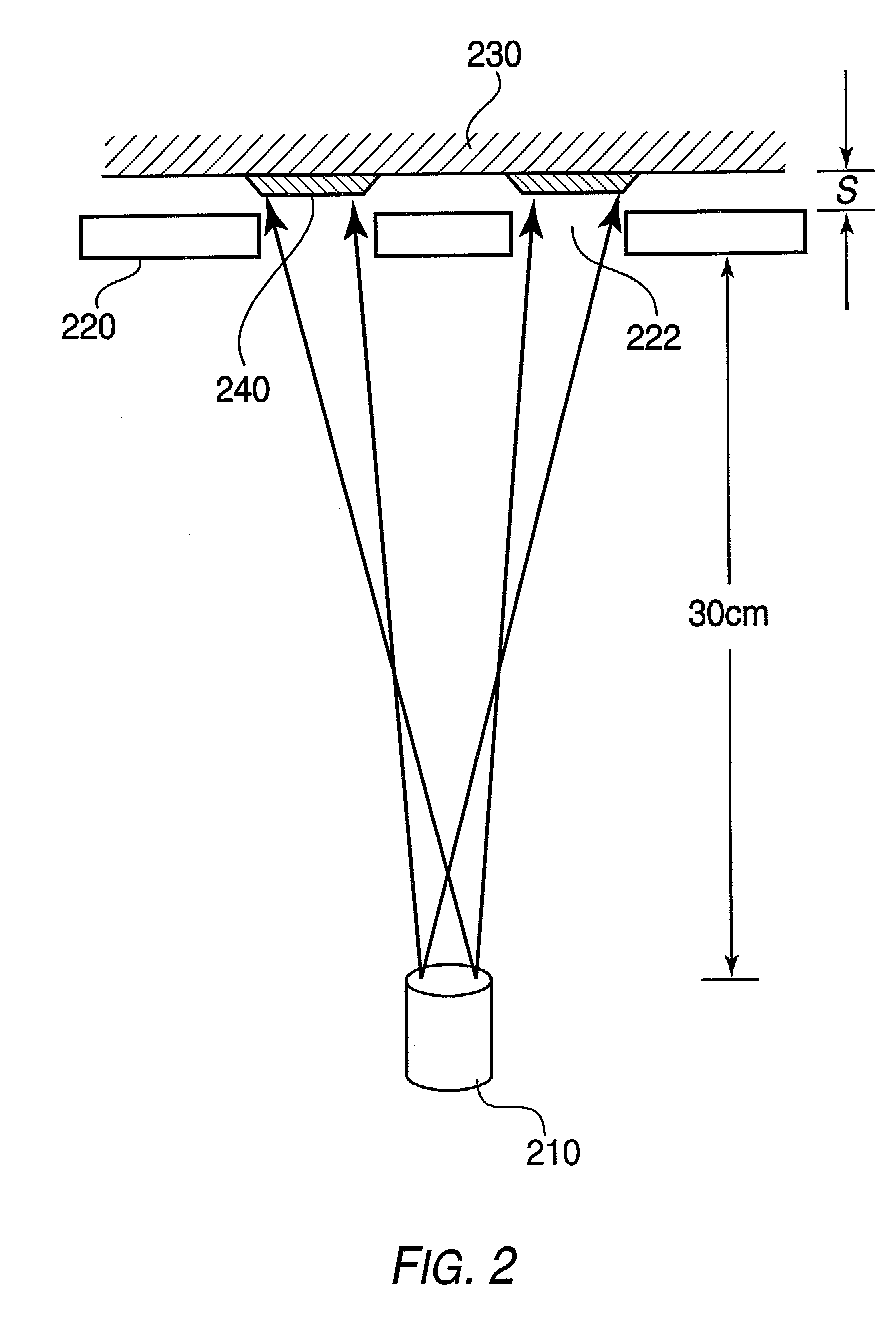

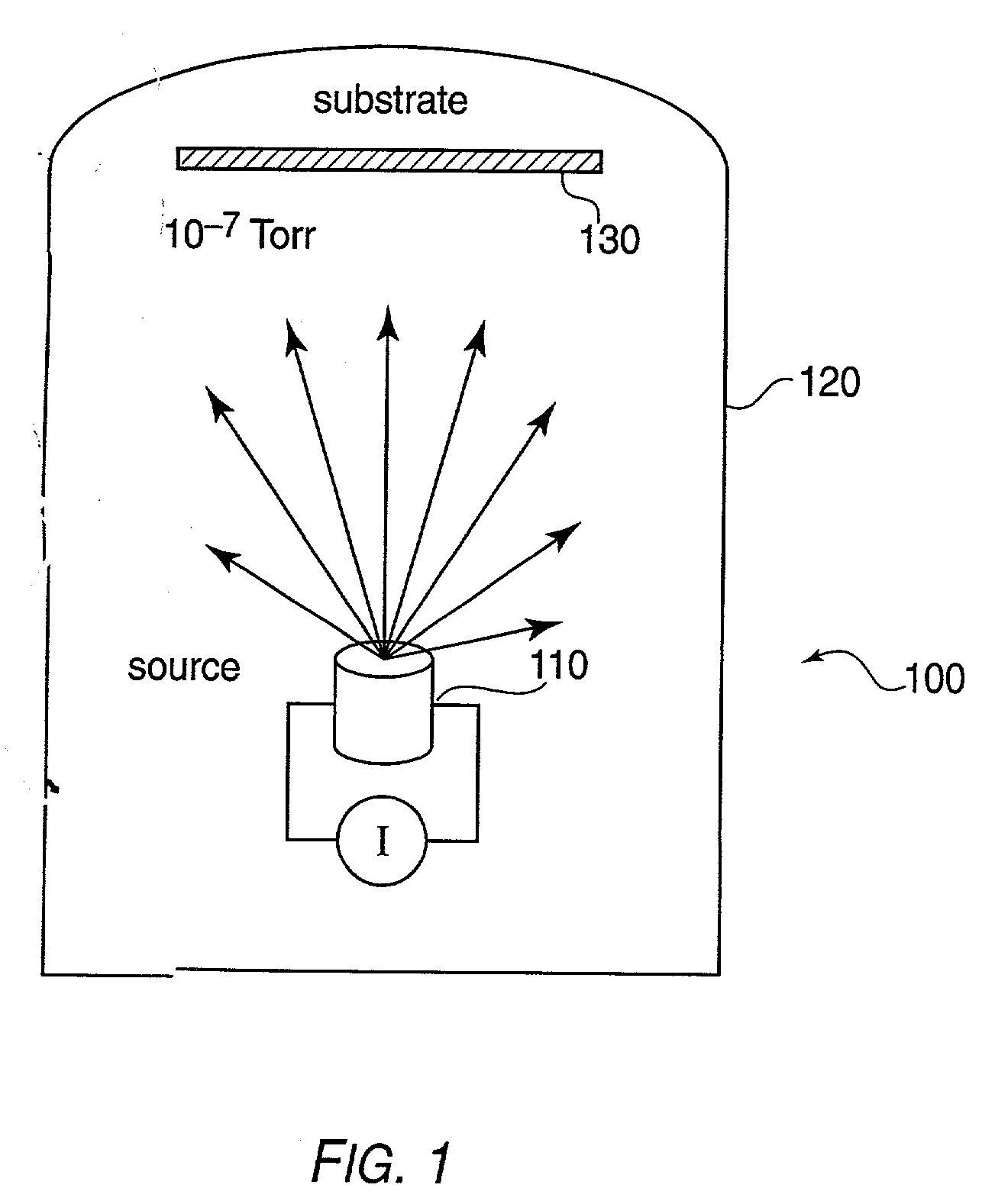

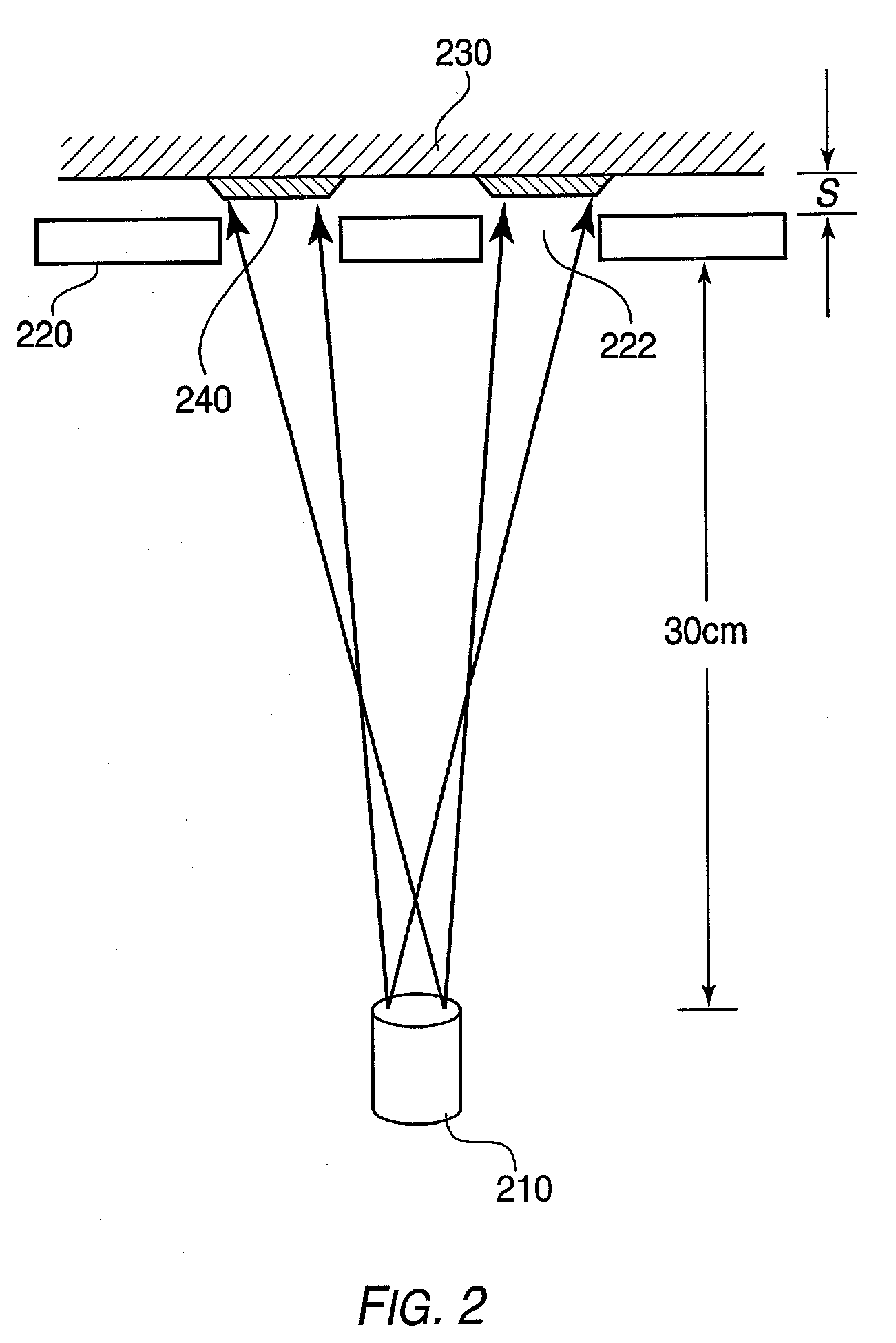

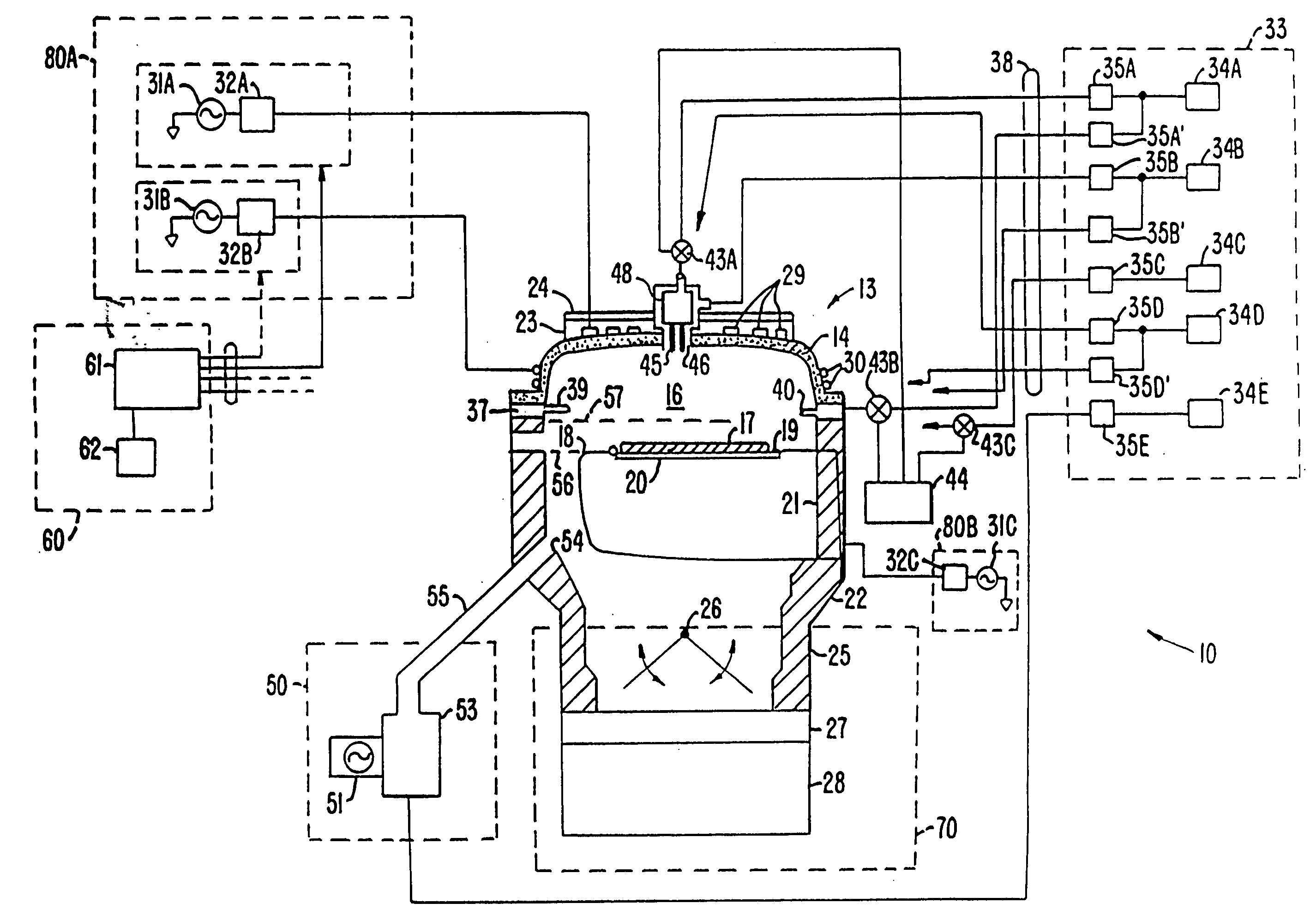

Process and apparatus for organic vapor jet deposition

ActiveUS7431968B1Good directionSharp pixelVacuum evaporation coatingSputtering coatingOrganic filmVacuum chamber

A method of fabricating an organic film is provided. A non-reactive carrier gas is used to transport an organic vapor. The organic vapor is ejected through a nozzle block onto a cooled substrate, to form a patterned organic film. A device for carrying out the method is also provided. The device includes a source of organic vapors, a source of carrier gas and a vacuum chamber. A heated nozzle block attached to the source of organic vapors and the source of carrier gas has at least one nozzle adapted to eject carrier gas and organic vapors onto a cooled substrate disposed within the vacuum chamber.

Owner:THE TRUSTEES FOR PRINCETON UNIV

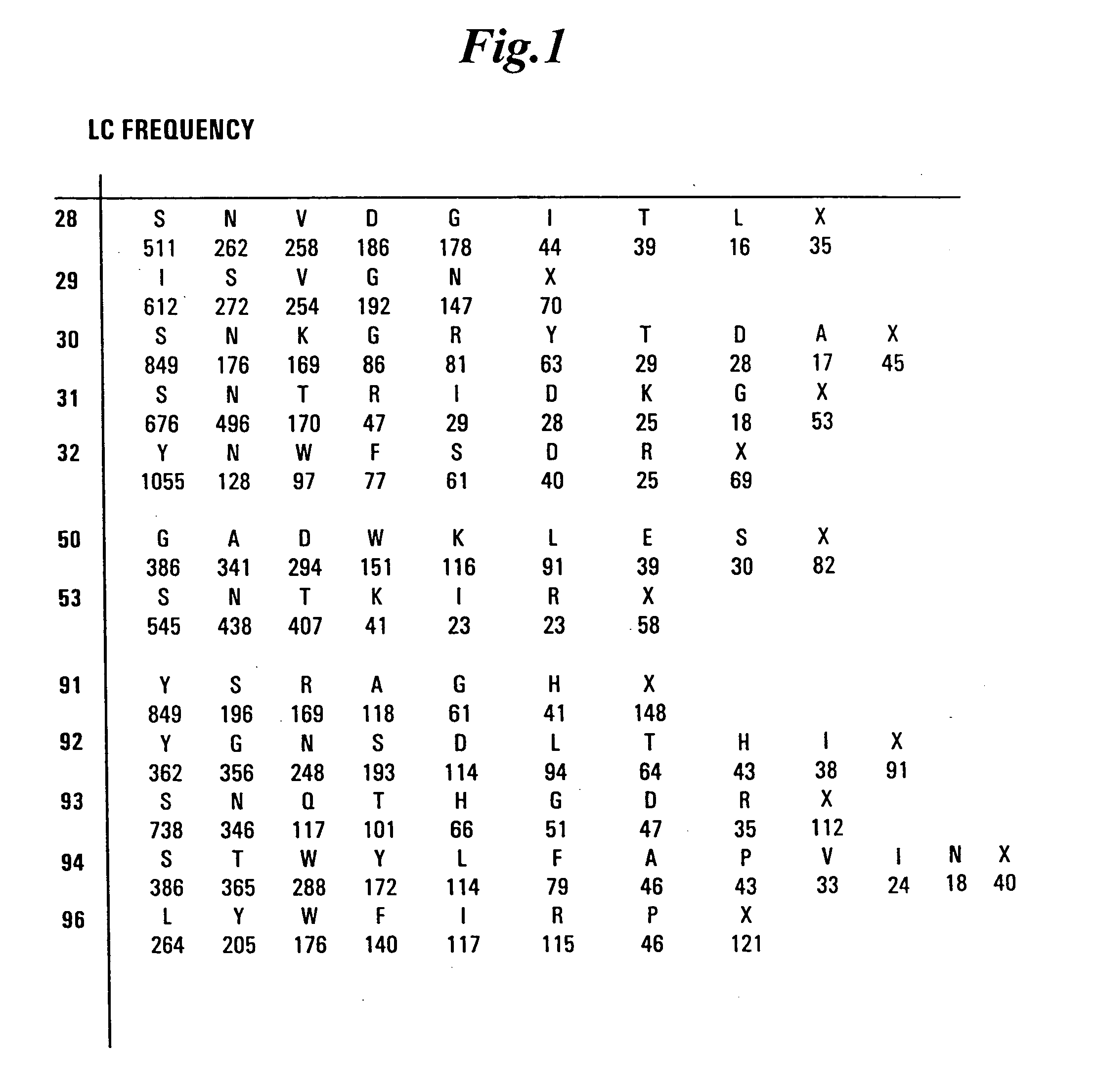

Synthetic antibody phage libraries

InactiveUS20050079574A1High-quality target binding characteristicGenerate efficientlyAntibody mimetics/scaffoldsImmunoglobulins against cell receptors/antigens/surface-determinantsHeterologousIntravenous gammaglobulin

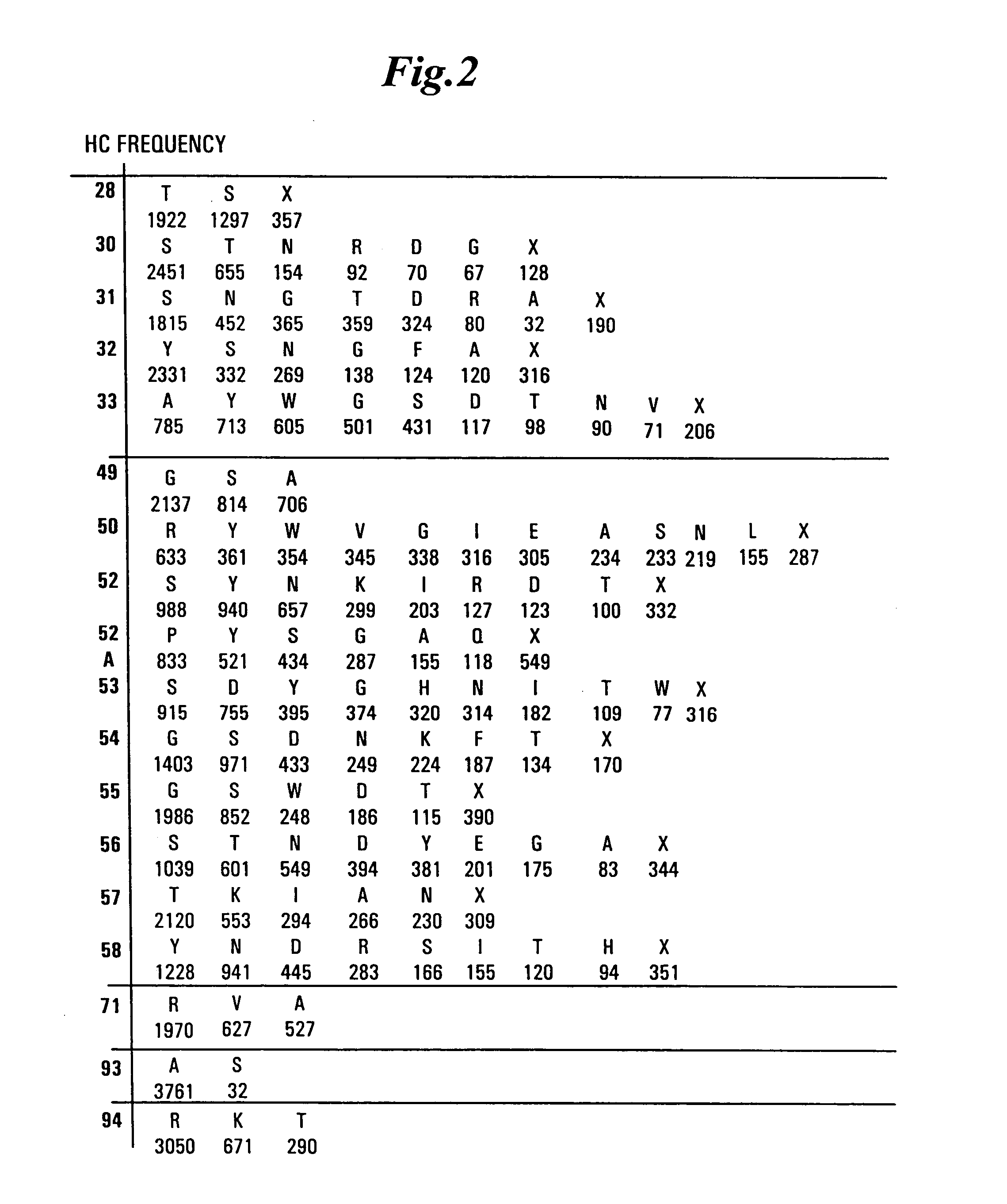

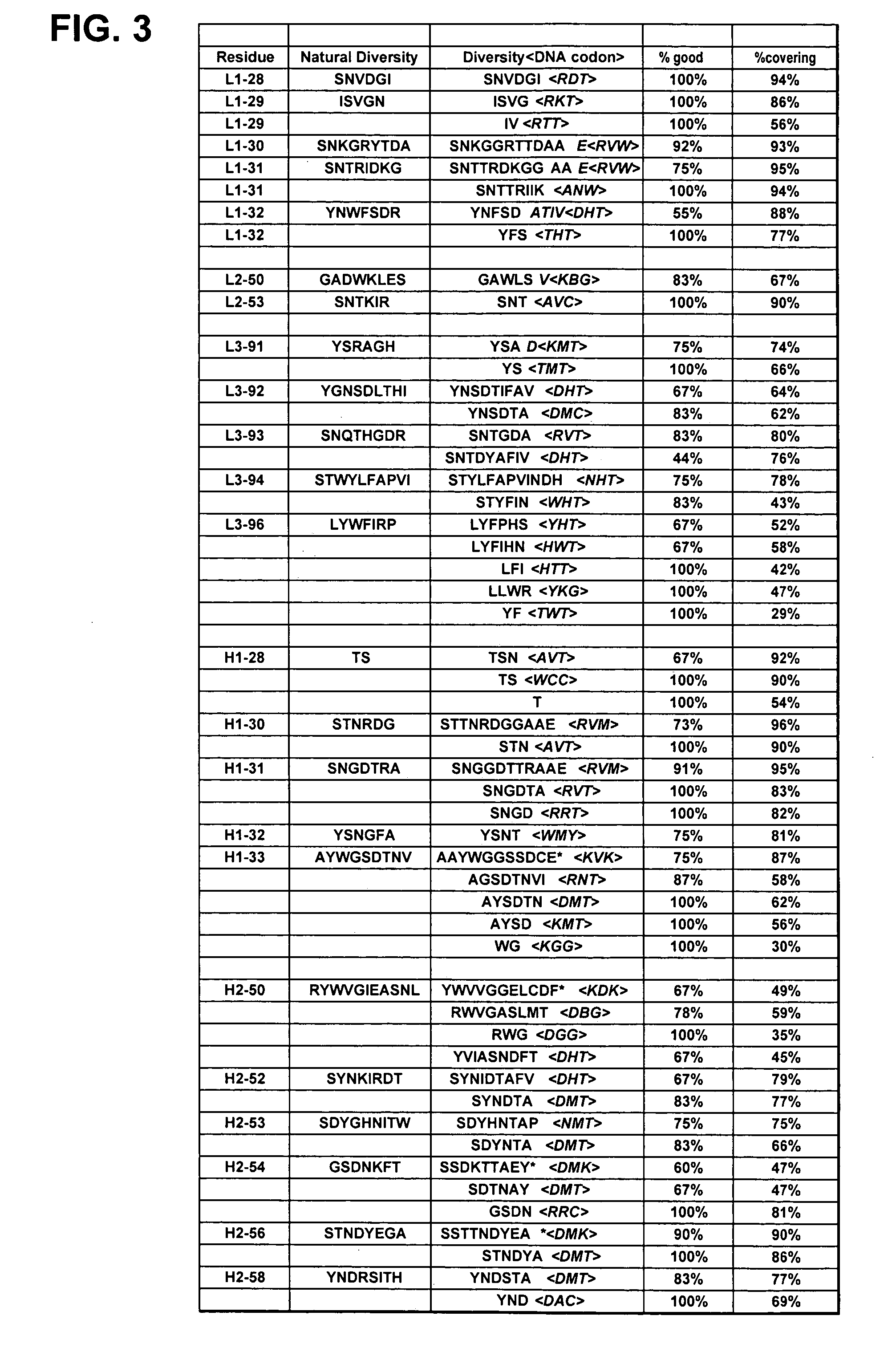

The invention provides immunoglobulin polypeptides comprising variant amino acids in CDRs of antibody variable domains. In one embodiment, the polypeptide is a variable domain of a monobody and has a variant CDRH3 region. These polypeptides provide a source of great sequence diversity that can be used as a source for identifying novel antigen binding polypeptides. The invention also provides these polypeptides as fusion polypeptides to heterologous polypeptides such as at least a portion of phage or viral coat proteins, tags and linkers. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

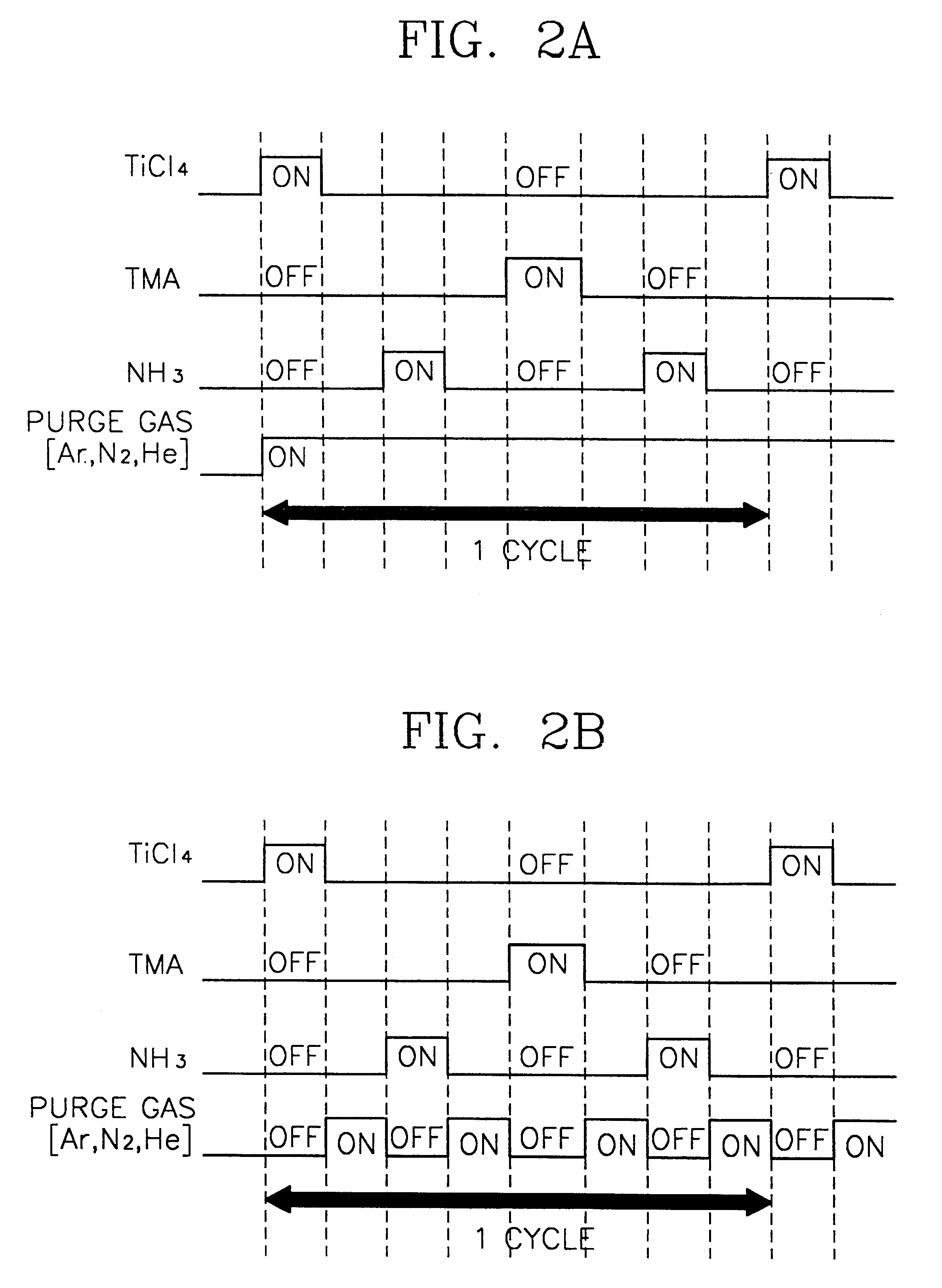

Method of forming metal layer using atomic layer deposition and semiconductor device having the metal layer as barrier metal layer or upper or lower electrode of capacitor

InactiveUS6287965B1High thermal resistantEasy to adjustSemiconductor/solid-state device manufacturingCapacitorsNiobiumDevice material

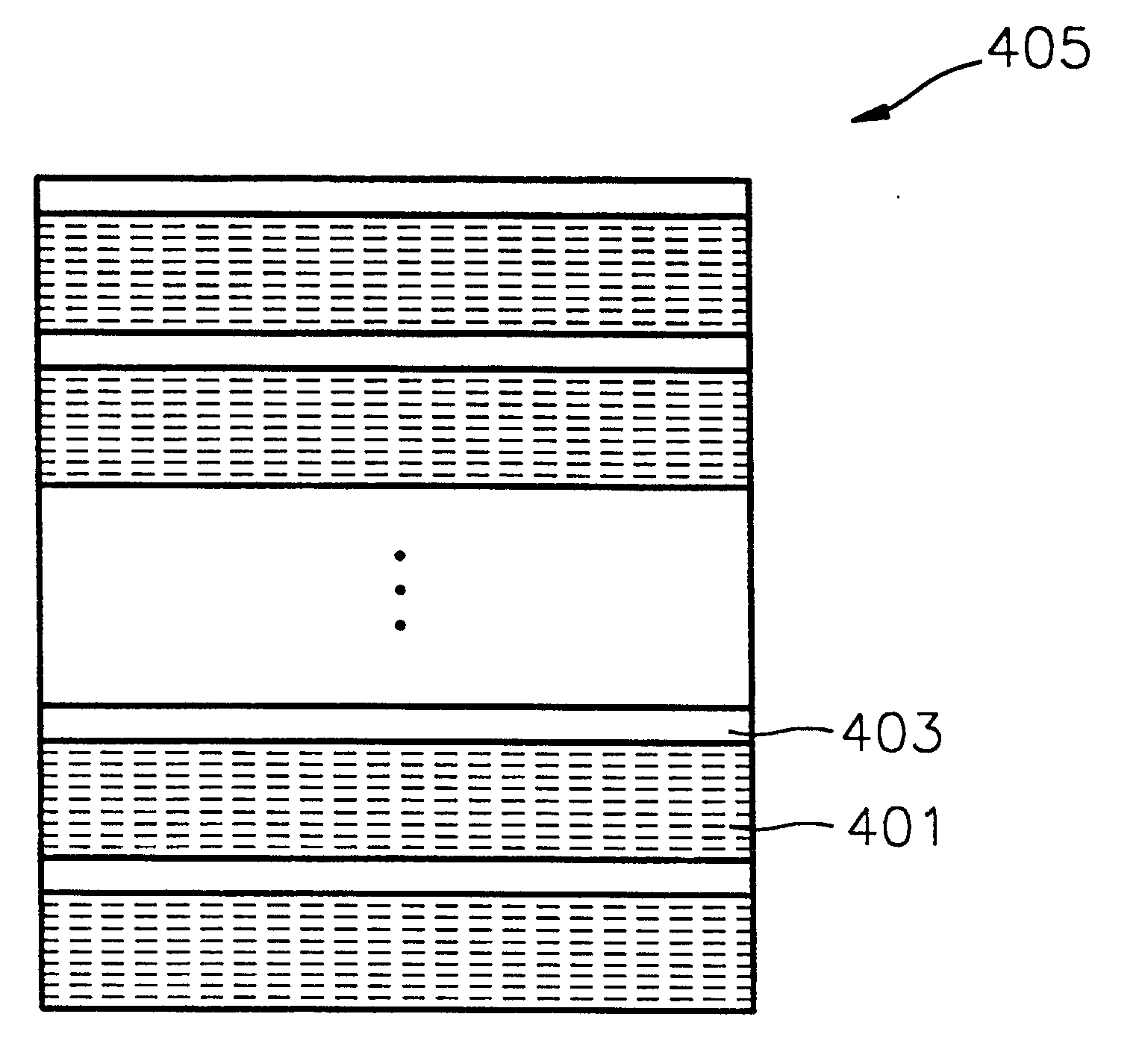

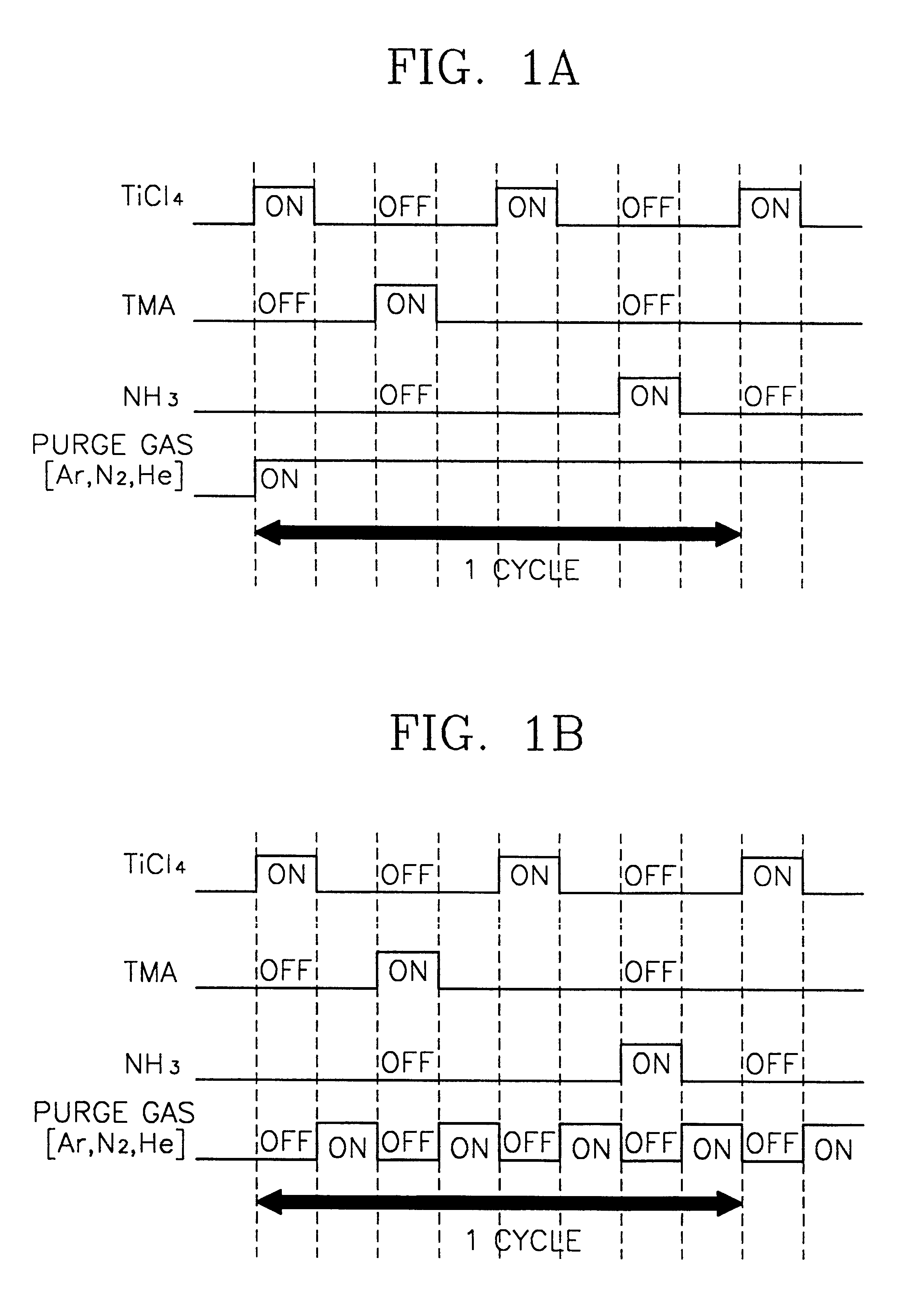

A method of forming a metal layer having excellent thermal and oxidation resistant characteristics using atomic layer deposition is provided. The metal layer includes a reactive metal (A), an element (B) for the amorphous combination between the reactive metal (A) and nitrogen (N), and nitrogen (N). The reactive metal (A) may be titanium (Ti), tantalum (Ta), tungsten (W), zirconium (Zr), hafnium (Hf), molybdenum (Mo) or niobium (Nb). The amorphous combination element (B) may be aluminum (Al), silicon (Si) or boron (B). The metal layer is formed by alternately injecting pulsed source gases for the elements (A, B and N) into a chamber according to atomic layer deposition to thereby alternately stack atomic layers. Accordingly, the composition ratio of a nitrogen compound (A-B-N) of the metal layer can be desirably adjusted just by appropriately determining the number of injection pulses of each source gas. According to the composition ratio, a desirable electrical conductivity and resistance of the metal layer can be accurately obtained. The atomic layers are individually deposited, thereby realizing excellent step coverage even in a complex and compact region. A metal layer formed by atomic layer deposition can be employed as a barrier metal layer, a lower electrode or an upper electrode in a semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

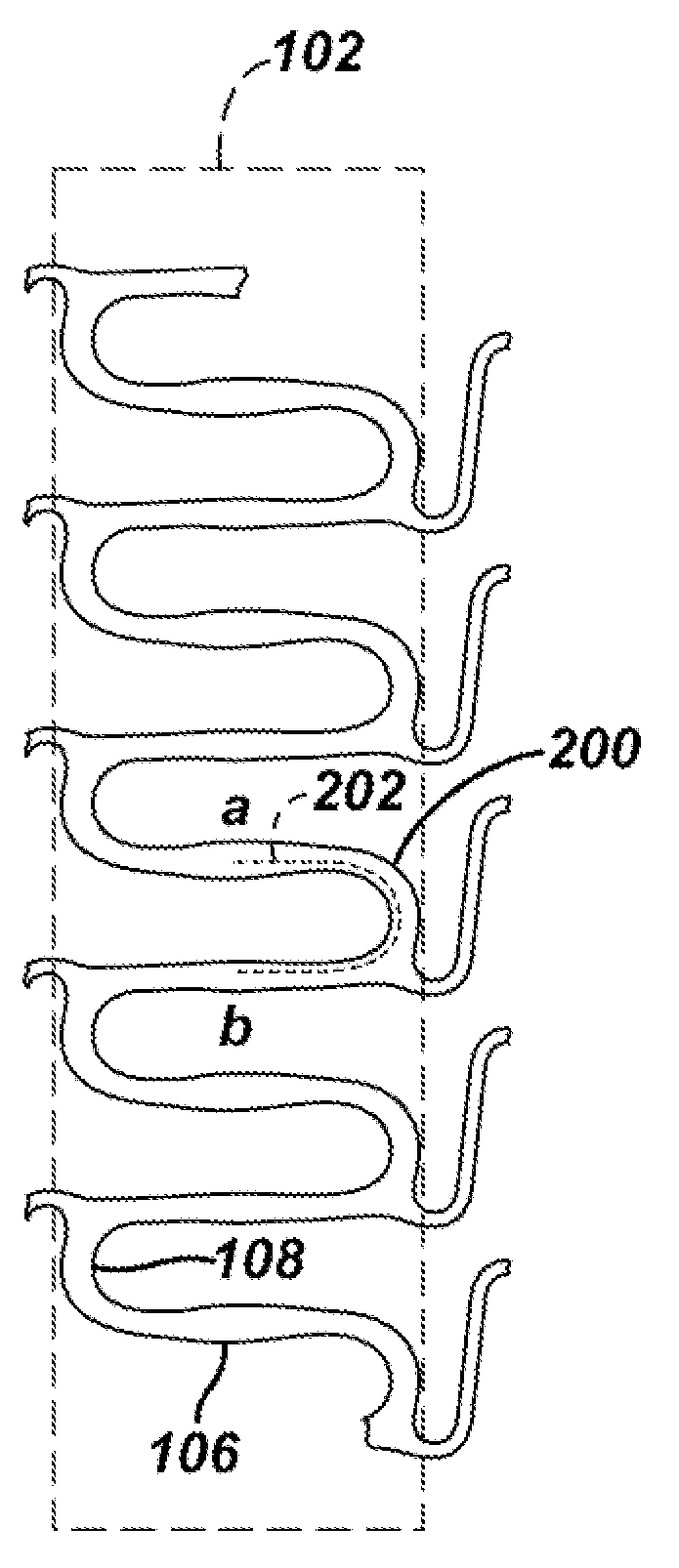

Sutures and surgical staples for anastamoses, wound closures, and surgical closures

InactiveUS8016881B2Improve featuresControlled release rateSuture equipmentsStentsSurgical stapleMicroparticle

The invention relates to sutures and surgical staples useful in anastomoses. Various aspects of the invention include wound closure devices that use amphiphilic copolymer or parylene coatings to control the release rate of an agent, such as a drug or a biological material, polymerizing a solution containing monomers and the agent to form a coating, using multiple cycles of swelling a polymer with a solvent-agent solution to increase loading, microparticles carrying the agent, biodegradable surgical articles with amphiphilic copolymer coatings, and sutures or surgical staples the deliver a drug selected from the group consisting of triazolopyrimidine, paclitaxol, sirolimus, derivatives thereof, and analogs thereof to a wound site.

Owner:MIRUS LLC

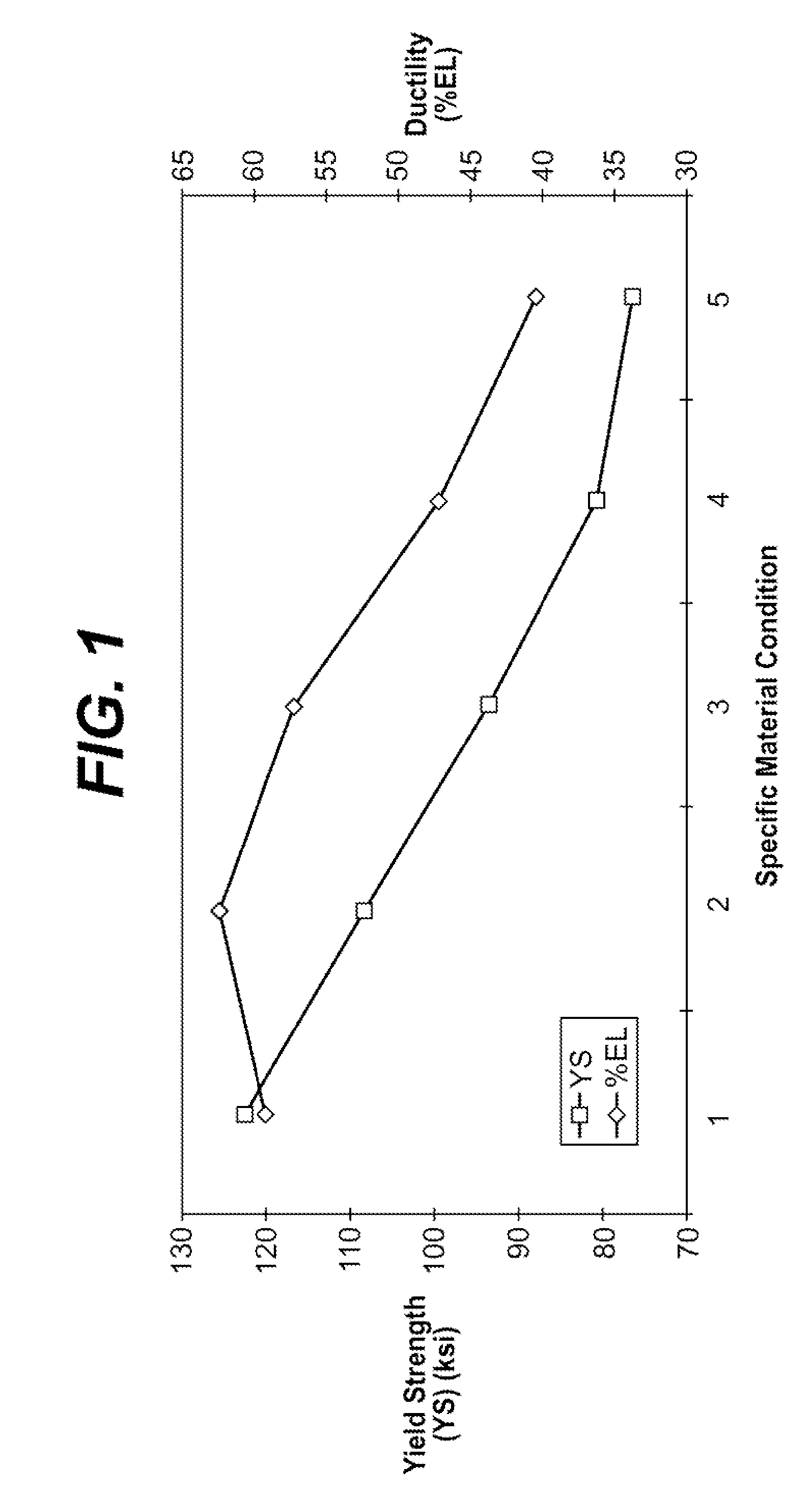

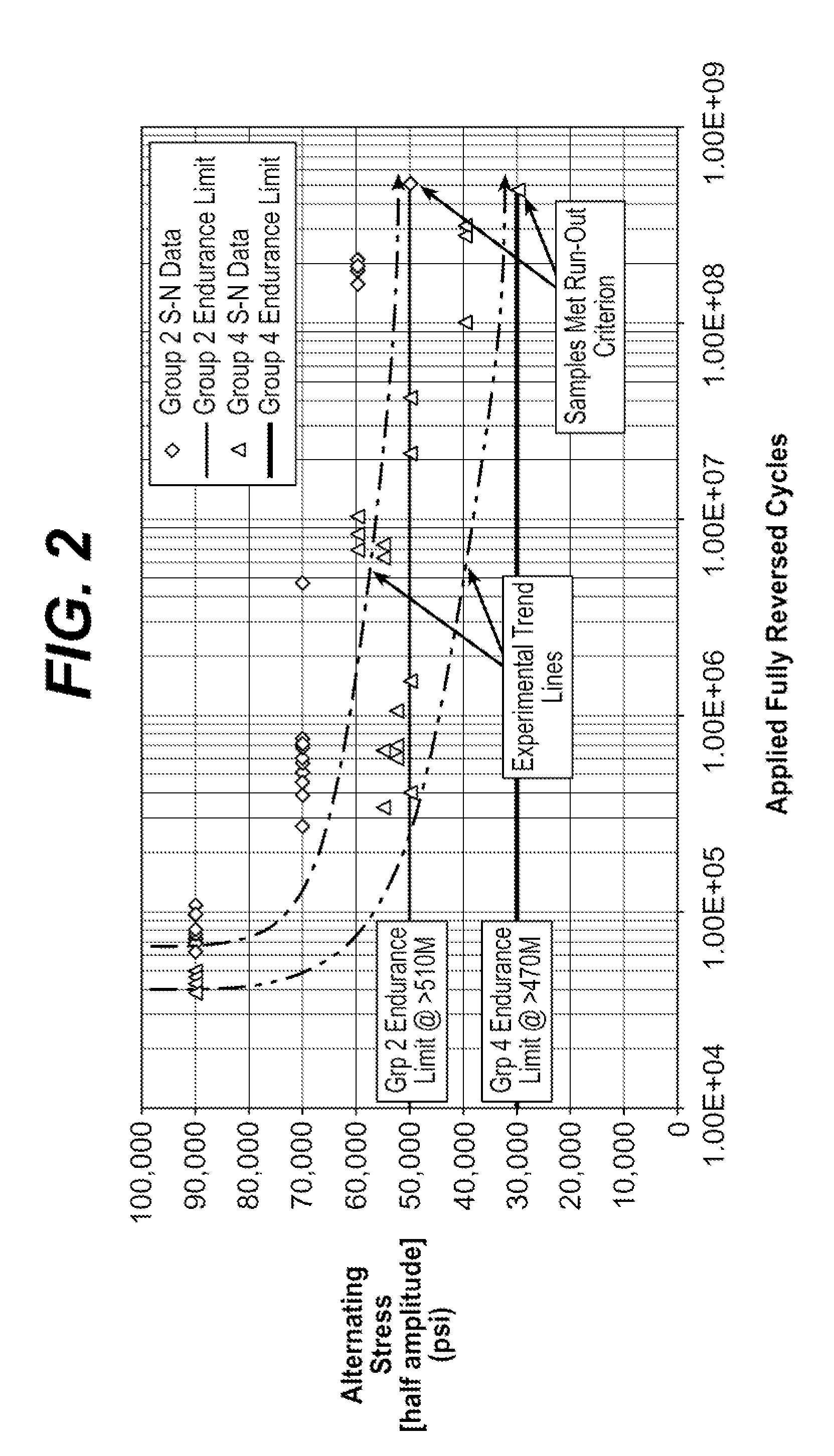

Bioabsorbable Polymer, Bioabsorbable Composite Stents

InactiveUS20080249608A1Simple and inexpensive to manufactureVarying of ductilityStentsSurgeryMetallic materialsMedical device

Biocompatible materials may be configured into any number of implantable medical devices including intraluminal stents. The biocompatible material may comprise metallic and non-metallic materials in hybrid structures. In one such structure, a device may be fabricated with one or more elements having an inner metallic core that is biodegradable with an outer shell formed from a polymeric material that is biodegradable. Additionally, therapeutic agents may be incorporated into the microstructure or the bulk material.

Owner:CORDIS CORP

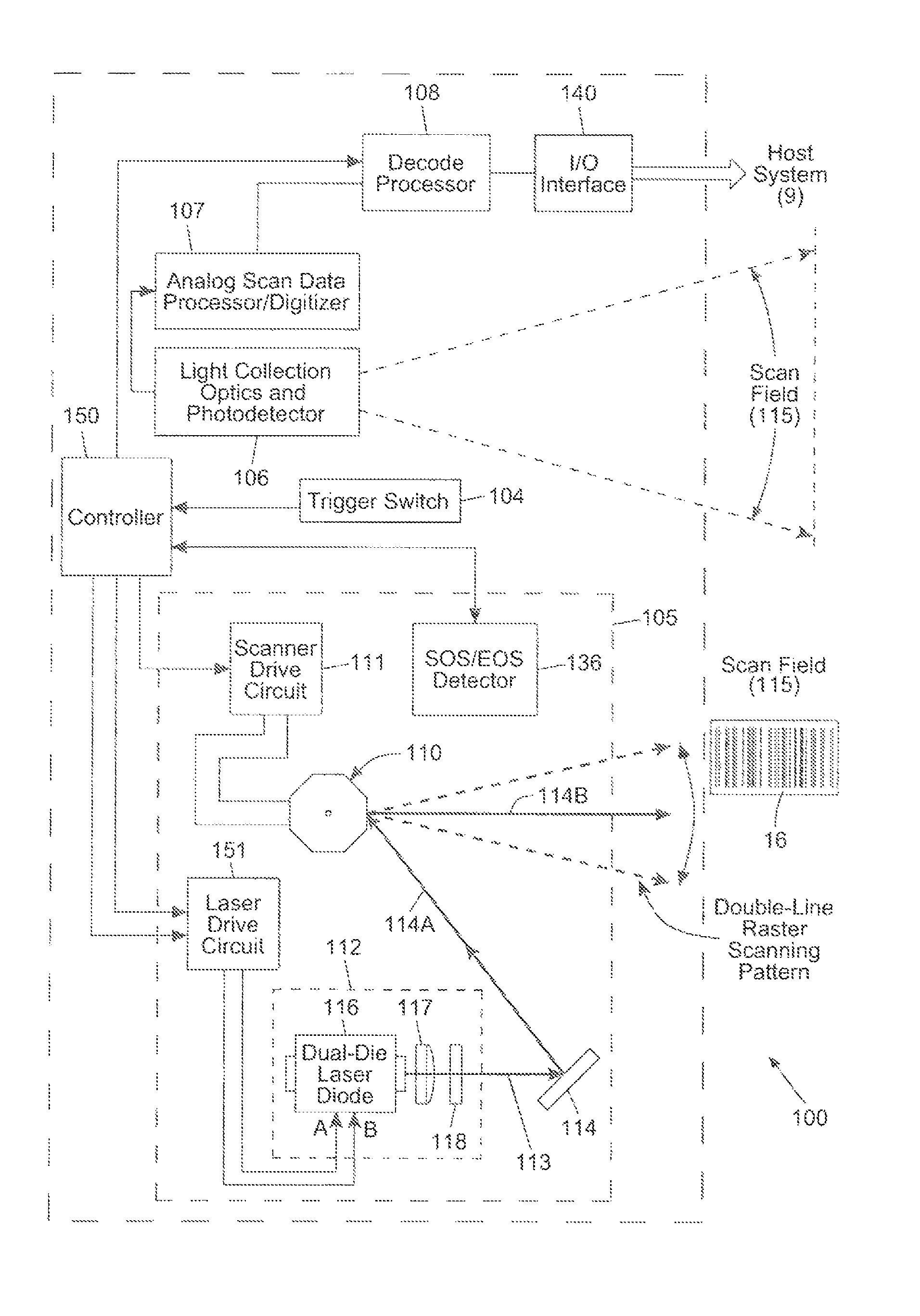

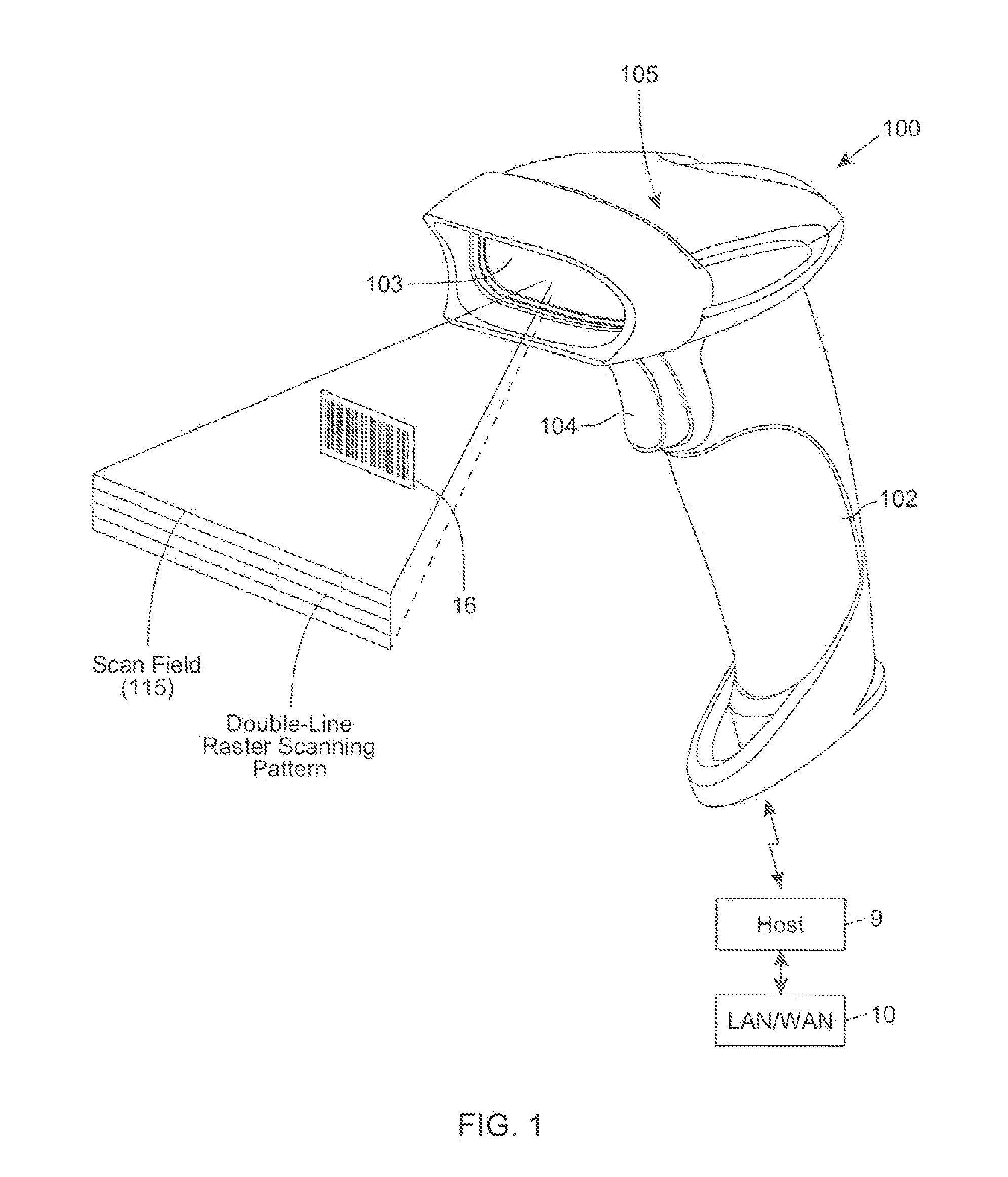

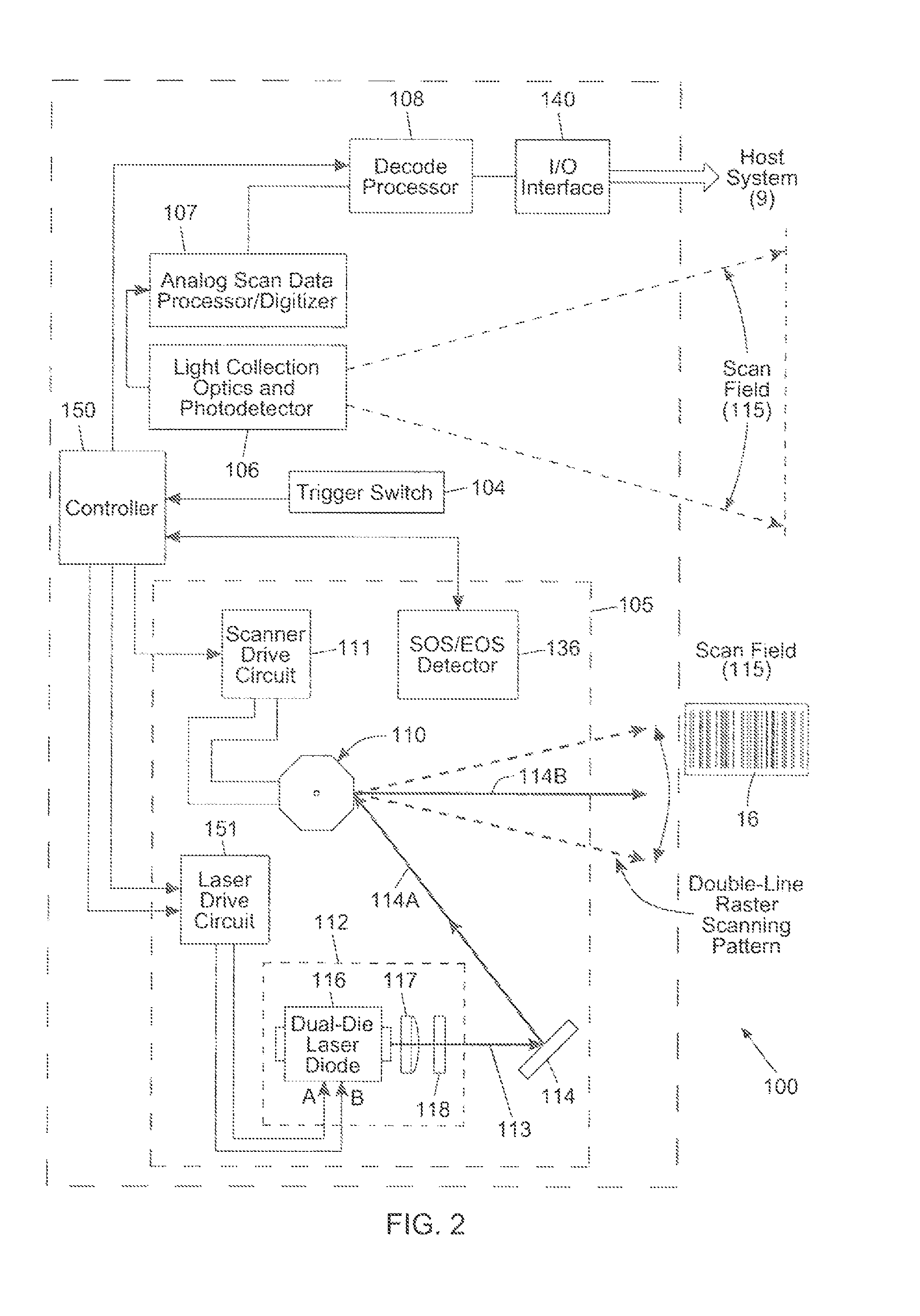

Method of and apparatus for multiplying raster scanning lines by modulating a multi-cavity laser diode

ActiveUS8678285B2Improve featuresHigh densityCharacter and pattern recognitionSensing by electromagnetic radiationGratingLaser scanning

A method of and apparatus for generating a multiple raster-type scanning pattern by modulating a multi-cavity laser diode in such a way that it sequentially generates different laser beams synchronously during different laser scanning cycles, while the output laser beams are directed incident upon a rotating polygonal laser scanning element. The system does not require additional moving parts beyond the rotating polygon scanning element so as to reduce complexity and simplify construction of the laser scanning mechanism.

Owner:METROLOGIC INSTR INC

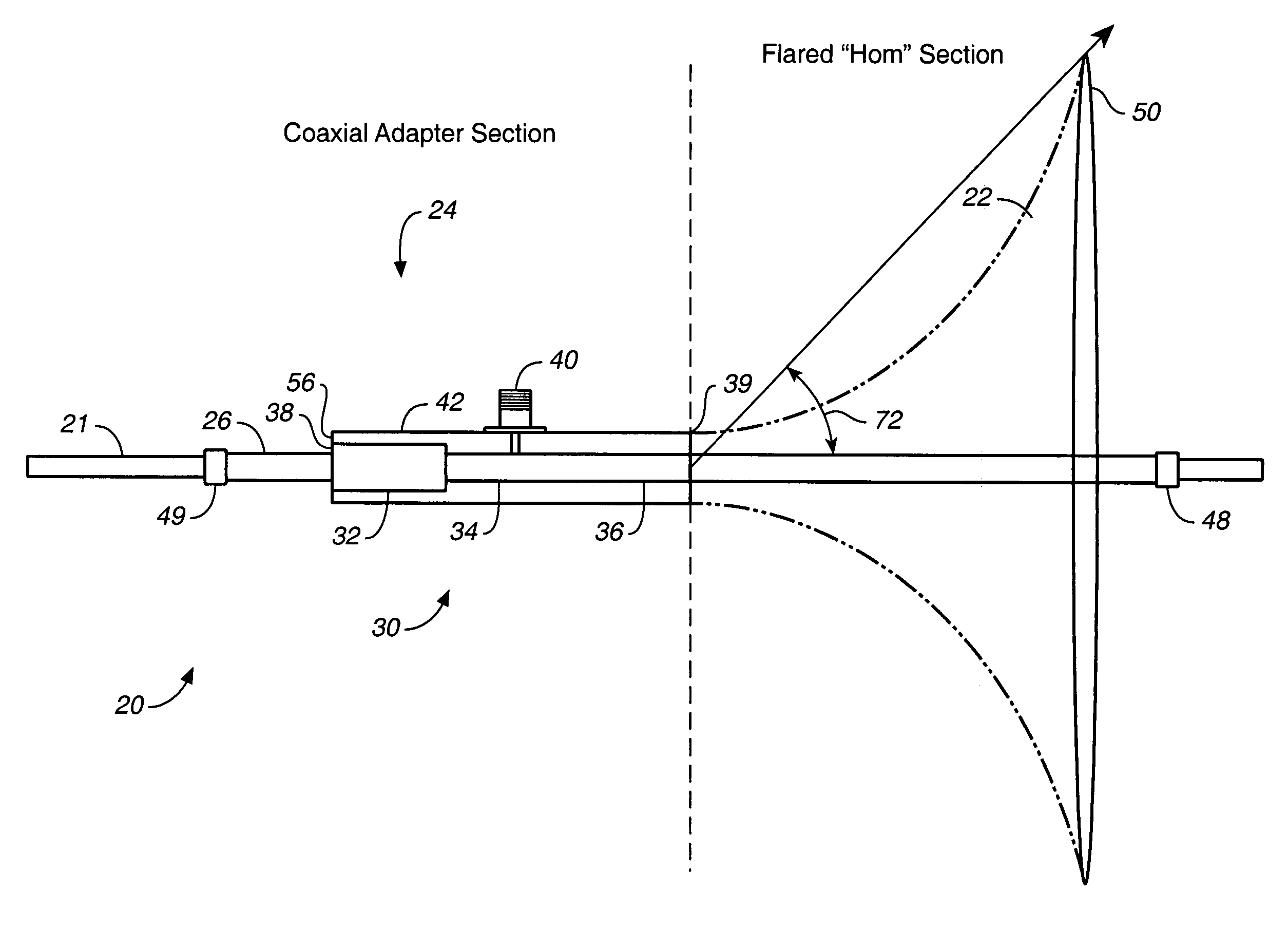

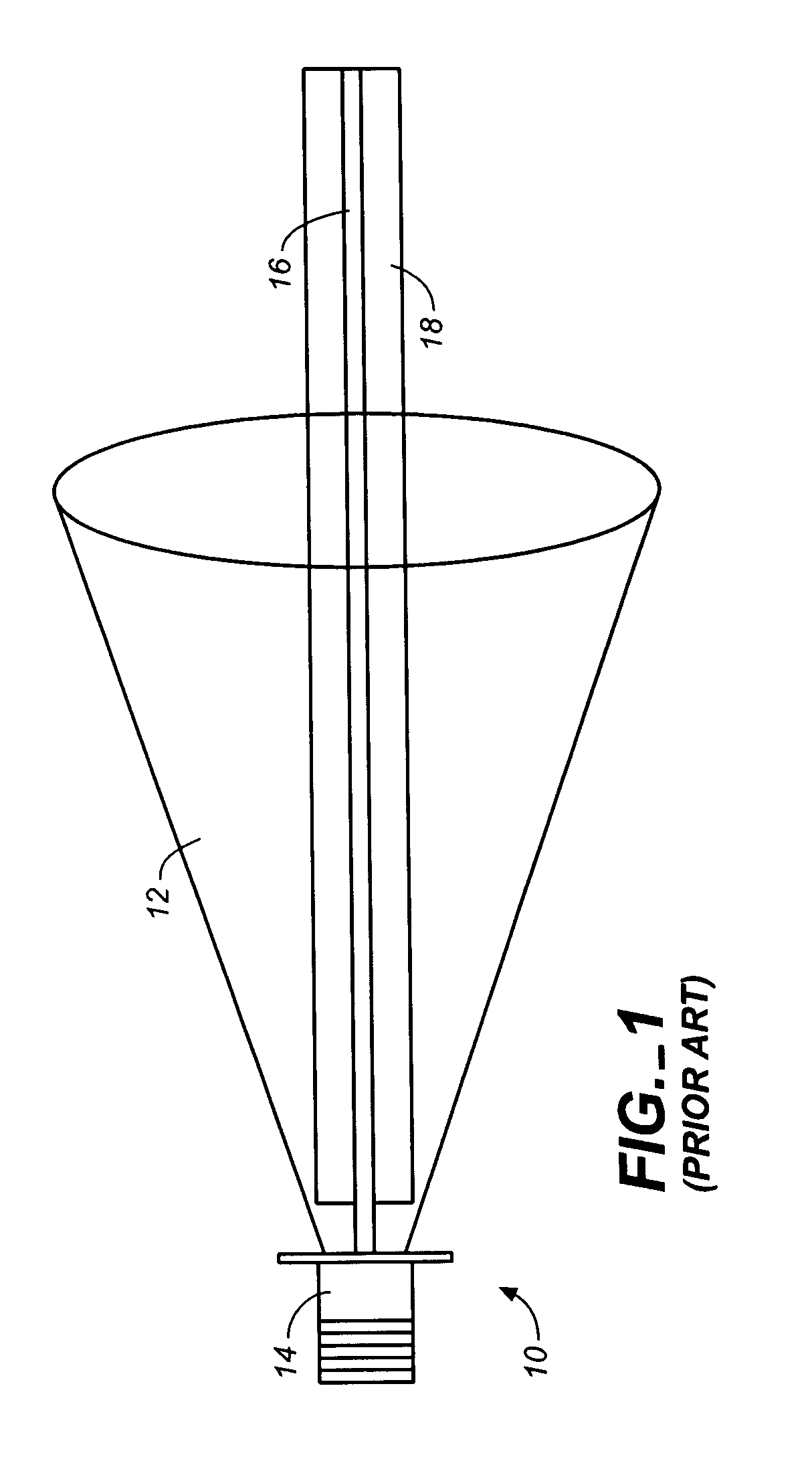

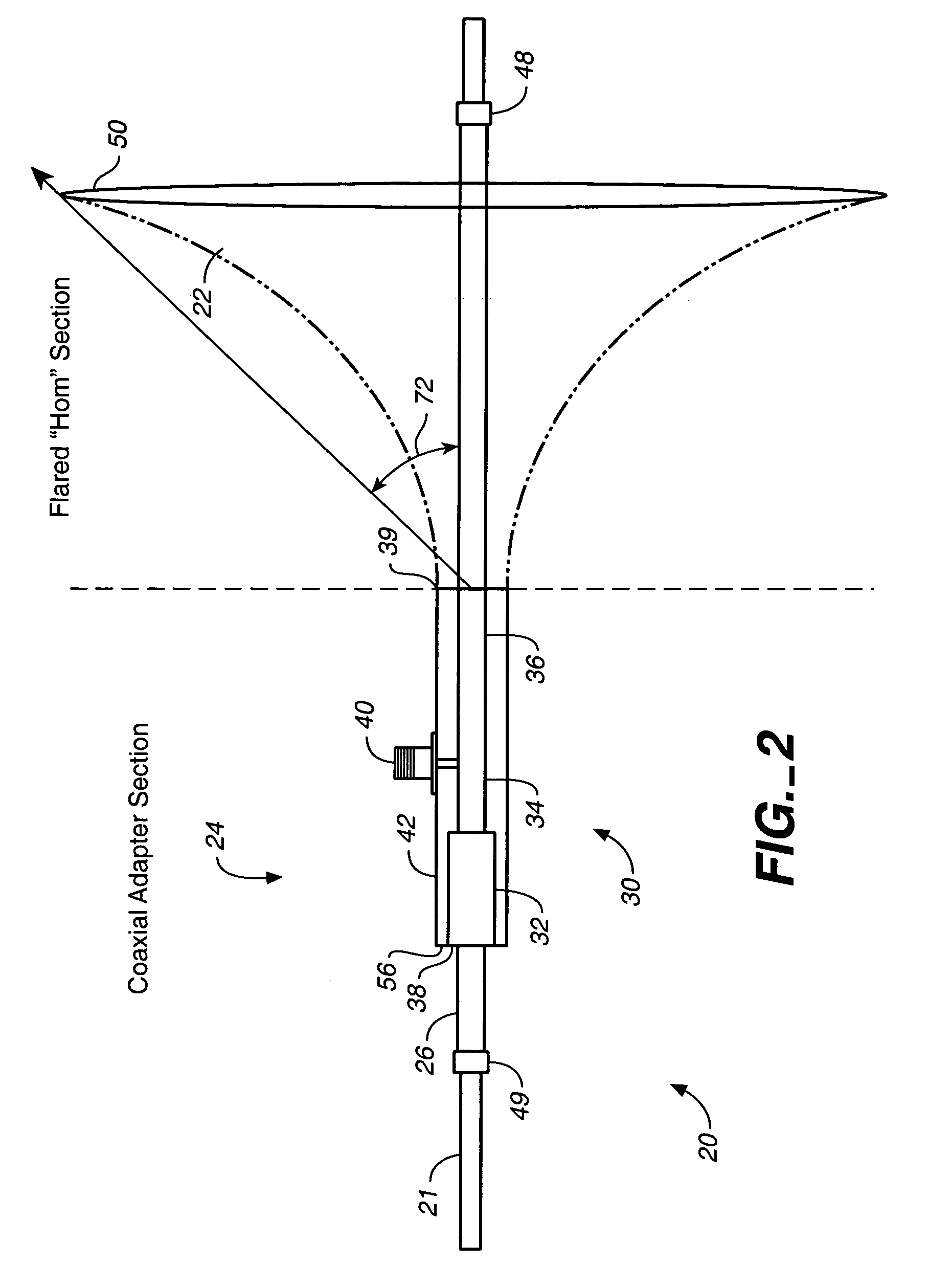

Method and apparatus for launching a surfacewave onto a single conductor transmission line using a slohed flared cone

ActiveUS7009471B2Avoid prolonged useImproving Impedance MatchingMultiple-port networksWaveguidesElectrical conductorEngineering

An apparatus for launching a surfacewave onto a single conductor transmission line provides a launch including a flared, continuously curving cone portion; a coaxial adapter portion; a wire adapter portion for contacting the wire conductor which allows for a multiplicity of wire dimensions for either insulated or uninsulated wire, or a tri-axial wire adapter device enabling non-contacting coupling to a wire; and a longitudinal slot added to the flared cone, wire adapter, and coaxial adapter portions of the launch to allow direct placement of the launch onto existing lines, without requiring cutting or threading of those lines for installation.

Owner:CORRIDOR SYST INC

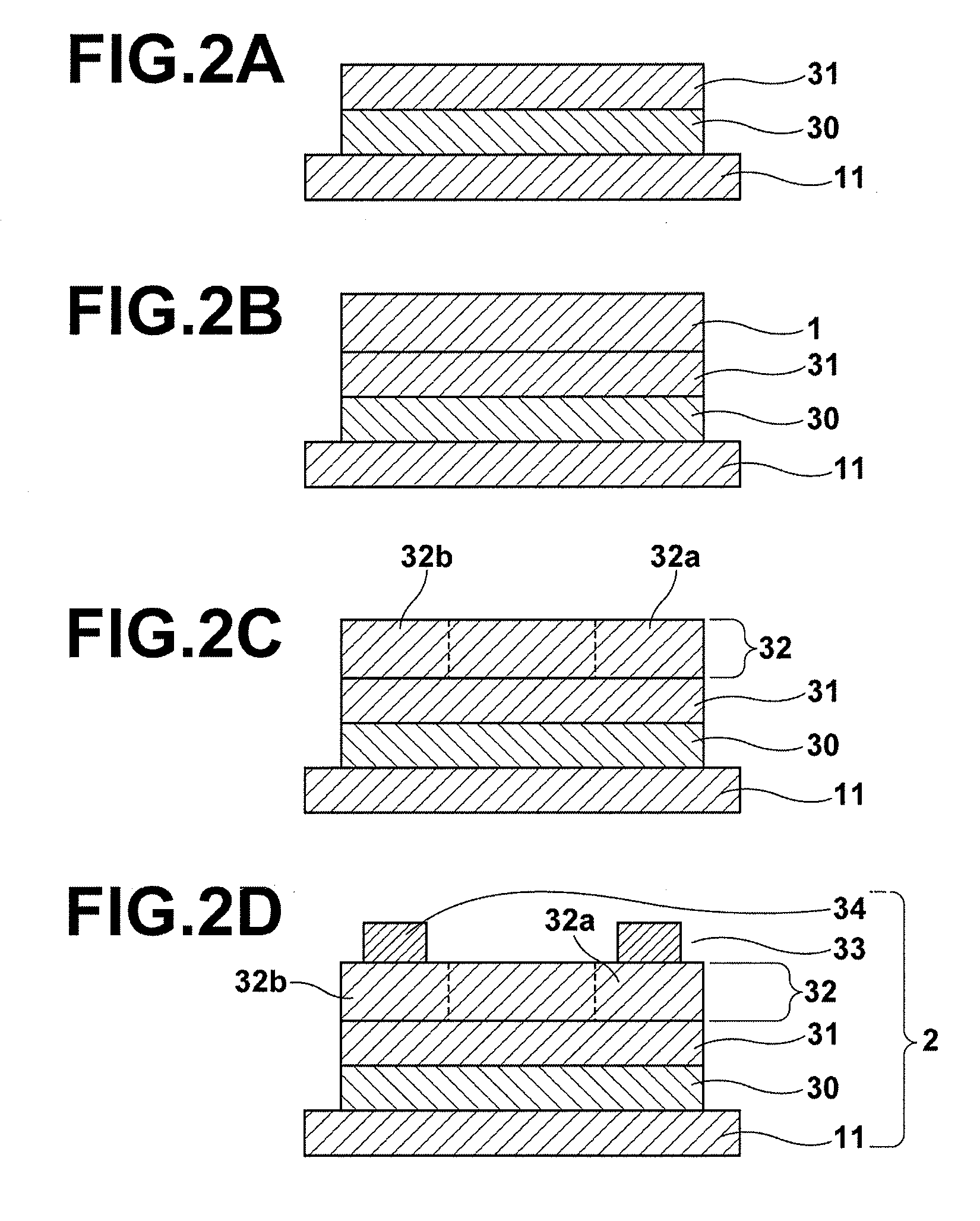

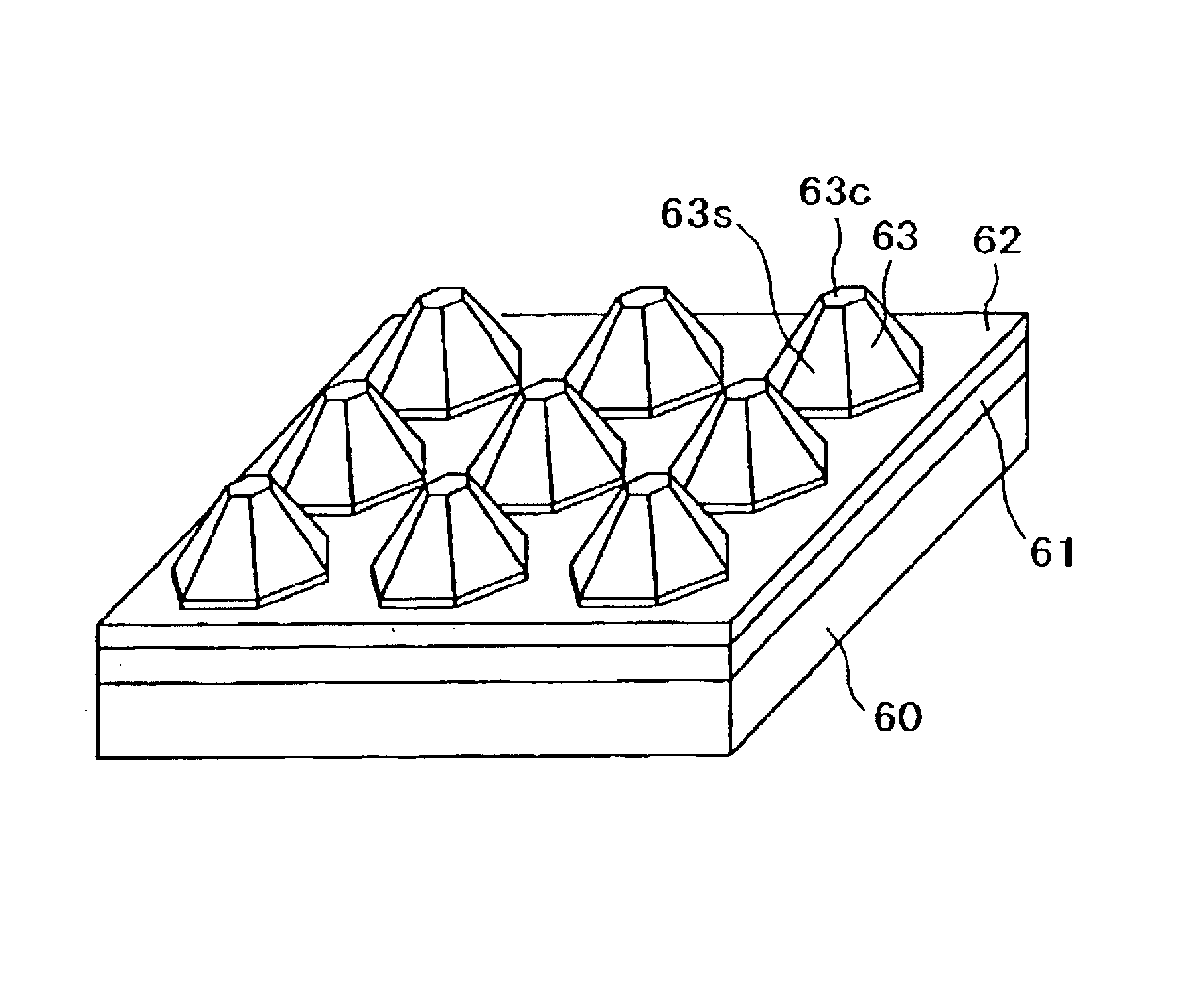

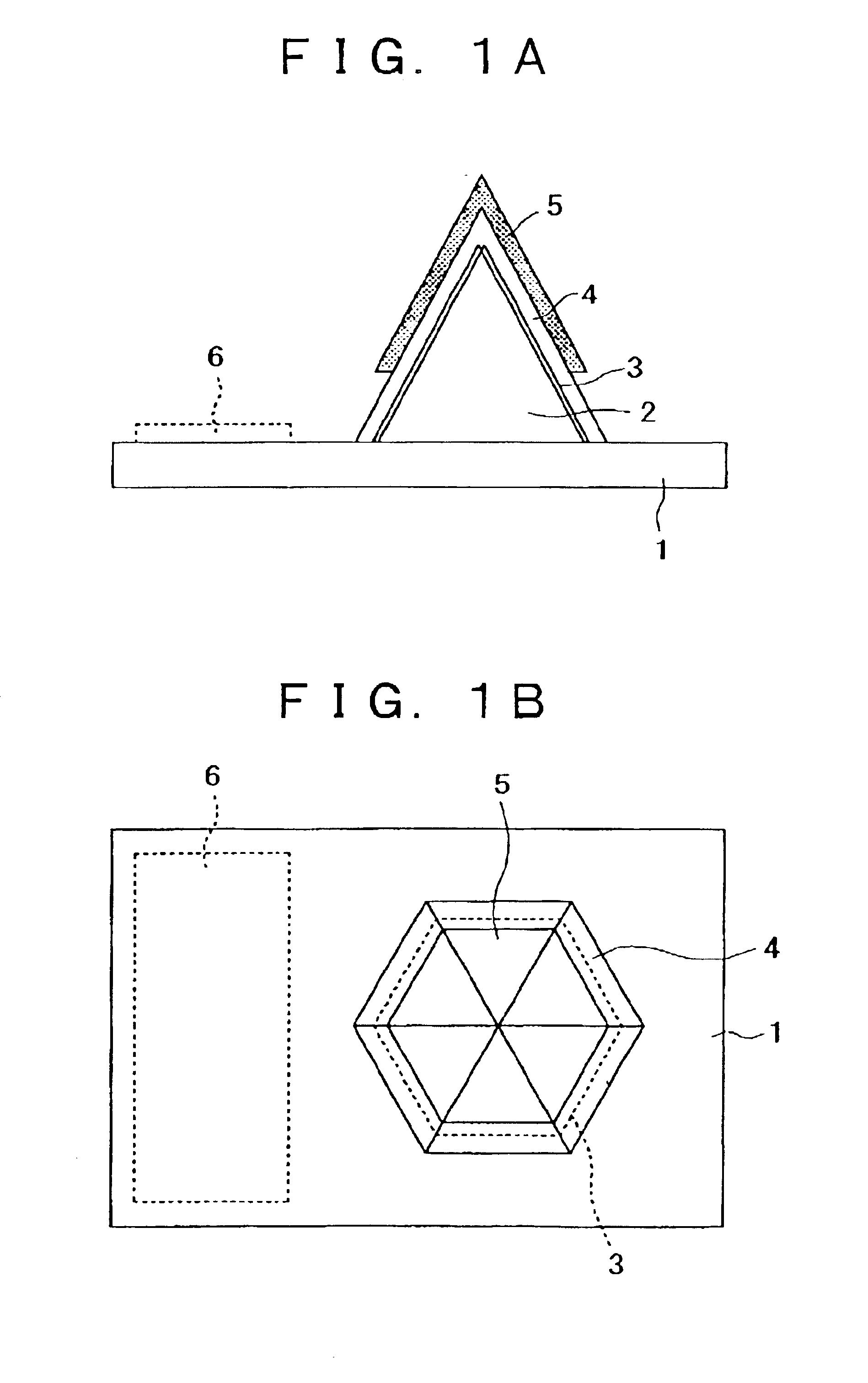

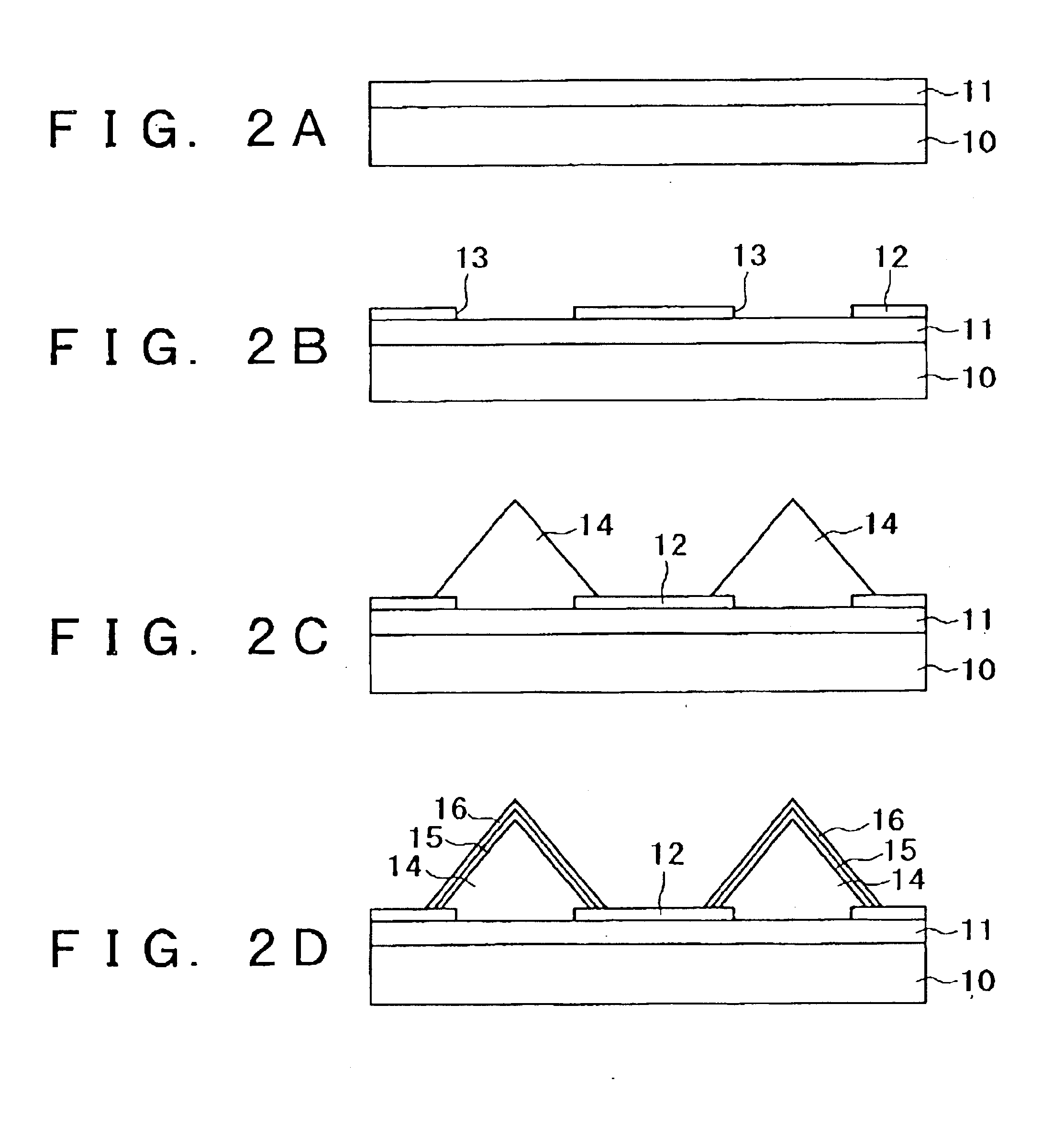

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

Collagen biofabric and methods of preparation and use therefor

InactiveUS20040048796A1Improved biophysical propertyImprove featuresSenses disorderPeptide/protein ingredientsSurgical GraftWound dressing

The present invention relates to collagenous membranes produced from amnion, herein referred to as a collagen biofabric. The collagen biofabric of the invention has the structural integrity of the native non-treated amniotic membrane, i.e., the native tertiary and quaternary structure. The present invention provides a method for preparing a collagen biofabric from a placental membrane, preferably a human placental membrane having a chorionic and amniotic membrane, by decellularizing the amniotic membrane. In a preferred embodiment, the amniotic membrane is completely decellularized. The collagen biofabric of the invention has numerous utilities in the medical and surgical field including for example, blood vessel repair, construction and replacement of a blood vessel, tendon and ligament replacement, wound-dressing, surgical grafts, ophthalmic uses, sutures, and others. The benefits of the biofabric are, in part, due to its physical properties such as biomechanical strength, flexibility, suturability, and low immunogenicity, particularly when derived from human placenta.

Owner:CELLULAR THERAPEUTICS DIV OF CELGENE +1

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

ActiveUS8202365B2Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventCrystal structure

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

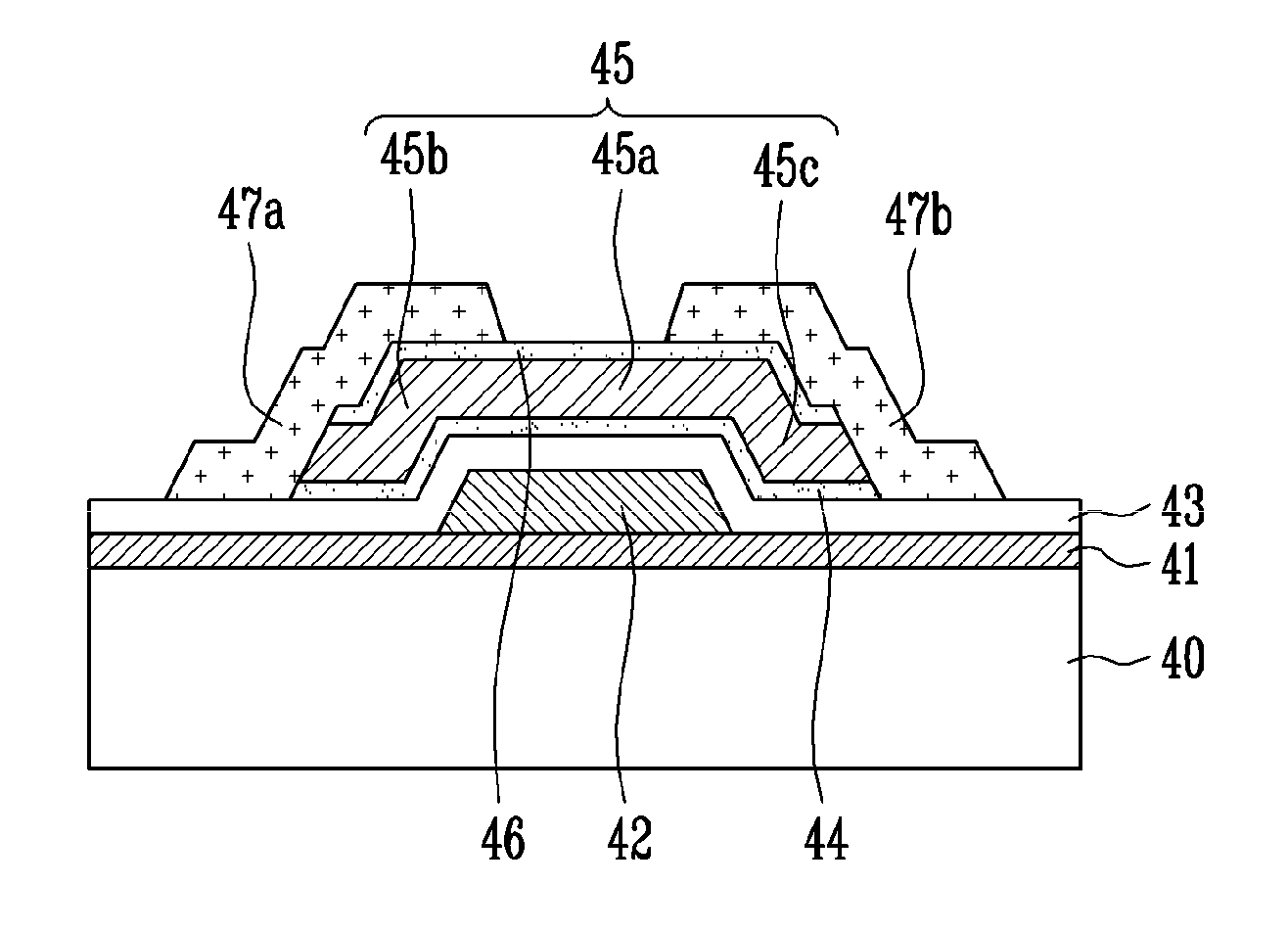

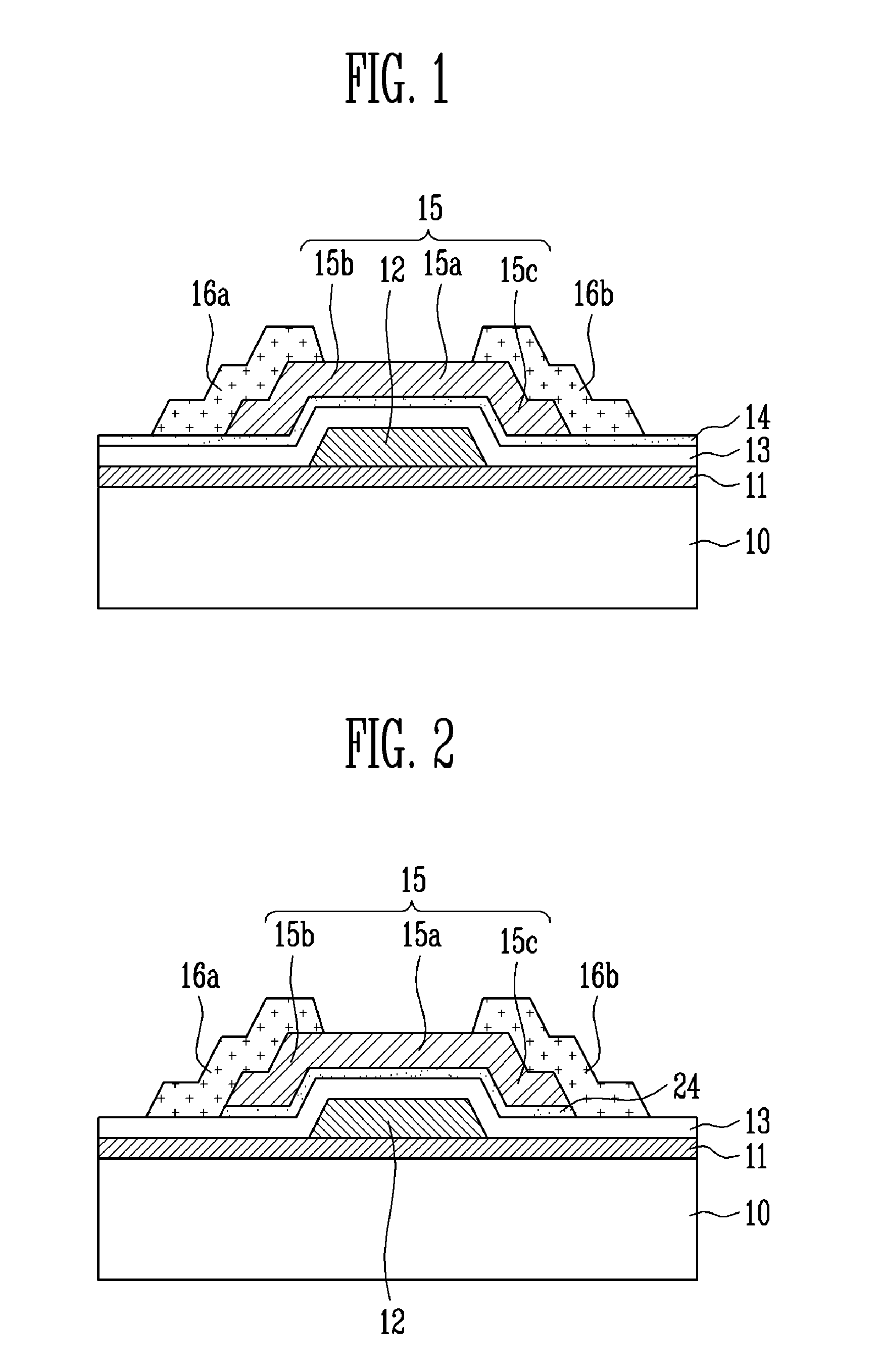

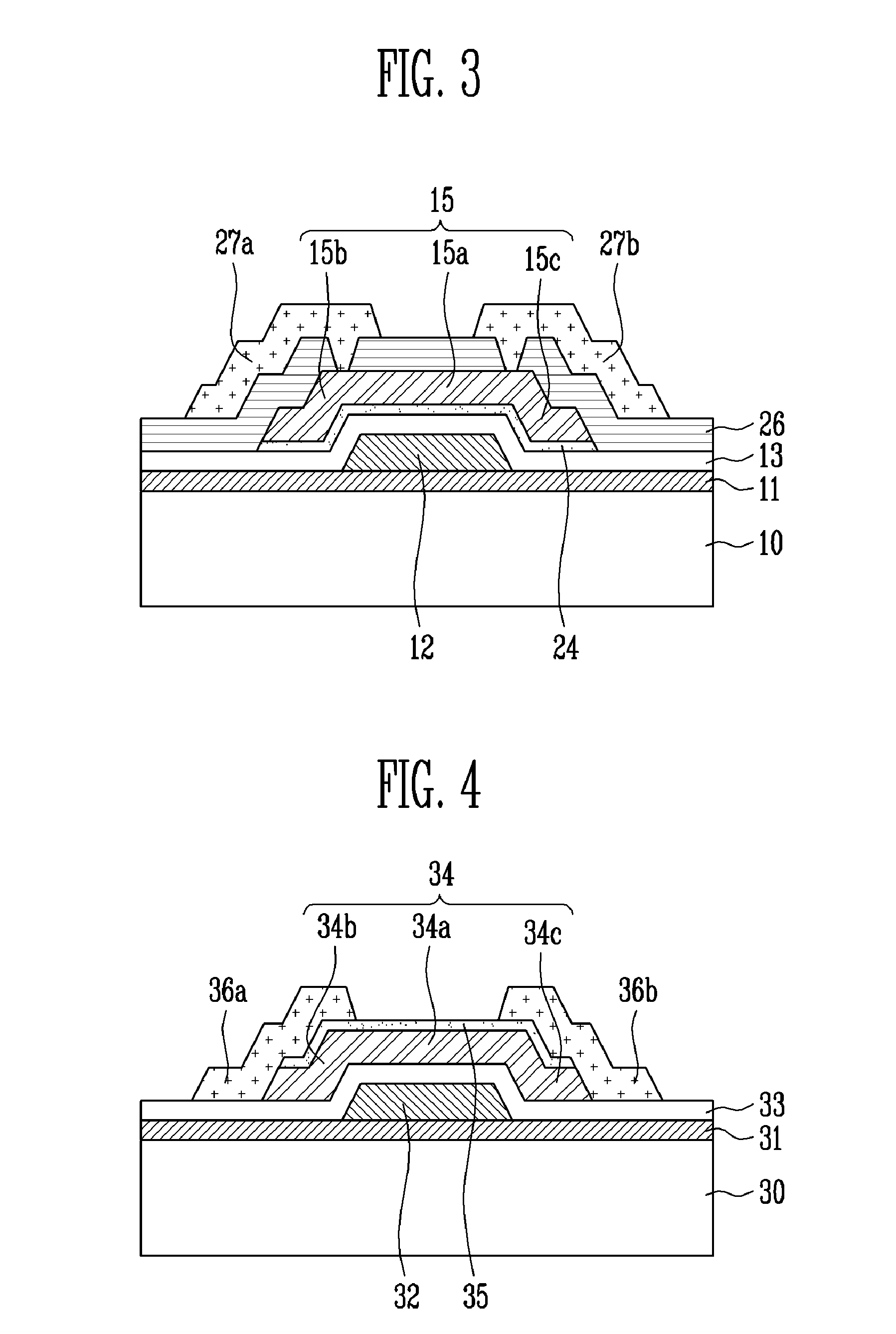

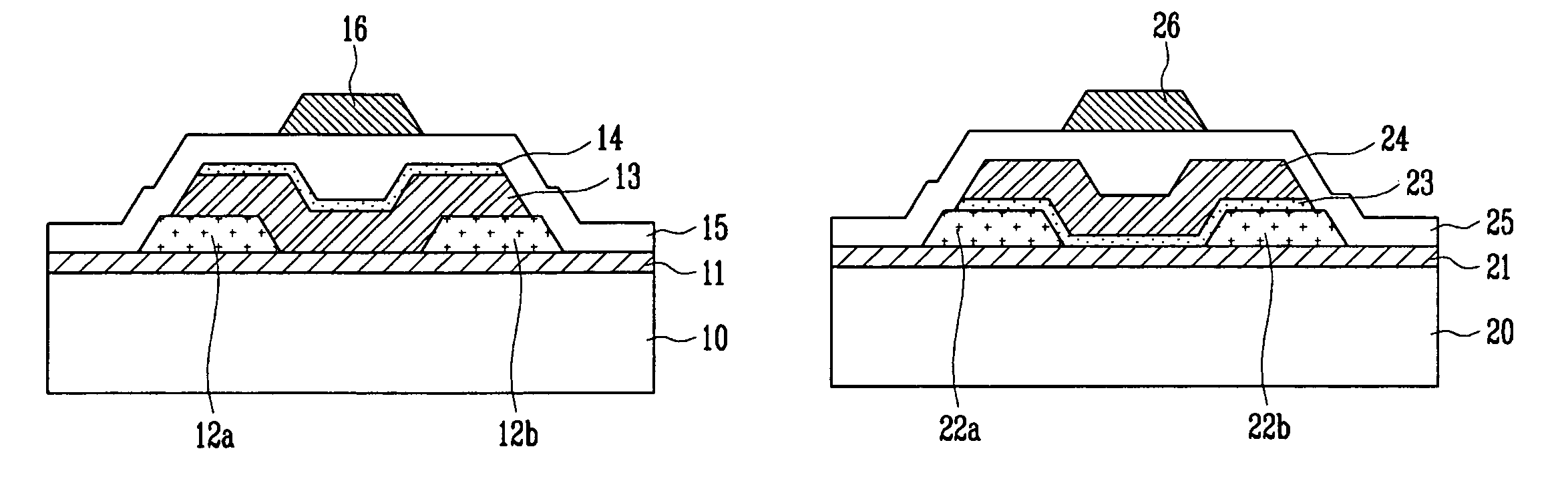

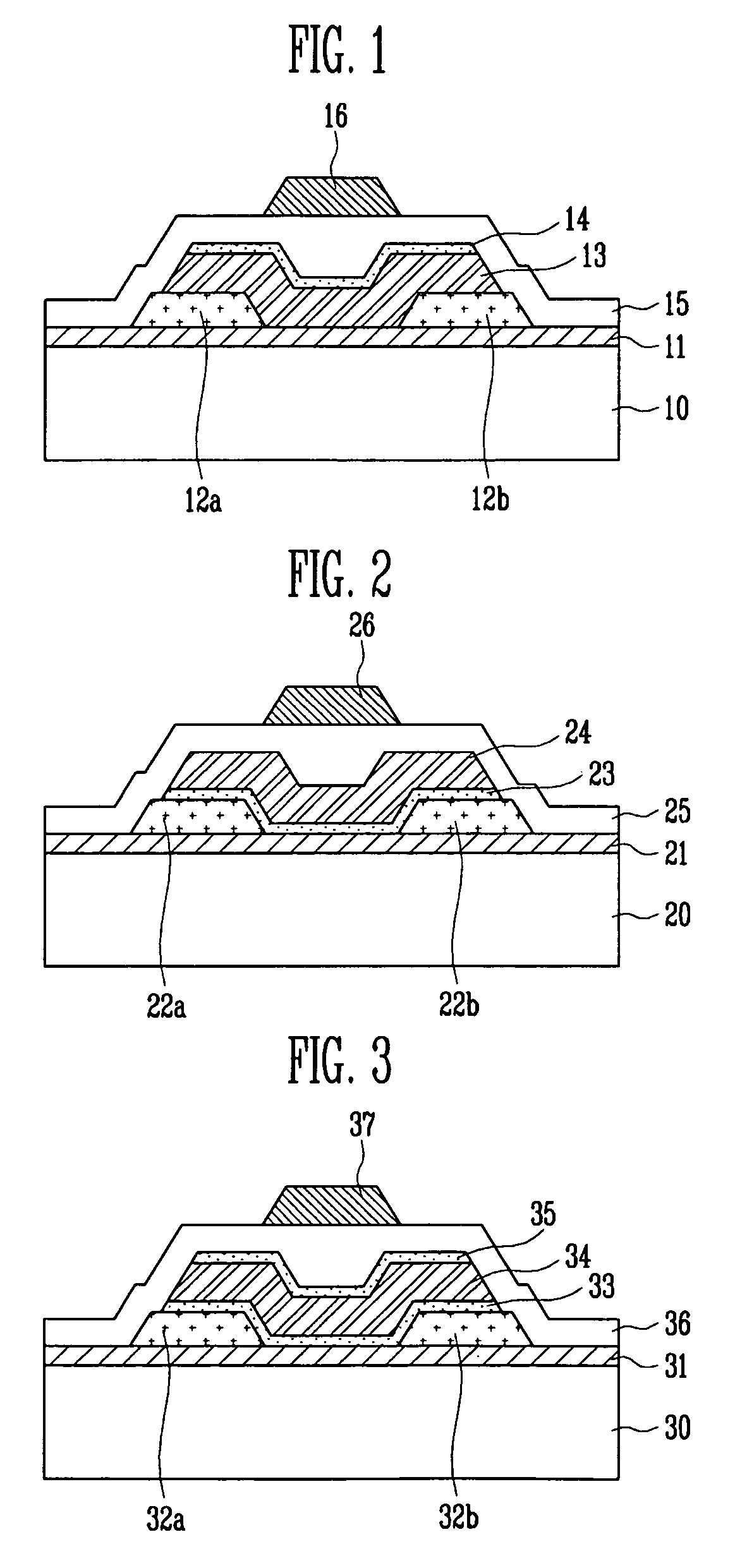

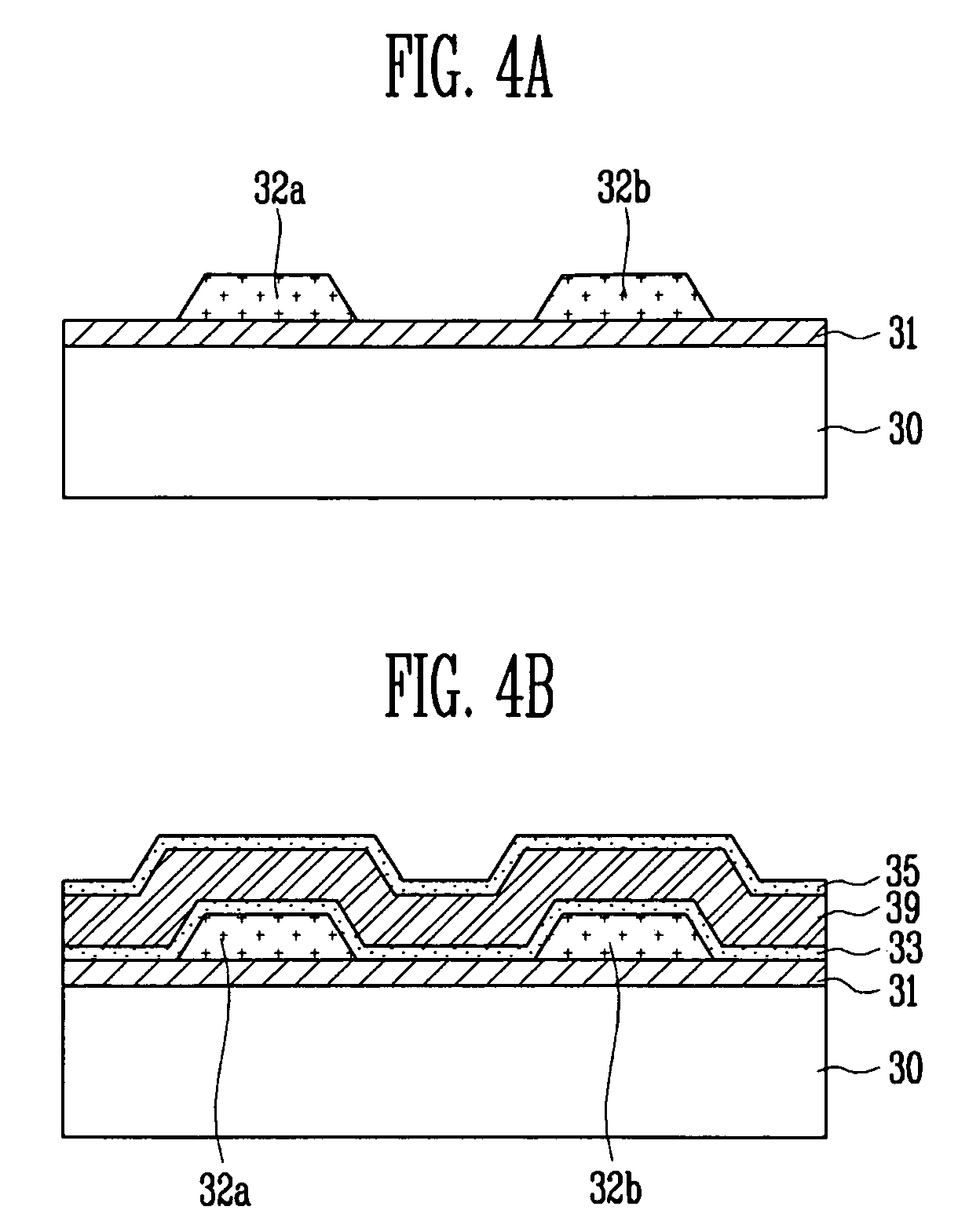

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS8148779B2Improve featuresAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

Process and apparatus for organic vapor jet deposition

ActiveUS20080233287A1Good directionalityMinimize material wasteVacuum evaporation coatingSputtering coatingOrganic vaporOrganic film

A method of fabricating an organic film is provided. A non-reactive carrier gas is used to transport an organic vapor. The organic vapor is ejected through a nozzle block onto a cooled substrate, to form a patterned organic film. A device for carrying out the method is also provided. The device includes a source of organic vapors, a source of carrier gas and a vacuum chamber. A heated nozzle block attached to the source of organic vapors and the source of carrier gas has at least one nozzle adapted to eject carrier gas and organic vapors onto a cooled substrate disposed within the vacuum chamber.

Owner:THE TRUSTEES FOR PRINCETON UNIV

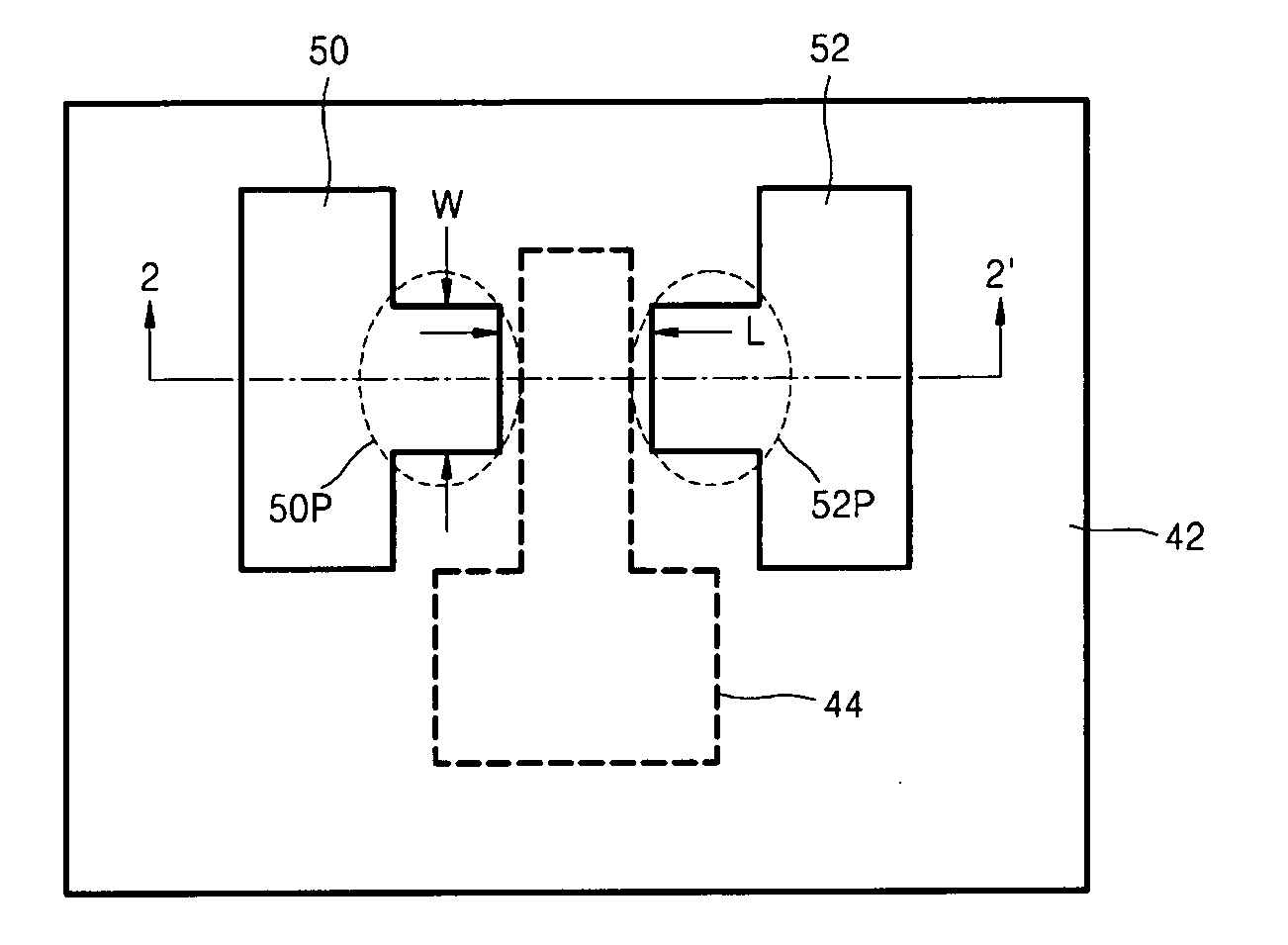

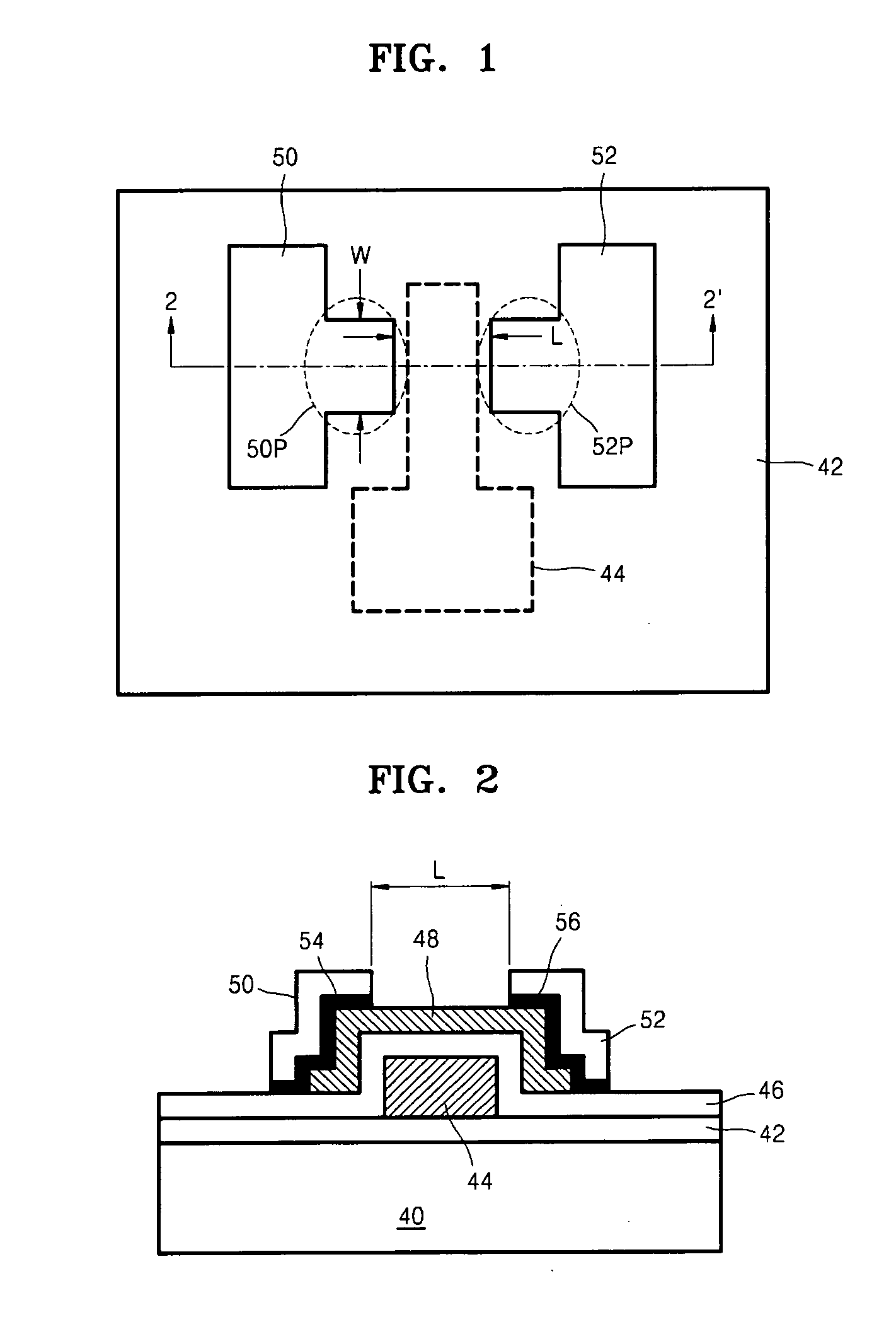

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor and method of manufacturing the same

ActiveUS20080203387A1Improve featuresSmooth connectionTransistorSolid-state devicesOptoelectronicsMaterials science

Provided are a thin film transistor and a method of manufacturing the same. The thin film transistor may include a gate; a channel layer; a source and a drain, the source and the drain being formed of metal; and a metal oxide layer, the metal oxide layer being formed between the channel layer and the source and the drain. The metal oxide layer may have a gradually changing metal content between the channel layer and the source and the drain.

Owner:SAMSUNG ELECTRONICS CO LTD

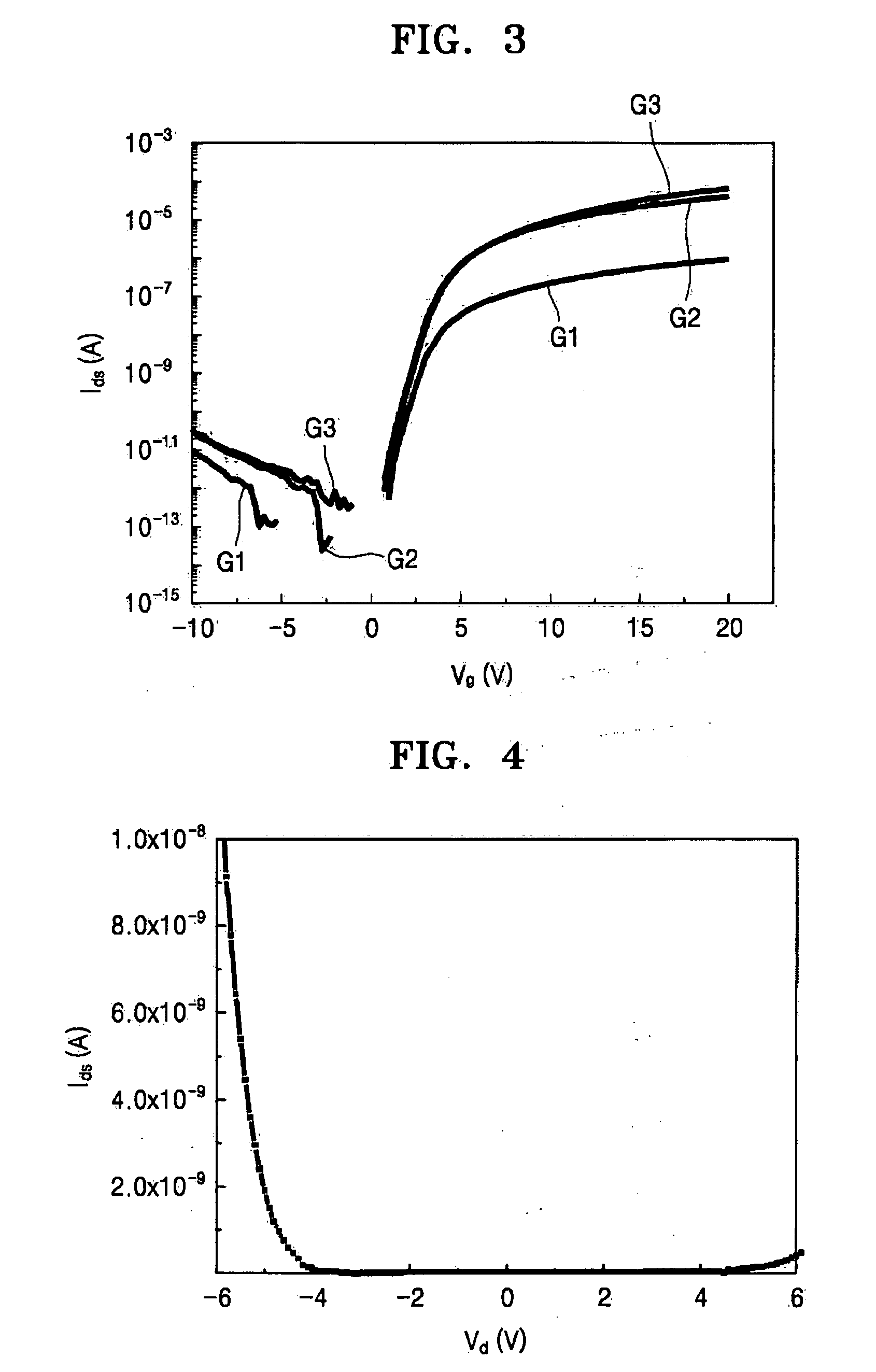

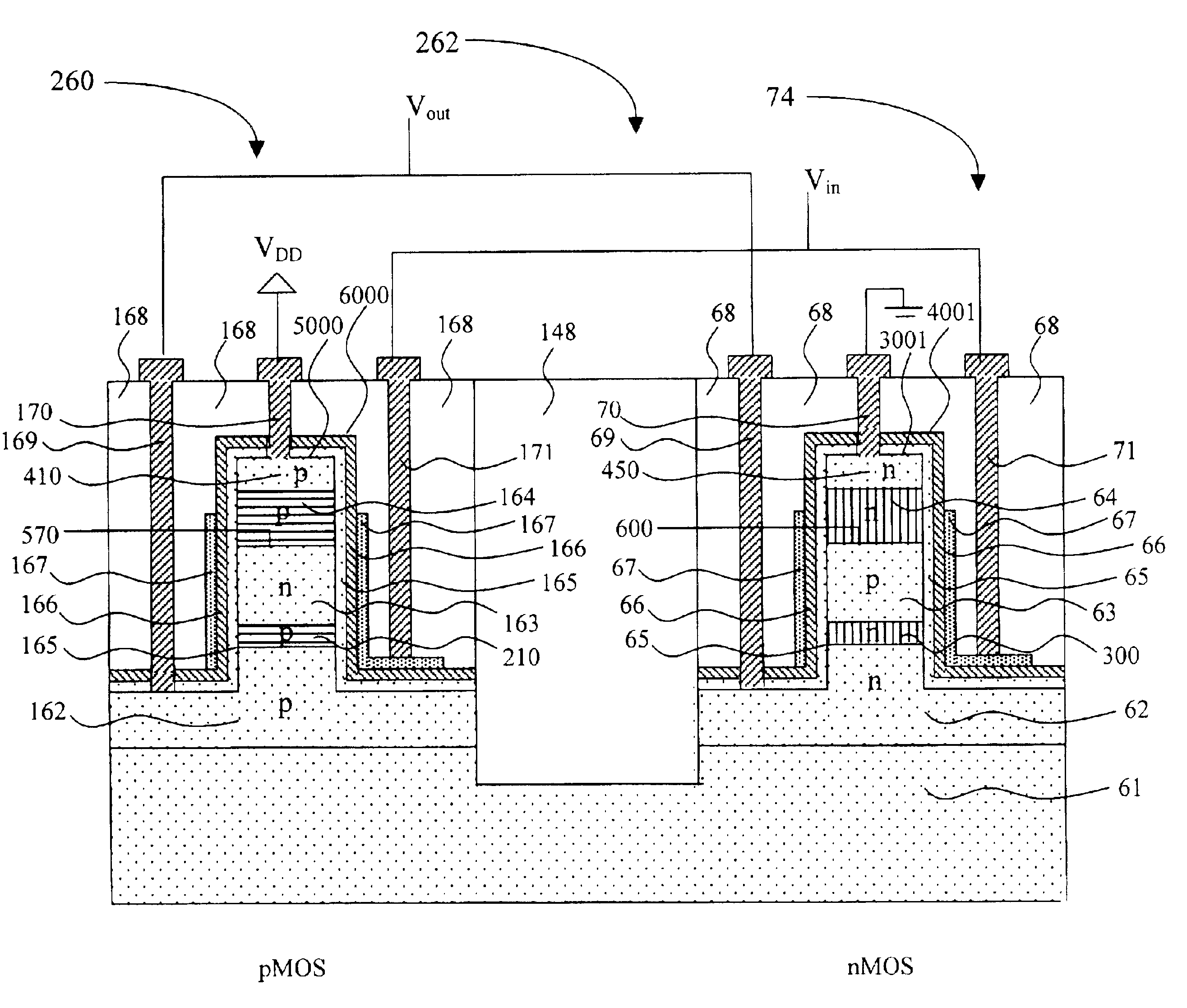

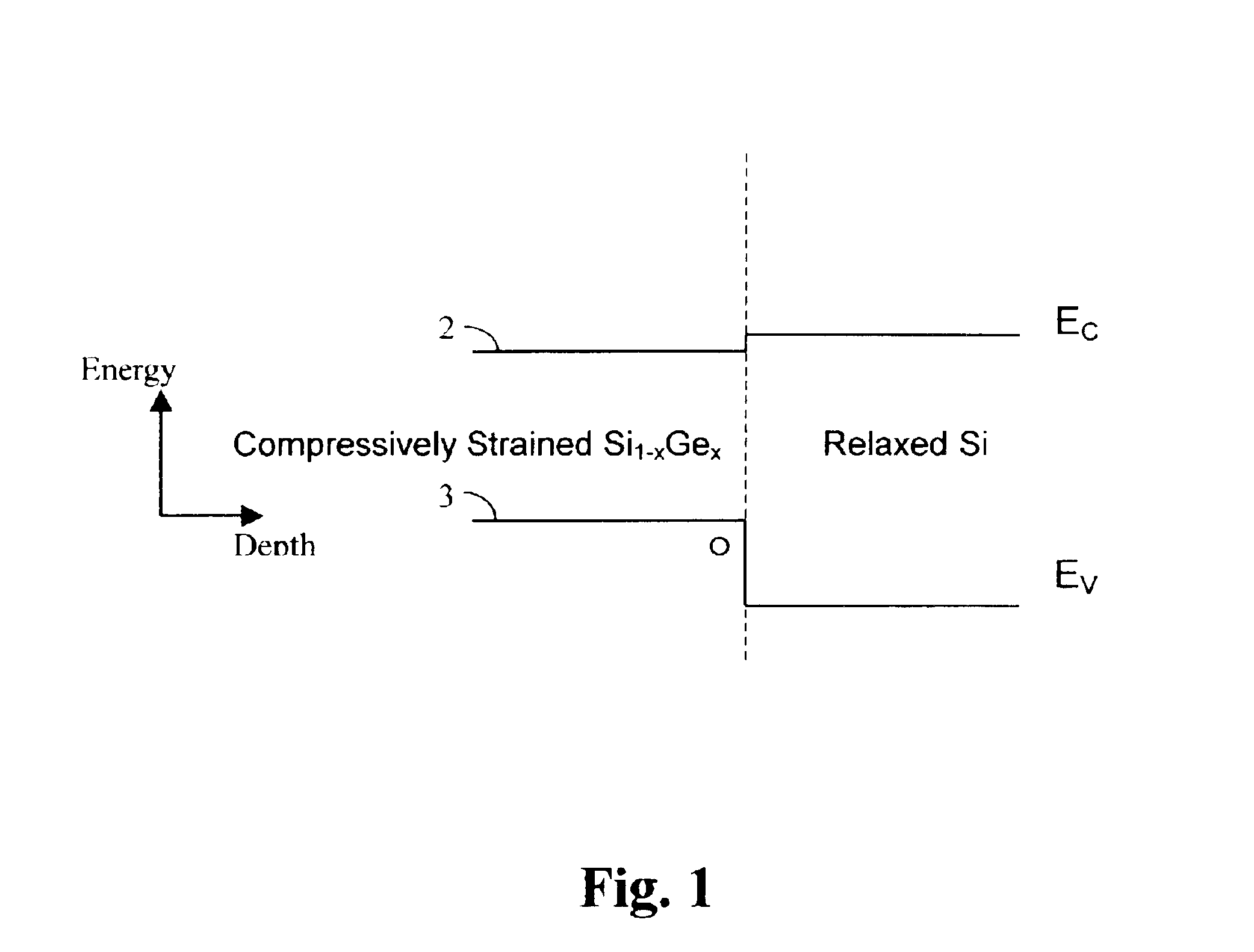

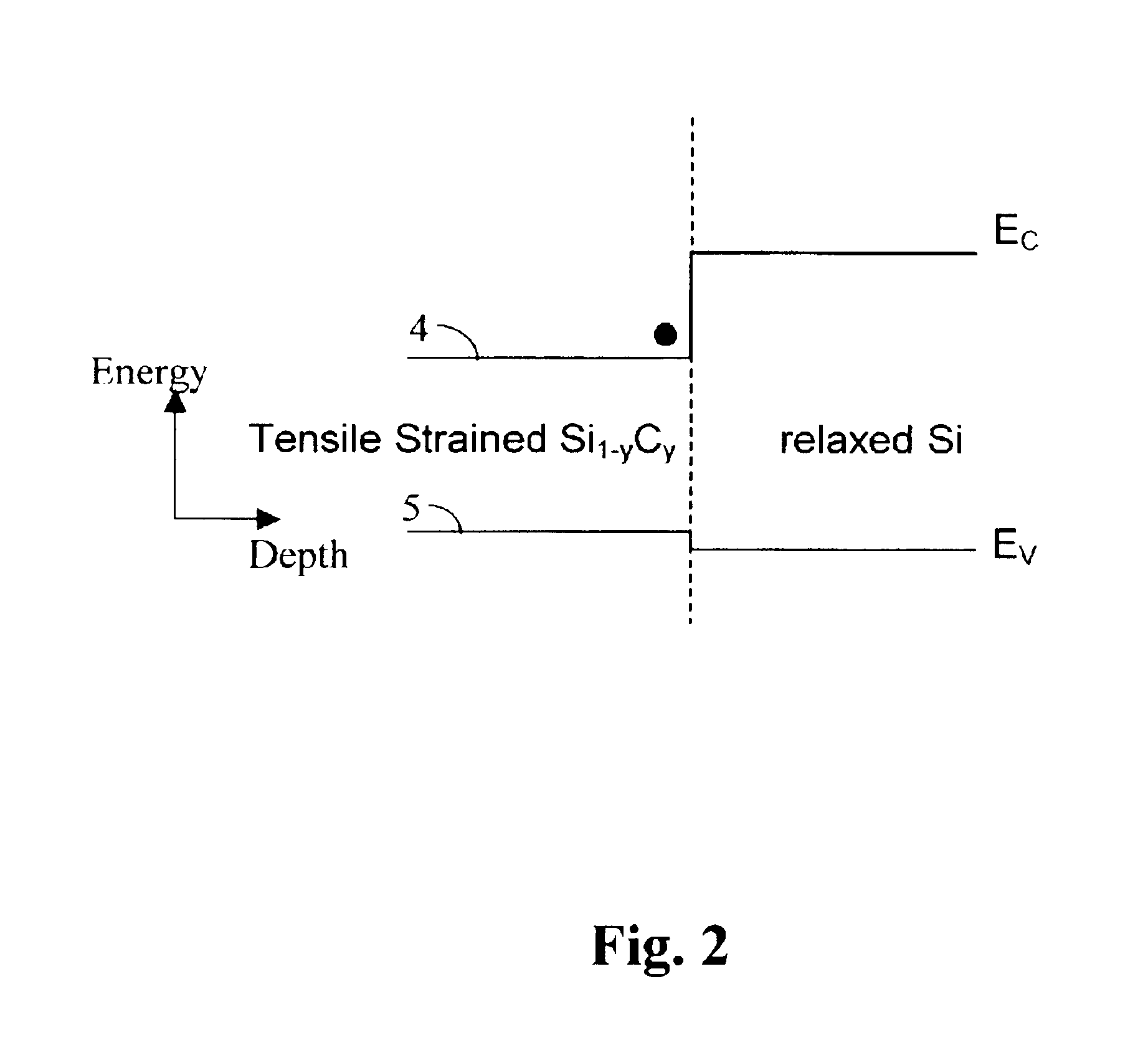

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

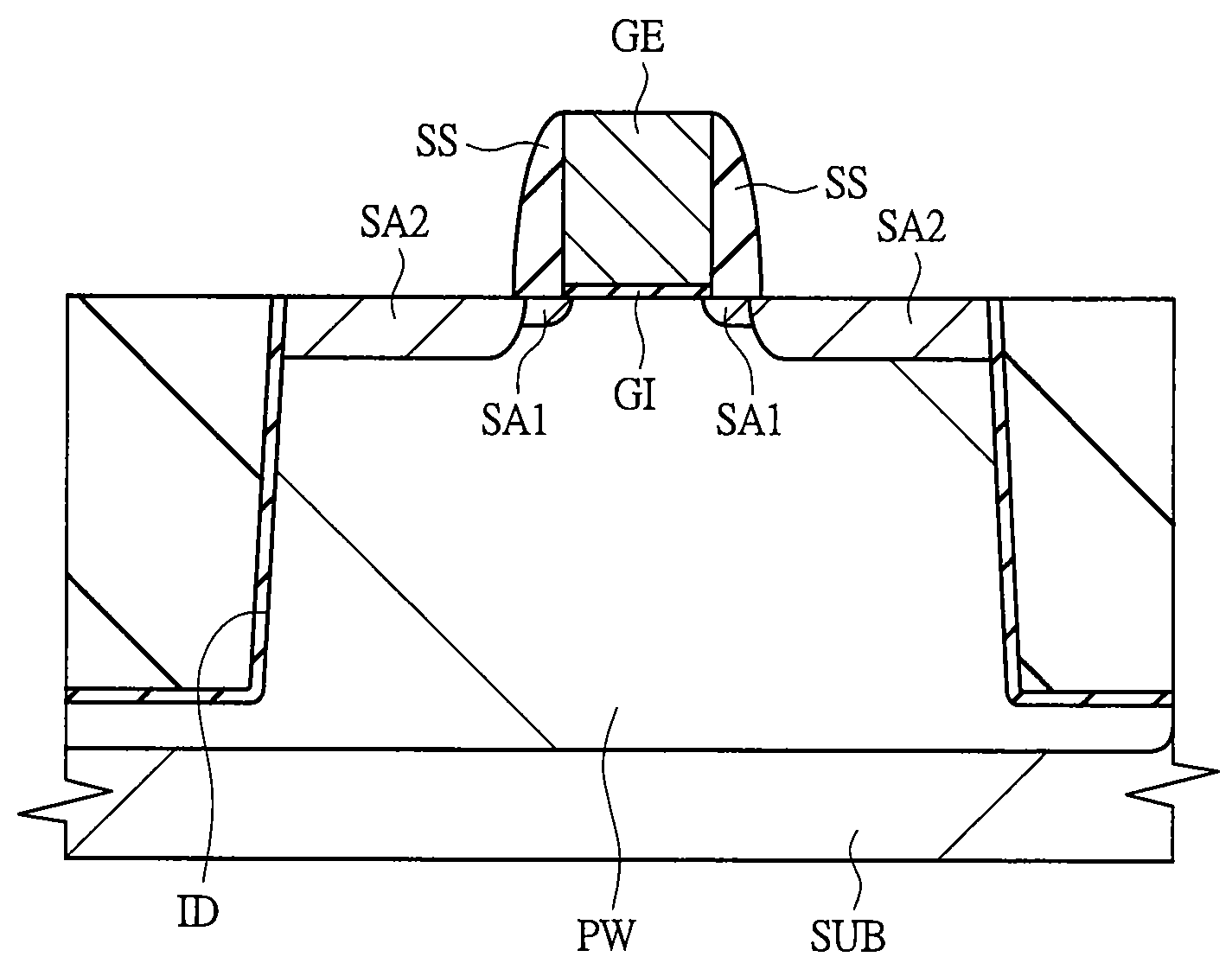

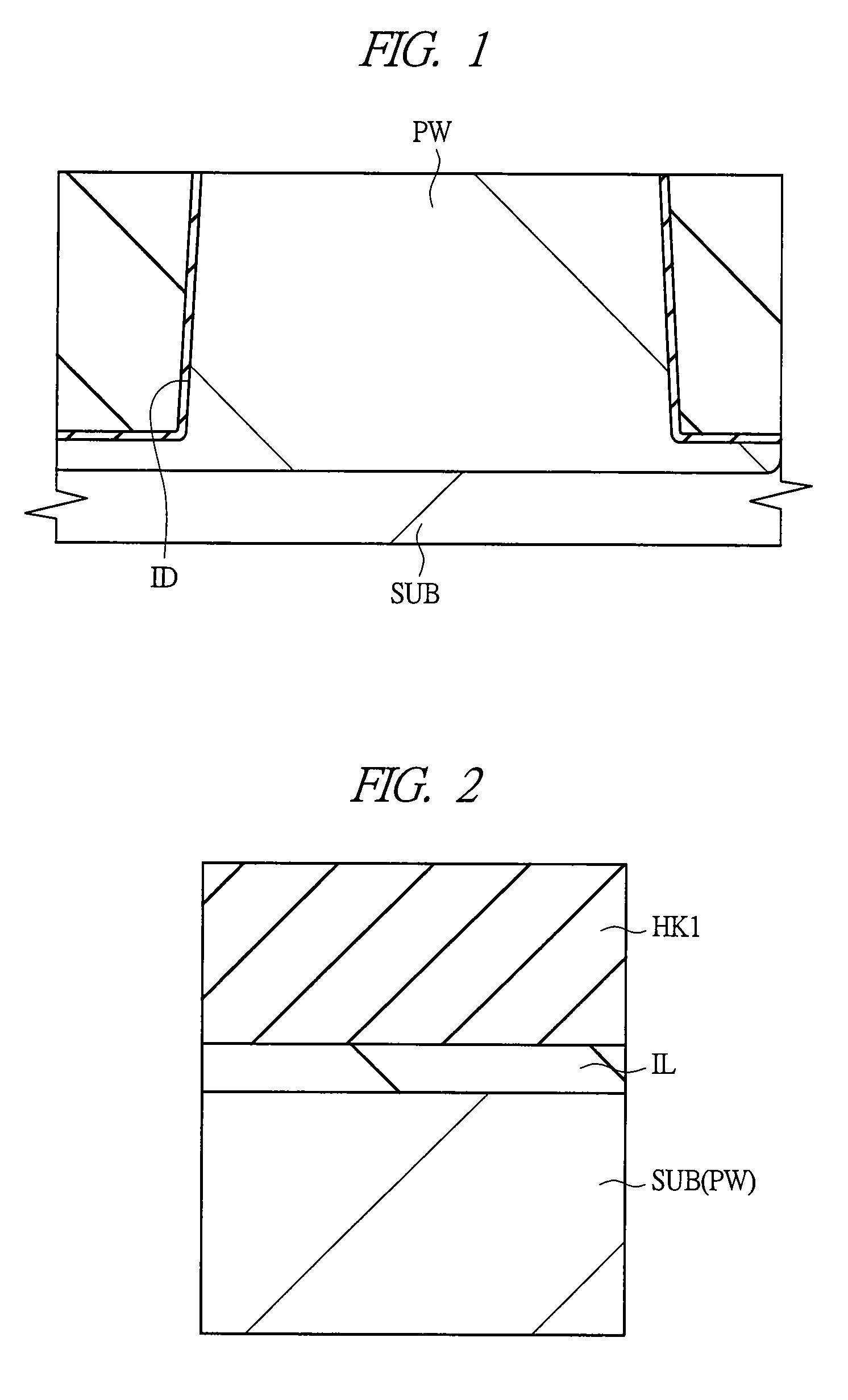

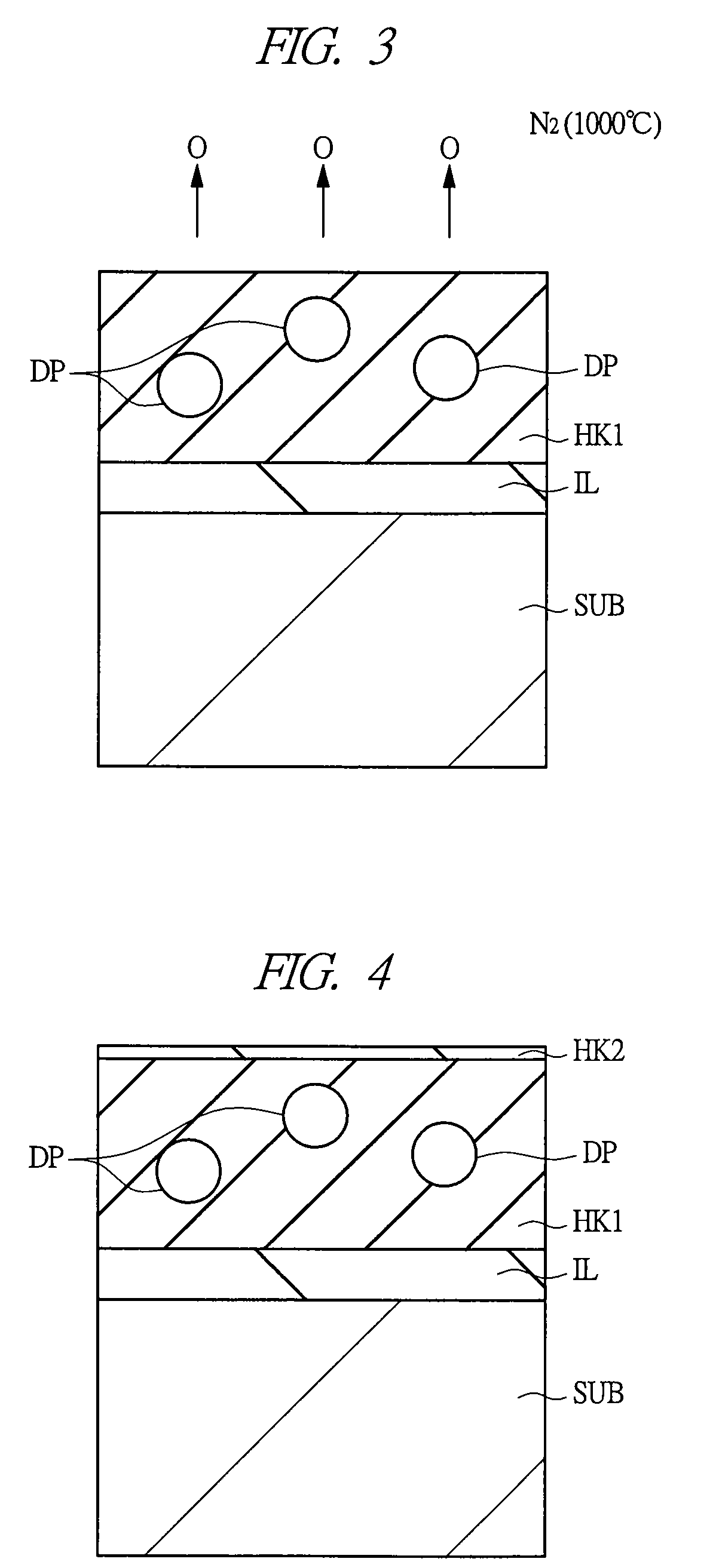

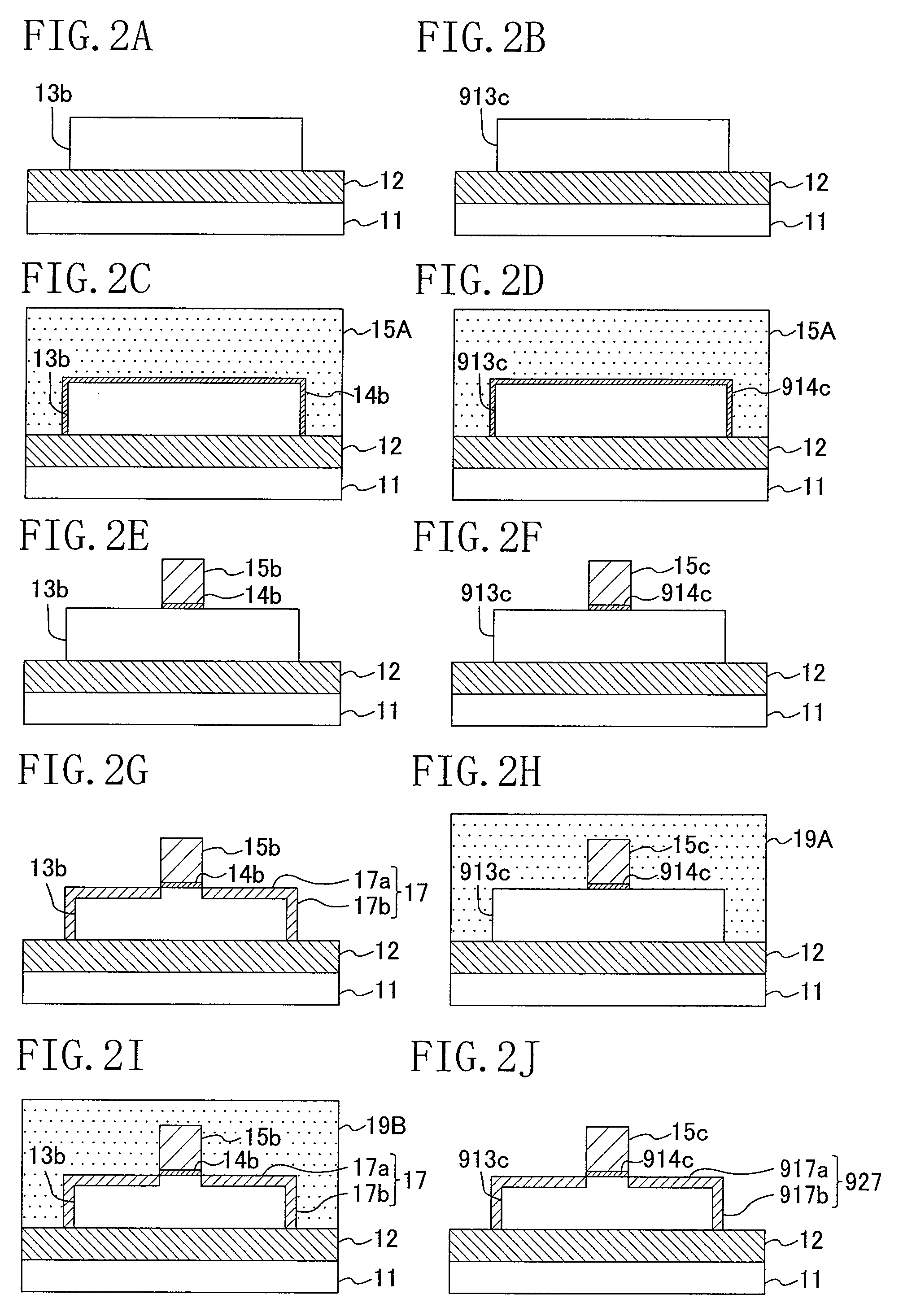

Manufacturing method of semiconductor device

InactiveUS20090011608A1Reduce hypoxiaSuppression of interface silicon oxide growthSemiconductor/solid-state device manufacturingSemiconductor devicesTantalum nitrideSilicon oxide

The transistor characteristics of a MIS transistor provided with a gate insulating film formed to contain oxide with a relative dielectric constant higher than that of silicon oxide are improved. After a high dielectric layer made of hafnium oxide is formed on a main surface of a semiconductor substrate, the main surface of the semiconductor substrate is heat-treated in a non-oxidation atmosphere. Next, an oxygen supplying layer made of hafnium oxide deposited by ALD and having a thickness smaller than that of the high dielectric layer is formed on the high dielectric layer, and a cap layer made of tantalum nitride is formed. Thereafter, the main surface of the semiconductor substrate is heat-treated.

Owner:RENESAS TECH CORP

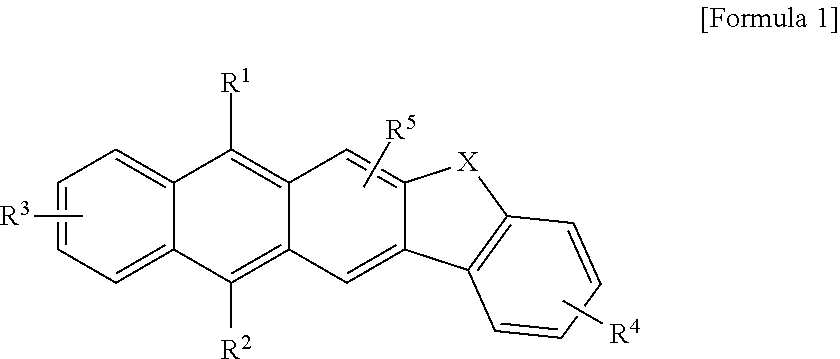

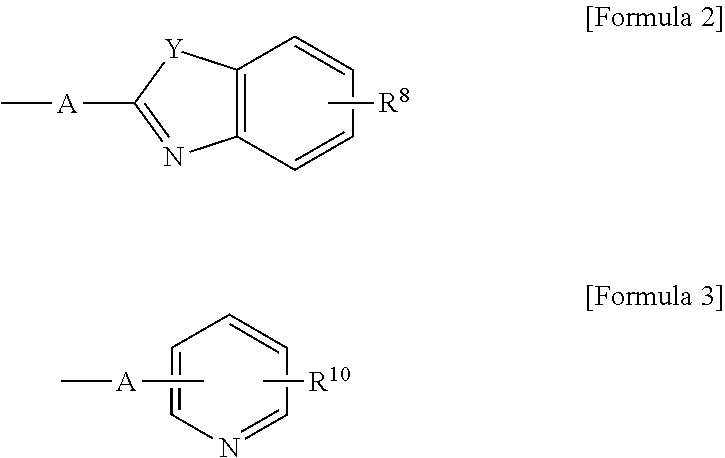

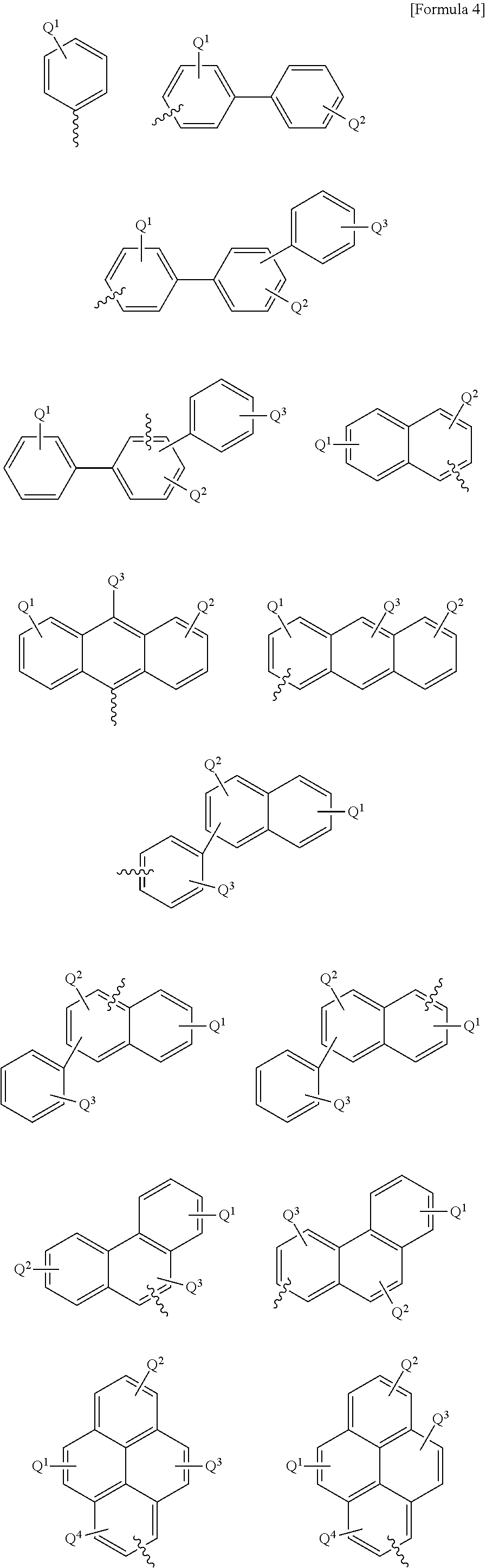

Anthracene derivative and organic electroluminescence element using the same

ActiveUS20110210320A1Enhanced electron transport capabilitiesImprove performanceOrganic chemistryElectroluminescent light sourcesBenzoxazoleAnthracene

The present invention relates to an anthracene derivative and an organic electroluminescent device using the same. More specifically, the present invention relates to: a novel compound which has a core (for example, an indenoanthracene core) where both an anthracene moiety with excellent device characteristics and a fluorene moiety with excellent fluorescent properties are fused, wherein substituents (for example, a heterocyclic group such as a benzimidazole group, a benzothiazole group, a benzoxazole group, a pyridinyl group or a bipyridinyl group) with an electron transfer capacity are substituted to the core; and an organic electroluminescence element which has improved luminous efficiency, brightness, thermal stability, driving voltage, and lifetime, by comprising an organic layer which is positioned between a positive electrode and negative electrode and contains the novel compound.

Owner:SOLUS ADVANCED MATERIALS CO LTD

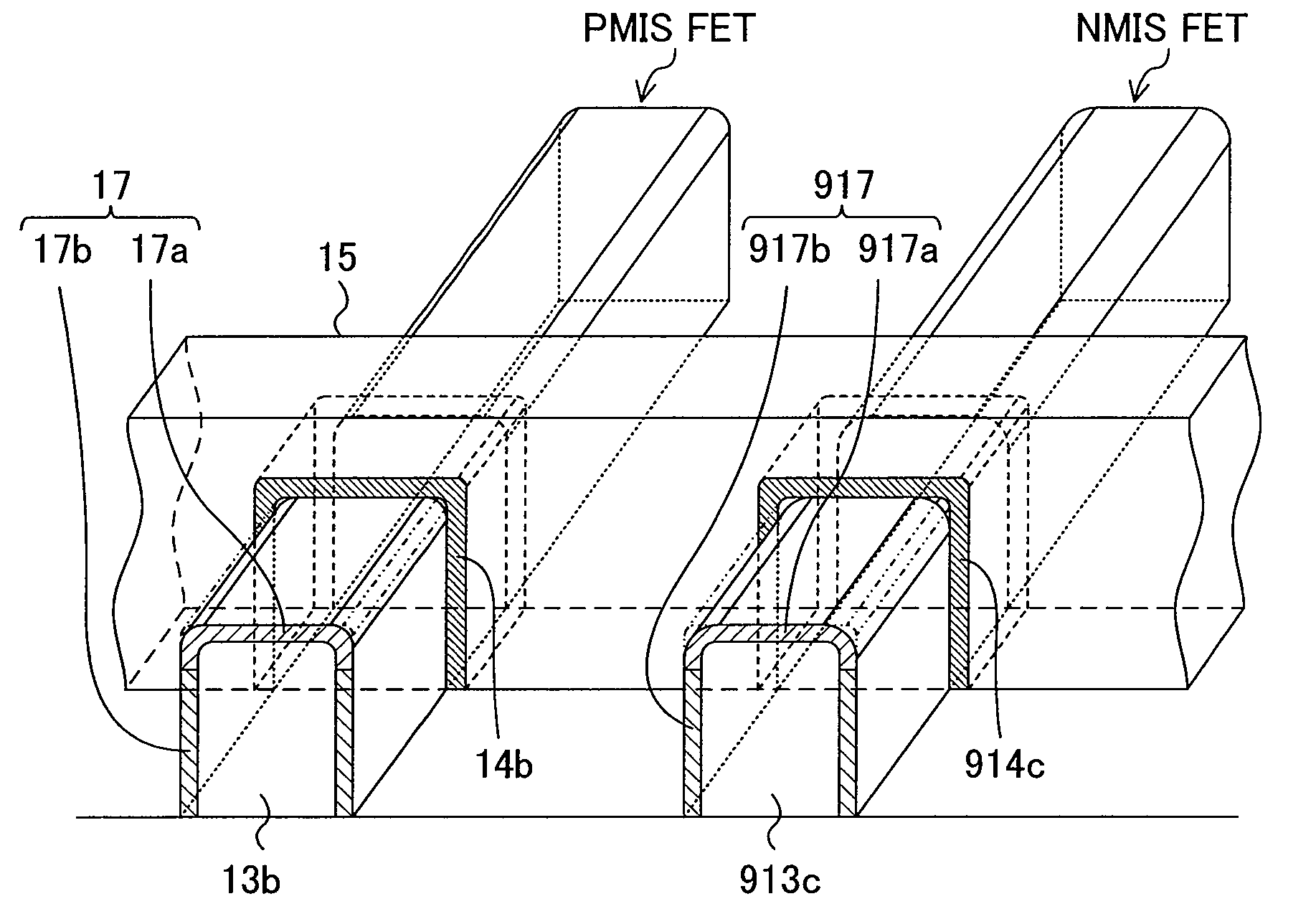

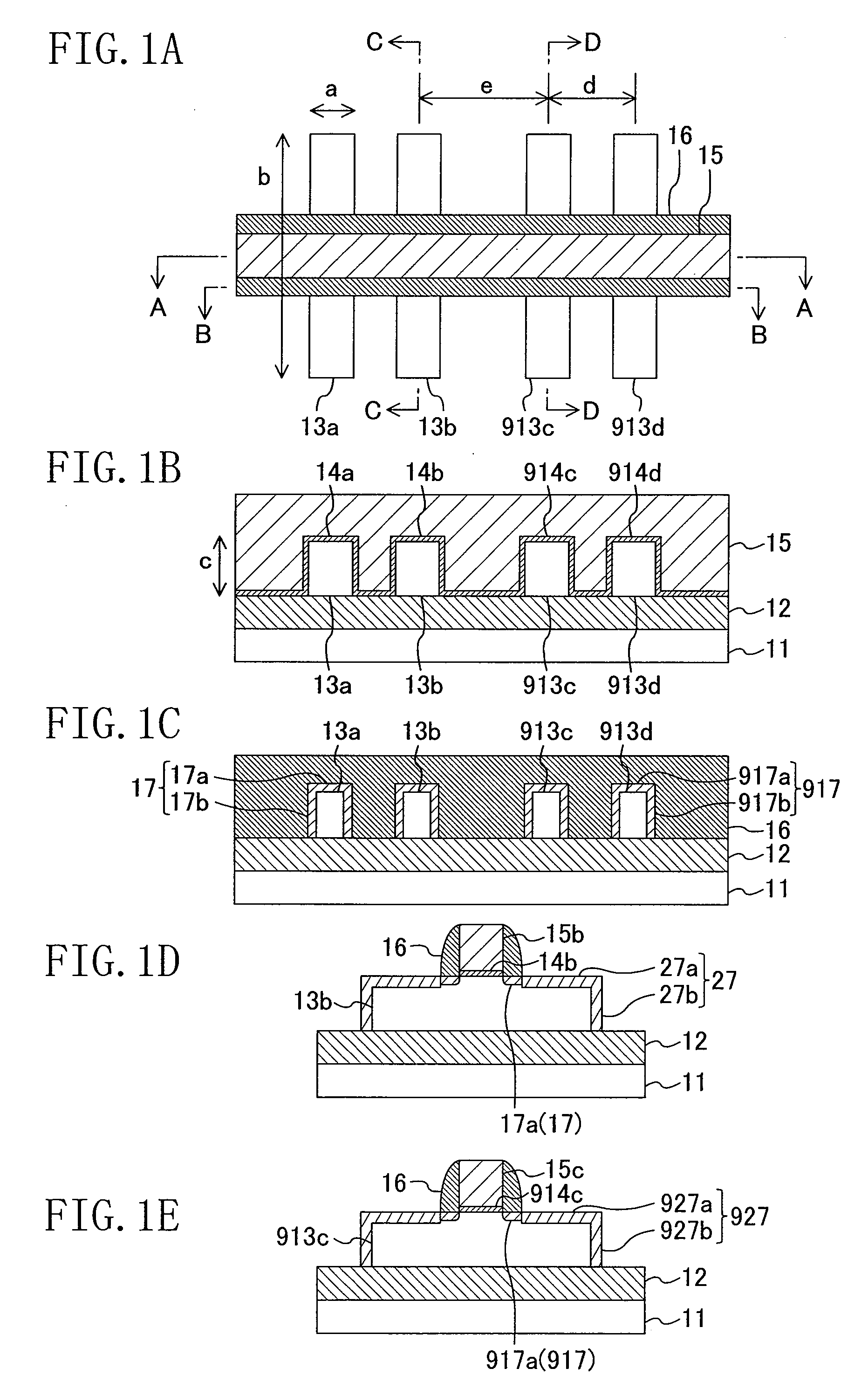

Semiconductor device and method for producing the same

ActiveUS20090289300A1Low ion densityReduce pressureTransistorSolid-state devicesEngineeringSemiconductor

First and second gate insulating films are formed so as to cover at least the upper corner of first and second fin-shaped semiconductor regions. The radius of curvature r1′ of the upper corner of the first fin-shaped semiconductor region located outside the first gate insulating film is greater than the radius of curvature r1 of the upper corner of the first fin-shaped semiconductor region located under the first gate insulating film and is less than or equal to 2×r1. The radius of curvature r2′ of the upper corner of the second fin-shaped semiconductor region located outside the second gate insulating film is greater than the radius of curvature r2 of the upper corner of the second fin-shaped semiconductor region located under the second gate insulating film and is less than or equal to 2×r2.

Owner:GK BRIDGE 1

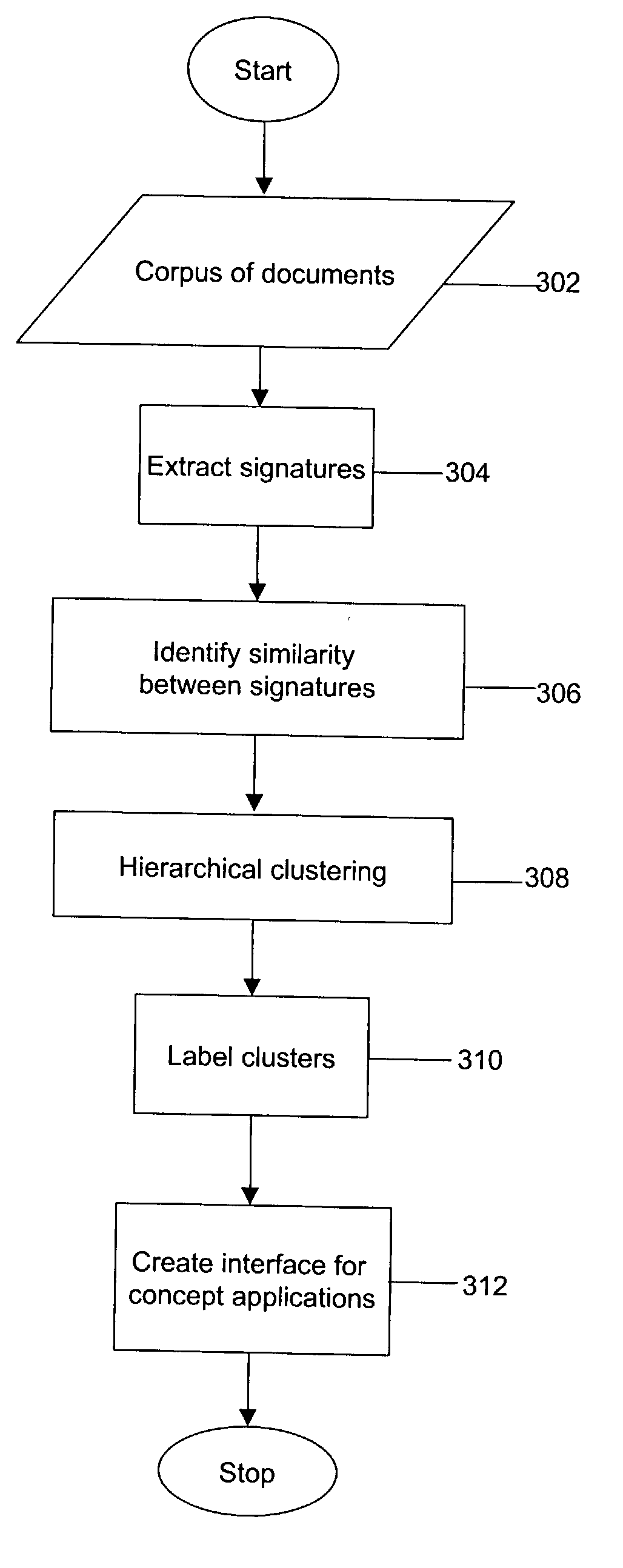

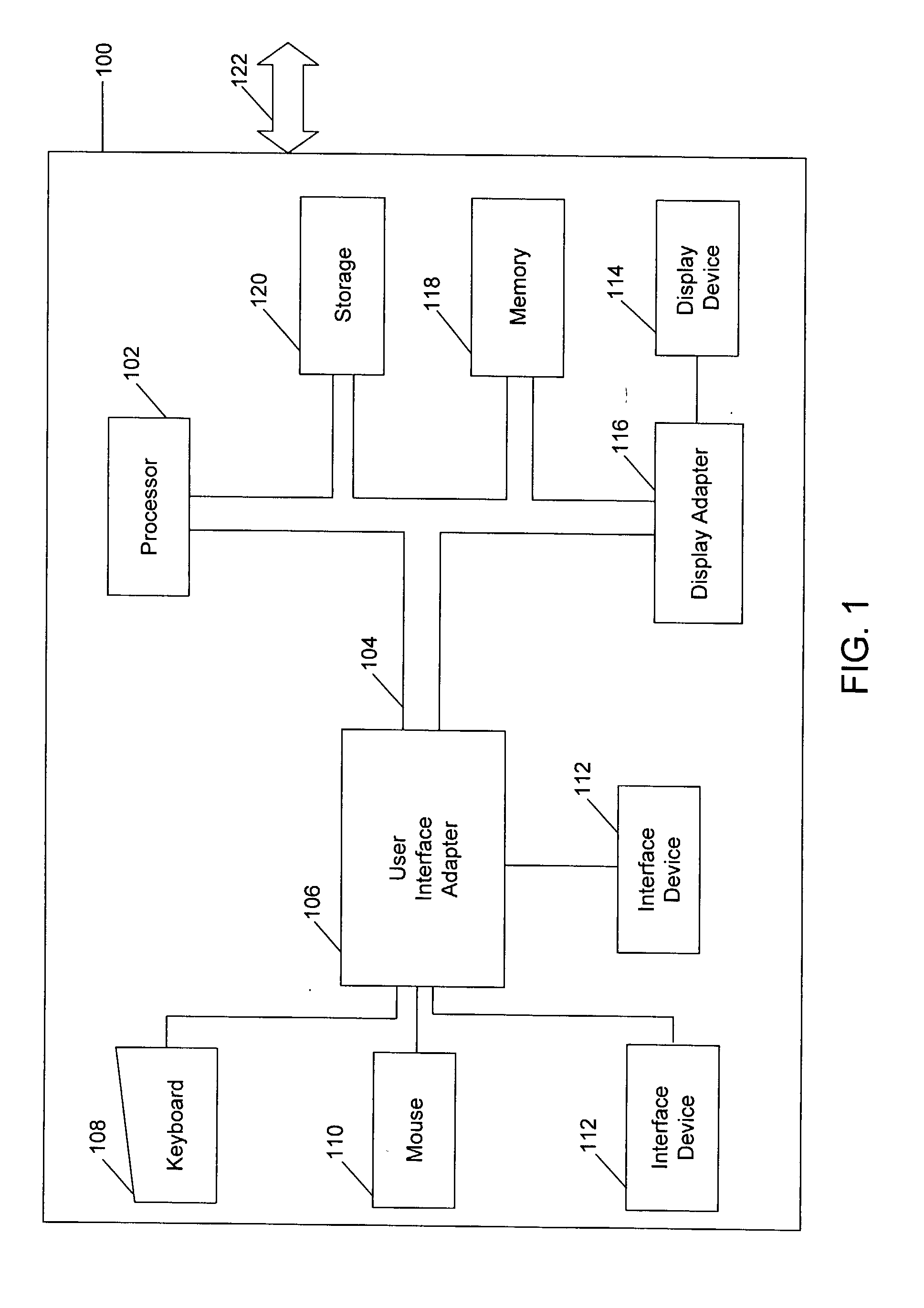

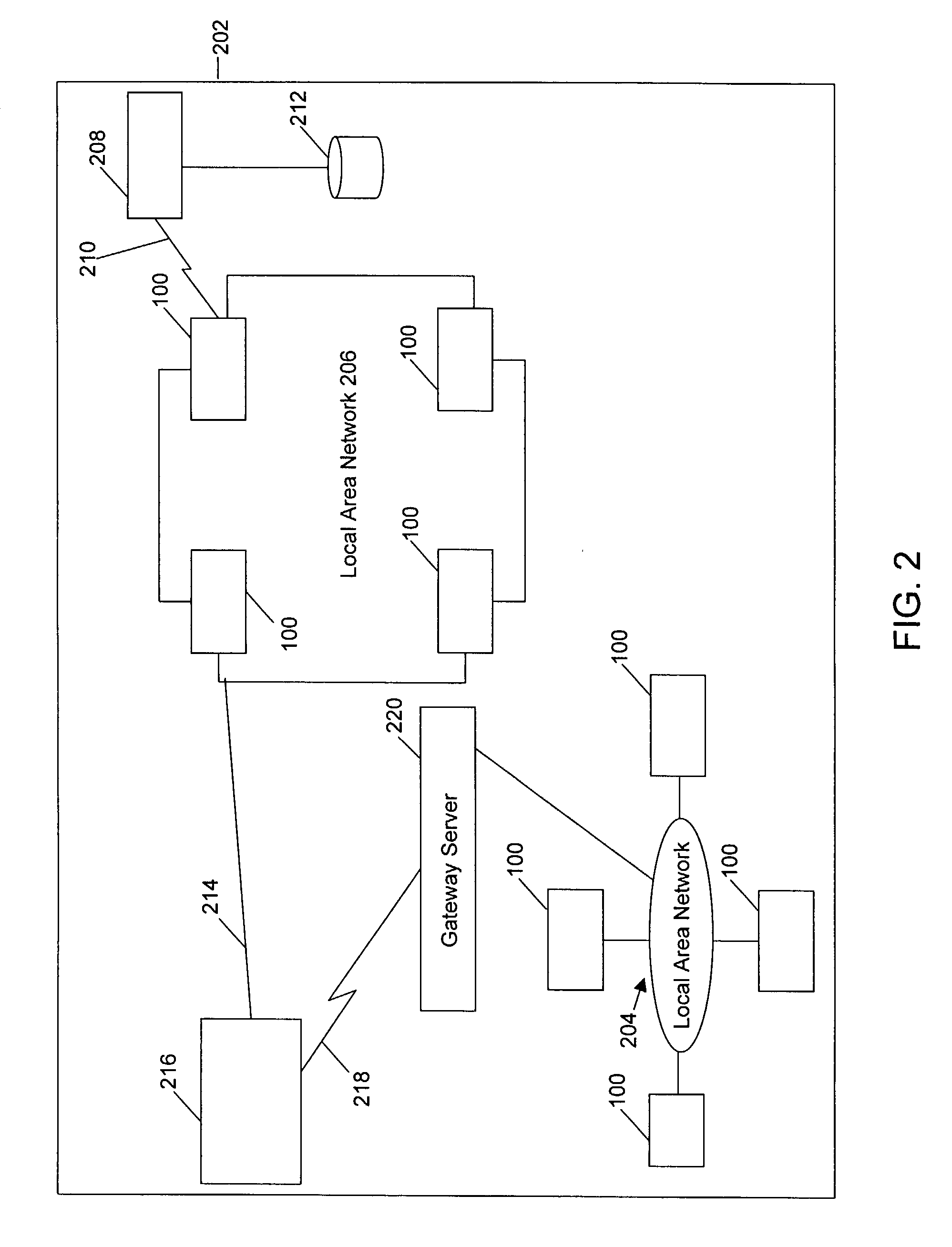

System and method for automatically discovering a hierarchy of concepts from a corpus of documents

InactiveUS20030217335A1Efficient retrievalUser-friendly interfaceDigital data information retrievalData processing applicationsInformation retrievalText corpus

The invention is a method, system and computer program for automatically discovering concepts from a corpus of documents and automatically generating a labeled concept hierarchy. The method involves extraction of signatures from the corpus of documents. The similarity between signatures is computed using a statistical measure. The frequency distribution of signatures is refined to alleviate any inaccuracy in the similarity measure. The signatures are also disambiguated to address the polysemy problem. The similarity measure is recomputed based on the refined frequency distribution and disambiguated signatures. The recomputed similarity measure reflects actual similarity between signatures. The recomputed similarity measure is then used for clustering related signatures. The signatures are clustered to generate concepts and concepts are arranged in a concept hierarchy. The concept hierarchy automatically generates query for a particular concept and retrieves relevant documents associated with the concept.

Owner:MICRO FOCUS LLC

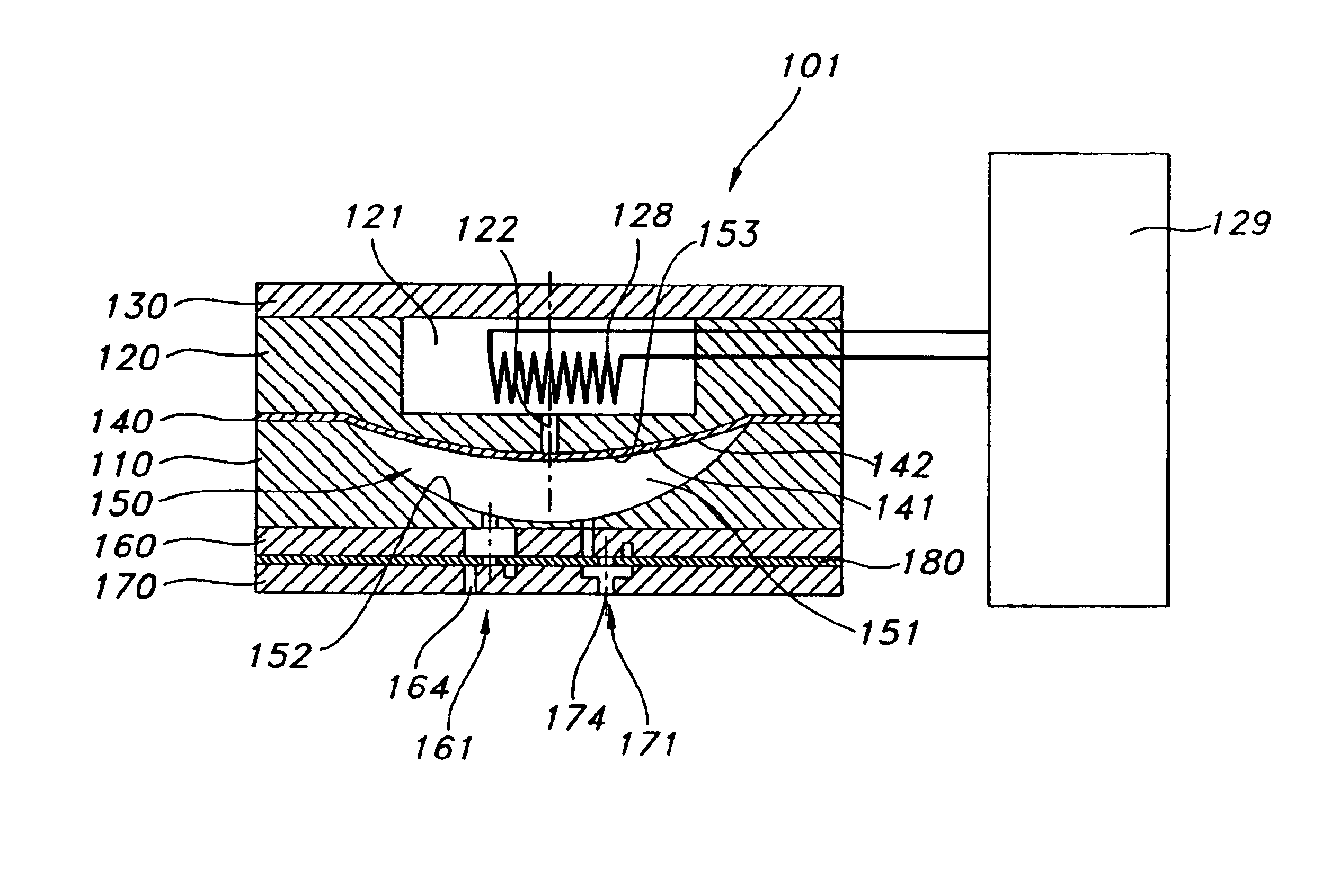

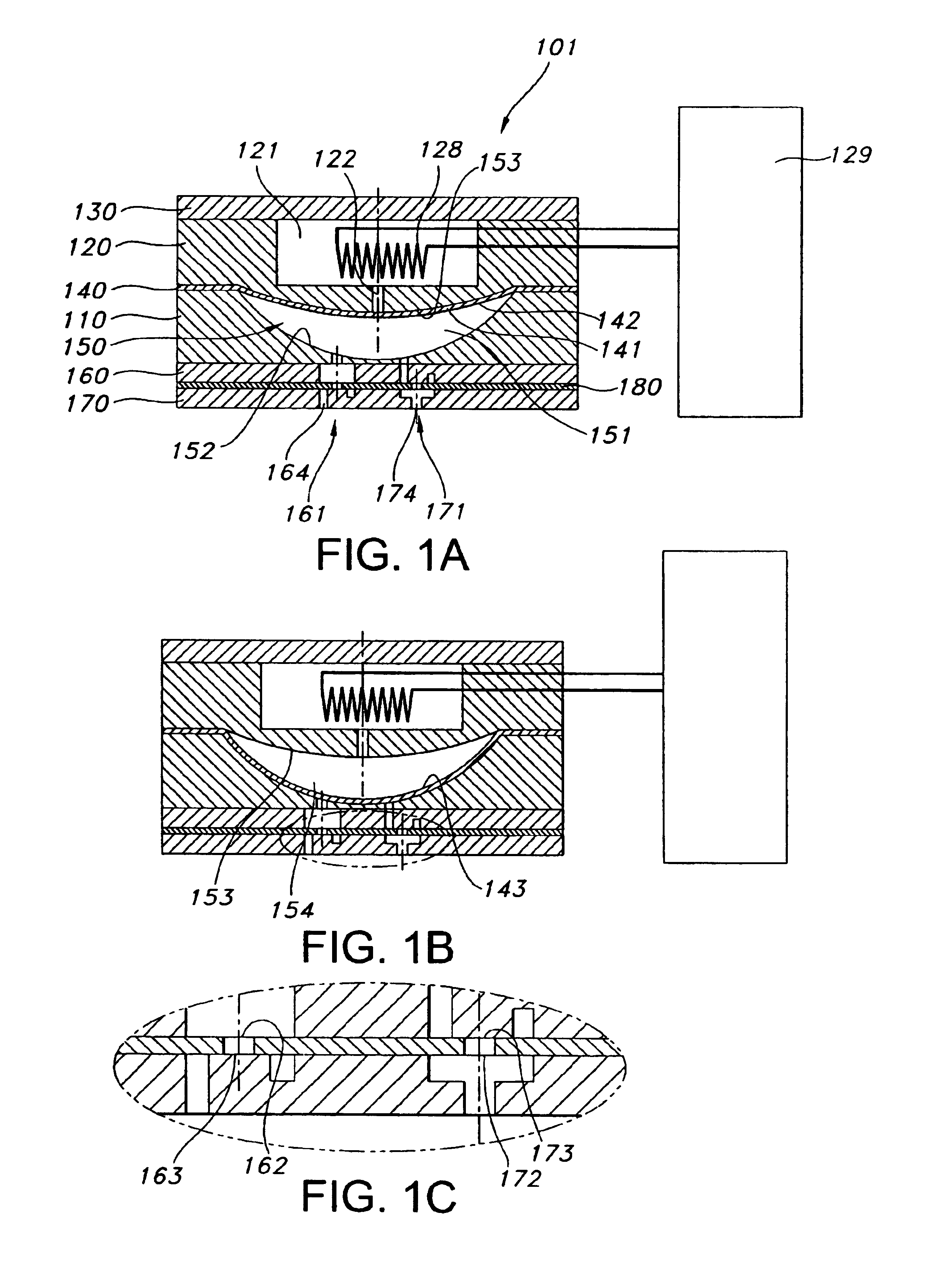

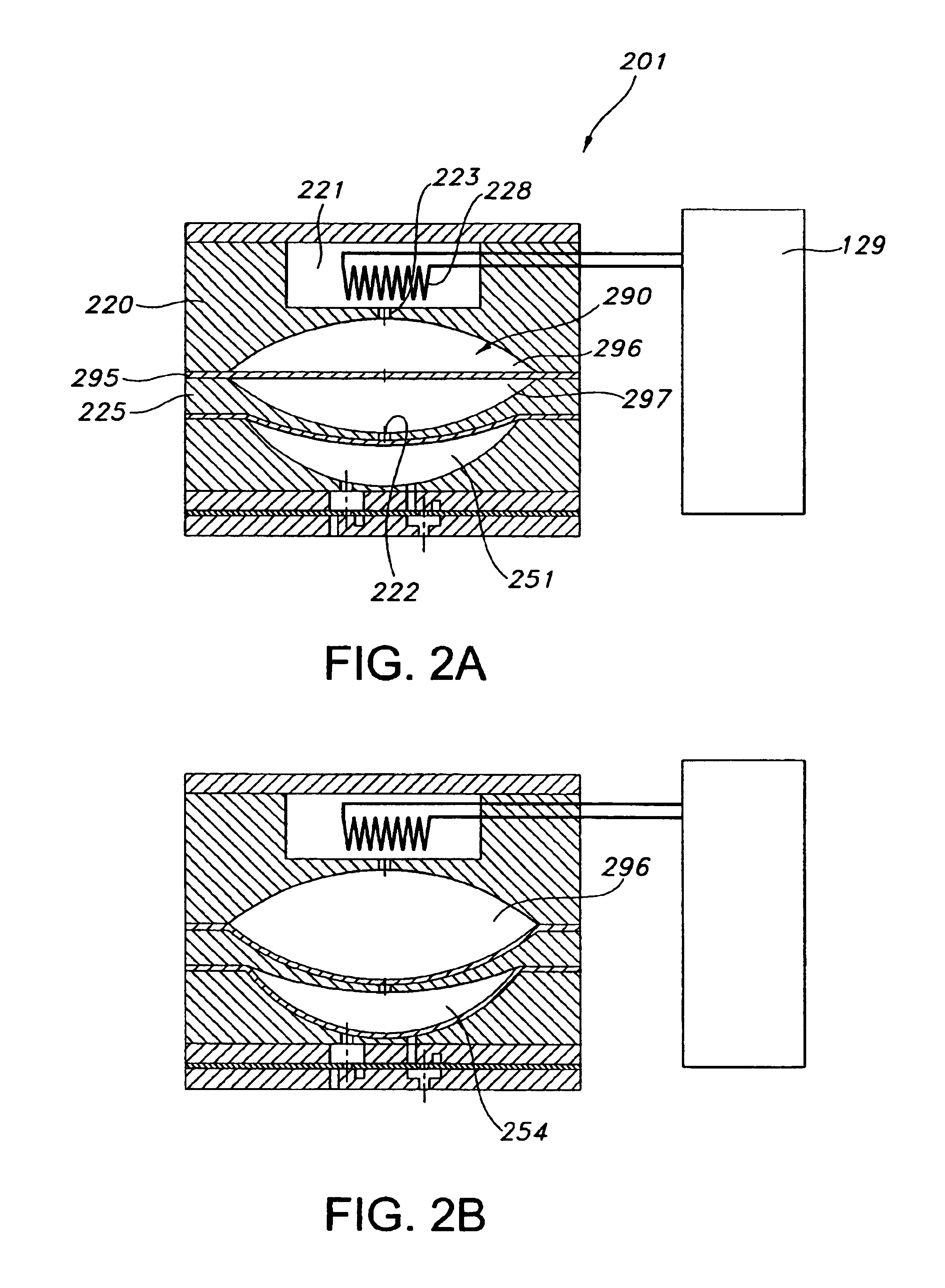

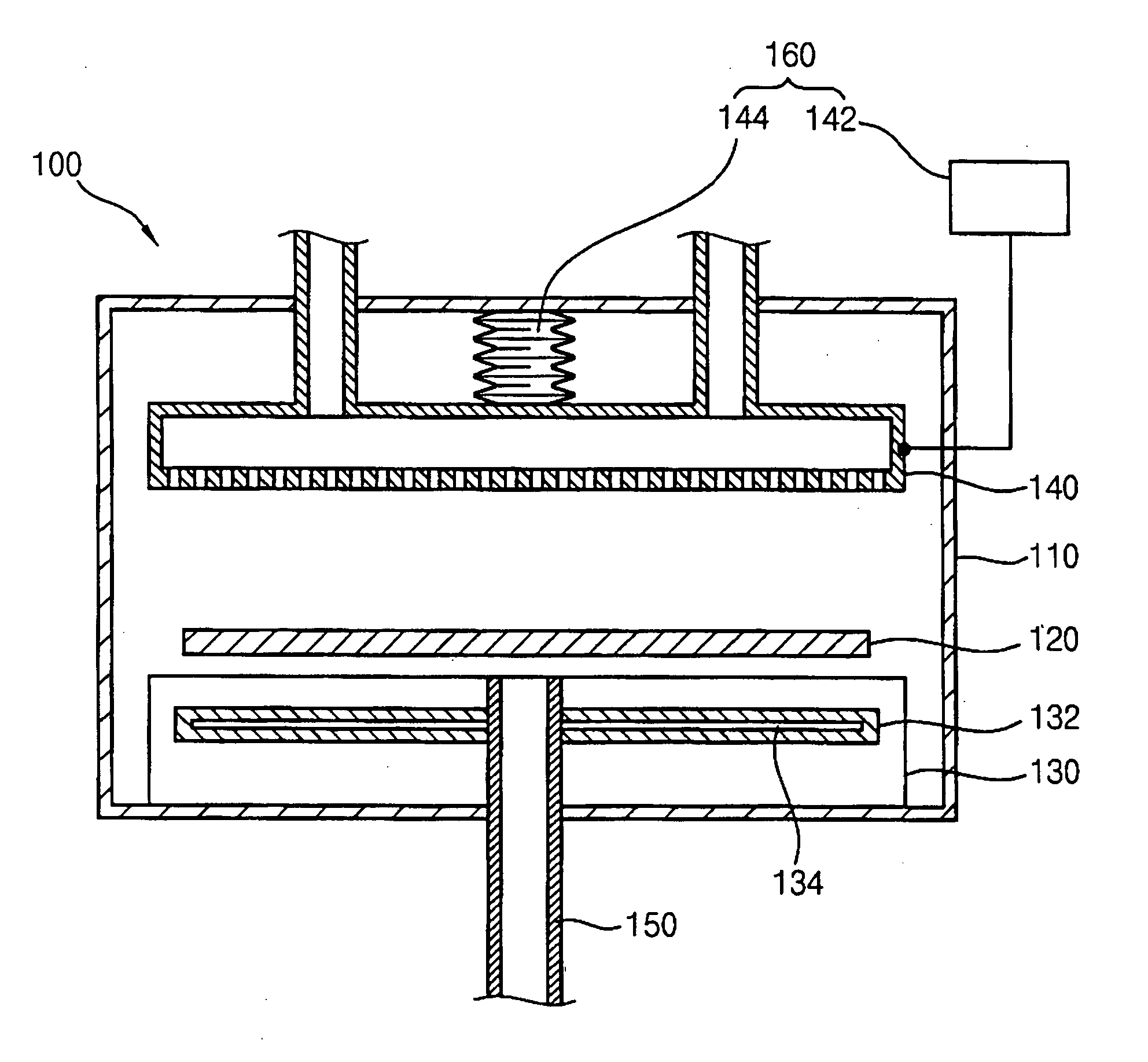

Membrane pump with stretchable pump membrane

InactiveUS6948918B2Stiff systemImprove accuracyValve arrangementsPositive displacement pump componentsPump chamberInlet valve

The invention relates to membrane pumps for delivering liquids. More specifically, a pump is provided having a pump housing with a pump cavity formed between first and second wall portions thereof, and an pump membrane pump membrane having first and second membrane surfaces arranged within the pump cavity, whereby a pump chamber is provided between the first wall portion and the first membrane surface, and an actuation chamber is provided between the second wall and the second membrane surface. Inlet means comprising an inlet valve in fluid communication with the pump chamber, and outlet means comprising an outlet valve in fluid communication with the pump chamber are provided. The pump membrane has a maximum volume position, and a drained volume position in which the first membrane surface in a stretched state abuts the first wall. To drive the membrane, actuating means for periodically shifting the pump membrane between the maximum volume position and the drained volume position is provided, thereby, in a situation of use, providing a flow of fluid.

Owner:NOVO NORDISK AS

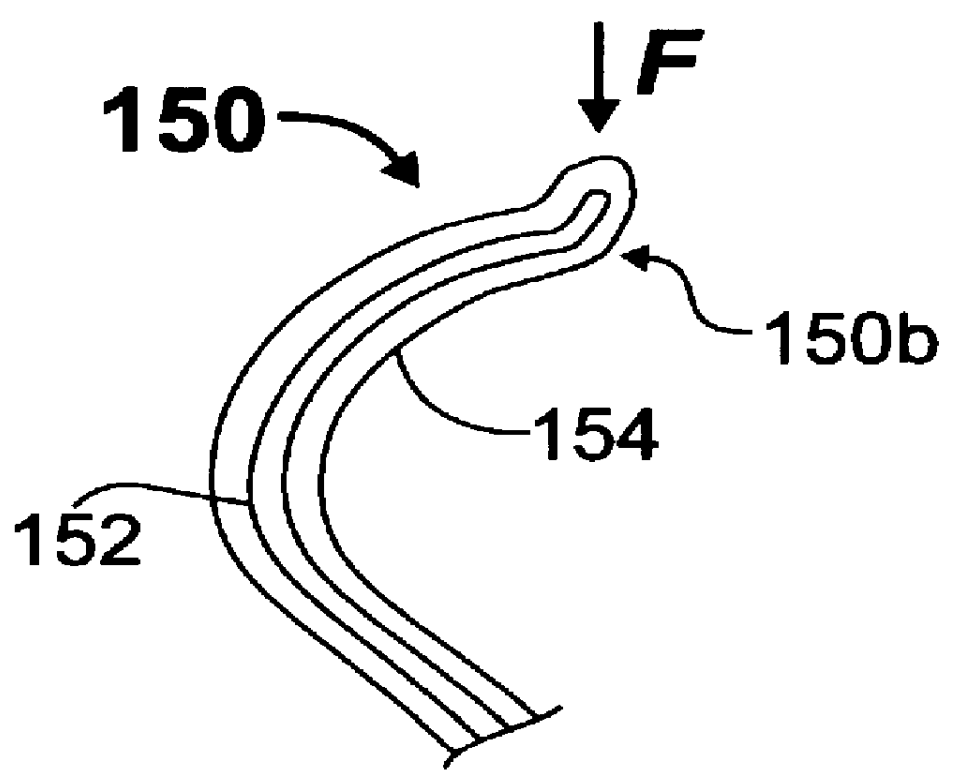

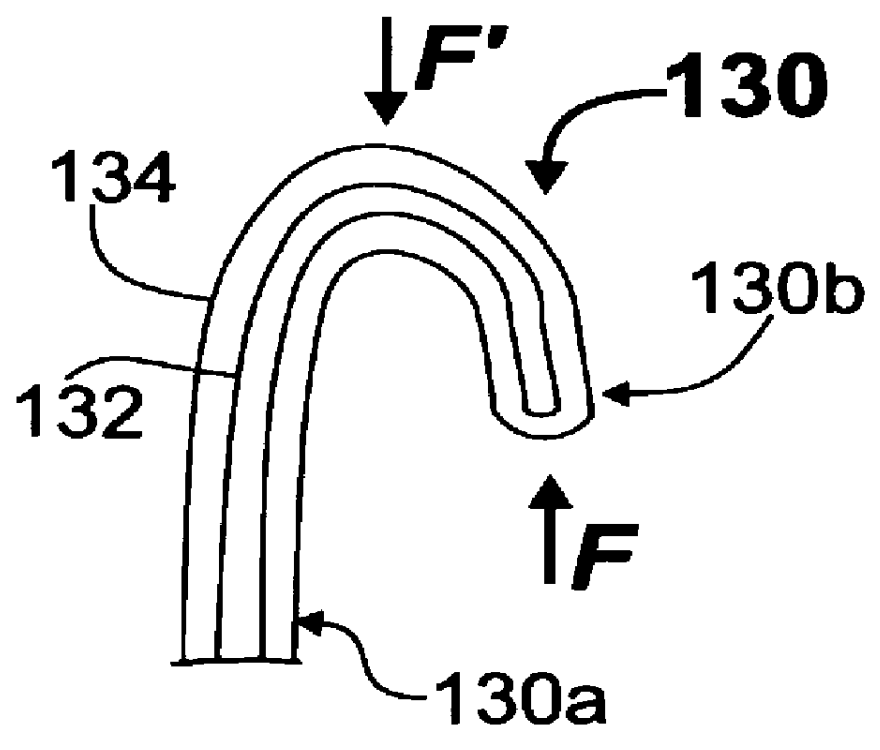

Composite interconnection element for microelectronic components, and method of making same

InactiveUS6029344AEliminate needImprove featuresSemiconductor/solid-state device testing/measurementFinal product manufactureMetal foilSolderability

Interconnection elements for electronic components, exhibiting desirable mechanical characteristics (such as resiliency, for making pressure contacts) are formed by shaping an elongate element (core) of a soft material (such as gold) to have a springable shape (including cantilever beam, S-shape, U-shape), and overcoating the shaped elongate element with a hard material (such as nickel and its alloys), to impart a desired spring (resilient) characteristic to the resulting composite interconnection element. A final overcoat of a material having superior electrical qualities (e.g., electrical conductivity and / or solderability) may be applied to the composite interconnection element. The elongate element may be formed from a wire, or from a sheet (e.g., metal foil). The resulting interconnection elements may be mounted to a variety of electronic components, including directly to semiconductor dies and wafers (in which case the overcoat material anchors the composite interconnection element to a terminal (or the like) on the electronic component), may be mounted to support substrates for use as interposers and may be mounted to substrates for use as probe cards or probe card inserts. In one embodiment, a hybrid composite interconnection element is formed by mounting a core to an end of an flat elongate element formed from a sheet, and overcoating at least the core, the flat elongate element providing a "floating" support for the overcoated core, capable of absorbing non-planarities (tolerances) of an electronic component. Methods of fabricating interconnection elements on sacrificial substrates are described. Methods of fabricating tip structures and contact tips at the end of interconnection elements are described.

Owner:FORMFACTOR INC

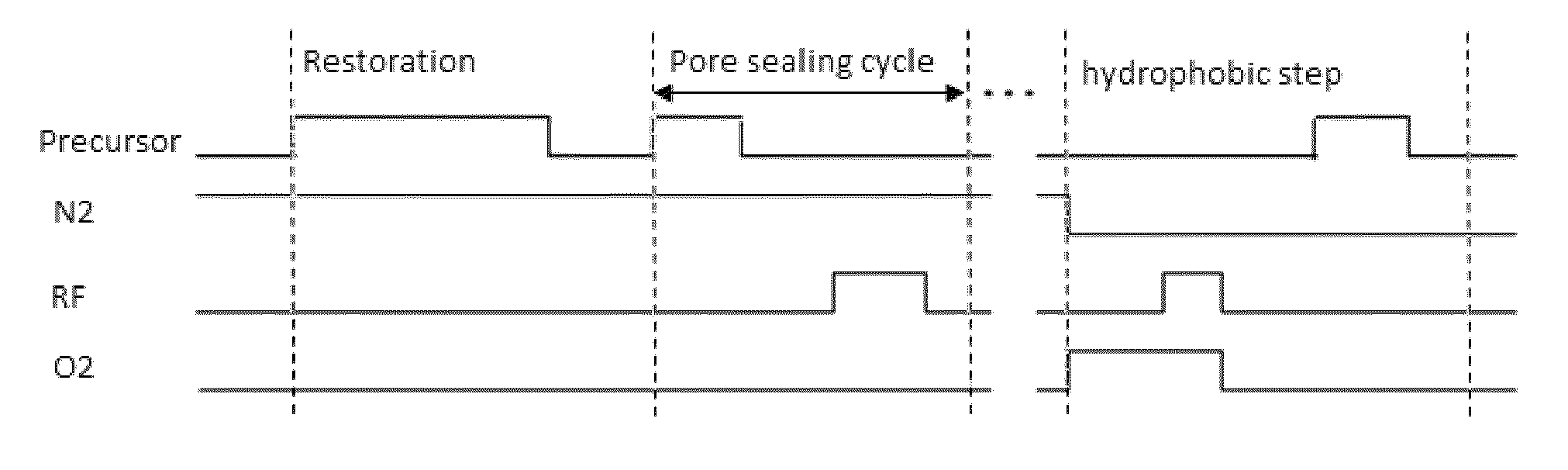

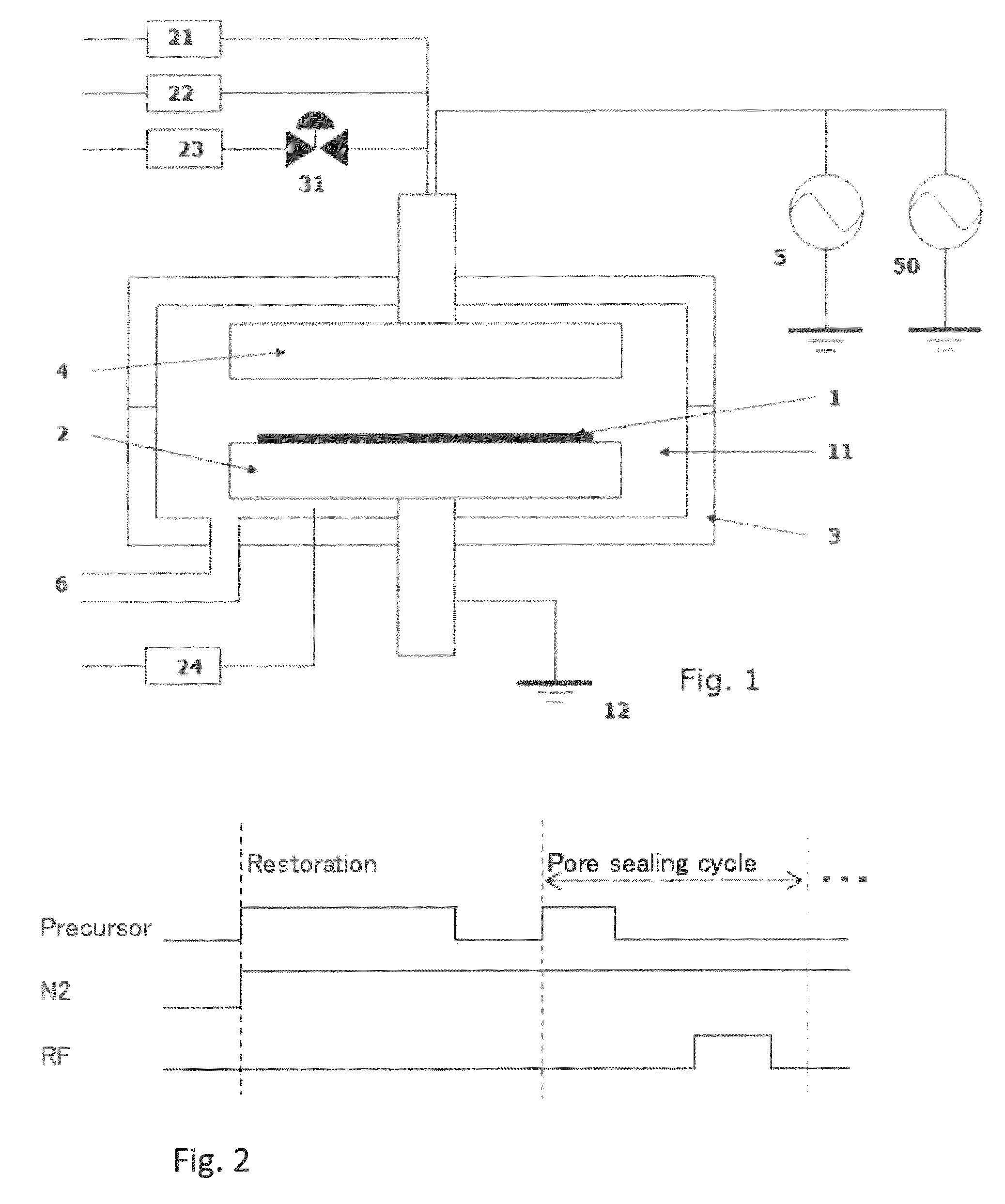

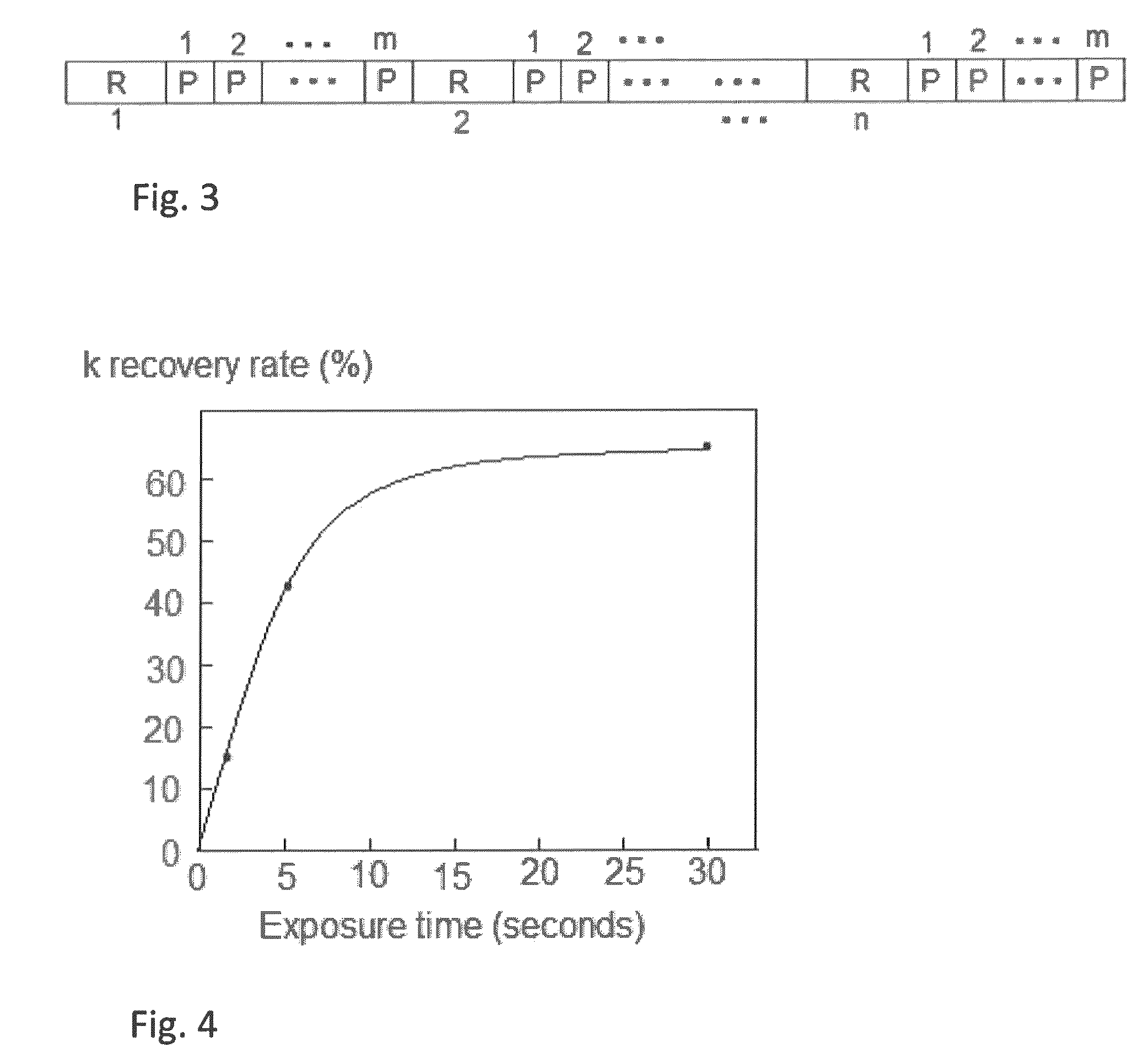

Method for repairing damage of dielectric film by cyclic processes

ActiveUS8785215B2Enhanced barrier functionPlasma-enhanced atomic layerSemiconductor/solid-state device manufacturingChemical vapor deposition coatingCyclic processSilicon

A method for repairing process-related damage of a dielectric film includes: (i) adsorbing a first gas containing silicon on a surface of the damaged dielectric film without depositing a film in the absence of reactive species, (ii) adsorbing a second gas containing silicon on a surface of the dielectric film, followed by applying reactive species to the surface of the dielectric film, to form a monolayer film thereon, and (iii) repeating step (ii). The duration of exposing the surface to the first gas in step (i) is longer than the duration of exposing the surface to the second gas in step (ii).

Owner:ASM IP HLDG BV

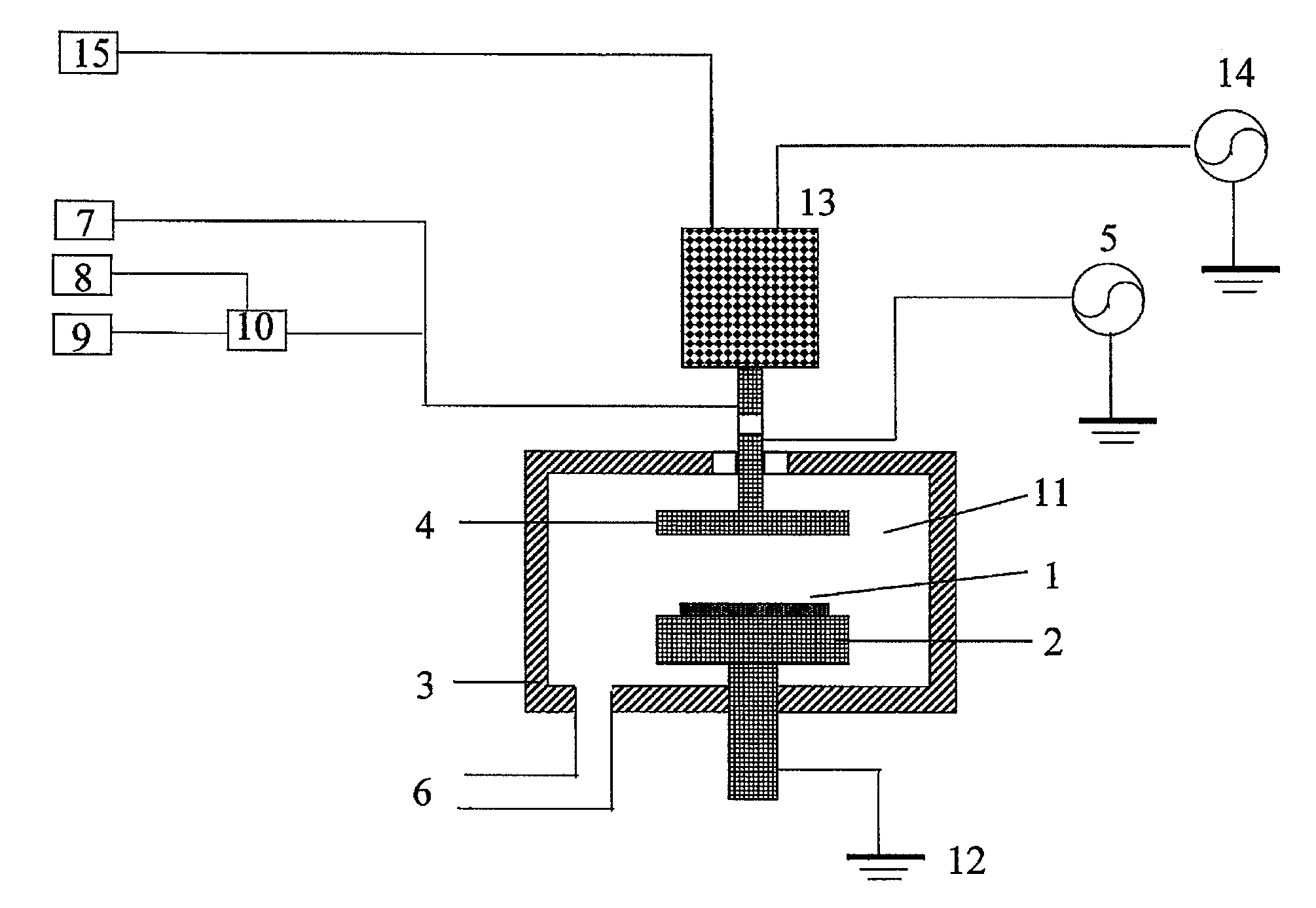

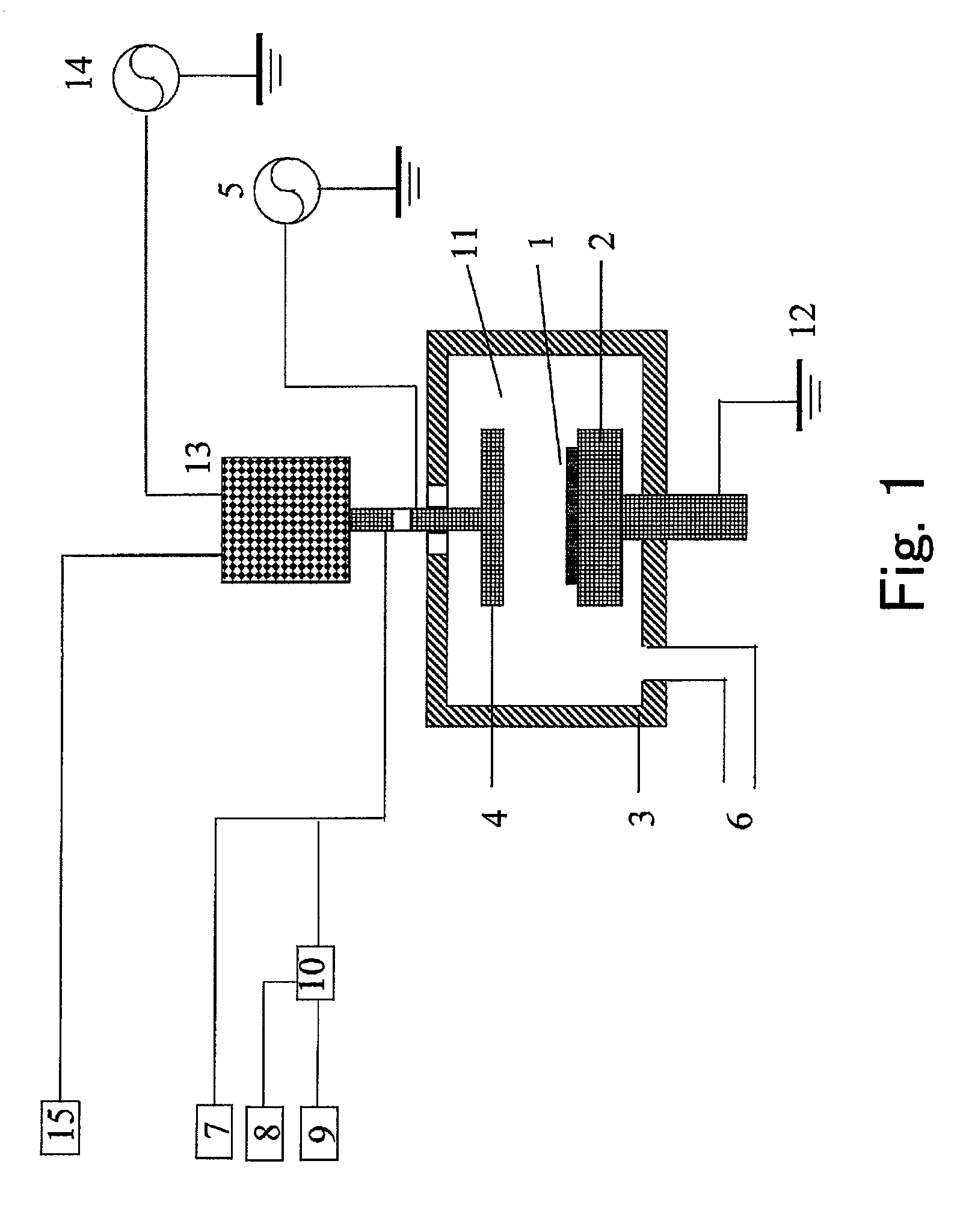

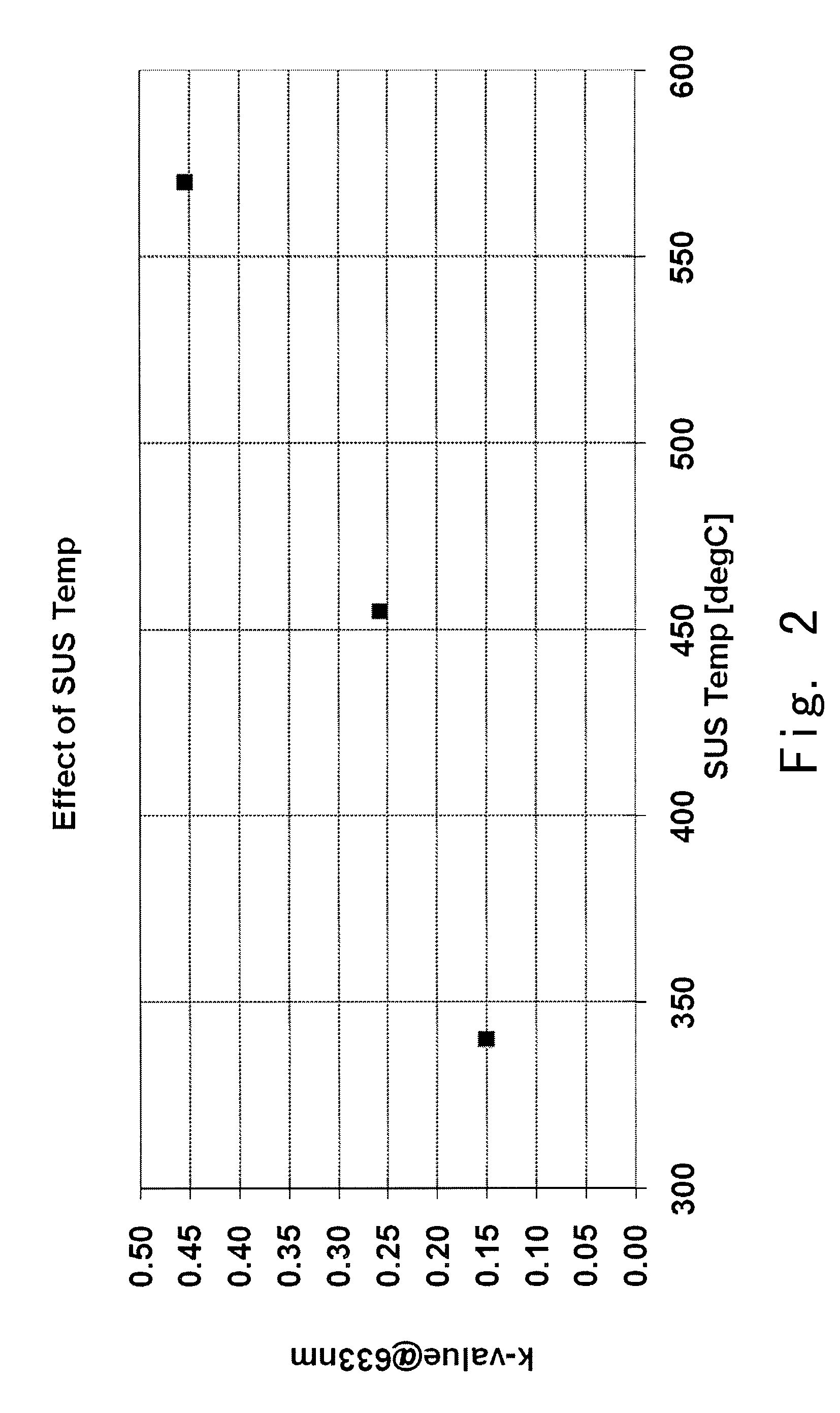

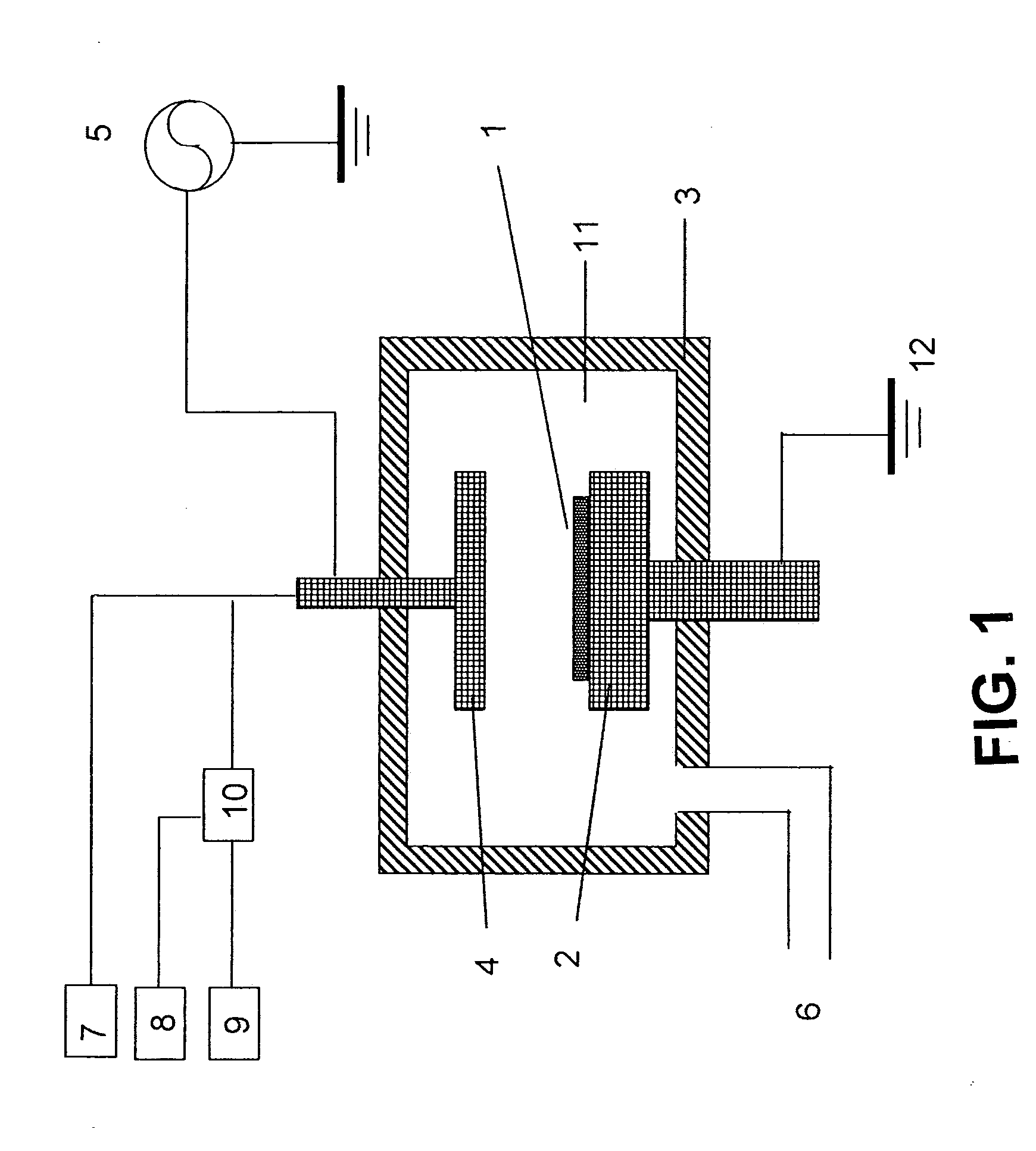

Method of forming a high transparent carbon film

ActiveUS7632549B2Improve featuresRich varietyLiquid surface applicatorsSemiconductor/solid-state device manufacturingCarbon filmProduct gas

A method of forming a transparent hydrocarbon-based polymer film on a substrate by plasma CVD includes: introducing a main gas consisting of a hydrocarbon gas (CαHβ, wherein α and β are natural numbers) and an inert gas at a flow ratio (R) of CαHβ / inert gas of 0.25 or less into a CVD reaction chamber inside which a substrate is placed; and forming a hydrocarbon-based polymer film on the substrate by plasma polymerization of the gas at a processing temperature (T) wherein T≦(−800R+500).

Owner:ASM JAPAN

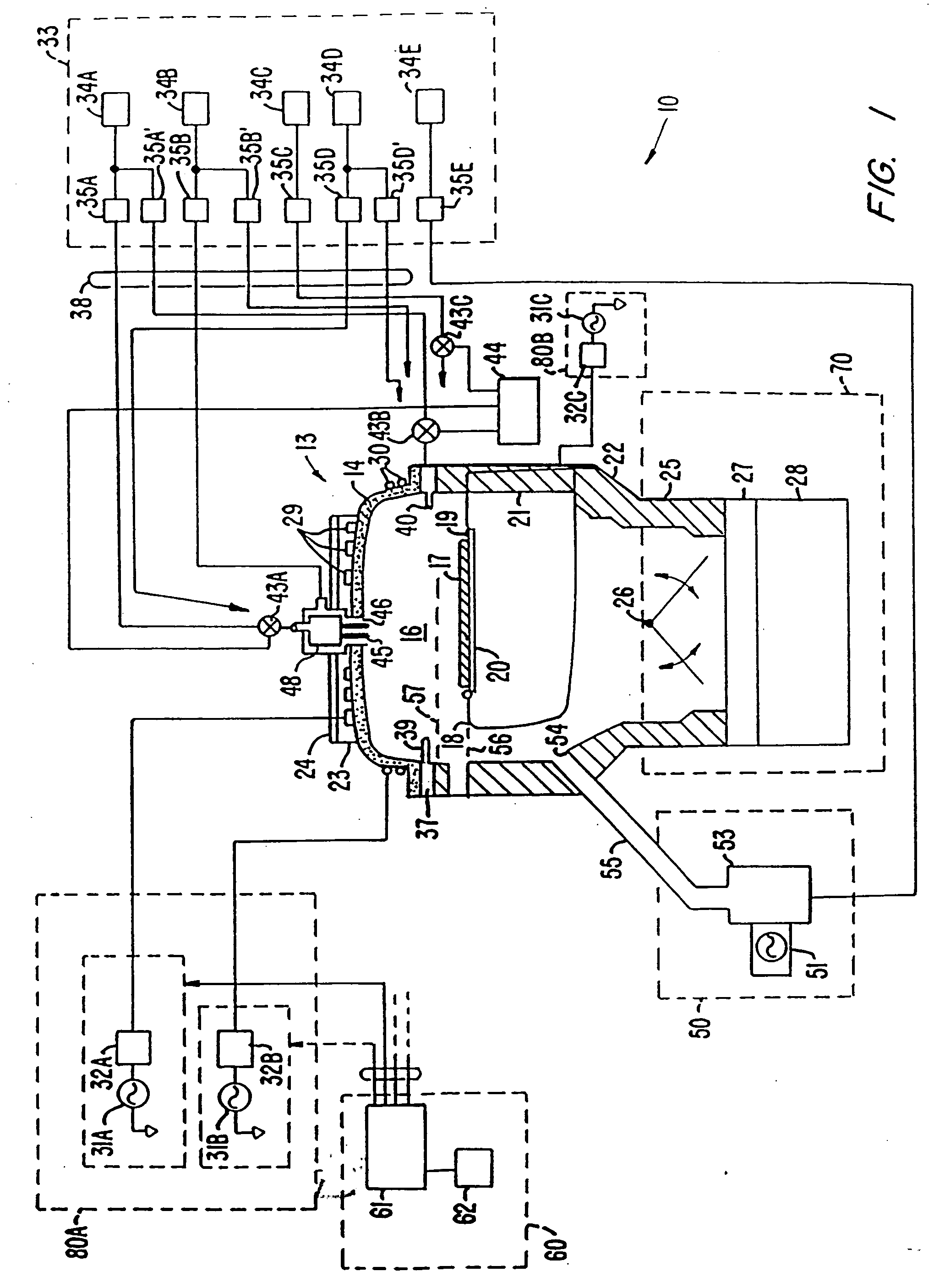

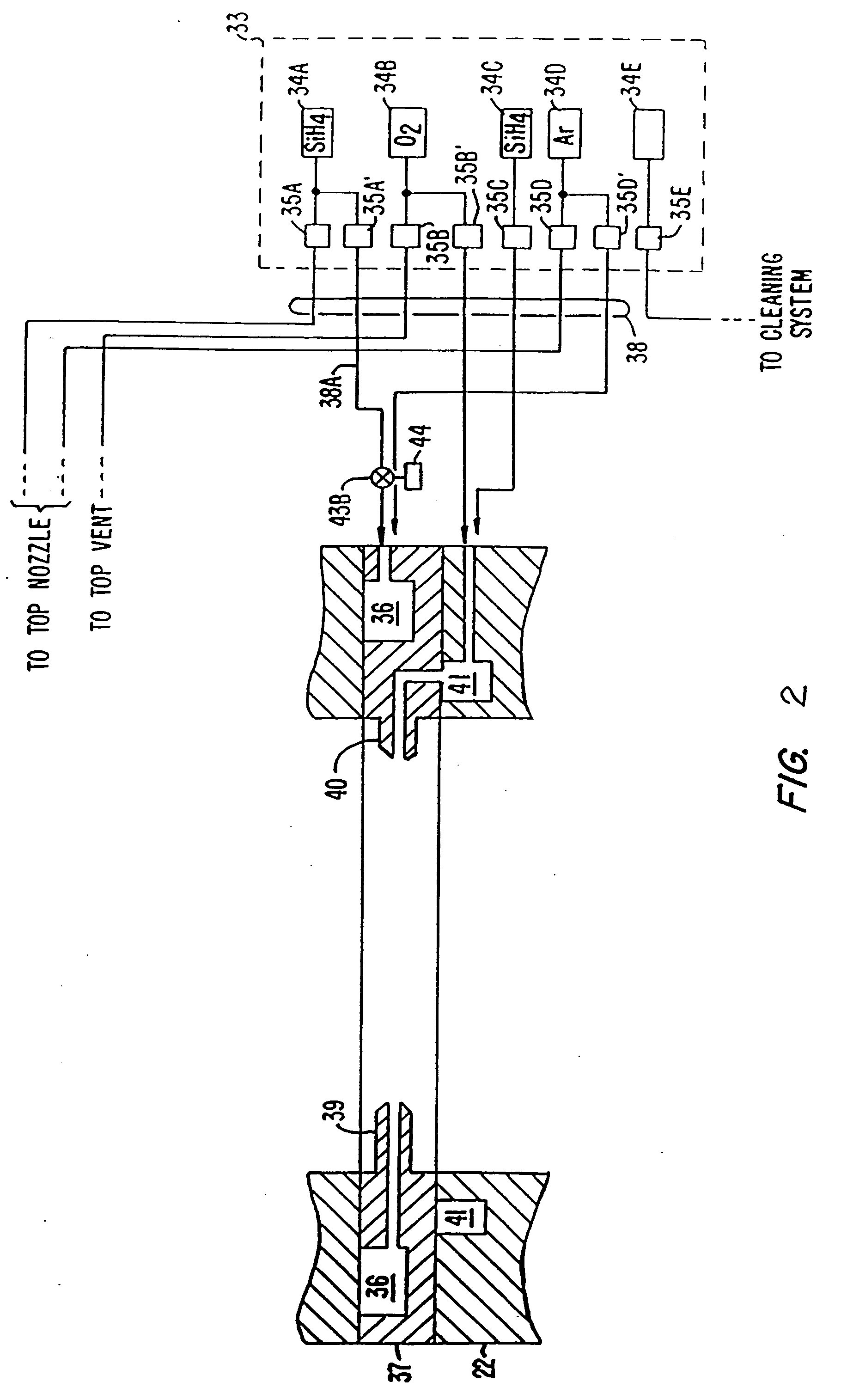

Gas distribution system for improved transient phase deposition

InactiveUS20060113038A1Good gapfill characteristicEnsuring quality of depositionDecorative surface effectsSemiconductor/solid-state device manufacturingDistribution systemEngineering

Embodiments of the present invention are directed to a gas distribution system which distributes the gas more uniformly into a process chamber. In one embodiment, a gas distribution system comprises a gas ring including an outer surface and an inner surface, and a gas inlet disposed at the outer surface of the gas ring. The gas inlet is fluidicly coupled with a first channel which is disposed between the outer surface and the inner surface of the gas ring. A plurality of gas outlets are distributed over the inner surface of the gas ring, and are fluidicly coupled with a second channel which is disposed between the outer surface and the inner surface of the gas ring. A plurality of orifices are fluidicly coupled between the first channel and the second channel. The plurality of orifices are spaced from the gas inlet by a plurality of distances, and have sizes which vary with the distances from the gas inlet as measured along the first channel, such that the size of the orifice increases with an increase in the distance between the orifice and the gas inlet as measured along the first channel.

Owner:APPLIED MATERIALS INC

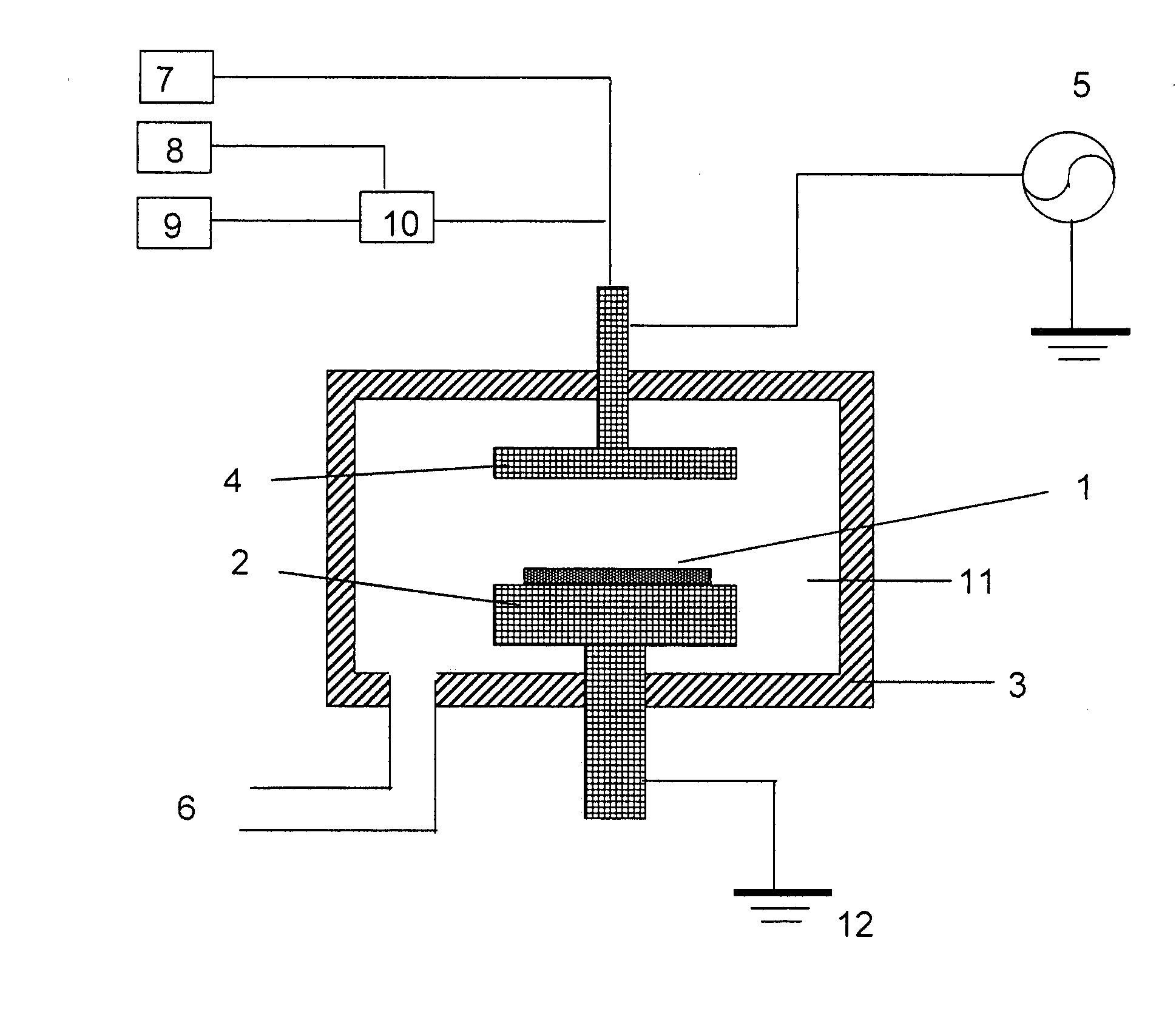

Method of forming a carbon polymer film using plasma CVD

ActiveUS20070218705A1Improve featuresFunction increaseLiquid surface applicatorsPhotomechanical apparatusCapacitanceBoiling point

A method forms a hydrocarbon-containing polymer film on a semiconductor substrate by a capacitively-coupled plasma CVD apparatus. The method includes the steps of: vaporizing a hydrocarbon-containing liquid monomer (CαHβXγ, wherein α and β are natural numbers of 5 or more; γ is an integer including zero; X is O, N or F) having a boiling point of about 20° C. to about 350° C.; introducing the vaporized gas into a CVD reaction chamber inside which a substrate is placed; and forming a hydrocarbon-containing polymer film on the substrate by plasma polymerization of the gas.

Owner:ASM JAPAN

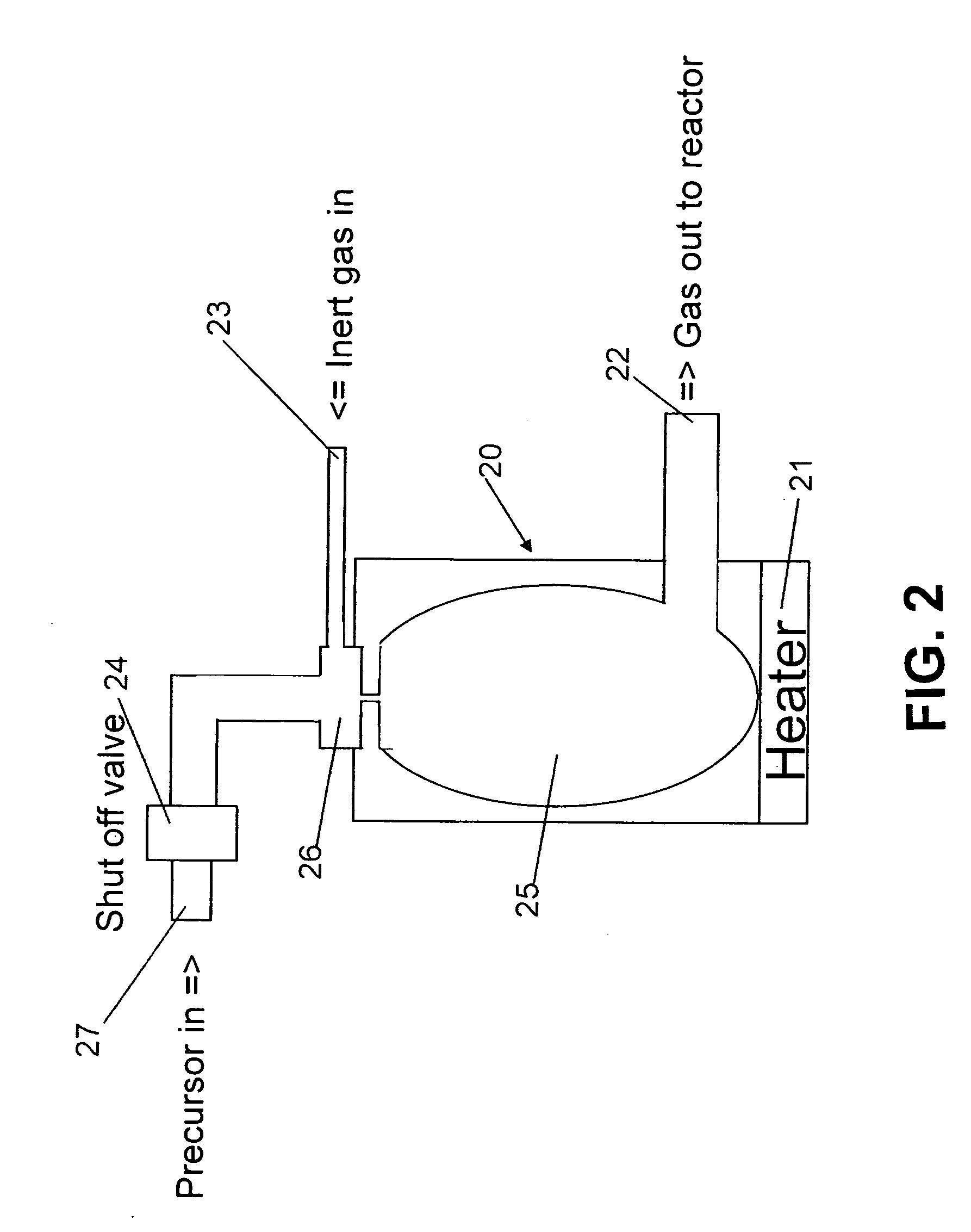

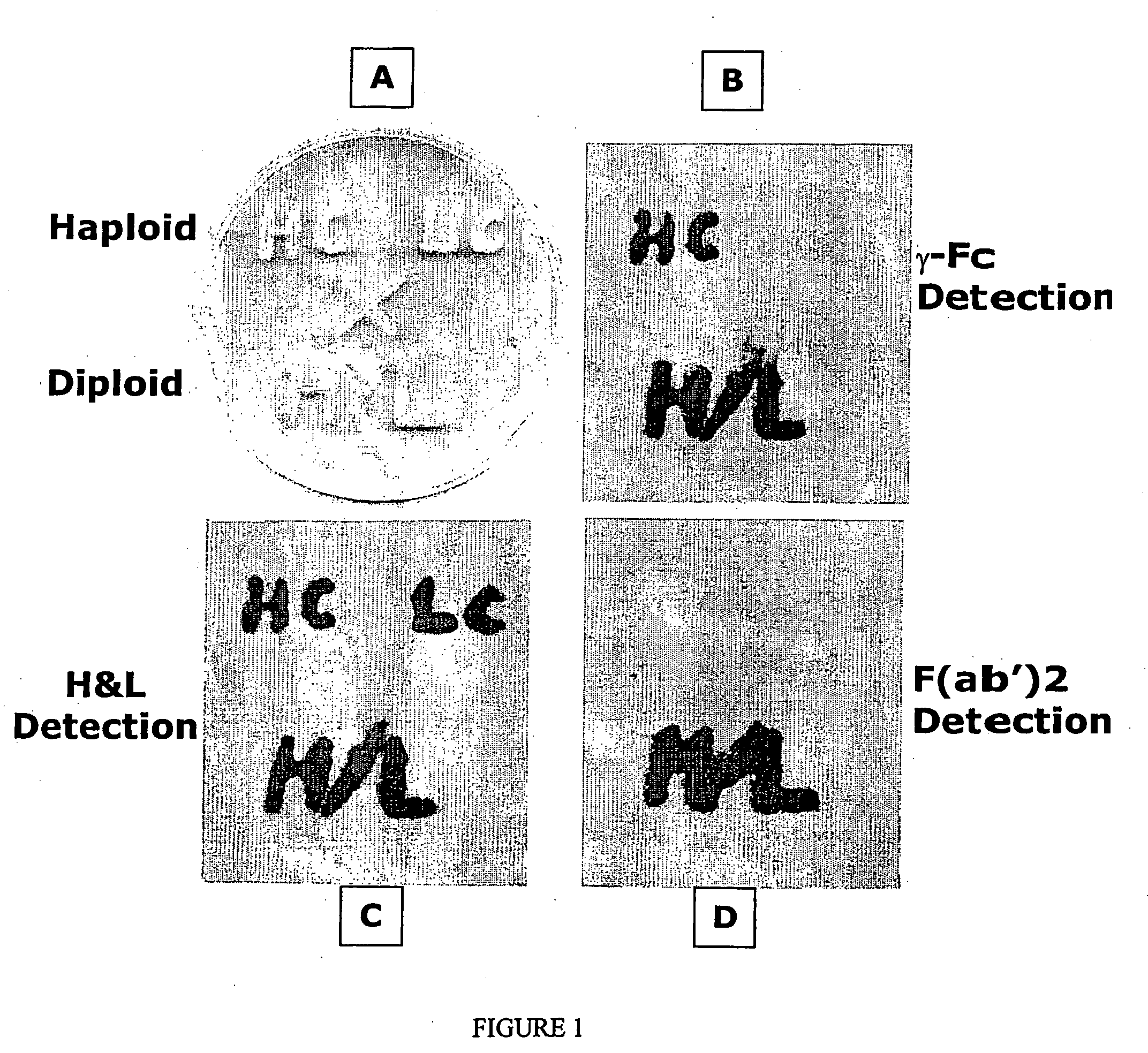

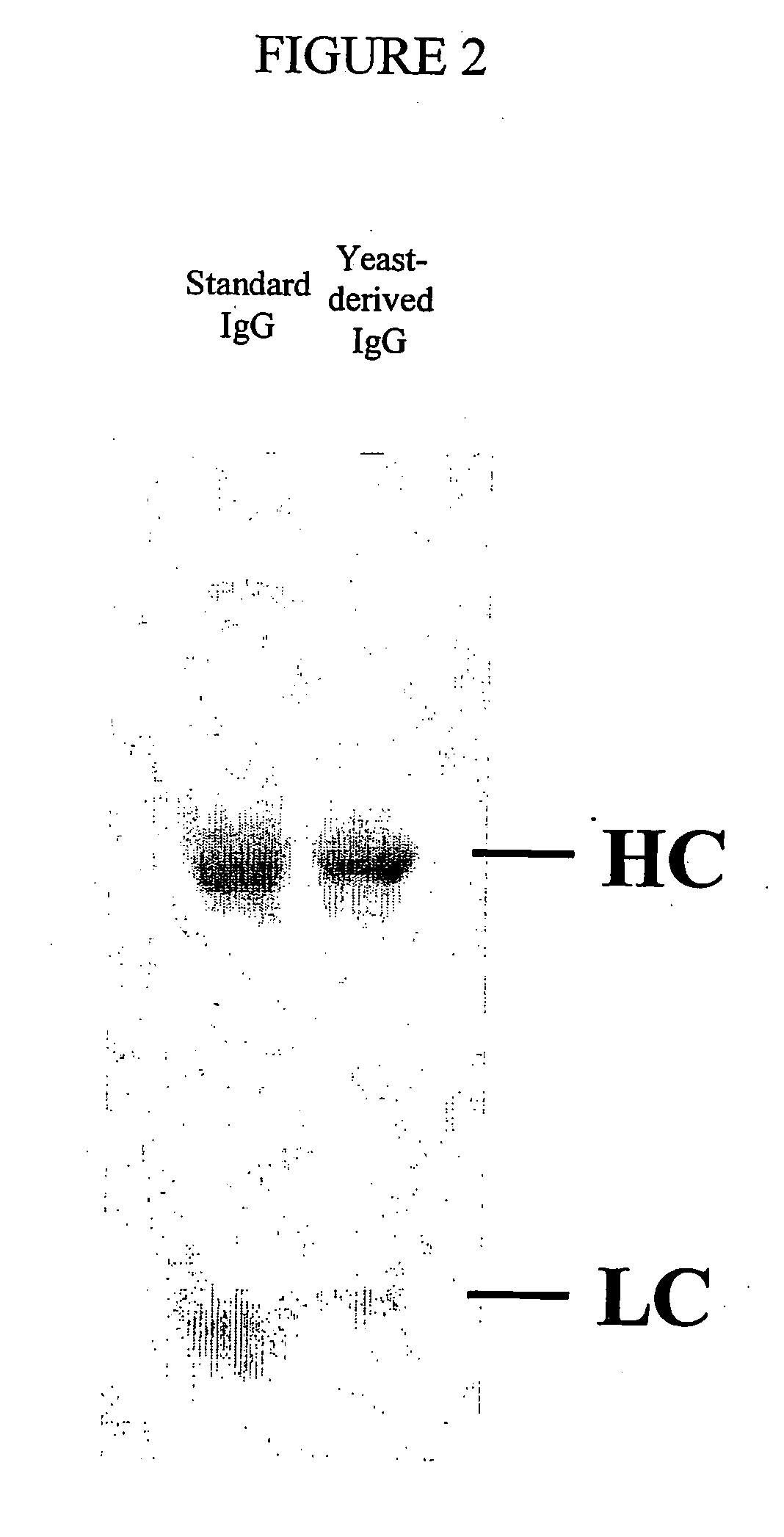

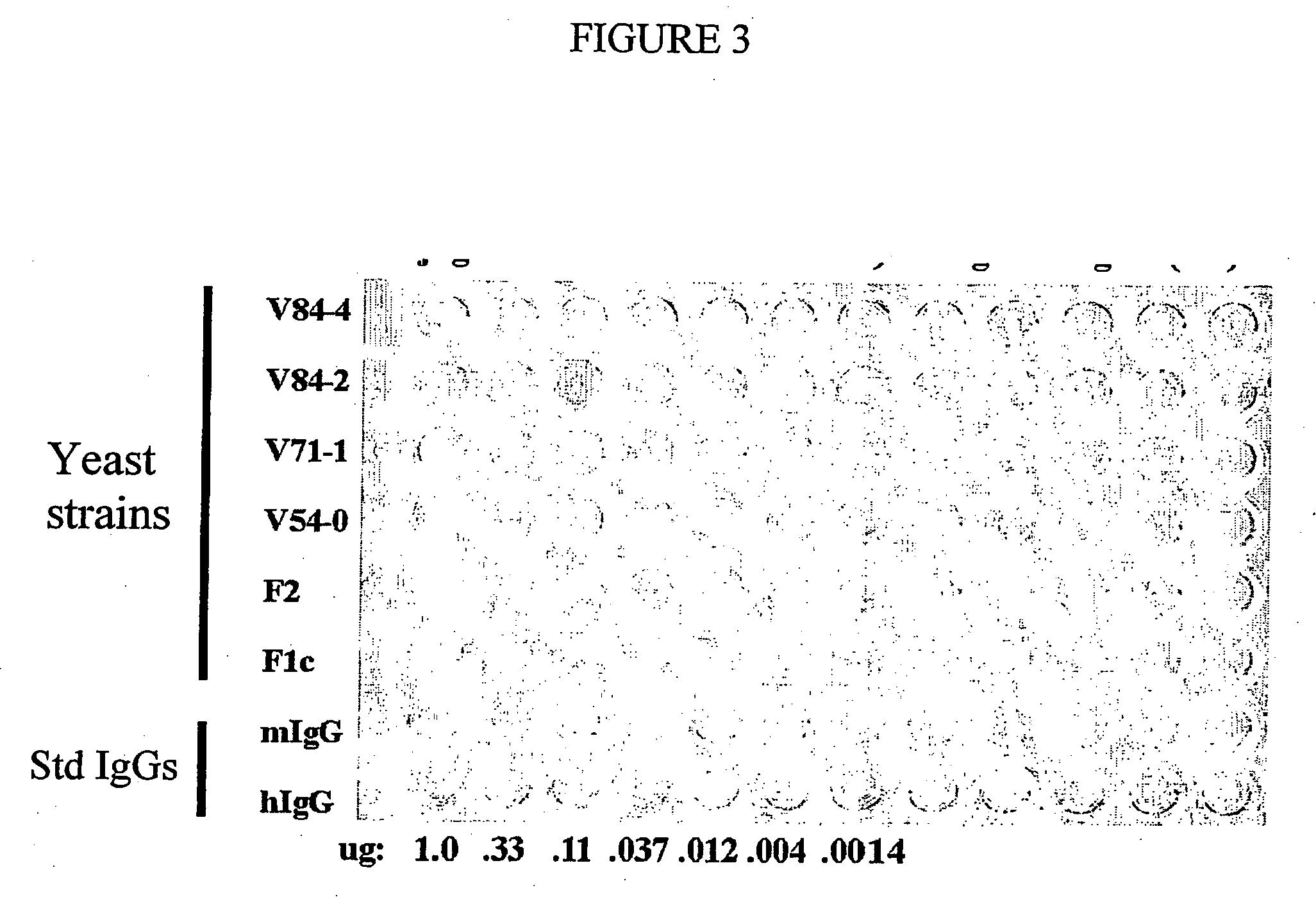

Methods of synthesizing heteromultimeric polypeptides in yeast using a haploid mating strategy

ActiveUS20060270045A1Enhance full-length product generationIncrease secretionFungiMicrobiological testing/measurementBiotechnologyMating

Methods are provided for the synthesis and secretion of recombinant proteins preferably large mammalian proteins or hetero-multimeric proteins at high levels and for prolonged time in polyploid, preferably diploid yeast. These methods use various mating competent yeast, including Pichia. In a preferred embodiment, a first expression vector is transformed into a first haploid cell; and a second expression vector is transformed into a second haploid cell. The transformed haploid cells, each individually synthesizing a non-identical polypeptide, are identified and then genetically crossed or fused. The resulting diploid strains are utilized to produce and secrete fully assembled and biologically functional hetero-multimeric protein.

Owner:KECK GRADUATE INST OF APPLIED LIFE SCI +1

Method of forming a layer on a semiconductor substrate and apparatus for performing the same

InactiveUS20060000411A1Preventing deterioration of layerIncrease total manufacturing throughputSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialThin layer

In a method of forming a thin layer for a semiconductor device through an ALD process and a CVD process in the same chamber, a semiconductor substrate is introduced into a processing chamber, and an interval between a showerhead and the substrate is adjusted to a first gap distance. A first layer is formed on the substrate at a first temperature through an ALD process. The interval between the showerhead and the substrate is additionally adjusted to a second gap distance, and a second layer is formed on the first layer at a second temperature through a CVD process. Accordingly, the thin layer has good current characteristics, and the manufacturing throughput of a semiconductor device is improved.

Owner:SAMSUNG ELECTRONICS CO LTD