Patents

Literature

7892 results about "Heterojunction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A heterojunction is the interface that occurs between two layers or regions of dissimilar crystalline semiconductors. These semiconducting materials have unequal band gaps as opposed to a homojunction. It is often advantageous to engineer the electronic energy bands in many solid-state device applications, including semiconductor lasers, solar cells and transistors ("heterotransistors") to name a few. The combination of multiple heterojunctions together in a device is called a heterostructure, although the two terms are commonly used interchangeably. The requirement that each material be a semiconductor with unequal band gaps is somewhat loose, especially on small length scales, where electronic properties depend on spatial properties. A more modern definition of heterojunction is the interface between any two solid-state materials, including crystalline and amorphous structures of metallic, insulating, fast ion conductor and semiconducting materials.

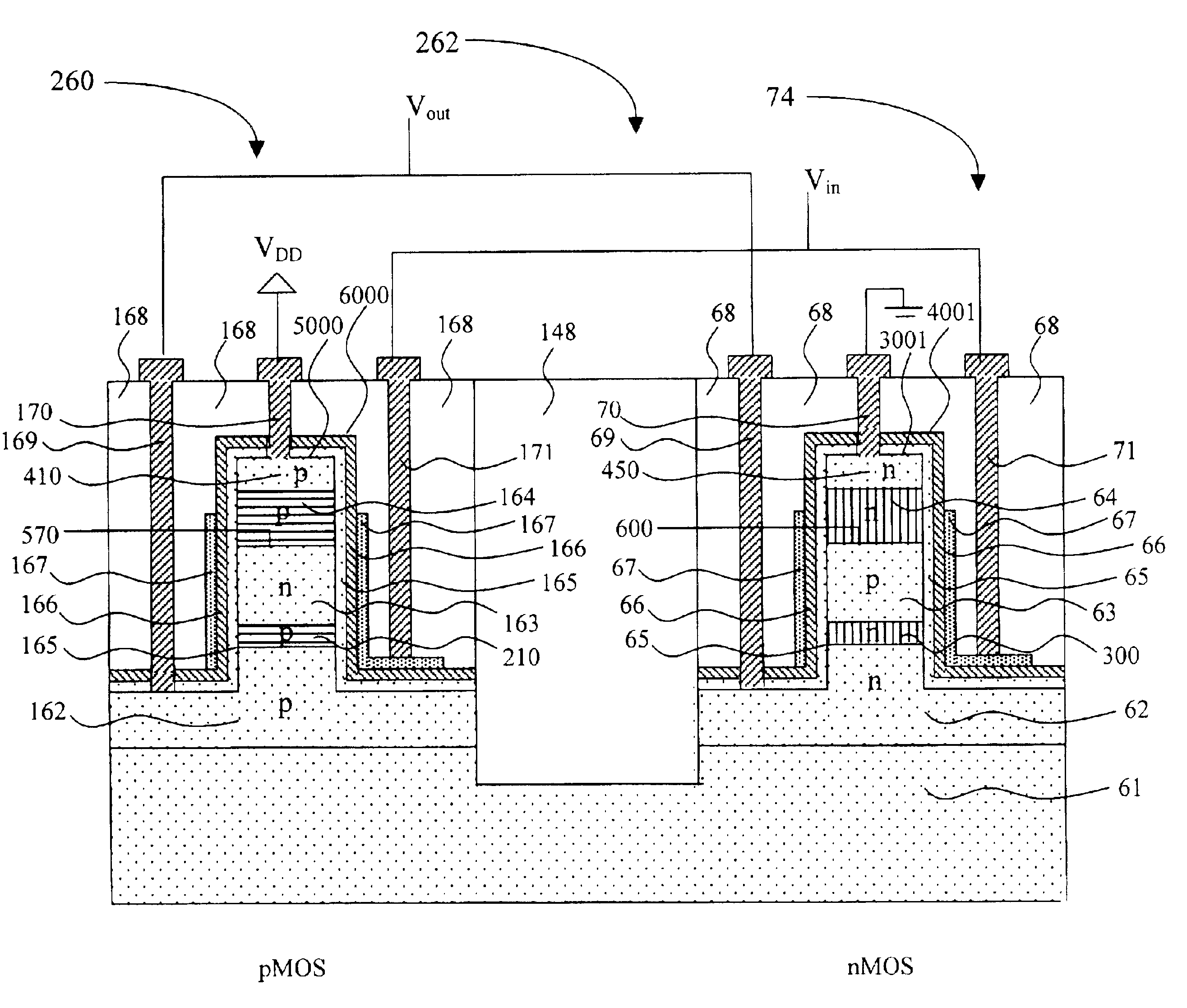

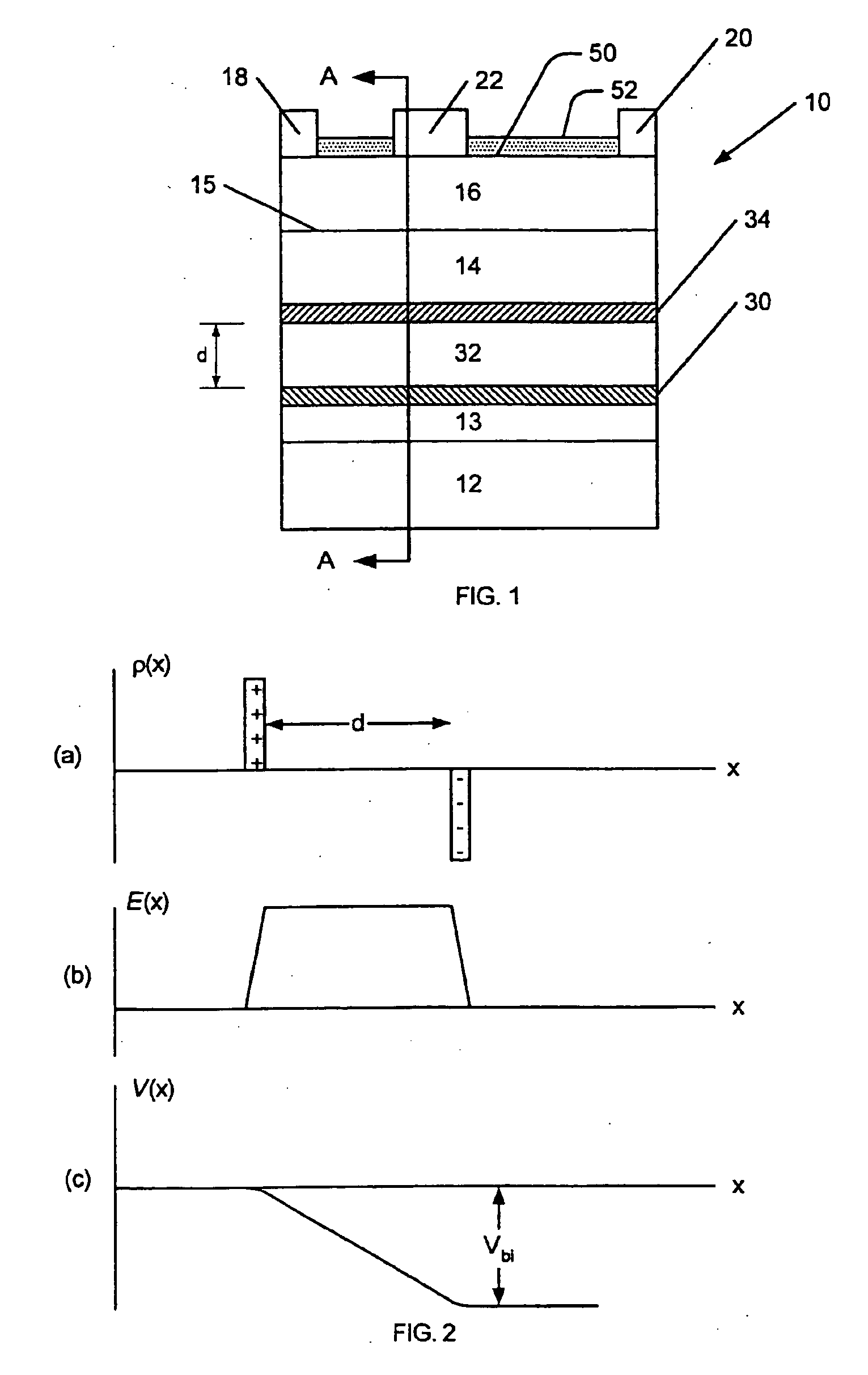

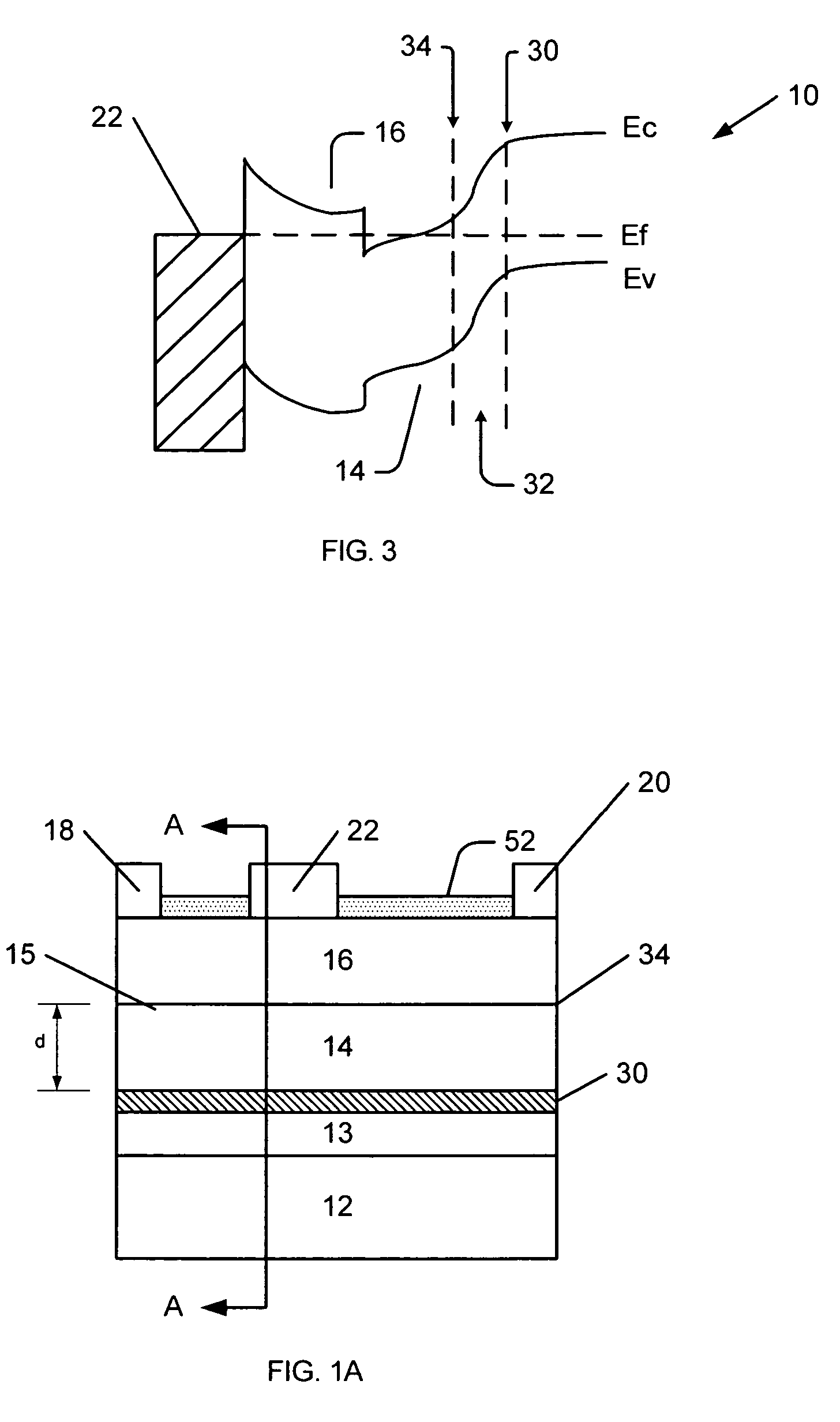

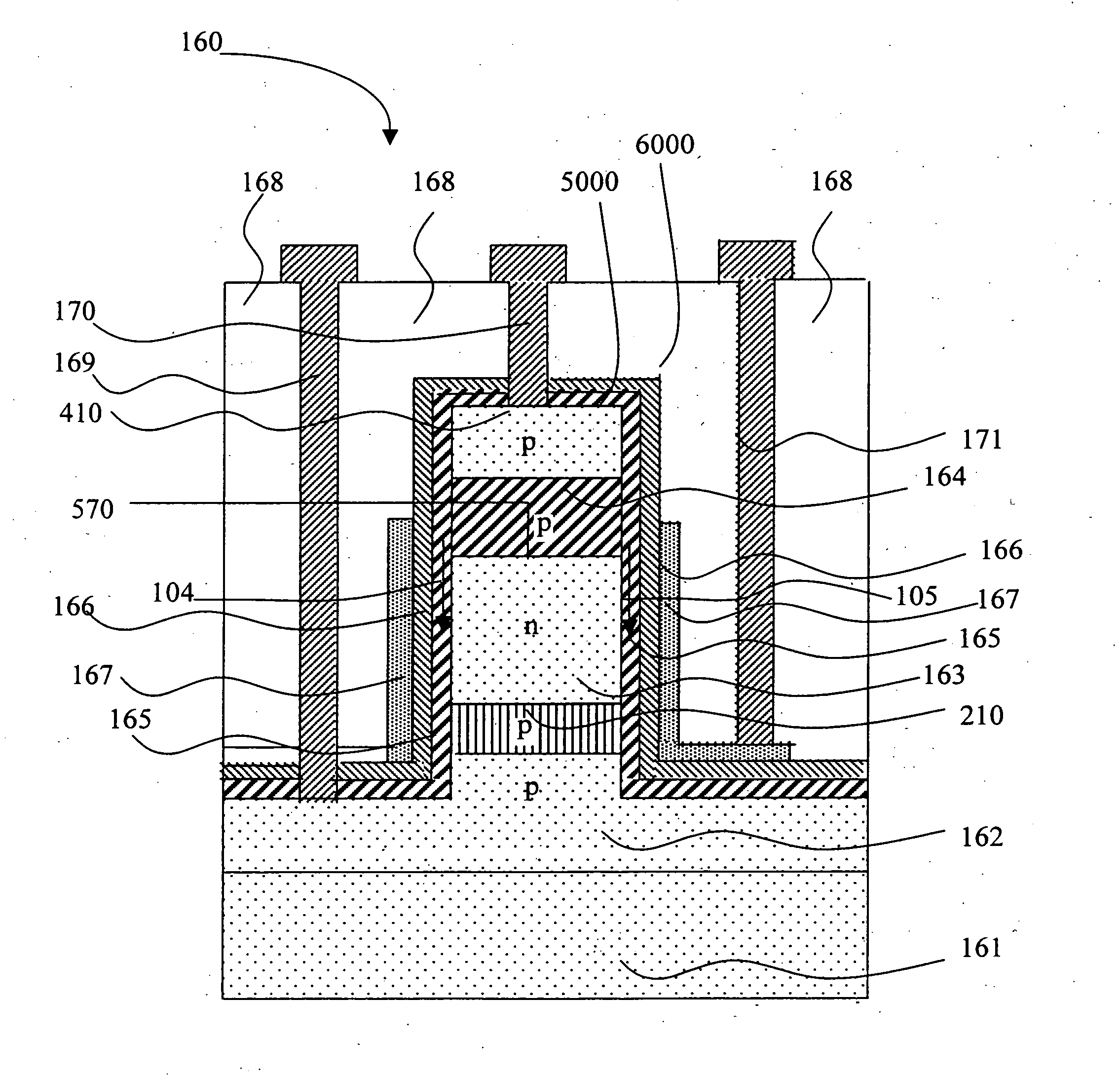

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

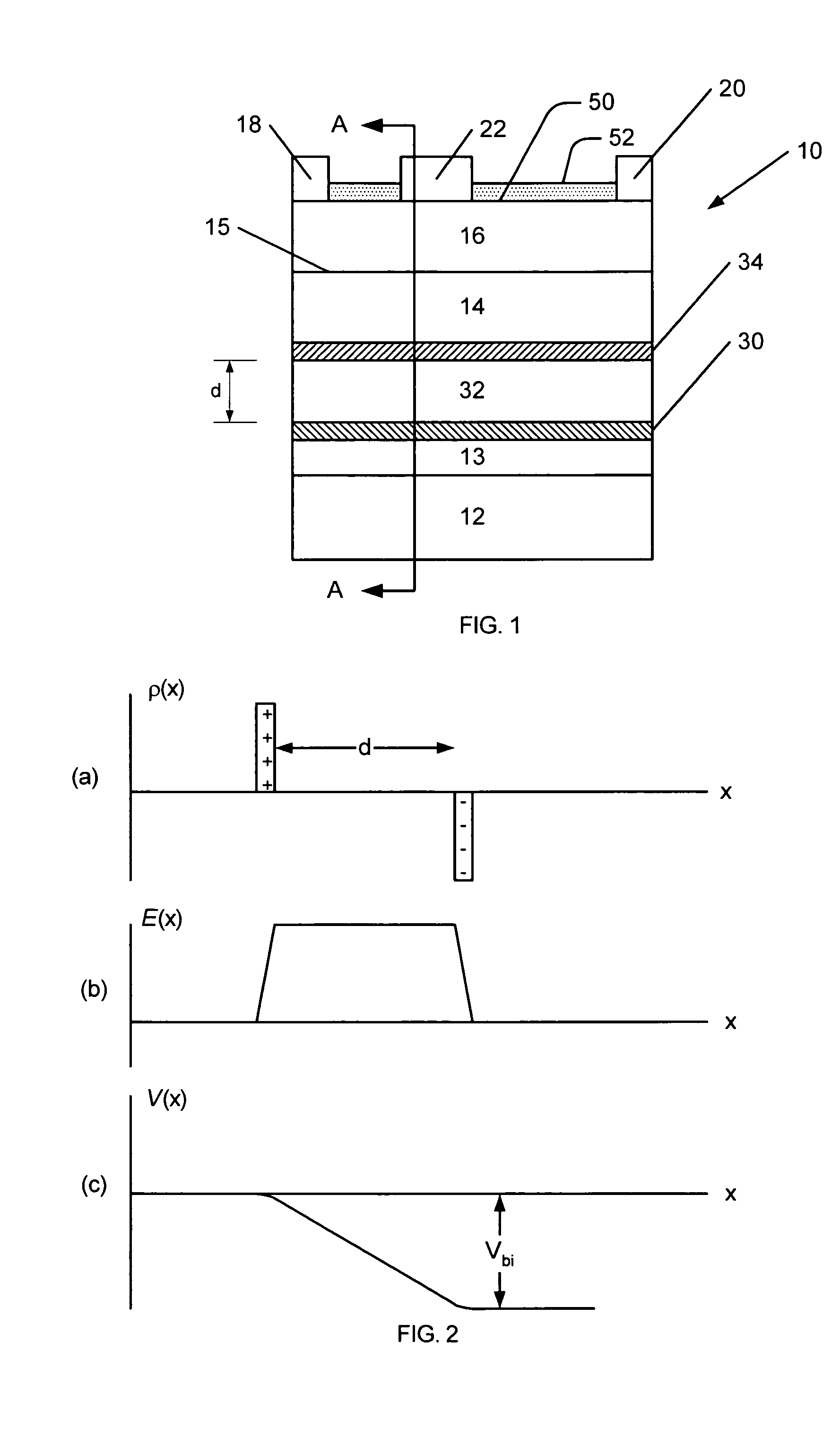

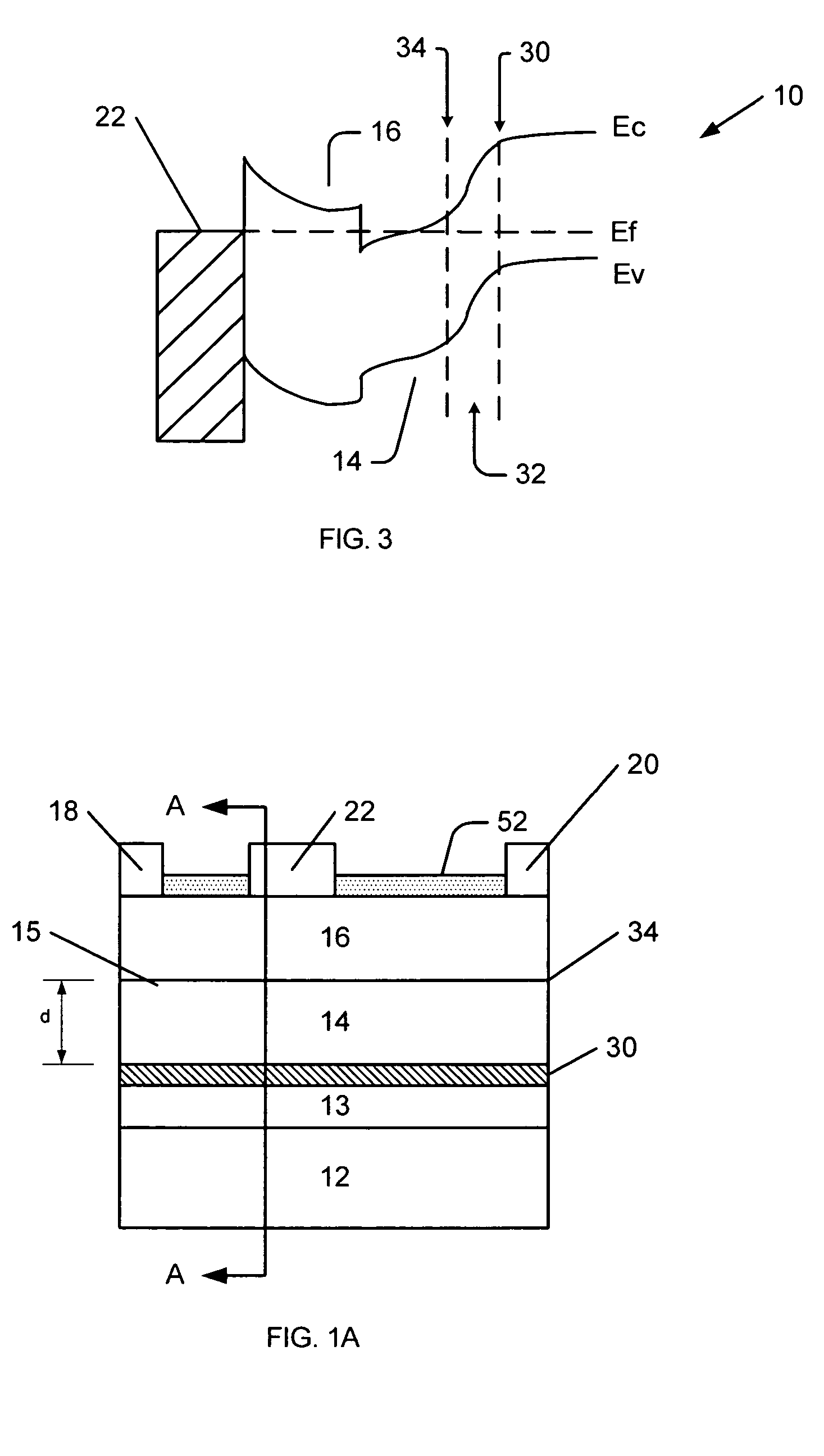

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

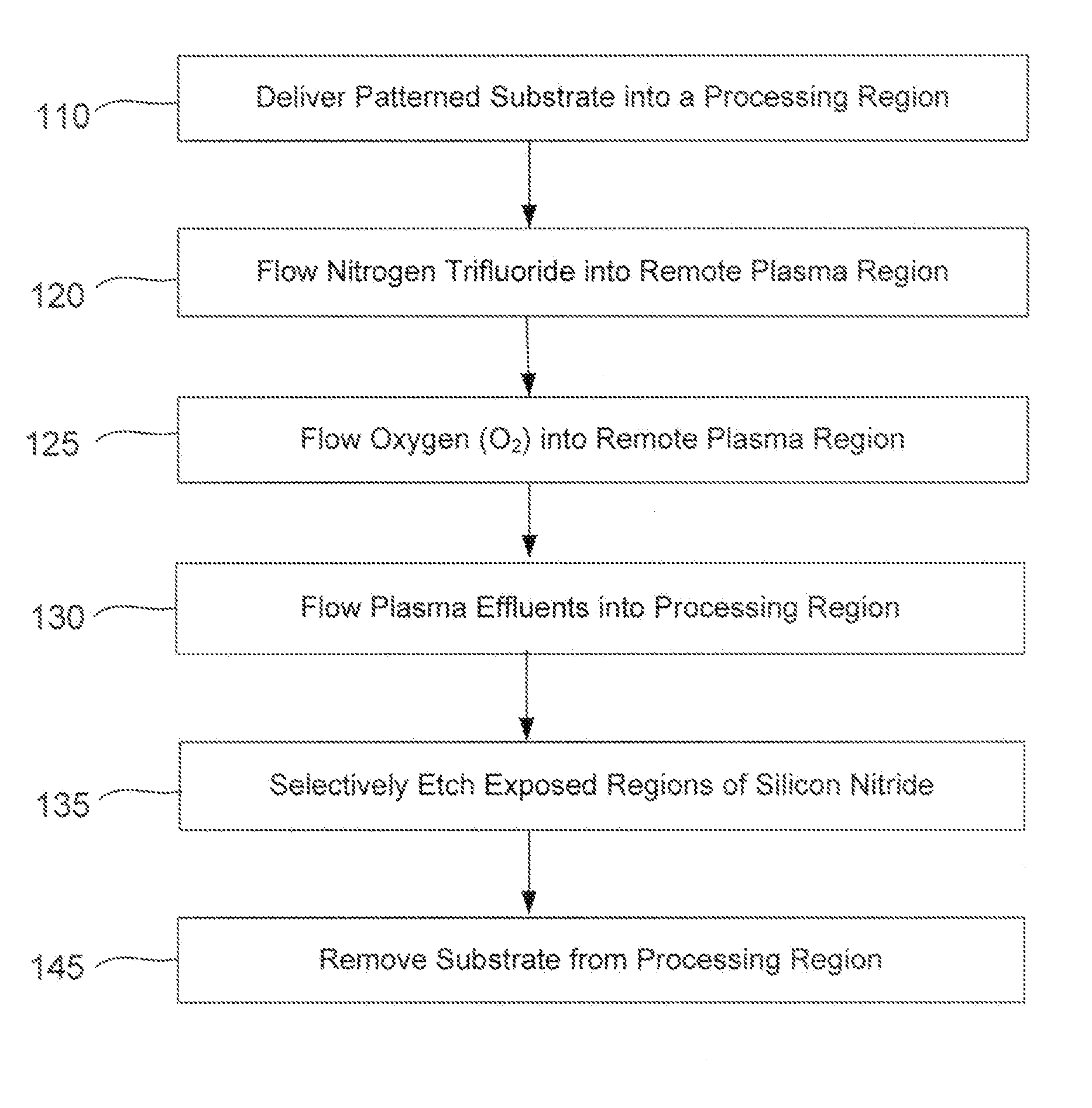

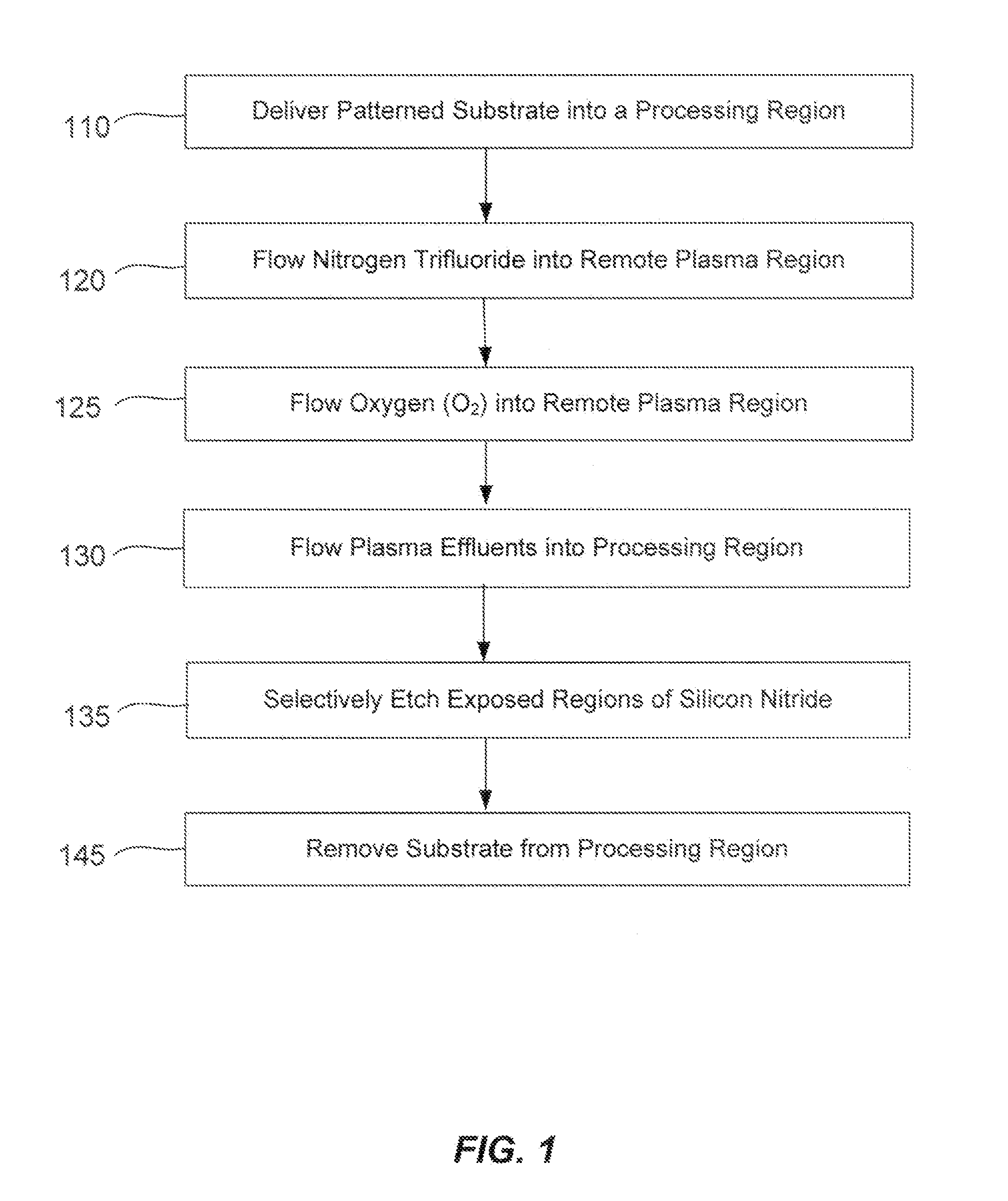

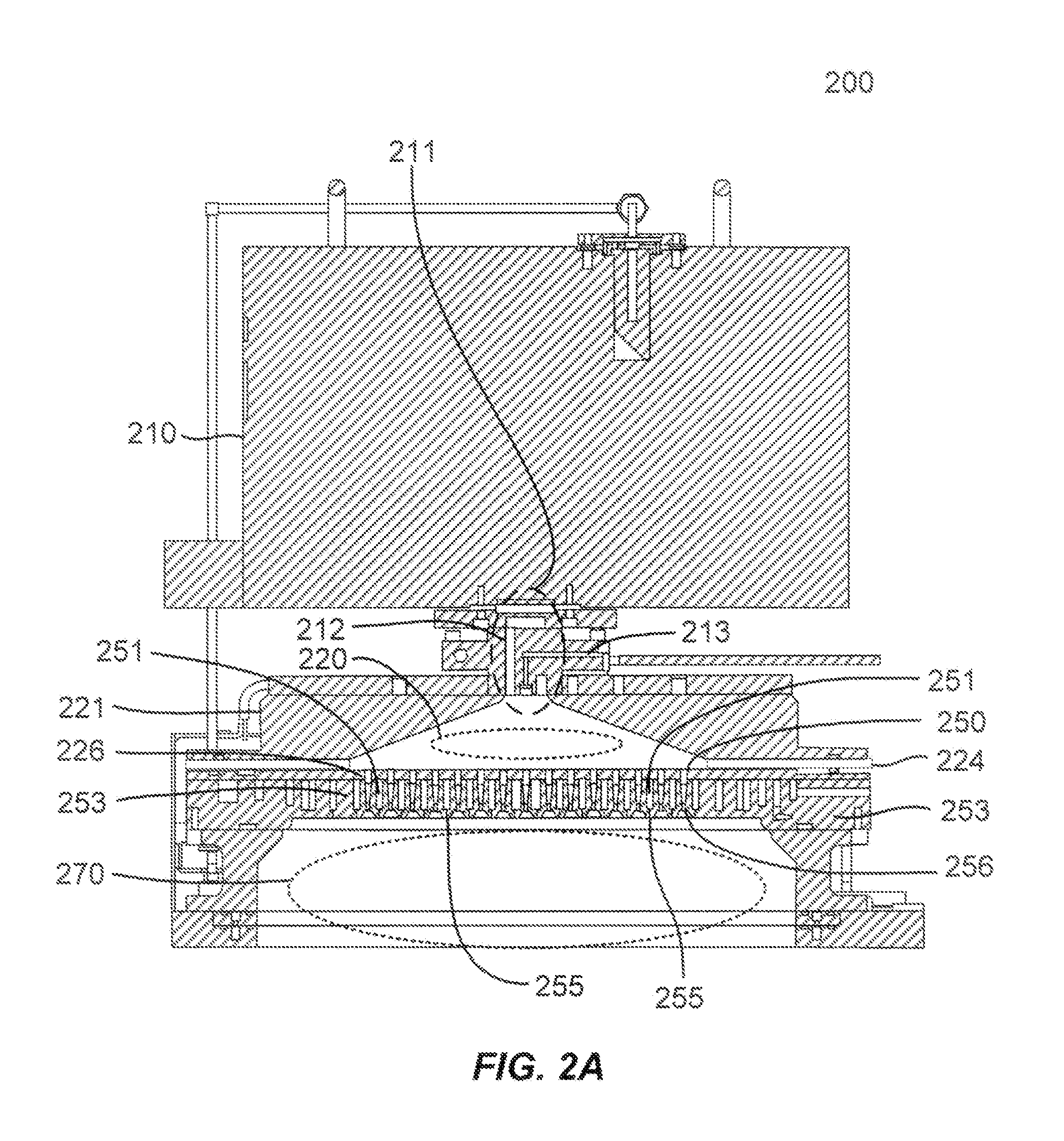

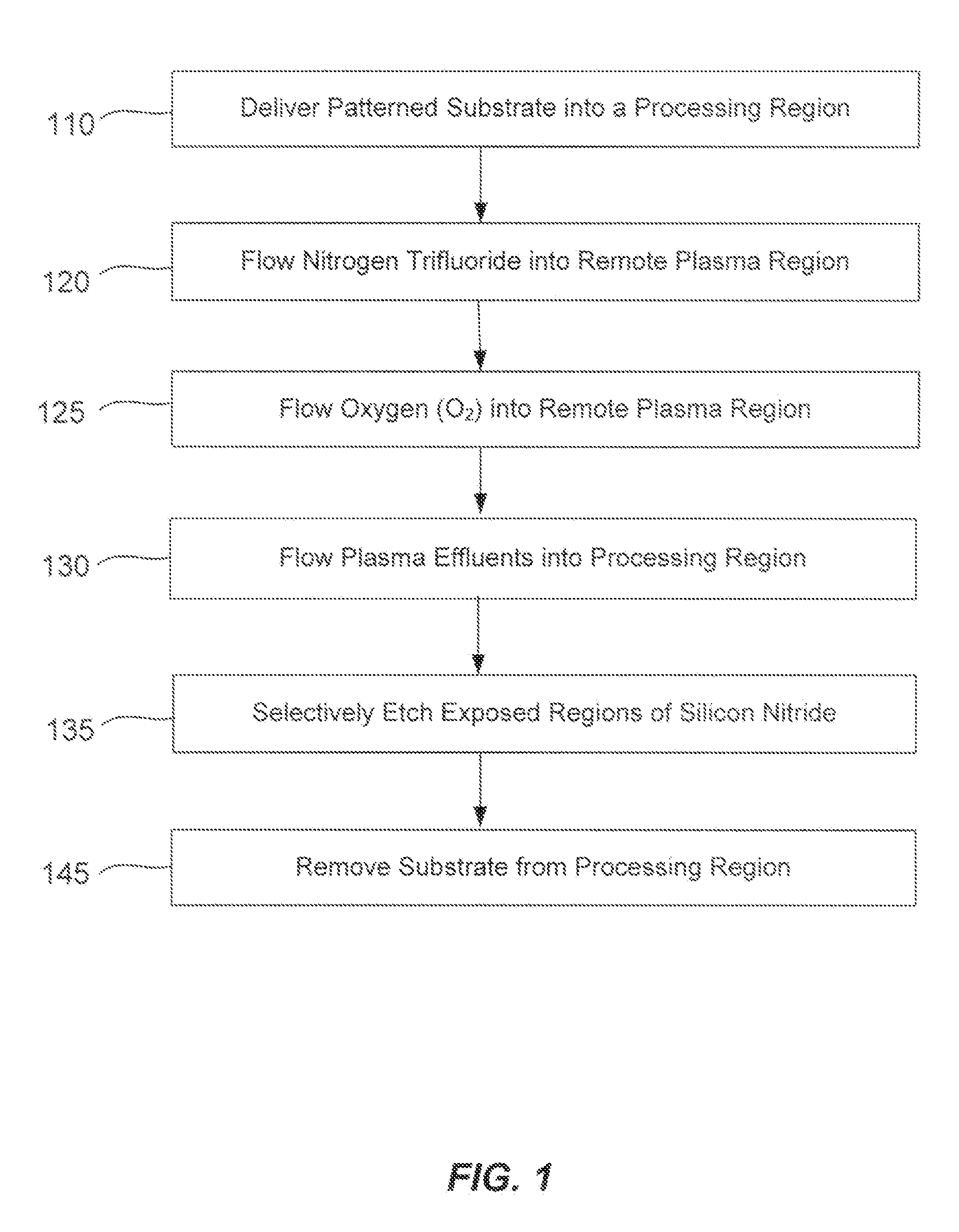

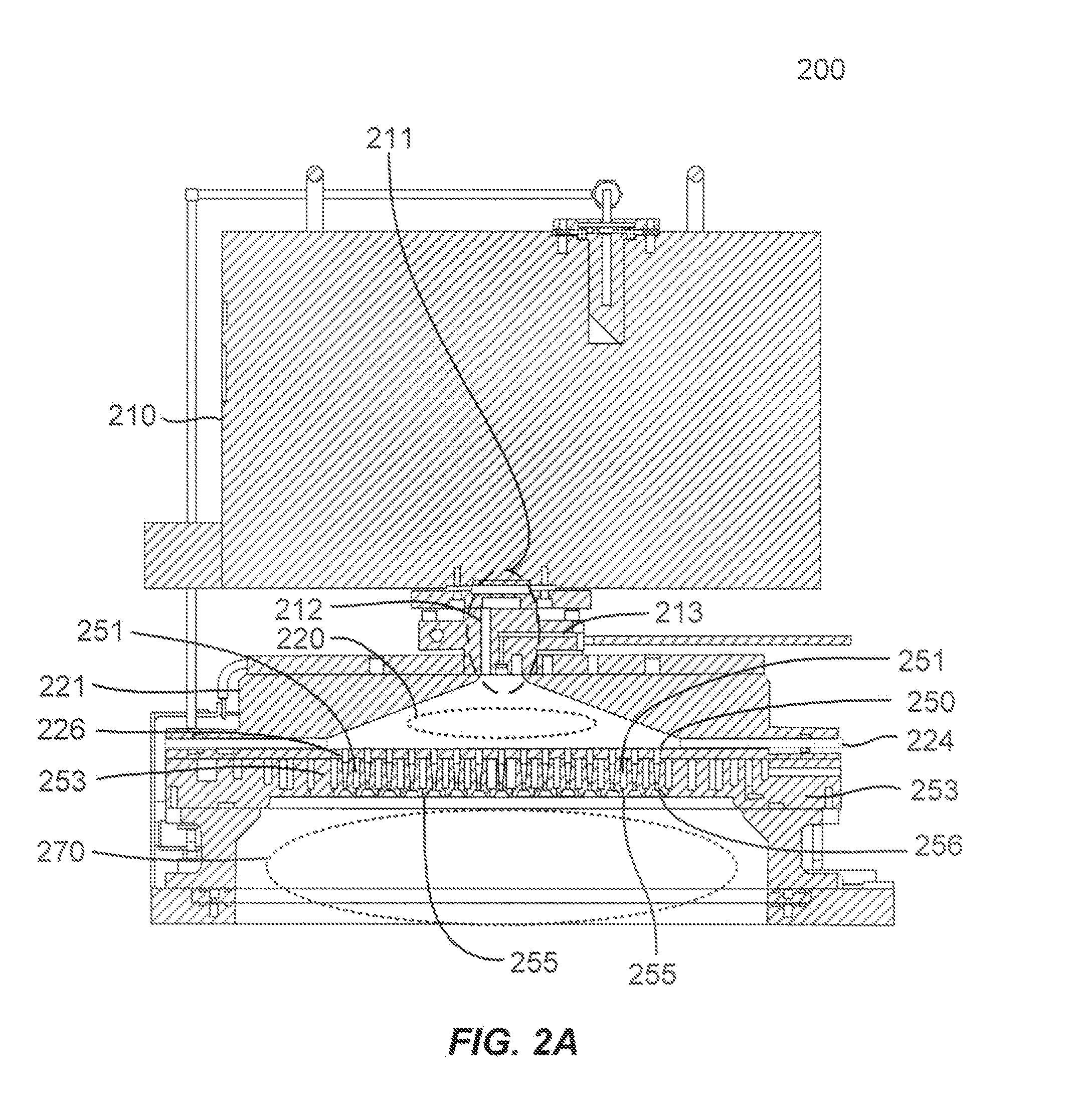

Dry-etch for silicon-and-nitrogen-containing films

InactiveUS20130045605A1Reduces and substantially eliminates numberMaterial removalElectric discharge tubesSemiconductor/solid-state device manufacturingHeterojunctionRemote plasma

A method of etching exposed silicon-and-nitrogen-containing material on patterned heterogeneous structures is described and includes a remote plasma etch formed from a fluorine-containing precursor and an oxygen-containing precursor. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents react with the exposed regions of silicon-and-nitrogen-containing material. The plasmas effluents react with the patterned heterogeneous structures to selectively remove silicon-and-nitrogen-containing material from the exposed silicon-and-nitrogen-containing material regions while very slowly removing other exposed materials. The silicon-and-nitrogen-containing material selectivity results partly from the presence of an ion suppression element positioned between the remote plasma and the substrate processing region. The ion suppression element reduces or substantially eliminates the number of ionically-charged species that reach the substrate. The methods may be used to selectively remove silicon-and-nitrogen-containing material at more than twenty times the rate of silicon oxide.

Owner:APPLIED MATERIALS INC

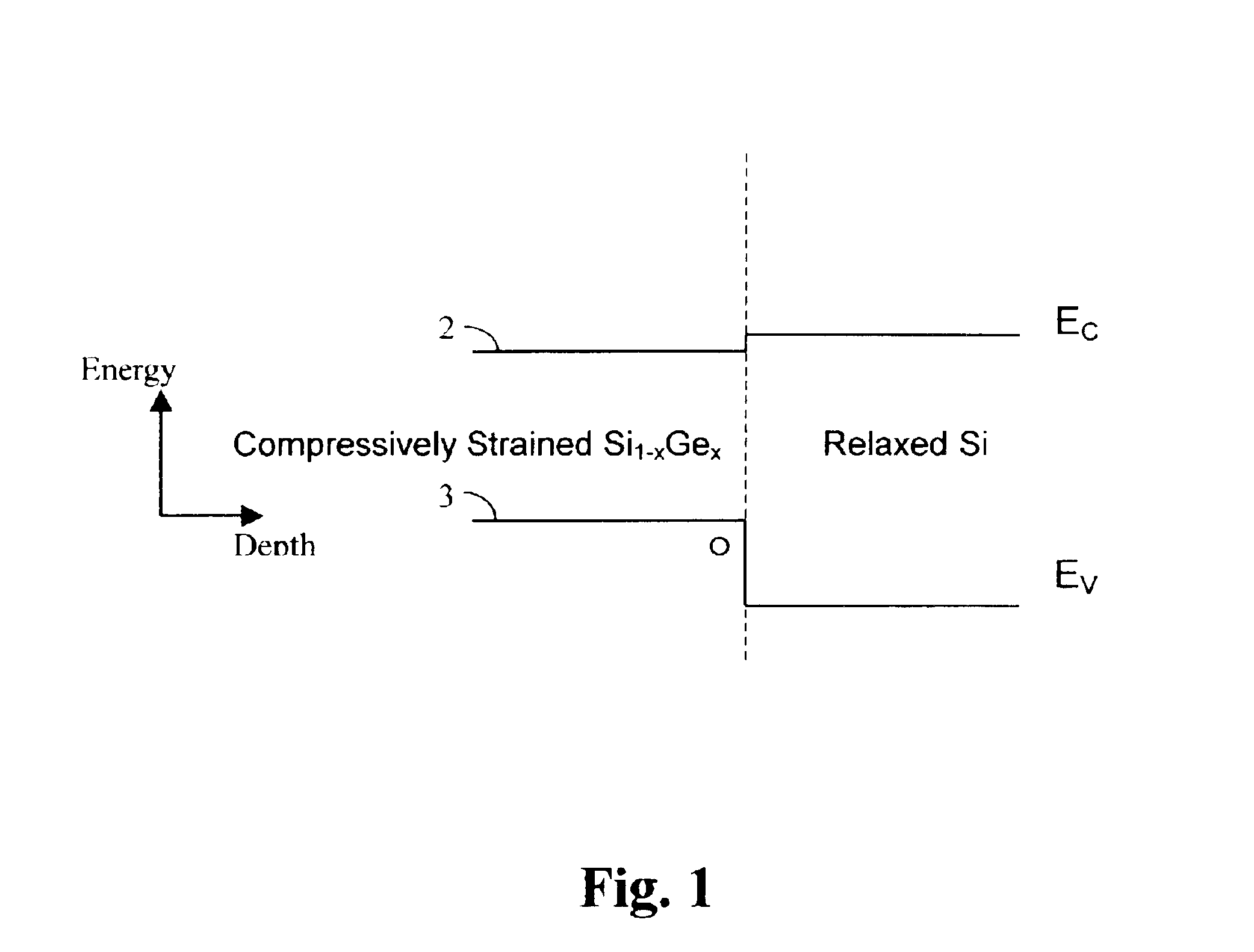

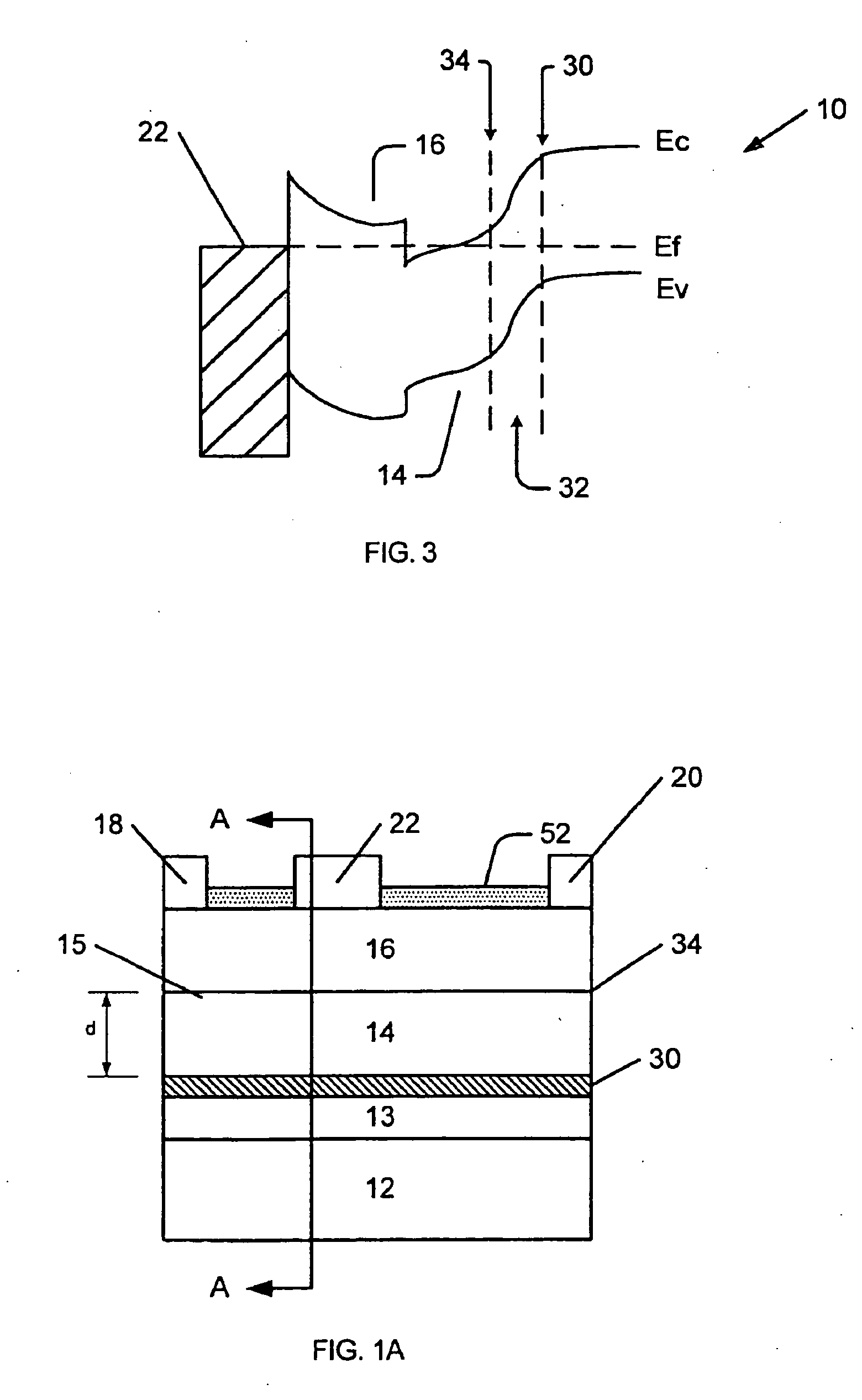

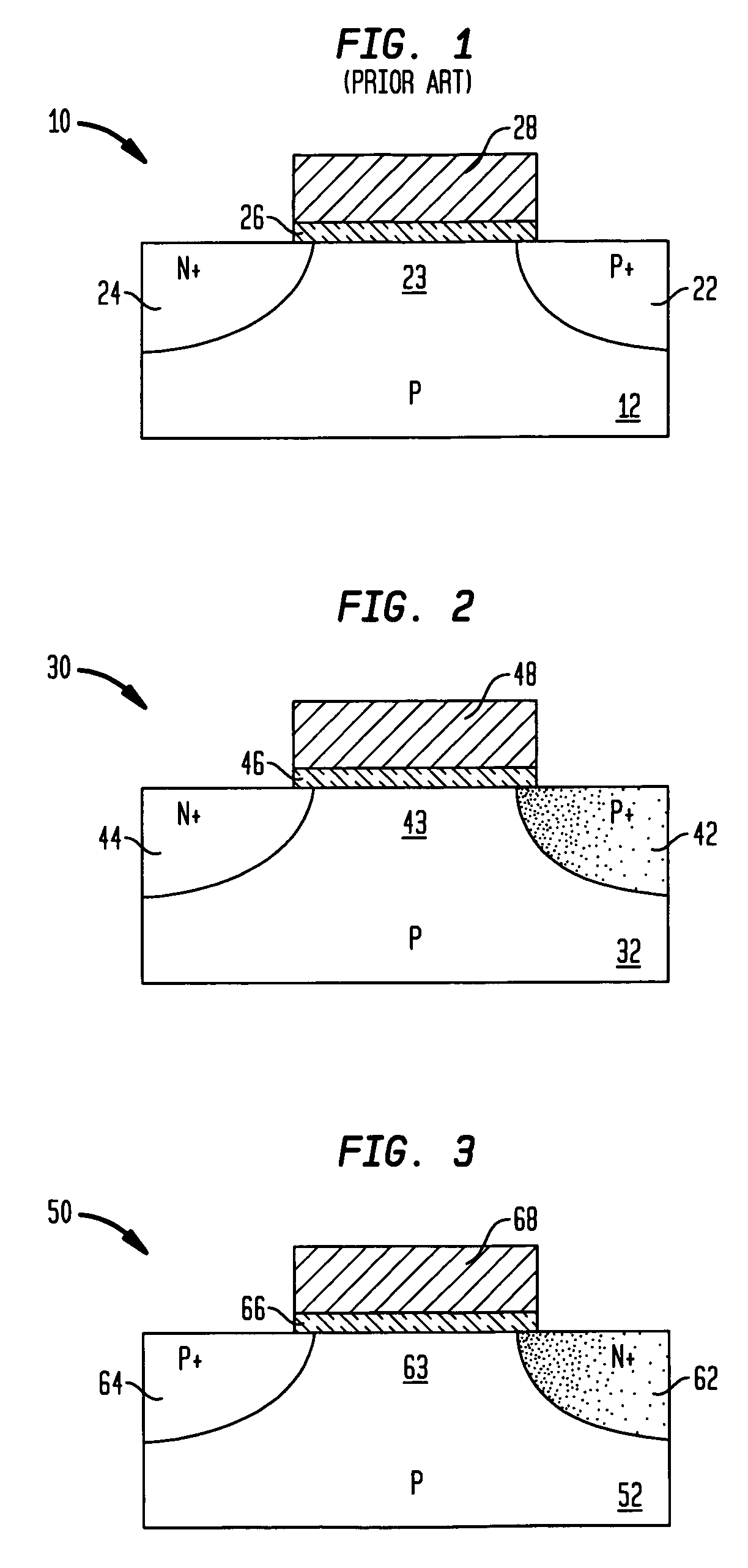

High mobility heterojunction complementary field effect transistors and methods thereof

ActiveUS20050093021A1Minimal toleranceHigh hole mobilityTransistorSolid-state devicesHeterojunctionCMOS

A structure, and method of fabrication, for high performance field effect devices is disclosed. The MOS structures include a crystalline Si body of one conductivity type, a strained SiGe layer epitaxially grown on the Si body serving as a buried channel for holes, a Si layer epitaxially grown on the SiGe layer serving as a surface channel for electrons, and a source and a drain containing an epitaxially deposited, strained SiGe of opposing conductivity type than the Si body. The SiGe source / drain forms a heterojunction and a metallurgical junction with the Si body that coincide with each other with a tolerance of less than about 10 nm, and preferably less than about 5 nm. The heterostructure source / drain is instrumental in reducing short channel effects. These structures are especially advantageous for PMOS due to increased hole mobility in the compressively strained SiGe channel. Representative embodiments include CMOS structures on bulk and on SOI.

Owner:GLOBALFOUNDRIES US INC

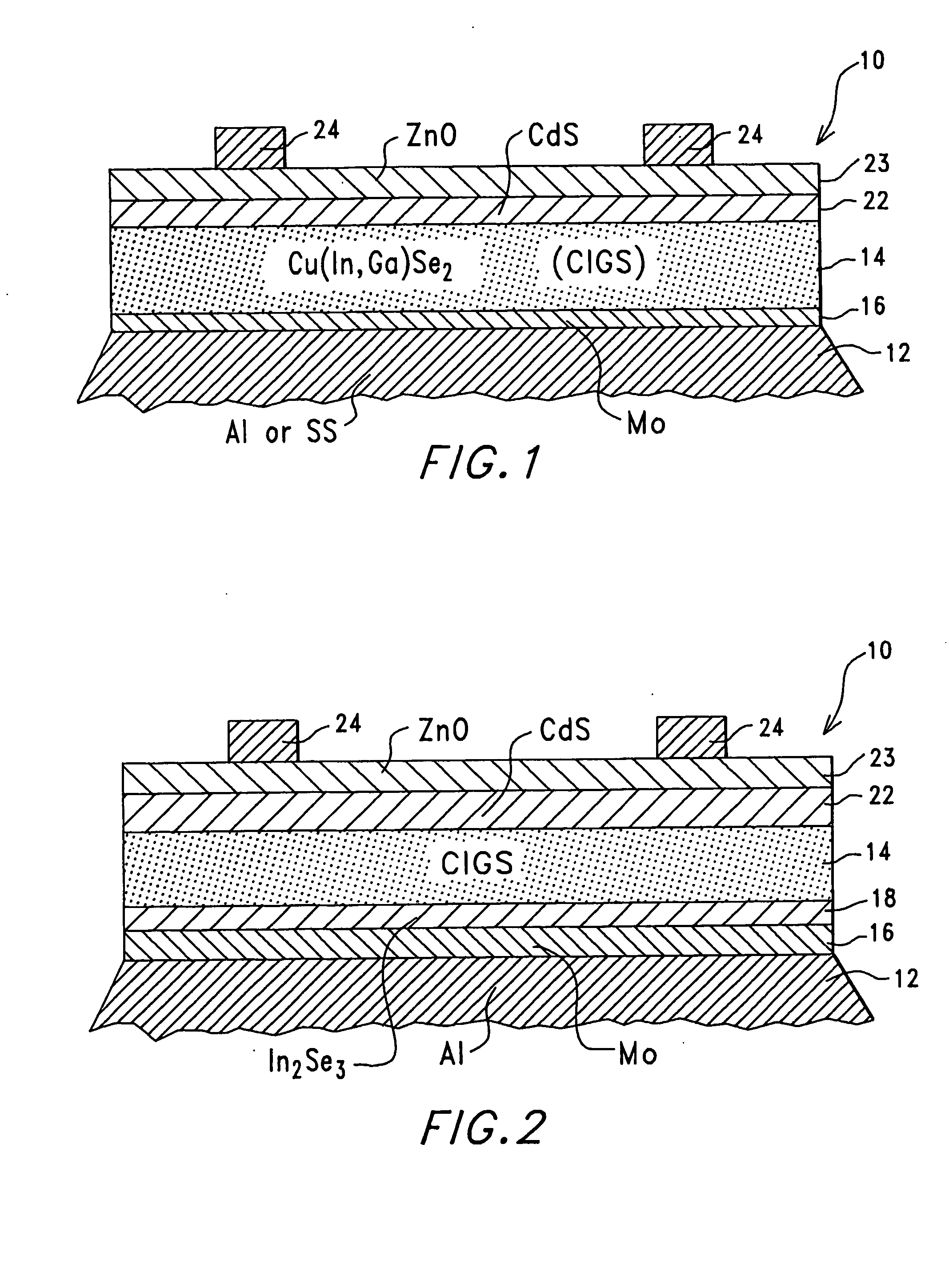

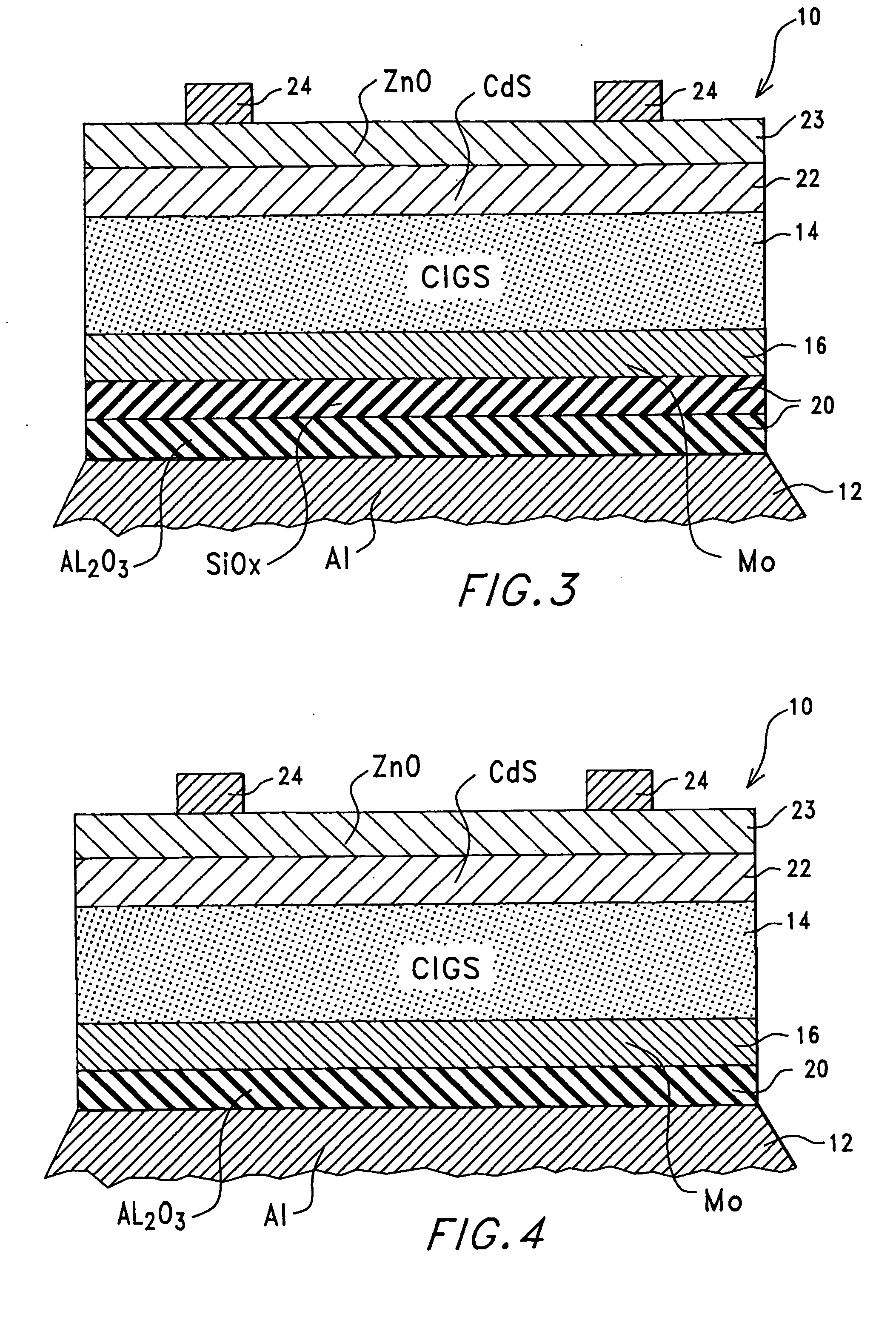

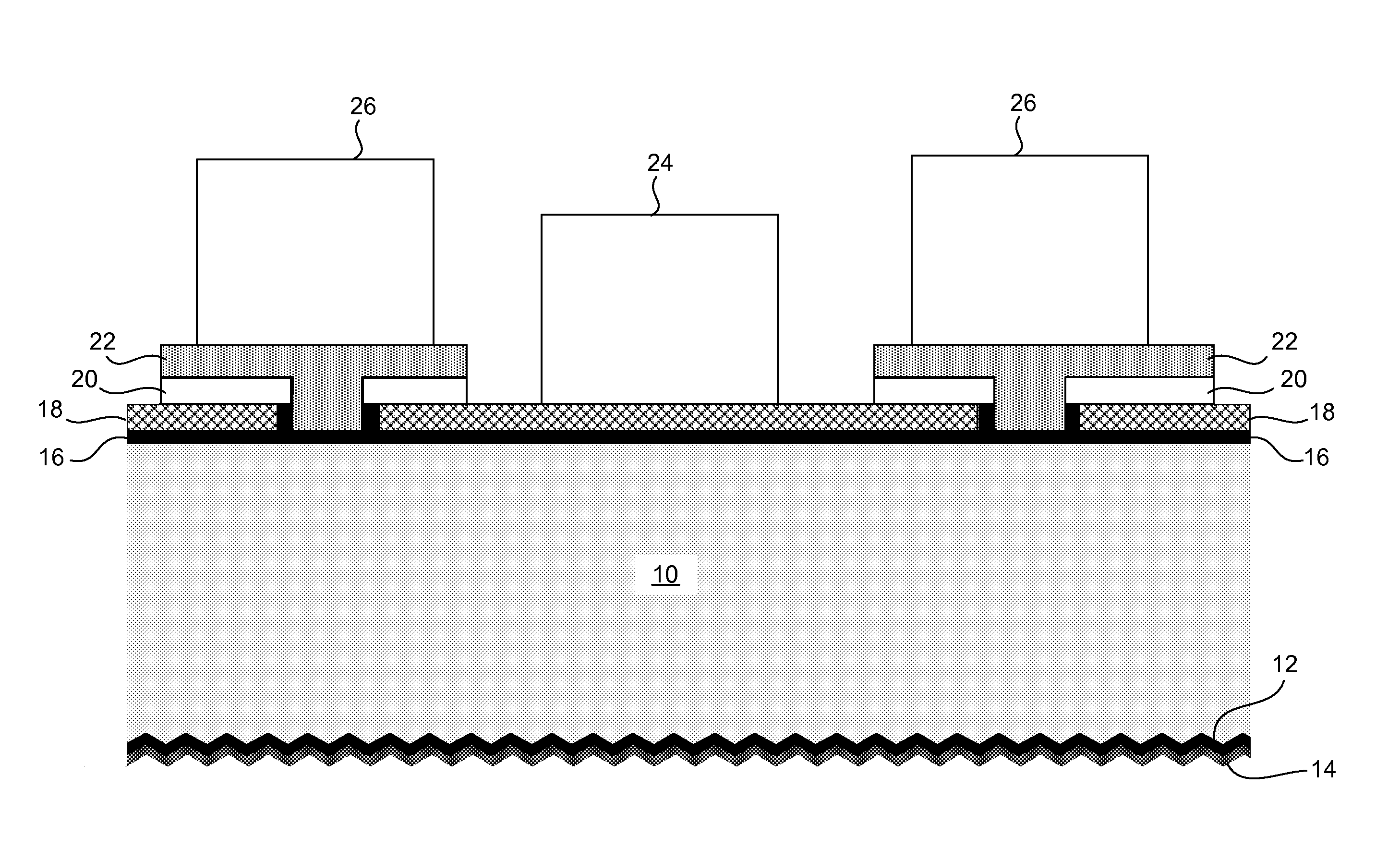

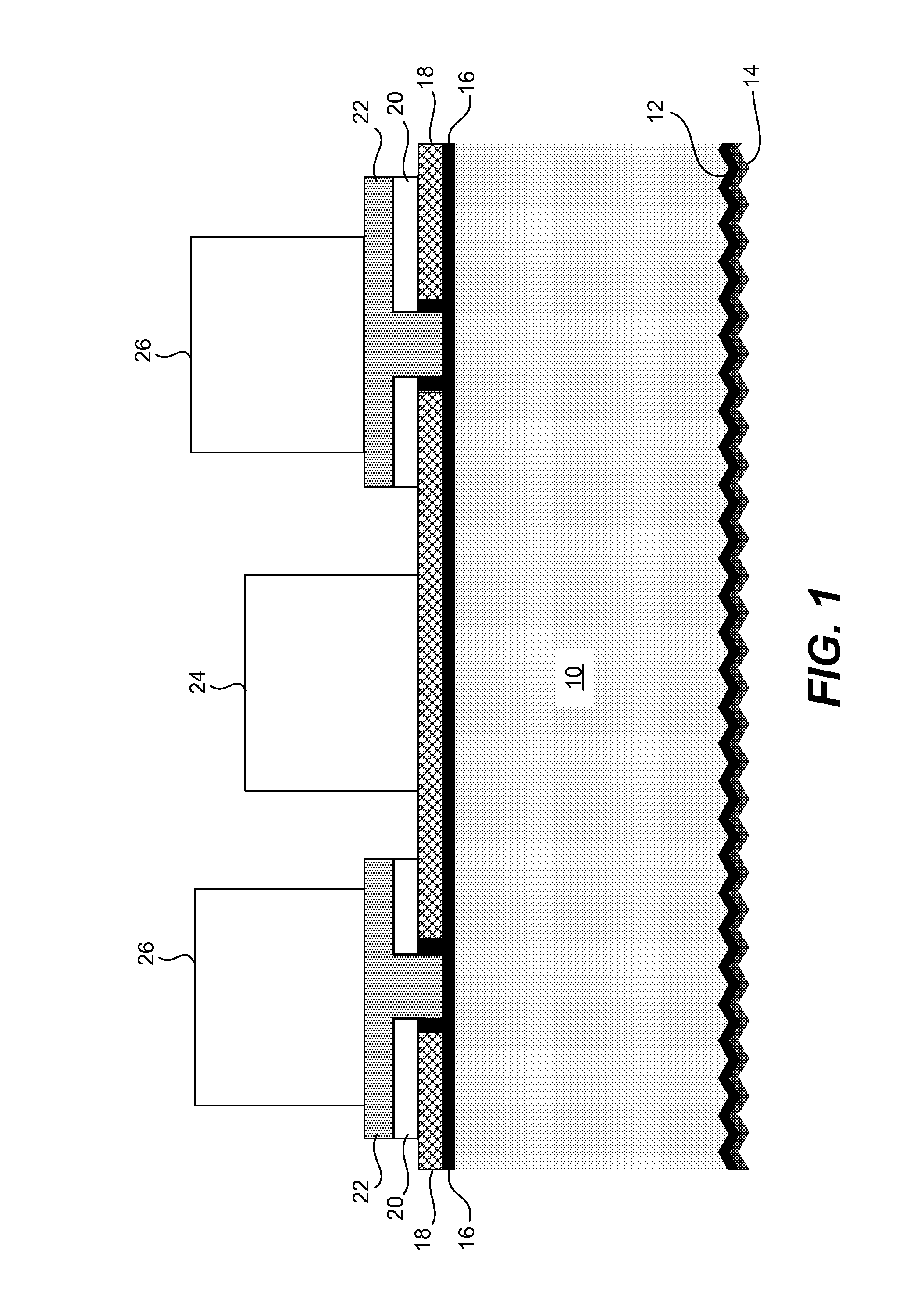

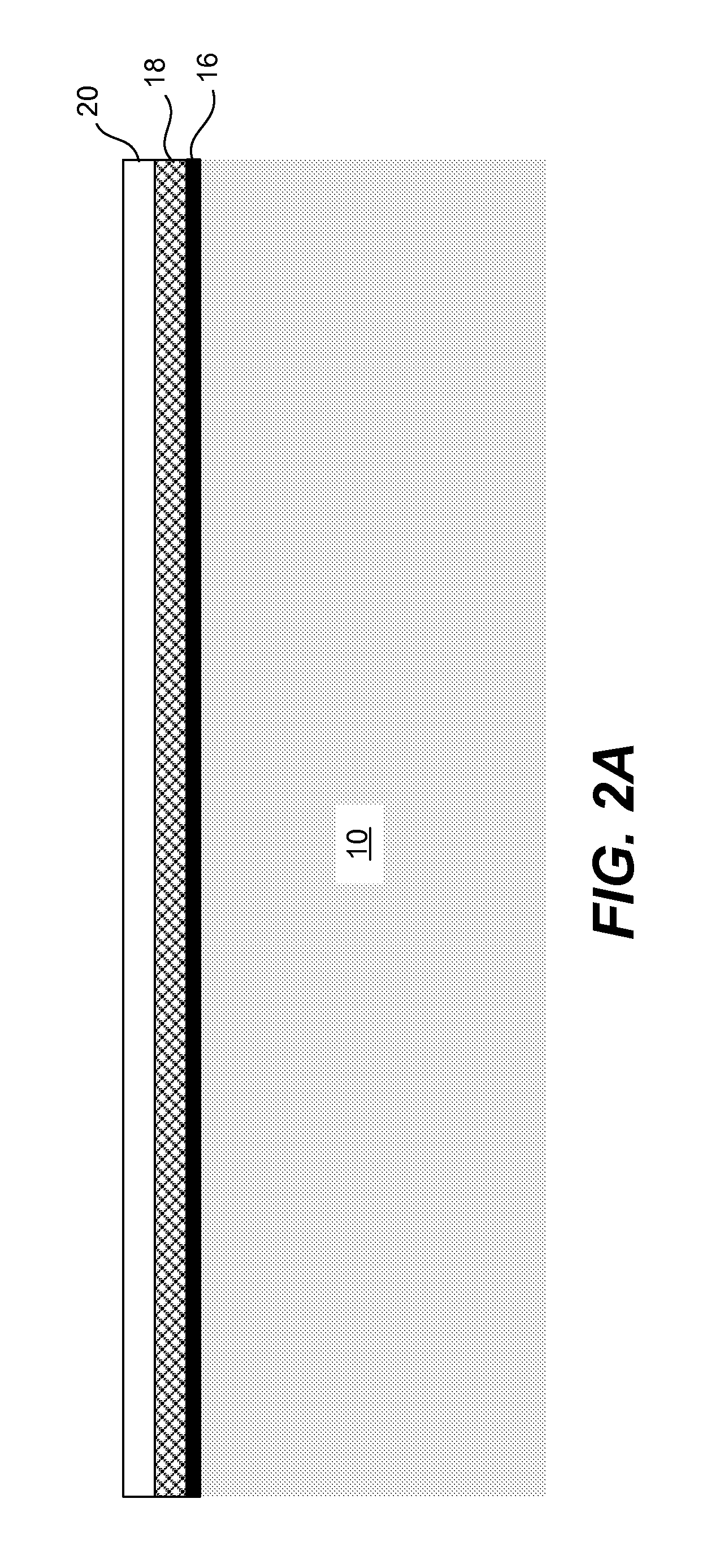

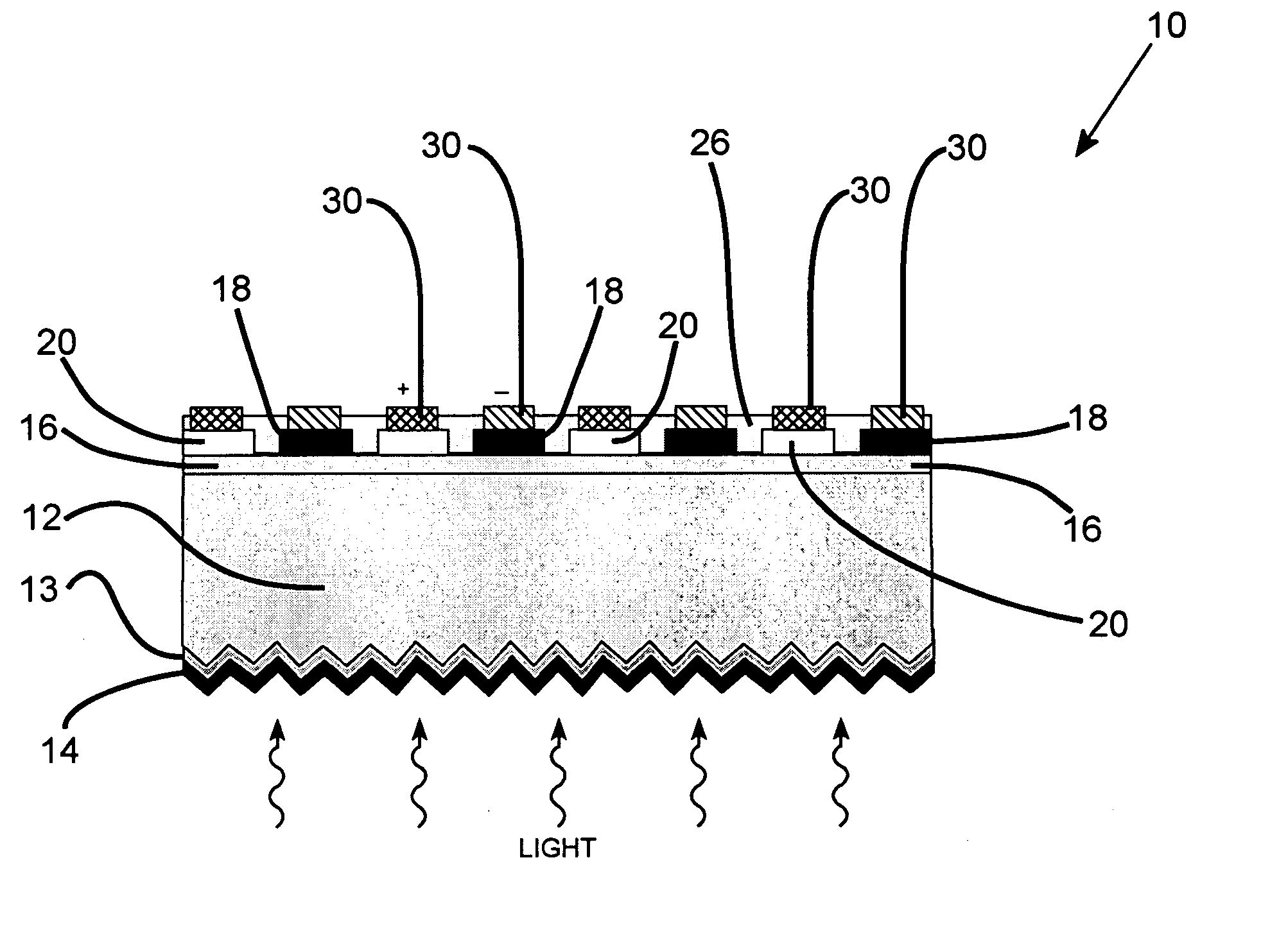

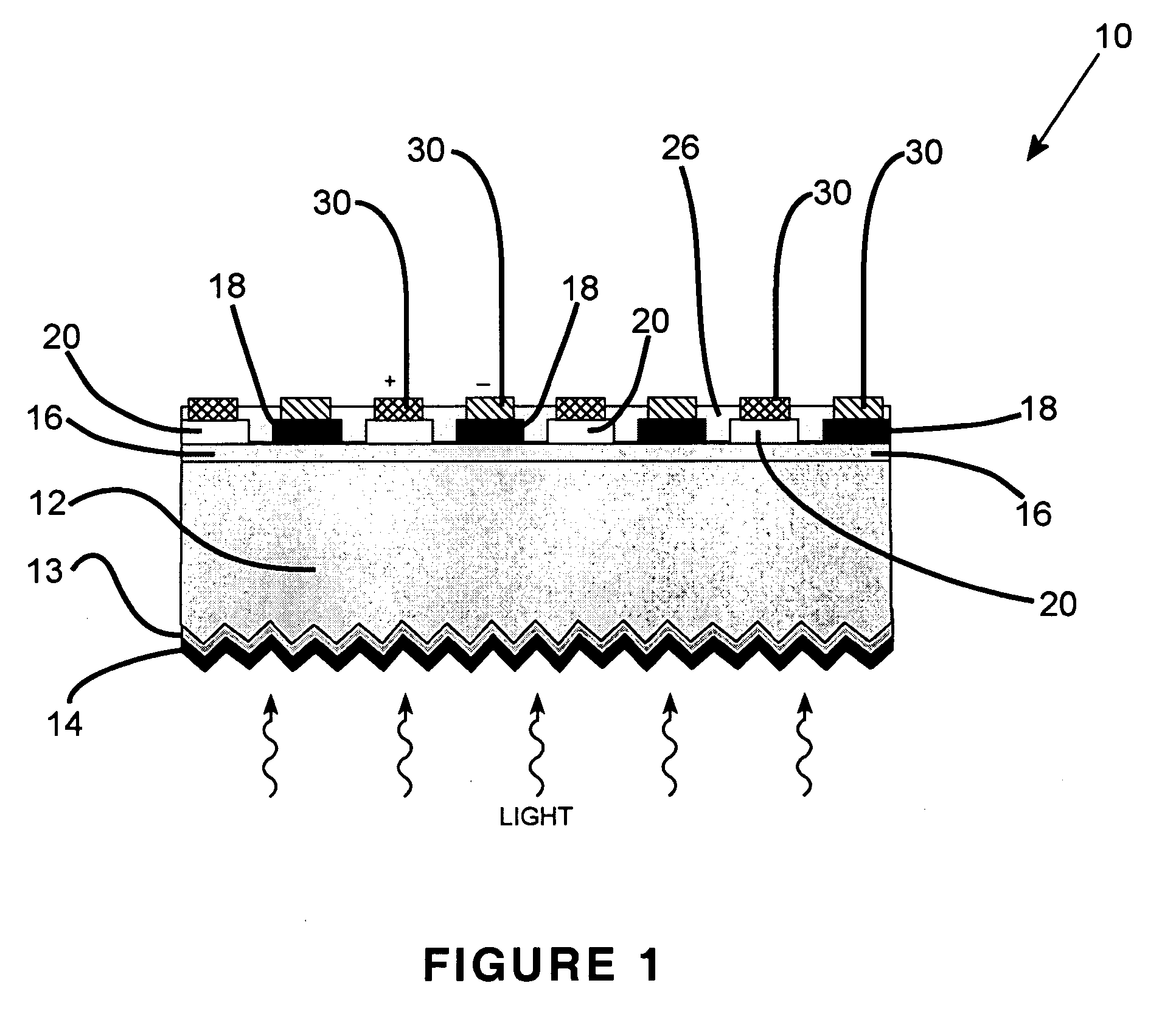

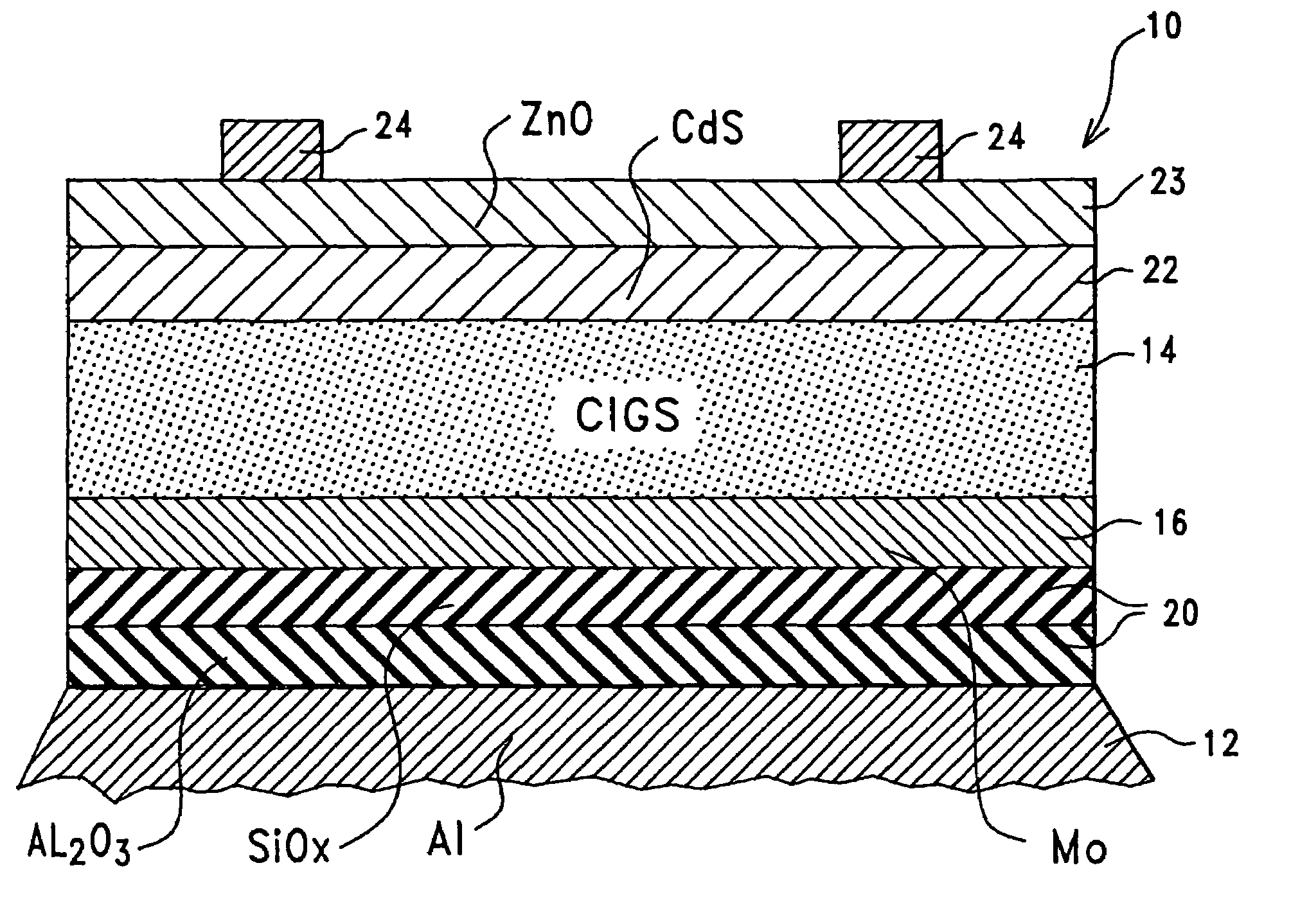

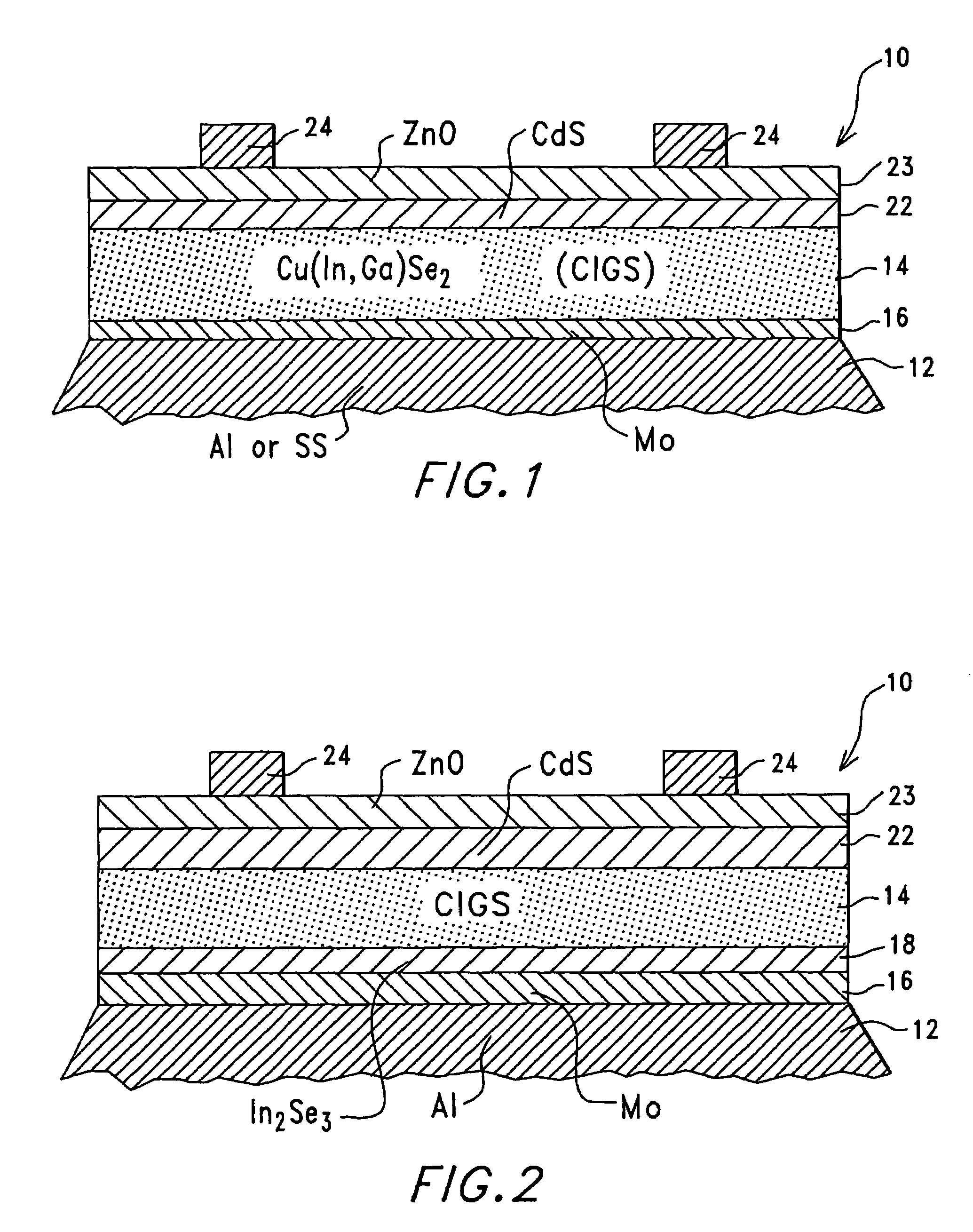

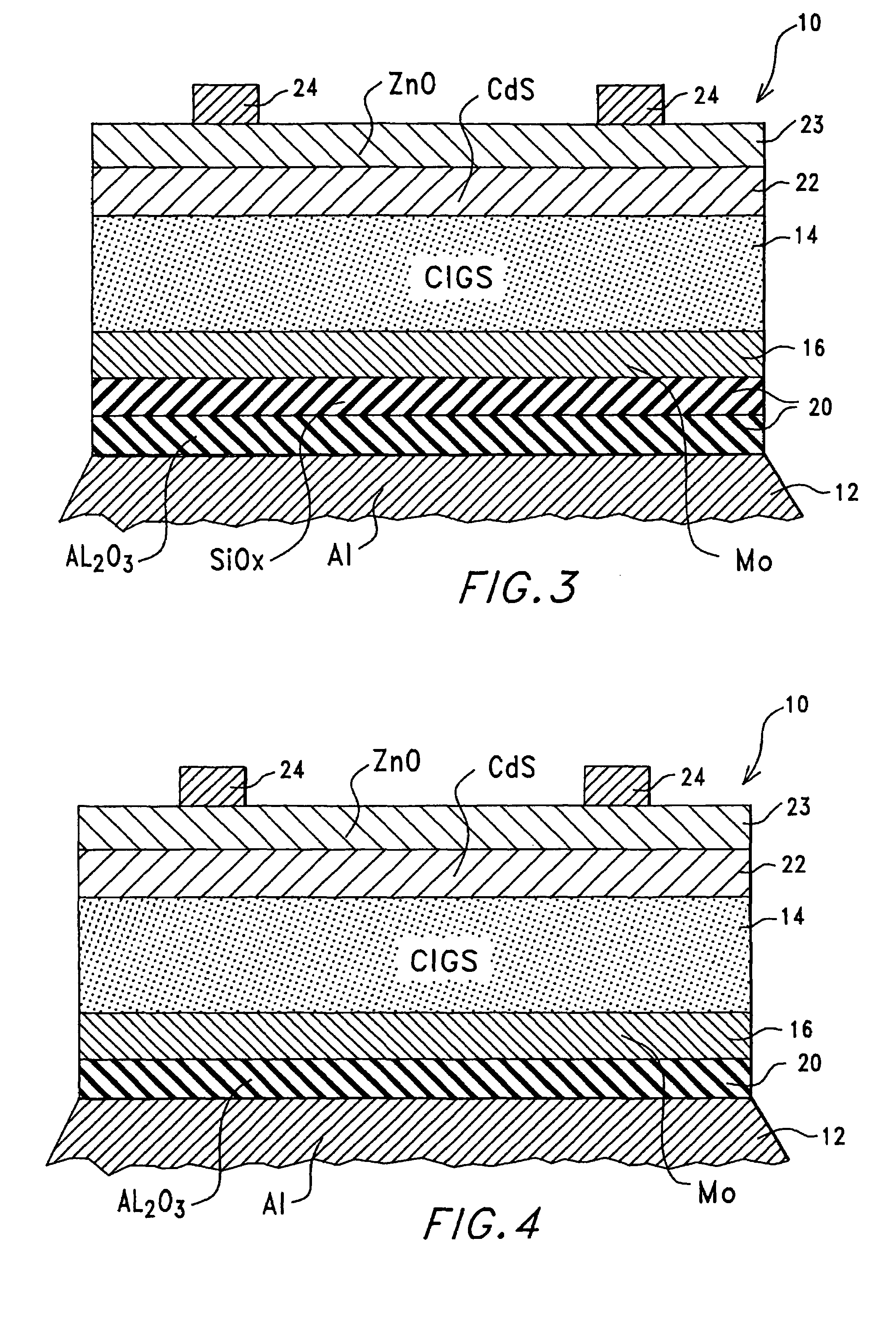

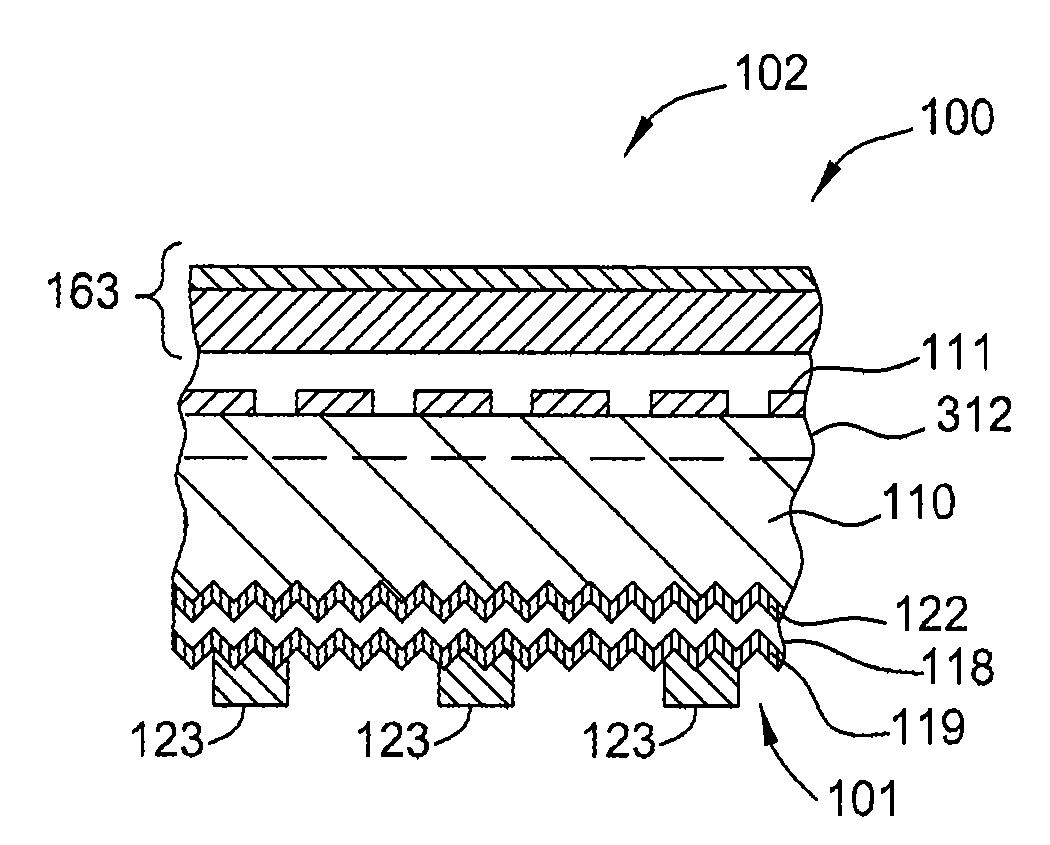

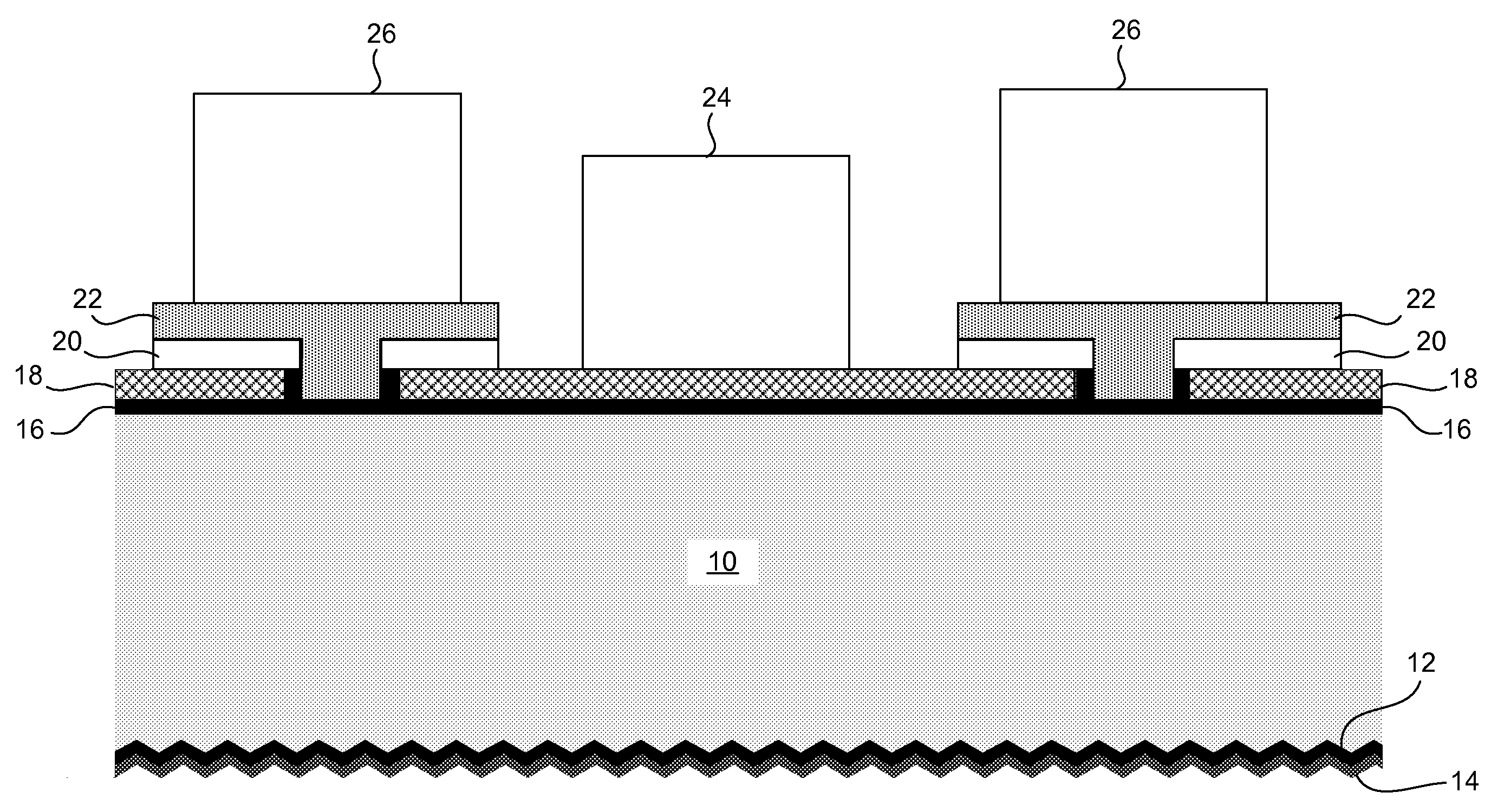

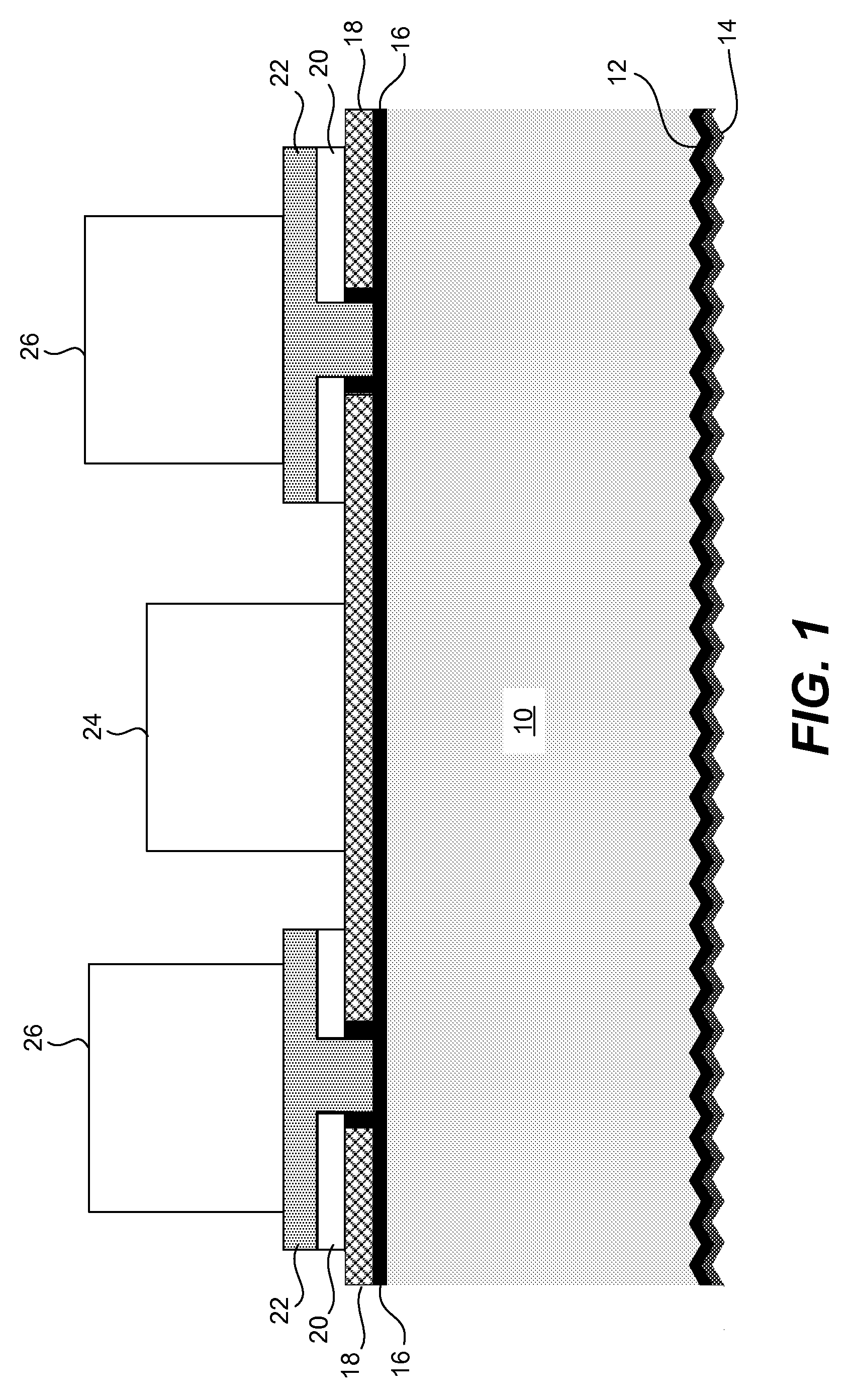

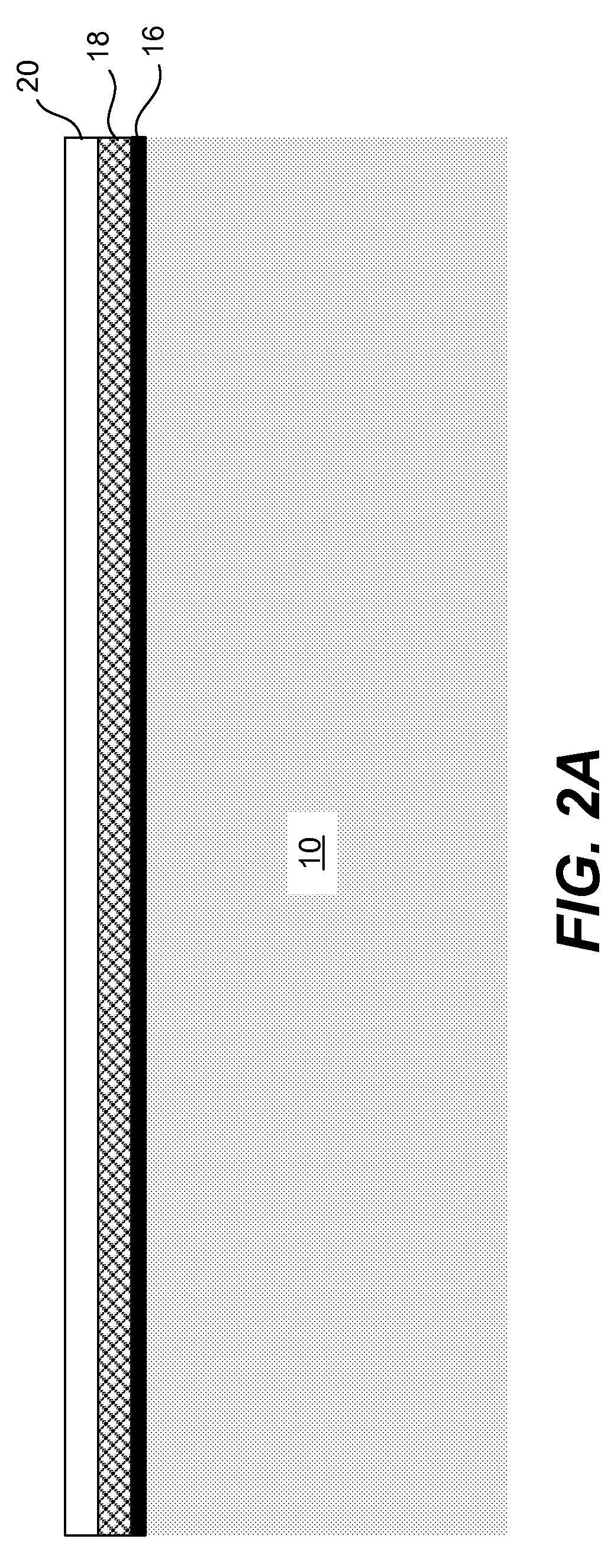

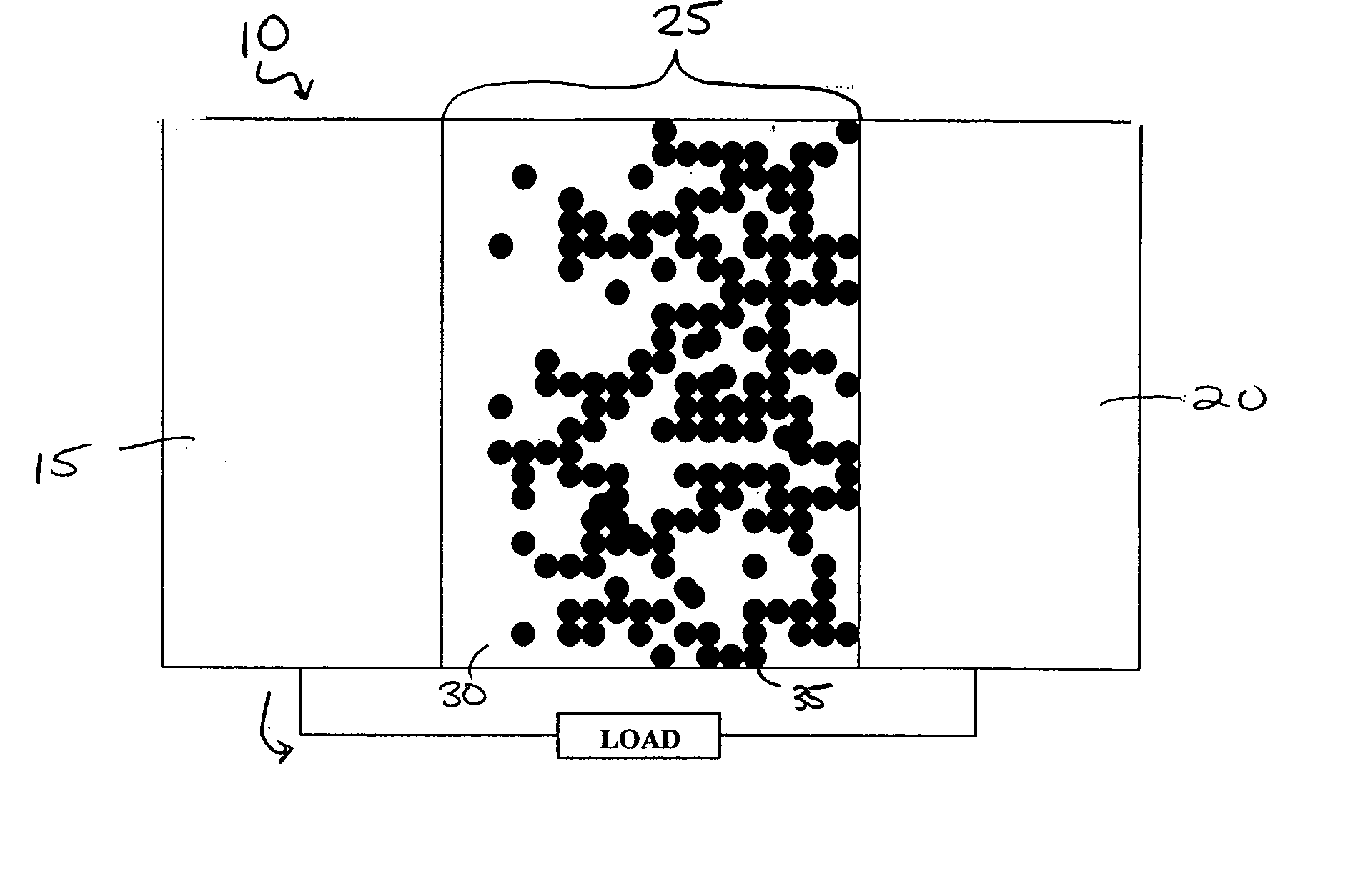

Thin-film solar cell fabricated on a flexible metallic substrate

A thin-film solar cell (10) is provided. The thin-film solar cell (10) comprises a flexible metallic substrate (12) a having a first surface and a second surface. A back metal contact layer (16) is deposited on the first surface of the flexible metallic substrate (12). A semiconductor absorber layer (14) is deposited on the back metal contact. A photoactive film deposited on the semiconductor absorber layer (14) forms a heterojunction structure and a grid contact (24) deposited on the heterjunction structure. The flexible metal substrate (12) can be constructed of either aluminium or stainless steel. Furthermore, a method of constructing a solar cell is provided. The method comprises providing an aluminum substrate (12), depositing a semiconductor absorber layer (14) on the aluminum substrate (12), and insulating the aluminum substrate (12) from the semiconductor absorber layer (14) to inhibit reaction between the aluminum substrate (12) and the semiconductor absorber layer (14).

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

Solar cell having doped semiconductor heterojunction contacts

ActiveUS20070256728A1Readily apparentPV power plantsFinal product manufactureHeterojunctionAmorphous silicon

A silicon solar cell has doped amorphous silicon contacts formed on a tunnel silicon oxide layer on a surface of a silicon substrate. High temperature processing is unnecessary in fabricating the solar cell.

Owner:MAXEON SOLAR PTE LTD

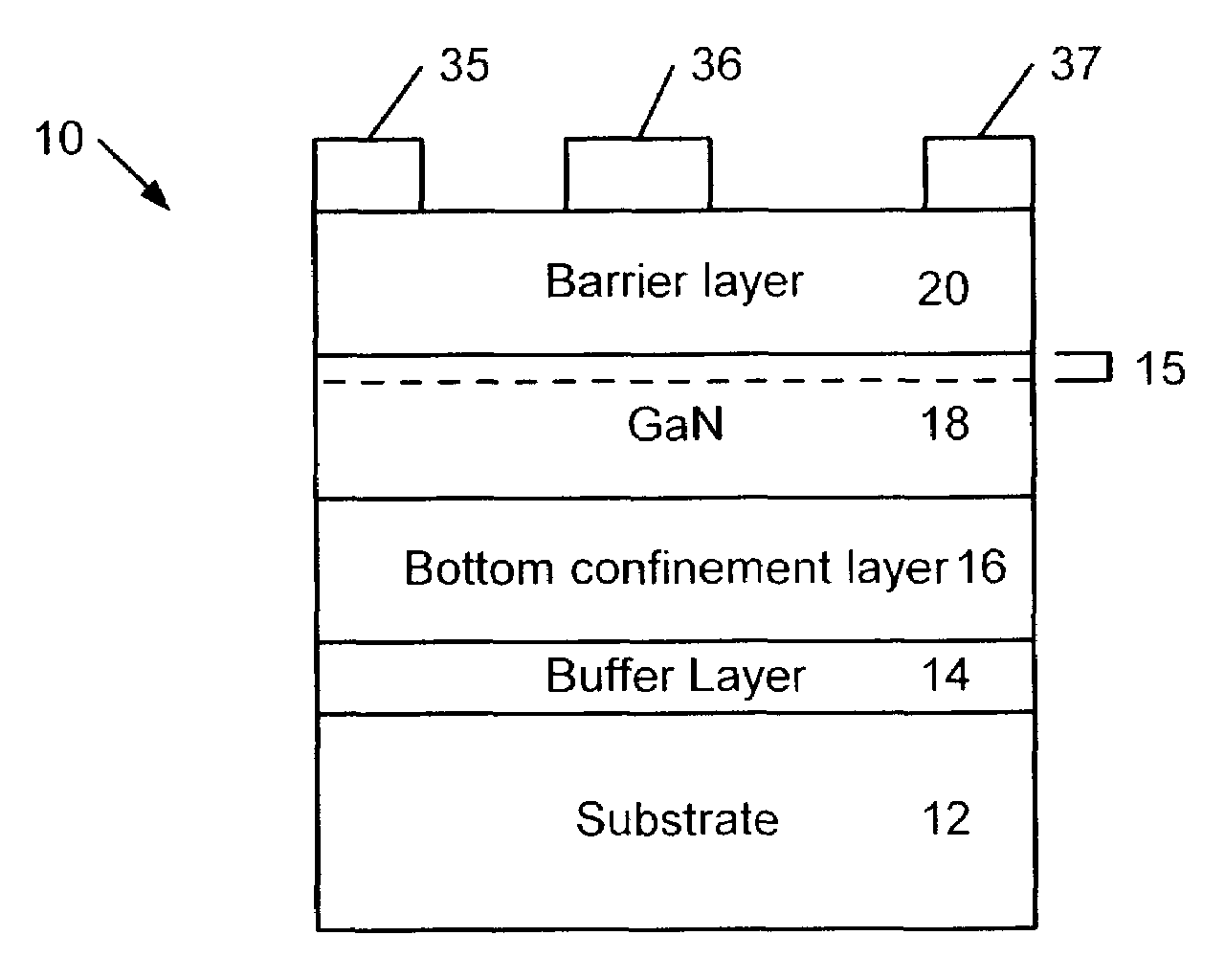

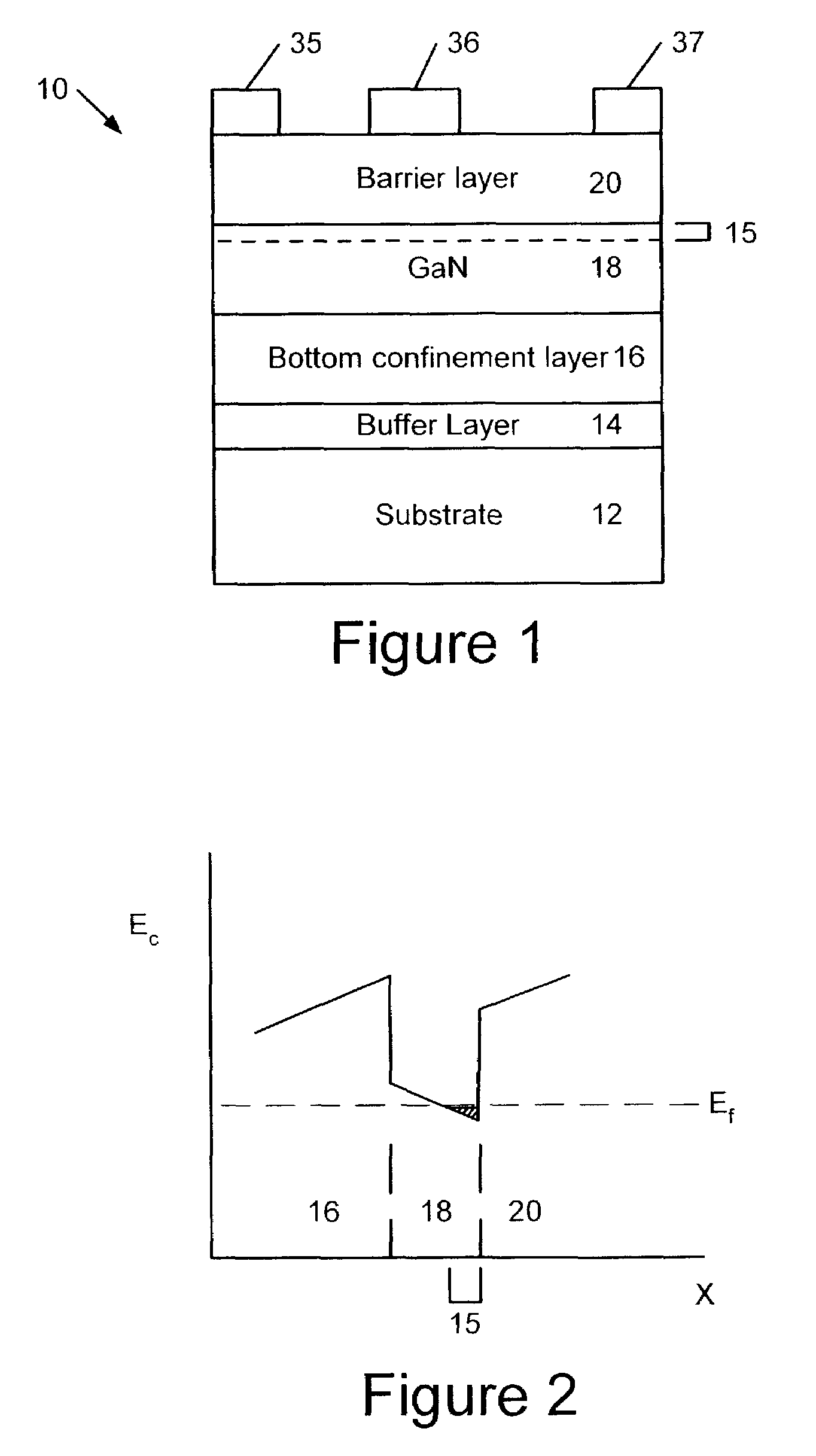

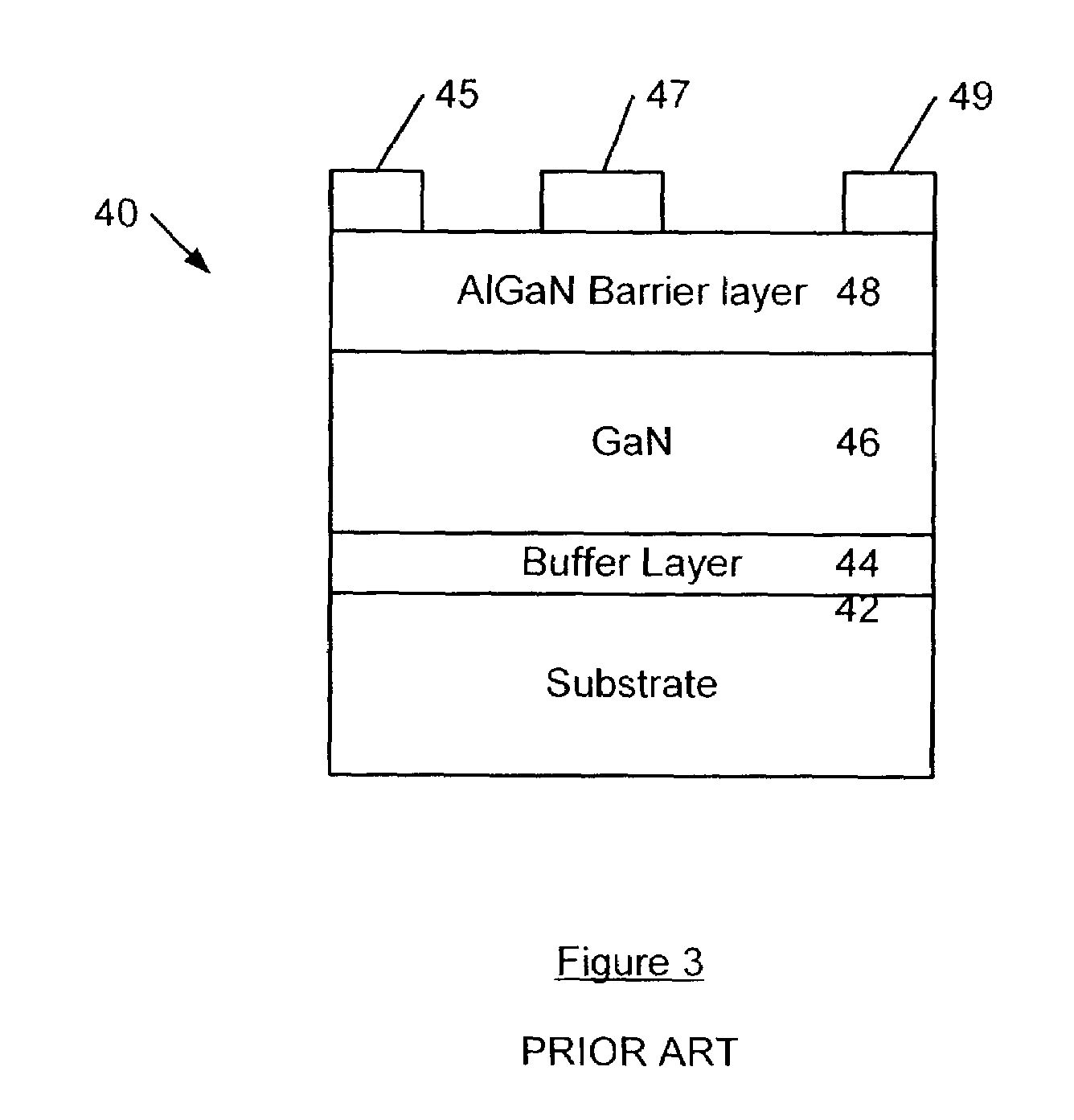

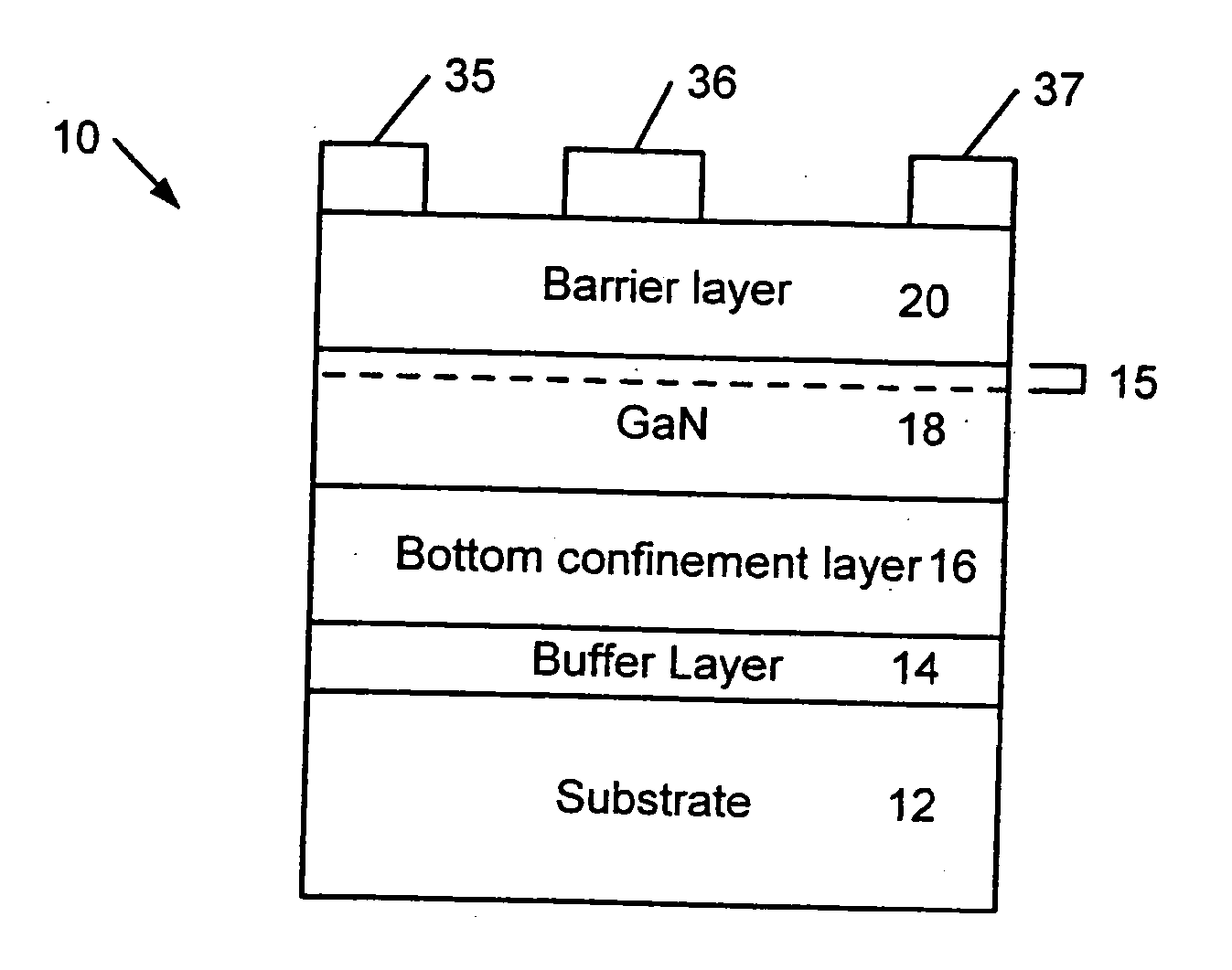

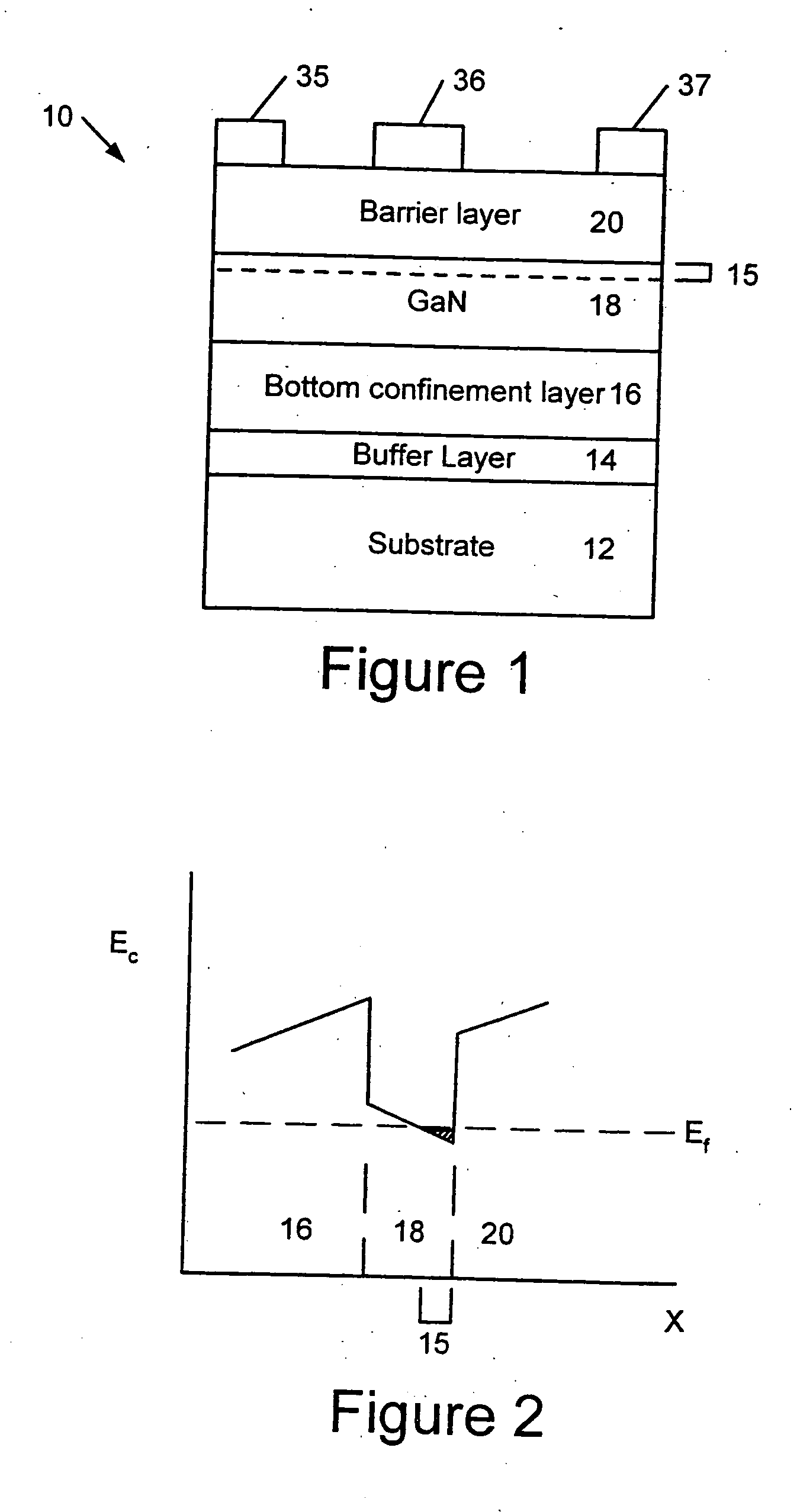

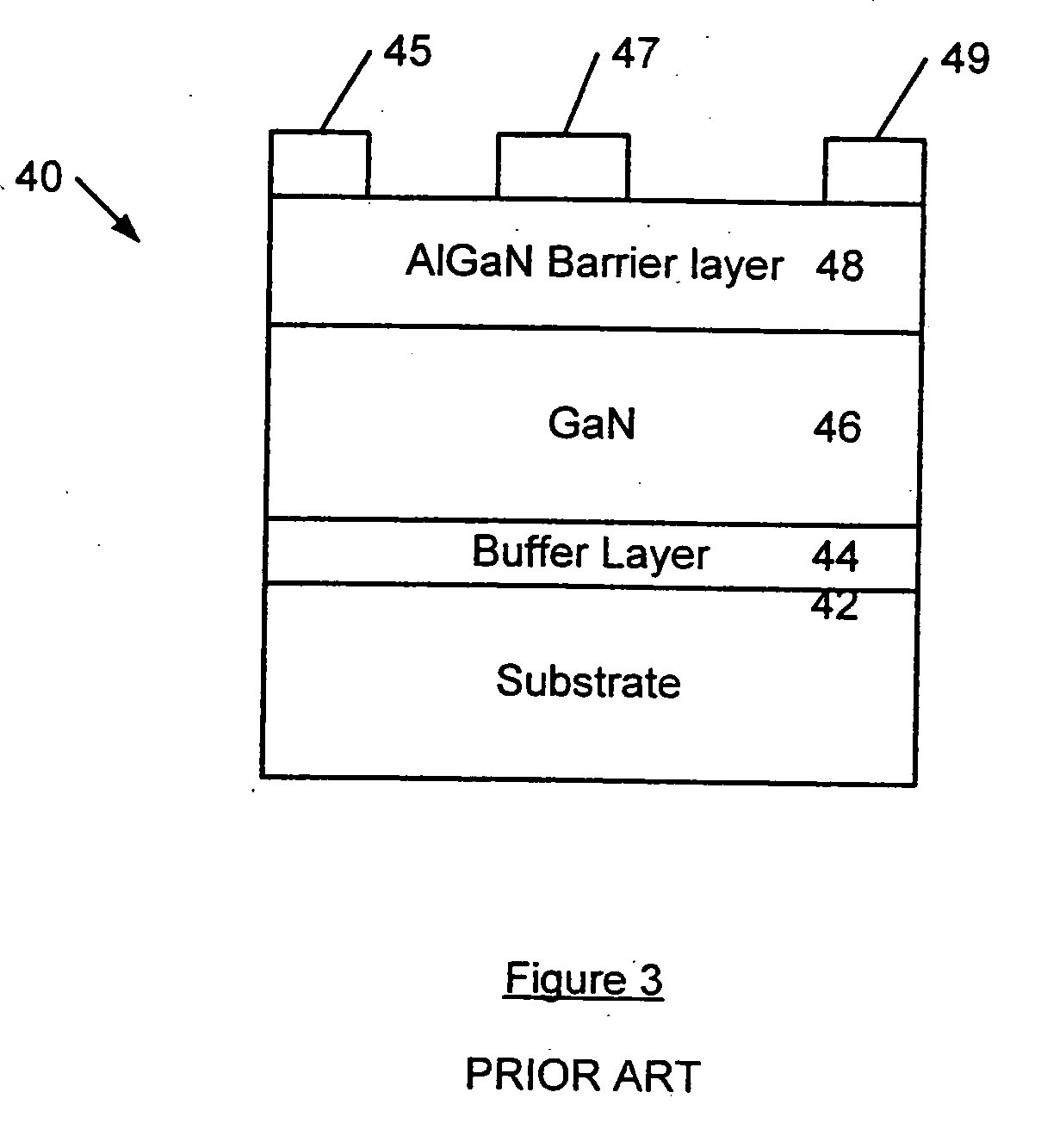

Strain balanced nitride heterojunction transistors

InactiveUS7030428B2Solid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationHeterojunction

A nitride based heterojunction transistor includes a substrate and a first Group III nitride layer, such as an AlGaN based layer, on the substrate. The first Group III-nitride based layer has an associated first strain. A second Group III-nitride based layer, such as a GaN based layer, is on the first Group III-nitride based layer. The second Group III-nitride based layer has a bandgap that is less than a bandgap of the first Group III-nitride based layer and has an associated second strain. The second strain has a magnitude that is greater than a magnitude of the first strain. A third Group III-nitride based layer, such as an AlGaN or AlN layer, is on the GaN layer. The third Group III-nitride based layer has a bandgap that is greater than the bandgap of the second Group III-nitride based layer and has an associated third strain. The third strain is of opposite strain type to the second strain. A source contact, a drain contact and a gate contact may be provided on the third Group III-nitride based layer. Nitride based heterojunction transistors having an AlGaN based bottom confinement layer, a GaN based channel layer on the bottom confinement layer and an AlGaN based barrier layer on the channel layer, the barrier layer having a higher concentration of aluminum than the bottom confinement layer, are also provided. Methods of fabricating such transistor are also provided.

Owner:CREE INC

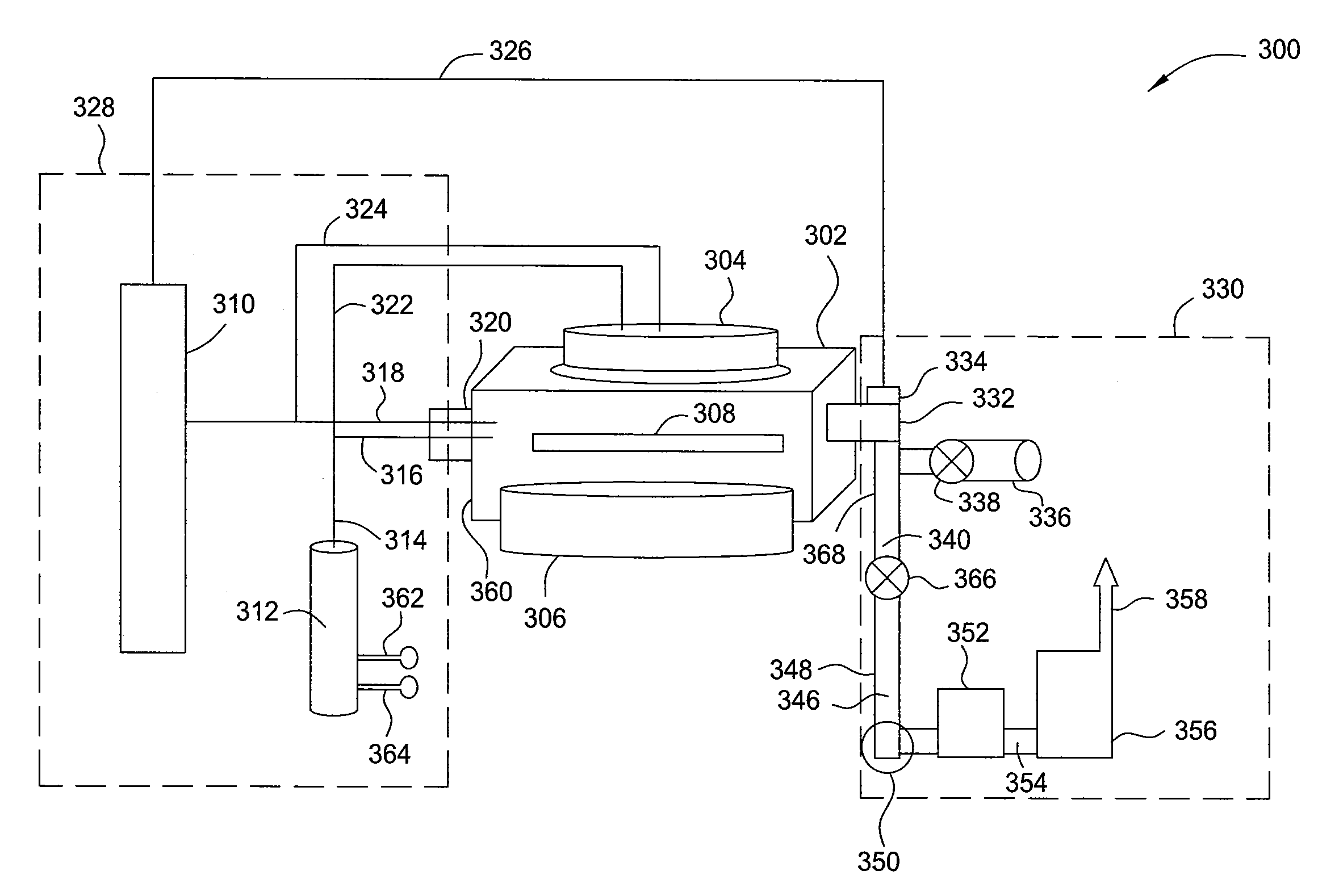

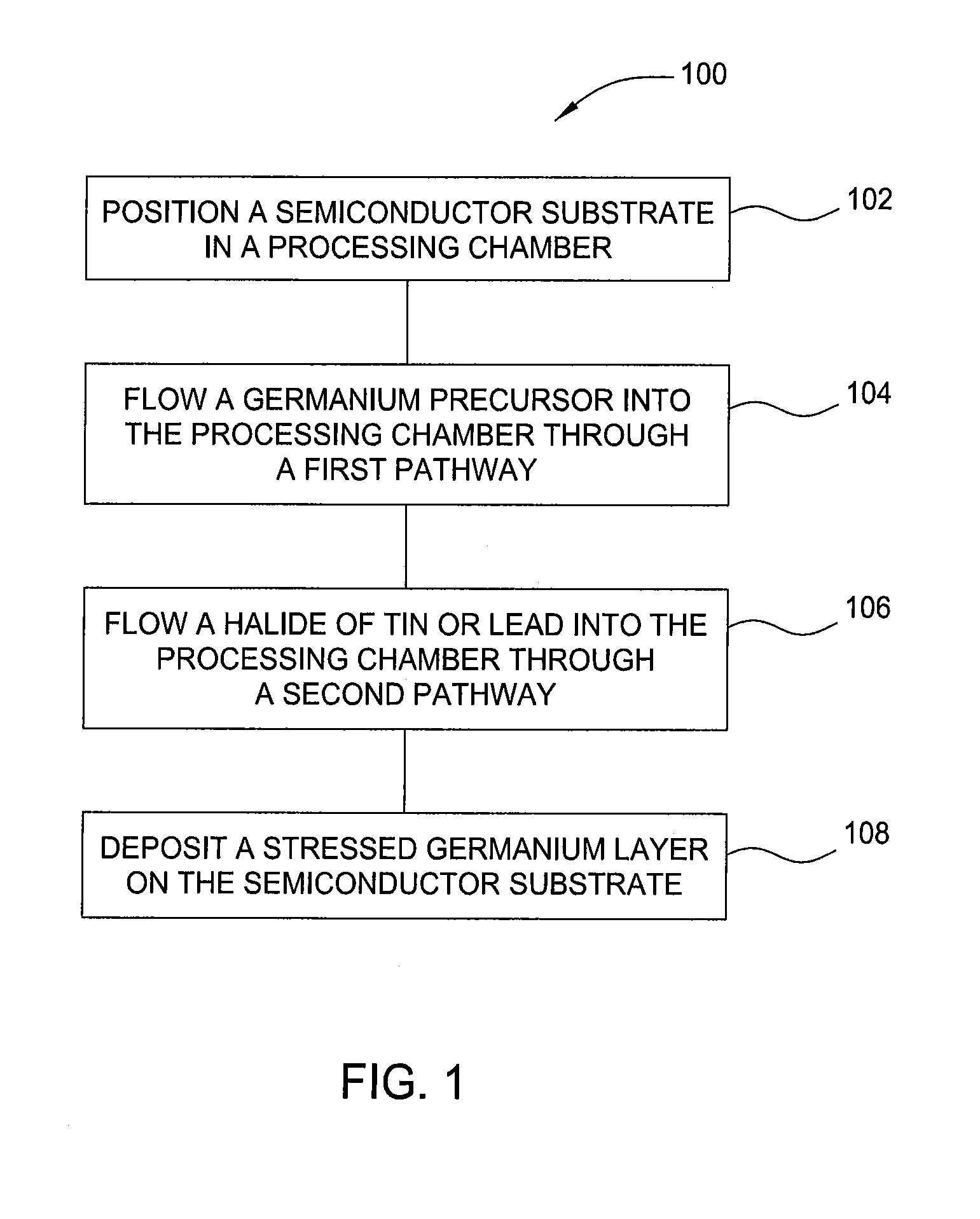

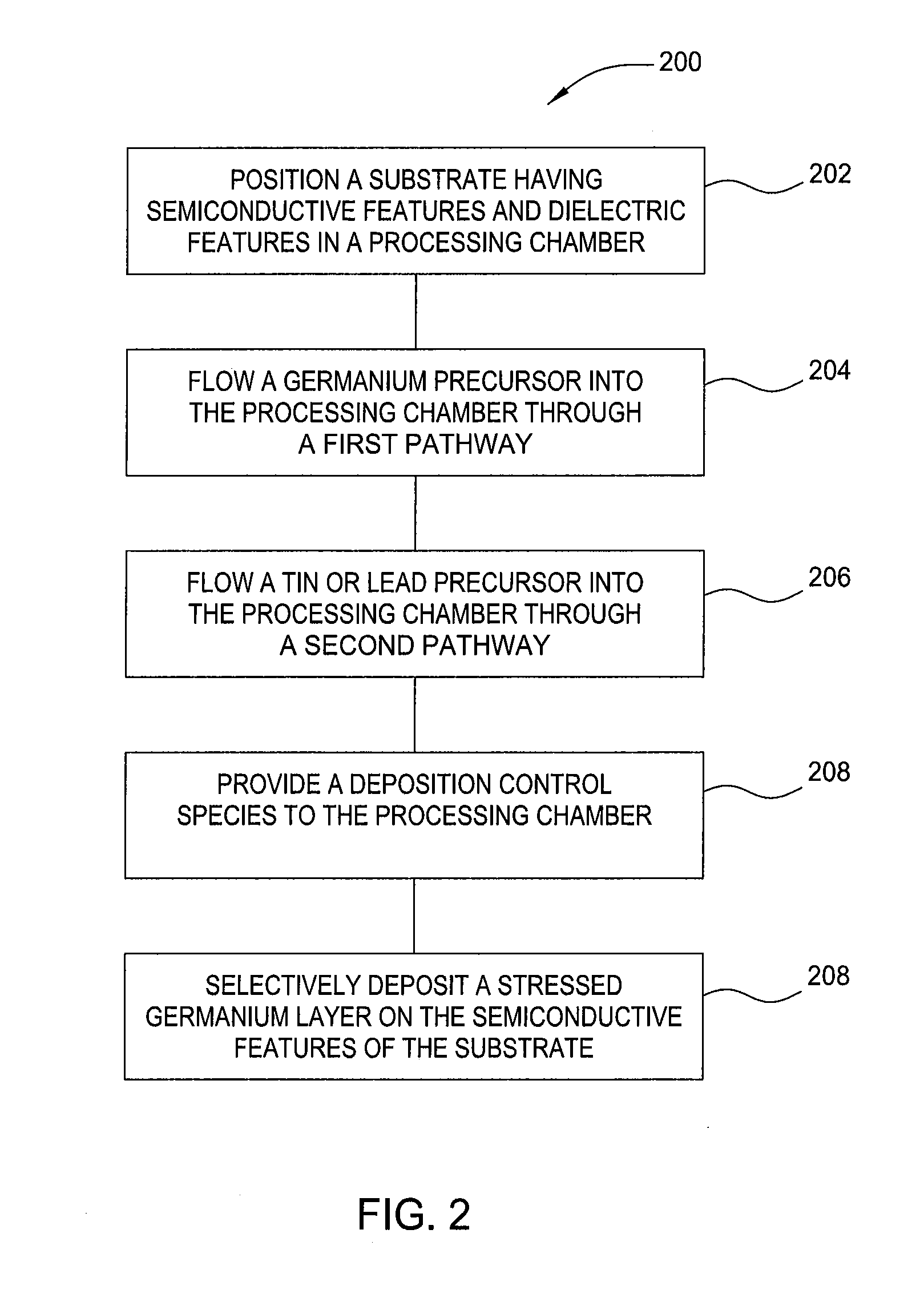

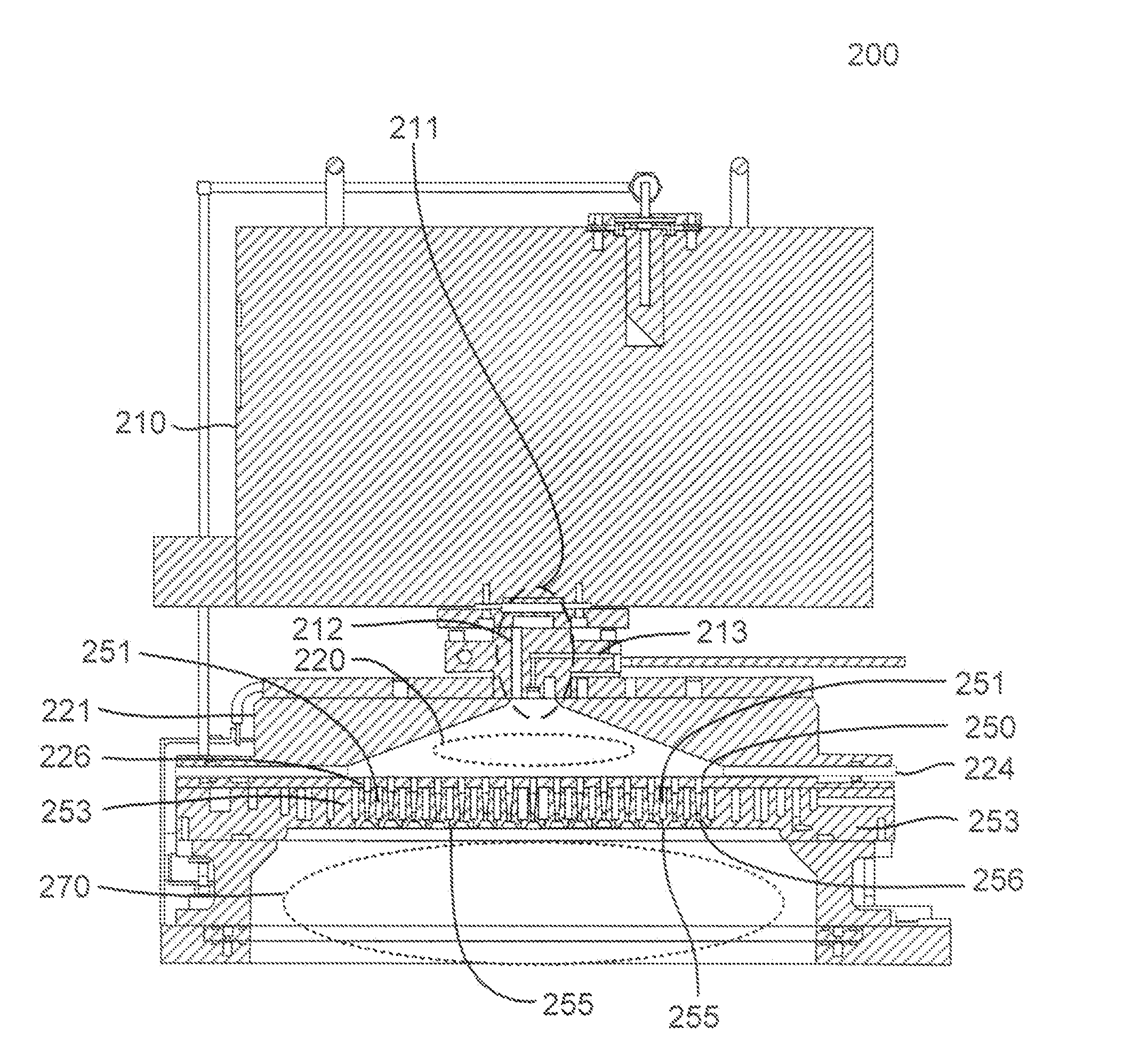

Method and apparatus for the selective deposition of epitaxial germanium stressor alloys

ActiveUS20120247386A1Reduce adhesionPolycrystalline material growthSemiconductor/solid-state device manufacturingHeterojunctionHalogen

A method and apparatus for forming heterojunction stressor layers is described. A germanium precursor and a metal precursor are provided to a chamber, and an epitaxial layer of germanium-metal alloy formed on the substrate. The metal precursor is typically a metal halide, which may be provided by subliming a solid metal halide or by contacting a pure metal with a halogen gas. The precursors may be provided through a showerhead or through a side entry point, and an exhaust system coupled to the chamber may be separately heated to manage condensation of exhaust components.

Owner:APPLIED MATERIALS INC

Dry-etch for silicon-and-nitrogen-containing films

ActiveUS20130130507A1Reduces and substantially eliminates numberMaterial removalElectric discharge tubesSemiconductor/solid-state device manufacturingHeterojunctionRemote plasma

A method of etching exposed silicon-and-nitrogen-containing material on patterned heterogeneous structures is described and includes a remote plasma etch formed from a fluorine-containing precursor and an oxygen-containing precursor. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents react with the exposed regions of silicon-and-nitrogen-containing material. The plasmas effluents react with the patterned heterogeneous structures to selectively remove silicon-and-nitrogen-containing material from the exposed silicon-and-nitrogen-containing material regions while very slowly removing other exposed materials. The silicon-and-nitrogen-containing material selectivity results partly from the presence of an ion suppression element positioned between the remote plasma and the substrate processing region. The ion suppression element reduces or substantially eliminates the number of ionically-charged species that reach the substrate. The methods may be used to selectively remove silicon-and-nitrogen-containing material at more than twenty times the rate of silicon oxide.

Owner:APPLIED MATERIALS INC

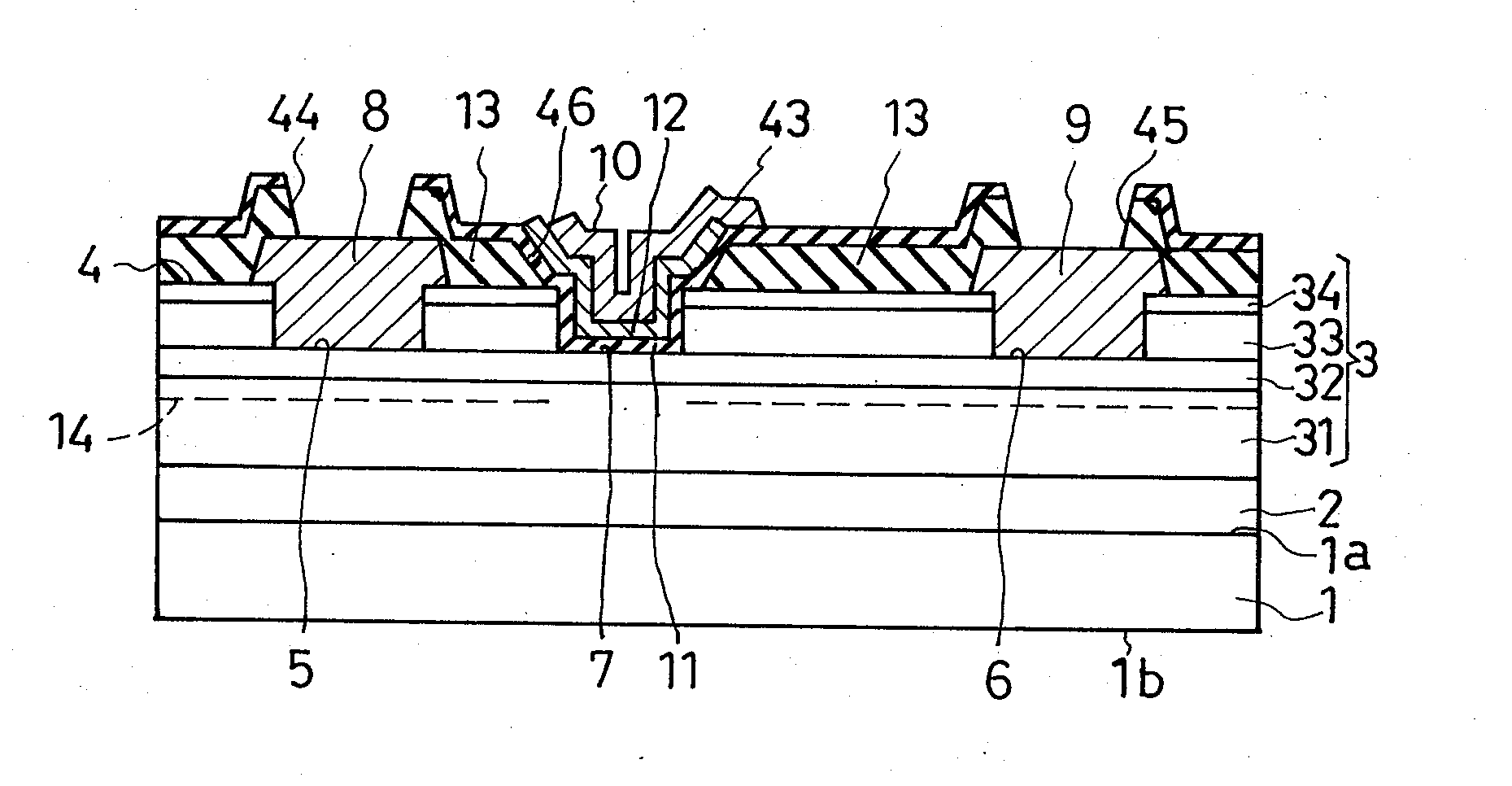

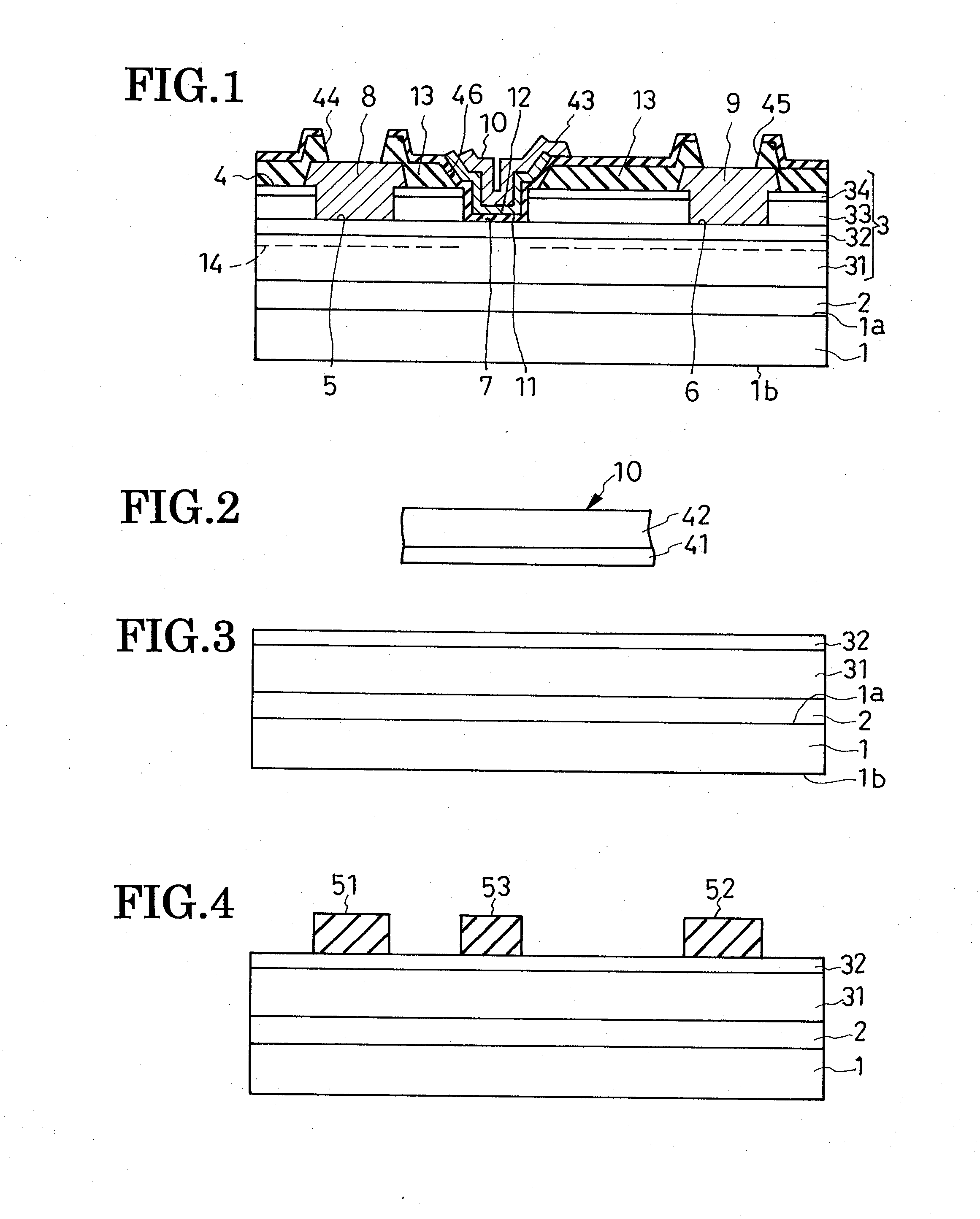

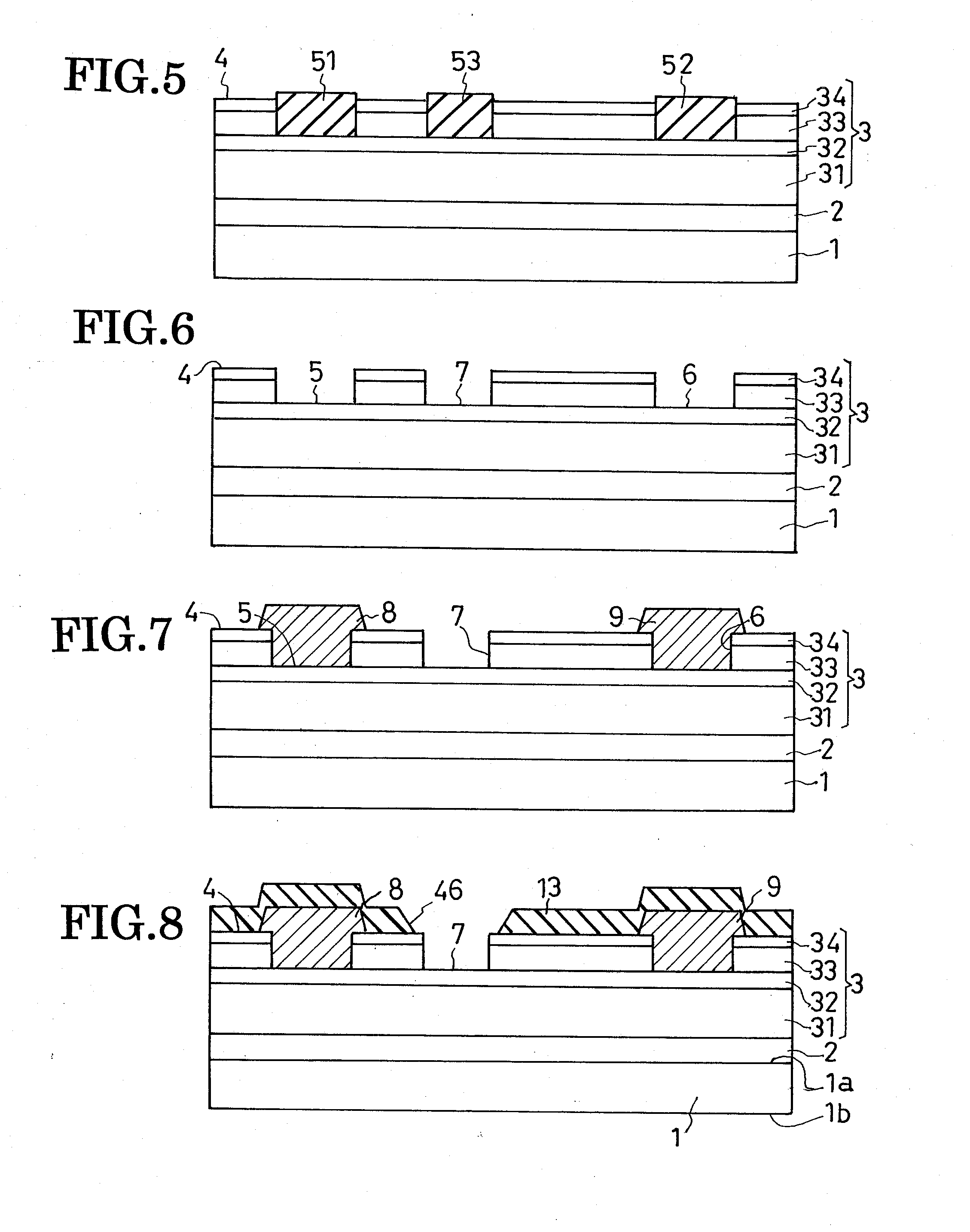

Solar cell

InactiveUS20070169808A1Low costEasy to usePhotovoltaic energy generationSemiconductor devicesHeterojunctionManufacturing technology

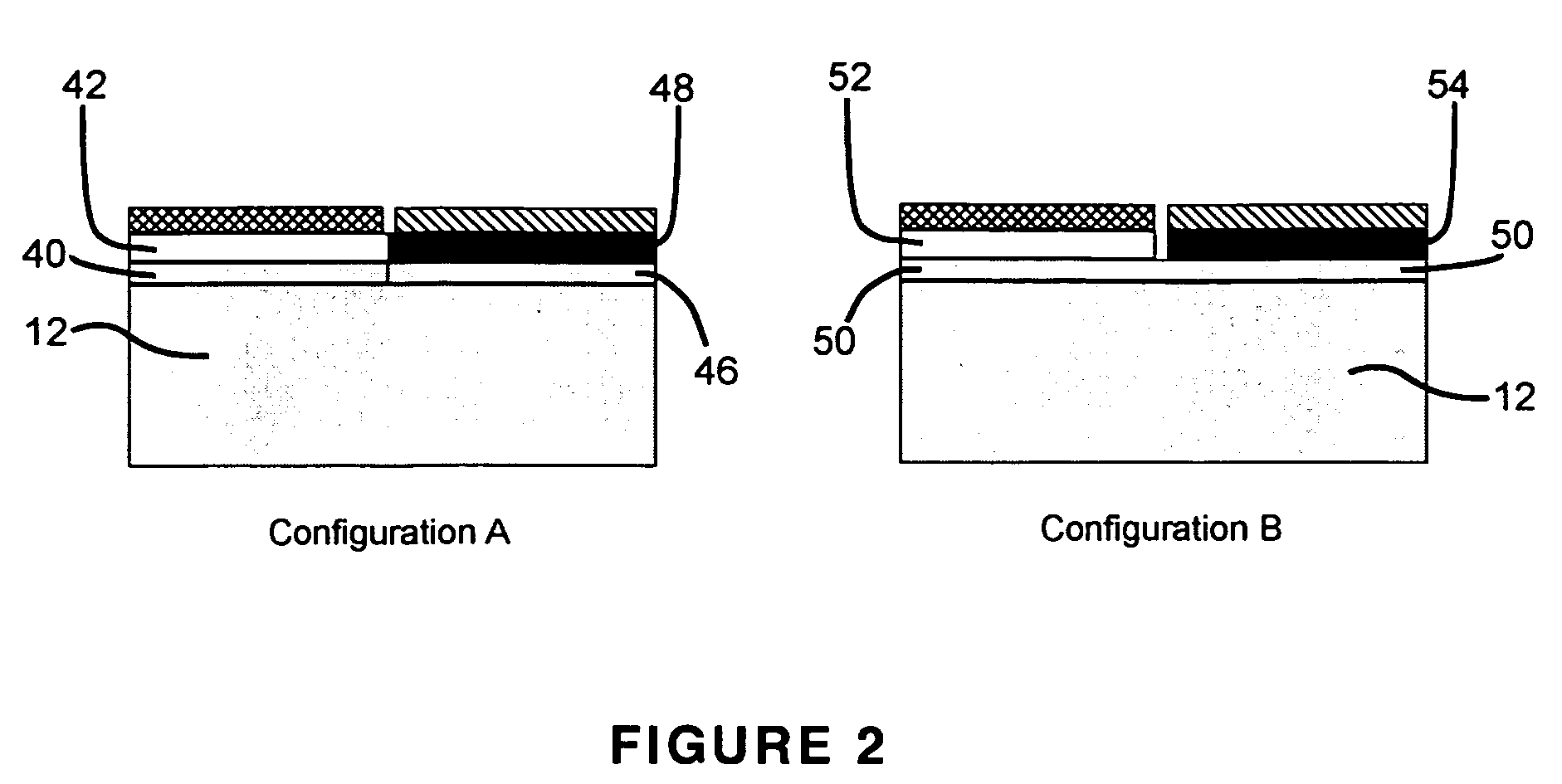

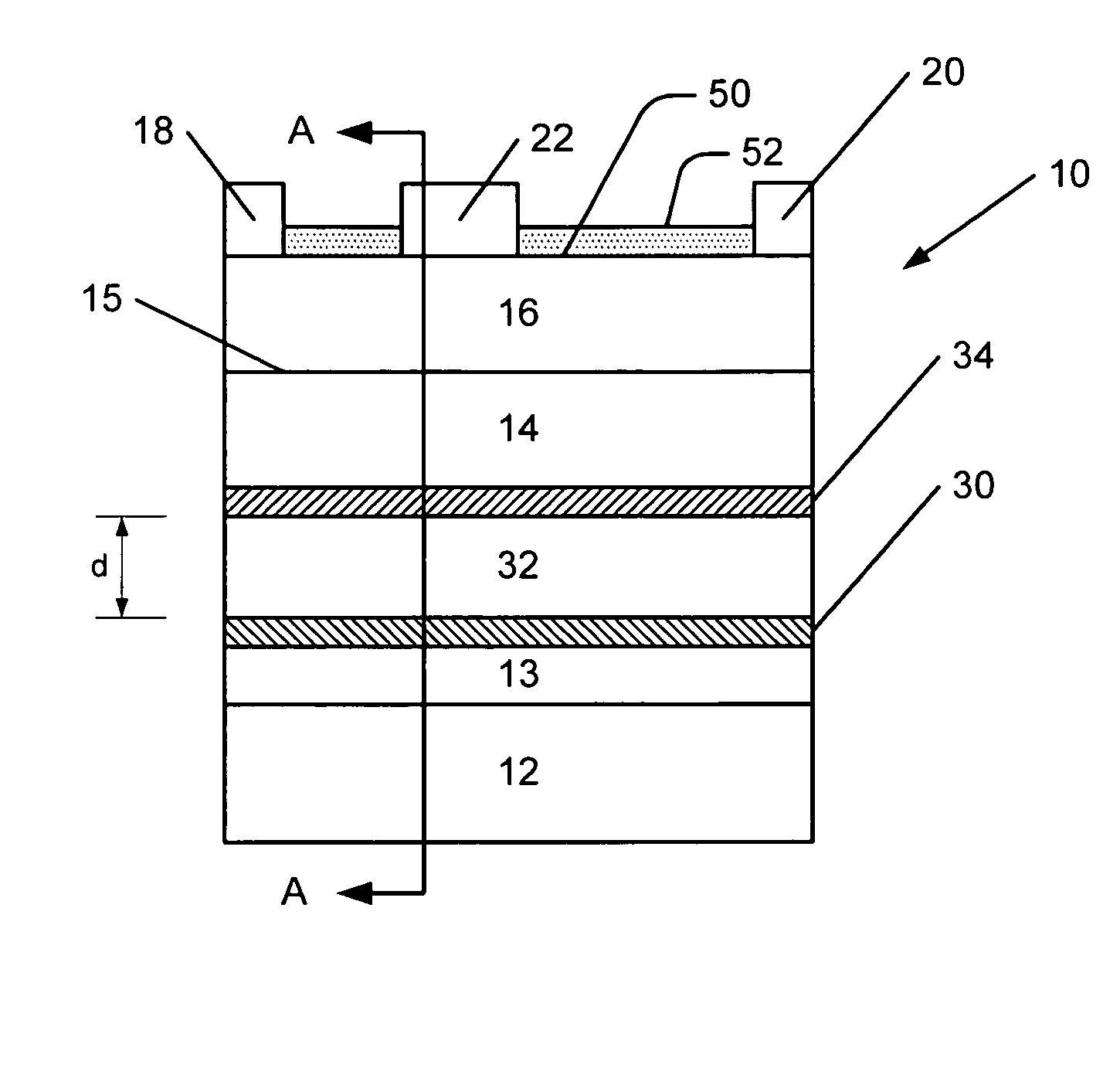

The present invention provides a thin film amorphous silicon-crystalline silicon back heterojunction and back surface field device configuration for a heterojunction solar cell. The configuration is attained by the formation of heterojunctions on the back surface of crystalline silicon at low temperatures. Low temperature fabrication allows for the application of low resolution lithography and / or shadow masking processes to produce the structures. The heterojunctions and interface passivation can be formed through a variety of material compositions and deposition processes, including appropriate surface restructing techniques. The configuration achieves separation of optimization requirements for light absorption and carrier generation at the front surface on which the light is incident, and in the bulk, and charge carrier collection at the back of the device. The shadowing losses are eliminated by positioning the electrical contacts at the back thereby removing them from the path of the incident light. Back contacts need optimization only for maximum charge carrier collection without bothering about shading losses. A range of elements / alloys may be used to effect band-bending. All of the above features result in a very high efficiency solar cell. The open circuit voltage of the back heterojunction device is higher than that of an all-crystalline device. The solar cell configurations are equally amenable to crystalline silicon wafer absorber as well as thin silicon layers formed by using a variety of fabrication processes. The configurations can be used for radiovoltaic and electron-voltaic energy conversion devices.

Owner:KHERANI NAZIR P +1

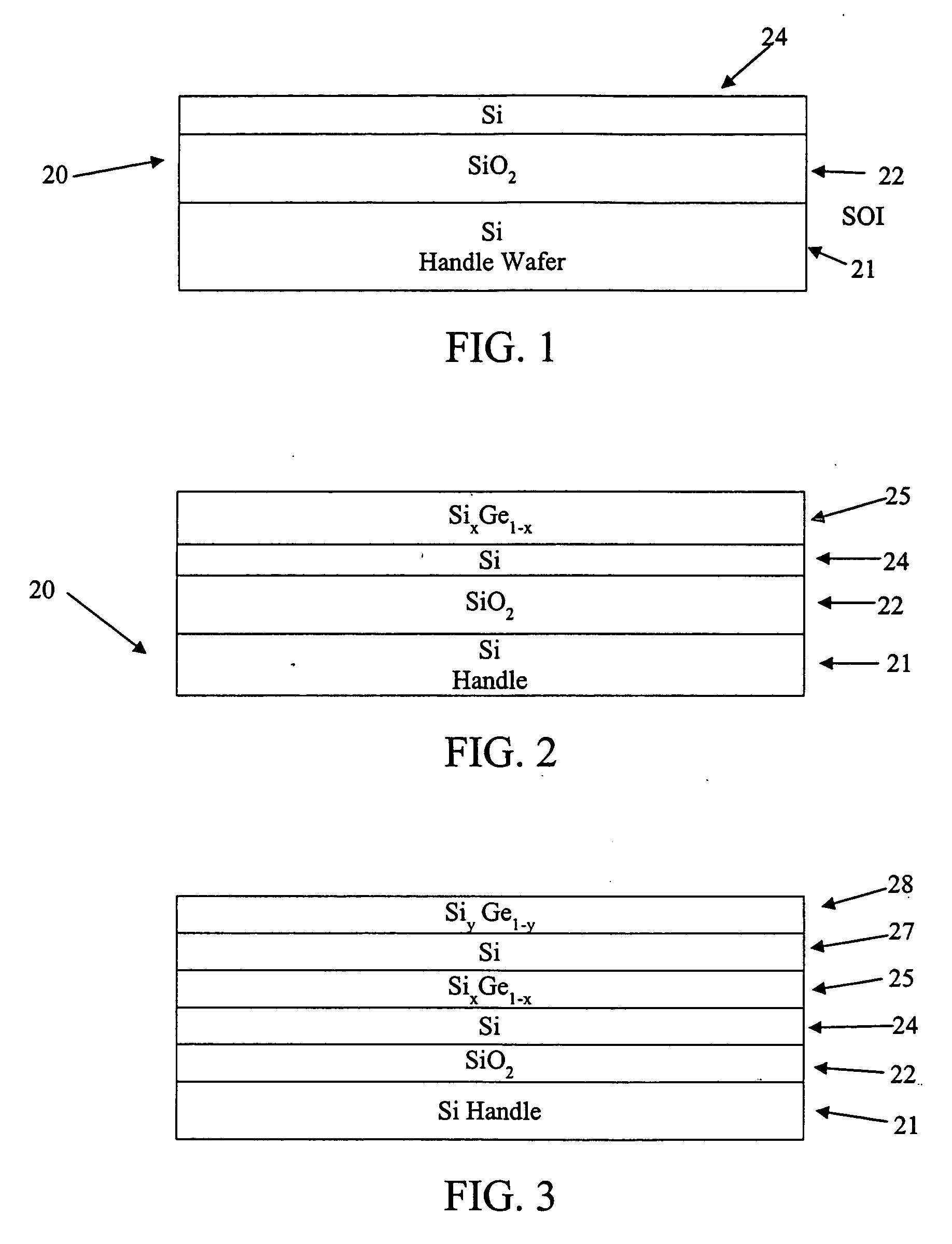

Nitride heterojunction transistors having charge-transfer induced energy barriers and methods of fabricating the same

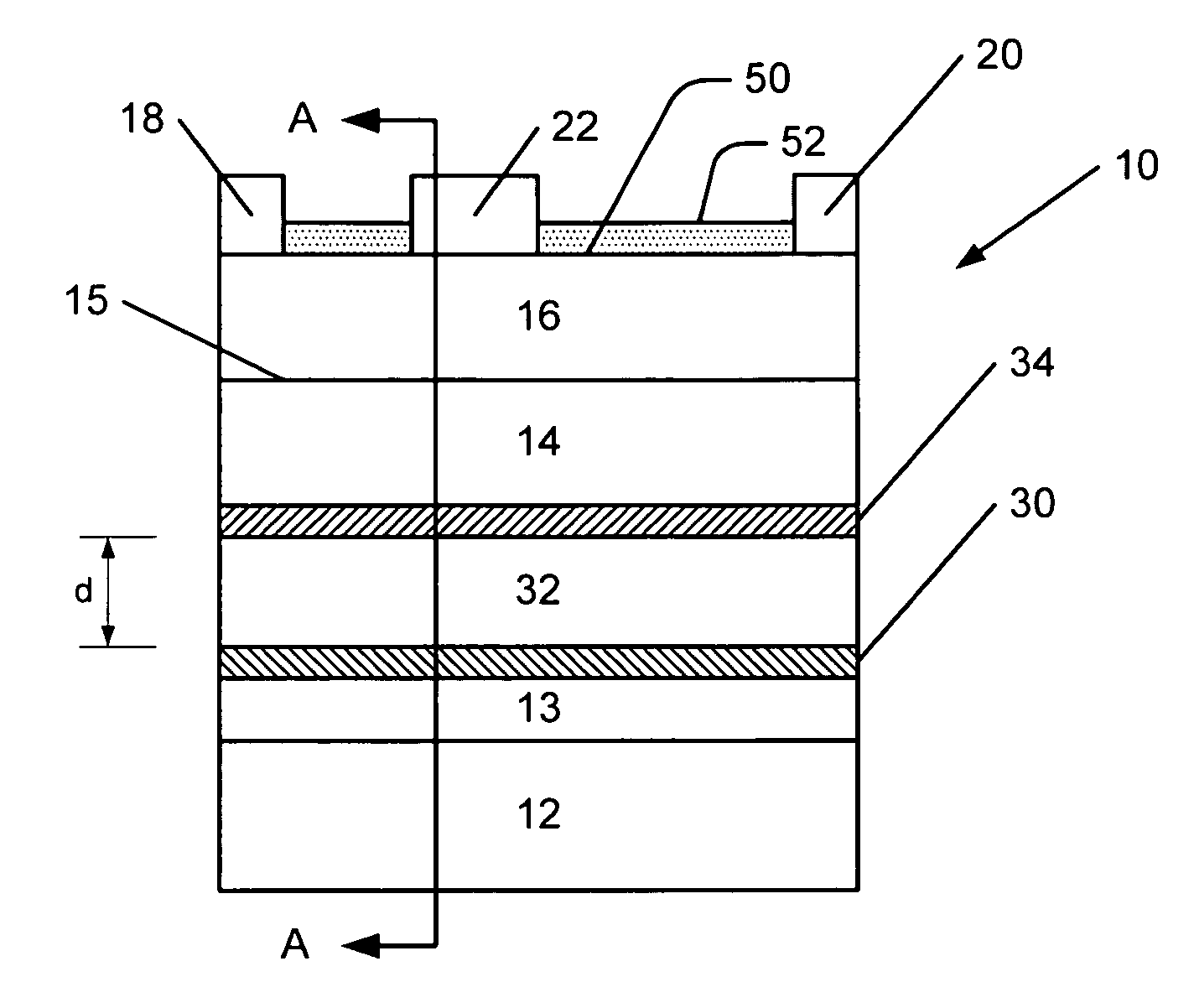

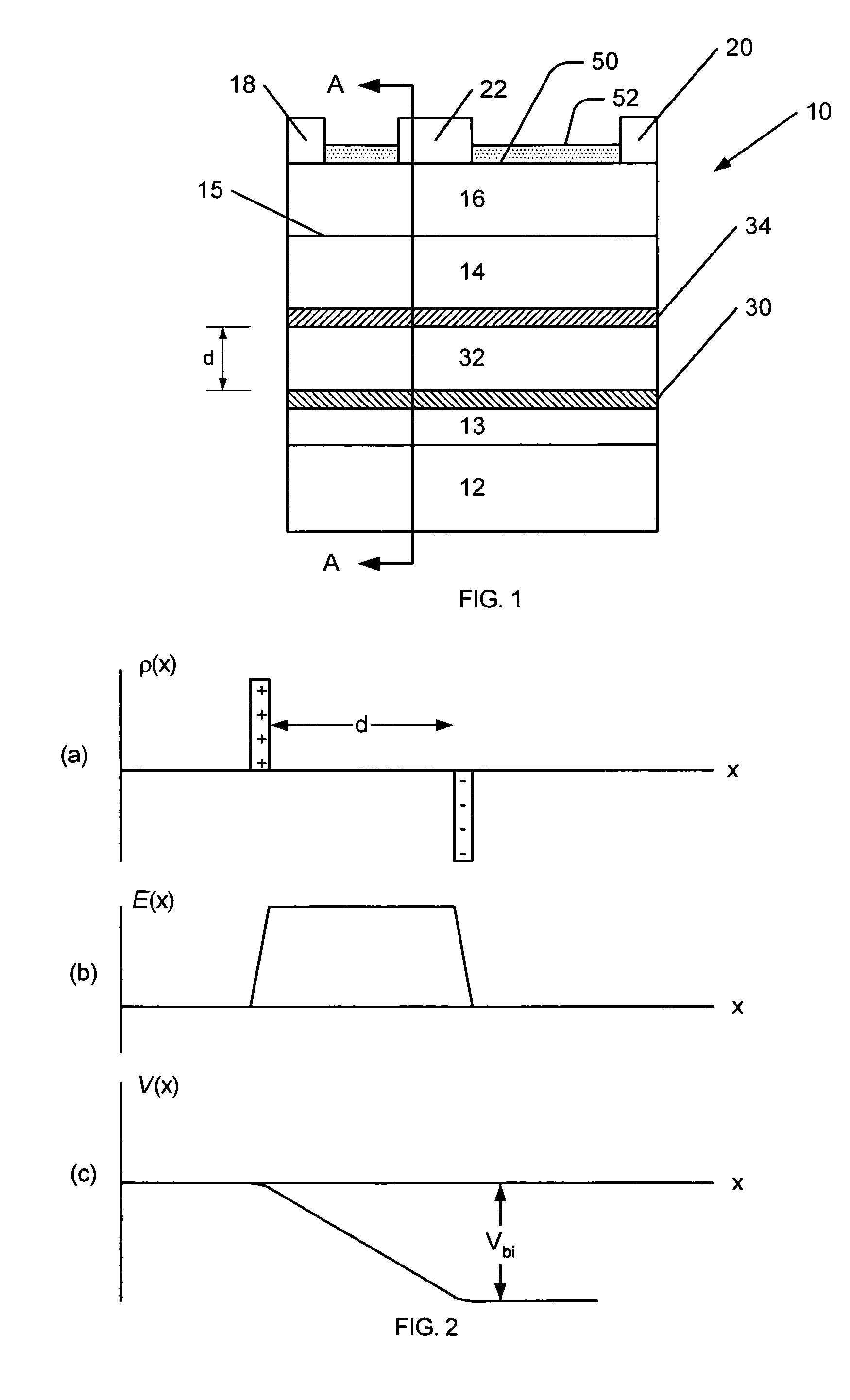

ActiveUS20050173728A1Affect performanceTransistorSemiconductor/solid-state device manufacturingHeterojunctionElectron source

A nitride-based field effect transistor includes a substrate, a channel layer comprising InAlGaN formed on the substrate, source and drain ohmic contacts in electrical communication with the channel layer, and a gate contact formed on the channel layer. At least one energy barrier opposes movement of carriers away from the channel layer. The energy barrier may comprise an electron source layer in proximity with a hole source layer which generate an associated electric field directed away from the channel. An energy barrier according to some embodiments may provide a built-in potential barrier in excess of about 0.5 eV. Method embodiments are also disclosed.

Owner:CREE INC

Thin-film solar cell fabricated on a flexible metallic substrate

A thin-film solar cell (10) is provided. The thin-film solar cell (10) comprises a flexible metallic substrate (12) having a first surface and a second surface. A back metal contact layer (16) is deposited on the first surface of the flexible metallic substrate (12). A semiconductor absorber layer (14) is deposited on the back metal contact. A photoactive film deposited on the semiconductor absorber layer (14) forms a heterojunction structure and a grid contact (24) deposited on the heterjunction structure. The flexible metal substrate (12) can be constructed of either aluminium or stainless steel. Furthermore, a method of constructing a solar cell is provided. The method comprises providing an aluminum substrate (12), depositing a semiconductor absorber layer (14) on the aluminum substrate (12), and insulating the aluminum substrate (12) from the semiconductor absorber layer (14) to inhibit reaction between the aluminum substrate (12) and the semiconductor absorber layer (14).

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

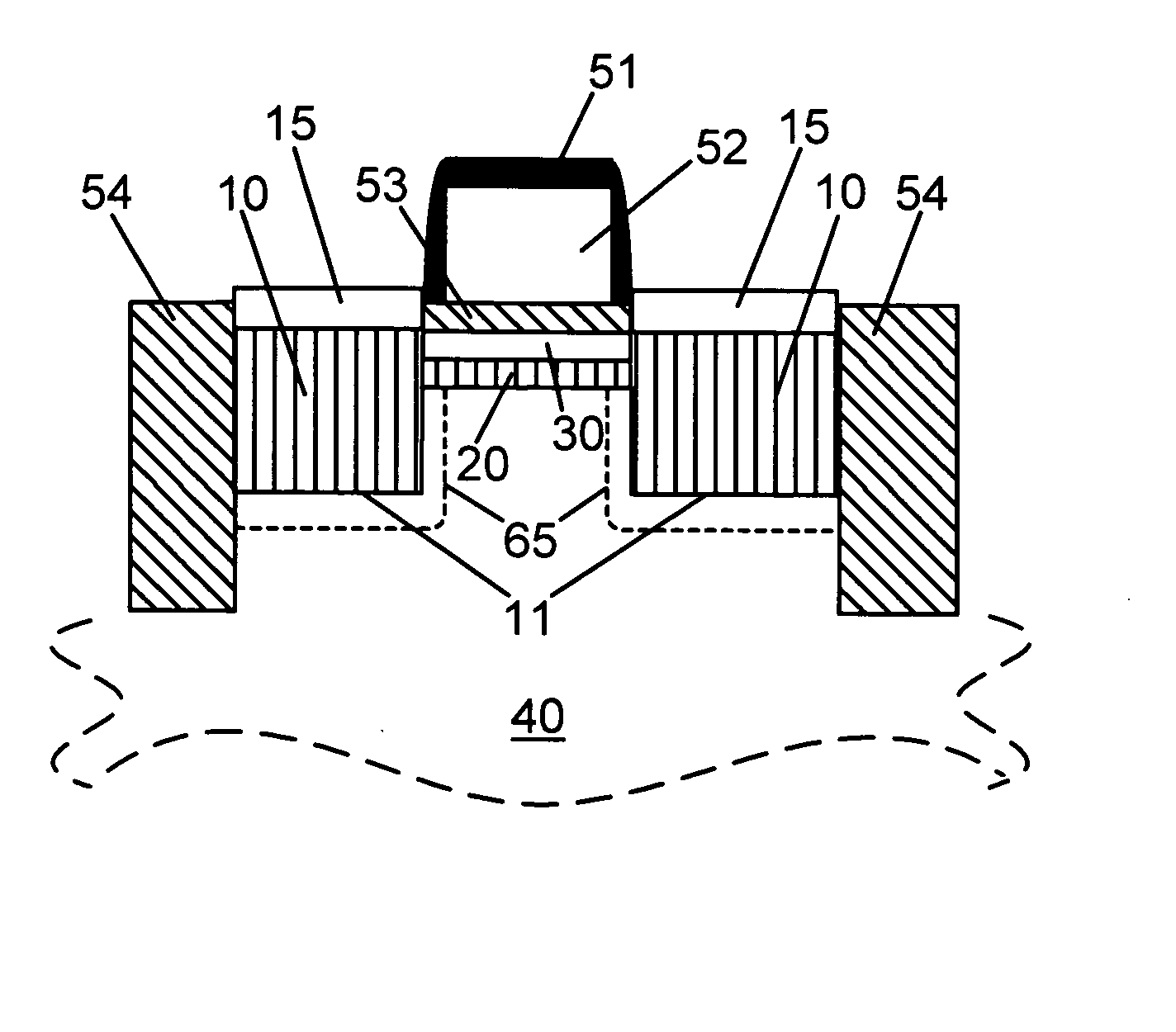

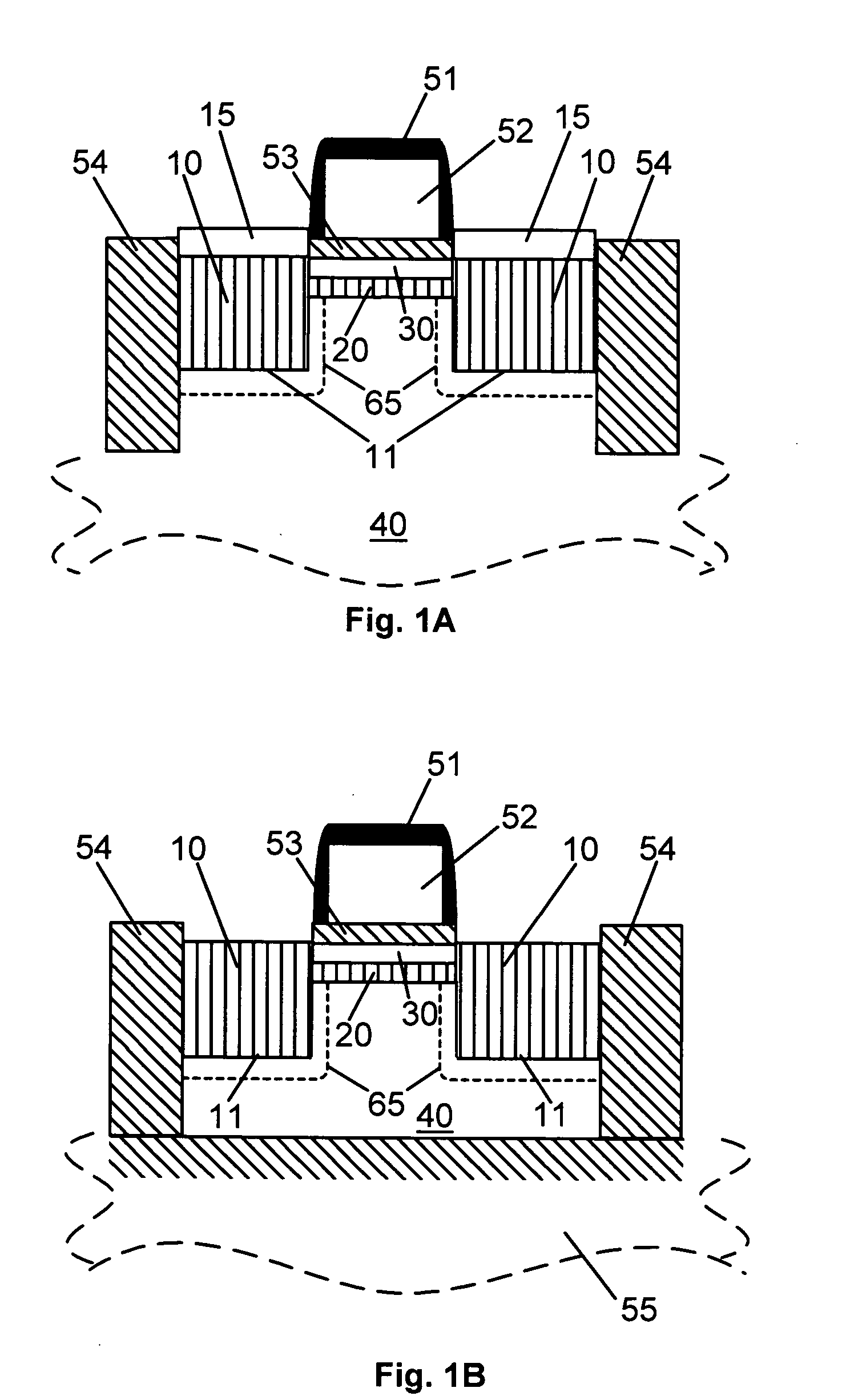

High mobility heterojunction complementary field effect transistors and methods thereof

InactiveUS7057216B2High hole mobilitySimilar current carrying capabilityTransistorSolid-state devicesHeterojunctionPresent day

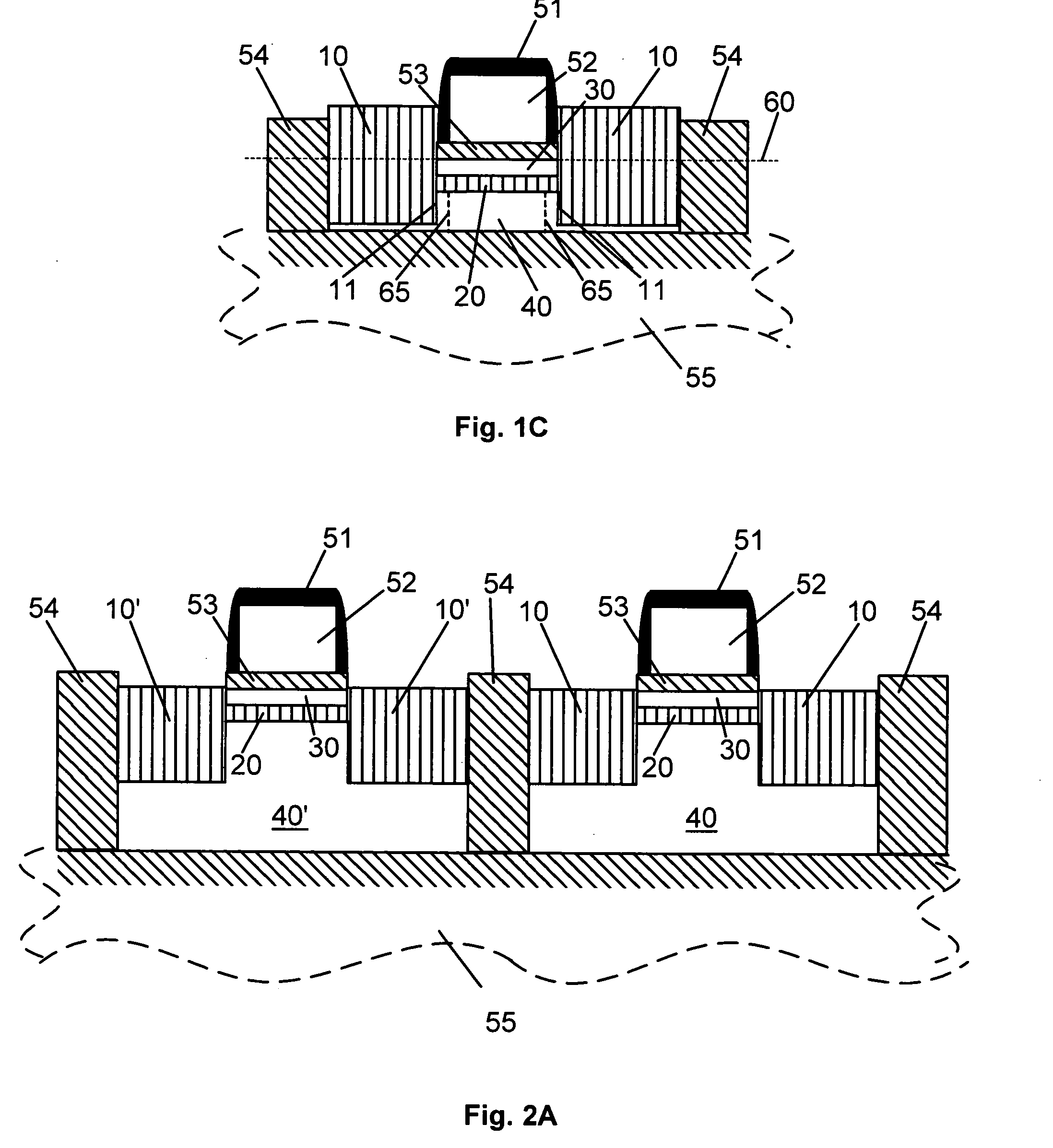

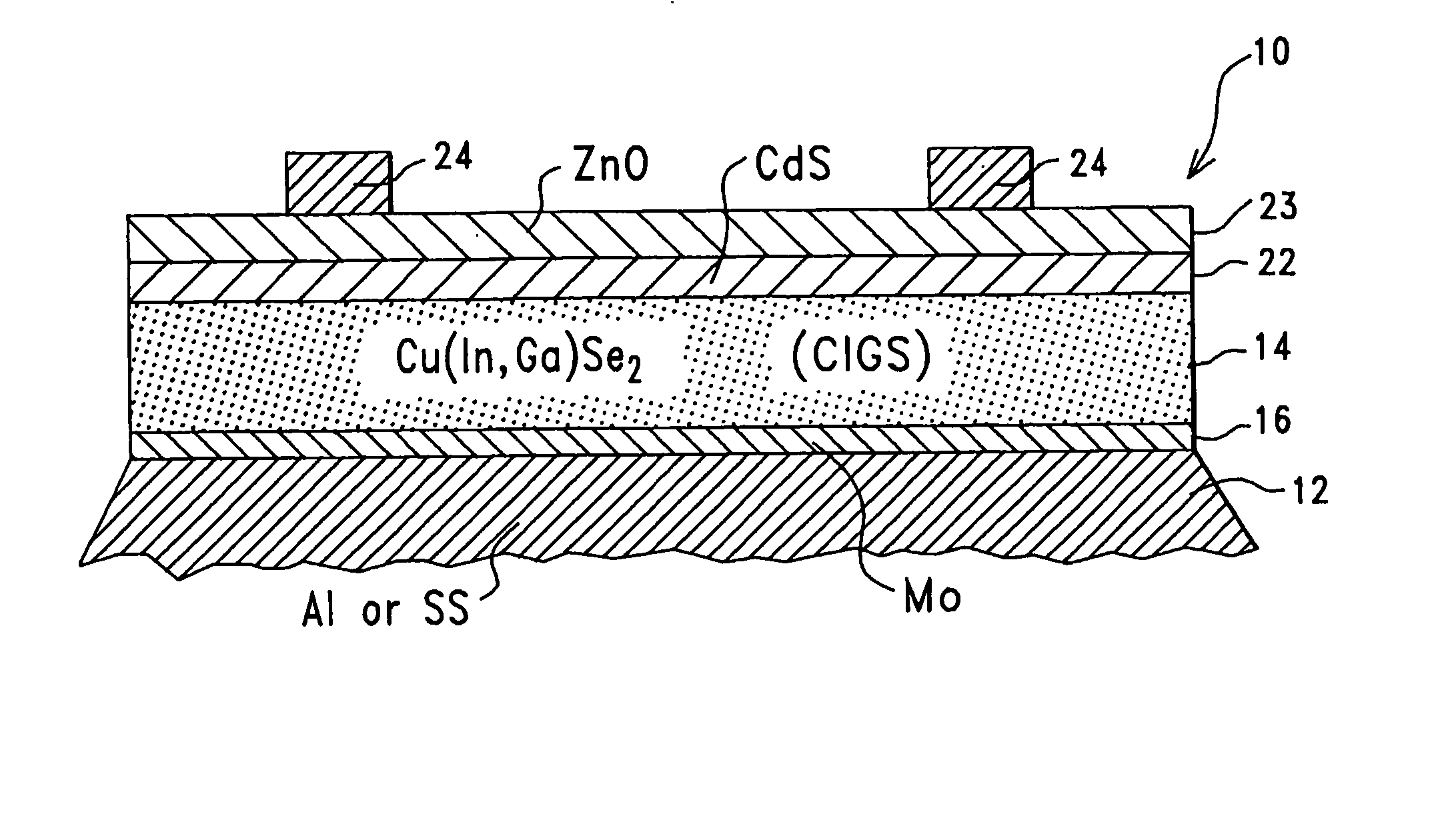

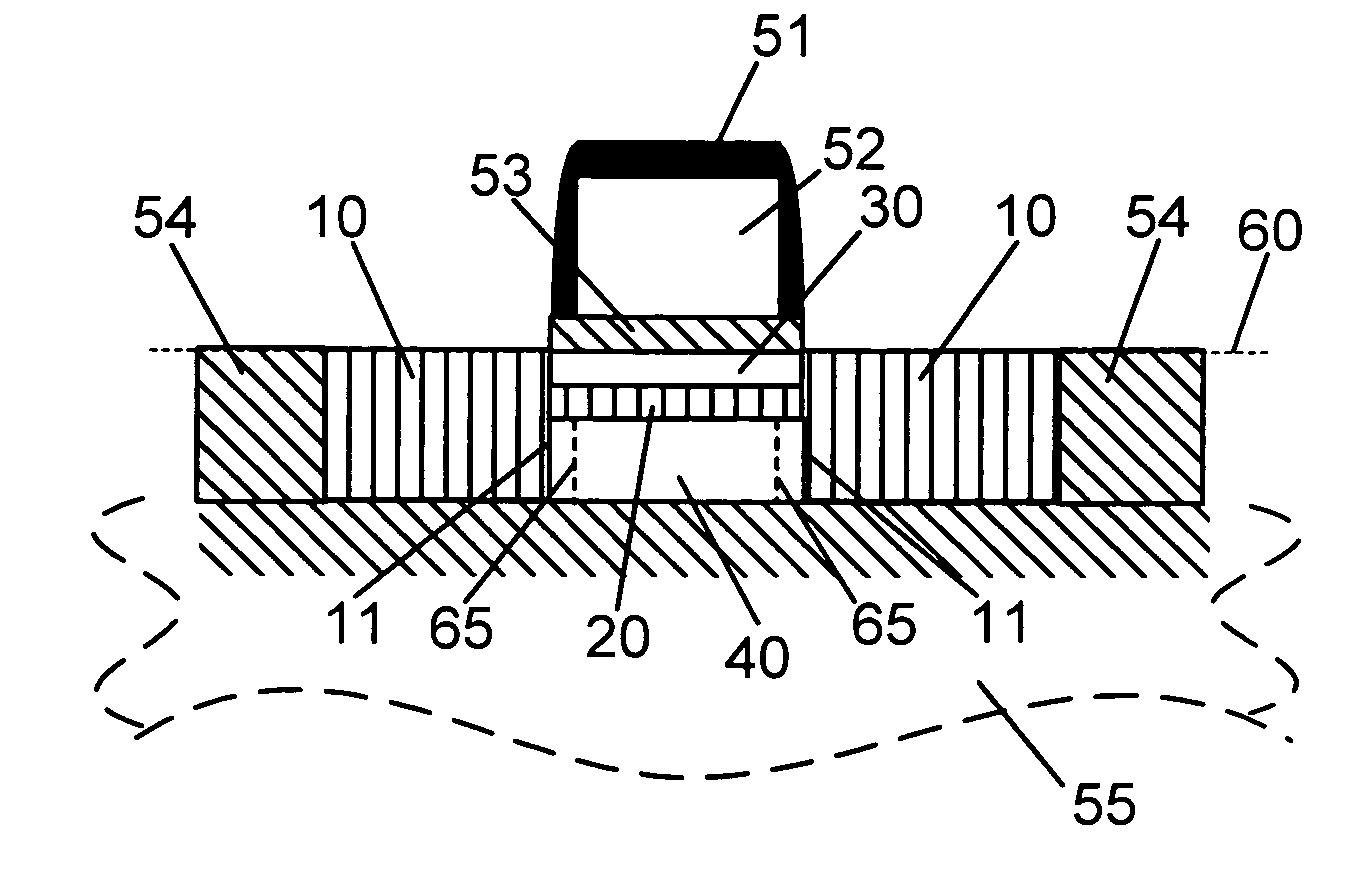

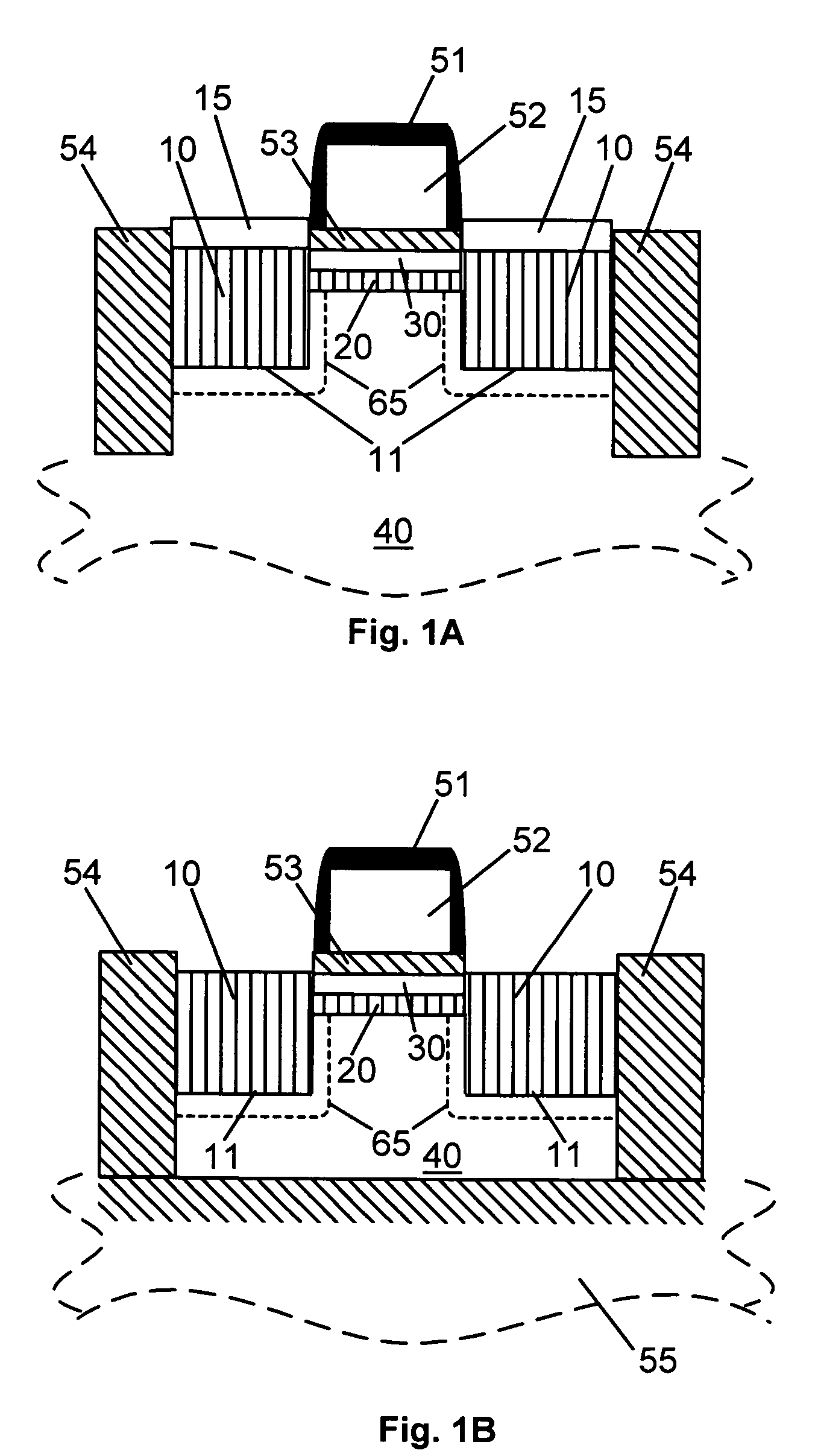

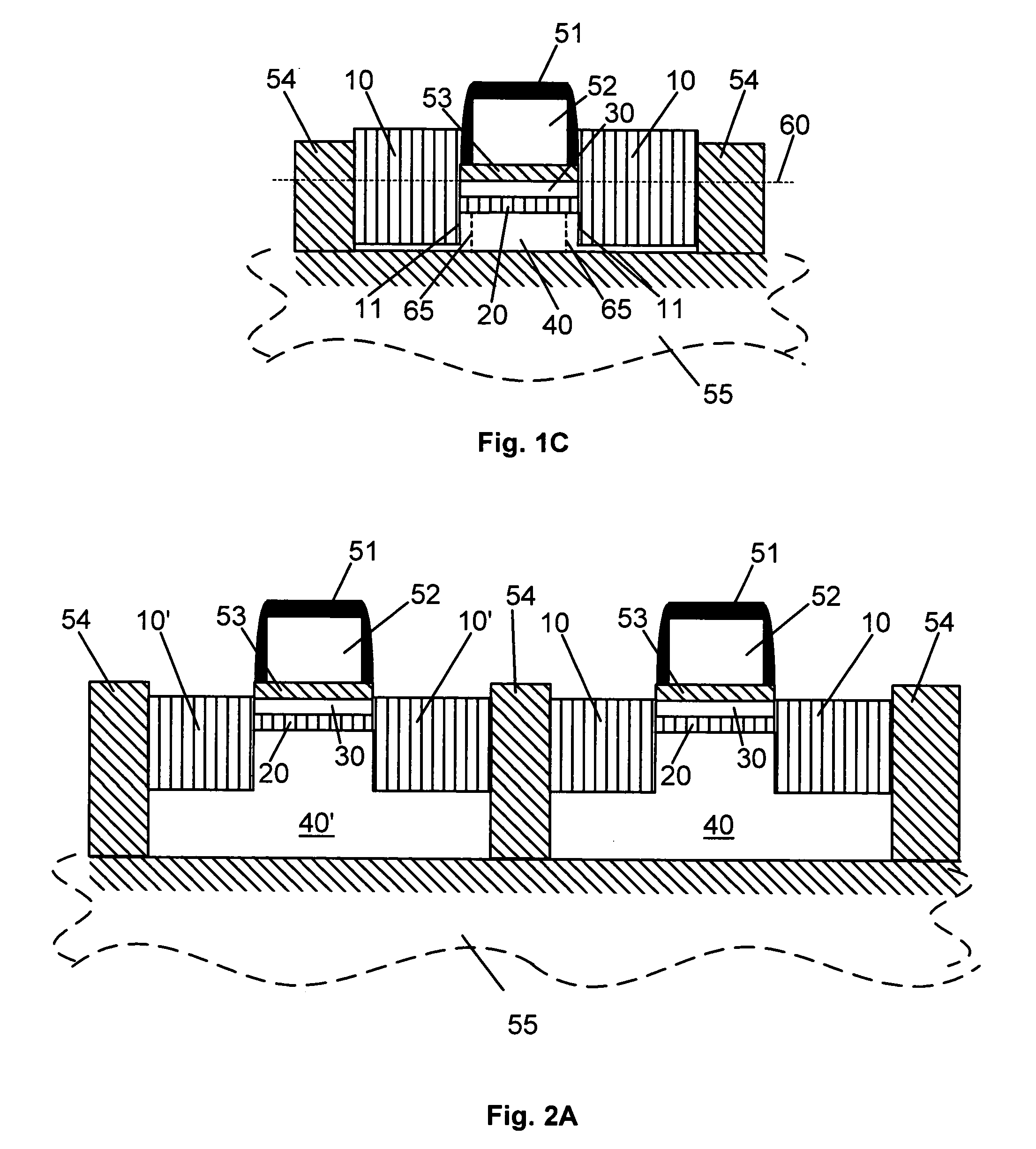

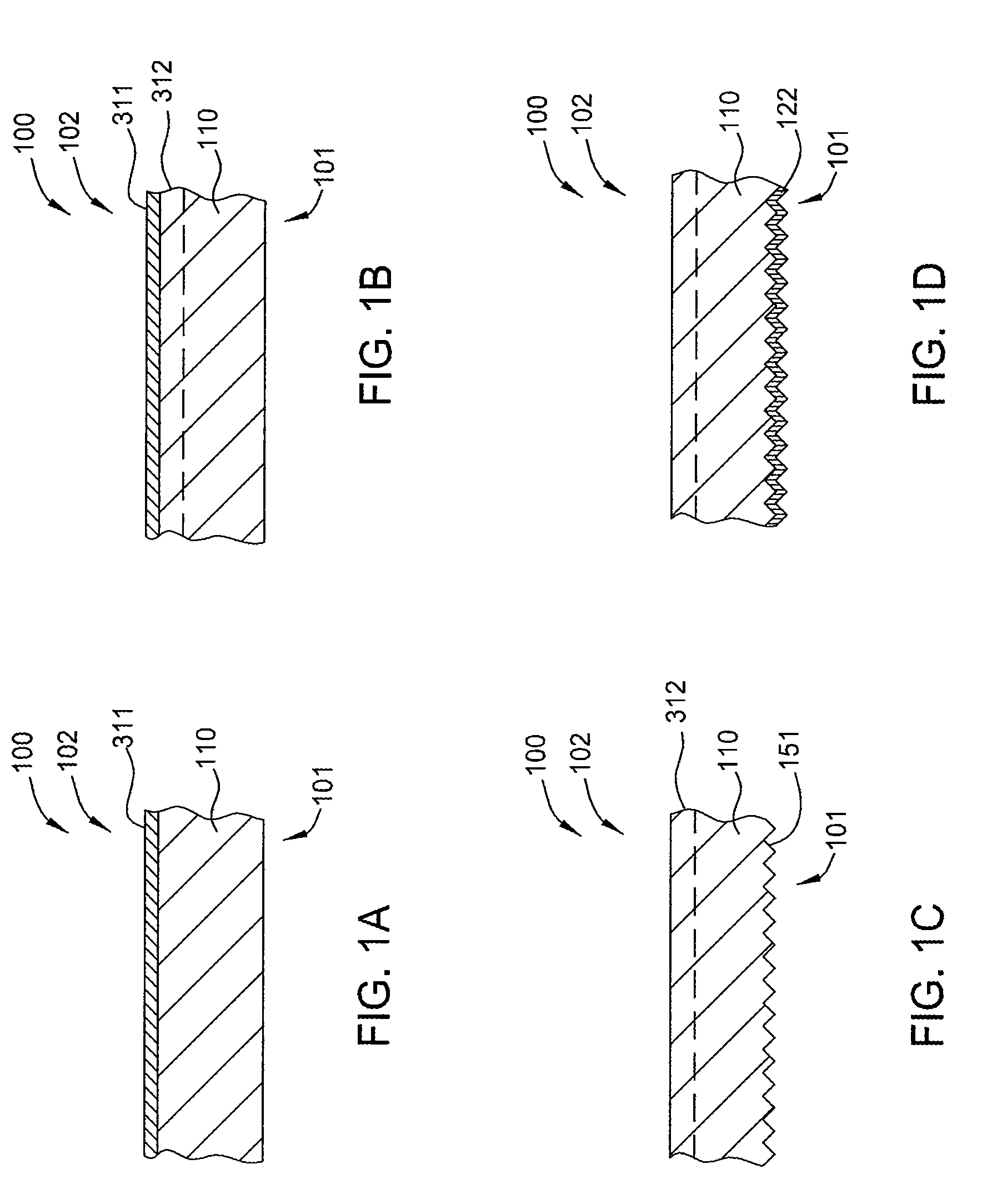

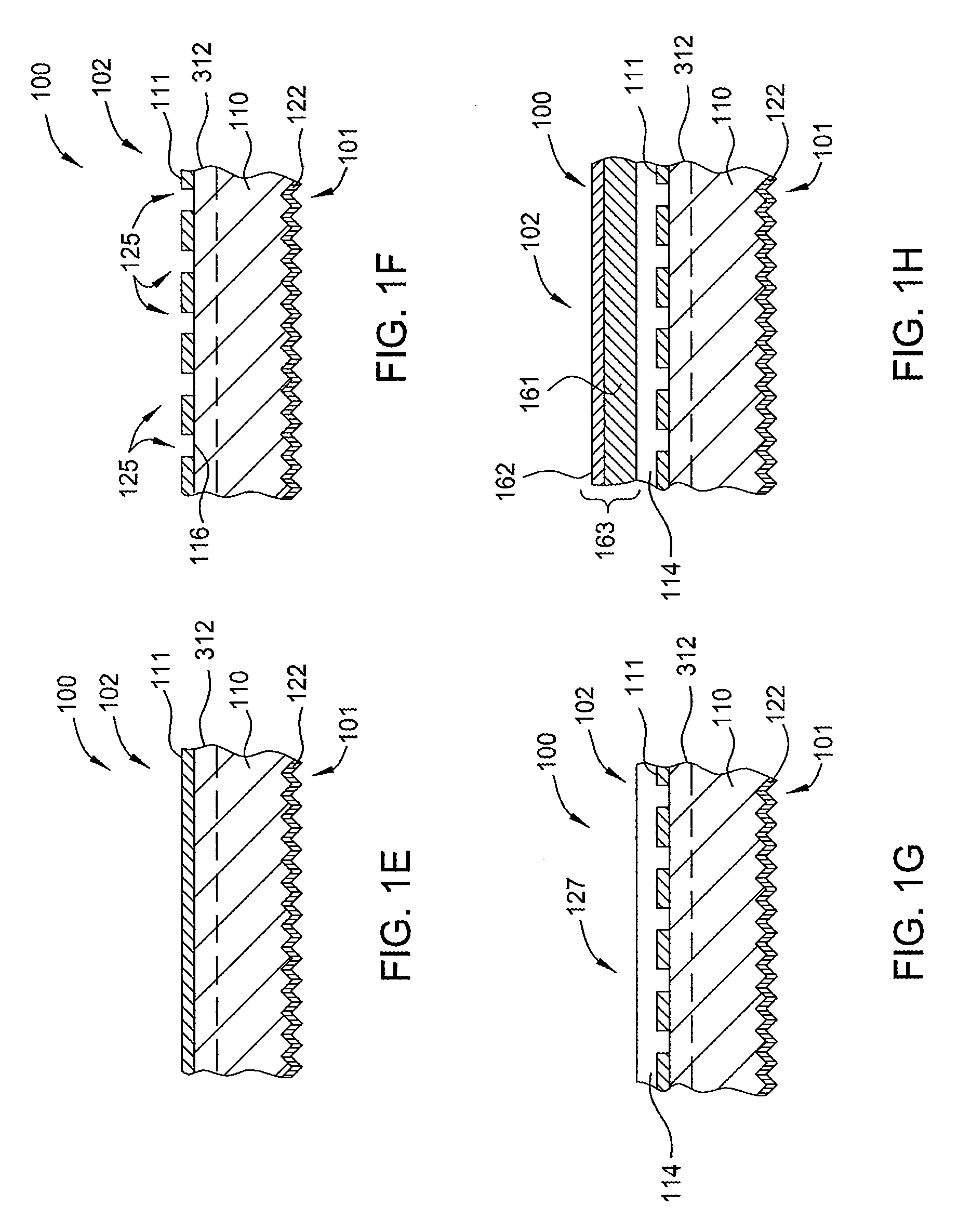

In all representative embodiments presented, the Ge concentration in the source and drain 10 and the SiGe epitaxial channel layer 20 is in the 15% to 50% range, preferably between about 20% to 40%. The SiGe thicknesses in the source / drain 10 are staying below the critical thickness for the given Ge concentration. The critical thickness is defined such that above it the SiGe will relax and defects and dislocations will form. The thickness of the SiGe epitaxial layer 20 typically is between about 5nm and 15nm. The thickness of the epitaxial Si layer 30 is typically between about 5nm and 15nm. FIG. 1A shows an embodiment where the body is bulk Si. These type of devices are the most common devices in present day microelectronics. FIGS. 1B and 1C show representative embodiment of the heterojunction source / drain FET device when the Si body 40 is disposed on top of an insulating material 55. This type of technology is commonly referred to as silicon on insulator (SOI) technology. The insulator material 55 usually, and preferably, is SiO2. FIG. 1B shows an SOI embodiment where the body 40 has enough volume to contain mobile charges. Such SOI devices are called partially depleted devices. FIG. 1C shows an SOI embodiment where the volume of the body 40 is insufficient to contain mobile charges. Such SOI devices are called fully depleted devices. For devices shown in FIG. 1B and 1C there is, at least a thin, layer of body underneath the source and drain 10. This body material serves as the seed material onto which the epitaxial SiGe source and drain 10 are grown. In an alternate embodiment, shown in FIG. 1D. for extremely thin fully depleted SOI devices, one could grow the source and drain 10 laterally, from a lateral seeding, in which case the source and drain 10 would penetrate all the way down to the insulating layer 55.

Owner:GLOBALFOUNDRIES US INC

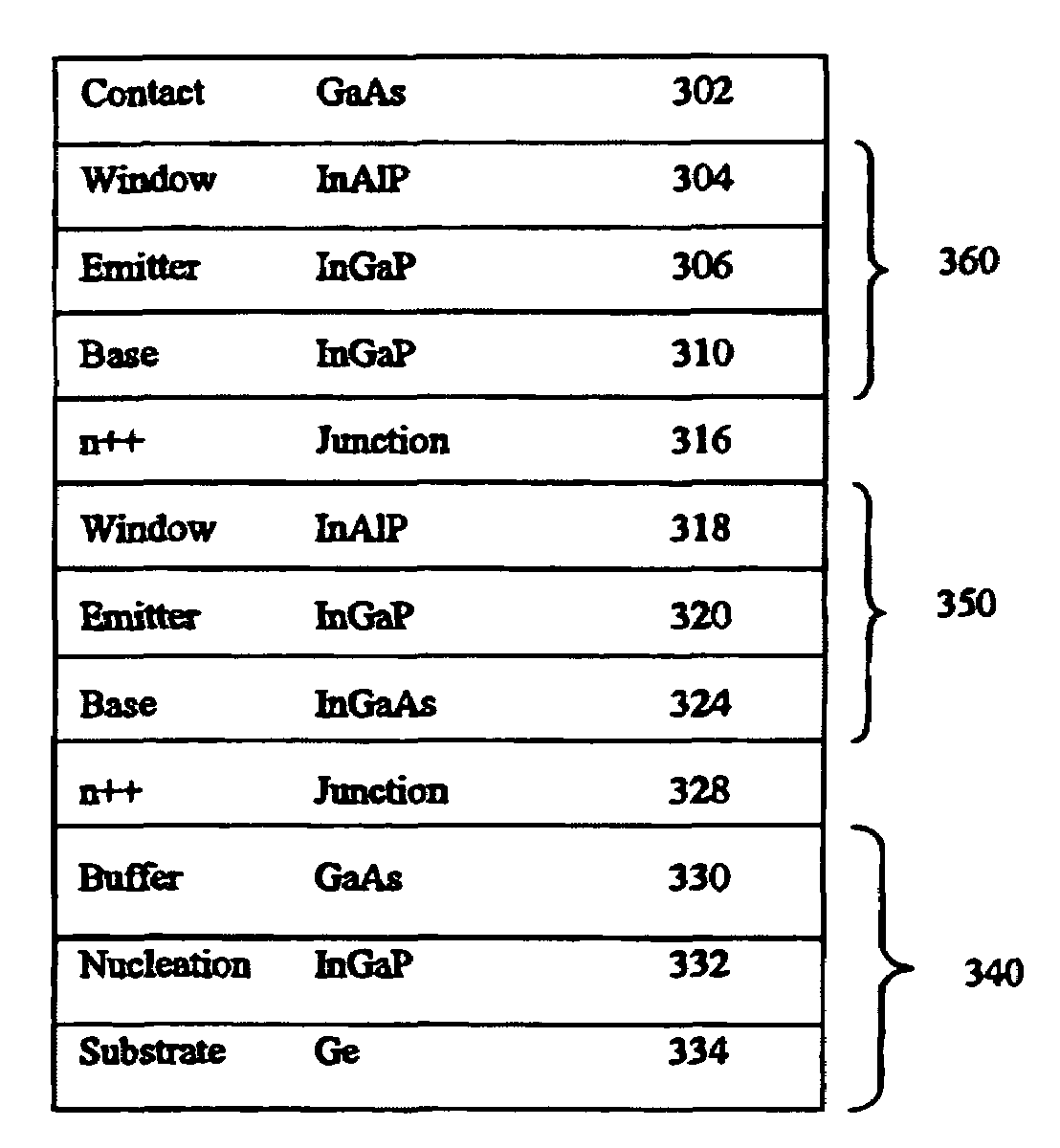

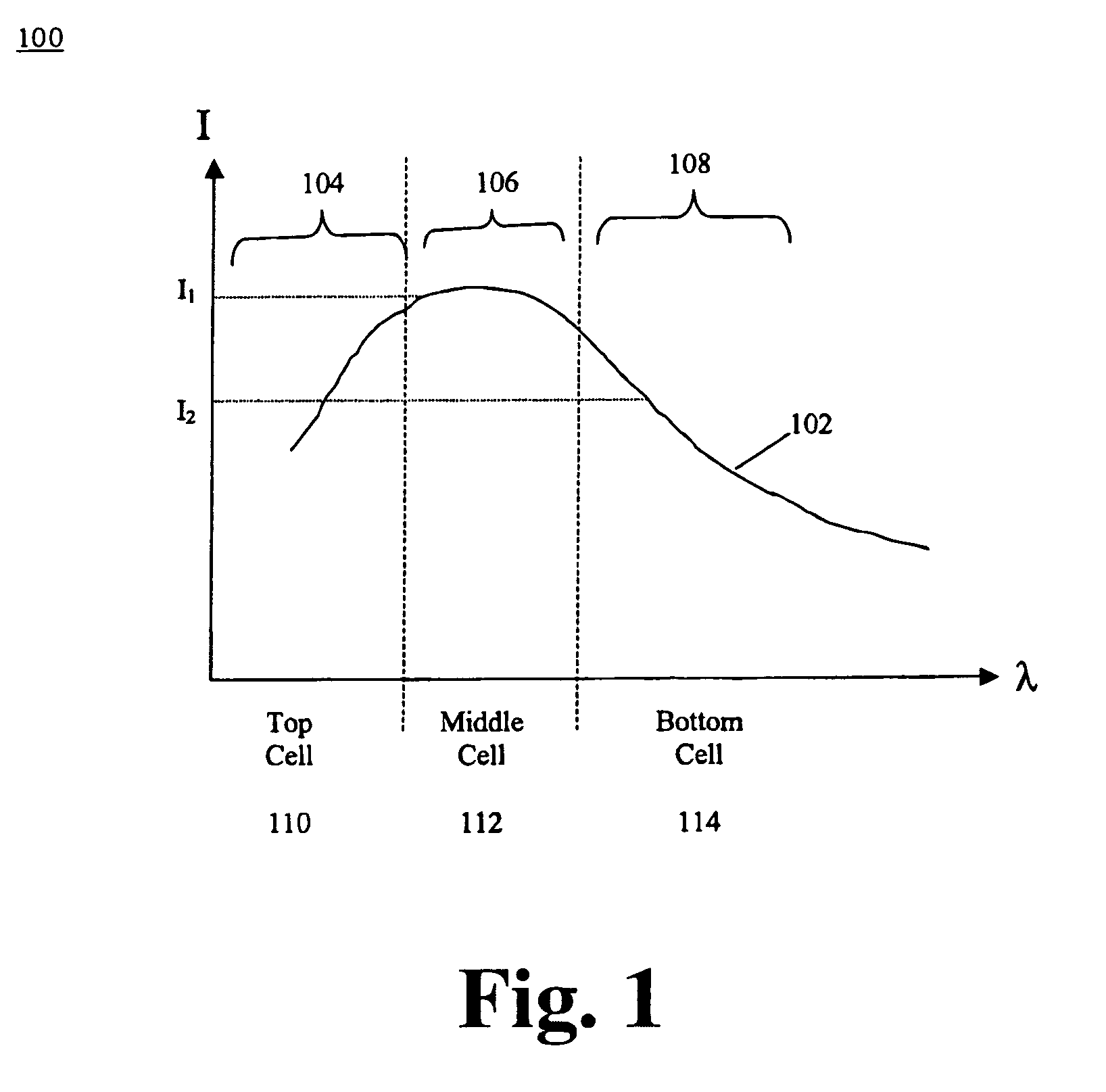

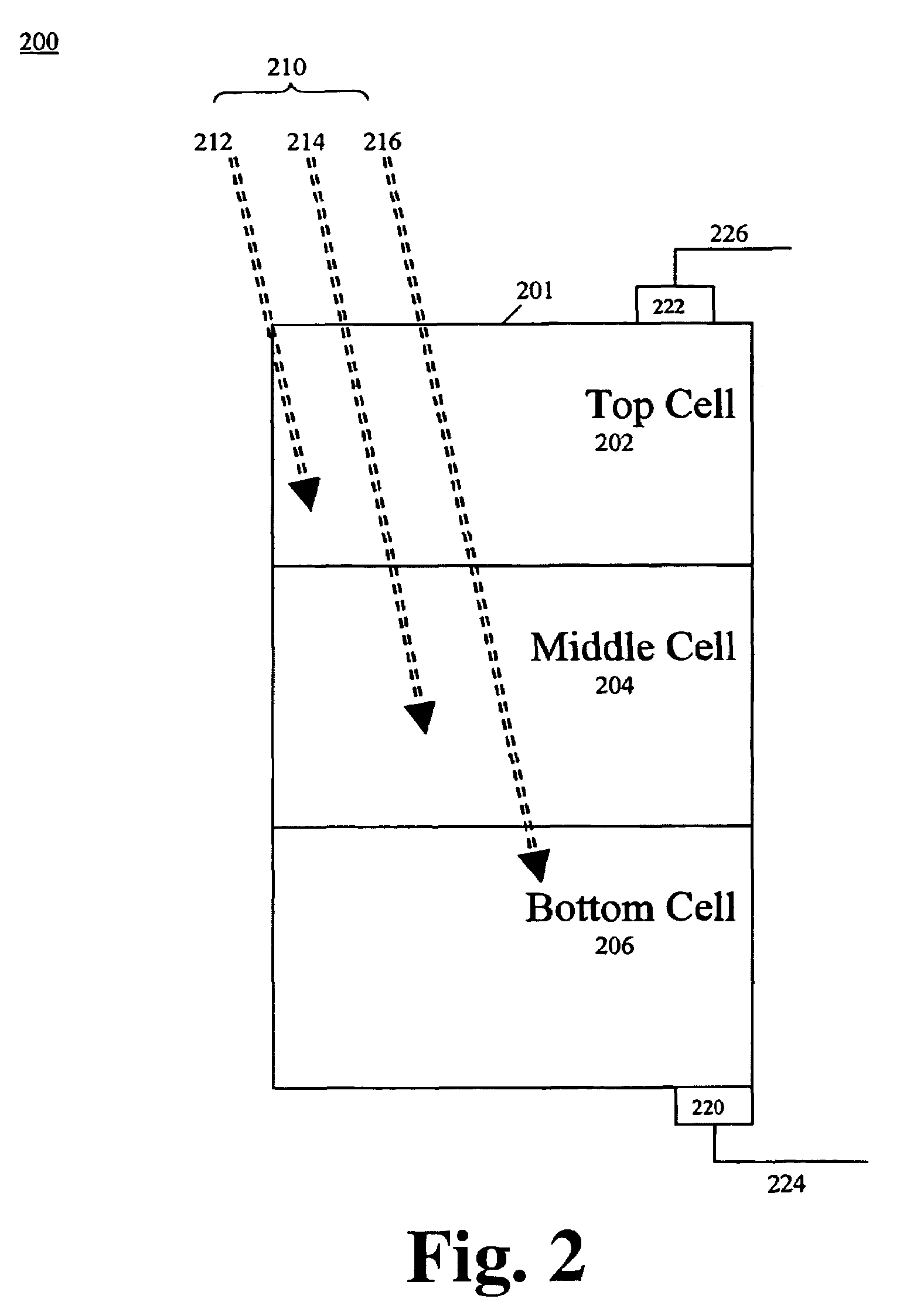

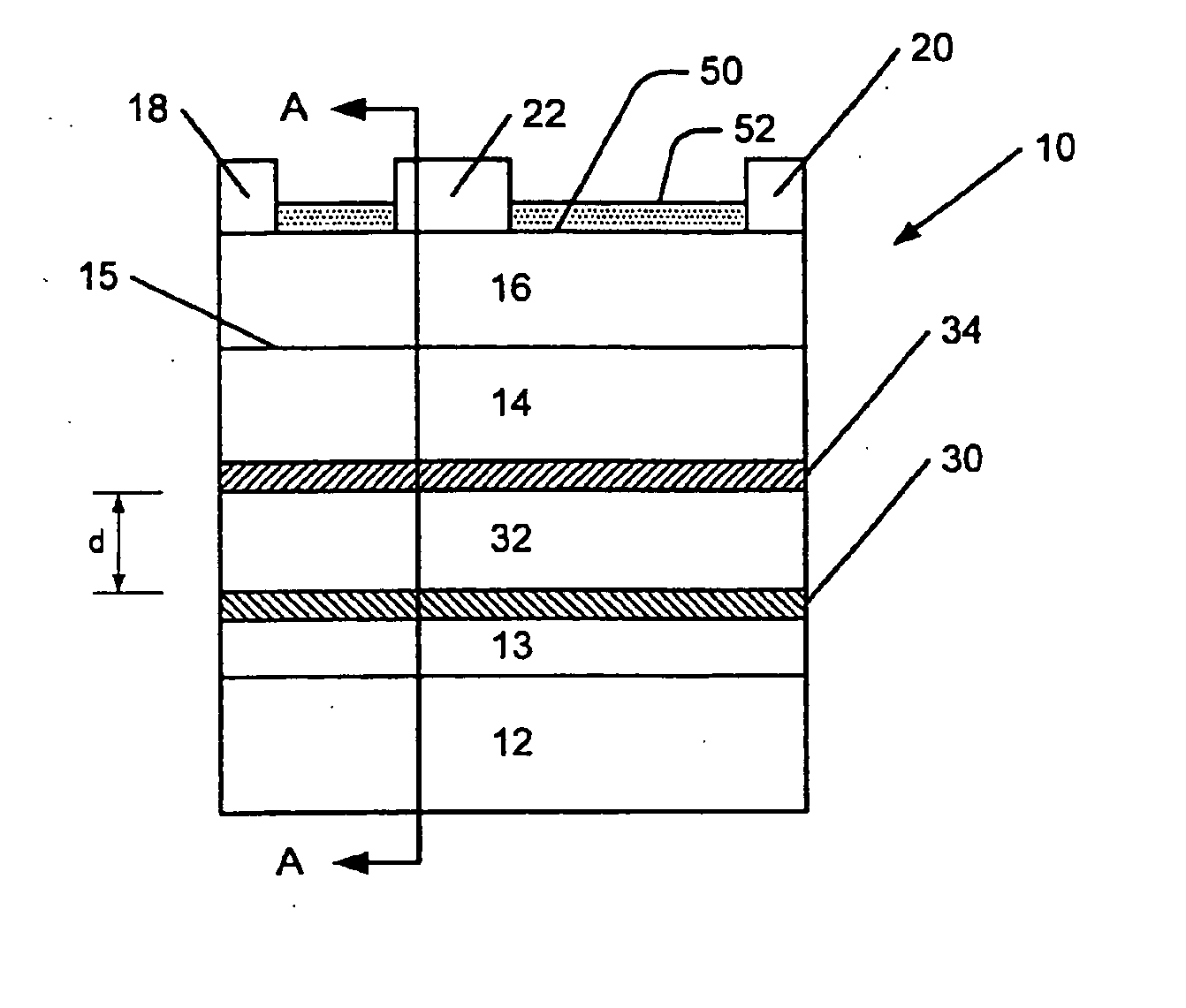

Method and apparatus of multiplejunction solar cell structure with high band gap heterojunction middle cell

InactiveUS7071407B2Final product manufactureSemiconductor/solid-state device manufacturingHeterojunctionTriple junction

A method and a multijunction solar device having a high band gap heterojunction middle solar cell are disclosed. In one embodiment, a triple-junction solar device includes bottom, middle, and top cells. The bottom cell has a germanium (Ge) substrate and a buffer layer, wherein the buffer layer is disposed over the Ge substrate. The middle cell contains a heterojunction structure, which further includes an emitter layer and a base layer that are disposed over the bottom cell. The top cell contains an emitter layer and a base layer disposed over the middle cell.

Owner:SOLAERO TECH CORP

Heterojunction transistors including energy barriers and related methods

A heterojunction transistor may include a channel layer comprising a Group III nitride, a barrier layer comprising a Group III nitride on the channel layer, and an energy barrier comprising a layer of a Group III nitride including indium on the channel layer such that the channel layer is between the barrier layer and the energy barrier. The barrier layer may have a bandgap greater than a bandgap of the channel layer, and a concentration of indium (In) in the energy barrier may be greater than a concentration of indium (In) in the channel layer. Related methods are also discussed.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

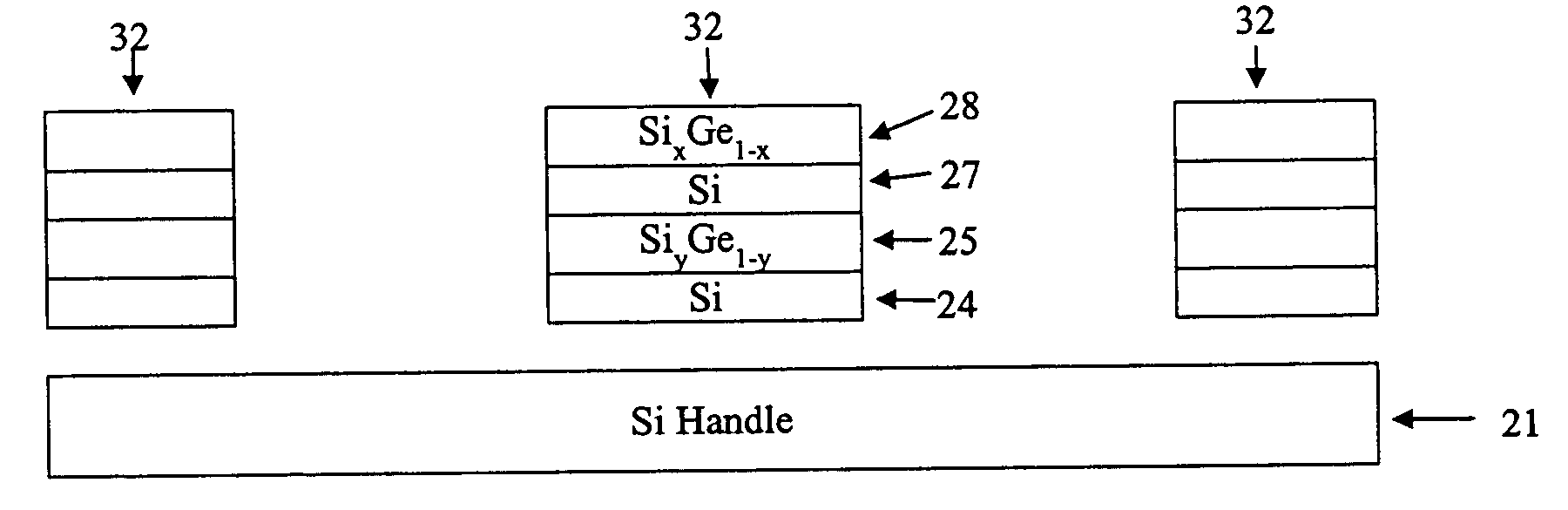

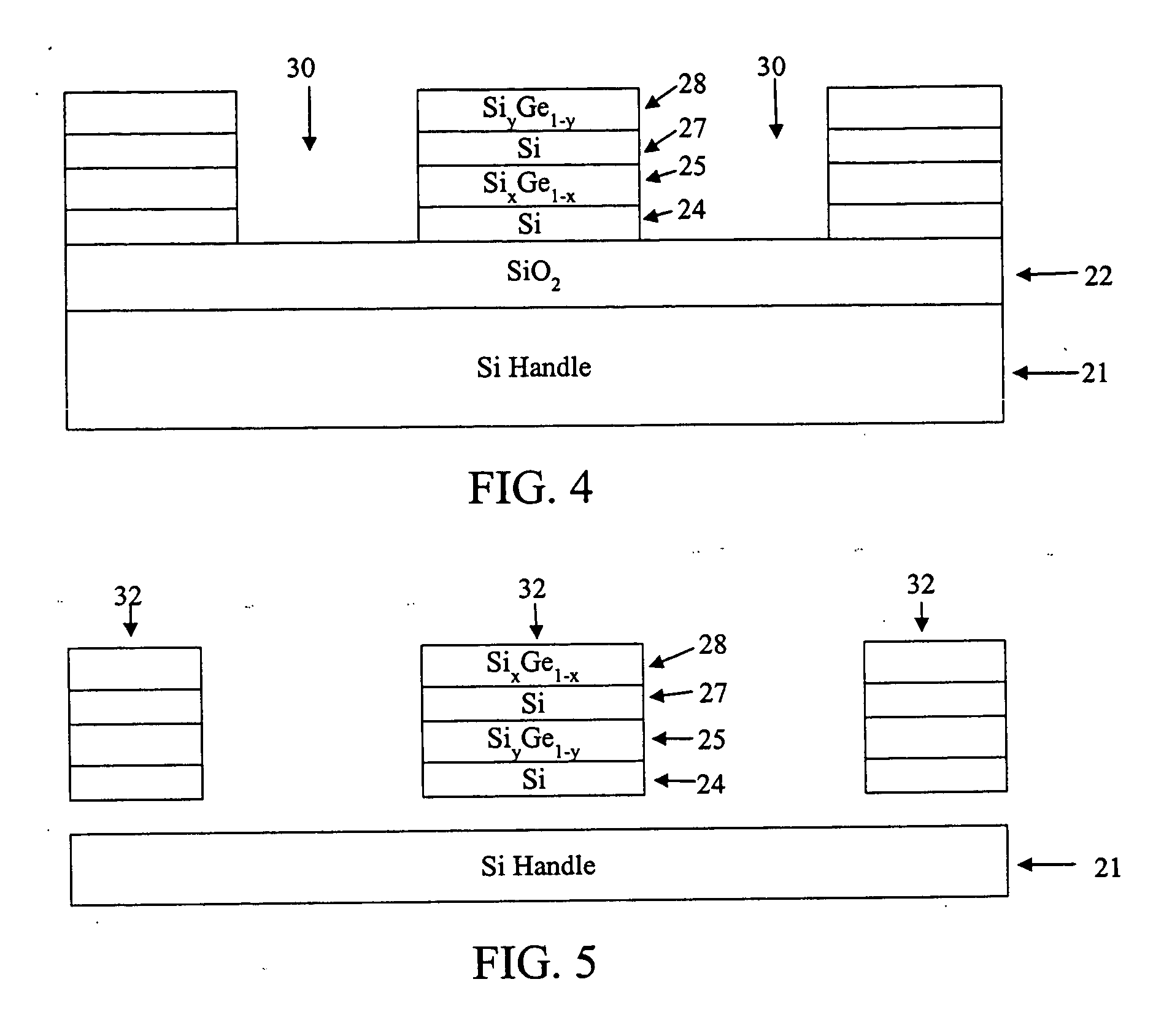

Fabrication of strained heterojunction structures

ActiveUS20060134893A1Improve featuresHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionLayer interface

Growth of multilayer films is carried out in a manner which allows close control of the strain in the grown layers and complete release of the grown films to allow mounting of the released multilayer structures on selected substrates. A layer of material, such as silicon-germanium, is grown onto a template layer, such as silicon, of a substrate having a sacrificial layer on which the template layer is formed. The grown layer has a lattice mismatch with the template layer so that it is strained as deposited. A top layer of crystalline material, such as silicon, is grown on the alloy layer to form a multilayer structure with the grown layer and the template layer. The sacrificial layer is preferentially etched away to release the multilayer structure from the sacrificial layer, relaxing the grown layer and straining the crystalline layers interfaced with it.

Owner:WISCONSIN ALUMNI RES FOUND

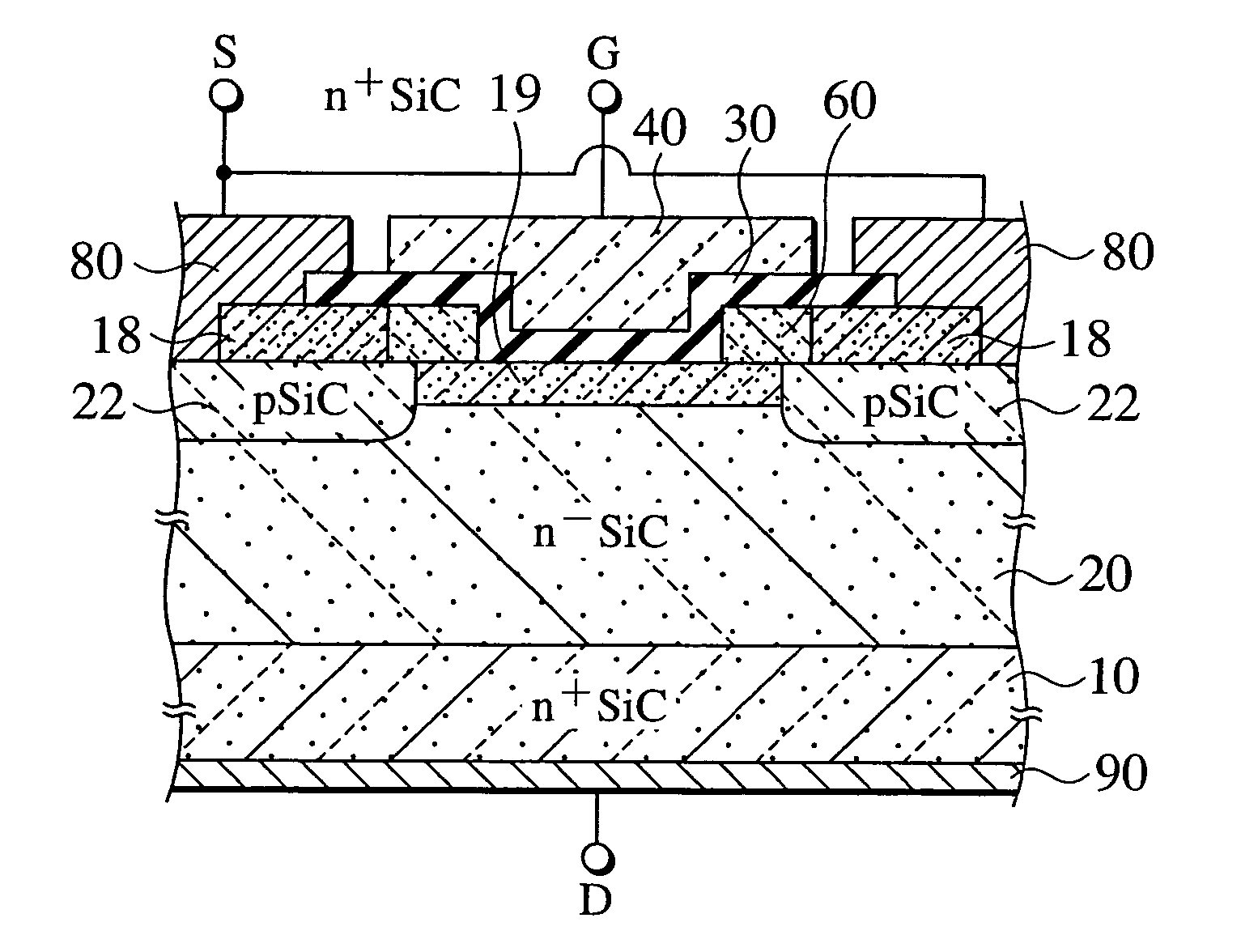

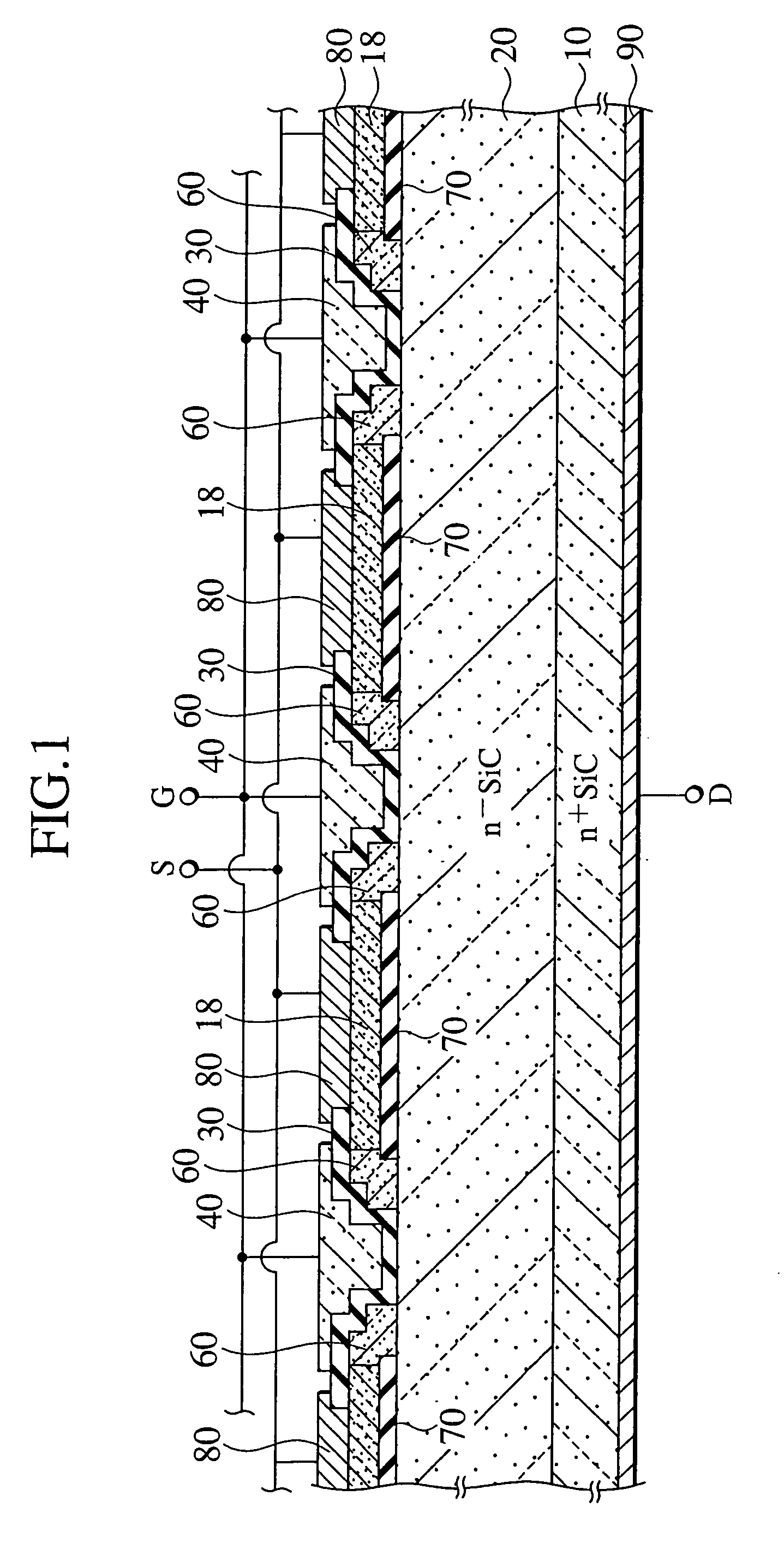

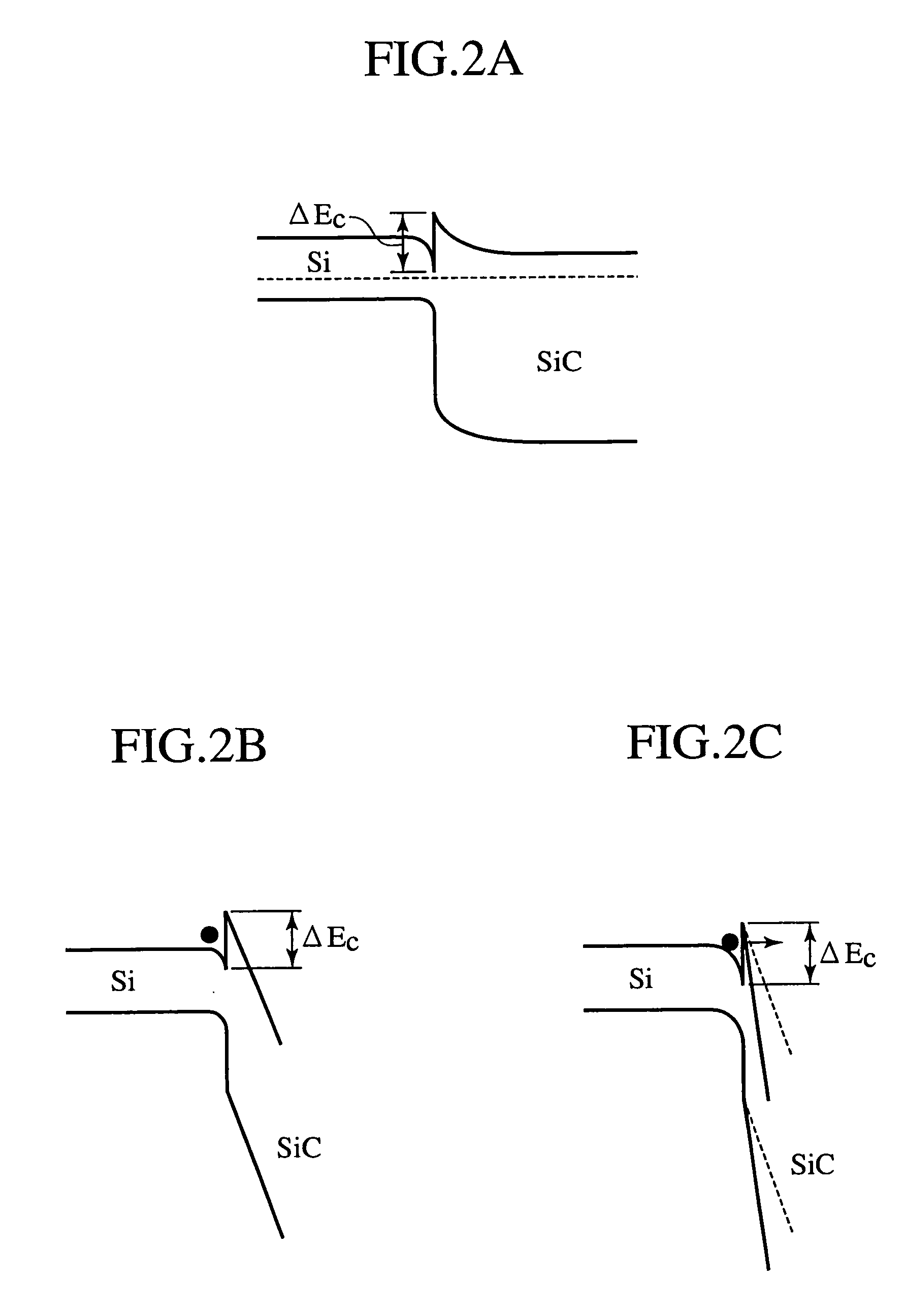

Insulated gate tunnel-injection device having heterojunction and method for manufacturing the same

InactiveUS20040079989A1High breakdown voltage of the gate insulation filmImprove mobilitySemiconductor/solid-state device manufacturingDiodeHeterojunctionTunnel injection

The present invention-provides a tunnel-injection device which encompasses, a reception layer made of a first semiconductor, a barrier-forming layer made of a second semiconductor having a bandgap-narrower than the first semiconductor, being in metallurgical contact with the reception layer, a gate insulating film disposed on the barrier-forming layer. The gate electrode controls the width of the barrier generated at the heterojunction interface between the reception layer and the barrier-forming layer so as to change the tunneling probability of carriers through the barrier. The device further encompasses a carrier receiving region being contact with the reception layer and a carrier-supplying region being contact with the barrier-forming layer.

Owner:NISSAN MOTOR CO LTD

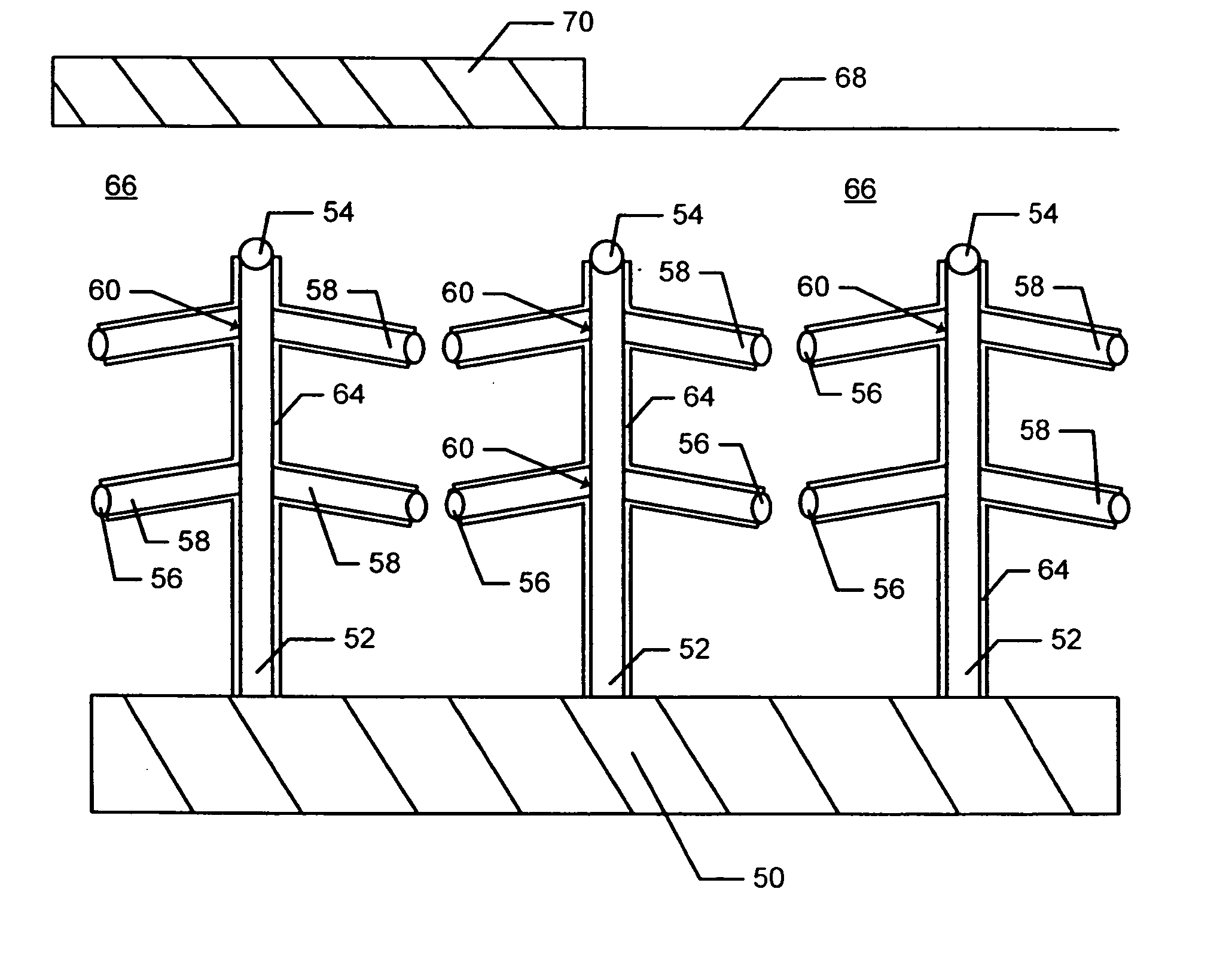

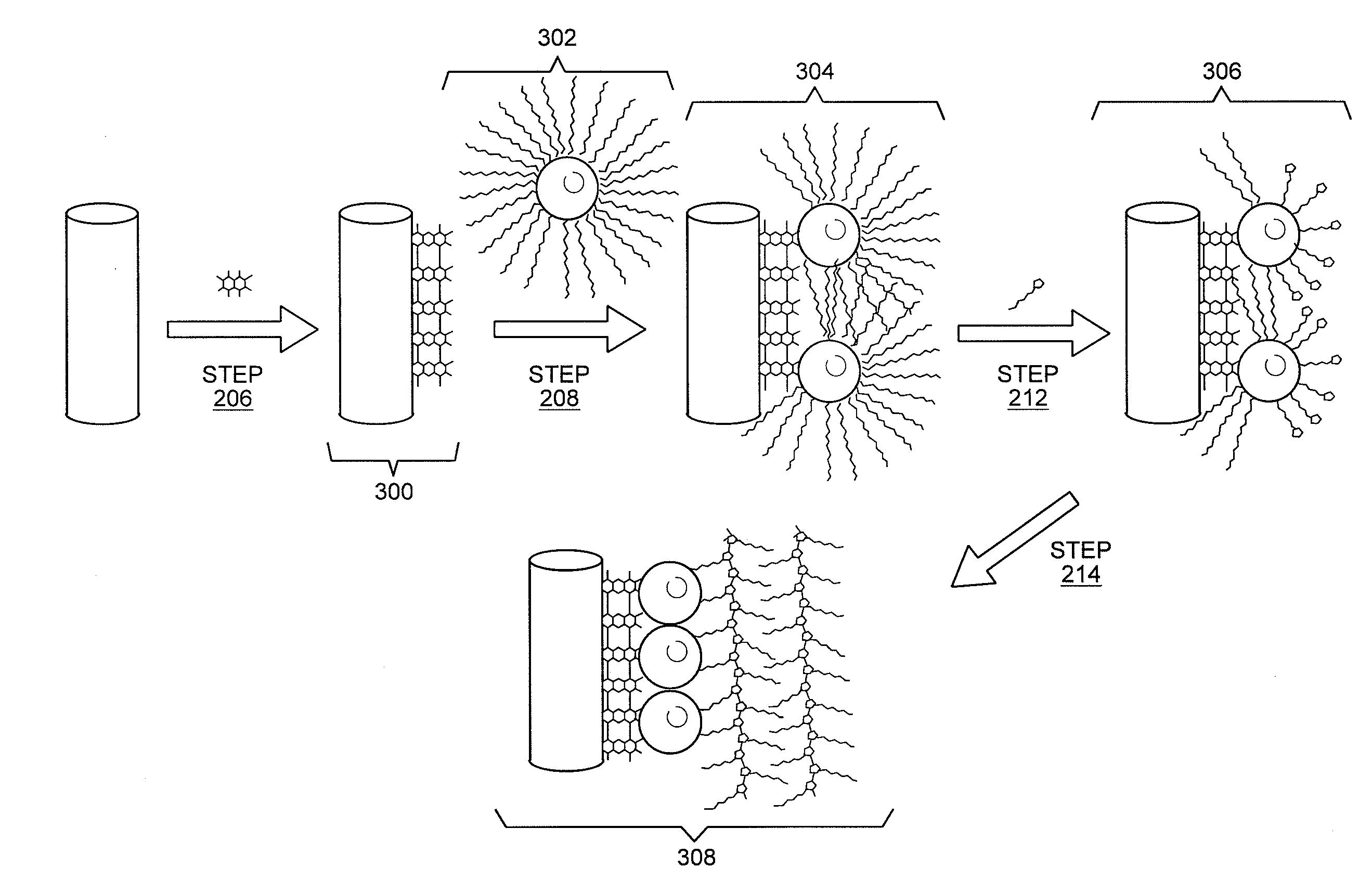

Nanostructures formed of branched nanowhiskers and methods of producing the same

InactiveUS20060057360A1Structure moreMaterial nanotechnologyLiquid surface applicatorsHeterojunctionEngineering

A method of forming a nanostructure having the form of a tree, comprises a first stage and a second stage. The first stage includes providing one or more catalytic particles on a substrate surface, and growing a first nanowhisker via each catalytic particle. The second stage includes providing, on the periphery of each first nanowhisker, one or more second catalytic particles, and growing, from each second catalytic particle, a second nanowhisker extending transversely from the periphery of the respective first nanowhisker. Further stages may be included to grow one or more further nanowhiskers extending from the nanowhisker(s) of the preceding stage. Heterostructures may be created within the nanowhiskers. Such nanostructures may form the components of a solar cell array or a light emitting flat panel, where the nanowhiskers are formed of a photosensitive material. A neural network may be formed by positioning the first nanowhiskers close together so that adjacent trees contact one another through nanowhiskers grown in a subsequent stage, and heterojunctions within the nanowhiskers create tunnel barriers to current flow.

Owner:QUNANO

Hybrid heterojunction solar cell fabrication using a doping layer mask

InactiveUS20100015756A1Prevent substantial etching of back surfaceFinal product manufactureSemiconductor/solid-state device manufacturingHeterojunctionSolar cell

Embodiments of the invention contemplate the formation of a high efficiency solar cell using a novel processing sequence to form a solar cell device. In one embodiment, the methods include forming a doping layer on a back surface of a substrate, heating the doping layer and substrate to cause the doping layer diffuse into the back surface of the substrate, texturing a front surface of the substrate after heating the doping layer and the substrate, forming a dielectric layer on the back surface of the substrate, removing portions of the dielectric layer from the back surface to from a plurality of exposed regions of the substrate, and depositing a metal layer over the back surface of the substrate, wherein the metal layer is in electrical communication with at least one of the plurality of exposed regions on the substrate, and at least one of the exposed regions has dopant atoms provided from the doping layer.

Owner:APPLIED MATERIALS INC

Nitride heterojunction transistors having charge-transfer induced energy barriers and methods of fabricating the same

ActiveUS7170111B2TransistorSemiconductor/solid-state device manufacturingHeterojunctionElectron source

A nitride-based field effect transistor includes a substrate, a channel layer comprising InAlGaN formed on the substrate, source and drain ohmic contacts in electrical communication with the channel layer, and a gate contact formed on the channel layer. At least one energy barrier opposes movement of carriers away from the channel layer. The energy barrier may comprise an electron source layer in proximity with a hole source layer which generate an associated electric field directed away from the channel. An energy barrier according to some embodiments may provide a built-in potential barrier in excess of about 0.5 eV. Method embodiments are also disclosed.

Owner:WOLFSPEED INC

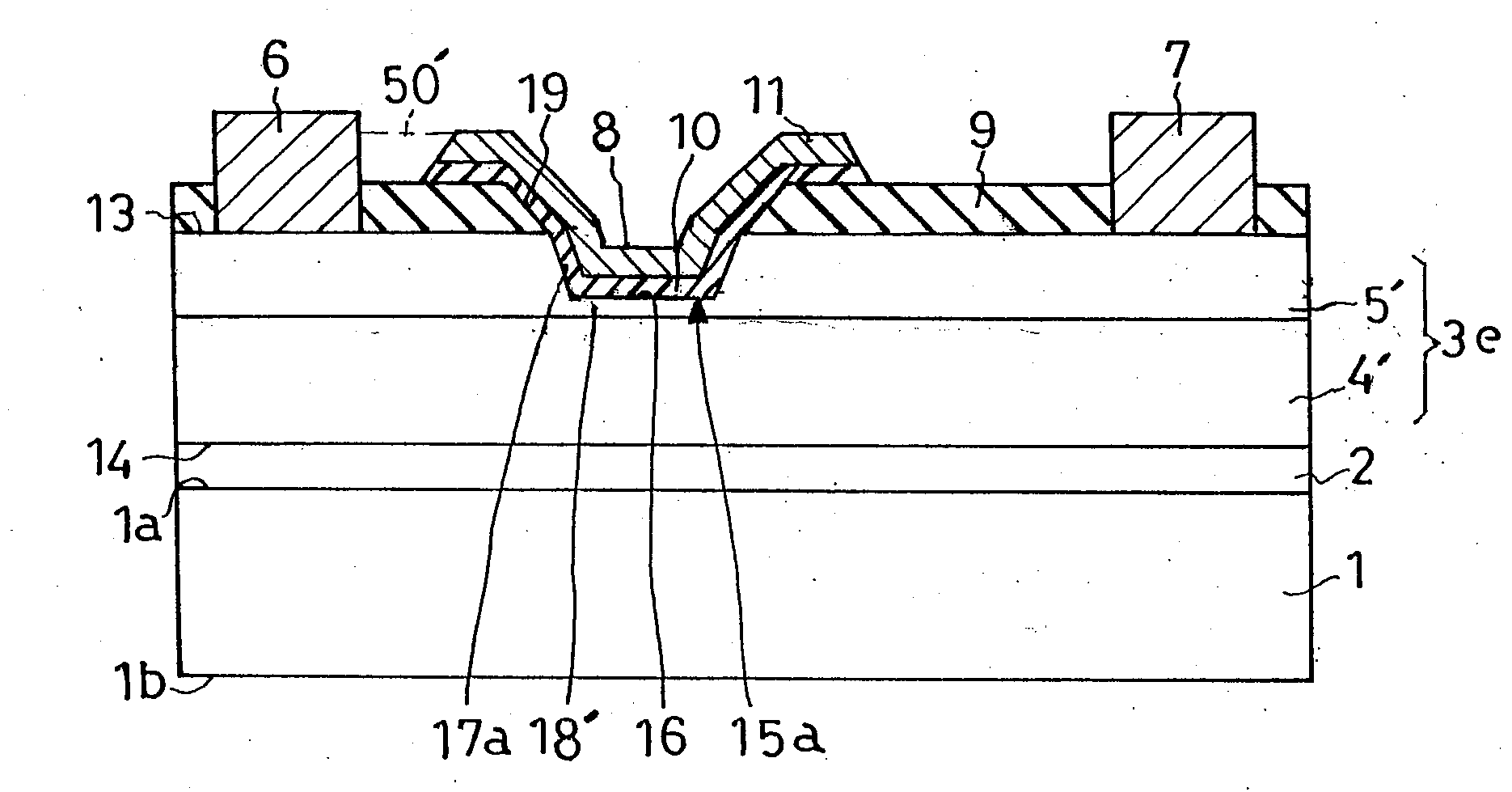

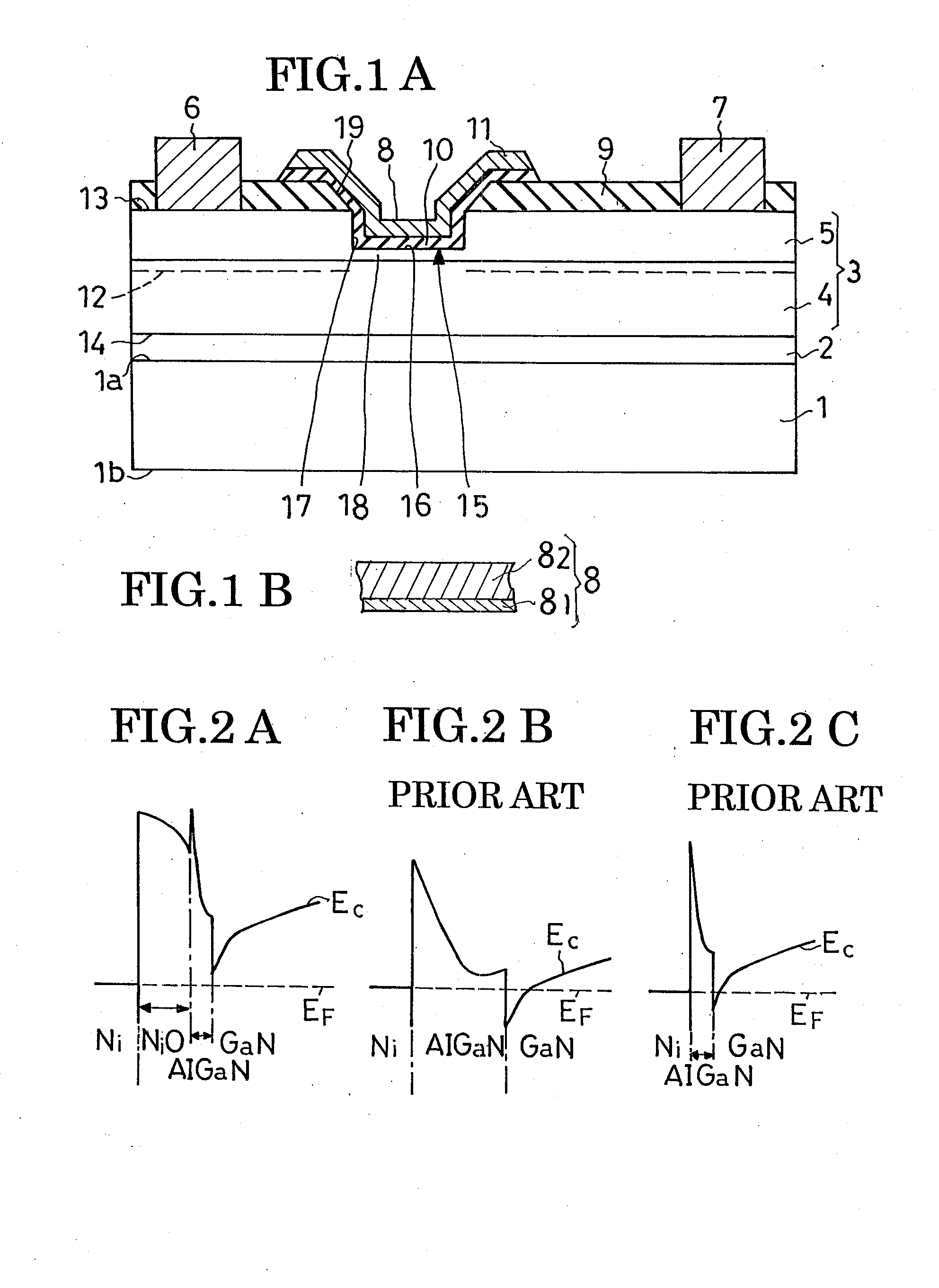

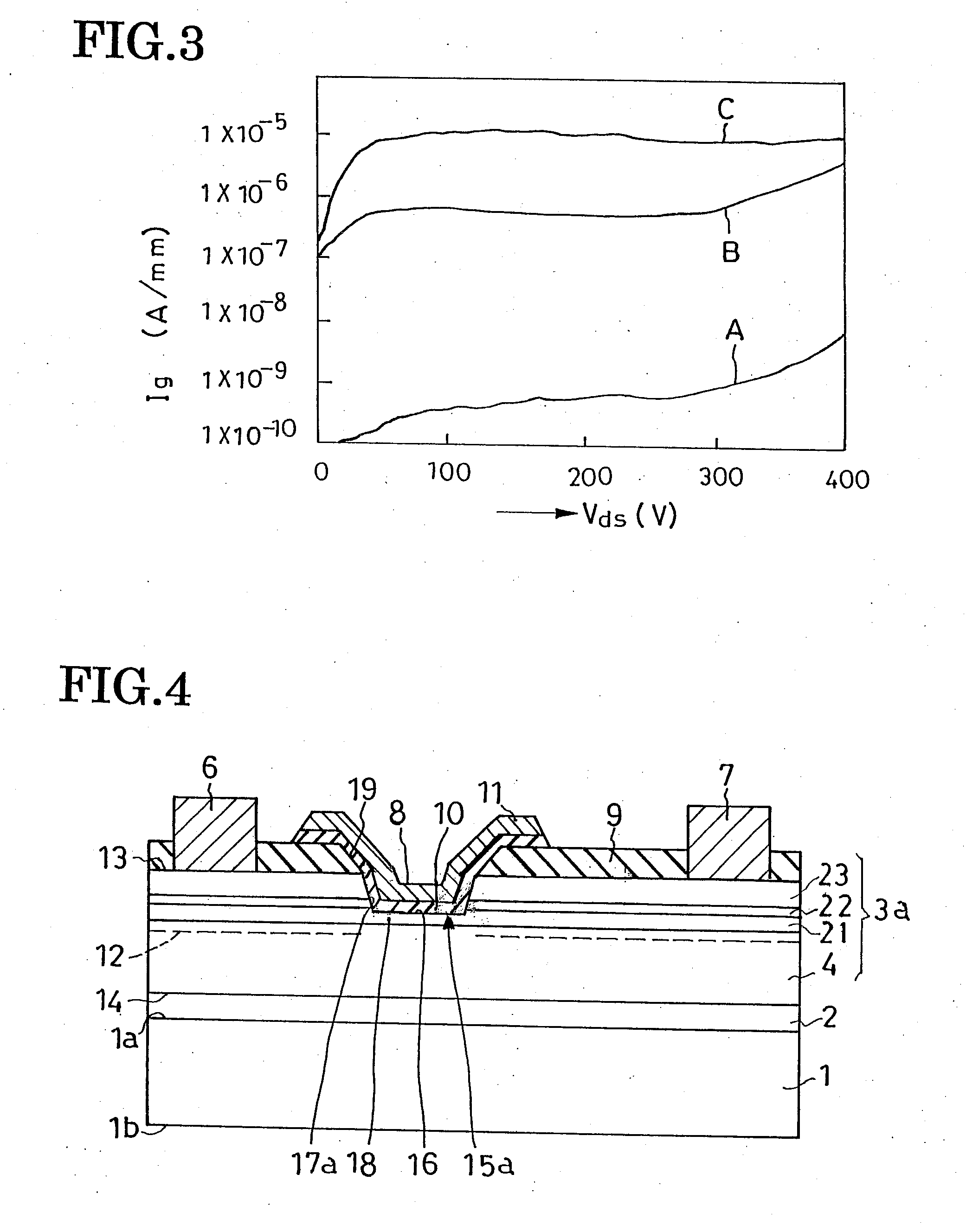

Field-Effect Semiconductor Device, and Method of Fabrication

ActiveUS20090057720A1Reduce leakage currentPreventing current collapseSemiconductor/solid-state device detailsSolid-state devicesHeterojunctionField effect

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film whereby a depletion zone is normally created in the electron gas layer, with a minimum of turn-on resistance and gate leak current.

Owner:SANKEN ELECTRIC CO LTD

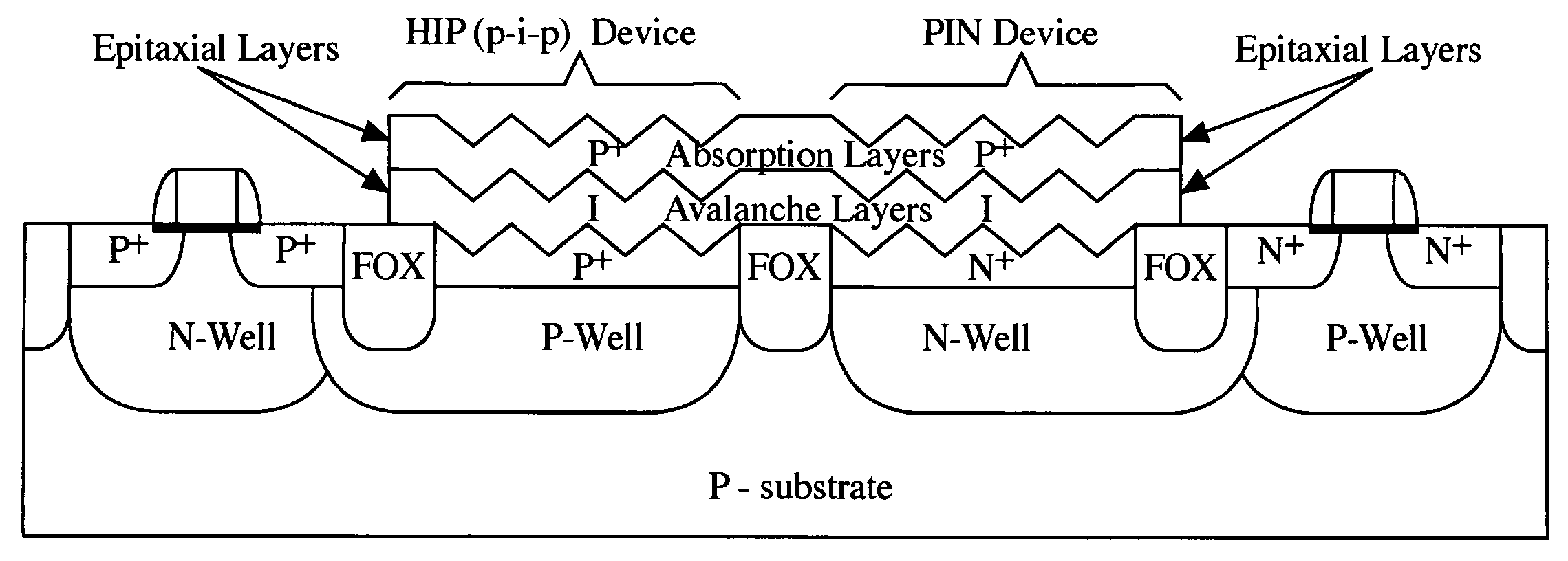

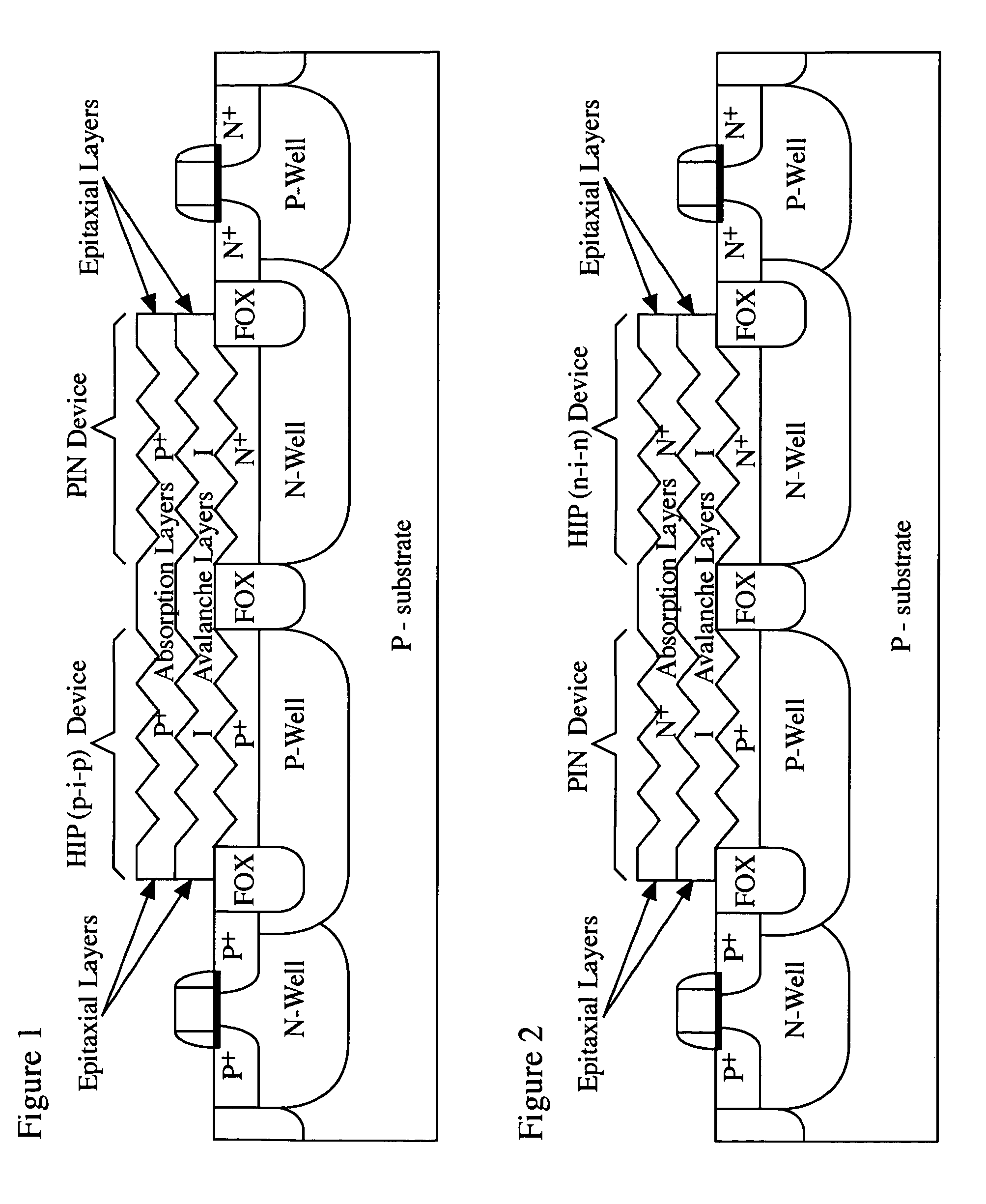

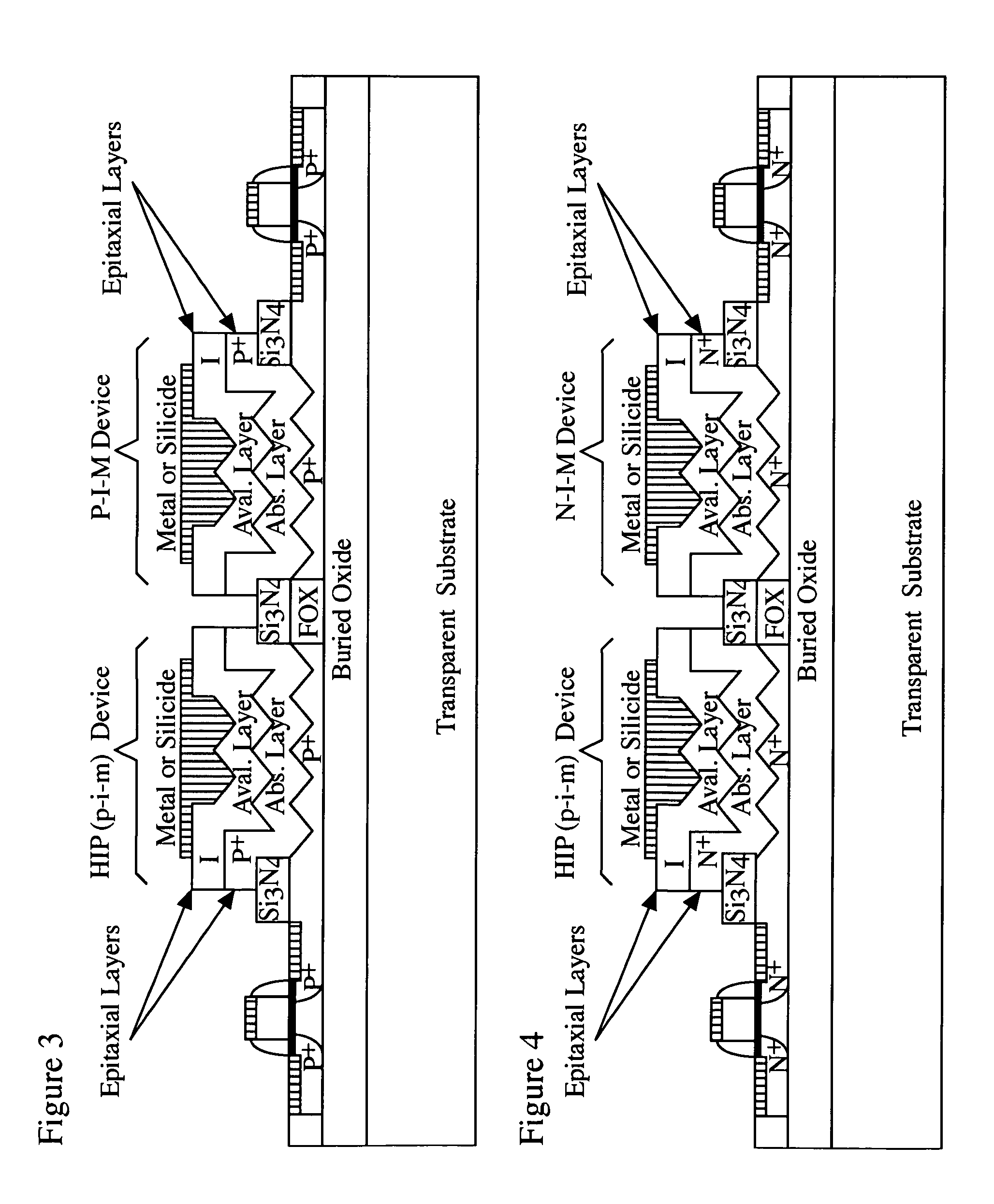

Light-sensing device

ActiveUS7521737B2Solid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionPixel density

A method of fabricating light-sensing devices including photodiodes monolithically integrated with CMOS devices. Several types of photodiode devices (PIN, HIP) are expitaxially grown in one single step on active areas implanted in a common semiconductor substrate, the active areas having defined polarities. The expitaxially grown layers for the photodiode devices may be either undoped or in-situ doped with profiles suitable for their respective operation. With appropriate choice of substrate materials, device layers and heterojunction engineering and process architecture, it is possible to fabricate silicon-based and germanium-based multi-spectral sensors that can deliver pixel density and cost of fabrication comparable to the state of the art CCDs and CMOS image sensors. The method can be implemented with epitaxially deposited films on the following substrates: Silicon Bulk, Thick-Film and Thin-Film Silicon-On-Insulator (SOI), Germanium Bulk, Thick-Film and Thin-Film Geranium-On-Insulator (GeOI).

Owner:QUANTUM SEMICON

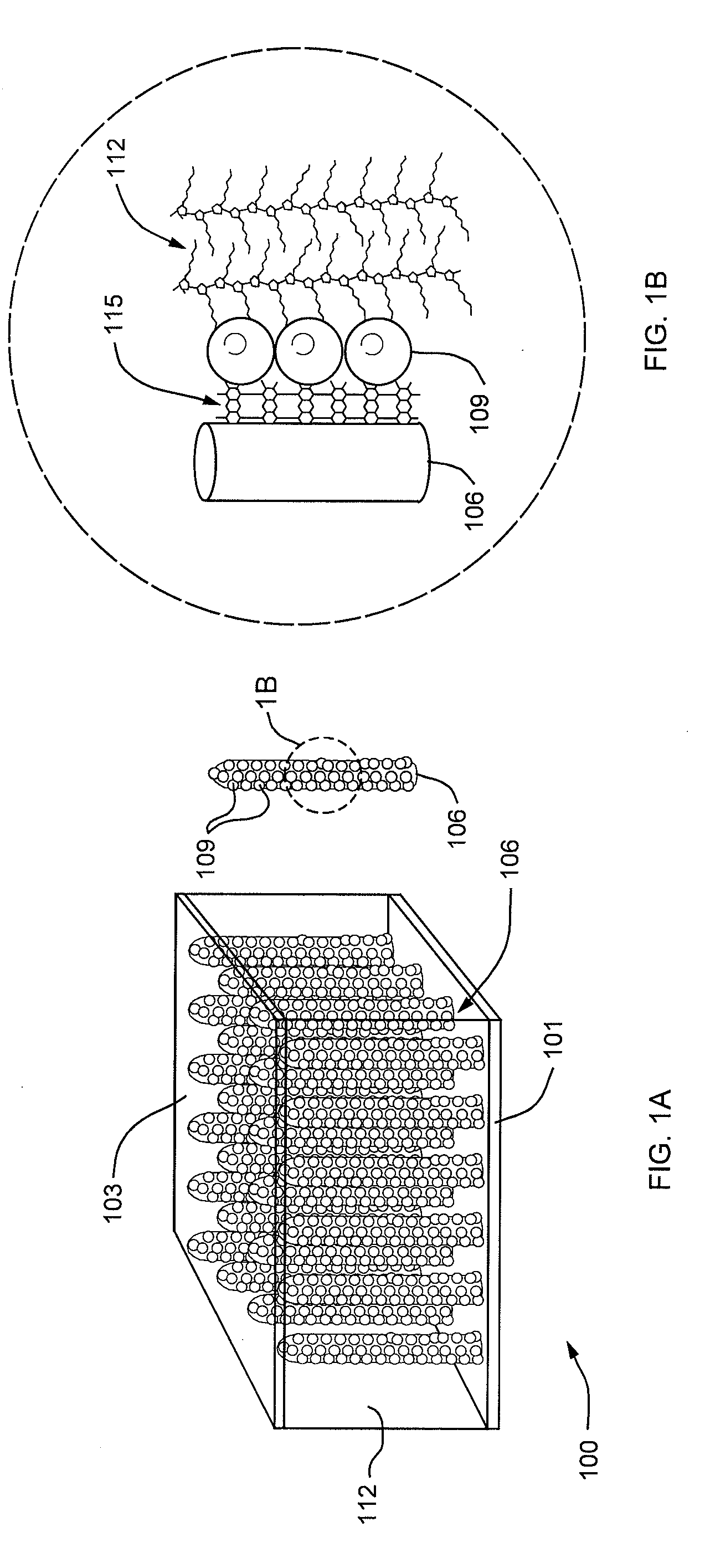

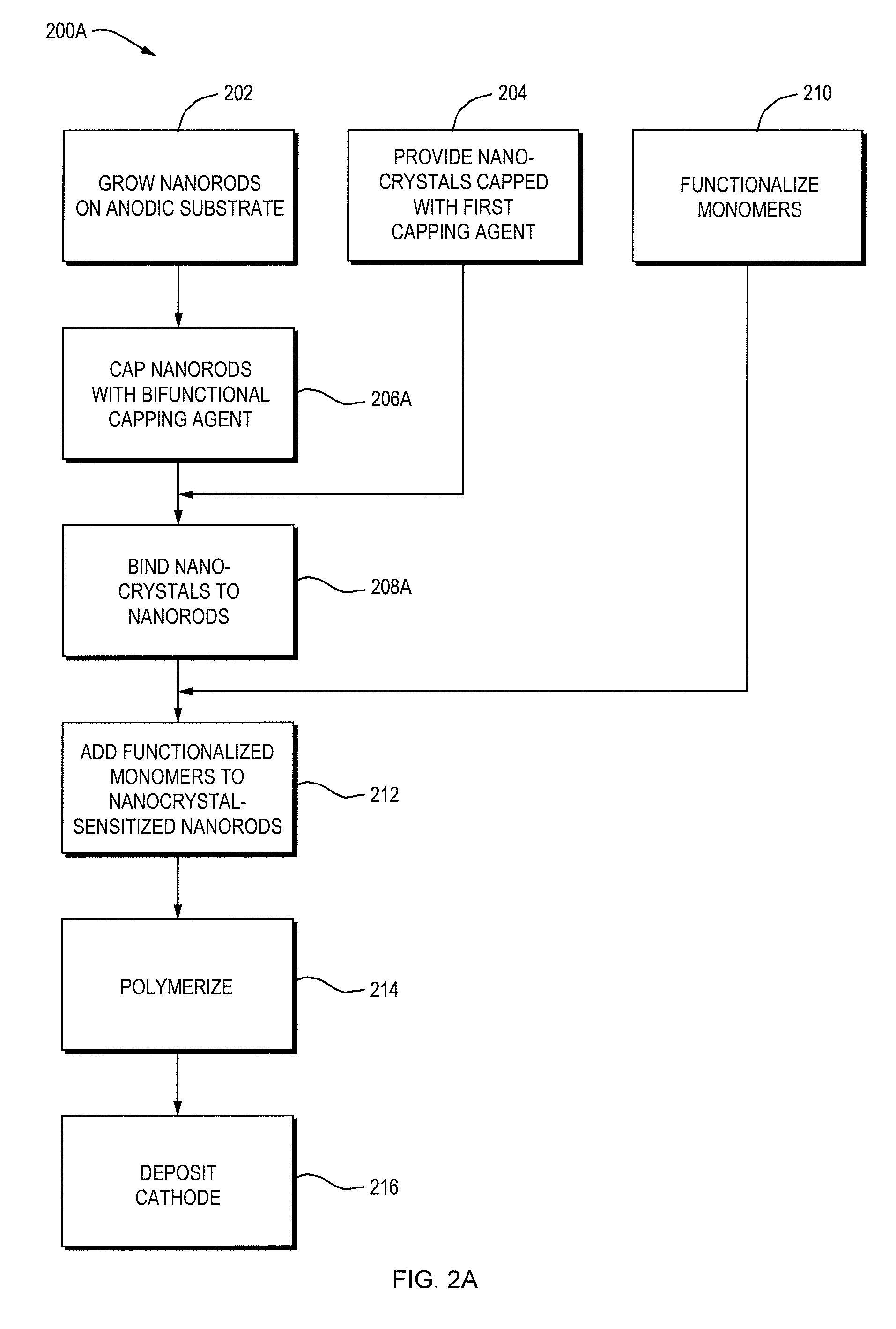

Hybrid Photovoltaic Cells and Related Methods

InactiveUS20080264479A1Reduce recombination lossImprove conversion efficiencyFinal product manufactureIndividual molecule manipulationElectron holeHeterojunction

Embodiments of the present invention involve photovoltaic (PV) cells comprising a semiconducting nanorod-nanocrystal-polymer hybrid layer, as well as methods for fabricating the same. In PV cells according to this invention, the nanocrystals may serve both as the light-absorbing material and as the heterojunctions at which excited electron-hole pairs split.

Owner:NANOCO TECH LTD

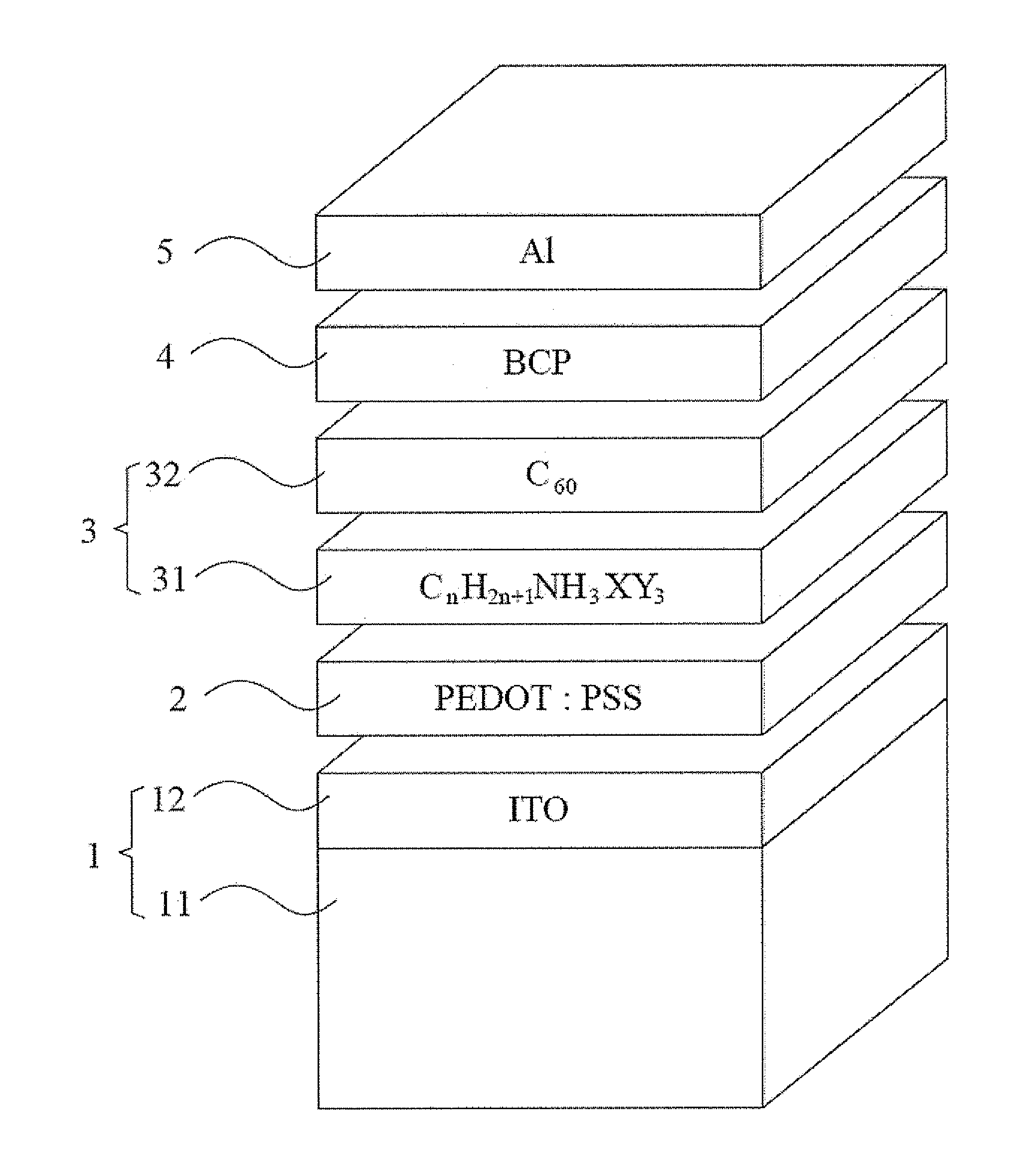

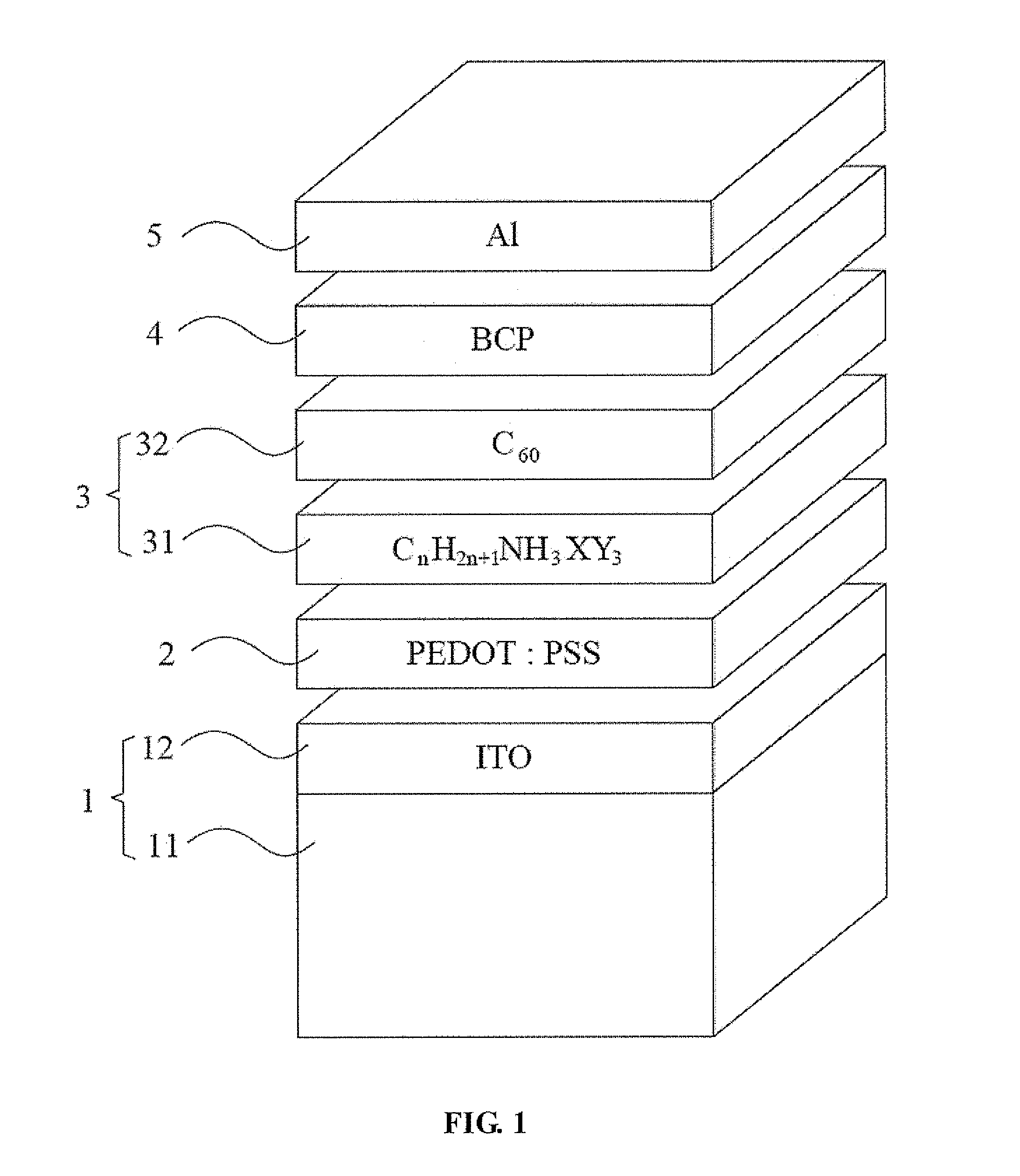

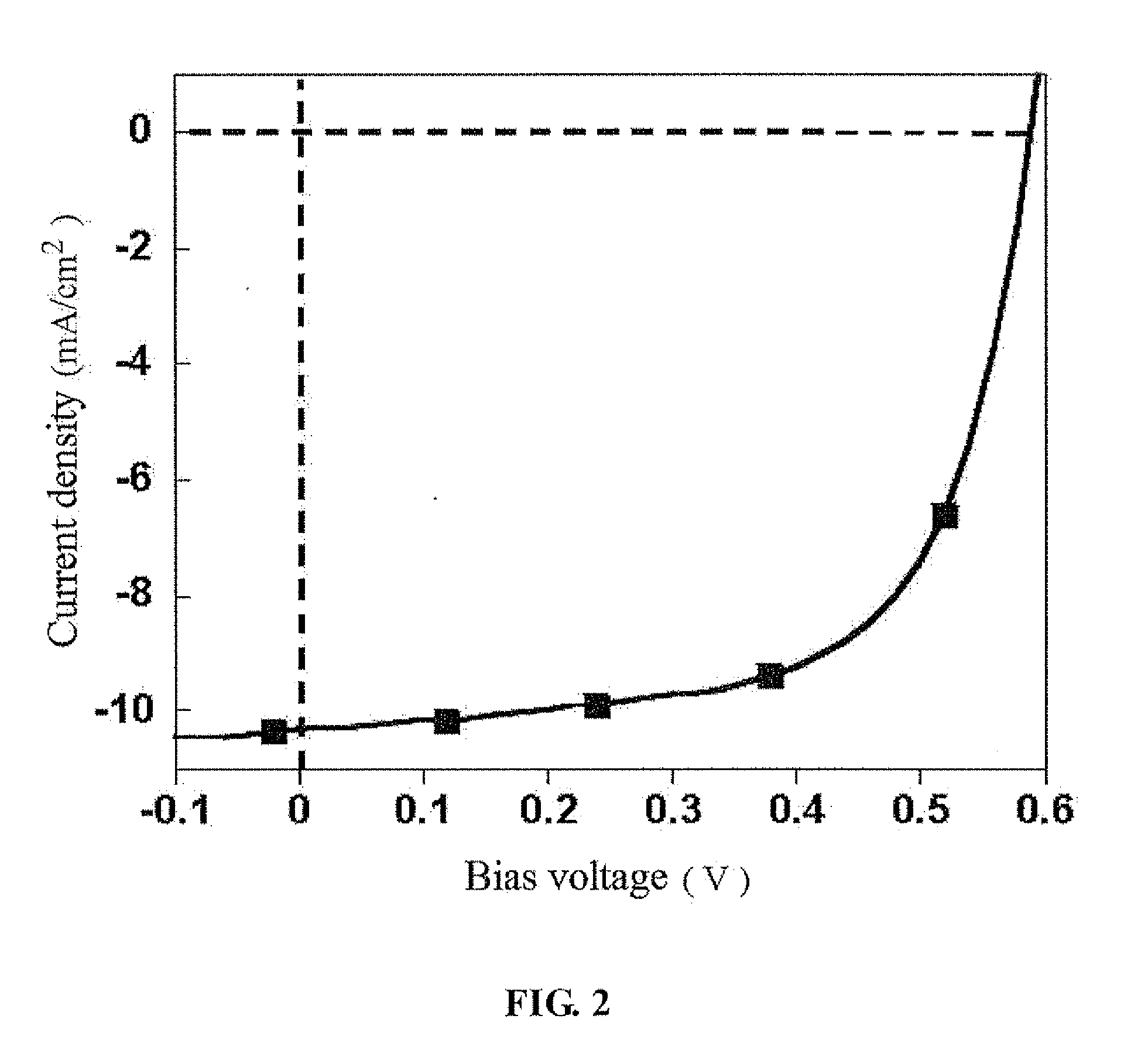

Hybrid organic solar cell with perovskite structure as absorption material and manufacturing method thereof

ActiveUS20140332078A1Low costSimple processFinal product manufactureSolid-state devicesHeterojunctionOrganic solar cell

A hybrid organic solar cell (HOSC) with perovskite structure as absorption material and a manufacturing method thereof are provided. The HOSC includes a conductive substrate, a hole transport layer, an active layer, a hole blocking layer and a negative electrode. The active layer has a light absorption layer (LAL) and an electron acceptor layer (EAL). The LAL is made of perovskite material represented by the following equation: CnH2n+1NH3XY3, n is positive integer form 1 to 9; X is Pb, Sn or Ge; and Y is at least one of I, Br or Cl. The EAL is made of at least one type of fullerene or derivatives thereof. A planar heterojunction (PHJ) is formed between the LAL and the EAL. The LAL has simple structure and fabricating process with relatively low cost, so that it is advantageous to carry out the mass production of HOSCs of flexible solid-state form.

Owner:NAT CHENG KUNG UNIV

Field-effect semiconductor device, and method of fabrication

ActiveUS20100155720A1Leakage currentLittle and no physical impairmentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionField effect

A heterojunction field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region and electrically coupled to the 2DEG layer. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film and insulating film, whereby a depletion zone is normally created in the 2DEG layer, making the device normally off. The p-type metal oxide semiconductor film of high hole concentration serves for the normally-off performance of the device with low gate leak current, and the insulating film for further reduction of gate leak current.

Owner:SANKEN ELECTRIC CO LTD

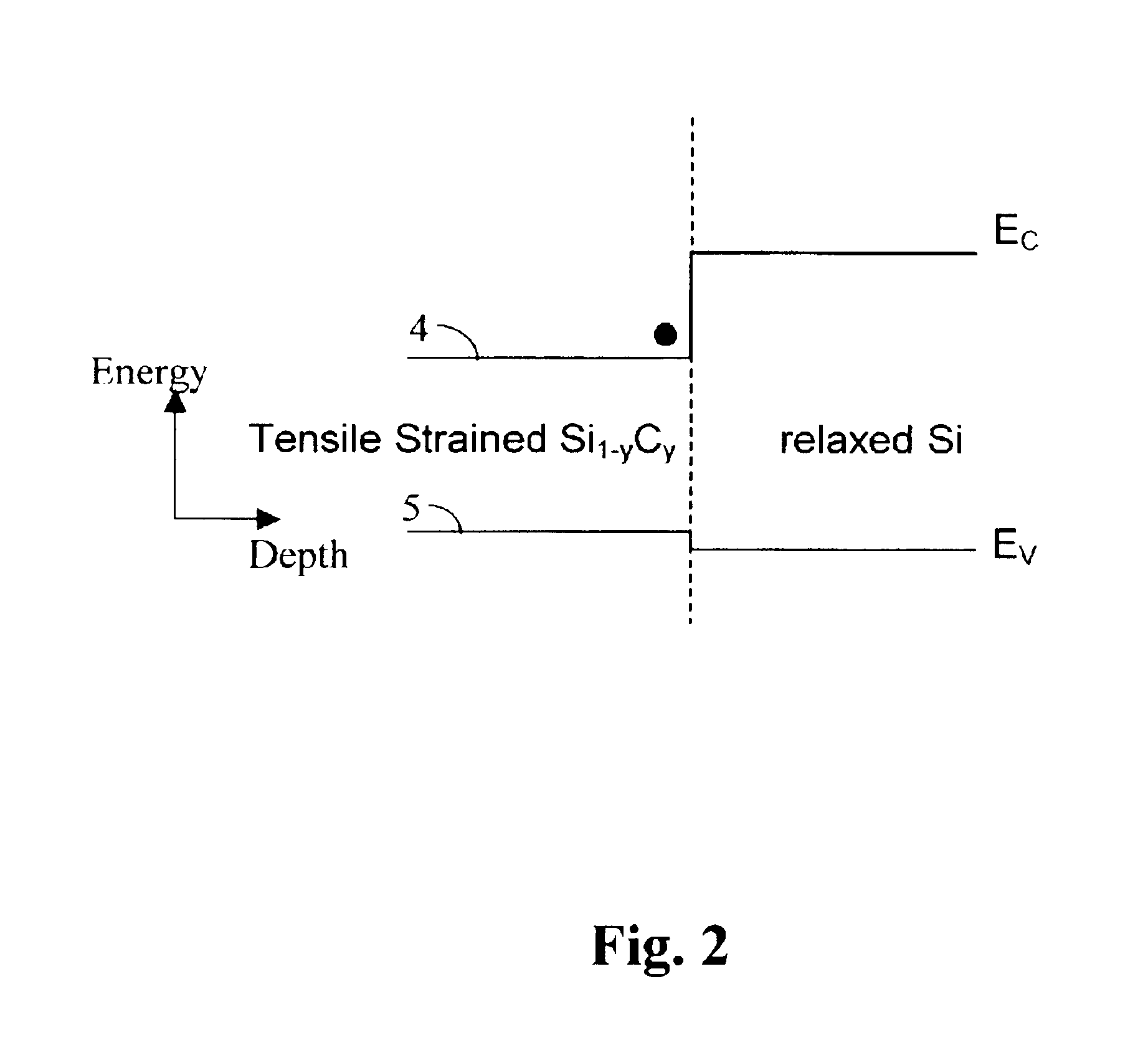

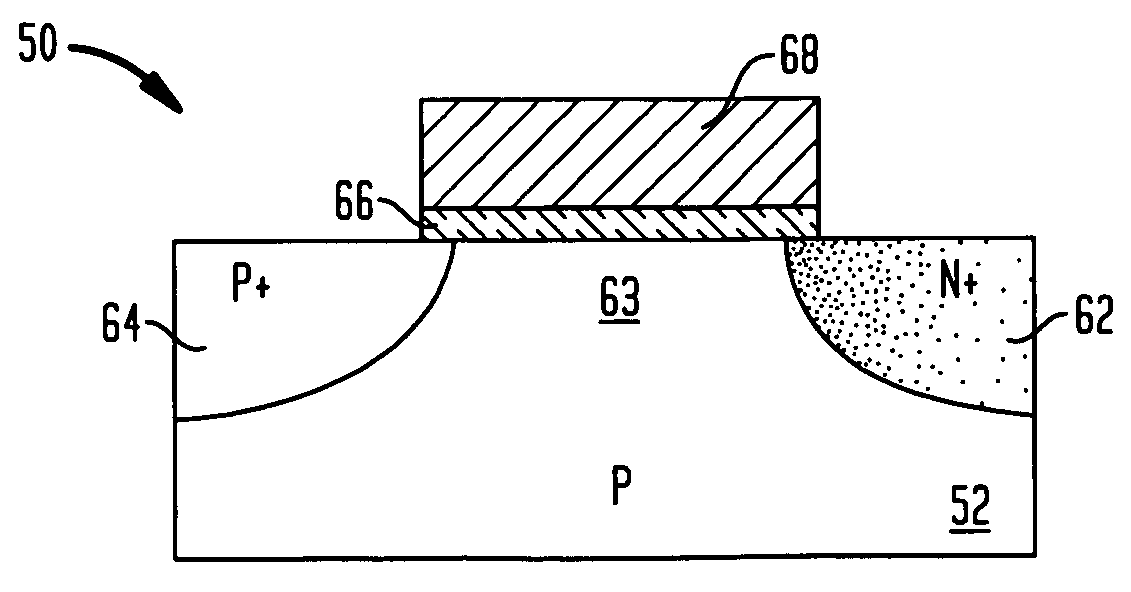

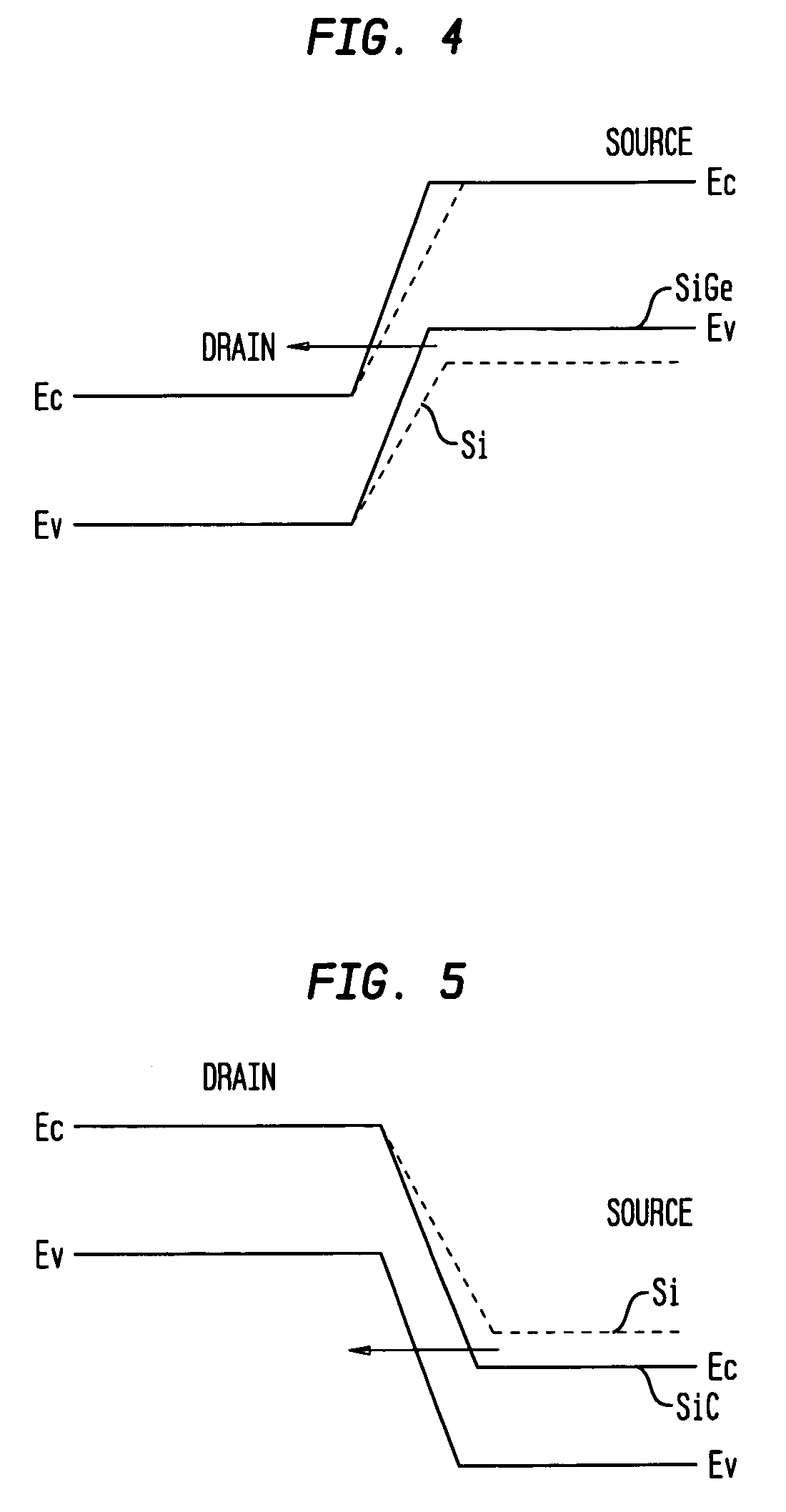

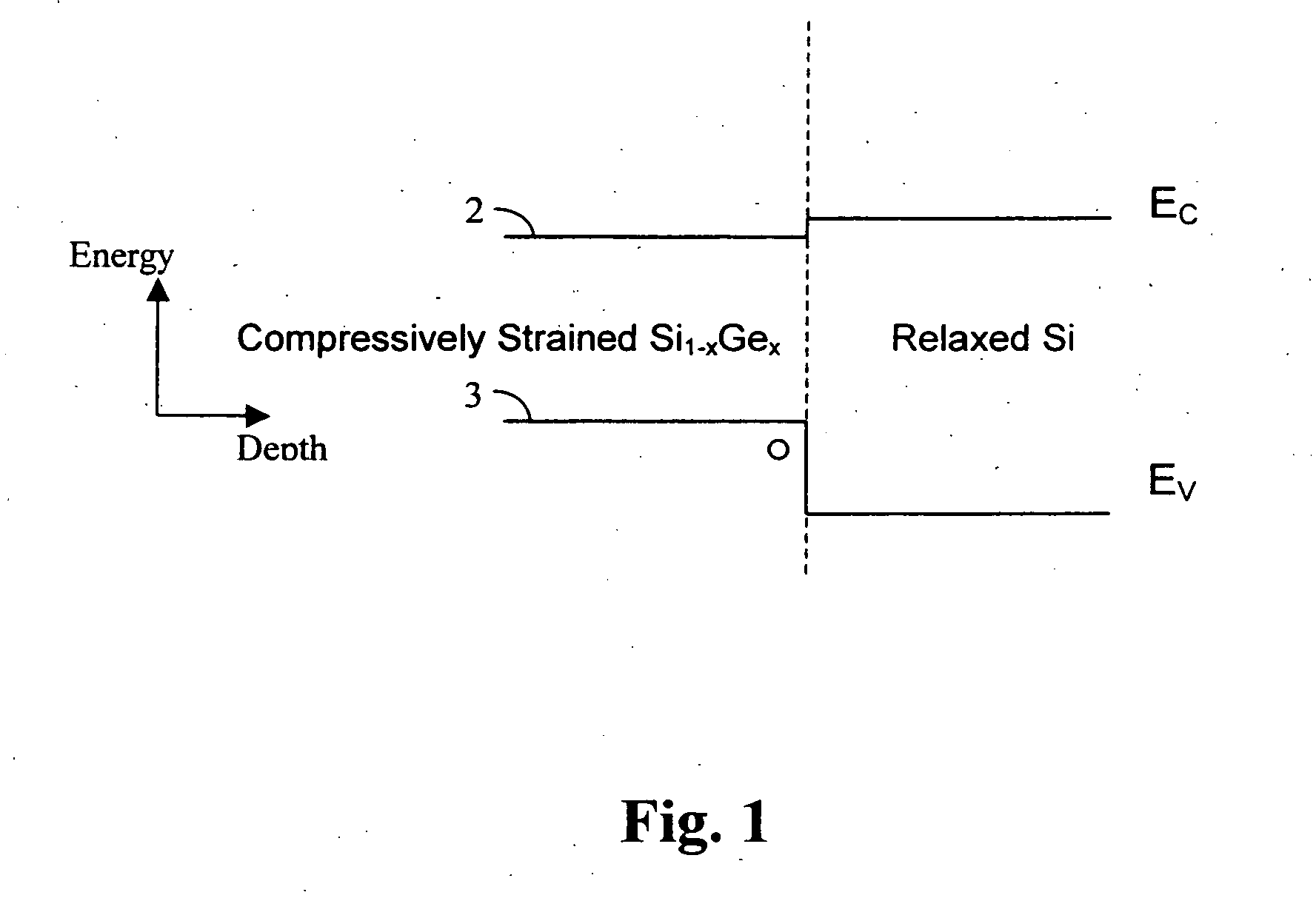

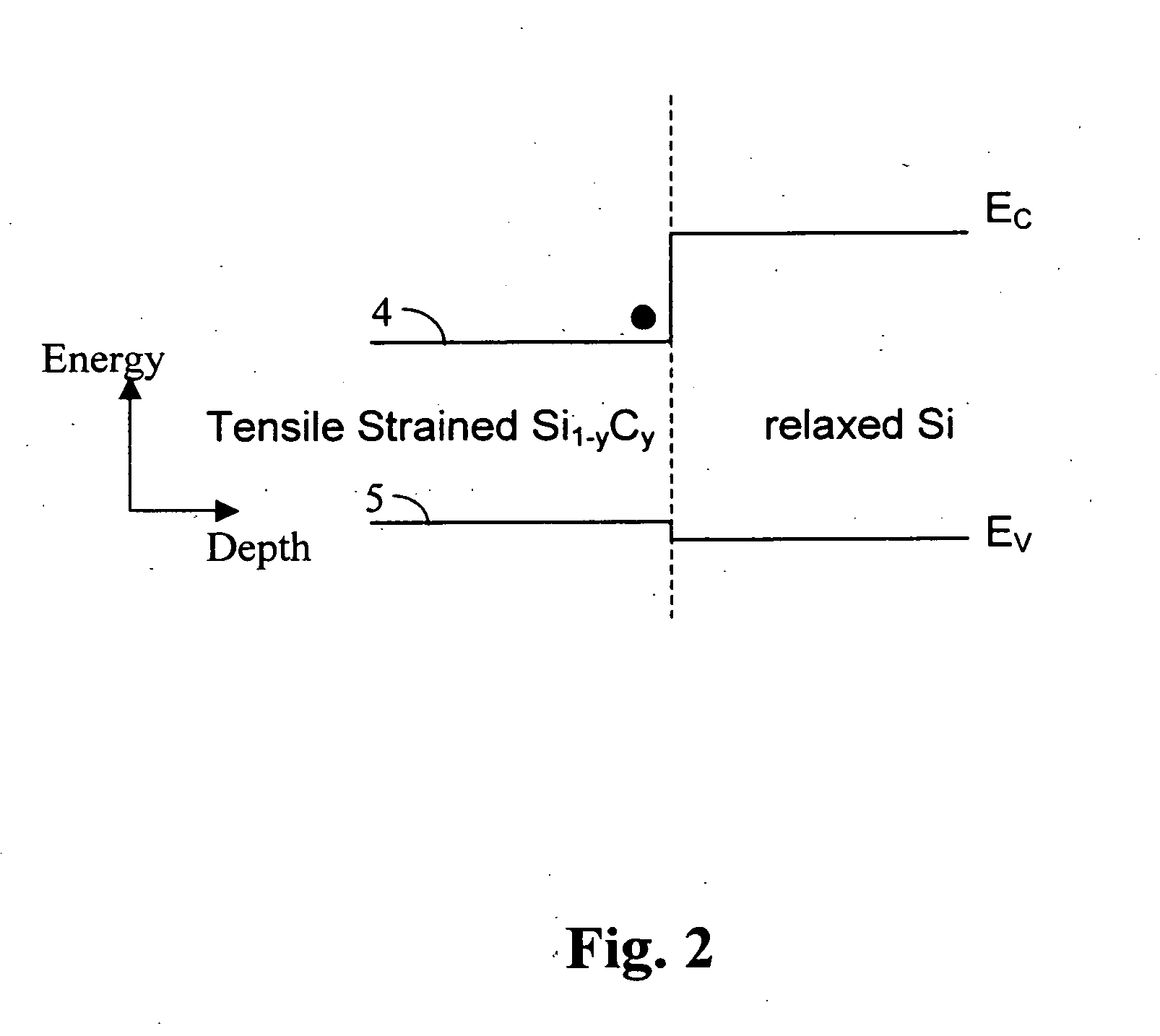

Heterojunction tunneling field effect transistors, and methods for fabricating the same

InactiveUS20070178650A1Increase currentEnhance junction currentSemiconductor/solid-state device manufacturingDiodeHeterojunctionDopant

The present invention relates to a heterojunction tunneling effect transistor (TFET), which comprises spaced apart source and drain regions with a channel region located therebetween and a gate stack located over the channel region. The drain region comprises a first semiconductor material and is doped with a first dopant species of a first conductivity type. The source region comprises a second, different semiconductor material and is doped with a second dopant species of a second, different conductivity type. The gate stack comprises at least a gate dielectric and a gate conductor. When the heterojunction TFET is an n-channel TFET, the drain region comprises n-doped silicon, while the source region comprises p-doped silicon germanium. When the heterojunction TFET is a p-channel TFET, the drain region comprises p-doped silicon, while the source region comprises n-doped silicon carbide.

Owner:IBM CORP

Strain balanced nitride heterojunction transistors and methods of fabricating strain balanced nitride heterojunction transistors

ActiveUS20060121682A1Semiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionHigh concentration

A nitride based heterojunction transistor includes a substrate and a first Group III nitride layer, such as an AlGaN based layer, on the substrate. The first Group III-nitride based layer has an associated first strain. A second Group III-nitride based layer, such as a GaN based layer, is on the first Group III-nitride based layer. The second Group III-nitride based layer has a bandgap that is less than a bandgap of the first Group III-nitride based layer and has an associated second strain. The second strain has a magnitude that is greater than a magnitude of the first strain. A third Group III-nitride based layer, such as an AlGaN or AlN layer, is on the GaN layer. The third Group III-nitride based layer has a bandgap that is greater than the bandgap of the second Group III-nitride based layer and has an associated third strain. The third strain is of opposite strain type to the second strain. A source contact, a drain contact and a gate contact may be provided on the third Group III-nitride based layer. Nitride based heterojunction transistors having an AlGaN based bottom confinement layer, a GaN based channel layer on the bottom confinement layer and an AlGaN based barrier layer on the channel layer, the barrier layer having a higher concentration of aluminum than the bottom confinement layer, are also provided. Methods of fabricating such transistor are also provided.

Owner:CREE INC

Solar cell having doped semiconductor heterojunction contacts

A silicon solar cell has doped amorphous silicon contacts formed on a tunnel silicon oxide layer on a surface of a silicon substrate. High temperature processing is unnecessary in fabricating the solar cell.

Owner:MAXEON SOLAR PTE LTD

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS20070148939A1Superb performanceSuperb scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

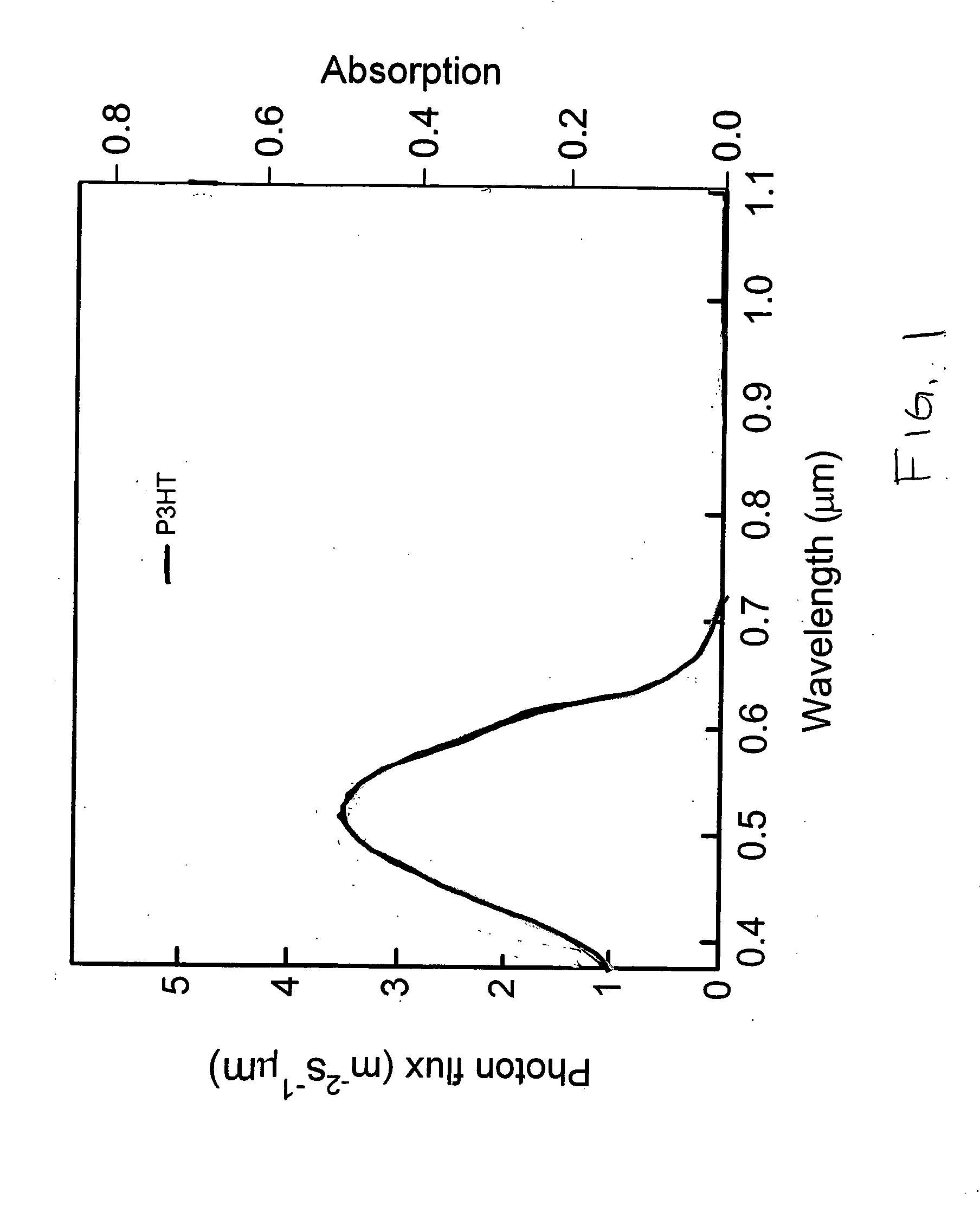

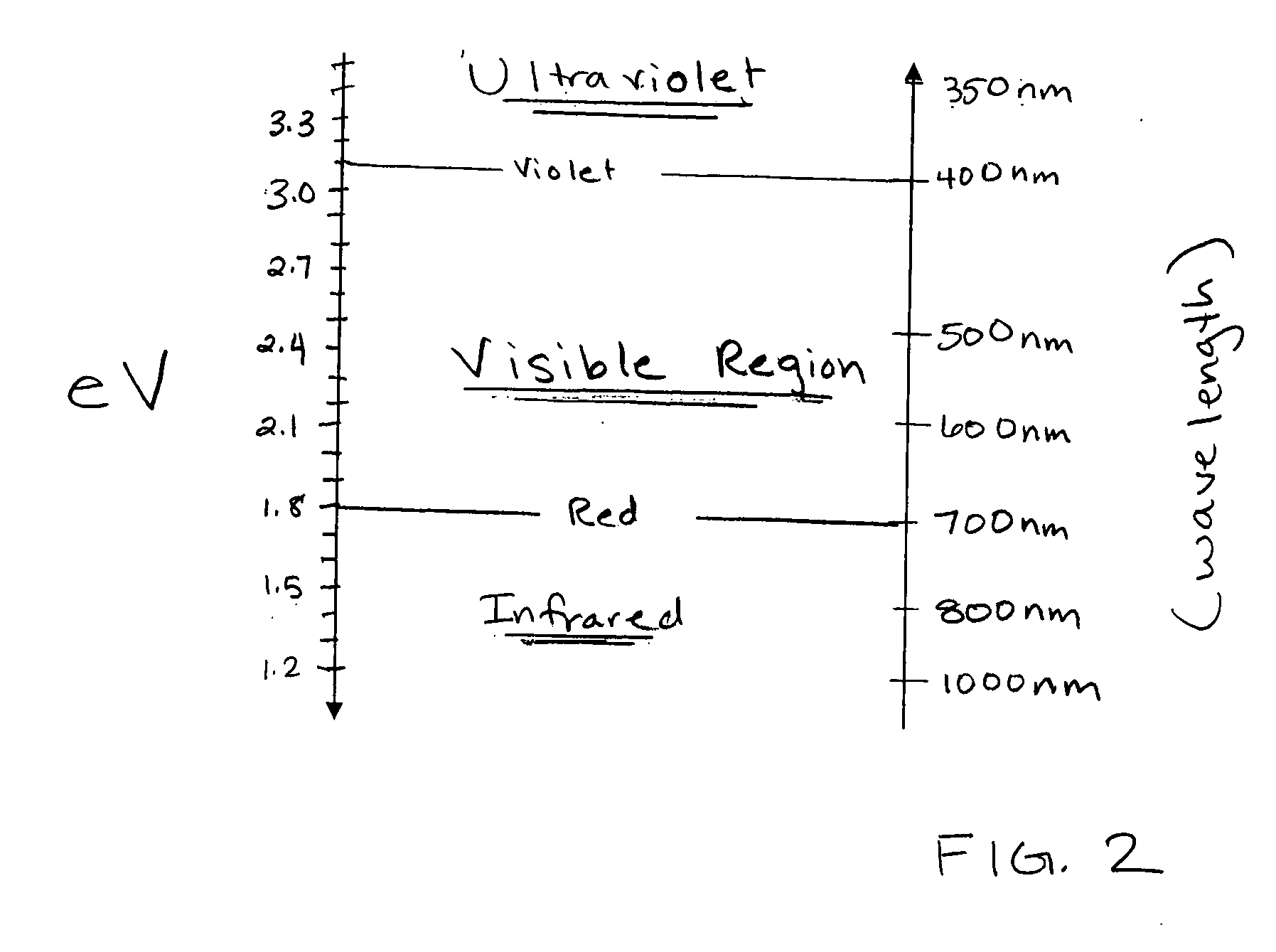

Organic solar cells including group IV nanocrystals and method of manufacture

InactiveUS20050061363A1Promote absorptionEasy to manufactureMaterial nanotechnologyFinal product manufactureHeterojunctionOrganic solar cell

An improved organic solar cell converts light into electricity. The organic solar cell includes a cathode, an anode, and a bulk heterojunction material disposed therebetween. The bulk heterojunction material includes a plurality of group IV nanocrystals (e.g., silicon nanocrystals) disposed within an organic absorber (e.g., an organic polymer).

Owner:EVERGREEN SOLAR

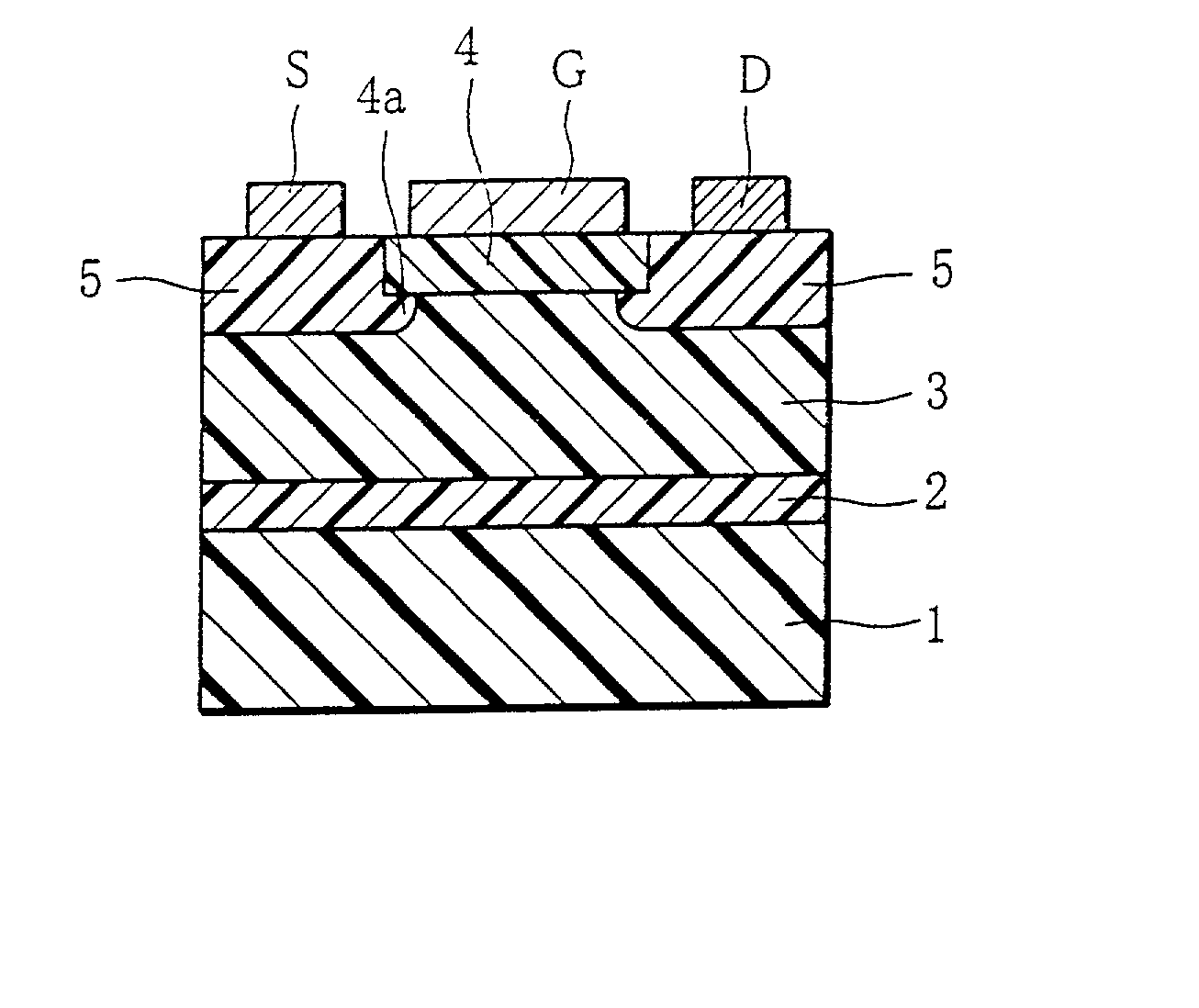

GaN-based high electron mobility transistor

InactiveUS20020079508A1Improve mobilityIncreased electrical resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectric resistivity

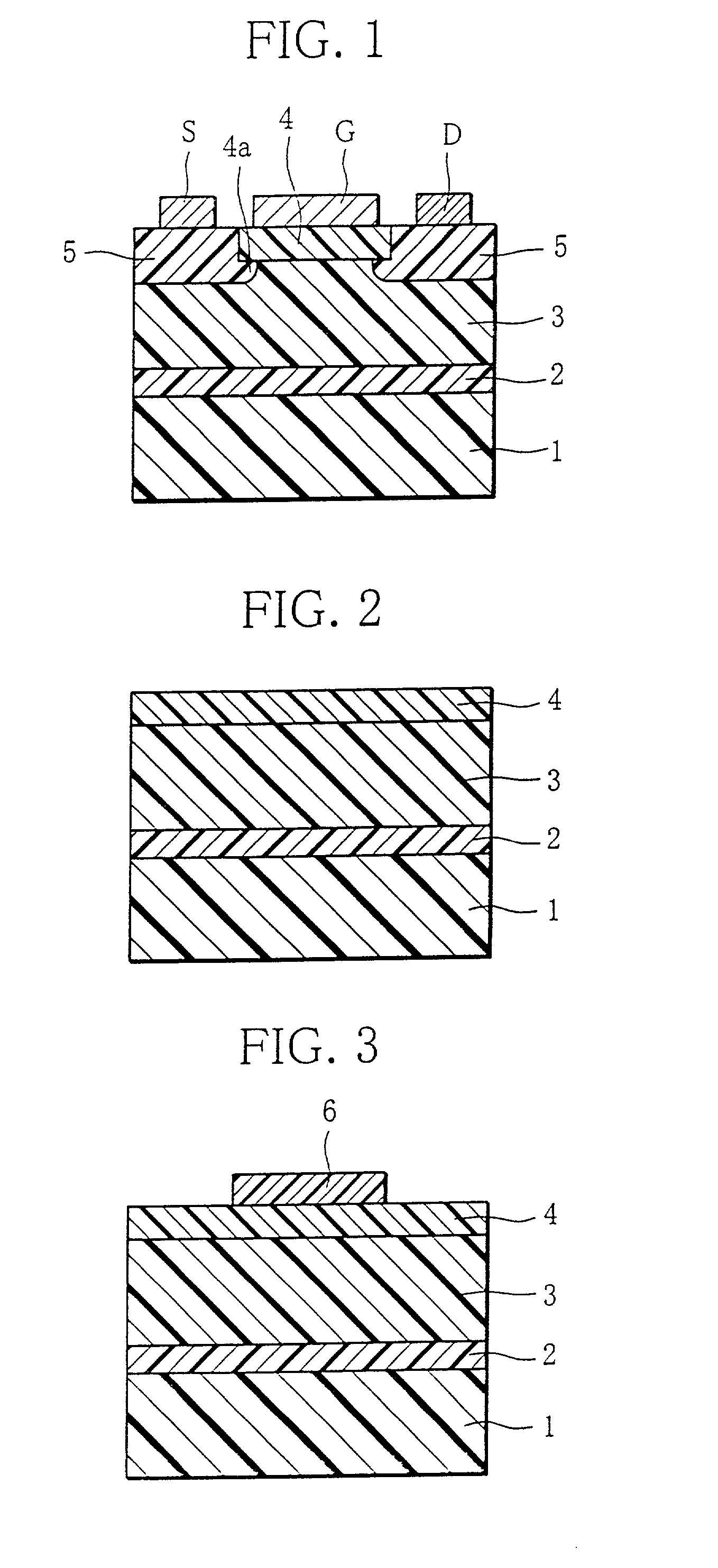

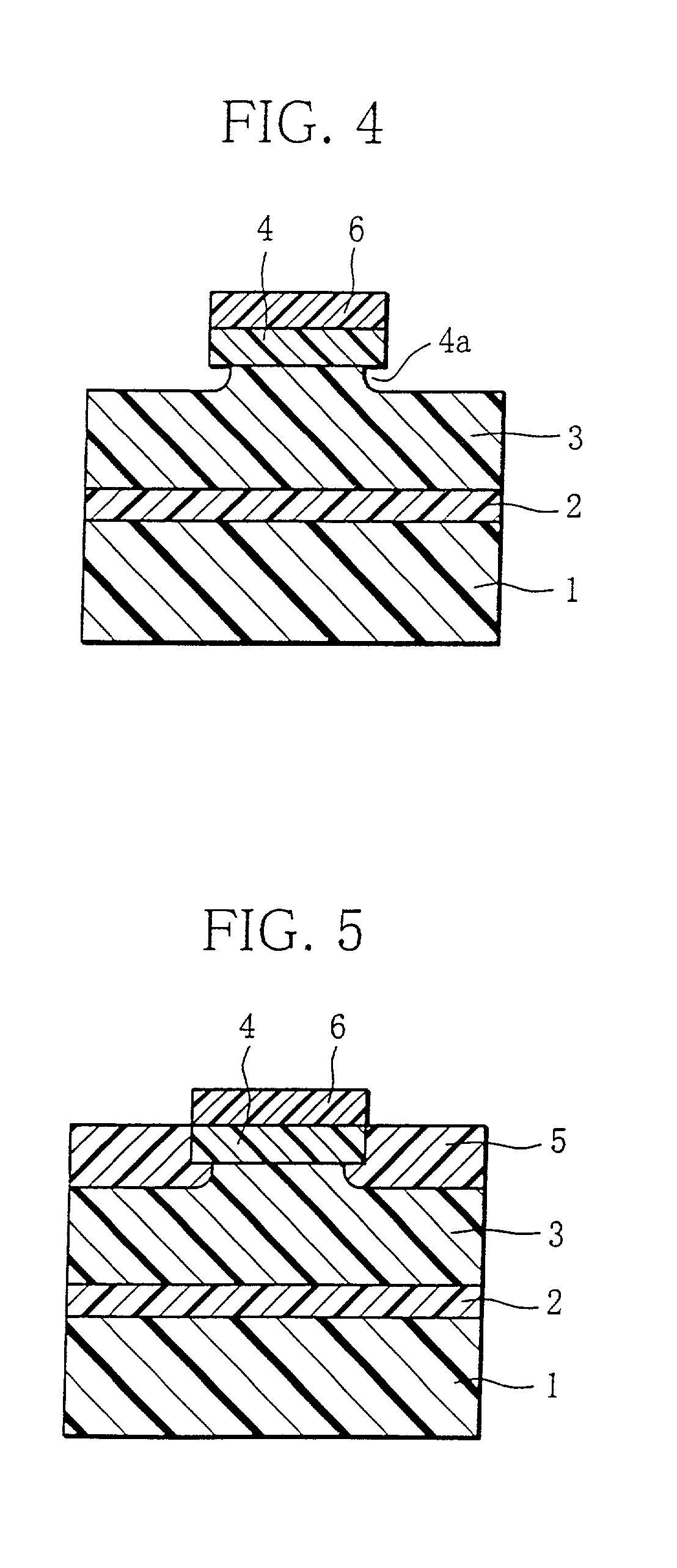

A GaN-based high electron mobility transistor (HEMT) has an undoped GaN layer where a two-dimensional electron gas layer is formed, the undoped GaN layer having a high electric resistivity enabling a pinch-off state to be obtained even when the gate bias voltage is 0 V. The GaN-based HEMT comprises a semi-insulating substrate on which a GaN buffer layer is formed. An undoped GaN layer is disposed on the GaN buffer layer and has an electric resistivity of not less than 1x106 OMEGA / cm2. An undoped AlGaN layer is disposed on the undoped GaN layer via a heterojunction such that an undercut portion is formed therebetween. An n-type GaN layer is further disposed in such a manner as to bury side portions of the undoped AlGaN layer and the undercut portion. The individual layers thus Ad form a layered structure. A gate electrode G is formed on the undoped AlGaN layer, and a source electrode S and a drain electrode D are formed on the n-type GaN layer.

Owner:FURUKAWA ELECTRIC CO LTD