Patents

Literature

5664 results about "Crystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Crystalline silicon (c-Si) is the crystalline forms of silicon, either multicrystalline silicon (multi-Si) consisting of small crystals, or monocrystalline silicon (mono-Si), a continuous crystal. Crystalline silicon is the dominant semiconducting material used in photovoltaic technology for the production of solar cells. These cells are assembled into solar panels as part of a photovoltaic system to generate solar power from sunlight.

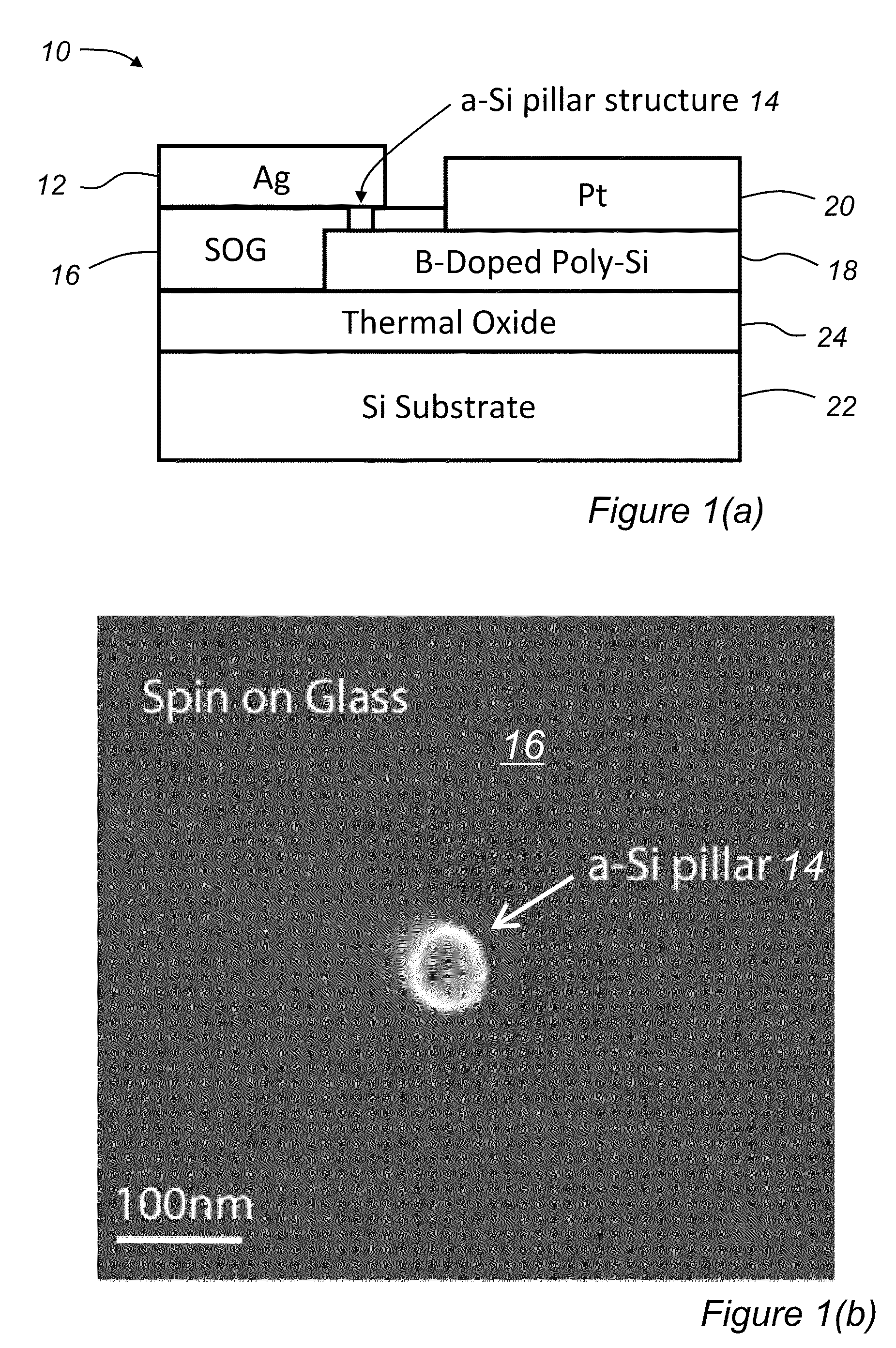

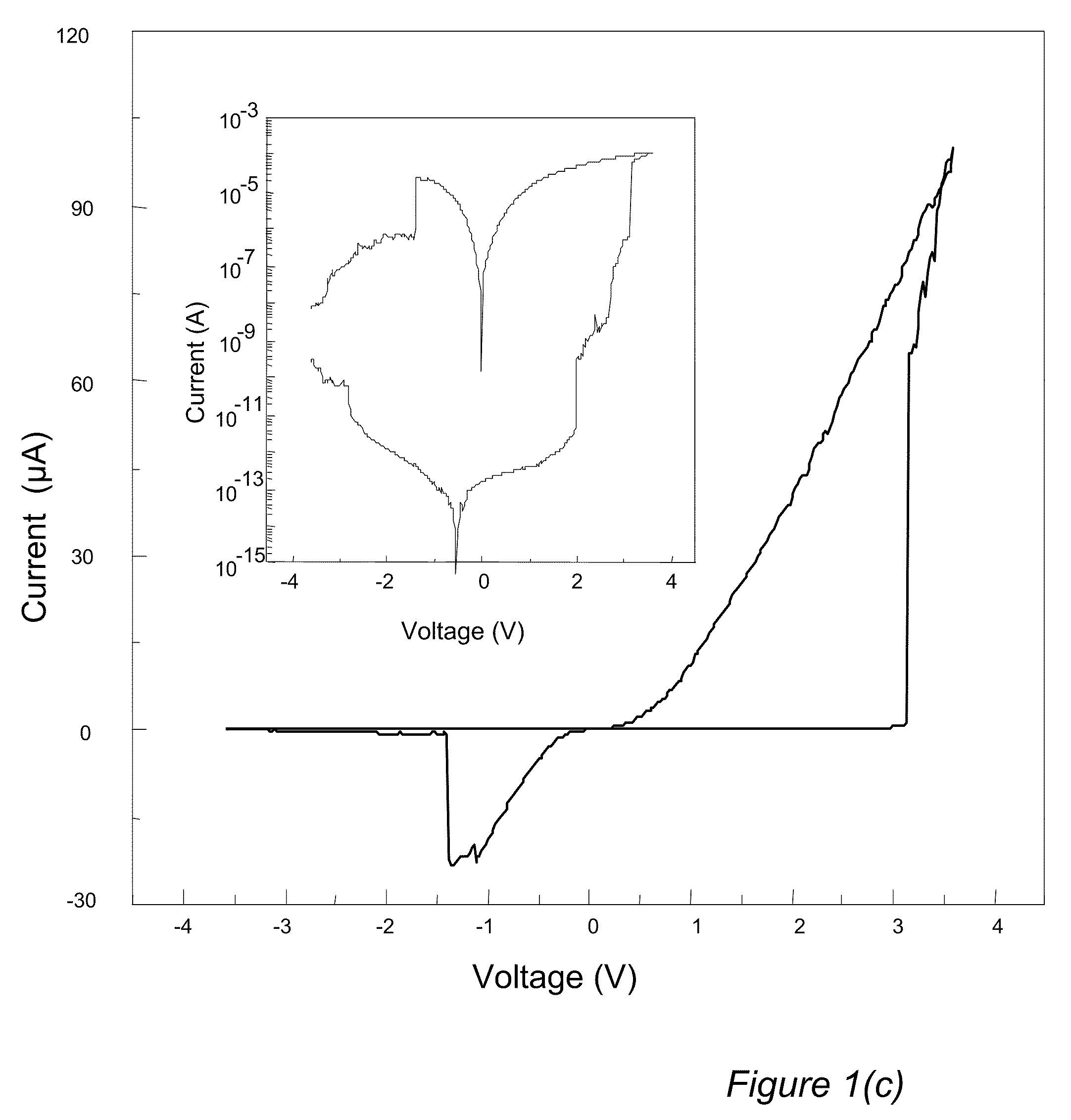

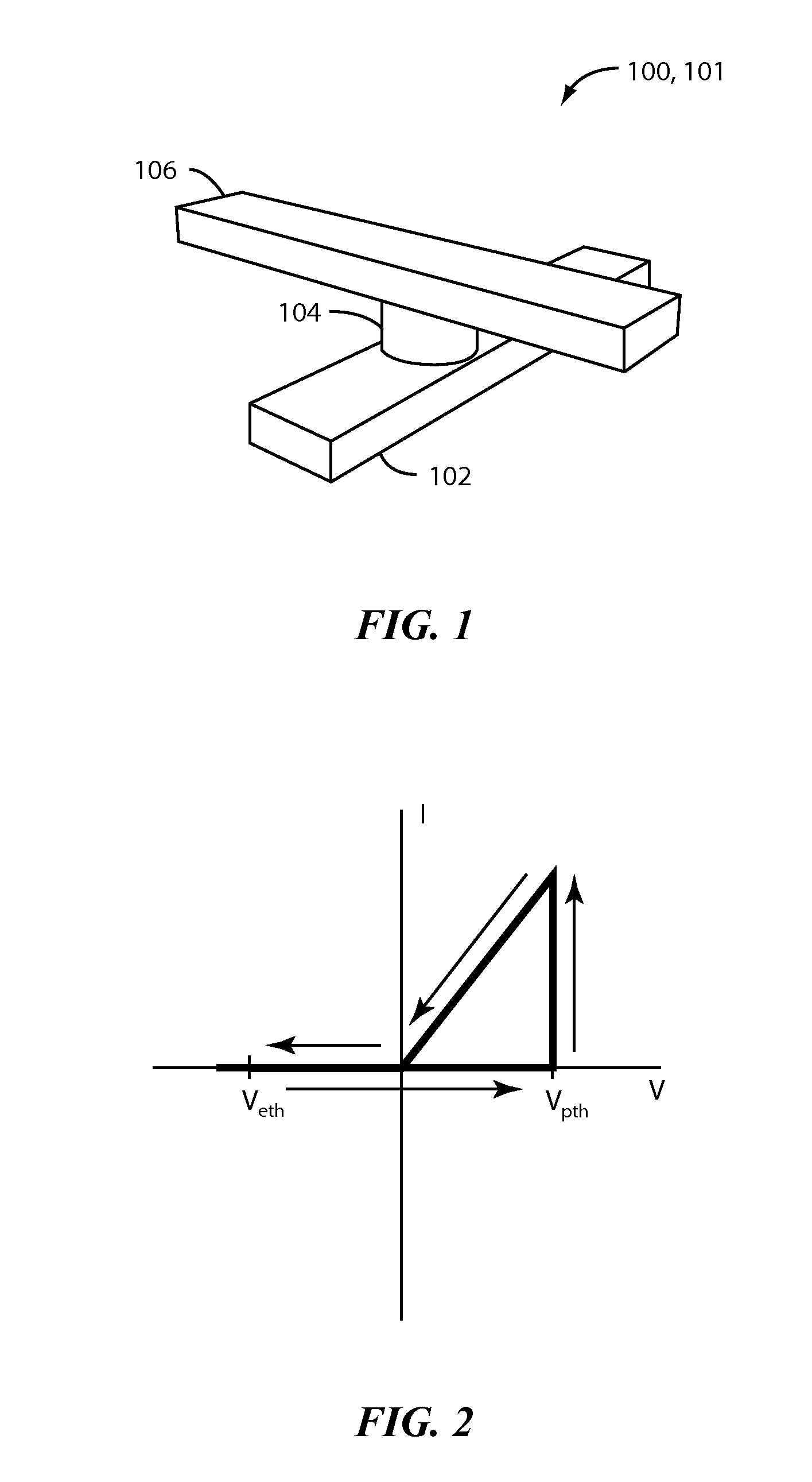

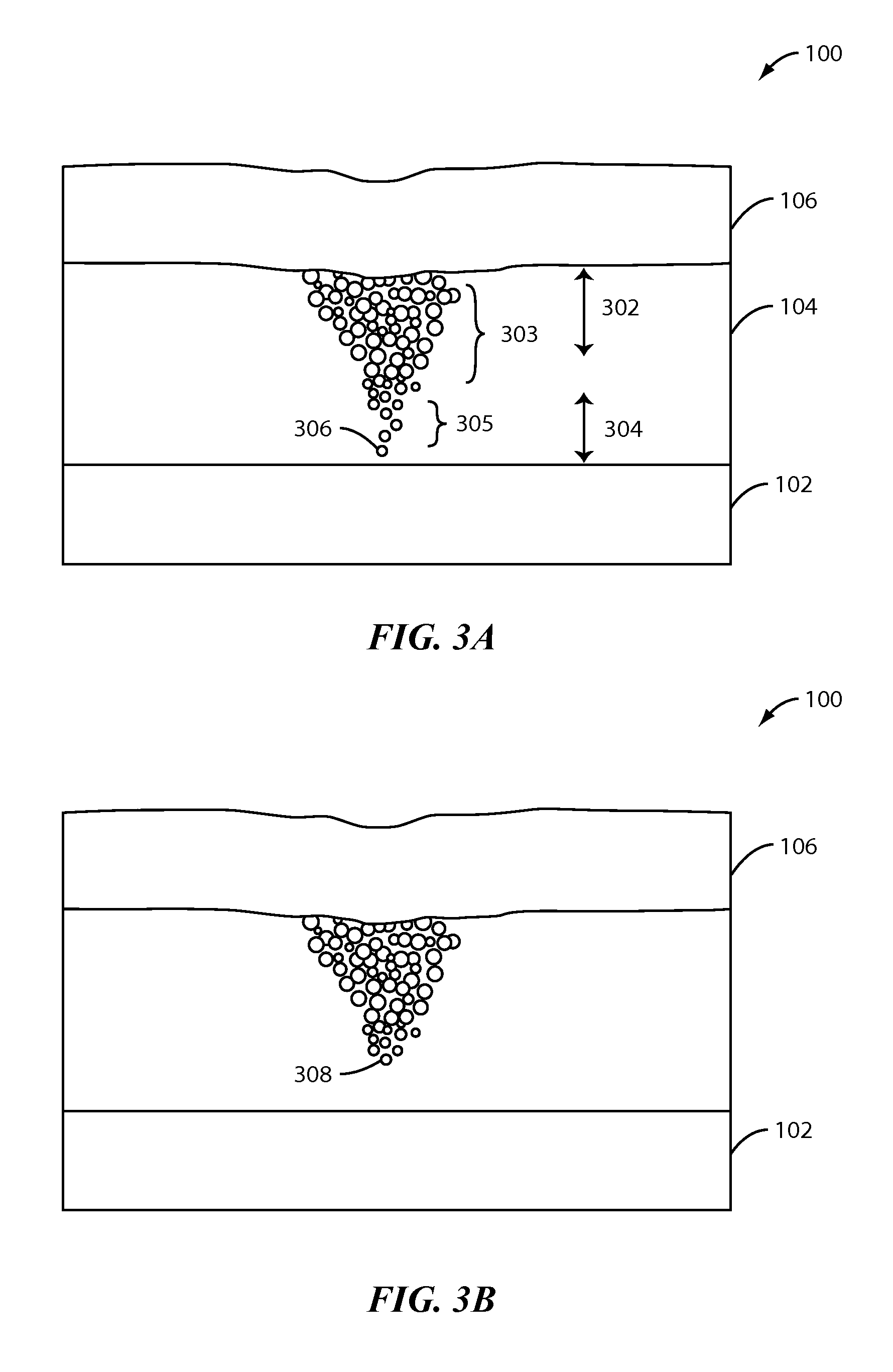

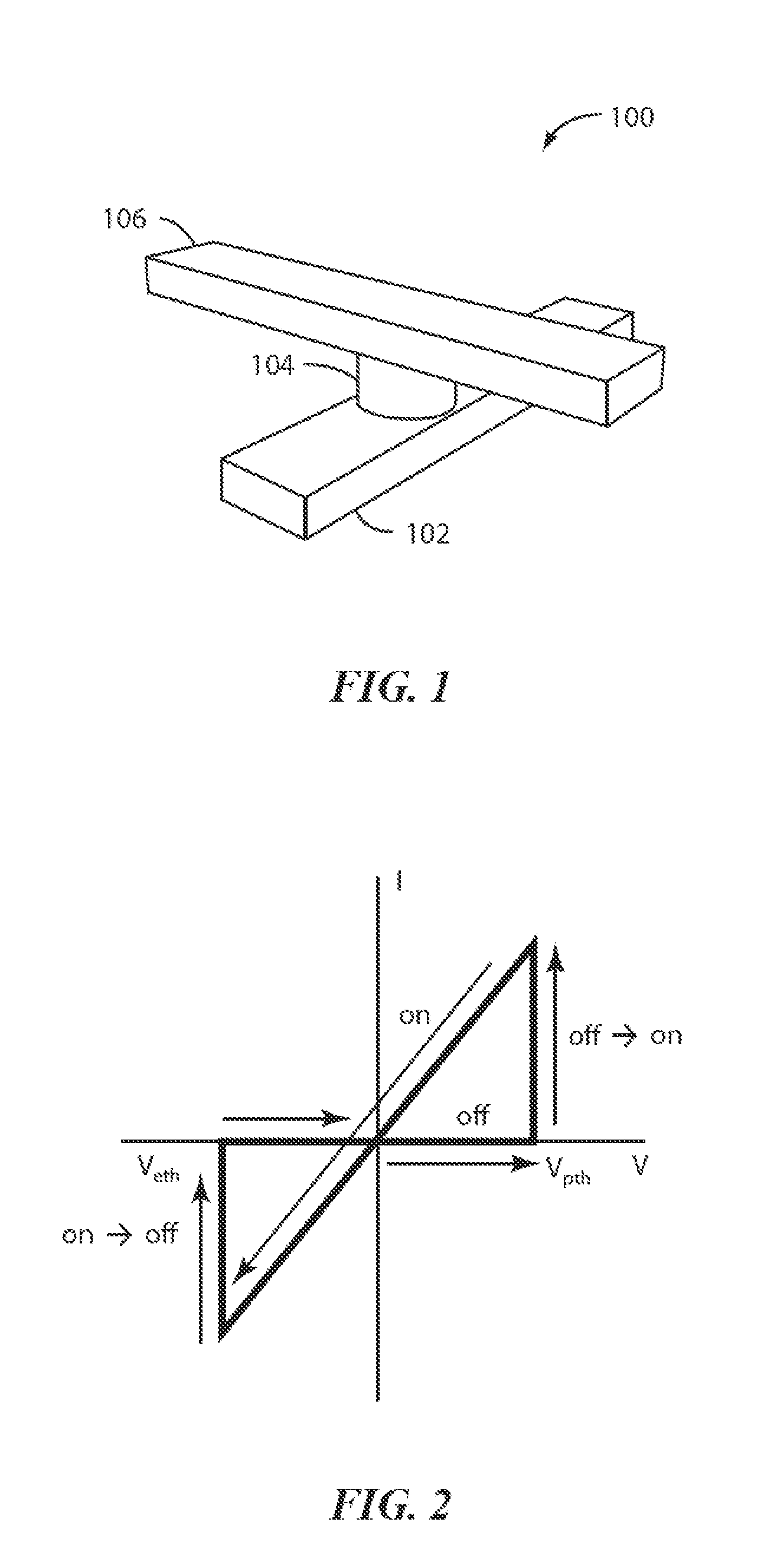

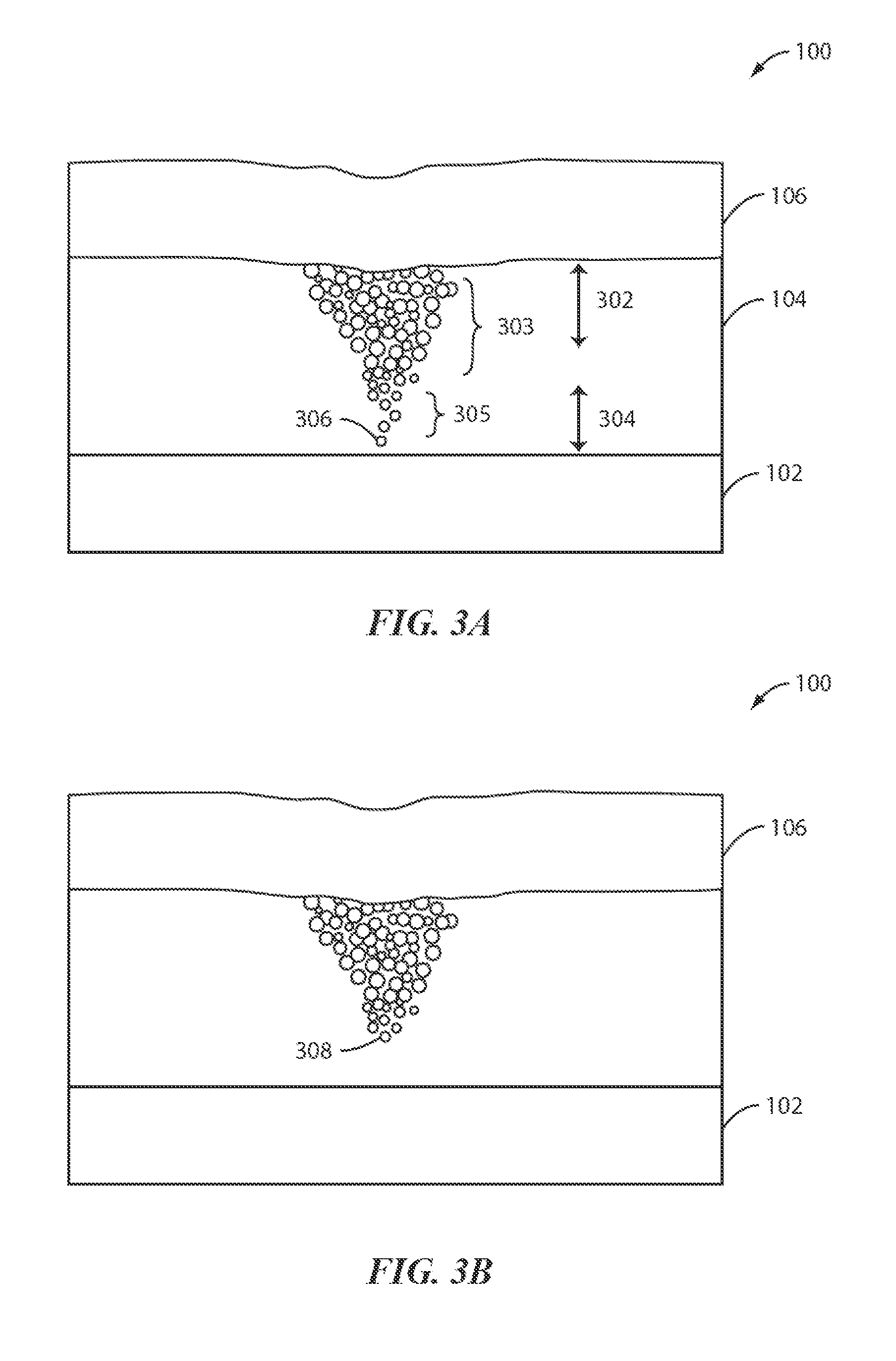

Silicon-based nanoscale resistive device with adjustable resistance

A non-volatile solid state resistive device that includes a first electrode, a p-type poly-silicon second electrode, and a non-crystalline silicon nanostructure electrically connected between the electrodes. The nanostructure has a resistance that is adjustable in response to a voltage being applied to the nanostructure via the electrodes. The nanostructure can be formed as a nanopillar embedded in an insulating layer located between the electrodes. The first electrode can be a silver or other electrically conductive metal electrode. A third (metal) electrode can be connected to the p-type poly-silicon second electrode at a location adjacent the nanostructure to permit connection of the two metal electrodes to other circuitry. The resistive device can be used as a unit memory cell of a digital non-volatile memory device to store one or more bits of digital data by varying its resistance between two or more values.

Owner:RGT UNIV OF MICHIGAN

Semiconductor device and method for fabricating the same

InactiveUS6077731AImprove featuresPromote crystallizationTransistorSolid-state devicesCrystalline siliconSemiconductor

A novel and very useful method for forming a crystal silicon film by introducing a metal element which promotes crystallization of silicon to an amorphous silicon film and for eliminating or reducing the metal element existing within the crystal silicon film thus obtained is provided. The method for fabricating a semiconductor device comprises steps of intentionally introducing the metal element which promotes crystallization of silicon to the amorphous silicon film and crystallizing the amorphous silicon film by a first heat treatment to obtain the crystal silicon film; eliminating or reducing the metal element existing within the crystal silicon film by implementing a second heat treatment within an oxidizing atmosphere; eliminating a thermal oxide film formed in the previous step; and forming another thermal oxide film on the surface of the region from which the thermal oxide film has been eliminated by implementing another thermal oxidation.

Owner:SEMICON ENERGY LAB CO LTD

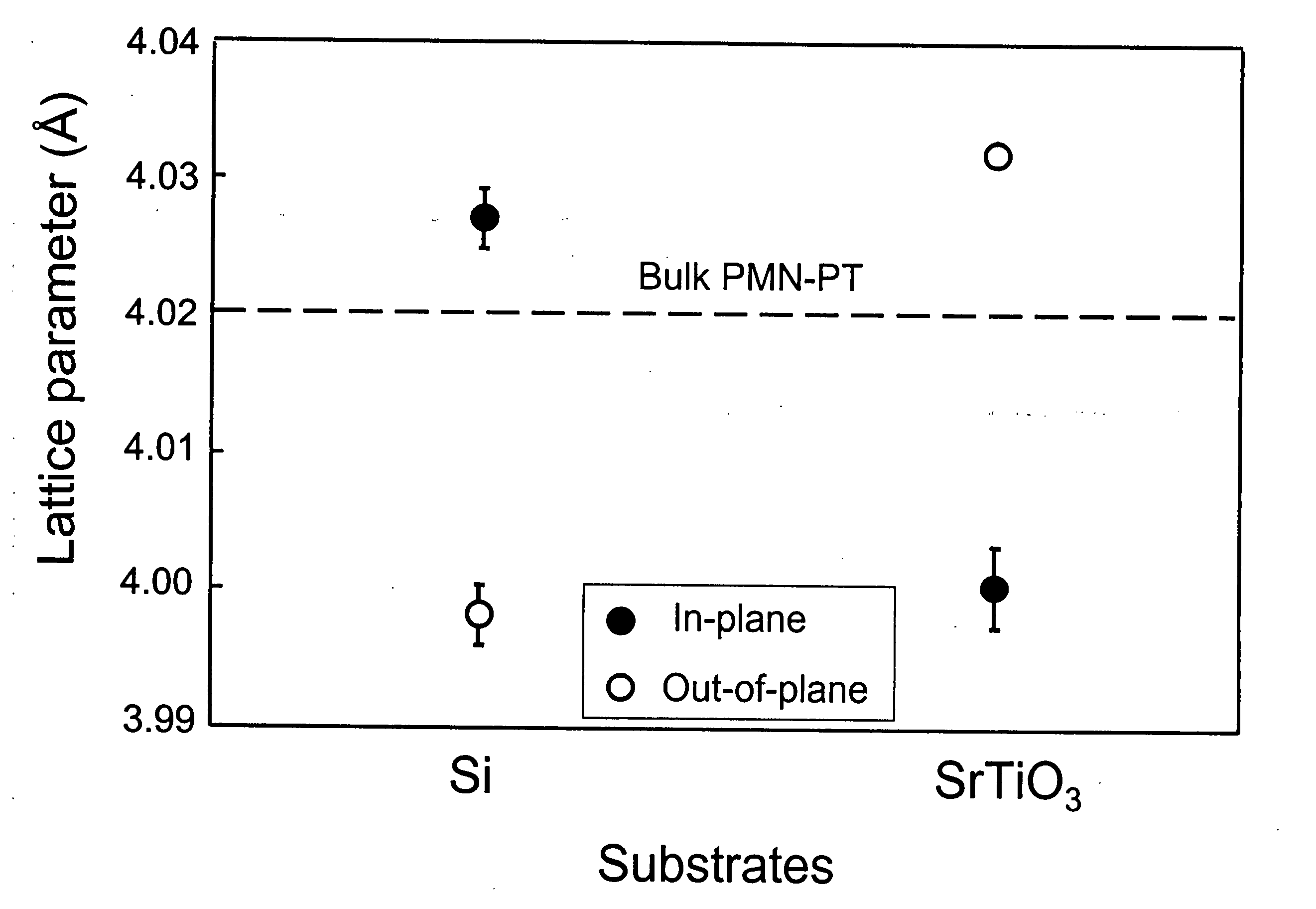

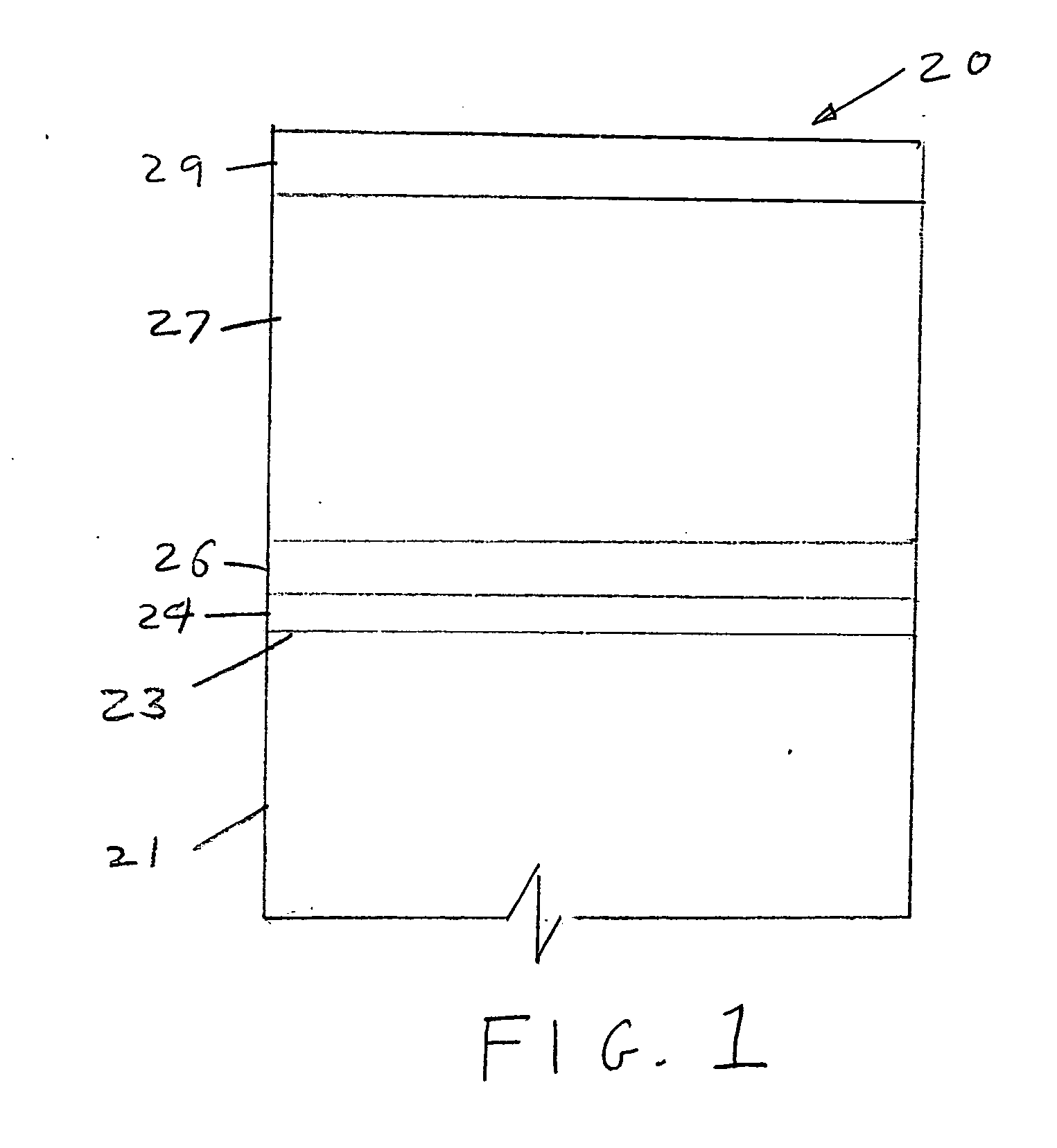

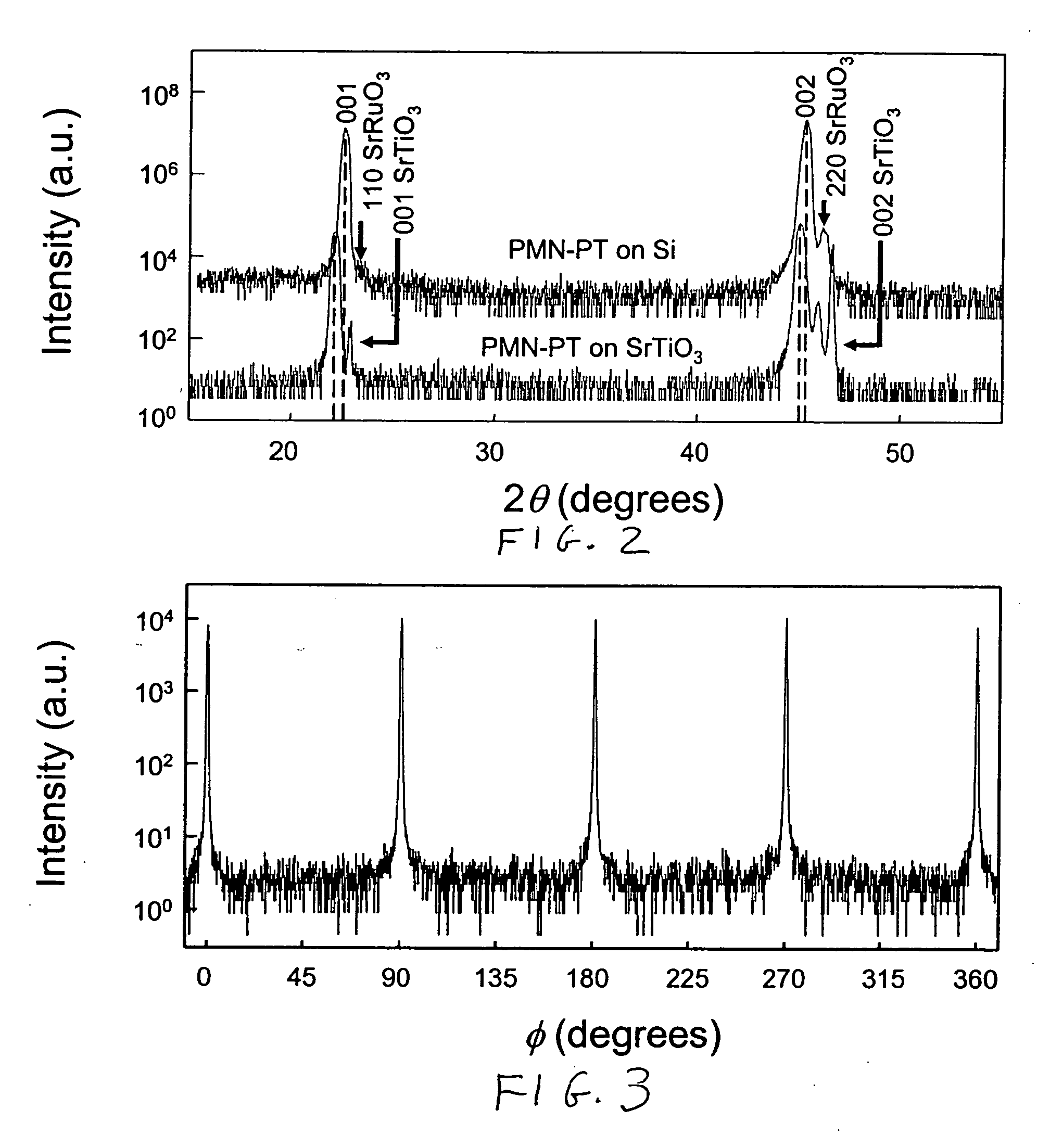

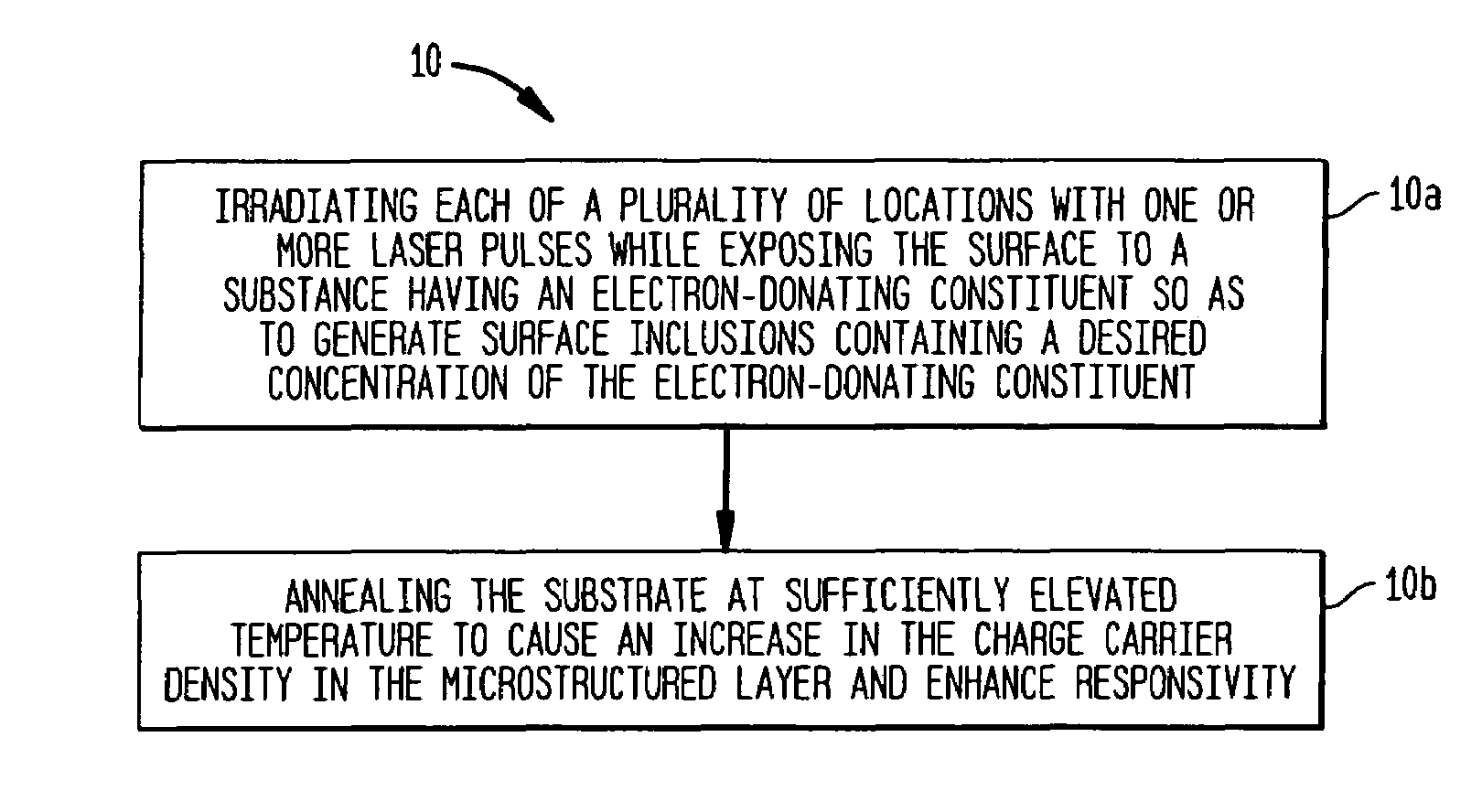

Perovskite-based thin film structures on miscut semiconductor substrates

InactiveUS20060288928A1Quality improvementGood metallic behaviorPolycrystalline material growthFrom chemically reactive gasesCrystal structureCrystal plane

A perovskite-based thin film structure includes a semiconductor substrate layer, such as a crystalline silicon layer, having a top surface cut at an angle to the (001) crystal plane of the crystalline silicon. A perovskite seed layer is epitaxially grown on the top surface of the substrate layer. An overlayer of perovskite material is epitaxially grown above the seed layer. In some embodiments the perovskite overlayer is a piezoelectric layer grown to a thickness of at least 0.5 μm and having a substantially pure perovskite crystal structure, preferably substantially free of pyrochlore phase, resulting in large improvements in piezoelectric characteristics as compared to conventional thin film piezoelectric materials.

Owner:PENN STATE RES FOUND +1

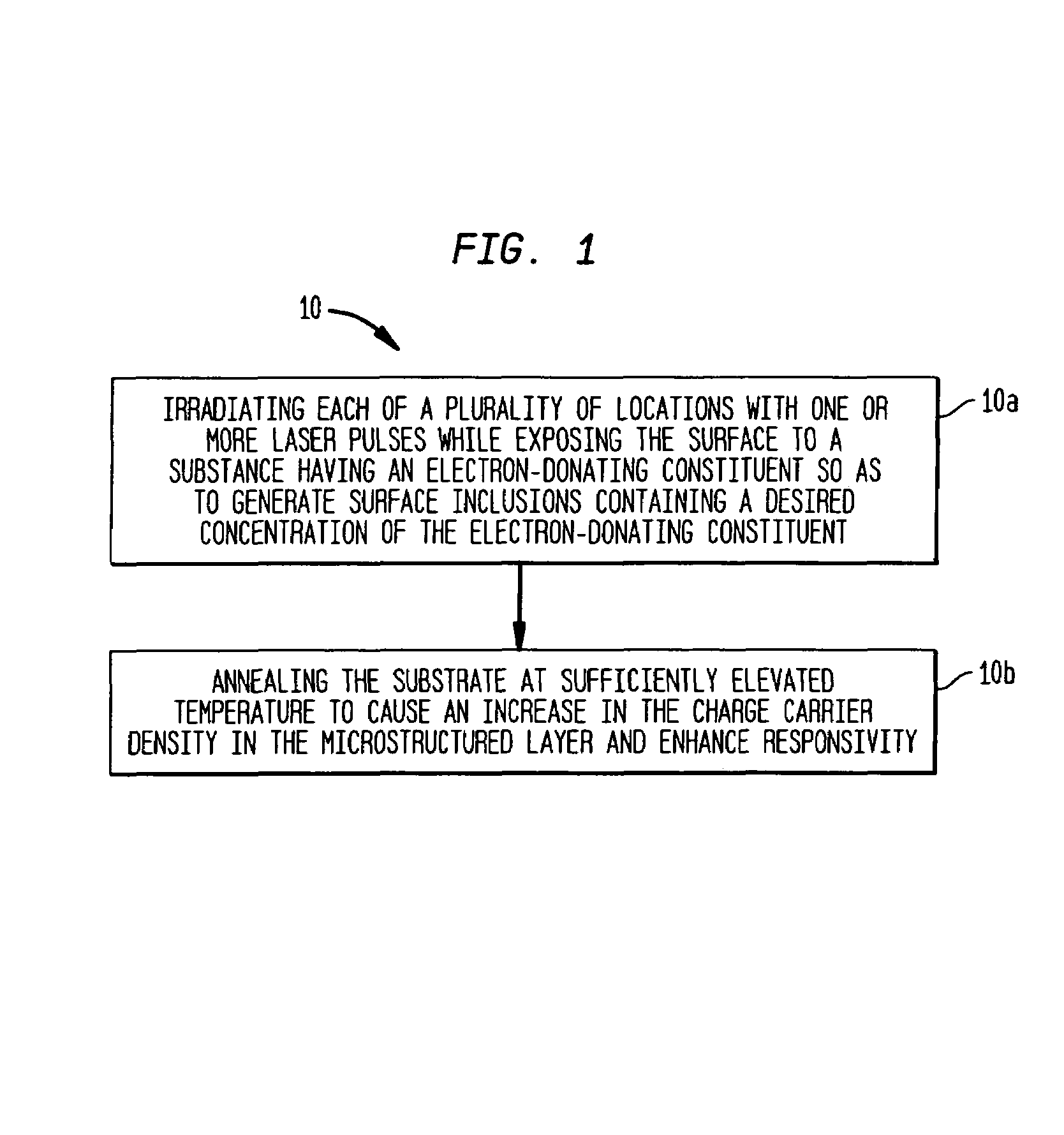

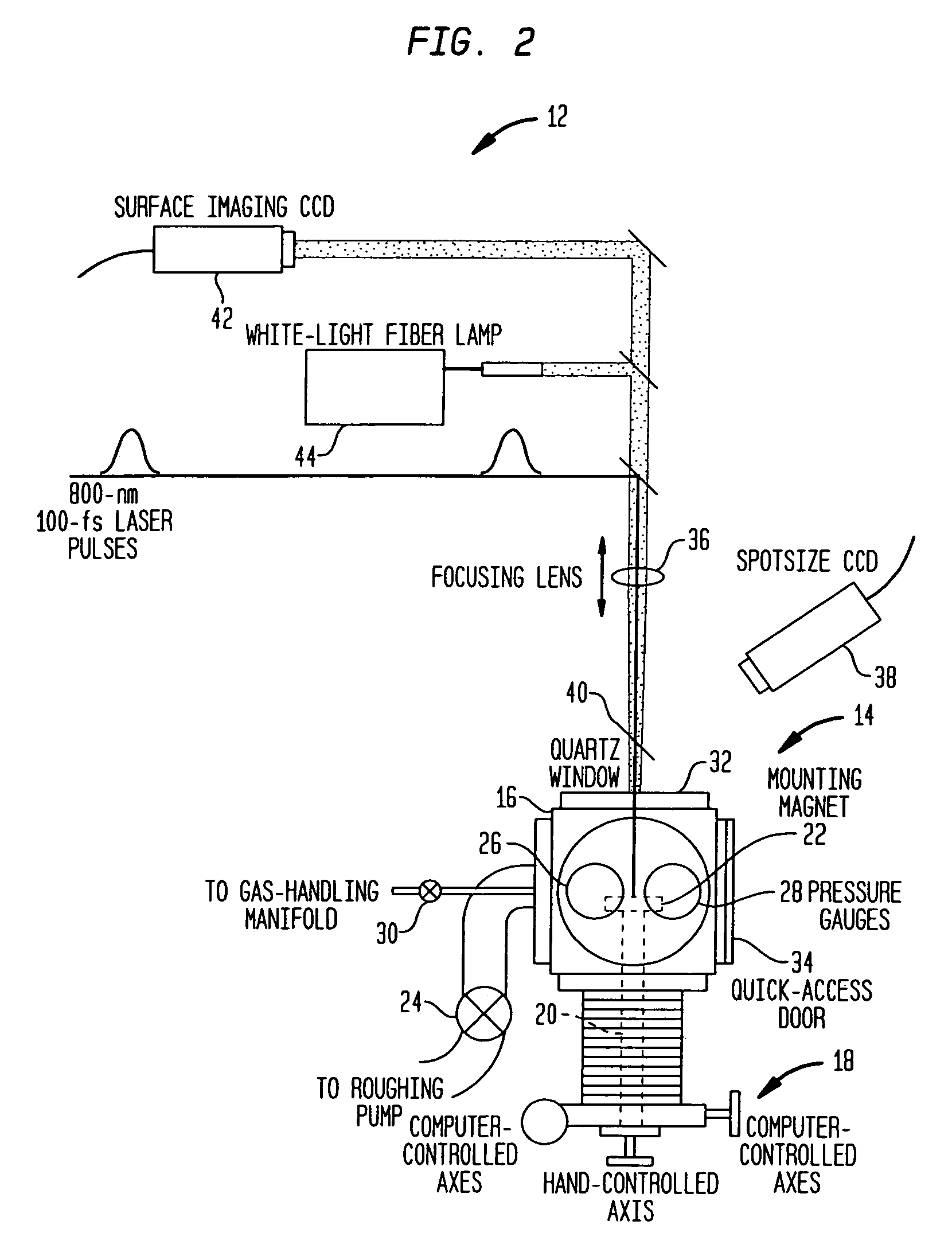

Manufacture of silicon-based devices having disordered sulfur-doped surface layers

InactiveUS7354792B2Final product manufactureSemiconductor/solid-state device manufacturingSurface layerCharge-carrier density

The present invention provides methods of fabricating a radiation-absorbing semiconductor wafer by irradiating at least one surface location of a silicon substrate, e.g., an n-doped crystalline silicon, by a plurality of temporally short laser pulses, e.g., femtosecond pulses, while exposing that location to a substance, e.g., SF6, having an electron-donating constituent so as to generate a substantially disordered surface layer (i.e., a microstructured layer) that incorporates a concentration of that electron-donating constituent, e.g., sulfur. The substrate is also annealed at an elevated temperature and for a duration selected to enhance the charge carrier density in the surface layer. For example, the substrate can be annealed at a temperature in a range of about 700 K to about 900 K.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Manufacturing method of fin-type field effect transistor

InactiveUS20080171407A1Inhibition formationIncrease etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A method for manufacturing a fin-type field effect transistor simply and securely by using a SOI (Silicon On Insulator) wafer, capable of suppressing an undercut formation, is disclosed. The method includes forming a fin-shaped protrusion by selectively dry-etching a single crystalline silicon layer until an underlying buried oxide layer is exposed; forming a sacrificial oxide film by oxidizing a surface of the protrusion including a damage inflicted thereon; and forming a fin having a clean surface by removing the sacrificial oxide film by etching, wherein an etching rate r1 of the sacrificial oxide film is higher than an etching rate r2 of the buried oxide layer during the etching.

Owner:TOKYO ELECTRON LTD

Method of manufacturing a semiconductor memory device

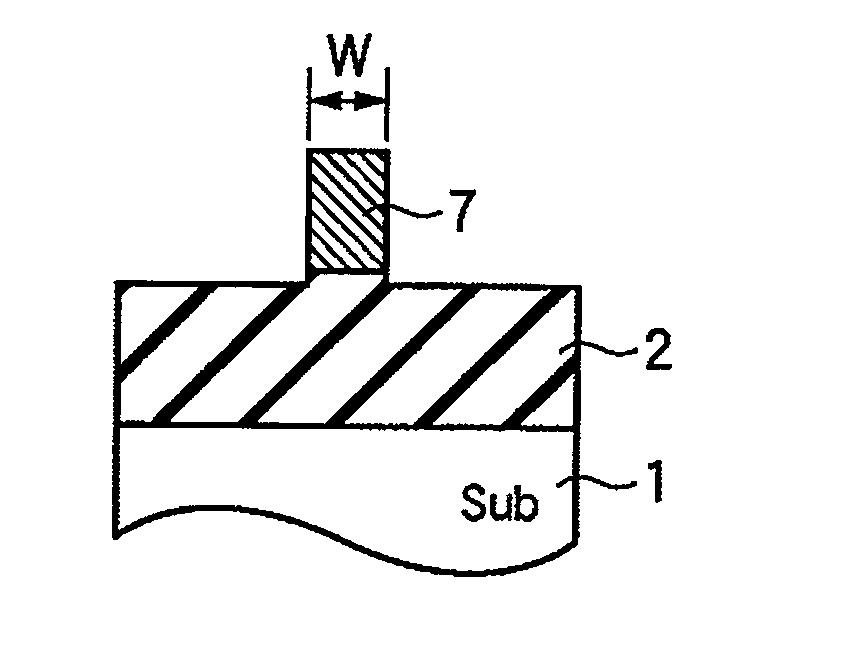

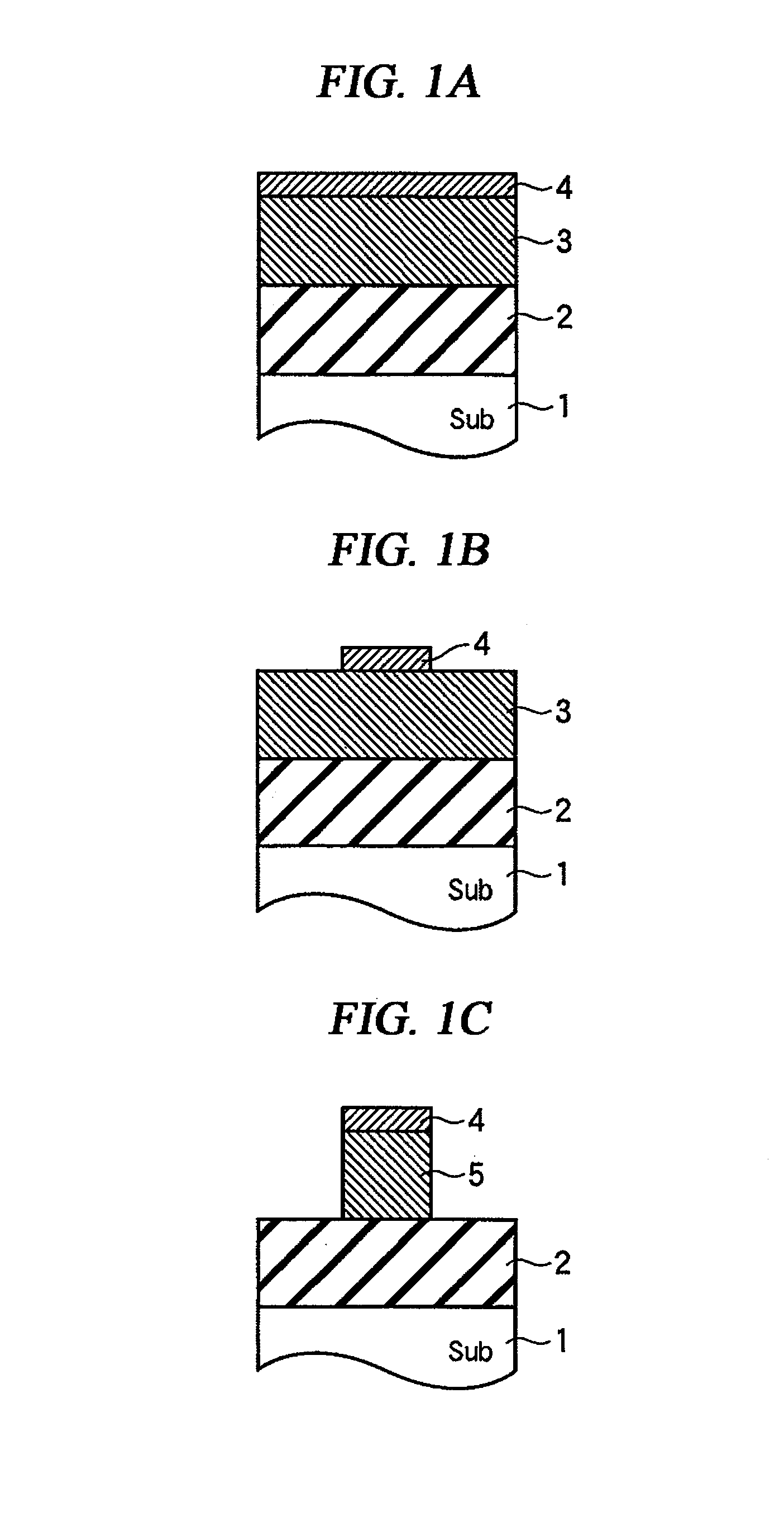

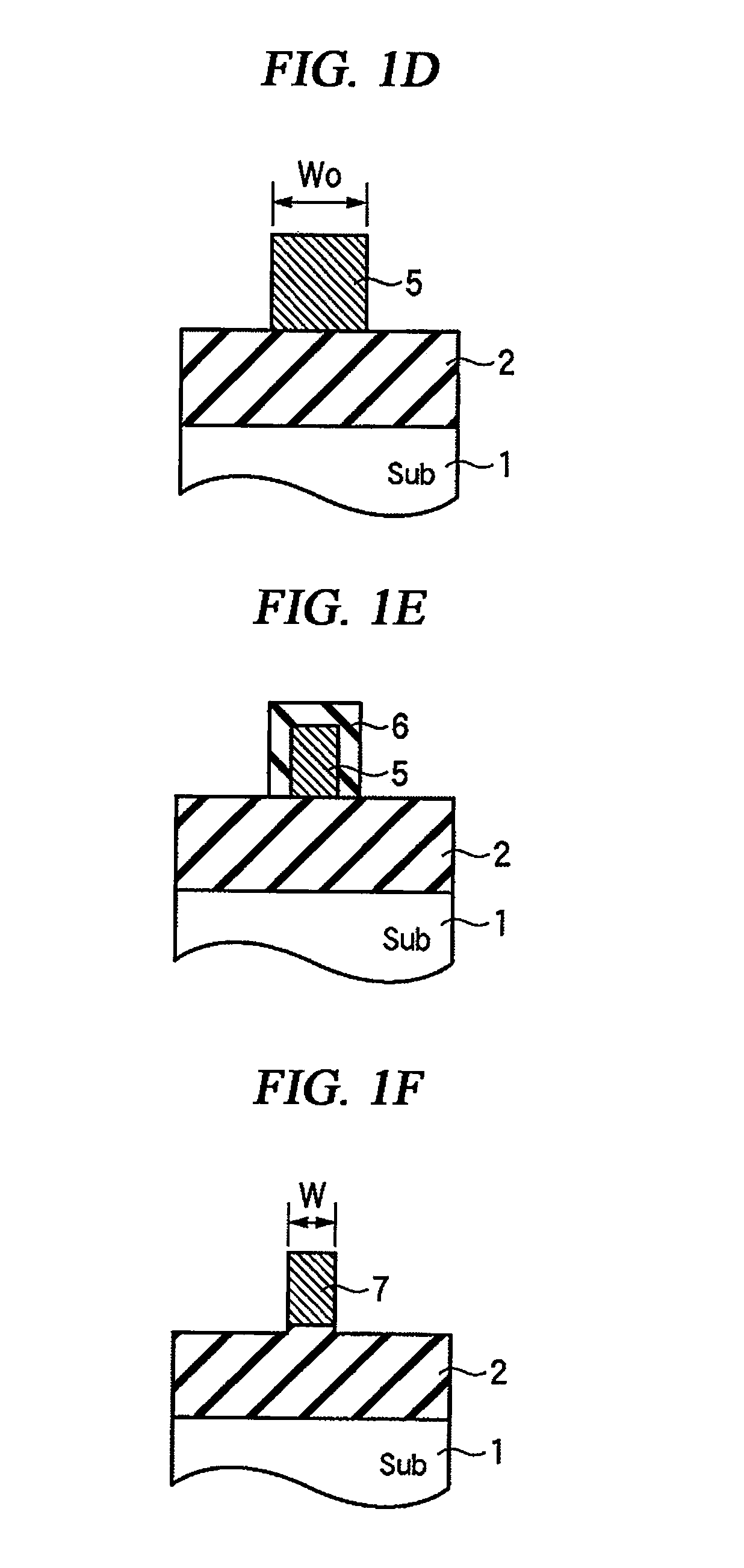

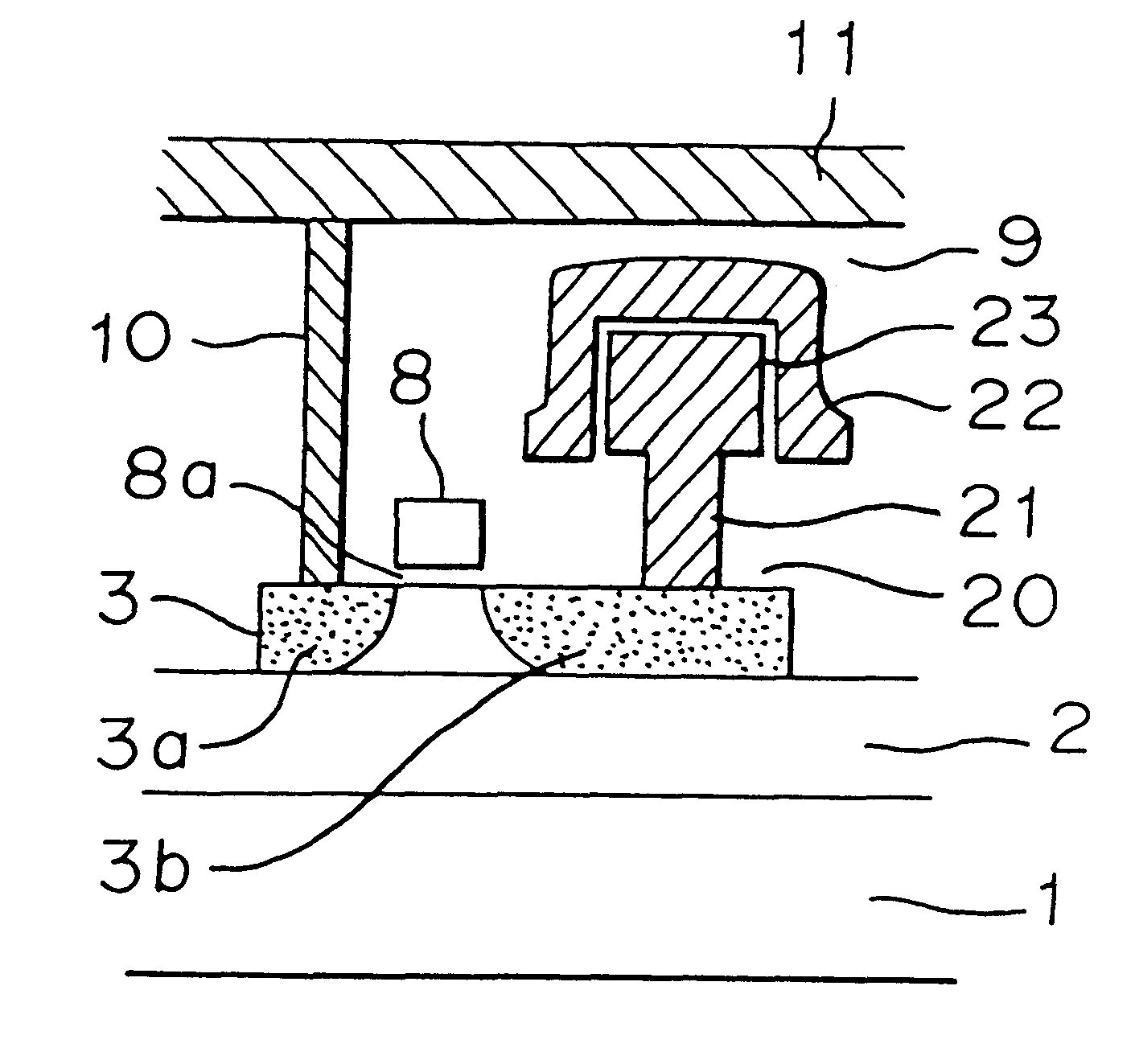

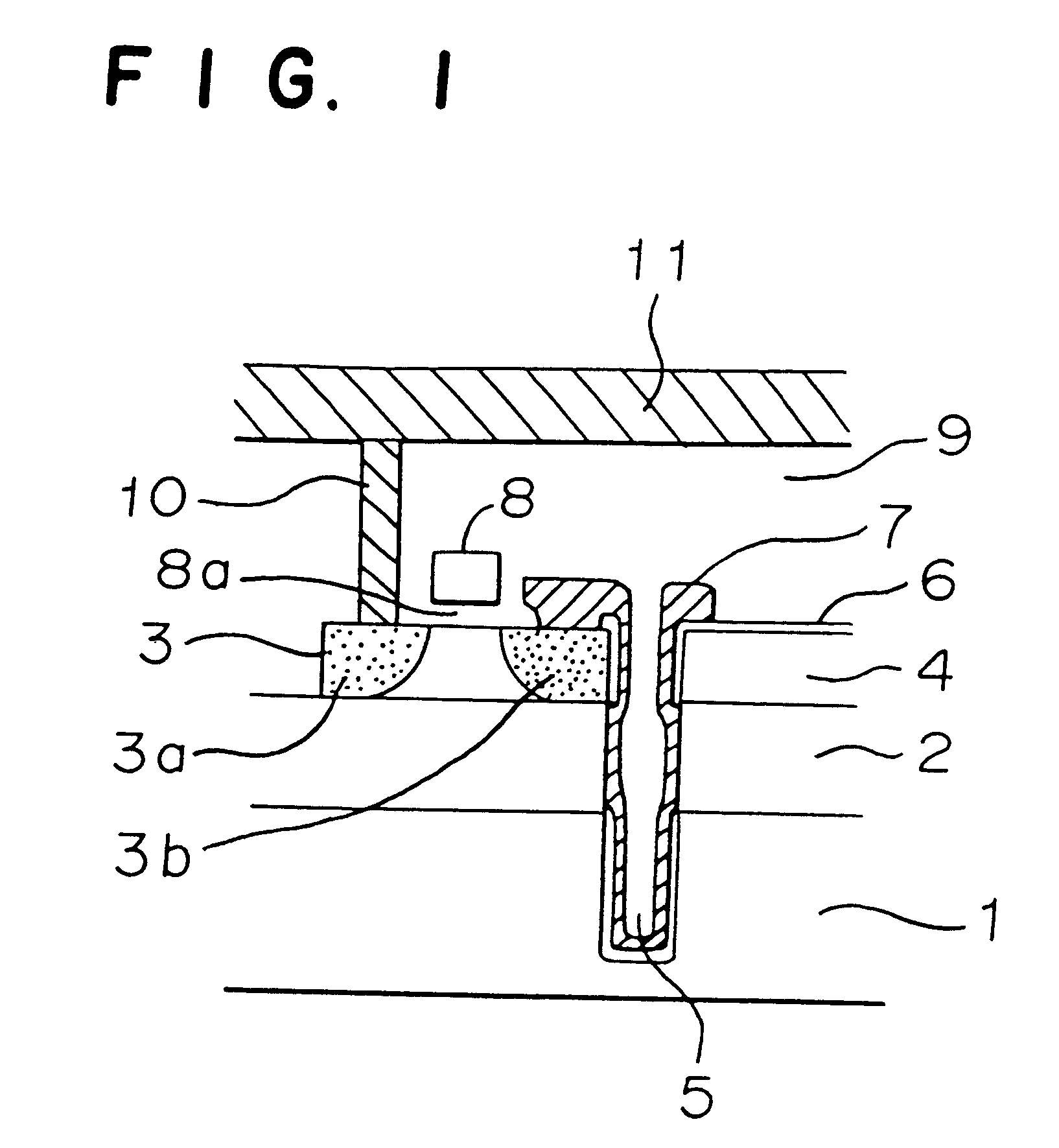

A method of manufacturing a semiconductor memory device comprising: a step of forming a storage node in which a conductive layer 7 to be the storage node is formed in the vicinity of single crystalline silicon 3 formed on an insulator 2, a gettering step for conducting heat treatment to the single crystalline silicon 3 after the step of forming the storage node and gettering contaminants contained in the single crystalline silicon 3 by the conductive layer 7 connected to the single crystalline silicon, and a step of forming a gate oxide film 8a on the single crystalline silicon 3 after the step of gettering is provided to thereby obtain a sufficient gettering effect even though the width of an element and / or the thickness of the element is reduced in accordance with microminiaturization of the element.

Owner:MITSUBISHI ELECTRIC CORP

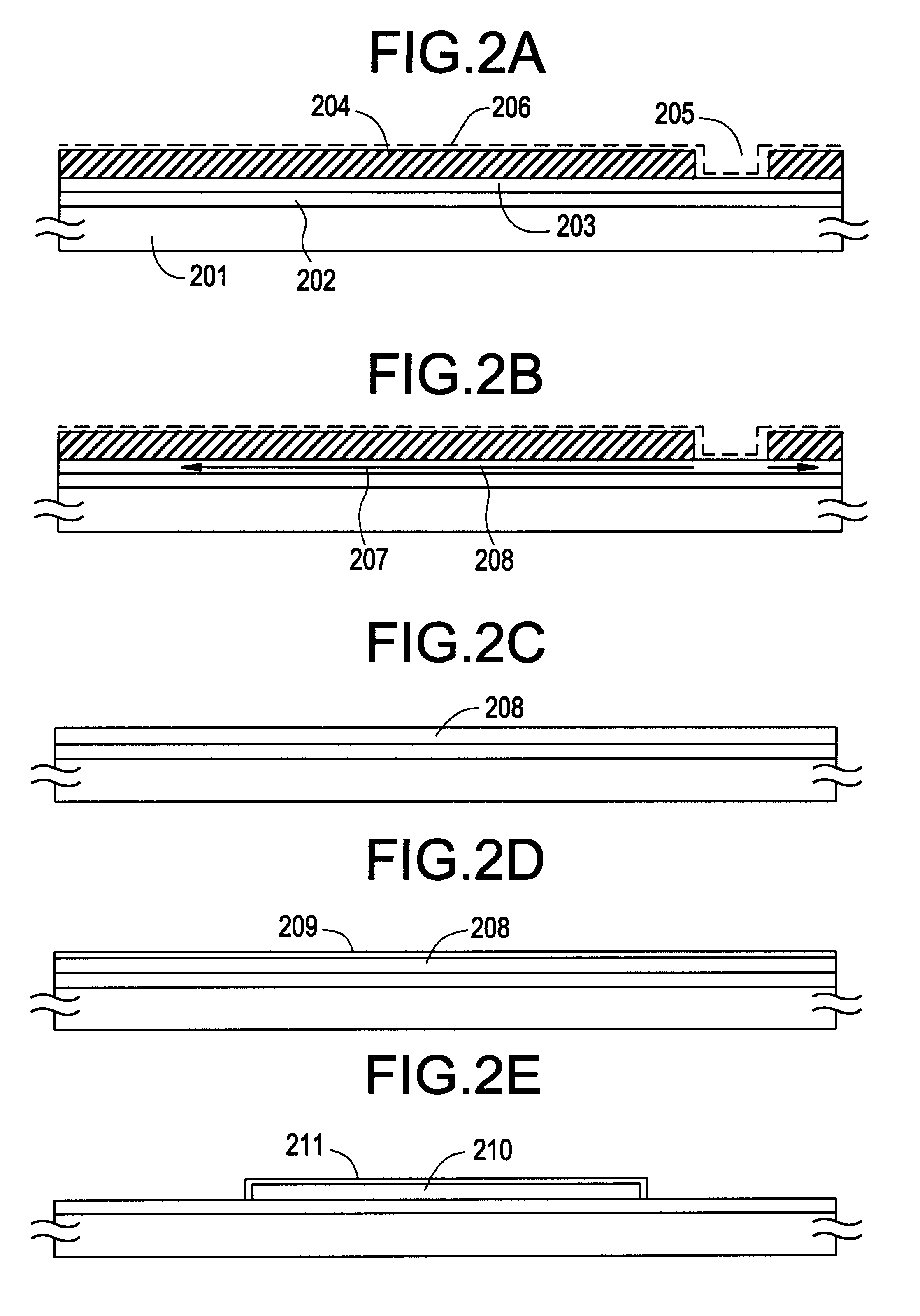

Method of manufacturing a semiconductor device

InactiveUS6998282B1Promote crystallizationHigh effectTransistorSolid-state devicesAmorphous siliconCrystalline silicon

A method of manufacturing a semiconductor device, comprises the steps of: forming a first insulating film on a first substrate; forming a second insulating film on the first insulating film; forming an amorphous silicon film on the second insulating film; holding a metal element that promotes the crystallization of silicon in contact with a surface of the amorphous silicon film; crystallizing the amorphous silicon film through a heat treatment to obtain a crystalline silicon film; forming a thin-film transistor using the crystalline silicon film; forming a sealing layer that seals the thin-film transistor; bonding a second substrate having a translucent property to the sealing layer; and removing the first insulating film to peel off the first substrate.

Owner:SEMICON ENERGY LAB CO LTD

Solar cell

InactiveUS20070169808A1Low costEasy to usePhotovoltaic energy generationSemiconductor devicesHeterojunctionManufacturing technology

The present invention provides a thin film amorphous silicon-crystalline silicon back heterojunction and back surface field device configuration for a heterojunction solar cell. The configuration is attained by the formation of heterojunctions on the back surface of crystalline silicon at low temperatures. Low temperature fabrication allows for the application of low resolution lithography and / or shadow masking processes to produce the structures. The heterojunctions and interface passivation can be formed through a variety of material compositions and deposition processes, including appropriate surface restructing techniques. The configuration achieves separation of optimization requirements for light absorption and carrier generation at the front surface on which the light is incident, and in the bulk, and charge carrier collection at the back of the device. The shadowing losses are eliminated by positioning the electrical contacts at the back thereby removing them from the path of the incident light. Back contacts need optimization only for maximum charge carrier collection without bothering about shading losses. A range of elements / alloys may be used to effect band-bending. All of the above features result in a very high efficiency solar cell. The open circuit voltage of the back heterojunction device is higher than that of an all-crystalline device. The solar cell configurations are equally amenable to crystalline silicon wafer absorber as well as thin silicon layers formed by using a variety of fabrication processes. The configurations can be used for radiovoltaic and electron-voltaic energy conversion devices.

Owner:KHERANI NAZIR P +1

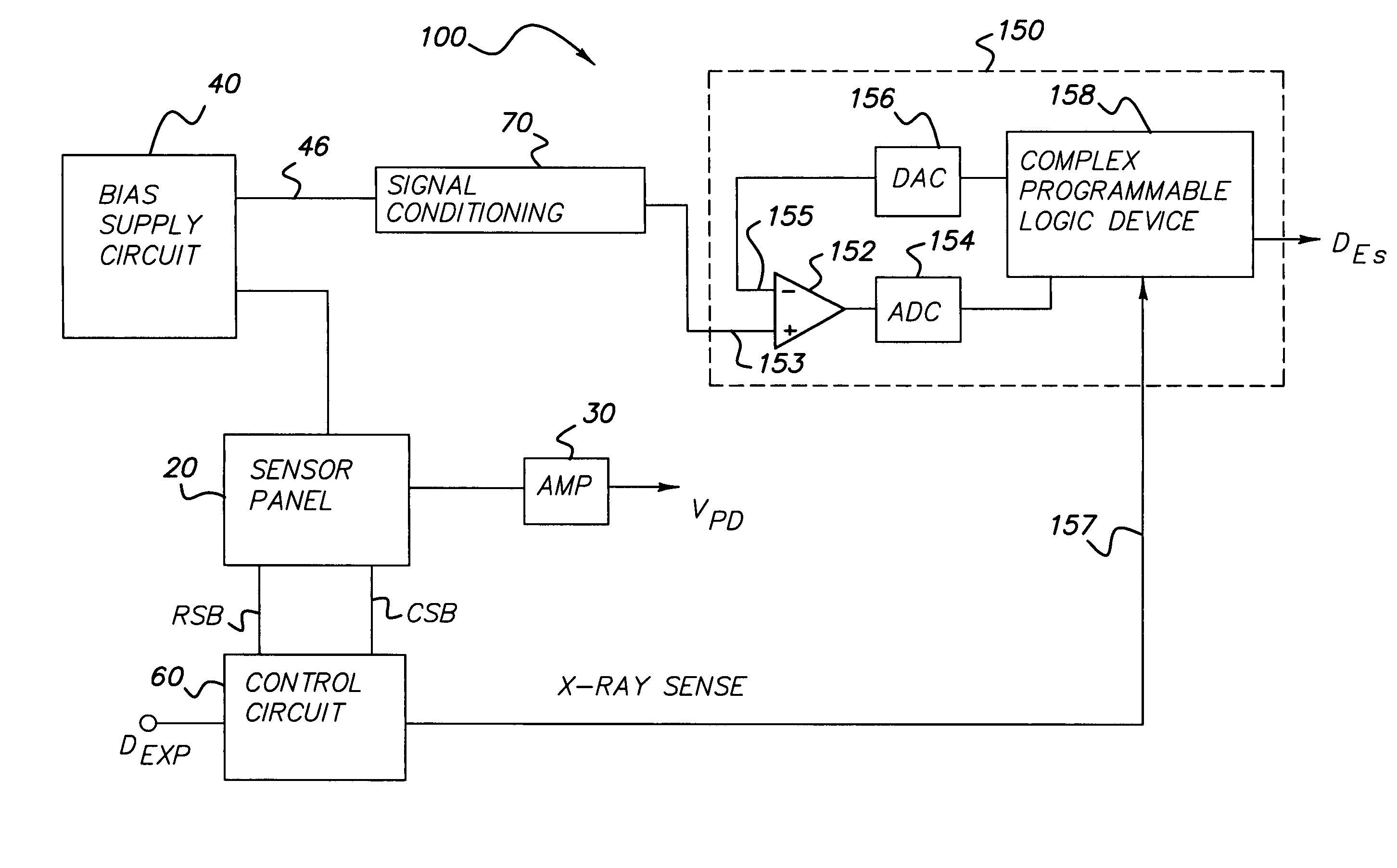

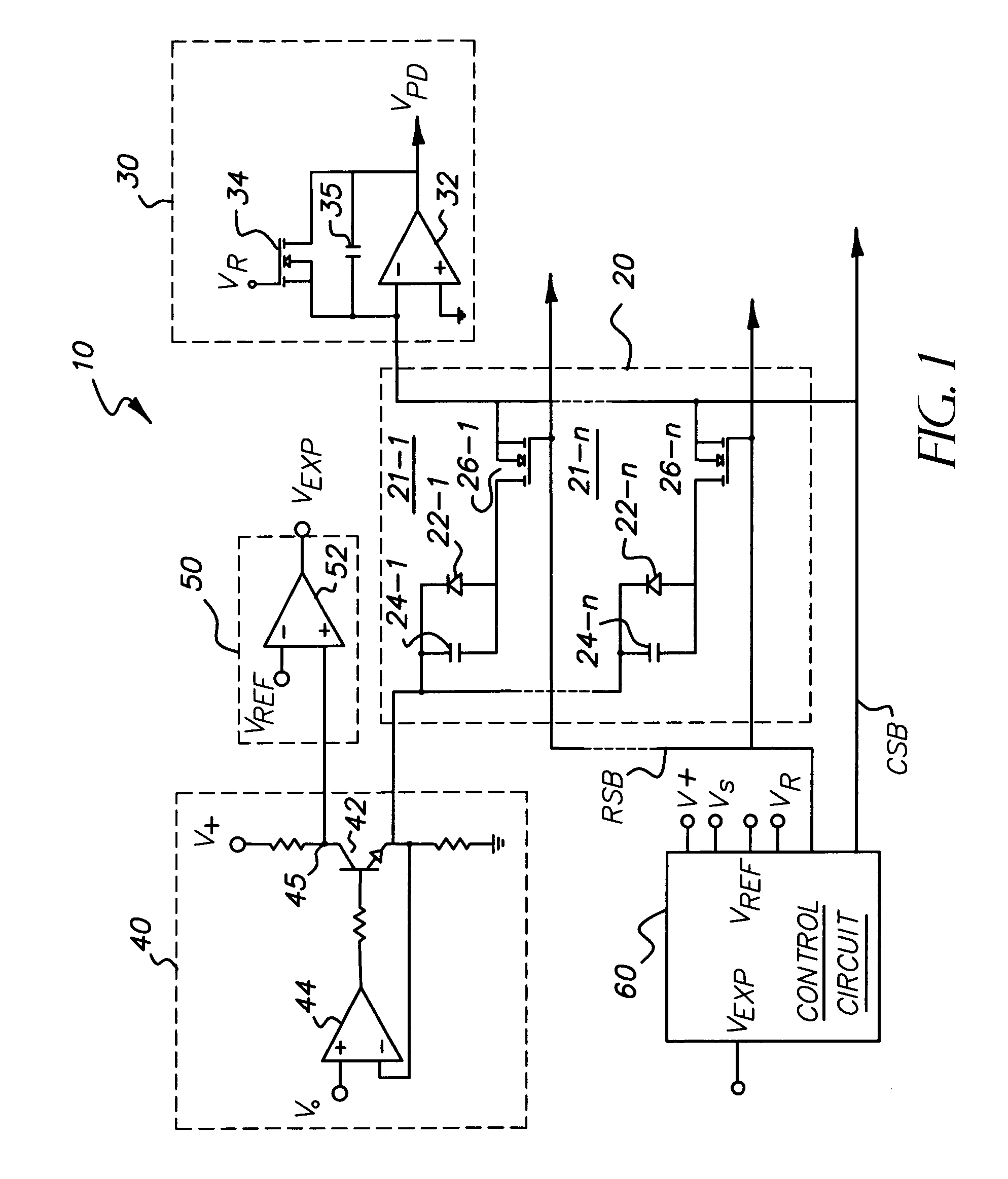

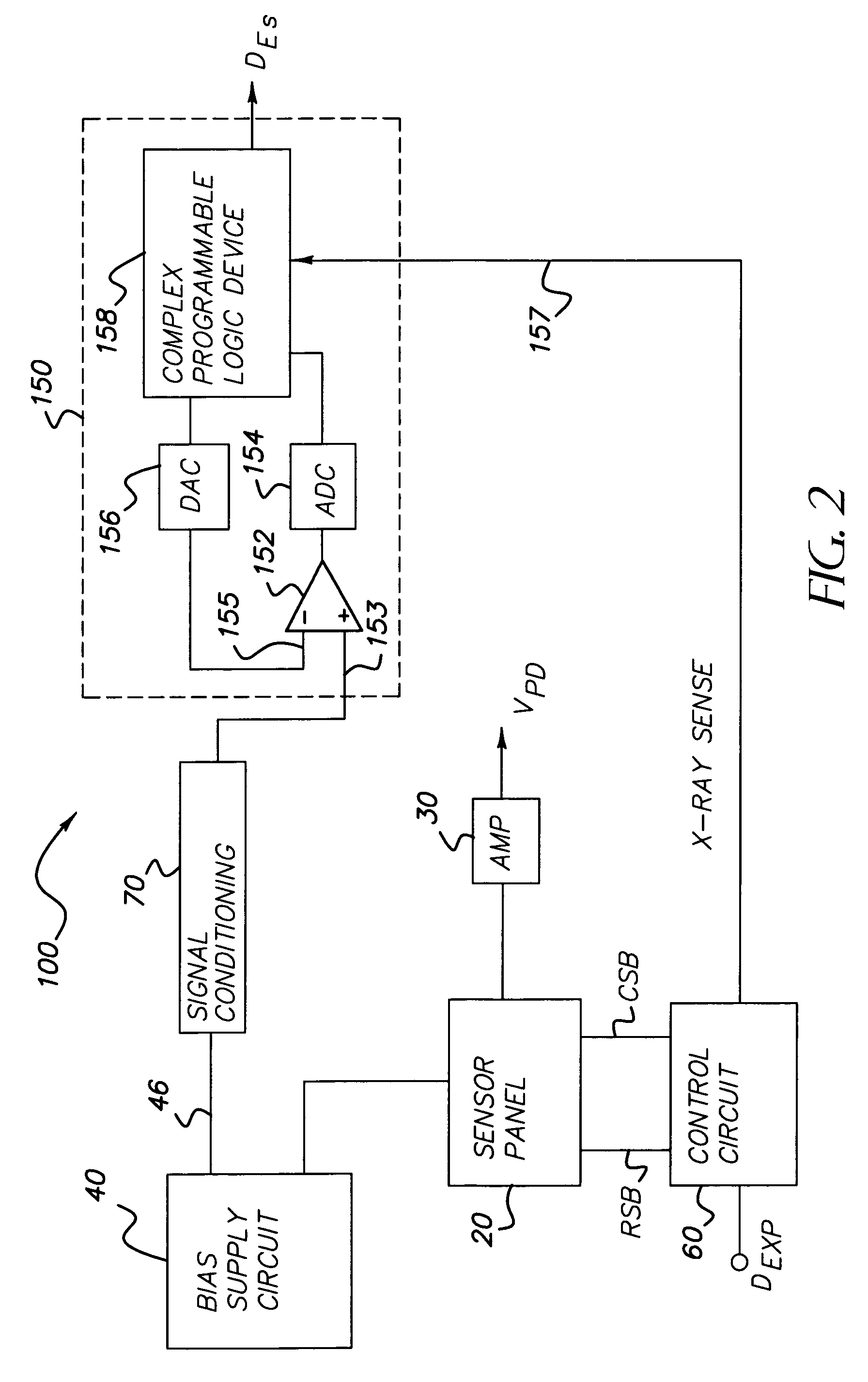

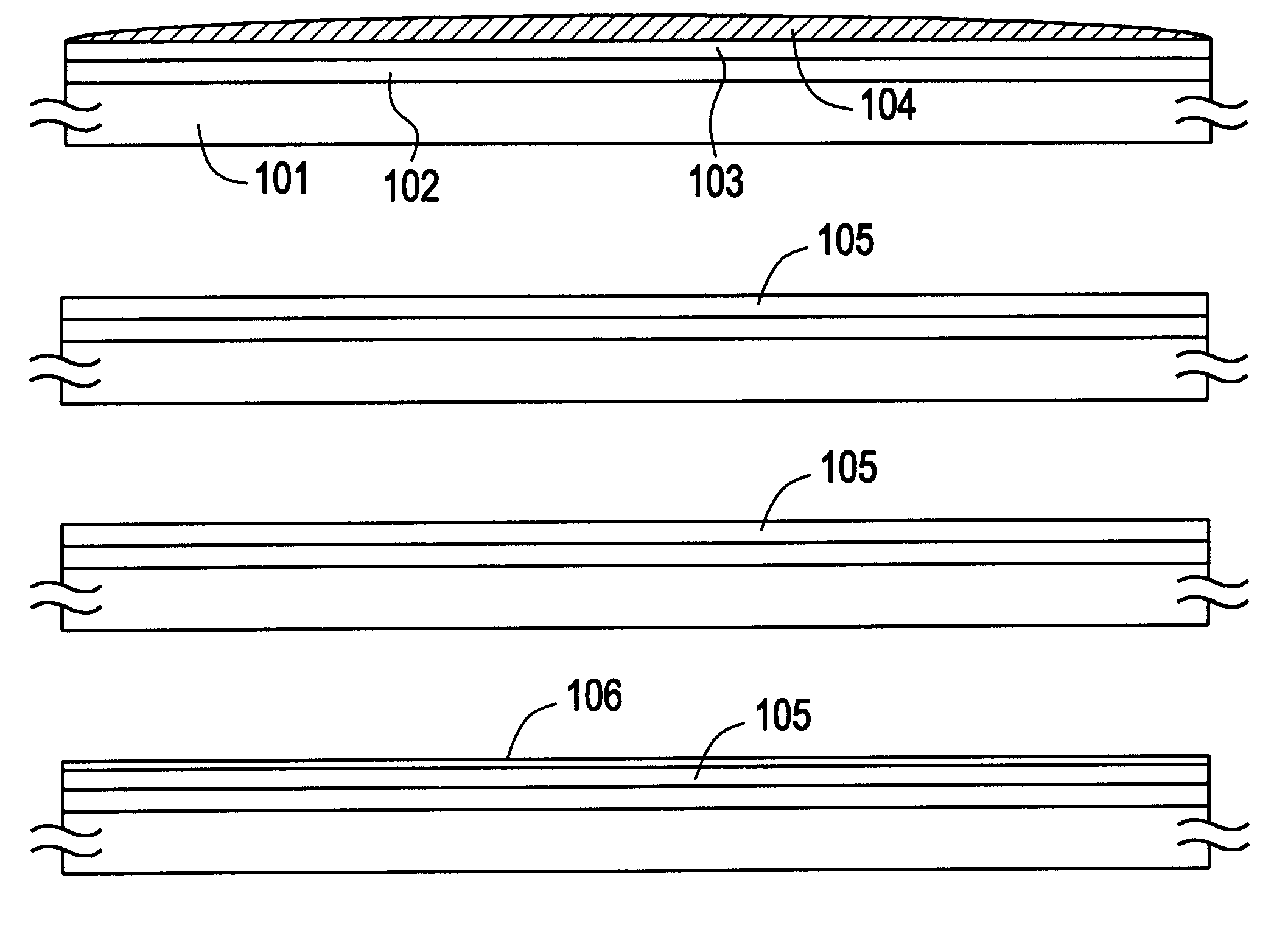

Wireless X-ray detector for a digital radiography system with remote X-ray event detection

ActiveUS7211803B1Improve signal-to-noise ratioQuick checkMaterial analysis using wave/particle radiationRadiation/particle handlingDetector circuitsX-ray

A wireless X-ray detector for a digital radiography system with remote detection of impinging radiation from the system X-ray source onto a sensor panel having amorphous or crystalline silicon photodiodes or metal insulated semiconductor (MIS) sensors. Changes in current in the photodiode bias supply circuit is sensed to generate a signal indicating presence of radiation. Improved detection of X-ray cessation is achieved either by leaving at least one line of sensors connected between the bias supply circuit to a virtual ground during charge accumulation or by using an X-ray presence detector circuit that increases the sensitivity of the detector circuit to bias circuit current changes occurring after onset of the radiation.

Owner:CARESTREAM HEALTH INC

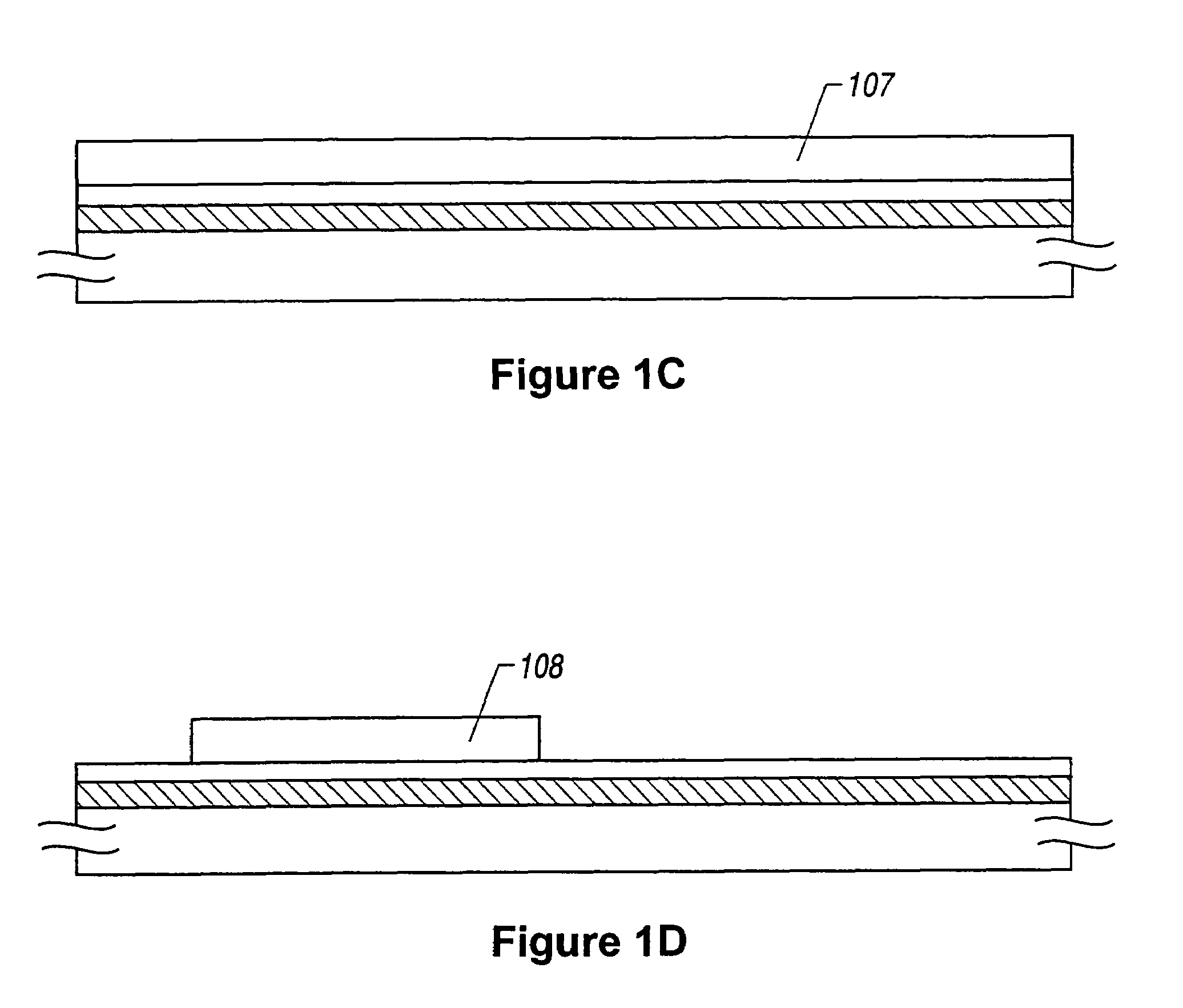

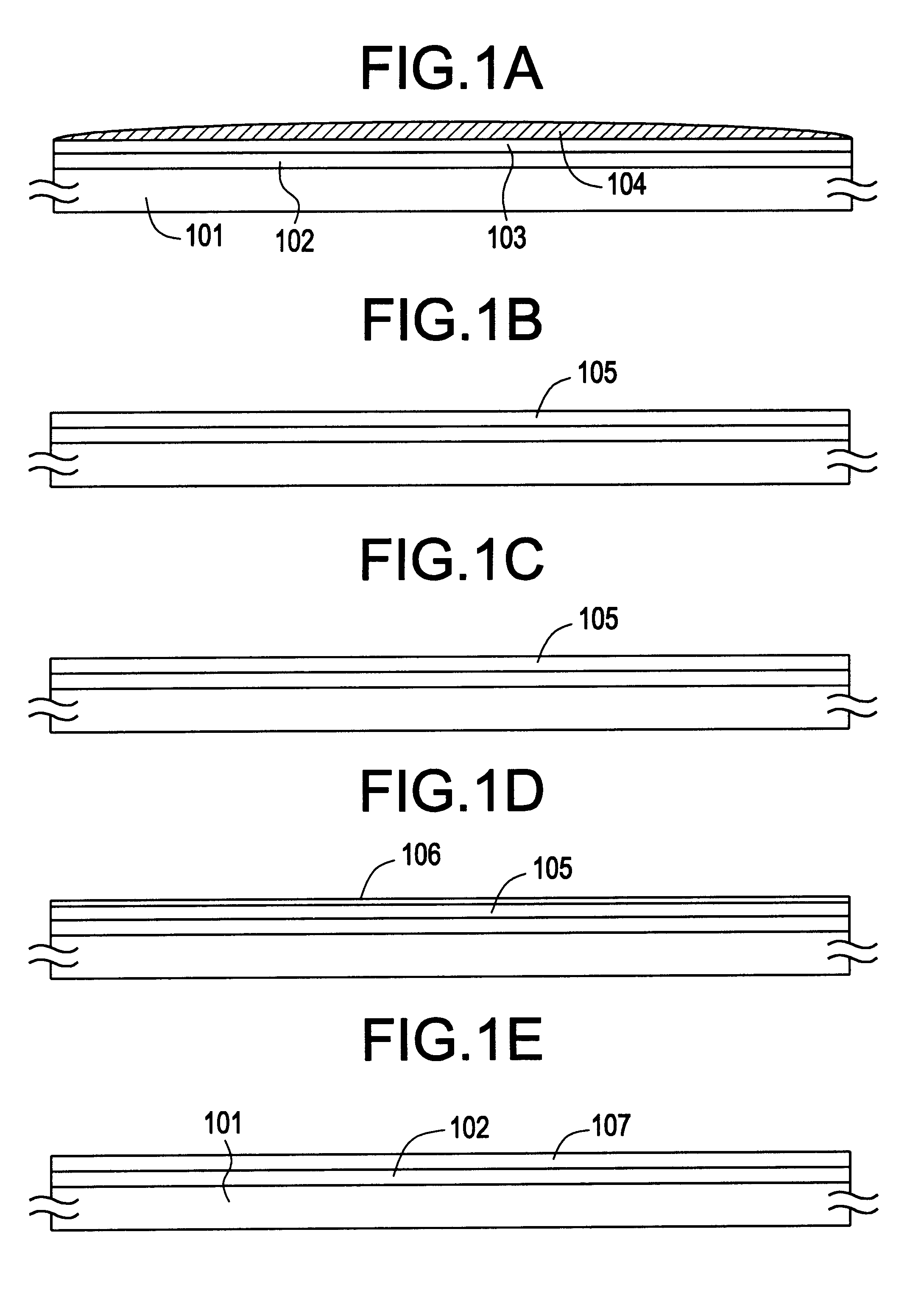

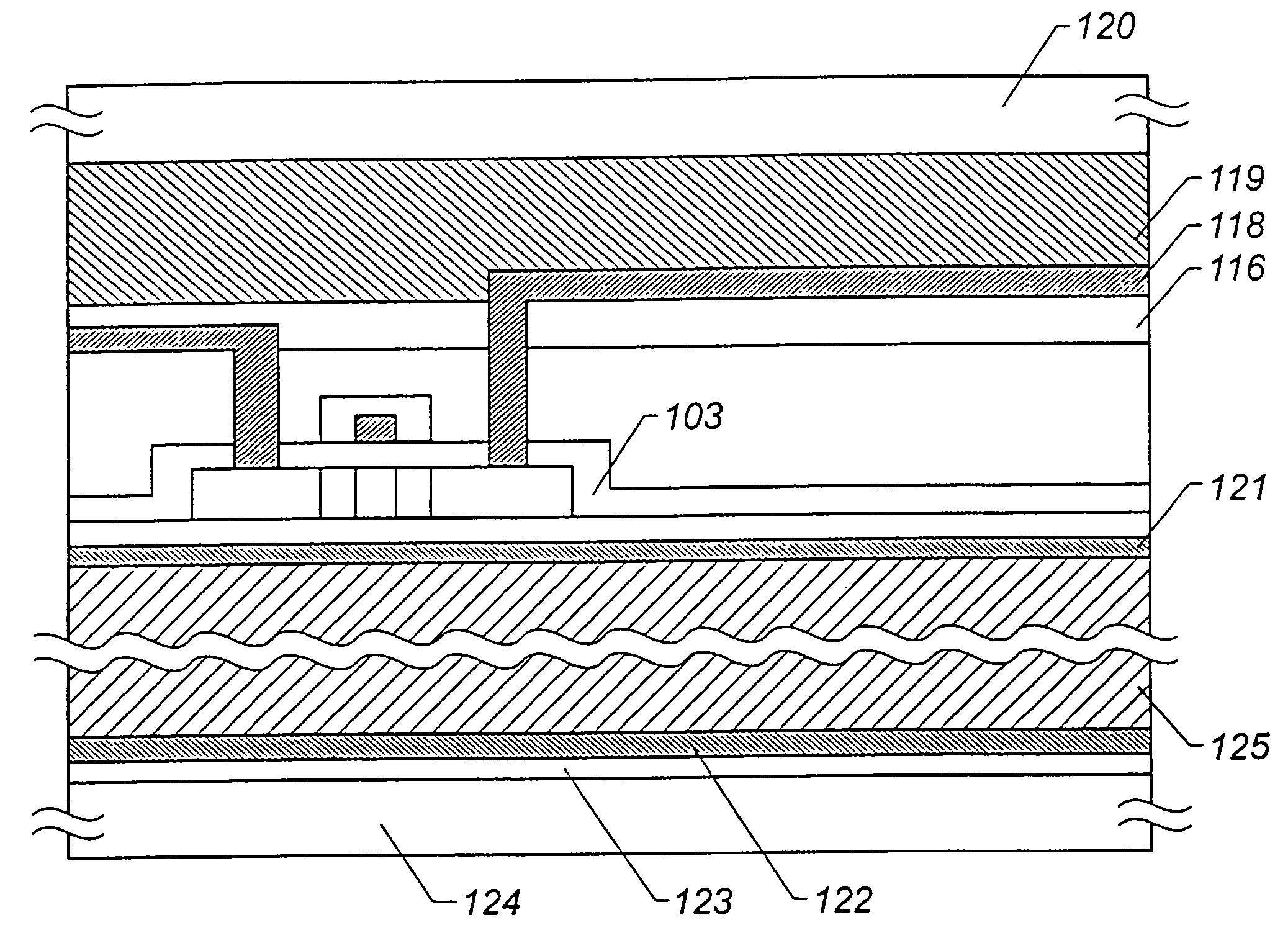

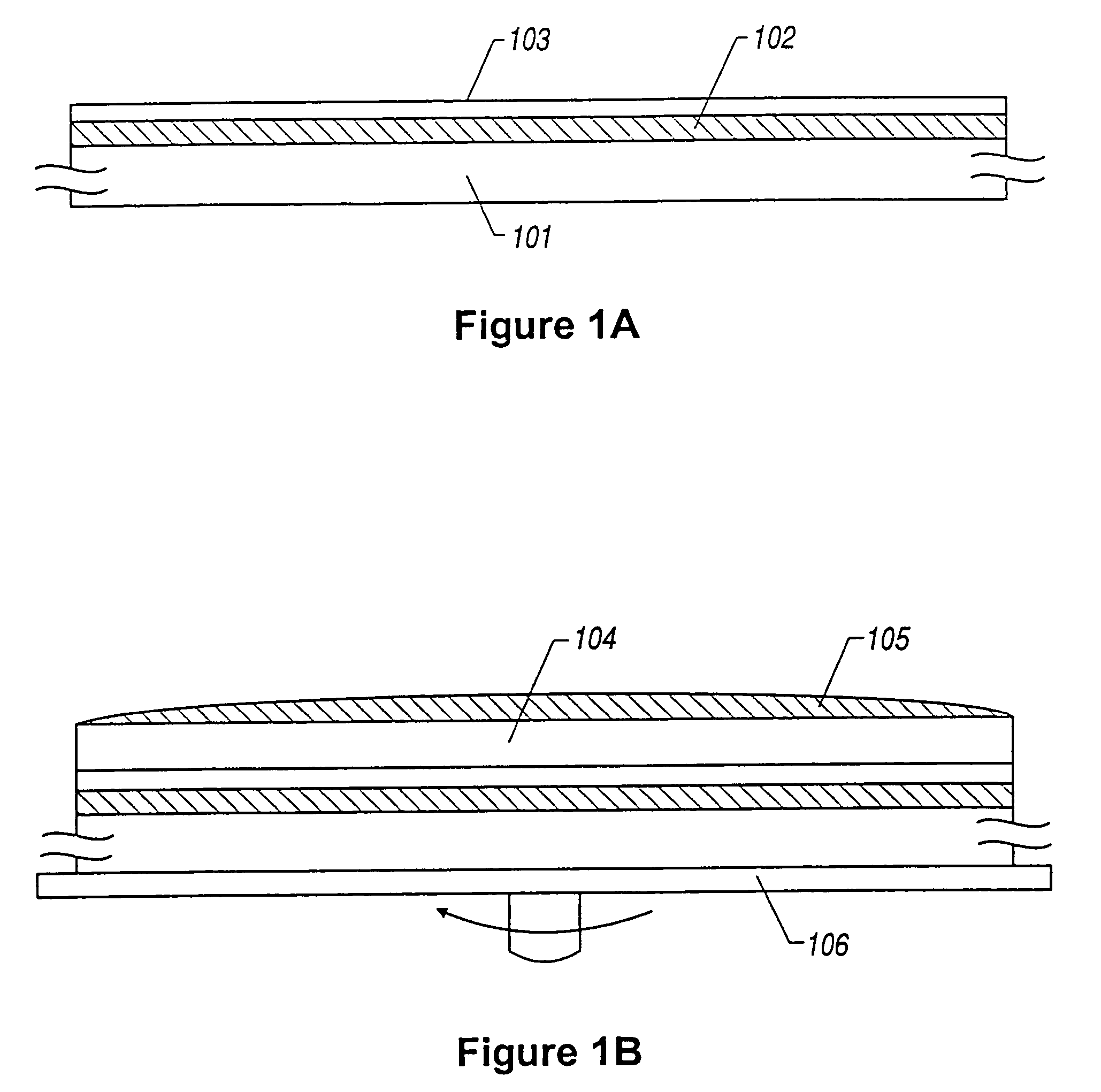

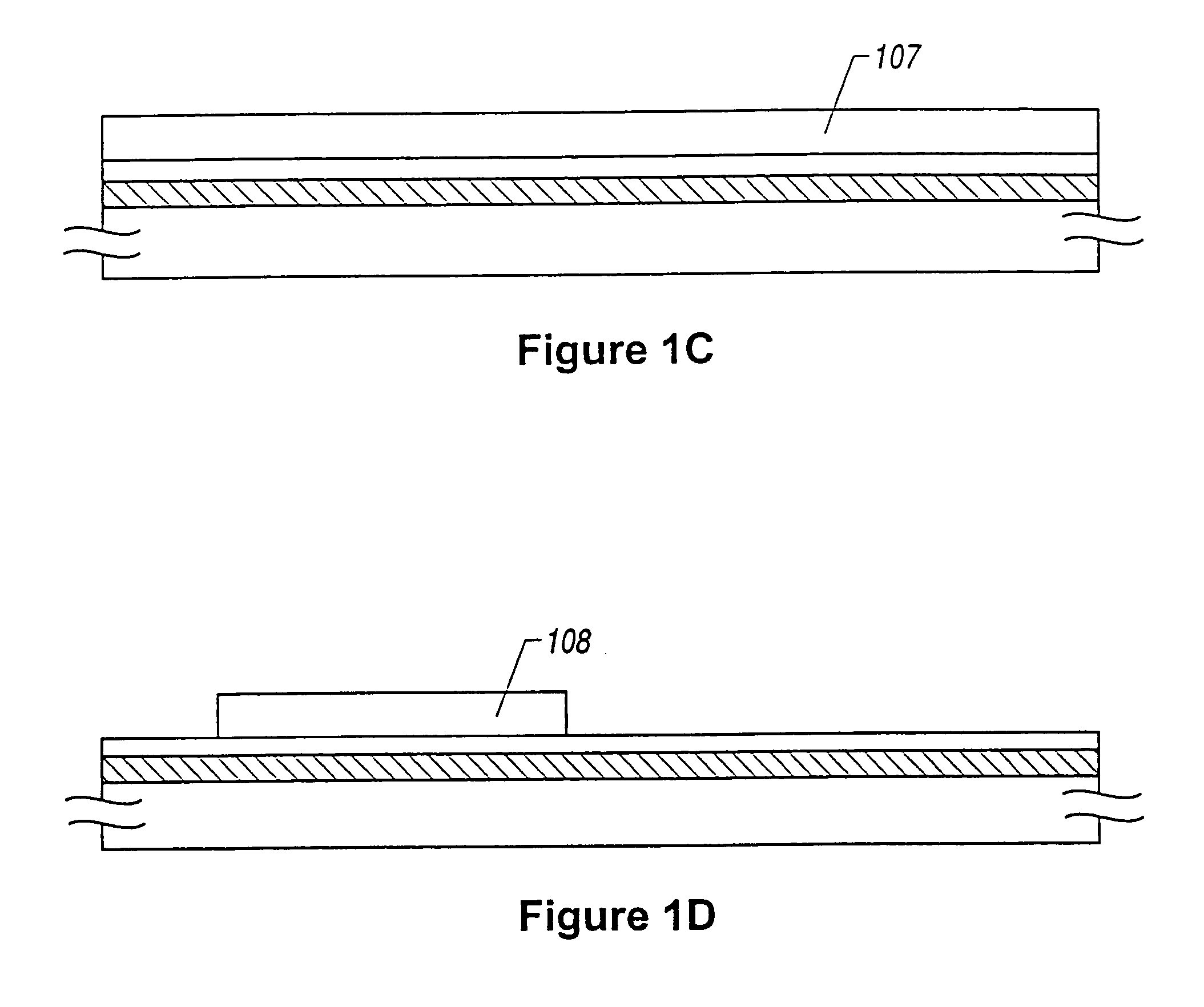

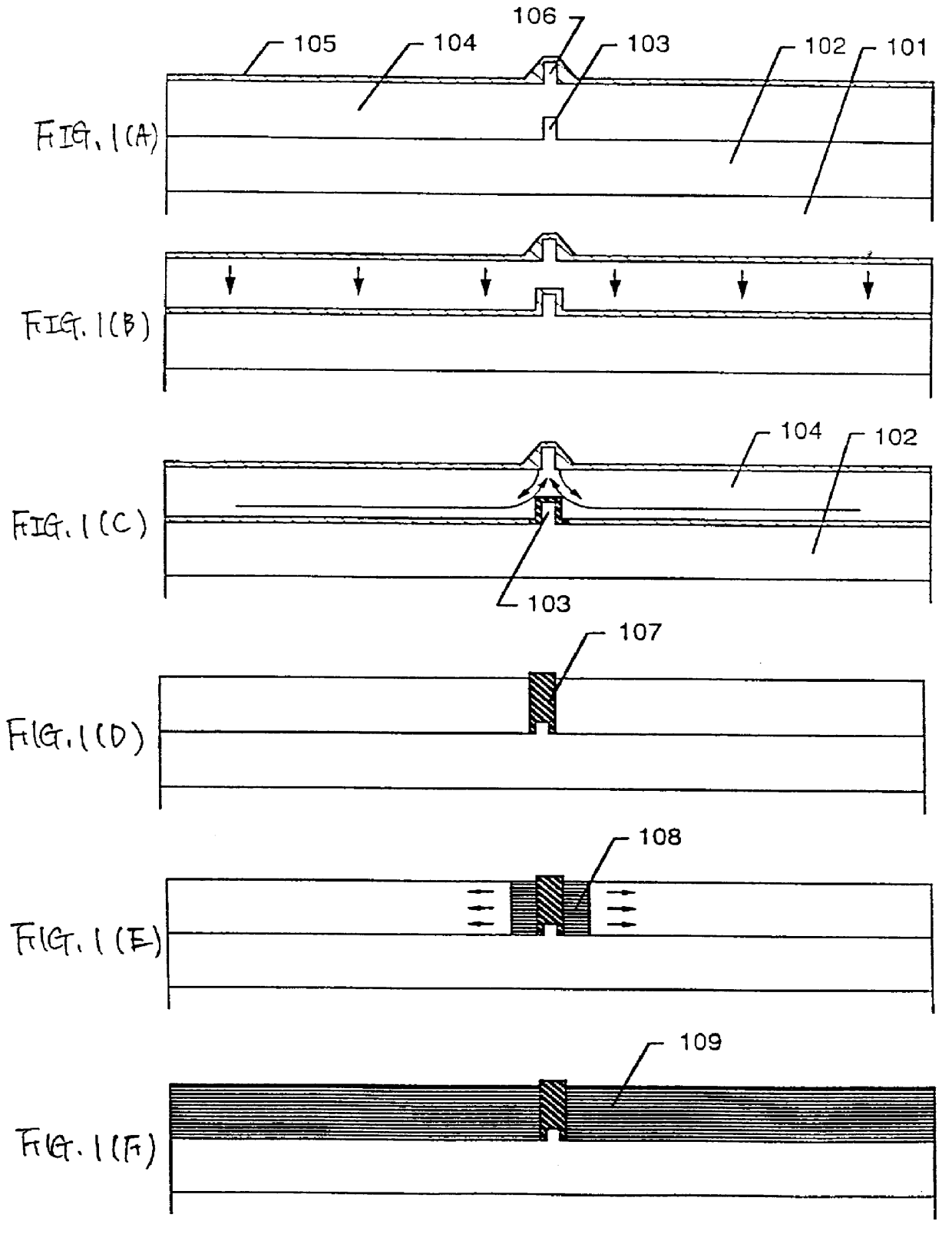

Method for fabricating a semiconductor device

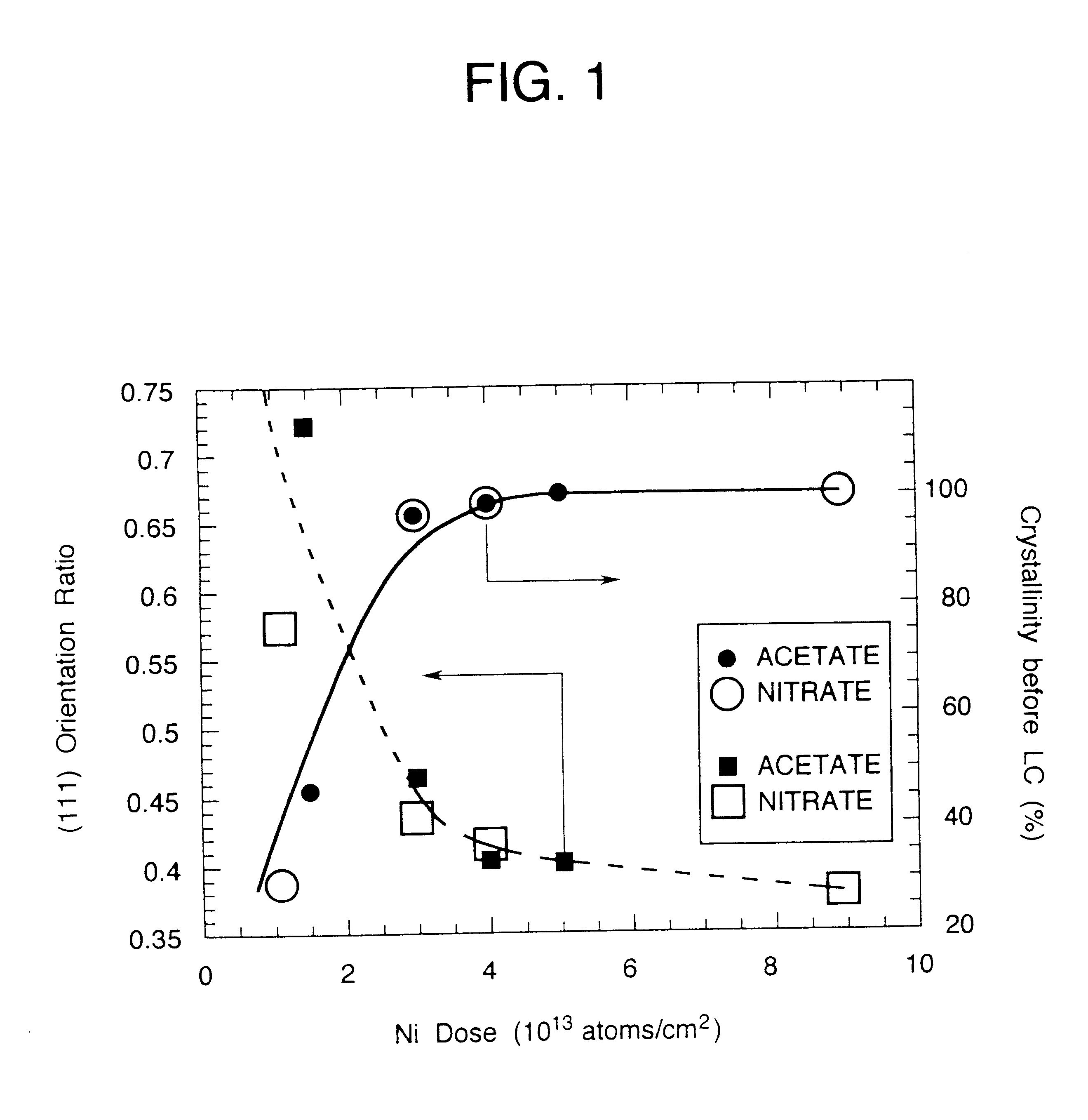

InactiveUS6180439B1Promote crystallizationReduce concentrationTransistorSolid-state devicesAtmospheric airLaser light

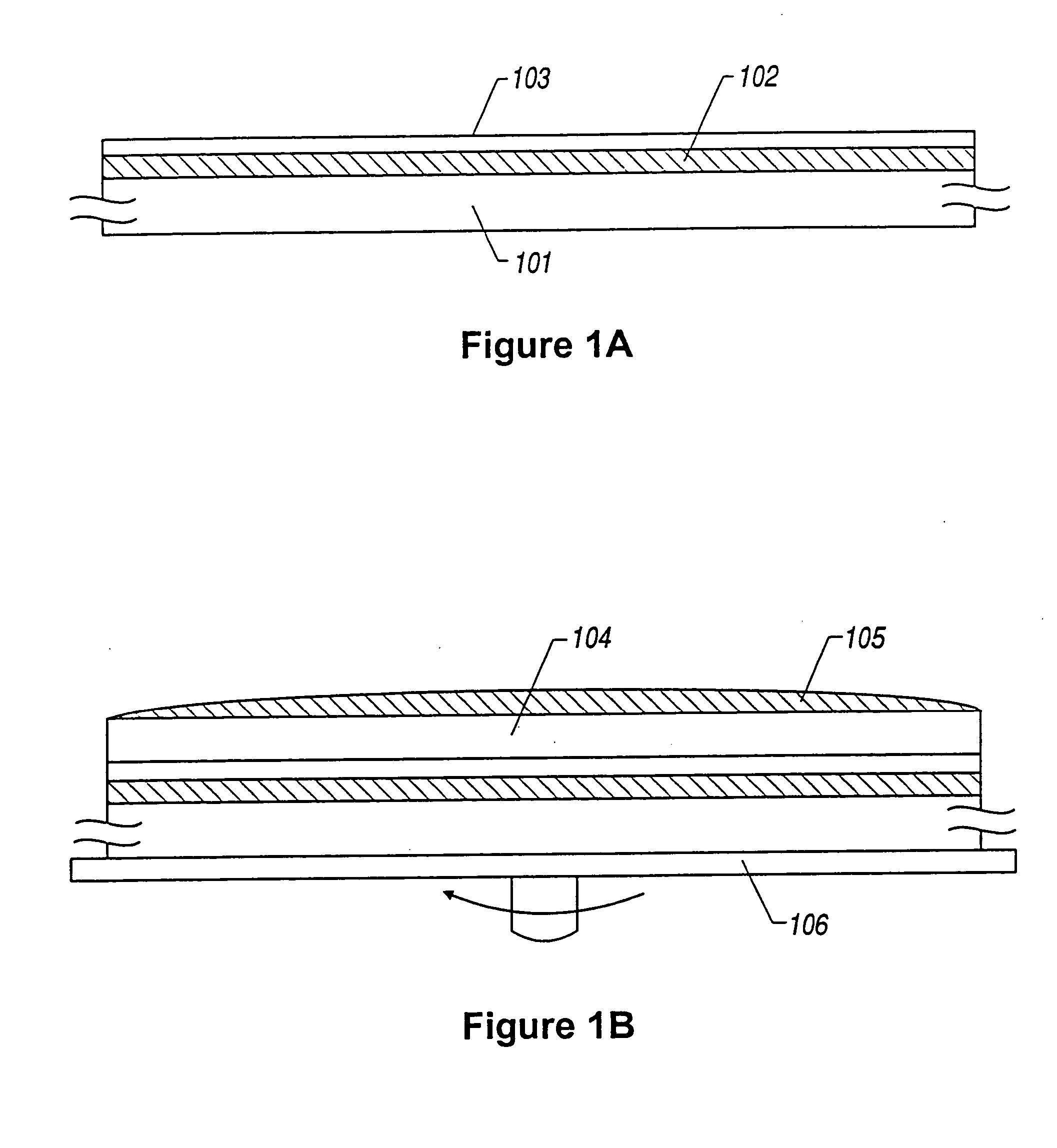

Concentration of metal element which promotes crystallization of silicon and which exists within a crystalline silicon film obtained by utilizing the metal element is reduced. A first heat treatment for crystallization is performed after introducing nickel to an amorphous silicon film 103. Then, laser light is irradiated to diffuse nickel element which is concentrated locally. After that, another heat treatment is performed within an oxidizing atmosphere at a temperature higher than that of the previous heat treatment. At this time, HCl or the like is added to the atmosphere. A thermal oxide film 106 is formed in this step. At this time, gettering of the nickel element into the thermal oxide film 106 takes place. Then, the thermal oxide film 106 is removed. Thereby, a crystalline silicon film 107 having low concentration of the metal element and a high crystallinity can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

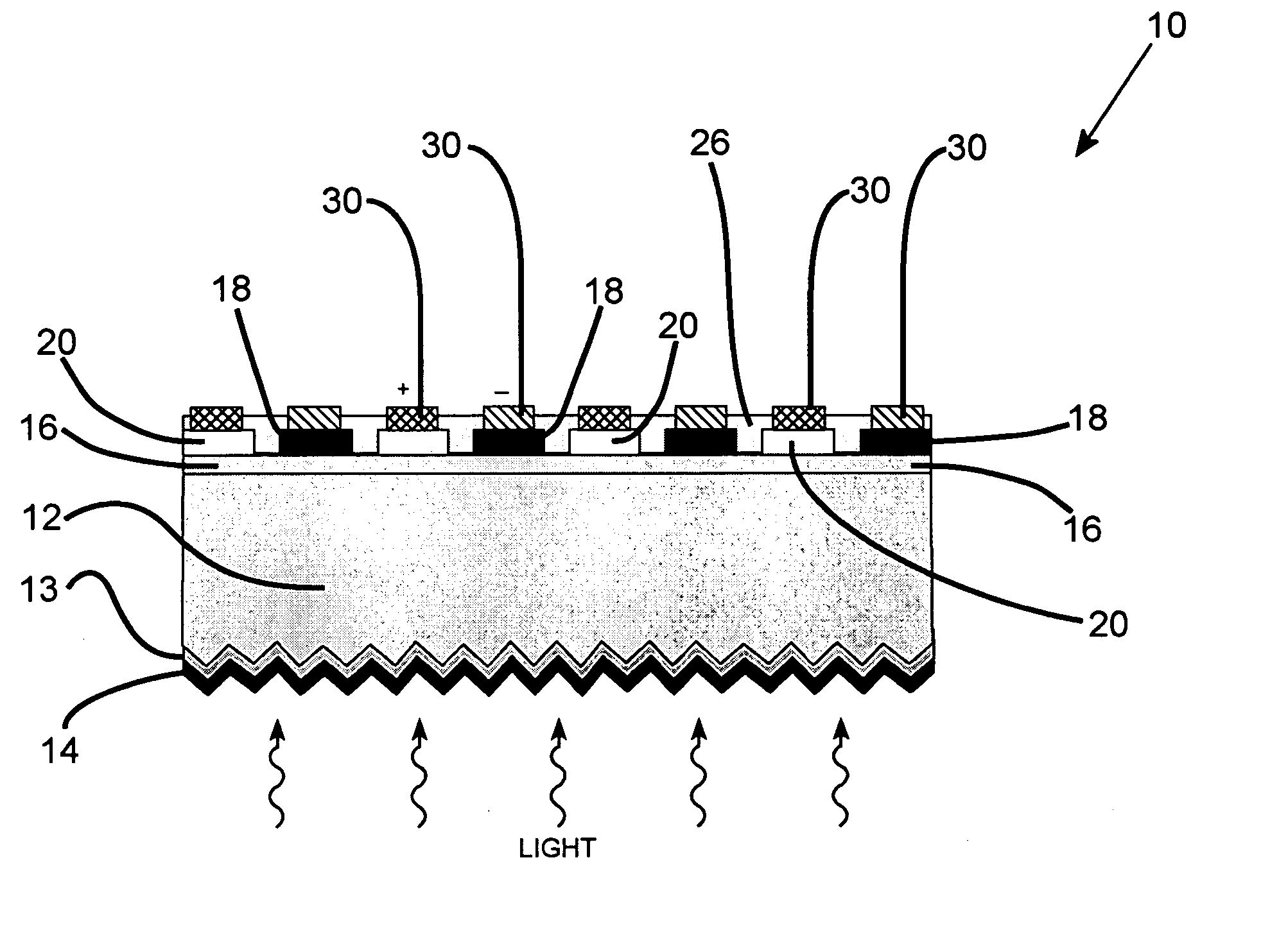

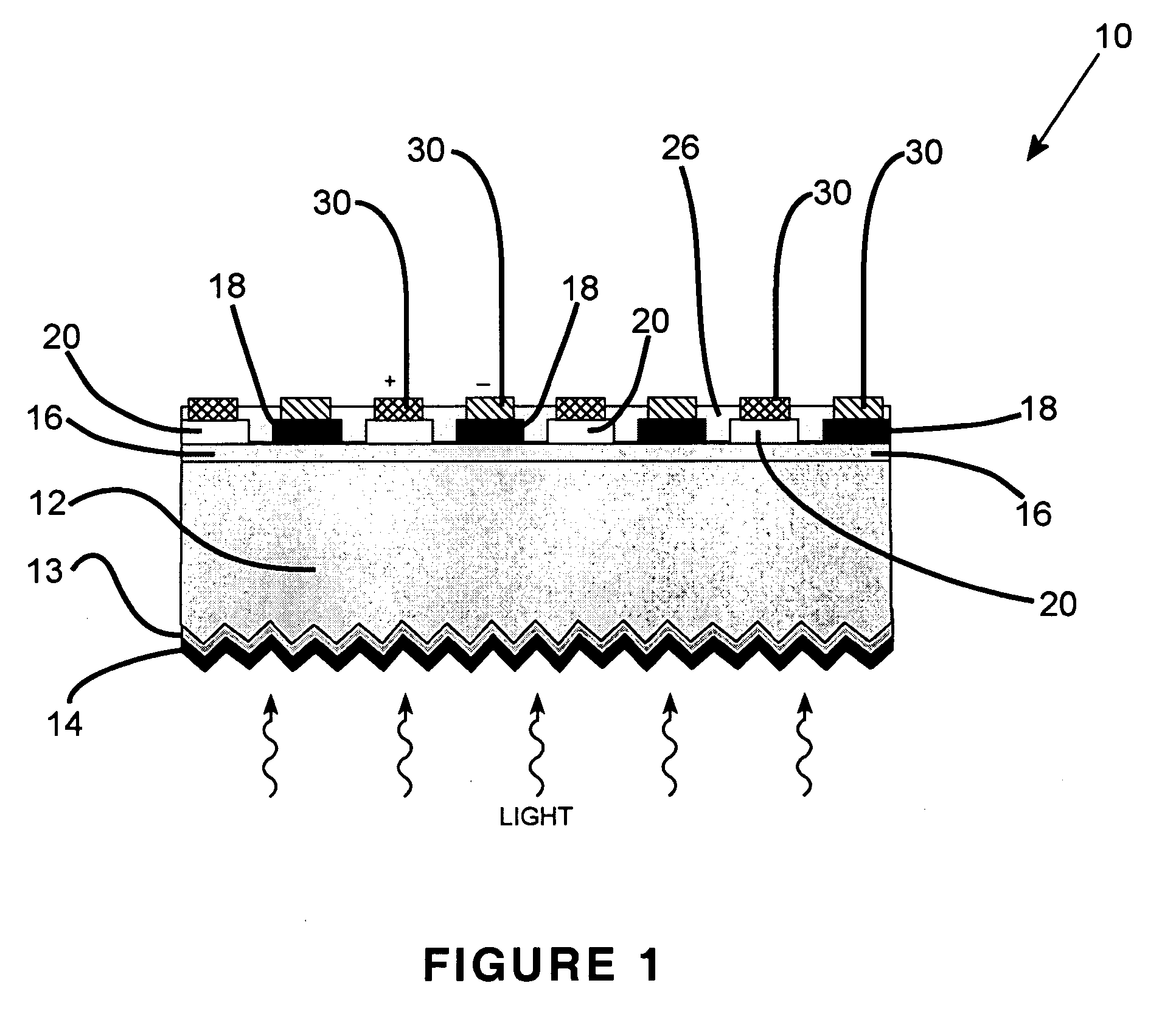

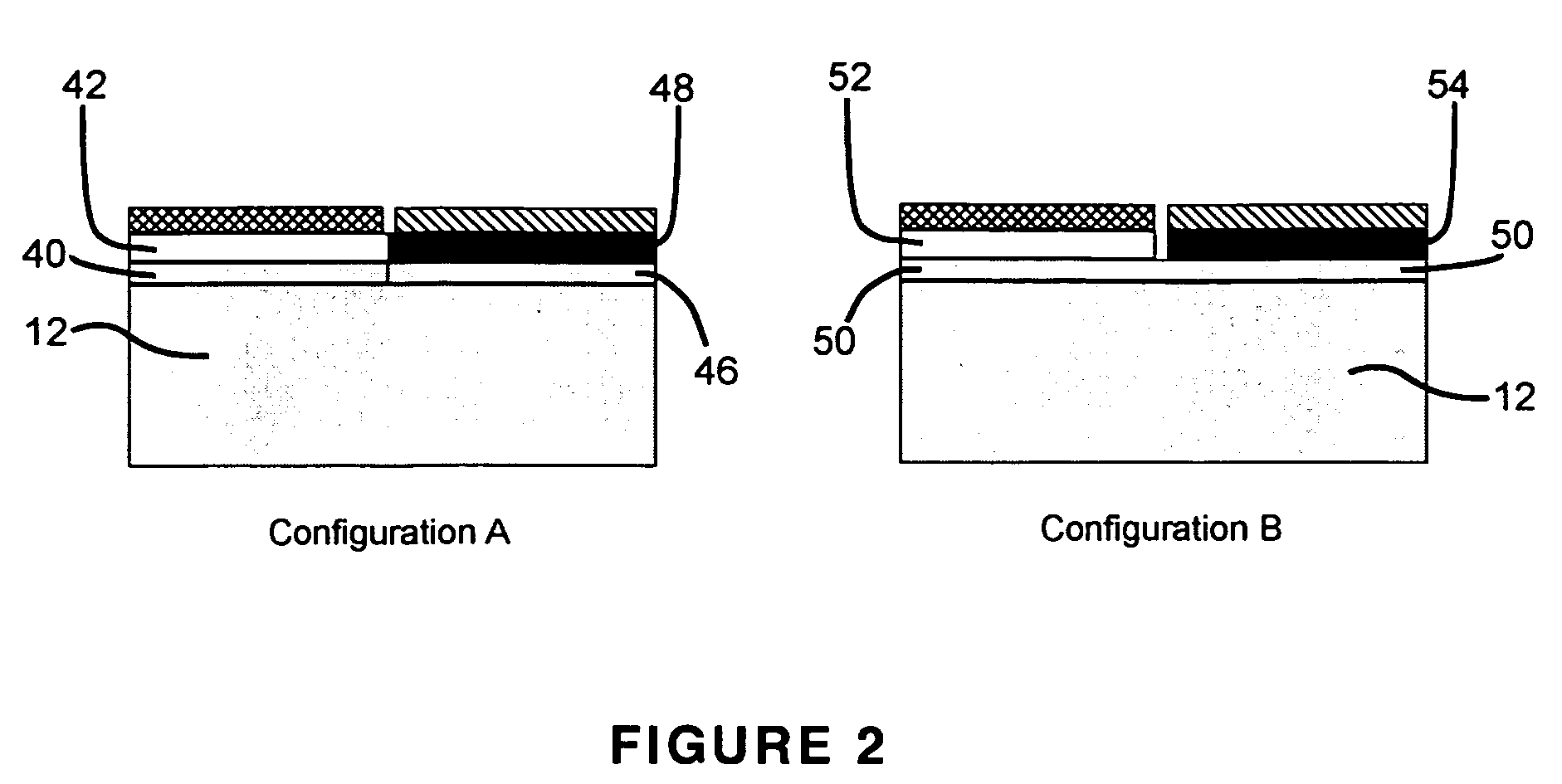

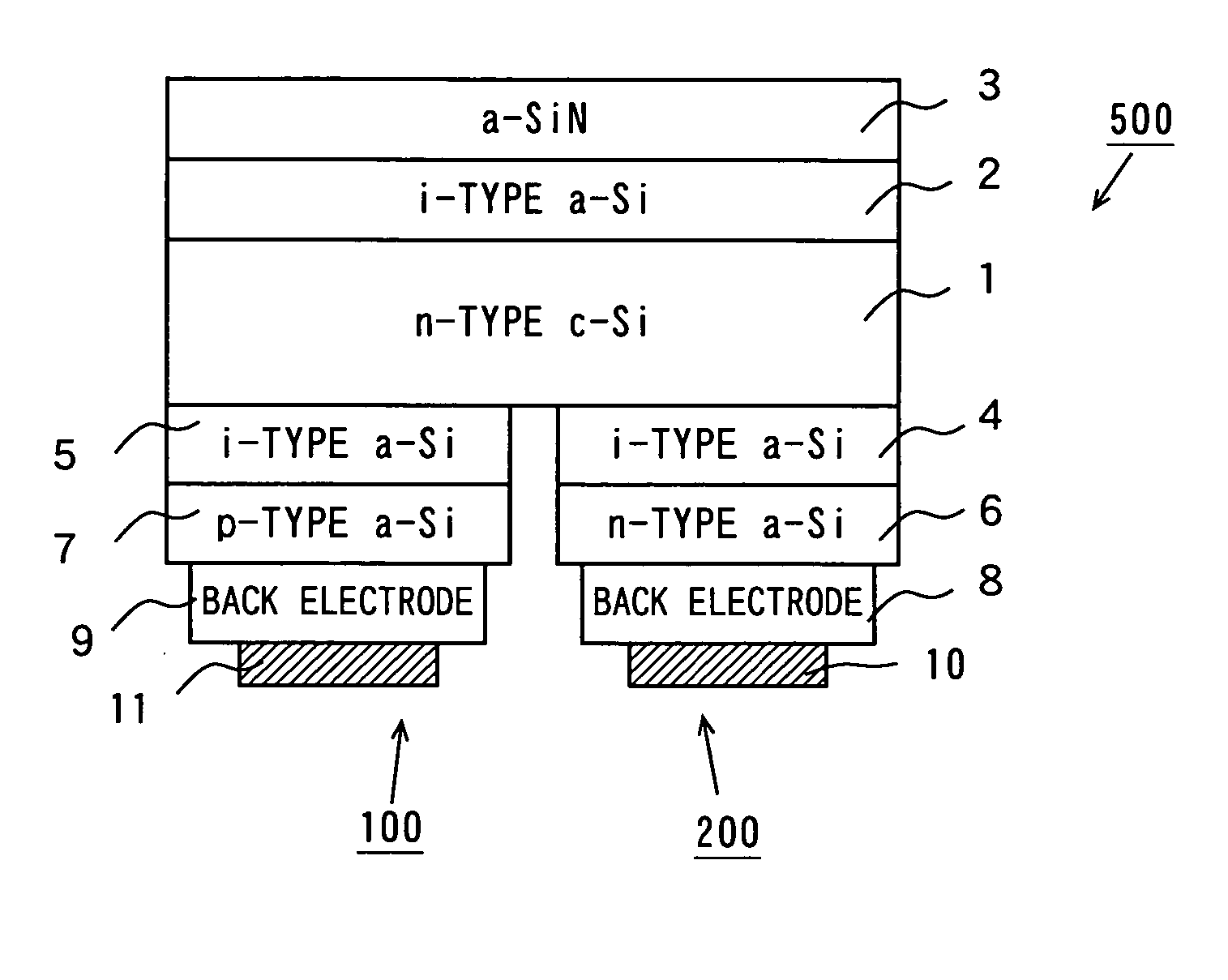

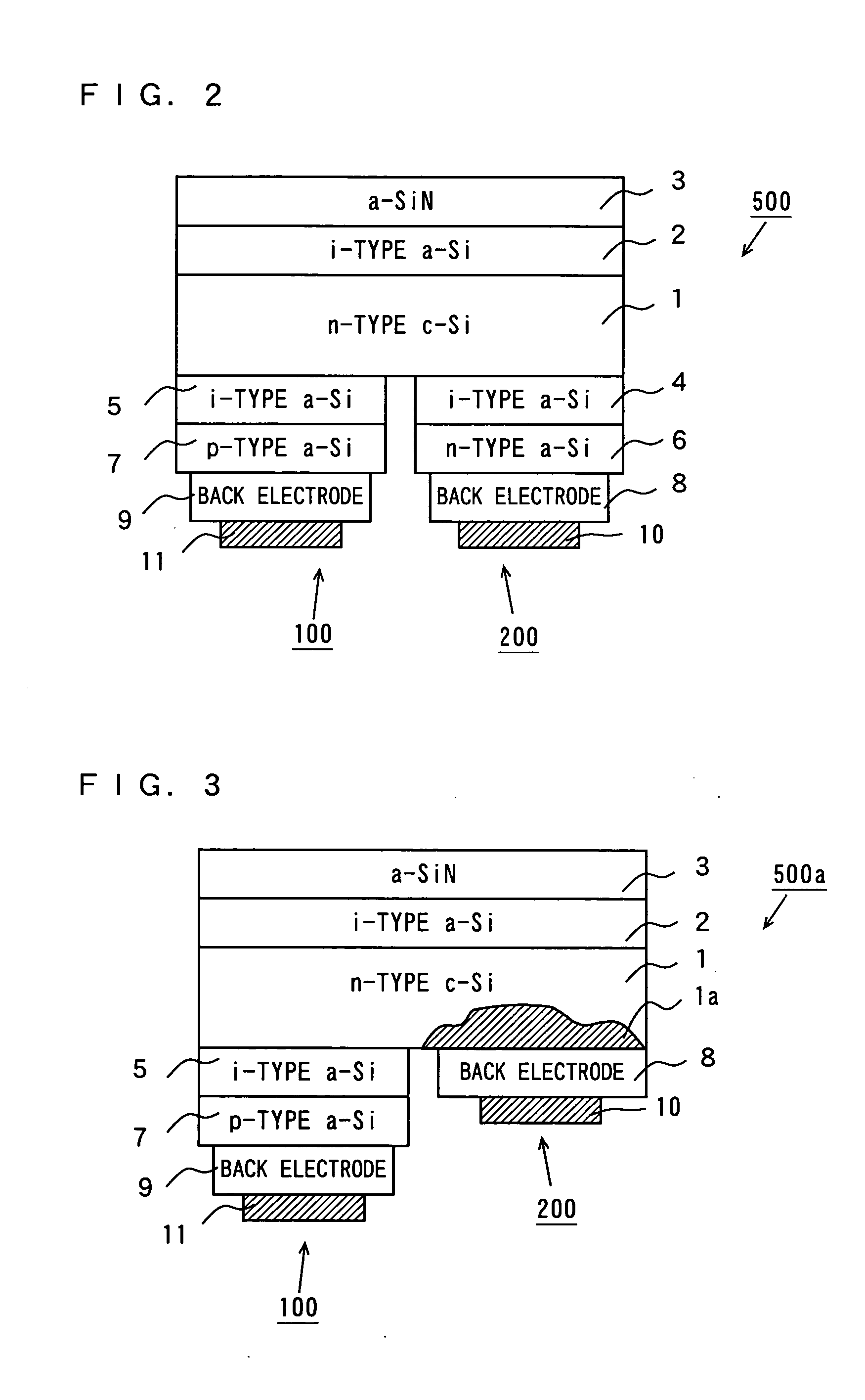

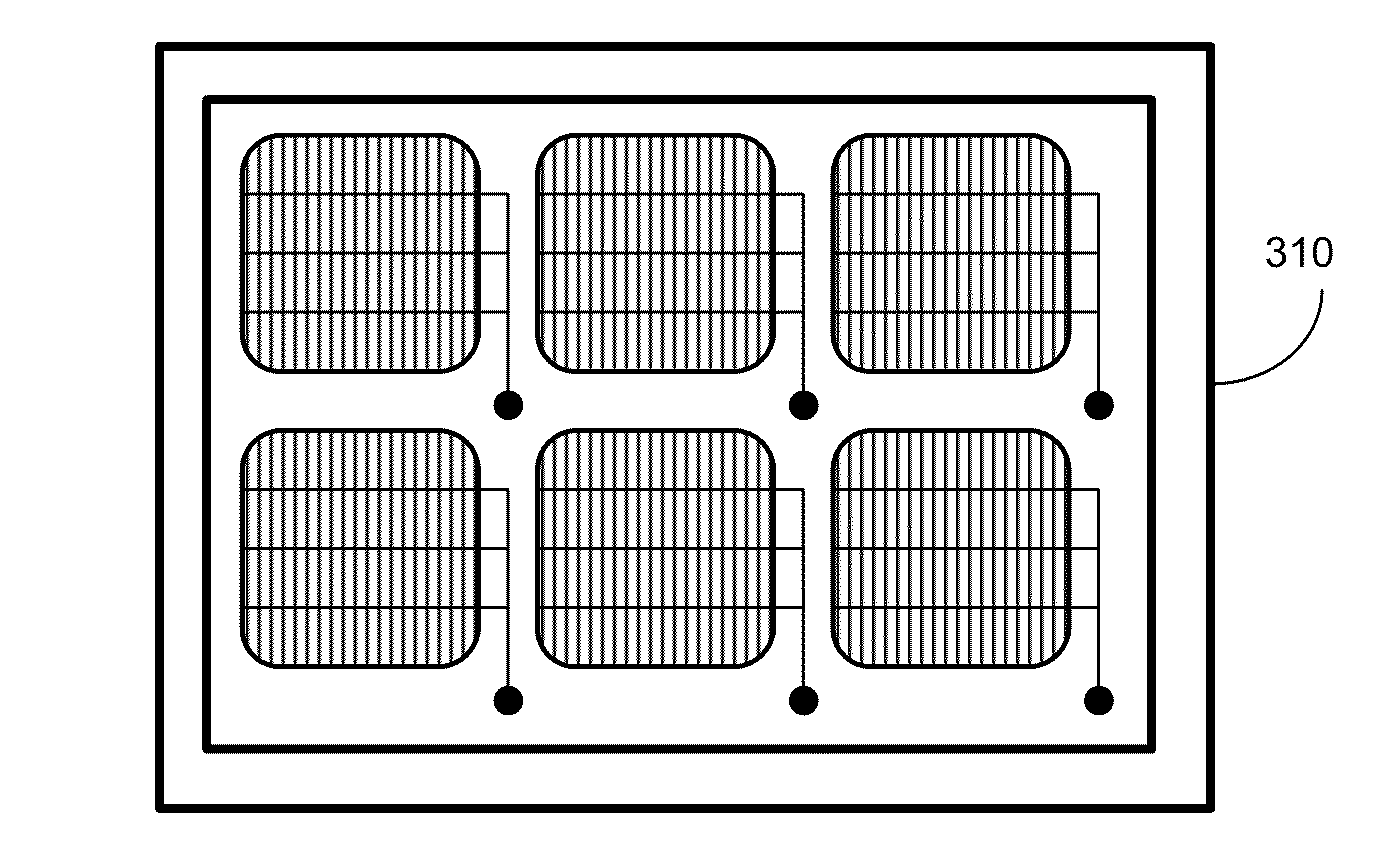

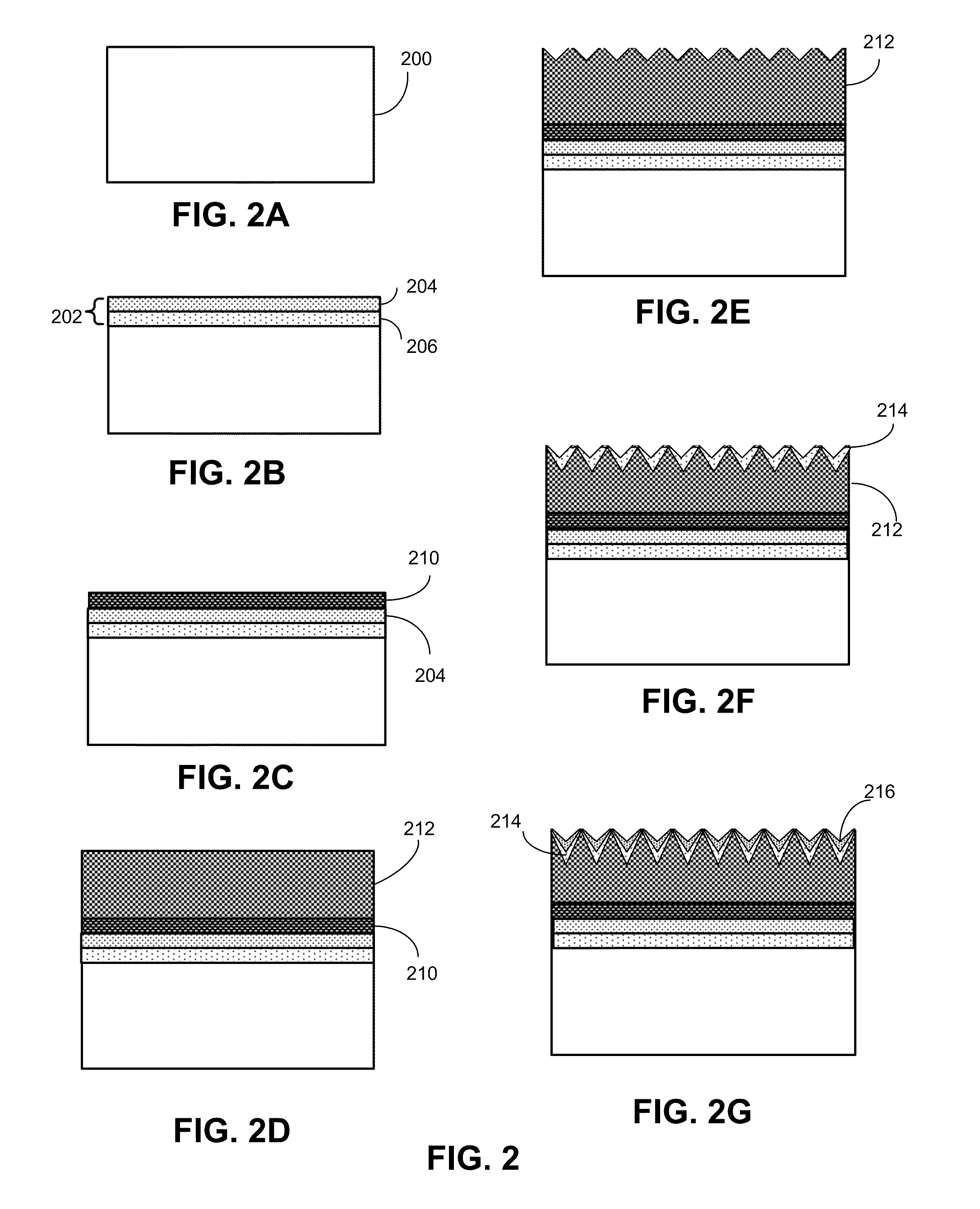

Photovoltaic cell and method of fabricating the same

ActiveUS20050062041A1Significant to useLow costPhotovoltaic energy generationSemiconductor devicesOptoelectronicsCrystalline silicon

An i-type amorphous silicon film and an anti-reflection film made of amorphous silicon nitride or the like are formed in this order on a main surface of an n-type single-crystalline silicon substrate. On a back surface of the n-type single-crystalline silicon substrate are provided a positive electrode and a negative electrode next to each other. The positive electrode includes an i-type amorphous silicon film, a p-type amorphous silicon film, a back electrode, and a collector electrode formed in this order on the back surface of the n-type single-crystalline silicon substrate. The negative electrode includes an i-type amorphous silicon film, an n-type amorphous silicon film, a back electrode, and a collector electrode formed in this order on the back surface of the n-type single-crystalline silicon substrate.

Owner:SANYO ELECTRIC CO LTD

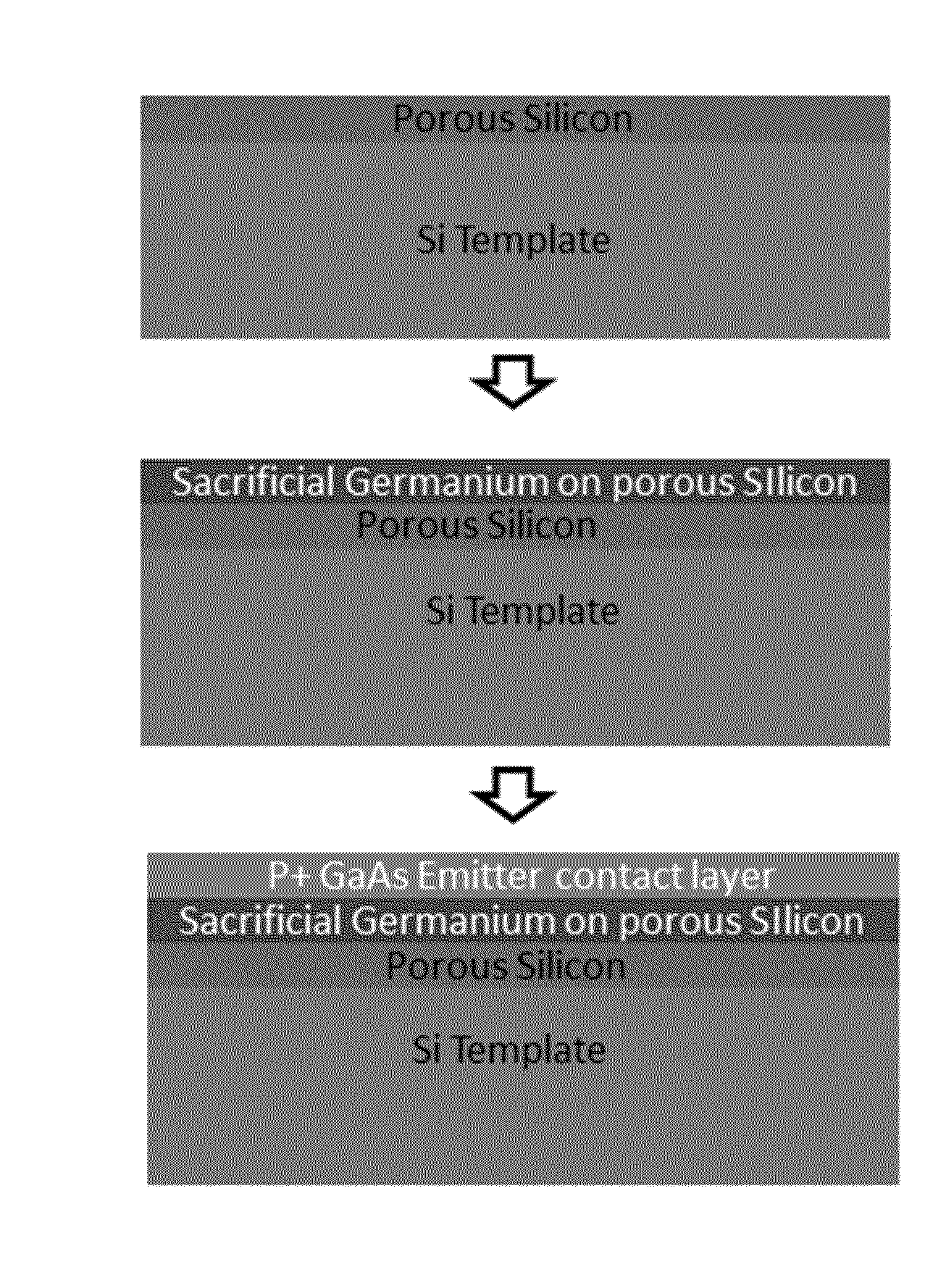

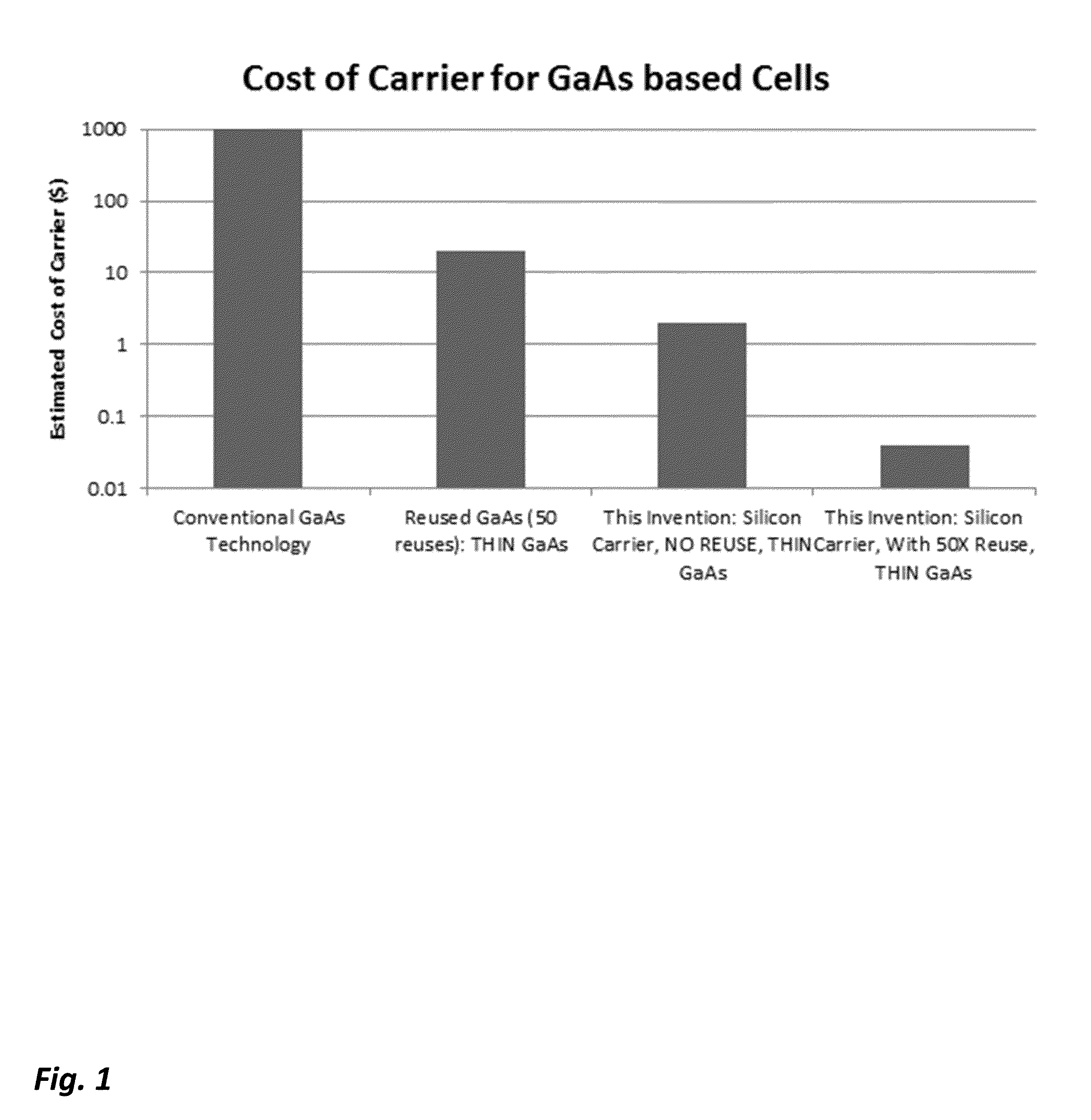

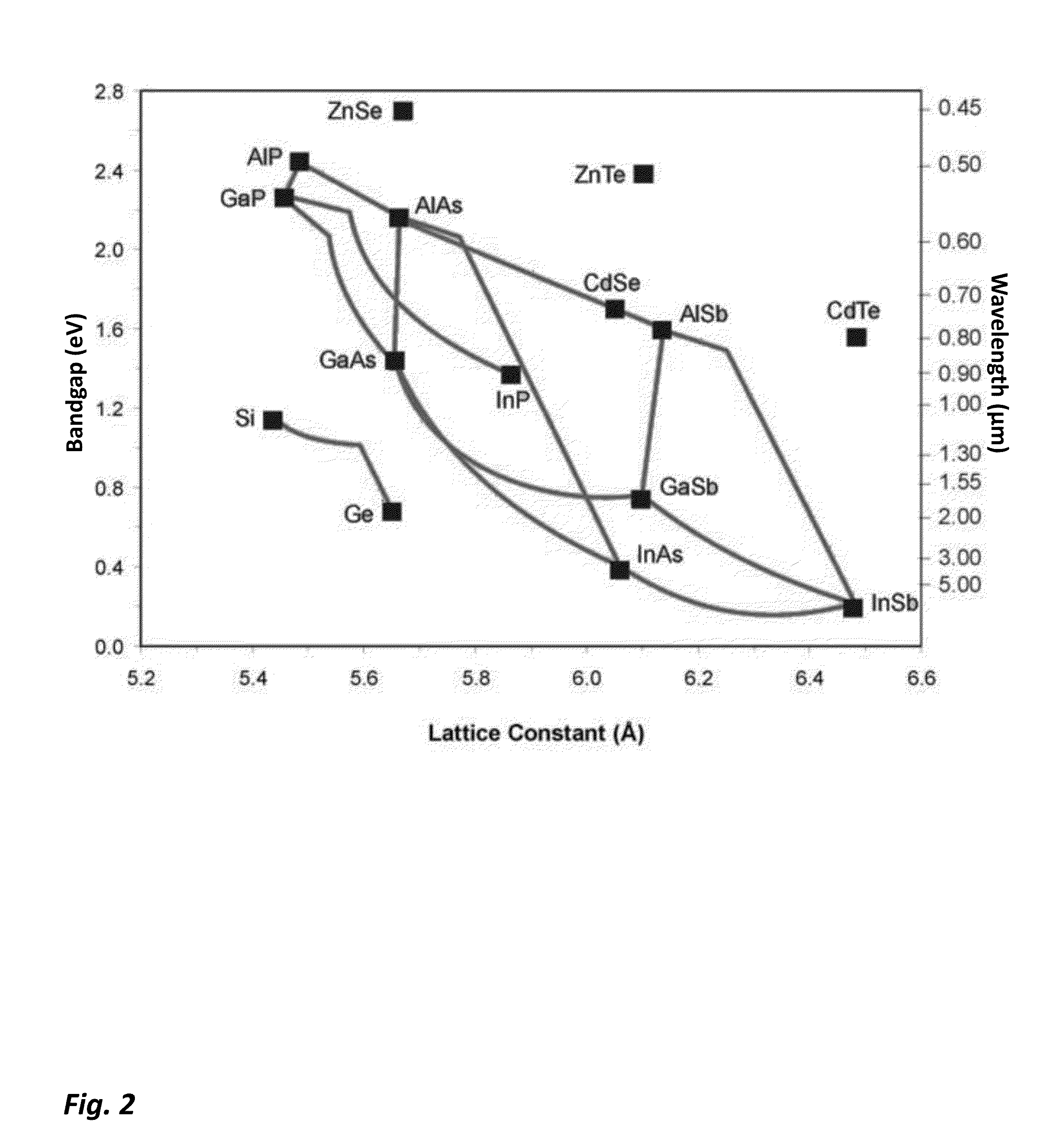

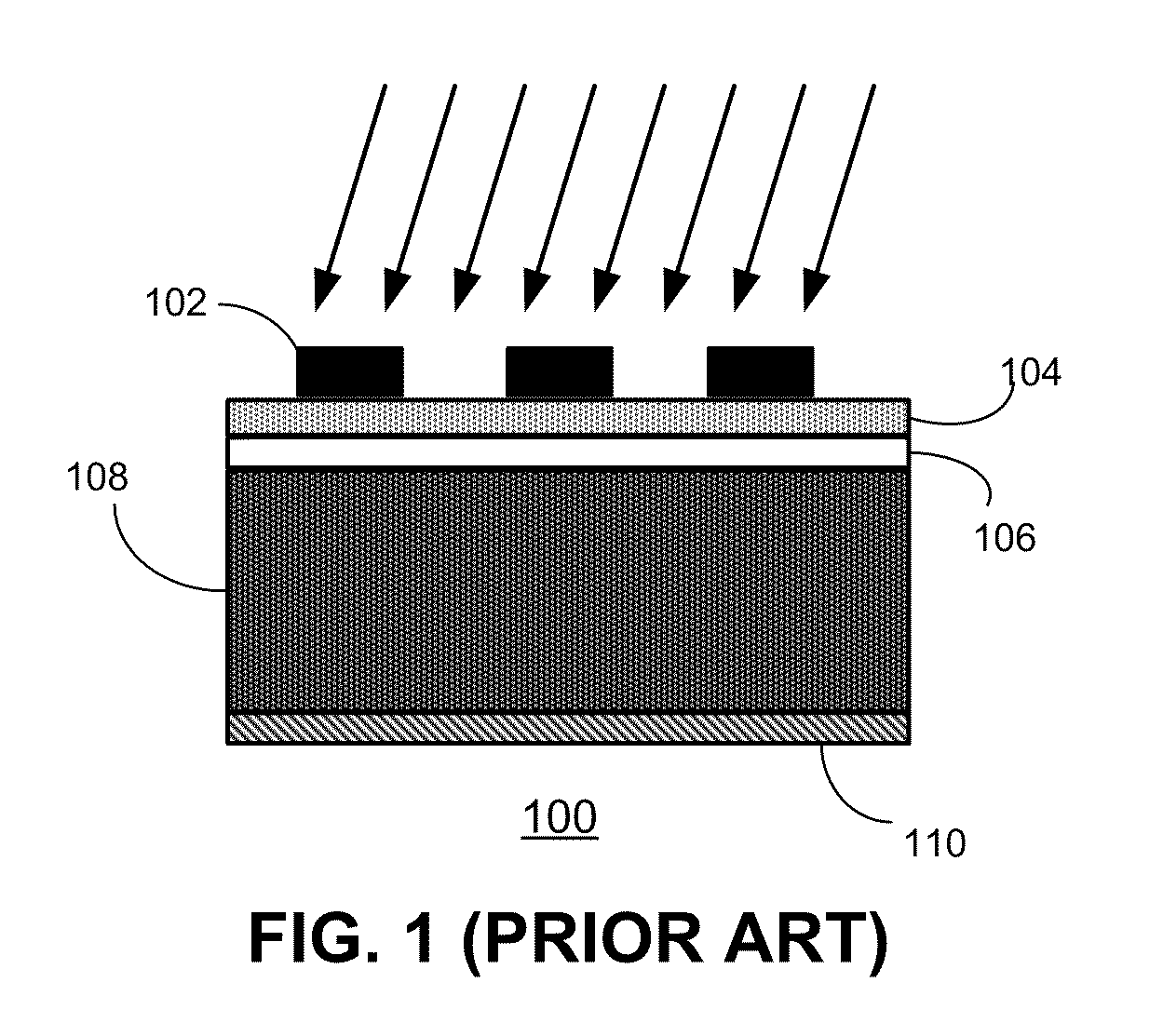

Structures and methods for high efficiency compound semiconductor solar cells

InactiveUS20130337601A1Eliminate and reduce cost and scaling disadvantageLow costFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsThin layer

Methods and structures are provided for the growth and separation of a relatively thin layer crystalline compound semiconductor material containing III-V device layers, including but not limited to Gallium Arsenide (GaAs), on top of a crystalline silicon template wafer. Solar cell structures and manufacturing methods based on the crystalline compound semiconductor material are described.

Owner:BEAMREACH SOLAR INC

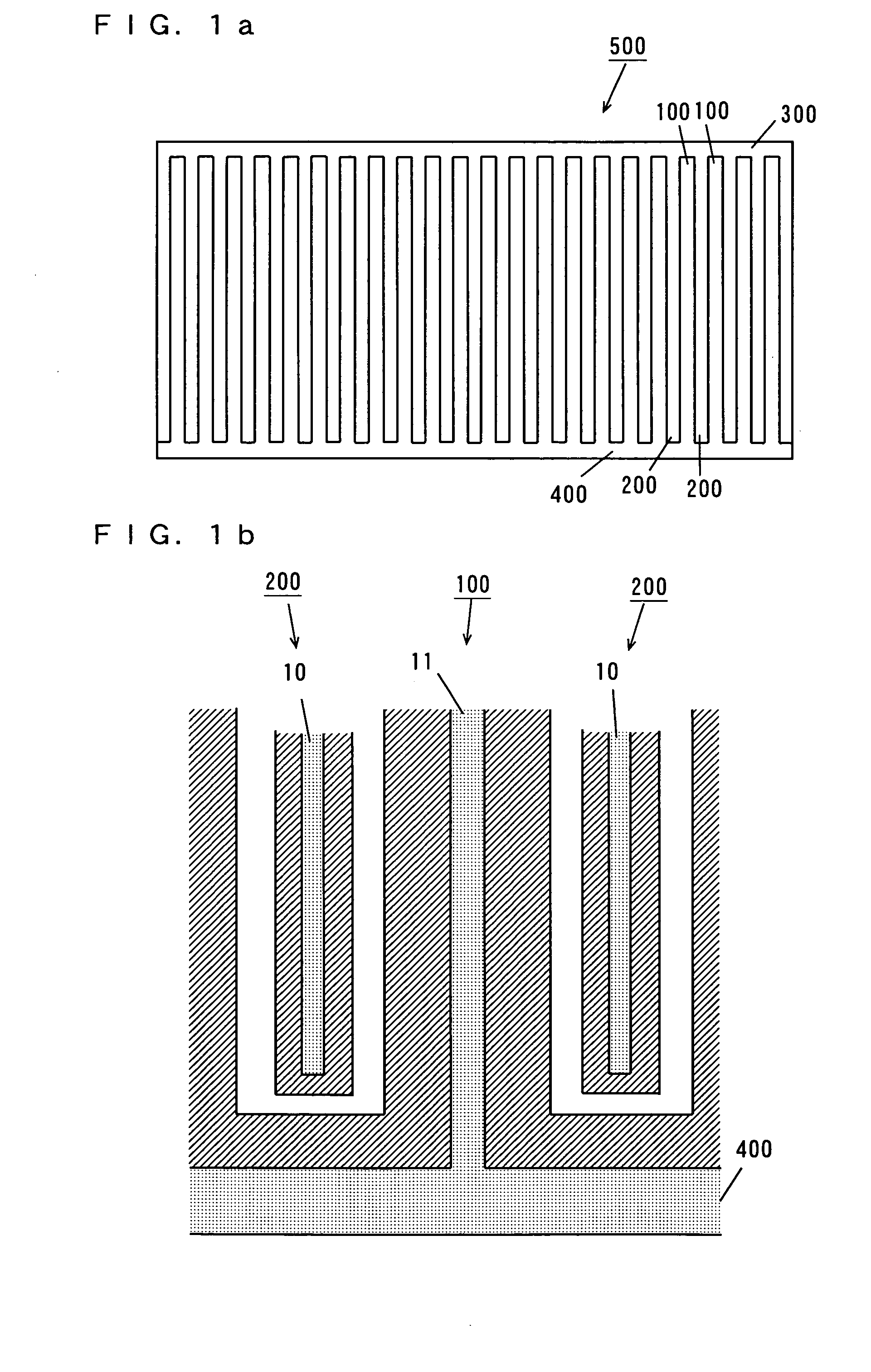

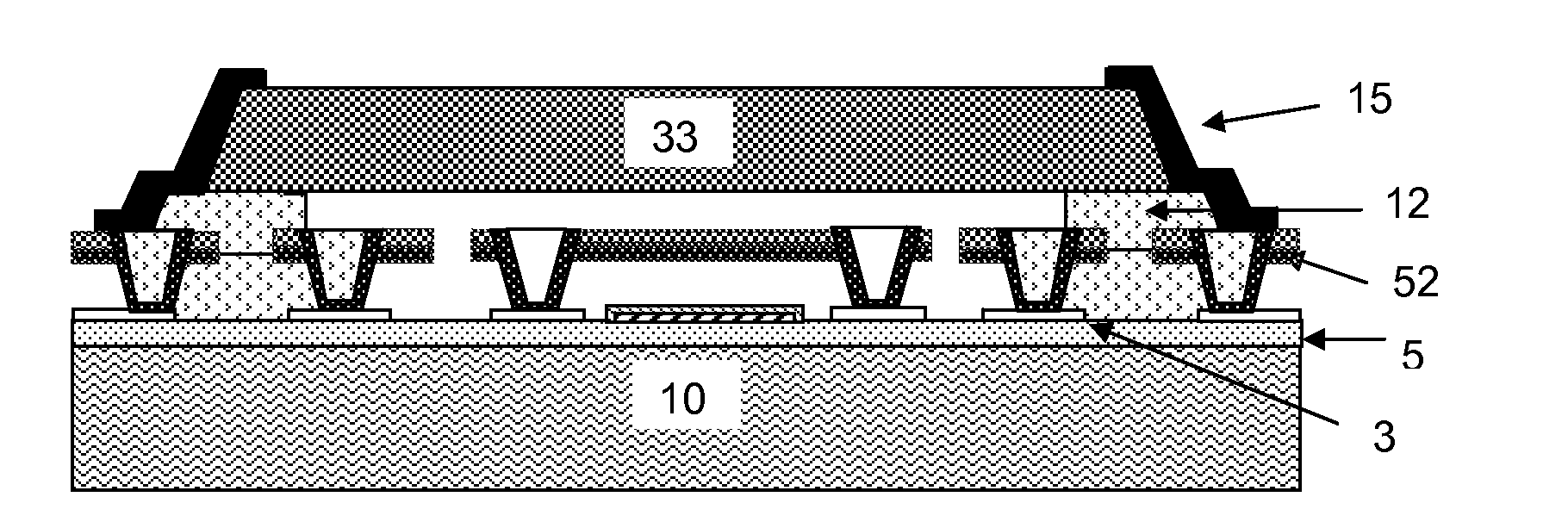

System and method of fabricating micro cavities

InactiveUS20080308920A1Decorative surface effectsSemiconductor/solid-state device detailsEpoxyMicroelectromechanical systems

A system and method for manufacturing micro cavity packaging enclosure at the wafer level using MEMS (MicroElectroMechanical Systems) process, wherein micro cavities are formed from epoxy-bonded single-crystalline silicon wafer as its cap, epoxy and deposited metal or insulator as at least part of its sidewall, on substrate wafers.

Owner:WAN CHANG FENG

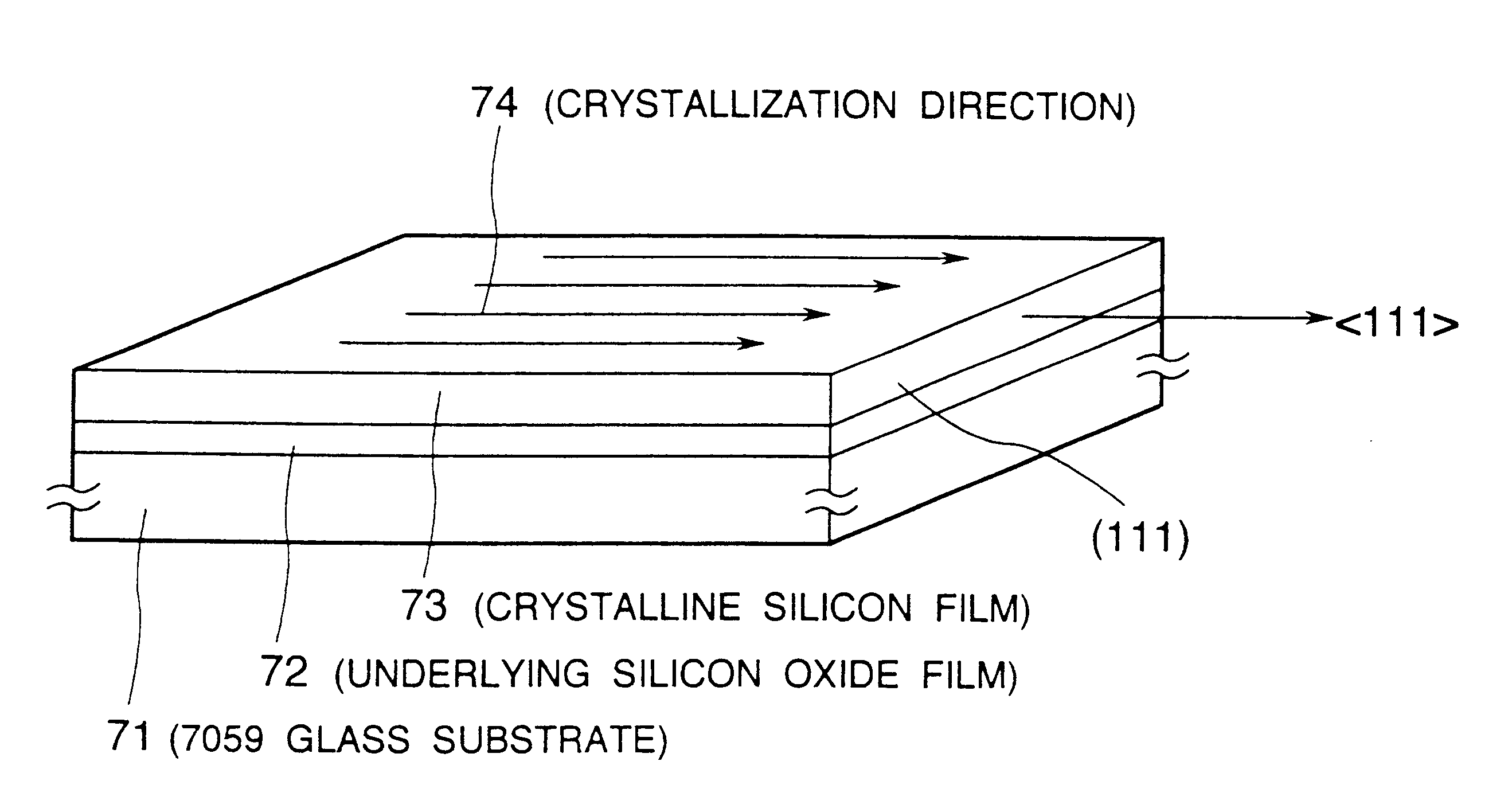

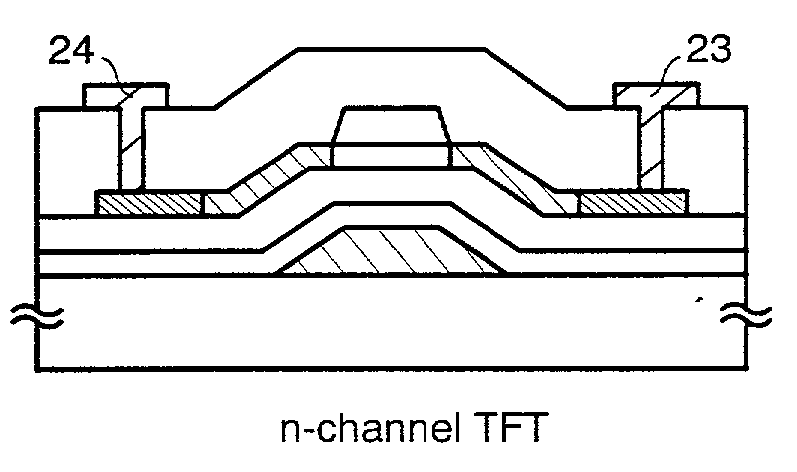

Method of preparing a semiconductor having controlled crystal orientation

InactiveUS6756657B1TransistorSemiconductor/solid-state device manufacturingAmorphous siliconCrystal orientation

A semiconductor device is disclosed. The semiconductor device has a crystalline silicon film as an active layer region. The crystalline silicon film has needle-like or columnar crystals oriented parallel to the substrate and having a crystal growth direction of (111) axis. A method for preparing the semiconductor device comprises steps of adding a catalytic element to an amorphous silicon film; and heating the amorphous silicon film containing the catalytic element at a low temperature to crystallize the silicon film.

Owner:SEMICON ENERGY LAB CO LTD

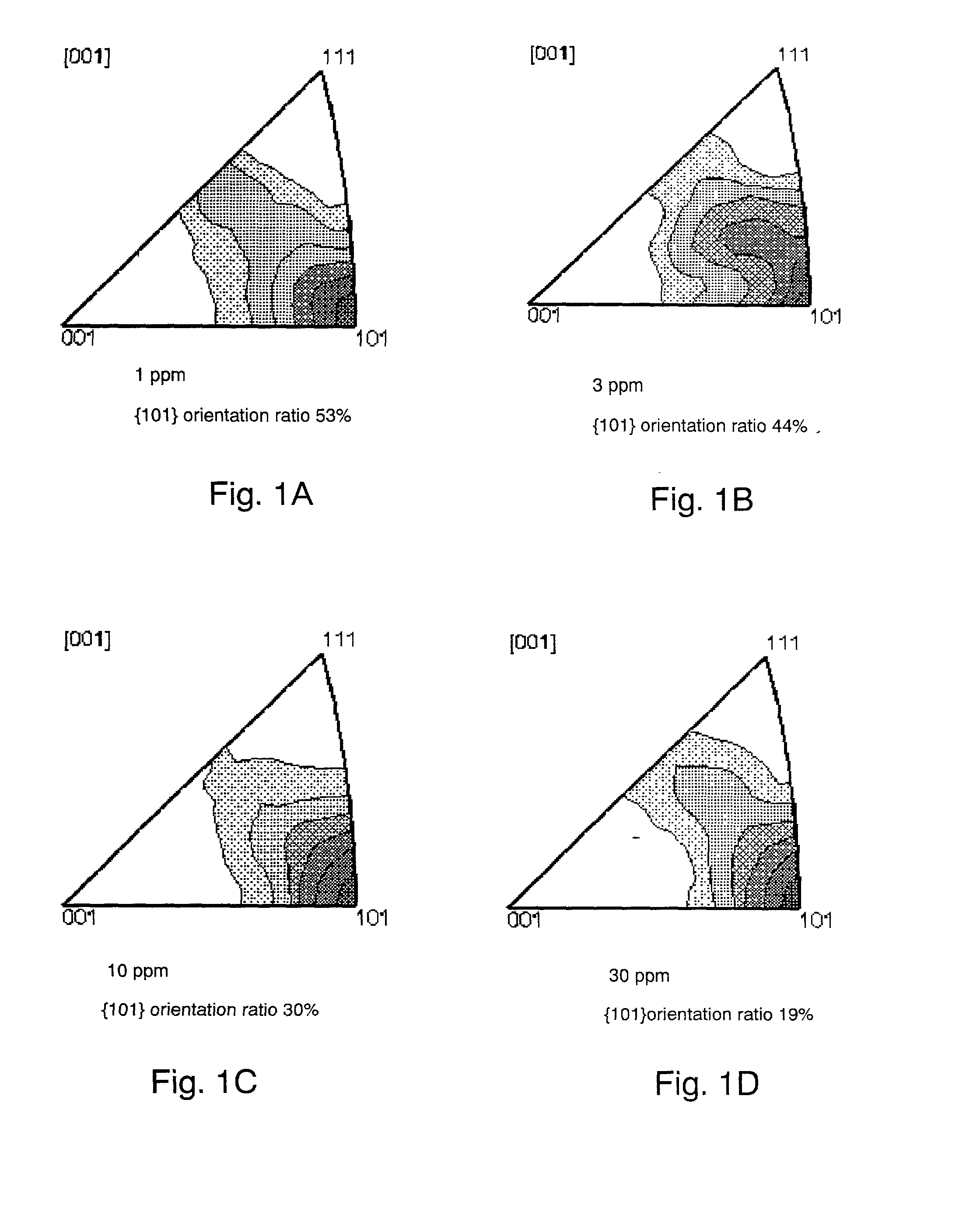

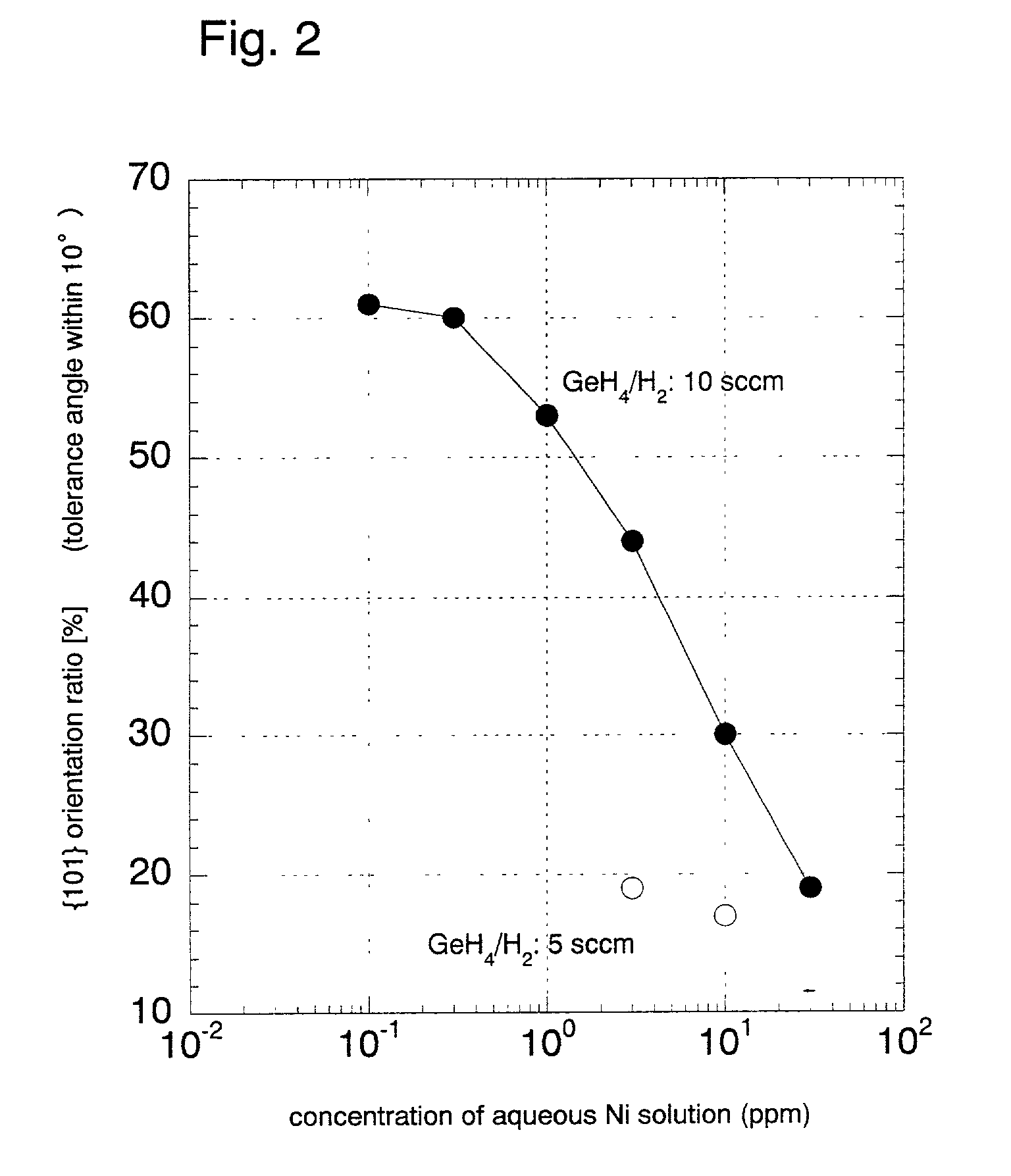

Semiconductor device

Crystal orientation planes exist randomly in a crystalline silicon film manufactured by a conventional method, and the orientation ratio is low with respect to a specific crystal orientation. A semiconductor film having a high orientation ratio for the {101} lattice plane is obtained if crystallization of an amorphous semiconductor film, which has silicon as its main constituent and contains from 0.1 to 10 atom % germanium, is performed after introduction of a metal element. A TFT is manufactured utilizing the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing a semiconductor device

InactiveUS7361519B2Promote crystallizationHigh effectTransistorSolid-state devicesAmorphous siliconCrystalline silicon

A method of manufacturing a semiconductor device, comprises the steps of: forming a first insulating film on a first substrate; forming a second insulating film on the first insulating film; forming an amorphous silicon film on the second insulating film; holding a metal element that promotes the crystallization of silicon in contact with a surface of the amorphous silicon film; crystallizing the amorphous silicon film through a heat treatment to obtain a crystalline silicon film; forming a thin-film transistor using the crystalline silicon film; forming a sealing layer that seals the thin-film transistor; bonding a second substrate having a translucent property to the sealing layer; and removing the first insulating film to peel off the first substrate.

Owner:SEMICON ENERGY LAB CO LTD

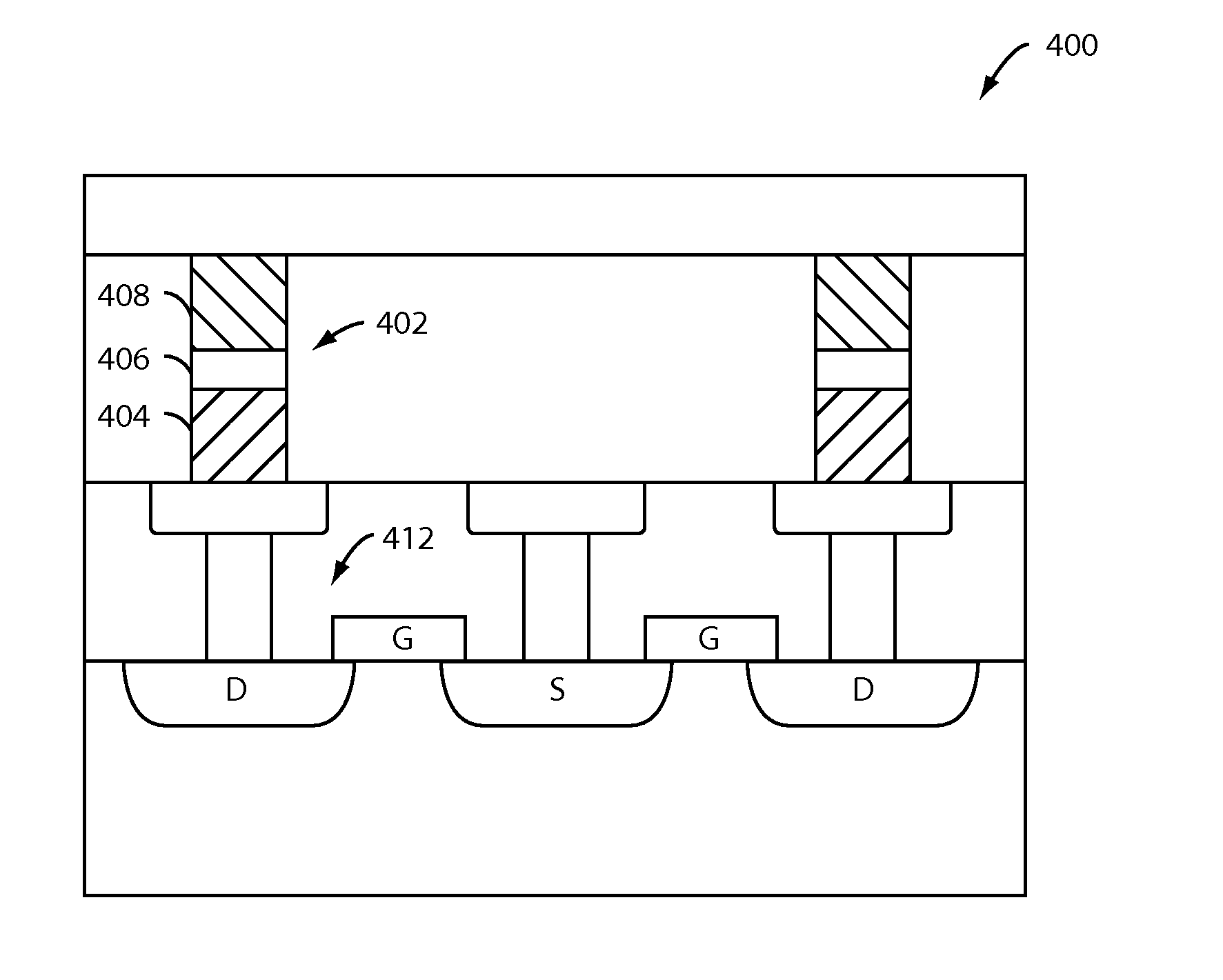

RESTIVE MEMORY USING SiGe MATERIAL

ActiveUS20120008366A1Solid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconCrystalline silicon

A resistive memory device includes a first electrode; a second electrode having a polycrystalline semiconductor layer that includes silicon; a non-crystalline silicon structure provided between the first electrode and the second electrode. The first electrode, second electrode and non-crystalline silicon structure define a two-terminal resistive memory cell.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

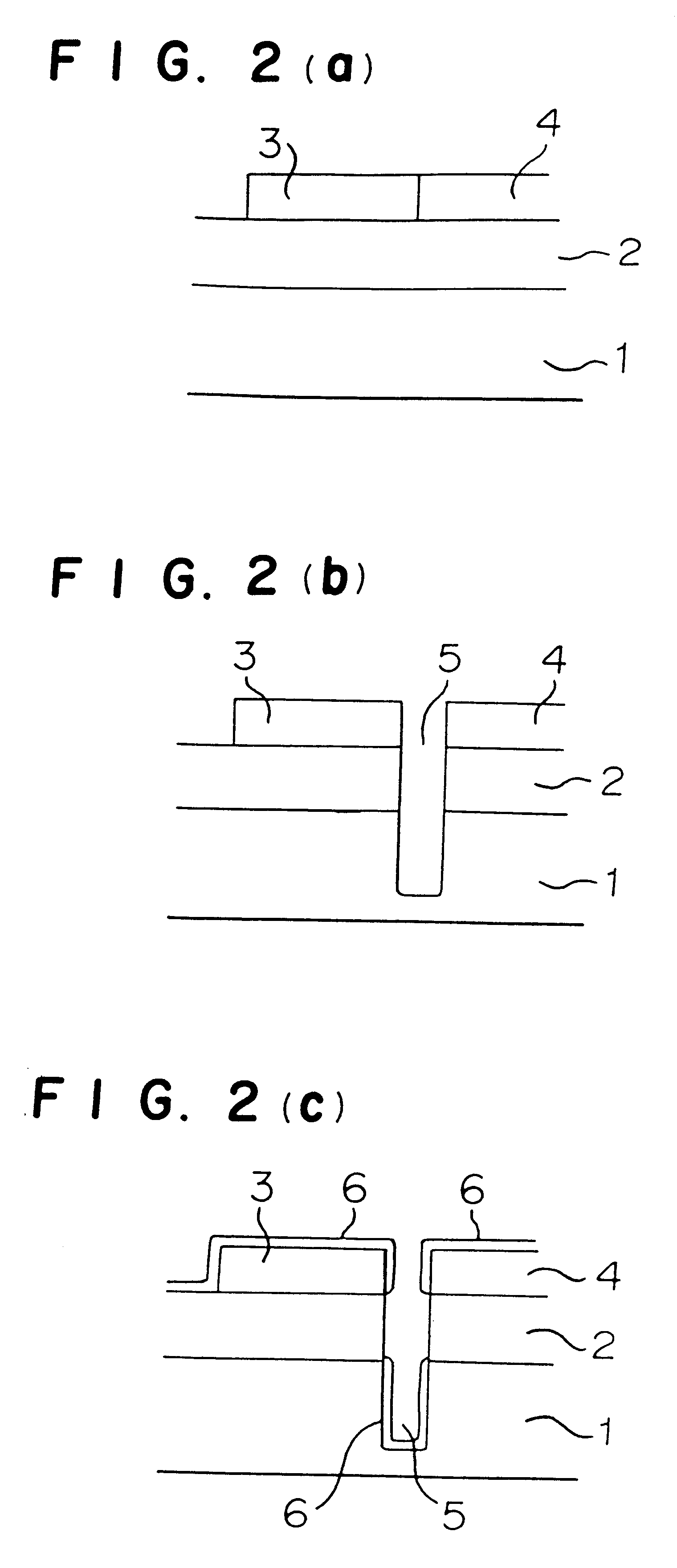

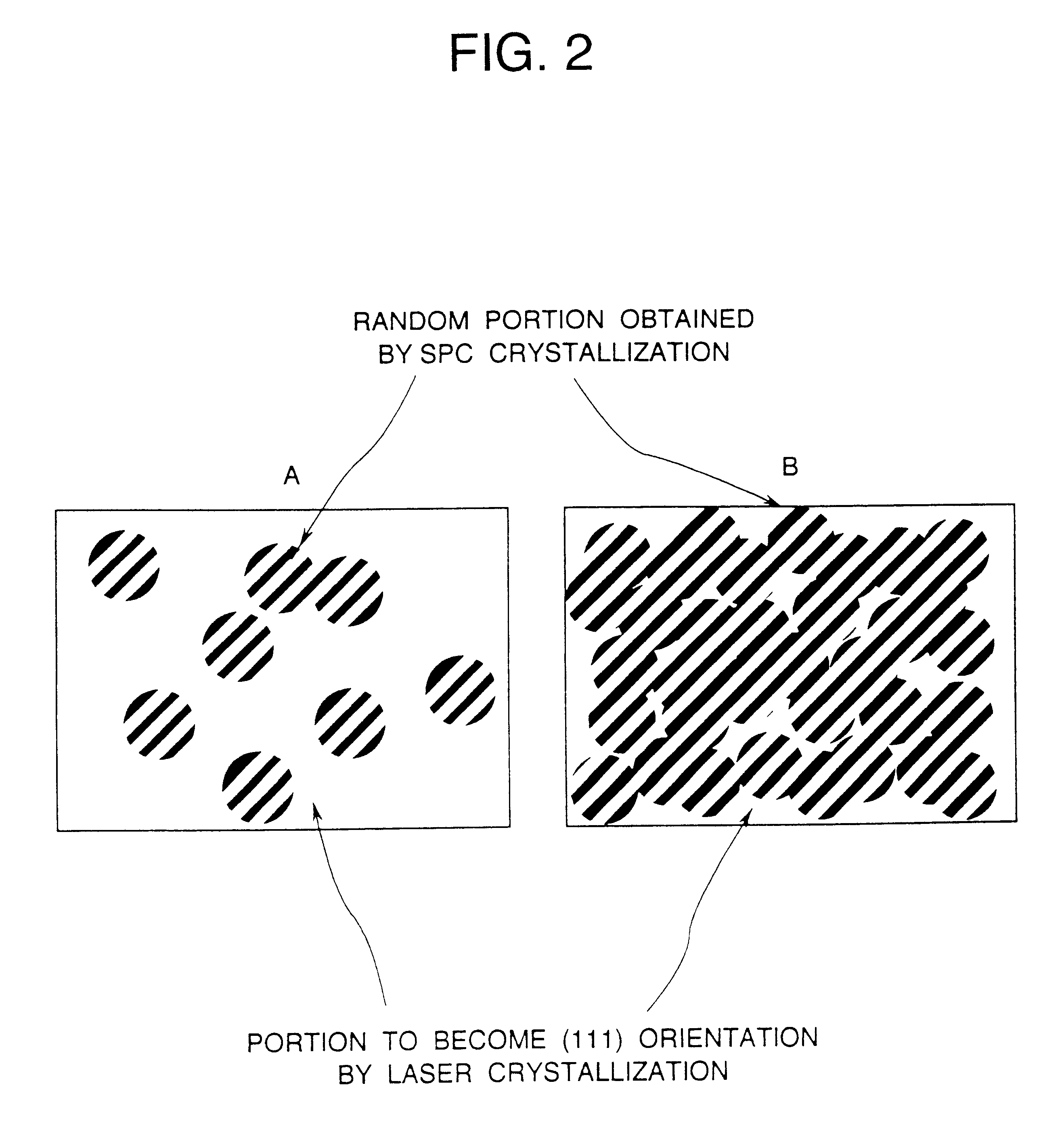

Thin film semiconductor and method for manufacturing the same, semiconductor device and method for manufacturing the same

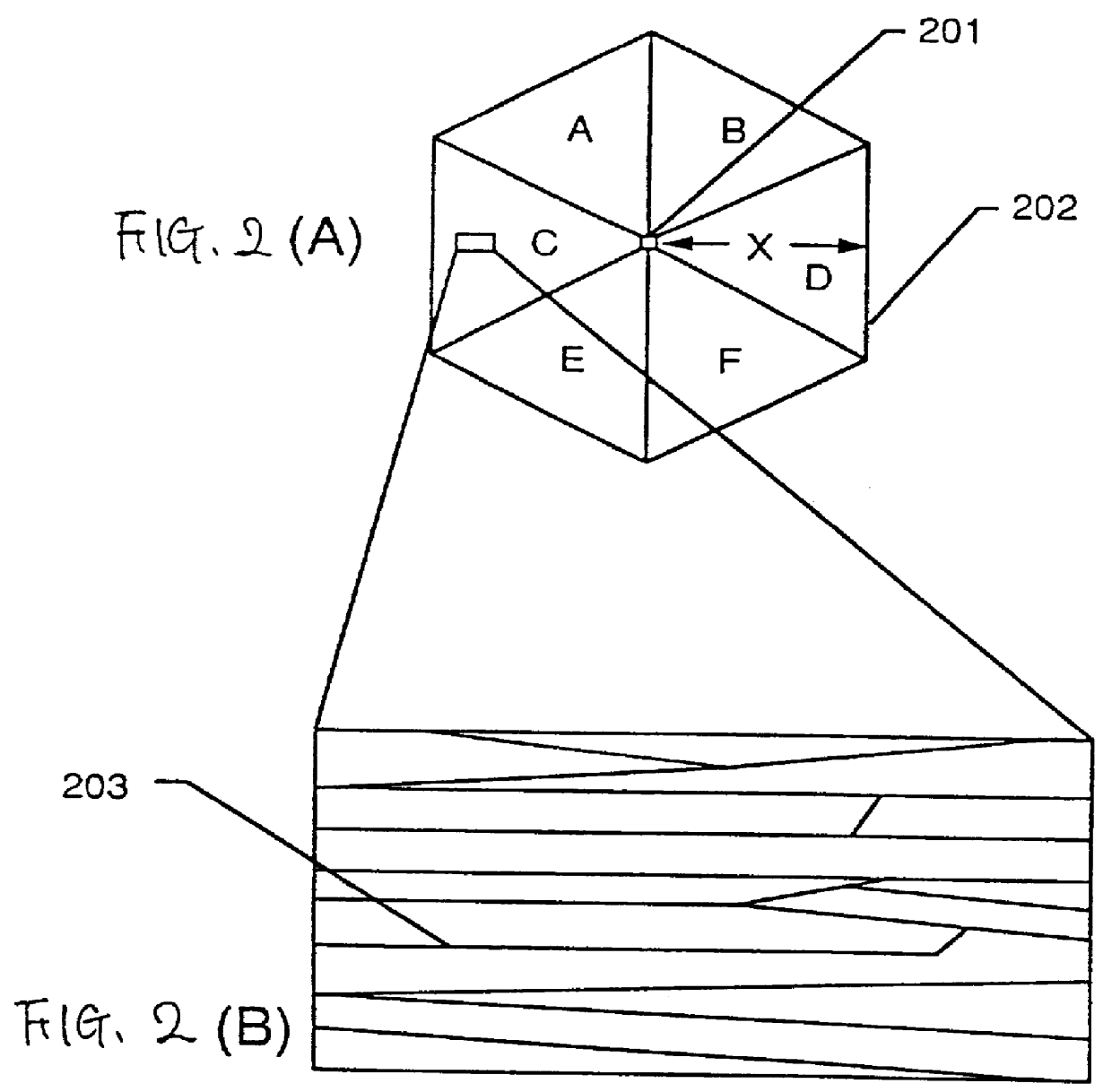

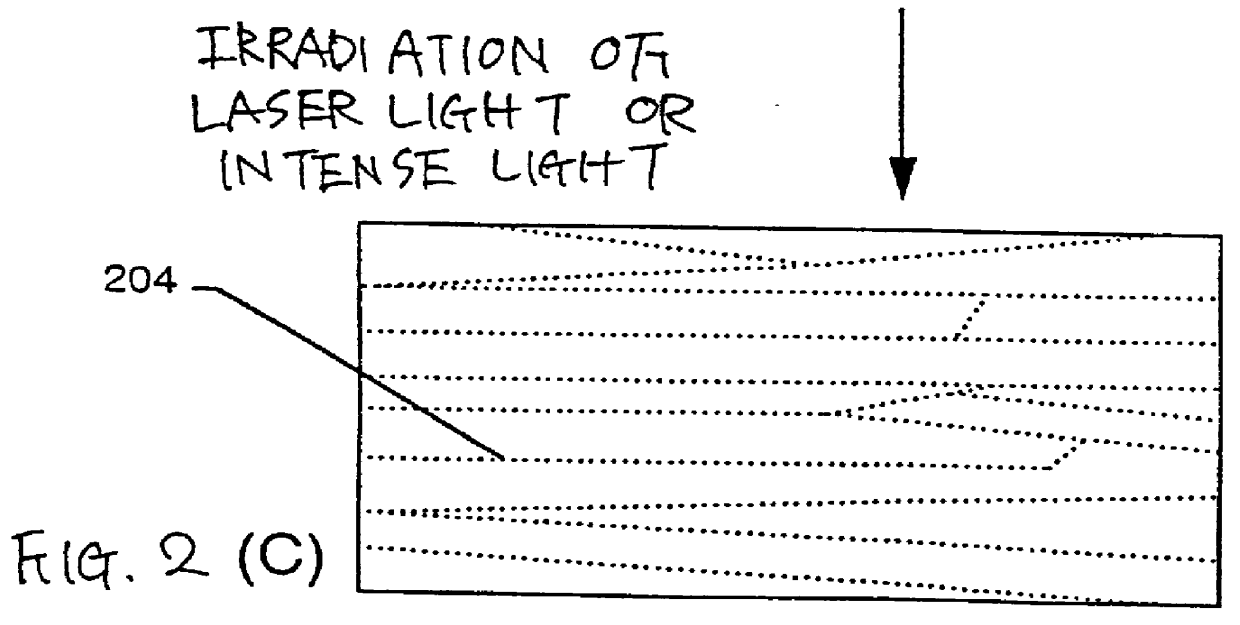

The present invention is related to a thin film semiconductor which can be regarded as substantially a single crystal and a semiconductor device comprising an active layer formed by the thin film semiconductor. At least a concave or convex pattern is formed intentionally on a insulating film provided in contact with the lower surface of an amorphous silicon film, whereby at least a site is formed in which a metal element for accelerating crystallization can be segregated. Therefore, a crystal nuclei is selectively formed in a portion where the concave or convex pattern is located, which carries out controlling a crystal diameter. Thus, a crystalline silicon film is obtained. A crystallinity of the crystalline silicon film is improved by the irradiation of a laser light or an intense light having an energy equivalent to that of the laser light, whereby a monodomain region in which no grain boundary substantially exit is formed.

Owner:SEMICON ENERGY LAB CO LTD

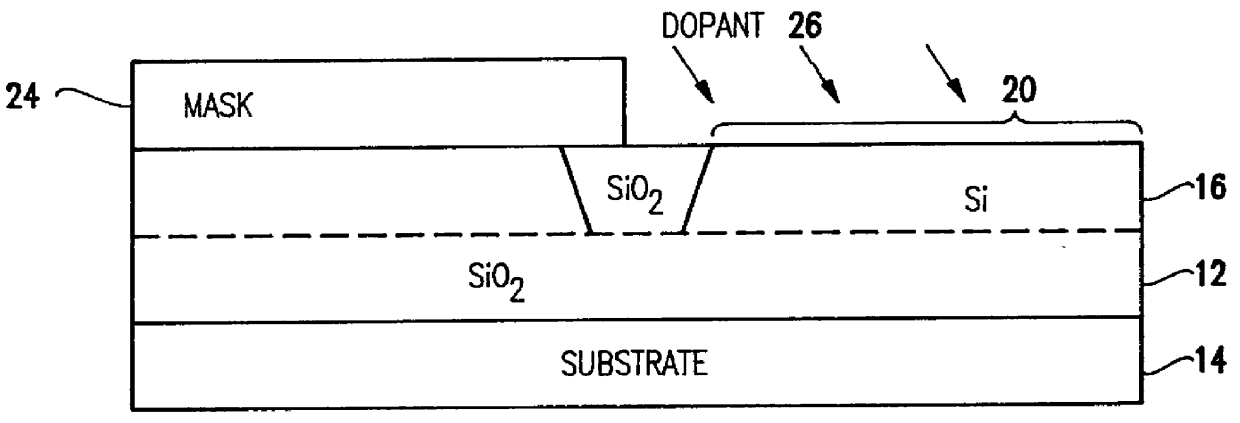

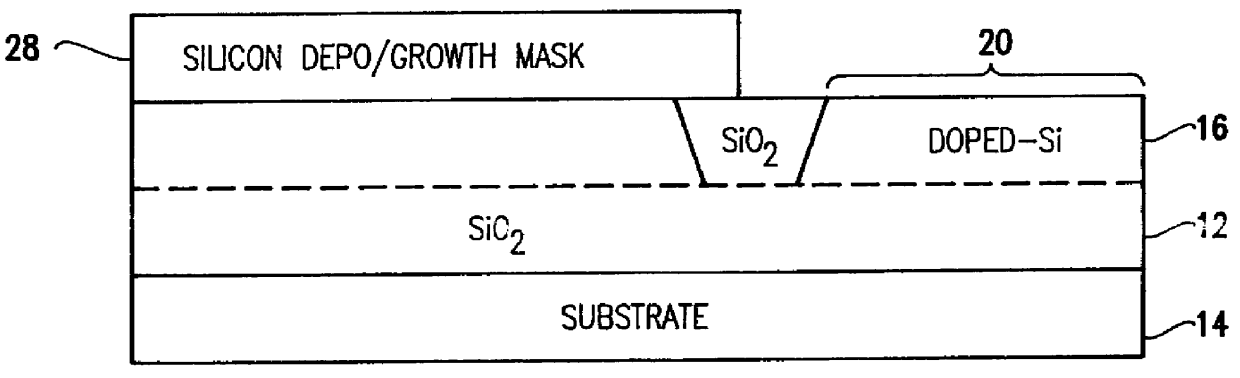

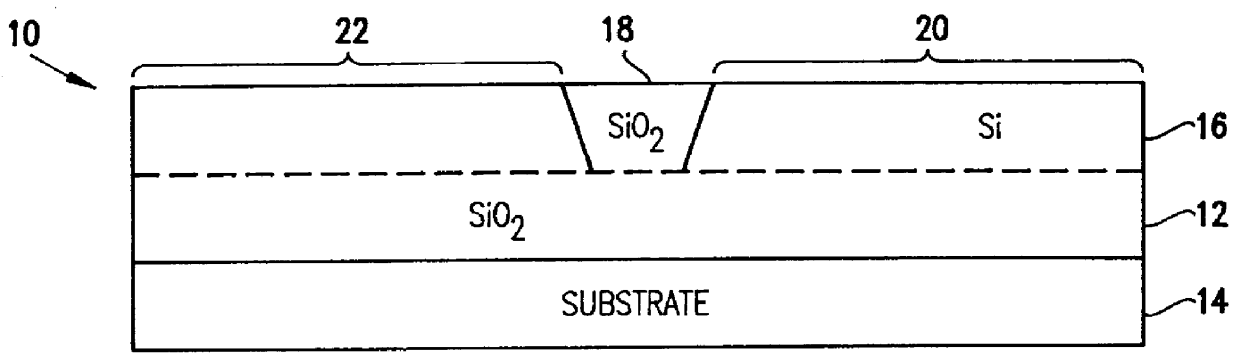

Silicon-on-insulator and CMOS-on-SOI double film fabrication process with a coplanar silicon and isolation layer and adding a second silicon layer on one region

InactiveUS6096584AHigher power-to-failure thresholdImprove protectionTransistorSolid-state devicesIsolation layerElectronic component

Silicon is formed at selected locations on a silicon-insulator (SOI) substrate during fabrication of selected electronic components, including resistors, capacitors, and diodes. The silicon location is defined using a patterned, removable mask, and the silicon may be applied by deposition or growth and may take the form of polysilicon or crystalline silicon. Electrostatic discharge (ESD) characteristics of the SOI device is significantly improved by having a thick double layer of silicon in selected regions.

Owner:GLOBALFOUNDRIES INC

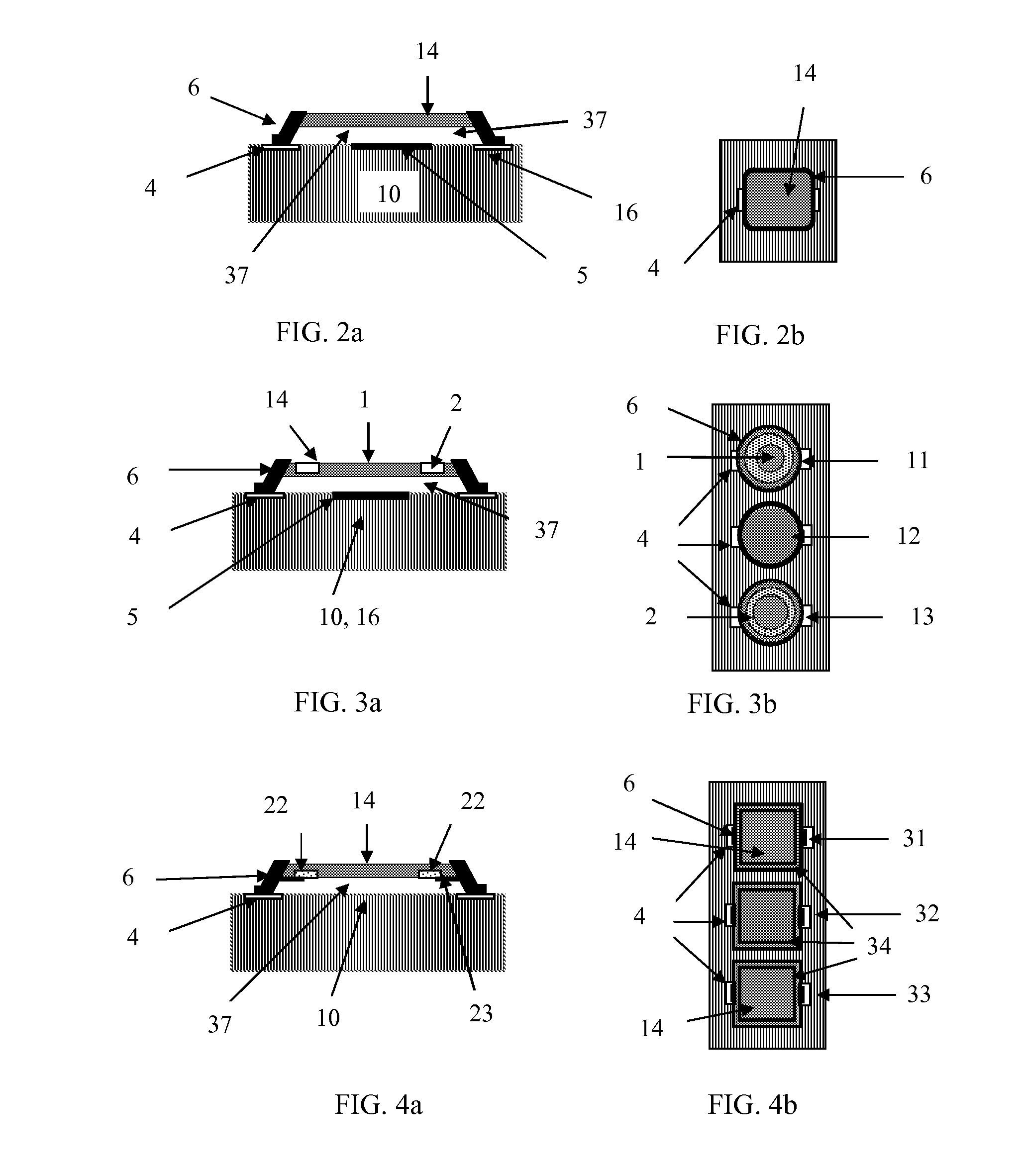

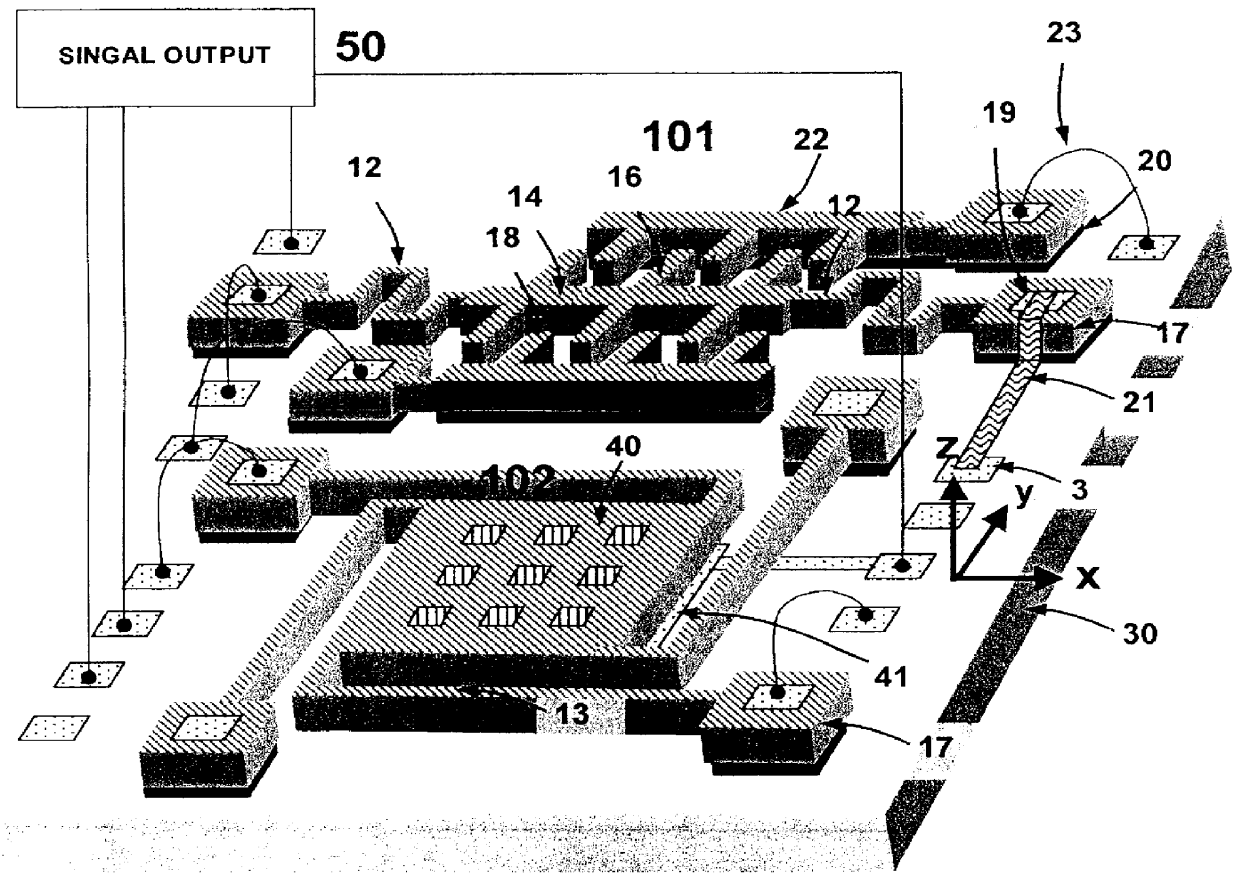

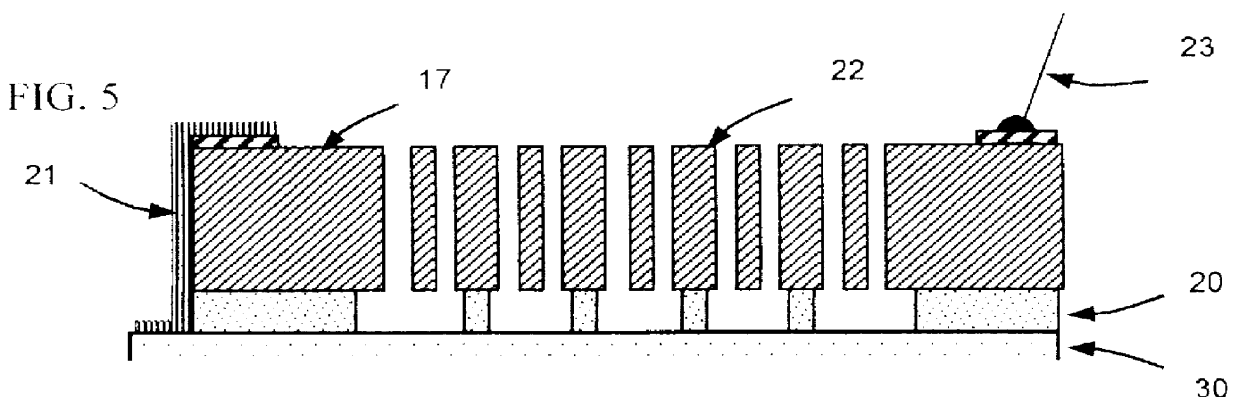

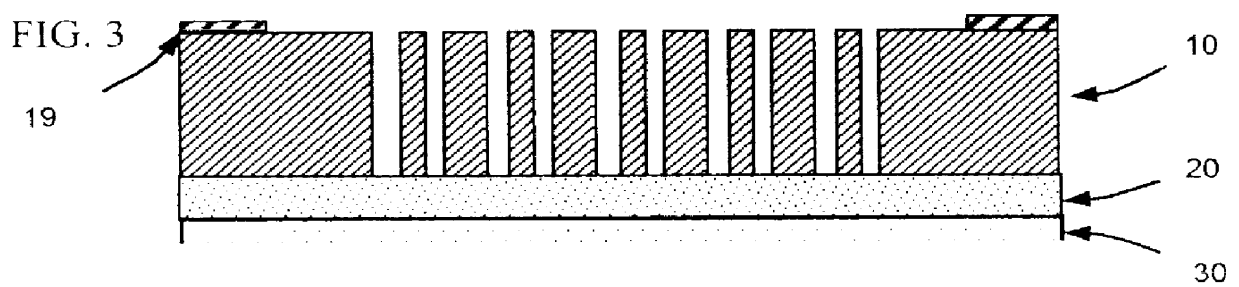

Micro-electro mechanical device made from mono-crystalline silicon and method of manufacture therefore

InactiveUS6060336ALow temperature processingReduce stressAcceleration measurement using interia forcesSemiconductor/solid-state device manufacturingAdhesiveEngineering

A micro-electro-mechanical device and method of manufacture therefore with a suspended structure formed from mono-crystalline silicon, bonded to a substrate wafer with an organic adhesive layer serving as support and spacer and the rest of the organic adhesive layer serving as a sacrificial layer, which is removed by a dry etch means. Said substrate wafer may contain integrated circuits for sensing and controlling the device.

Owner:C F WAN

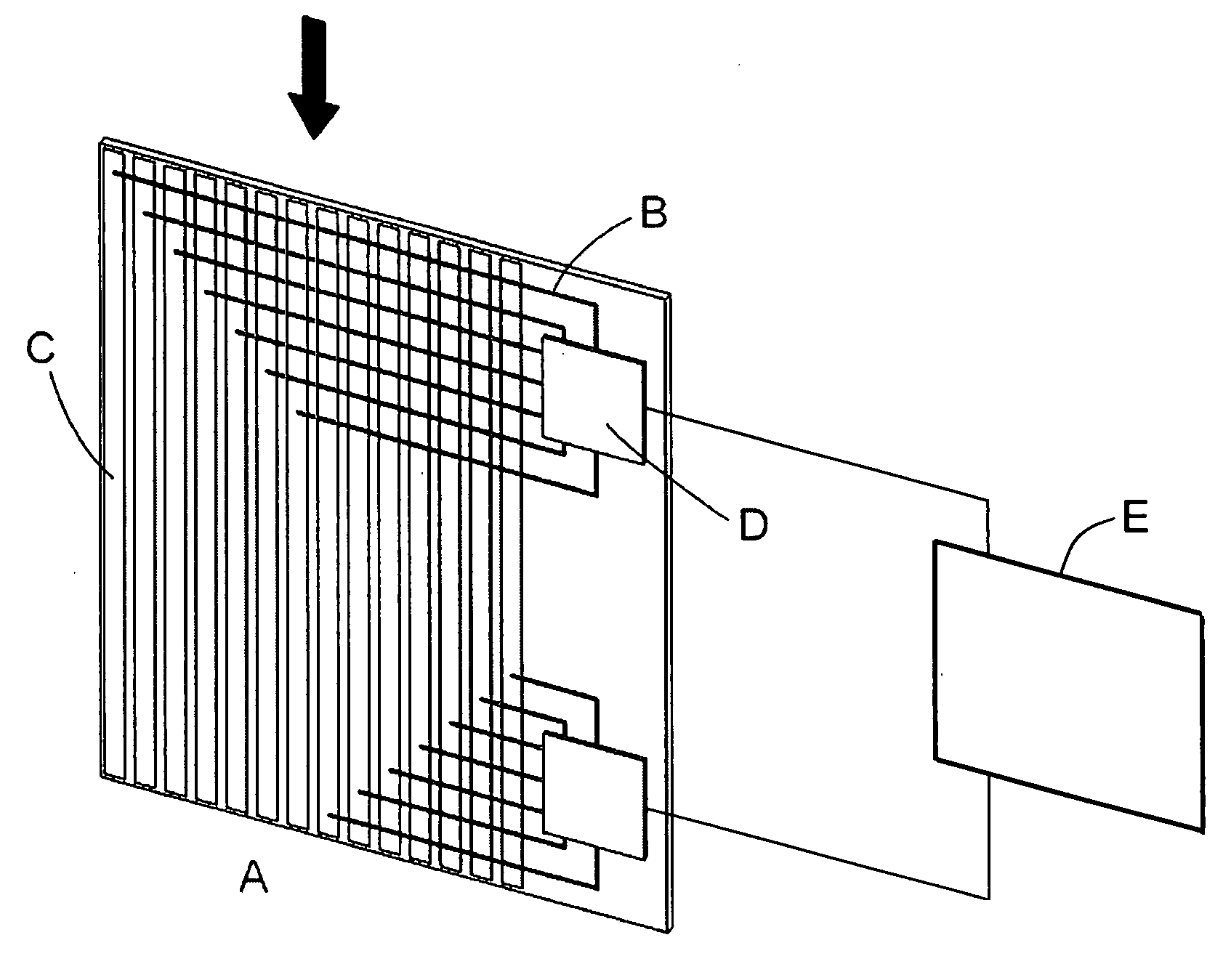

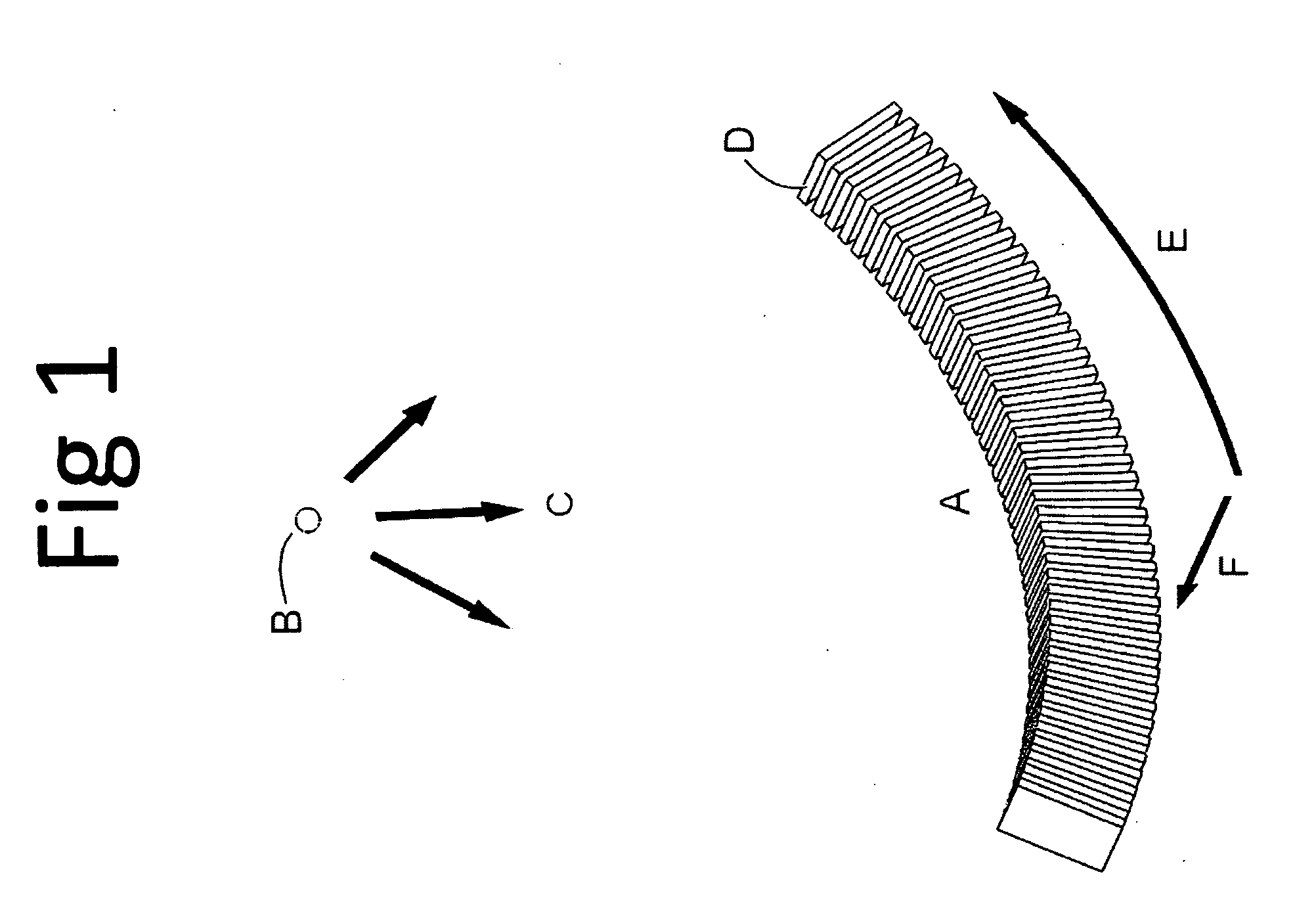

Silicon detector assembly for x-ray imaging

A Silicon detector for x-ray imaging is based on multiple semiconductor detector modules (A) arranged together to form an overall detector area, where each semiconductor detector module includes an x-ray sensor of crystalline Silicon oriented edge-on to incoming x-rays and connected to integrated circuitry for registration of x-rays interacting in the x-ray sensor through the photoelectric effect and through Compton scattering and for an incident x-ray energy between 40 keV and 250 keV to provide the spatial and energy information from these interactions to enable an image of an object. Further, anti-scatter modules (B) are interfolded between at least a subset of the semiconductor detector modules to at least partly absorb Compton scattered x-rays.

Owner:PRISMATIC SENSORS

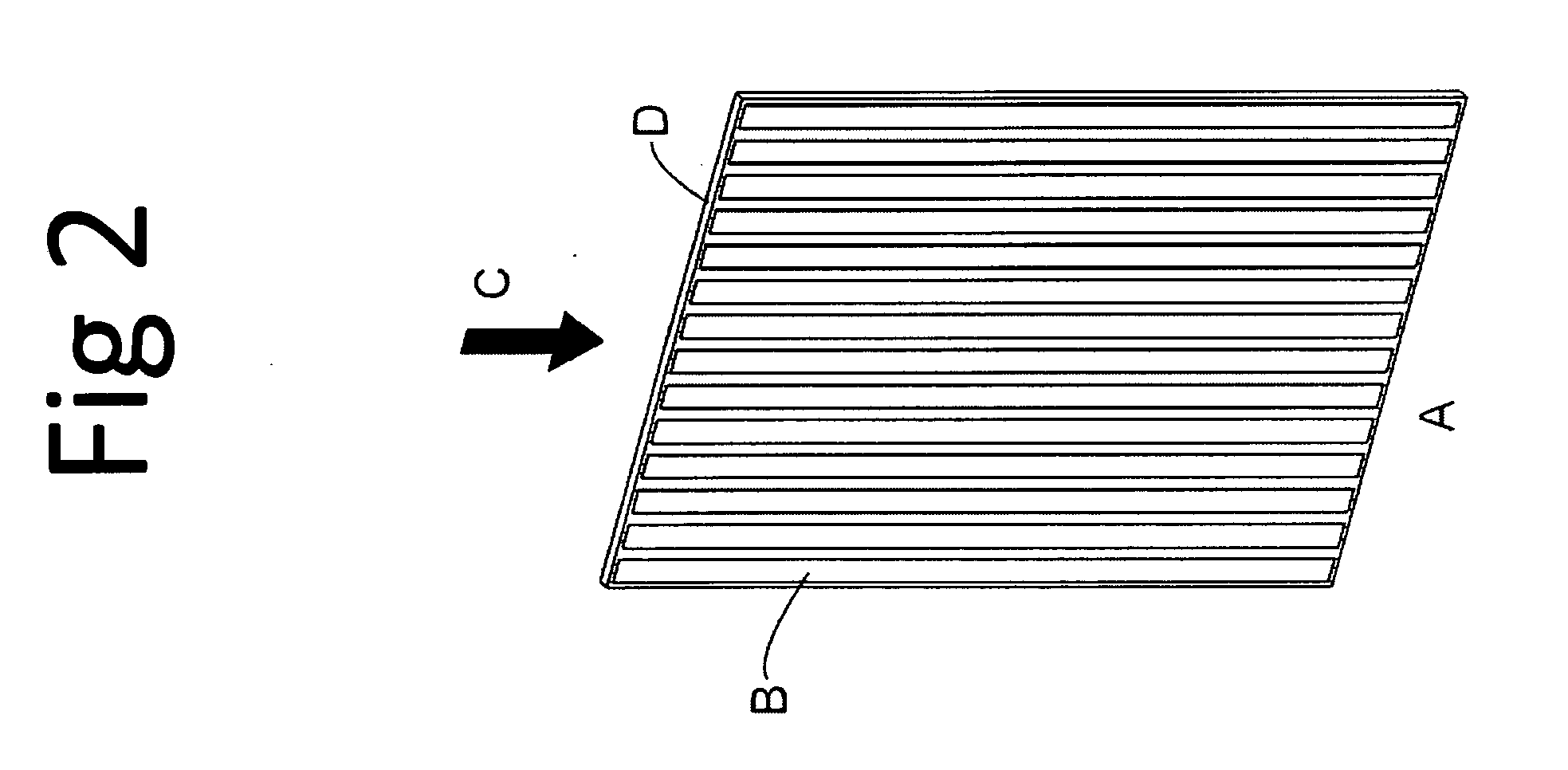

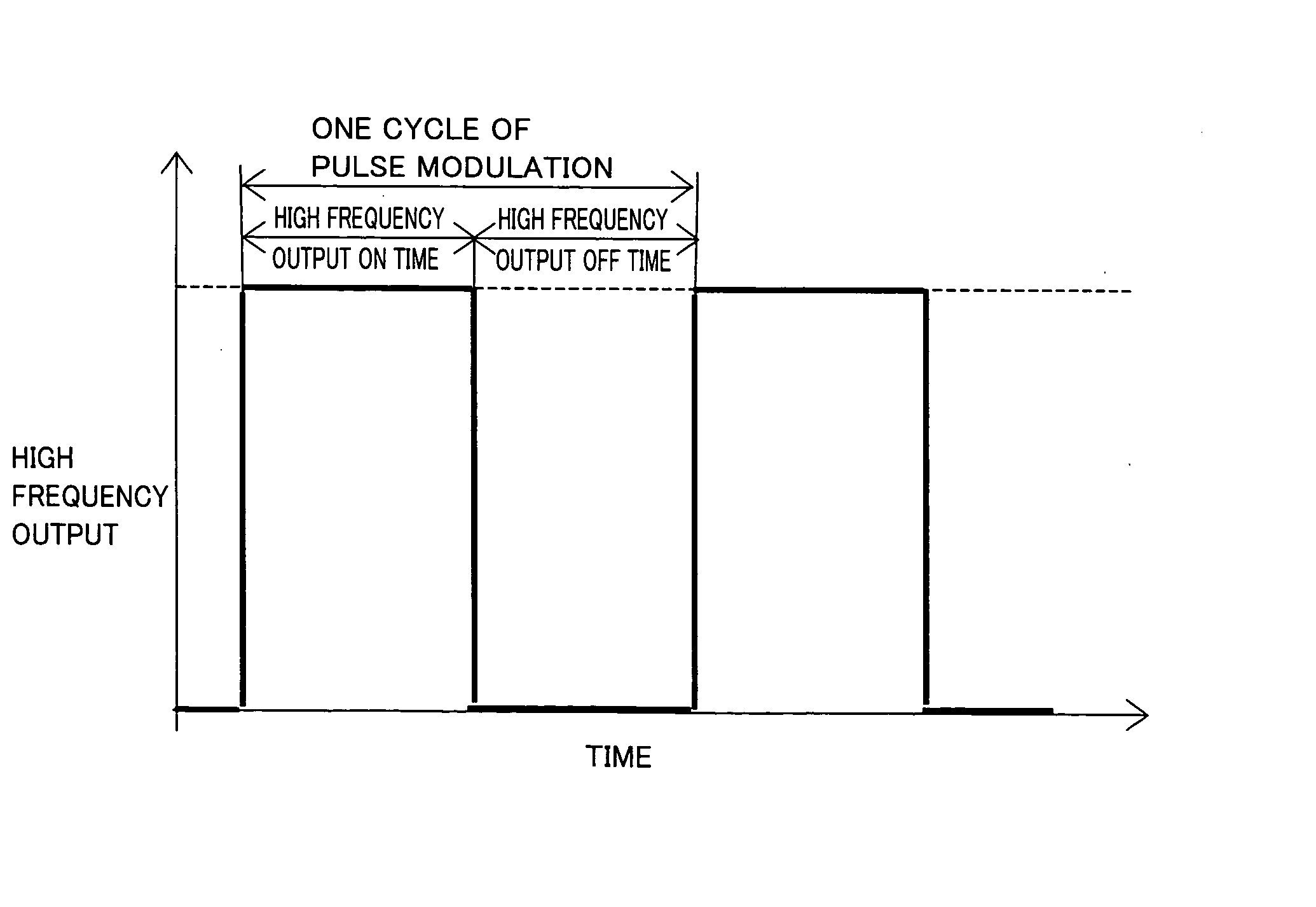

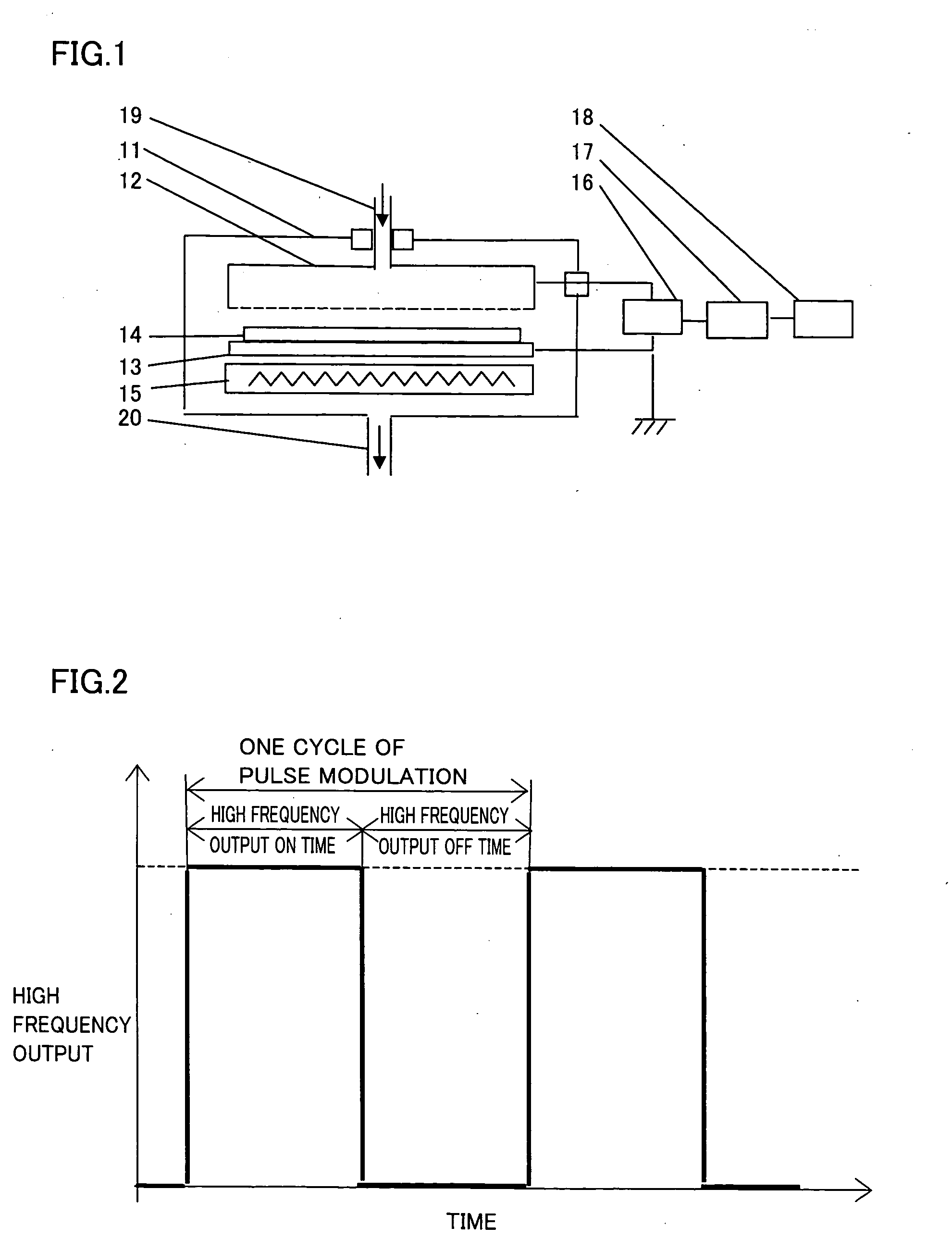

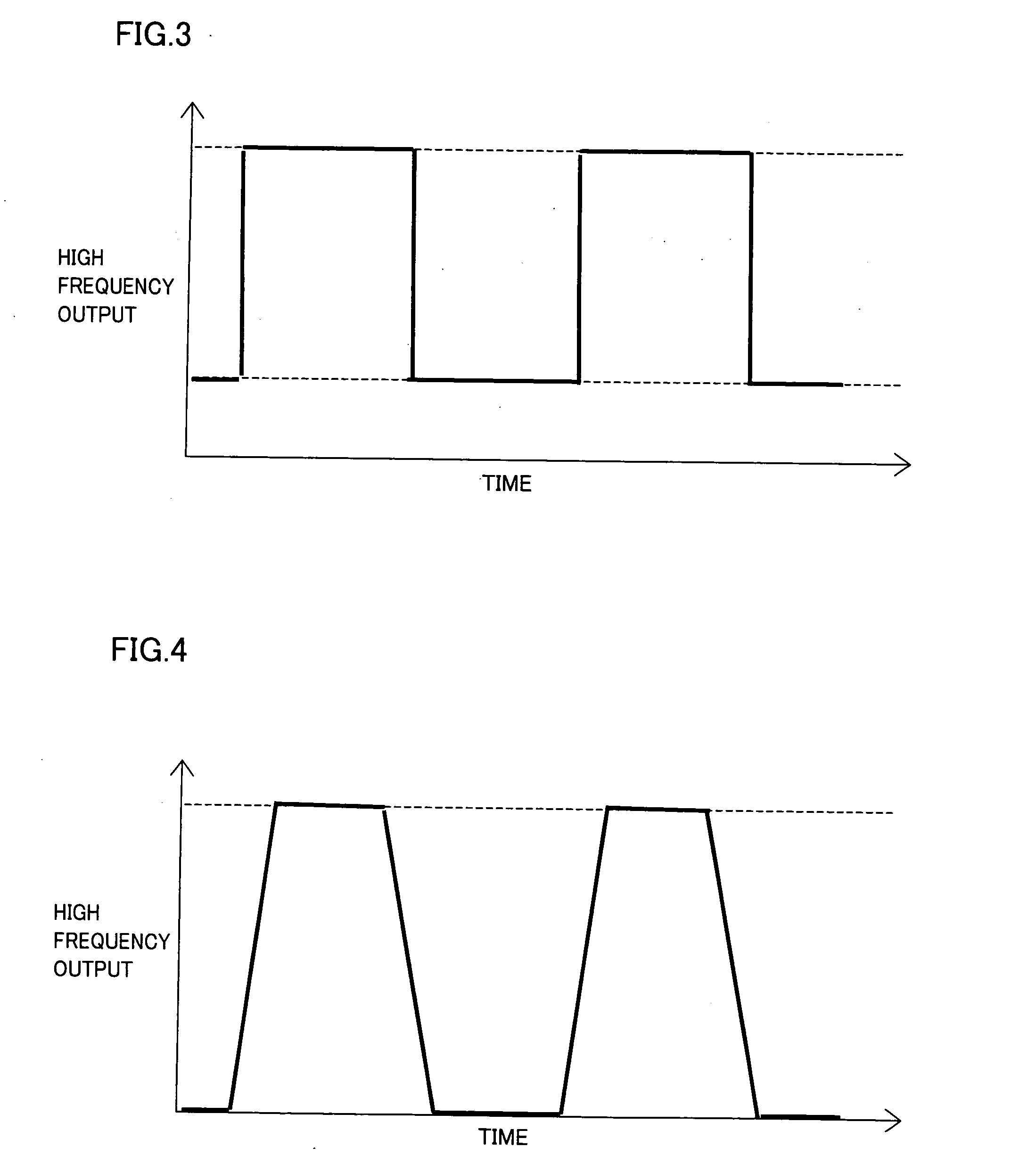

Manufacturing method of silicon thin film solar cell

InactiveUS20050022864A1Lower performance requirementsIncrease currentFinal product manufactureSemiconductor/solid-state device manufacturingHigh frequency powerSilicon thin film

To uniformly form a silicon thin film for a solar cell, having an i layer formed with crystalline silicon, on a substrate of a large area to provide a high power solar cell, in a manufacturing method of a silicon thin film solar cell, a silicon thin film, having a structure such that an i layer is sandwiched between a p layer and an n layer, is formed on a substrate with a high frequency plasma CVD method, wherein i layer is formed with crystalline silicon using plasma with pulse-modulated high frequency power, one cycle of pulse modulation includes an ON state for outputting high frequency power and an OFF state for not outputting, an output waveform is modulated to be rectangular, a time of the ON state is 1-100 microseconds, and a time of the OFF state is 5 microseconds or longer.

Owner:SHARP KK

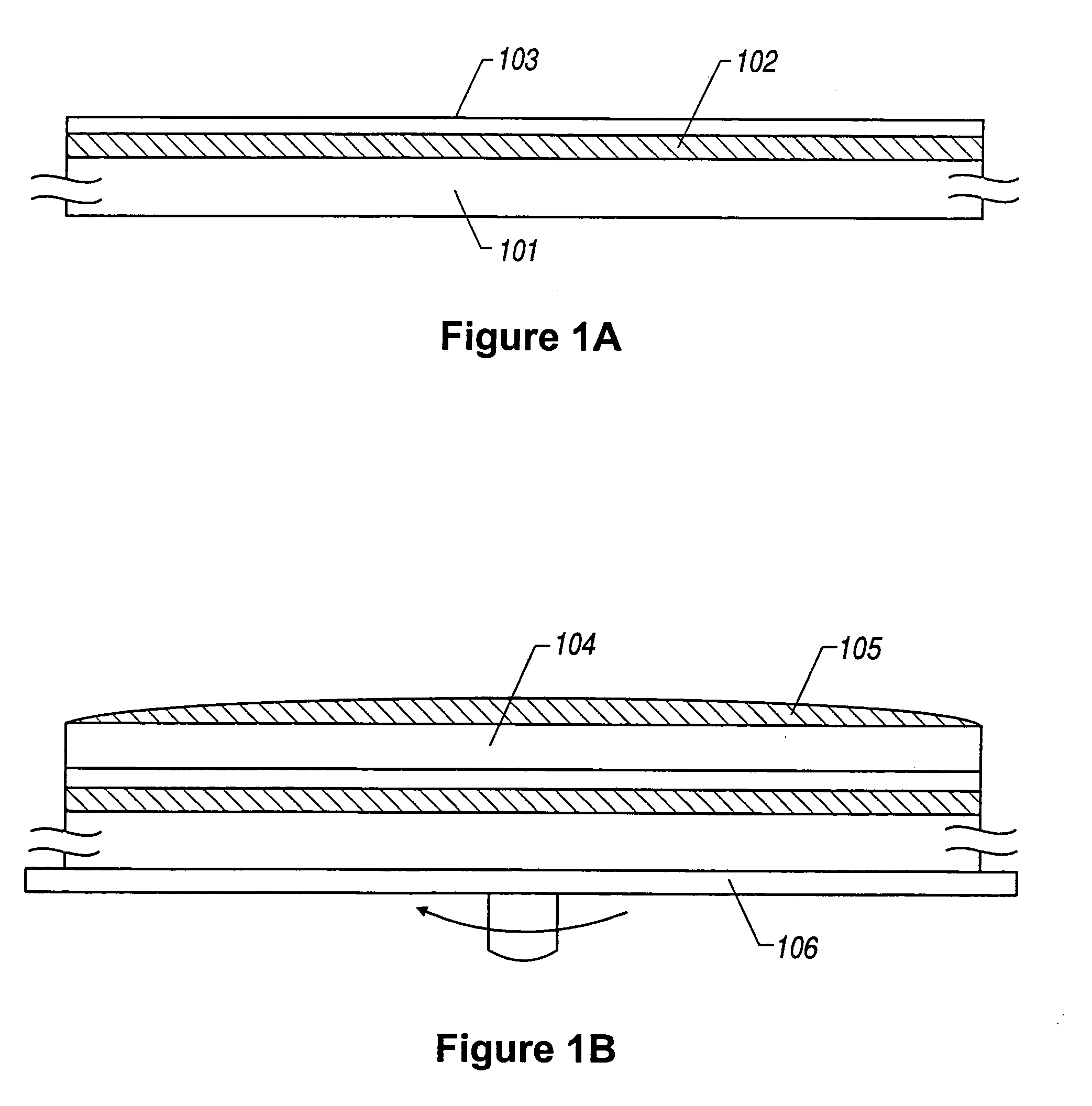

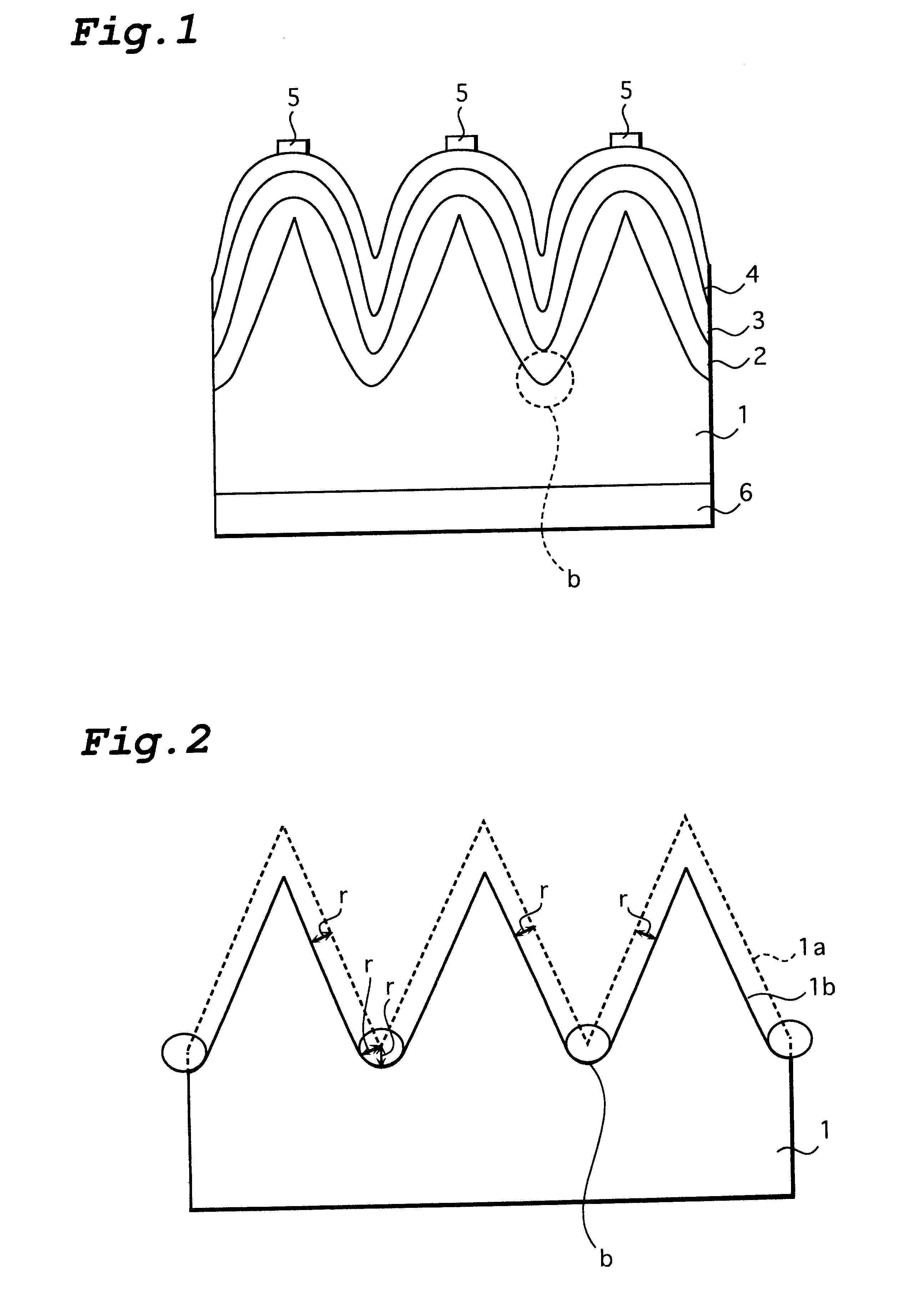

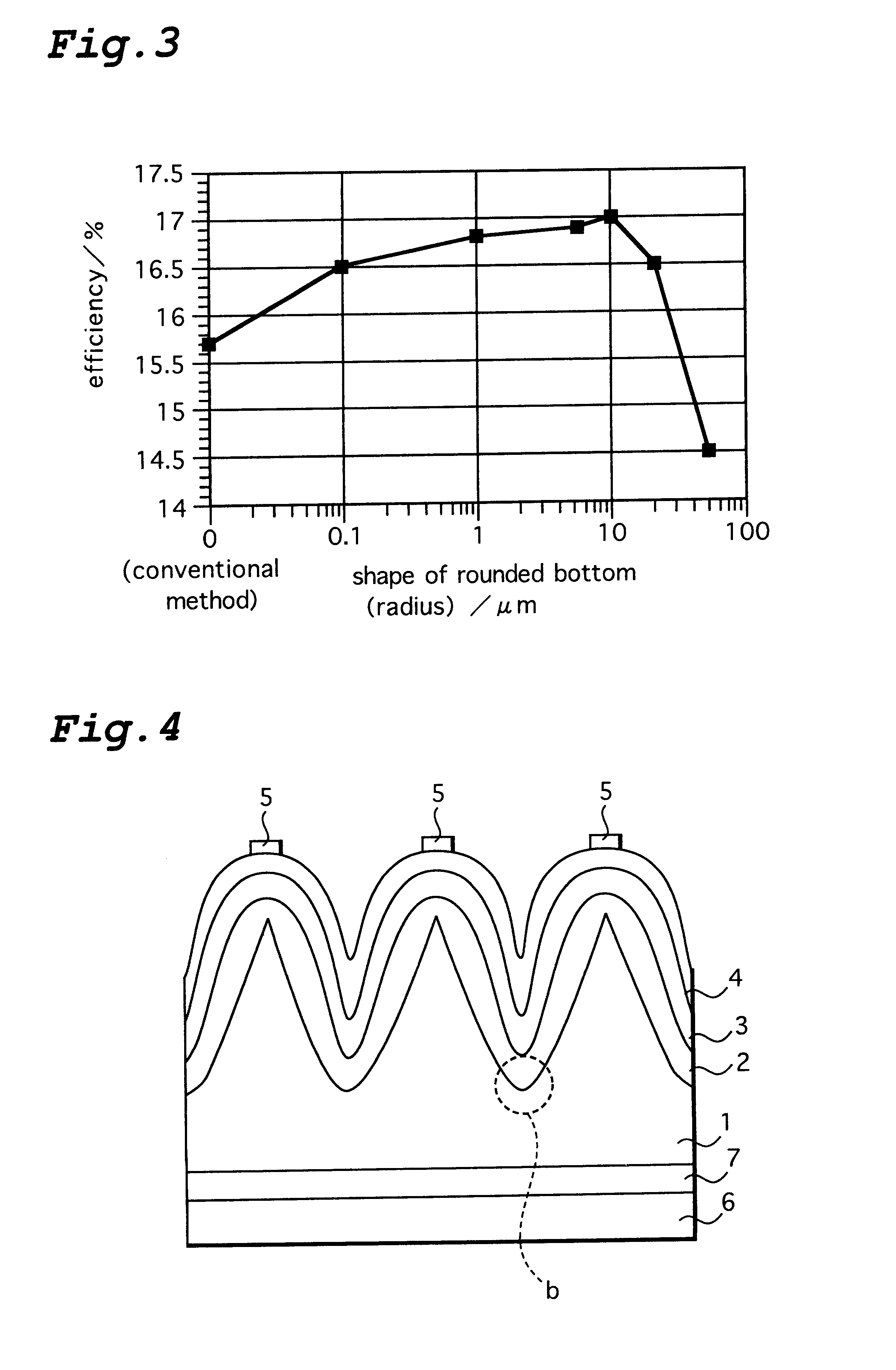

Photovoltaic element and method for manufacture thereof

InactiveUS6207890B1Lowered open circuit voltage circuitLowered circuit short circuitPV power plantsSolid-state devicesSolar lightAmorphous silicon

A photovoltaic element which directly converts an optical energy such as solar light into an electric energy. After many uneven sections are formed on the surface of an n-type crystalline silicon substrate (1), the surface of the substrate (1) is isotropically etched. Then the bottoms (b) of the recessed sections are rounded and a p-type amorphous silicon layer (3) is formed on the surface of the substrate (1) through an intrinsic amorphous silicon layer (2). The shape of the surface of the substrate (1) after isotropic etching is such that the bottoms of the recessed sections are slightly rounded and therefore the amorphous silicon layer can be deposited in a uniform thickness.

Owner:SANYO ELECTRIC CO LTD

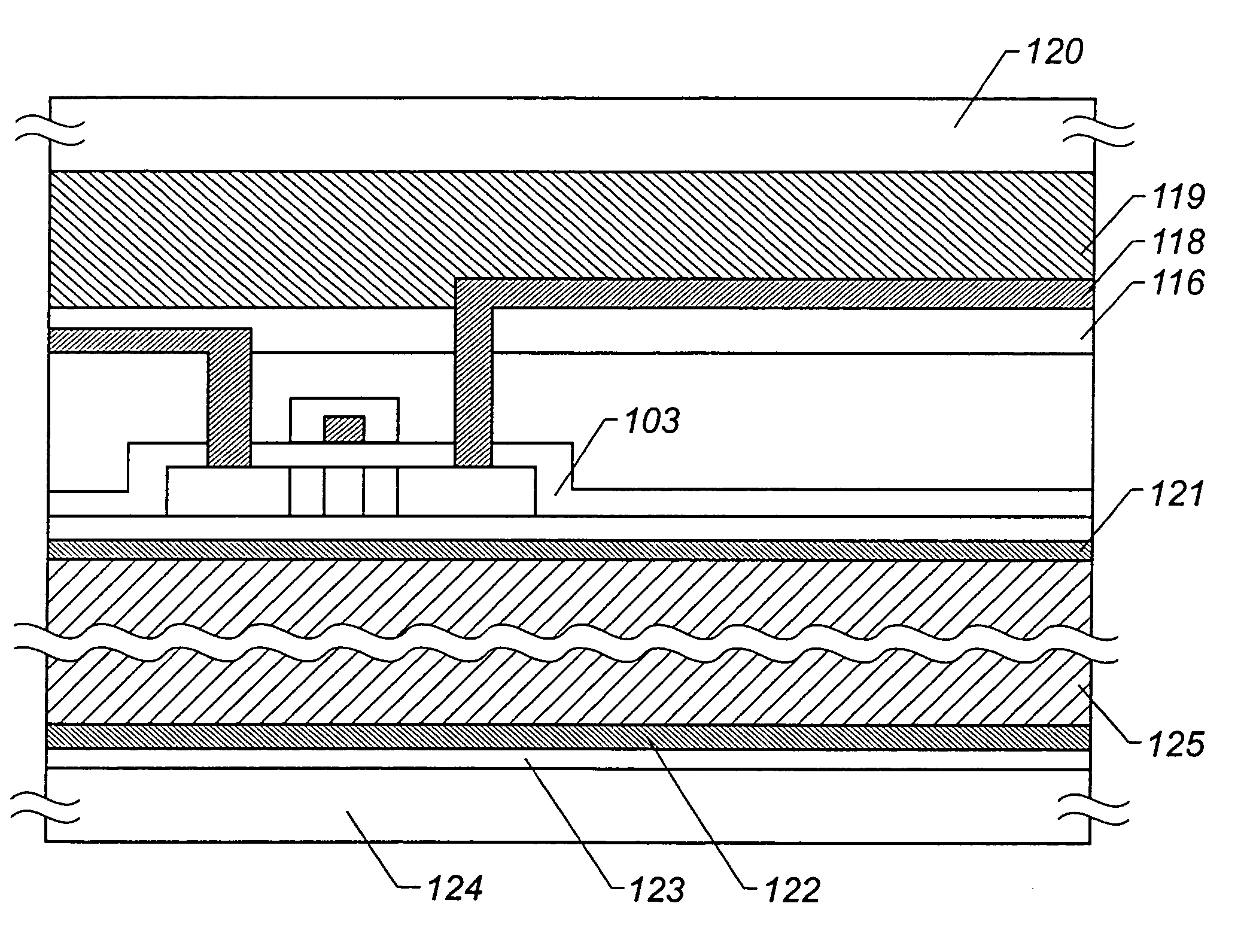

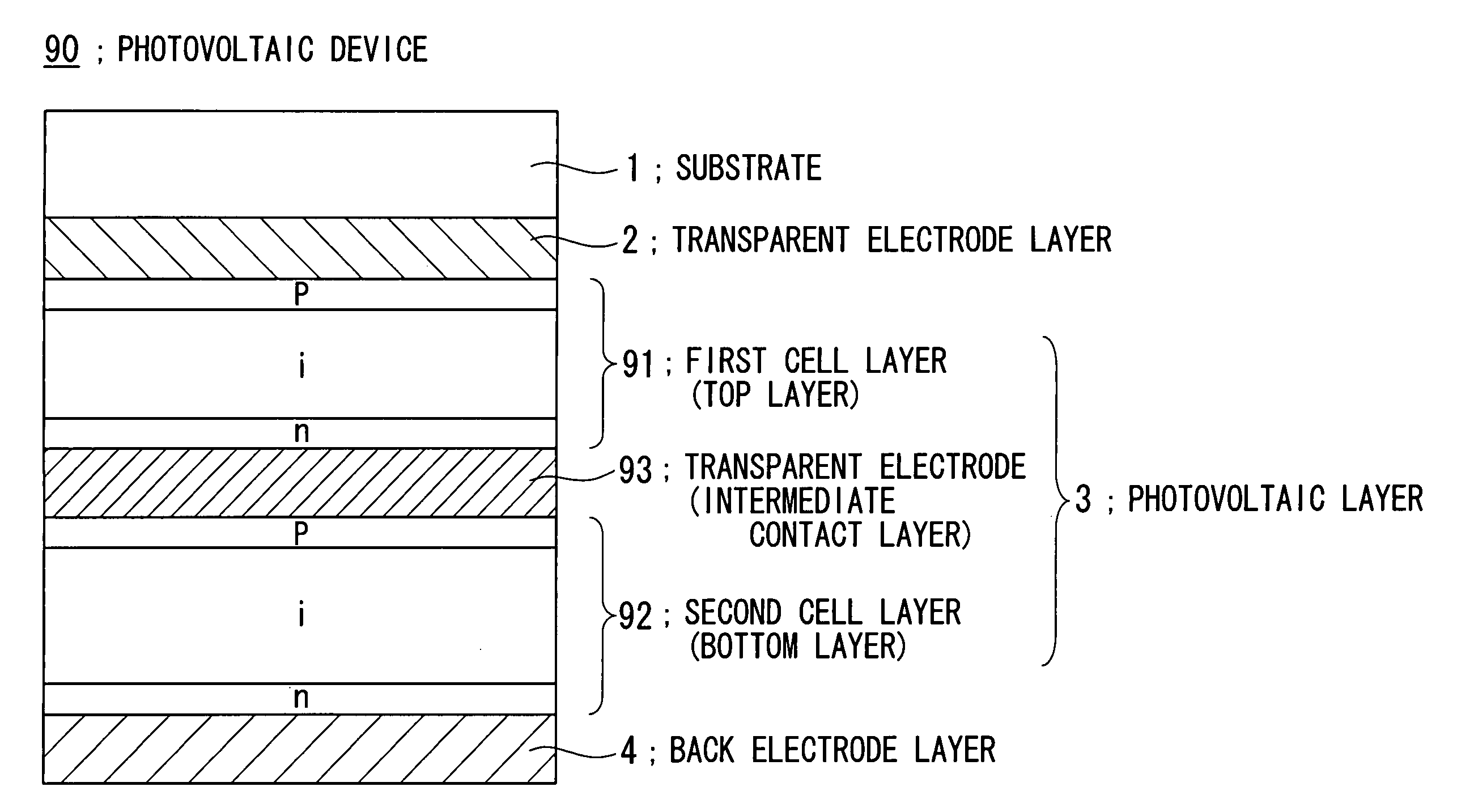

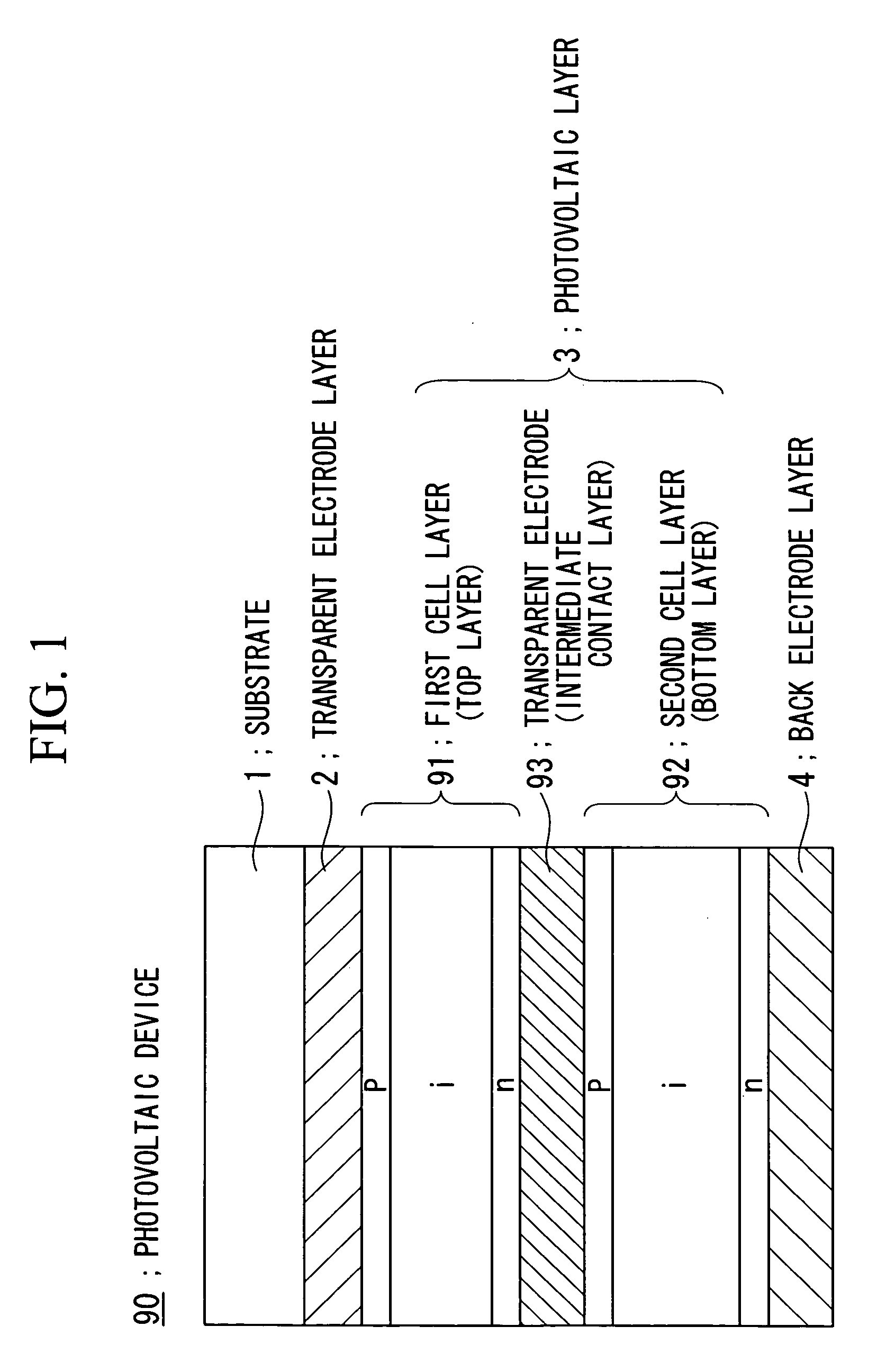

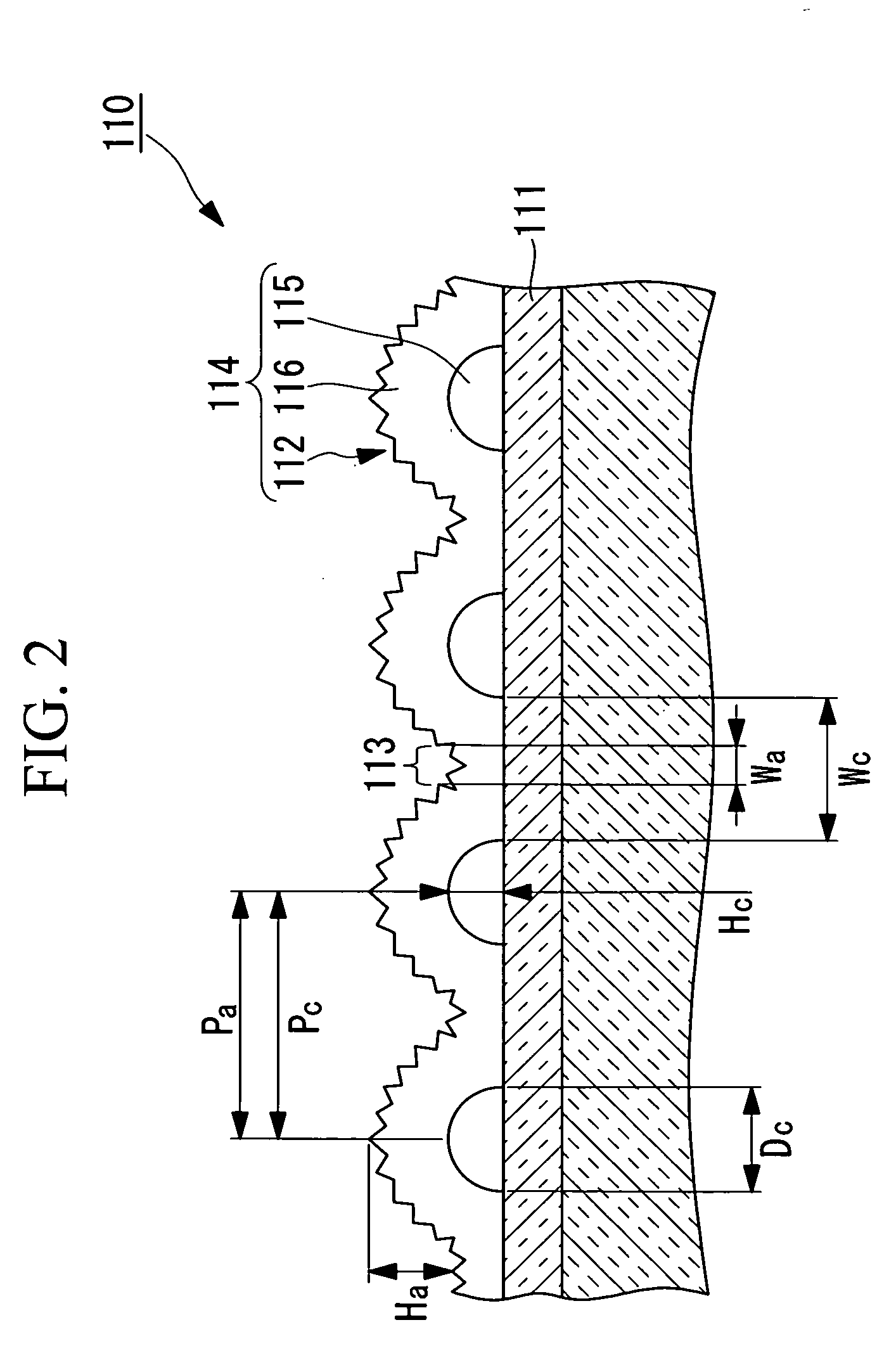

Photovoltaic device and process for producing same

InactiveUS20080196761A1Improve efficiencyHigh levelFinal product manufactureSolid-state devicesProduction rateLength wave

A photovoltaic device and a process for producing the photovoltaic device that combine a high photovoltaic conversion efficiency with a high level of productivity. The photovoltaic device includes at least a transparent electrode-bearing substrate, prepared by providing a transparent electrode layer on a transparent, electrically insulating substrate, and a photovoltaic layer containing mainly crystalline silicon-based semiconductors and a back electrode layer formed sequentially on the transparent electrode layer of the transparent electrode-bearing substrate, wherein the surface of the transparent electrode layer of the transparent electrode-bearing substrate has a shape that contains a mixture of coarse and fine roughness, and exhibits a spectral haze ratio of 20% or greater for wavelengths of from 550 nm to 800 nm, and the photovoltaic layer containing mainly crystalline silicon-based semiconductors has a film thickness of from 1.2 μm to 2 μm, and a Raman ratio of from 3.0 to 8.0.

Owner:MITSUBISHI HEAVY IND LTD

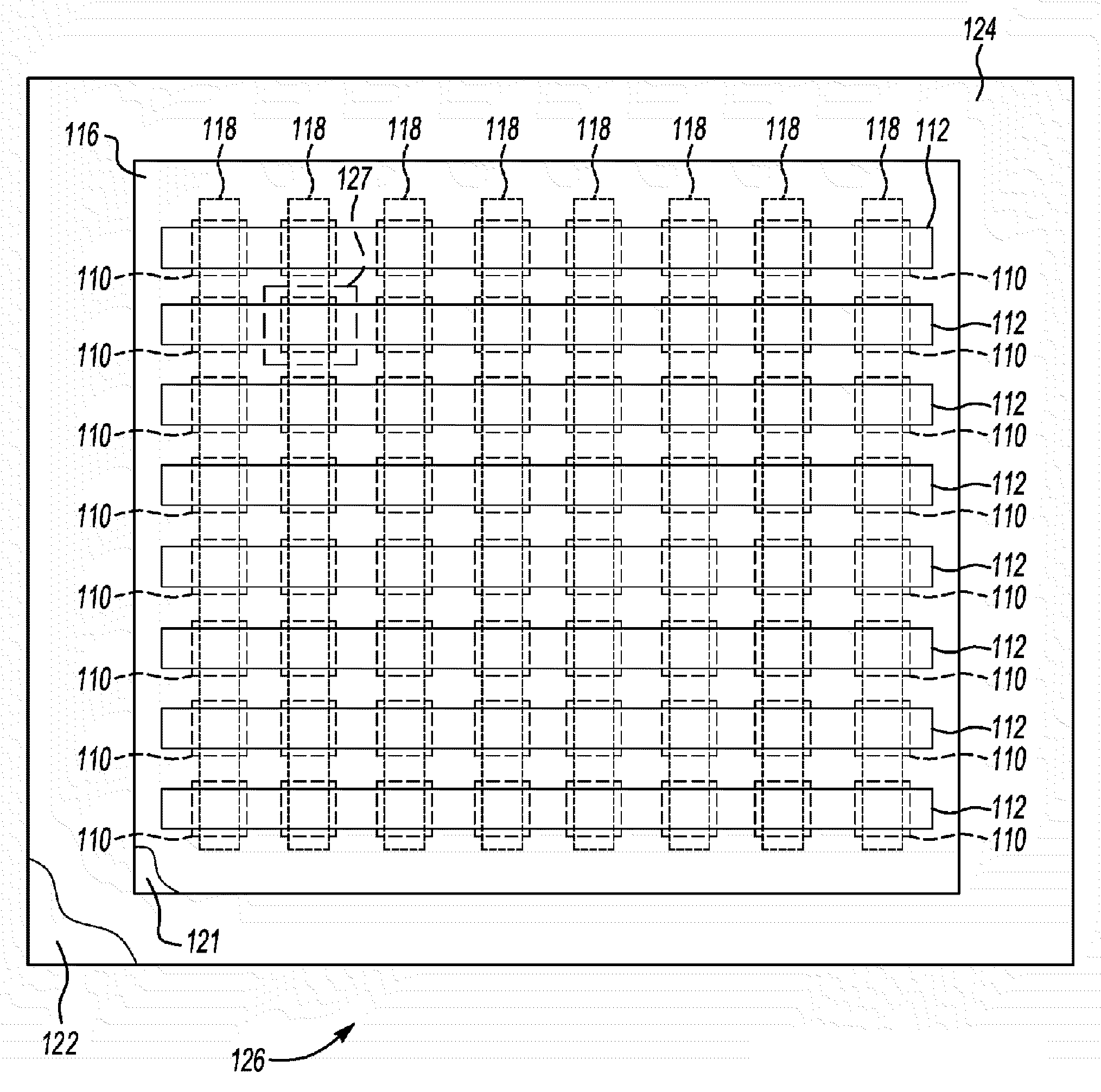

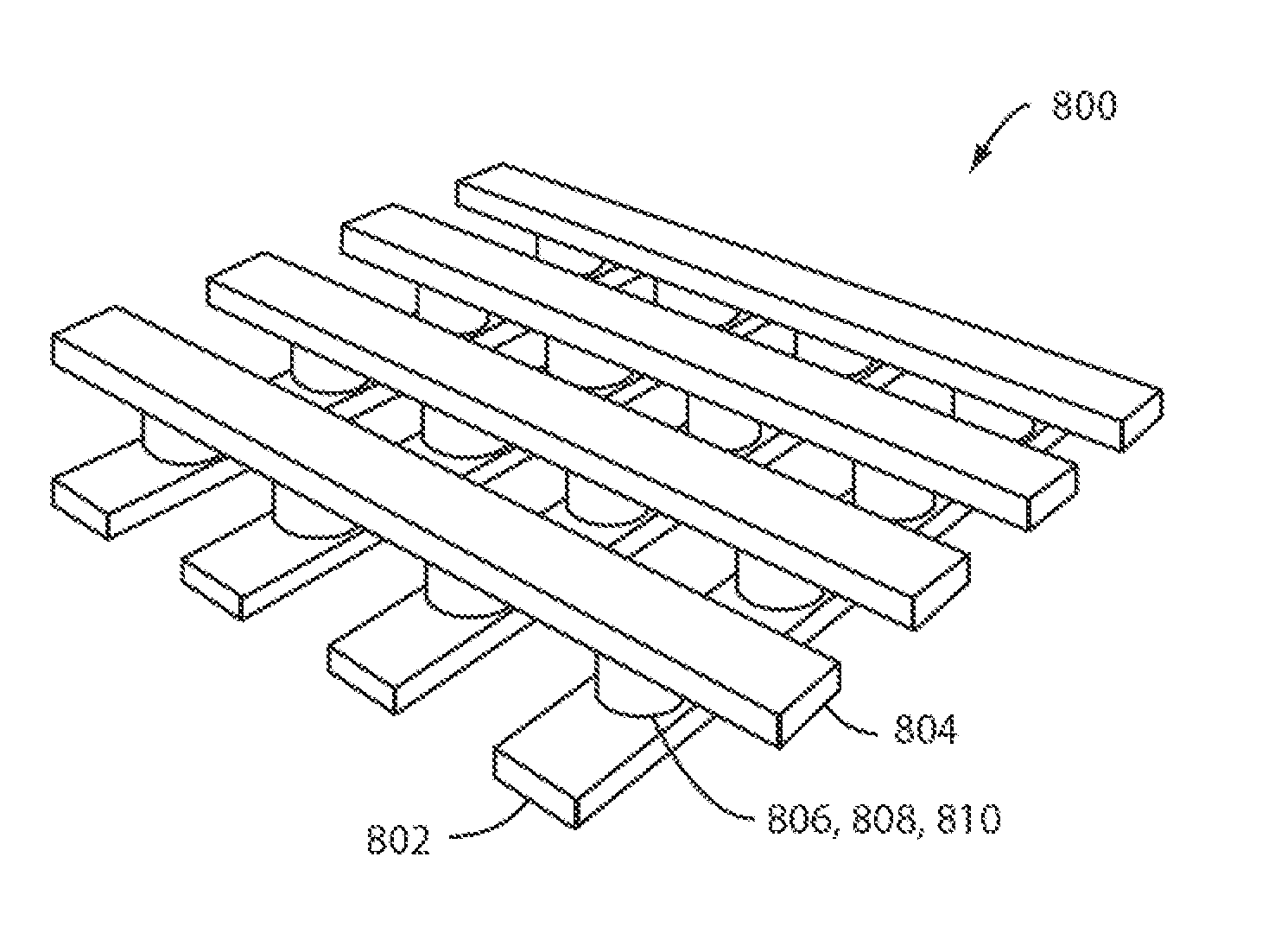

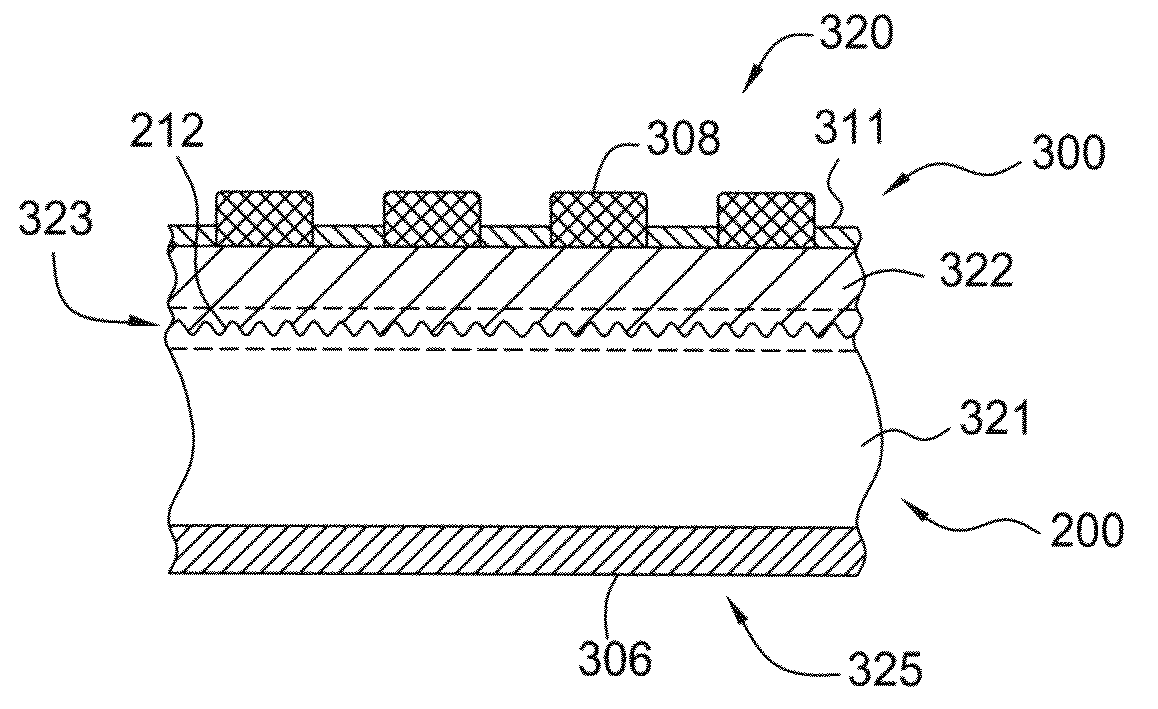

Interface control for improved switching in rram

ActiveUS20110305064A1Solid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

A memory device has a crossbar array including a first array of first electrodes extending along a first direction. A second array of second electrodes extends along a second direction. A non-crystalline silicon structure provided between the first electrode and the second electrode at an intersection defined by the first array and the second array. The non-crystalline silicon structure has a first layer having a first defect density and a second layer having a second defect density different from the first defect density. Each intersection of the first array and the second array defines a two-terminal memory cell.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

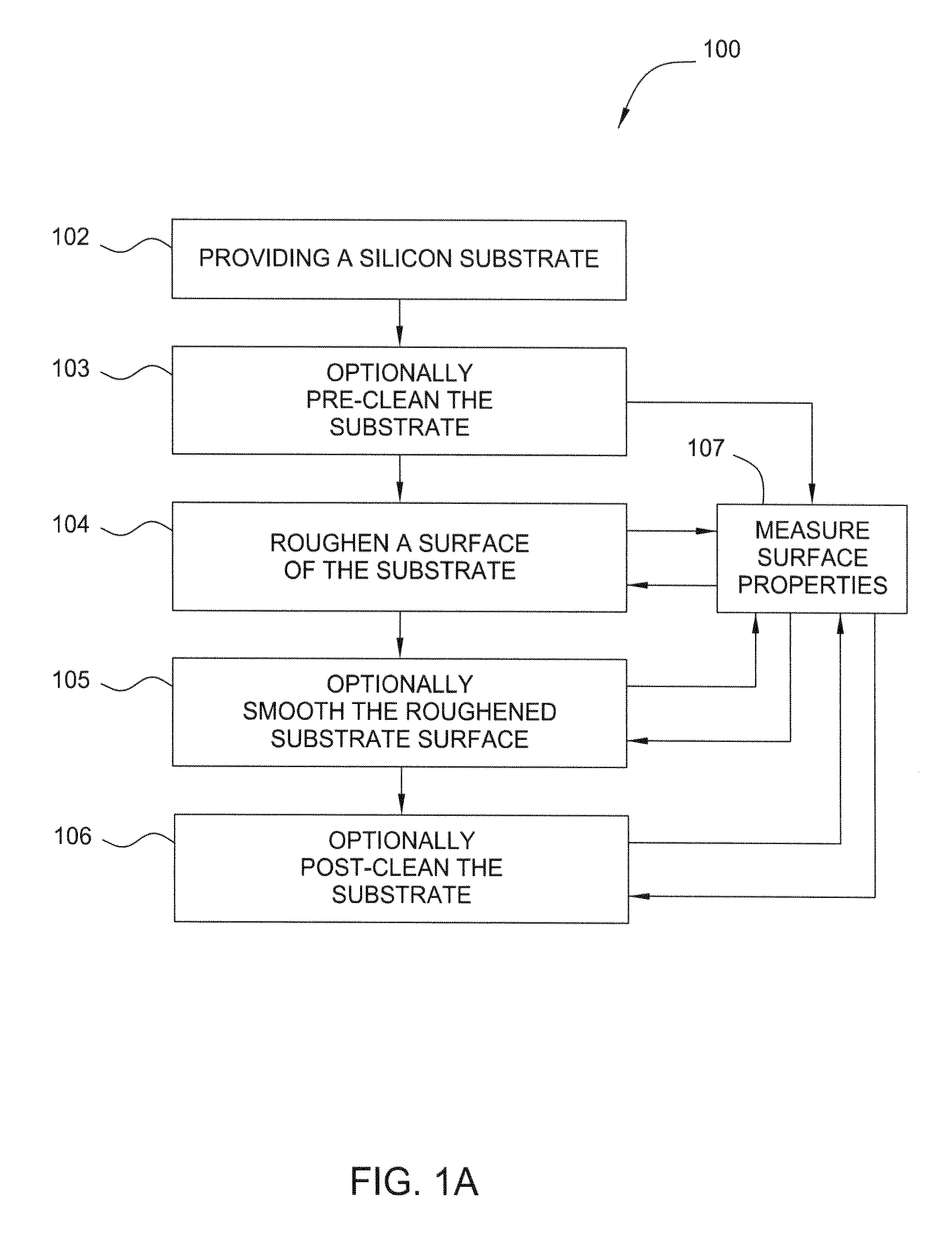

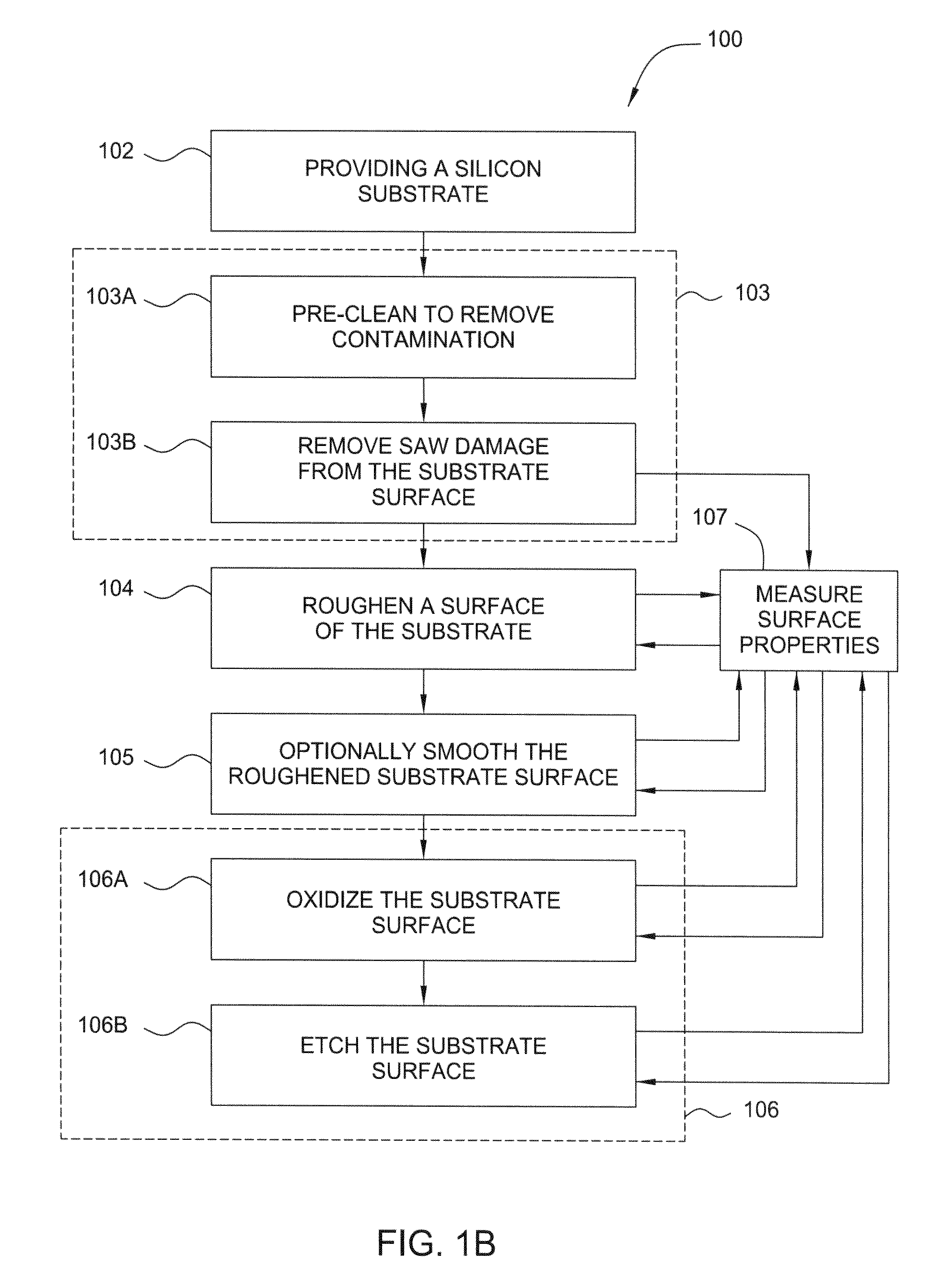

Surface cleaning and texturing process for crystalline solar cells

InactiveUS20090280597A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationCrystallographySurface cleaning

Methods for surface texturing a crystalline silicon substrate are provided. In one embodiment, the method includes providing a crystalline silicon substrate, wetting the substrate with an alkaline solution comprising a wetting agent, and forming a textured surface with a structure having a depth about 1 μm to about 10 μm on the substrate. In another embodiment, a method of performing a substrate texture process includes providing crystalline silicon substrate, pre-cleaning the substrate in a HF aqueous solution, wetting the substrate with a KOH aqueous solution comprising polyethylene glycol (PEG) compound, and forming a textured surface with a structure having a depth about 3 μm to about 8 μm on the substrate.

Owner:APPLIED MATERIALS INC

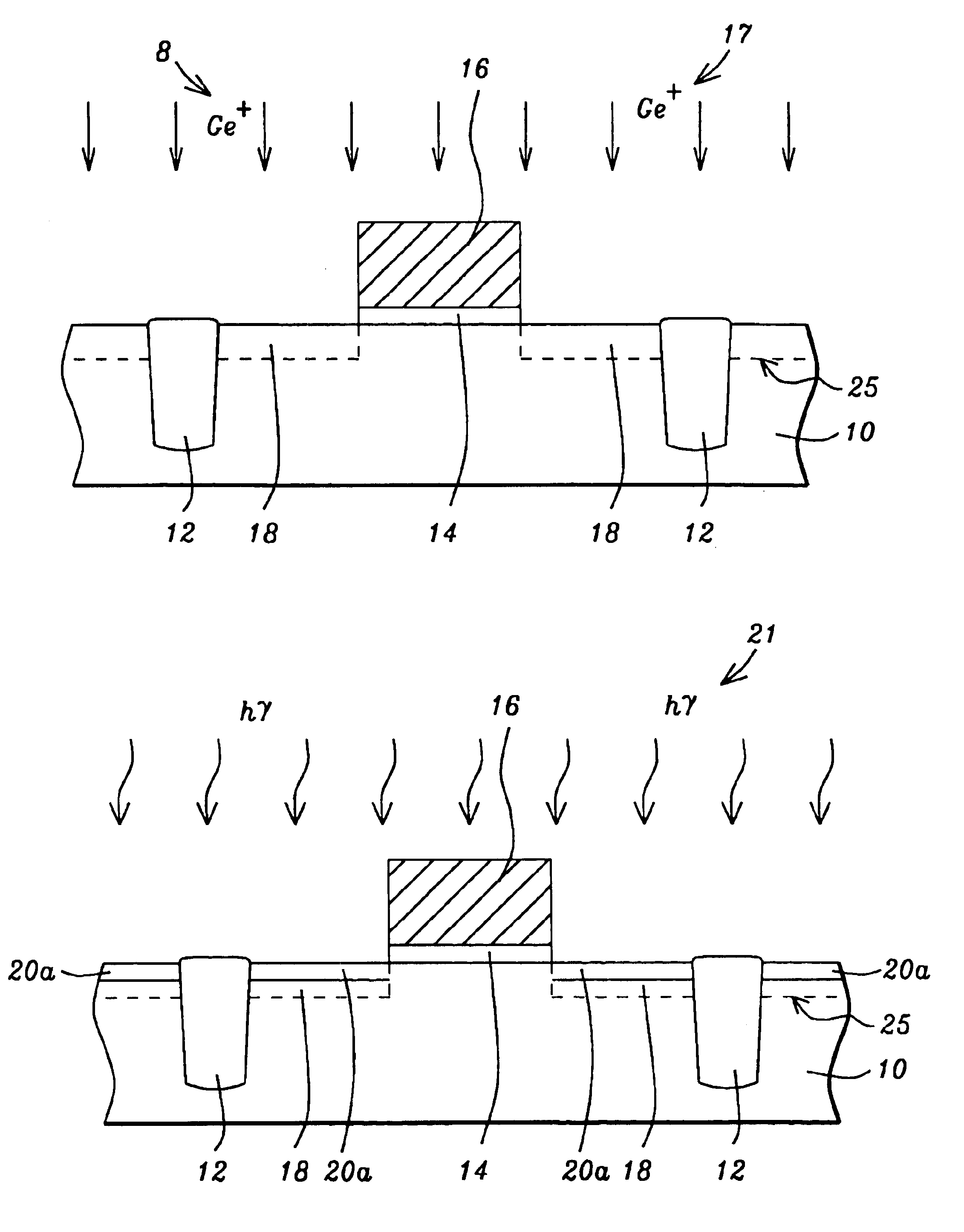

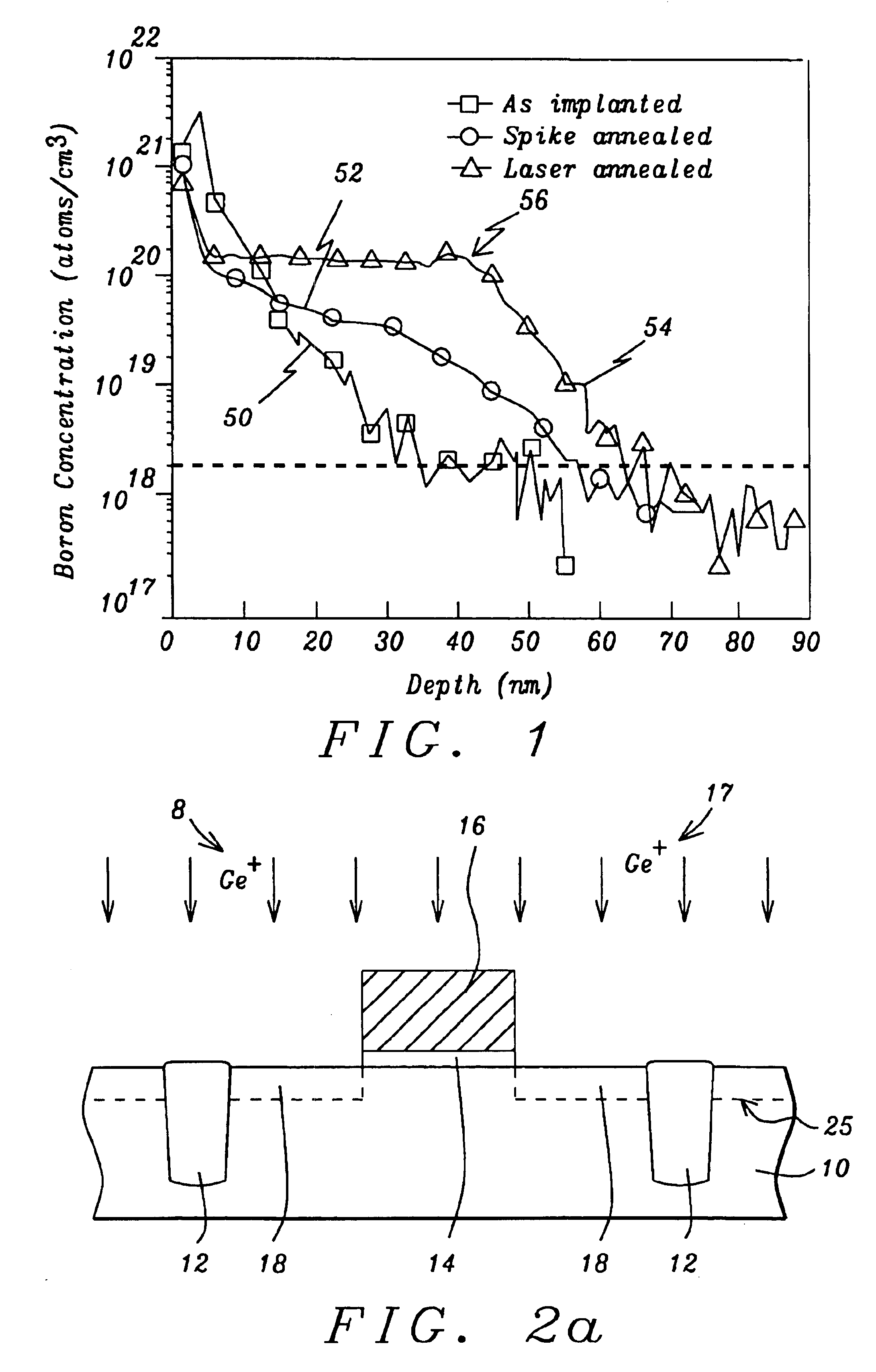

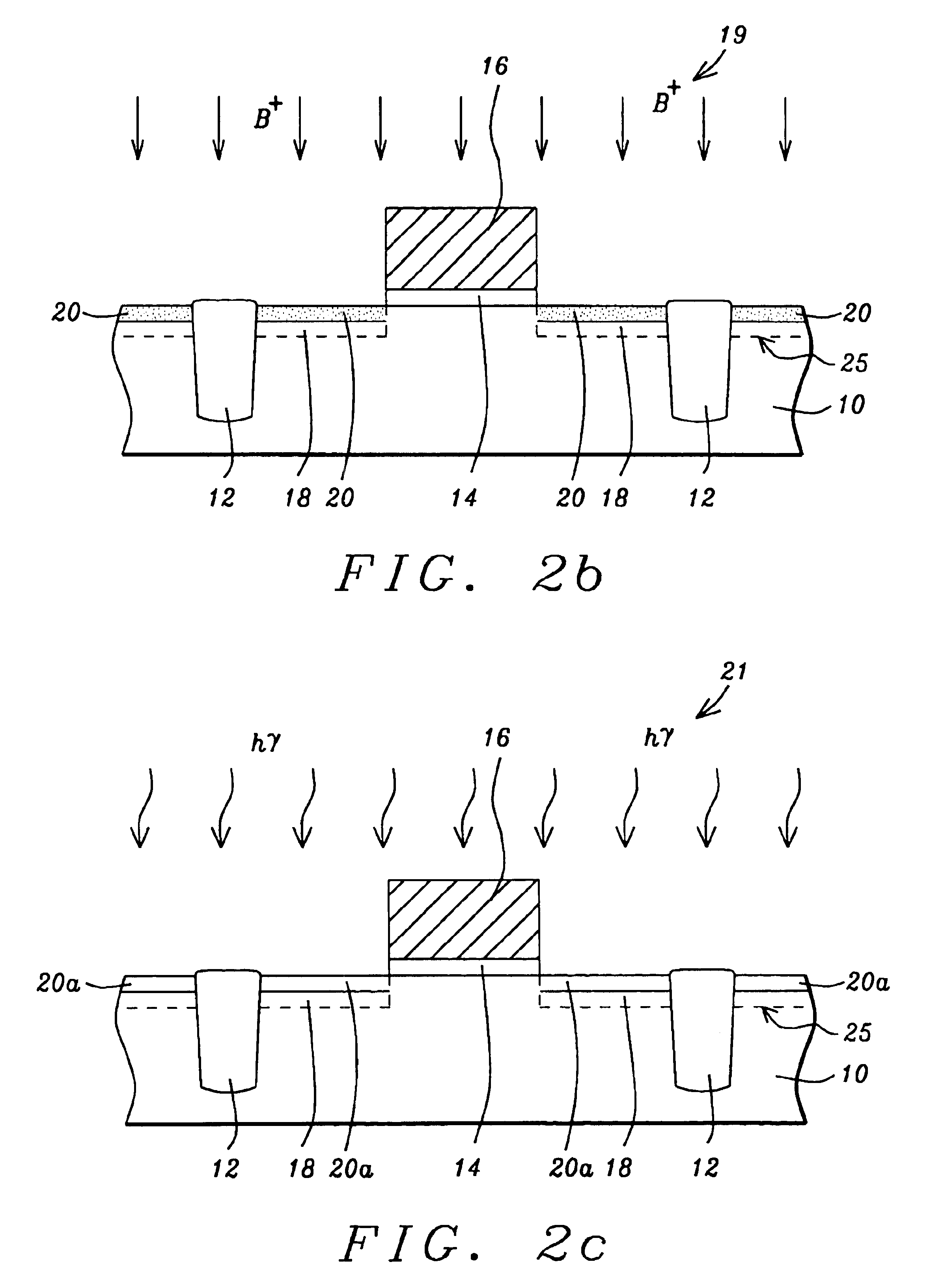

Method of multiple pulse laser annealing to activate ultra-shallow junctions

A method for forming a highly activated ultra shallow ion implanted semiconductive elements for use in sub-tenth micron MOSFET technology is described. A key feature of the method is the ability to activate the implanted impurity to a highly active state without permitting the dopant to diffuse further to deepen the junction. A selected single crystalline silicon active region is first amorphized by implanting a heavy ion such as silicon or germanium. A semiconductive impurity for example boron is then implanted and activated by pulsed laser annealing whereby the pulse fluence, frequency, and duration are chosen to maintain the amorphized region just below it's melting temperature. It is found that just below the melting temperature there is sufficient local ion mobility to secure the dopant into active positions within the silicon matrix to achieve a high degree of activation with essentially no change in concentration profile. The selection of the proper laser annealing parameters is optimized by observation of the reduction of sheet resistance and concentration profile as measured on a test site. Application of the method is applied to forming a MOS FET and a CMOS device. The additional processing steps required by the invention are applied simultaneously to both n-channel and p-channel devices of the CMOS device pair.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

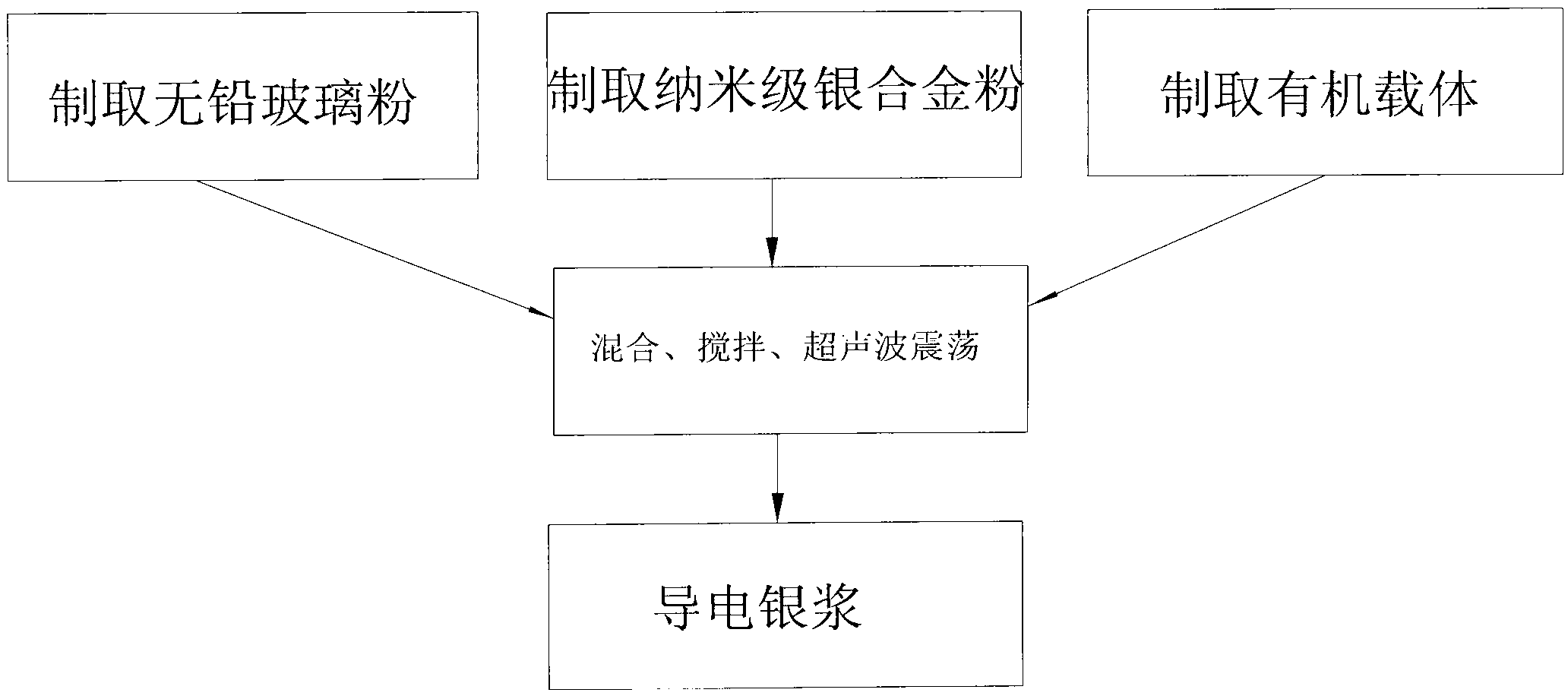

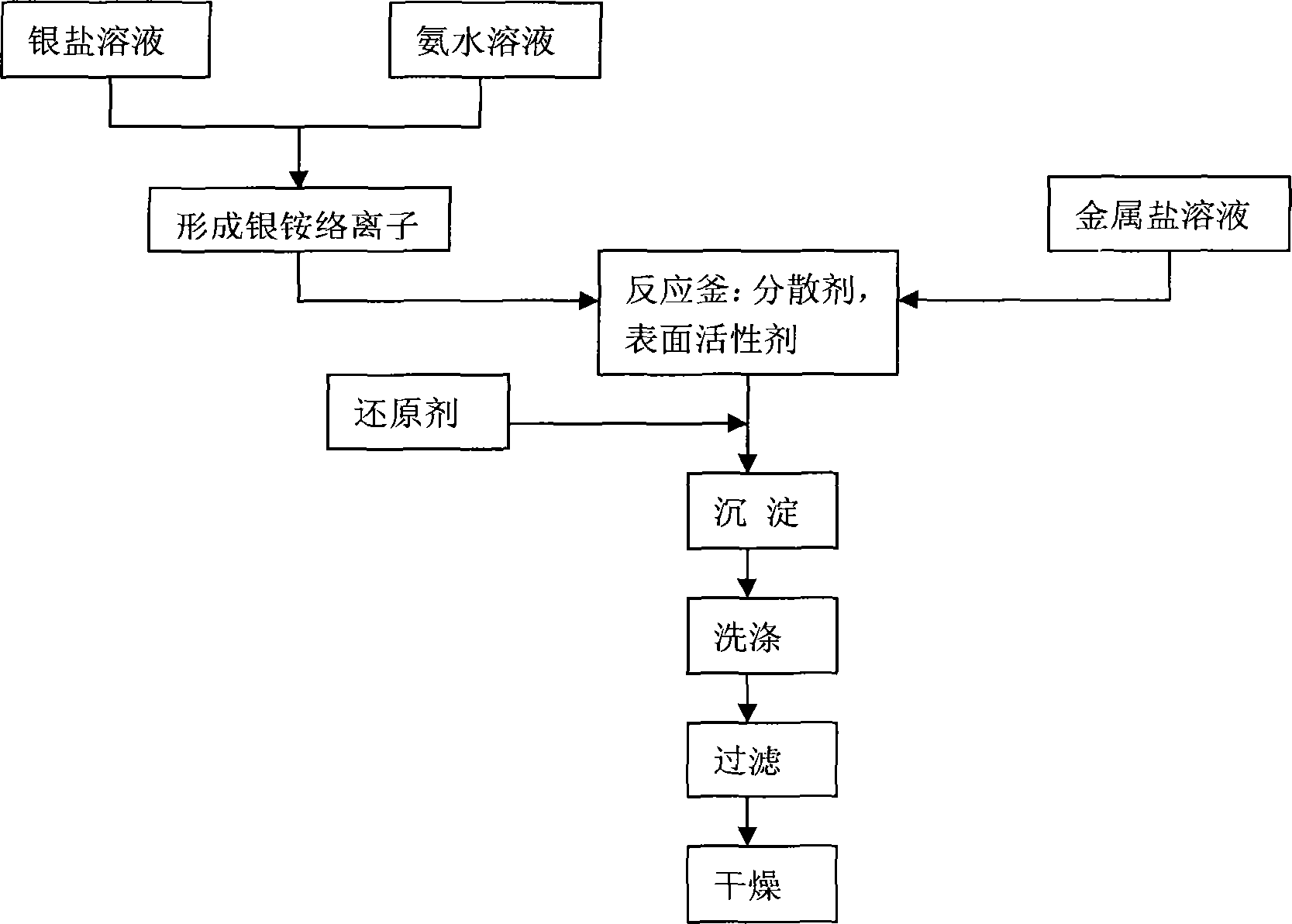

Electric conductive silver paste and manufacturing method thereof

ActiveCN103258584AEnhanced interconnectionIncrease contact areaNon-conductive material with dispersed conductive materialCable/conductor manufactureSilver pasteMetal alloy

The invention discloses electric conductive silver paste and a manufacturing method of the electric conductive silver paste. The electric conductive silver paste comprises, by mass percentage, 35 - 65 % of micron-sized silver powder, 1-10 % of nanometer-sized silver powder of or 1-20 % of nanometer-sized silver and other metal alloy powder, and 1-10 % of an organic carrier; for ceramics, solar cell silver paste comprises 2-15 % of unleaded glass powder, each component is manufactured in parts, weighed, mixed and stirred or mixed and rapidly scattered, and ultrasonic-vibrated or fine adjusted of viscosity of solvent, and therefore the electric conductive silver paste is obtained. Due to the fact that the nanometer-sized silver powder or the nanometer-sized silver alloy powder is mixed with the micron-sized silver powder, intensity of conductivity and a circuit is improved, adhesive force of crushing resistance and a base plate is improved, at the same time unleaded slurry good in thixotropy, low in contacting resistance and low in piece-needed slurry amount replaces lead slurry materials, the electric conductive silver paste is used for manufacturing crystalline silicon solar cells, improves photoelectric conversion efficiency, accords with environmental-protection ideas, and can be produced in large scales continuously.

Owner:SHENZHEN CHENGGONG CHEM

Method of manufacturing a semiconductor device

InactiveUS20050162578A1Promote crystallizationHigh effectTransistorSolid-state devicesCrystalline siliconSemiconductor

A method of manufacturing a semiconductor device, comprises the steps of: forming a first insulating film on a first substrate; forming a second insulating film on the first insulating film; forming an amorphous silicon film on the second insulating film; holding a metal element that promotes the crystallization of silicon in contact with a surface of the amorphous silicon film; crystallizing the amorphous silicon film through a heat treatment to obtain a crystalline silicon film; forming a thin-film transistor using the crystalline silicon film; forming a sealing layer that seals the thin-film transistor; bonding a second substrate having a translucent property to the sealing layer; and removing the first insulating film to peel off the first substrate.

Owner:SEMICON ENERGY LAB CO LTD

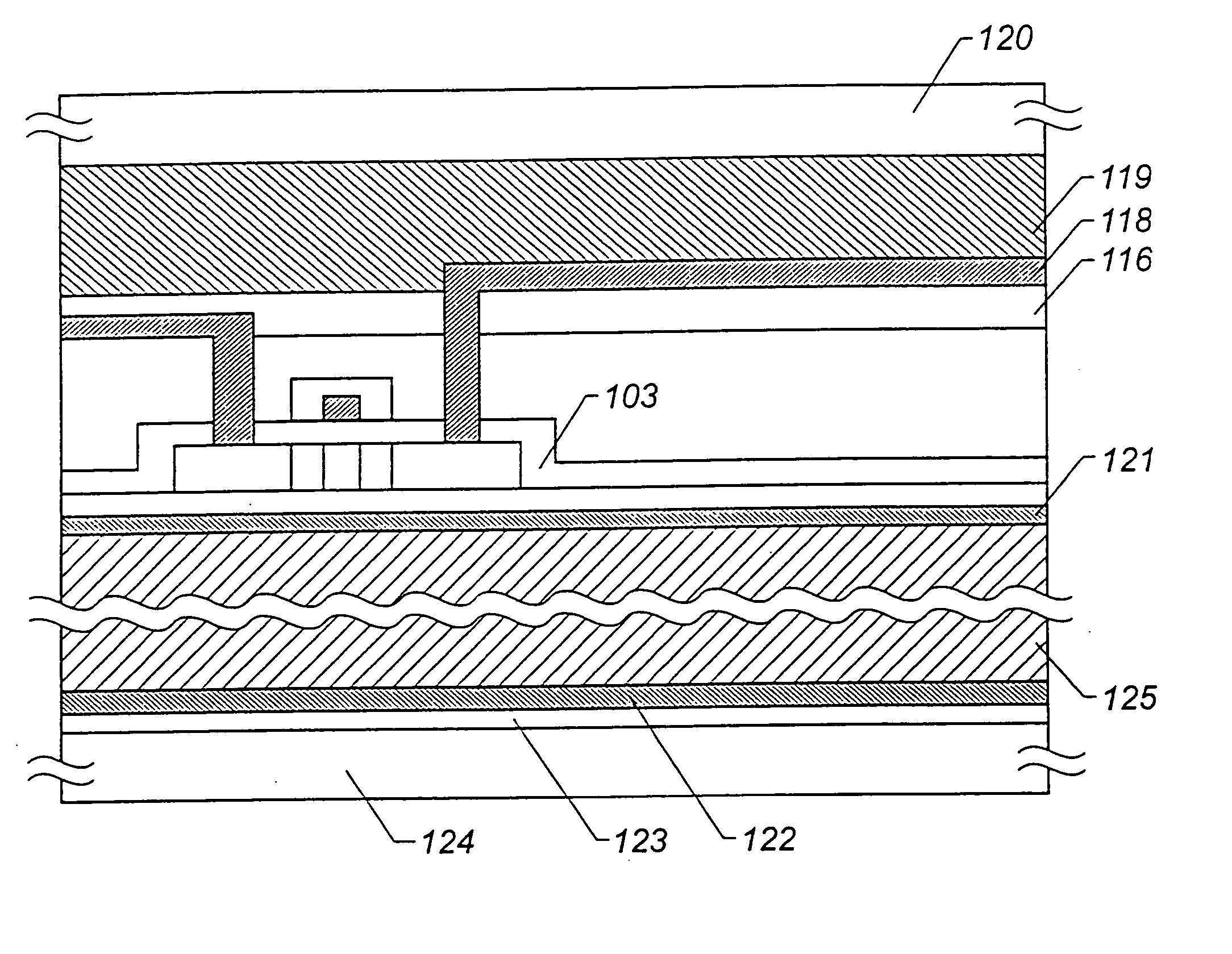

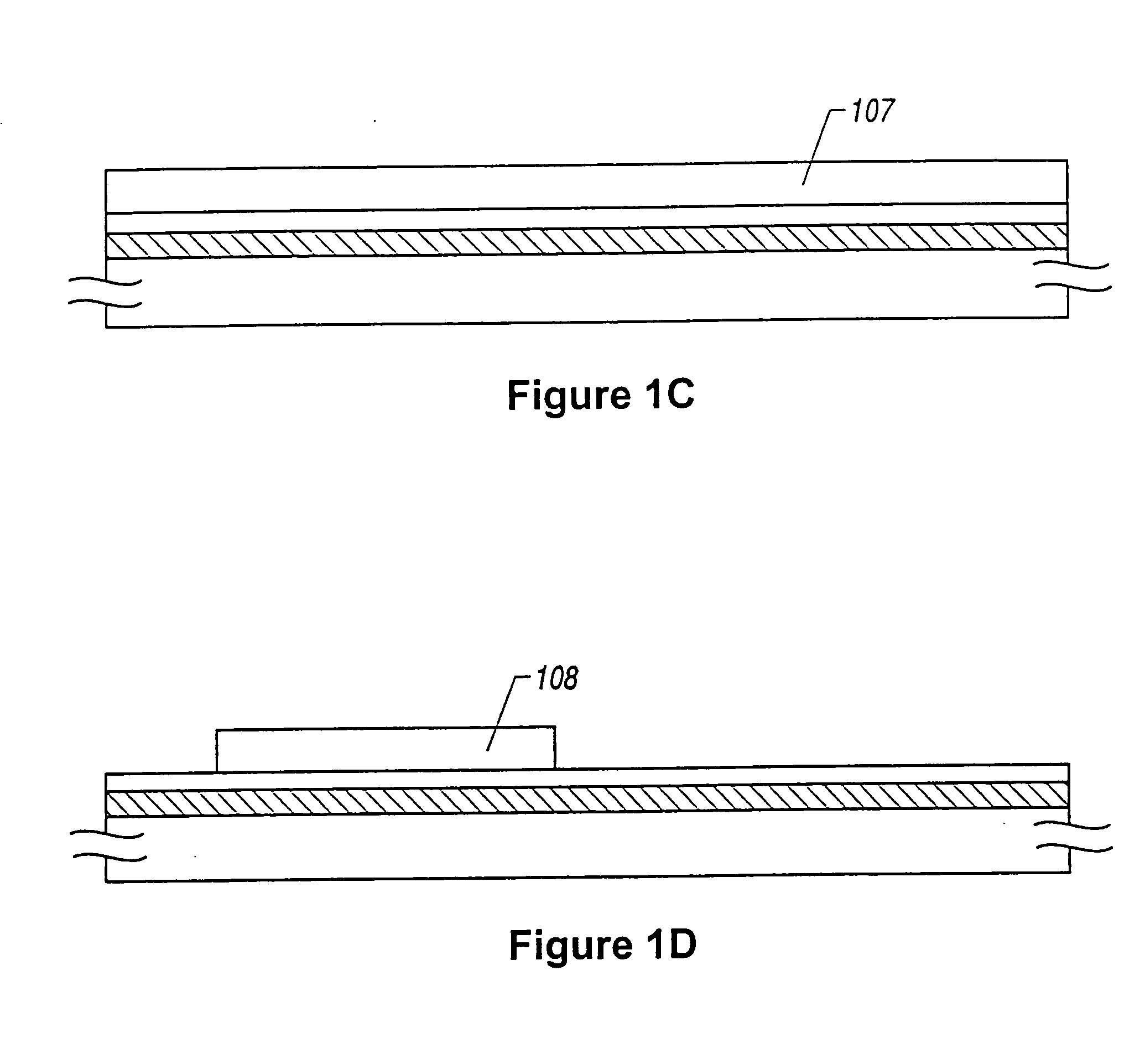

High efficiency low cost crystalline-si thin film solar module

One embodiment of the present invention provides a double-sided heterojunction solar cell module. The solar cell includes a frontside glass cover, a backside cover situated below the frontside glass cover, and a number of solar cells situated between the frontside glass cover and the backside glass cover. Each solar cell includes a semiconductor multilayer structure situated below the frontside glass cover, including: a frontside electrode grid, a first layer of heavily doped amorphous Si (a-Si) situated below the frontside electrode, a layer of lightly doped crystalline-Si (c-Si) situated below the first layer of heavily doped a-Si, and a layer of heavily doped c-Si situated below the lightly doped c-Si layer. The solar cell also includes a second layer of heavily doped a-Si situated below the multilayer structure; and a backside electrode situated below the second layer of heavily doped a-Si.

Owner:SOLARCITY +1