Patents

Literature

732 results about "Overlayer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An overlayer is a layer of adatoms adsorbed onto a surface, for instance onto the surface of a single crystal.

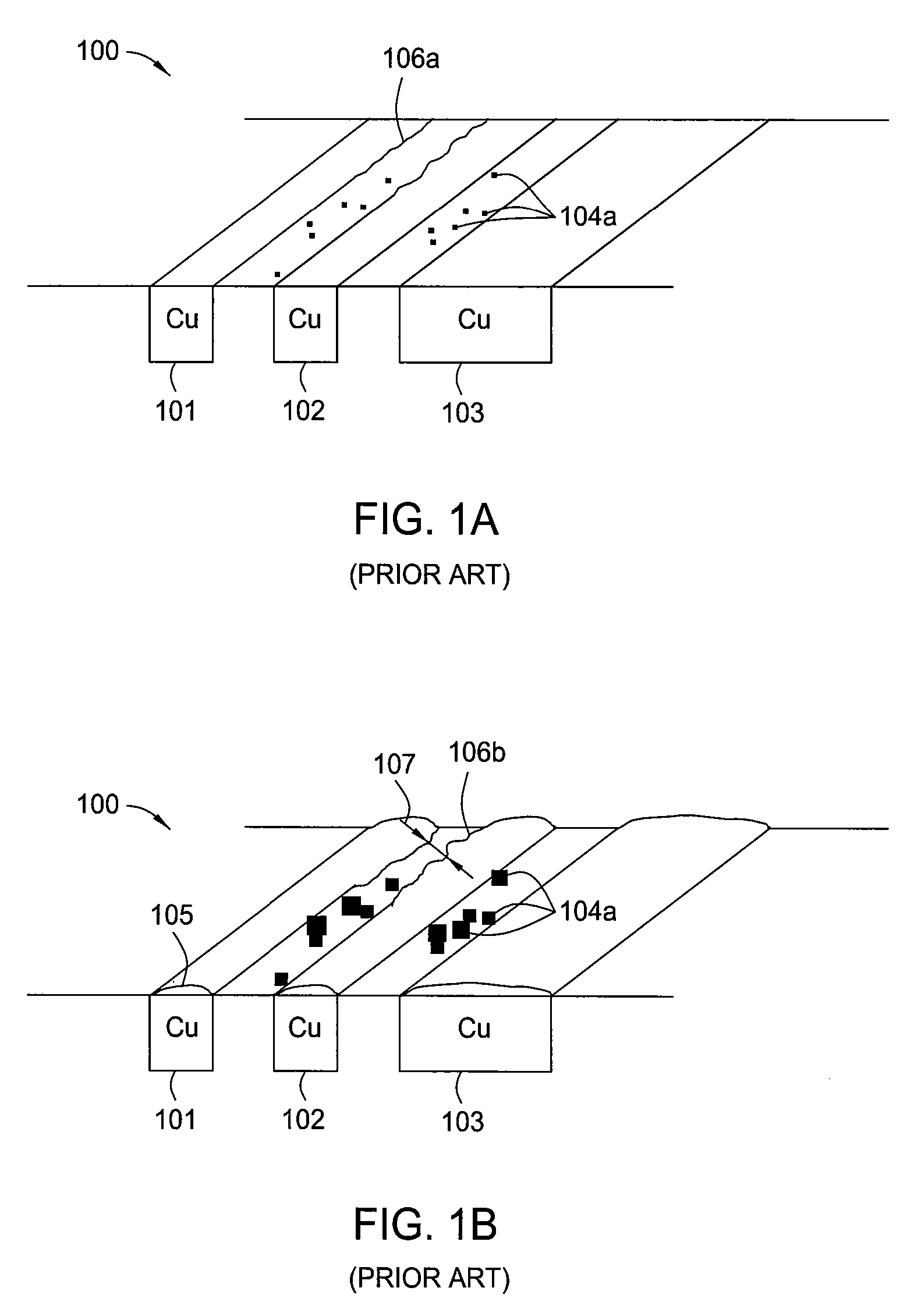

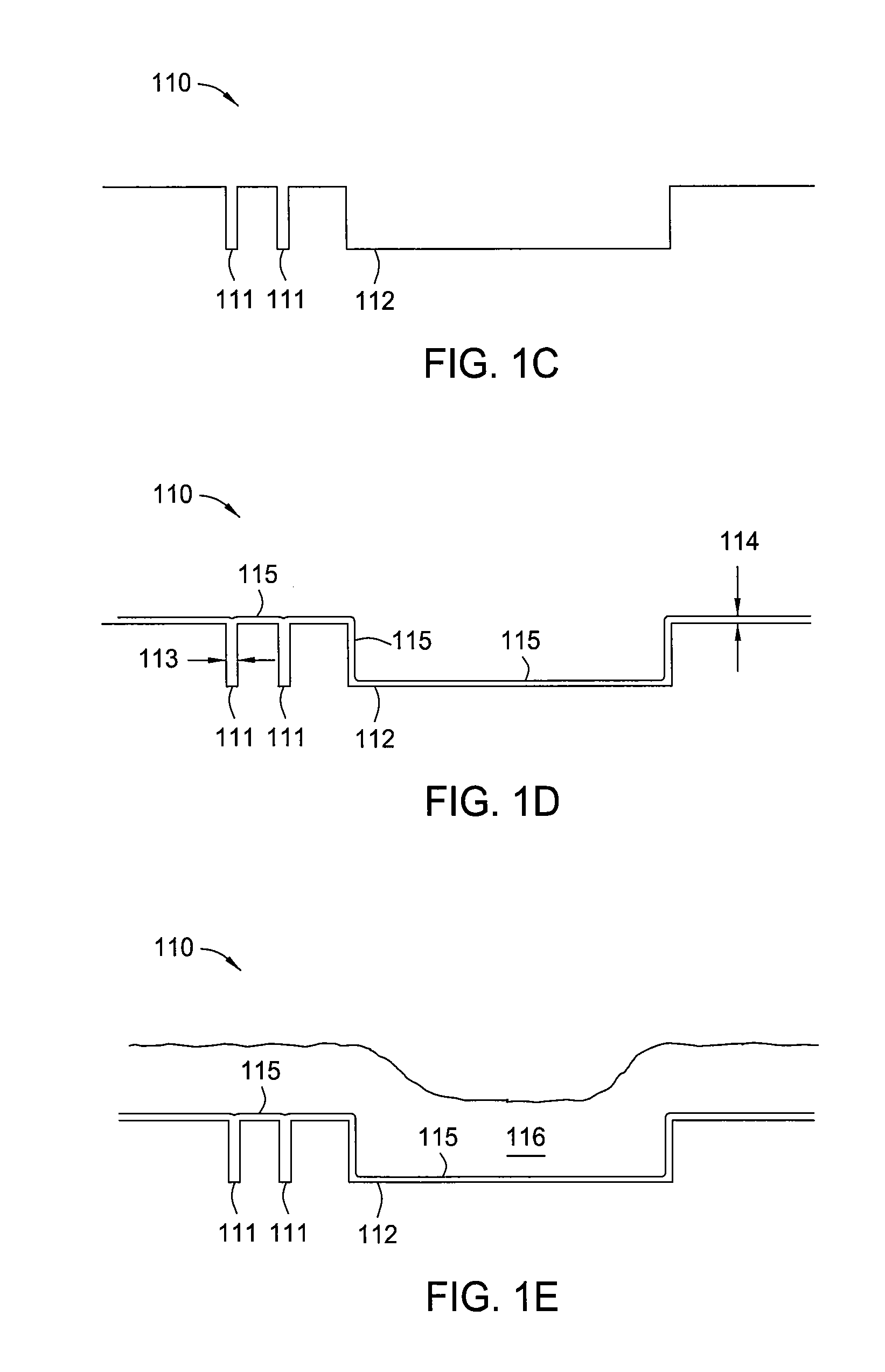

Forming capping layer over metal wire structure using selective atomic layer deposition

InactiveUS7084060B1Material nanotechnologySemiconductor/solid-state device detailsDielectricSemiconductor structure

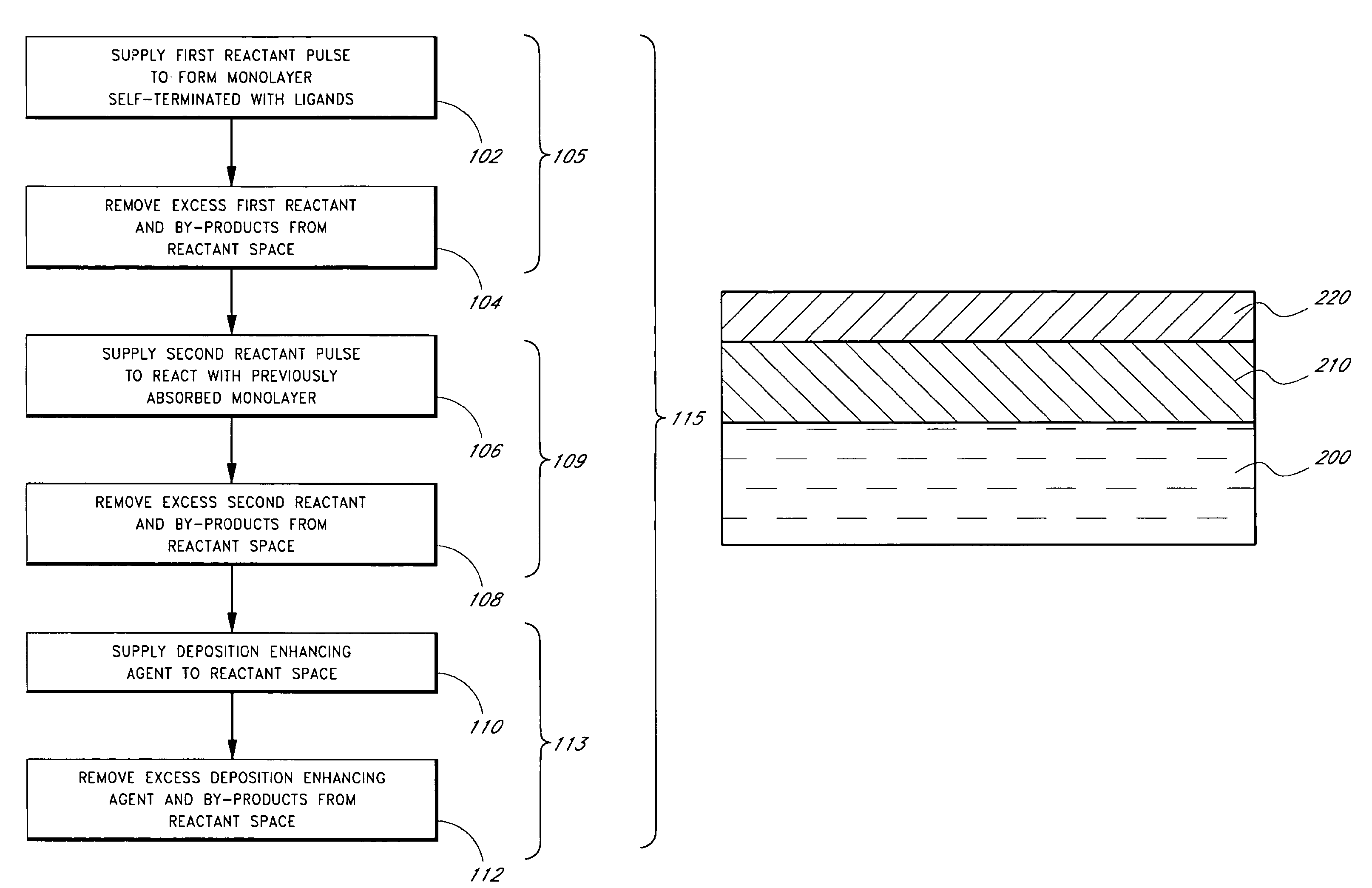

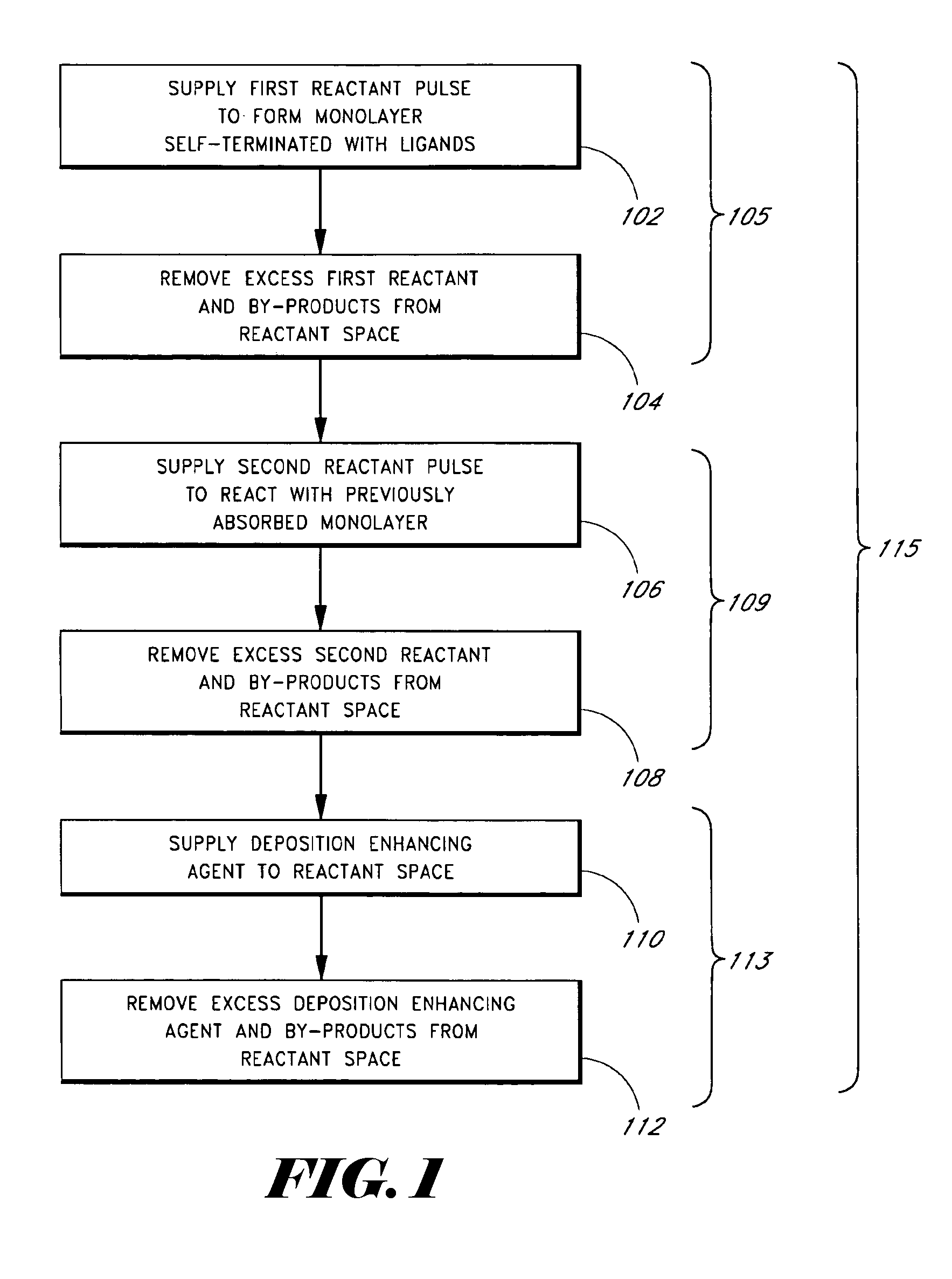

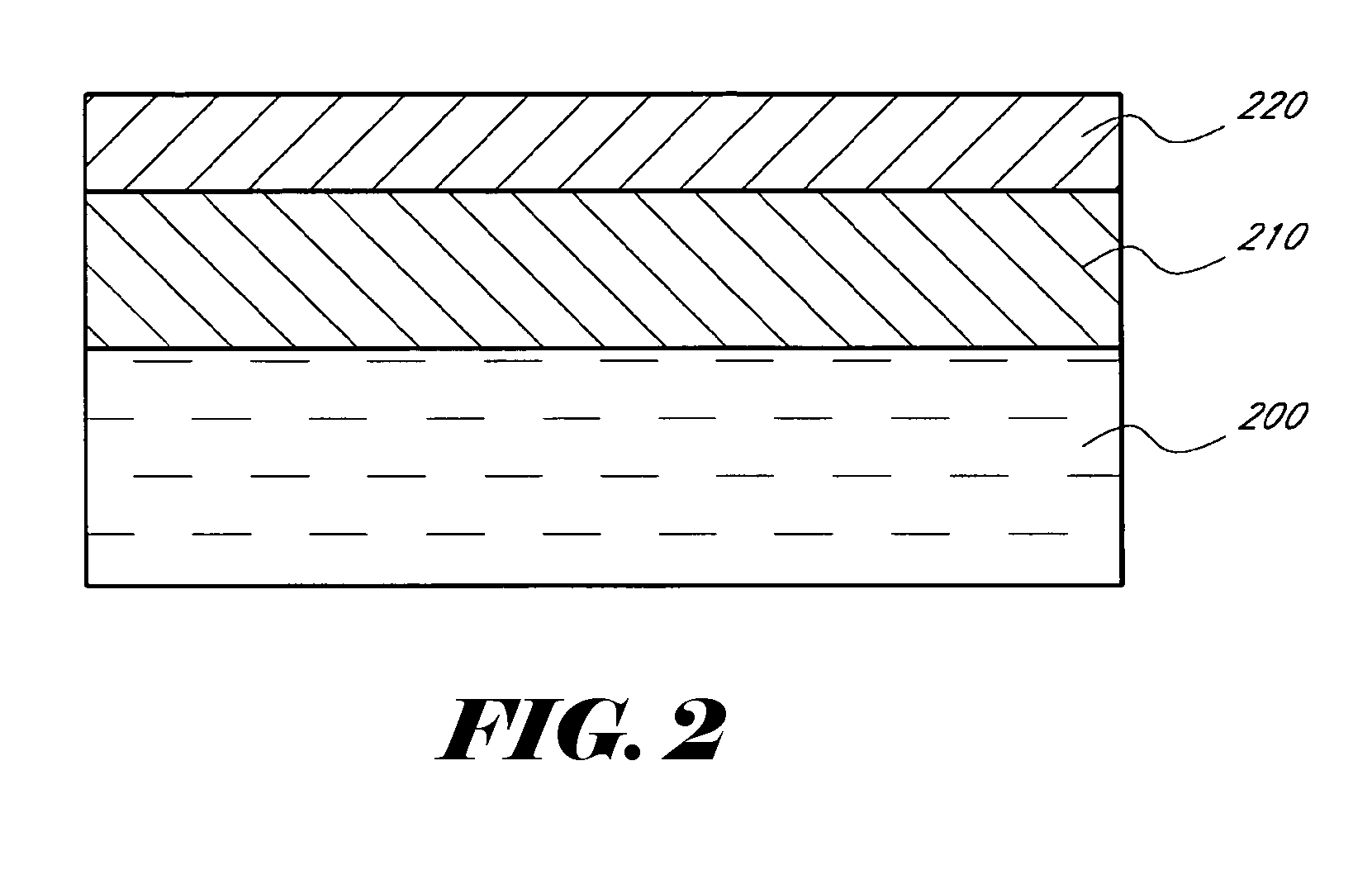

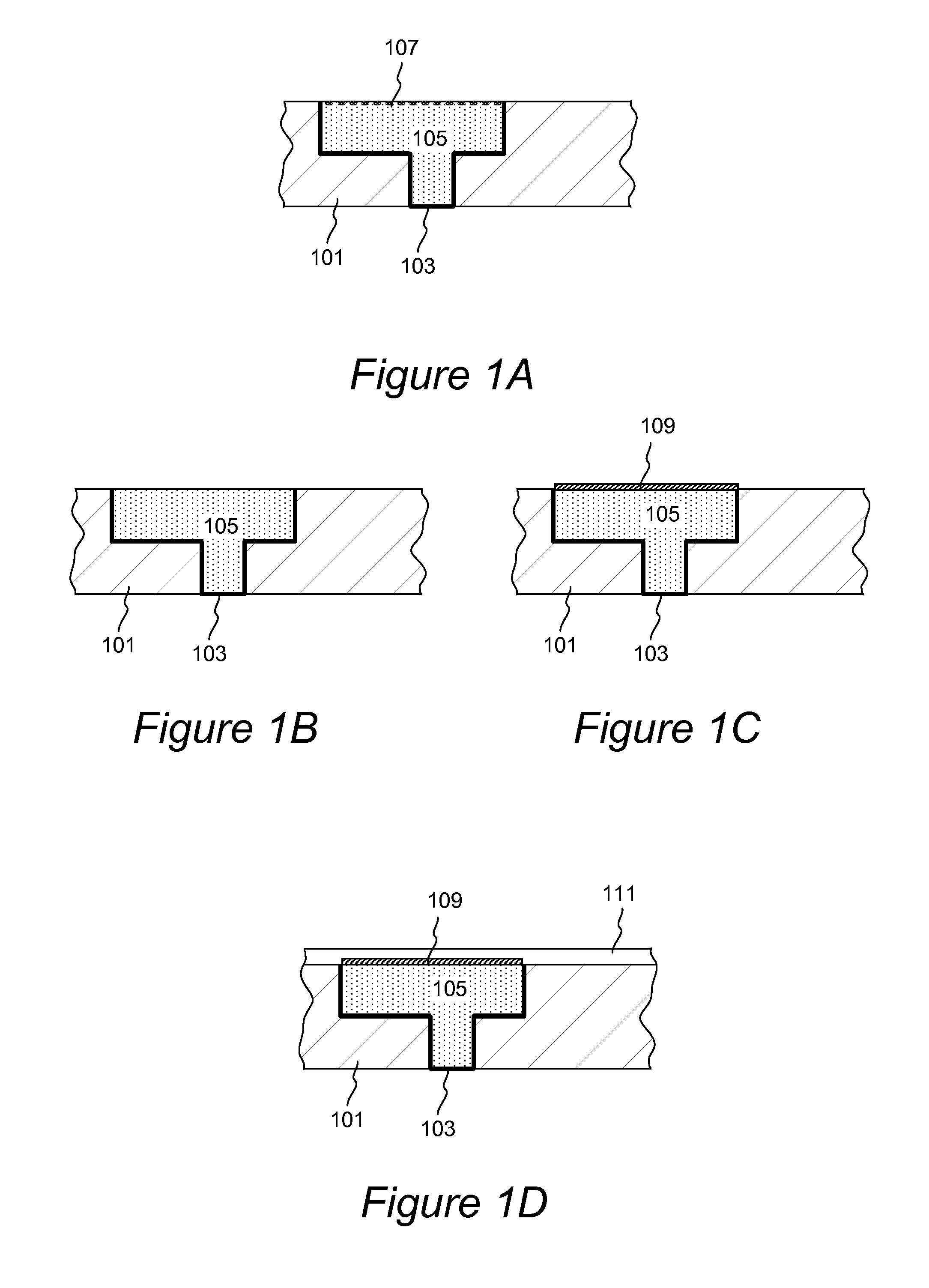

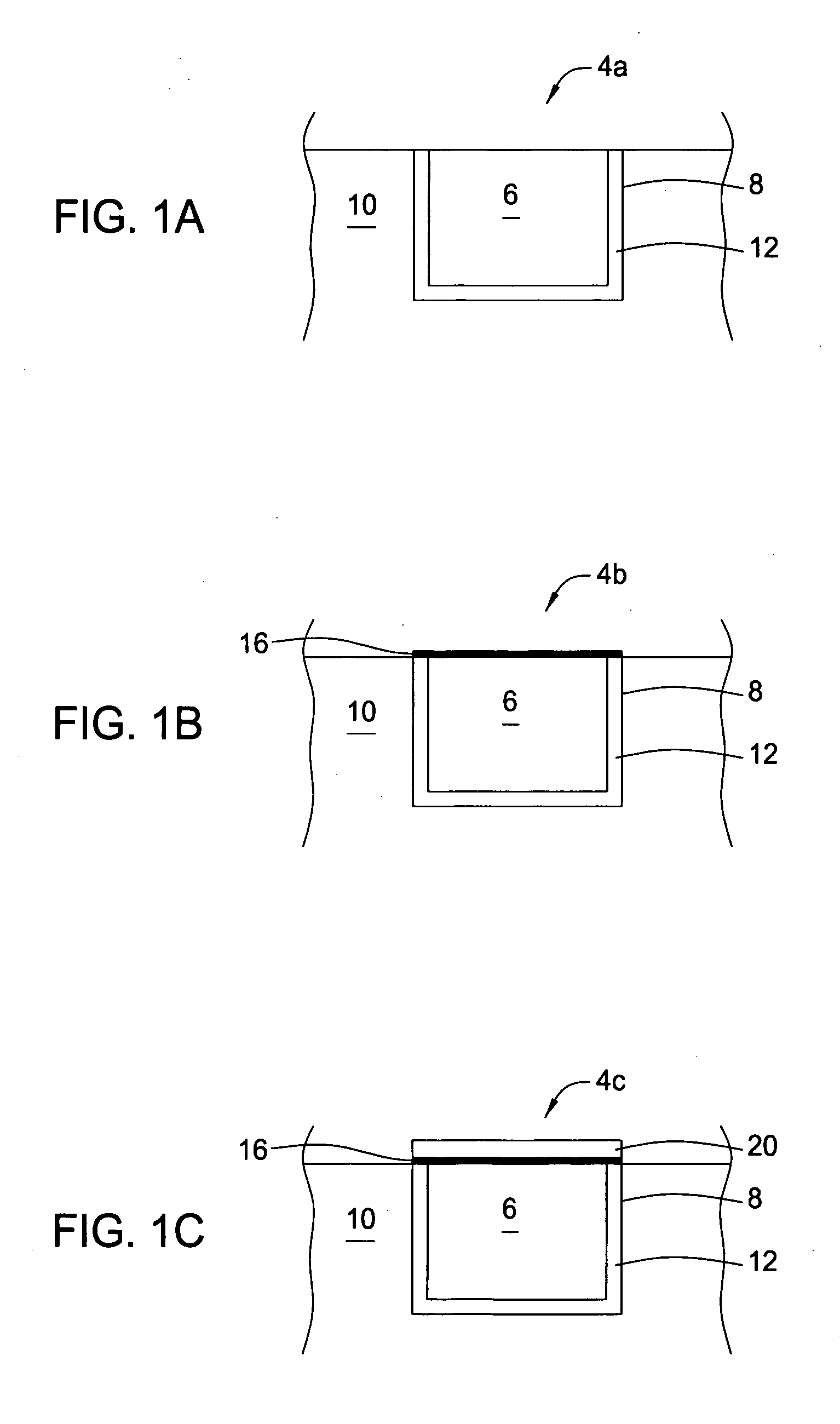

Methods of forming a capping layer over a metal wire structure of a semiconductor device are disclosed. In one embodiment, the method includes providing a partially fabricated semiconductor device having exposed surfaces of the metal (e.g., copper) wire structure and a dielectric around the metal wire structure. The exposed surface of the metal wire structure is then activated by forming a seed layer thereon. The capping layer is then formed over the exposed surface of the metal wire structure by performing a selective atomic layer deposition (ALD) of a capping layer material onto the metal wire structure. As an alternative, the dielectric may be masked off to further assist the selectivity of the ALD. The invention also includes a semiconductor structure including the metal wire structure having an atomic layer deposition capping layer over an upper surface thereof.

Owner:IBM CORP

Silane and borane treatments for titanium carbide films

ActiveUS8841182B1Reduce oxidized portionPrevent oxidationSemiconductor/solid-state device manufacturingSilanesCompound (substance)

Methods of treating metal-containing thin films, such as films comprising titanium carbide, with a silane / borane agent are provided. In some embodiments a film including titanium carbide is deposited on a substrate by an atomic layer deposition (ALD) process. The process may include a plurality of deposition cycles involving alternating and sequential pulses of a first source chemical that includes titanium and at least one halide ligand, a second source chemical that includes metal and carbon, where the metal and the carbon from the second source chemical are incorporated into the thin film, and a third source chemical, where the third source chemical is a silane or borane that at least partially reduces oxidized portions of the titanium carbide layer formed by the first and second source chemicals. The treatment can form a capping layer on the metal carbide film.

Owner:ASM IP HLDG BV

Integrated circuit and manufacturing method of copper germanide and copper silicide as copper capping layer

ActiveUS7858519B2Improve barrier propertiesAvoiding Cu out diffusingSemiconductor/solid-state device detailsSolid-state devicesGermanideCopper silicide

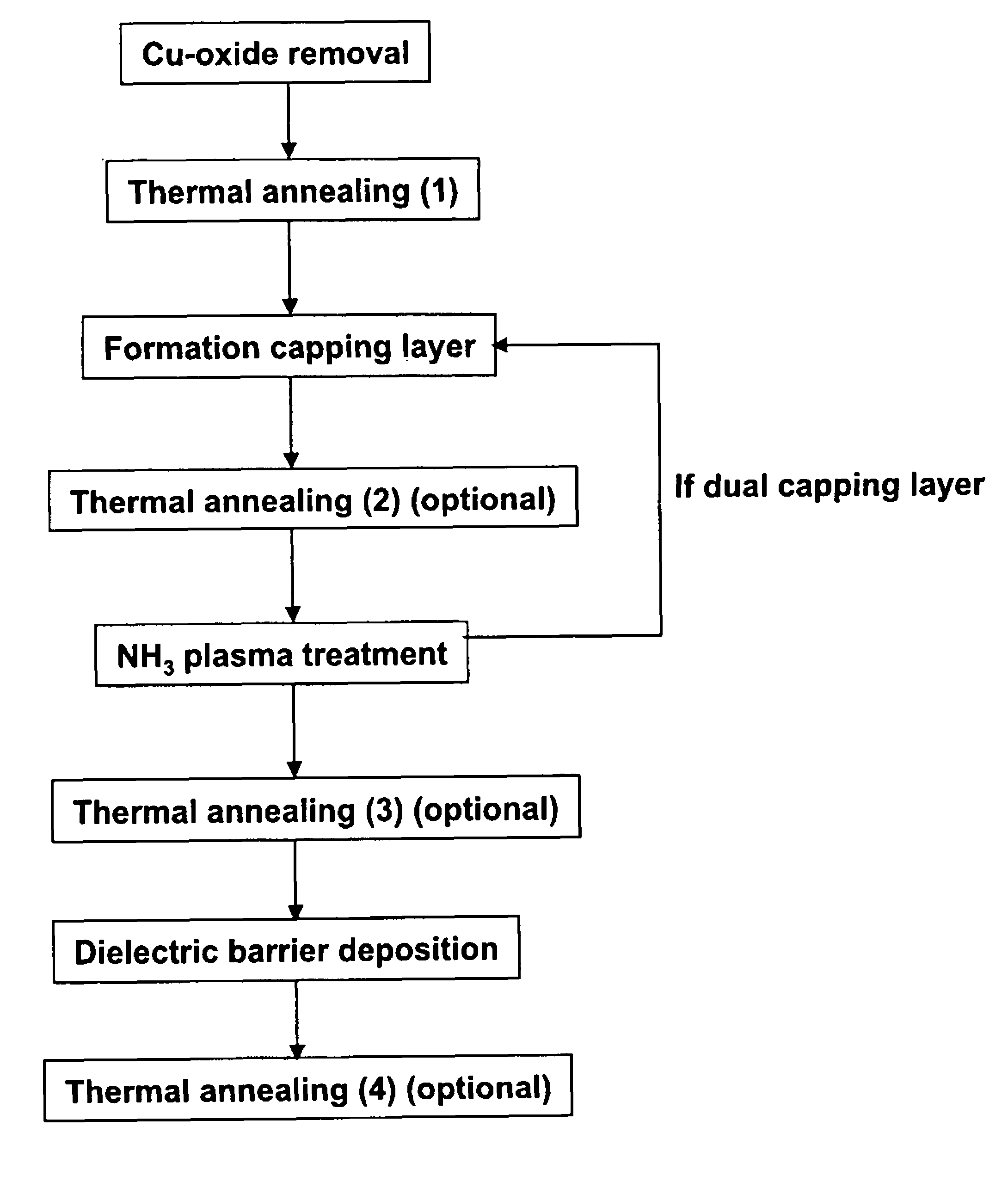

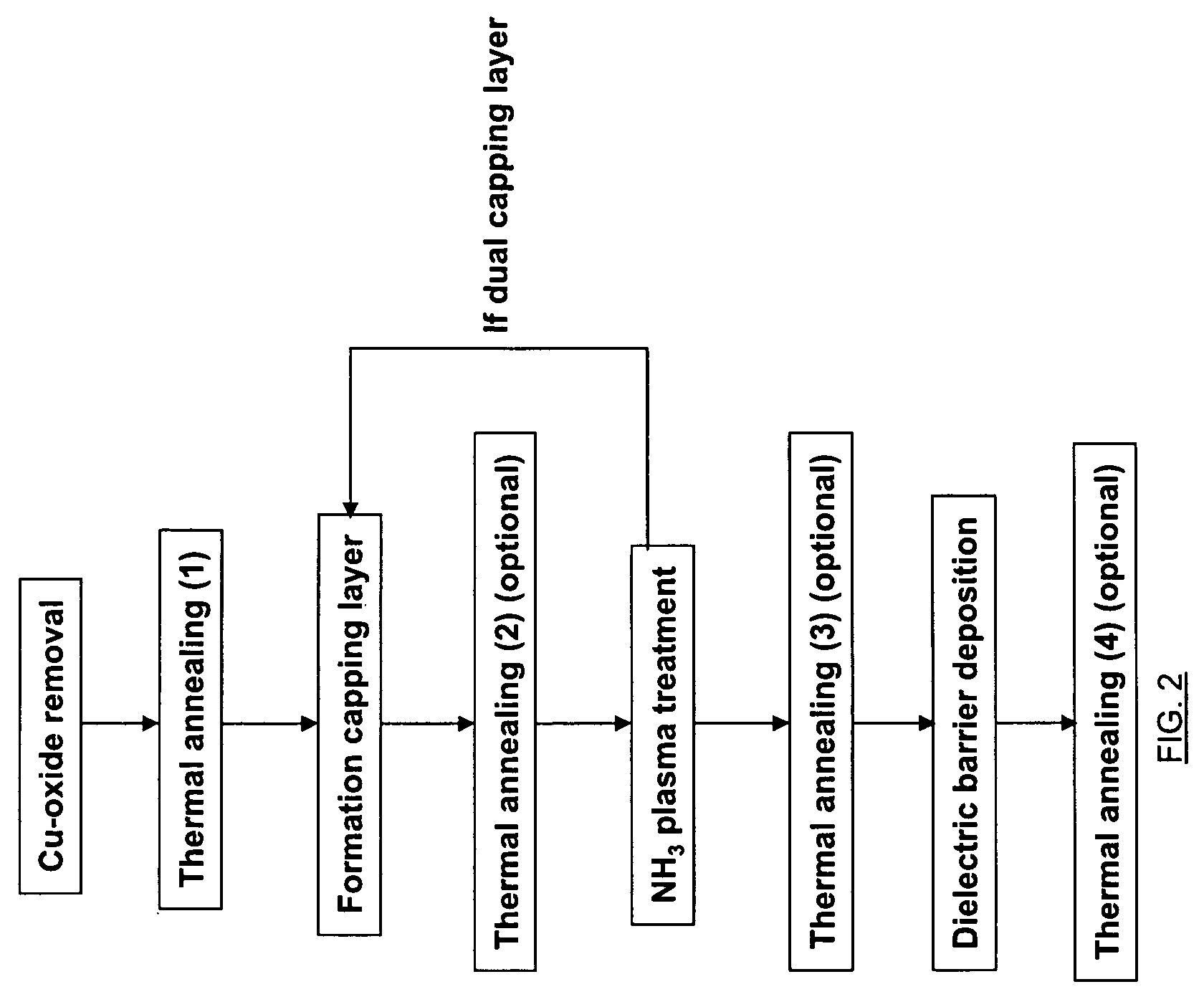

A method is provided for forming a capping layer comprising Cu, N, and also Si and / or Ge onto a copper conductive structure, said method comprising the sequential steps of: forming, at a temperature range between 200° C. up to 400° C., at least one capping layer onto said copper conductive structure by exposing said structure to a GeH4 and / or a SiH4 comprising ambient, performing a NH3 plasma treatment thereby forming an at least partly nitrided capping layer, forming a dielectric barrier layer onto said at least partly nitrided capping layer, wherein prior to said step of forming said at least one capping layer a pre-annealing step of said copper conductive structure is performed at a temperature range between 250° C. up to 450° C.

Owner:TAIWAN SEMICON MFG CO LTD +1

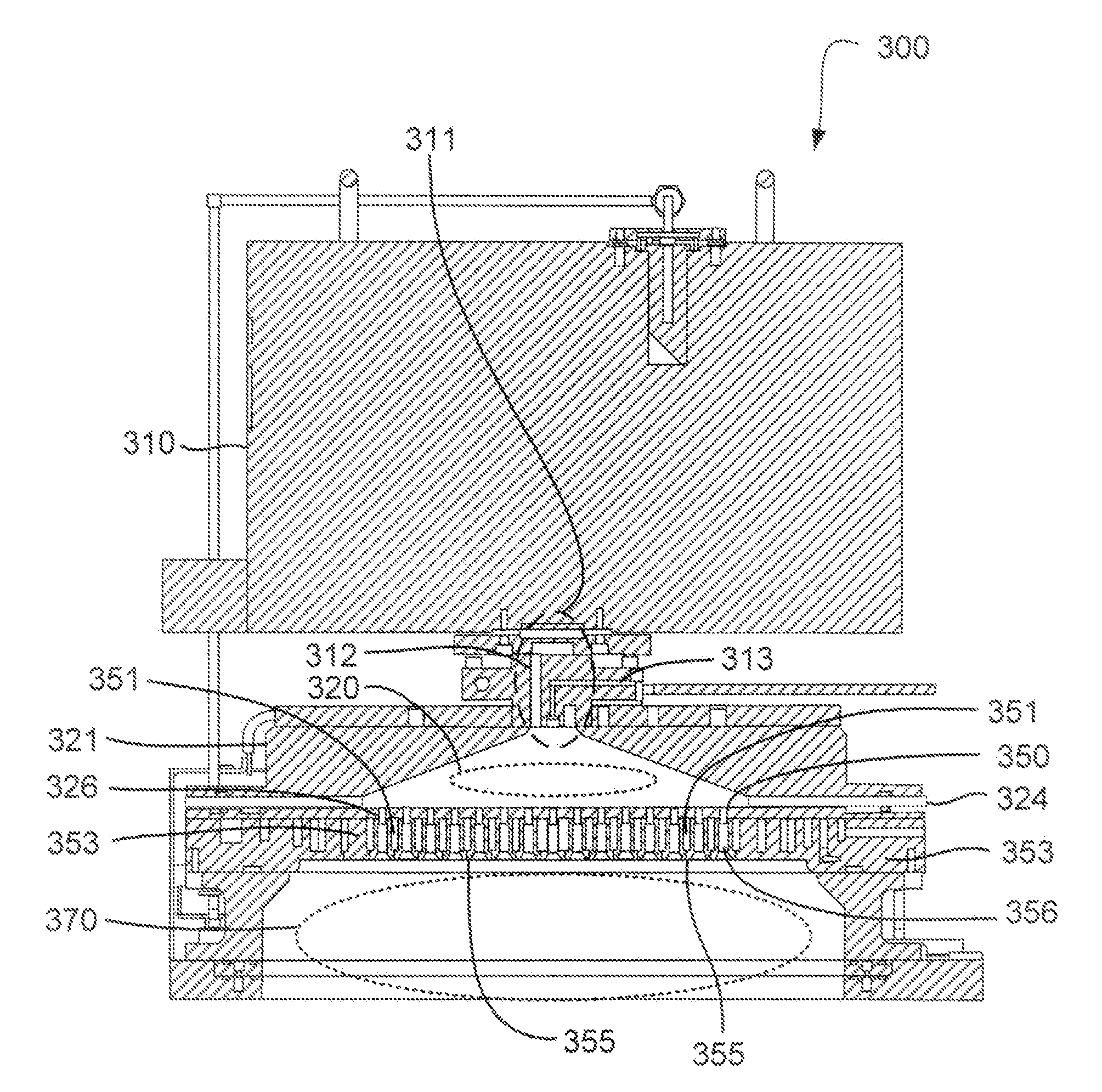

Removal of surface dopants from a substrate

InactiveUS20090162996A1Semiconductor/solid-state device detailsSolid-state devicesDopantHigh concentration

A method and apparatus for removing excess dopant from a doped substrate is provided. In one embodiment, a substrate is doped by surfaced deposition of dopant followed by formation of a capping layer and thermal diffusion drive-in. A reactive etchant mixture is provided to the process chamber, with optional plasma, to etch away the capping layer and form volatile compounds by reacting with excess dopant. In another embodiment, a substrate is doped by energetic implantation of dopant. A reactive gas mixture is provided to the process chamber, with optional plasma, to remove excess dopant adsorbed on the surface and high-concentration dopant near the surface by reacting with the dopant to form volatile compounds. The reactive gas mixture may be provided during thermal treatment, or it may be provided before or after at temperatures different from the thermal treatment temperature. The volatile compounds are removed. Substrates so treated do not form toxic compounds when stored or transported outside process equipment.

Owner:APPLIED MATERIALS INC

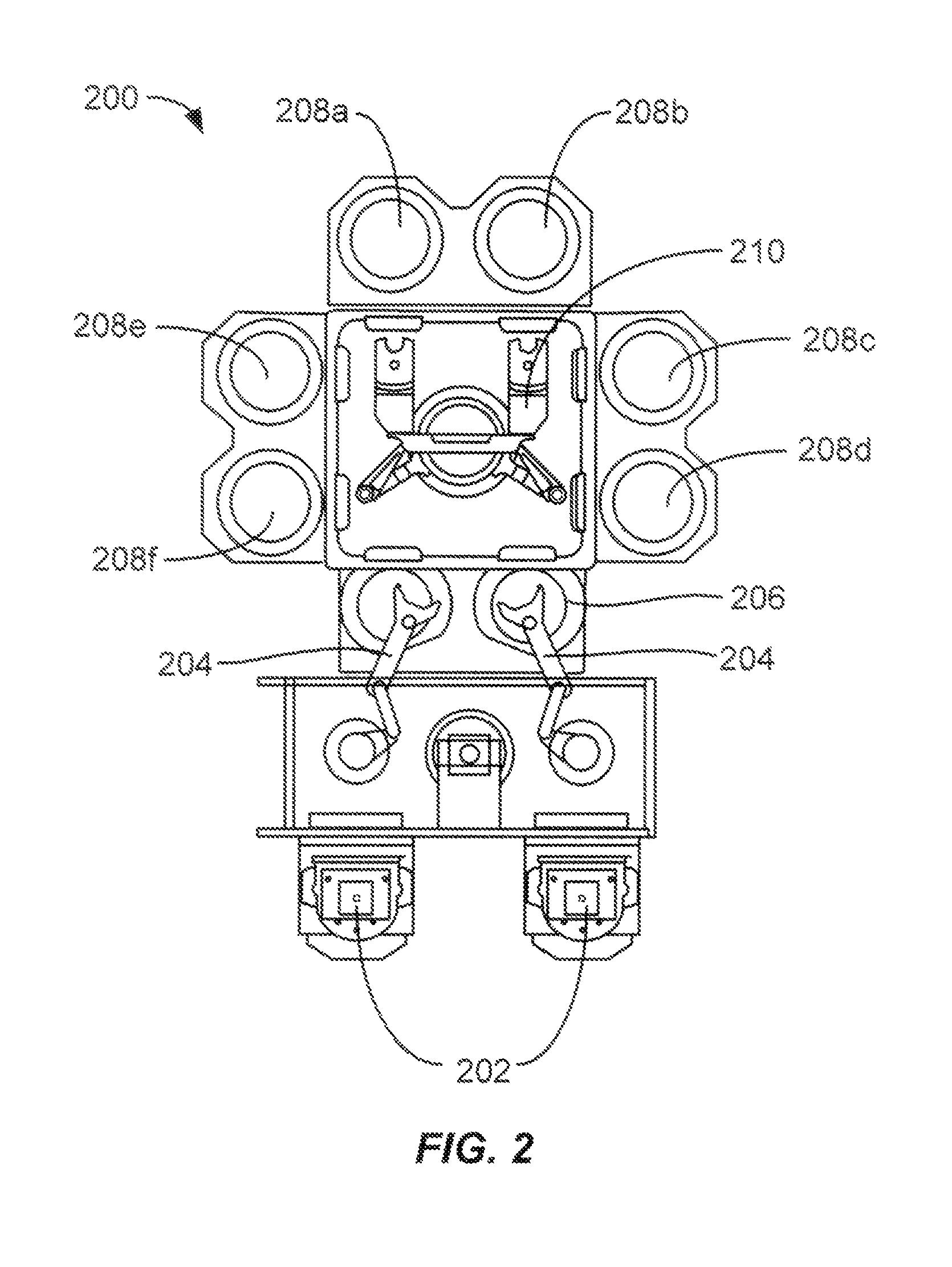

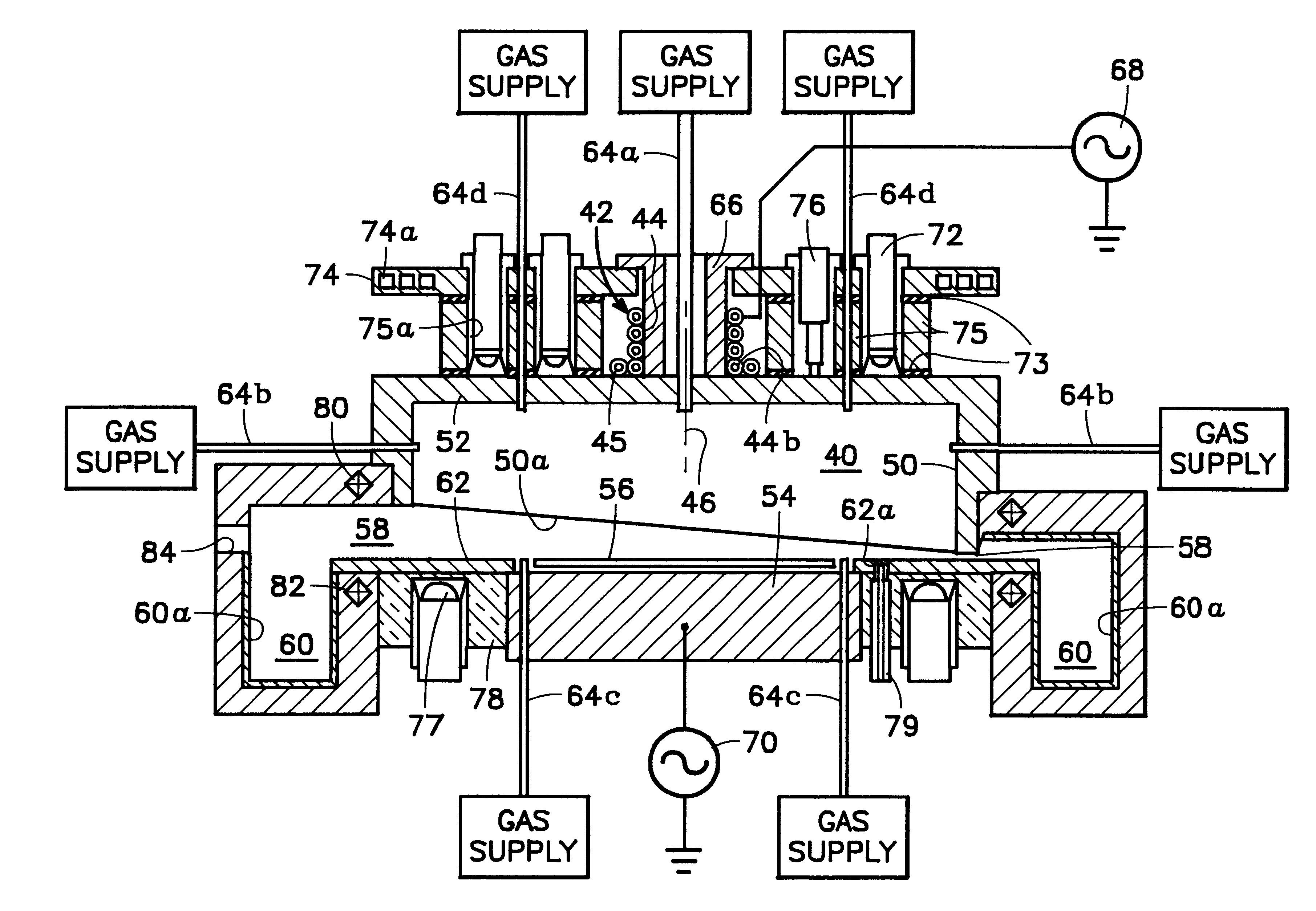

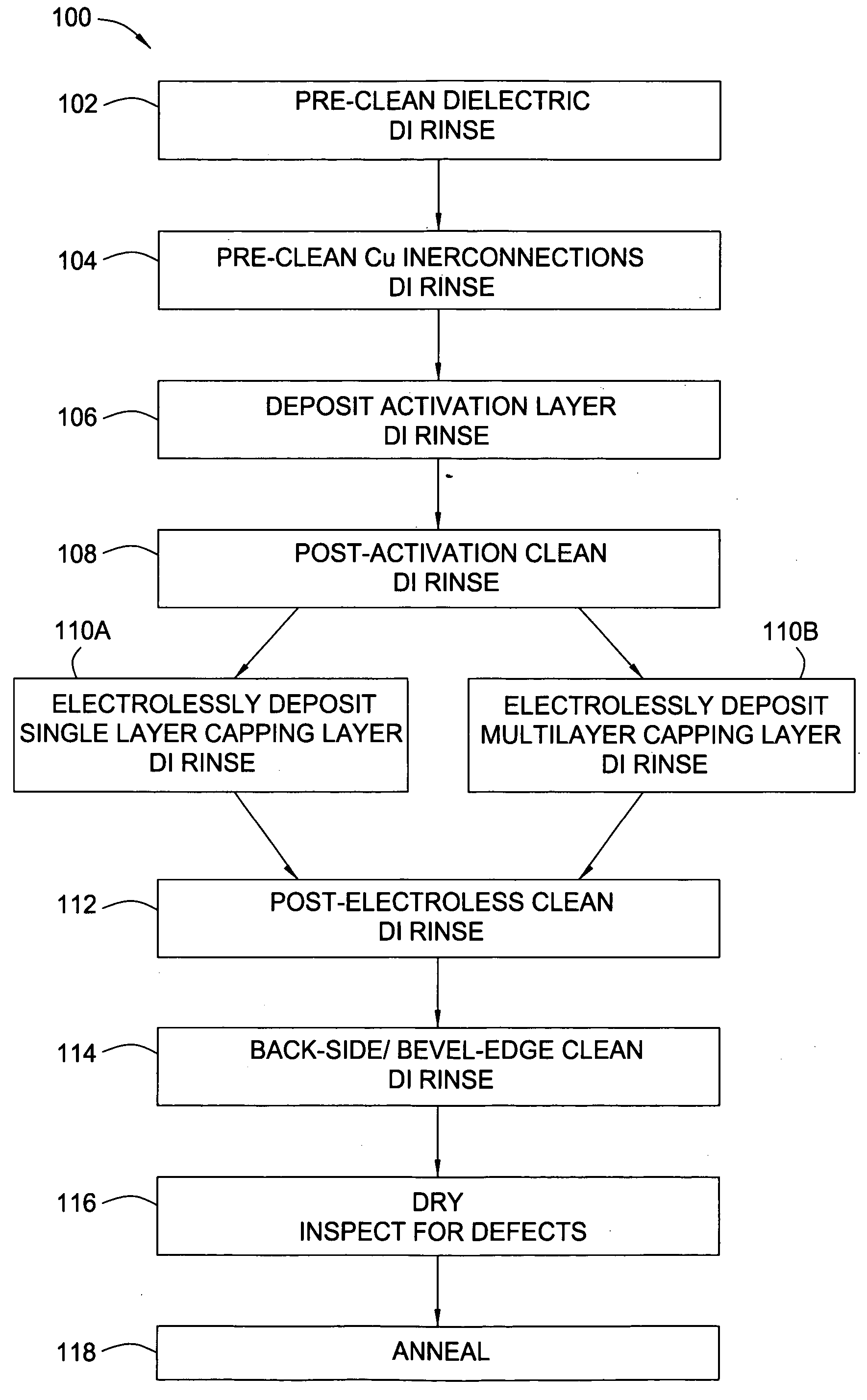

Integrated electroless deposition system

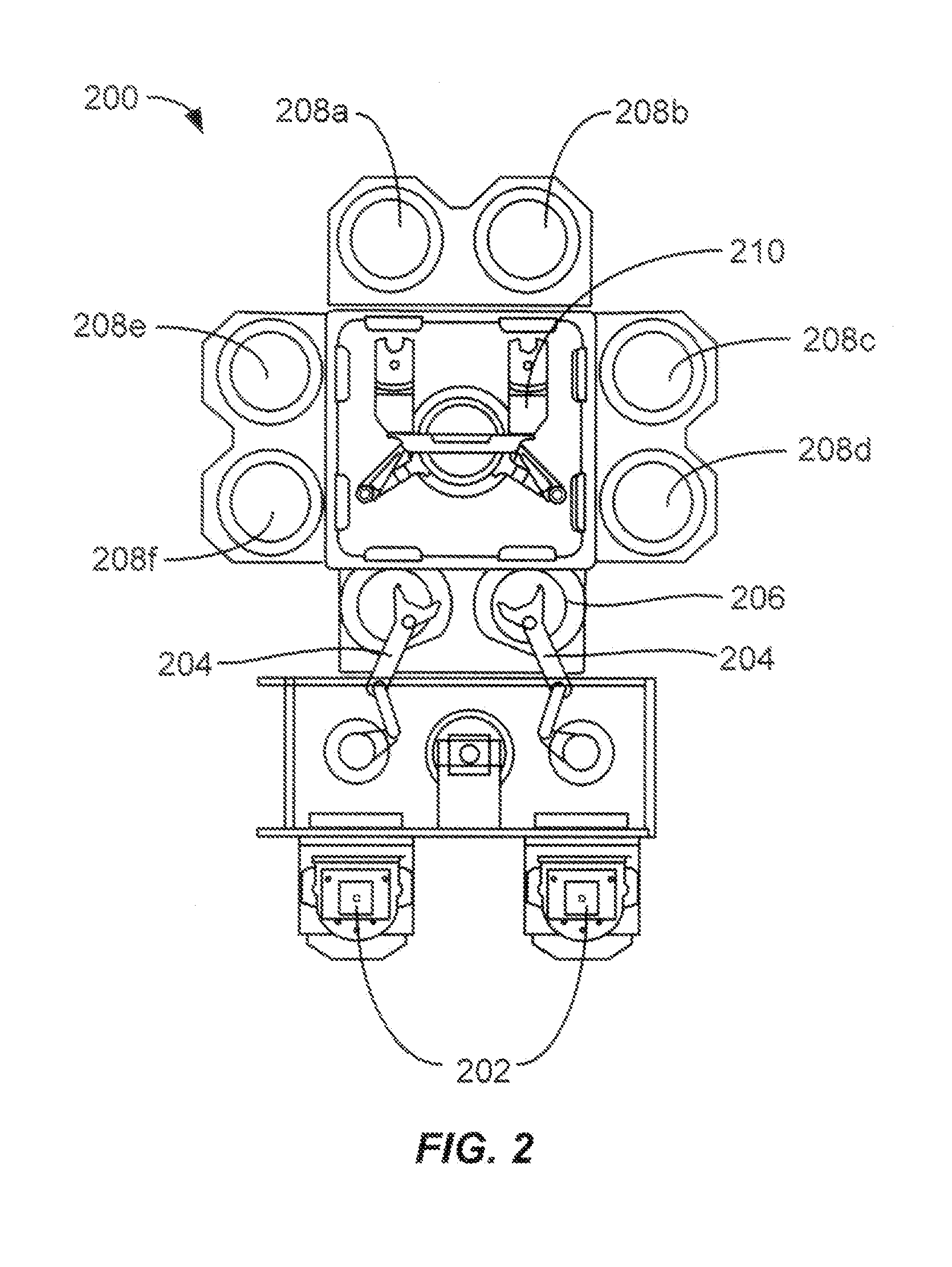

InactiveUS20070111519A1Electrolysis componentsSemiconductor/solid-state device manufacturingEngineeringElectroless deposition

Embodiments of the invention provide methods for depositing a material onto a surface of a substrate by using one or more electroless, electrochemical plating, CVD and / or ALD processes. Embodiments of the invention provide a method for depositing a seed layer on a substrate with an electroless process and to subsequently fill interconnect features on the substrate with an ECP process on a single substrate processing platform. Other aspects provide a method for depositing a seed layer on a substrate, fill interconnect features on a substrate, or sequentially deposit both a seed layer and fill interconnect features on the substrate. One embodiment provides a method for forming a capping layer over substrate interconnects. Methods include the use of a vapor dryer for pre- and post-deposition cleaning of substrates as well as a brush box chamber for post-deposition cleaning.

Owner:APPLIED MATERIALS INC

Cleaning of carbon-based contaminants in metal interconnects for interconnect capping applications

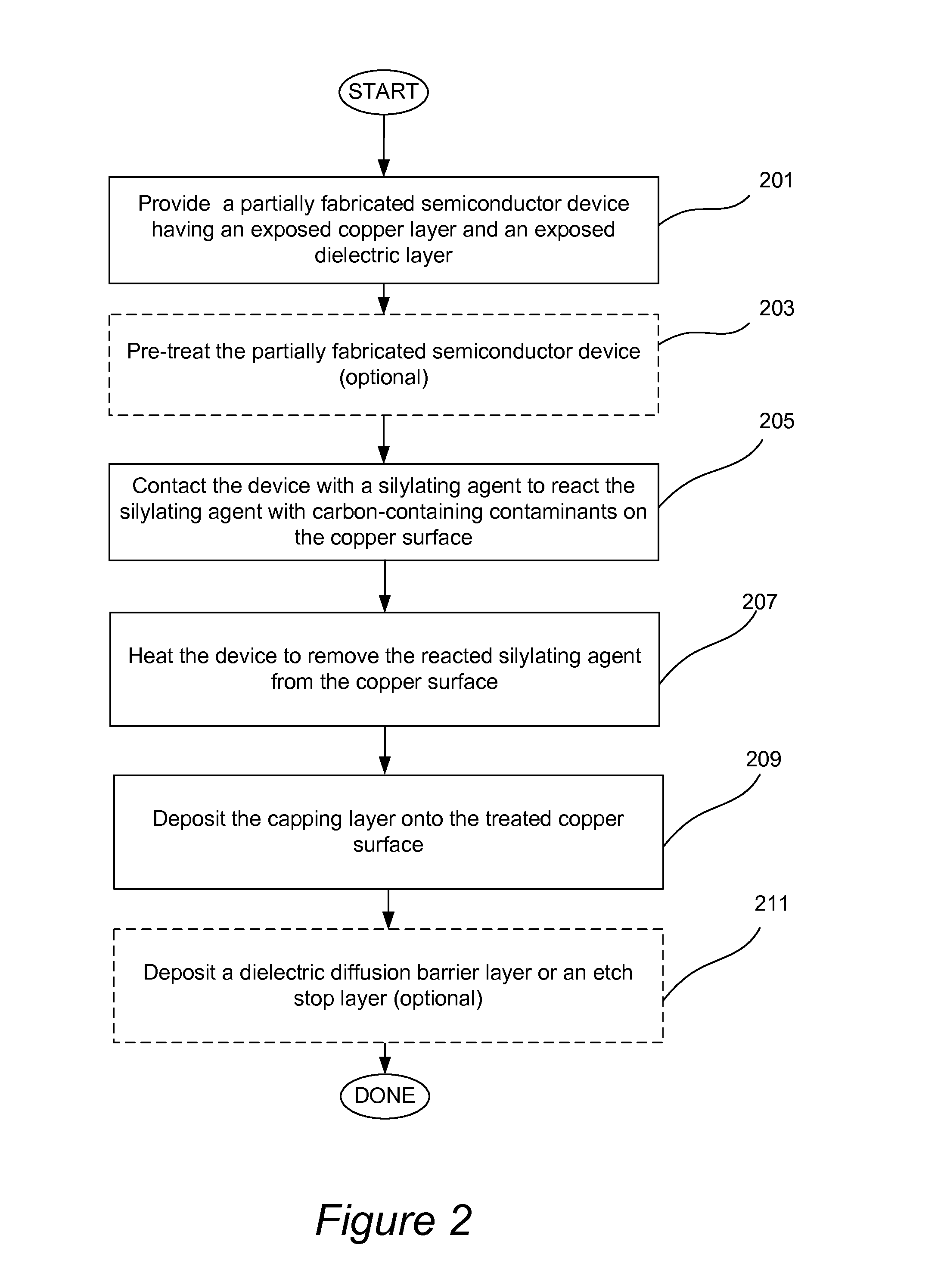

InactiveUS20150380296A1Avoid depositionLow deposition rateLiquid surface applicatorsSemiconductor/solid-state device manufacturingMetal interconnectSilylation

Protective caps residing at an interface between copper lines and dielectric diffusion barrier layers are used to improve various performance characteristics of interconnects. The caps, such as cobalt-containing caps or manganese-containing caps, are selectively deposited onto exposed copper lines in a presence of exposed dielectric using CVD or ALD methods. The deposition of the capping material is affected by the presence of carbon-containing contaminants on the surface of copper, which may lead to poor or uneven growth of the capping layer. A method of removing carbon-containing contaminants from the copper surface prior to deposition of caps involves contacting the substrate containing the exposed copper surface with a silylating agent at a first temperature to form a layer of reacted silylating agent on the copper surface, followed by heating the substrate at a higher temperature to release the reacted silylating agent from the copper surface.

Owner:LAM RES CORP

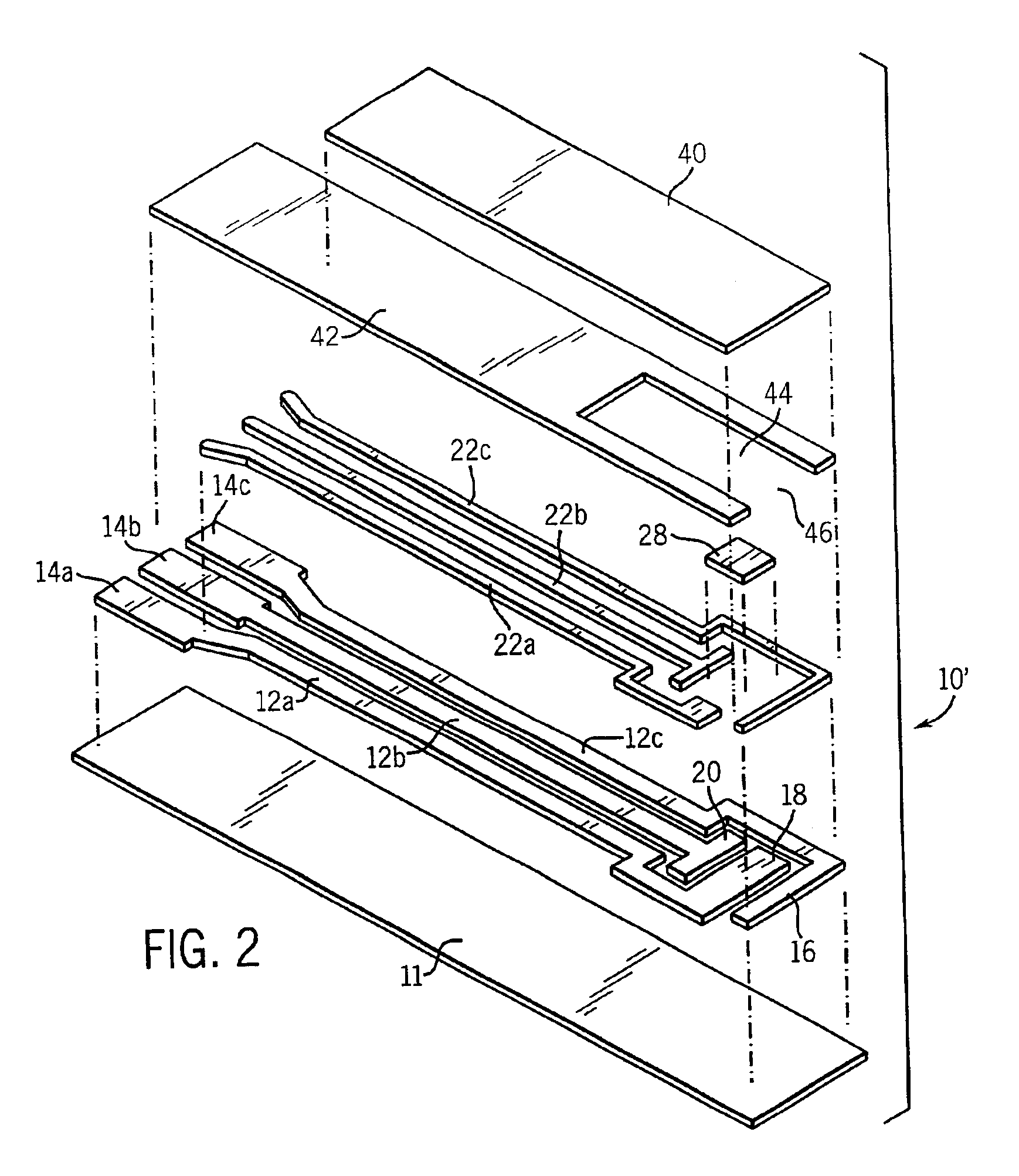

Electrochemical biosensor strip for analysis of liquid samples

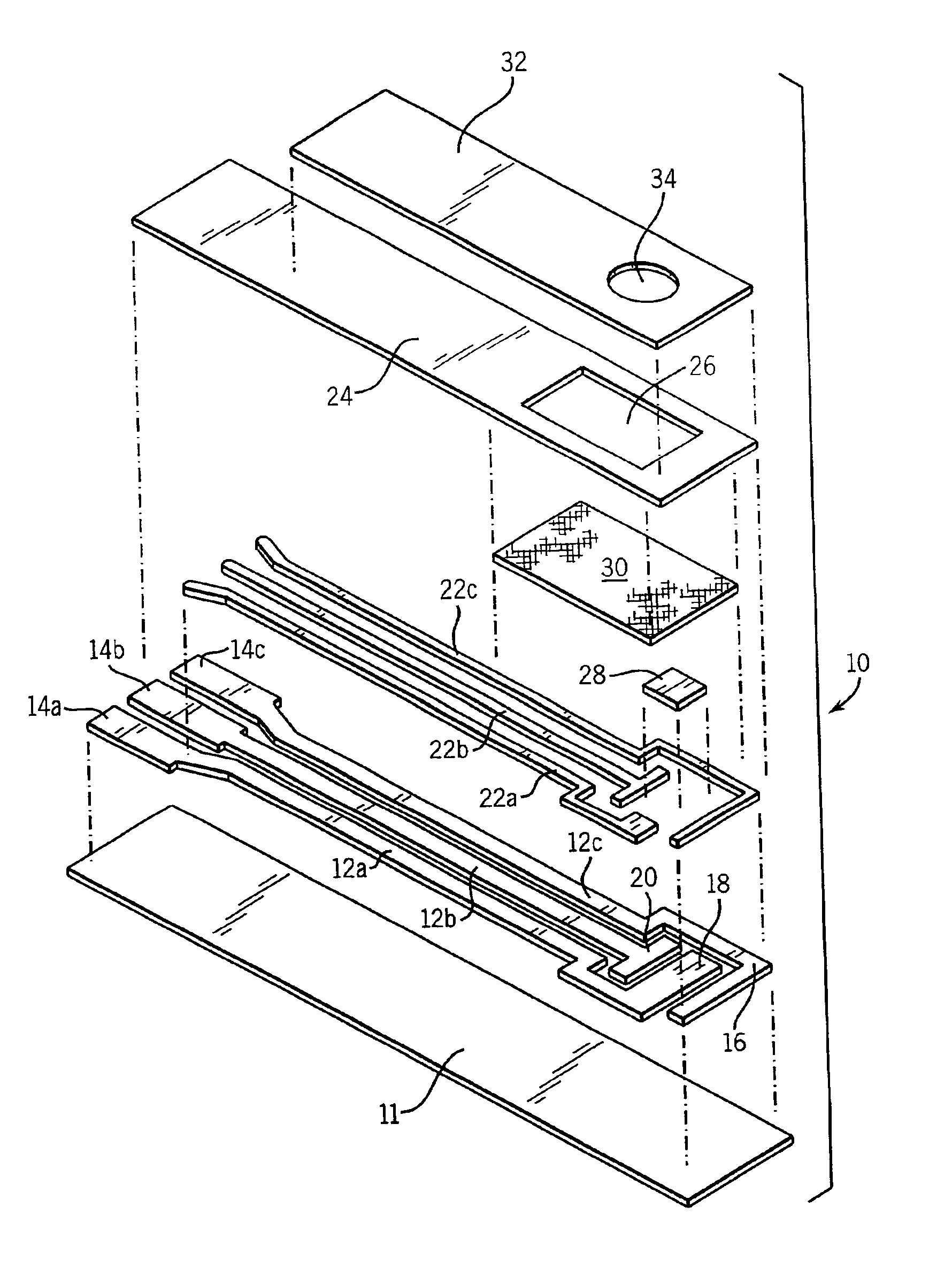

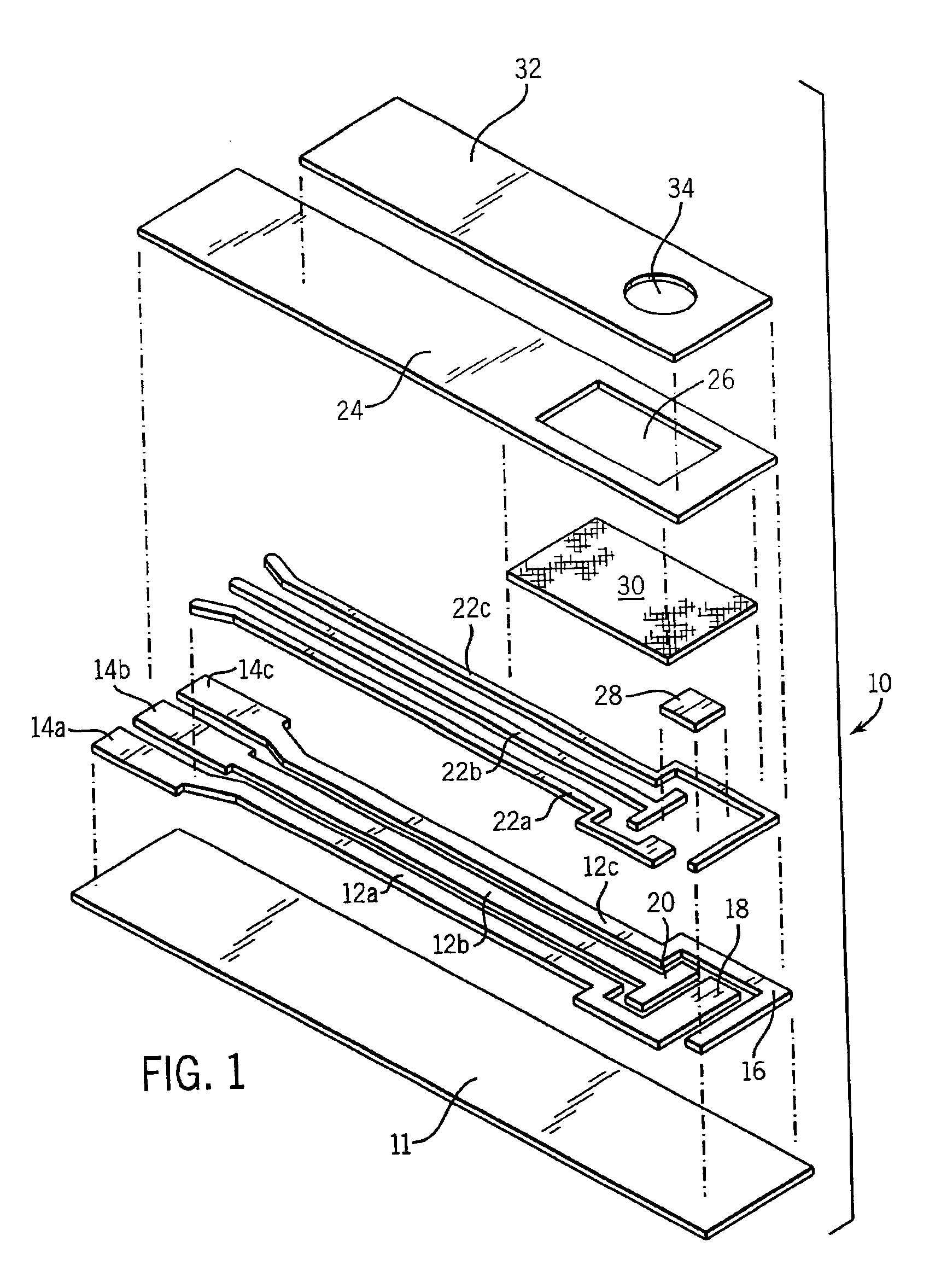

InactiveUS6863800B2Easy to transportImmobilised enzymesBioreactor/fermenter combinationsElectrochemical biosensorConcentrations glucose

A biosensor in the form of a strip. In one embodiment, the biosensor strip comprises an electrode support, a first electrode, i.e., a working electrode, a second electrode, i.e., a counter electrode, and a third electrode, i.e., a reference electrode. Each of the electrodes is disposed on and supported by the electrode support. Each of the electrodes is spaced apart from the other two electrodes. The biosensor strip can include a covering layer, which defines an enclosed space over the electrodes. This enclosed space includes a zone where an analyte in the sample reacts with reagent(s) deposited at the working electrode. This zone is referred to as the reaction zone. The covering layer has an aperture for receiving a sample for introduction into the reaction zone. The biosensor strip can also include at least one layer of mesh interposed in the enclosed space between the covering layer and the electrodes in the reaction zone. This layer of mesh facilitates transporting of the sample to the electrodes in the reaction zone. In another embodiment, a biosensor strip can be constructed to provide a configuration that will allow the sample to be introduced to the reaction zone by action of capillary force. In this embodiment, the layer of mesh can be omitted. The invention also provides a method for determining the concentration of glucose in a sample of whole blood by using the biosensor of this invention.

Owner:ABBOTT LAB INC

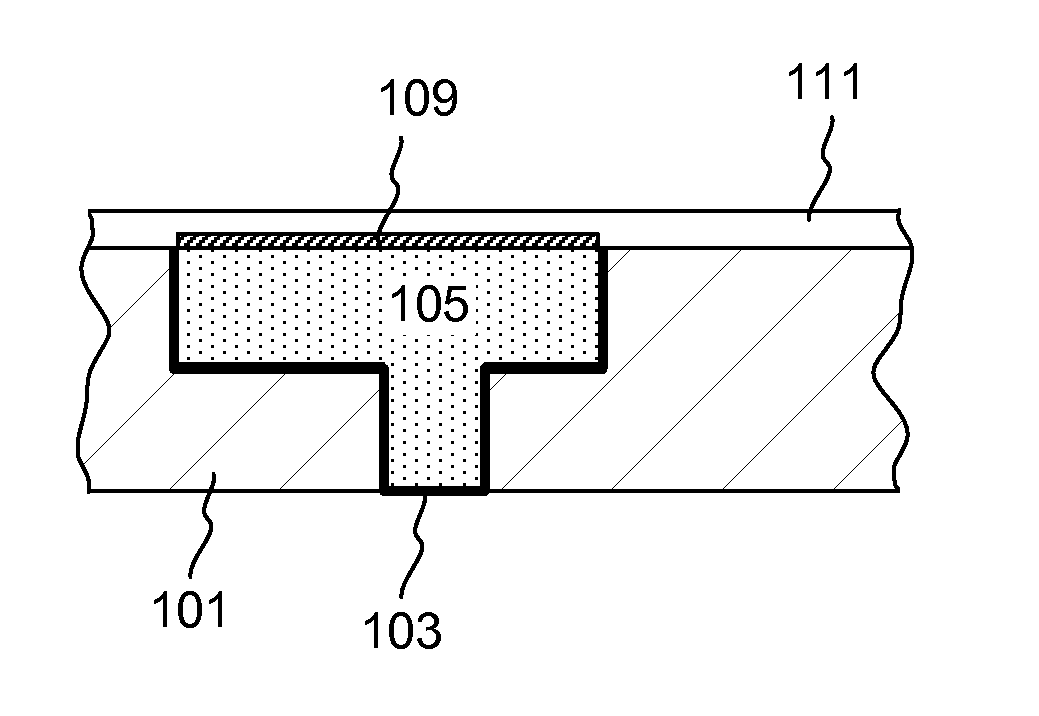

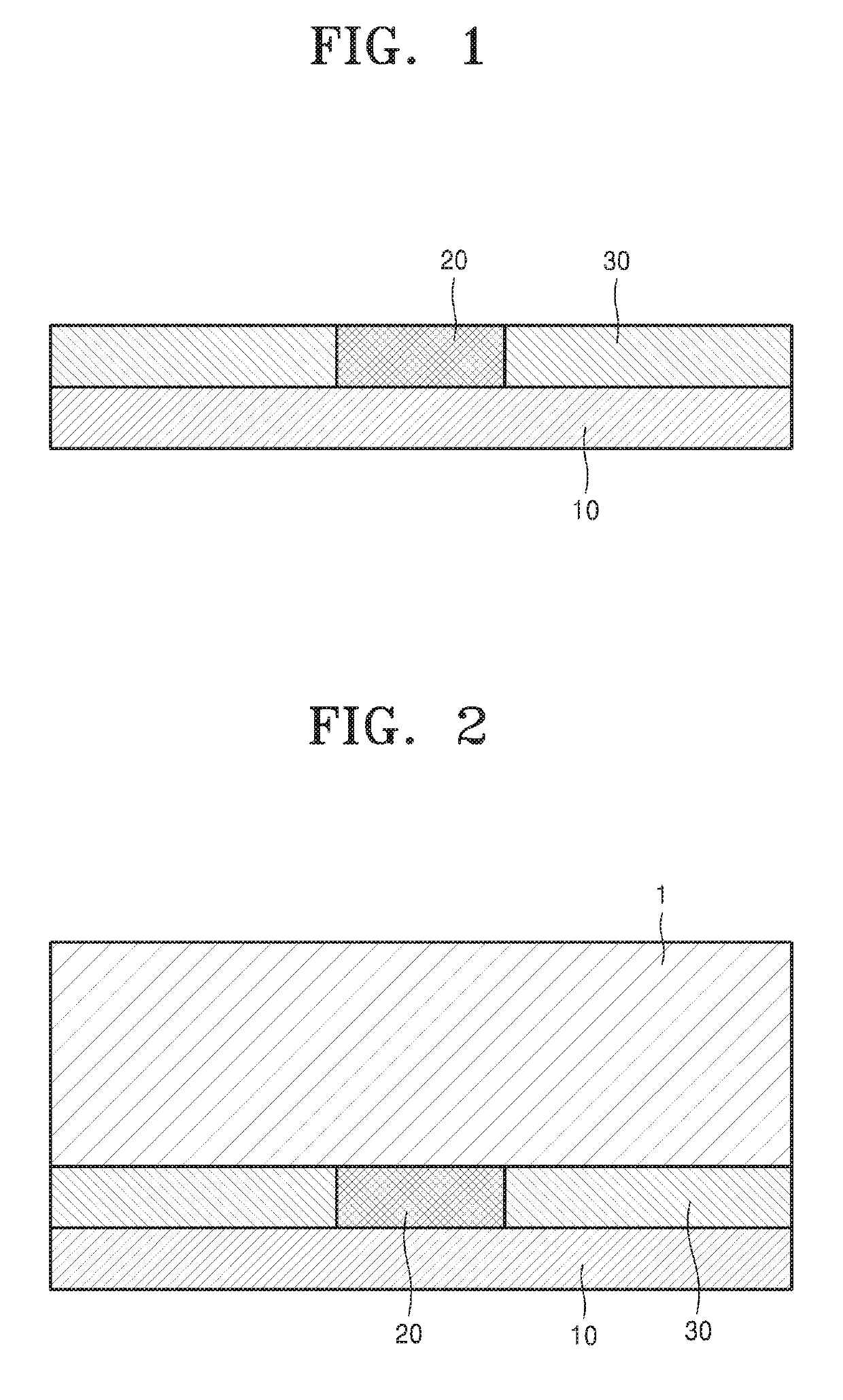

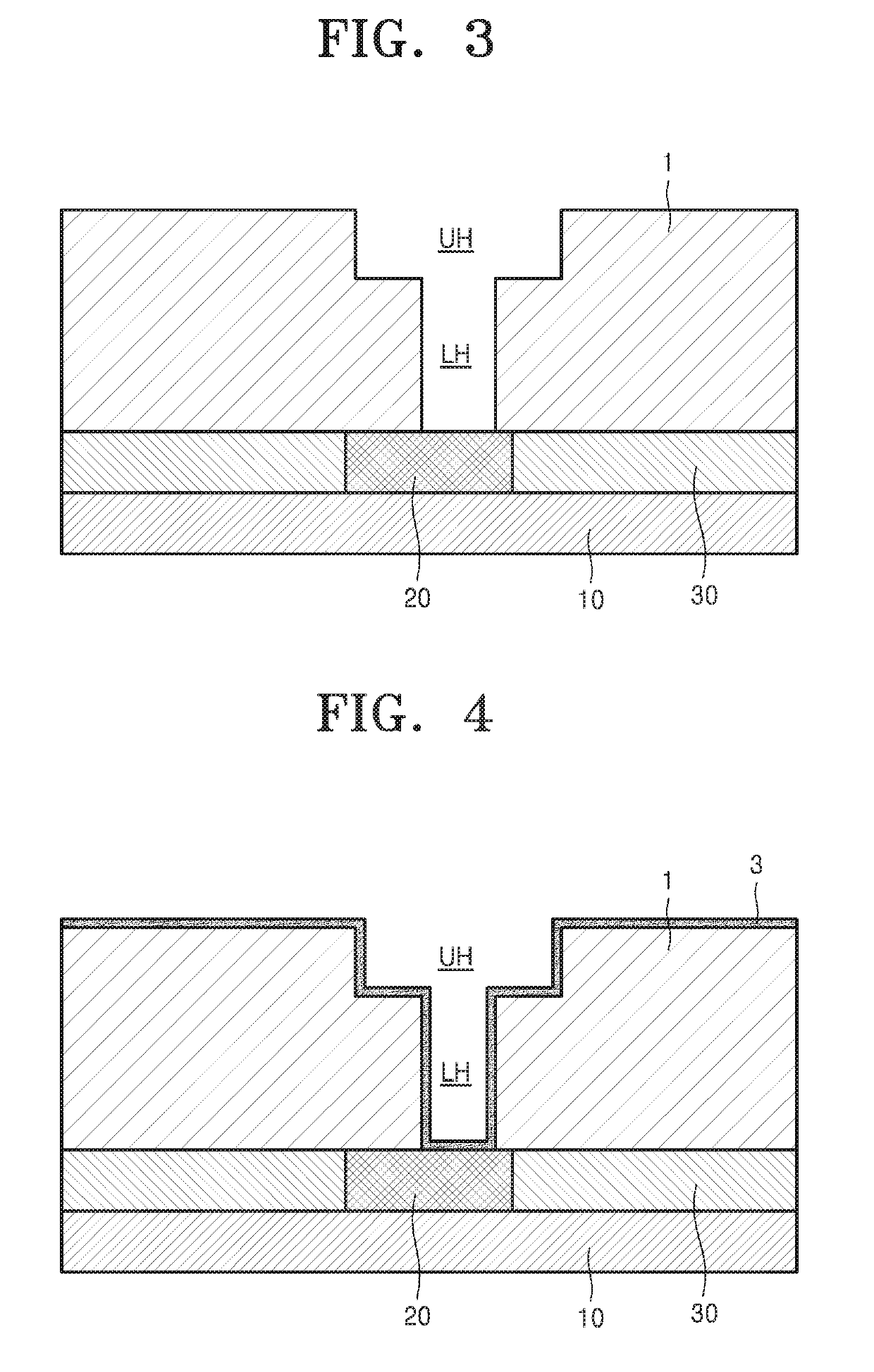

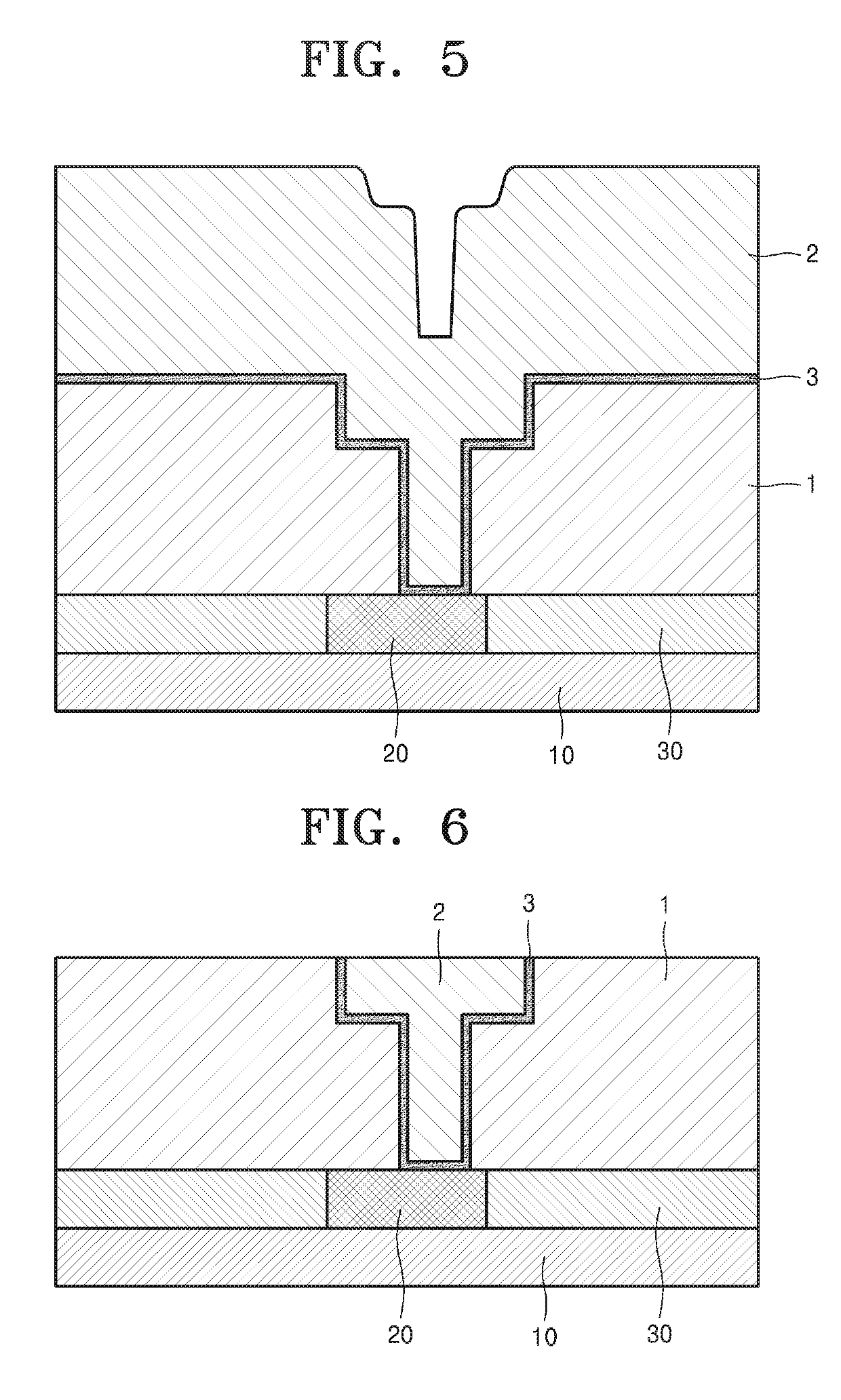

Method of forming metal interconnection and method of fabricating semiconductor apparatus using the method

ActiveUS10249577B2Improve air tightnessSemiconductor/solid-state device detailsSolid-state devicesInterconnectionFiller metal

A semiconductor manufacturing method includes depositing a low-k dielectric layer, forming a trench in the low-k dielectric layer, forming a barrier layer in the trench, filling a metal on the barrier layer, planarizing the metal, and forming a capping layer on the planarized metal, wherein the capping layer includes at least two layers.

Owner:ASM IP HLDG BV

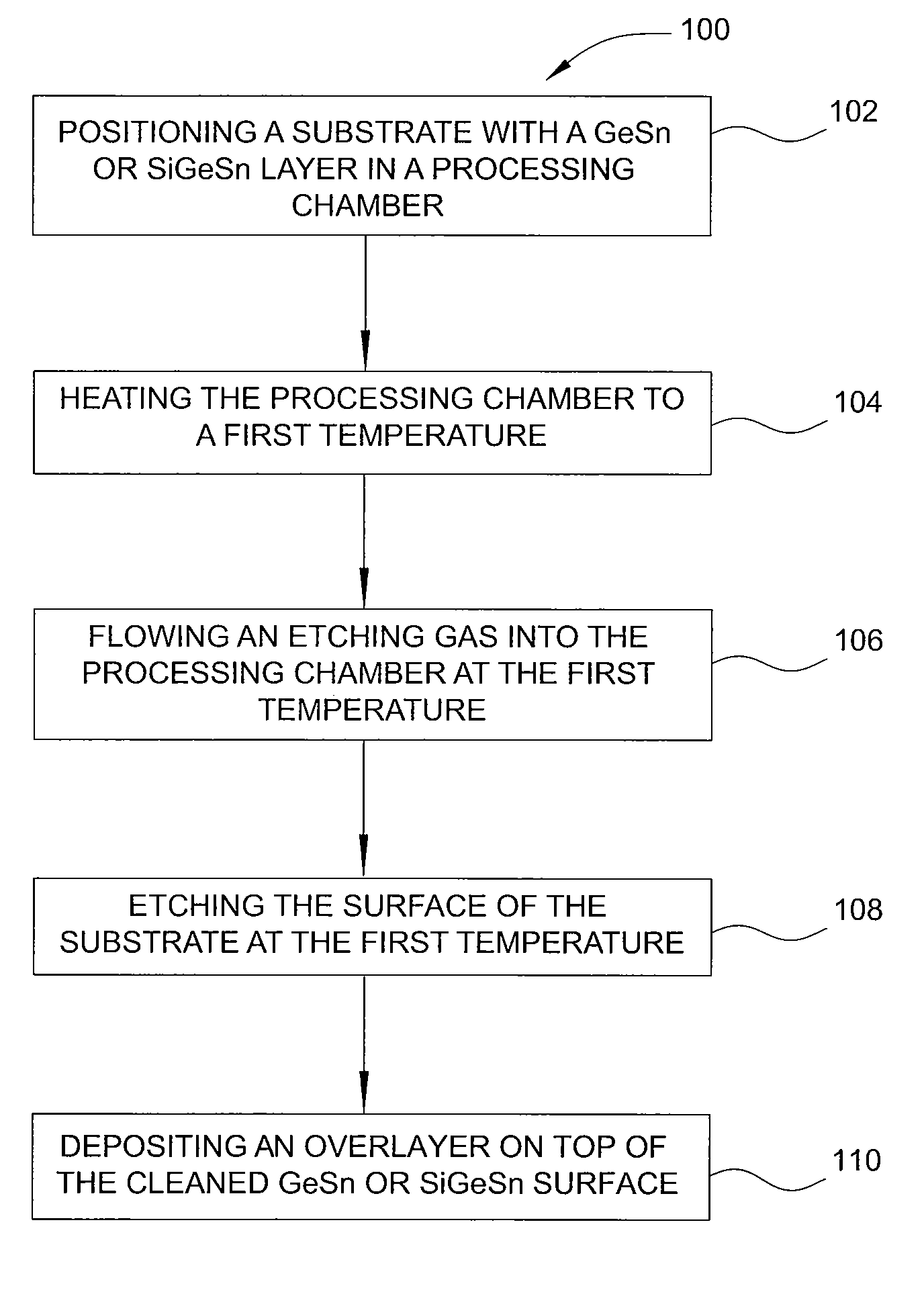

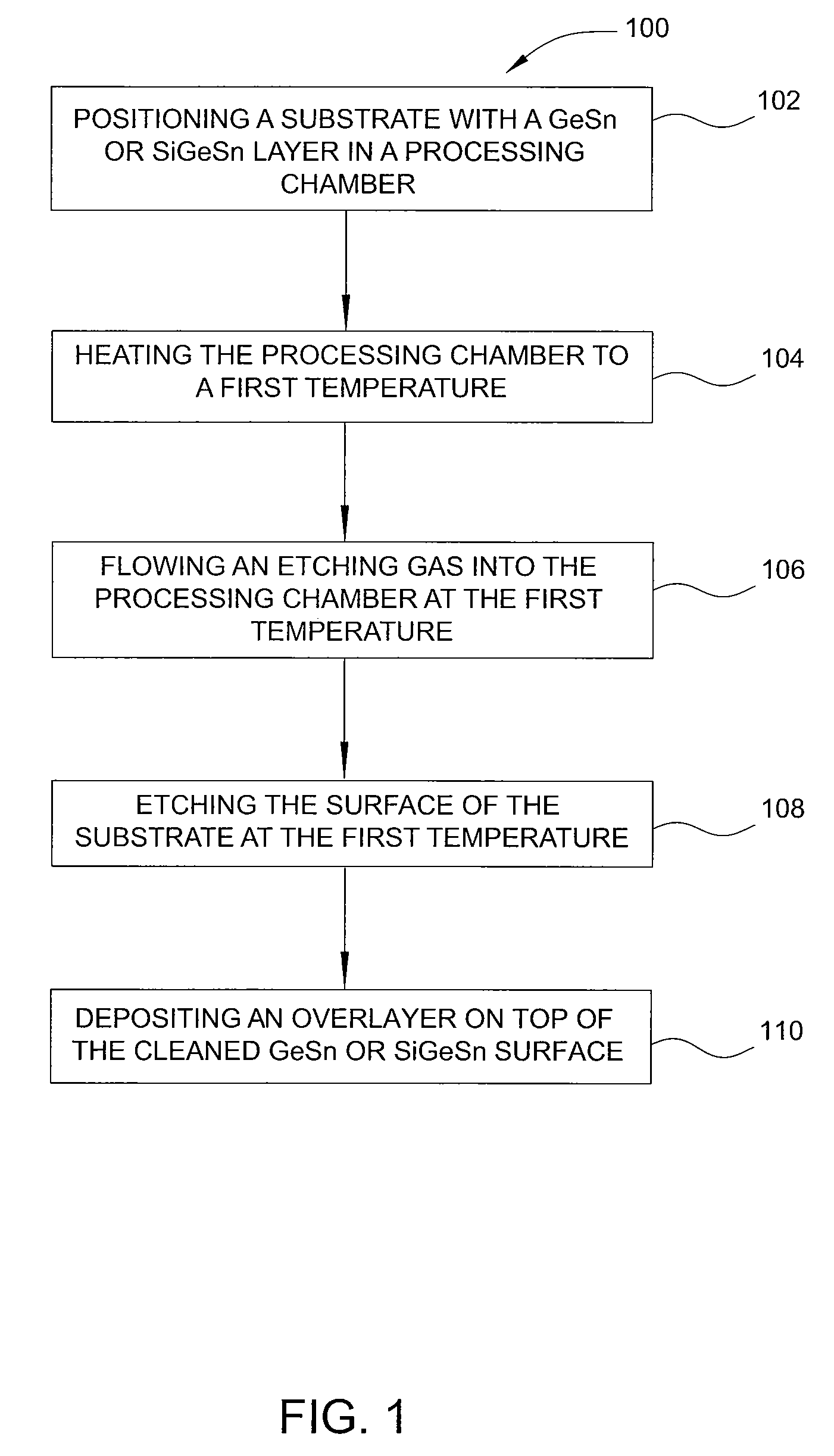

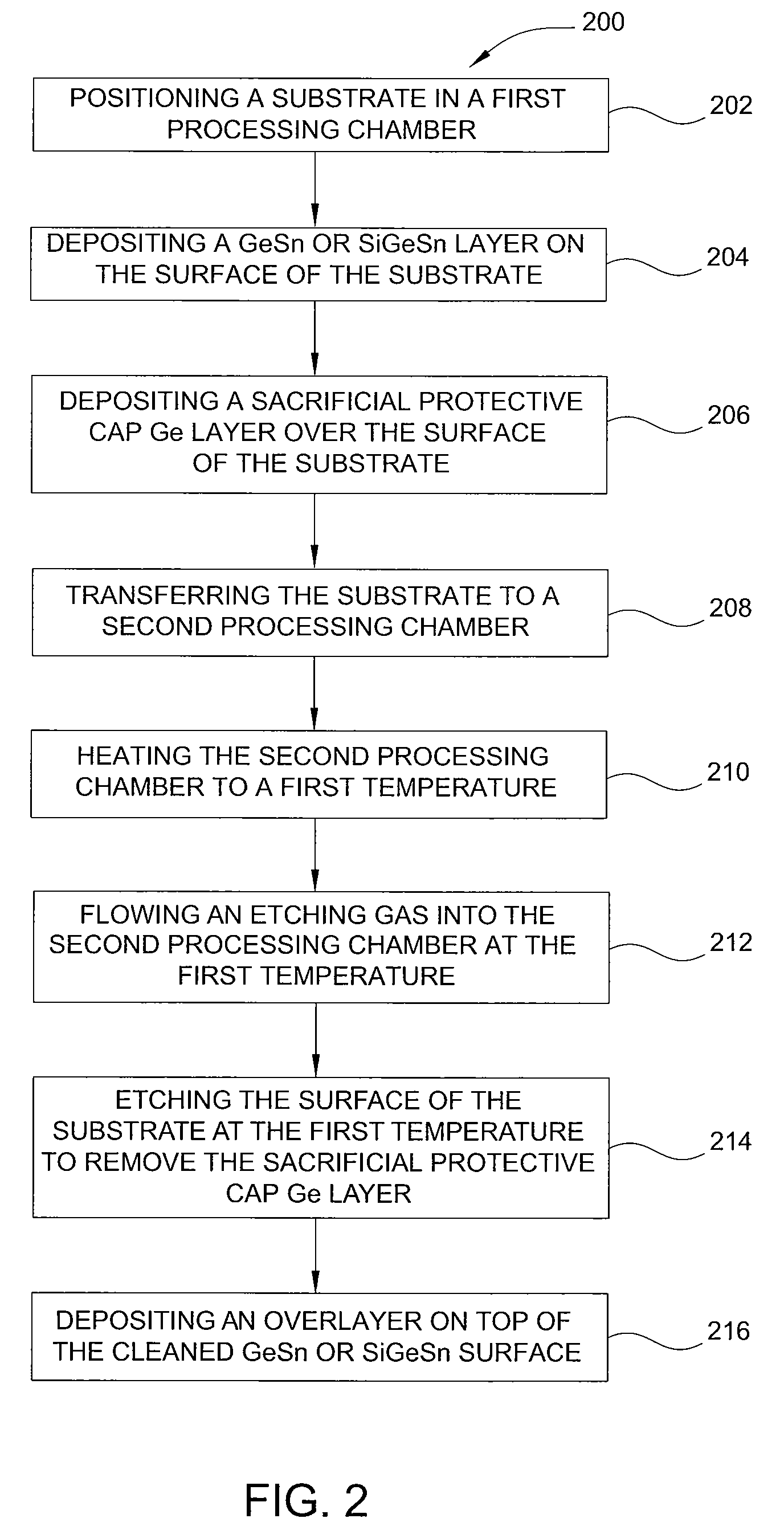

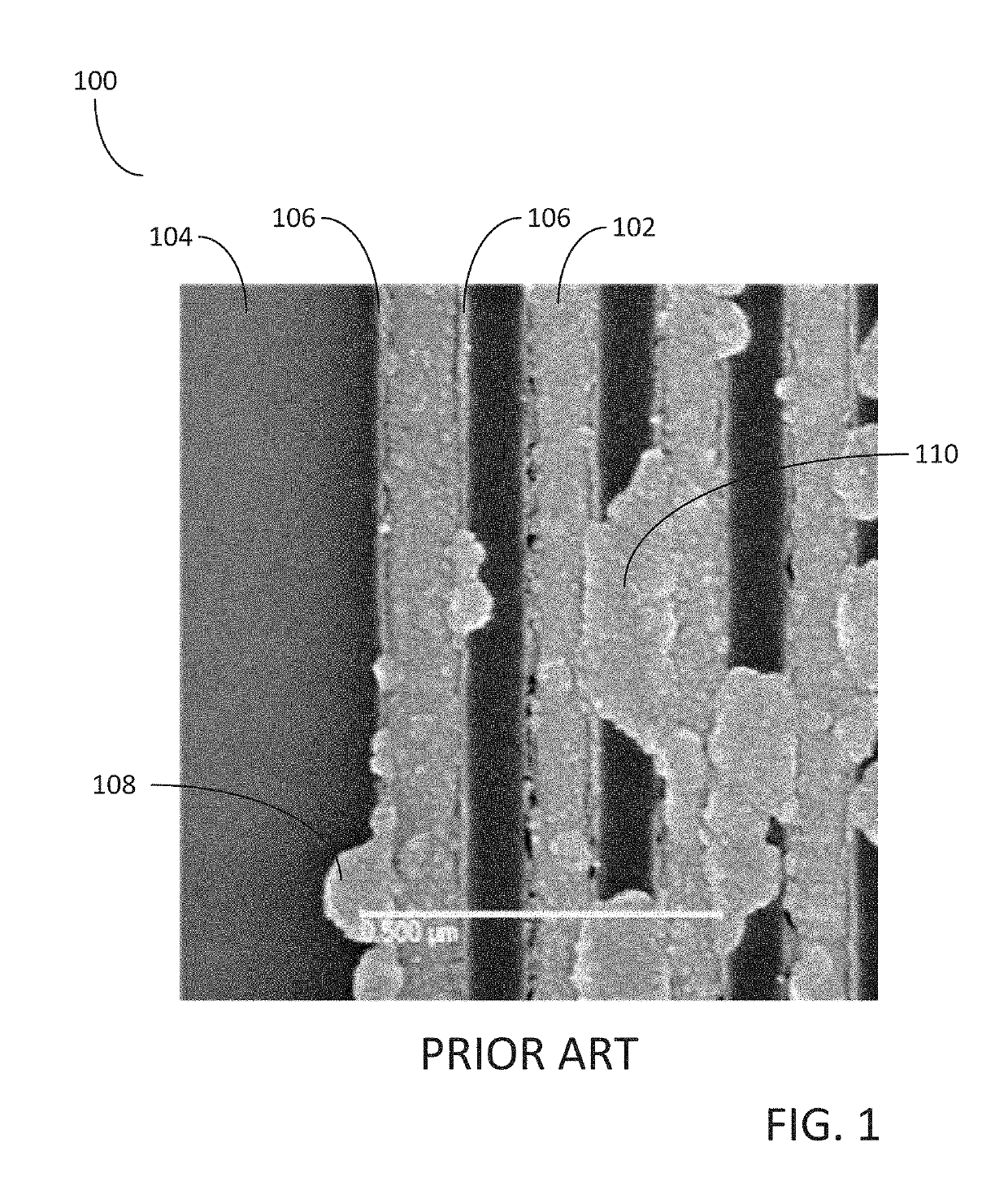

Method of epitaxial germanium tin alloy surface preparation

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

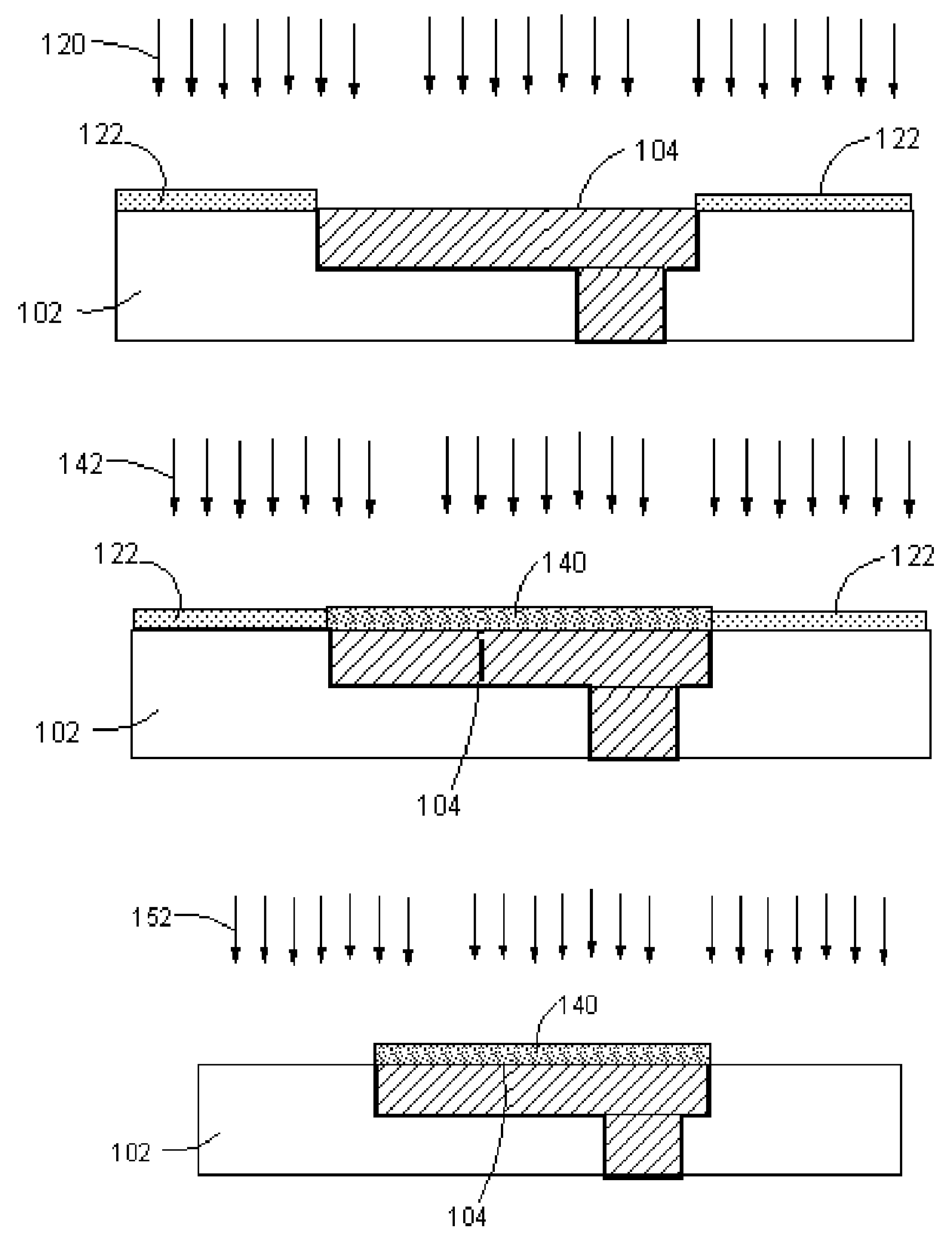

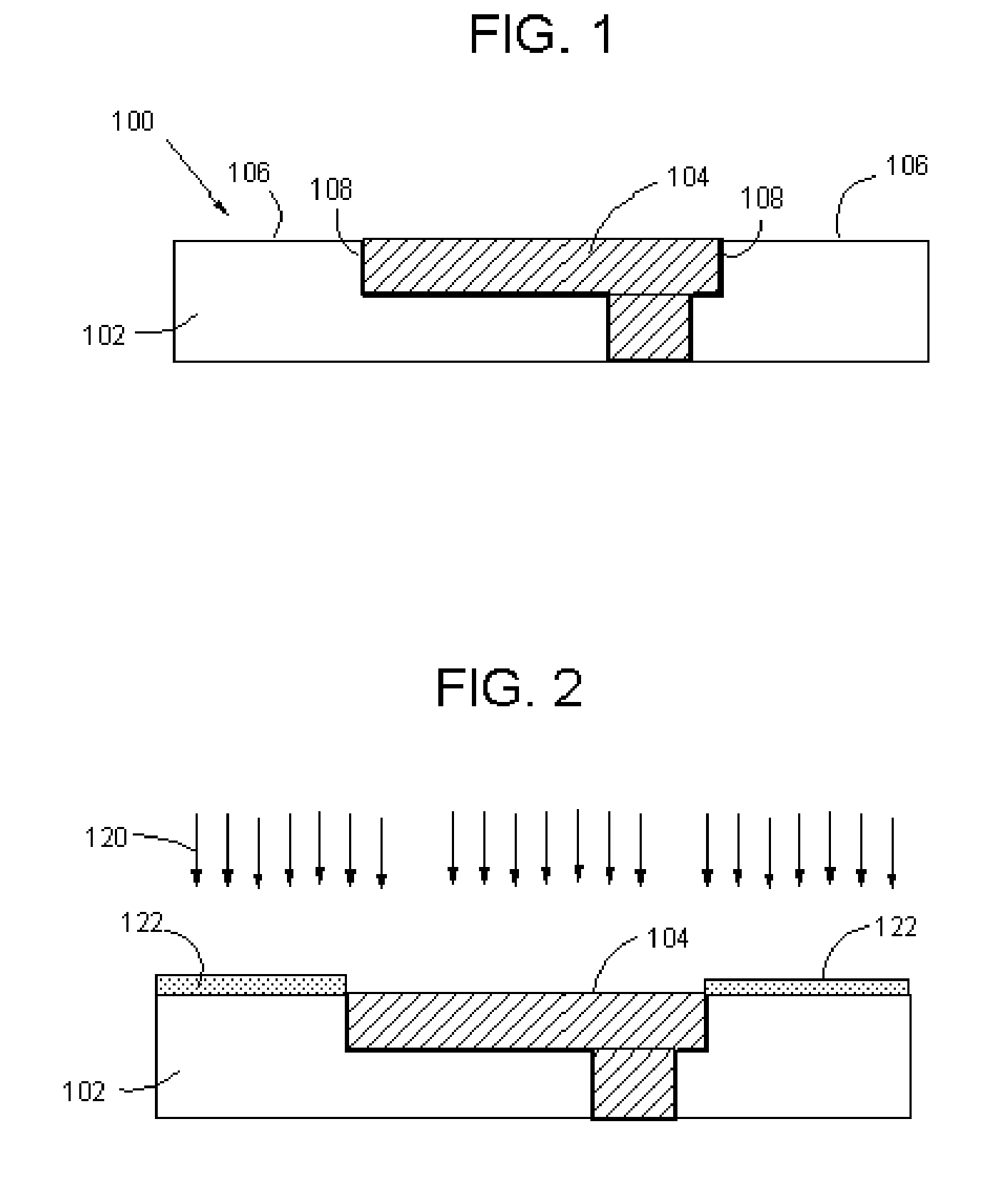

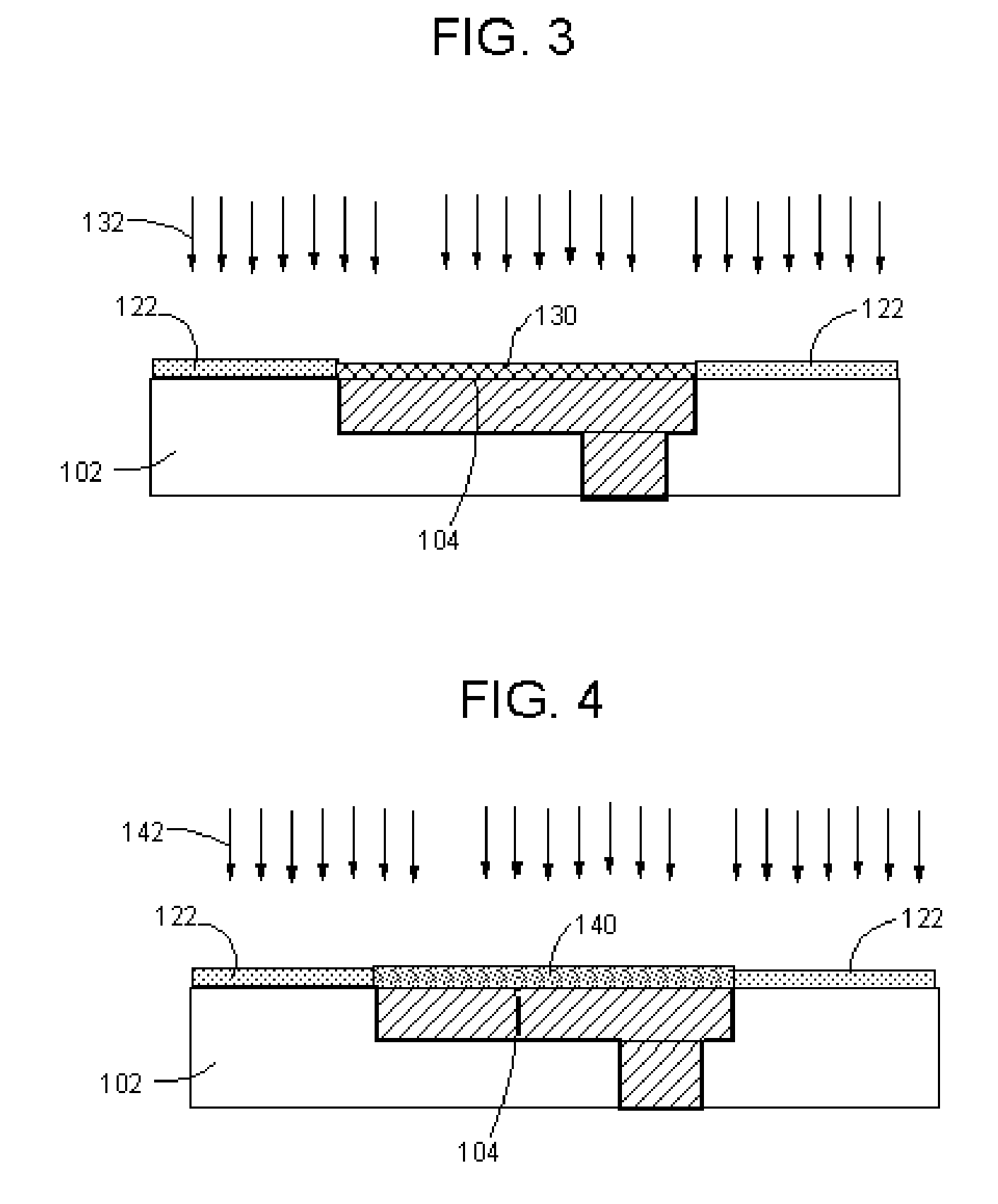

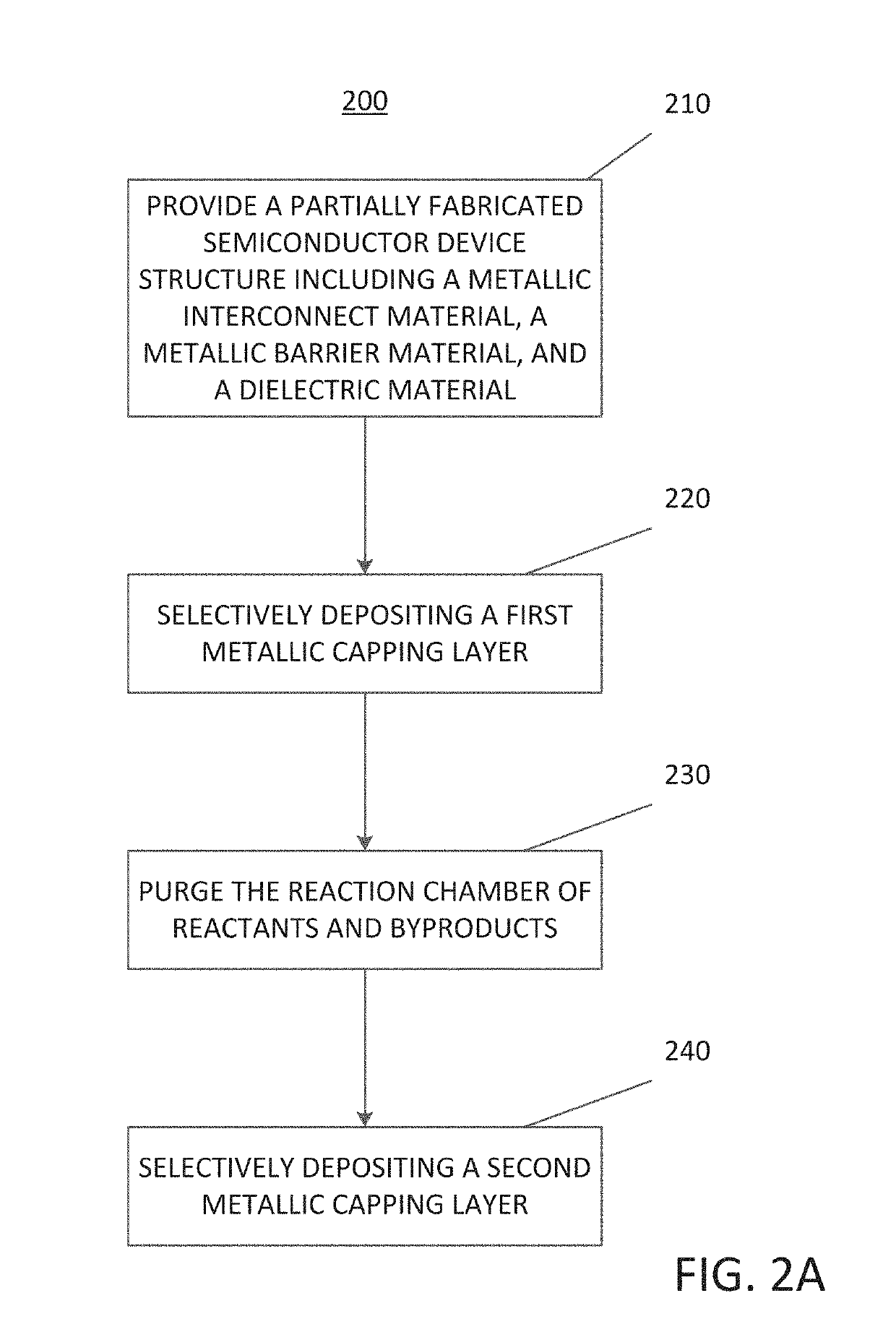

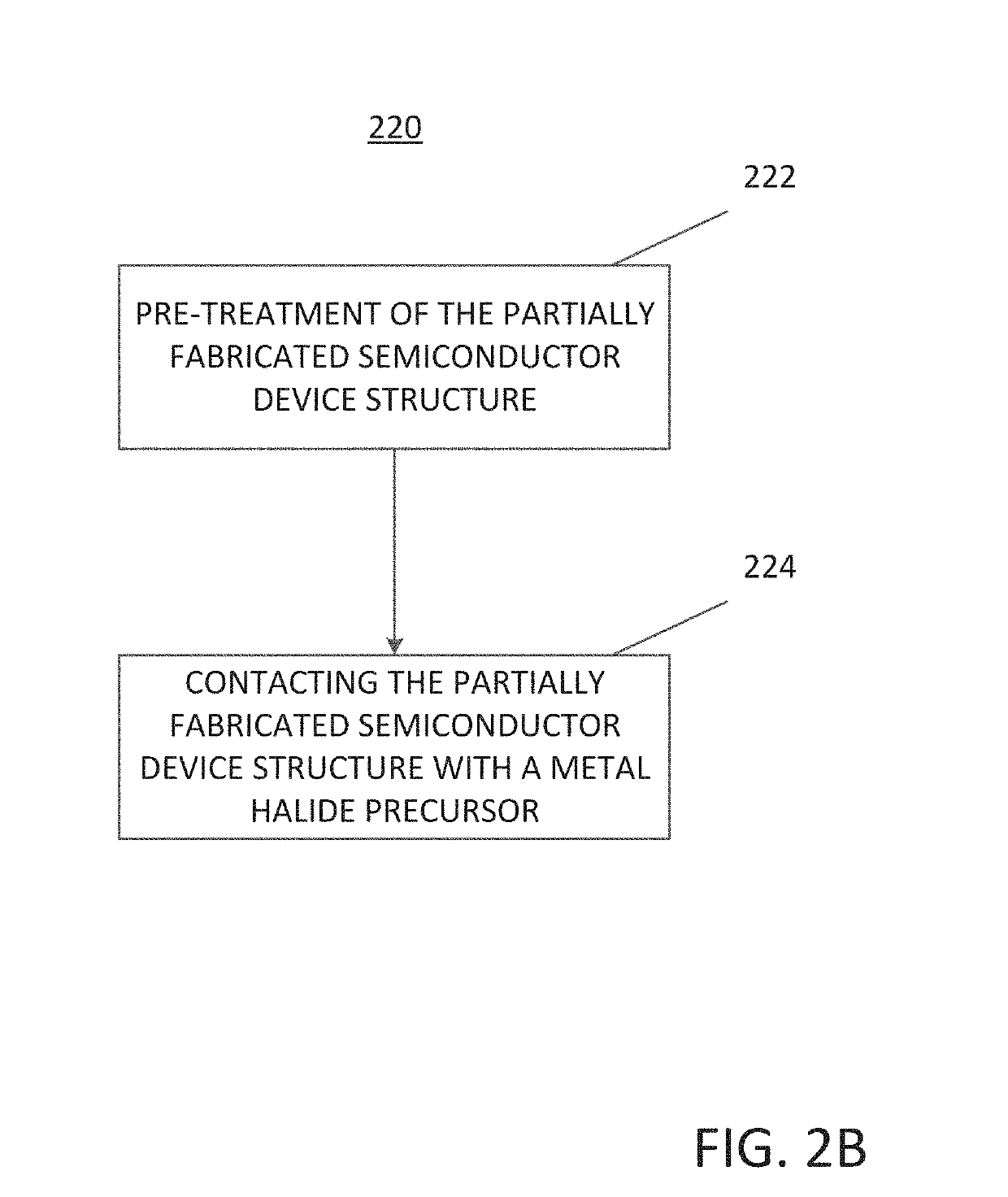

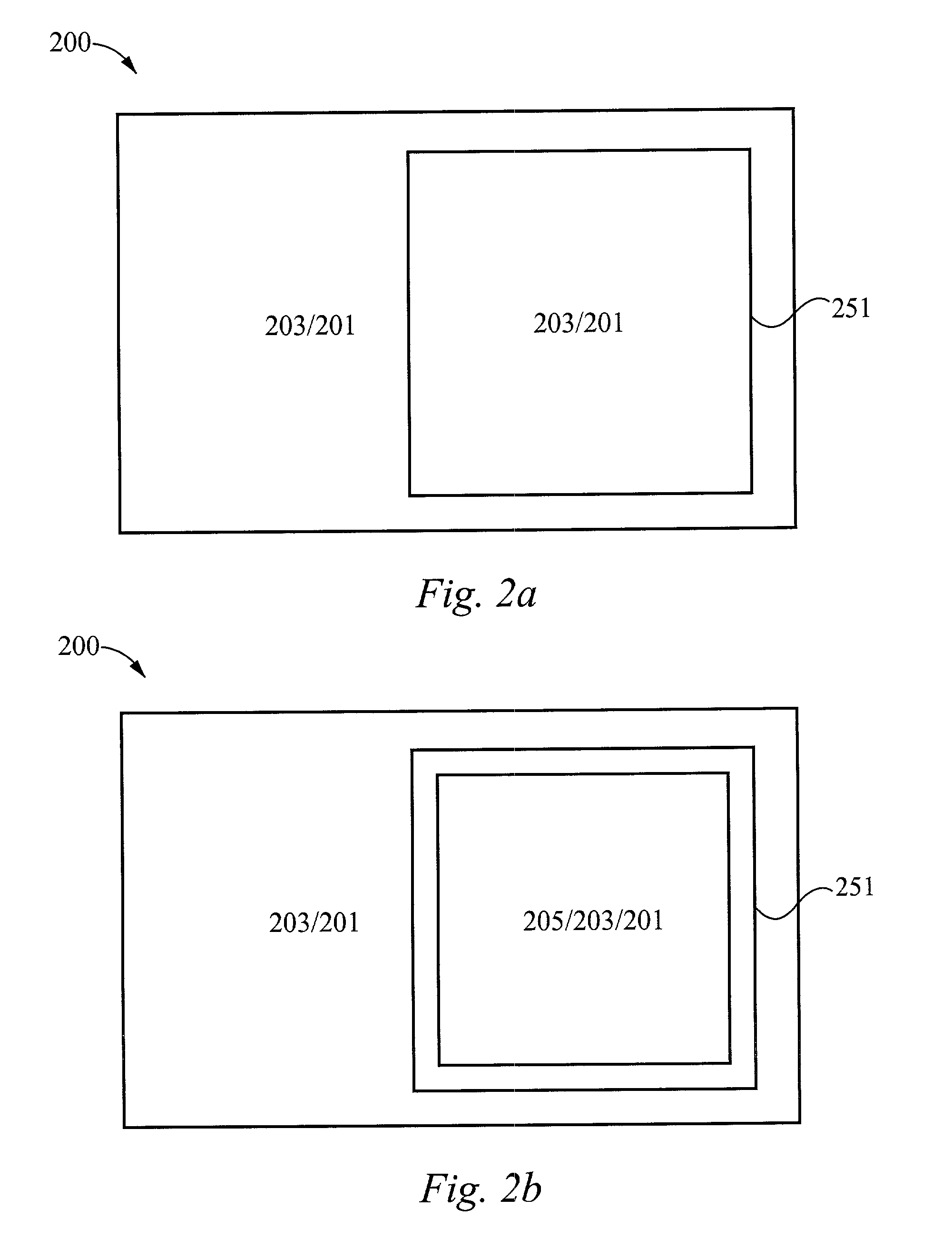

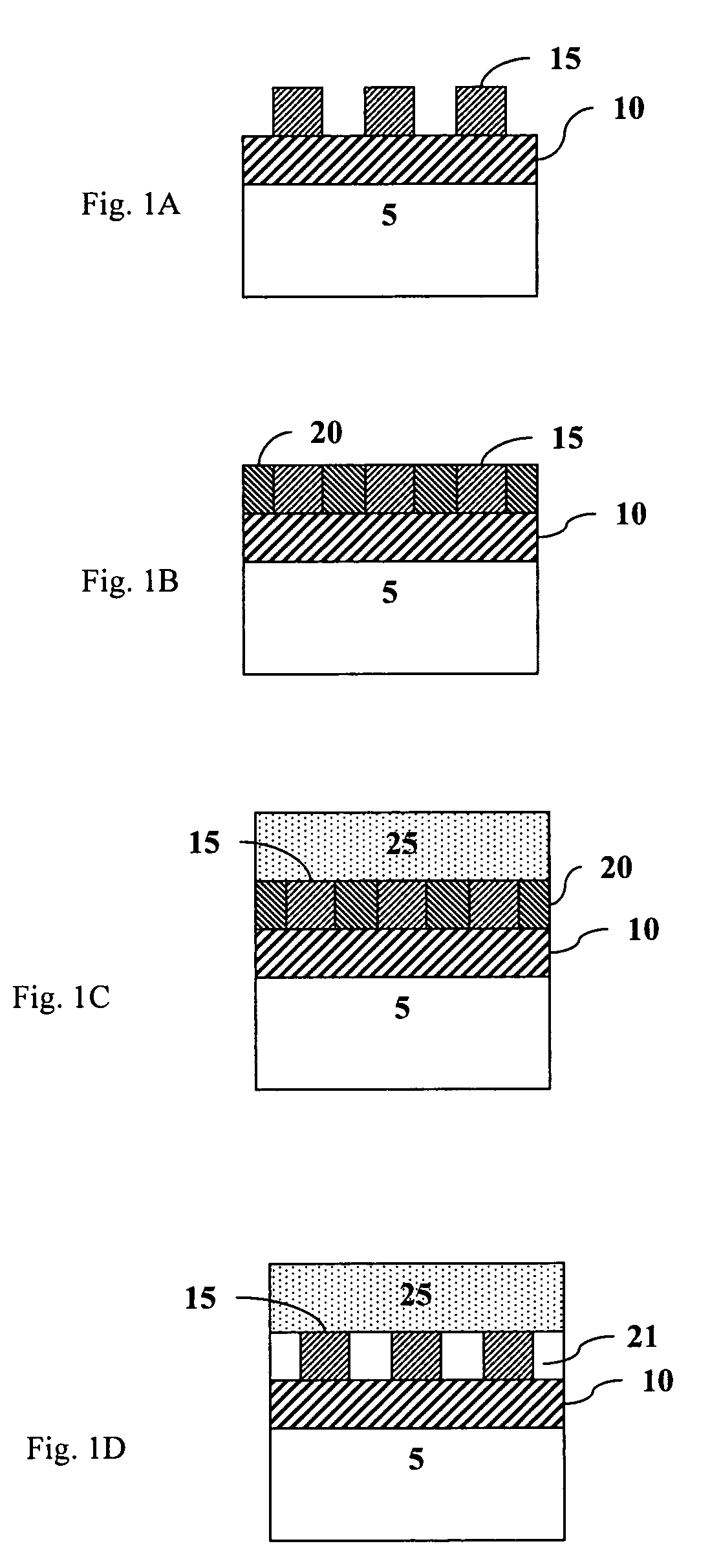

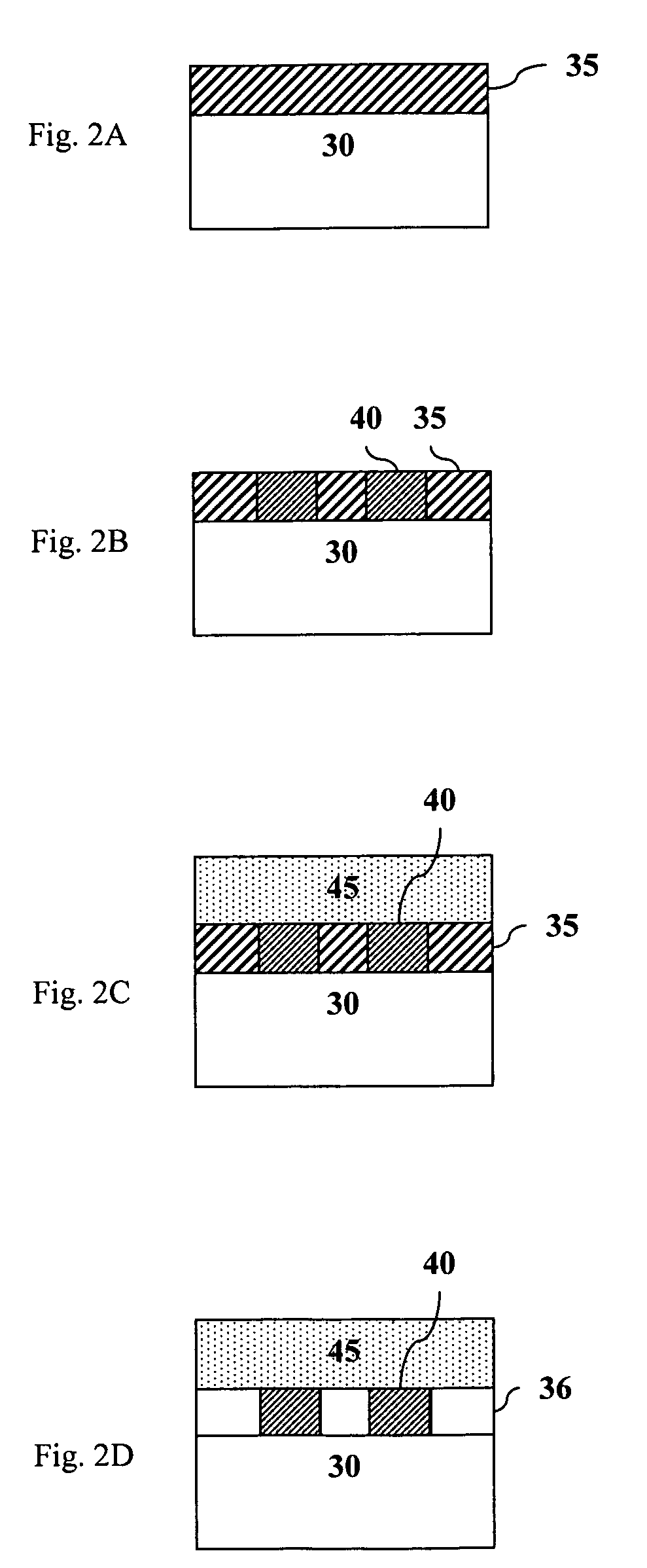

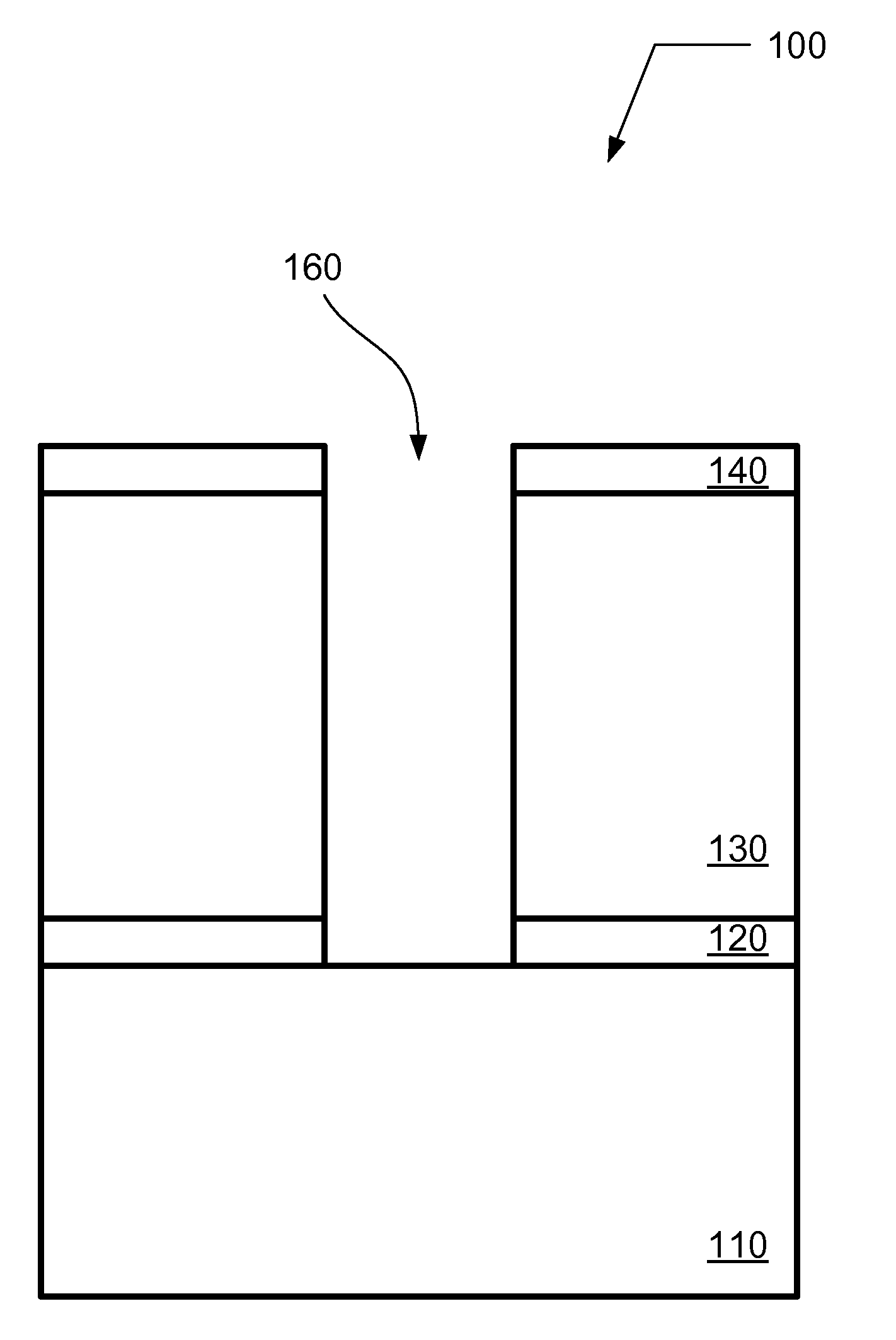

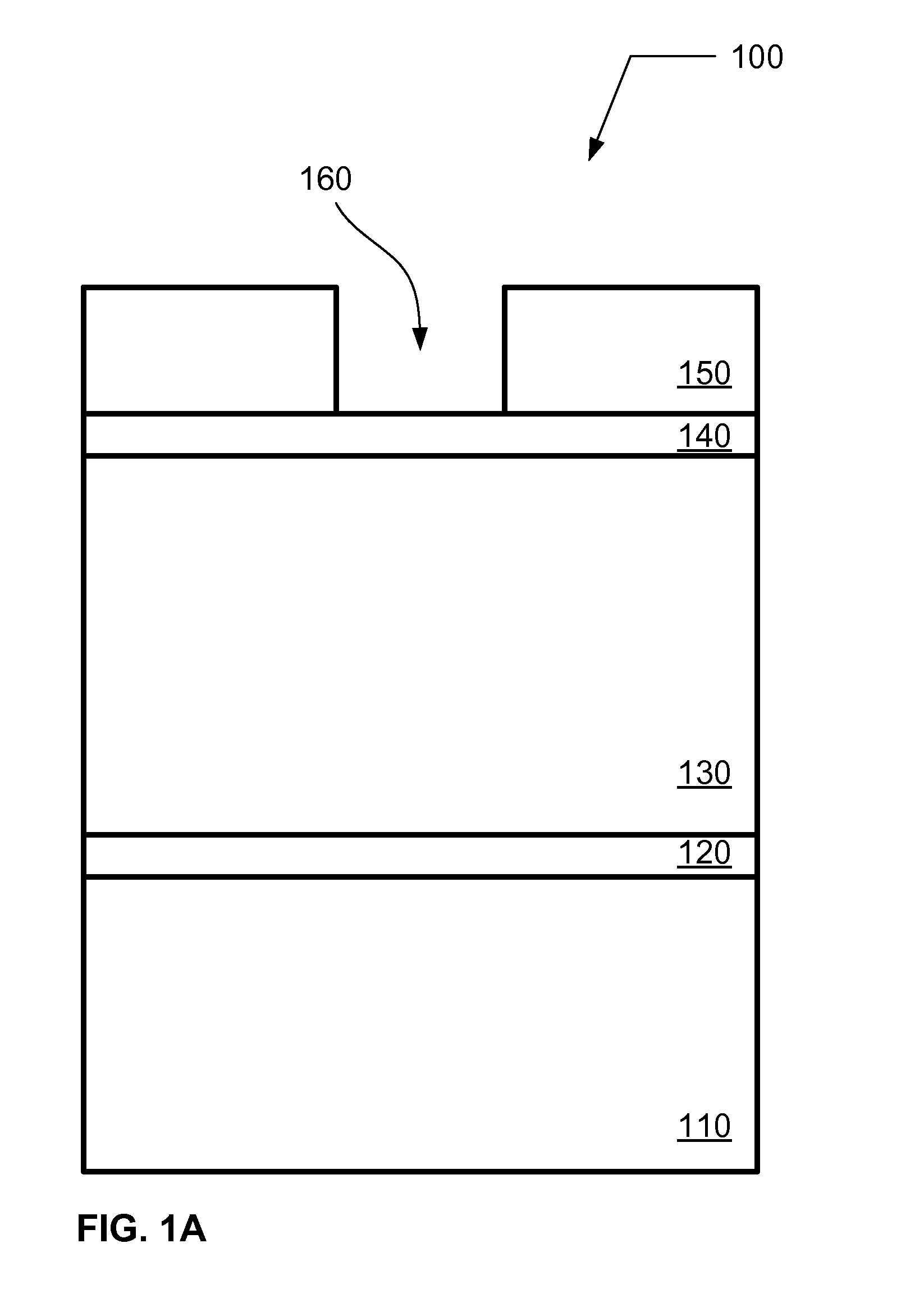

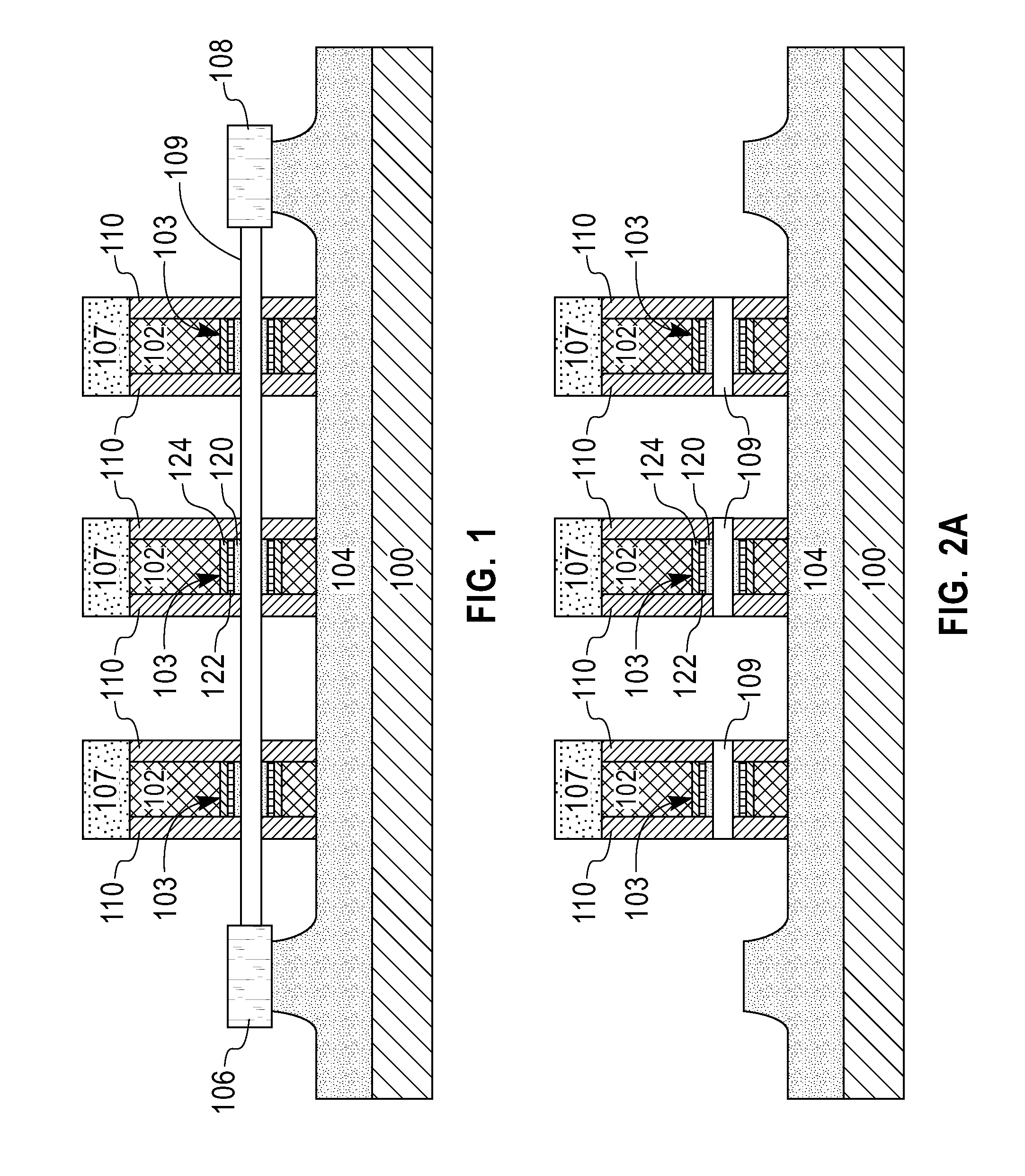

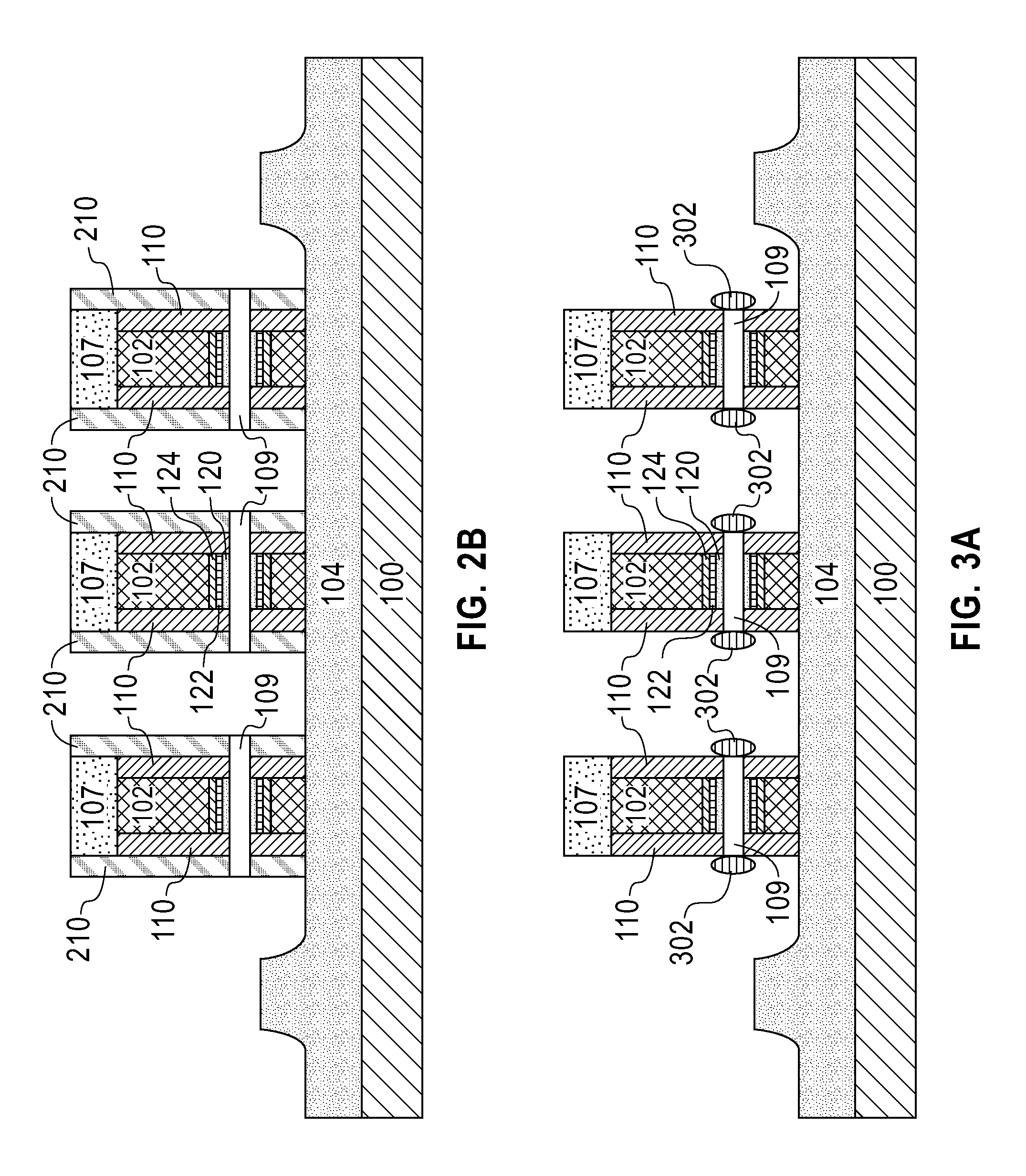

Method of selectively depositing a capping layer structure on a semiconductor device structure

A method of selectively depositing a capping layer structure on a semiconductor device structure is disclosure. The method may include; providing a partially fabricated semiconductor device structure comprising a surface including a metallic interconnect material, a metallic barrier material, and a dielectric material. The method may also include; selectively depositing a first metallic capping layer over the metallic barrier material and over the metallic interconnect material relative to the dielectric material; and selectively depositing a second metallic capping layer over the first metallic capping layer relative to the dielectric material. Semiconductor device structures including a capping layer structure are also disclosed.

Owner:ASM IP HLDG BV

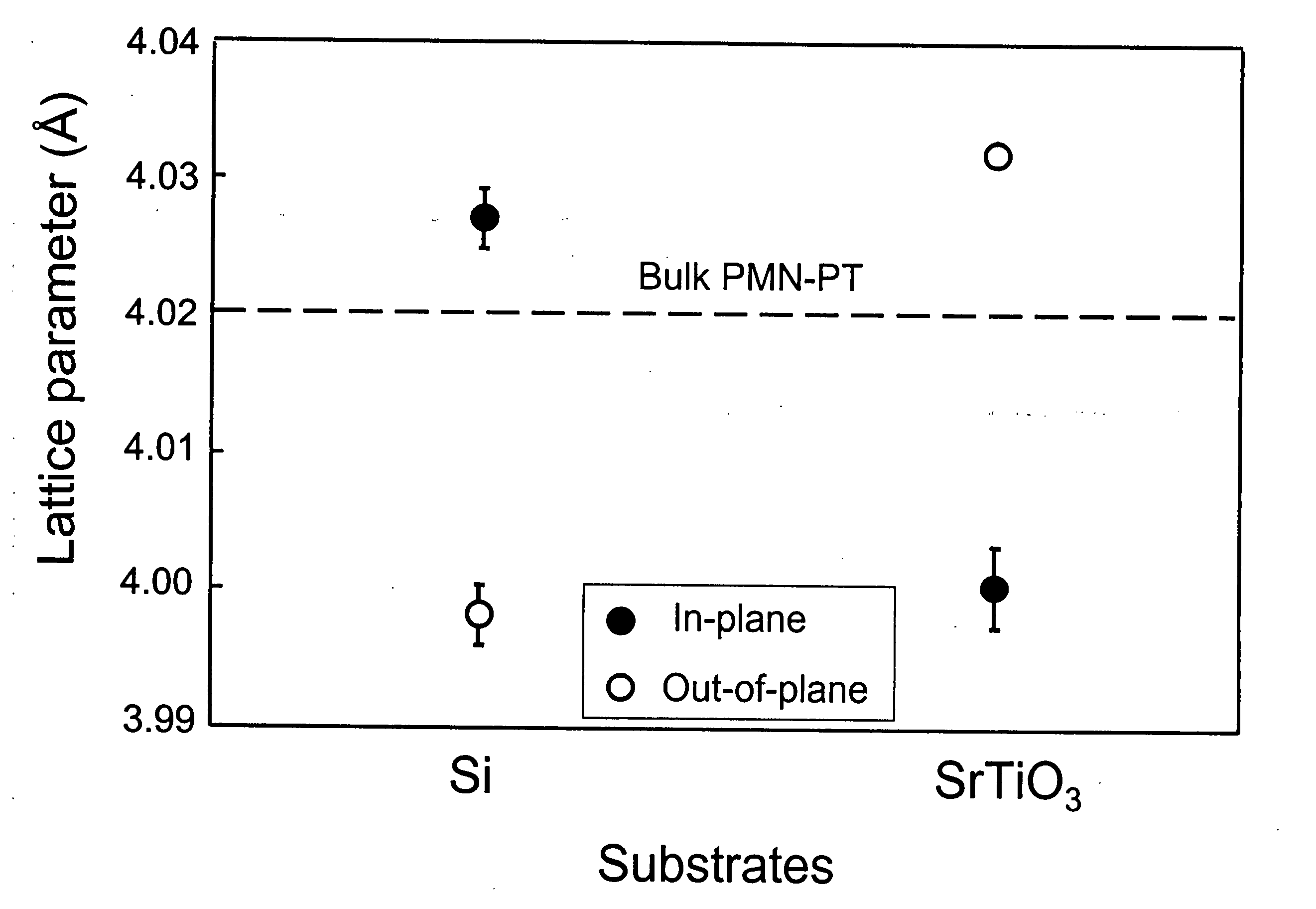

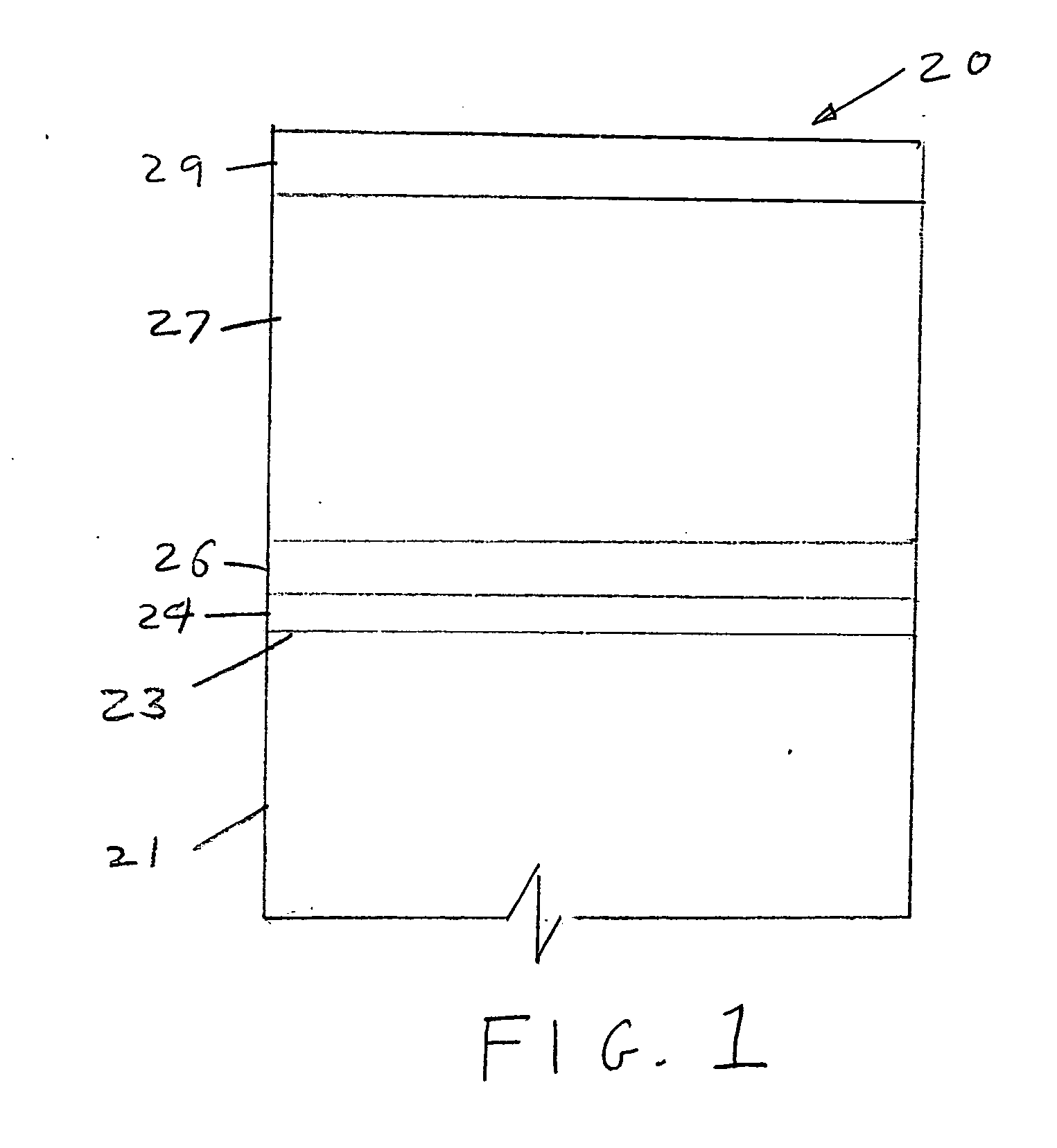

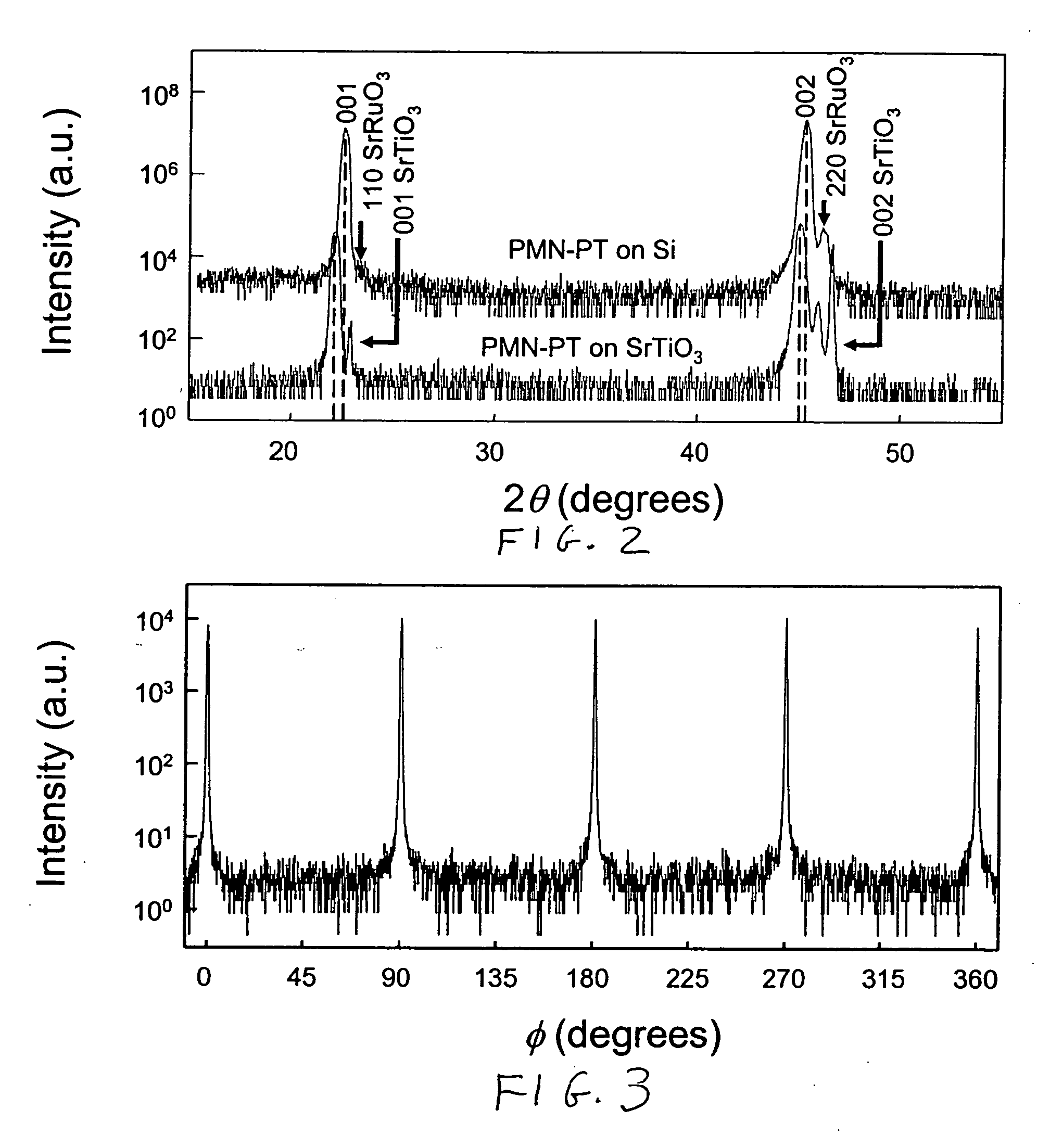

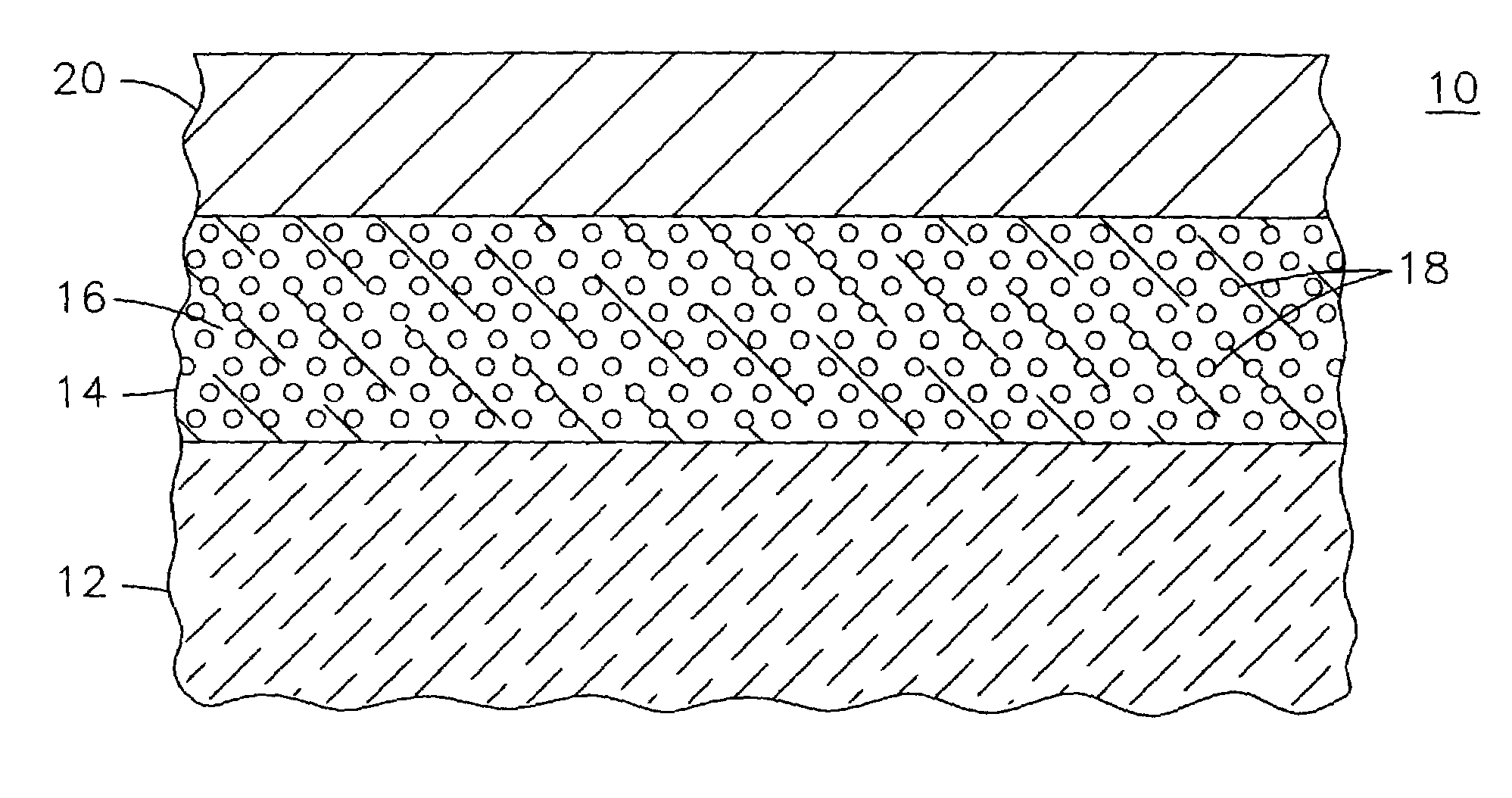

Perovskite-based thin film structures on miscut semiconductor substrates

InactiveUS20060288928A1Quality improvementGood metallic behaviorPolycrystalline material growthFrom chemically reactive gasesCrystal structureCrystal plane

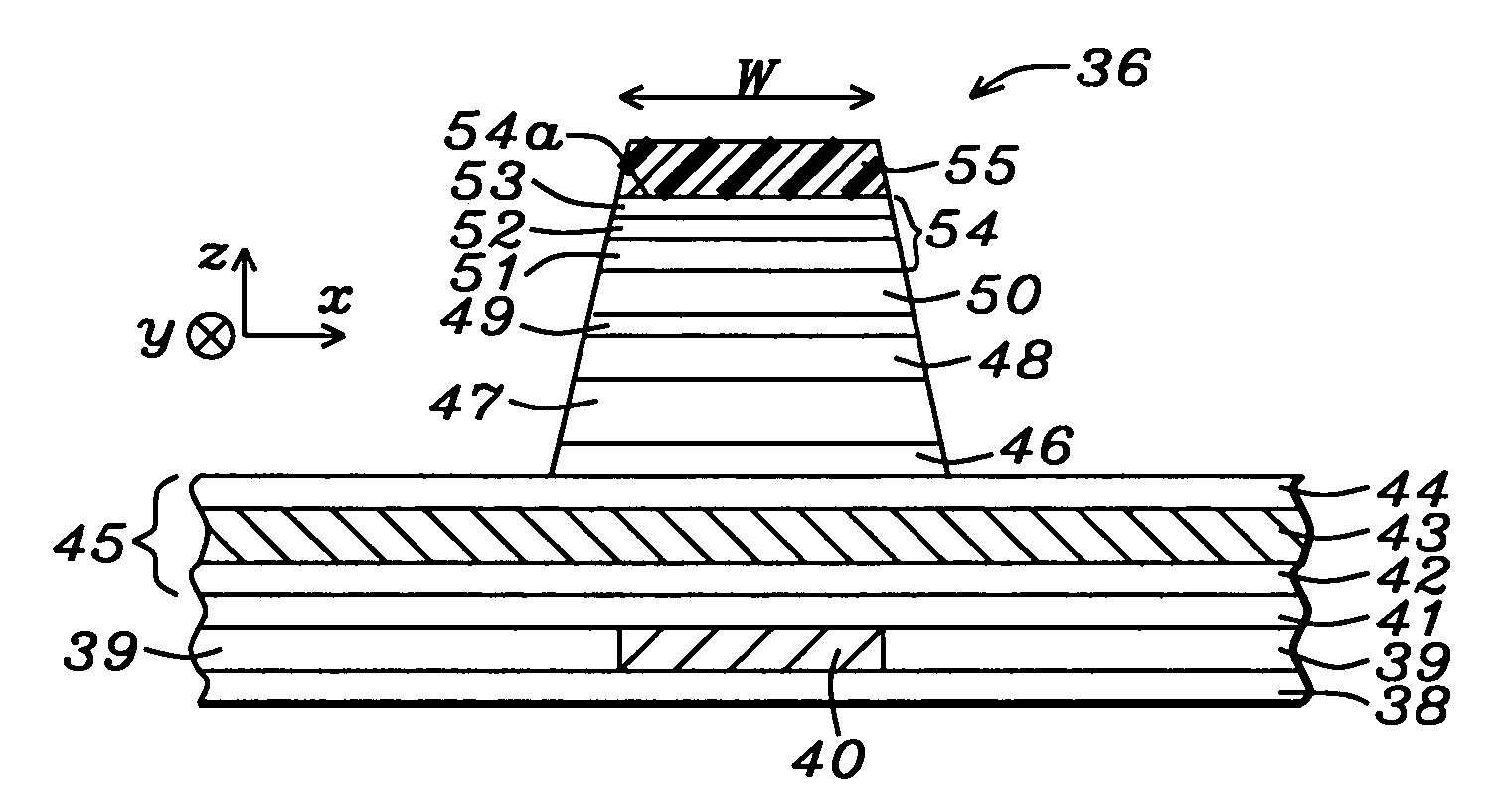

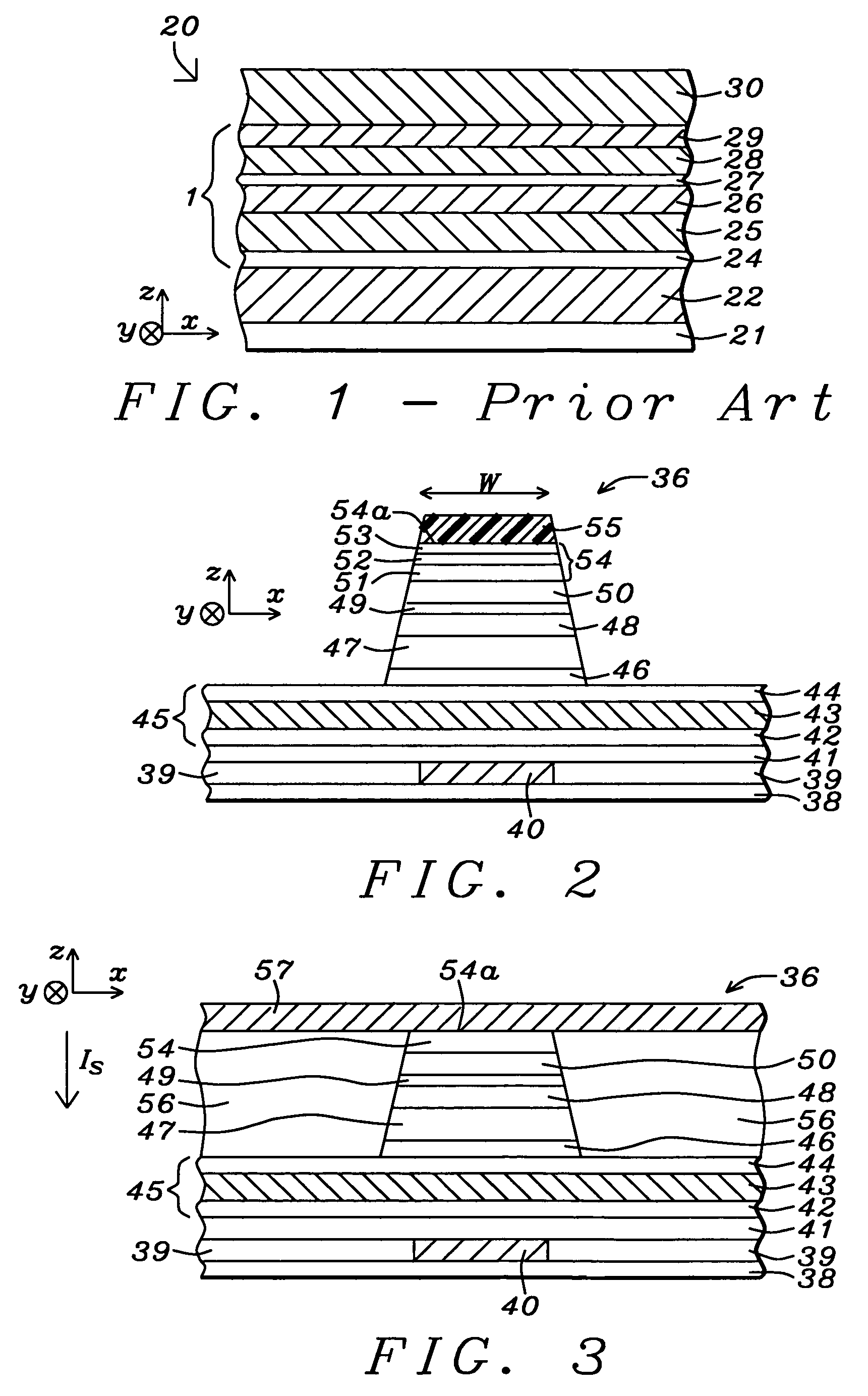

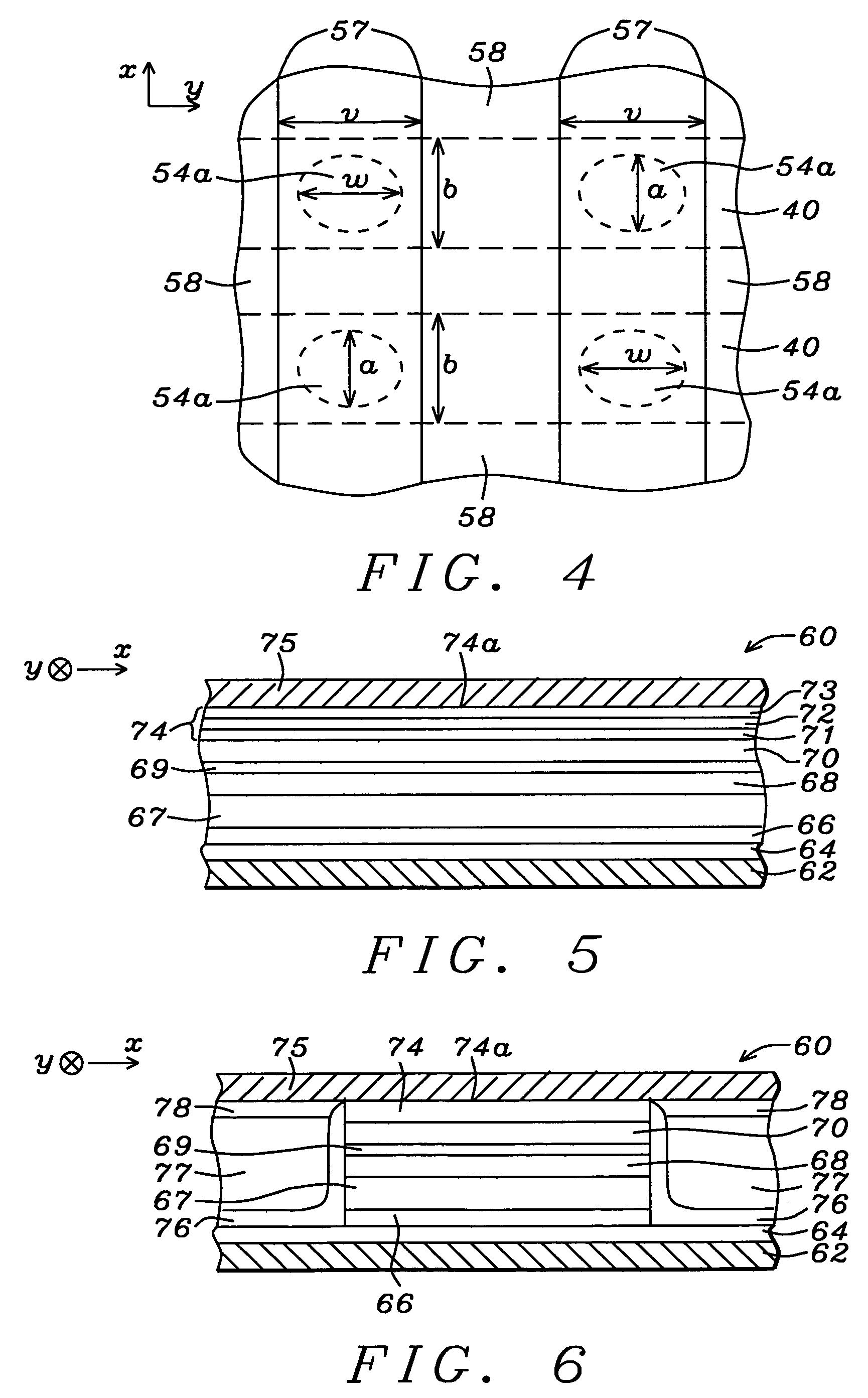

A perovskite-based thin film structure includes a semiconductor substrate layer, such as a crystalline silicon layer, having a top surface cut at an angle to the (001) crystal plane of the crystalline silicon. A perovskite seed layer is epitaxially grown on the top surface of the substrate layer. An overlayer of perovskite material is epitaxially grown above the seed layer. In some embodiments the perovskite overlayer is a piezoelectric layer grown to a thickness of at least 0.5 μm and having a substantially pure perovskite crystal structure, preferably substantially free of pyrochlore phase, resulting in large improvements in piezoelectric characteristics as compared to conventional thin film piezoelectric materials.

Owner:PENN STATE RES FOUND +1

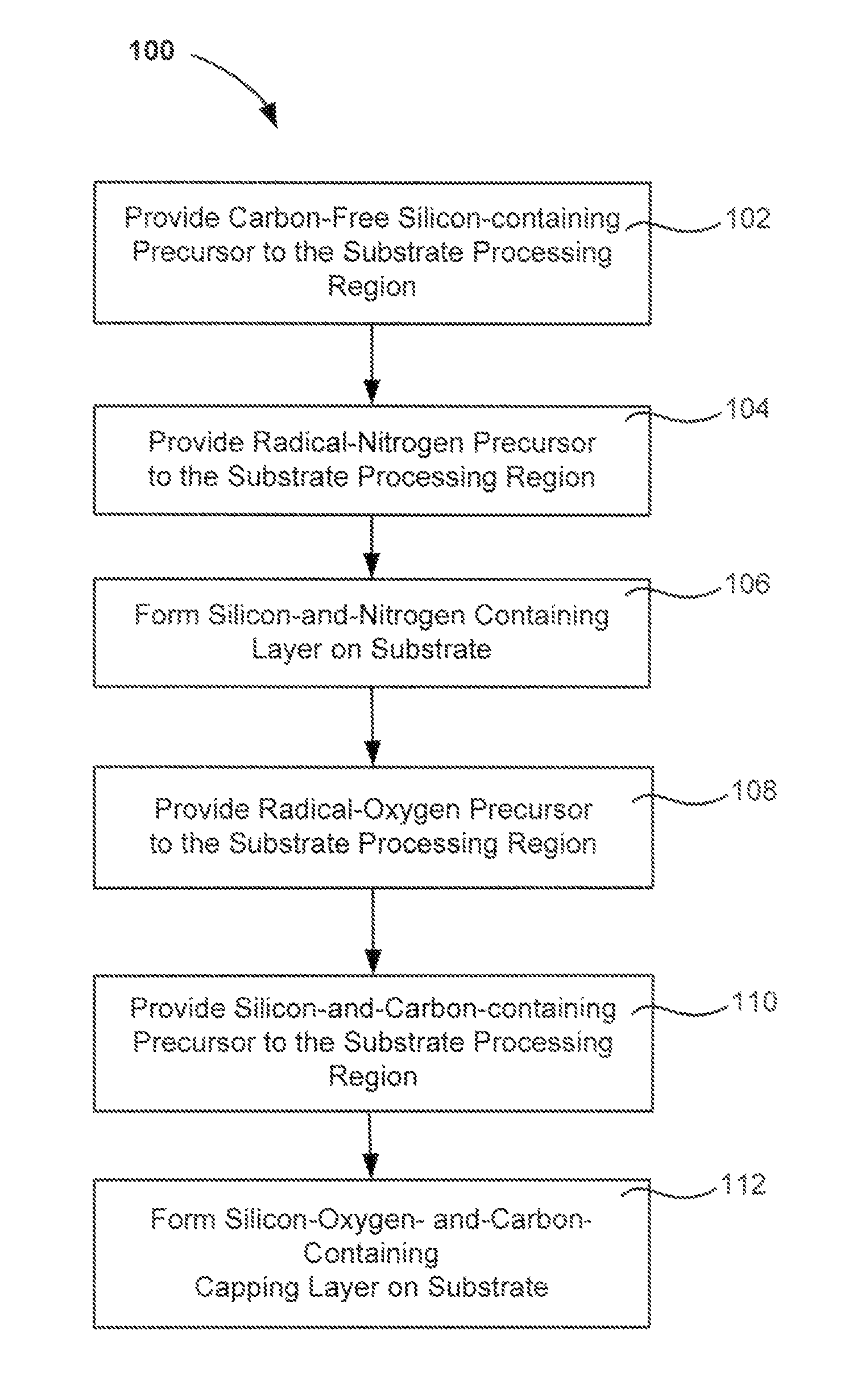

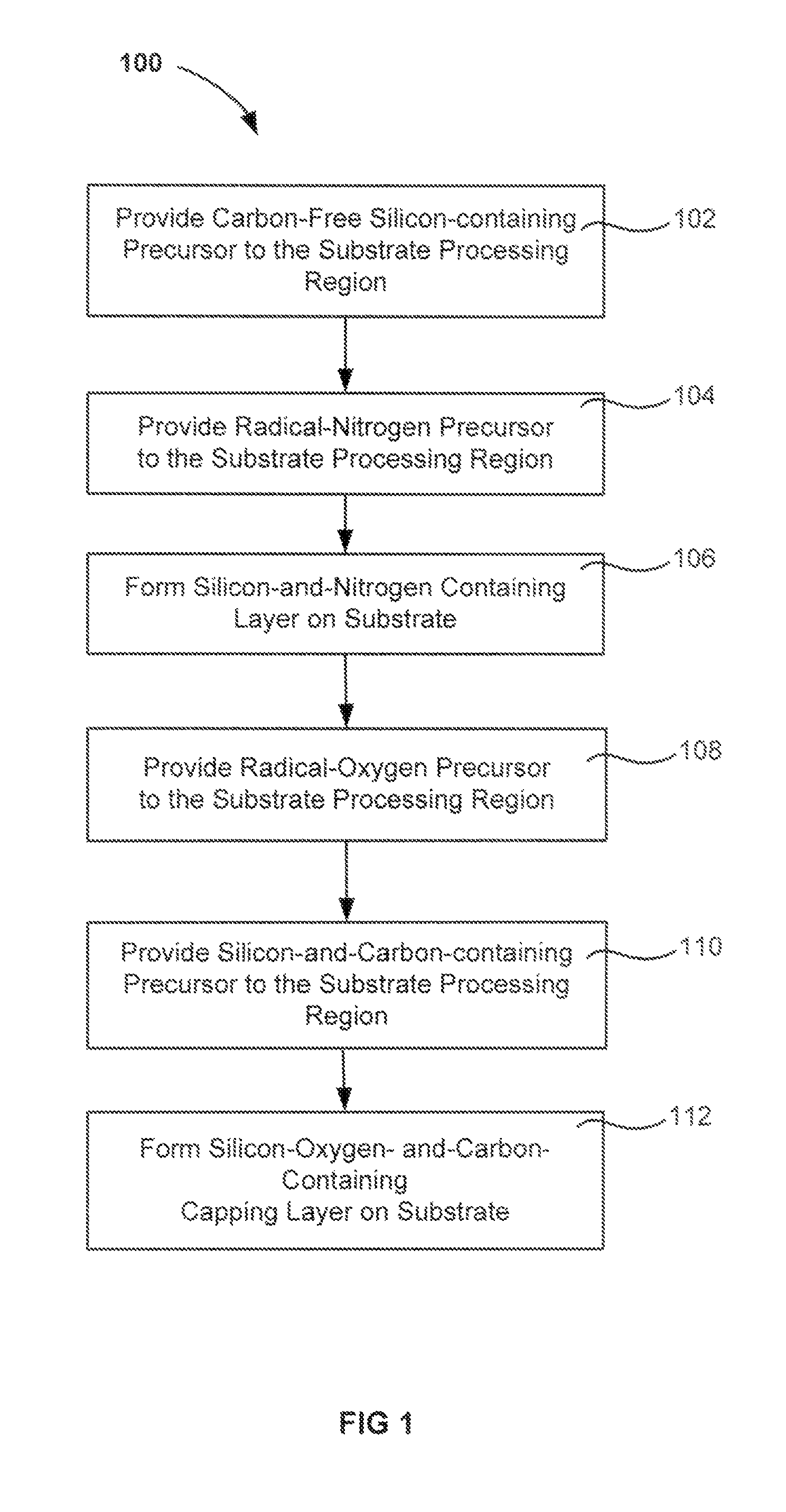

Capping layer for reduced outgassing

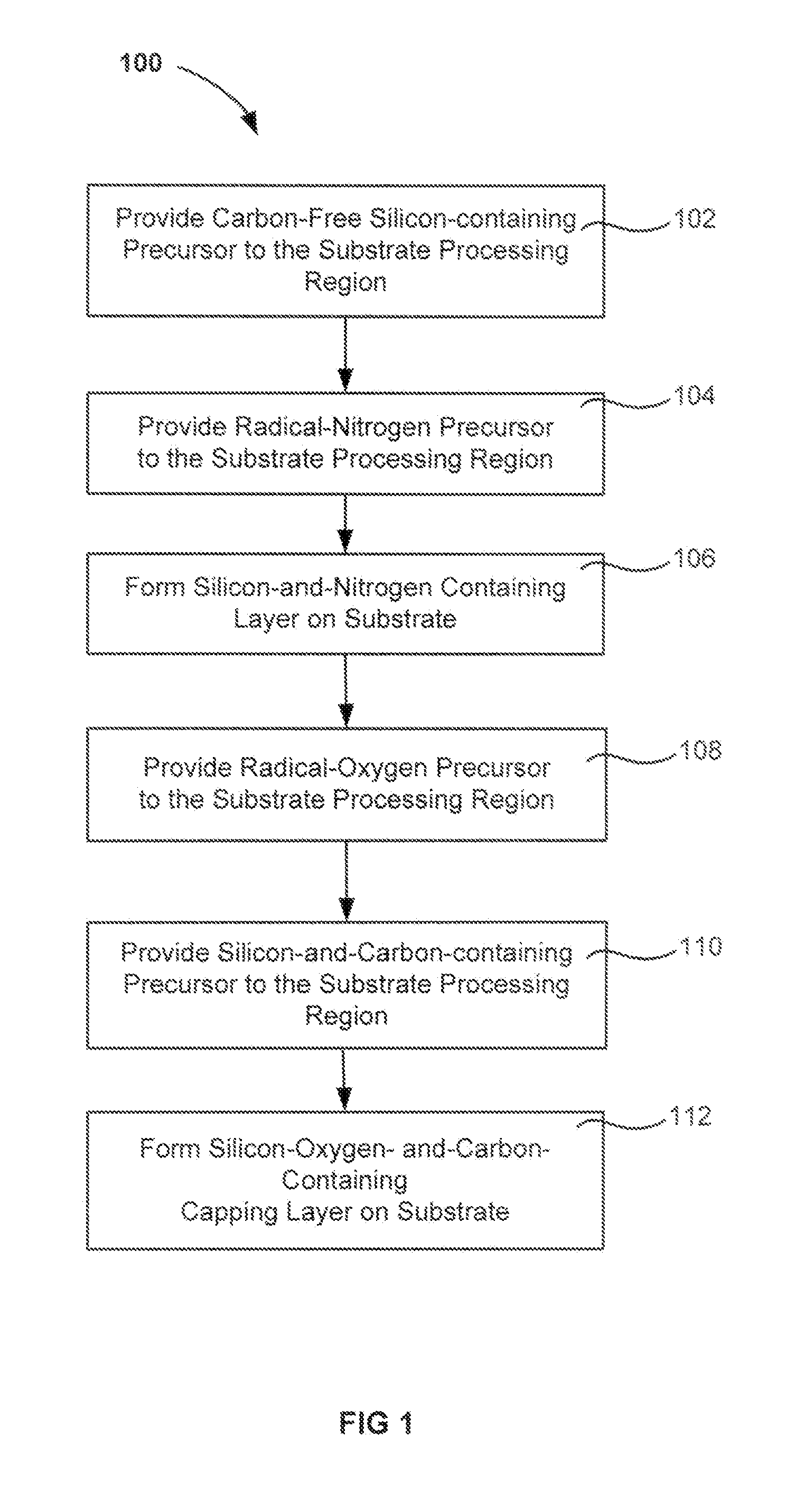

InactiveUS8466073B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaHydrogen

A method of forming a silicon oxide layer is described. The method first deposits a silicon-nitrogen-and-hydrogen-containing (polysilazane) film by radical-component chemical vapor deposition (CVD). The silicon-nitrogen-and-hydrogen-containing film is formed by combining a radical precursor (excited in a remote plasma) with an unexcited carbon-free silicon precursor. A capping layer is formed over the silicon-nitrogen-and-hydrogen-containing film to avoid time-evolution of underlying film properties prior to conversion into silicon oxide. The capping layer is formed by combining a radical oxygen precursor (excited in a remote plasma) with an unexcited silicon-and-carbon-containing-precursor. The films are converted to silicon oxide by exposure to oxygen-containing environments. The two films may be deposited within the same substrate processing chamber and may be deposited without breaking vacuum.

Owner:APPLIED MATERIALS INC

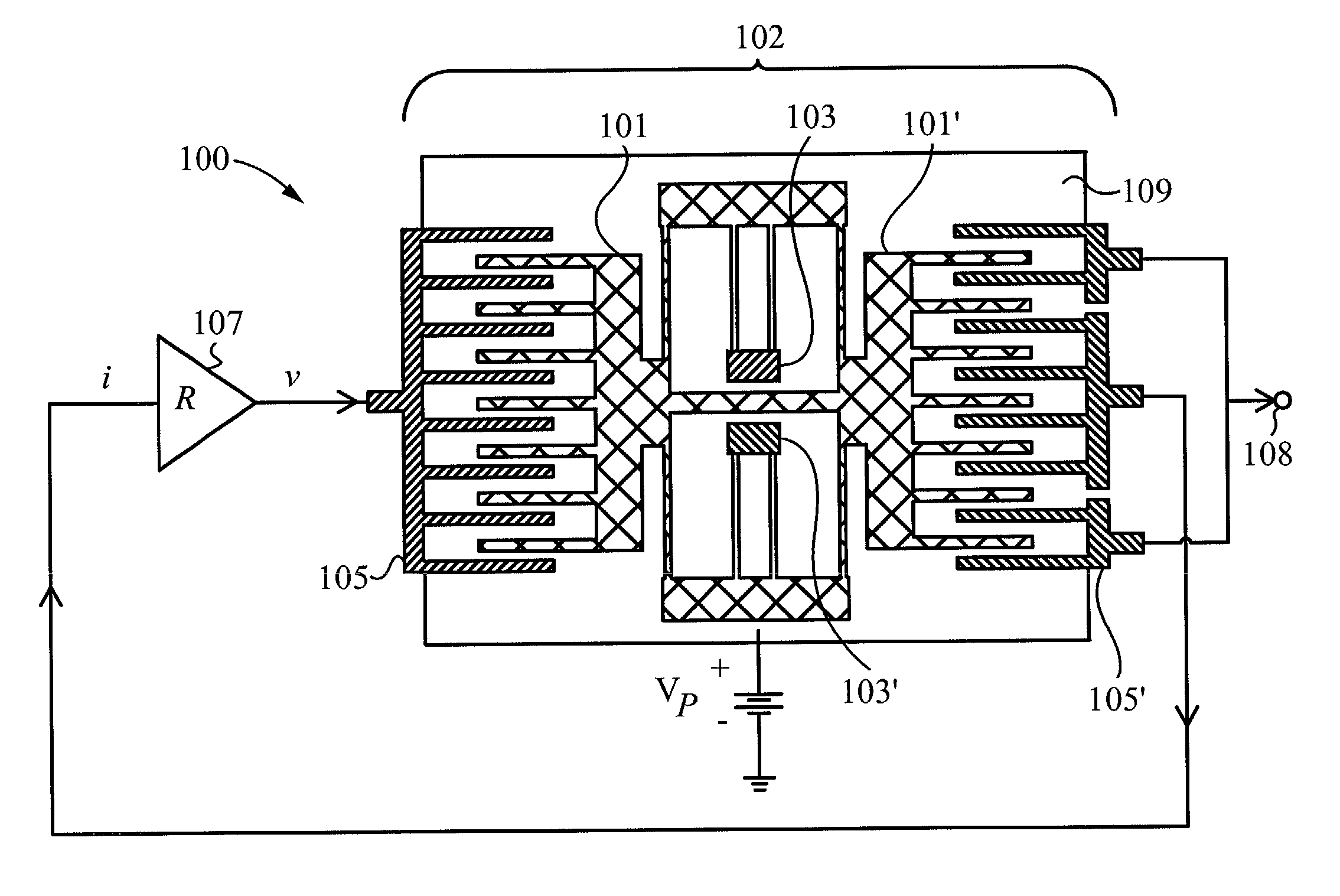

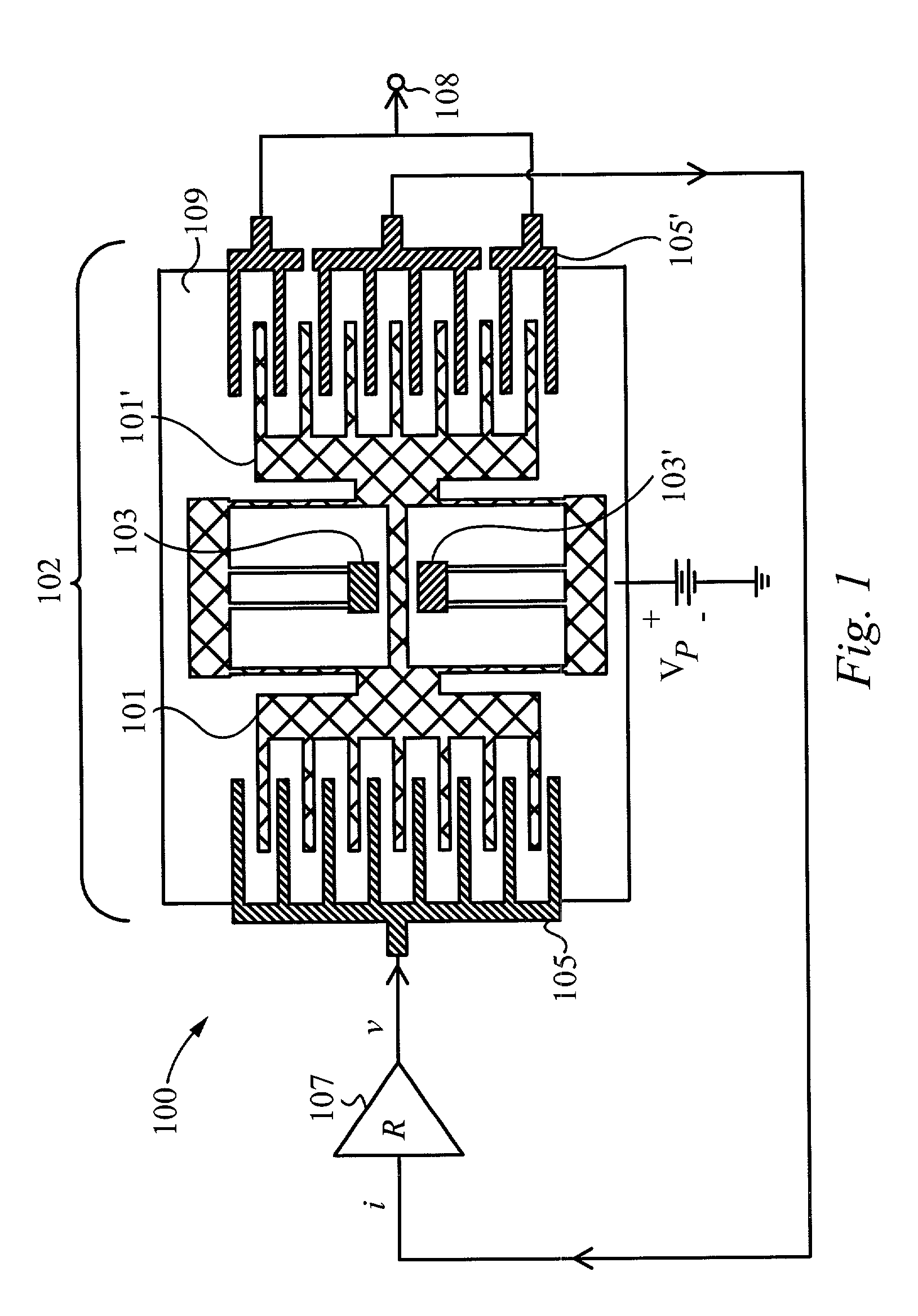

Microelectronic mechanical system and methods

InactiveUS20040053434A1Decorative surface effectsSemiconductor/solid-state device detailsNoble gasSilicon oxide

The current invention provides for encapsulated release structures, intermediates thereof and methods for their fabrication. The multi-layer structure has a capping layer, that preferably comprises silicon oxide and / or silicon nitride, and which is formed over an etch resistant substrate. A patterned device layer, preferably comprising silicon nitride, is embedded in a sacrificial material, preferably comprising polysilicon, and is disposed between the etch resistant substrate and the capping layer. Access trenches or holes are formed in to capping layer and the sacrificial material are selectively etched through the access trenches, such that portions of the device layer are release from sacrificial material. The etchant preferably comprises a noble gas fluoride NGF2x (wherein Ng=Xe, Kr or Ar: and where x=1, 2 or 3). After etching that sacrificial material, the access trenches are sealed to encapsulate released portions the device layer between the etch resistant substrate and the capping layer. The current invention is particularly useful for fabricating MEMS devices, multiple cavity devices and devices with multiple release features.

Owner:SILICON LIGHT MACHINES CORP

Capping layer for reduced outgassing

InactiveUS20120309205A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaHydrogen

Owner:APPLIED MATERIALS INC

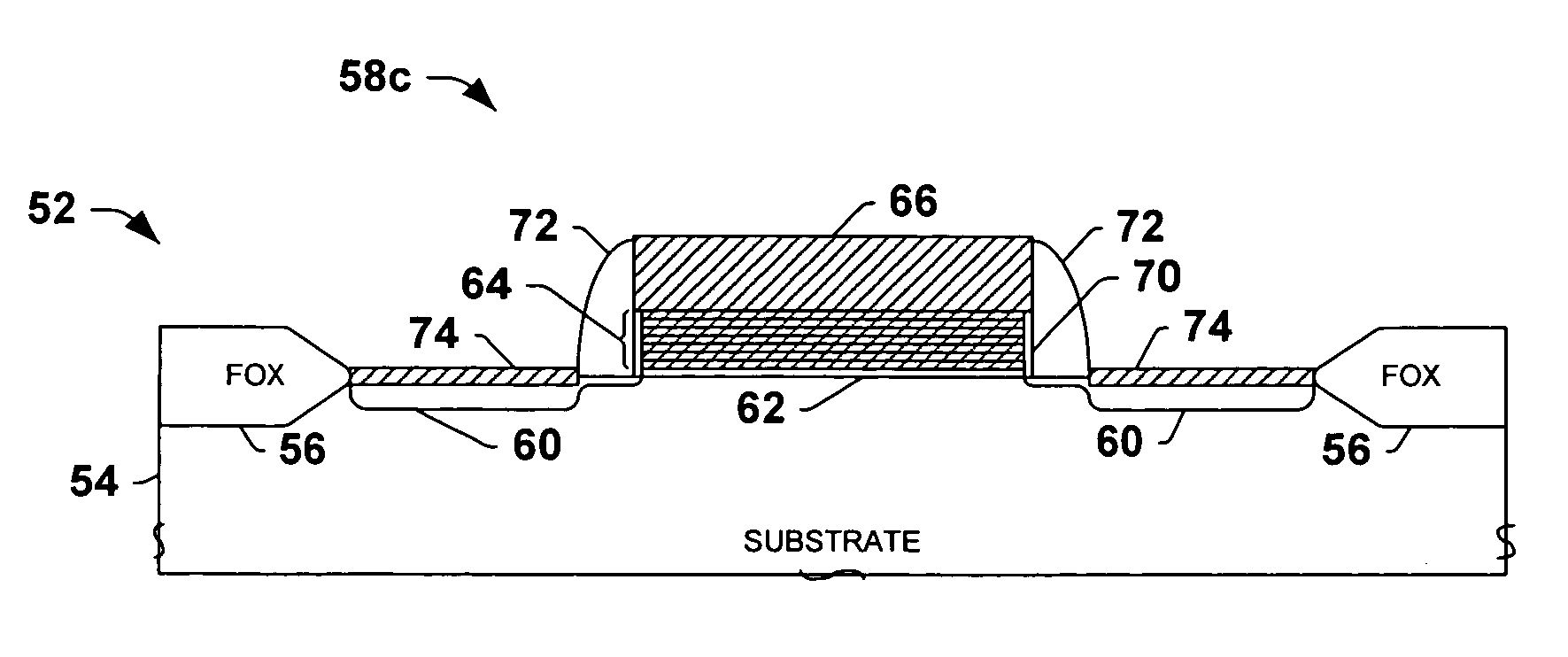

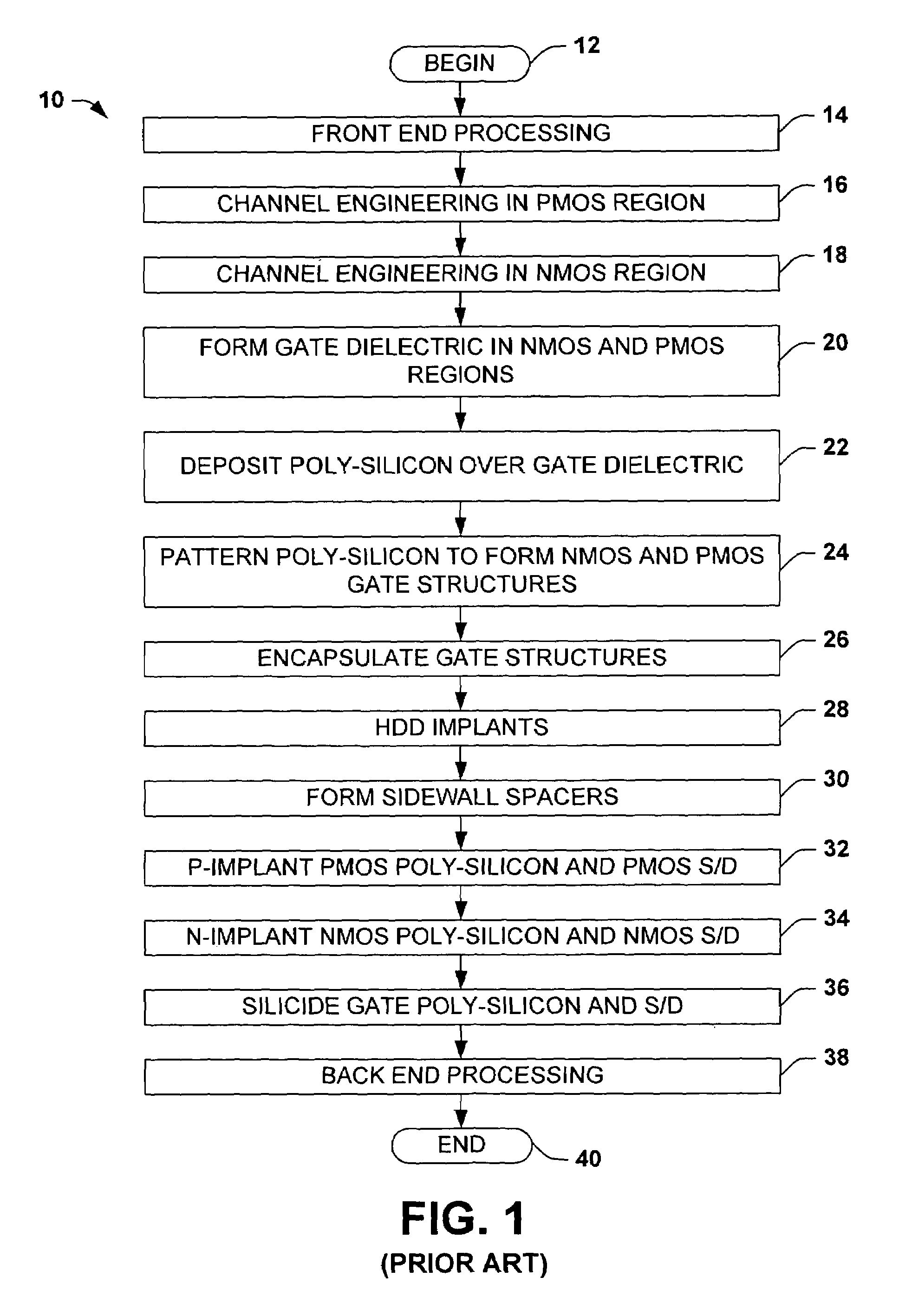

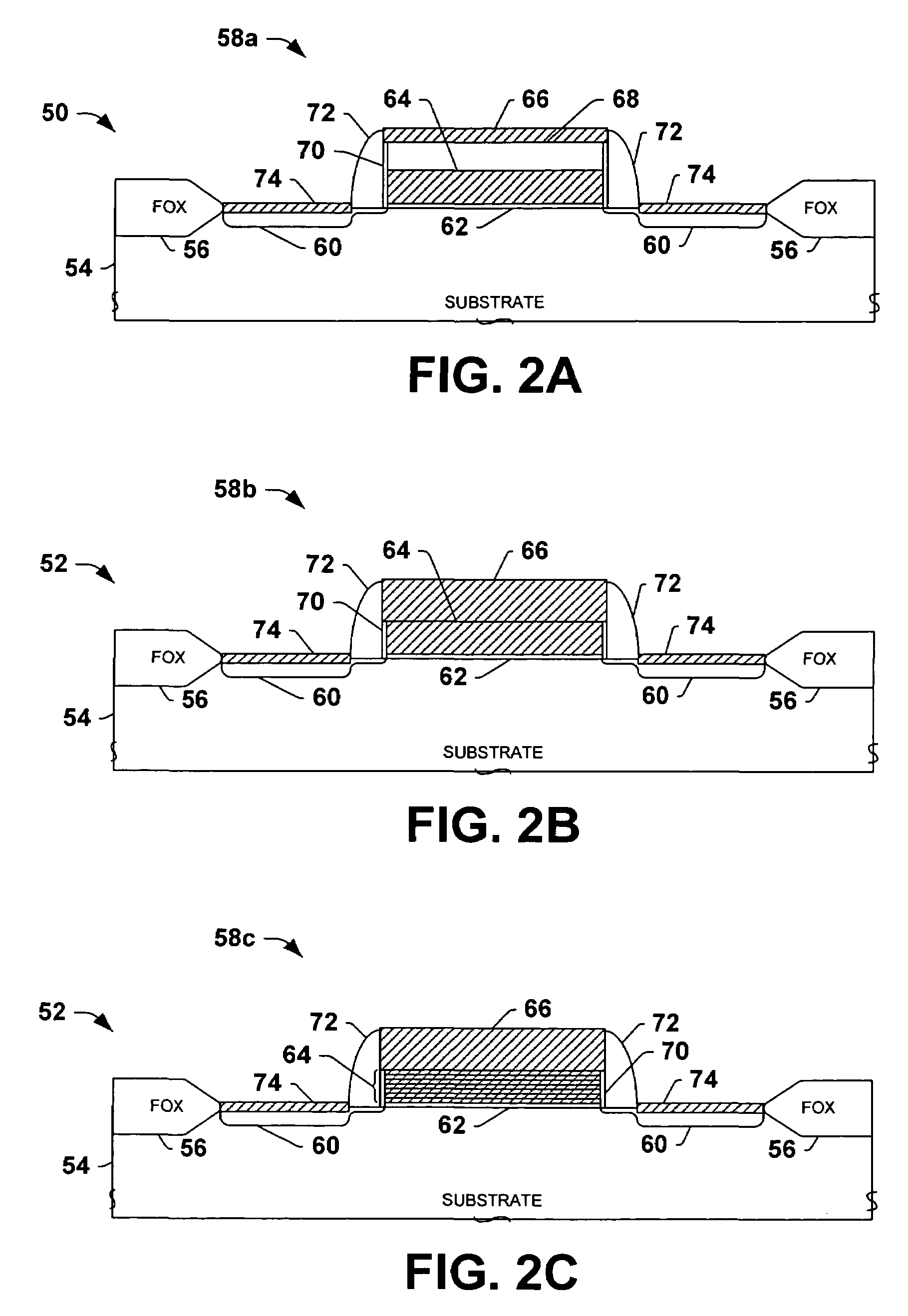

MOS transistor gates with thin lower metal silicide and methods for making the same

ActiveUS7045456B2Easy to implantEasy to controlTransistorSemiconductor/solid-state device manufacturingSalicideGate dielectric

Methods are presented for fabricating transistor gate structures, wherein upper and lower metal suicides are formed above a gate dielectric. In one example, the lower silicide is formed by depositing a thin first silicon-containing material over the gate dielectric, which is implanted and then reacted with a first metal by annealing to form the lower silicide. A capping layer can be formed over the first metal prior to annealing, to prevent oxidation of the metal prior to silicidation, and a barrier layer can be formed over the lower silicide to prevent reaction with subsequently formed silicon material. In another example, the lower silicide is a multilayer silicide structure including a plurality of metal silicide sublayers.

Owner:TEXAS INSTR INC

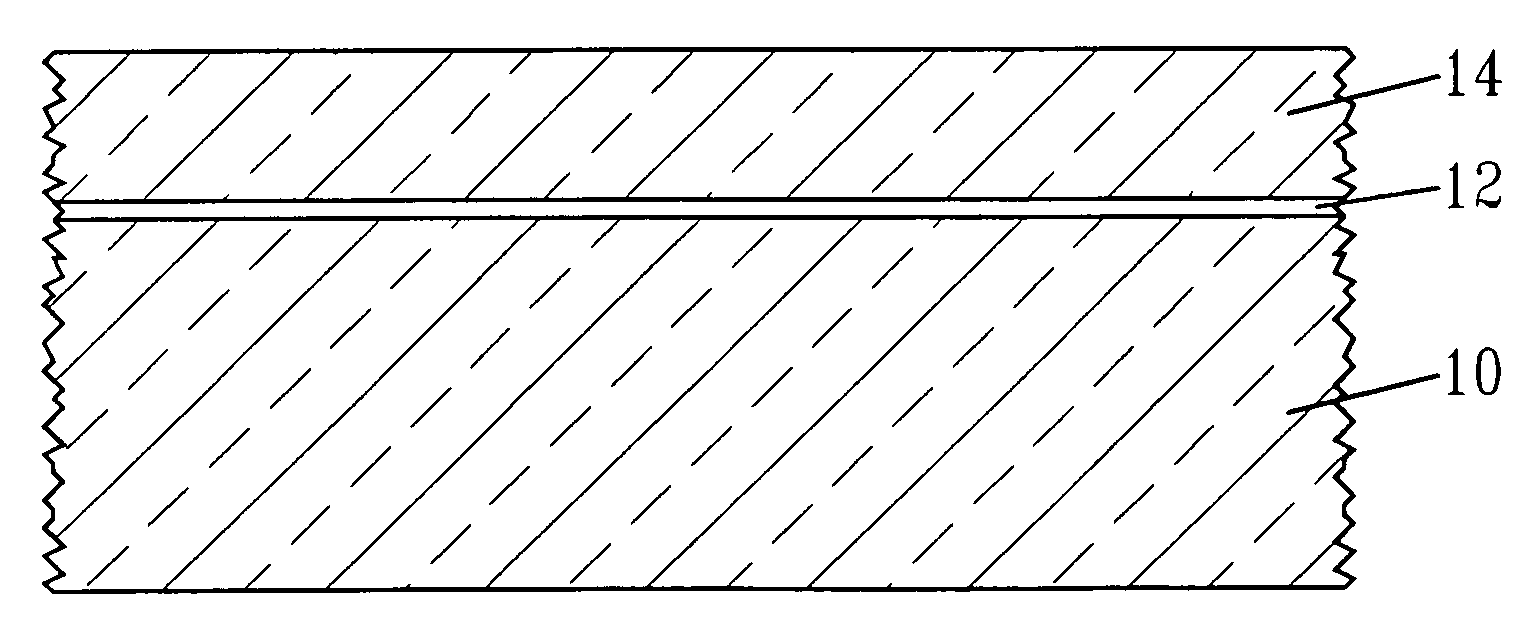

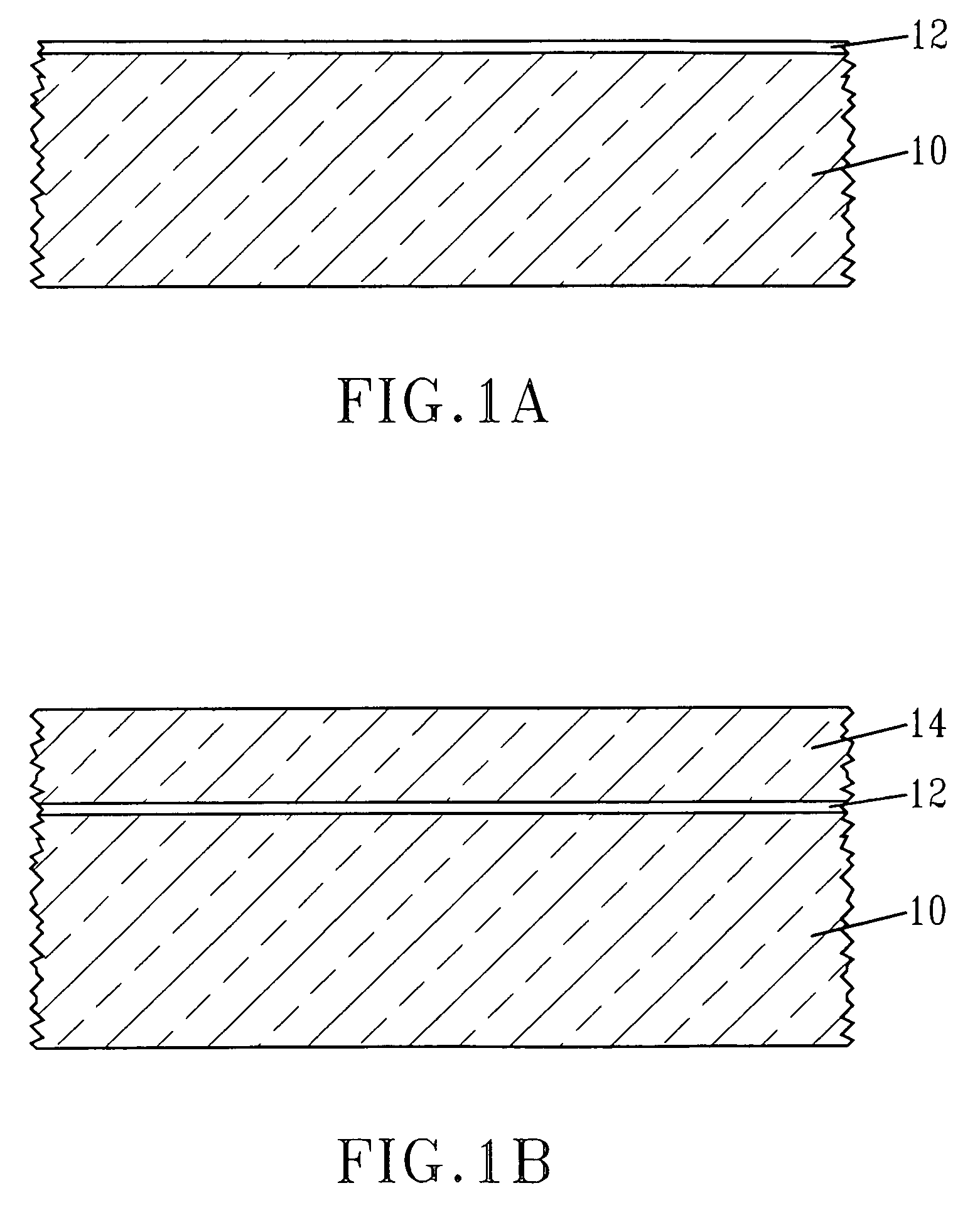

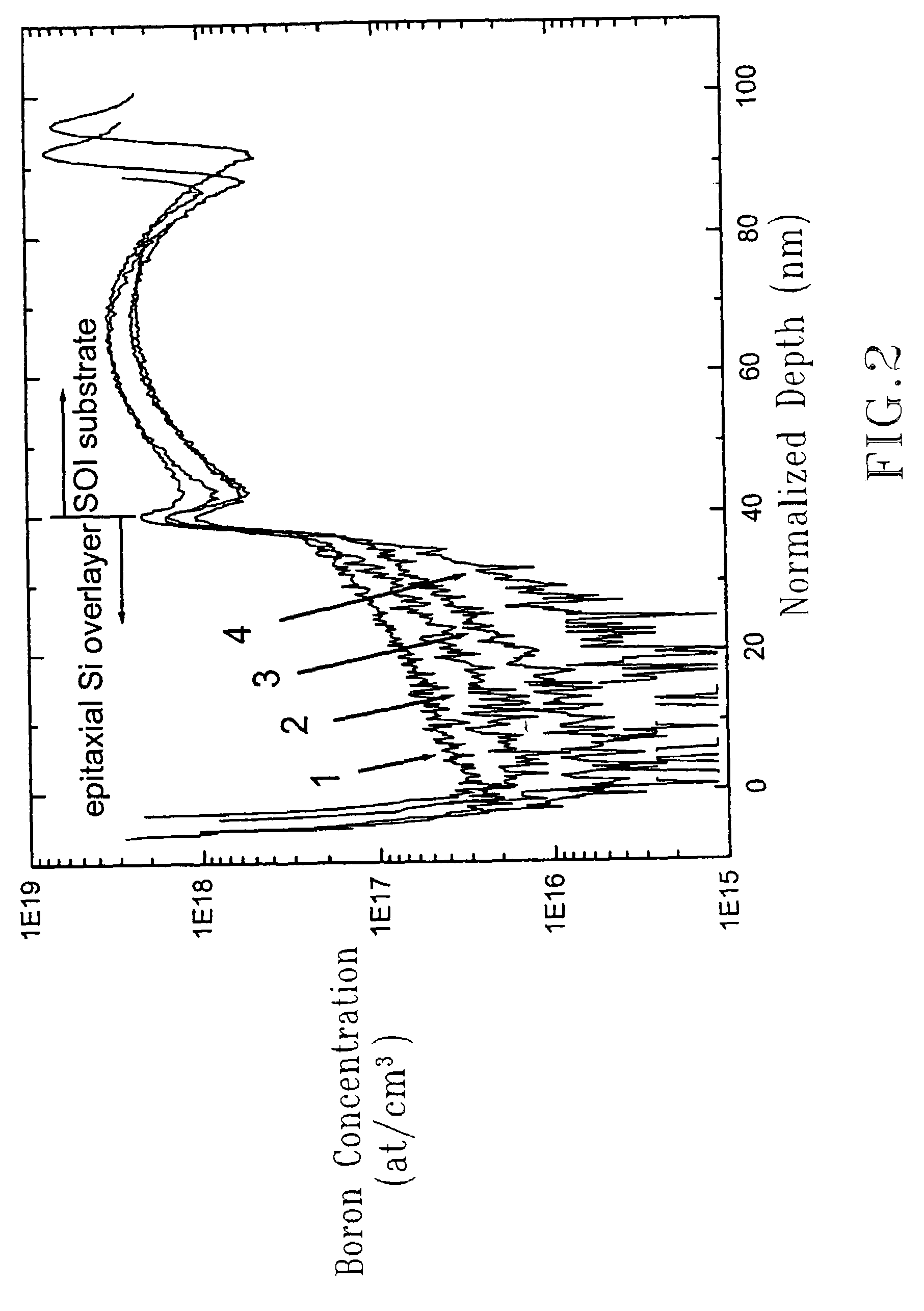

Chemical treatment to retard diffusion in a semiconductor overlayer

InactiveUS7071103B2Diffusion slowSimple technologySemiconductor/solid-state device manufacturingDopantChemical treatment

Owner:INT BUSINESS MASCH CORP

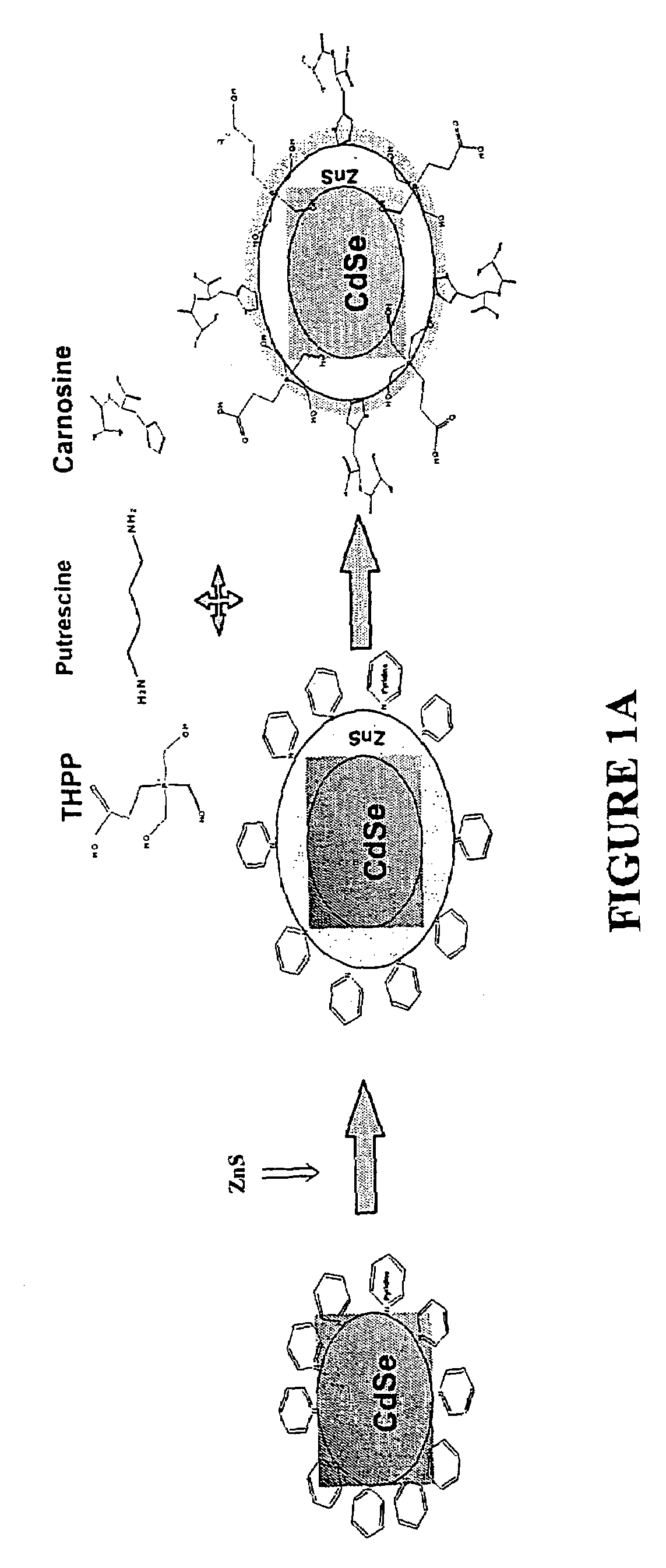

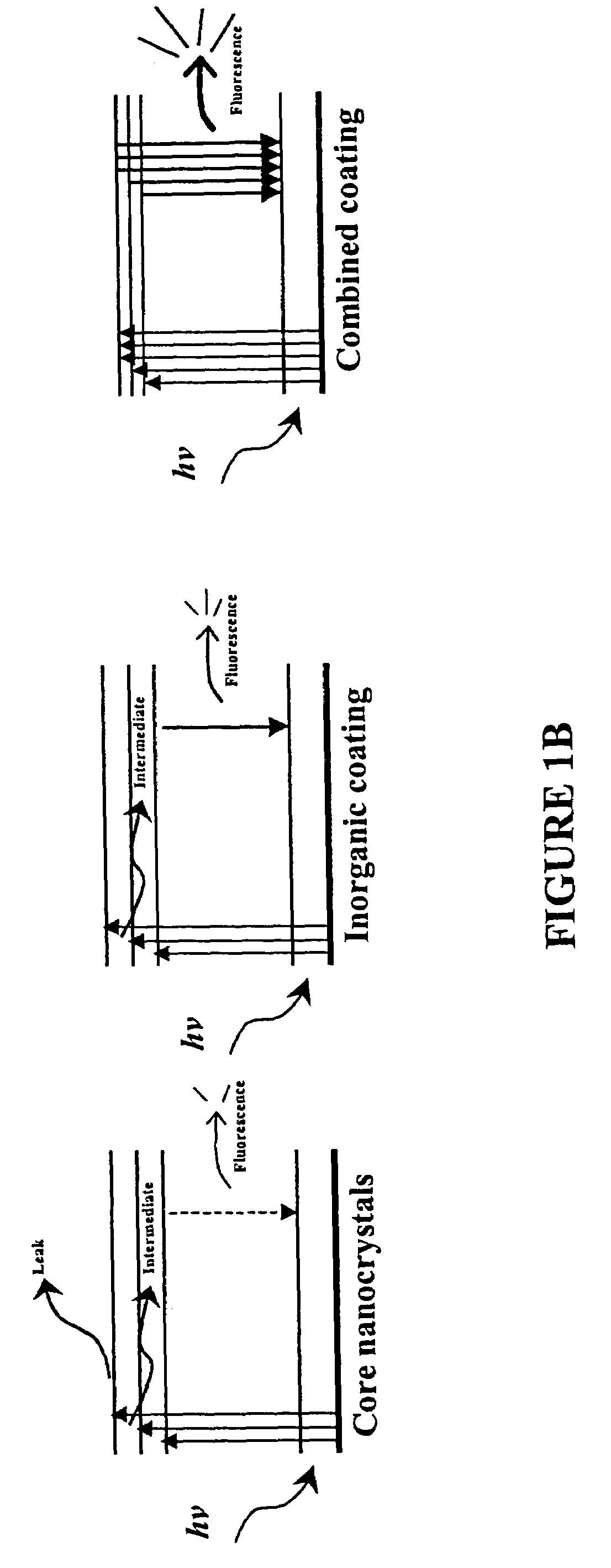

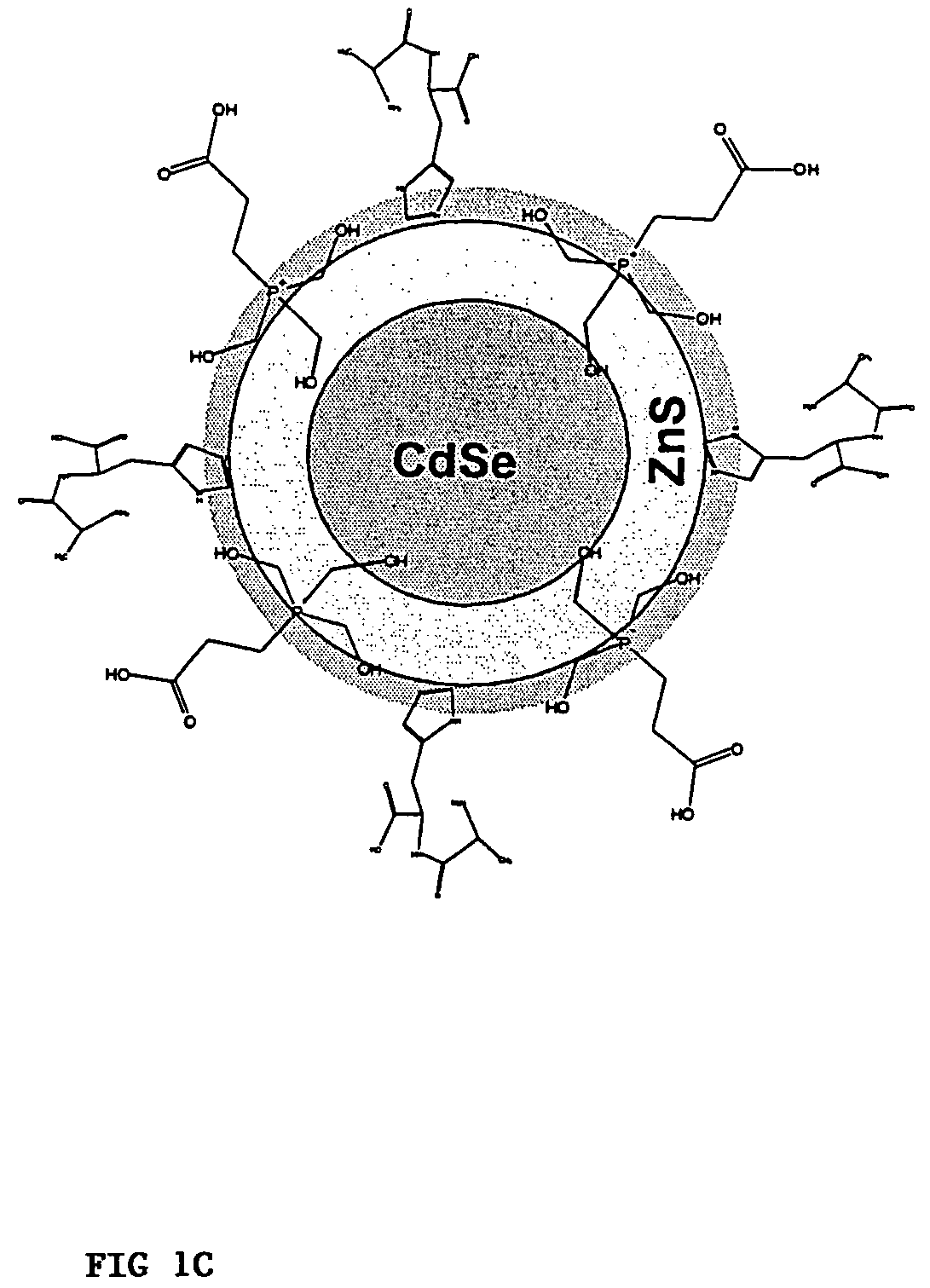

Functionalized fluorescent nanocrystal compositions and methods of making

InactiveUS7205048B2Improve efficiencyImprove solubilityInksRecord information storageSolubilityQuantum yield

The present invention provides for functionalized fluorescent nanocrystal compositions and methods for making these compositions. The compositions are fluorescent nanocrystals coated with at least one material. The coating material has chemical compounds or ligands with functional groups or moieties with conjugated electrons and moieties for imparting solubility to coated fluorescent nanocrystals in aqueous solutions. The coating material provides for functionalized fluorescent nanocrystal compositions which are water soluble, chemically stable, and emit light with a high quantum yield and / or luminescence efficiency when excited with light. The coating material may also have chemical compounds or ligands with moieties for bonding to target molecules and cells as well as moieties for cross-linking the coating. In the presence of reagents suitable for reacting to form capping layers, the compounds in the coating may form a capping layer on the fluorescent nanocrystal with the coating compounds operably bonded to the capping layer.

Owner:LIFE TECH CORP

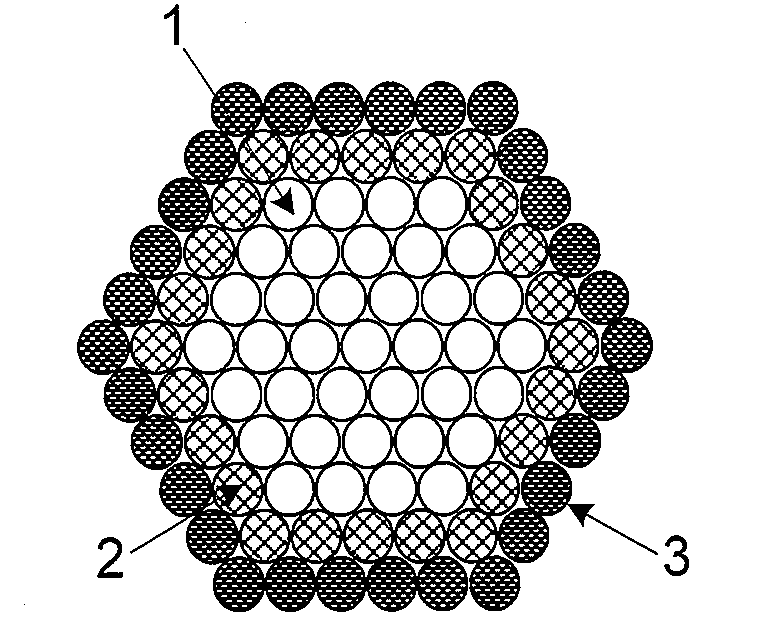

Platinum-Coated Non-Noble Metal-Noble Metal Core-Shell Electrocatalysts

InactiveUS20100197490A1Minimal loadingEfficiently formedMaterial nanotechnologyCell electrodesAlloyPt element

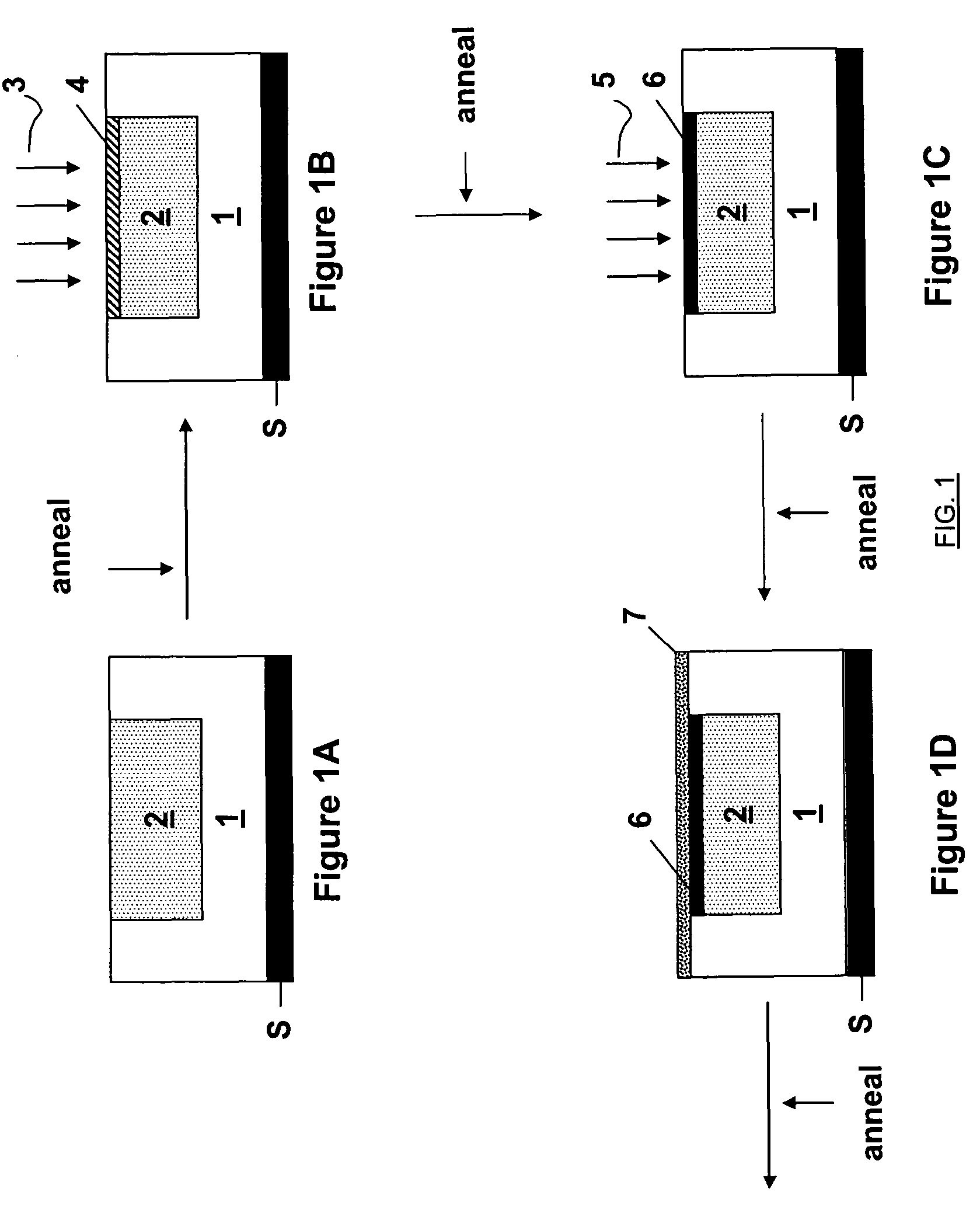

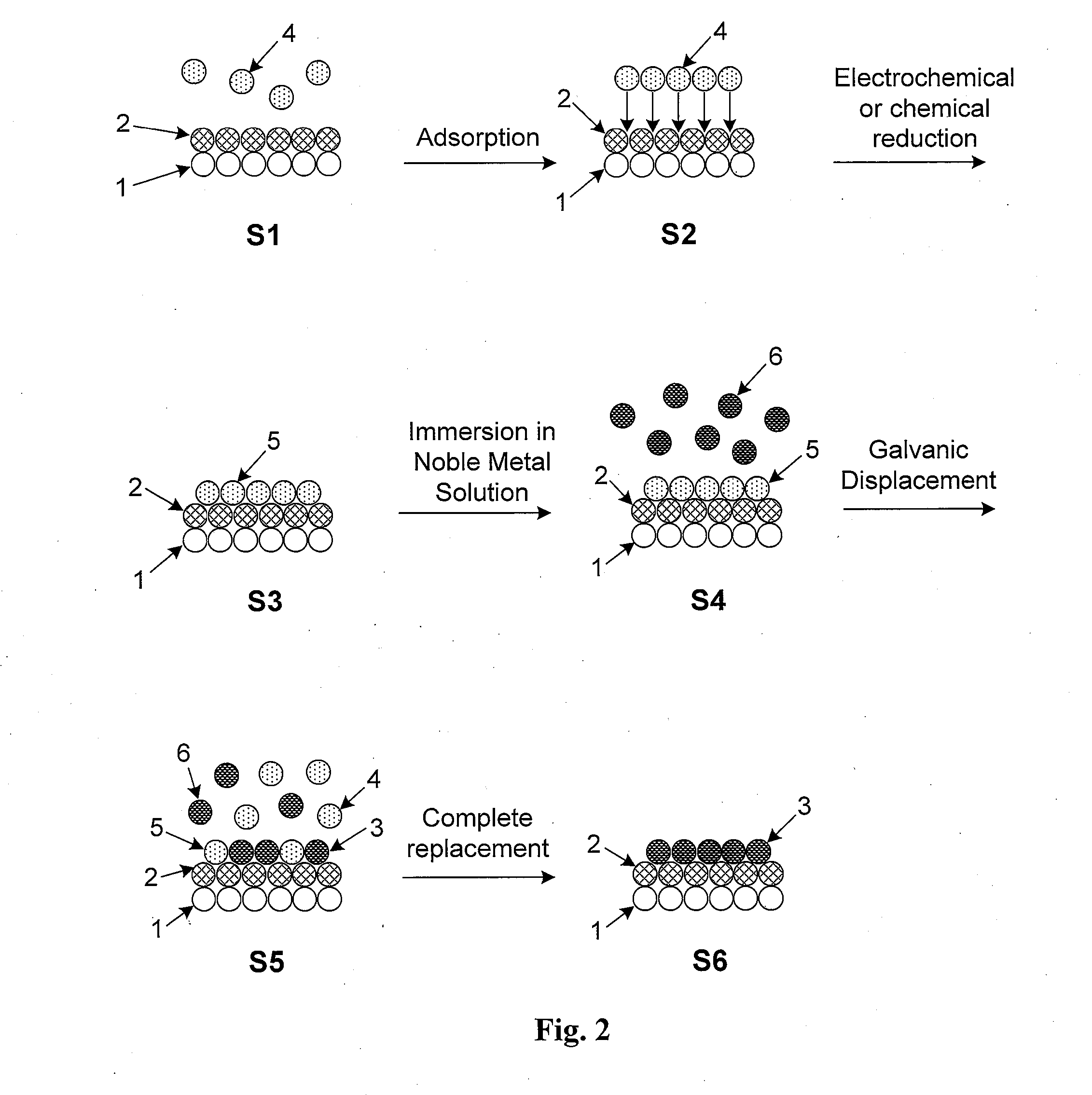

Core-shell particles encapsulated by a thin film of a catalytically active metal are described. The particles are preferably nanoparticles comprising a non-noble core with a noble metal shell which preferably do not include Pt. The non-noble metal-noble metal core-shell nanoparticles are encapsulated by a catalytically active metal which is preferably Pt. The core-shell nanoparticles are preferably formed by prolonged elevated-temperature annealing of nanoparticle alloys in an inert environment. This causes the noble metal component to surface segregate and form an atomically thin shell. The Pt overlayer is formed by a process involving the underpotential deposition of a monolayer of a non-noble metal followed by immersion in a solution comprising a Pt salt. A thin Pt layer forms via the galvanic displacement of non-noble surface atoms by more noble Pt atoms in the salt. The overall process is a robust and cost-efficient method for forming Pt-coated non-noble metal-noble metal core-shell nanoparticles.

Owner:BROOKHAVEN SCI ASSOCS

Method of forming poly-si pattern, diode having poly-si pattern, multi-layer cross point resistive memory device having poly-si pattern, and method of manufacturing the diode and the memory device

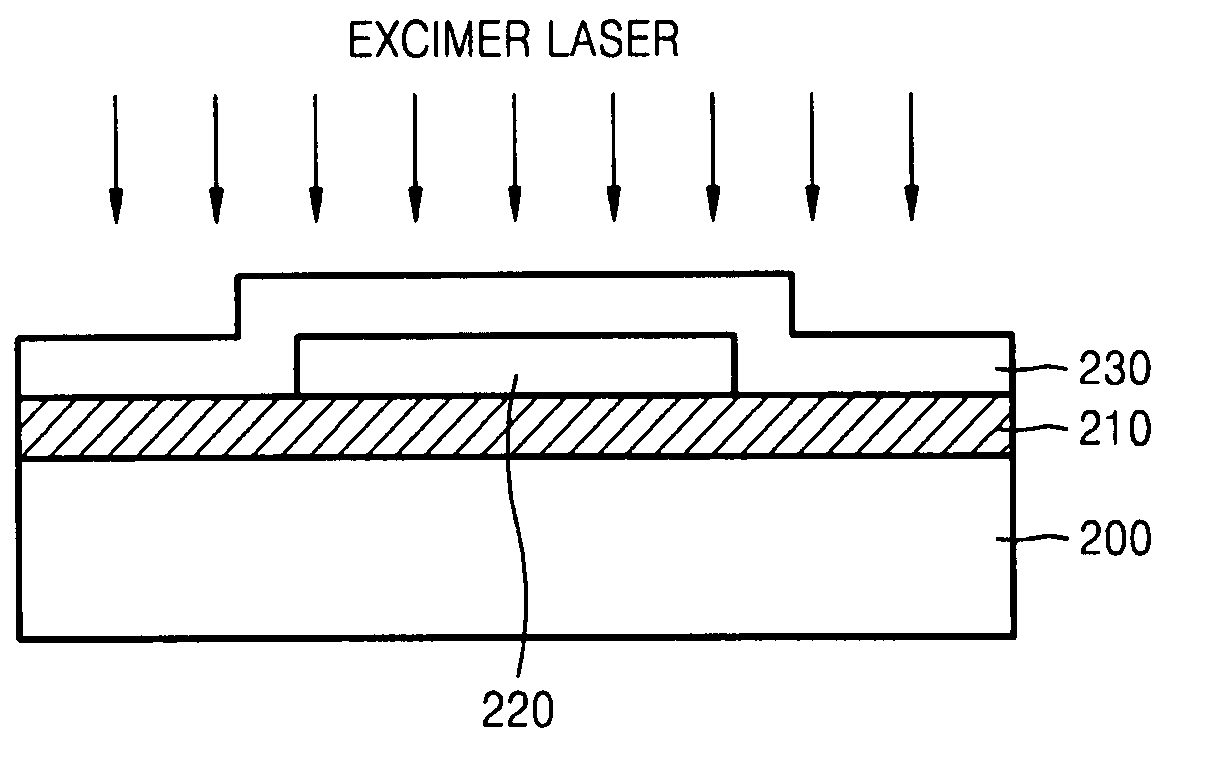

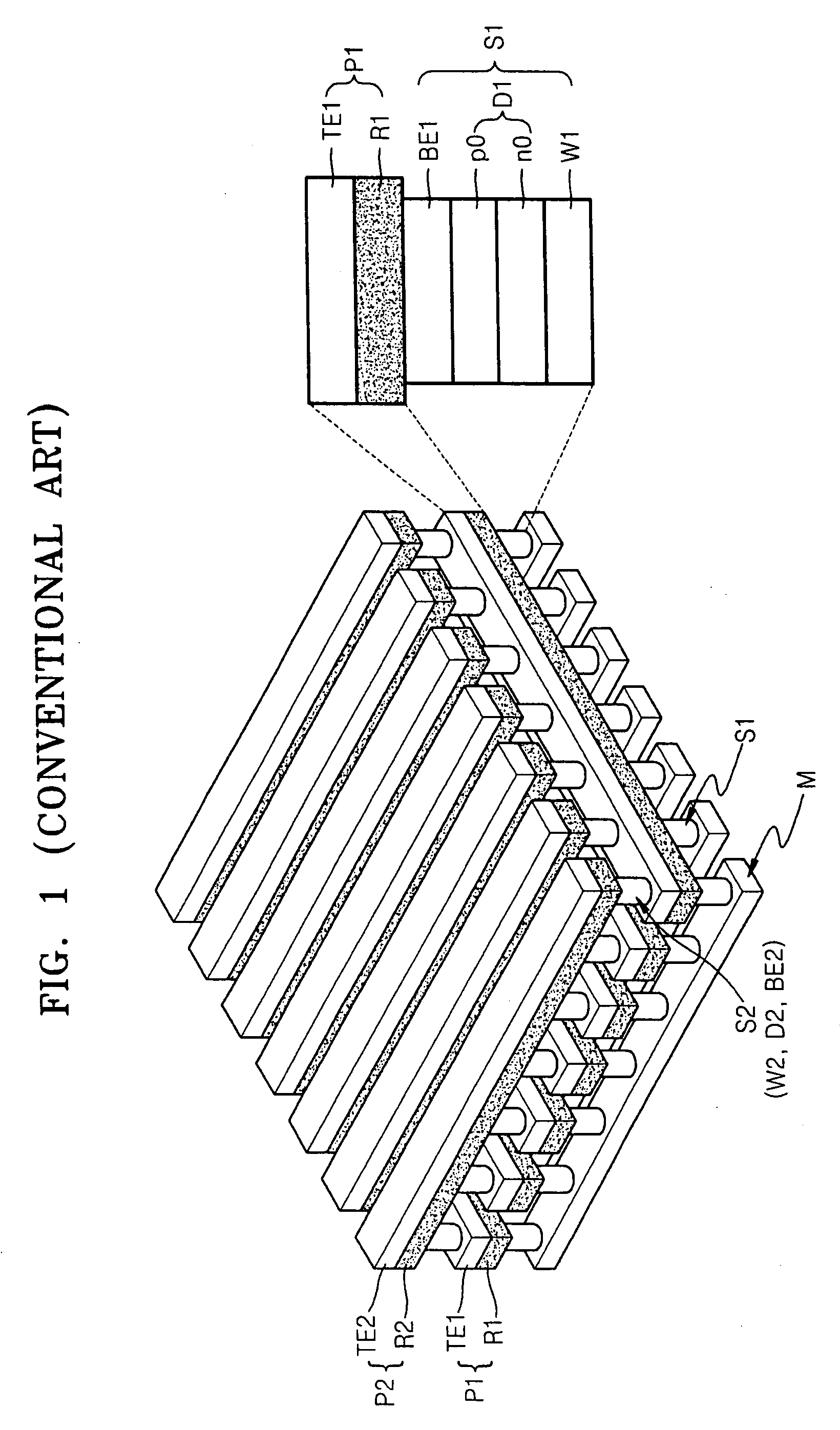

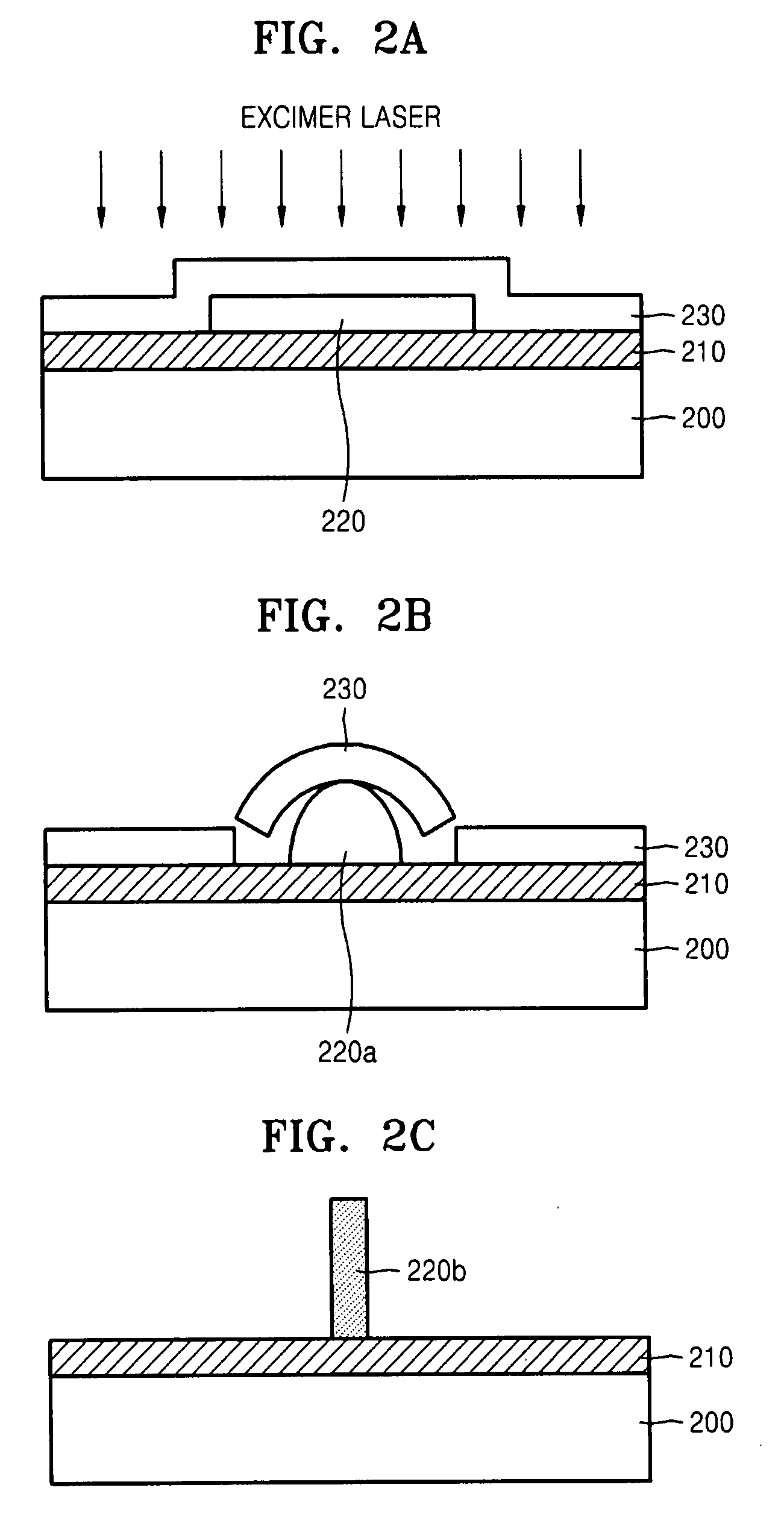

ActiveUS20080026547A1Improve rectification effectSolid-state devicesSemiconductor/solid-state device manufacturingPolycrystalline siliconOverlayer

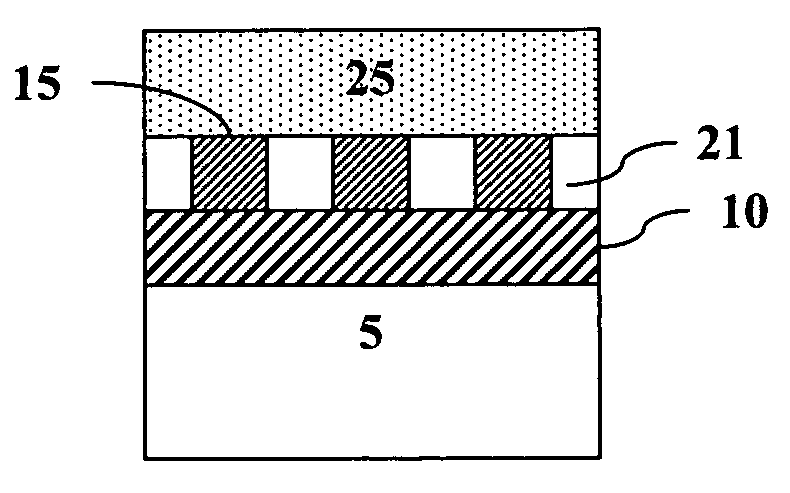

A method of forming a poly-silicon pattern may include forming an amorphous silicon pattern on a lower layer; forming a capping layer on the substrate covering the amorphous silicon pattern; poly-crystallizing the amorphous silicon pattern using an excimer laser annealing process; and removing the capping layer.

Owner:SAMSUNG ELECTRONICS CO LTD

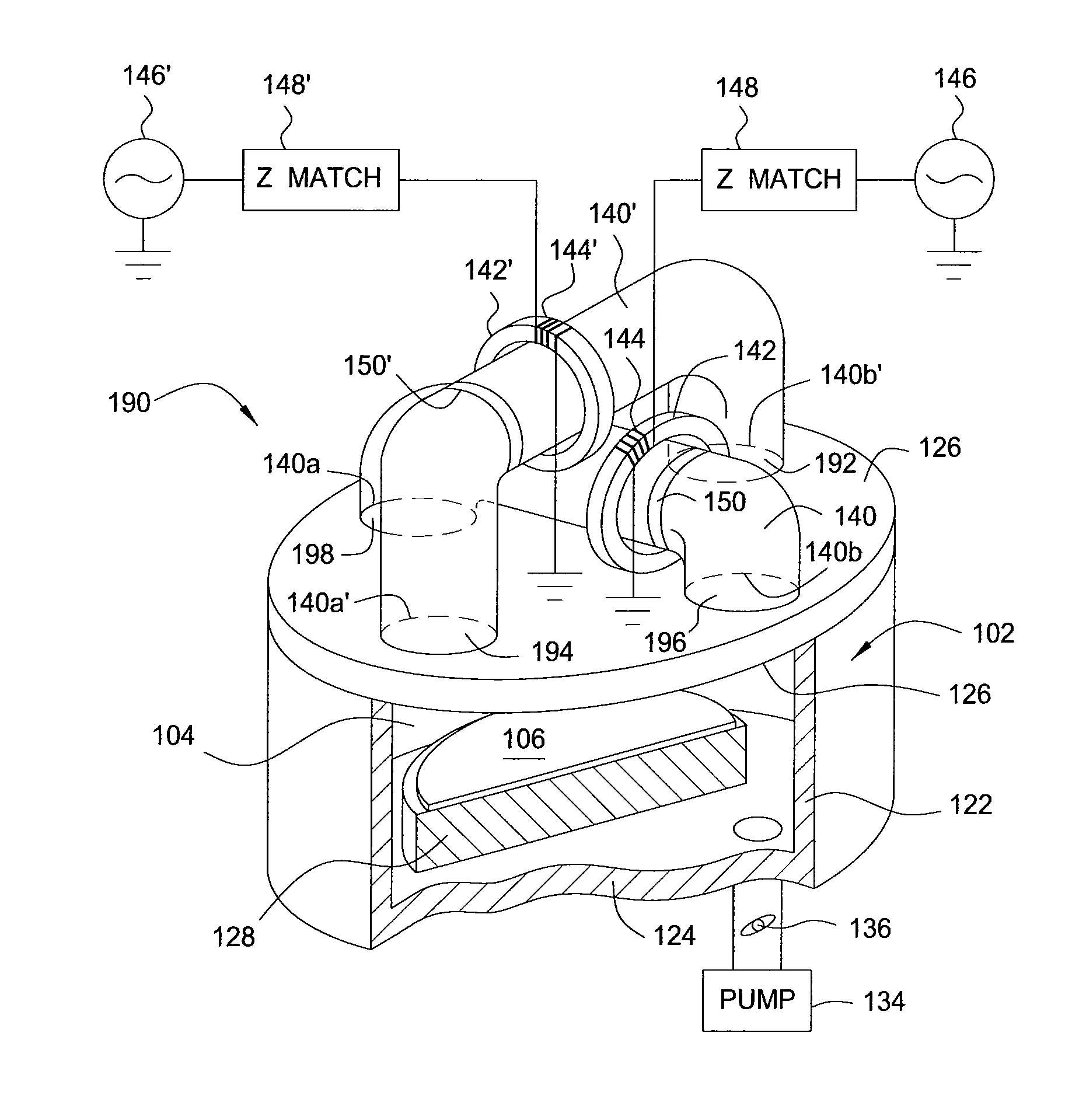

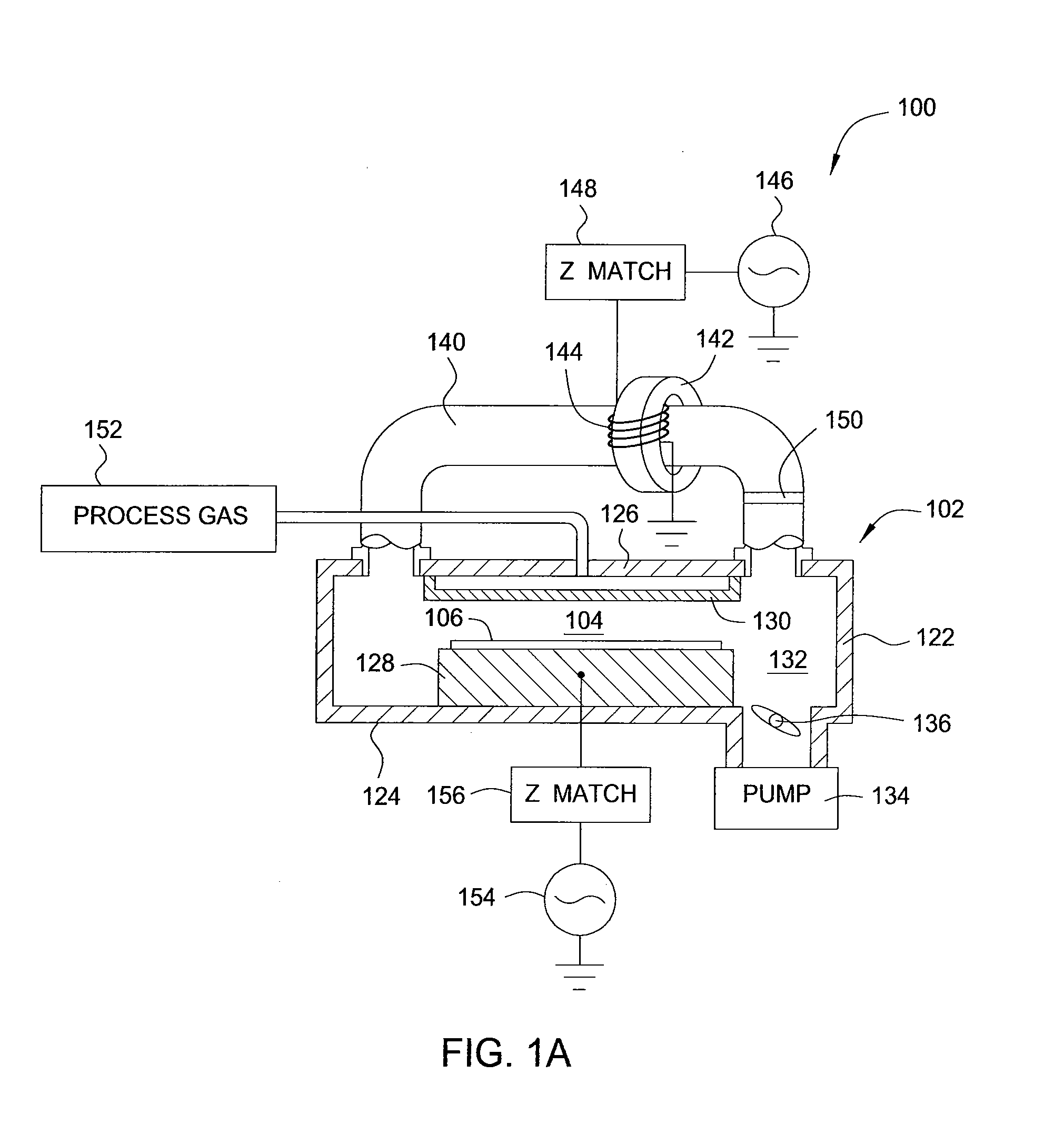

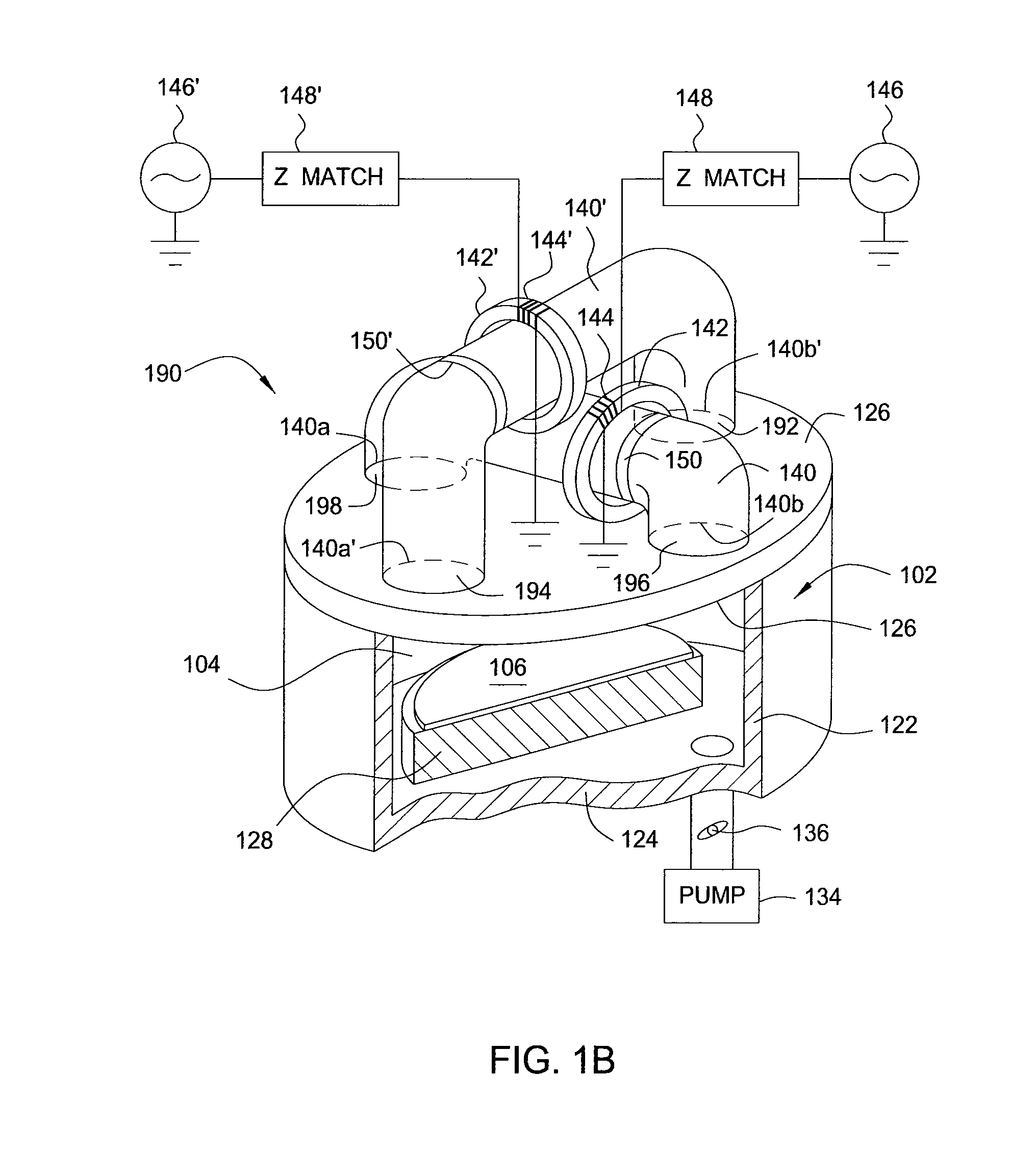

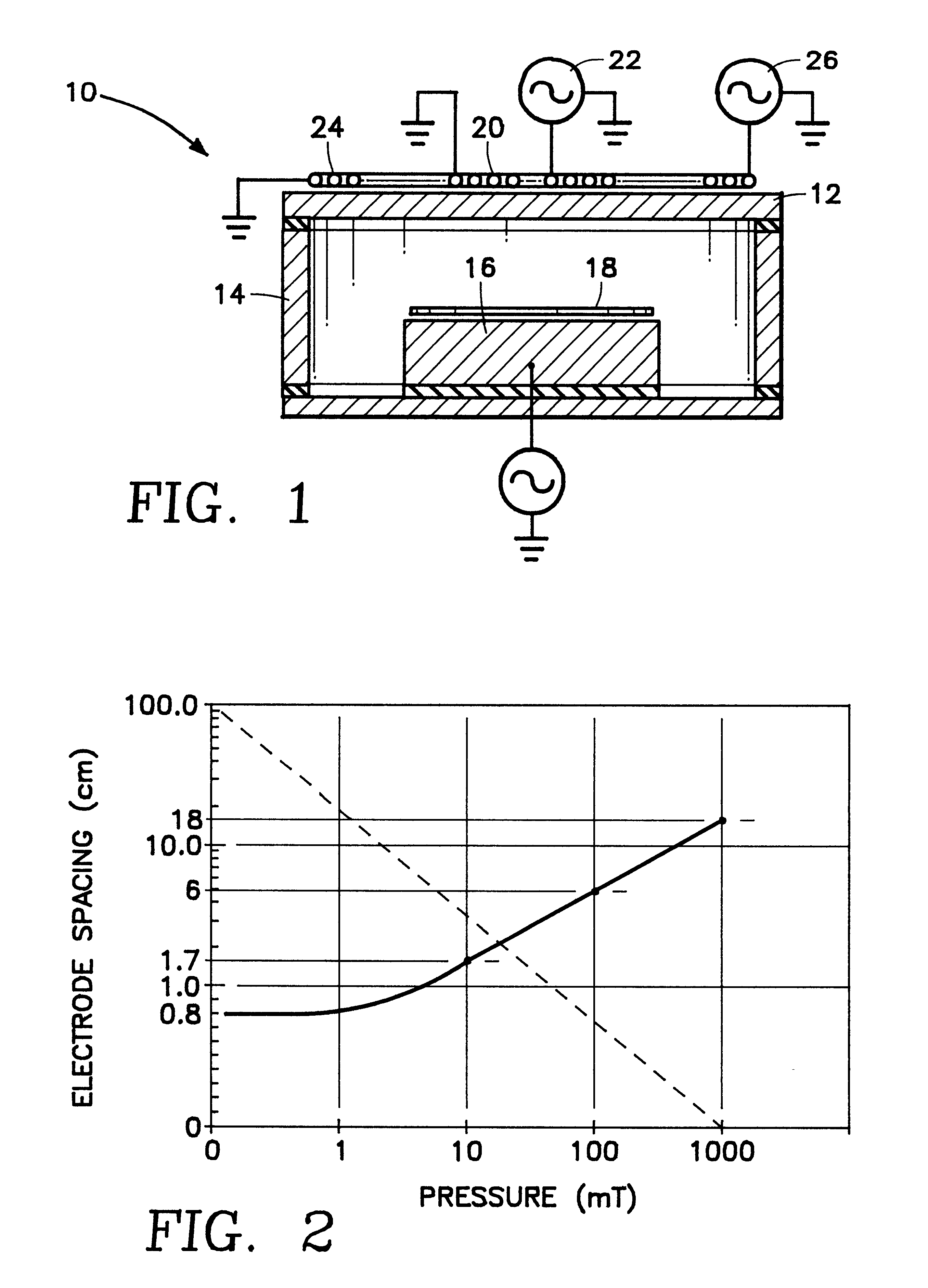

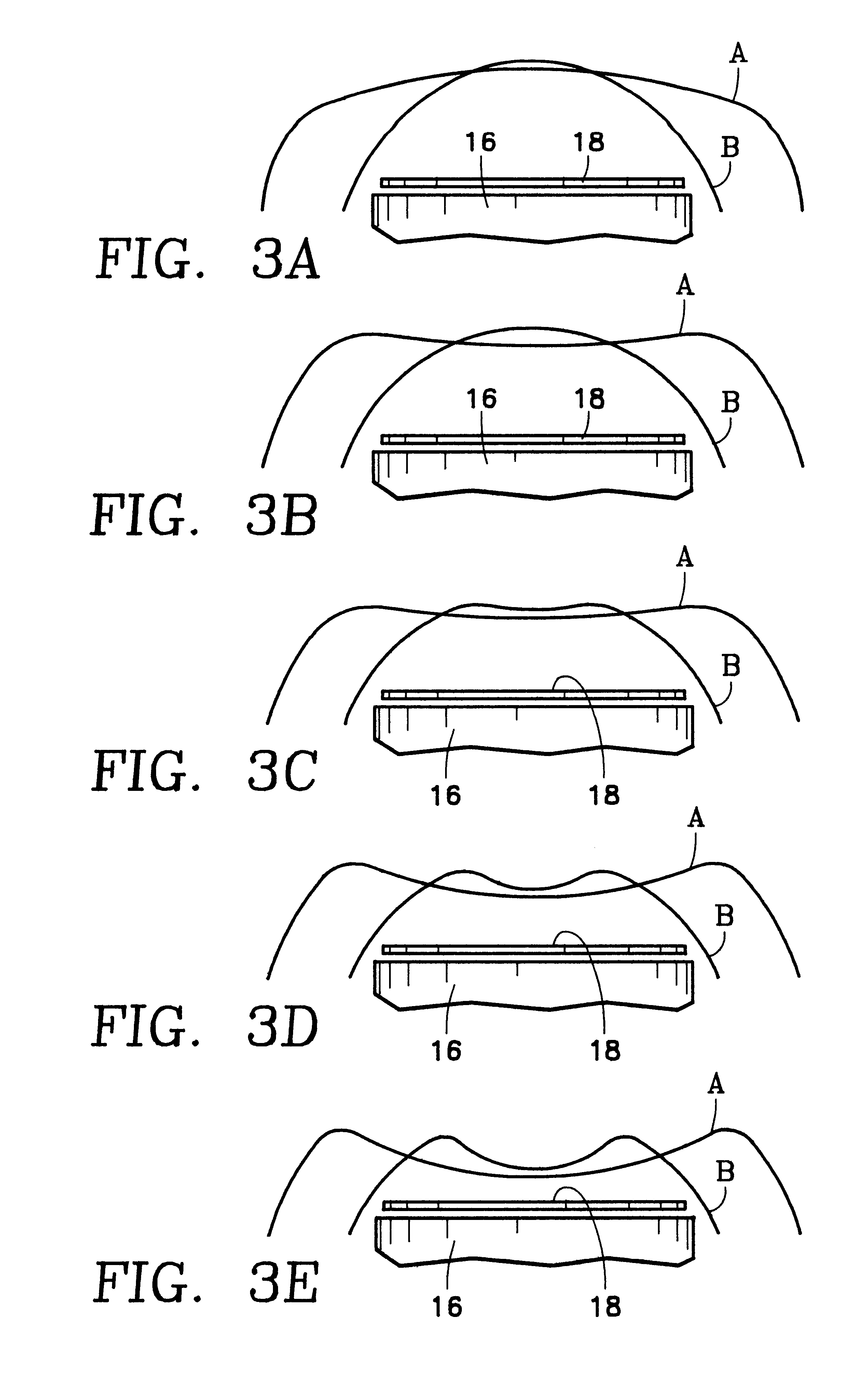

High pressure high non-reactive diluent gas content high plasma ion density plasma oxide etch process

InactiveUS6238588B1Increase pressureHigh strengthElectric discharge tubesDecorative surface effectsHigh plasmaOxygen

The invention is embodied in a method of processing a semiconductor workpiece in a plasma reactor chamber, including supplying a polymer and etchant precursor gas containing at least carbon and fluorine into the chamber at a first flow rate sufficient of itself to maintain a gas pressure in the chamber in a low pressure range below about 20 mT, supplying a relatively non-reactive gas into the chamber at second flow rate sufficient about one half or more of the total gas flow rate into the chamber, in combination with the first flow rate of the precursor gas, to maintain the gas pressure in the chamber in a high pressure range above 20 mT, and applying plasma source power into the chamber to form a high ion density plasma having an ion density in excess of 1010 ions per cubic centimeter. In one application of the invention, the workpiece includes an oxygen-containing overlayer to be etched by the process and a non-oxygen-containing underlayer to be protected from etching, the precursor gas dissociating in the plasma into fluorine-containing etchant species which etch the oxygen-containing layer and carbon-containing polymer species which accumulate on the non-oxygen-containing underlayer. Alternatively, the high pressure range may be defined as a pressure at which the skin depth of the inductive field exceeds {fraction (1 / 10)} of the gap between the inductive antenna and the workpiece.

Owner:APPLIED MATERIALS INC

Method and tool of chemical doping CoW alloys with Re for increasing barrier properties of electroless capping layers for IC Cu interconnects

InactiveUS20050101130A1Semiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingRheniumAlloy

A method for fabricating a capping layer with enhanced barrier resistance to both copper and oxygen diffusion, comprises forming a capping layer on a conductive surface of an interconnect, wherein the capping layer comprises cobalt (Co), tungsten (W), rhenium (Re), and at least one of phosphorus (P) and boron (B). In an embodiment of the invention, forming the capping layer comprises exposing the conductive surface to an electroless capping solution comprising a cobalt source, a tungsten source, a rhenium source, and at least one of a phosphorus source and a boron source, and annealing the capping layer.

Owner:APPLIED MATERIALS INC

Label film with improved adhesion

The invention relates to the use of a biaxially oriented polyolefin film as a label film. The inventive film consists of a base layer and at least one cover layer. Said cover layer contains as the main component a copolymer or terpolymer consisting of one alkene and unsaturated carboxylic acids or the esters thereof and low amounts of an additive. The cover layer is characterized by excellent and divers adhesion to various polymer materials from which containers are formed. It is no longer necessary to apply adhesives, primers, coatings etc. in a separate step after production of the film.

Owner:TRESPAPHAN

Capping layer for a magnetic tunnel junction device to enhance dR/R and a method of making the same

An MTJ in an MRAM array or TMR read head is disclosed in which a low magnetization capping layer is a composite having a NiFeHf inner layer formed on a NiFe or CoFeB / NiFe free layer, a Ta middle layer, and a Ru outer layer on the Ta layer. For example, a low magnetization NiFeHf layer is achieved by co-sputtering NiFe and Hf targets with a forward power of 400 W and 200 W, respectively. A higher Hf content increases the oxygen gettering power of the NiFeHf layer and the thickness is modified to change dR / R, RA, and magnetostriction values. A so-called dead layer between the free layer and capping layer is restored by incorporating a NiFeHf layer on the free layer to improve lattice matching. The Fe content in the NiFe target used to make the NiFeHf layer is preferably the same as in the NiFe free layer.

Owner:TAIWAN SEMICON MFG CO LTD

High performance rear-projection screen

A rear-projection screen and a method for forming same are provided. The screen can include a substrate including a first side and a second side, apertures disposed on the first side of the substrate, and an opaque layer disposed on the second side of the substrate. In a particular embodiment, the opaque layer includes a plurality of apertures therethrough. A surface relief diffuser can be provided in the substrate at the plurality of apertures. A bulk diffuser can be provided at the plurality of apertures to diffuse the projected image. A cover can be attached to the opaque layer, for example, with an adhesive. An overlayer can be provided on the opaque layer for providing deep apertures that can be filled with bulk diffuser to further diffuse the projected image. The overlayer disposed on the opaque layer can include a light-absorbing material in and / or on the overlayer.

Owner:REFLEXITE

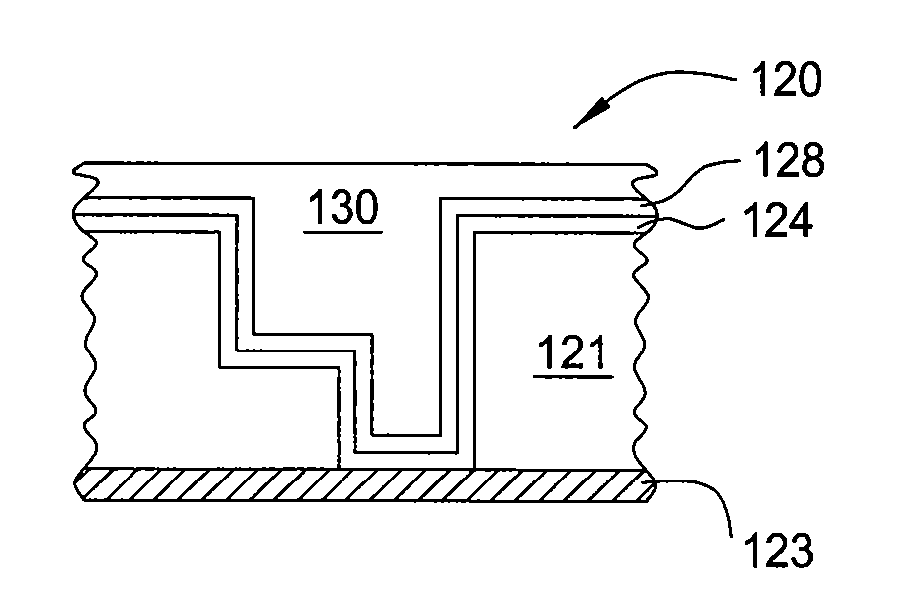

Air gap formation

ActiveUS7256127B2Reduce the amount requiredSemiconductor/solid-state device detailsSolid-state devicesSolid structureEngineering

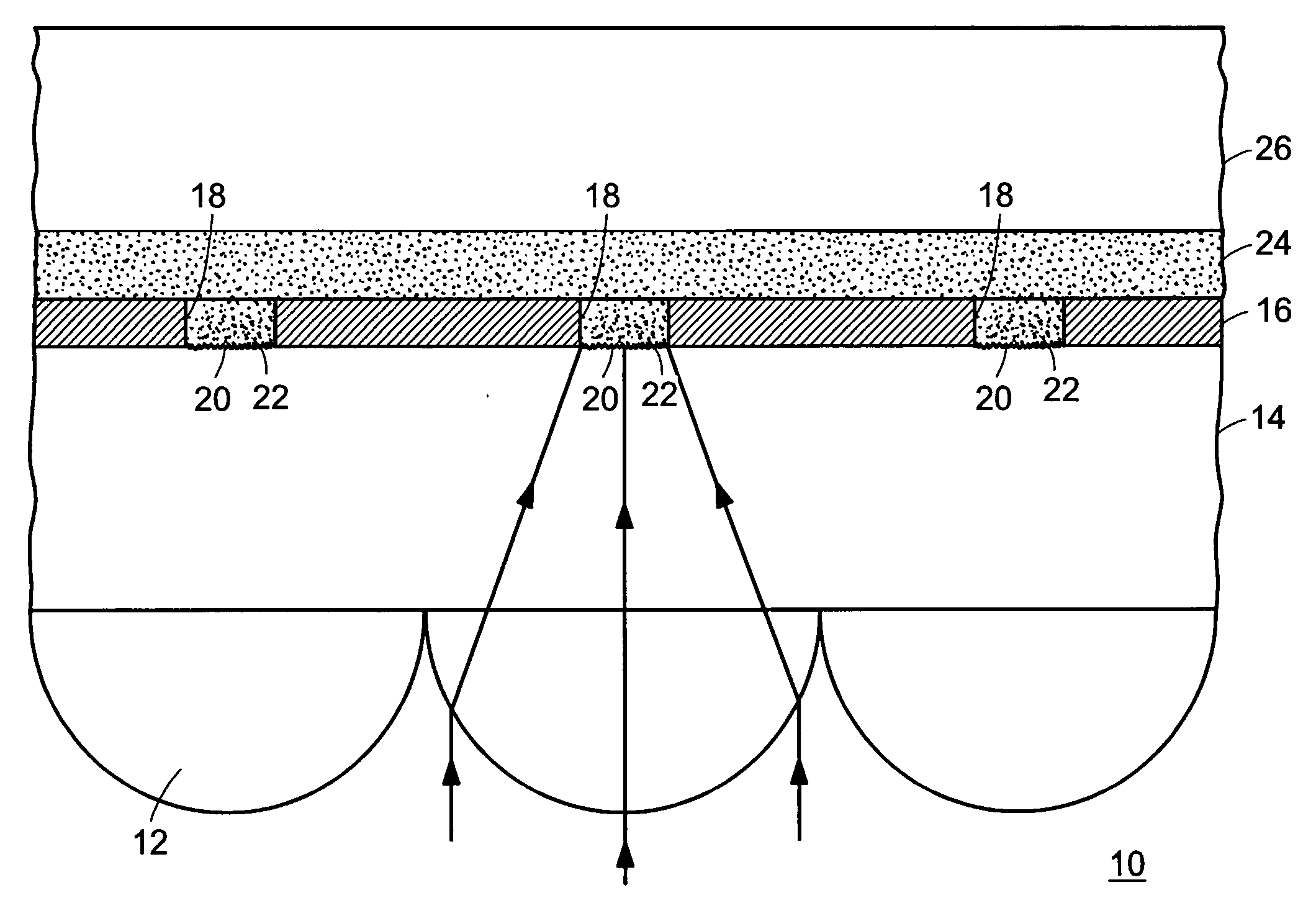

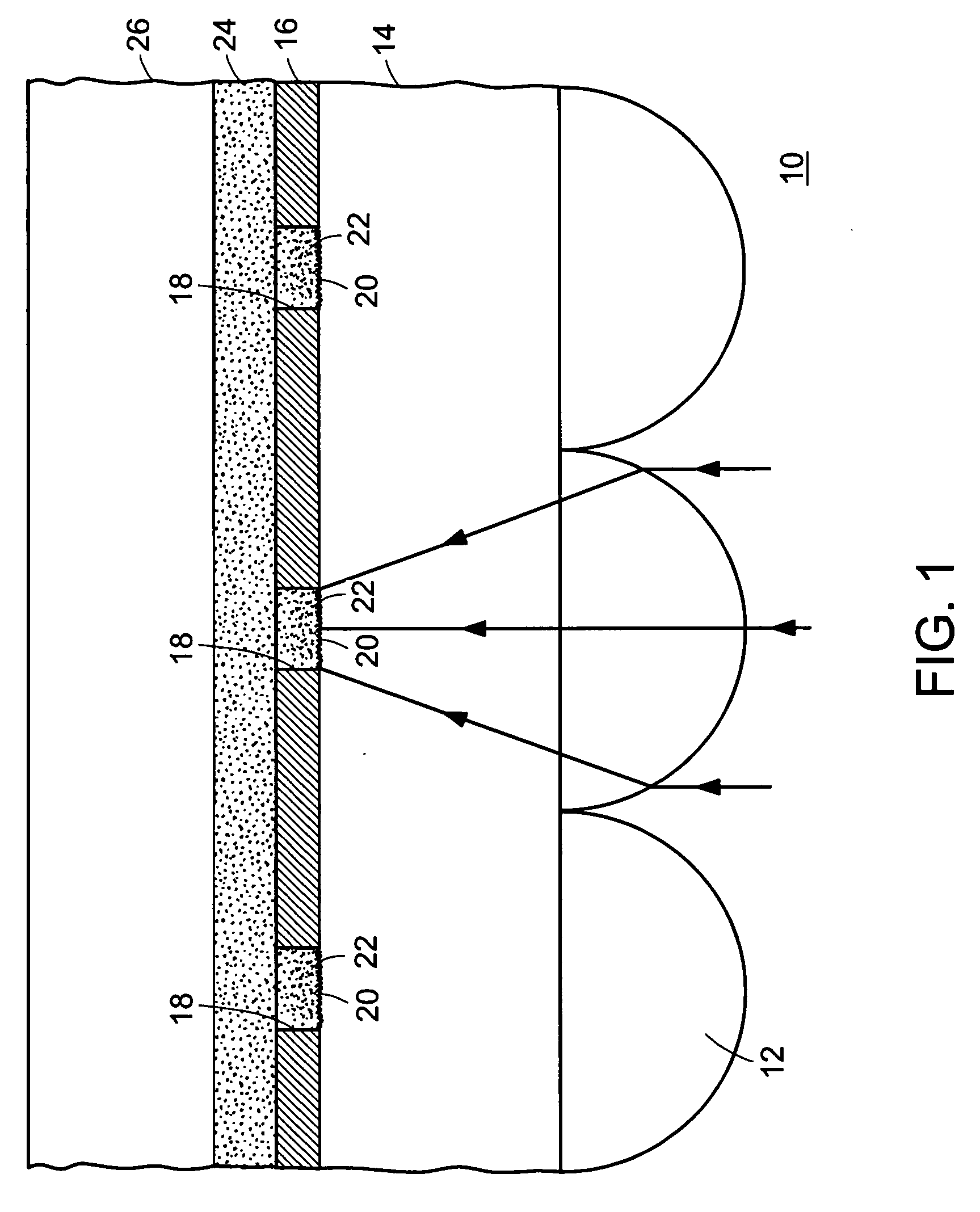

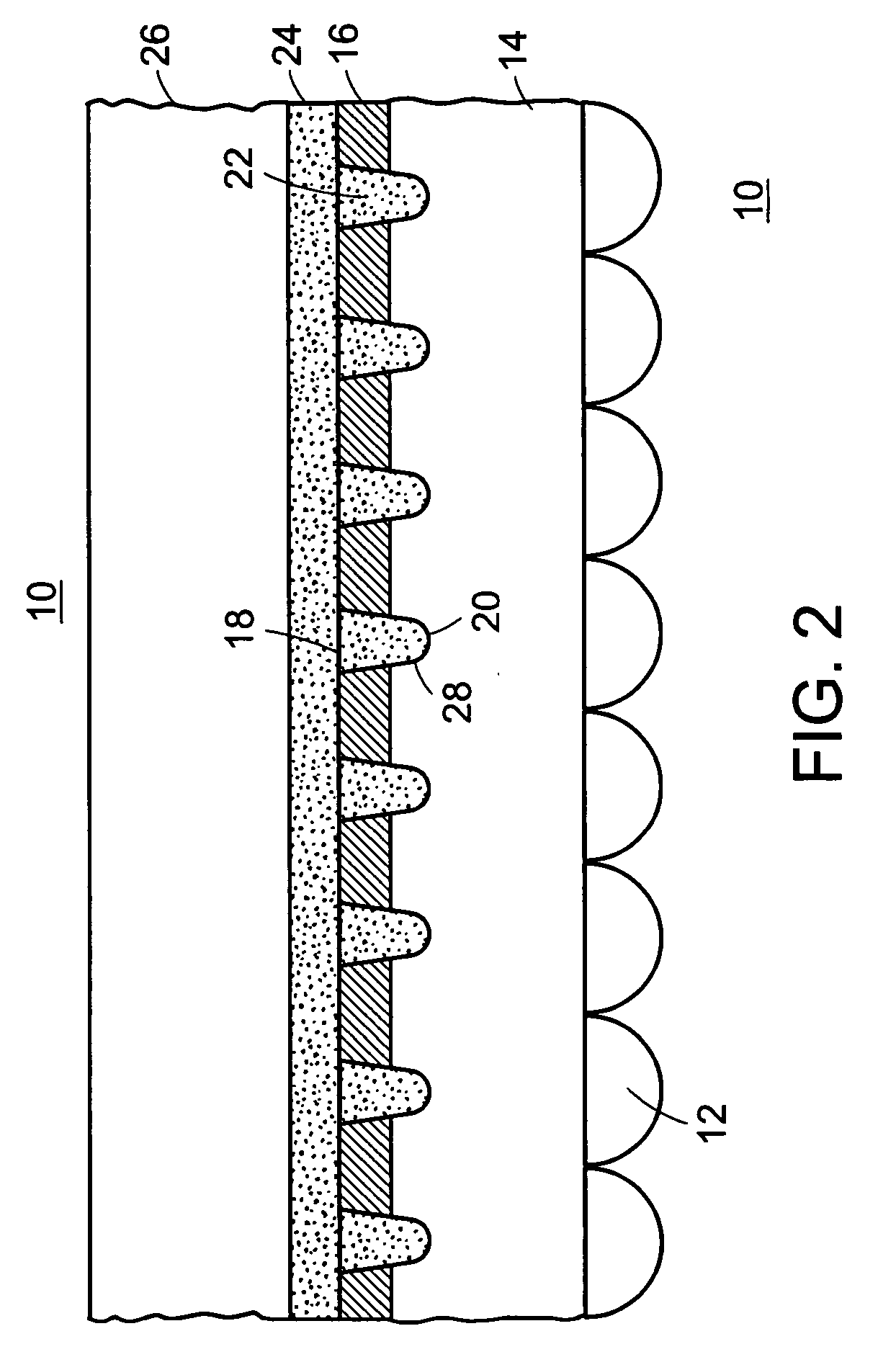

A method of forming air gaps within a solid structure is provided. In this method, a sacrificial material is covered by an overlayer. The sacrificial material is then removed through the overlayer to leave an air gap. Such air gaps are particularly useful as insulation between metal lines in an electronic device such as an electrical interconnect structure. Structures containing air gaps are also provided.

Owner:SHIPLEY CO LLC

Method of selectively etching an insulation stack for a metal interconnect

ActiveUS20110306214A1Electric discharge tubesSemiconductor/solid-state device manufacturingTemperature controlMetal interconnect

A method of patterning an insulation layer is described. The method includes preparing a film stack on a substrate, wherein the film stack comprises a cap layer, a SiCOH-containing layer overlying the cap layer, and a hard mask overlying the SiCOH-containing layer. The method further includes transferring a pattern through the film stack by performing a series of etch processes in a plasma etching system, wherein the series of etch processes utilize a temperature controlled substrate holder in the plasma etching system according to a substrate temperature control scheme that achieves etch selectivity between the SiCOH-containing layer and the underlying cap layer.

Owner:TOKYO ELECTRON LTD

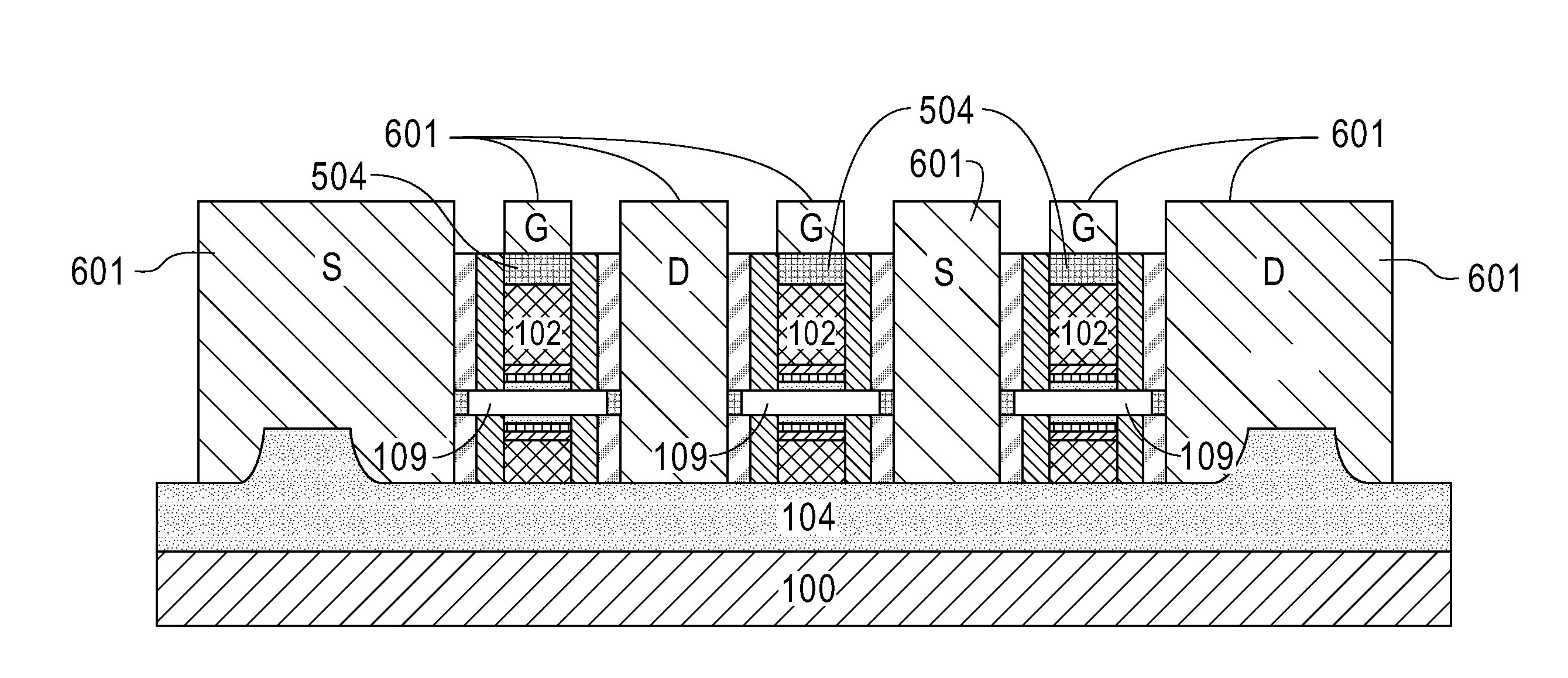

Self-aligned contacts for nanowire field effect transistors

A method for forming a nanowire field effect transistor (FET) device includes forming a nanowire over a semiconductor substrate, forming a gate structure around a portion of the nanowire, forming a capping layer on the gate structure; forming a first spacer adjacent to sidewalls of the gate and around portions of nanowire extending from the gate, forming a hardmask layer on the capping layer and the first spacer, removing exposed portions of the nanowire, epitaxially growing a doped semiconductor material on exposed cross sections of the nanowire to form a source region and a drain region, forming a silicide material in the epitaxially grown doped semiconductor material, and forming a conductive material on the source and drain regions.

Owner:GLOBALFOUNDRIES US INC

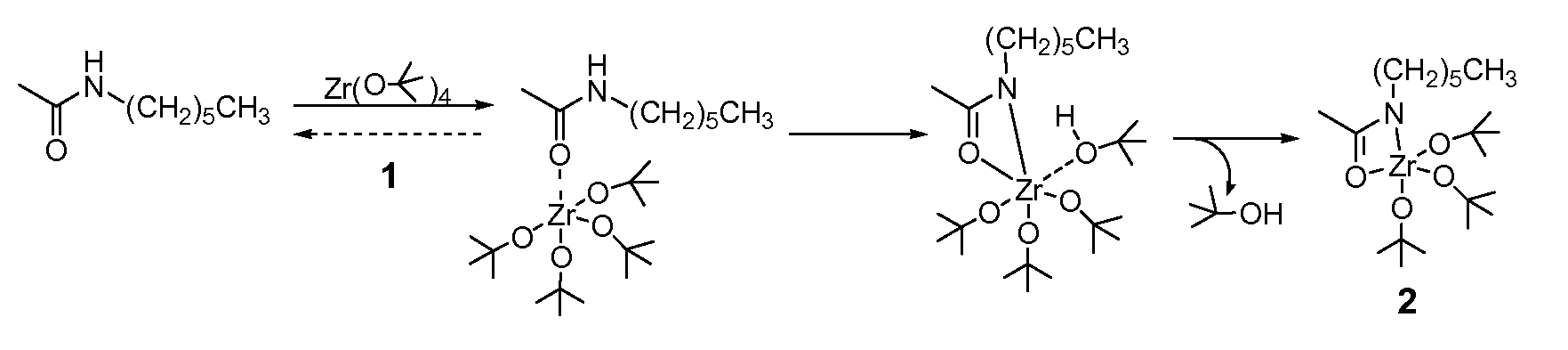

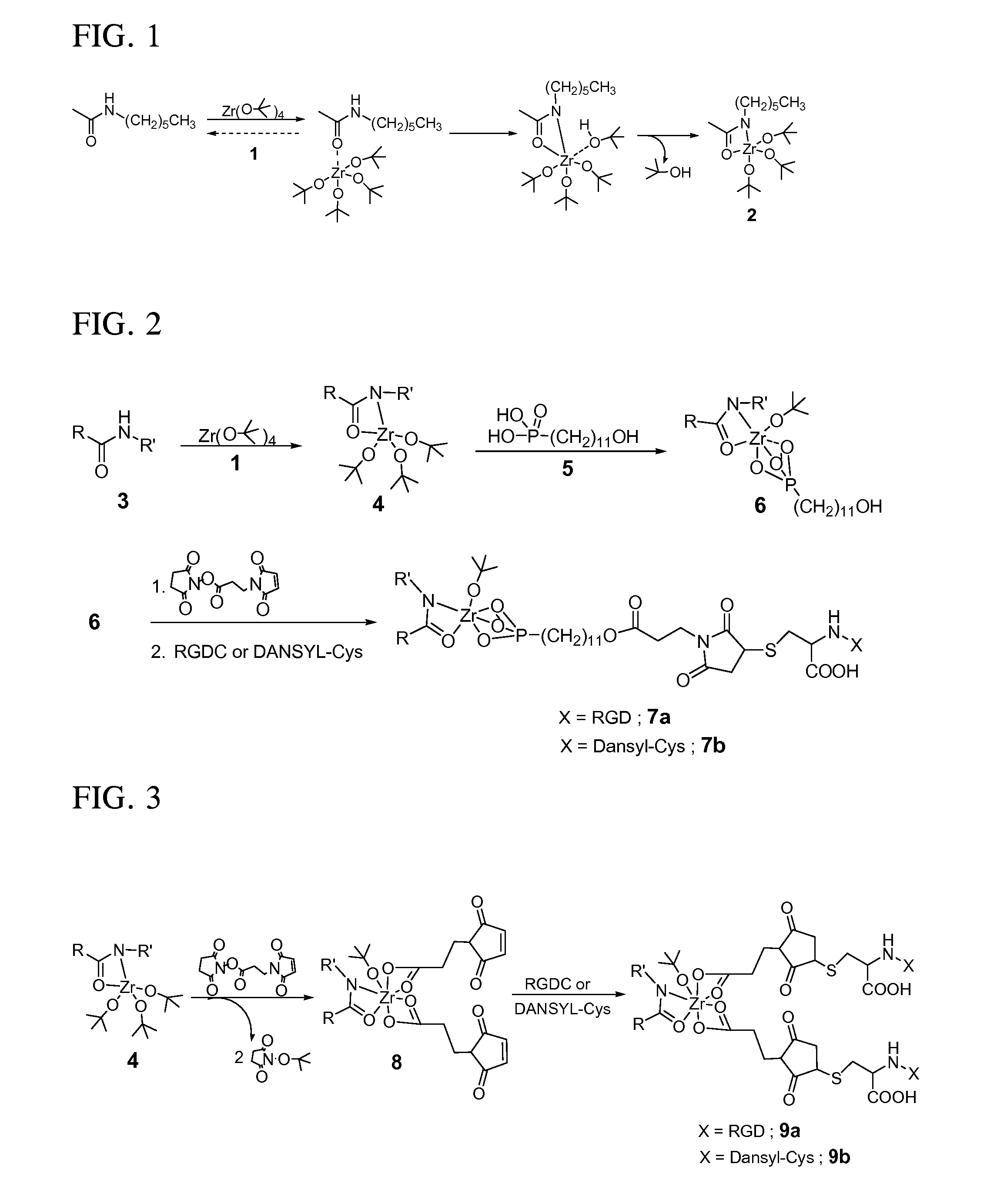

High-yield activation of polymer surfaces for covalent attachment of molecules

InactiveUS20070196663A1High yieldMild reaction conditionsSurgeryPretreated surfacesPolymeric surfaceBiological activation

Polymer surfaces coated with organometallic layers, wherein the organometallic layers and polymer surfaces have functional groups that react to bond the organometallic layer to the polymer surface with organometallic functional groups remaining unreacted for the subsequent covalent attachment of organic overlayers. Coating methods and coated articles are also disclosed.

Owner:THE TRUSTEES FOR PRINCETON UNIV

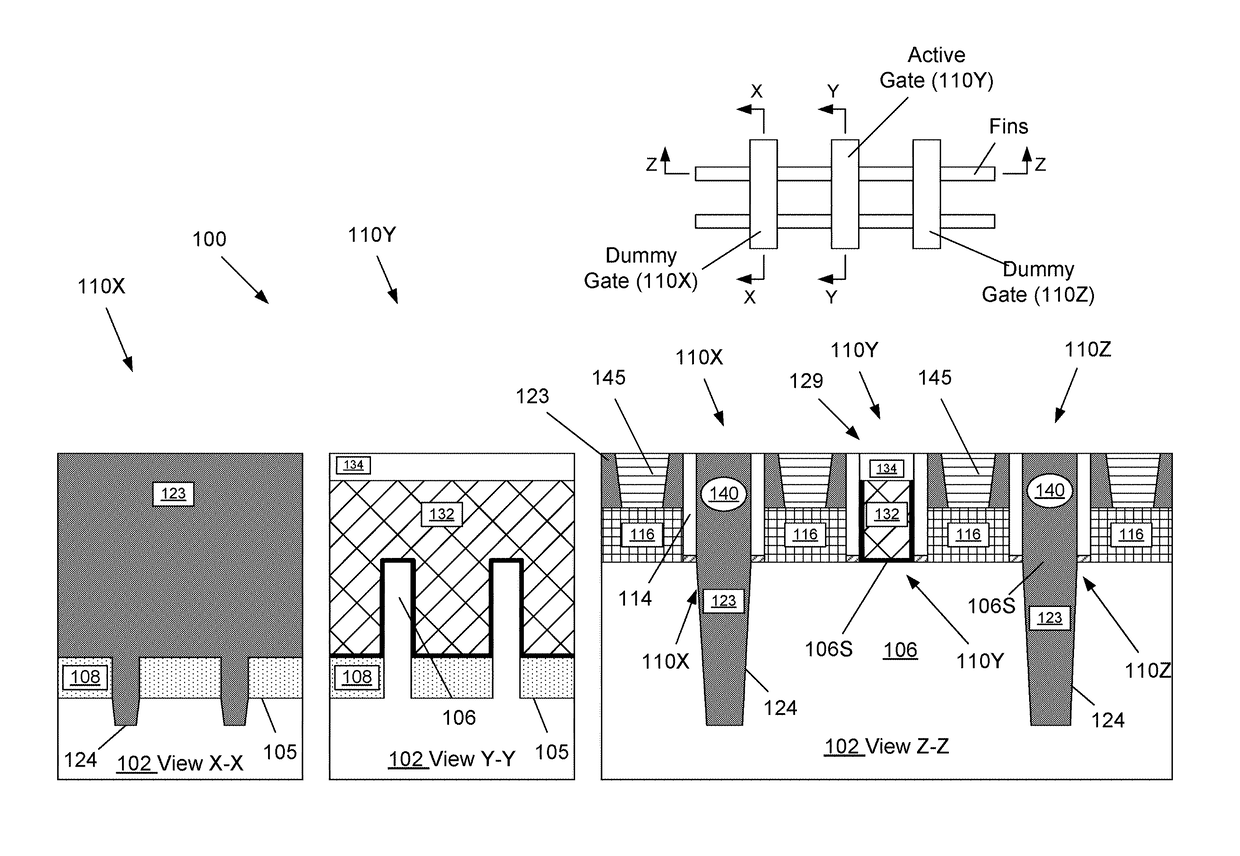

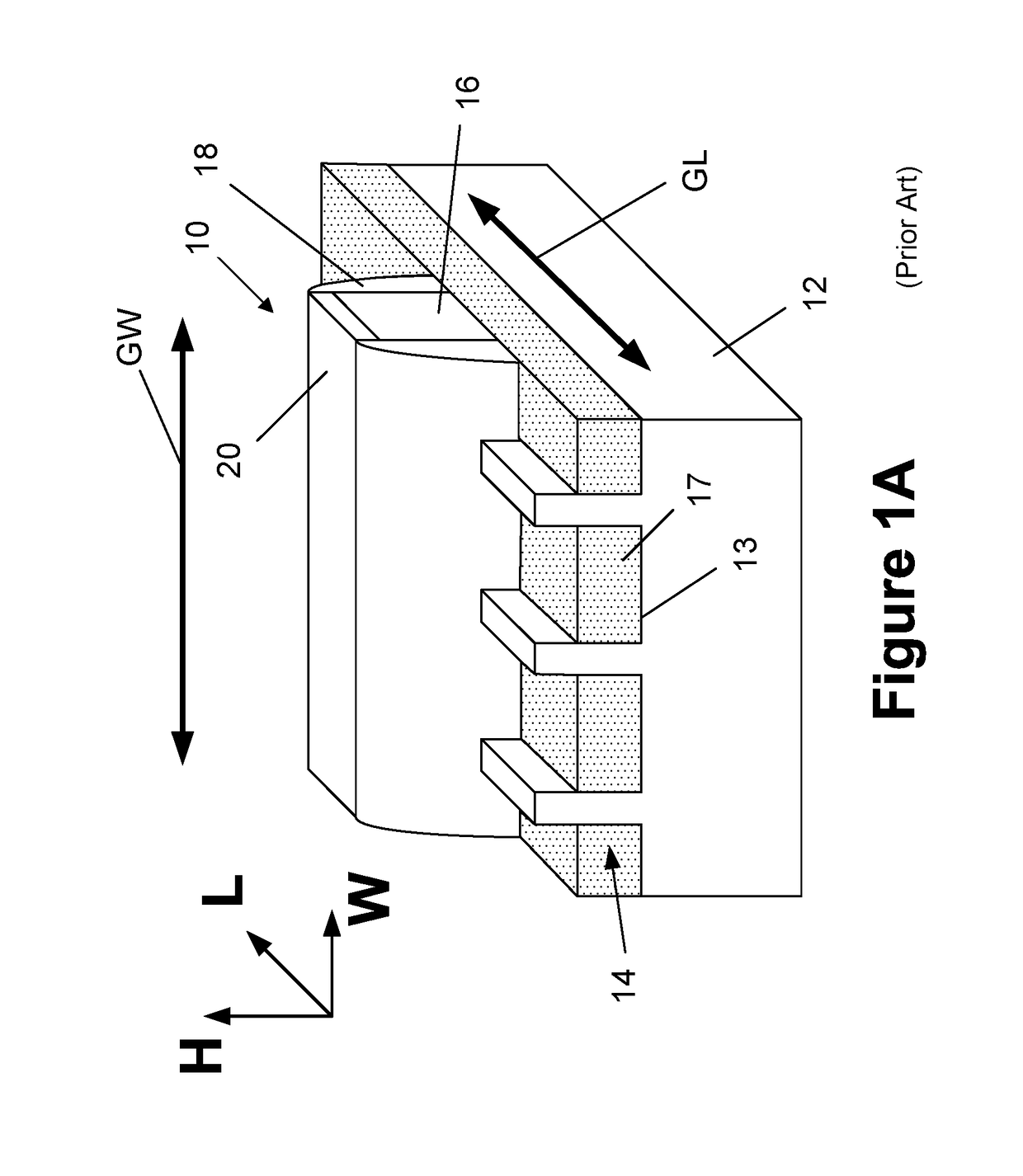

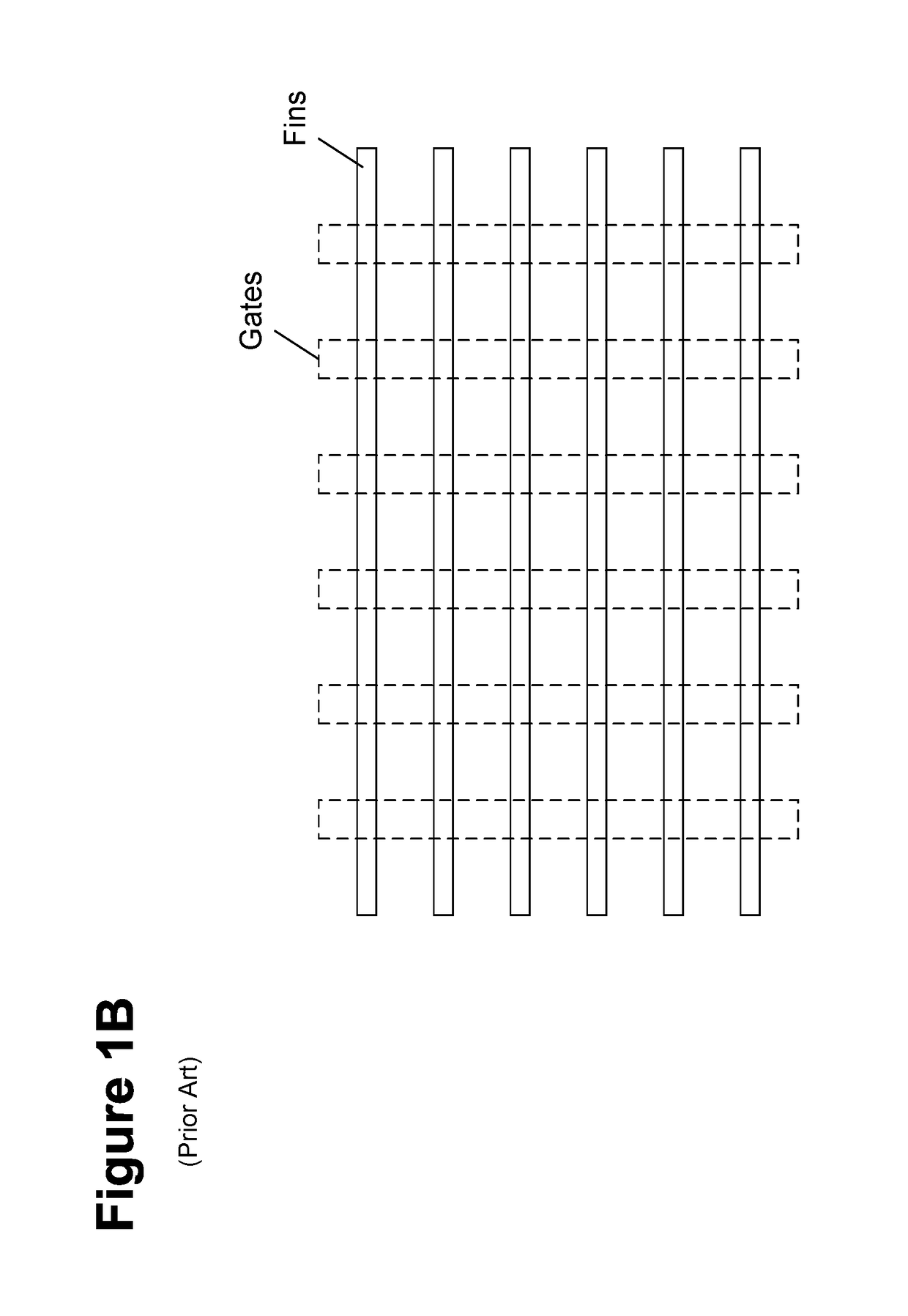

Methods of forming diffusion breaks on integrated circuit products comprised of finFET devices

ActiveUS9653583B1Well formedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

One illustrative method disclosed herein includes, among other things, forming a first gate structure above a fin, forming epi semiconductor material on the fin, performing at least one first etching process through a patterned sacrificial layer of material to remove at least a gate cap layer and sacrificial gate materials of the first gate structure so as to define a first isolation cavity that exposes the fin while leaving the second gate structure intact, performing at least one second etching process through the first isolation cavity to remove at least a portion of a vertical height of the fin and thereby form a first isolation trench, removing the patterned sacrificial layer of material, and forming a layer of insulating material above the epi semiconductor material and in the first isolation trench and in the first isolation cavity.

Owner:GLOBALFOUNDRIES US INC

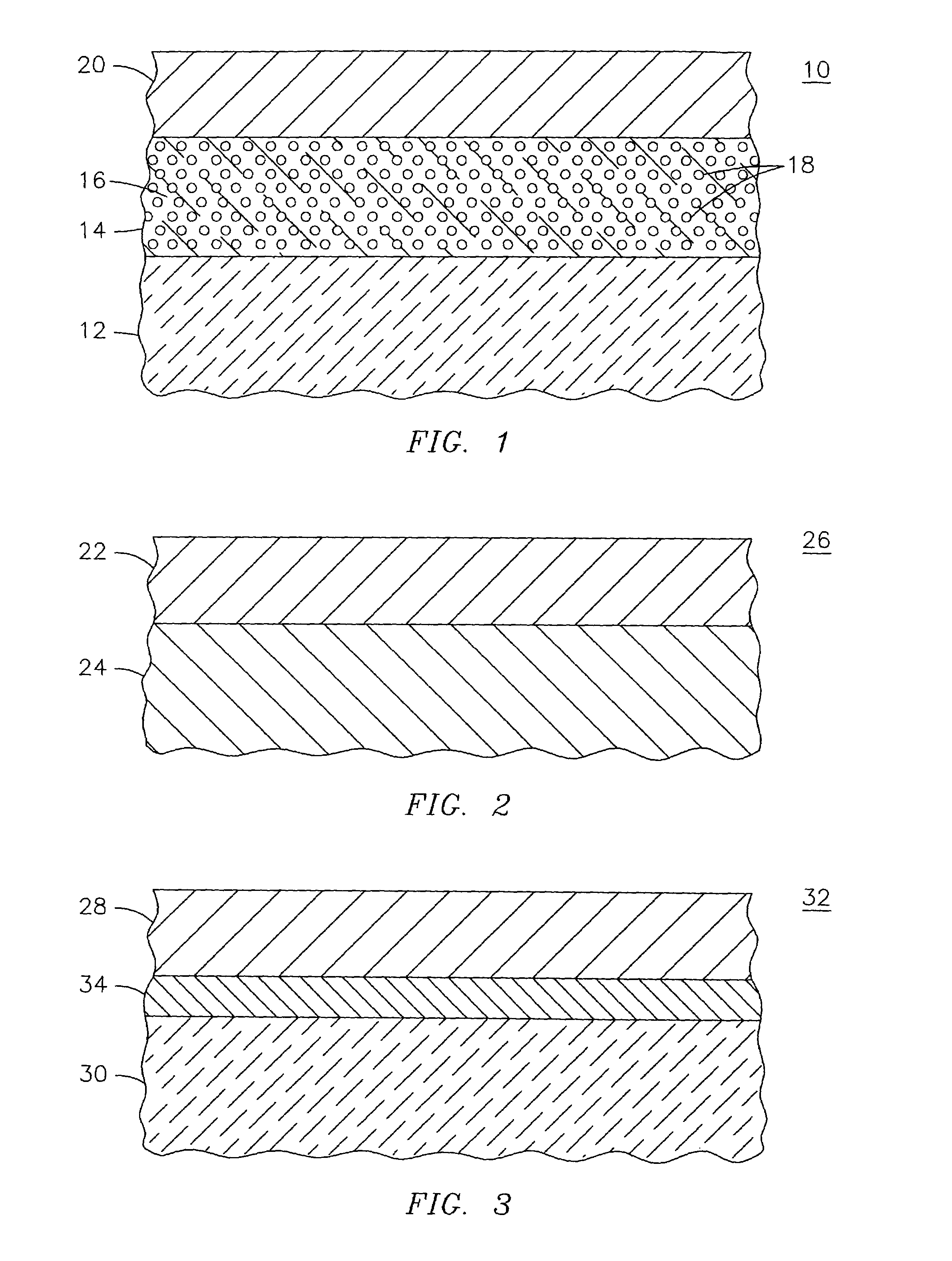

Protective overlayer for ceramics

A xenotime phosphate protective overlayer (22) for protecting a ceramic material (24) from a high temperature, moisture-containing environment. Yttrium phosphate may be used as a protective overlayer to protect an underlying mullite layer to temperatures in excess of 1,500° C. The coating may have porosity of greater than 15% for improved thermal shock protection. To prevent the ingress of oxygen to an underlying ceramic non-oxide material, such as silicon carbide or silicon nitride, an oxygen barrier layer (34) is disposed between the xenotime phosphate coating and the non-oxide material. Such a protective overlayer may be used for an article having a ceramic matrix composite substrate.

Owner:SIEMENS ENERGY INC