Patents

Literature

107 results about "Germanide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A germanide is any binary compound of germanium and a more electropositive element. The composition of most germanides is analogous to that of the corresponding silicides and does not follow formal valence rules. The germanides of alkali and alkaline earth metals, are readily decomposed by water and acids to give germanium hydrides; most germanides of the transition metals resist the action of acids and alkalies. The main method of producing germanides is the melting or sintering of the components.

Methods for depositing nickel films and for making nickel silicide and nickel germanide

ActiveUS20130115768A1Semiconductor/solid-state device manufacturingSemiconductor devicesGas phaseMetal silicide

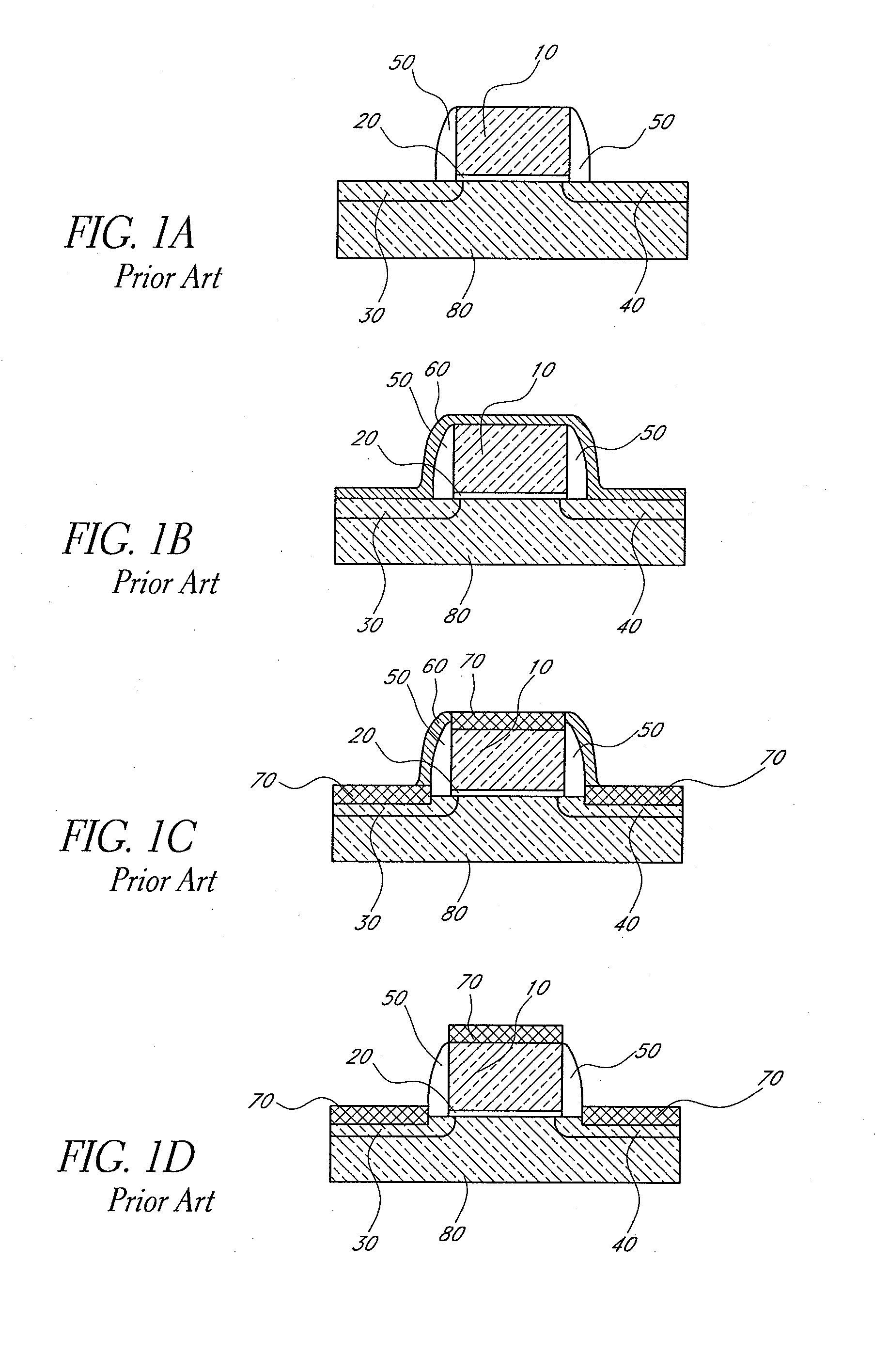

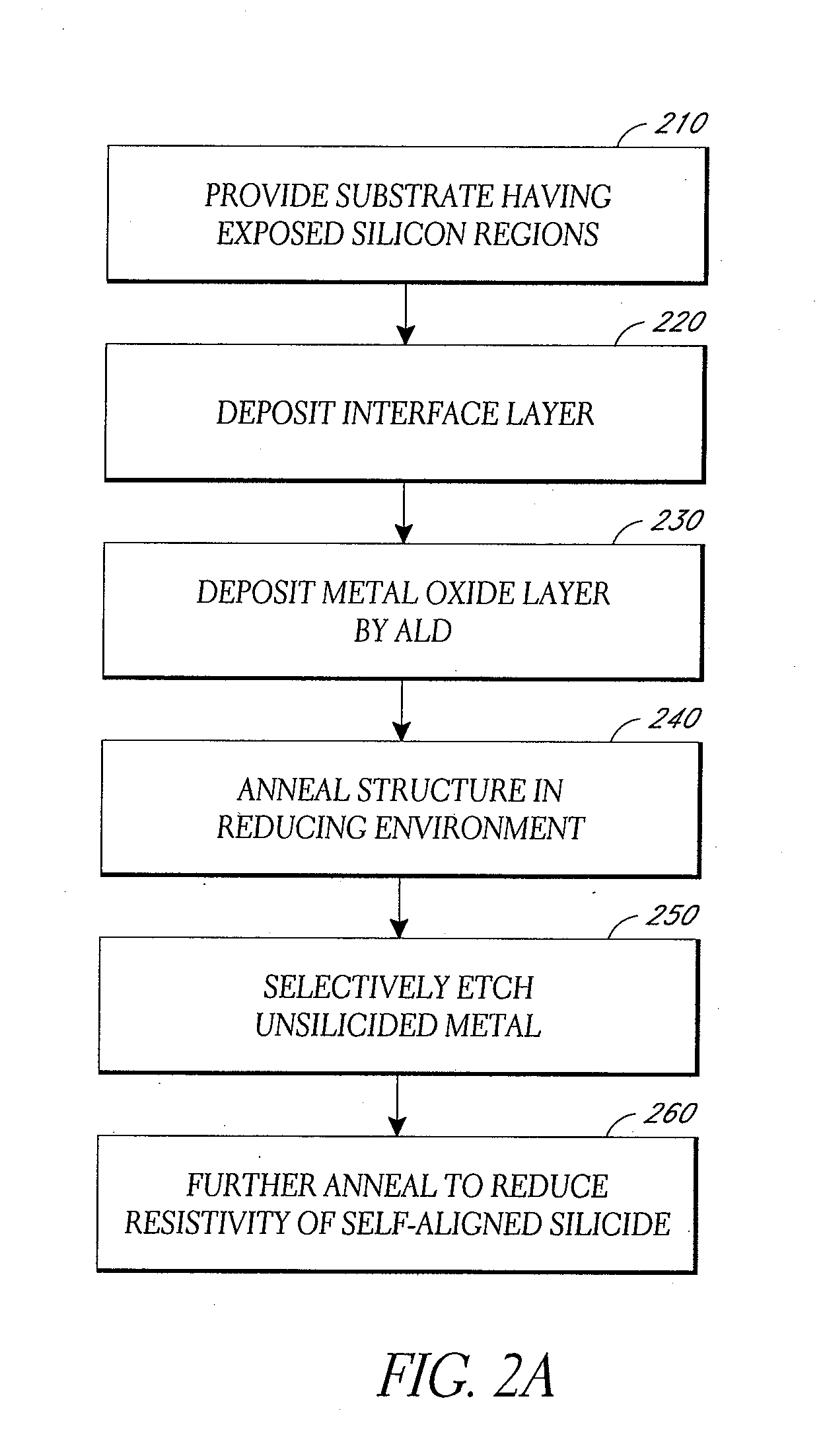

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD. Nickel thin films can be used directly in silicidation and germanidation processes.

Owner:ASM INTERNATIONAL

Metal silicide, metal germanide, methods for making the same

ActiveUS20120270393A1Prevent oxidationSelective silicidationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal silicideGermanide

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD.

Owner:ASM INTERNATIONAL

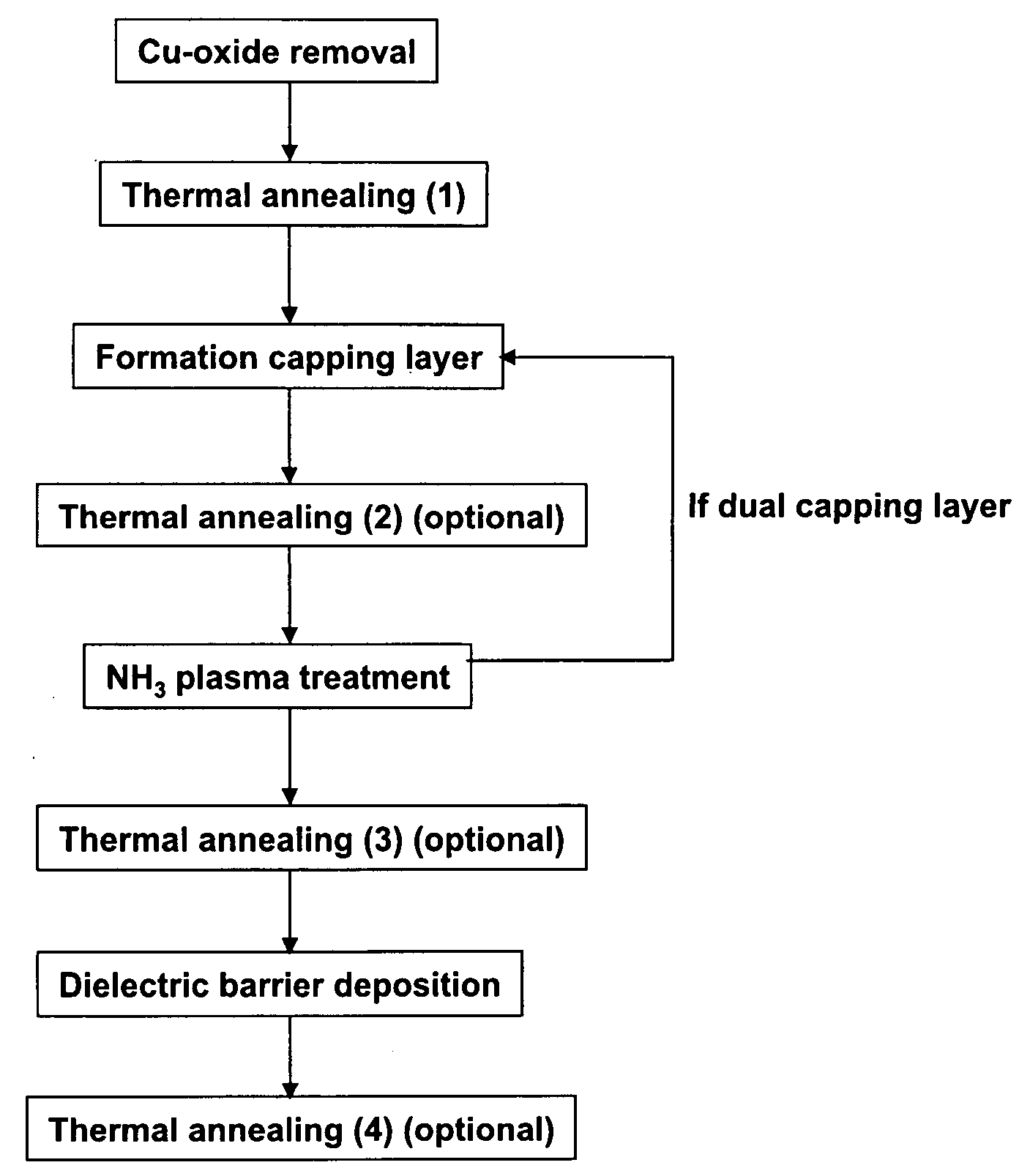

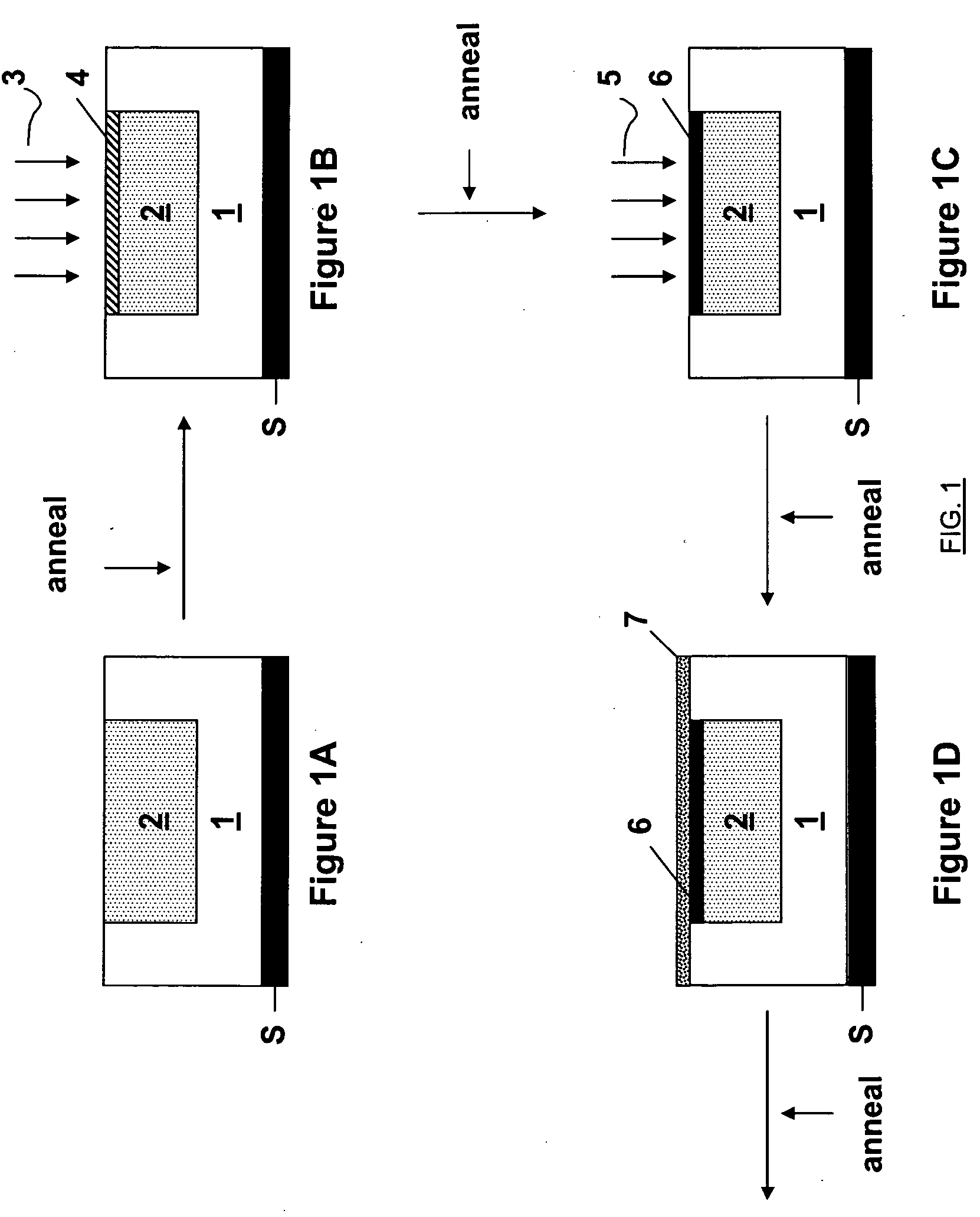

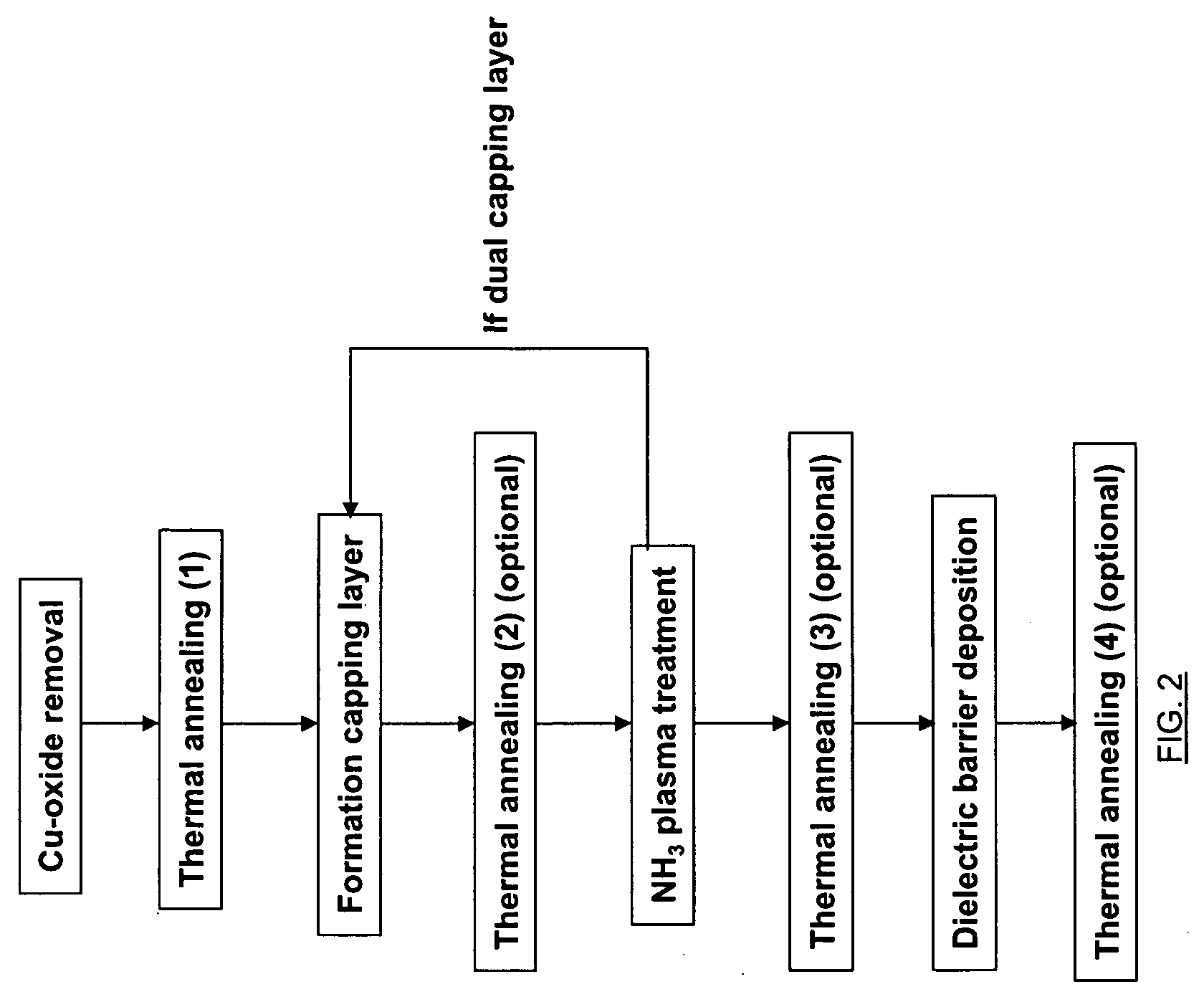

Integrated circuit and manufacturing method of copper germanide and copper silicide as copper capping layer

ActiveUS7858519B2Improve barrier propertiesAvoiding Cu out diffusingSemiconductor/solid-state device detailsSolid-state devicesGermanideCopper silicide

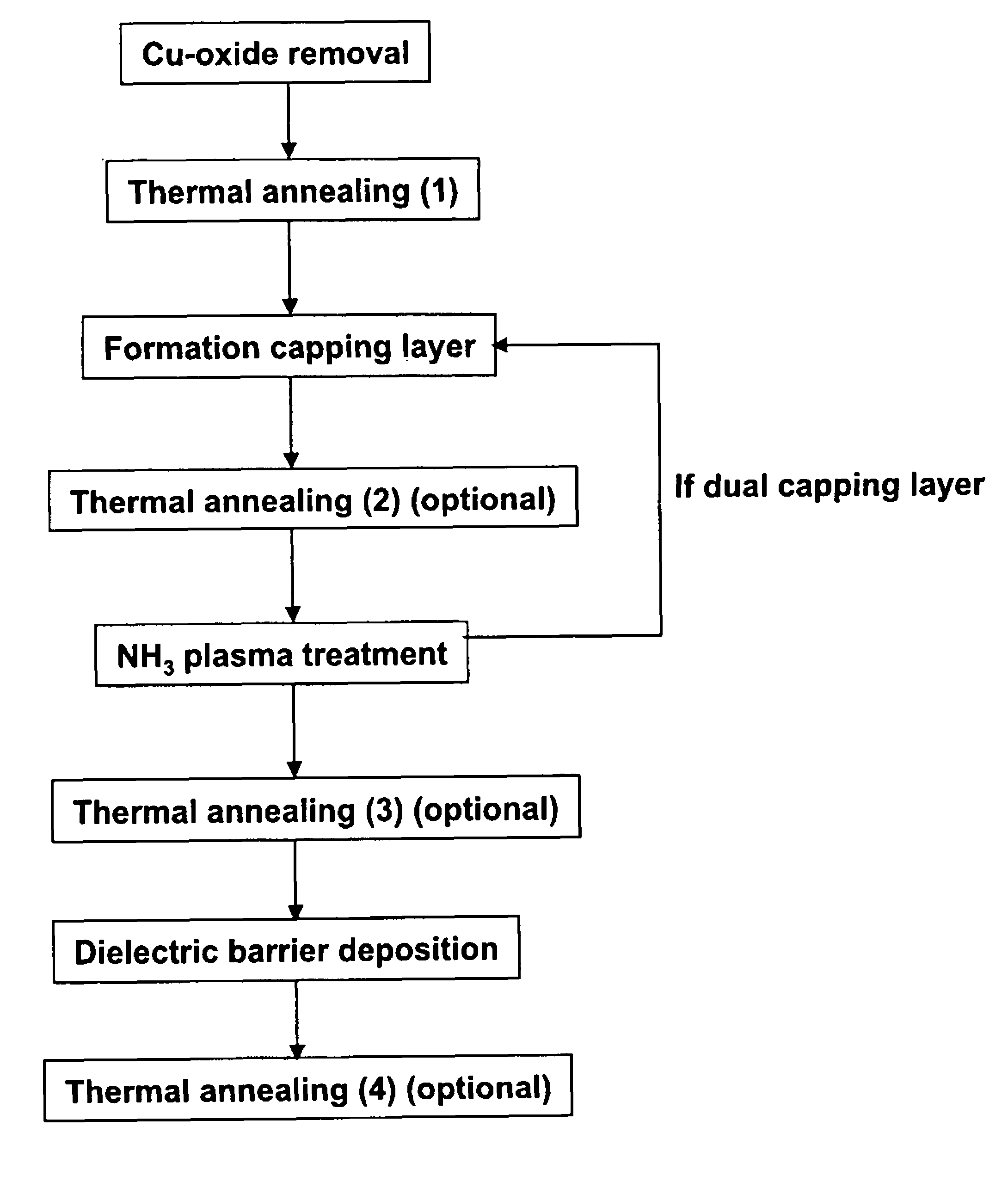

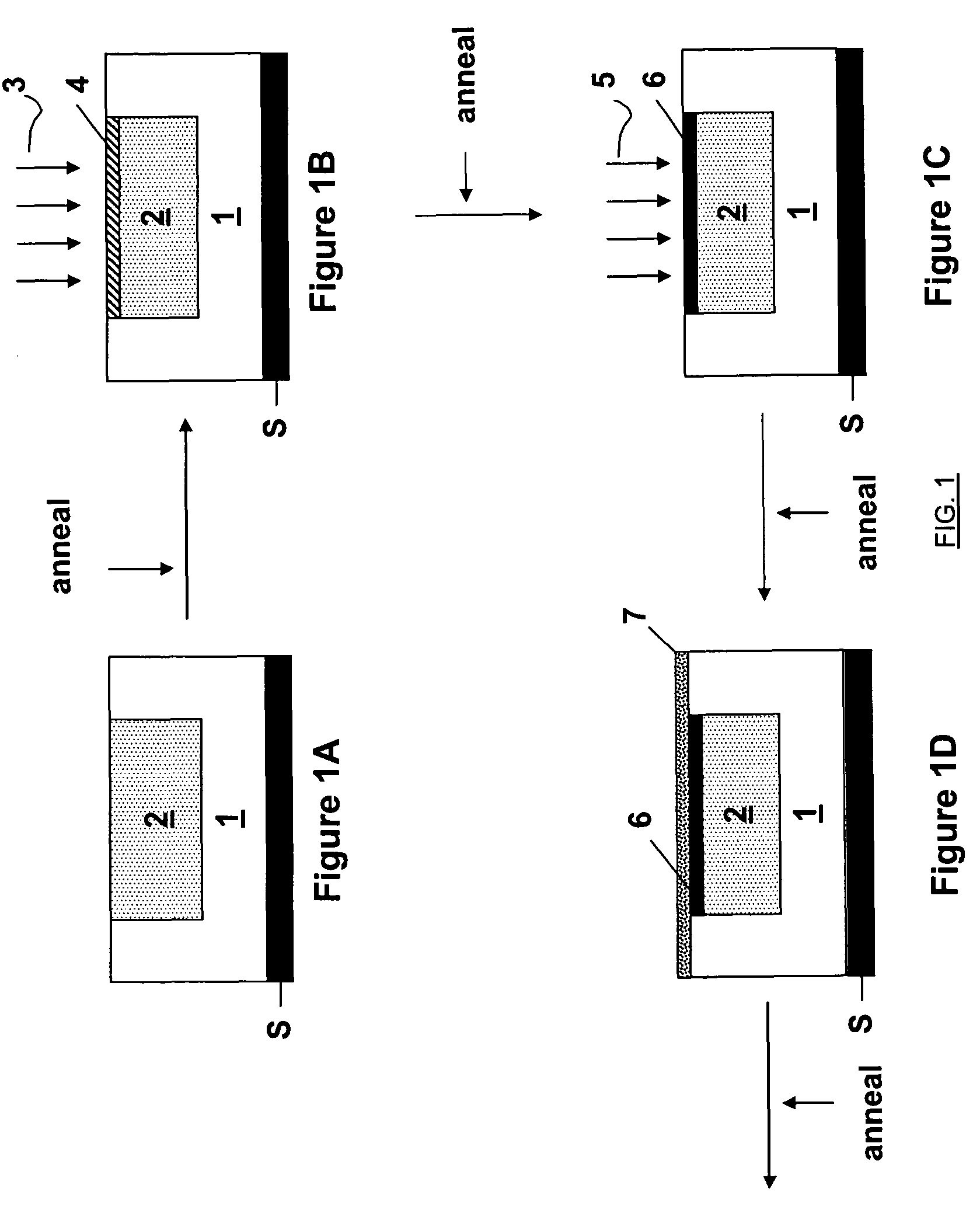

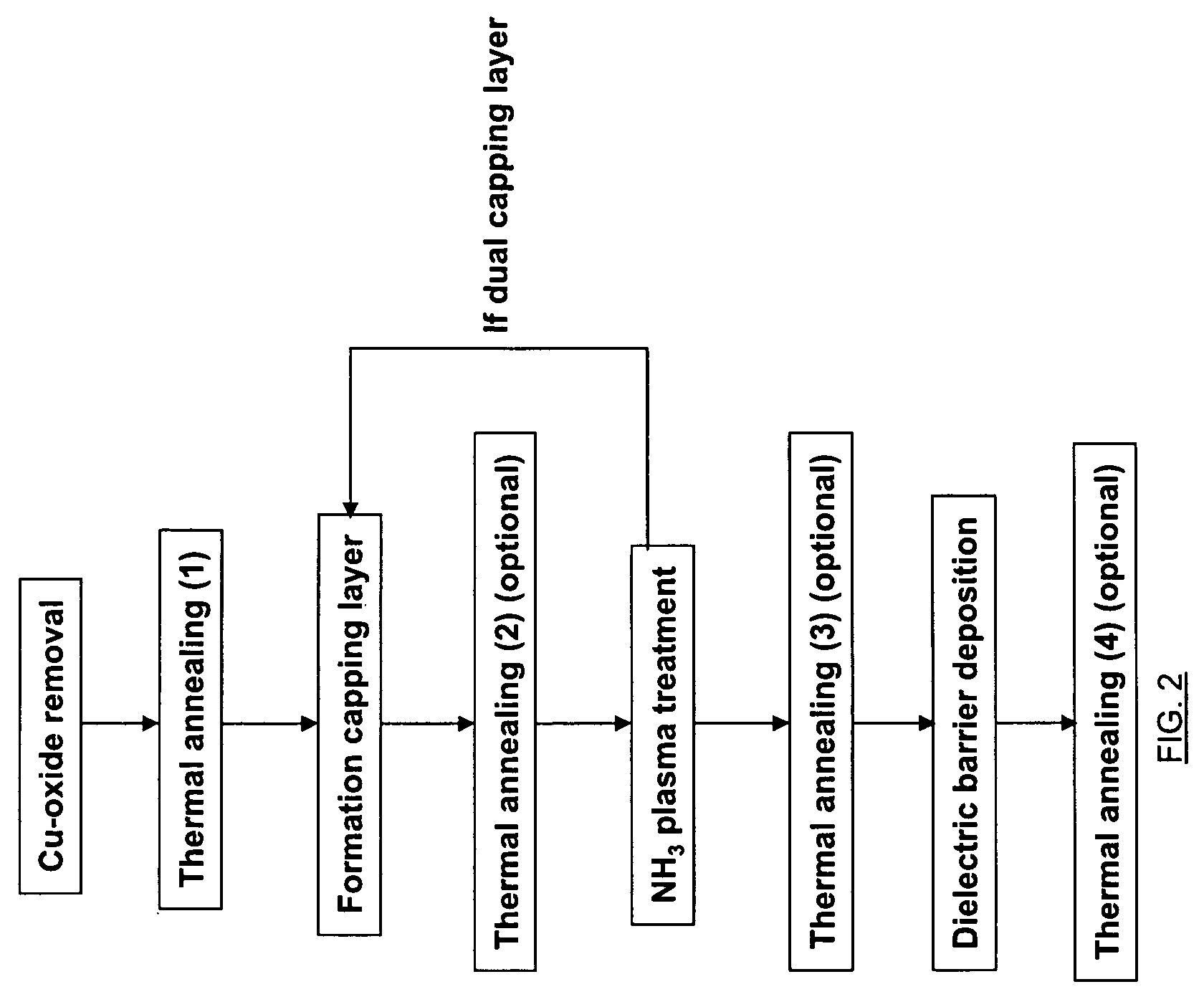

A method is provided for forming a capping layer comprising Cu, N, and also Si and / or Ge onto a copper conductive structure, said method comprising the sequential steps of: forming, at a temperature range between 200° C. up to 400° C., at least one capping layer onto said copper conductive structure by exposing said structure to a GeH4 and / or a SiH4 comprising ambient, performing a NH3 plasma treatment thereby forming an at least partly nitrided capping layer, forming a dielectric barrier layer onto said at least partly nitrided capping layer, wherein prior to said step of forming said at least one capping layer a pre-annealing step of said copper conductive structure is performed at a temperature range between 250° C. up to 450° C.

Owner:TAIWAN SEMICON MFG CO LTD +1

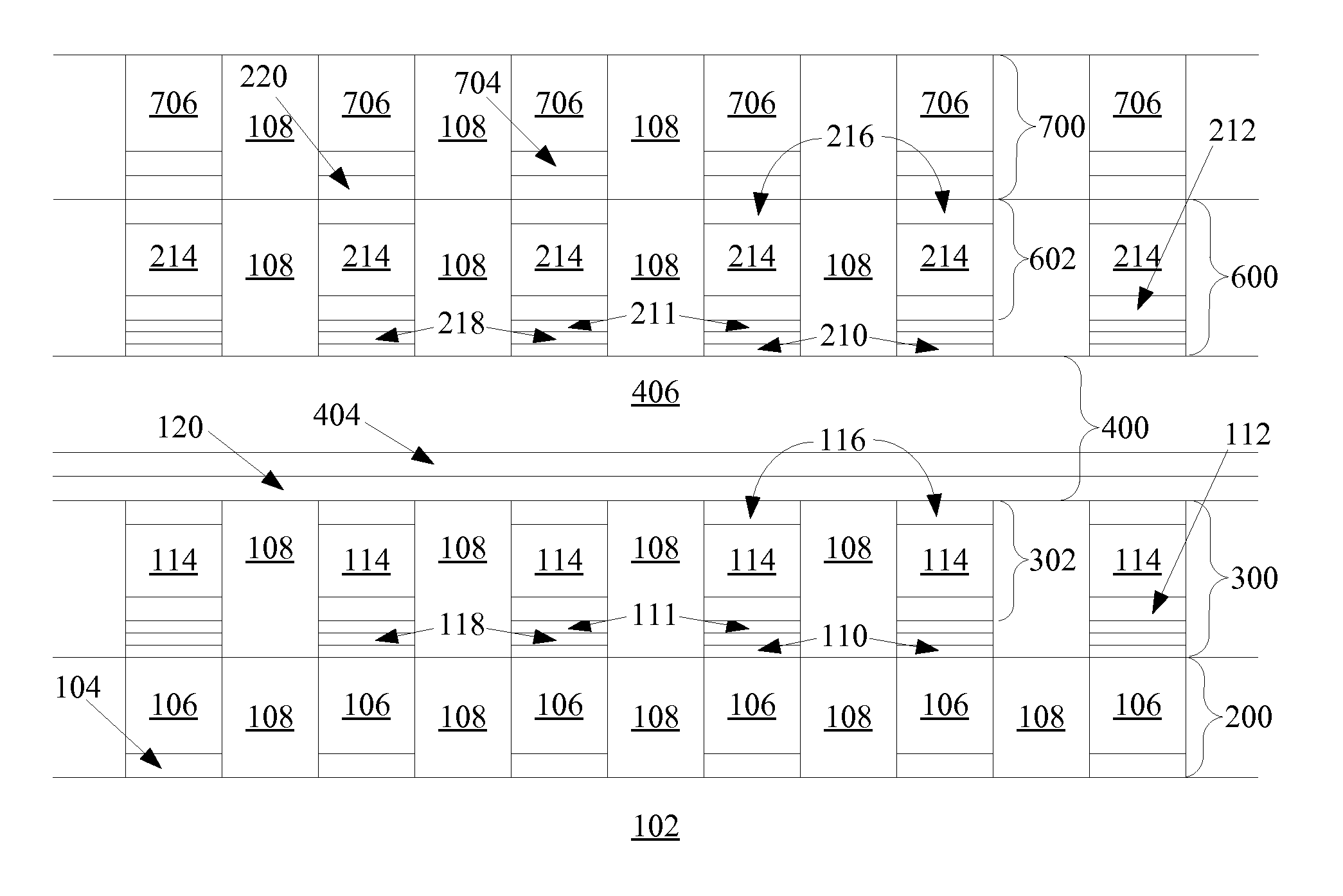

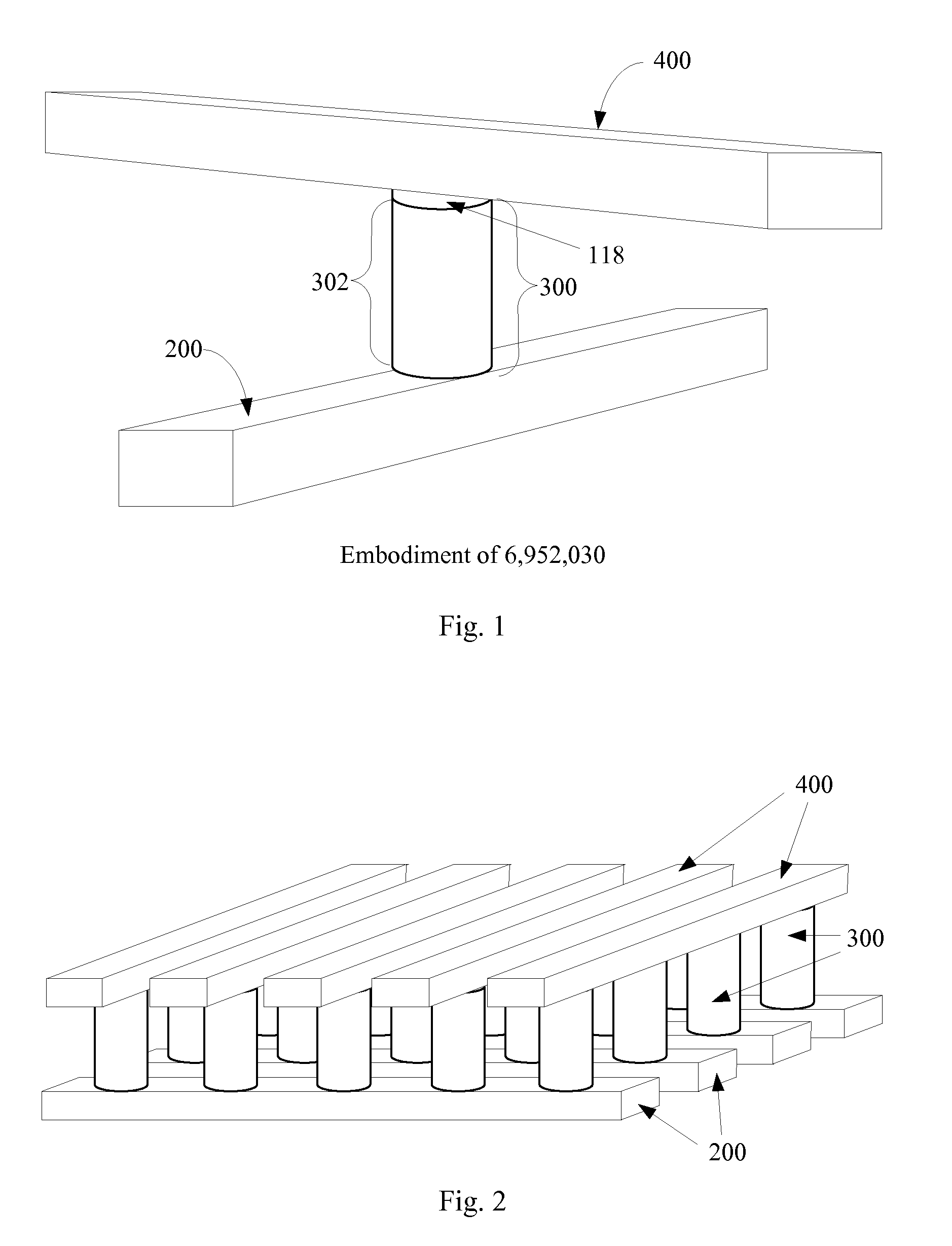

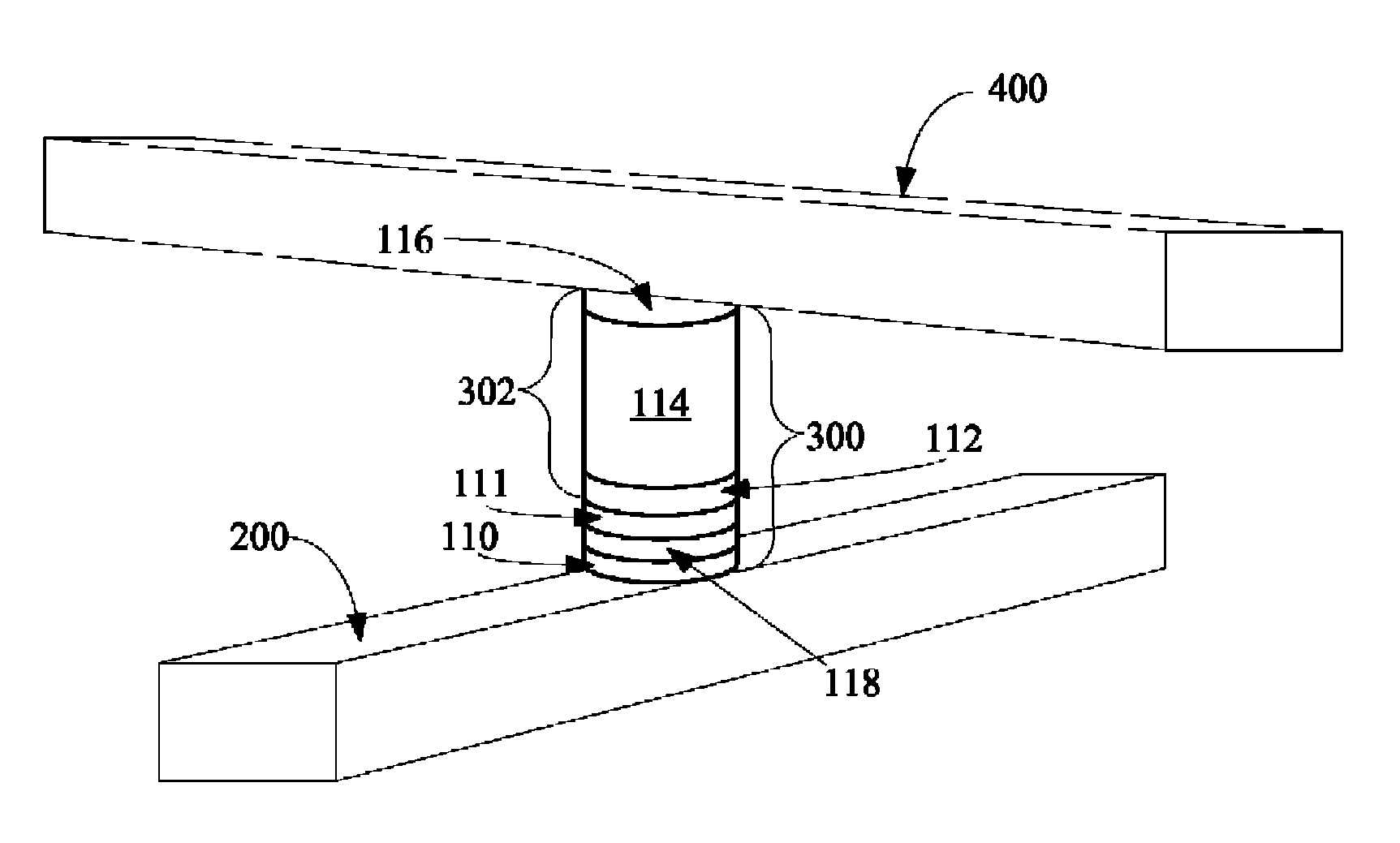

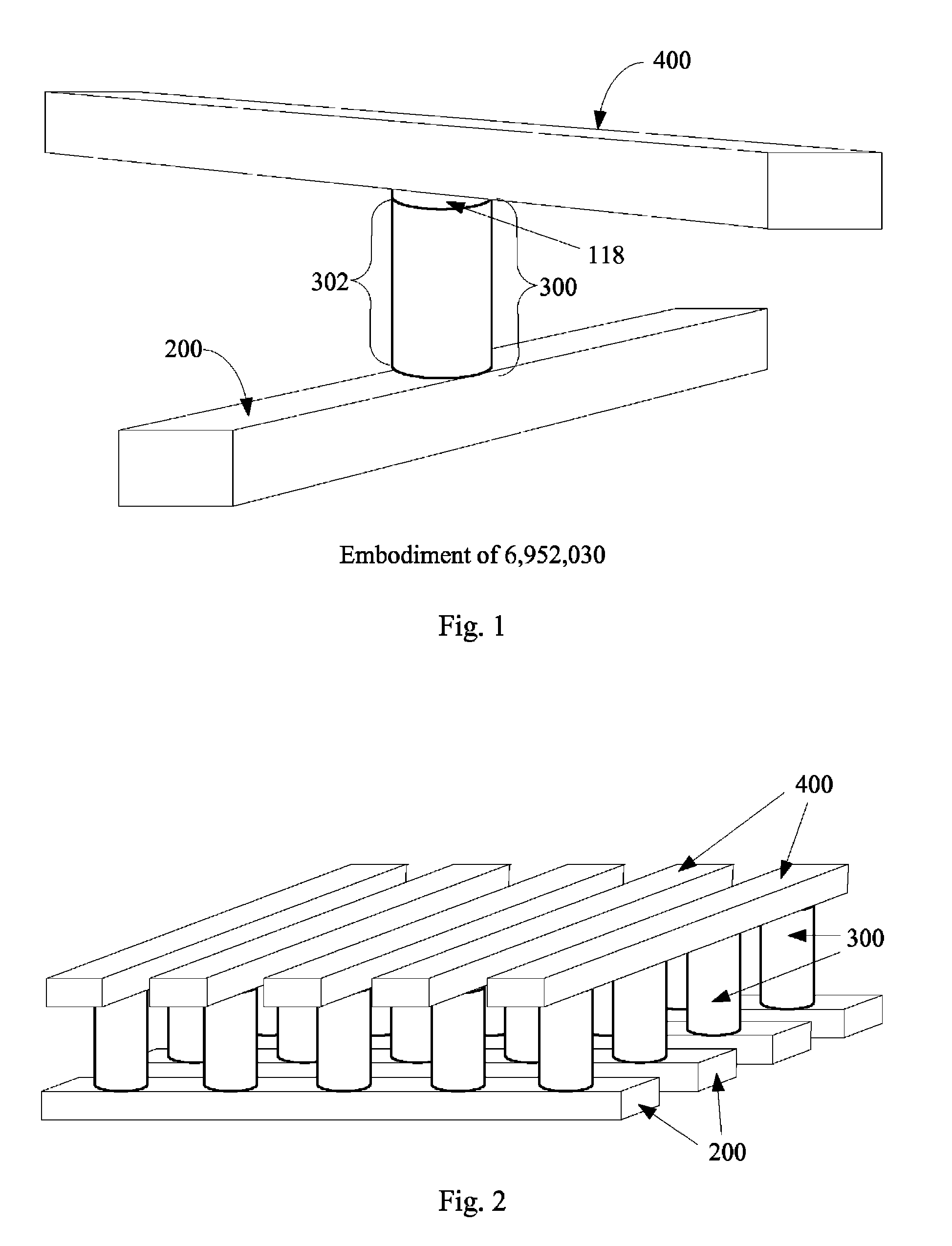

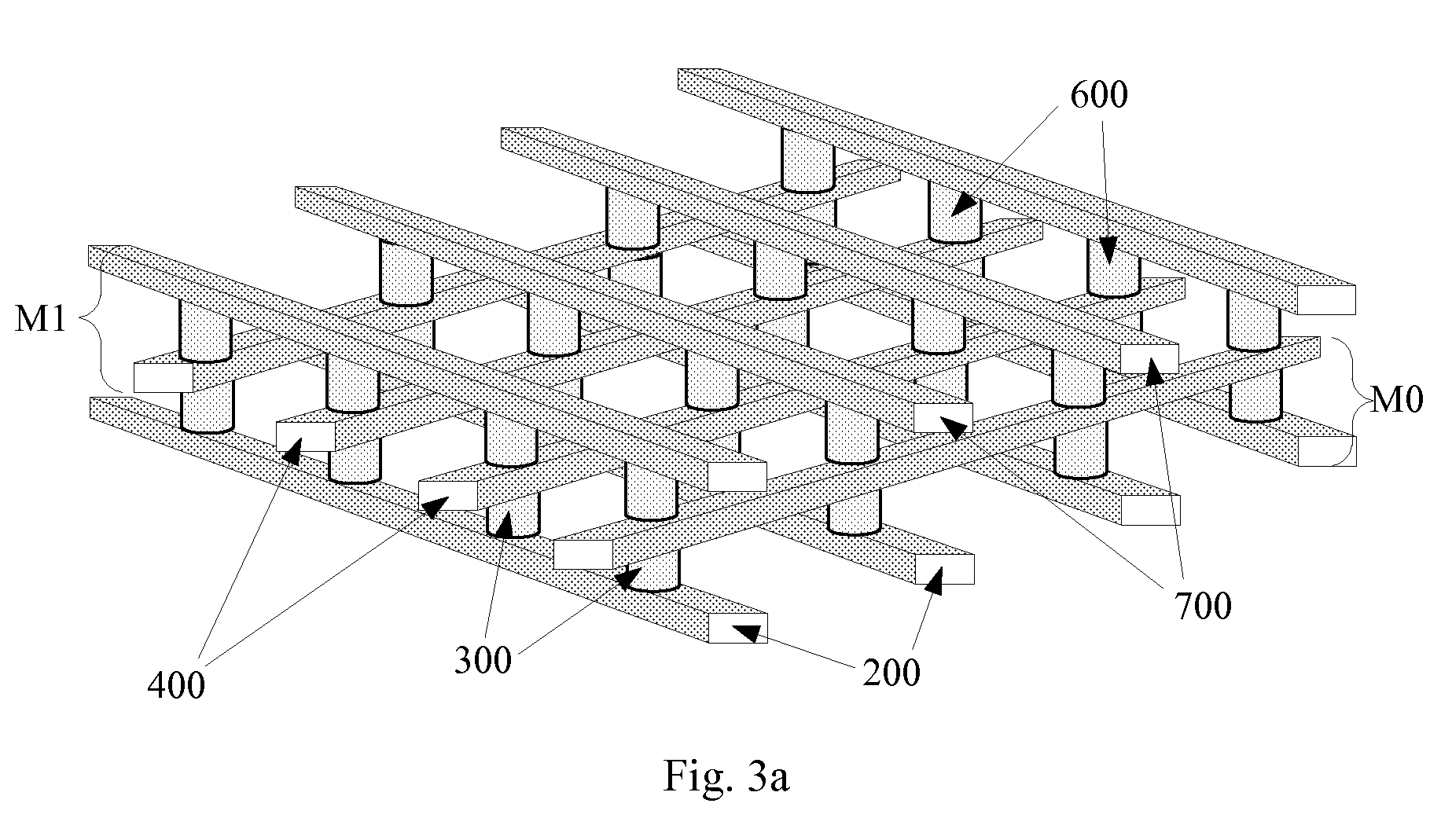

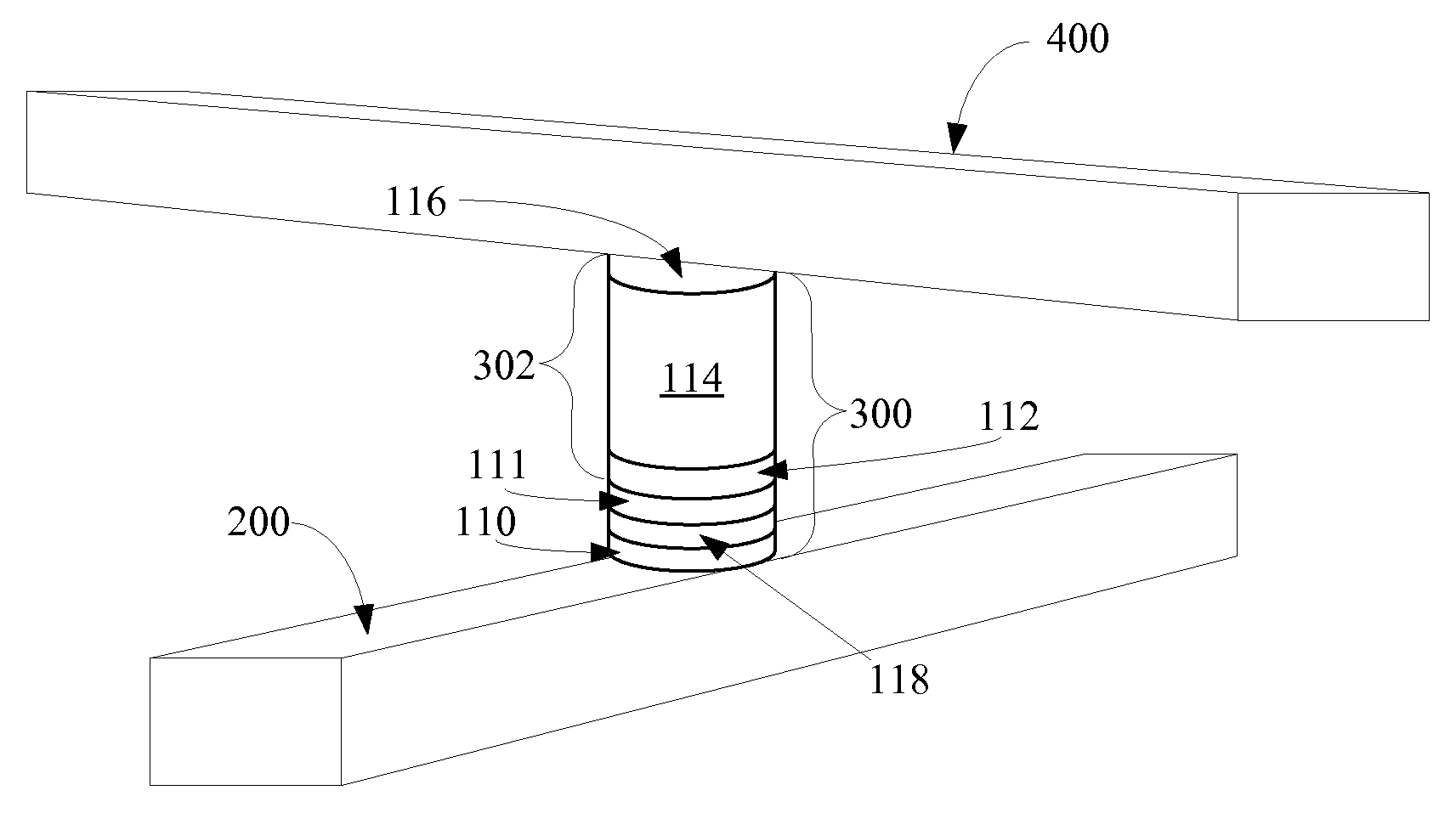

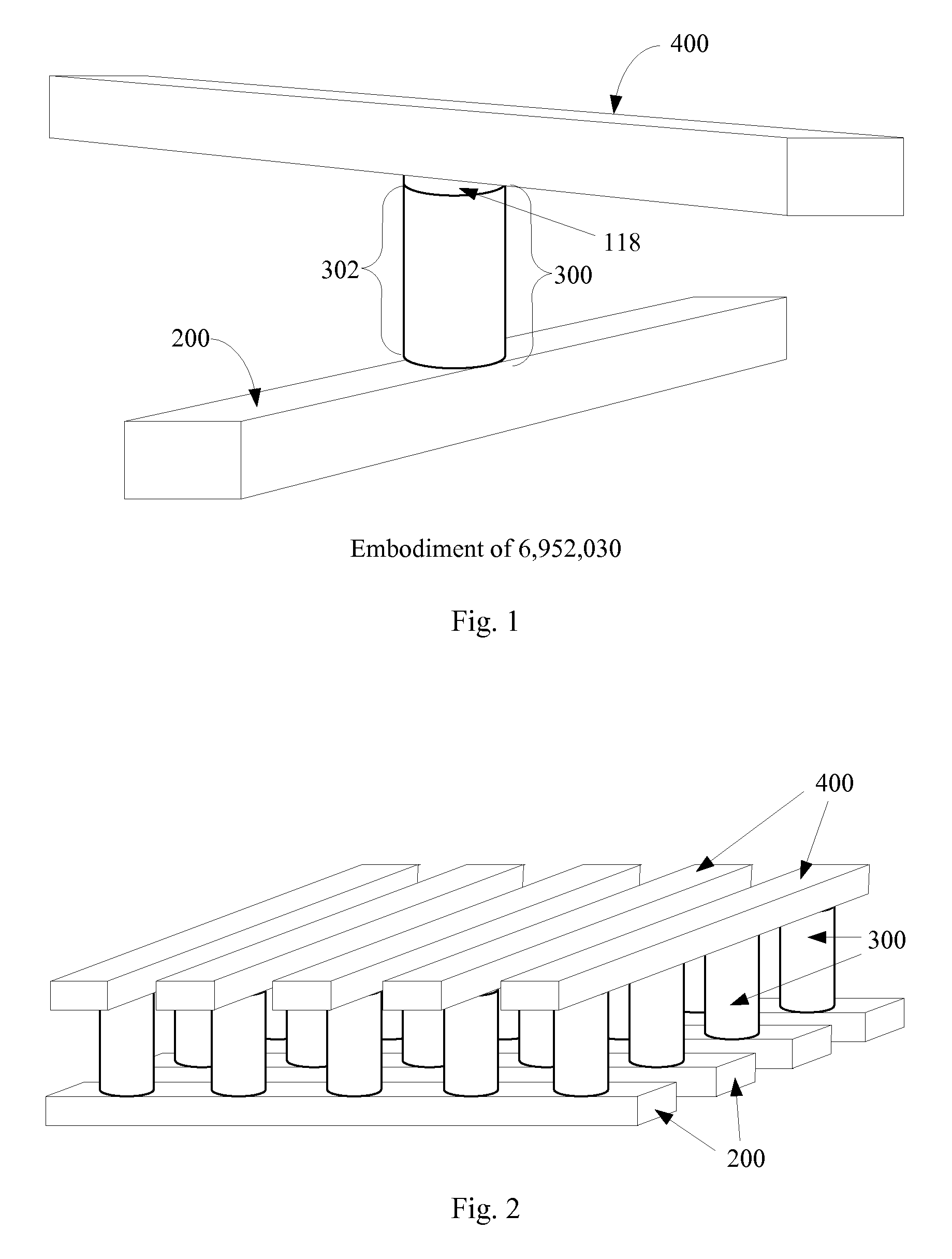

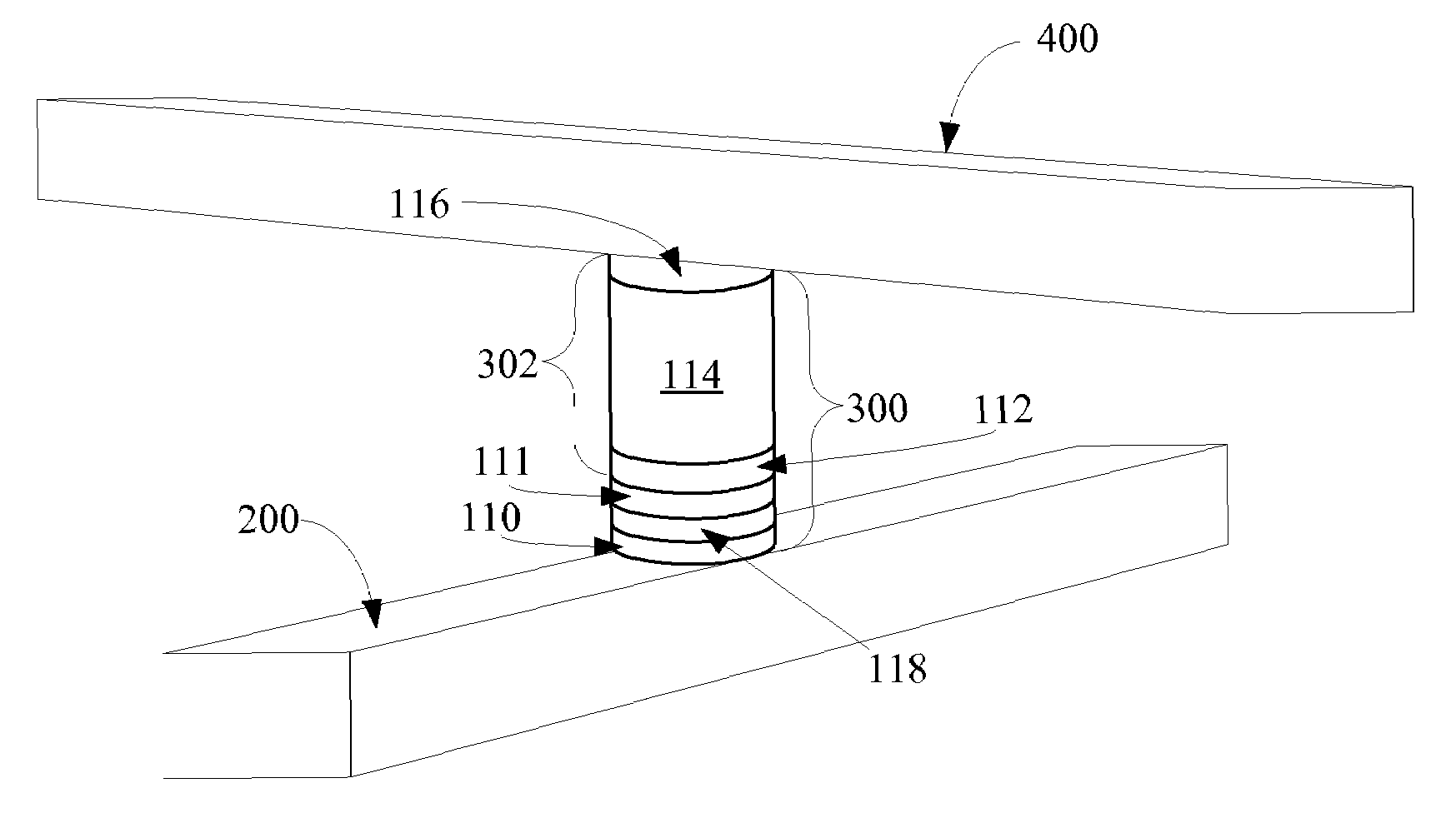

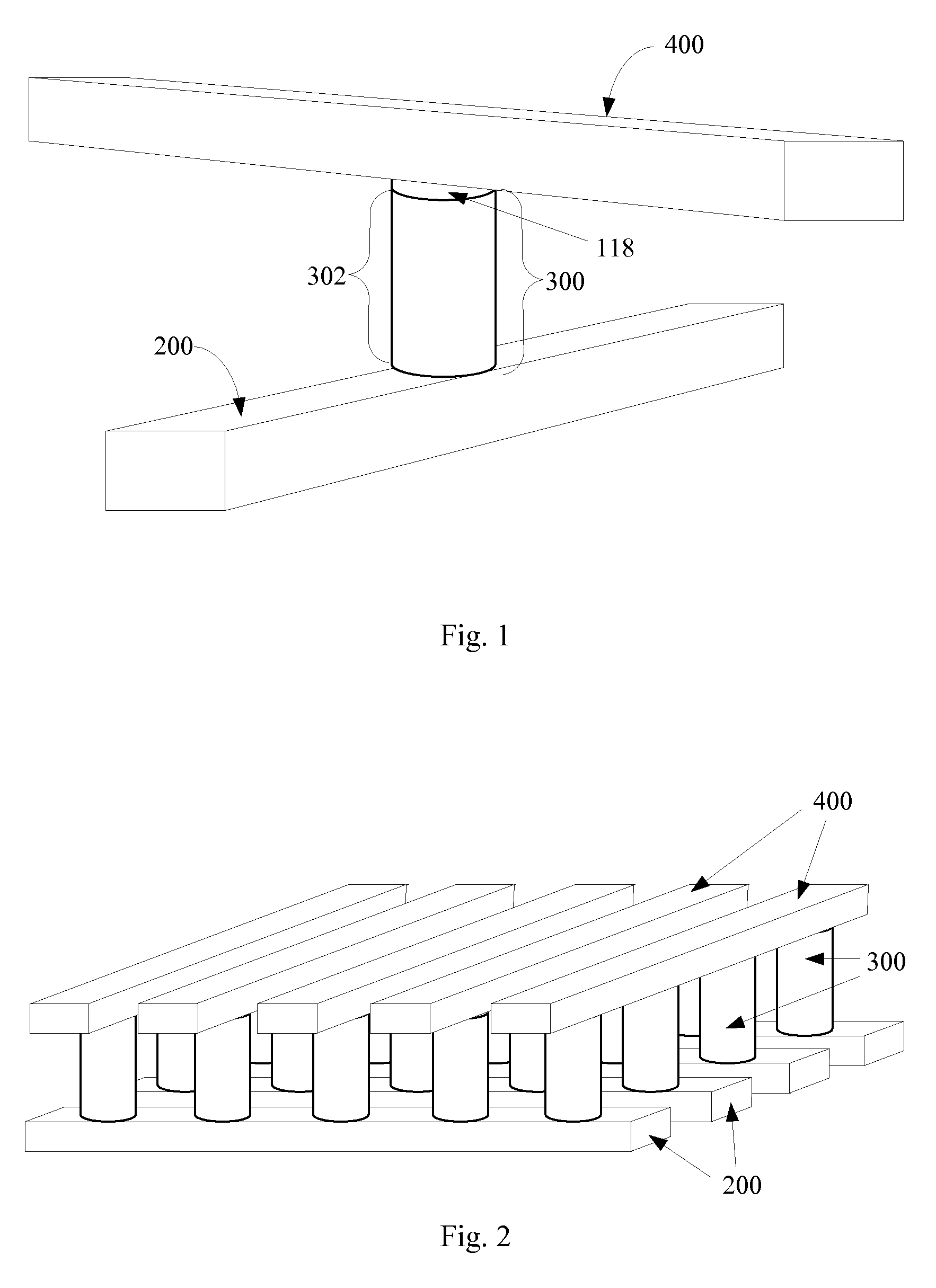

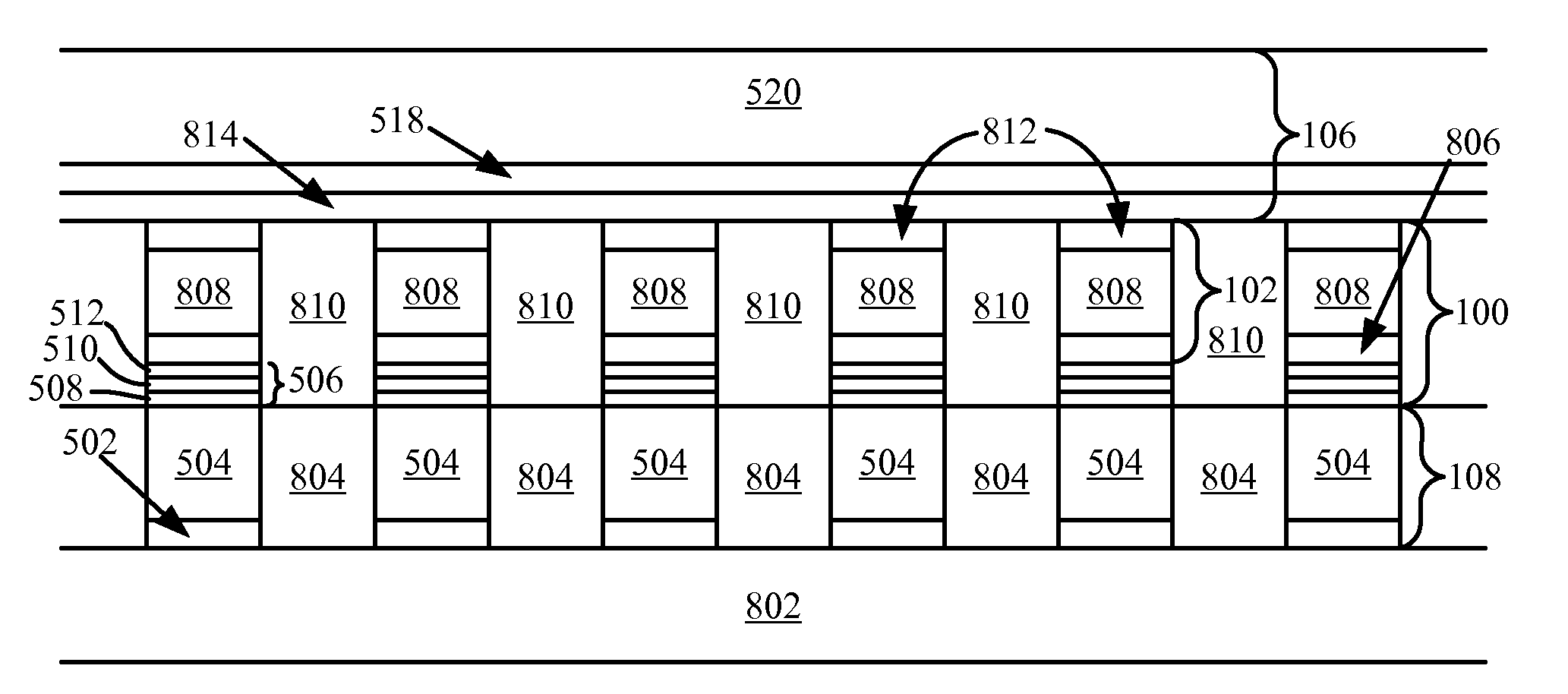

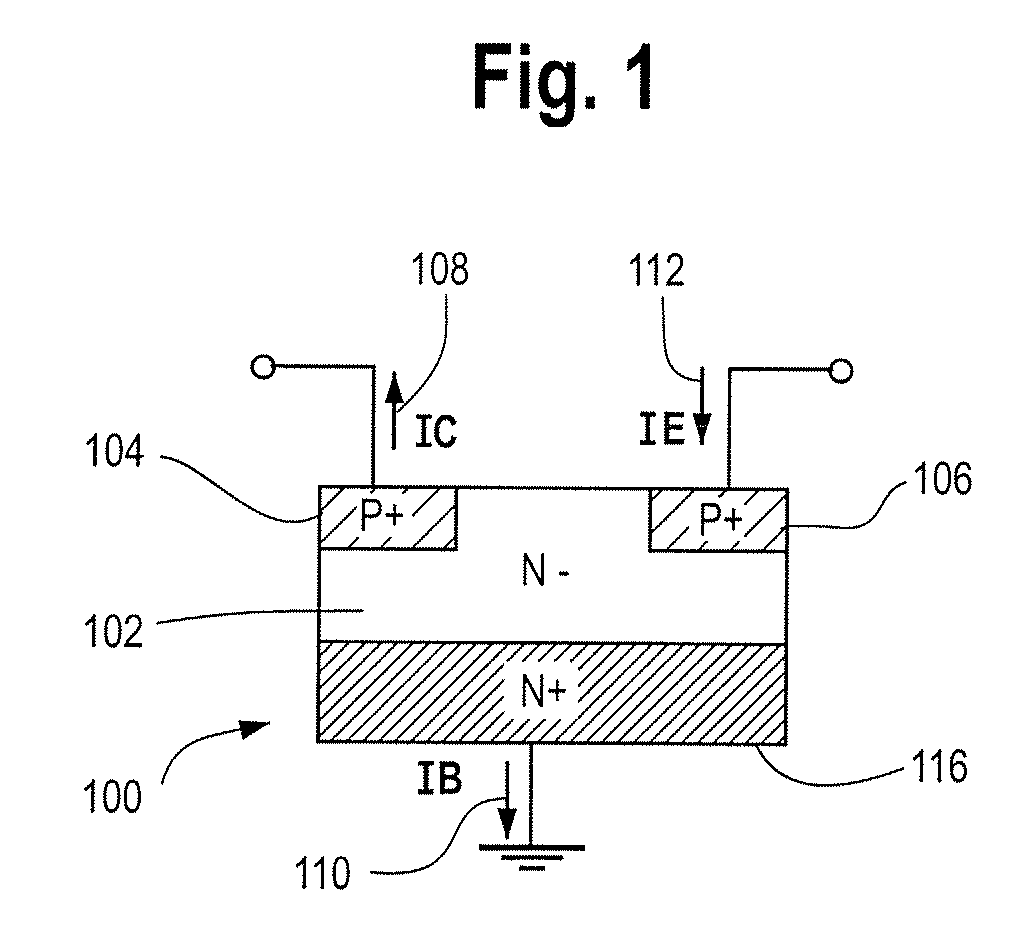

Method to form upward pointing p-i-n diodes having large and uniform current

A method is disclosed to form an upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

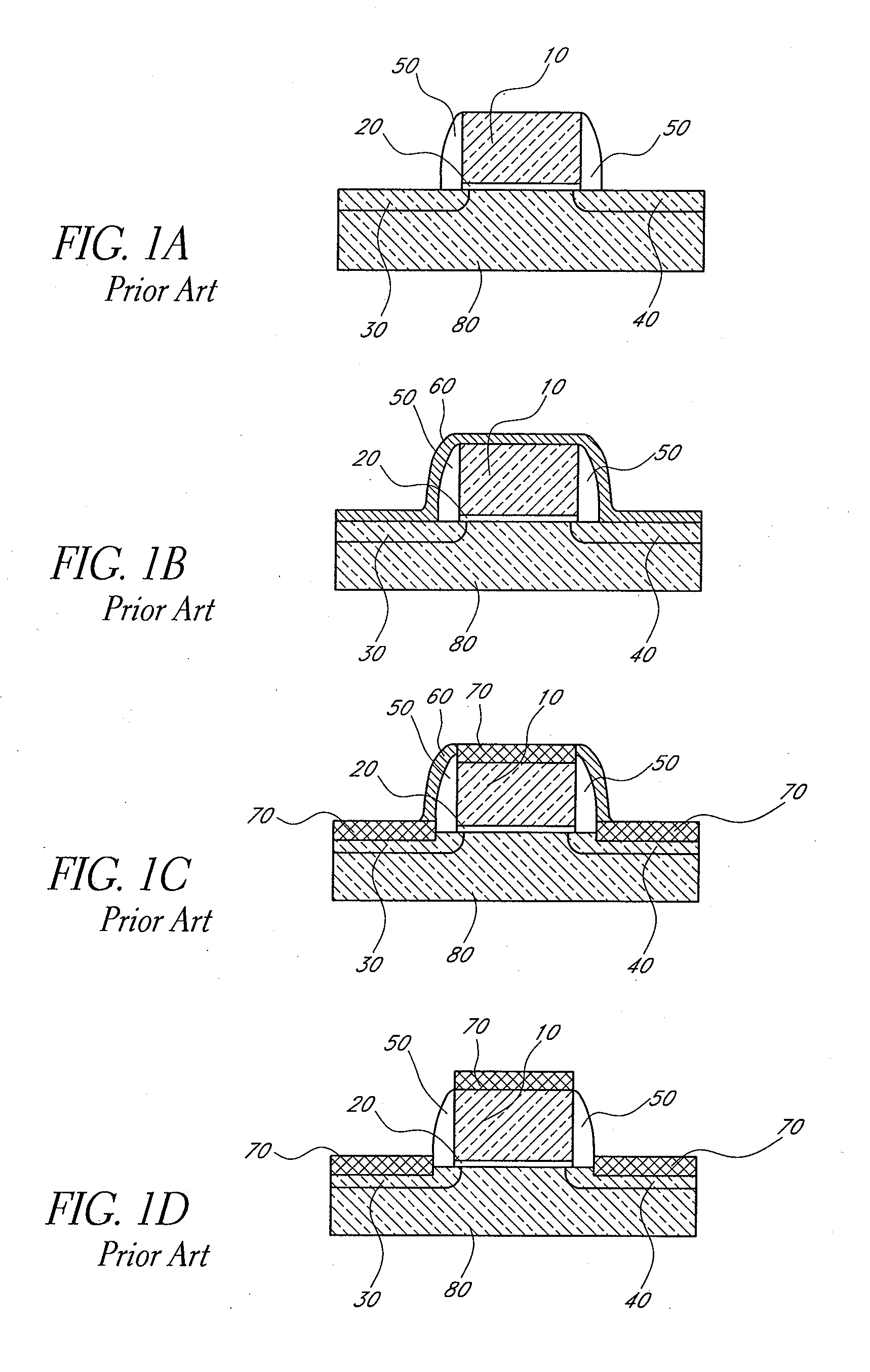

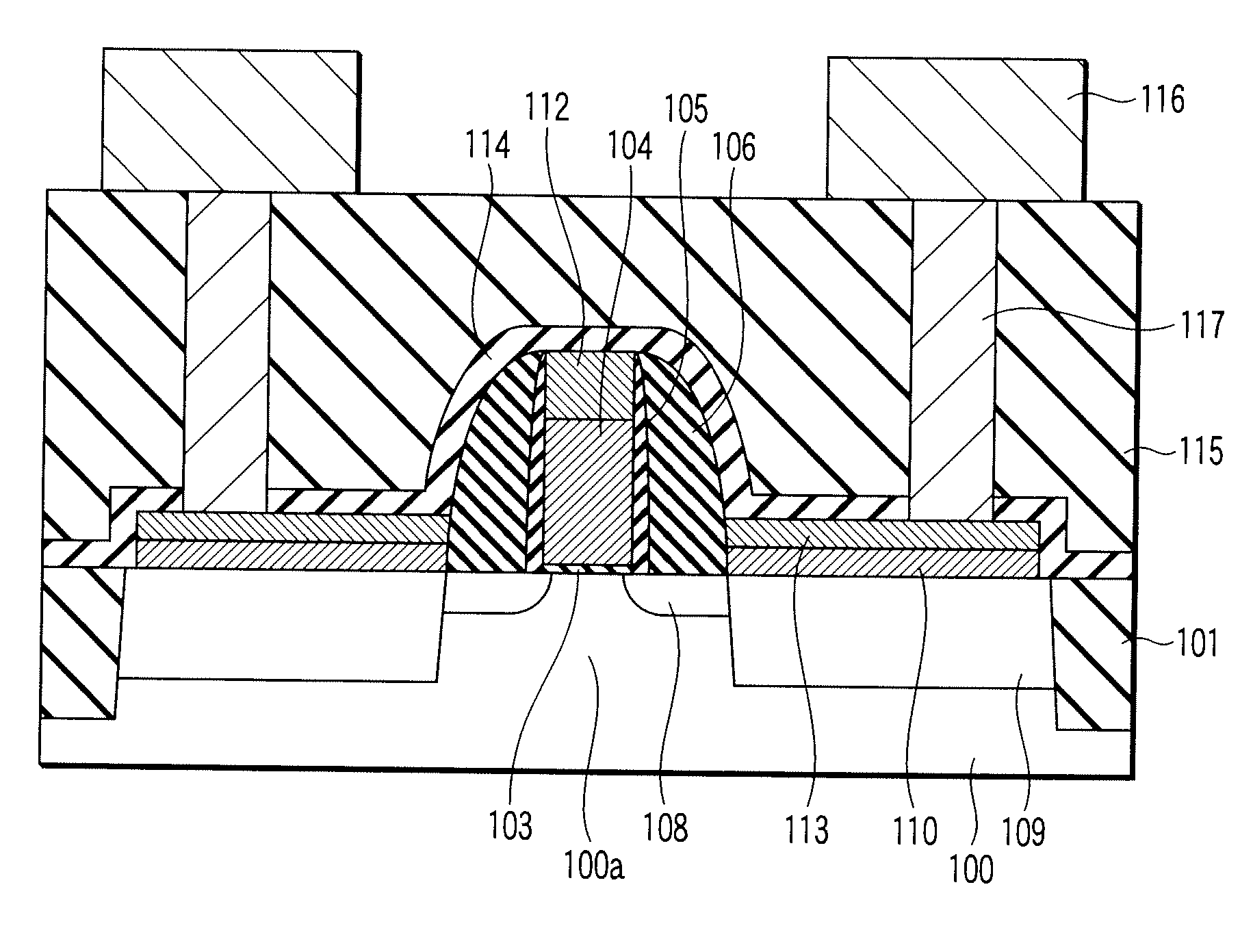

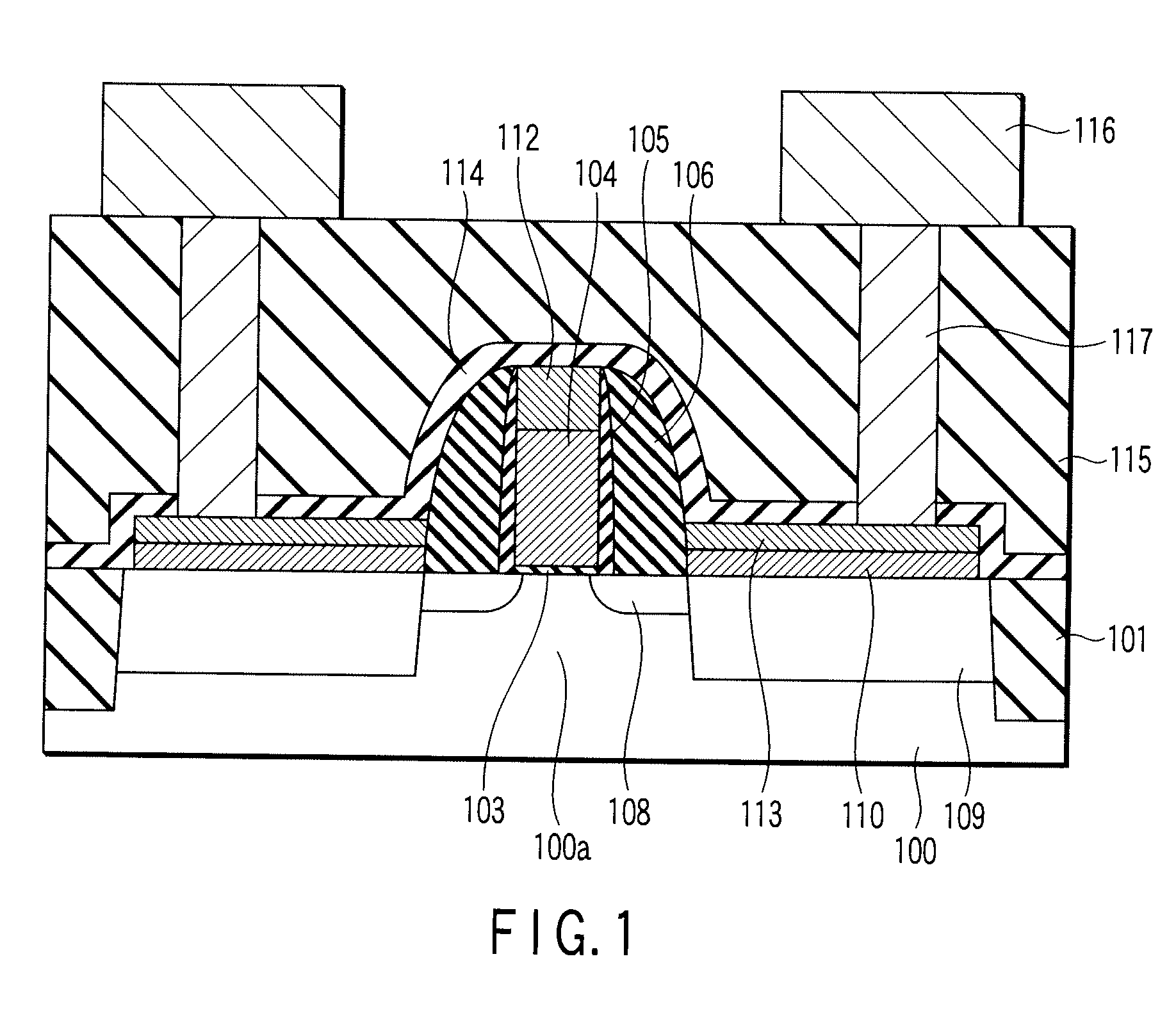

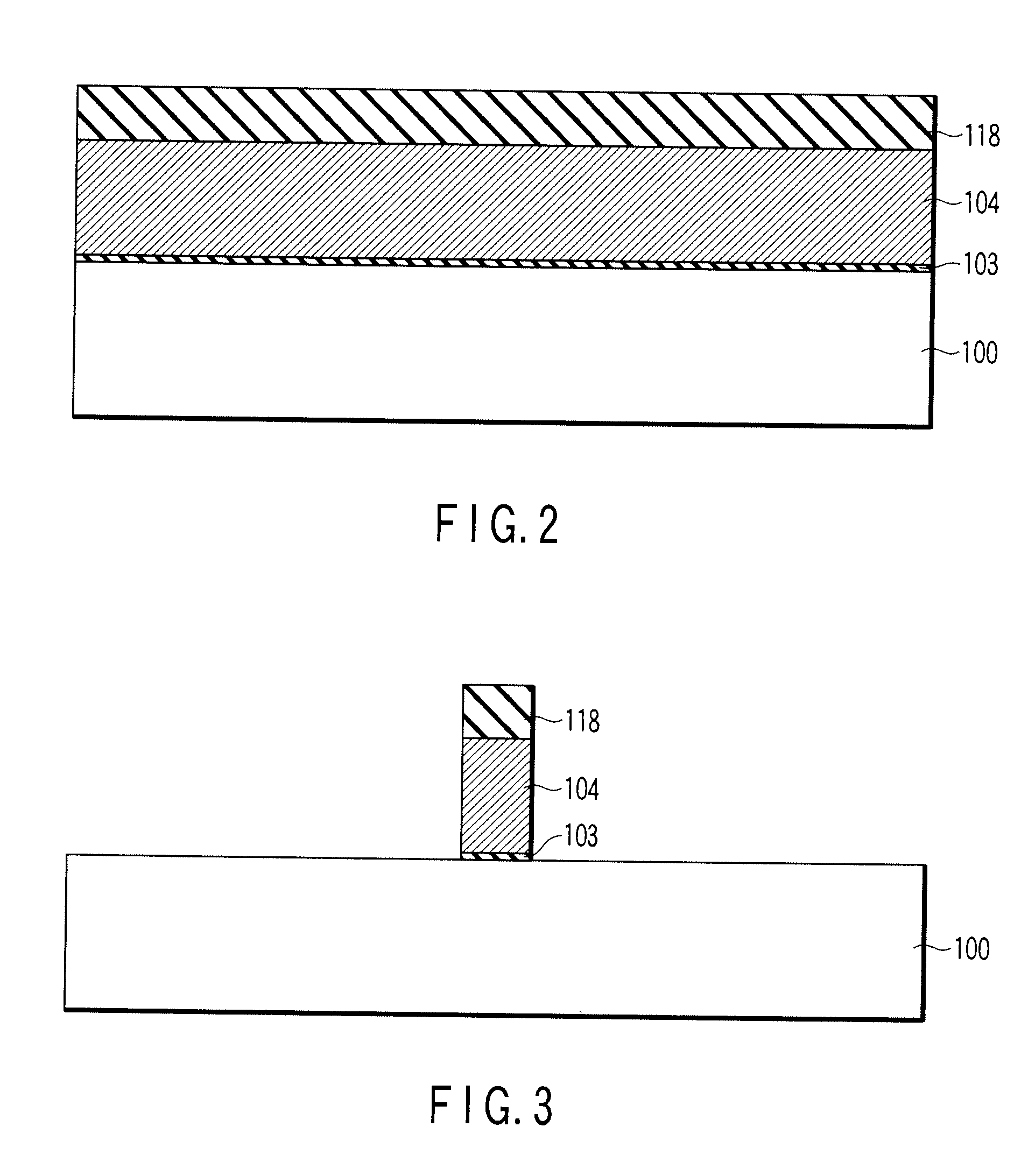

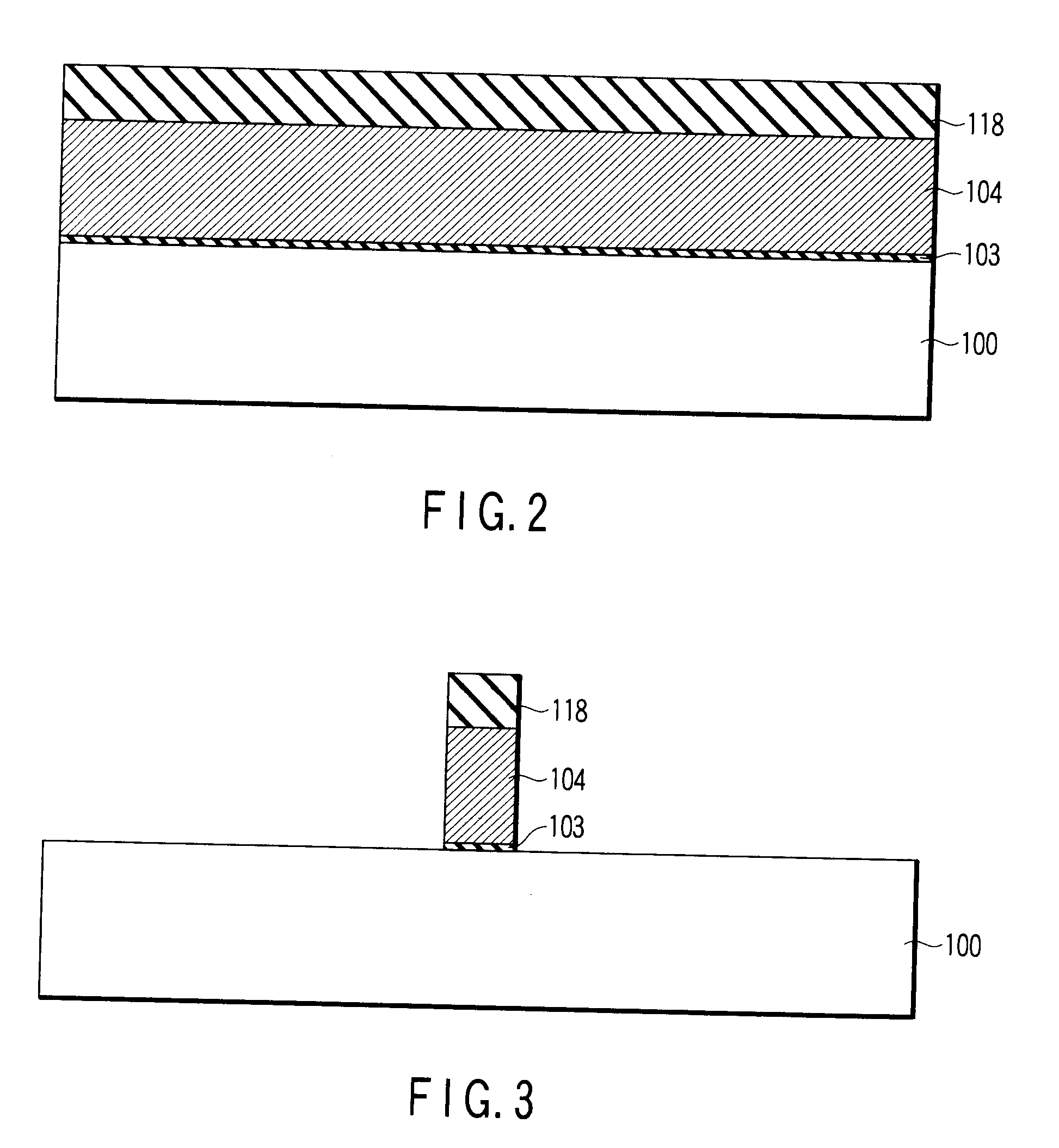

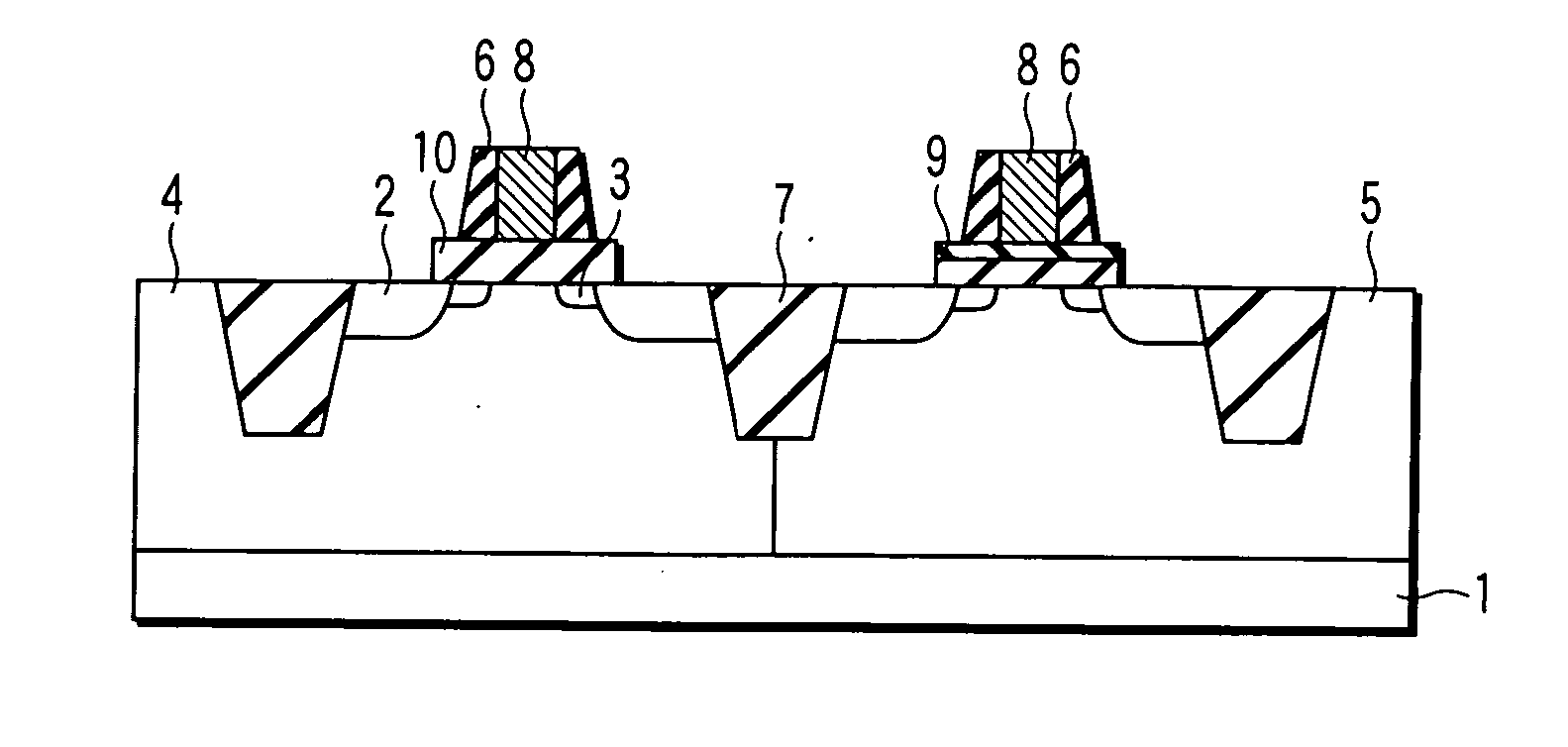

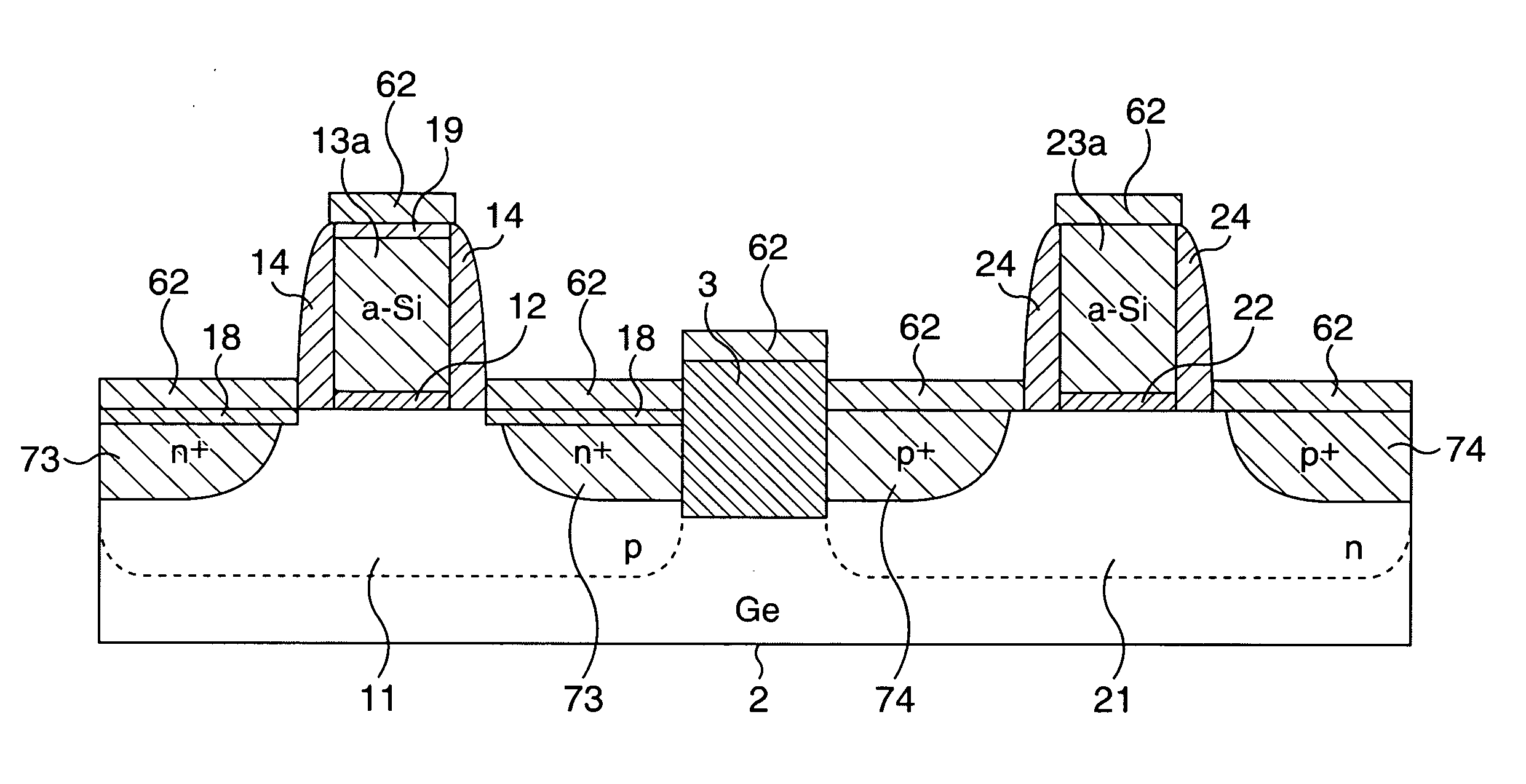

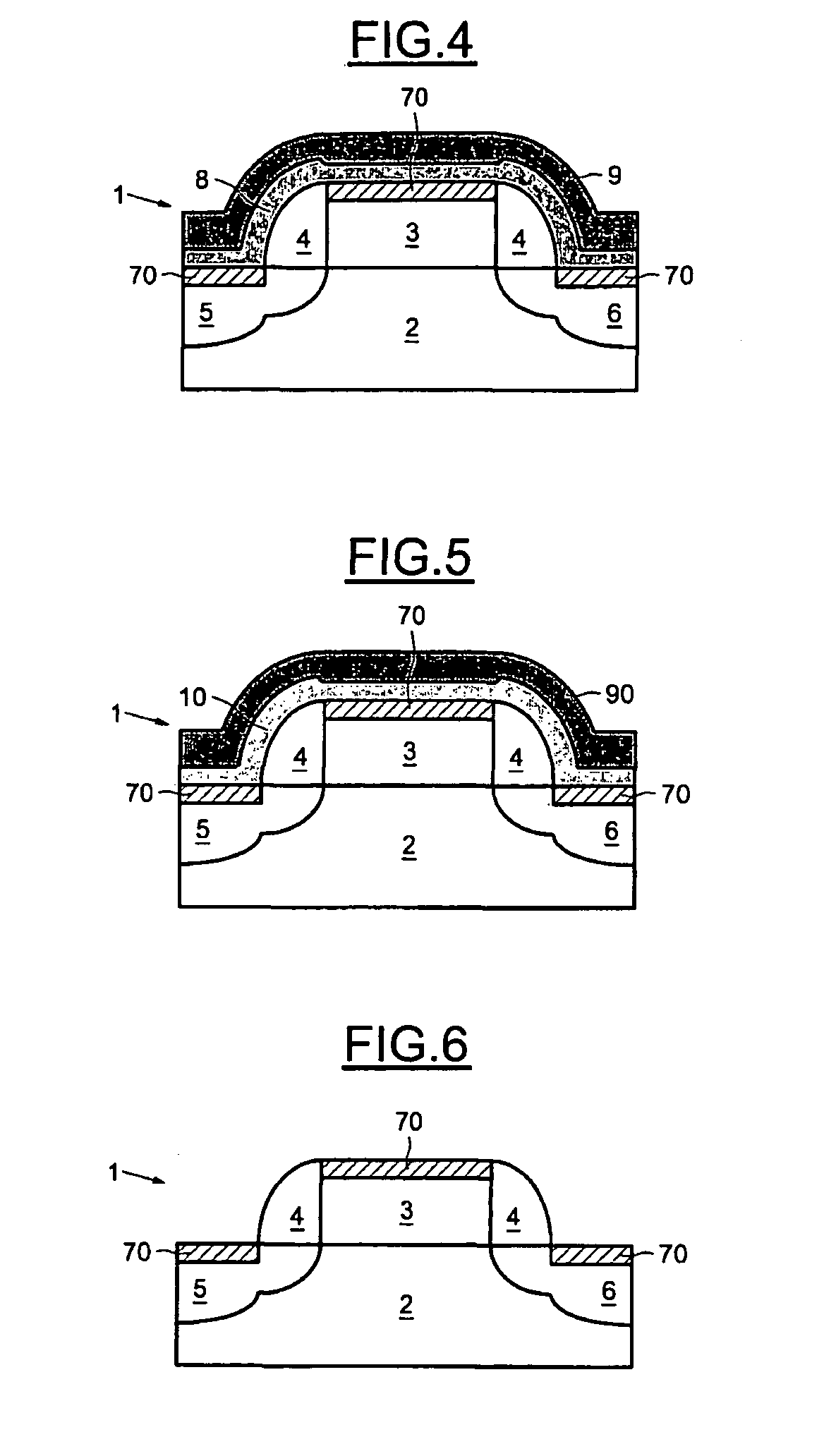

Semiconductor device including misfet

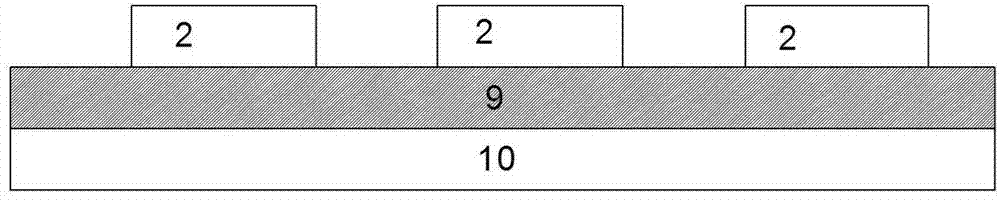

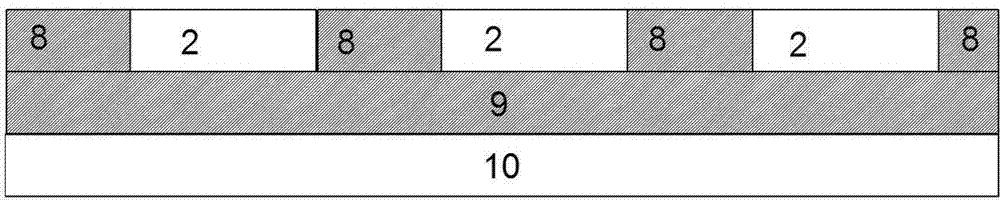

InactiveUS20070187767A1Semiconductor/solid-state device manufacturingSemiconductor devicesSurface layerDevice material

A semiconductor device includes a semiconductor substrate, a gate insulating film, a gate electrode, a source / drain layer, and a germanide layer. The gate insulating film is formed on the semiconductor substrate. The gate electrode is formed on the gate insulating film. The source / drain layer is formed on both sides of the gate electrode, contains silicon germanium, and has a germanium layer in a surface layer portion. The germanide layer is formed on the germanium layer of the source / drain layer.

Owner:KK TOSHIBA

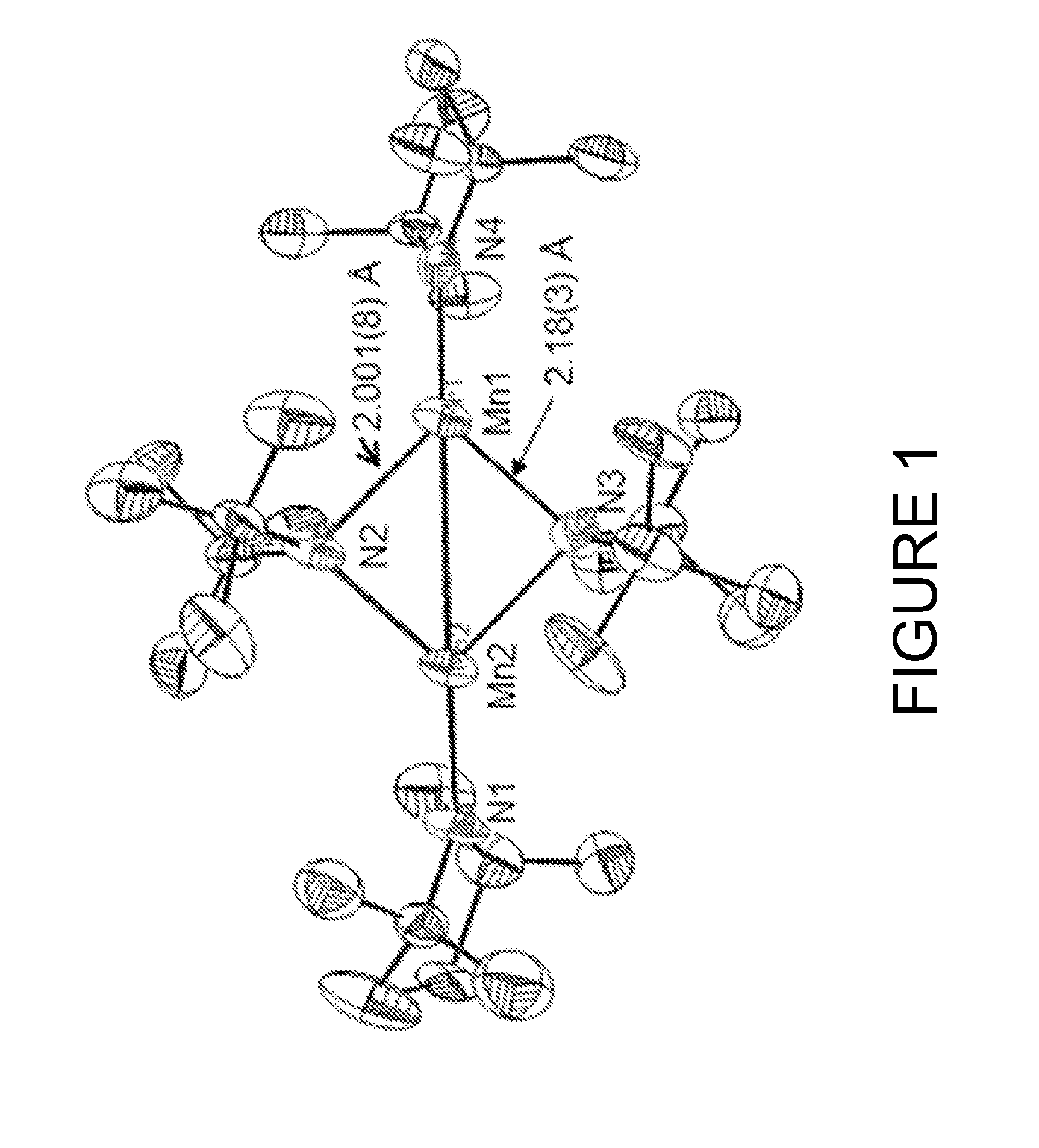

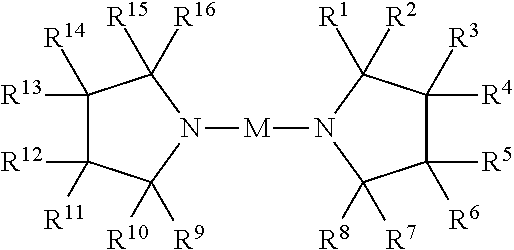

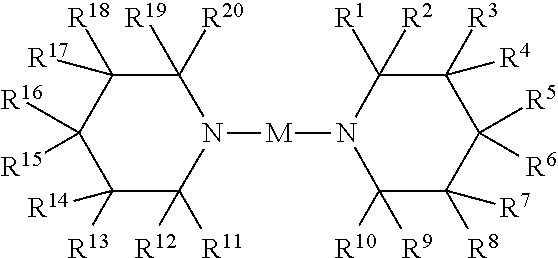

Metal amides of cyclic amines

ActiveUS20160152649A1Improve thermal stabilityImprove conductivityIron group organic compounds without C-metal linkagesNickel organic compoundsGermanideMetal silicide

Compounds, and oligomers of the compounds, are synthesized with cyclic amine ligands attached to a metal atom. These compounds are useful for the synthesis of materials containing metals. Examples include pure metals, metal alloys, metal oxides, metal nitrides, metal phosphides, metal sulfides, metal selenides, metal tellurides, metal borides, metal carbides, metal silicides and metal germanides. Techniques for materials synthesis include vapor deposition (chemical vapor deposition and atomic layer deposition), liquid solution methods (sol-gel and precipitation) and solid-state pyrolysis. Suitable applications include electrical interconnects in microelectronics and magnetoresistant layers in magnetic information storage devices. The films have very uniform thickness and high step coverage in narrow holes.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

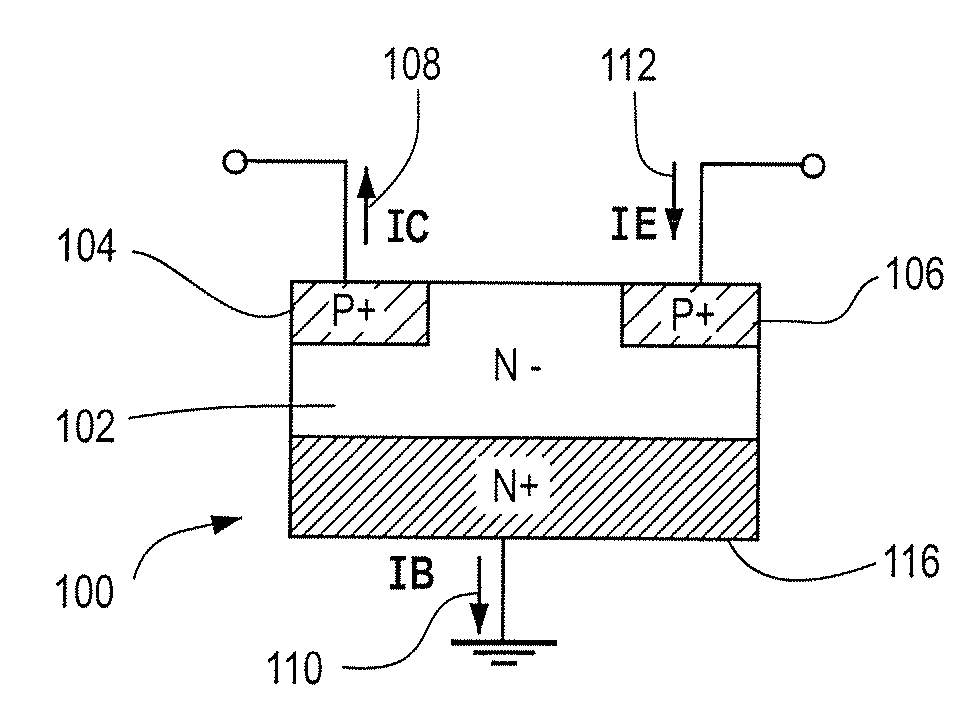

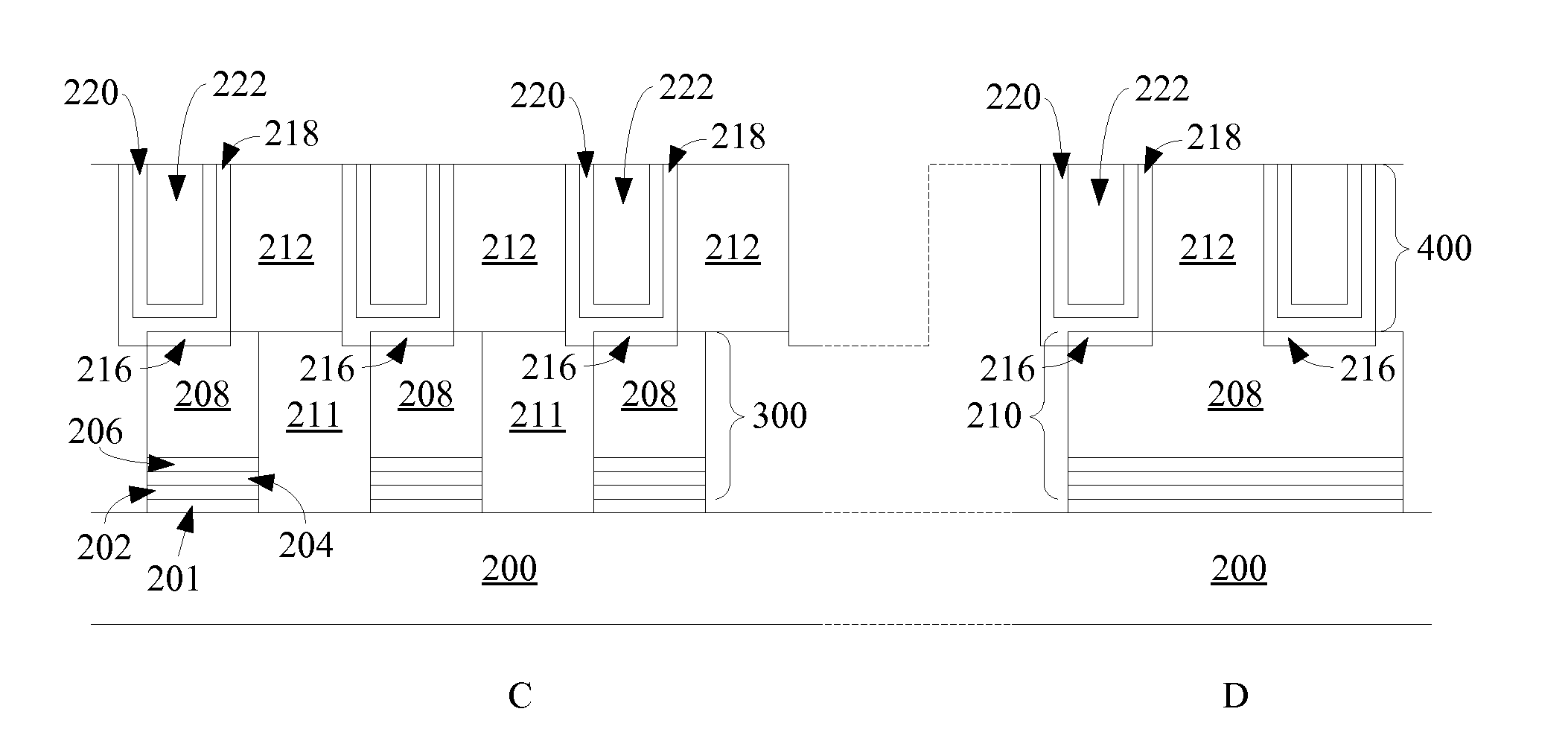

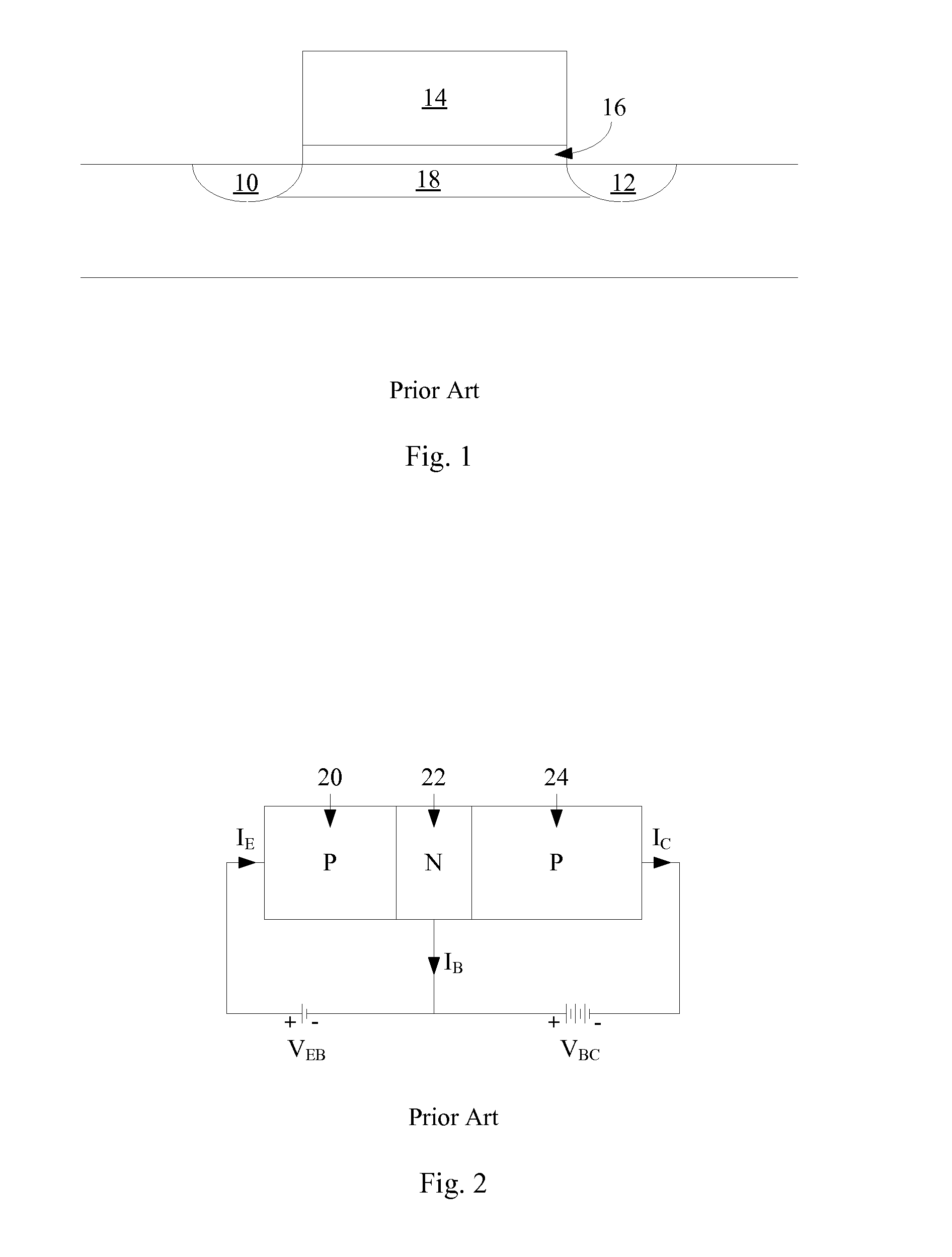

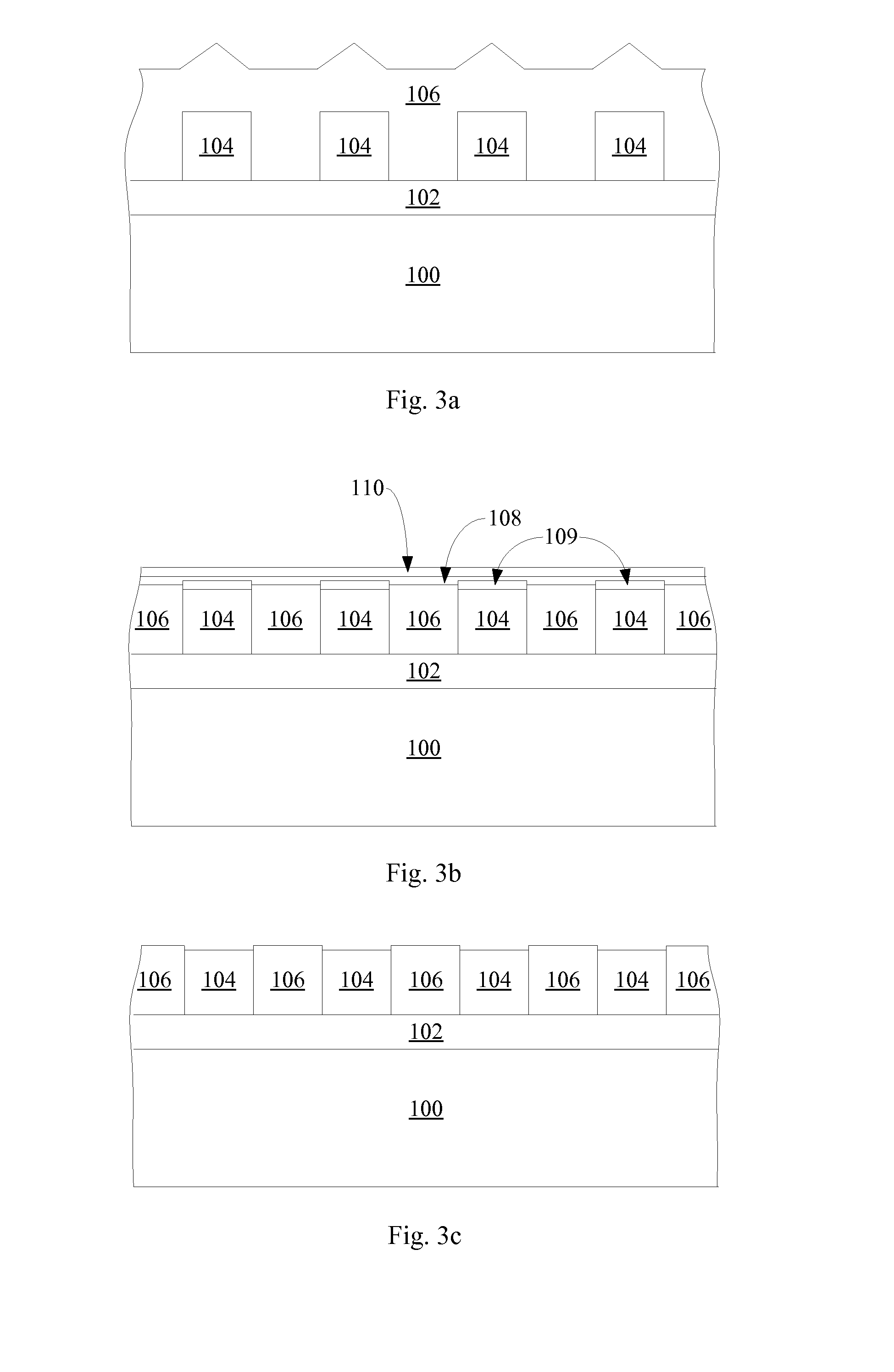

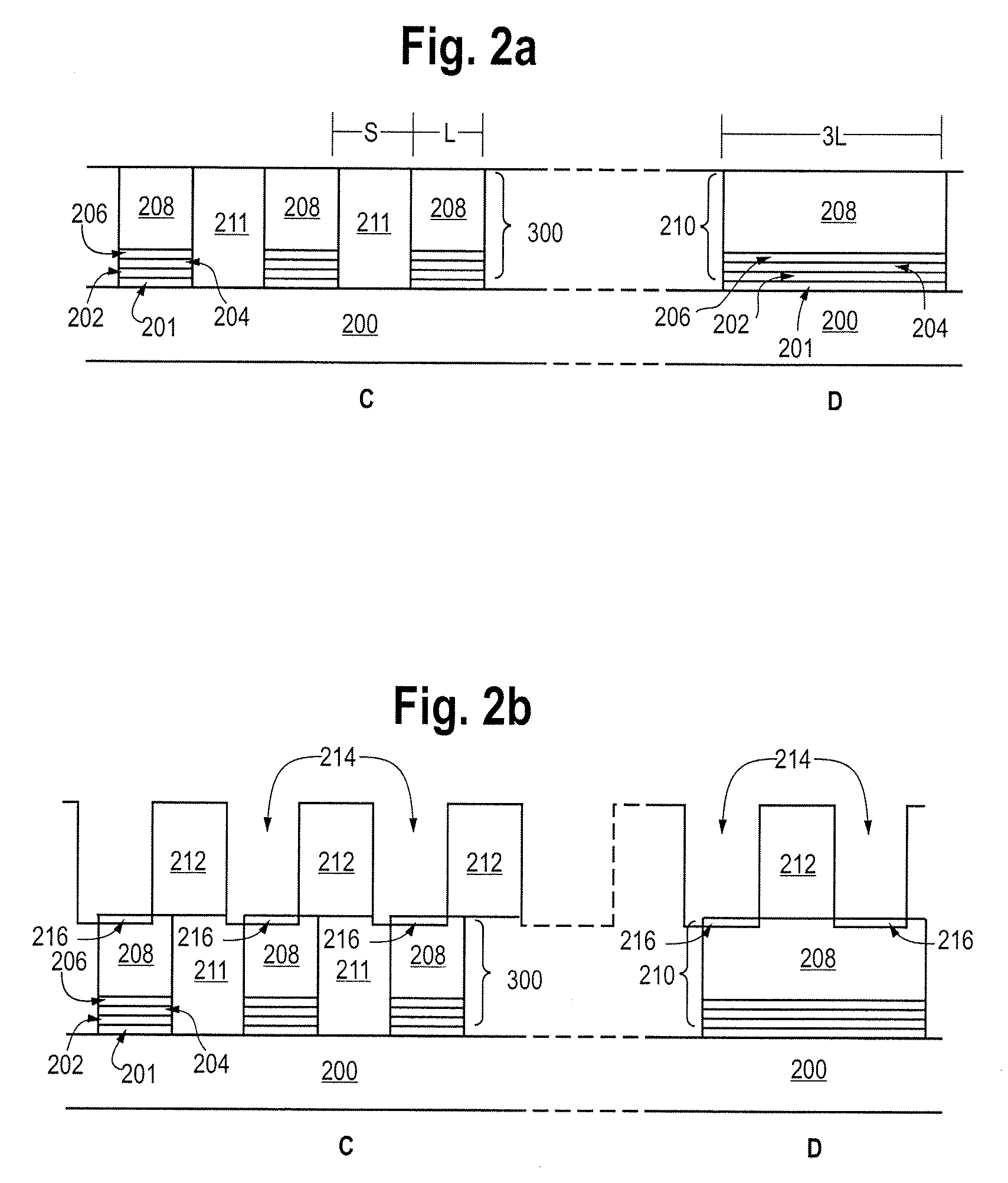

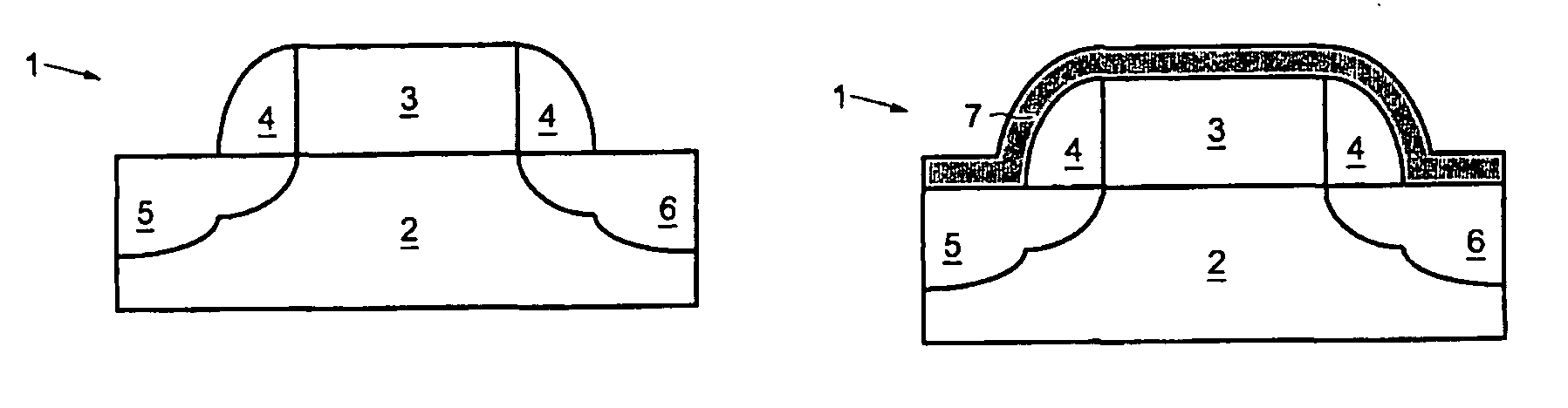

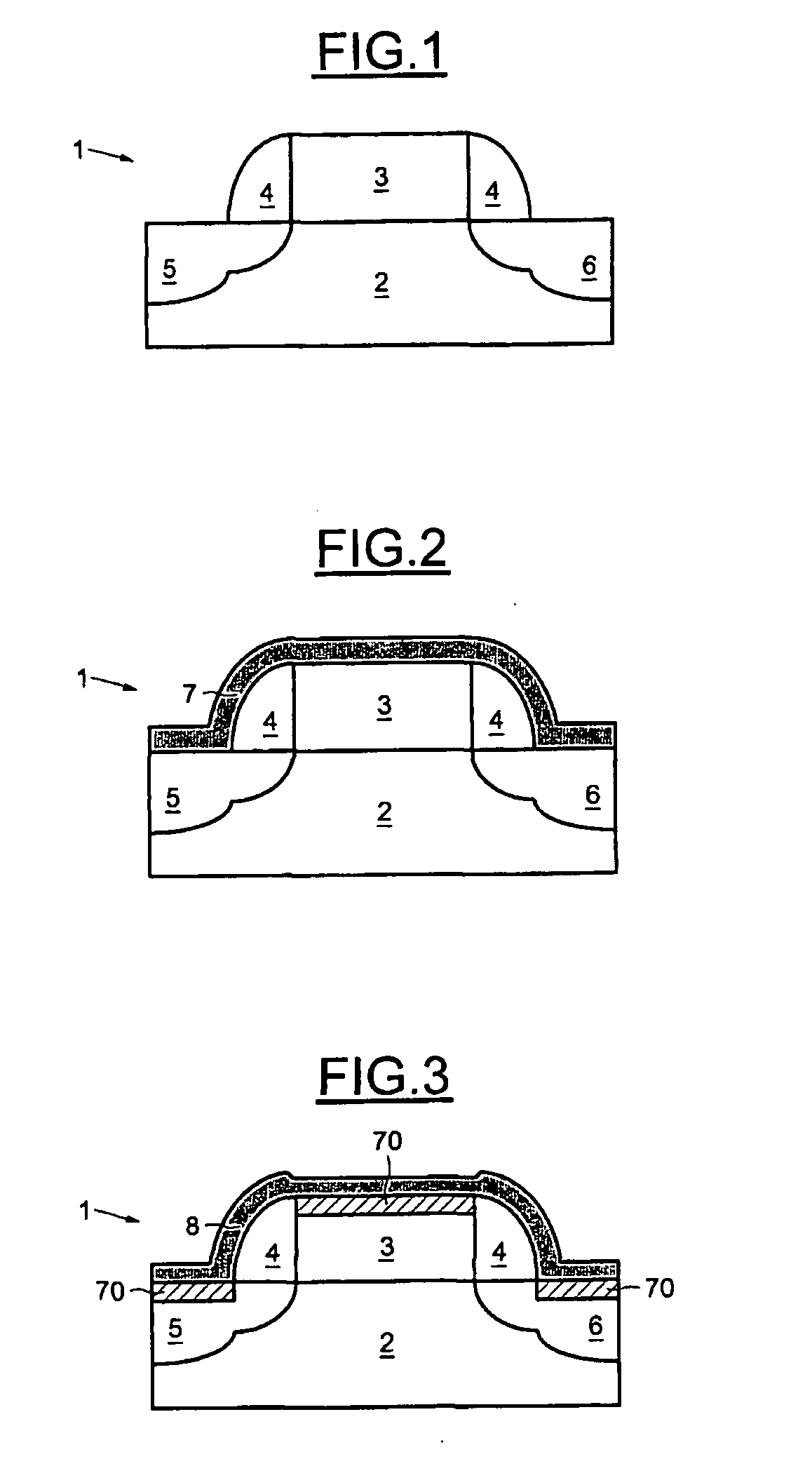

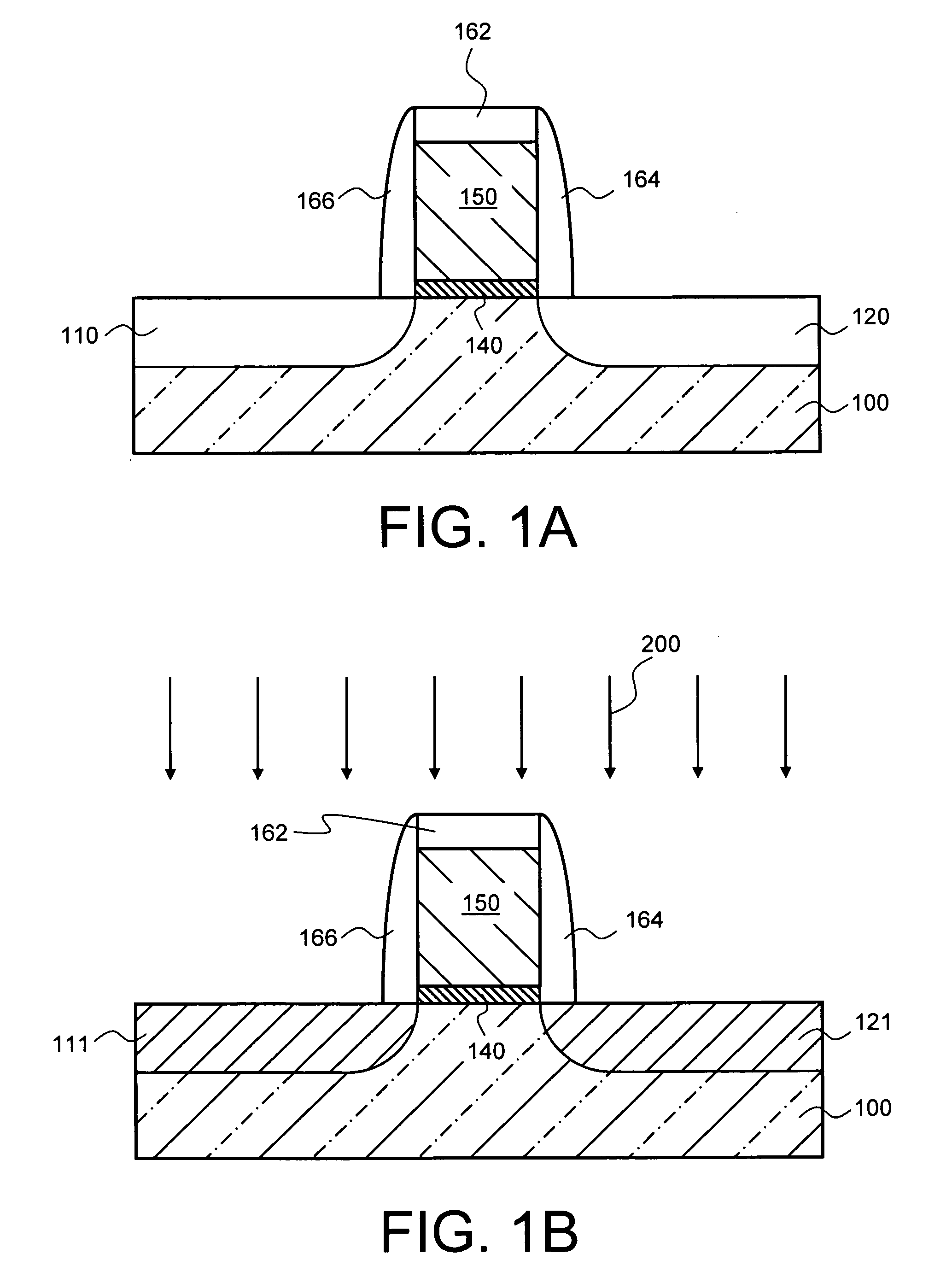

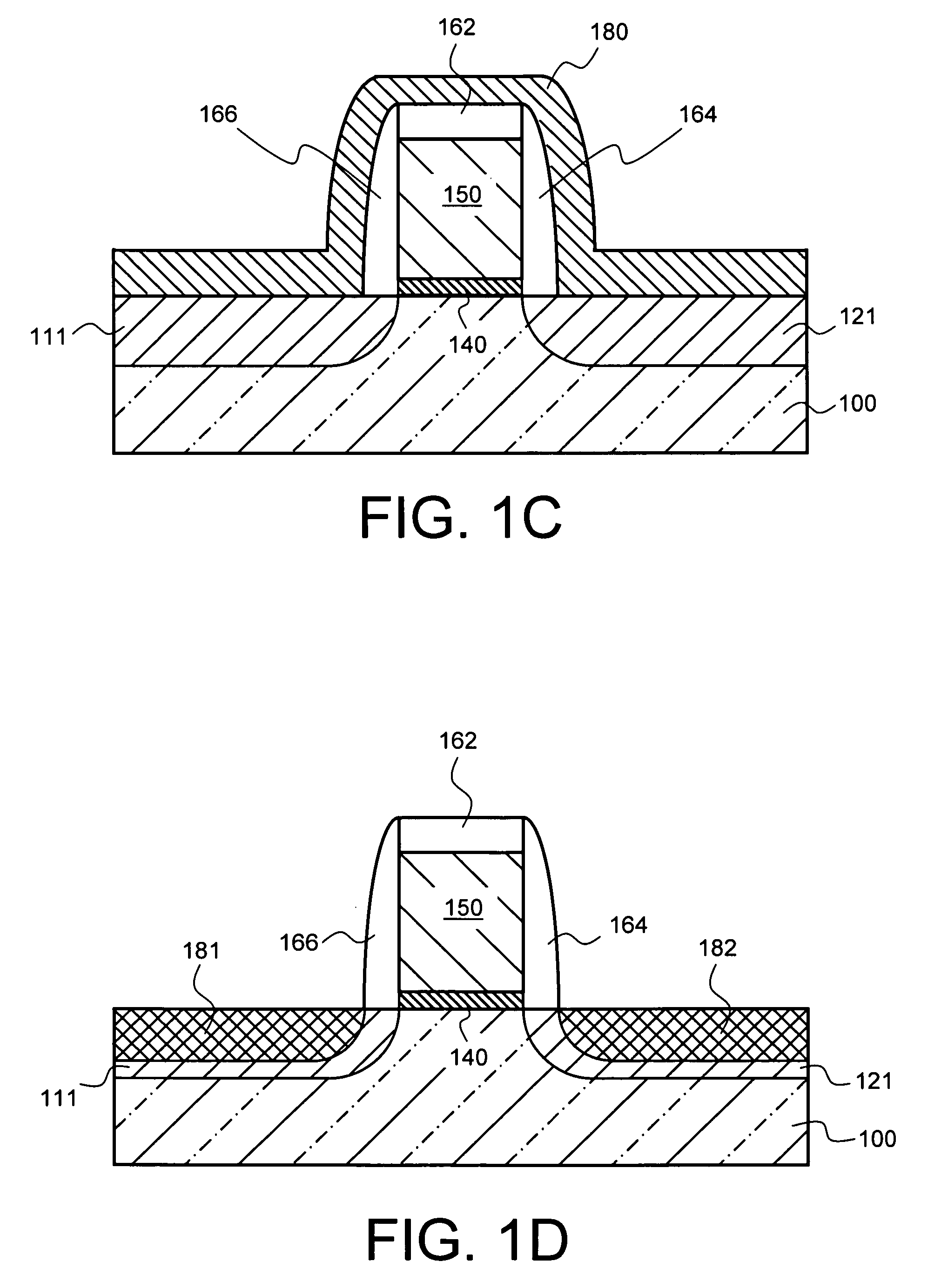

Method for forming polycrystalline thin film bipolar transistors

ActiveUS20080311722A1Read-only memoriesSemiconductor/solid-state device manufacturingGermanideMaterials science

A method is described for forming a semiconductor device comprising a bipolar transistor having a base region, an emitter region and a collector region, wherein the base region comprises polycrystalline semiconductor material formed by crystallizing silicon, germanium or silicon germanium in contact with a silicide, germanide or silicide germanide. The emitter region and collector region also may be formed from polycrystalline semiconductor material formed by crystallizing silicon, germanium or silicon germanium in contact with a silicide, germanide or silicide germanide forming metal. The polycrystalline semiconductor material is preferably silicided polysilicon, which is formed in contact with C49 phase titanium silicide.

Owner:SANDISK TECH LLC

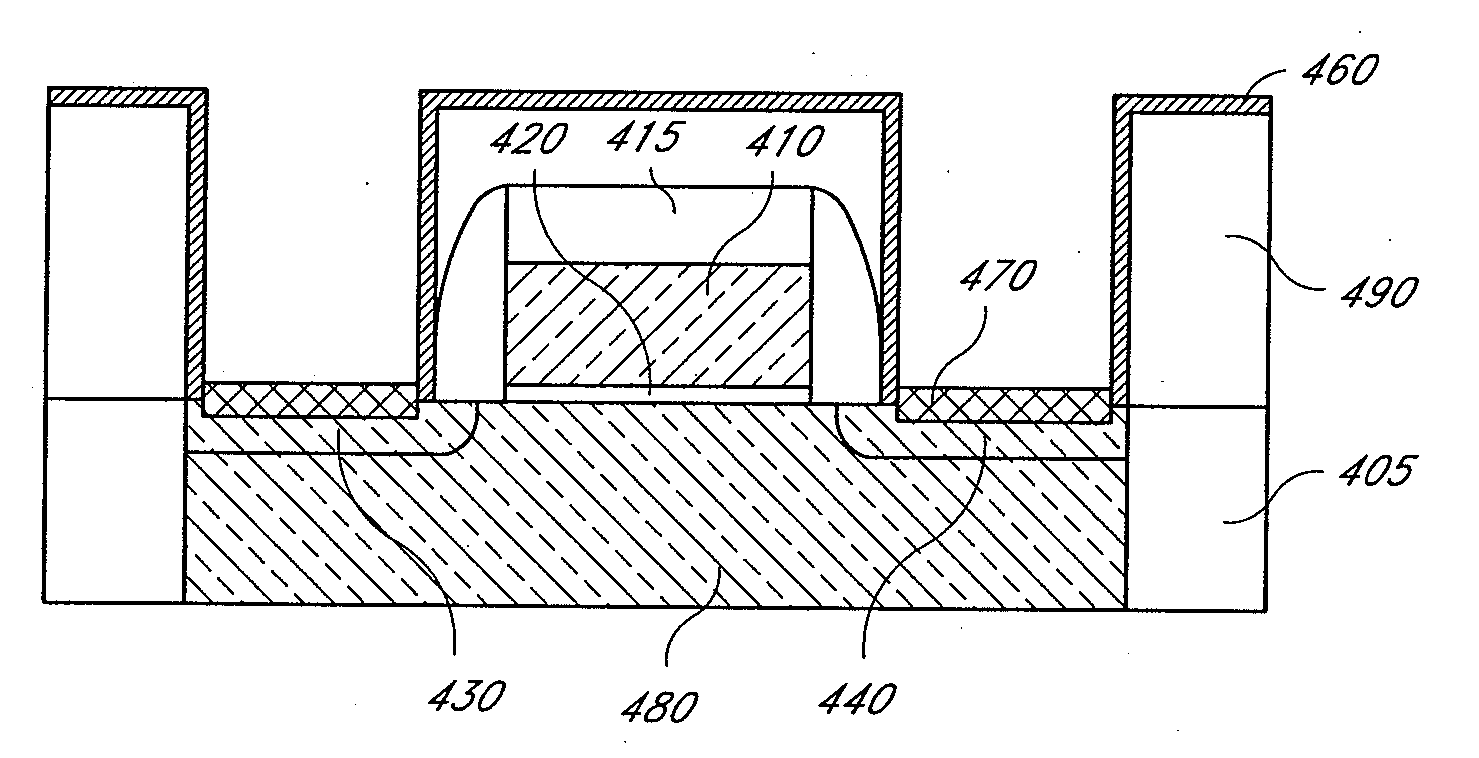

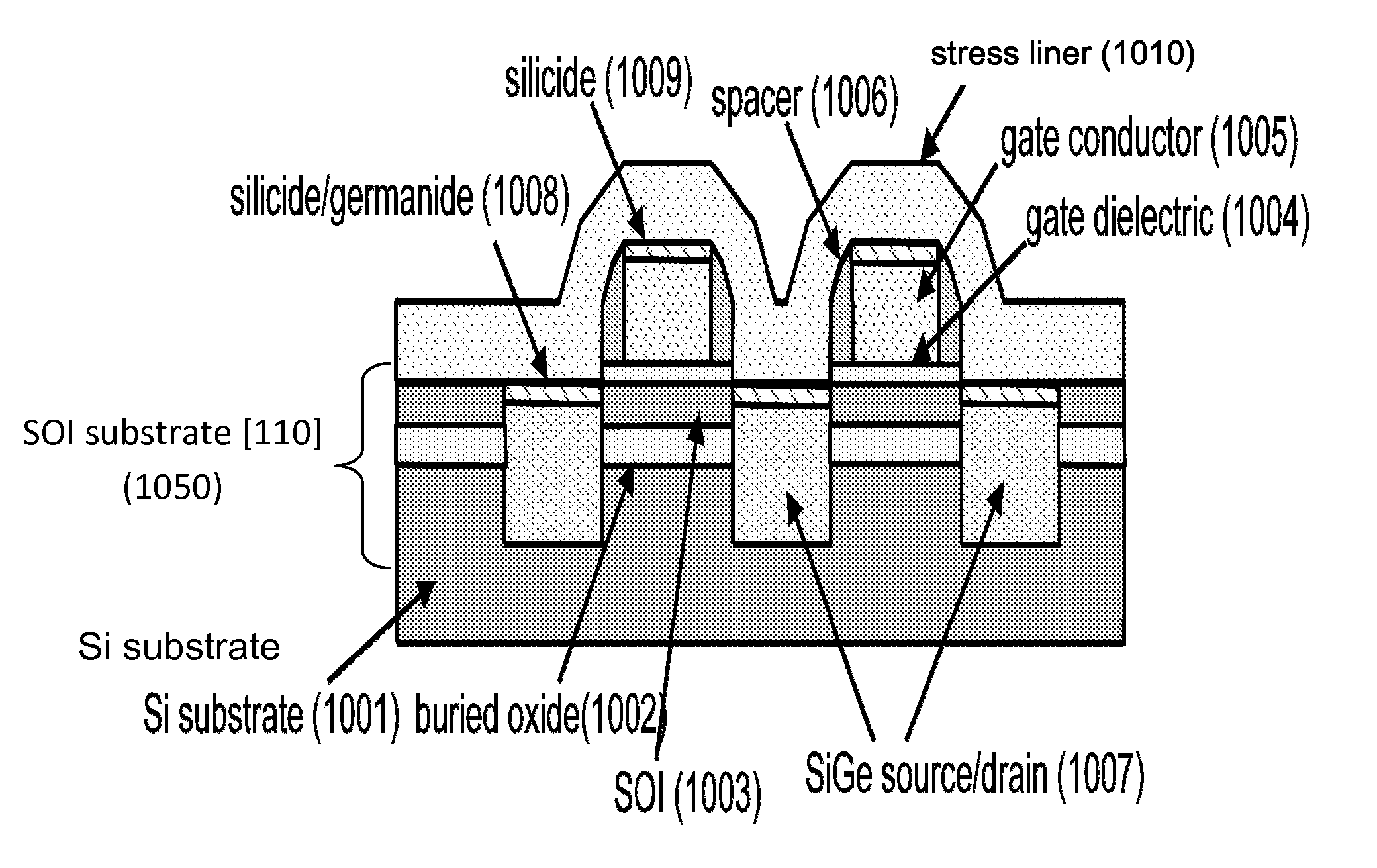

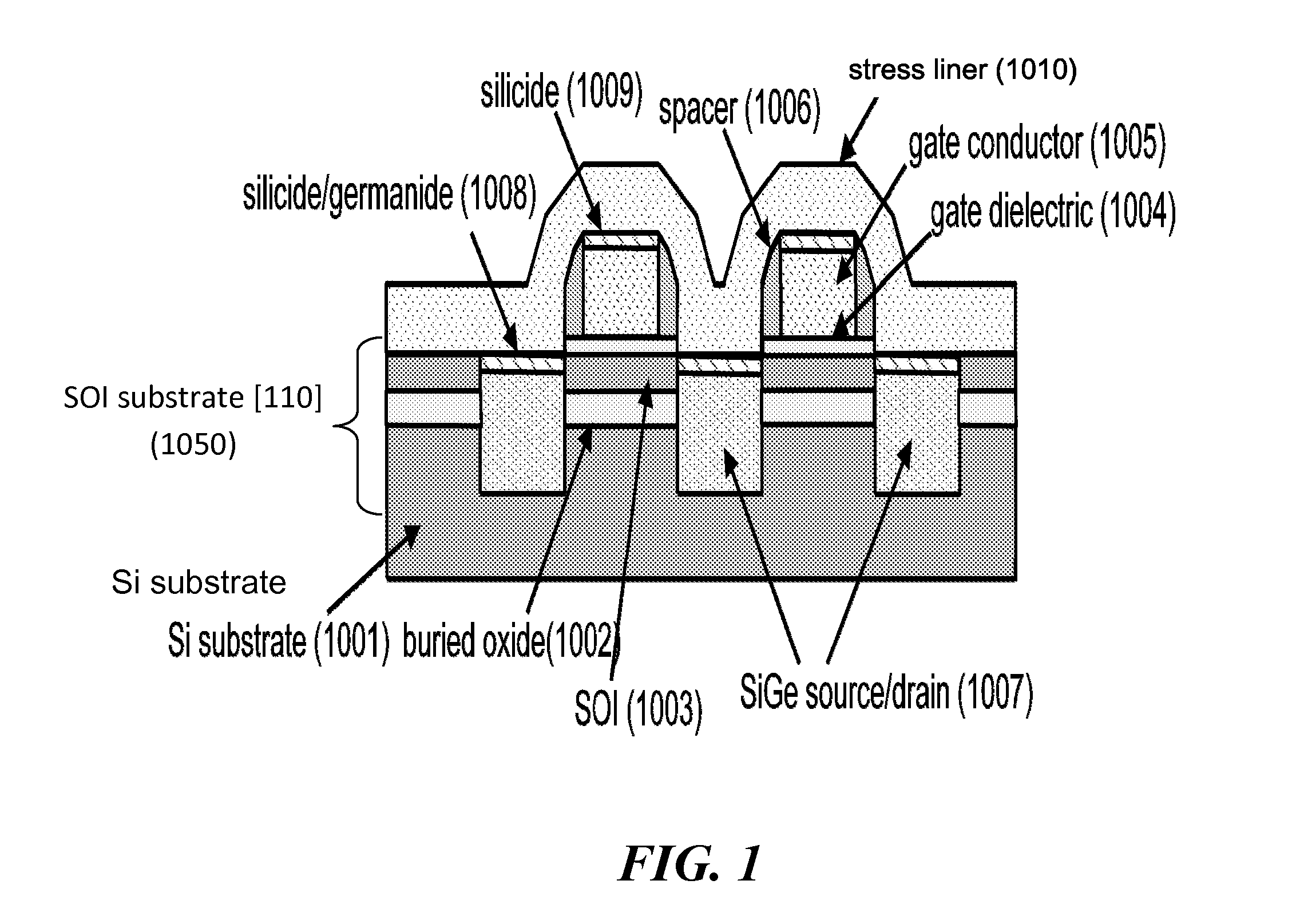

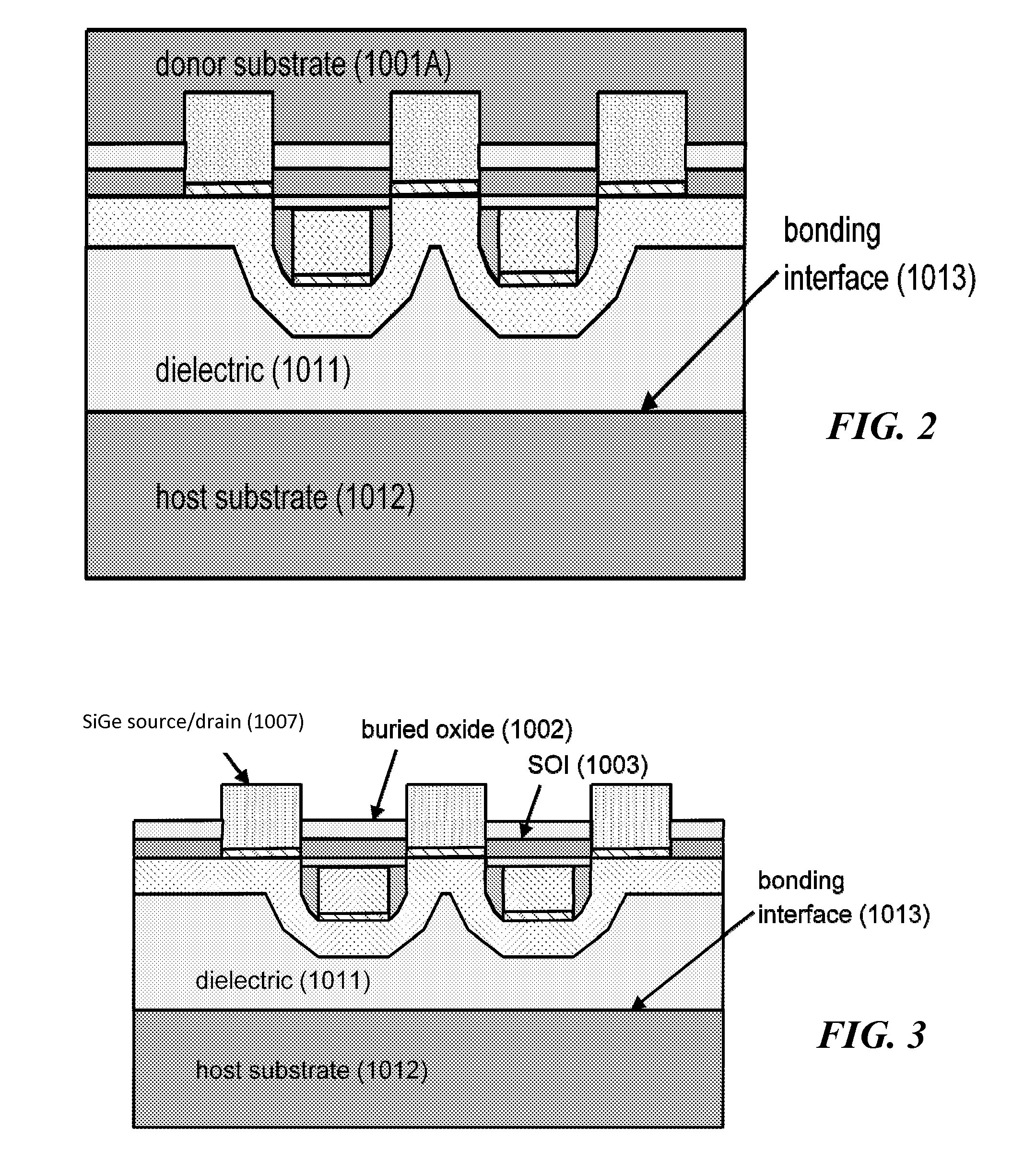

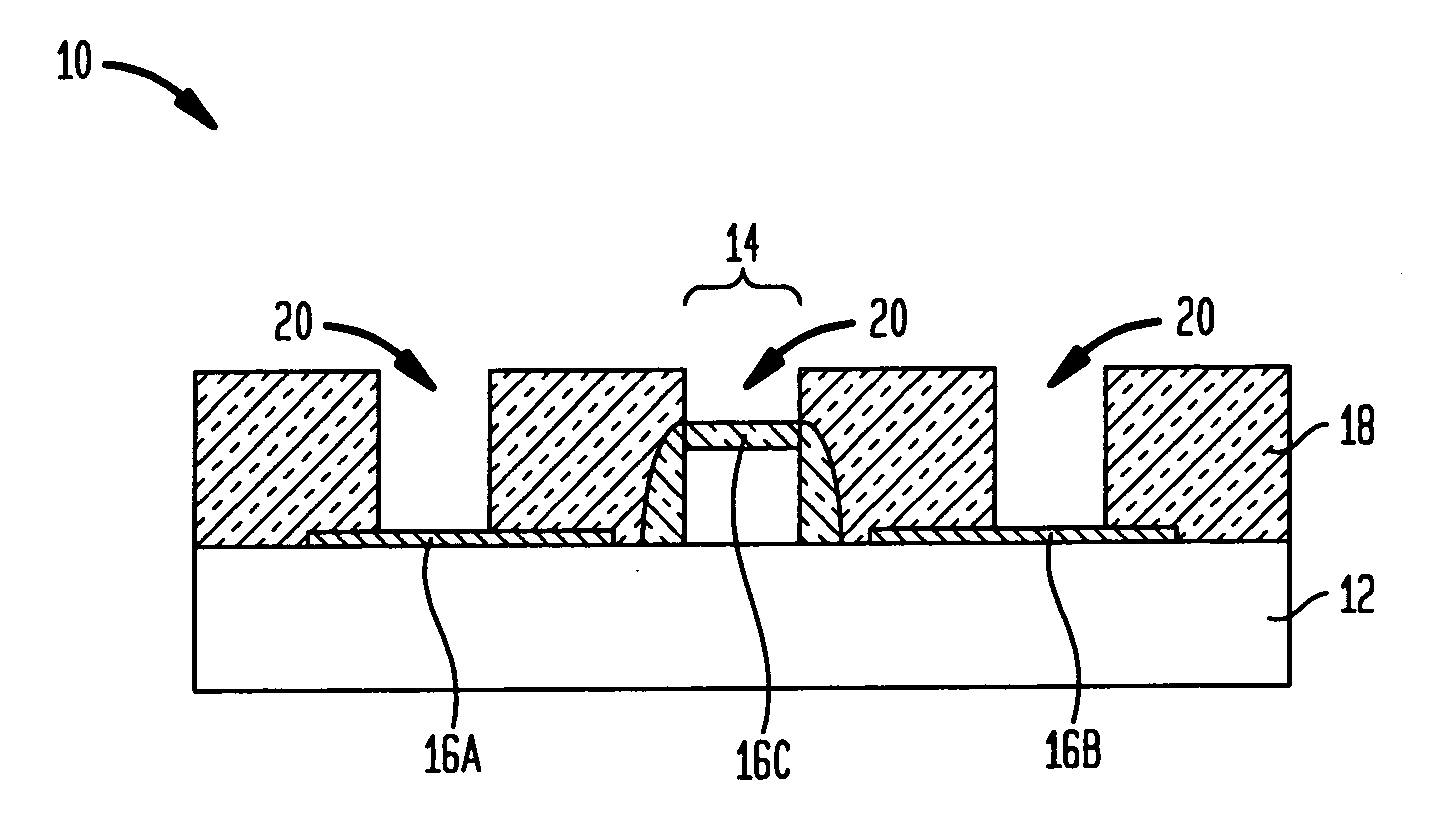

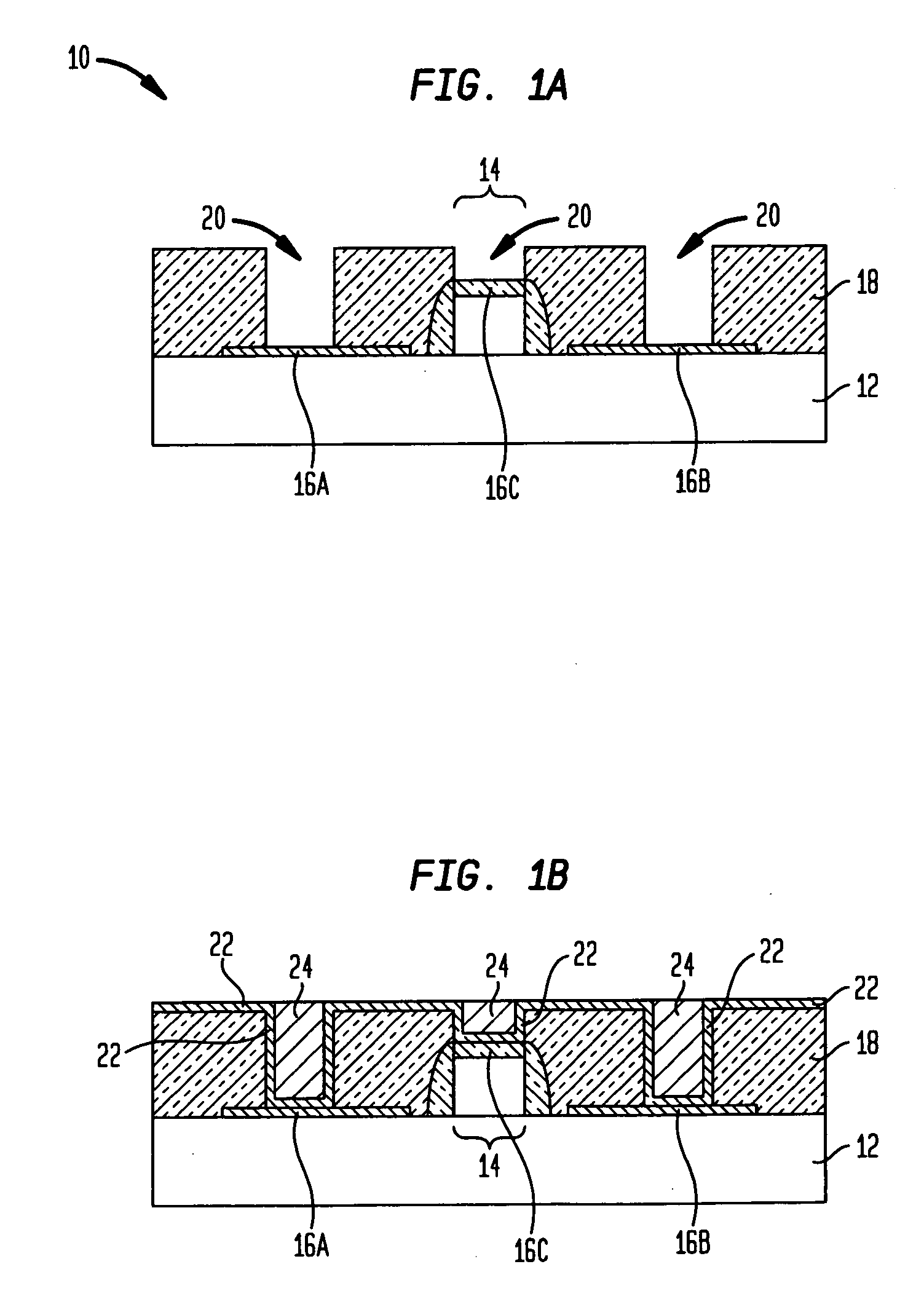

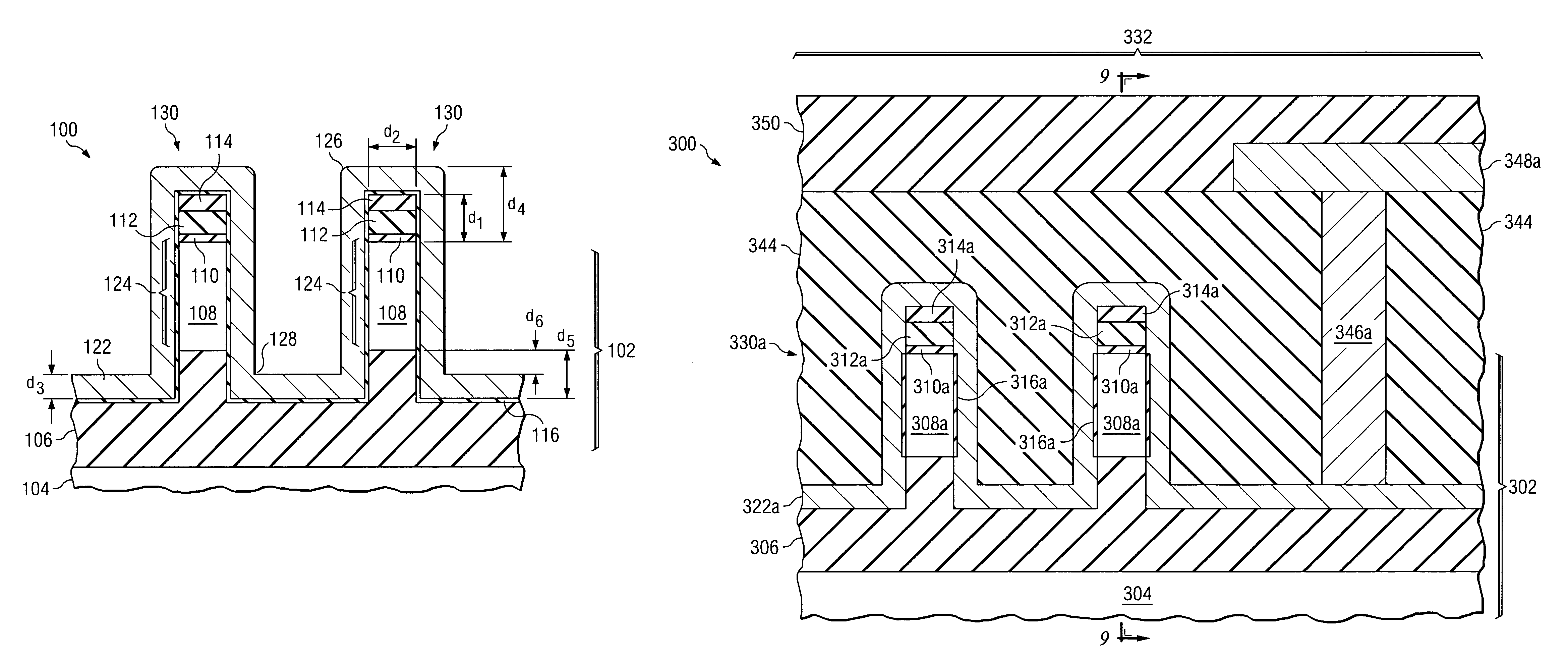

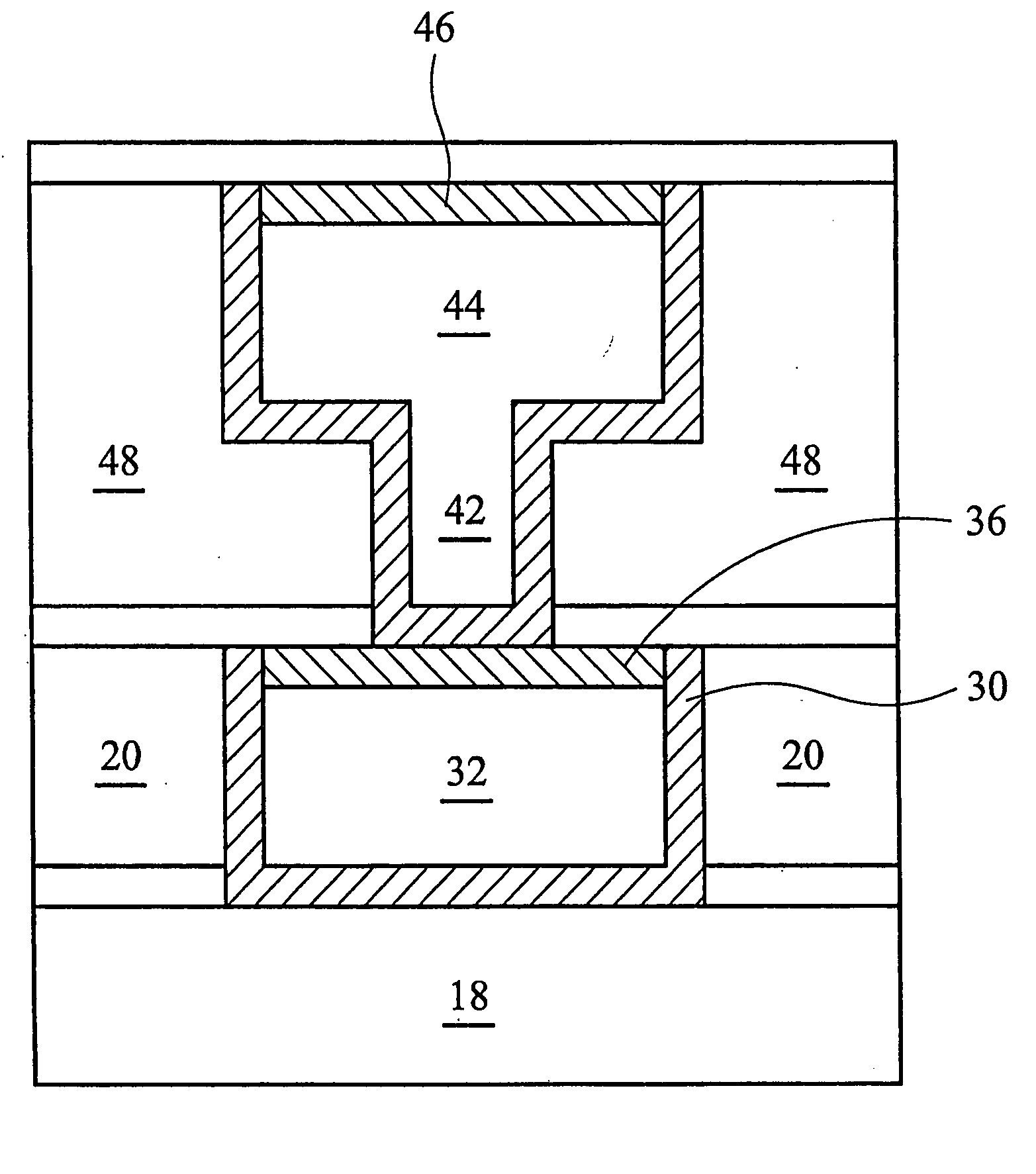

Structure for self-aligned silicide contacts to an upside-down fet by epitaxial source and drain

InactiveUS20110241073A1Induce strainTransistorSemiconductor/solid-state device detailsSalicideDielectric

A method for fabricating an upside-down p-FET includes: fully etching source and drain regions in a donor substrate by etching a silicon-on-insulator layer through buried oxide and partially etching the silicon substrate; refilling a bottom and sidewall surfaces of the etched source and drain regions with epitaxial silicide / germanide to form e-SiGe source and drain regions; capping the source and drain regions with self-aligning silicide / germanide; providing a silicide layer formed over the gate conductor line; providing a first stress liner over the gate and the e-SiGe source and drain regions; depositing a planarized dielectric over the self-aligning silicide / germanide; inverting the donor substrate; bonding the donor substrate to a host wafer; and selectively exposing the buried oxide and the e-SiGe source and drain regions by removing the donor wafer.

Owner:GLOBALFOUNDRIES US INC

Method to form upward pointing p-i-n diodes having large and uniform current

A method is disclosed to form an upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

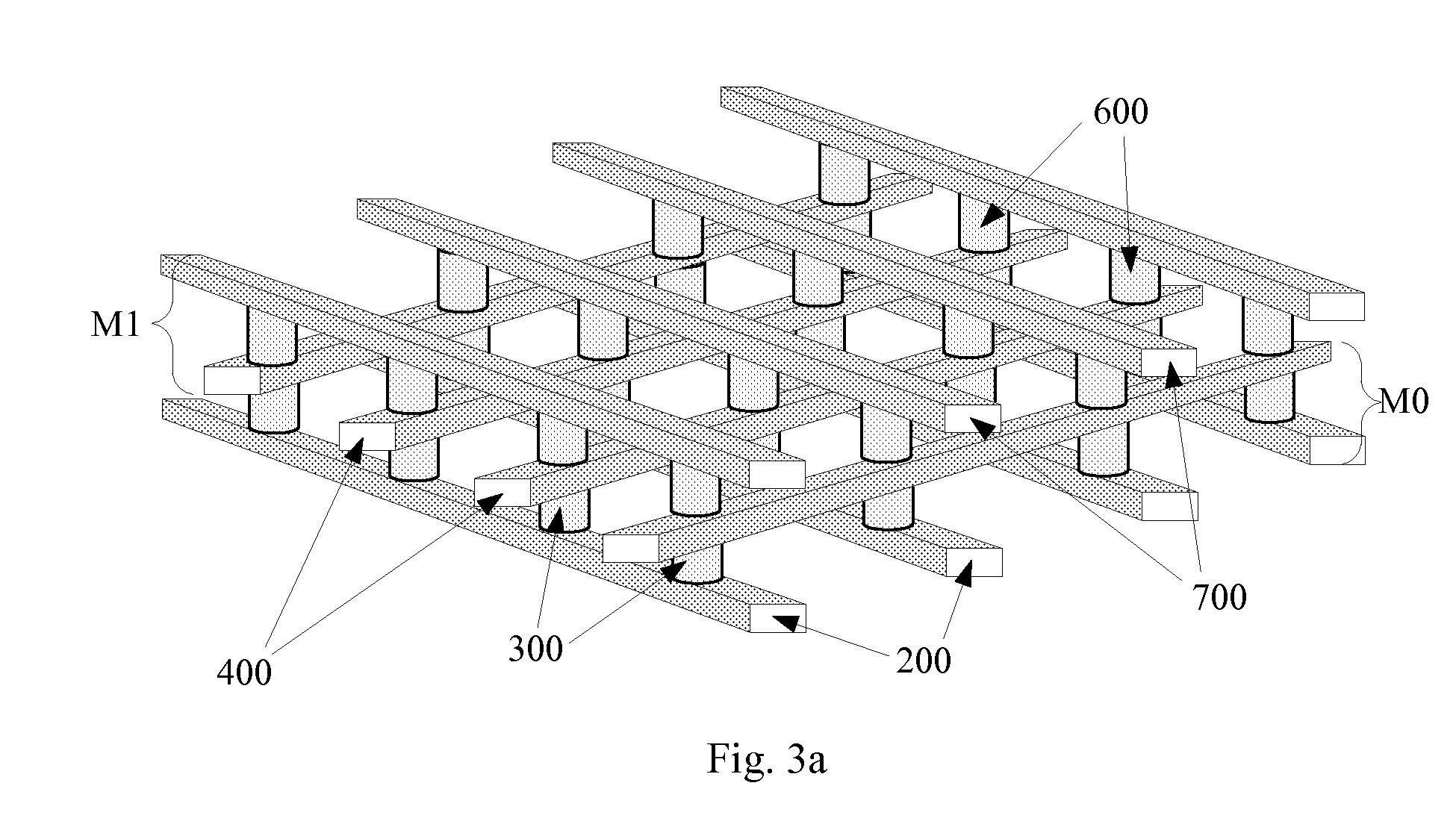

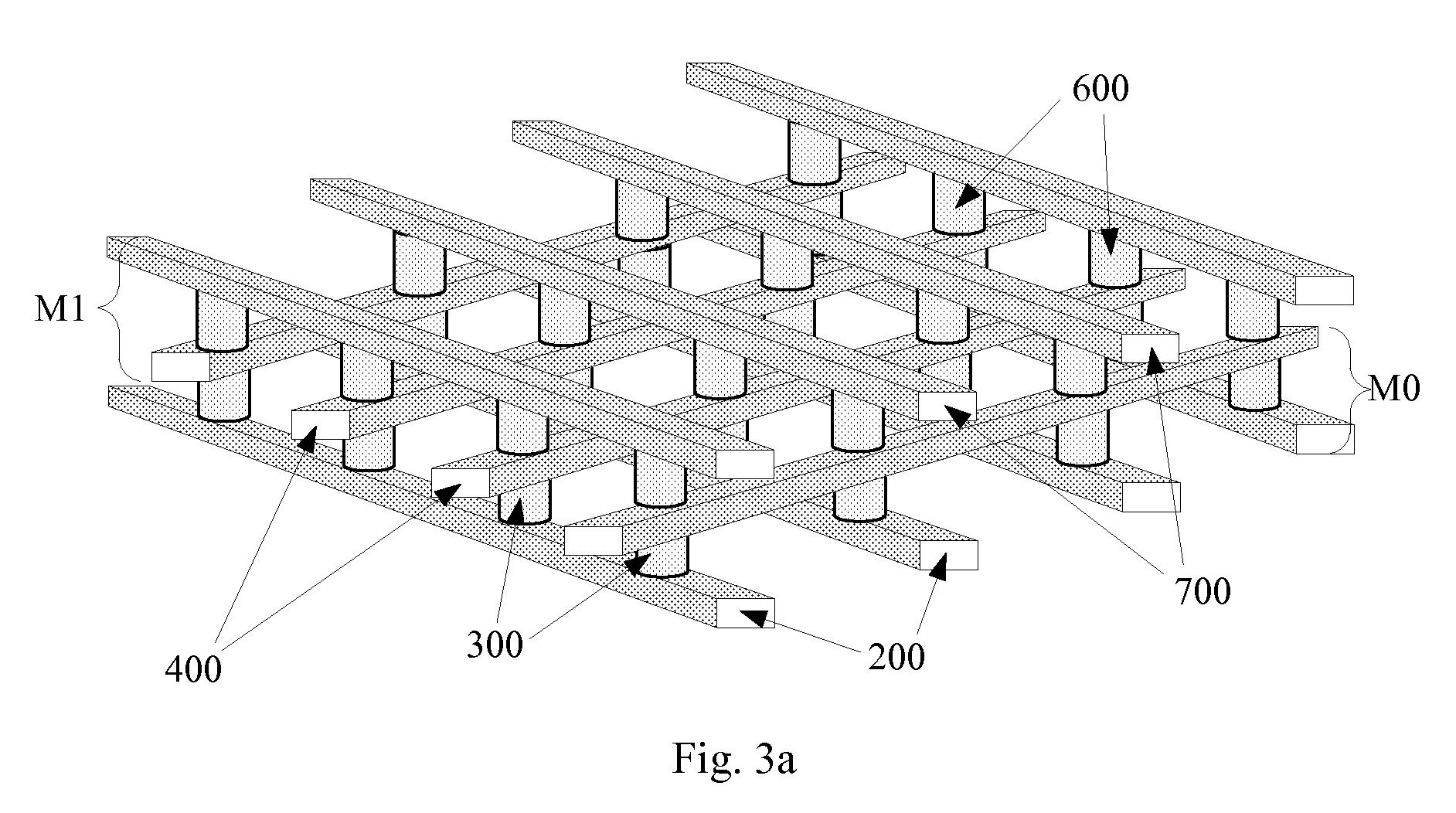

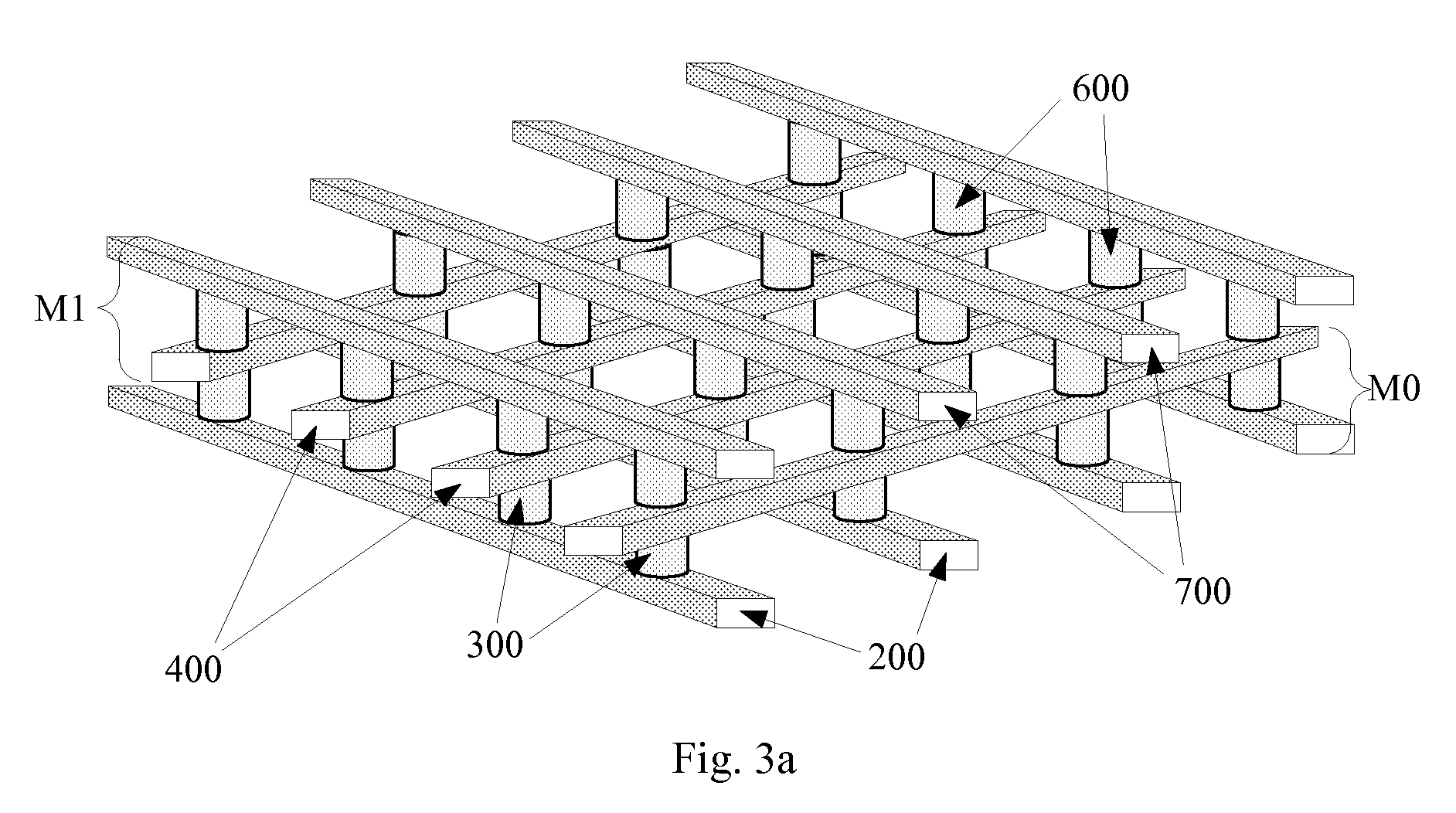

Large array of upward pointing p-i-n diodes having large and uniform current

An upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium is disclosed. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

Large array of upward pointing p-i-n diodes having large and uniform current

An upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium is disclosed. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

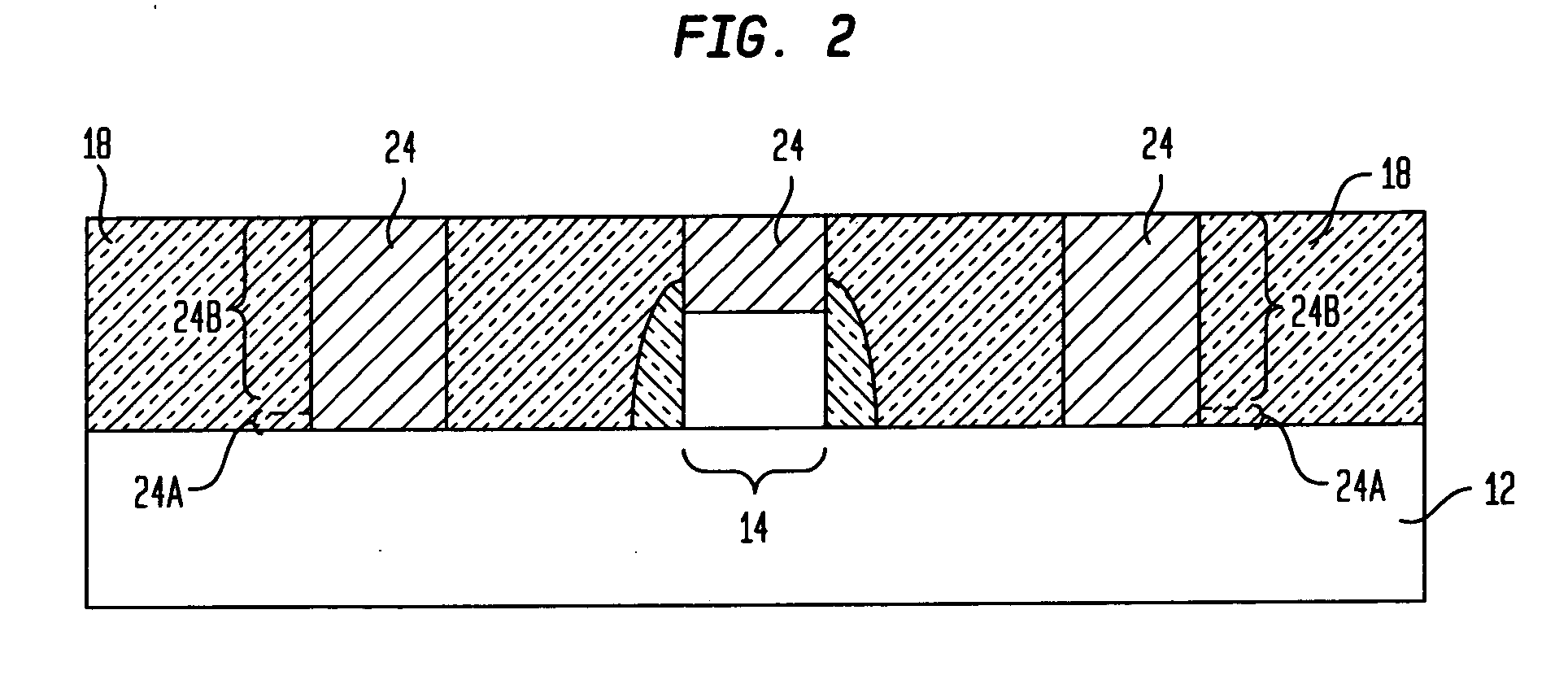

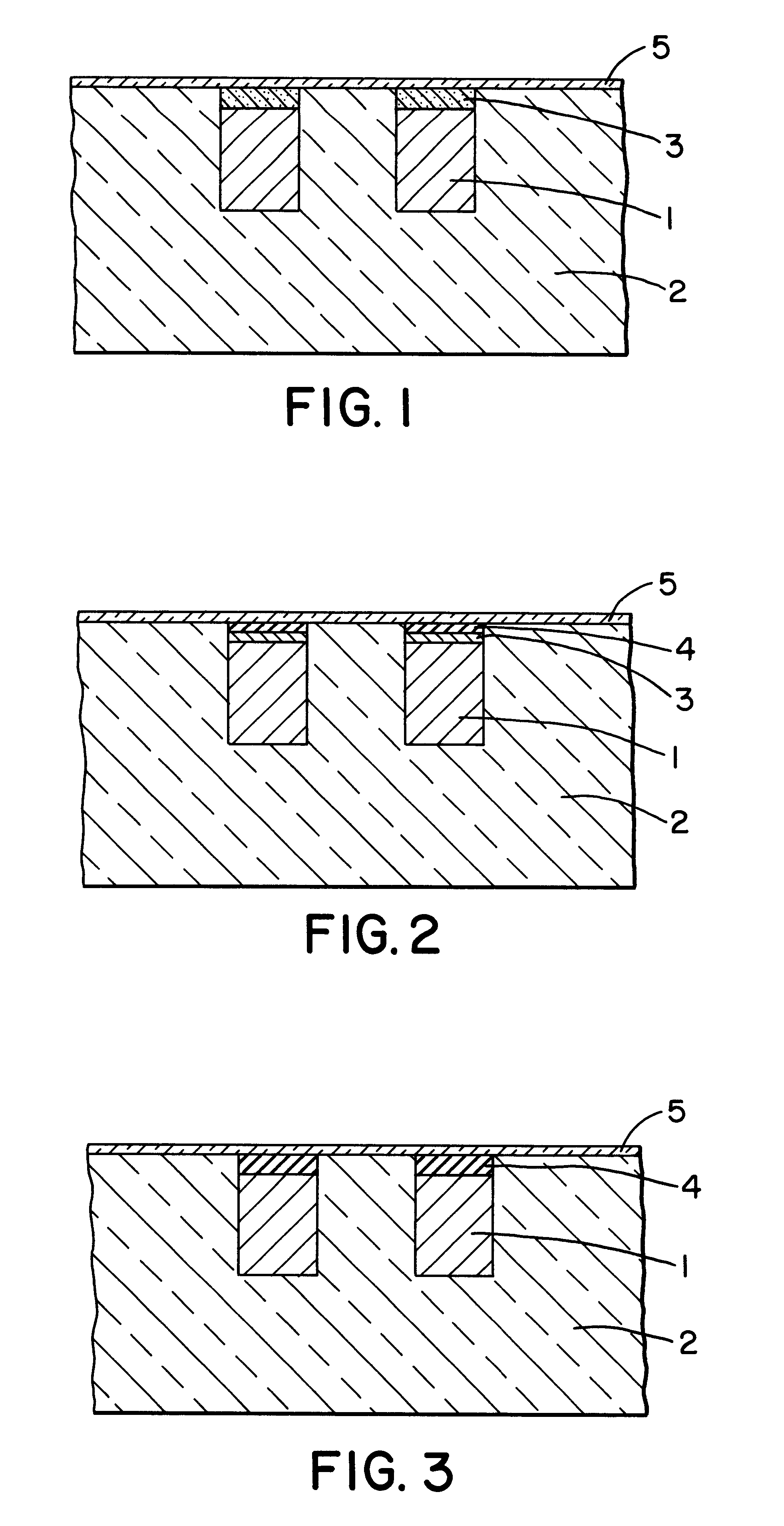

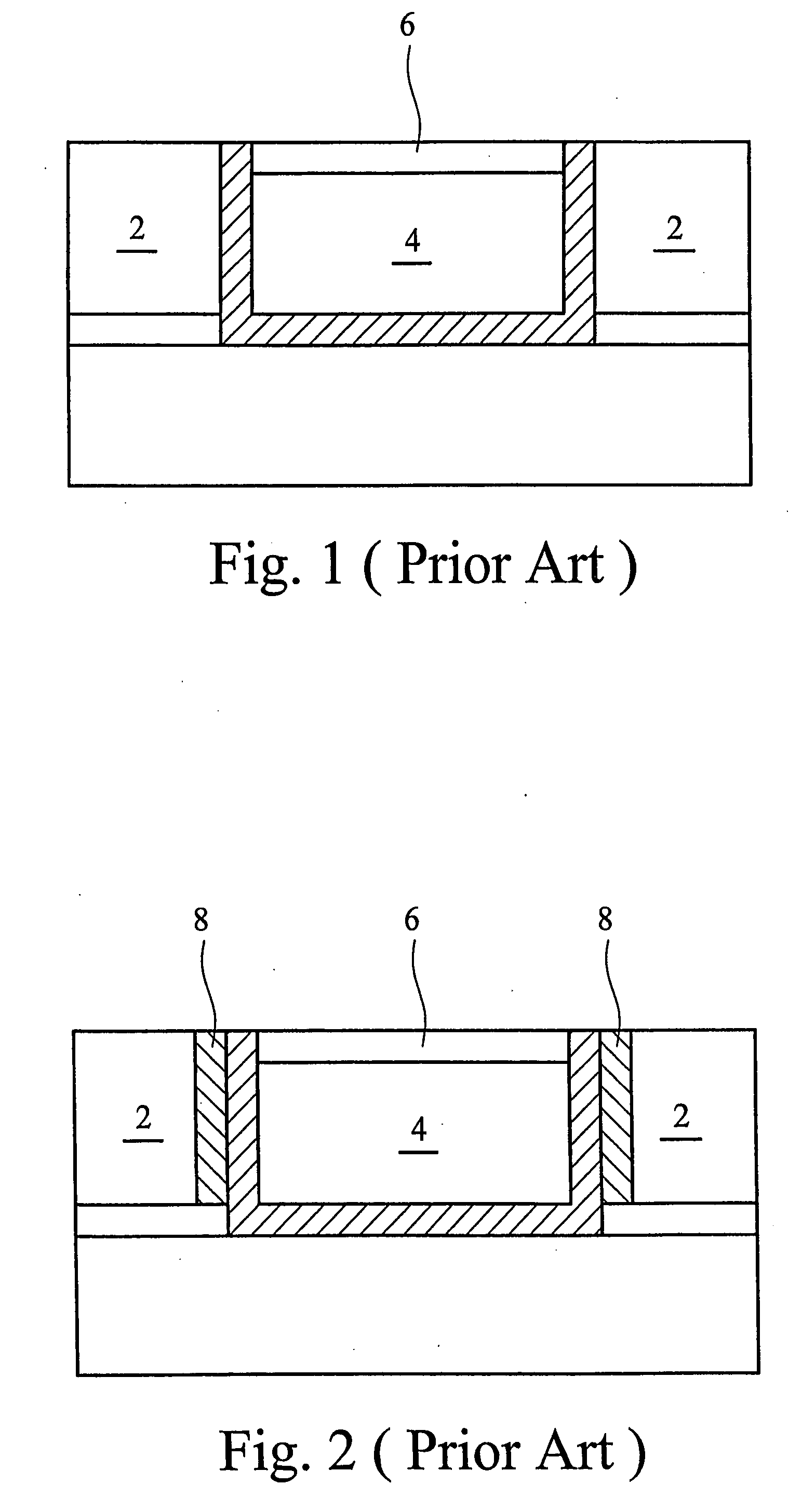

Method and structure for reducing contact resistance between silicide contact and overlying metallization

InactiveUS20070275548A1Lower resistance contactReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMetal silicide

A semiconductor structure in which the contact resistance in the contact opening is reduced as well as a method of forming the same are provided. This is achieved in the present invention by replacing conventional contact metallurgy, such as tungsten, or a metal silicide, such as Ni silicide or Cu silicide, with a metal germanide-containing contact material. The term “metal germanide-containing” is used in the present application to denote a pure metal germanide (i.e., MGe alloy) or a metal germanide that includes Si (i.e., MSiGe alloy).

Owner:GLOBALFOUNDRIES INC

Method for improving adhesion to copper

InactiveUS6271595B1Poor materialImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesGermanideOptoelectronics

Poorly adherent layers such as silicon nitride and silicon dioxide exhibit improved adhesion to copper member by providing an intervening germanium-containing layer. The germanium-containing layer is copper germanide, germanium oxide, germanium bitride or combinations thereof. The germanium-containing layer enhances the adhesion such that the poorly adherent layer is less susceptible to delamination from the copper member.

Owner:GLOBALFOUNDRIES INC

Interconnect structure having a silicide/germanide cap layer

InactiveUS20070228571A1Improve reliabilityIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesSalicideElectrical conductor

An interconnect structure of an integrated circuit and a method for forming the same are provided. The interconnect structure includes a semiconductor substrate, a low-k dielectric layer over the semiconductor substrate, a conductor in the low-k dielectric layer, and a cap layer on the conductor. The cap layer has at least a top portion comprising a metal silicide / germanide.

Owner:TAIWAN SEMICON MFG CO LTD

Integrated circuit and manufacturing method of copper germanide and copper silicide as copper capping layer

ActiveUS20090134521A1Avoid damageImprove barrier propertiesSemiconductor/solid-state device detailsSolid-state devicesGermanideCopper silicide

A method is provided for forming a capping layer comprising Cu, N, and also Si and / or Ge onto a copper conductive structure, said method comprising the sequential steps of: forming, at a temperature range between 200° C. up to 400° C., at least one capping layer onto said copper conductive structure by exposing said structure to a GeH4 and / or a SiH4 comprising ambient, performing a NH3 plasma treatment thereby forming an at least partly nitrided capping layer, forming a dielectric barrier layer onto said at least partly nitrided capping layer, wherein prior to said step of forming said at least one capping layer a pre-annealing step of said copper conductive structure is performed at a temperature range between 250° C. up to 450° C.

Owner:TAIWAN SEMICON MFG CO LTD +1

Semi-gate controlled source schottky barrier type tunneling field effect transistor

InactiveCN103500758AReduce processing difficultyReduce manufacturing costSemiconductor devicesGermanideGate voltage

The invention relates to a semi-gate controlled source schottky barrier type tunneling field effect transistor. On the premise of no requirements on the introduction of a material such as a compound semiconductor, silicon germanide and germanium with a smaller forbidden bandwidth into the generation of a tunneling part of a device, a source schottky barrier is formed between a metal source and intrinsic silicon, and a semi-gate is used for controlling the barrier width of the source schottky barrier and the energy band bending degree of the intrinsic silicon to control the switching of the device. An asymmetrical semi-gate structural design is adopted, so that gate-induced drain leakage current is remarkably reduced on the premise of keeping gate voltage well controlling the width of the schottky barrier and the energy band bending degree. The semi-gate controlled source schottky barrier type tunneling field effect transistor has the advantages of process simplicity, low cost, high sub-threshold slope, high breakover current, low reverse leakage current and the like, and is suitable to be popularized and used.

Owner:SHENYANG POLYTECHNIC UNIV

Semiconductor device including misfet

InactiveUS20100244154A1Semiconductor/solid-state device manufacturingSemiconductor devicesSurface layerGermanide

Owner:KK TOSHIBA

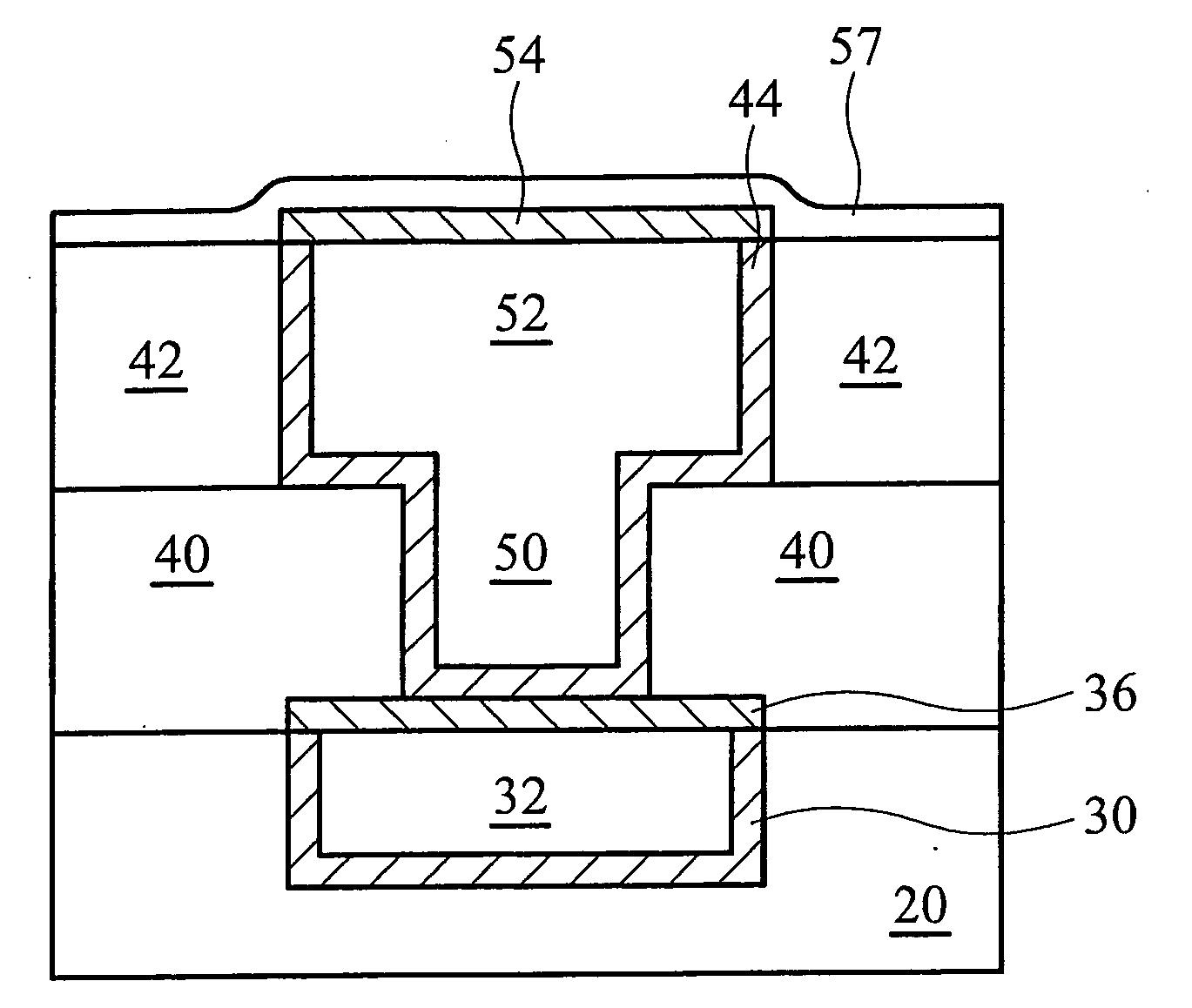

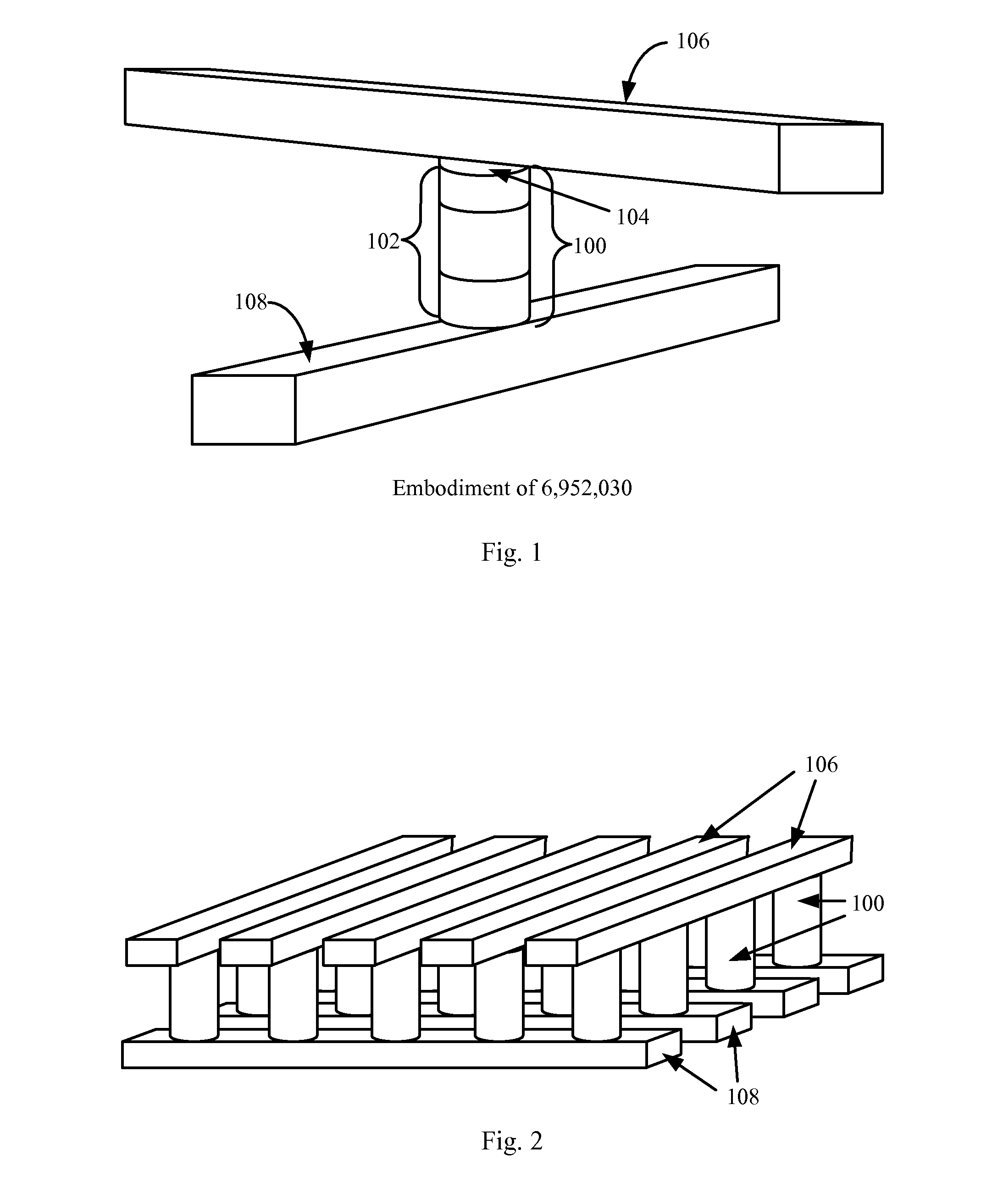

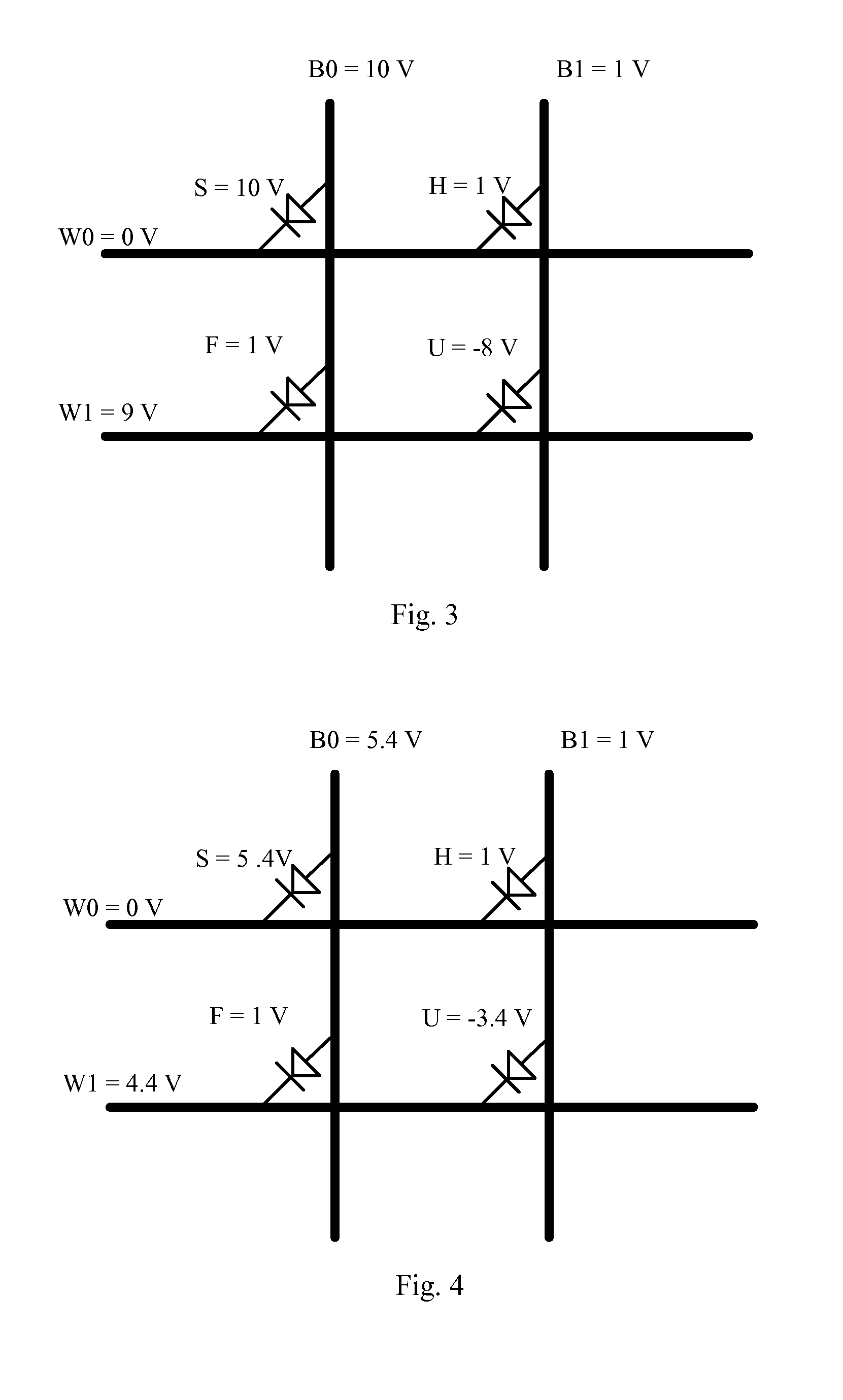

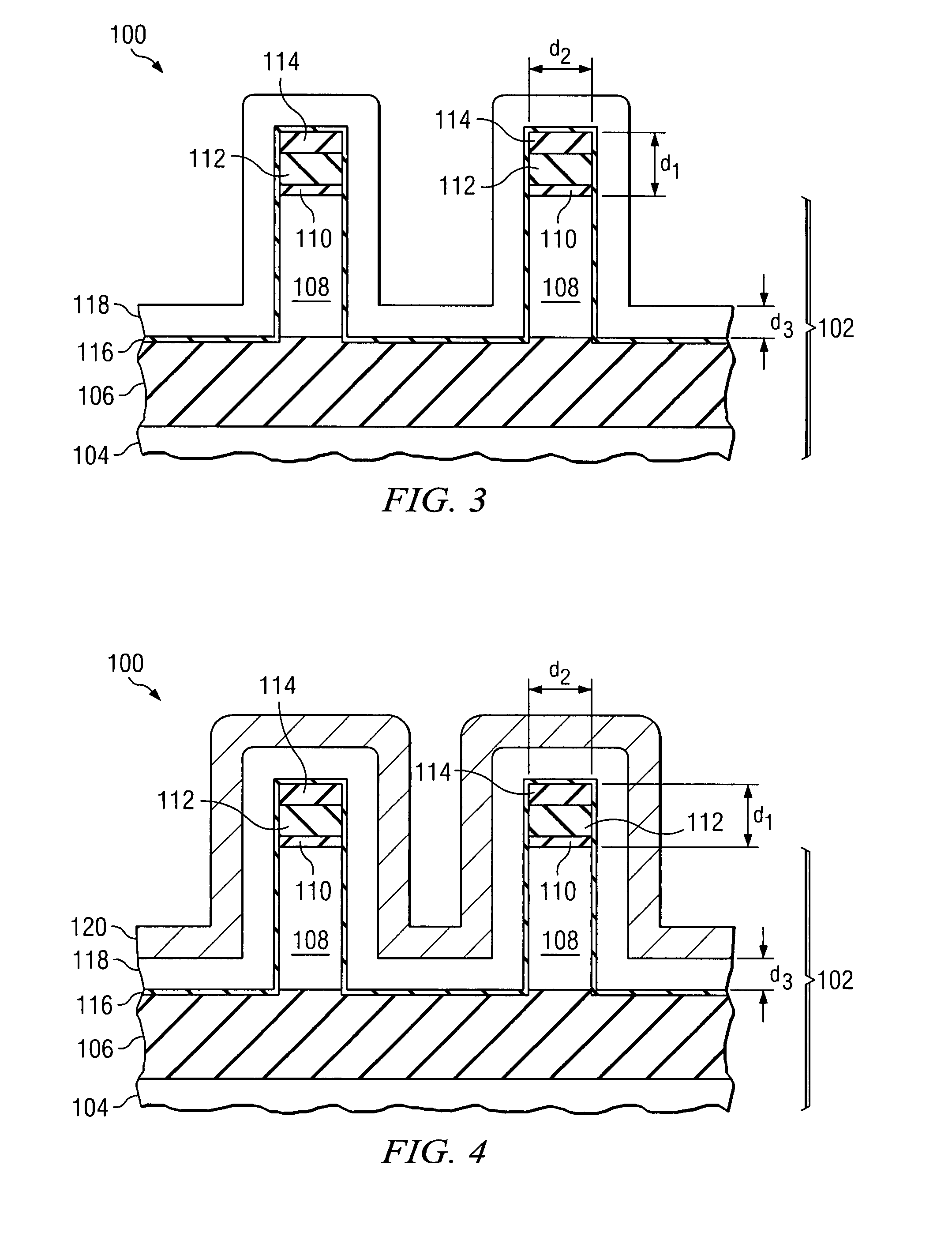

Vertical diode based memory cells having a lowered programming voltage and methods of forming the same

ActiveUS20090085154A1TransistorSemiconductor/solid-state device detailsMetal-insulator-metalSemiconductor materials

In a first aspect, a method for forming a non-volatile memory cell is provided. The method includes (1) forming a metal-insulator-metal (MIM) antifuse stack including (a) a first metal layer; (b) a silicon dioxide, oxynitride or silicon nitride antifuse layer formed above the first metal layer; and (c) a second metal layer formed above the antifuse layer. The method also includes (2) forming a contiguous p-i-n diode above the MIM stack, the contiguous p-i-n diode comprising deposited semiconductor material; (3) forming a layer of a silicide, silicide-germanide, or germanide in contact with the deposited semiconductor material; and (4) crystallizing the deposited semiconductor material in contact with the layer of silicide, silicide-germanide, or germanide. The memory cell comprises the contiguous p-i-n diode and the MIM stack. Other aspects are provided.

Owner:SANDISK TECH LLC

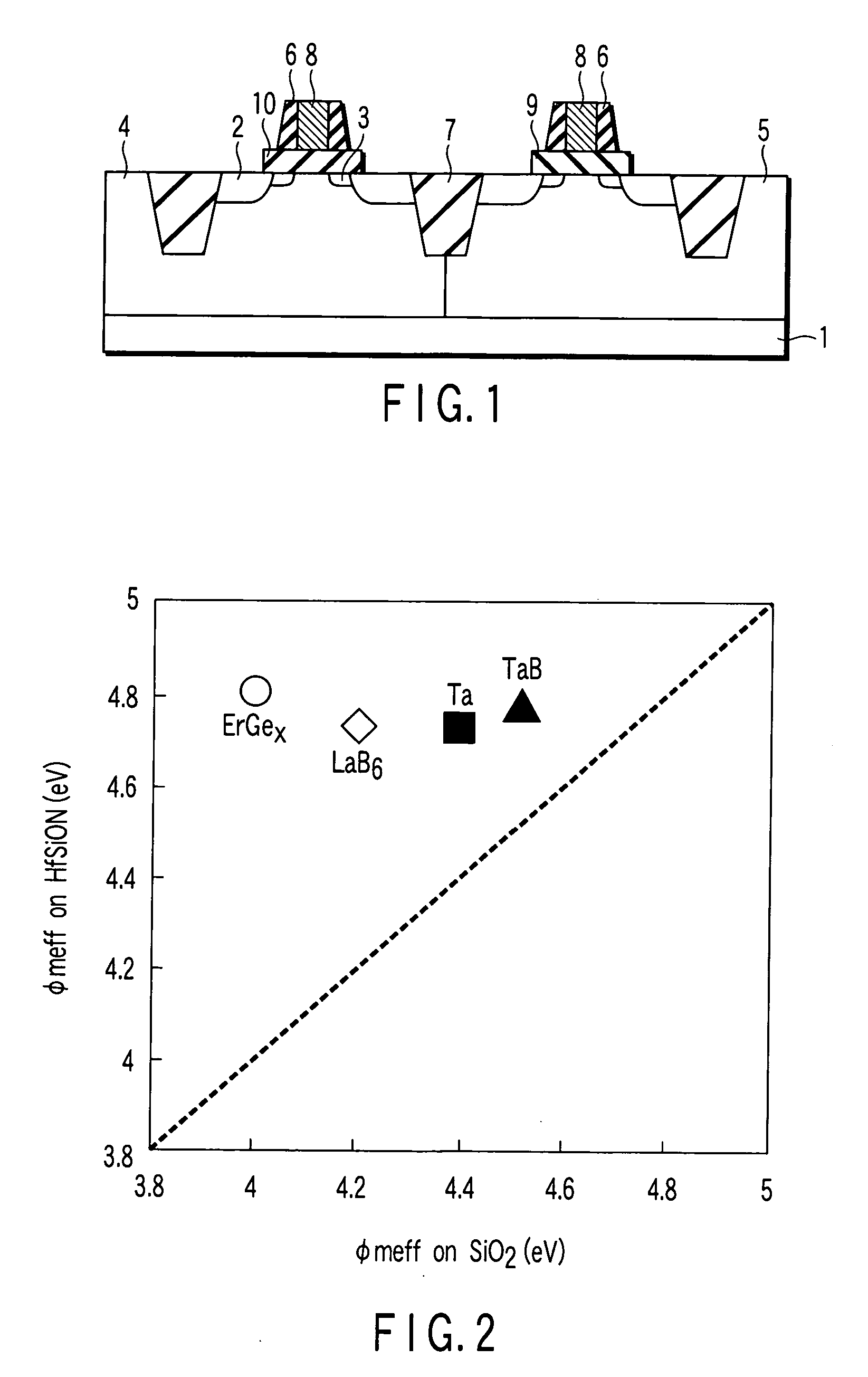

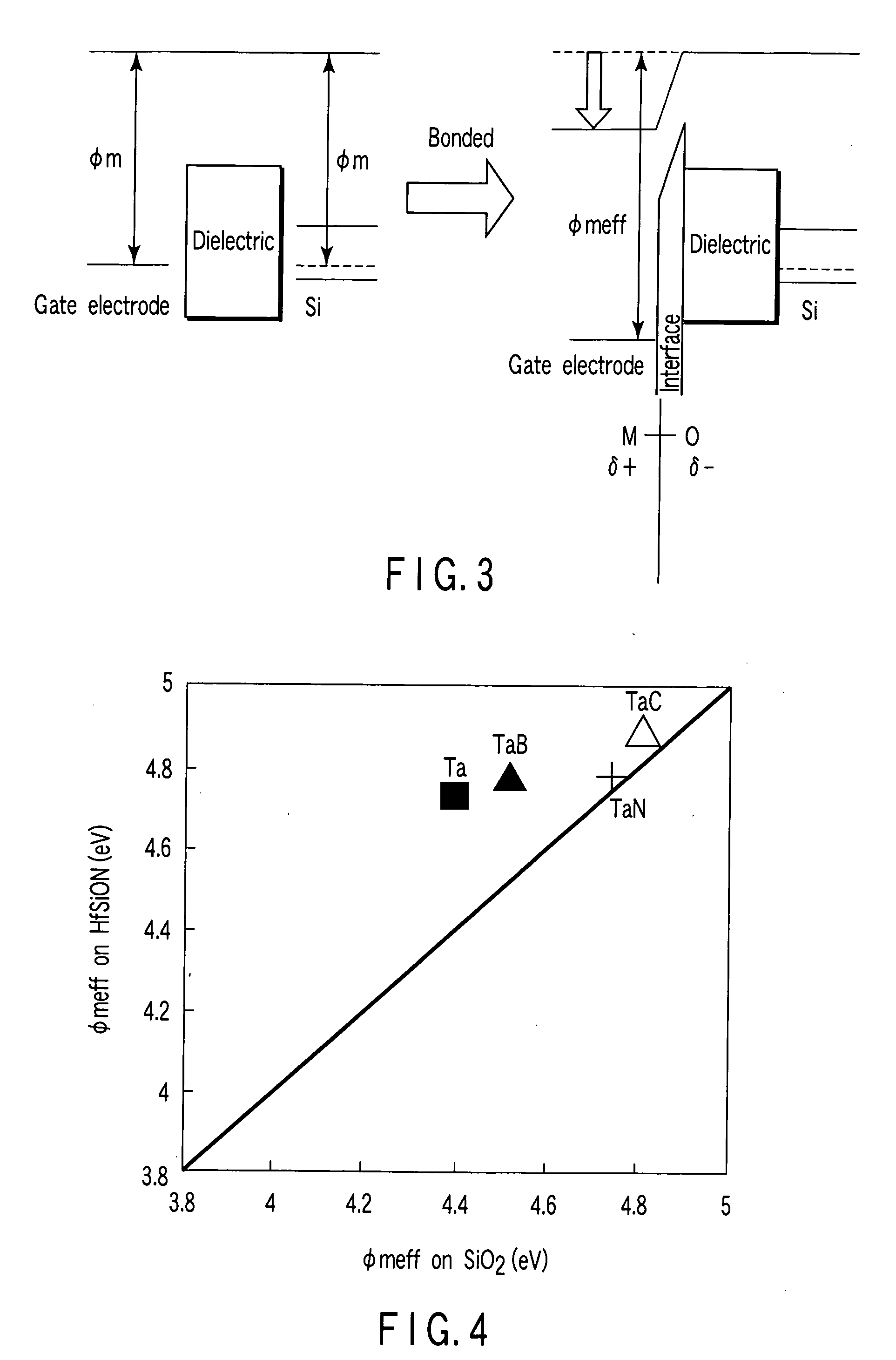

Semiconductor device

A semiconductor device includes a semiconductor substrate, an nMISFET formed on the substrate, the nMISFET including a first dielectric formed on the substrate and a first metal gate electrode formed on the first dielectric and formed of one metal element selected from Ti, Zr, Hf, Ta, Sc, Y, a lanthanoide and actinide series and of one selected from boride, silicide and germanide compounds of the one metal element, and a pMISFET formed on the substrate, the pMISFET including a second dielectric formed on the substrate and a second metal gate electrode formed on the second dielectric and made of the same material as that of the first metal gate electrode, at least a portion of the second dielectric facing the second metal gate electrode being made of an insulating material different from that of at least a portion of the first dielectric facing the first metal gate electrode.

Owner:KK TOSHIBA

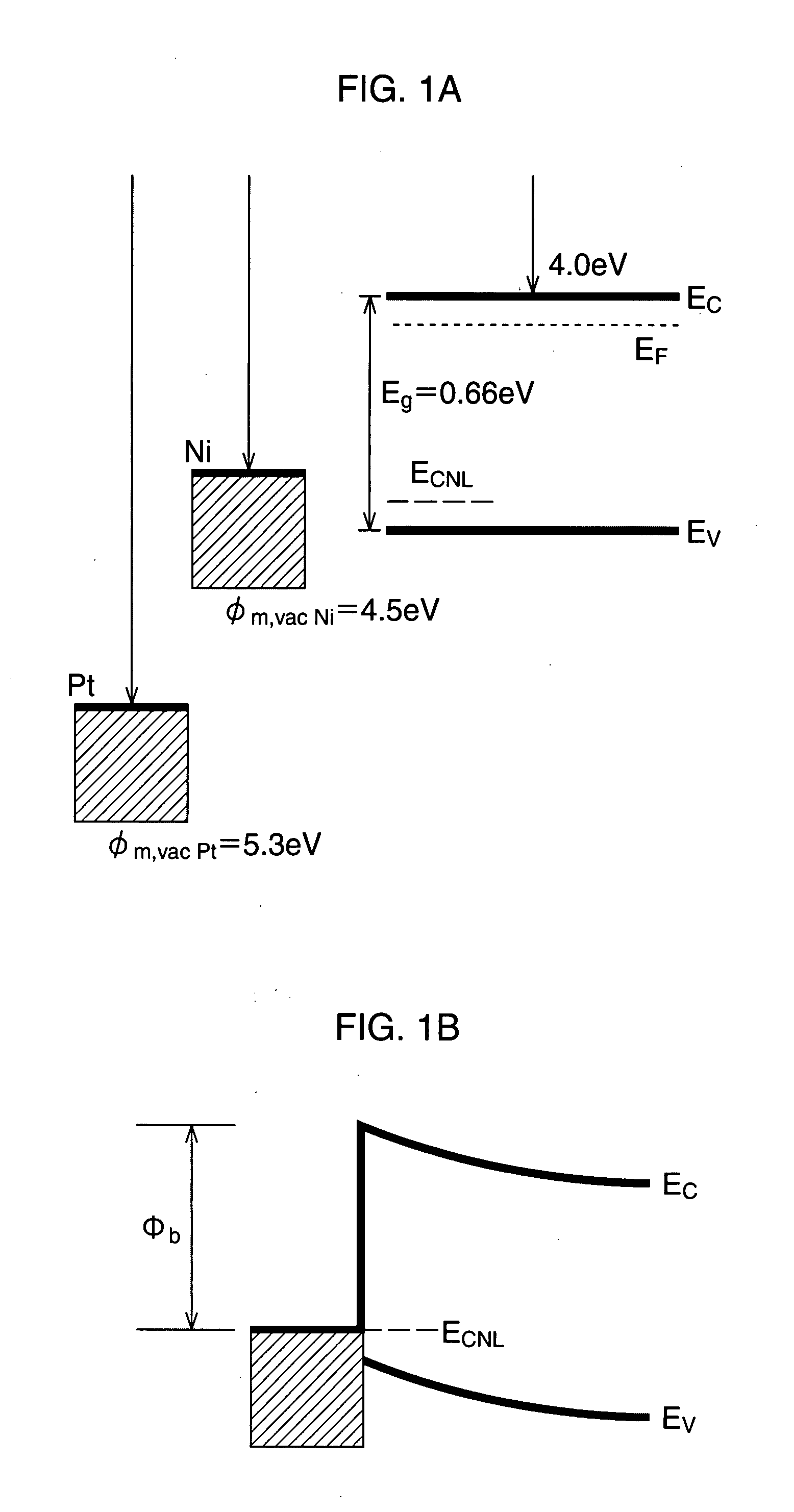

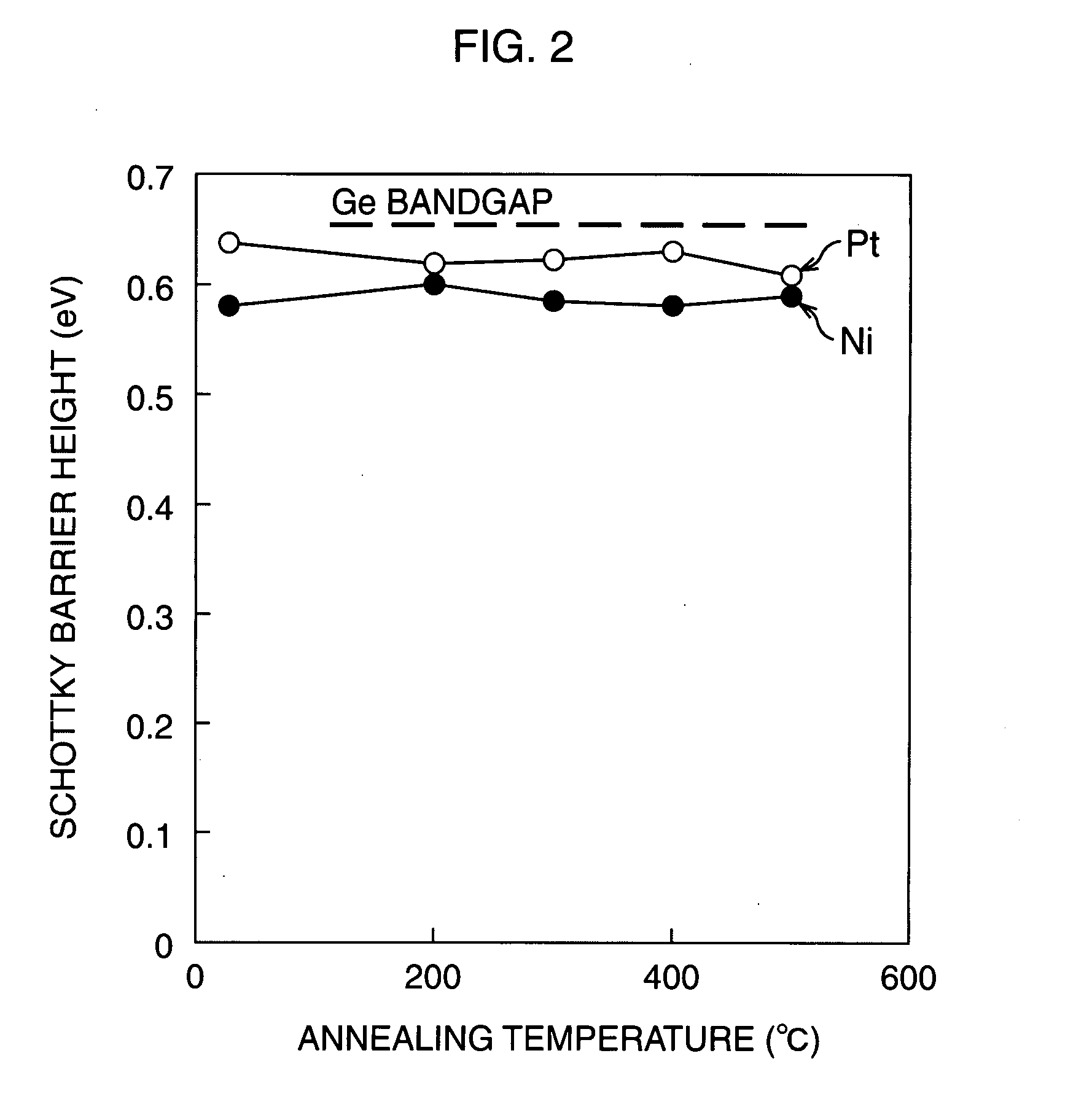

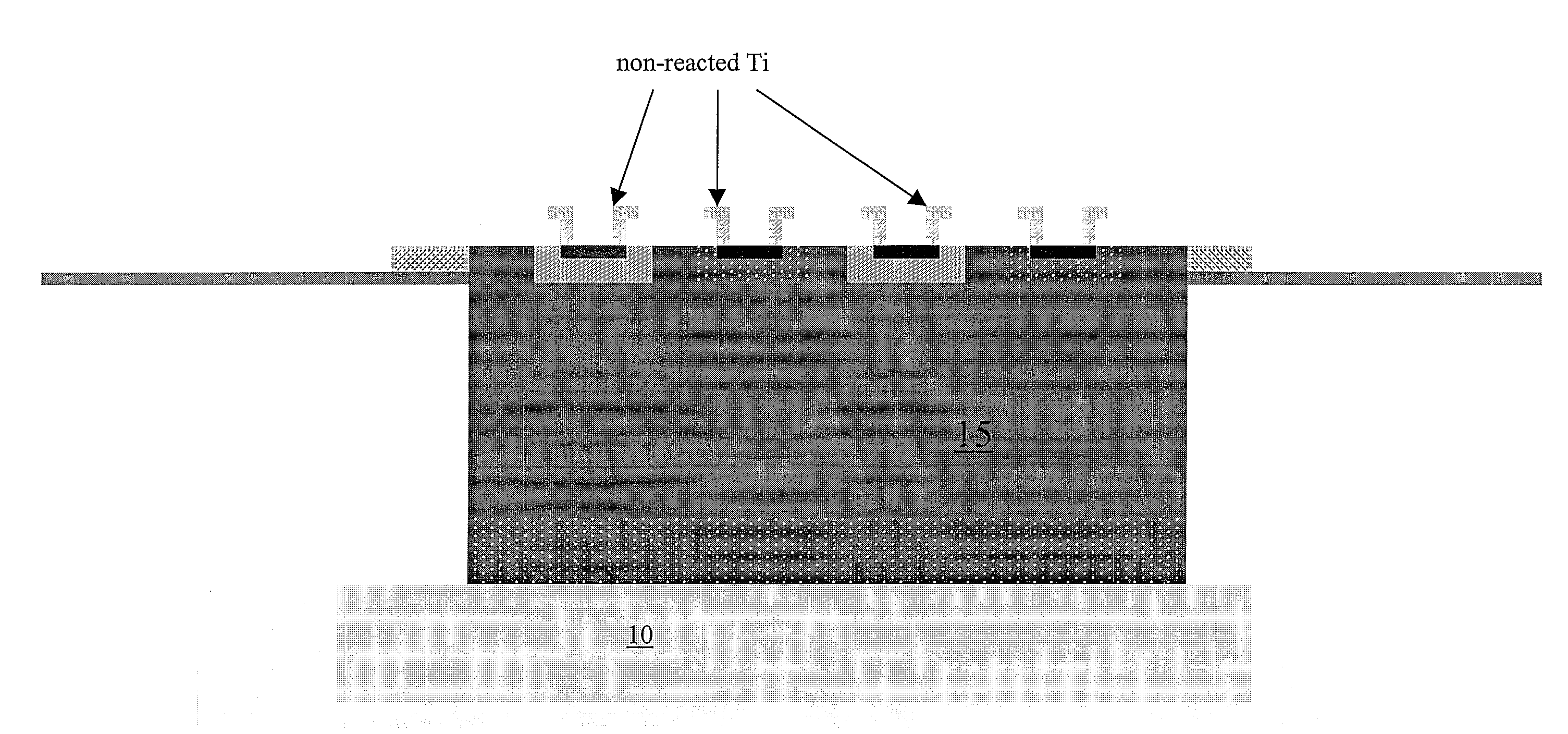

Preparation method of germanium-base schottky transistor

ActiveCN101635262AGood lookingImprove performanceSemiconductor/solid-state device manufacturingVery large scale integrated circuitsManufacturing technology

The invention discloses a preparation method of a germanium-base schottky transistor, which belongs to the technical field of a manufacturing process of ultra large scale integrated circuits (ULSI). The method comprises the following steps: manufacturing an MOS transistor structure on a germanium-base substrate; depositing a metal thin film; carrying out heat treatment for the first time for quick heat annealing so as to ensure that the metal thin film layer and the germanium layer below the metal thin film layer react to form metal germanide; removing the unreacted metal thin film layer; doping impurities in the germanide layer generated by the reaction; carrying out heat treatment for the second time for annealing so as to ensure that the doped impurities are activated to drive in; and finally forming contact holes and metal connection wires. The method carries out the impurity doping and the activated drive-in annealing after forming the germanide through the first annealing and can effectively regulate and control a barrier height of the contact of a metal semiconductor and also improve the surface appearance of the germanide.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

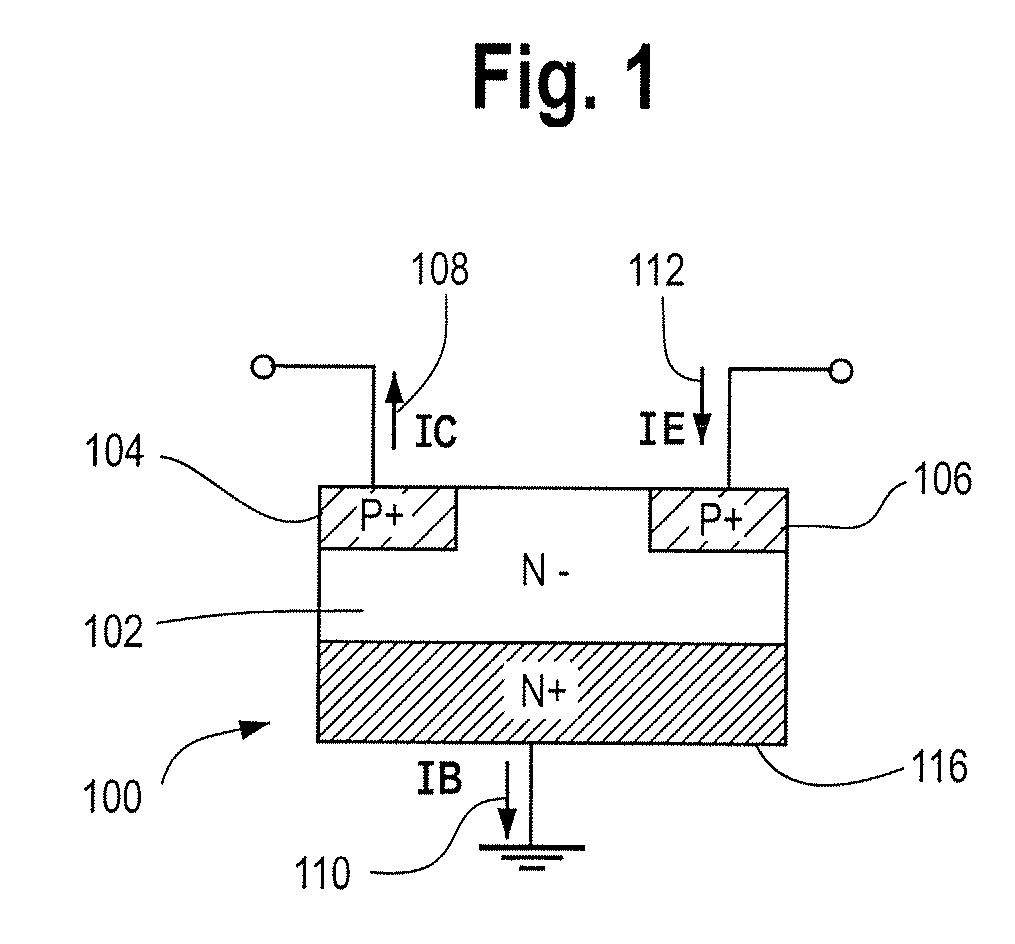

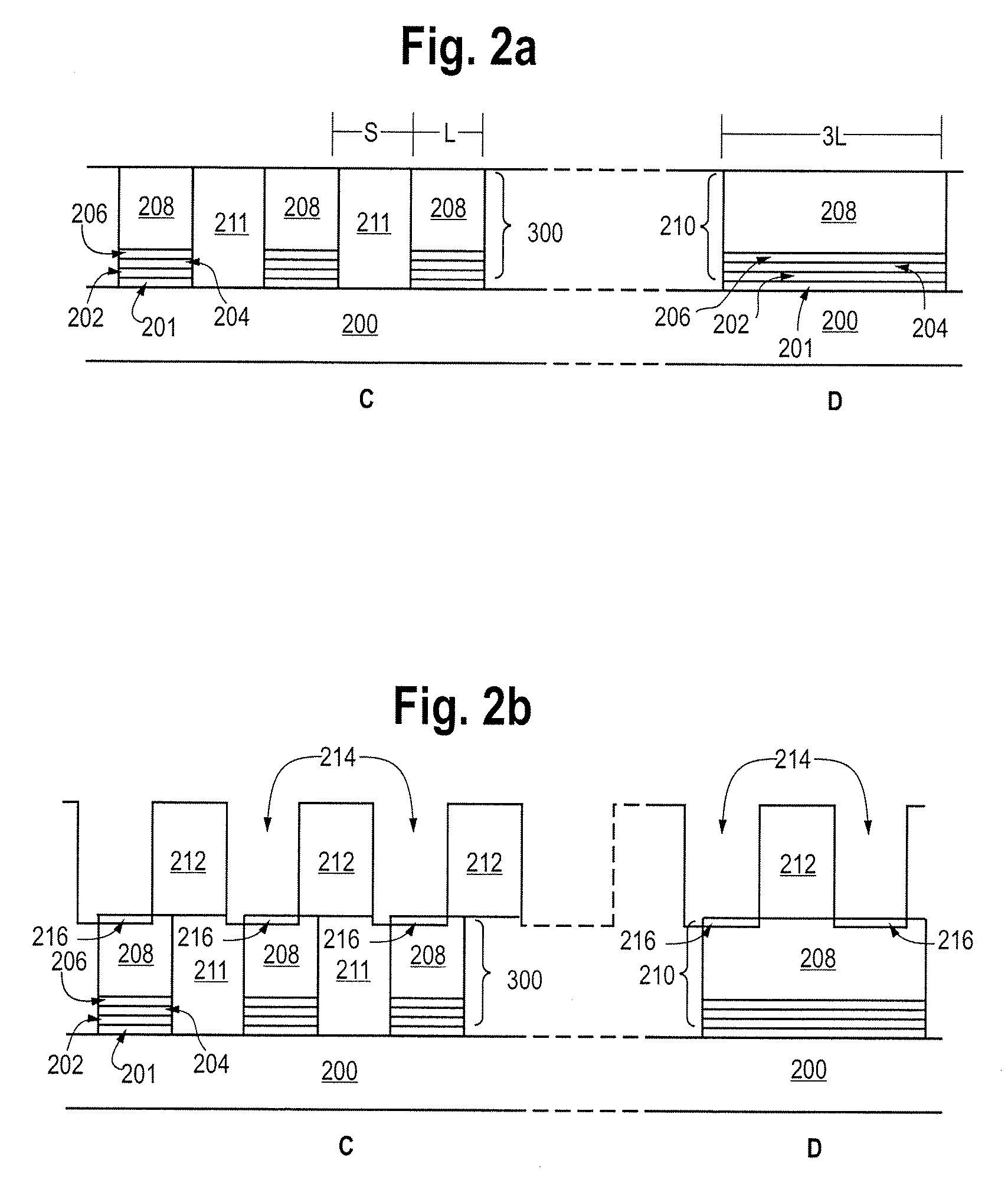

Method to form low-defect polycrystalline semiconductor material for use in a transistor

ActiveUS20080311710A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsGermanide

A method is described for forming a thin film transistor having its current-switching region in polycrystalline semiconductor material which has been crystallized in contact with titanium silicide, titanium silicide-germanide, or titanium germanide. The titanium silicide, titanium silicide-germanide, or titanium germanide is formed having feature size no more than 0.25 micron in the smallest dimension. The small feature size tends to inhibit the phase transformation from C49 to C54 phase titanium silicide. The C49 phase of titanium silicide has a very close lattice match to silicon, and thus provides a crystallization template for the silicon as it forms, allowing formation of large-grain, low-defect silicon. Titanium does not tend to migrate through the silicon during crystallization, limiting the danger of metal contamination. In preferred embodiments, the transistors thus formed may be, for example, field-effect transistors or bipolar junction transistors.

Owner:SANDISK TECH LLC

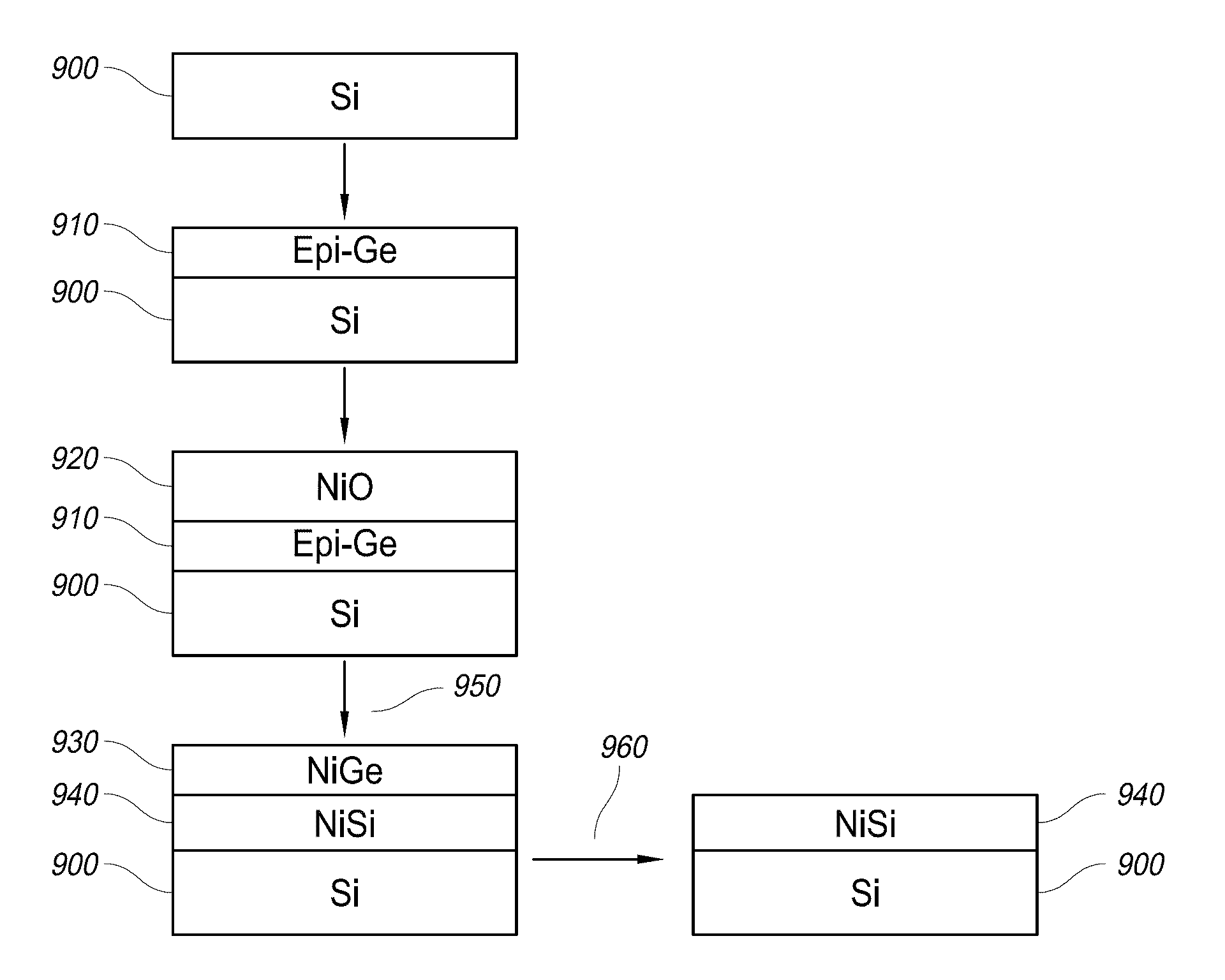

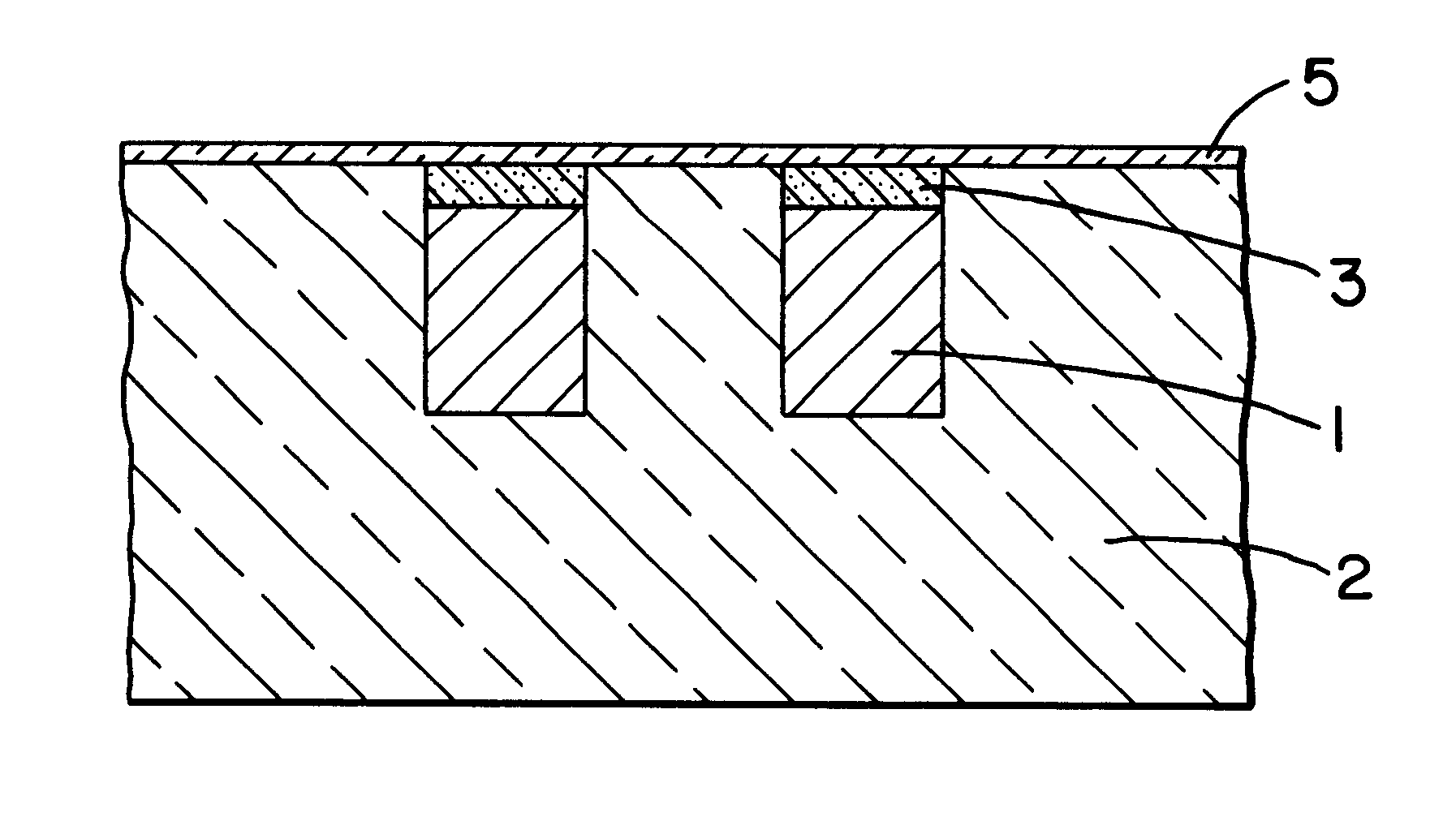

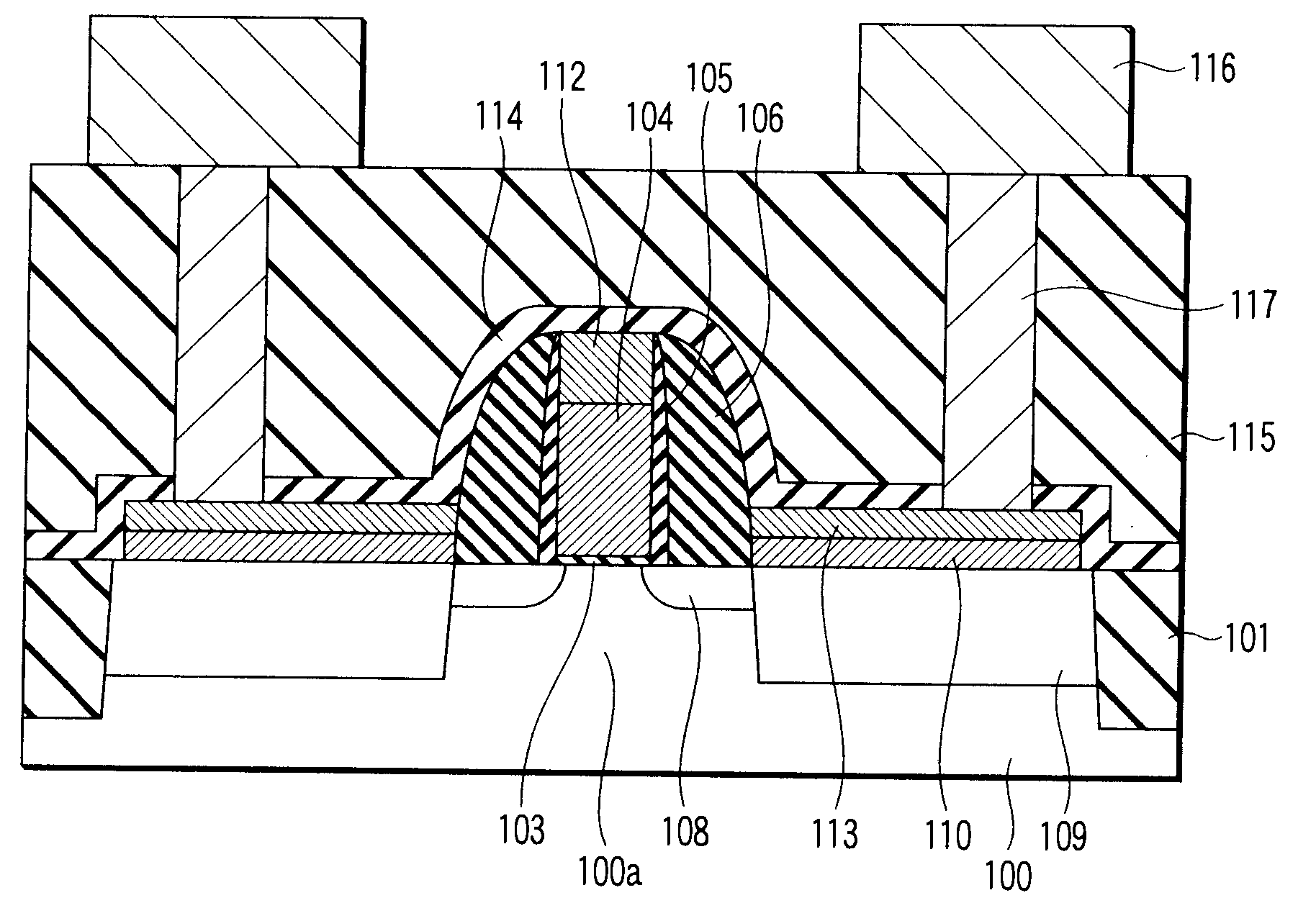

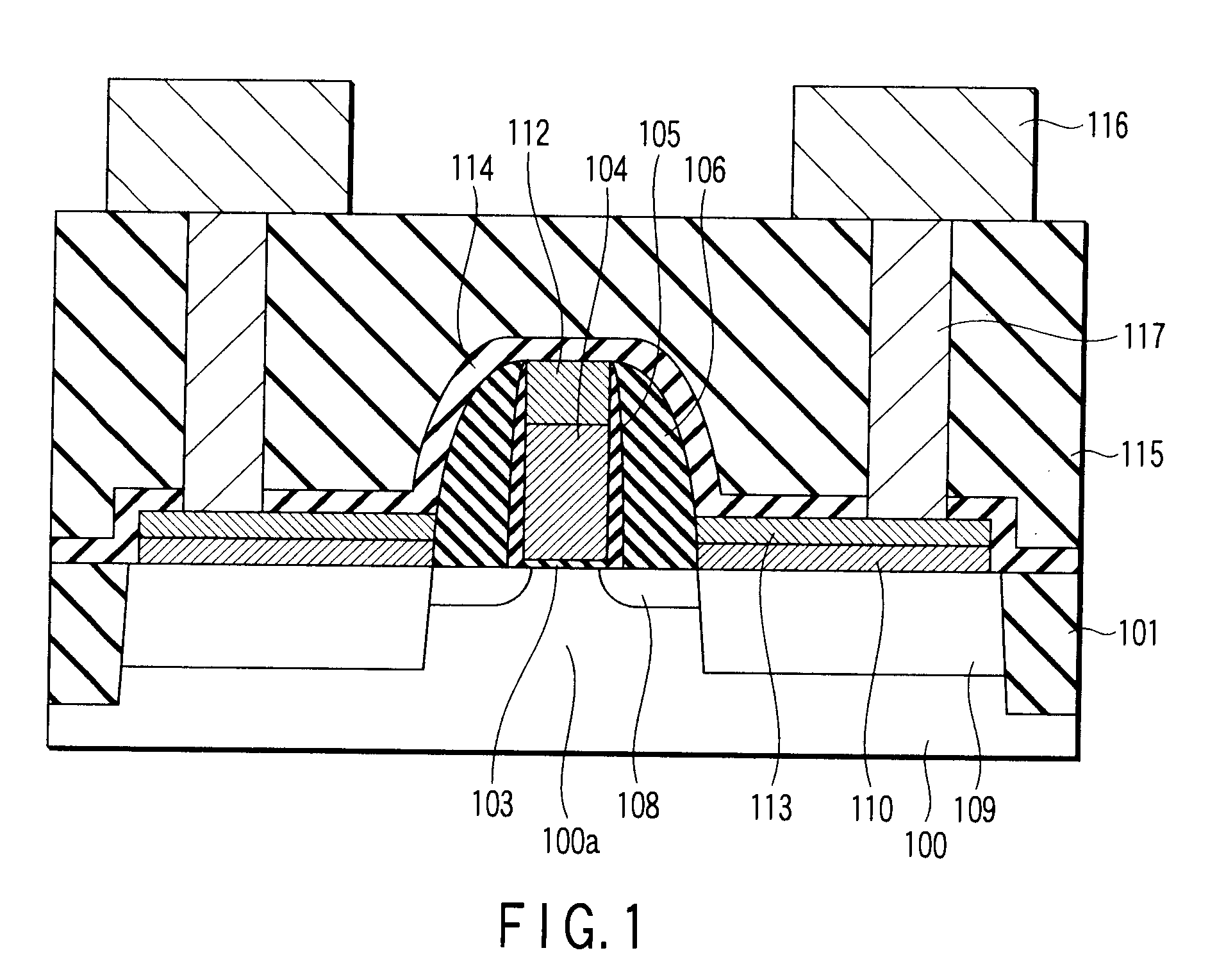

Semiconductor device and method of manufacturing the same

InactiveUS20080064156A1Run at high speedDesired threshold voltage controlSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationSurface layer

In an nMOSFET, a gate electrode is formed by a silicide layer comprised of NiSi. In a surface layer of a Ge substrate on both sides of the gate electrode, NiGe layers which are germanide layers comprised of NiGe are formed. On junction interfaces between the NiGe layers and the Ge substrate, first layers are formed which are formed by segregating a predetermined atom with high concentration, and on an interface between the gate electrode and an insulation film, a second layer is formed which is formed by segregating the same atom as that of the first layer with high concentration.

Owner:FUJITSU SEMICON LTD

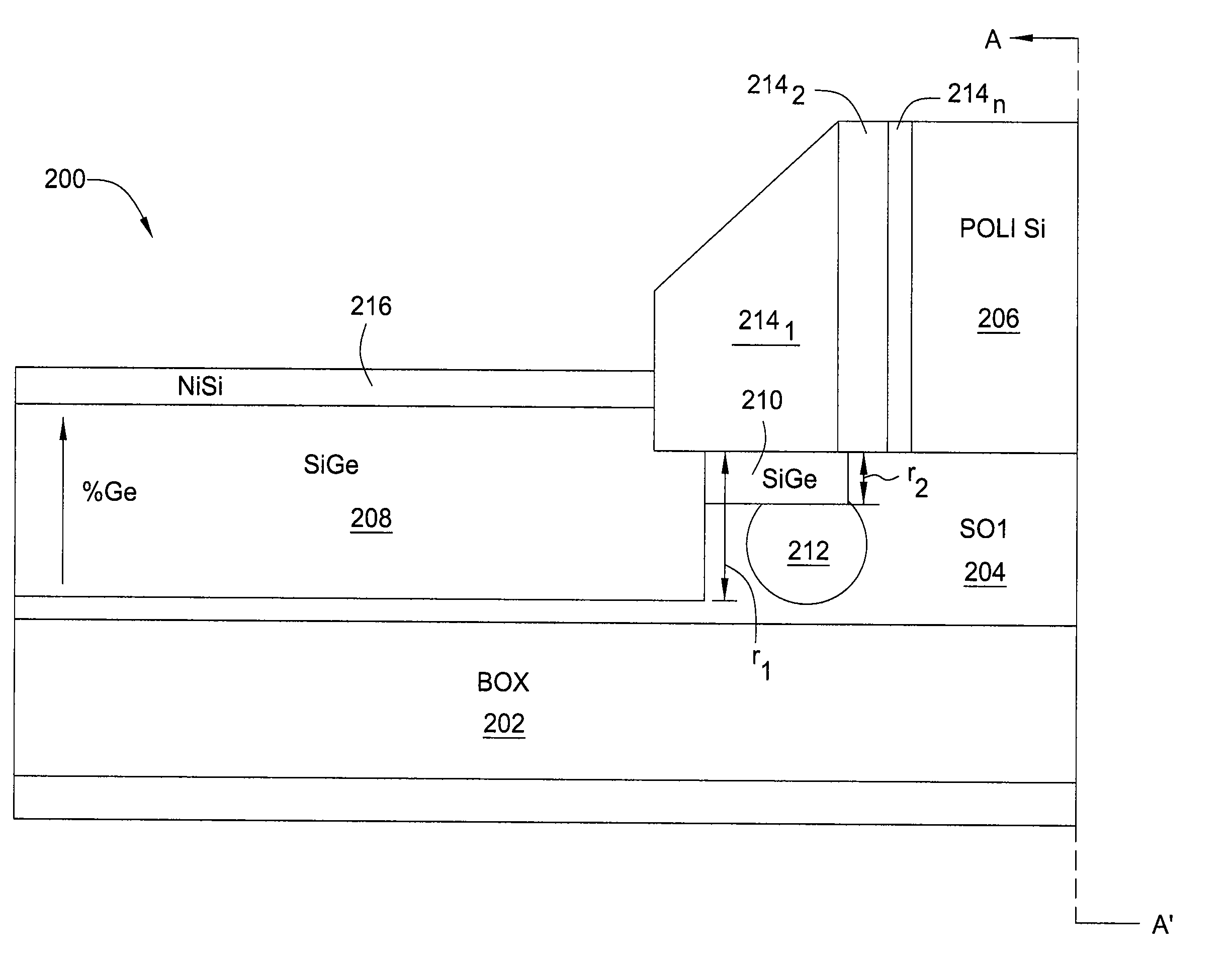

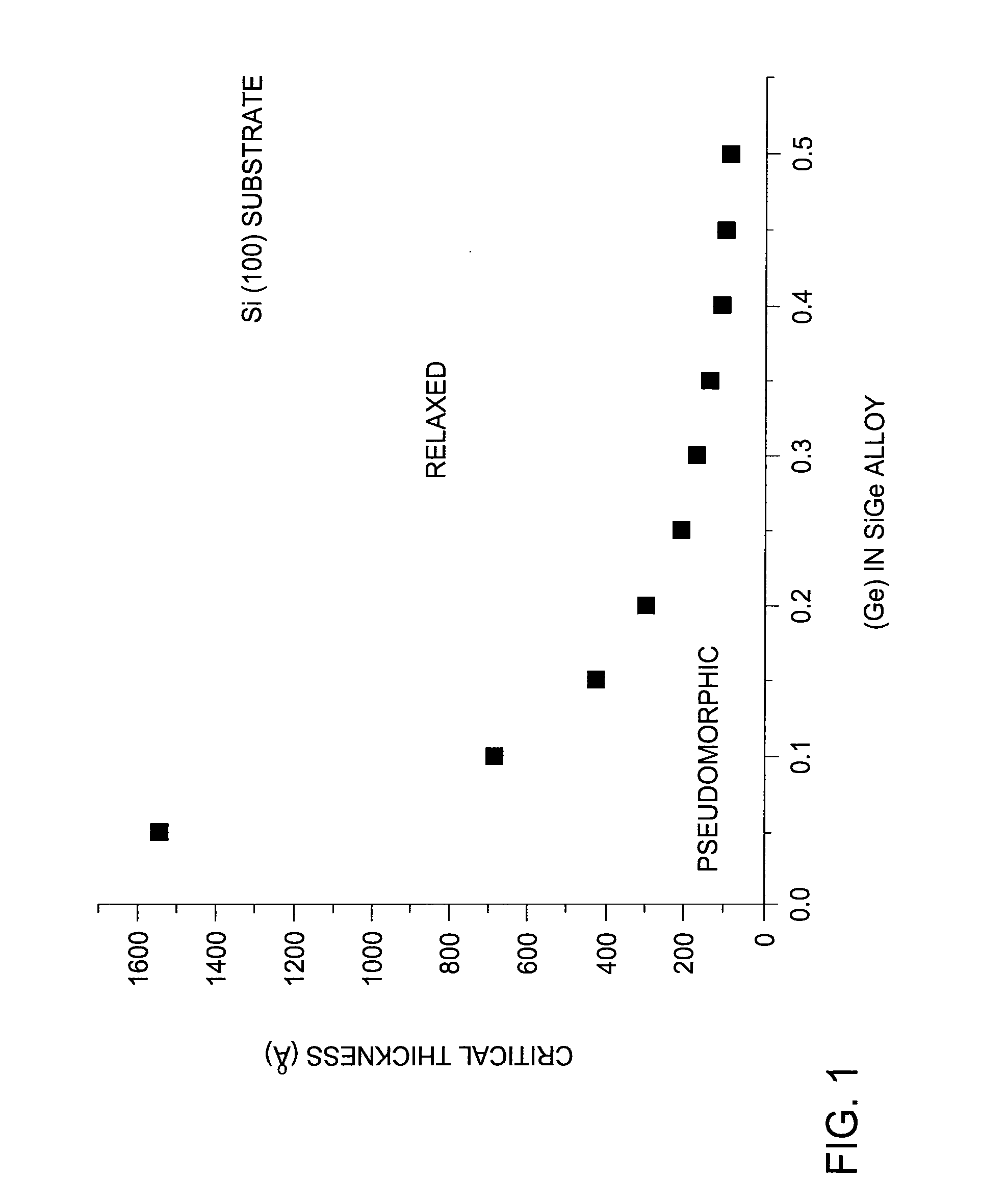

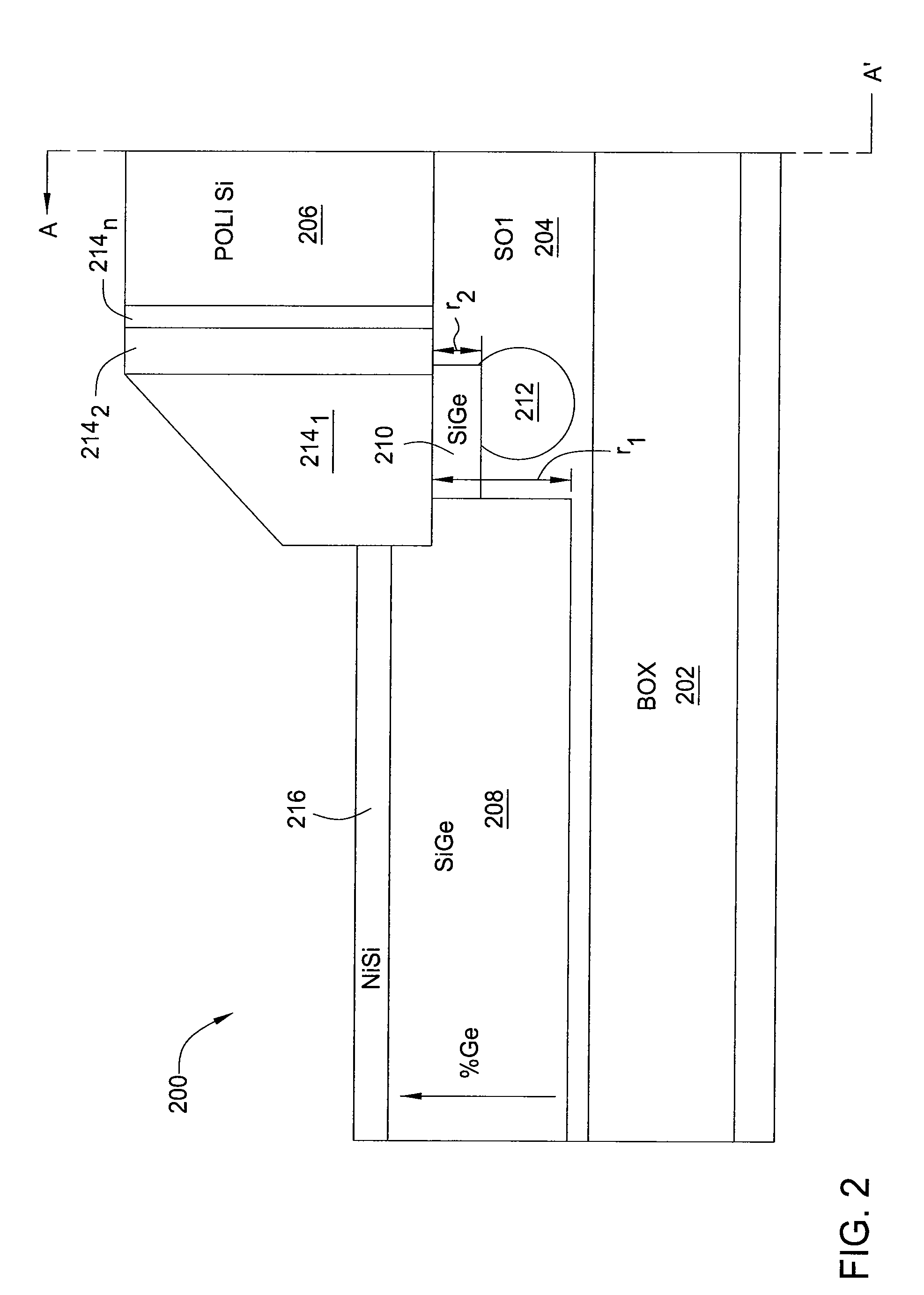

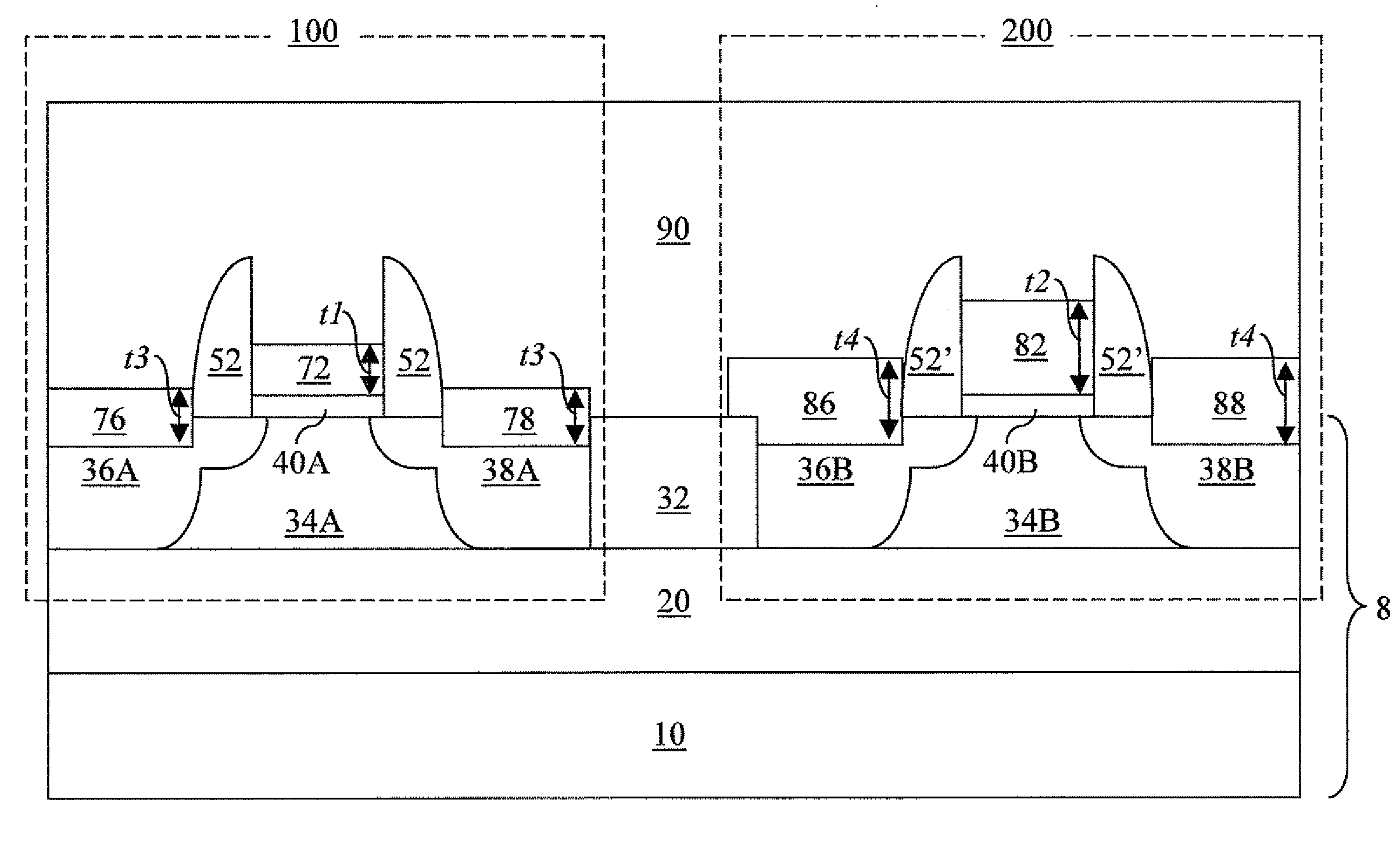

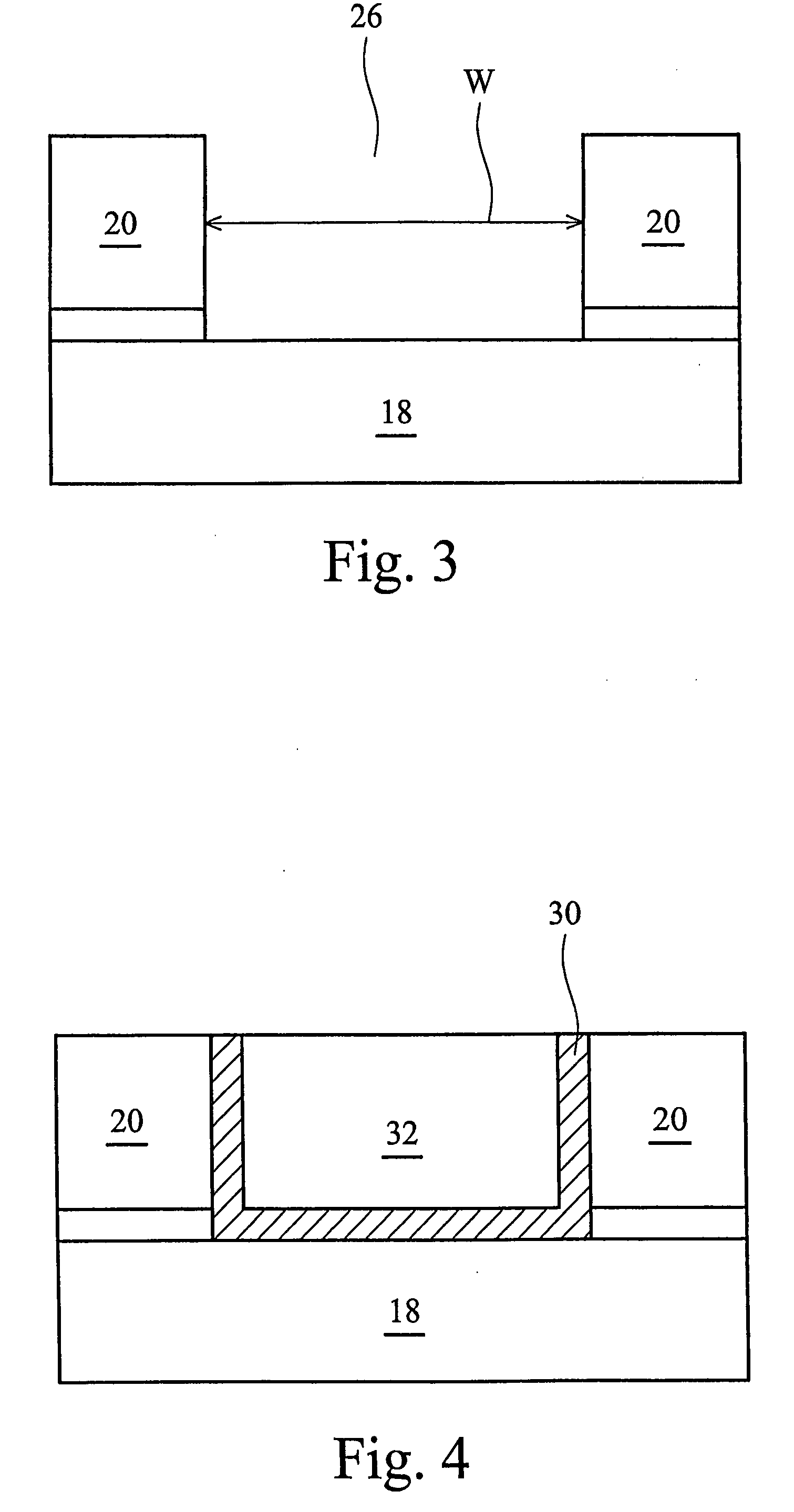

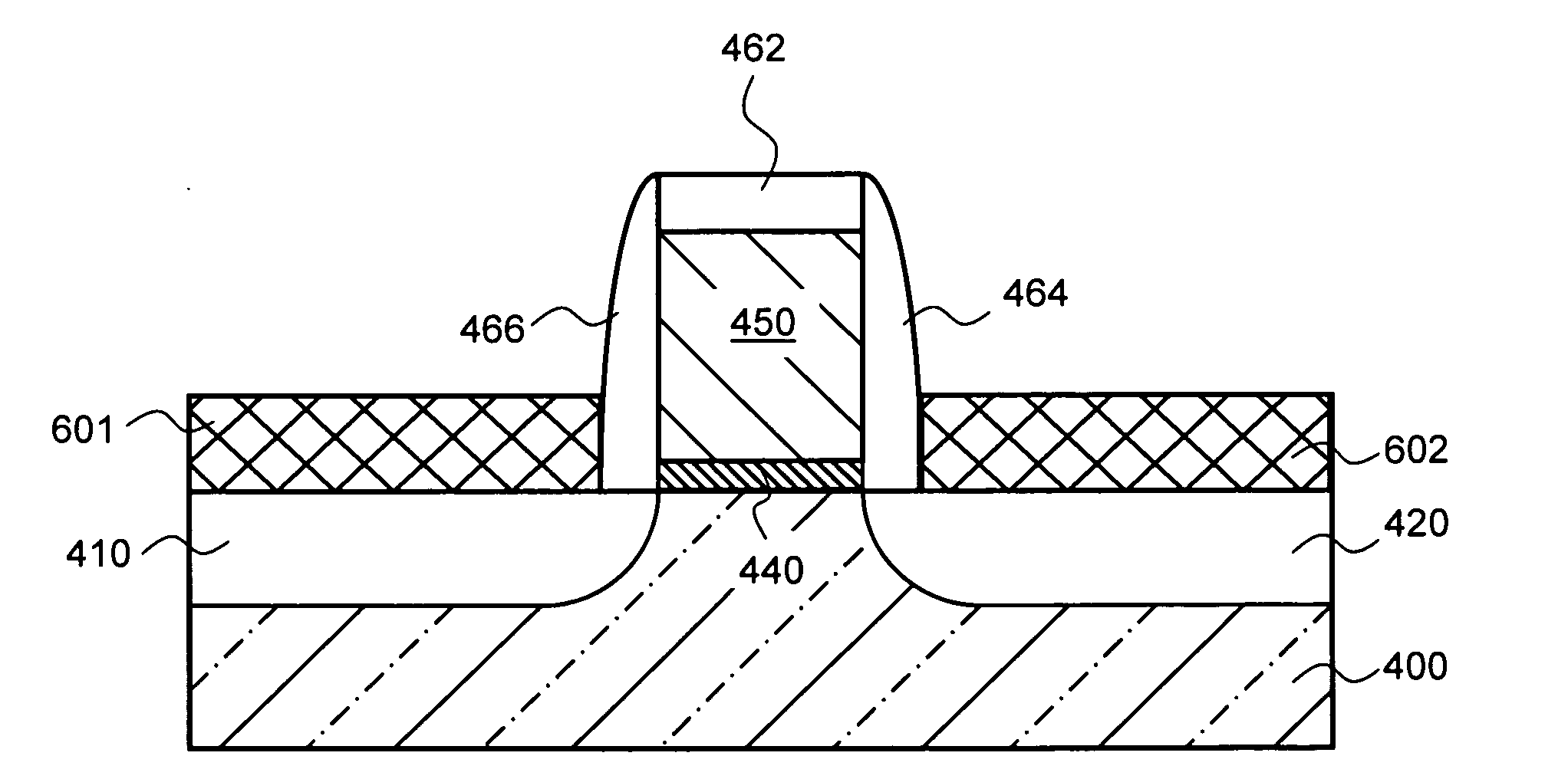

Complementary metal-oxide-semiconductor device with embedded stressor

InactiveUS20090242989A1Solid-state devicesSemiconductor/solid-state device manufacturingGermanideAlloy

In one embodiment, the invention is a complementary metal-oxide-semiconductor device with an embedded stressor. One embodiment of a field effect transistor includes a silicon on insulator channel, a gate electrode coupled to the silicon on insulator channel, and a stressor embedded in the silicon on insulator channel and spaced laterally from the gate electrode, where the stressor is formed of a silicon germanide alloy whose germanium content gradually increases in one direction.

Owner:IBM CORP +2

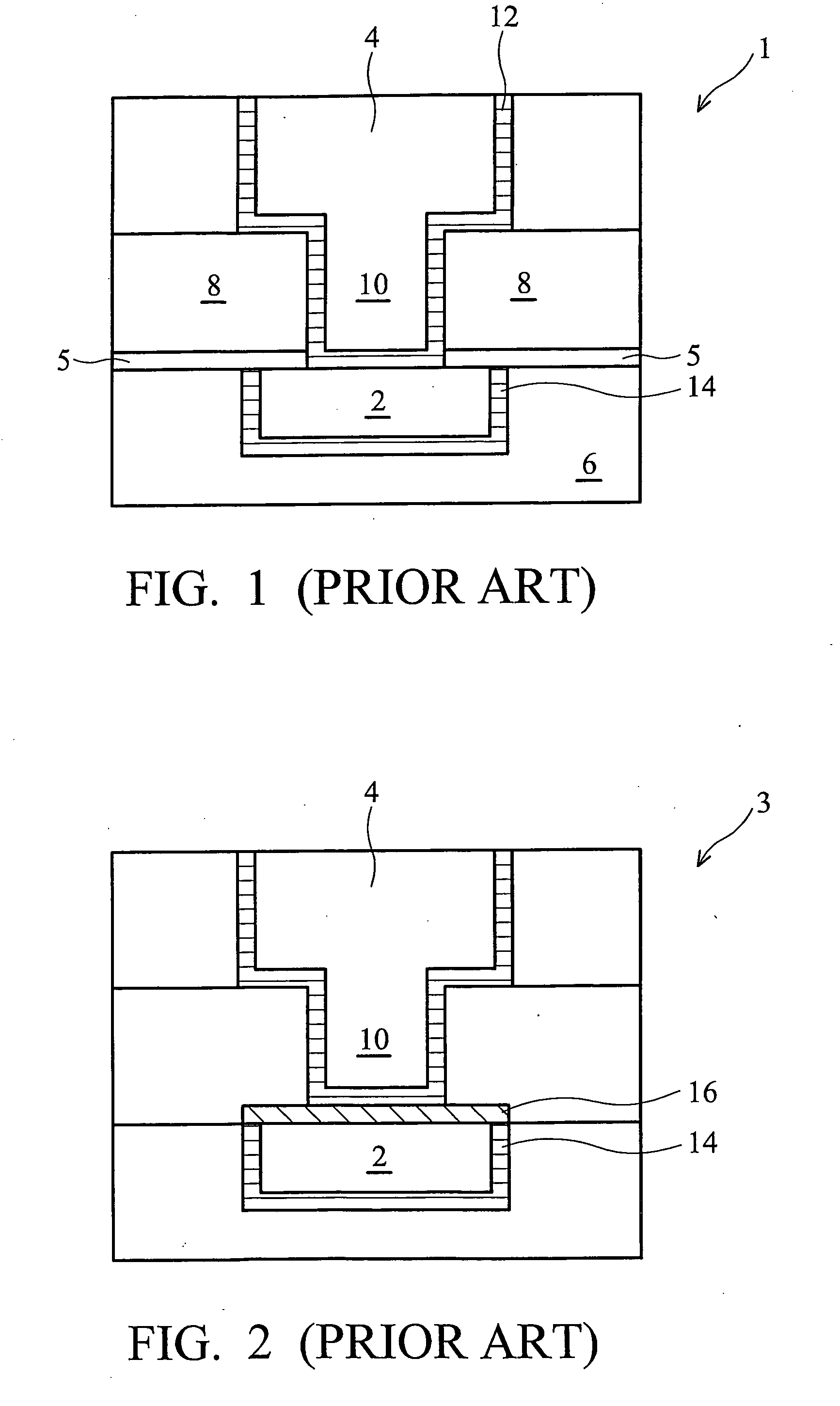

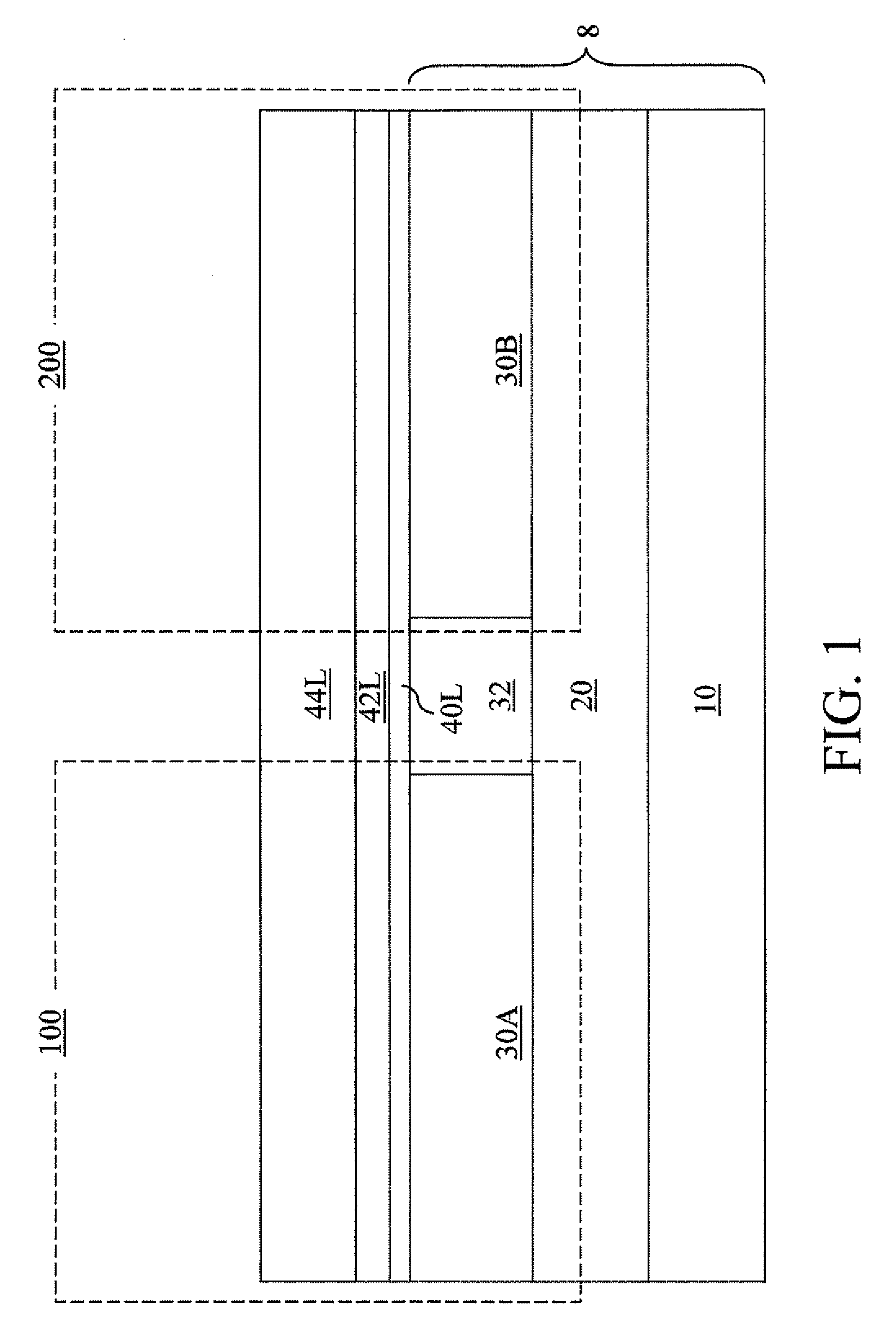

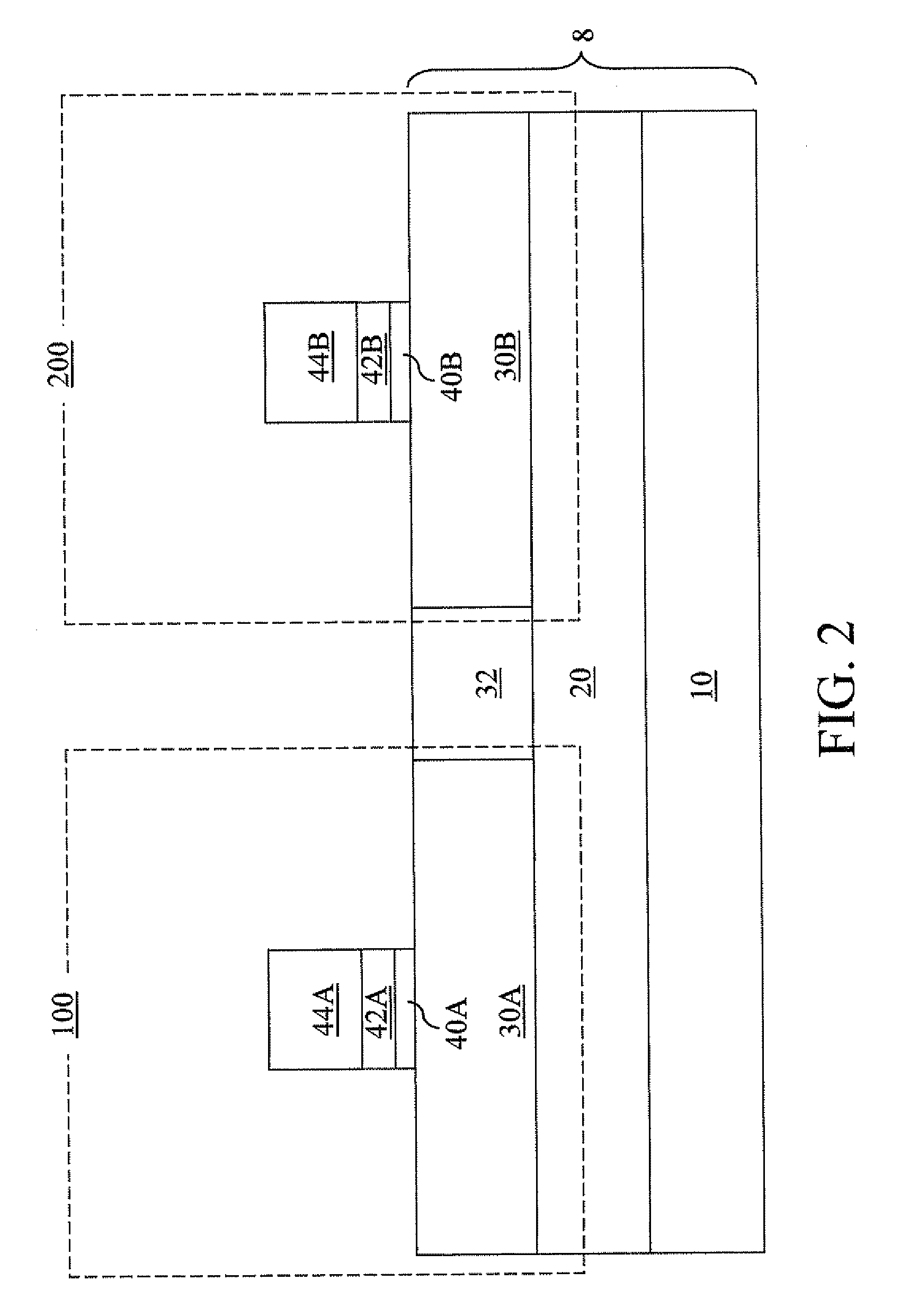

CMOS integration scheme employing a silicide electrode and a silicide-germanide alloy electrode

InactiveUS20090206413A1Reduce complexityLow costTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor materials

A p-type field effect transistor (PFET) and an n-type field effect transistor (NFET) are formed by patterning of a gate dielectric layer, a thin silicon layer, and a silicon-germanium alloy layer. After formation of the source / drain regions and gate spacers, silicon germanium alloy portions are removed from gate stacks. A dielectric layer is formed and patterned to cover an NFET gate electrode, while exposing a thin silicon portion for a PFET. Germanium is selectively deposited on semiconductor surfaces including the exposed silicon portion. The dielectric layer is removed and a metal layer is deposited and reacted with underlying semiconductor material to form a metal silicide for a gate electrode of the NFET, while forming a metal silicide-germanide alloy for a gate electrode of the PFET.

Owner:IBM CORP

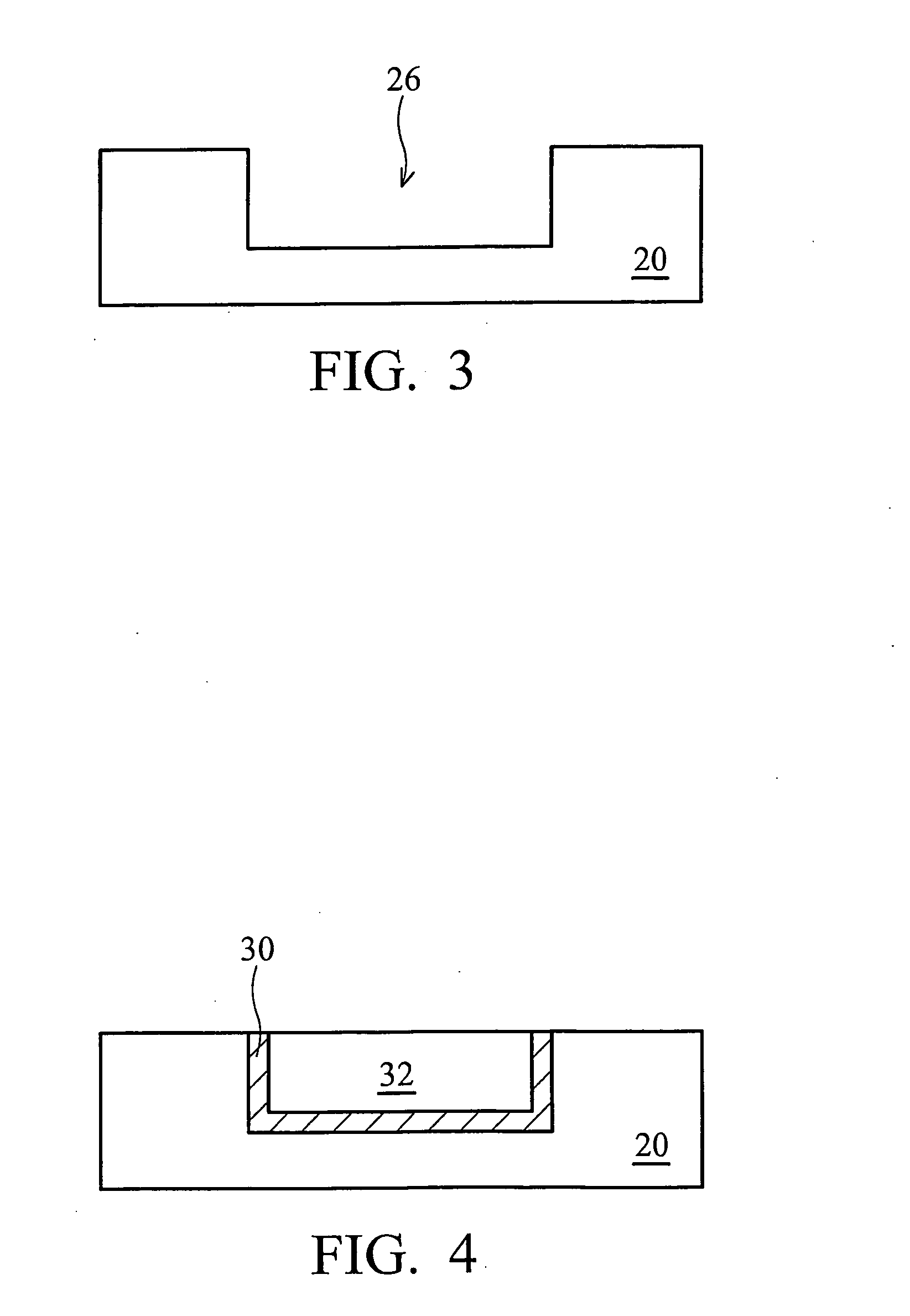

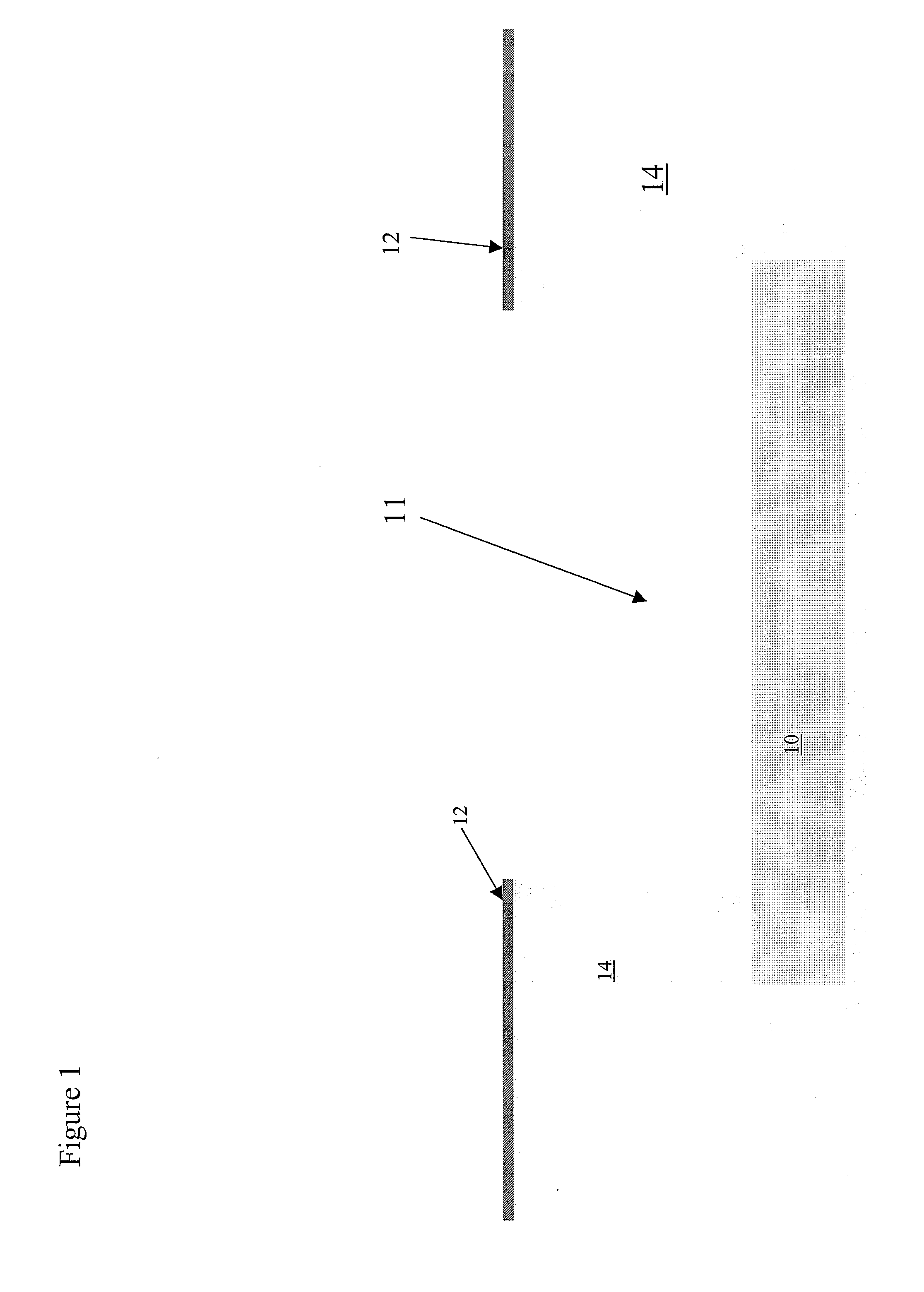

Method for Manufacturing Lateral Germanium Detectors

InactiveUS20120252158A1Solid-state devicesSemiconductor/solid-state device manufacturingGermanideResist

An improved method for manufacturing a lateral germanium detector is disclosed. A detector window is opened through an oxide layer to expose a doped single crystalline silicon layer situated on a substrate. Next, a single crystal germanium layer is grown within the detector window, and an amorphous germanium layer is grown on the oxide layer. The amorphous germanium layer is then polished to leave only a small portion around the single crystal germanium layer. A dielectric layer is deposited on the amorphous germanium layer and the single crystal germanium layer. Using resist masks and ion implants, multiple doped regions are formed on the single crystal germanium layer. After opening several oxide windows on the dielectric layer, a refractory metal layer is deposited on the doped regions to form multiple germanide layers.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

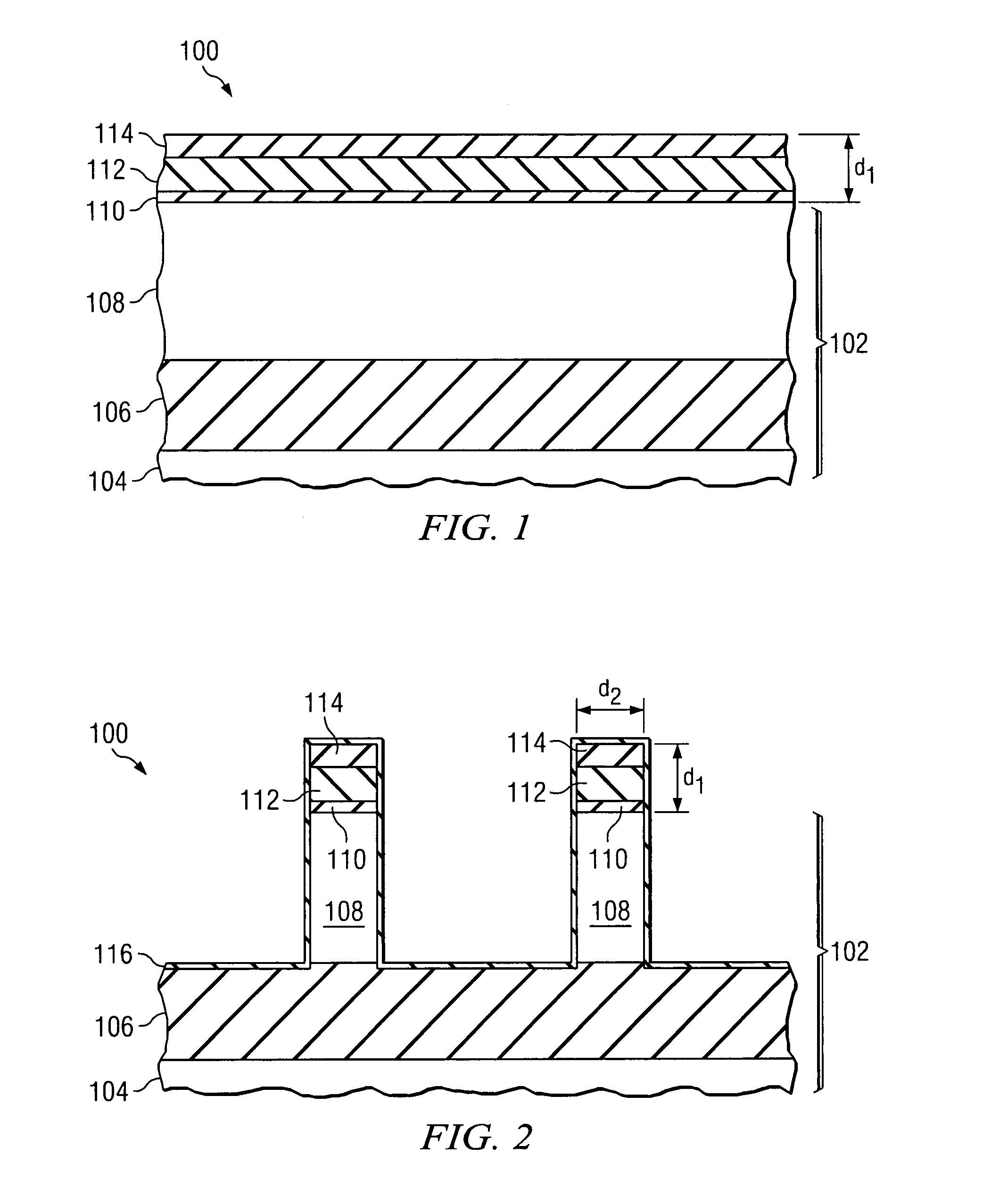

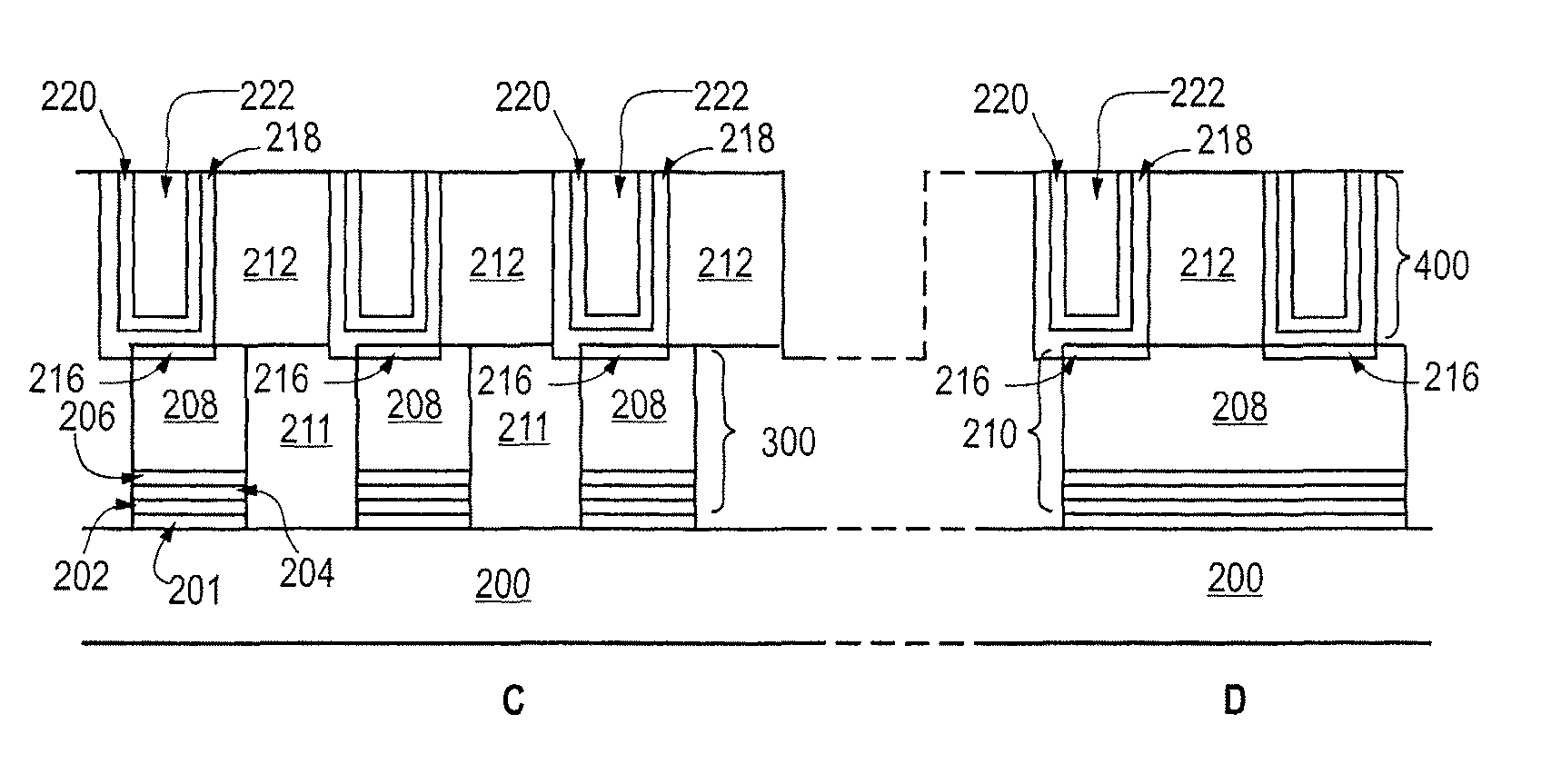

Semiconductor devices and methods of manufacture thereof

ActiveUS8124483B2Semiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGermanide

Semiconductor devices and methods of manufacture thereof are disclosed. In a preferred embodiment, a method of manufacturing a semiconductor device includes forming a transistor, the transistor including a fin having a first side and a second side opposite the first side. The transistor includes a first gate electrode disposed on the first side of the fin and a second gate electrode disposed on the second side of the fin. The method includes forming a silicide or germanide of a metal on the first gate electrode and the second gate electrode of the transistor. The amount of the metal of the silicide or germanide is substantially homogeneous over the first gate electrode and the second gate electrode proximate the fin.

Owner:INFINEON TECH AG

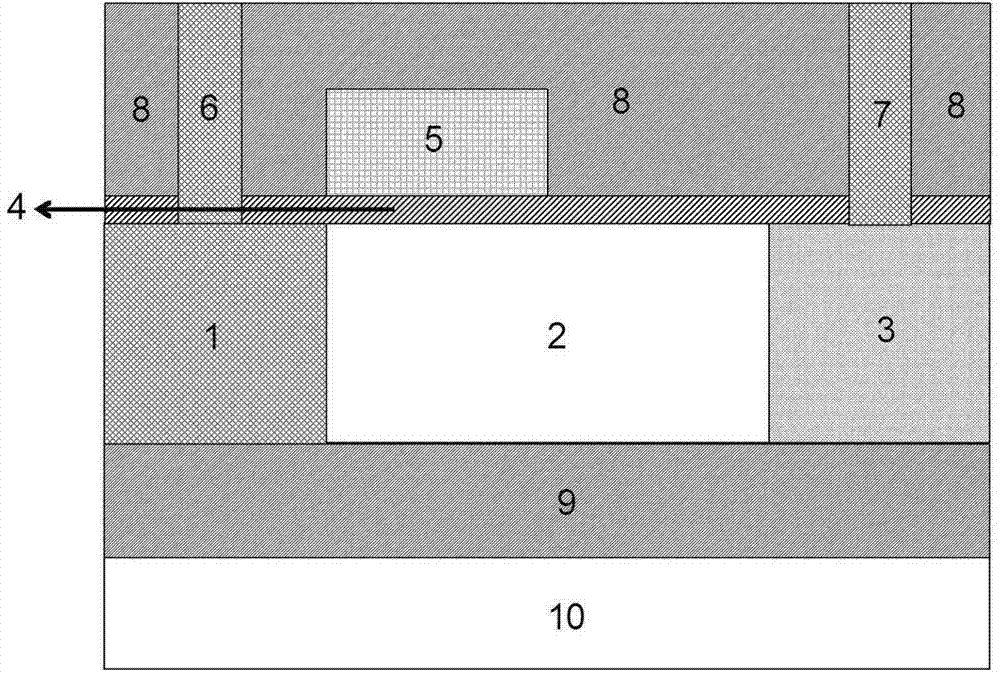

Germanium-containing dielectric barrier for low-k process

ActiveUS20080136029A1Reduce diffuseStable layerSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureGermanide

A semiconductor structure and methods of forming the same are provided. The semiconductor structure includes a semiconductor substrate; a first dielectric layer over the semiconductor substrate; a conductive wiring in the first dielectric layer; and a copper germanide nitride layer over the conductive wiring.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming polycrystalline thin film bipolar transistors

ActiveUS7855119B2Read-only memoriesSemiconductor/solid-state device manufacturingGermanideMaterials science

Owner:SANDISK TECH LLC

Method for the selective removal of an unsilicided metal

InactiveUS20070197029A1Dissolution of the metal germanideSemiconductor/solid-state device manufacturingChemical solutionGermanide

An integrated circuit is silicided by depositing at least one metal on a silicon-containing region and forming a metal silicide. Residue metal that has not been silicided during the formation of the metal silicide is then removed. The removal of the residue metal involves the conversion of the residue metal to an alloy containing the germanide of said metal with minimal if any adverse affect on the silicide. Next, the alloy is removed, in a manner selective to the silicide, by dissolving the alloy in a chemical solution.

Owner:STMICROELECTRONICS (CROLLES 2) SAS

Method of forming self-aligned low resistance contact layer

ActiveUS20100035399A1Semiconductor/solid-state device manufacturingSemiconductor devicesGermanideContact layer

Embodiments of the present invention describe a method of fabricating low resistance contact layers on a semiconductor device. The semiconductor device comprises a substrate having source and drain regions. The substrate is alternatingly exposed to a first precursor and a second precursor to selectively deposit an amorphous semiconductor layer onto each of the source and drain regions. A metal layer is then deposited over the amorphous semiconductor layer on each of the source and drain regions. An annealing process is then performed on the substrate to allow the metal layer to react with amorphous semiconductor layer to form a low resistance contact layer on each of the source and drain regions. The low resistance contact layer on each of the source and drain regions can be formed as either a silicide layer or germanide layer depending on the type of precursors used.

Owner:INTEL CORP