Patents

Literature

462 results about "Reverse leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

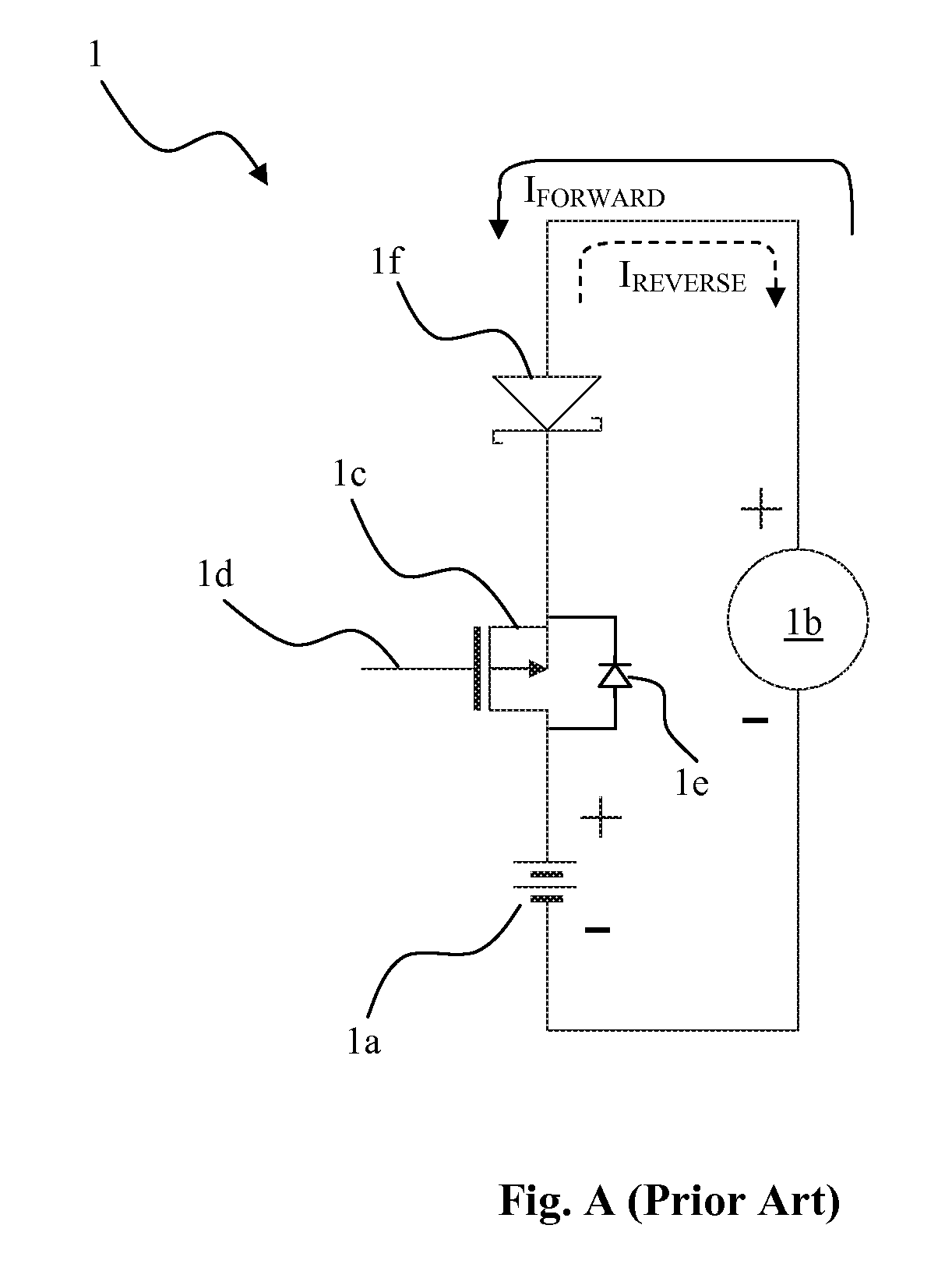

Reverse leakage current in a semiconductor device is the current from that semiconductor device when the device is reverse biased. When a semiconductor device is reverse biased it should not conduct any current, however, due to an increased barrier potential, the free electrons on the p side are dragged to the battery's positive terminal, while holes on the n side are dragged to the battery's negative terminal. This produces a current of minority charge carriers and hence its magnitude is extremely small. For constant temperatures, the reverse current is almost constant although the applied reverse voltage is increased up to a certain limit. Hence, it is also called reverse saturation current.

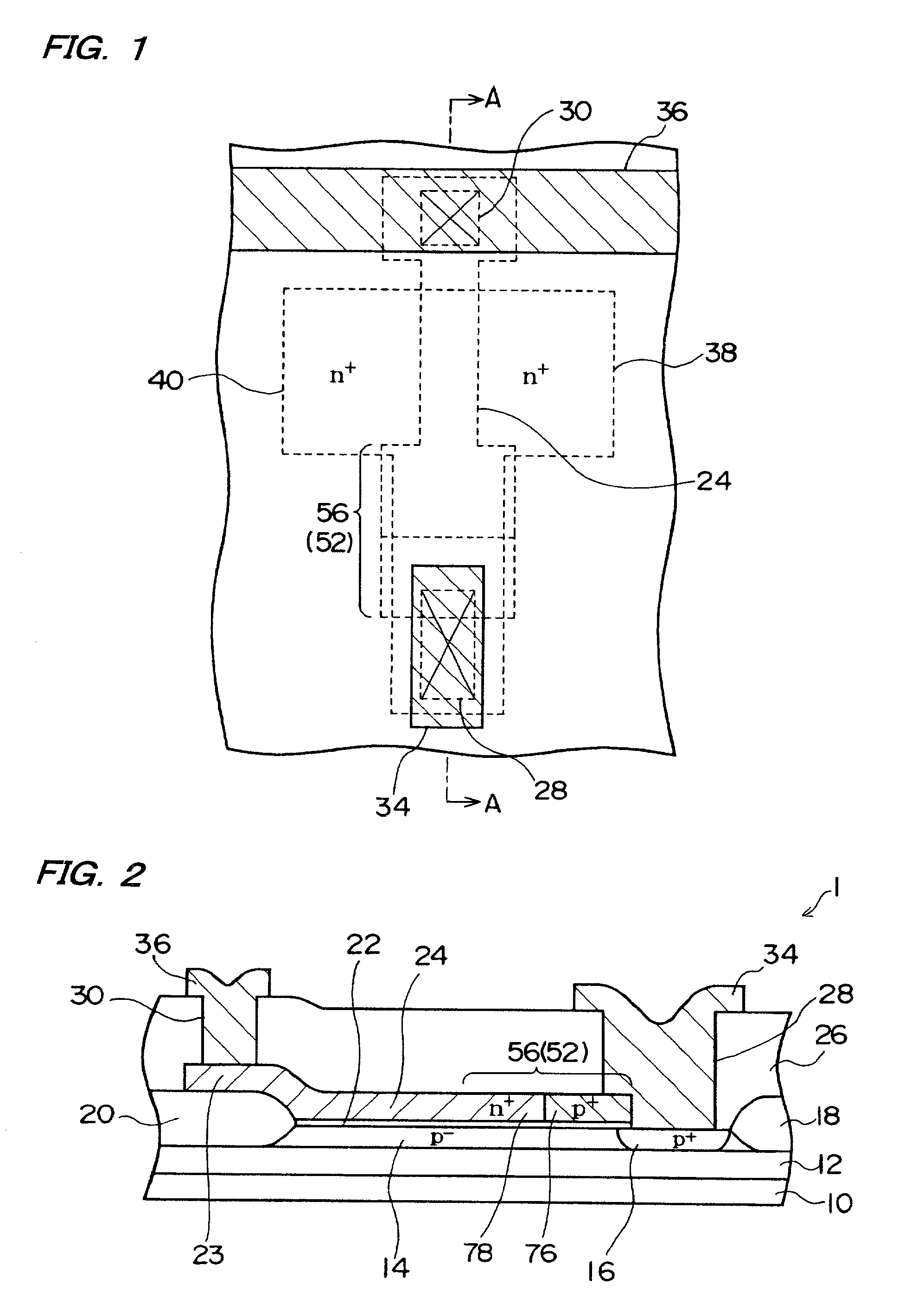

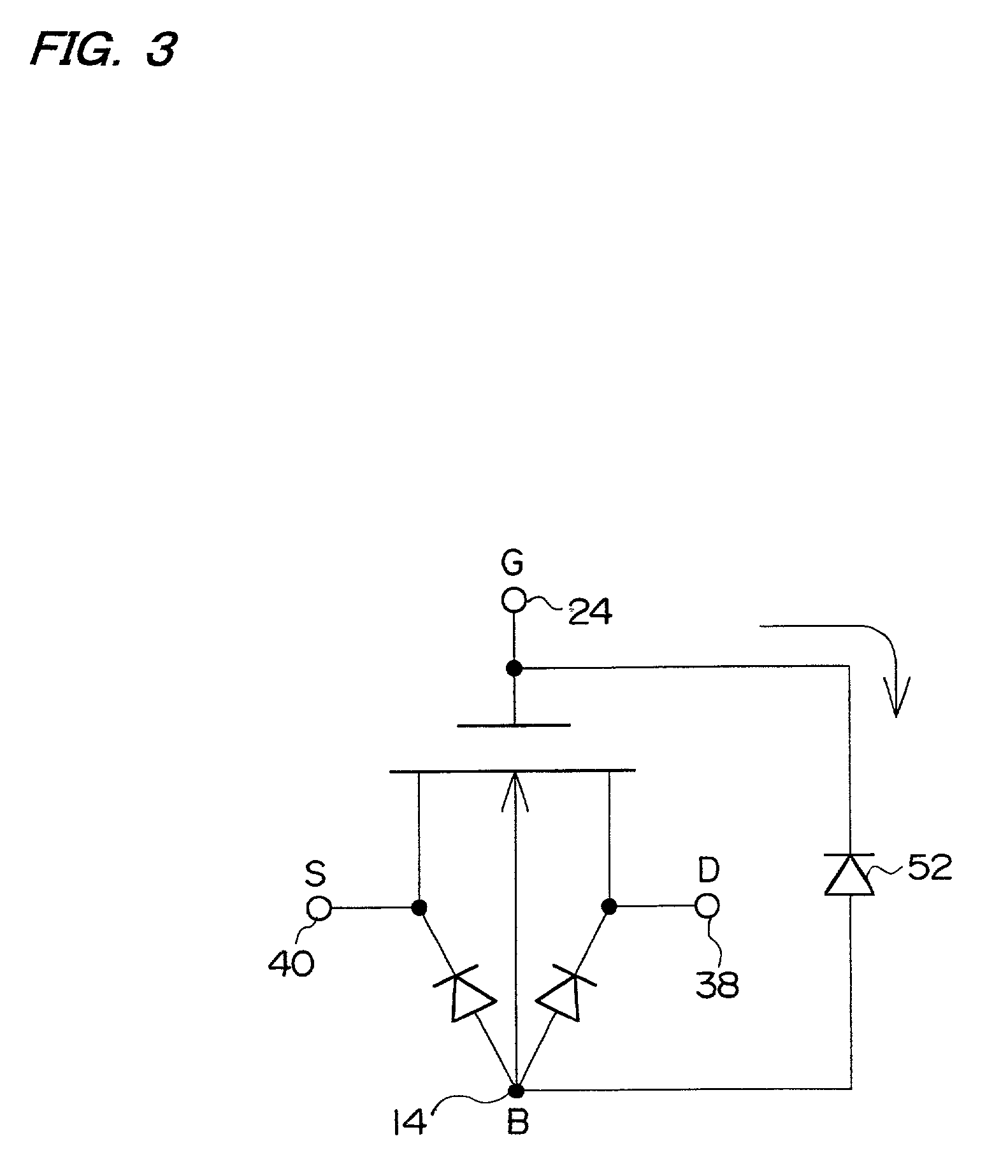

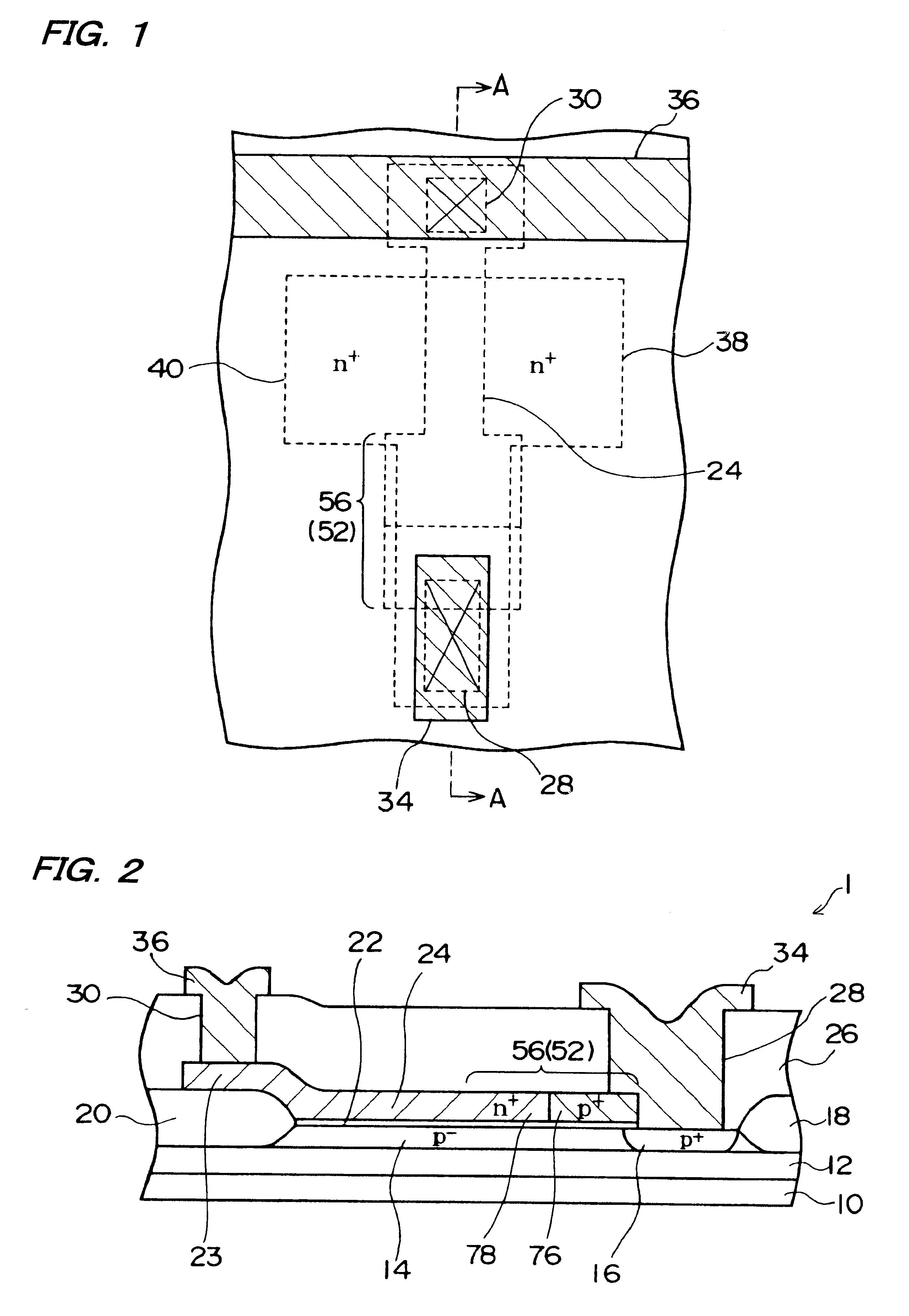

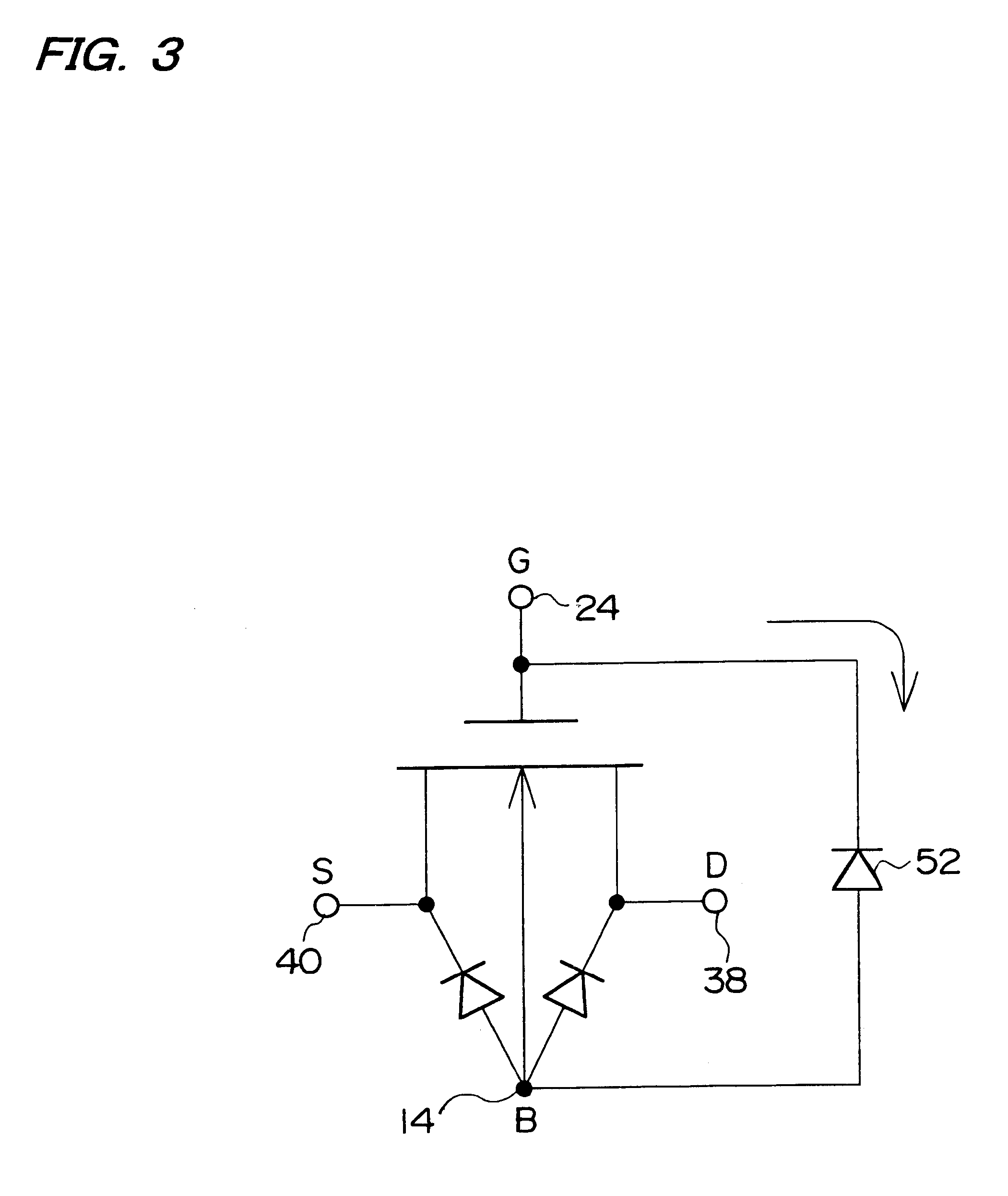

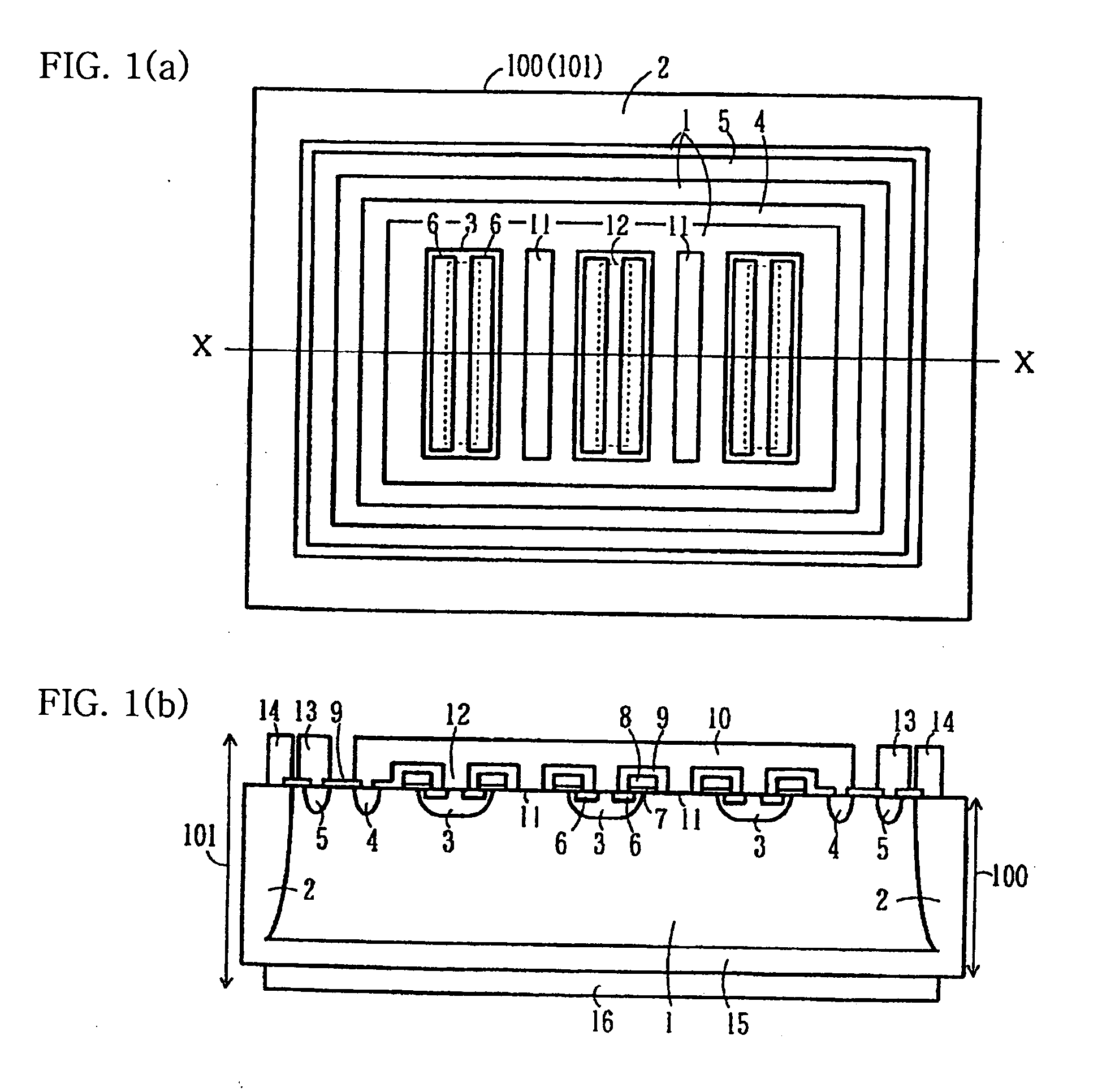

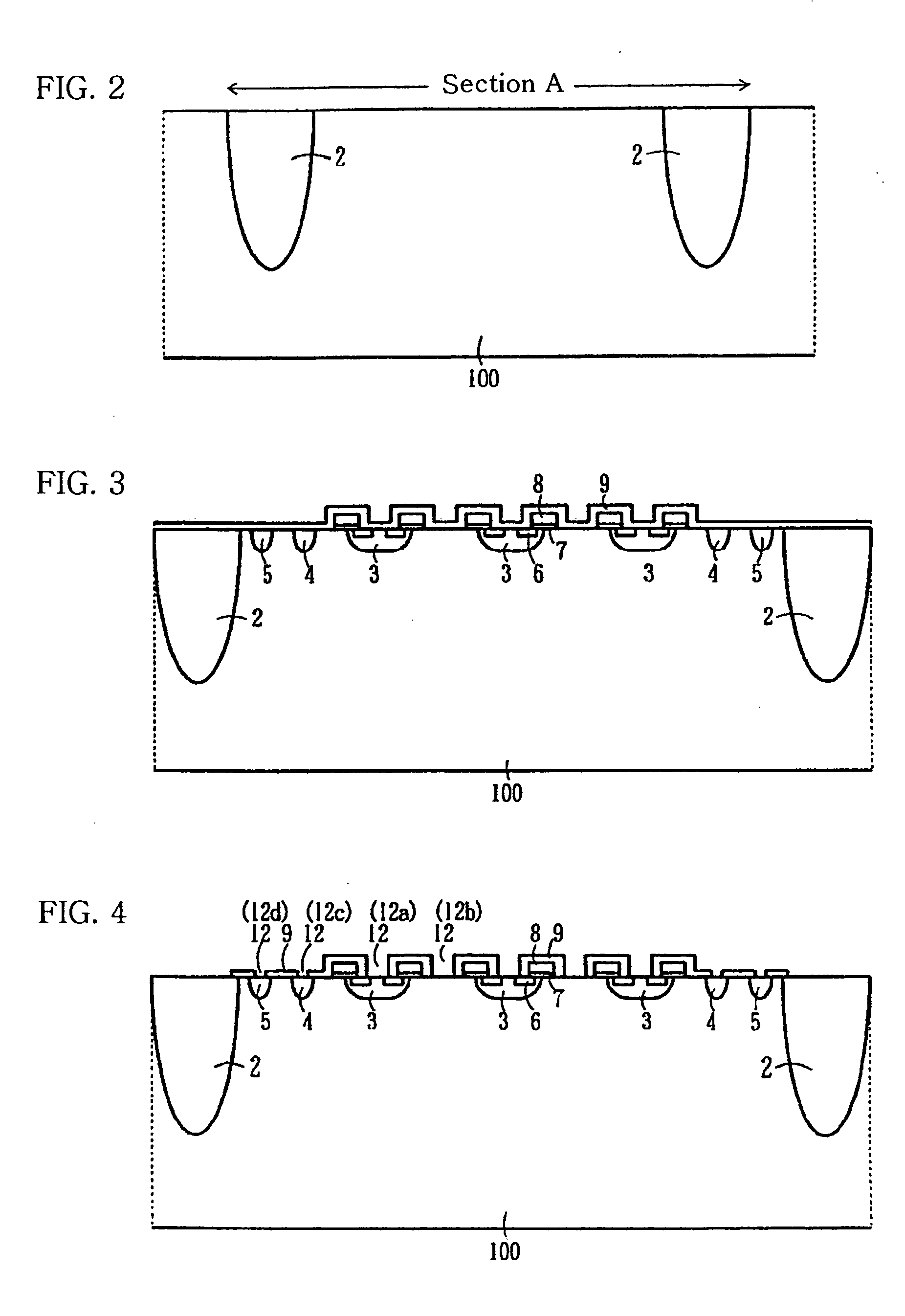

SOI-structure MIS field-effect transistor and method of manufacturing the same

A SOI-structure MOS field-effect transistor. In this transistor, agate electrode and a p- region that is a body region are placed into electrical contact by a PN junction portion. An n+-type portion of the PN junction portion is in electrical contact with the gate electrode and a p+-type portion of the PN junction portion is in electrical contact with a p- region. When a positive voltage is applied to the gate electrode, the above configuration ensures that a reverse voltage is applied to the PN junction portion, so that only a small current on the order of the reverse leakage current of the PN junction flows along the path from the gate electrode, to the PN junction portion and the body region, and into the source region.

Owner:SEIKO EPSON CORP

Method of fabricating Schottky diode and related structure

InactiveUS6261932B1Easy to optimizeReduce parasitic capacitanceTransistorSolid-state devicesDopantMetal silicide

A method of forming an improved Schottky diode structure as part of an integrated circuit fabrication process that includes the introduction of a selectable concentration of dopant into the surface of an epitaxial layer so as to form a barrier-modifying surface dopant layer. The epitaxial layer forms the cathode of the Schottky diode and a metal-silicide layer on the surface of the epitaxial layer forms the diode junction. The surface dopant layer positioned between the cathode and the diode junction is designed to raise or lower the barrier height between those two regions either to reduce the threshold turn-on potential of the diode, or to reduce the reverse leakage current of the transistor. The particular dopant conductivity used to form the surface dopant layer is dependent upon the conductivity of the epitaxial layer and the type of metal used to form the metal-silicide junction.

Owner:SEMICON COMPONENTS IND LLC

SOI-structure MIS field-effect transistor with gate contacting body region

A SOI-structure MOS field-effect transistor. In this transistor, a gate electrode and a p- region that is a body region are placed into electrical contact by a PN junction portion. An n+-type portion of the PN junction portion is in electrical contact with the gate electrode and a p+-type portion of the PN junction portion is in electrical contact with a p- region. When a positive voltage is applied to the gate electrode, the above configuration ensures that a reverse voltage is applied to the PN junction portion, so that only a small current on the order of the reverse leakage current of the PN junction flows along the path from the gate electrode, to the PN junction portion and the body region, and into the source region.

Owner:SEIKO EPSON CORP

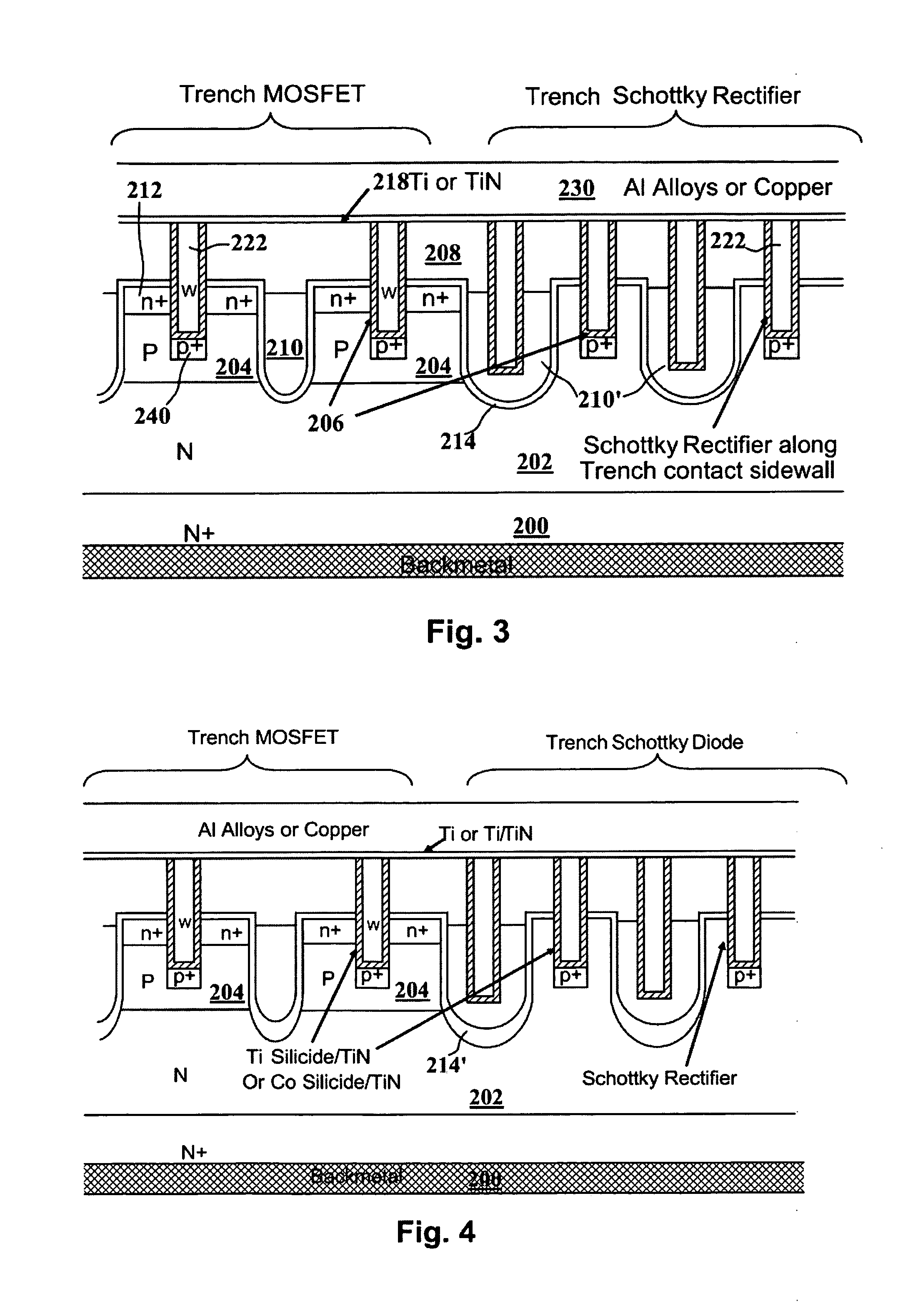

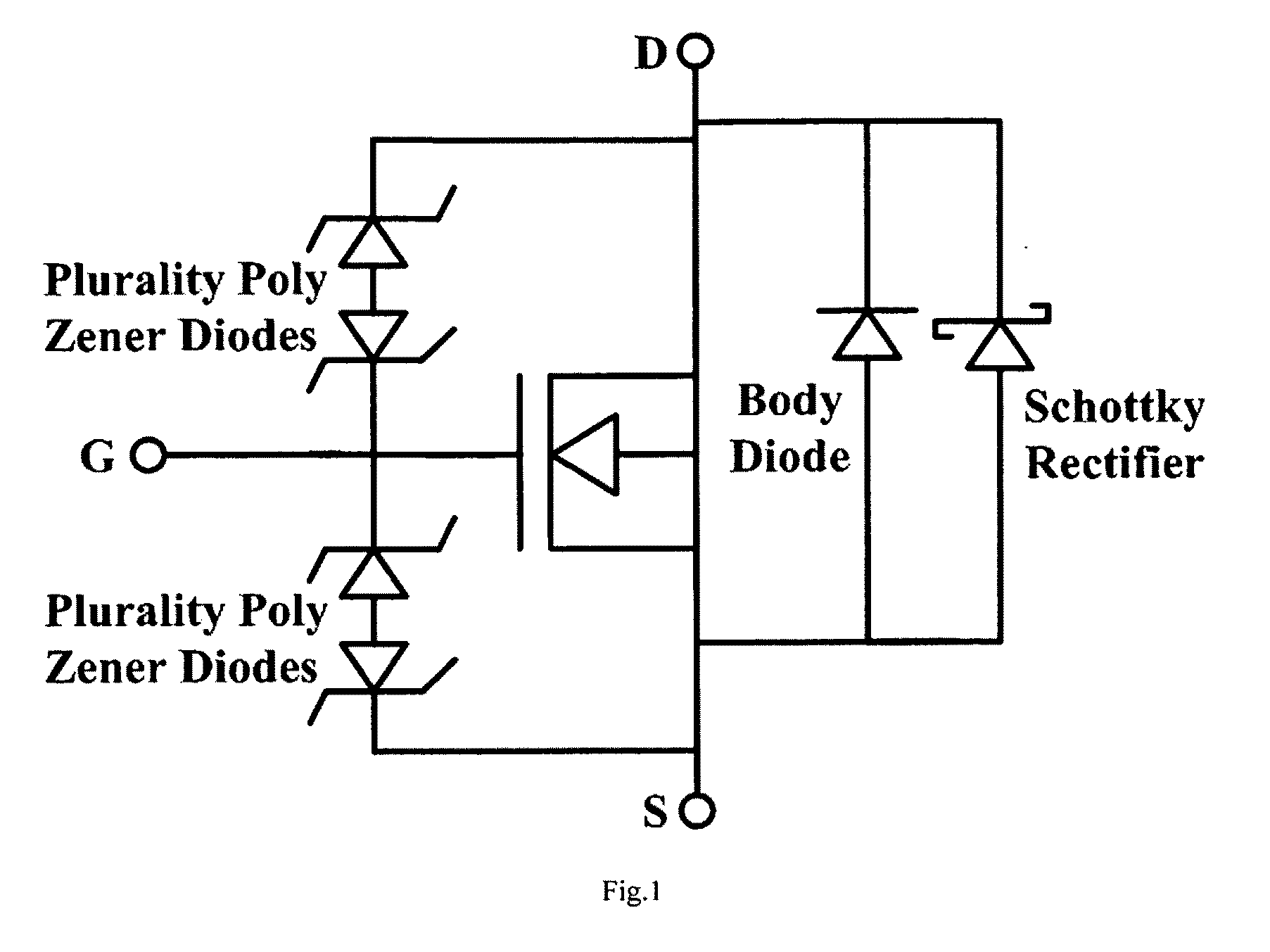

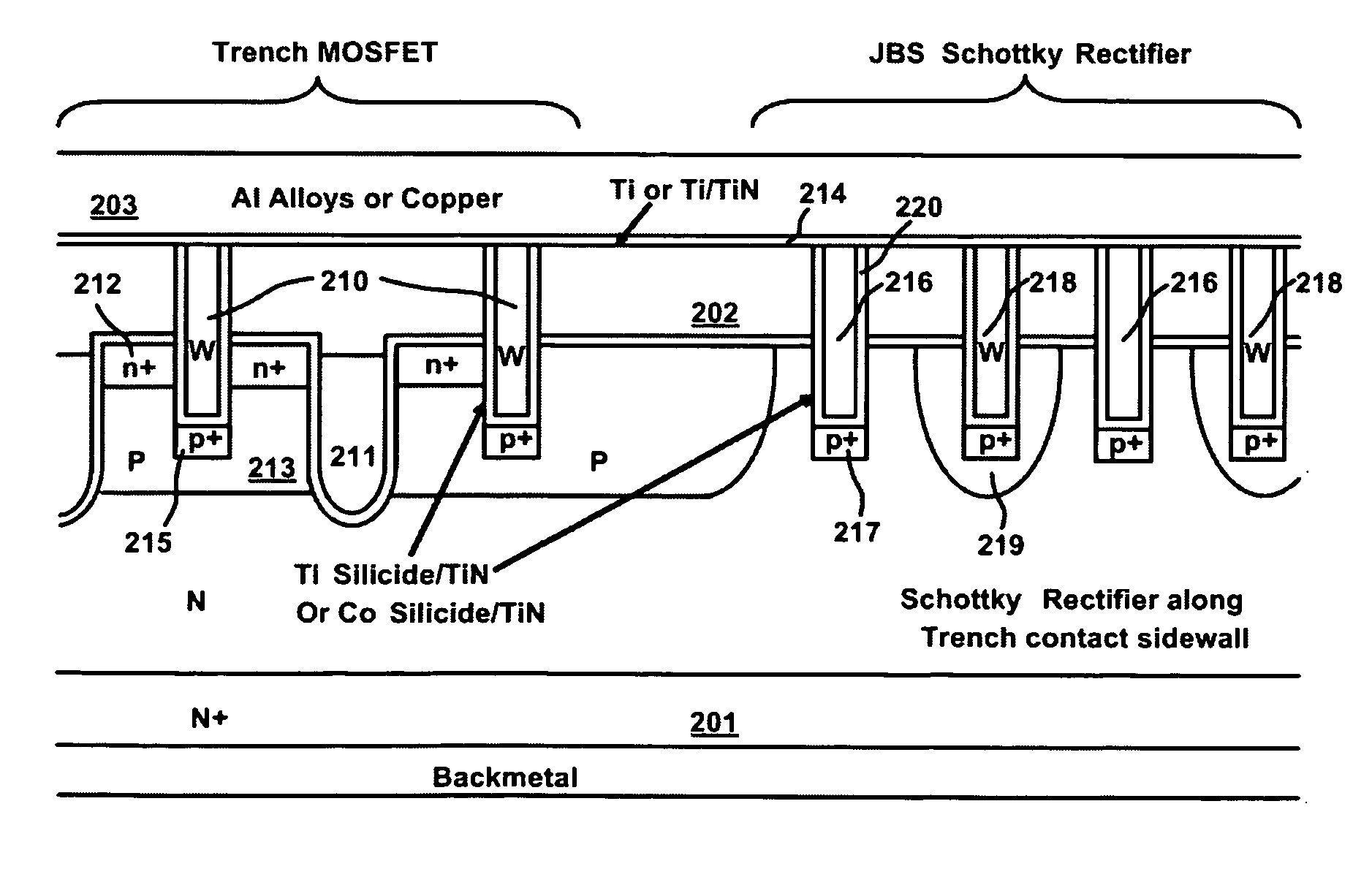

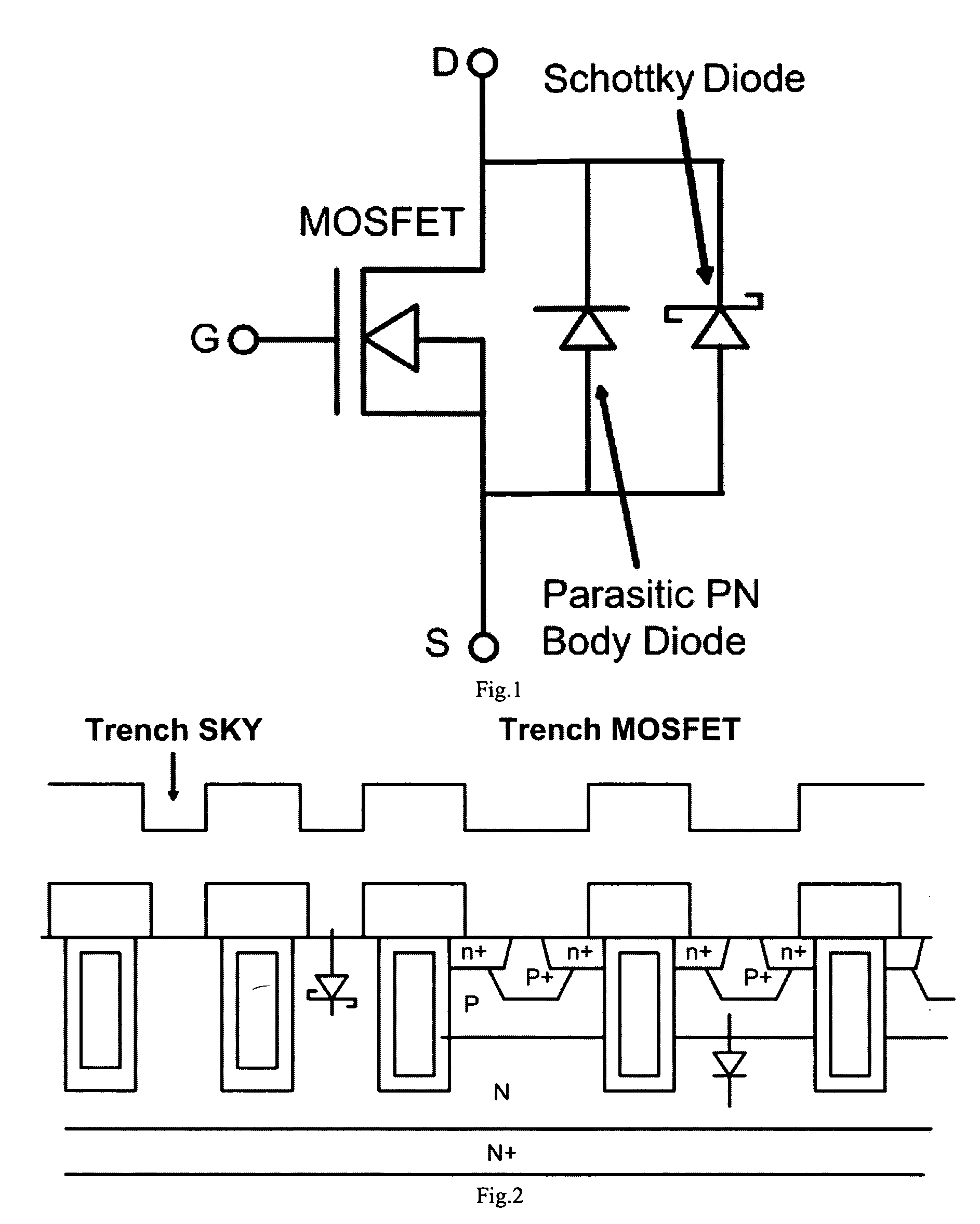

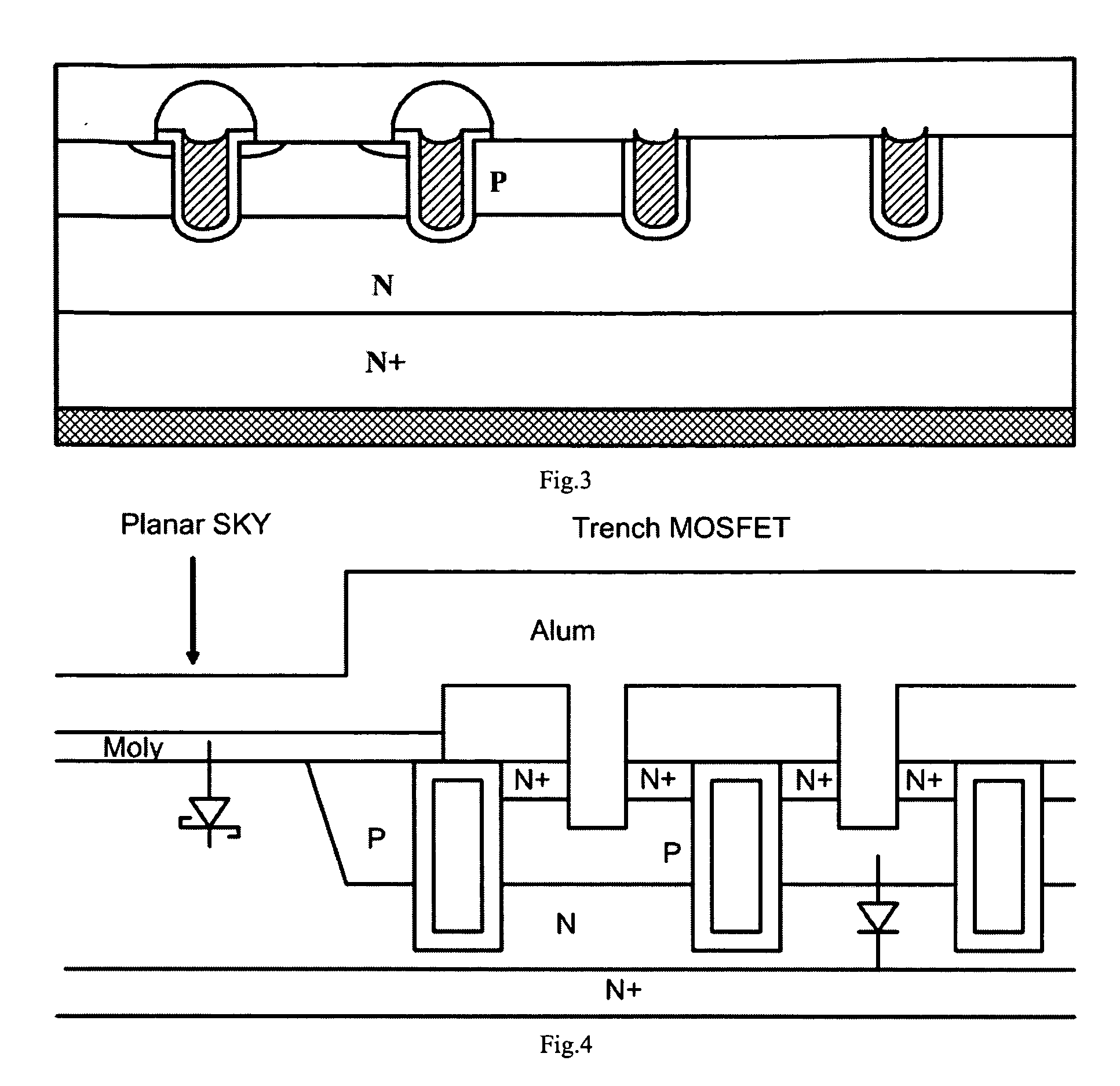

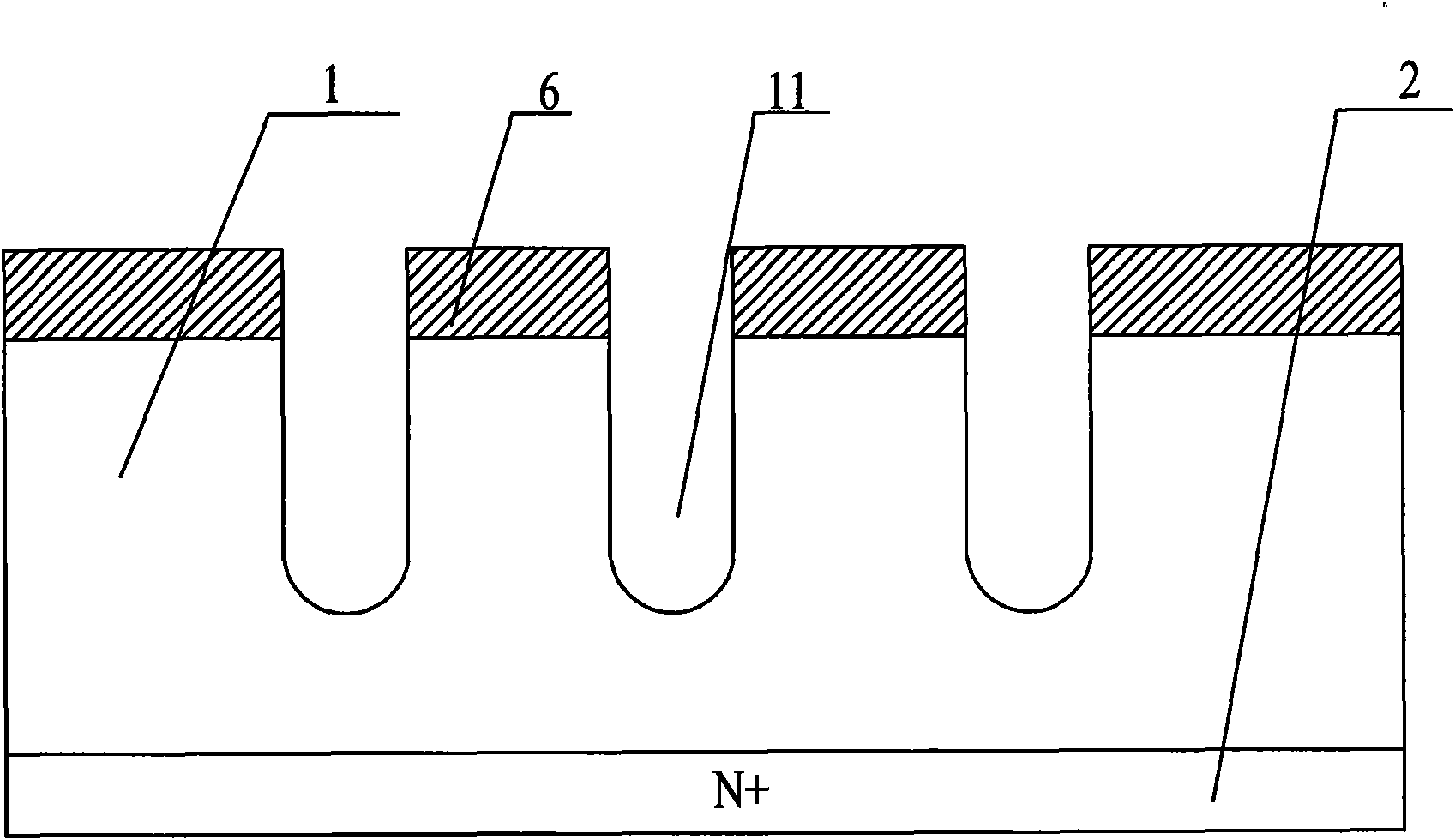

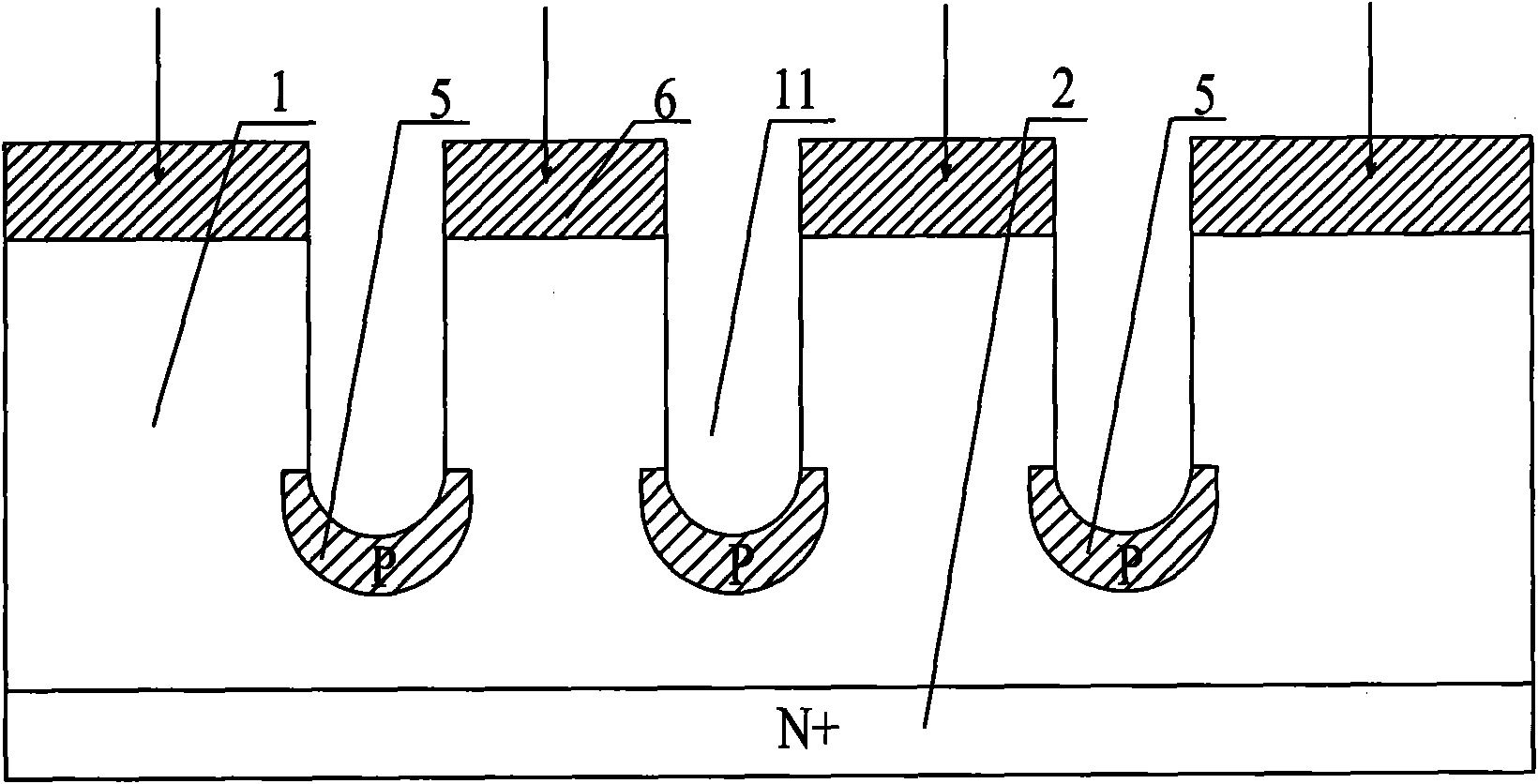

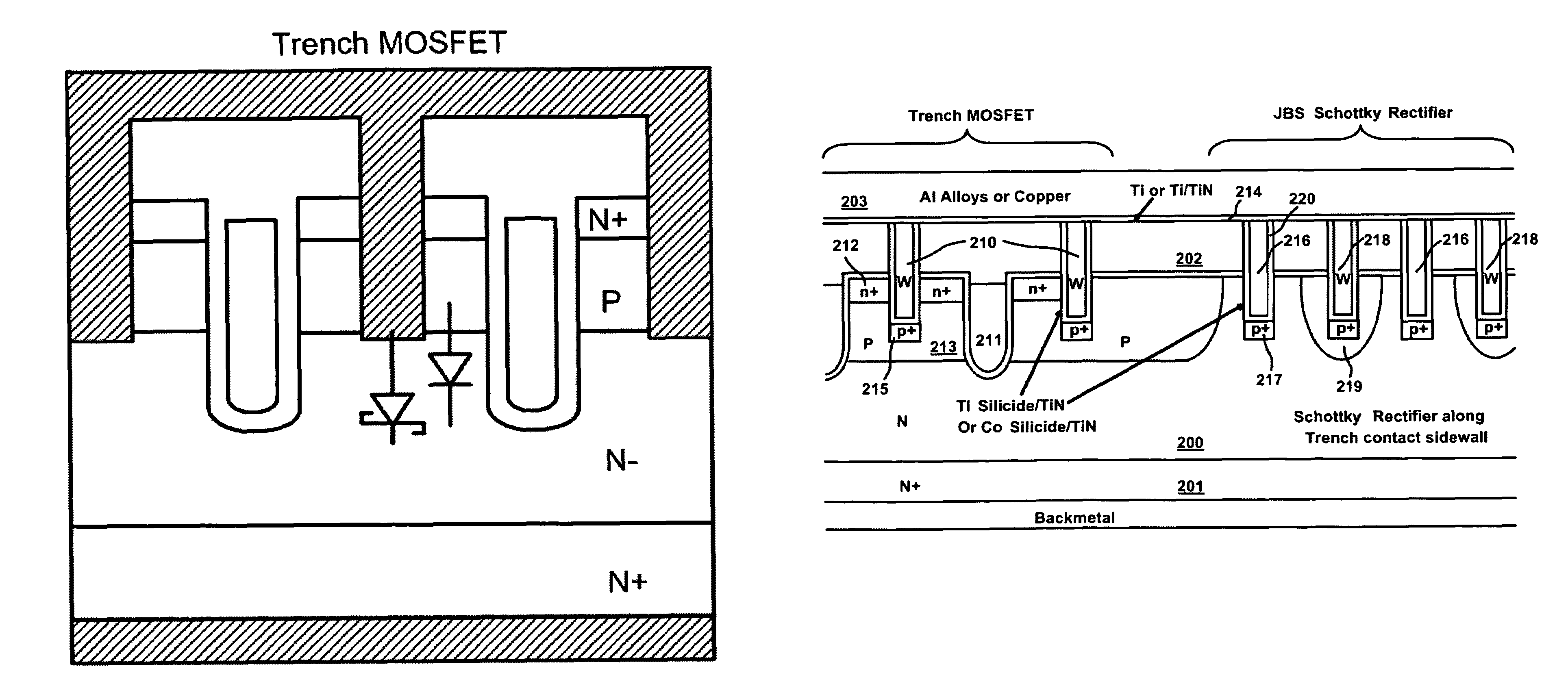

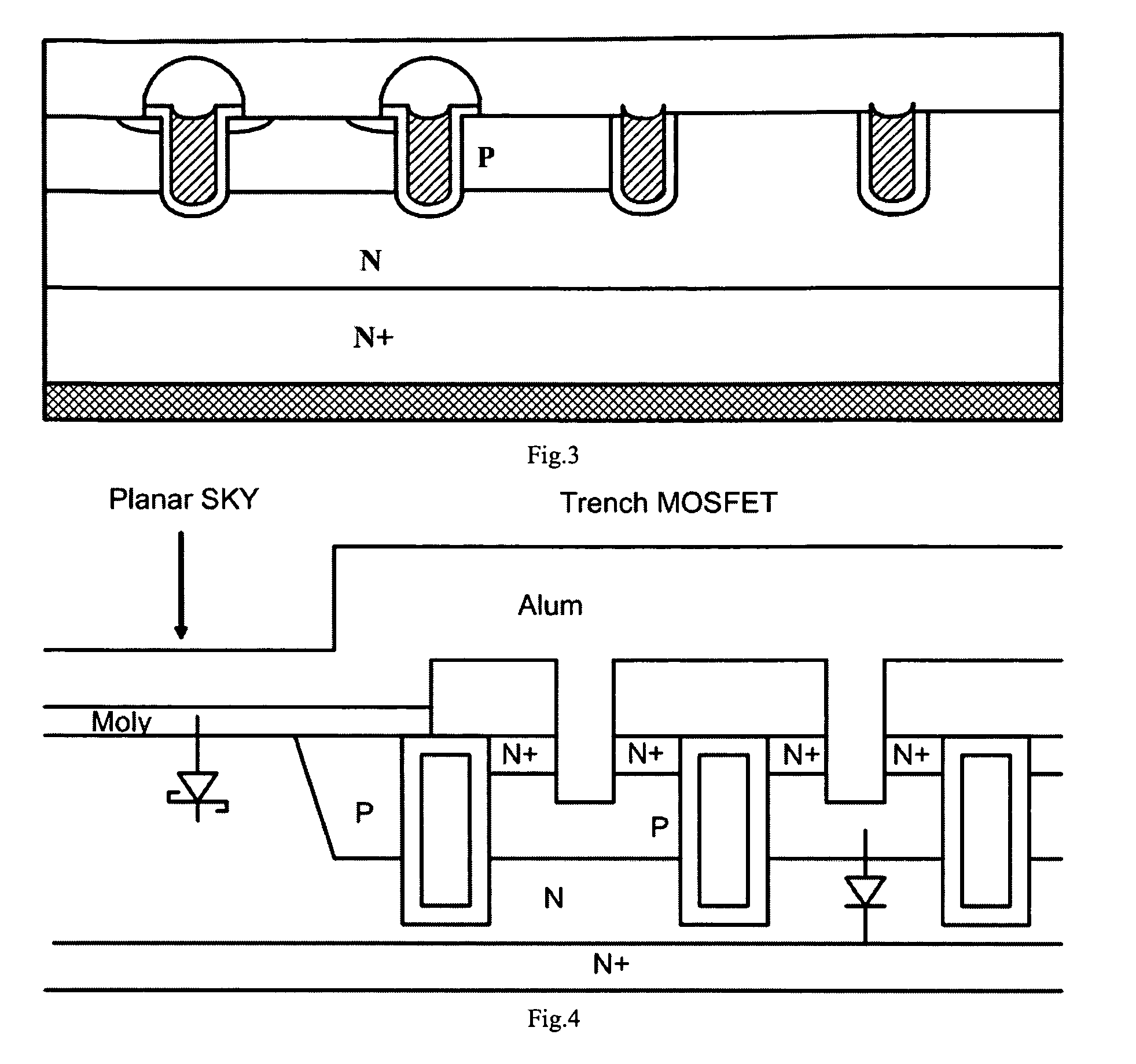

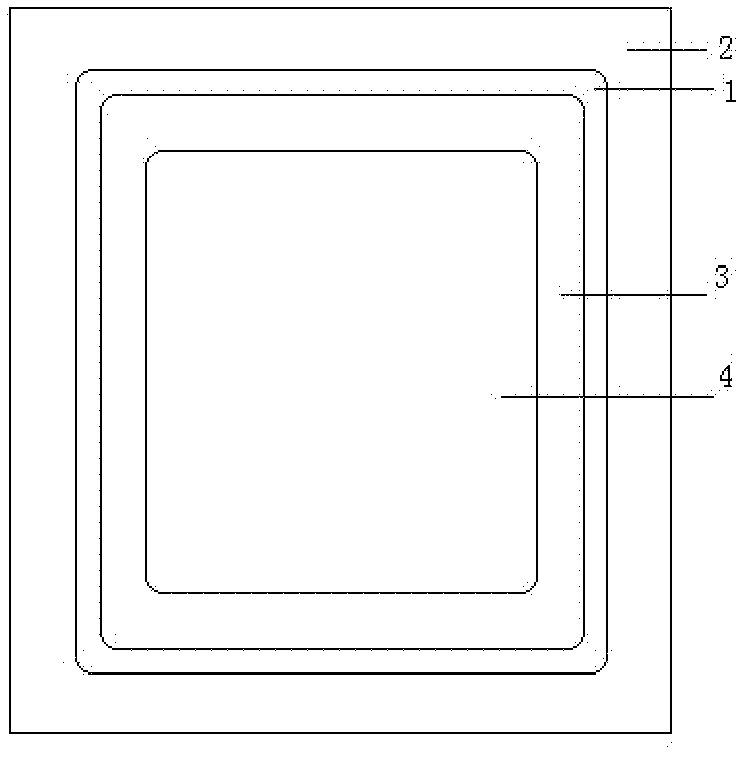

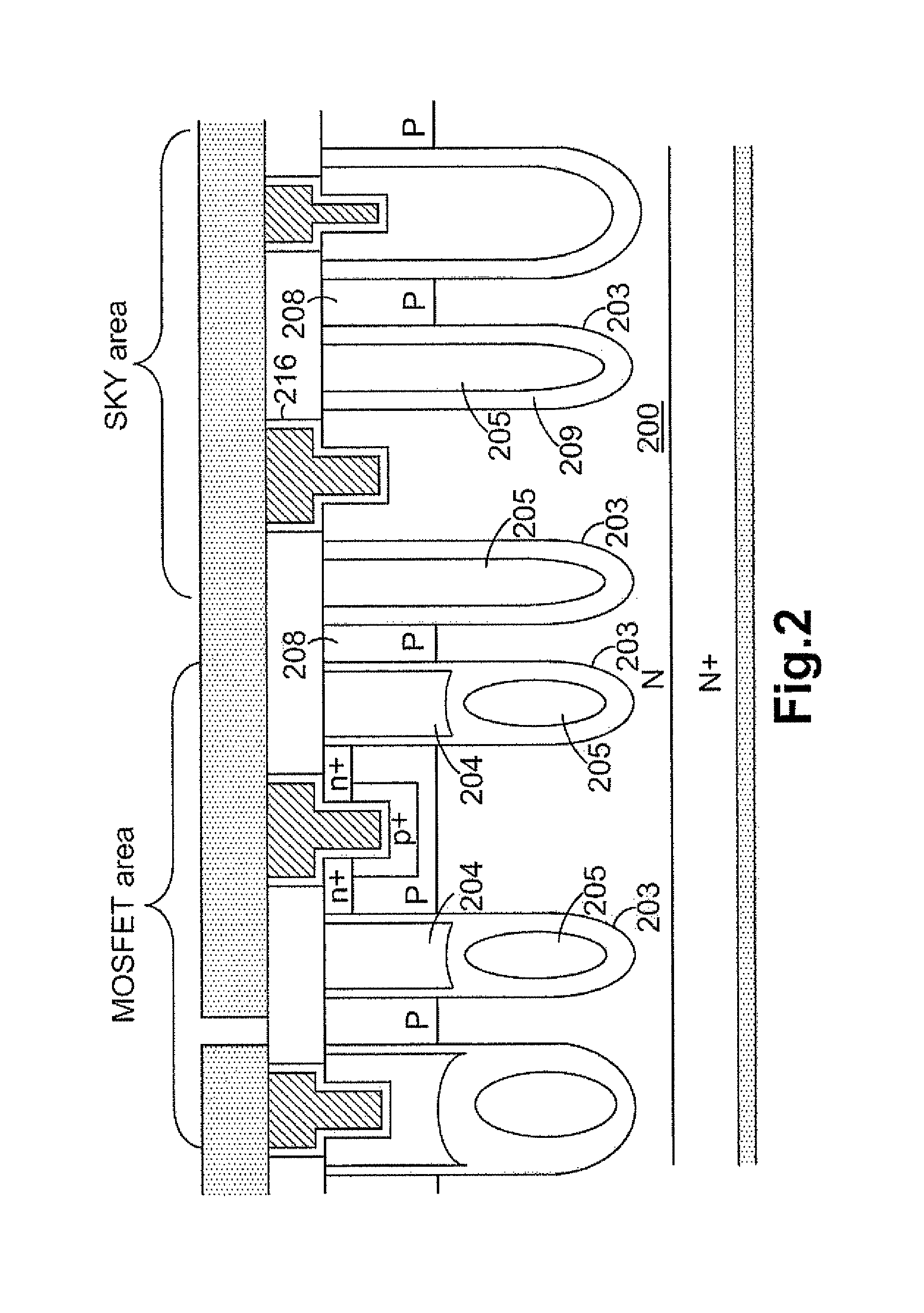

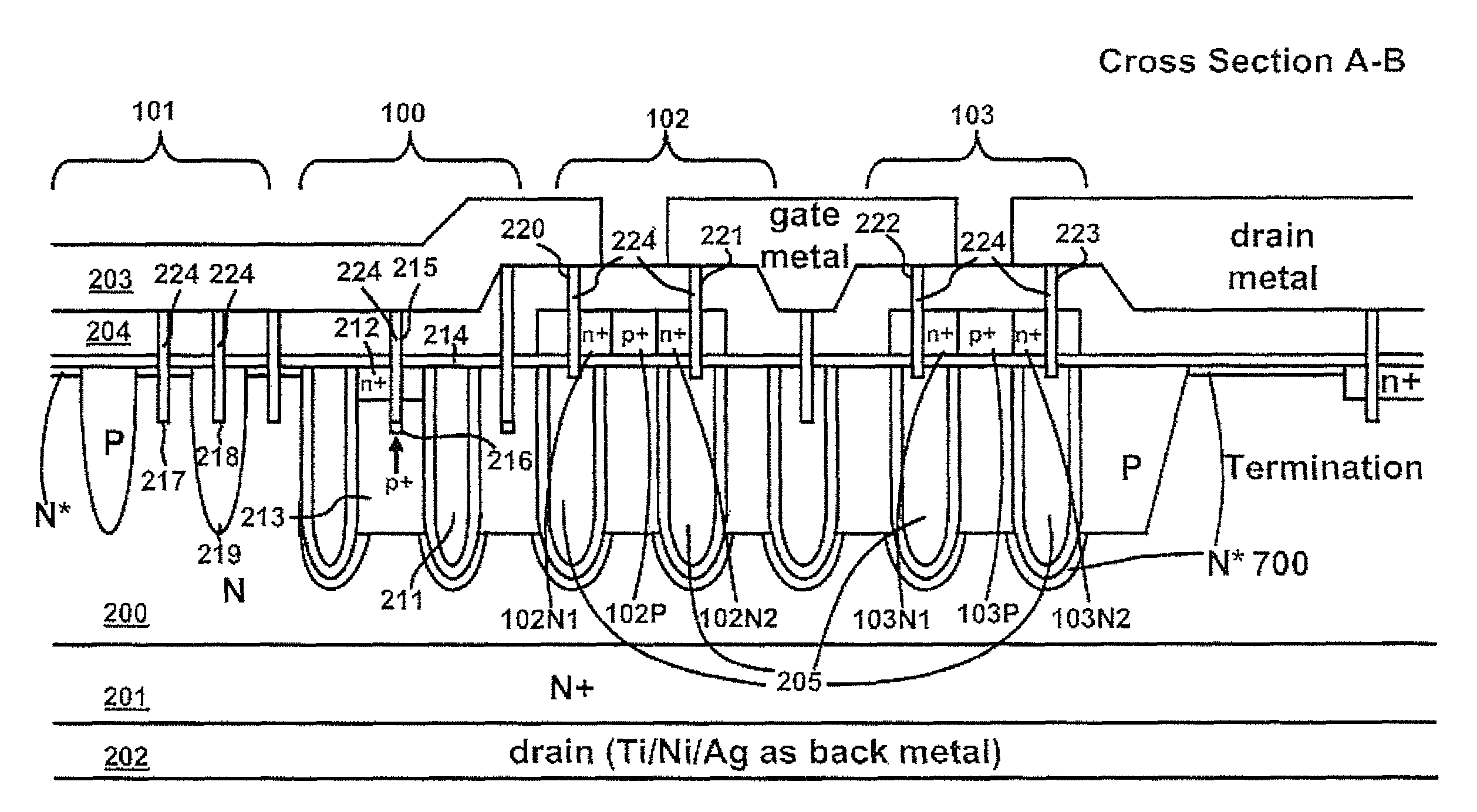

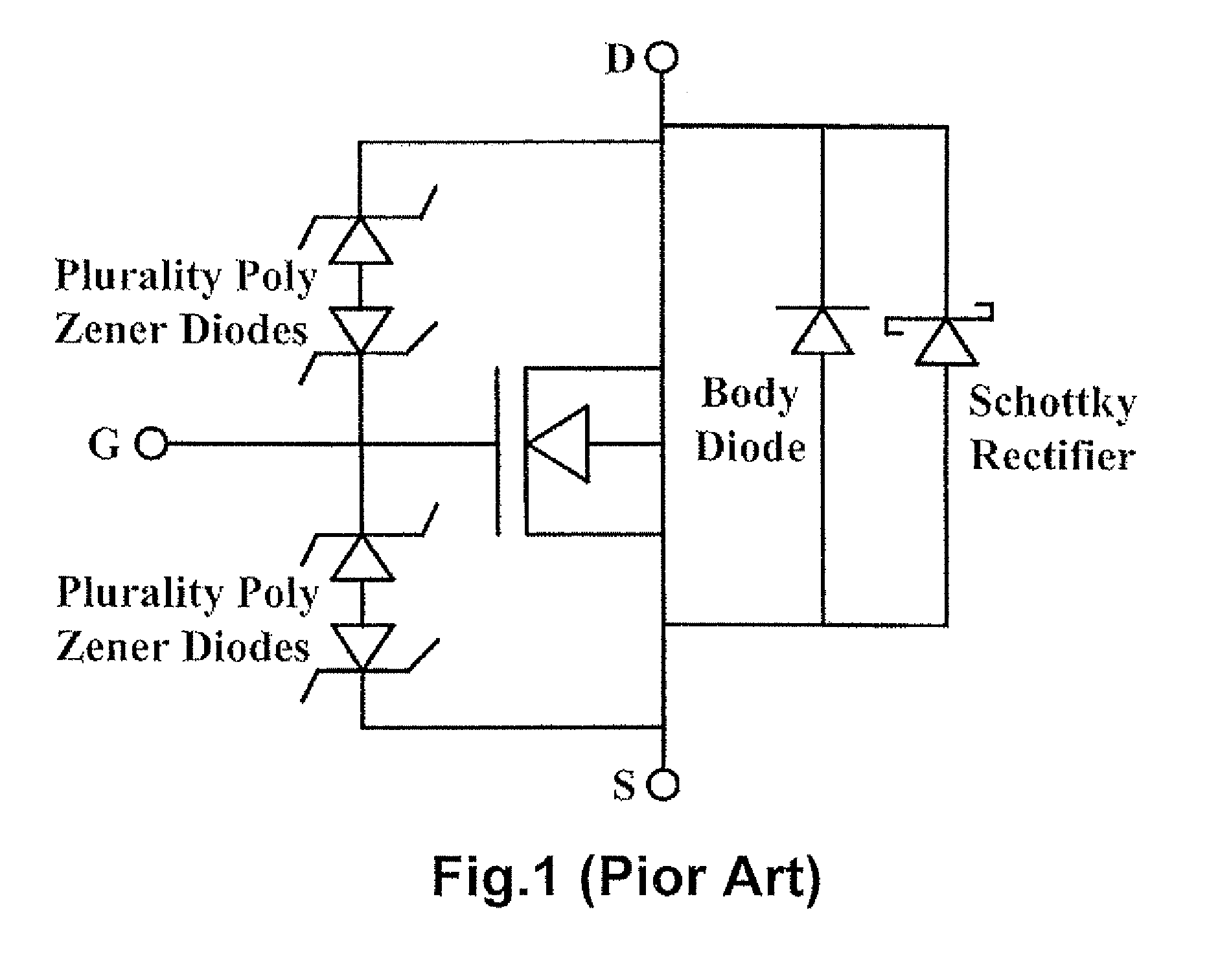

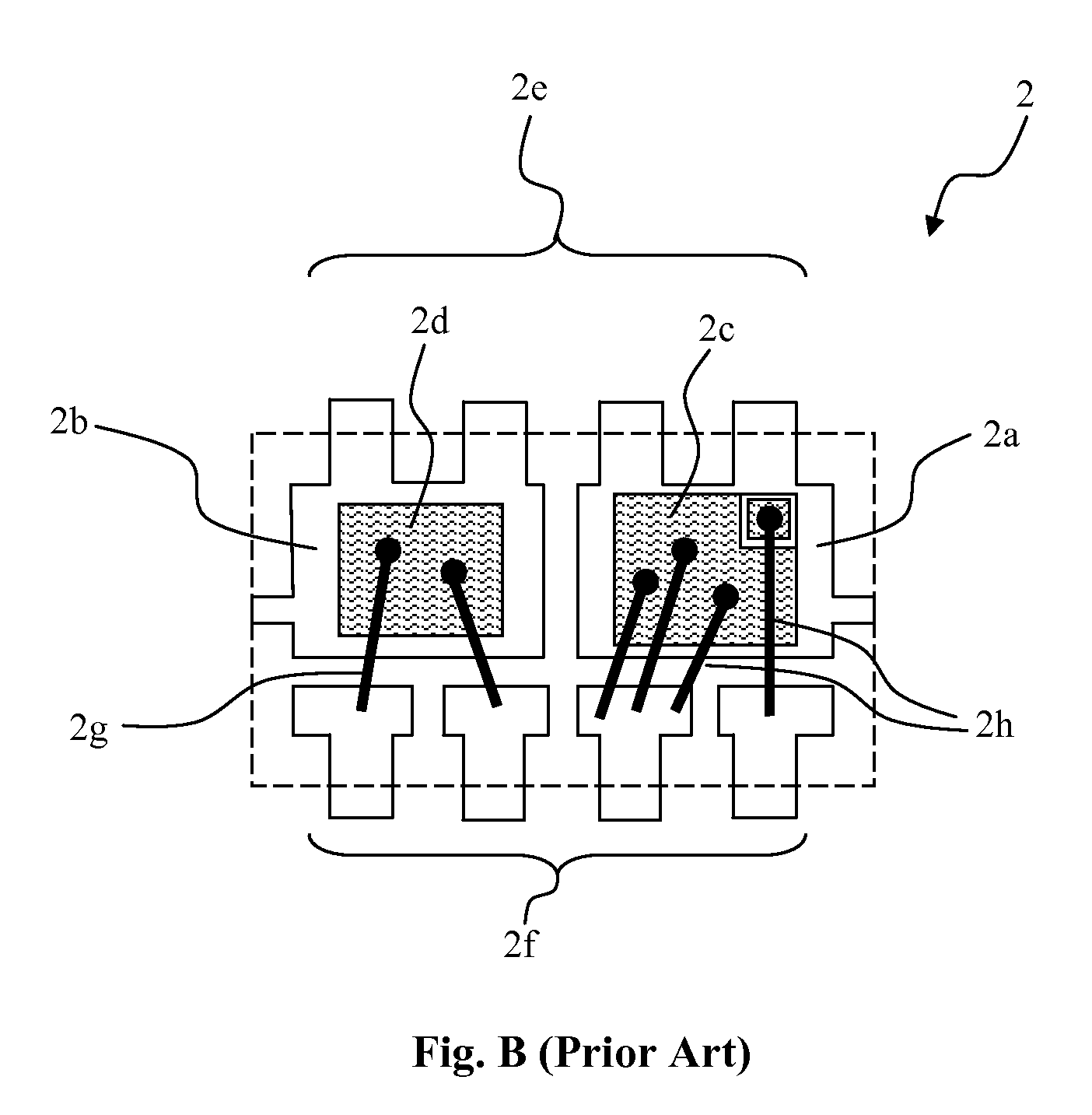

Integrated trench Mosfet and Schottky Rectifier with trench contact structure

InactiveUS20090315106A1Lower on-resistanceLow VfTransistorSolid-state devicesTrench mosfetReverse leakage current

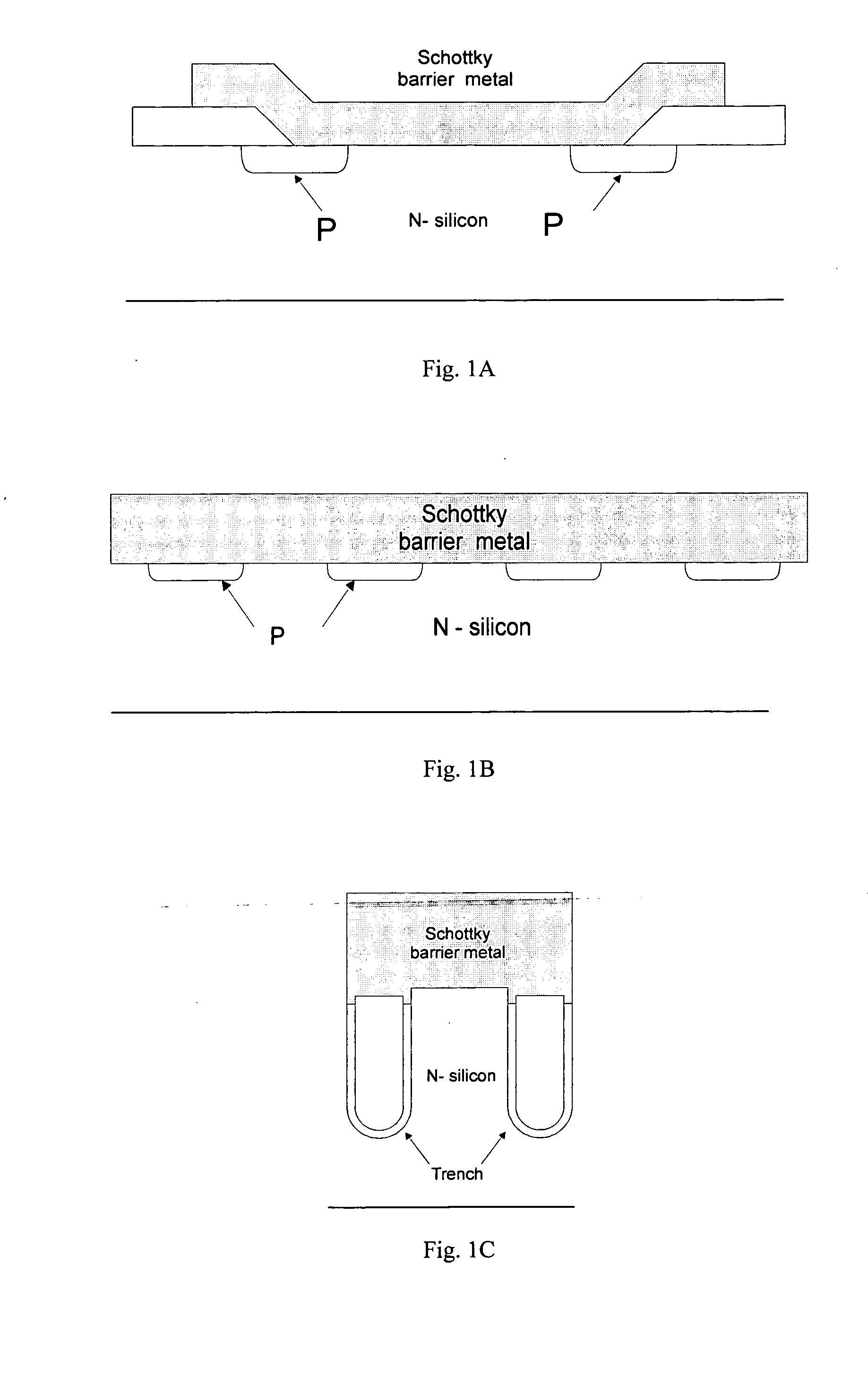

A trench MOSFET in parallel with trench Schottky barrier rectifier is formed on a single substrate. The present invention solves the constrains brought by planar contact of Schottky, for example, the large area occupied by planar structure. As the size of present device is getting smaller and smaller, the trench Schottky structure of this invention is able to be shrink and, at the same time, to achieve low specific on-resistance. By applying a double epitaxial layer in trench Schottky barrier rectifier, the device performance is enhanced for lower Vf and lower reverse leakage current Ir is achieved.

Owner:FORCE MOS TECH CO LTD

Semiconductor device, the method of manufacturing the same, and two-way switching device using the semiconductor devices

InactiveUS20050082640A1Reduce leakage currentReducing the on-voltage of the IGBTConversion constructional detailsSolid-state devicesEngineeringReverse bias

A semiconductor device is disclosed that reduces the reverse leakage current caused by reverse bias voltage application and reduces the on-voltage of the IGBT. A two-way switching device using the semiconductor devices is provided, and a method of manufacturing the semiconductor device is disclosed. The reverse blocking IGBT reduces the reverse leakage current and the on-voltage by bringing portions of an n−-type drift region 1 that extend between p-type base regions and an emitter electrode into Schottky contact to form Schottky junctions.

Owner:FUJI ELECTRIC CO LTD

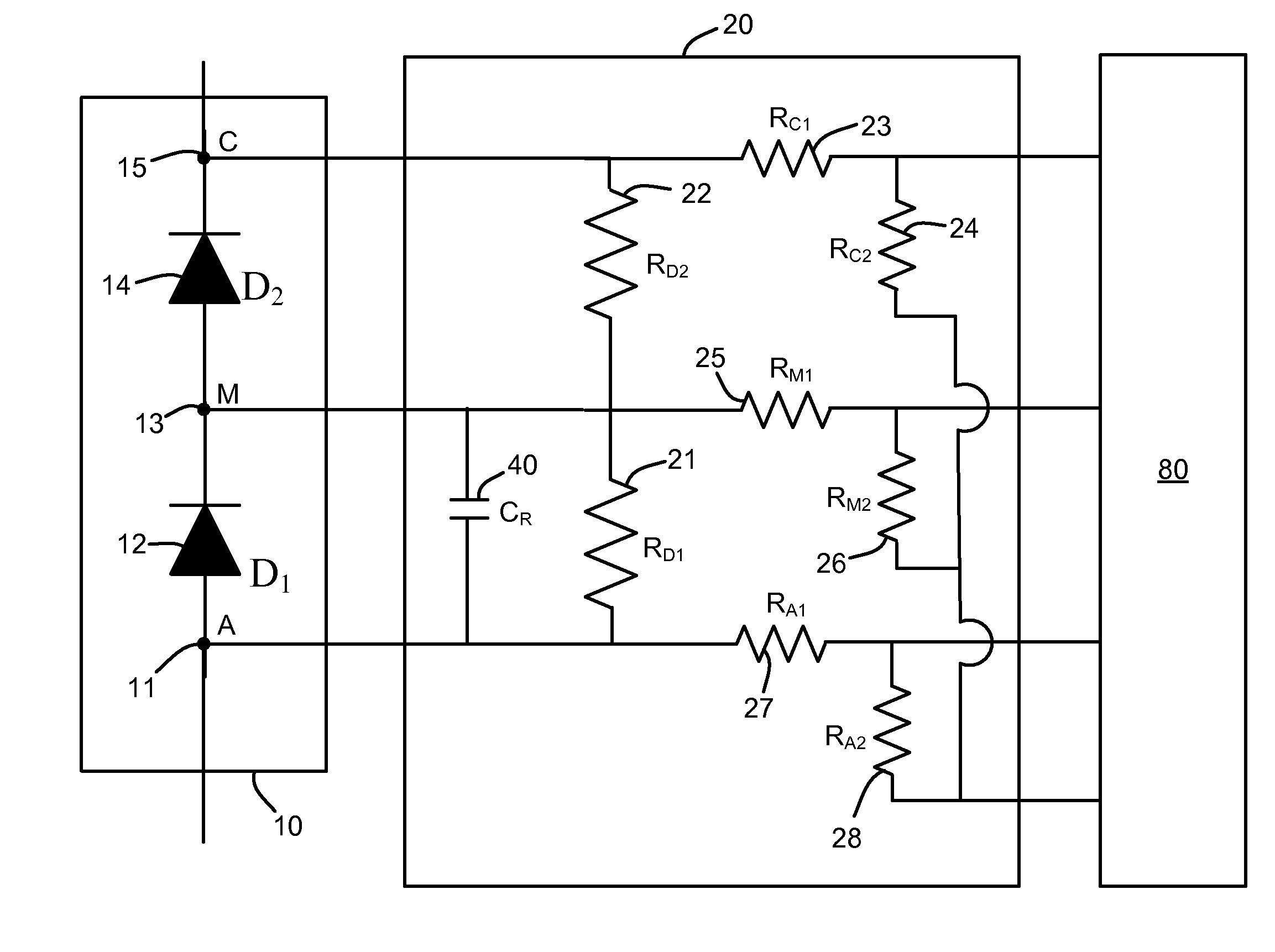

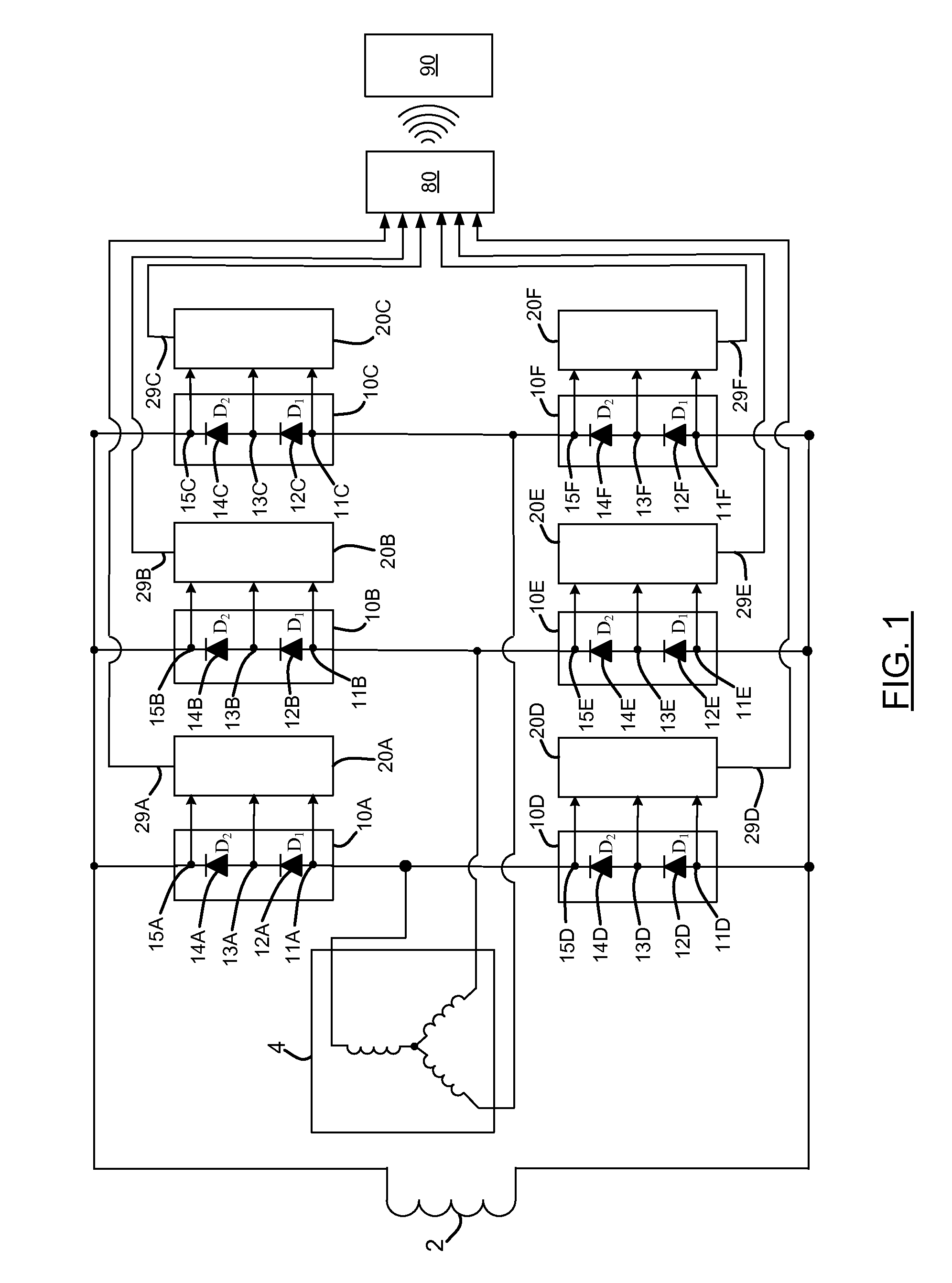

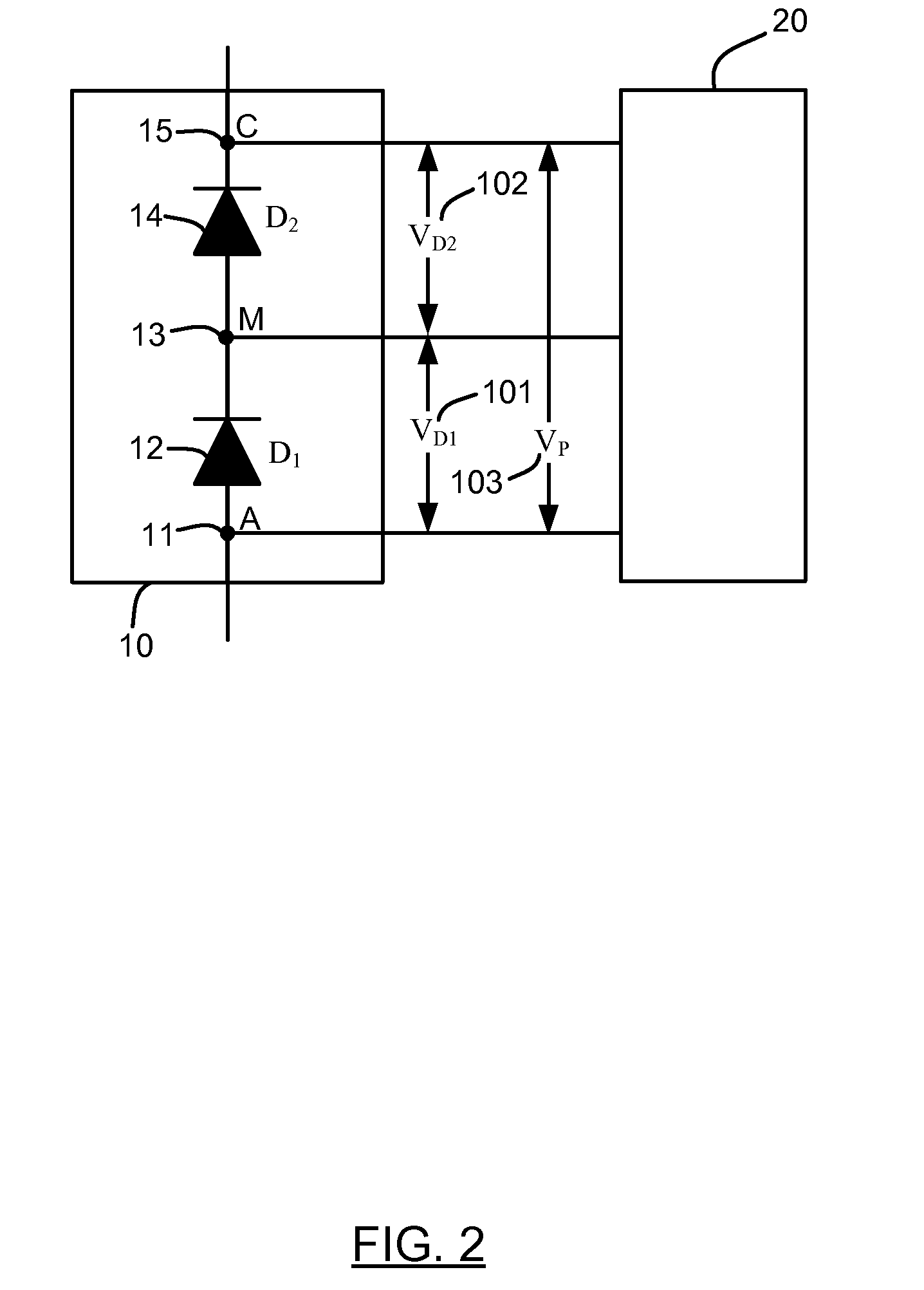

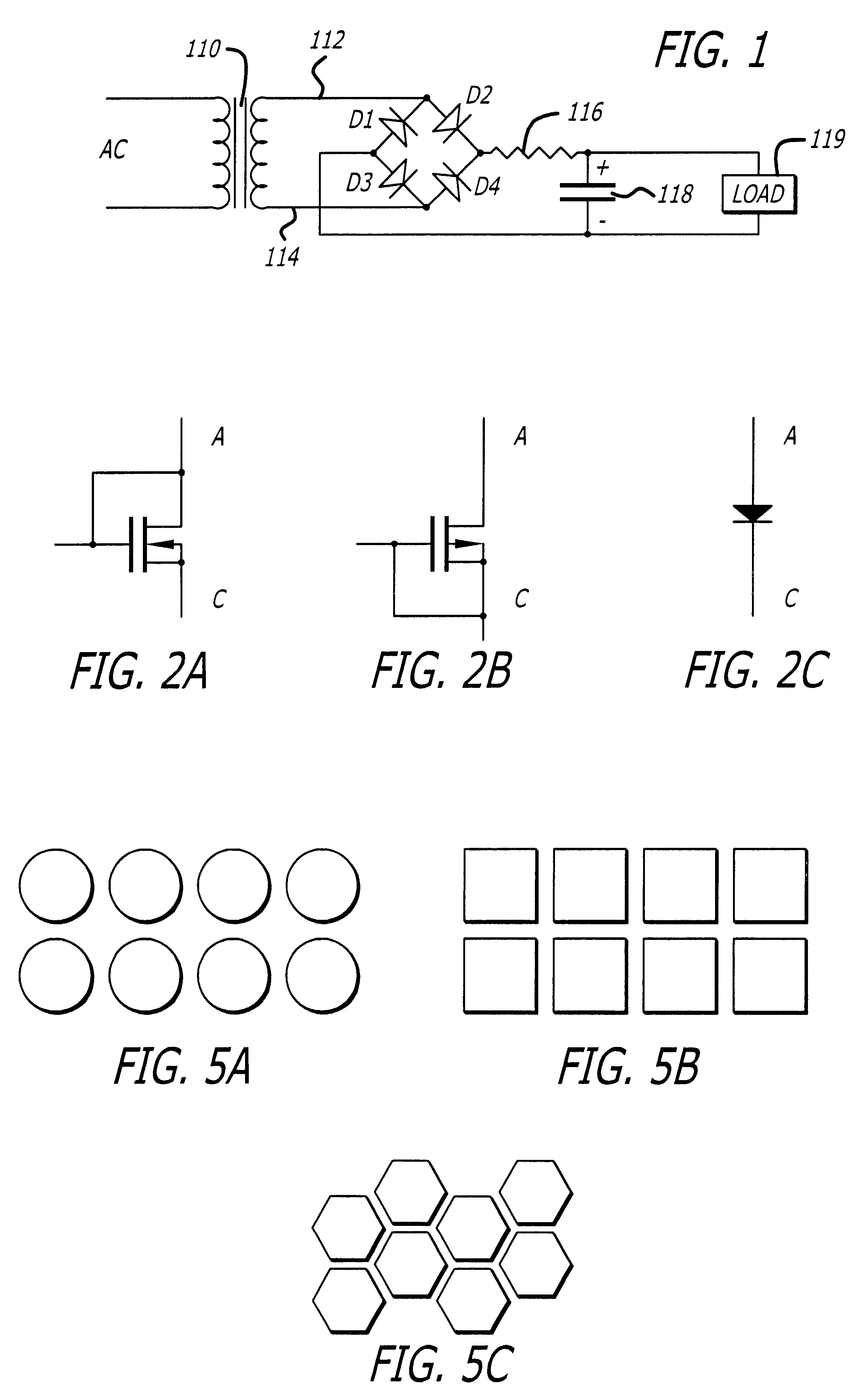

Method and apparatus for fault detection of series diodes in rectifiers

ActiveUS20110216449A1Minimize potentialEasy to detectDiode testingEmergency protective arrangements for limiting excess voltage/currentReverse recoveryEngineering

A method and apparatus for fault detection of series diodes in rectifiers is disclosed, wherein the voltages across one or both of the individual diodes, and / or the voltage across the pair of diodes are measured to determine a ratio between two of those voltages. The ratio is then analyzed to determine if a fault (e.g., a short circuit or an open circuit) is present. In some embodiments, circuitry can be included to compensate for the normal variations in diode characteristics (e.g., reverse leakage current, reverse recovery charge) between the pair of series diodes to minimize the potential for erroneous fault detection.

Owner:ACCUMETRICS INC +1

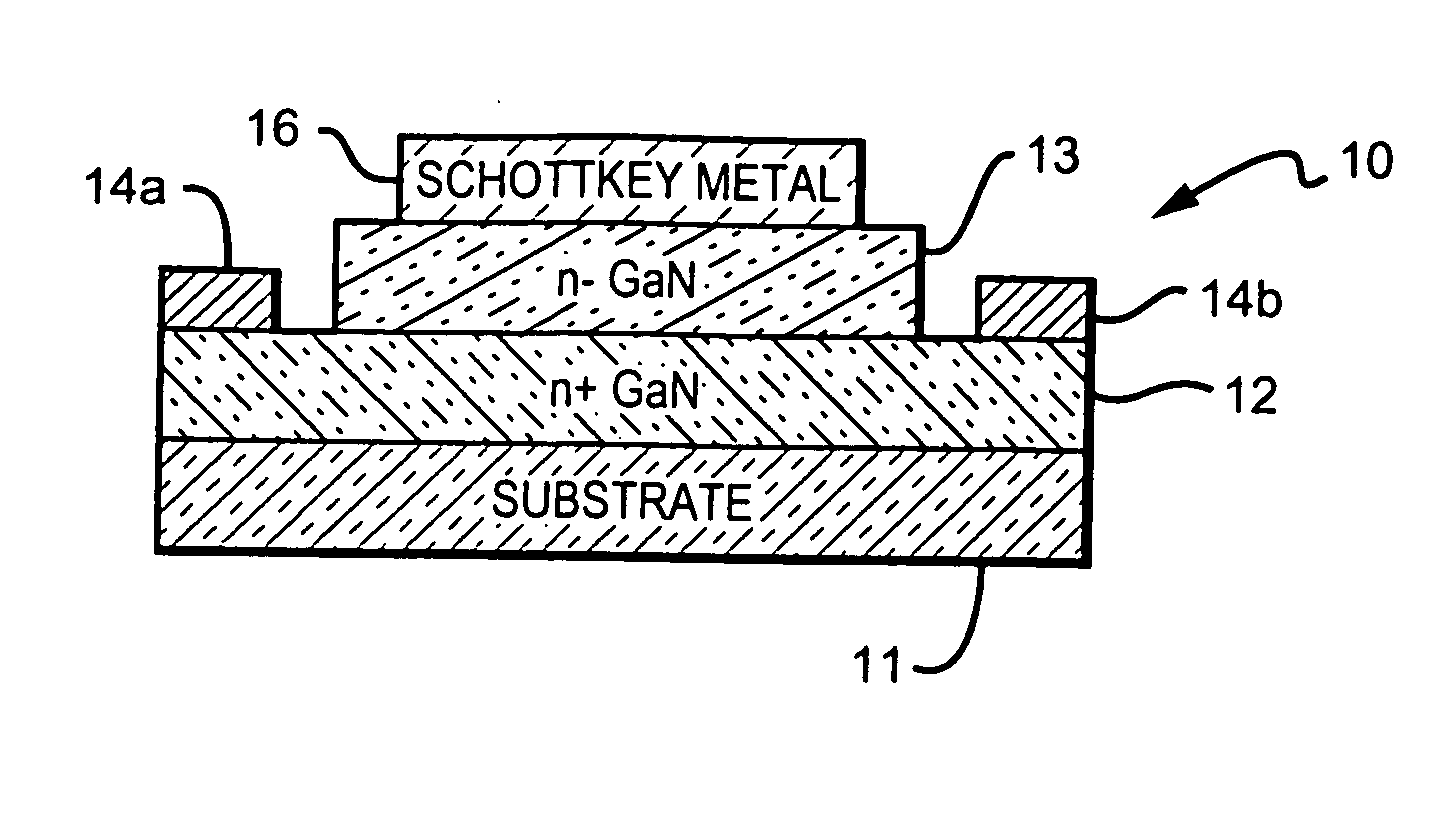

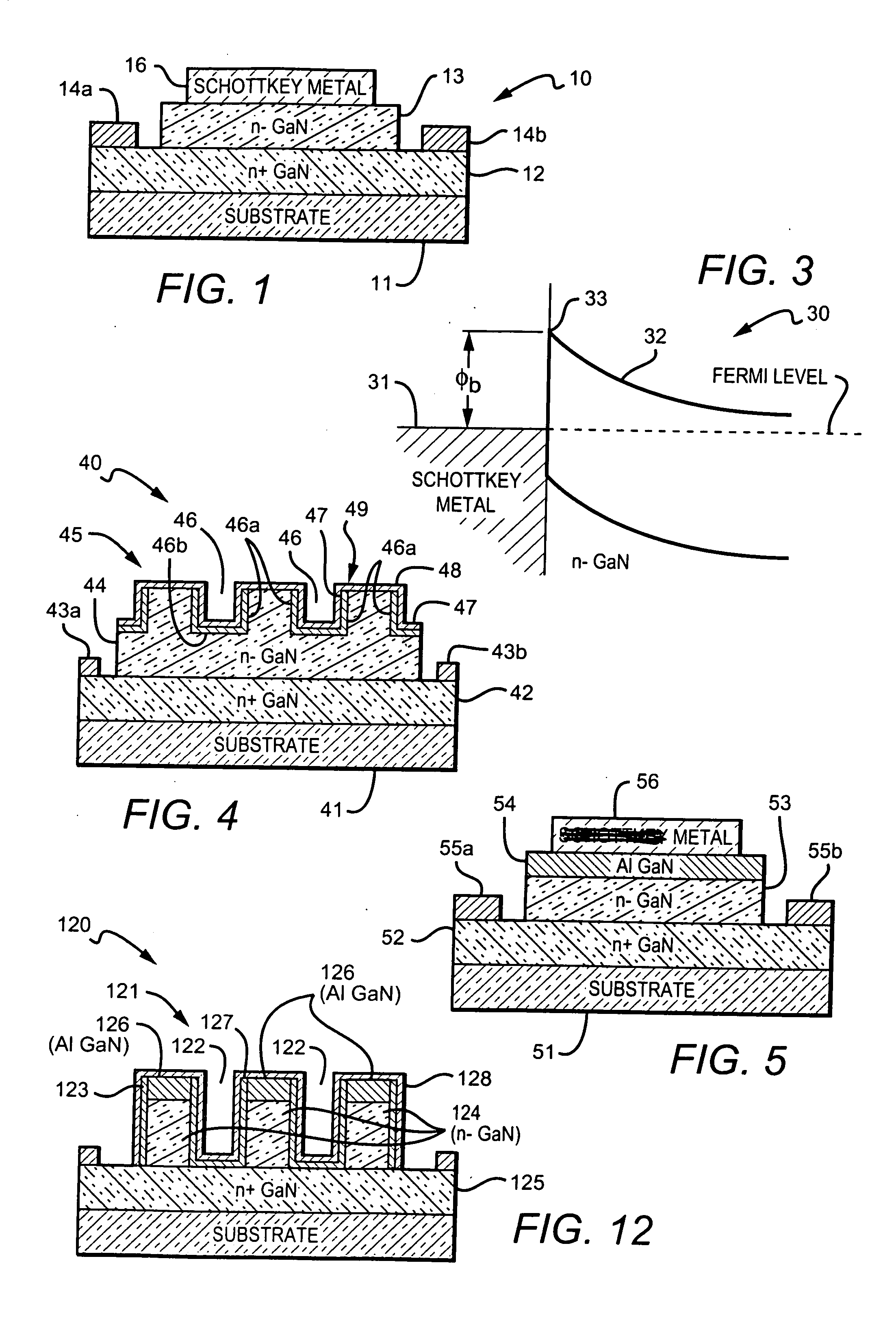

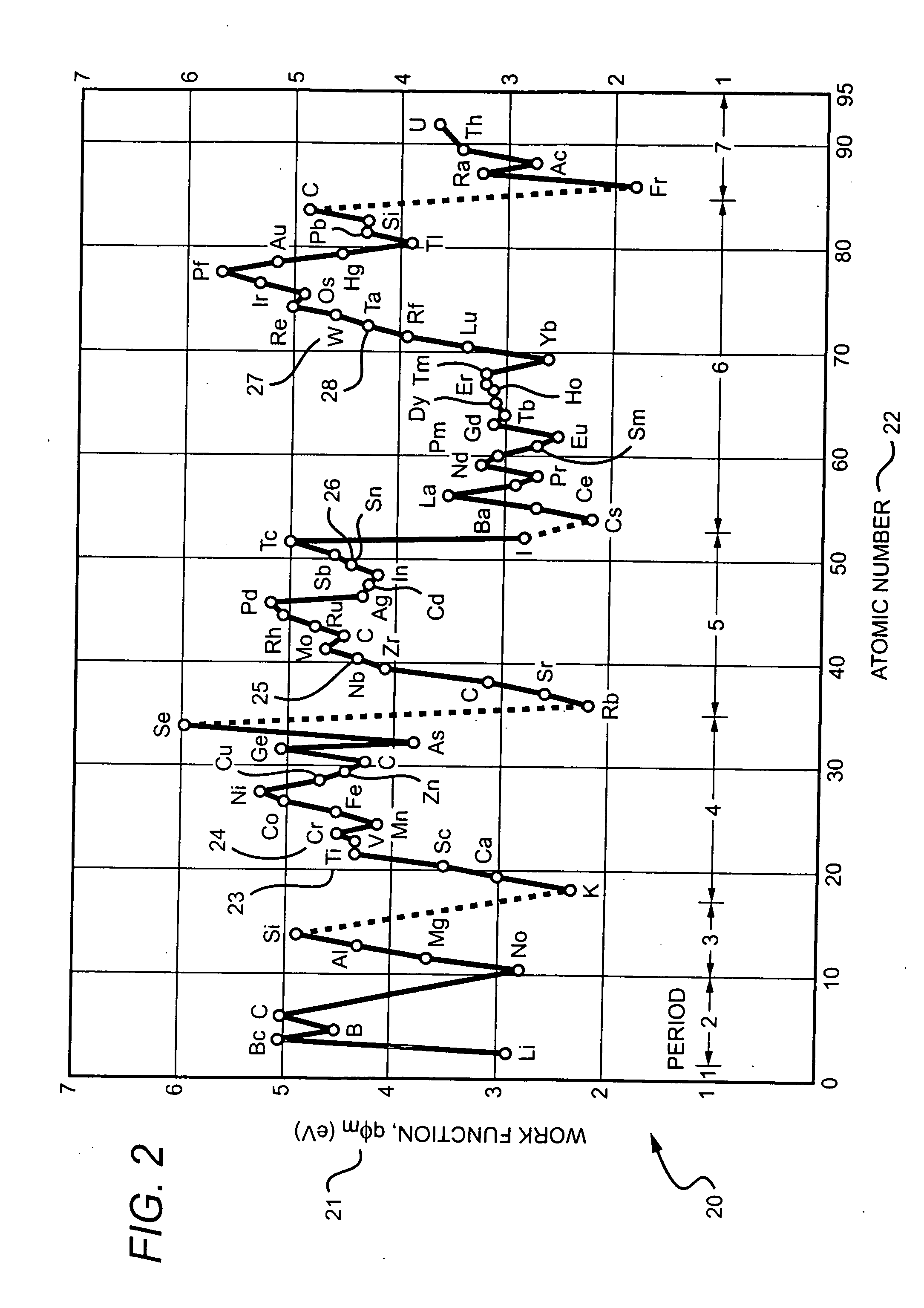

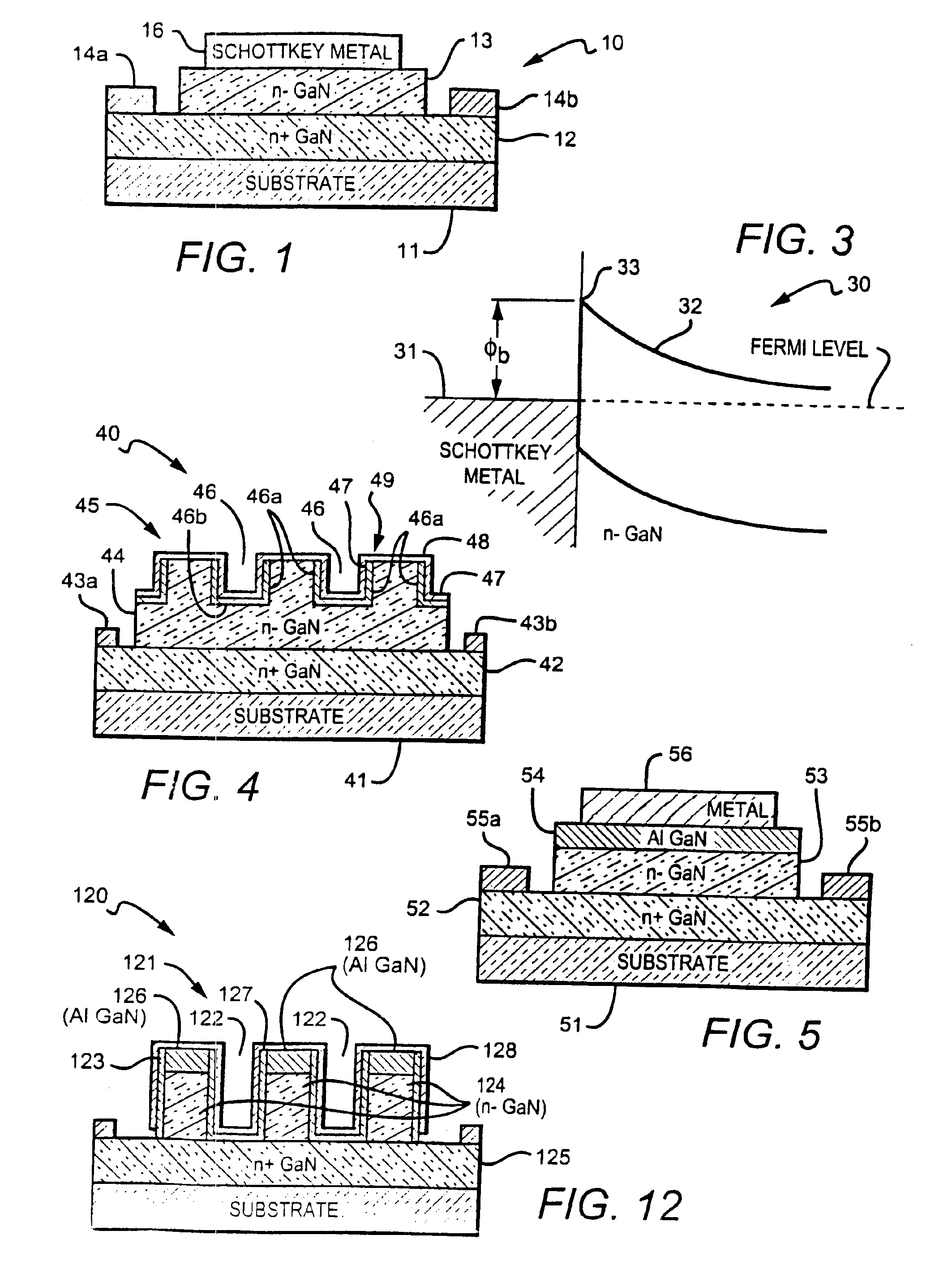

Gallium nitride based diodes with low forward voltage and low reverse current operation

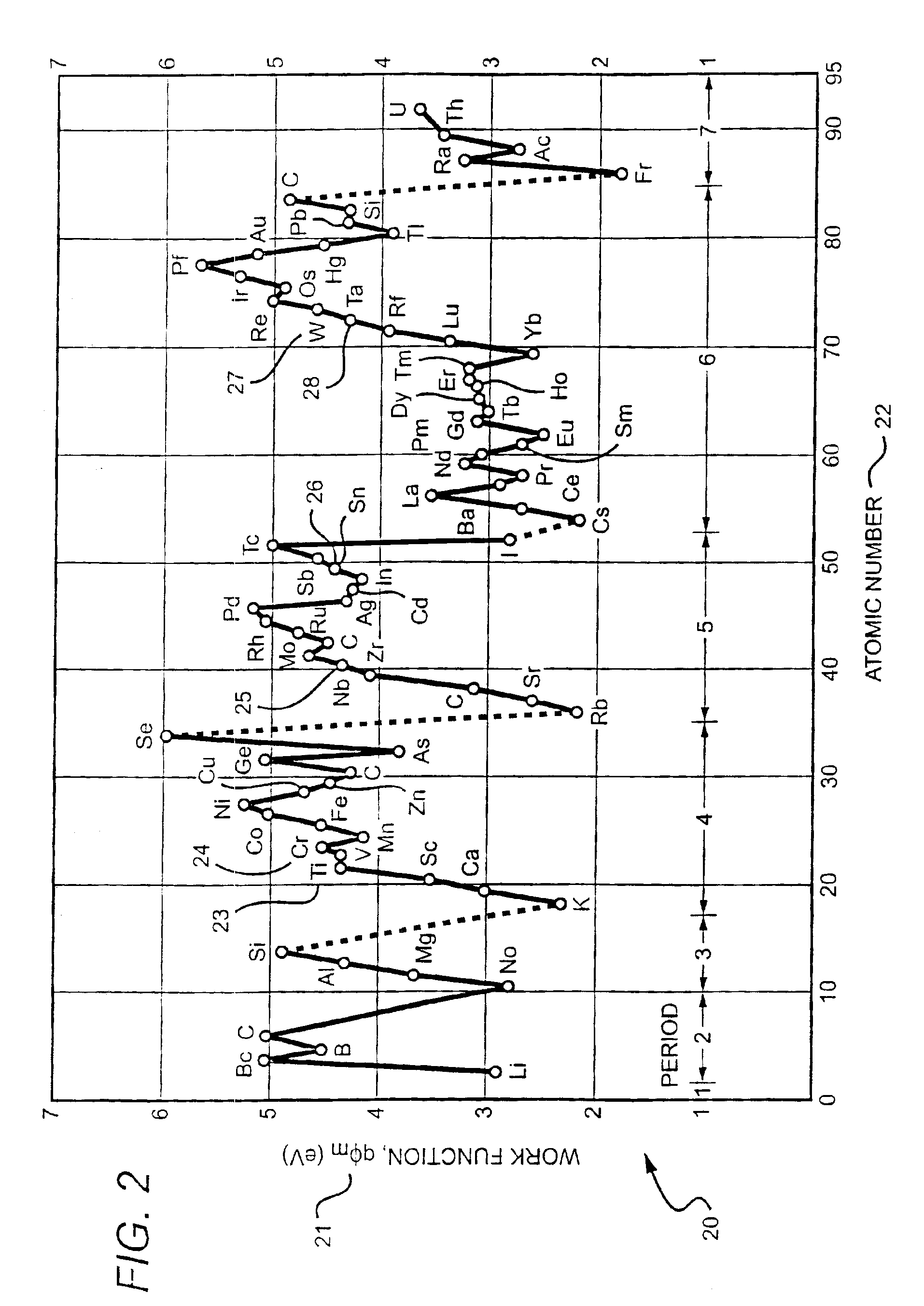

InactiveUS20050242366A1Prevents an increase in the electric fieldSchottky barrier potential is loweredDiodeSemiconductor materialsTunnel diode

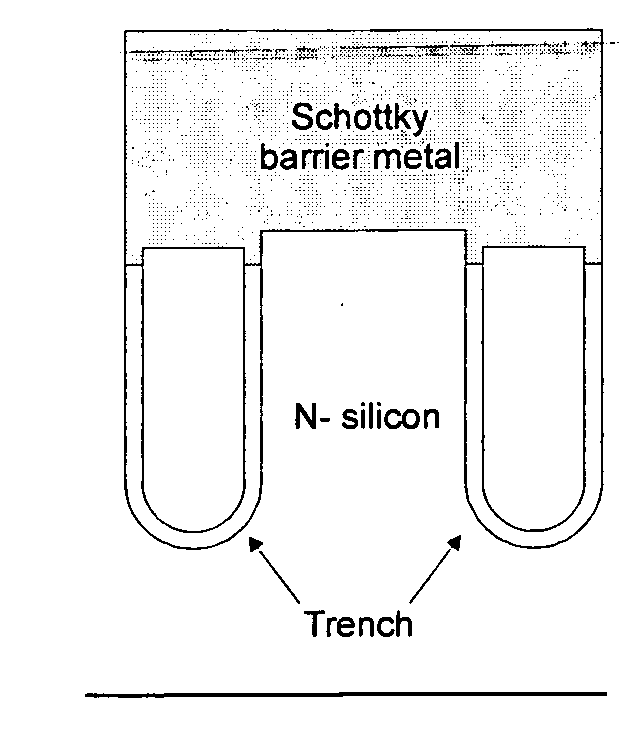

New Group III based diodes are disclosed having a low on state voltage (Vf) and structures to keep reverse current (Irev) relatively low. One embodiment of the invention is Schottky barrier diode made from the GaN material system in which the Fermi level (or surface potential) of is not pinned. The barrier potential at the metal-to-semiconductor junction varies depending on the type of metal used and using particular metals lowers the diode's Schottky barrier potential and results in a Vf in the range of 0.1-0.3V. In another embodiment a trench structure is formed on the Schottky diodes semiconductor material to reduce reverse leakage current. and comprises a number of parallel, equally spaced trenches with mesa regions between adjacent trenches. A third embodiment of the invention provides a GaN tunnel diode with a low Vf resulting from the tunneling of electrons through the barrier potential, instead of over it. This embodiment can also have a trench structure to reduce reverse leakage current.

Owner:CREE INC

Trench junction barrier controlled Schottky

ActiveUS20070034901A1Silicon area utilization is greatly improvedEliminate requirementsTransistorSolid-state devicesDopantSemiconductor

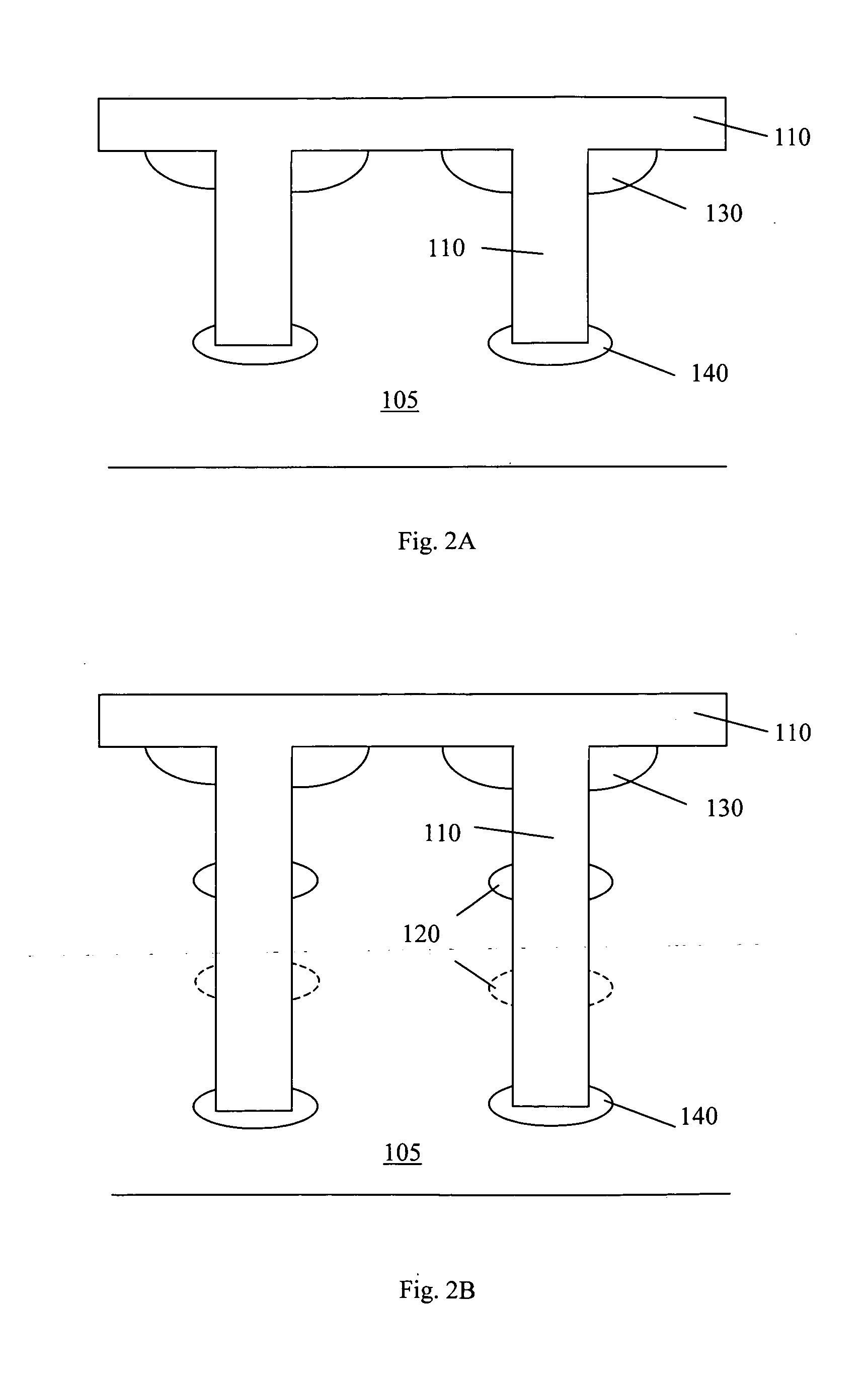

A Schottky diode includes at least a trenched opened in a semiconductor substrate doped with a dopant of a first conductivity type wherein the trench is filled with a Schottky junction barrier metal. The Schottky diode further includes one or more dopant region of a second conductivity type surrounding sidewalls of the trench distributed along the depth of the trench for shielding a reverse leakage current through the sidewalls of the trench. The Schottky diode further includes a bottom-doped region of the second conductivity type surrounding a bottom surface of the trench and a top-doped region of the second conductivity type surrounding a top portion of the sidewalls of the trench. In a preferred embodiment, the first conductivity type is a N-type conductivity type and the middle-depth dopant region comprising a P-dopant region.

Owner:ALPHA & OMEGA SEMICON LTD

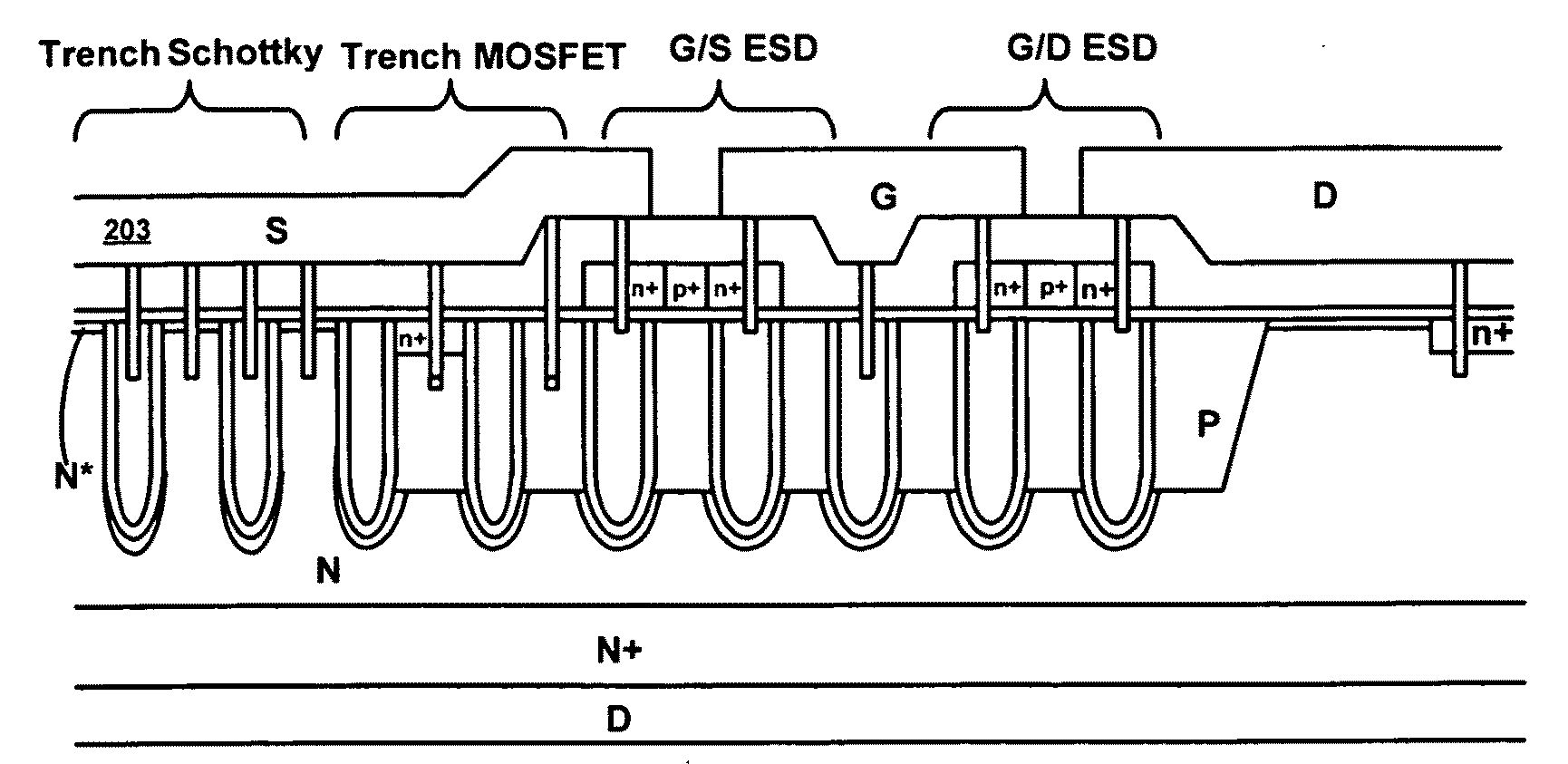

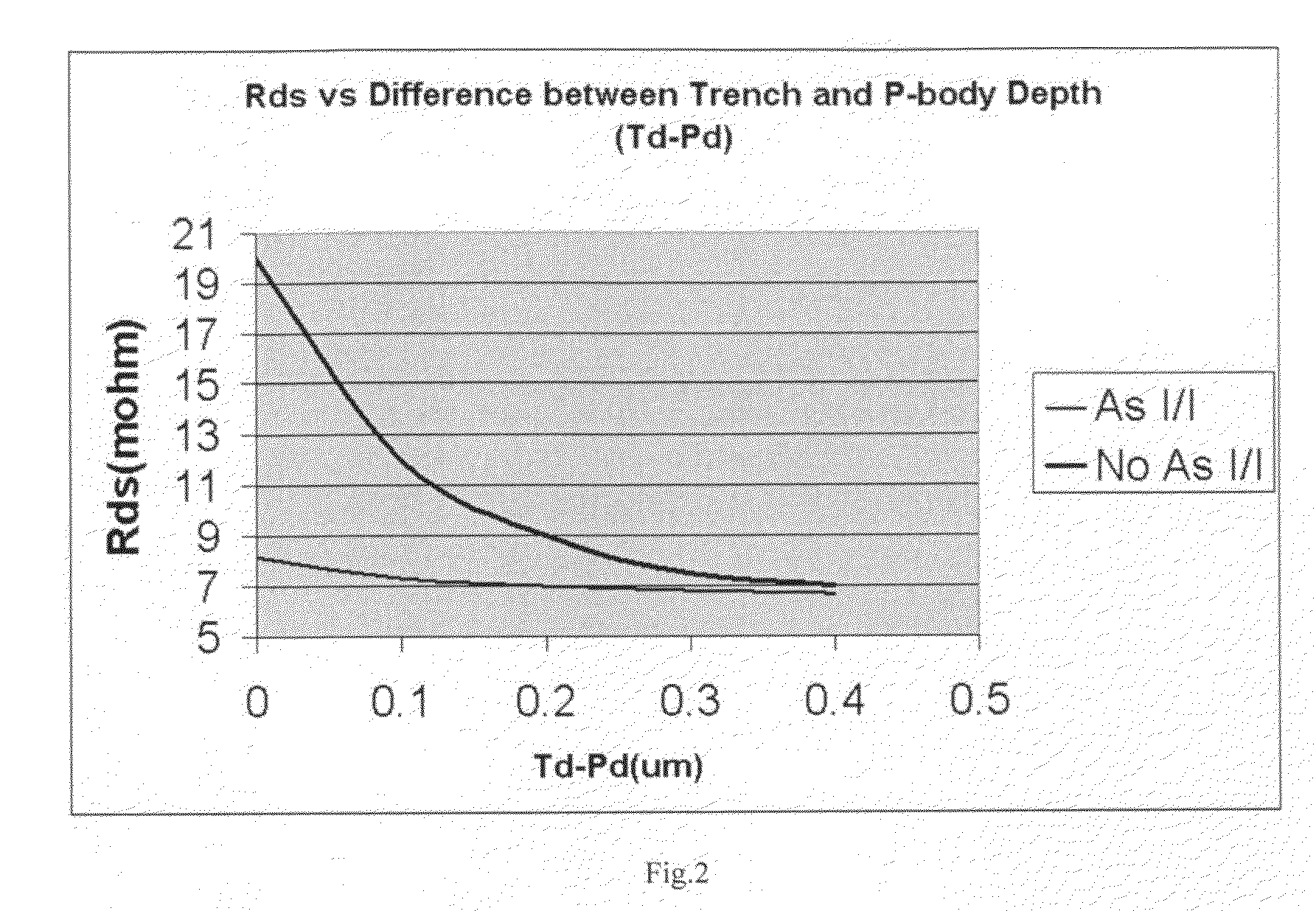

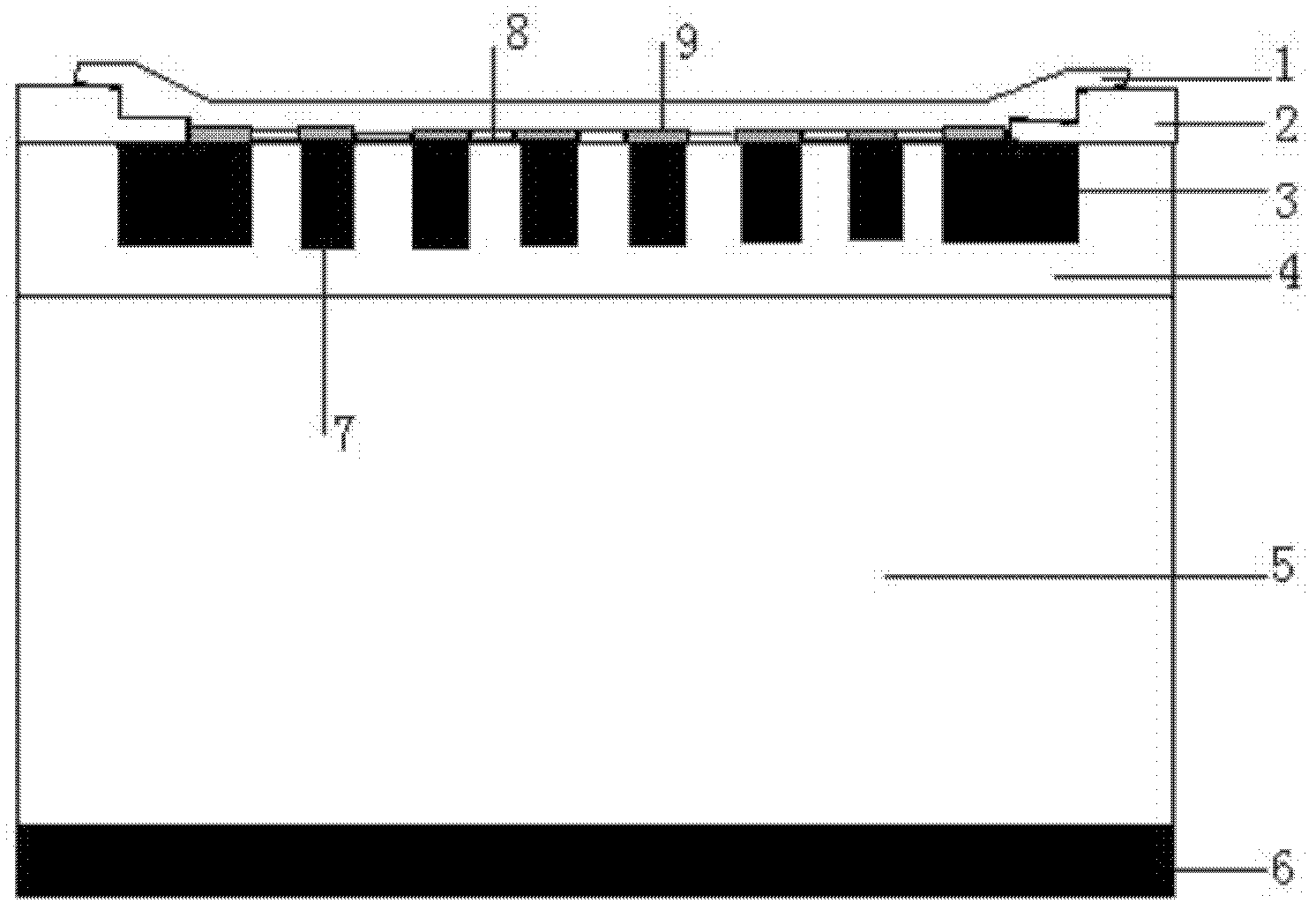

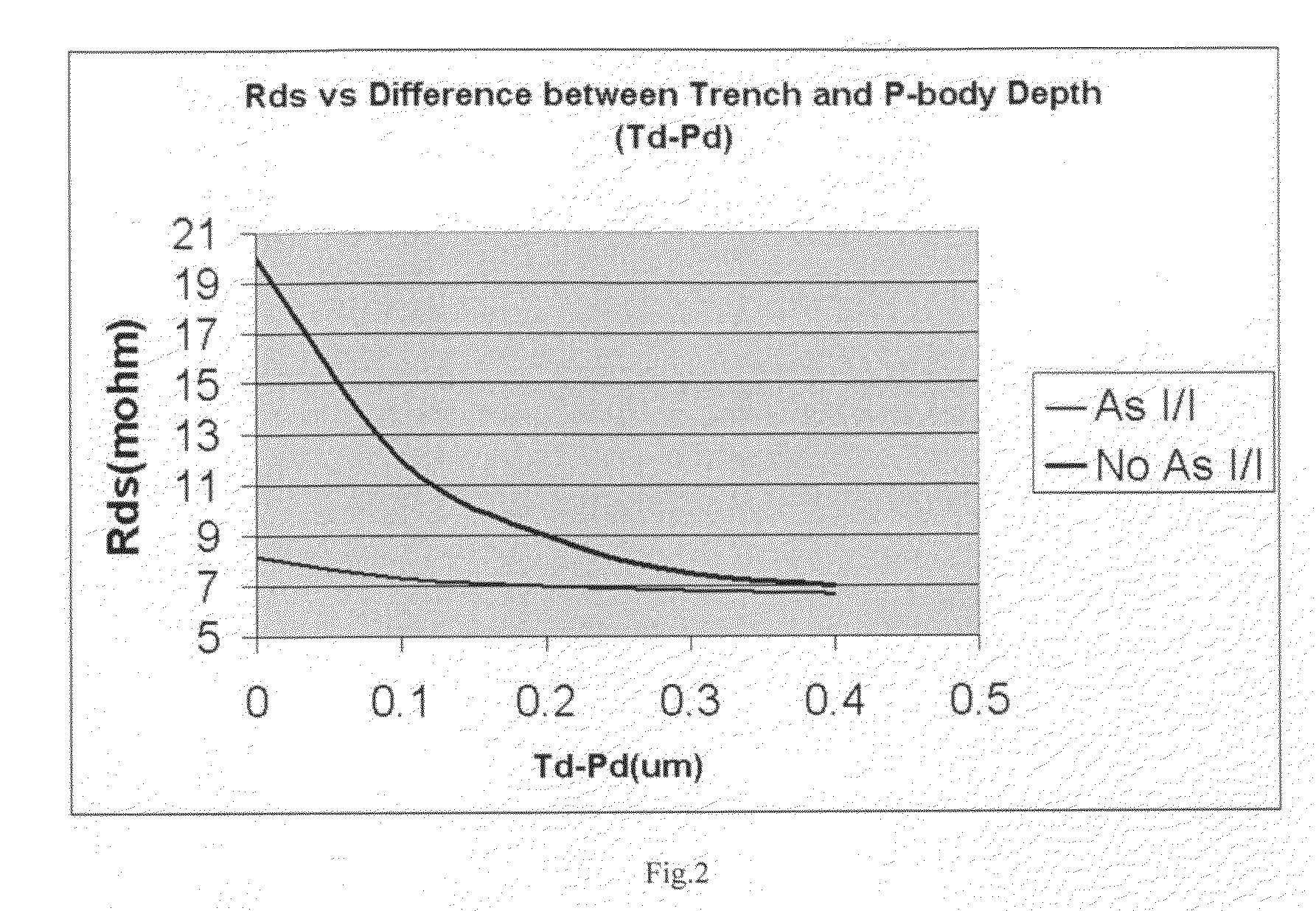

MSD integrated circuits with shallow trench

InactiveUS20100237414A1Reduce extra spaceImprove performanceSemiconductor/solid-state device detailsSolid-state devicesOvervoltageEngineering

A trench MOSFET device with embedded Schottky rectifier, gate-drain and gate-source diodes on single chip is formed with shallow trench structure to achieve device shrinkage and performance improvement. The present semiconductor devices achieve low Vf and reverse leakage current for embedded Schottky rectifier, have overvoltage protection for GS clamp diodes and avalanche protection for GD clamp diodes. More particularly, gate charge of the present semiconductor device is reduced due to the shallow trench surrounded by an additional N doped area around the bottom while keeping Rds low enough and at the same time, maintaining BV at a certain level

Owner:FORCE MOS TECH CO LTD

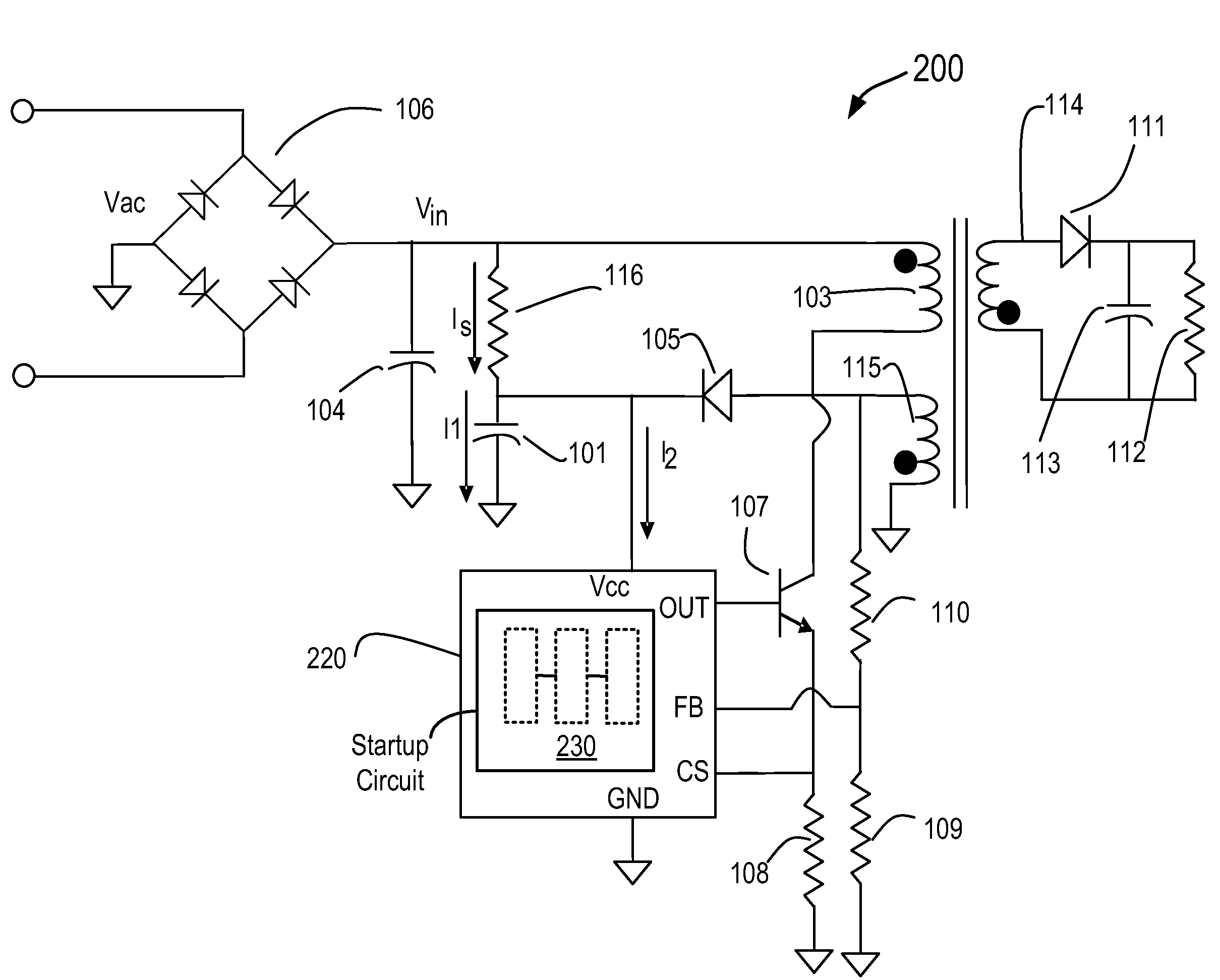

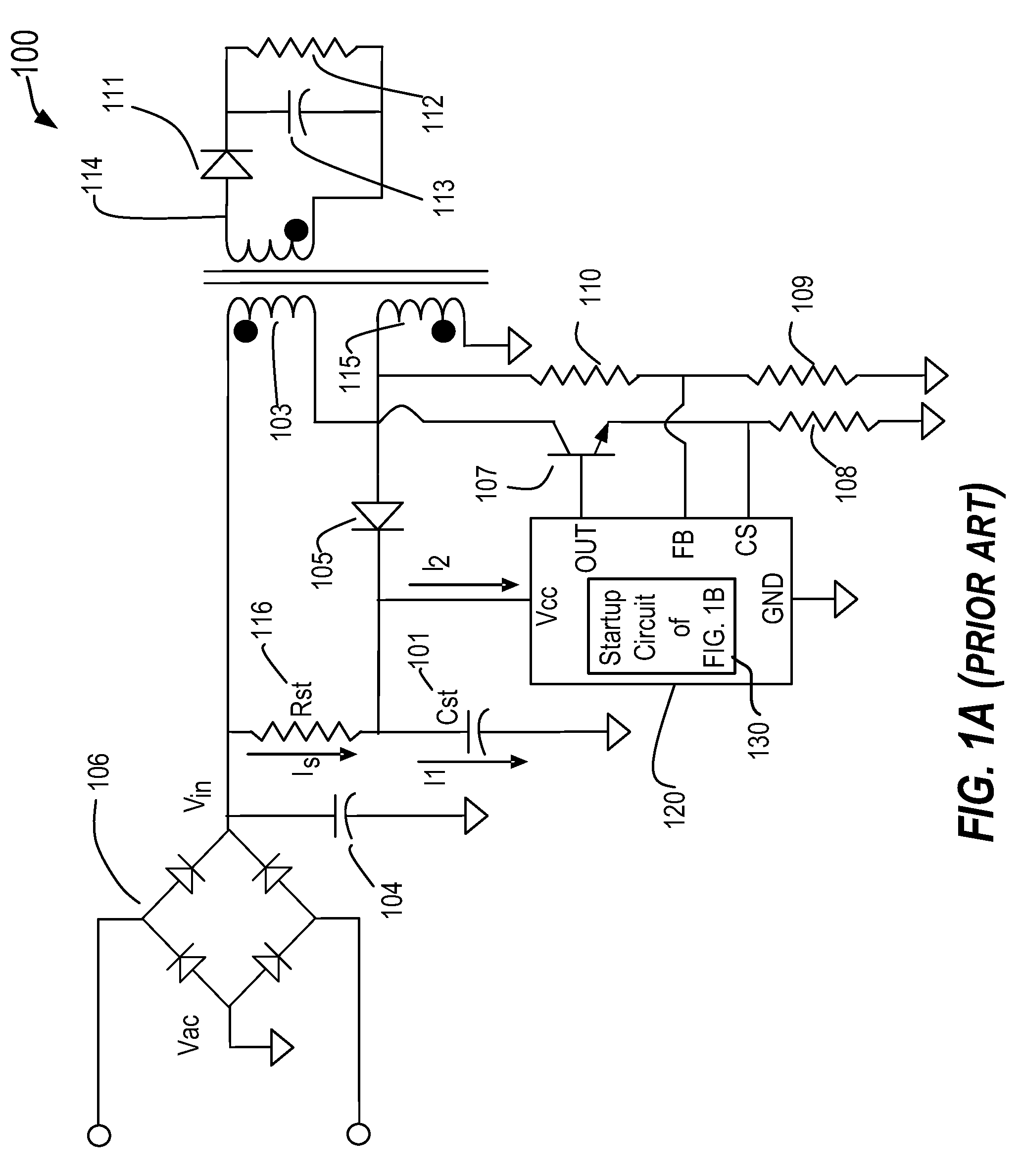

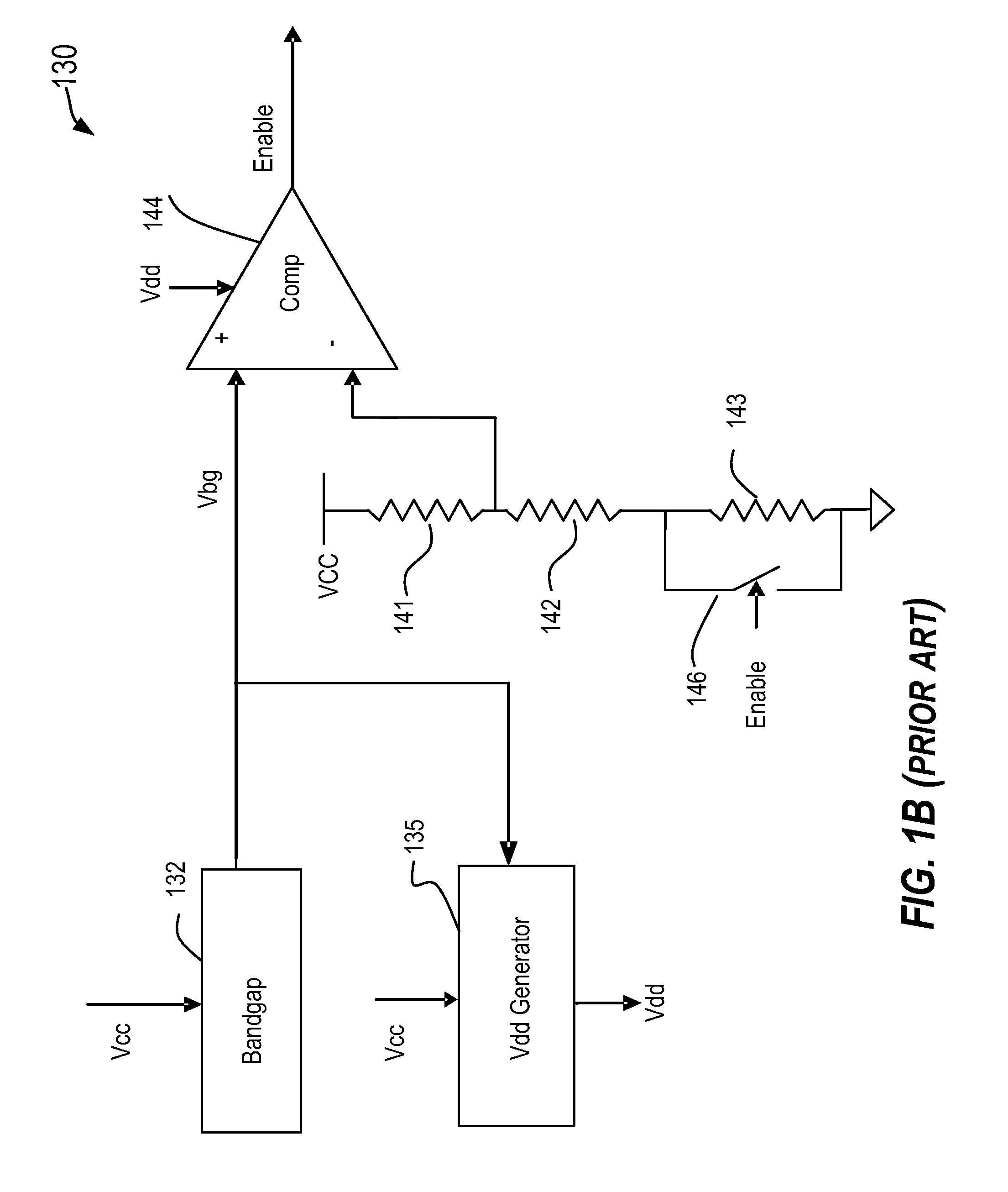

Method and apparatus of low current startup circuit for switching mode power supplies

ActiveUS20100244804A1Reduce standby powerTotal current dropDc-dc conversionElectric variable regulationEngineeringFeedback circuits

A startup circuit for a switching-mode power supply (SMPS) includes a first voltage detector configured to trigger the switching-mode power supply from a startup mode to a normal operation mode when an input supply voltage exceeds a first threshold voltage, a current consumption in the first voltage detector in the startup mode being determined by a reverse leakage current of a diode. A feedback circuit is coupled to the first voltage detector and being capable of maintaining a positive feedback loop with a current consumption of no more than a microampere. A second voltage detector is coupled to the first voltage detector and the feedback circuit, and is configured to trigger the switching-mode power supply to switch from the normal operation mode to the startup mode when the input supply voltage is below a second threshold voltage.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

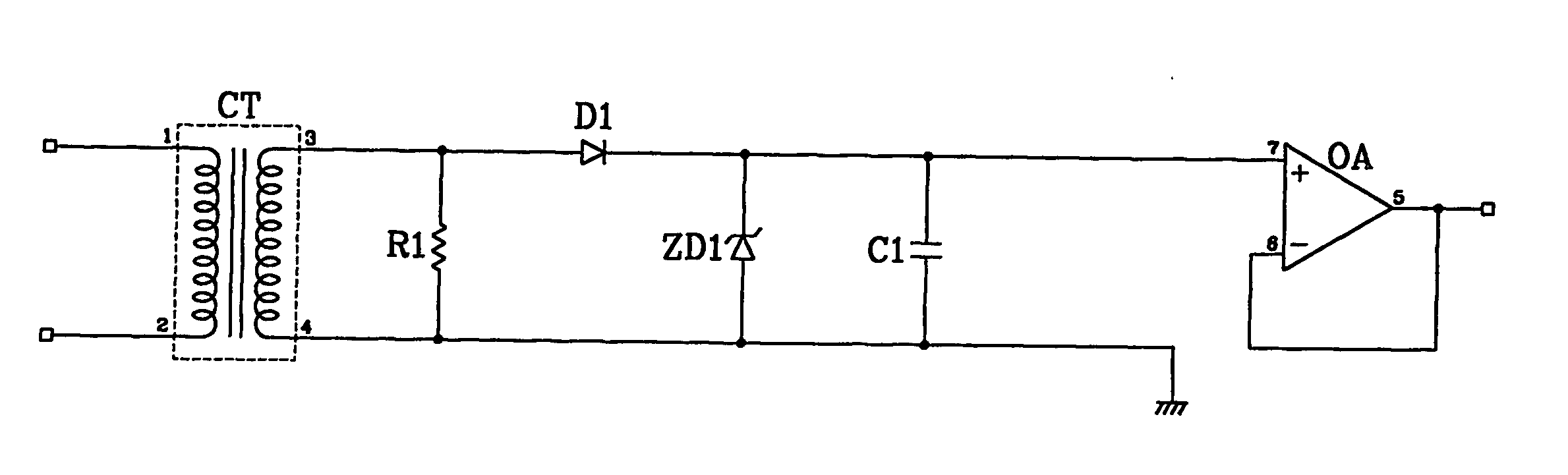

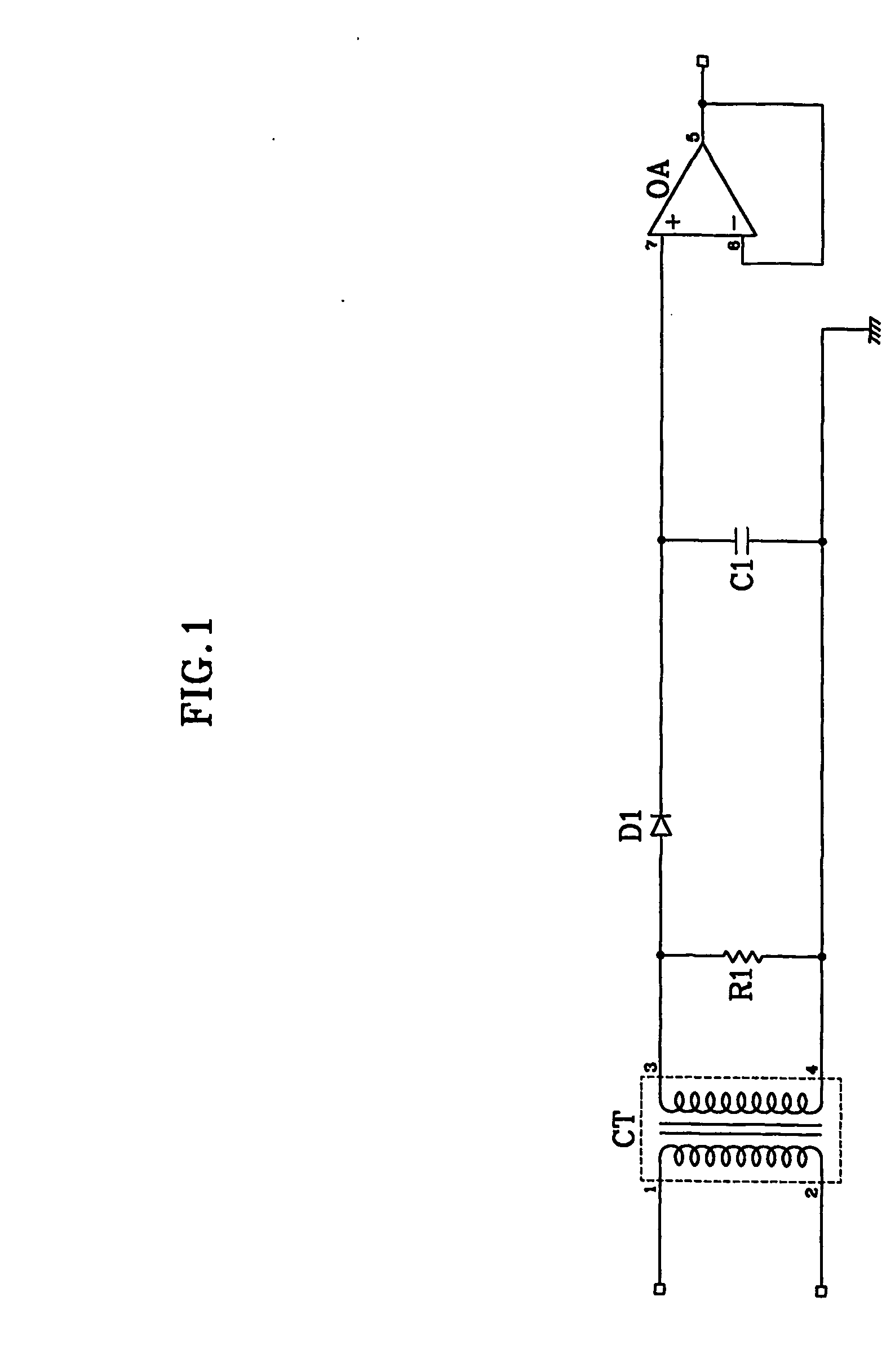

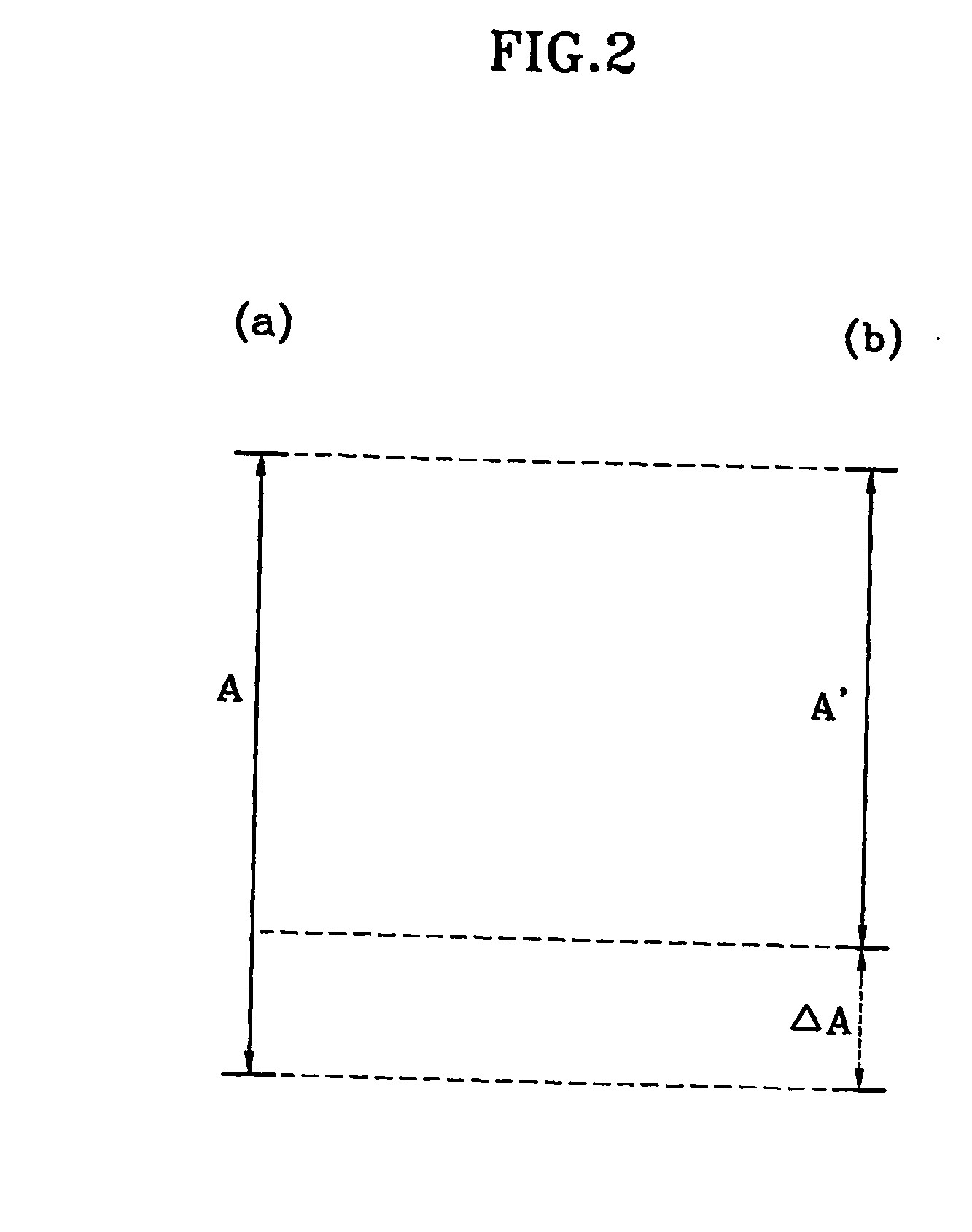

Circuit for detecting electric current

ActiveUS20060164096A1Improve accuracyImprove reliabilityResistance/reactance/impedenceAc/pulses peak value measurementsInduction heaterEngineering

A circuit for detecting an electric current by which a loss portion of a forward current caused by a backward leakage current of a diode generated by the influence of temperature increase can be compensated such that error in the peak value of a load current detected by surrounding high temperature can be minimized, and credibility reliability can be increased for electric instruments that call for an accurate control of the load current and that generate a high temperature such as induction heating cookers, induction heaters and the like.

Owner:KWON YONG JAI

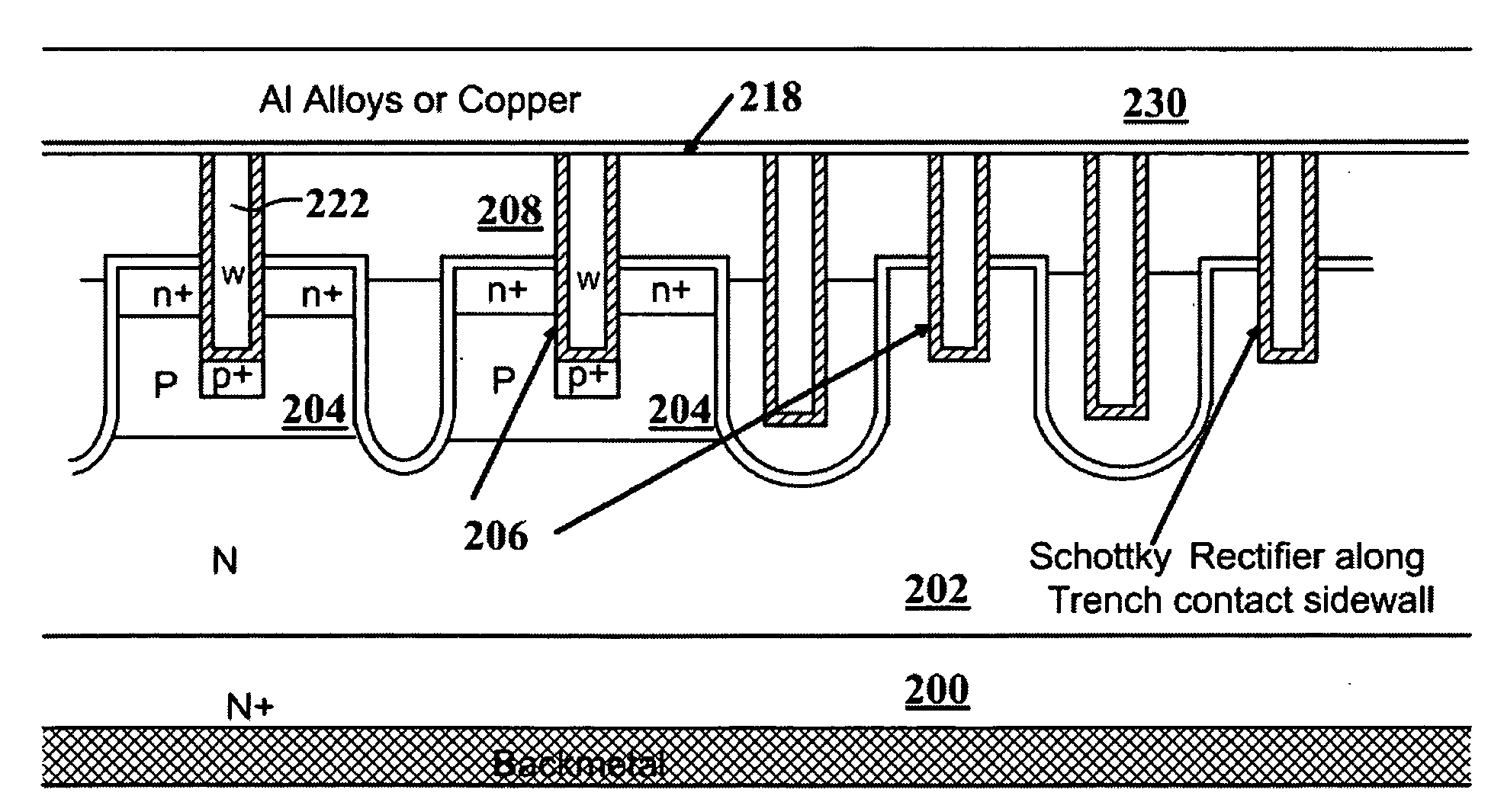

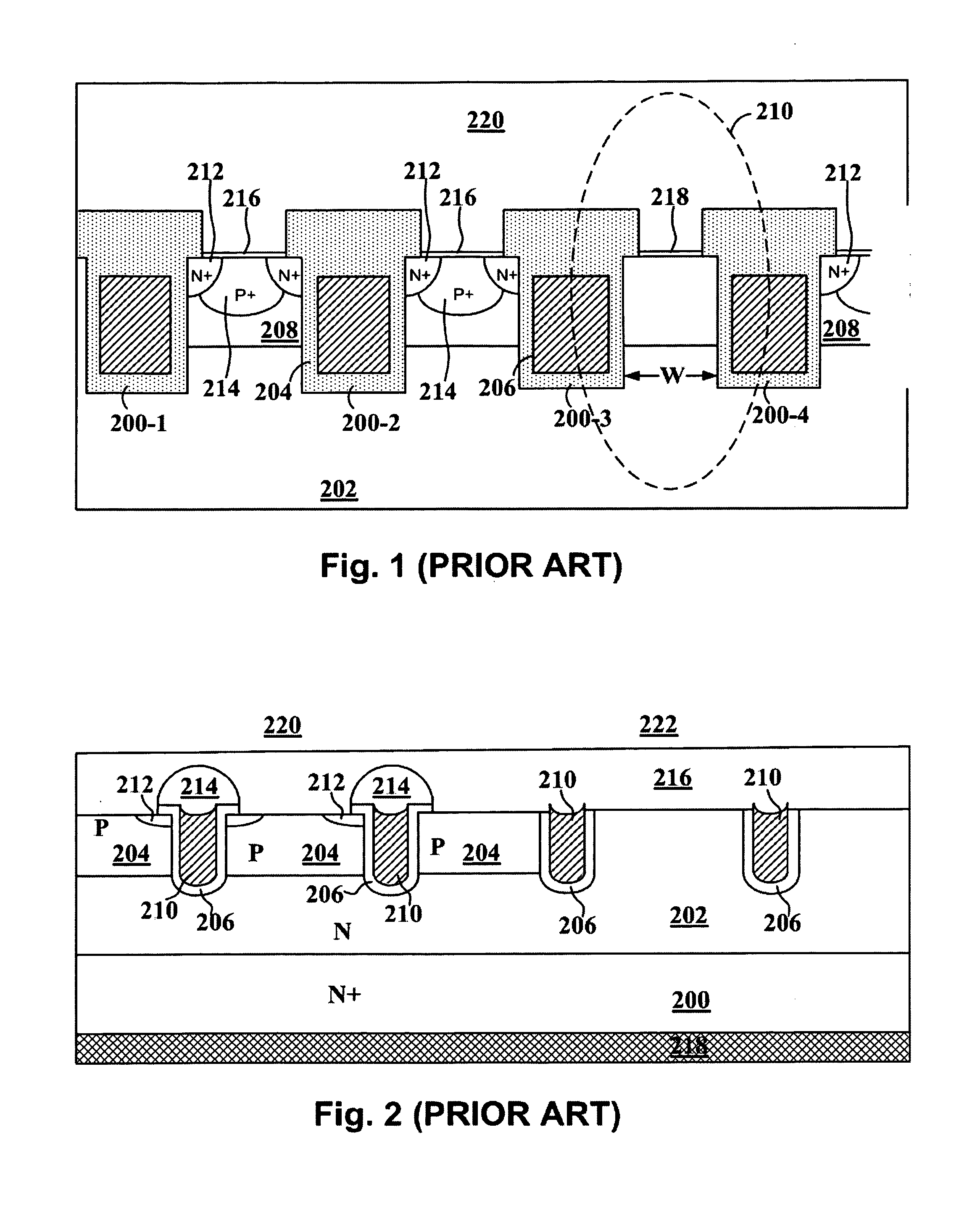

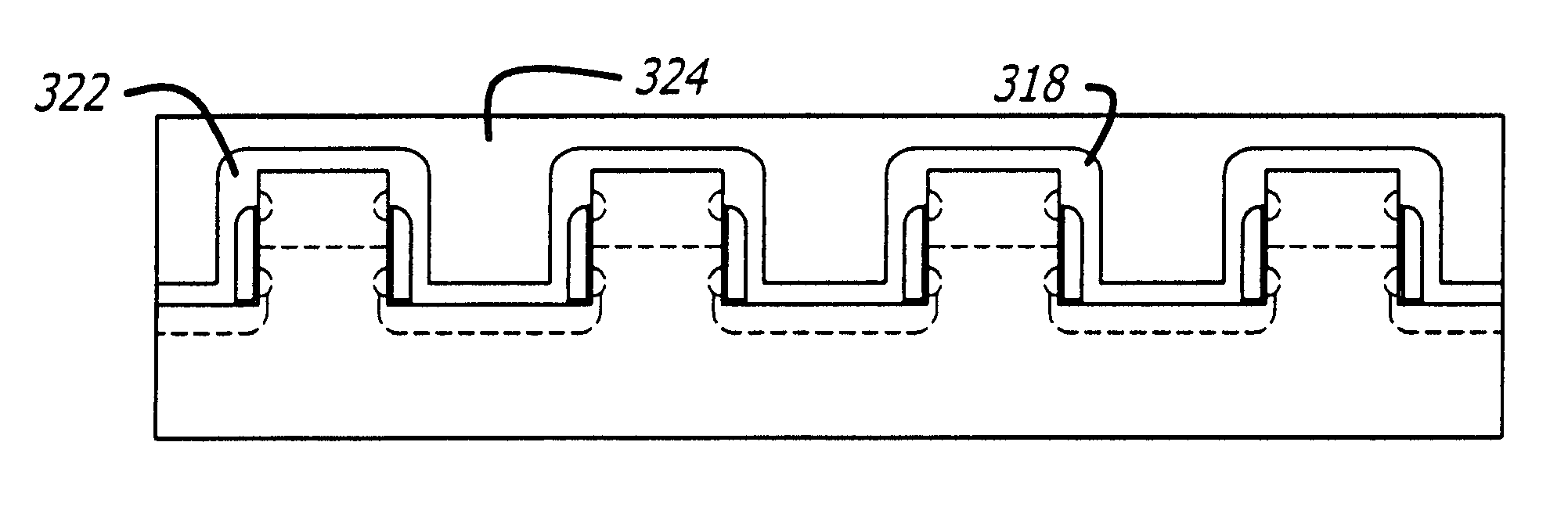

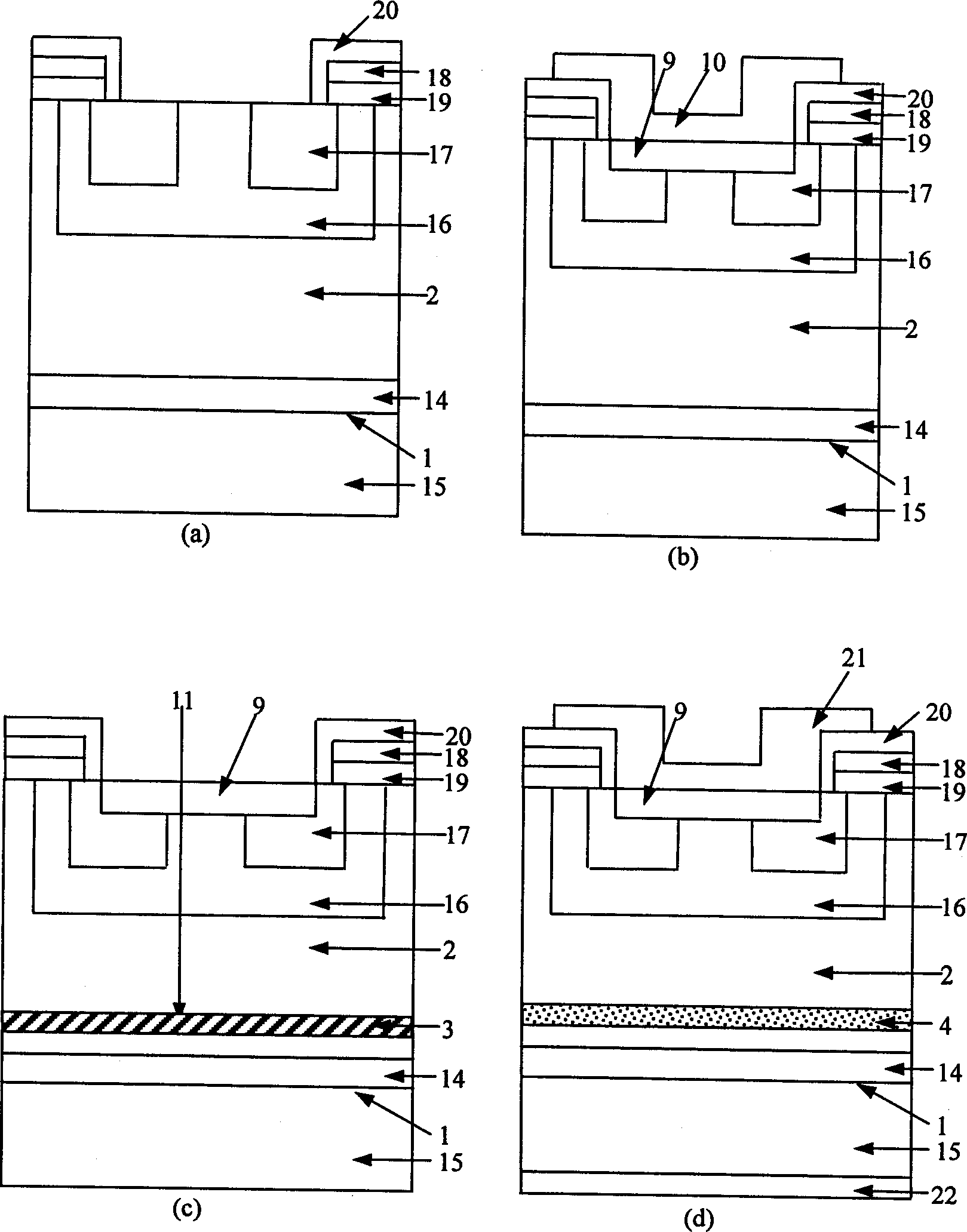

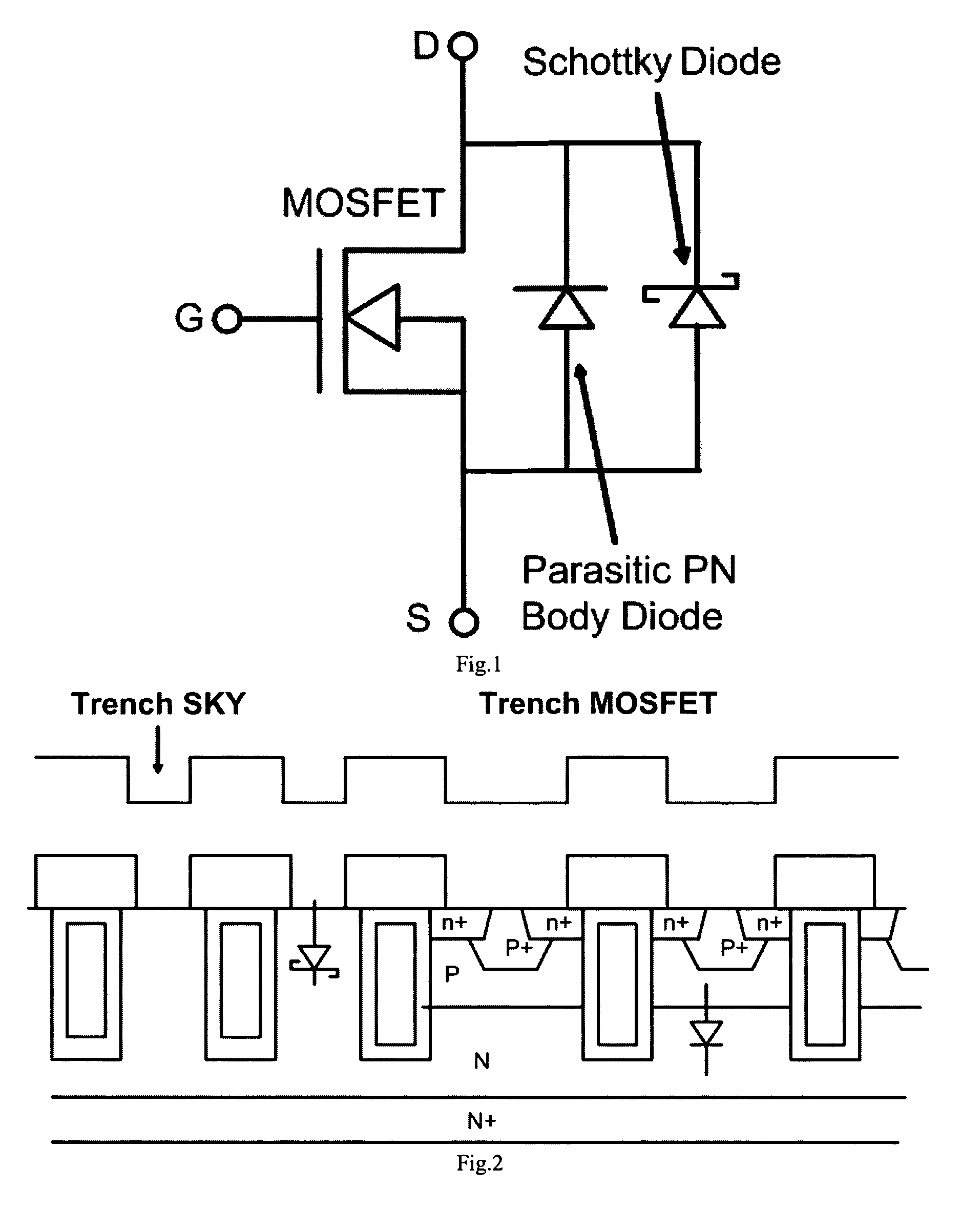

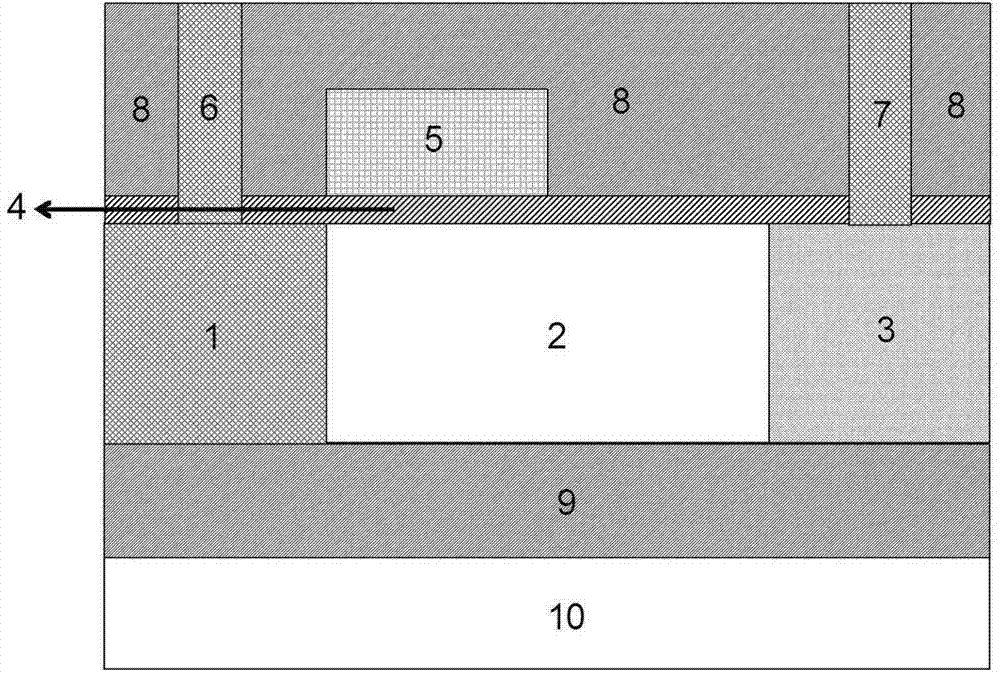

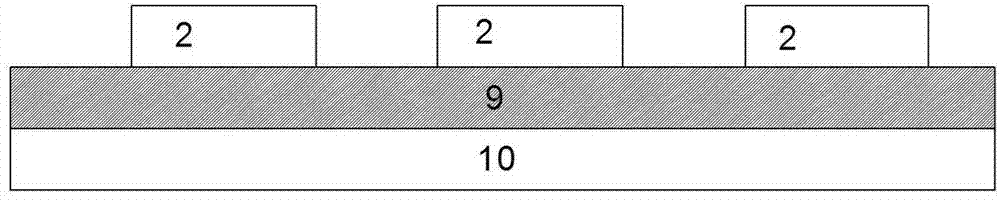

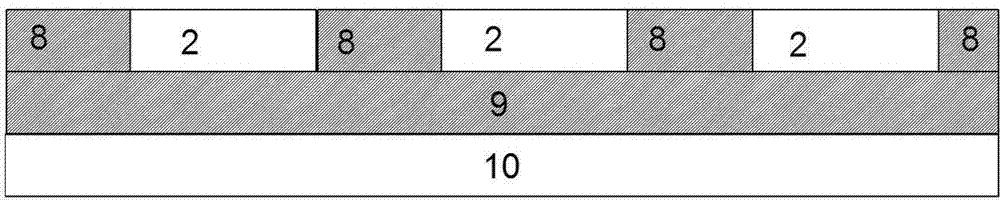

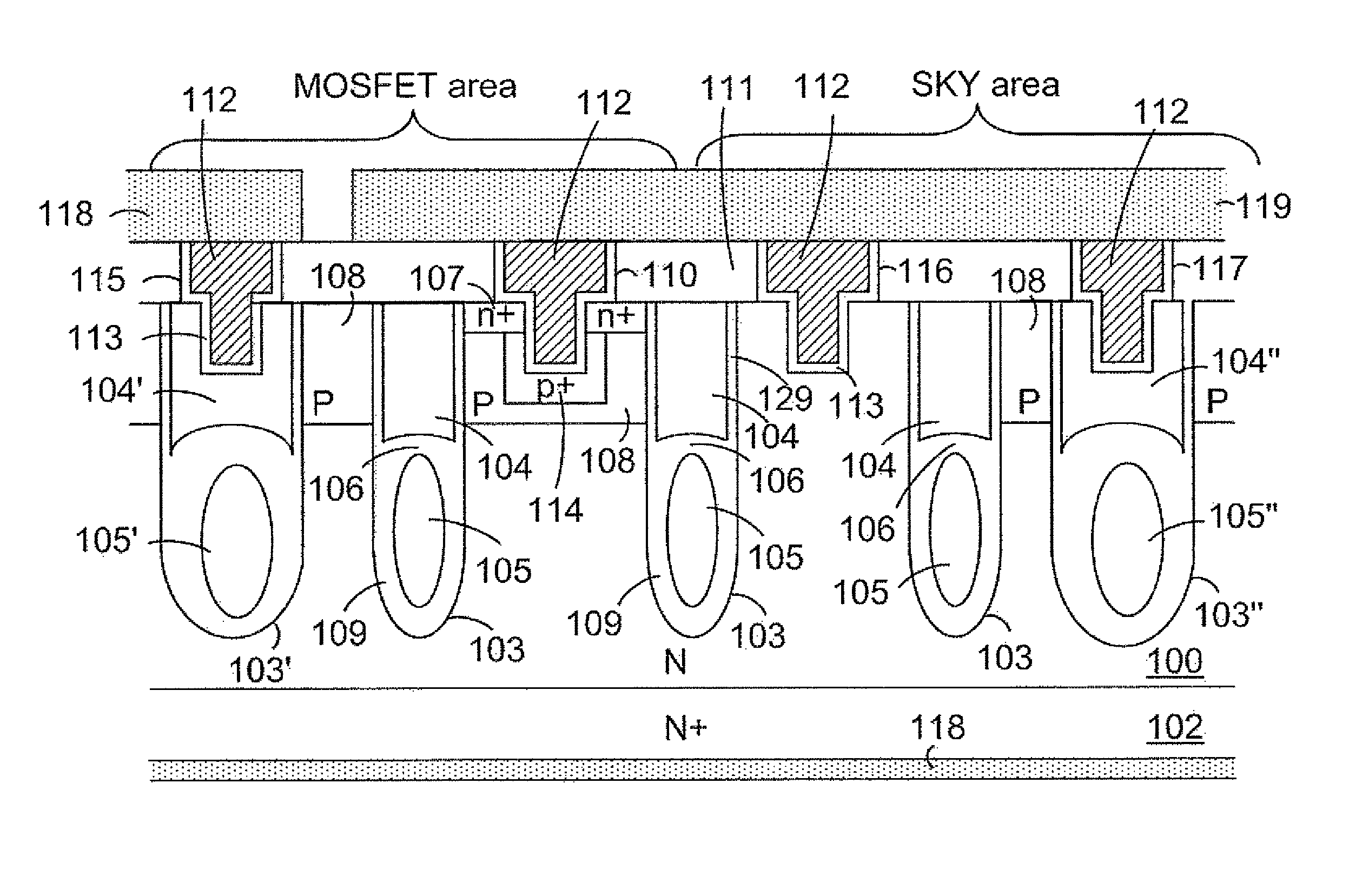

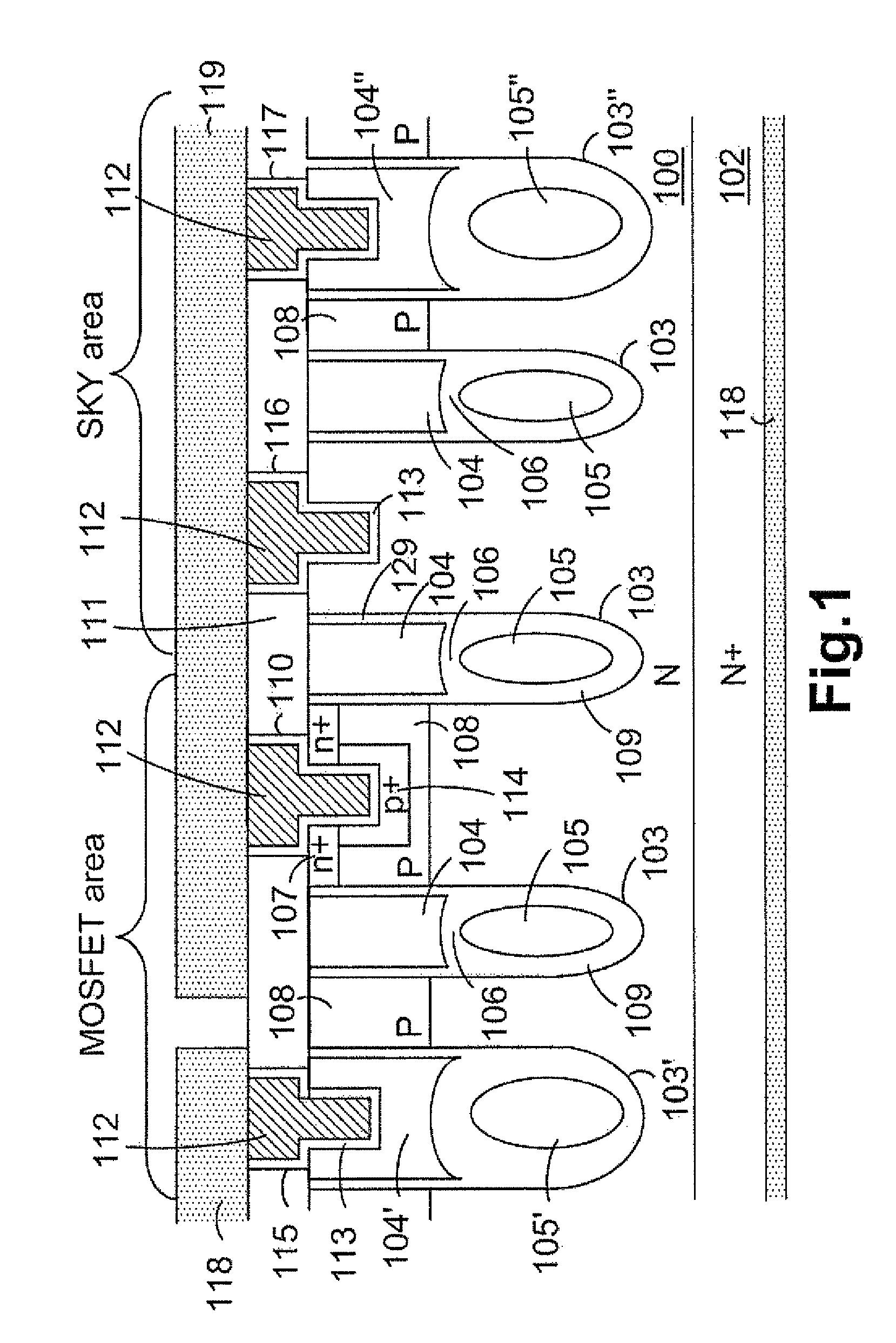

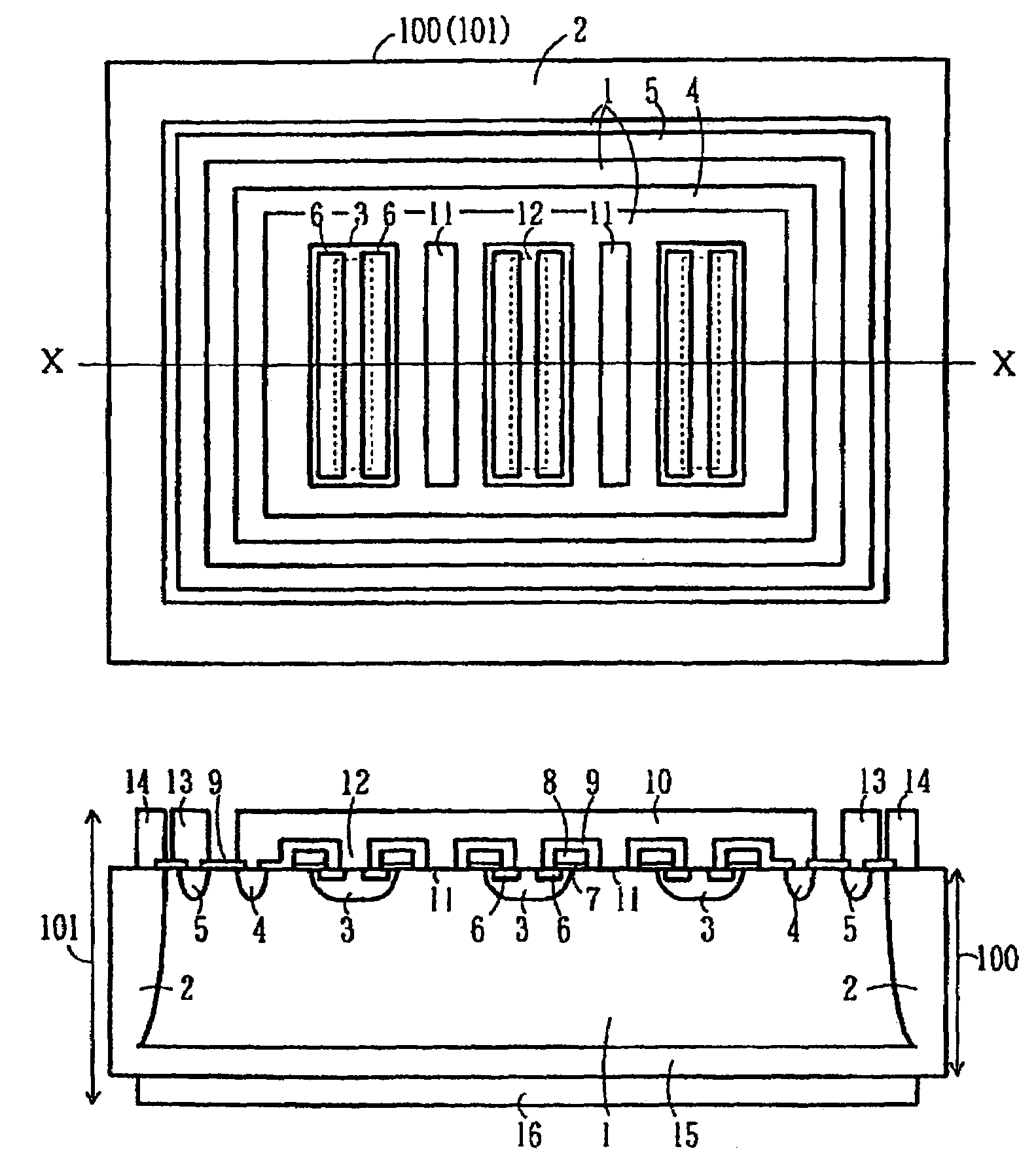

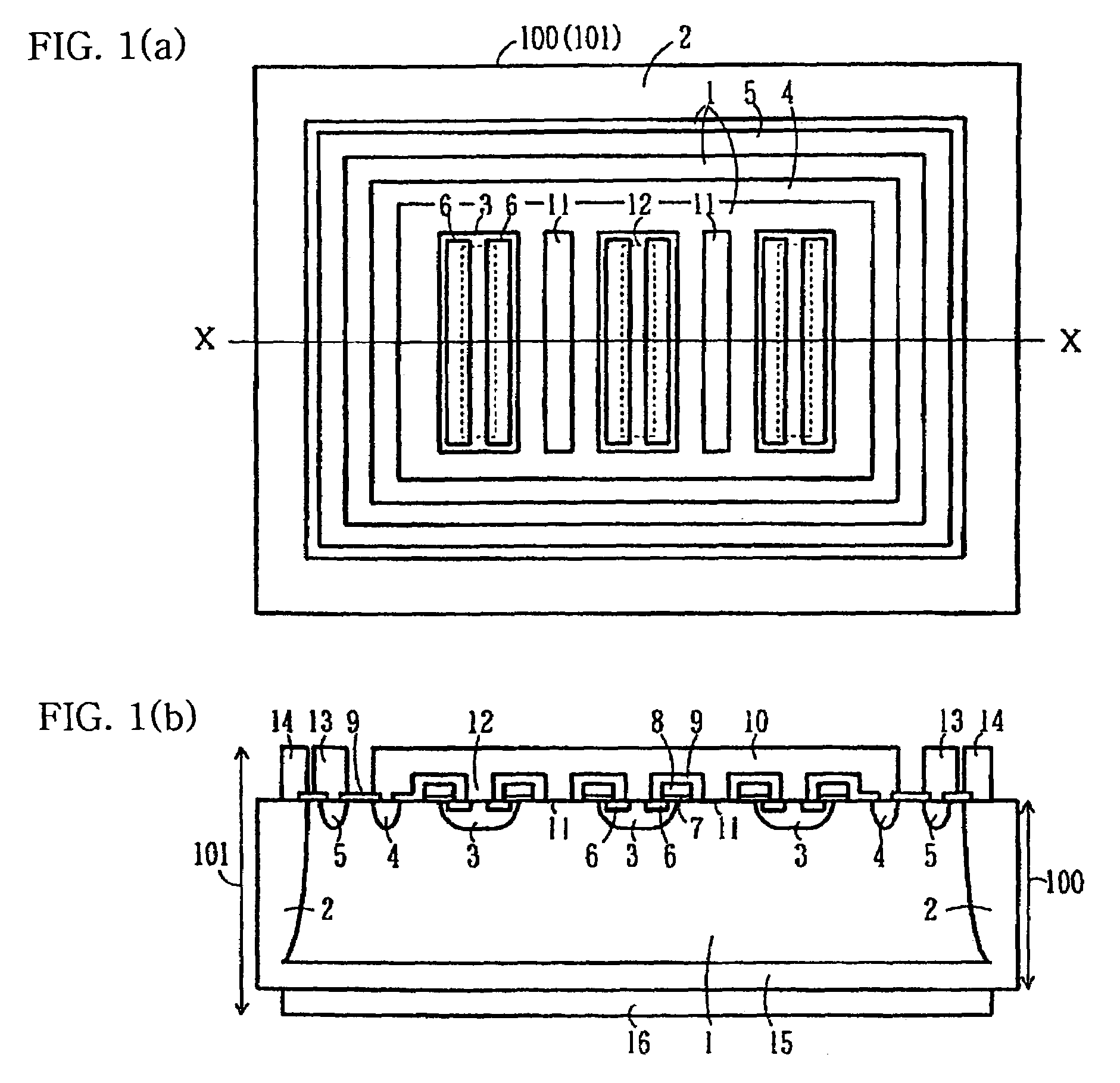

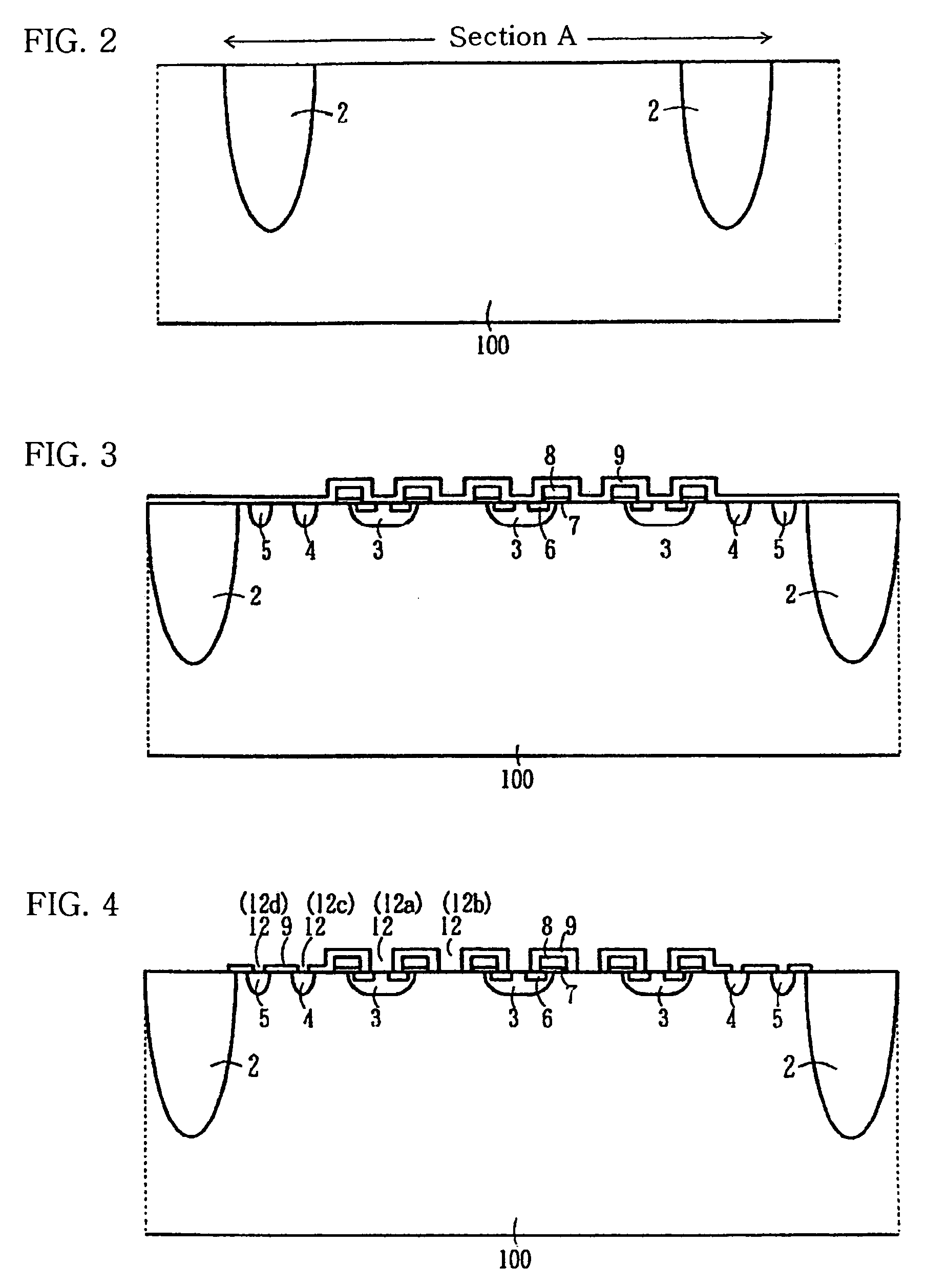

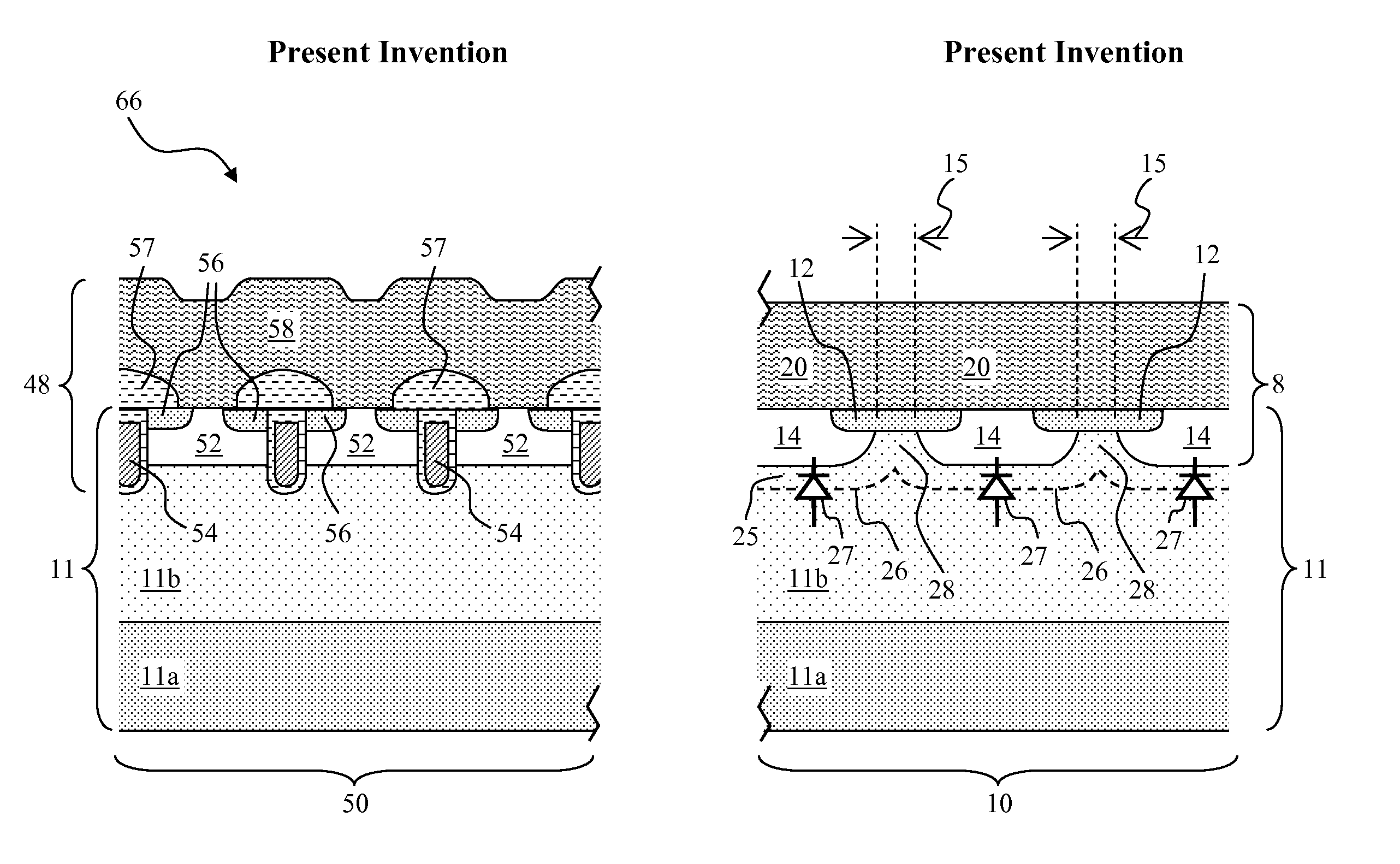

Integrated trench mosfet and junction barrier schottky rectifier with trench contact structures

ActiveUS20090315107A1Improve configurationImproved manufactureSolid-state devicesSemiconductor devicesTrench mosfetMiniaturization

A trench MOSFET in parallel with trench junction barrier Schottky rectifier with trench contact structures is formed in single chip. The present invention solves the drawback brought by some prior arts, for example, the large area occupied by planar contact structure and high gate-source capacitance. As the electronic devices become more miniaturized, the trench contact structures of this invention are able to be shrunk to achieve low specific on-resistance of Trench MOSFET, and low Vf and reverse leakage current of the Schottky Rectifier.

Owner:FORCE MOS TECH CO LTD

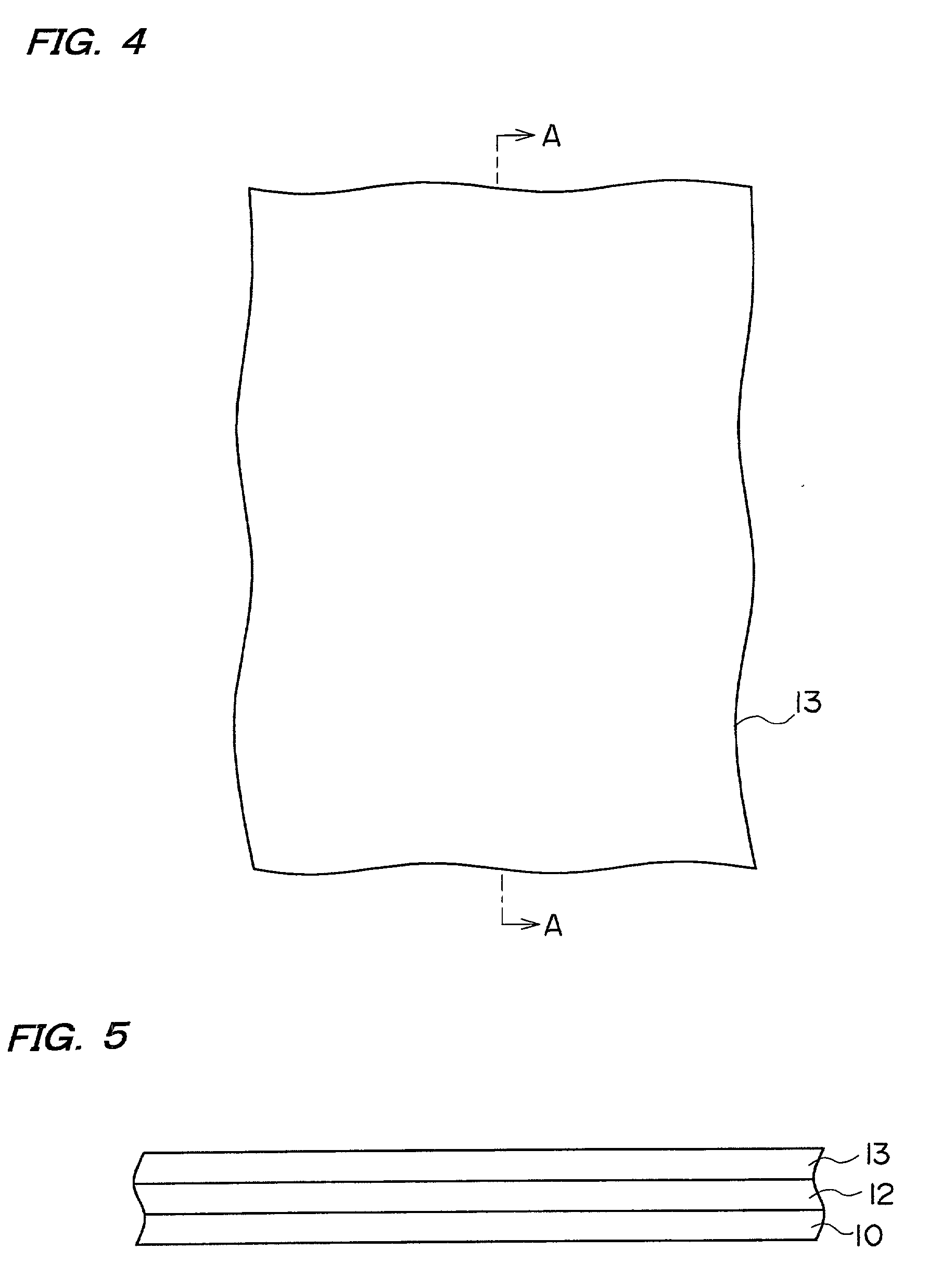

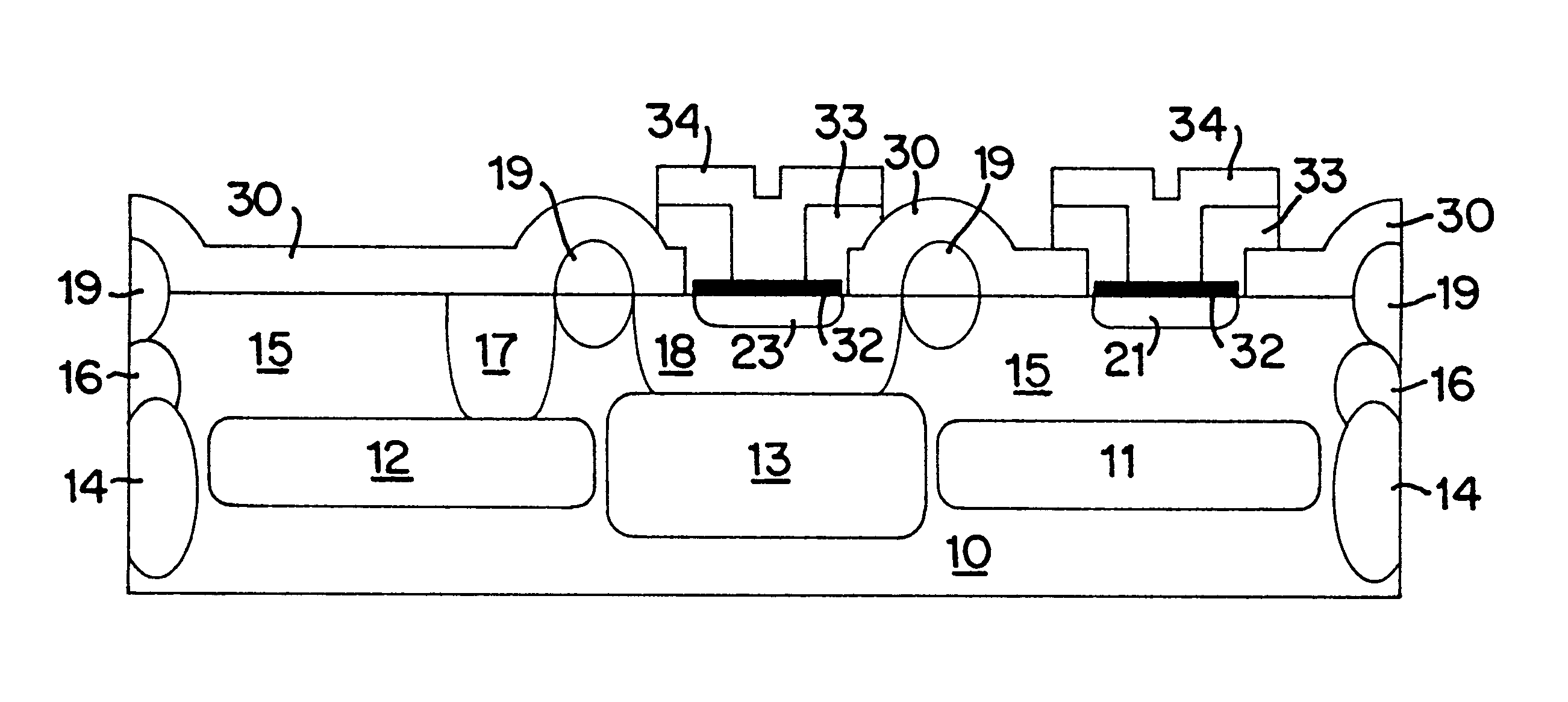

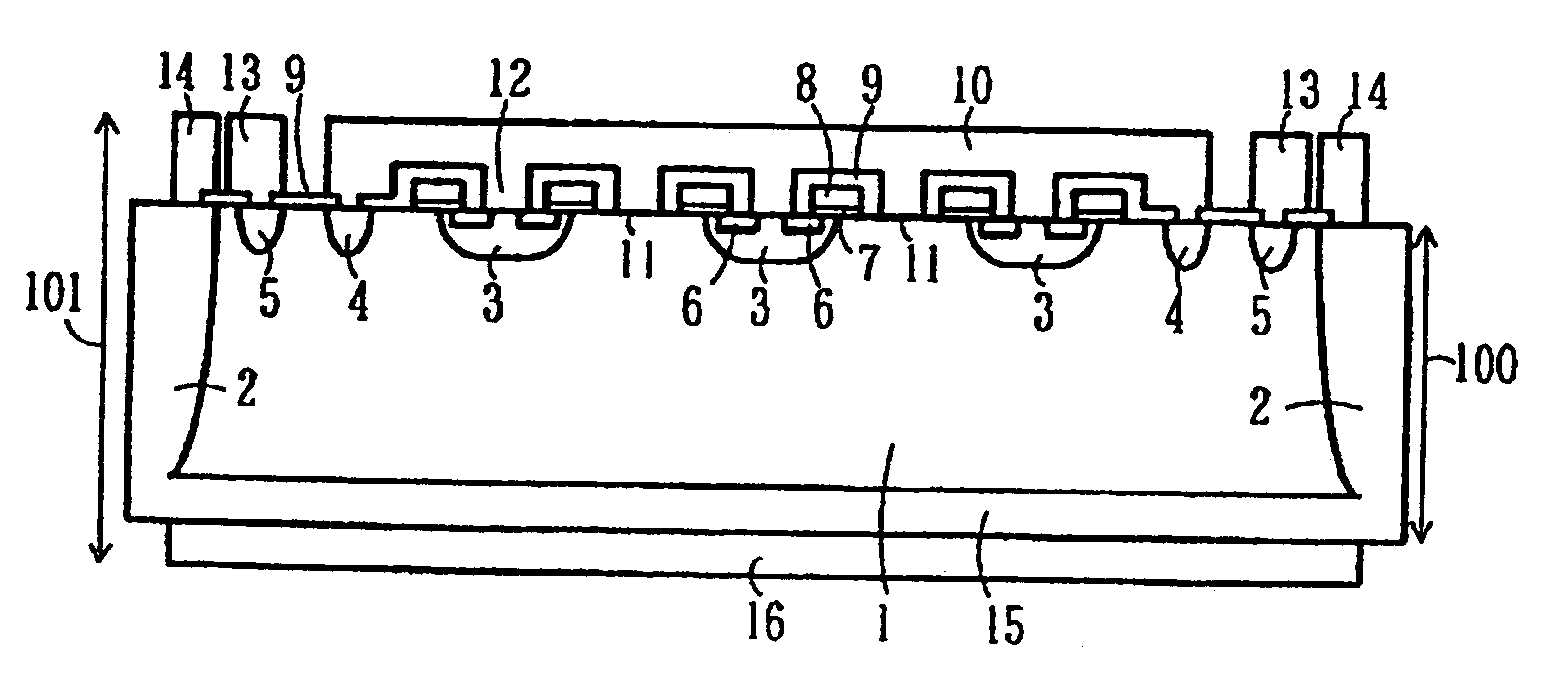

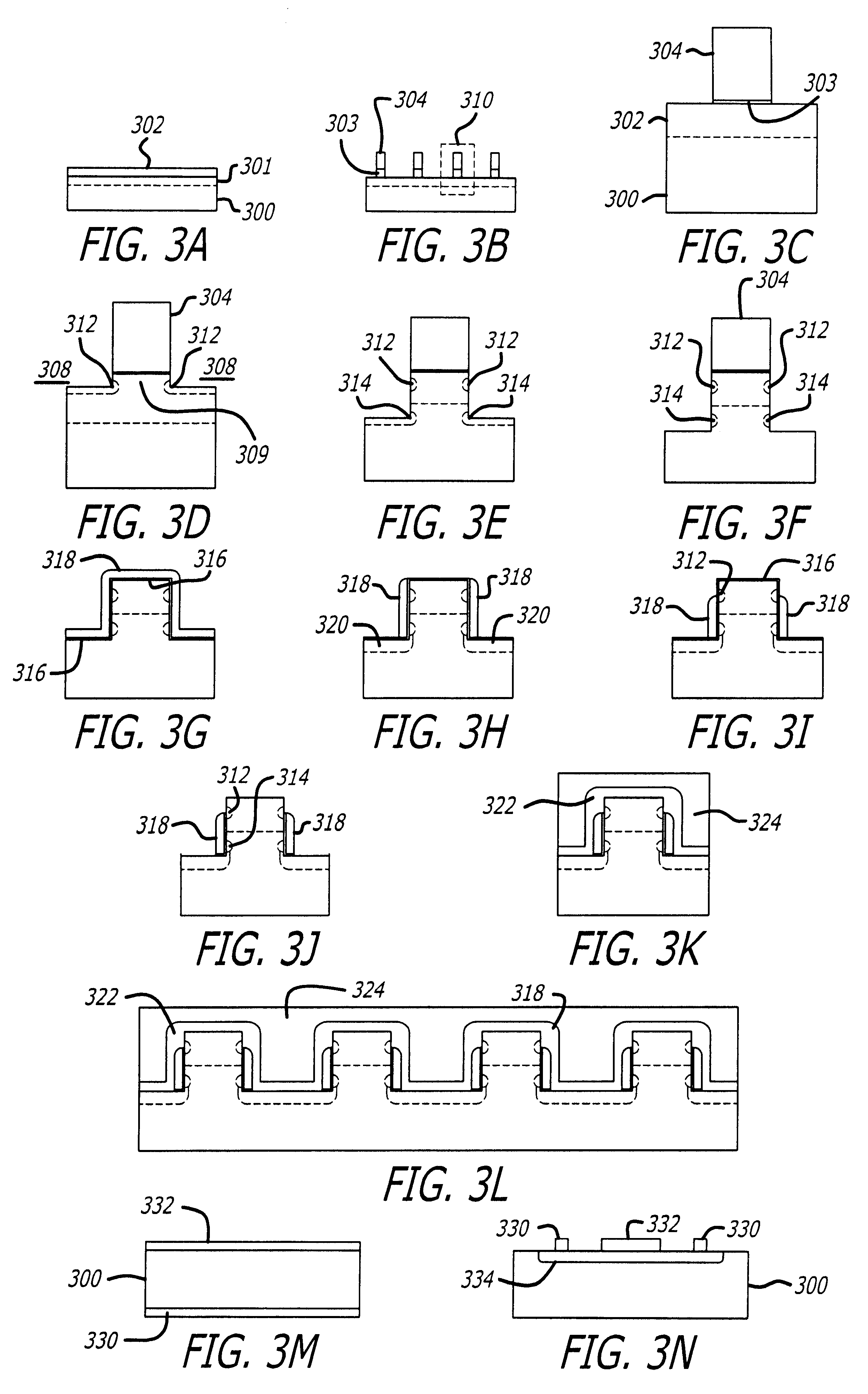

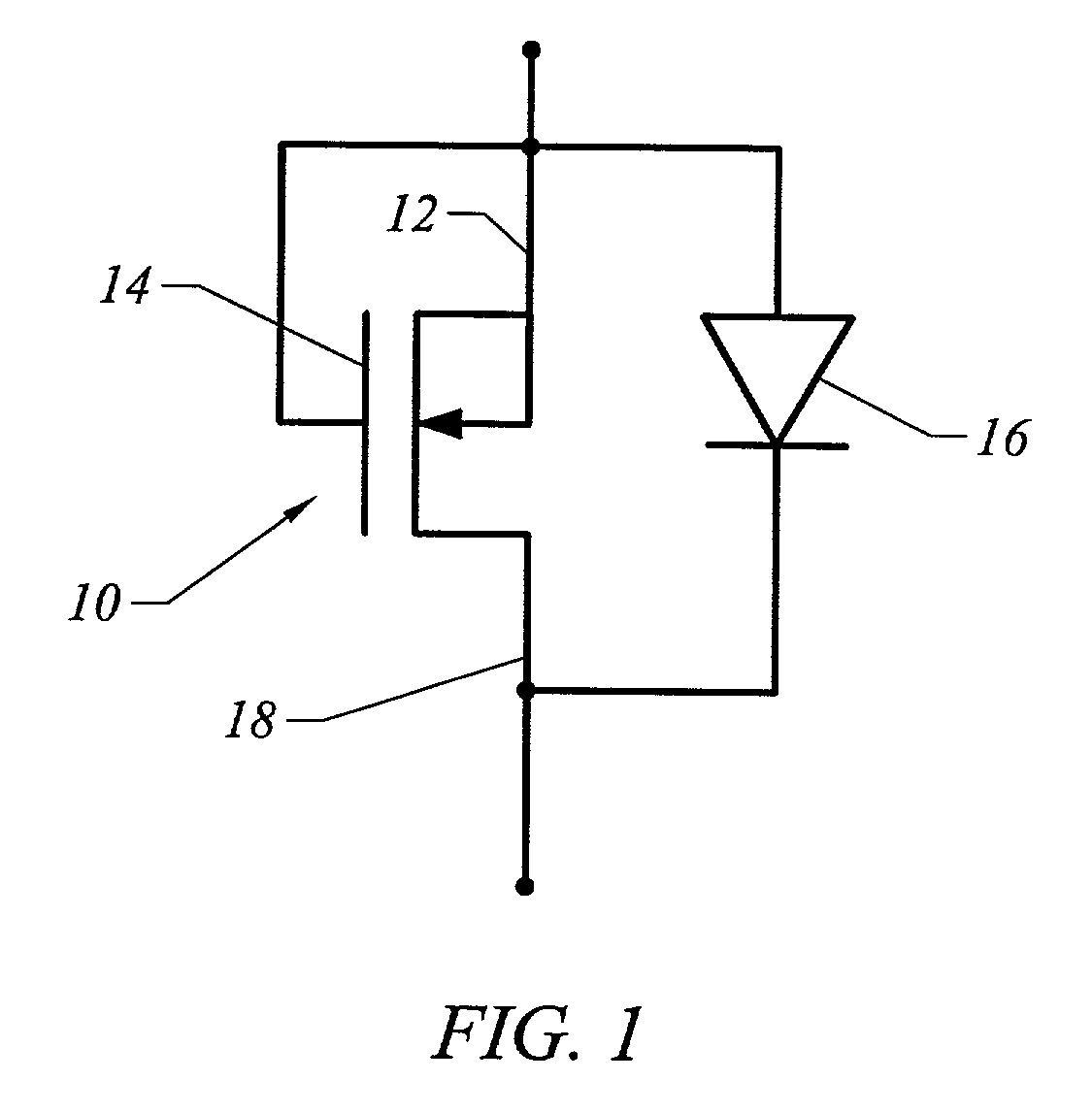

Vertical metal oxide silicon field effect semiconductor diodes

InactiveUS6537921B2Solid-state devicesSemiconductor/solid-state device manufacturingVoltage dropField effect

The present invention includes methods and apparatus as described in the claims. Briefly, semiconductor diodes having a low forward conduction voltage drop, a low reverse leakage current, a high voltage capability and avalanche energy capability, suitable for use in integrated circuits as well as for discrete devices are disclosed. The semiconductor diodes are diode configured vertical cylindrical metal oxide semiconductor field effect devices having one diode terminal as the common connection between the gates and drains of the vertical cylindrical metal oxide semiconductor field effect devices, and one diode terminal as the common connection with the sources of the vertical cylindrical metal oxide semiconductor field effect devices. The method of manufacturing the vertical cylindrical metal oxide semiconductor field effect devices is disclosed. Various device terminations can be employed to complete the diode devices. Various embodiments are disclosed.

Owner:ARRAY OPTRONIX

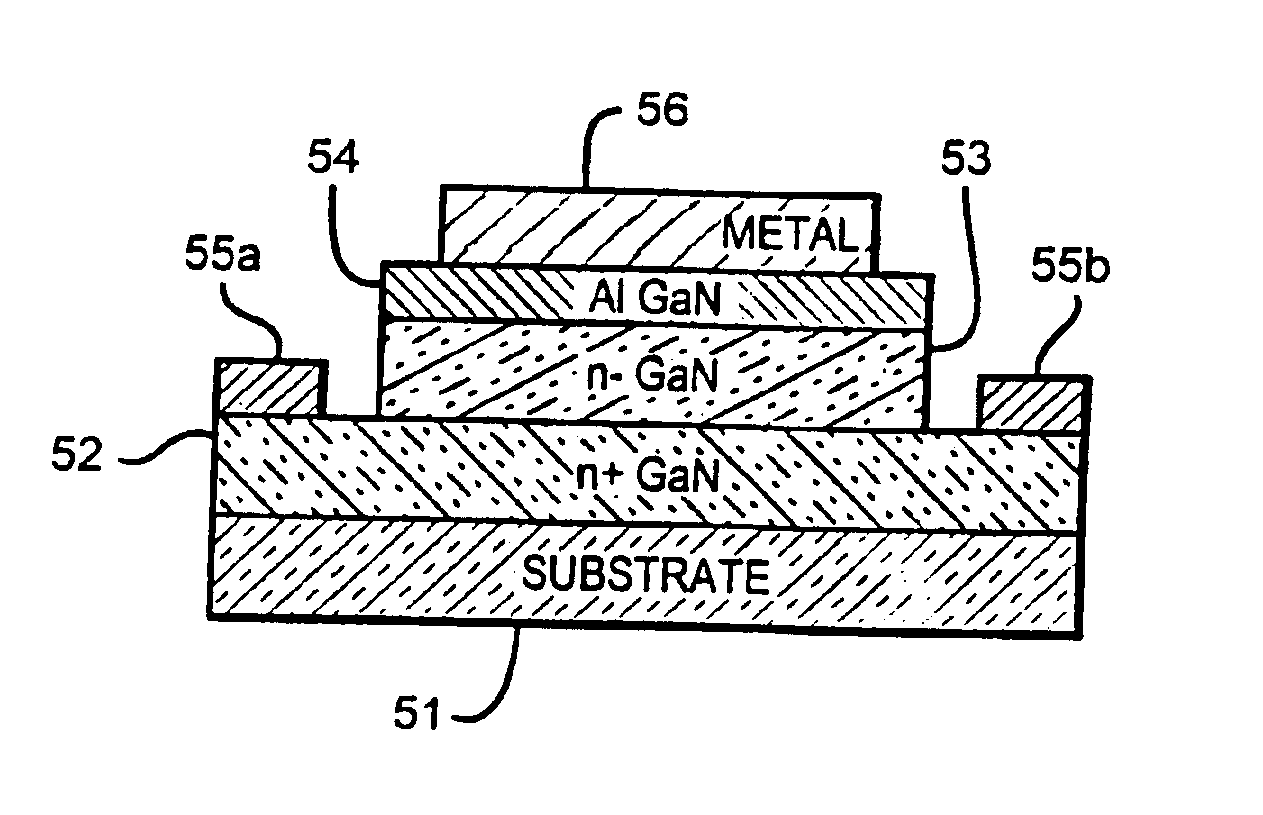

Gallium nitride based diodes with low forward voltage and low reverse current operation

InactiveUS6949774B2Maximizes forward tunneling probabilityLow VfDiodeTunnel diodeSemiconductor materials

New Group III based diodes are disclosed having a low on state voltage (Vf), and structures to keep reverse current (Irev) relatively low. One embodiment of the invention is Schottky barrier diode made from the GaN material system in which the Fermi level (or surface potential) of is not pinned. The barrier potential at the metal-to-semiconductor junction varies depending on the type of metal used and using particular metals lowers the diode's Schottky barrier potential and results in a Vf in the range of 0.1-0.3V. In another embodiment a trench structure is formed on the Schottky diodes semiconductor material to reduce reverse leakage current. and comprises a number of parallel, equally spaced trenches with mesa regions between adjacent trenches. A third embodiment of the invention provides a GaN tunnel diode with a low Vf resulting from the tunneling of electrons through the barrier potential, instead of over it. This embodiment can also have a trench structure to reduce reverse leakage current.

Owner:CREE INC

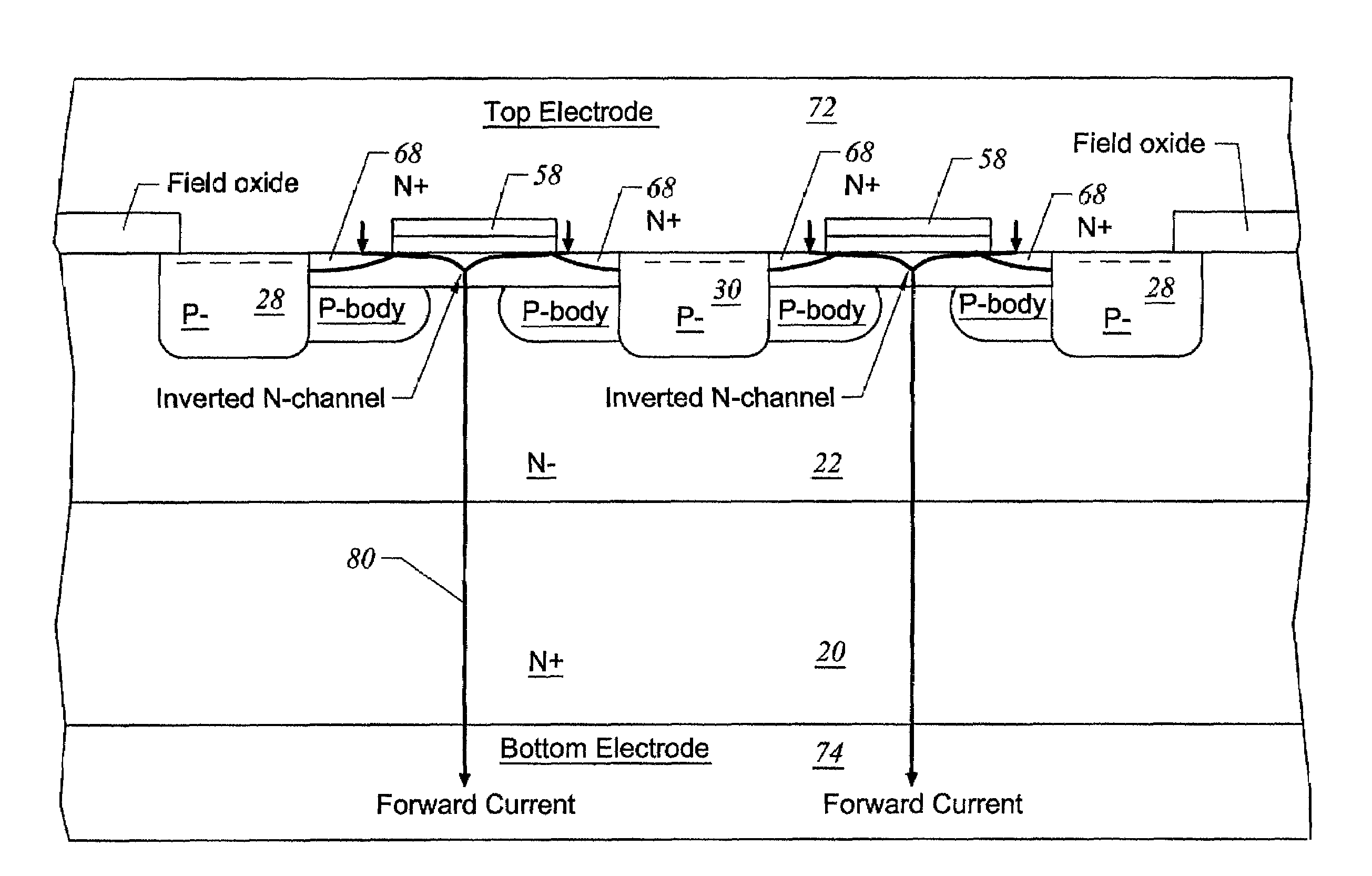

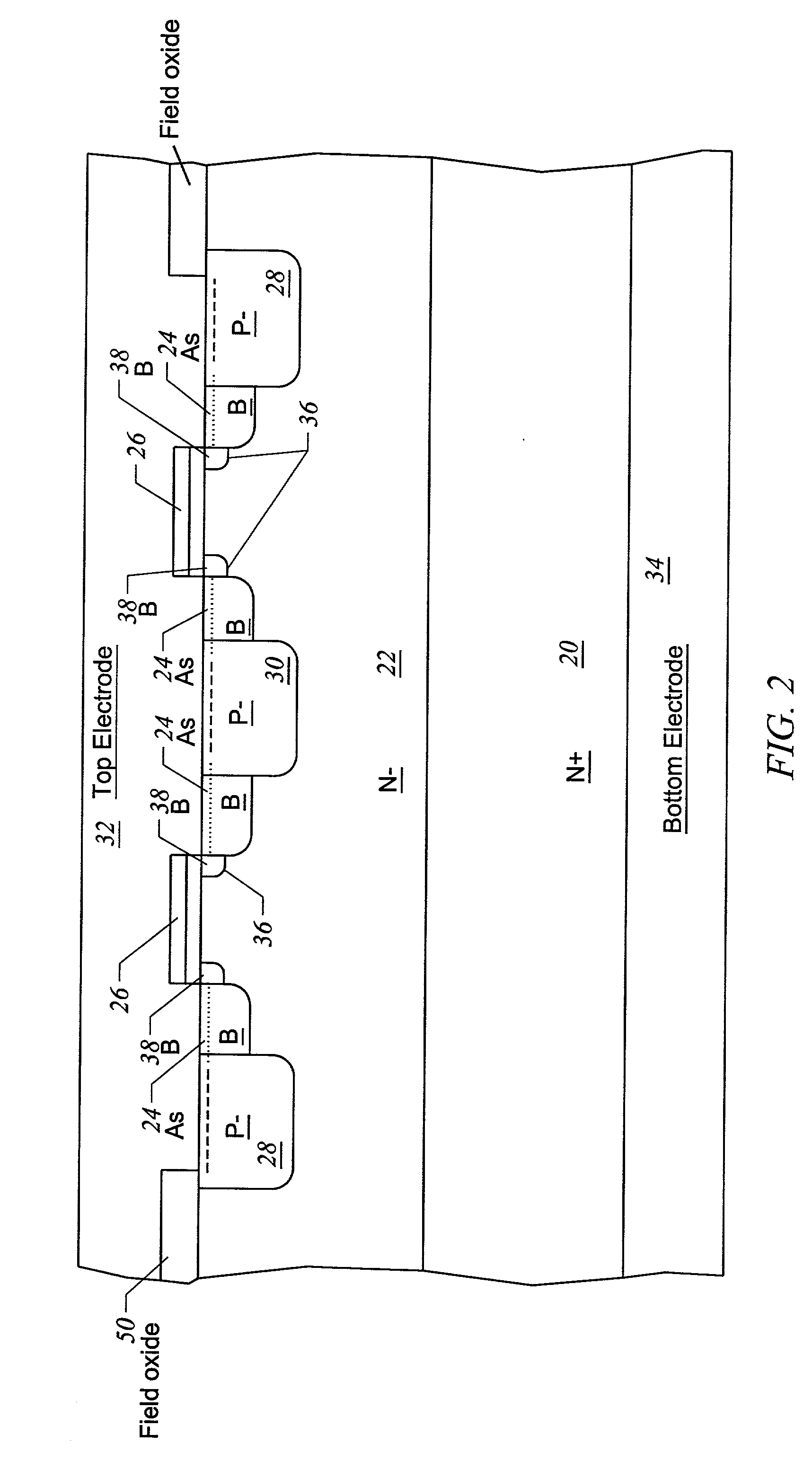

Power device having reduced reverse bias leakage current

InactiveUS6979861B2Improve blockageWell formedSemiconductor/solid-state device manufacturingSemiconductor devicesGate insulatorReverse bias

A power device having vertical current flow through a semiconductor body of one conductivity type from a top electrode to a bottom electrode includes at least one gate electrode overlying a gate insulator on a first surface of the body, a channel region of second conductivity type in the surface of the body underlying all of the gate electrode, a first doped region of the second conductivity type contiguous with the channel region and positioned deeper in the body than the channel region and under a peripheral region of the gate electrode, and a second doped source / drain region in the surface of the body abutting the channel region and adjacent to the gate electrode. When the gate is forward biased, an inversion region extends through the channel region and electrically connects the first electrode and the second electrode with a small Vf near to the area between adjacent P bodies being flooded with electrons and denuded of holes. Therefore, at any forward bias this area conducts as an N-type region. When the gate electrode is reverse biased, the long channel region underlying the full length of the gate electrode reduces reverse leakage current.

Owner:DIODES INC

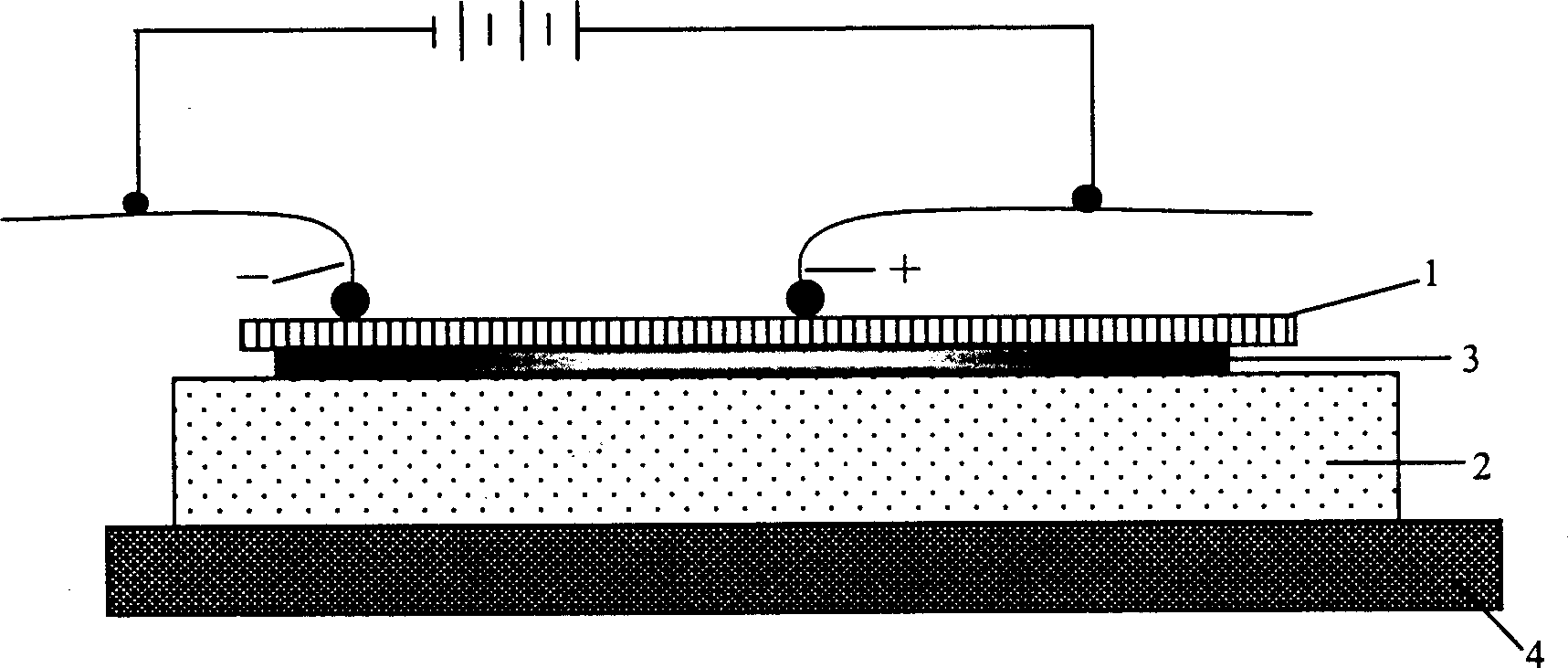

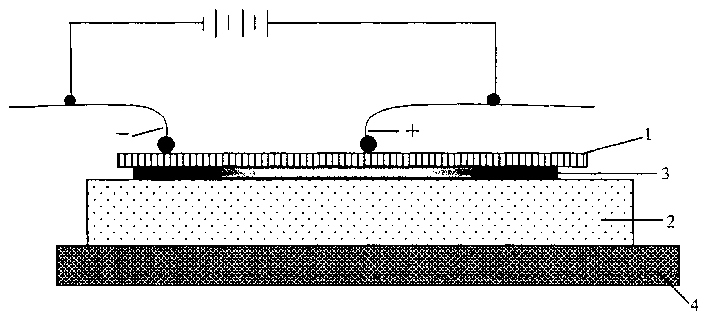

LED epitaxial wafer electroluminescent nondestructive detection method

InactiveCN1395305ATo achieve the purpose of detectionMeasurement method directSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingFluorescenceLuminescence

The invented method for testing the pitaxial wafer of the light emitting diode (LED) belongs to the area of the test instrument. The positive and negative electrodes are set upon the surface of the epitaxial wafer of LED. The high-voltage constant current source is connected to the positive and negative electrode, making the p type layer and the n type layer in the epitaxial wafer of LED form thebackward diode. The breakdown of the backward diode caused by the high-voltage makes the entire circuit turn on so as to trigger off the luminescence of the luminous layer of the epitaxial wafer of LED. Thus, the target of the test is reached. The method is direct, safe and convenient. Moreover, the electric parameters such as the forward direction on-state voltage, the reverse-leakage current can be obtained if it is photo fluorescence.

Owner:TSINGHUA UNIV

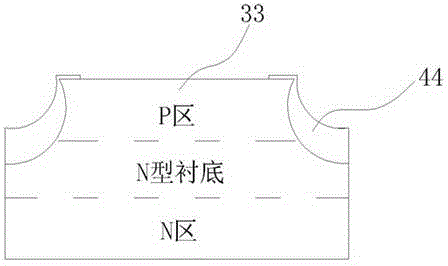

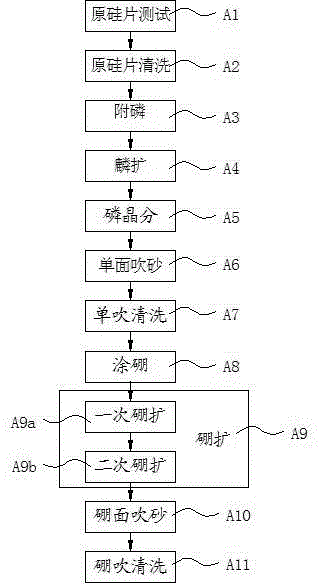

Manufacturing process of transient voltage suppression diode chip

ActiveCN103606521AStress reliefReduce defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a manufacturing process of a transient voltage suppression diode chip. The manufacturing process of the transient voltage suppression diode chip includes two production processes: a diffusion process and a GPP process. The steps of the diffusion process include original silicon wafer testing, original silicon wafer washing, phosphorus attachment, phosphorus diffusion, phosphorus wafer separation, single side sand blasting, single blasting washing, boron coating, boron diffusion, boron wafer separation, boron side sand blasting, and boron blasting washing, wherein the step of boron diffusion comprises primary boron diffusion and secondary boron diffusion; and the steps of the GPP process sequentially include oxidation, primary photoetching, groove etching, photoresist sintering, groove washing, SIPOS passive film formation, glassivation, secondary photoetching, surface etching, and nickel-gold plating. The manufacturing process of the transient voltage suppression diode chip in the invention reduces defects of the chip, enables voltage distribution to be relatively concentrated, and reduces reverse leakage current at the same time.

Owner:南通康芯半导体科技有限公司

Method for avoiding or reducing V-defect of blue-green light LED material

ActiveCN1905222AAvoid or reduce V-shaped defectsAvoid or reduce the occurrence ofSemiconductor devicesGreen-lightLight-emitting diode

The invention is a method for avoiding or reducing V-type defect of blue-green light emitting diode material which has in turn sapphire substrate, low-temperature grown GaN buffer layer, high-temperature grown n-GaN layer, InGa1-Yn / GaN multi-quantum trap layer, and p-Alx Ga1-xN / p-GaN layer, characterized in that: there is a grown n-AlxGa1-xN / GaN superlattice layer between the high-temperature grown n-GaN layer and InGa1-Yn / GaN multi-quantum trap layer, where 0<x<1, the growth temperature is between 1100deg.C and 1200deg.C, the pressure is 30Torr-100Torr, the AlxGa1-xN layer is 1nm-5nm thick, the GaN layer is 1nm-5nm thick, the periodicity is 5-10, the doping concentration is between 1*1016cm-3 and 1*1018cm-3; there is also a weak n-type doped GaN layer between the high-temperature grown n-GaN layer and InGa1-Yn / GaN multi-quantum trap layer, where the growth temperature is 1150 deg.C-1200 deg.C, the growth pressure is 30Torr-80Torr, and the thickness is 1m-50nm, the doping concentration is between 1*1016cm-3 and 5*1017cm-3. And it can avoid or reduce V-type defect and reverse leakage current generated by this.

Owner:HC SEMITEK SUZHOU

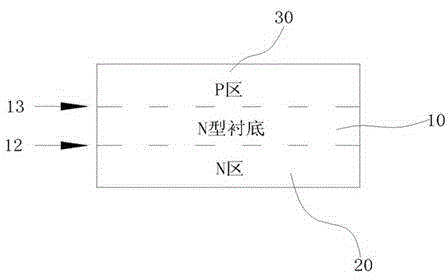

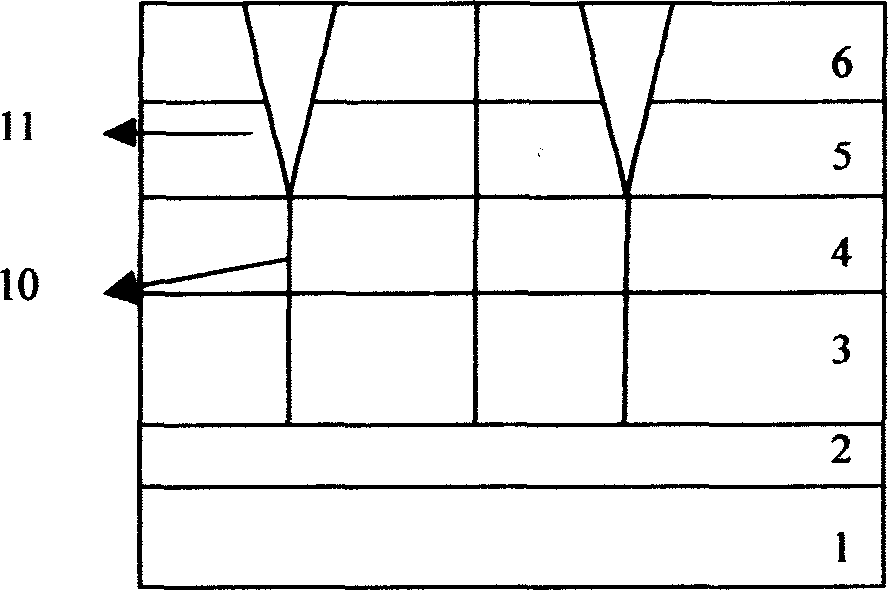

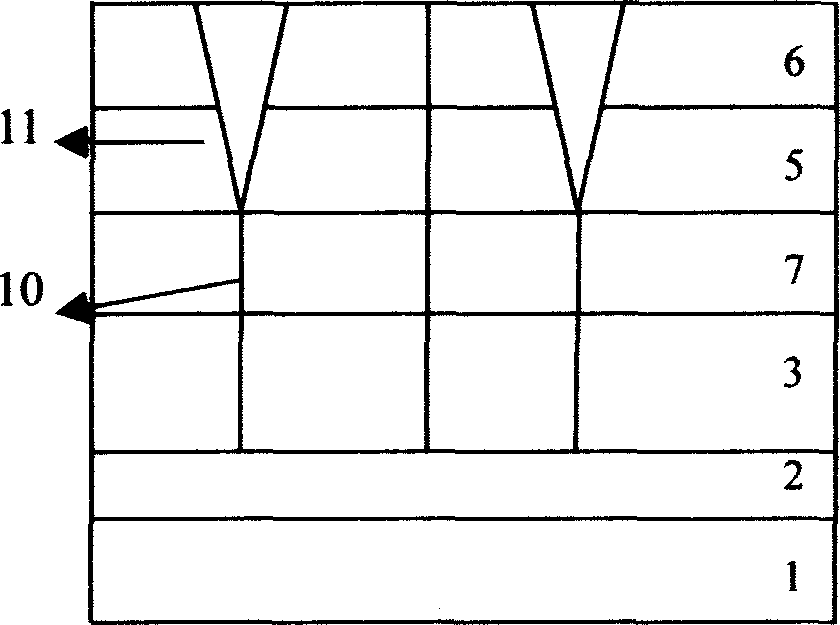

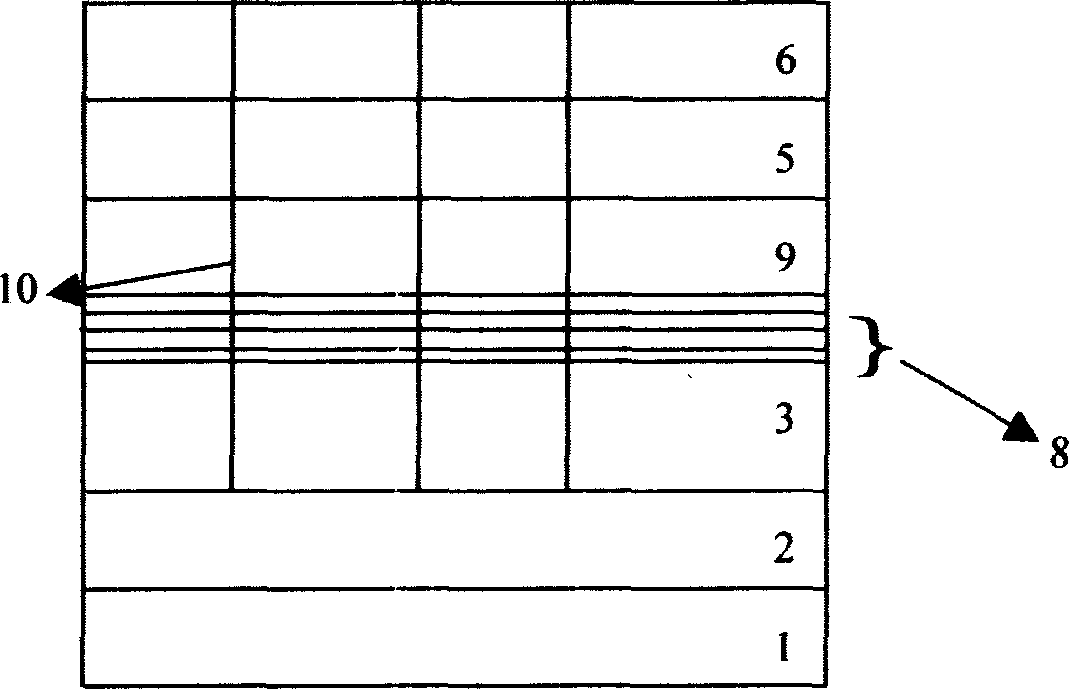

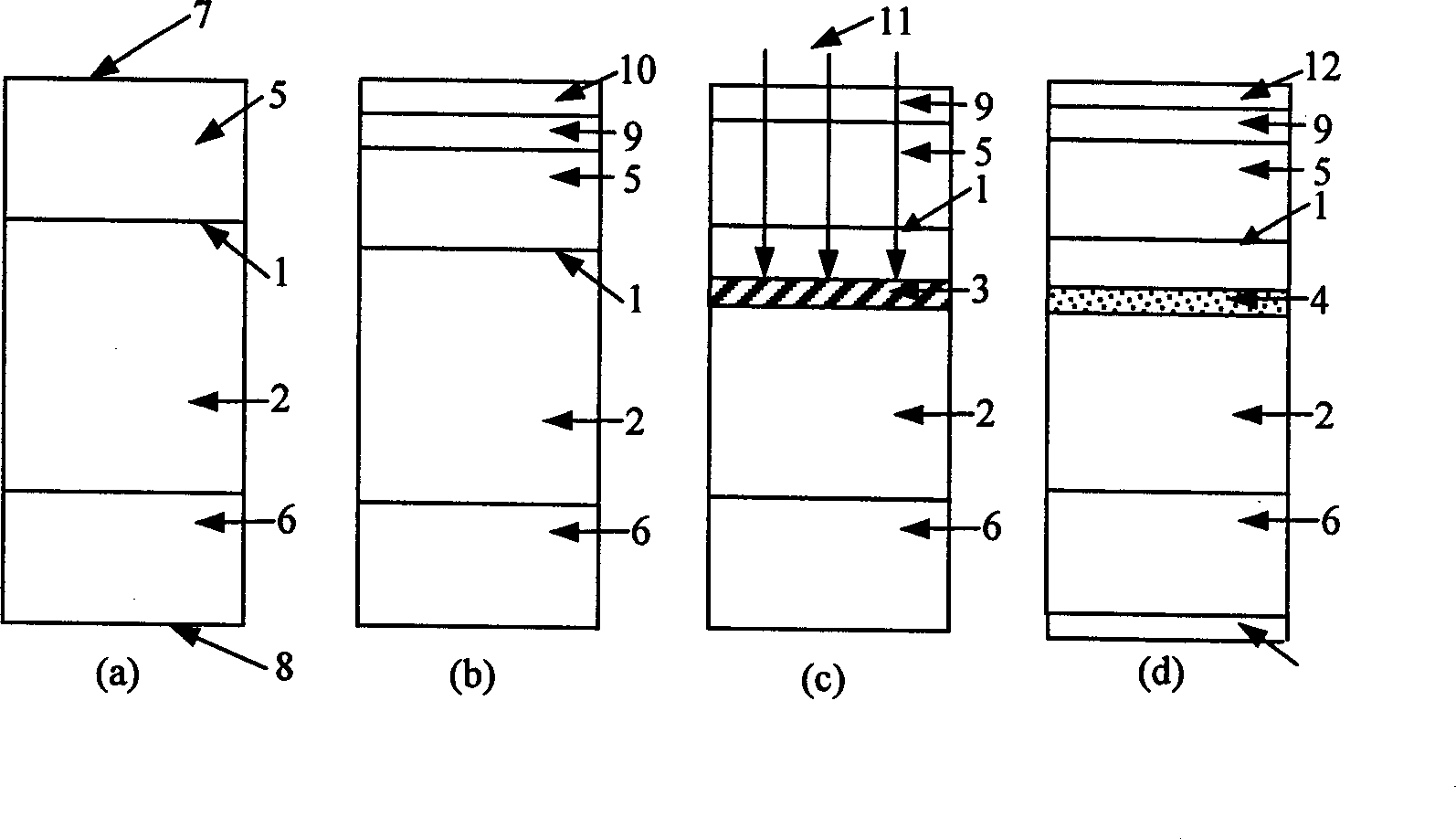

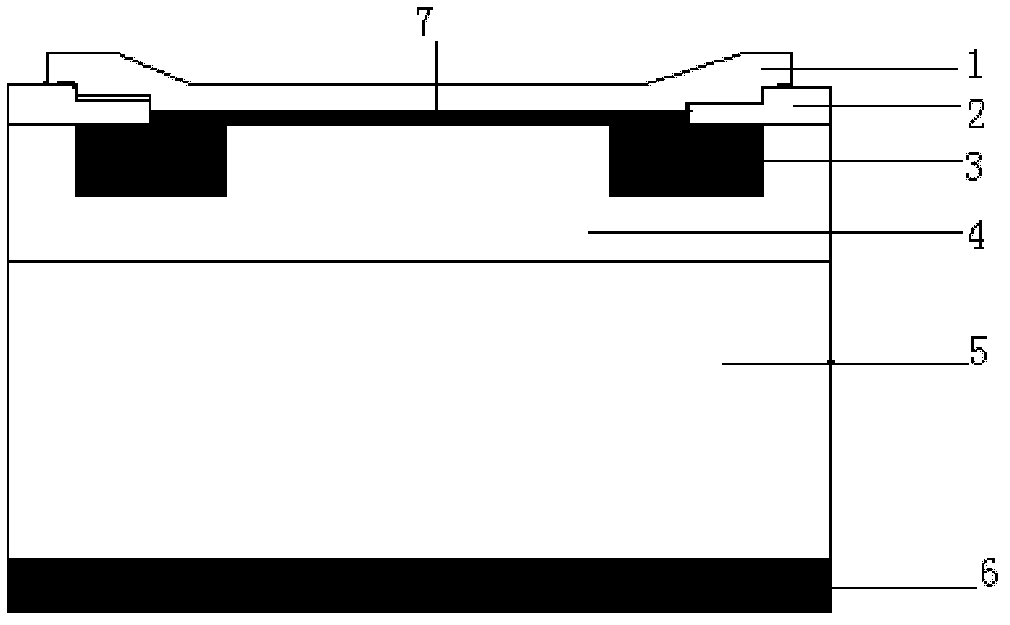

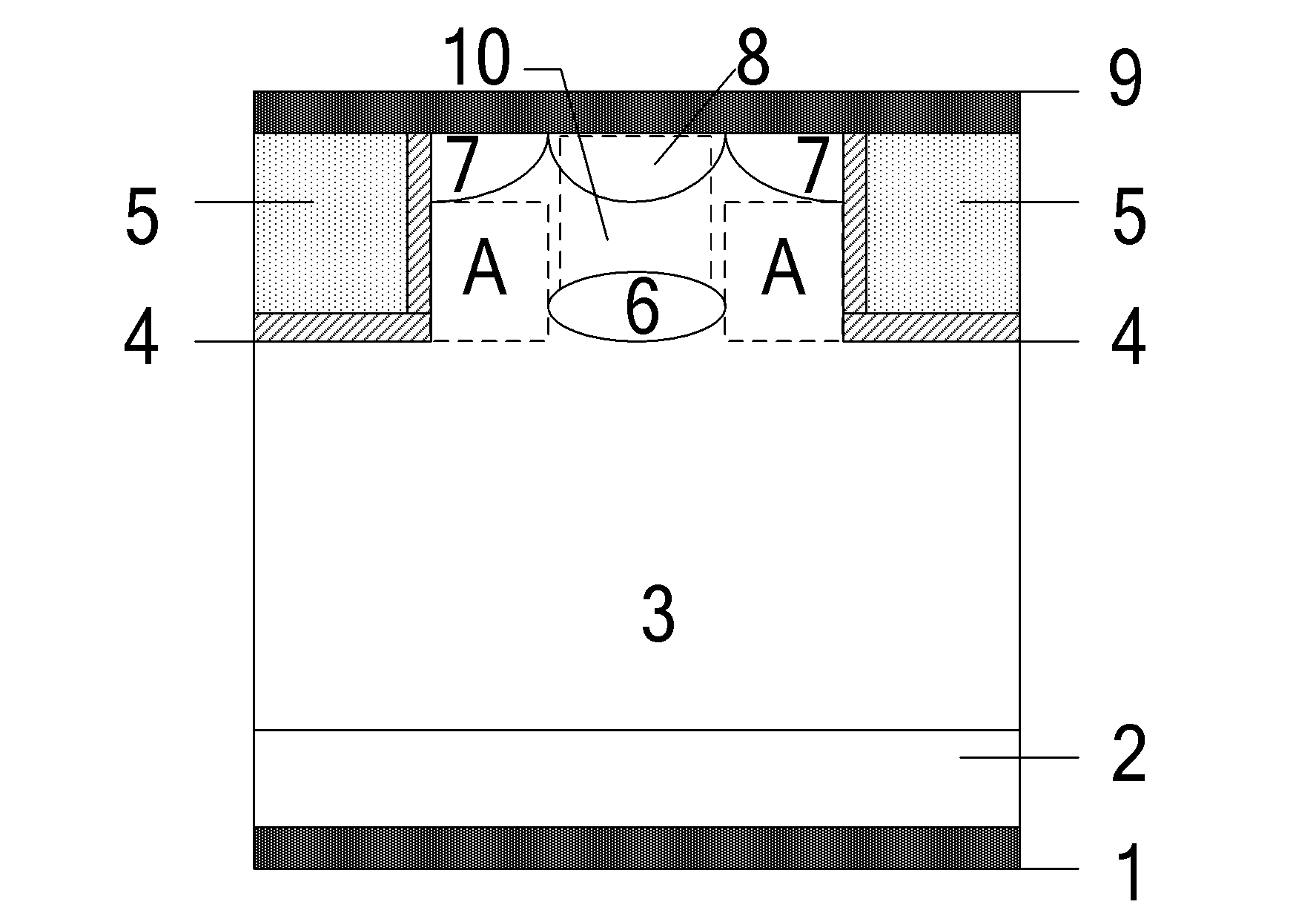

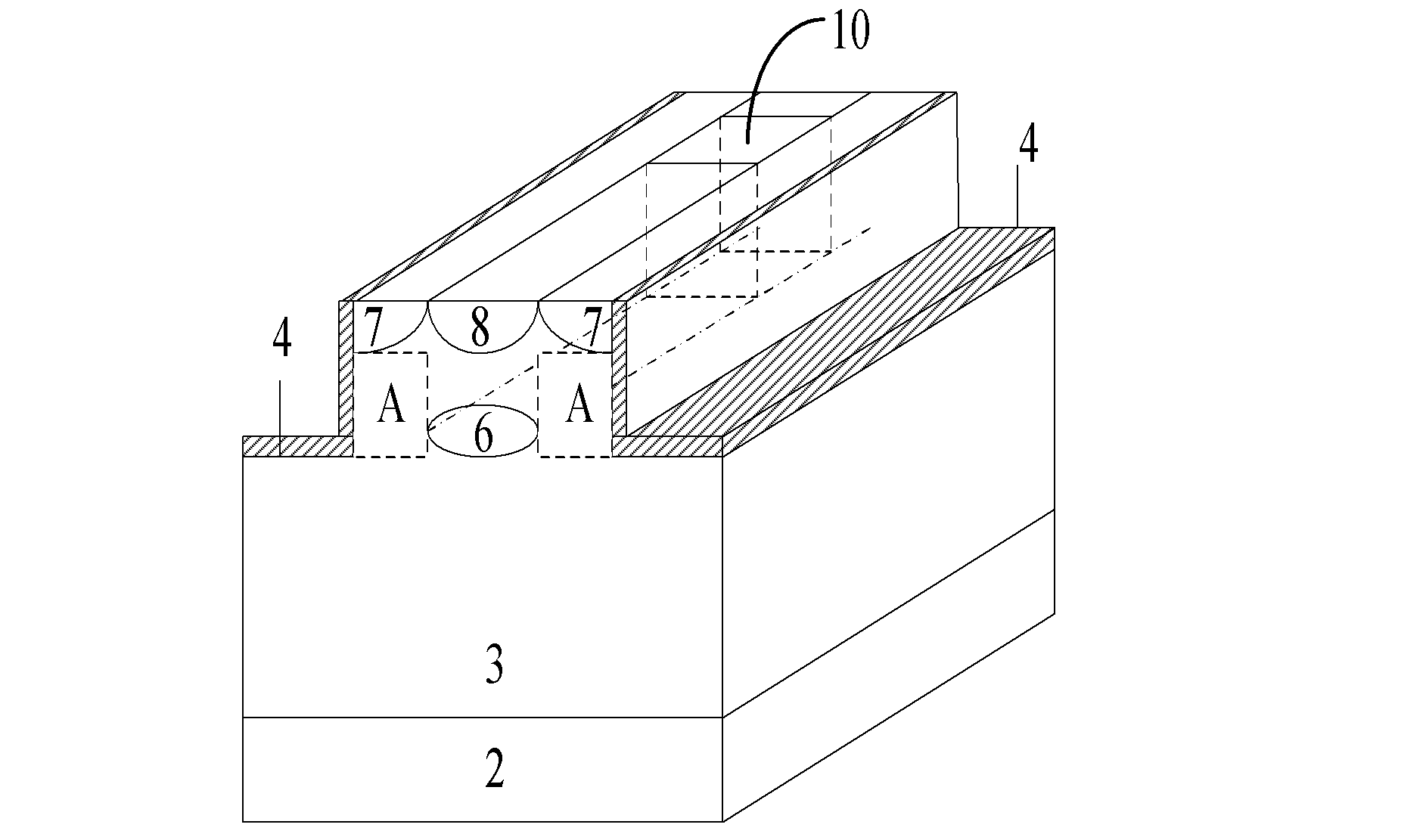

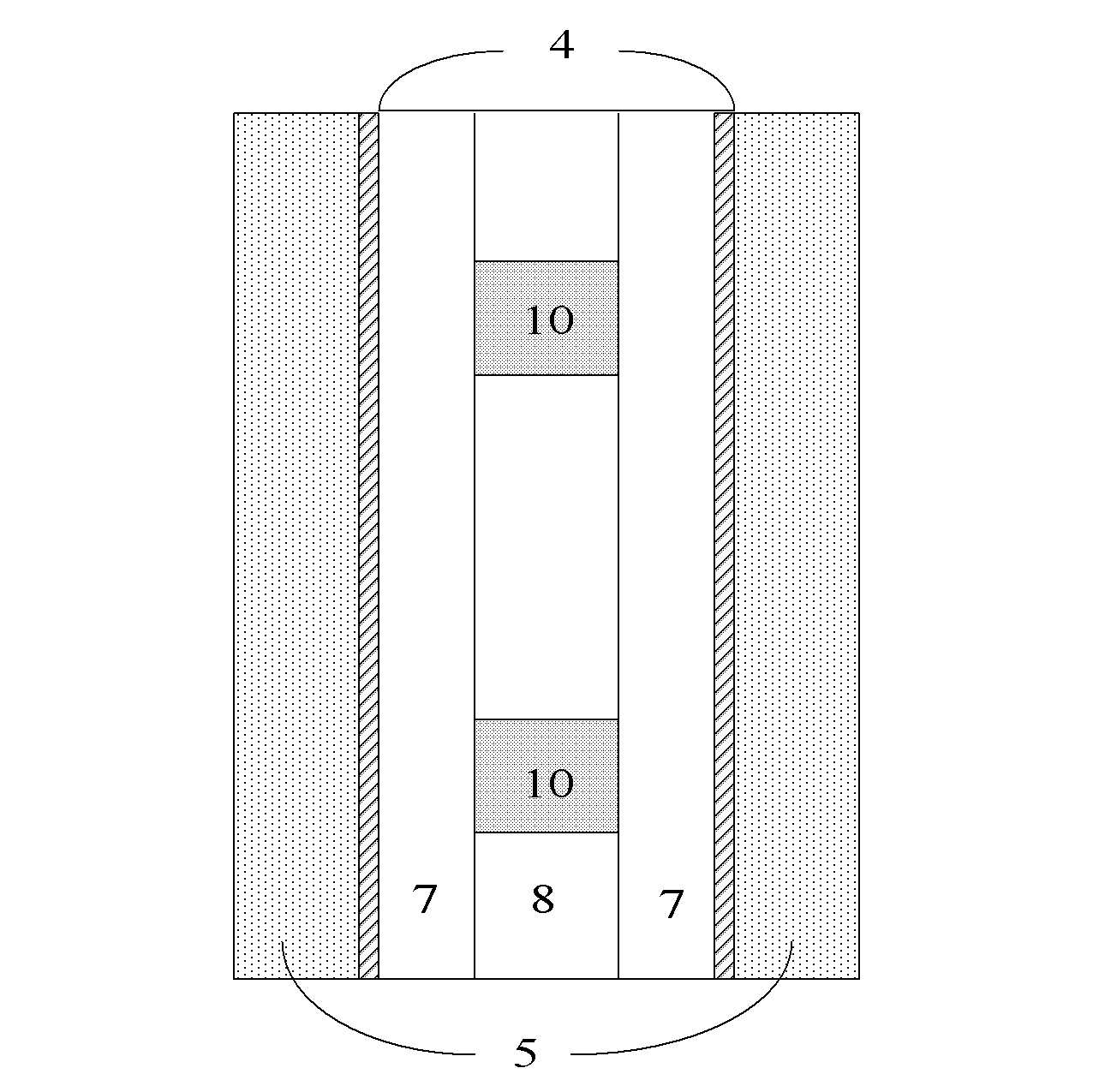

Grooved semiconductor rectifier and manufacturing method thereof

InactiveCN101783345AReduce forward voltage dropReduce reverse leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention relates to a grooved semiconductor rectifier and a manufacturing method thereof. The grooved semiconductor rectifier comprises a semiconductor baseplate, a first conduction type substrate and a first conduction type drift region, wherein one or more grooves extend from the first main plane to the first conduction type drift region, one or more mesa parts are limited at the upper part of the first conduction type drift region, and the upper part of the mesa part is provided with a first conduction type injection layer; the inner wall of the groove is covered with an insulation oxide layer, and a first electrode is deposited in the groove covered with the insulation oxide layer; the first conduction type drift region is provided with a second conduction type enclosure layer corresponding to the bottom of the groove, and the bottom of the groove is coated by the second conduction type enclosure layer; a first metal layer corresponding to the upper part of the first plane is deposited on the semiconductor baseplate; and the second plane of the semiconductor baseplate is covered with a second metal layer. The invention has the advantage of low manufacturing cost, and reduces the reverse leakage current and the forward conduction voltage drop of the Schottky rectifier.

Owner:无锡新洁能功率半导体有限公司

Method for manufacturnig silicon high-speed semiconductor switch device

InactiveCN1471146AExcellent electrical performanceDensity Spatial Distribution OptimizationSemiconductor/solid-state device manufacturingGate turn-off thyristorPlatinum

The method is applicable to manufacture silicon semiconductor binistor with at least one PN junction such as GTO, IGBT etc. General manufacturing steps is carried out till the step of making metalized electrode. Platinum-silicon alloy is made on surface of silicon. Using proton or particle injection forms local high density defect area. Heating and annealing makes the defect area absorb platinum to convert to platinum impurity range. Then, General manufacturing steps is carried out till manufacturing completion. The performances of the invention are better than present life control technique. The parts made by the invention possesses higher switching speed and backward recovery speed, but the forward voltage drop and reverse leakage are not increased visibly.

Owner:BEIJING UNIV OF TECH

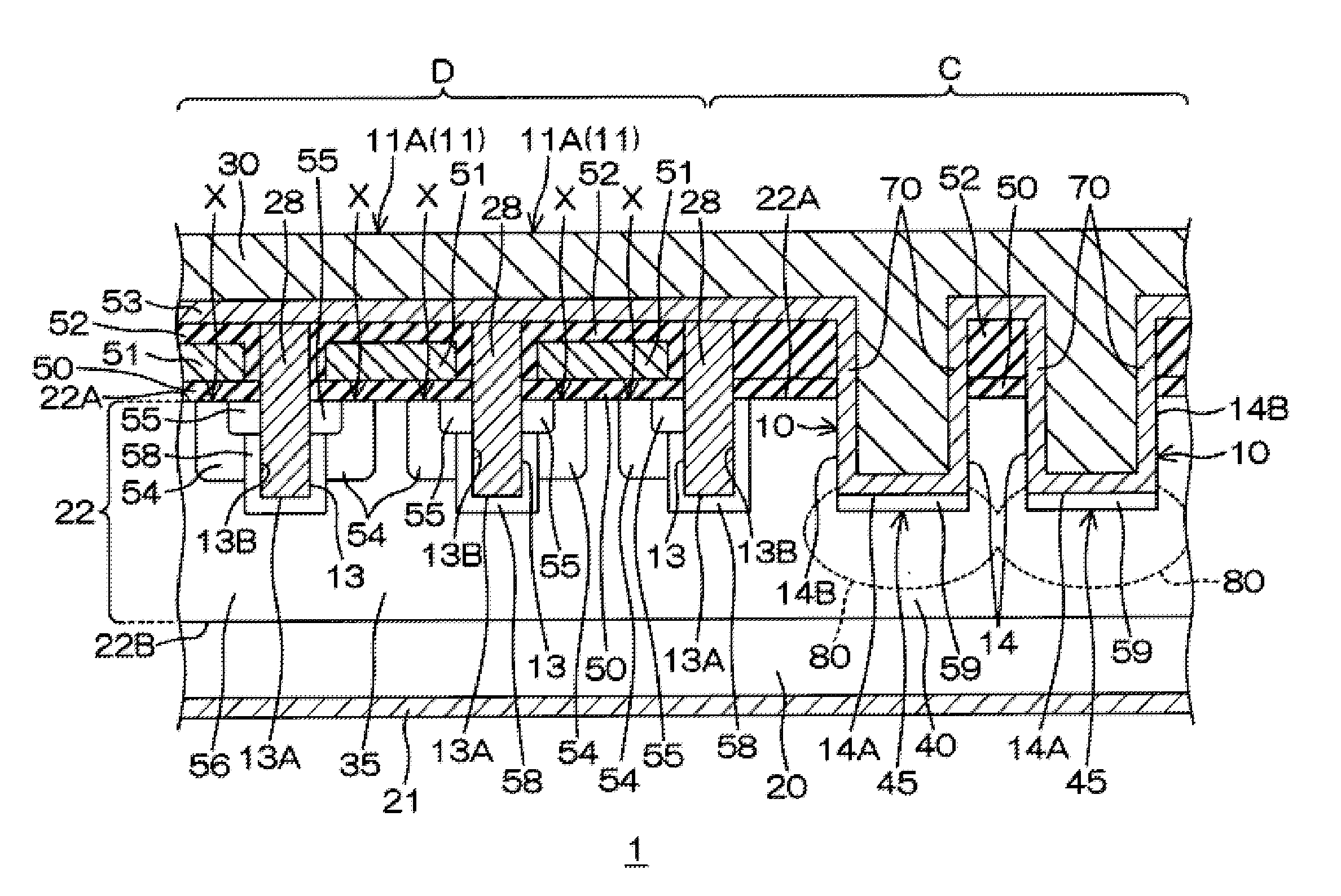

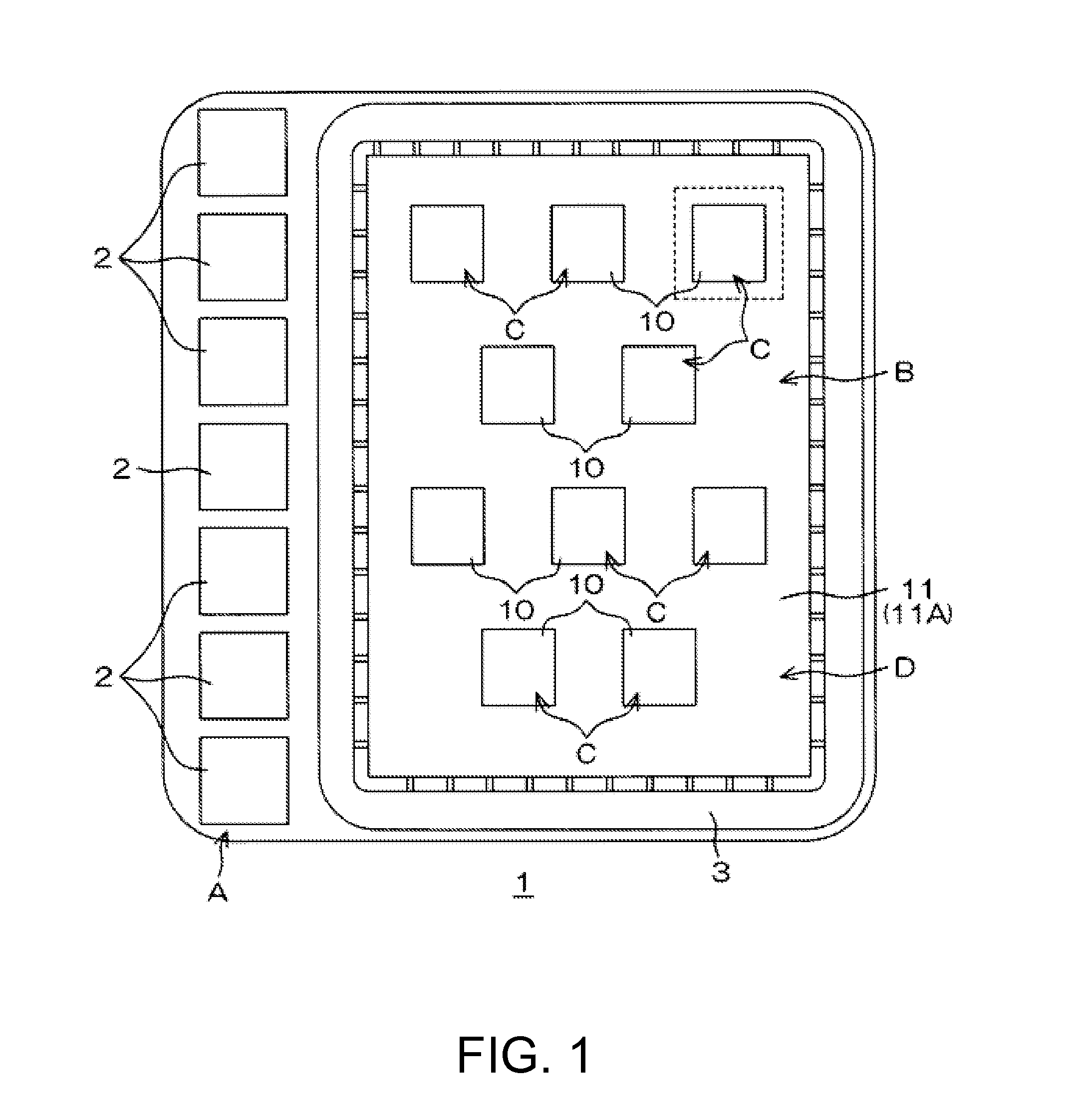

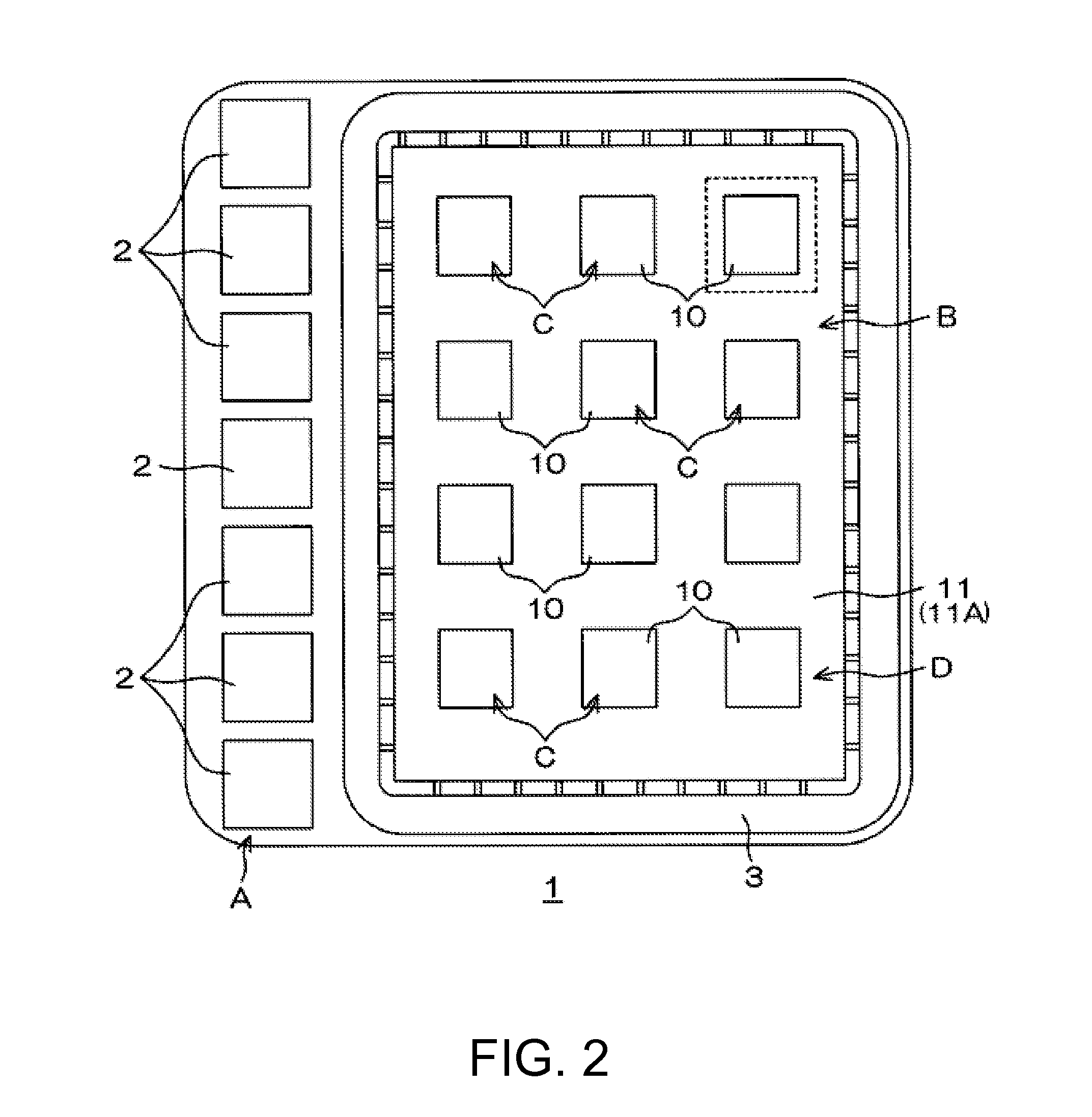

Integrated trench MOSFET and junction barrier schottky rectifier with trench contact structures

ActiveUS7626231B1Improved device configurationReduce spacingSemiconductor devicesTrench mosfetMiniaturization

A trench MOSFET in parallel with trench junction barrier Schottky rectifier with trench contact structures is formed in single chip. The present invention solves the drawback brought by some prior arts, for example, the large area occupied by planar contact structure and high gate-source capacitance. As the electronic devices become more miniaturized, the trench contact structures of this invention are able to be shrunk to achieve low specific on-resistance of Trench MOSFET, and low Vf and reverse leakage current of the Schottky Rectifier.

Owner:FORCE MOS TECH CO LTD

Semi-gate controlled source schottky barrier type tunneling field effect transistor

InactiveCN103500758AReduce processing difficultyReduce manufacturing costSemiconductor devicesGermanideGate voltage

The invention relates to a semi-gate controlled source schottky barrier type tunneling field effect transistor. On the premise of no requirements on the introduction of a material such as a compound semiconductor, silicon germanide and germanium with a smaller forbidden bandwidth into the generation of a tunneling part of a device, a source schottky barrier is formed between a metal source and intrinsic silicon, and a semi-gate is used for controlling the barrier width of the source schottky barrier and the energy band bending degree of the intrinsic silicon to control the switching of the device. An asymmetrical semi-gate structural design is adopted, so that gate-induced drain leakage current is remarkably reduced on the premise of keeping gate voltage well controlling the width of the schottky barrier and the energy band bending degree. The semi-gate controlled source schottky barrier type tunneling field effect transistor has the advantages of process simplicity, low cost, high sub-threshold slope, high breakover current, low reverse leakage current and the like, and is suitable to be popularized and used.

Owner:SHENYANG POLYTECHNIC UNIV

Semiconductor device and manufacturing method thereof

ActiveUS20130313638A1Difficult to manufactureLow costTransistorSolid-state devicesDevice materialEngineering

Provided is a semiconductor device that can be manufactured at low cost and that can reduce a reverse leak current, and a manufacturing method thereof. A semiconductor device has: a source region and a drain region having a body region therebetween; a source trench that reaches the body region, penetrating the source region; a body contact region formed at the bottom of the source trench; a source electrode embedded in the source trench; and a gate electrode that faces the body region. The semiconductor device also has: an n-type region for a diode; a diode trench formed reaching the n-type region for a diode; a p+ region for a diode that forms a pn junction with the n-type region for a diode at the bottom of the diode trench; and a schottky electrode that forms a schottky junction with the n-type region for a diode at side walls of the diode trench.

Owner:ROHM CO LTD

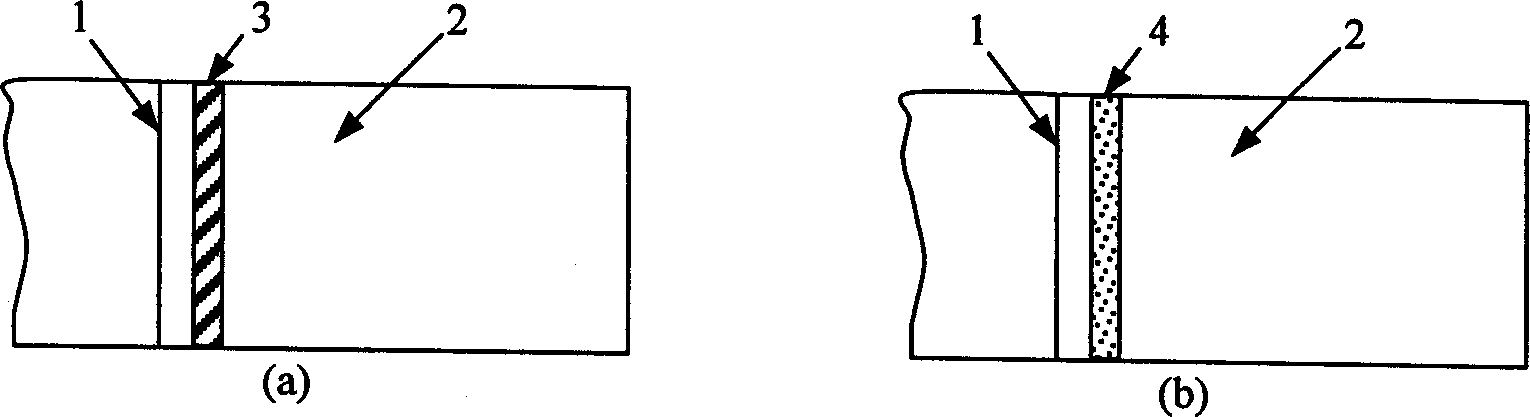

Schottky diode with high reverse-blocking performance and manufacturing method thereof

InactiveCN102354704AAvoid lowering effectAvoid reducing reverse leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesEffective potentialDot matrix

The invention provides a schottky diode with high reverse-blocking performance and a manufacturing method thereof. The schottky diode core is structurally characterized in that: a lightly doped epitaxial layer of a drift region is provided with a P-type structure region which is composed of a P-type ring and P-type dot matrixes uniformly spaced on the epitaxial layer in the P-type ring; the surface of the epitaxial layer in the P-type ring is provided with a schottky potential barrier contact metal layer; and the surface of the P-type structure region is in Ohm metal contact. When the schottky diode is in reverse application, a PN junction depletion region gradually spreads to a channel region along with the increase of the reverse voltage until the depletion region is communicated, and extends towards the substrate along with further increase of the reverse voltage to form an effective potential barrier in the channel region and effectively shield the schottky potential barrier region, thereby improving the reverse blocking ability that the reverse blocking voltage can reach 200 V or above; and moreover, the schottky diode also has good technical indexes such as reverse recovery time, reverse leakage current and the like, realizes low working loss of switches and prevents noise.

Owner:丹东安顺微电子有限公司

Trench MOSFET having shielded electrode integrated with trench Schottky rectifier

A trench MOSFET having shielded gate in parallel with trench Schottky rectifier is formed on a single chip to further increase the efficiency of the trench MOSFET having shielded electrode. As the size of present device is getting smaller and smaller, the trench Schottky rectifier of this invention is able to be shrink and, at the same time, to achieve lower forward voltage drop and lower reverse leakage current.

Owner:FORCE MOS TECH CO LTD

Semiconductor device, the method of manufacturing the same, and two-way switching device using the semiconductor devices

InactiveUS7157785B2Reduce leakage currentReducing the on-voltage of the IGBTTransistorConversion constructional detailsEngineeringReverse bias

Owner:FUJI ELECTRIC CO LTD

MSD integrated circuits with shallow trench

InactiveUS8101993B2Improve configurationImproved manufactureSemiconductor/solid-state device detailsSolid-state devicesOvervoltageTrench mosfet

A trench MOSFET device with embedded Schottky rectifier, gate-drain and gate-source diodes on single chip is formed with shallow trench structure to achieve device shrinkage and performance improvement. The present semiconductor devices achieve low Vf and reverse leakage current for embedded Schottky rectifier, have overvoltage protection for GS clamp diodes and avalanche protection for GD clamp diodes. More particularly, gate charge of the present semiconductor device is reduced due to the shallow trench surrounded by an additional N doped area around the bottom while keeping Rds low enough and at the same time, maintaining BV at a certain level.

Owner:FORCE MOS TECH CO LTD

Semiconductor Device Die with Integrated MOSFET and Low Forward Voltage Diode-Connected Enhancement Mode JFET and Method

A semiconductor die with integrated MOSFET and diode-connected enhancement mode JFET is disclosed. The MOSFET-JFET die includes common semiconductor substrate region (CSSR) of type-1 conductivity. A MOSFET device and a diode-connected enhancement mode JFET (DCE-JFET) device are located upon CSSR. The DCE-JFET device has the CSSR as its DCE-JFET drain. At least two DCE-JFET gate regions of type-2 conductivity located upon the DCE-JFET drain and laterally separated from each other with a DCE-JFET gate spacing. At least a DCE-JFET source of type-1 conductivity located upon the CSSR and between the DCE-JFET gates. A top DCE-JFET electrode, located atop and in contact with the DCE-JFET gate regions and DCE-JFET source regions. When properly configured, the DCE-JFET simultaneously exhibits a forward voltage Vf substantially lower than that of a PN junction diode while the reverse leakage current can be made comparable to that of a PN junction diode.

Owner:ALPHA & OMEGA SEMICON INC

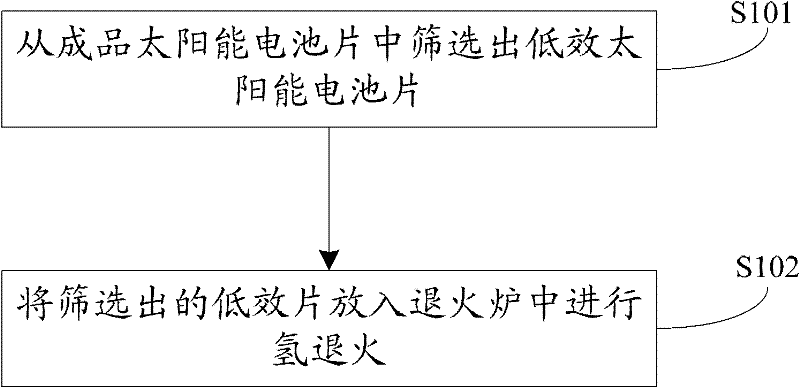

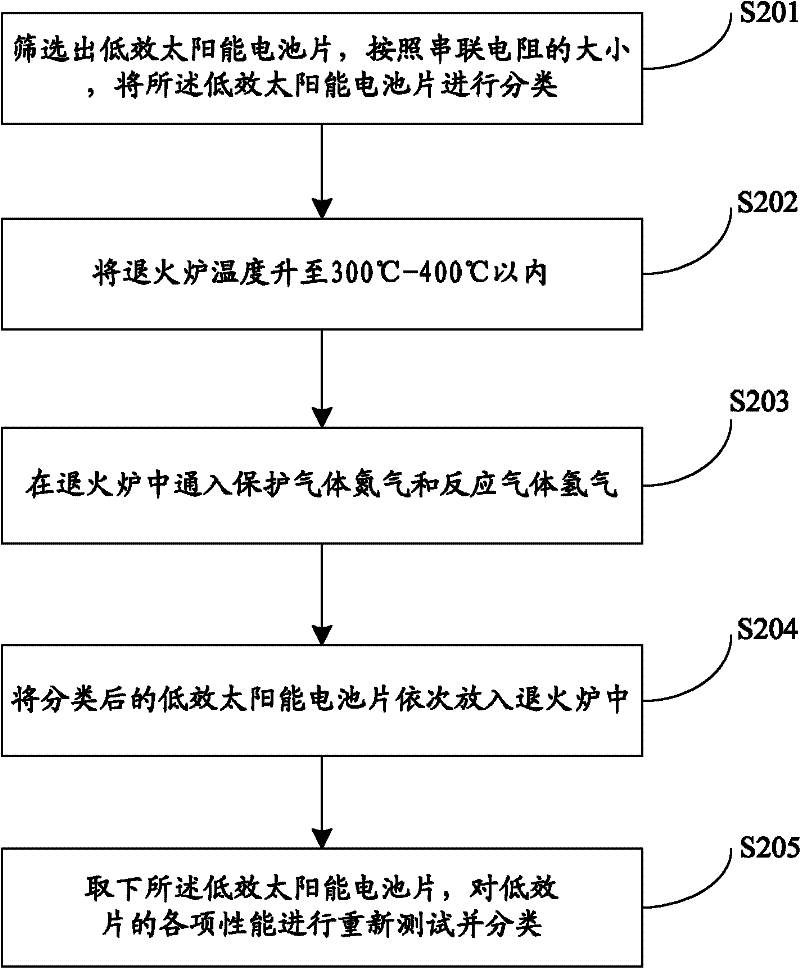

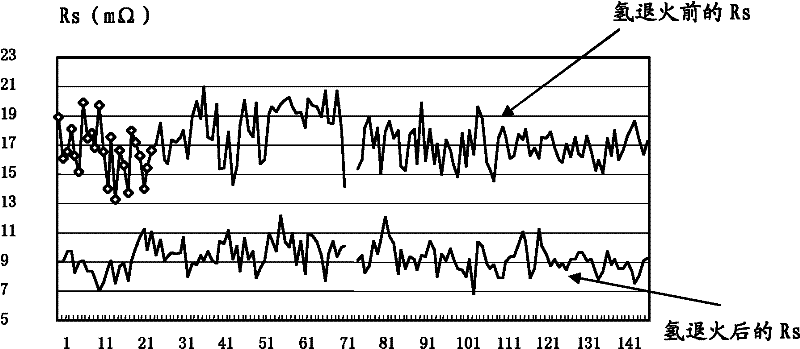

A processing method of inefficient solar cell sheets

InactiveCN102185008AReduce the series resistance RsImprove conductivityFinal product manufactureSemiconductor devicesSolar cellMetal electrodes

The invention discloses a processing method of inefficient solar cell sheets. The processing method comprises the steps of screening out inefficient solar cell sheets from solar cell sheet products, and disposing the inefficient solar cell sheets into an annealing furnace for annealing with hydrogen. In the embodiment of the invention, the inefficient cell sheets are annealed with hydrogen. Since hydrogen can reduce oxide on metal electrodes, the contact resistance between the metal electrodes and silicon is thereby reduced, and accordingly the total series resistance of the inefficient cell sheets is reduced. Moreover, since hydrogen possesses a passivation function, the electroactive impurities are passivated, the recombination rate of carriers on cell surfaces and the lifetime of minority carriers are prolonged. Therefore, the shunt resistance of the cell sheets is improved and the reverse leakage current density is reduced, accordingly the filling factors of the cell sheets are increased and the conversion efficiency is improved.

Owner:JETION SOLAR HLDG

Accumulation type grooved-gate diode

InactiveCN102544114AImprove featuresImproved reverse recovery featureSemiconductor devicesPeak valueSilicon dioxide

The invention relates to an accumulation type grooved-gate diode, belonging to the technical field of semiconductor devices. The accumulation type grooved-gate diode comprises an N<+> substrate, a metallized cathode on the back surface of the N<+> substrate and an N<-> drift region on the front surface of the N<+> substrate, wherein a slotted grid electrode and a silicon dioxide grid oxidation layer are arranged outside the two sides of the top of the N<-> drift region; two N-type heavily doped regions are respectively arranged on the two sides of the top of the N<-> drift region, and a P-type heavily doped region is arranged between the two N-type heavily doped regions; a P-type buried layer region is arranged just above the P-type heavily doped region; and a plurality of separately distributed P-type column regions are arranged between the P-type buried layer region and the P-type heavily doped region. The P-type buried layer region, the N-type heavily doped region and the silicon dioxide grid oxidation layer form a charge carrier accumulation region. According to the accumulation type grooved-gate diode disclosed by the invention, a device has smaller conduction voltage drop, shorter reverse recovery time and ultralow reverse recovery peak value current by guiding one P-type buried layer region without influencing reverse breakdown voltage and reverse leakage current.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1