Patents

Literature

361 results about "Integrated circuit fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Integrated Circuits Fabrication Process: IC Types – An Integrated Circuits Fabrication Process consists of several interconnected transistors, resistors, etc., all contained in one small package with external connecting terminals.

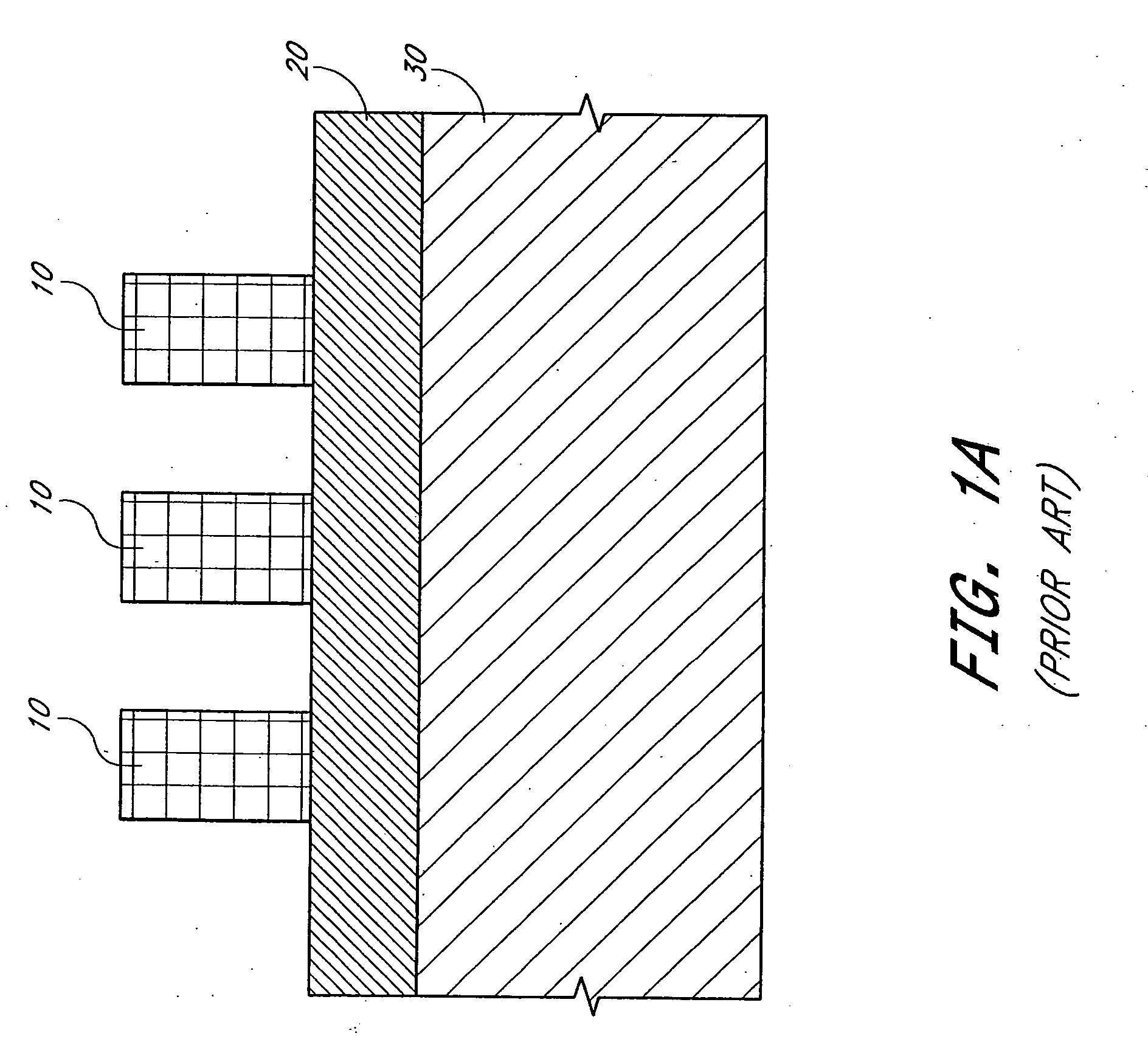

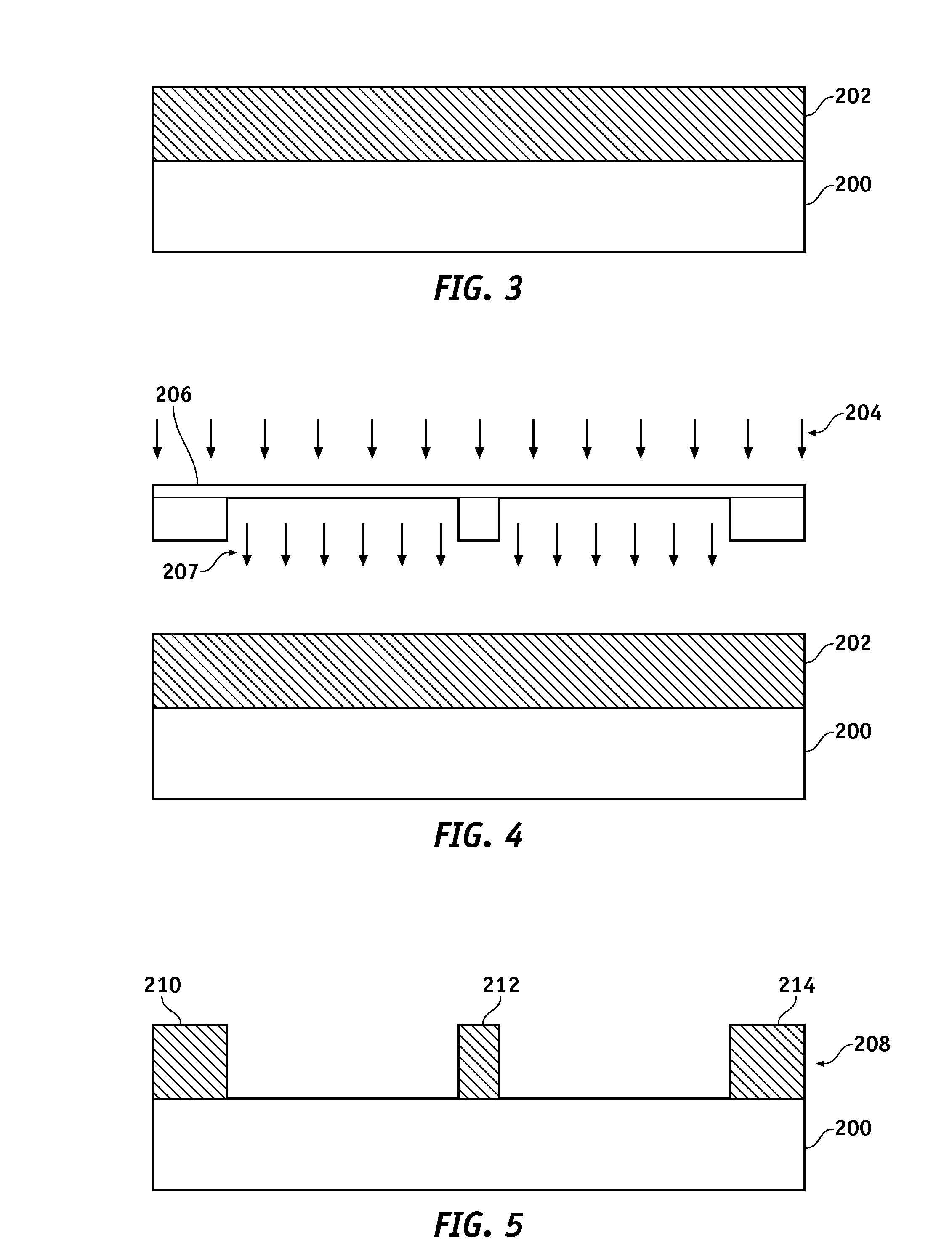

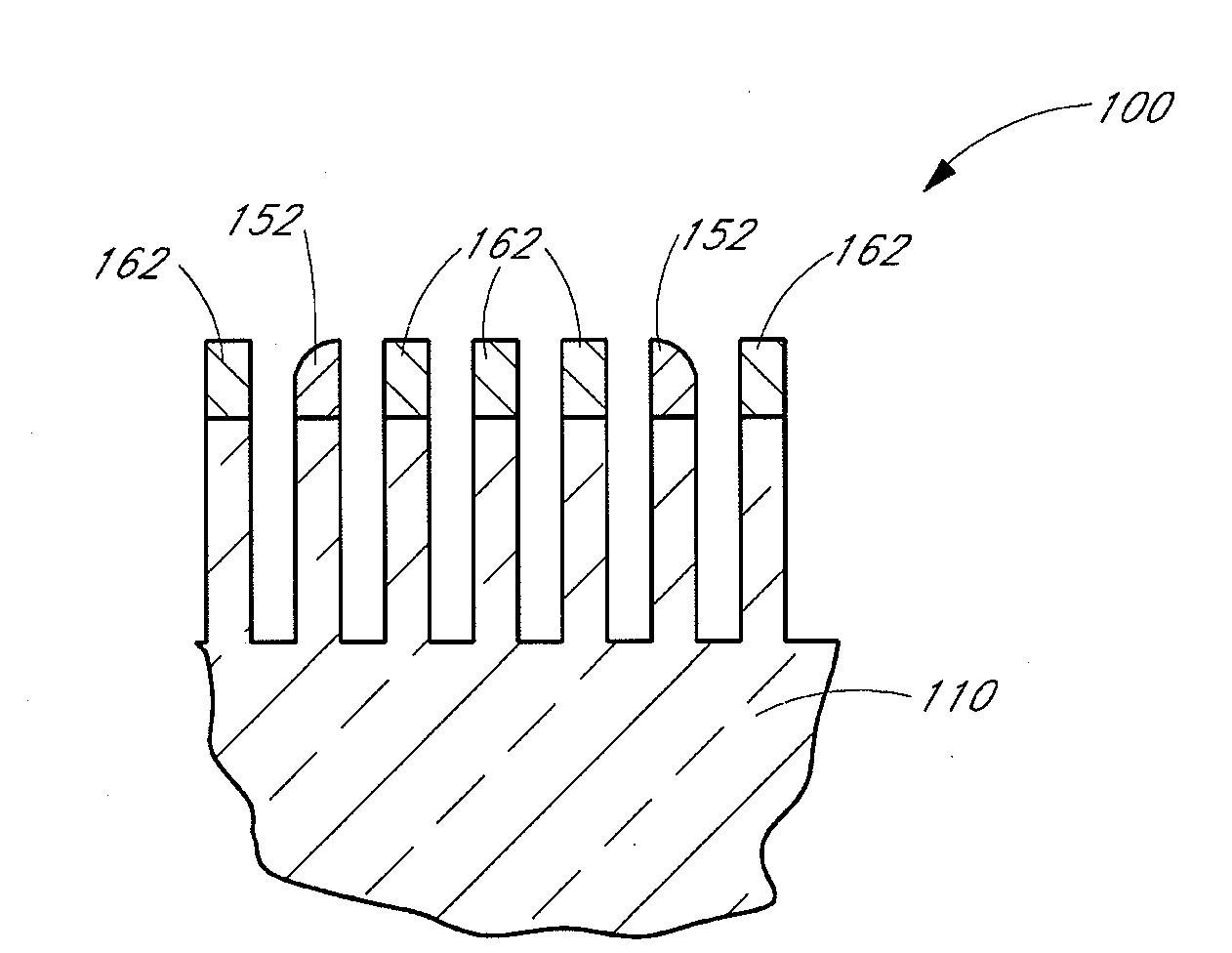

Method for integrated circuit fabrication using pitch multiplication

InactiveUS7115525B2Electric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

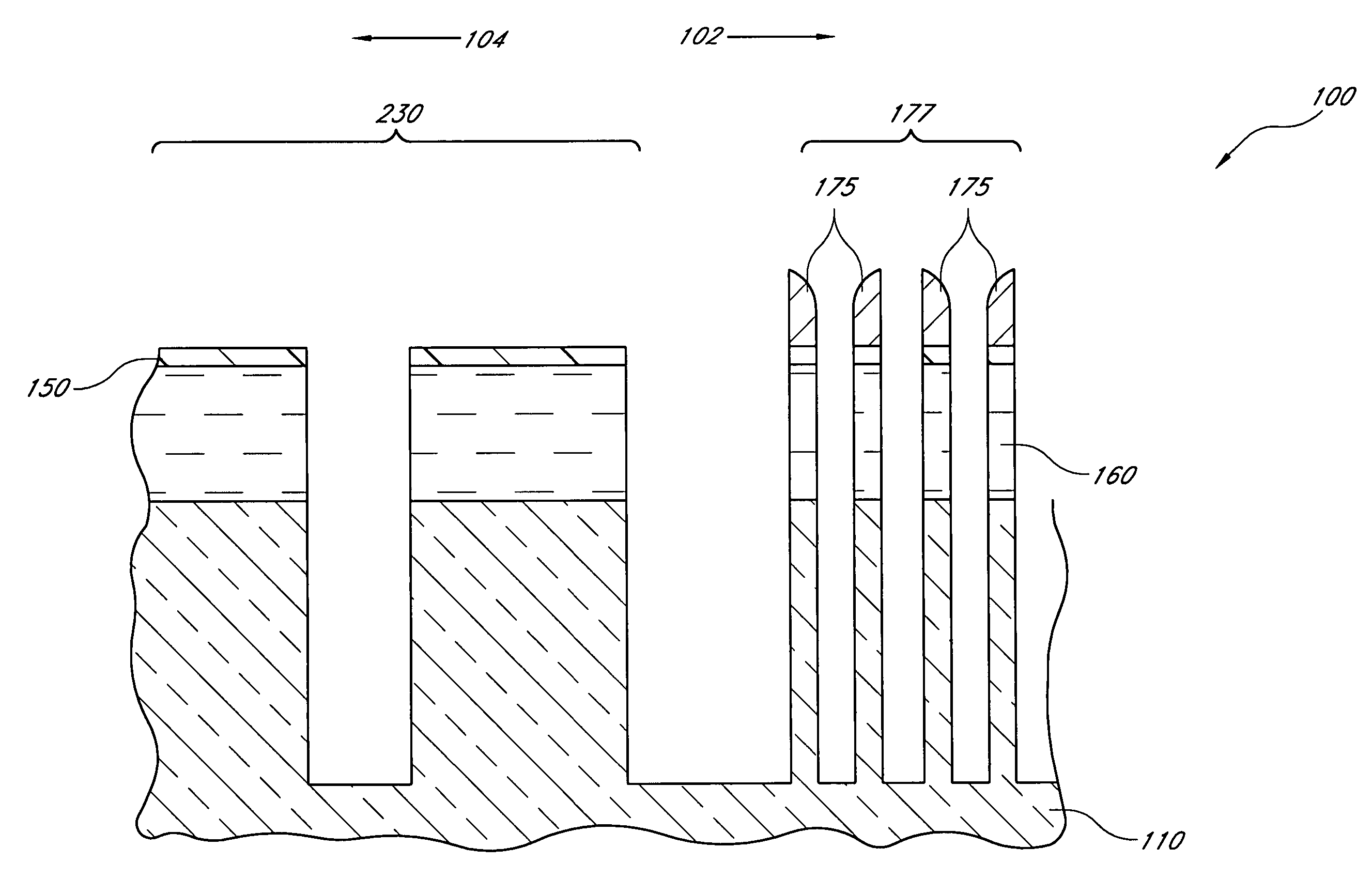

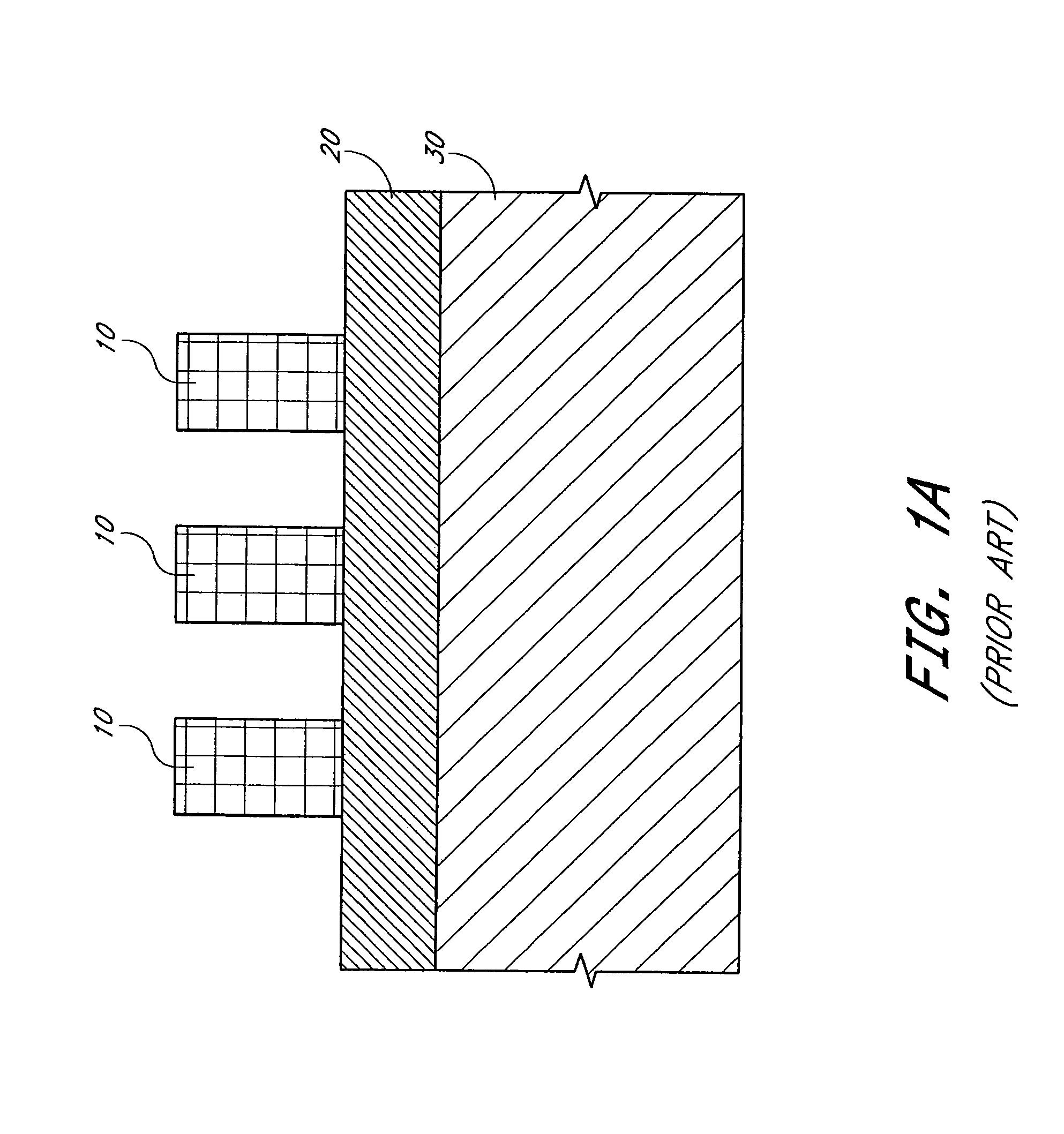

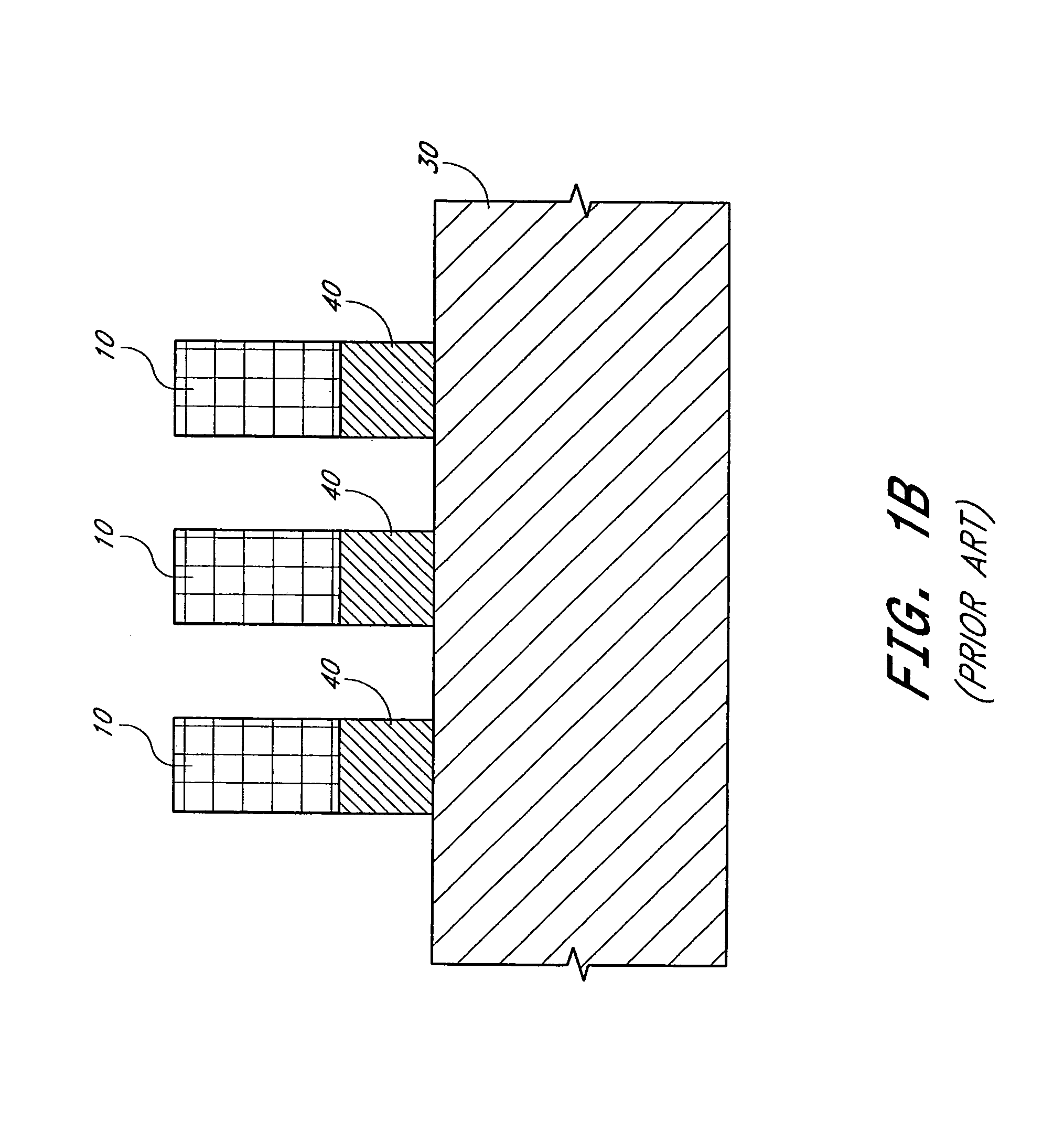

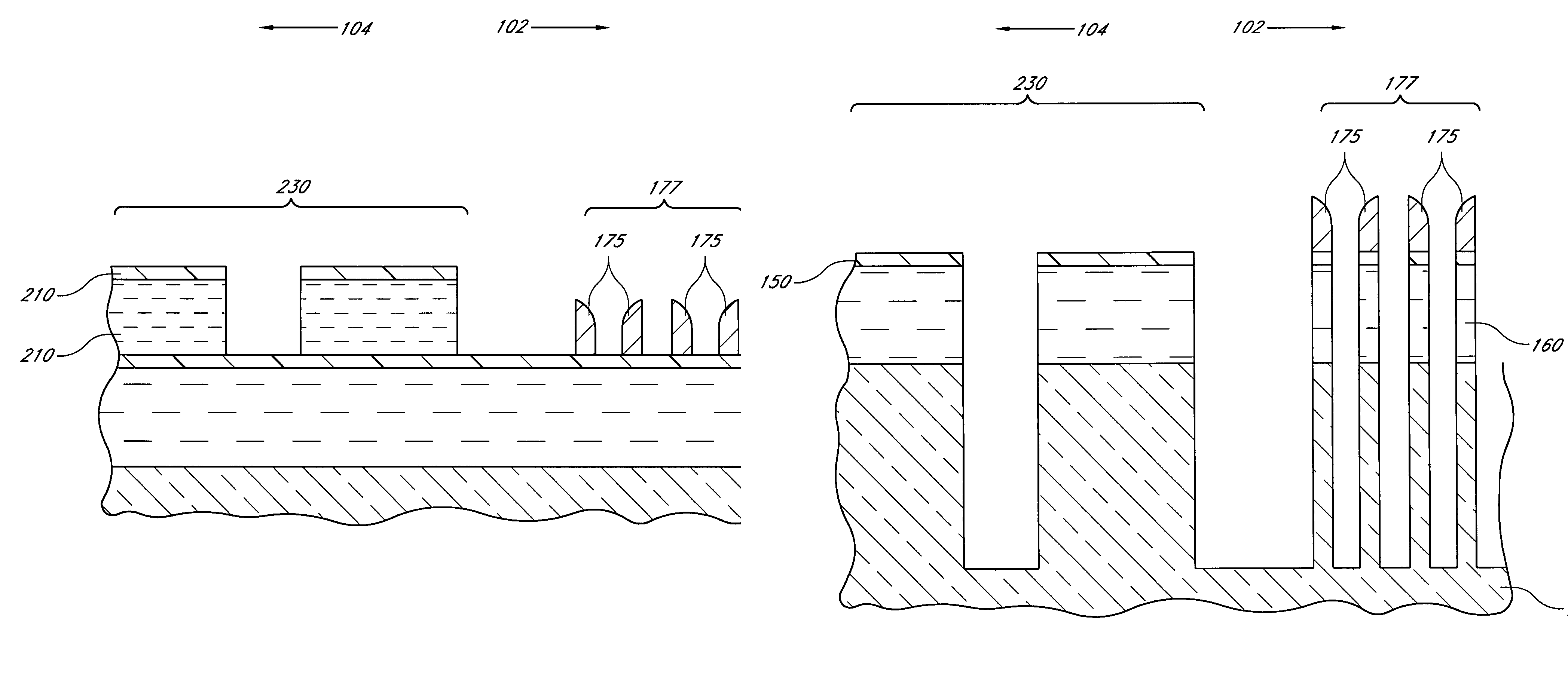

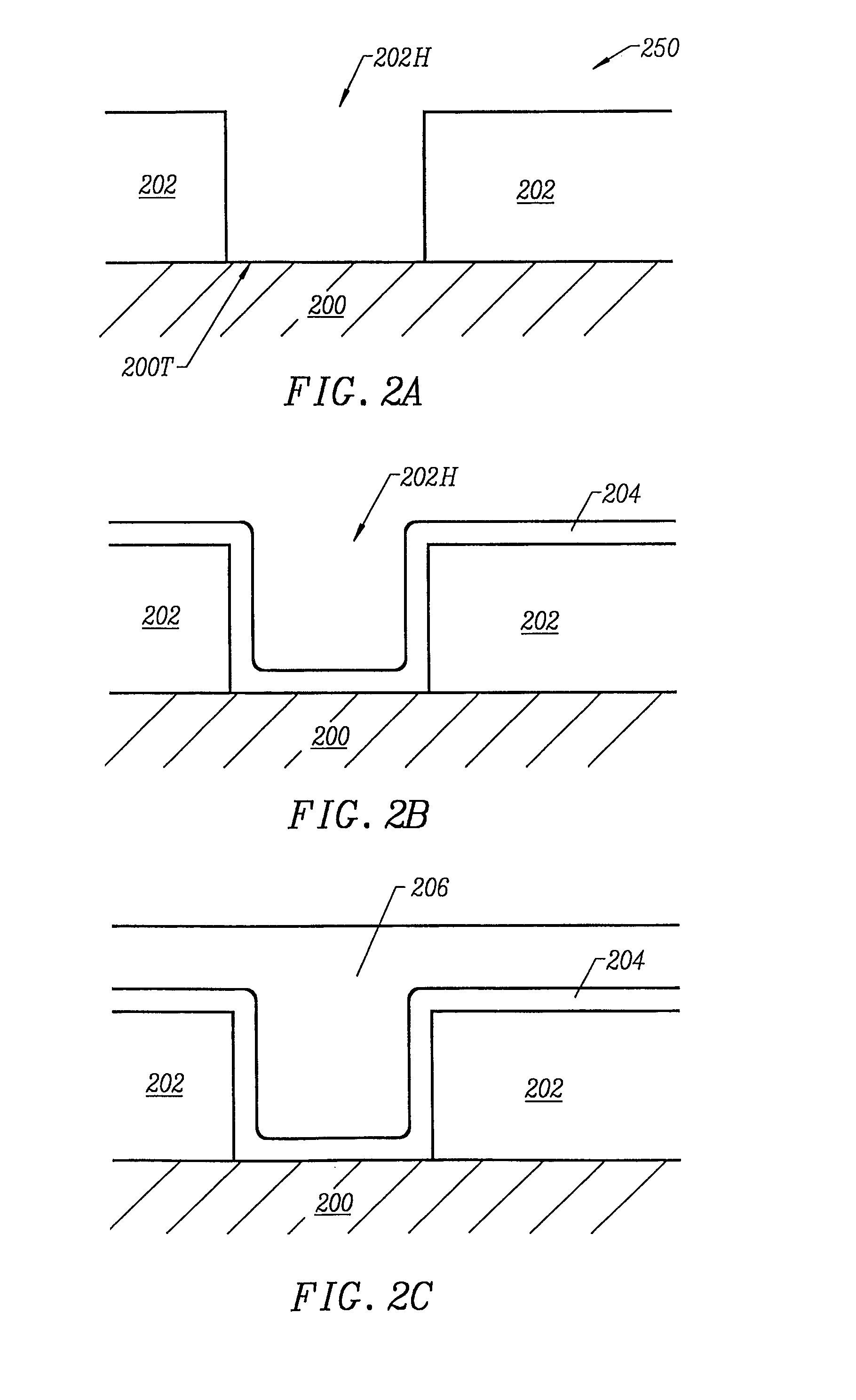

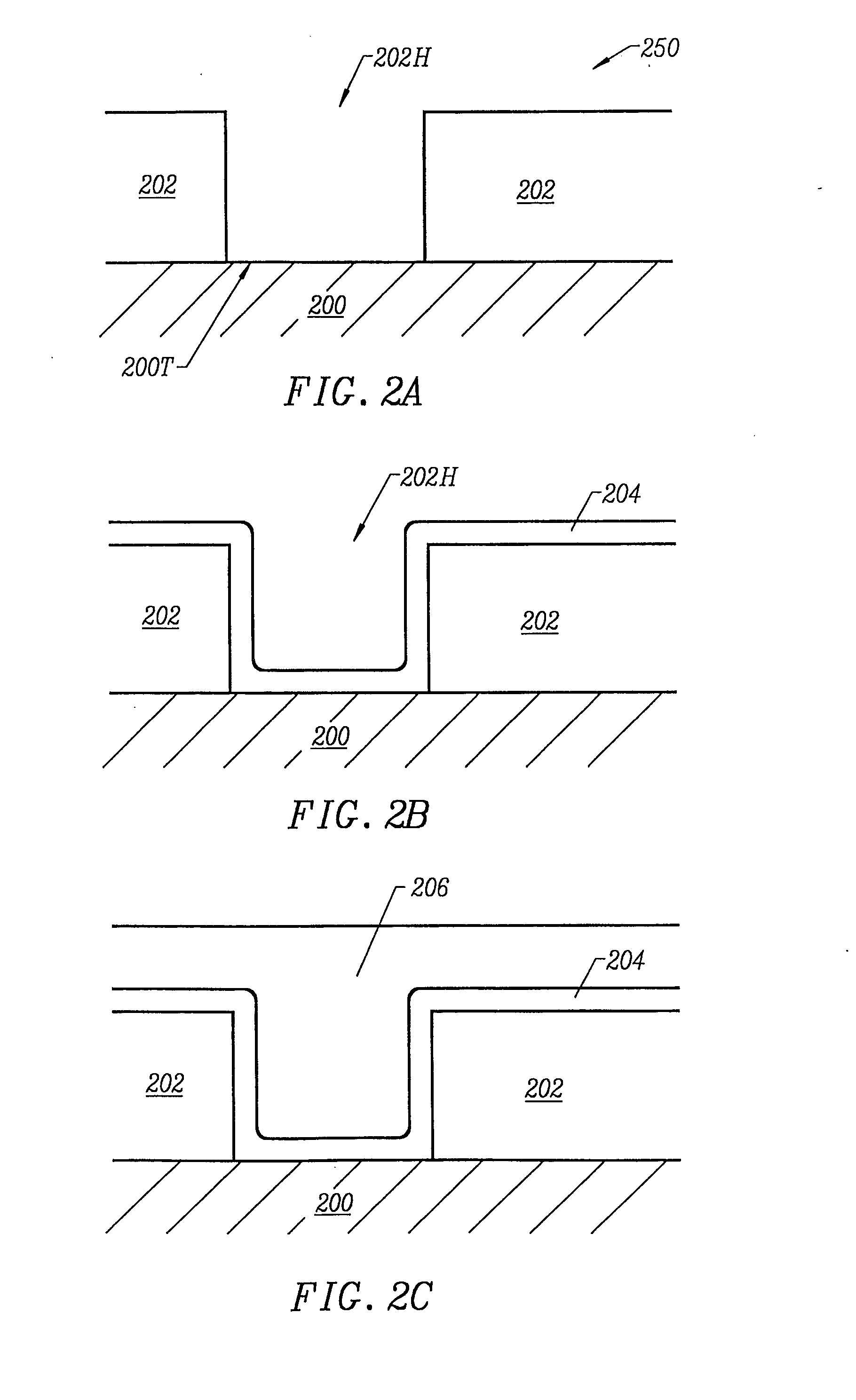

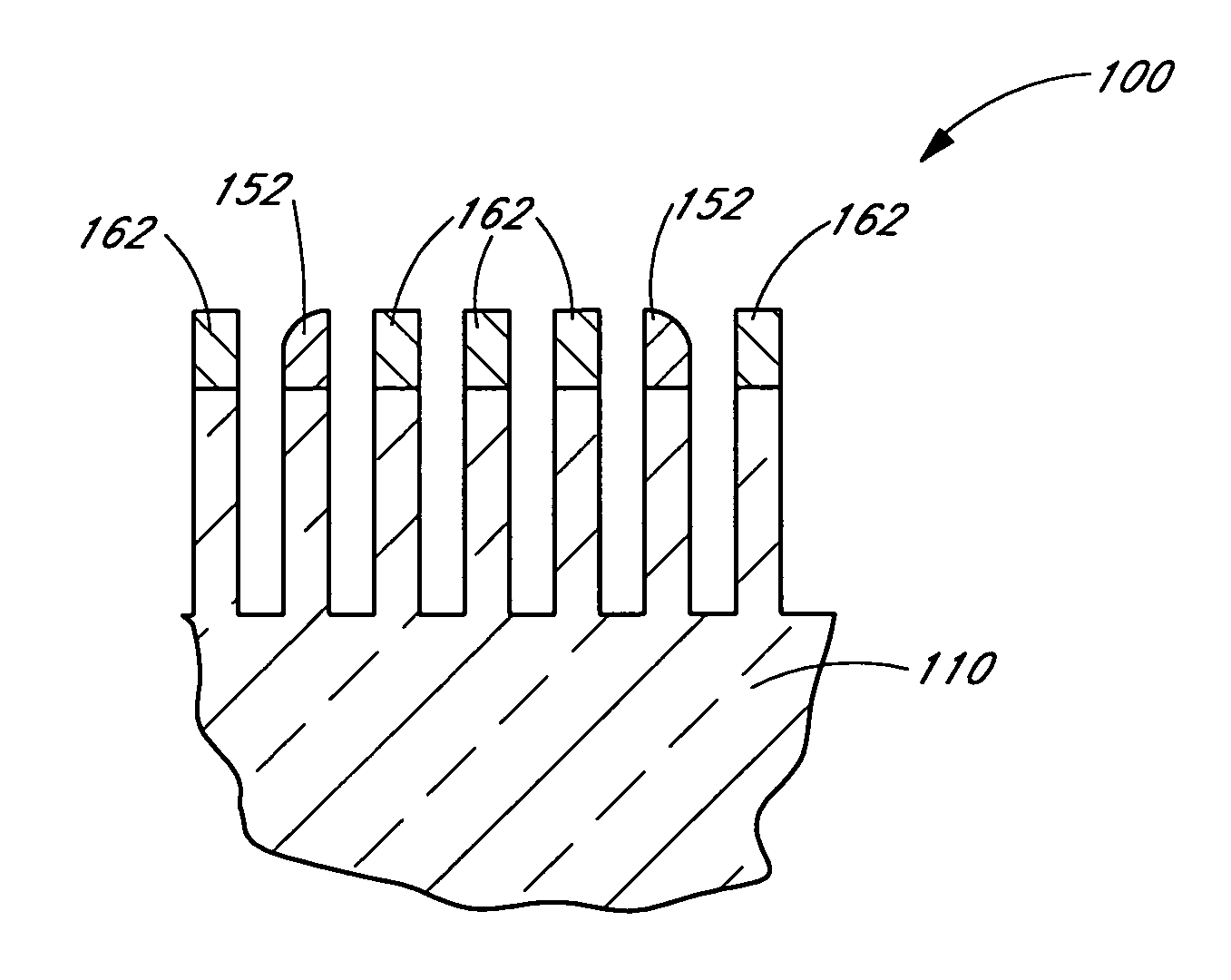

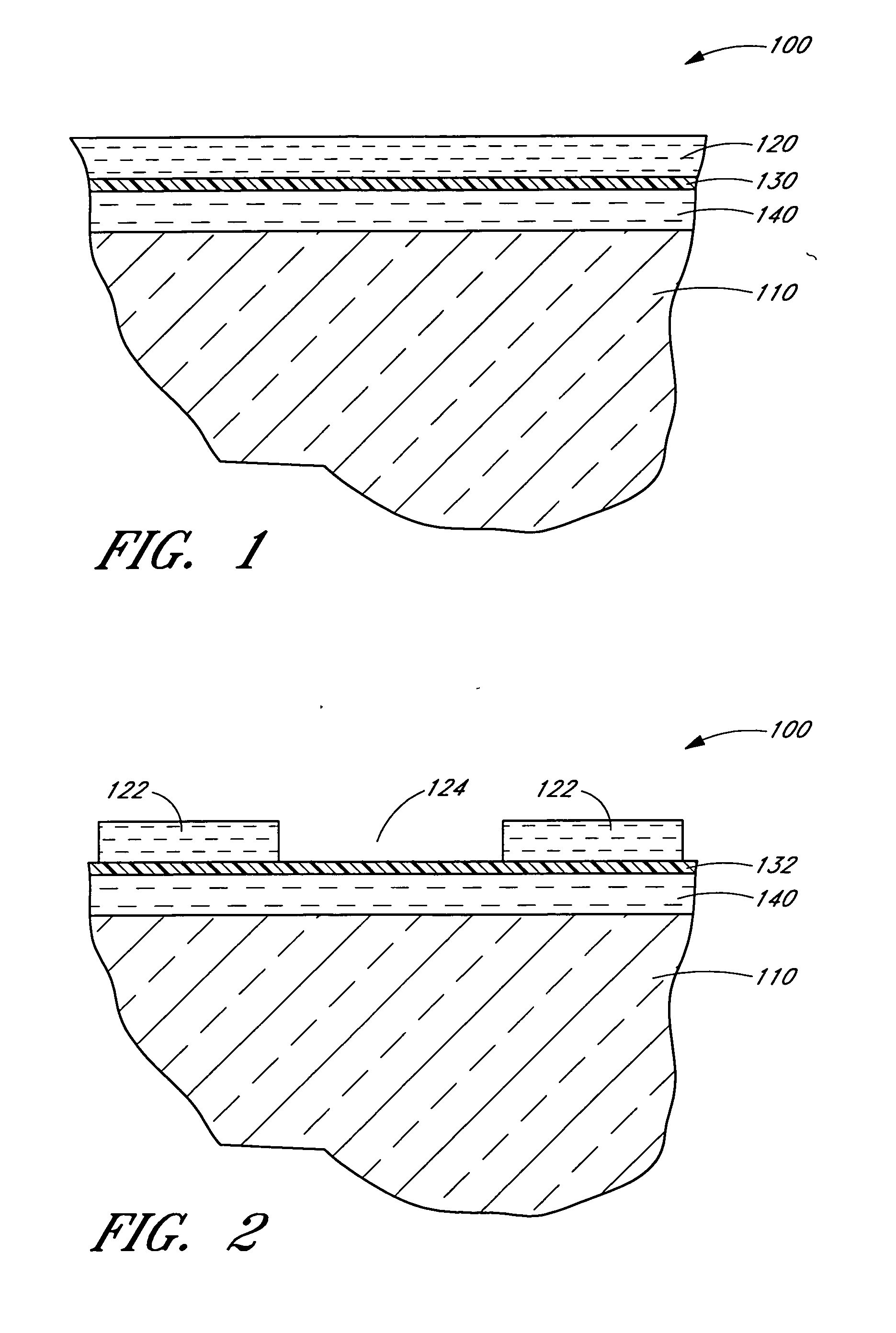

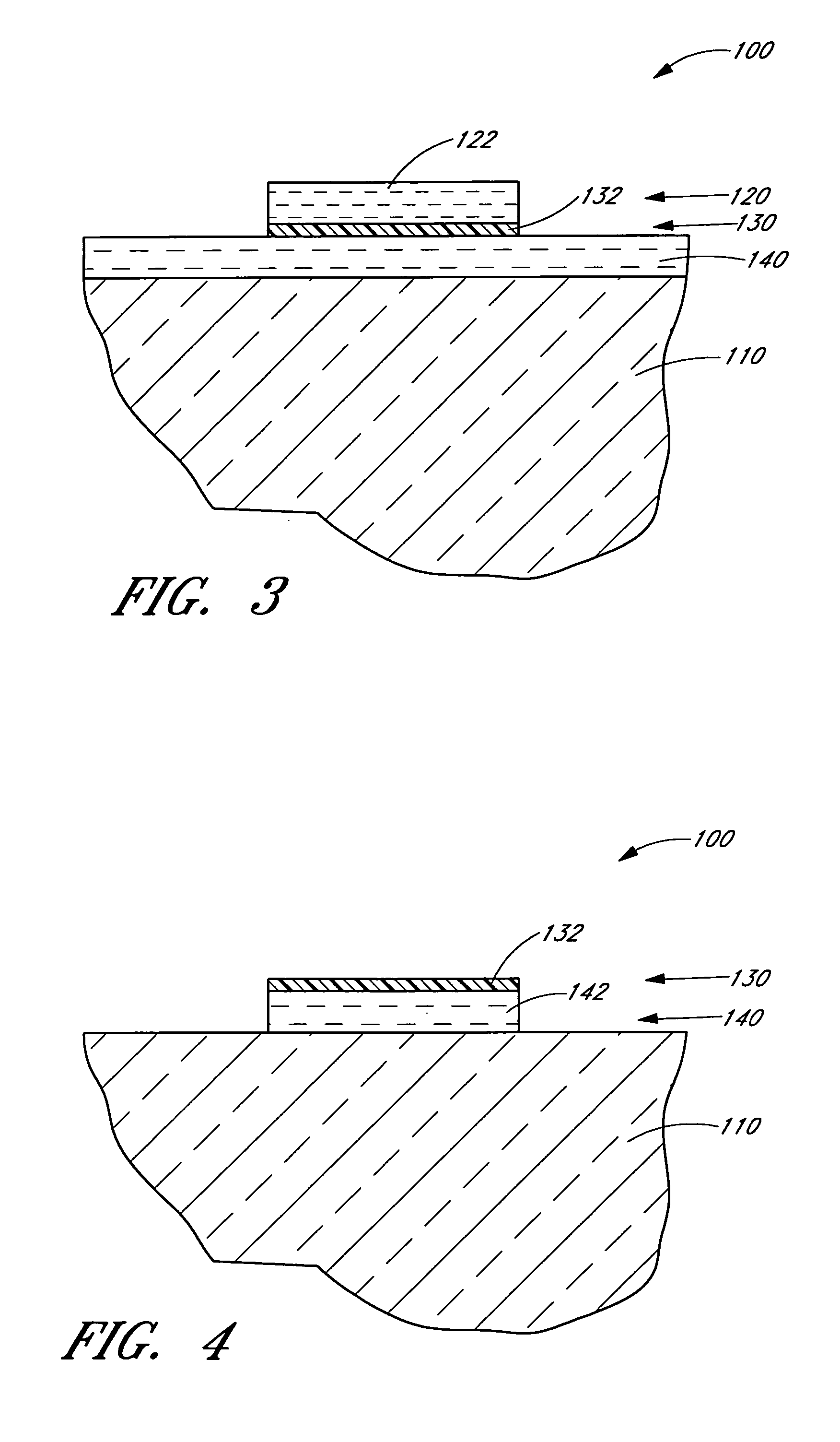

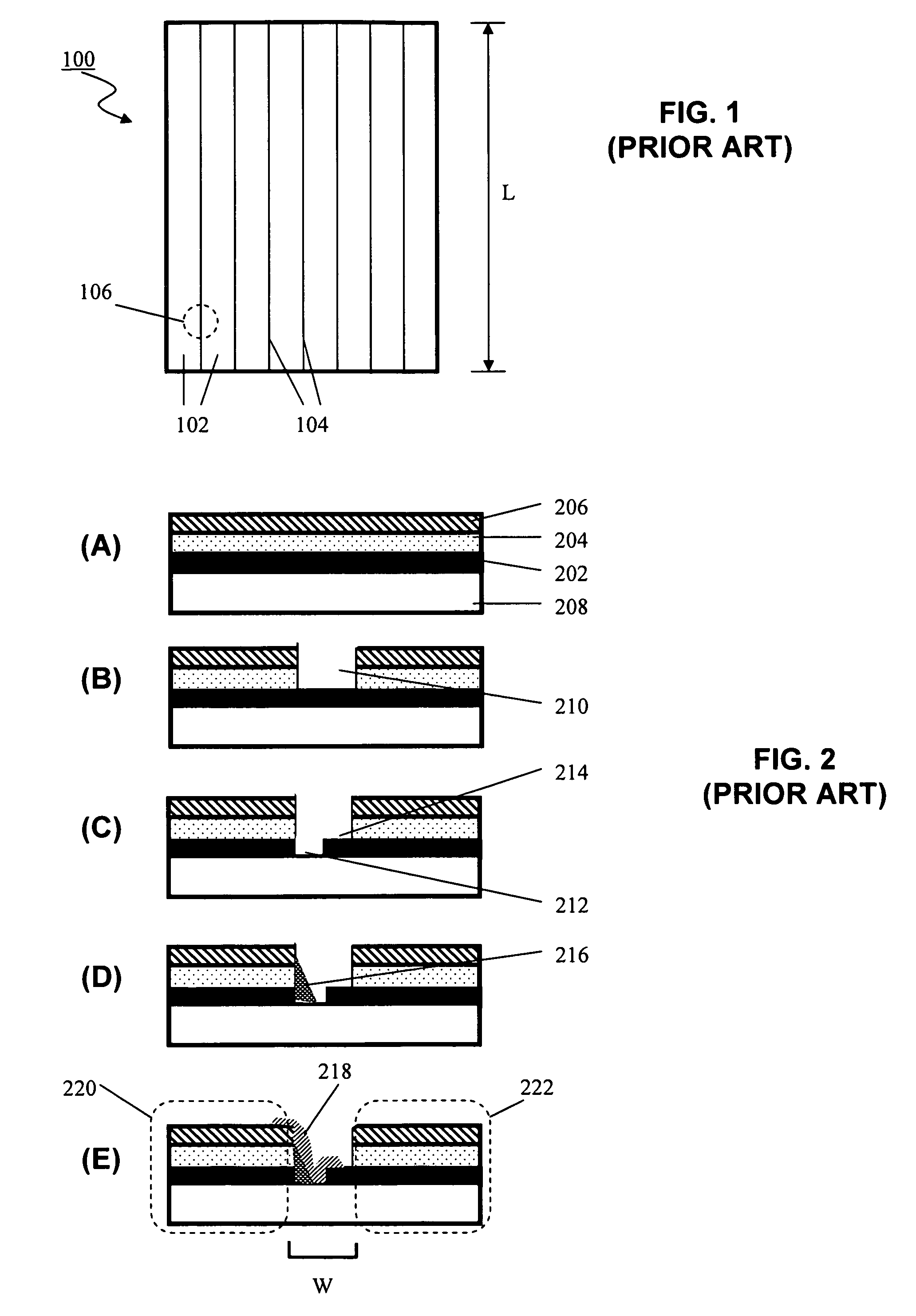

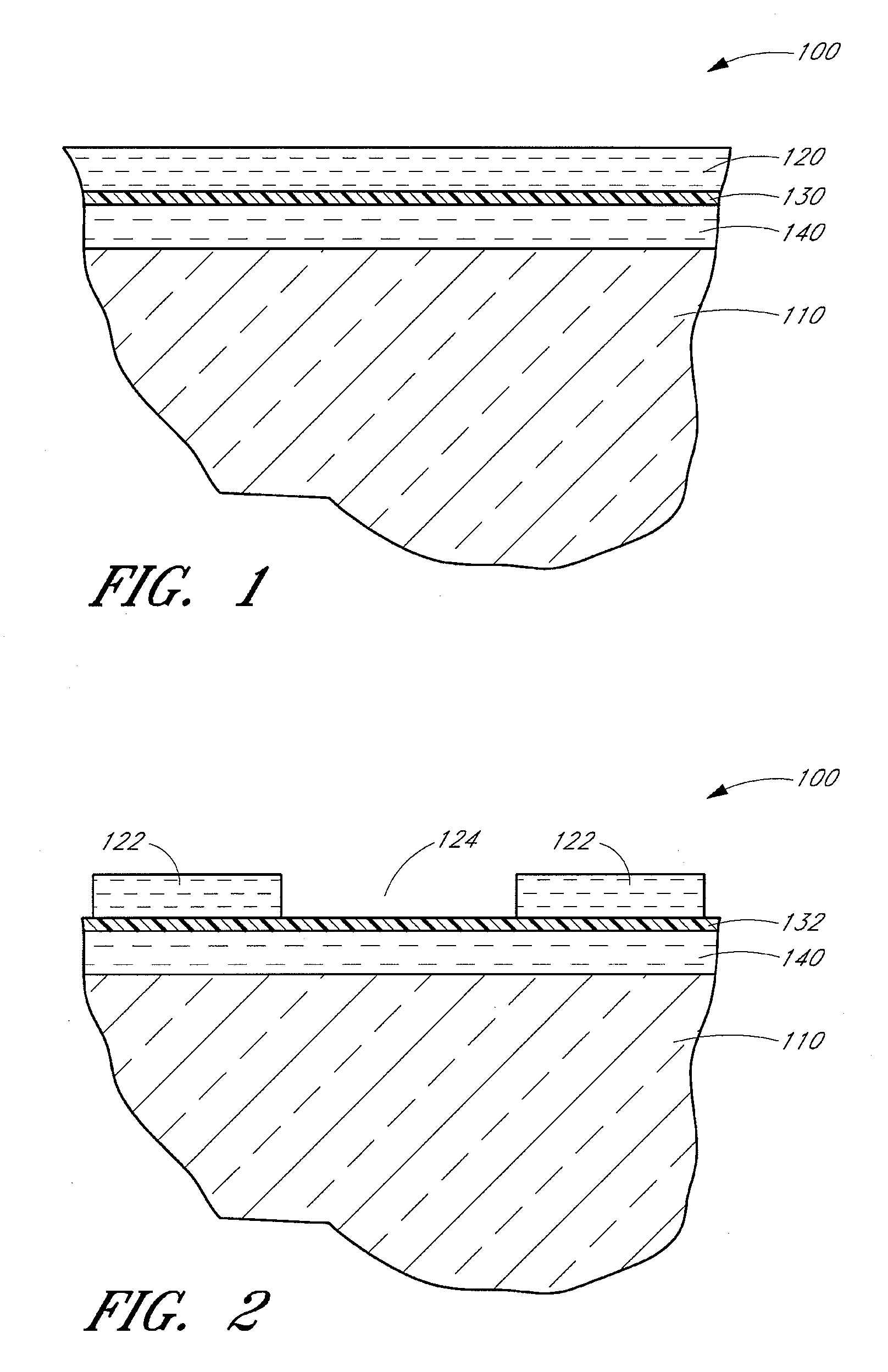

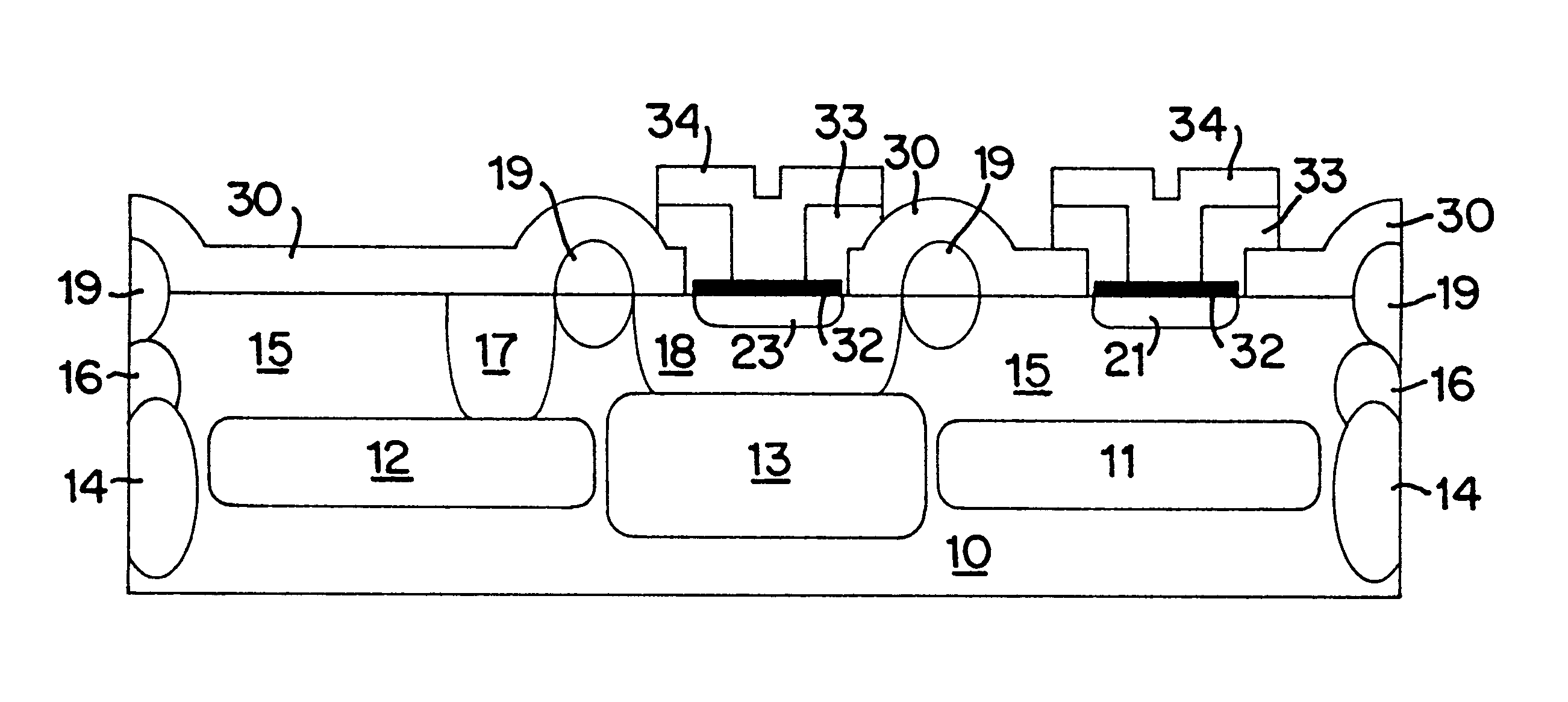

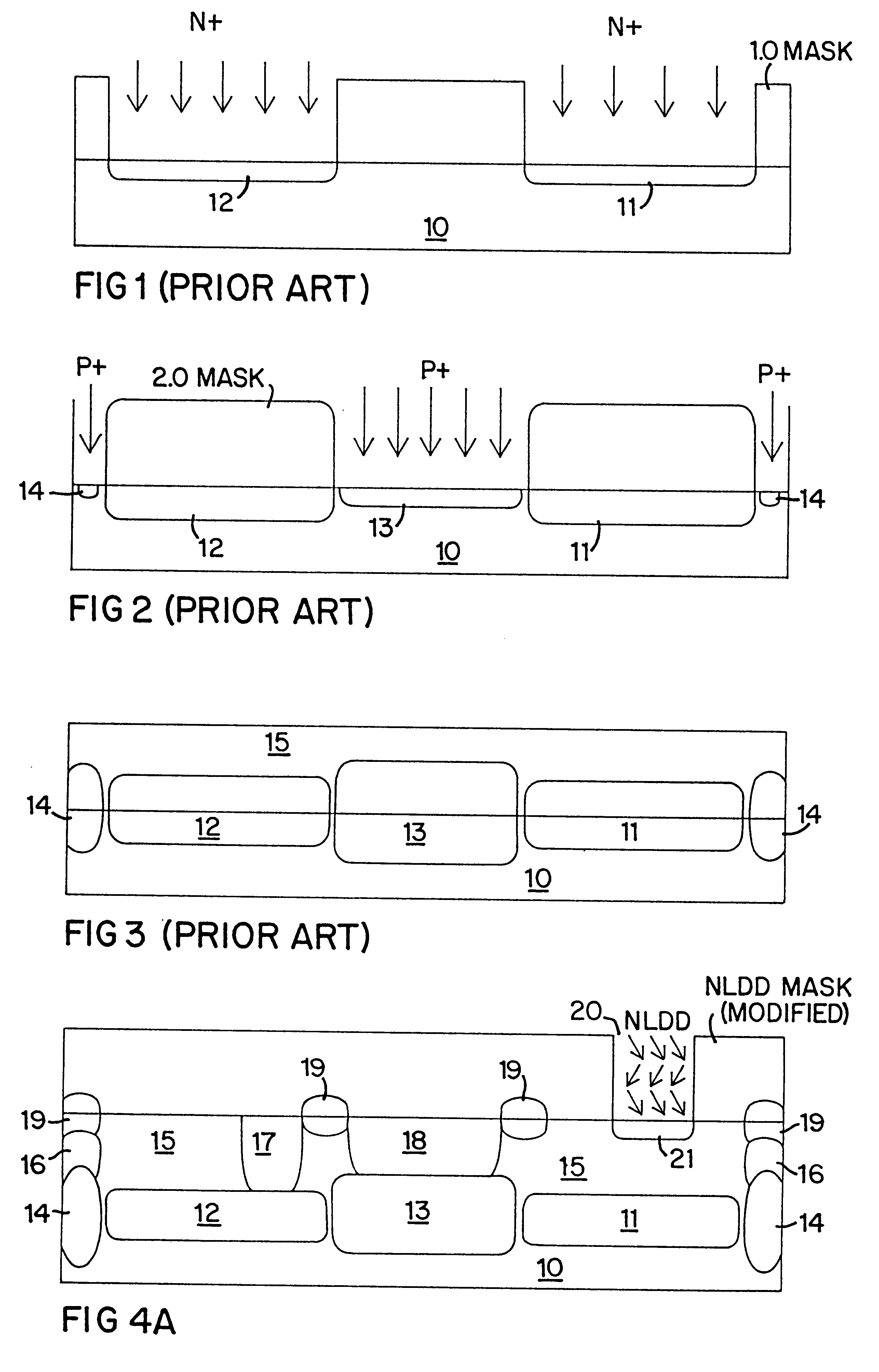

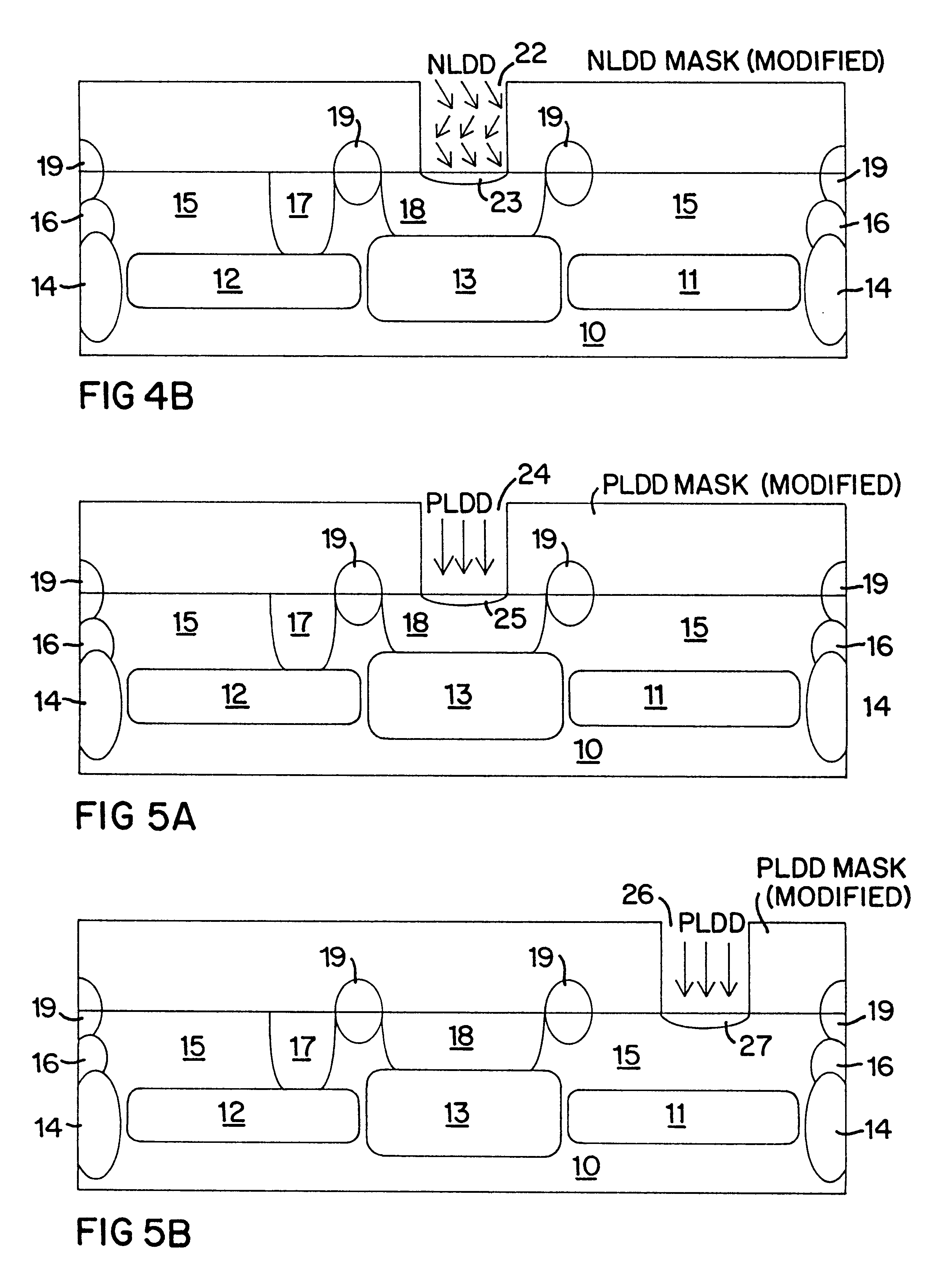

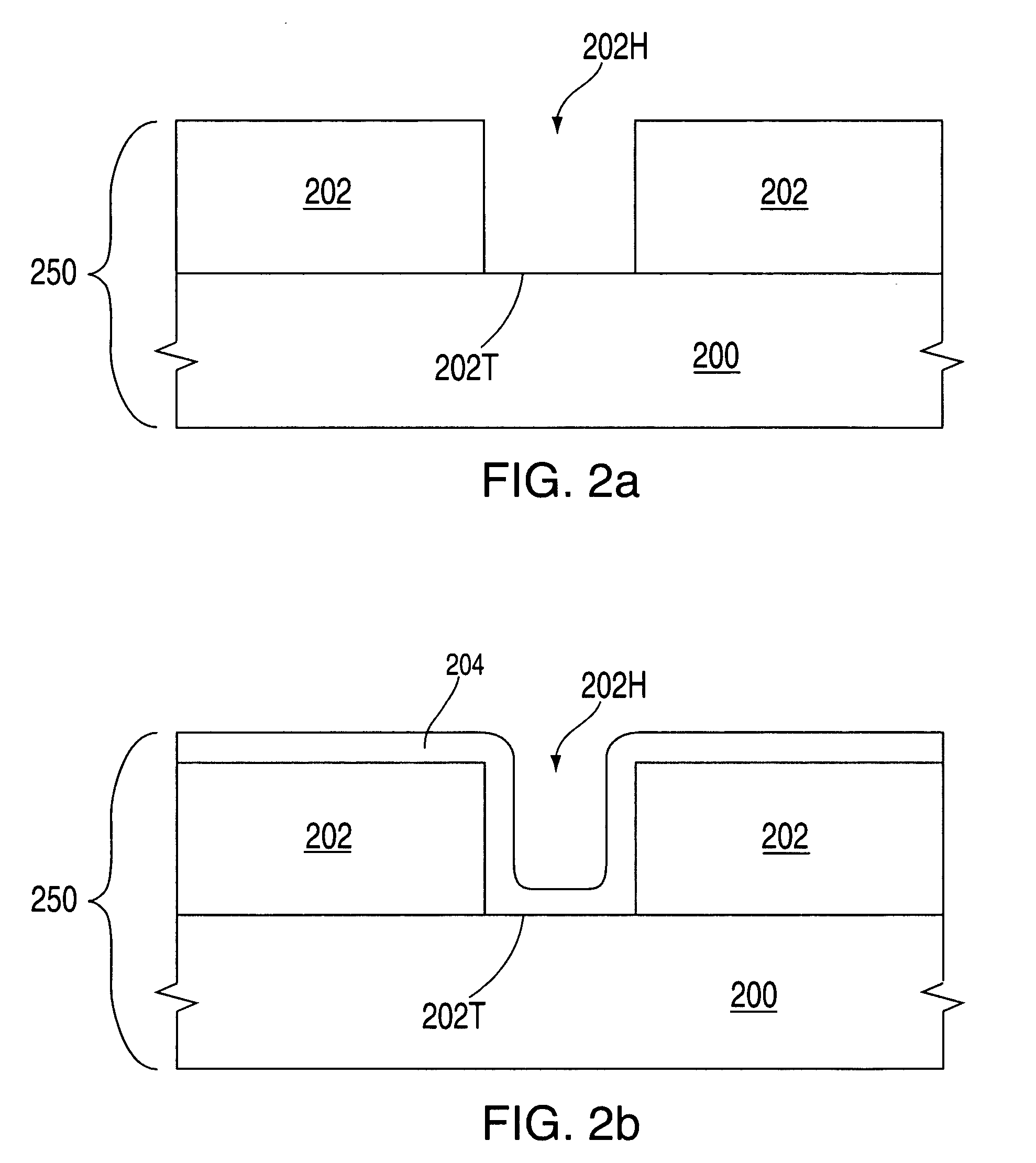

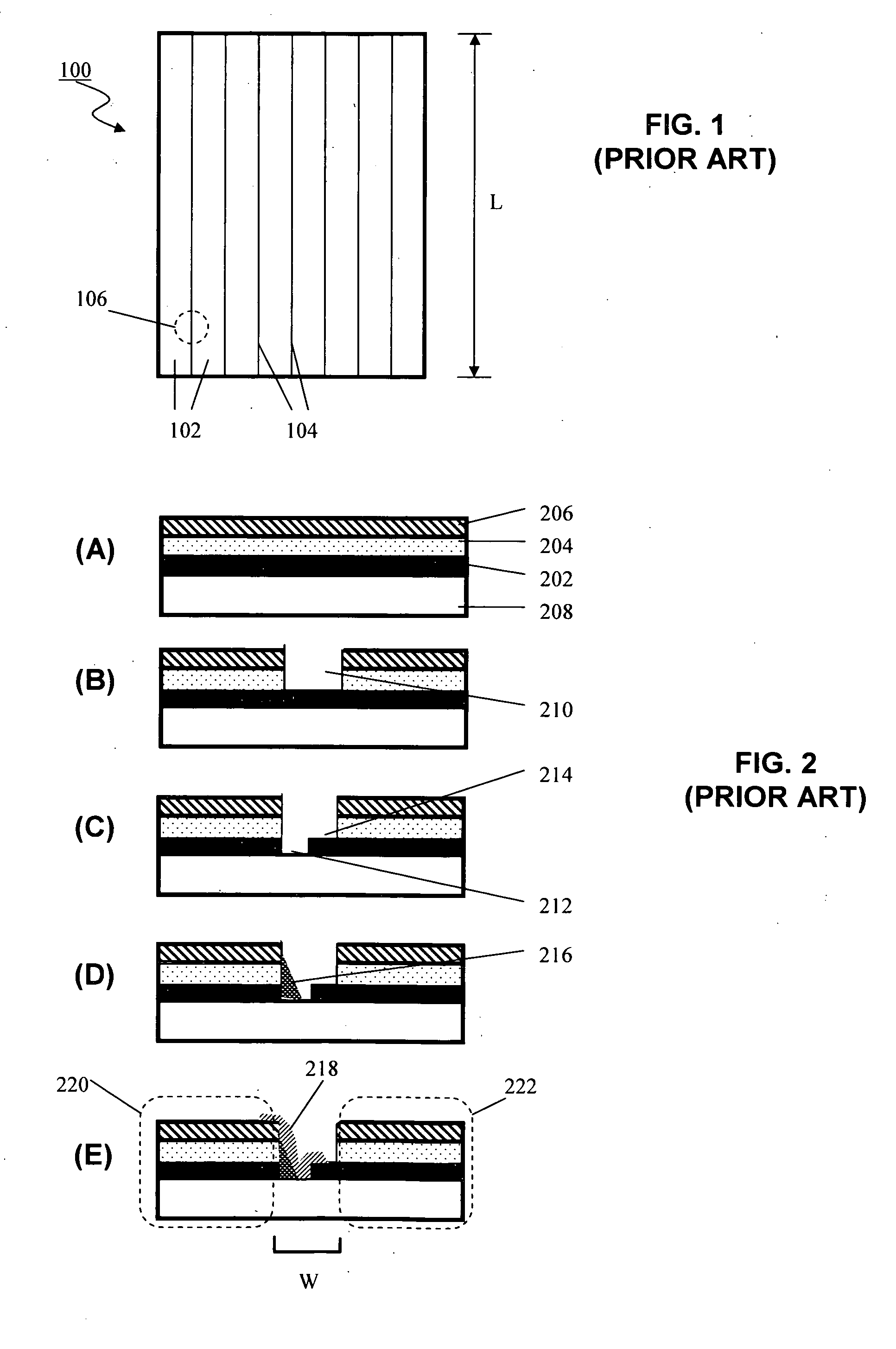

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Method for integrated circuit fabrication using pitch multiplication

InactiveUS20060046484A1Electric discharge tubesSemiconductor/solid-state device manufacturingImage resolutionDifferences size

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Formation of boride barrier layers using chemisorption techniques

InactiveUS7208413B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingBorideBoron containing

A method of forming a boride layer for integrated circuit fabrication is disclosed. In one embodiment, the boride layer is formed by chemisorbing monolayers of a boron-containing compound and one refractory metal compound onto a substrate. In an alternate embodiment, the boride layer has a composite structure. The composite boride layer structure comprises two or more refractory metals. The composite boride layer is formed by sequentially chemisorbing monolayers of a boron compound and two or more refractory metal compounds on a substrate.

Owner:APPLIED MATERIALS INC

Formation of boride barrier layers using chemisorption techniques

InactiveUS20050118804A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingBorideChemisorption

A method of forming a boride layer for integrated circuit fabrication is disclosed. In one embodiment, the boride layer is formed by chemisorbing monolayers of a boron-containing compound and one refractory metal compound onto a substrate. In an alternate embodiment, the boride layer has a composite structure. The composite boride layer structure comprises two or more refractory metals. The composite boride layer is formed by sequentially chemisorbing monolayers of a boron compound and two or more refractory metal compounds on a substrate.

Owner:APPLIED MATERIALS INC

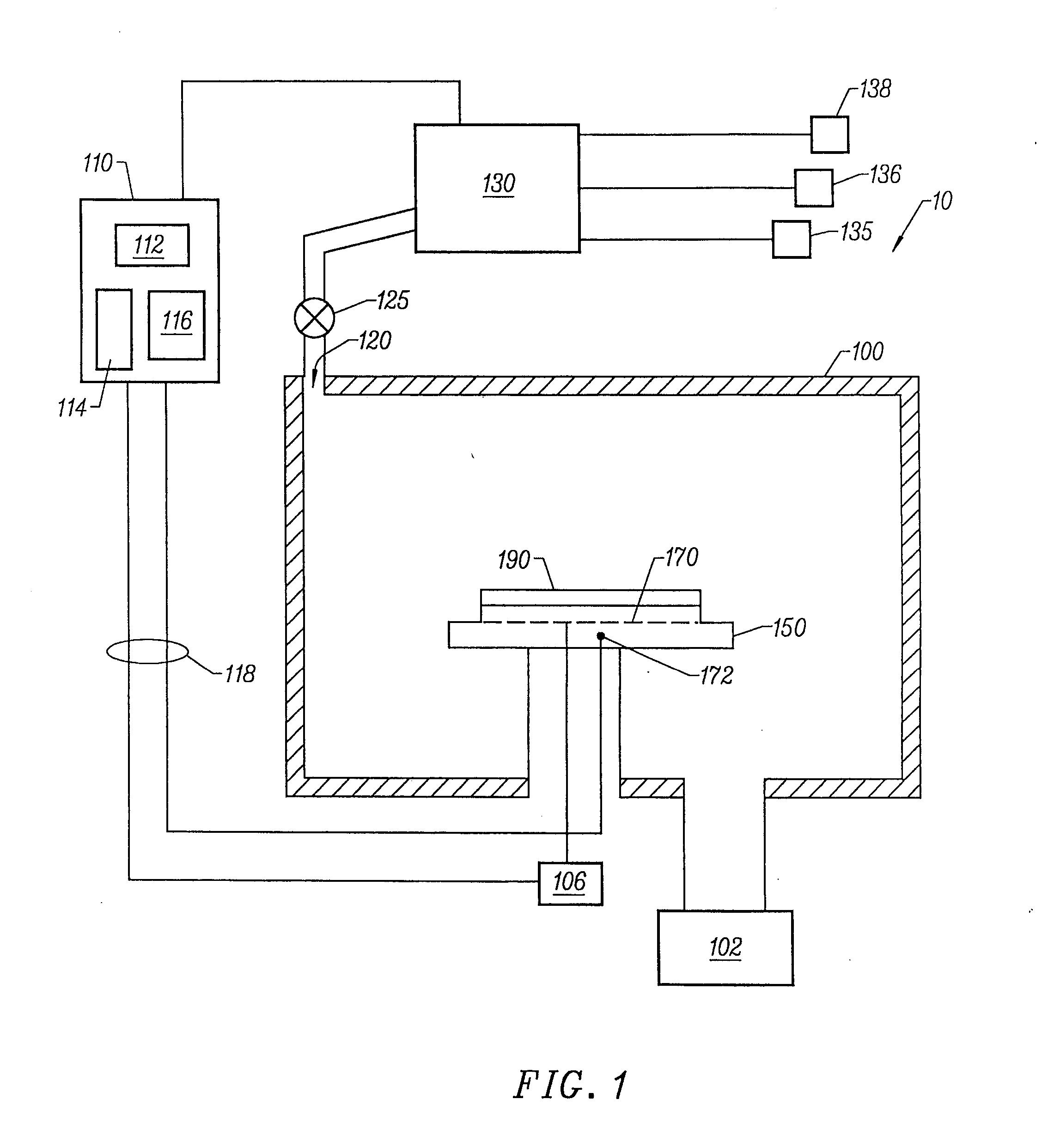

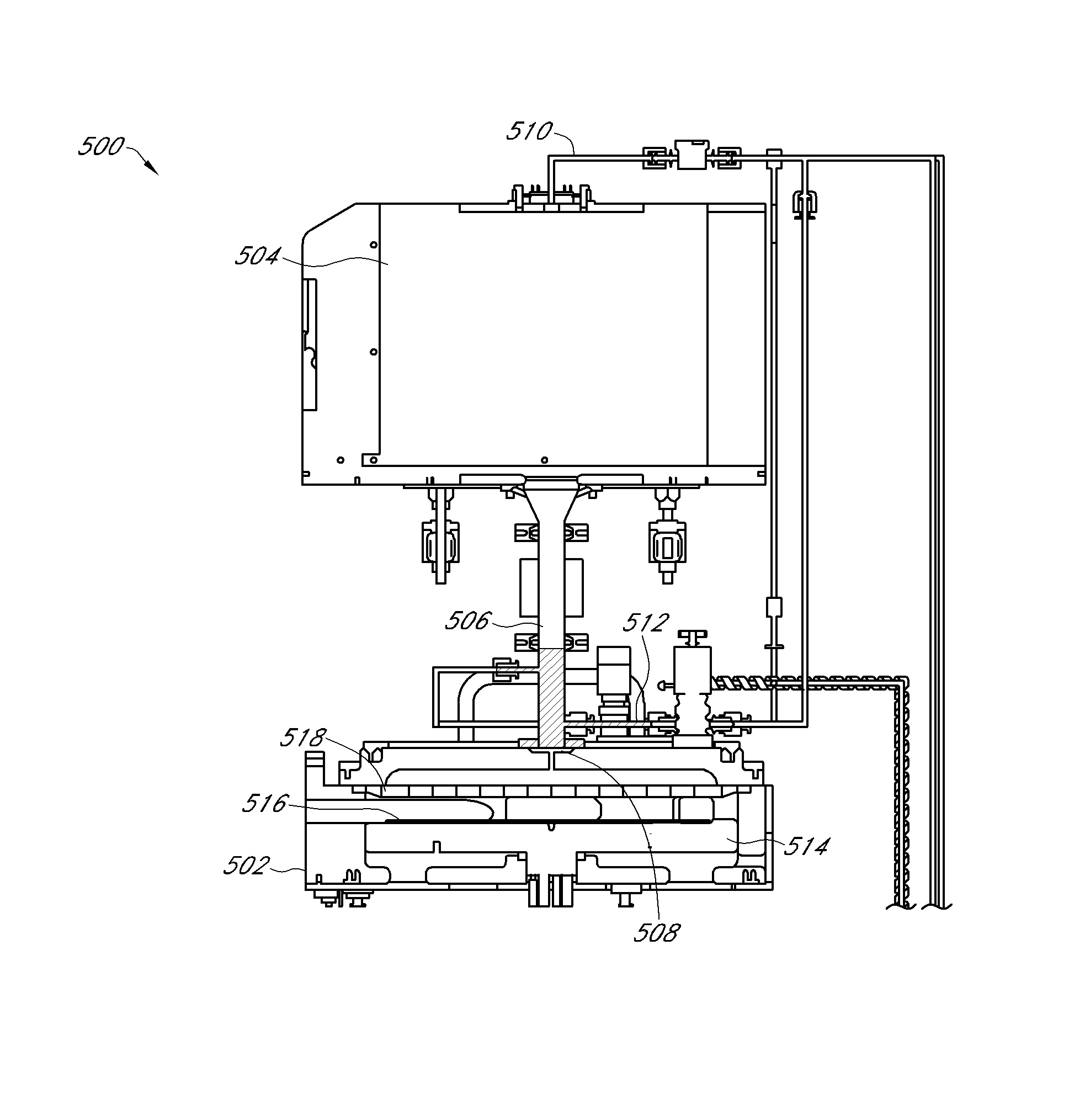

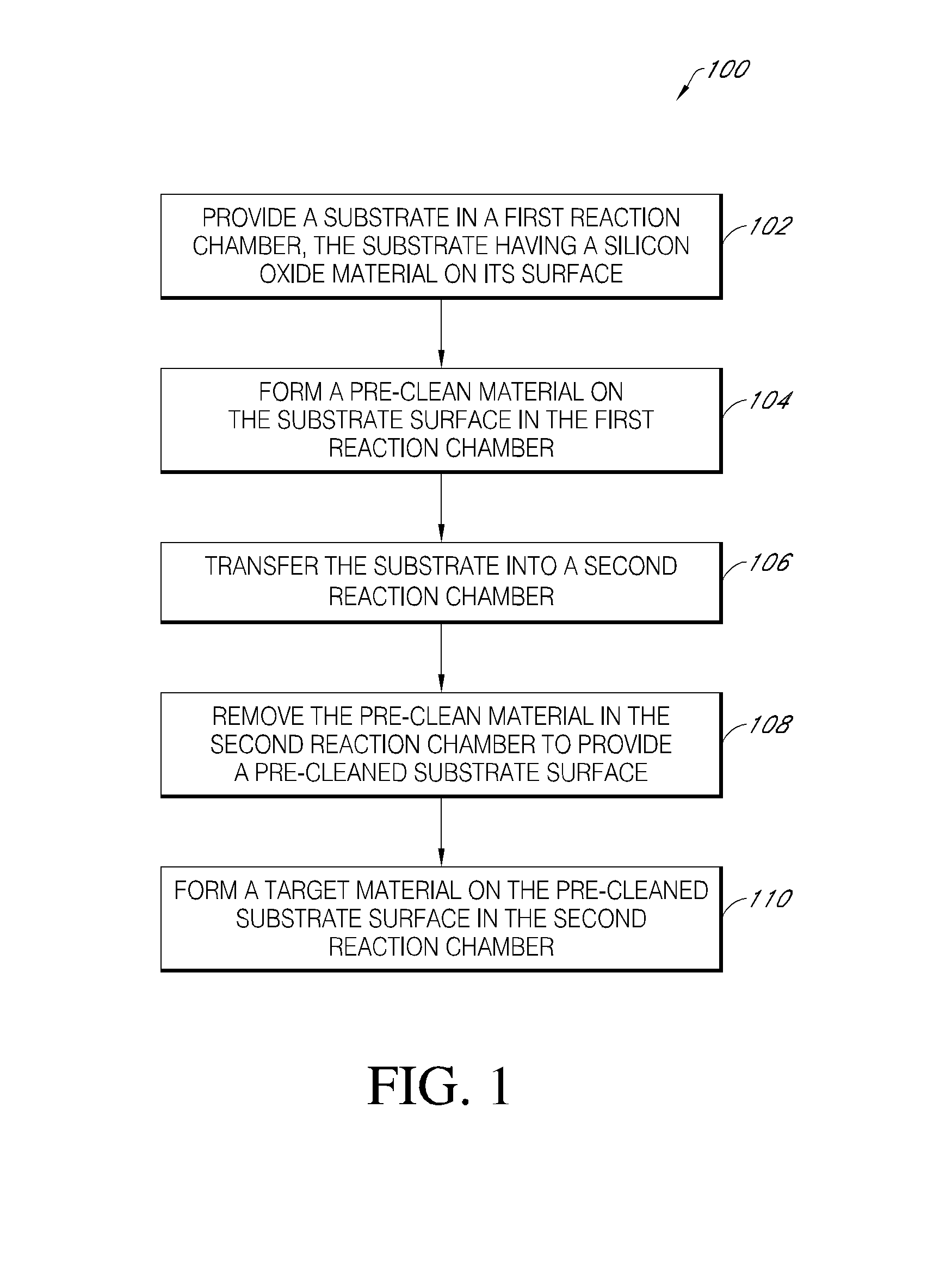

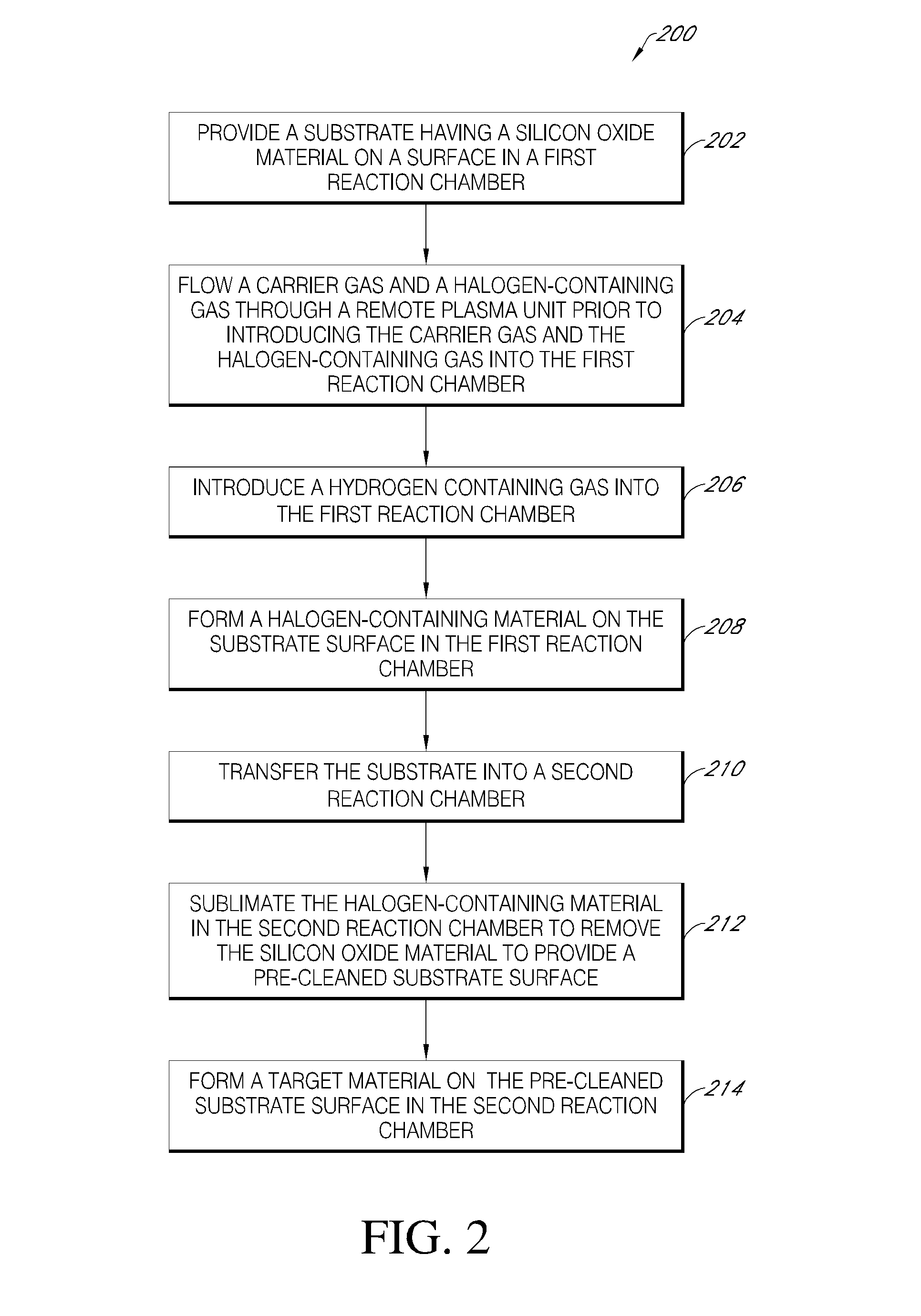

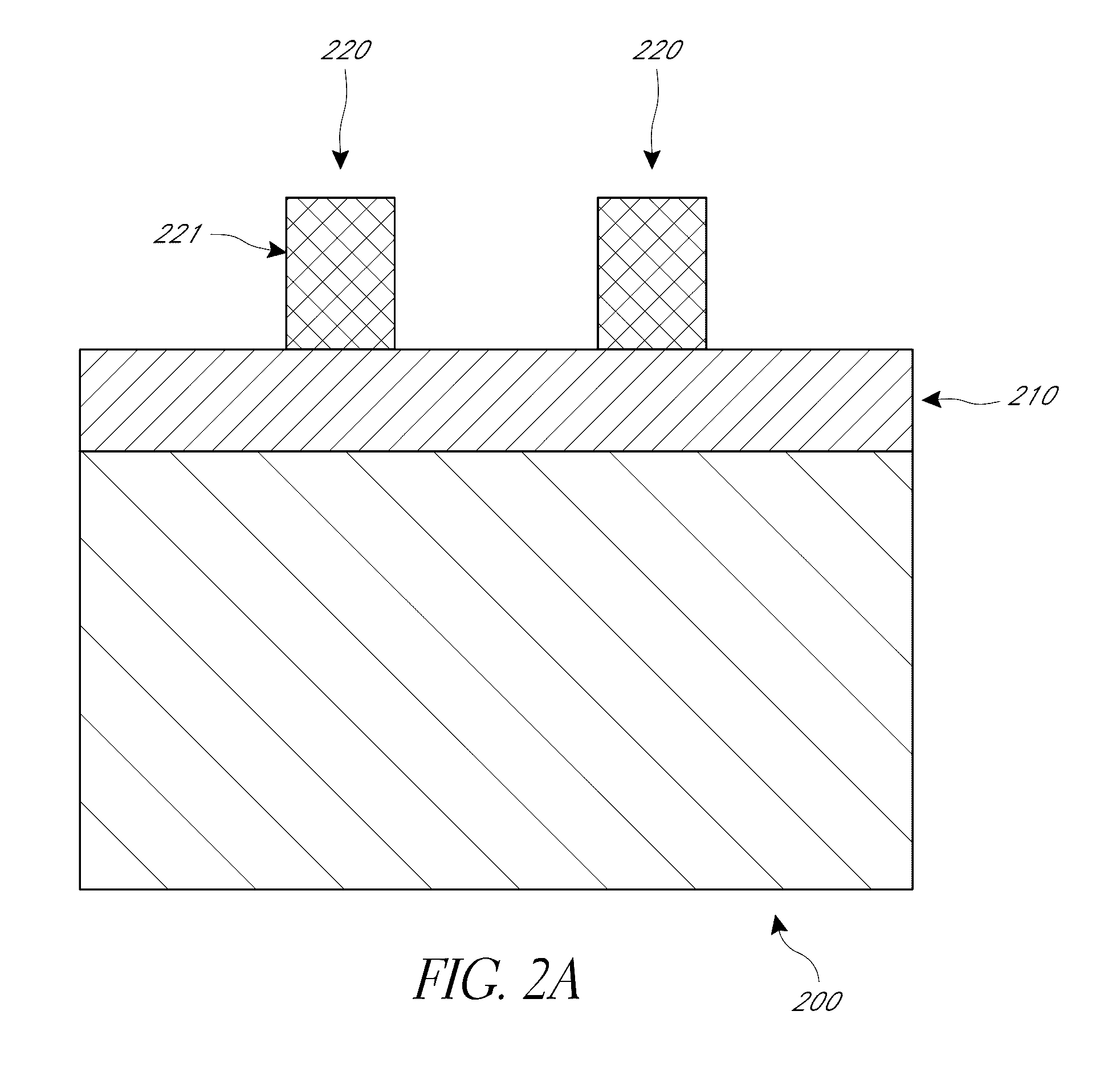

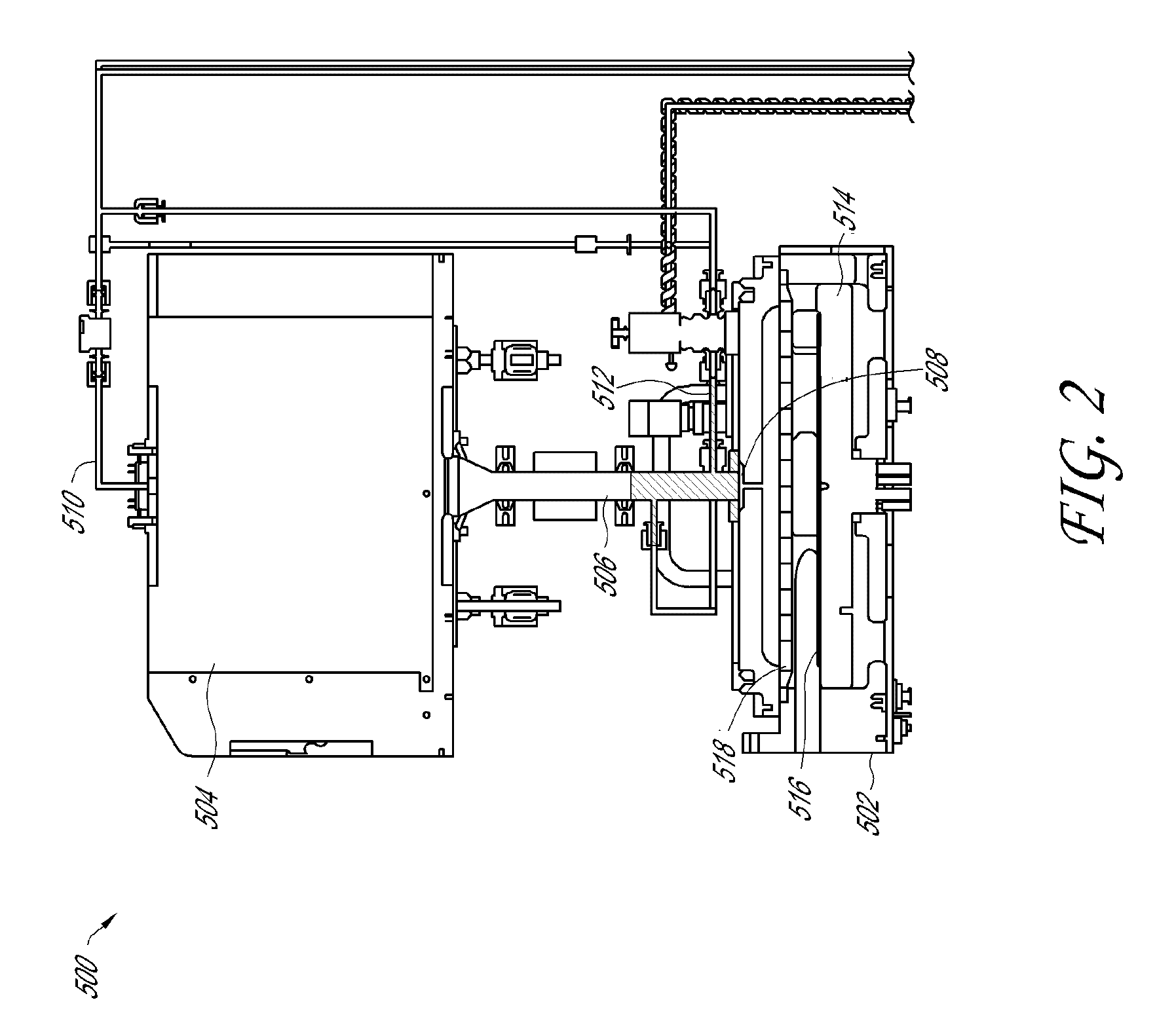

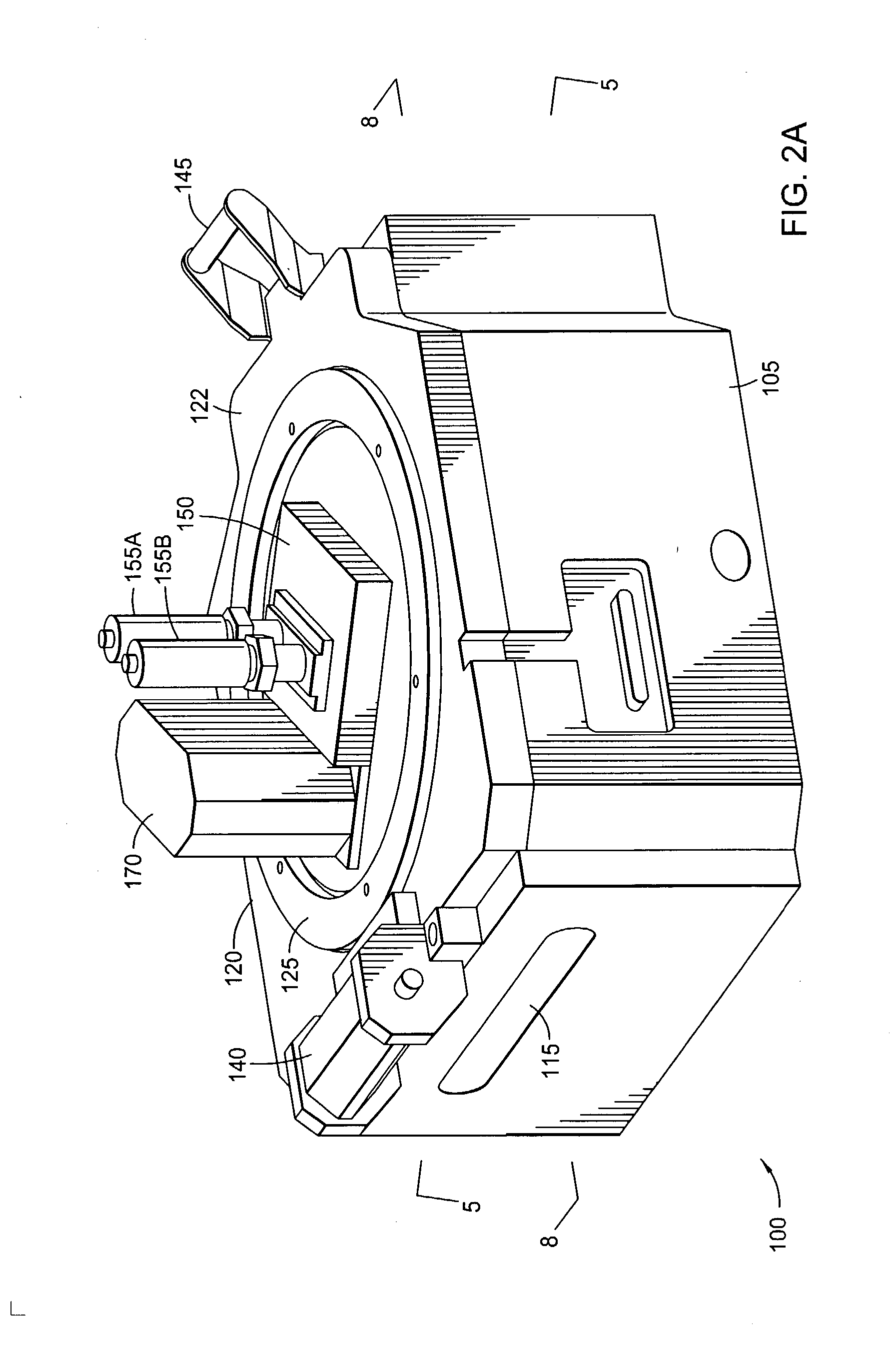

Plasma pre-clean module and process

ActiveUS9299557B2Polycrystalline material growthSemiconductor/solid-state device manufacturingConductive materialsSilicon oxide

A method for integrated circuit fabrication can include removing silicon oxide by a pre-clean process. The pre-clean process can include depositing a halogen-containing material on the surface of a substrate in a first reaction chamber, and transferring the substrate having the halogen-containing material to a second reaction chamber. Silicon oxide material can be removed from a surface of the substrate by sublimating the halogen-containing material in the second reaction chamber. A target material, such as a conductive material, may subsequently be deposited on the substrate surface in the second reaction chamber.

Owner:ASM IP HLDG BV

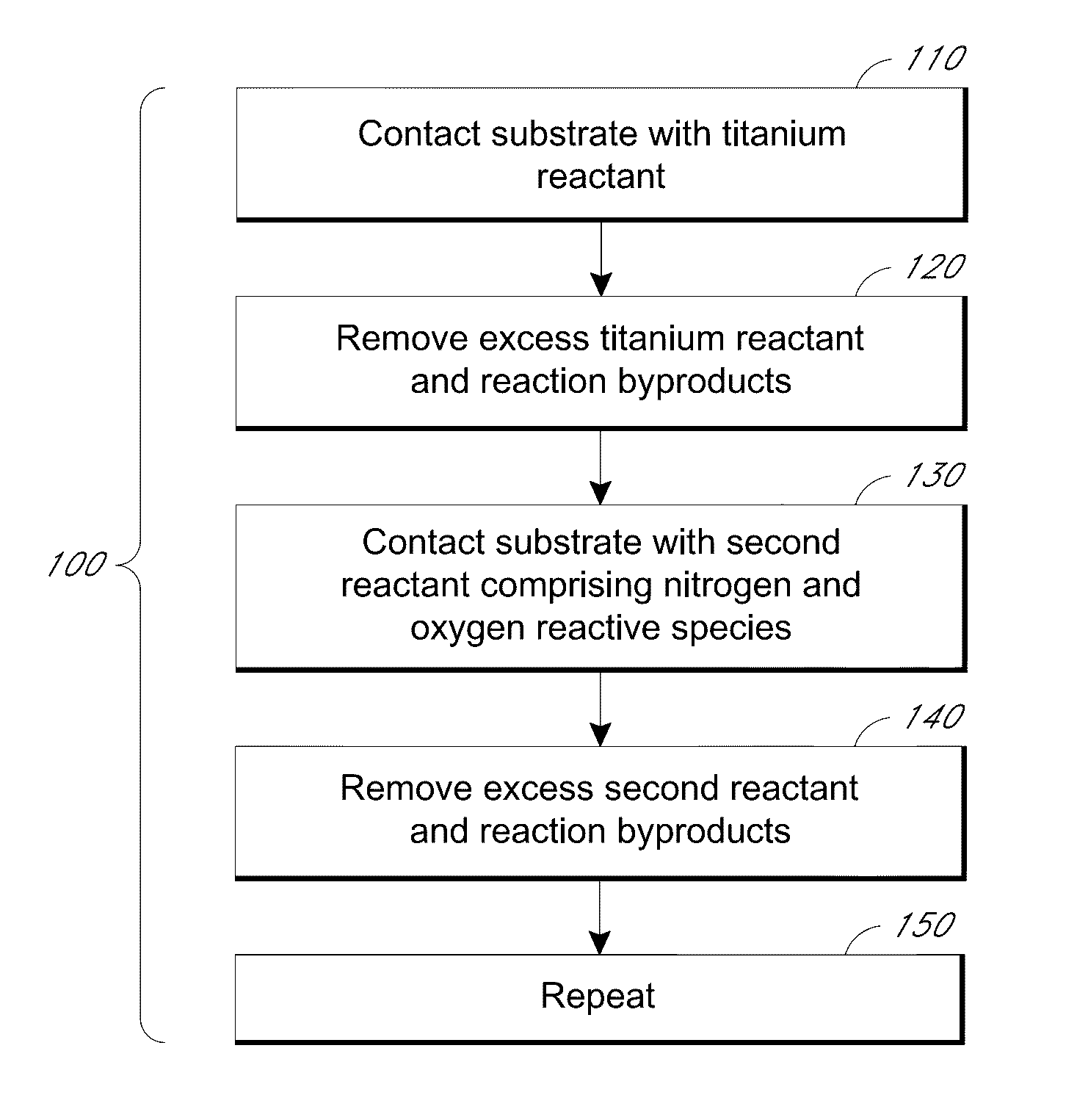

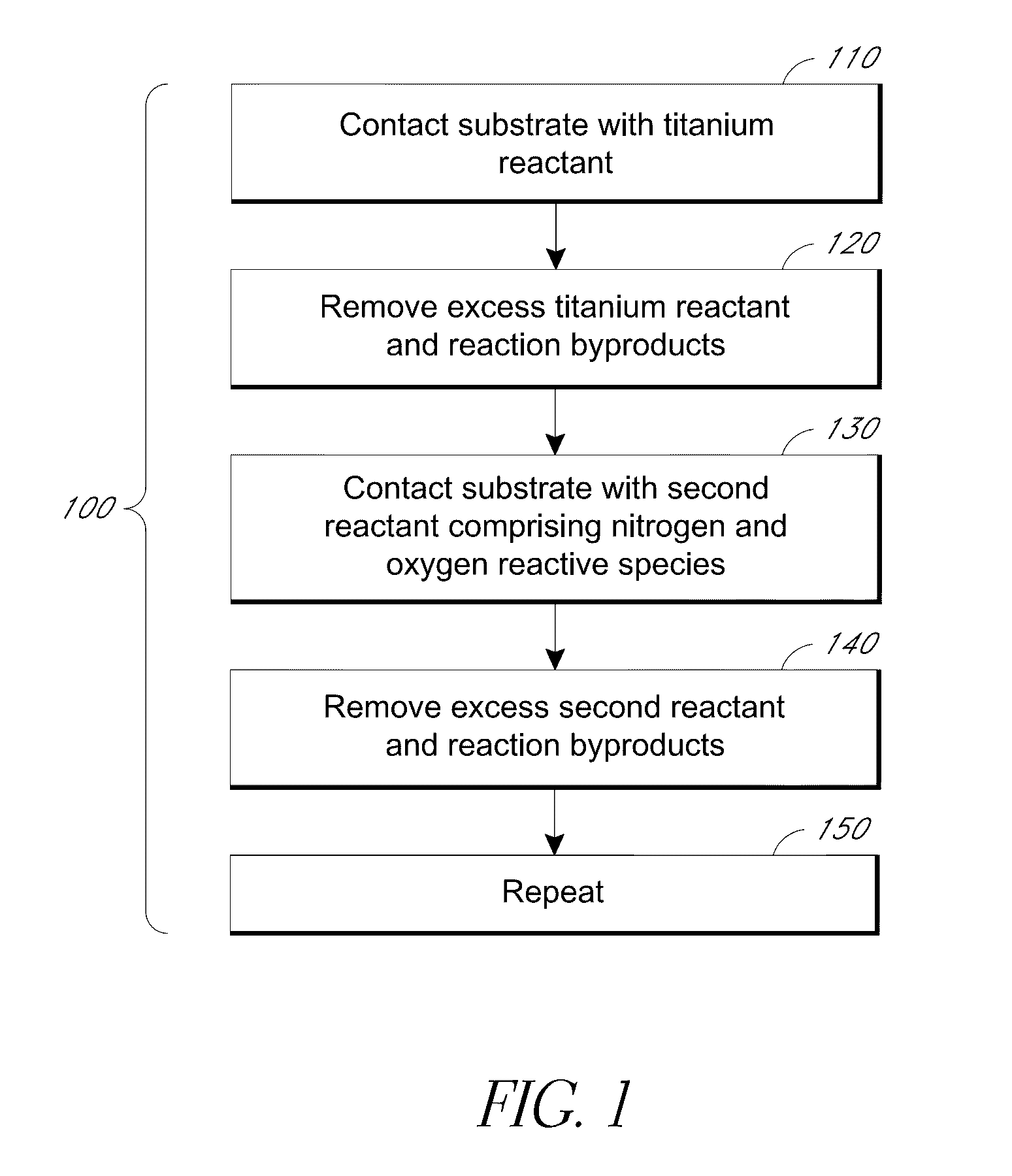

Process for deposition of titanium oxynitride for use in integrated circuit fabrication

A process is provided for depositing a substantially amorphous titanium oxynitride thin film that can be used, for example, in integrated circuit fabrication, such as in forming spacers in a pitch multiplication process. The process comprises contacting the substrate with a titanium reactant and removing excess titanium reactant and reaction byproducts, if any. The substrate is then contacted with a second reactant which comprises reactive species generated by plasma, wherein one of the reactive species comprises nitrogen. The second reactant and reaction byproducts, if any, are removed. The contacting and removing steps are repeated until a titanium oxynitride thin film of desired thickness has been formed.

Owner:ASM IP HLDG BV

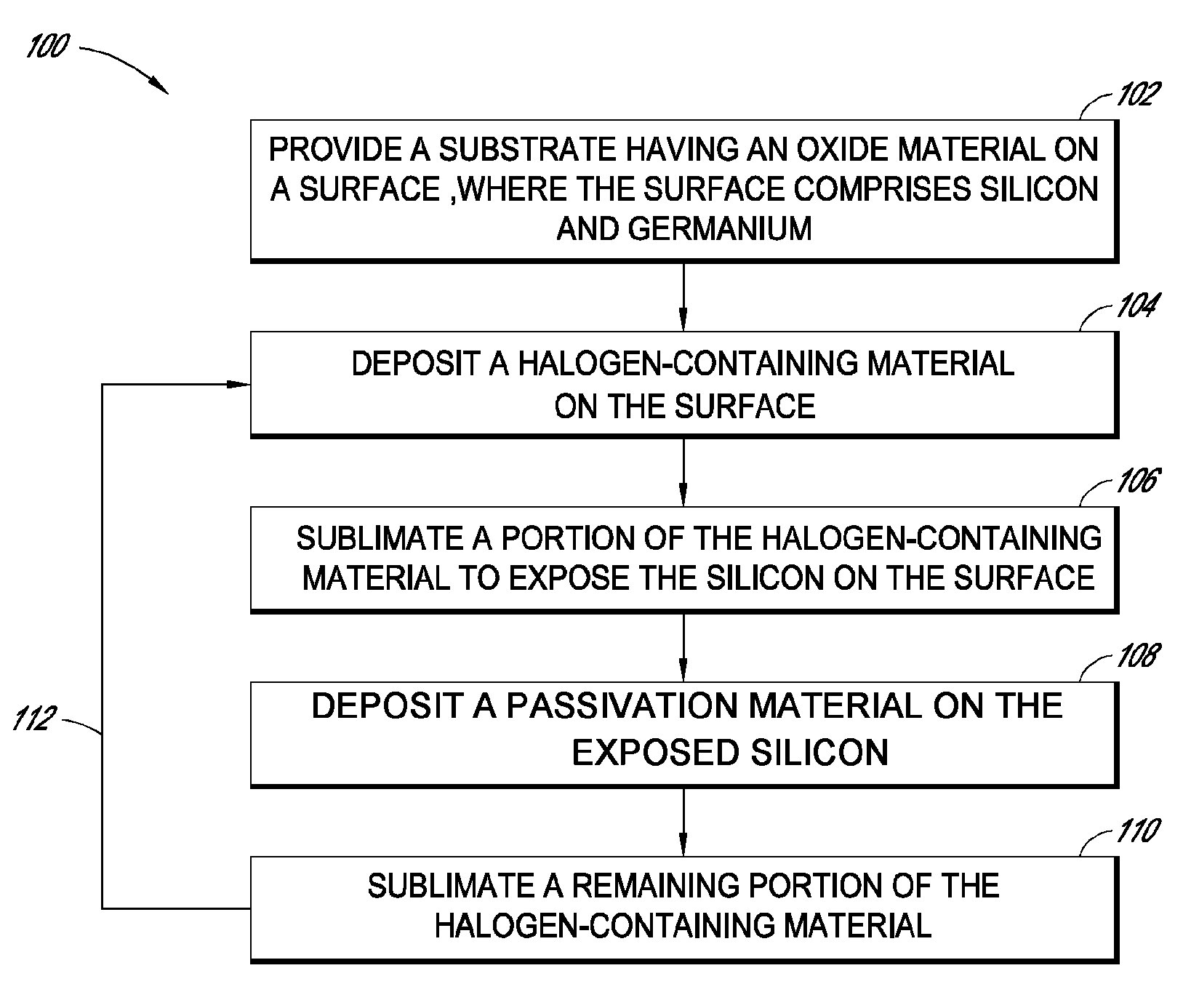

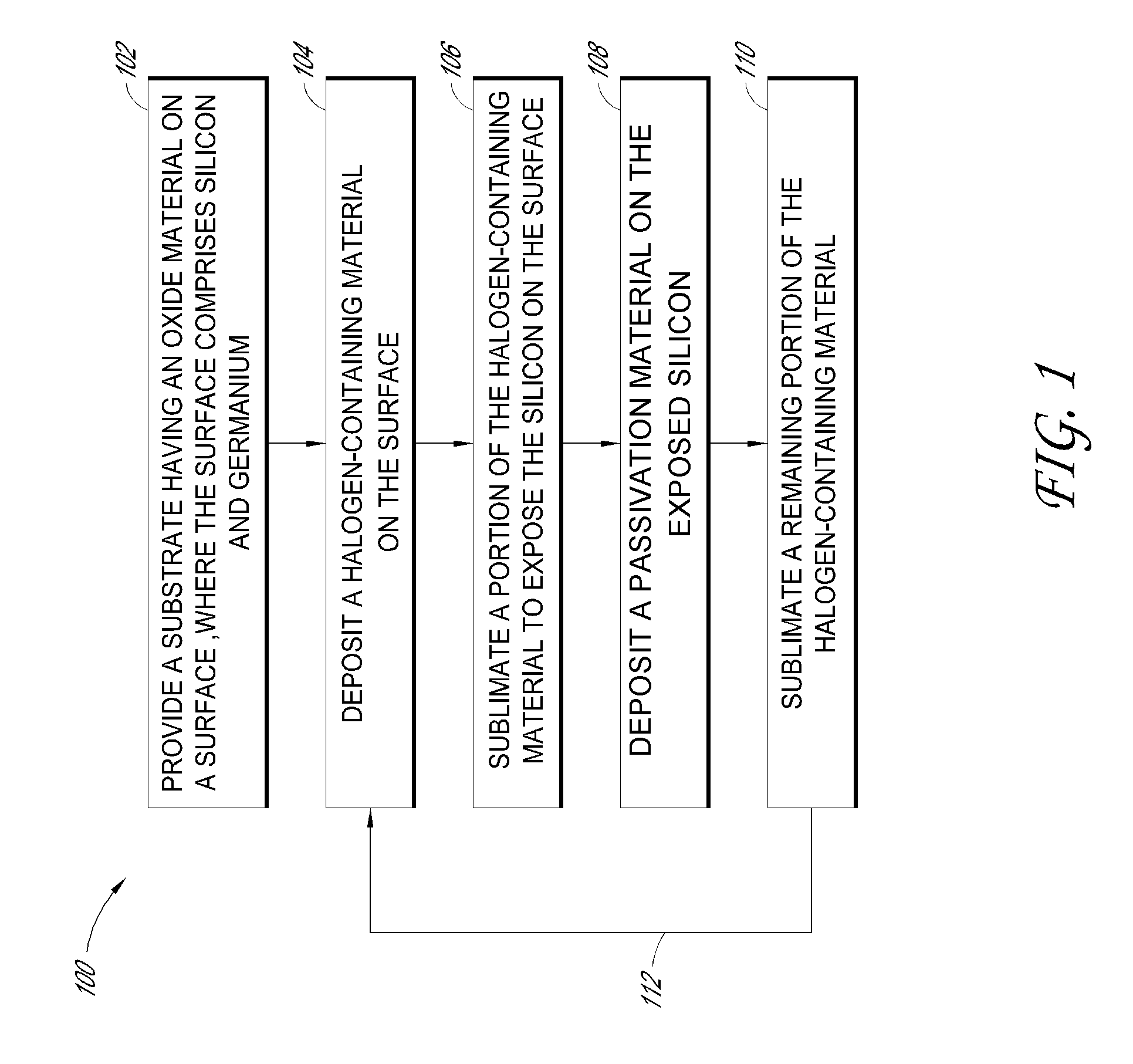

Germanium oxide pre-clean module and process

ActiveUS9474163B2Printed circuit liquid treatmentSemiconductor/solid-state device manufacturingChemical speciesHalogen

In some embodiments, a method for integrated circuit fabrication includes removing oxide material from a surface of a substrate, where the surface includes silicon and germanium. Removing the oxide material includes depositing a halogen-containing pre-clean material on a silicon oxide-containing surface and sublimating a portion of the halogen-containing pre-clean material to expose the silicon on the surface. A passivation film is deposited on the exposed silicon. The passivation film may include chlorine. The passivation film may prevent contamination of the silicon surface by chemical species from the later sublimation, which may be at a higher temperature than the earlier sublimation. Subsequently, a remaining portion of the halogen-containing pre-clean material and the passivation film are sublimated. A target material, such as a conductive material, may subsequently be deposited on the substrate surface.

Owner:ASM IP HLDG BV

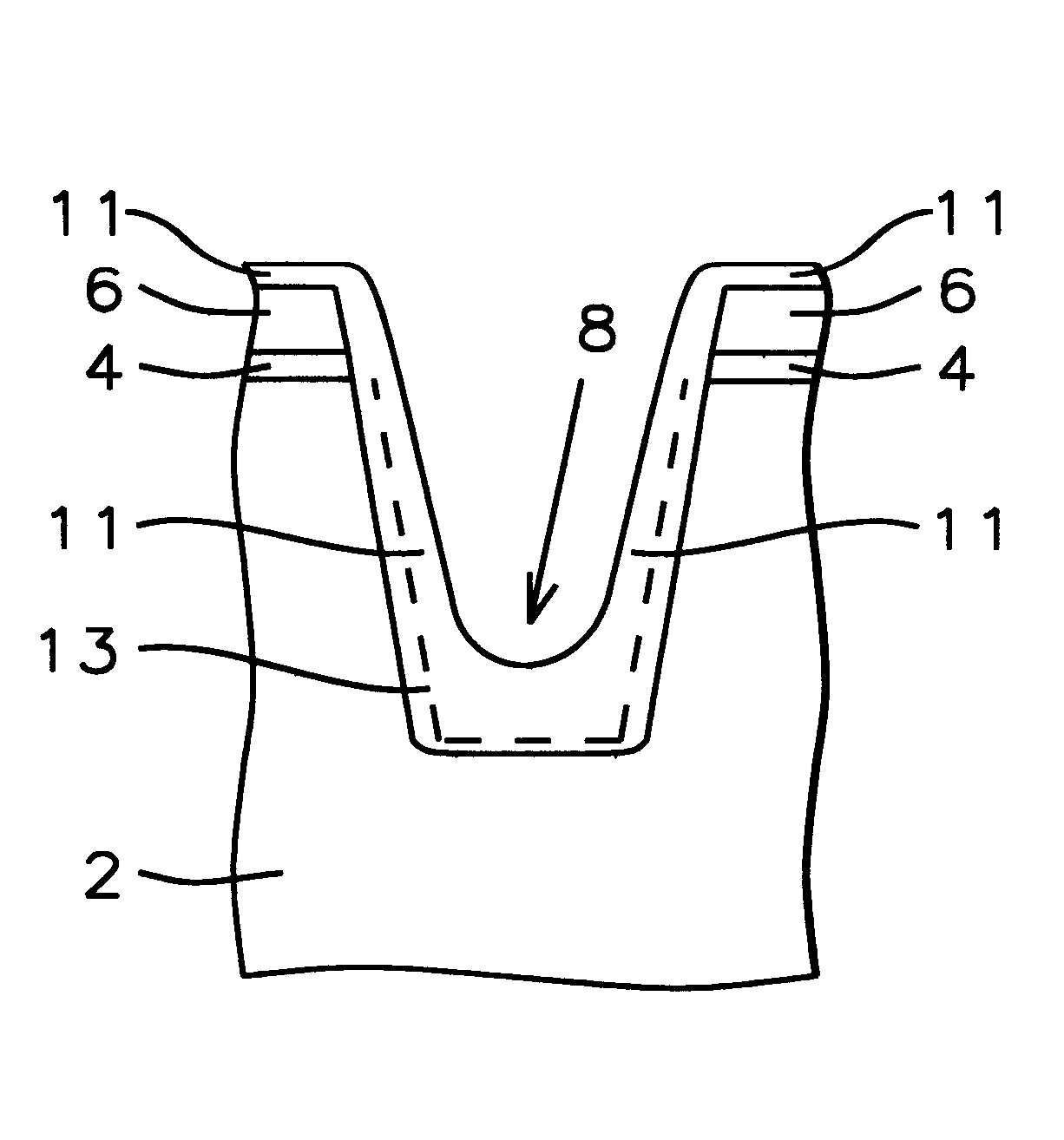

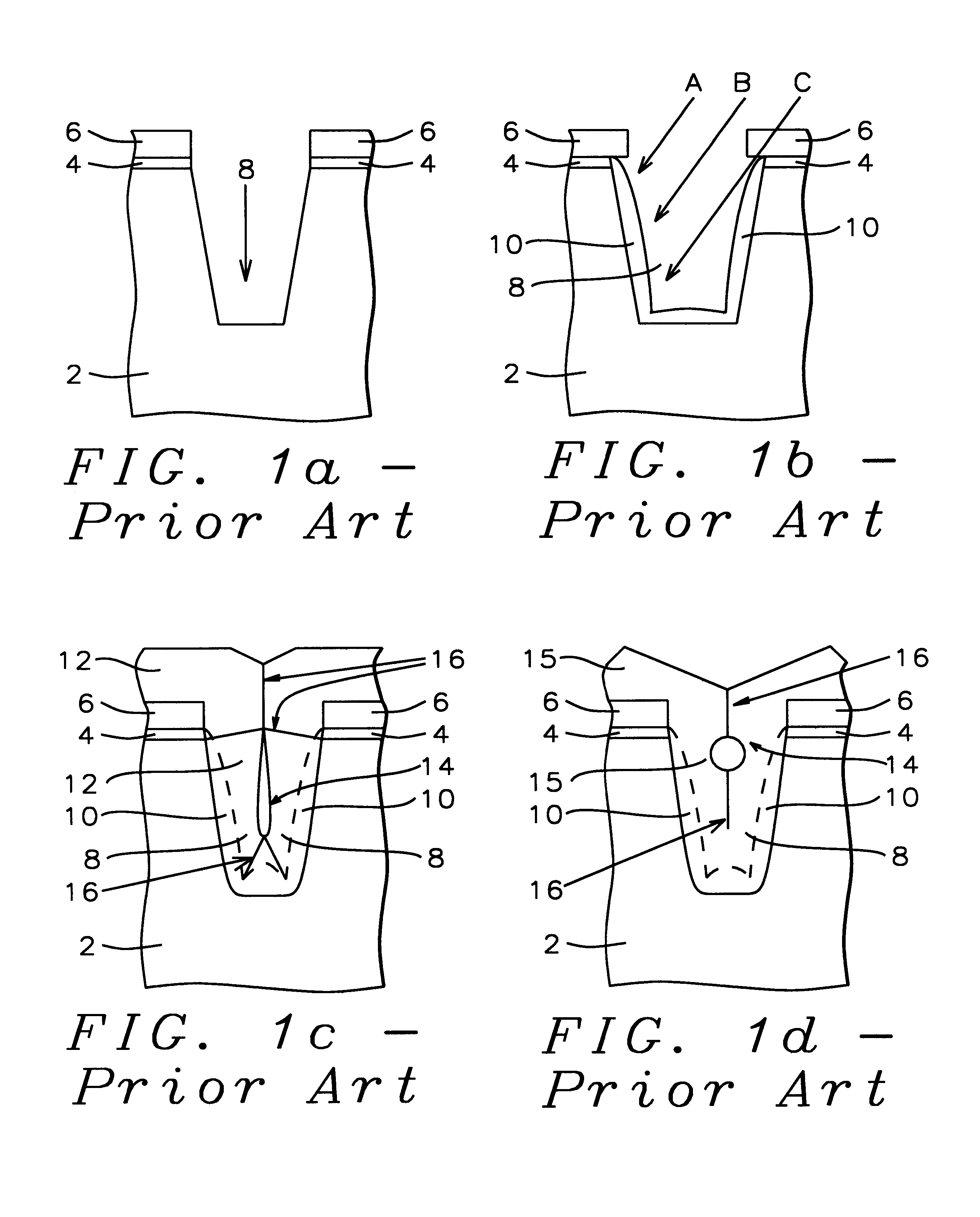

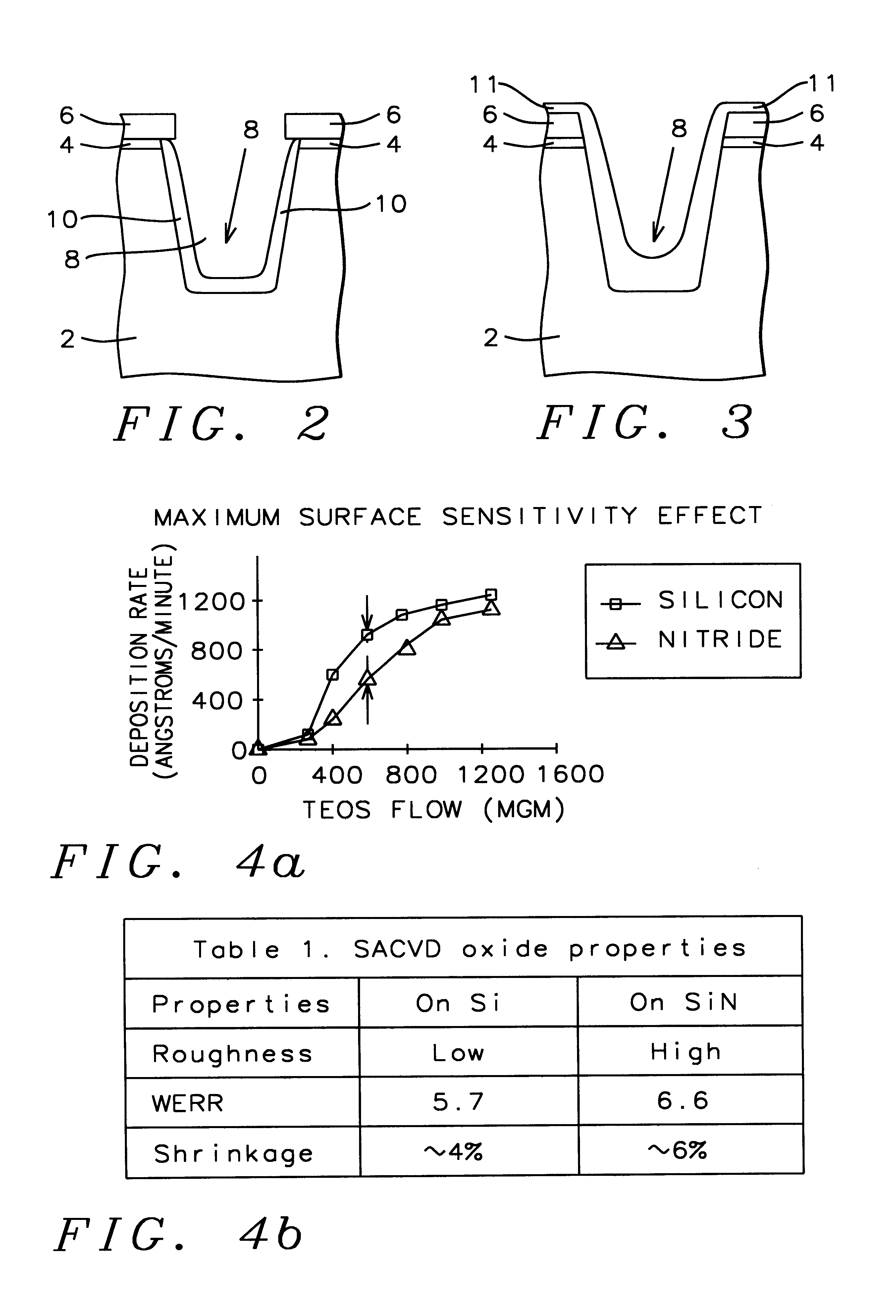

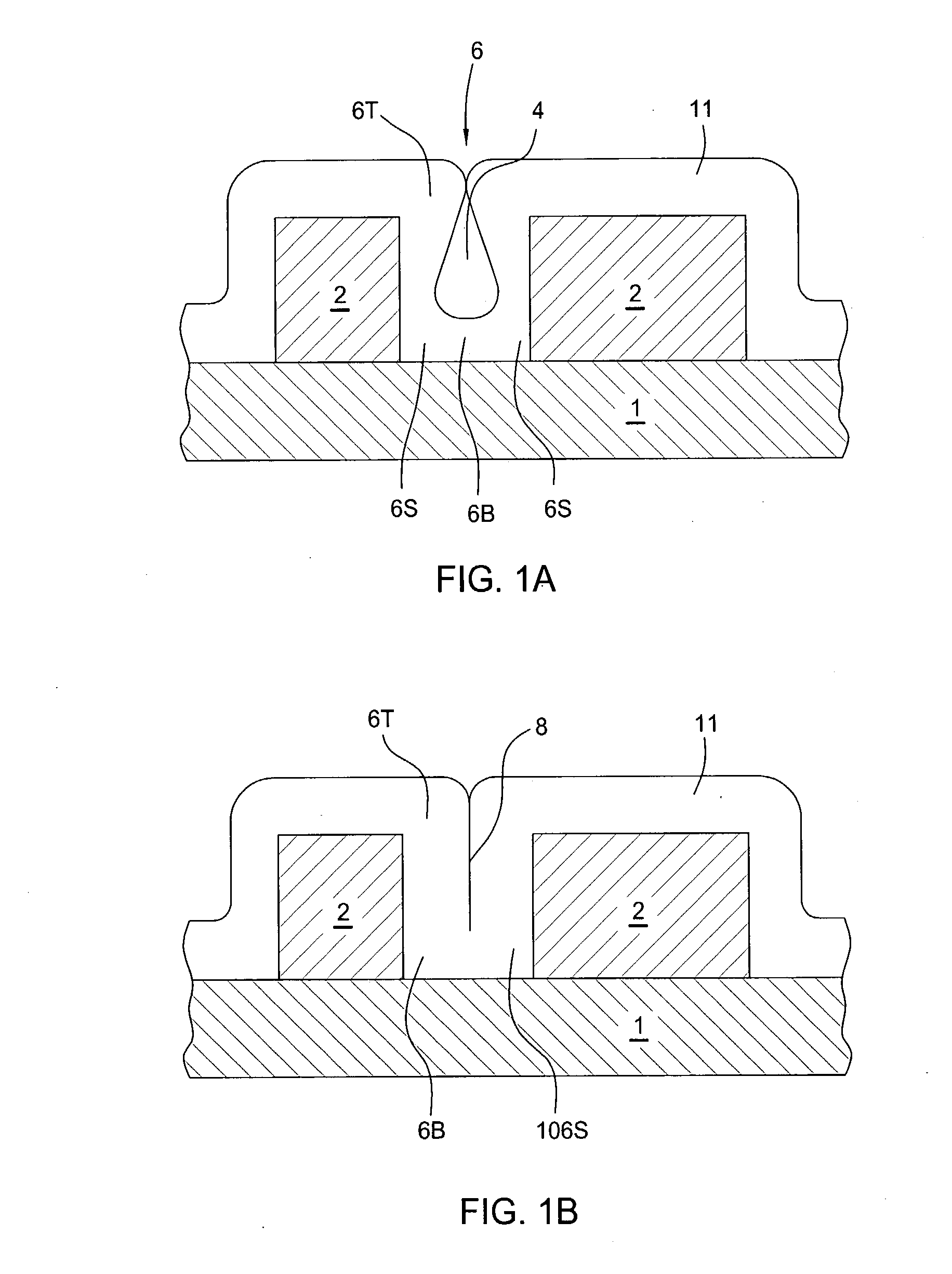

Method of filling shallow trenches

InactiveUS6180490B1Semiconductor/solid-state device manufacturingUnderlayIntegrated circuit fabrication

This invention relates to a method of fabrication used for semiconductor integrated circuit devices, and more specifically to an improved method of filling shallow trenches, in shallow trench isolation, STI sub-quarter micron technology. The present method relates to a process for forming trench gap filling with chemically vapor deposited (CVD) silicon dioxide layers within trenches within substrates employed in integrated circuit fabrication.There is first provided a silicon substrate having a trench formed therein. There is then formed a silicon dioxide layer through tetraethylorthosilicate (TEOS) and ozone reaction, at either sub-atmospheric, or atmospheric pressure, with enhanced surface sensitivity features, which lines the trench providing corner rounding. Then there is a thermal oxidation to form within the trench a thermal silicon dioxide layer underneath the TEOS-ozone trench silicon dioxide liner. Finally, there is formed on top of the trench a silicon dioxide layer formed by either low pressure CVD using TEOS, or non-surface sensitive TEOS ozone CVD, or a high-density plasma CVD process. All layers are further annealed to form a void-free trench fill.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

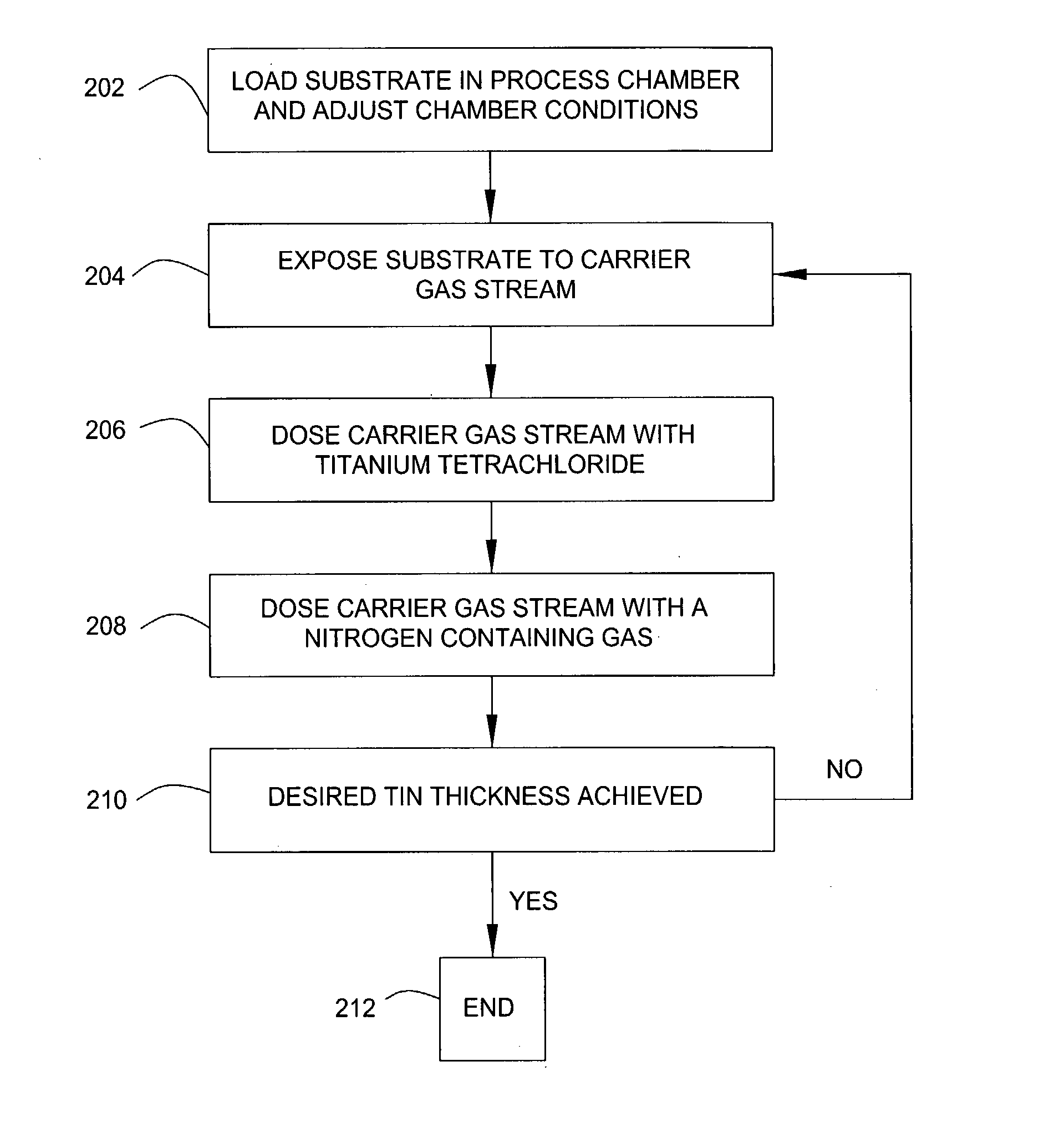

Formation of titanium nitride films using a cyclical deposition process

InactiveUS20040013803A1Natural mineral layered productsChemical vapor deposition coatingTitanium nitrideDeposition process

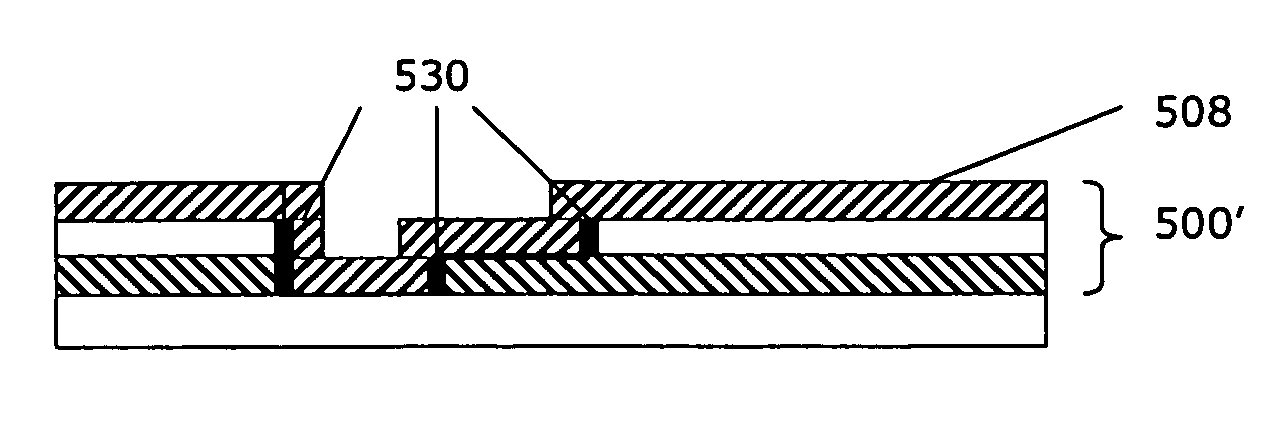

Methods of depositing titanium nitride (TiN) films on a substrate are disclosed. The titanium nitride (TiN) films may be formed using a cyclical deposition process by alternately adsorbing a titanium-containing precursor and a NH3 gas on the substrate. The titanium-containing precursor and the NH3 gas react to form the titanium nitride (TiN) layer on the substrate. The titanium nitride (TiN) films are compatible with integrated circuit fabrication processes. In one integrated circuit fabrication process, an interconnect structure is fabricated. The titanium nitride films may also be used as an electrode of a three-dimensional capacitor structure such as for example, trench capacitors and crown capacitors.

Owner:APPLIED MATERIALS INC

Process for reducing copper oxide during integrated circuit fabrication

InactiveUS6033584ADecorative surface effectsSemiconductor/solid-state device manufacturingCopper interconnectCopper oxide

A method of integrated circuit fabrication creating copper interconnect structures wherein the formation of copper oxide is reduced or eliminated by etching away the copper oxide performing an H2 plasma treatment in a plasma enhanced chemical vapor deposition chamber.

Owner:ADVANCED MICRO DEVICES INC

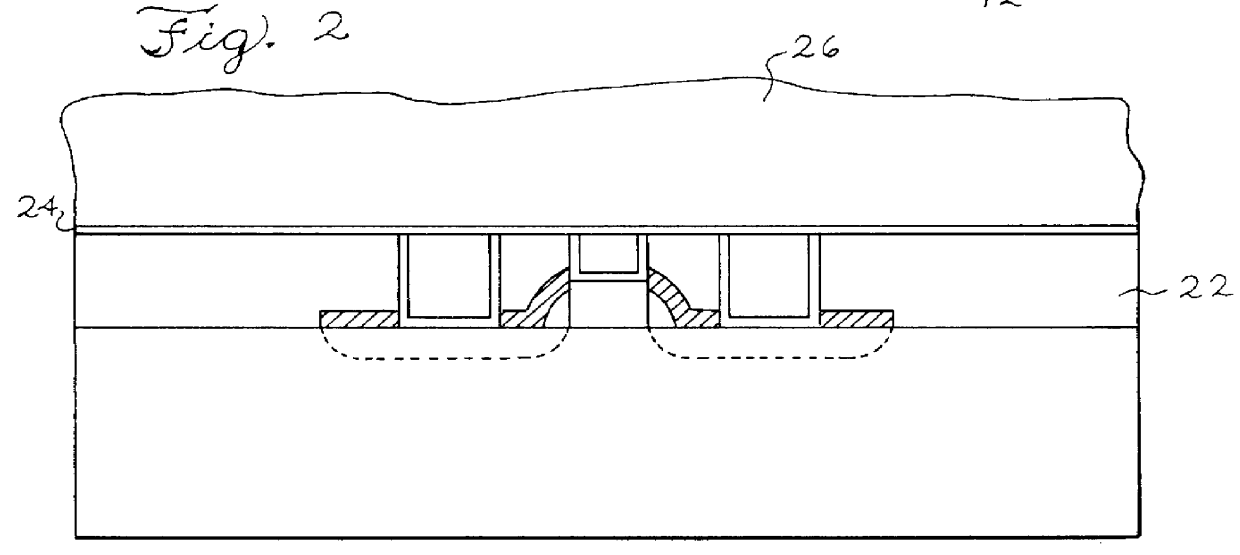

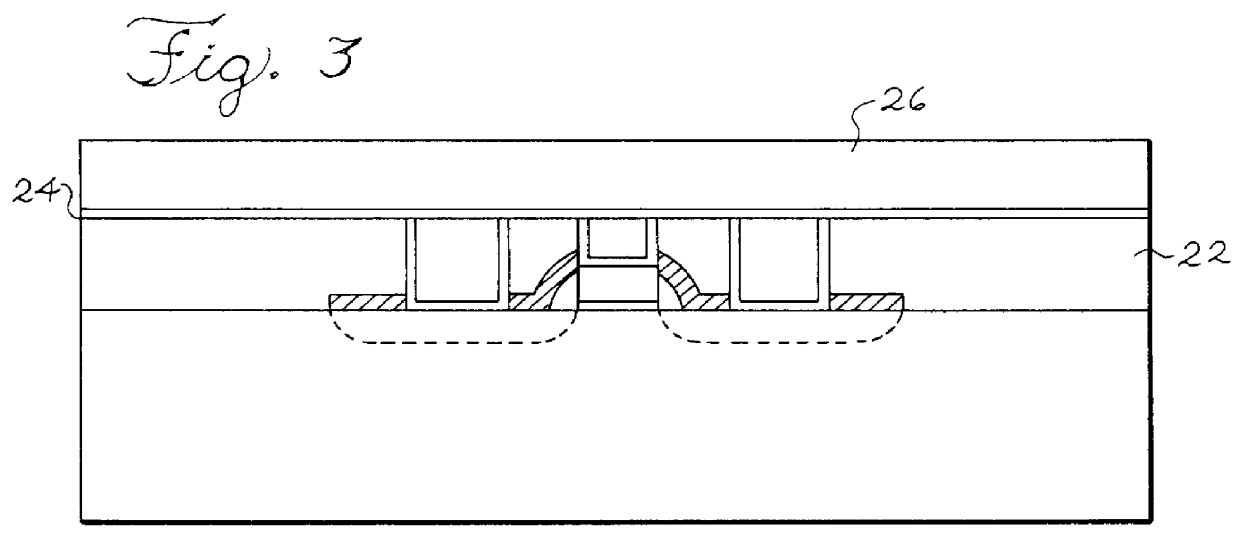

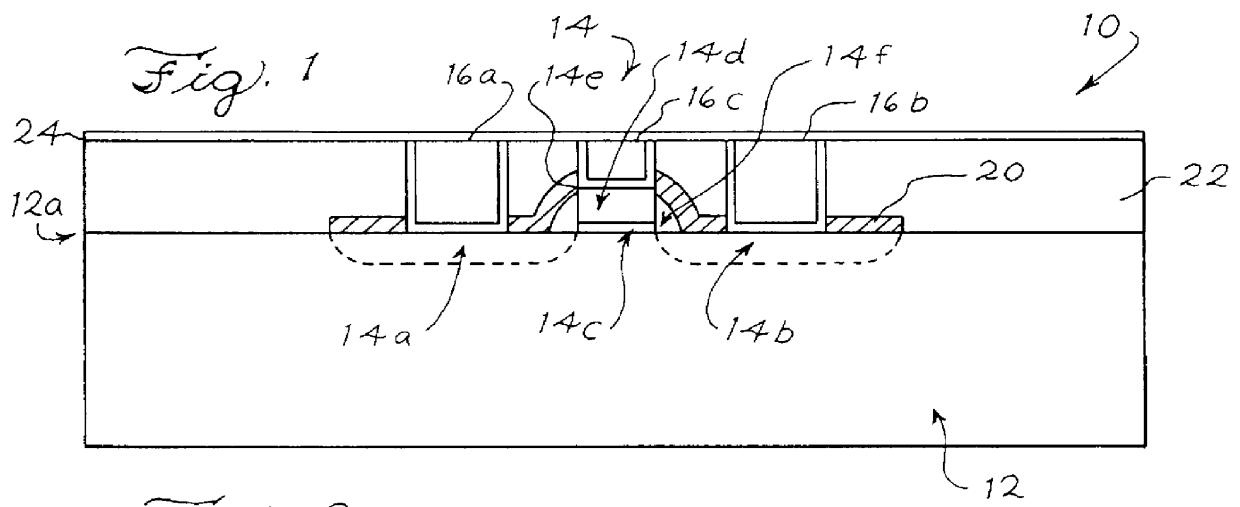

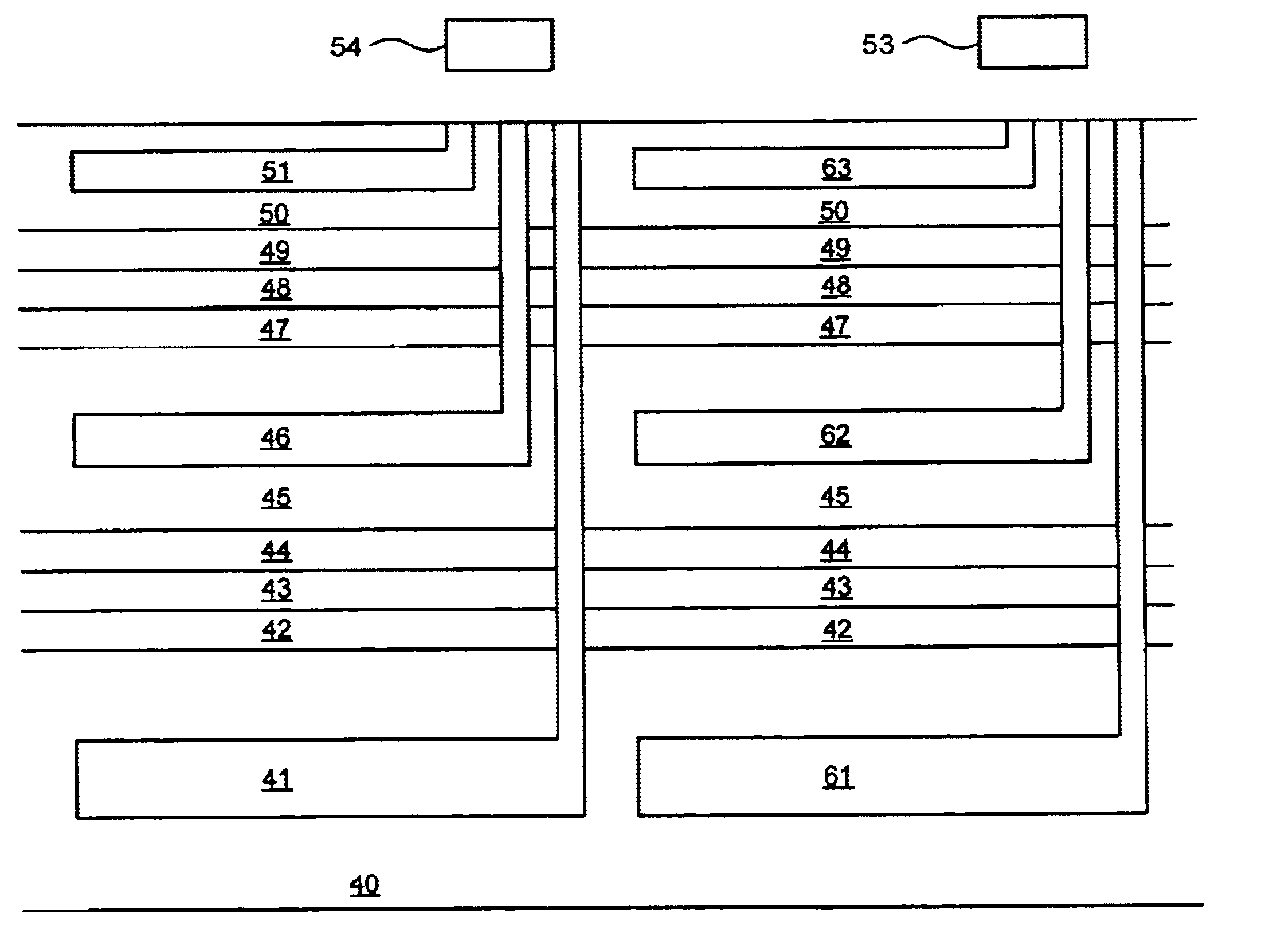

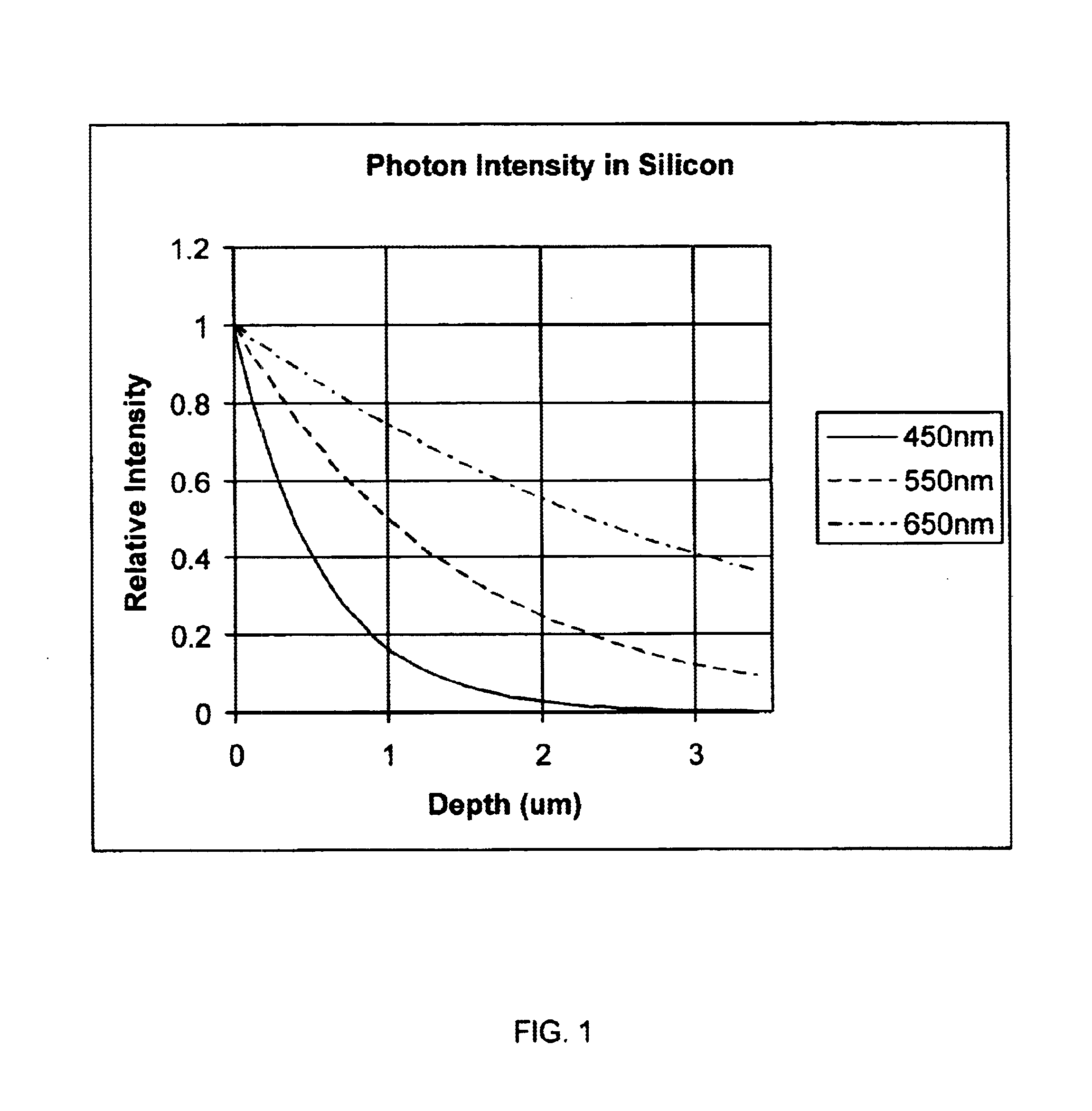

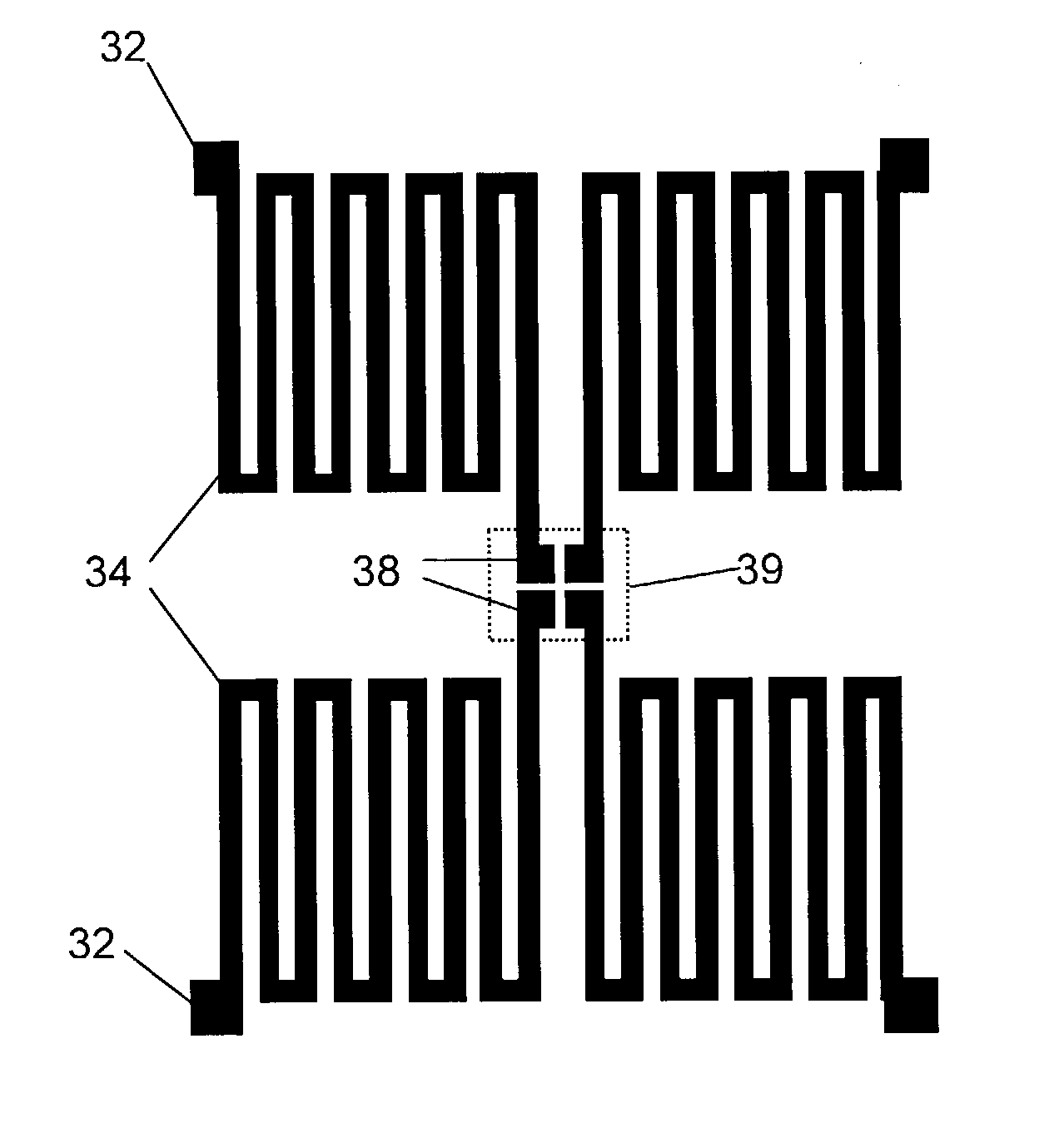

Vertical color filter sensor group with non-sensor filter and method for fabricating such a sensor group

InactiveUS6841816B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorMicrolens

A vertical color filter sensor group formed on a substrate (preferably a semiconductor substrate) and including at least two vertically stacked, photosensitive sensors. In preferred embodiments, the sensor group includes at least one filter positioned relative to the sensors such that radiation that has propagated through or reflected from the filter will propagate into at least one sensor. Preferably, the filter is or includes a layer that has been integrated with the sensors by a semiconductor integrated circuit fabrication process. In other embodiments, the sensor group includes a micro-lens. Other aspects of the invention are arrays of vertical color filter sensor groups, some or all of which include at least one filter or micro-lens, and methods for fabricating vertical color filter sensor groups and arrays thereof.

Owner:FOVEON

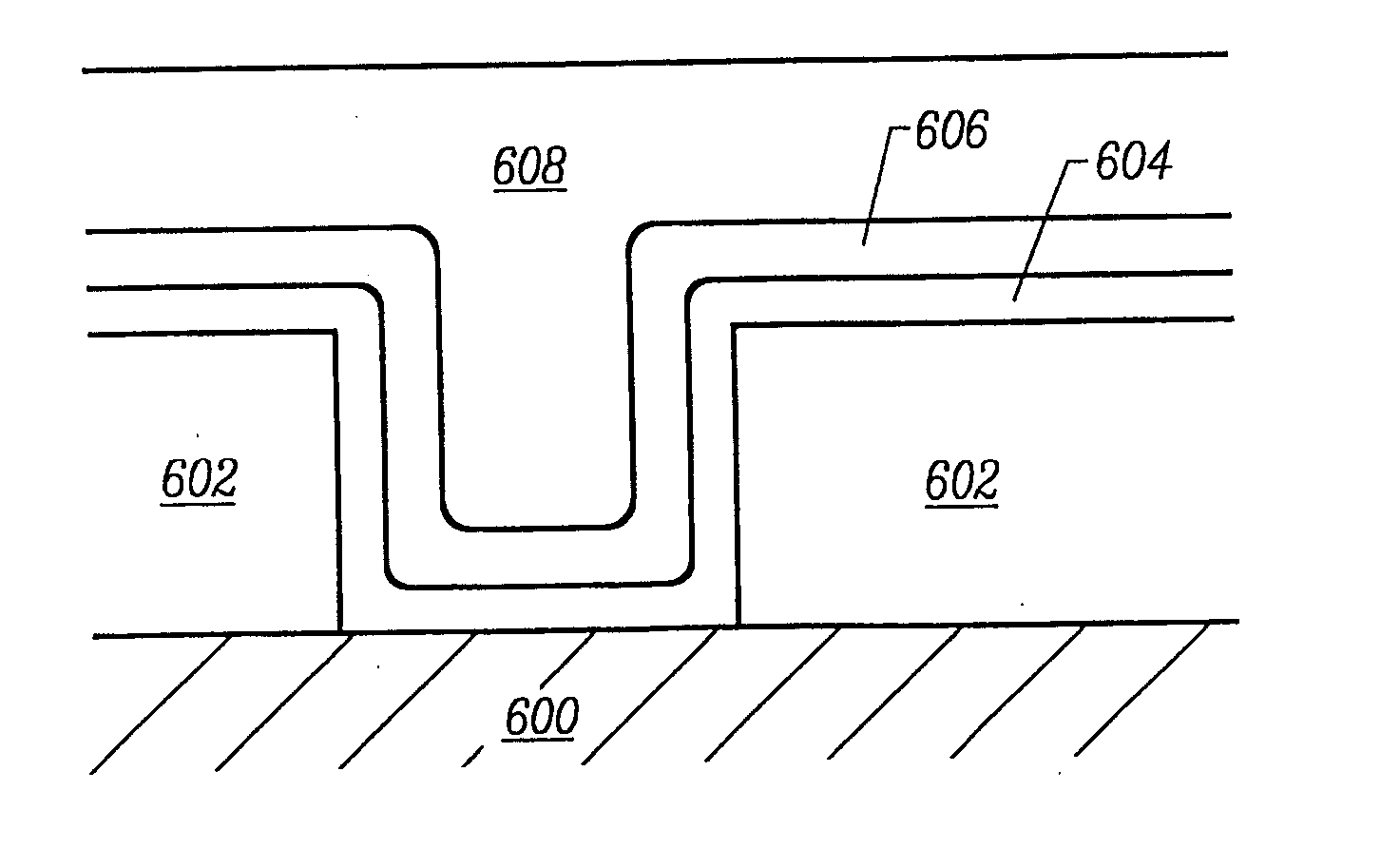

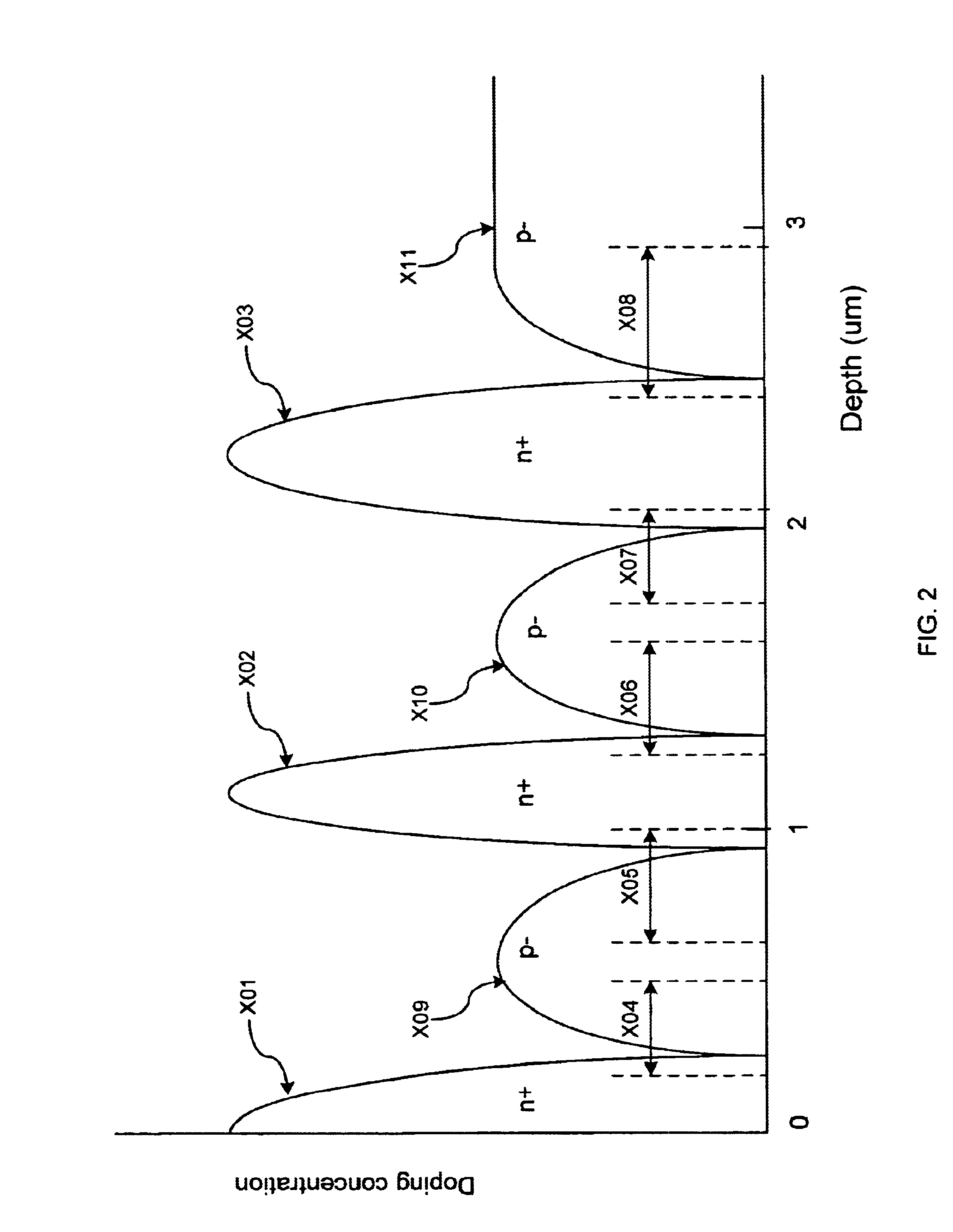

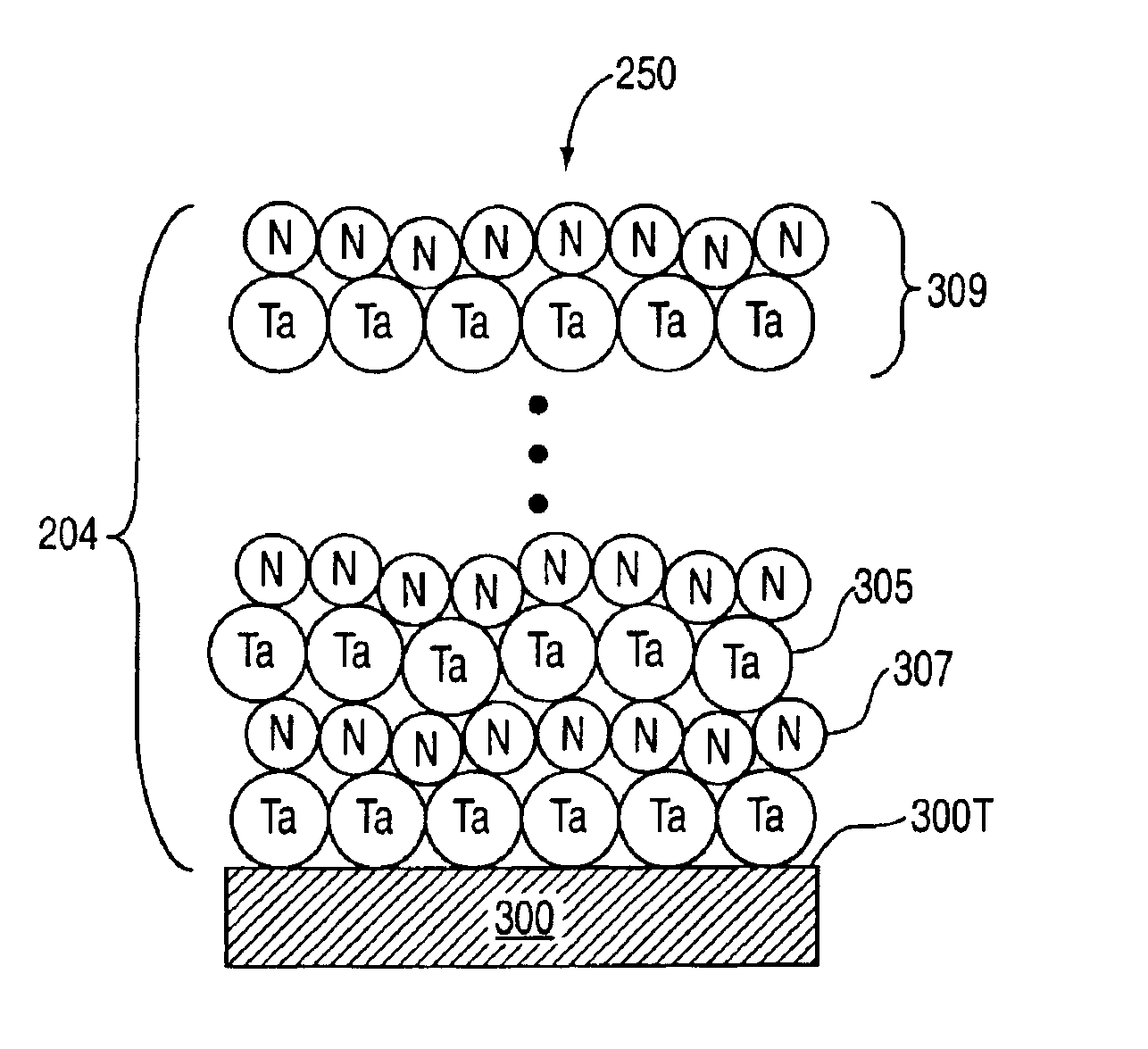

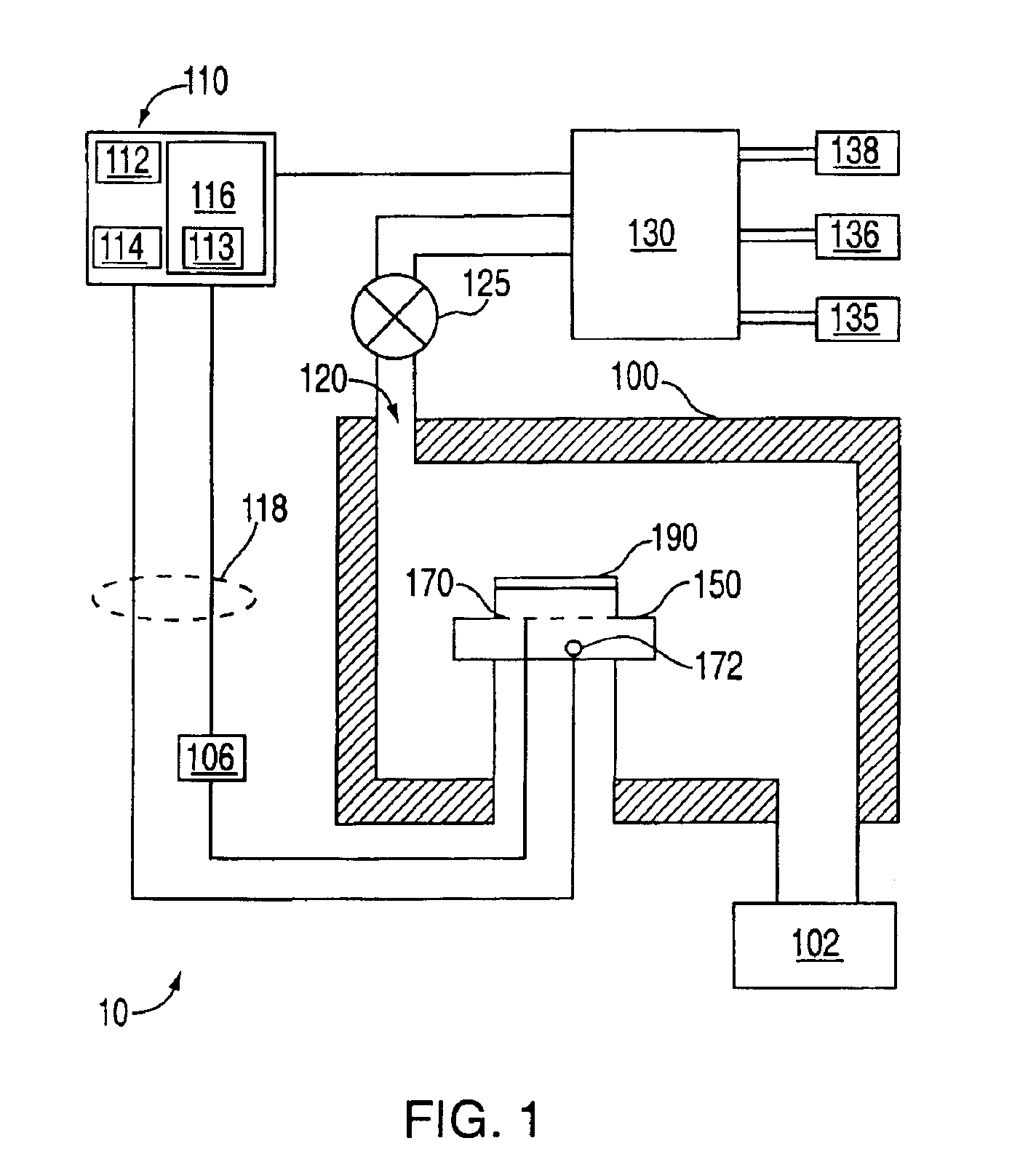

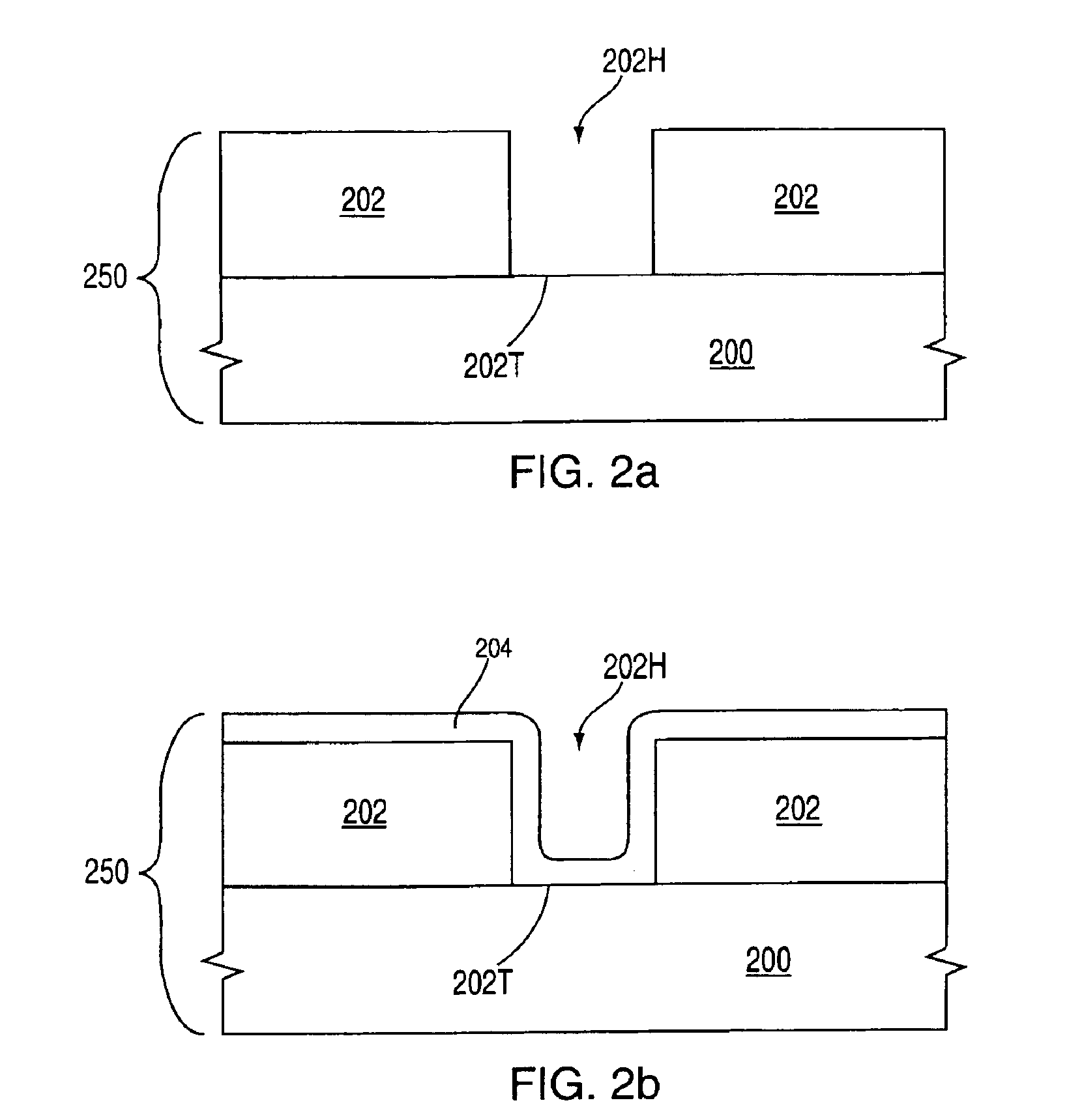

Formation of a tantalum-nitride layer

InactiveUS6951804B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal interconnectTantalum nitride

A method of forming a tantalum-nitride layer (204) for integrated circuit fabrication is disclosed. Alternating or co-reacting pulses of a tantalum containing precursor and a nitrogen containing precursor are provided to a chamber (100) to form layers (305, 307) of tantalum and nitrogen. The nitrogen precursor may be a plasma gas source. The resultant tantalum-nitride layer (204) may be used, for example, as a barrier layer. As barrier layers may be used with metal interconnect structures (206), at least one plasma anneal on the tantalum-nitride layer may be performed to reduce its resistivity and to improve film property.

Owner:APPLIED MATERIALS INC

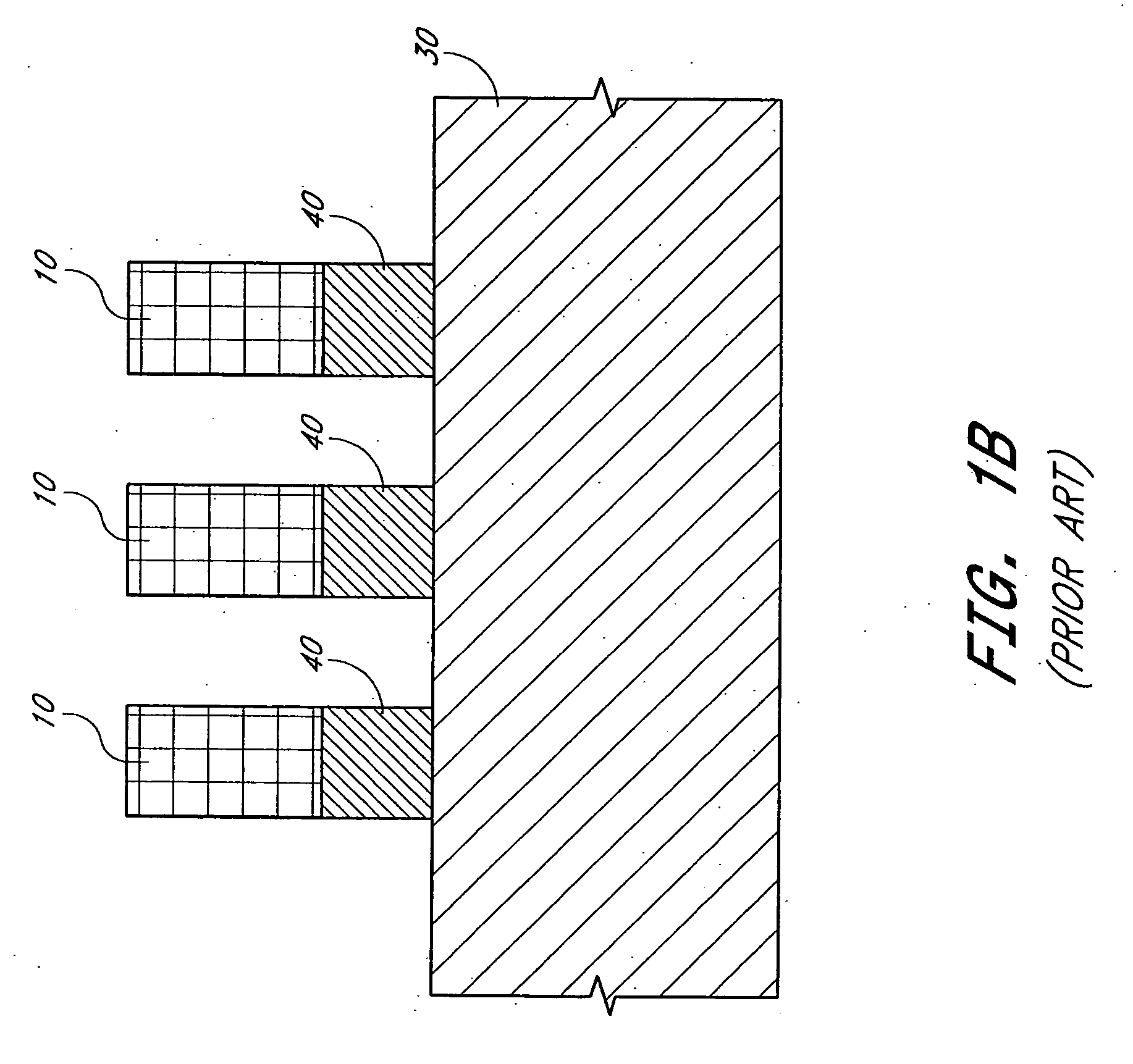

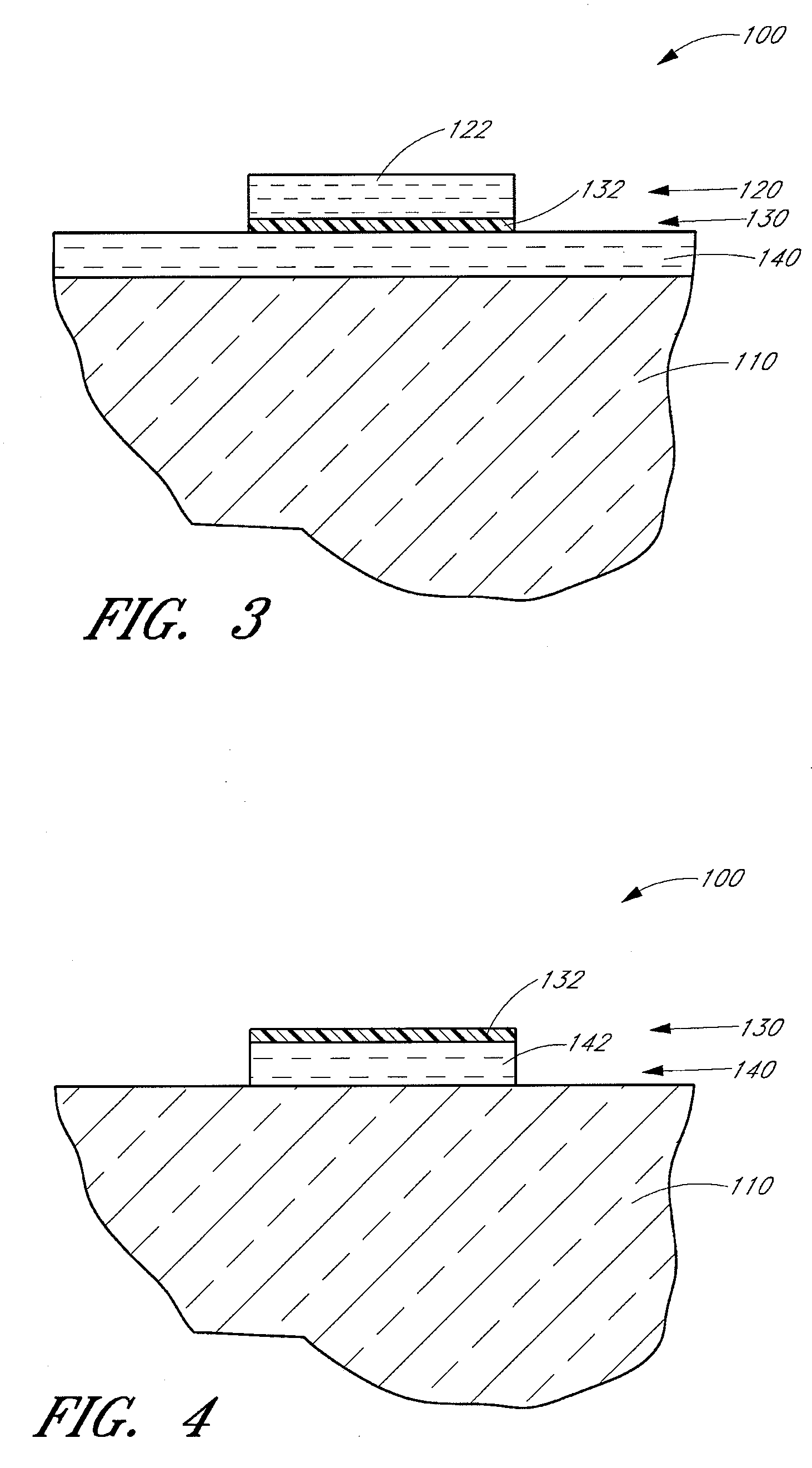

Topography directed patterning

A pattern having exceptionally small features is formed on a partially fabricated integrated circuit during integrated circuit fabrication. The pattern comprises features formed by self-organizing material, such as diblock copolymers. The organization of the copolymers is directed by spacers which have been formed by a pitch multiplication process in which spacers are formed at the sides of sacrificial mandrels, which are later removed to leave spaced-apart, free-standing spacers. Diblock copolymers, composed of two immiscible block species, are deposited over and in the space between the spacers. The copolymers are made to self-organize, with each block species aggregating with other block species of the same type.

Owner:MICRON TECH INC

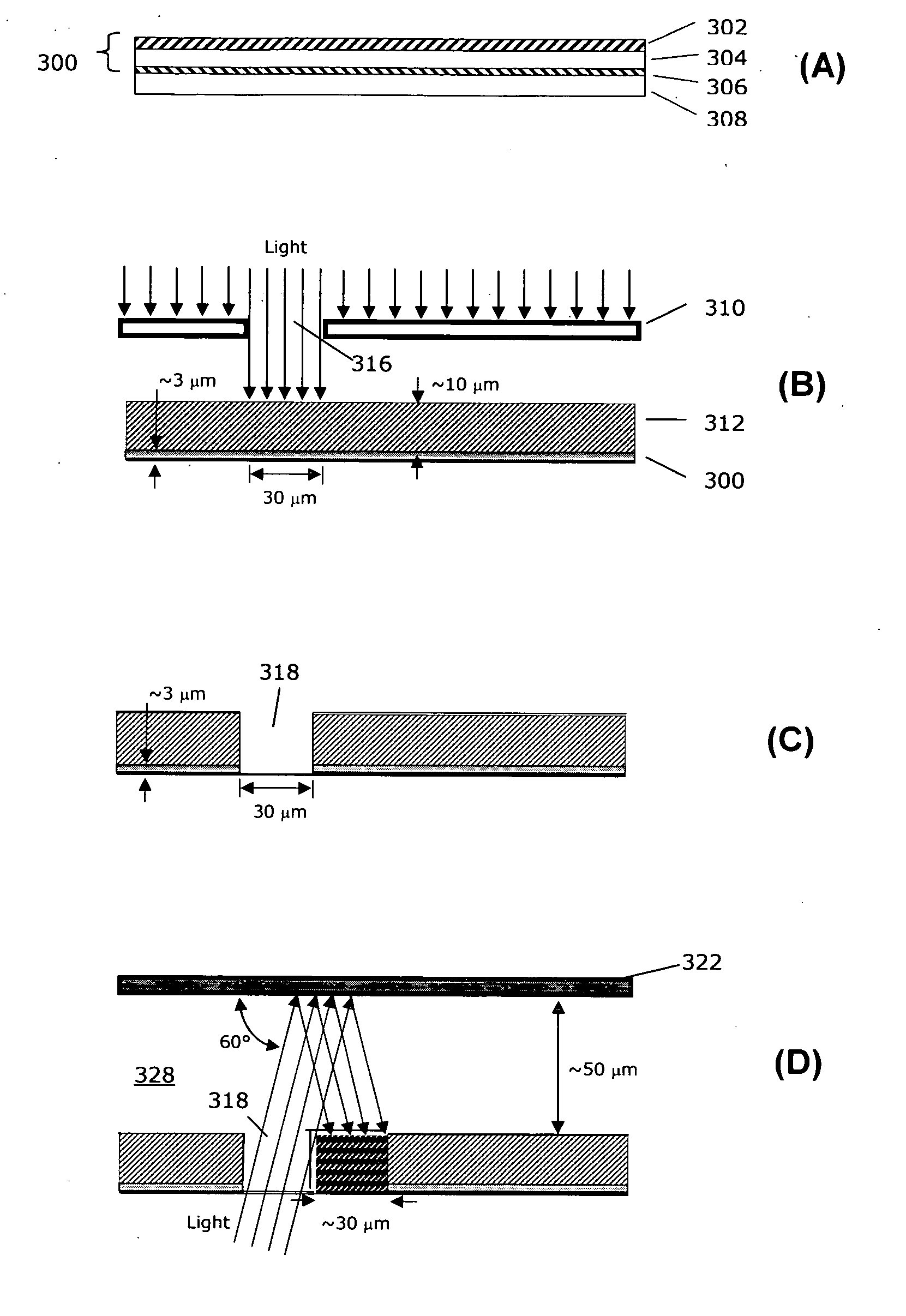

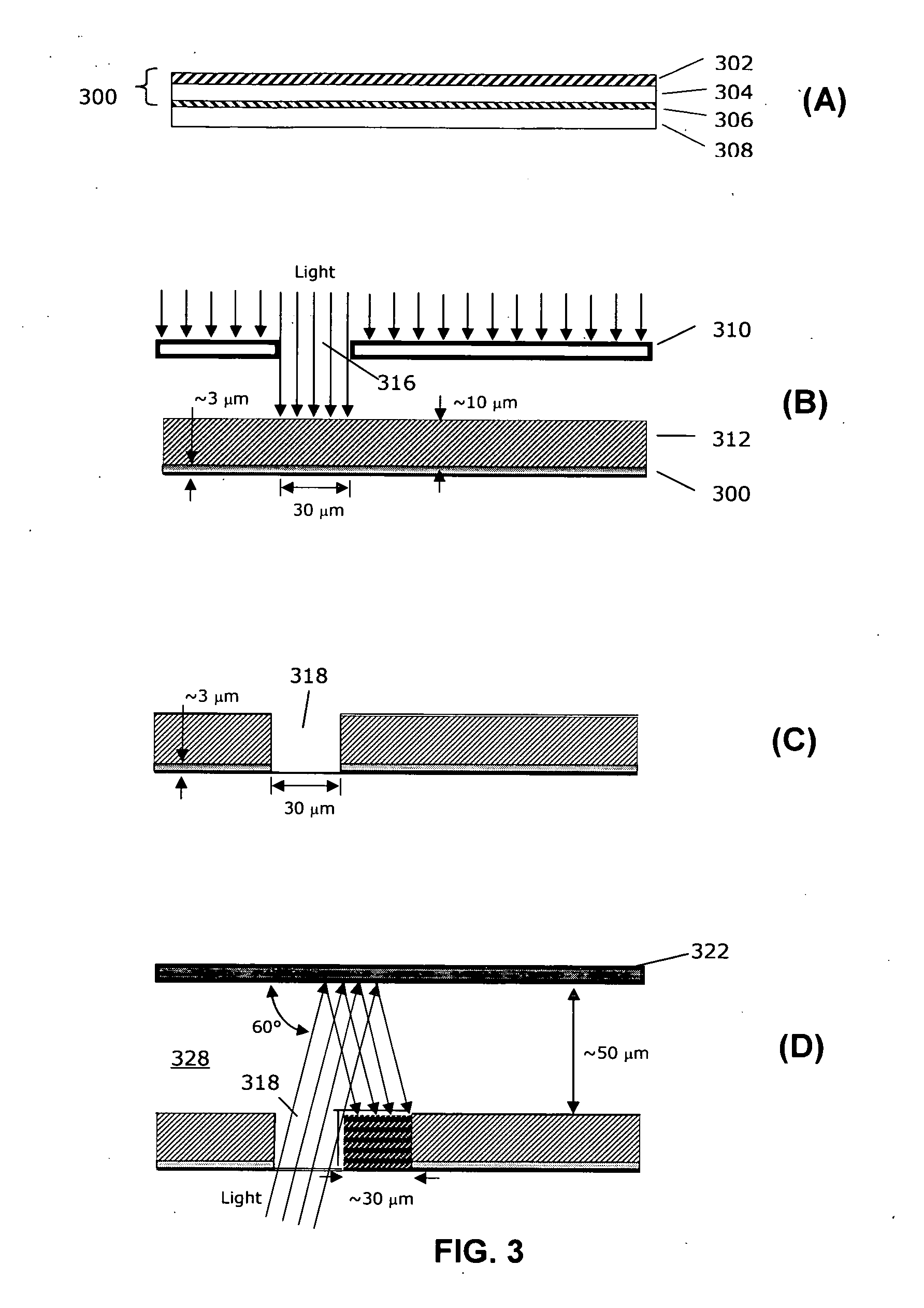

Method for making an improved thin film solar cell interconnect using etch and deposition process

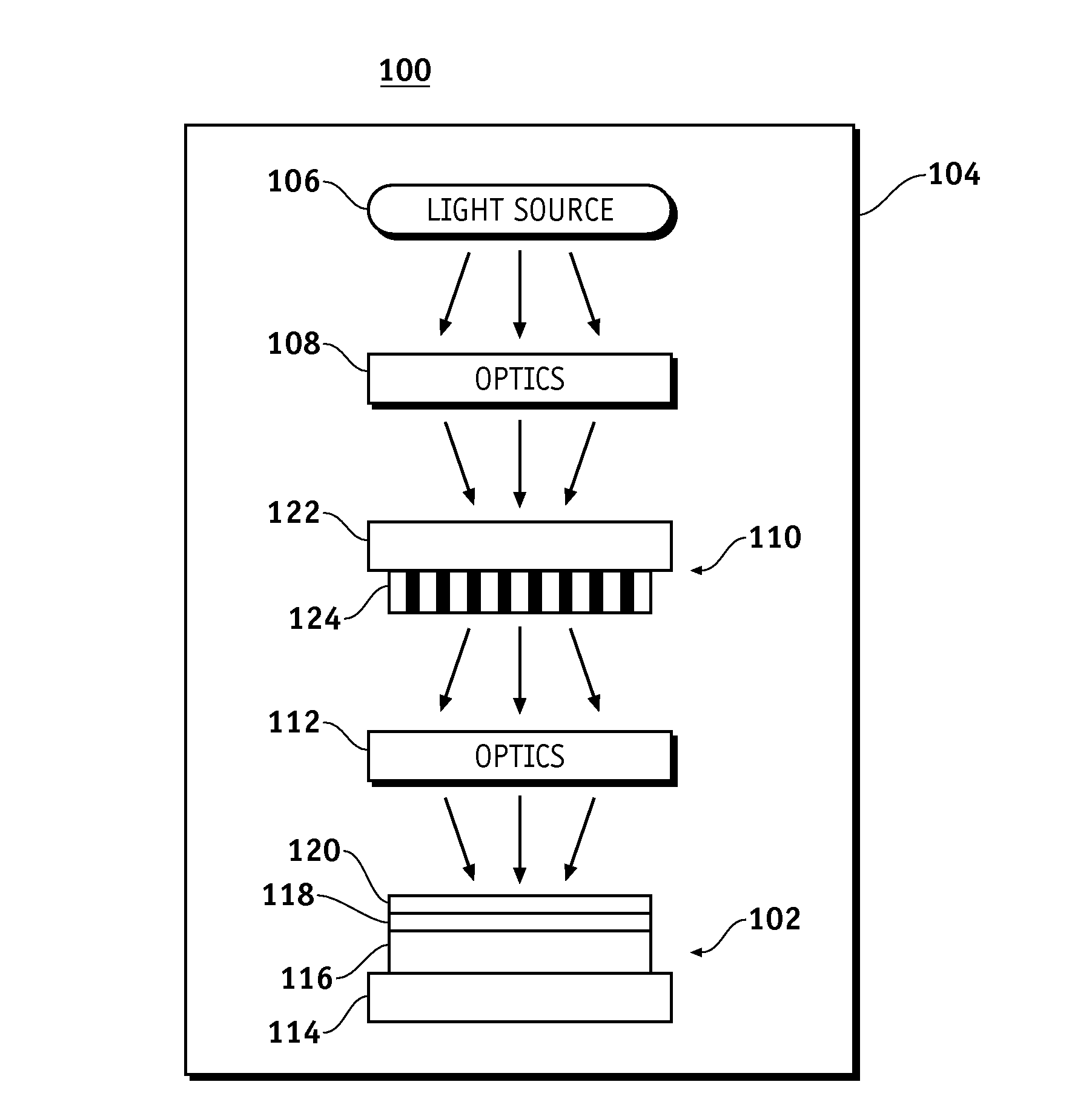

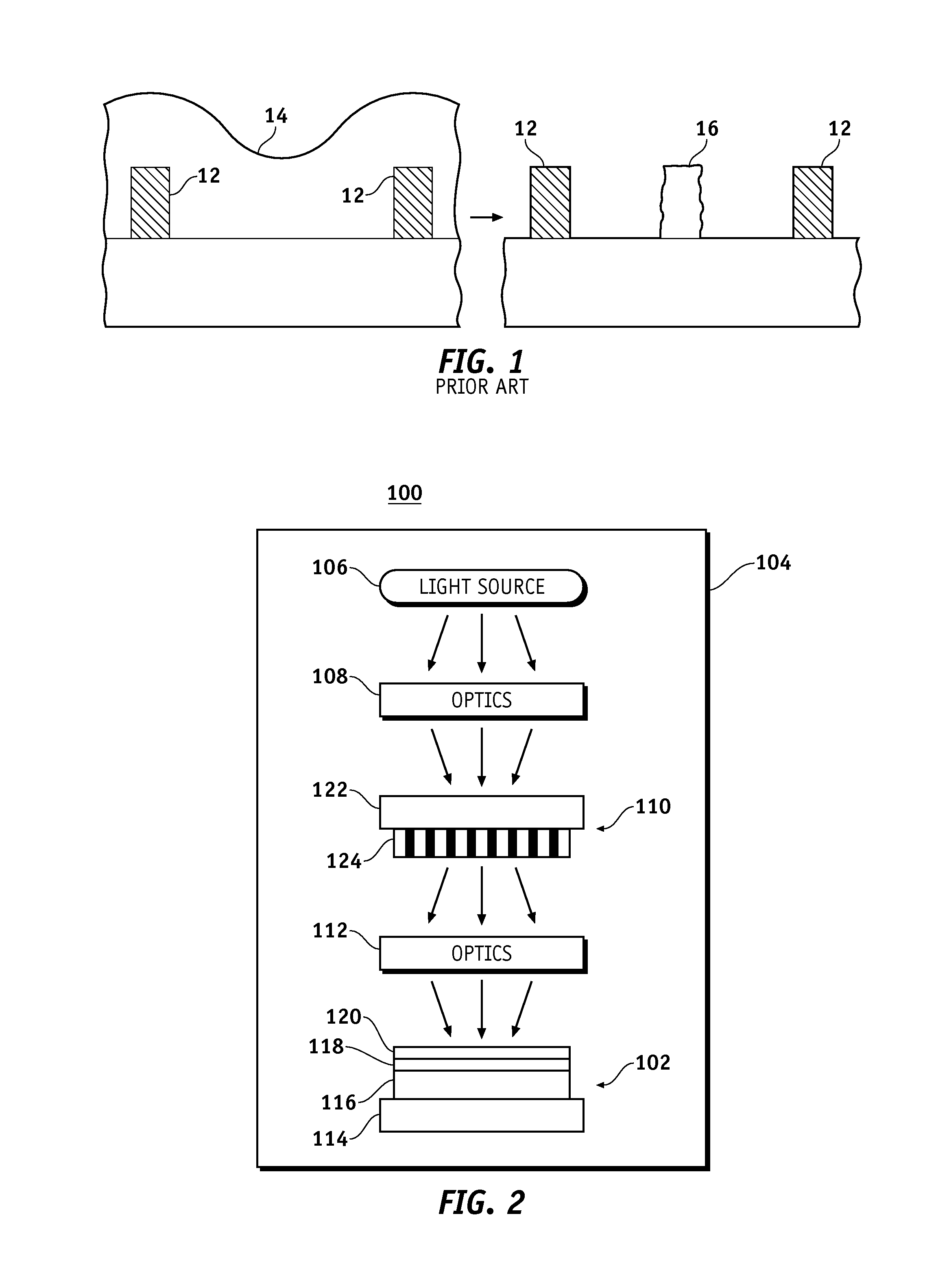

InactiveUS20070238285A1Improve current transportPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringDeposition process

The present invention provides a method of forming interconnects in a photovoltaic module. According to one aspect, a method according to the invention includes processing steps that are similar to those performed in conventional integrated circuit fabrication. For example, the method can include masks and etches to form isolation grooves between cells, and additional etches to form a conductive step adjacent to the grooves that can be used to form interconnects between cells. According to another aspect the method for forming the conductive step can be self-aligned, such as by positioning a mirror above the module and exposing photoresist from underneath the substrate at an angle one or more times, and etching to expose the conductive step. According to another aspect, the process can include steps to form grid lines in the module to improve current transport in the structure.

Owner:APPLIED MATERIALS INC

High fidelity multiple resist patterning

InactiveUS20080292991A1Accurate featuresPhotomechanical apparatusSemiconductor/solid-state device manufacturingPhotoresistHigh fidelity

An integrated circuit fabrication process as described herein employs a double photoresist exposure technique. After creation of a first pattern of photoresist features on a wafer, a second photoresist layer is formed over the first pattern of photoresist features. The second photoresist layer is subjected to a reflow step that softens and relaxes the second photoresist material. This reflow step causes the exposed surface of the second photoresist layer to become substantially planar. Thereafter, the second photoresist layer can be exposed and developed to create a second pattern of photoresist features on the wafer. The planar surface of the second photoresist layer, which results from the reflow step, facilitates the creation of accurate, precise, and “high fidelity” photoresist features from the second photoresist material.

Owner:GLOBALFOUNDRIES INC

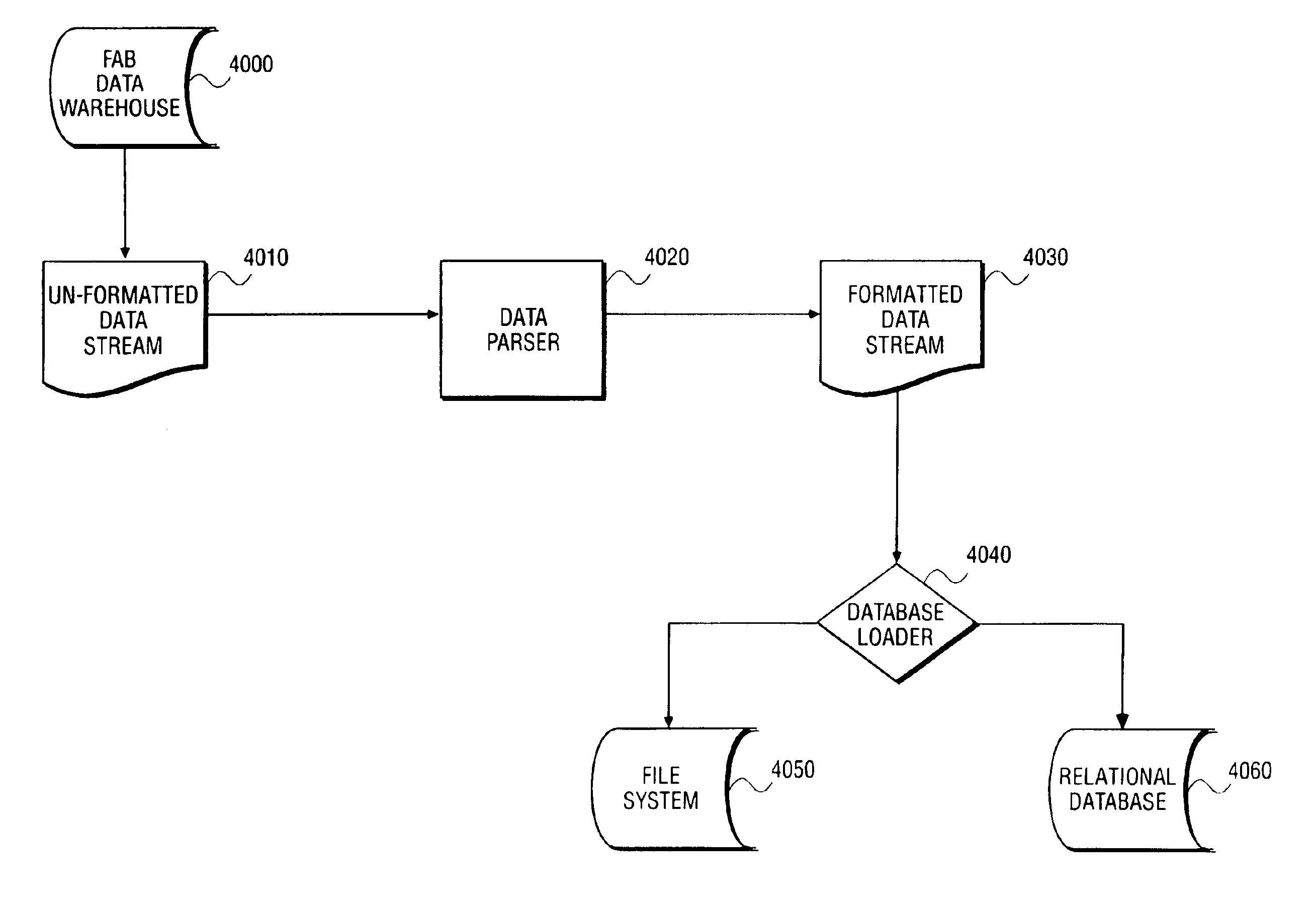

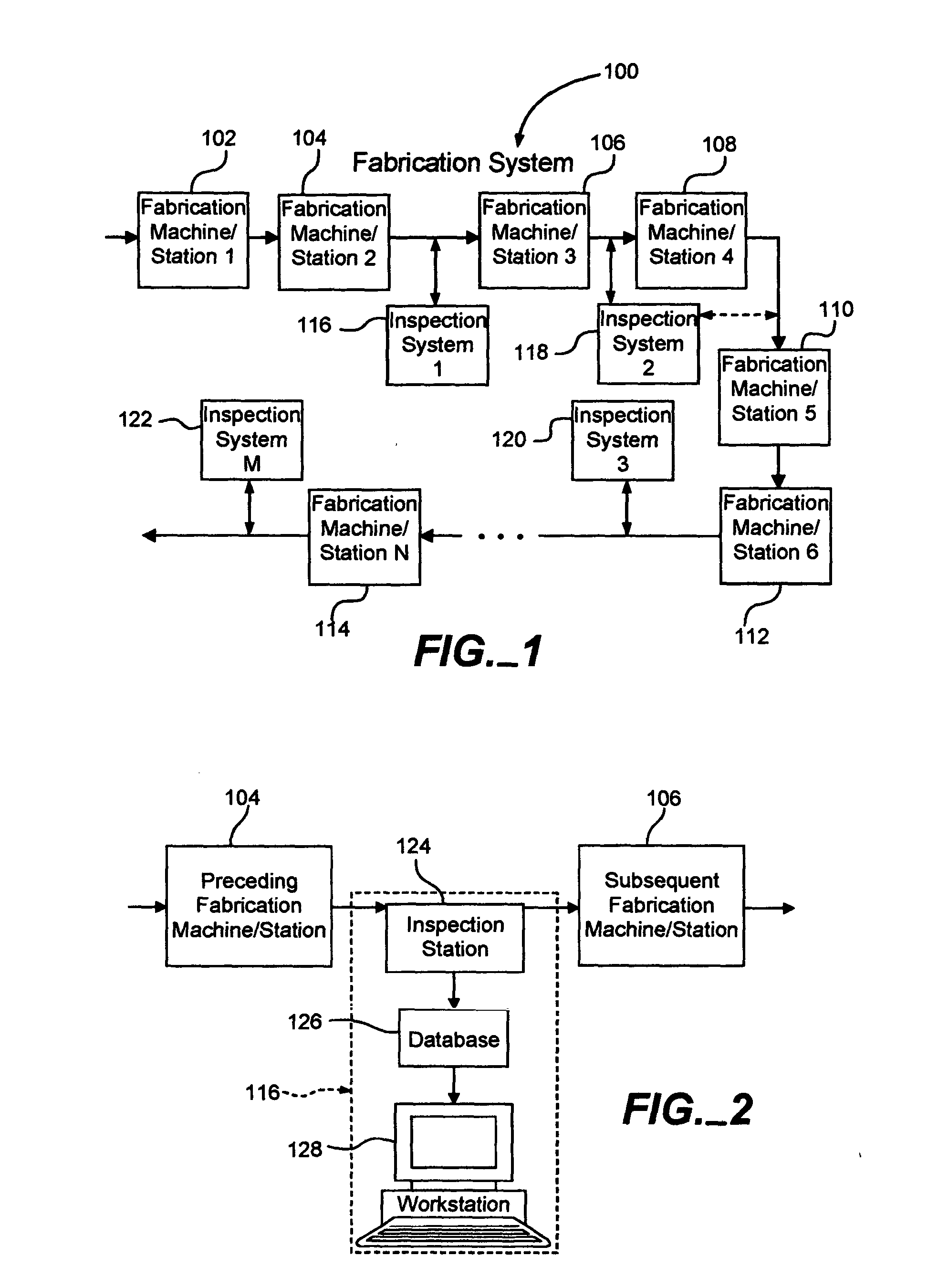

Method and apparatus for analyzing manufacturing data

A method for data mining information obtained in an integrated circuit fabrication factory (“fab”) that includes steps of: (a) gathering data from the fab from one or more of systems, tools, and databases that produce data in the fab or collect data from the fab; (b) formatting the data and storing the formatted data in a source database; (c) extracting portions of the data for use in data mining in accordance with a user specified configuration file; (d) data mining the extracted portions of data in response to a user specified analysis configuration file; (e) storing results of data mining in a results database; and (f) providing access to the results.

Owner:APPLIED MATERIALS INC

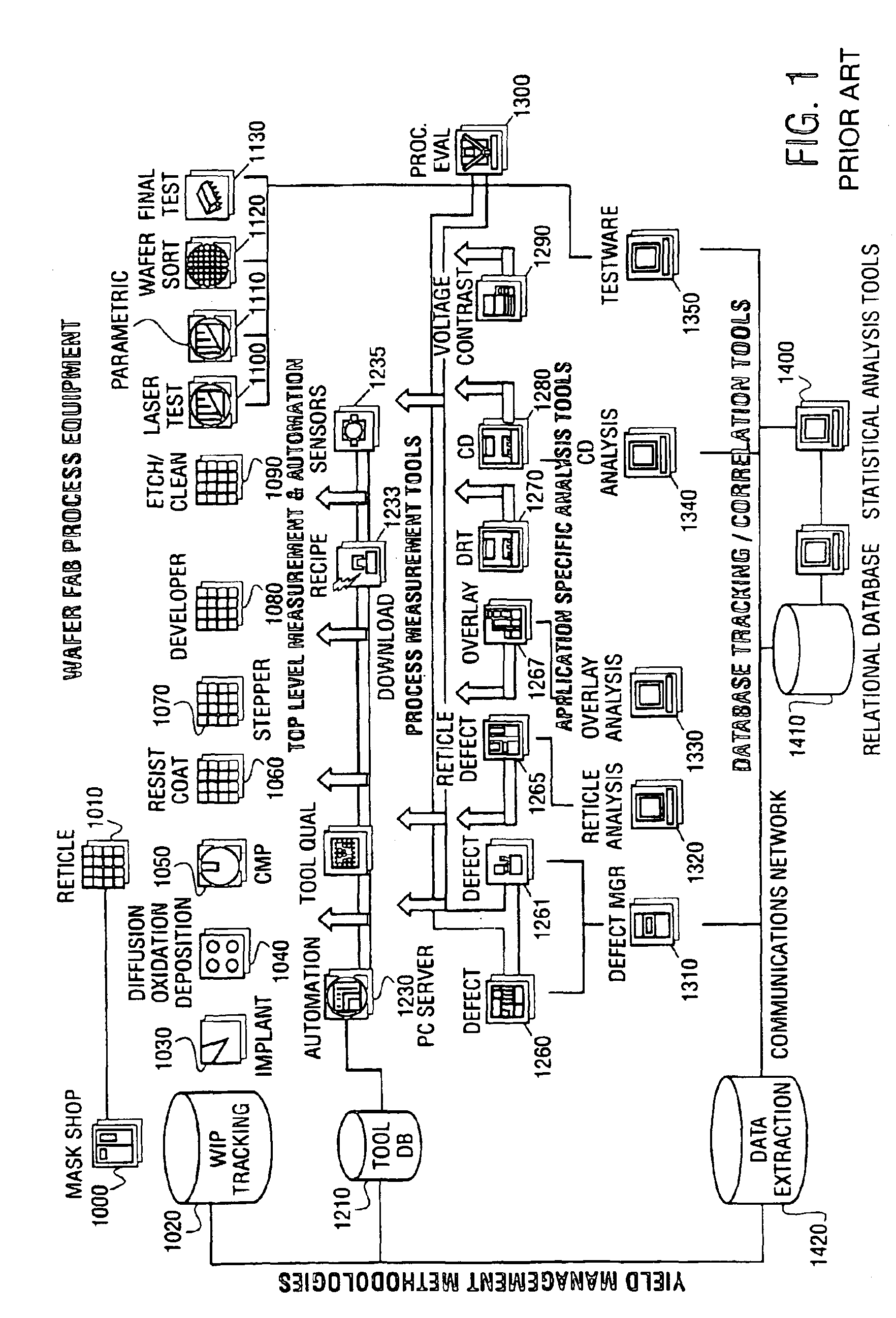

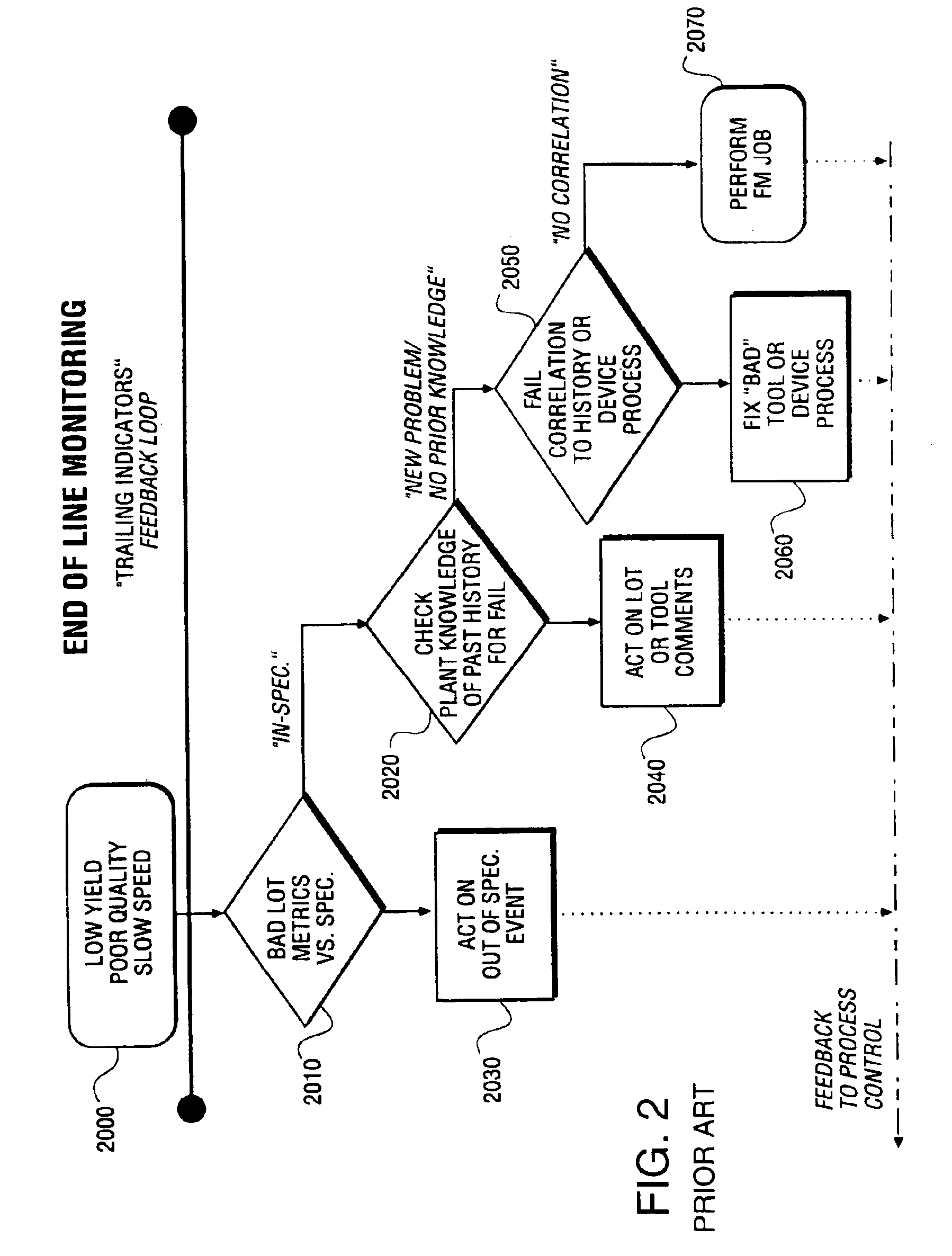

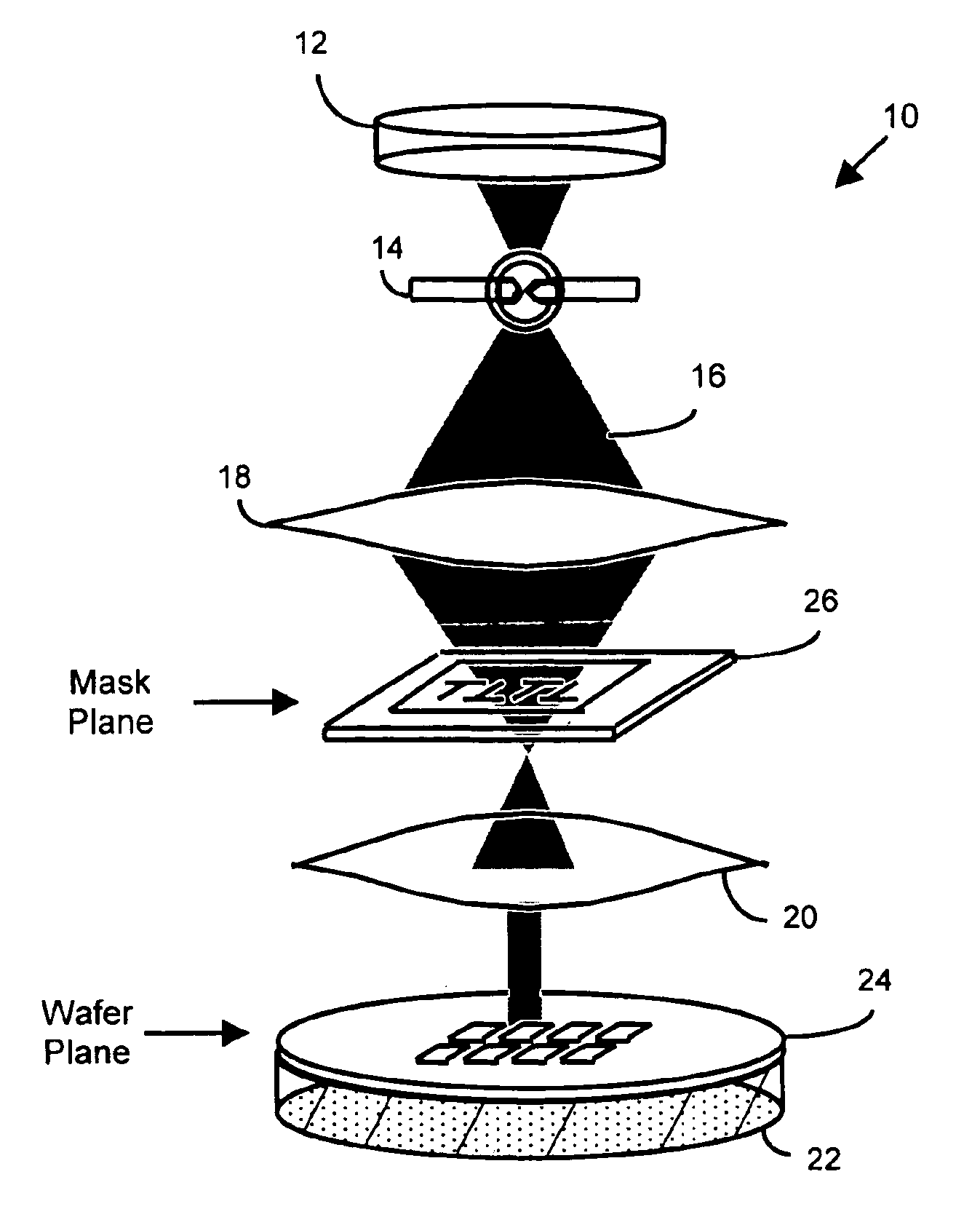

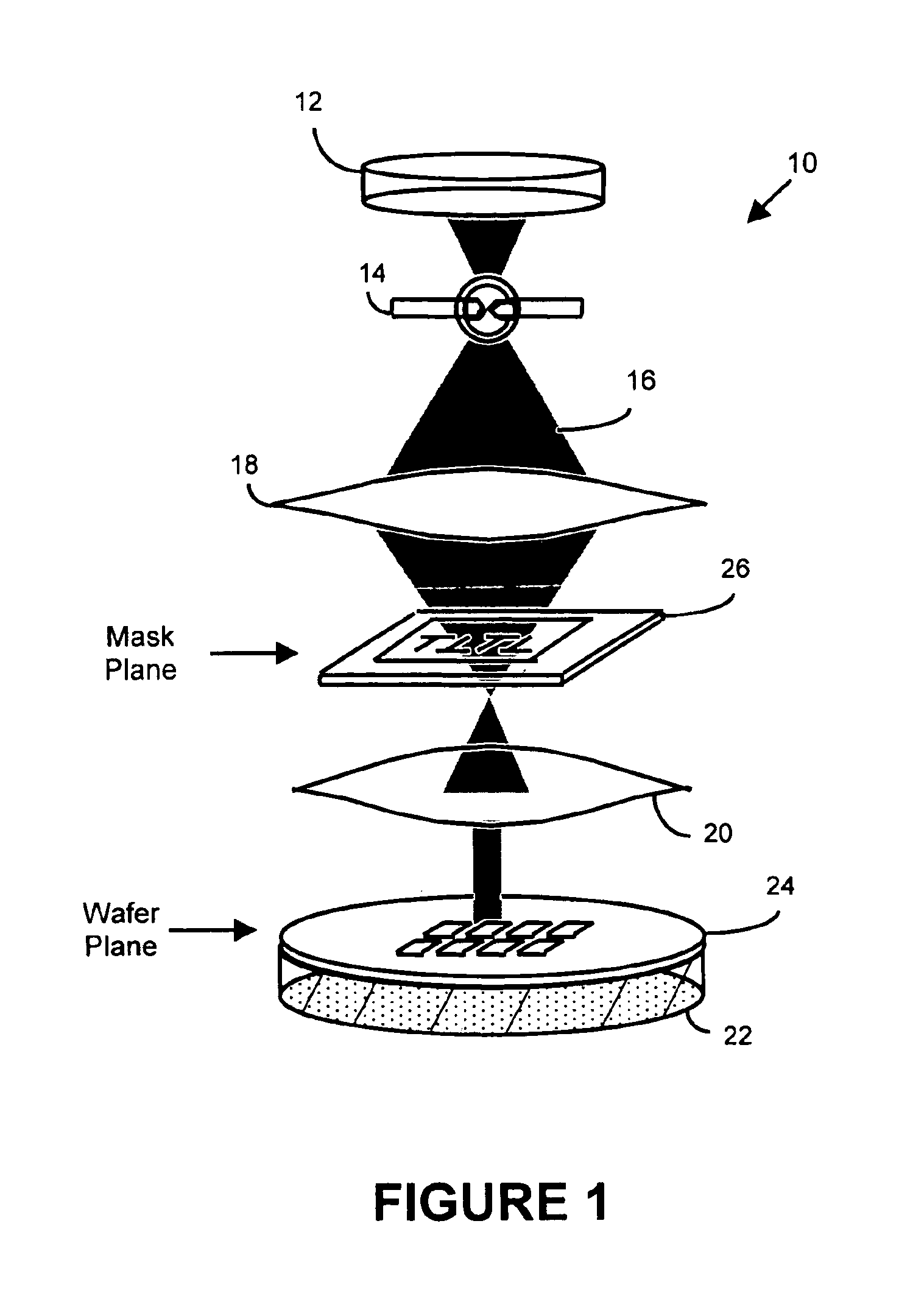

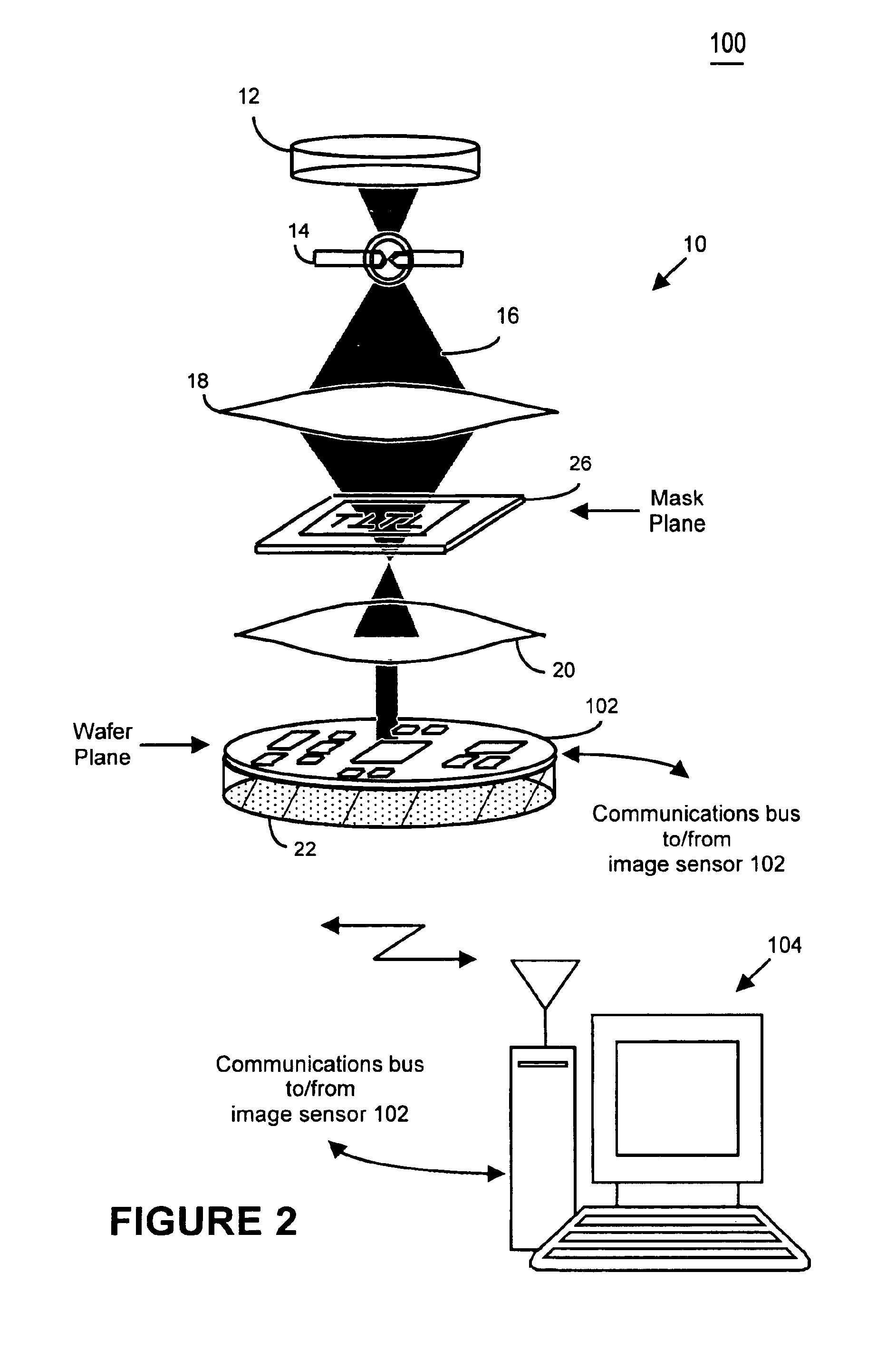

System and method for lithography process monitoring and control

InactiveUS6884984B2Highly precise moveable platformPhotometrySolid-state devicesLithography processEngineering

In one aspect, the present invention is a technique of, and a system and sensor for measuring, inspecting, characterizing and / or evaluating optical lithographic equipment, methods, and / or materials used therewith, for example, photomasks. In one embodiment, the system, sensor and technique measures, collects and / or detects an aerial image (or portion thereof) produced or generated by the interaction between the photomask and lithographic equipment. An image sensor unit may measure, collect, sense and / or detect the aerial image in situ—that is, the aerial image at the wafer plane produced, in part, by a production-type photomask (i.e., a wafer having integrated circuits formed during the integrated circuit fabrication process) and / or by associated lithographic equipment used, or to be used, to manufacture of integrated circuits. A processing unit, coupled to the image sensor unit, may measure the critical dimensions of features of the photomask, using data which is representative of the intensity of light sampled by the image sensor unit, to control at least one operating parameter of the lithographic equipment.

Owner:ASML NETHERLANDS BV

Topography directed patterning

A pattern having exceptionally small features is formed on a partially fabricated integrated circuit during integrated circuit fabrication. The pattern comprises features formed by self-organizing material, such as diblock copolymers. The organization of the copolymers is directed by spacers which have been formed by a pitch multiplication process in which spacers are formed at the sides of sacrificial mandrels, which are later removed to leave spaced-apart, free-standing spacers. Diblock copolymers, composed of two immiscible block species, are deposited over and in the space between the spacers. The copolymers are made to self-organize, with each block species aggregating with other block species of the same type.

Owner:MICRON TECH INC

Voltage contrast test structure

InactiveUS7217579B2Increase speedNo wasteMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityVoltage contrast

A method for electrically testing a semiconductor wafer during integrated-circuit fabrication process, the method including: (i) providing a scanning charged-particle microscope (SCPM), having a defined scanning plane and operative, while in any one mechanical state, to scan a surface in the scanning plane within a two-dimensional scanning window, which has a given maximum size; (ii) providing in association with any layer of the wafer, it being a test layer, one or more test structures, each test structure including normally conductive areas within a normally non-conductive background in one or more layers, which include said test layer, the conductive areas formed as one or more patterns; the patterns in said test layer include one or more clusters of mutually isolated pads; each pad is conductively connected with a corresponding distinct point on the patterns and all the pads in any one cluster are sized and arranged so that at least a significant portion of each pad falls within a common window whose size does not exceed said maximum size of said scanning window; (iii) with said test layer forming the top surface of the wafer, placing the wafer on the SCPM and adjusting the mechanical state of the SCPM so that at least a significant portion of each pad in any one of said clusters is within said scanning window; (iv) causing the SCPM, while in said mechanical state, to scan all of the pads of said one cluster and thereby to provide information about the electrical state of the respective test structure.

Owner:APPL MATERIALS ISRAEL LTD

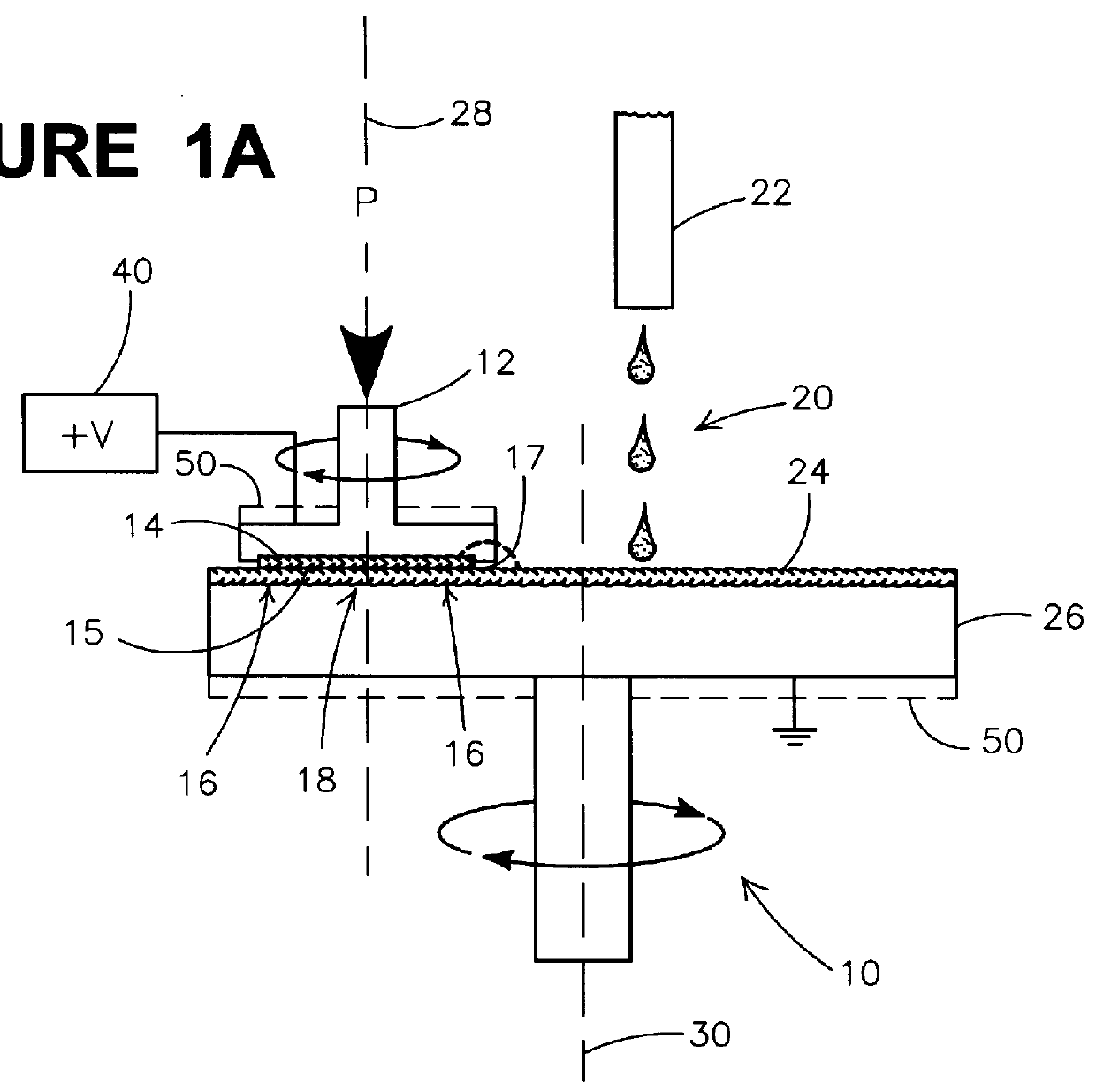

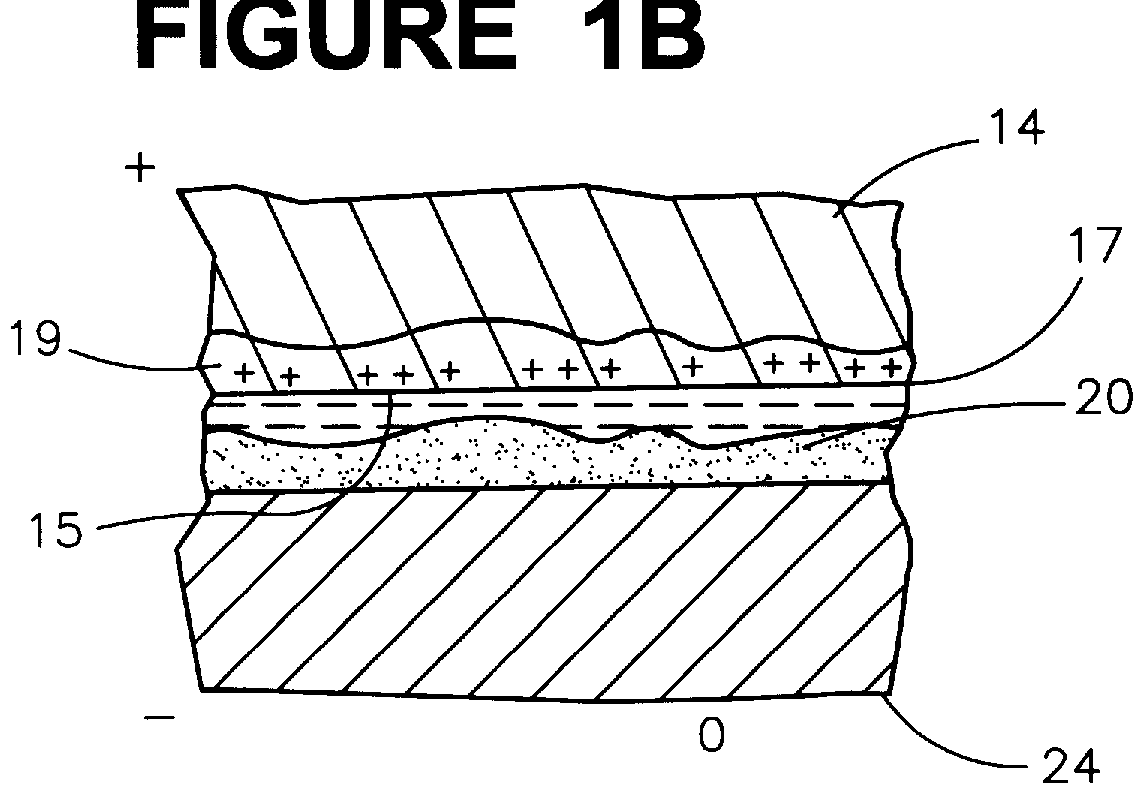

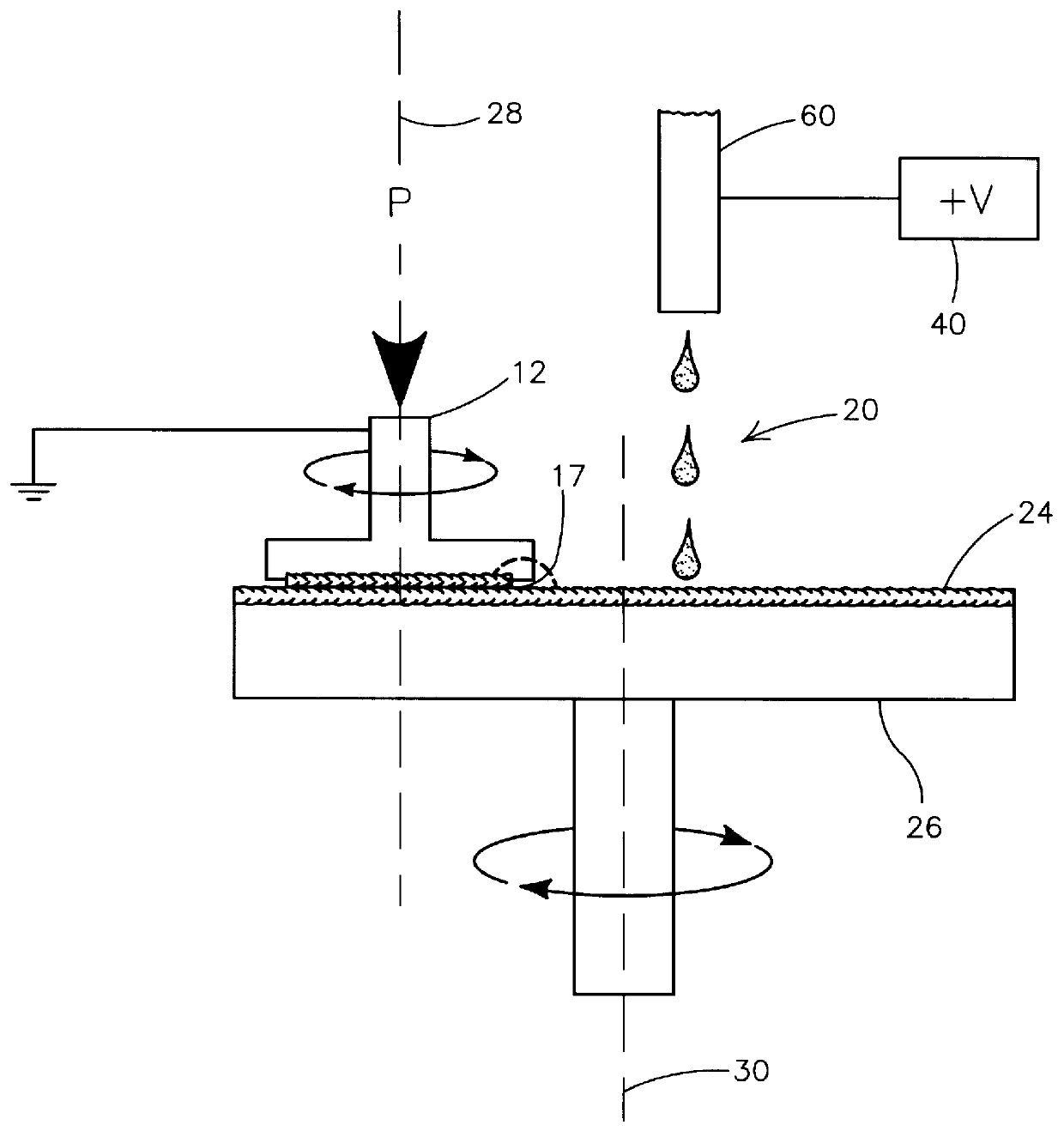

Wafer surface treatment methods and systems using electrocapillarity

InactiveUS6010964ADecorative surface effectsPhotomechanical apparatusBiomedical engineeringElectric potential

A surface treatment method for use in integrated circuit fabrication includes providing a substrate assembly having a surface. A liquid is provided adjacent the surface resulting in an interface therebetween. An electrical potential difference is applied across the interface and the surface is treated as the electrical potential difference is applied across the interface. The liquid may be a planarization liquid when the treatment of the surface includes planarizing a substrate assembly or the liquid may be a coating material when the treatment of the surface includes applying a coating material on the surface.

Owner:MICRON TECH INC

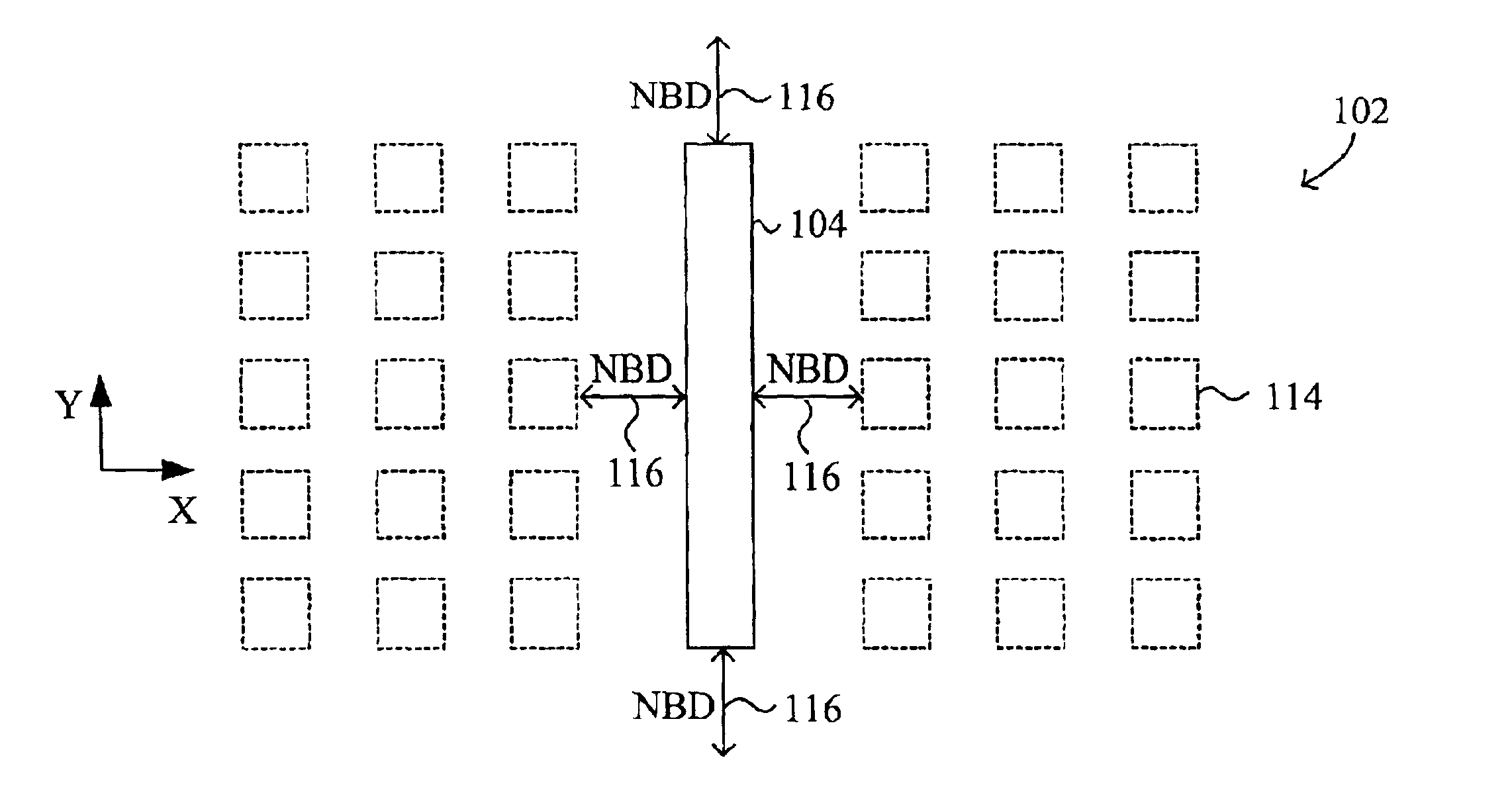

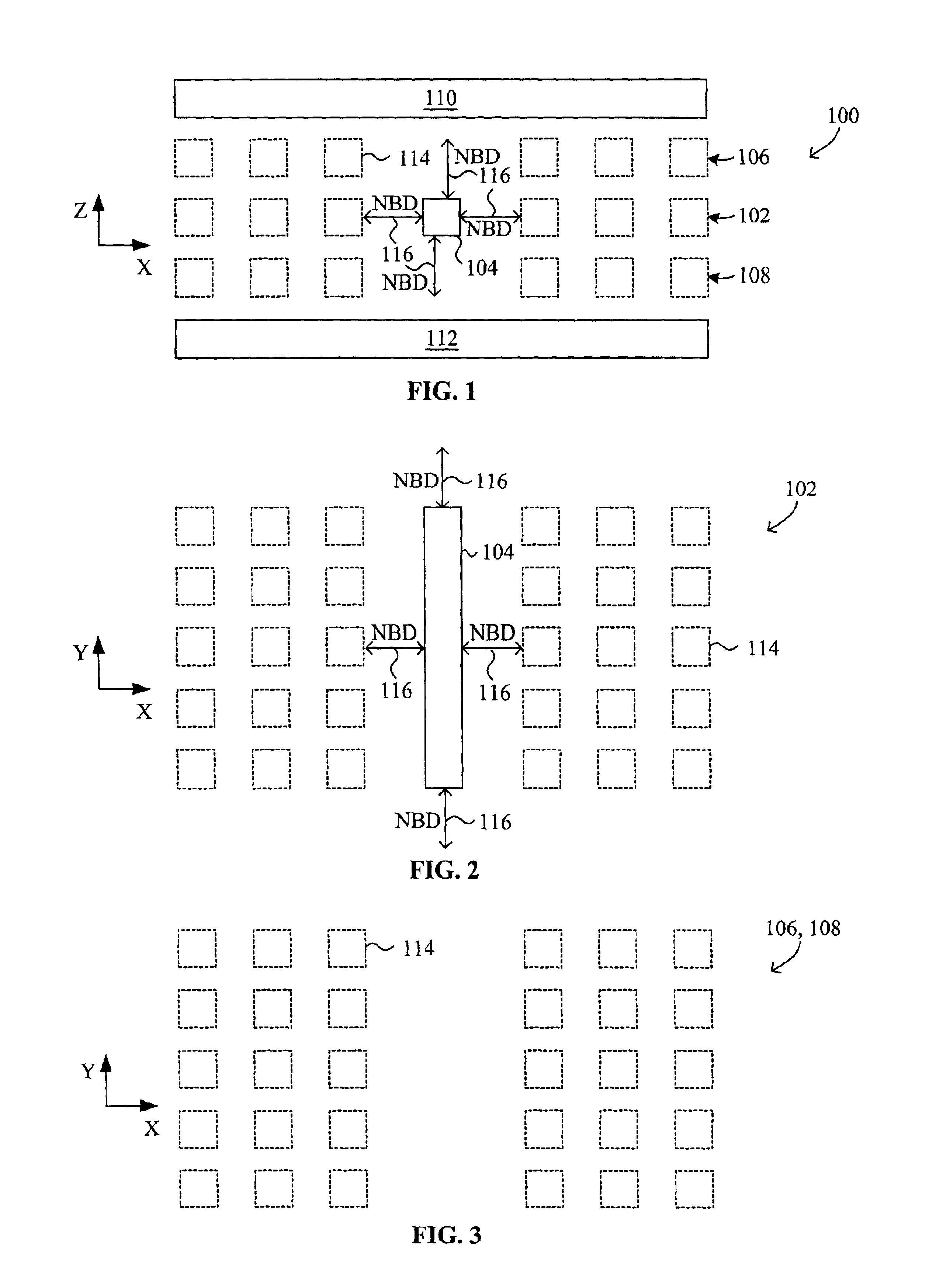

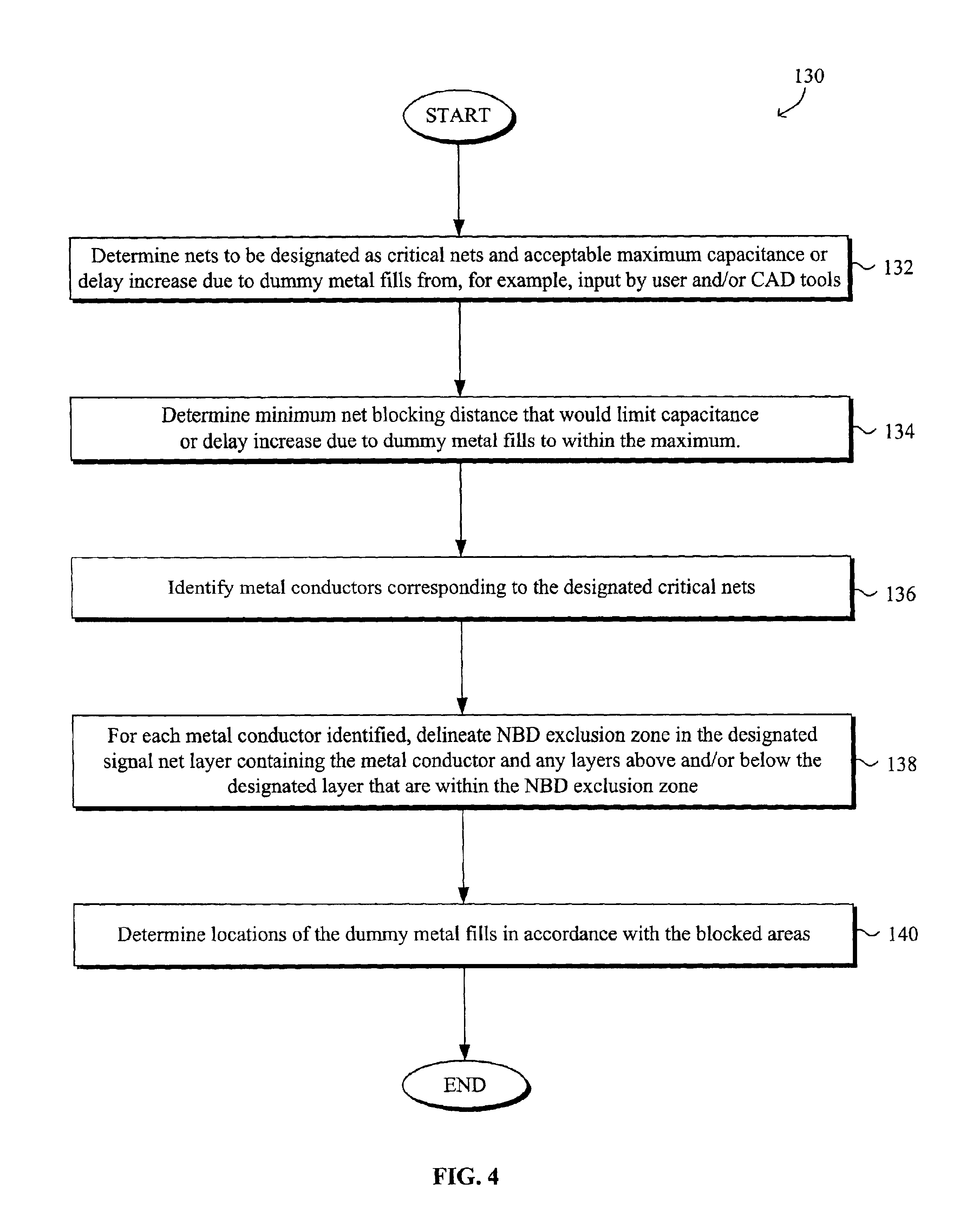

System and method for limiting increase in capacitance due to dummy metal fills utilized for improving planar profile uniformity

InactiveUS6751785B1CAD circuit designSoftware simulation/interpretation/emulationCapacitanceElectrical conductor

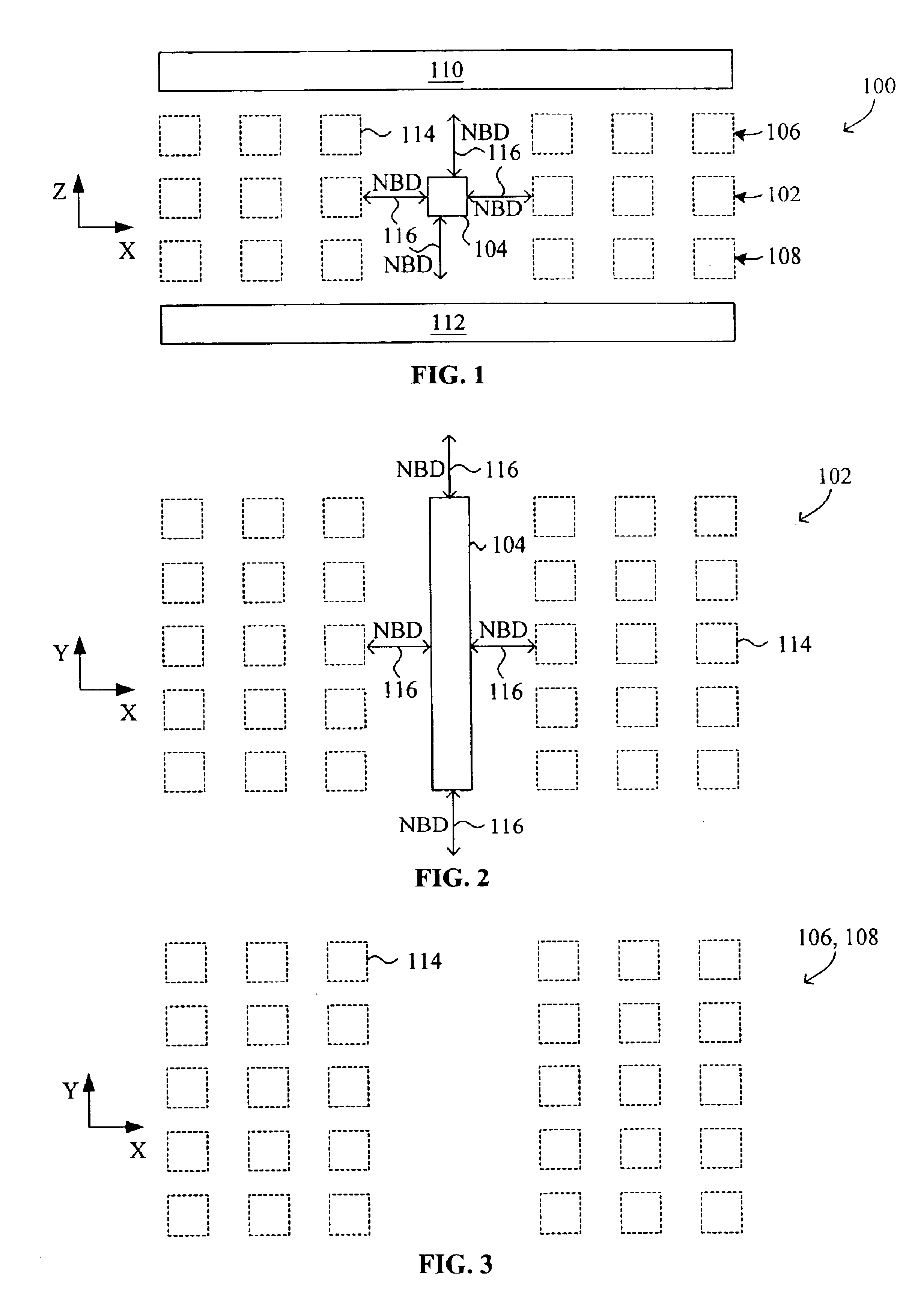

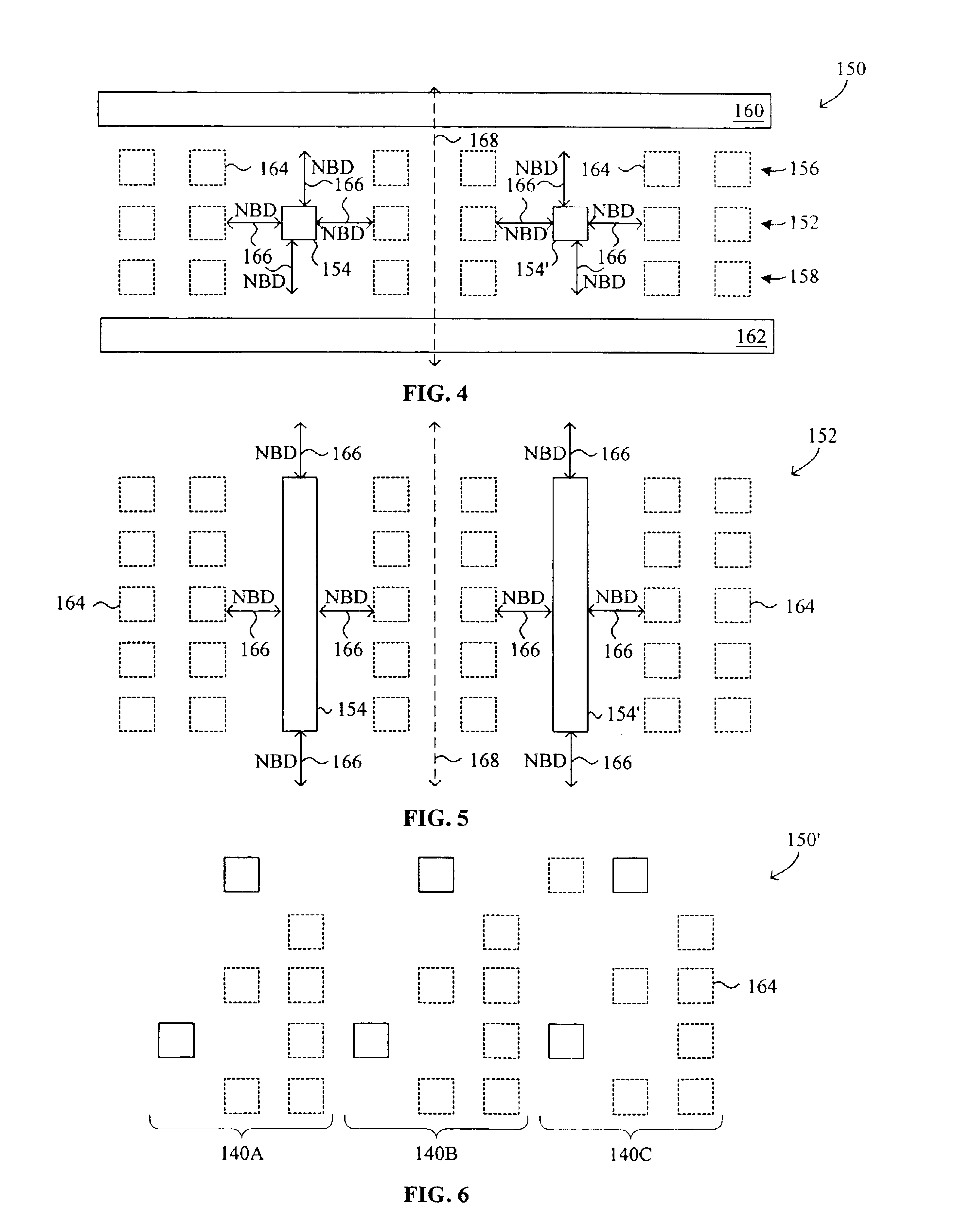

Systems and methods for limiting capacitance increase due to dummy fill metals utilized to improve planar profile uniformity are disclosed. A computer-automated method for locating dummy fills in an integrated circuit fabrication process generally comprises reading a layout file specifying layout of the integrated circuit, designating at least one net of the integrated circuit as a critical net, the critical nets being only a subset of all nets of the integrated circuit, identifying metal conductors corresponding to each designated critical net from the layout file, delineating a net blocking exclusion zone extending a distance of a minimum net blocking distance (NBD) from the metal conductor for each metal conductor identified, and locating the dummy fills outside of the net blocking exclusion zone.

Owner:SYNOPSYS INC

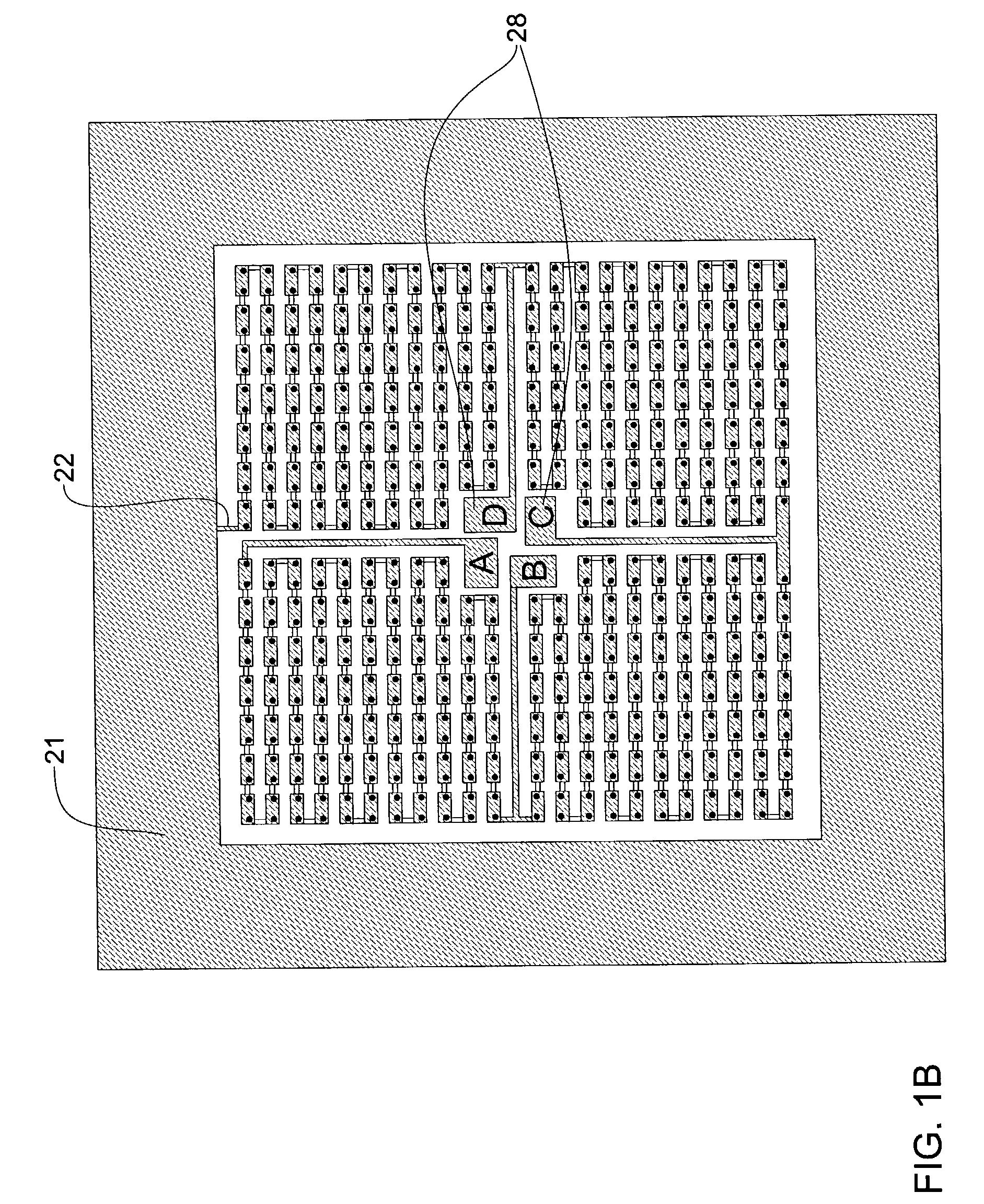

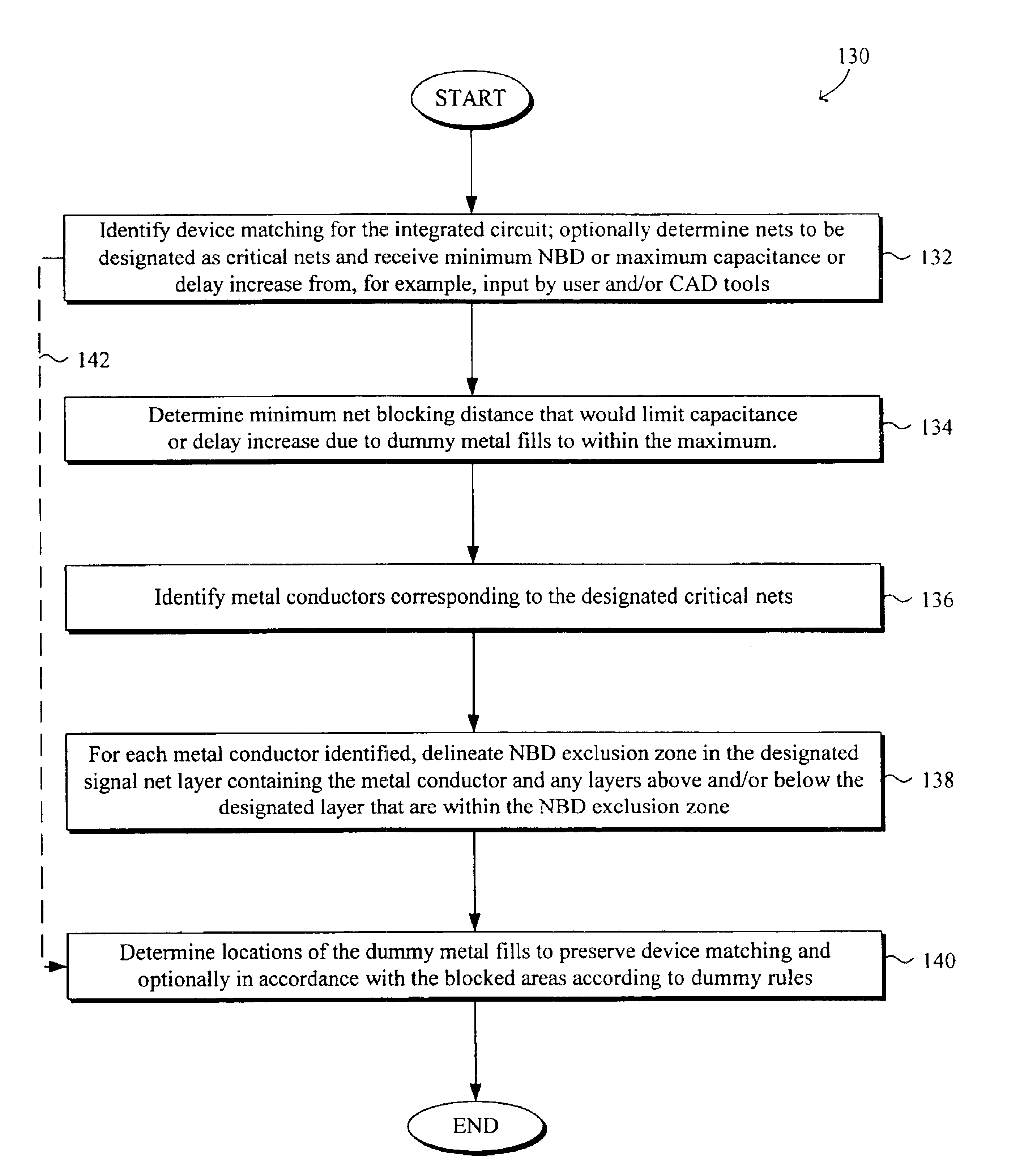

System and method for placement of dummy metal fills while preserving device matching and/or limiting capacitance increase

InactiveUS6904581B1CAD circuit designSoftware simulation/interpretation/emulationCapacitanceElectrical conductor

Systems and methods for placement of dummy metal fills while preventing disturbance of device matching and optionally limiting capacitance increase are disclosed. A computer-automated method for locating dummy fills in an integrated circuit fabrication process generally comprises receiving an input layout of the integrated circuit and specification of device matching for the integrated circuit and locating the dummy fills in the integrated circuit according to dummy rules while preserving device matching. Locating the dummy fills may include locating the dummy fills along the at least one axis of symmetry where device matching is along an axis of symmetry and locating the dummy fills so as to preserve matching of the repeated elements where device matching is repeated matched elements. The method may also include designating at least one net of the integrated circuit as a critical net, the critical nets being only a subset of all nets of the integrated circuit, identifying metal conductors corresponding to each designated critical net from the layout file, and delineating a net blocking exclusion zone extending a distance of a minimum net blocking distance (NBD) from the metal conductor for each metal conductor identified, wherein the step of locating locates the dummy fills outside of the net blocking exclusion zone.

Owner:MAGMA DESIGN AUTOMATION

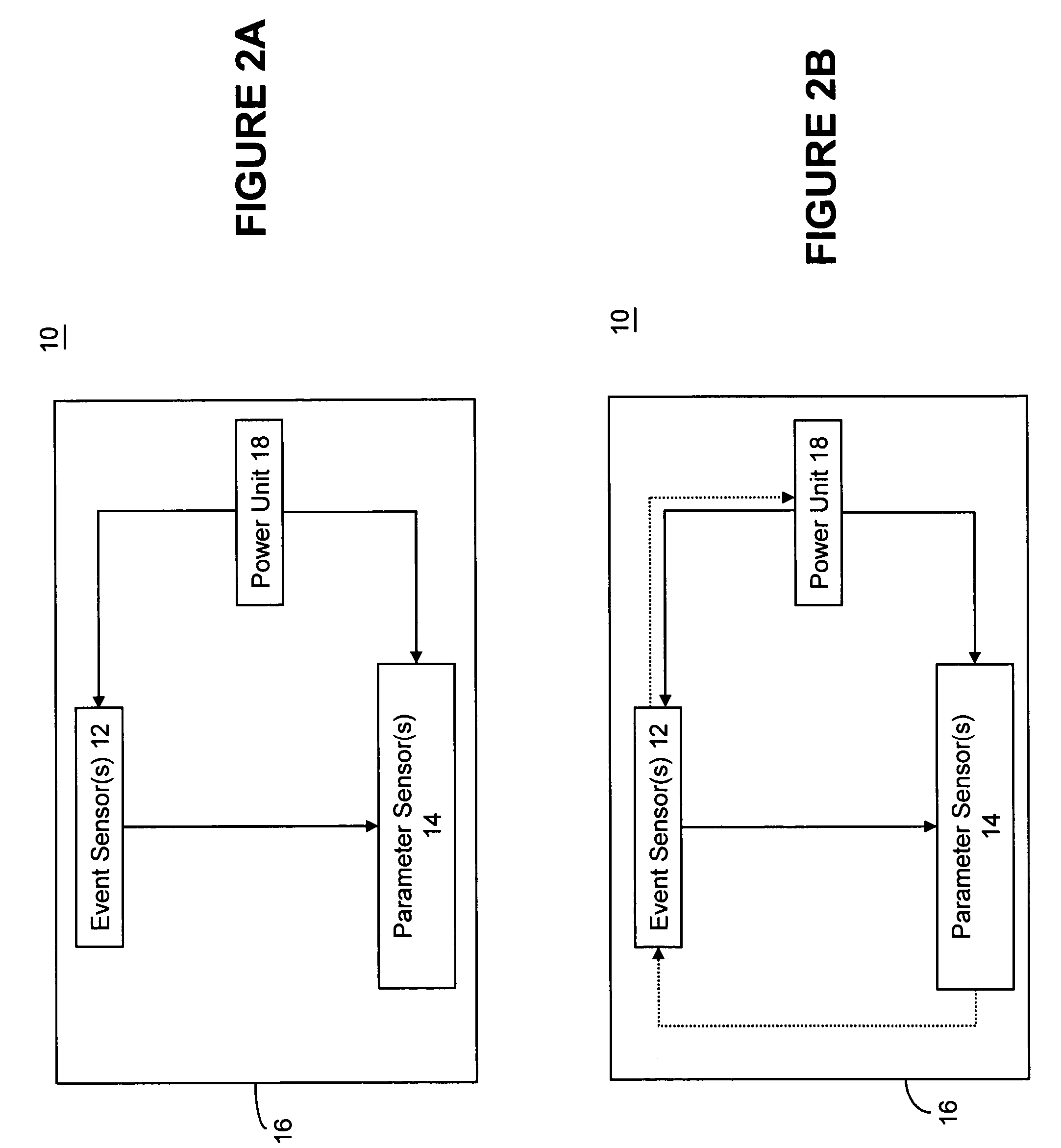

Method and apparatus for synchronizing data acquisition of a monitored IC fabrication process

ActiveUS7171334B2Semiconductor/solid-state device testing/measurementResistance/reactance/impedenceData acquisitionEngineering

Owner:ASML NETHERLANDS BV

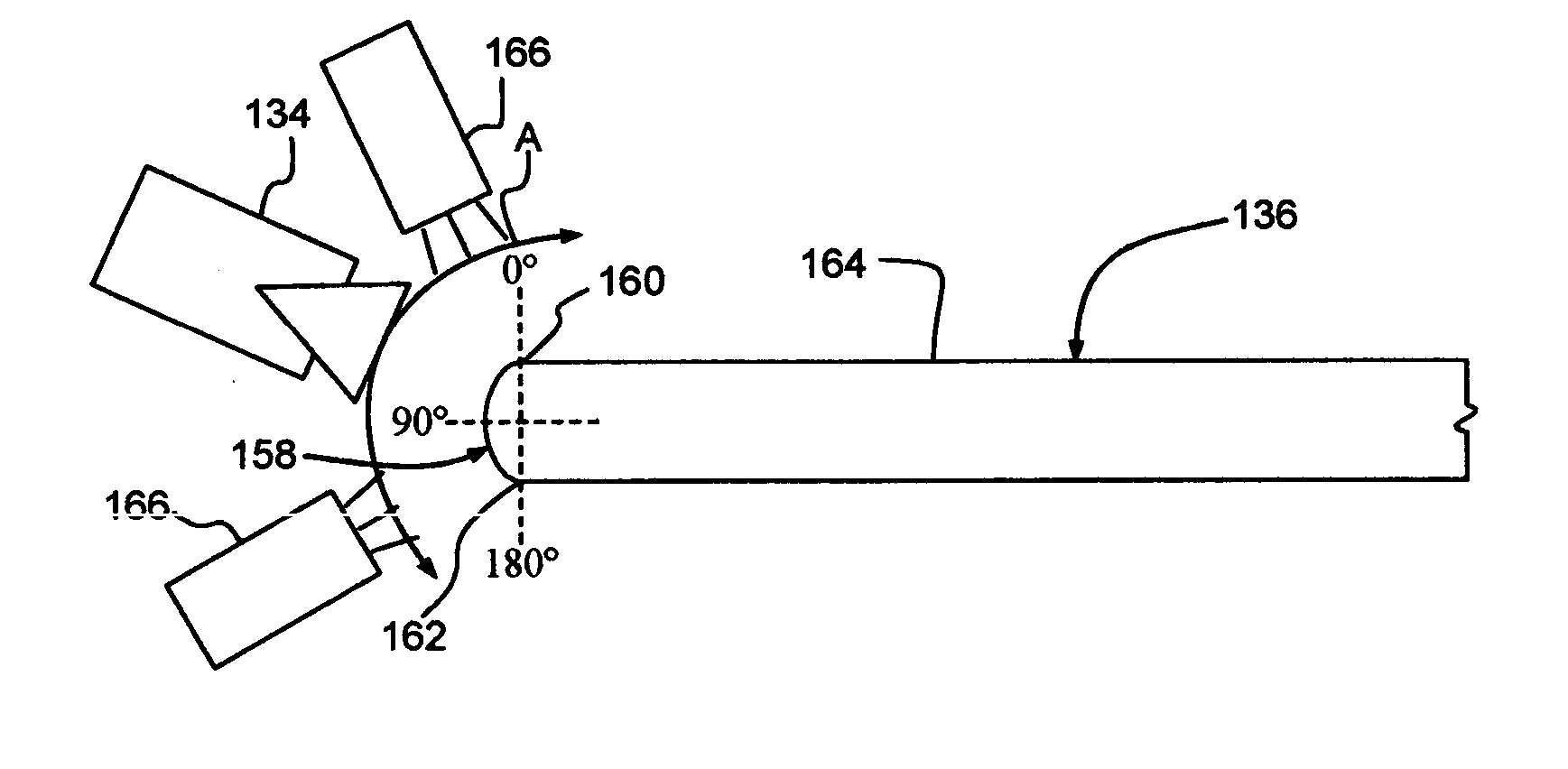

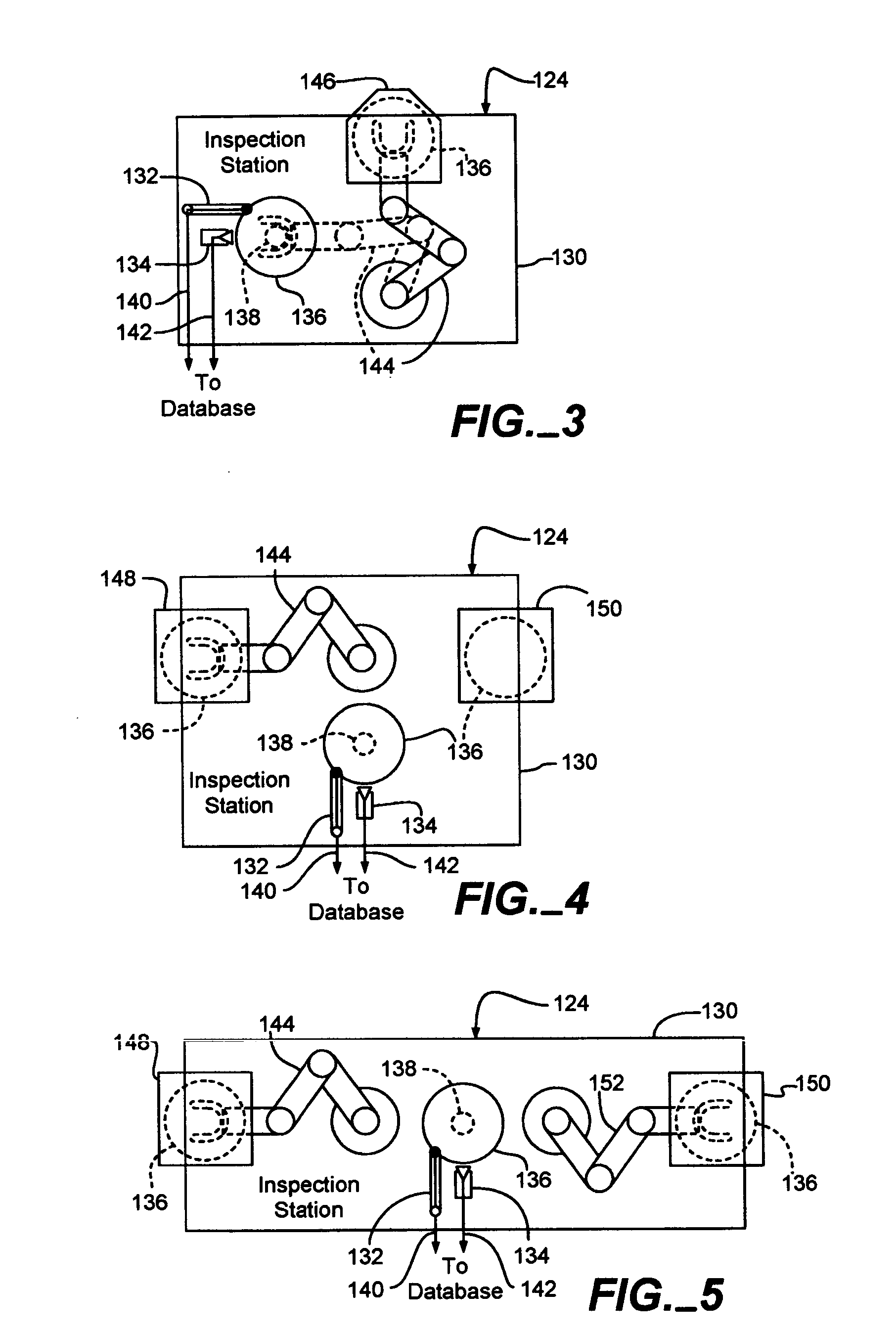

Wafer edge defect inspection

ActiveUS20050023491A1Great considerationInvestigating moving sheetsCounting objects on conveyorsManufacturing technologyImage capture

A wafer edge defect inspection method and apparatus for use in an integrated circuit fabrication system includes an image capturing device for capturing images of the edges of wafers, a database in which the images are stored and accessible for analysis and a computer for analyzing the images of one or more wafer edges to locate edge defects and for evaluating the performance of the fabrication system. The inspection and data storage are performed automatically. The database storage enables detailed analysis of many wafers and fabrication process steps.

Owner:BELL SEMICON LLC

Method of fabricating Schottky diode and related structure

InactiveUS6261932B1Easy to optimizeReduce parasitic capacitanceTransistorSolid-state devicesDopantMetal silicide

A method of forming an improved Schottky diode structure as part of an integrated circuit fabrication process that includes the introduction of a selectable concentration of dopant into the surface of an epitaxial layer so as to form a barrier-modifying surface dopant layer. The epitaxial layer forms the cathode of the Schottky diode and a metal-silicide layer on the surface of the epitaxial layer forms the diode junction. The surface dopant layer positioned between the cathode and the diode junction is designed to raise or lower the barrier height between those two regions either to reduce the threshold turn-on potential of the diode, or to reduce the reverse leakage current of the transistor. The particular dopant conductivity used to form the surface dopant layer is dependent upon the conductivity of the epitaxial layer and the type of metal used to form the metal-silicide junction.

Owner:SEMICON COMPONENTS IND LLC

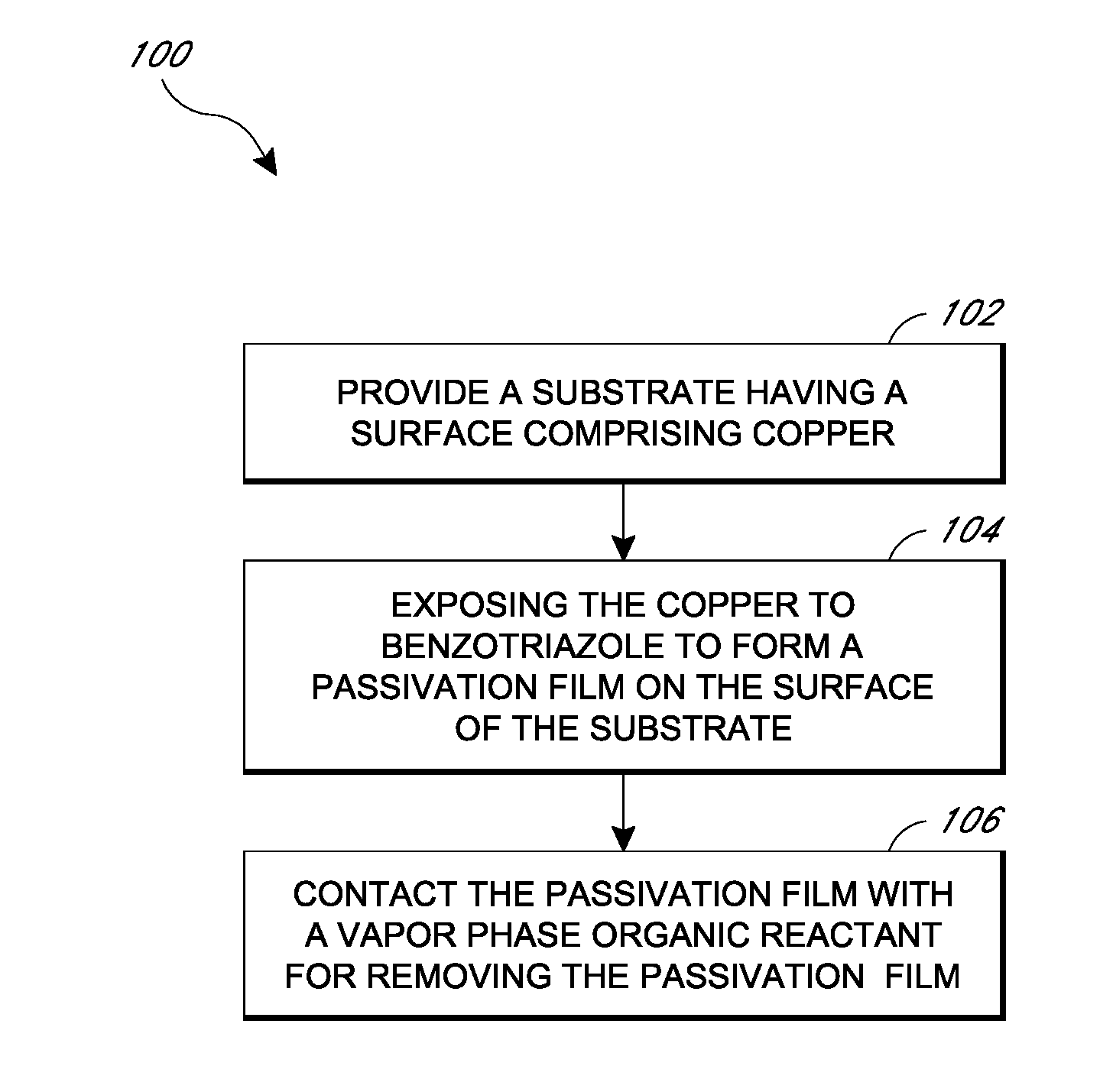

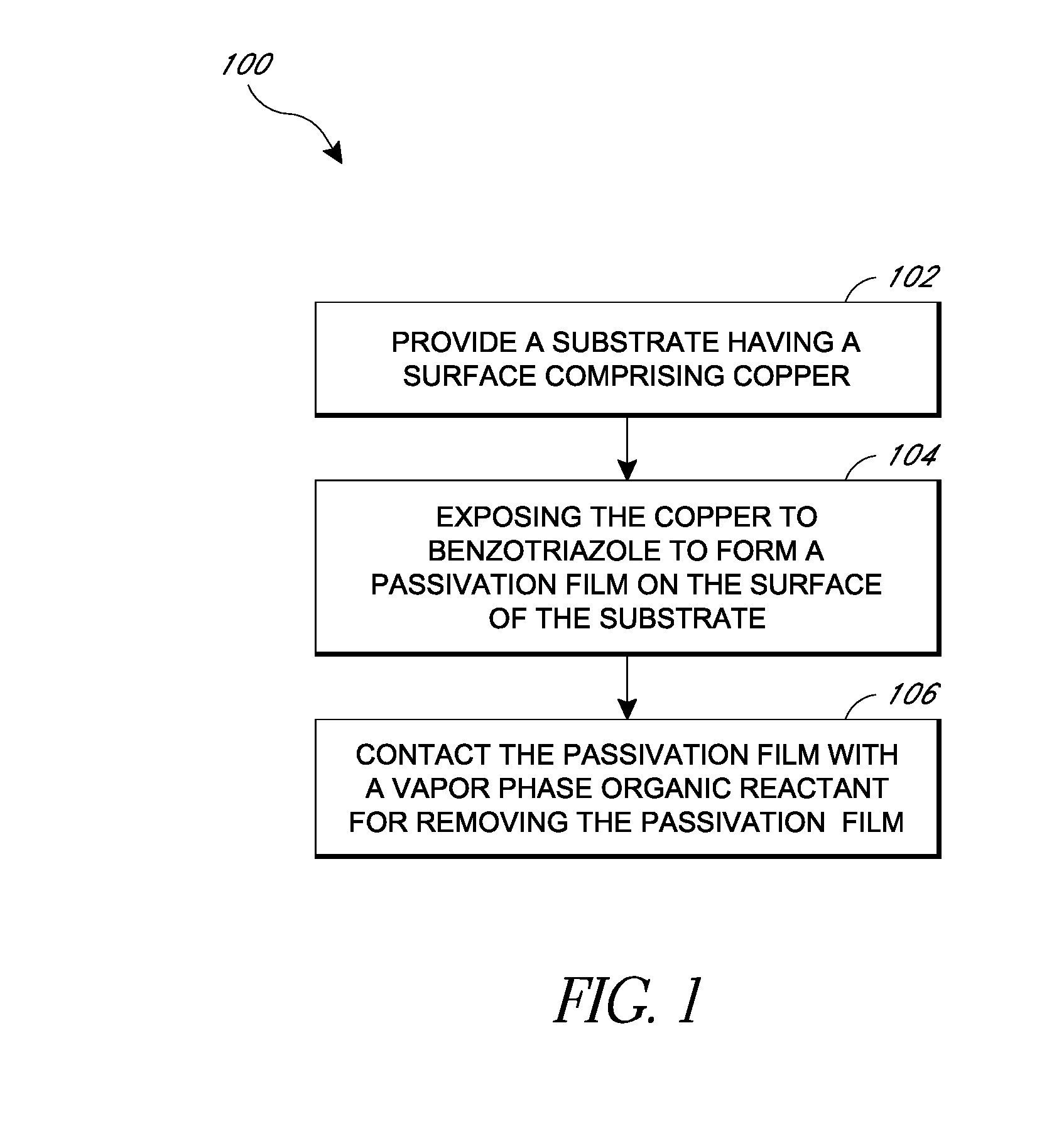

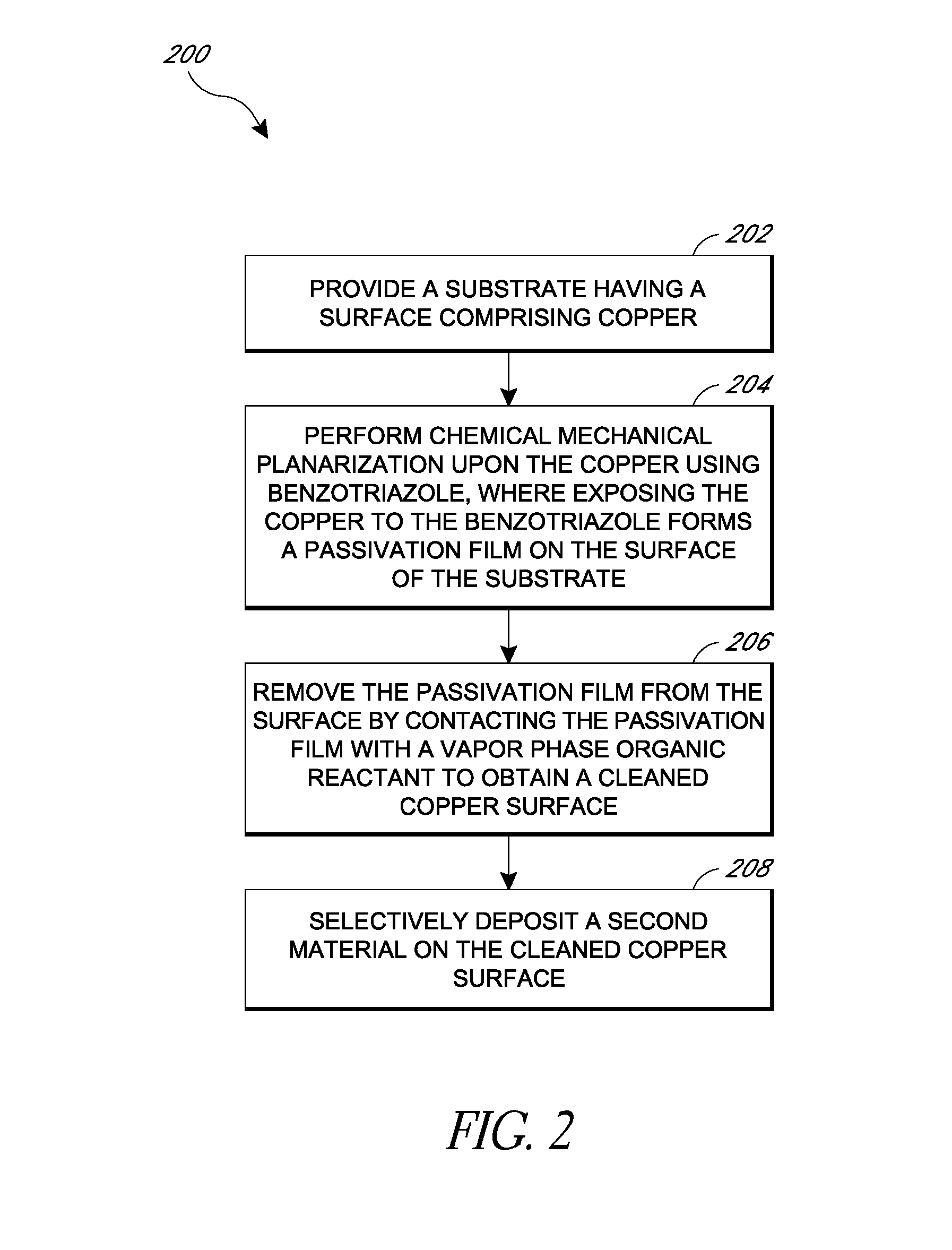

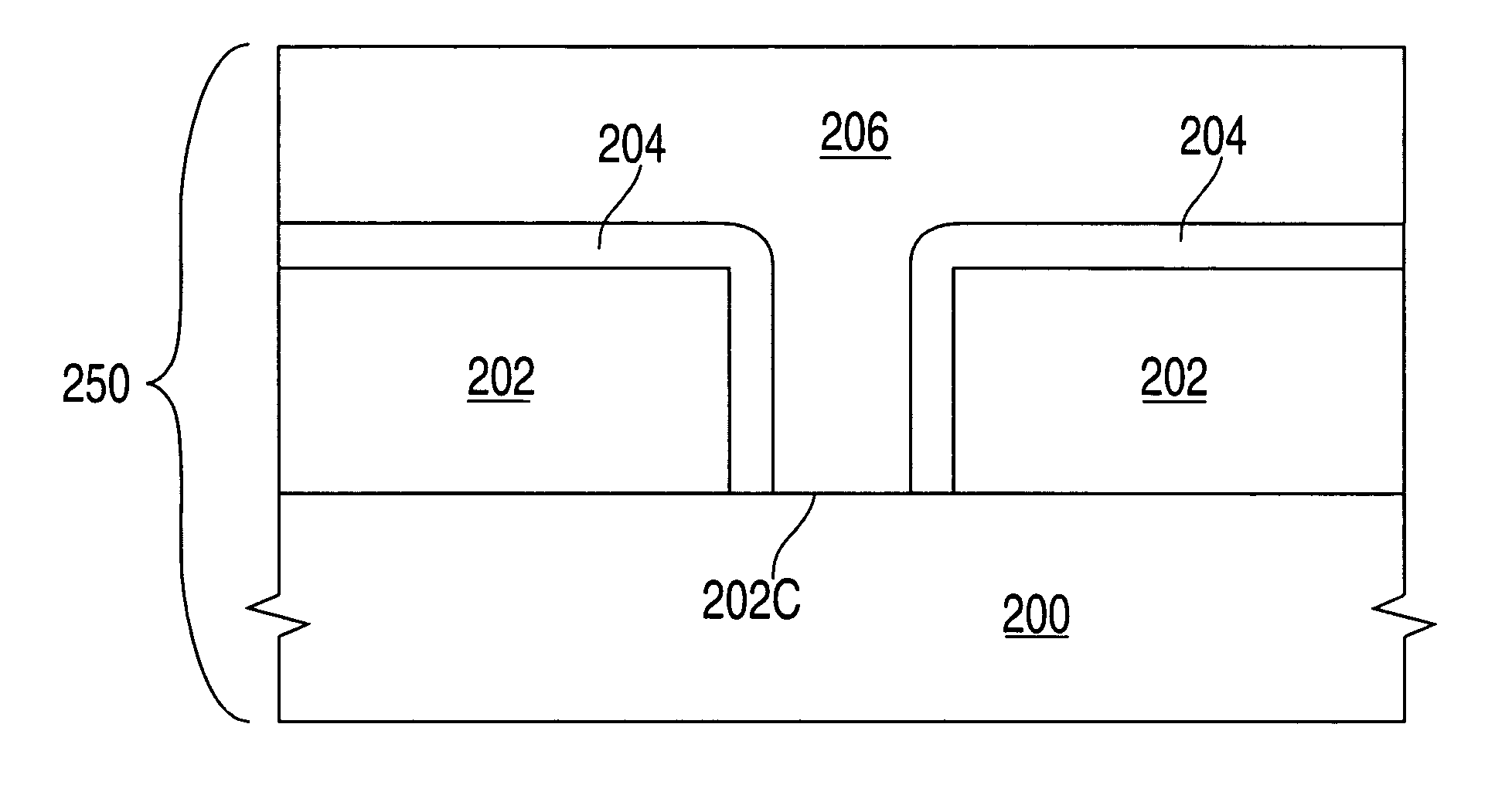

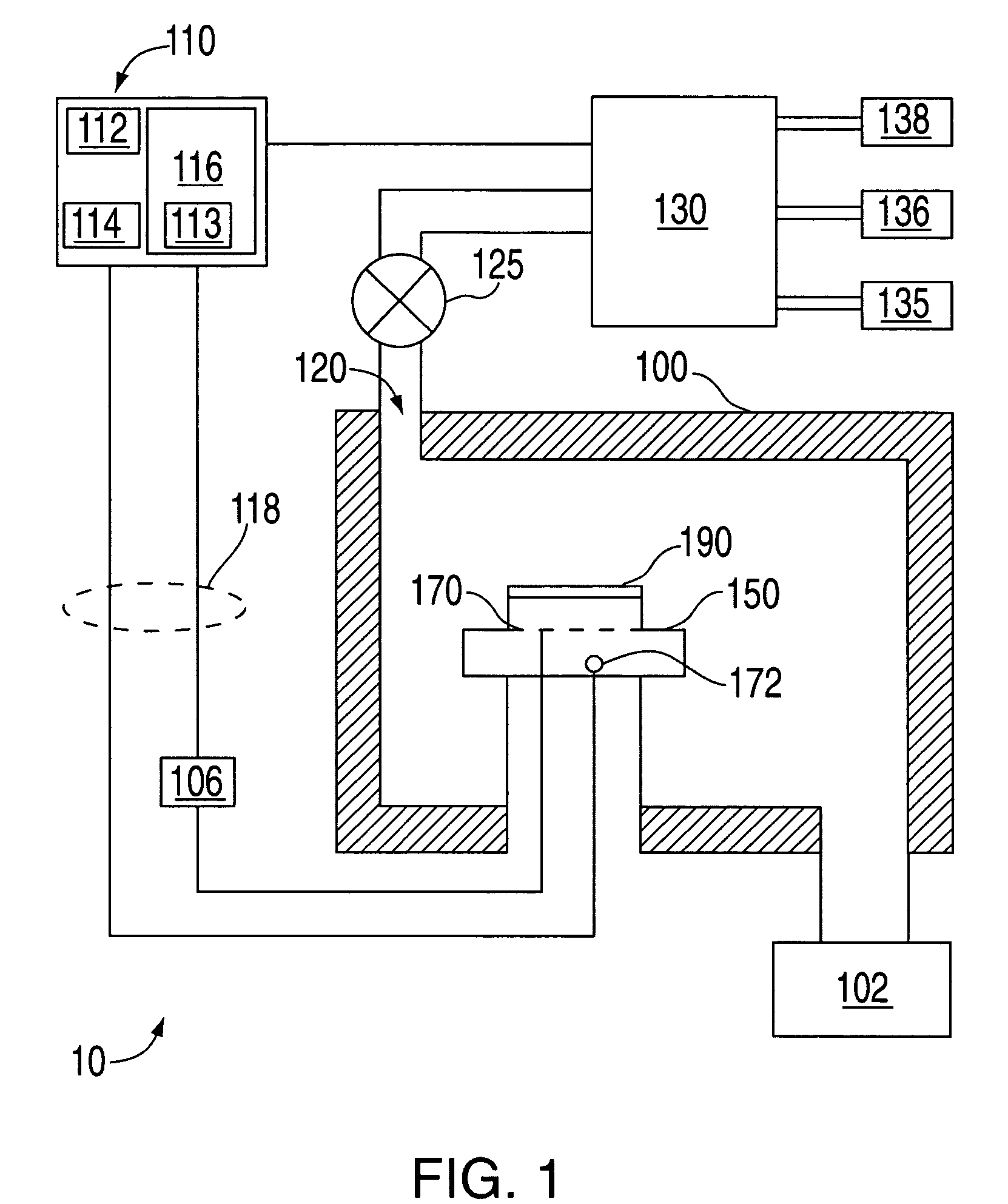

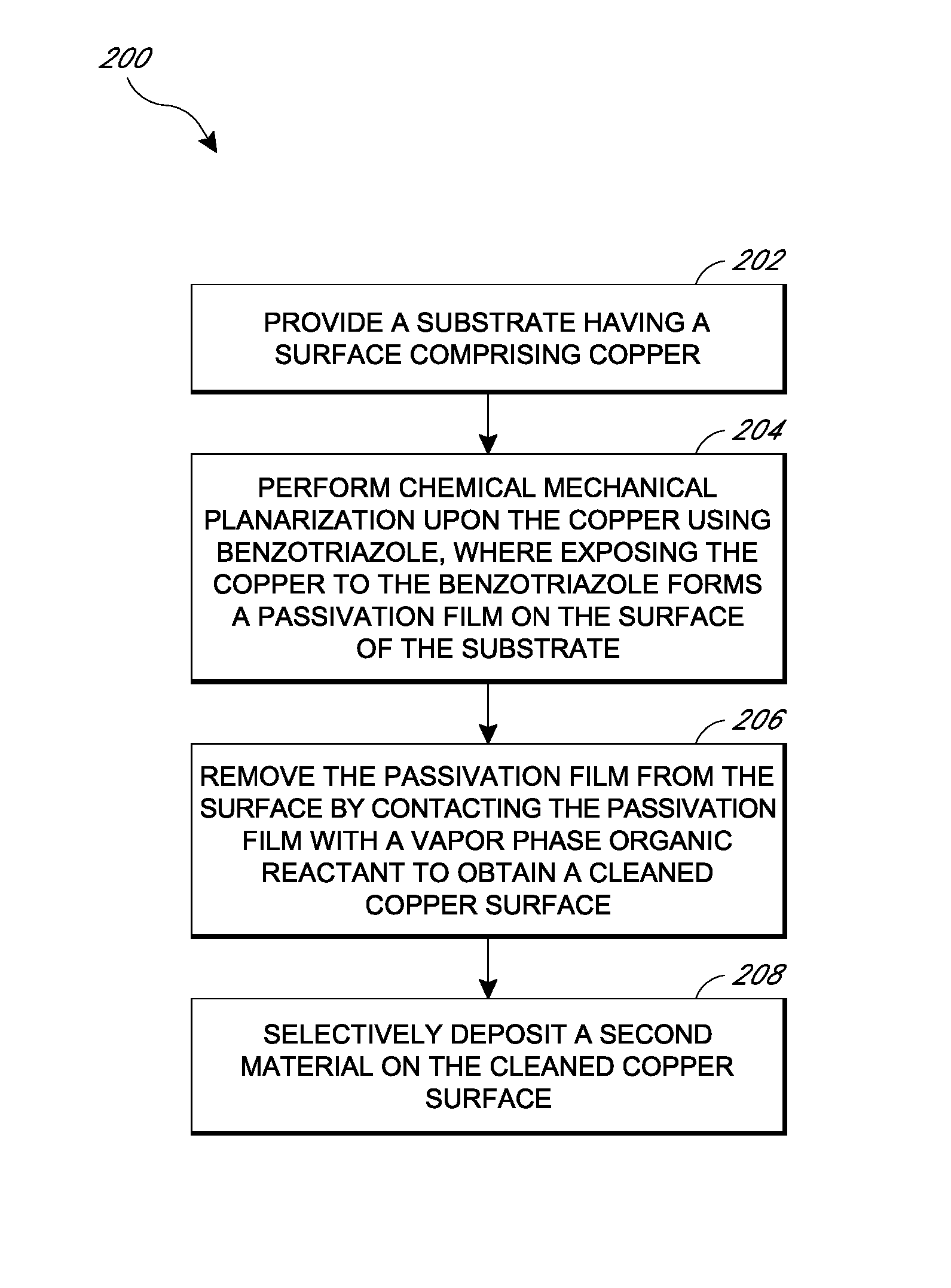

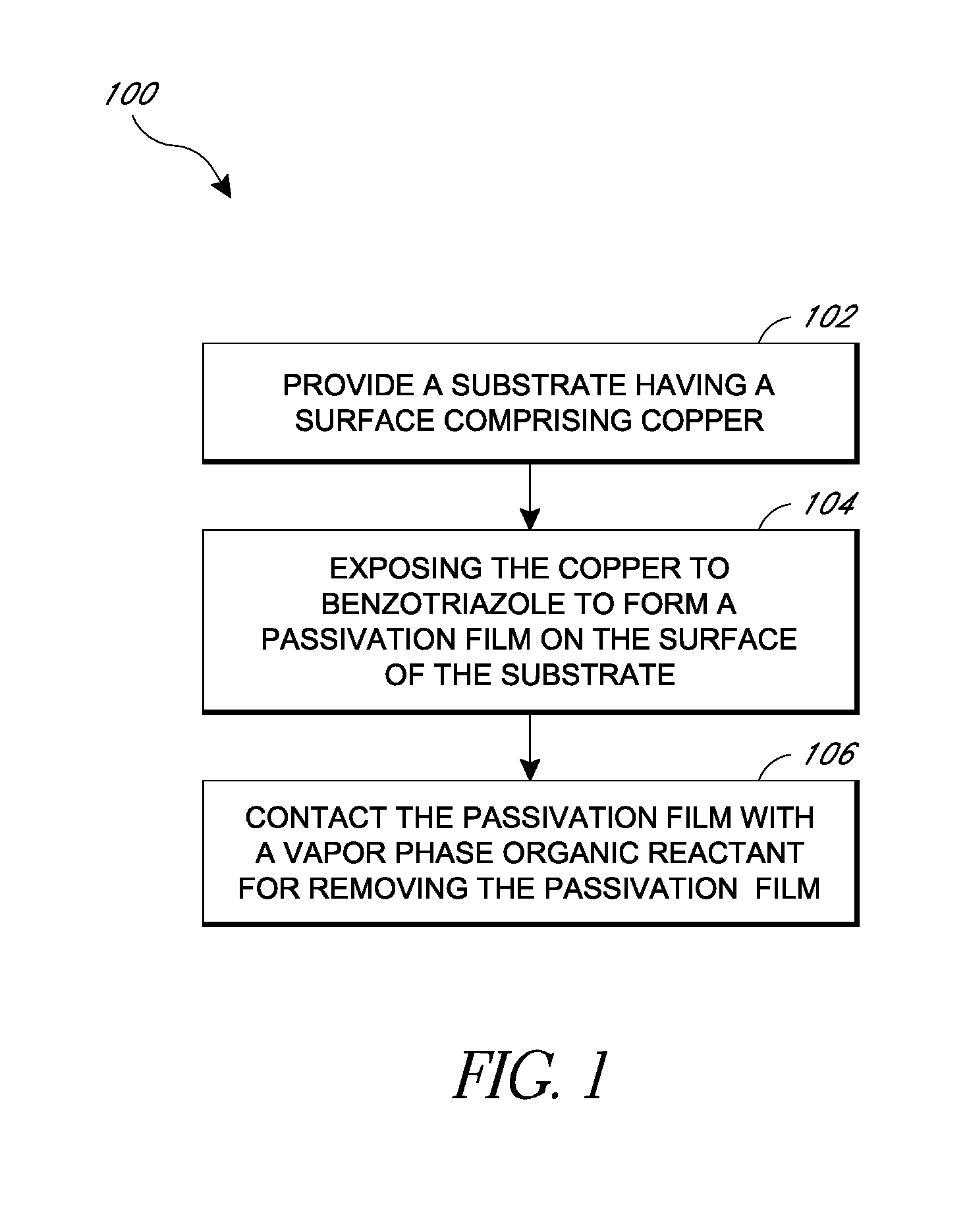

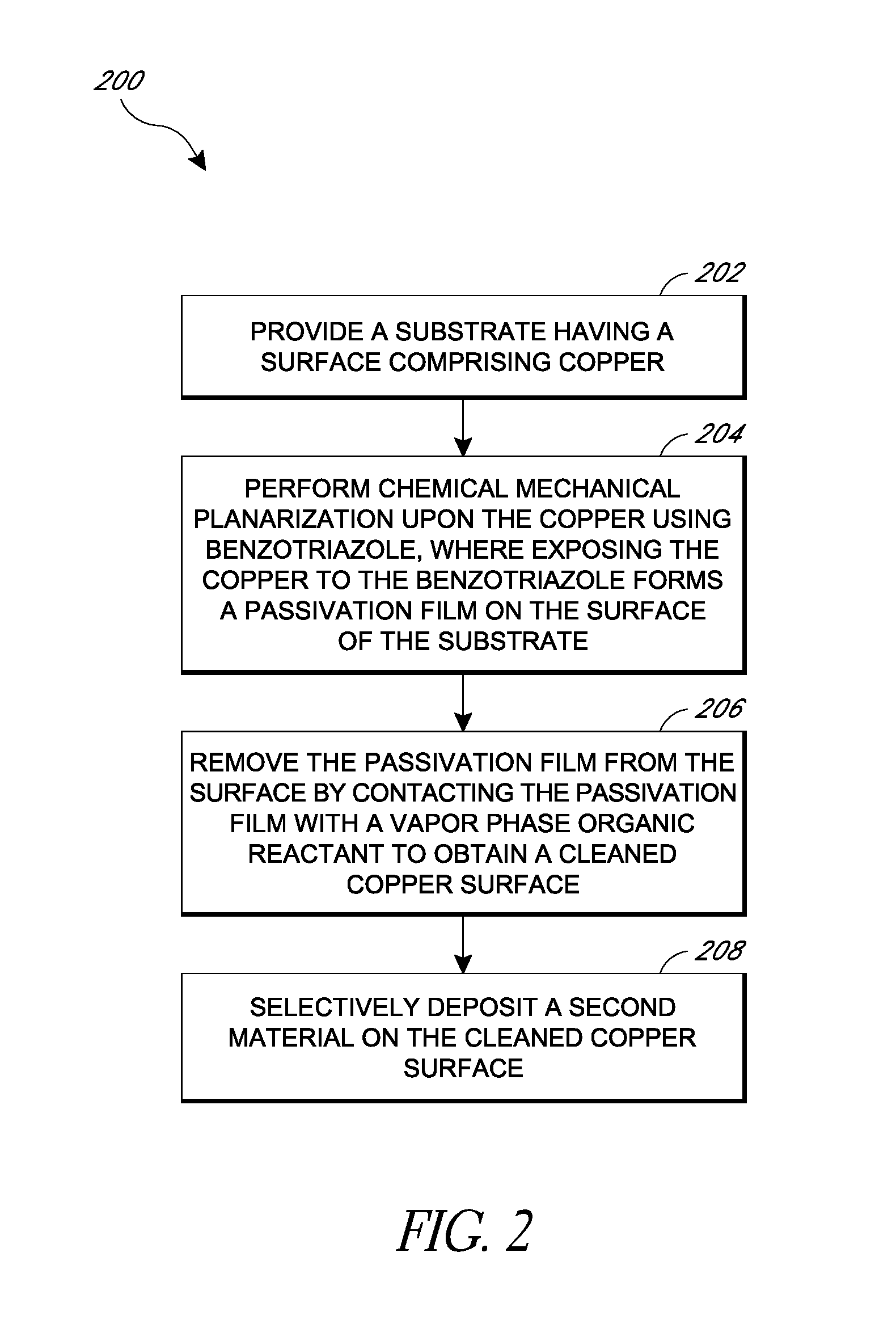

Removal of surface passivation

Methods for removing a passivation film from a copper surface can include exposing the passivation film to a vapor phase organic reactant, for example at a temperature of 100° C. to 400° C. In some embodiments, the passivation film may have been formed by exposure of the copper surface to benzotriazole, such as can occur during a chemical mechanical planarization process. The methods can be performed as part of a process for integrated circuit fabrication. A second material can be selectively deposited on the cleaned copper surface relative to another surface of the substrate.

Owner:ASM IP HLDG BV

Formation of a tantalum-nitride layer

InactiveUS20050164487A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTantalum nitrideNitrogen

A method of forming a tantalum nitride layer for integrated circuit fabrication is disclosed. In one embodiment, the method includes forming a tantalum nitride layer by chemisorbing a tantalum precursor and a nitrogen precursor on a substrate disposed in a process chamber. A nitrogen concentration of the tantalum nitride layer is reduced by exposing the substrate to a plasma annealing process. A metal-containing layer is then deposited on the tantalum nitride layer by a deposition process.

Owner:APPLIED MATERIALS INC

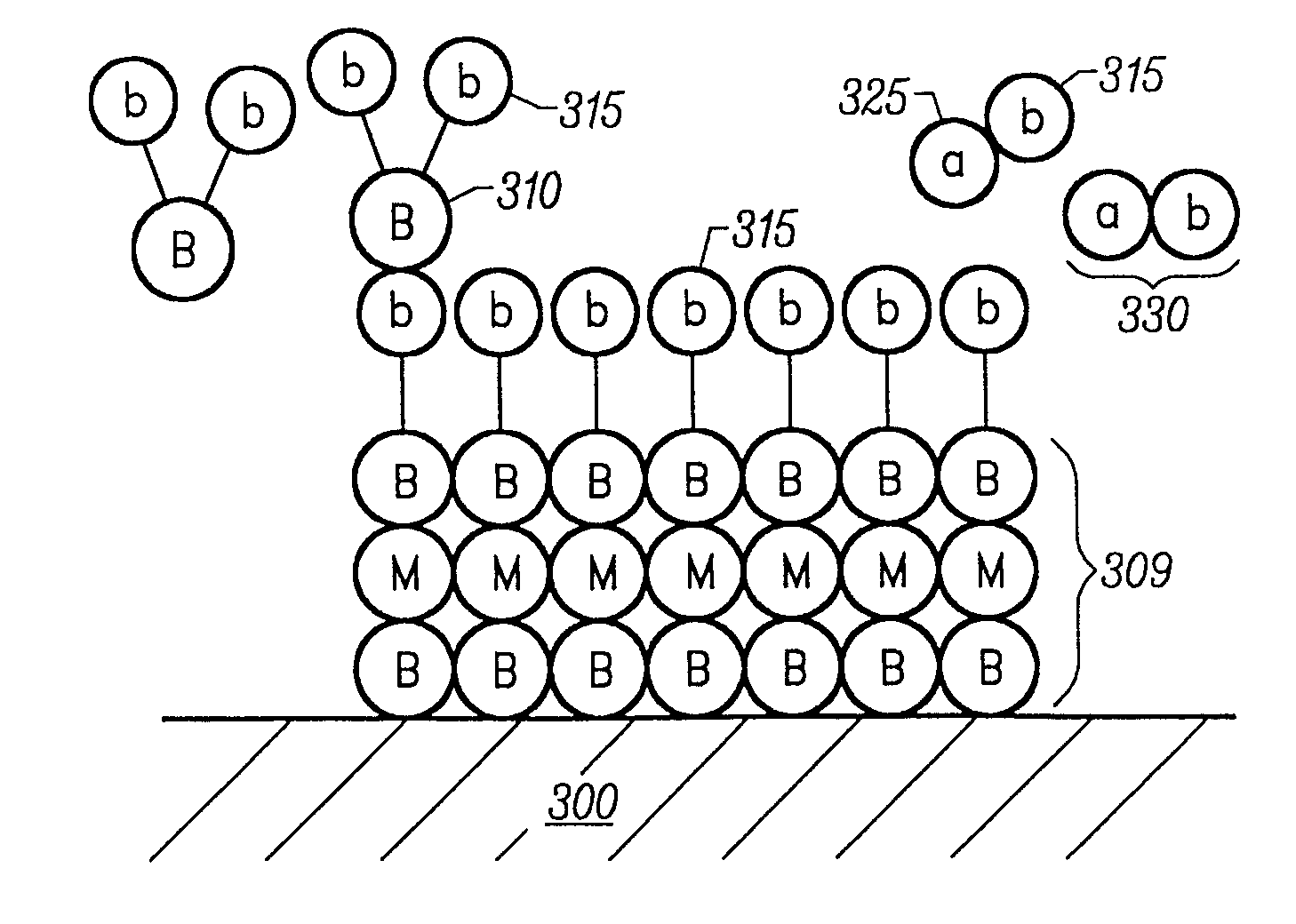

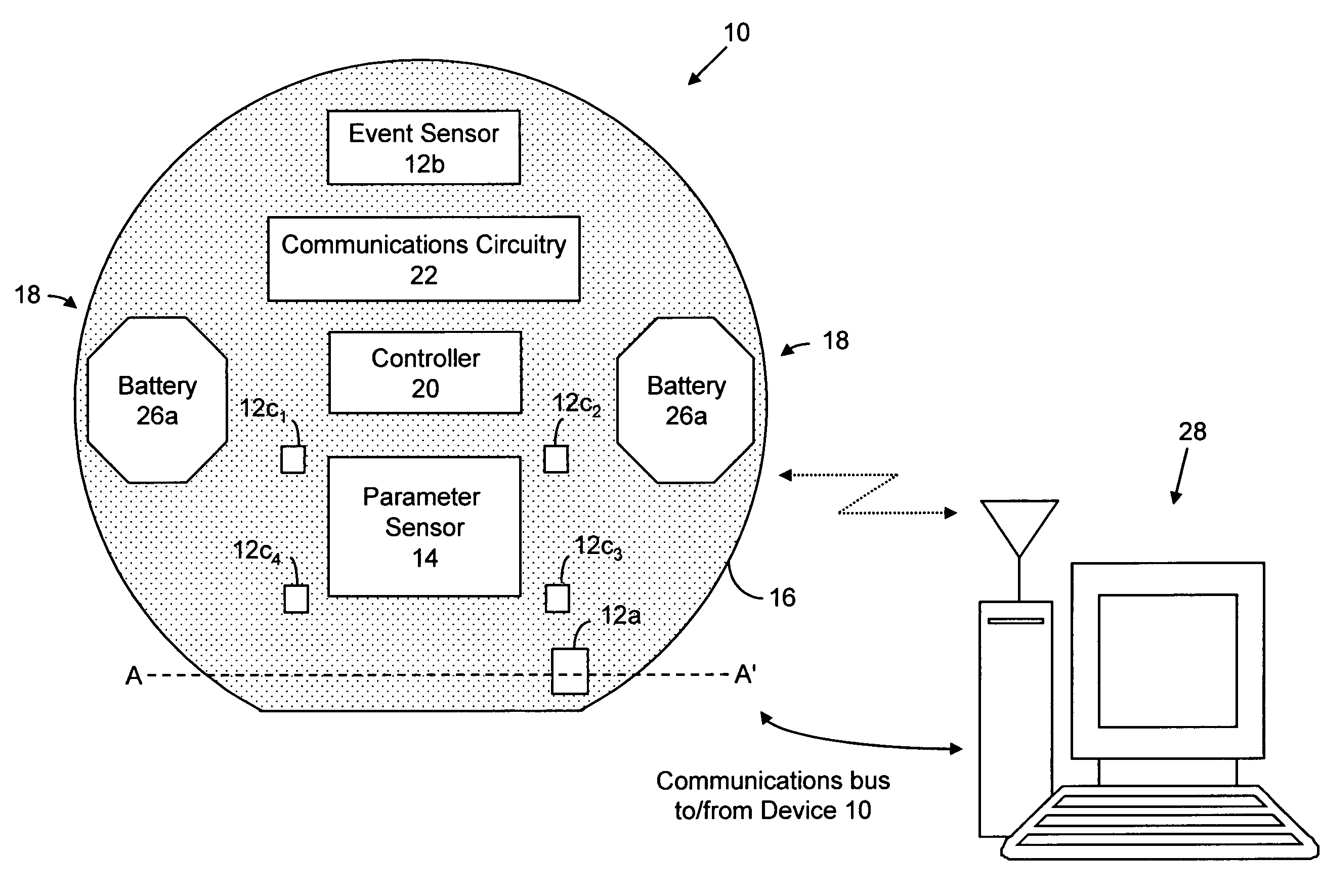

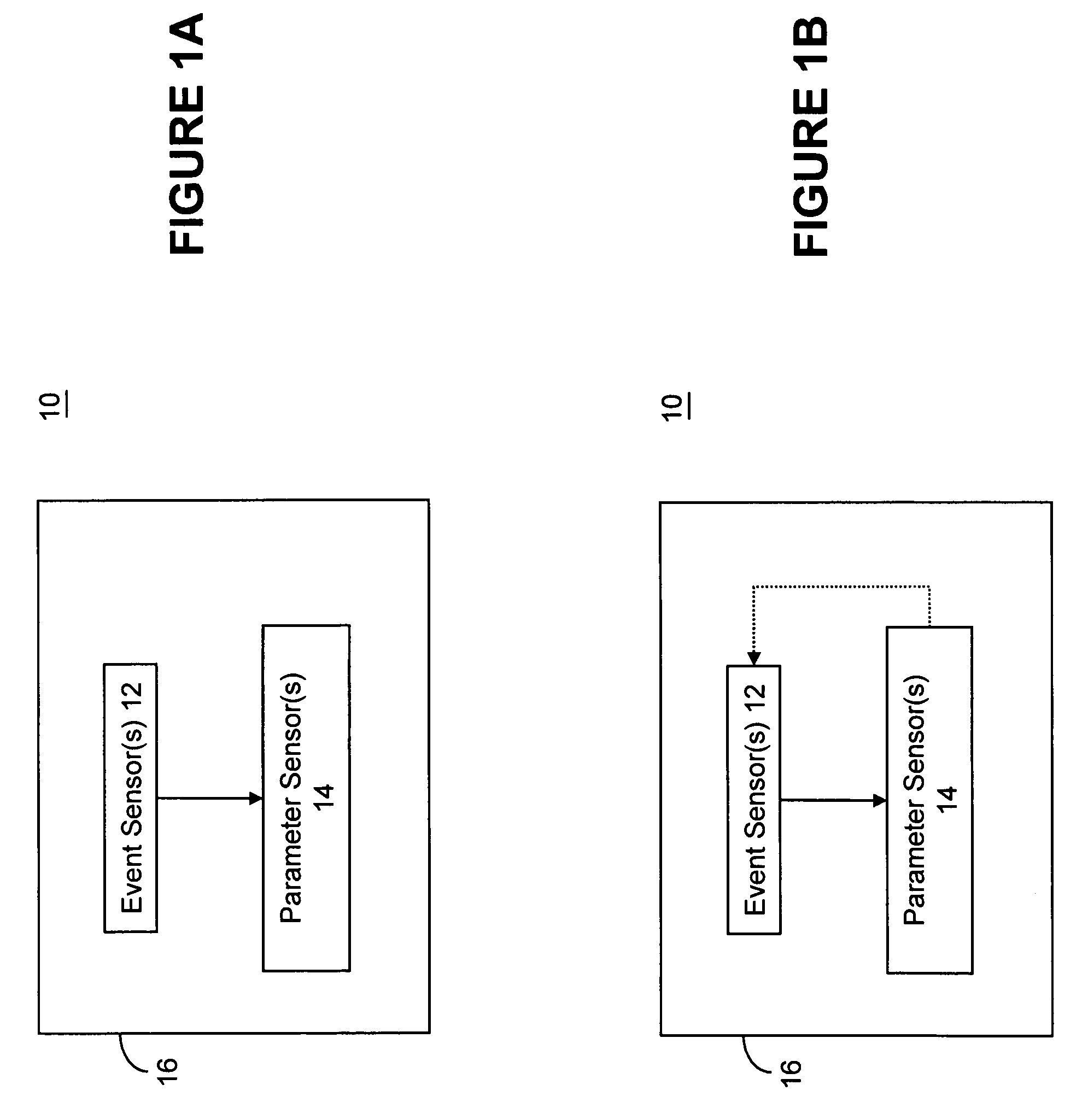

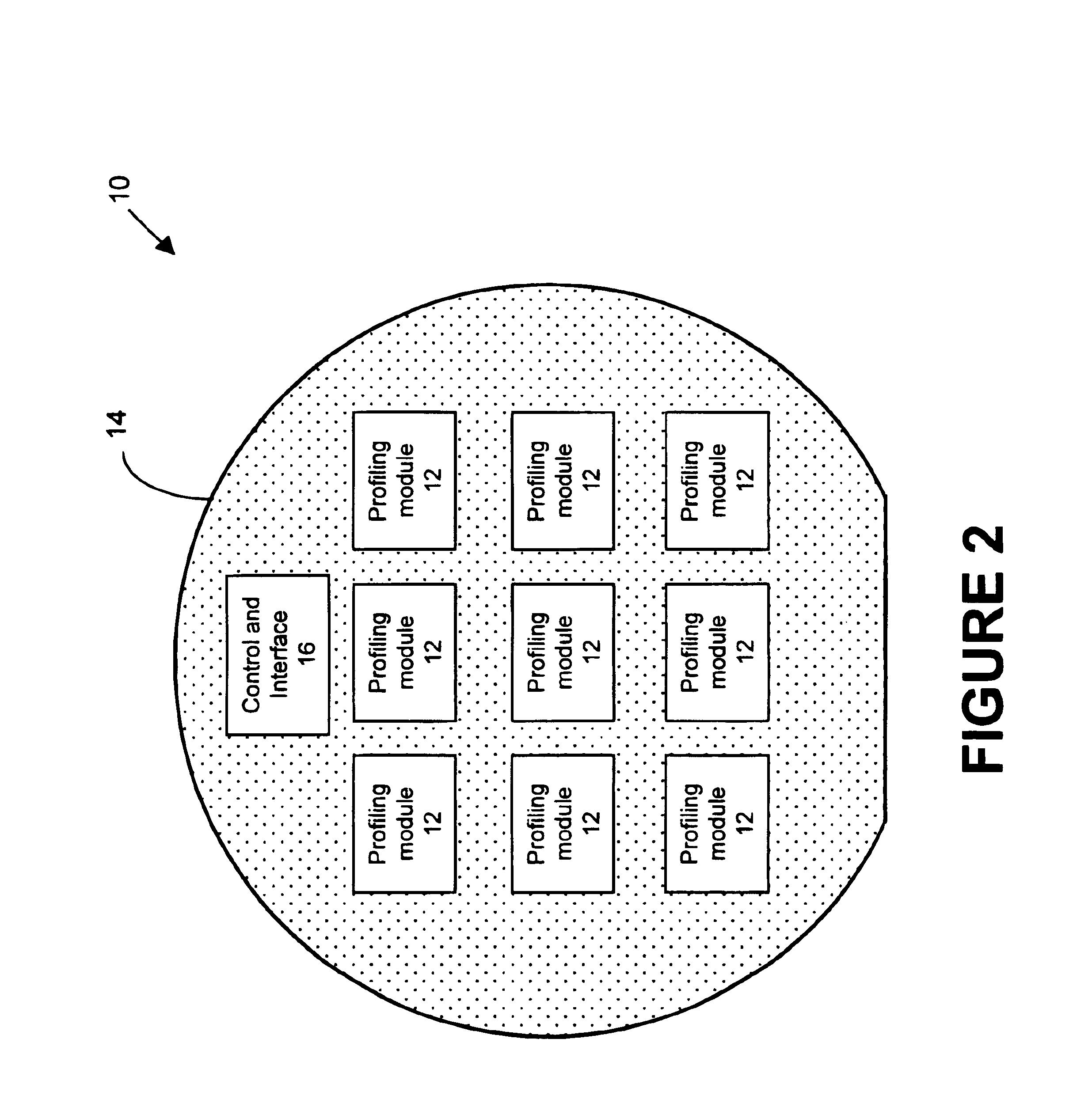

Method and apparatus for monitoring integrated circuit fabrication

ActiveUS6879924B2Accelerate lead optimization processChange is minimalSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceSurface stressEngineering

In one aspect, the present invention is a sensor unit for sensing process parameters of a process to manufacture an integrated circuit using integrated circuit processing equipment. In one embodiment, the sensor unit includes a substrate having a wafer-shaped profile and a first sensor, disposed on or in the substrate, to sample a first process parameter. The sensor unit of this embodiment also includes a second sensor, disposed on or in the substrate, to sample a second process parameter wherein the second process parameter is different from the first process parameter. In one embodiment, the sensor unit includes a first source, disposed on or in the substrate, wherein first source generates an interrogation signal and wherein the first sensor uses the interrogation signal from the first source to sample the first process parameter. The sensor unit may also include a second source, disposed on or in the substrate, wherein second source generates an interrogation signal and wherein the second sensor uses the interrogation signal from the second source to sample the second process parameter. The first sensor and the first source may operate in an end-point mode or in a real-time mode. In this regard, the first sensor samples the first parameter periodically or continuously while the sensor unit is disposed in the integrated circuit processing equipment and undergoing processing. In one embodiment, the first sensor is a temperature sensor and the second sensor is a pressure sensor, a chemical sensor, a surface tension sensor or a surface stress sensor.

Owner:ASML NETHERLANDS BV

Removal of surface passivation

Methods for removing a passivation film from a copper surface can include exposing the passivation film to a vapor phase organic reactant, for example at a temperature of 100° C. to 400° C. In some embodiments, the passivation film may have been formed by exposure of the copper surface to benzotriazole, such as can occur during a chemical mechanical planarization process. The methods can be performed as part of a process for integrated circuit fabrication. A second material can be selectively deposited on the cleaned copper surface relative to another surface of the substrate.

Owner:ASM IP HLDG BV

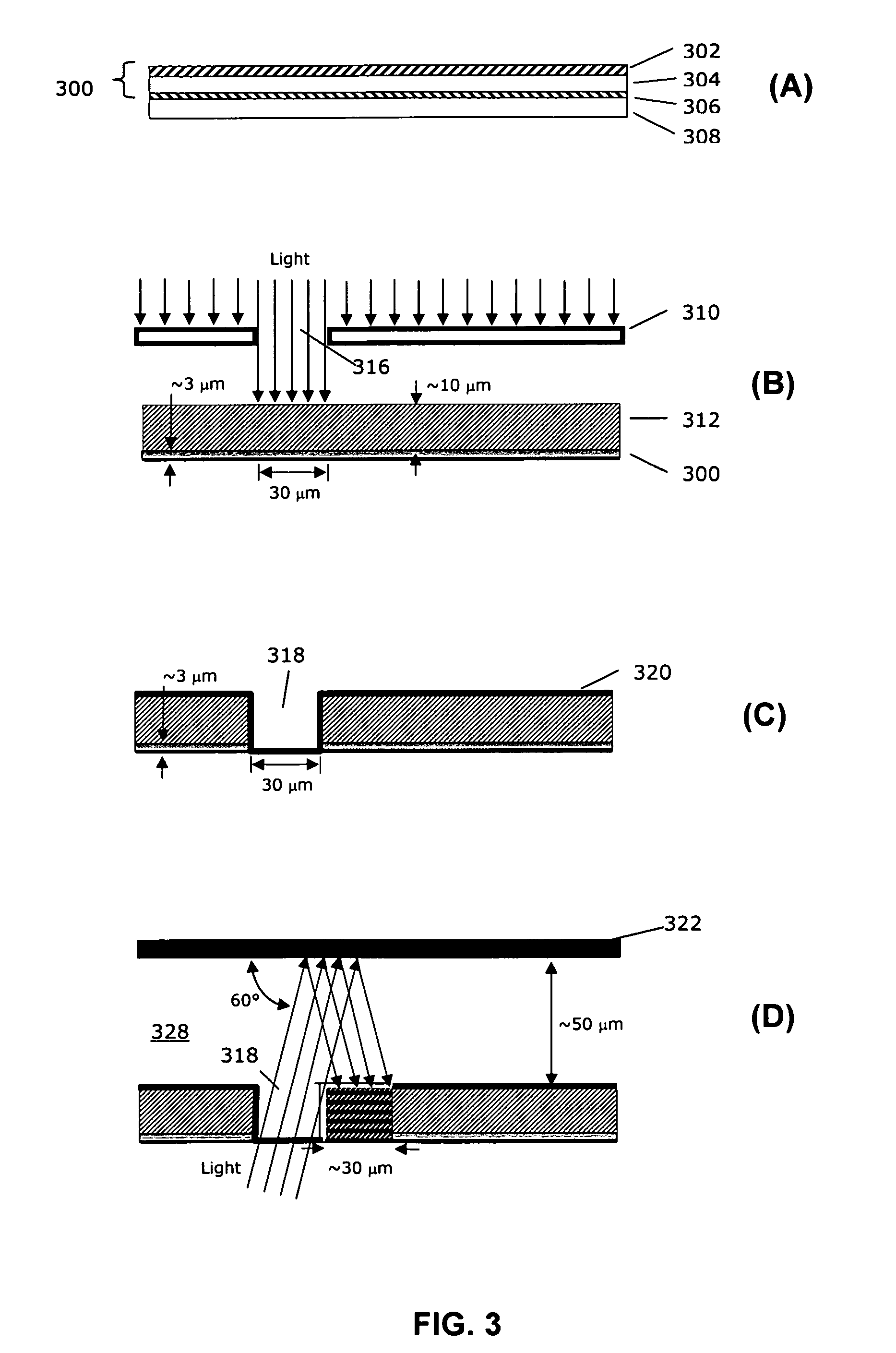

Method for forming thin film photovoltaic interconnects using self-aligned process

InactiveUS20070232057A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationEngineeringPhotoresist

Processing steps that are useful for forming interconnects in a photovoltaic module are described herein. According to one aspect, a method according to the invention includes processing steps that are similar to those performed in conventional integrated circuit fabrication. For example, the method can include etches to form a conductive step adjacent to the grooves that can be used to form interconnects between cells. According to another aspect the method for forming the conductive step can be self-aligned, such as by positioning a mirror above the module and exposing photoresist from underneath the substrate at an angle one or more times, and etching to expose the conductive step.

Owner:APPLIED MATERIALS INC