Patents

Literature

2961 results about "Test structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Structural testing is the type of testing carried out to test the structure of code. It is also known as White Box testing or Glass Box testing. This type of testing requires knowledge of the code, so, it is mostly done by the developers.

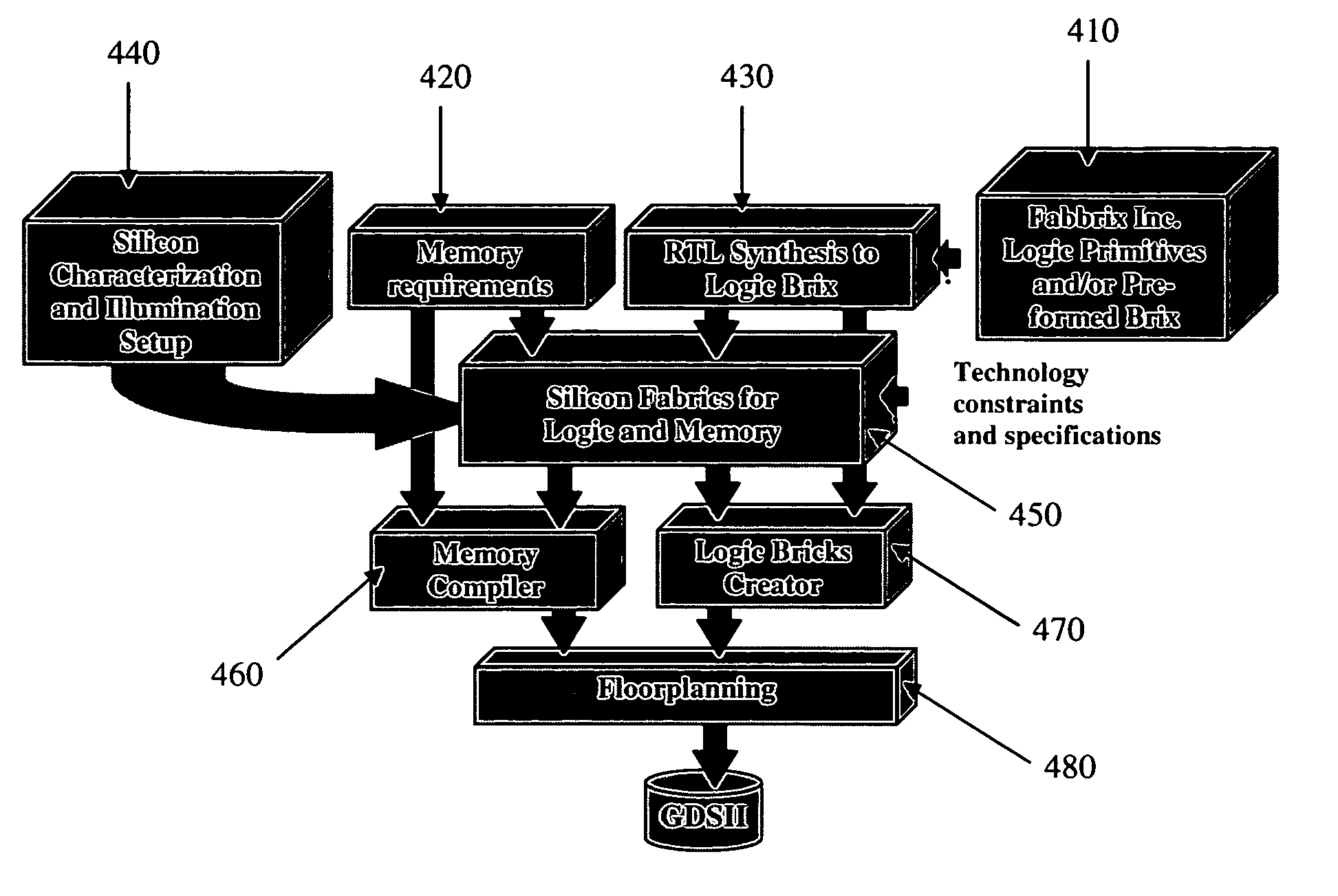

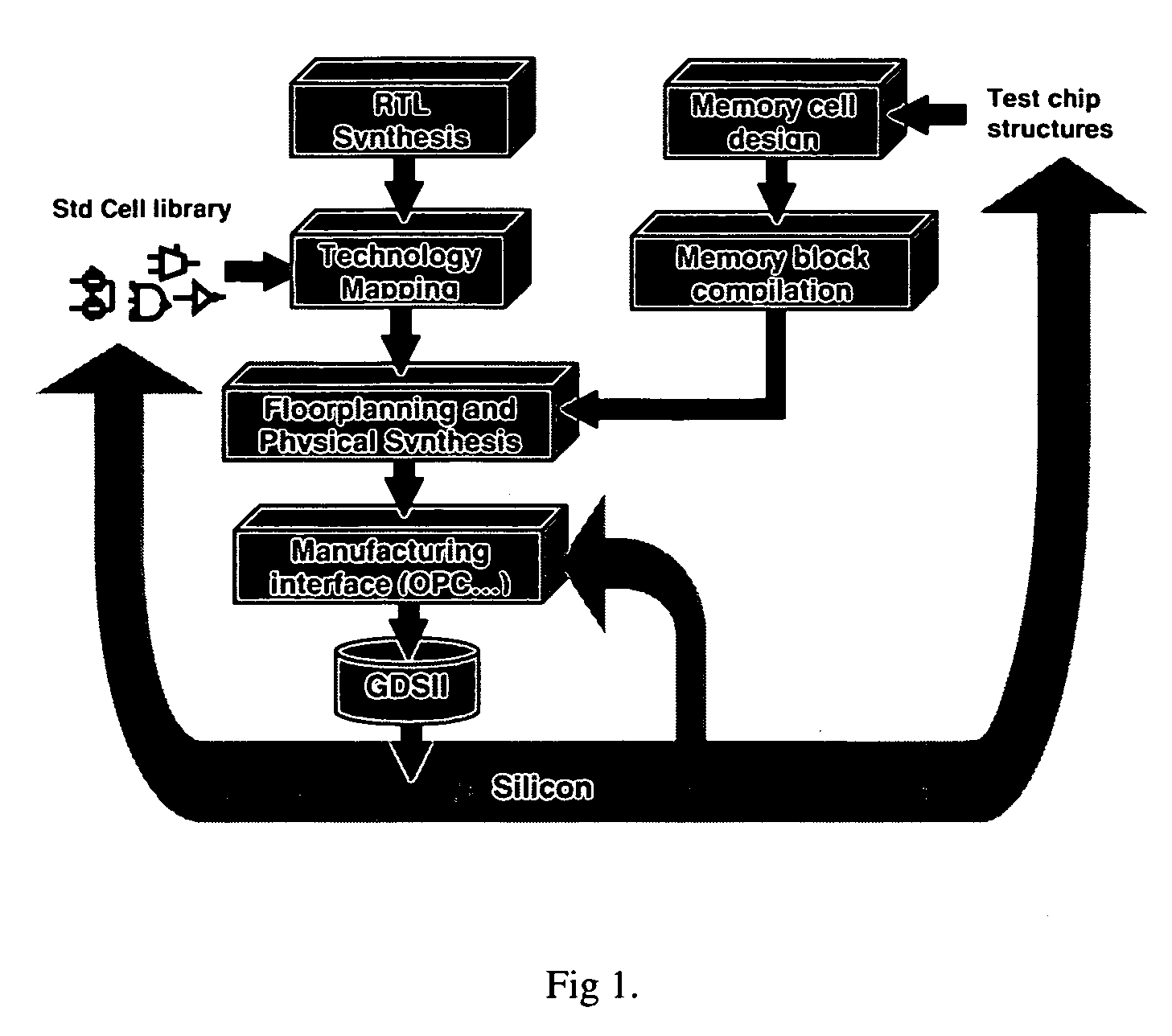

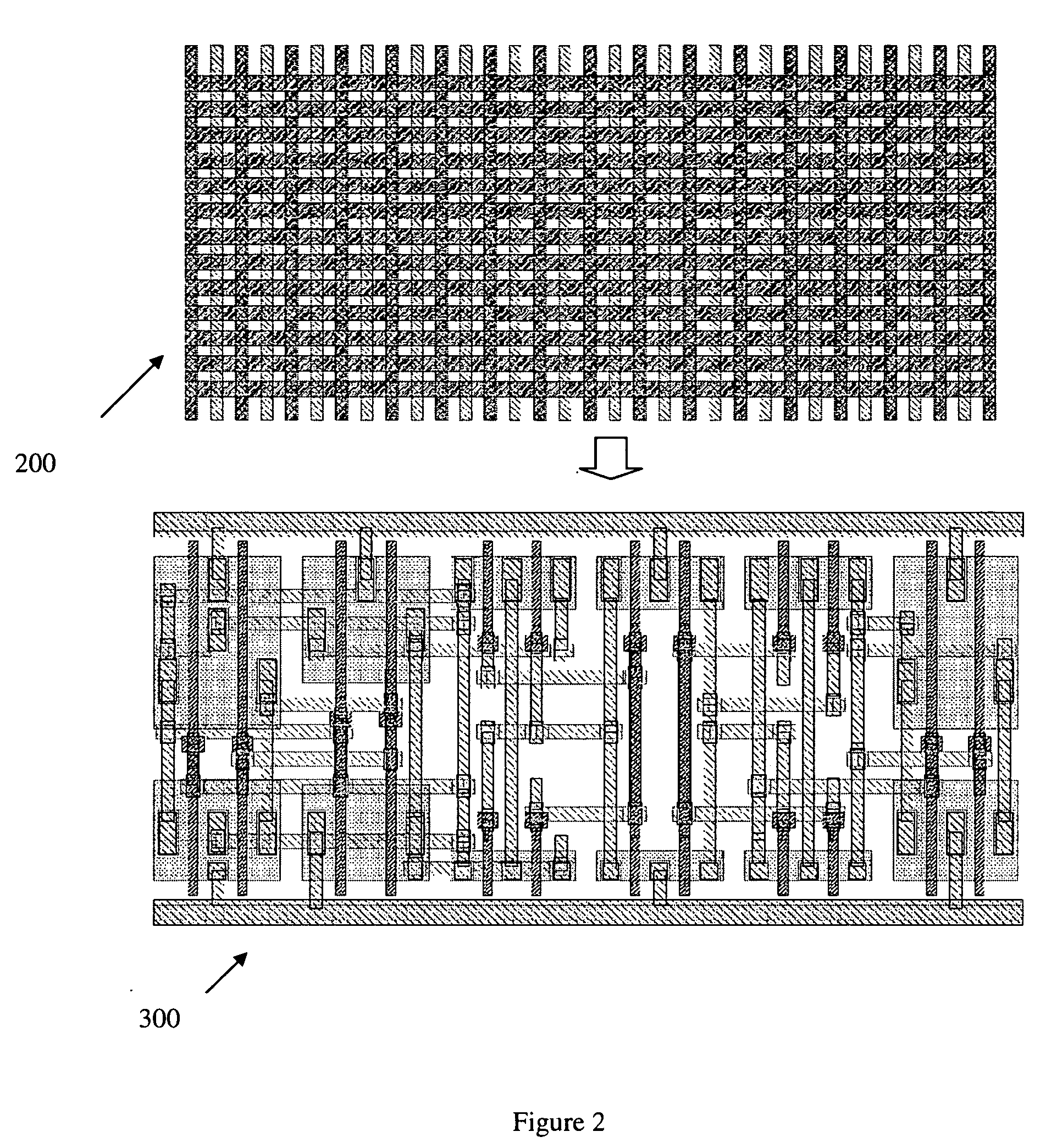

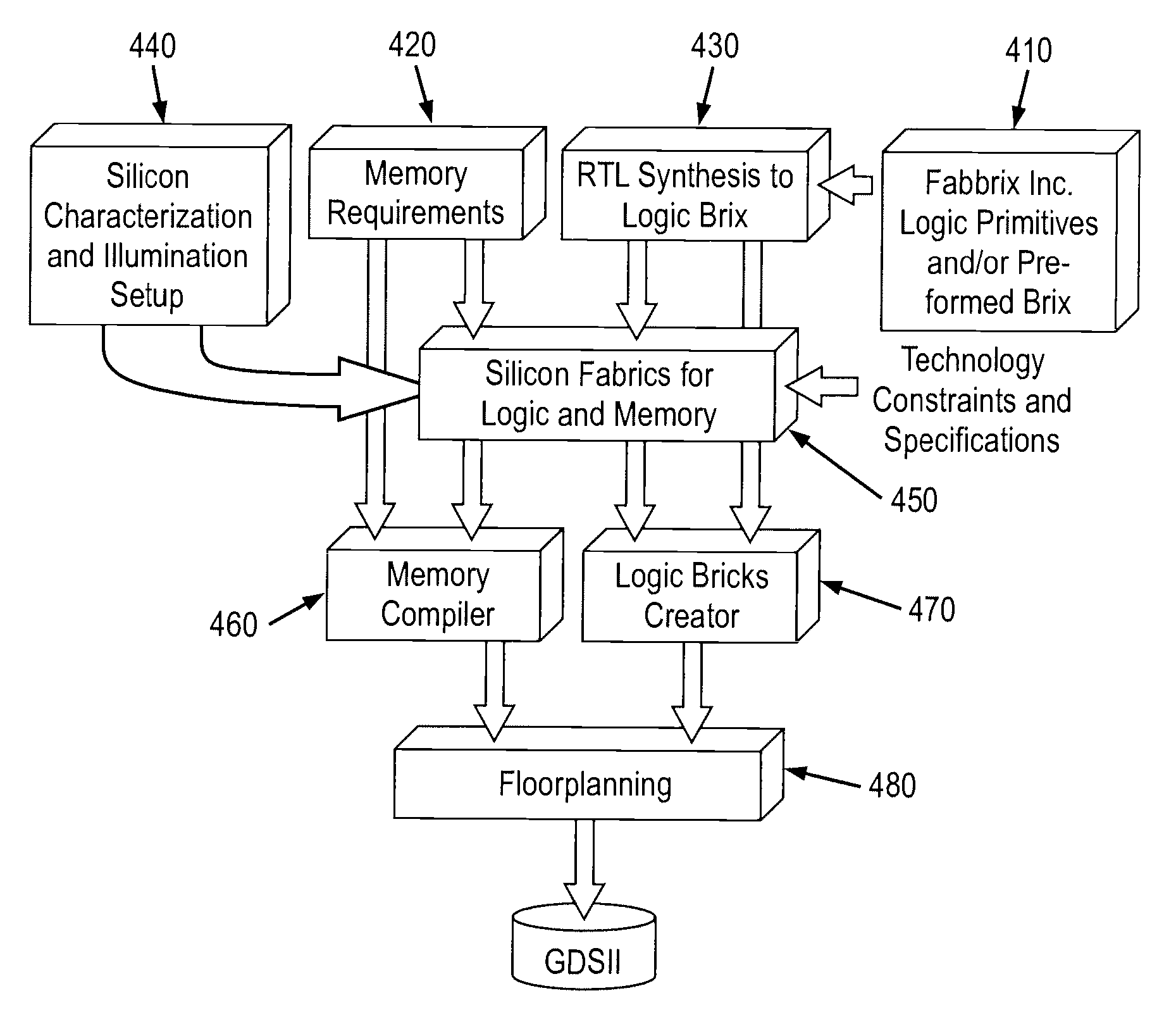

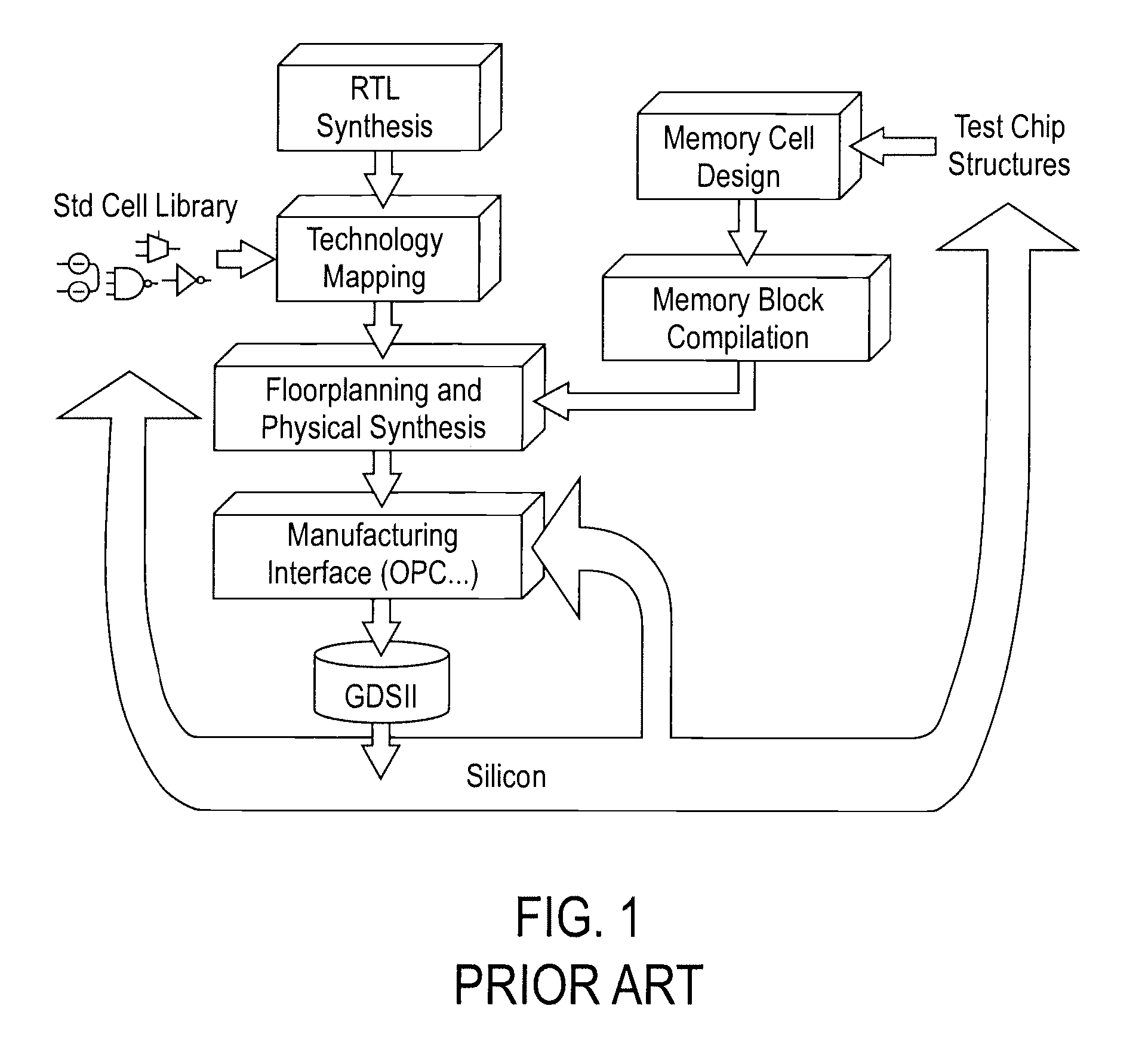

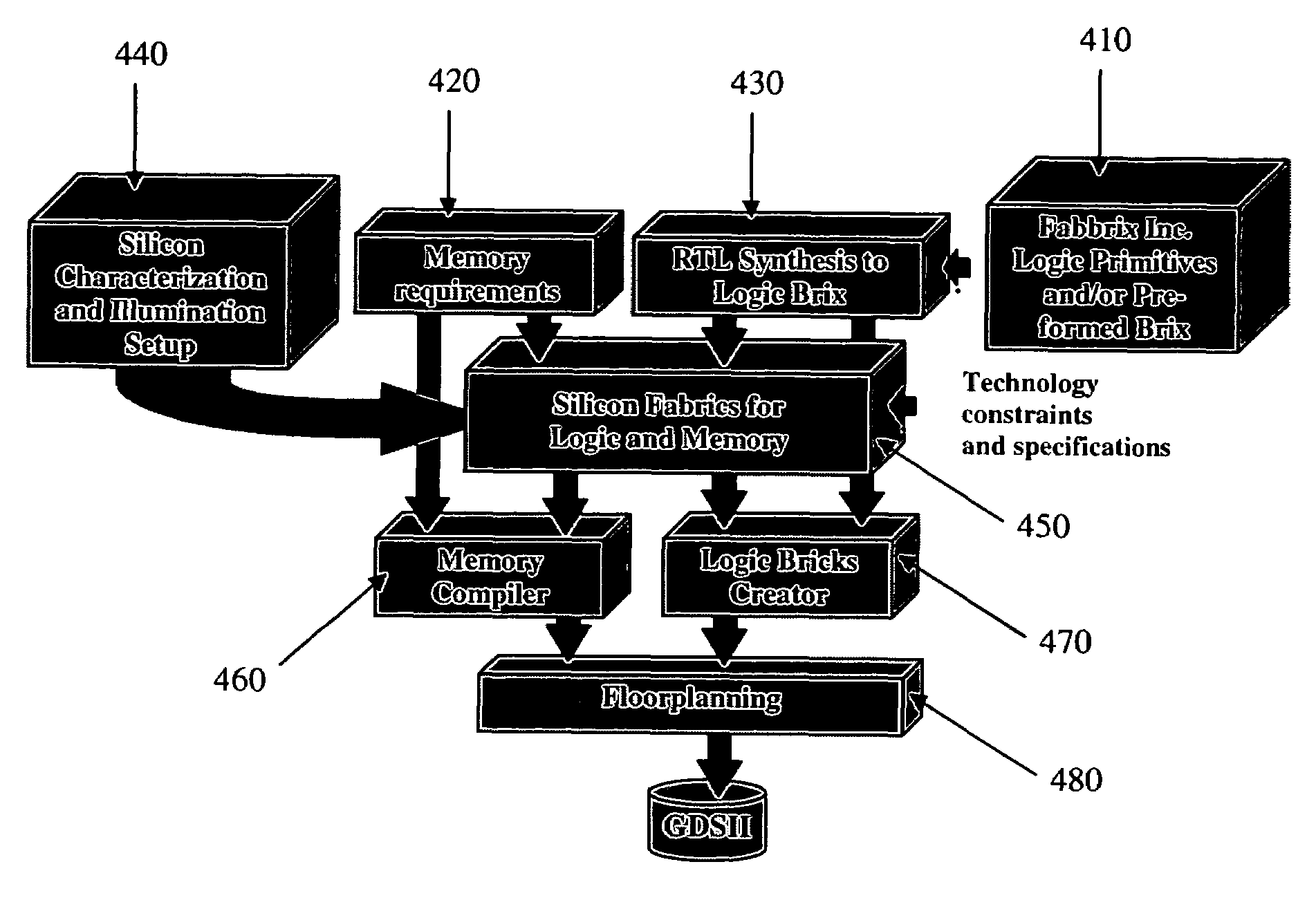

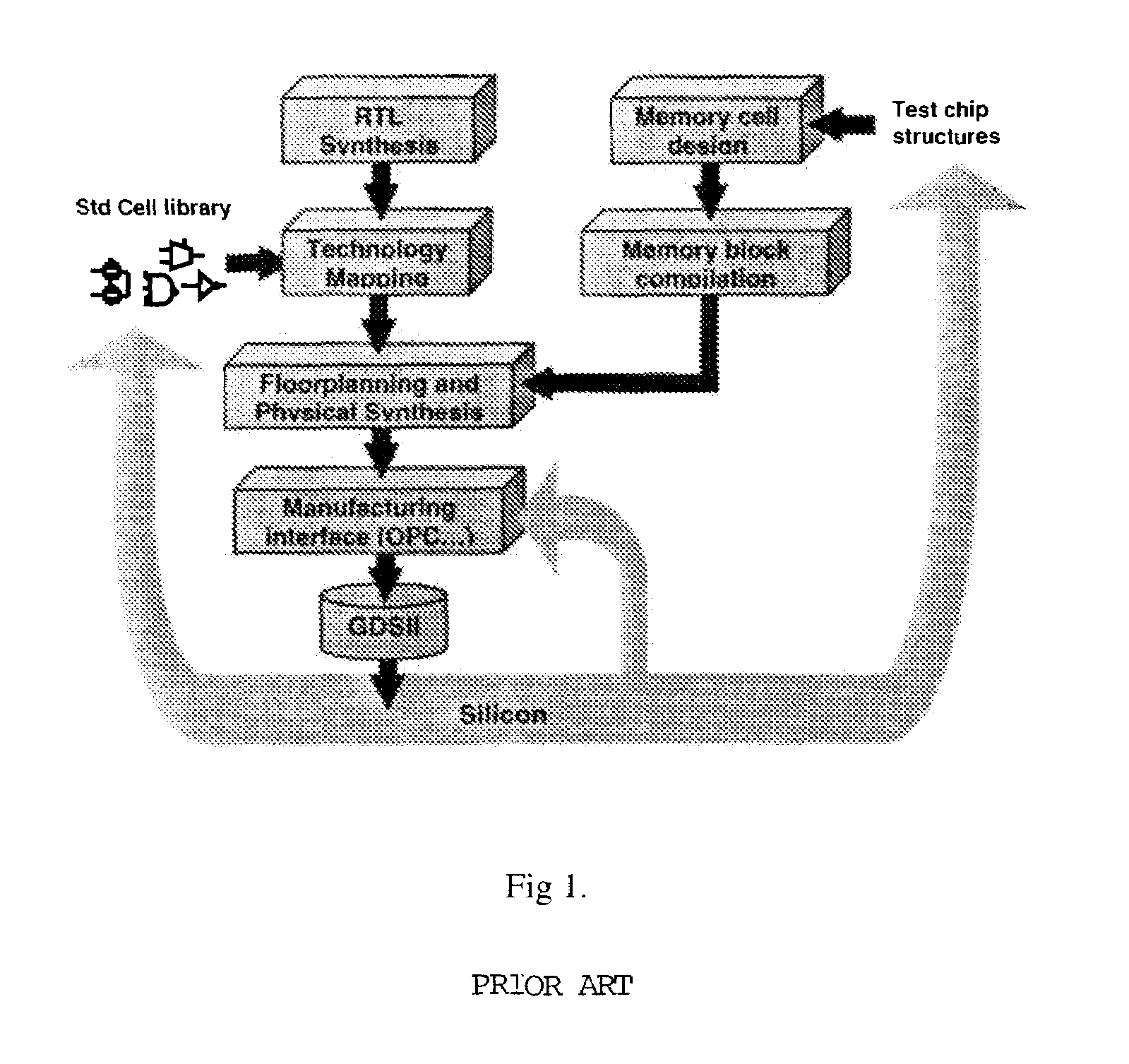

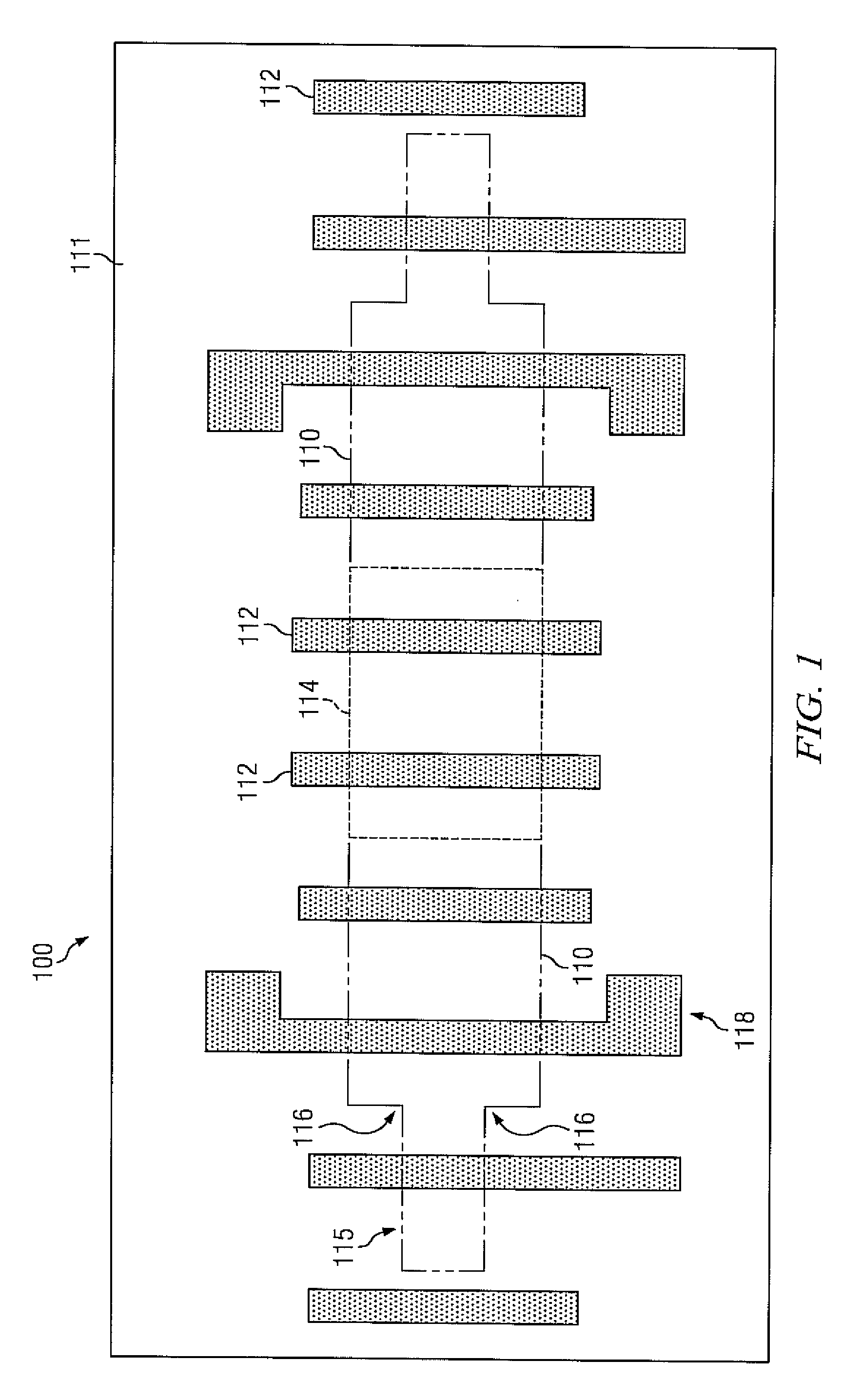

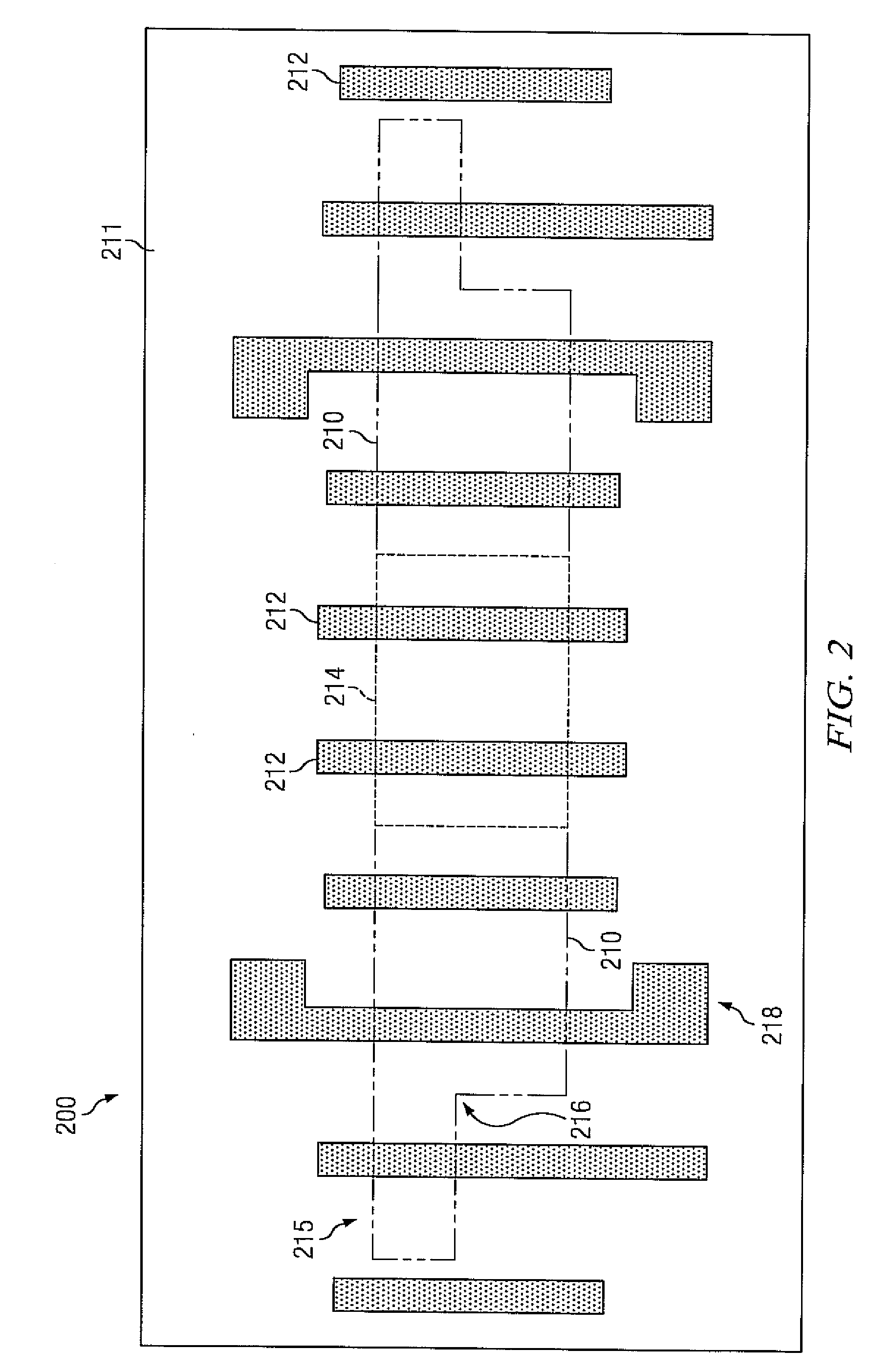

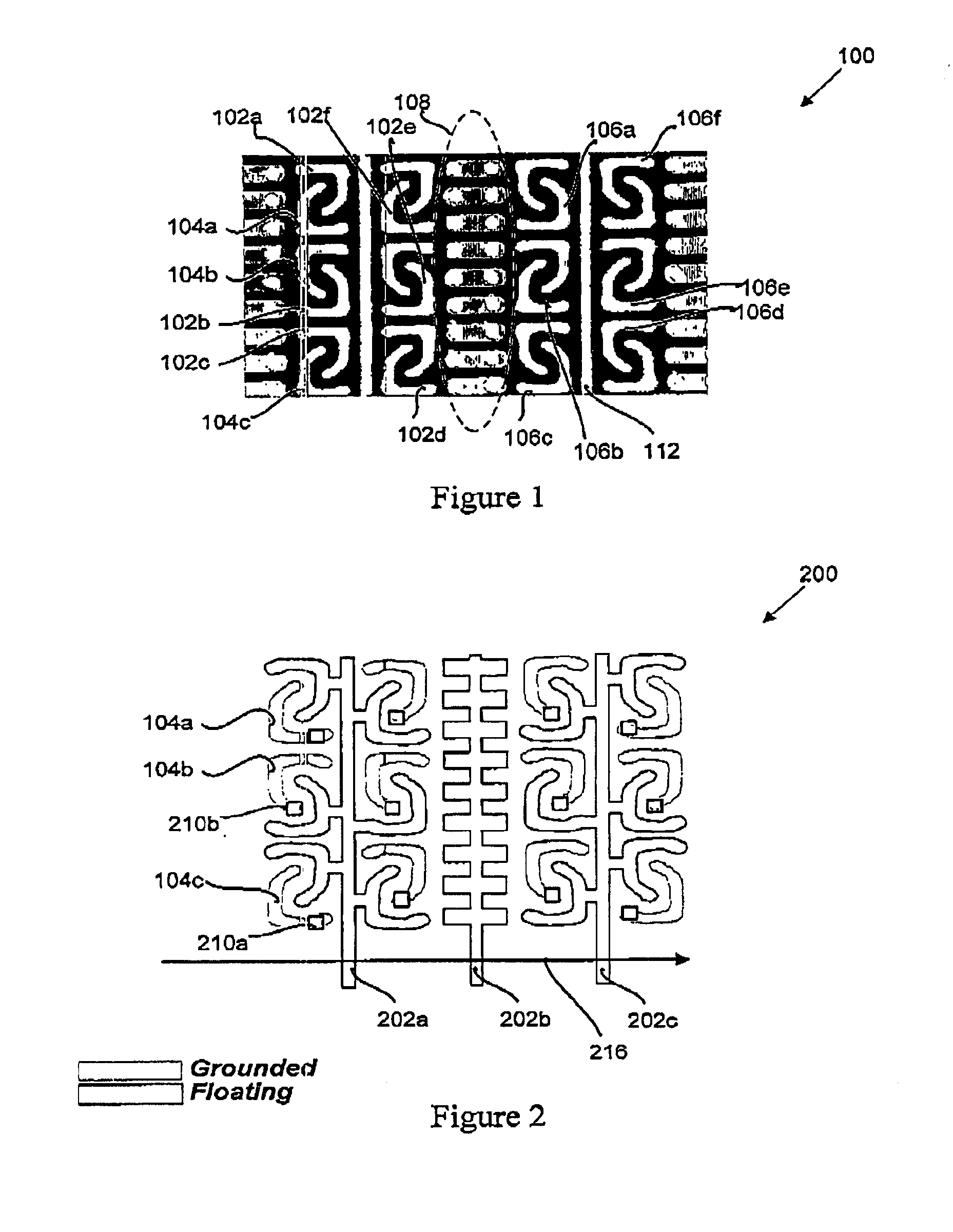

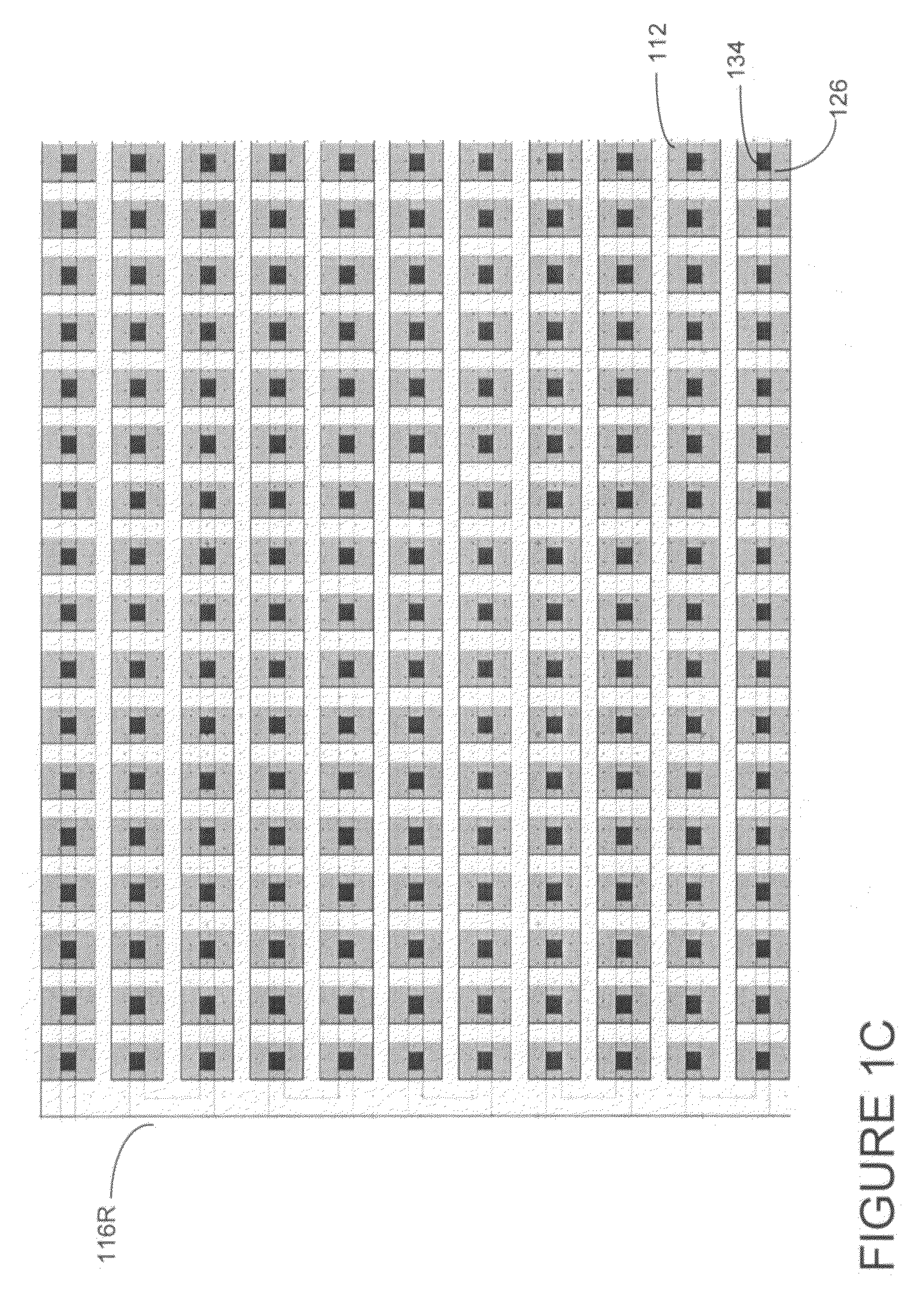

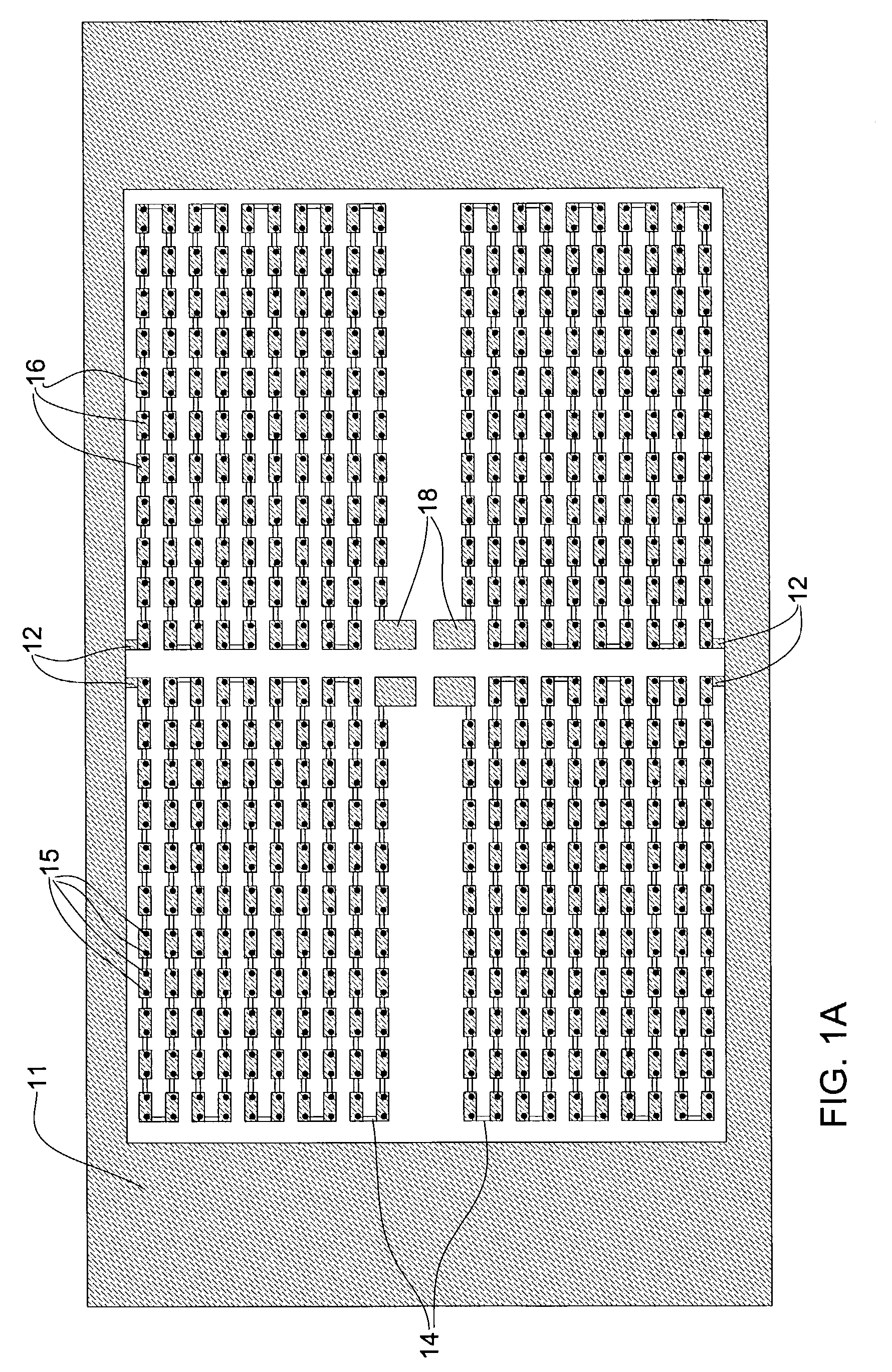

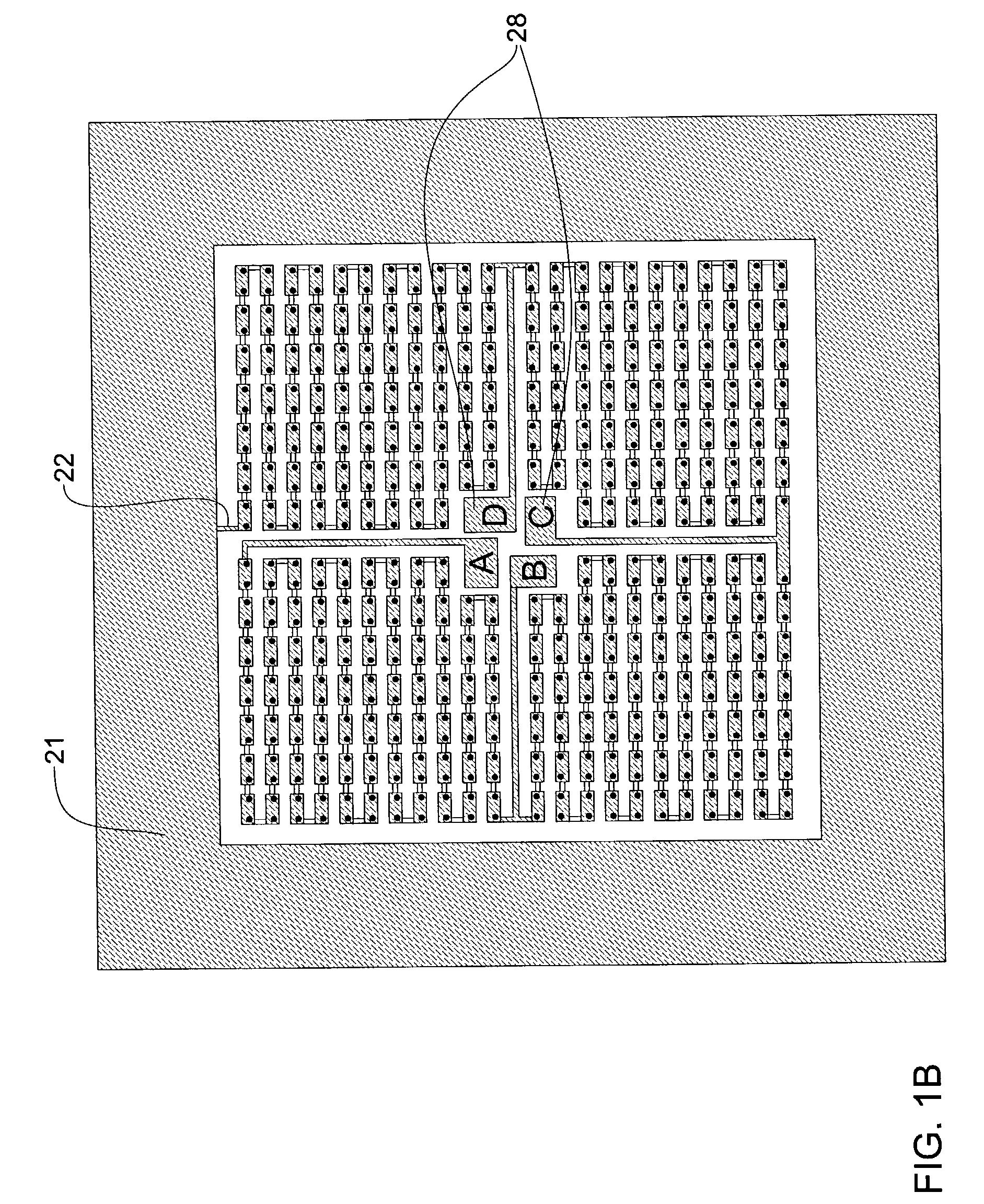

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

ActiveUS20060112355A1CAD circuit designSpecial data processing applicationsComputer architectureBrick

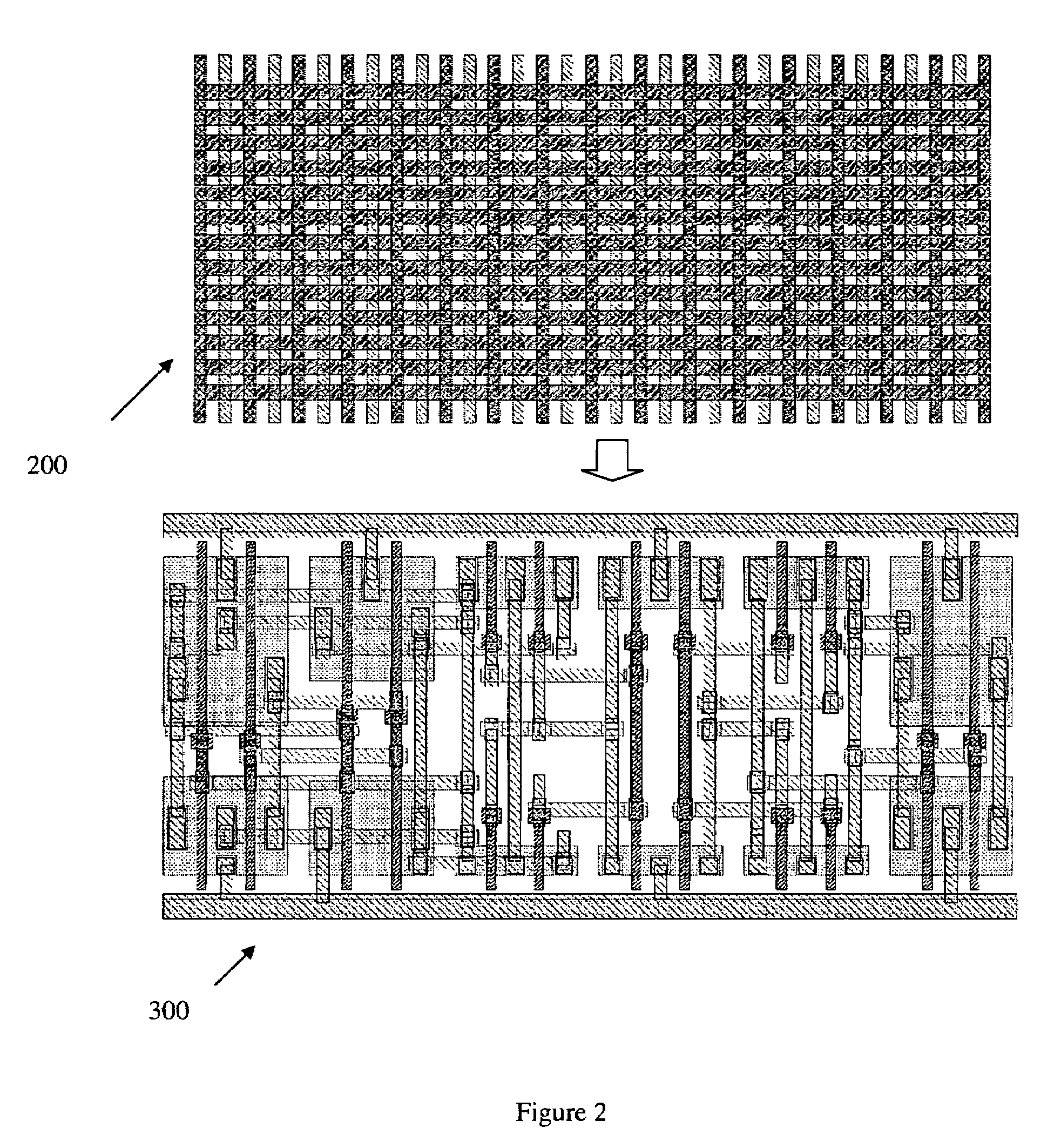

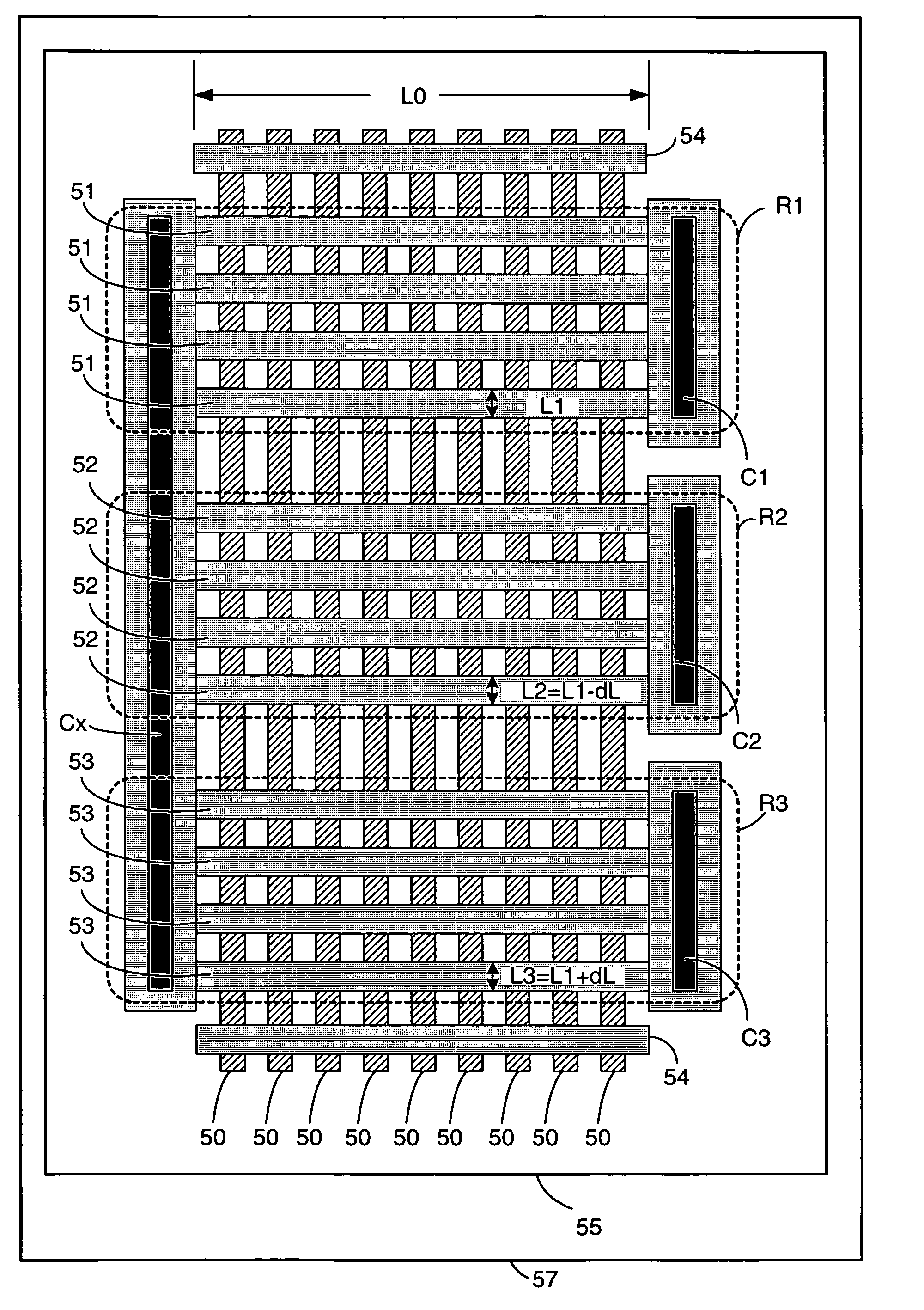

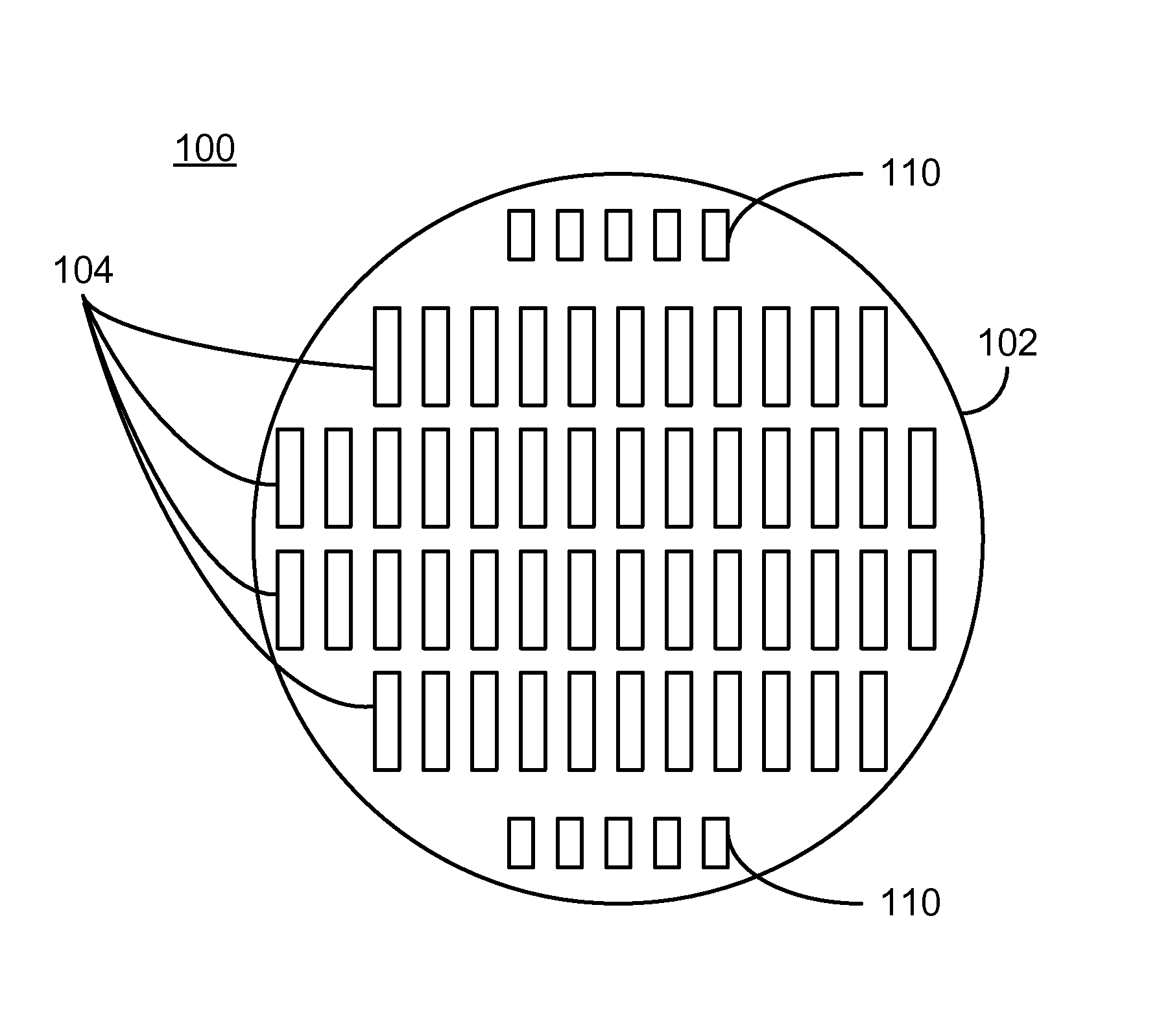

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

InactiveUS20080098334A1CAD circuit designOriginals for photomechanical treatmentComputer architectureBrick

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

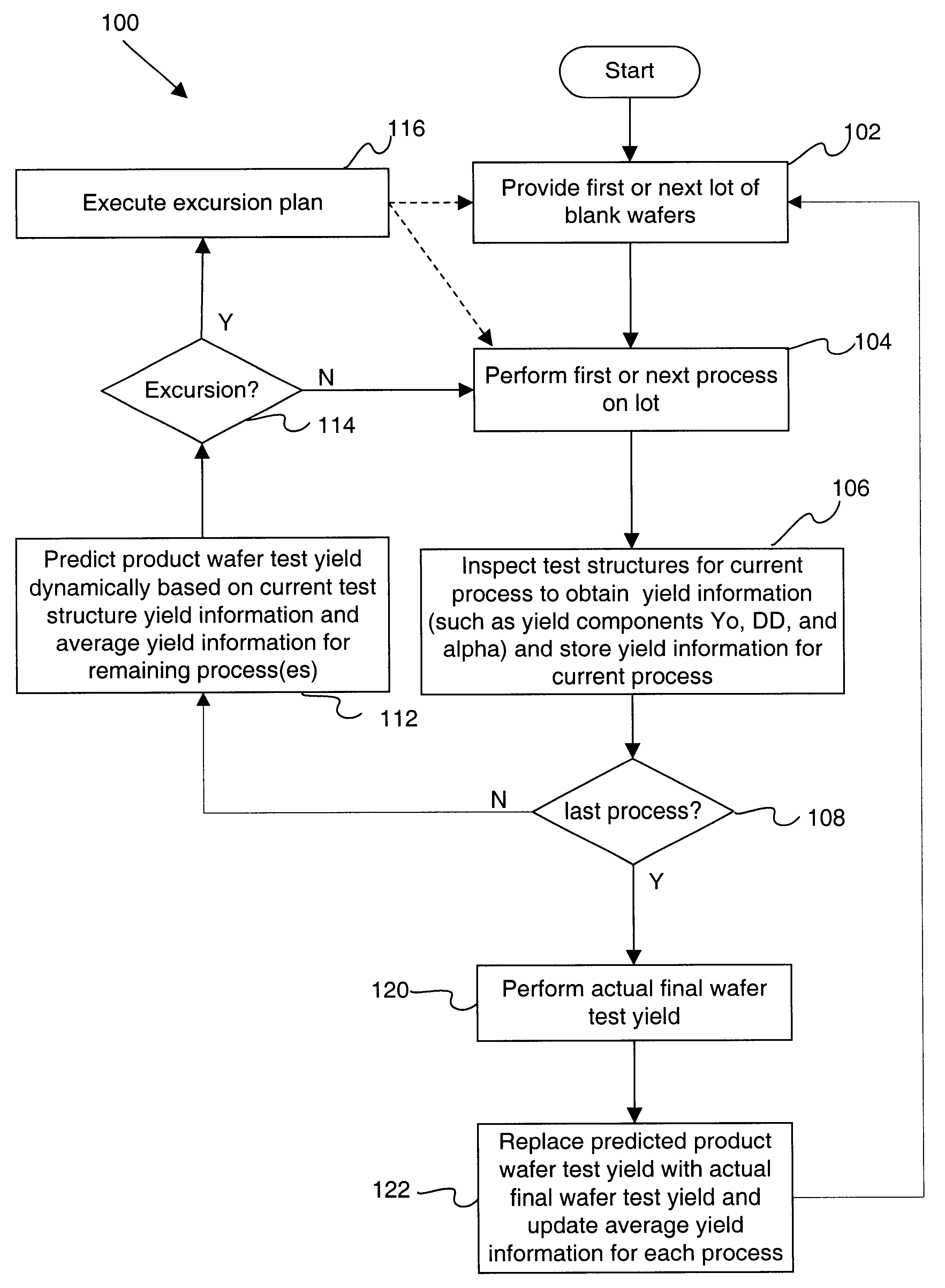

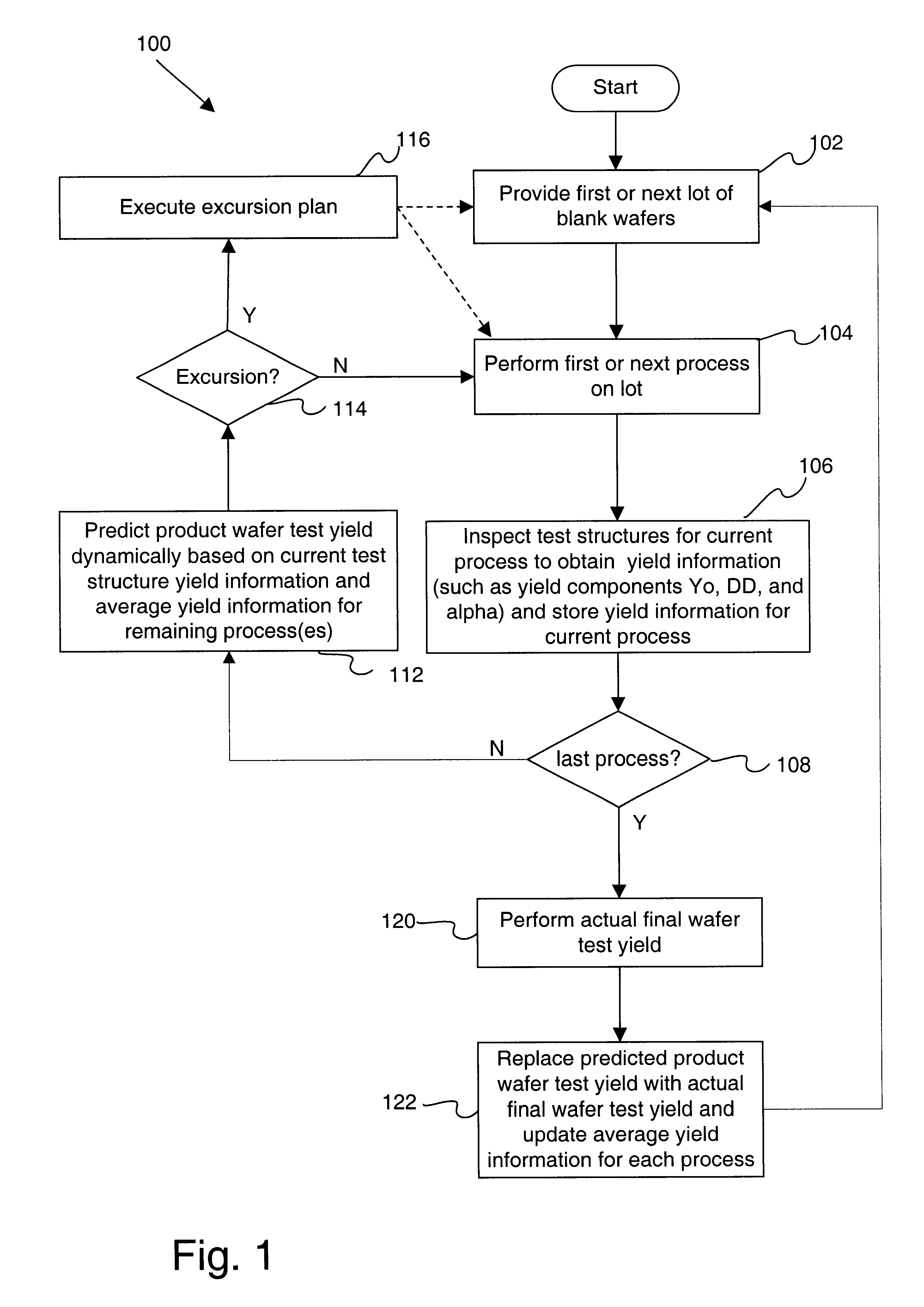

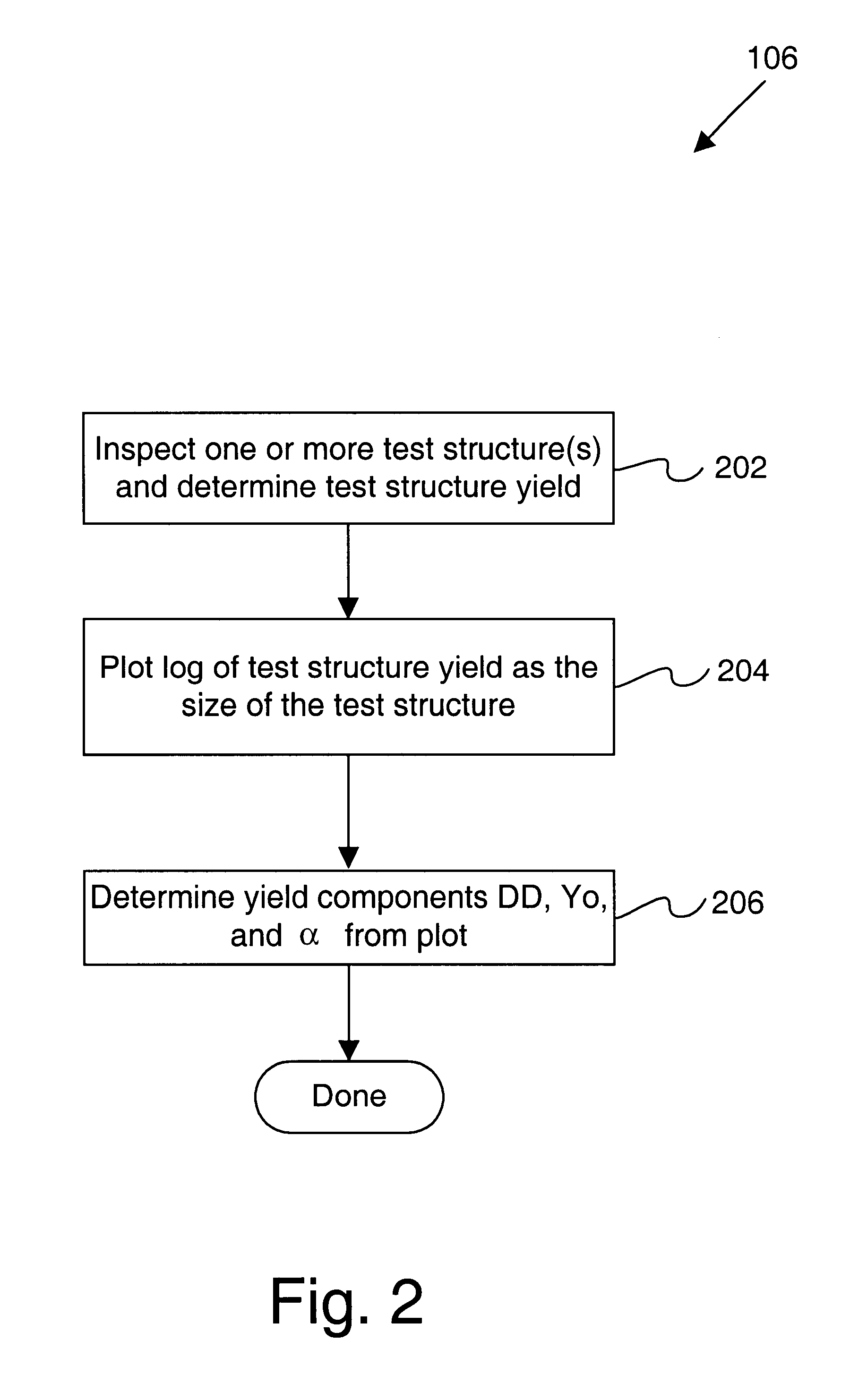

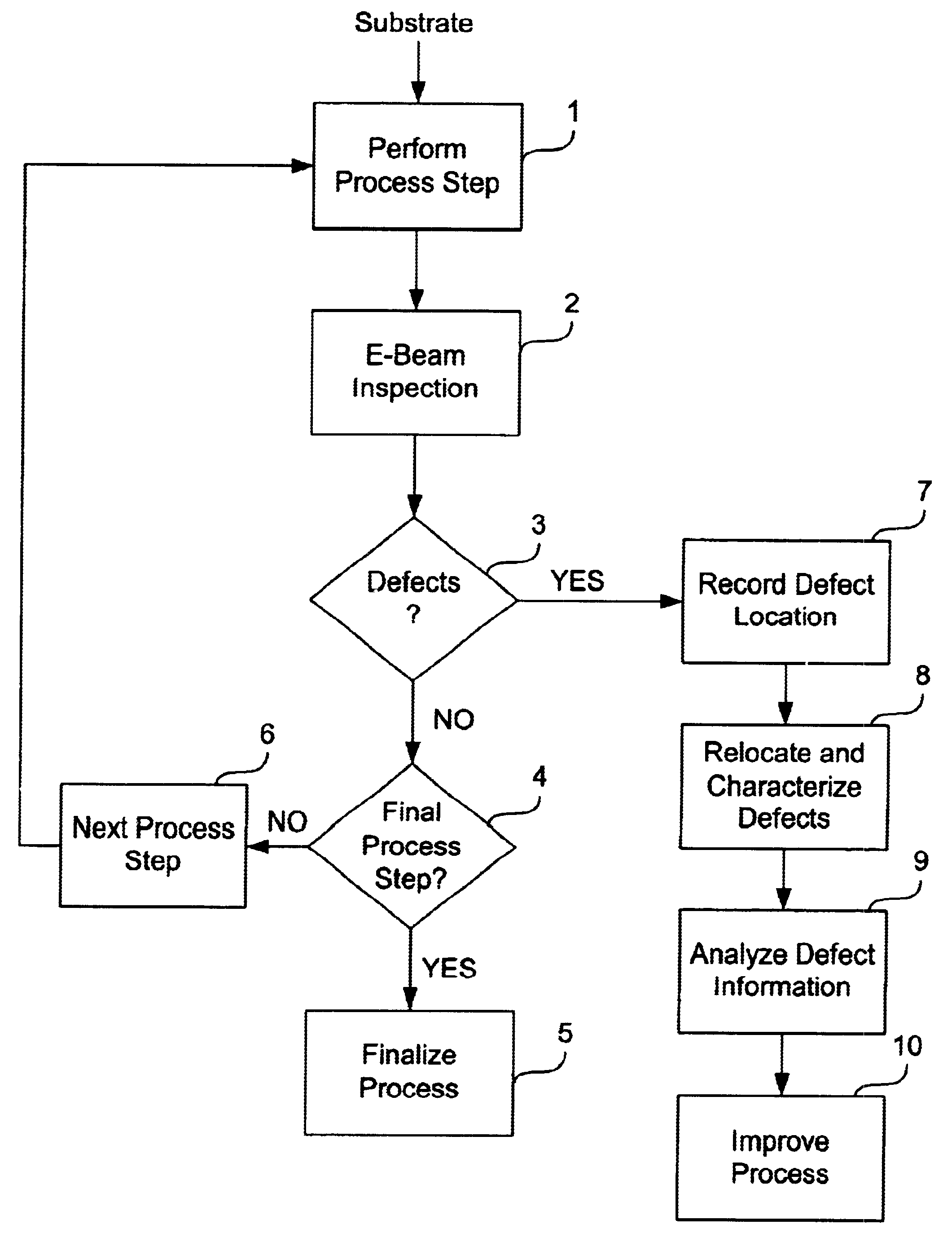

Methods and systems for predicting IC chip yield

InactiveUS6751519B1Semiconductor/solid-state device testing/measurementNuclear monitoringProcess engineeringReliability engineering

Disclosed are methods and apparatus for efficiently managing IC chip yield learning. In general terms, as each wafer lot moves through fabrication, yield information is obtained from each set of test structures for a particular process or defect mechanism. The nature of the yield information is such that it may be used directly or indirectly to predict product wafer test yield. In one implementation, the yield information includes a systematic yield (Y.sub.0), a defect density (DD), and a defect clustering factor (.alpha.) determined based on the inspected test structure's yield. A running average of the yield information for each process or defect mechanism is maintained as each wafer lot is processed. As a particular wafer lot moves through the various processes, a product wafer-sort test yield may be predicted at any stage in the fabrication process based on the running-average yield information maintained for previously fabricated wafer lots.

Owner:KLA TENCOR TECH CORP

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

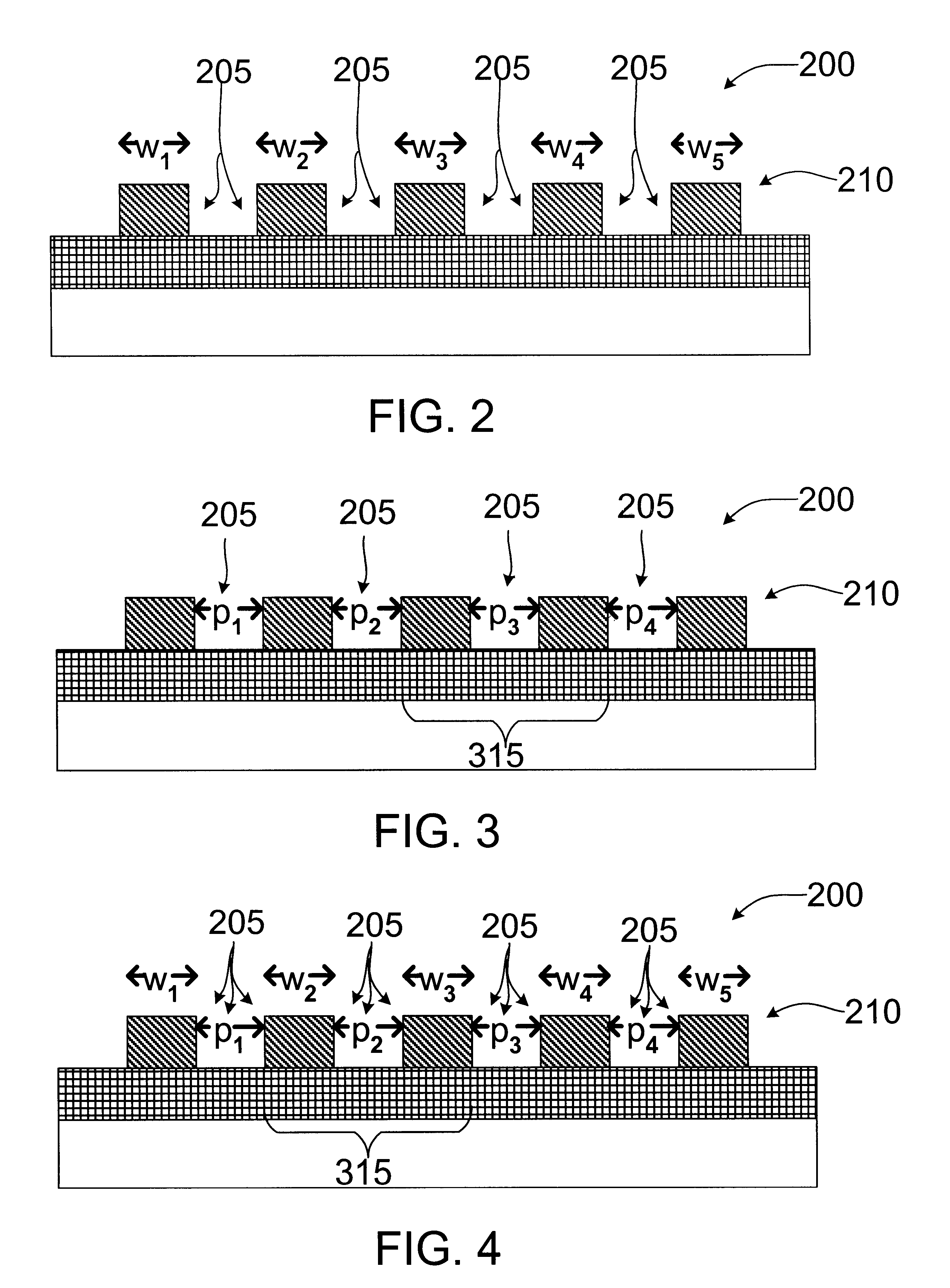

Polysilicon conductor width measurement for 3-dimensional FETs

InactiveUS7227183B2Sure easyImprove accuracyTransistorSemiconductor/solid-state device testing/measurementElectrical resistance and conductanceElectrical conductor

An apparatus and method is disclosed for determining polysilicon conductor width for 3-dimensional field effect transistors (FinFETs). Two or more resistors are constructed using a topology in which polysilicon conductors are formed over a plurality of silicon “fins”. A first resistor has a first line width. A second resistor has a second line width. The second line width is slightly different than the first line width. Advantageously, the first line width is equal to the nominal design width used to make FET gates in the particular semiconductor technology. Resistance measurements of the resistors and subsequent calculations using the resistance measurements are used to determine the actual polysilicon conductor width produced by the semiconductor process. A composite test structure not only allows calculation of the polysilicon conductor width, but provides proof that differences in the widths used in the calculations do not introduce objectionable etching characteristics of the polysilicon conductors.

Owner:IBM CORP

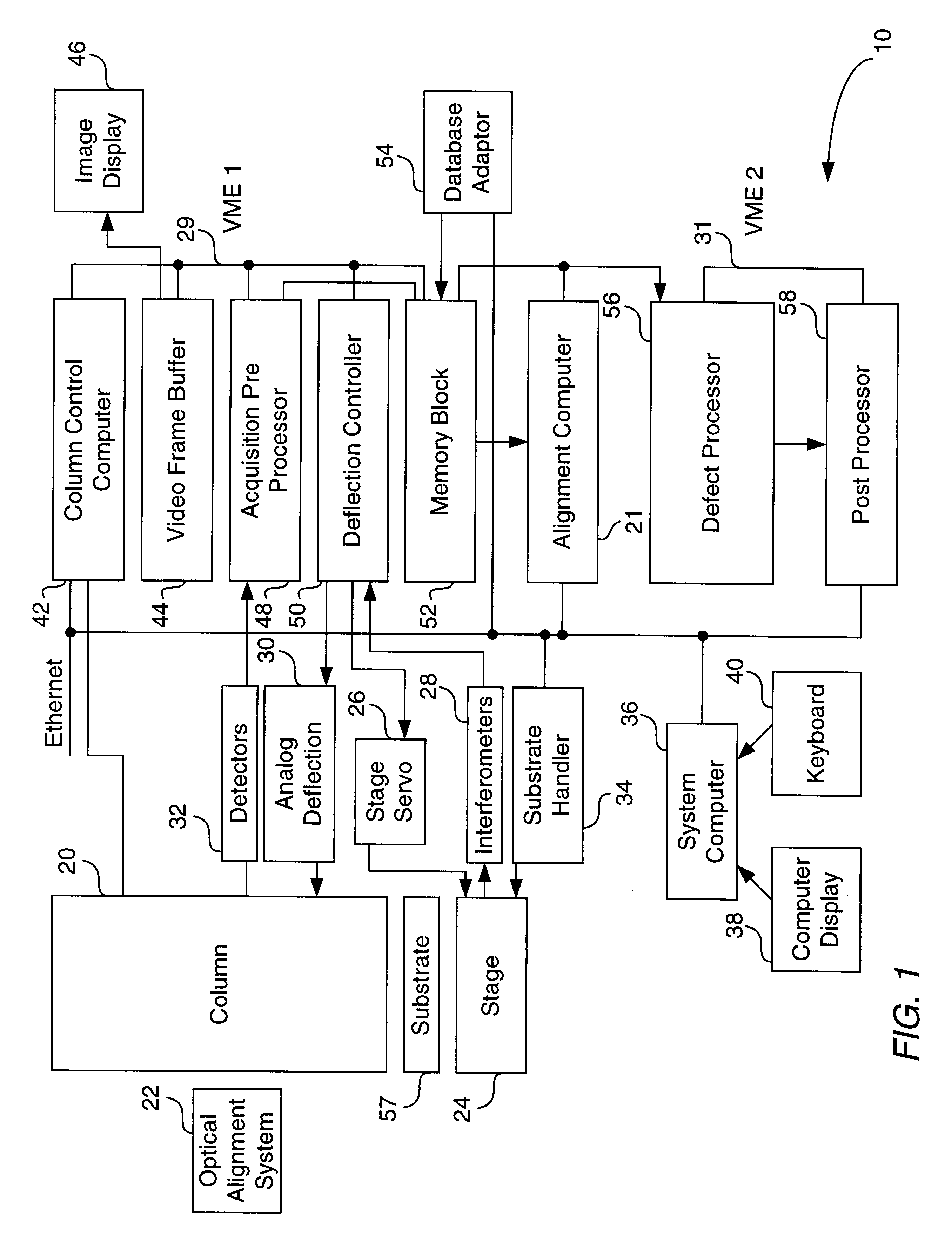

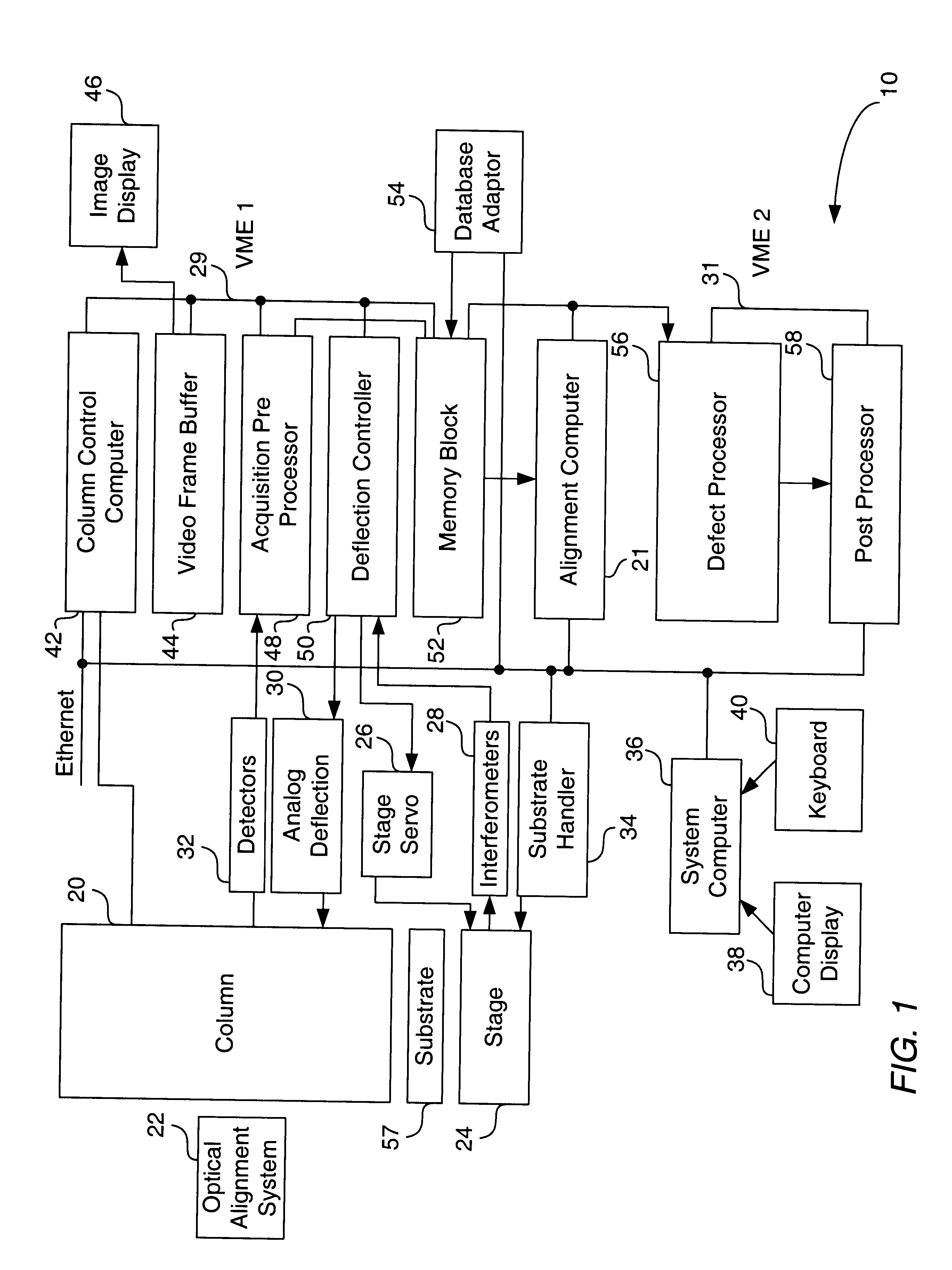

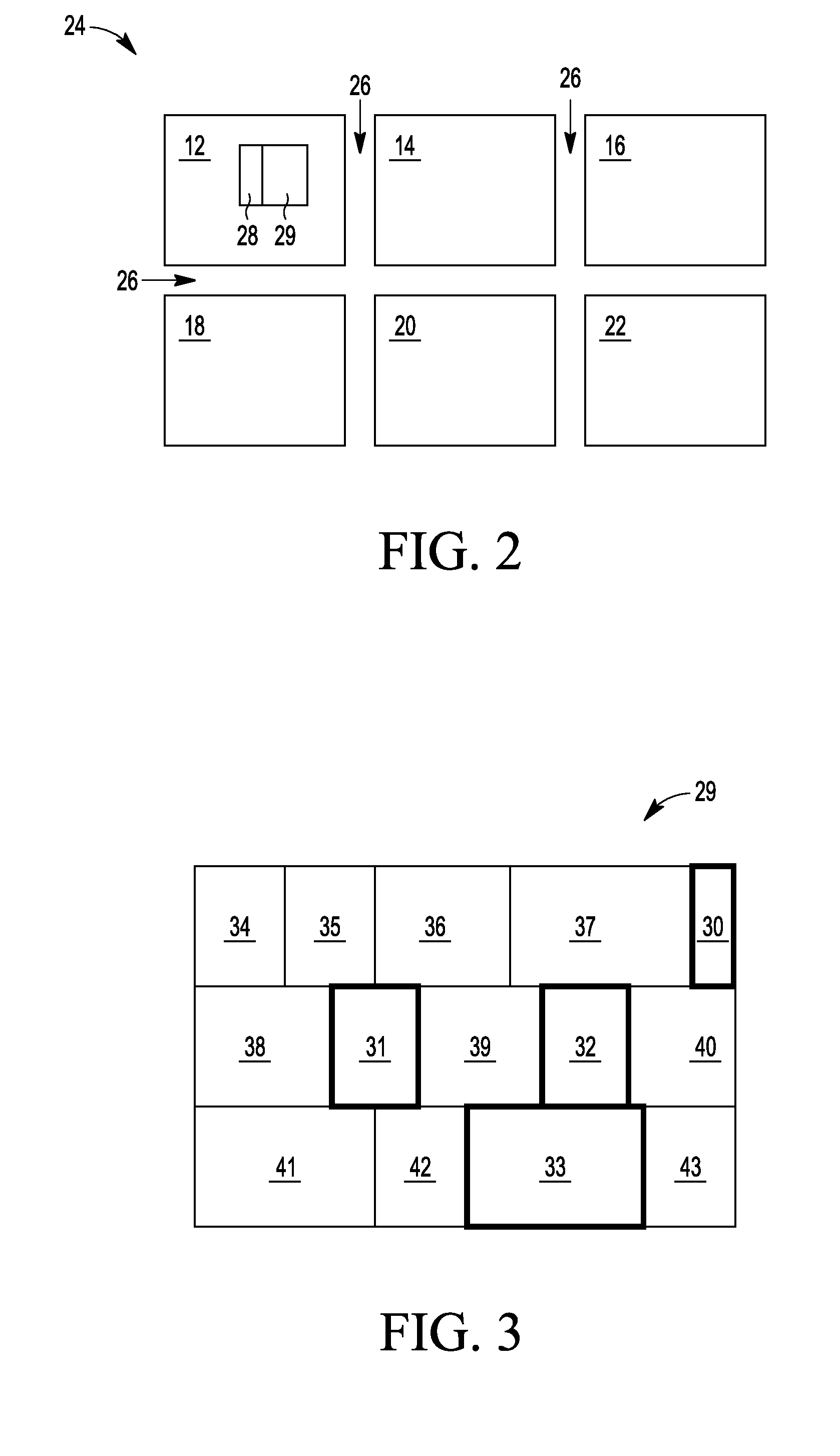

Stepper type test structures and methods for inspection of semiconductor integrated circuits

InactiveUS6633174B1Reduce pressureNanotechSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

Disclosed is a method of inspecting a sample. The method includes moving to a first field associated with a first group of test structures. The first group of test structures are partially within the first field. The method further includes scanning the first field to determine whether there are any defects present within the first group of test structures. When it is determined that there are defects within the first group of test structures, the method further includes repeatedly stepping to areas and scanning such areas so as to determine a specific defect location within the first group of test structures. A suitable test structure for performing this method is also disclosed.< / PTEXT>

Owner:KLA TENCOR TECH CORP

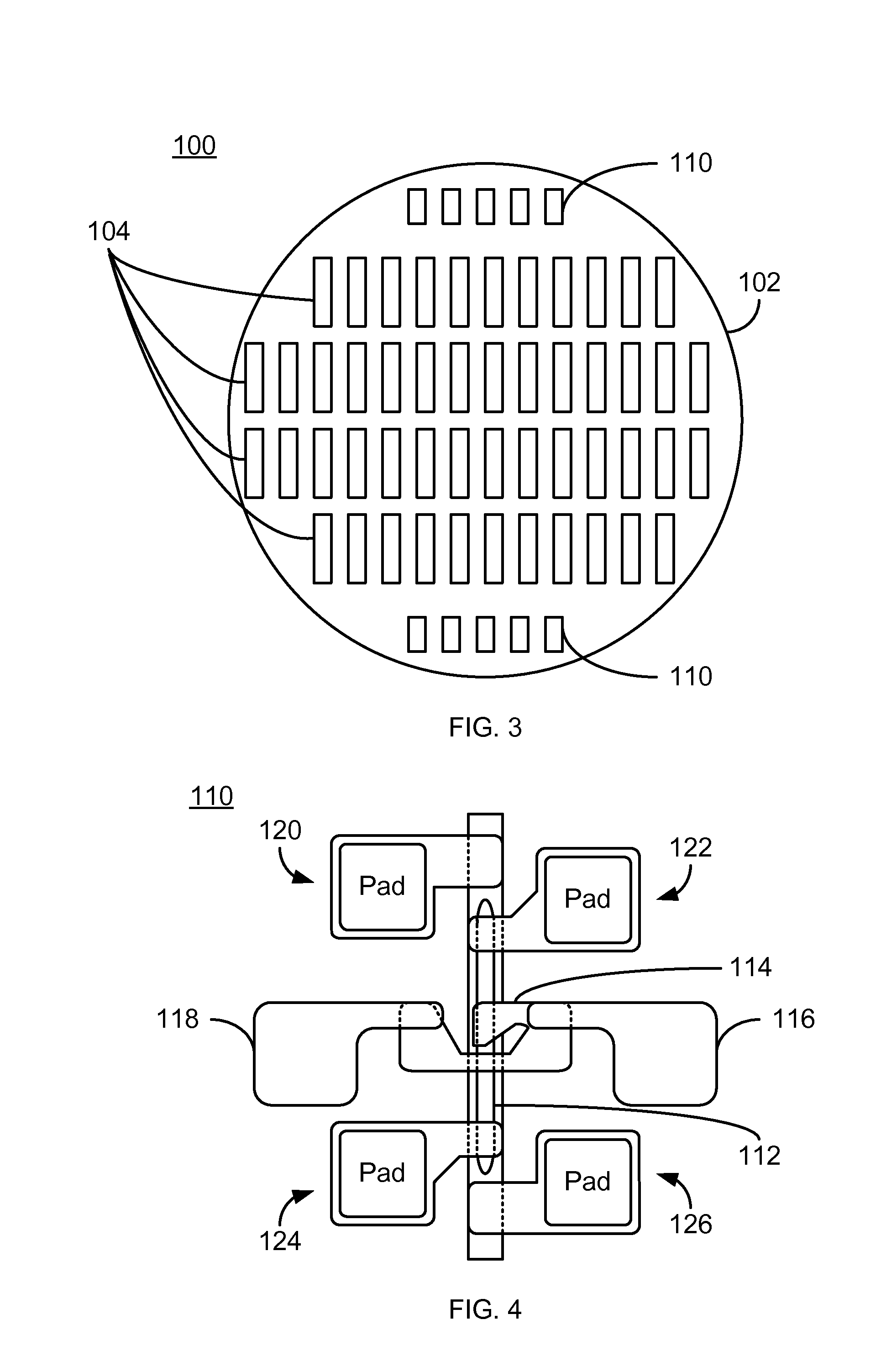

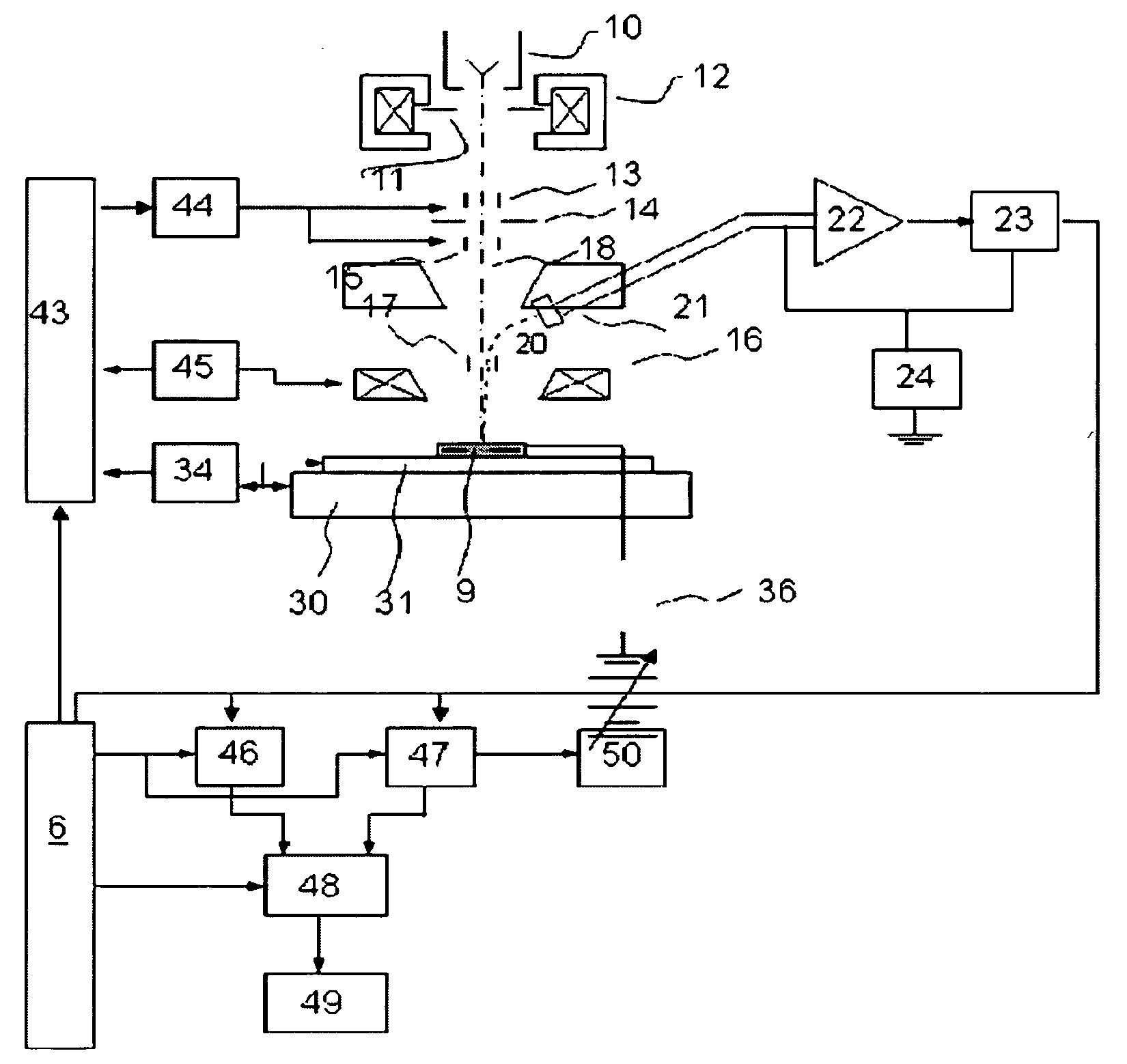

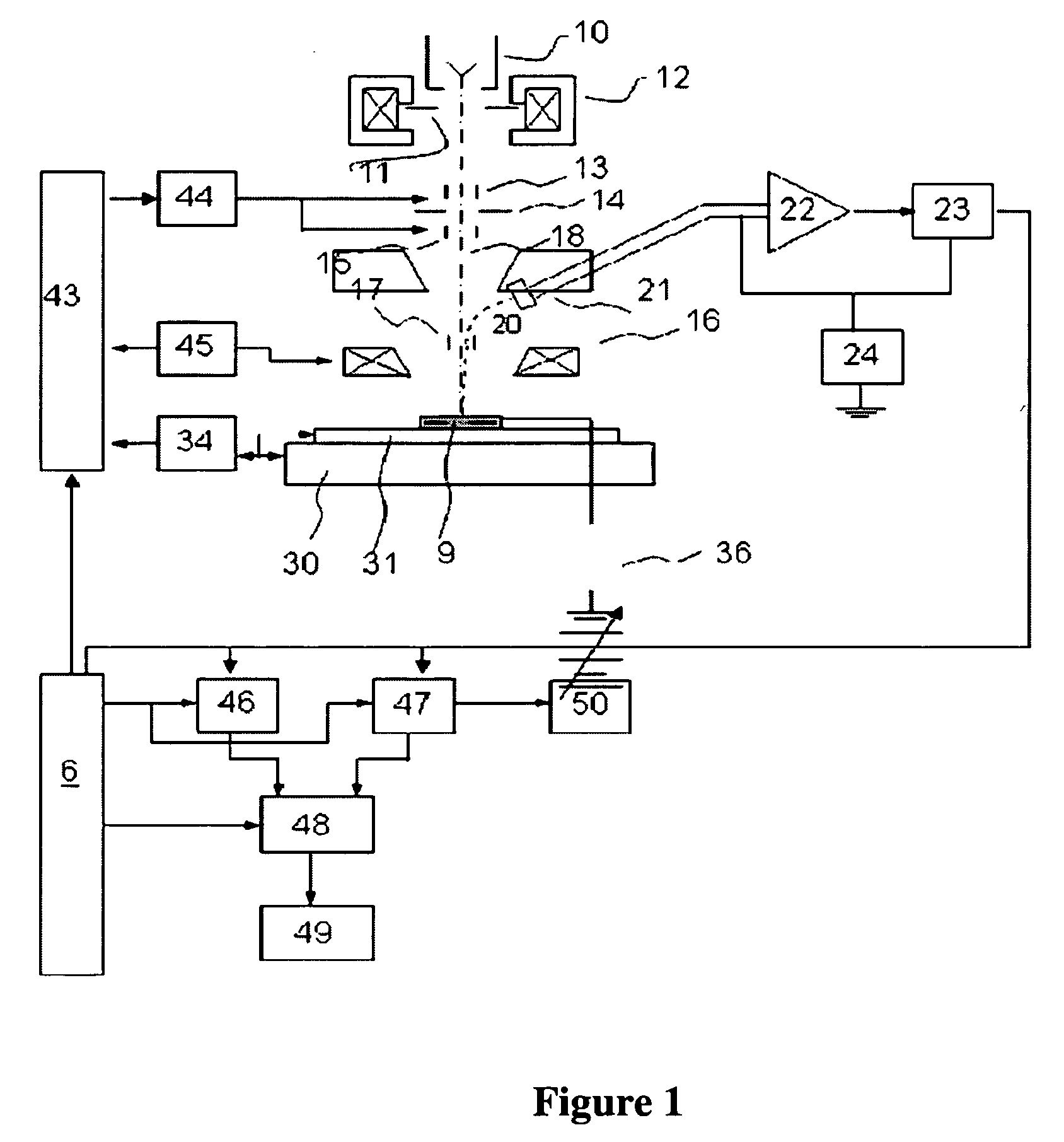

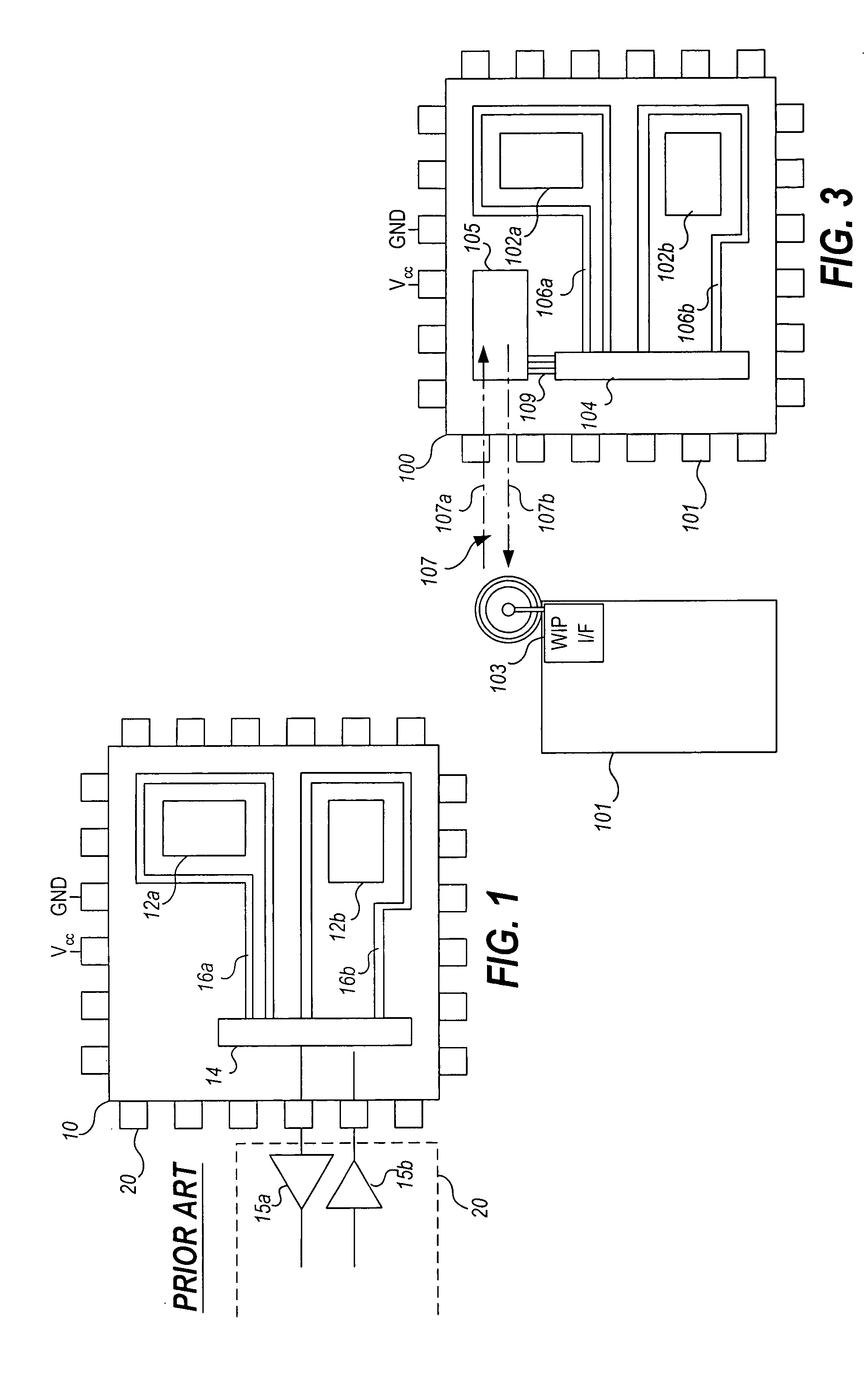

Method and system for performing on-wafer testing of heads

InactiveUS20130257421A1Electronic circuit testingMagnetic property measurementsPhysicsTest structure

A method and system for testing a read transducer are described. The read transducer includes a read sensor fabricated on a wafer. A system includes a test structure that resides on the wafer. The test structure includes a test device and a heater. The test device corresponds to the read sensor. The heater is in proximity to the test device and is configured to heat the test device substantially without heating the read sensor. Thus, the test structure allows for on-wafer testing of the test device at a plurality of temperatures above an ambient temperature.

Owner:WESTERN DIGITAL TECH INC

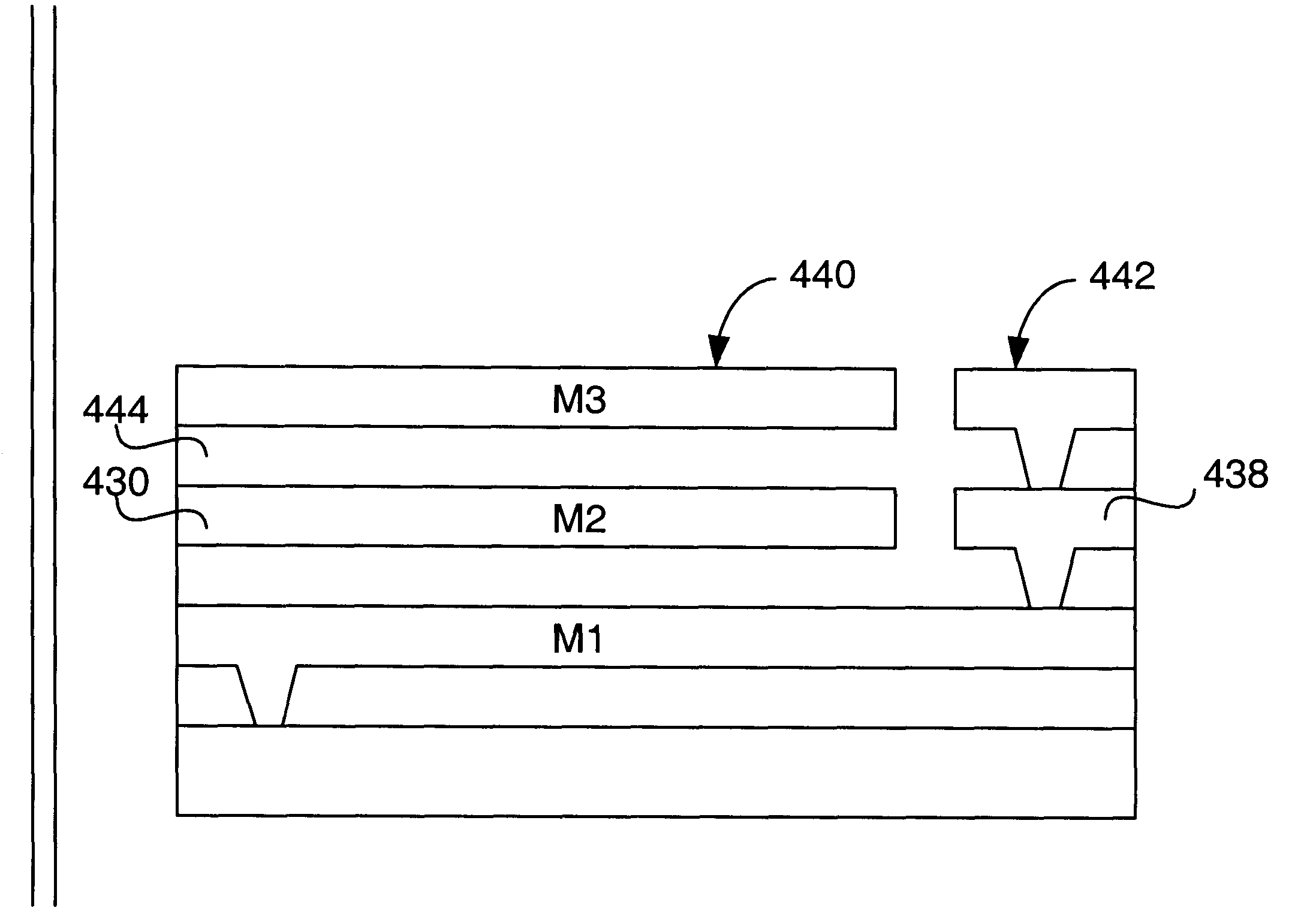

Inspectable buried test structures and methods for inspecting the same

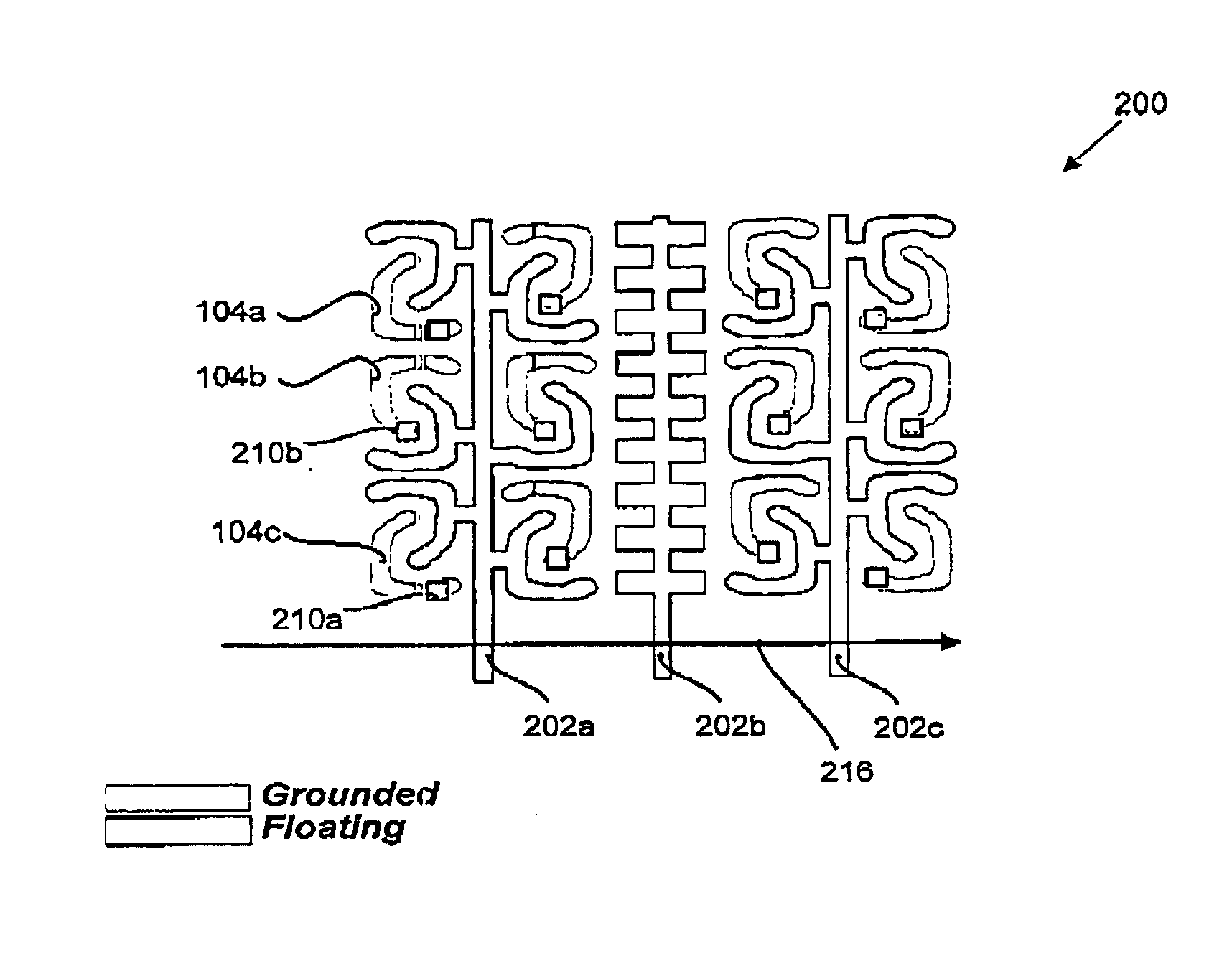

InactiveUS6509197B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesVoltage contrastSemiconductor

Disclosed is a semiconductor die having a lower test structure formed in a lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end. The first end is coupled to a predetermined voltage level. The semiconductor die also includes an insulating layer formed over the lower metal layer. The die further includes an upper test structure formed in an upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure. The upper metal layer is formed over the insulating layer. In a specific implementation, the first end of the lower test structure is coupled to ground. In another embodiment, the semiconductor die also includes a substrate and a first via coupled between the first end of the lower test structure and the substrate. In yet another aspect, the lower test structure is an extended metal line, and the upper test structure is a voltage contrast element. Methods for inspecting and fabricating such semiconductor die are also disclosed.

Owner:KLA TENCOR CORP

Dual probe test structures for semiconductor integrated circuits

InactiveUS6636064B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

Disclosed is a semiconductor die having an upper layer and a lower layer. The die includes a lower test structure formed in the lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end, wherein the first end is coupled to a predetermined voltage level. The die also has an insulating layer formed over the lower metal layer and an upper test structure formed in the upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure, and the upper metal layer being formed over the insulating layer. The die further includes at least one probe pad coupled with the upper test structure. Preferably, the first end of the lower test structure is coupled to a nominal ground potential. In another implementation, the upper test structure is a voltage contrast element. In another embodiment, a semiconductor die having a scanning area is disclosed. The semiconductor die includes a first plurality of test structures wherein each of the test structures in the first plurality of test structures is located entirely within the scanning area. The die includes a second plurality of test structures wherein each of the test structures in the first plurality of test structures is located only partially within the scanning area. The first plurality of test structures or the second plurality of test structures has a probe pad coupled to at least one test structure.

Owner:KLA TENCOR TECH CORP

Inspectable buried test structures and methods for inspecting the same

InactiveUS6576923B2Reduce pressureNanotechSemiconductor/solid-state device testing/measurementEngineeringVoltage contrast

Disclosed is a semiconductor die having a lower test structure formed in a lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end. The first end is coupled to a predetermined voltage level. The semiconductor die also includes an insulating layer formed over the lower metal layer. The die further includes an upper test structure formed in an upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure. The upper metal layer is formed over the insulating layer. In a specific implementation, the first end of the lower test structure is coupled to ground. In another embodiment, the semiconductor die also includes a substrate and a first via coupled between the first end of the lower test structure and the substrate. In yet another aspect, the lower test structure is an extended metal line, and the upper test structure is a voltage contrast element. Methods for inspecting and fabricating such semiconductor die are also disclosed.

Owner:KLA CORP

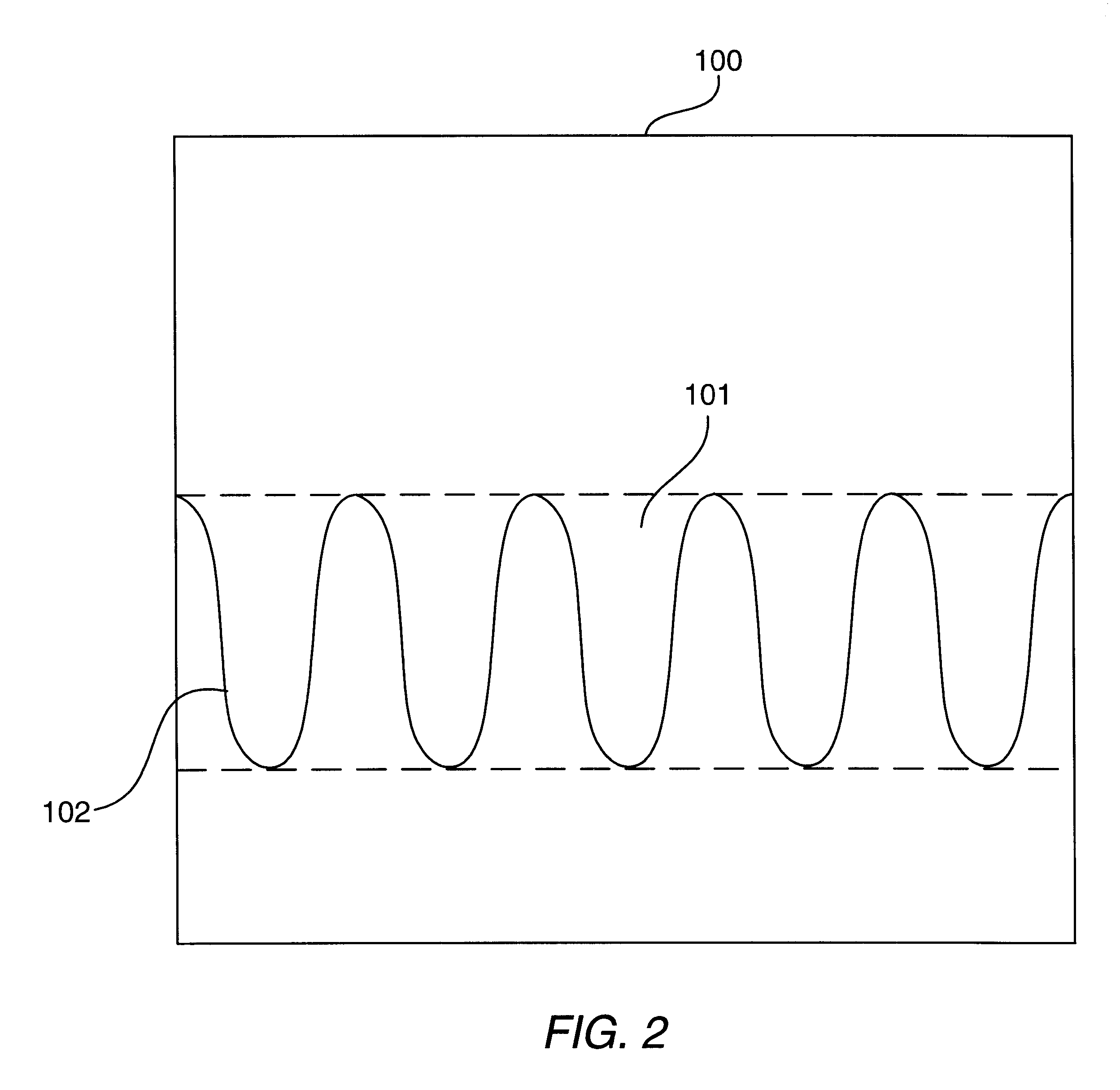

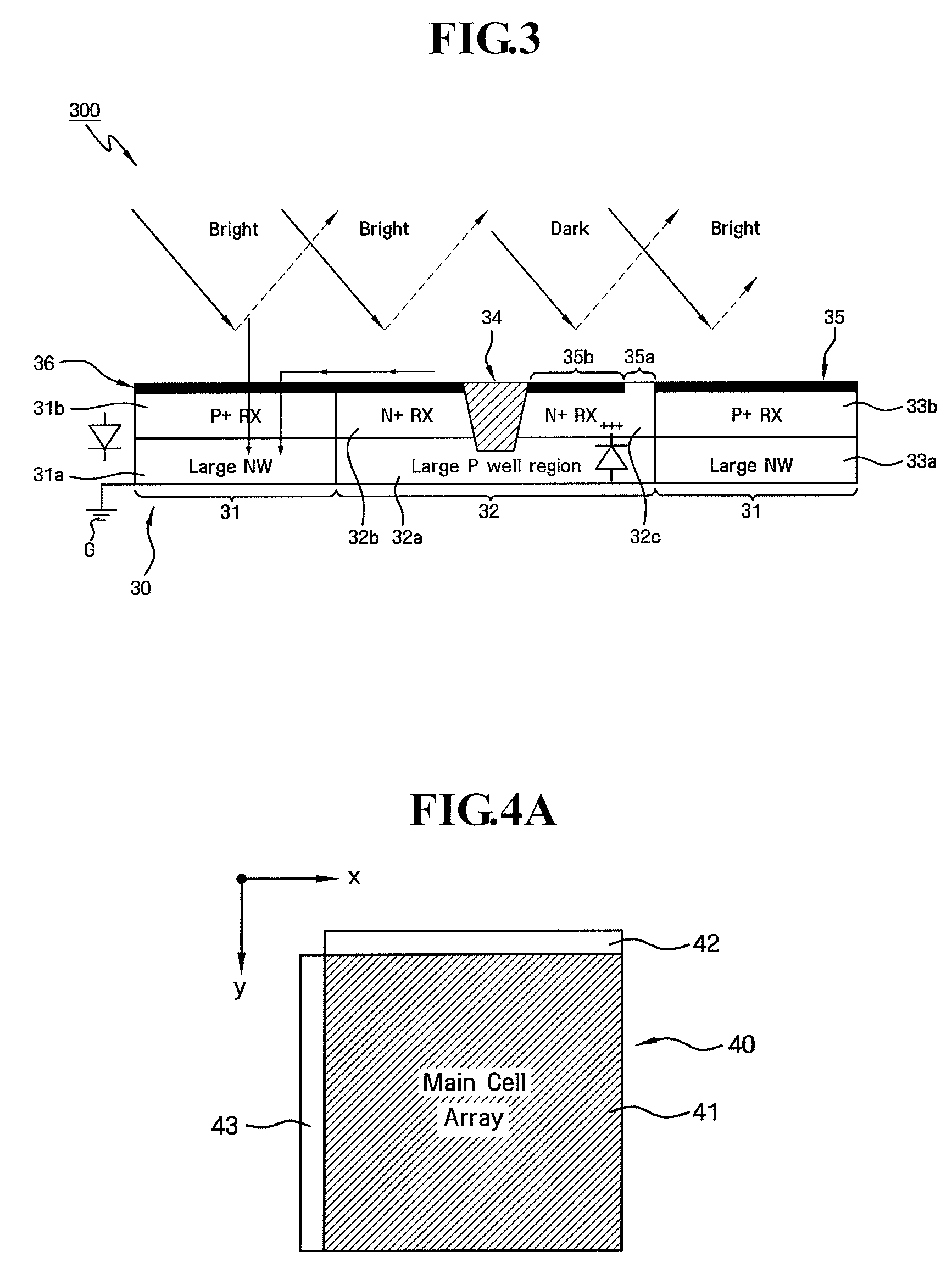

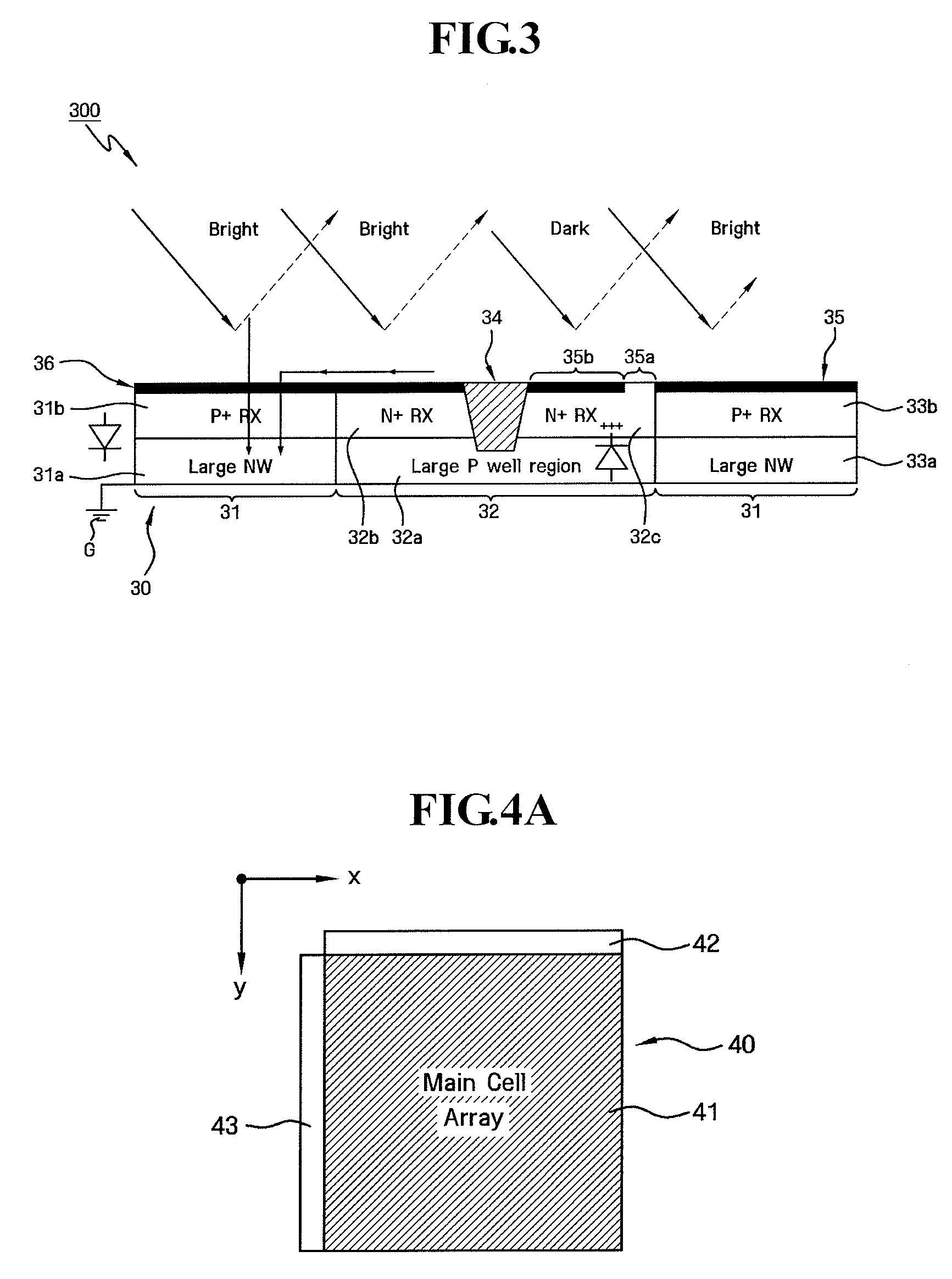

Apparatus and methods for detection of systematic defects

ActiveUS7280945B1Electrical testingComputation using non-denominational number representationResistSystem failure

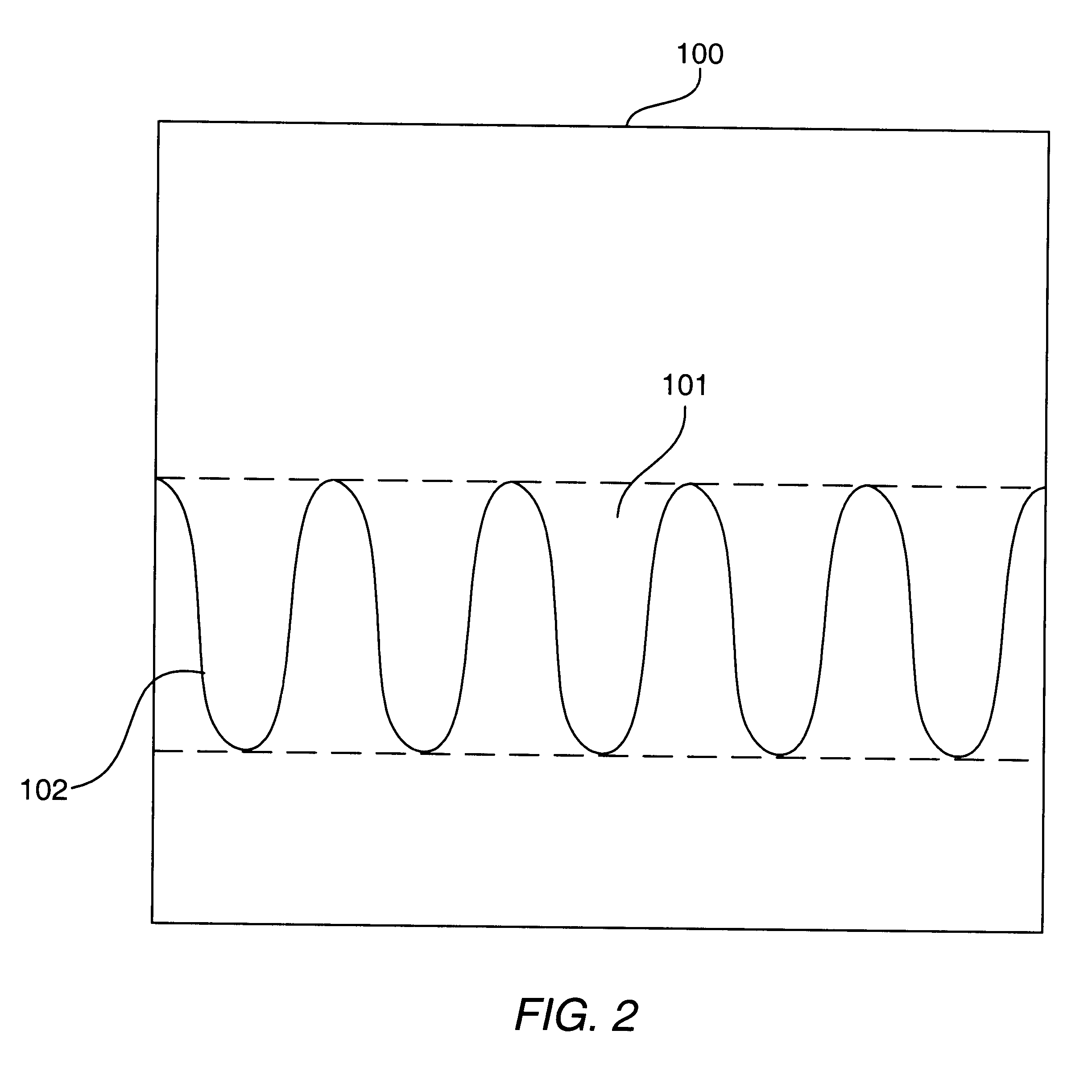

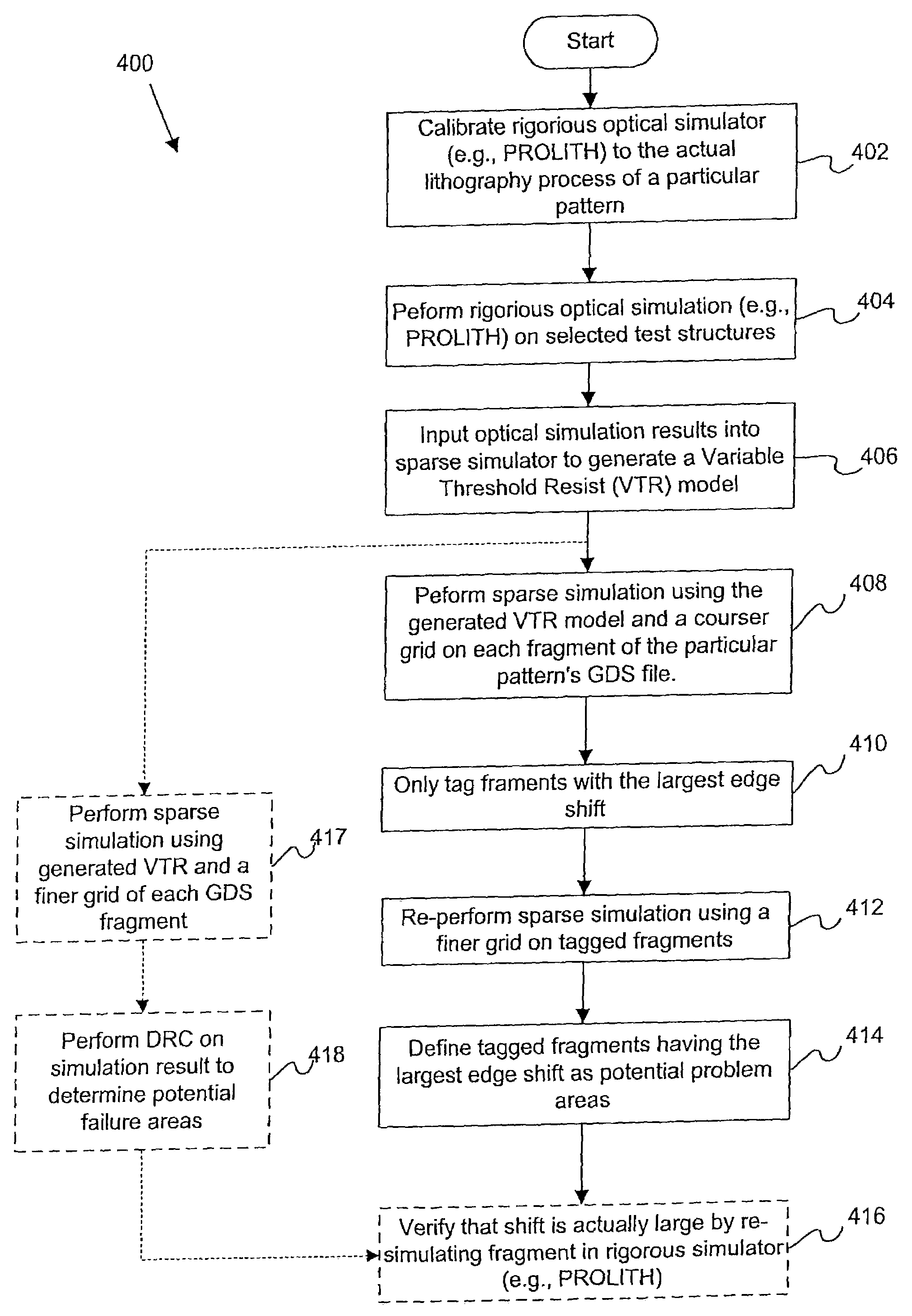

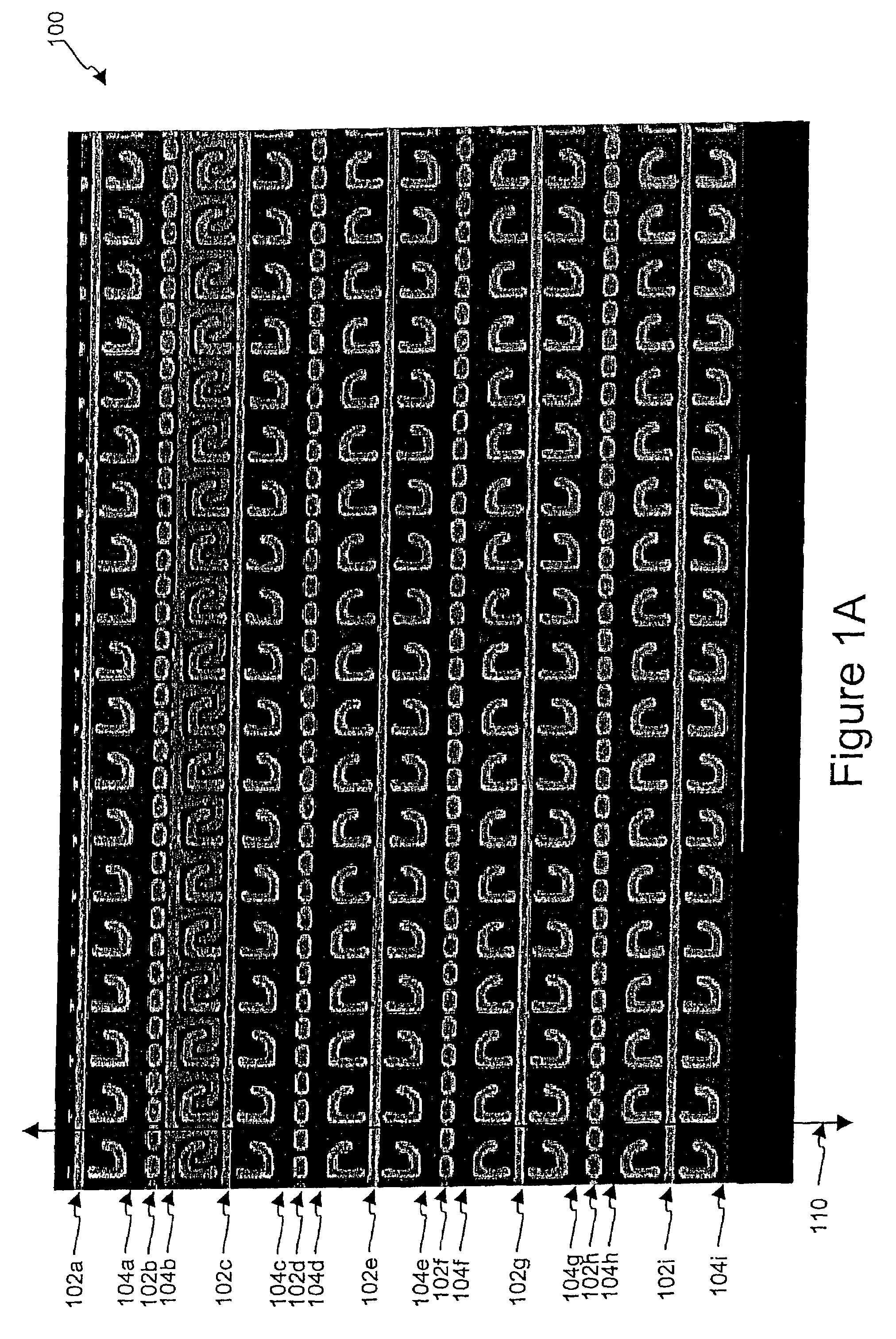

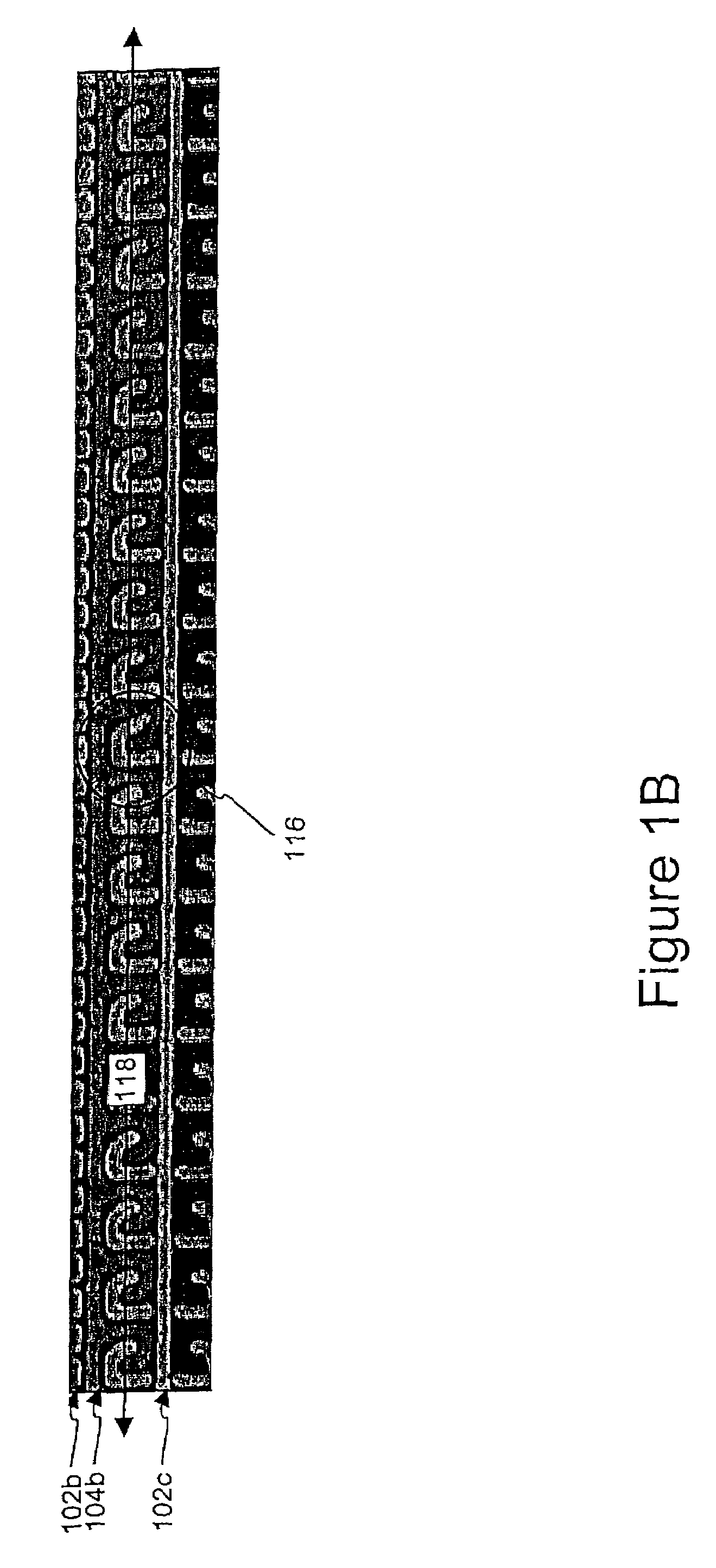

Disclosed are mechanisms are provided for determining whether a particular integrated circuit (IC) pattern is susceptible to systematic failure, e.g., due to process fluctuations. In one embodiment, final resist patterns for such IC pattern are simulated using a sparse type simulator under various process settings. The sparse type simulator uses a model (e.g., a variable threshold resist model) for a particular photolithography process in which the IC pattern is to be fabricated. The model is generated from measurements taken from a plurality of simulated structures output from a rigorous type simulator. The simulated final resist patterns may then be analyzed to determine whether the corresponding IC pattern is susceptible to systematic failure. After an IC pattern which is susceptible to systematic failure has been found, a test structure may be fabricated from a plurality of IC patterns or cells. The cells of the test structure are arranged to have a particular pattern of voltage potential or brightness levels during a voltage contrast inspection. Mechanisms for quickly inspecting such test structures to thereby predict systematic yield of a product device containing patterns similar to the test structure cells are also disclosed.

Owner:KLA TENCOR TECH CORP

Integrated circuit having a filler standard cell

InactiveUS20100258798A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsFunctional testingEngineering

An integrated circuit includes a functional block having a plurality of standard cells. The plurality of standard cells includes a plurality of functional standard cells and a filler standard cell. Each functional standard cell of the plurality of functional standard cells has a rectangular boundary. The filler standard cell has a rectangular boundary adjacent to at least one of the functional standard cells. The filler standard cell is selectable between a first state and a second state. The filler standard cell is non-functional in the first state. The filler standard cell has functional test structures coupled to a first metal layer in the second state. This allows for test structures helpful in analyzing functionality of circuit features such as transistors without requiring additional space on the integrated circuit.

Owner:NXP USA INC

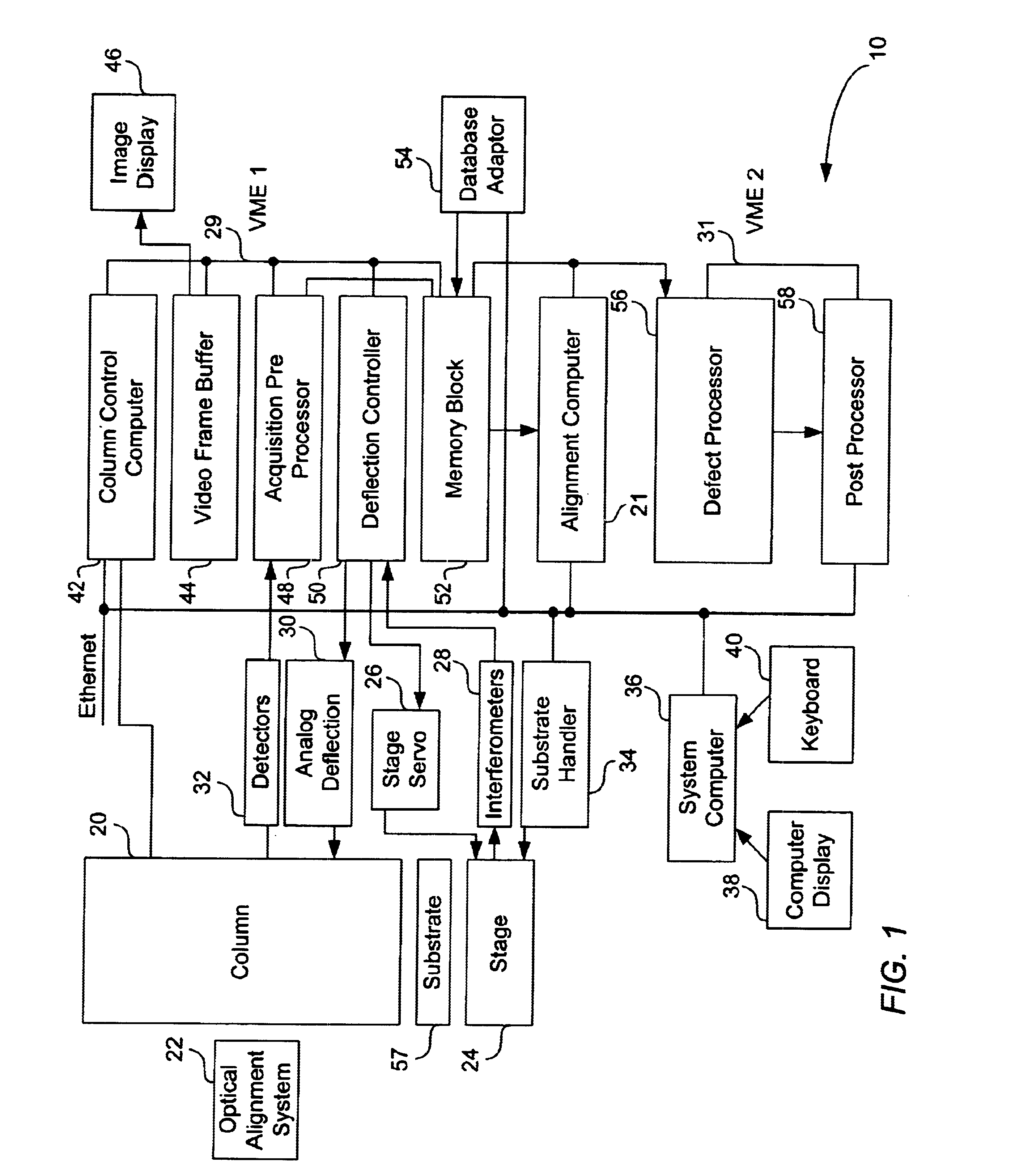

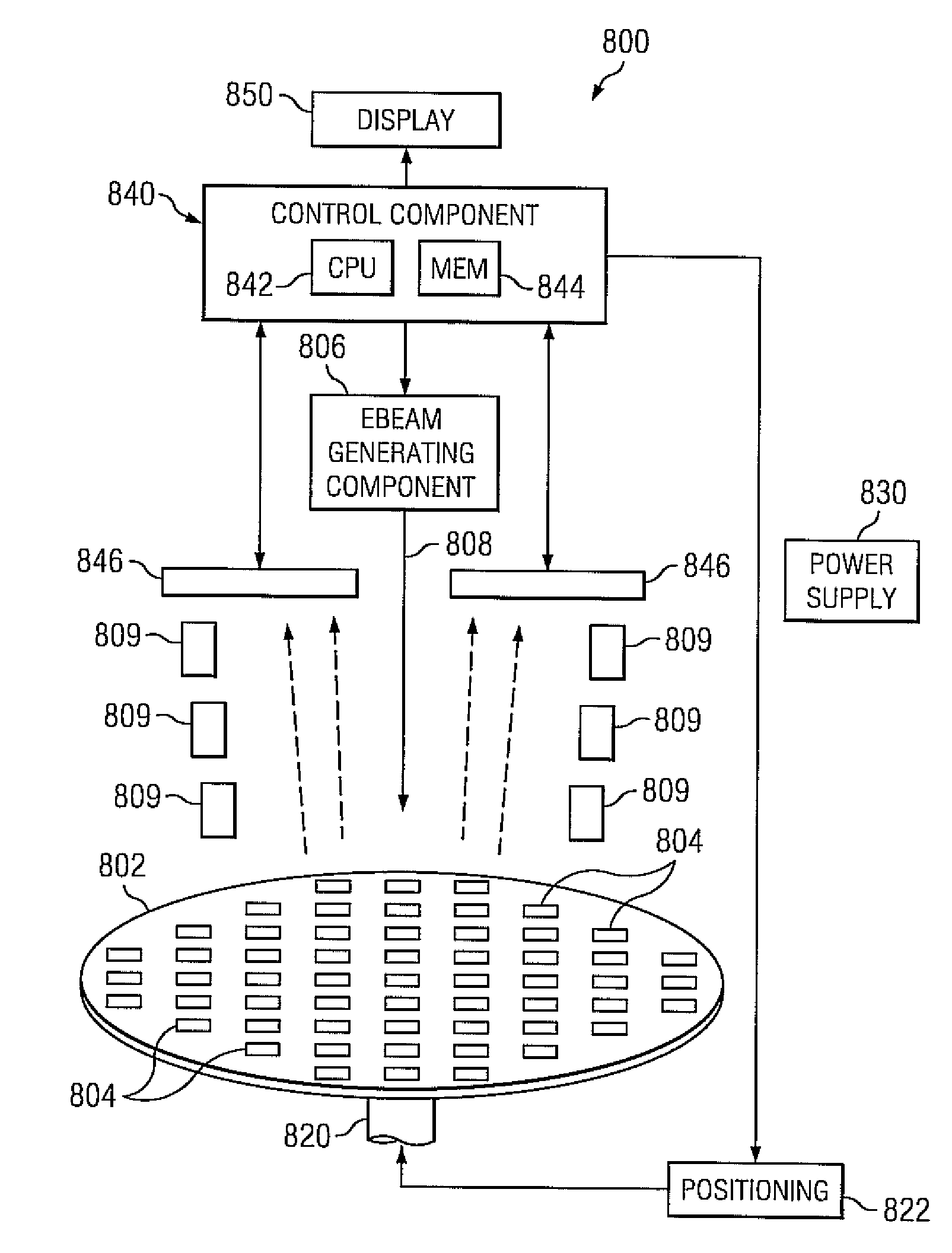

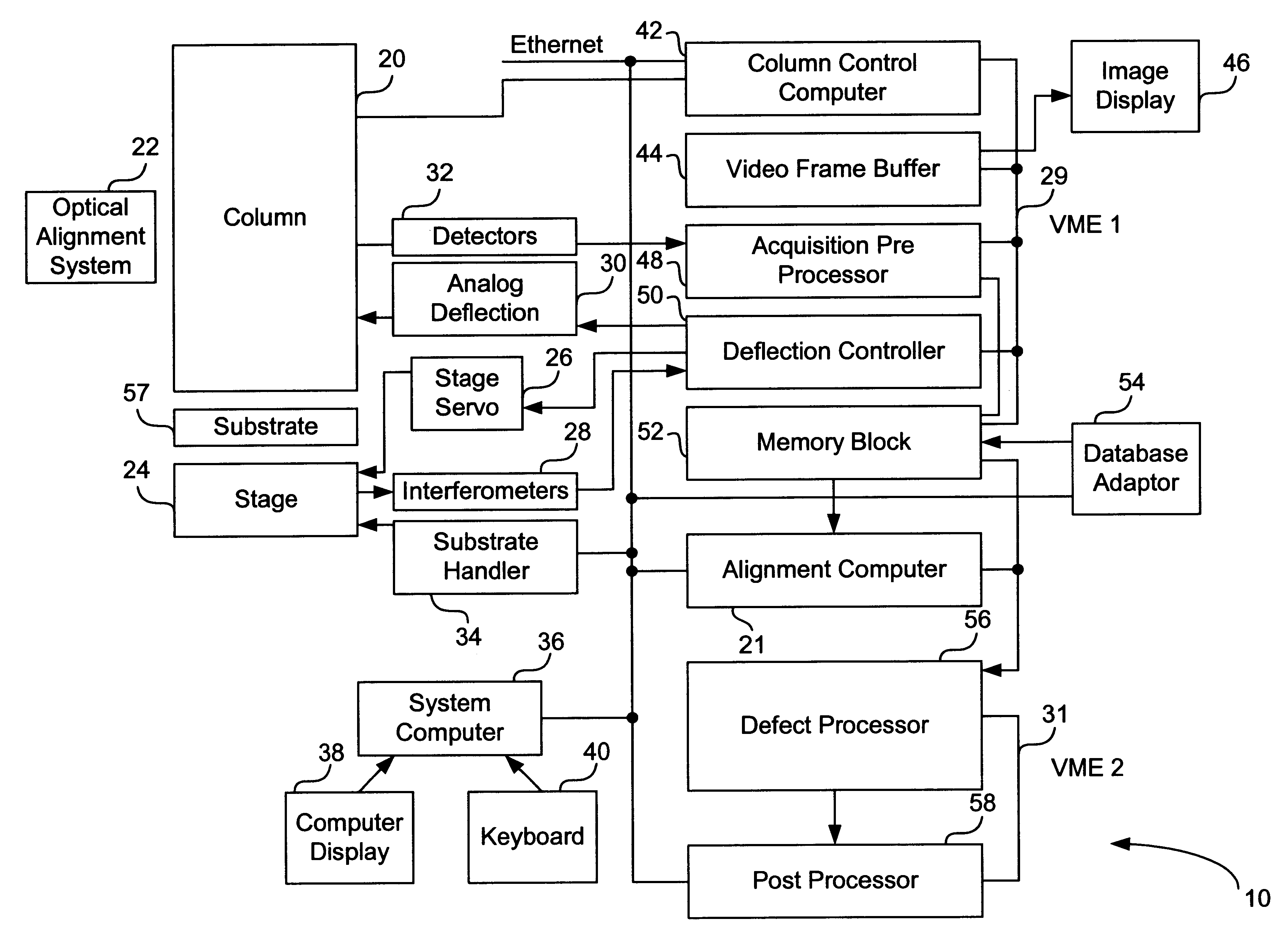

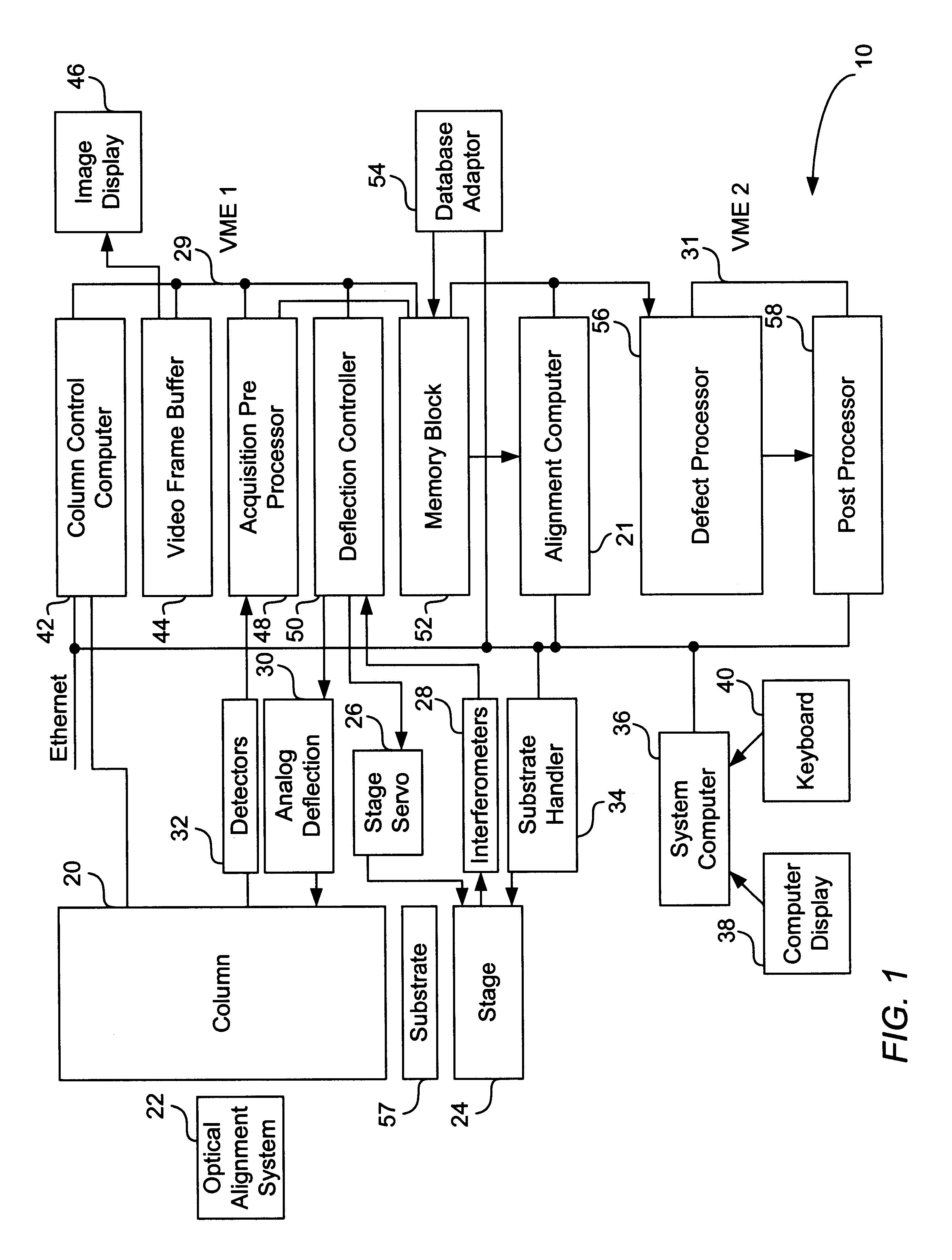

Test structures for e-beam testing of systematic and random defects in integrated circuits

InactiveUS20090102501A1Non-uniform stressMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectron beam testingDislocation

In accordance with the invention, there are electron beam inspection systems, electron beam testable semiconductor test structures, and methods for detecting systematic defects, such as, for example contact-to-gate shorts, worm hole leakage paths, holes printing issues, and anomalies in sparse holes and random defects, such as, current leakage paths due to dislocations and pipes during semiconductor processing.

Owner:TEXAS INSTR INC

Method for determining abnormal characteristics in integrated circuit manufacturing process

A method for determining abnormal characteristics in integrated circuit manufacturing process is disclosed. The method comprises obtaining a charged particle microscope image of a sample test structure, wherein the sample including a reference pattern and a test pattern; measuring gray levels of the reference pattern and the test pattern; calculating a standard deviation from a distribution of the gray levels of the reference pattern measured; and determining the abnormal characteristics of the test pattern based on the gray levels measured and the standard deviation.

Owner:ASML NETHERLANDS BV

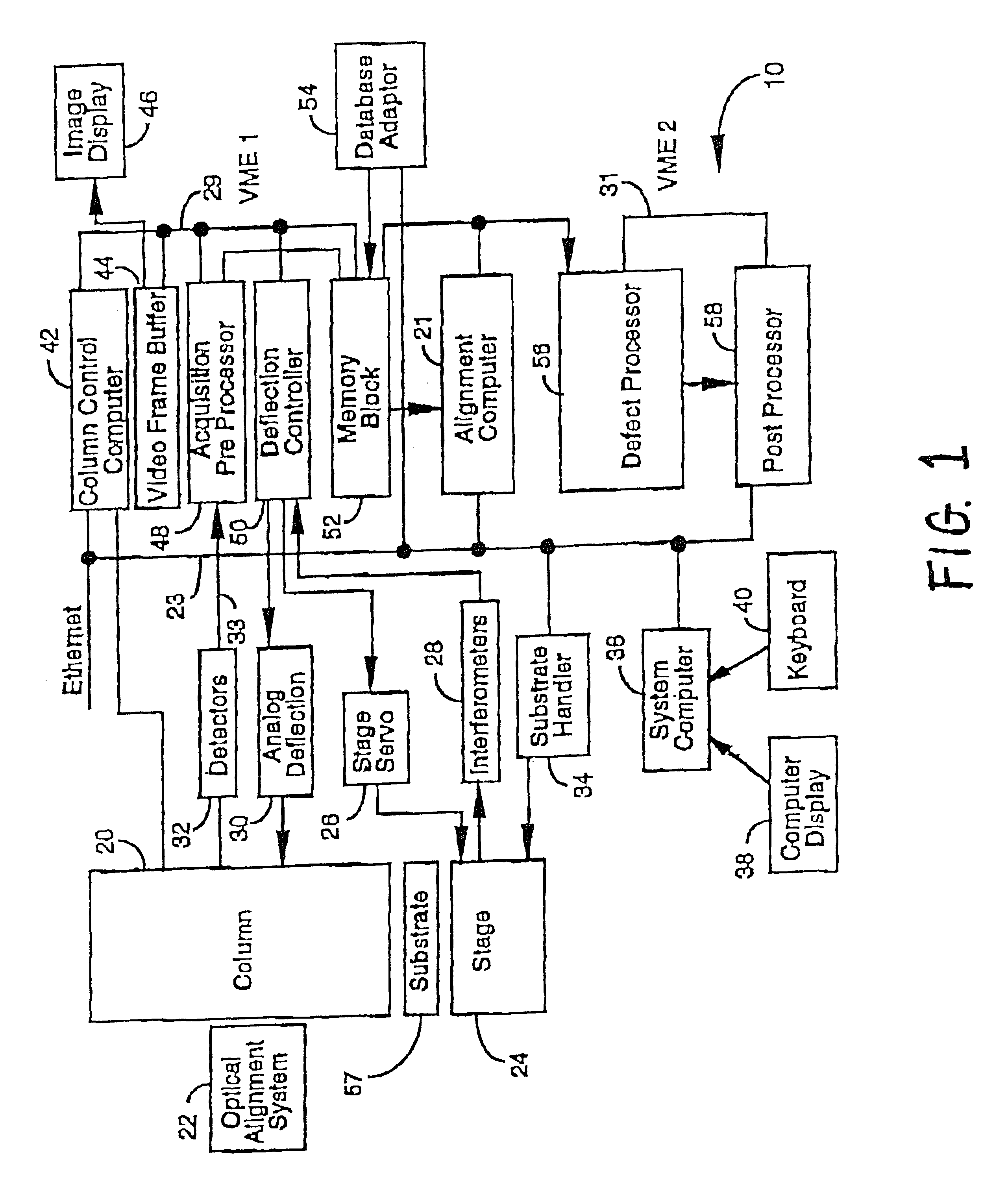

Methods and apparatus for generating spatially resolved voltage contrast maps of semiconductor test structures

InactiveUS6445199B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesSpatially resolvedEngineering

Disclosed is a method of inspecting a sample. The sample is illuminated with an incident beam, thereby causing voltage contrast within structures present on the sample. Voltage contrast is detected within the structures. Information from the detected voltage contrast is stored, and position data concerning the location of features corresponding to at least a portion of the stored voltage contrast information is also stored. In a specific embodiment, the features represent electrical defects present on the sample. In another embodiment, the stored position data is in the form of a two dimensional map. In another aspect, the sample is re-inspected and the stored position data is used in analyzing data resulting from the re-inspection.

Owner:KLA CORP

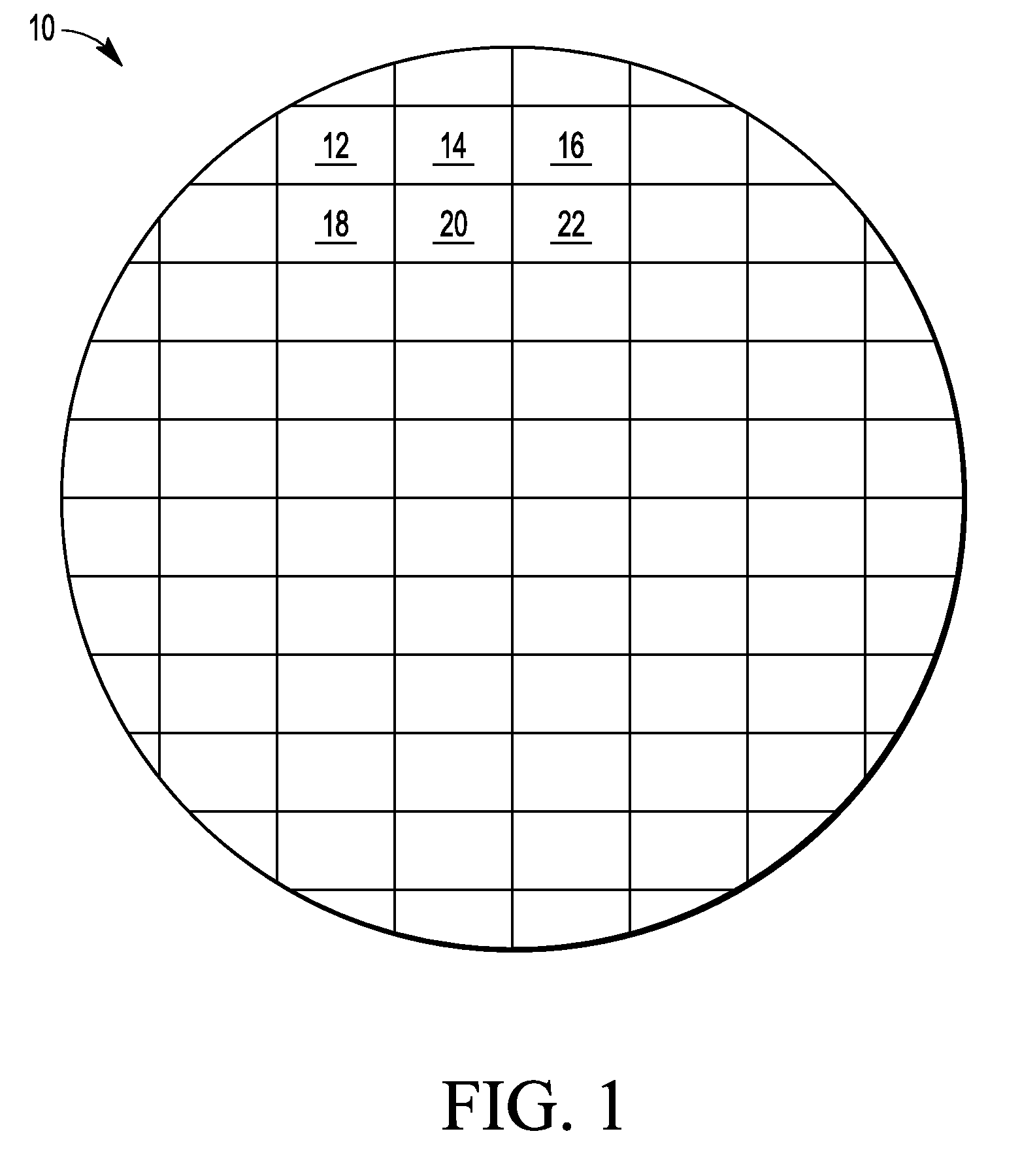

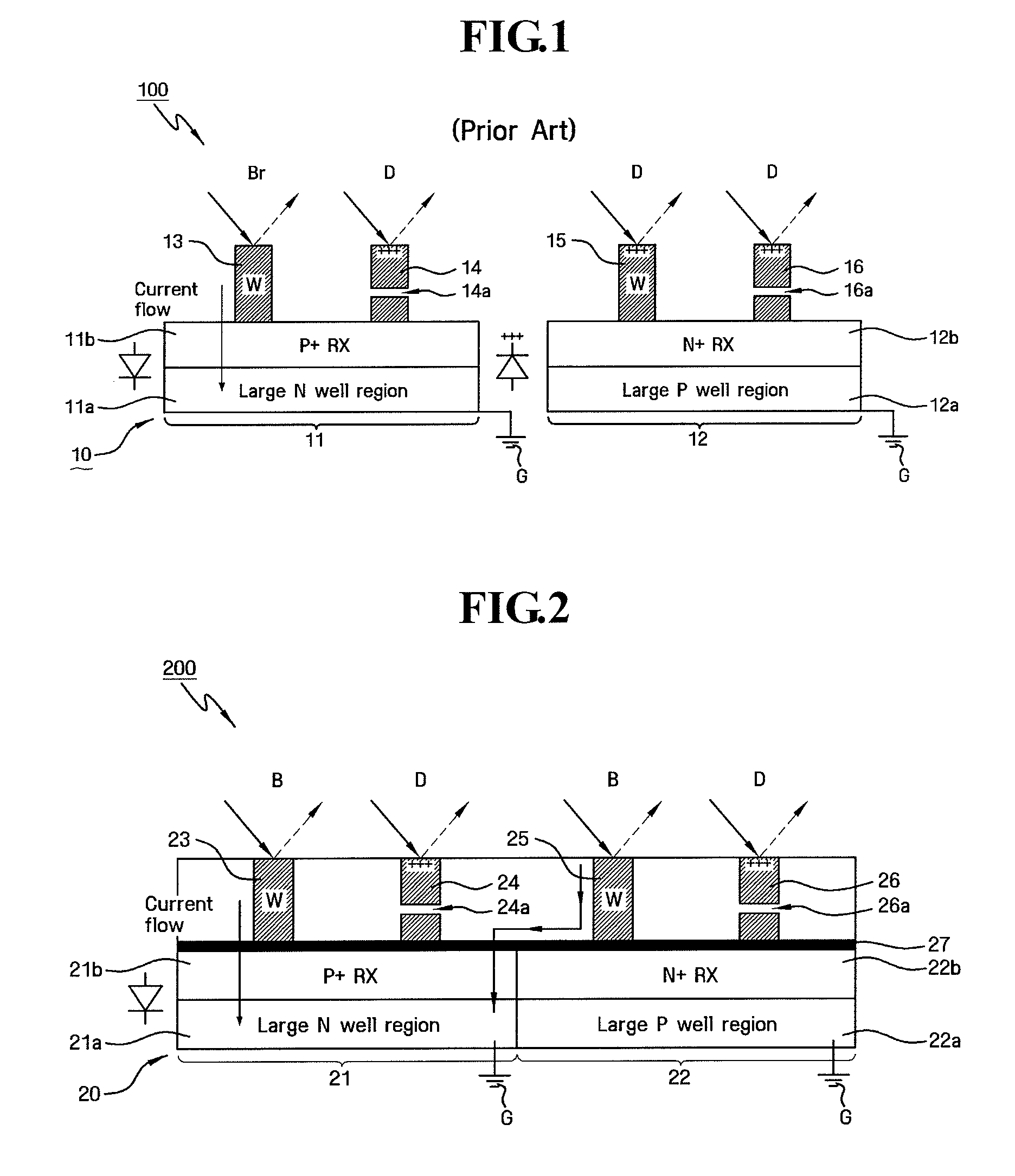

Semiconductor integrated test structures for electron beam inspection of semiconductor wafers

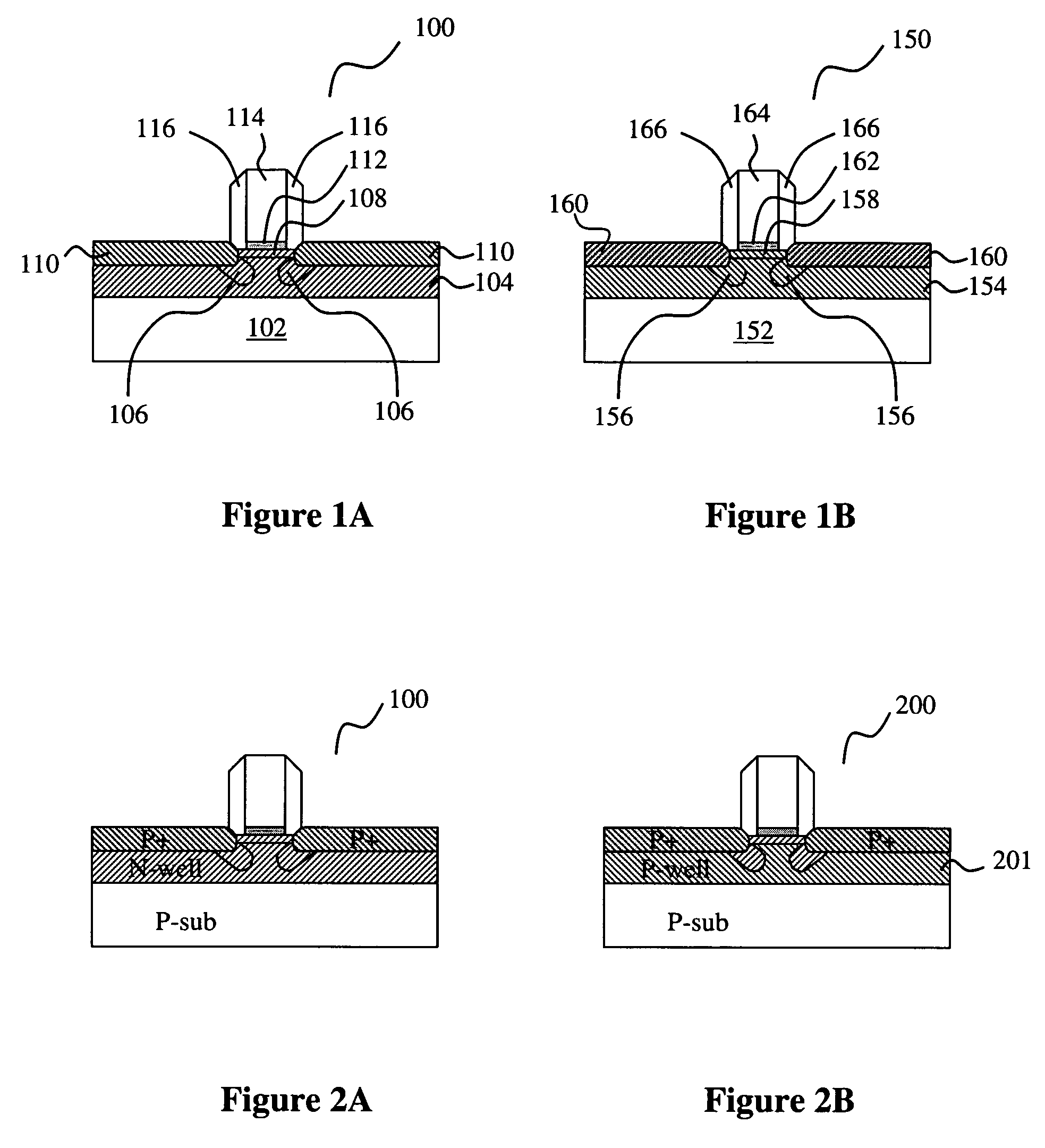

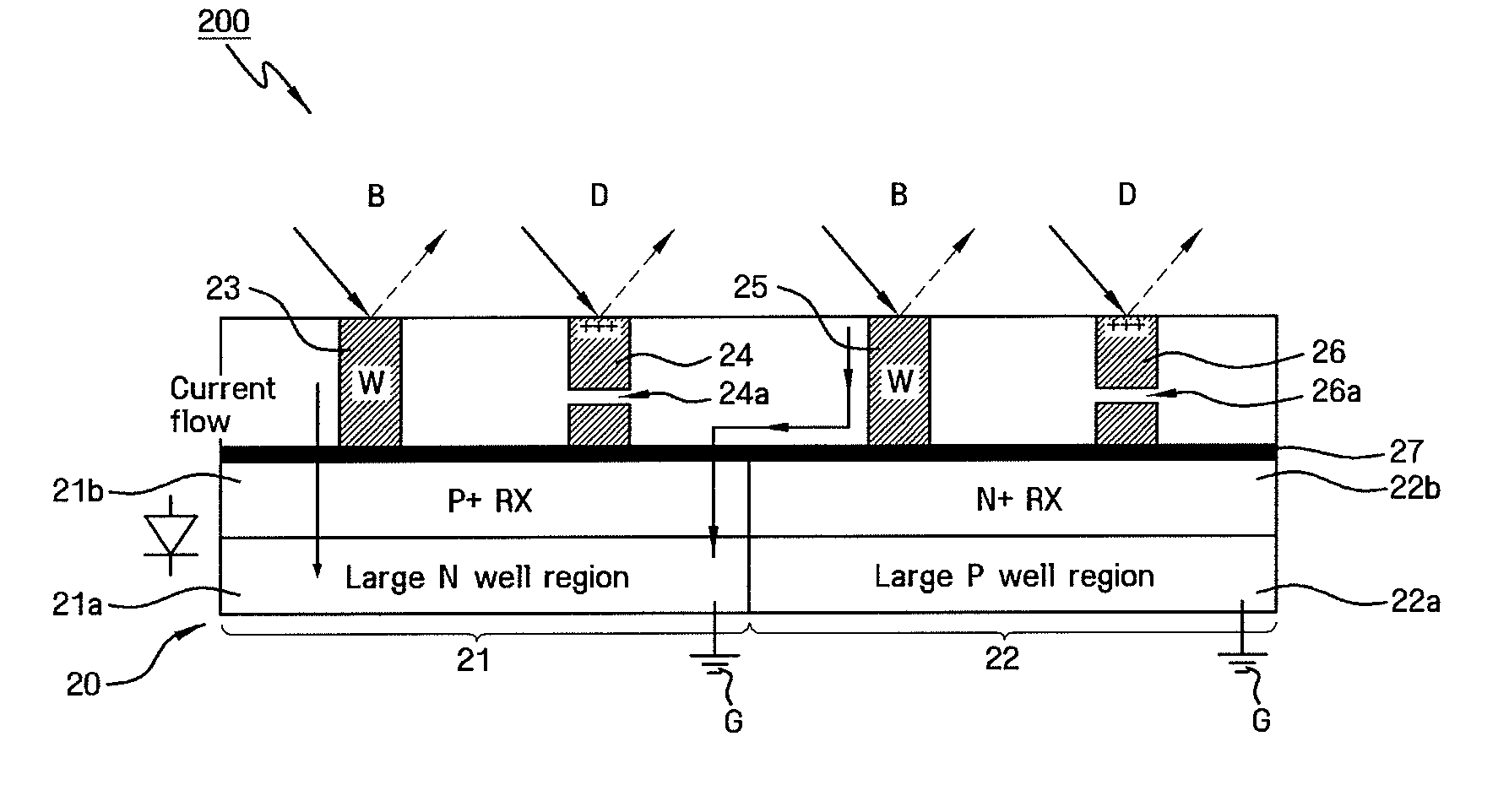

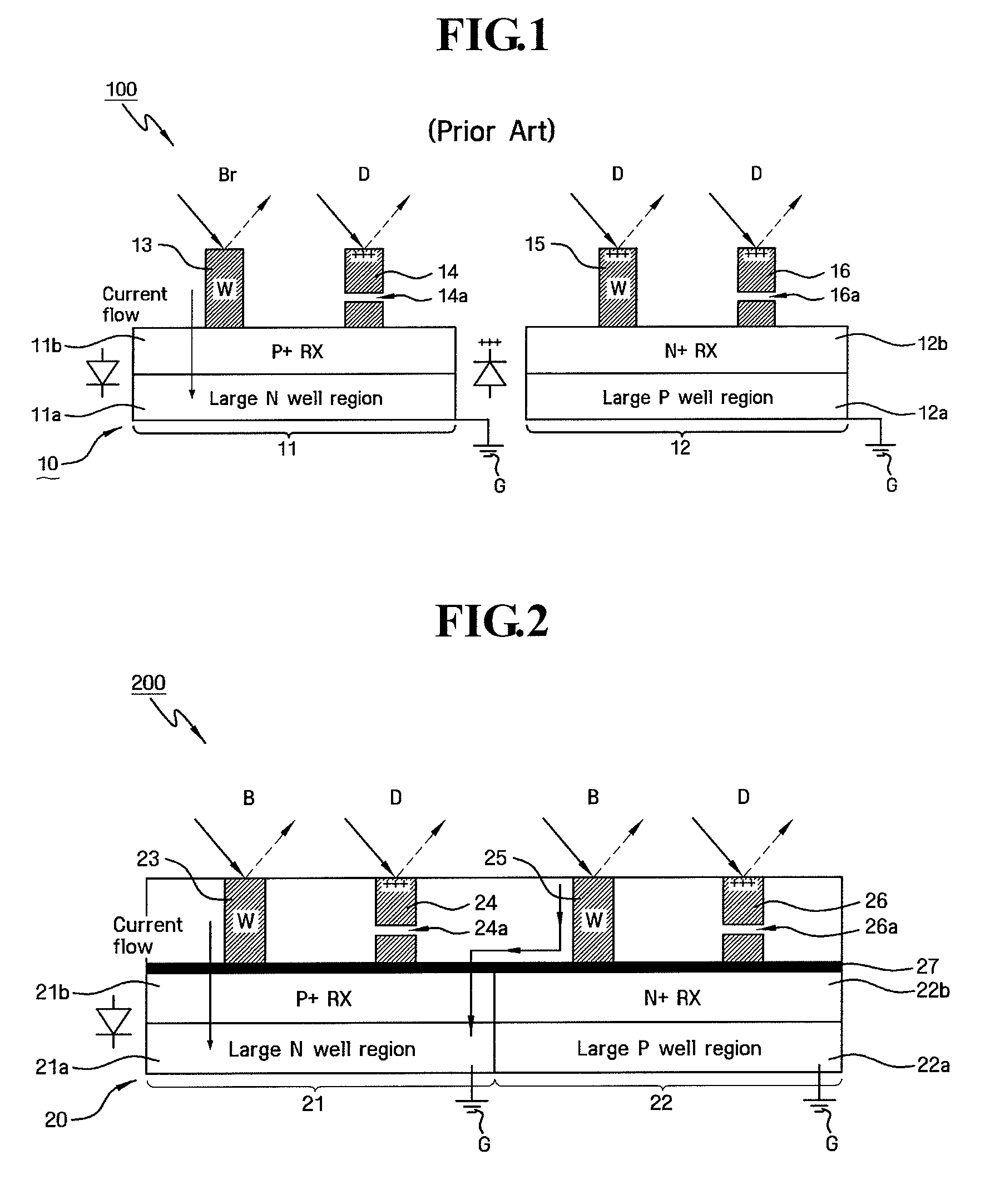

ActiveUS7679083B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCMOSEngineering

Semiconductor integrated test structures are designed for electron beam inspection of semiconductor wafers. The test structures include pattern features that are formed in designated test regions of the wafer concurrently with pattern features of integrated circuits formed on the wafer. The test structures include conductive structures that are designed to enable differential charging between defective and non-defective features (or defective and non-defection portions of a given feature) to facilitate voltage contrast defect detection of CMOS devices, for example, using a single, low energy electron beam scan, notwithstanding the existence of p / n junctions in the wafer substrate or other elements / features.

Owner:SAMSUNG ELECTRONICS CO LTD +2

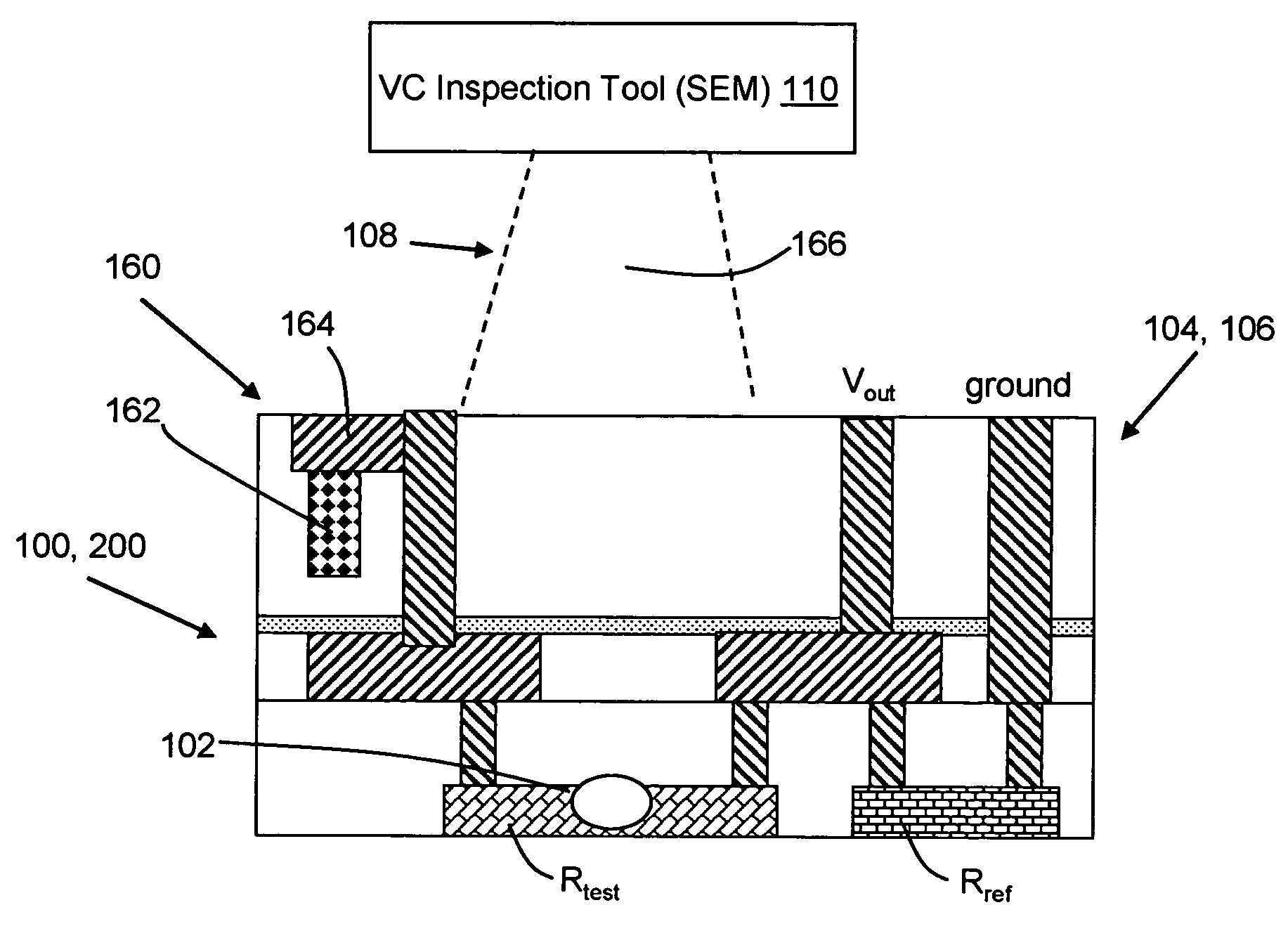

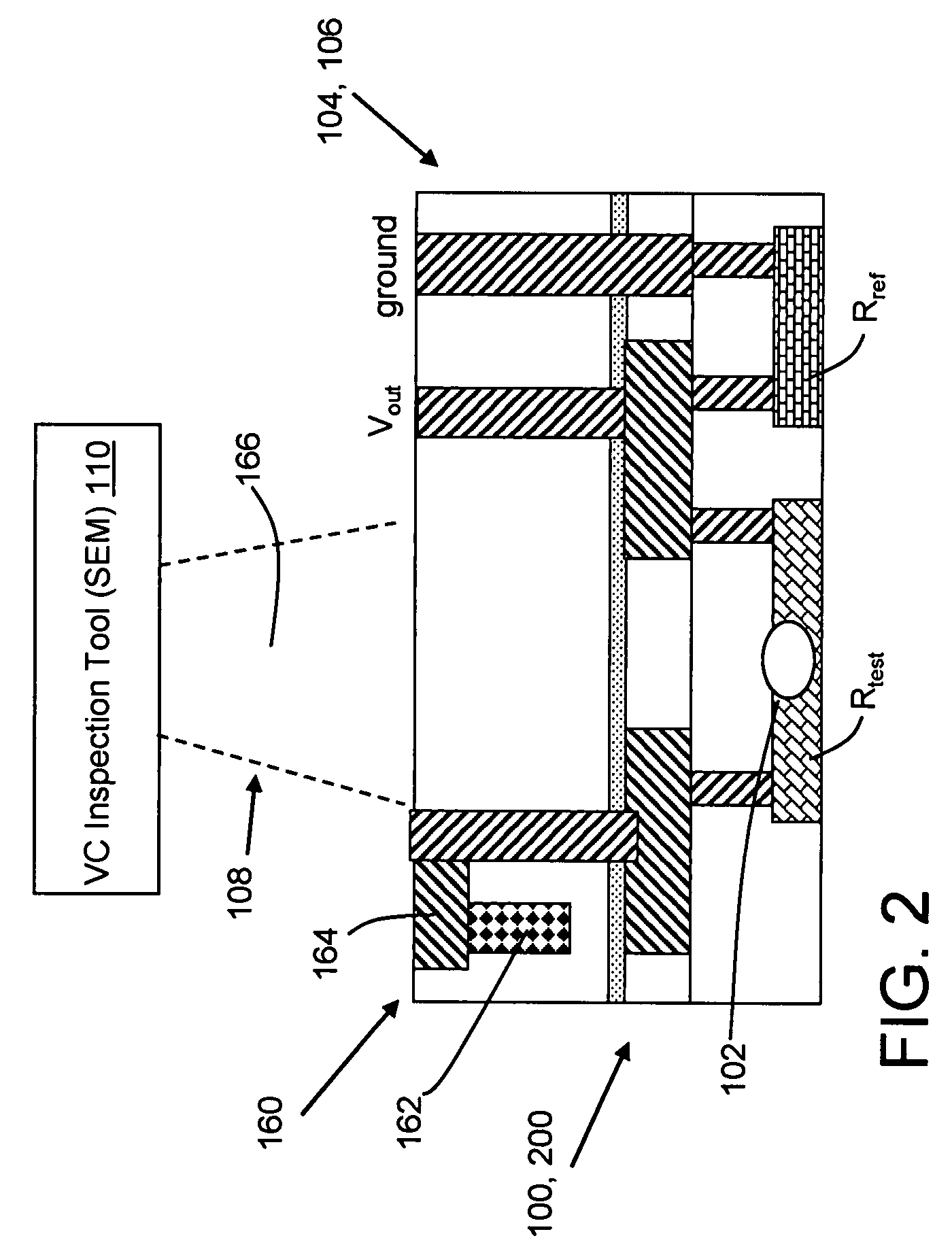

Apparatus and methods for determining and localization of failures in test structures using voltage contrast

InactiveUS6861666B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVoltage contrastProduct layer

Disclosed is test structure that can be fabricated with minimal photolithography masking steps and in which defects may be localized to specific layers. Mechanisms for fabricating such test structures are also provided. In one embodiment, a semiconductor test structure suitable for a voltage contrast inspection is provided. The test structure includes one or more test layers corresponding to one or more product layers selected from a plurality of product layers of an integrated circuit (IC) product structure. The number of the selected one or more test layers is less than a total number of the plurality of product layers of the product structure, and the test layers include at least a first portion that is designed to have a first potential during the voltage contrast inspection and a second portion that is designed to have a second potential during the voltage contrast inspection. The first potential differs from the second potential. The selected one or more test layers which correspond to product layers are selected from the plurality of product layers such that defects found in the test layers of the test structure during the voltage contrast inspection represent a prediction of defects in the corresponding product structure.

Owner:KLA TENCOR TECH CORP

Buried short location determination using voltage contrast inspection

Structure and methods of determining the complete location of a buried short using voltage contrast inspection are disclosed. In one embodiment, a method includes providing a test structure having a PN junction thereunder; and using the PN junction to determine the location of the buried short using voltage contrast (VC) inspection. A test structure may include a plurality of test elements each having a PN junction thereunder, wherein a location of the buried short within the test structure can be determined using the PN junction and the VC inspection. The PN junction forces a change in illumination brightness of a test element including the buried short, thus allowing determination of the complete location of a buried short.

Owner:GLOBALFOUNDRIES INC

Mobile ionic contamination detection in manufacture of semiconductor devices

InactiveUS6348808B1Efficient detectionElectronic circuit testingIndividual semiconductor device testingEngineeringSemiconductor device fabrication

A test transistor structure formed in a semiconductor device has a thick-oxide transistor with an elongated serpentine-shaped metal gate. The gate is used to first measure the threshold voltage of the thick-oxide test structure. Then, a current is passed through the elongated metal line which forms the serpentine gate to heat the area of the test structure. While being heated, a stress voltage is applied between the substrate and one end of the gate electrode, this stress voltage being much larger than the logic voltage used in operating thin-oxide transistors on the chip. After a selected time, the current is removed, the stress voltage is removed, and the threshold voltage of the thick-oxide transistor is again measured and compared to the original value. Any reduction in threshold voltage can be attributed to the migration of positive charge to the silicon-to-oxide interface beneath the gate, and is proportional to the area between the source and drain regions of the test transistor.

Owner:BELL SEMICON LLC

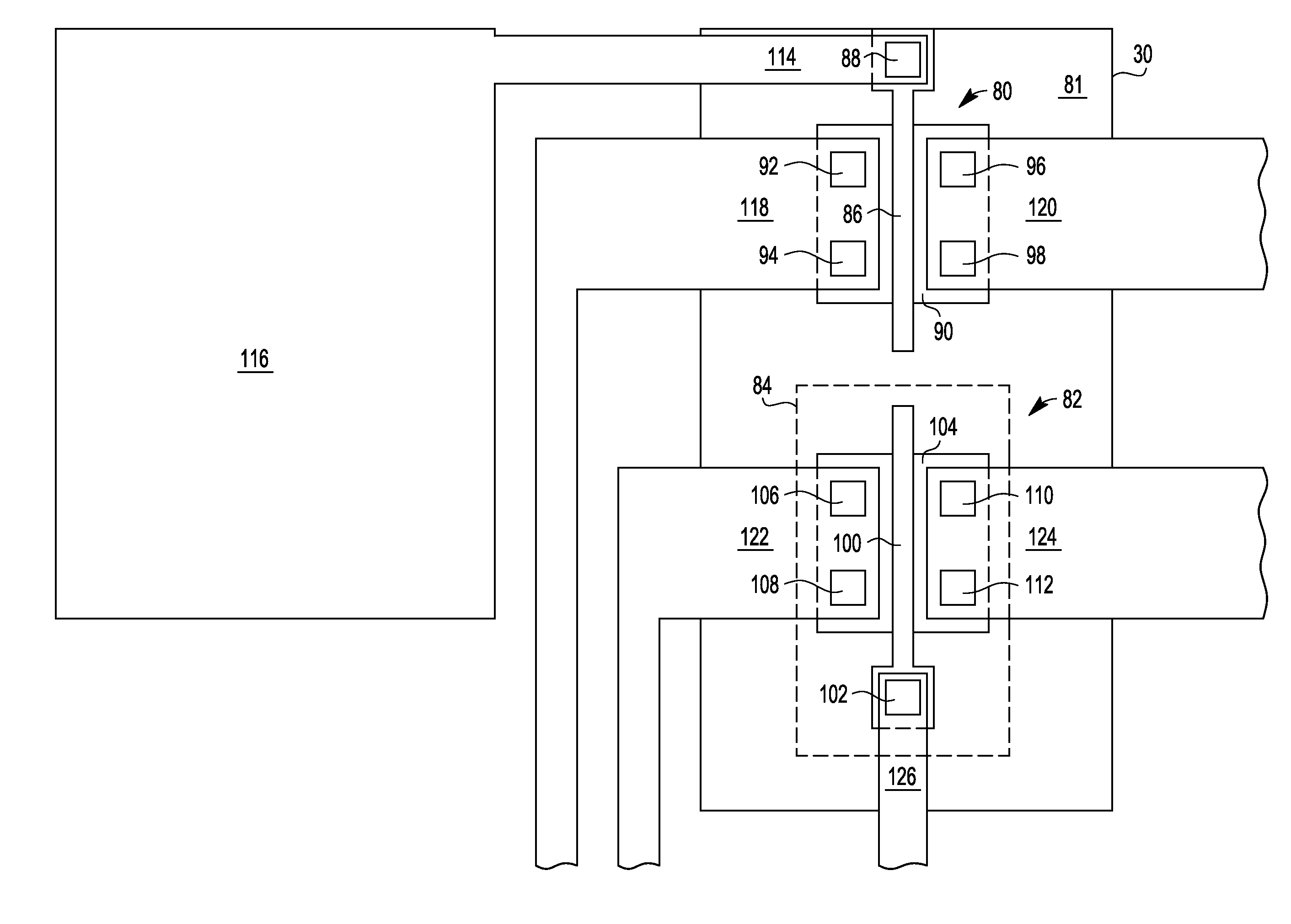

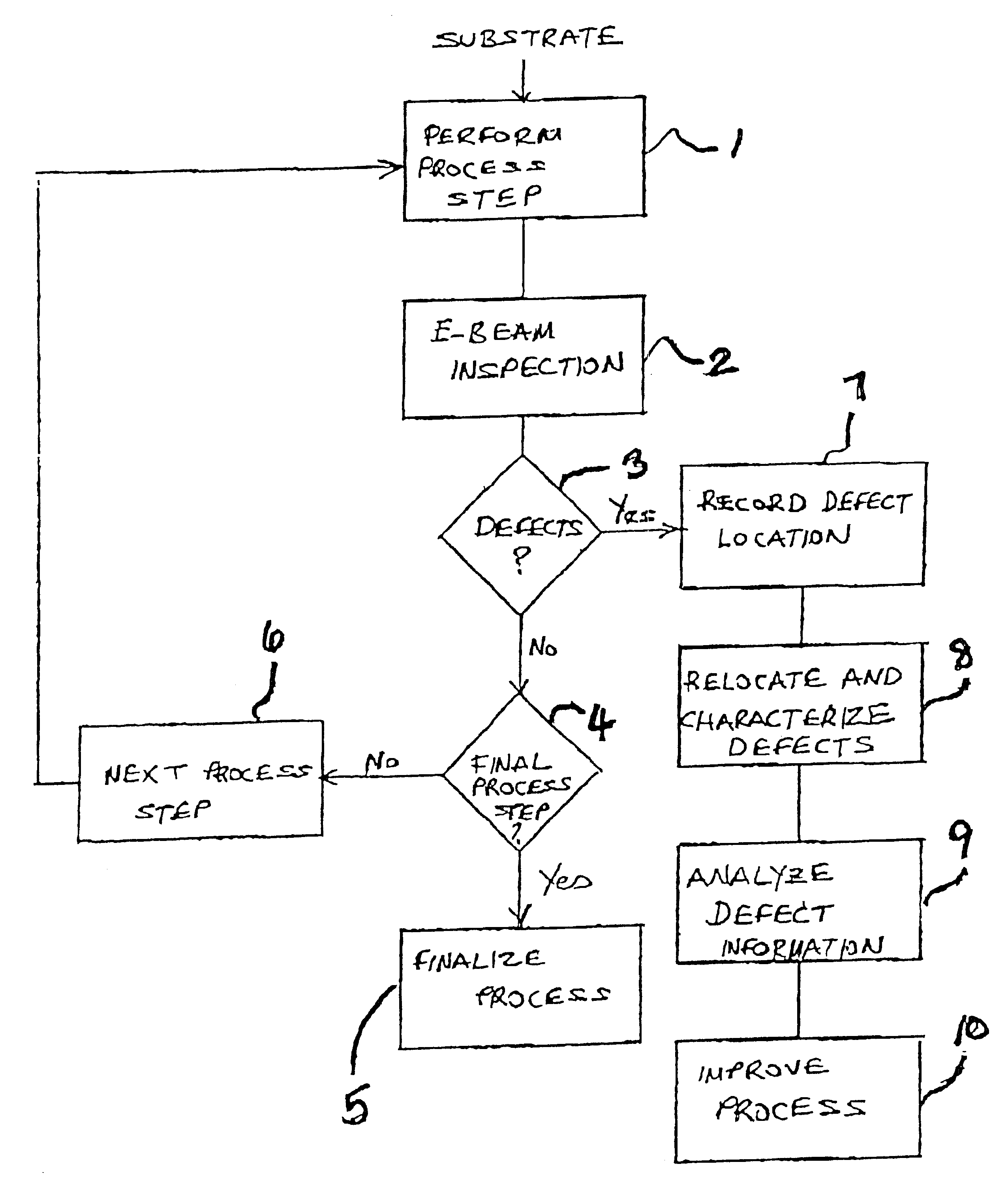

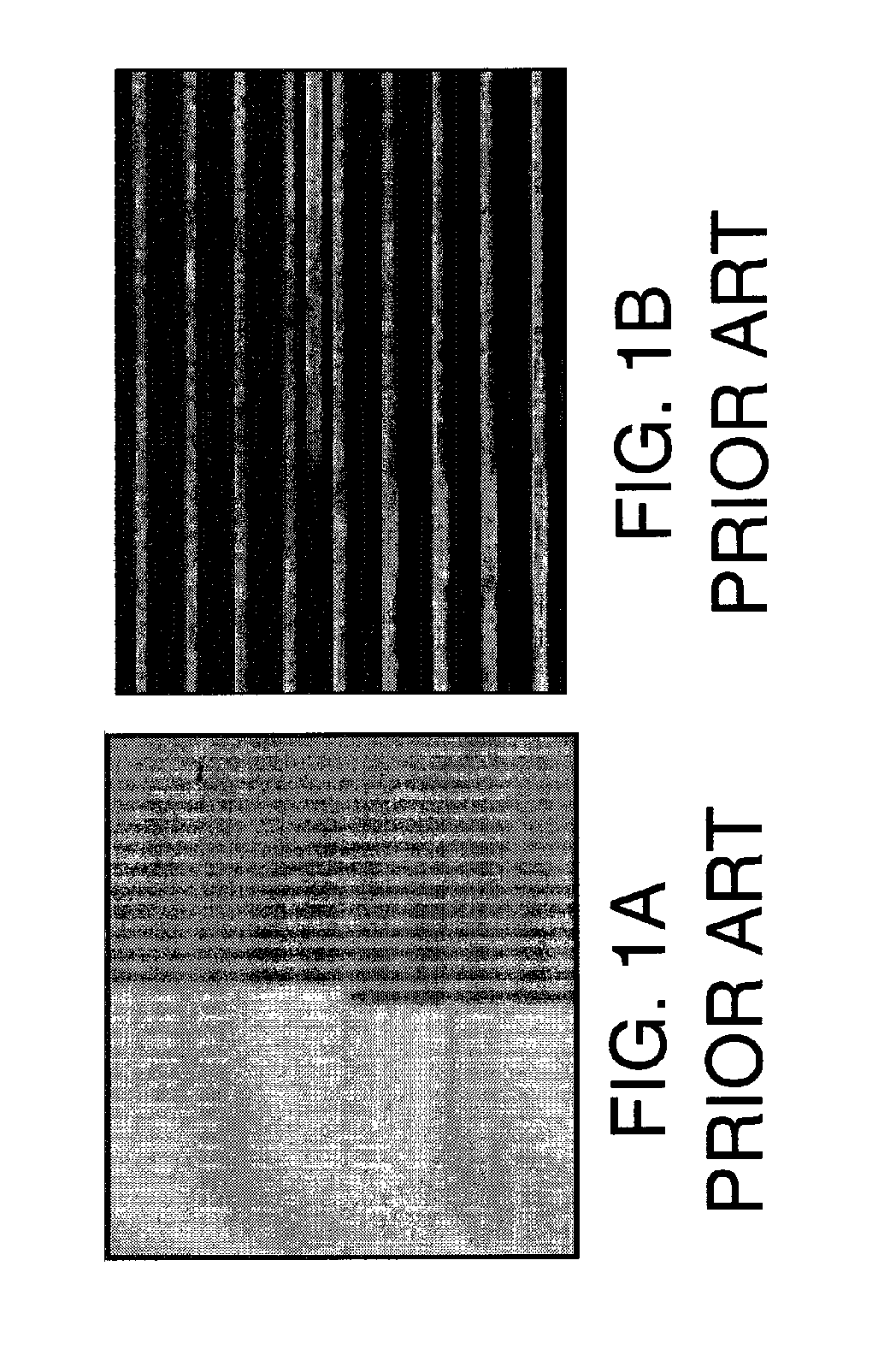

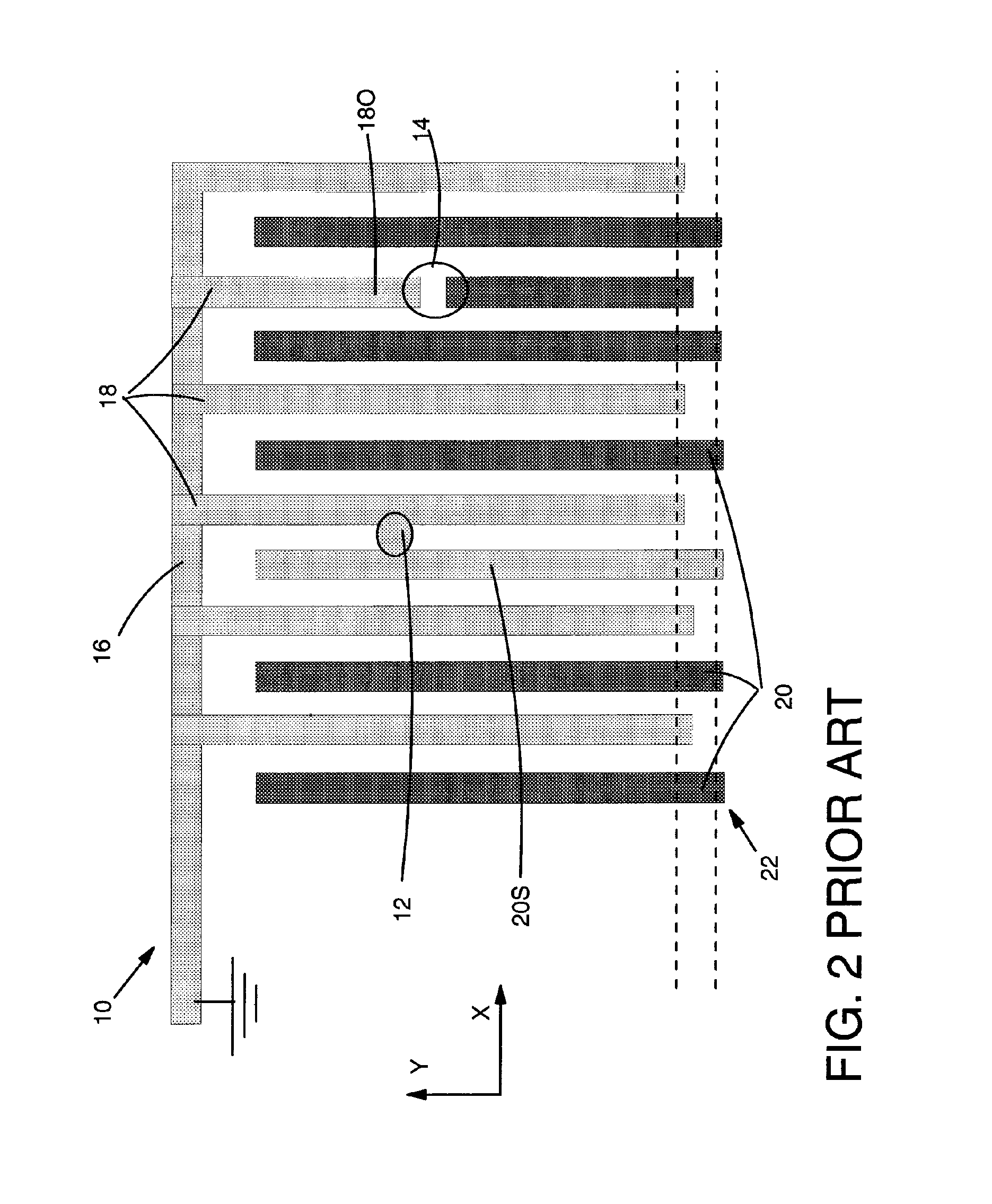

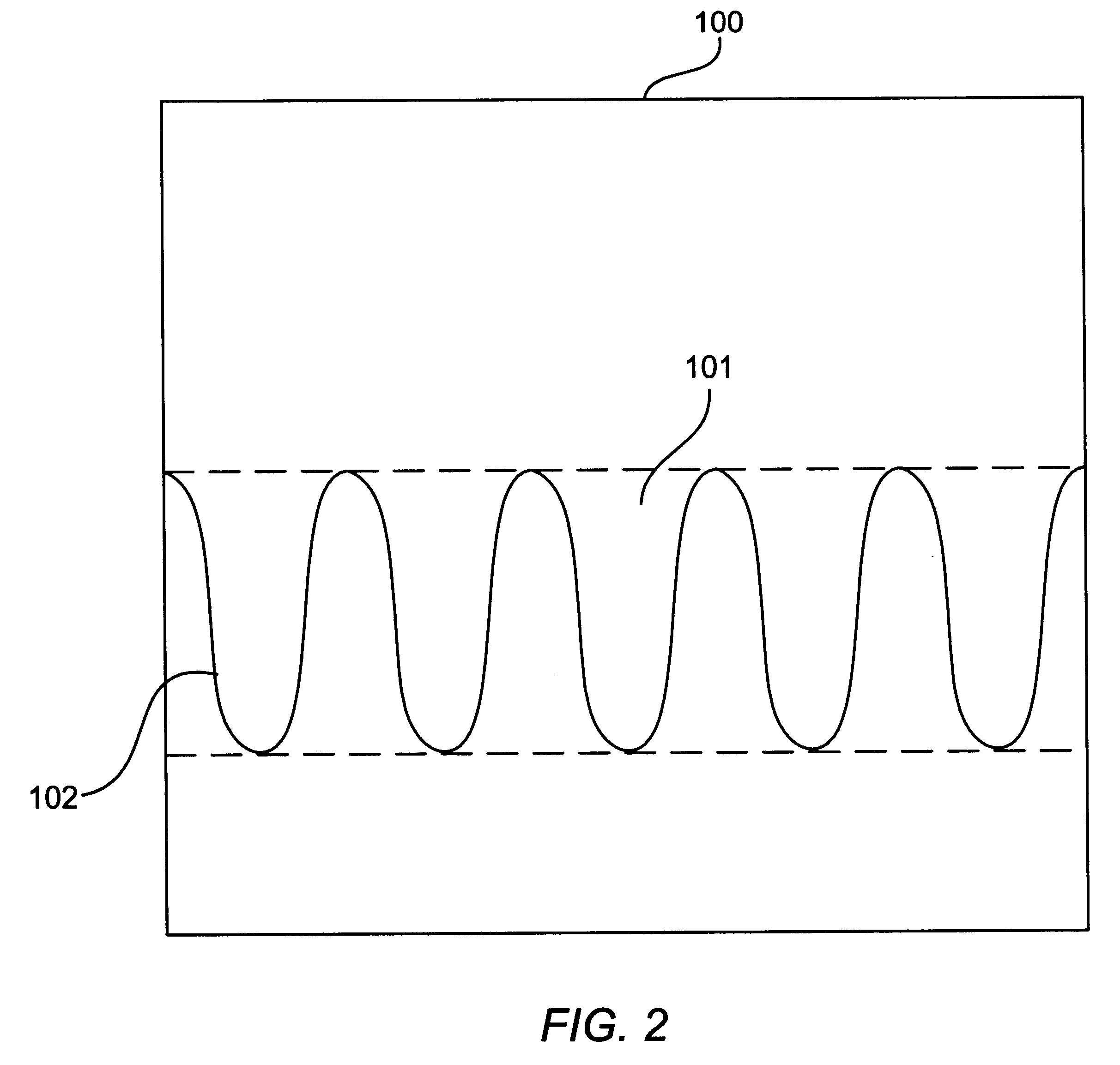

Continuous movement scans of test structures on semiconductor integrated circuits

InactiveUS6524873B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesElectricityEngineering

Disclosed is, a method for detecting electrical defects on test structures of a semiconductor die. The semiconductor die includes a plurality of electrically-isolated test structures and a plurality of non-electrically-isolated test structures. Voltages are established for the plurality of electrically-isolated test structures. These voltages are different than the voltages of the plurality of non-electrically-isolated test structures. A region of the semiconductor die is continuously inspected in a first direction thereby obtaining voltage contrast data indicative of whether there are defective test structures. The voltage contrast data is analyzed to determine whether there are one or more defective test structures.

Owner:KLA CORP

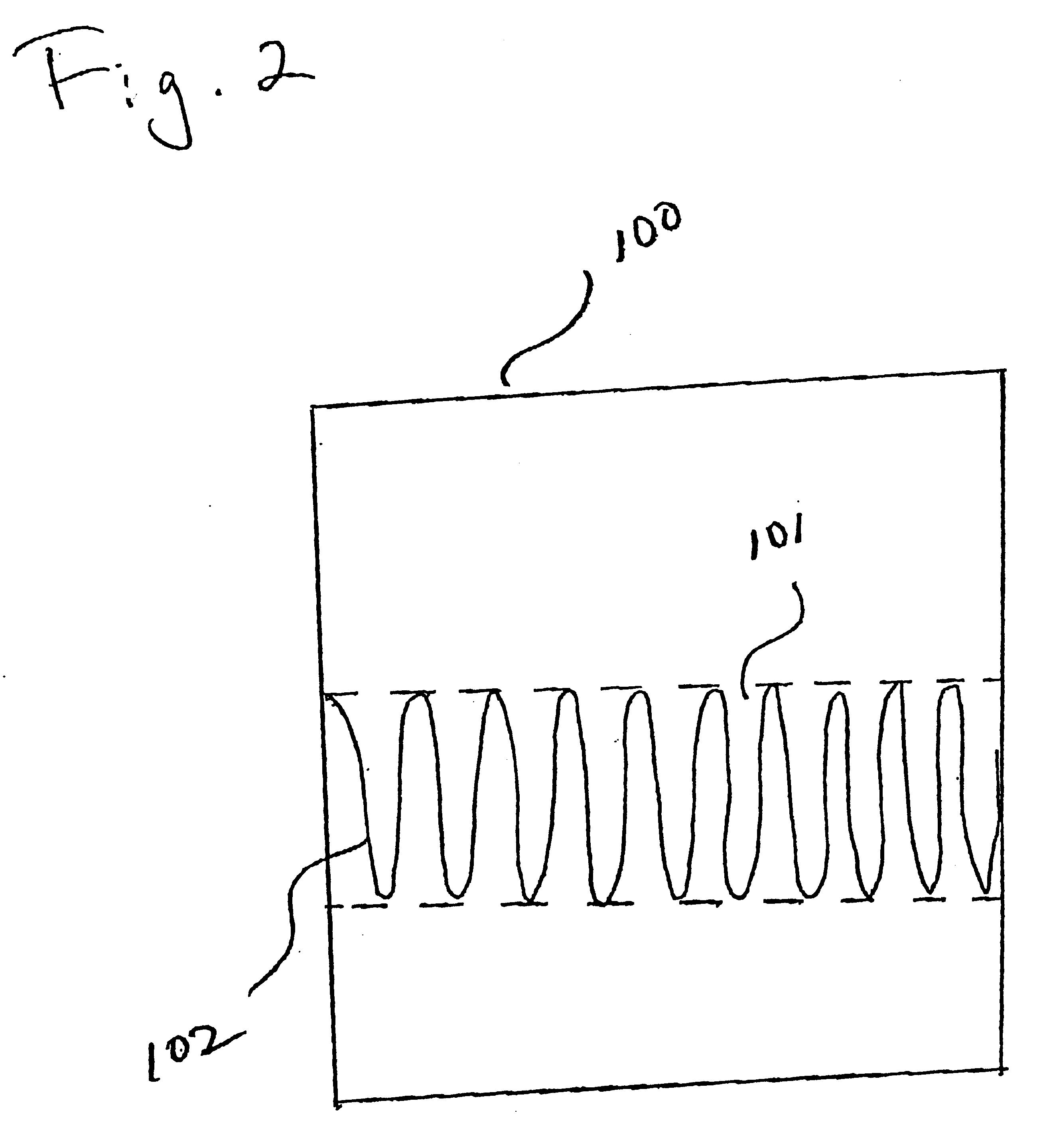

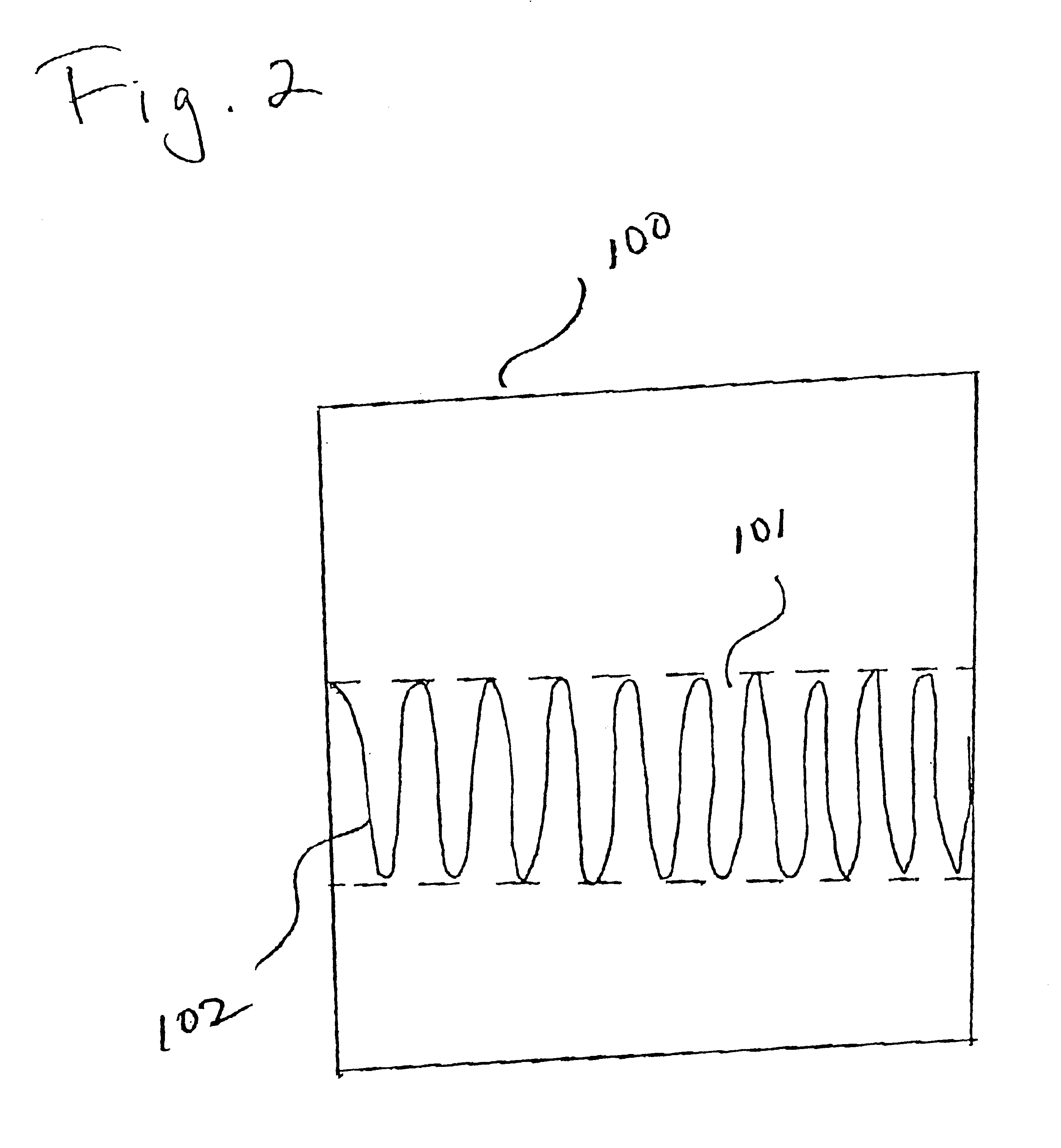

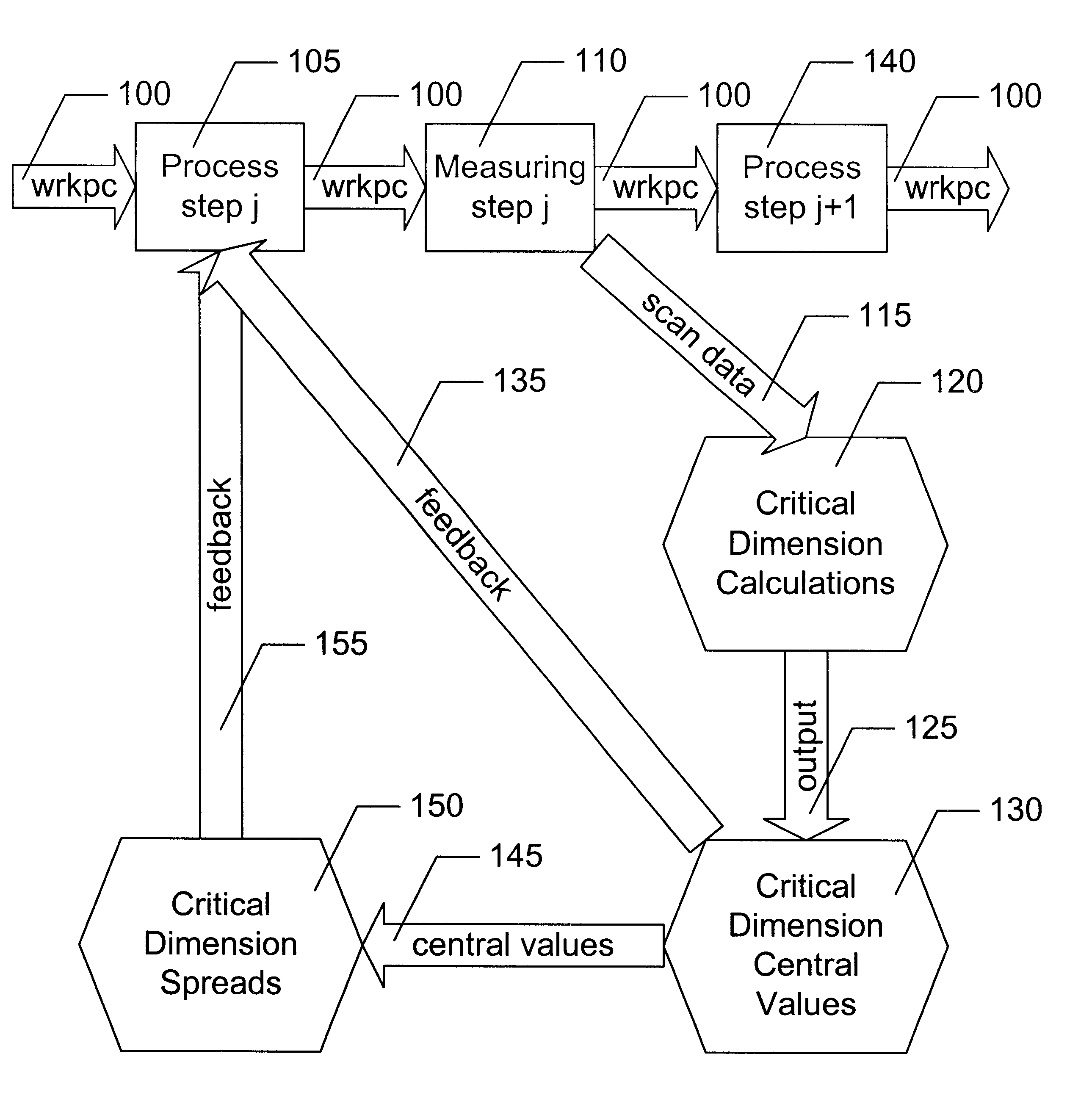

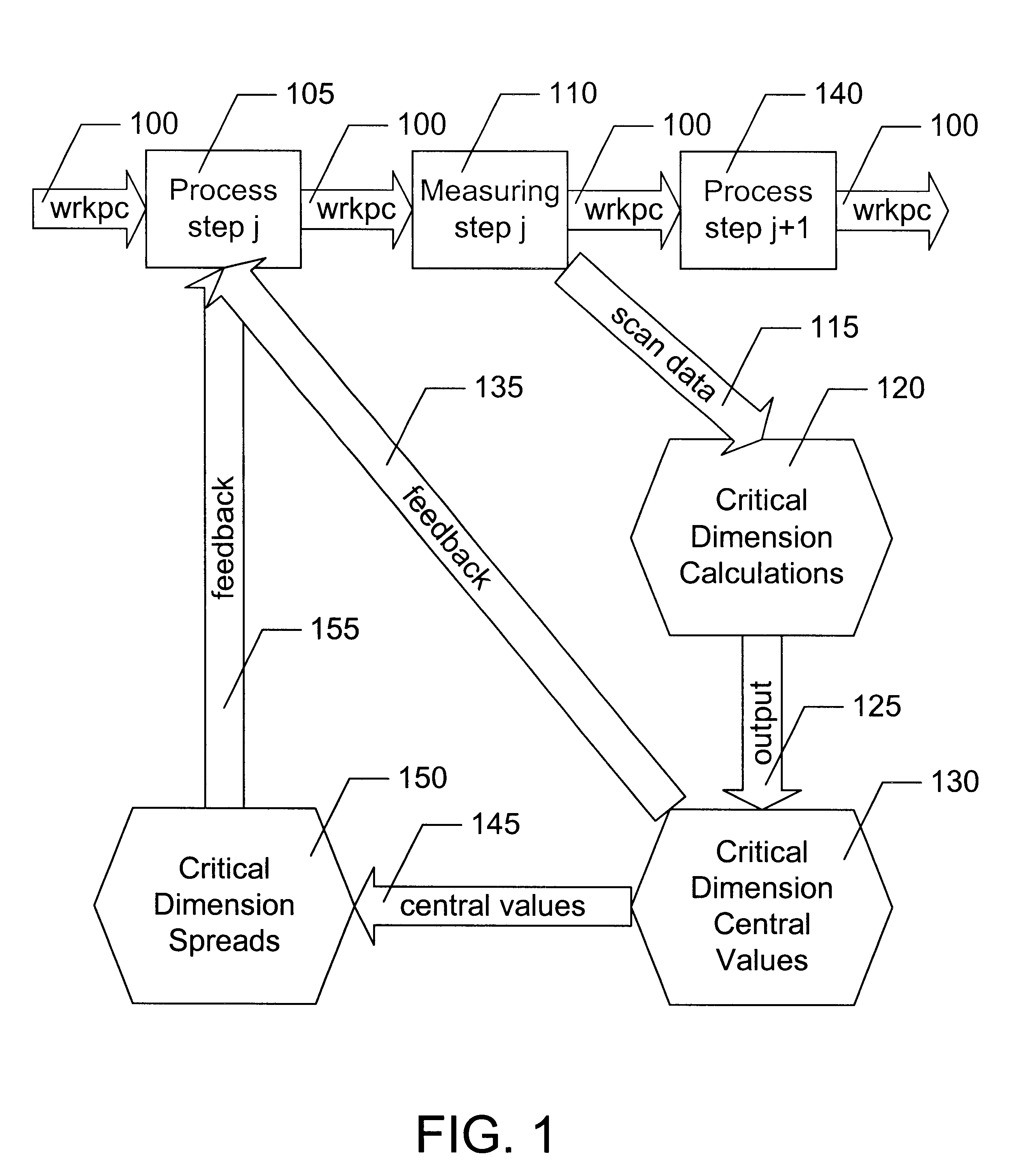

Process control with control signal derived from metrology of a repetitive critical dimension feature of a test structure on the work piece

InactiveUS6368879B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMetrologyControl signal

A method is provided for manufacturing, the method including processing a workpiece in a processing step, measuring a critical dimension of features formed on the workpiece using a test structure formed on the workpiece, the test structure including a plurality of the features, and forming an output signal corresponding to the critical dimension measurements. The method also includes feeding back a control signal based on the output signal to adjust the processing performed in the processing step if the output signal corresponding to the critical dimension measurements indicates a predetermined tolerance value has been exceeded.

Owner:GLOBALFOUNDRIES INC

E-beam inspection structure for leakage analysis

InactiveUS20090057664A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityGate dielectric

A testing structure, and method of using the testing structure, where the testing structure comprised of at least one of eight test structures that exhibits a discernable defect characteristic upon voltage contrast scanning when it has at least one predetermined structural defect. The eight test structures being: 1) having an Active Area (AA) / P-N junction leakage; 2) having an isolation region to ground; 3) having an AA / P-N junction and isolation region; 4) having a gate dielectric leakage and gate to isolation region to ground; 5) having a gate dielectric leakage through AA / P-N junction to ground leakage; 6) having a gate dielectric to ground and gate / one side isolation region leakage to ground; 7) having an oversized gate dielectric through AA / P-N junction to ground leakage; and 8) having an AA / P-N junction leakage gate dielectric leakage.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

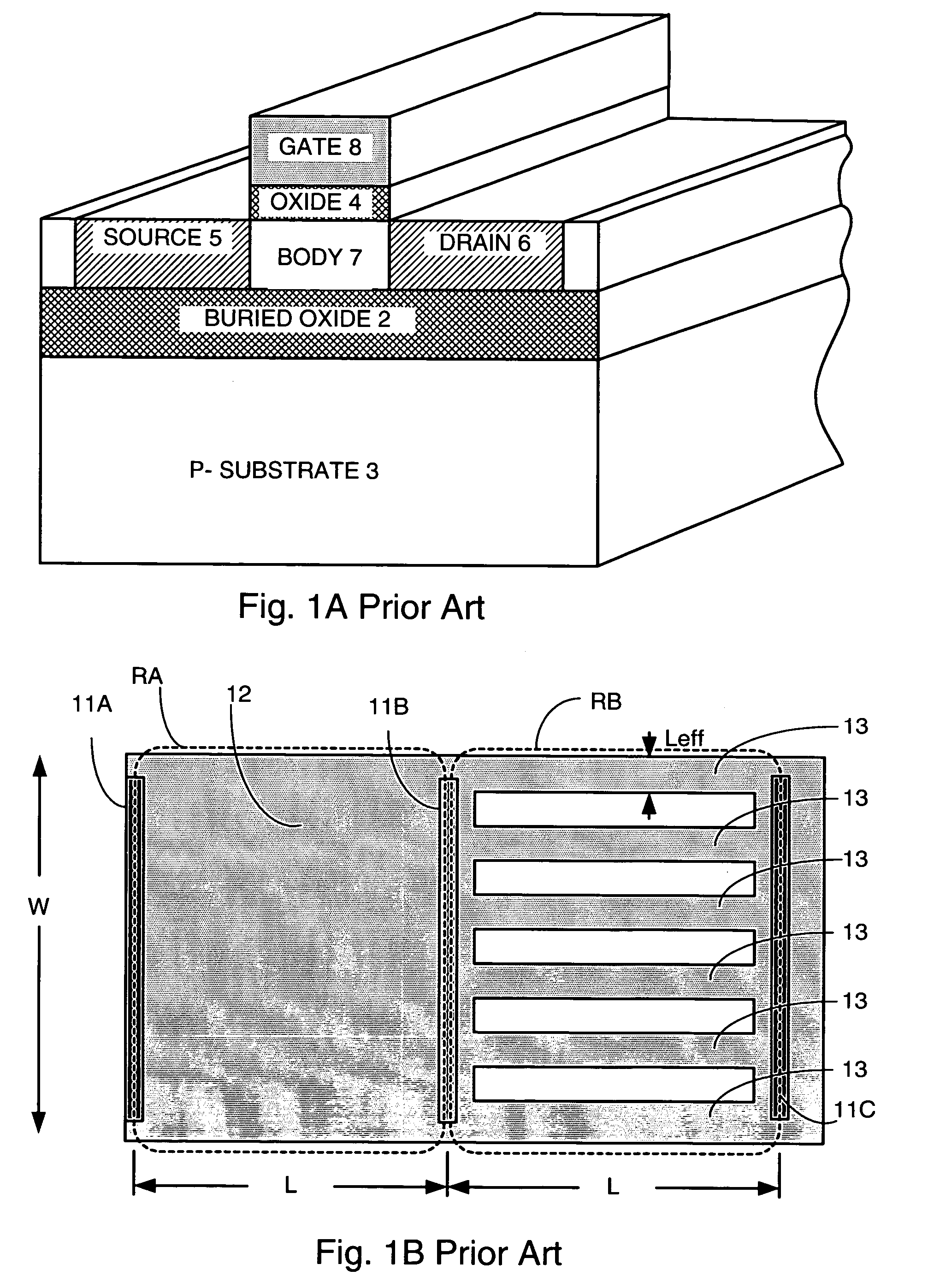

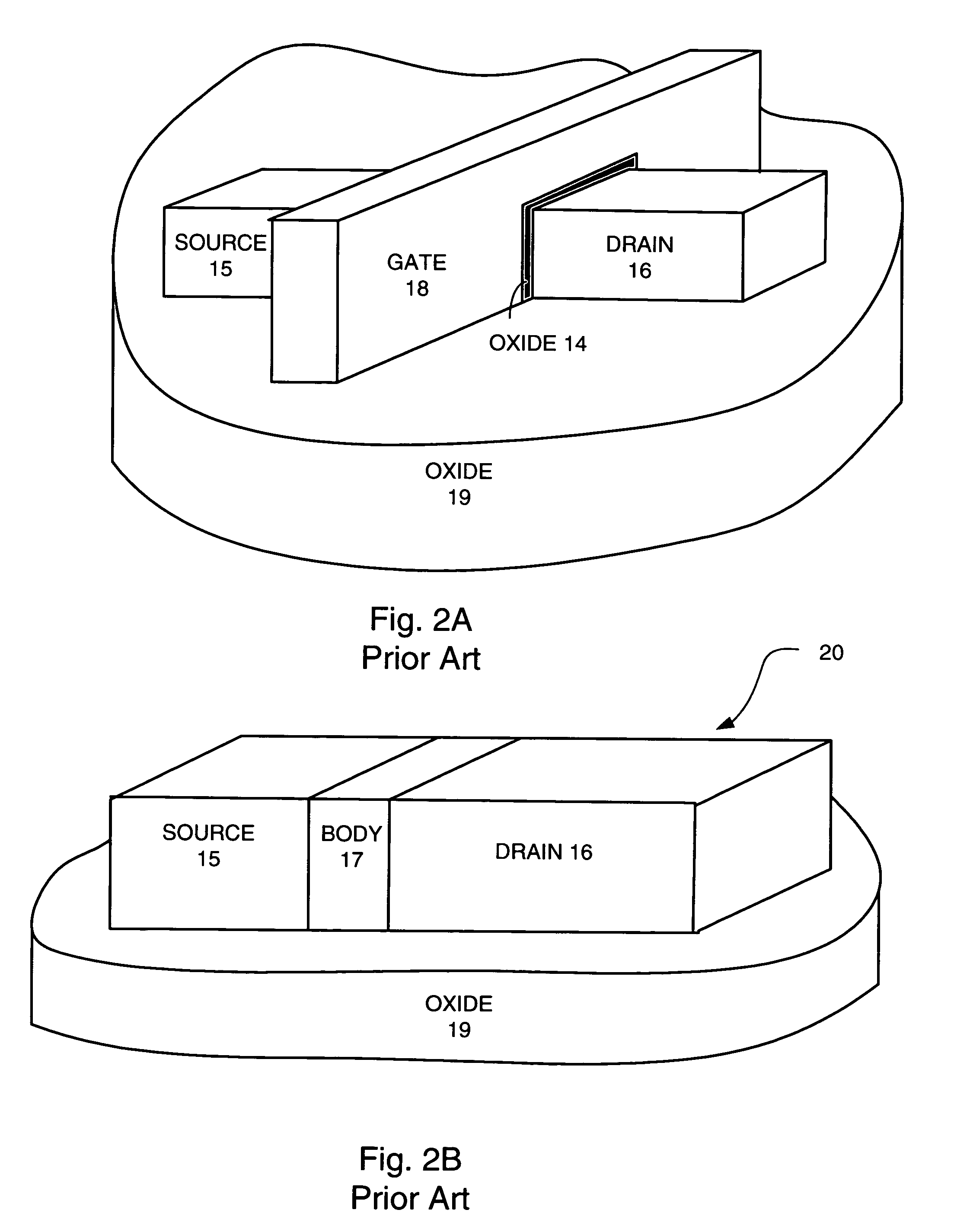

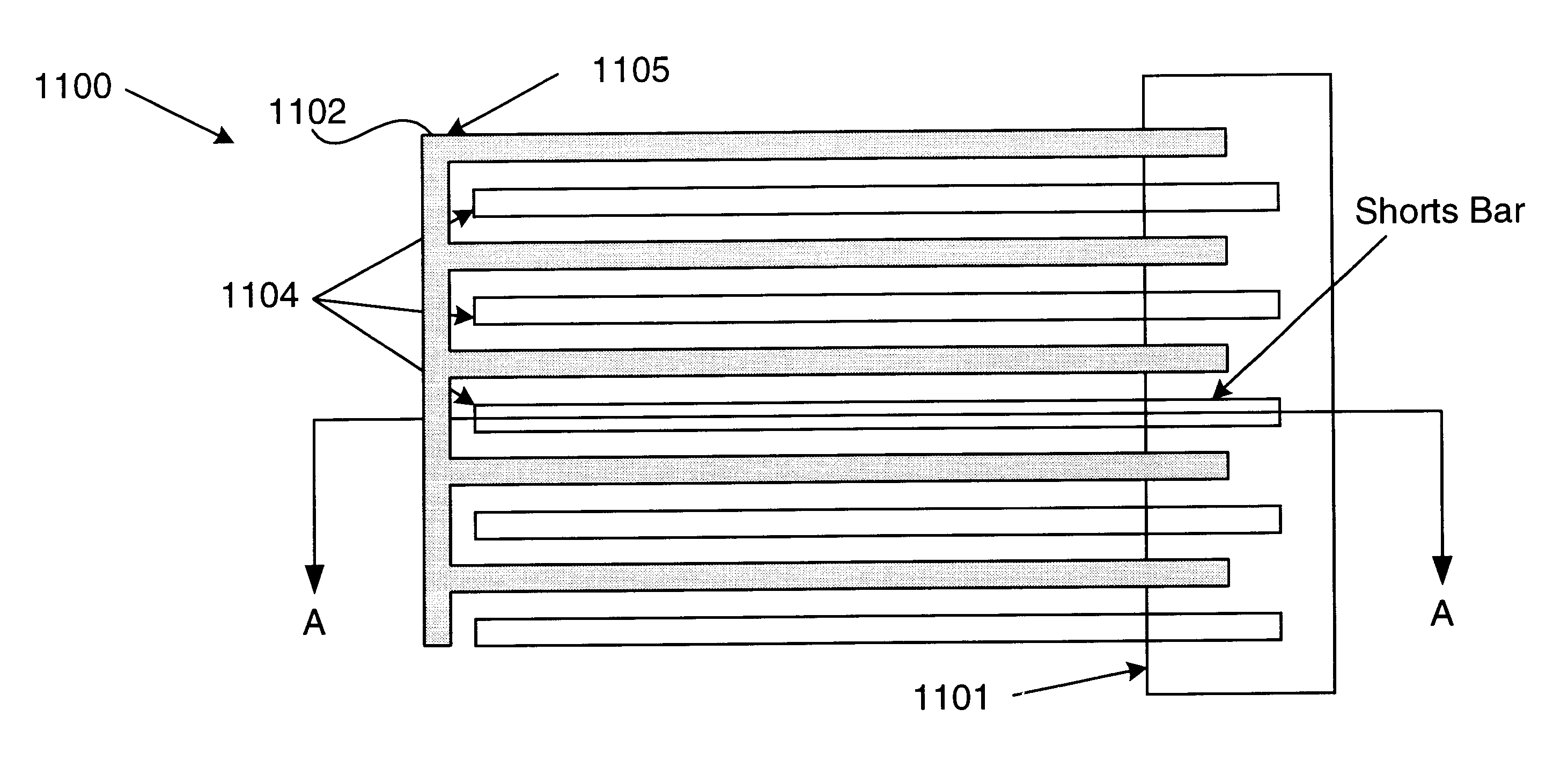

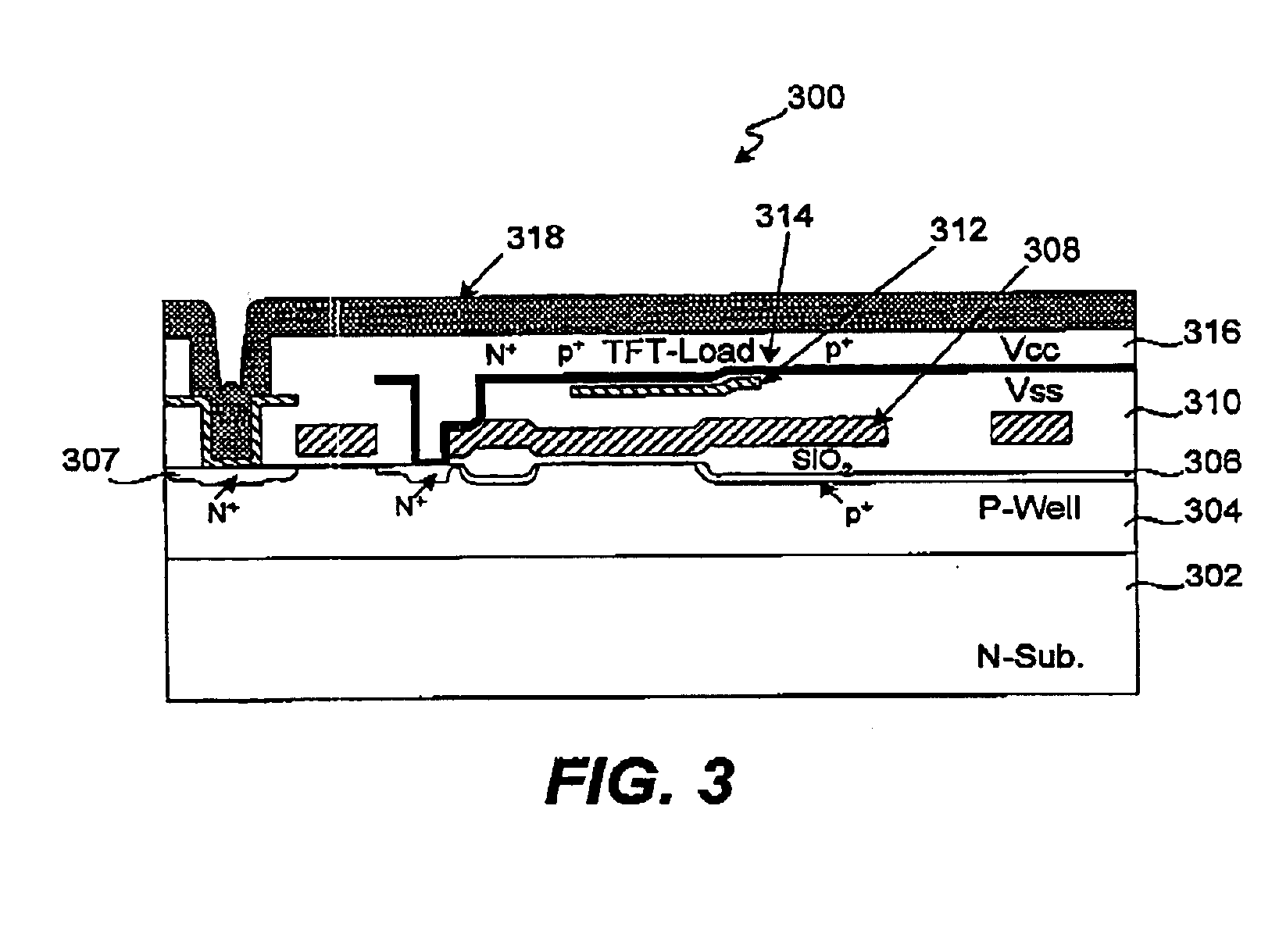

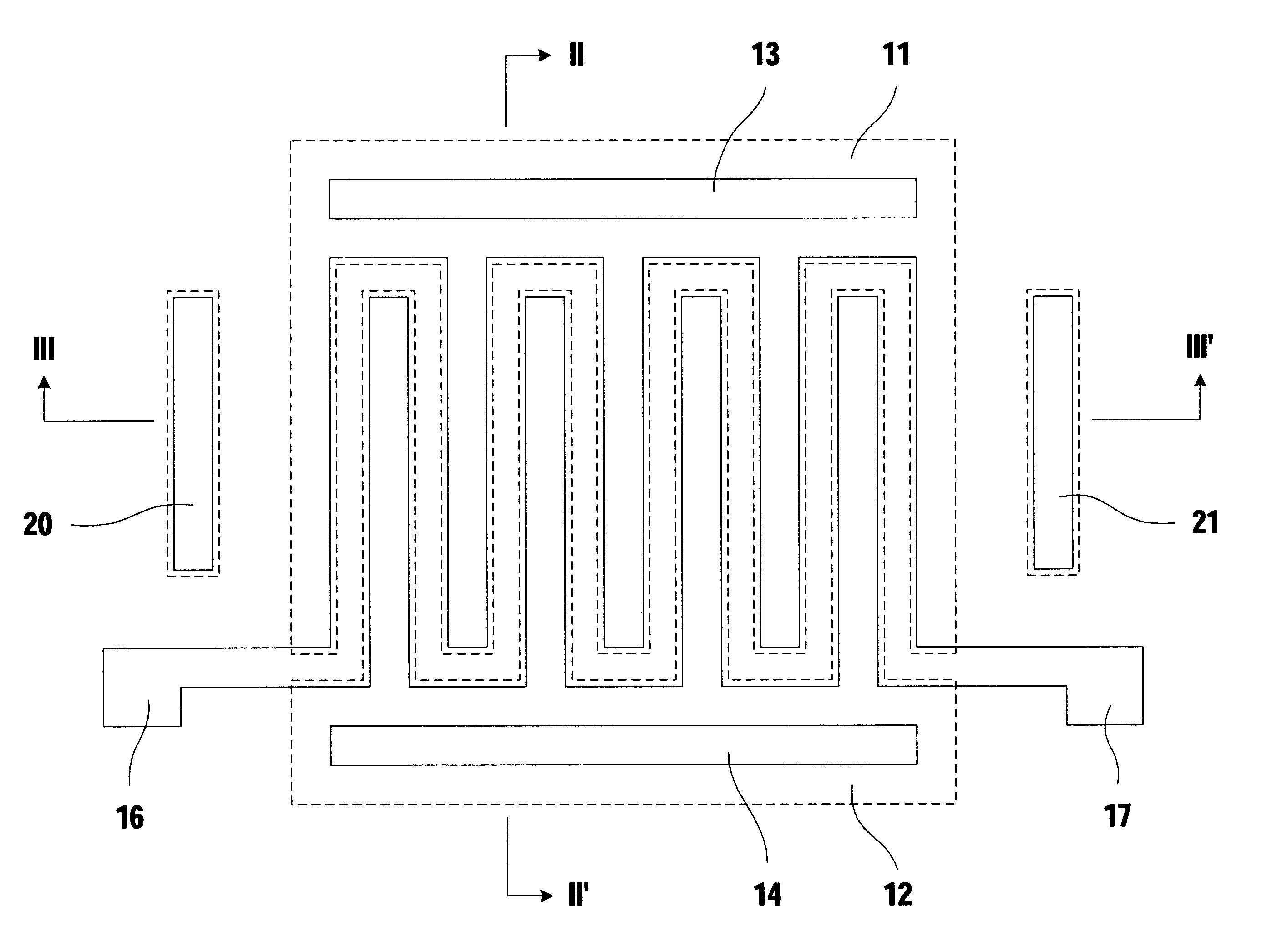

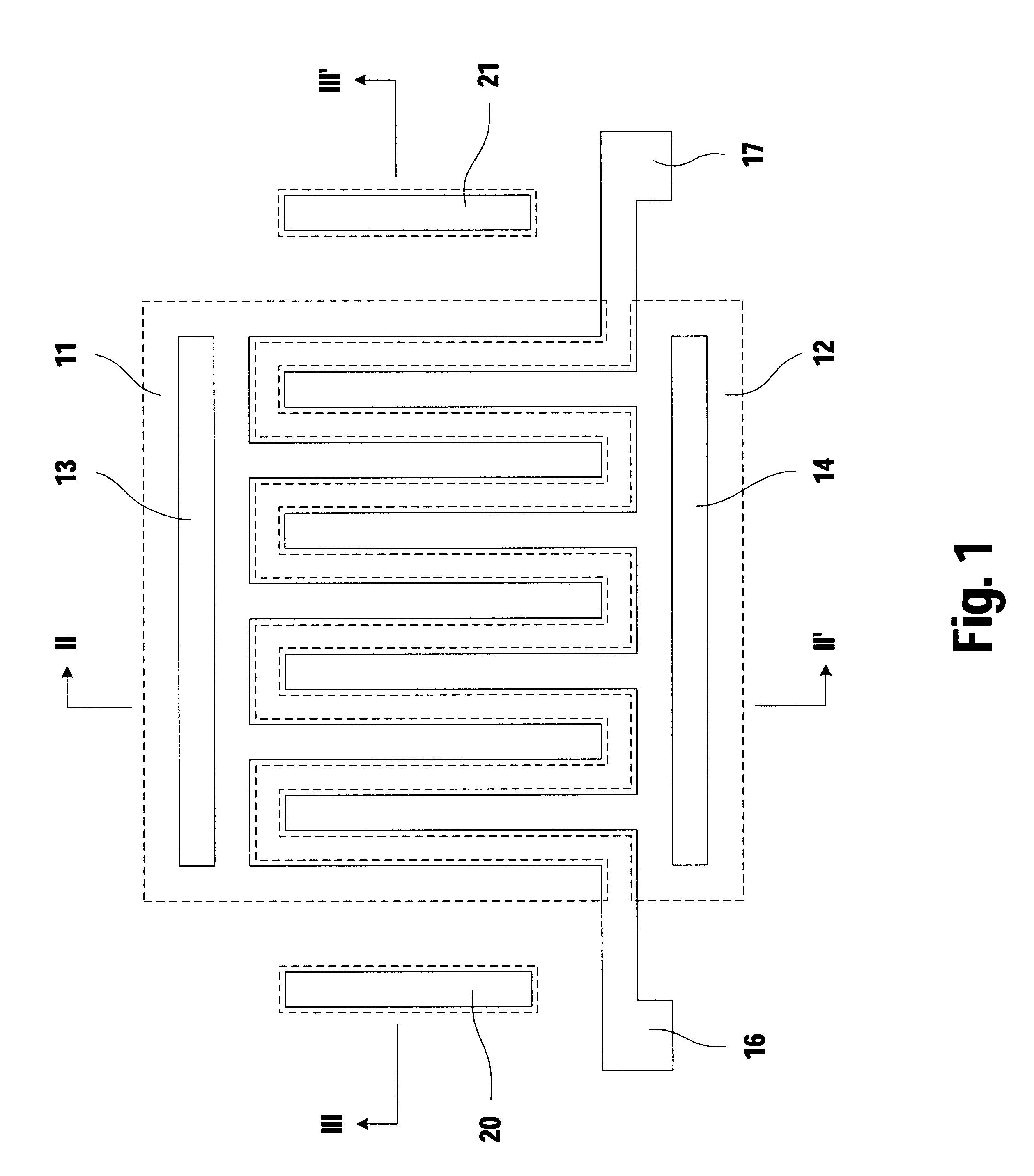

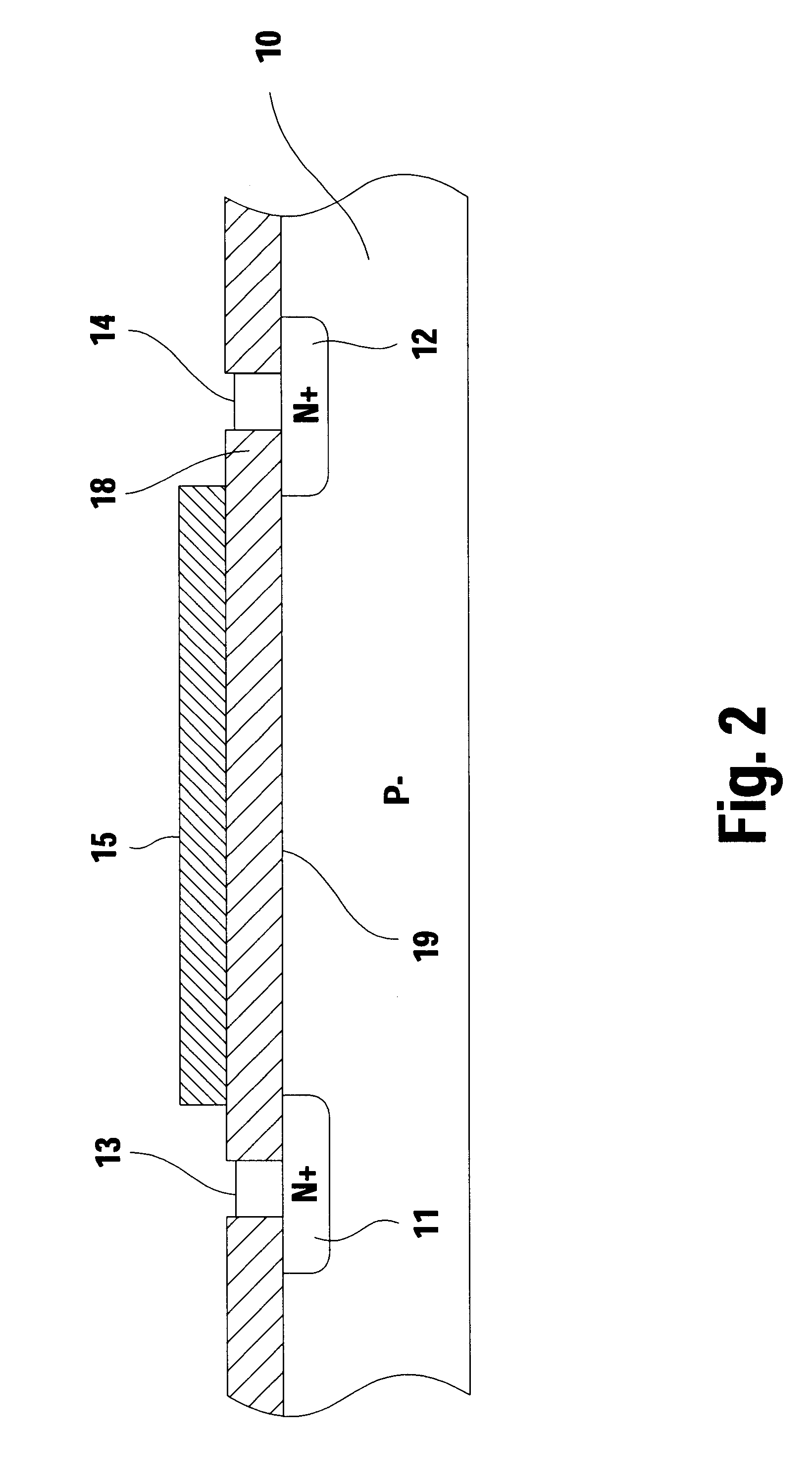

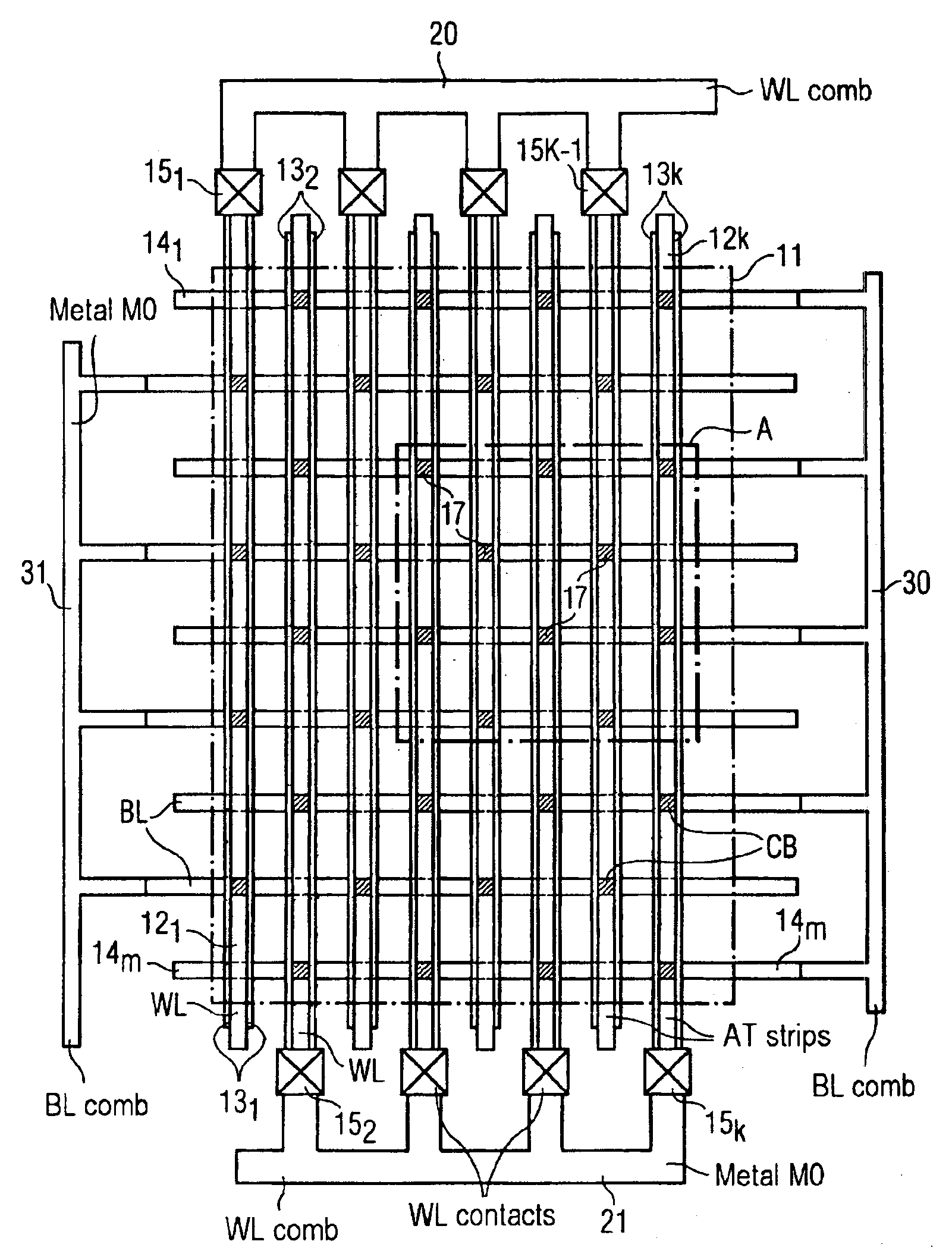

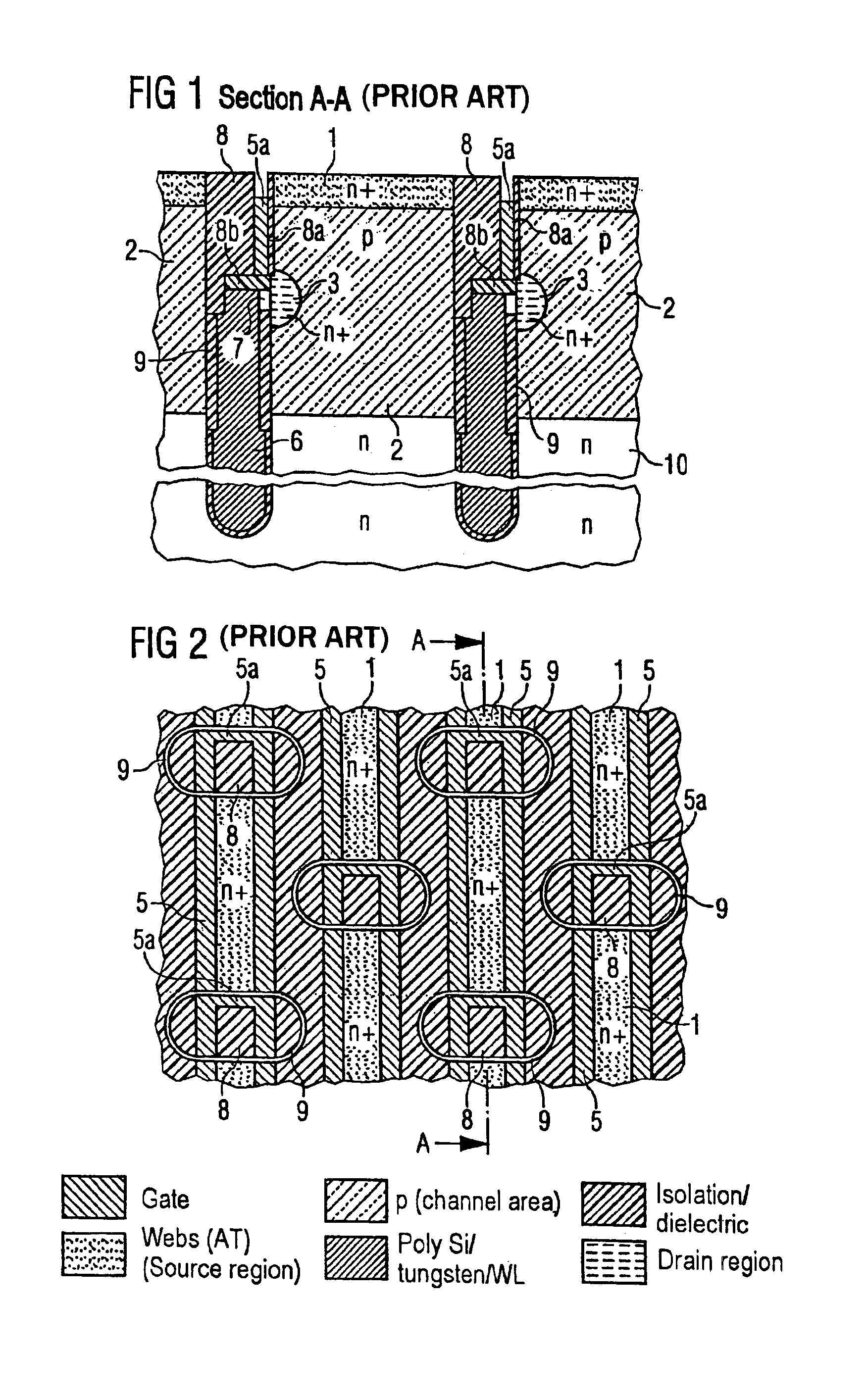

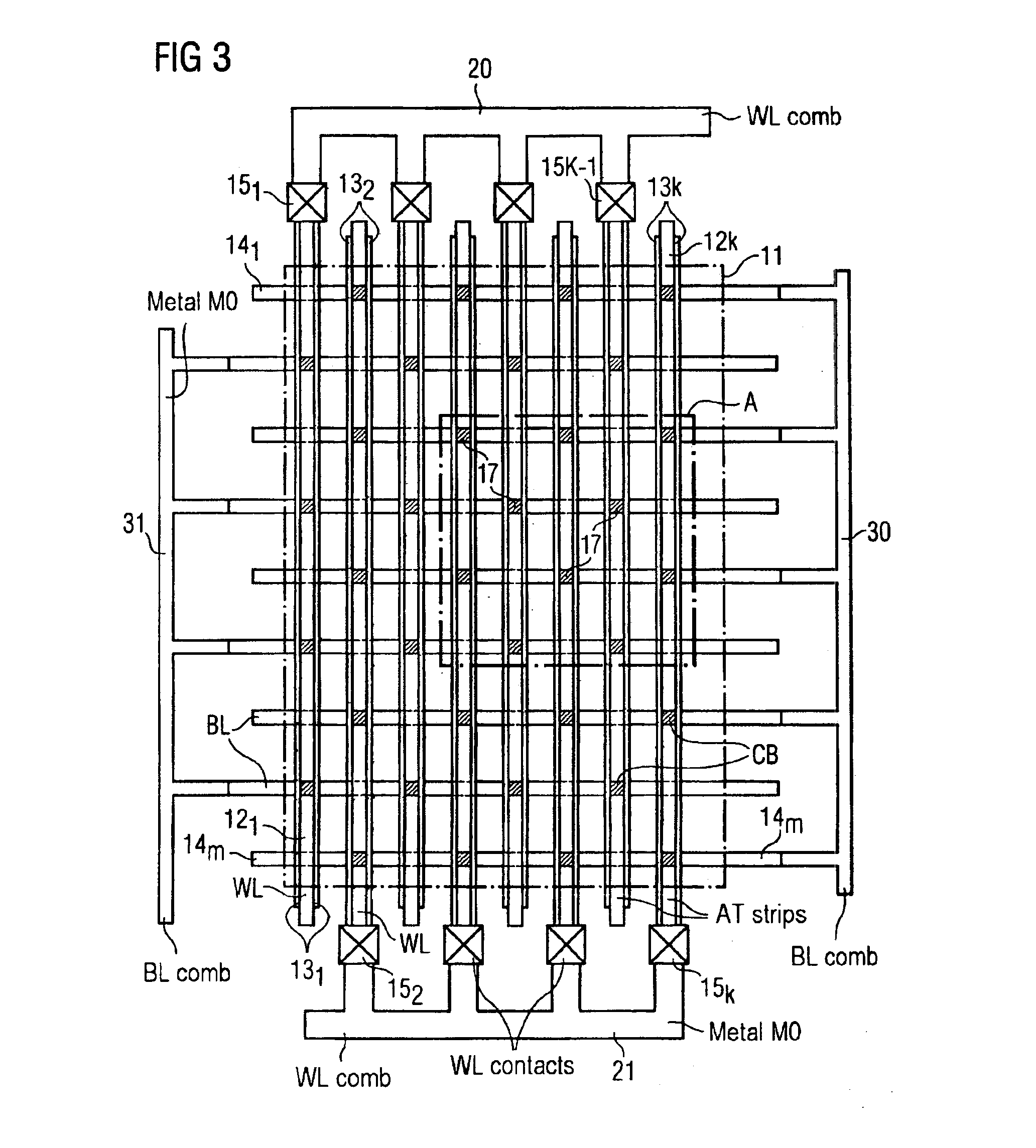

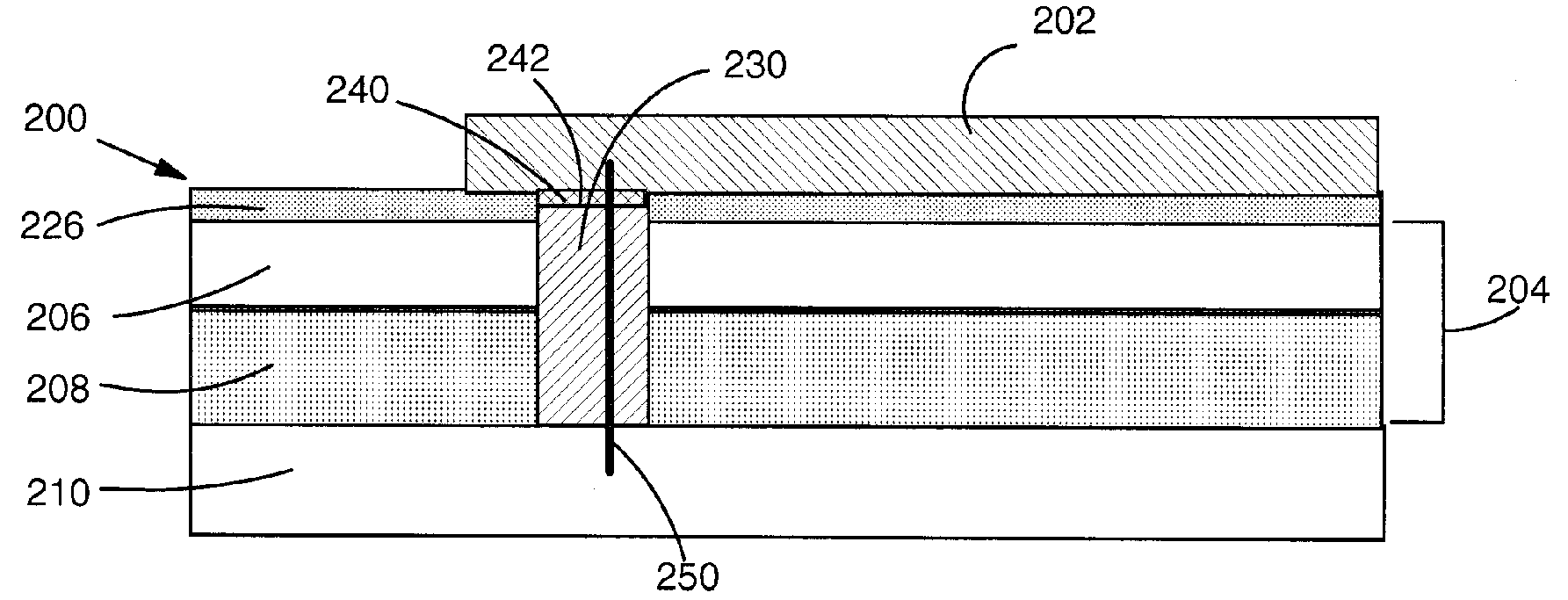

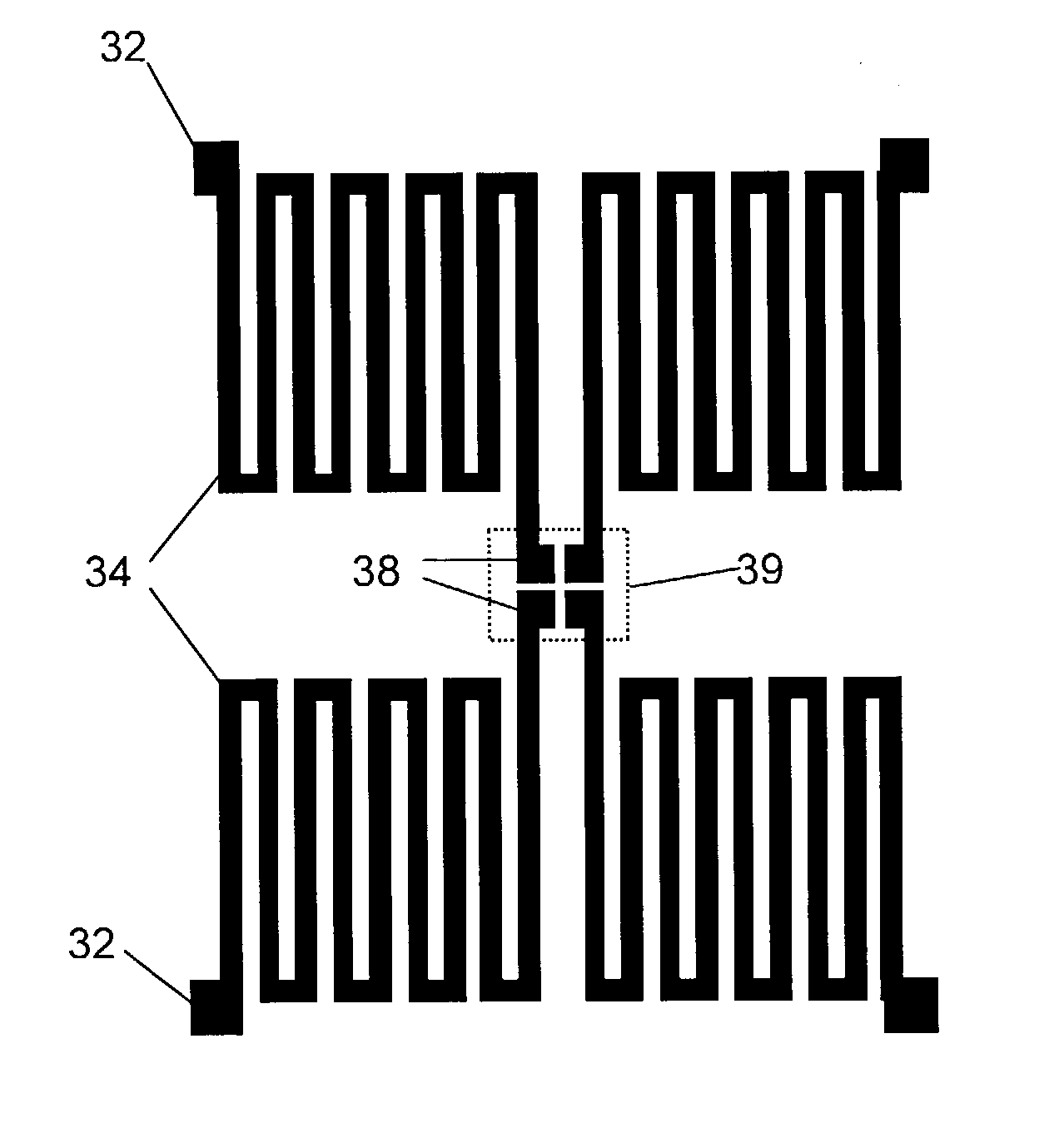

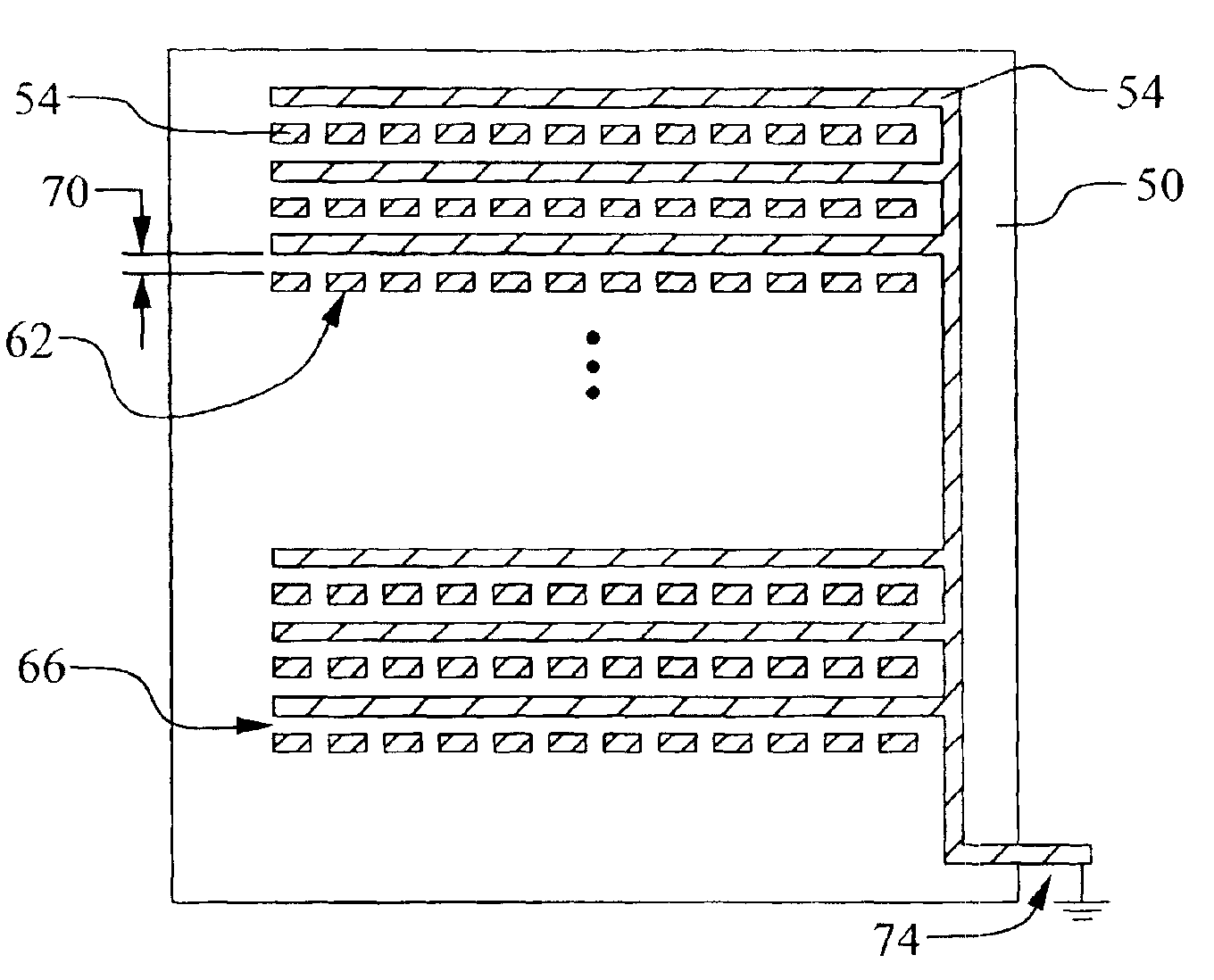

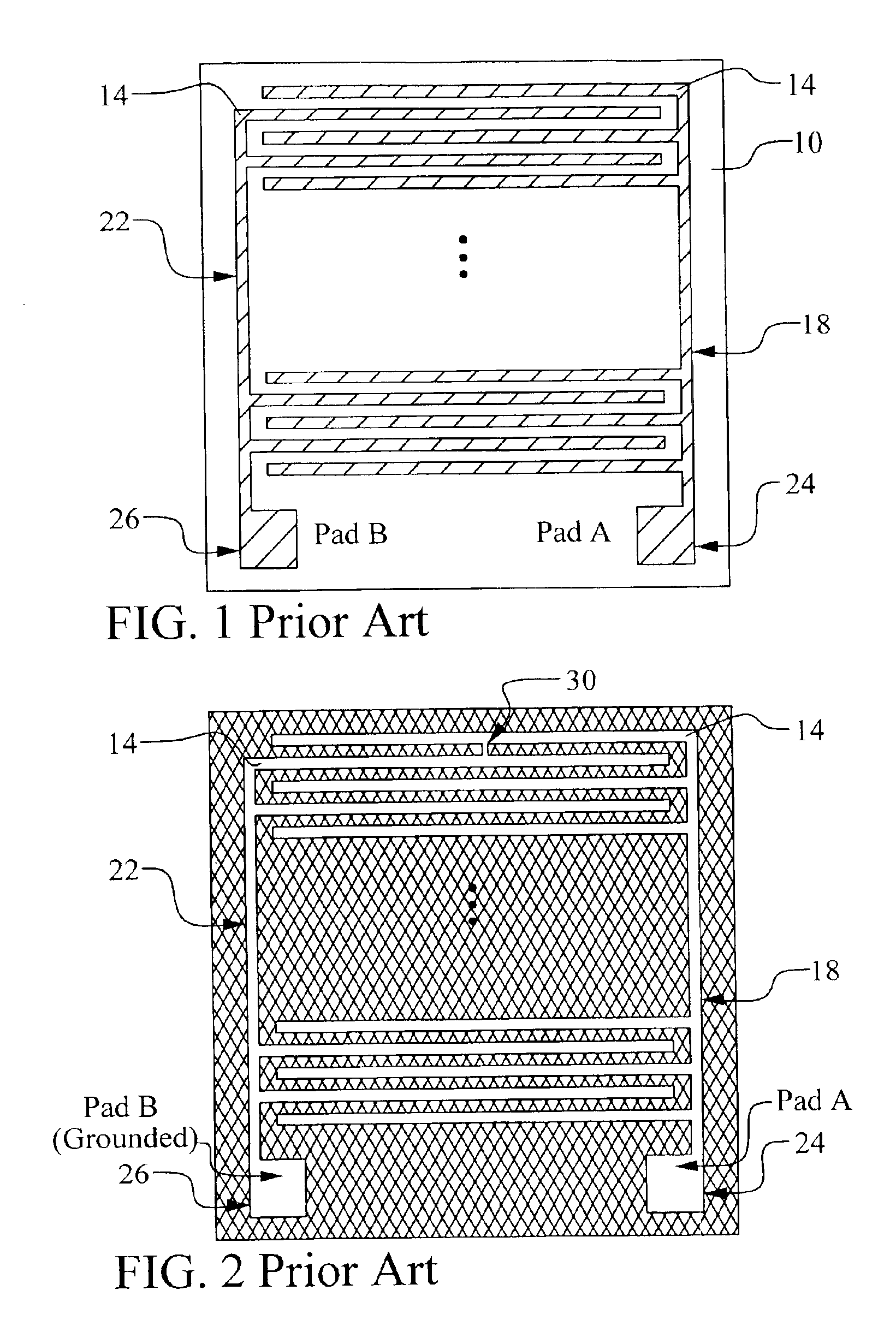

Device architecture and process for improved vertical memory arrays

InactiveUS6930324B2TransistorSemiconductor/solid-state device testing/measurementTransistor arrayDielectric

An array process diagnosis test structure for an integrated circuit including a transistor array composed of vertical FET memory cell access transistors, which are formed into the depth of a substrate in the form of active webs which run parallel in the lateral direction of the circuit is disclosed. Memory cell storage capacitors in the array test structure are formed in deep trenches on the end faces of those sections of the active webs which form the vertical FET transistors. Word lines are arranged along the webs and along parallel intersecting bit lines of the array, outside of which, and on two mutually opposite edges, are located a first and second word line comb. The wordline combs are offset and connected alternately to different word lines. In addition, a first and a second bit line comb are formed on the two other opposing edges of the transistor array mutually offset and each connected to different bit lines. The test structure provides a convenient means to carry out reliability investigations on the gate oxide of the vertical FET transistors and on the capacitor dielectric in the deep trenches, capacitance measurements between the word lines, and between the word lines and other circuit layers, as well as capacitance measurements between the bit lines and between the bit lines and other circuit layers, and thus facilitates diagnosis of possible fault sources arising during the production process.

Owner:POLARIS INNOVATIONS

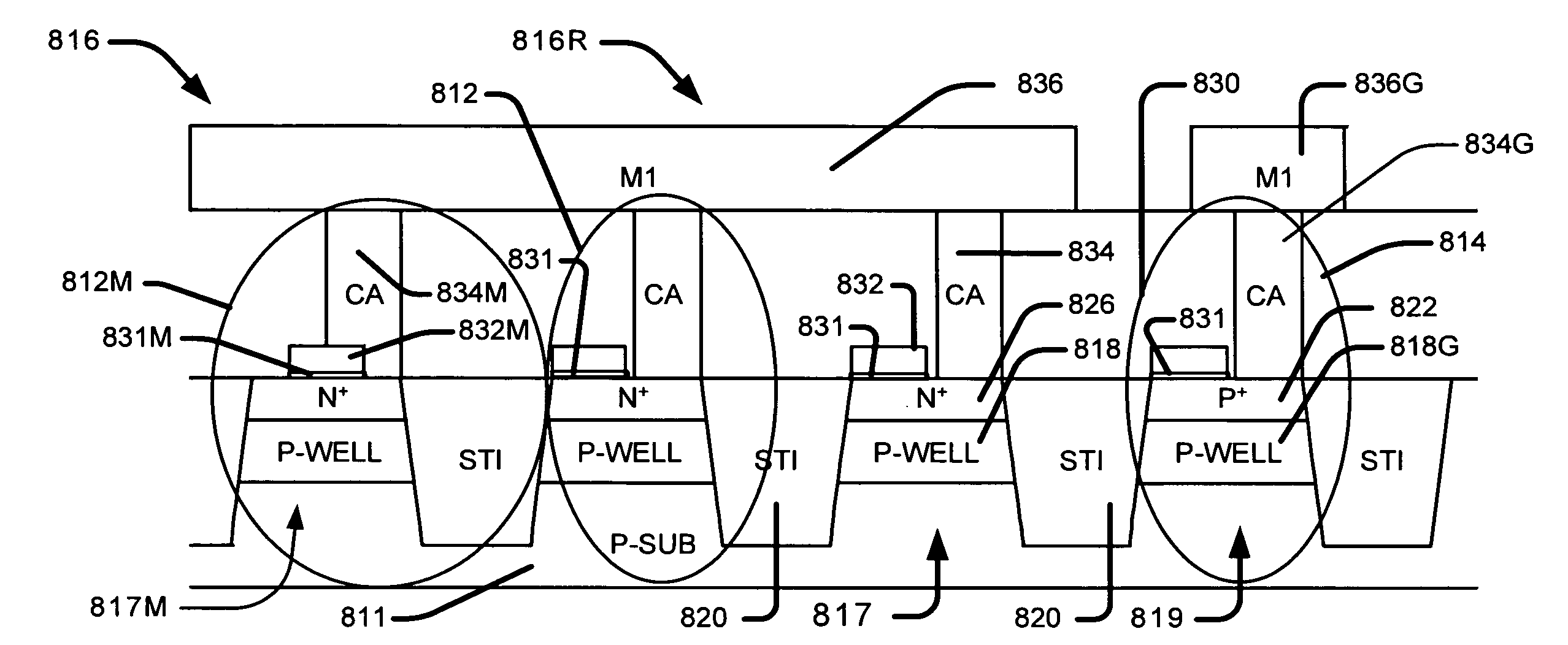

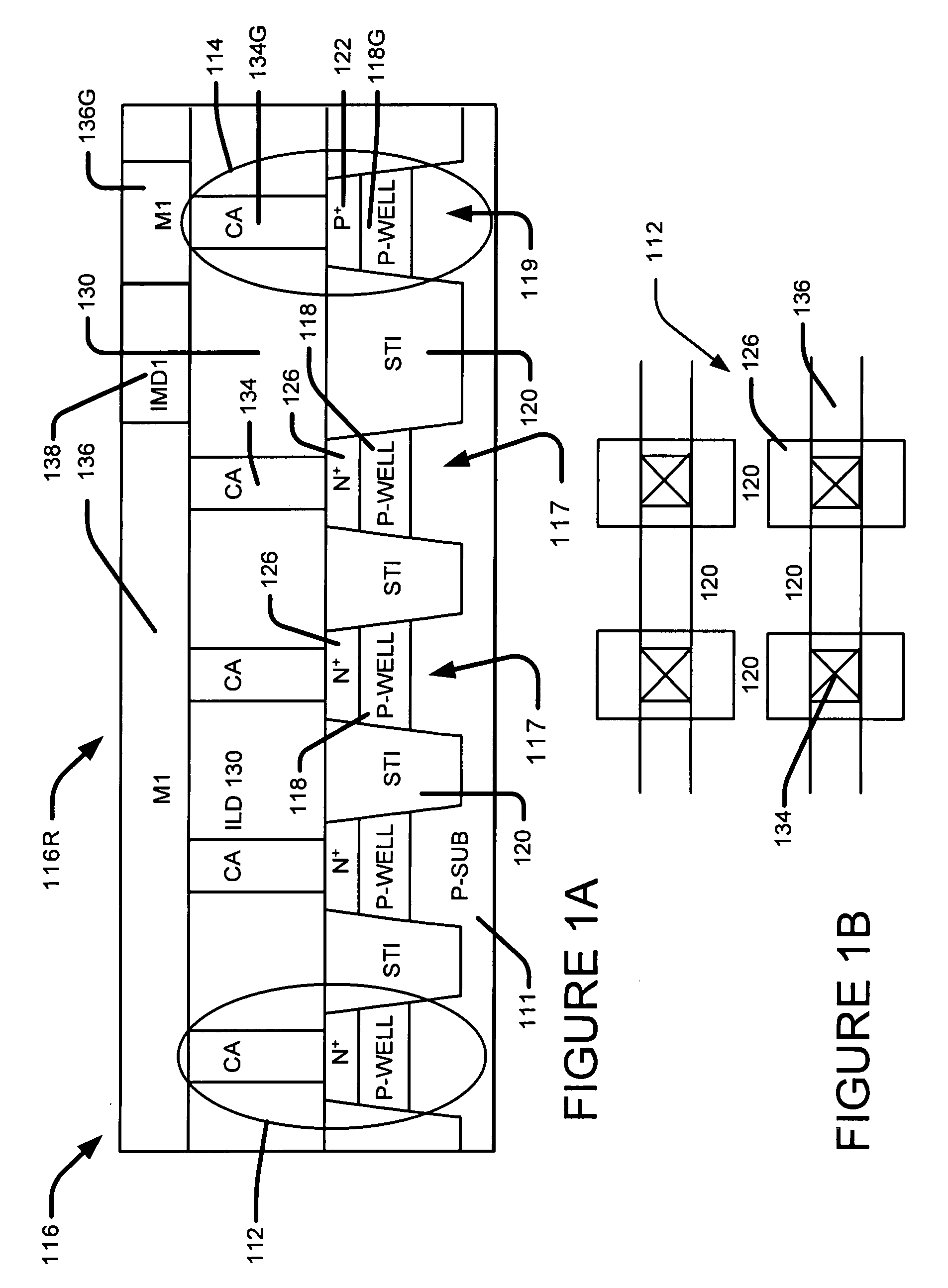

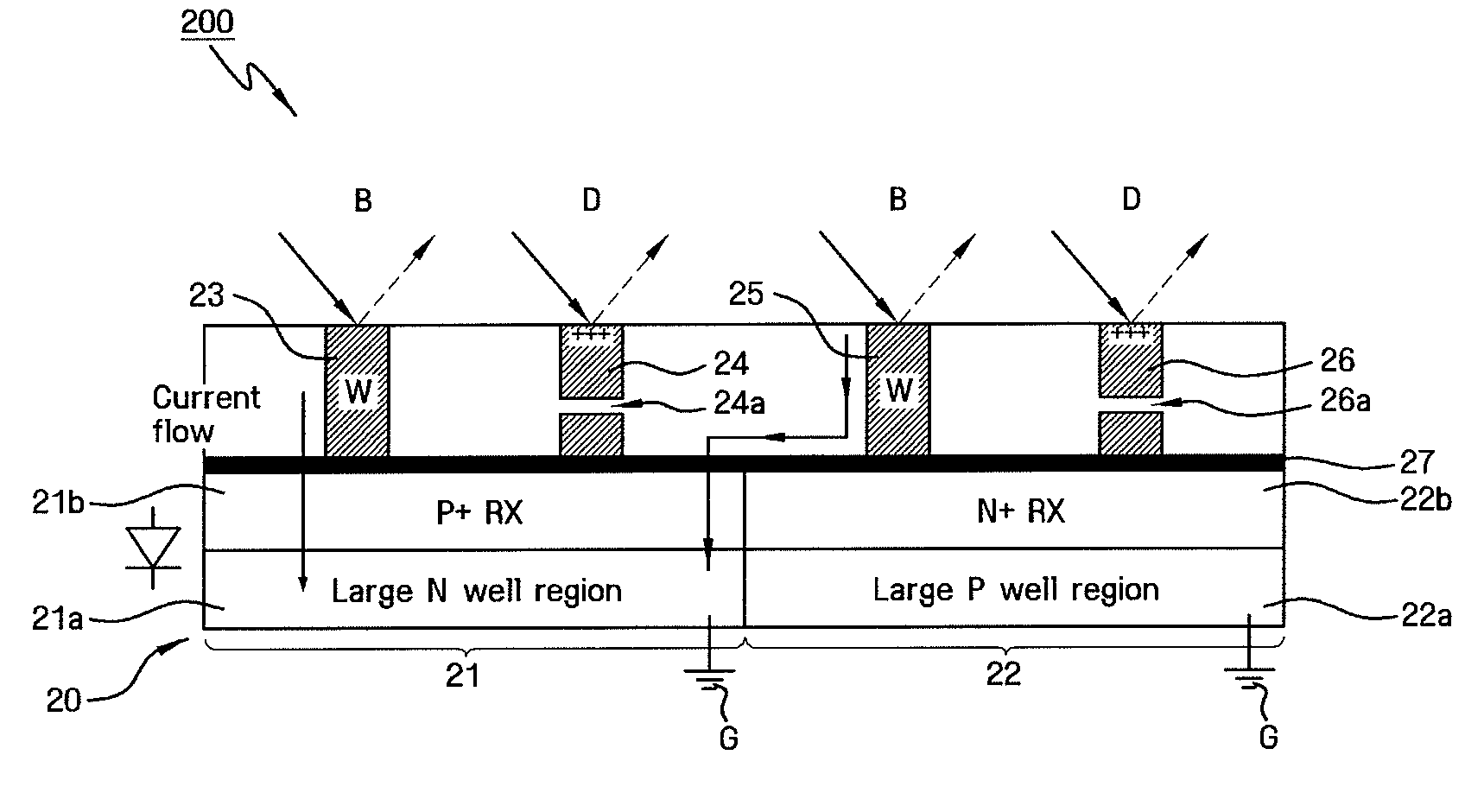

Semiconductor Integrated Test Structures For Electron Beam Inspection of Semiconductor Wafers

ActiveUS20080237586A1Easy to detectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCMOSEngineering

Semiconductor integrated test structures are designed for electron beam inspection of semiconductor wafers. The test structures include pattern features that are formed in designated test regions of the wafer concurrently with pattern features of integrated circuits formed on the wafer. The test structures include conductive structures that are designed to enable differential charging between defective and non-defective features (or defective and non-defection portions of a given feature) to facilitate voltage contrast defect detection of CMOS devices, for example, using a single, low energy electron beam scan, notwithstanding the existence of p / n junctions in the wafer substrate or other elements / features.

Owner:SAMSUNG ELECTRONICS CO LTD +2

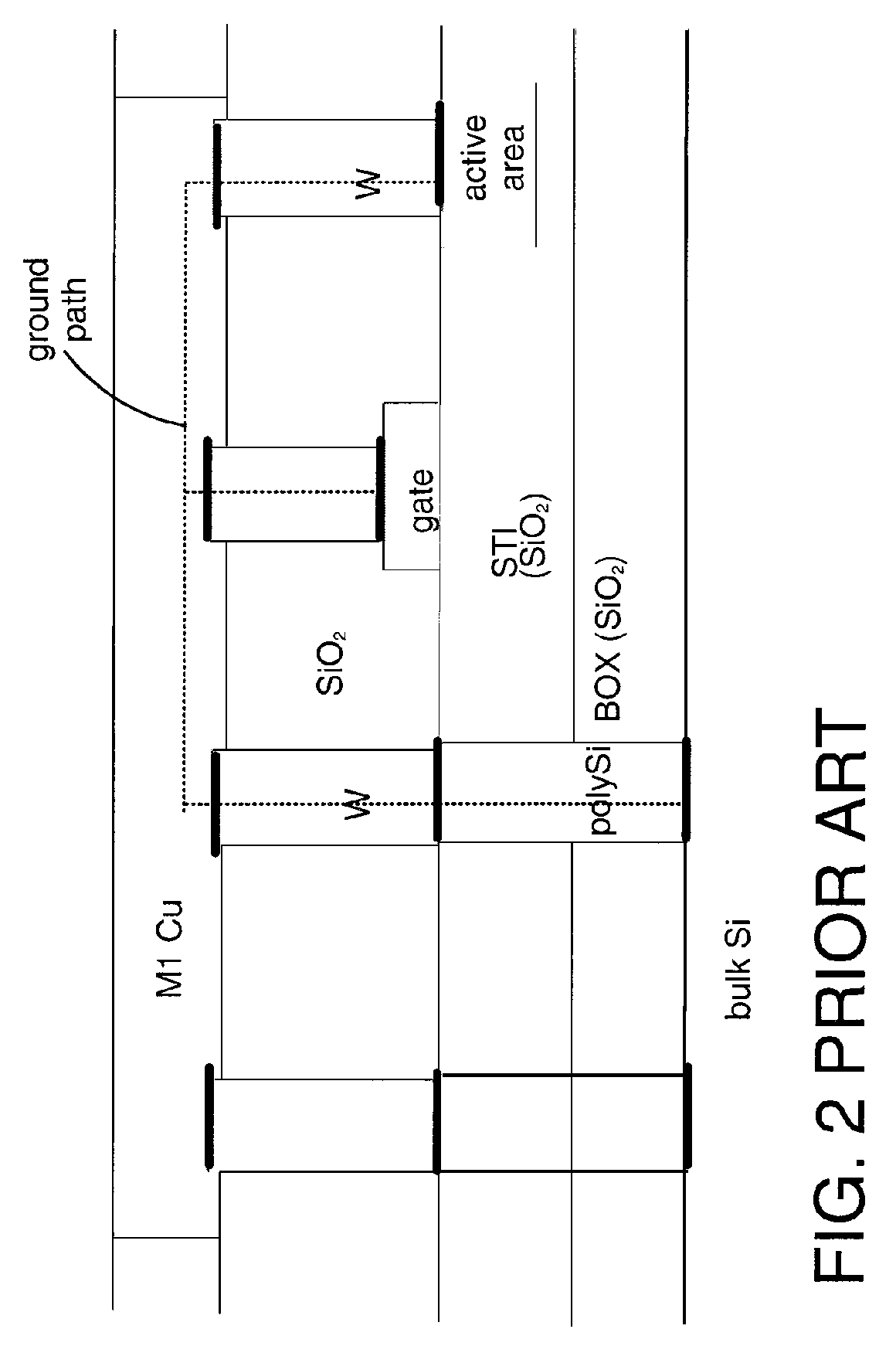

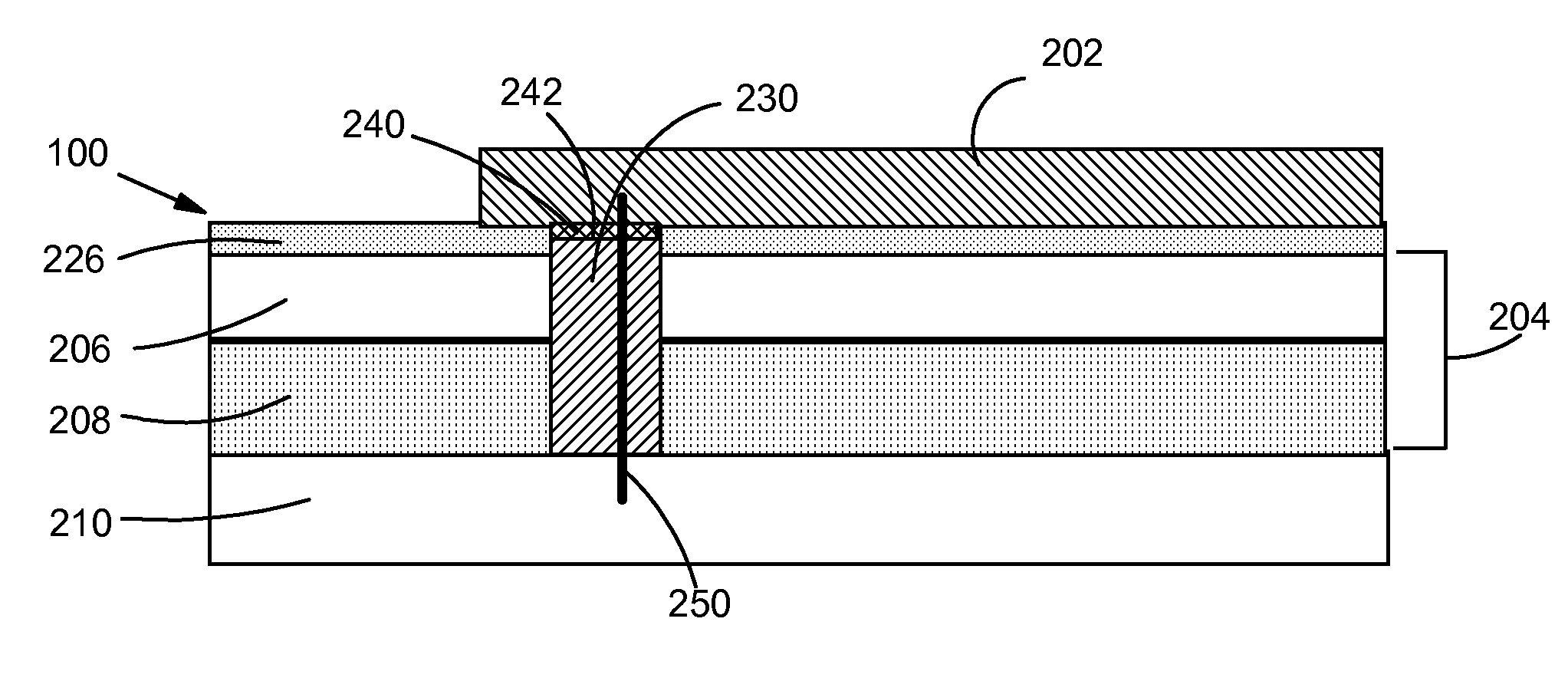

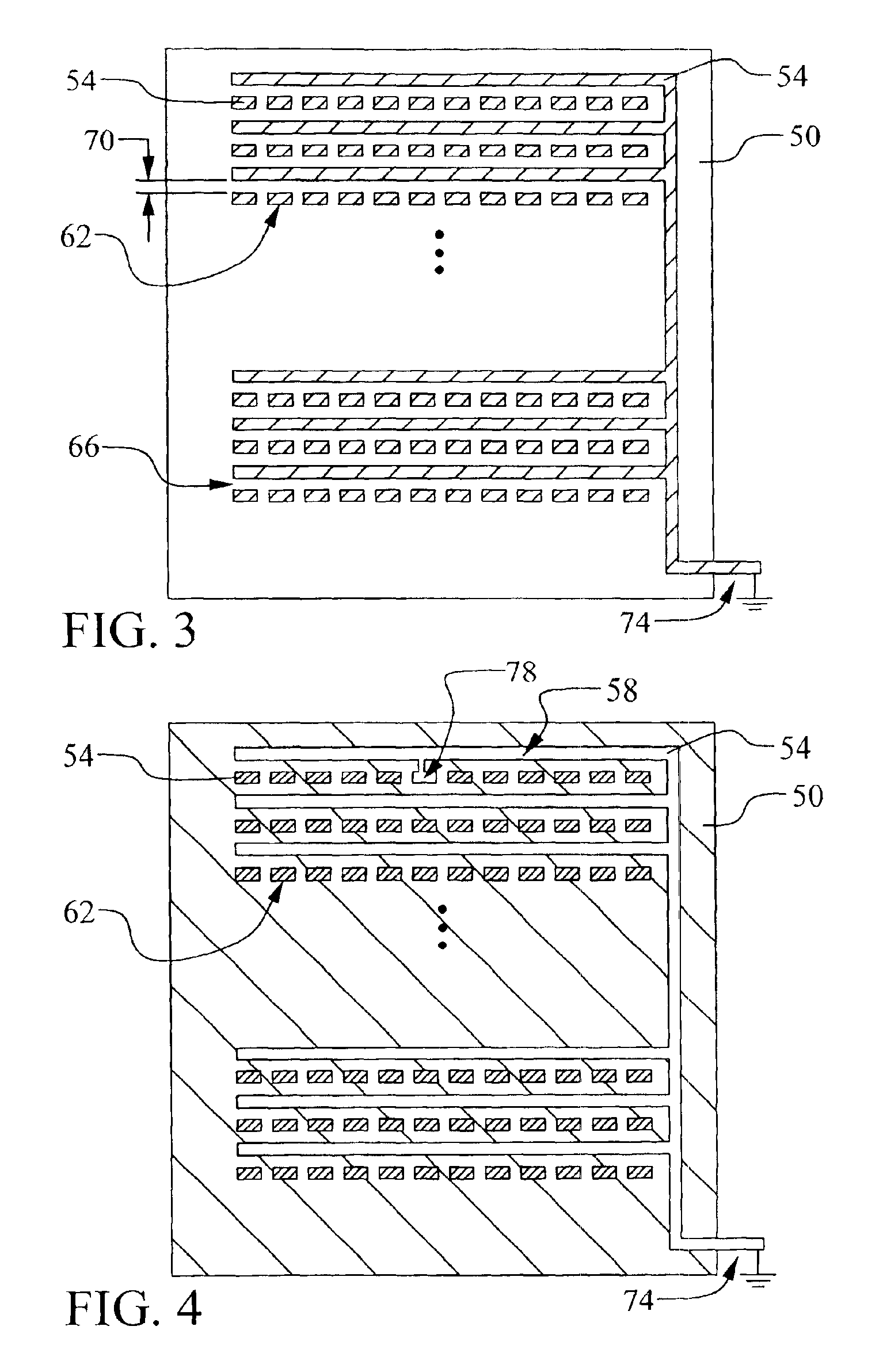

Grounding front-end-of-line structures on a SOI substrate

ActiveUS7518190B2Semiconductor/solid-state device detailsSolid-state devicesGround contactGate stack

Owner:TAIWAN SEMICON MFG CO LTD

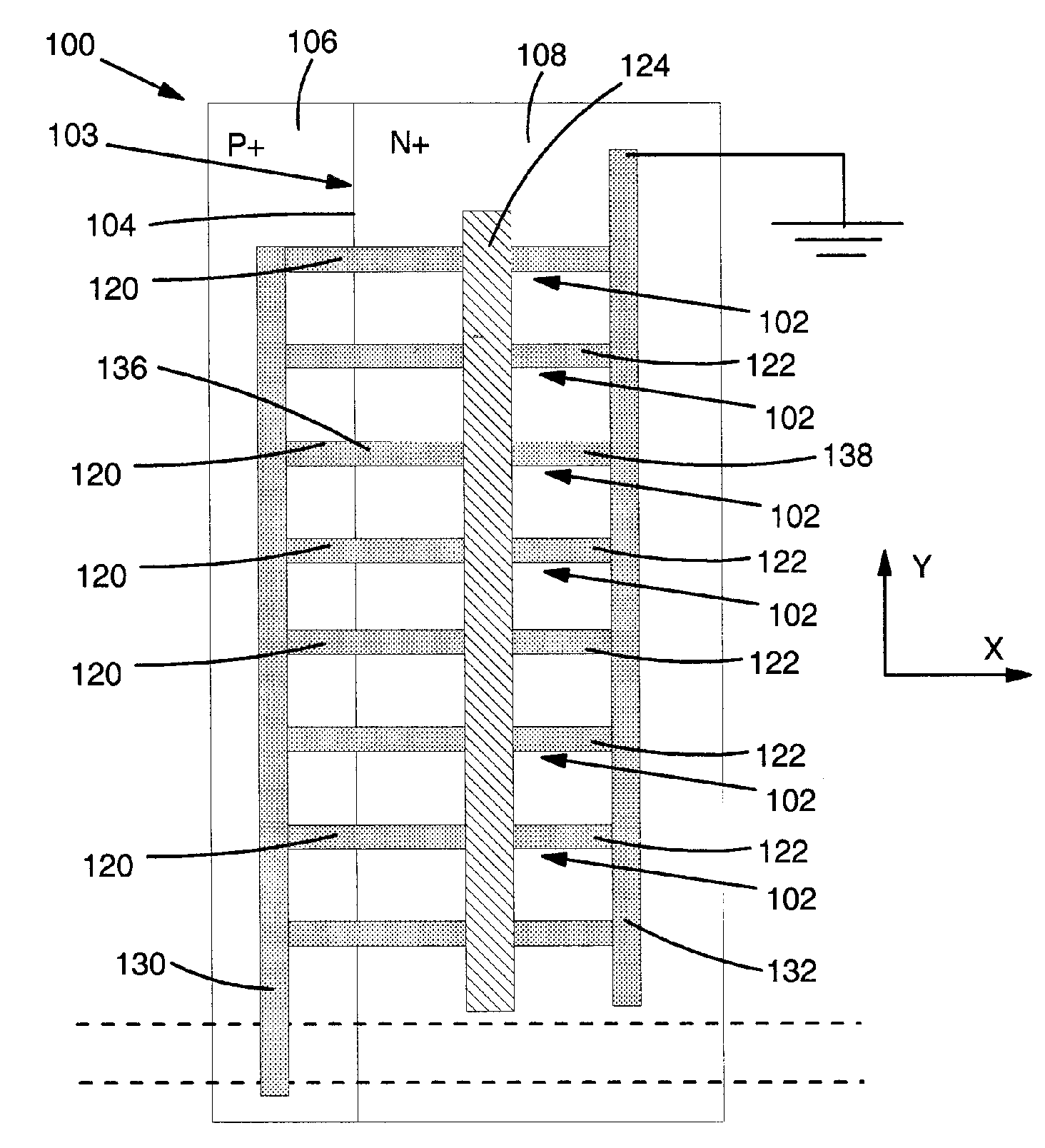

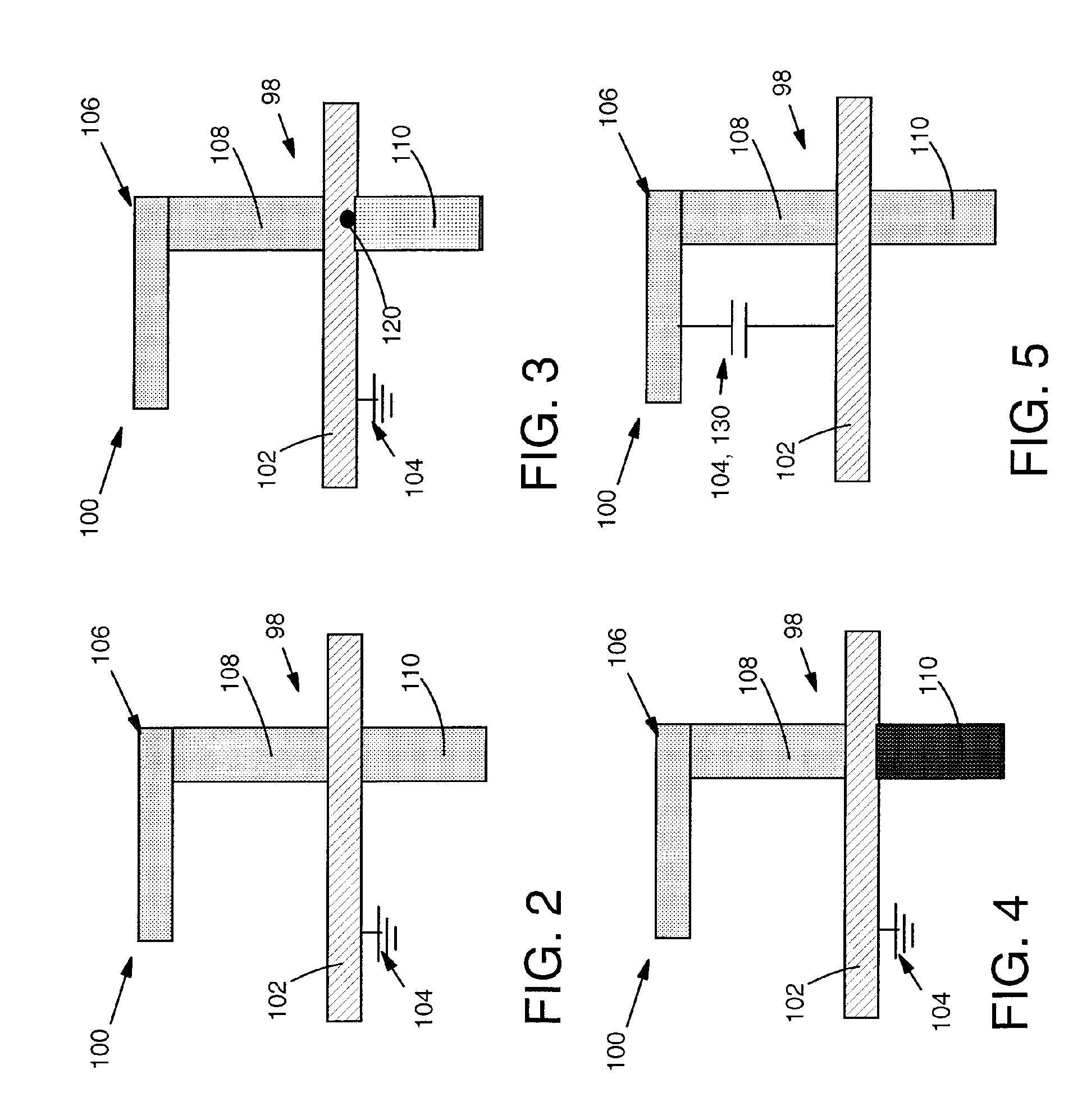

Test structures and method of defect detection using voltage contrast inspection

InactiveUS7456636B2Shorter learning cycleSemiconductor/solid-state device detailsSolid-state devicesDielectricElectricity

Test structures and a method for voltage contrast (VC) inspection are disclosed. In one embodiment, the test structure includes: a gate stack that is grounded by a ground to maintain the gate stack in an off state during VC inspection, which allows NFET defect detection using VC inspection prior to contact dielectric deposition. The test structure may alternatively include a gate stack that is biased by a bias to maintain the gate stack in an on state during VC inspection. The method may detect source-to-drain shorts in a transistor using VC inspection by providing a gate stack over a source and drain region of the transistor that is grounded by a ground to maintain the gate stack in an off state during VC inspection; and inspecting the transistor using voltage contrast. If the drain of the NFET brightens during VC inspection, this indicates a source to drain short.

Owner:INT BUSINESS MASCH CORP

Voltage contrast test structure

InactiveUS7217579B2Increase speedNo wasteMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityVoltage contrast

A method for electrically testing a semiconductor wafer during integrated-circuit fabrication process, the method including: (i) providing a scanning charged-particle microscope (SCPM), having a defined scanning plane and operative, while in any one mechanical state, to scan a surface in the scanning plane within a two-dimensional scanning window, which has a given maximum size; (ii) providing in association with any layer of the wafer, it being a test layer, one or more test structures, each test structure including normally conductive areas within a normally non-conductive background in one or more layers, which include said test layer, the conductive areas formed as one or more patterns; the patterns in said test layer include one or more clusters of mutually isolated pads; each pad is conductively connected with a corresponding distinct point on the patterns and all the pads in any one cluster are sized and arranged so that at least a significant portion of each pad falls within a common window whose size does not exceed said maximum size of said scanning window; (iii) with said test layer forming the top surface of the wafer, placing the wafer on the SCPM and adjusting the mechanical state of the SCPM so that at least a significant portion of each pad in any one of said clusters is within said scanning window; (iv) causing the SCPM, while in said mechanical state, to scan all of the pads of said one cluster and thereby to provide information about the electrical state of the respective test structure.

Owner:APPL MATERIALS ISRAEL LTD

Test structure for resistive open detection using voltage contrast inspection and related methods

ActiveUS7733109B2Semiconductor/solid-state device testing/measurementElectric discharge tubesElectrical resistance and conductanceOutput compare

A test structure for resistive open detection using voltage contrast (VC) inspection and method for using such structure are disclosed. The test structure may include a comparator within the IC chip for comparing a resistance value of a resistive element under test to a reference resistance and outputting a result of the comparing that indicates whether the resistive open exists in the resistive element under test, wherein the result is detectable by the voltage contrast inspection.

Owner:TWITTER INC

Padless structure design for easy identification of bridging defects in lines by passive voltage contrast

InactiveUS6949765B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementEngineeringElectron microscope

A new test structure to locate bridging defects in a conductive layer of an integrated circuit device is achieved. The test structure comprises a line comprising a conductive layer overlying a substrate. The line is coupled to ground. A plurality of rectangles comprises the conductive layer. The rectangles are not connected to the line or to other rectangles. Near edges of the rectangles and of the line are parallel. The rectangles are floating. The test structure is used with a passive voltage contrast test in a scanning electron microscope. A test structure and method to measure critical dimensions is disclosed.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

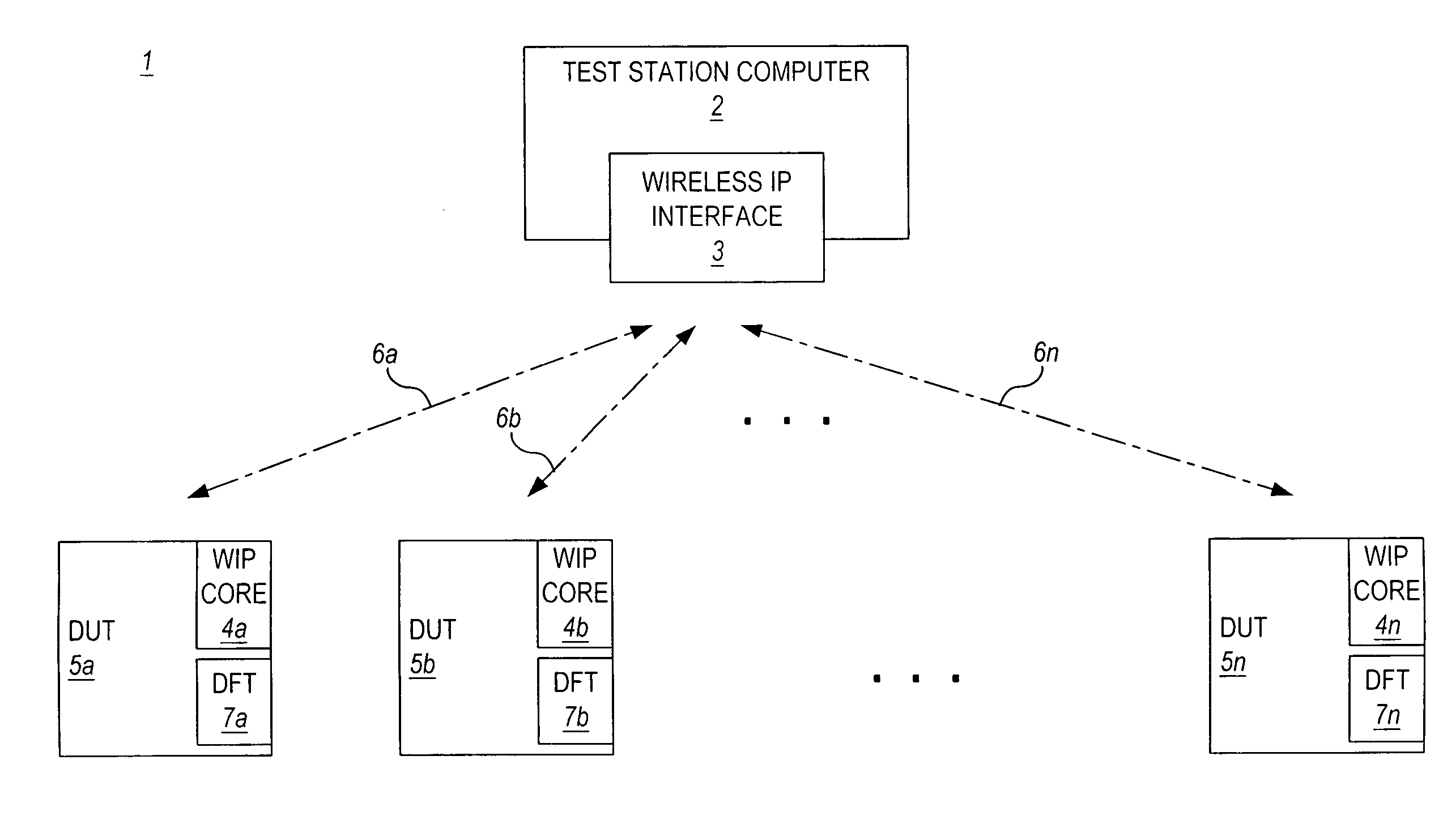

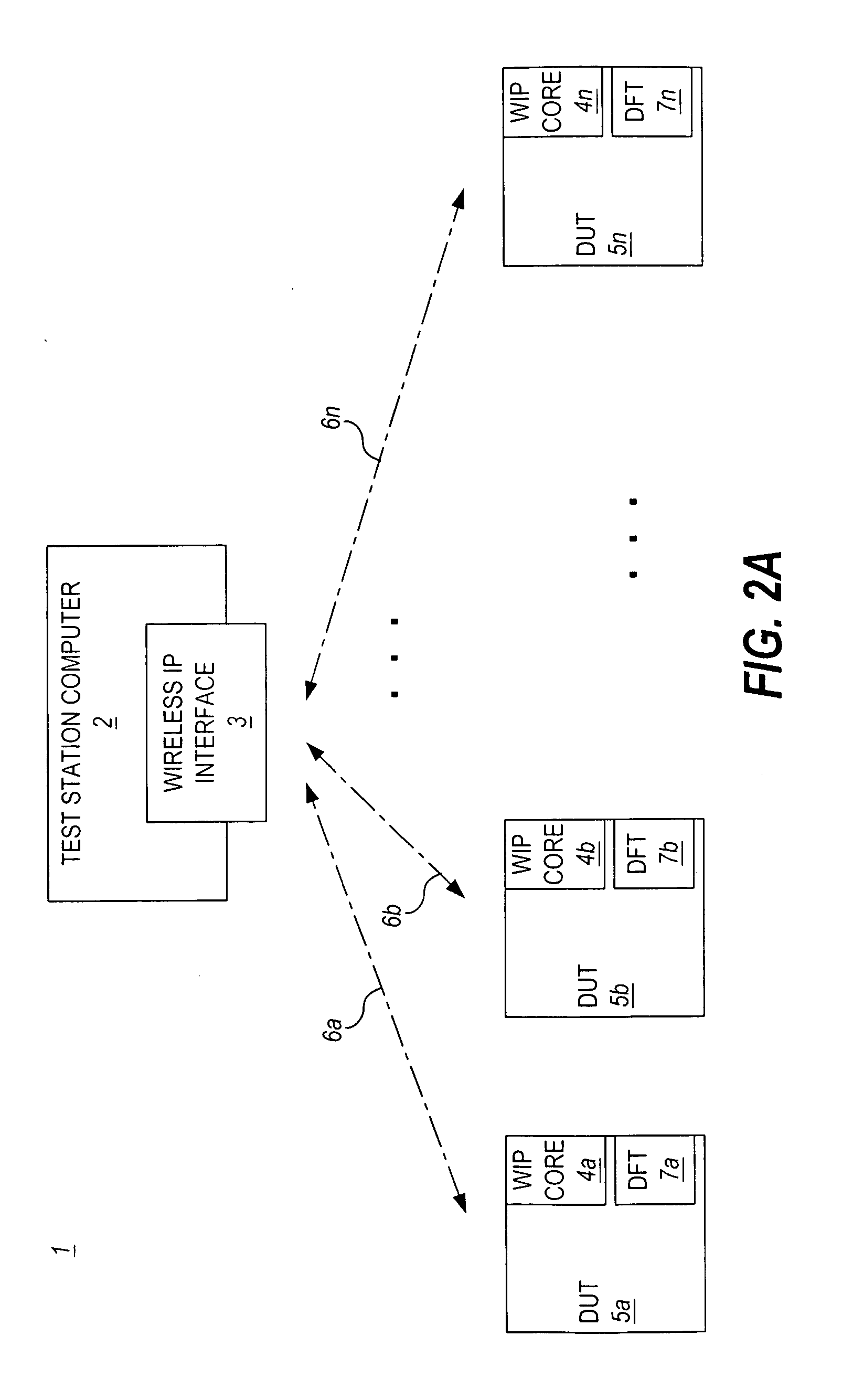

Wireless no-touch testing of integrated circuits

ActiveUS20050193294A1Immediate cost-reduction impactIncrease speedDigital circuit testingSemiconductor/solid-state device testing/measurementCircuit under testEngineering

A wireless integrated circuit test method and system is presented. The invention allows testing of one or more integrated circuits configured with a wireless interface and a test access mechanism which controls input of test data received over a wireless connection from a test station to test structures which test functional blocks on the integrated circuit. Via the wireless connection, multiple integrated circuits or similarly equipped devices under test can be tested simultaneously. The invention also enables concurrent testing of independently testable functional blocks on any given integrated circuit under test.

Owner:ADVANTEST CORP