Patents

Literature

827 results about "Output compare" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Output compare is the ability to trigger an output based on a timestamp in memory, without interrupting the execution of code by a processor or microcontroller. This is a functionality provided by many embedded systems.

Passive remote sensor of chemicals

InactiveUS6853452B1Minimize eliminateImprove accuracyColor/spectral properties measurementsOutput compareHand held

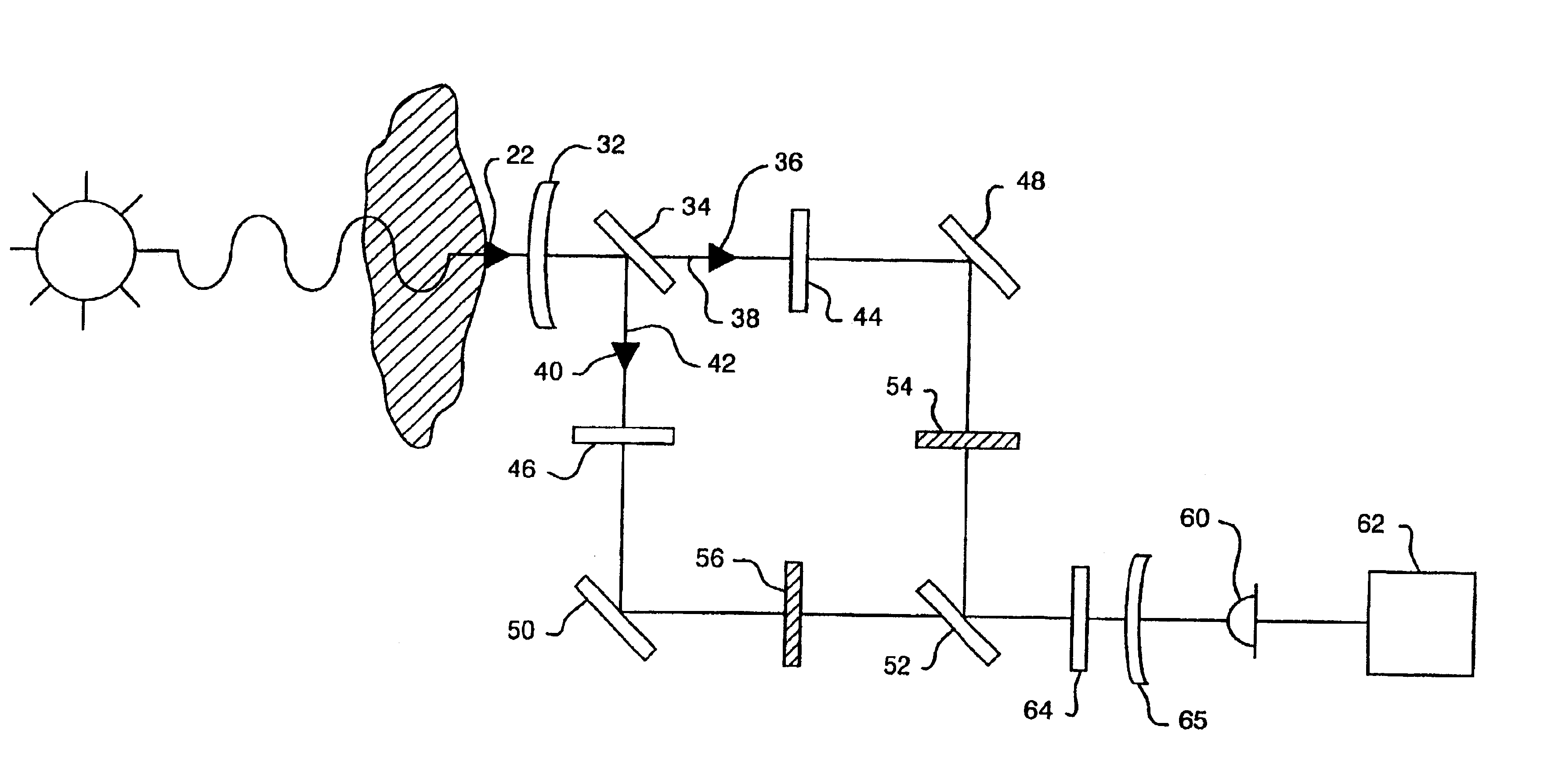

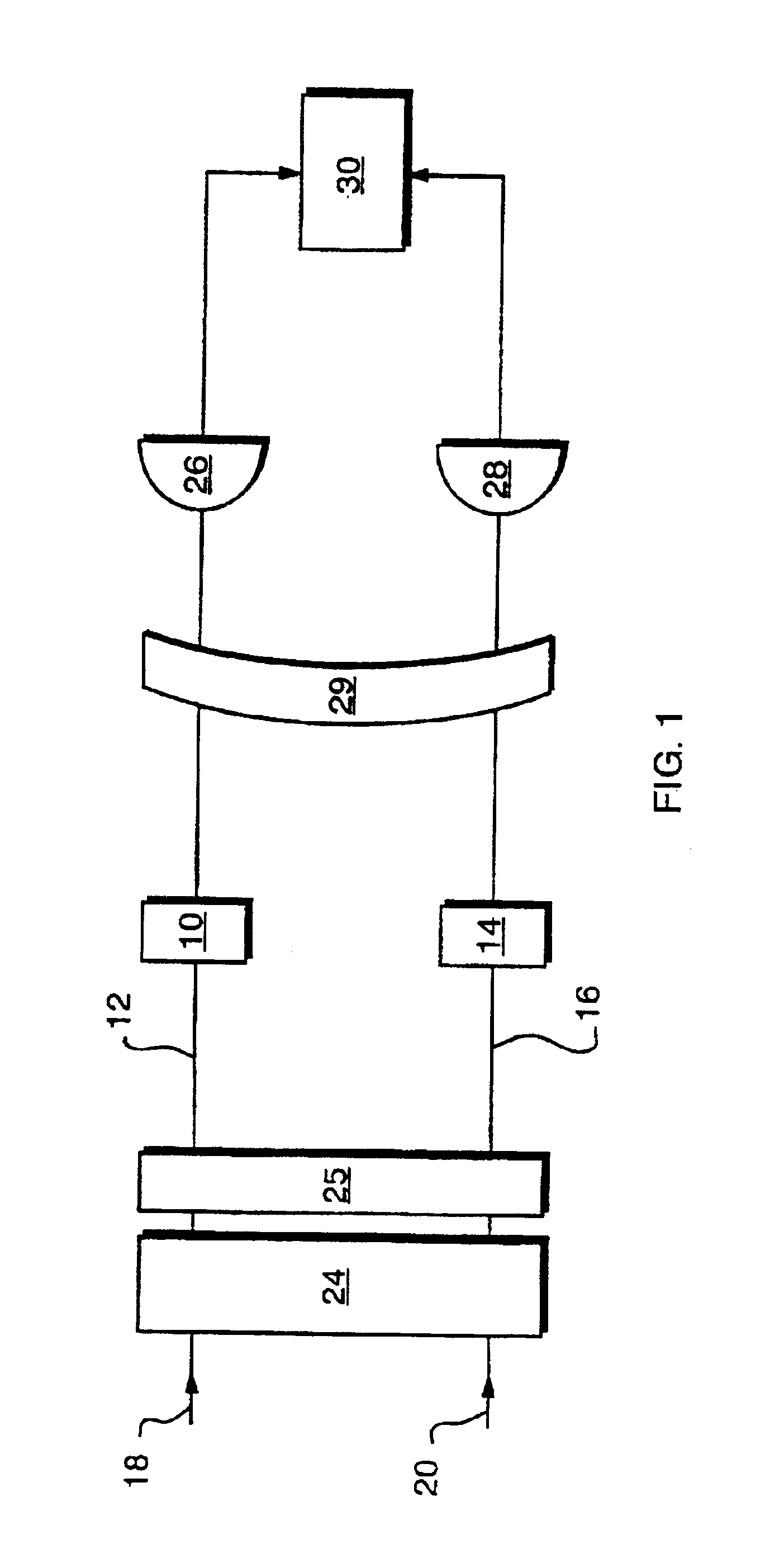

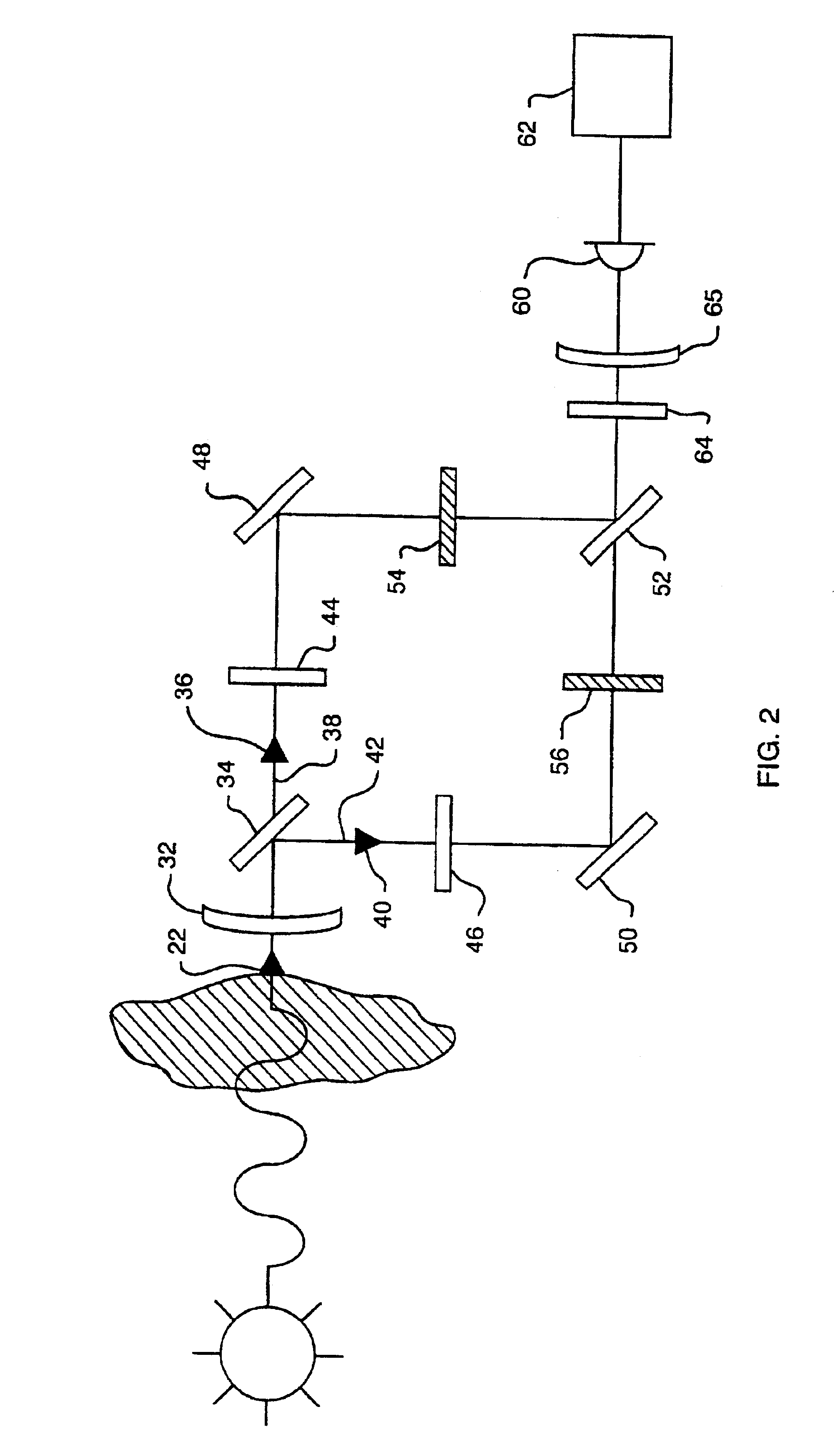

A remote sensor for use as a handheld, mobile or stand-alone sensor has first (12) and second (16) optical paths, light collecting optics, a sample filter (10) assembly positioned in a first optical Path (12), a reference filter (14) assembly positioned in a second optical path (16), a detector assembly to detect the filtered light r other radiation, and a detector output comparison device such as BRD to minimize the effects of common background noise components, differences in light or other radiation source power, and absorption or emission by interfering species.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

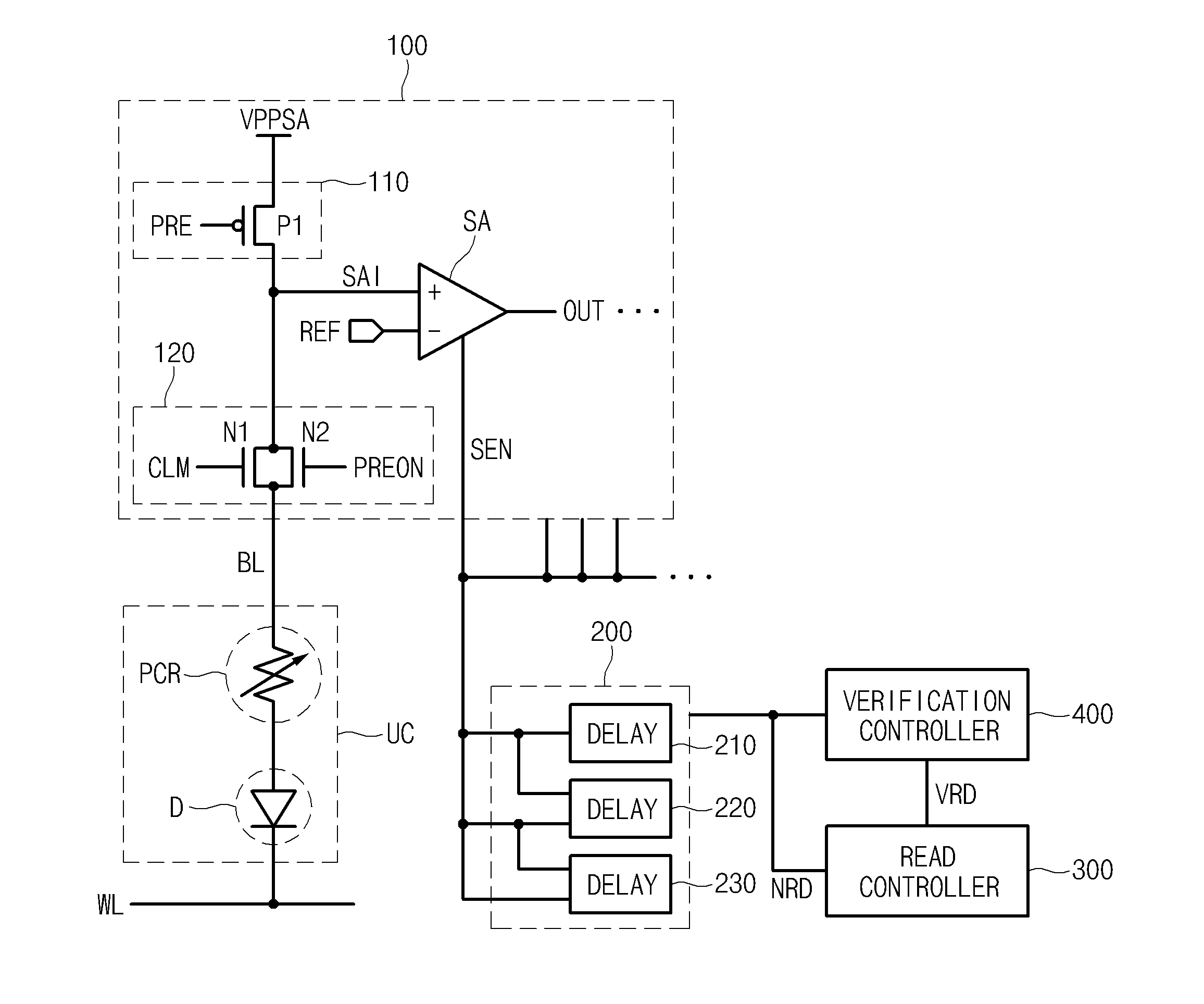

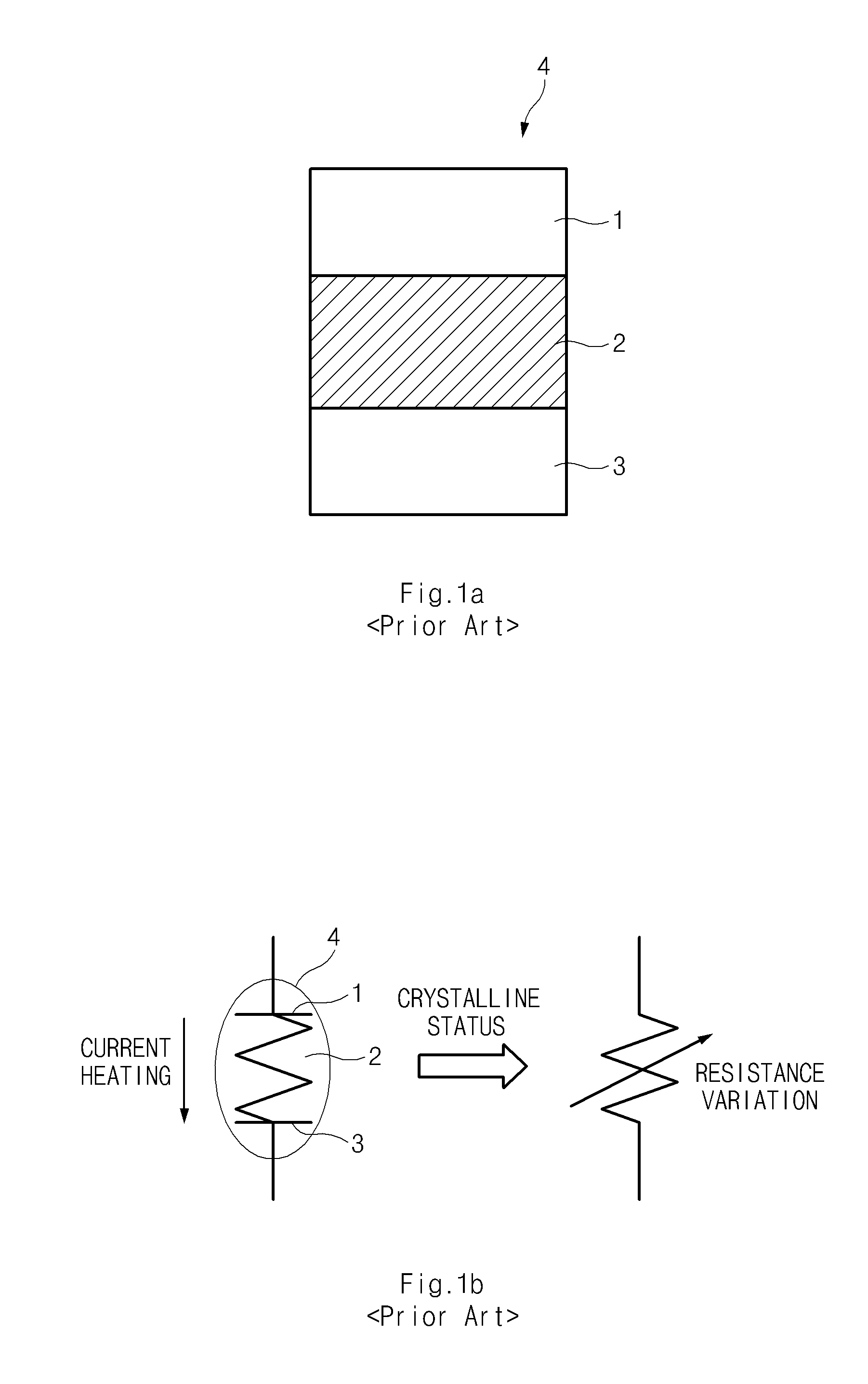

Method of reading nonvolatile memory device and nonvolatile memory device for implementing the method

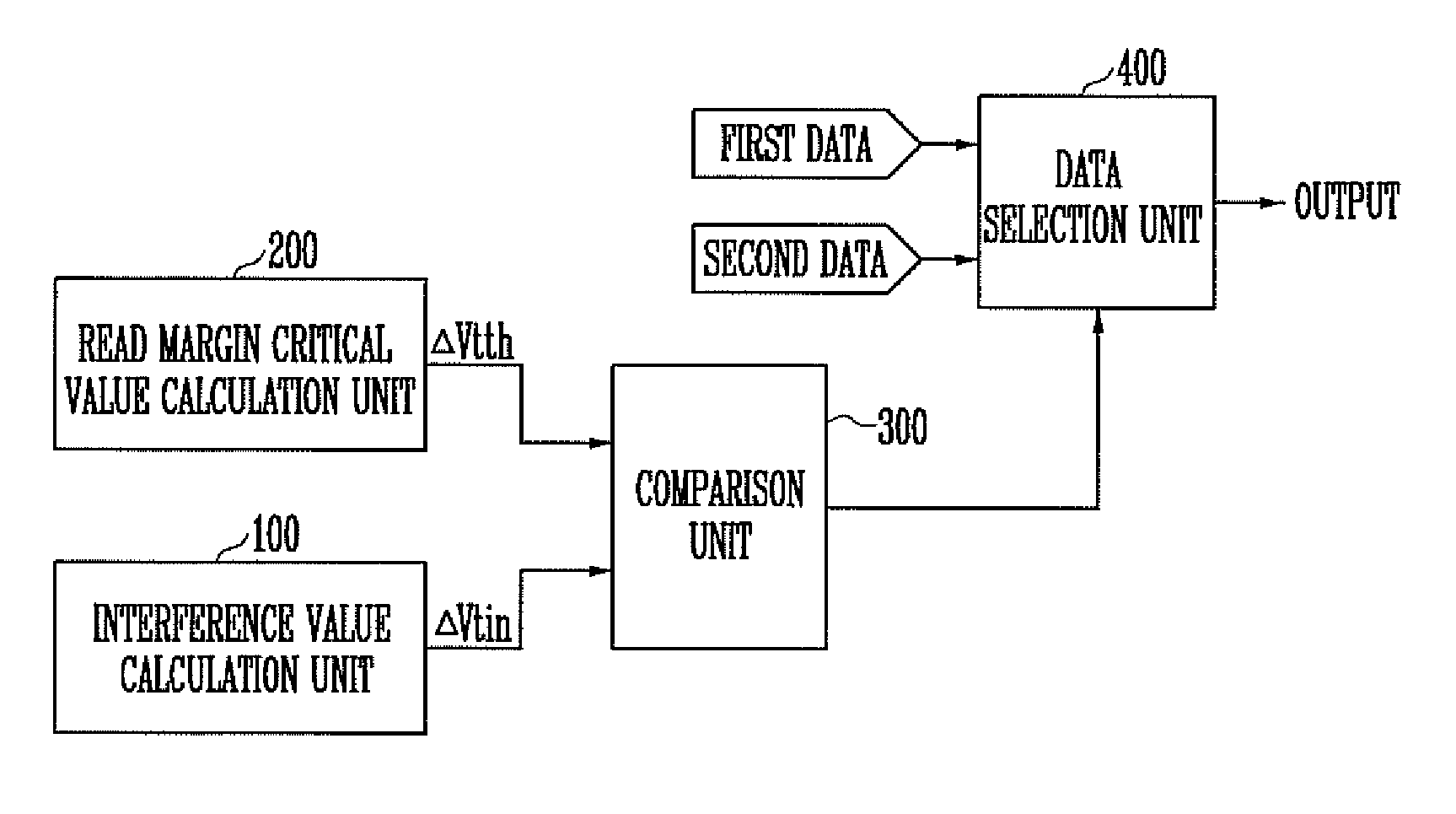

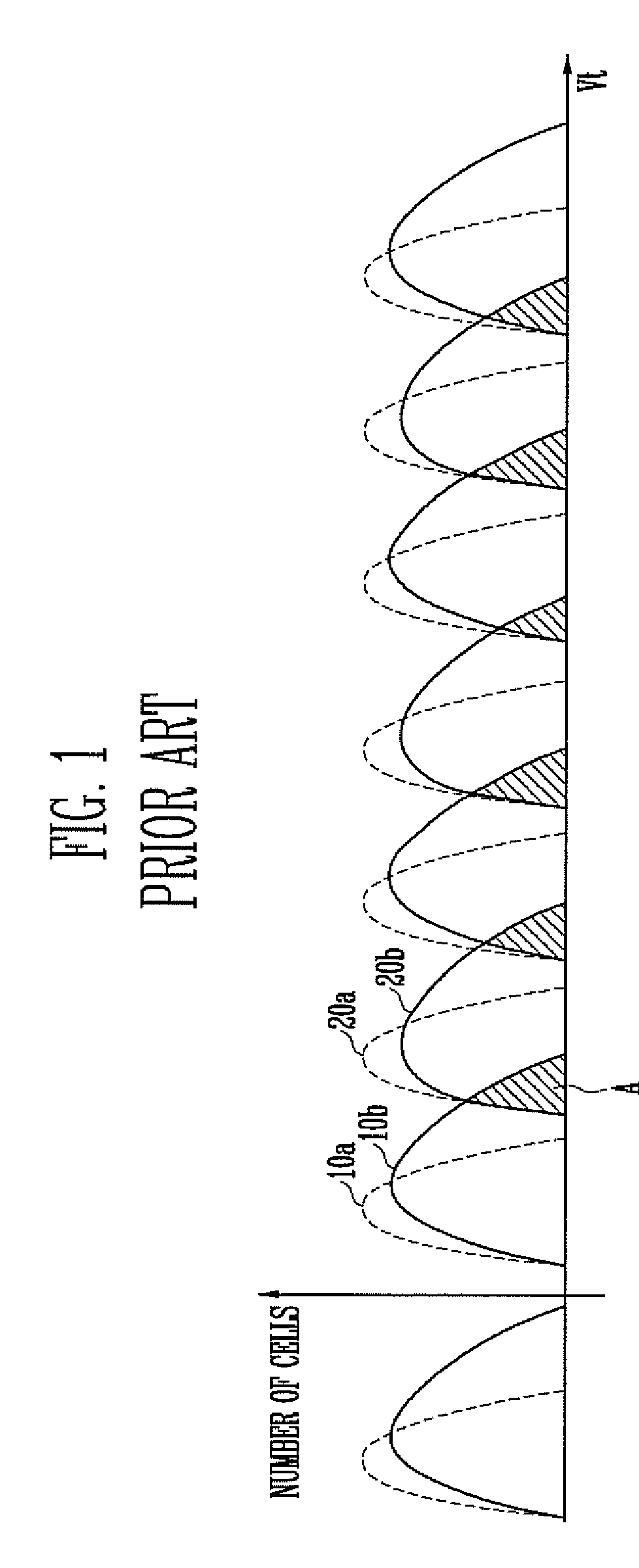

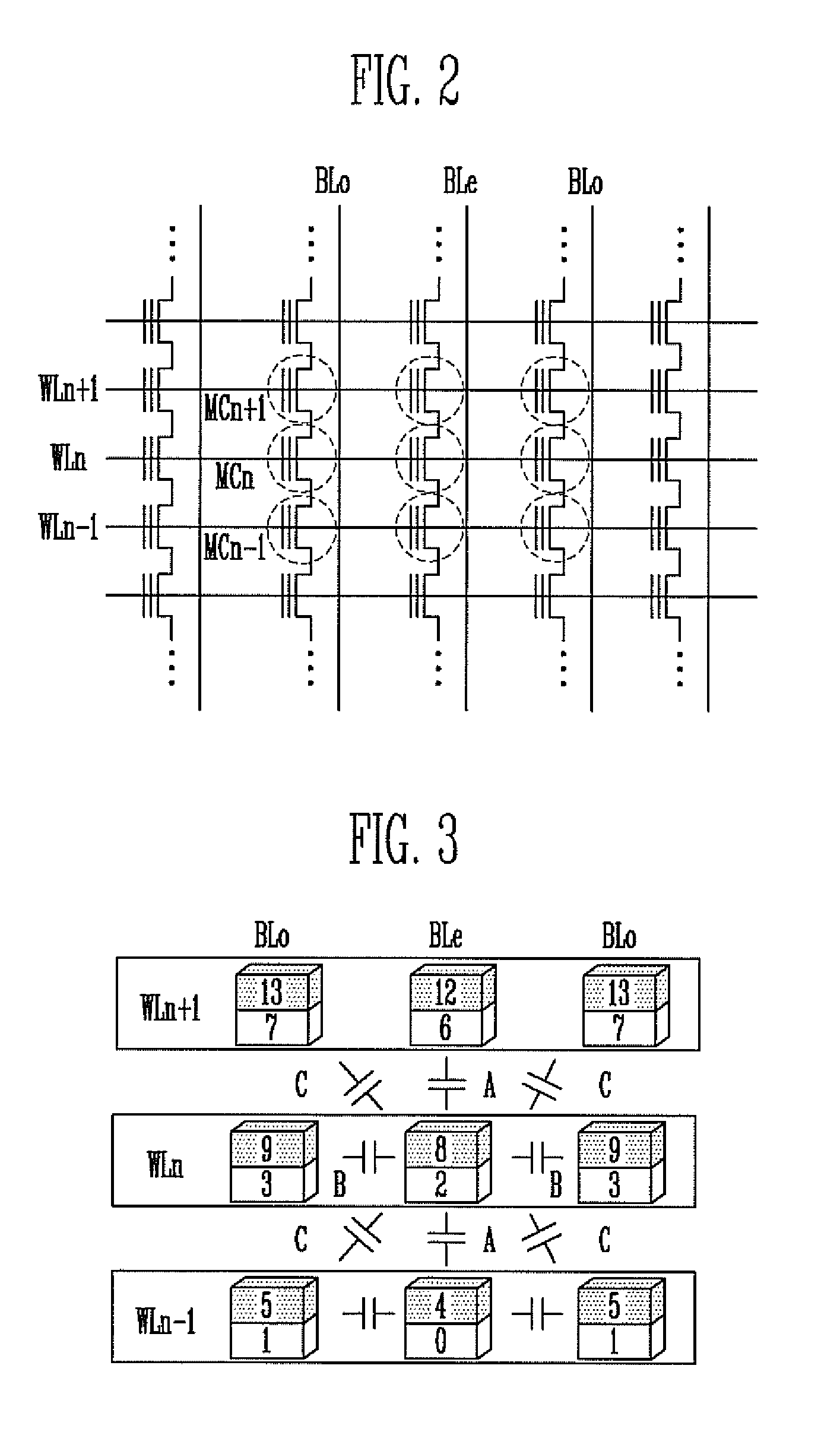

A nonvolatile memory device includes a read margin critical value calculation unit configured to calculate a critical value of a read margin between a read voltage and a threshold voltage of a specific cell, an interference value calculation unit configured to calculate an interference value affecting the threshold voltage of the specific cell, a comparison unit configured to compare the critical value and the interference value and to output a result of the comparison, and a data selection unit configured to output either first data, read from the specific cell using a first read voltage, or second data, read from the specific cell using a second read voltage, based on the result outputted from the comparison unit.

Owner:SK HYNIX INC

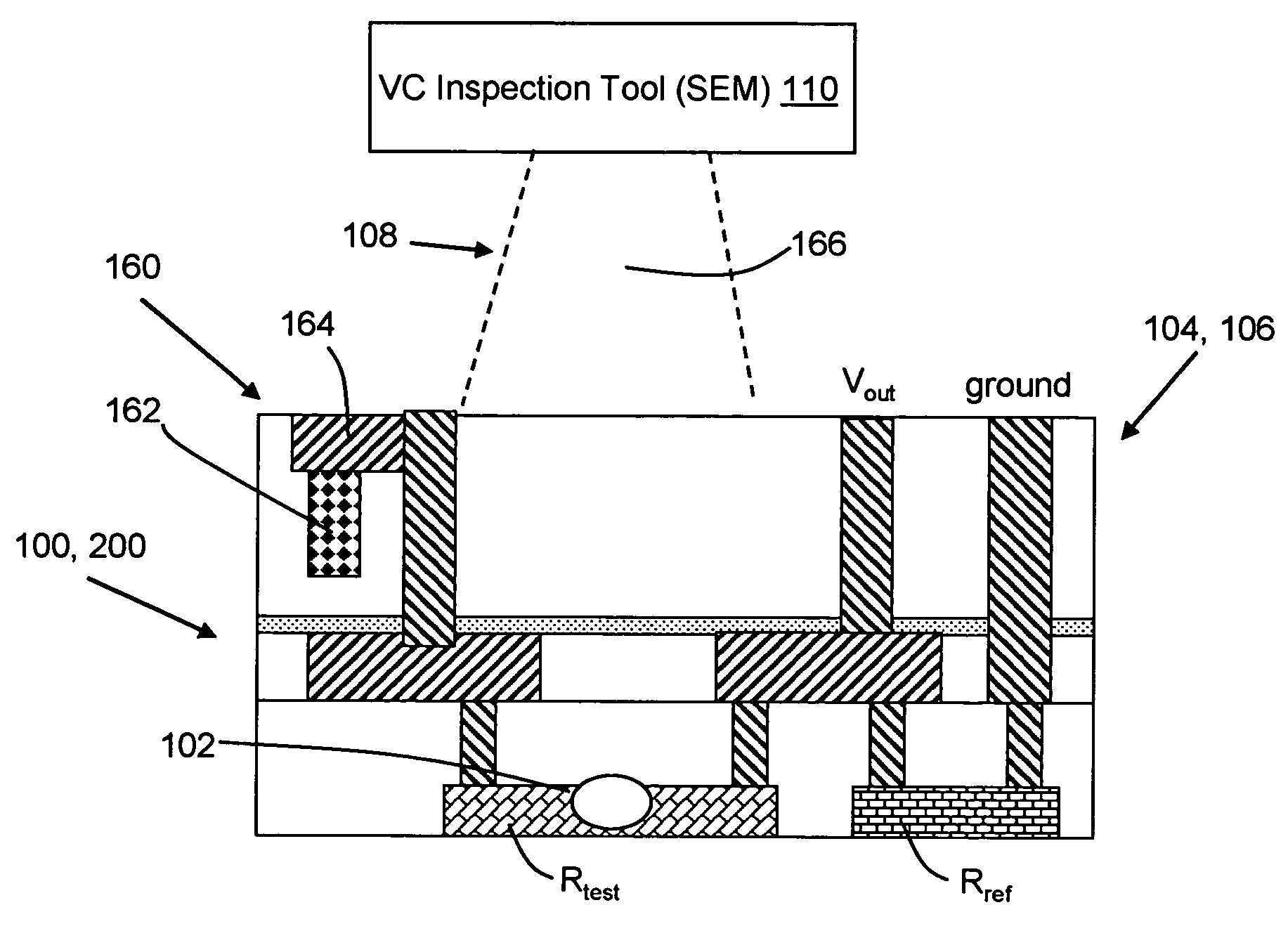

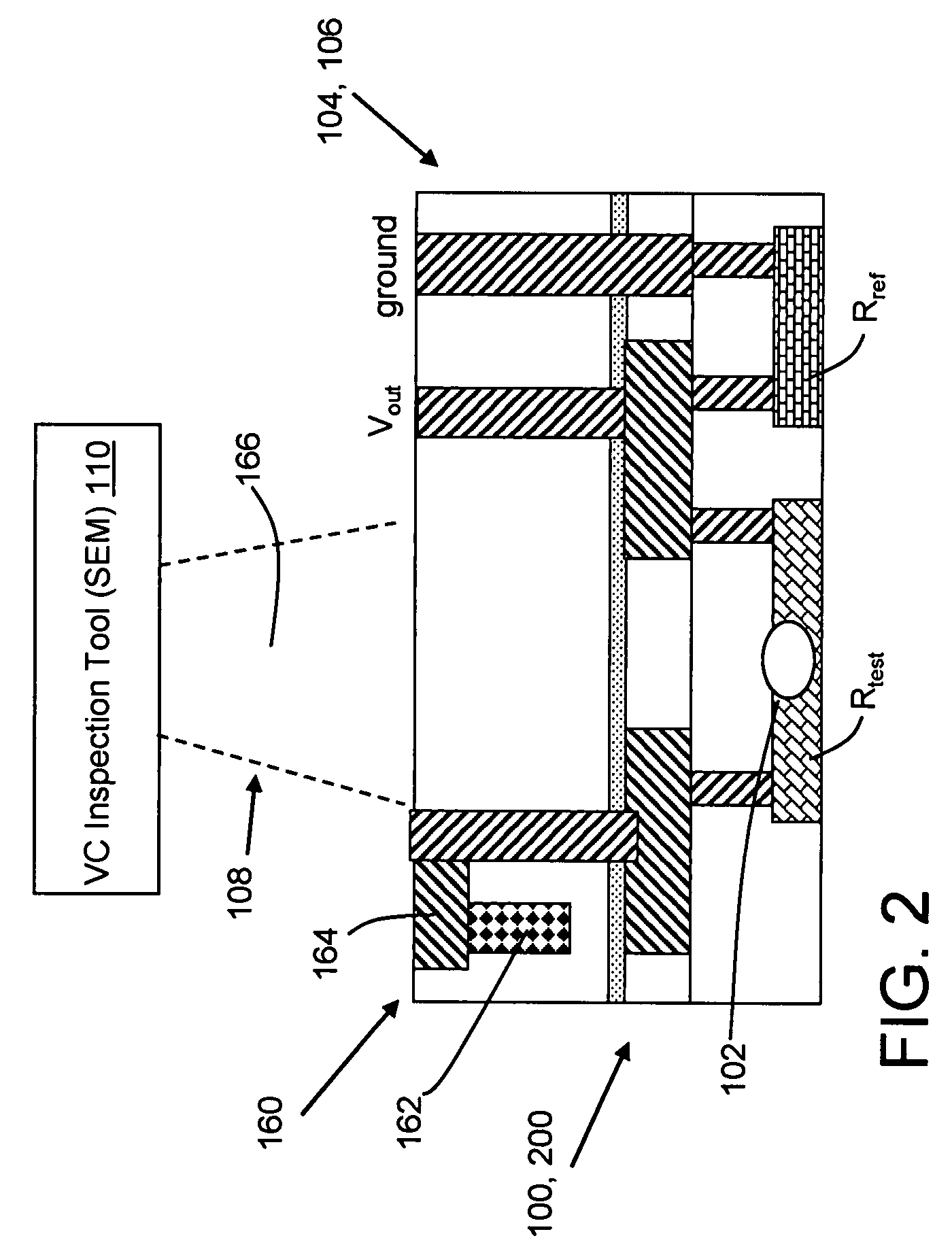

Test structure for resistive open detection using voltage contrast inspection and related methods

ActiveUS7733109B2Semiconductor/solid-state device testing/measurementElectric discharge tubesElectrical resistance and conductanceOutput compare

A test structure for resistive open detection using voltage contrast (VC) inspection and method for using such structure are disclosed. The test structure may include a comparator within the IC chip for comparing a resistance value of a resistive element under test to a reference resistance and outputting a result of the comparing that indicates whether the resistive open exists in the resistive element under test, wherein the result is detectable by the voltage contrast inspection.

Owner:TWITTER INC

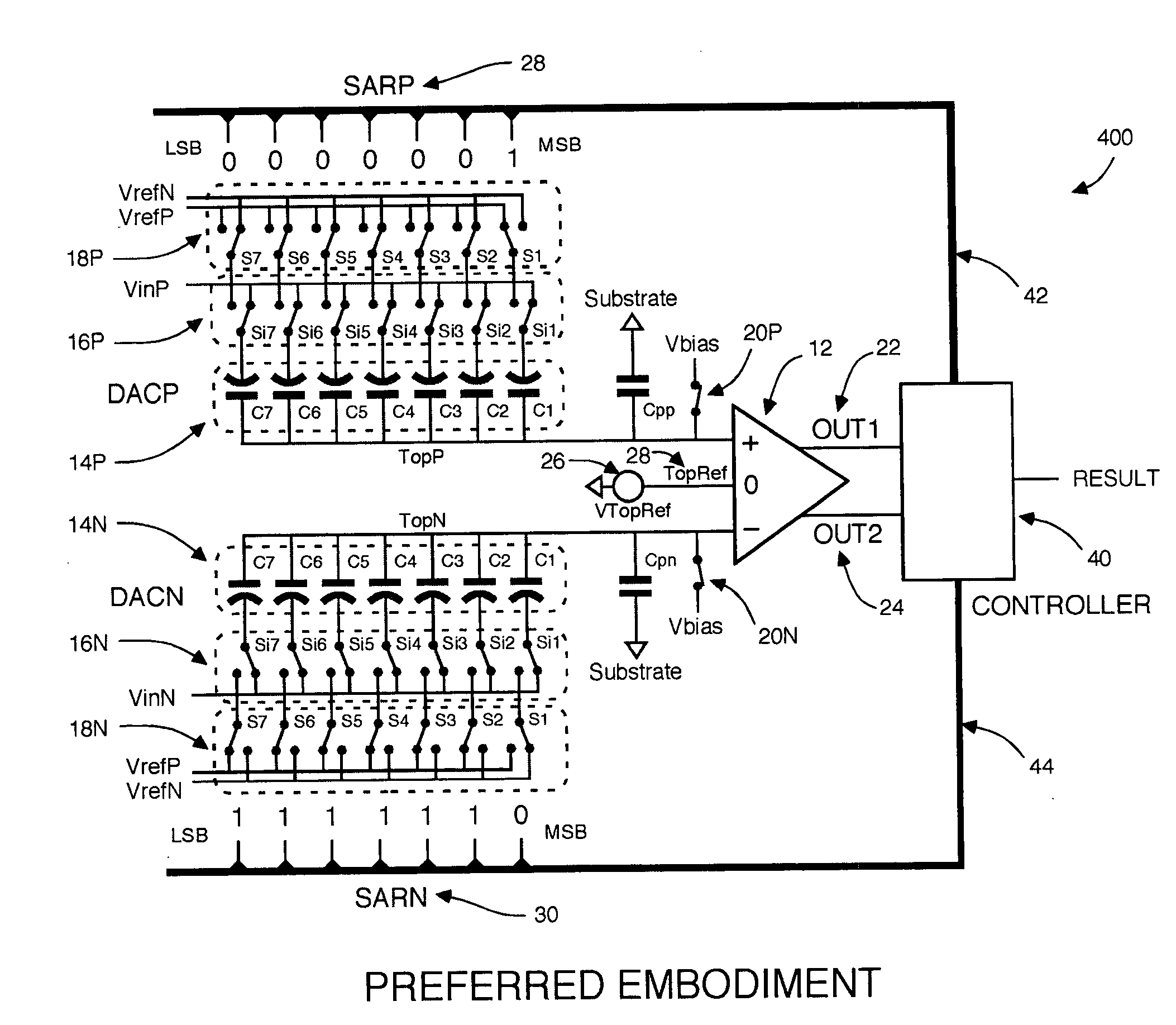

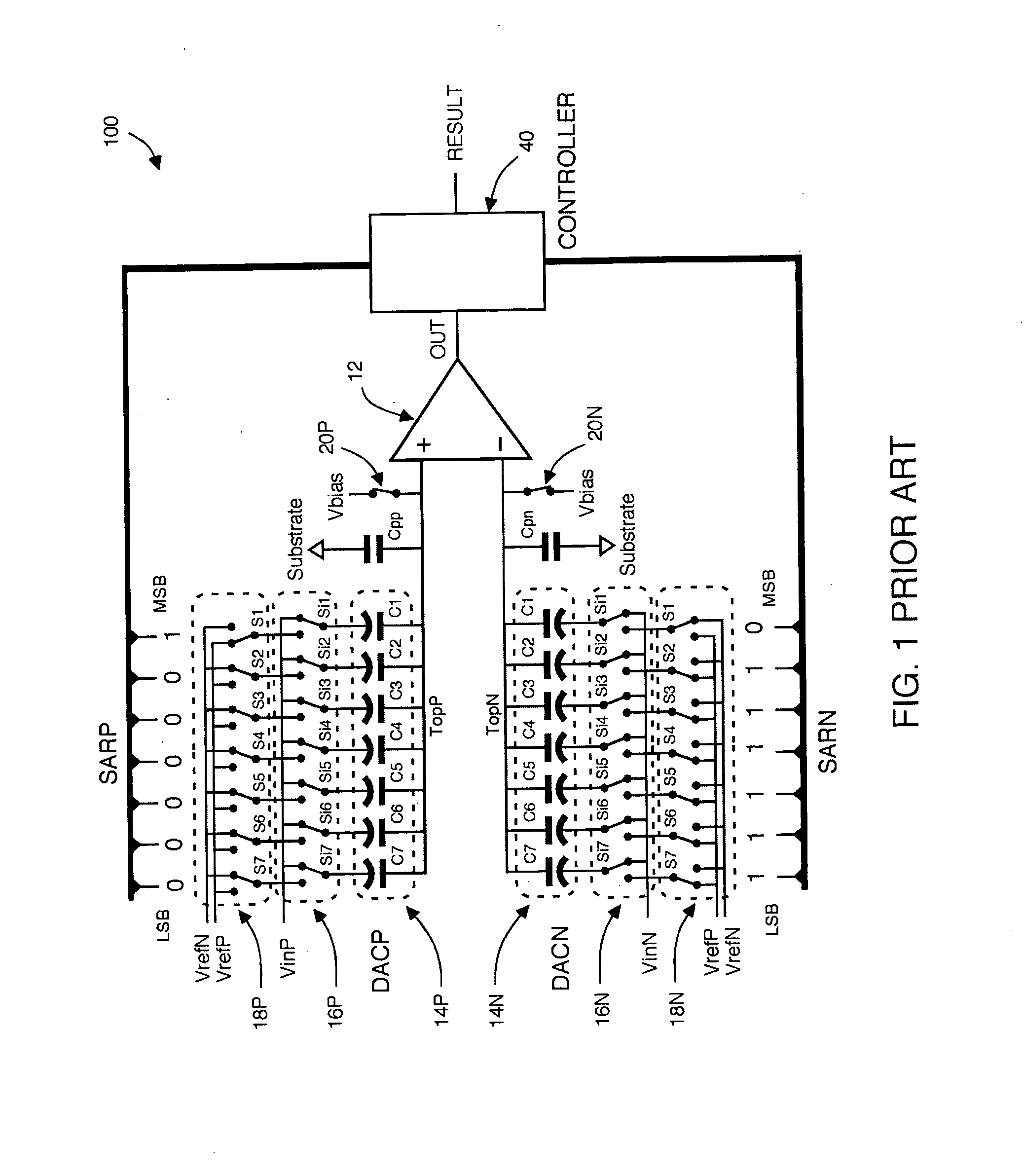

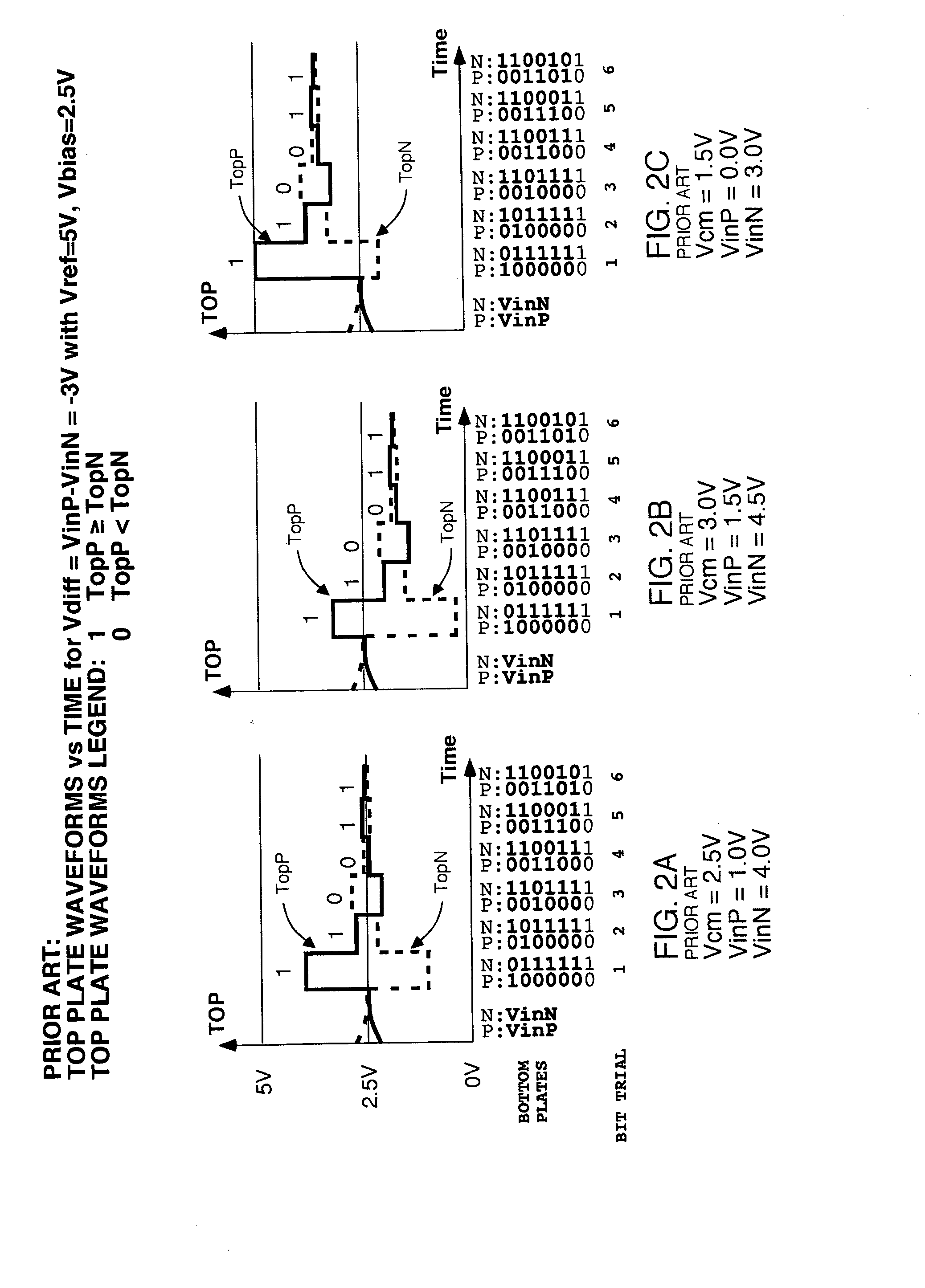

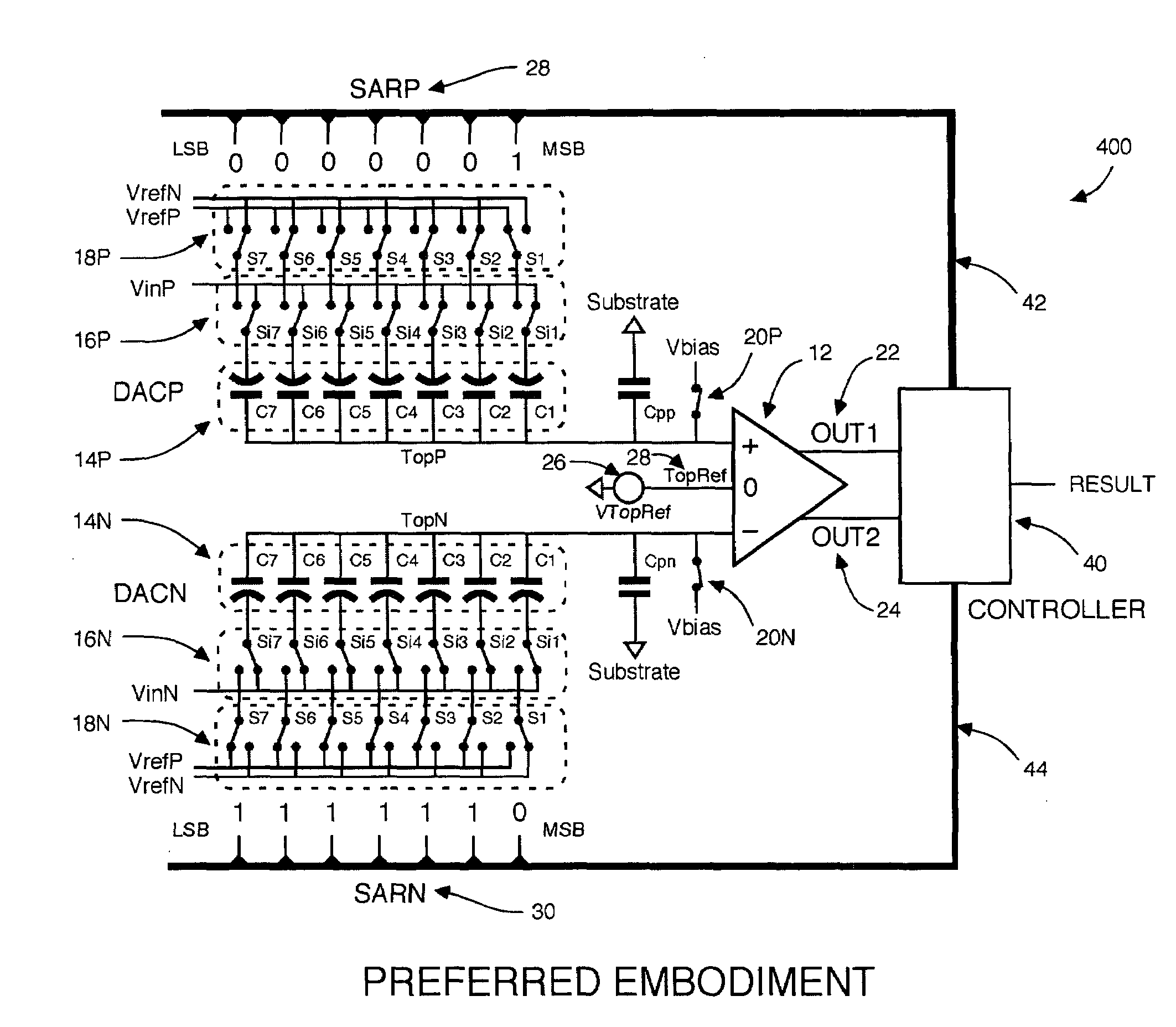

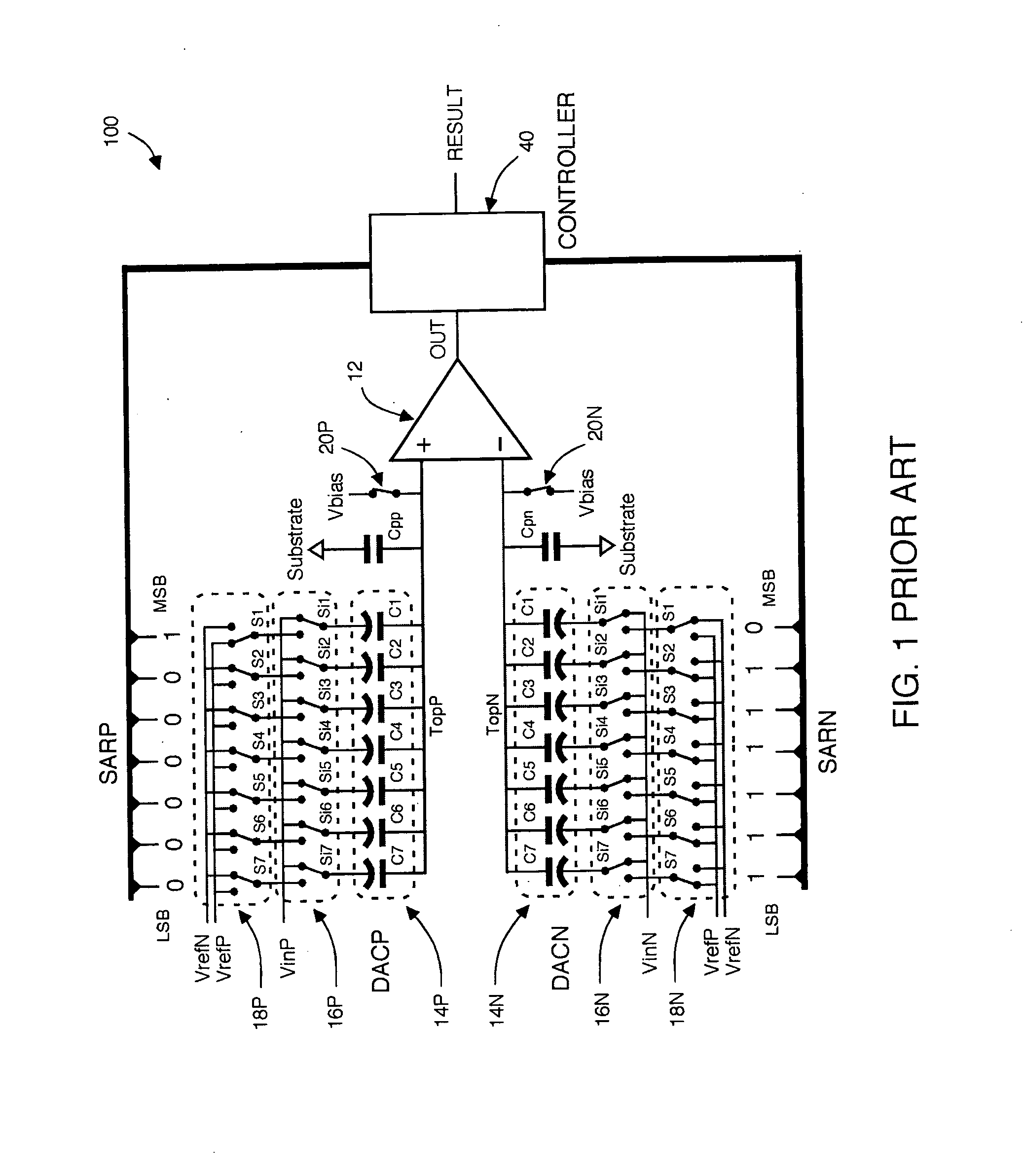

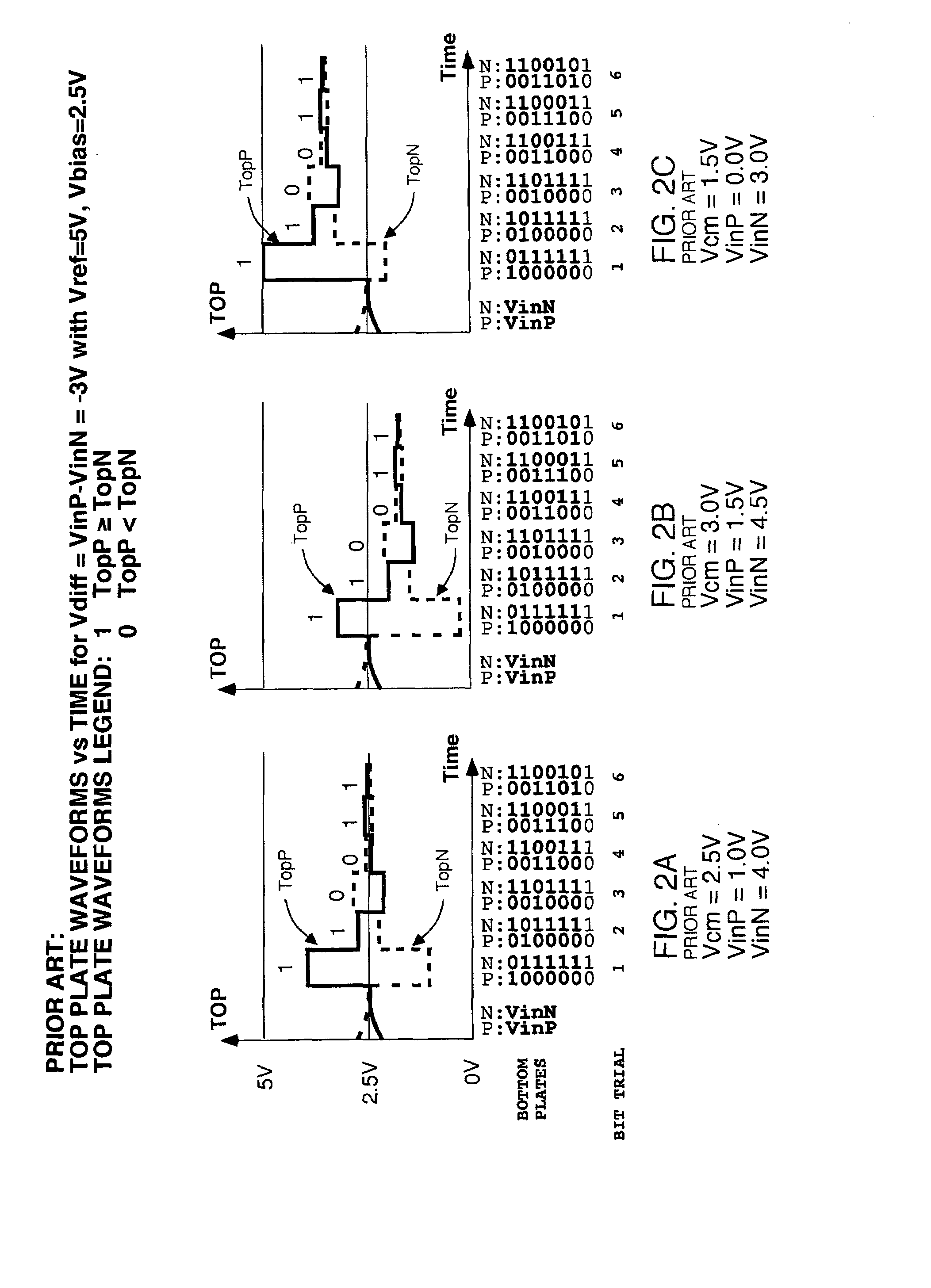

Differential input successive approximation analog to digital converter with common mode rejection

ActiveUS20080129573A1Analogue/digital conversionElectric signal transmission systemsOutput compareA d converter

A Successive Approximation Routine converter is provided in which a comparator is responsive to an output of a first Digital to Analog Converter, and an output of a second Digital to Analog Converter and to a DAC common mode output reference voltage, and wherein the comparator provides data to a SAR controller indicating which one of the DAC outputs is greater than the other, and how a common mode voltage on the DAC outputs compares to the reference voltage. On this basis the SAR controller can add or subtract a common mode offset to the trial words being presented at a given bit trial such that both differential and common mode convergence is achieved.

Owner:ANALOG DEVICES INC

Differential input successive approximation analog to digital converter with common mode rejection

ActiveUS7432844B2Analogue/digital conversionElectric signal transmission systemsOutput compareVoltage reference

A Successive Approximation Routine converter is provided in which a comparator is responsive to an output of a first Digital to Analog Converter, and an output of a second Digital to Analog Converter and to a DAC common mode output reference voltage, and wherein the comparator provides data to a SAR controller indicating which one of the DAC outputs is greater than the other, and how a common mode voltage on the DAC outputs compares to the reference voltage. On this basis the SAR controller can add or subtract a common mode offset to the trial words being presented at a given bit trial such that both differential and common mode convergence is achieved.

Owner:ANALOG DEVICES INC

Non-volatile memory device and sensing method thereof

ActiveUS20120287730A1Shorten the timeReduce circuit areaRead-only memoriesDigital storageElectrical resistance and conductanceOutput compare

A non-volatile memory device and a sensing method thereof are disclosed, which can sense multi-level data using resistance variation. The non-volatile memory device includes a cell array and a sensing unit. The cell array includes a plurality of unit cells where data is read out or written. The sensing unit compares a sensing voltage corresponding to data stored in the unit cell with a reference voltage, amplifies / outputs the compared result, measures a difference in discharge time where the sensing voltage is discharged in response to a resistance value of the unit cell during an activation period of a sensing enable signal after a bit line is precharged, and senses the data in response to the measured result.

Owner:SK HYNIX INC

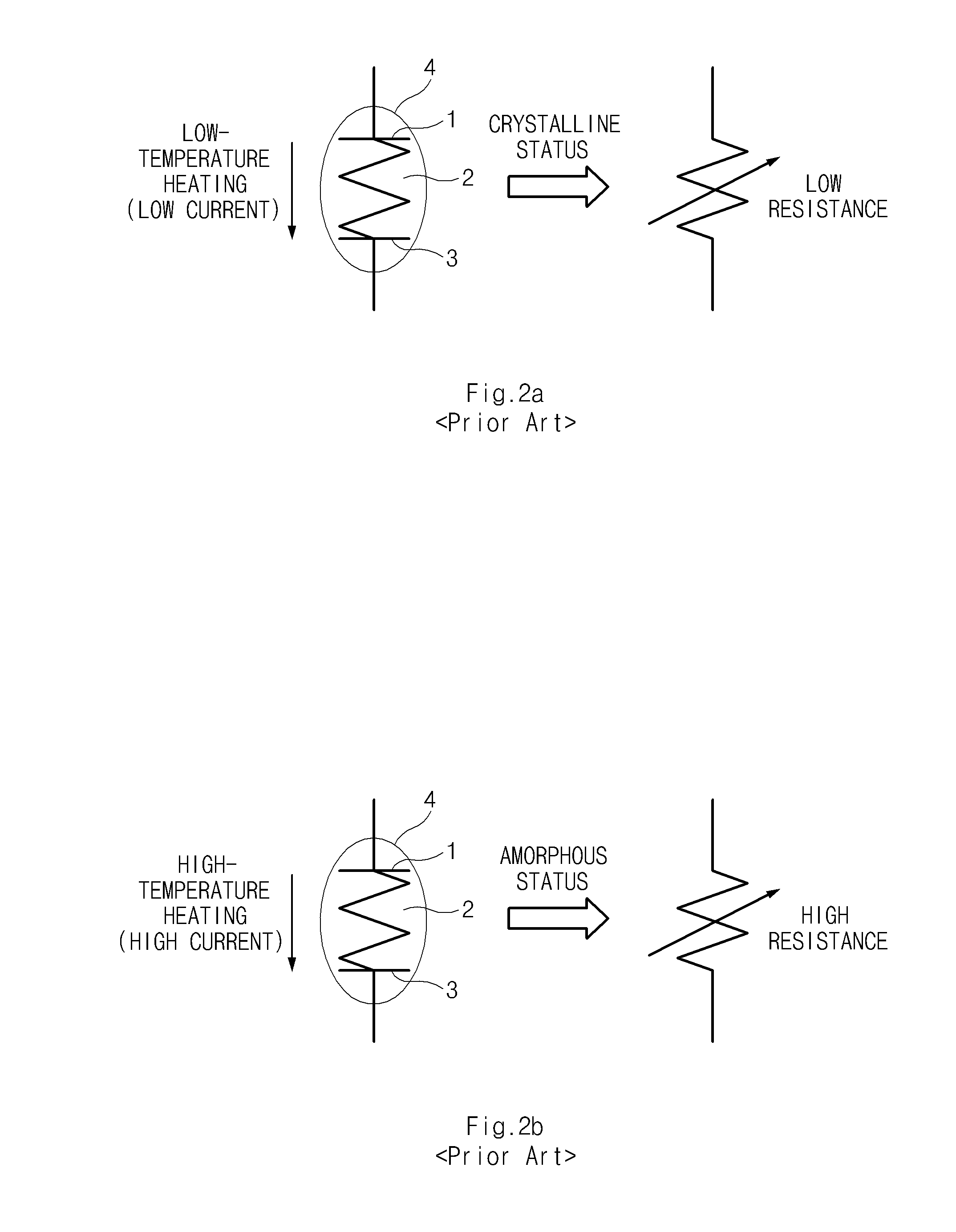

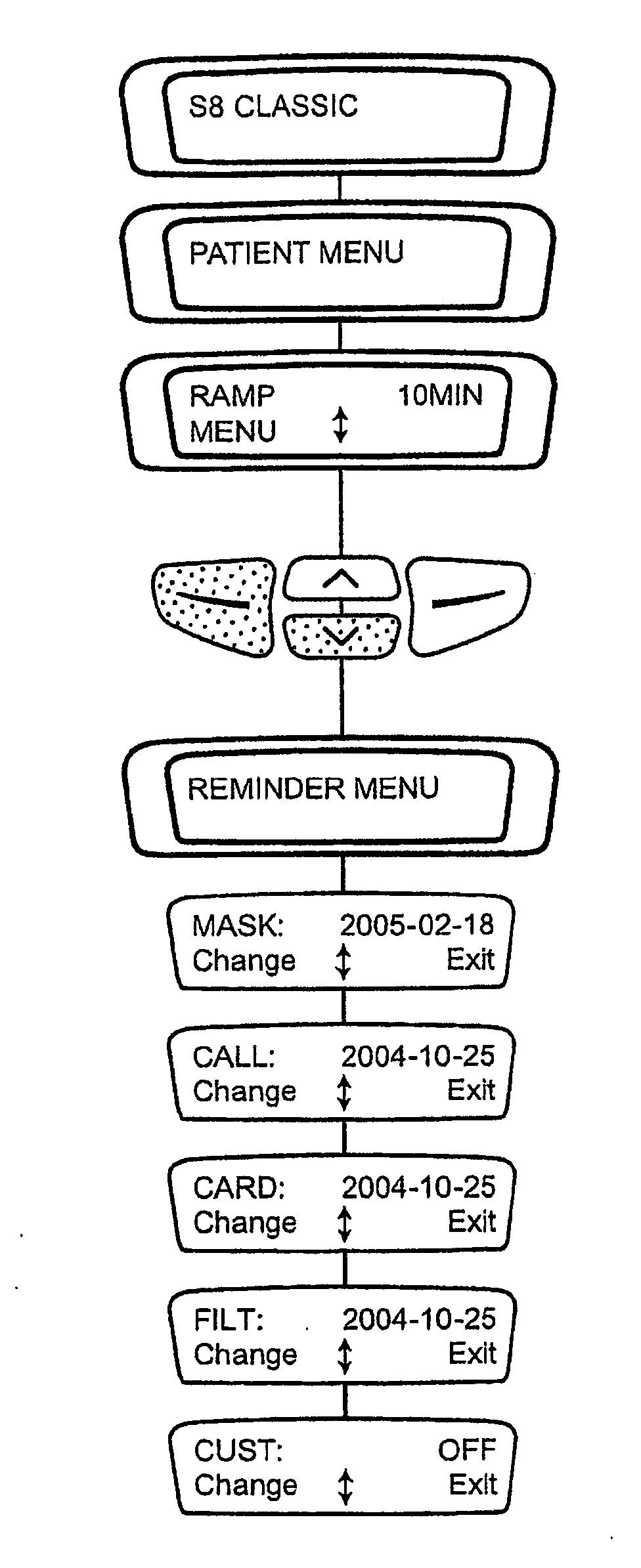

Flow generator with patient reminder

ActiveUS20100192094A1Simple and economical structureEasy to useRespiratorsOperating means/releasing devices for valvesPatient dataEngineering

A flow generator and humidifier construction is described, including a flow generator construction adapted to reduce noise output compared to known flow generators of comparable size. The flow generator includes a chassis forming first and second muffler volumes and a venturi-shaped connection portion, and a metal / polymer composite material blower enclosure which suppresses noise from the blower. The flow generator may be programmed to include a reminder system including a menu from which the user may request a reminder to take specific action, e.g., replace a component, call a physician, and / or enter patient data card, etc.

Owner:JOHN SNOW & COMPANY +1

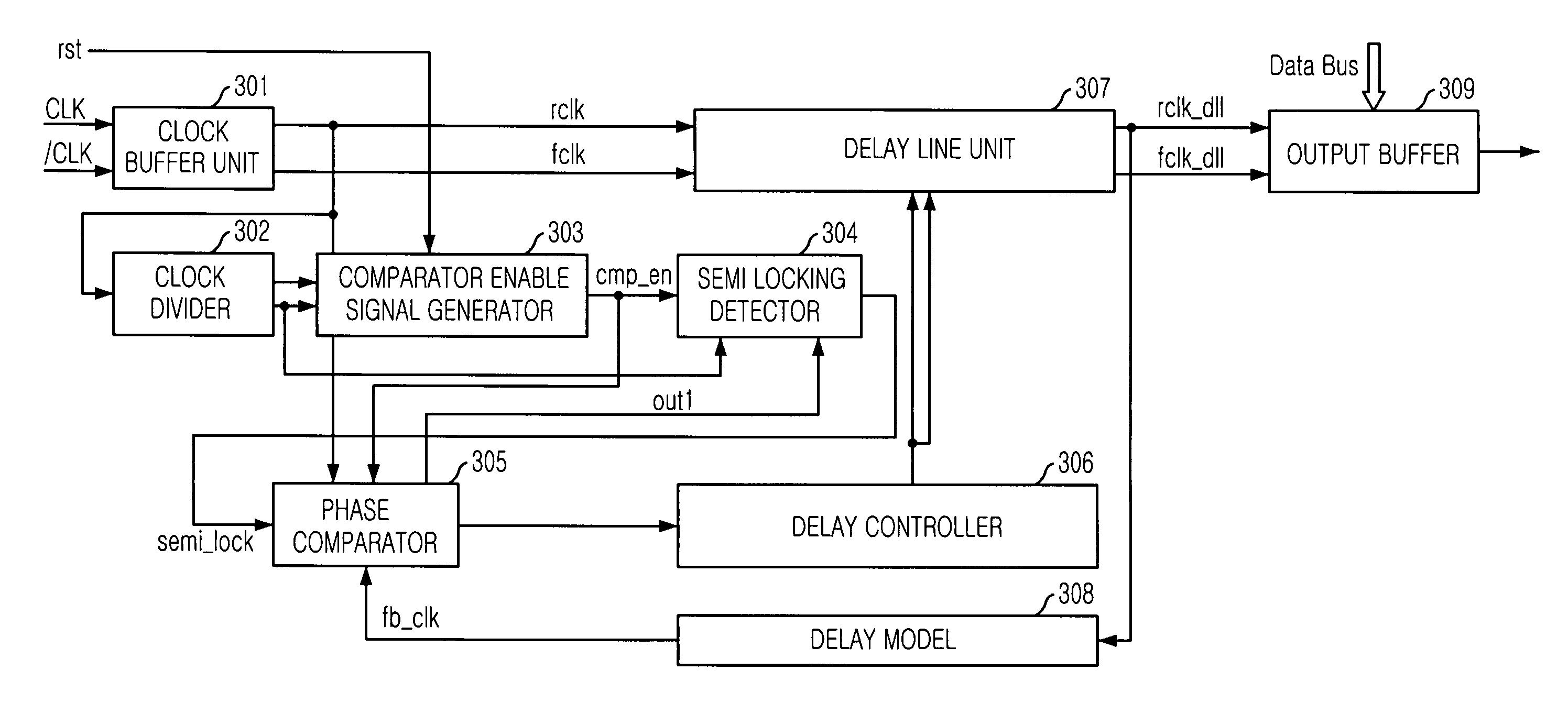

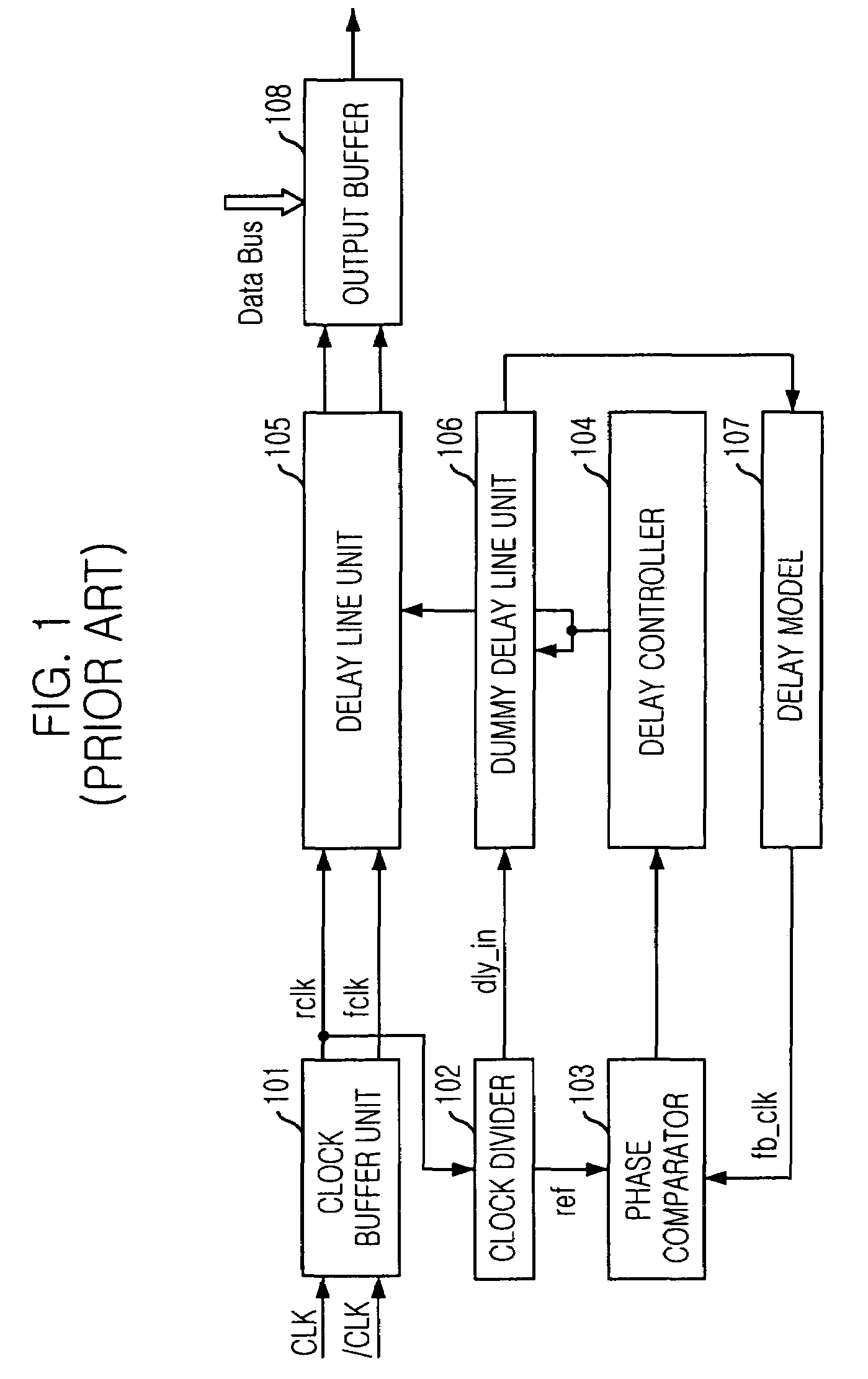

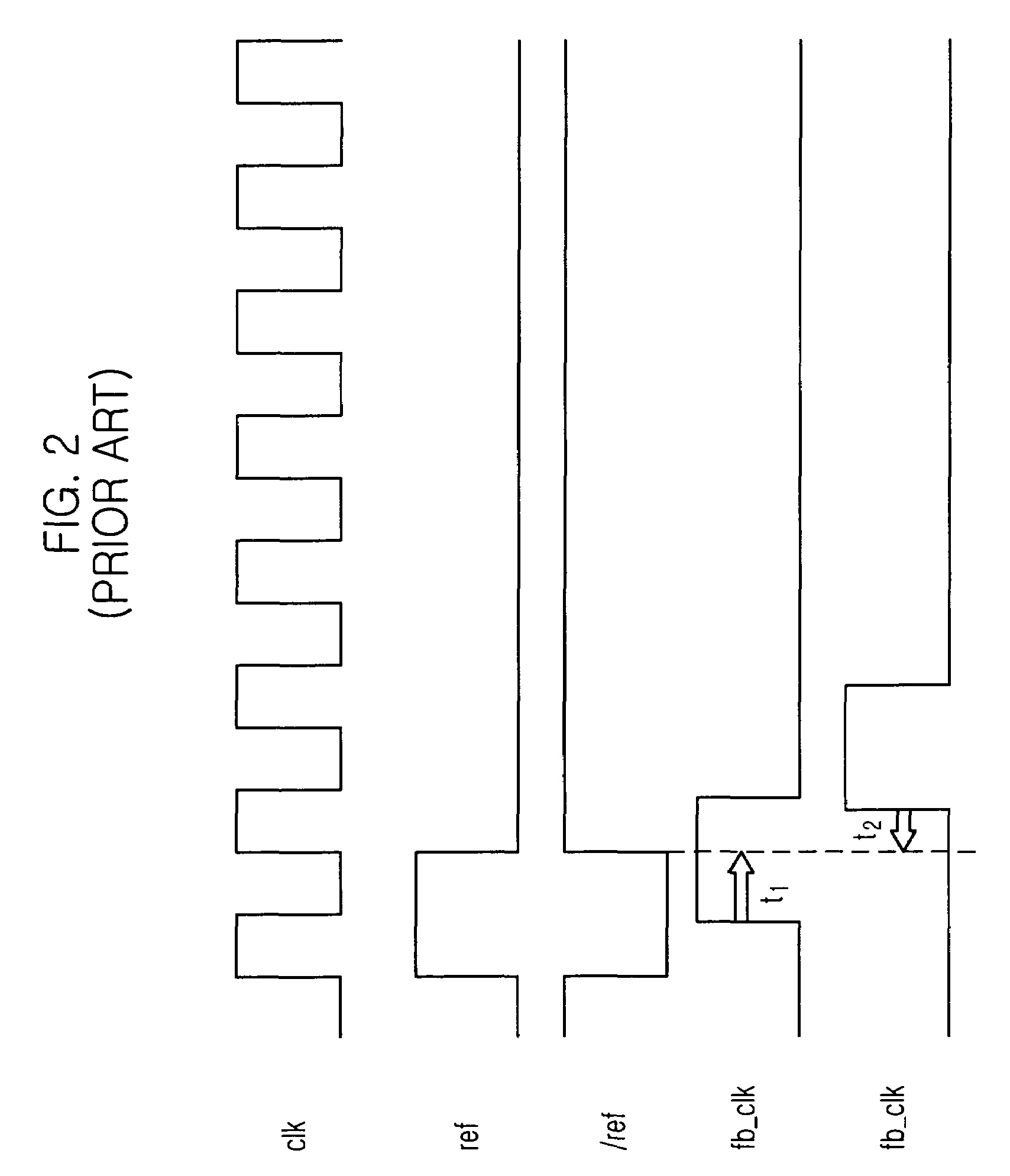

Delay locked loop in semiconductor memory device and its clock locking method

ActiveUS6989700B2Increase working frequencyGuaranteed uptimeMultiple input and output pulse circuitsPulse automatic controlOutput compareDelay-locked loop

A delay locked loop (DLL) for generating a delay locked clock signal, including: a comparator enable signal generator for generating a comparator enable signal in response to a reset signal and a plurality of clock divided signals; a semi locking detector for generating a semi locking detection signal in response to the comparator enable signal; a phase comparator enabled by the comparator enable signal for receiving a rising edge clock signal and a feed-backed clock signal in order to compare phases of the rising edge clock signal and the feed-backed clock signal and output the comparison result; and a DLL generator for generating the delay locked clock signal in response to the comparison result, wherein the comparator enable signal is generated by enlarging a pulse width of the reset signal by a predetermined amount.

Owner:SK HYNIX INC

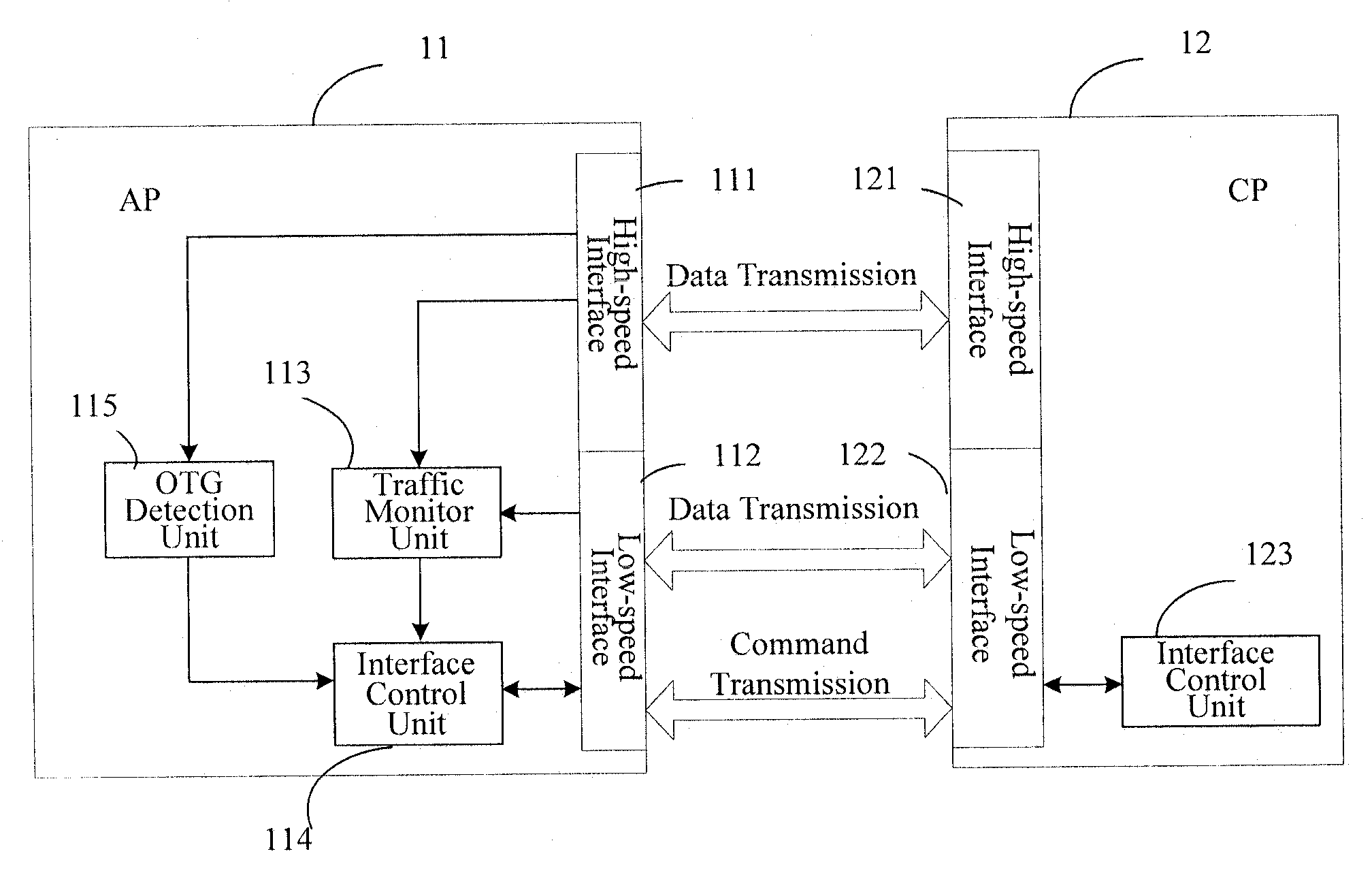

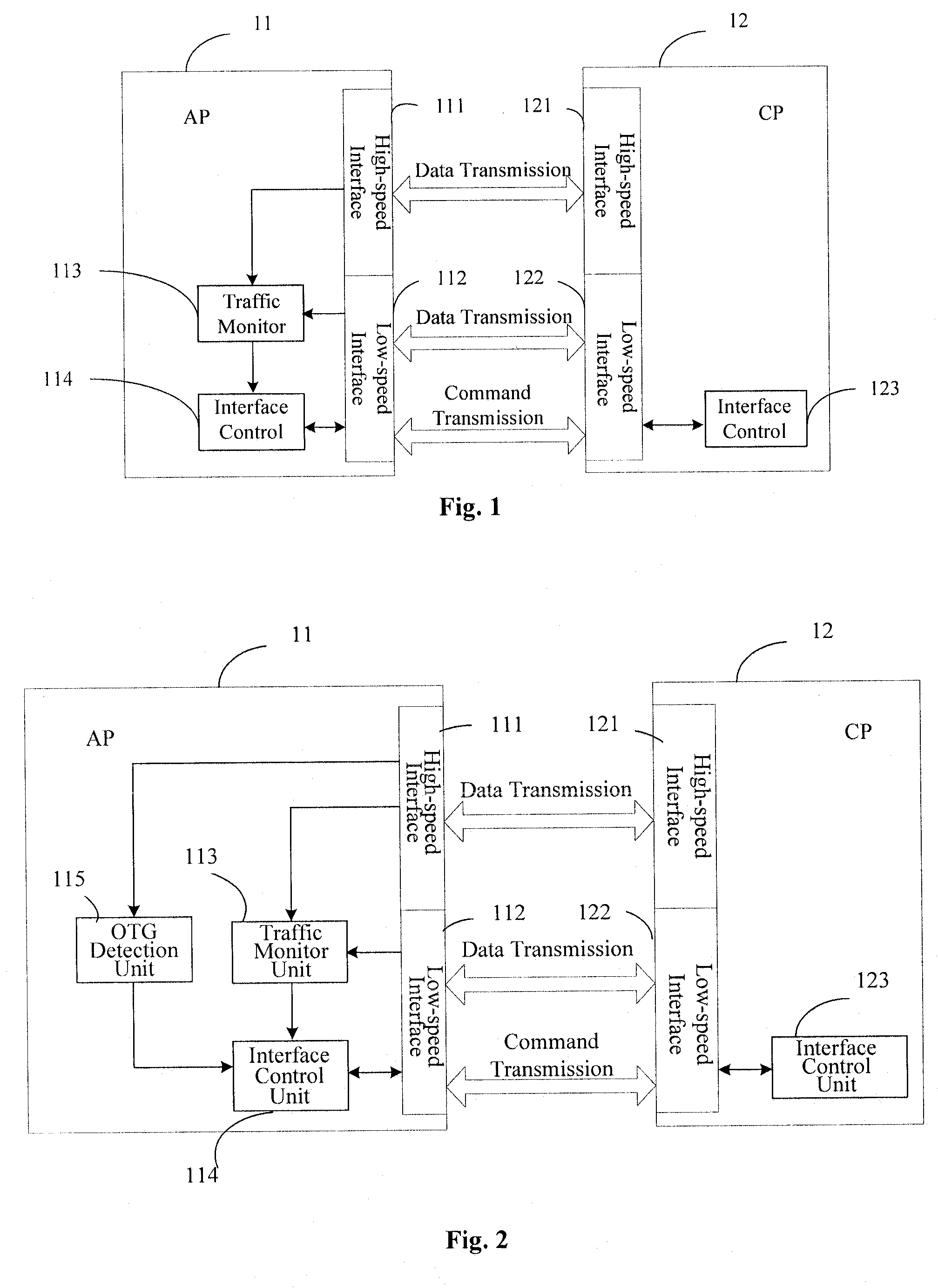

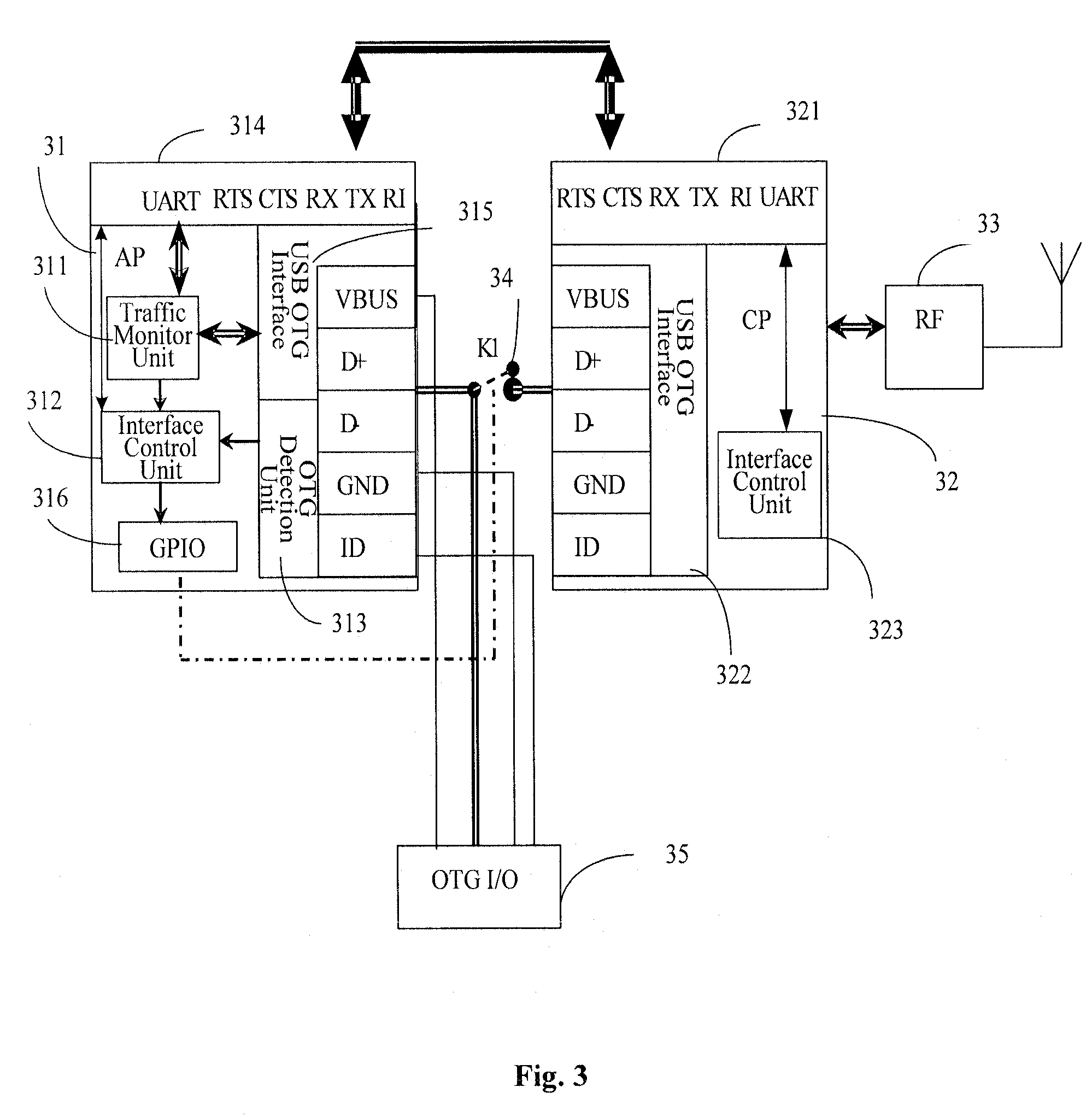

Mobile terminal and switching method for controlling data transmission interface thereof

ActiveUS20100161842A1Improve data transfer efficiencyImprove efficiencyEnergy efficient ICTError preventionData transmissionOutput compare

A mobile terminal and switching method for controlling data transmission interface thereof are provided. The mobile terminal comprises an application processor, a communication processor and data transmission interfaces thereof, the application processor comprising a traffic monitor unit and an interface control unit, wherein the traffic monitor unit is configured to detect data traffic of data transmission, compare the data traffic with a preset threshold to obtain a comparison result, and output the comparison result; and the interface control unit is configured to control, on receipt of the comparison result, the connection or disconnection of a high-speed data line between the application processor and the communication processor, and to transmit a corresponding interface switching command to the communication processor for switching the data transmission interface. With the present invention, the power consumption of the system can be reduced and the efficiency of the data transmission can be improved.

Owner:LENOVO (BEIJING) CO LTD

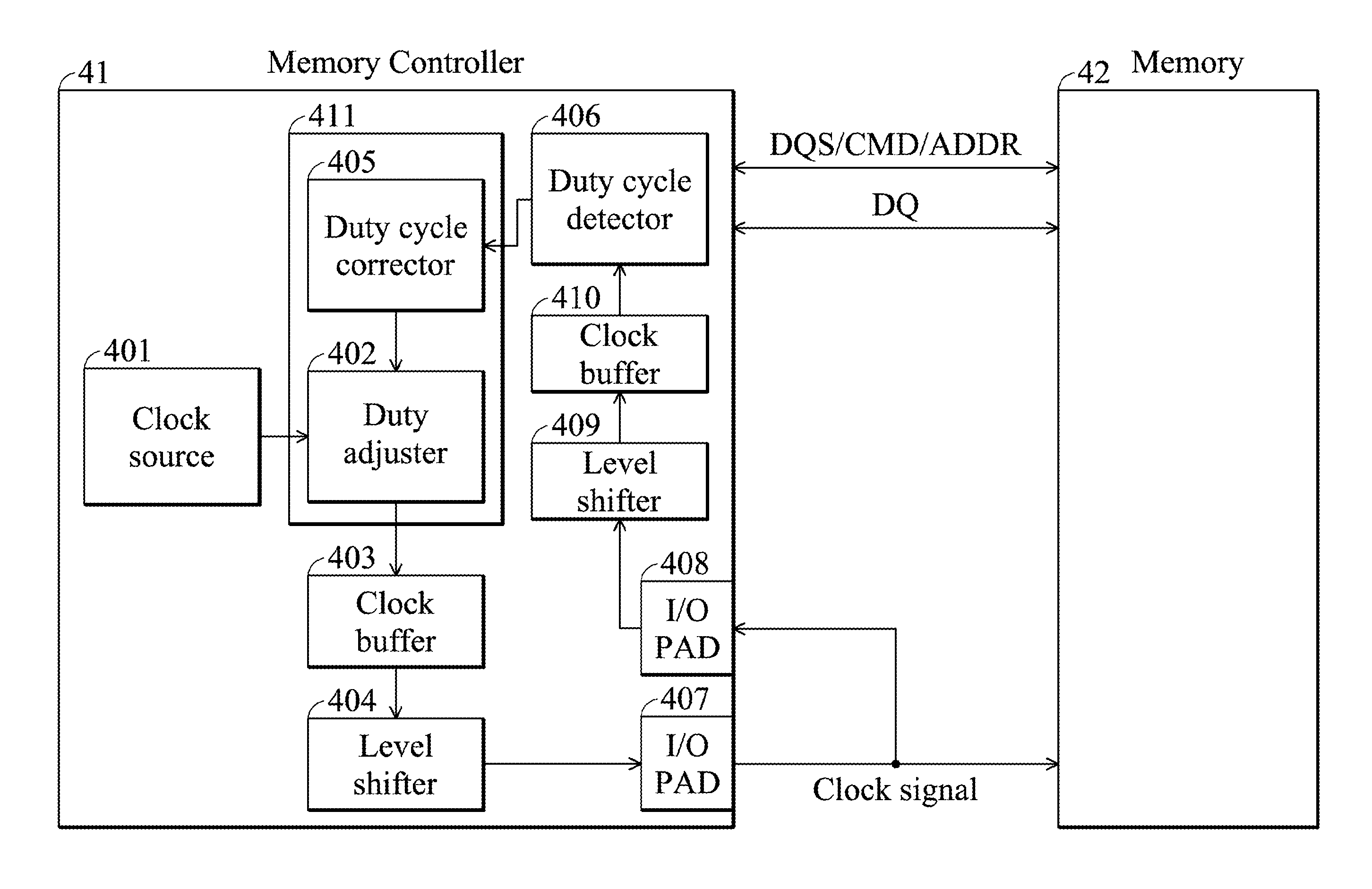

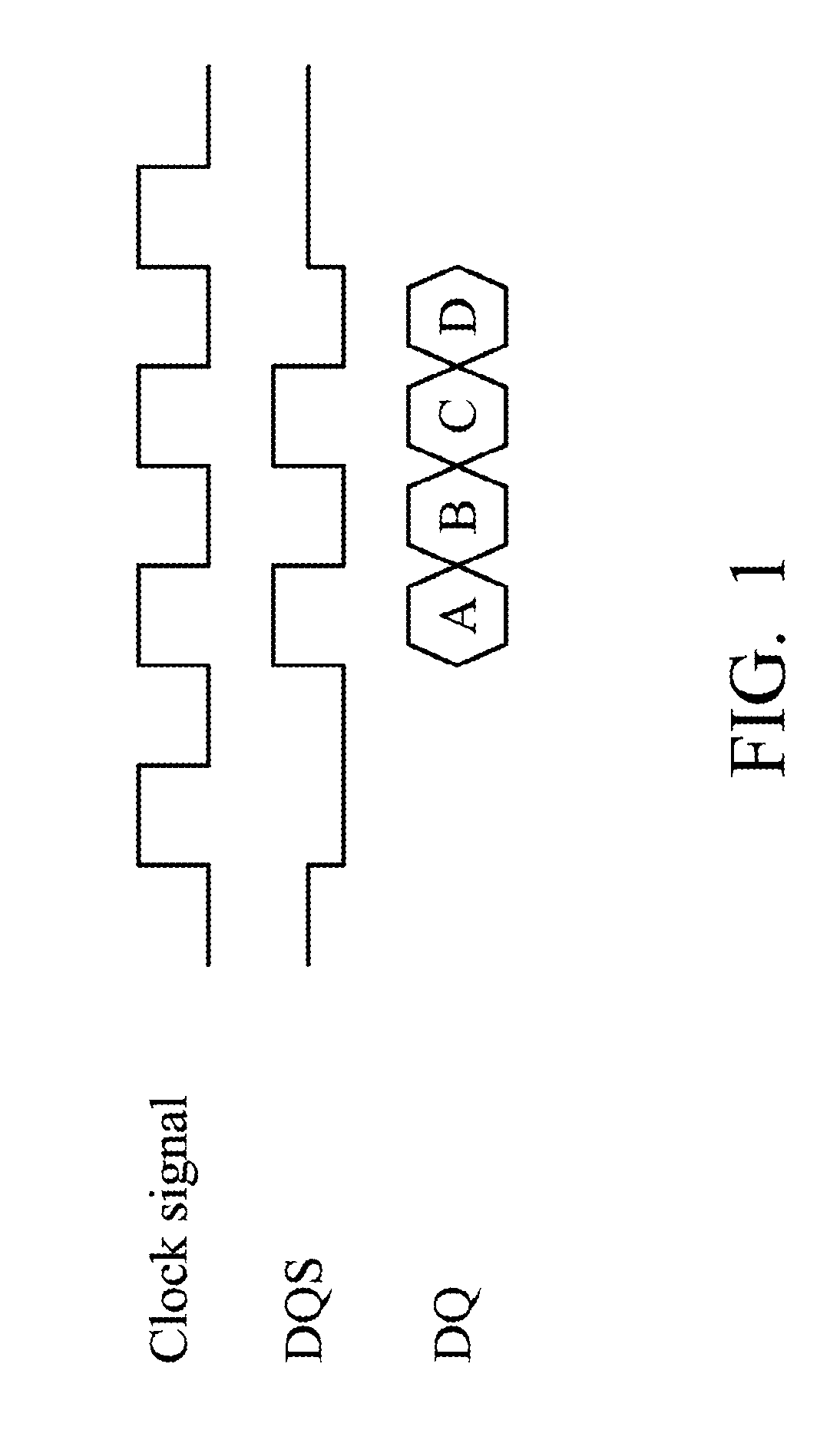

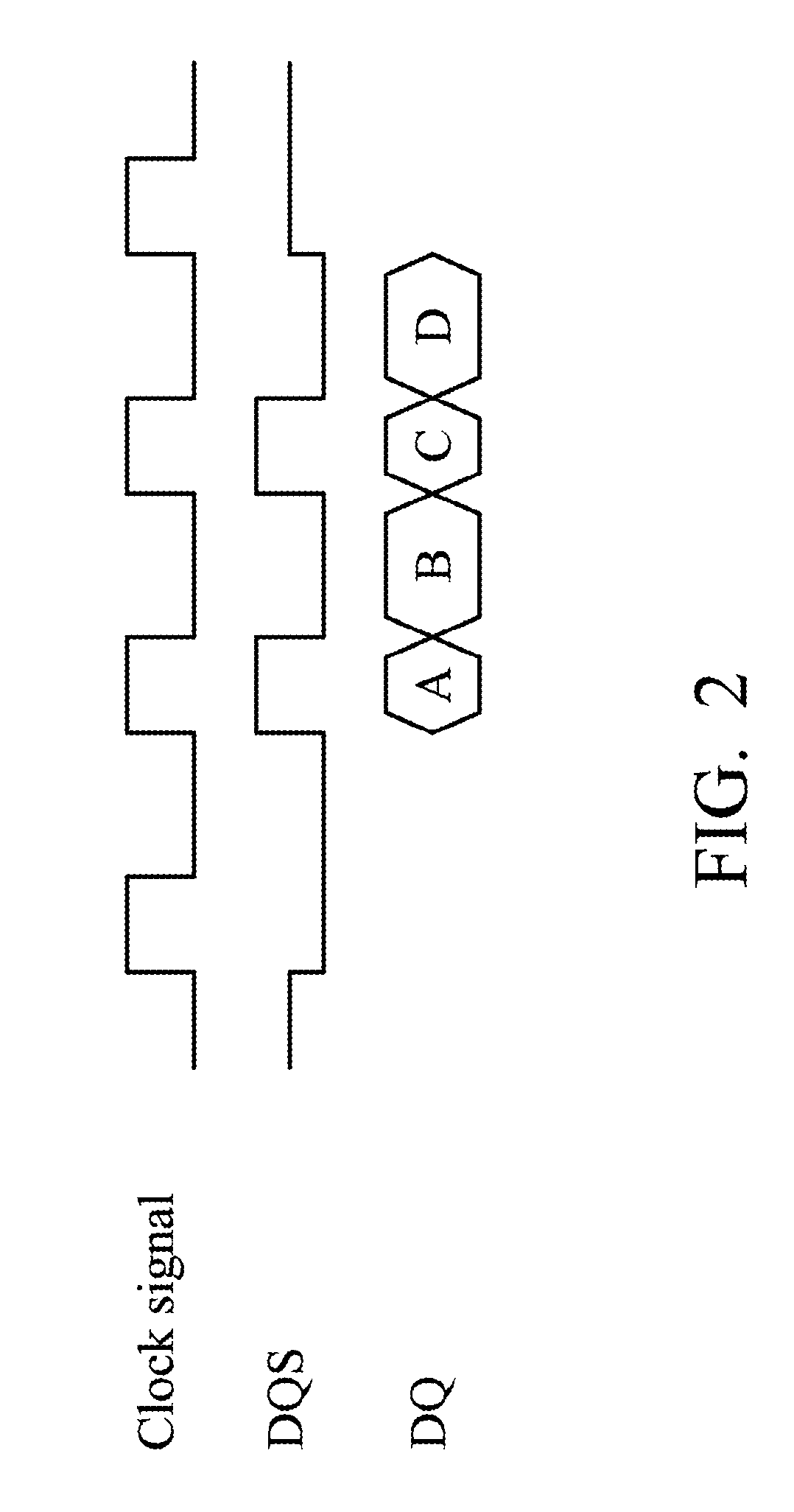

Apparatus and Method to Adjust Clock Duty Cycle of Memory

An embodiment of the invention provides a memory controller for controlling a memory. The memory controller comprises a pulse width modulation module, a voltage comparator and a duty cycle calibration device. The pulse width modulation module is suitable for receiving a clock signal to generate a first voltage. The voltage comparator is suitable for receiving and comparing a reference voltage with the first voltage to output a comparison signal. The duty cycle calibration device is suitable for adjusting a duty cycle of the clock signal according to the comparison signal.

Owner:MEDIATEK INC

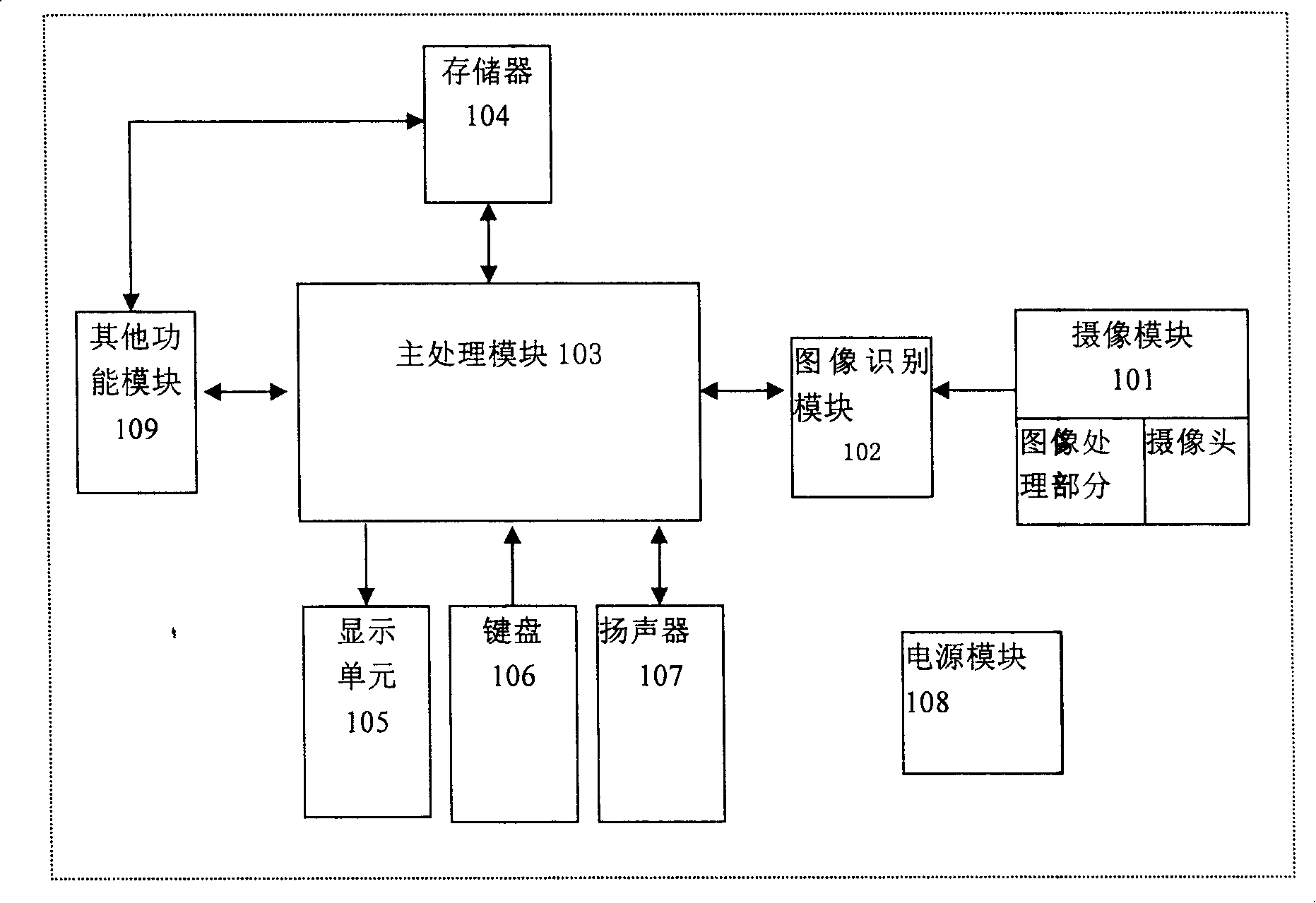

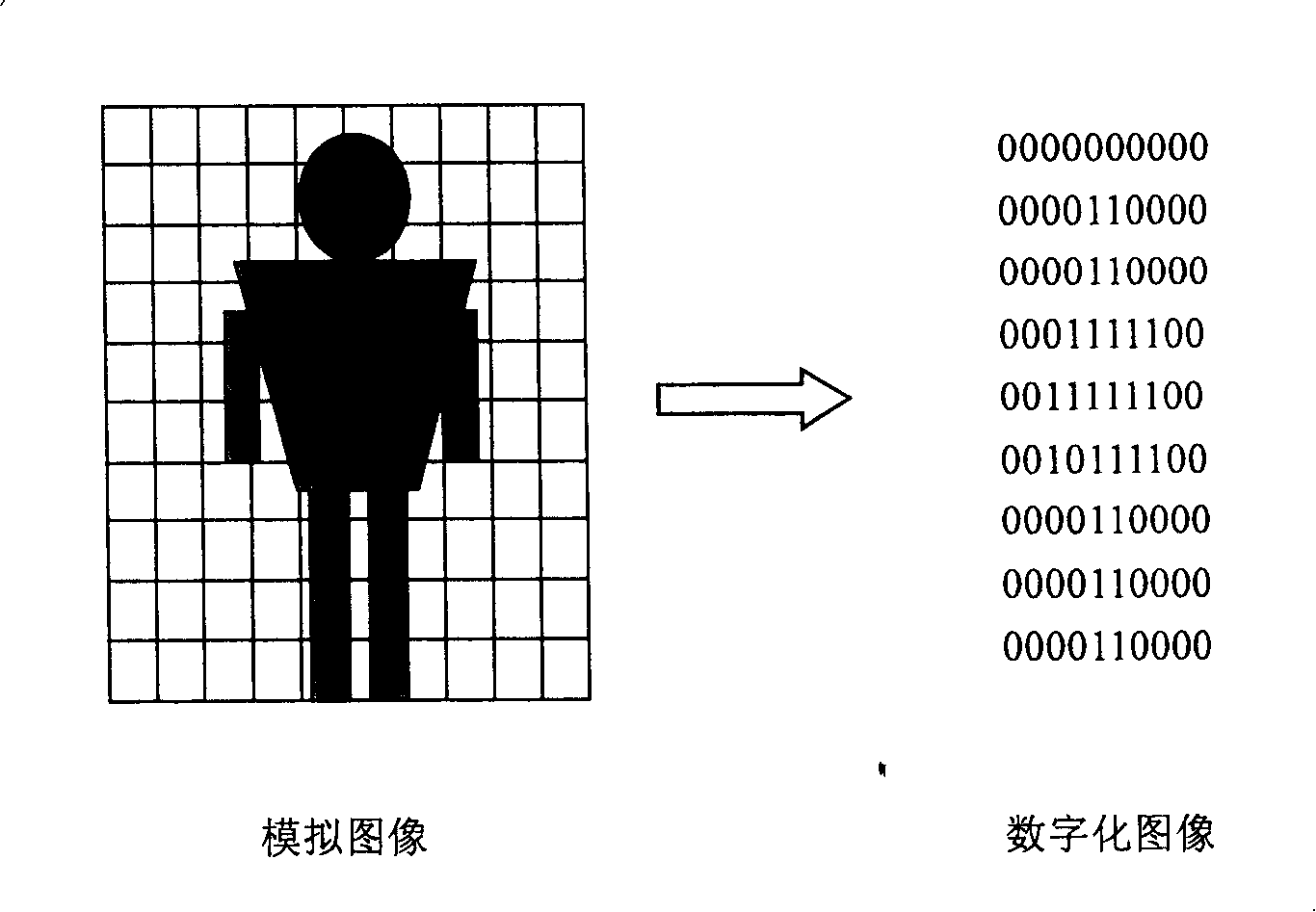

Method and device assistant to user for body-building

ActiveCN101202994AGood fitness effectImprove fitness effectRadio/inductive link selection arrangementsTelephone set constructionsHuman bodyOutput compare

The invention discloses a device of assisting a user in body building, which comprises a memory, a display unit, a keyboard, a loudspeaker, a power module, and also a shooting module which is used for converting external scenes into corresponding digital image files; an image recognition module which is used for recognizing human body movements in the images and extracting features of human body movements; and a main processing module which is used for controlling movements of every module and outputting comparing results. The device of the invention is equipped with a human body movement recognition system, compares human body building movements with standard movement templates, can provide guides like a body building coach for users at any time and any place, is used for pointing out non-standard places in user body building movements and helps users achieve ideal body building effects.

Owner:BEIJING SAMSUNG TELECOM R&D CENT +1

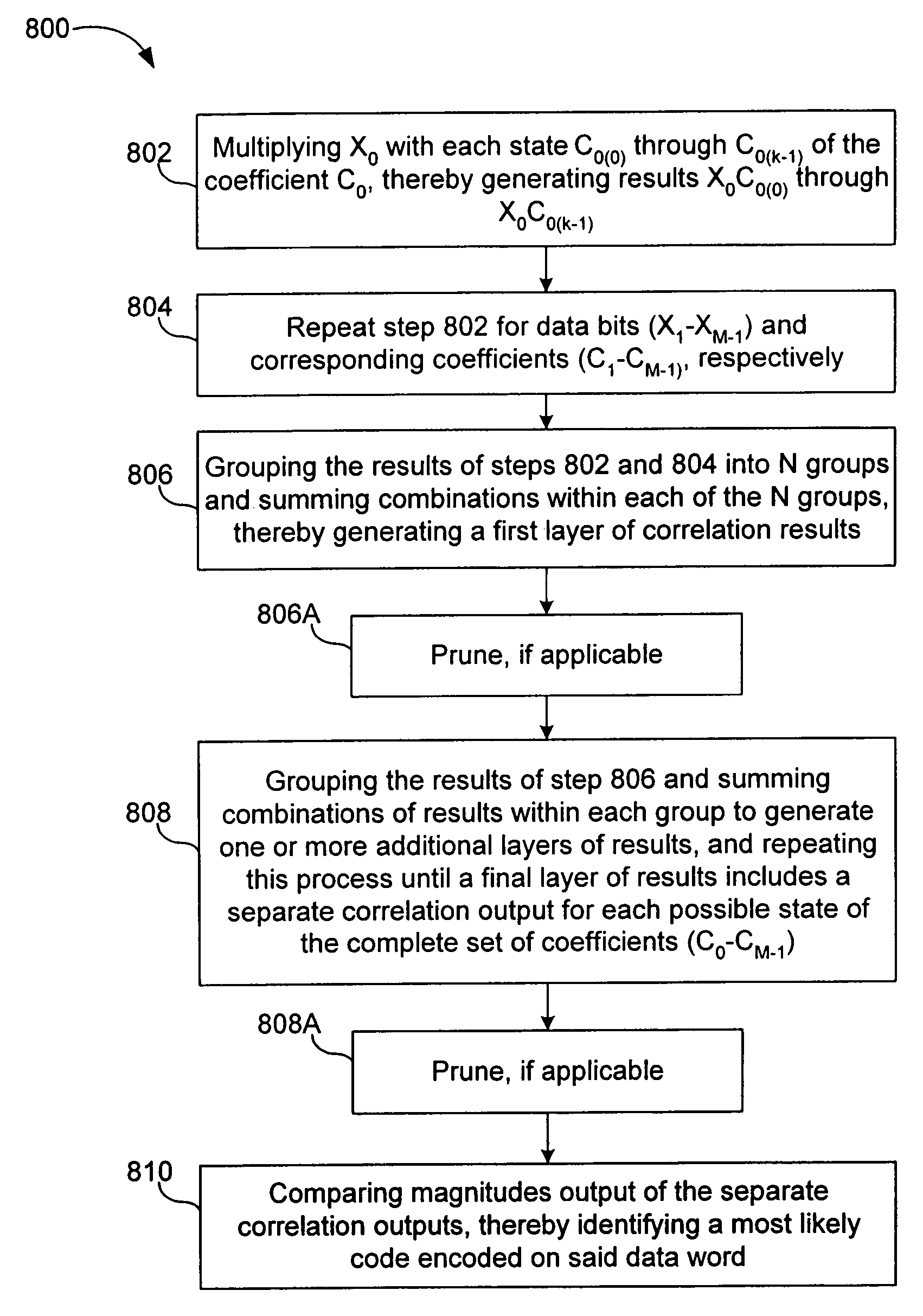

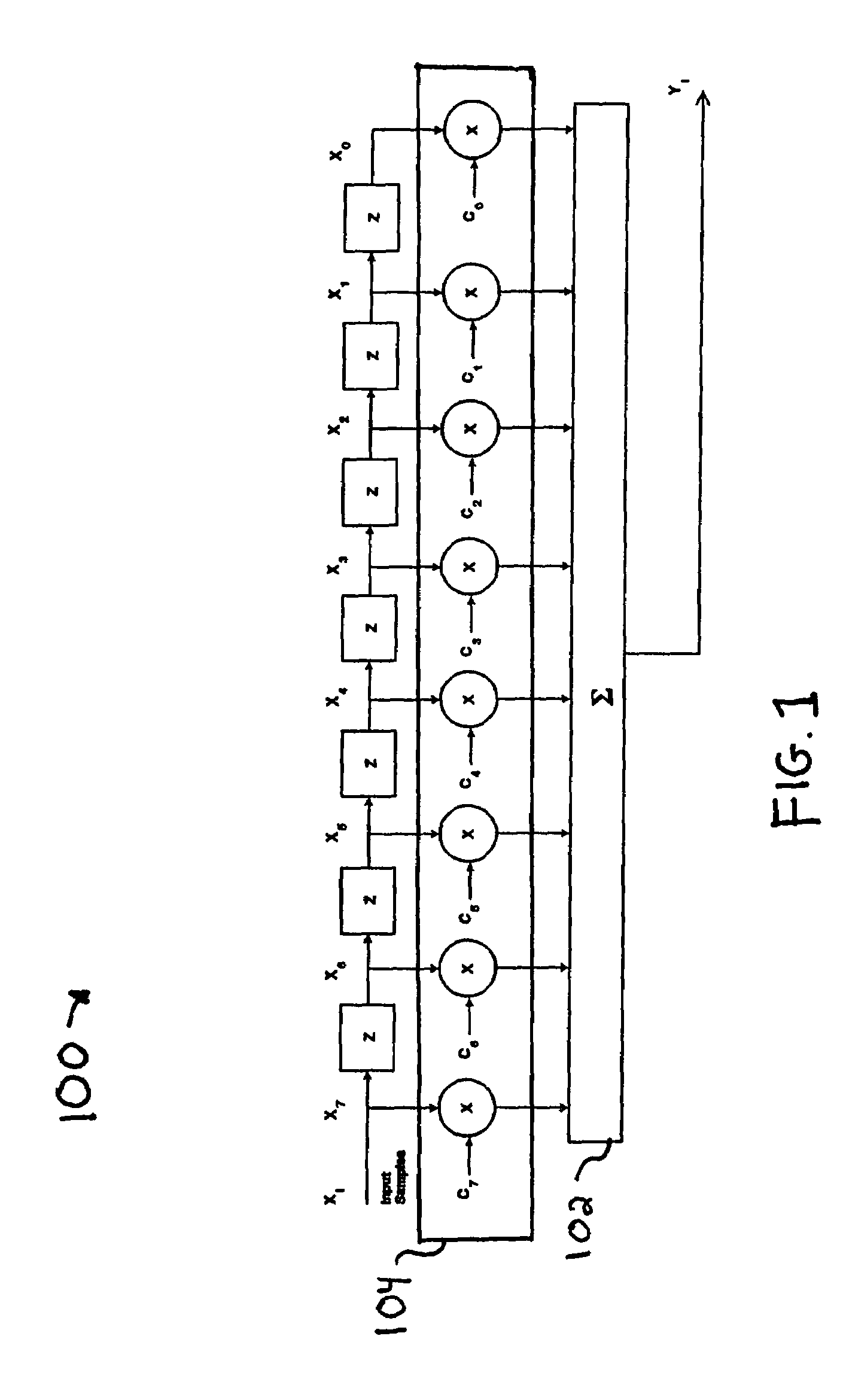

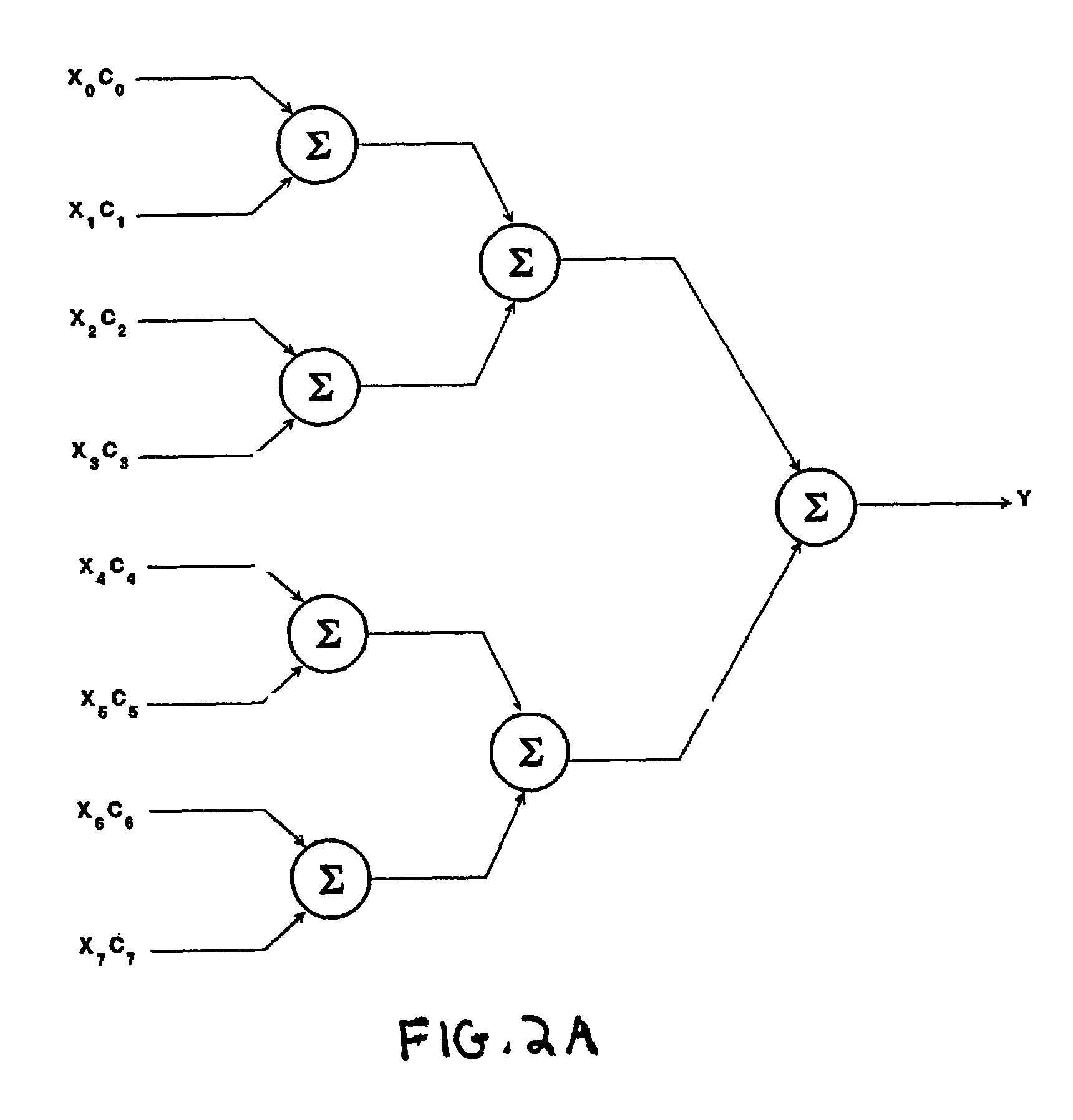

Methods, systems, and computer program products for parallel correlation and applications thereof

A fast correlator transform (FCT) algorithm and methods and systems for implementing same, correlate an encoded data word (X0-XM−1) with encoding coefficients (C0-CM−1), wherein each of (X0-XM−1) is represented by one or more bits and each said coefficient is represented by one or more bits, wherein each coefficient has k possible states, and wherein M is greater than 1. X0 is multiplied by each state (C0(0) through C0(k−1)) of the coefficient C0, thereby generating results X0C0(0) through X0C0(k−1). This is repeated for data bits (X1-XM−1) and corresponding coefficients (C1-CM−1), respectively. The results are grouped into N groups. Members of each of the N groups are added to one another, thereby generating a first layer of correlation results. The first layer of results is grouped and the members of each group are summed with one another to generate a second layer of results. This process is repeated until a final layer of results is generated. The final layer of results includes a separate correlation output for each possible state of the complete set of coefficients (C0-CM−1). The final layer of results is compared to identify a most likely code encoded on the data word. The summations can be optimized to exclude summations that would result in invalid combinations of the encoding coefficients (C0-CM−1). Substantially the same hardware can be utilized for processing in-phase and quadrature phase components of the data word (X0-XM−1). The coefficients (C0-CM−1) can represent real numbers and / or complex numbers. The coefficients (C0-CM−1) can be represented with a single bit or with multiple bits (e.g., magnitude). The coefficients (C0-CM−1) represent, for example, a cyclic code keying (“CCK”) code set substantially in accordance with IEEE 802.11 WLAN standard.

Owner:PARKER VISION INC

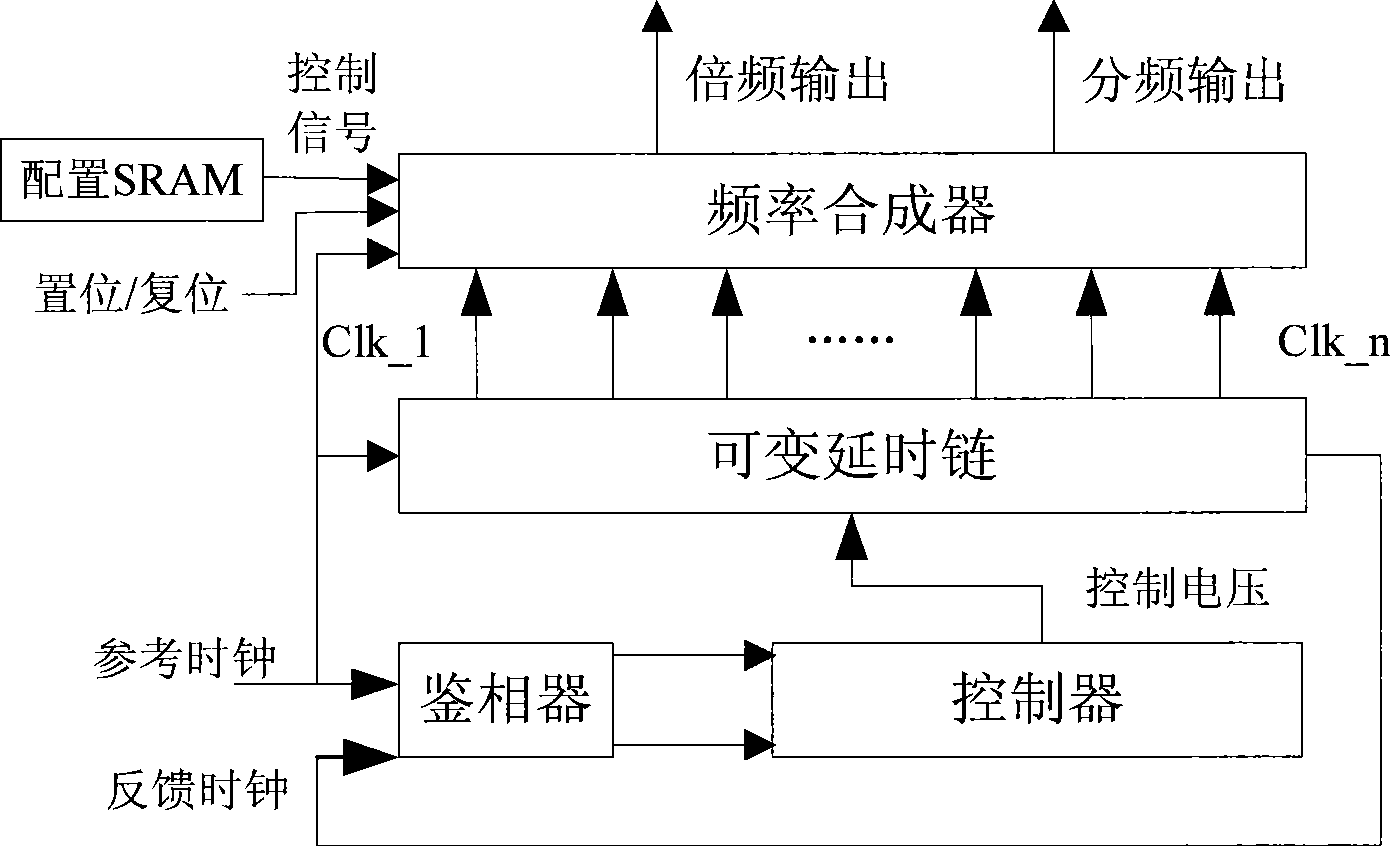

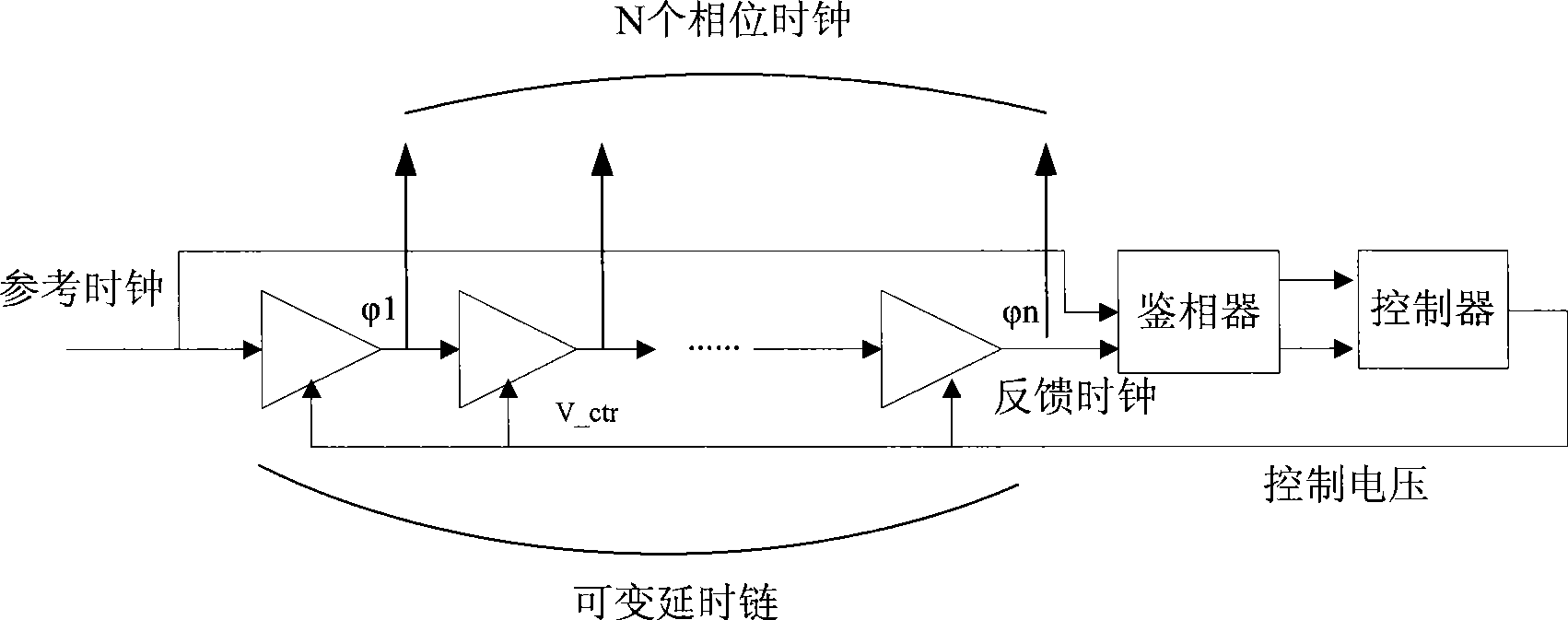

Configurable frequency synthesizer circuit based on time-delay lock loop

ActiveCN101478308AImprove reusabilityAbsolute stabilityPulse automatic controlDiscriminatorTime delays

The invention relates to a configurable frequency synthesis circuit based on a delay locked loop. The circuit comprises the delay locked loop, a frequency synthesizer and a configuring SRAM, wherein, the delay locked loop consists of a phase discriminator, a controller and a variable delay chain; and the frequency synthesizer consists of a frequency doubling synthesizer and a frequency division synthesizer. The phase discriminator receives a reference clock and a feedback clock and outputs comparison signals and locking signals after phase demodulation comparison; the comparison signals and the locking signals are processed by the controller, and the controller outputs control voltage then in order to enable the variable delay chain to generate N phase clocks that are output to the frequency synthesizer; and the frequency doubling synthesizer and the frequency division synthesizer enable the set / reset time of a R / S trigger in the frequency doubling synthesizer to generate frequency doubling clock signals under the control of the configuring SRAM, and lead the set / reset time of the R / S trigger in the frequency division synthesizer to generate frequency division clock signals. The configurable frequency synthesis circuit has simple circuit organization, flexibly changes a frequency synthesis coefficient by changing the code flow value in the embedded configuring SRAM so as to obtain a frequency division coefficient and a frequency doubling coefficient as required, and can be applied to a field programmable logic array.

Owner:BEIJING MXTRONICS CORP +1

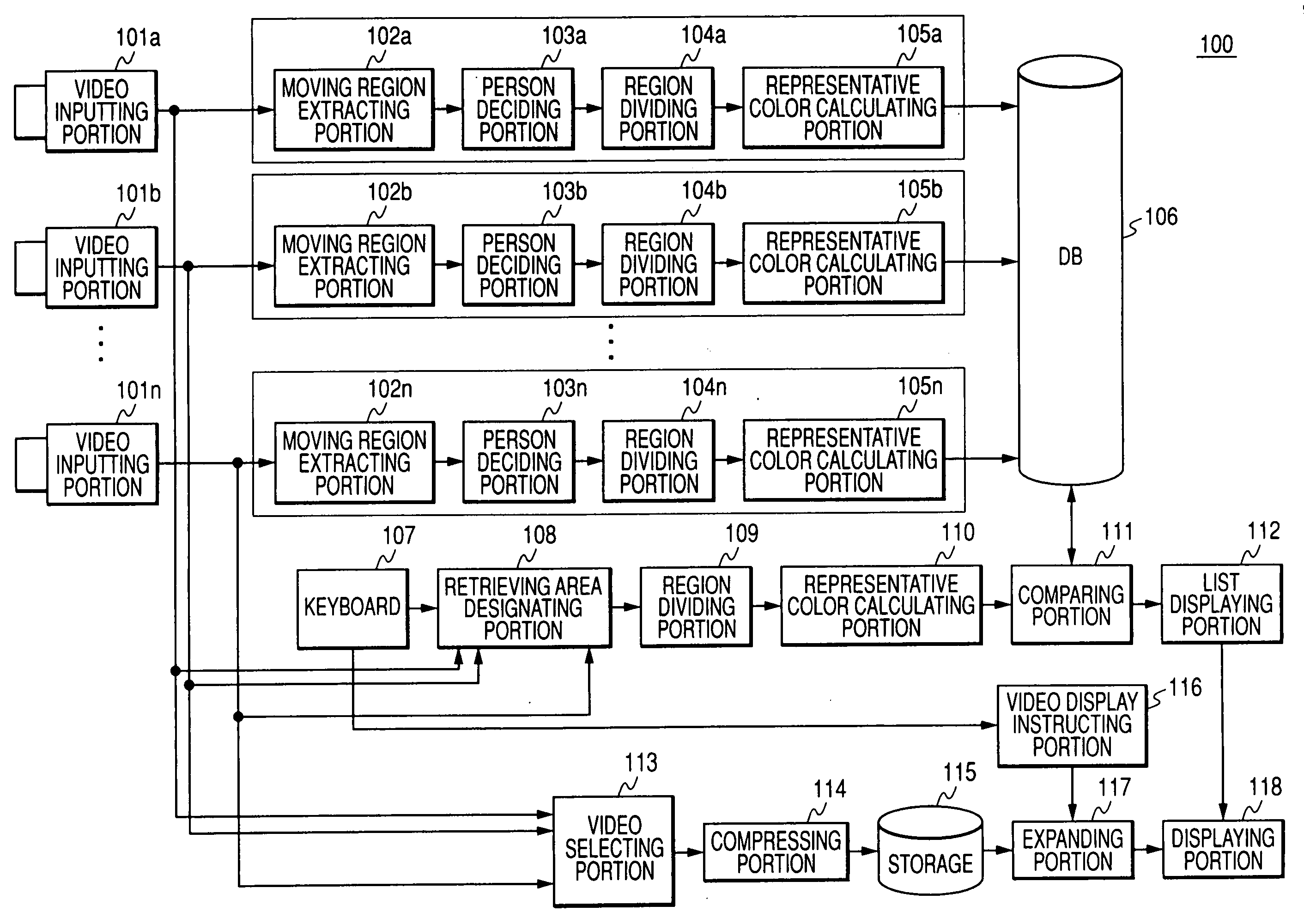

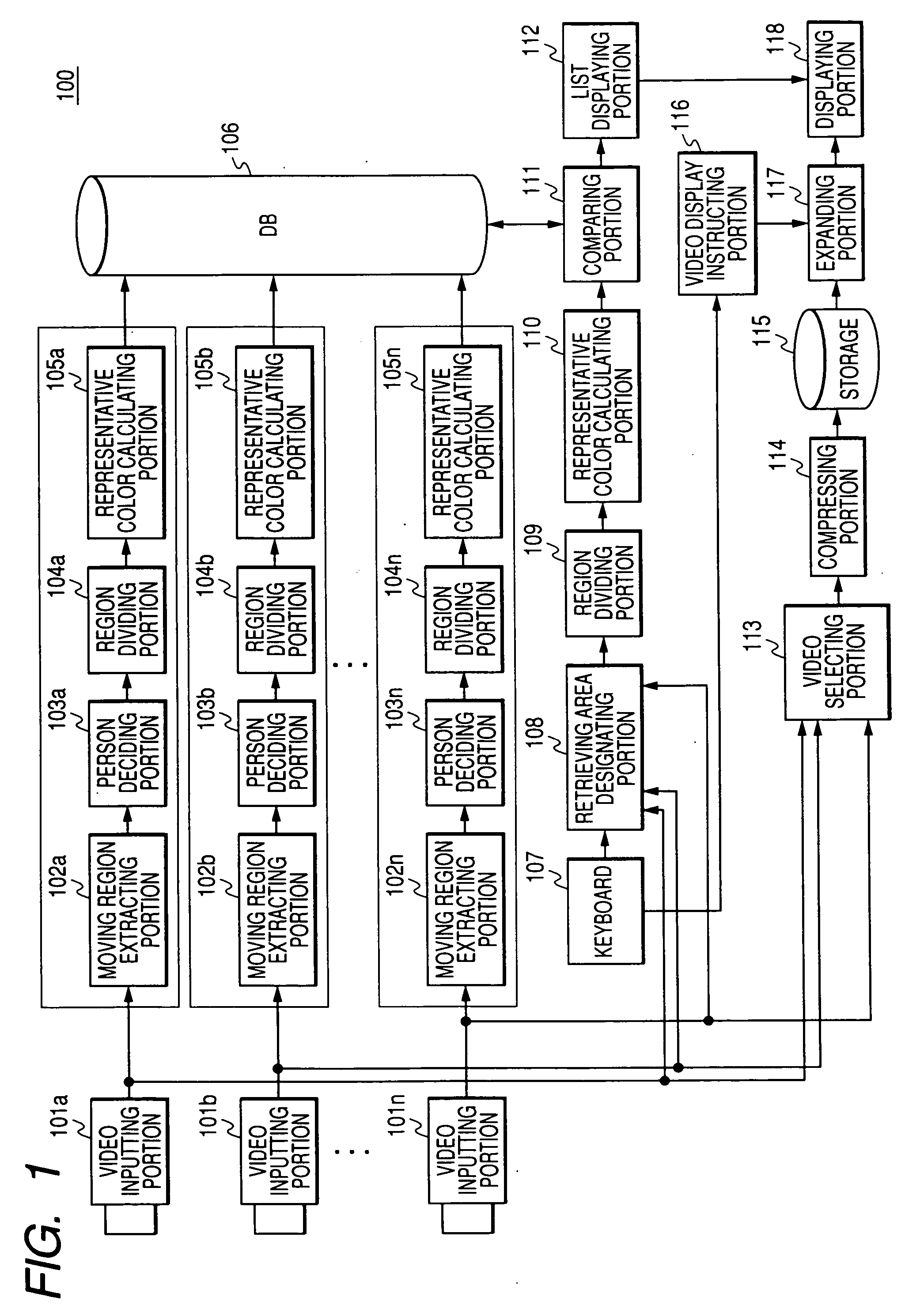

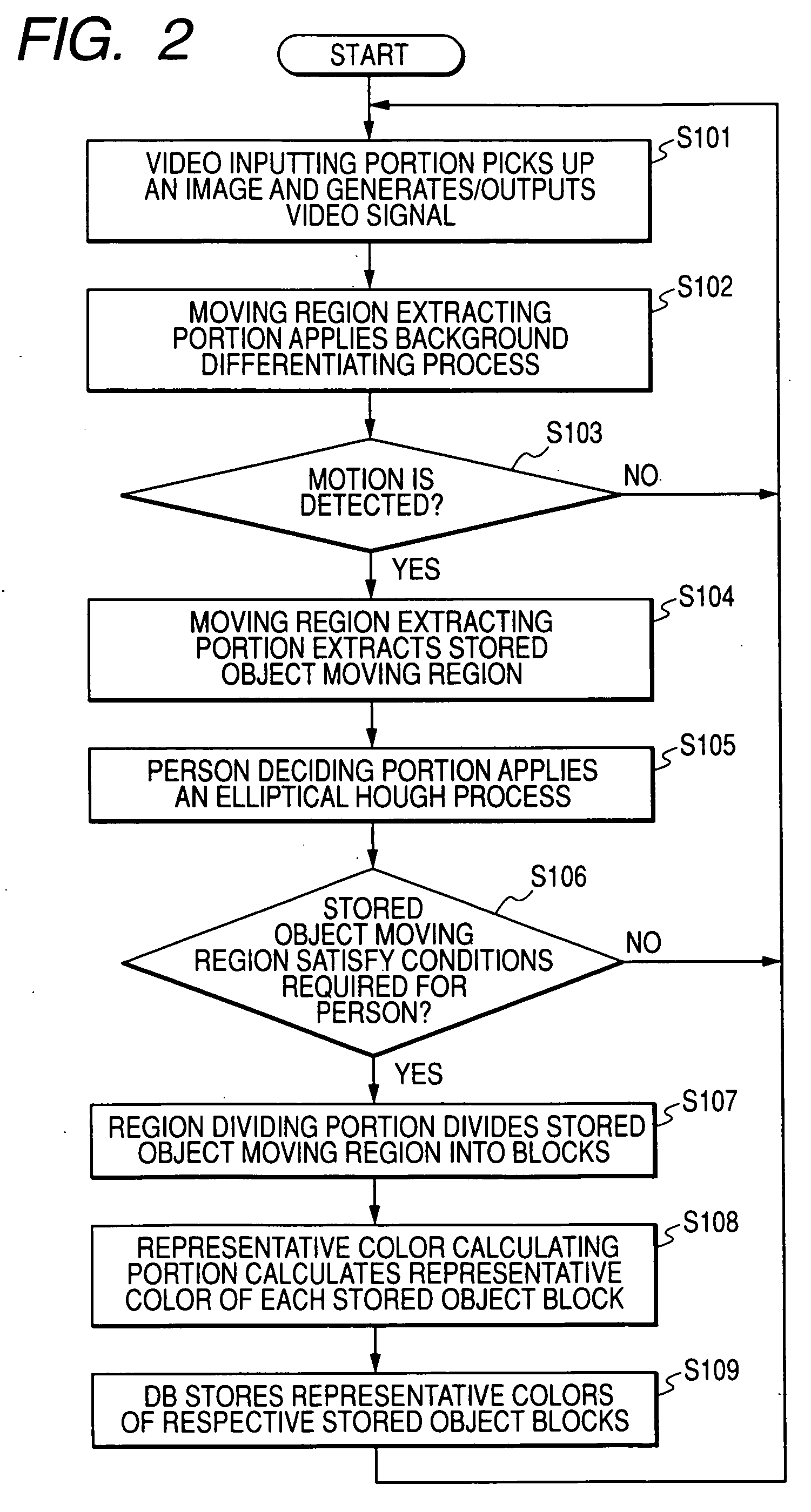

Video retrieval system and video retrieval method

InactiveUS20060159370A1Easy to specifyEfficient retrievalTelevision system detailsImage analysisPattern recognitionVideo retrieval

A video retrieval apparatus and a video retrieval method capable of executing appropriately a video retrieval and executing an effective retrieval by easily designating a retrieved object are provided. A video retrieval apparatus, includes a moving region extracting portion 102 that extracts a stored object moving region in a video, a region dividing portion 104 that divides the stored object moving region into stored object block regions, a representative color deriving portion 105 that derives representative colors of respective stored object block regions constituting the stored object moving region, a DB 106 that stores respective representative colors of respective stored object block regions constituting the stored object moving region, a retrieved object region designating portion 108 that extracts a retrieved object region in a video, a region dividing portion 109 that divides the retrieved object region into retrieved object block regions, a representative color calculating portion 110 that derives representative colors of respective retrieved object block regions constituting the retrieved object region, and a comparing portion 111 that compares respective representative colors of the stored object block regions with respective representative colors of the retrieved object block regions, and outputs compared results.

Owner:PANASONIC CORP

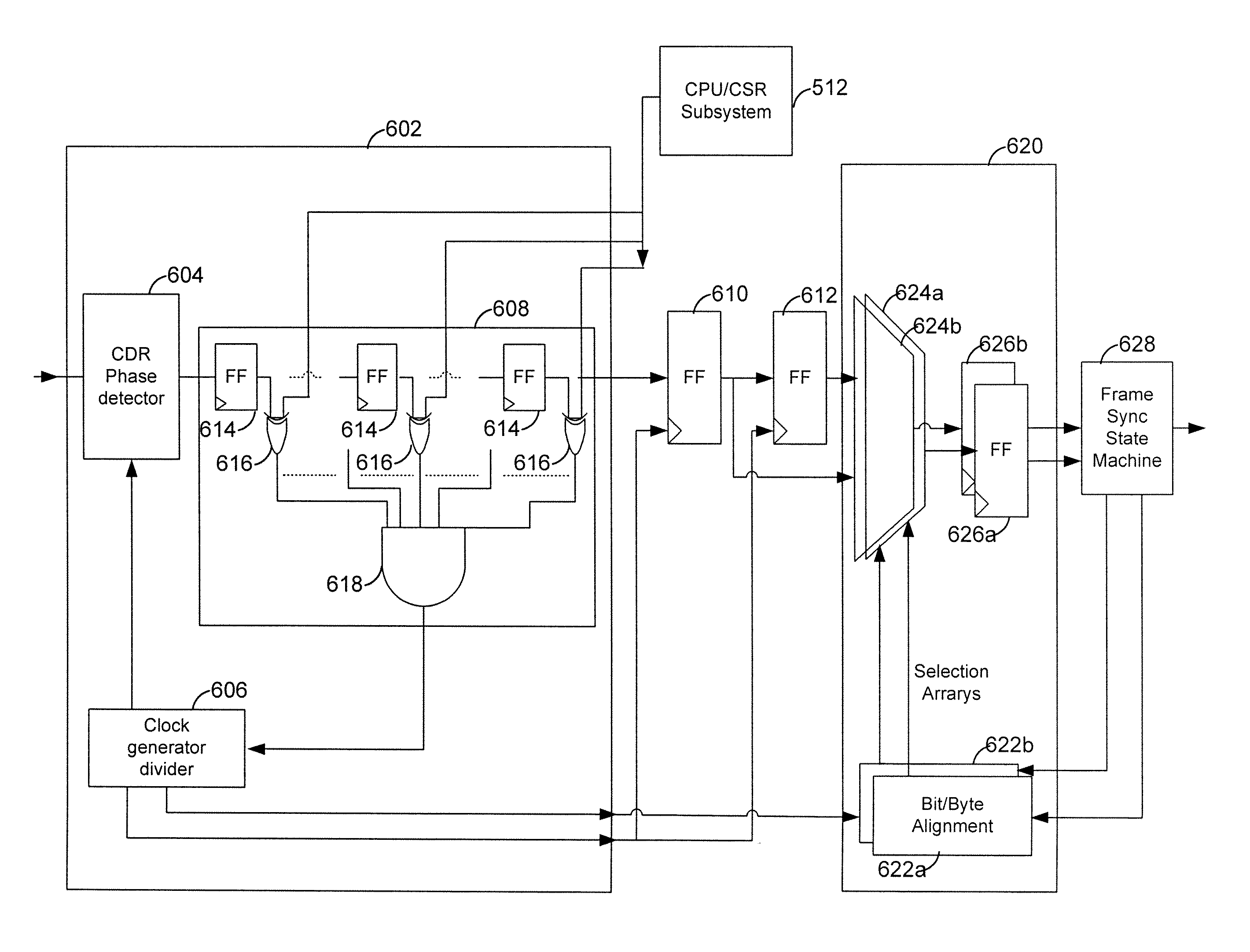

Method and apparatus for data frame synchronization

InactiveUS7983308B1Multiplex system selection arrangementsTime-division multiplexSerial transferData synchronization

A circuit to synchronize with a data transmission includes a comparator to read a set of data within a serialized data transmission, compare the set of data to a predetermined data pattern and output a comparison result. For a serialized data transmission, the comparator receives the serialized transmission and a shift register serially coupled to the comparator to hold the data pattern. A synchronization detector receives a comparison hit vector based on the comparison result from the comparator and aligns a boundary of a data frame according to the comparison hit vector if the comparison hit vector indicates a match between the data pattern in the set of data and the predetermined data pattern. For a deserialized data transmission, each stage of a multistage shift register read a set of data from the deserialized data transmission and selectively outputs the set of data to a comparator which compares each set to a predetermined data pattern and output a comparison result. A synchronization detector receives the comparison result from the comparator and aligns a boundary of a data frame according to the comparison result if the comparison result indicates a match between a data pattern sub-set within a combined data pattern and the predetermined data pattern, where the sets of deserialized data comprise the combined data pattern.

Owner:MARVELL INT LTD

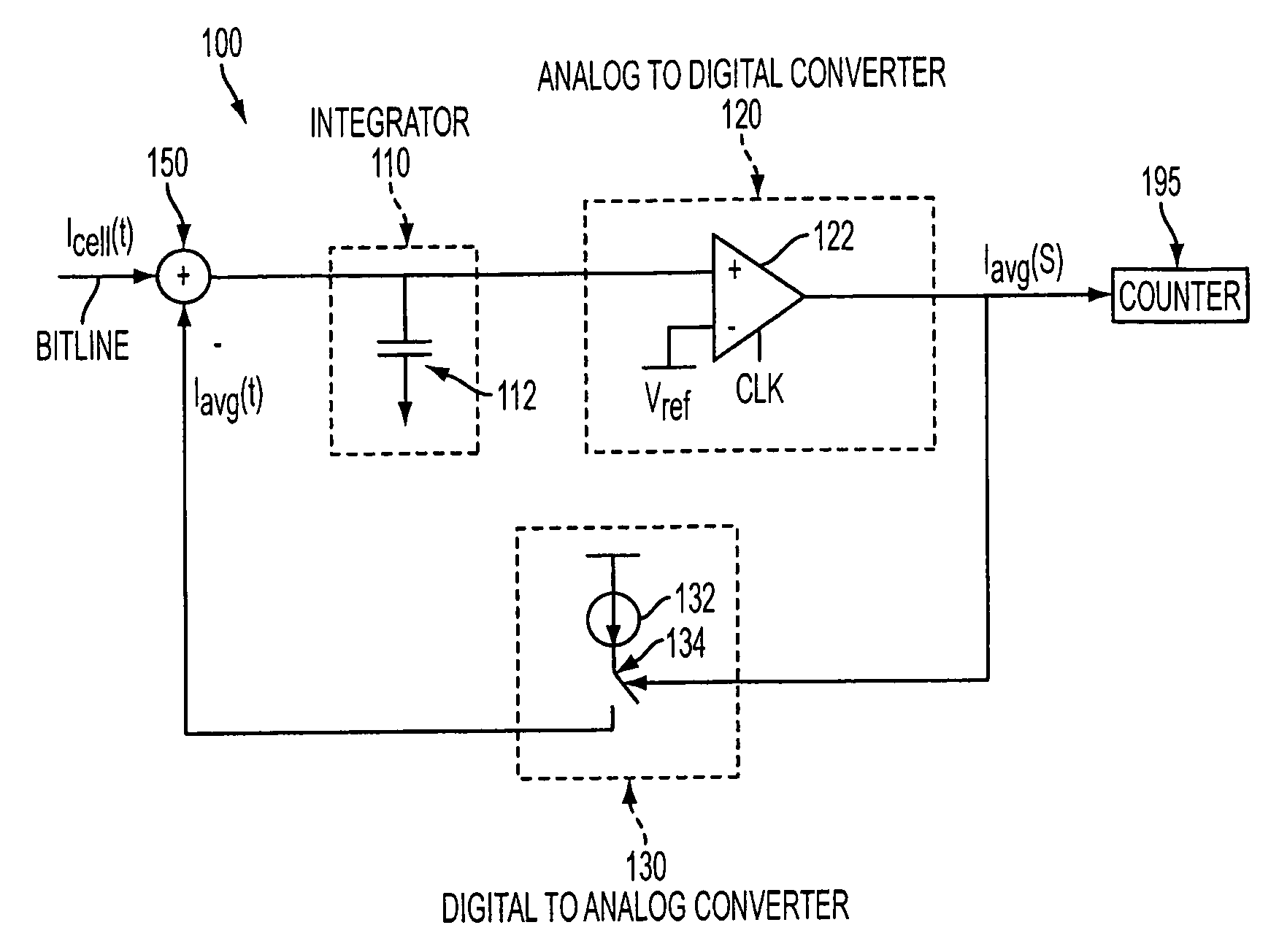

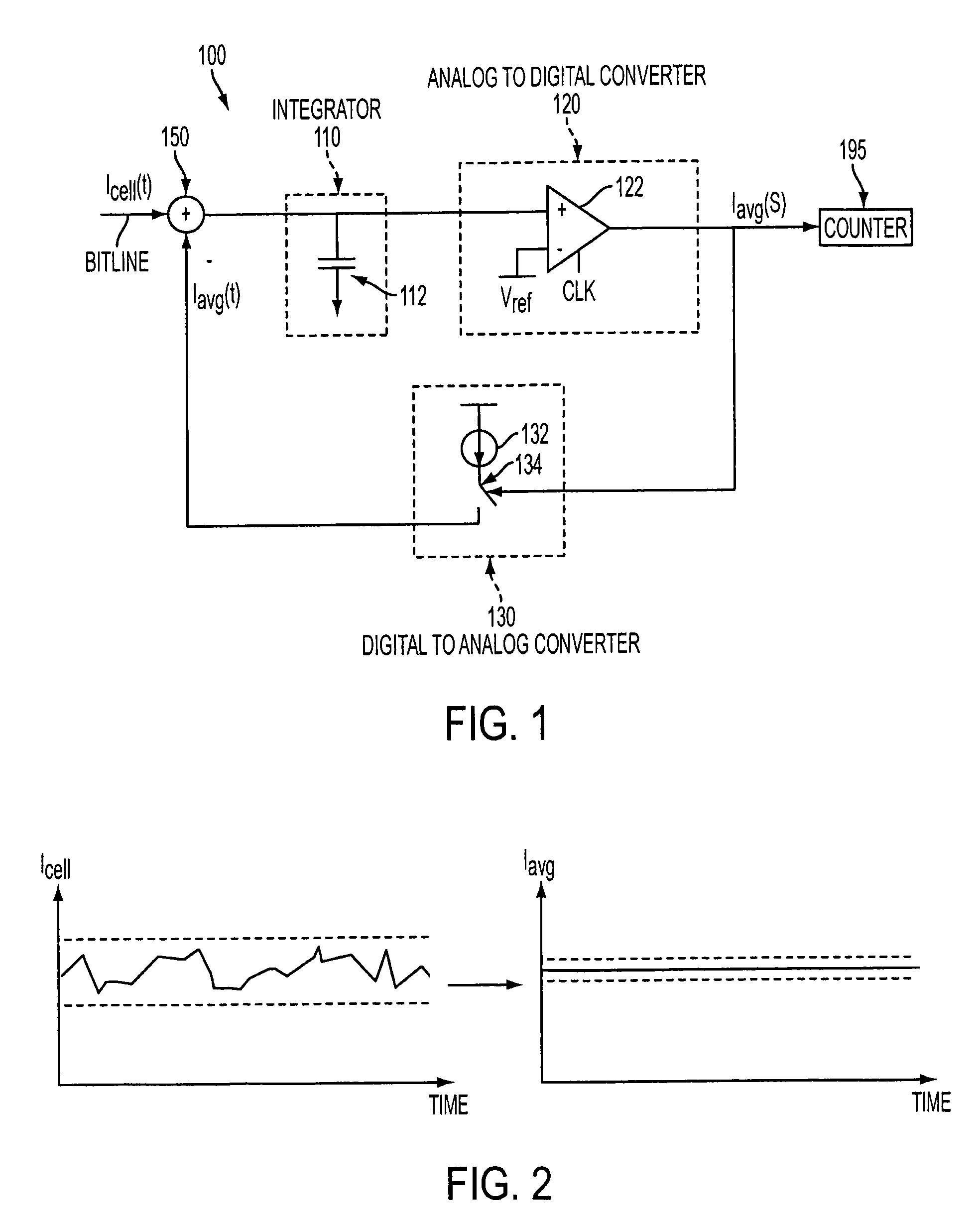

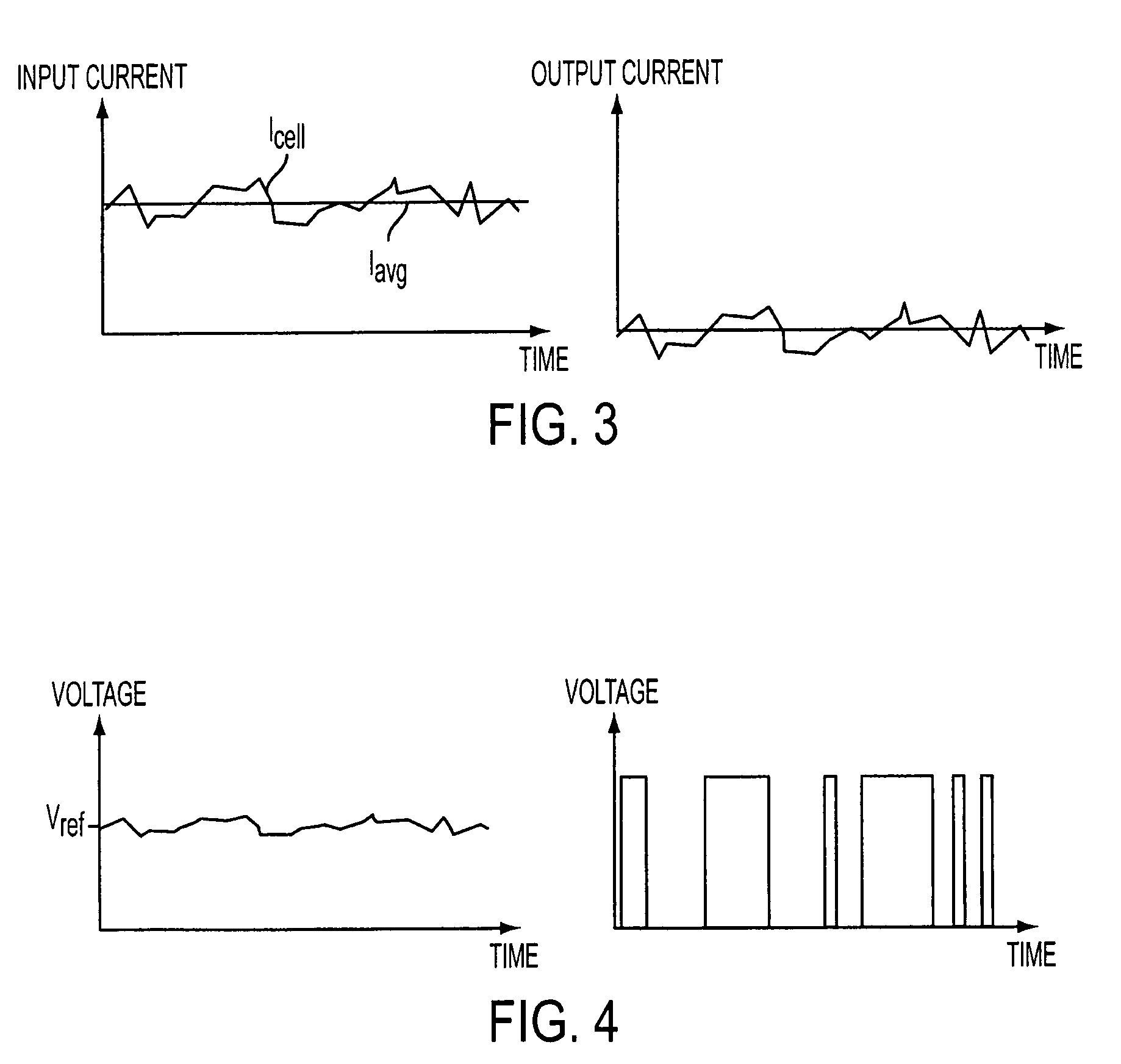

Method and apparatus for sensing flash memory using delta sigma modulation

ActiveUS7366021B2Accurate inductionHigh circuitryRead-only memoriesDigital storageIntegratorAverage current

Owner:MICRON TECH INC

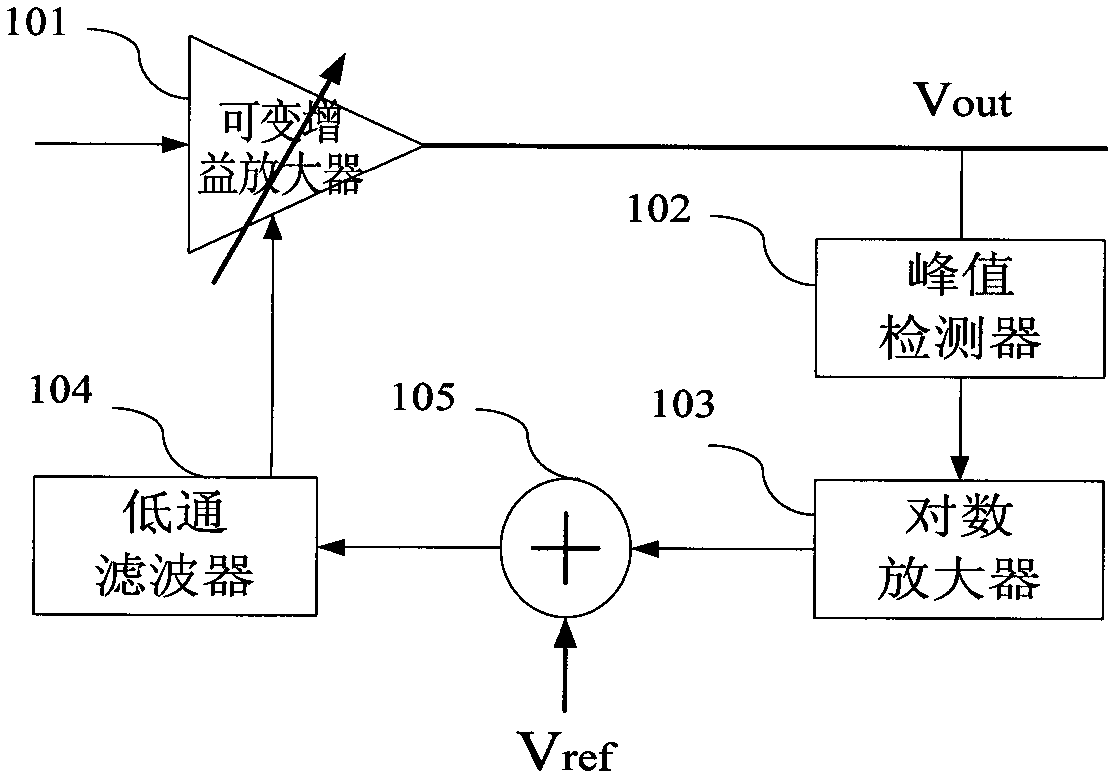

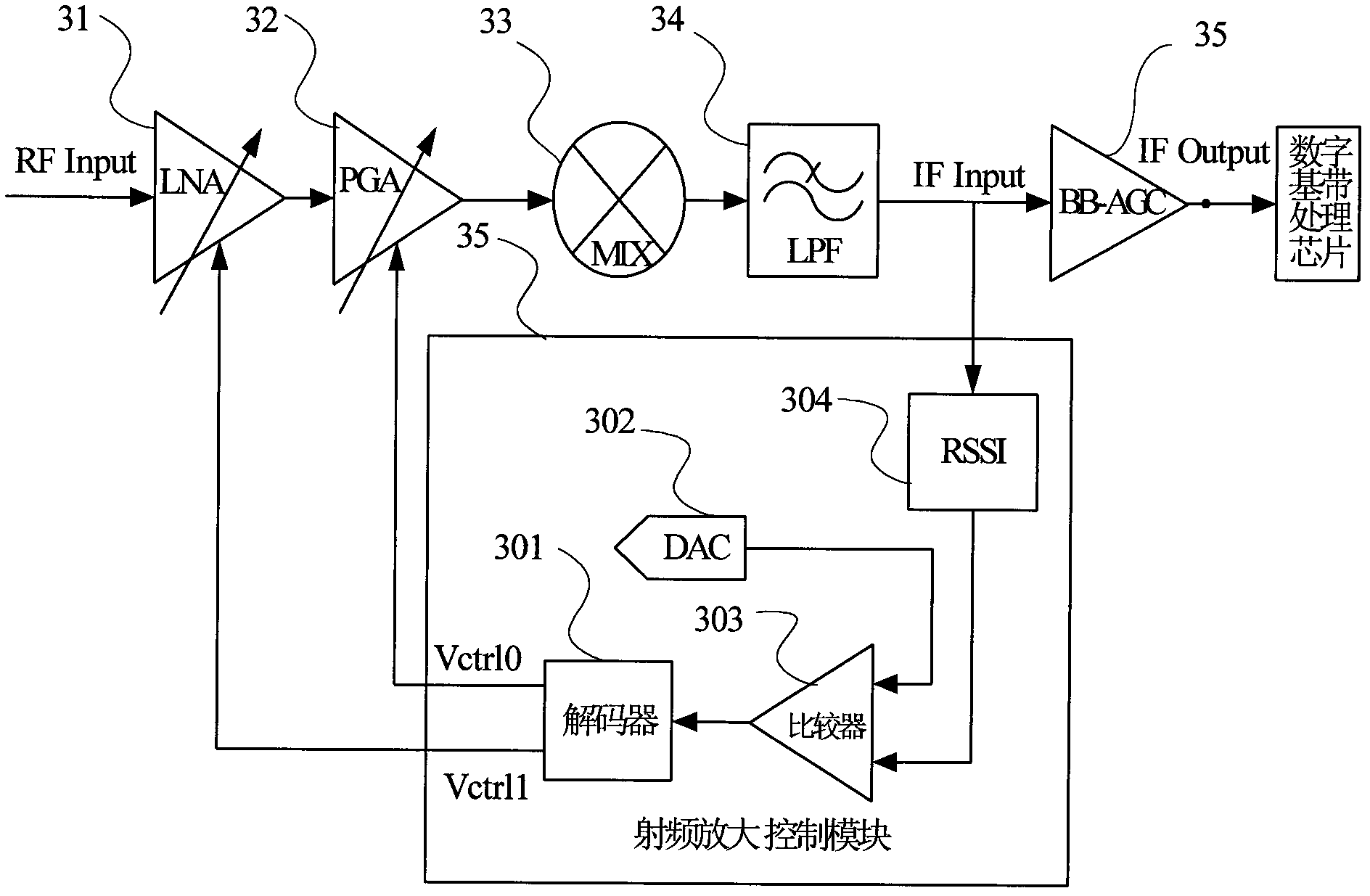

Radio frequency automatic gain control amplifier

ActiveCN102868369AReduce signal to noise ratioSimple designAmplifier modifications to reduce noise influenceLow-pass filterIntermediate frequency

The invention discloses a radio frequency automatic gain control amplifier. The radio frequency automatic gain control amplifier comprises a radio frequency receiving unit, a radio frequency amplifier control unit and an intermediate frequency amplifier, wherein the radio frequency receiving unit is composed of an adjustable low noise amplifier (LNA), a programmable gain amplifier (PGA), a down-conversion frequency mixer and a low-pass filter; the radio frequency amplifier control unit comprises a signal strength detector, a DAC (digital-to-analog converter), a comparator and a decoder; the signal strength detector is used for detecting the strength of an intermediate frequency signal; a comparator circuit is used for comparing an output signal of the signal strength detector with a fixed comparing level output from the DAC so as to output a comparison result; the decoder is used for inputting the comparison result into a gain control digital module and outputting a digital control signal so as to carry out the feedback control to the signal at the front end of the radio frequency, so that the gains of the LNA and the PGA are controlled, the signal to noise ratio of a receiving system is increased, and the requirements on dynamic ranges and high linearity of an input signal are met. The automatic gain control amplifier can be used in various radio frequency receiving chips flexibly, and particularly is applicable to radio frequency front-end circuit which has a wider input range of a radio frequency signal.

Owner:杭州中科微电子有限公司

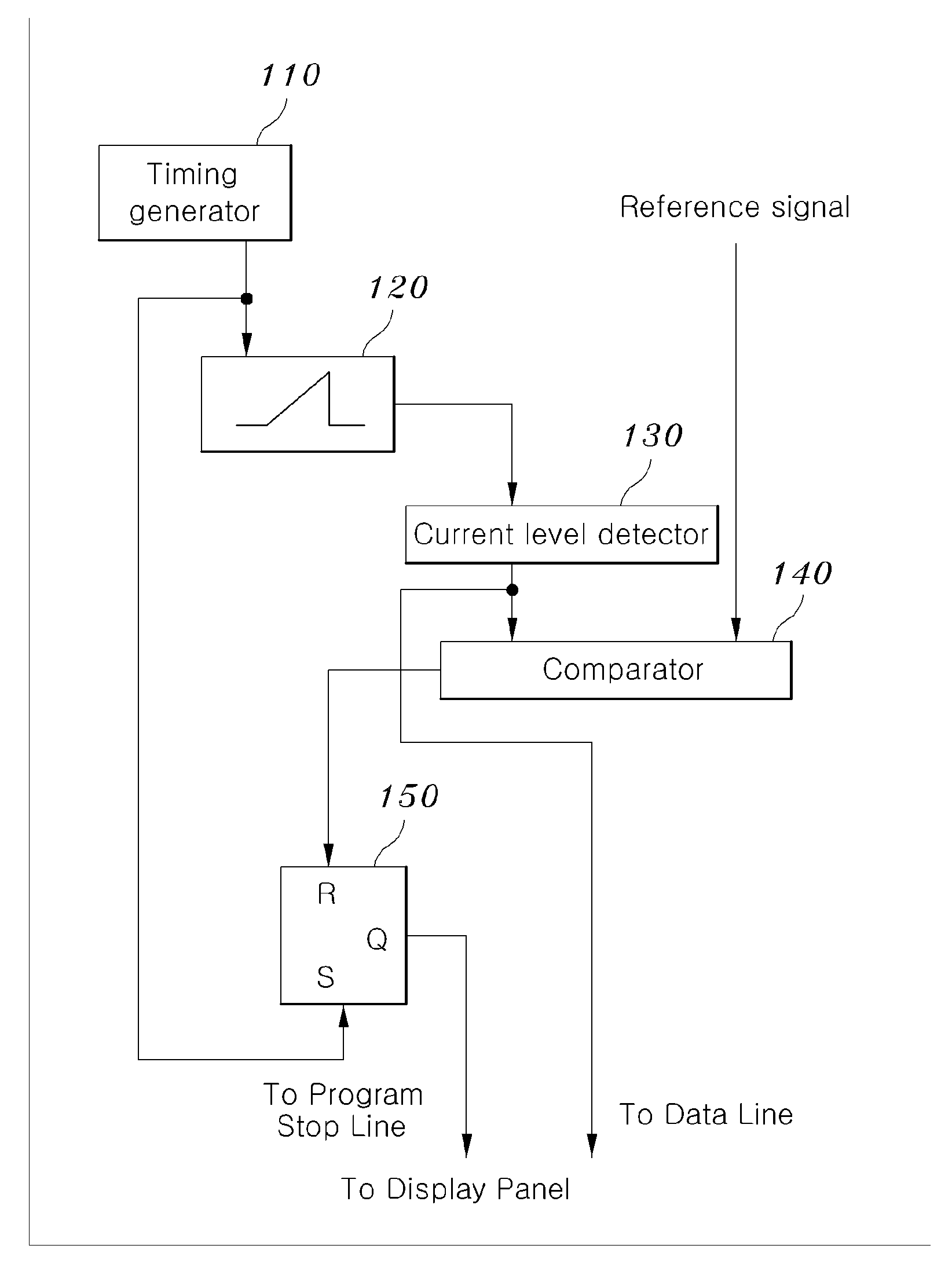

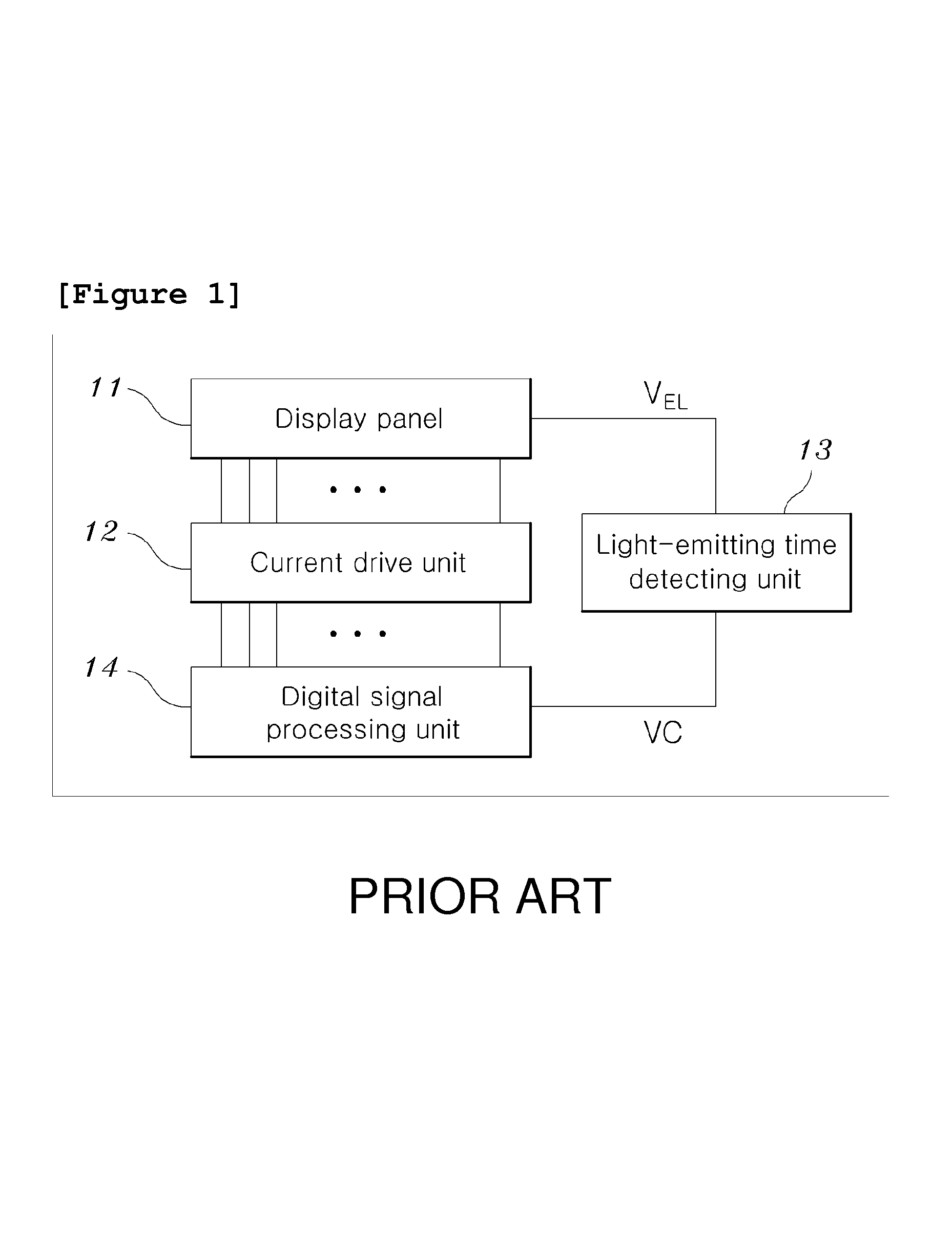

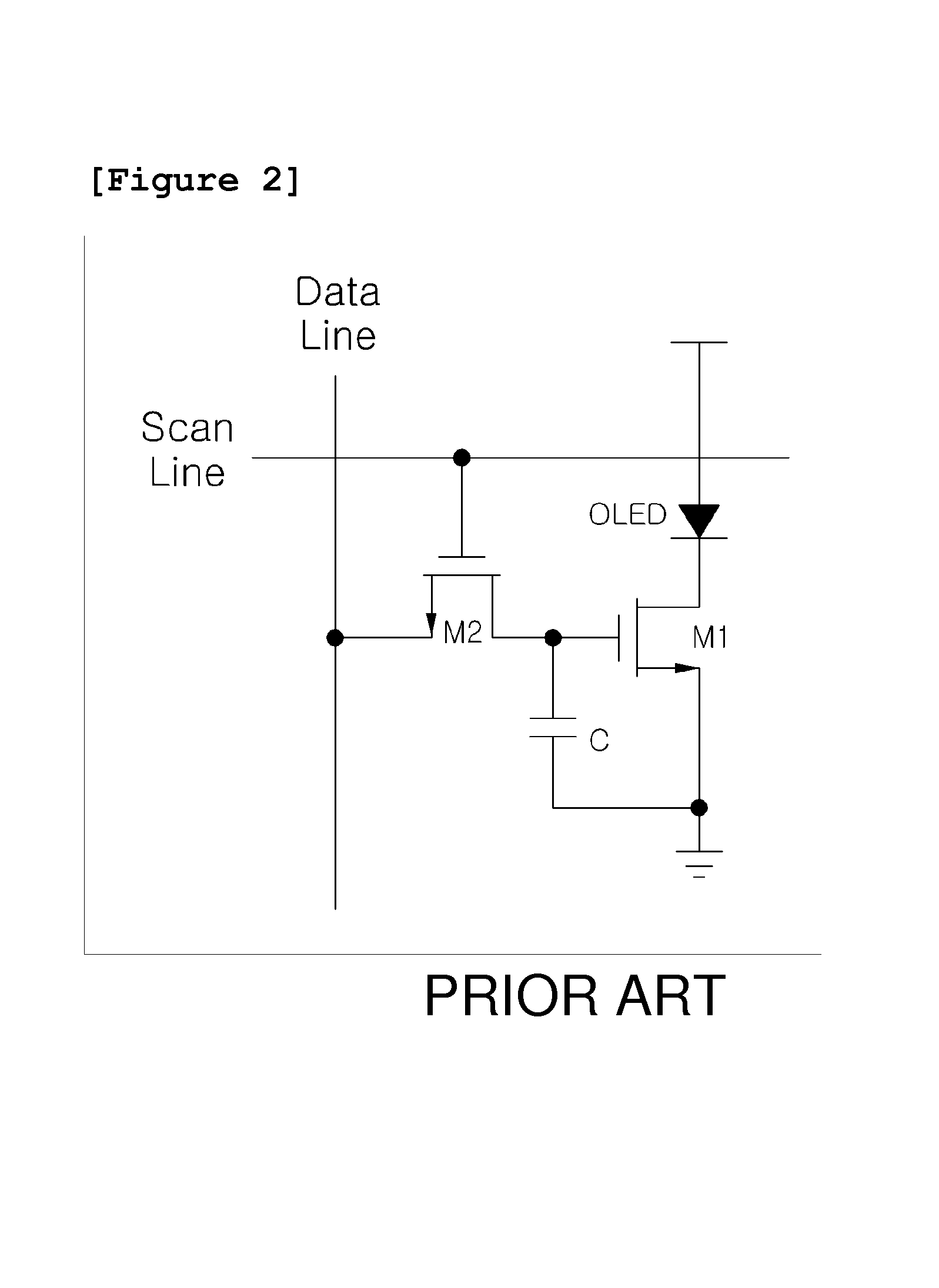

Driving method and circuit for automatic voltage output of active matrix organic light emitting device and data drive circuit using the same

InactiveUS7605792B2Uniform brightnessImprove current drive capabilityElectrical apparatusCathode-ray tube indicatorsControl signalActive matrix

Disclosed herein is a driving method and circuit for the automatic voltage output of an active matrix organic light emitting device, which is capable of resolving the non-uniformity of brightness between pixels. The circuit of the present invention includes timing generation means for generating a data drive start signal; sweep voltage generation means for generating a sweep voltage signal in response to output of the timing generation means; current level detection means for sensing an amount of current, which flows into pixels, based on output of the sweep voltage generation means, and outputting a sensing result to a data line; comparison means for comparing output of the current level detection means with a reference signal that determines stop timing for data writing, and outputting a comparison result; and data writing start / end control signal generation means for starting to operate in response to the output of the timing generation means, and generating data writing start and end control signals to a program stop line of a display panel. The invention can shorten data writing time and improve the precision of data writing. Furthermore, the present invention can simplify a data drive circuit and achieve the uniformity of brightness between pixels.

Owner:IKAIST CO LTD

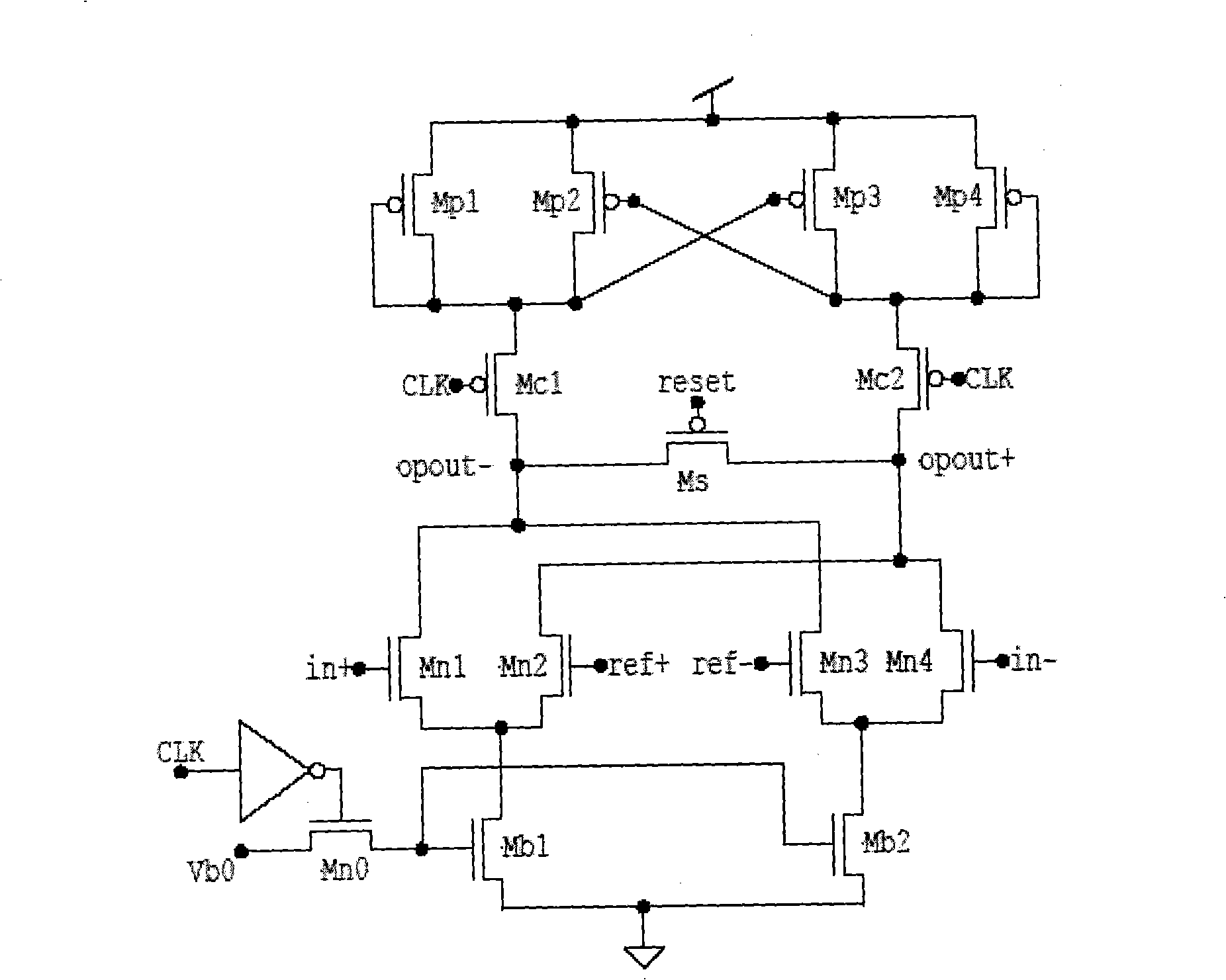

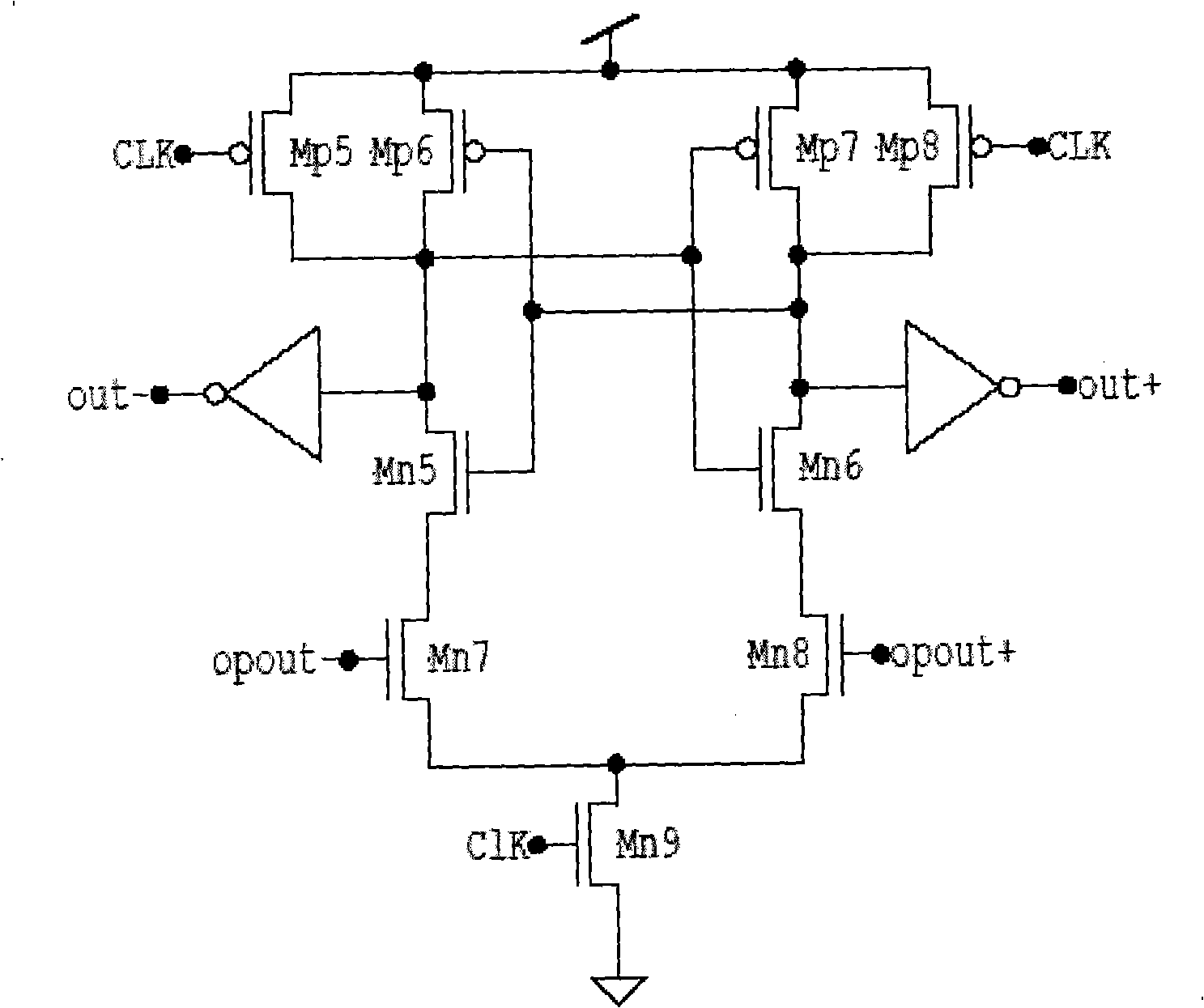

Dynamic comparer

ActiveCN101282117AImprove build speedReduce feedback noiseAnalogue/digital conversionElectric signal transmission systemsOutput compareControl signal

The invention discloses a dynamic comparator including a preamplifier and a positive feedback latch with drive, the preamplifier is controlled by the clock signal CLK and the asynchronous control signal reset, the positive feedback latch with drive is controlled by CLK; when the CLK is in low level, the reset is in high level, tubes connecting two output ends of the preamplifier are cut off, the preamplifier performs amplification for the input signal, the positive feedback latch is reset; when the CLK is in high level, the tail current tube of the preamplifier is cut off and the output end and the load of the preamplifier are cut off, the positive feedback latch works, when the positive feedback latch outputs the compared result, the reset is in the low level, tubes connecting the output end of the preamplifier are closed to make the output end of the preamplifier reset. The invention improces speed of the clock control preamplifier, makes the comparator work in higher frequency and greatly reduces feedback noise of the dynamic comparator, under condition of having advantage of low power dissipation of traditional dynamic comparator.

Owner:北京中科微知识产权服务有限公司

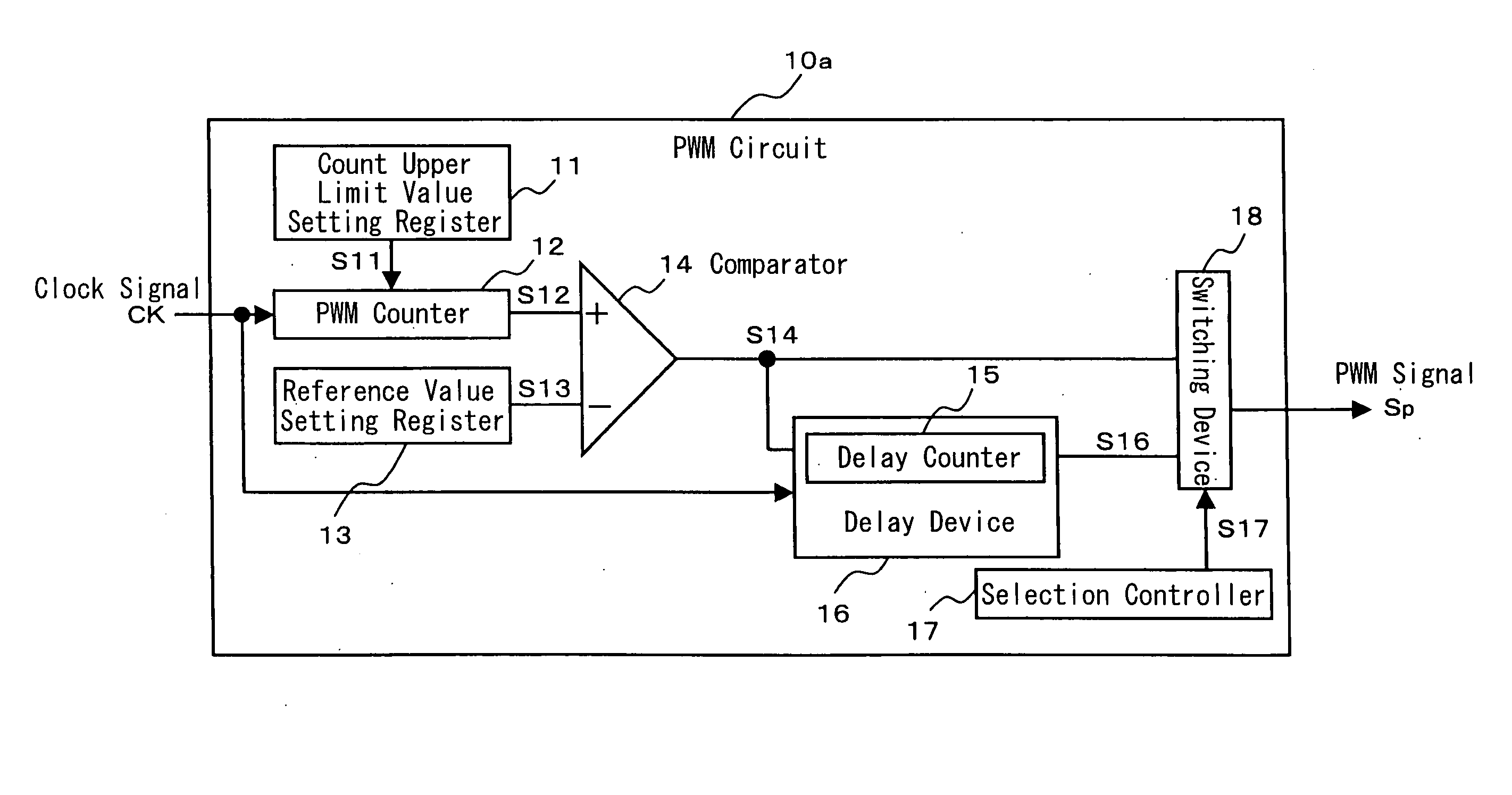

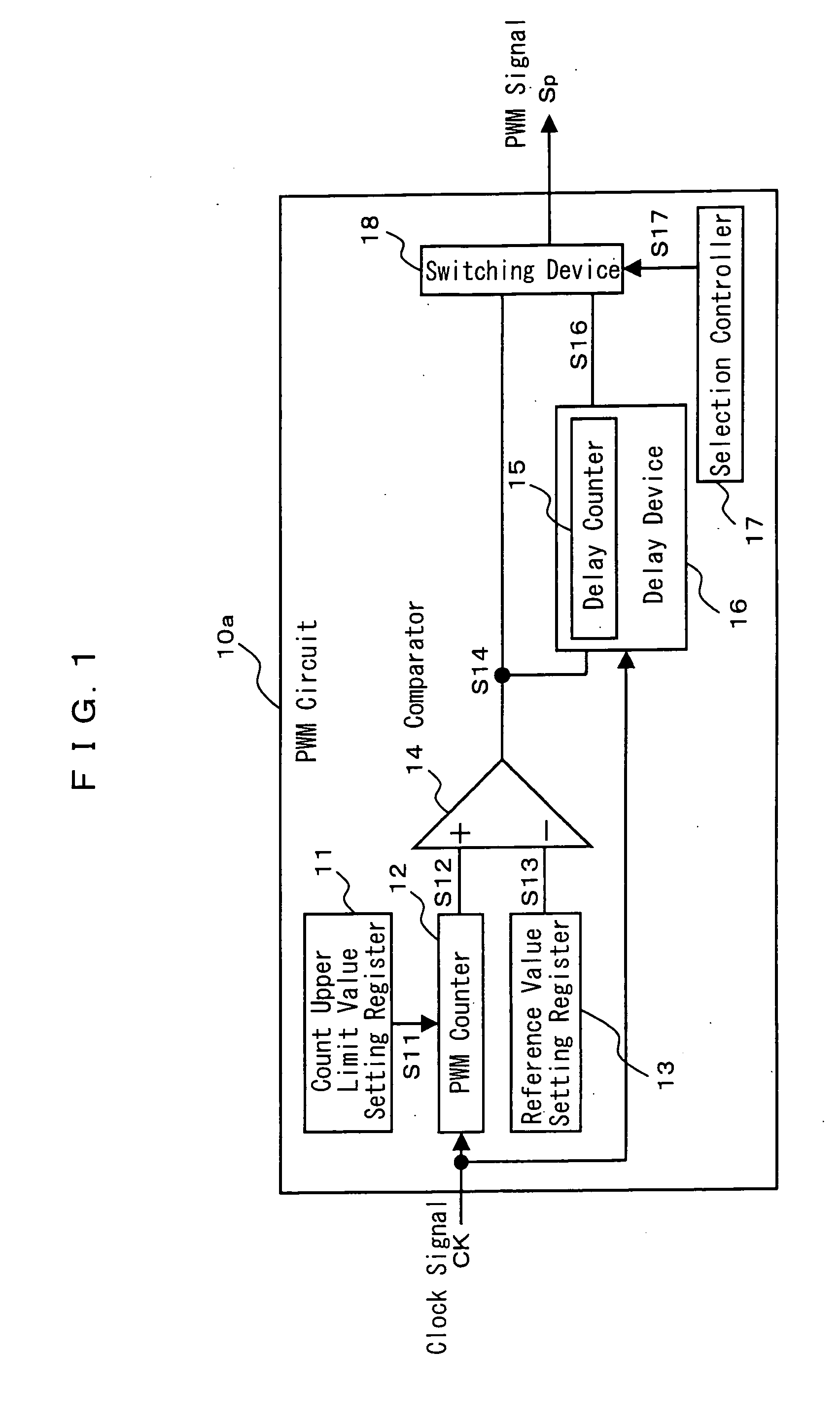

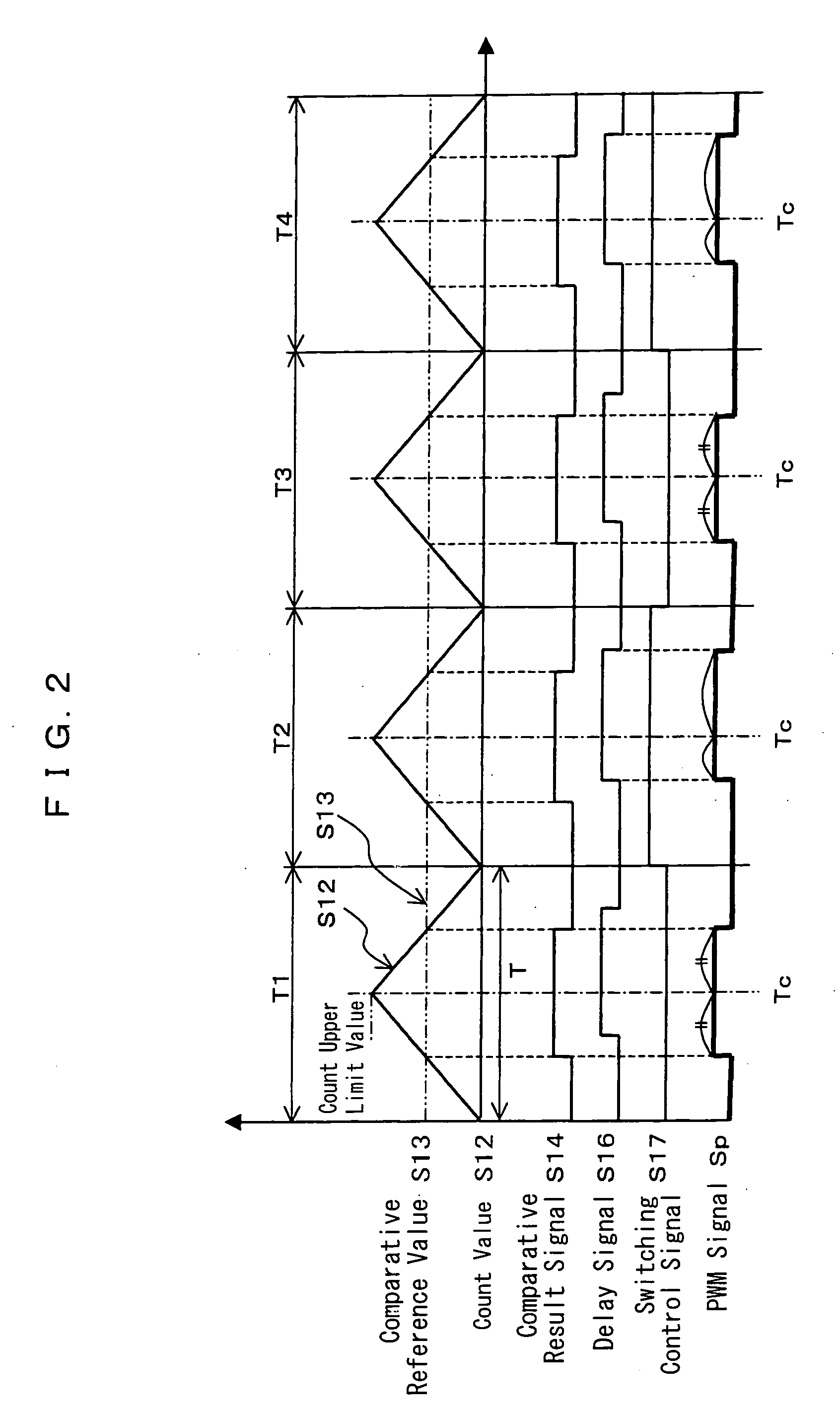

PWM circuit control method

ActiveUS20050285582A1Good dispersion propertiesAvoid noiseAC motor controlDc-dc conversionOutput compareEngineering

In the PWM circuit of the present invention, a PWM counter counts clock signals. A reference value setting register sets a comparative reference value for determining a duty ratio of a PWM signal. A comparator generates the PWM signals based on a comparative result of the comparative reference value and a count value of the PWM counter. A delay device delays the PWM signal. A switching device switchably outputs the output of the comparator and the output of the delay device in order of time sequence. Thereby, the pulse phase of the PWM signal can be adjusted.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

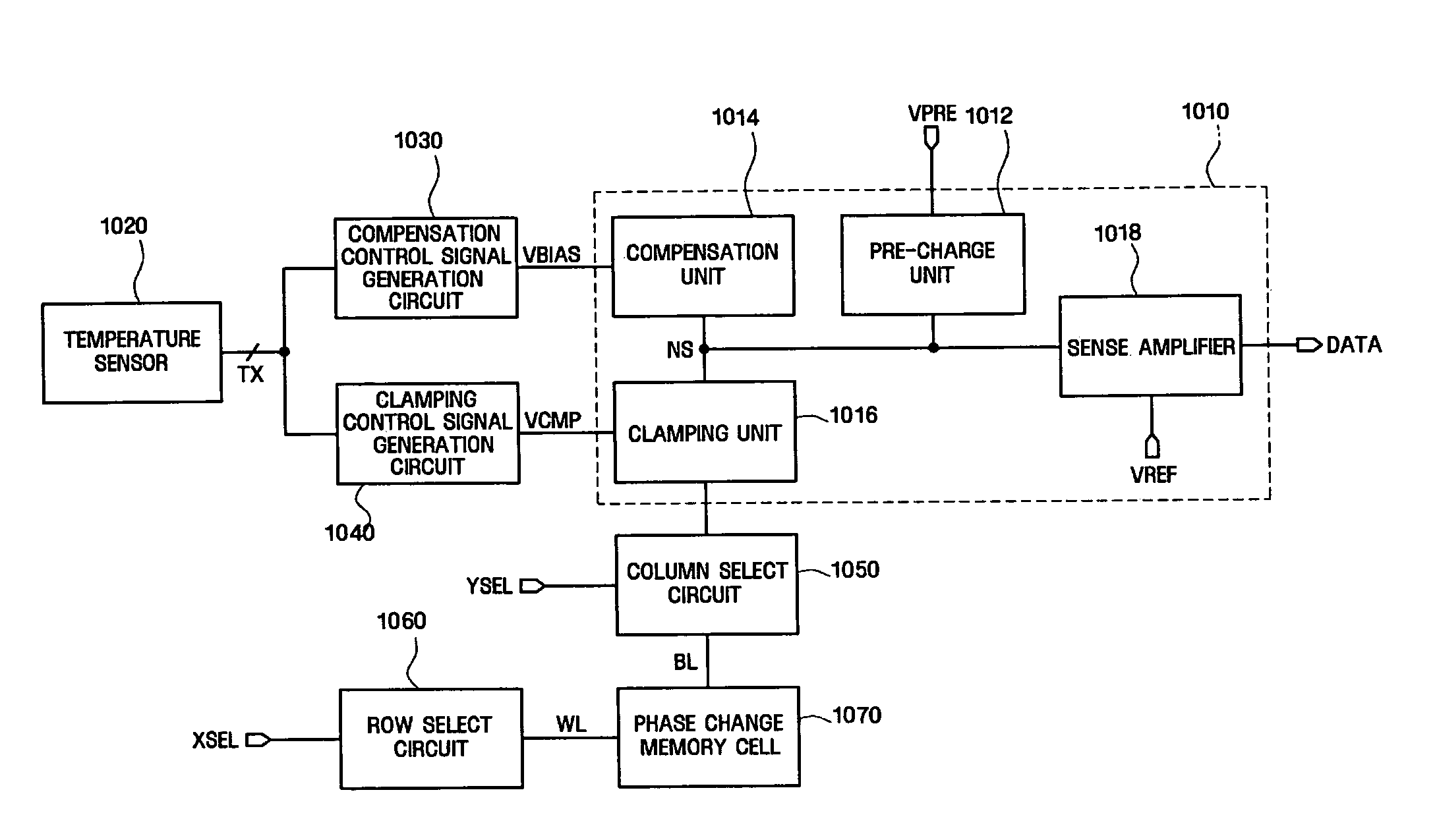

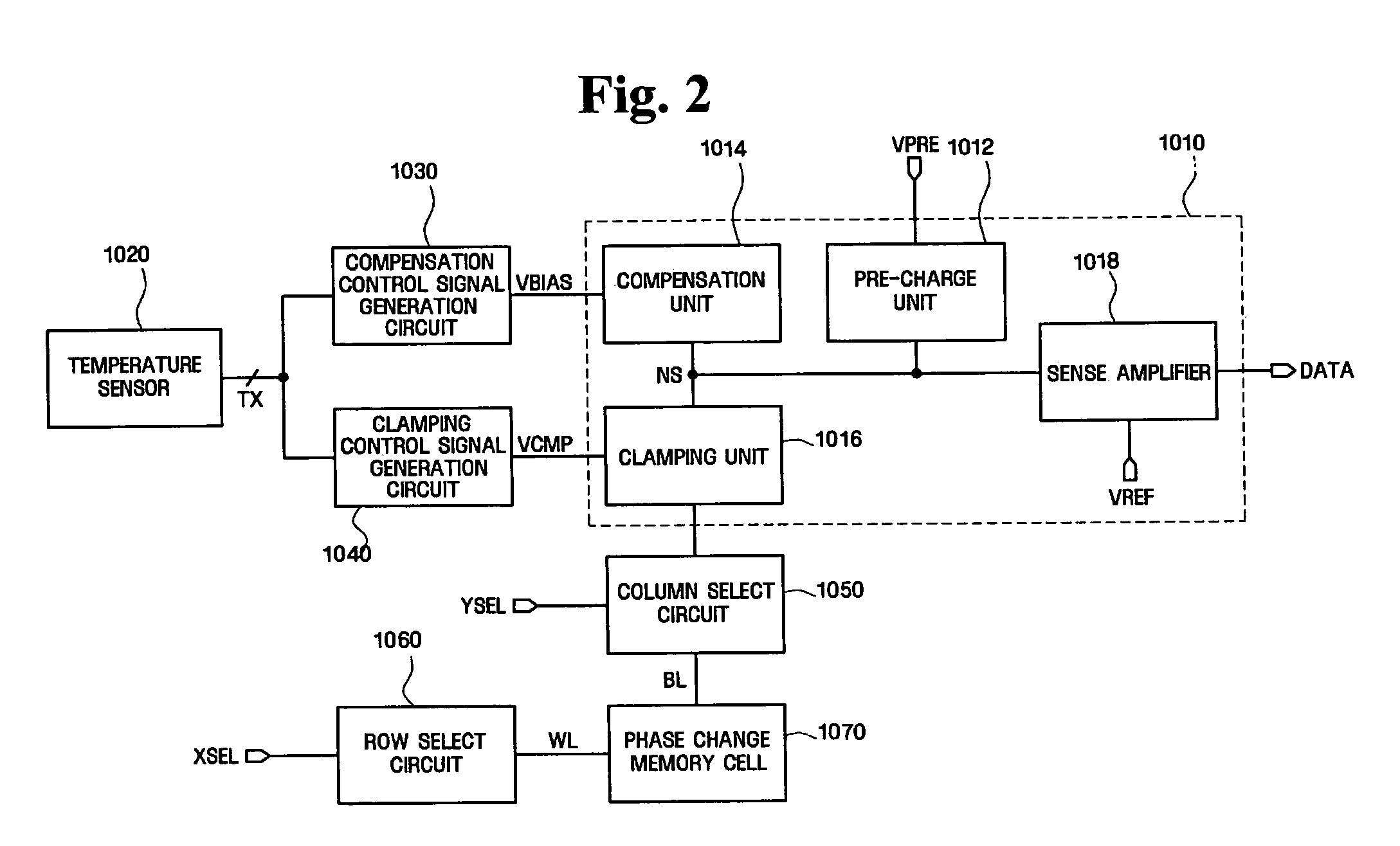

Nonvolatile memory device, storage system having the same, and method of driving the nonvolatile memory device

A nonvolatile memory device includes a memory cell array including a plurality of nonvolatile memory cells each having a resistance corresponding to one of a plurality of first resistance distributions, a temperature compensation circuit including one or more reference cells each having a resistance corresponding to one among one or more second resistance distributions, and a data read circuit including a compensation unit and a sense amplifier, the compensation unit being adapted to supply compensation current to a sensing node, an amount of the compensation current varying based on the resistance of each reference cell, and the sense amplifier being adapted to compare the level of the sensing node with a reference level and to output a comparison result.

Owner:SAMSUNG ELECTRONICS CO LTD

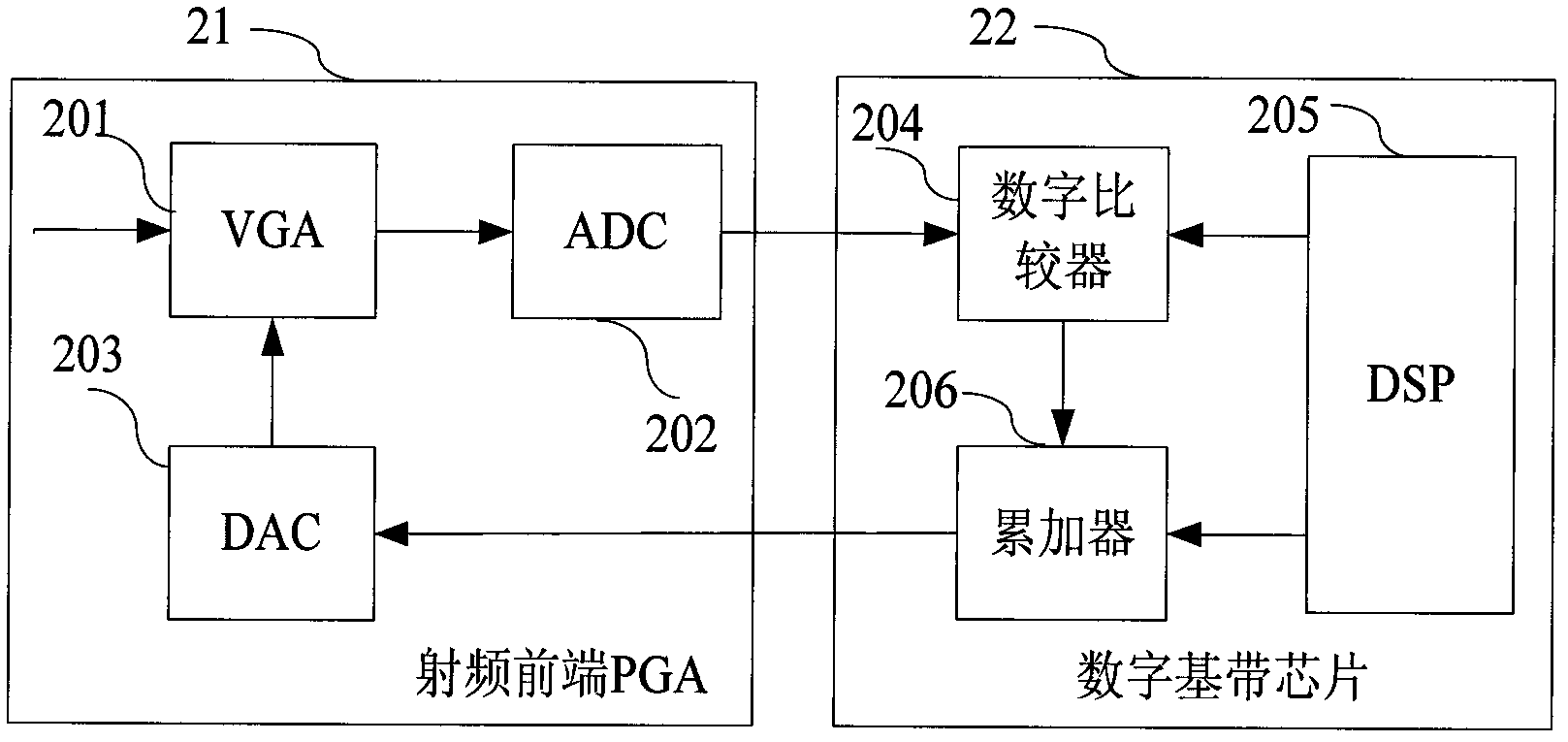

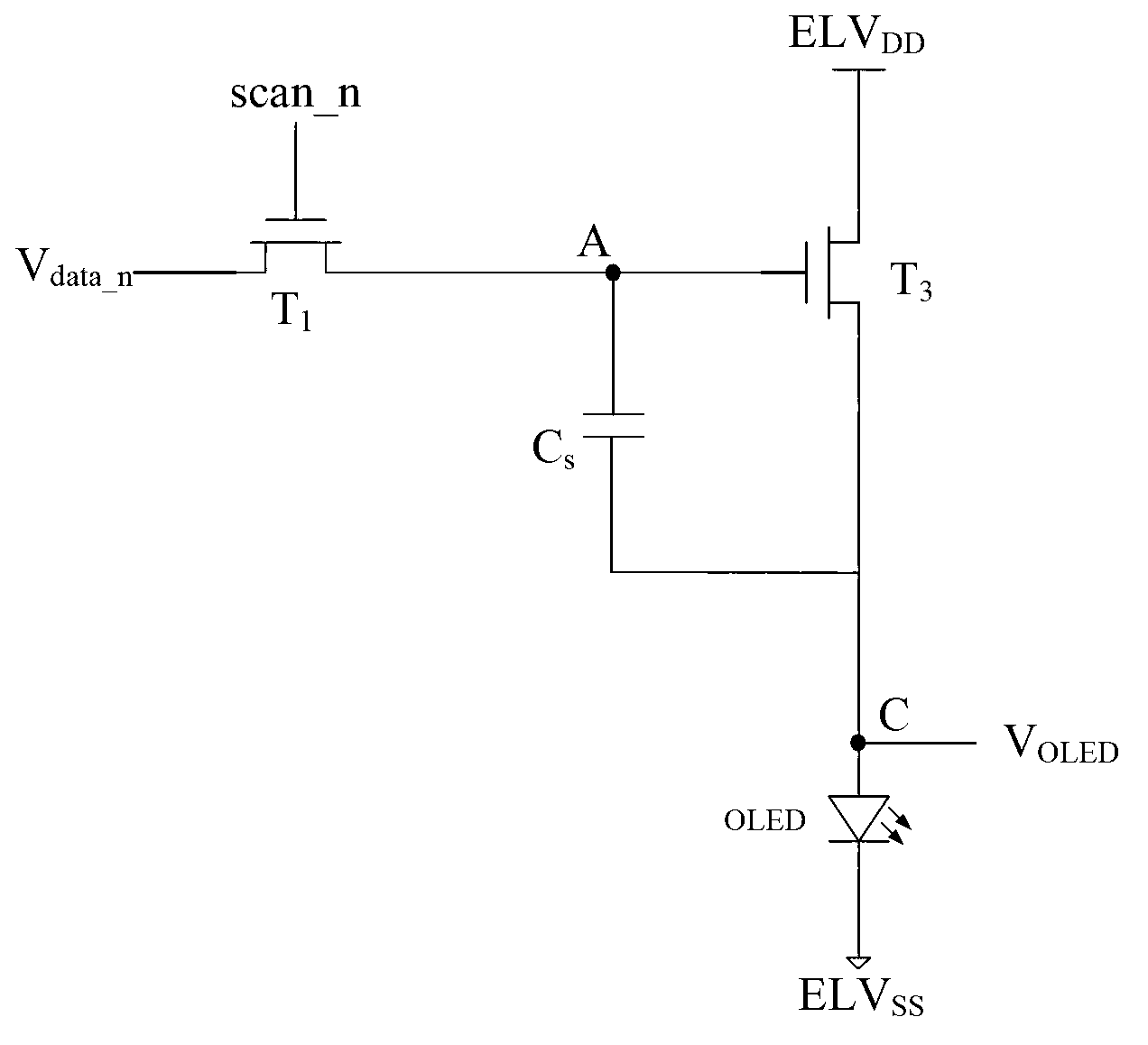

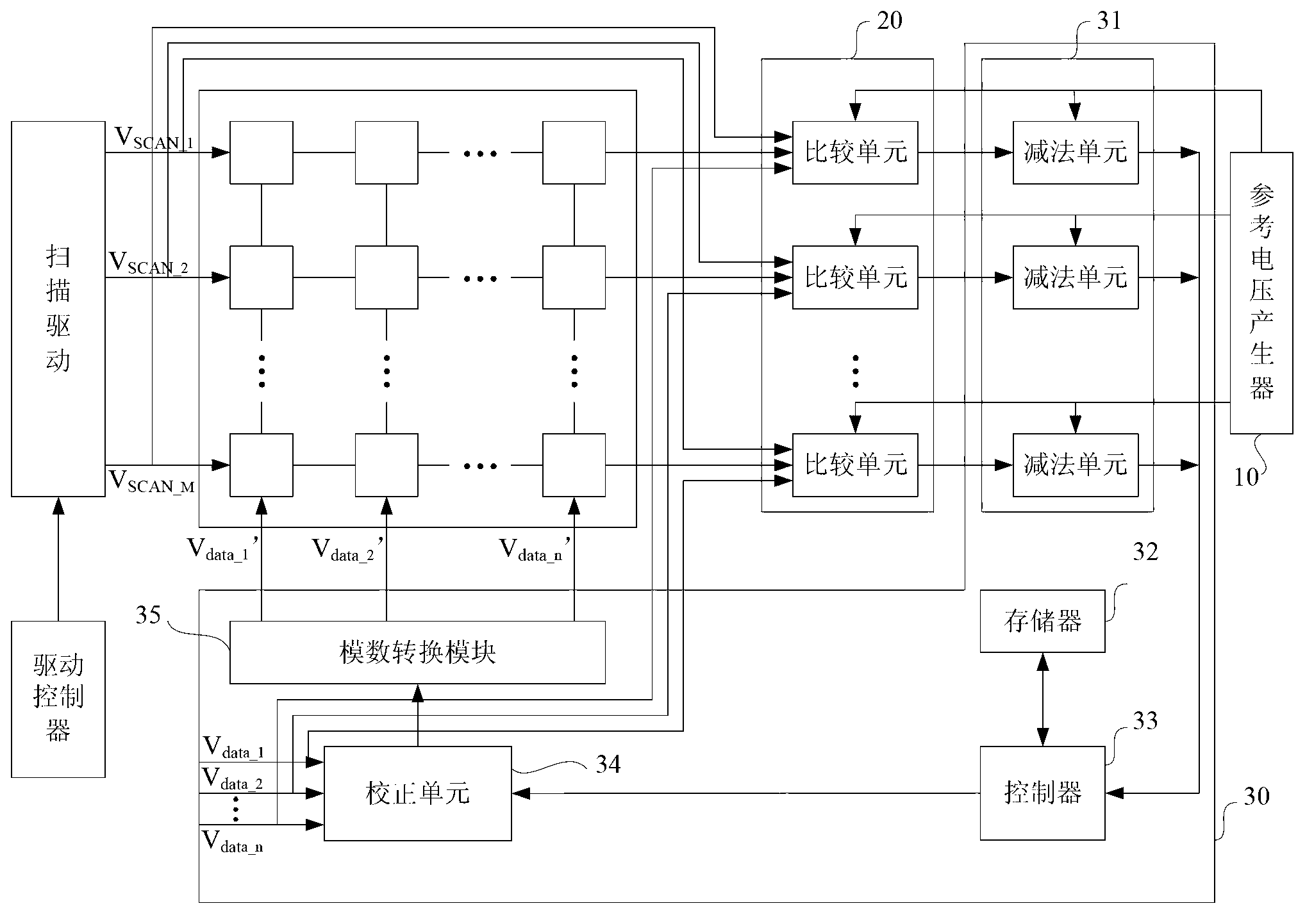

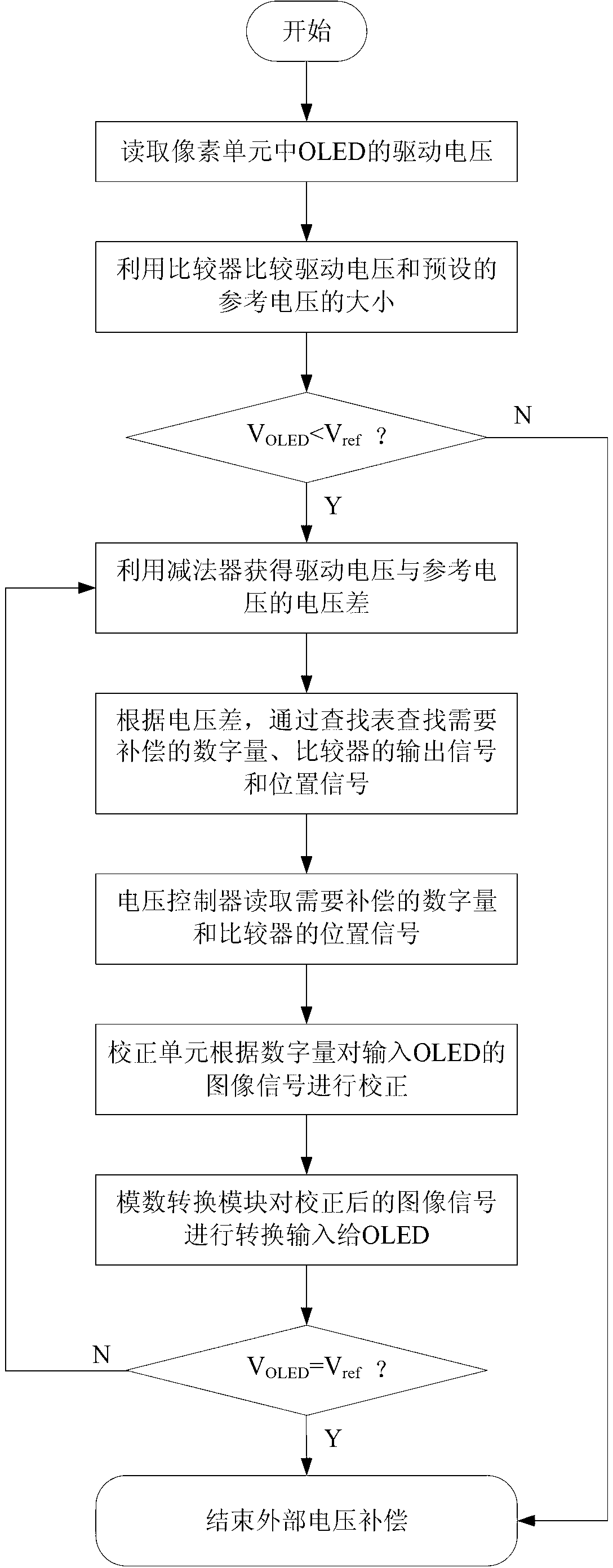

AMOLED voltage external compensation method and system

ActiveCN103268756AIncrease duty cycleShorten the timeStatic indicating devicesVoltage referenceAMOLED

The invention provides an AMOLED voltage external compensation method and circuit. The method includes the following steps of comparing the magnitude of a driving voltage of an OLED with the magnitude of a preset reference voltage through a comparator and beginning voltage compensation if the magnitude of the driving voltage of the OLED is less than the magnitude of the preset reference voltage. The voltage compensation includes the following steps of obtaining a voltage difference of between the driving voltage and the preset reference voltage through a subtractor, outputting a position signal of the comparator, looking up digital quantity which needs to be compensated, an output signal of the comparator and the position signal of the comparator according to the voltage difference, controlling a correction unit to correct an image signal which is input into the OLED according to the digital quantity through a voltage controller; conducting conversion on the corrected image signal through a digital-to-analog conversion module, obtaining a corrected image voltage signal and inputting the corrected image voltage signal to the OLED, repeating the voltage compensation process until the driving voltage is equal to the preset reference voltage, and stopping the voltage compensation. According to the AMOLED voltage external compensation method and circuit, a duty ratio of a pixel unit is improved, time for displaying an image is shortened, the luminance of the OLED is only related to the magnitude of Vdata_n, and the luminance of the OLED is not related to a threshold voltage which drives a TFT or electron mobility.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

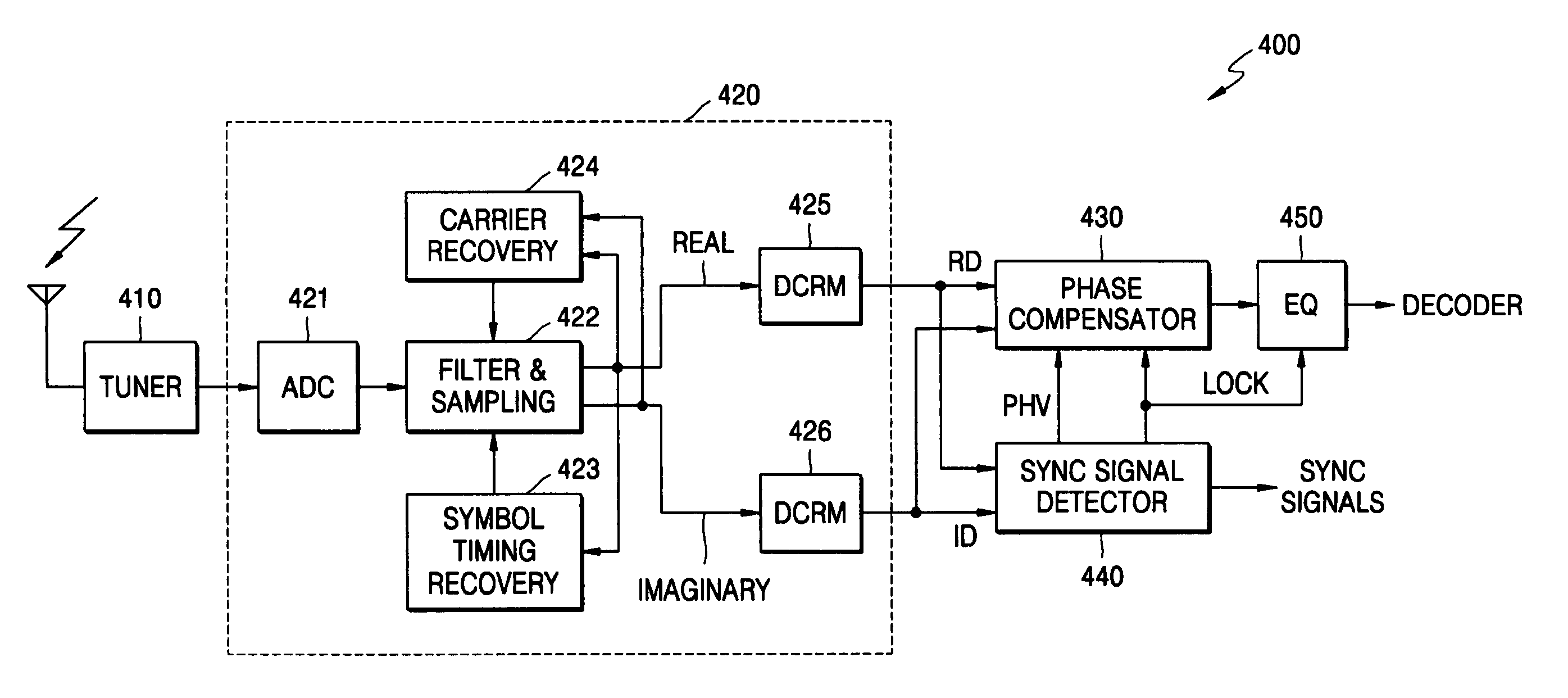

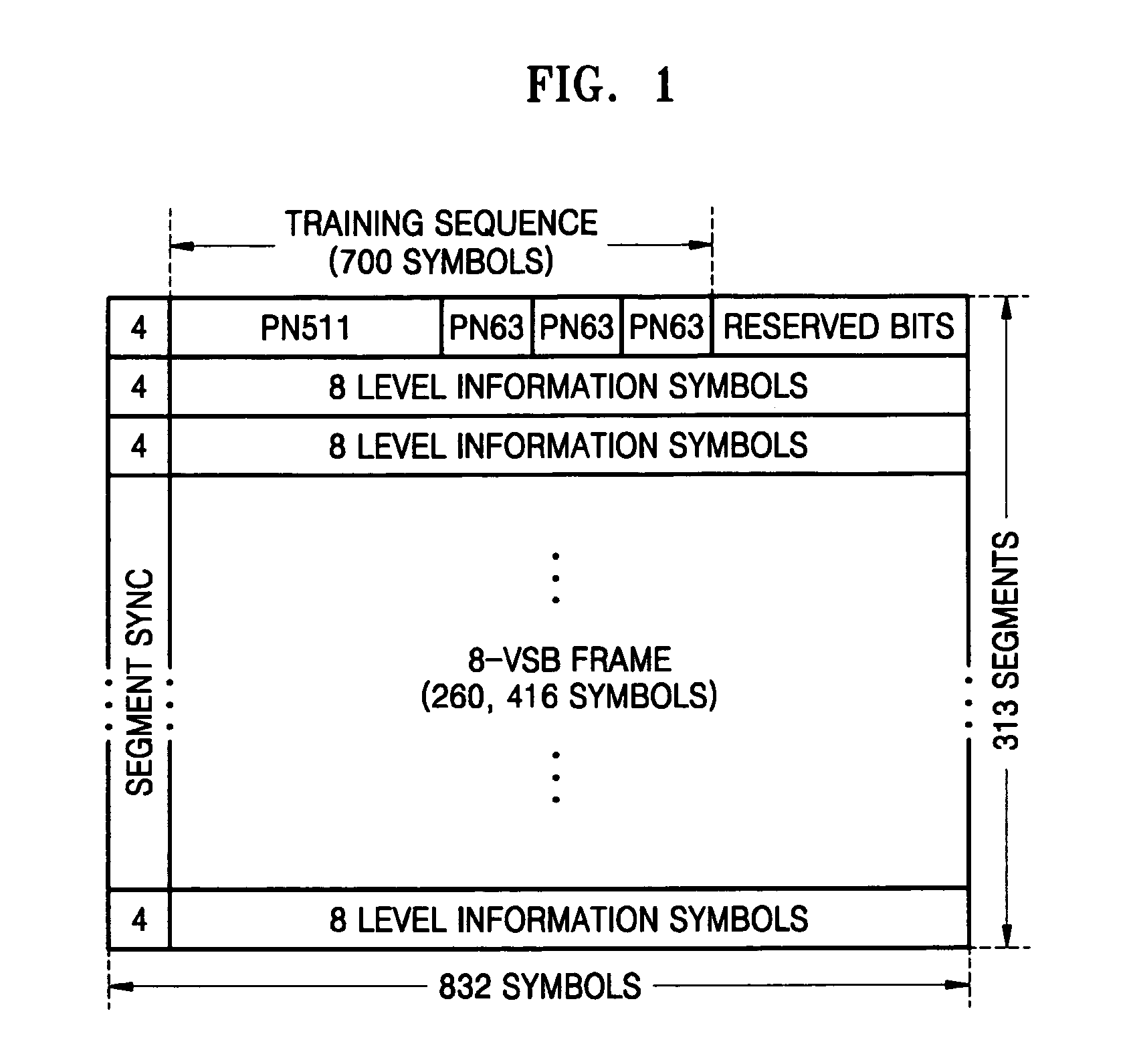

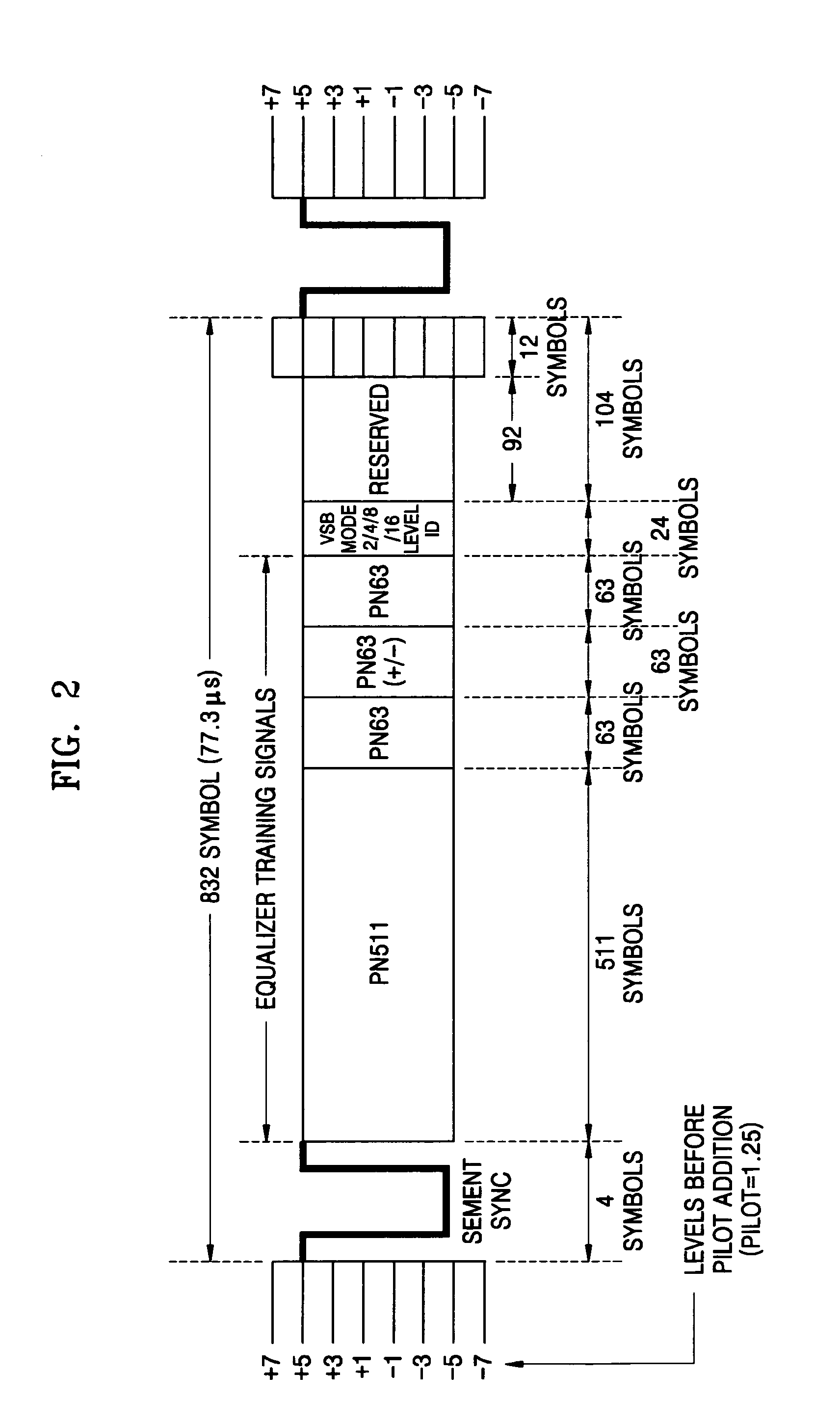

Synchronization signal detection in a digital television receiver

A digital television (DTV) receiver is provided, comprising: a demodulator that demodulates television signals and outputs equalizer training signals in the form of real (I) and imaginary (Q) data; a sync signal detector, and a phase compensator that offsets the phase of the I and Q data based on the phase offset signal and outputs phase adjusted I data under control of the lock control signal. The sync signal detector comprises: a correlator that correlates the equalizer training signals including the I and Q data; a power calculator that calculates the sum of the power of the correlated I and Q data; a comparator that compares (the sum) against a preset threshold and outputs a compare indication signal; a sync lock controller that monitors the compare indication signal and outputs a lock control signal; and a phase calculator that calculates a phase of the equalizer training signals based on the I and Q data and outputs a phase offset signal based on the compare indication signal.

Owner:SAMSUNG ELECTRONICS CO LTD

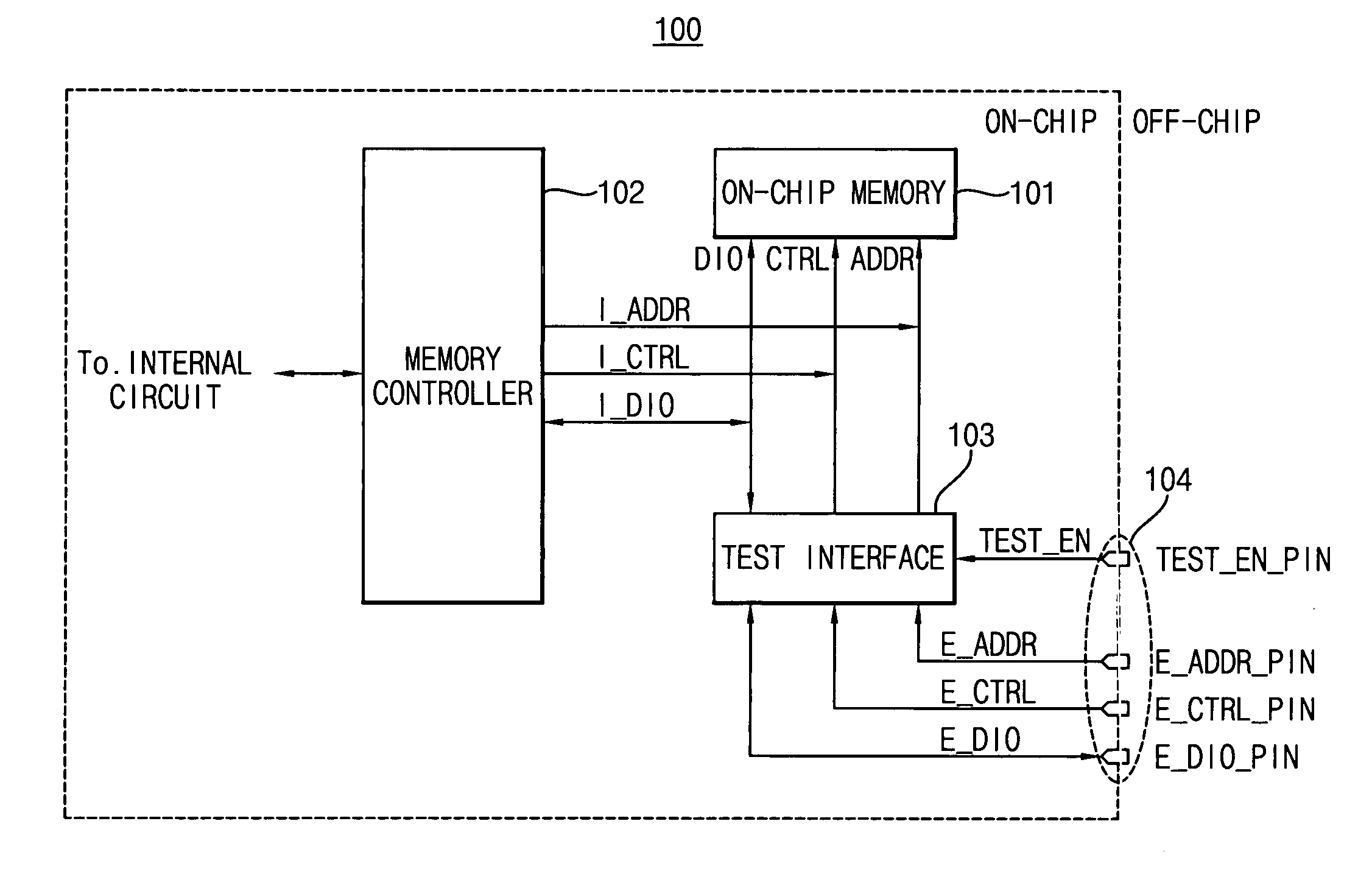

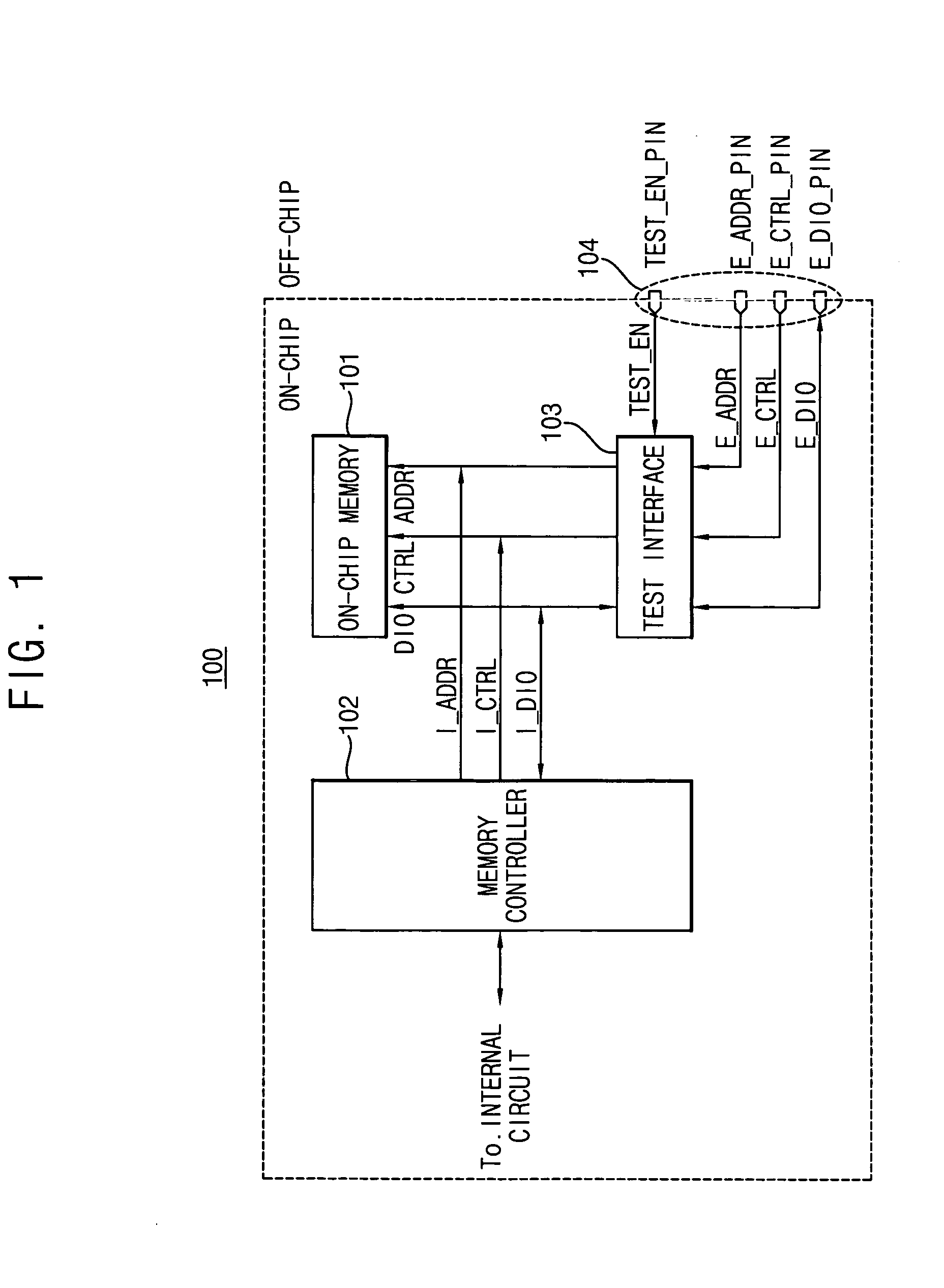

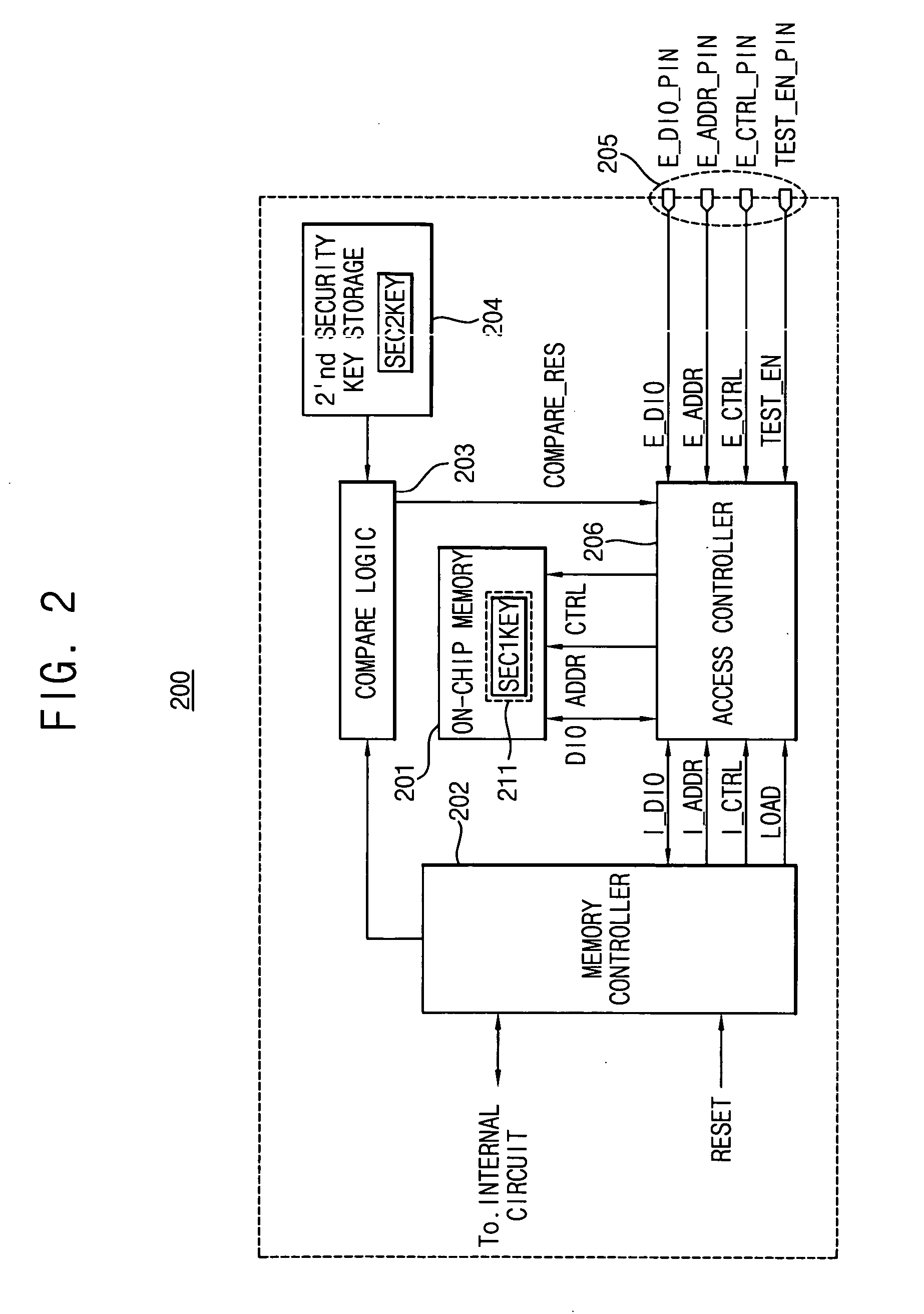

Security circuit and method to secure information in a device

InactiveUS20060184799A1Avoid destructionInternal/peripheral component protectionPackaging under special atmospheric conditionsExternal storageOutput compare

A circuit and method for securing information (e.g., a product serial number or certification key) stored in non-volatile on-chip memory from unauthorized read-out or destruction. External access is prevented by writing a first n-bit security key-word into the memory. A compare circuit compares the first security key-word with a second n-bit security key-word and outputs a comparison signal that either grants or denies external access to the memory based on a predetermined compare condition. The values of each of the first and second key-word and the comparison algorithm (predetermined compare condition) may be selected to avoid any interference with external memory-testing. The predetermined compare condition may be a pre-selected one of a match and a mismatch between the first security key word and the second security key word. At least one bit of the first or second security key word may be a fuse programmable bit.

Owner:SAMSUNG ELECTRONICS CO LTD

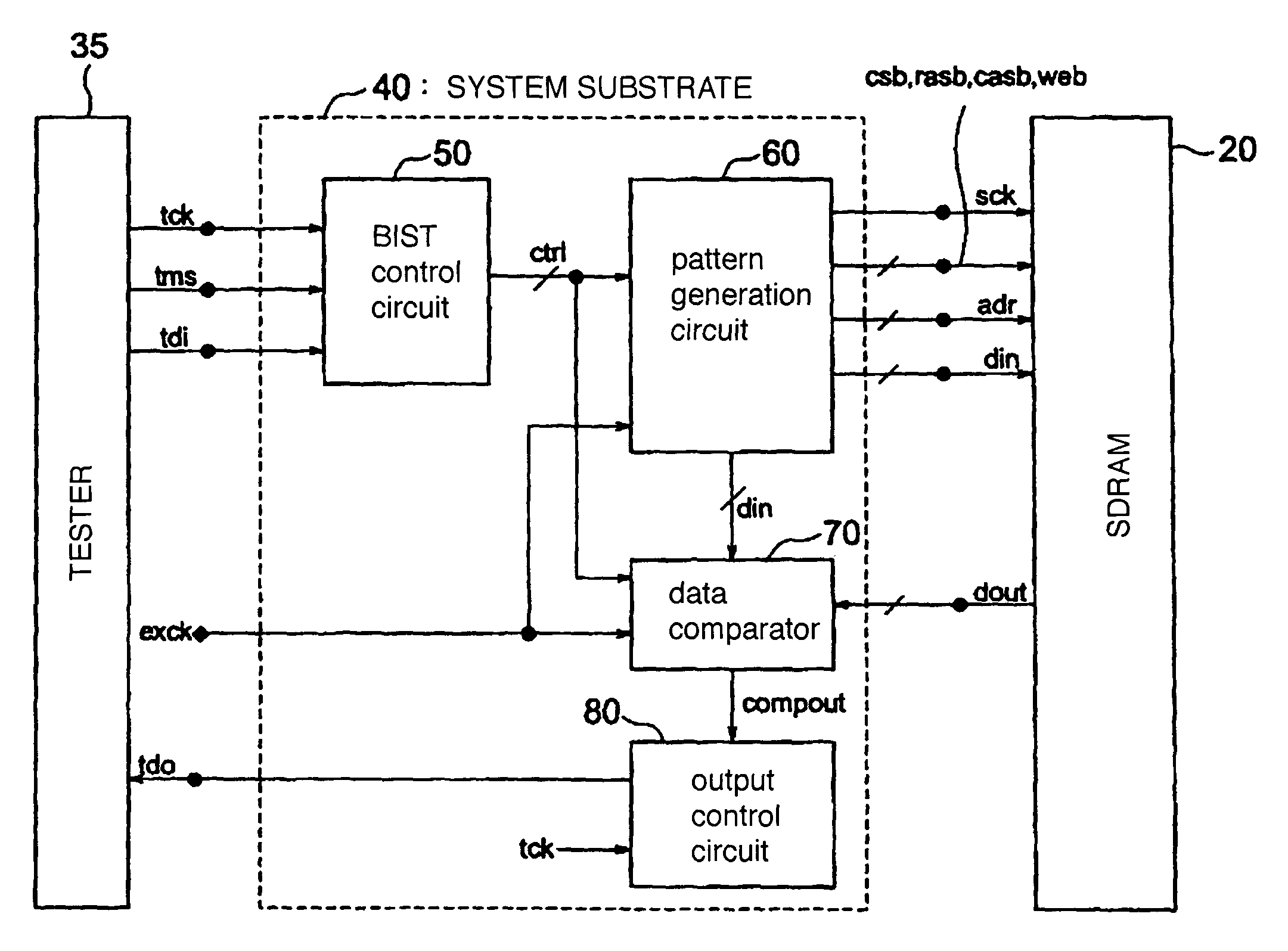

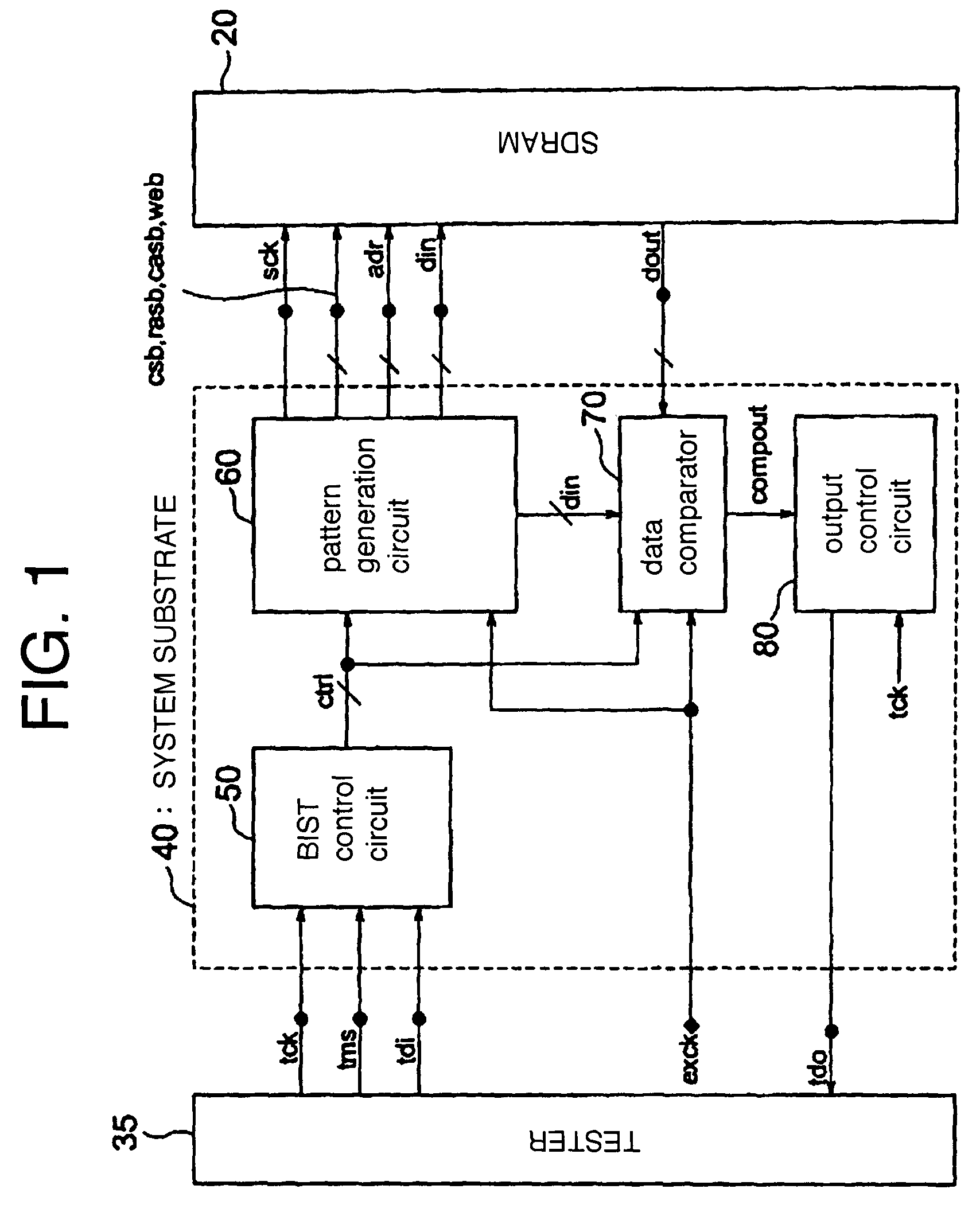

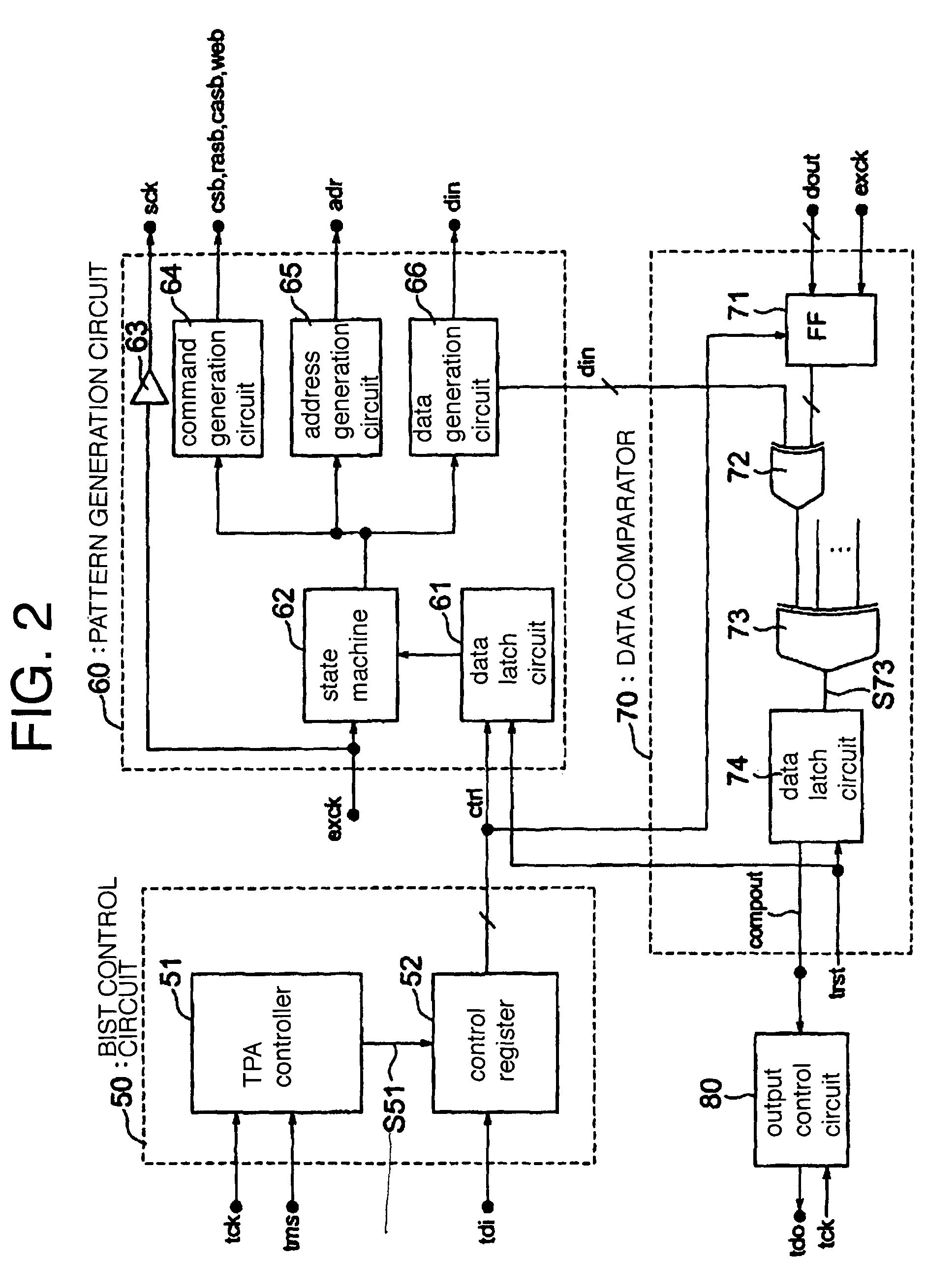

Test circuit provided with built-in self test function

A test circuit includes an input circuit for inputting data to select a test mode relative to a circuit to be tested and outputting result of selection of the test mode in synchronization with a first clock, a pattern generation circuit for responding to result of selection of the test mode, generating a test pattern in synchronization with a second clock and outputting the test pattern to the circuit to be tested and a comparator circuit for inputting result of test of the circuit to be tested in synchronization with the second clock, and comparing coincidence / non-coincidence between the result of the test and the test pattern supplied to the circuit to be tested. The test circuit further includes an output circuit for holding result of comparison by the comparator circuit and outputting the result of comparison in synchronization with the first clock.

Owner:LAPIS SEMICON CO LTD

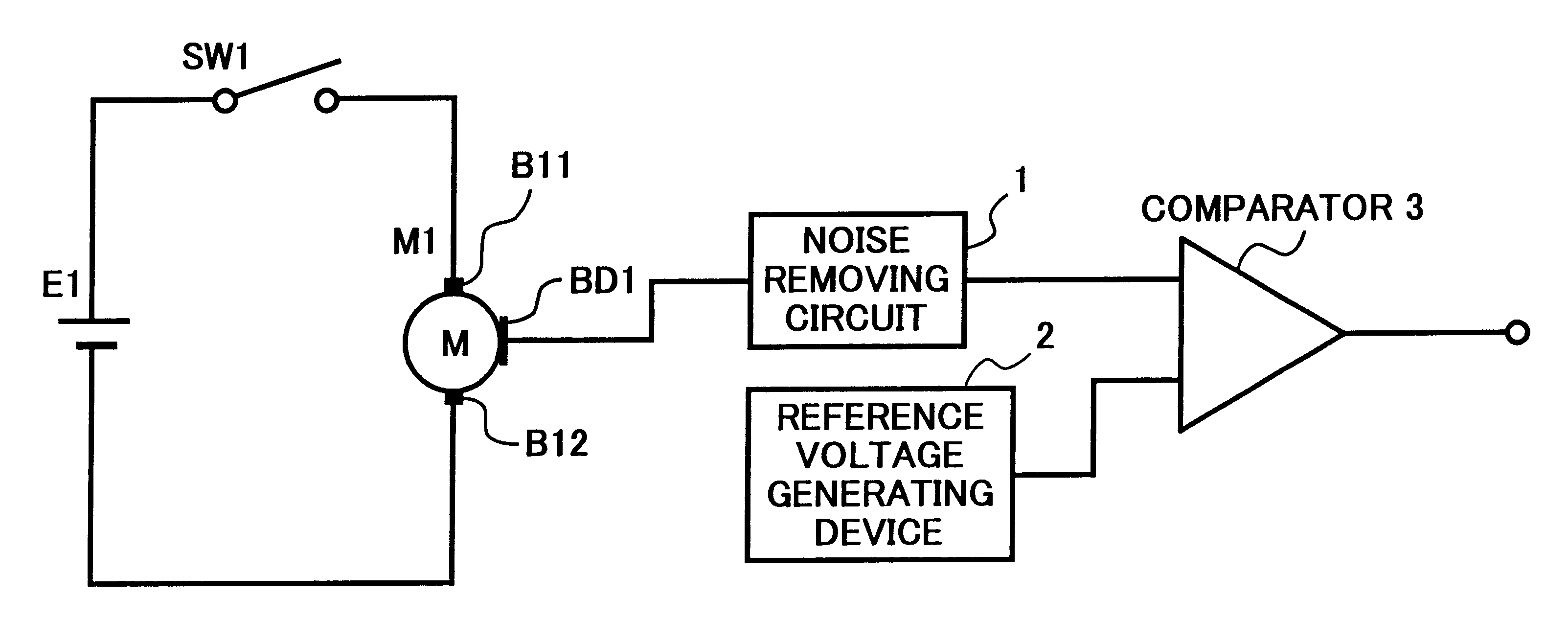

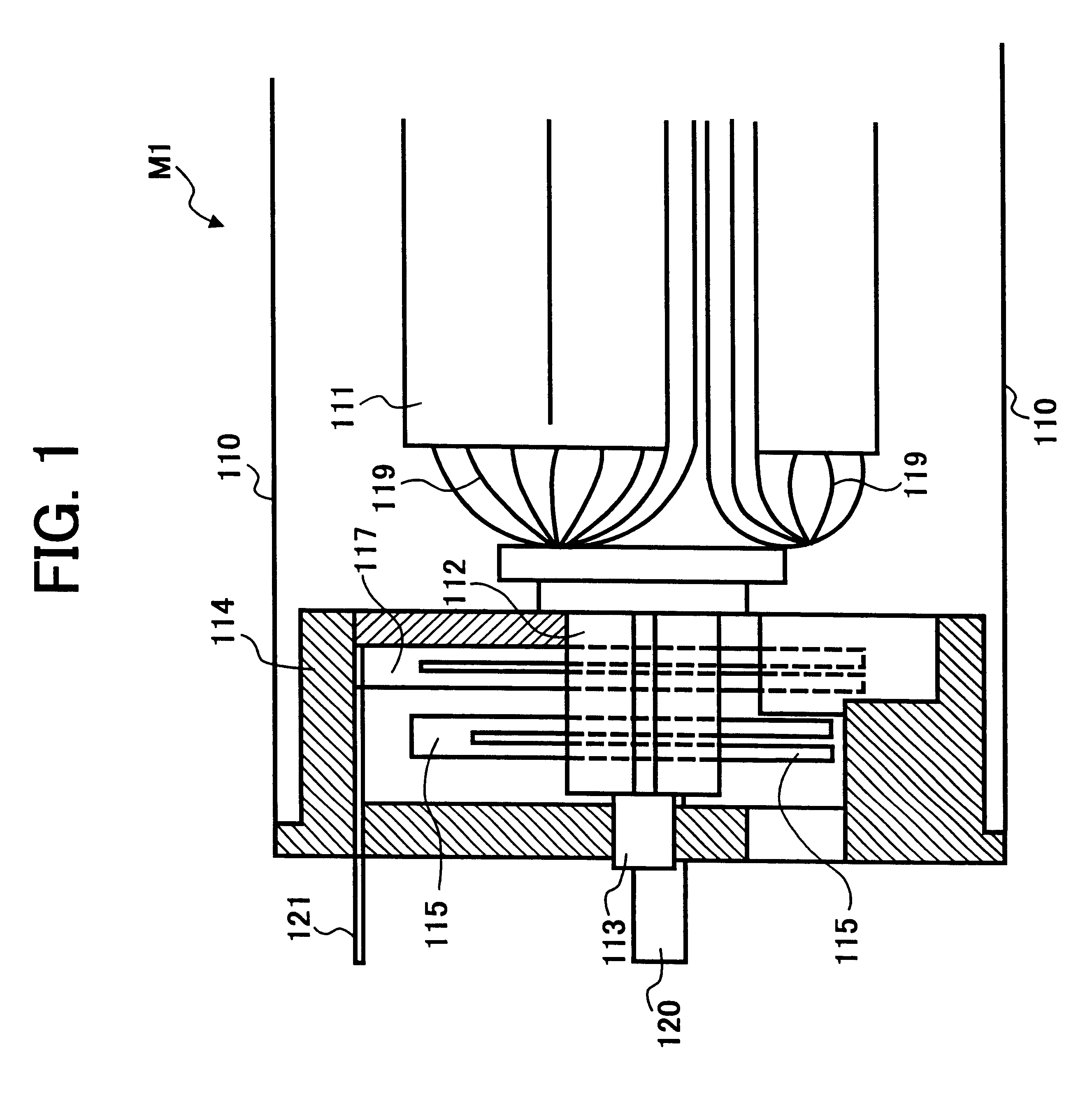

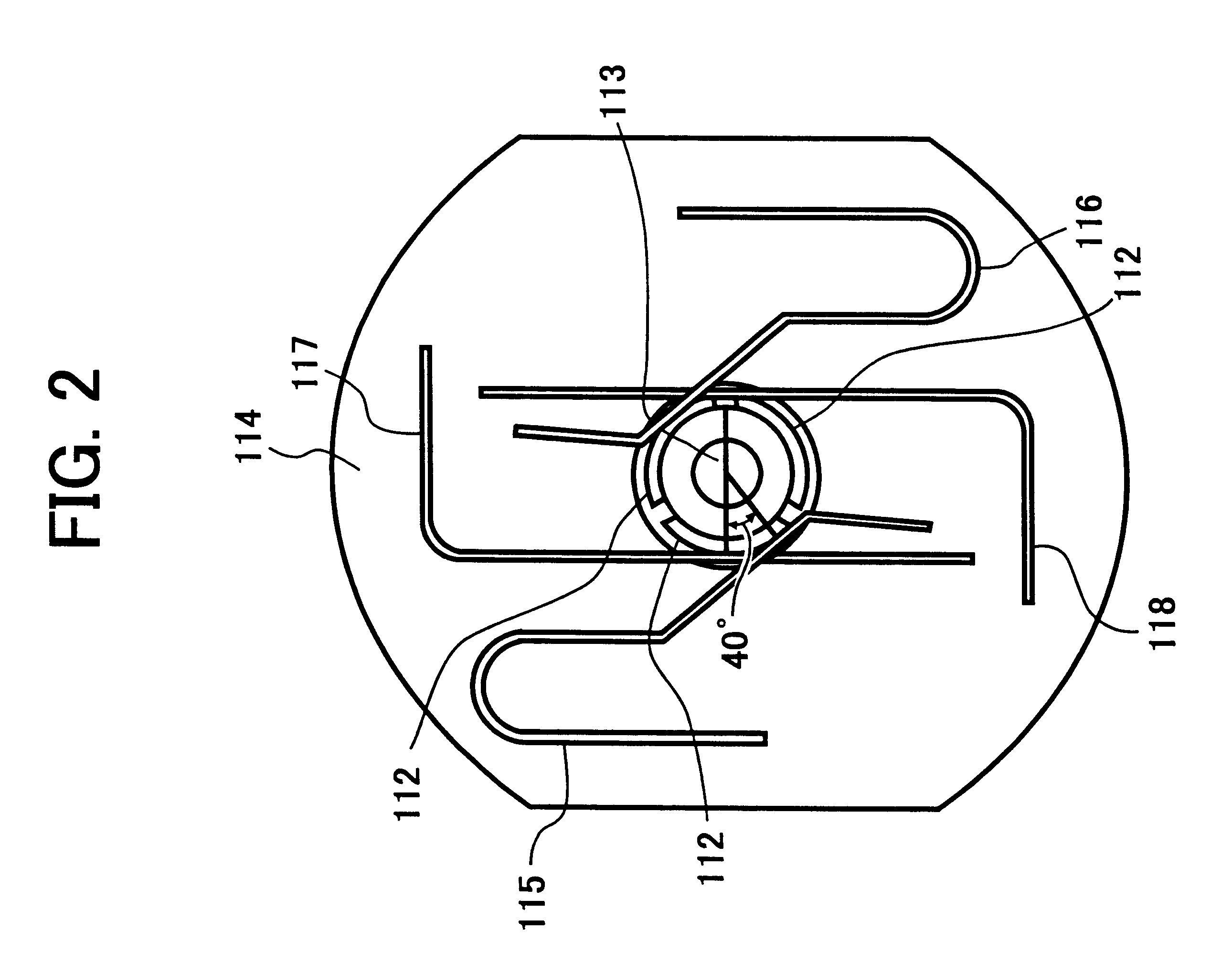

DC motor rotation control apparatus

A direct current motor rotation control apparatus, a method and device for controlling a rotational speed of a direct current motor, and an apparatus having the direct current motor rotation control apparatus. The apparatus and device control rotational operations of a direct current motor such that the direct current motor rotation control apparatus includes at least one rotation detecting brush which detects a signal indicative of an operation of the direct current motor, a motor driving circuit which drives the direct current motor by applying the direct current drive voltage to the pair of electrode brushes, a reference voltage generating device which generates a reference voltage a comparator which compares a voltage detected by the rotation detecting brush with the reference voltage generated by the reference voltage generating device and produces an output comparison voltage, and a motor control circuit which adjusts the direct current drive voltage based on the output comparison voltage. The direct current motor includes including a stator, a rotor with a rotation shaft and rotor coils, a commutator connected to the rotor coils, and a pair of electrode brushes in sliding contact with the commutator. The at least one rotation detecting brush contacts the commutator at a different axial position from an axial position contacted by the pair of electrode brushes. The comparator can compare a voltage detected by the rotation detecting brush with the reference voltage generated by the reference voltage generating device and produces as a comparison voltage output pulses of voltage. As such, the motor control circuit can determine an instantaneous rotational speed and adjust the drive voltage to the pair of electrode brushes accordingly.

Owner:RICOH KK

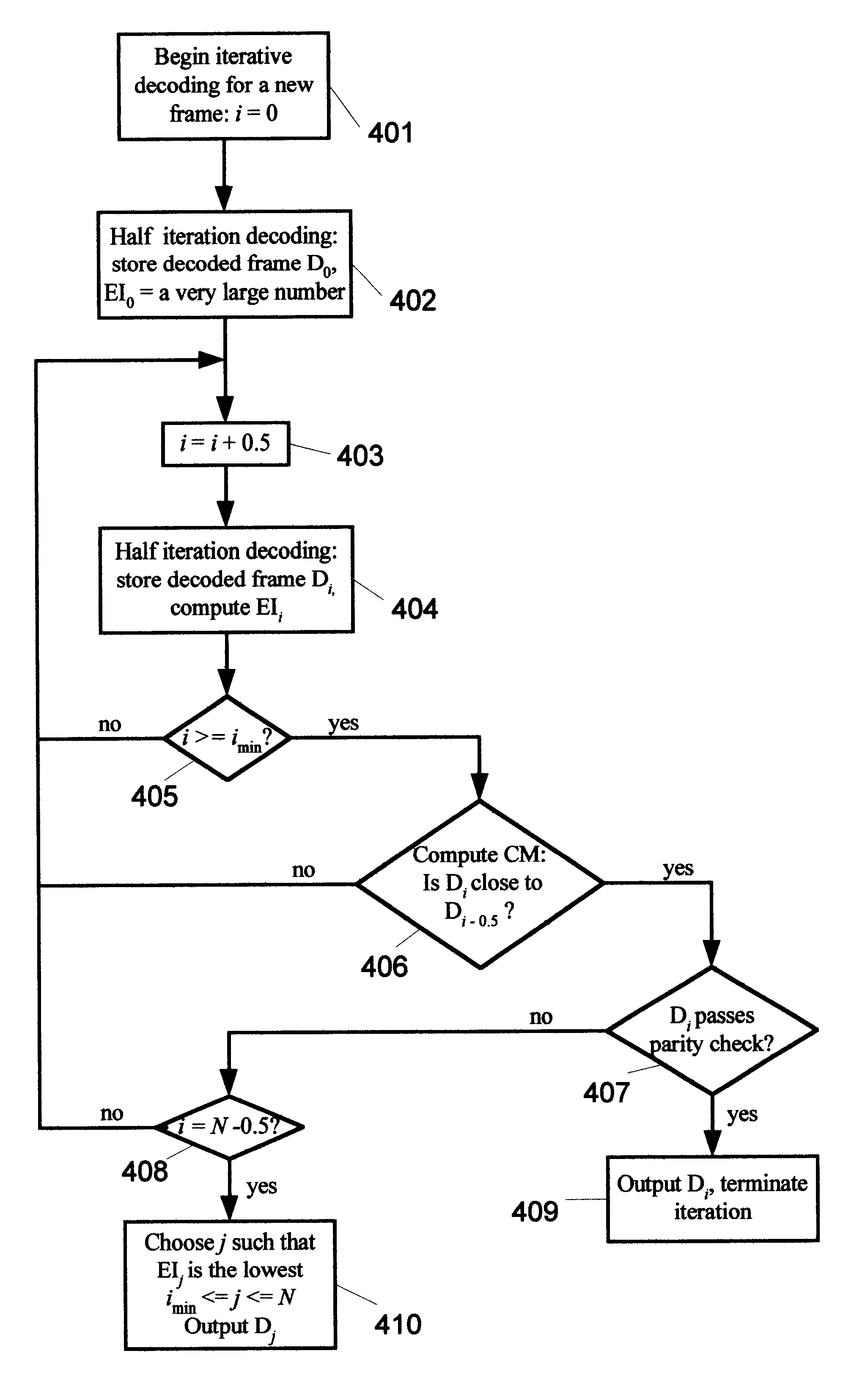

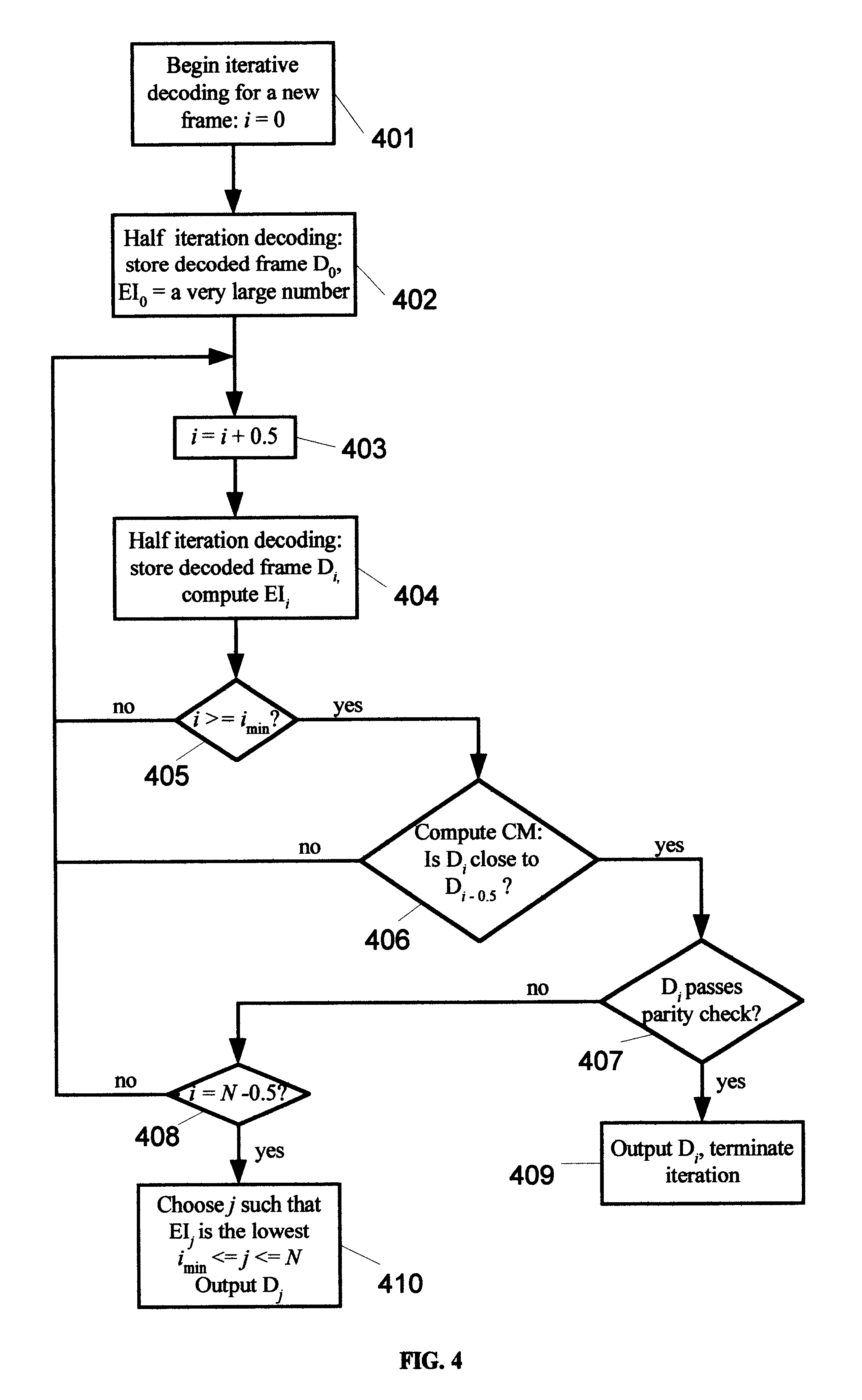

Hybrid early-termination methods and output selection procedure for iterative turbo decoders

InactiveUS6865708B2Accurately determineReliably terminatesData representation error detection/correctionOther decoding techniquesHybrid approachAlgorithm

Methods of early-termination and output selection for iterative decoders are disclosed. A hybrid early-termination method combines the output-comparison-based method with the parity-check-based method. The hybrid approach is far more superior in termination reliability in either of the two individual approaches, without their disadvantages. The hybrid termination method effectively and reliably terminates the iterative decoding process, cutting the majority of the computational load while eliminating the degradation in the bit error rate (BER) and frame-error-rate (FER) performance due to incorrectly terminated frames. An output selection procedure chooses the best possible decoded frame among those from all iterations if the iterative decoding process cannot be early-terminated during the decoding of a received frame and if the iterative decoder has reached the maximum number of iterations, thereby eliminating the iteration abnormality that is inherent in the iterative decoding approach, and improving the BER performance of the standard iterative decoders.

Owner:MINERAL LASSEN

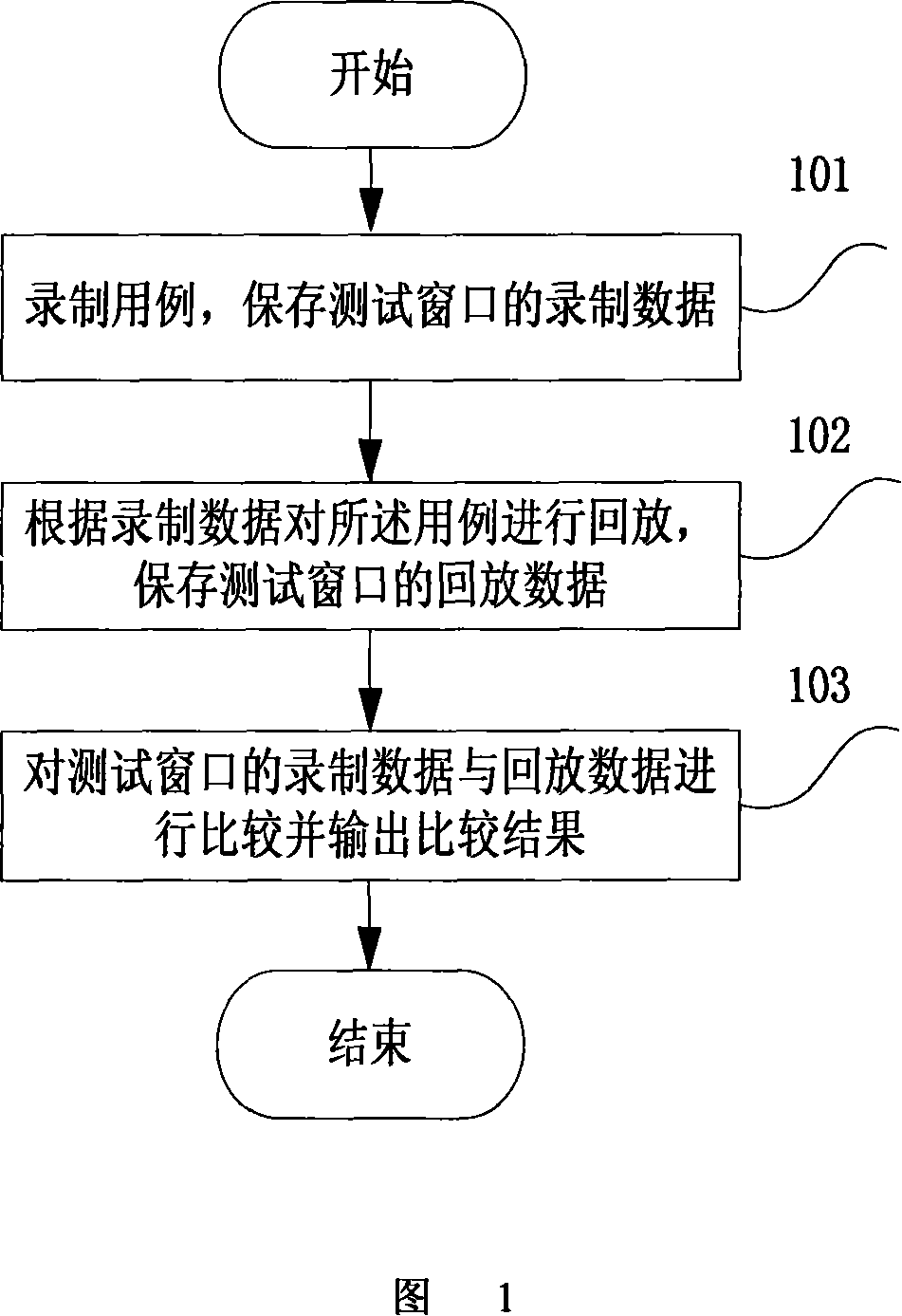

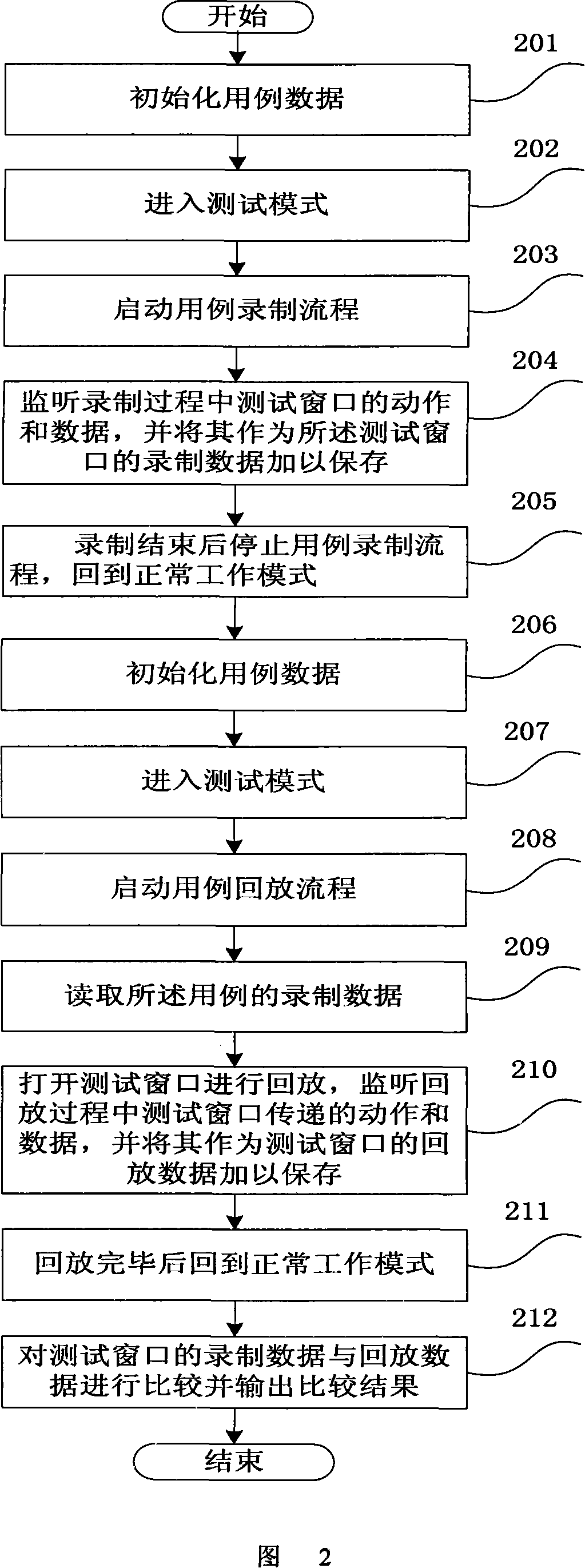

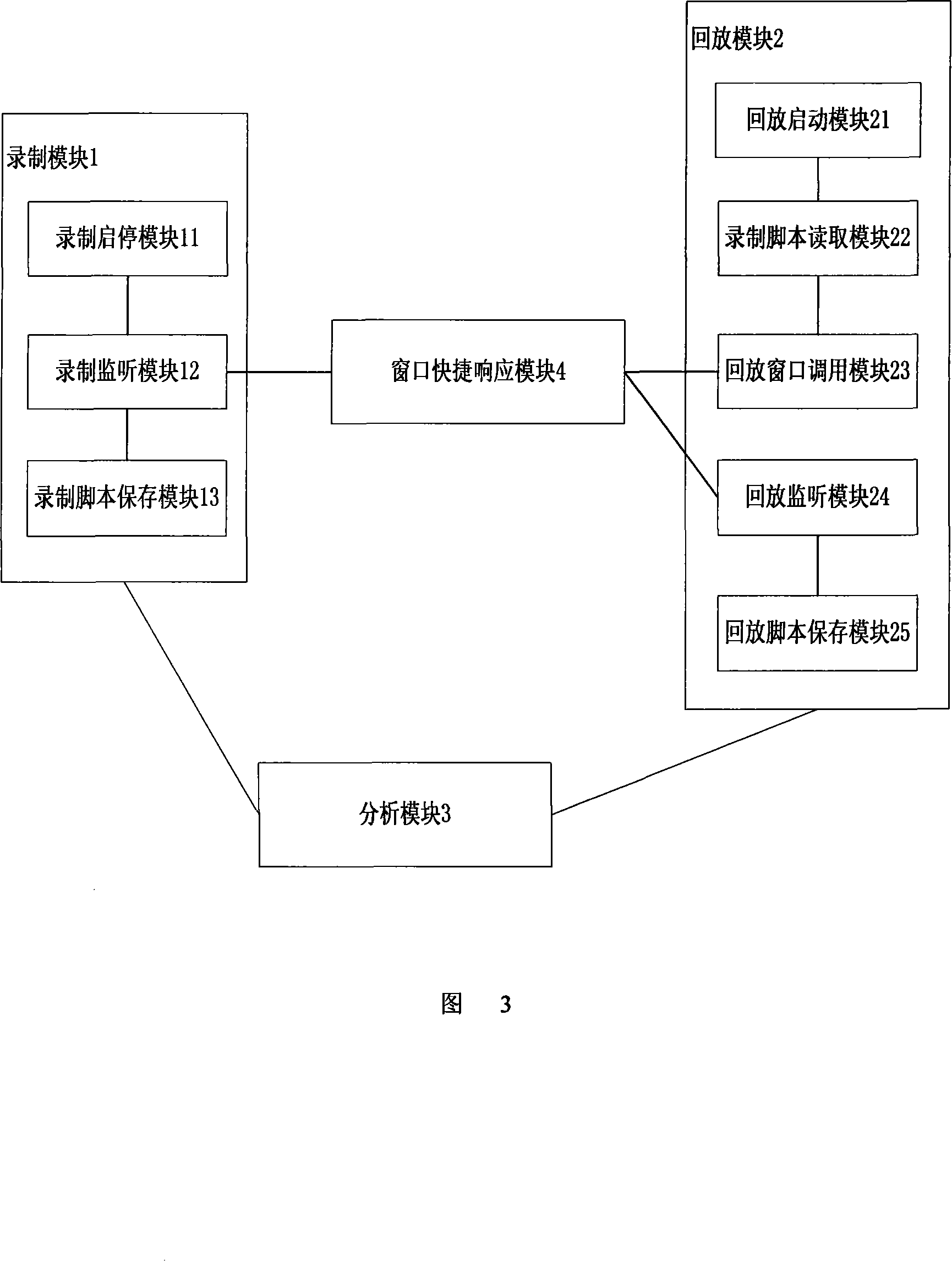

An automatic testing method and system based on interface

InactiveCN101242621AImprove test efficiencyImprove test qualitySupervisory/monitoring/testing arrangementsRadio/inductive link selection arrangementsComputer hardwareOutput compare

The invention discloses a automatic test method based on interface, which includes record test case at first, and saving recorded data in the test window; then, replaying the mentioned test case according to the mentioned recorded data, saving replaying data of the mentioned test window; finally, comparing recorded data of the test window with replaying data and outputting comparing result. The inventive technical scheme improves efficiency of automatic test and expands supported area.

Owner:ZTE CORP

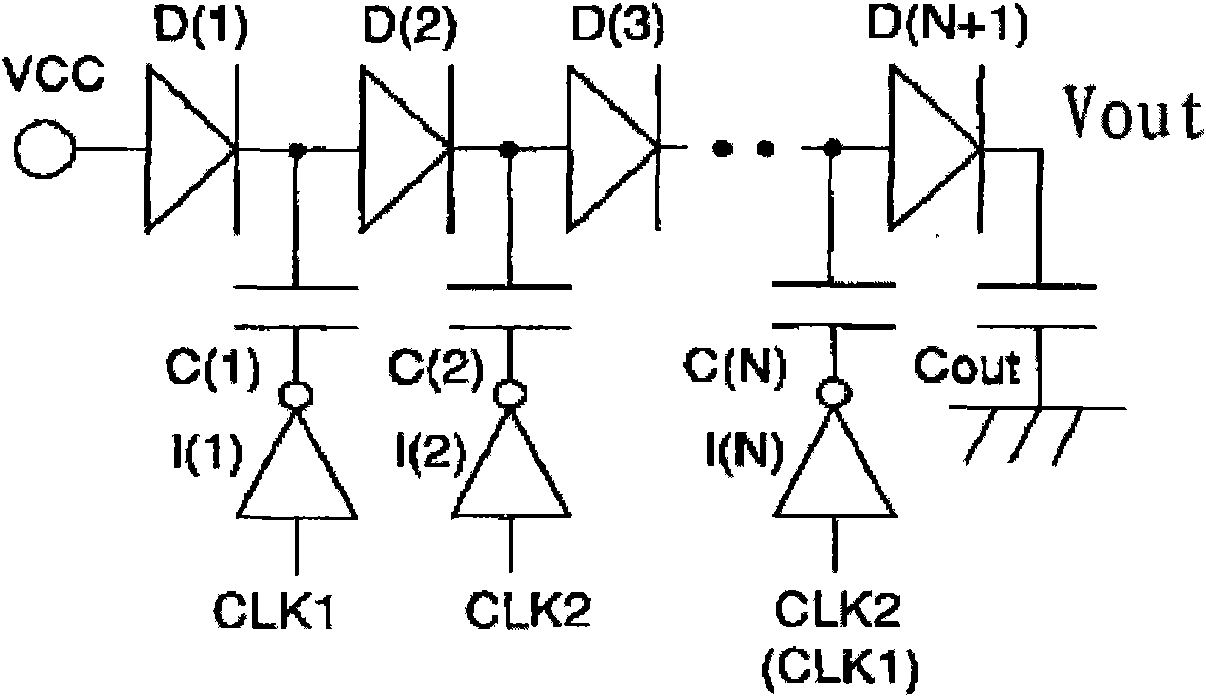

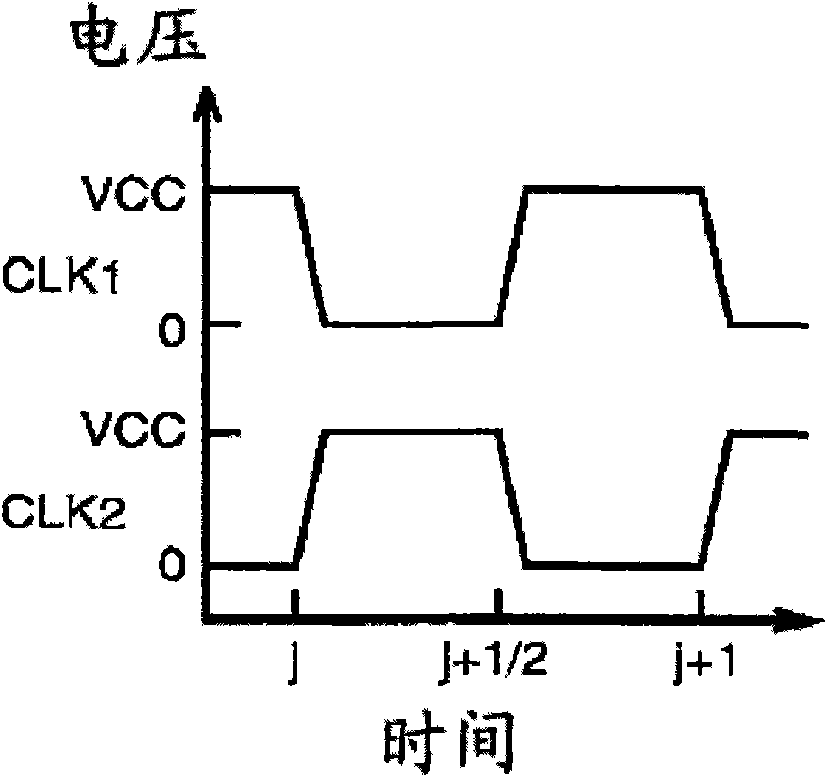

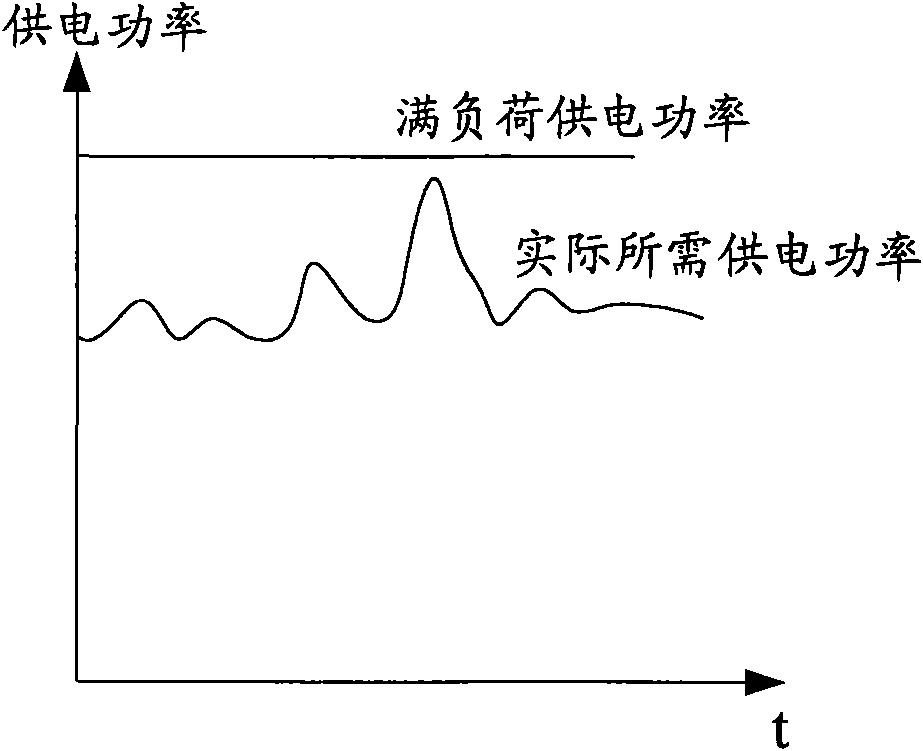

Closed-loop control charge pump circuit

ActiveCN101667774AGood power following characteristicsStable output voltageApparatus without intermediate ac conversionOutput compareControl signal

The invention relates to a closed-loop control charge pump circuit, which comprises a basic charge pump circuit and a control loop. The control loop comprises the following circuits which are connected in turn: a sampling circuit, a comparer, an oscillation control circuit, and an oscillator, wherein the sampling circuit is connected with a voltage output end (Vout) of a basic charge pump, and isused for sampling the voltage value of the Vout and generating a sampling voltage value V1 corresponding to the voltage value of the Vout according to a predefined function mapping relation f; the comparer is used for comparing the voltage value V1 with a preset reference voltage Vref and outputting the comparison result V2; the oscillation control circuit receives the comparison result V2 and generates a control signal Ctr1 according to the V2 value; and the oscillation frequency of the oscillator is controlled by the control signal Ctr1 to change continuously, and the oscillator outputs theoscillation frequency as the working frequency of the basic charge pump. Thus, the frequency of the oscillator of the charge pump circuit can be adjusted continuously and dynamically, and the whole charge pump circuit has good power following characteristics and reduces the energy consumption.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Chip pin open circuit and short circuit tester and method therefor

InactiveCN1632605ASimple structureLow costSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingDisplay deviceEngineering

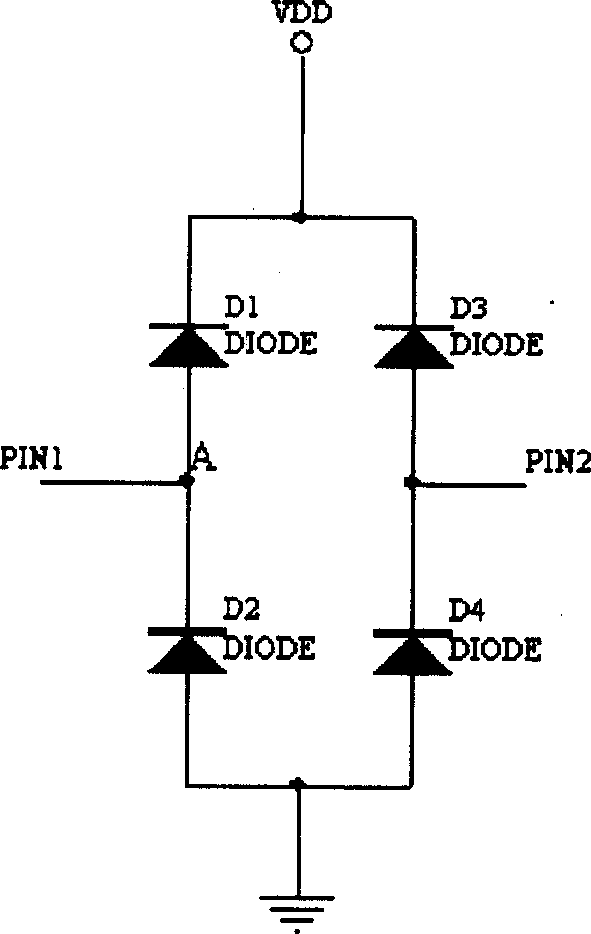

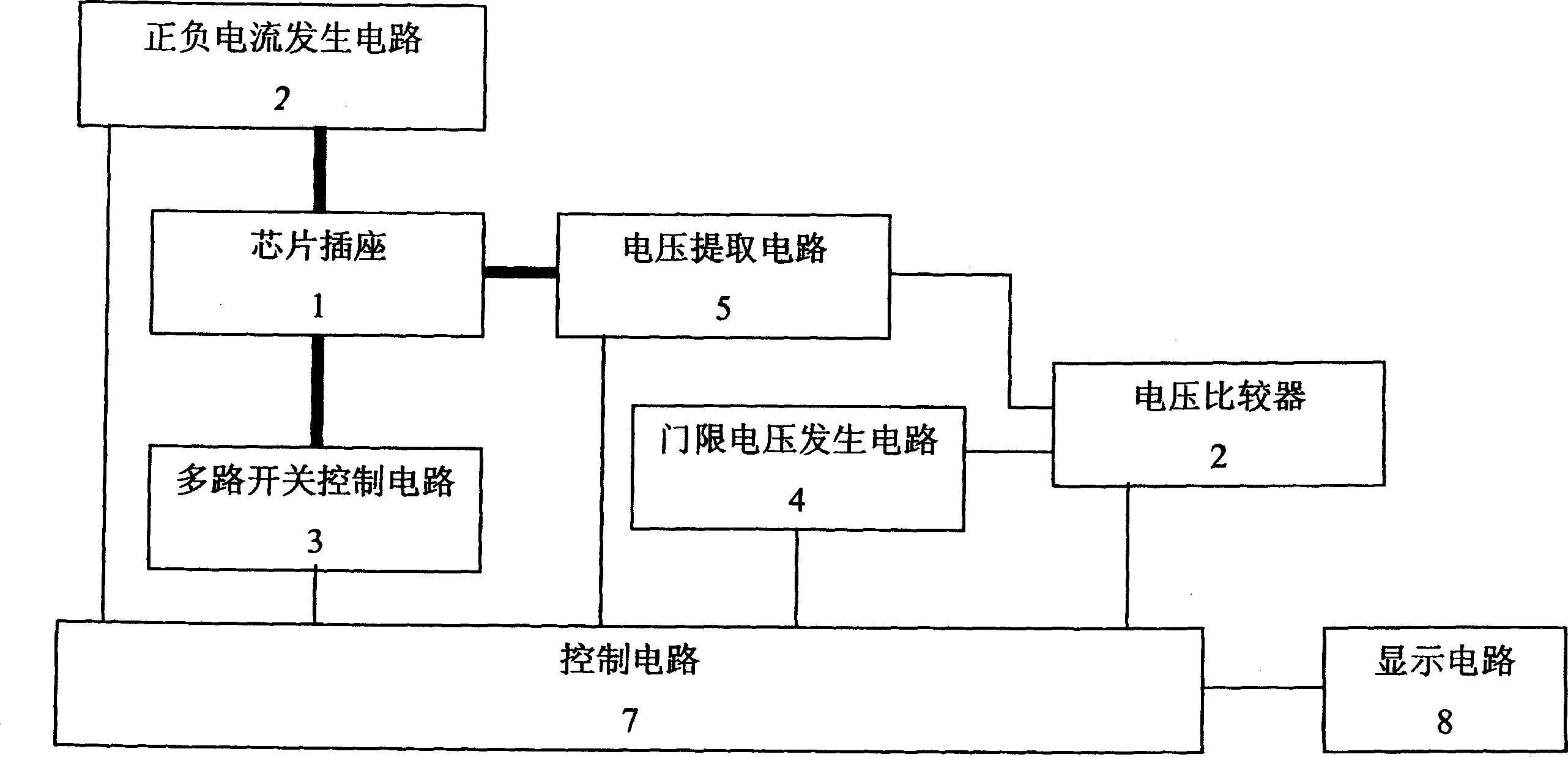

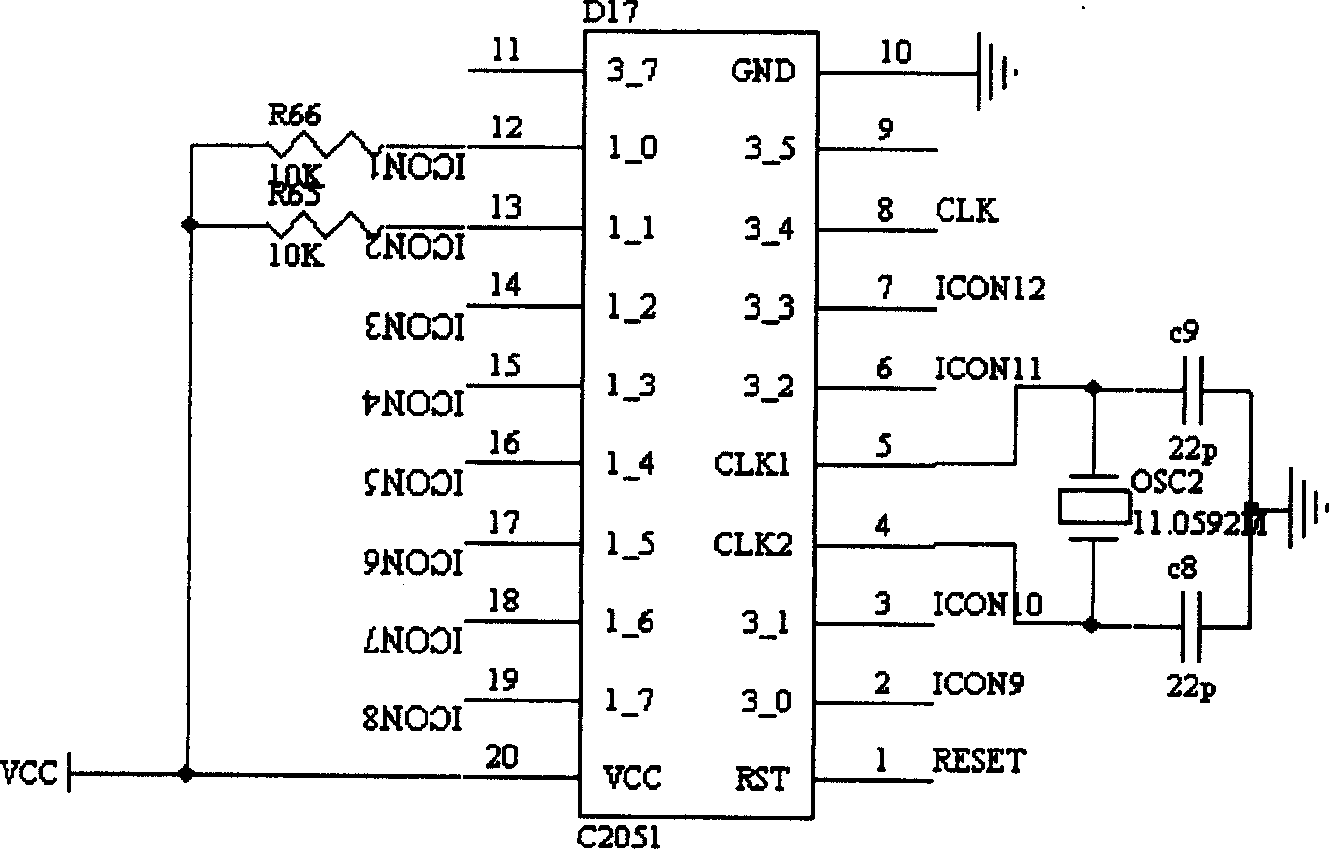

This invention relates to chip pin switch or short circuit test machine, which comprise the following: chip socket; positive or negative current generator circuit to provide positive or negative current to the chip pin; multi-path switch control circuit to control the rest chip pin ground connection; voltage extraction circuit to extract the output voltage from the chip pin; threshold voltage generation circuit to generate positive or negative threshold voltage; voltage comparer to compare the pin output voltage and threshold voltage and to output comparison results; control circuit to whole control the above circuit; display device to receive the signals of the above control circuit and to display the output signals.

Owner:ASE ASSEMBLY & TEST SHANGHAI