Patents

Literature

280results about How to "Improve current drive capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

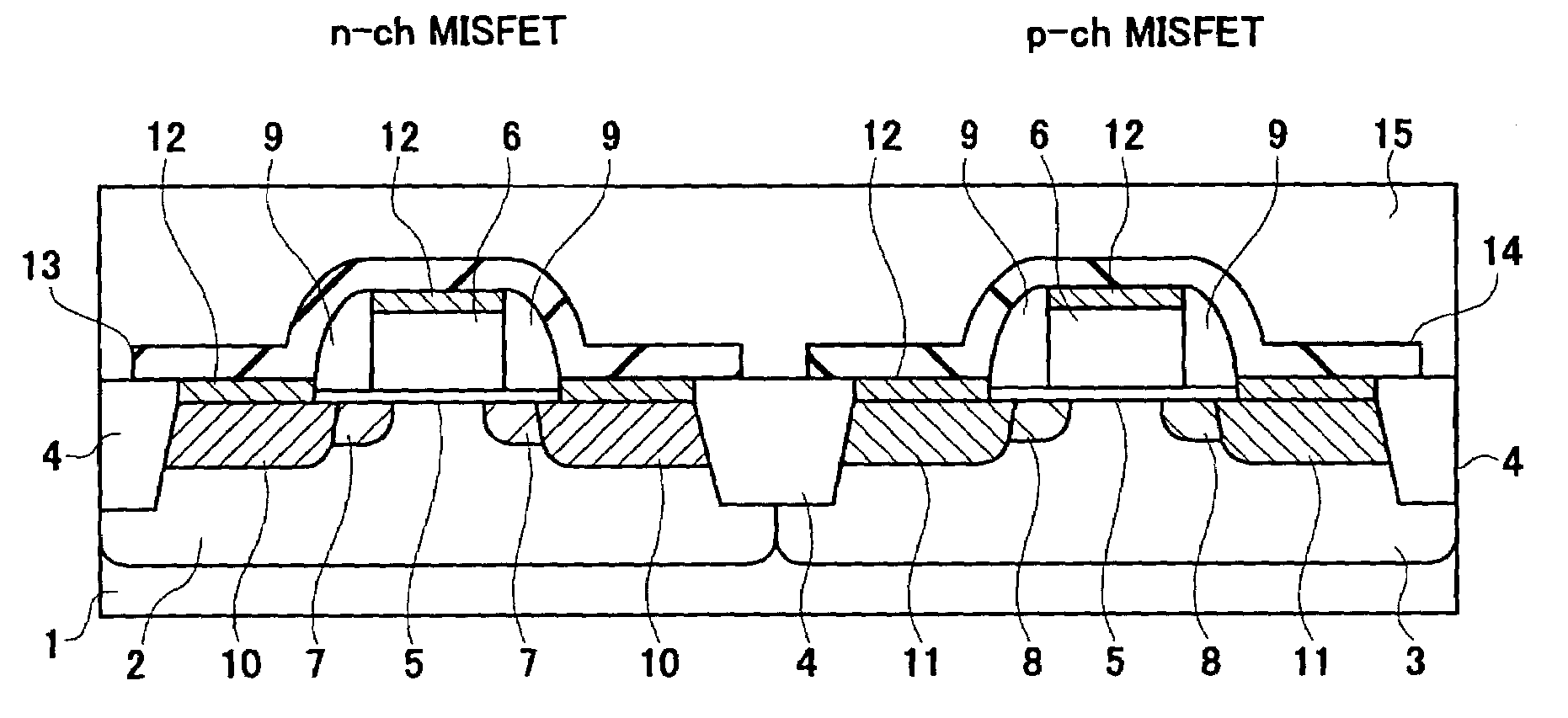

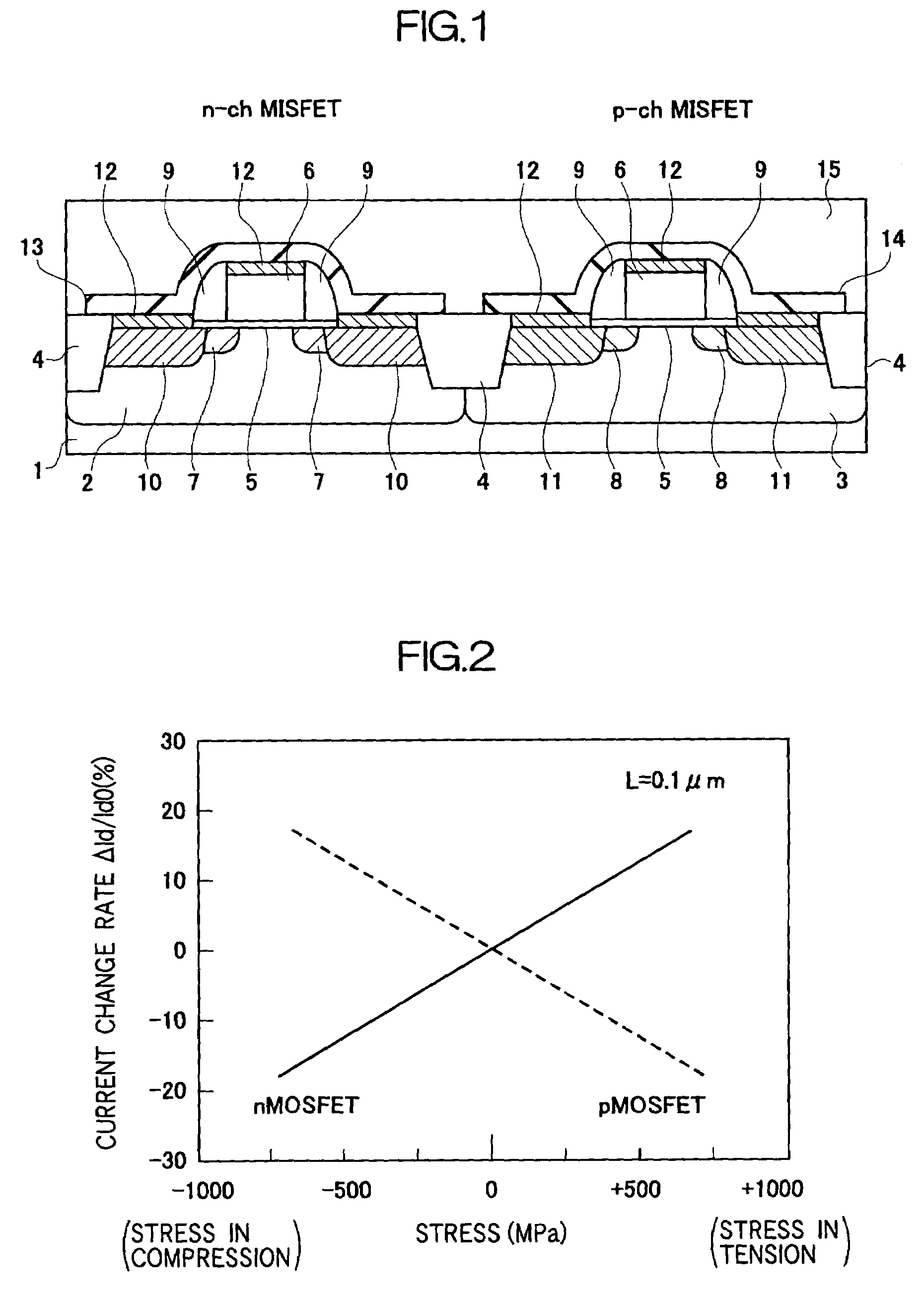

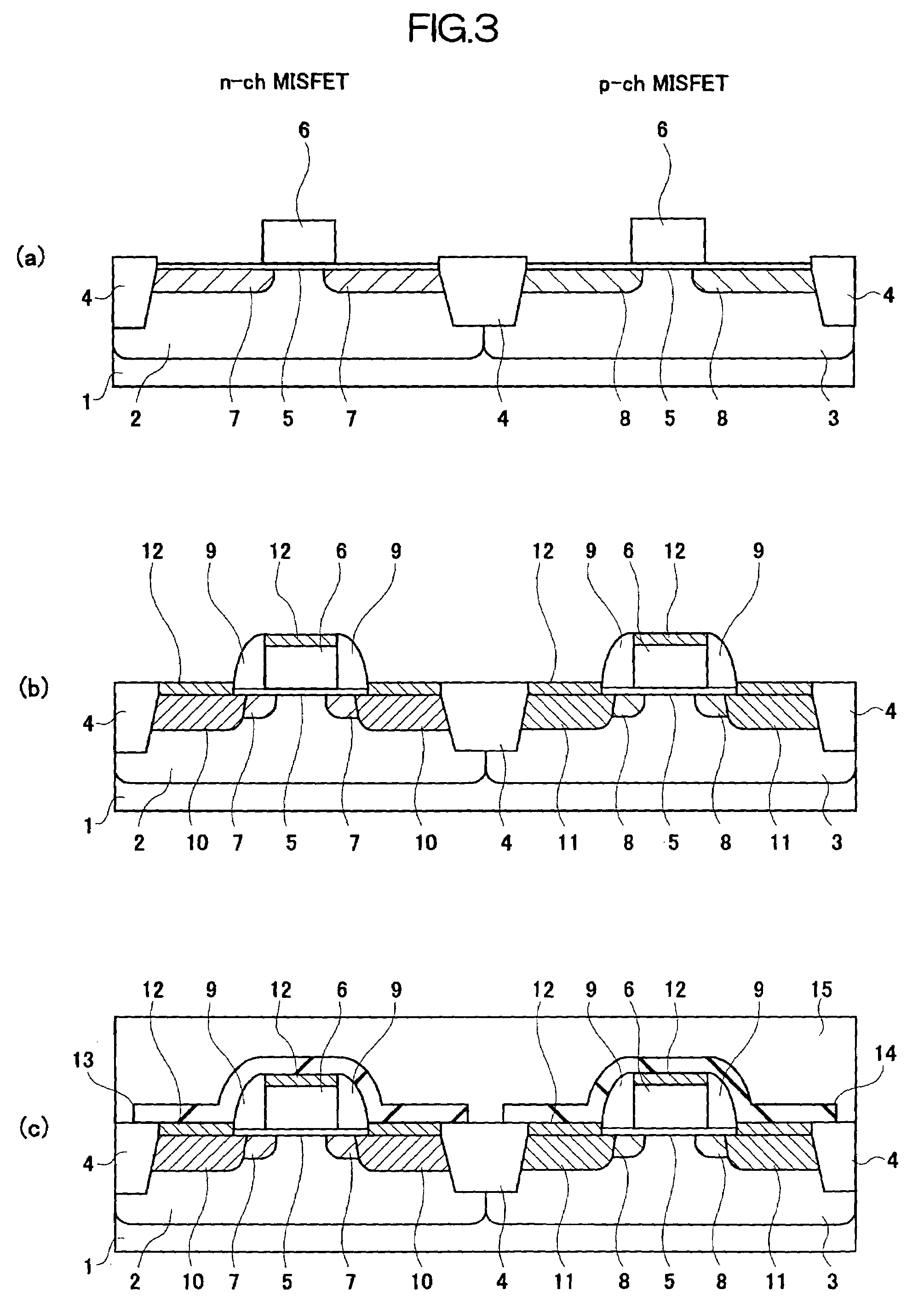

Semiconductor device including stress inducing films formed over n-channel and p-channel field effect transistors and a method of manufacturing the same

InactiveUS7115954B2Improve driving abilityImprove current drive capabilityTransistorSemiconductor/solid-state device detailsStress inducedField-effect transistor

A semiconductor device has an n channel conductivity type field effect transistor having a channel formation region formed in a first region on one main surface of a semiconductor substrate and a p channel conductivity type field effect transistor having a channel formation region formed in a second region on the main surface of the semiconductor substrate, which second region is different from the first region. An internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is different from an internal stress generated in the channel formation region of the p channel conductivity type field effect transistor. The internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is a tensile stress, while the internal stress generated in the channel formation region of the p channel conductivity type field effect transistor is a compressive stress.

Owner:RENESAS ELECTRONICS CORP

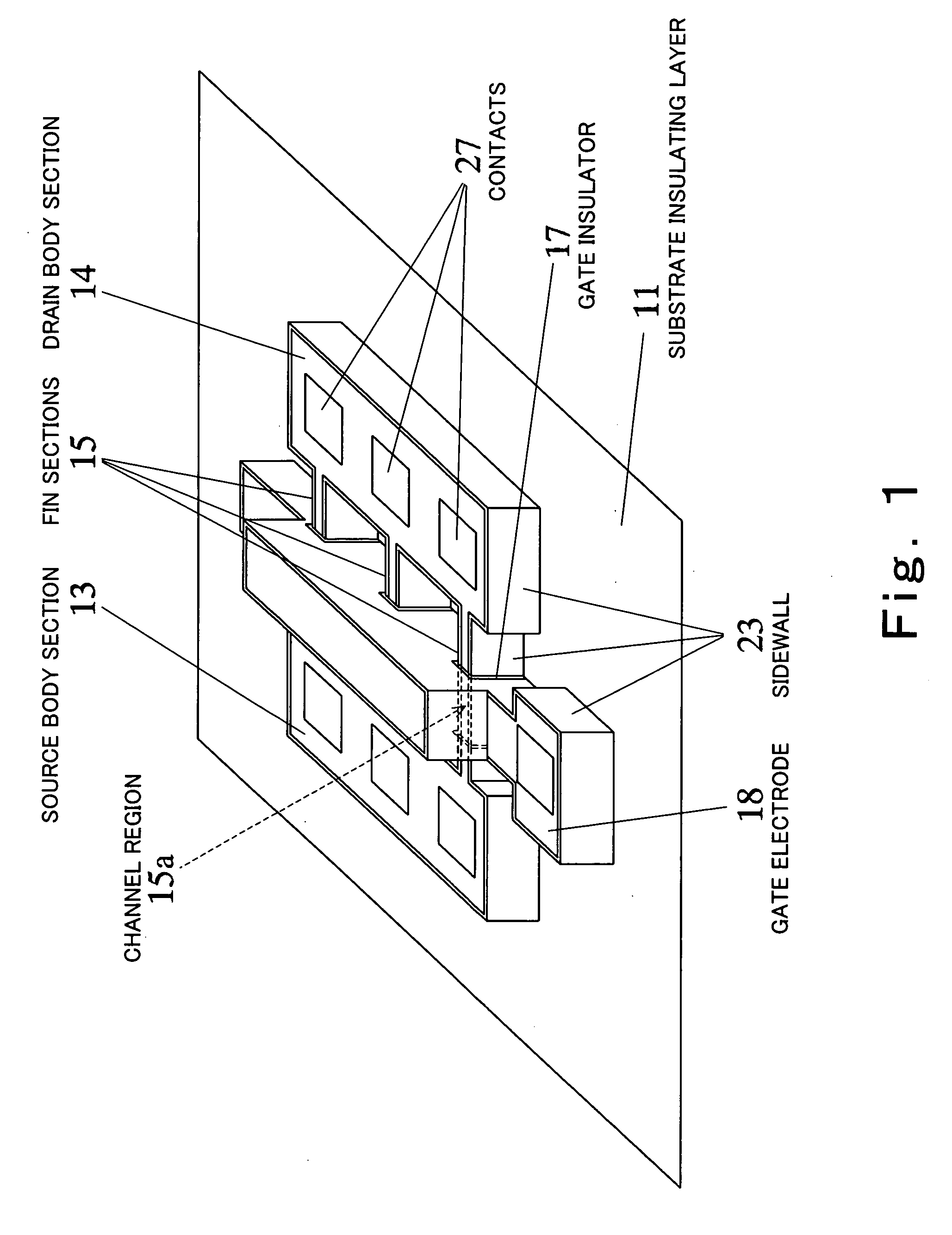

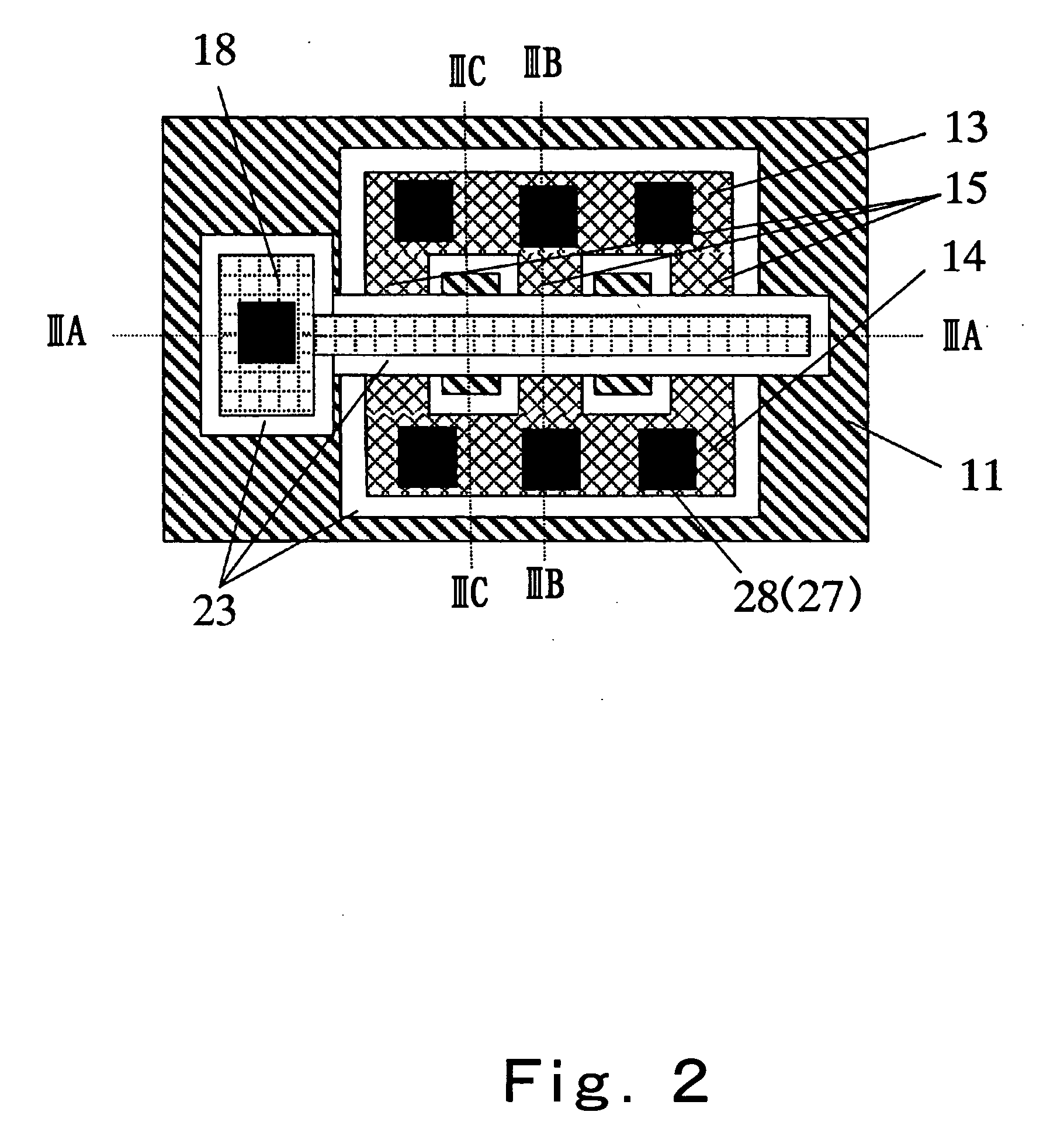

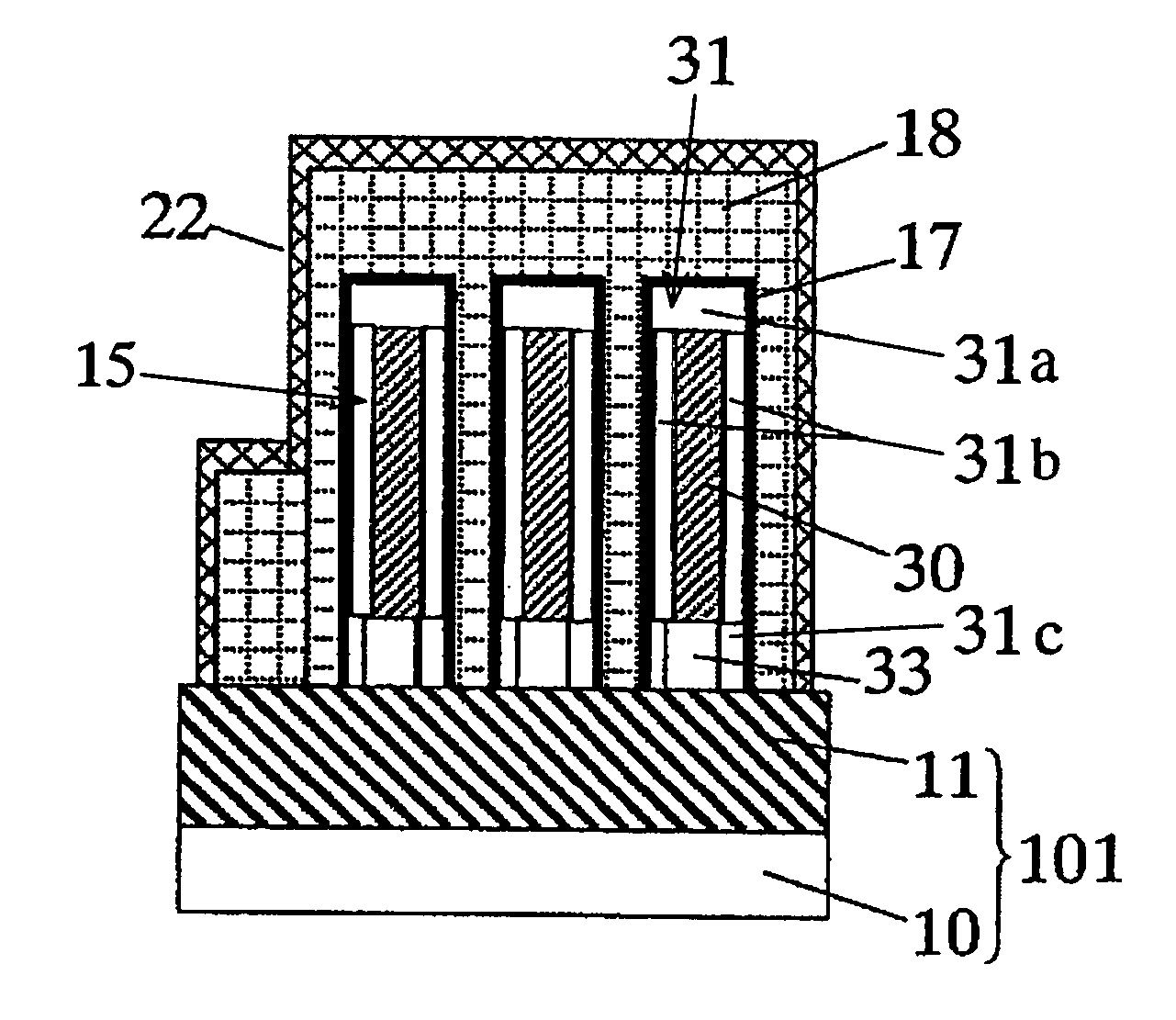

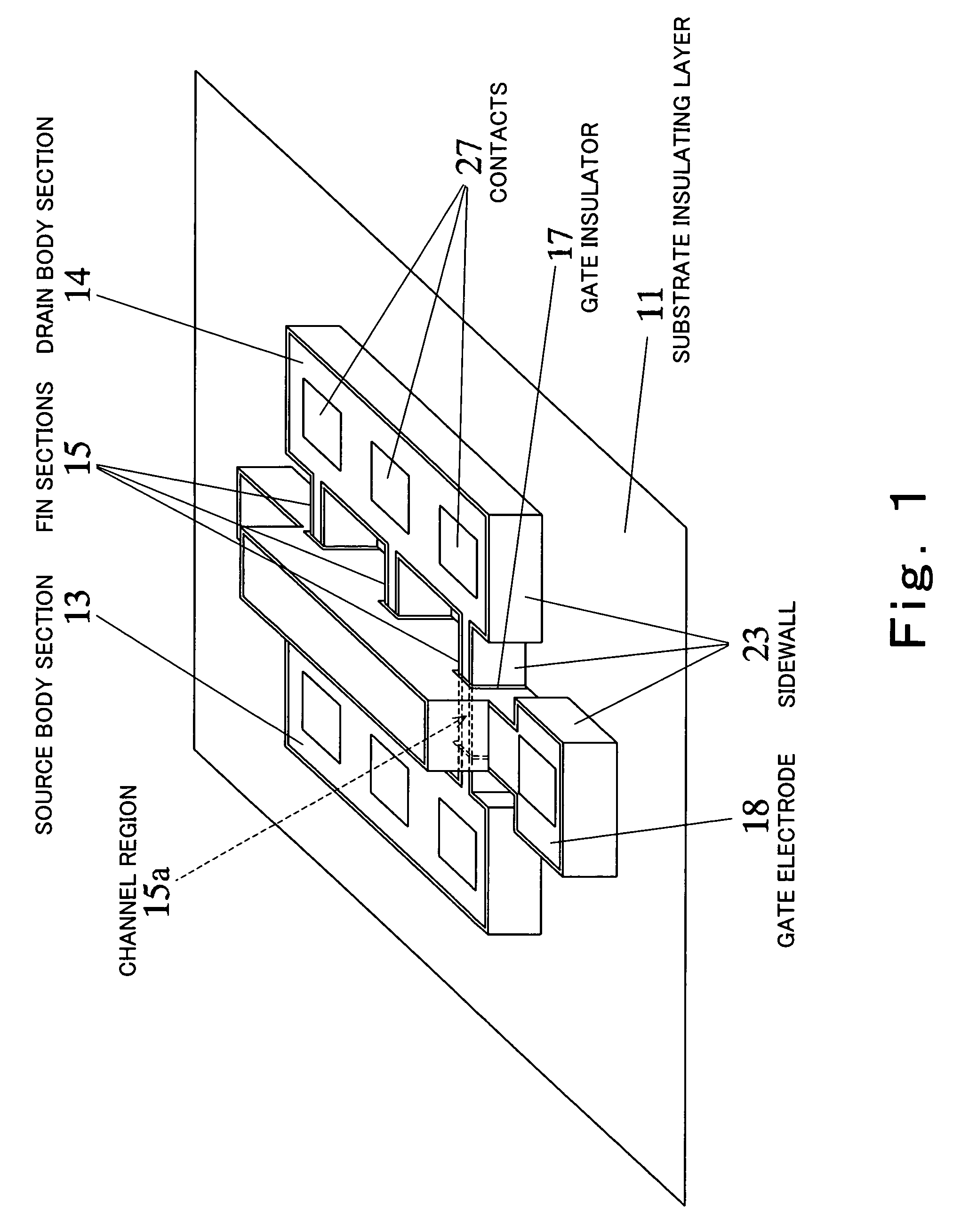

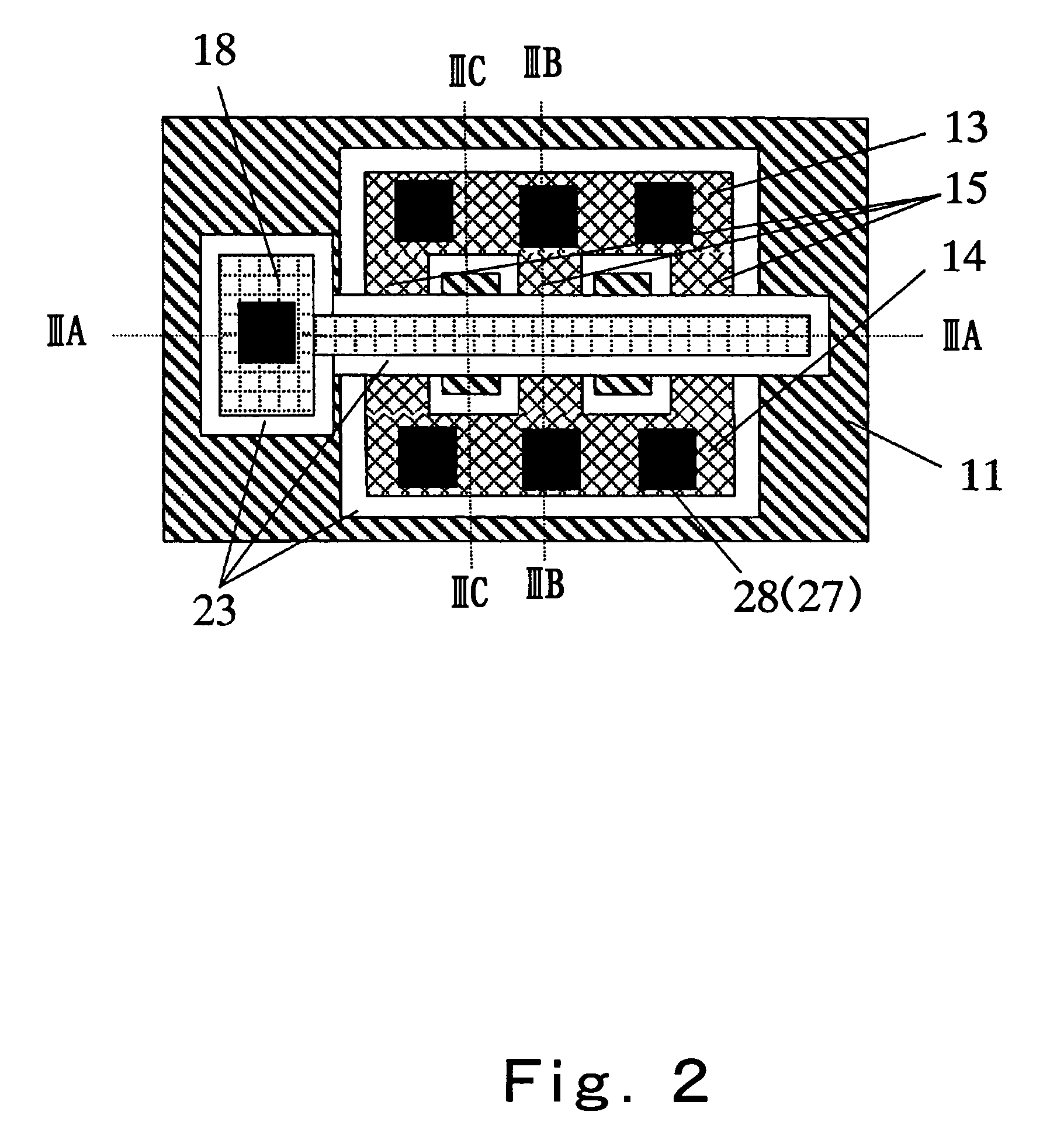

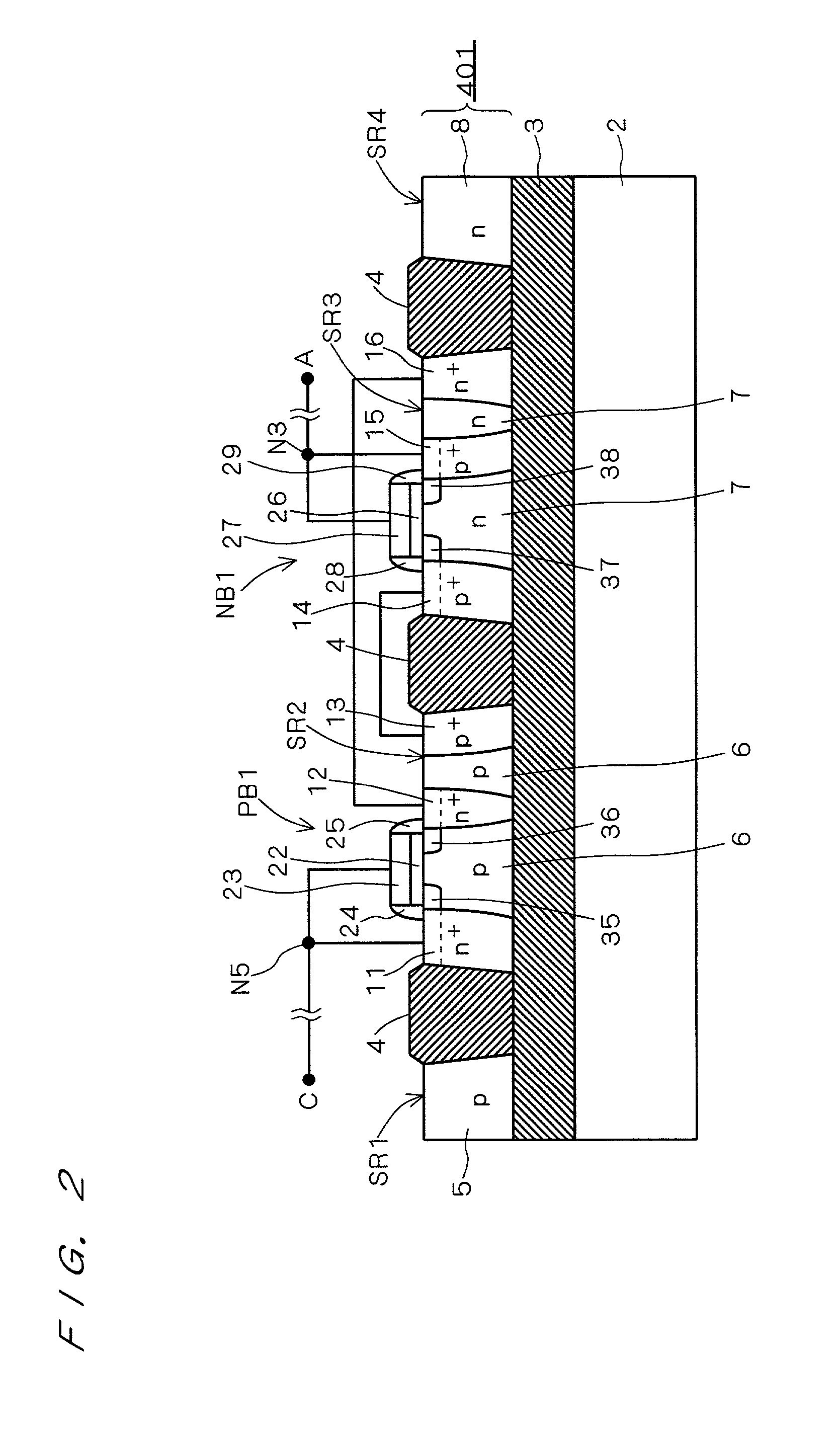

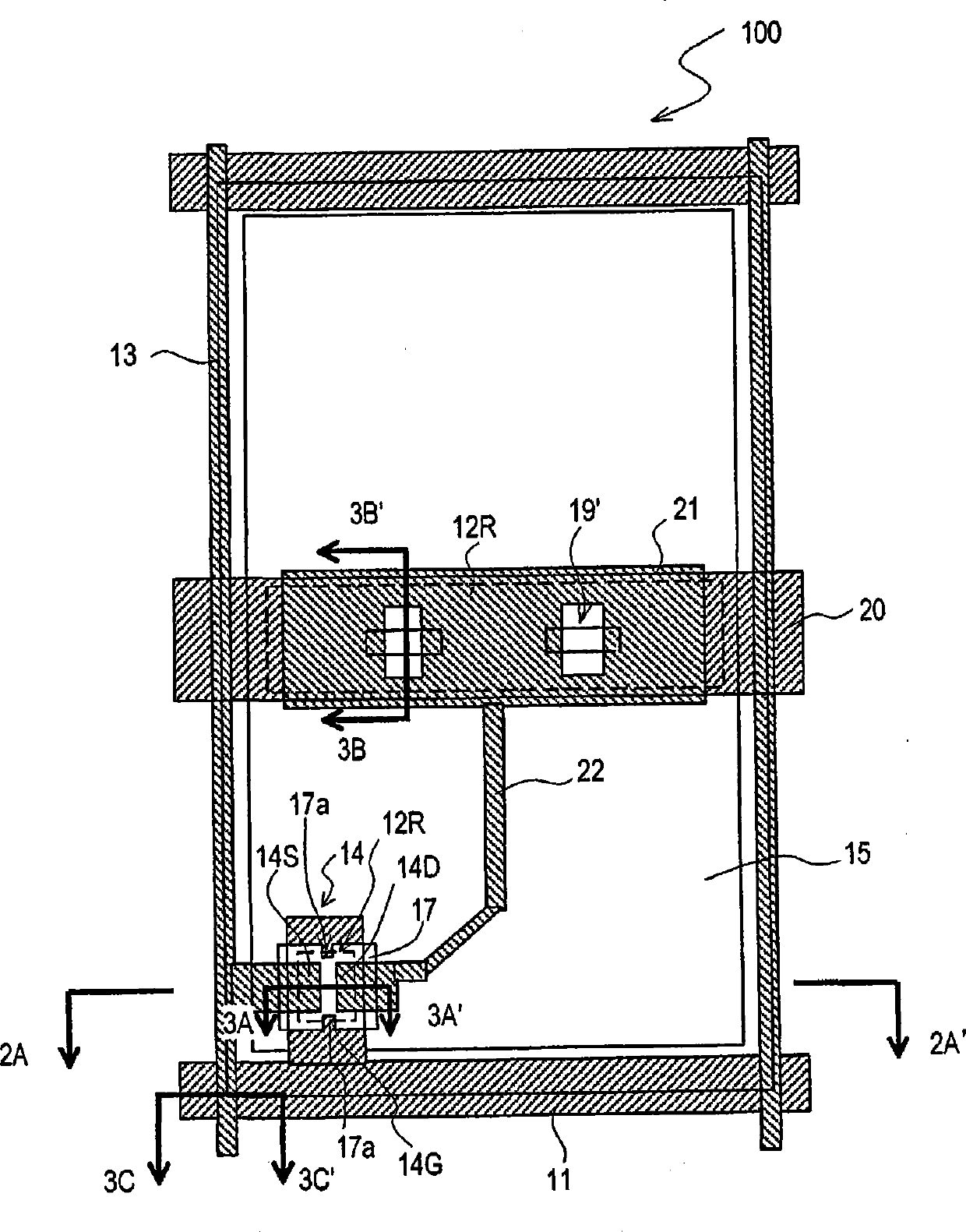

Semiconductor device and method of fabricating the same

InactiveUS20070052041A1Easily fabricateReduce difficultyTransistorSolid-state devicesEngineeringRidge

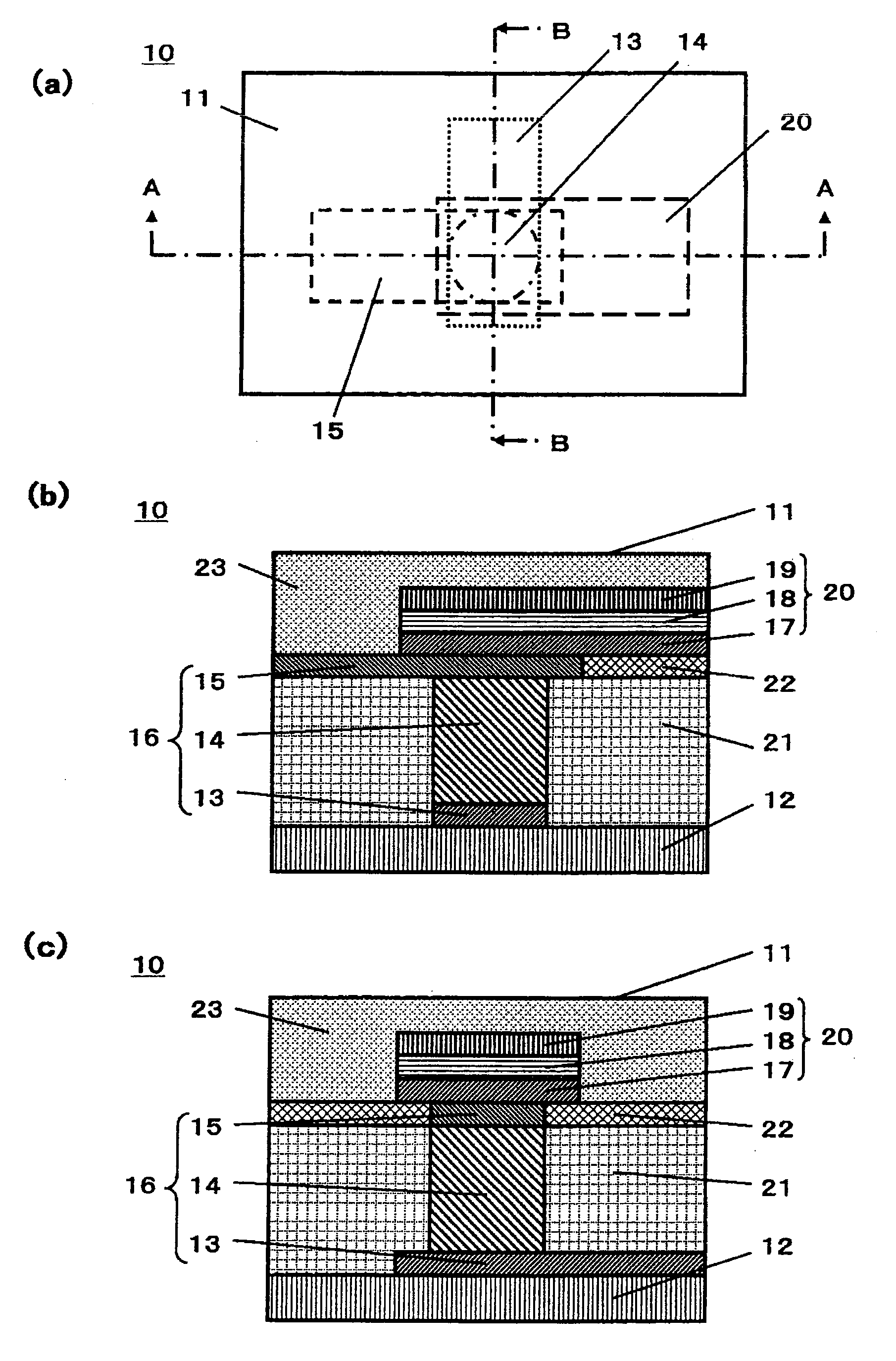

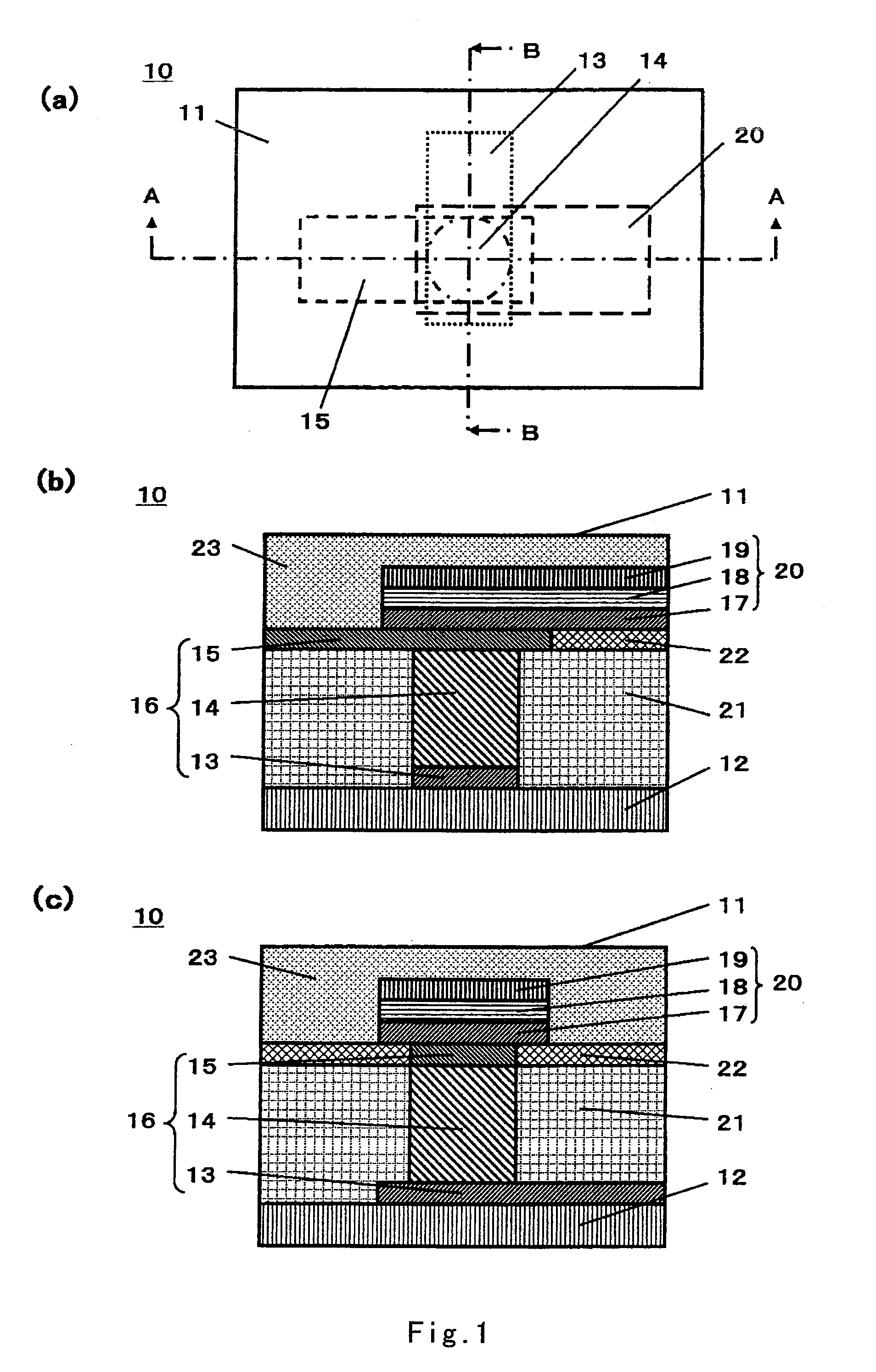

A semiconductor device according to this invention includes: a first insulating layer (11); a first body section (13) including an island-shaped semiconductor formed on the first insulating layer; a second body section (14) including an island-shaped semiconductor formed on the first insulating layer; a ridge-shaped connecting section (15) formed on the first insulating layer to interconnect the first body section and the second body section; a channel region (15a) formed by at least a part of the connecting section in lengthwise direction of the connecting section; a gate electrode (18) formed to cover a periphery of the channel region, with a second insulating layer intervening therebetween; a source region formed to extend over the first body section and a portion of the connecting section between the first body section and the channel region; and a drain region formed to extend over the second body section and a portion of the connecting section between the second body section and the channel region, wherein a semiconductor forming the channel region has a lattice strain.

Owner:PANASONIC CORP

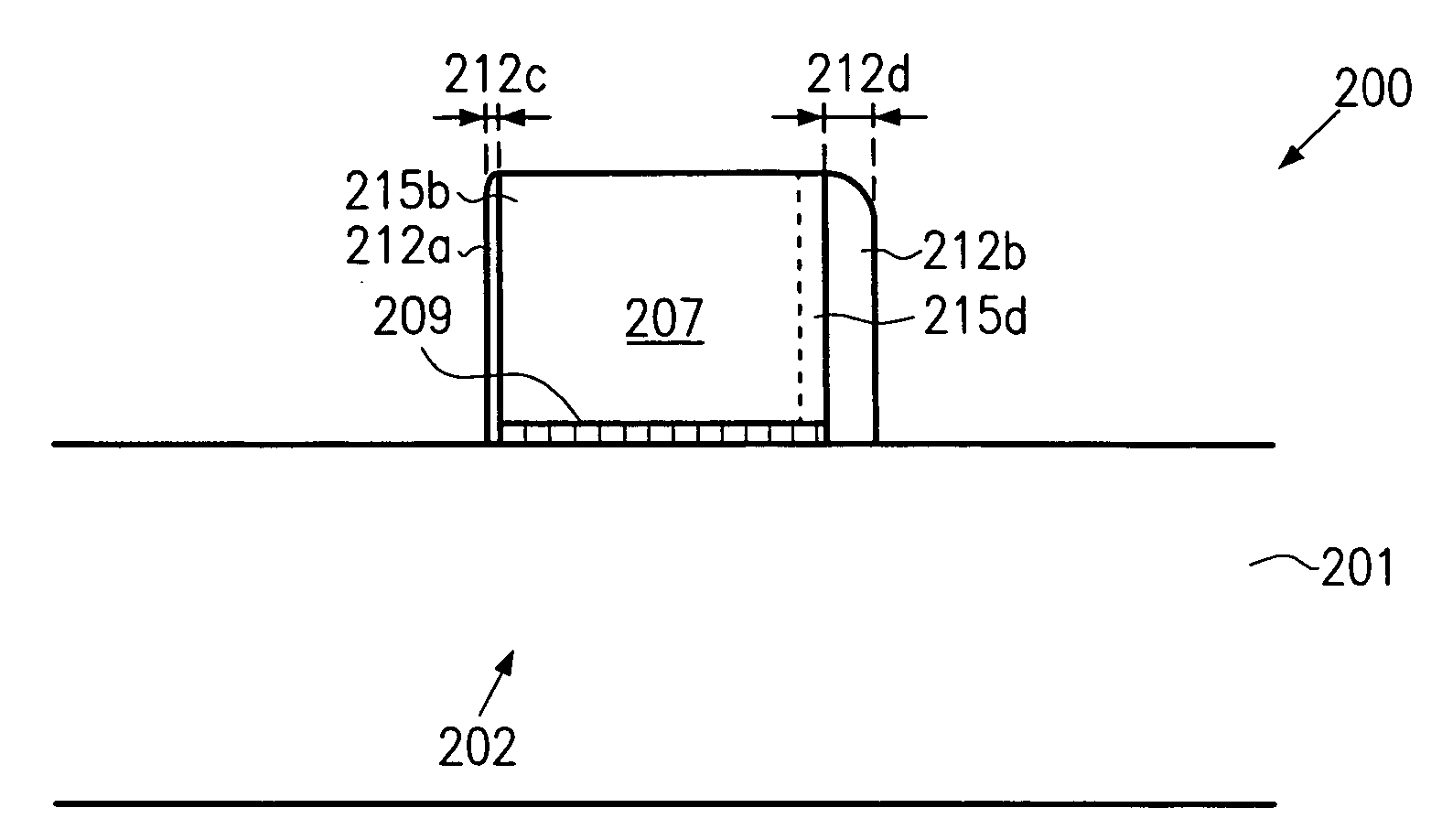

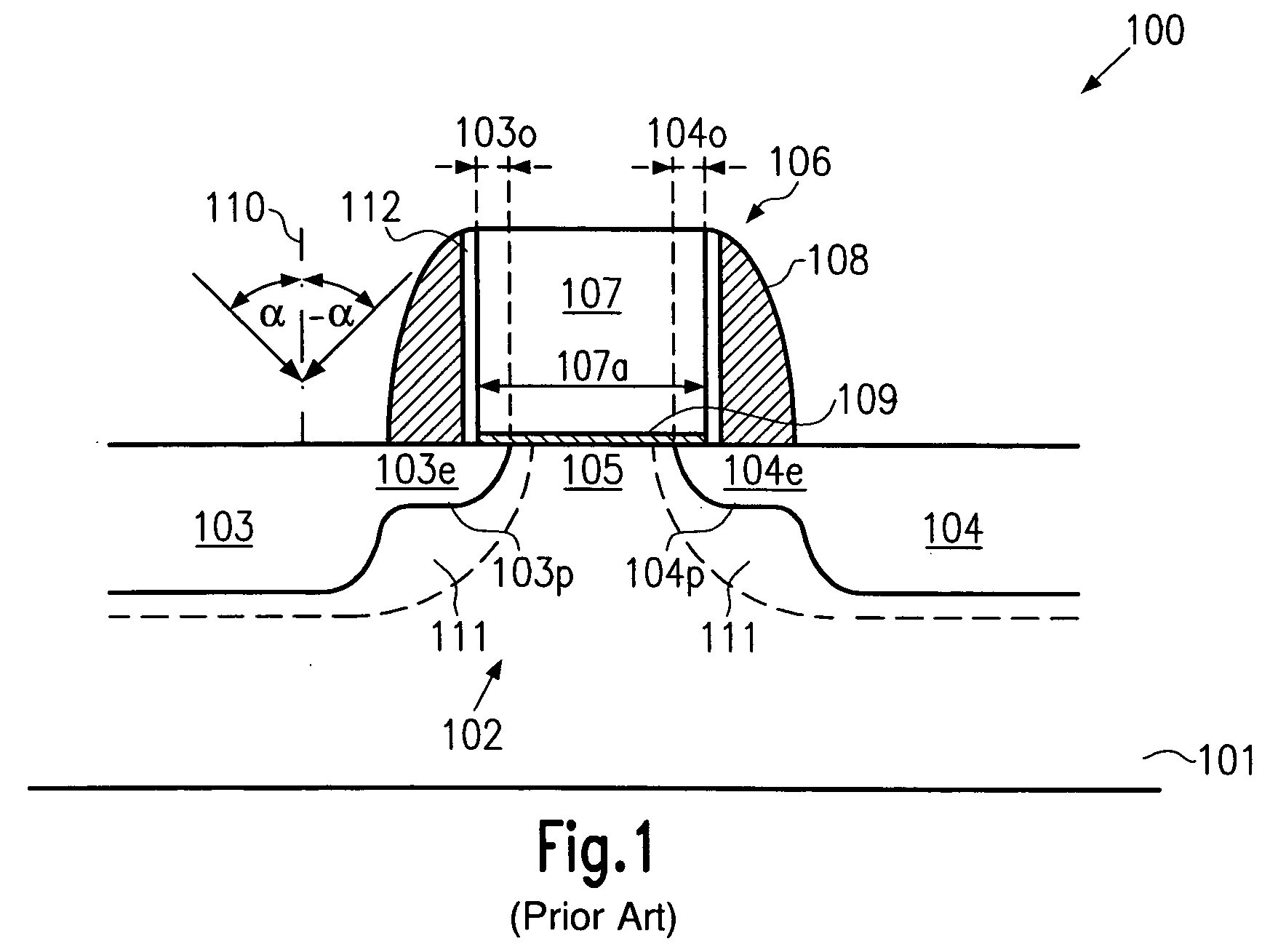

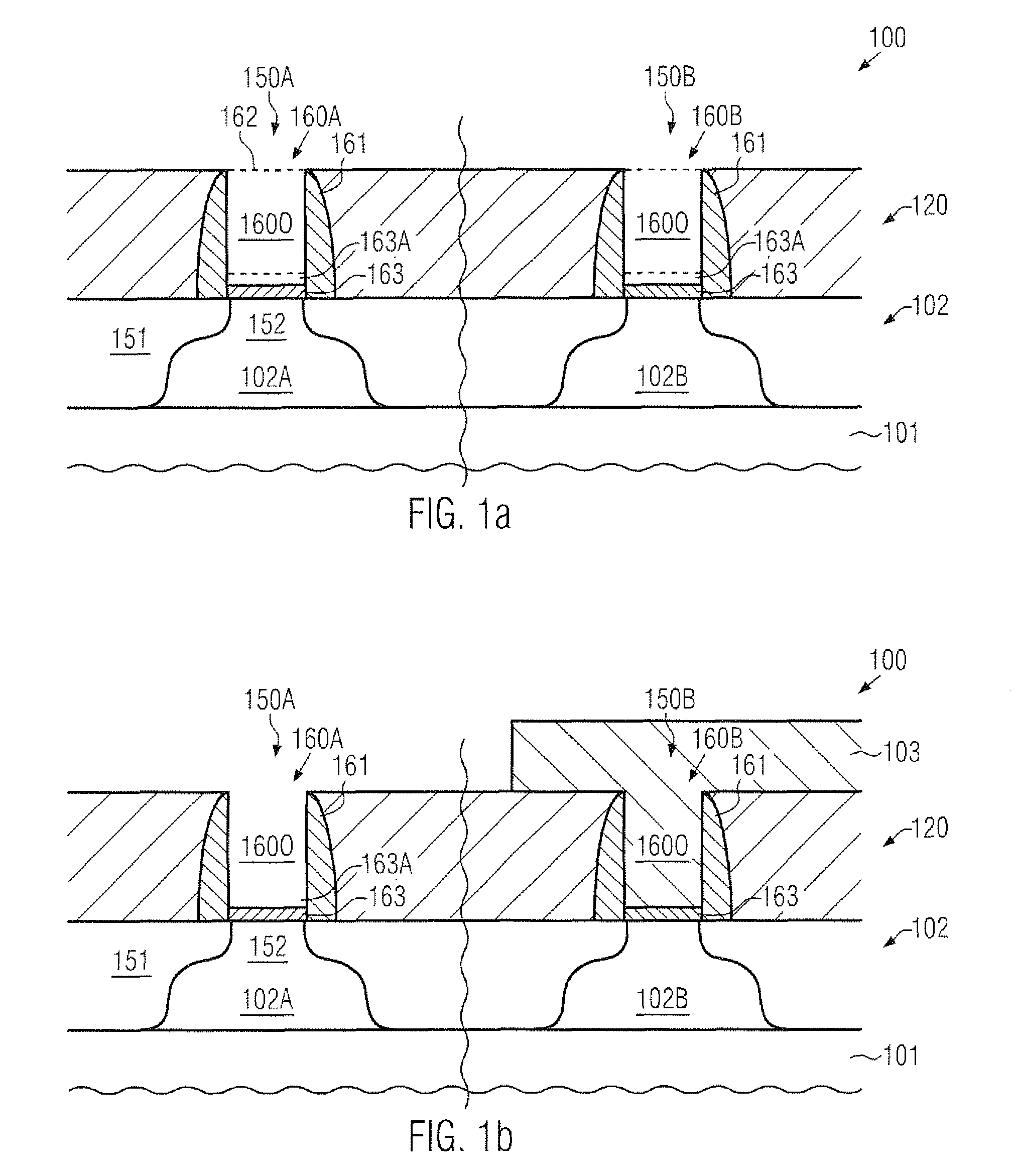

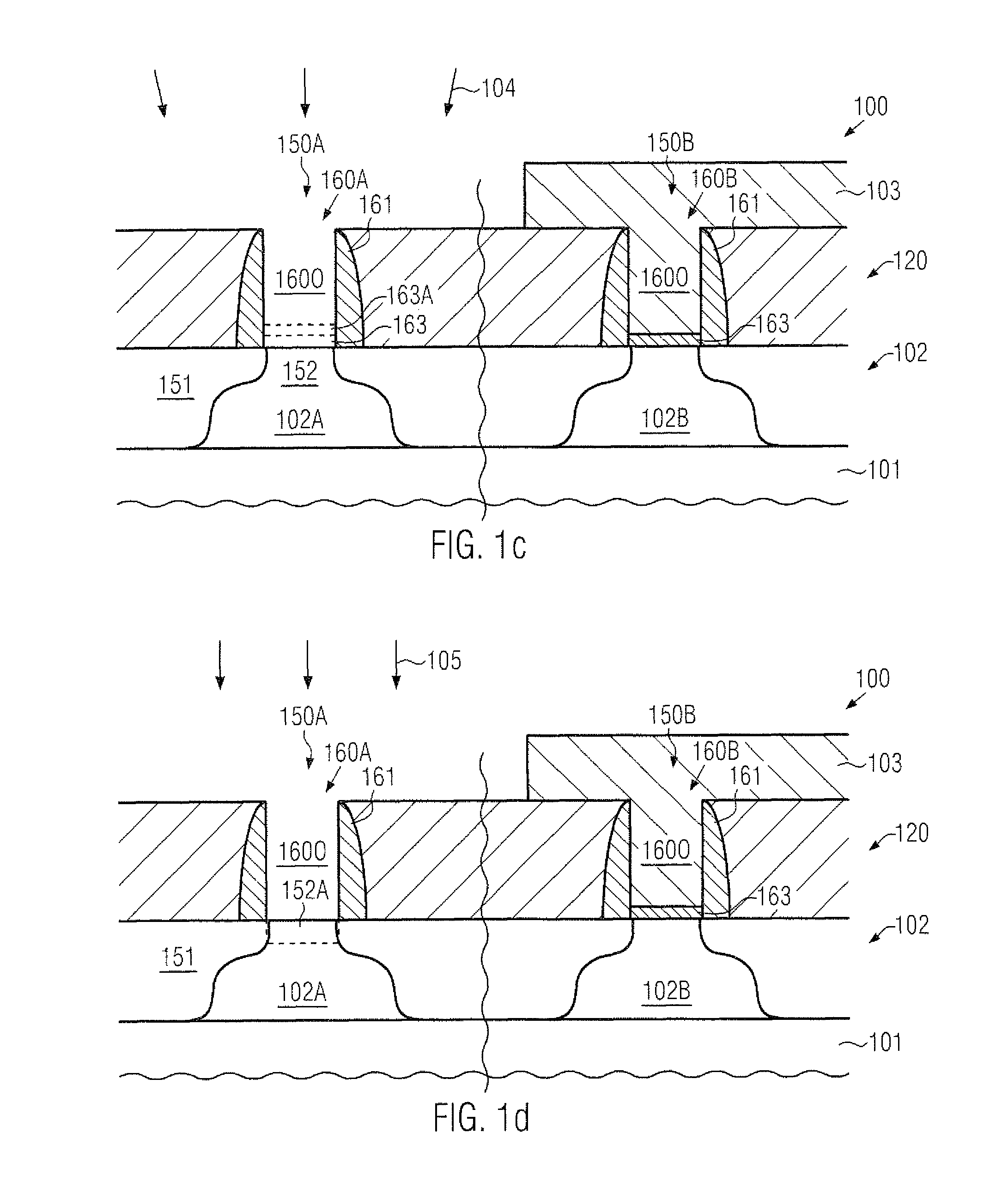

Gate structure and a transistor having asymmetric spacer elements and methods of forming the same

ActiveUS20060194381A1Improve current drive capabilityReduce staticSemiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricEngineering

Methods for forming asymmetric gate structures comprising spacer elements disposed on the opposed sides of a gate electrode and having a different width are disclosed. The asymmetric gate structures are employed to form an asymmetric design of a halo region and extension regions of a field effect transistor using a symmetric implantation scheme, or to further enhance the effectiveness of asymmetric implantation schemes. The transistor performance may be significantly enhanced for a given basic transistor architecture. In particular, a large overlap area may be created at the source side with a steep concentration gradient of the PN junction due to the provision of the halo region, whereas the drain overlap may be significantly reduced or may even be completely avoided to further enhance the transistor performance.

Owner:ADVANCED MICRO DEVICES INC

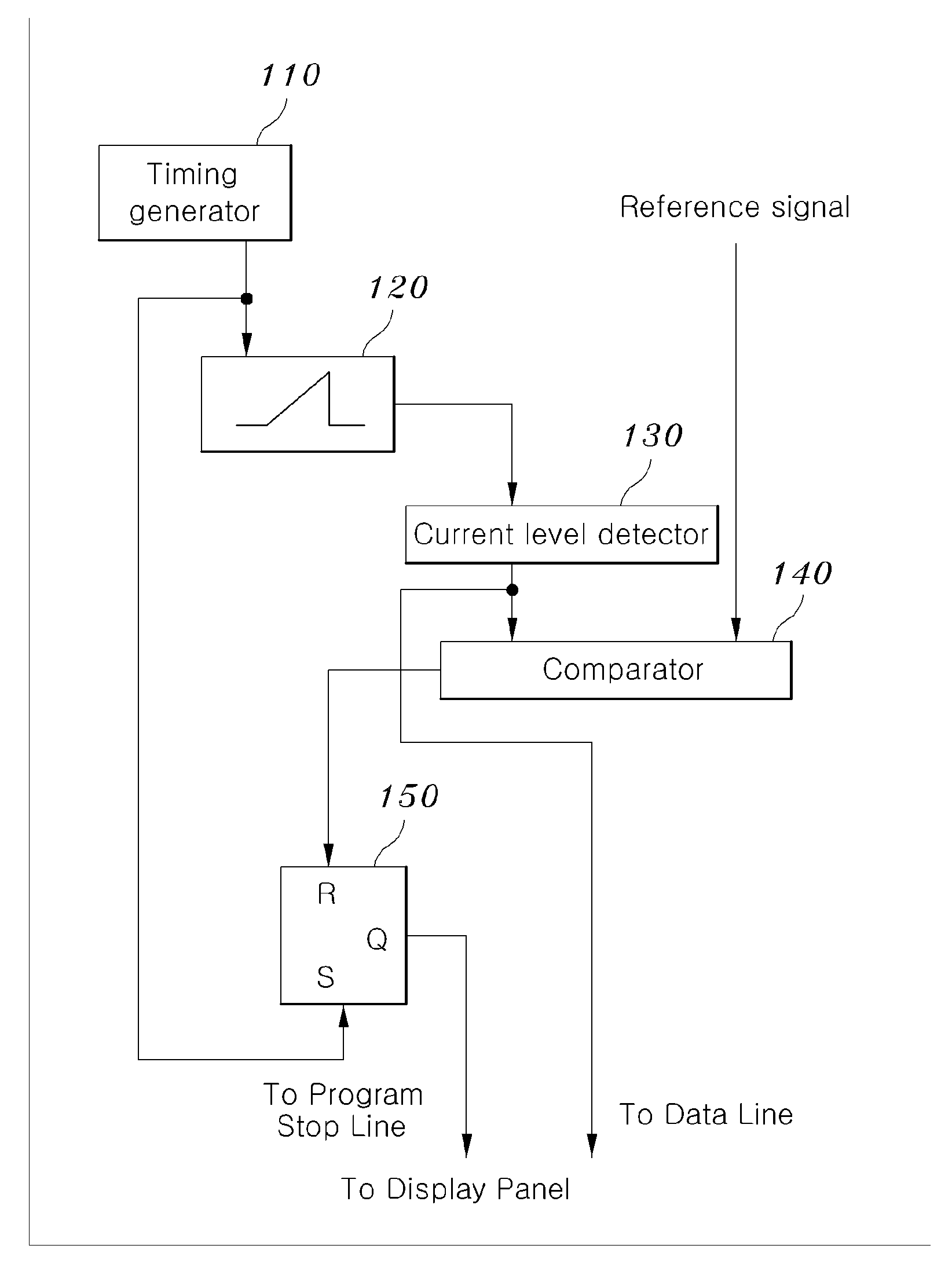

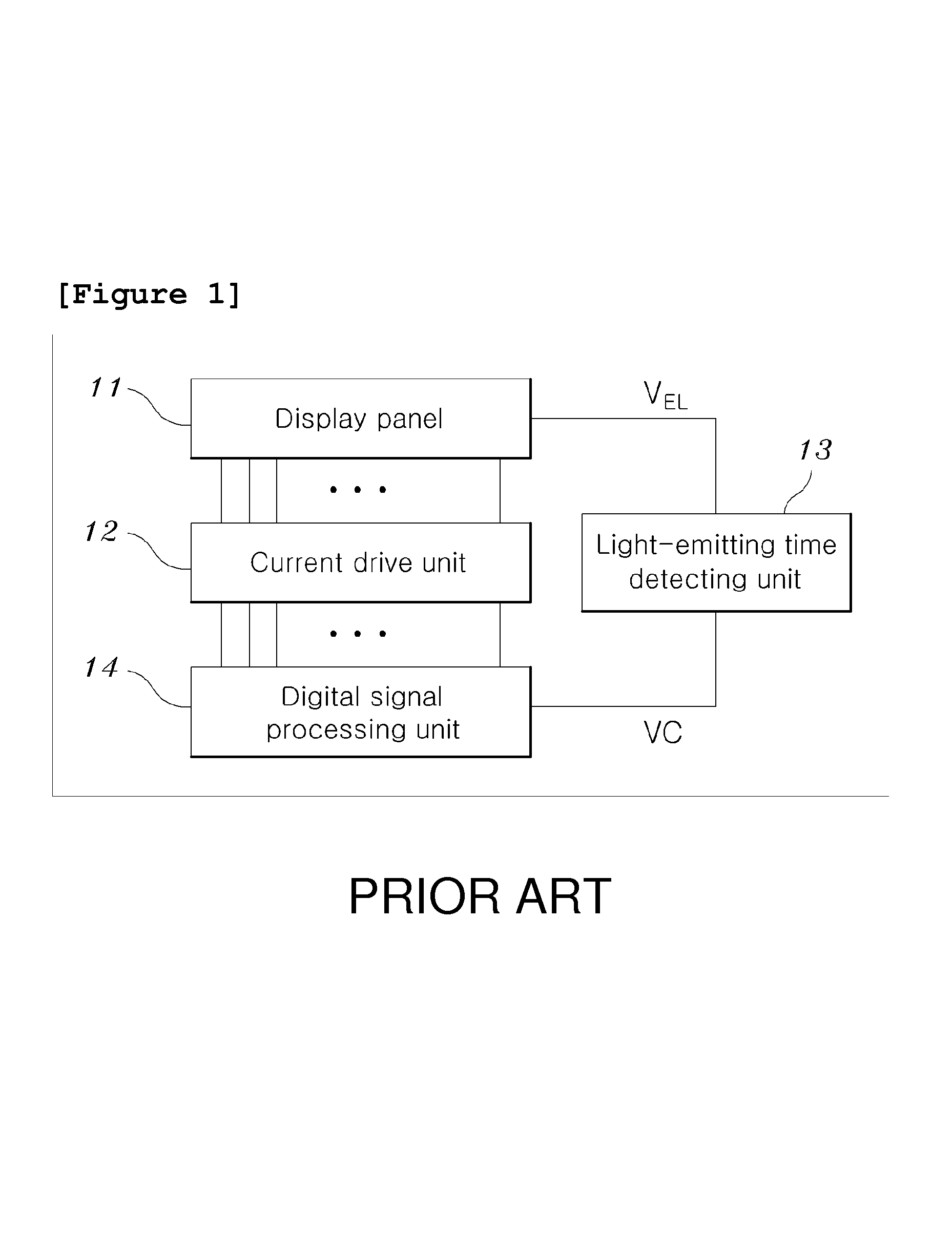

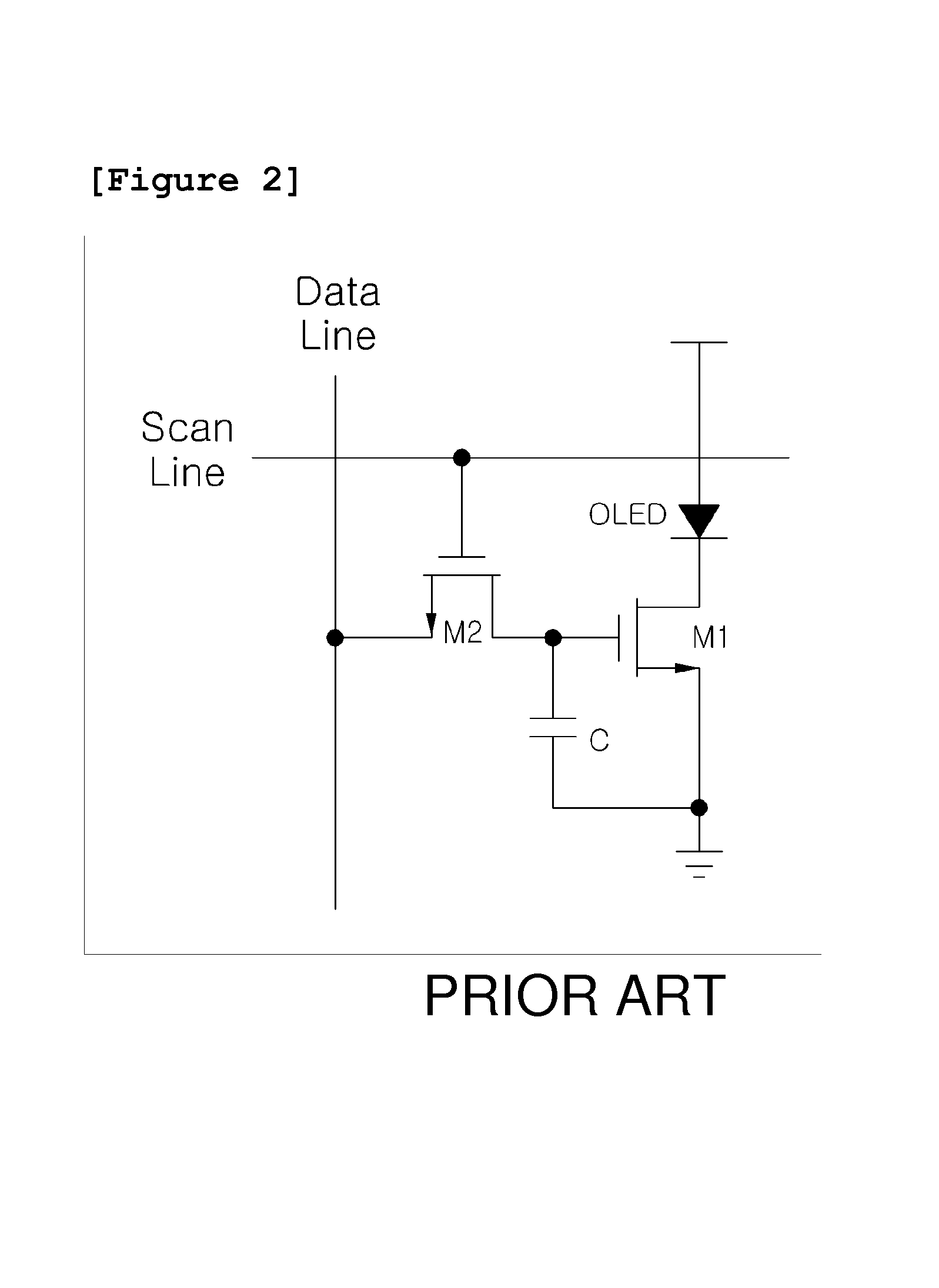

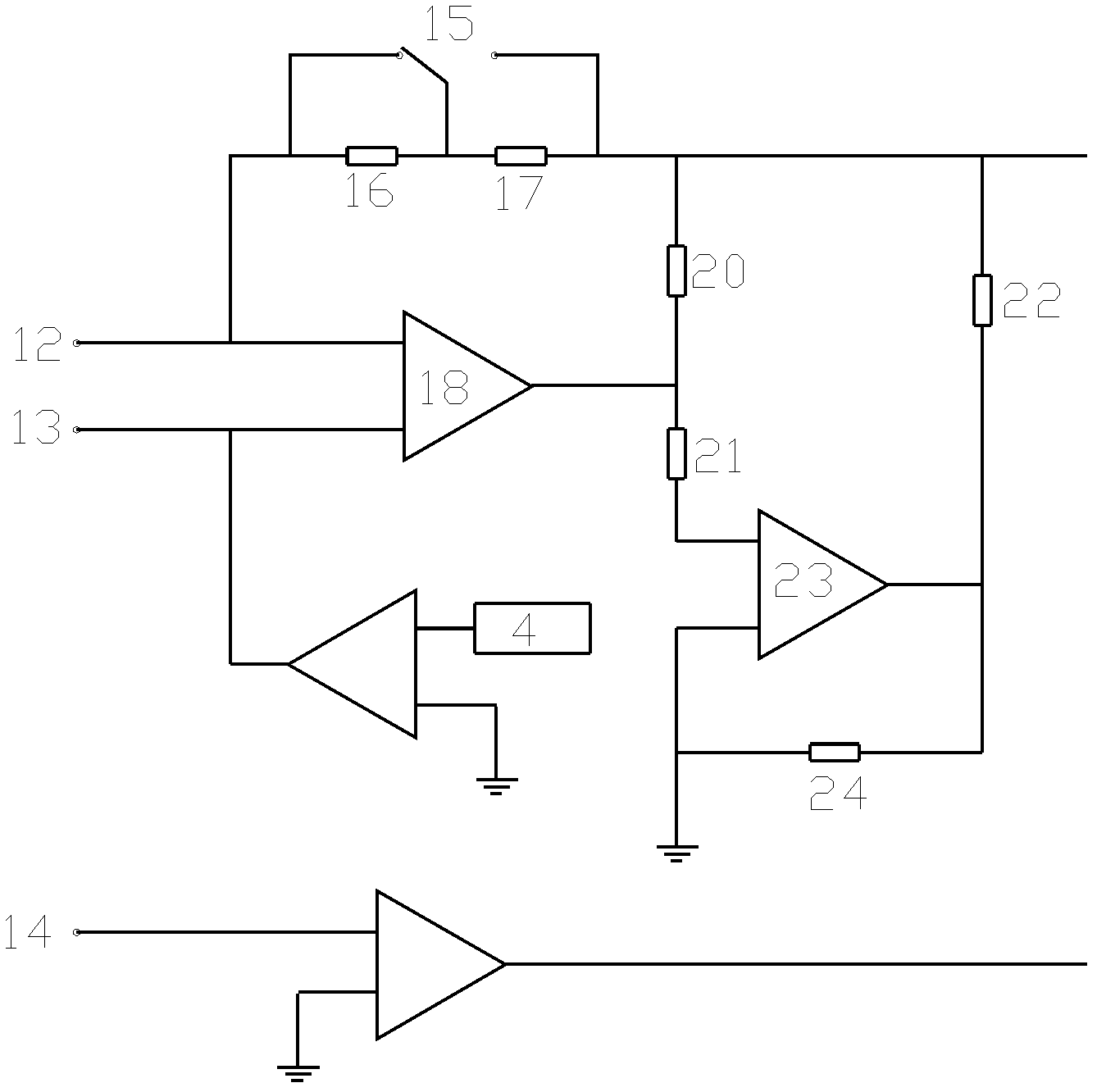

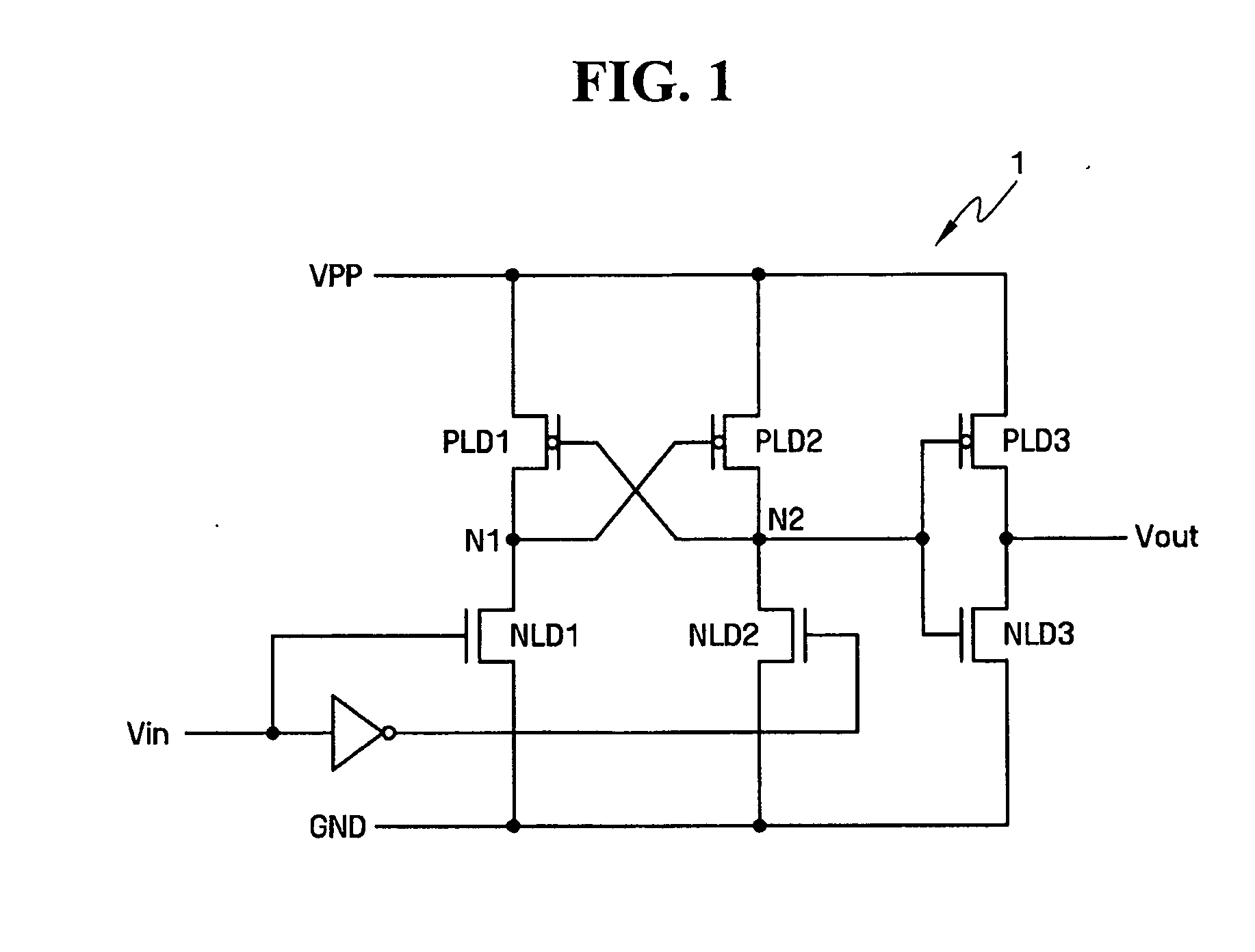

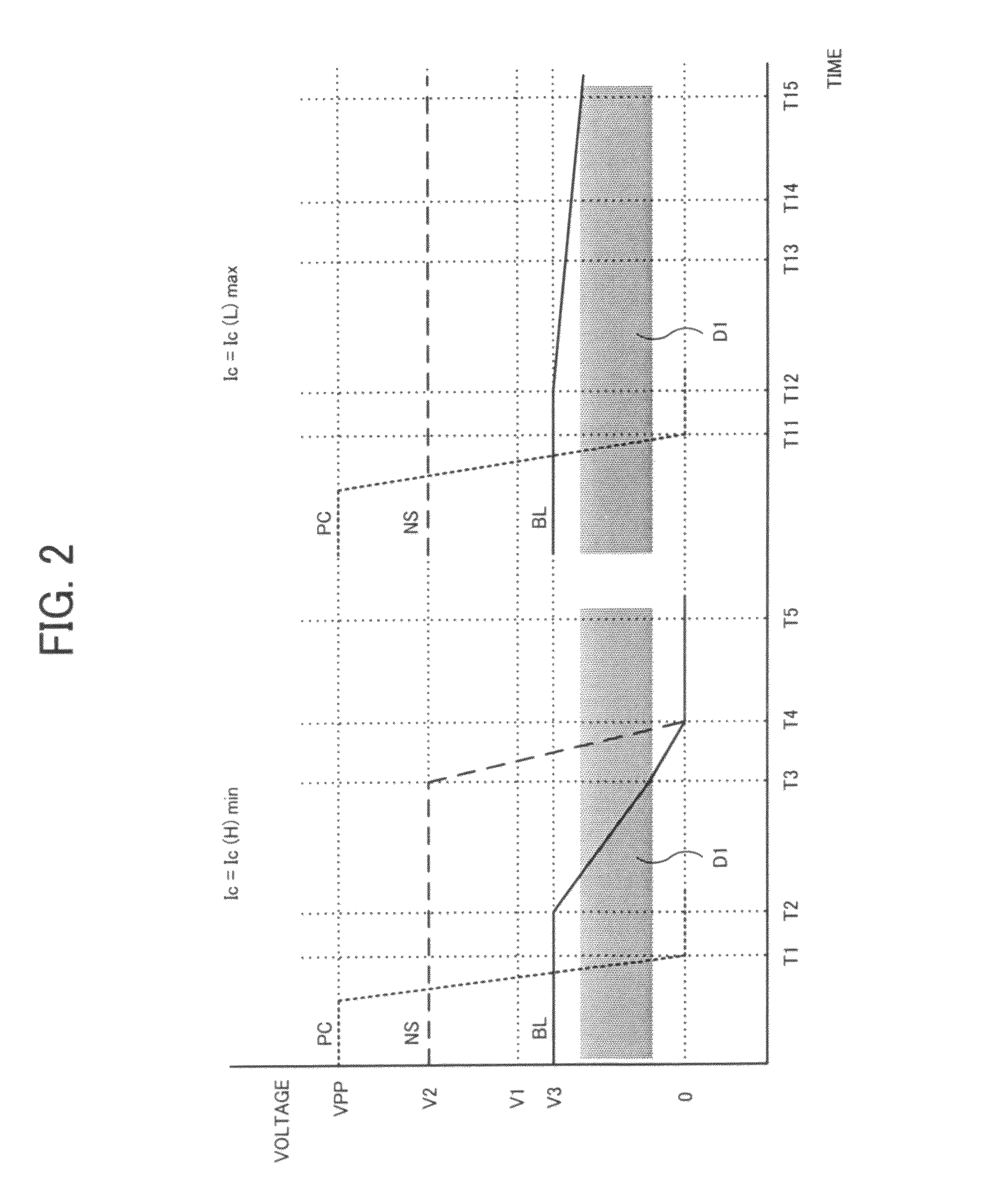

Driving method and circuit for automatic voltage output of active matrix organic light emitting device and data drive circuit using the same

InactiveUS7605792B2Uniform brightnessImprove current drive capabilityElectrical apparatusCathode-ray tube indicatorsControl signalActive matrix

Disclosed herein is a driving method and circuit for the automatic voltage output of an active matrix organic light emitting device, which is capable of resolving the non-uniformity of brightness between pixels. The circuit of the present invention includes timing generation means for generating a data drive start signal; sweep voltage generation means for generating a sweep voltage signal in response to output of the timing generation means; current level detection means for sensing an amount of current, which flows into pixels, based on output of the sweep voltage generation means, and outputting a sensing result to a data line; comparison means for comparing output of the current level detection means with a reference signal that determines stop timing for data writing, and outputting a comparison result; and data writing start / end control signal generation means for starting to operate in response to the output of the timing generation means, and generating data writing start and end control signals to a program stop line of a display panel. The invention can shorten data writing time and improve the precision of data writing. Furthermore, the present invention can simplify a data drive circuit and achieve the uniformity of brightness between pixels.

Owner:IKAIST CO LTD

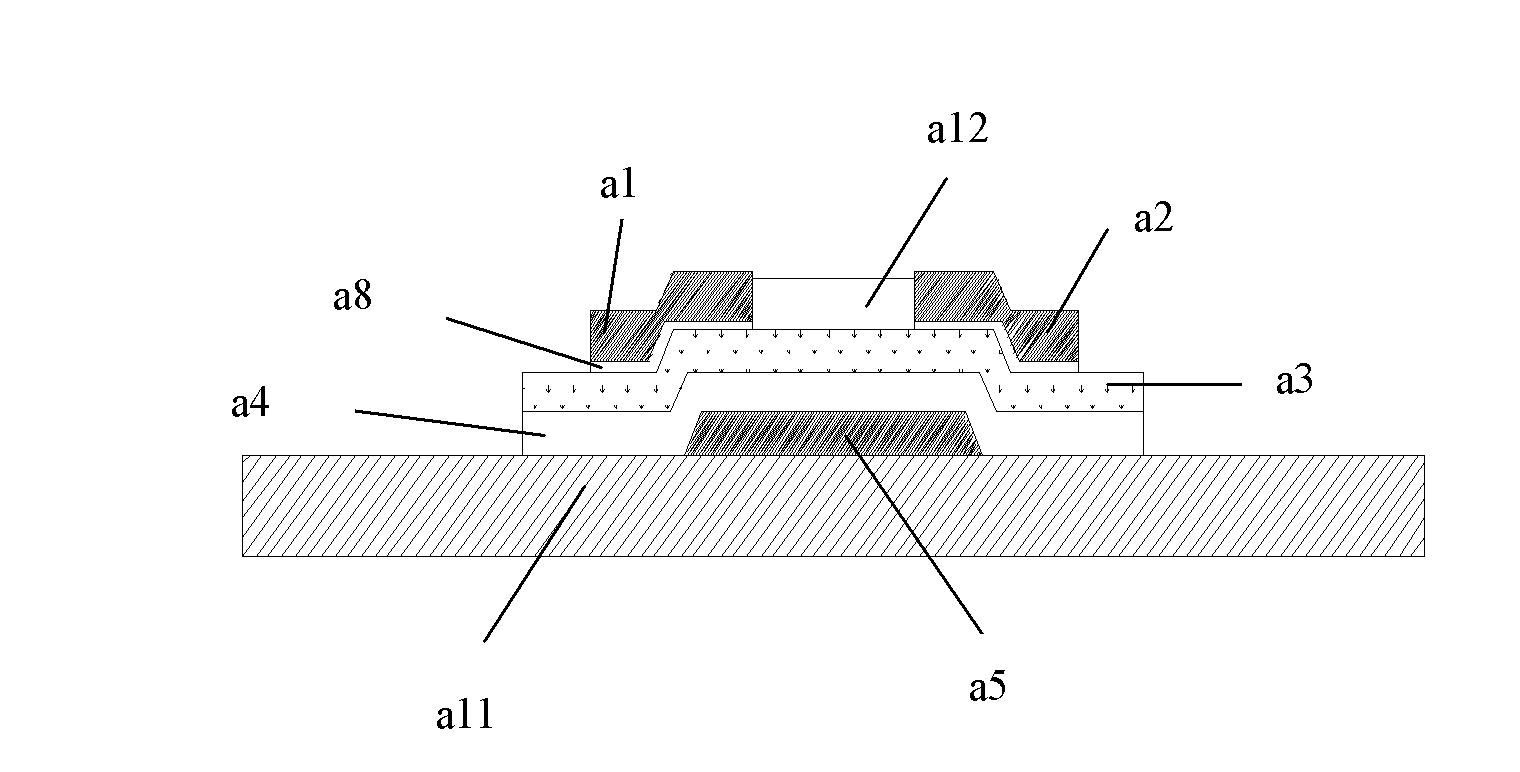

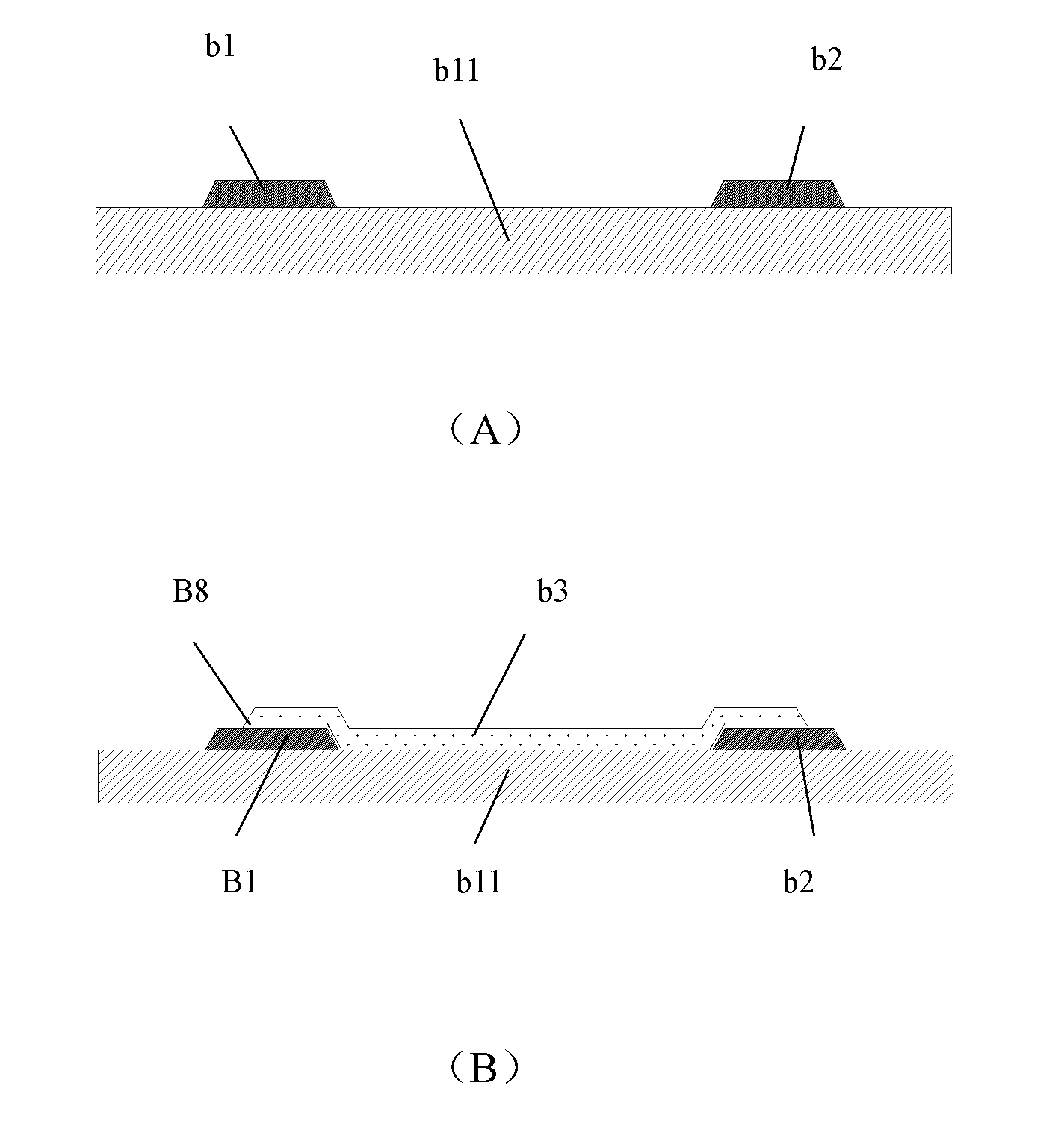

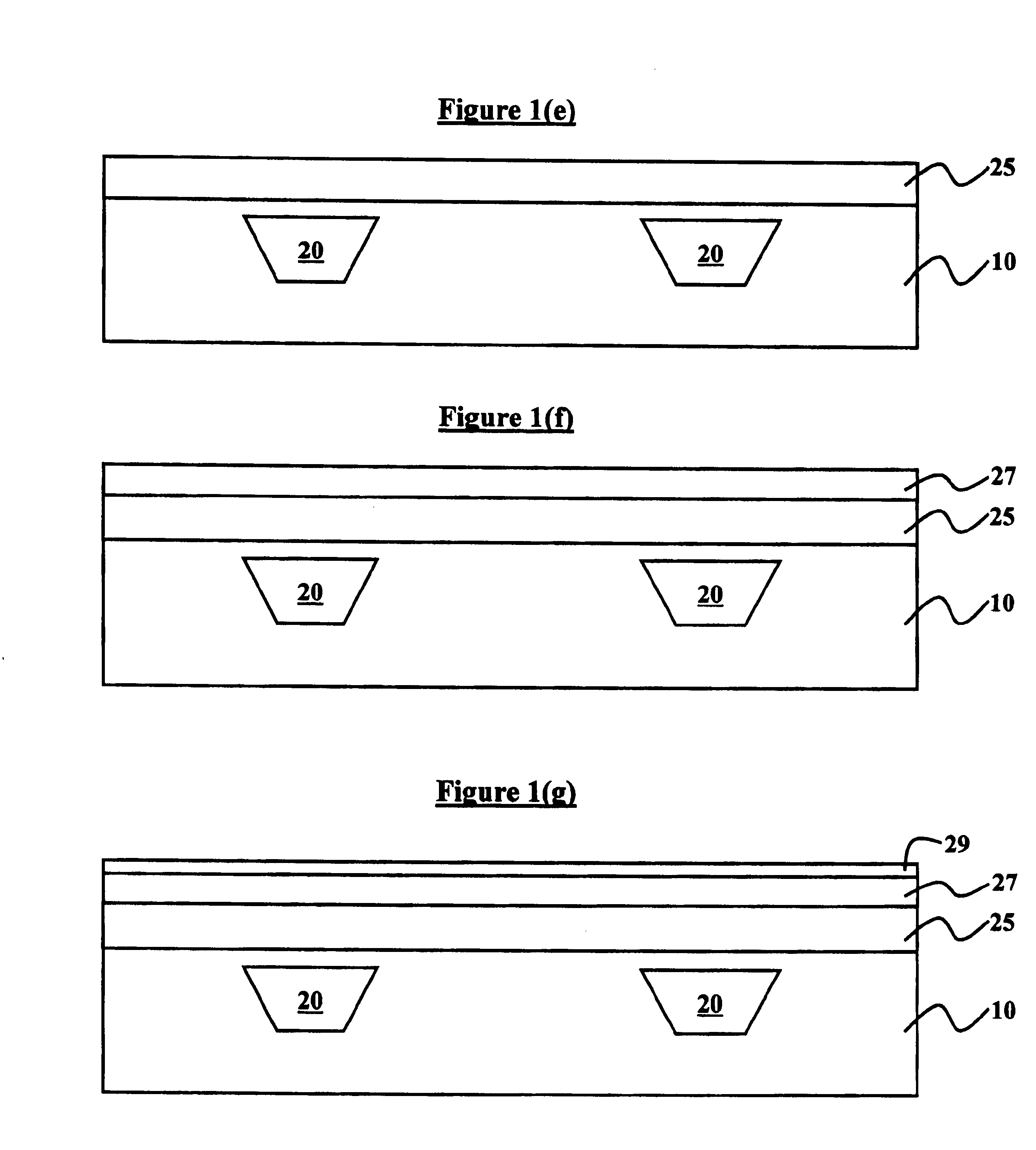

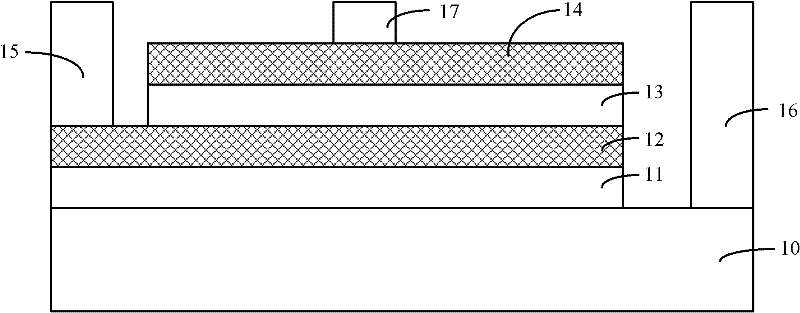

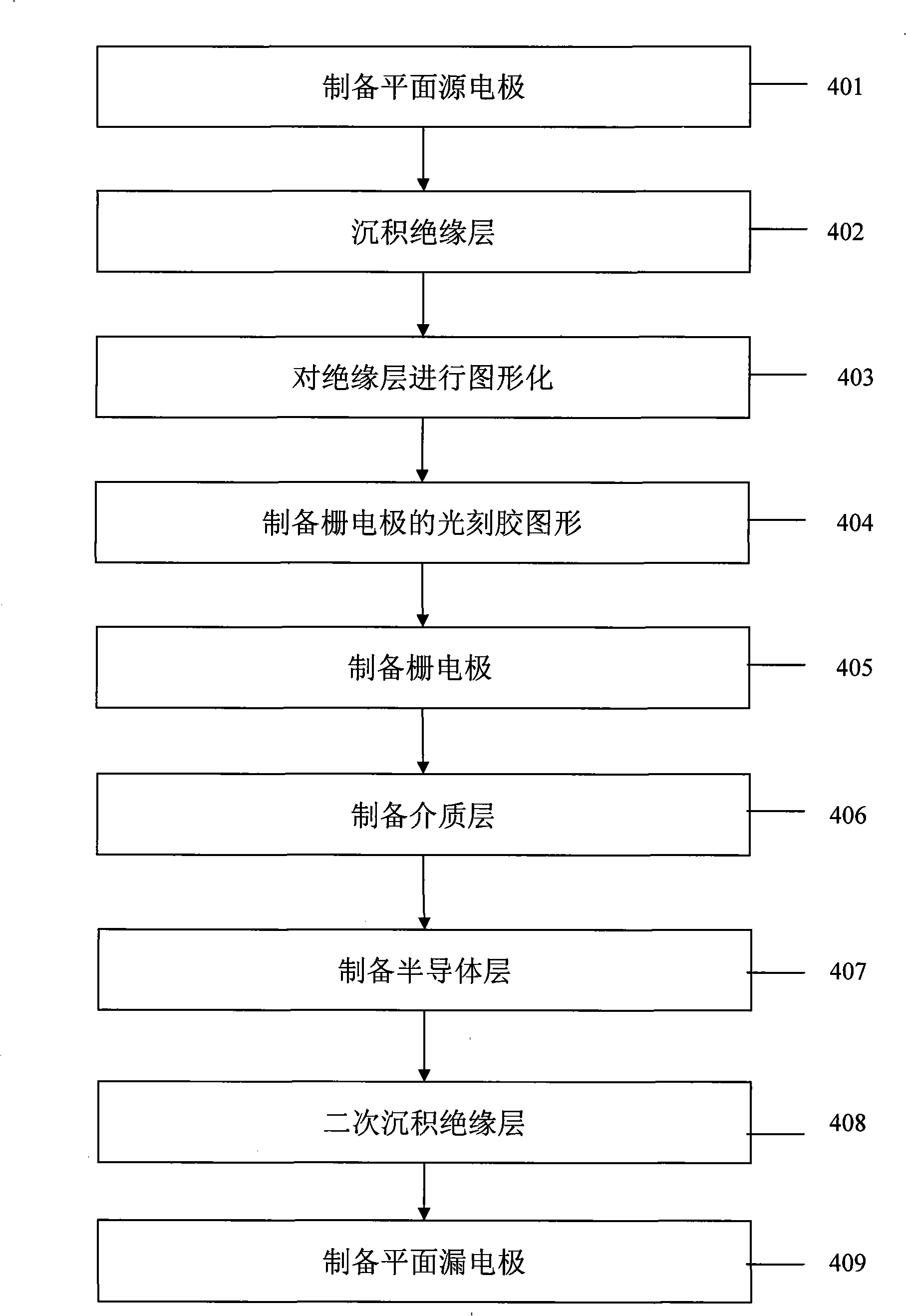

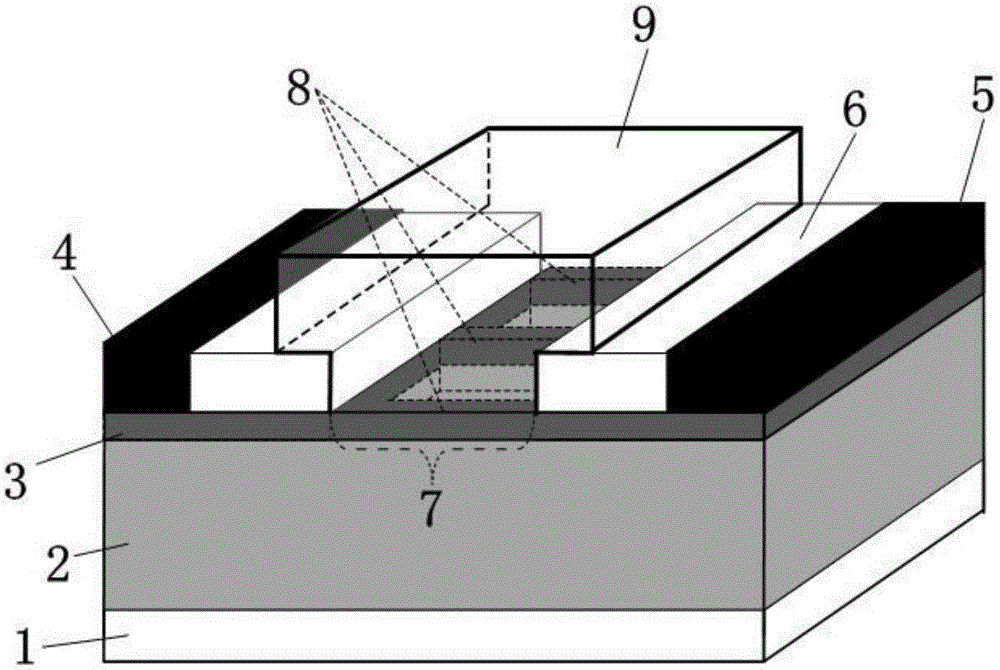

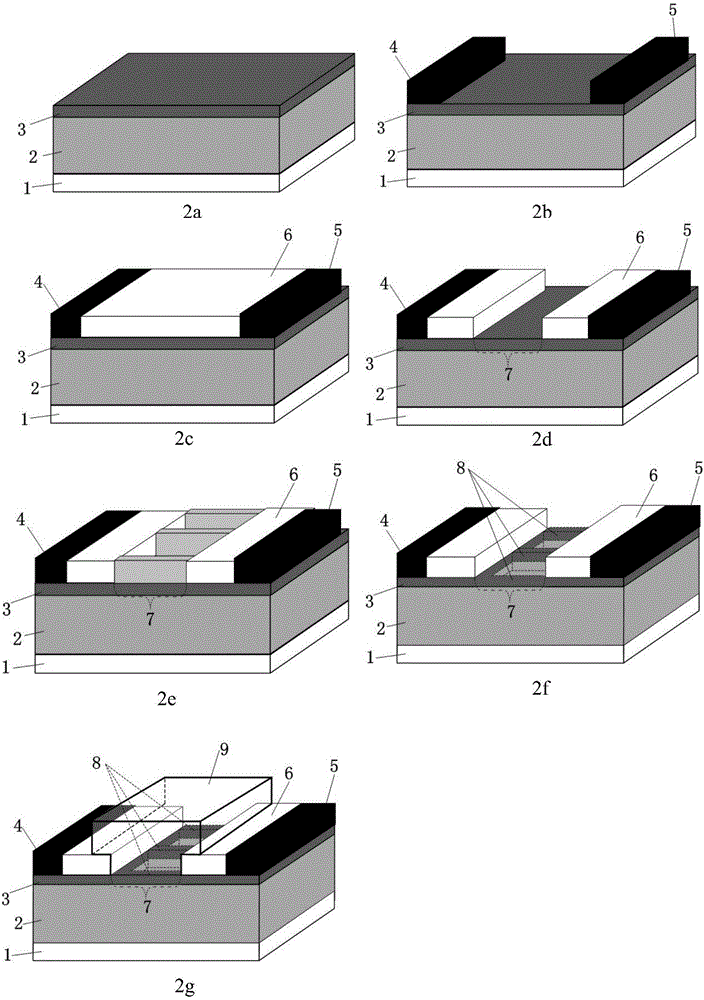

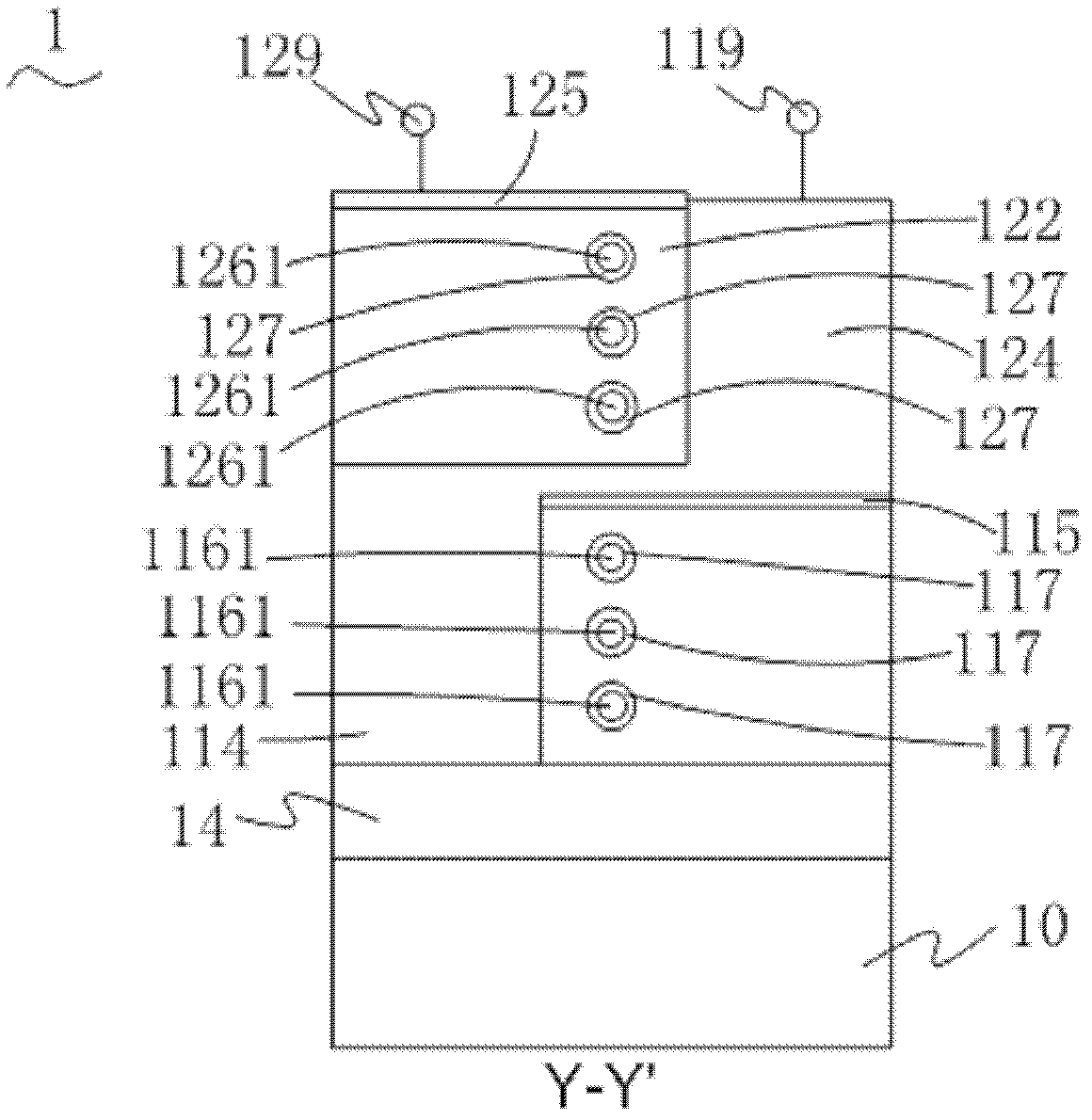

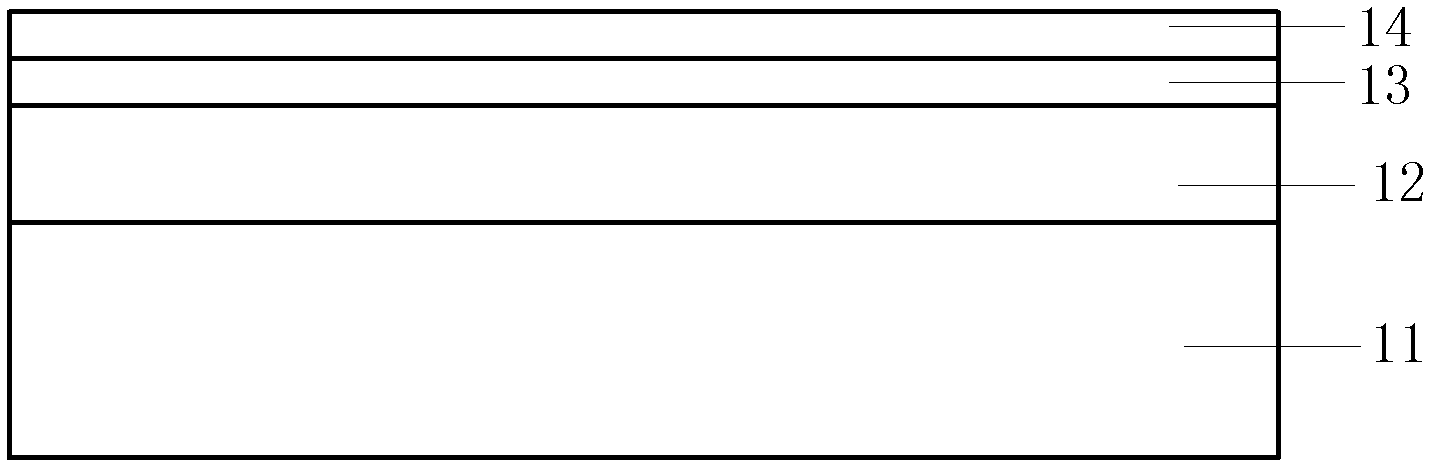

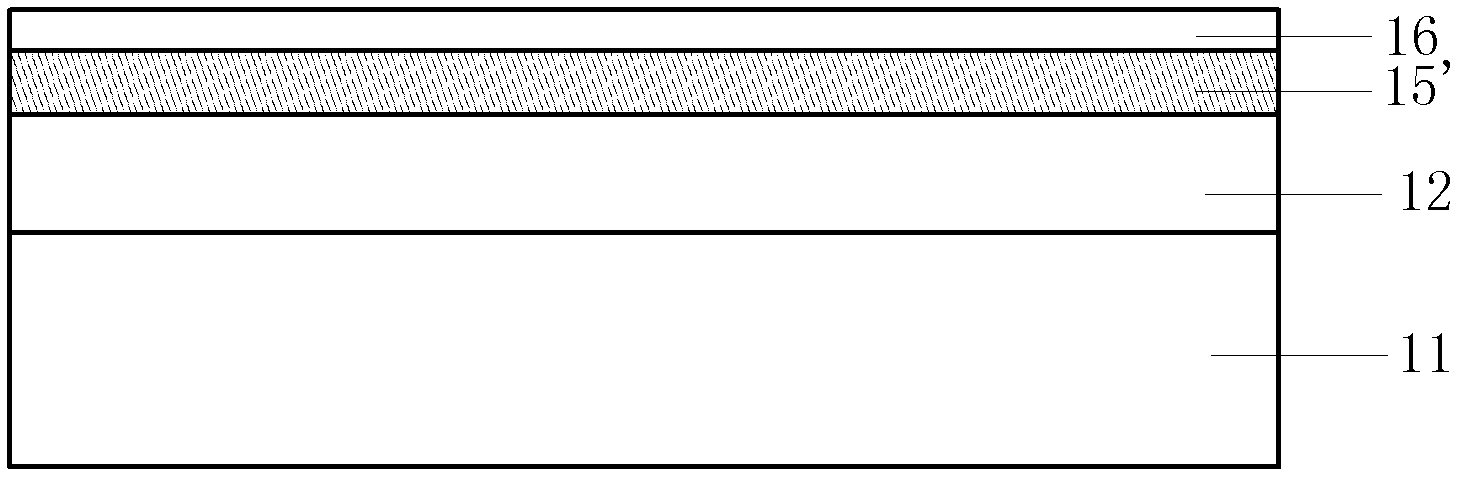

Thin film transistor with single-gate double-channel structure and manufacturing method thereof

ActiveCN102184968AIncrease the on-state currentImprove current drive capabilityTransistorSemiconductor/solid-state device manufacturingInsulation layerHemt circuits

The invention discloses a thin film transistor with a single-gate double-channel structure and a manufacturing method thereof. The manufacturing method comprises the steps of forming a first source electrode and a first drain electrode on a base plate; depositing a first active layer, wherein the edge of the active layer is overlapped with the edges of the first source electrode and the first drain electrode; then sequentially forming a first insulation layer, a gate electrode and a second insulation layer on the first active layer; forming a second active layer on the second insulation layerin a way of corresponding to the first active layer; and forming a second source electrode and a second drain electrode on the second active layer in a way of corresponding to the first source electrode and the first drain electrode to further form the thin film transistor with the single-gate double-channel structure. The thin film transistor with the single-gate double-channel structure has the advantages that: the thin film transistor can serve as a two-way switch device or a three-state device, can be used for controlling two circuit branches with a uniform circuit behavior, has a high on state current and can serve as an inverter.

Owner:王磊 +1

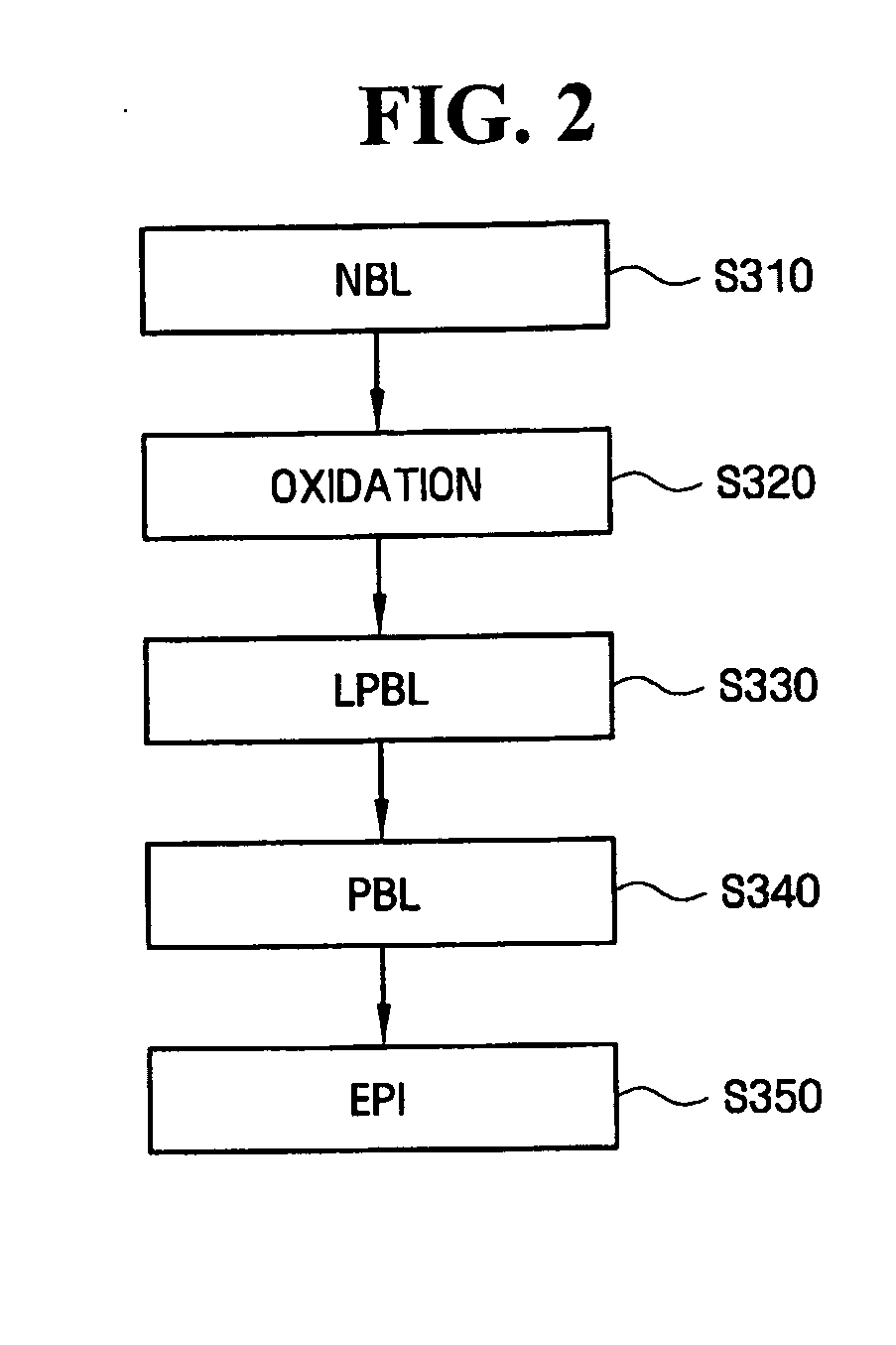

BICMOS technology on SIMOX wafers

InactiveUS6888221B1Reduce power consumptionImprove current drive capabilityTransistorSemiconductor/solid-state device manufacturingEngineeringSingle crystal

A method and structure for a bipolar transistor comprising a patterned isolation region formed below an upper surface of a semiconductor substrate and a single crystal extrinsic base formed on an upper surface of the isolation region. The single crystal extrinsic base comprises a portion of the semiconductor substrate located between the upper surface of the isolation region and the upper surface of the semiconductor substrate. The bipolar transistor further comprises a single crystal intrinsic base, wherein a portion of the single crystal extrinsic base merges with a portion of the single crystal intrinsic base. The isolation region electrically isolates the extrinsic base from a collector. The intrinsic and extrinsic bases separate the collector from an emitter. The extrinsic base comprises epitaxially-grown silicon. The isolation region comprises an insulator, which comprises oxide, and the isolation region comprises any of a shallow trench isolation region and a deep trench isolation region.

Owner:GLOBALFOUNDRIES INC

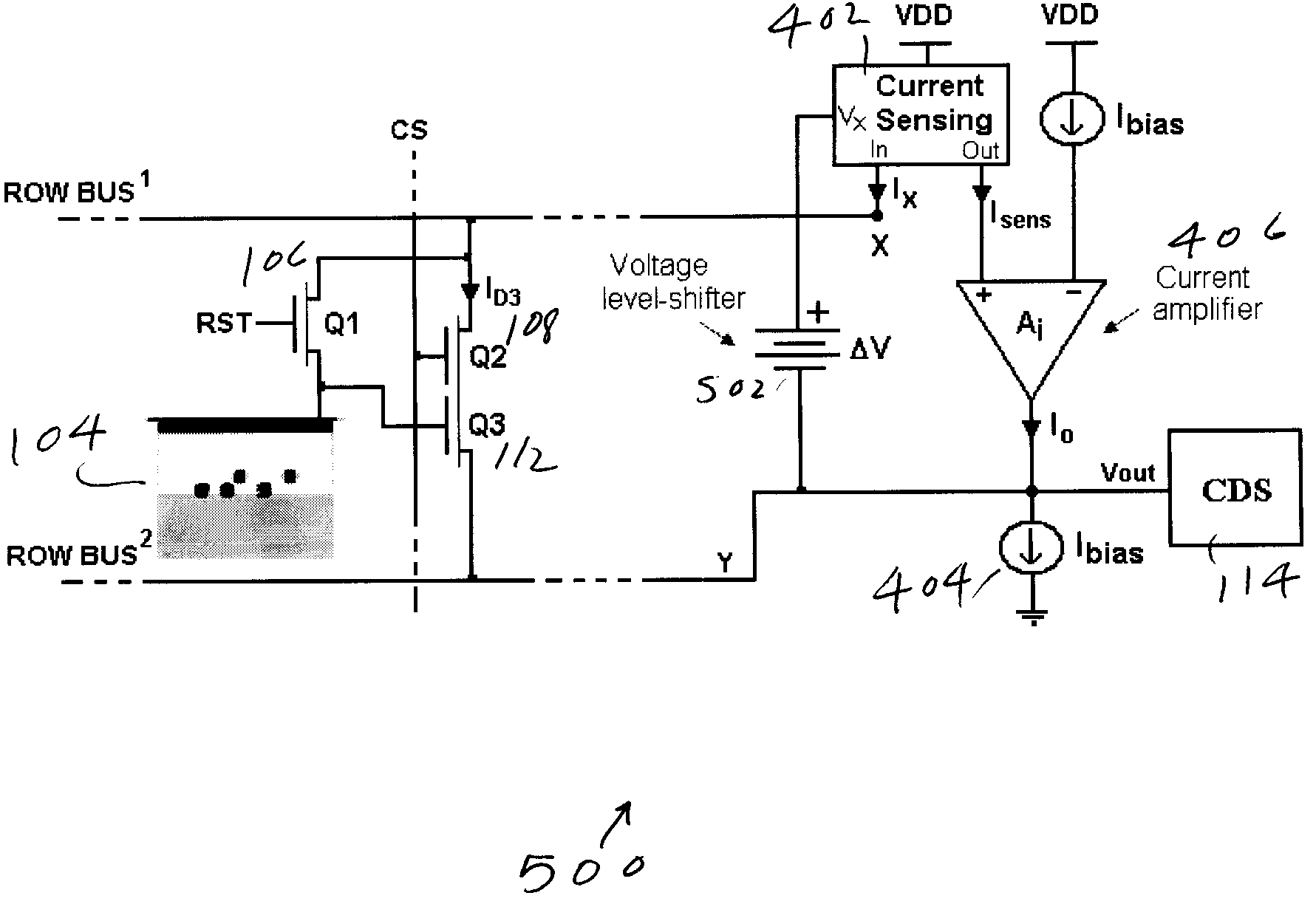

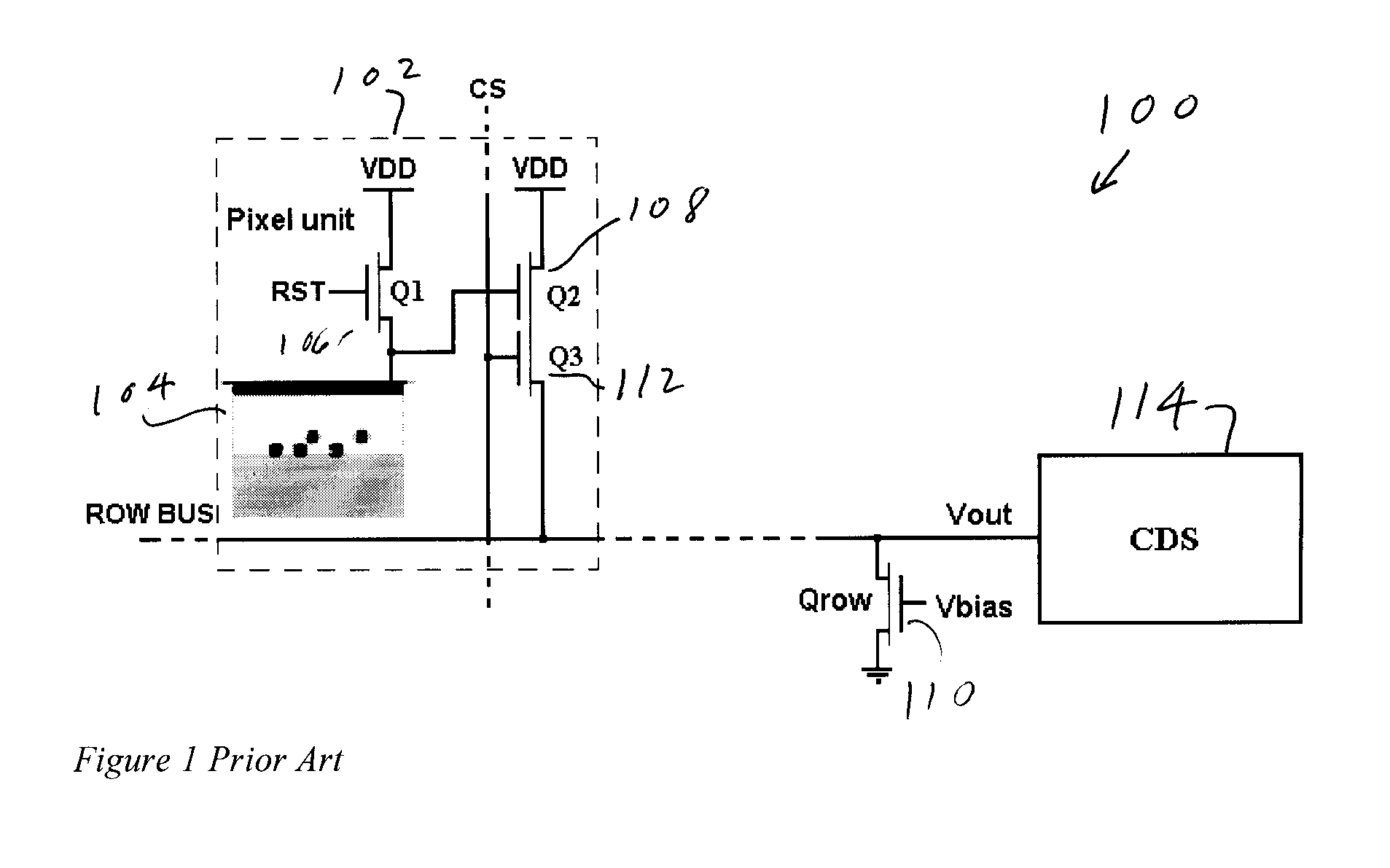

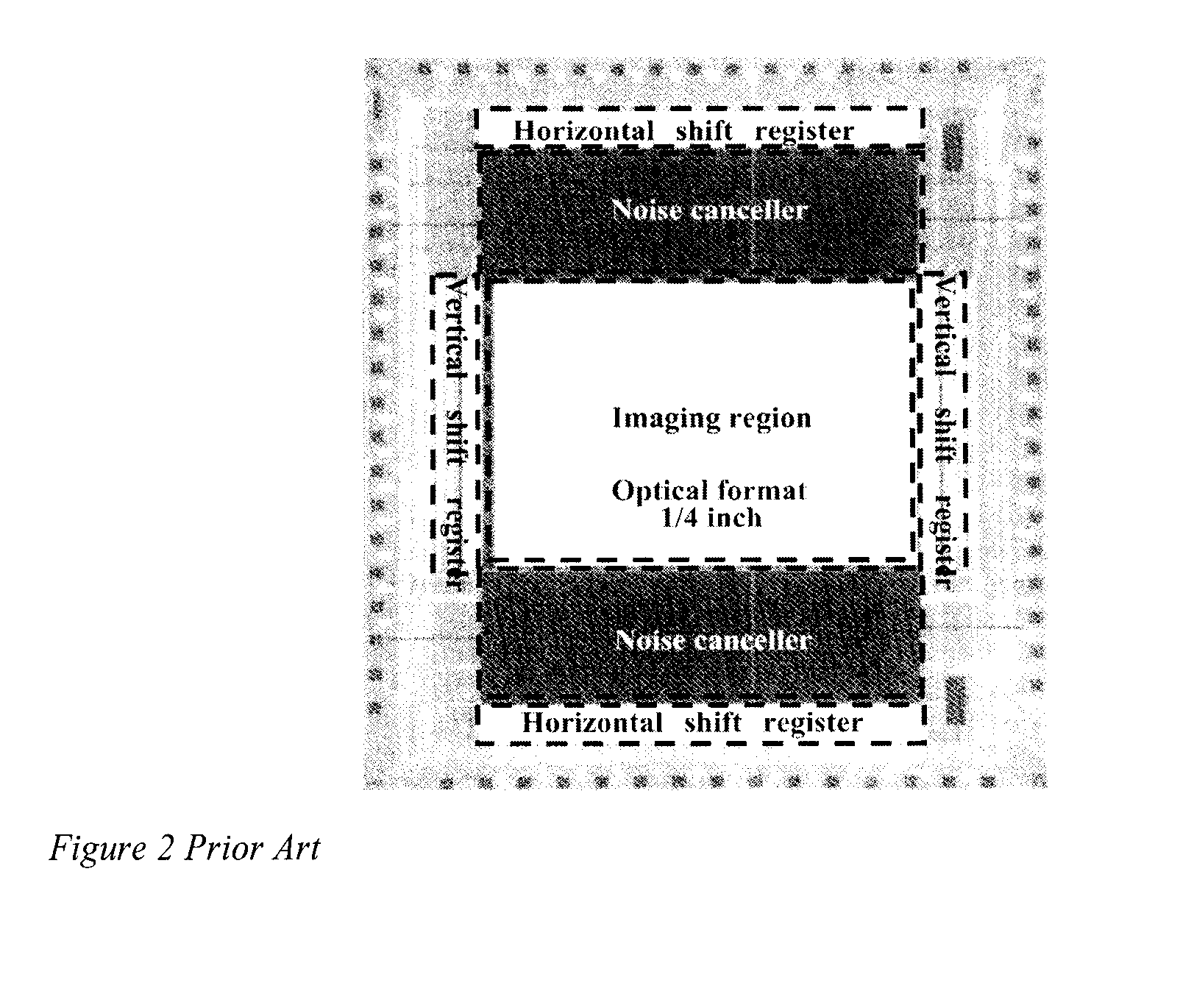

CMOS image sensor readout employing in-pixel transistor current sensing

ActiveUS7847846B1Reduce read noiseIncrease frame rateTelevision system detailsTelevision system scanning detailsCMOSParasitic capacitance

In an image sensor, the current through the in-pixel readout transistor is sensed by a circuit that is external to the pixel, and according to the measured current value a feedback current is supplied to charge the read-line parasitic capacitance. The feedback current is supplied by a circuit that also is external to the pixel area. The amplifier structure is reconfigurable so that it can be used both to read out and to reset the pixel.

Owner:UNIVERSITY OF ROCHESTER

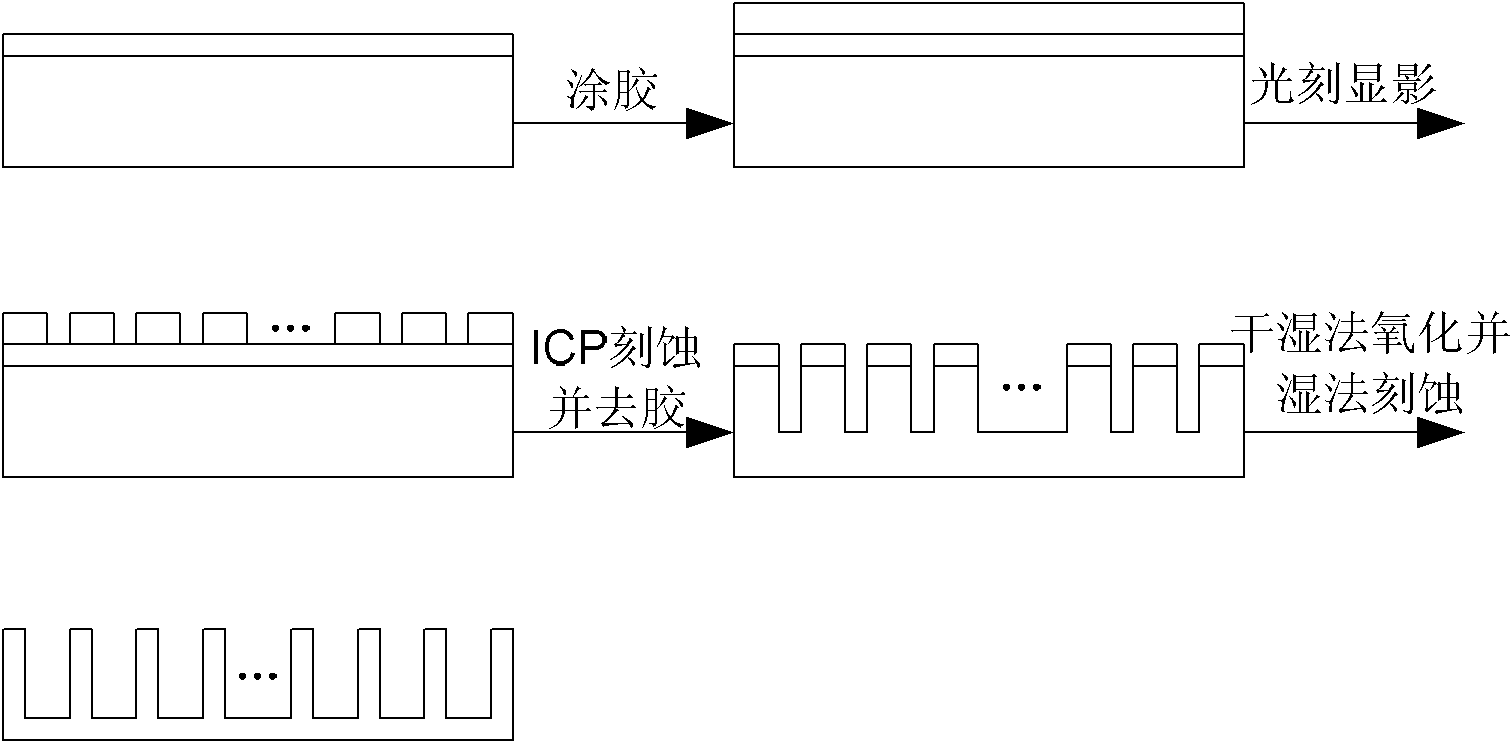

Preparation method of silicon nano-wire field-effect transistor

InactiveCN102214586AEasy to controlSmooth and steep etch effectSemiconductor/solid-state device manufacturingNanotechnologySilicon nanowiresField effect

The invention relates to the field of microelectronic apparatus manufacture, and discloses a top-down preparation method of a vertical silicon nano-wire gate field-effect transistor. The vertical silicon nano-wire gate field-effect transistor includes a semiconductor substrate, a nano-wire channel region vertically arranged on the semiconductor substrate and an annular grid conductive layer arranged out of the channel. The nano-wire channel region is provided with an active conductive layer; the upper part is doped with n impurity to serve as a source end n area; the semiconductor substrate contacting with the bottom of the drain conductive layer is doped with n impurity to serve as a drain end n area; and a non-symmetrical Halo-doped structure p+ region is added between the source end and the channel. The method for preparing the vertical silicon nano-wire gate field-effect transistor can well control the consistency of the position and size of the nano-wire, thus simplifying the manufacture process and reducing the manufacture cost.

Owner:XI AN JIAOTONG UNIV

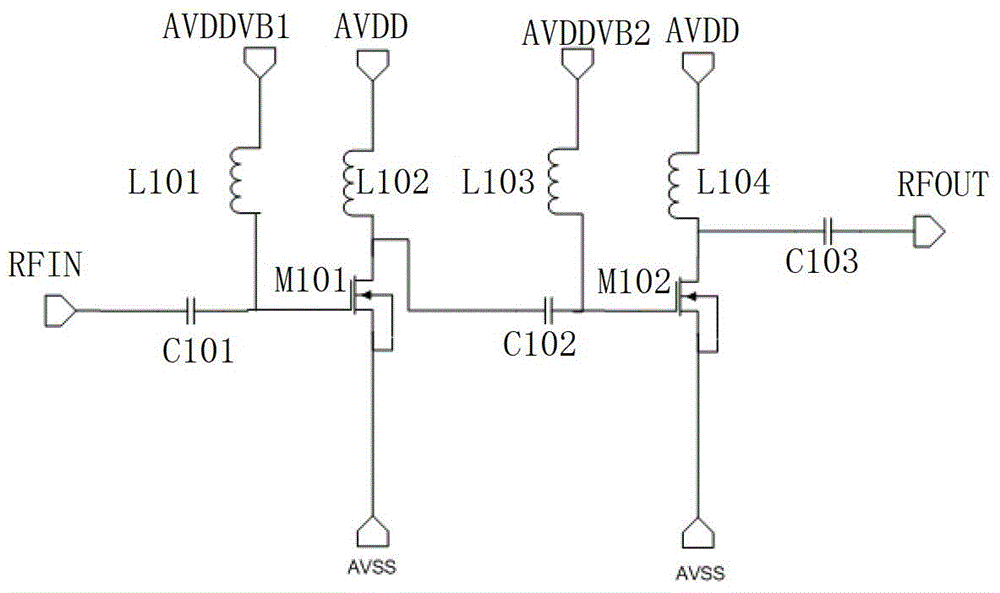

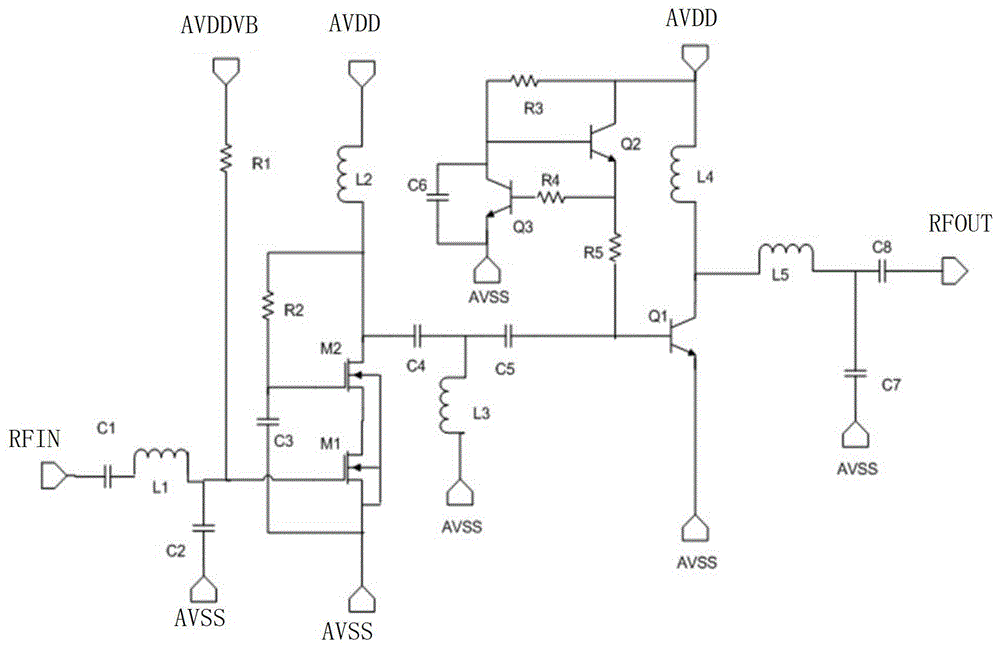

Radio frequency power amplifier

ActiveCN104158500AImprove pressure resistanceImprove isolationHigh frequency amplifiersAmplifier modifications to extend bandwidthCommon emitterAudio power amplifier

The invention discloses a radio frequency power amplifier integrated on a same chip. The radio frequency power amplifier comprises two stages of amplifying circuits. An automatic biasing cascode CMOS amplifier is adopted in the first-stage amplifying circuit, and a SiGe HBT connected through a common emitter is adopted in the second-stage amplifying circuit. According to the radio frequency power amplifier, the withstand voltage, the isolation and the bandwidth of the circuits can be improved, the voltage swing and working current of the circuits can be improved, the gain and the maximum output power of the circuits can be improved, the frequency performance of the power amplifier can be improved, full-chip integration can be achieved, and accordingly, the integration degree is improved, cost is reduced, and the application is simplified.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

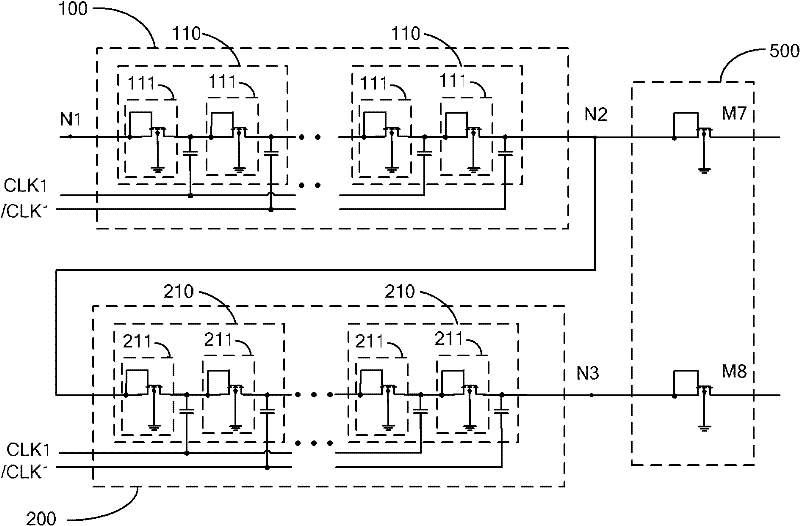

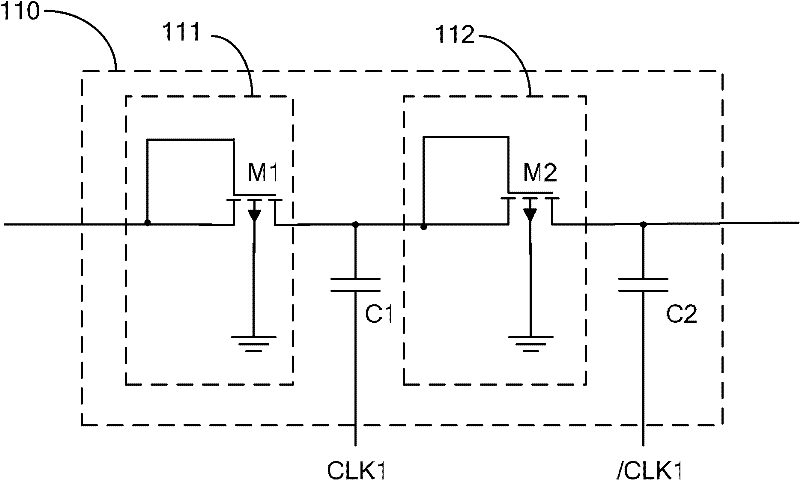

A charge pump circuit and flash memory using the charge pump circuit

ActiveCN102290981AReduce areaHighly integratedRead-only memoriesApparatus without intermediate ac conversionCapacitanceEngineering

A charge pump circuit, wherein a first charge pump unit, a second charge pump unit and an output unit are connected in series in sequence, the output ends of the first charge pump unit and the second charge pump unit are connected to the output unit, and the first charge pump The unit and the second charge pump unit are formed by cascading several basic units. The basic unit at least includes a switch unit and an output capacitor. An output capacitor is connected between two series-connected switch units. The first charge pump unit of the first charge pump unit The first output capacitor is a PPS capacitor, and the second output capacitor of the second charge pump unit is a MOS capacitor; the output unit is used to output the voltage output by the first charge pump unit and the voltage output by the second charge pump unit. Also provided is a flash memory using the charge pump circuit. Using the PPS capacitor as the output capacitor of the first charge pump unit can greatly reduce the area of the output capacitor, improve chip integration, and improve the current driving capability of the first charge pump unit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

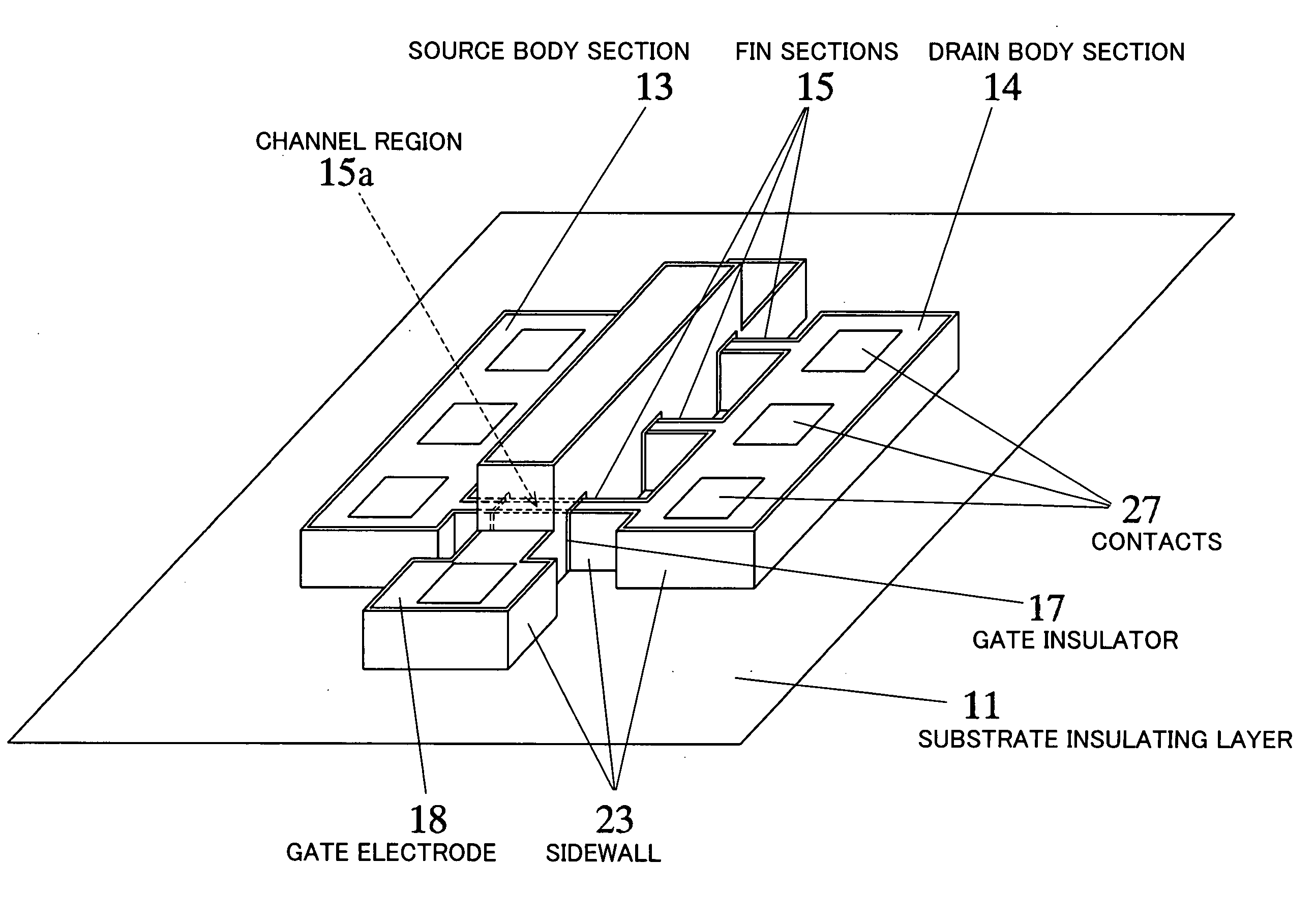

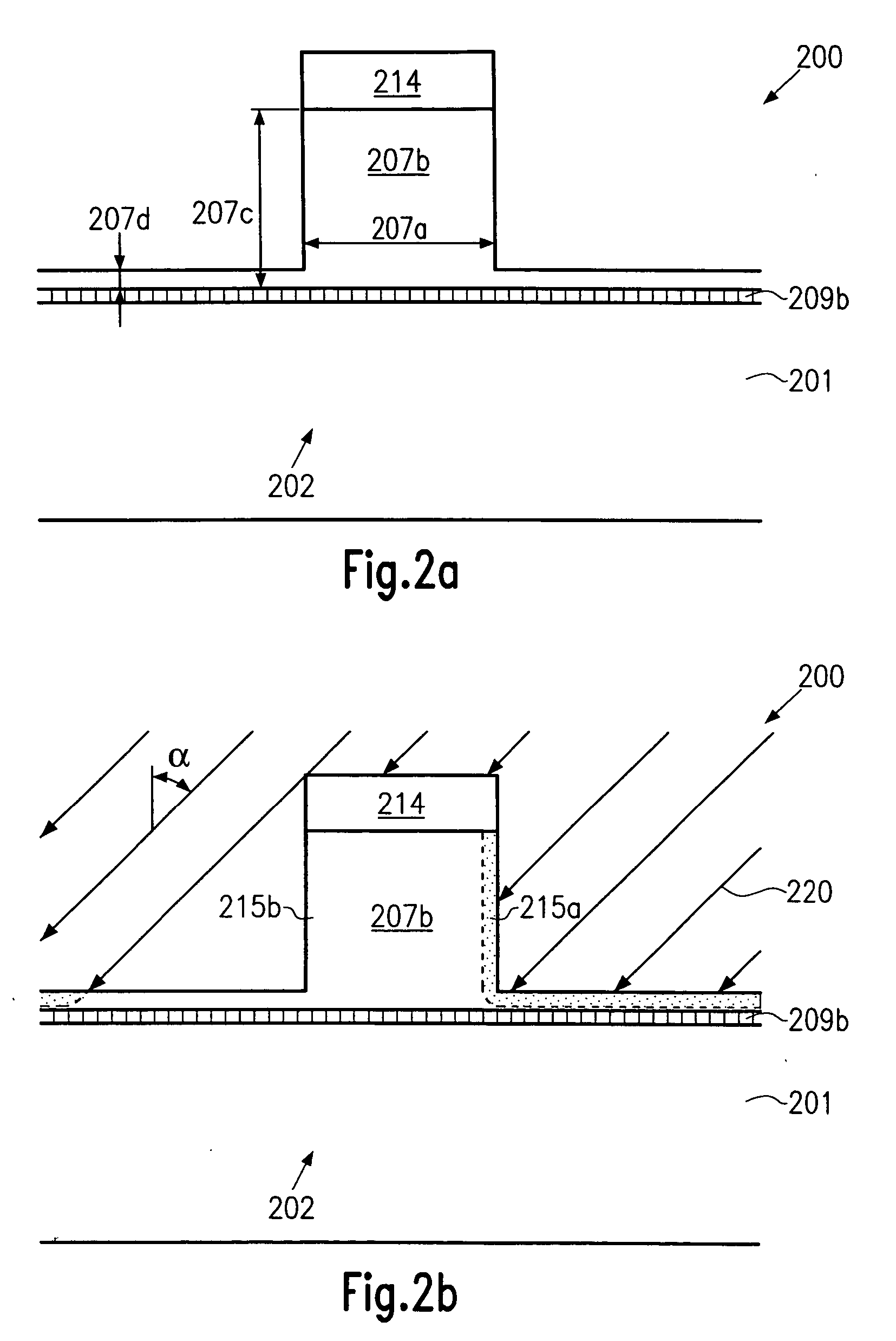

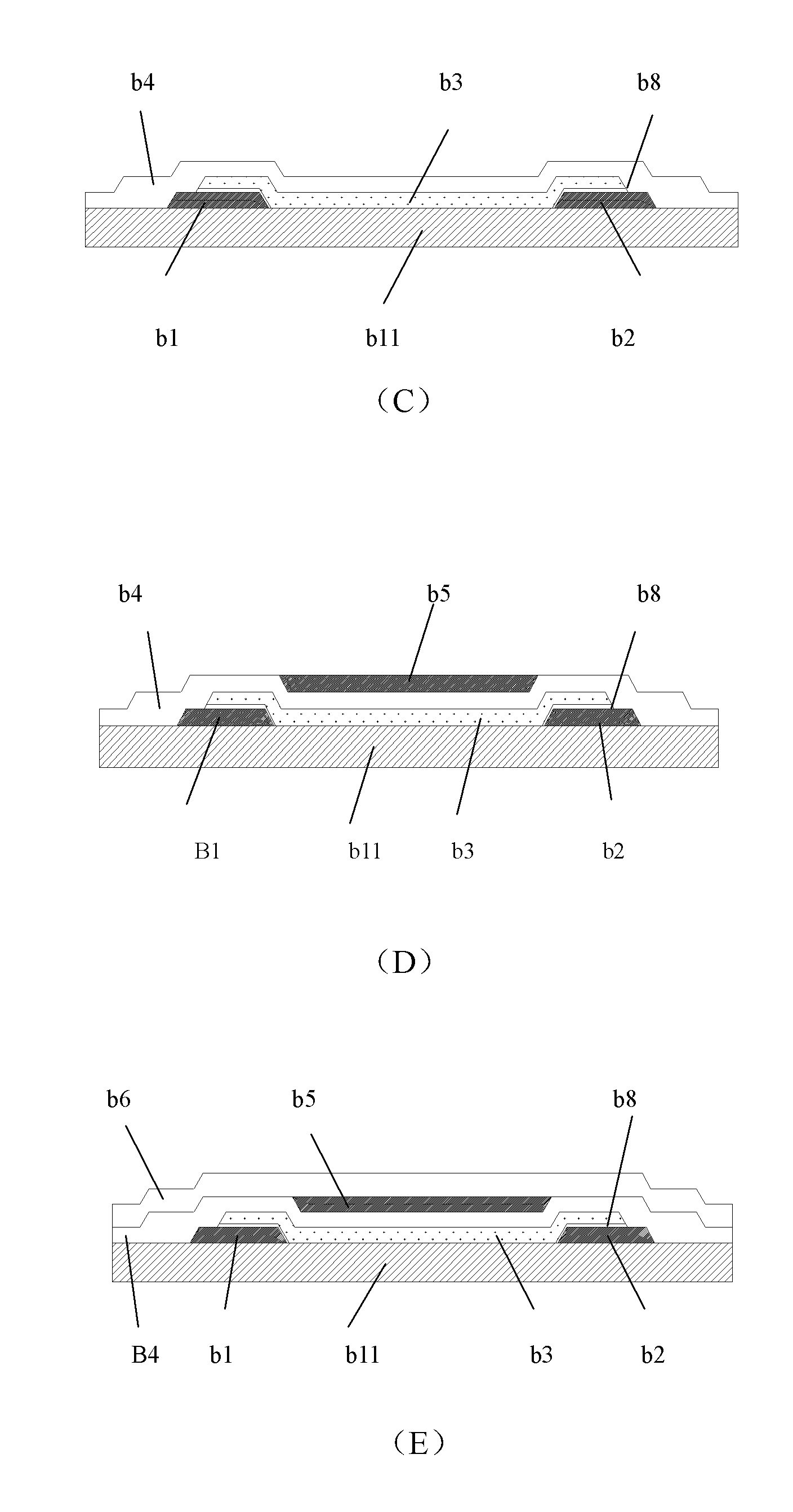

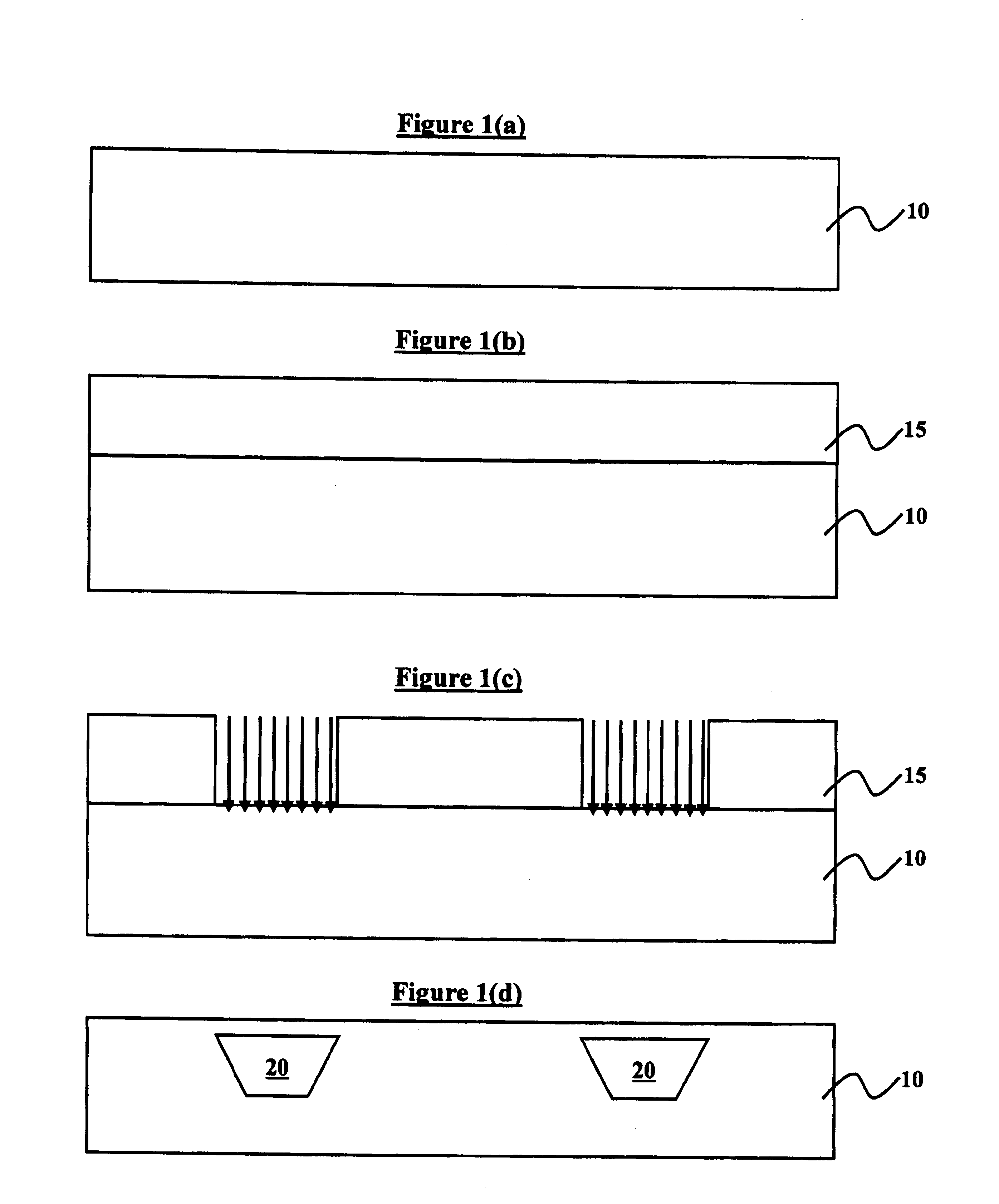

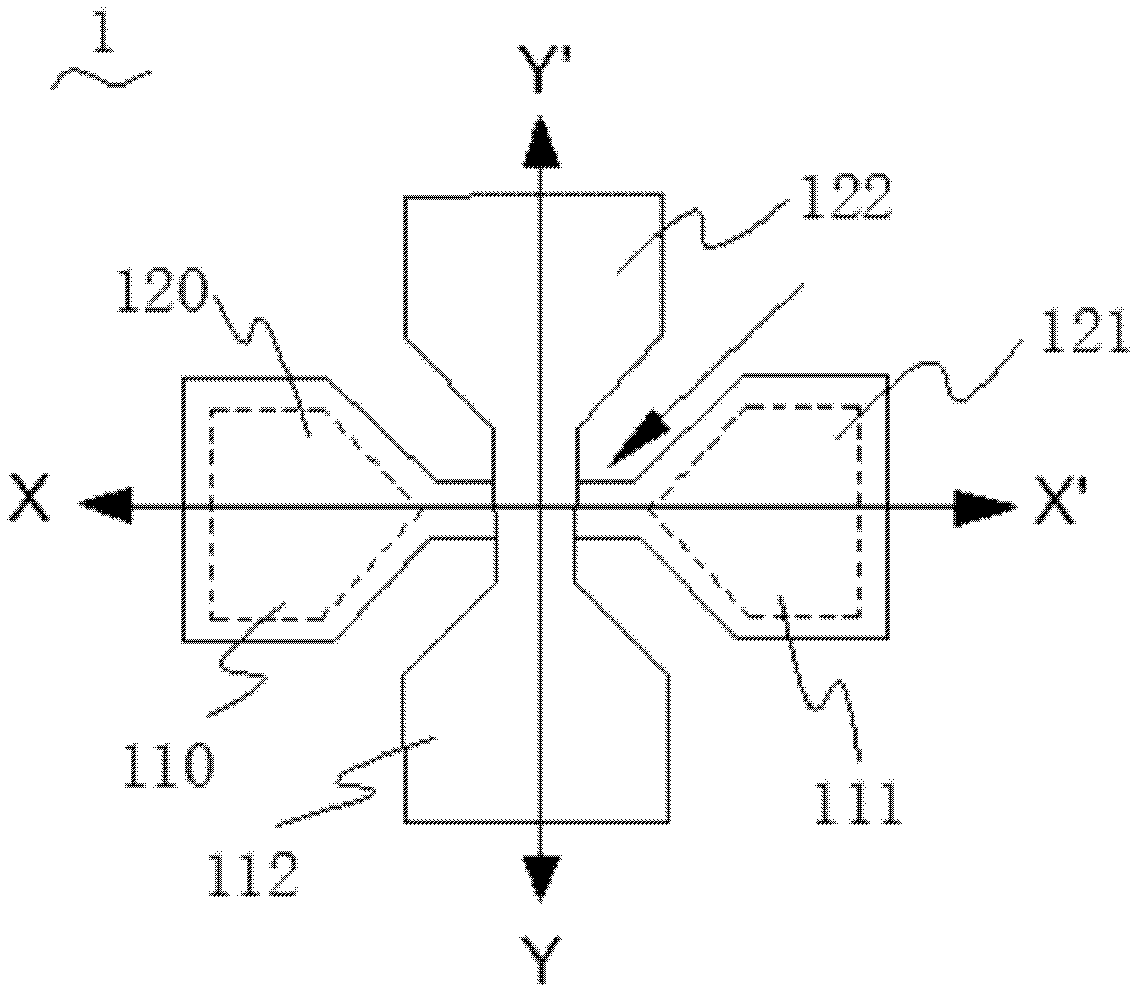

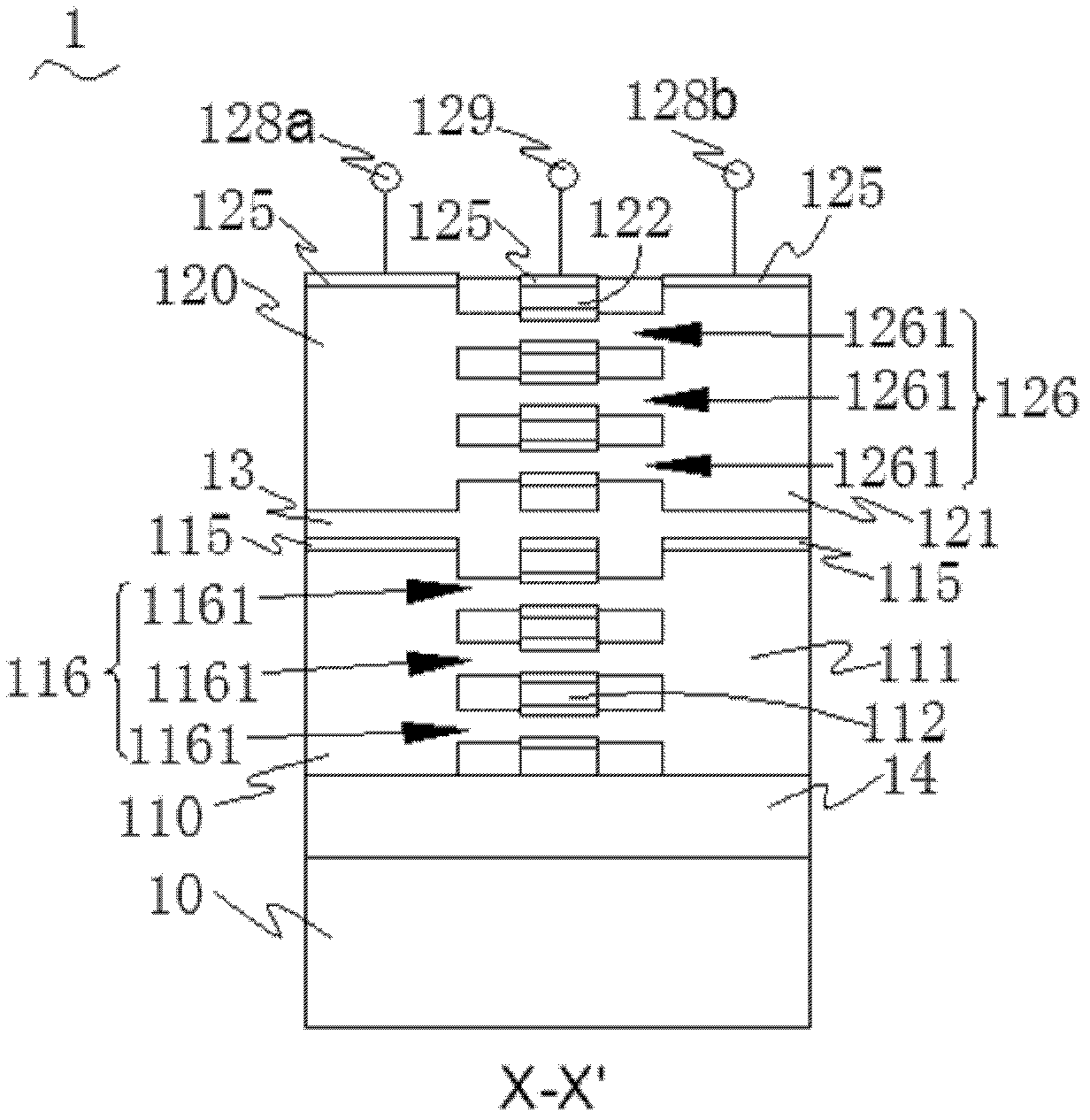

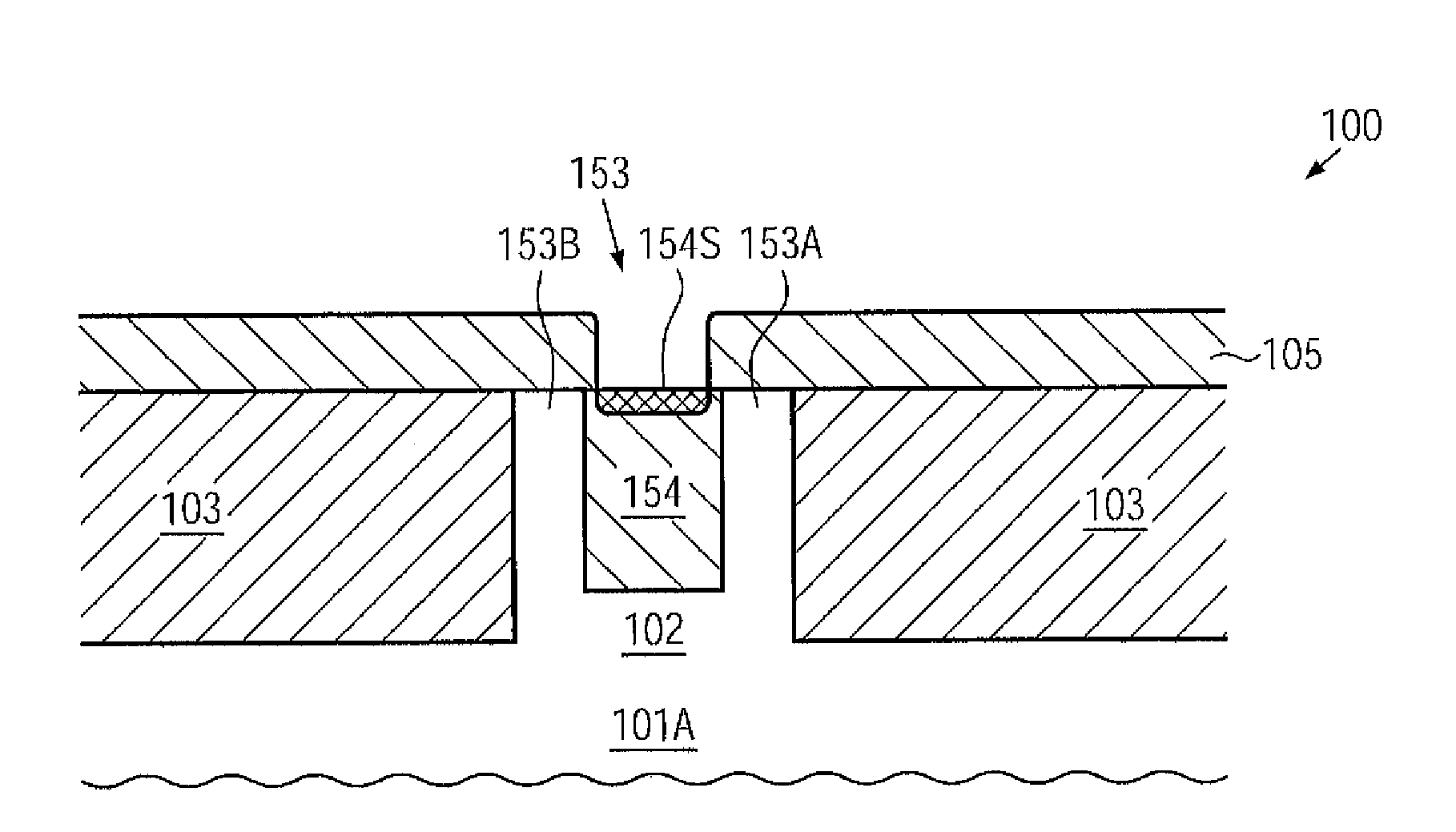

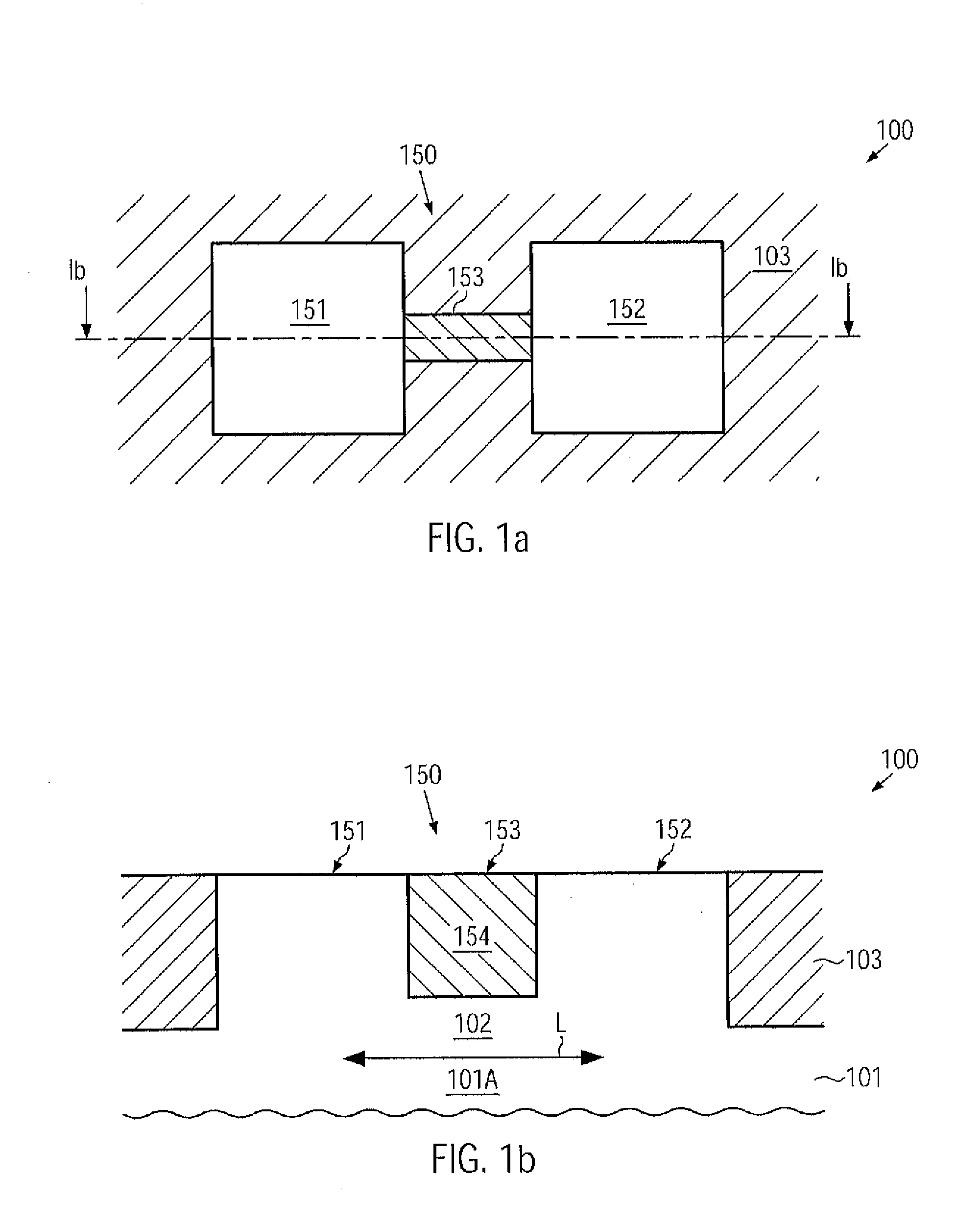

Strained channel finFET device

InactiveUS7473967B2High carrier mobilityImprove current drive capabilityTransistorSolid-state devicesSemiconductorLattice strain

A semiconductor device according to this invention includes: a first insulating layer (11); a first body section (13) including an island-shaped semiconductor formed on the first insulating layer; a second body section (14) including an island-shaped semiconductor formed on the first insulating layer; a ridge-shaped connecting section (15) formed on the first insulating layer to interconnect the first body section and the second body section; a channel region (15a) formed by at least a part of the connecting section in lengthwise direction of the connecting section; a gate electrode (18) formed to cover a periphery of the channel region, with a second insulating layer intervening therebetween; a source region formed to extend over the first body section and a portion of the connecting section between the first body section and the channel region; and a drain region formed to extend over the second body section and a portion of the connecting section between the second body section and the channel region, wherein a semiconductor forming the channel region has a lattice strain.

Owner:PANASONIC CORP

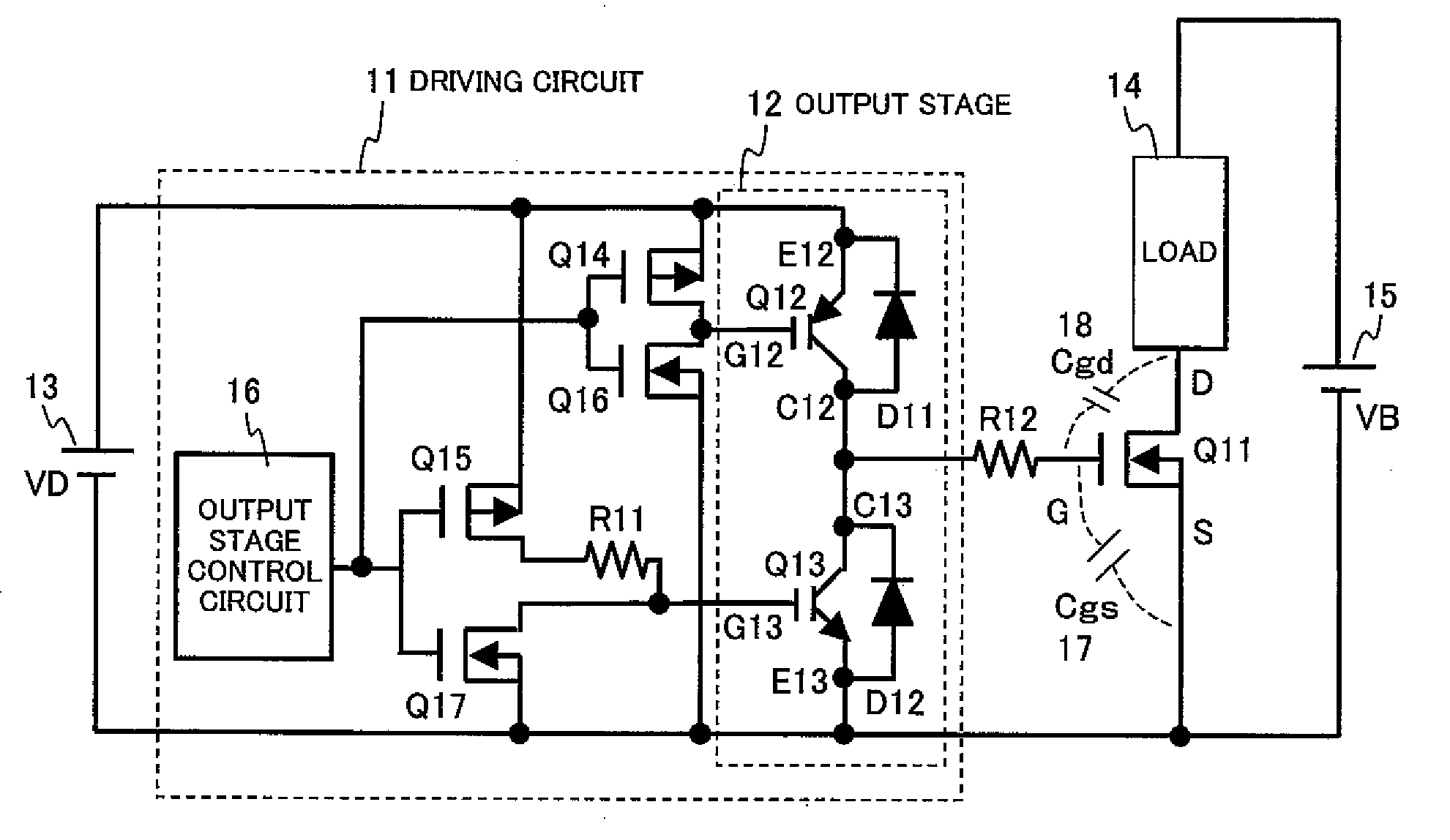

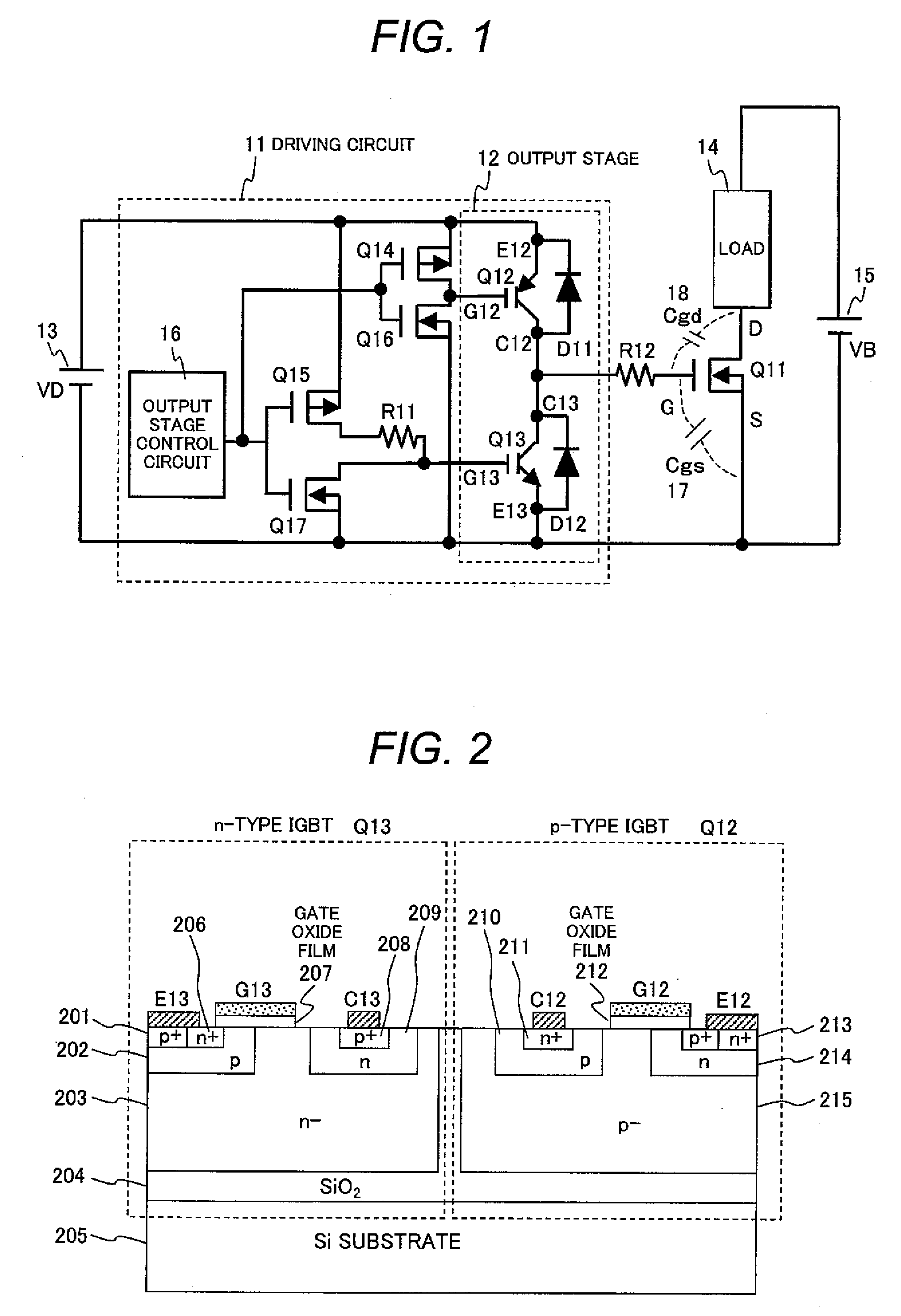

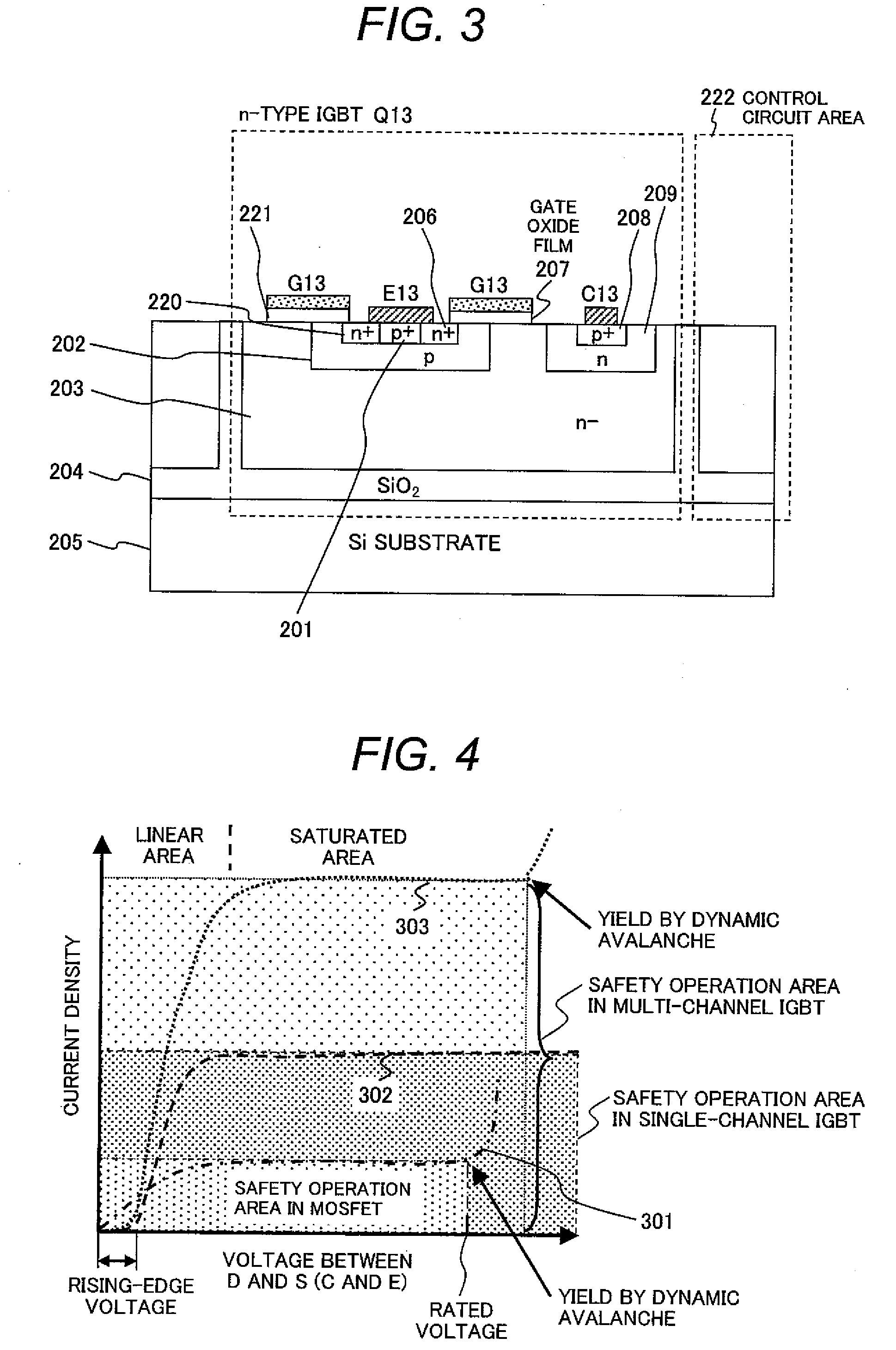

Semiconductor device and power converter using the same

InactiveUS20100165681A1Improve performanceImprove current drive capabilityAc-dc conversion without reversalElectronic switchingPower semiconductor deviceEngineering

In a driving circuit, for controlling the turning on and off of a main semiconductor switching device of an insulated gate type, in an insulated gate semiconductor switching device for electric power conversion, bipolar semiconductor devices of an insulated gate control type, particularly insulated gate bipolar transistors (IGBTs) are used at the output stage of a circuit that controls the gate voltage of the main semiconductor switching device.

Owner:HITACHI LTD

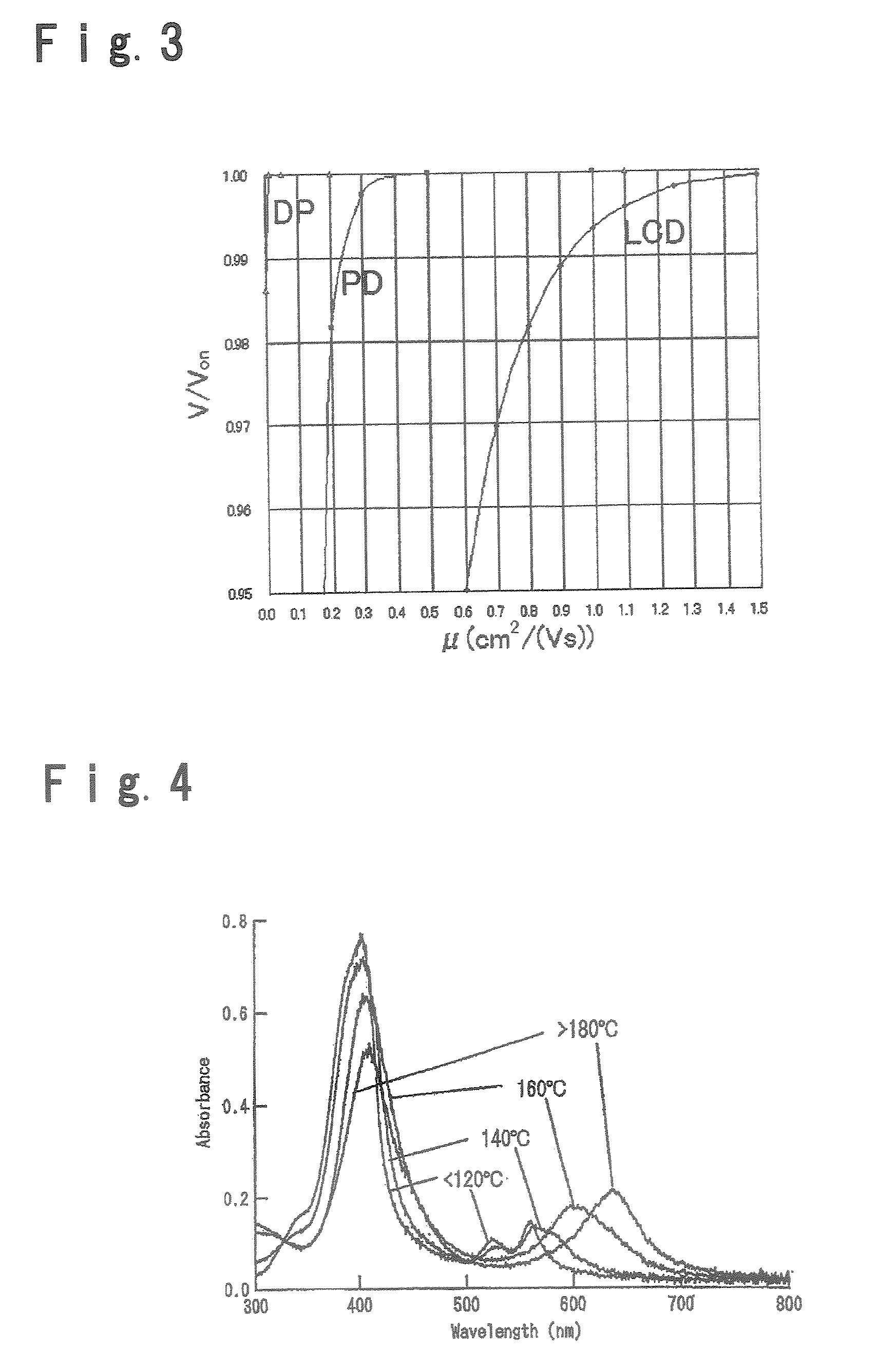

Field effect transistor

InactiveUS20090072224A1Improve driving stabilityImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringOrganic semiconductor

A field effect transistor including a gate isulation portion, an organic semiconductor portion, a source electrode and a drain electrode, wherein when a voltage is applied to the gate at 70° C. for 5.0±0.1 hours so that the field strength in the gate insulation portion would be 100±5 MV / m, the change in the threshold voltage is within 5 V. The organic semiconductor portion has a high driving stability, of which the change in characteristics by driving is thereby small.

Owner:MITSUBISHI CHEM CORP

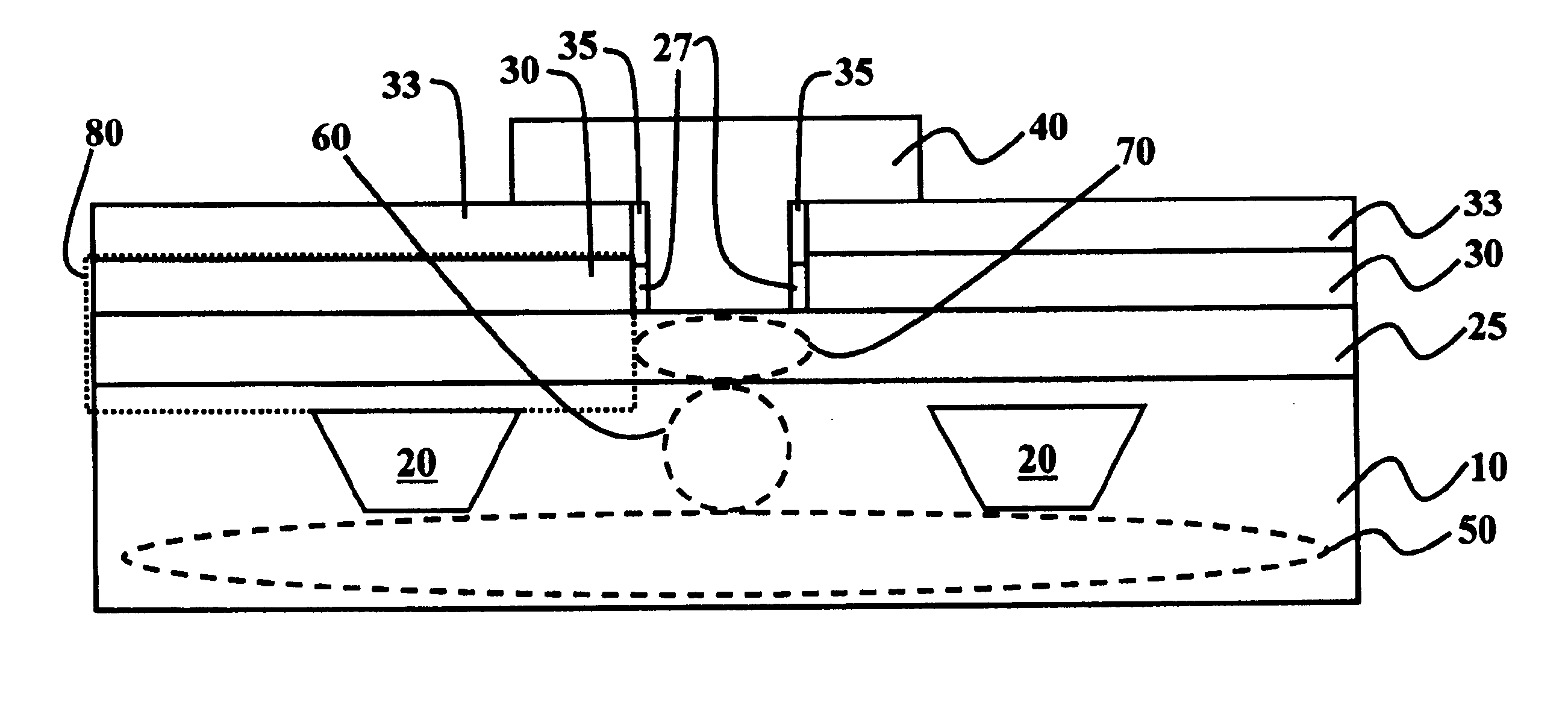

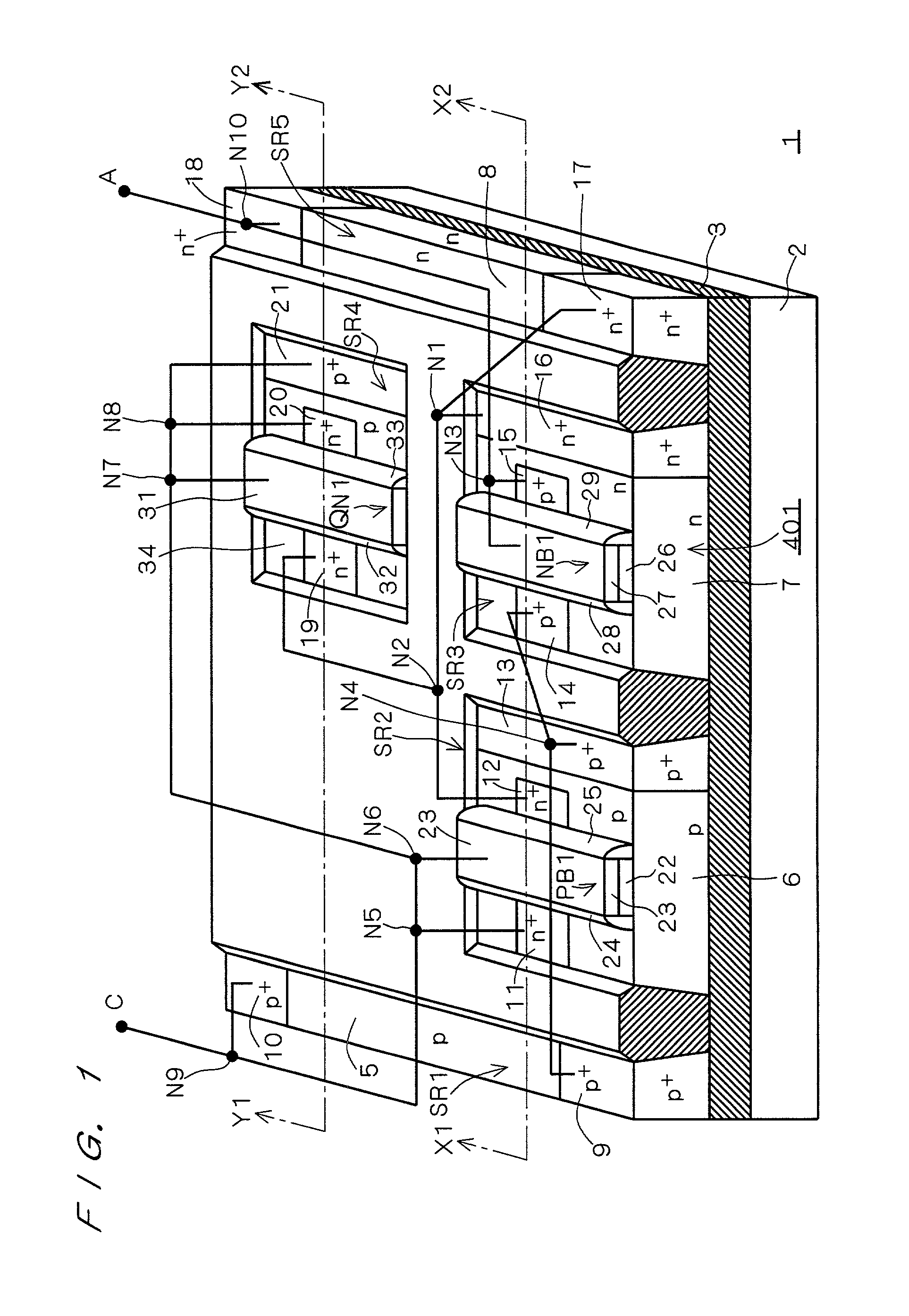

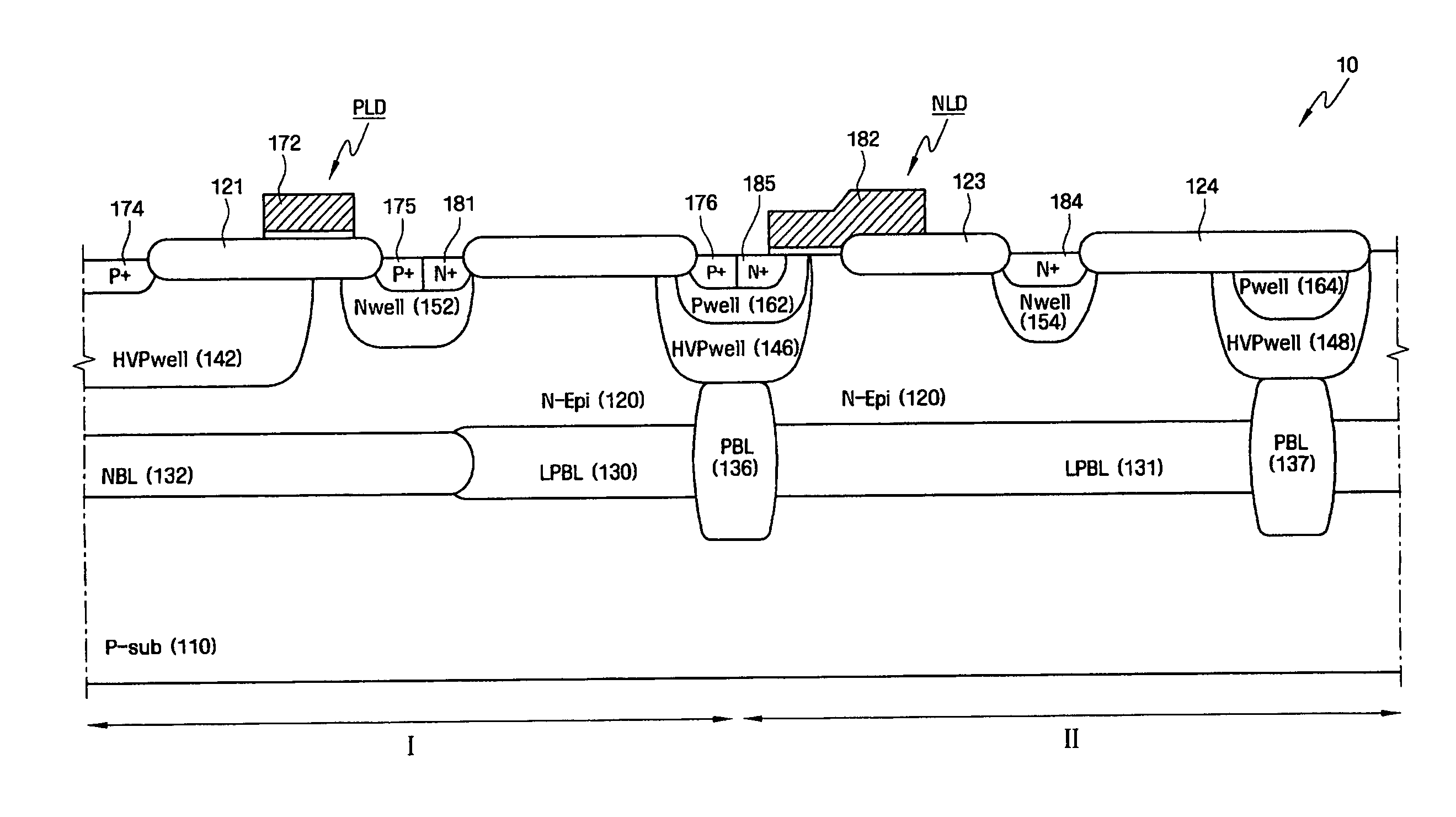

SOI semiconductor controlled rectifier and diode for electrostatic discharge protection

InactiveUS6429505B1Improve current drive capabilityAccelerating turn-on operationTransistorSemiconductor/solid-state device detailsSemiconductorElectrostatic discharge protection

Owner:RENESAS ELECTRONICS CORP

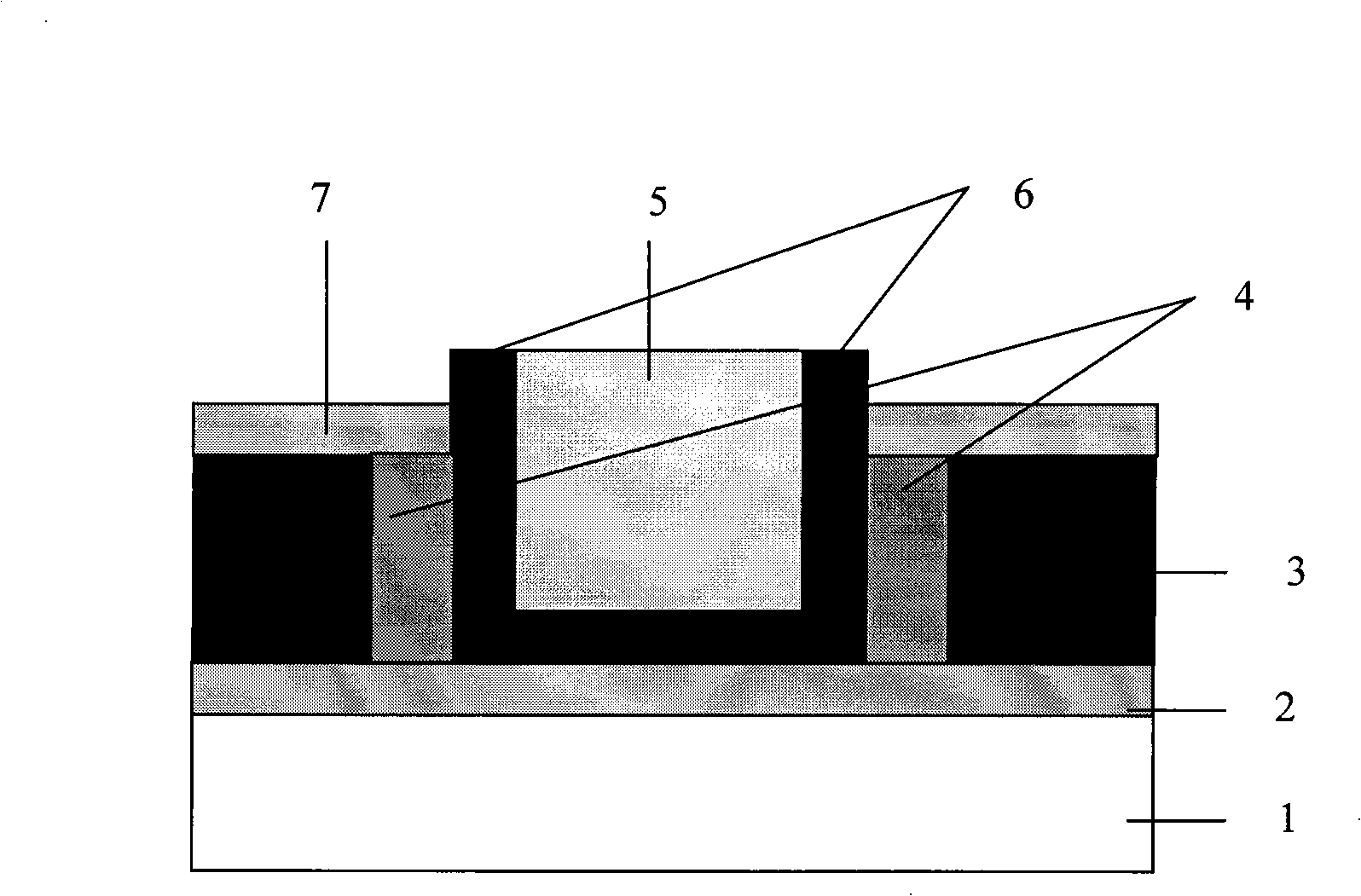

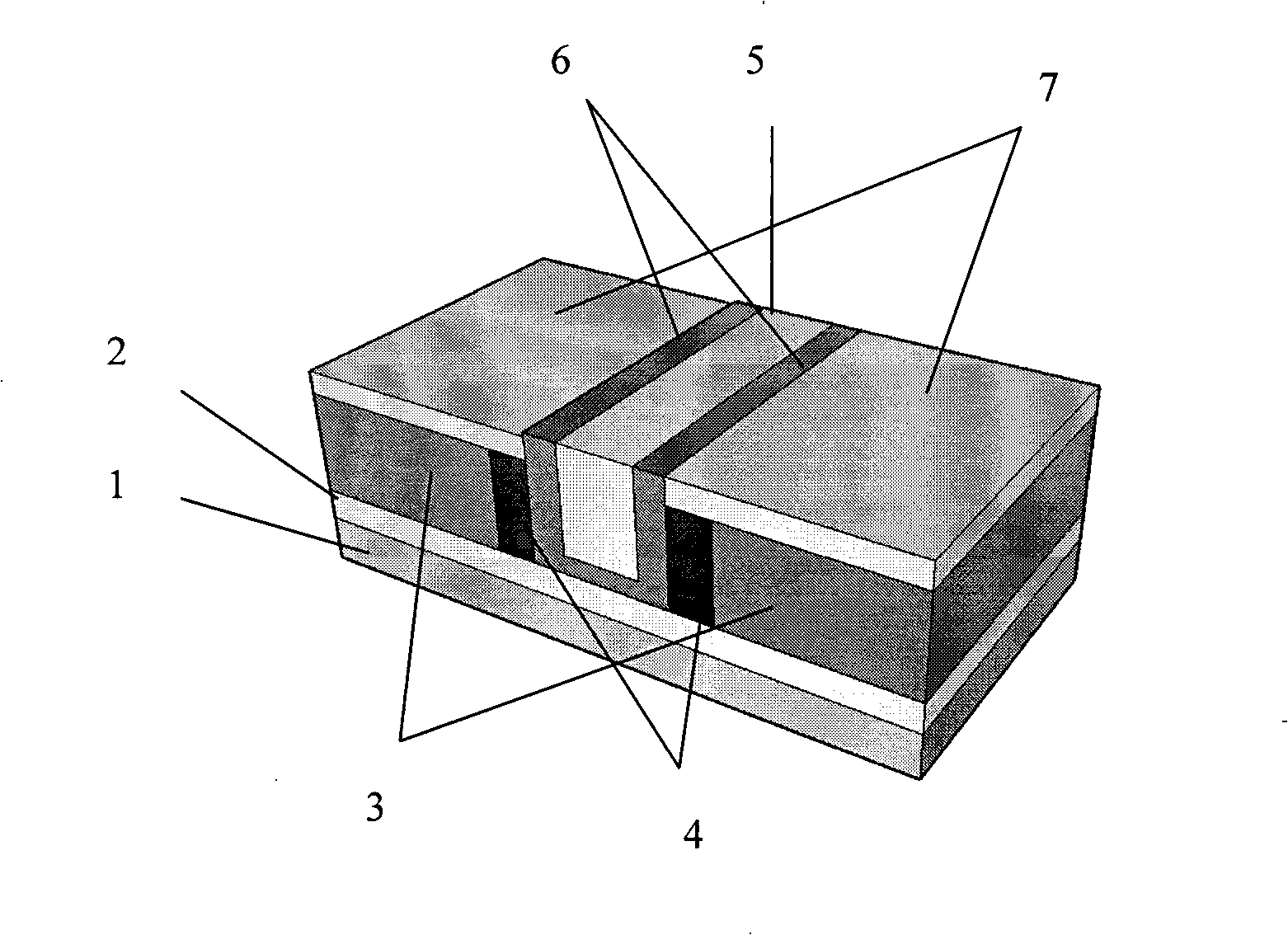

Vertical channel organic field effect transistor and method for producing the same

ActiveCN101404321AReduce difficultyReduce the occupied areaSolid-state devicesSemiconductor/solid-state device manufacturingPlanar electrodeGate dielectric

The invention discloses a vertical channel organic field effect transistor, and belongs to the field of organic microelectronics. The structure of the vertical channel organic field effect transistor comprises a metal source electrode at an insulating substrate, a gate dielectric layer, an insulating layer, an organic semiconductor layer, a gate electrode and a metal drain electrode, wherein, the long strip-shaped gate electrode is surrounded at the exact center of the device by the dielectric layer and the organic semiconductor material; both the source electrode and the drain electrode are planar electrodes, and by changing the direction of the channel from horizontal direction to vertical direction, the length of the channel can be effectively controlled only by controlling the growth thickness of a thin film, thus avoiding the expensive electron beam lithography, and providing a simple and convenient and low-cost method for preparing a short-channel organic field effect transistor. A method for preparing the vertical channel organic field effect transistor is also provided.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Nonvolatile memory element, nonvolatile memory element array, and method for manufacturing nonvolatile memory element

ActiveUS20100065807A1Improve drivabilityConfiguration of memory can be made compact and simplifiedSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenEngineering

The present invention is configured such that a resistance variable element (16) and a rectifying element (20) are formed on a substrate (12). The resistance variable element (16) is configured such that a resistance variable layer (14) made of a metal oxide material is sandwiched between a lower electrode (13) and an upper electrode (15). The rectifying element (20) is connected to the resistance variable element (16), and is configured such that a blocking layer (18) is sandwiched between a first electrode layer (17) located on a lower side of the blocking layer (18) and a second electrode layer (19) located on an upper side of the blocking layer (18). The resistance variable element (16) and the rectifying element (20) are connected to each other in series in a thickness direction of the resistance variable layer (14), and the blocking layer (18) is formed as a barrier layer having a hydrogen barrier property.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

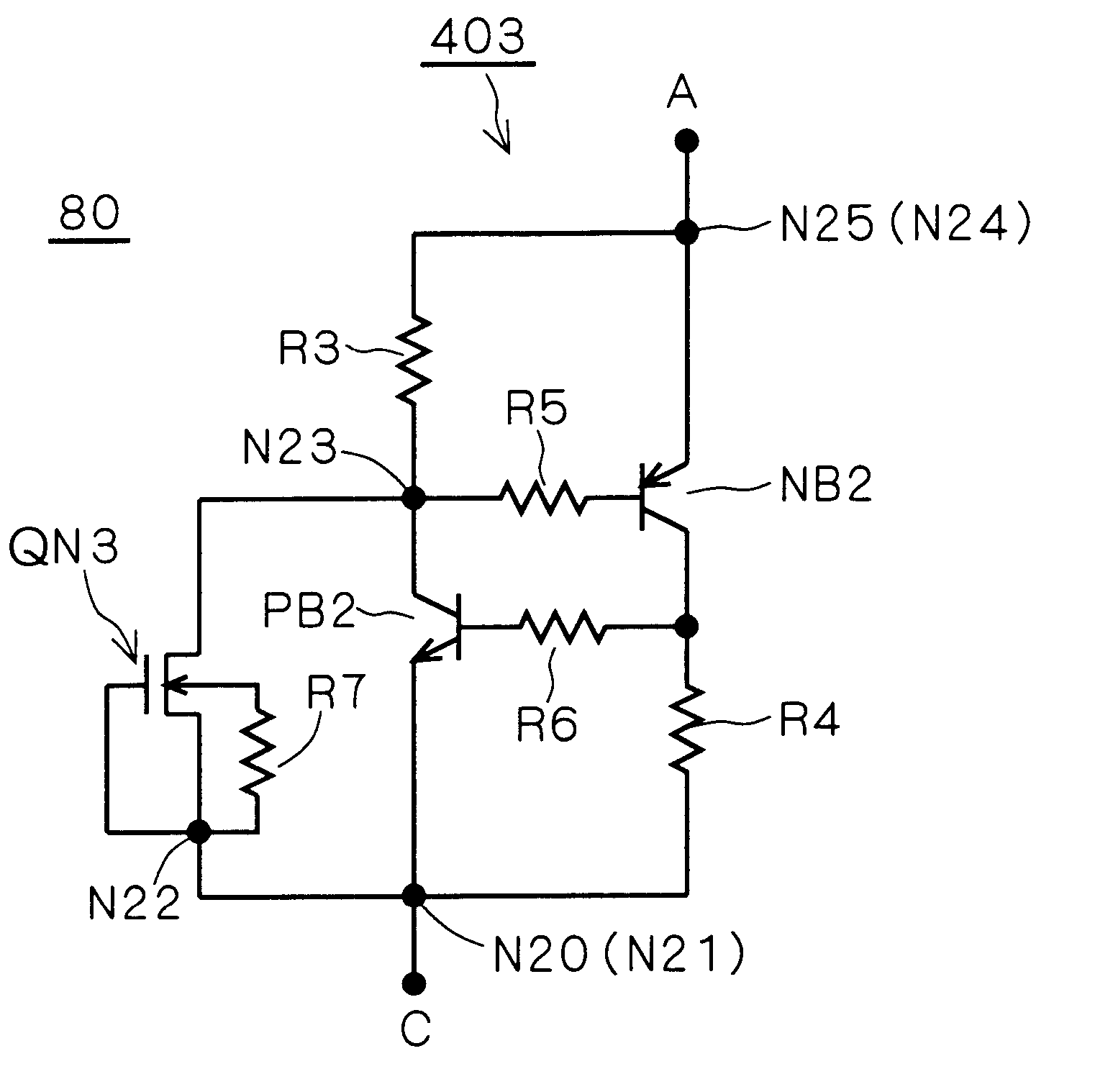

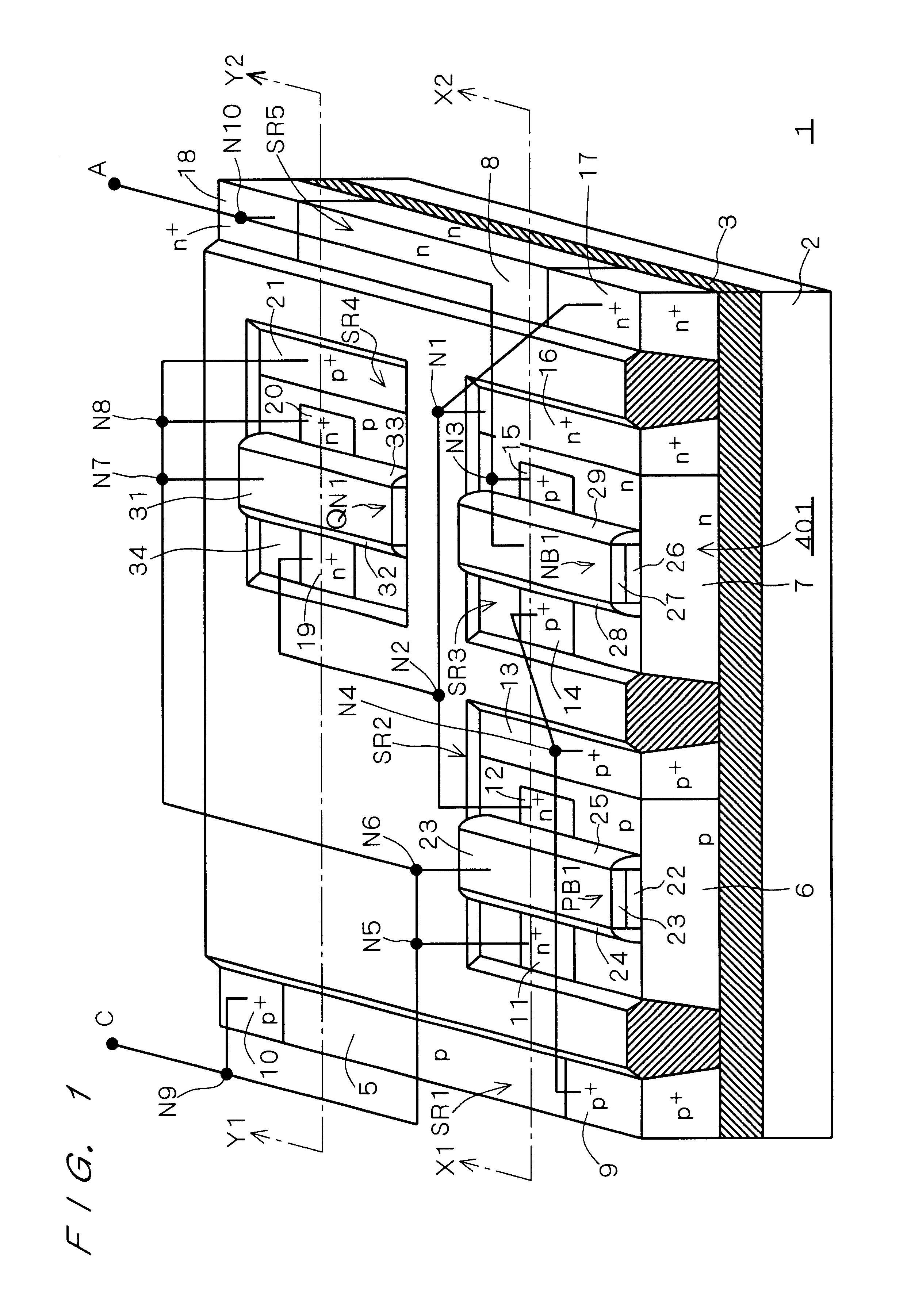

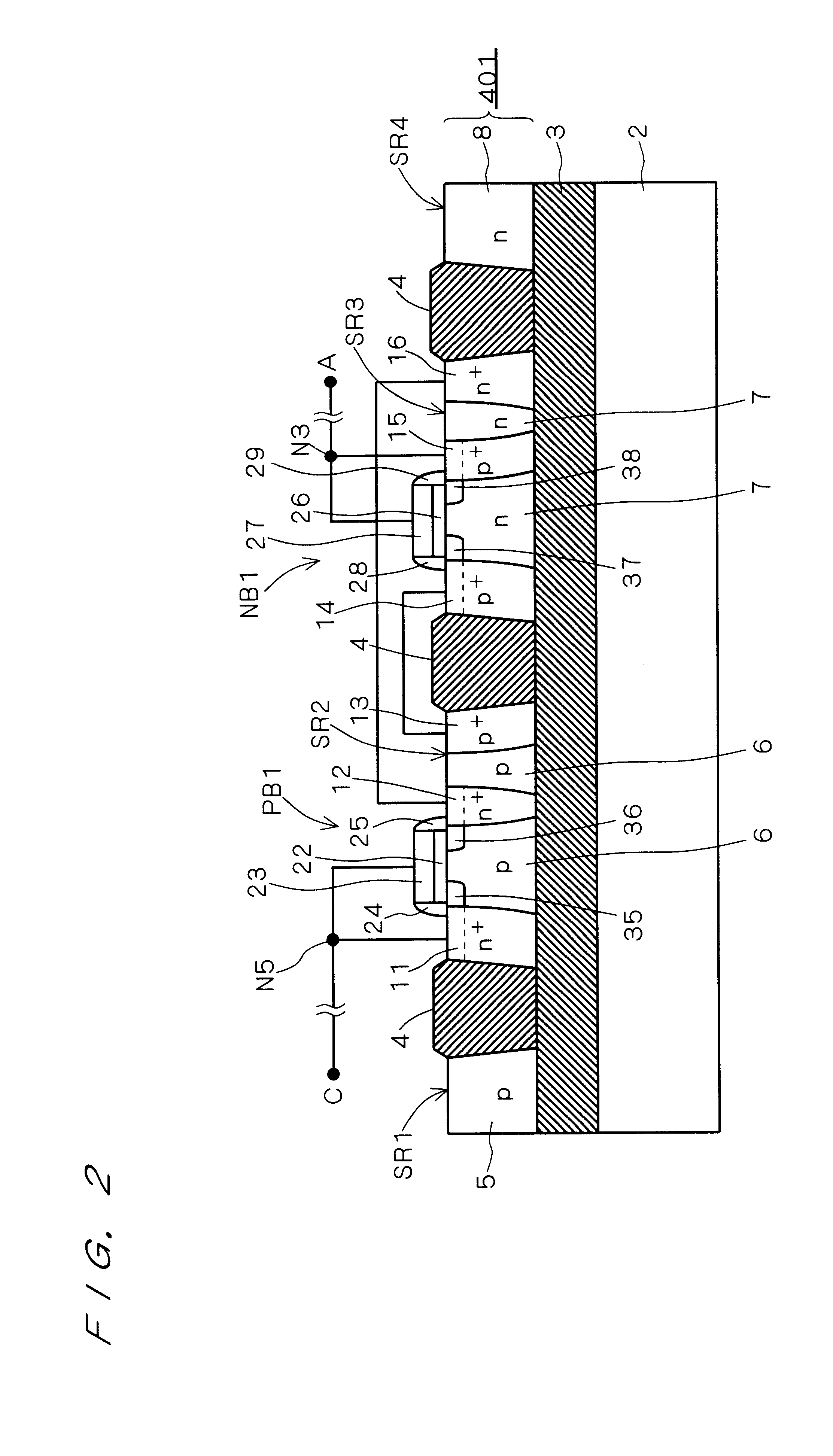

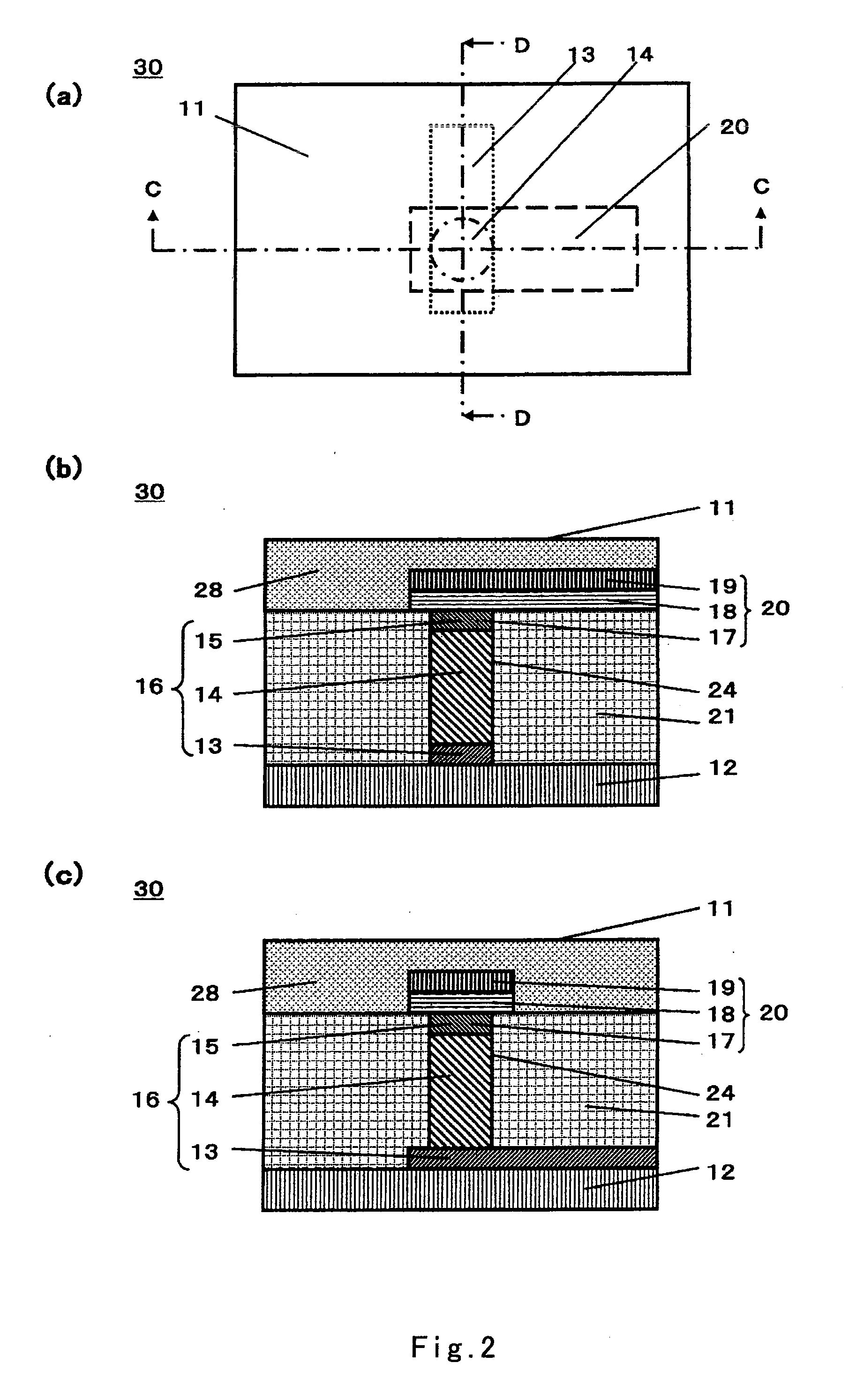

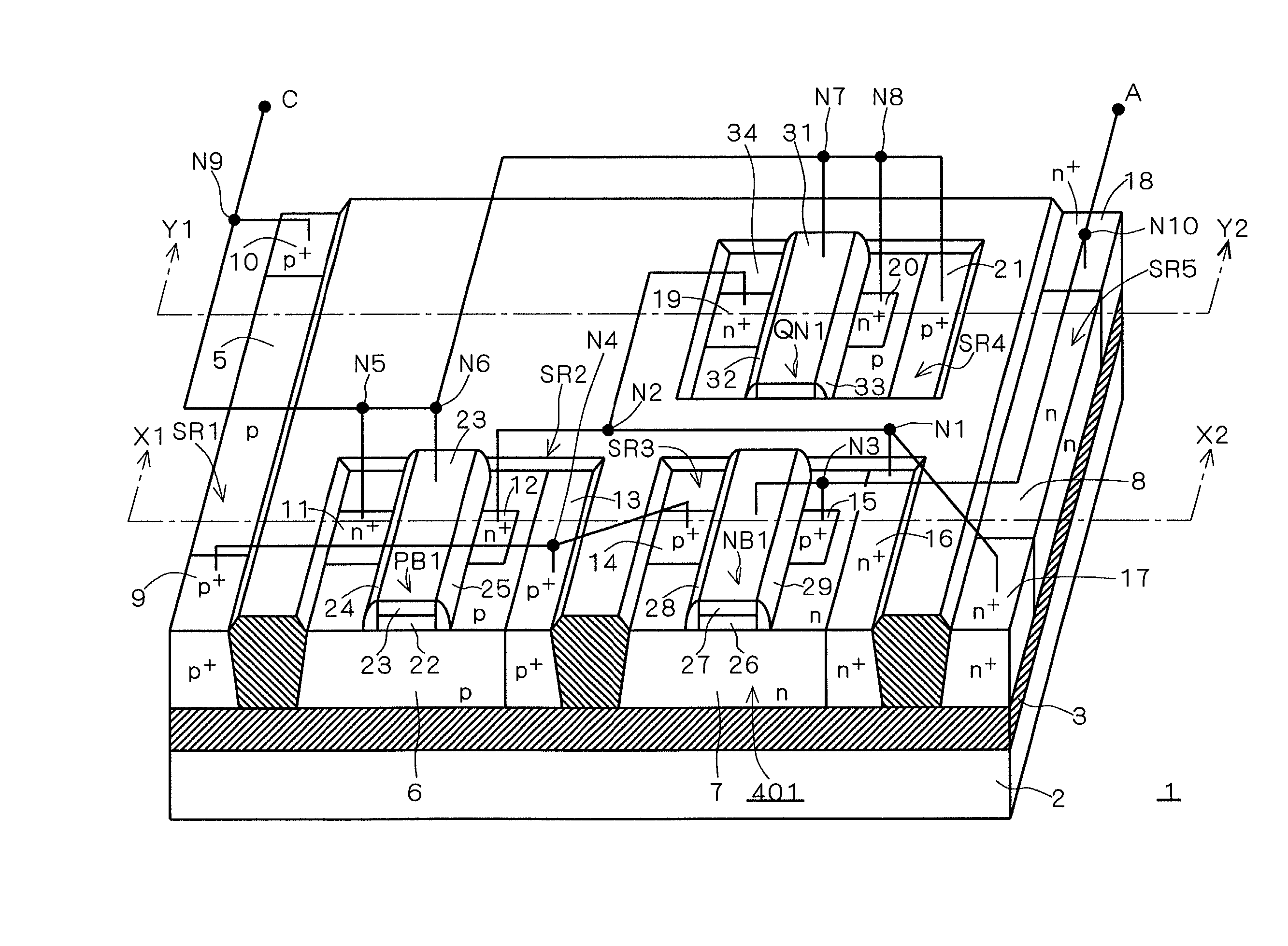

Semiconductor device

InactiveUS20020033520A1Improve current drive capabilityAccelerating turn-on operationTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A diode (QN1) is connected in parallel to one of two bipolar transistors (PB1, NB1) constituting a semiconductor-controlled rectifier or SCR (400) in such a direction as to encourage positive feedback. This enhances current drivability and accelerates a turn-on operation.

Owner:RENESAS ELECTRONICS CORP

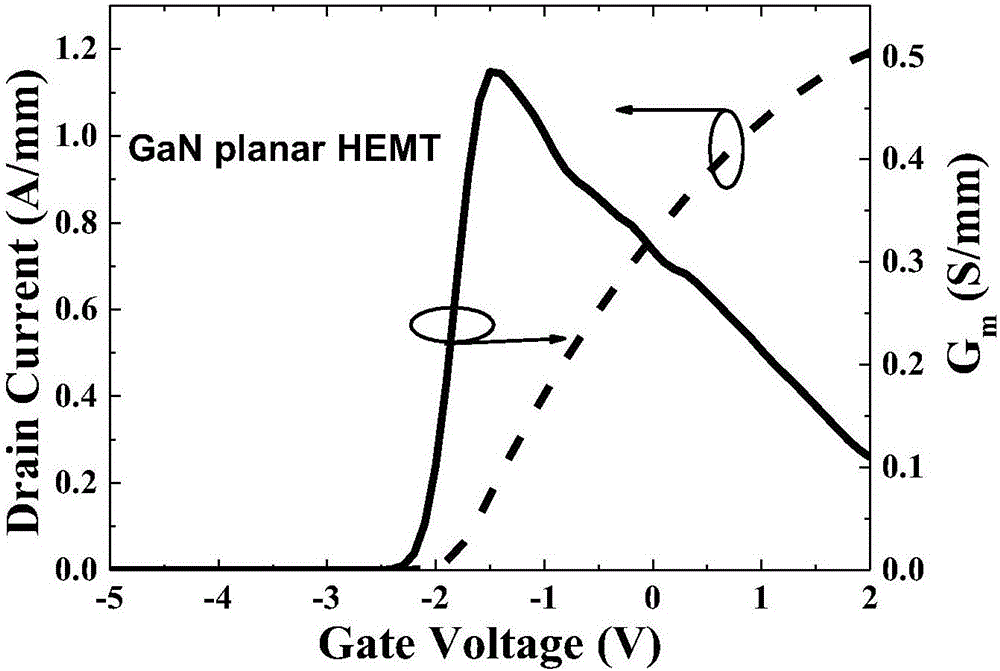

High linearity GaN fin-type high electron mobility transistor and manufacture method thereof

InactiveCN106684141AImprove linearityIncrease the maximum oscillation frequencySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMicrowave power

The present invention relates to a high linearity GaN fin-type high electron mobility transistor and a manufacture method thereof. From bottom to top, the transistor sequentially comprises a substrate, a buffer layer, a barrier layer, and a passivation layer. A source electrode is arranged at one end above the barrier layer and a drain electrode is arranged at the other end. The passivation layer is arranged above the barrier layer between the source electrode and the drain electrode. A groove is arranged in the passivation layer. A T-shaped gate is arranged in the groove. The transistor is characterized in that GaN-based three-dimensional fins in periodical arrangement are etched only on the barrier layer and the buffer layer in an area below the groove, the length of the GaN-based three-dimensional fins is equal to the length of the groove, and an isolation groove that is etched is arranged between adjacent GaN-based three-dimensional fins. The transistor has high linearity and output current, strong gate control capability, good heat dissipation performance, and high frequency characteristic. The manufacture method is simple and reliable, and is applicable to high power, high linearity microwave power devices.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

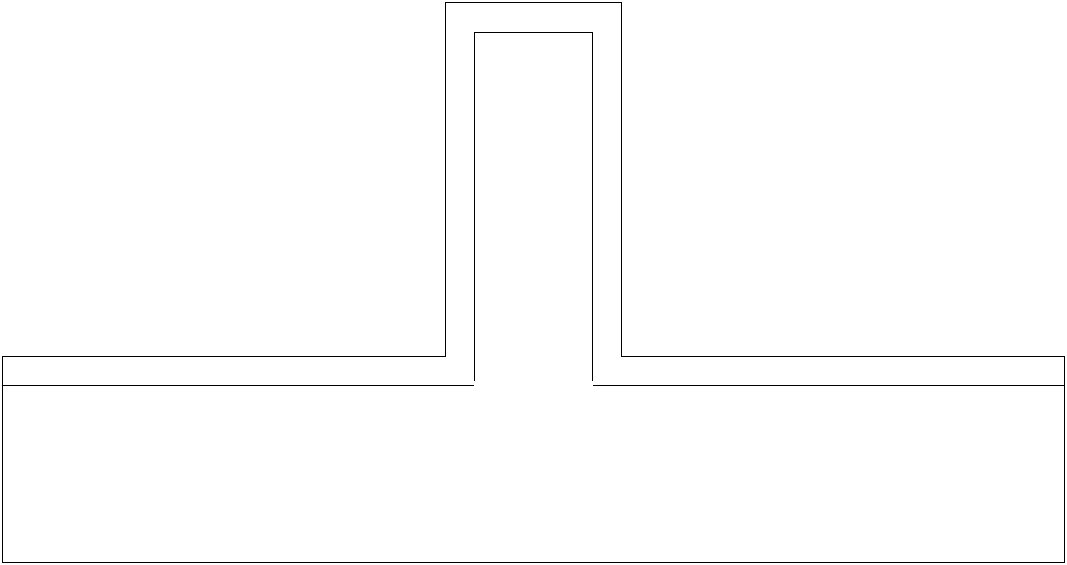

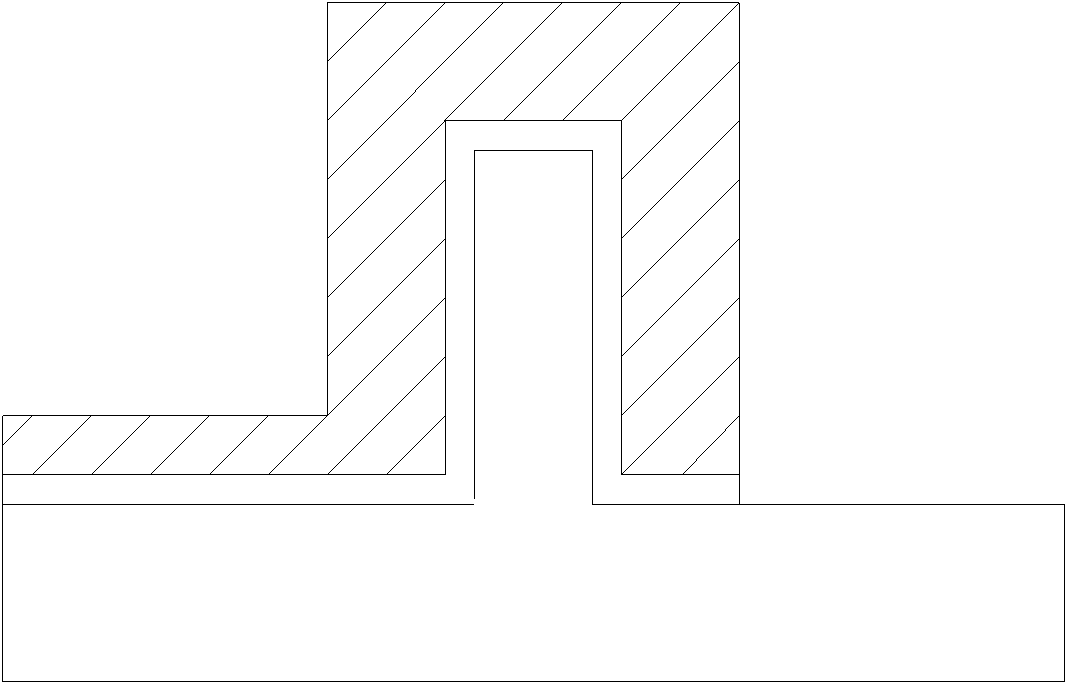

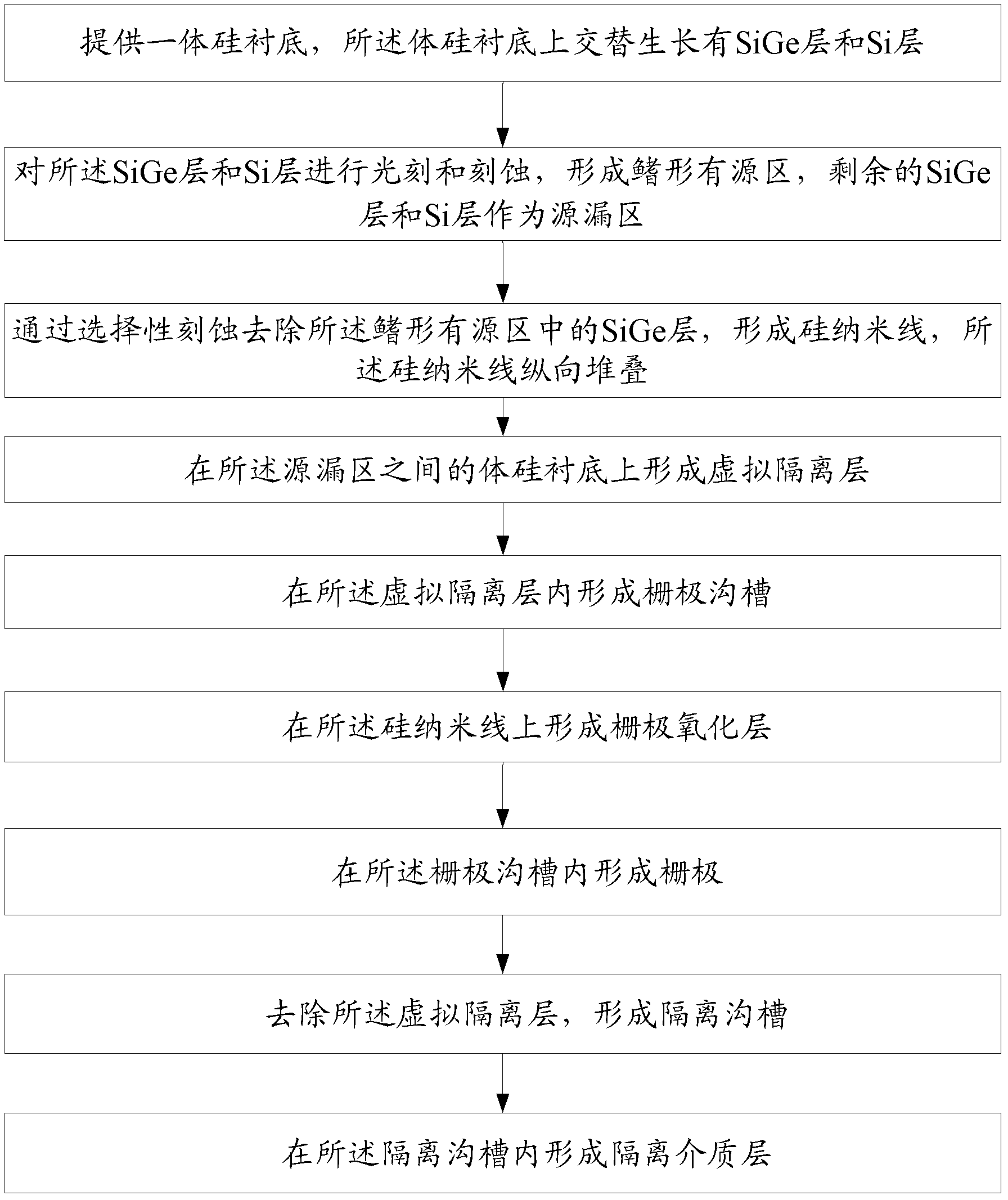

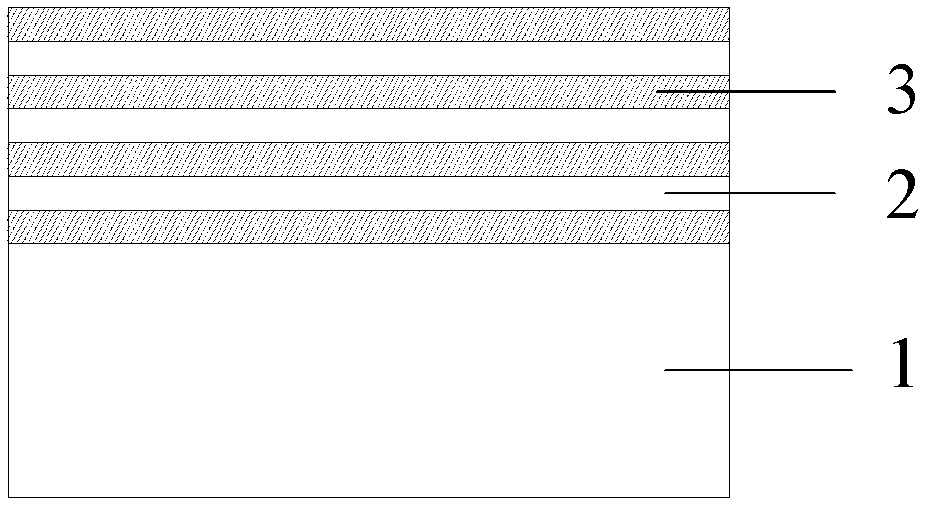

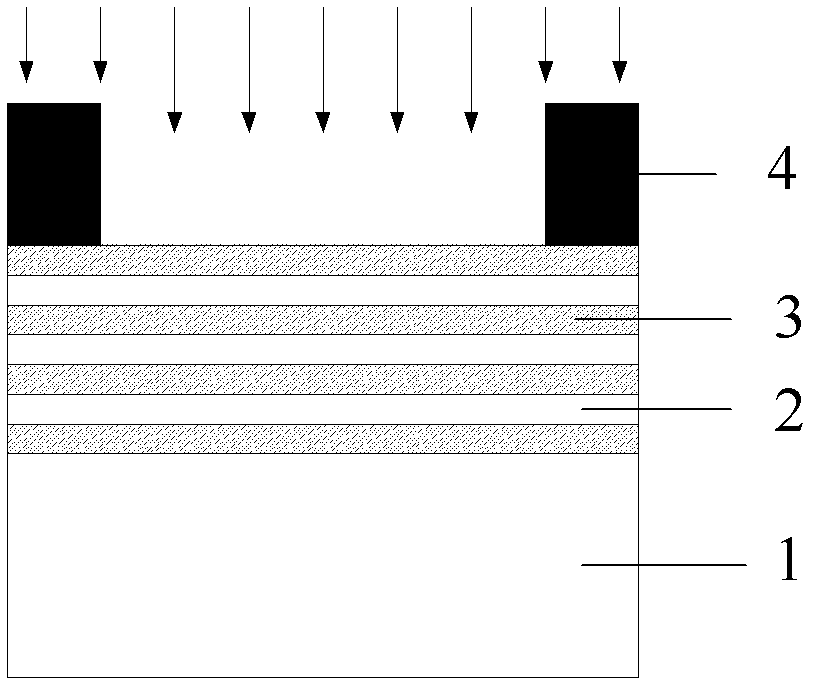

Bulk-silicon-based manufacturing method for vertically stacked under-gate type silicon nano-wire metal oxide semiconductor field effect transistor (SiNWFET)

InactiveCN102623383AEfficient releaseNo self-heating effectSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerGate oxide

The invention discloses a bulk-silicon-based manufacturing method for a vertically stacked under-gate type silicon nano-wire metal oxide semiconductor field effect transistor (SiNWFET). The method comprises the following steps of: providing a bulk silicon substrate on which SiGe layers and Si layers are alternately grown; photo-etching and etching the SiGe layers and the Si layers to form fin-shaped active regions, and taking the residual SiGe layers and the residual Si layers as source and drain regions; selectively etching and removing the SiGe layers in the fin-shaped active regions to form silicon nano-wires which are vertically stacked; forming a virtual isolation layer on the bulk silicon substrate between the source region and the drain region; forming a gate trench in the virtual isolation layer; forming gate oxide layers on the silicon nano-wires; forming a gate in the gate trench; removing the virtual isolation layer to form an isolated trench; and forming an isolation dielectric layer in the isolated trench. Due to the adoption of the virtual isolation layer, control over the contour of the gate trench is facilitated; the conventional gate oxide layers are adopted; and the silicon nano-wires are vertically stacked, so that the integration level and current driving capability of a device can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

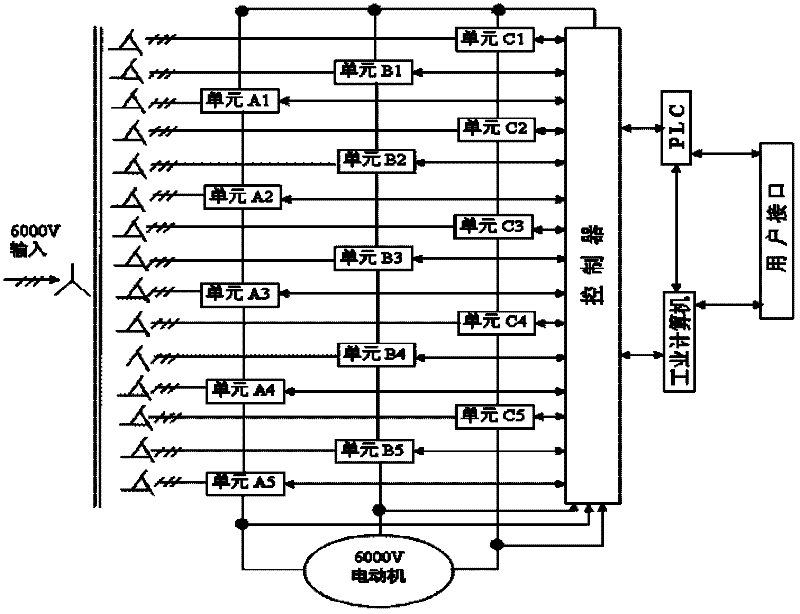

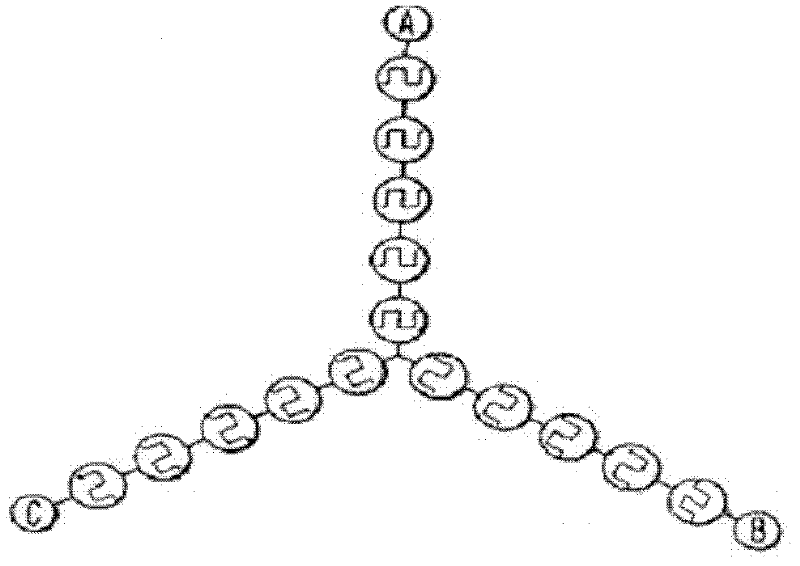

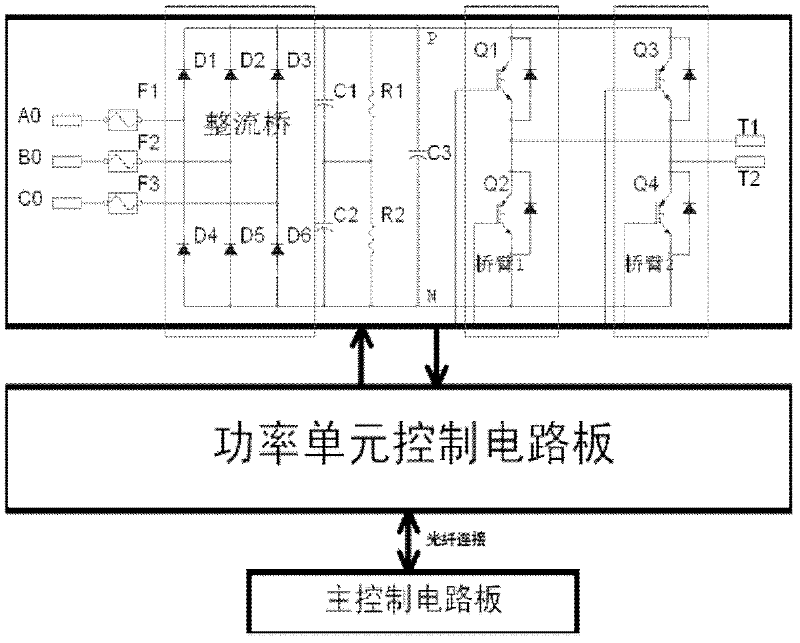

Power unit control plate of high-voltage frequency converter

InactiveCN102457196AImprove current drive capabilityMeet current drive requirementsAc-ac conversionProgrammable logic deviceElectromagnetic interference

The invention relates to a power unit control plate of a high-voltage frequency converter. The power unit control plate is connected between a main control plate of the high-voltage frequency converter and a power unit of the high-voltage frequency converter, and is a receiving-transmitting serial communication structure; receiving serial communication is defined from the main control plate to the power unit, and transmitting serial communication is defined from the power unit to the main control plate; and an input serial communication signal firstly passes through an input buffer filter circuit to filter out an interfering signal so as to enhance the current drive capability and interference-free feature of the signal, thereby furthest reducing the electromagnetic interference influence in communication. The power unit control plate comprises an address dip switch which is connected with a programmable logic device and is corresponding to the address of a component in the power unit, thereby guaranteeing that a command is accurately and reliably transferred. A temperature sensor is used for measuring the temperature of the component in the power unit and transferring a characteristic curve to adjust the opening voltage of the component so that the opening loss of the component reaches the optimum.

Owner:上海中发变频科技有限公司

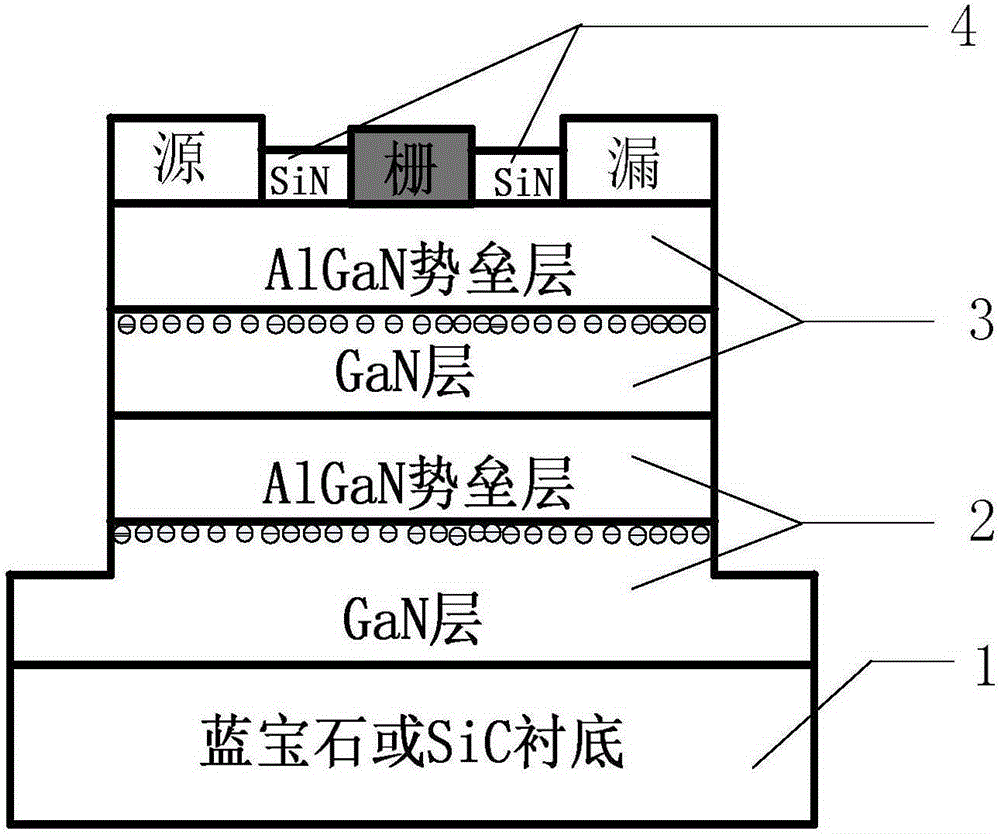

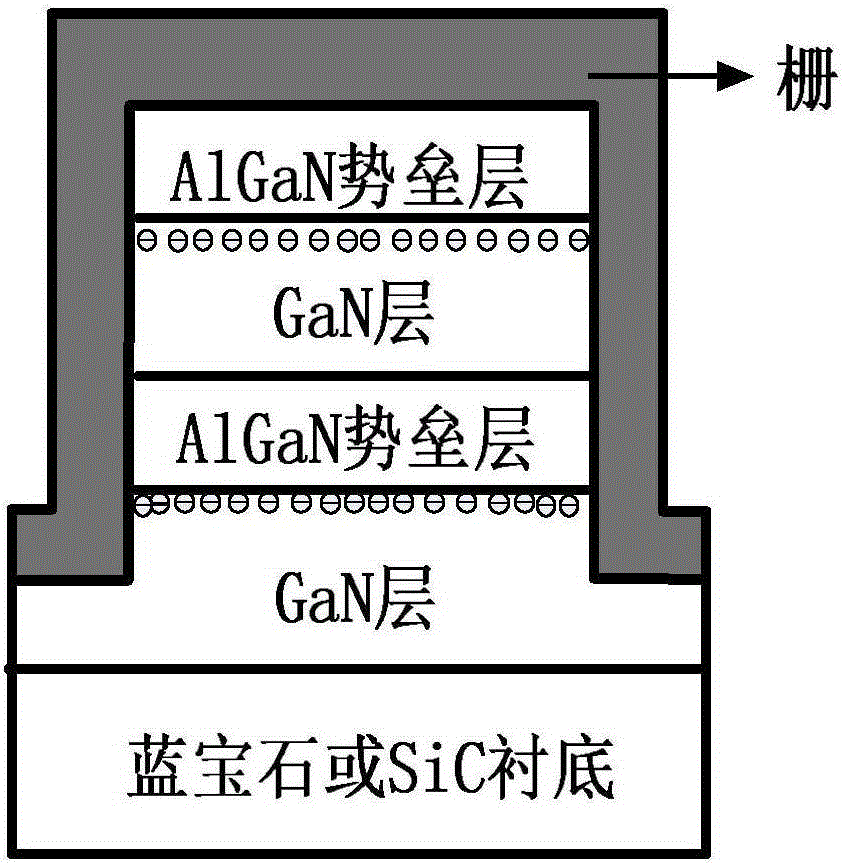

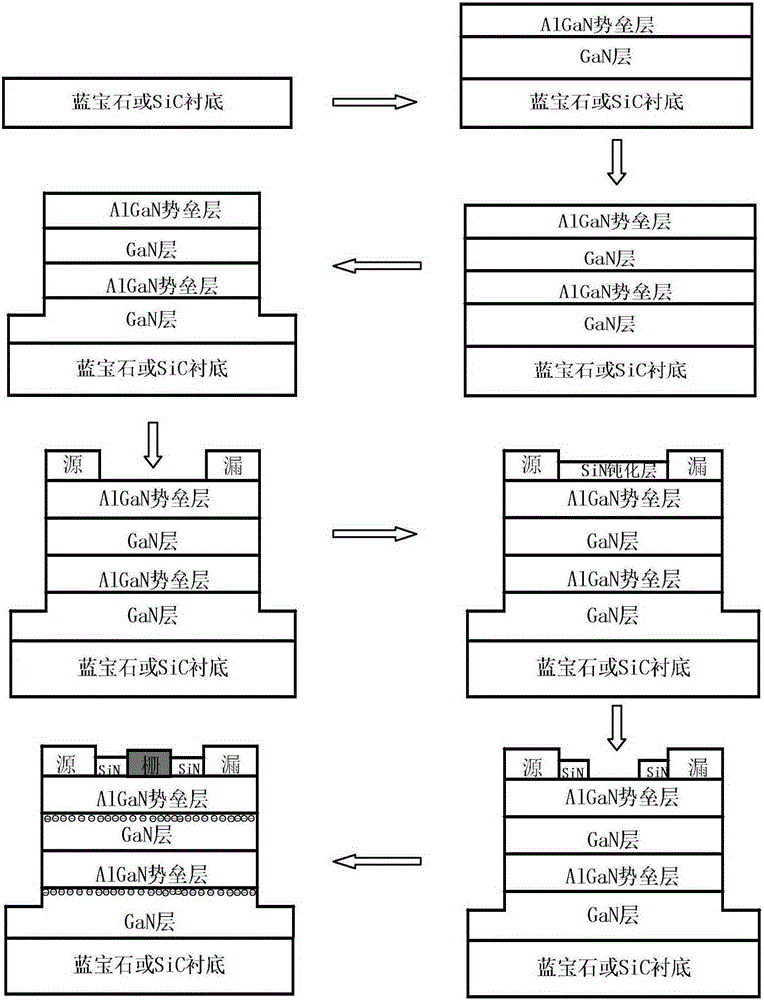

AlGaN/GaN high electron mobility transistor with multi-channel fin-type structure

InactiveCN105280696AReduce widthLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLow noise

The invention discloses a AlGaN / GaN high electron mobility transistor structure with a multi-channel fin-type structure and a manufacturing method, wherein the AlGaN / GaN high electron mobility transistor is designed mainly to solve the problems of the poor gate control ability of a multi-channel apparatus and low electric current of a FinFET apparatus; the AlGaN / GaN high electron mobility transistor comprises a substrate (1), a first layer AlGaN / GaN heterojunction (2), a SiN passivation layer (4) and a source electrode, a drain electroce, and a gate electrode successively from bottom to top; the source electrode and the drain electrode are located on AlGaN potential barrier layers on top layers at two sides of the SiN passivation layer respectively; the AlGaN / GaN high electron mobility transistor is characterized in that a GaN layer and the AlGaN potential barrier layer are set between the first layer AlGaN / GaN heterojunction and the SiN passivation layer so as to form a second layer AlGaN / GaN heterojuntion (3); and the gate electrode covers the top portion of a second layer heterojuntion and the two side walls of the first and the second heterojunctions. According to the invention, the gate control ability is strong; the saturation current is large; the subthreshold property is good; and the AlGaN / GaN high electron mobility transistor can be used for microwave power apparatus with a shrot gate length, low power consumption and low noise.

Owner:XIDIAN UNIV

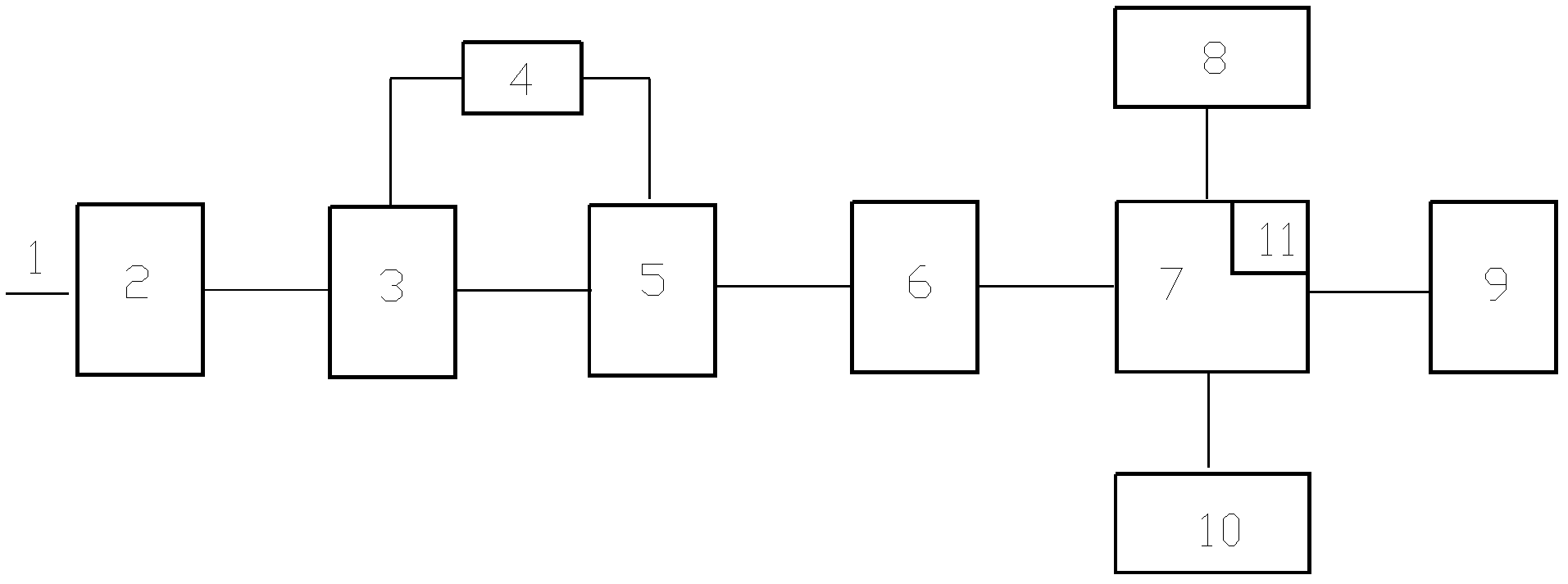

Multi-channel galvanic corrosion measurement device

ActiveCN102507431AEliminate mutual interferenceHigh linear precisionWeather/light/corrosion resistanceMeasurement deviceMetallic materials

The invention belongs to the technical field of galvanic corrosion measurement for metal materials, in particular relates to a multi-channel galvanic corrosion measurement device. According to the multi-channel galvanic corrosion measurement device, an SOC (System on a Chip) processor structural design is adopted; the front end of an electrode connection cable is connected with an electrode; the rear end of the electrode connection cable is connected into a voltage / current measurement switching unit; two ends of a front end signal conditioning circuit are bridged with a reference source afterbeing electrically communicated with an A / D (Analog-to-Digital) conversion circuit; the front end of the front end signal conditioning circuit is electrically connected with the voltage / current measurement switching unit; the output end of the A / D conversion circuit is electrically communicated with a main control module after being connected in series with a multi-channel electric isolation unit; an SOC processor is arranged in the main control module; the main control module is electrically connected with a display module, a storage module and a communication module respectively, so that electric information control is realized; and a signal input by a reference electrode is incorporated into the front end signal conditioning circuit after being amplified, so that a signal processing system is formed. The multi-channel galvanic corrosion measurement device has the characteristics of simple overall structure, reliable principle, convenience for use and operation, accuracy in measurement data, flexibility for control and wide application range.

Owner:725TH RES INST OF CHINA SHIPBUILDING INDAL CORP

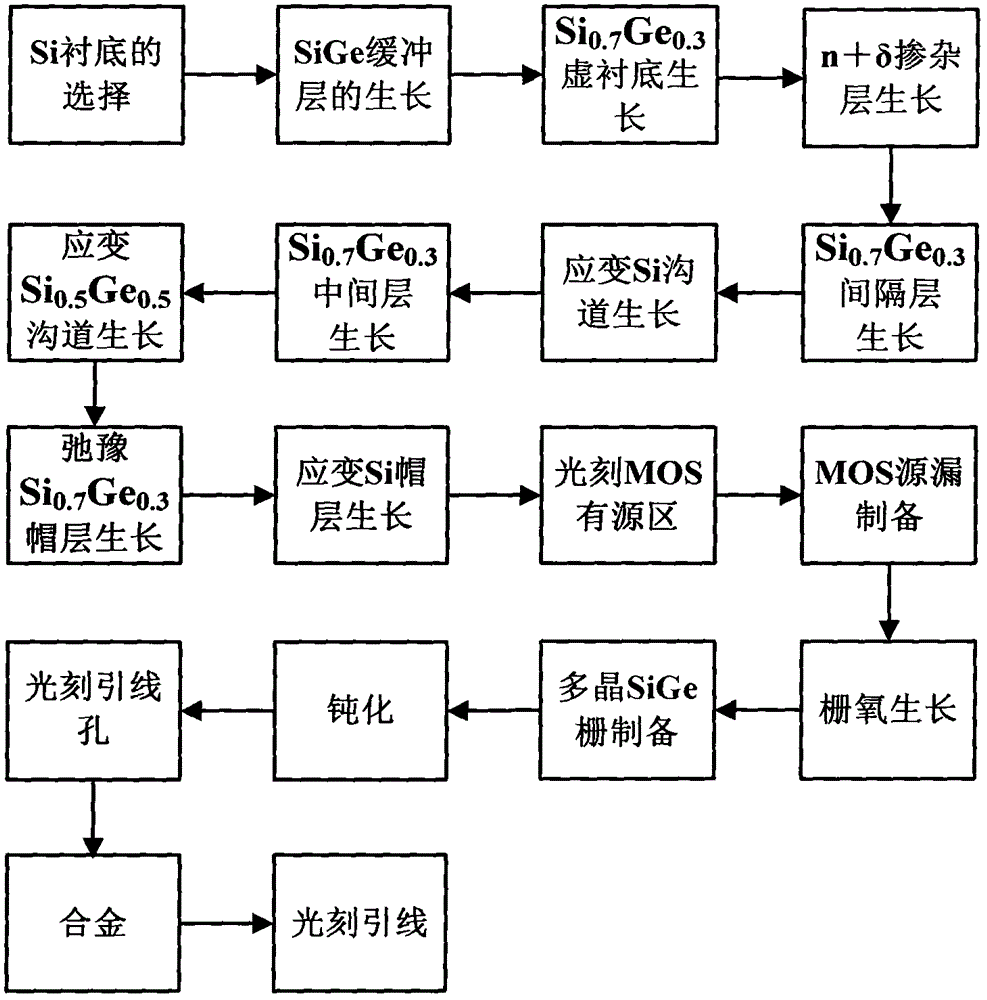

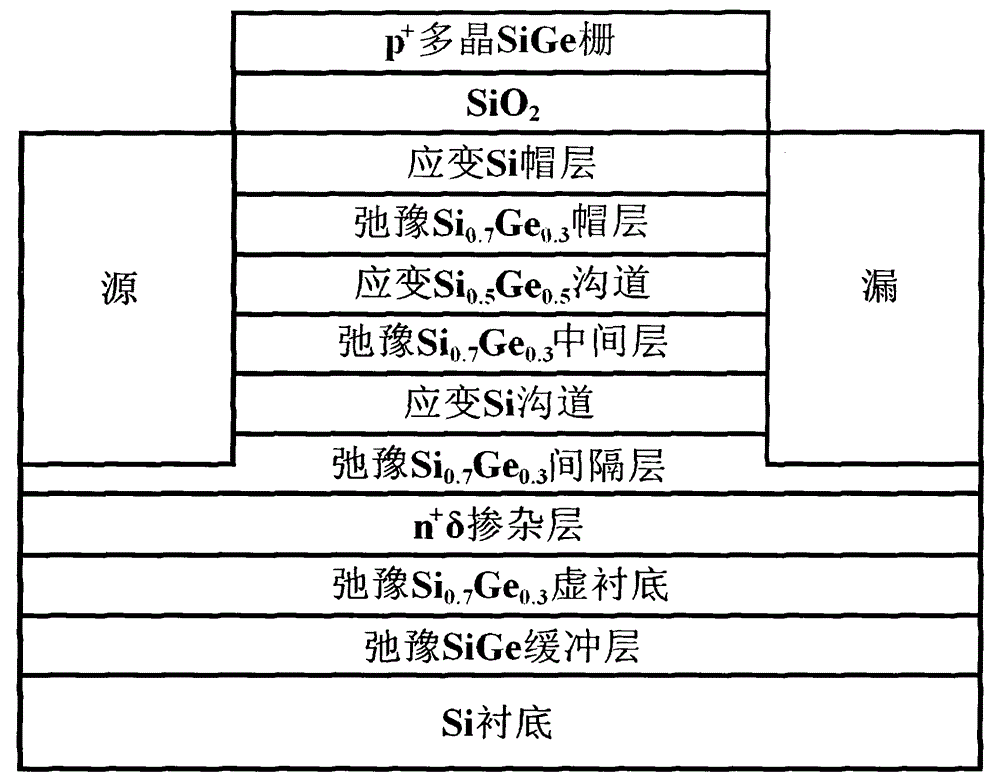

Vertically-stacked strain Si/SiGe heterojunction CMOS device structure and preparation method thereof

ActiveCN104992942AImprove mobilityHigh speedTransistorSemiconductor/solid-state device manufacturingTensile strainMOSFET

The invention discloses a vertically-stacked strain Si / SiGe heterojunction CMOS device structure and a preparation method thereof. The device comprises a silicon substrate, a relaxation SiGe buffer layer, a relaxation Si0.7Ge0.3 virtual substrate, an n<+> delta doping layer, a relaxation Si0.7Ge0.3 interval layer, a strain Si trench, a relaxation Si0.7Ge0.3 intermediate layer, a strain Si0.5Ge0.5 trench, a relaxation Si0.7Ge0.3 cap layer and a Si cap layer from the bottom up in sequence. An n-MOSFET trench adopts a tensile strain Si material, a p-MOSFET trench adopts a compression strain SiGe material, and the n-MOSFET and the p-MOSFET adopt a vertically-stacked structure, and share one polycrystalline SiGe gate electrode, so that electron and hole migration rates are improved greatly, speed and integration level of chips are improved, and new technological approaches are provided for high speed and high frequency development of the Si device and an integrated circuit.

Owner:XIDIAN UNIV

Double-layer isolation longitudinal stacked semiconductor nanowire MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

ActiveCN102569409AImprove device integrationImprove electrical propertiesSemiconductor devicesOxide semiconductorMOSFET

The invention provides a double-layer isolation longitudinal stacked semiconductor nanowire MOSFET (Metal Oxide Semiconductor Field Effect Transistor). The double-layer isolation longitudinal stacked semiconductor nanowire MOSFET comprises a semiconductor substrate, a first semiconductor nanowire MOSFET, a second semiconductor nanowire MOSFET, an isolation medium layer and a buried oxide layer, wherein the first semiconductor nanowire MOSFET further comprises a first semiconductor nanowire group and a first gate oxide layer; the second semiconductor nanowire MOSFET further comprises a second semiconductor nanowire group and a second gate oxide layer; the isolation medium layer is arranged between the first semiconductor nanowire MOSFET and the second semiconductor nanowire MOSFET; and the buried oxide layer is arranged between the first semiconductor nanowire MOSFET and the semiconductor substrate. According to the invention, by using the structural design that the first semiconductor nanowire MOSFET has the longitudinal stacked first semiconductor nanowire group and the second semiconductor nanowire MOSFET has the longitudinal stacked second semiconductor nanowire group, the process can be debugged in a completely independent way and high integration level of the device is obtained. At the same time, by using the double-layer isolation longitudinal stacked semiconductor nanowire MOSFET provided by the invention, the electrical property of the field effect transistor is improved and the device current driving capability is improved in multiples; and the double-layer isolation longitudinal stacked semiconductor nanowire MOSFET provided by the invention is suitable for the technical field of advanced nanodevices.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

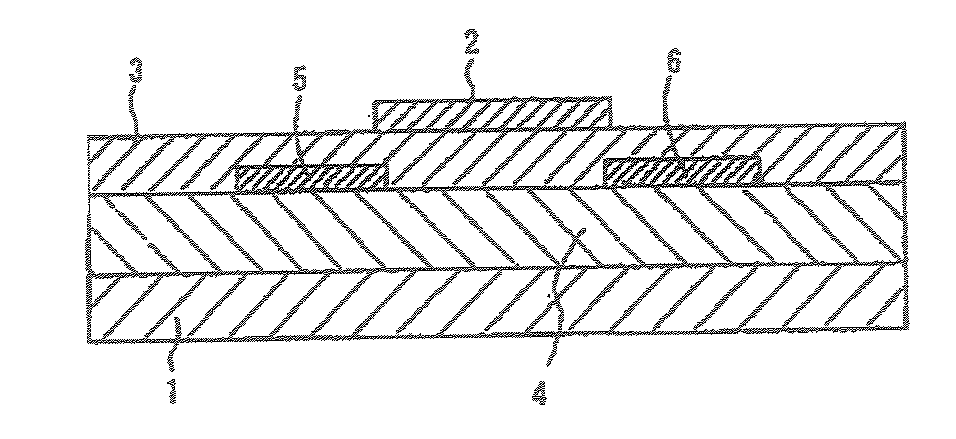

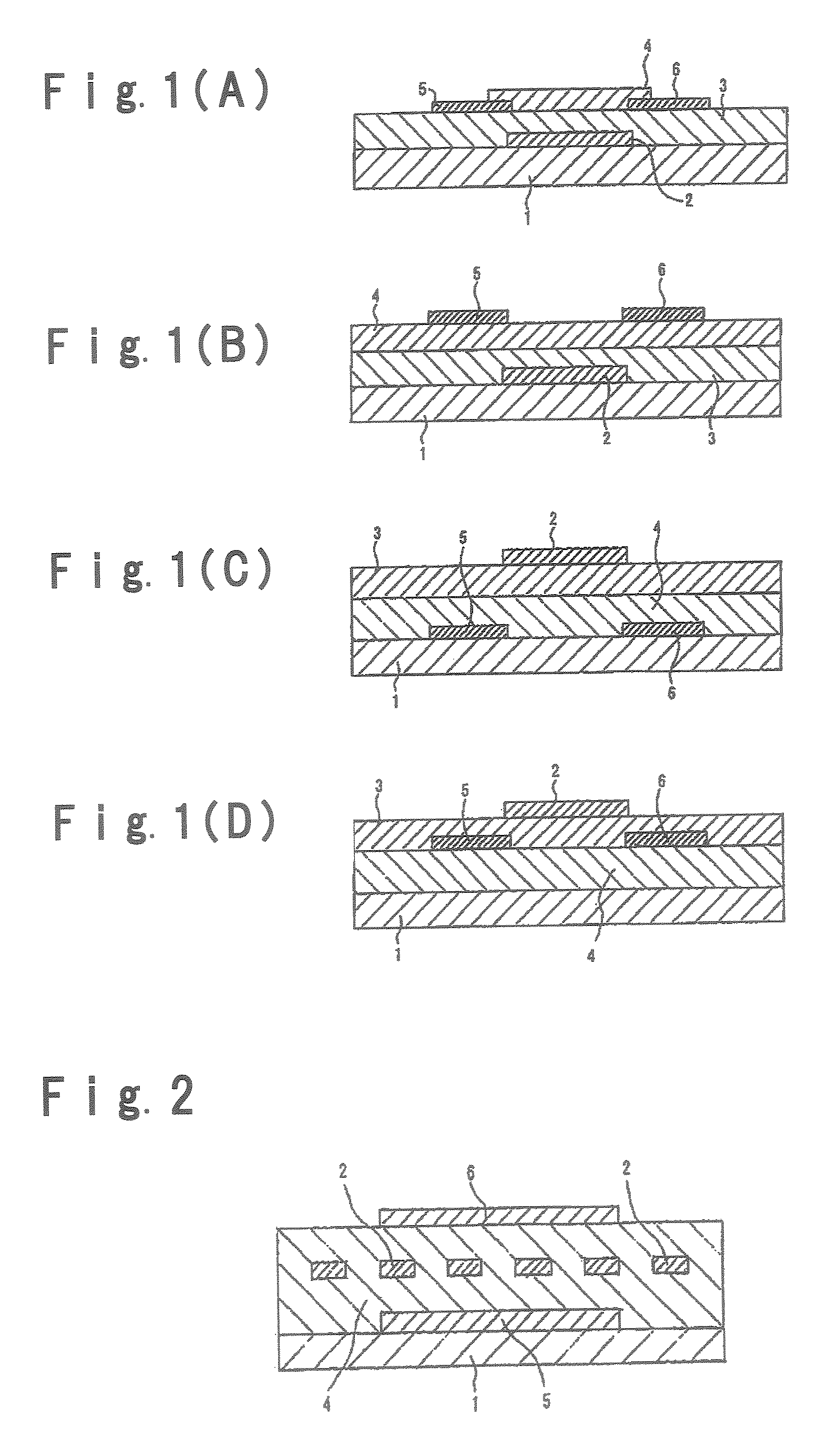

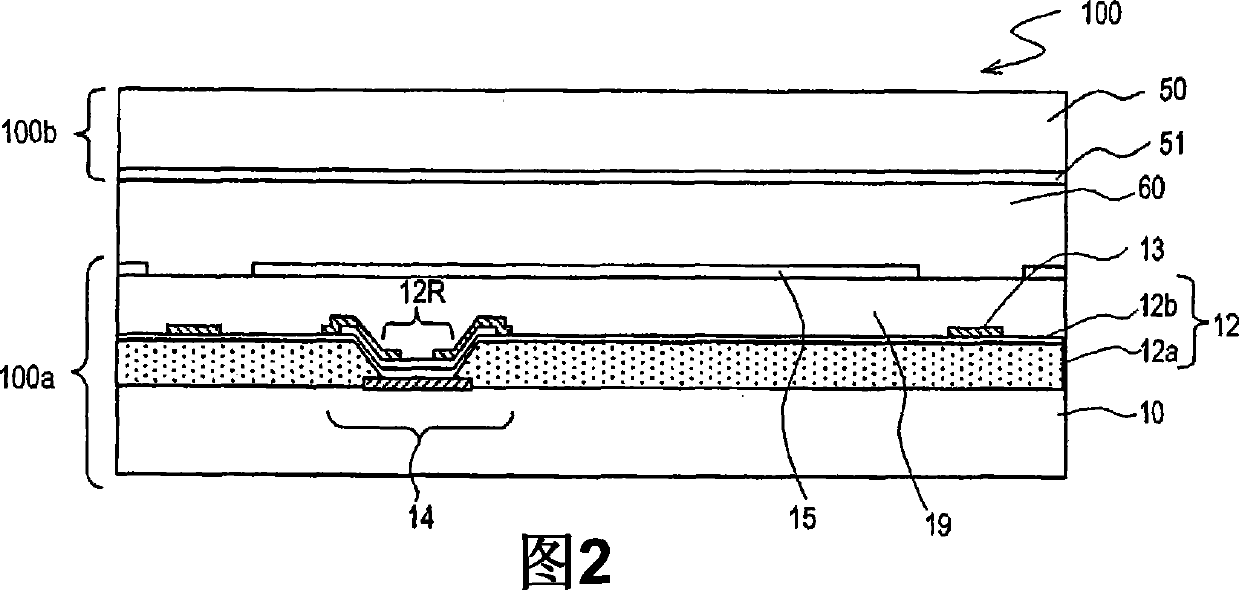

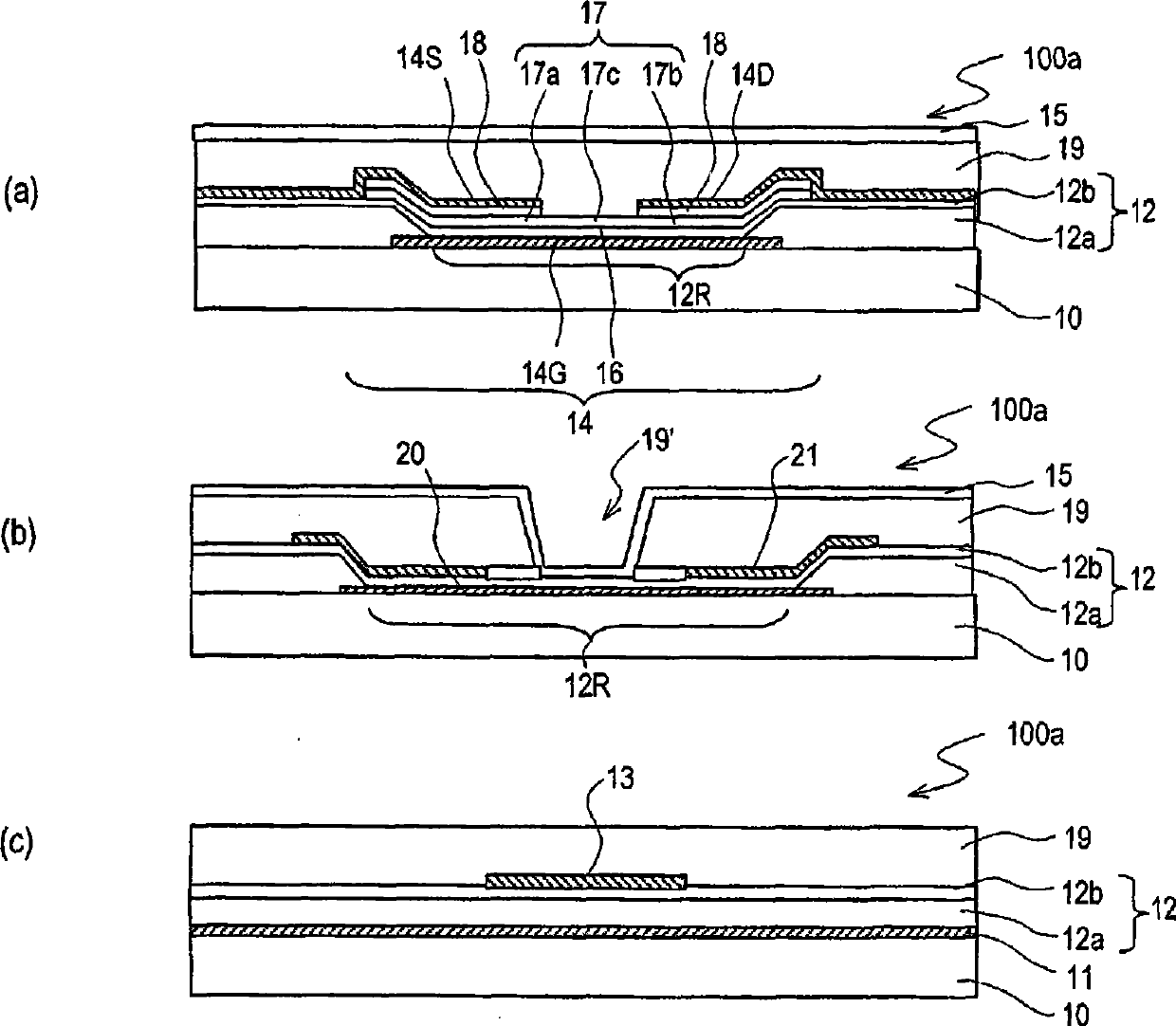

Thin film transistor, and active matrix substrate and display device provided with such thin film transistor

InactiveCN101375406AImprove current drive capabilityImprove yieldTransistorSolid-state devicesActive matrixDisplay device

The invention provides a film transistor and a source matrix substrate with the film transistor and the display device. The invention improves the electric current driving capability of a thin film transistor without the yield being decreased due to a defective leak between a source electrode / drain electrode and a gate electrode or due to a decrease in an off-characteristic. A thin film transistor according to the present invention includes a gate electrode; an insulating film covering the gate electrode; a semiconductor layer provided on the insulating film; and a source electrode and a drain electrode provided on the insulating film and the semiconductor layer. The insulating film is a multiple layer insulating film including a first insulating layer and a second insulating layer provided on the first insulating layer. The multiple layer insulating film has a low stacking region excluding the first insulating layer and a high stacking region in which the first insulating layer and the second insulating layer are stacked. The first insulating layer is provided so as to cover at least an edge of the gate electrode. The semiconductor layer is provided on both the low stacking region and the high stacking region of the multiple layer insulating film. The semiconductor layer and the low stacking region are arranged such that a path of a current flowing between the source electrode and the drain electrode necessarily passes a part of the semiconductor layer which is located above the low stacking region.

Owner:SHARP KK

Method of fabricating semiconductor integrated circuit device and semiconductor integrated circuit device fabricated using the method

ActiveUS20110241171A1Improve current drive capabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringImpurity

Owner:SAMSUNG ELECTRONICS CO LTD

Manufacturing method of three-dimensional array grid-last type Si-NWFET (Nanowire Field Effect Transistor) based on SOI (Silicon On Insulator)

InactiveCN102623385AImprove the isolation effectImprove etch selectivityNanoinformaticsSemiconductor/solid-state device manufacturingSilicon nanowiresField-effect transistor

The invention discloses a manufacturing method of a three-dimensional array grid-last type Si-NWFET (Silicon-Nanowire Field Effect Transistor) based on an SOI (Silicon On Insulator). The manufacturing method comprises the following steps of: alternatively growing silicon layers and germanium-silicon layers on the SOI, forming a fin-shaped active region, forming silicon nanowires in the fin-shaped active region, depositing amorphous carbon in a groove as a virtual isolating layer, then carrying out a grid-last process, and finally and simultaneously carrying out deposition on a groove isolating medium and an interlayer isolating medium. The manufacturing method disclosed by the invention has the advantages that due to existence of an oxygen embedding layer in the SOI, the isolating effect between a grid and an SOI substrate is effectively improved, and the adoption of the grid-last process is beneficial to the control of the profile of the grid and the electrical property of a device; the utilization of the amorphous carbon as the virtual isolating layer is beneficial to the control of the profiles of the grid and the grid groove; and in addition, the silicon-nanowire field effect transistor (Si-NWFET) structure is designed by adopting a three-dimensional array silicon-nanowire structure, so that the number of the nanowires is increased, and the current driving capability of the device is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

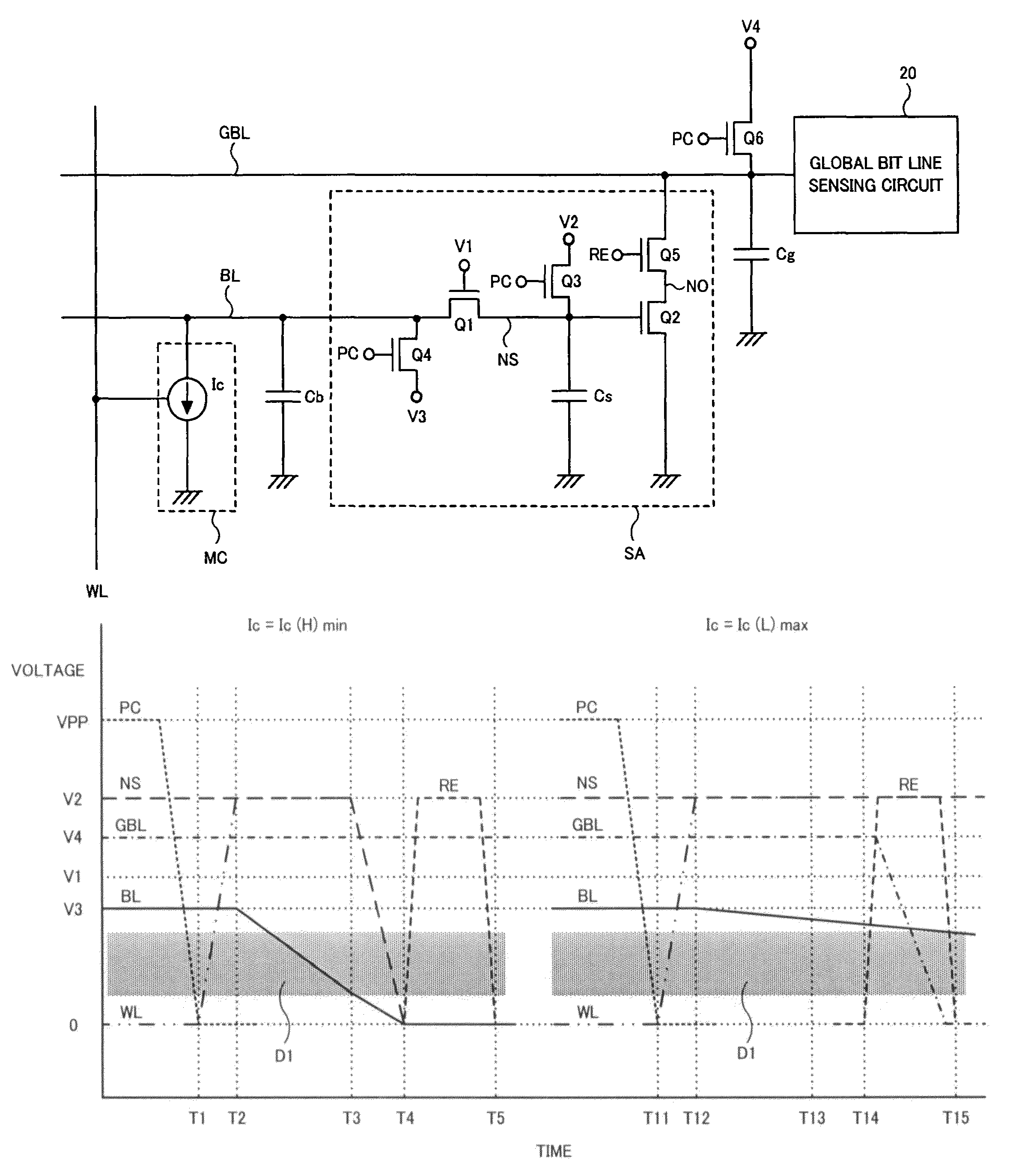

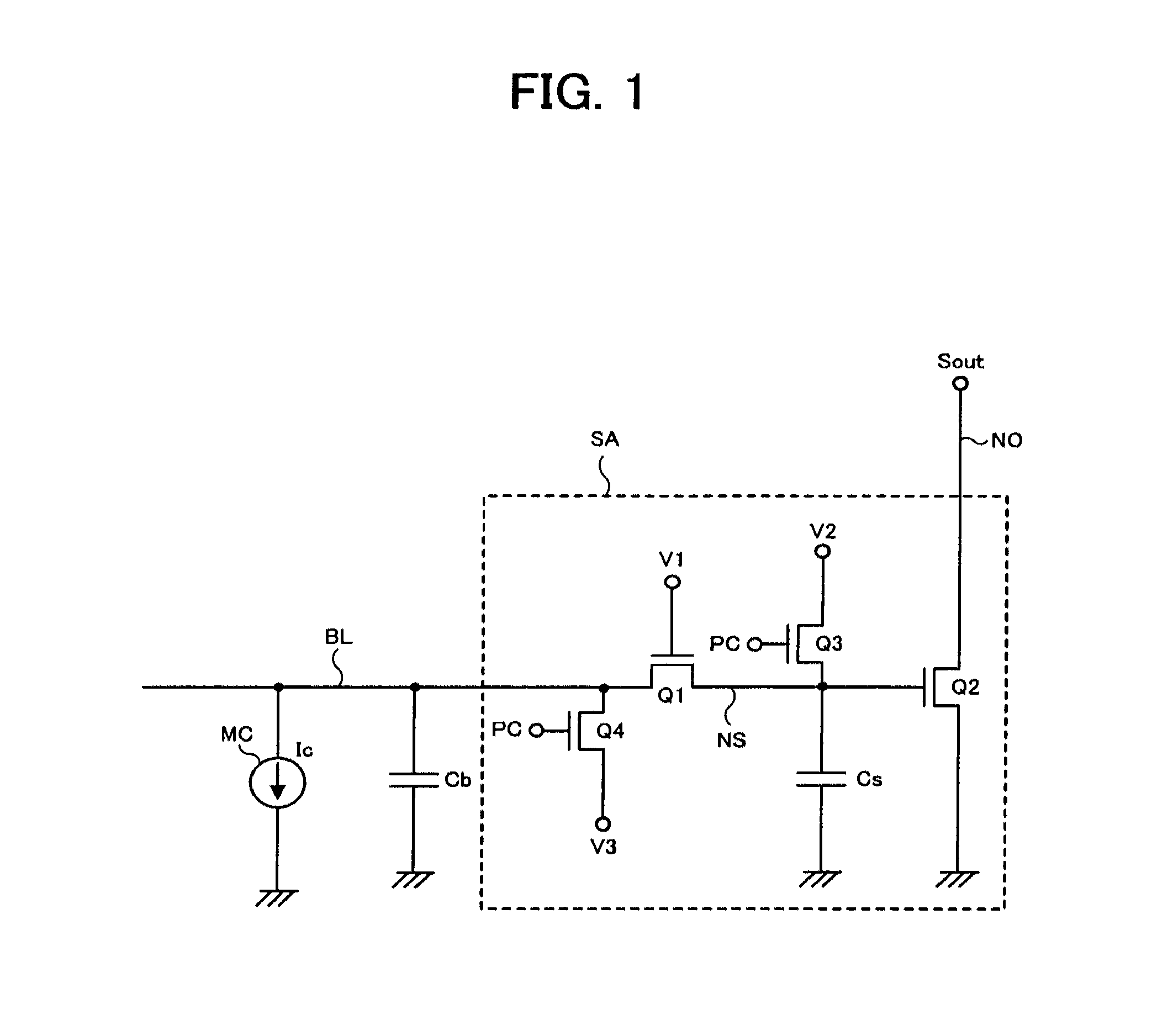

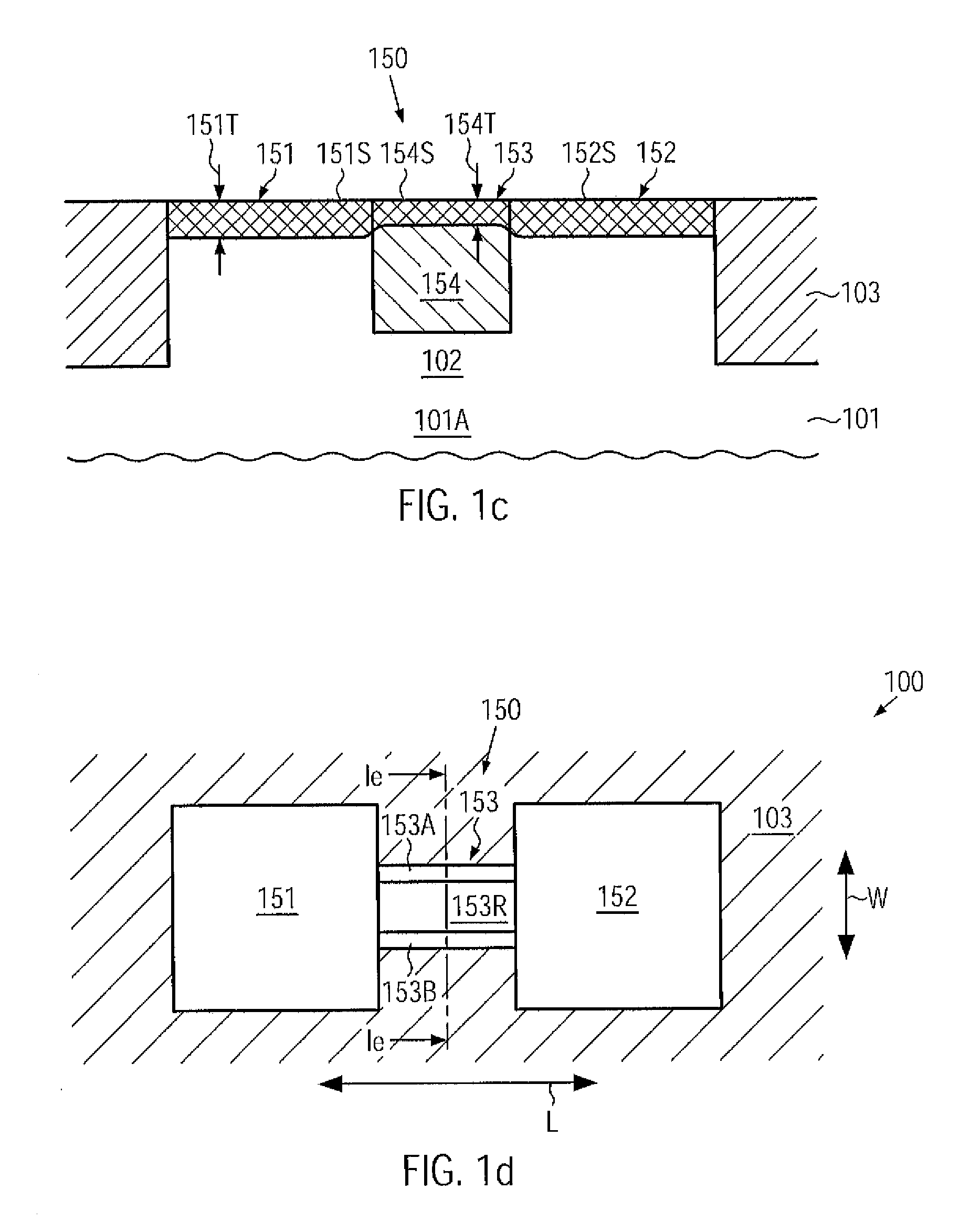

Semiconductor device having current change memory cell

InactiveUS8588019B2Improve current drive capabilityReduced operating requirementsElectric analogue storesDigital storageBit lineSemiconductor

A semiconductor device comprises a first transistor connected between a bit line and a sense node, and a second transistor amplifying a signal of the sense node. A first potential applied to a gate of the first transistor, a second potential supplied to the sense node, and a third potential supplied to the bit line are controlled so that the first potential applied to a gate of the first transistor is between the second and third potentials, the second potential is set larger than the third potential, and a predetermined potential obtained by subtracting a threshold voltage of the first transistor from the first potential is smaller than the third potential and higher than a low potential supplied to the second transistor. A potential of the bit line transitions from the third potential toward the low potential in accordance with data of a current change memory cell.

Owner:LONGITUDE LICENSING LTD

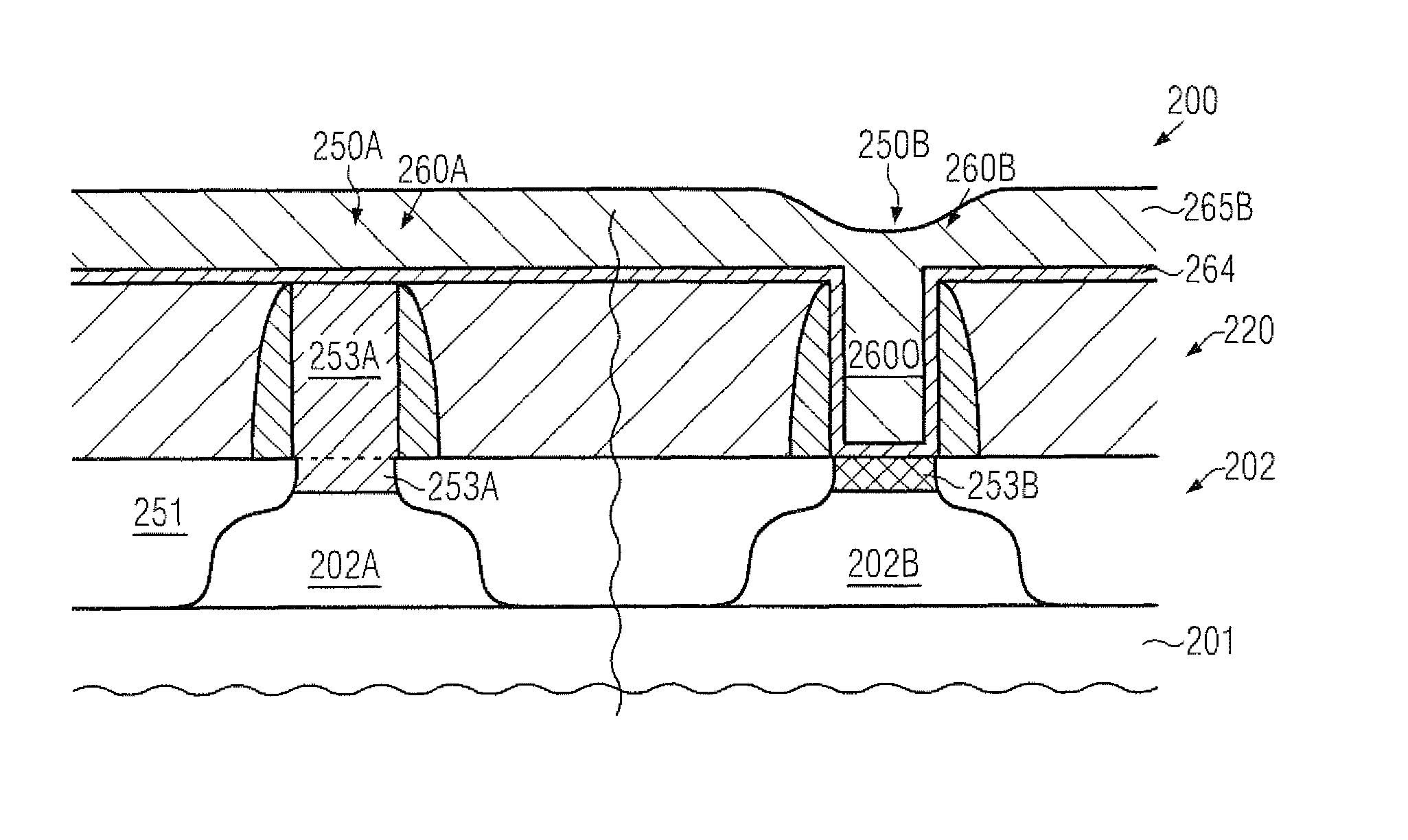

Semiconductor Device Comprising High-K Metal Gate Electrode Structures and Precision eFuses Formed in the Active Semiconductor Material

ActiveUS20120001295A1Low thermal conductivitySuperior heat conductivitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsEngineering

In a complex semiconductor device, electronic fuses may be formed in the active semiconductor material by using a semiconductor material of reduced heat conductivity selectively in the fuse body, wherein, in some illustrative embodiments, the fuse body may be delineated by a non-silicided semiconductor base material.

Owner:GLOBALFOUNDRIES US INC