Patents

Literature

2652 results about "Electrostatic discharge protection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

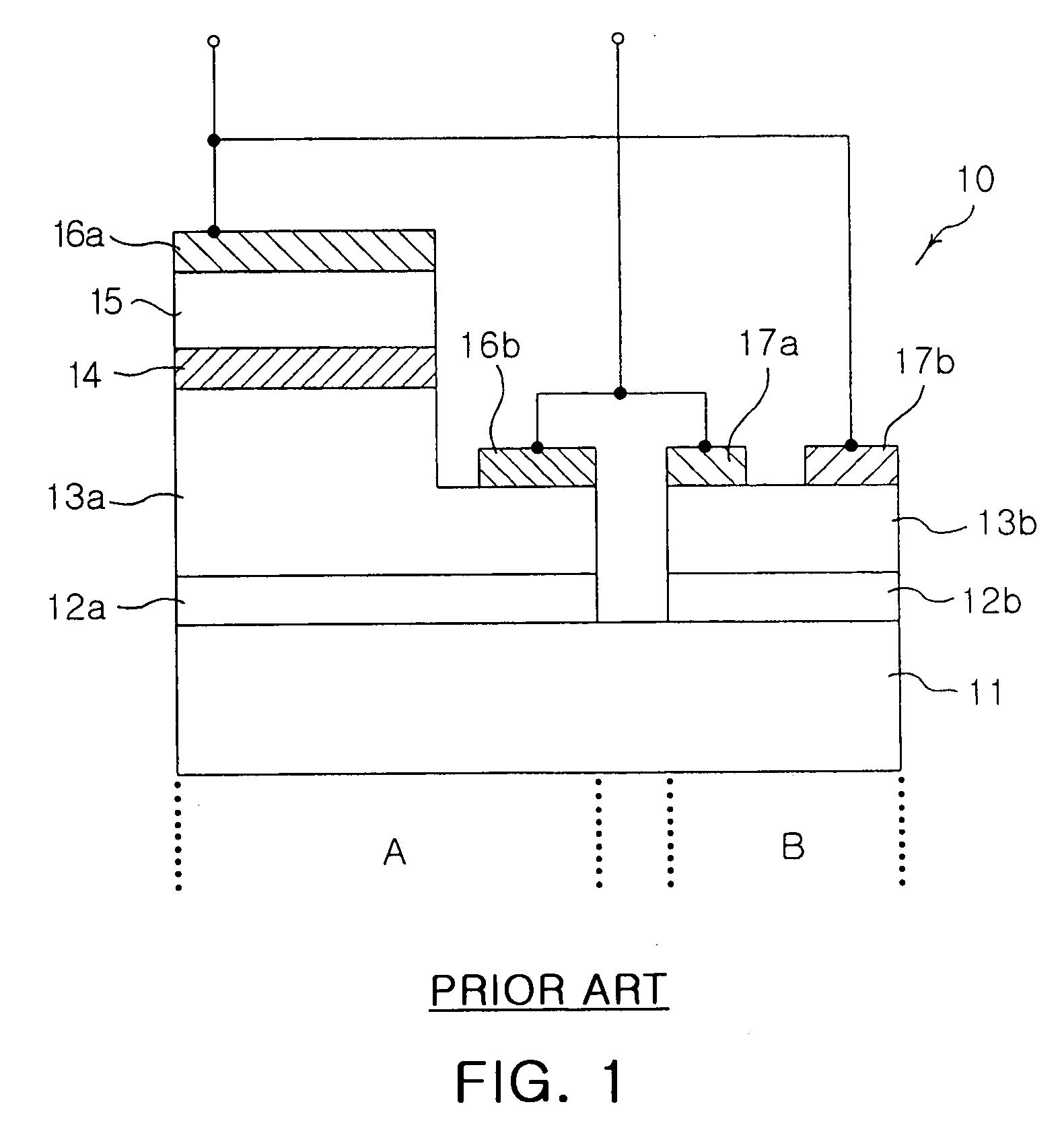

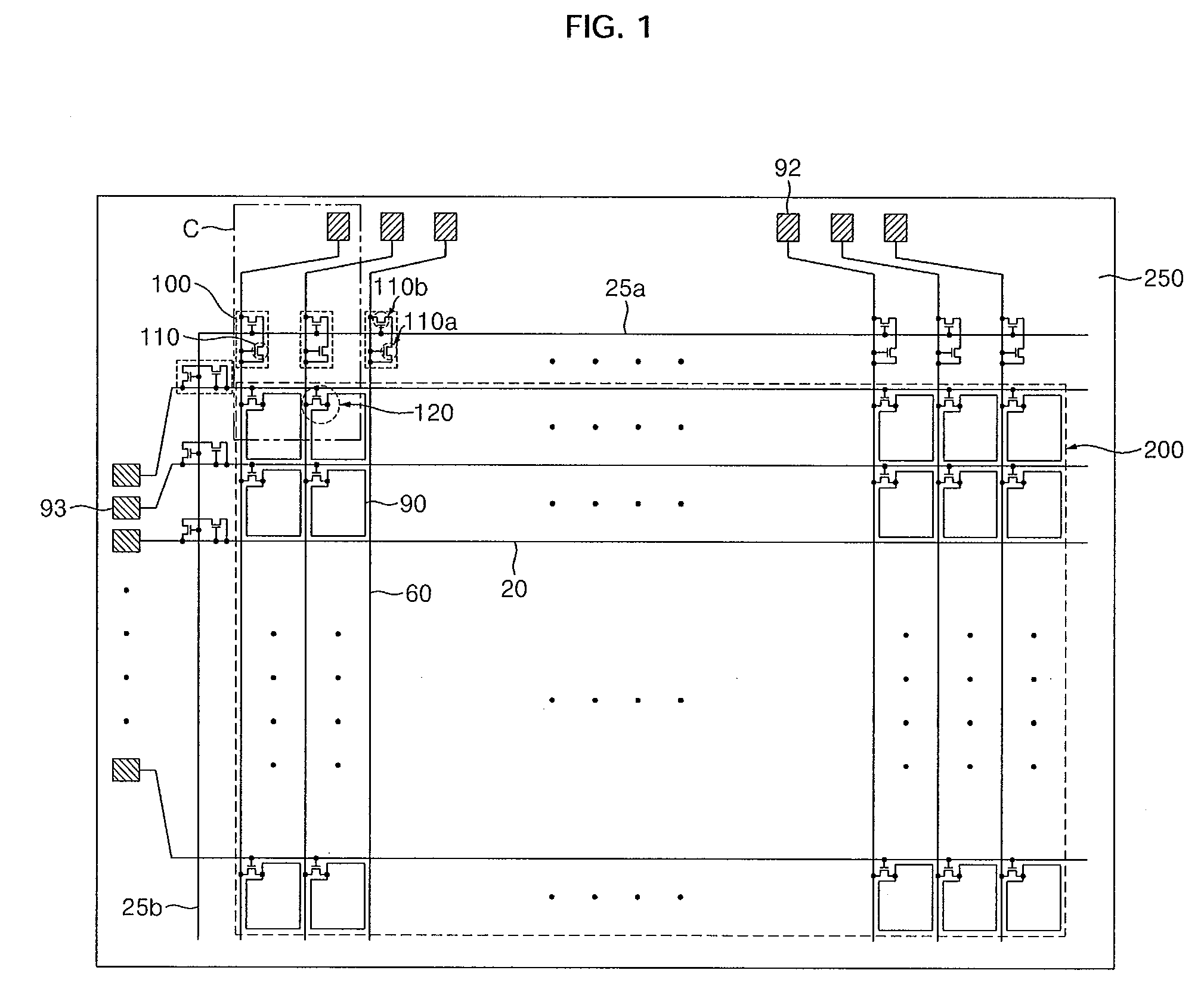

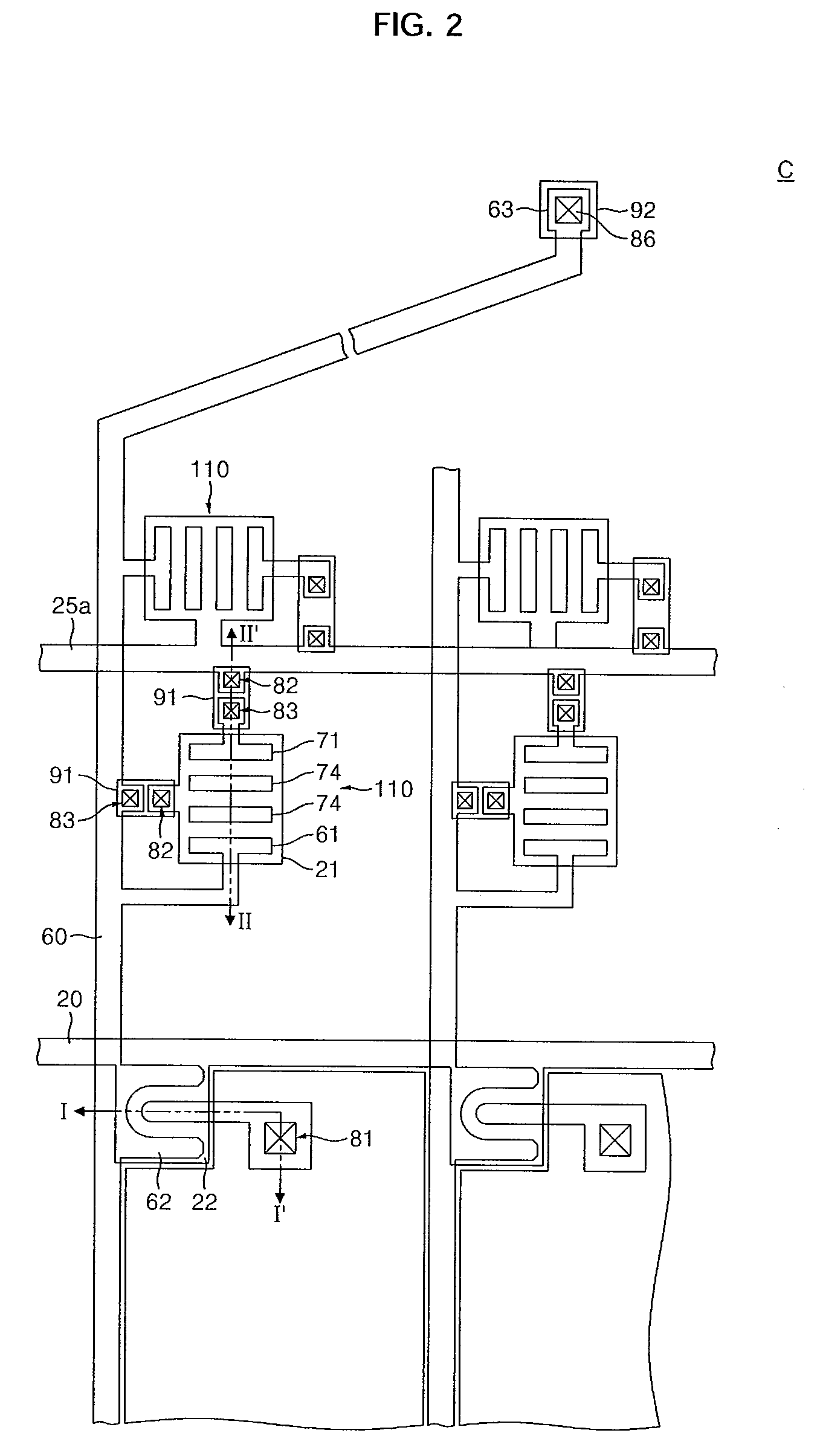

Electrostatic discharge protection device for liquid crystal display using a COG package

InactiveUS6043971AEmergency protective arrangements for limiting excess voltage/currentNon-linear opticsEngineeringElectrostatic discharge protection

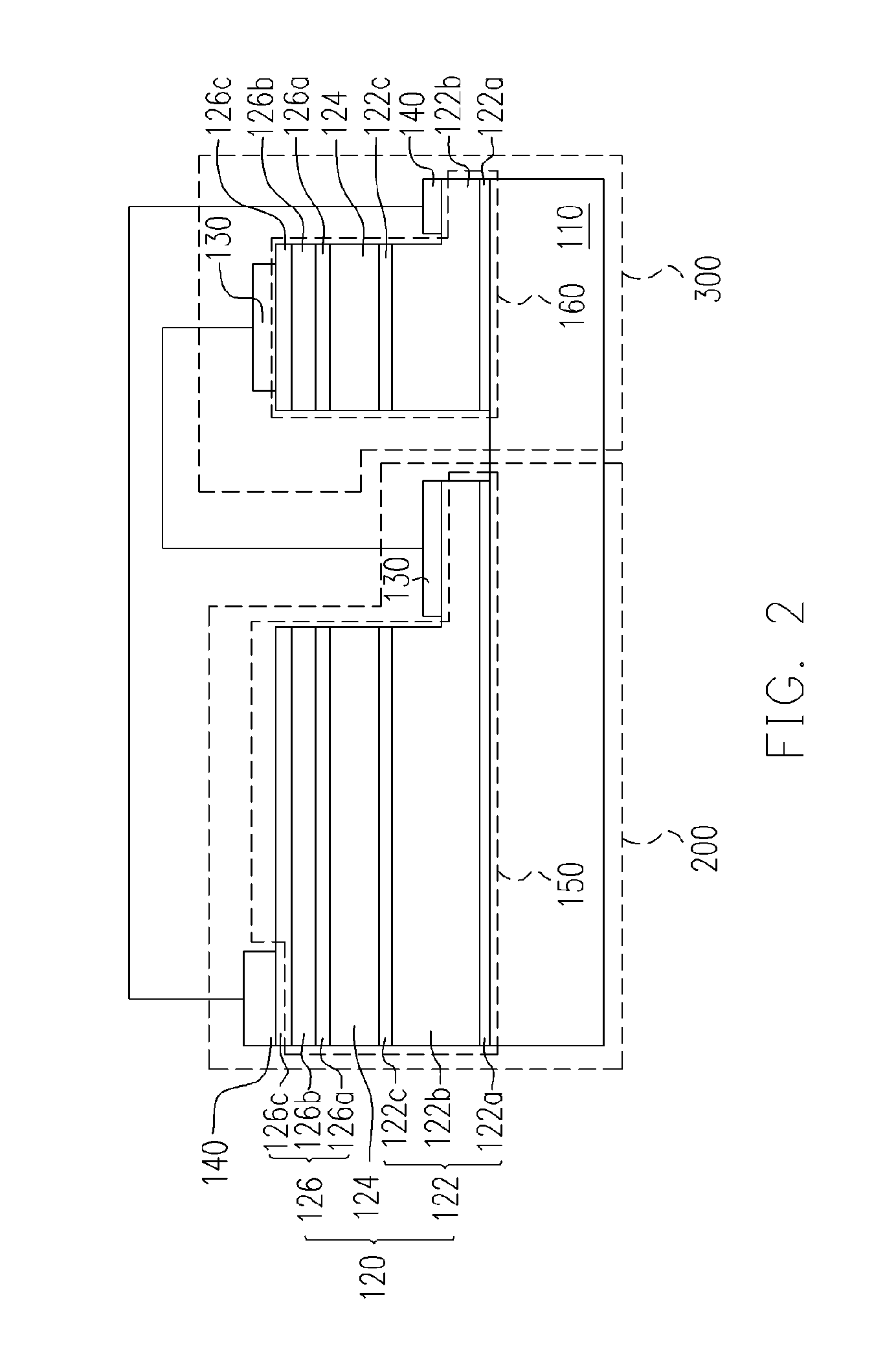

The electrostatic discharge (ESD) protection device for a liquid crystal display using a chip on glass (COG) package is provided. The ESD protection device includes a plurality of gate lines and data lines each of which has an output pad at its end. A plurality of gate line input pads and data line input pads are formed opposite to the output pads of the gate lines and data lines, respectively. A common electrode is formed between the plurality of gate line input pads and output pads and between the data line input pads and output pads. A plurality of electrostatic discharge protection circuits are connected between the input pads and the common electrodes to protect the input pads from electrostatic discharge.

Owner:LG DISPLAY CO LTD

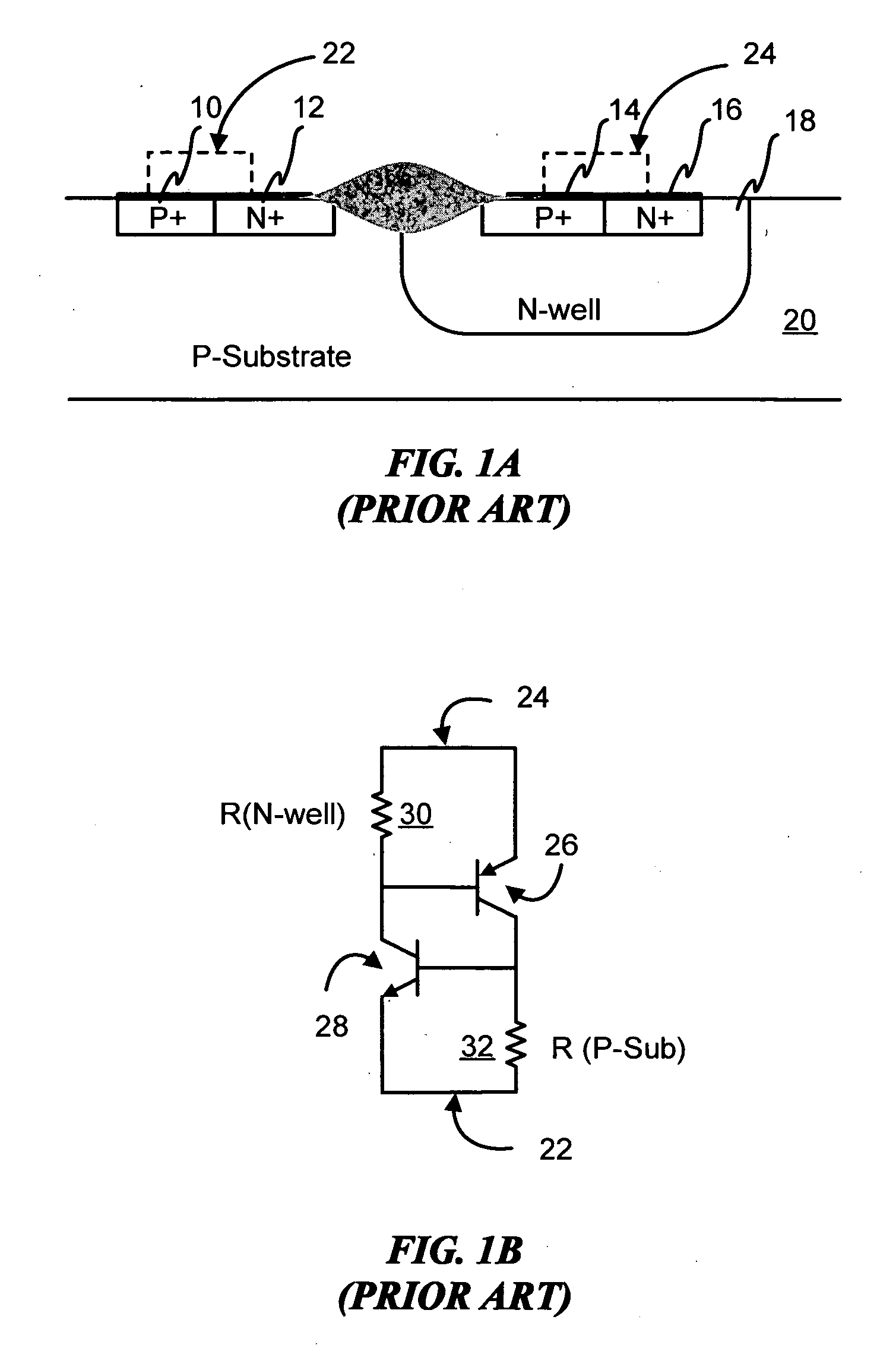

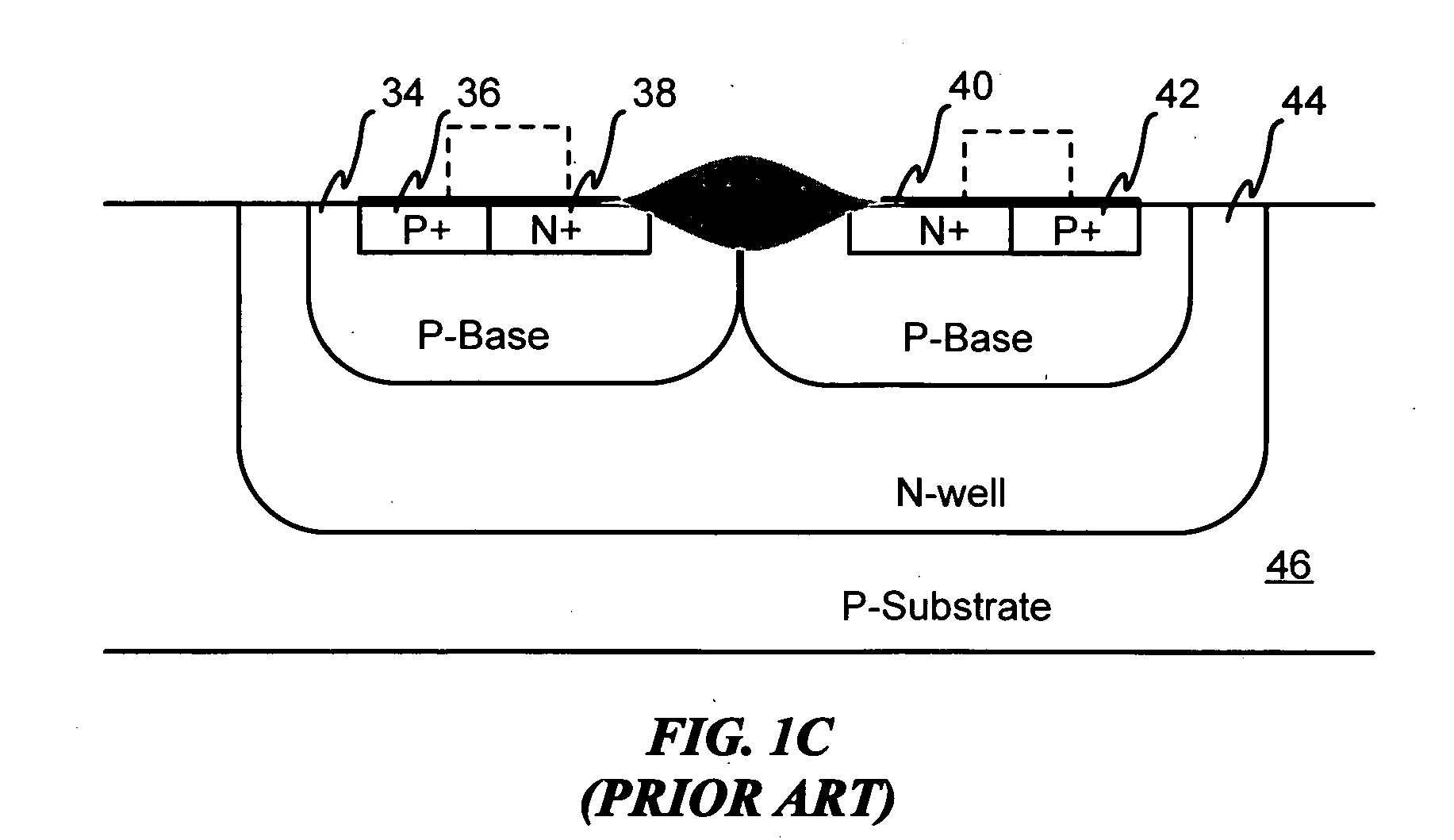

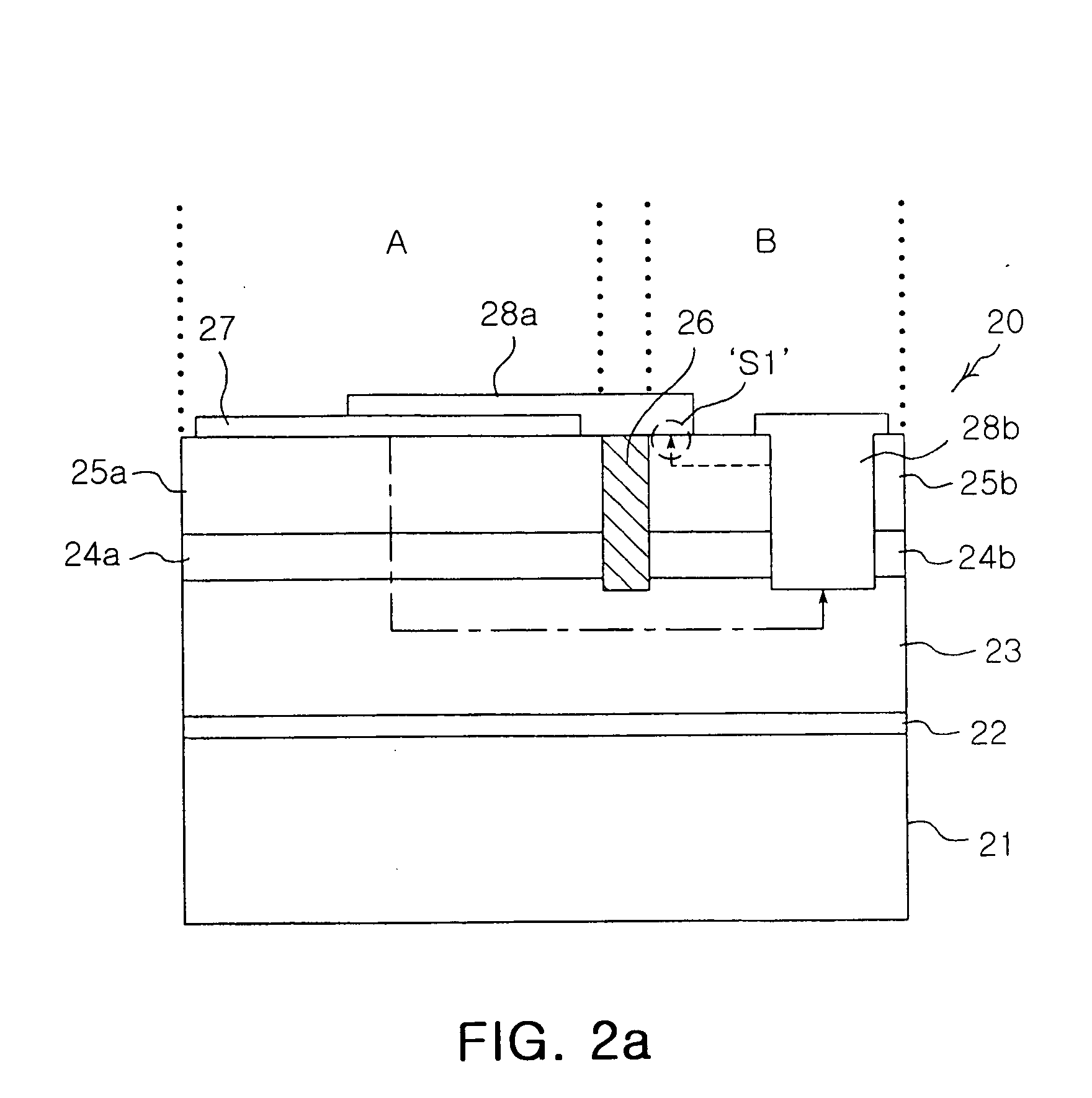

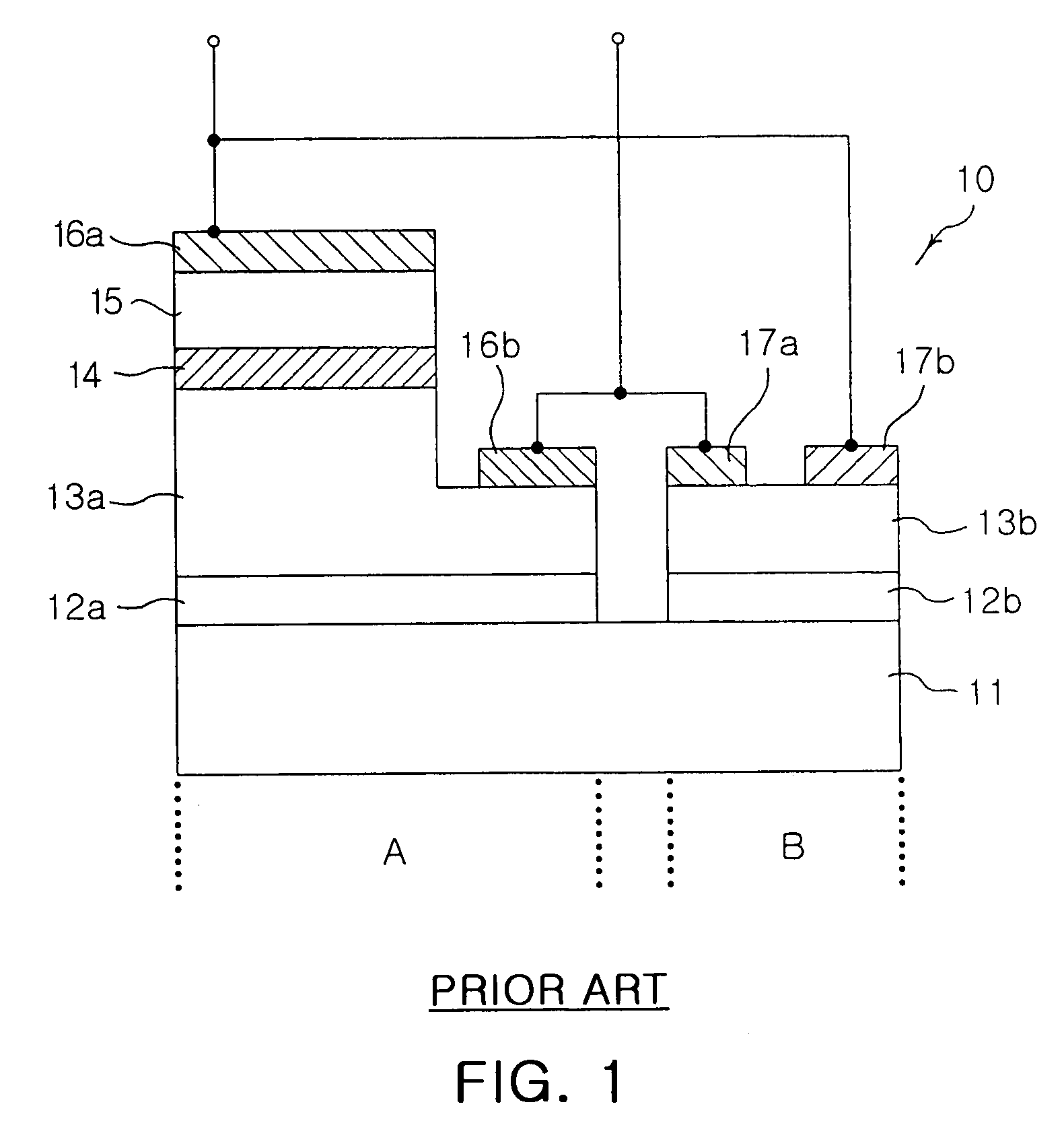

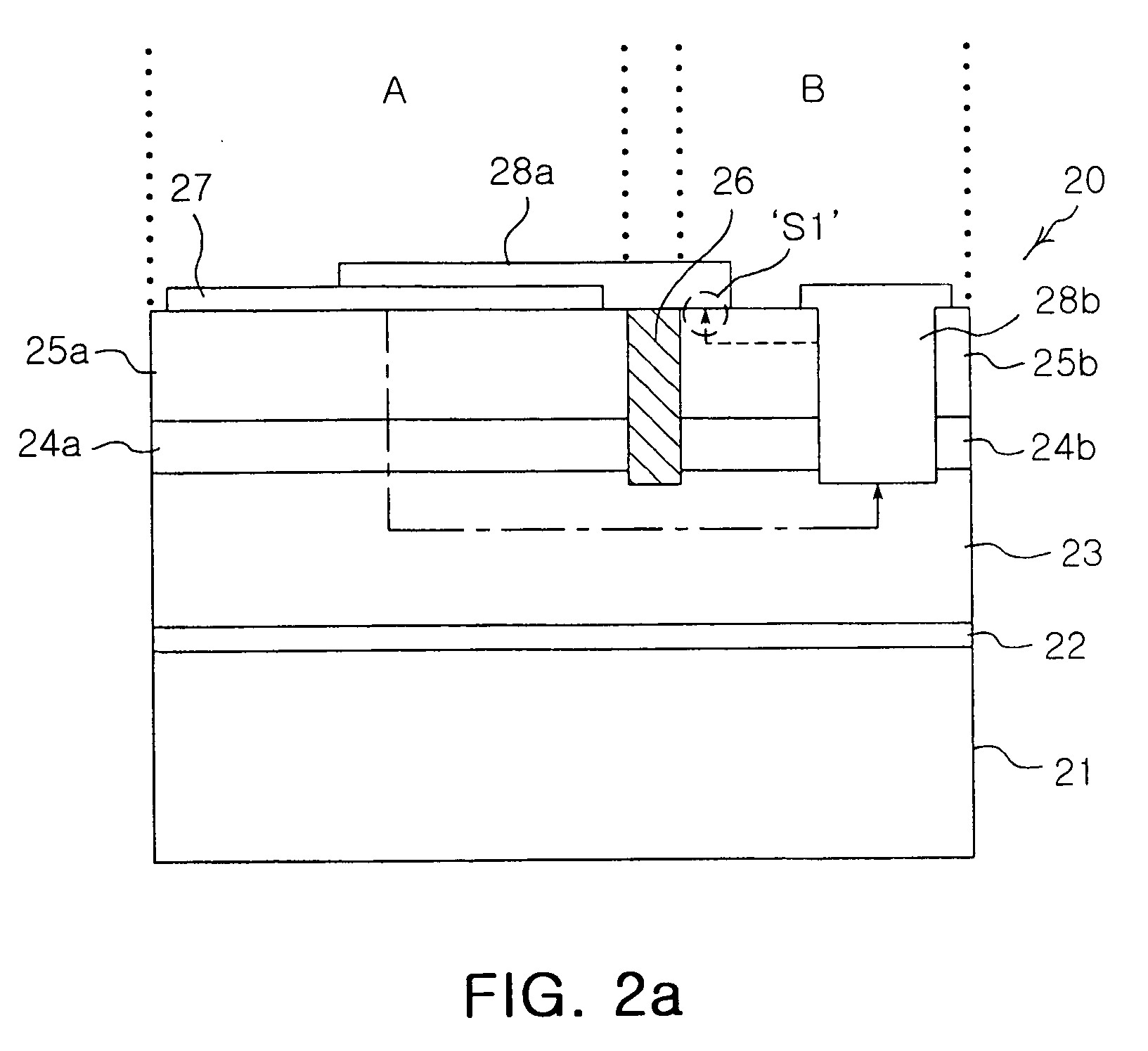

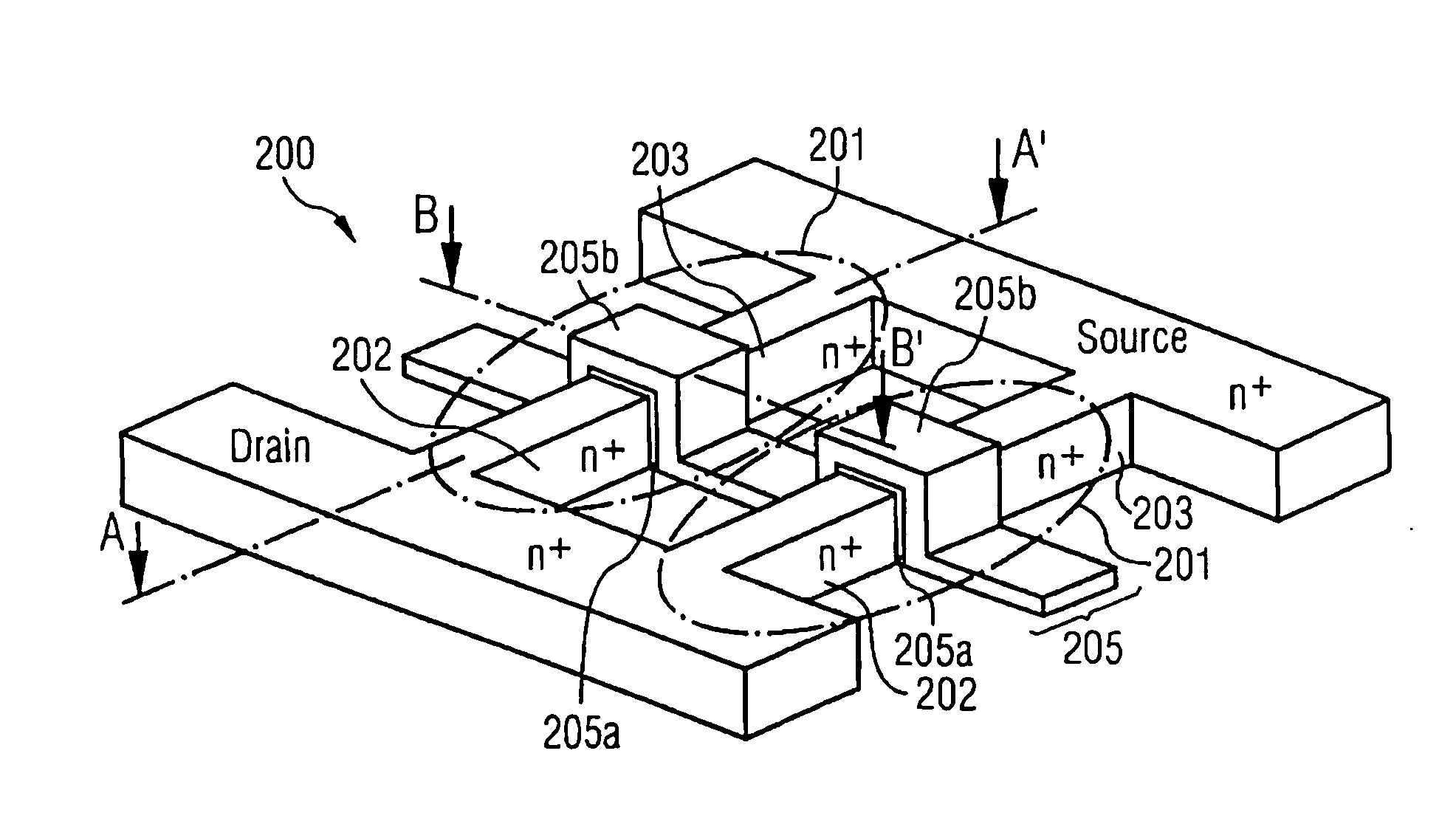

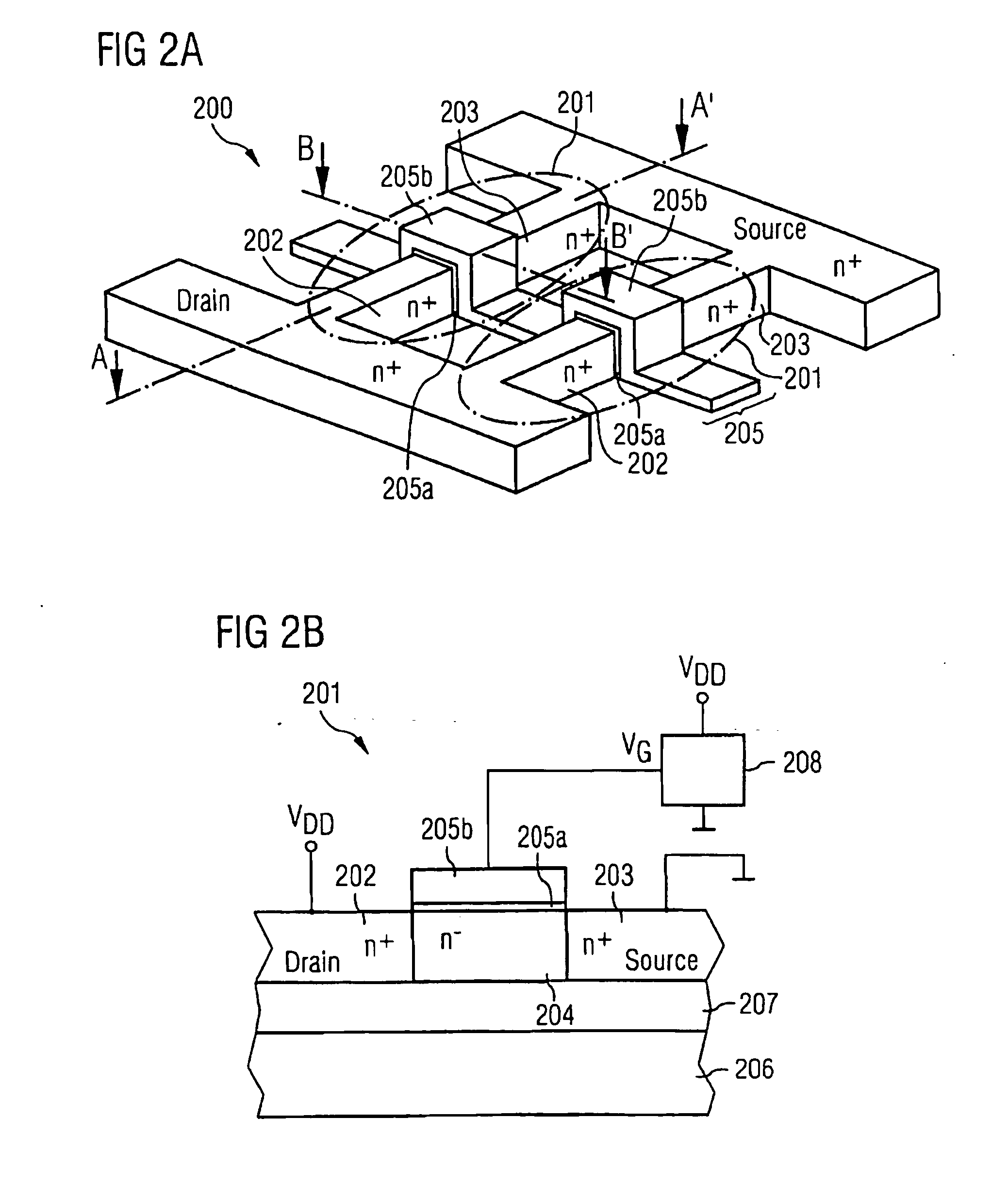

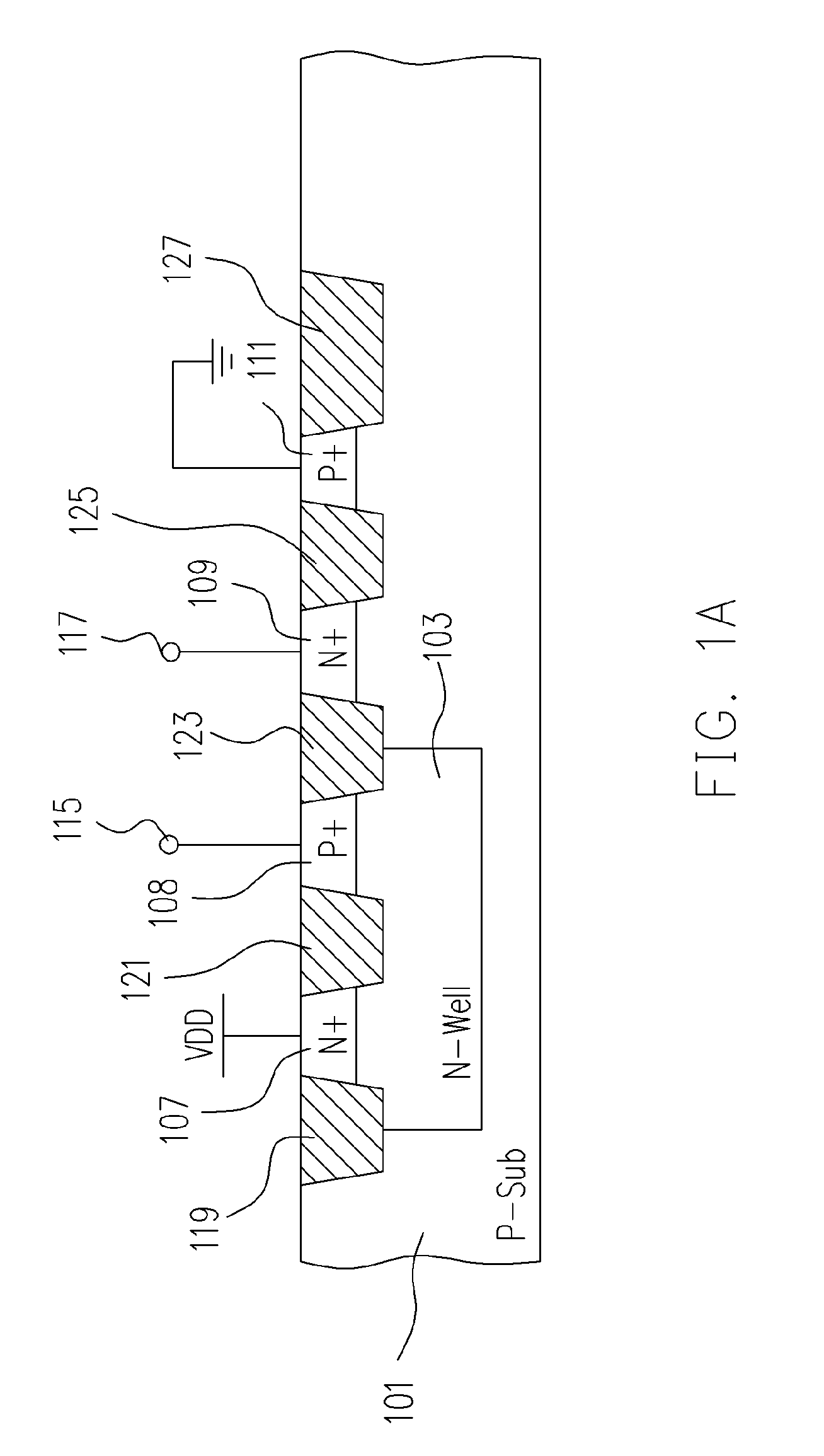

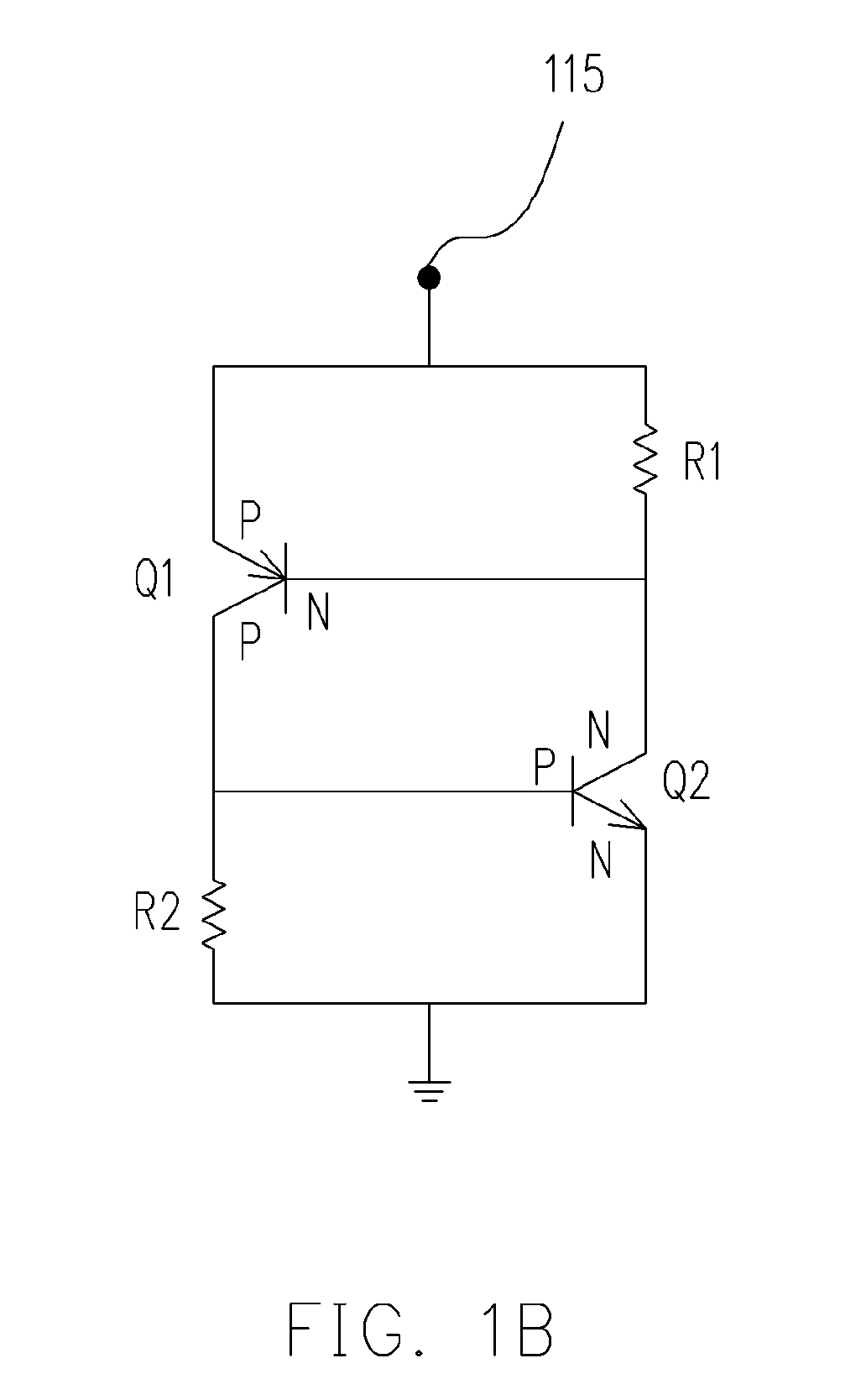

SCR devices in silicon-on-insulator CMOS process for on-chip ESD protection

InactiveUS20030146474A1TransistorSemiconductor/solid-state device detailsSilicon-controlled rectifierSilicon on insulator

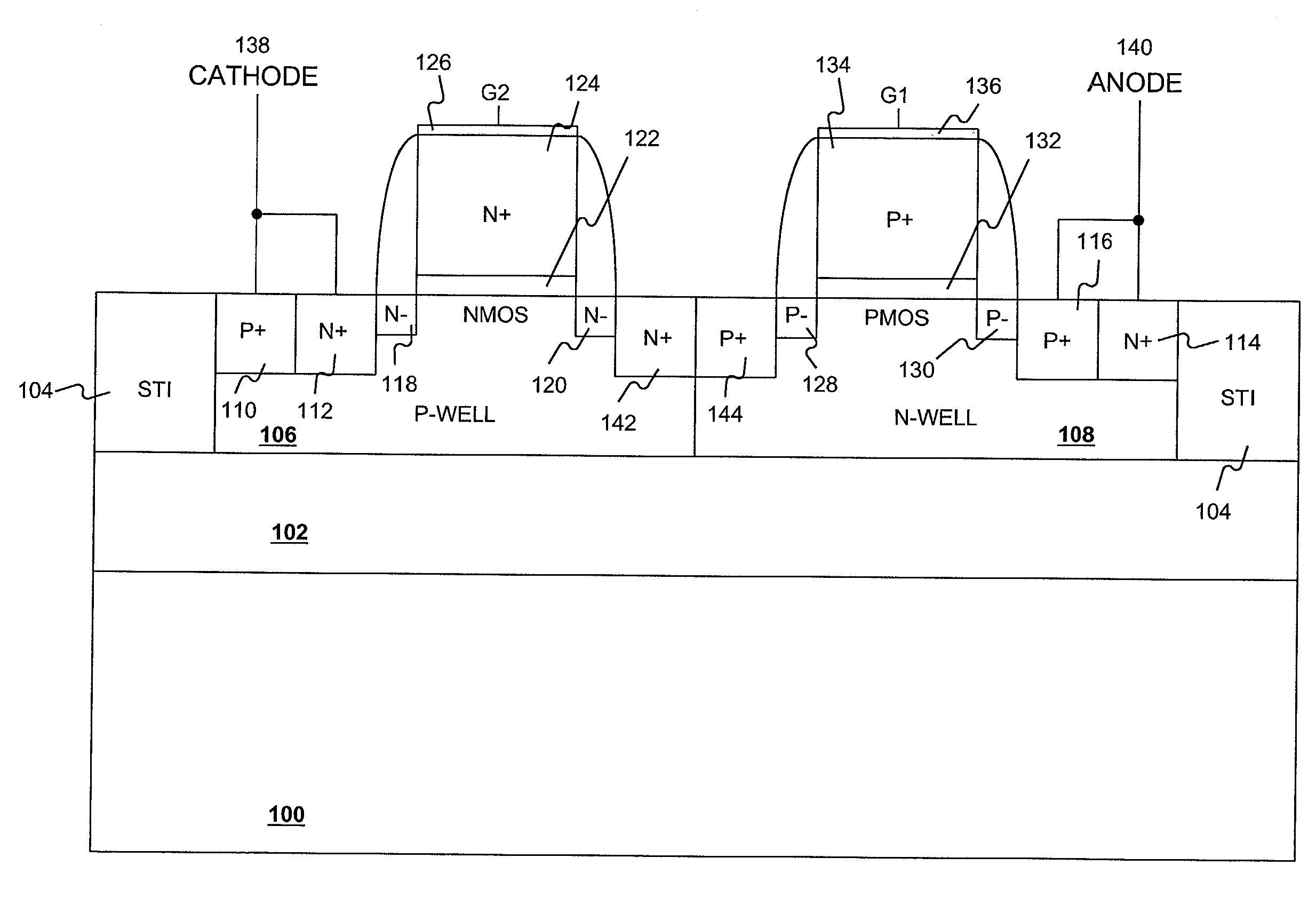

A silicon-on-isolator CMOS integrated circuit device includes a semiconductor substrate, an isolation layer formed over the semiconductor substrate, an n-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer, and a p-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer and contiguous with the n-type MOS transistor, wherein the n-type MOS transistor and the p-type MOS transistor form a silicon controlled rectifier to provide electrostatic discharge protection.

Owner:TRANSPACIFIC IP LTD

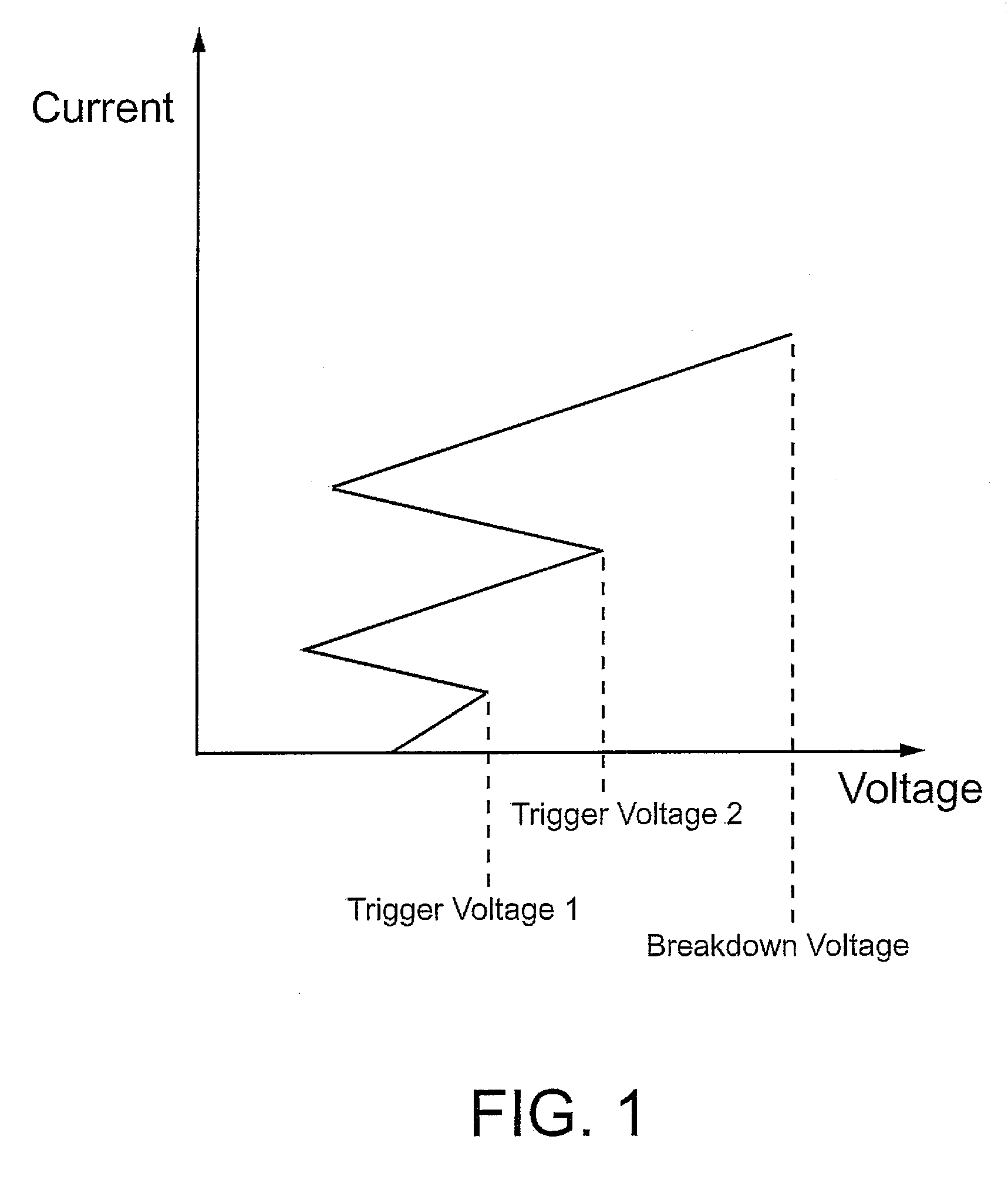

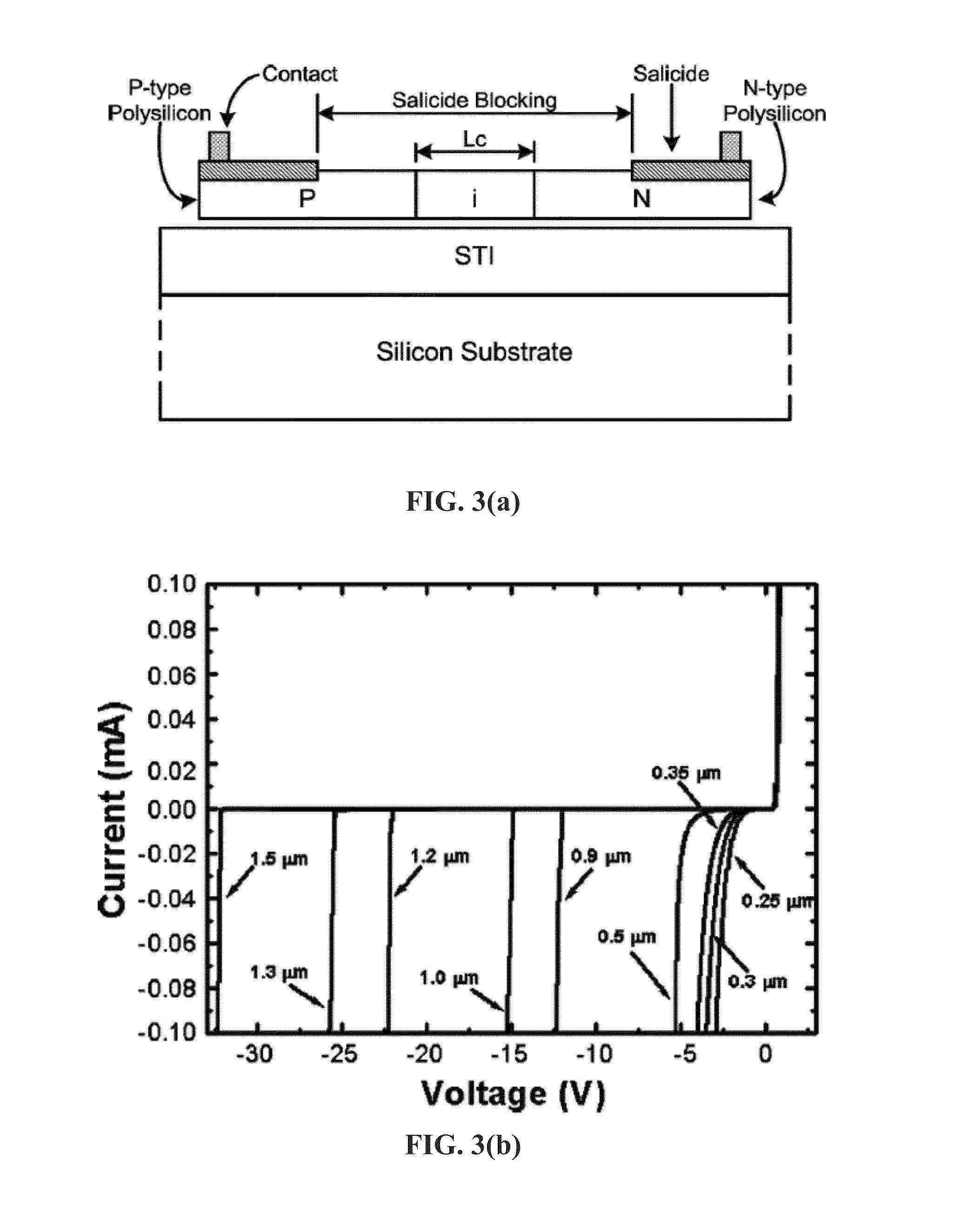

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

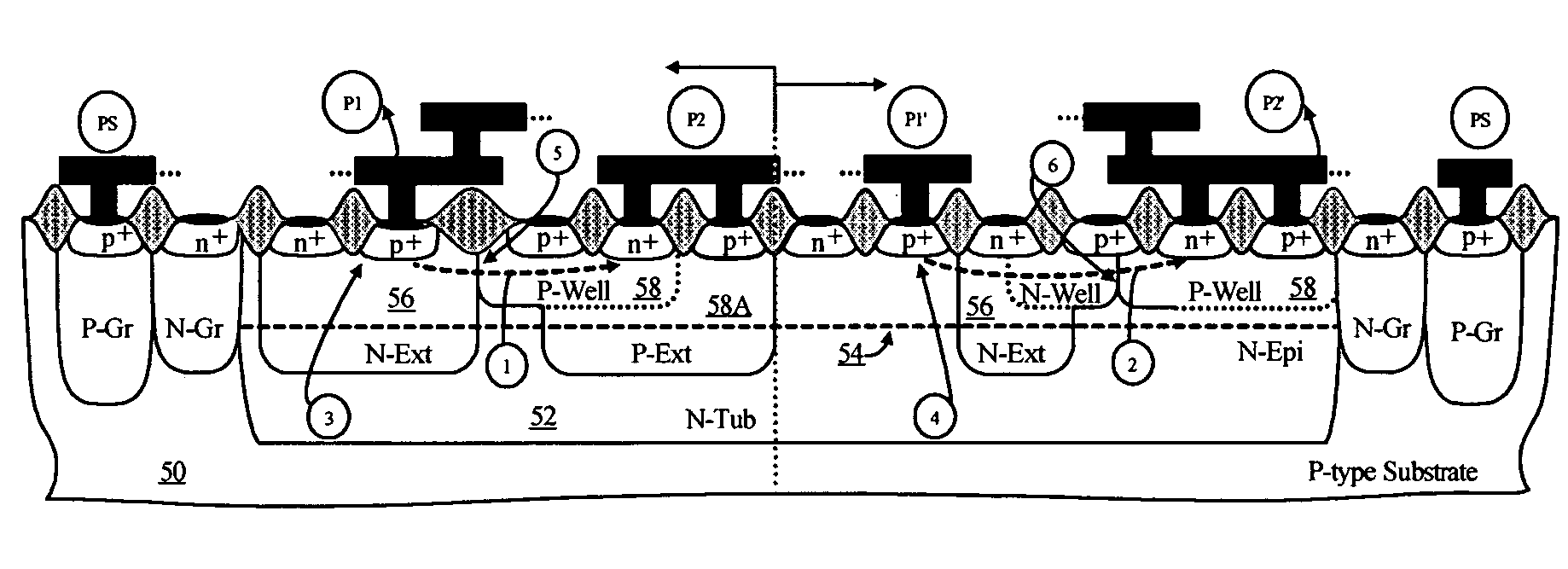

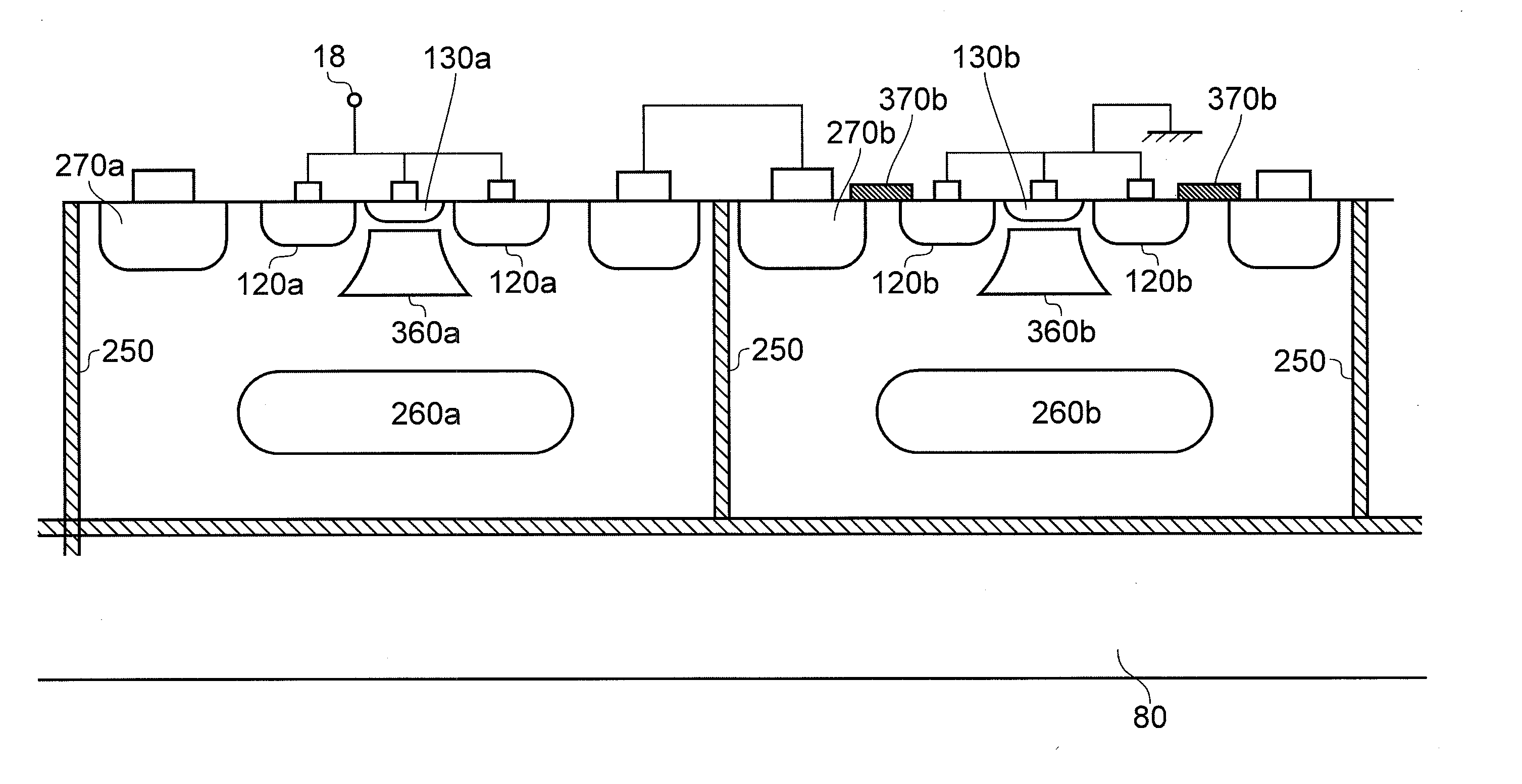

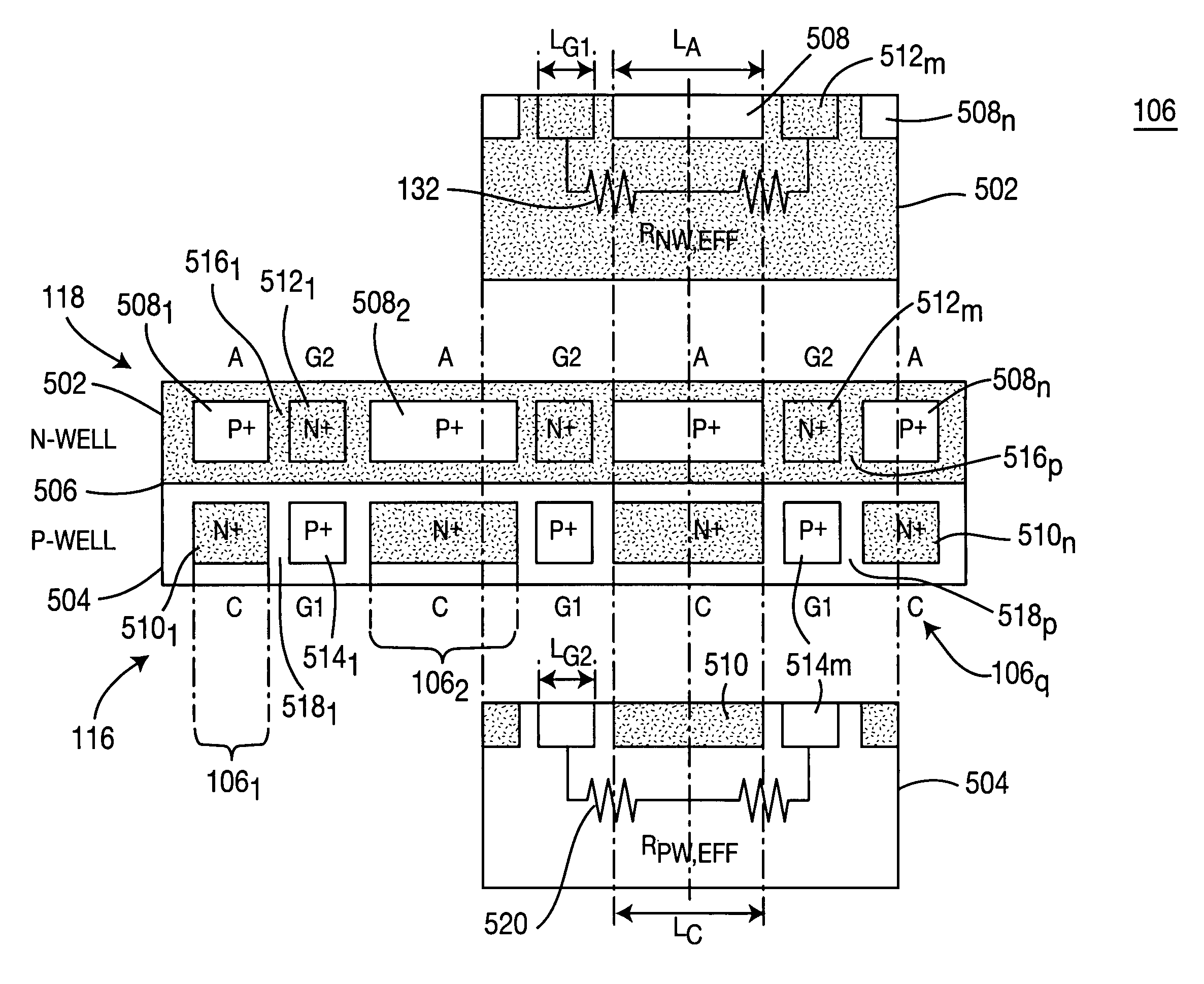

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

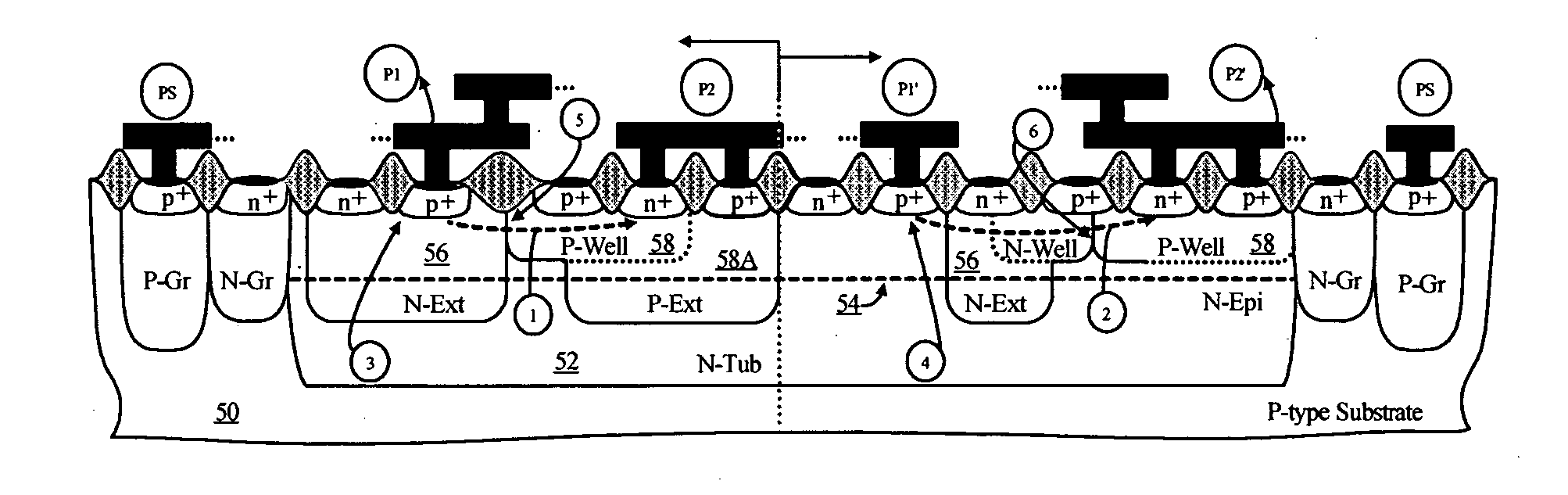

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

Electrostatic discharge protection semiconductor structure

ActiveUS20070004150A1Improve ESD protection capabilityTransistorSemiconductor/solid-state device detailsPower semiconductor deviceDevice material

An electrostatic discharge (ESD) protection device with adjustable single-trigger or multi-trigger voltage is provided. The semiconductor structure has multi-stage protection semiconductor circuit finction and adjustable discharge capacity. The single-trigger or multi-trigger semiconductor structure may be fabricated by using the conventional semiconductor process, and can be applied to IC semiconductor design and to effectively protect the important semiconductor devices and to prevent the semiconductor devices from ESD damage. In particular, the present invention can meet the requirements of high power semiconductor device and has better protection function compared to conventional ESD protection circuit. In the present invention, a plurality of N-wells or P-wells connected in parallel are used to adjust the discharge capacity of various wells in the P-substrate so as to improve the ESD protection capability and meet different power standards.

Owner:SEMICON COMPONENTS IND LLC

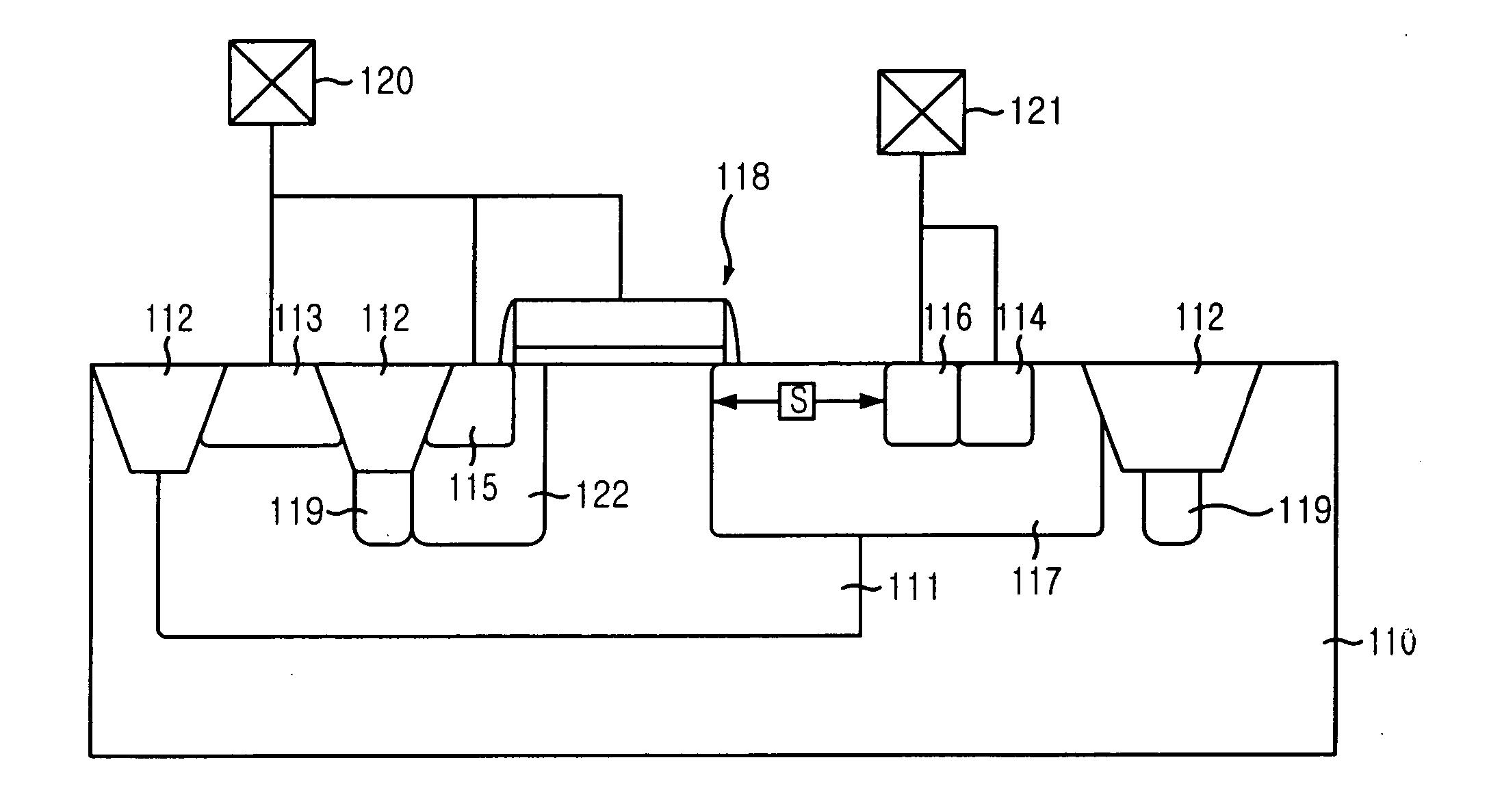

Electro-static discharge protection device, semiconductor device, and method for manufacturing electro-static discharge protection device

An electrostatic discharge protection device including a gate electrode formed on a substrate. First and second diffusion regions of a first conductivity type are formed in the substrate with the gate electrode located in between. A first silicide layer is formed in the first diffusion region. A silicide block region is formed between the gate electrode and the first suicide layer. A third diffusion region is formed below the first silicide layer to partially overlap the first diffusion region. The third diffusion region and first silicide layer have substantially the same shapes and dimensions. The third diffusion region and a portion below the gate electrode located at the same depth as the third diffusion region contain impurities of a second conductivity type. The third diffusion region has an impurity concentration that is higher than that of the portion below the gate electrode.

Owner:SOCIONEXT INC

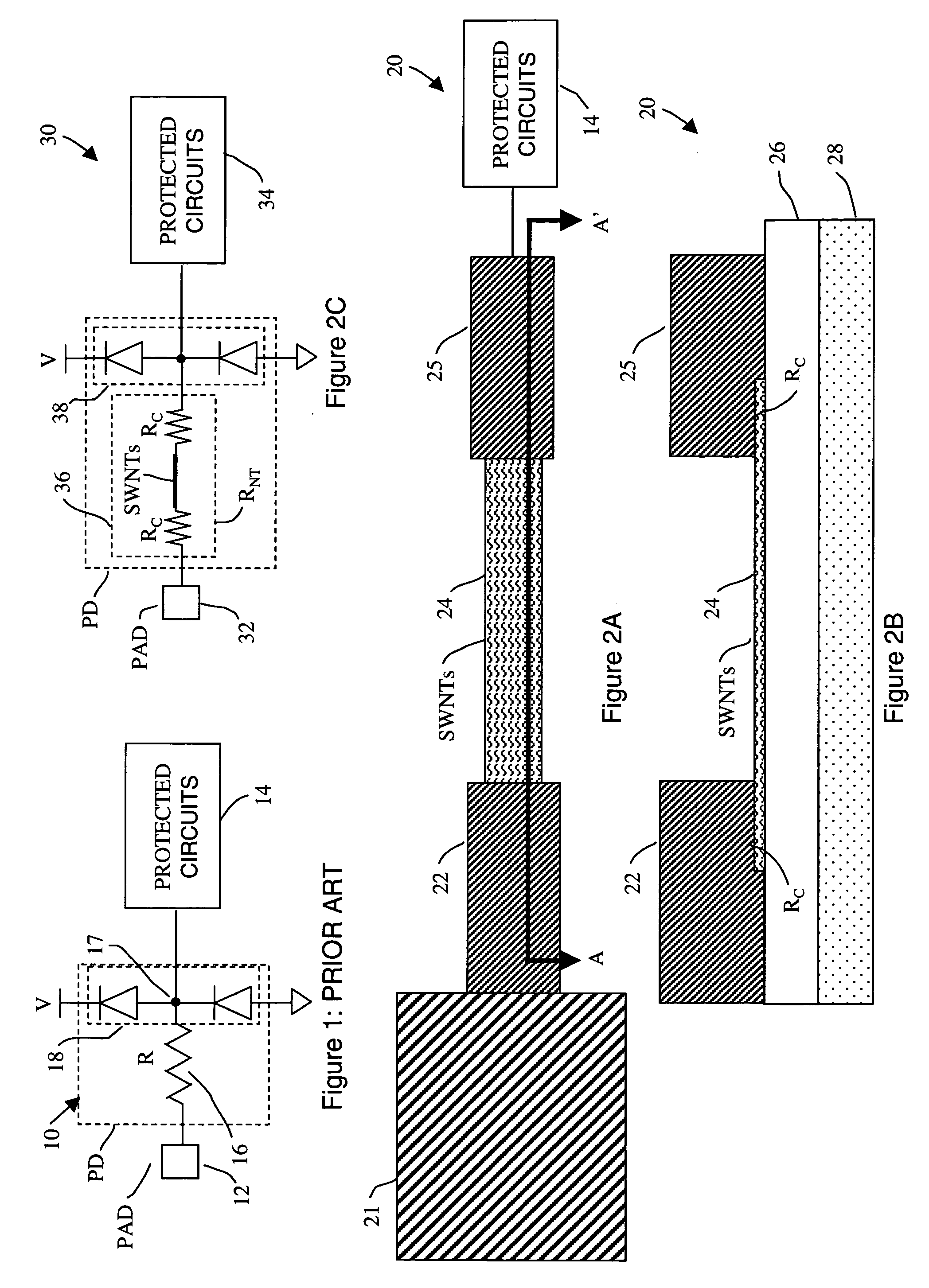

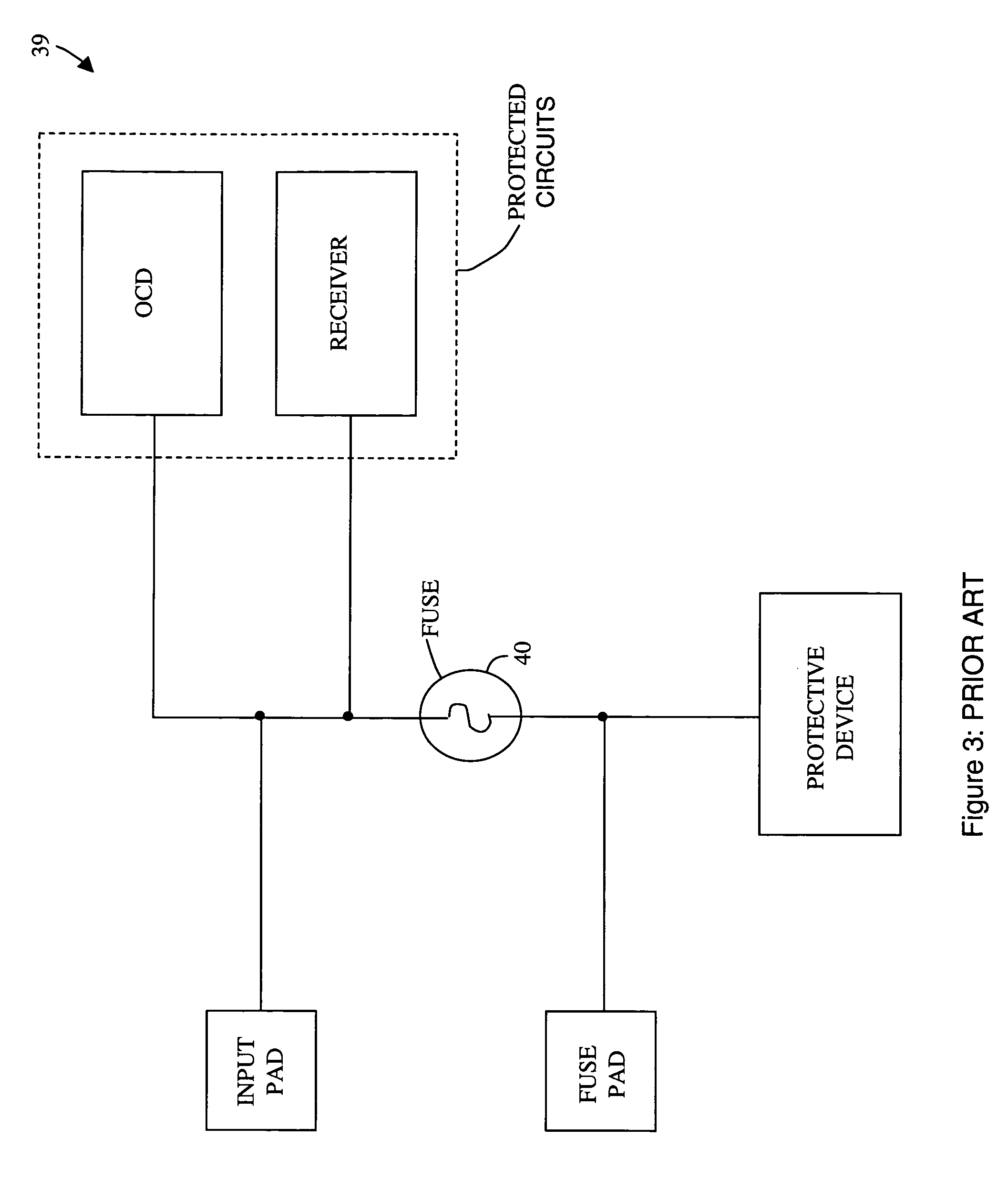

Nanotube ESD protective devices and corresponding nonvolatile and volatile nanotube switches

InactiveUS20060193093A1Nanoelectromechanical switchesSemiconductor/solid-state device detailsSignal onSemiconductor chip

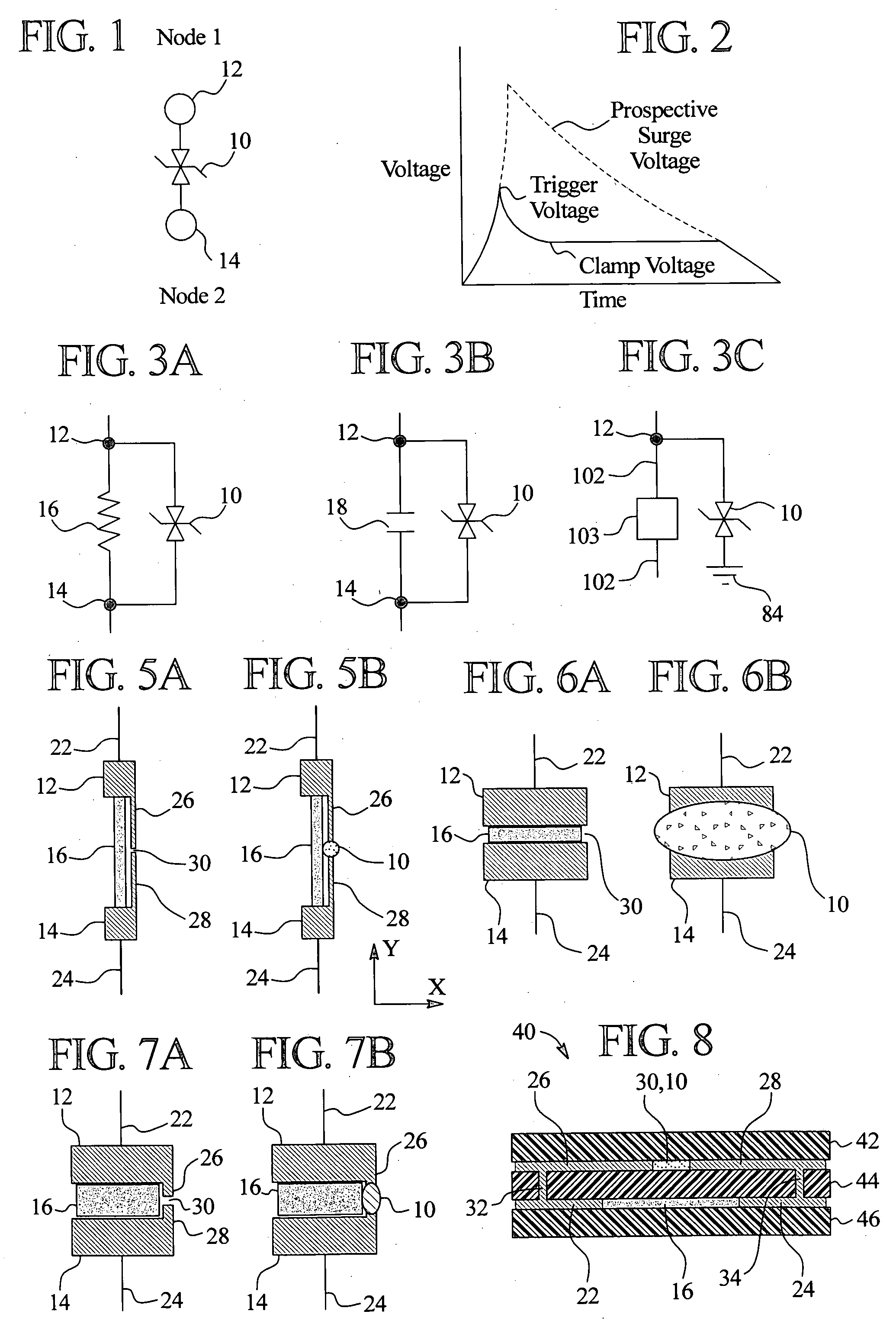

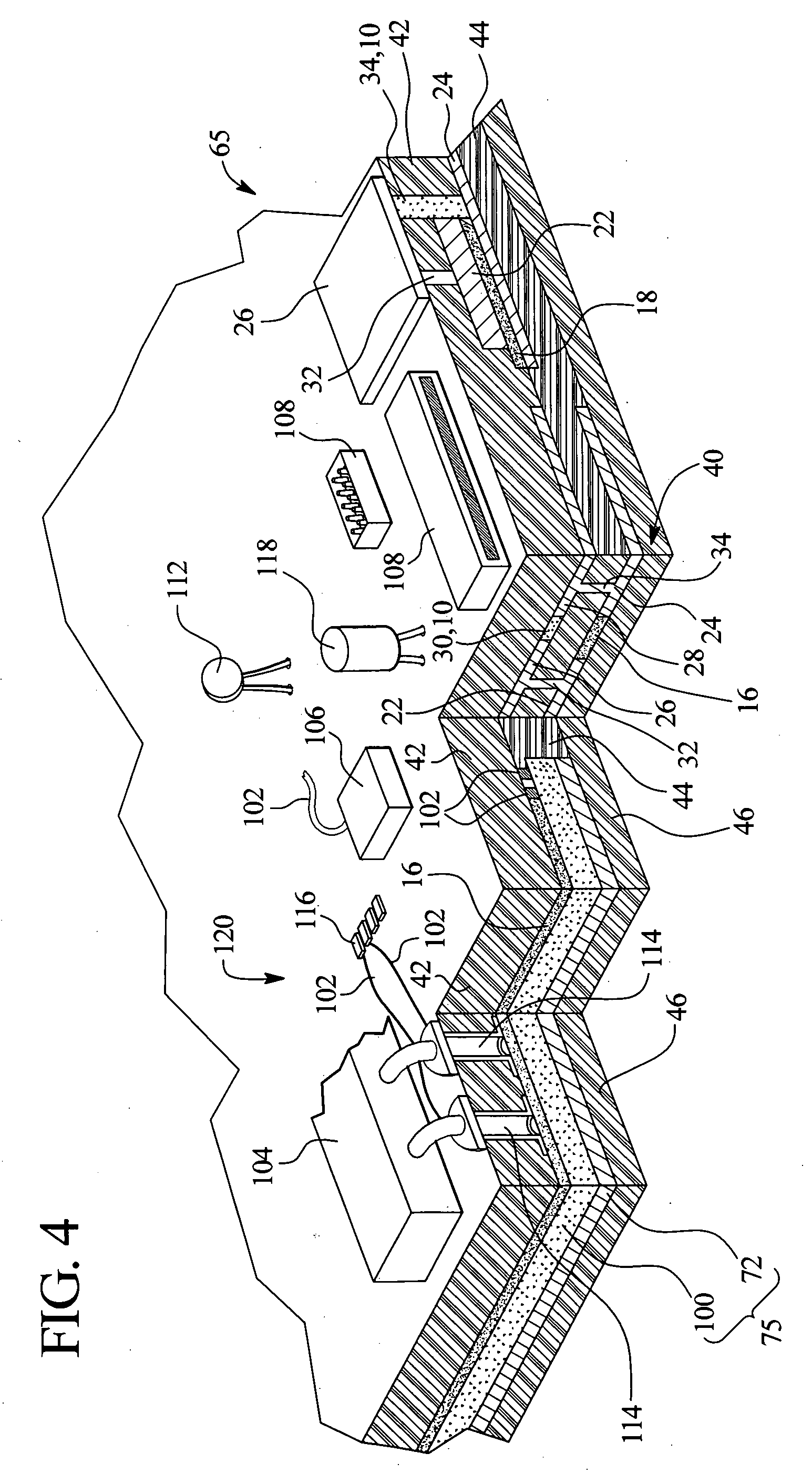

Nanotube ESD protective devices and corresponding nonvolatile and volatile nanotube switches. An electrostatic discharge (ESD) protection circuit for protecting a protected circuit is coupled to an input pad. The ESD circuit includes a nanotube switch electrically having a control. The switch is coupled to the protected circuit and to a discharge path. The nanotube switch is controllable, in response to electrical stimulation of the control, between a de-activated state and an activated state. The activated state creates a current path so that a signal on the input pad flows to the discharge path to cause the signal at the input pad to remain within a predefined operable range for the protected circuit. The nanotube switch, the input pad, and the protected circuit may be on a semiconductor chip. The nanotube switch may be on a chip carrier. The deactivated and activated states may be volatile or non-volatile depending on the embodiment. The ESD circuit may be repeatedly programmed between the activated and deactivated states so as to repeatedly activate and deactivate ESD protection of the protected circuit. The nanotube switch provides protection based on the magnitude of the signal on the input pad.

Owner:NANTERO

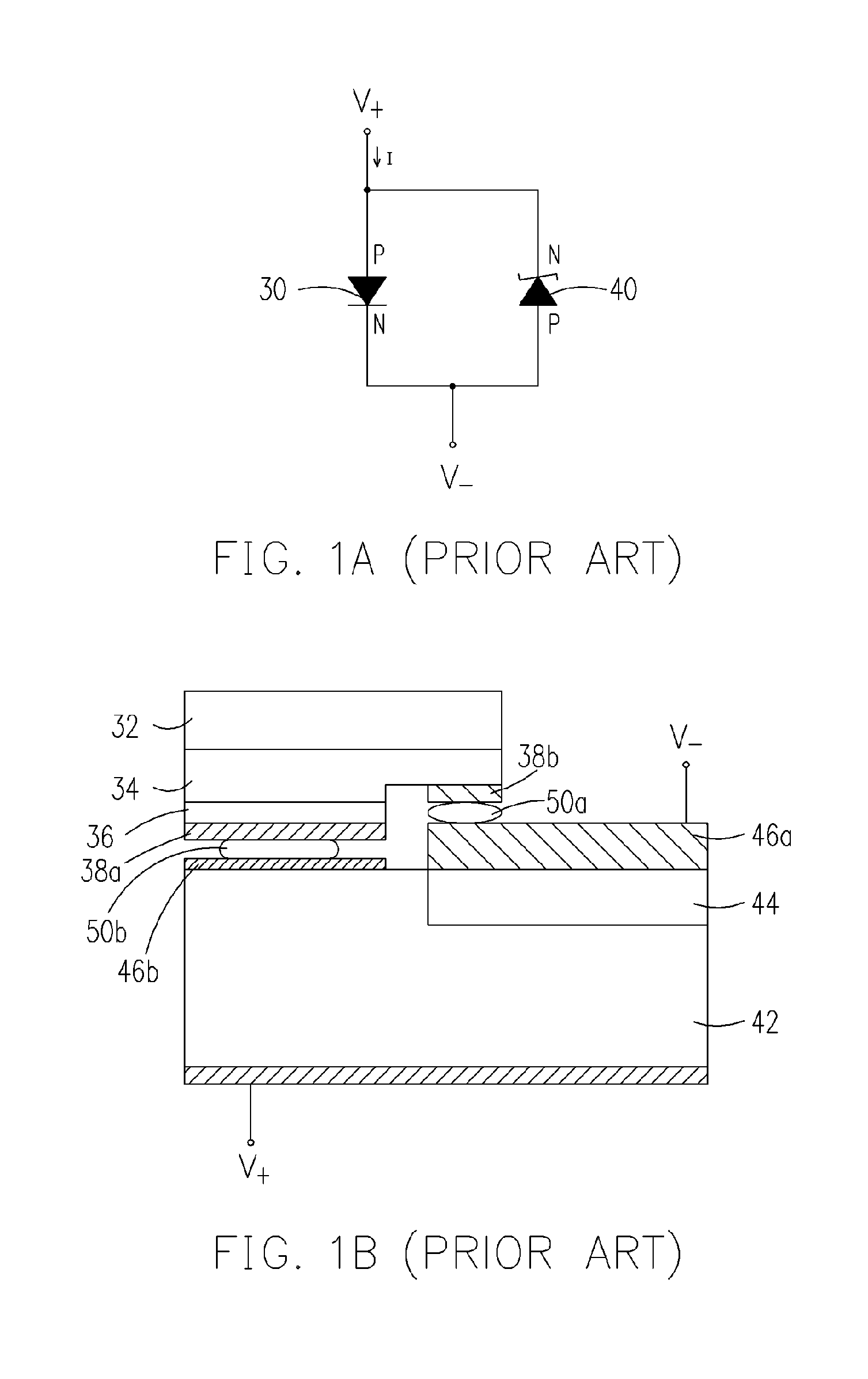

Light-emitting diode structure with electrostatic discharge protection

InactiveUS20050167680A1Protection from damageLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringLead structure

A light-emitting diode (LED) structure with electrostatic discharge (ESD) protection is described. The LED includes a substrate, a patterned semiconductor layer, a first electrode and a second electrode. The patterned semiconductor layer is disposed over the substrate, and is divided into at least a first island structure and a second island structure. The first electrode and the second electrode are connected between the first island structure and the second island structure. A shunt diode is formed by the first electrode, the second electrode and the second island structure. The shunt diode is connected in parallel to the LED with an inverse voltage compared to the LED. In the LED structure of the invention, the first island structure and the second island structure are manufactured simultaneously by the epitaxy procedure. Therefore, the LED could be protected from damage due to electrostatic discharge (ESD).

Owner:EPISTAR CORP

On-chip structure for electrostatic discharge (ESD) protection

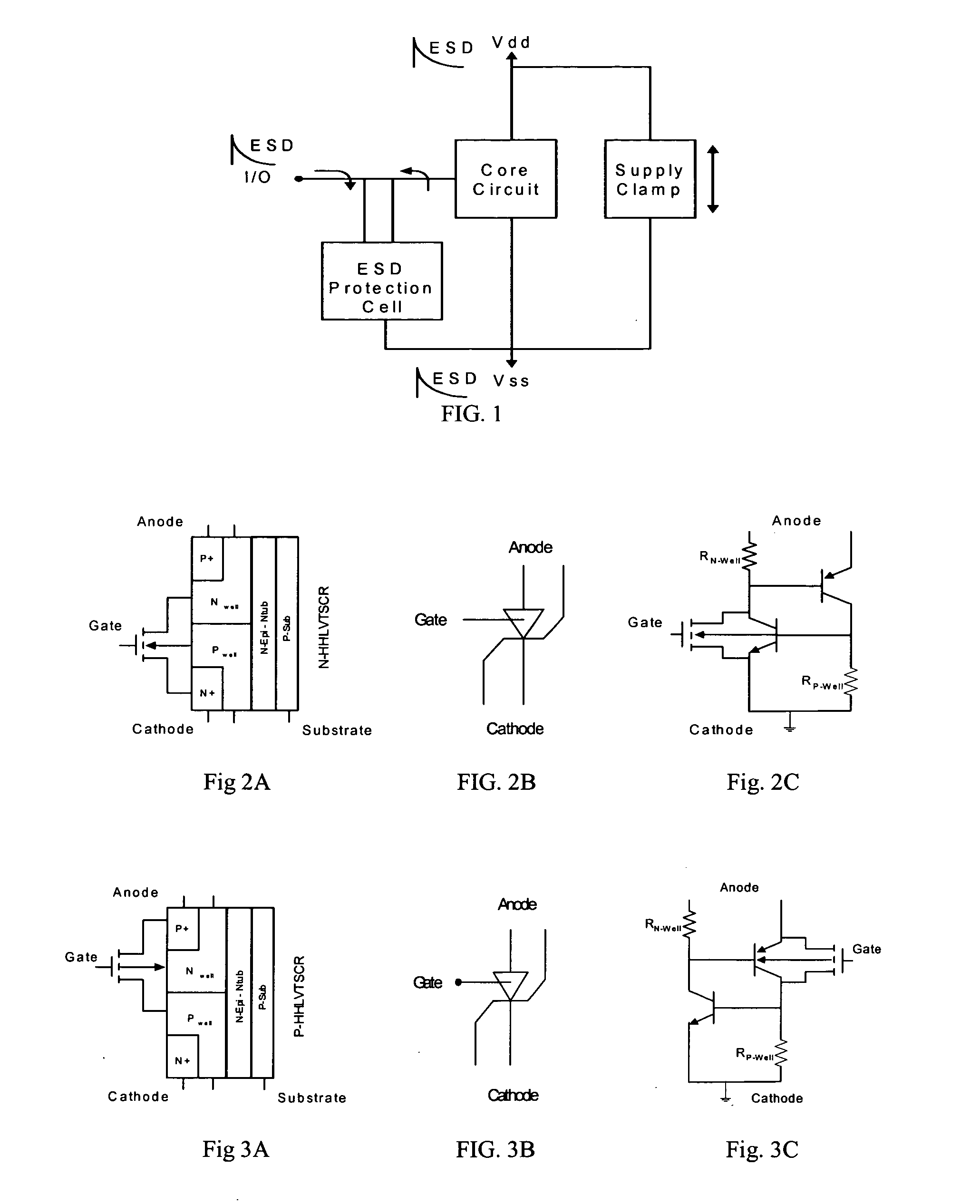

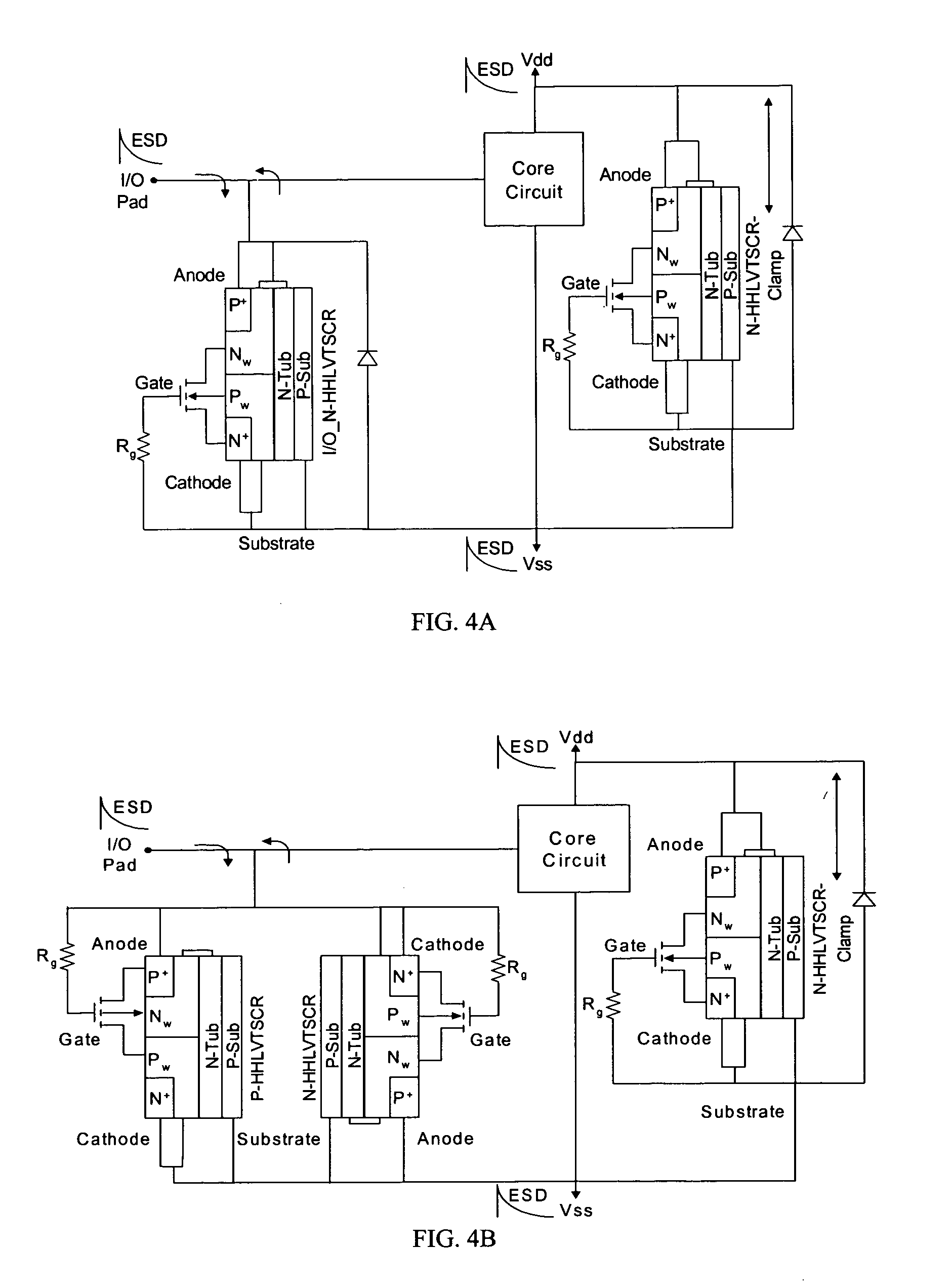

InactiveUS20050151160A1Efficient and reliableRobust and ESD protectionTransistorSemiconductor/solid-state device detailsCMOSLow voltage

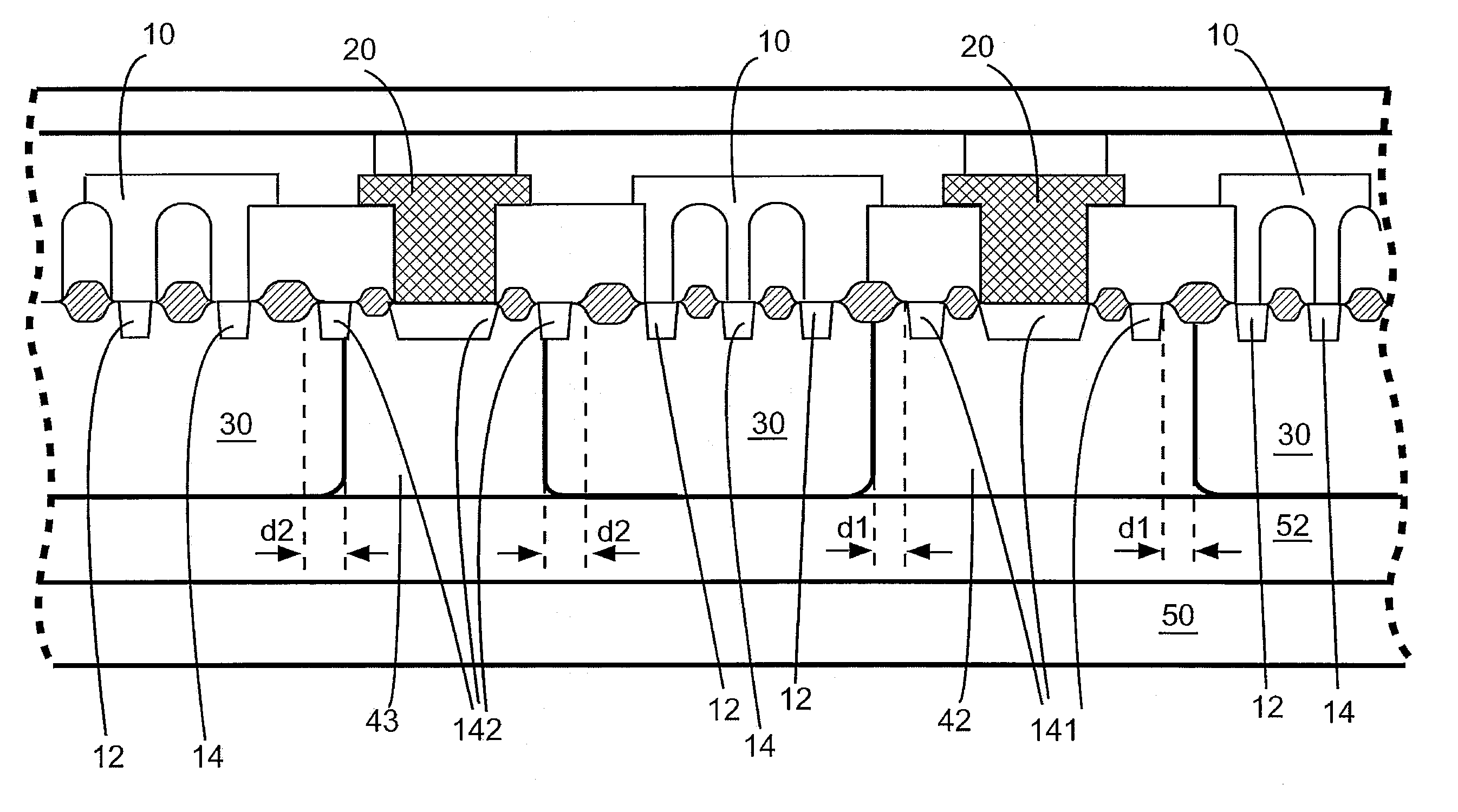

A complementary SCR-based structure enables a tunable holding voltage for robust and versatile ESD protection. The structure are n-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (N-HHLVTSCR) device and p-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (P-HHLVTSCR) device. The regions of the N-HHLVTSCR and P-HHLVTSCR devices are formed during normal processing steps in a CMOS or BICMOS process. The spacing and dimensions of the doped regions of N-HHLVTSCR and P-HHLVTSCR devices are used to produce the desired characteristics. The tunable HHLVTSCRs makes possible the use of this protection circuit in a broad range of ESD applications including protecting integrated circuits where the I / O signal swing can be either within the range of the bias of the internal circuit or below / above the range of the bias of the internal circuit.

Owner:INTERSIL INC

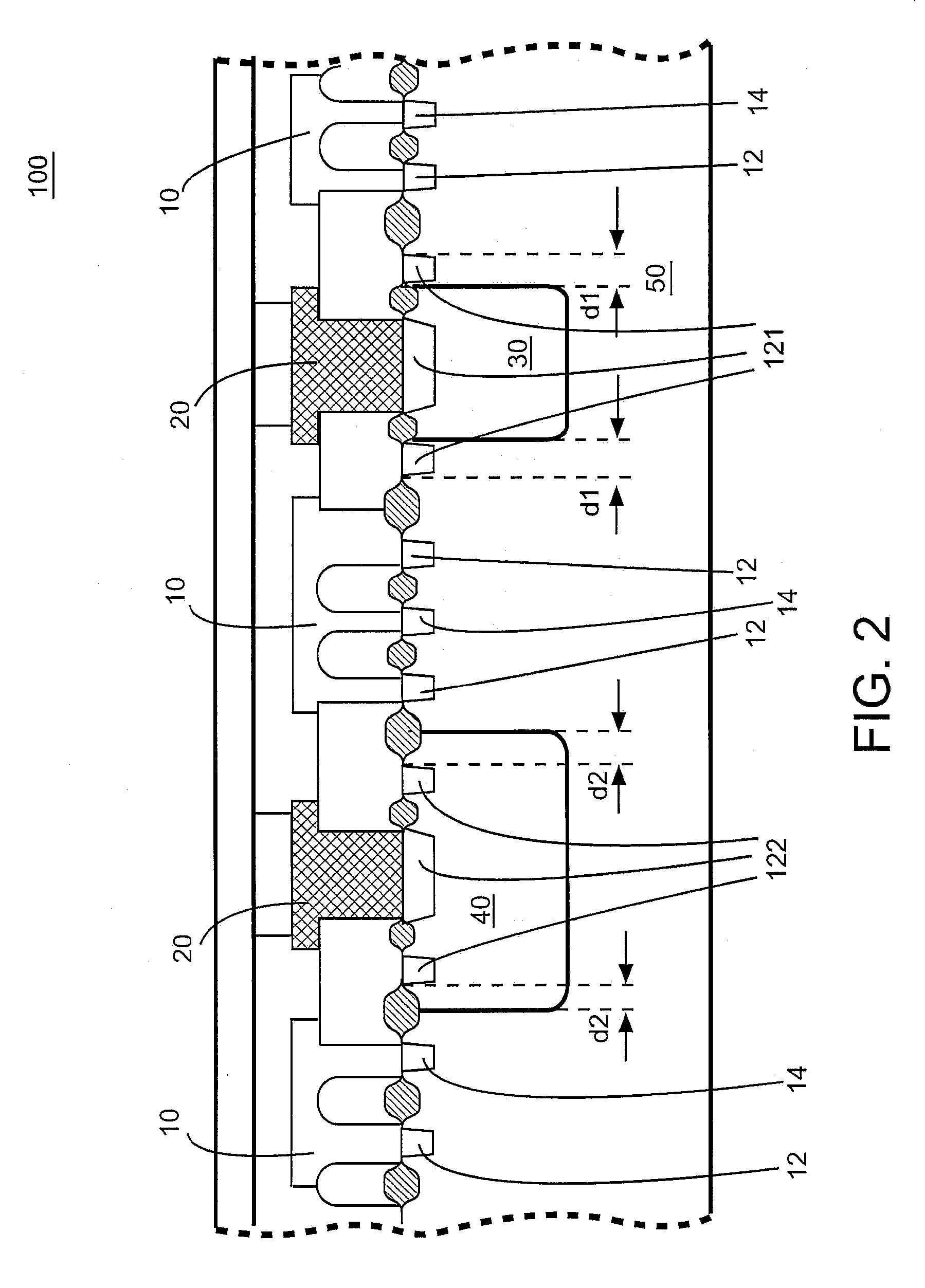

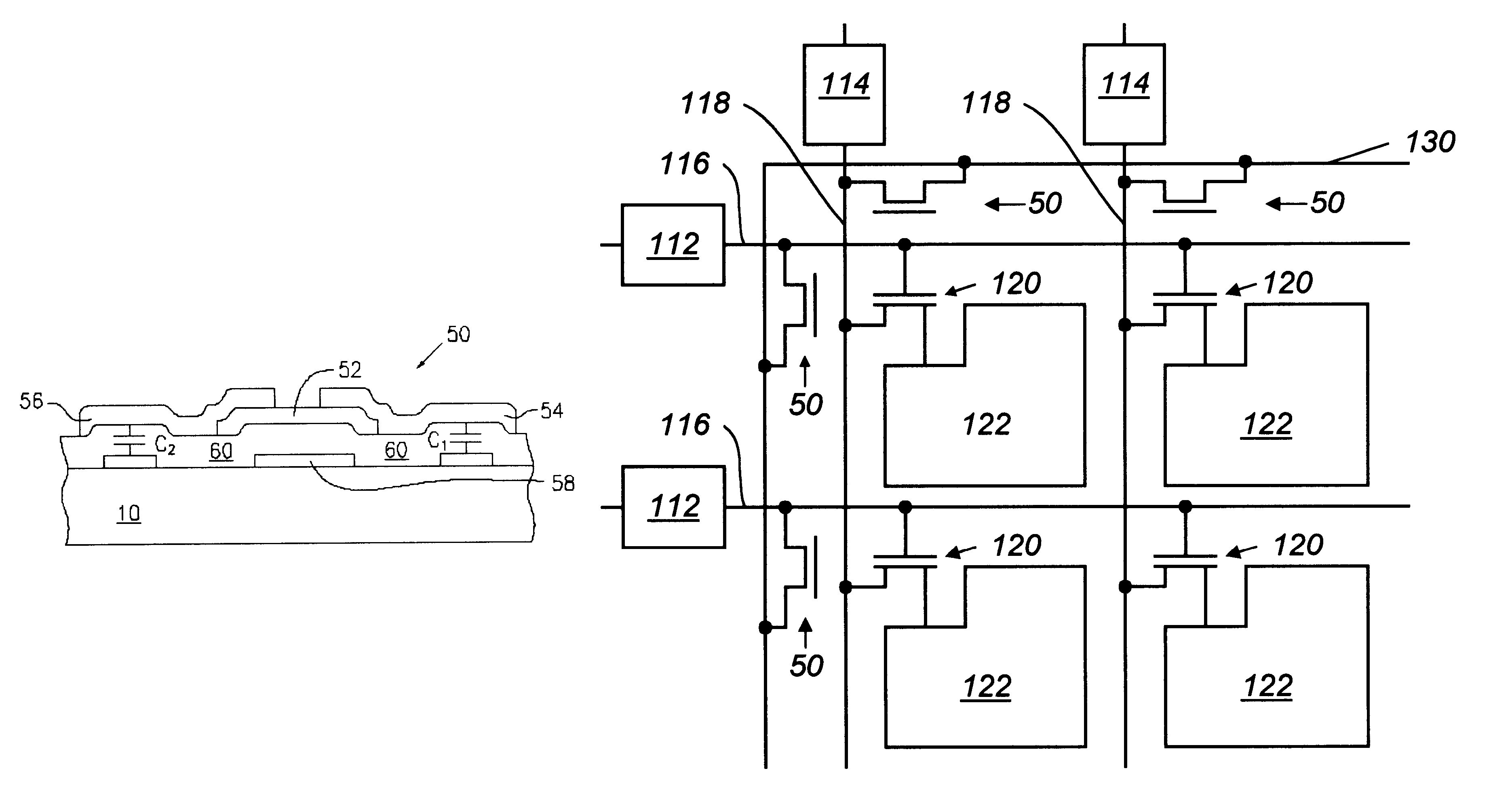

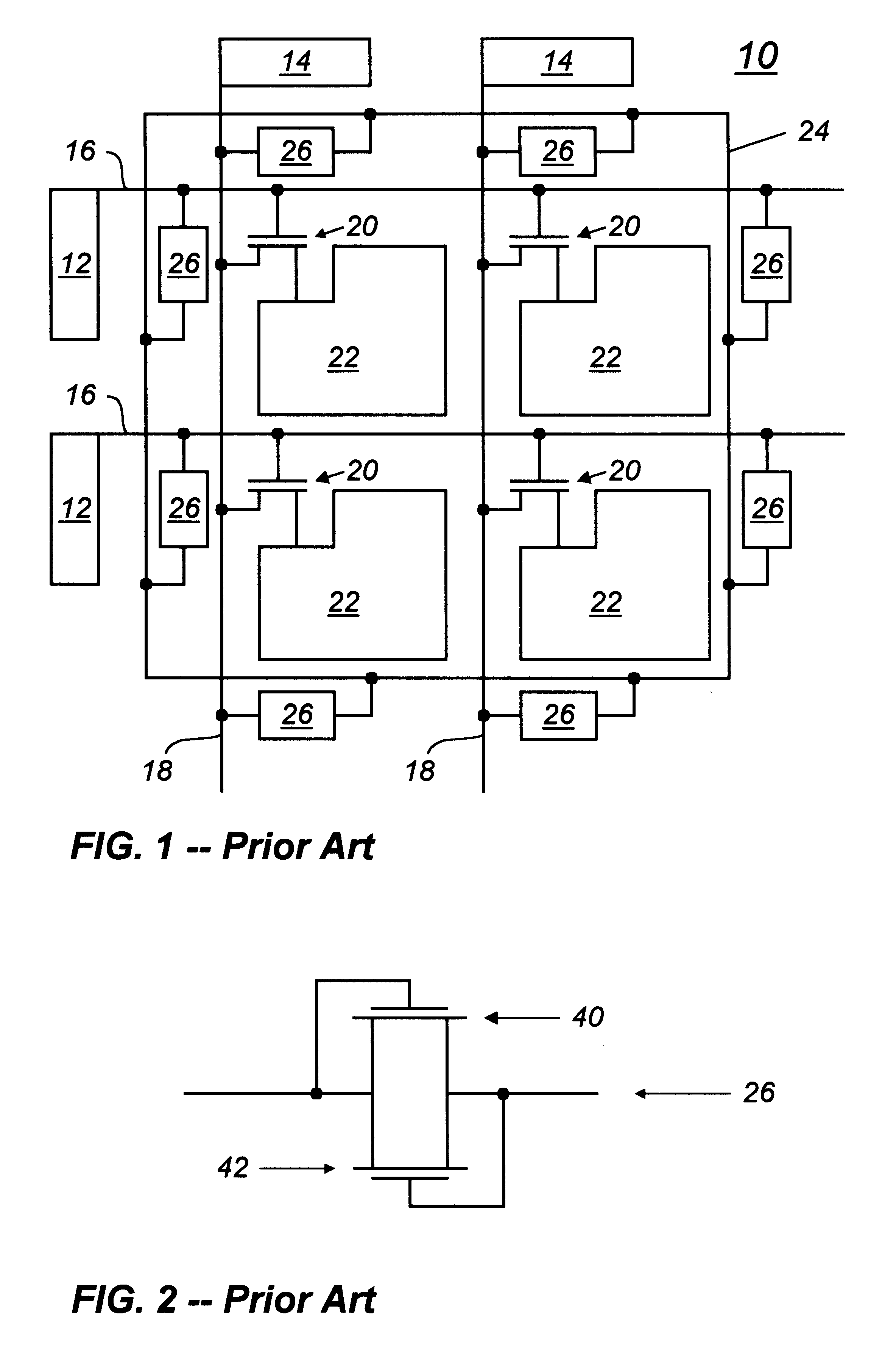

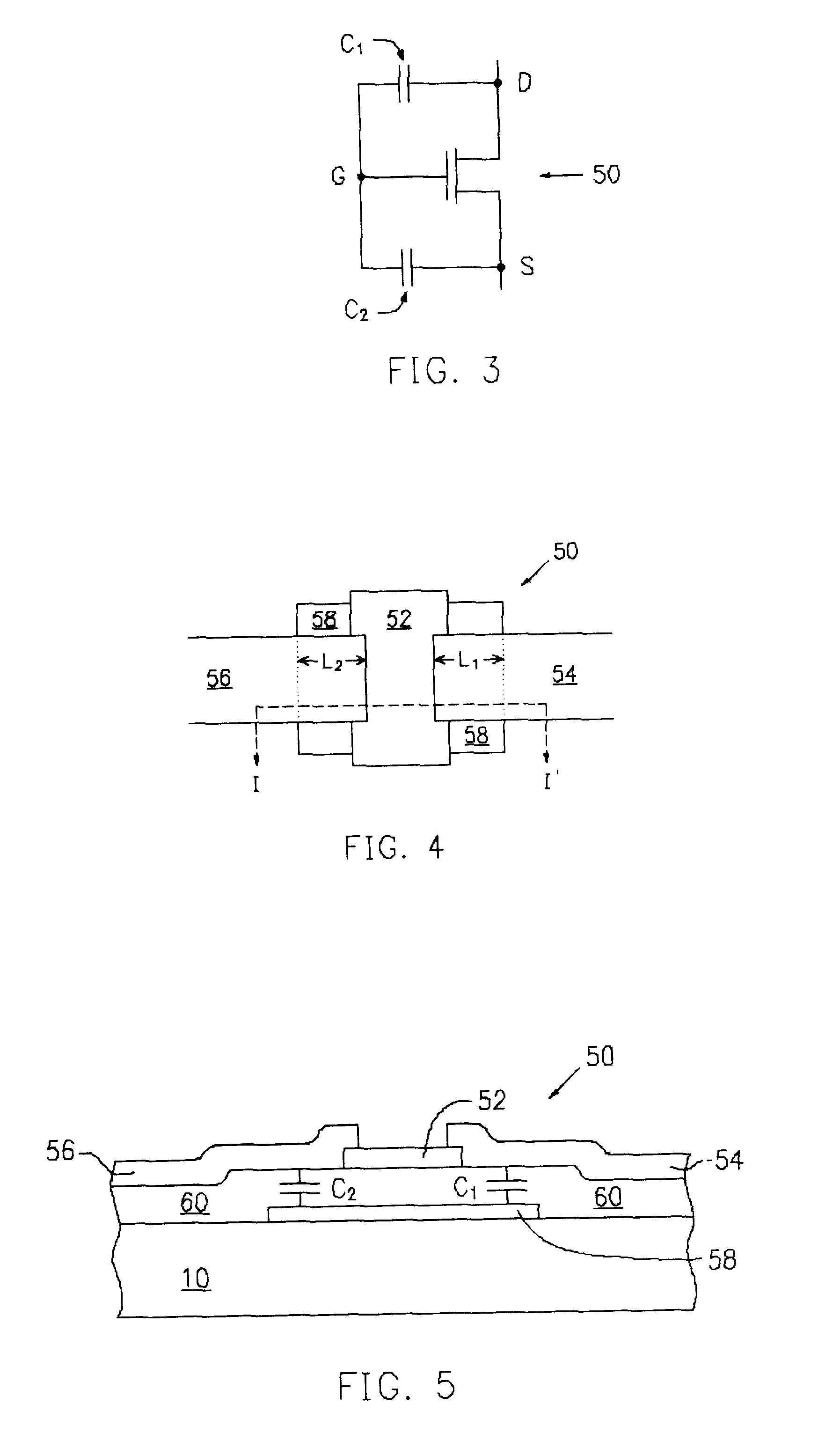

Capacitively coupled field effect transistors for electrostatic discharge protection in flat panel displays

A flat panel display includes a plurality of parallel row select lines and a plurality of column drive lines, with the row select lines and the column drive lines intersecting to define a matrix of pixel locations. Signals are provided to contact pads located on the periphery of the display and the signals flow over the row select lines and the column drive lines to thin film transistors located adjacent a pixel electrode at each of the pixel locations. The signals provided to each thin film transistor cause the transistor to charge a corresponding pixel electrode to control a pixel of the display. ESD protection for the display comprises a guard ring adjacent the contact pads. Capacitively coupled field effect transistors (CCFETs) connect the row select lines to the guard ring and connect the column drive lines to the guard ring. A CCFET is formed as a thin film transistor and typically has a floating gate capacitively coupled to the drain and source of the thin film transistor.

Owner:AU OPTRONICS CORP

Nitride semiconductor light emitting device having electrostatic discharge(ESD) protection capacity

ActiveUS20060060880A1Increase the number ofIncrease in sizeSolid-state devicesSemiconductor devicesOhmic contactIsolation layer

A nitride semiconductor light emitting device including a light emitting diode and a diode formed on a single substrate, in which the light emitting diode and the diode use a common electrode. According to the present invention, an active layer and a p-type nitride semiconductor layer are each divided into a first region and a second region by an insulative isolation layer, and an ohmic contact layer is formed on the p-type nitride semiconductor layer contained in the first region. A p-type electrode is formed on the ohmic contact layer and is extended to the p-type nitride semiconductor layer contained in the second region. An n-type electrode is formed on the p-type nitride semiconductor layer contained in the second region, passes through the p-type nitride semiconductor layer and the active layer contained in the second region, and is connected to the first n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

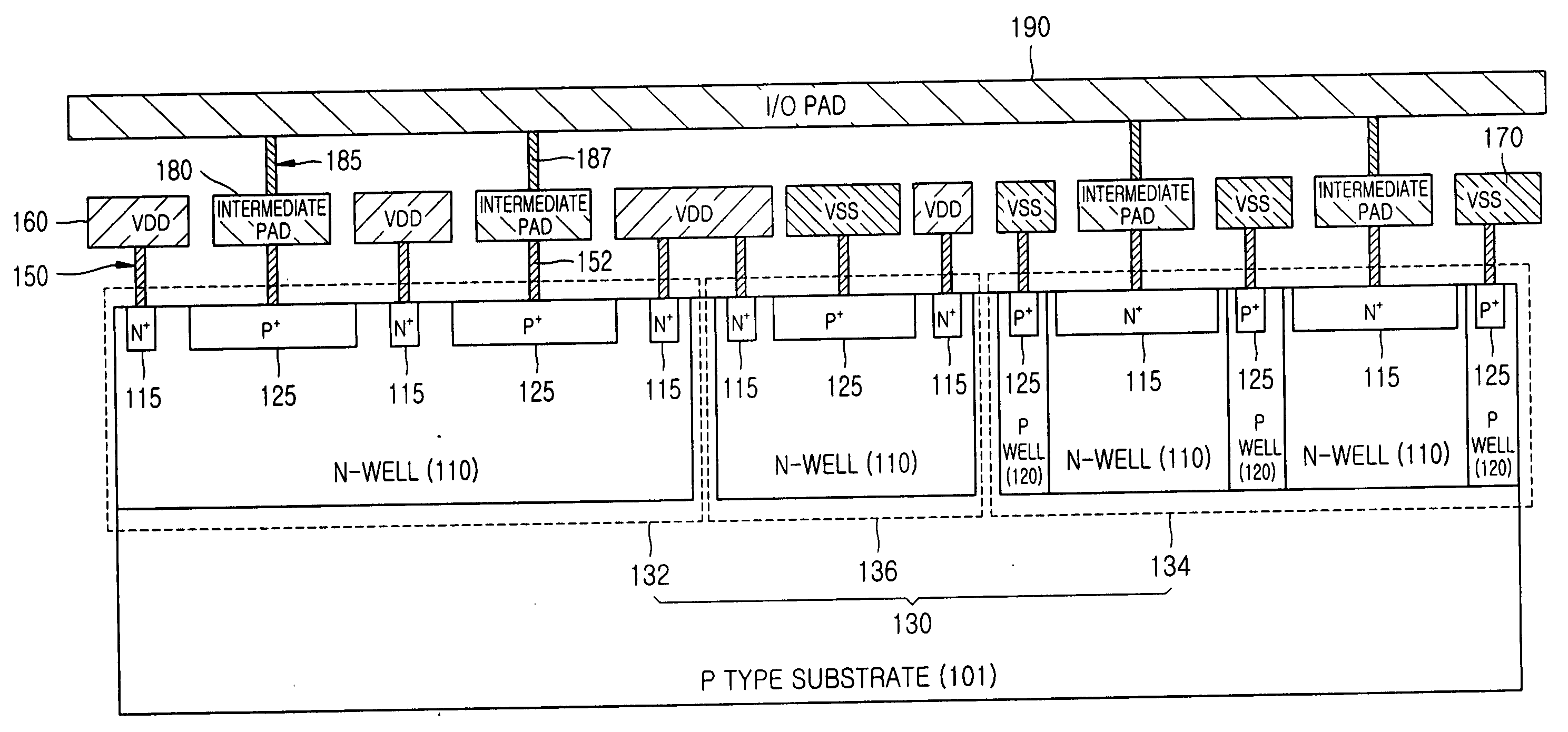

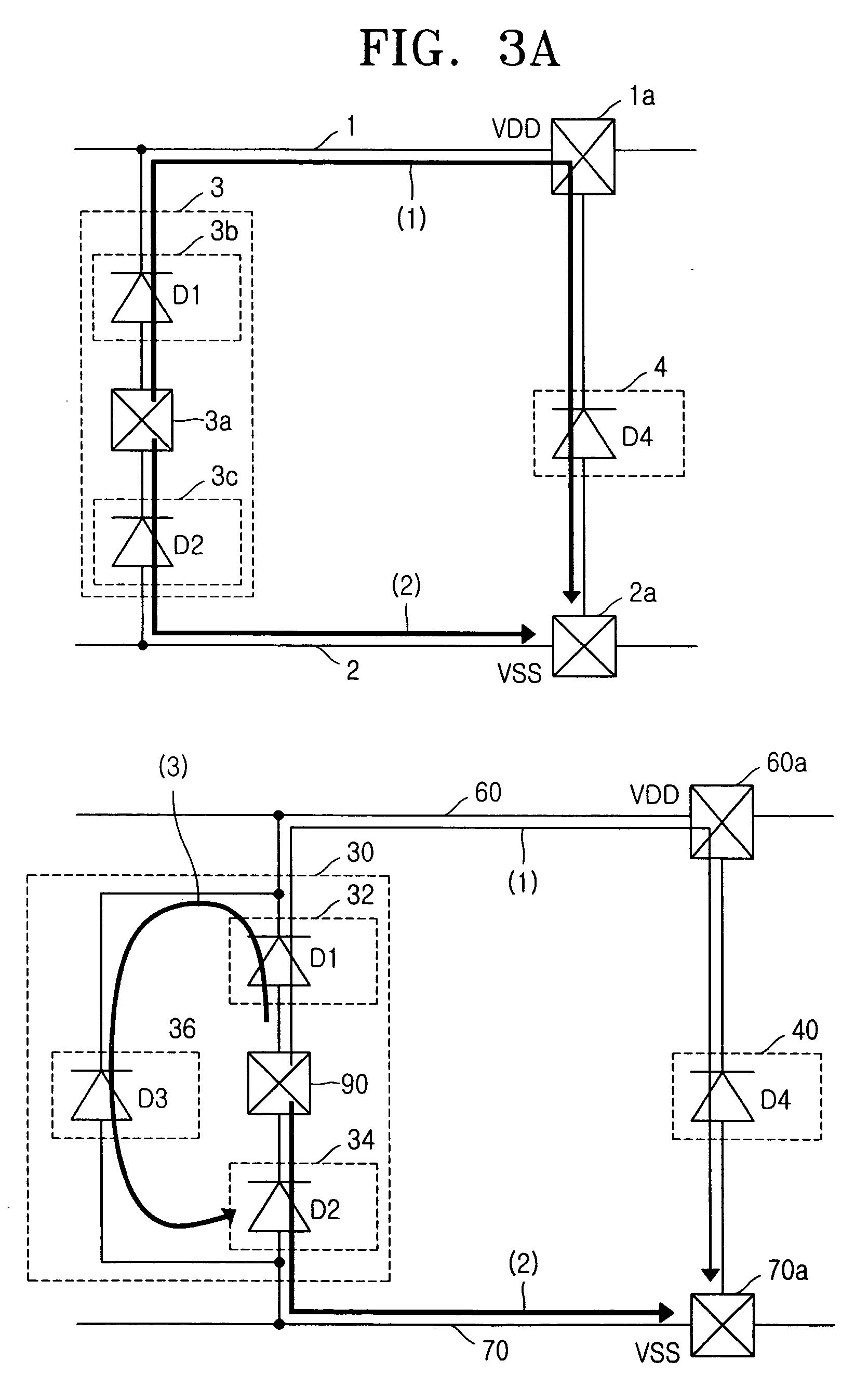

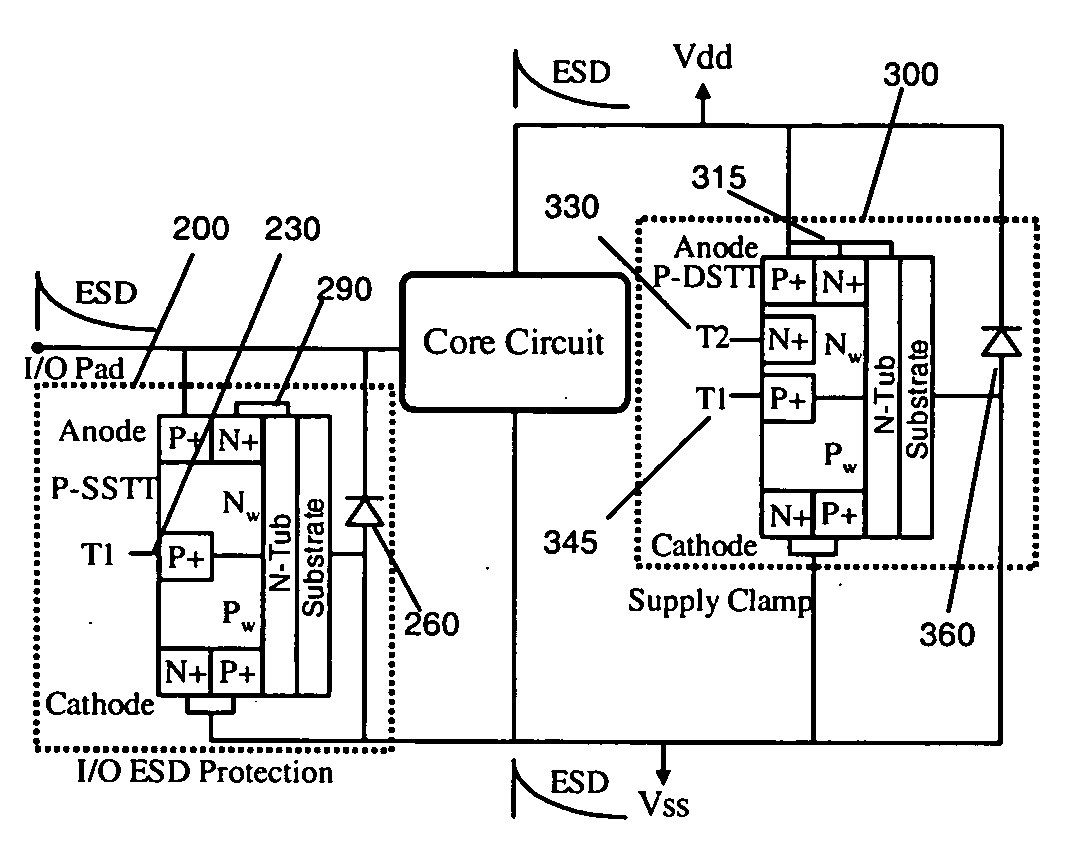

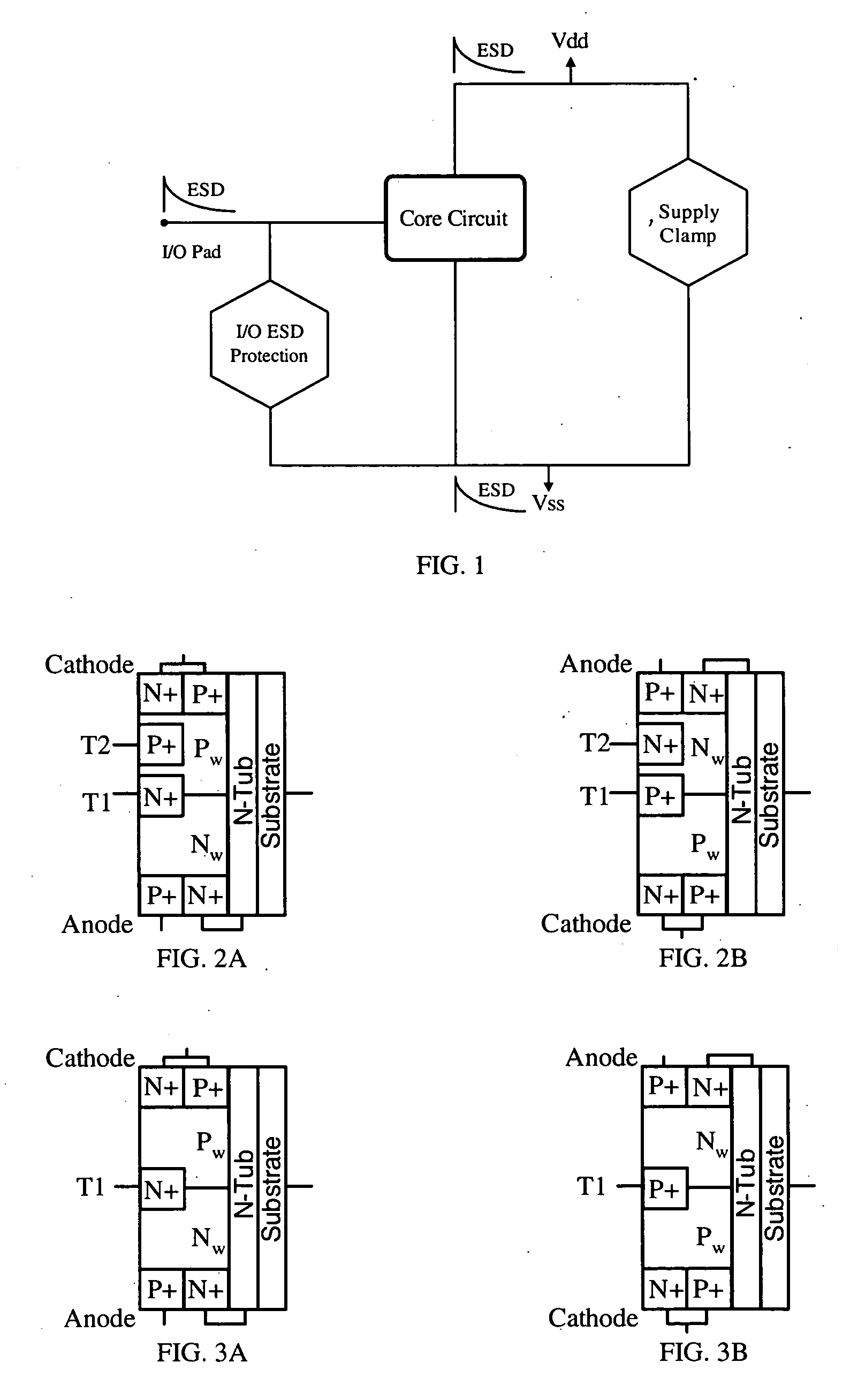

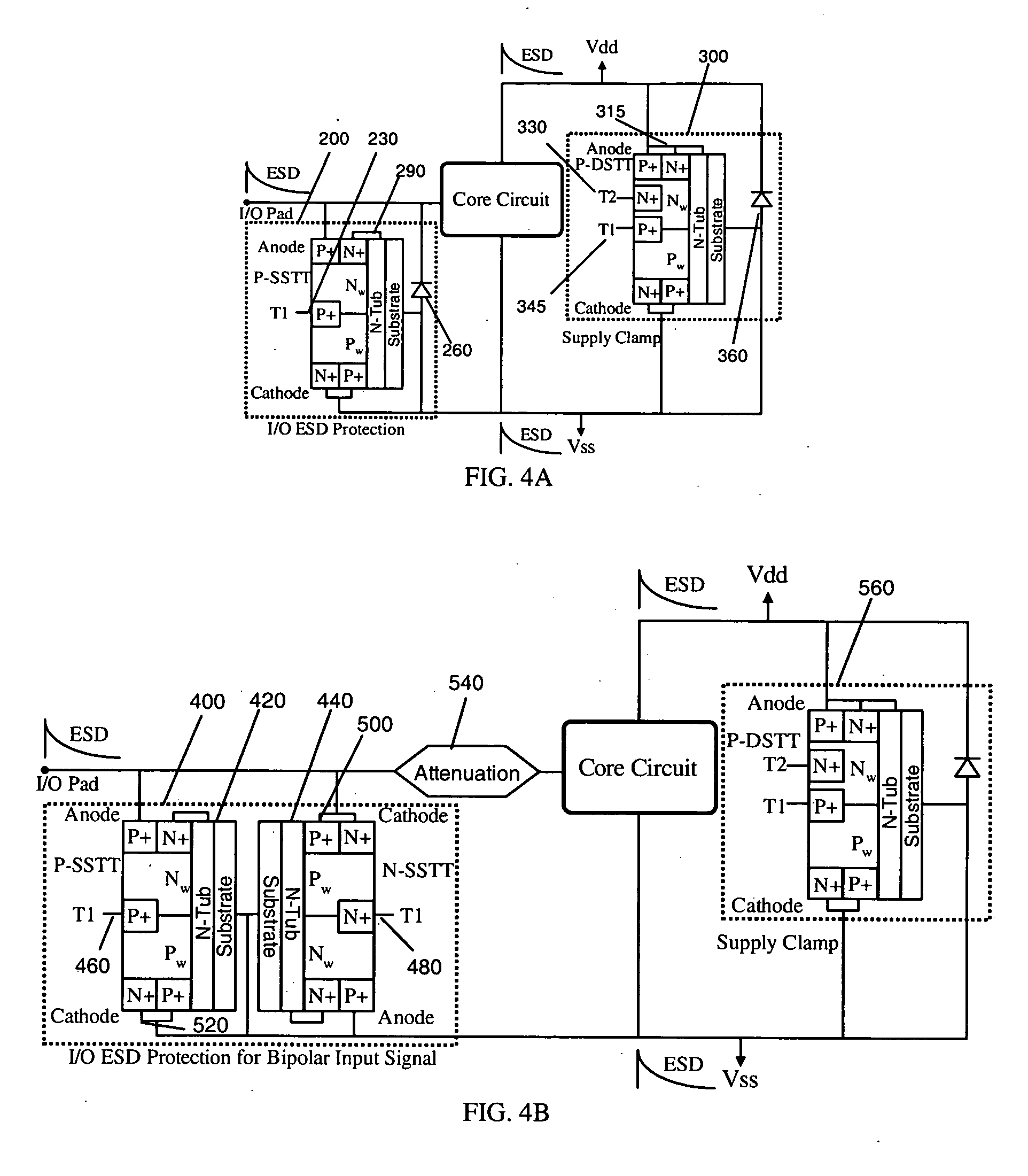

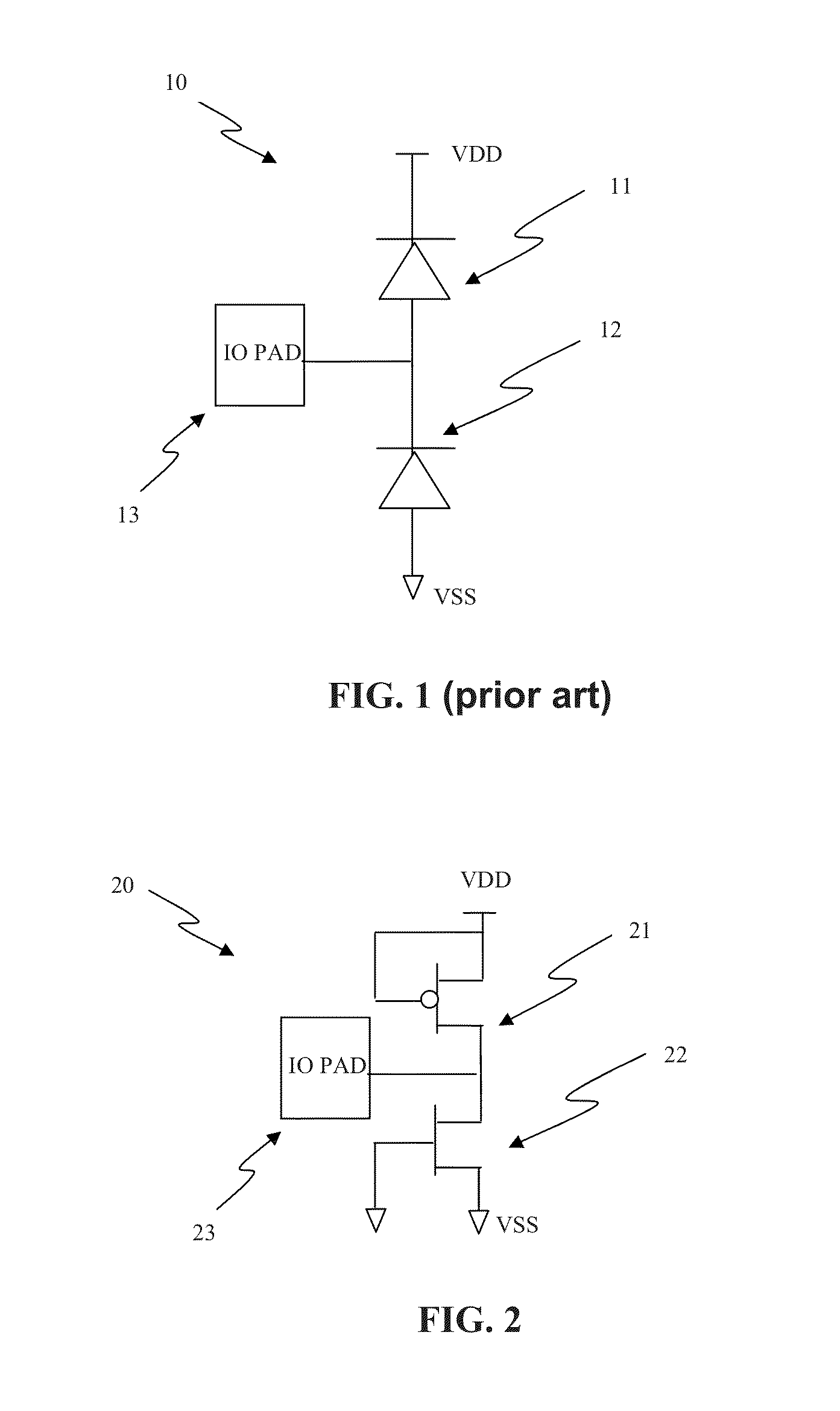

Integrated circuit device having input/output electrostatic discharge protection cell equipment with electrostatic discharge protection element and power clamp

There is provided an integrated circuit device having an input / output electrostatic discharge (I / O ESD) protection cell. The integrated circuit device includes an I / O ESD protection cell comprising a VDD ESD protection element connected between an I / O pad and a VDD line, a ground voltage (VSS) ESD protection element connected between the I / O pad and a VSS line, and a power clamp element connected between the VDD line and the VSS line, and wherein the VDD ESD protection element, the power clamp element, and the VSS ESD protection element in the I / O ESD protection cell are adjacent to each other so they can be connected in a straight line or are arranged to partially overlap.

Owner:SAMSUNG ELECTRONICS CO LTD

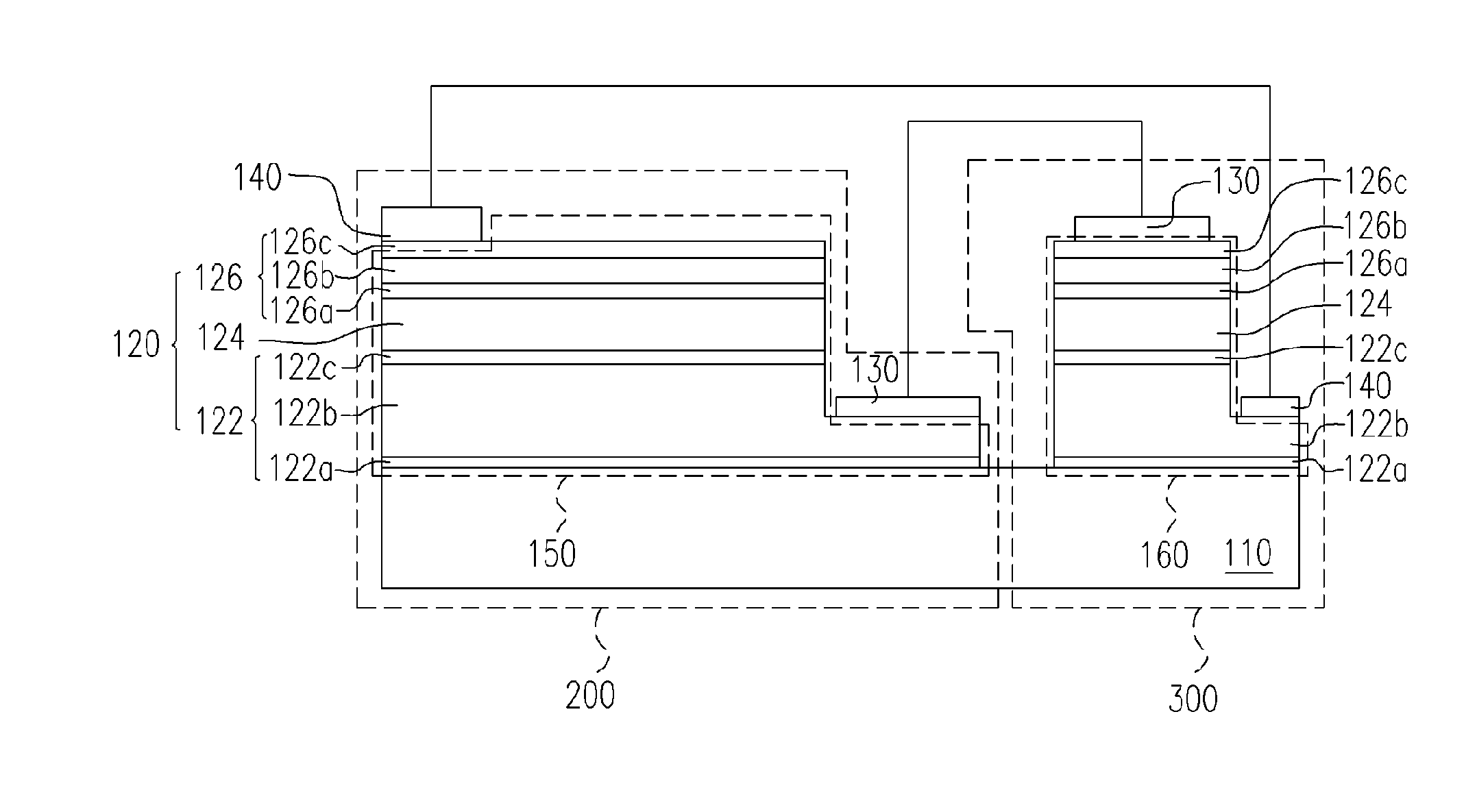

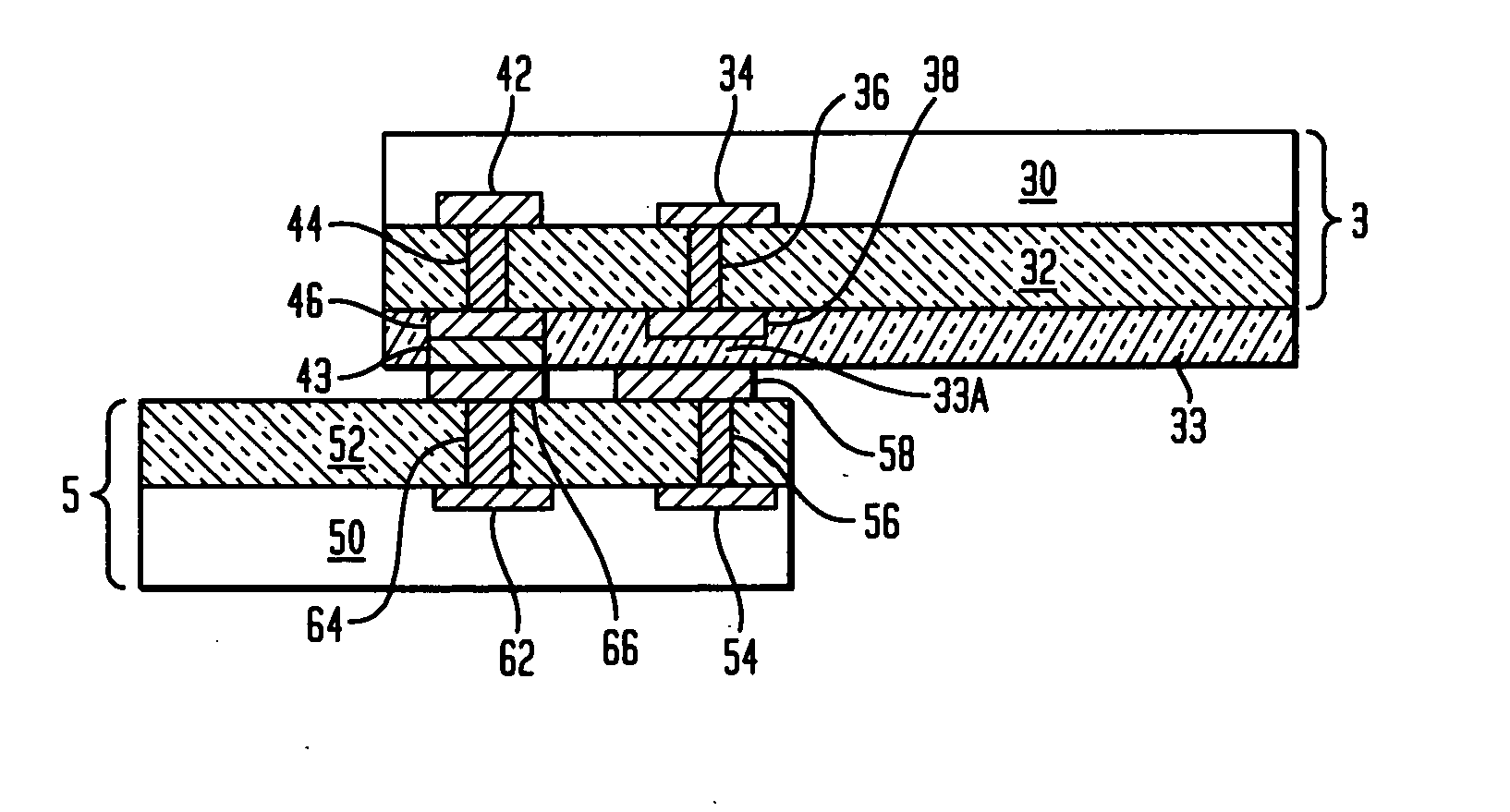

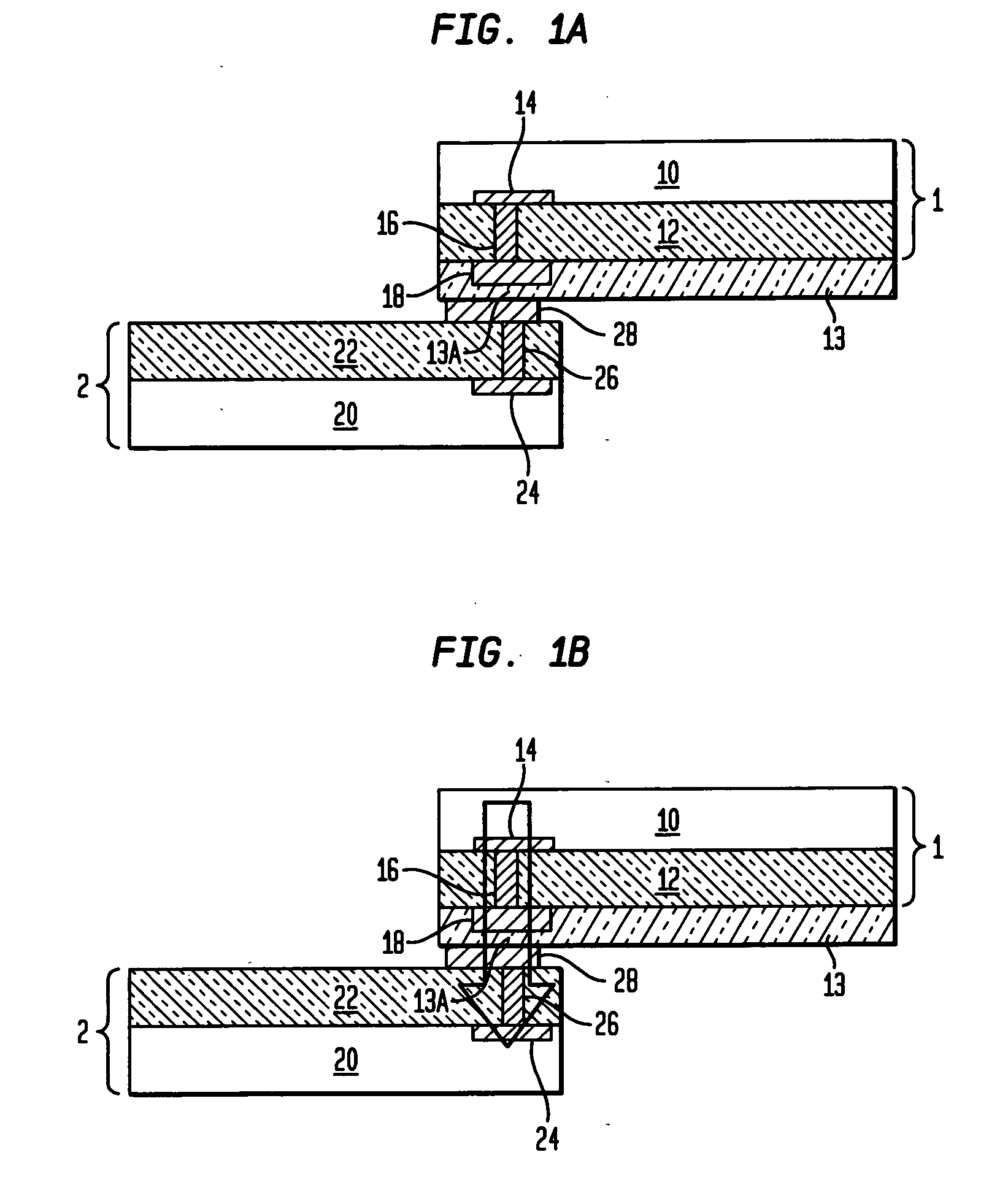

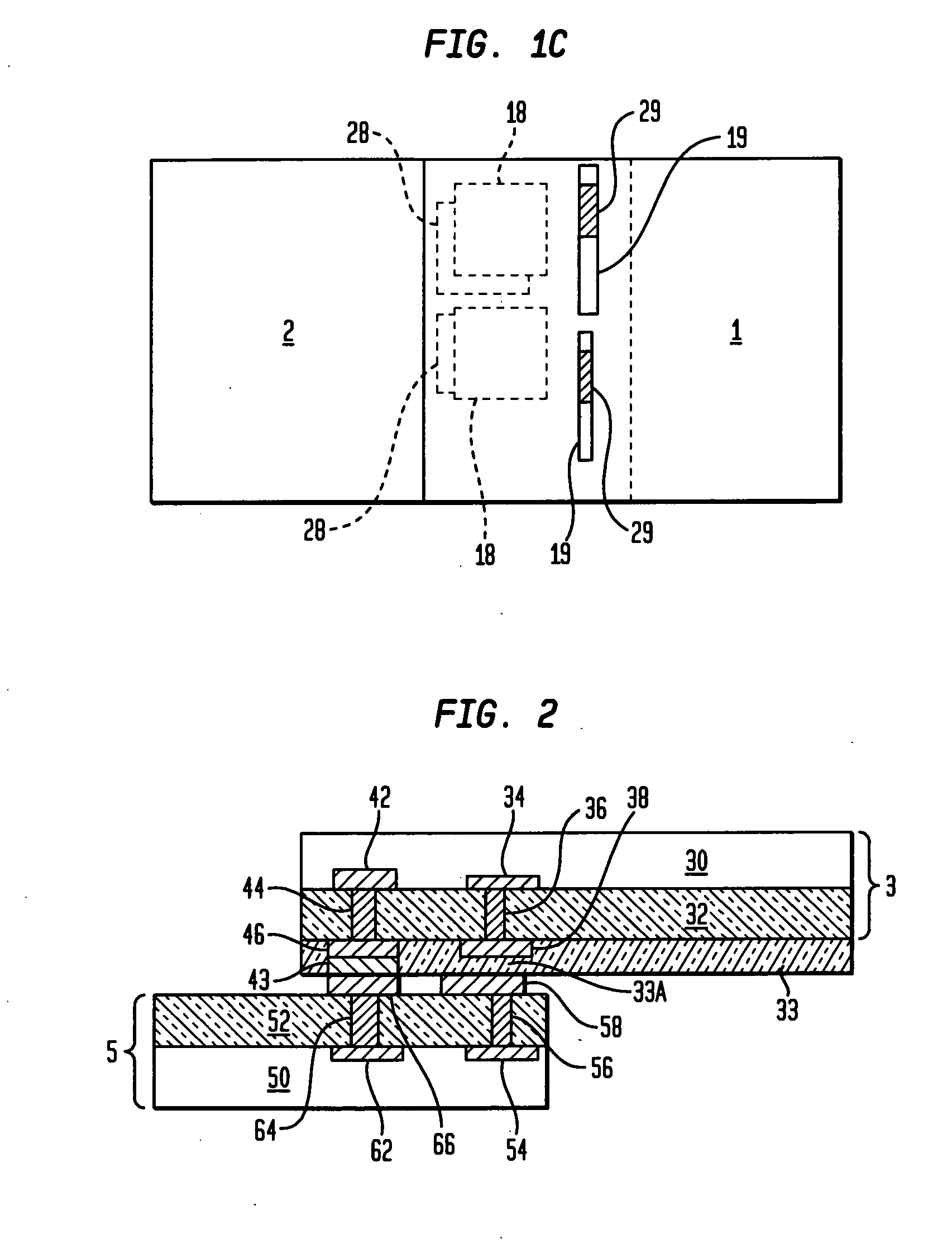

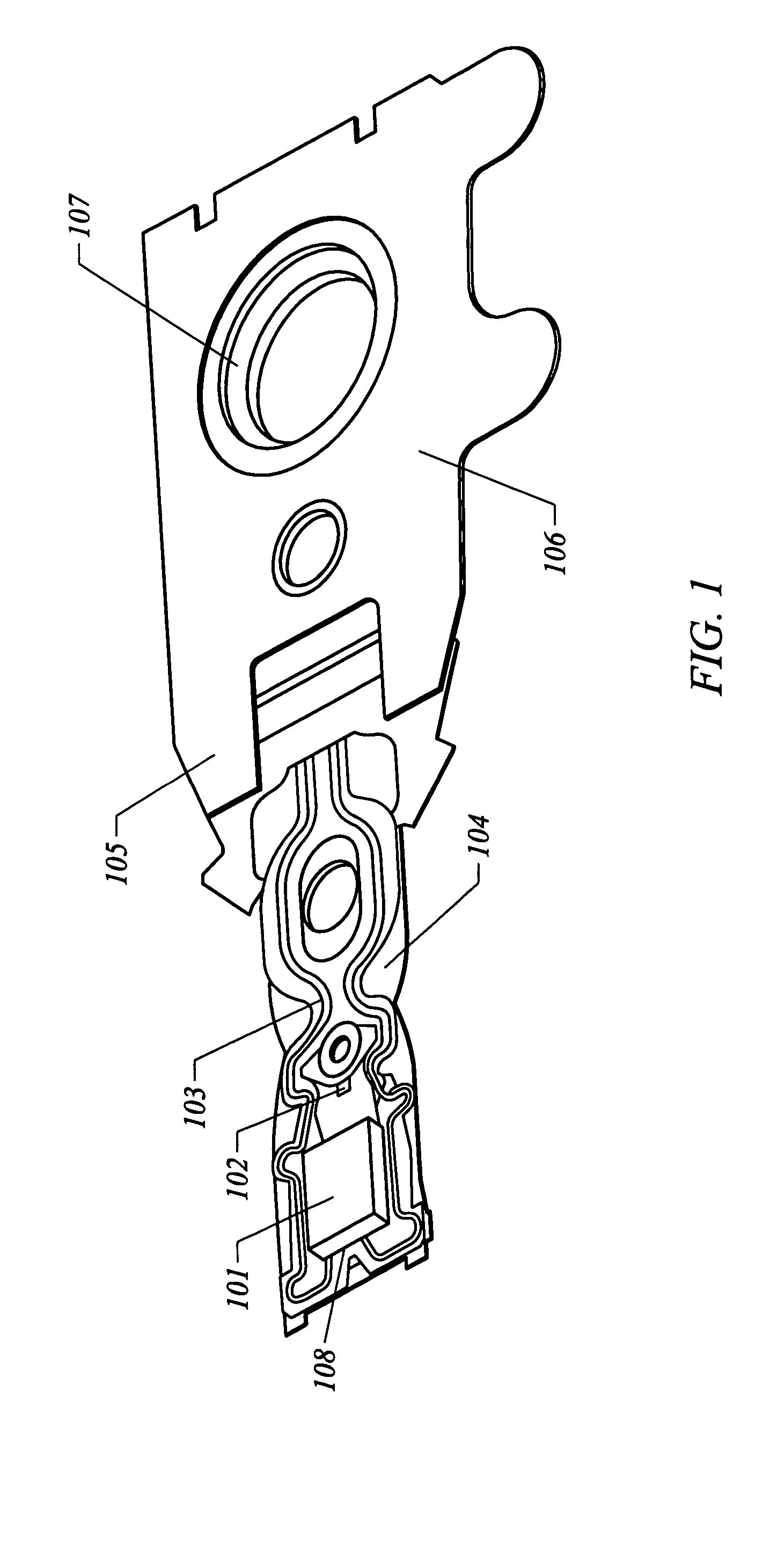

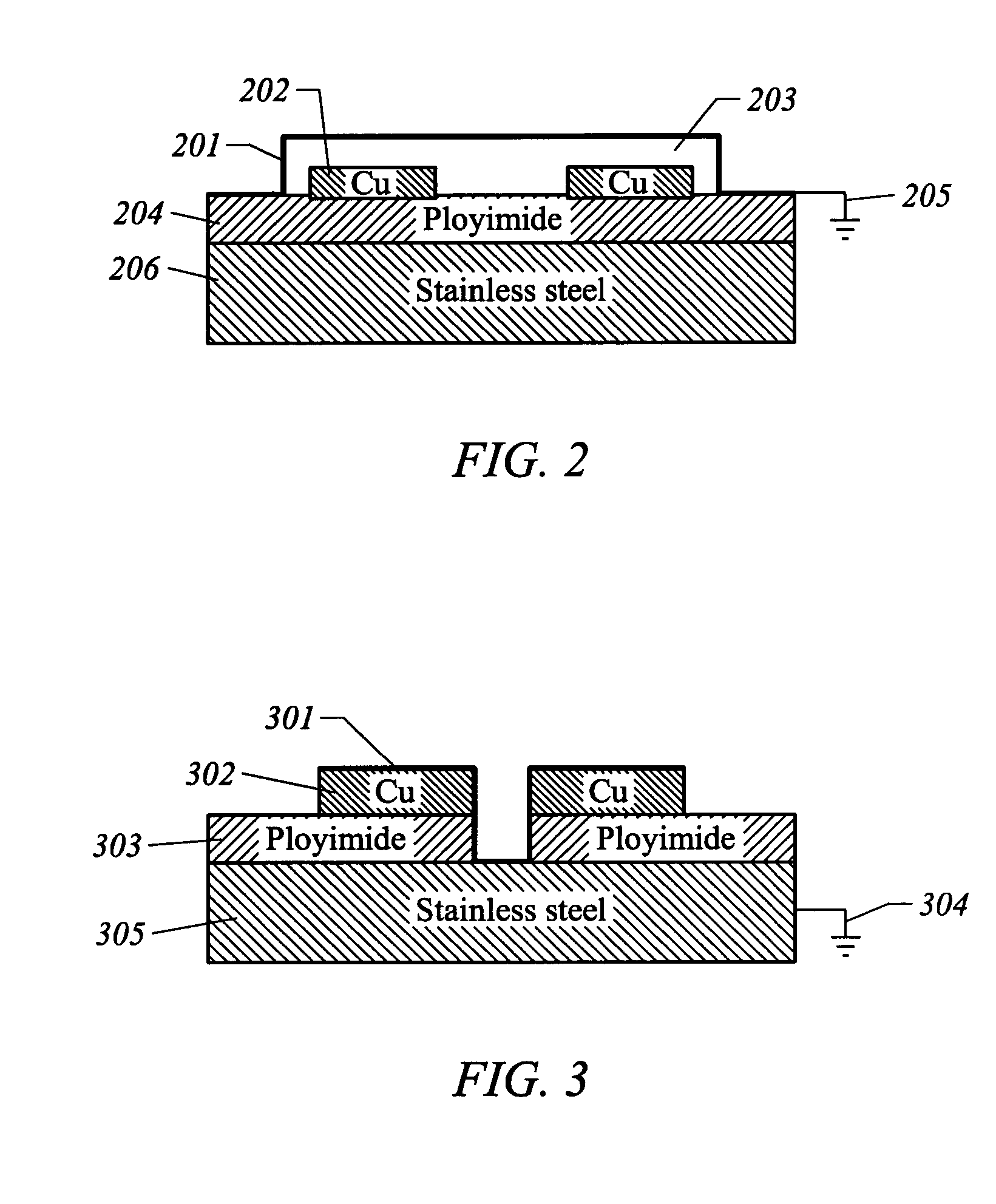

Inter-chip ESD protection structure for high speed and high frequency devices

ActiveUS20070029646A1Reduce load capacitanceImprove system performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringHigh velocity

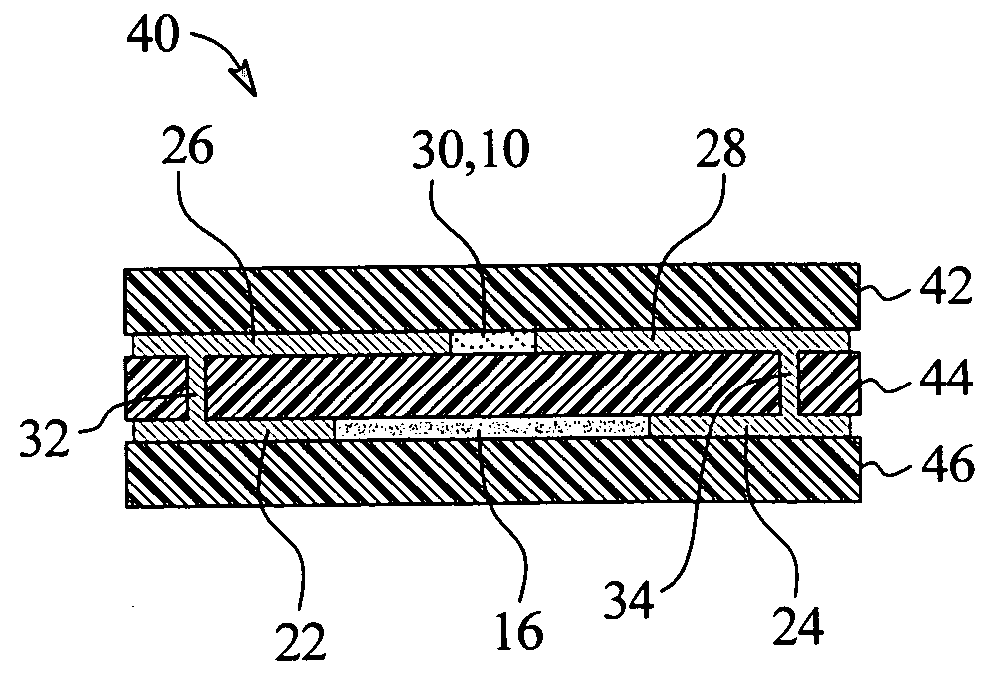

The present invention relates to inter-chip electrostatic discharge (ESD) protection structures for high speed, and high frequency devices that contain one or more direct, inter-chip signal transmission paths. Specifically, the present invention relates to a structure that contains: (1) a first chip including a first circuit, (2) a second chip including a second circuit, (3) an intermediate insulator layer located between the first and second chips, wherein the first and second circuits form a signal transmission path for transmitting signals through the intermediate insulator layer. An electrostatic discharge (ESD) protection path is provided in the structure between the first and the second chip through the intermediate insulator layer, to protect the signal transmission path from ESD damages.

Owner:GLOBALFOUNDRIES US INC

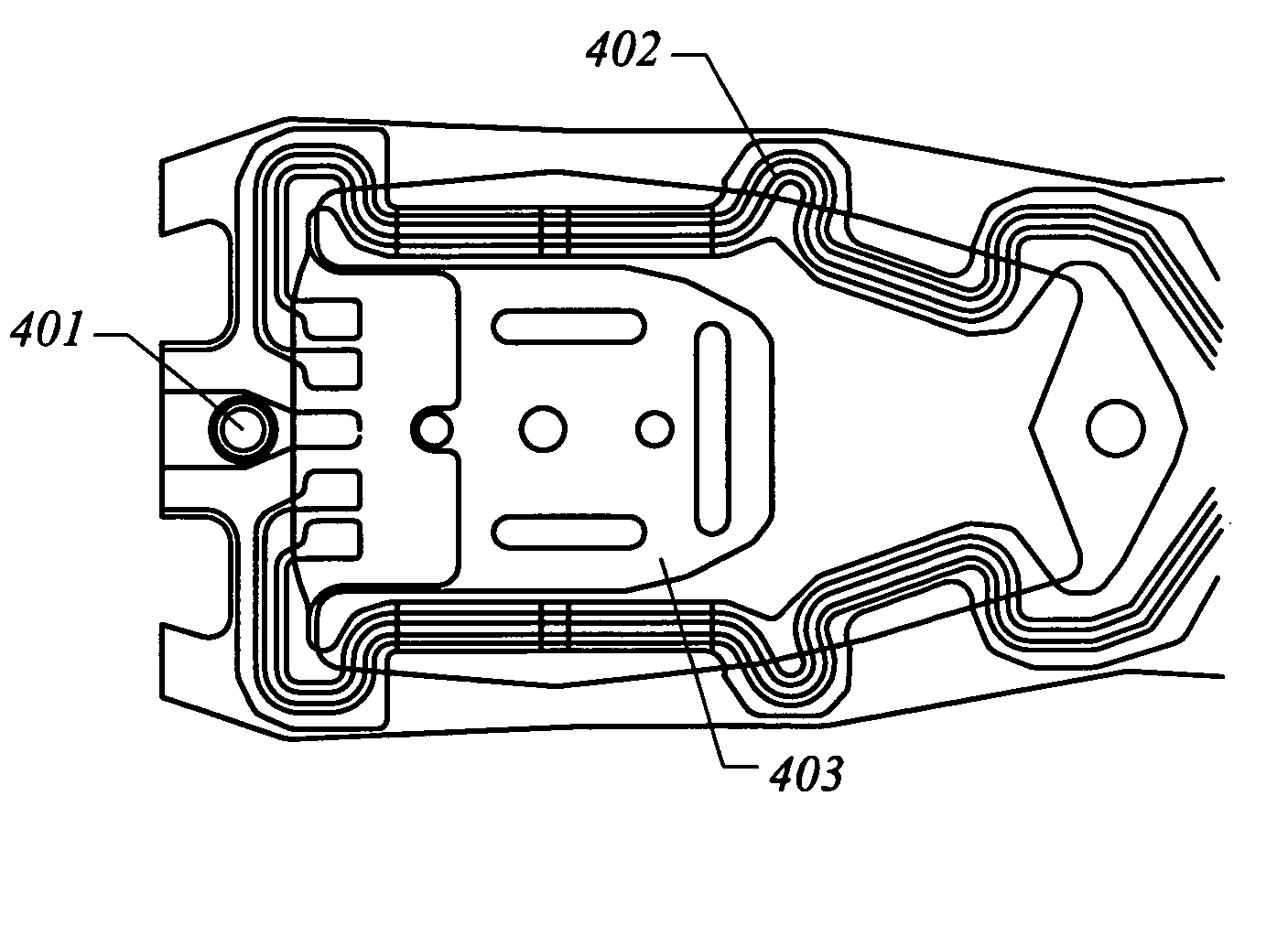

Method to form electrostatic discharge protection on flexible circuits

ActiveUS20050117257A1Avoid noisePreventing ESD damageSubstation/switching arrangement detailsRecord information storageFlexible circuitsIon deposition

Techniques for preventing electrostatic discharge (ESD) and circuit noise are provided. More particularly, the present invention provides a method to prevent ESD damage during the assembly of computer disk commonly called a hard disk for memory applications. The coating mainly involves a ion-deposition process. Merely by way of example, the present invention is implemented by using filtered cathodic vacuum arc (FCVA) with a dissipative crystalline and / or amorphous carbon base thin film coating on a flexible circuit to drain the potential electrostatic charges during circuit assembly and interconnect processes, yet it would be recognized that the invention has a much broader range of applicability on any electronic apparatus that is susceptible to electrostatic damage and static noise.

Owner:MAGNECOMP

Electrostatic discharge protection device for digital circuits and for applications with input/output bipolar voltage much higher than the core circuit power supply

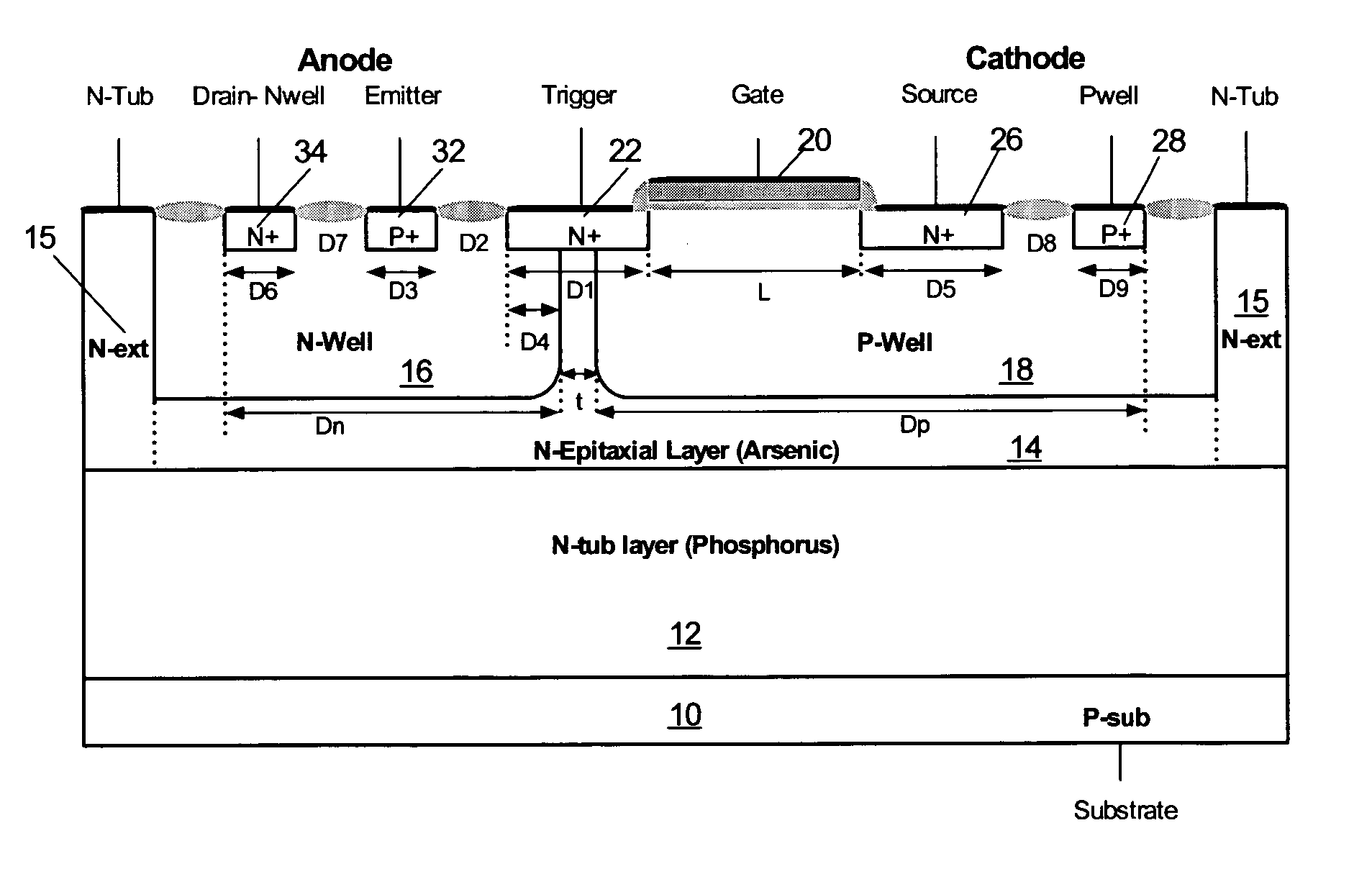

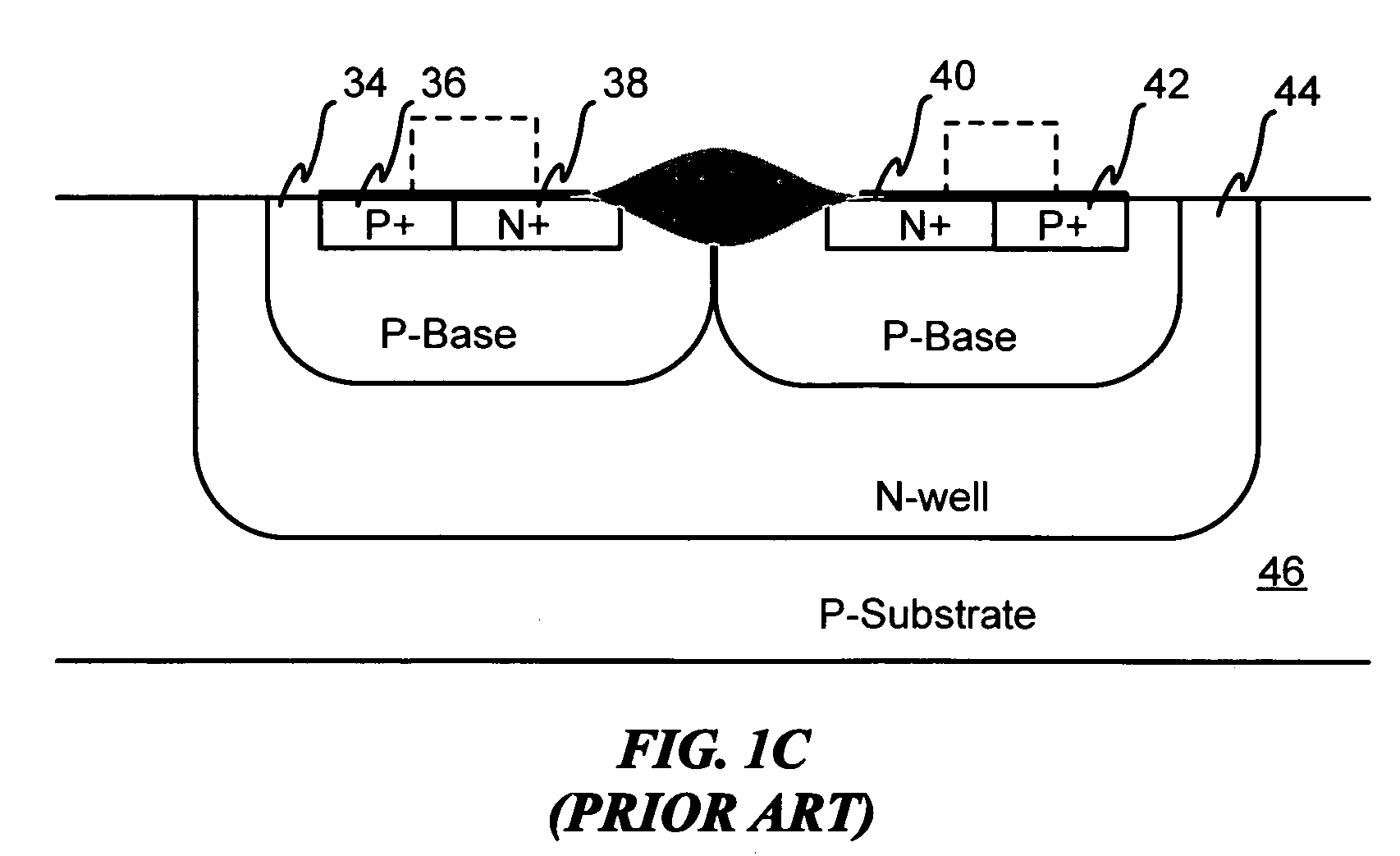

InactiveUS20060151836A1Robust implementationTransistorSemiconductor/solid-state device detailsBipolar voltageCondensed matter physics

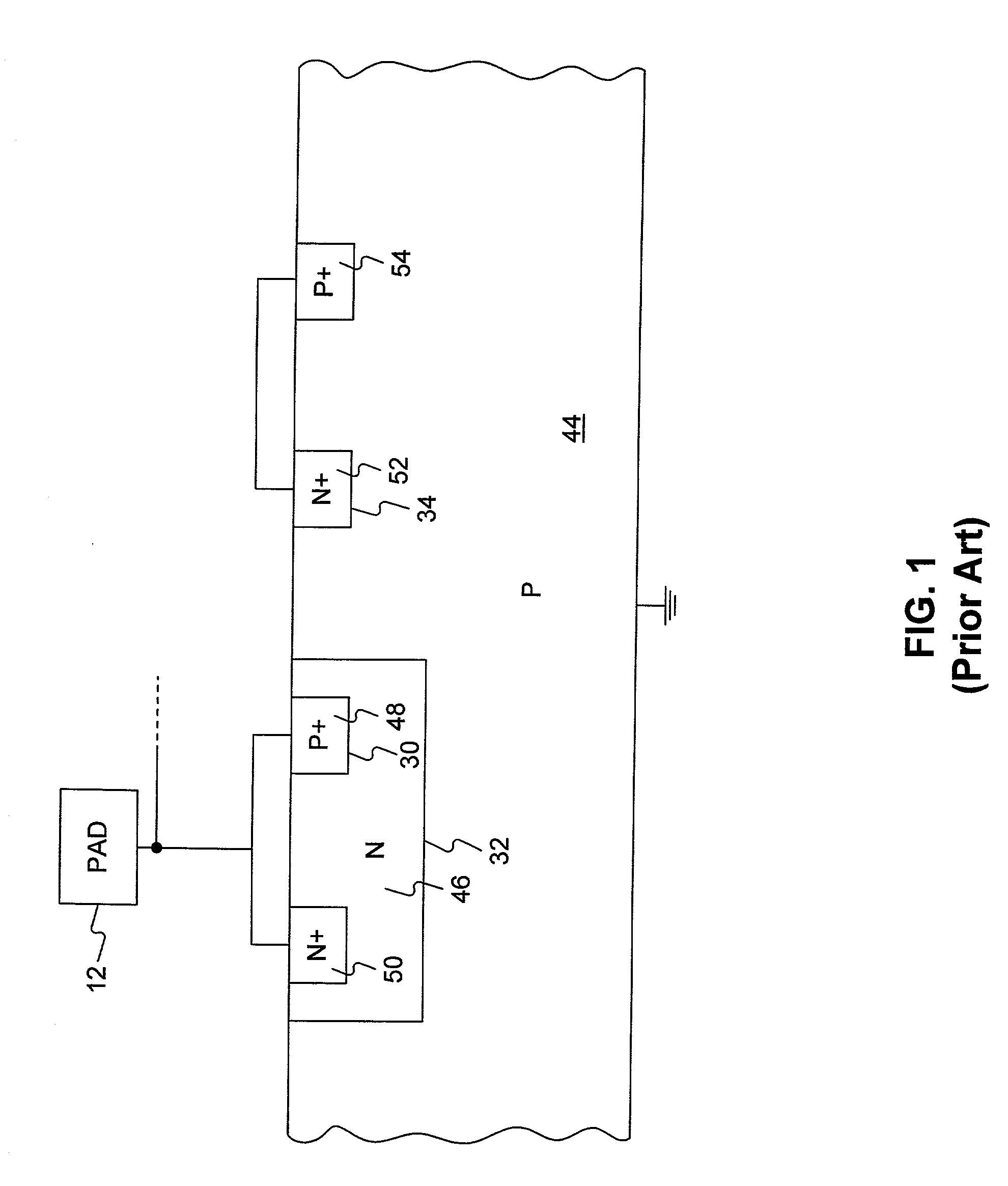

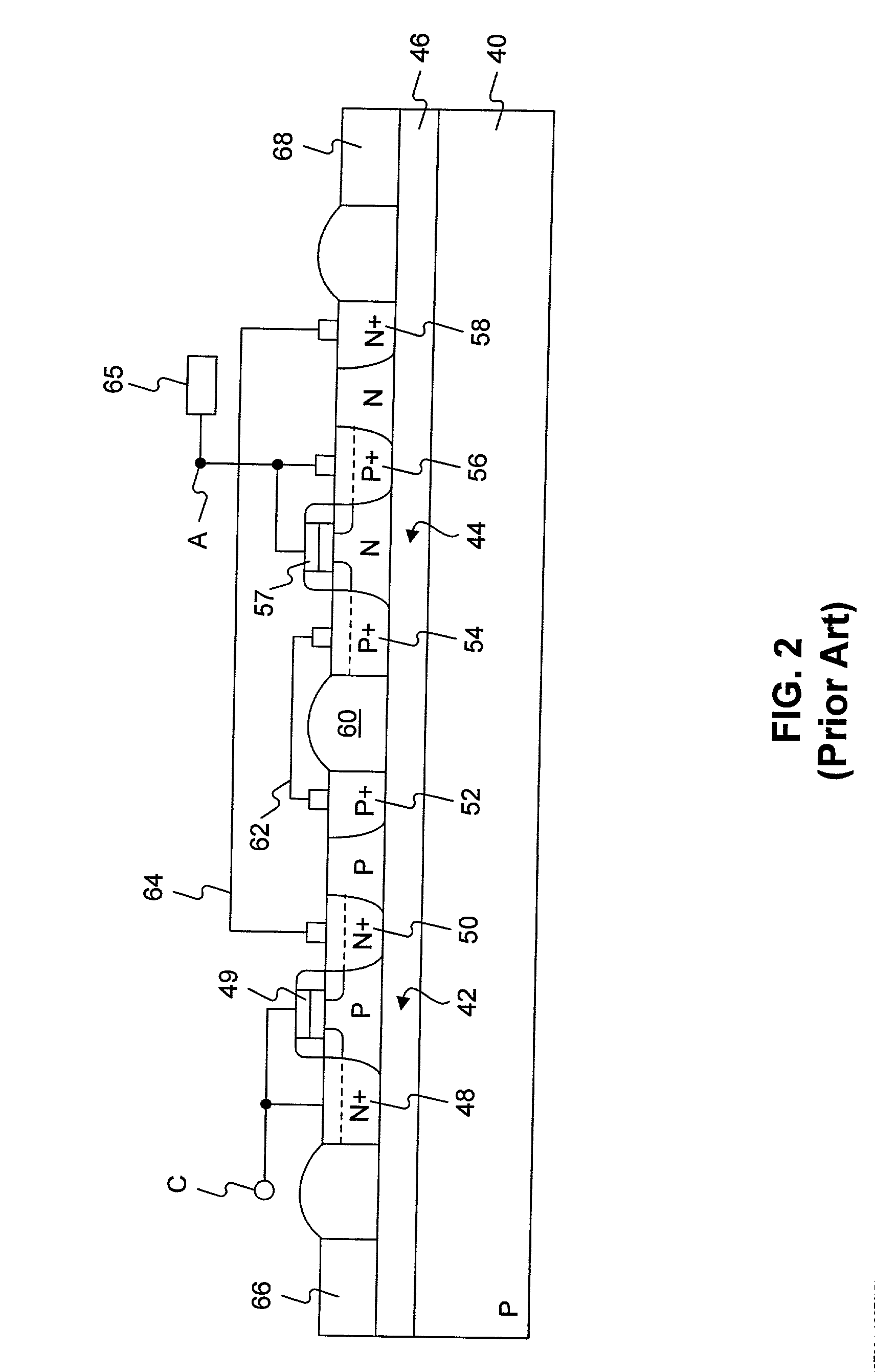

An electrostatic discharge (ESD) device and method is provided. The ESD device can comprise a substrate doped to a first conductivity type, an epitaxial region doped to the second conductivity type, and a first well doped to the first conductivity type disposed in the substrate. The first well can comprise a first region doped to the first conductivity type, a second region doped to a second conductivity type, and a first isolation region disposed between the first region and the second region. The ESD device can also comprise a second well doped to a second conductivity type disposed in the substrate adjacent to the first well, where the second well can comprise a third region doped to the first conductivity type, a fourth region doped to the second conductivity type, and a second isolation region disposed between the third region and the fourth region. Still further, the ESD device can include a first trigger contact and second trigger contact comprising highly doped regions of either conductivity type, the first trigger contact disposed at a junction between the first well and the second well, and the second trigger contact disposed at either well.

Owner:UNIV OF CENT FLORIDA RES FOUND INC +1

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

Electrostatic protection device

ActiveUS20110101444A1Easy to modifyTransistorSemiconductor/solid-state device detailsEngineeringImpurity

An apparatus including an electrostatic discharge (ESD) protection device comprising a semiconductor having first, second and third regions arranged to form a transistor, wherein the first region is doped with a first impurity of a first conductivity type and is separated from the second region which is doped with a second impurity of a second conductivity type opposite the first type, and wherein a dimensional constraint of the regions defines an operational threshold of the ESD protection device. In one example, the separation between a collector and an emitter of a bipolar transistor defines a trigger voltage to cause the electrostatic discharge protection device to become conducting. In another example, a width of a bipolar transistor base controls a holding voltage of the electrostatic discharge protection device.

Owner:ANALOG DEVICES INC

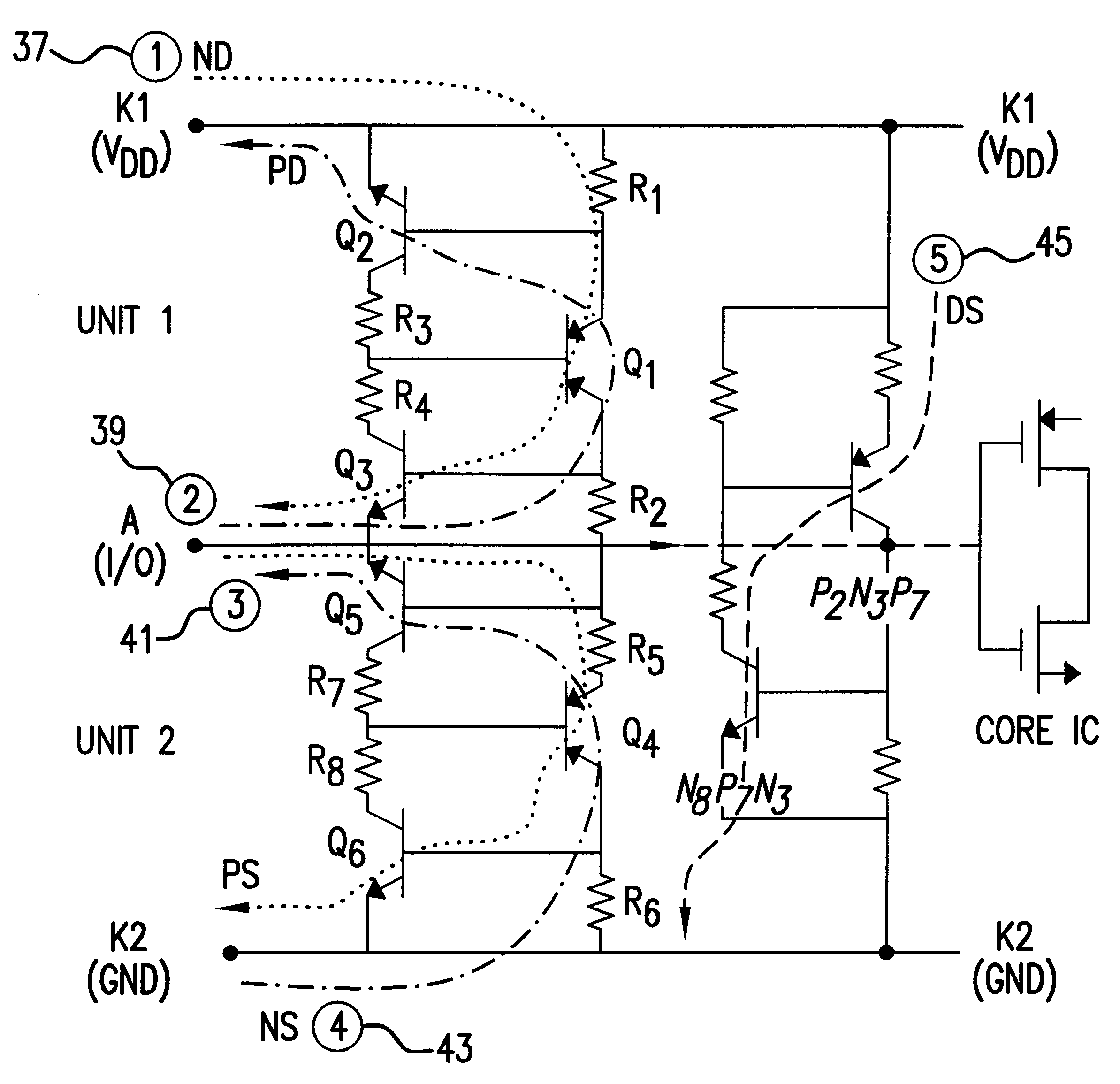

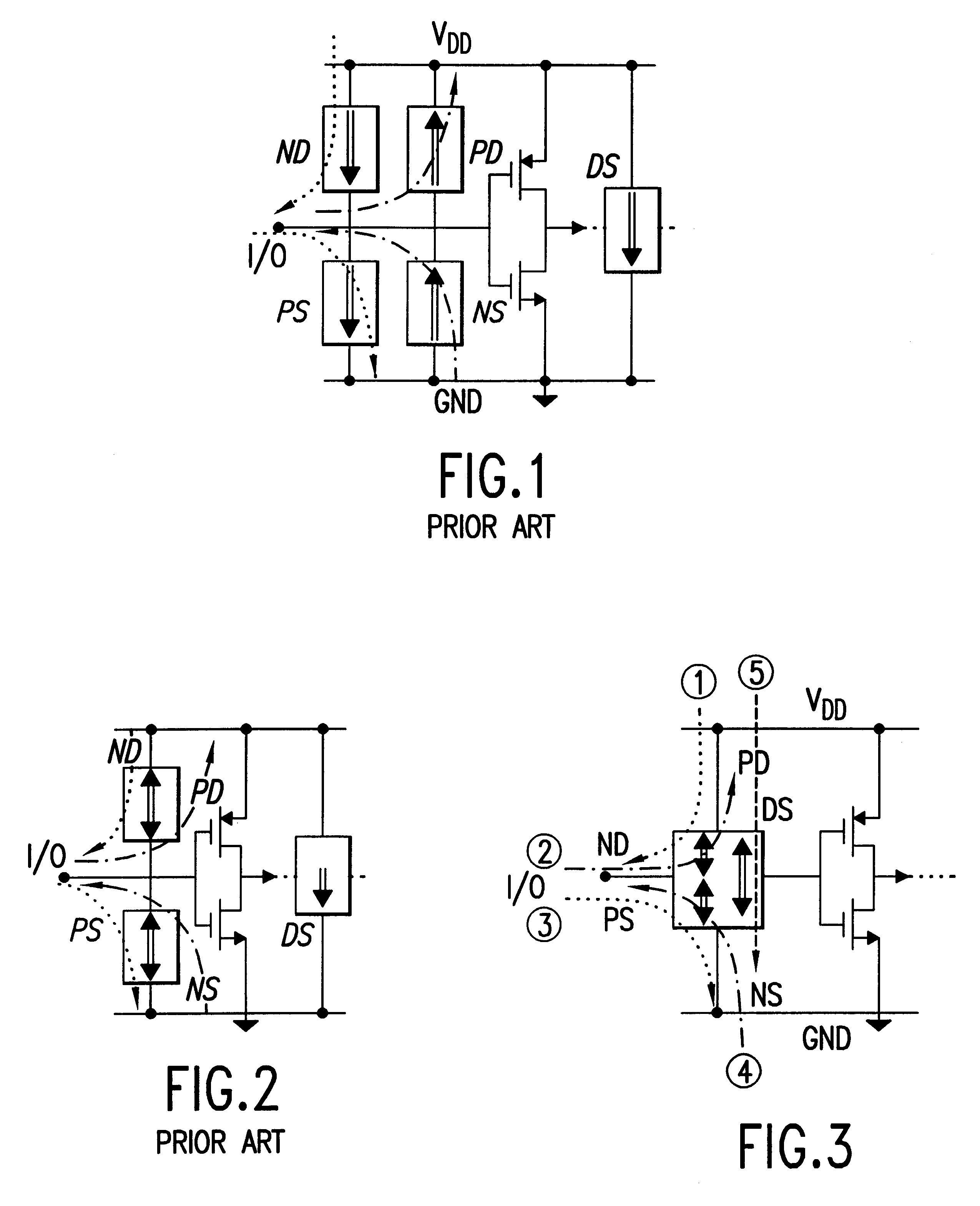

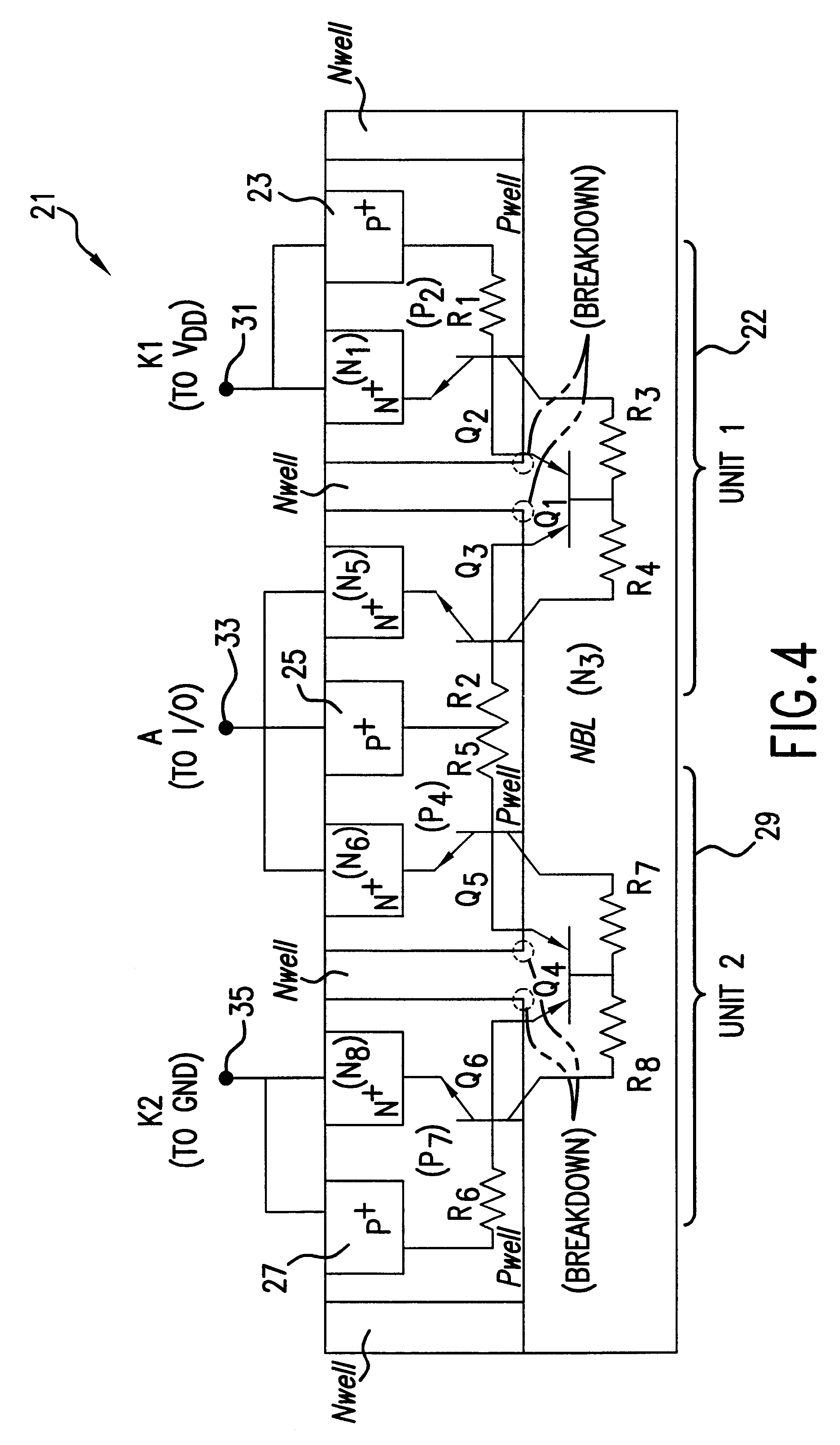

Single structure all-direction ESD protection for integrated circuits

InactiveUS6512662B1Solid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectrical resistance and conductanceOvervoltage

An overvoltage / overcurrent electrostatic discharge protection single circuit structure for Integrated Circuits protects on all paths and polarities between In / Out, Supply, and Ground pins. The structure is built on the chip substrate with an N well with three P Diffusions therein each containing N+ and P+ diffusions therein to form 6 transistors and 8 parasitic resistors to yield 5 thyristors. The structure provides very fast, symmetrical, full protection while using minimal chip area.

Owner:ILLINOIS INSTITUTE OF TECHNOLOGY

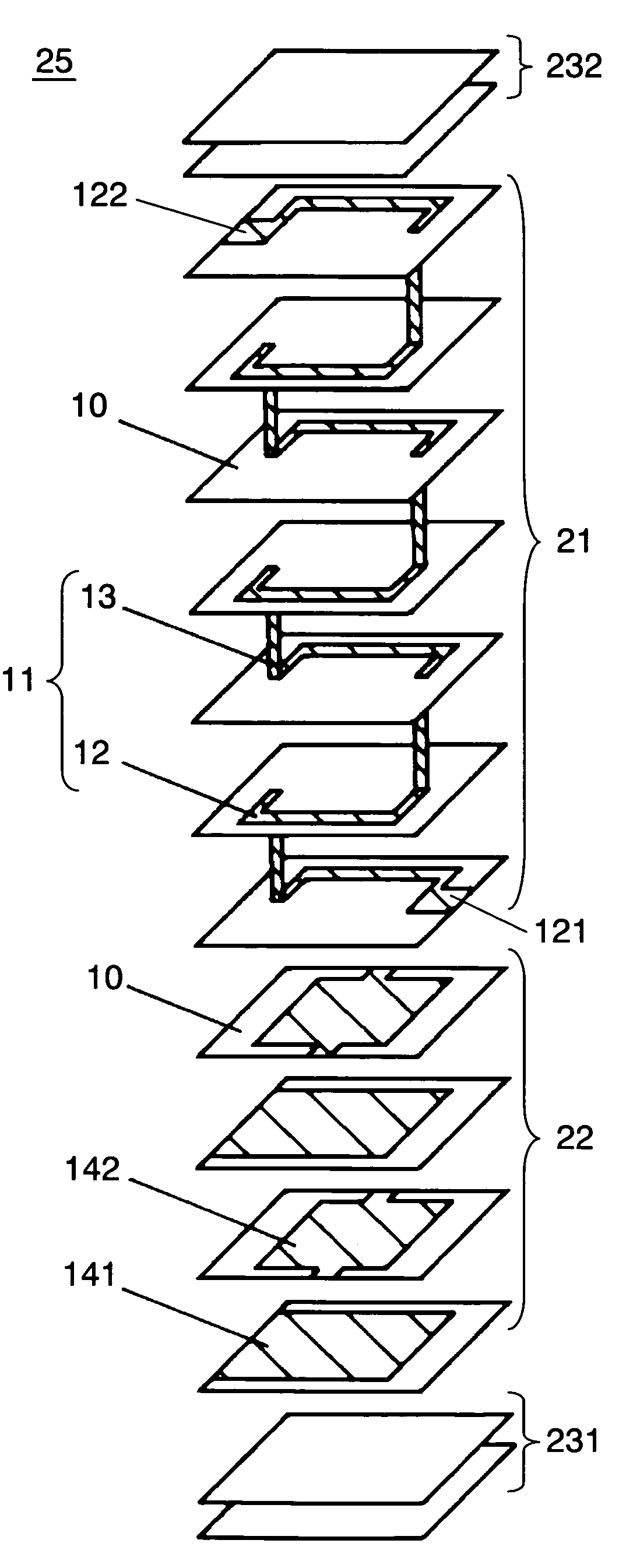

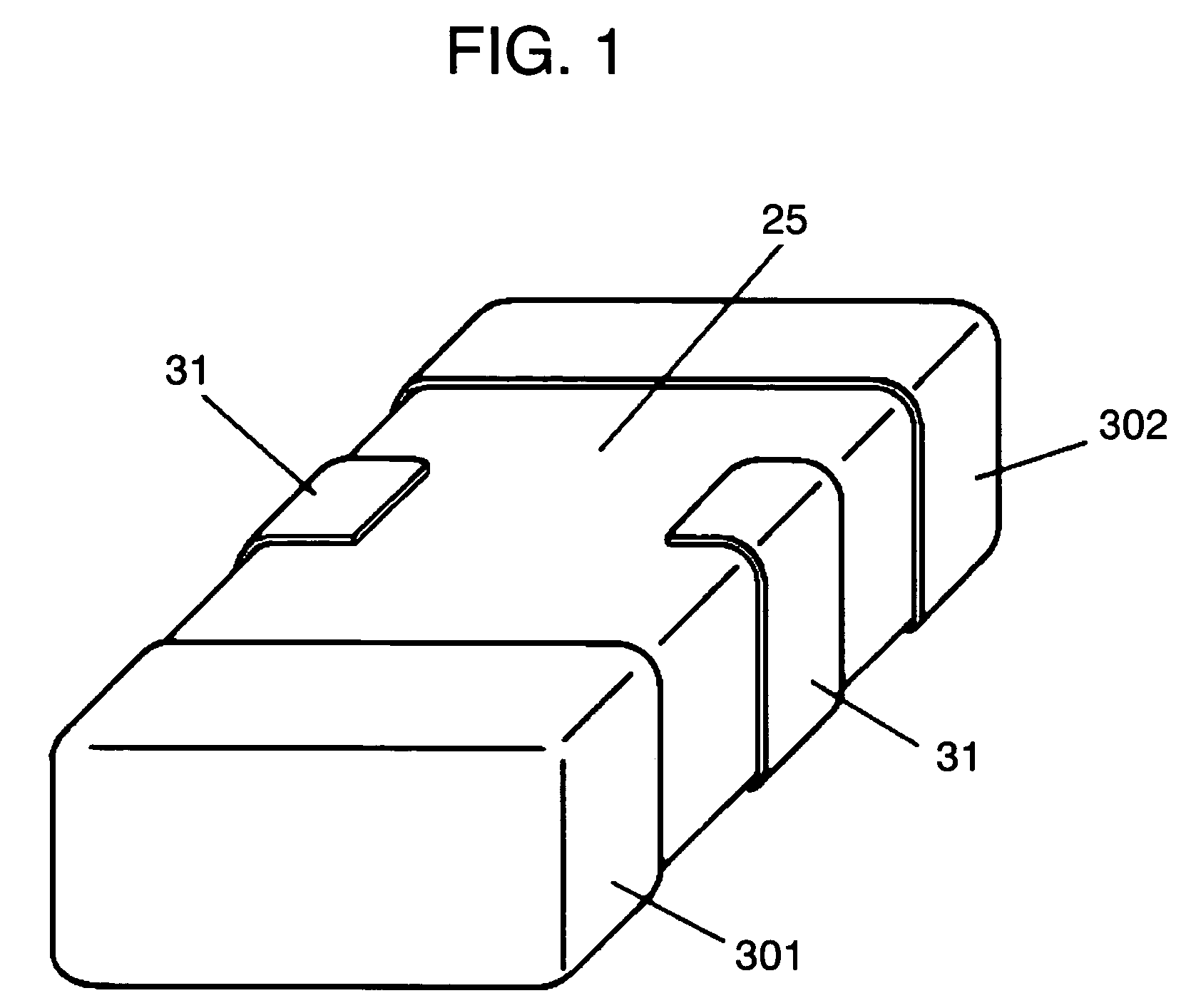

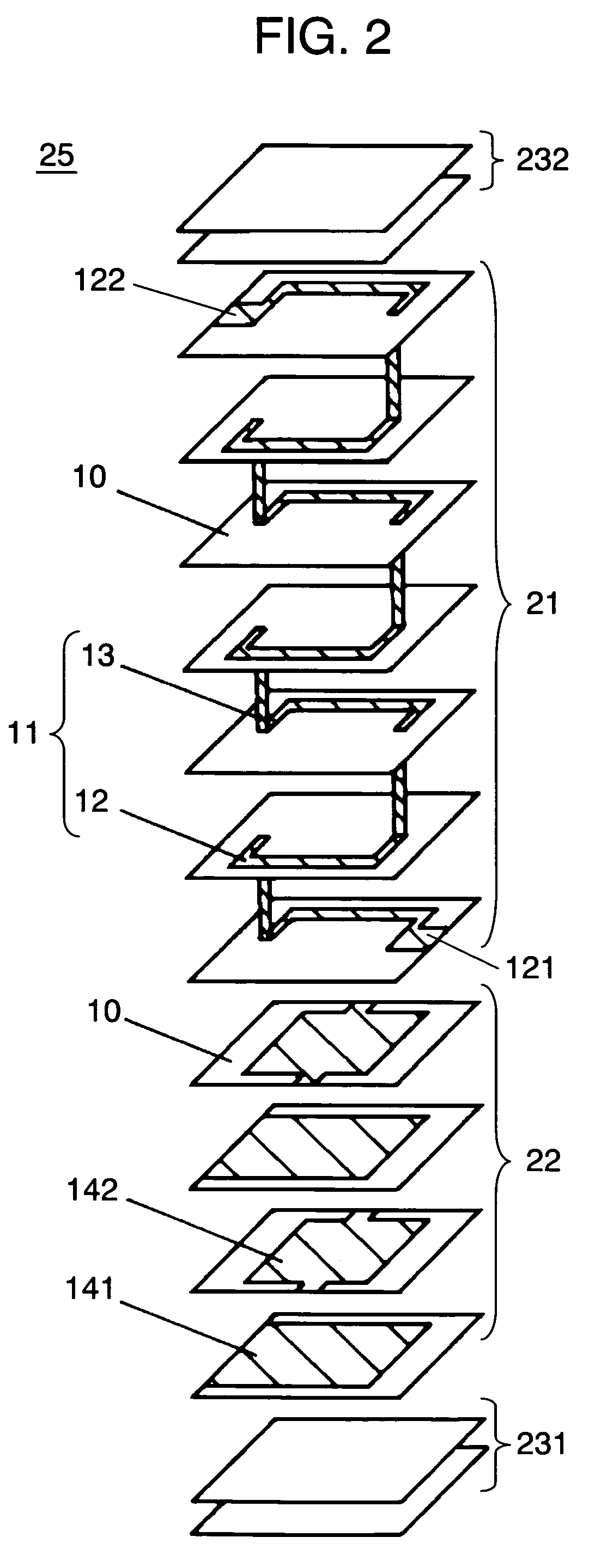

Electrostatic discharge protection component

InactiveUS7085118B2Prevent electrostatic dischargeHigh impedanceOther resistor networksEmergency protective arrangement detailsEngineeringInductor

On the surface of a ceramic sinter, at least an external electrode for input, an external electrode for output, and external electrodes for grounding are disposed, and the ceramic sinter includes an inductor electrically connected to the external electrode for input and external electrode for output, and a varistor electrically connected to the external electrode for input and external electrodes for grounding. By connecting the inductor to the signal line of the circuit of an electronic appliance and connecting the varistor between the input side of the signal line and the ground, electrostatic discharge pulses of about 0.5 to 2 nanoseconds can be suppressed efficiently.

Owner:PANASONIC CORP

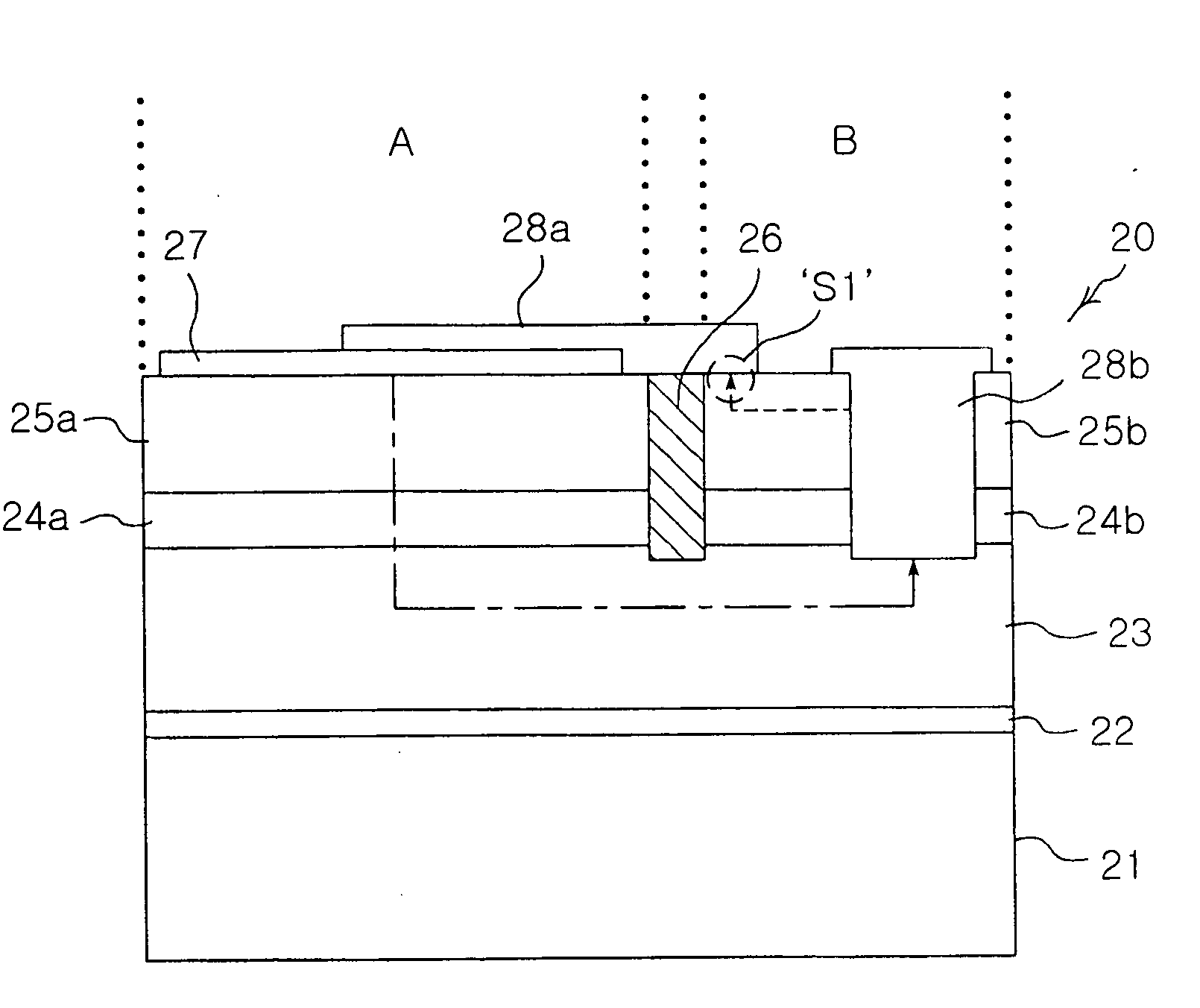

Nitride semiconductor light emitting device having electrostatic discharge (ESD) protection capacity

ActiveUS7173288B2Increase the number ofIncrease in sizeSolid-state devicesSemiconductor devicesOhmic contactIsolation layer

A nitride semiconductor light emitting device including a light emitting diode and a diode formed on a single substrate, in which the light emitting diode and the diode use a common electrode. According to the present invention, an active layer and a p-type nitride semiconductor layer are each divided into a first region and a second region by an insulative isolation layer, and an ohmic contact layer is formed on the p-type nitride semiconductor layer contained in the first region. A p-type electrode is formed on the ohmic contact layer and is extended to the p-type nitride semiconductor layer contained in the second region. An n-type electrode is formed on the p-type nitride semiconductor layer contained in the second region, passes through the p-type nitride semiconductor layer and the active layer contained in the second region, and is connected to the first n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

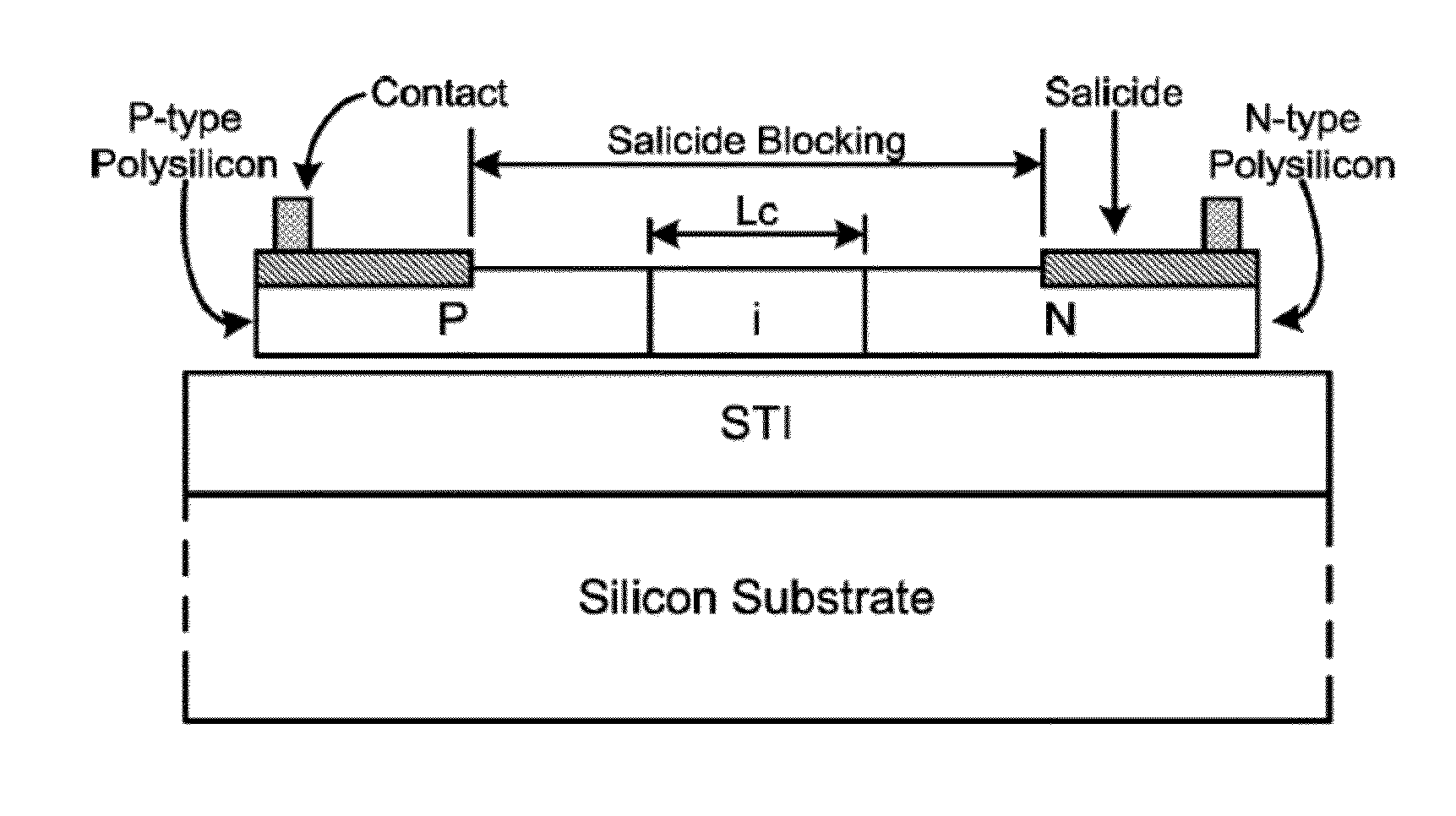

Electrostatic discharge protection element

ActiveUS20070040221A1Increase resistanceEnhanced ESD robustnessSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceEngineering

A gate controlled fin resistance element for use as an electrostatic discharge (ESD) protection element in an electrical circuit has a fin structure having a first connection region, a second connection region and a channel region formed between the first and second connection regions. Furthermore, the fin resistance element has a gate region formed at least over a part of the surface of the channel region. The gate region is electrically coupled to a gate control device, which gate control device controls an electrical potential applied to the gate region in such a way that the gate controlled fin resistance element has a high electrical resistance during a first operating state of the electrical circuit and a lower electrical resistance during a second operating state, which is characterized by the occurrence of an ESD event.

Owner:INFINEON TECH AG

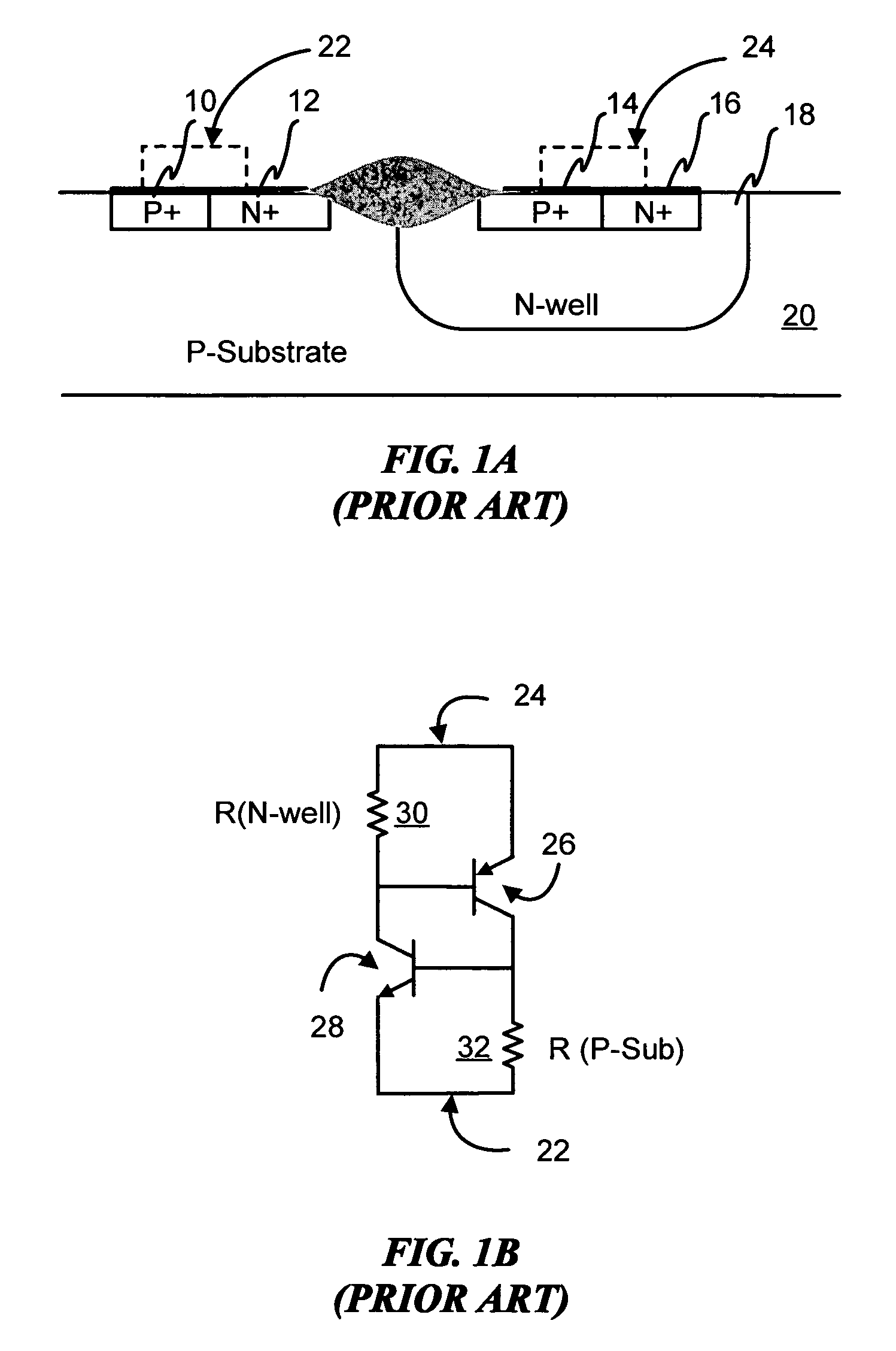

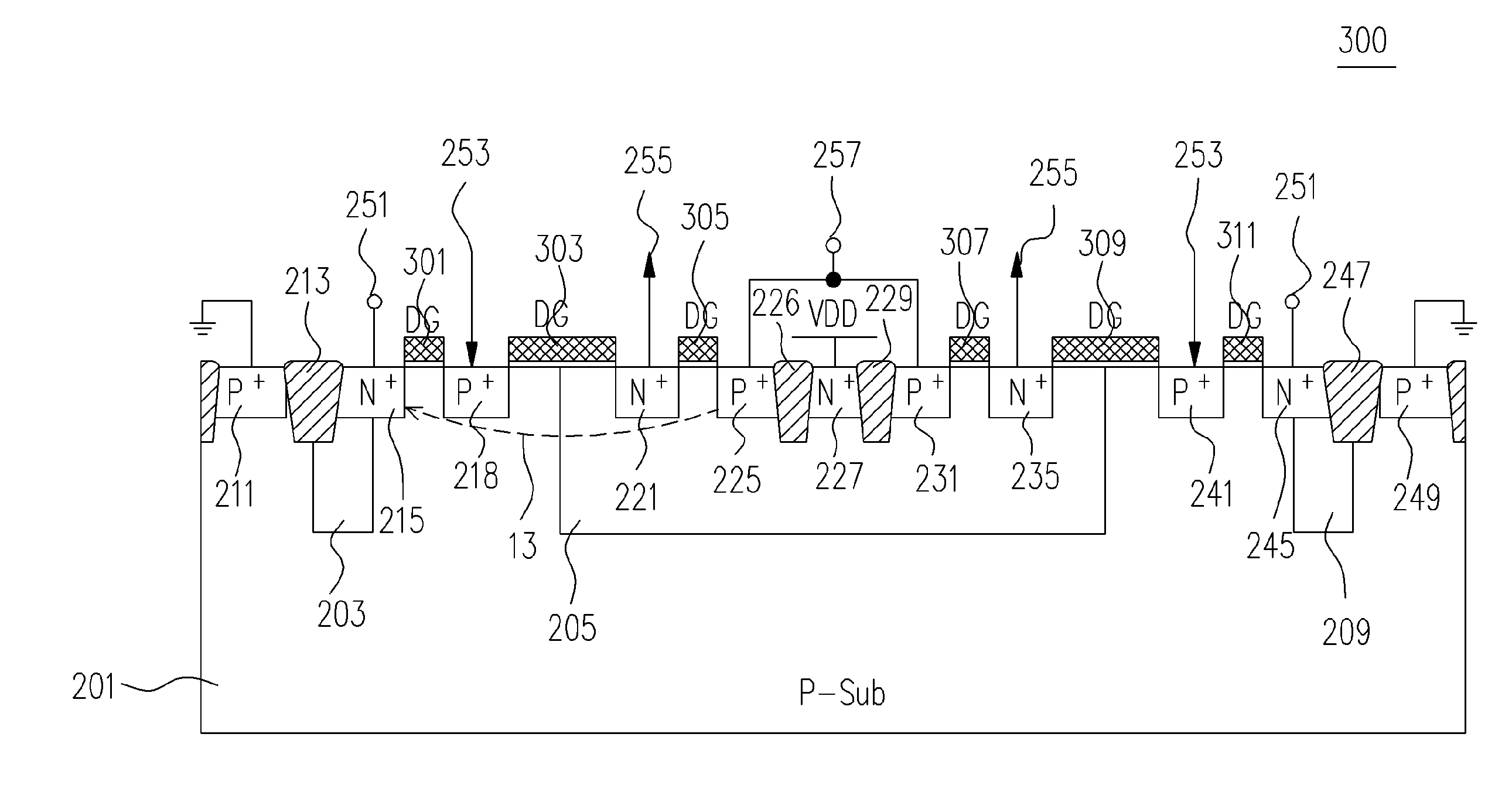

Double-triggered silicon controlling rectifier and electrostatic discharge protection circuit thereof

A double-triggered silicon controller rectifier (SCR) comprises a plurality of N+ diffusion areas, a plurality of P+ diffusion areas, a first N-well region, a second N-well region and a third N-well region formed in a P-substrate. The N+ diffusion areas and the P+ diffusion areas are isolated by shallow trench isolation (STI) structures. Two of the N+ diffusion areas are N-type trigger terminals. Two of the P+ diffusion areas are the P-type trigger terminal.

Owner:NAT CHIAO TUNG UNIV

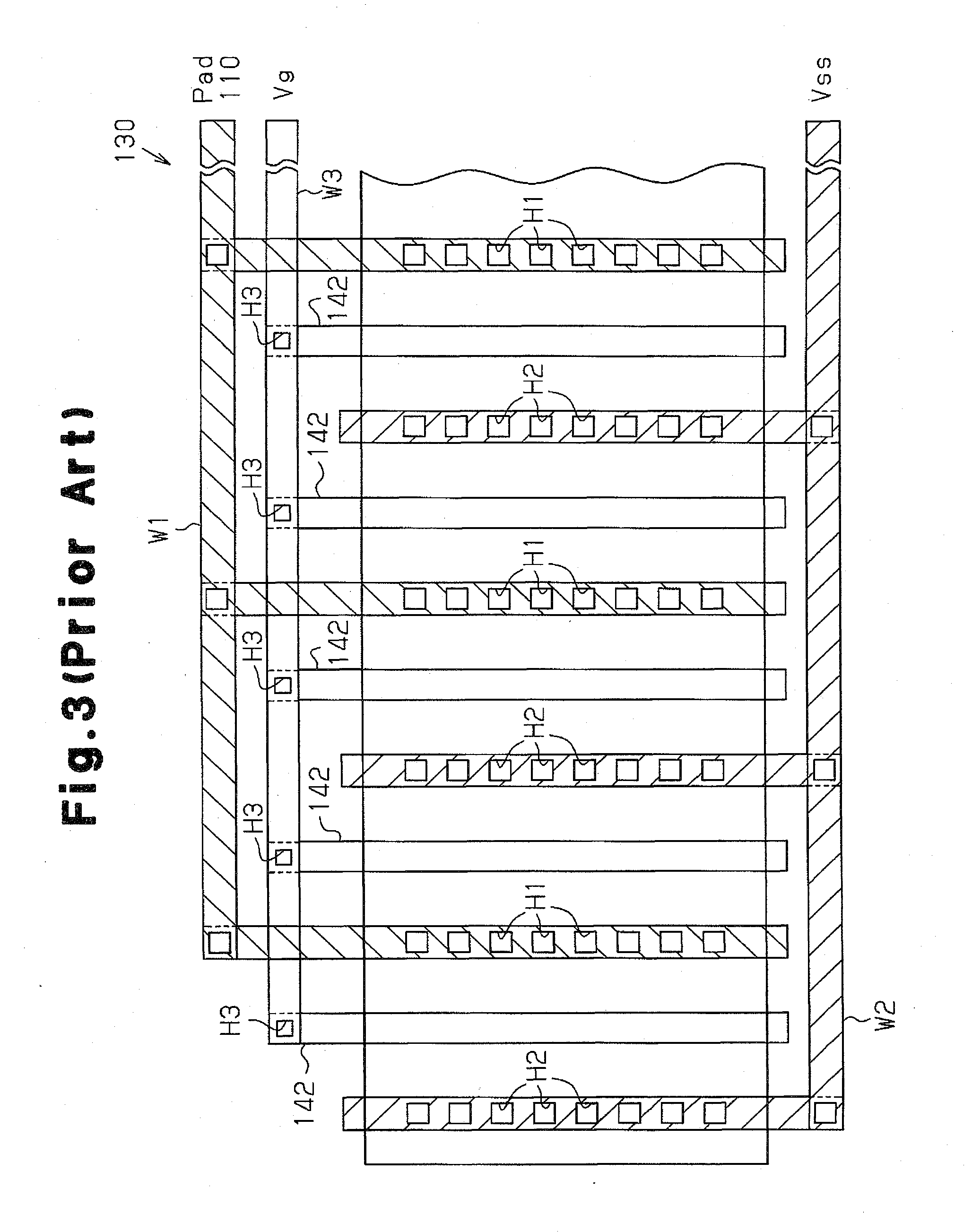

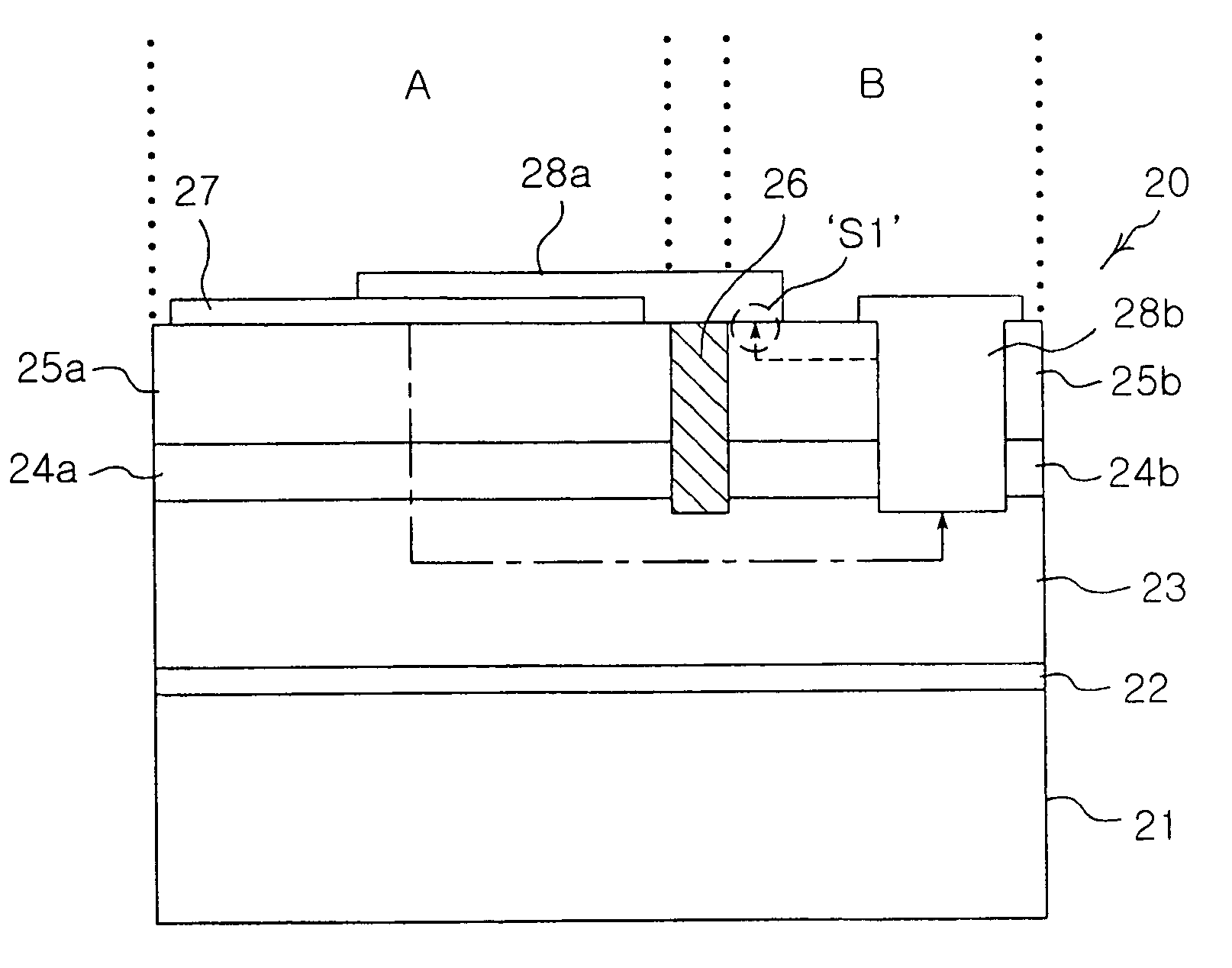

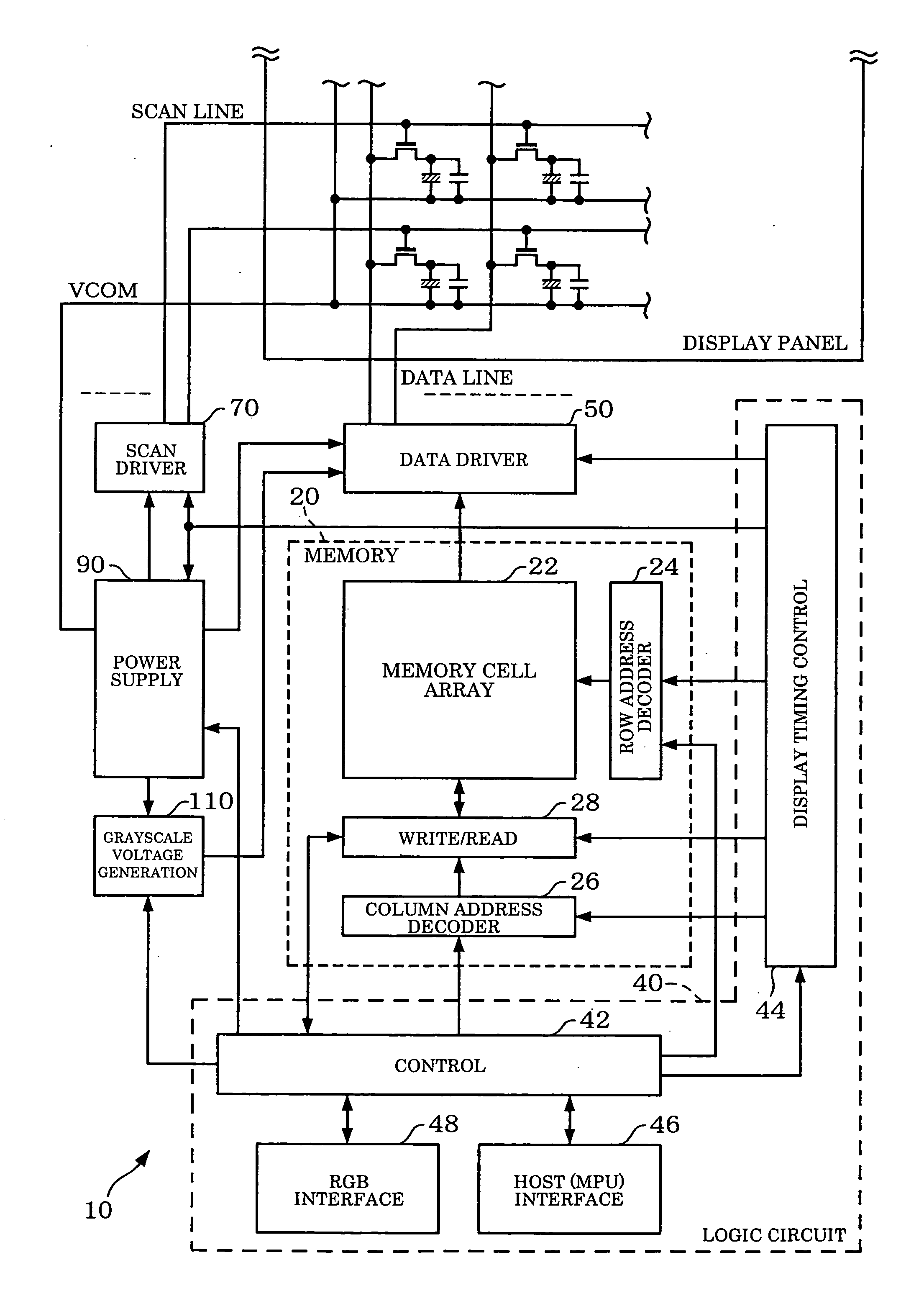

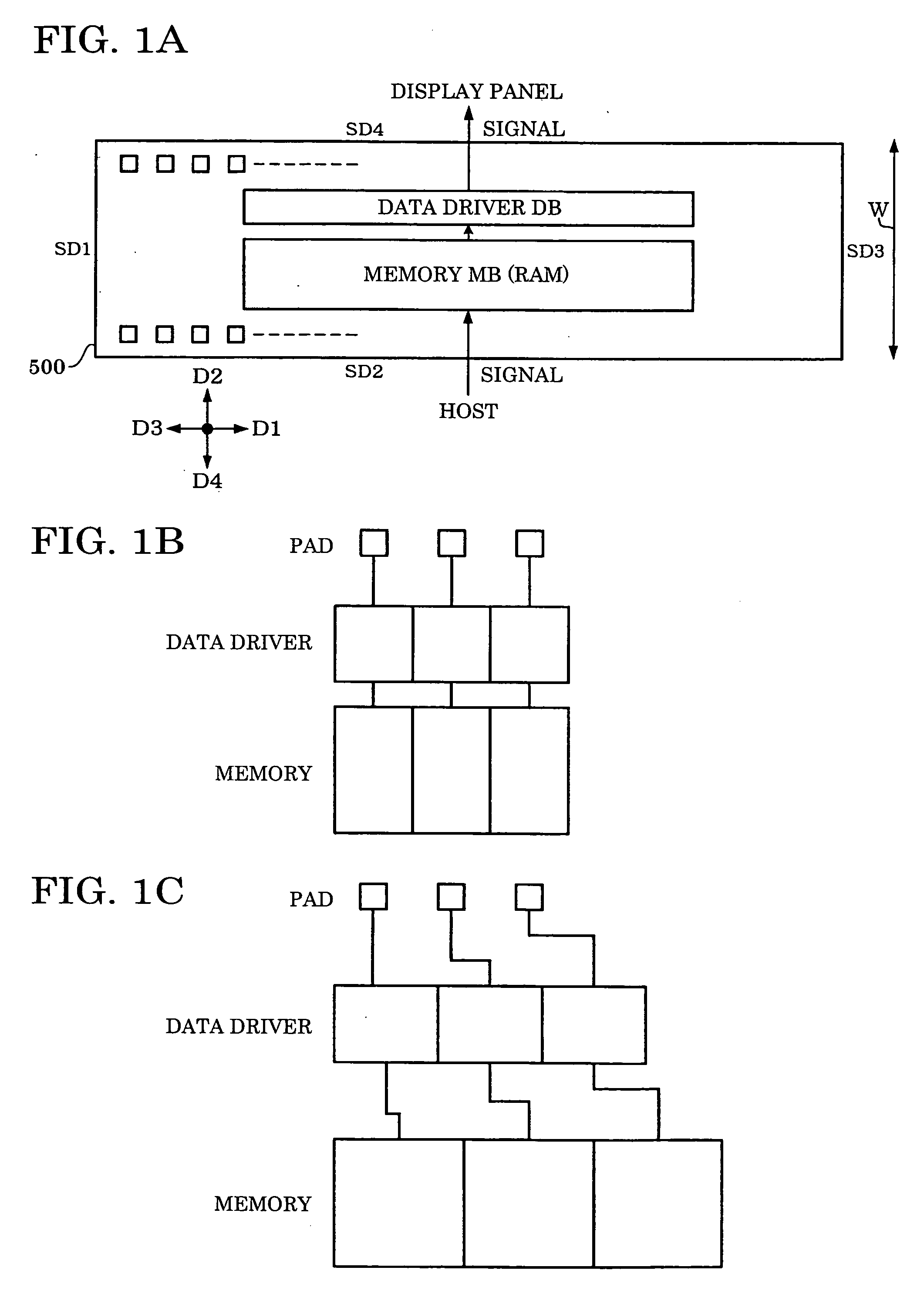

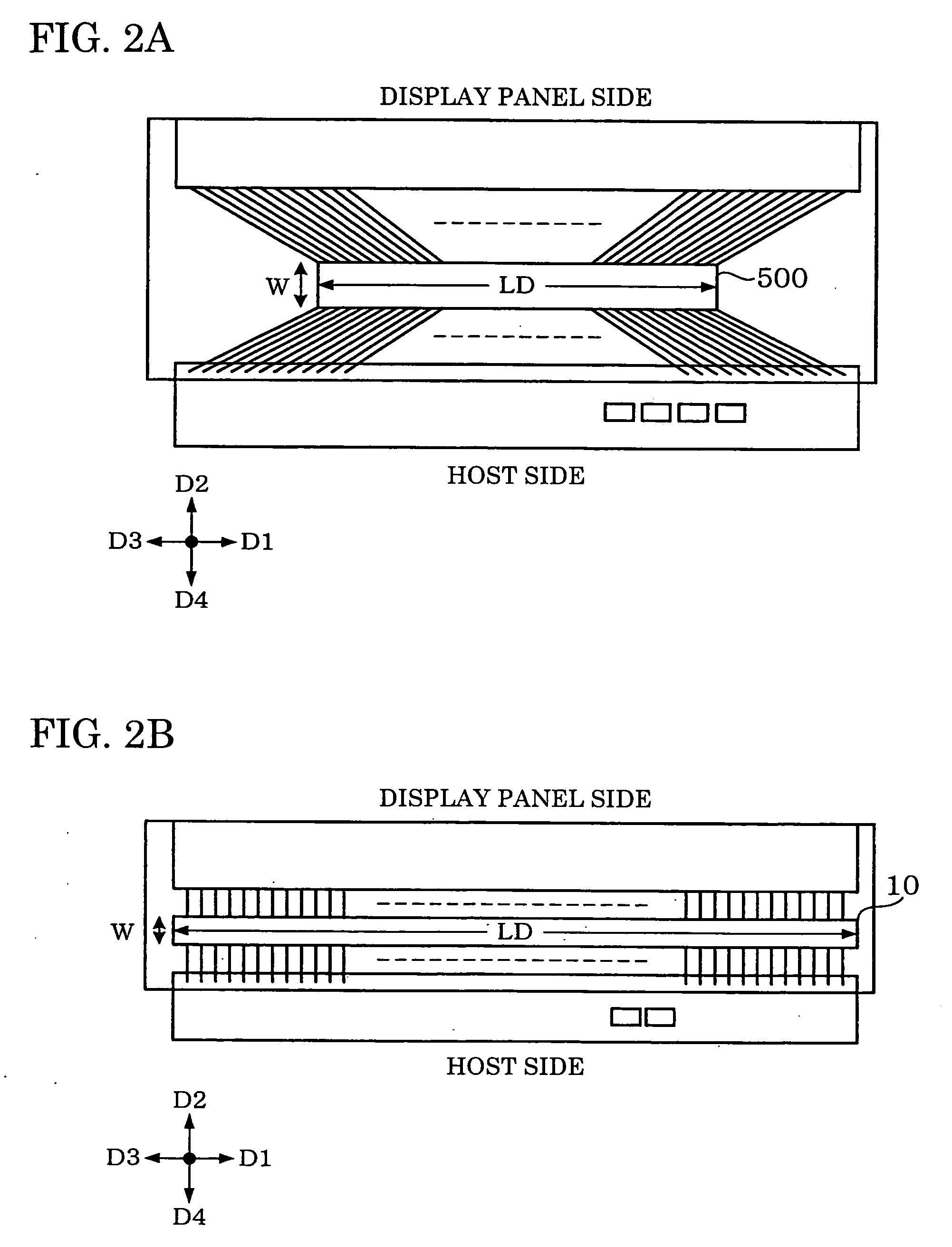

Integrated circuit device and electronic instrument

ActiveUS20070002509A1Static indicating devicesSemiconductor/solid-state device detailsElectronic instrumentElectronic instruments

Owner:SEIKO EPSON CORP

Structures and techniques for electro-static discharge (ESD) protection using ring structured diodes

InactiveUS20140131710A1High ESD immunityReduce input capacitanceTransistorSemiconductor/solid-state device manufacturingLOCOSEngineering

Electro-Static Discharge (ESD) protection using at least one ring-shape diode is disclosed. The ring-shape diode can be constructed from polysilicon, active region body on insulated substrate, or junction diode on silicon substrate. The diodes can have a first type of implant in an outer ring and a second type of implant in an inner ring to serve as two terminals of a diode coupled through contacts, vias, or metals. The two types of implant ring regions are separated with an isolation structure. The isolation can be LOCOS, STI, dummy gate, or silicide block layer (SBL). The ESD structure has at least a ring-shape diode with a first terminal coupled to an I / O pad and the second terminal coupled to a first supply voltage. The contours of the ring-shape diode can be circles, polygons, or other shapes. The ring-shape ESD structures can be multiple and be constructed in concentric manner.

Owner:ATTOPSEMI TECH CO LTD

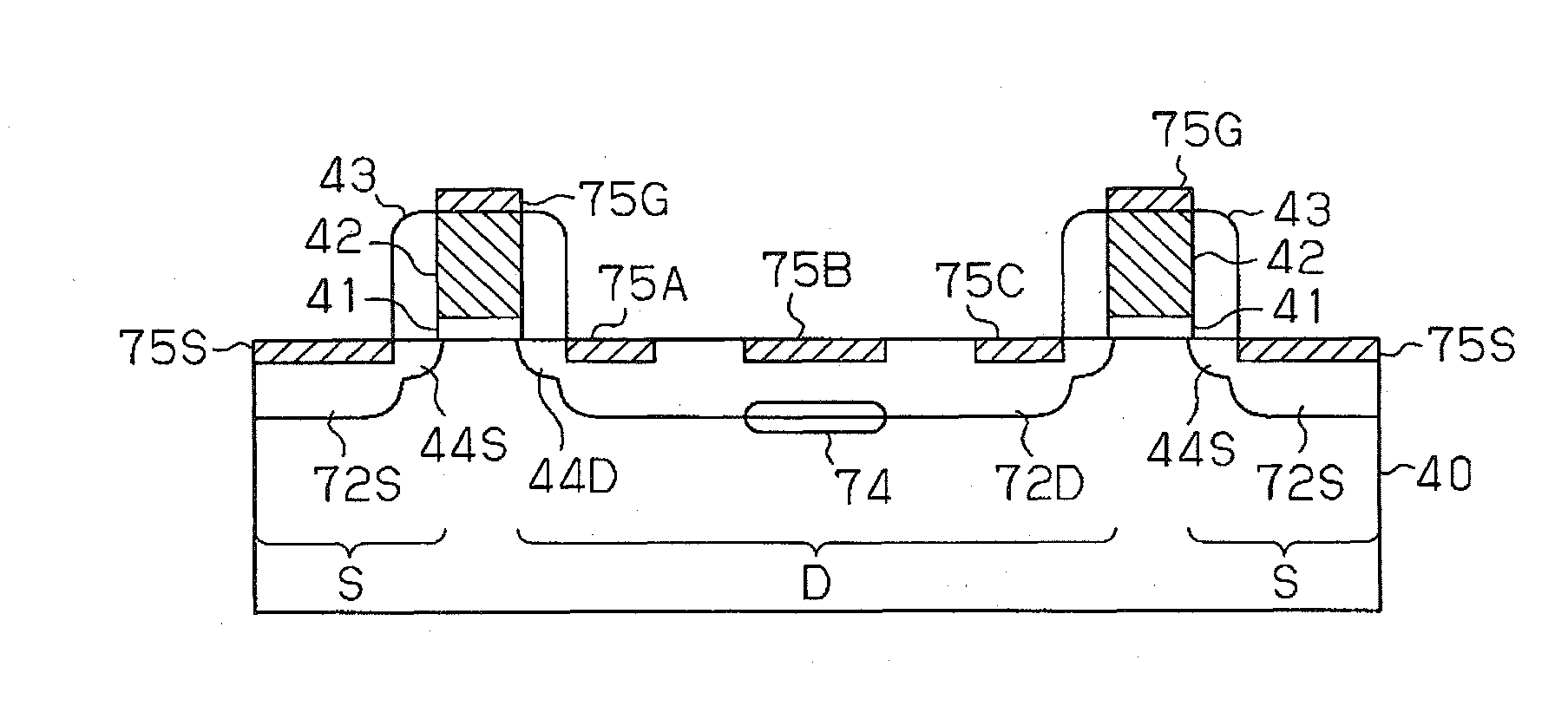

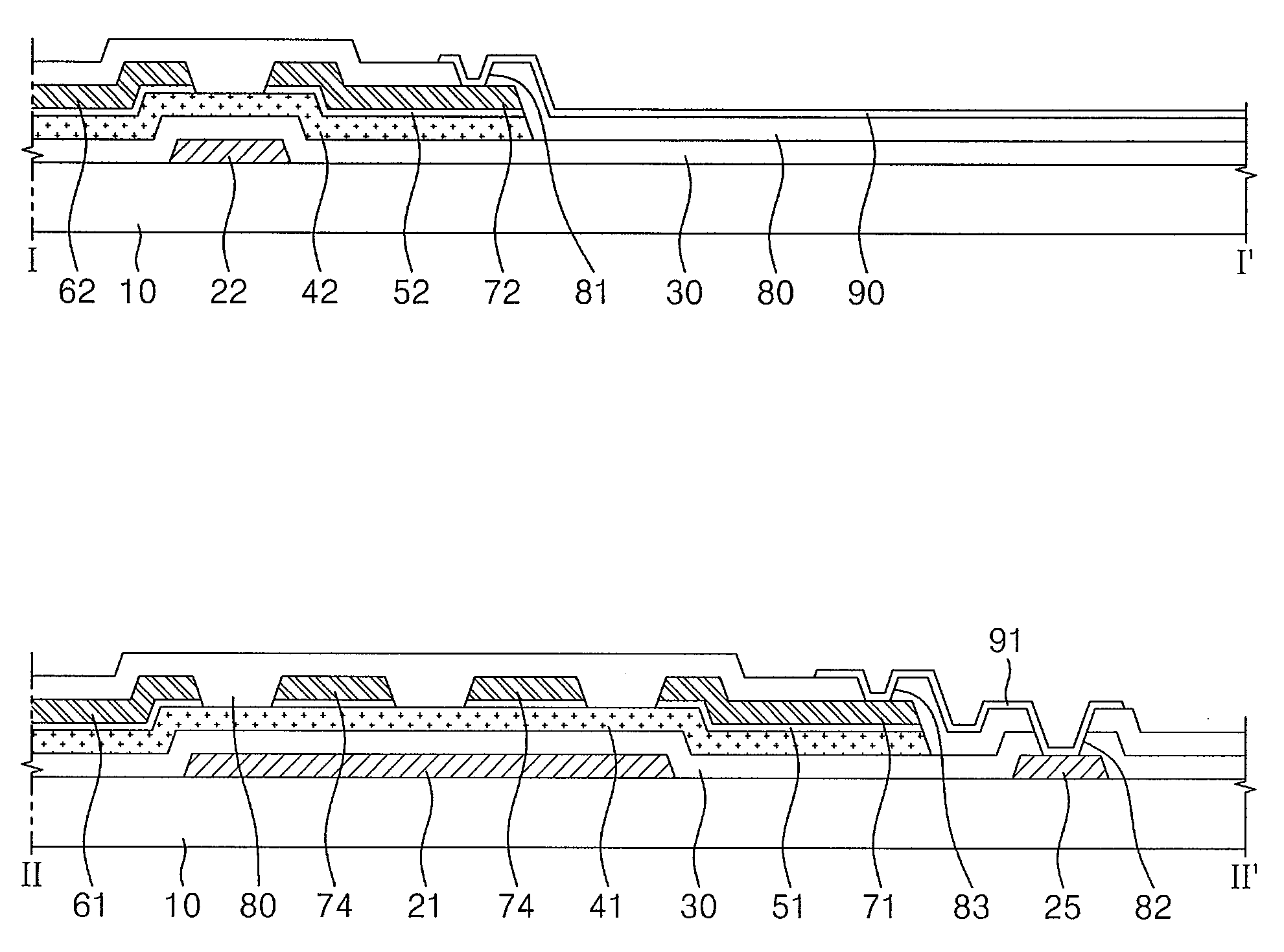

Thin film transistor substrate and method of manufacture

ActiveUS20080135846A1Increase the aperture ratioAvoid defectsSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectrostatic discharge protection

A thin film transistor (“TFT”) substrate in which the size of a pixel TFT formed in a display area is reduced using a single slit mask, and the length of the channel area of a protection TFT constituting an electrostatic discharge protection circuit formed in a non-display area is formed larger than that of the pixel TFT using the same mask pattern. The TFT substrate includes a signal line and a discharge line formed on a substrate, a signal supply pad formed on one end of the signal line to supply a signal to the signal line, and an electrostatic discharge protection circuit including at least one protection TFT including a plurality of channels formed between the signal supply pad and the discharge line and / or between the signal line and the discharge line.

Owner:KLA TENCOR TECH CORP +1

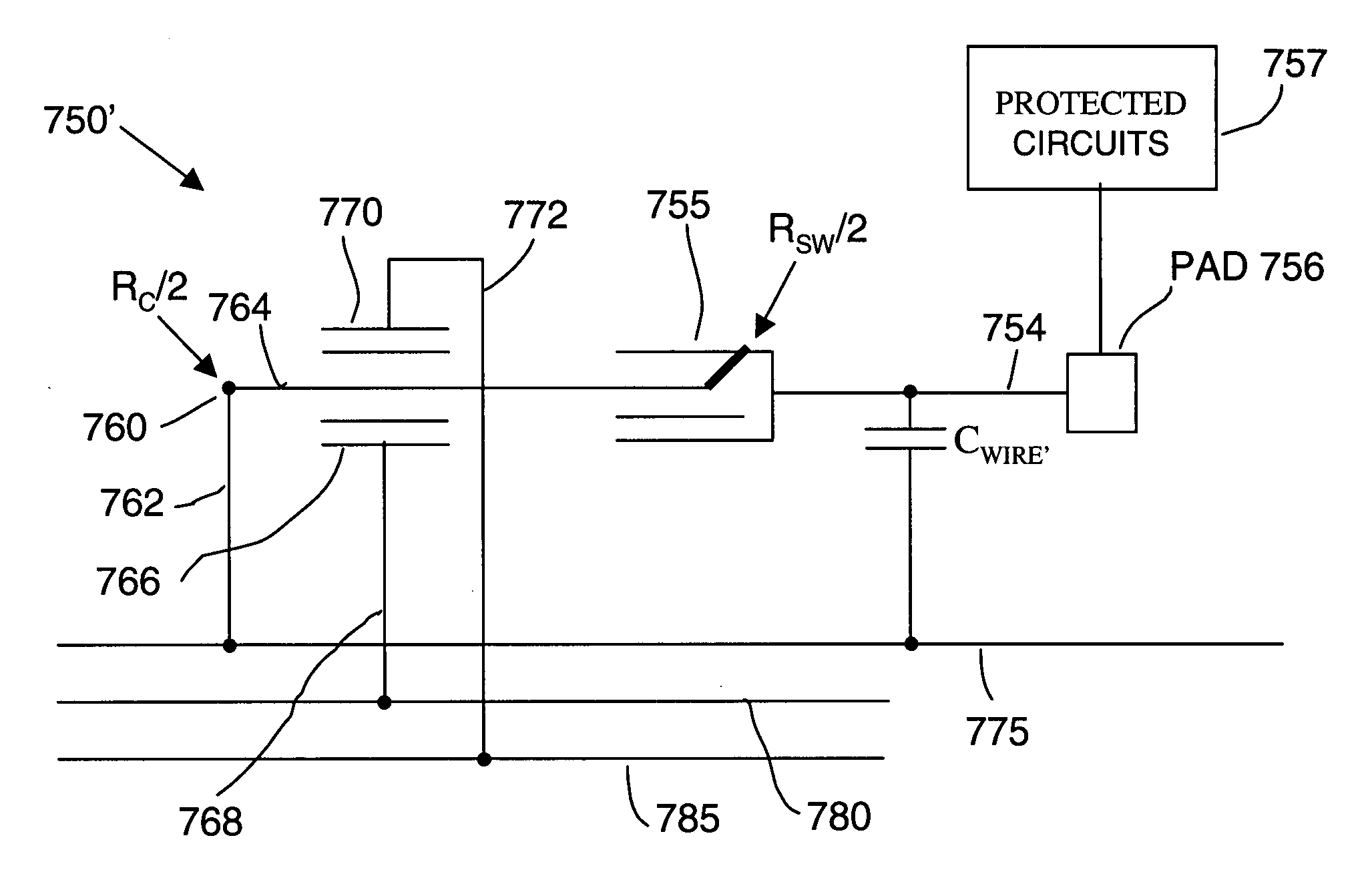

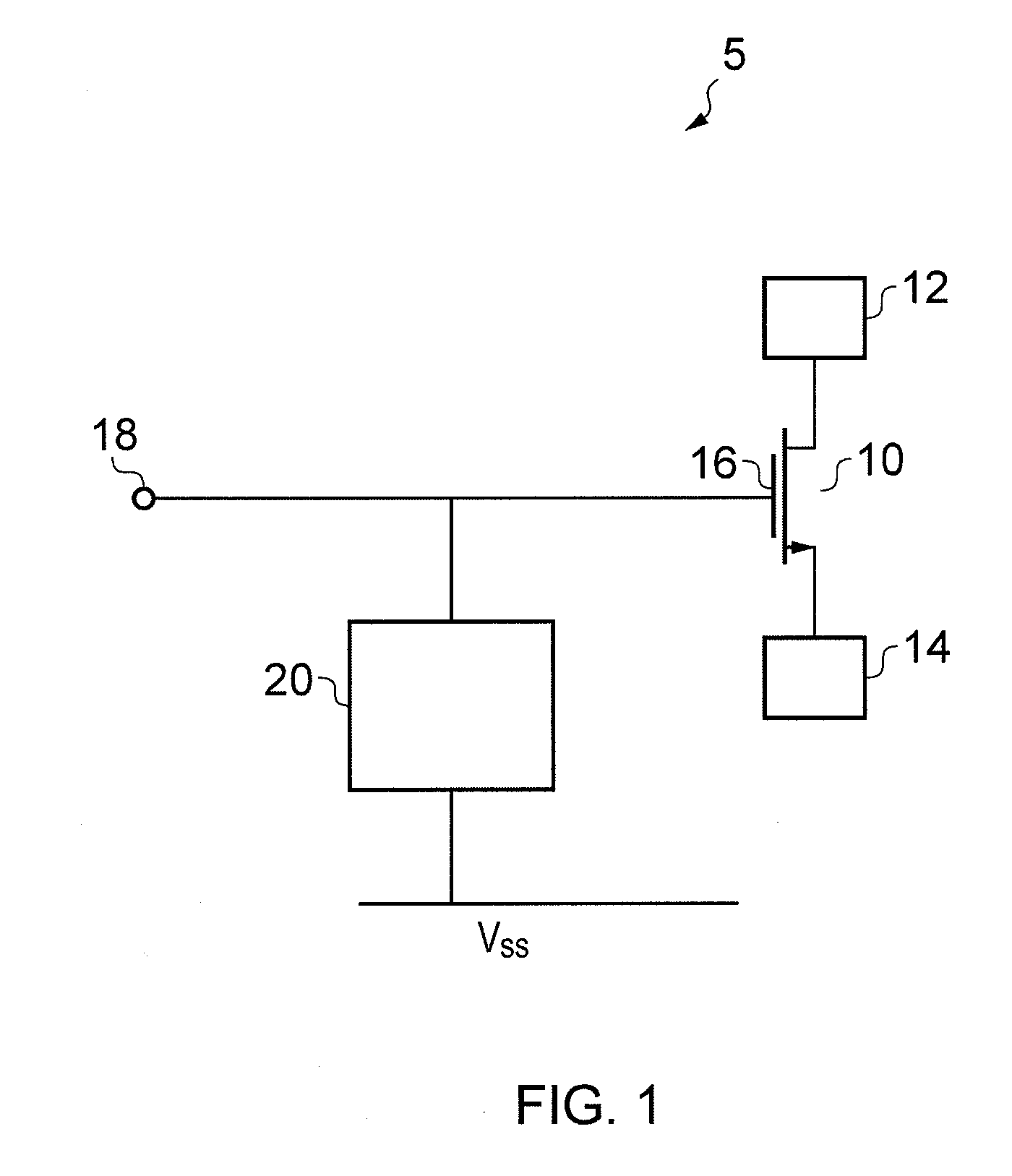

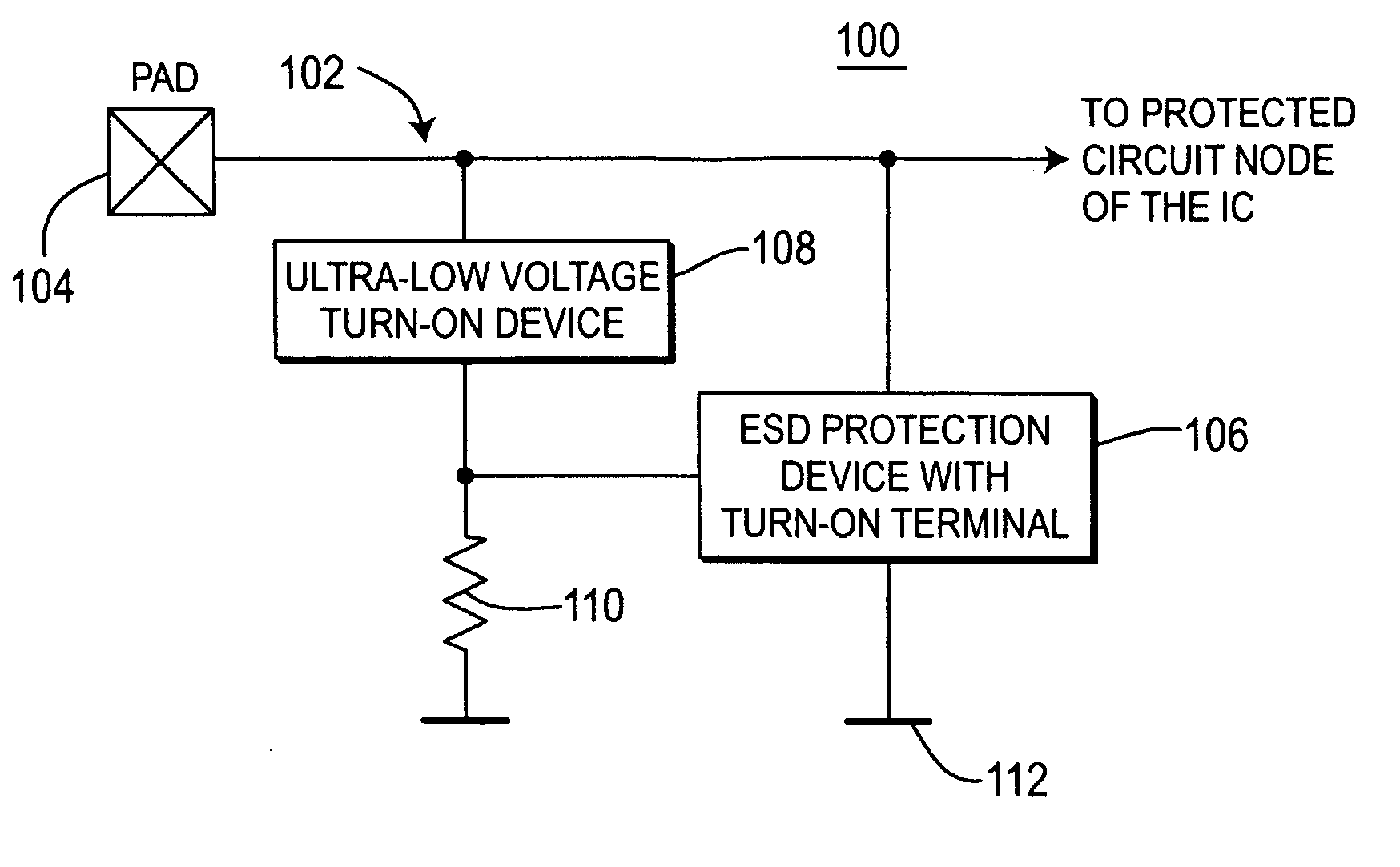

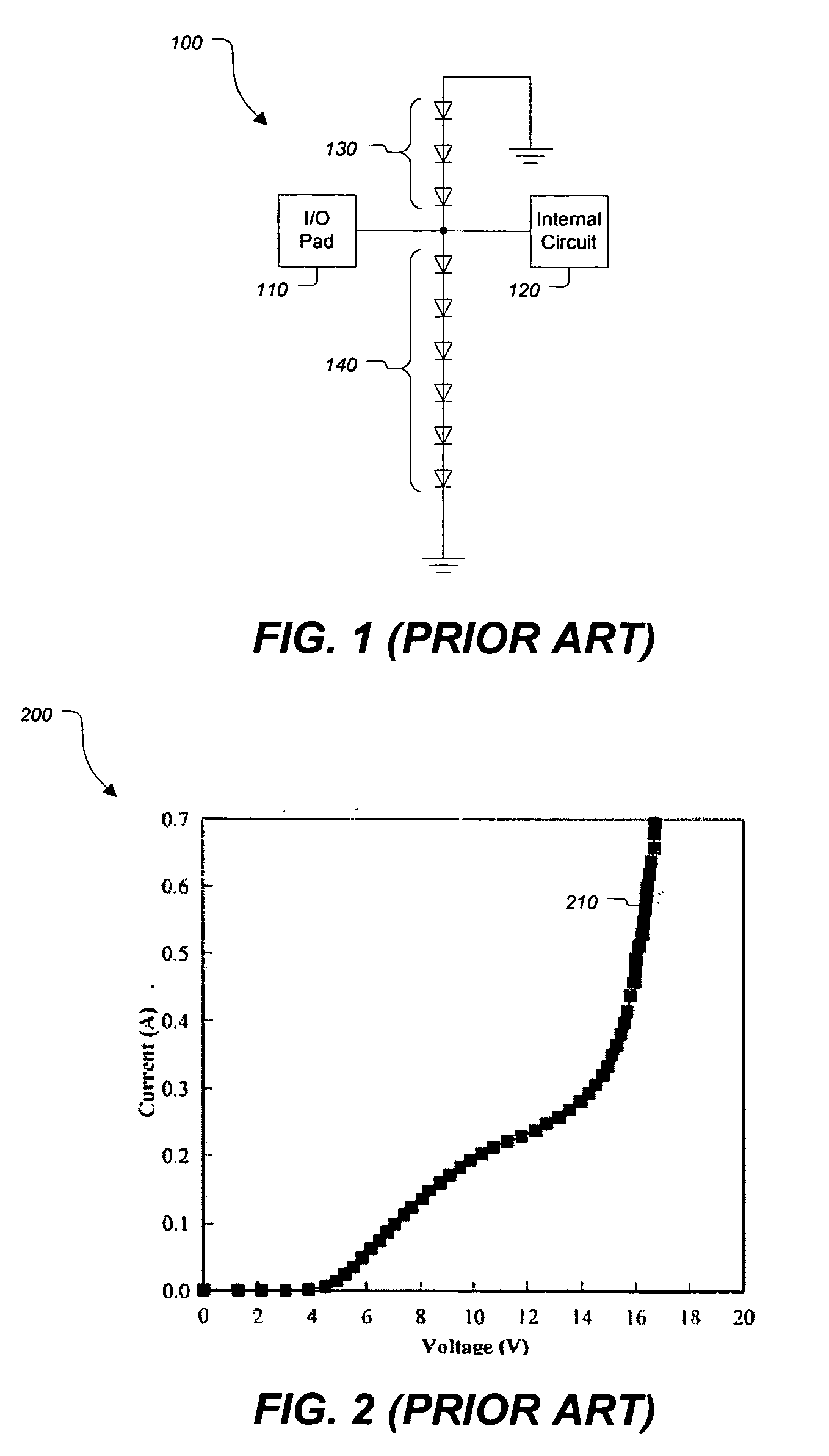

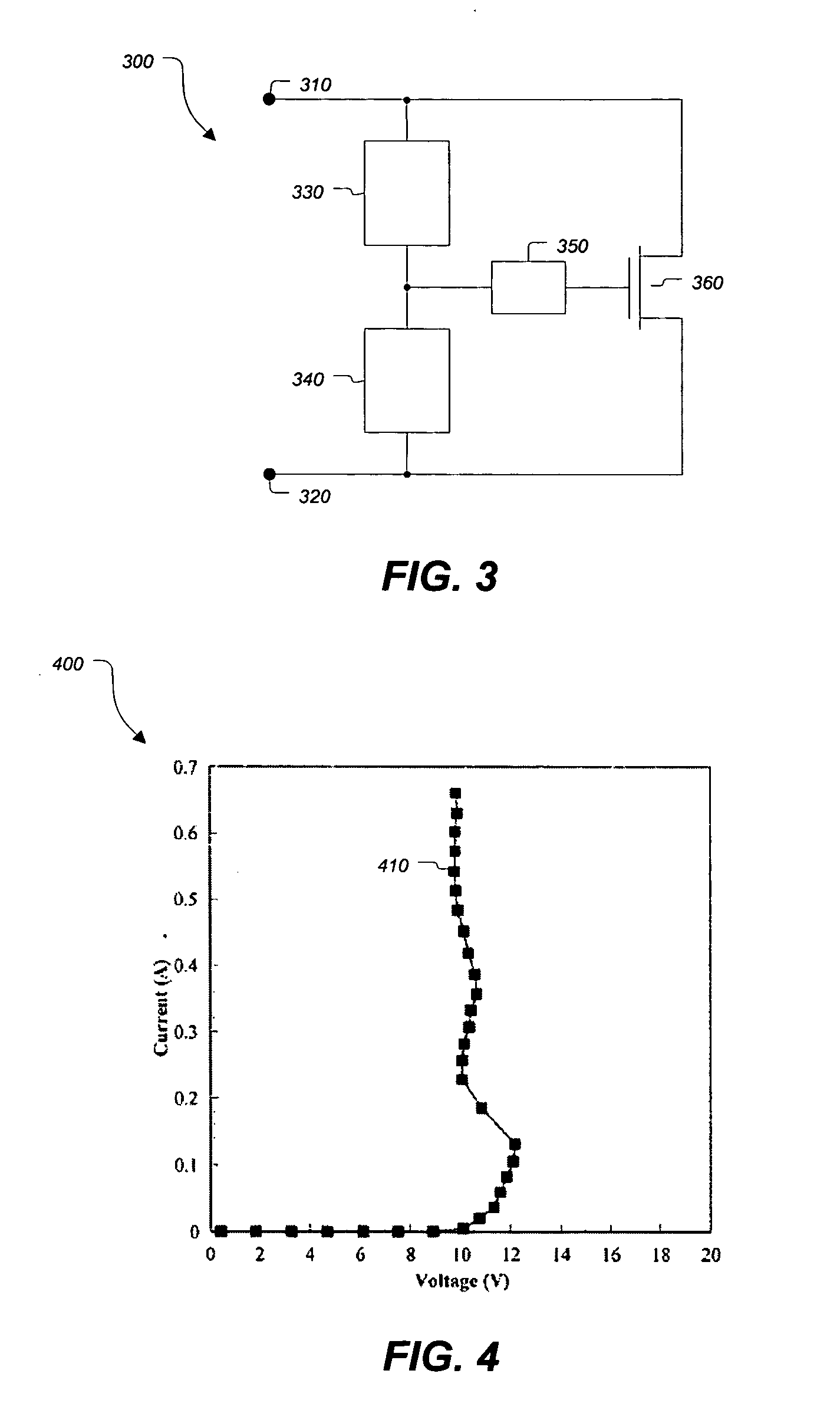

Electrostatic discharge protection structures for high speed technologies with mixed and ultra-low voltage supplies

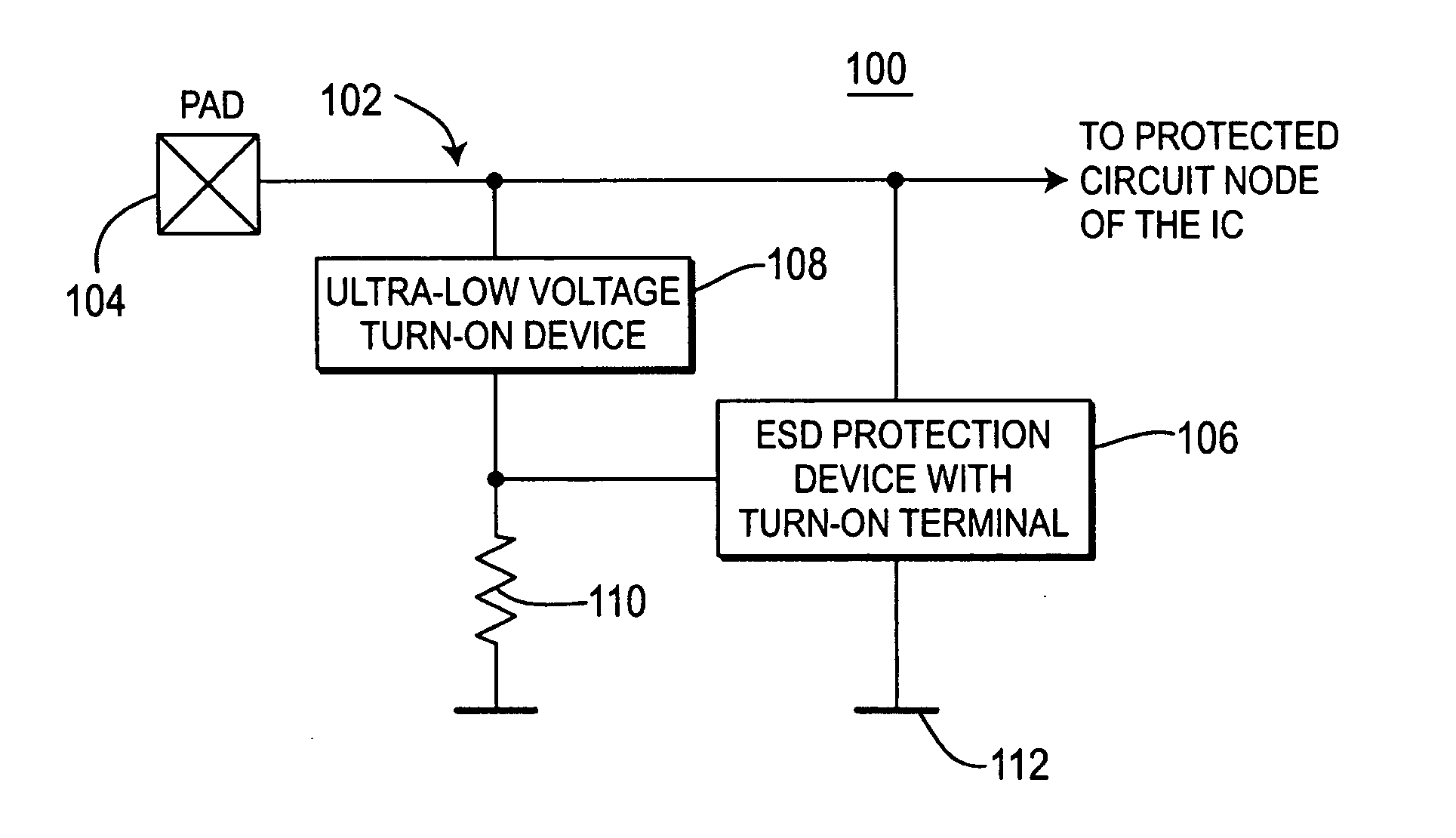

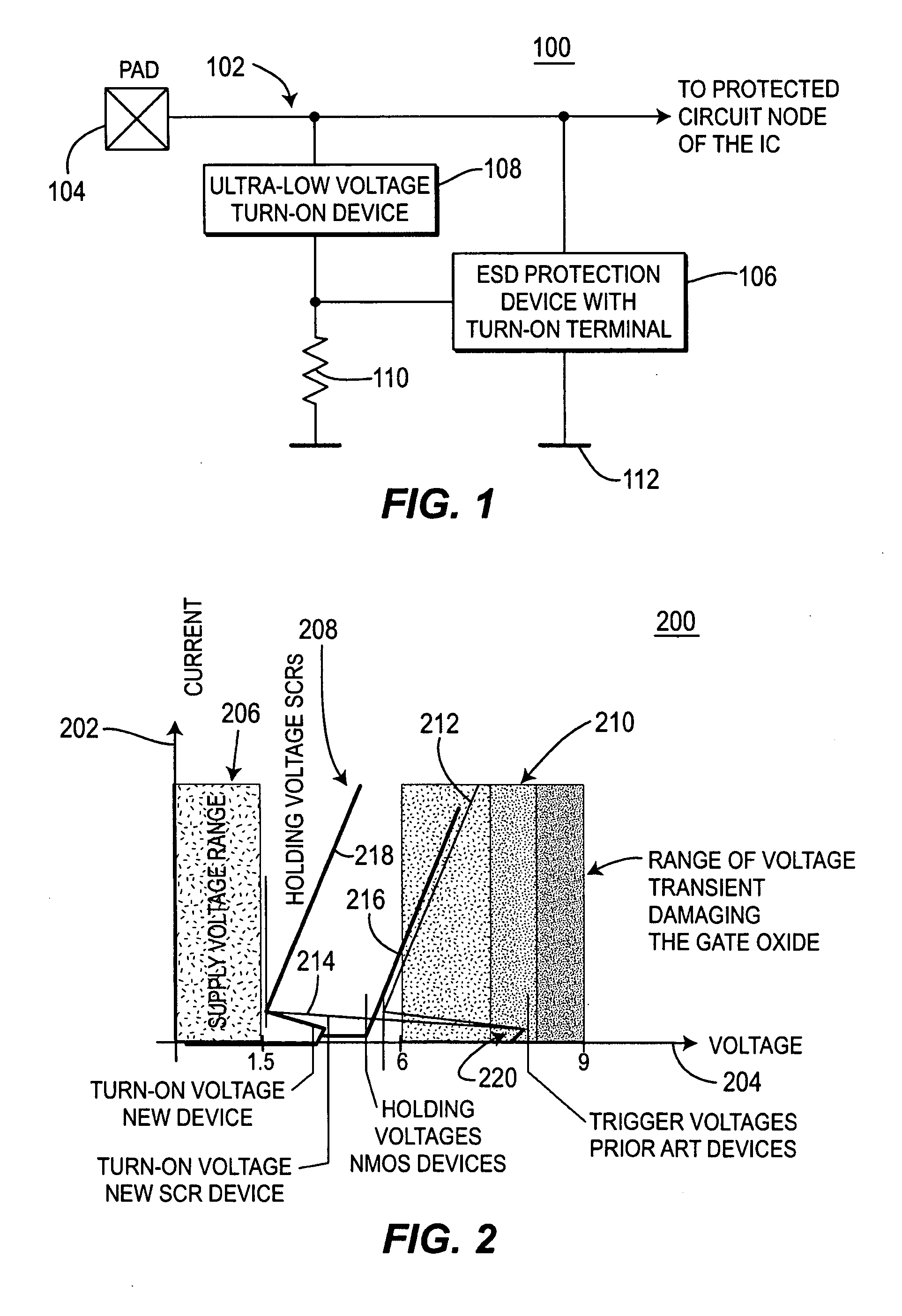

An electrostatic discharge (ESD) protection circuit in a semiconductor integrated circuit (IC) having protected circuitry is provided herein. In one embodiment, a circuit for protecting an integrated circuit from ESD includes a protected circuit node in the integrated circuit, a multiple stage transistor pump circuit coupled to the protected circuit node, and an electrostatic discharge protection circuit having a trigger coupled to the multiple stage transistor pump circuit. The multiple stage transistor pump circuit may comprise a Darlington transistor pump circuit.

Owner:SOFICS BVBA

Electro-static discharge protection circuit and method for fabricating the same

ActiveUS20060145260A1TransistorSemiconductor/solid-state device detailsElectrostatic discharge protectionElectrical and Electronics engineering

An ESD protection circuit using an N-type extended drain silicon controlled rectifier (N-EDSCR) and a method for fabricating the same are provided. An electro-static discharge (ESD) protection circuit includes a substrate, a well formed in the substrate, a drift region having a predetermined portion overlapped with the well, a plurality of first diffusion layers respectively formed in the well and the drift region, a plurality of second diffusion layers respectively formed in the well and the drift region, wherein corresponding first and second diffusion layers in the well are formed separately from each other and those in the drift region are formed adjacent to each other, a source region formed in a manner of surrounding a second conductive type diffusion layer inside the well, and a gate electrode formed on the well between the source and the drift region.

Owner:KEY FOUNDRY CO LTD

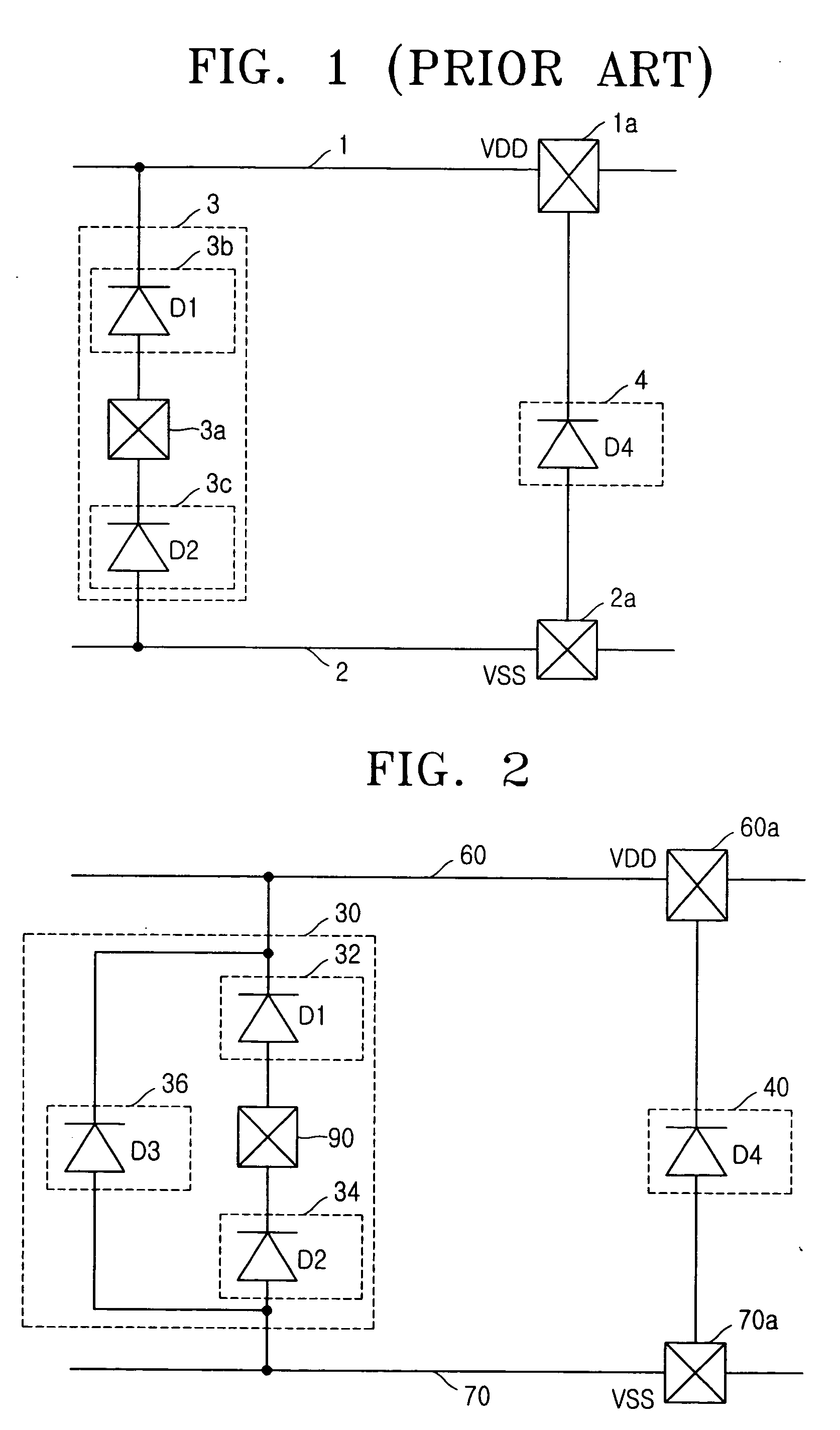

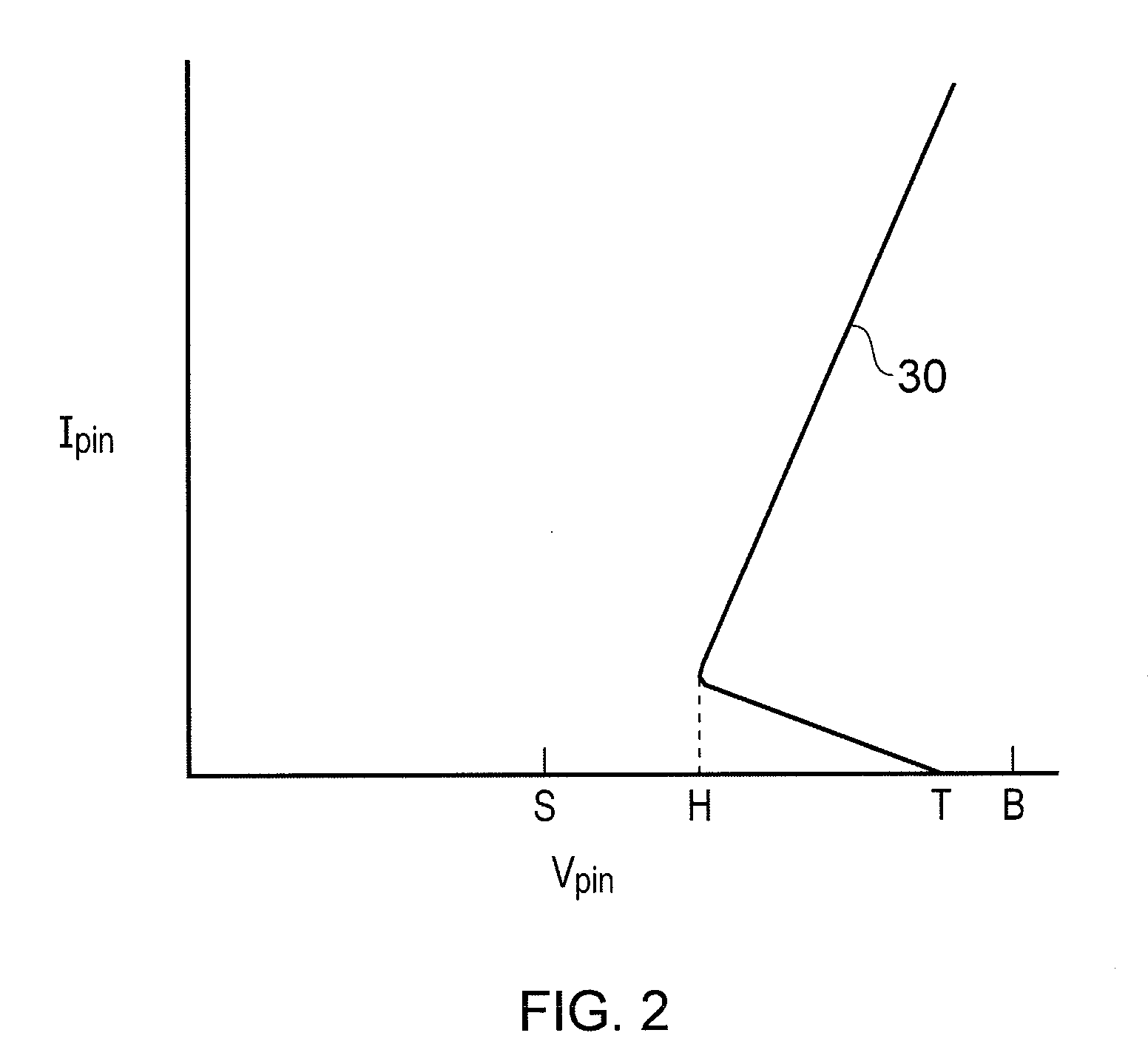

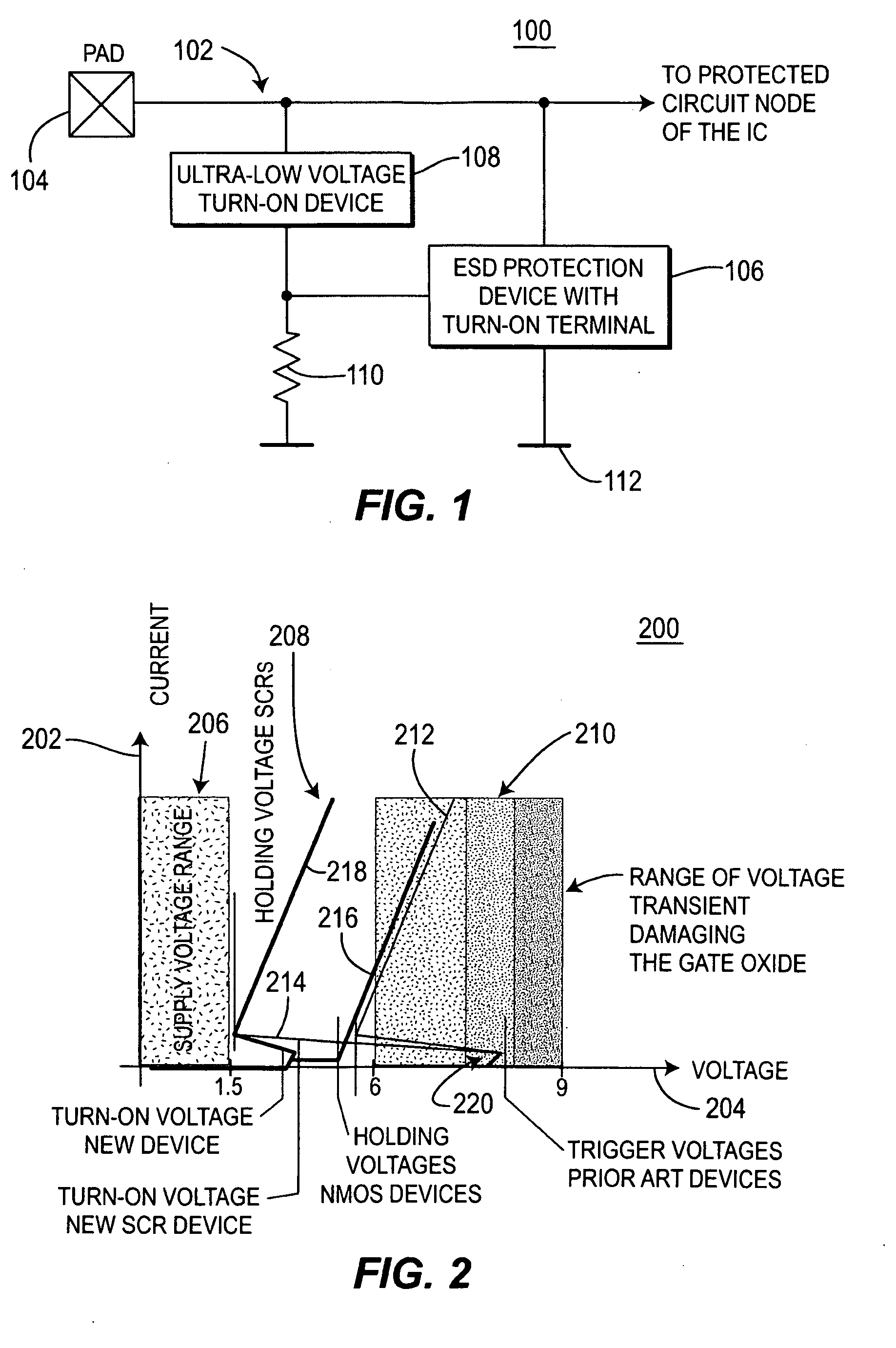

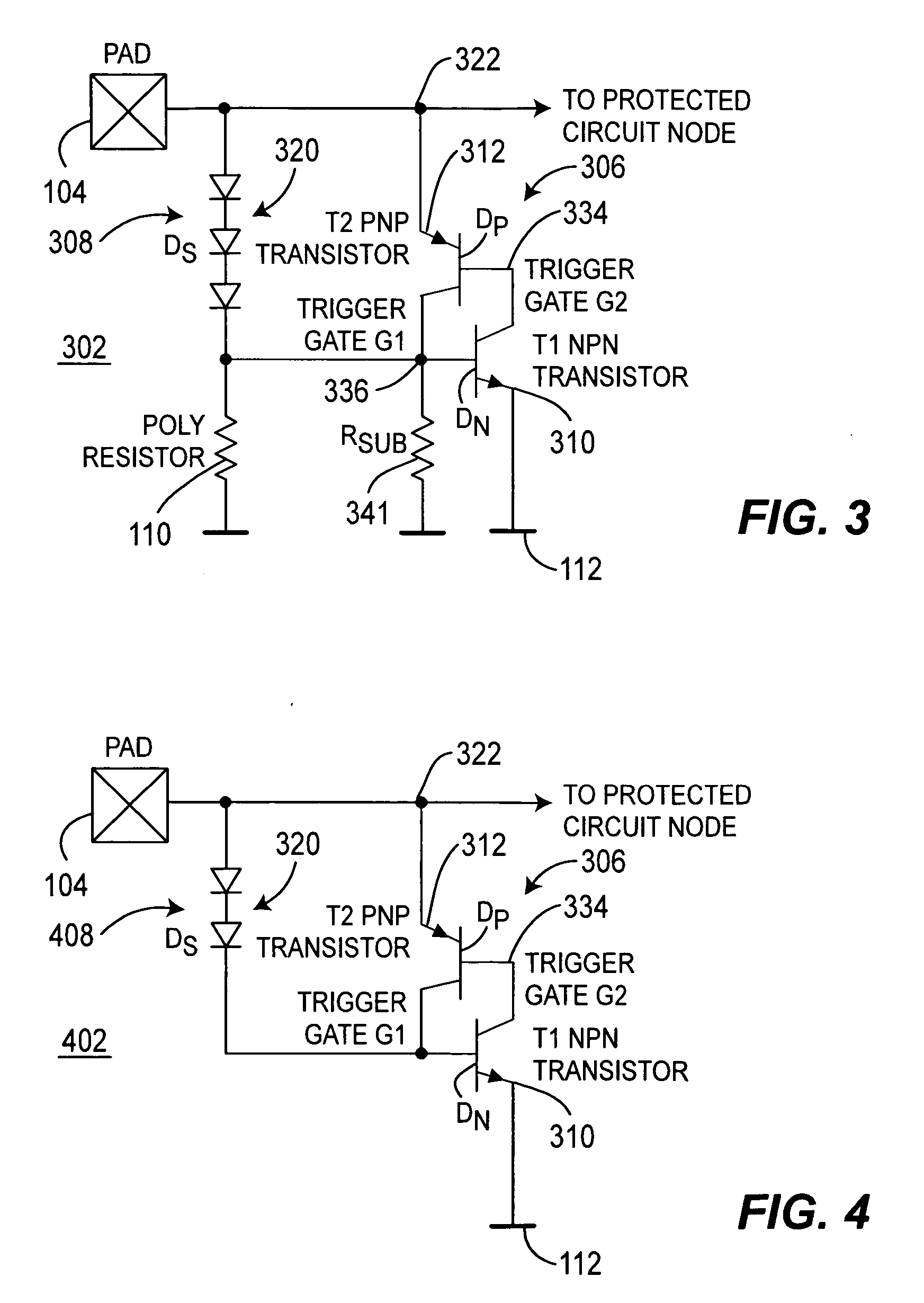

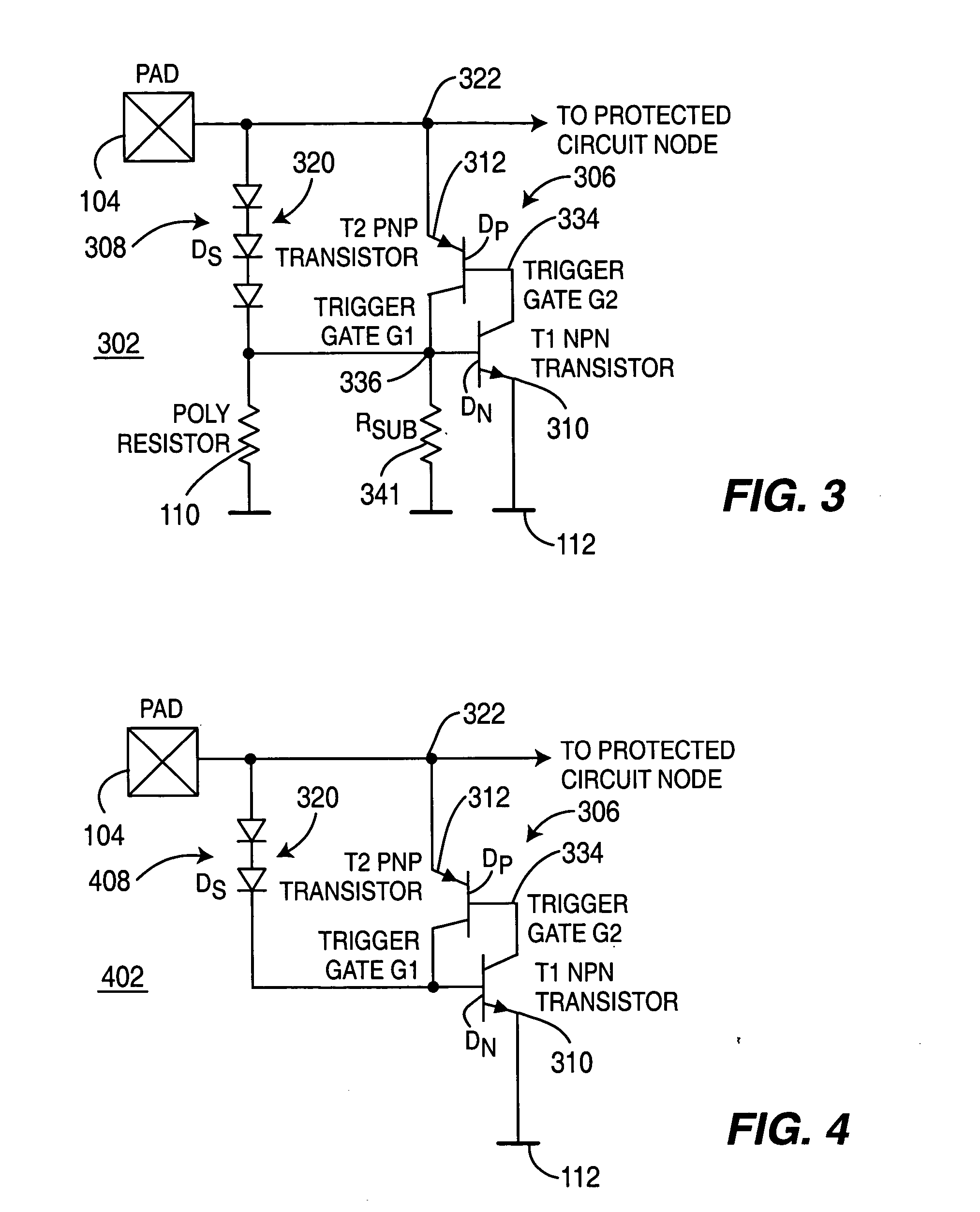

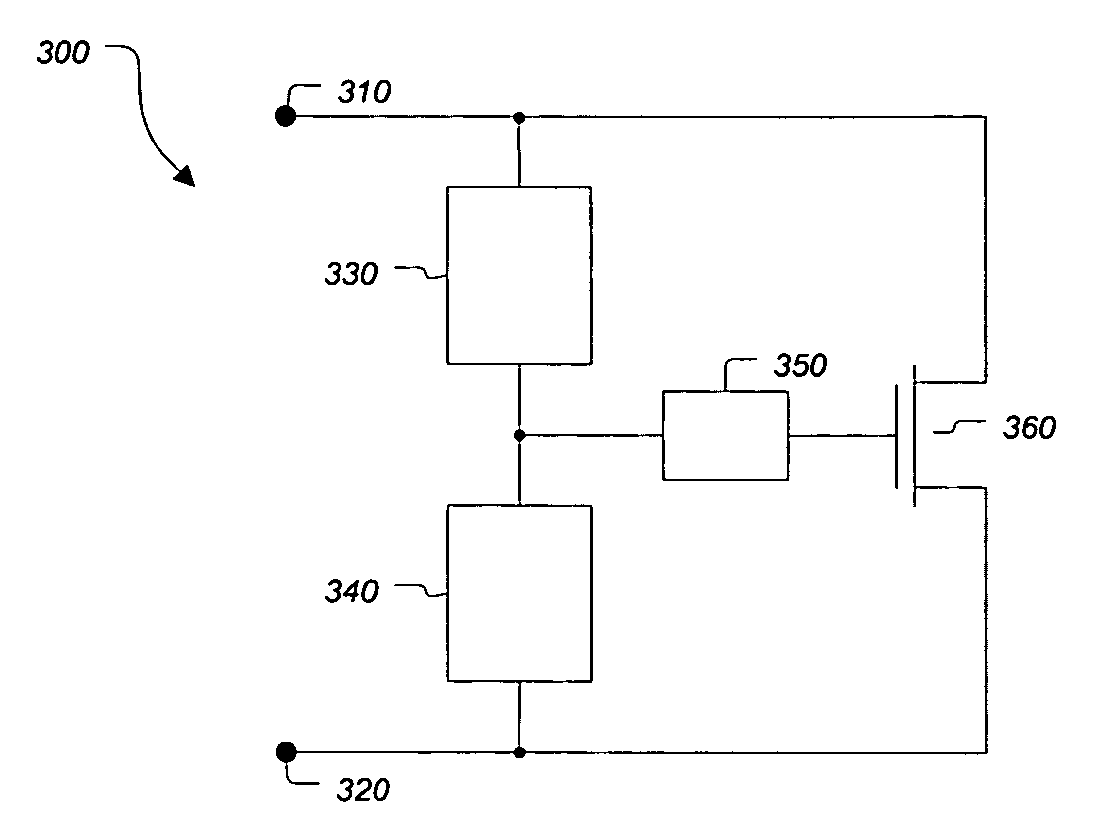

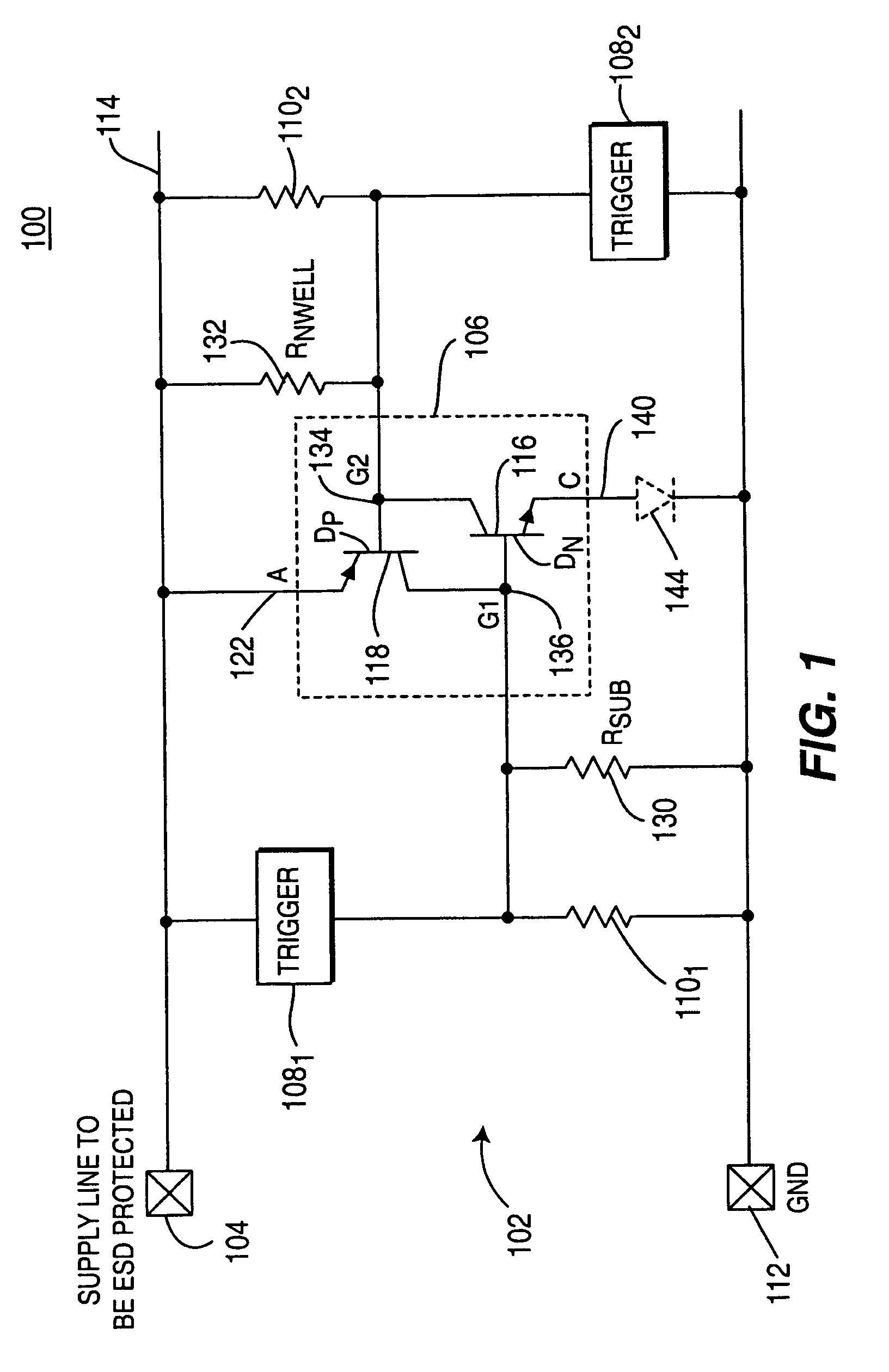

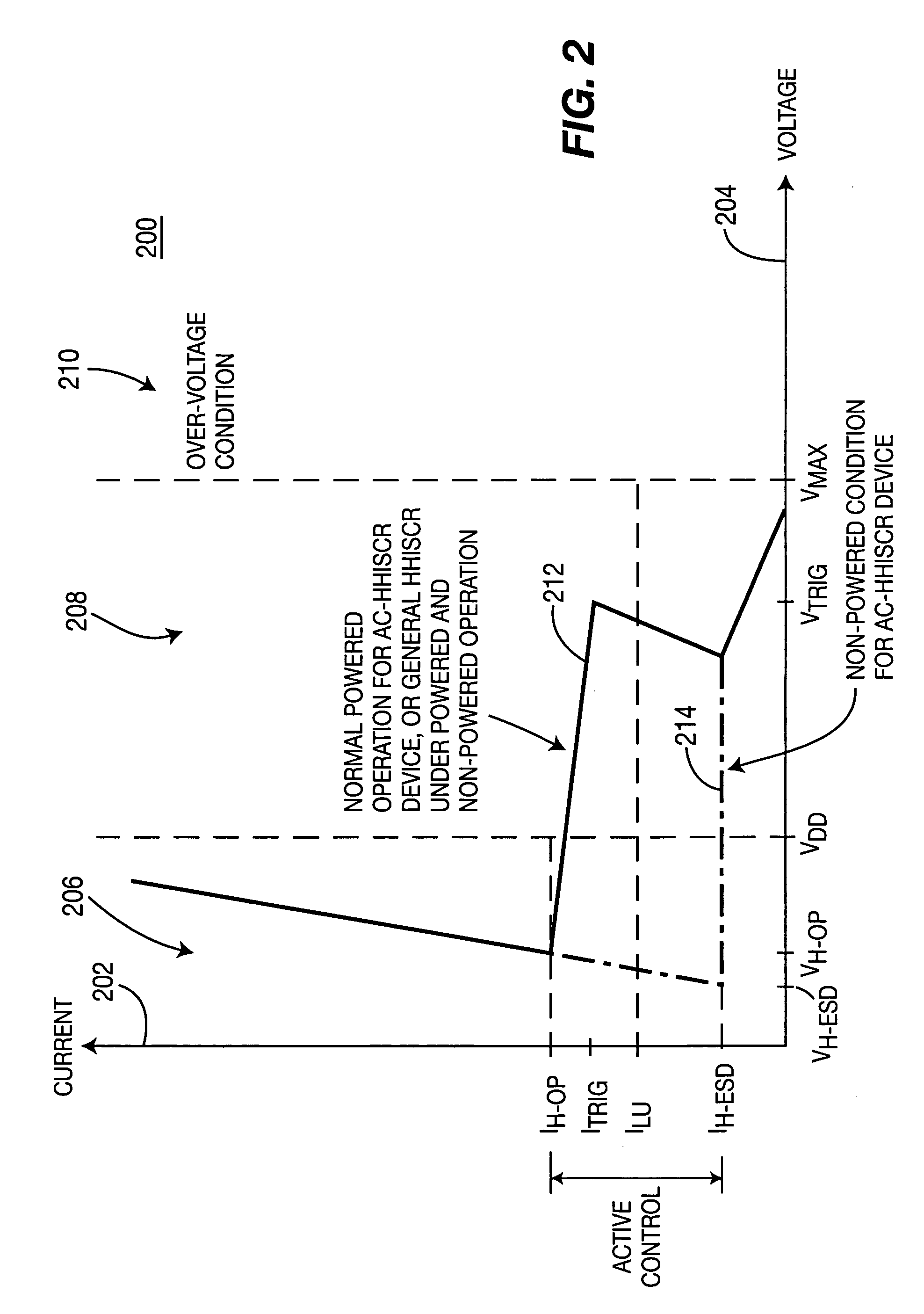

Electrostatic discharge protection structures for high speed technologies with mixed and ultra-low voltage supplies

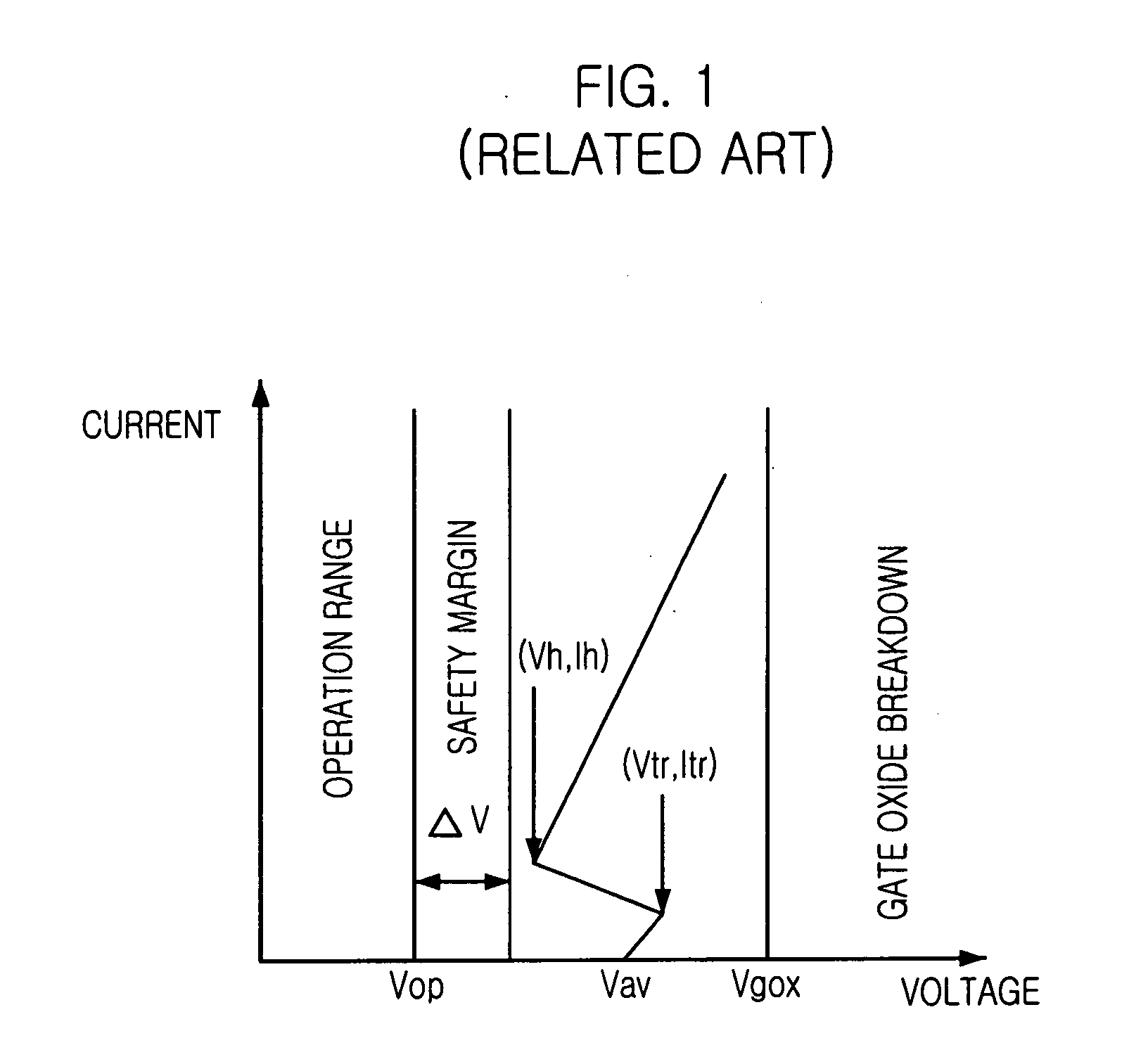

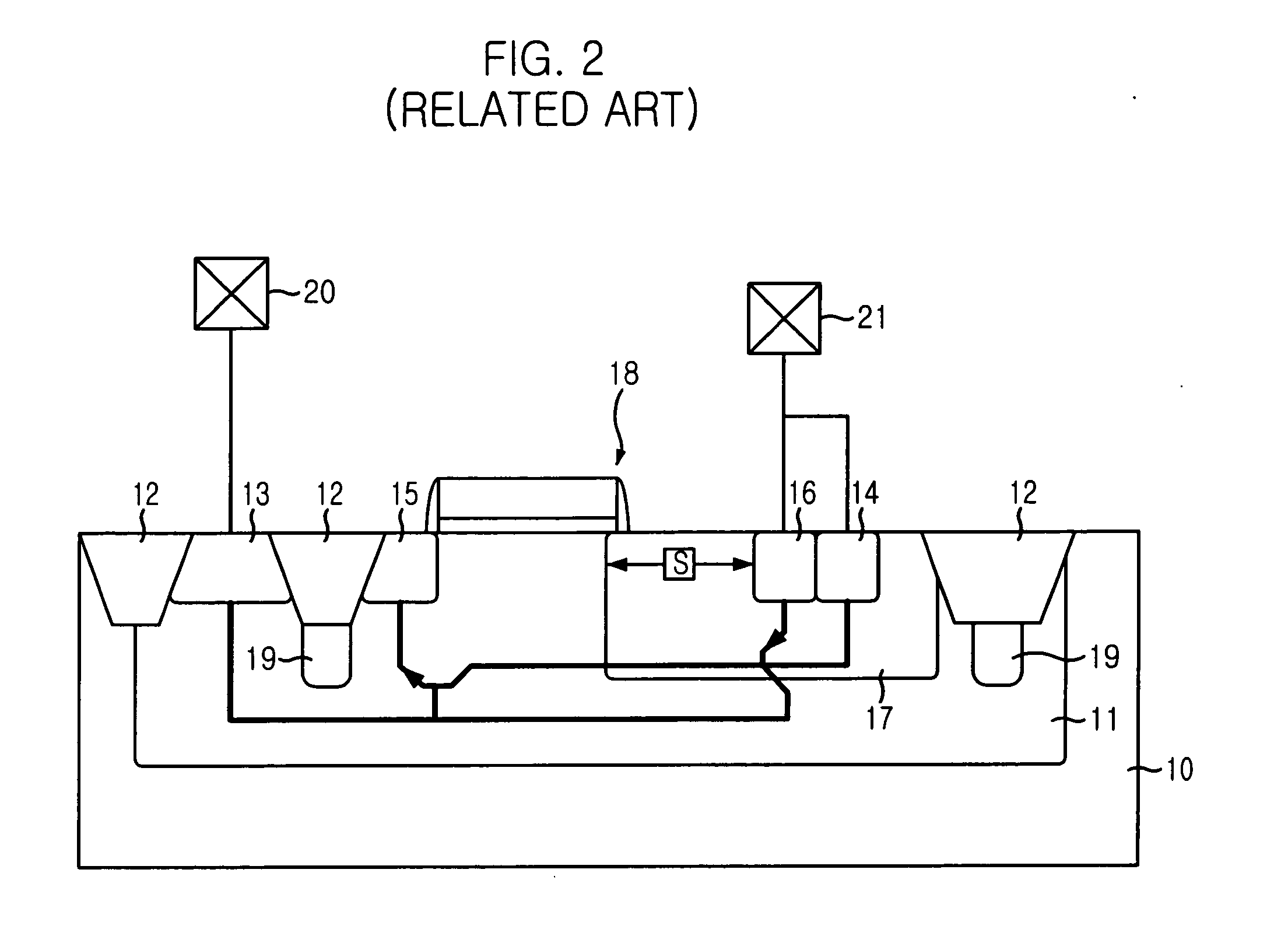

InactiveUS20050057866A1Reduce voltageProtection from damageTransistorThyristorSilicon-controlled rectifierLow voltage

An electrostatic discharge (ESD) protection circuit in a semiconductor integrated circuit (IC) having protected circuitry. In one embodiment, the ESD protection circuit includes a pad adapted for connection to a first voltage source of a protected circuit node of the IC, and a silicon controlled rectifier (SCR) having an anode adapted for coupling to the first voltage source, and a cathode adapted for coupling to a second voltage source. At least one capacitive turn-on device respectively coupled between at least one of a first gate of the SCR and the first voltage source, and a second gate of the SCR and the second voltage source.

Owner:SOFICS BVBA

Electrostatic discharge protection circuit for compound semiconductor devices and circuits

ActiveUS20080062595A1TransistorEmergency protective arrangements for limiting excess voltage/currentEngineeringElectrostatic discharge protection

An apparatus and method is disclosed for providing an electrostatic discharge protection circuit for compound semiconductor devices and circuits. The electrostatic discharge protection circuit comprises a first terminal and a second terminal. The electrostatic discharge protection circuit further comprises a transistor shunt element that is operably coupled between the first terminal and the second terminal; the transistor shunt element is capable of providing a bi-directional discharge path between the first terminal and the second terminal. The electrostatic discharge protection circuit further comprises a shut-off element that is operably coupled with the second terminal; the shut-off element is capable of keeping the transistor shunt element turned-off.

Owner:QORVO US INC

Electrostatic discharge protection for embedded components

InactiveUS20060152334A1Protection elementLow costPrinted circuit aspectsHigh voltage circuit adaptationsCapacitanceElectrical resistance and conductance

An improved electrical circuit that includes an embedded electrical component and an embedded voltage variable material (“VVM”) is provided. In one embodiment, the embedded VVM is provided as a voltage variable substrate, which is used in combination with an embedded electrical component, such as an embedded resistive material or an embedded capacitive material.

Owner:LITTELFUSE INC

Electrostatic discharge protection structures having high holding current for latch-up immunity

InactiveUS7064393B2High holding currentOvercome disadvantagesTransistorThyristorElectrical resistance and conductanceSilicon-controlled rectifier

An electrostatic discharge (ESD) protection device having high holding current for latch-up immunity. The ESD protection circuit is formed in a semiconductor integrated circuit (IC) having protected circuitry. The ESD protection device includes a silicon controlled rectifier (SCR) coupled between a protected supply line of the IC and ground. A trigger device is coupled from the supply line to a first gate of the SCR, and a first substrate resistor is coupled between the first gate and ground. A first shunt resistor is coupled between the first gate and ground, wherein the shunt resistor has a resistance value lower than the substrate resistor.

Owner:SOFICS BVBA