Patents

Literature

8049 results about "Isolation layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Layer isolate will isolate objects in a layer, and lock the rest of available layers. When you have complex drawings, you might want to lock and unlock layers quickly. Locking layers from layer manager definitely not good enough.

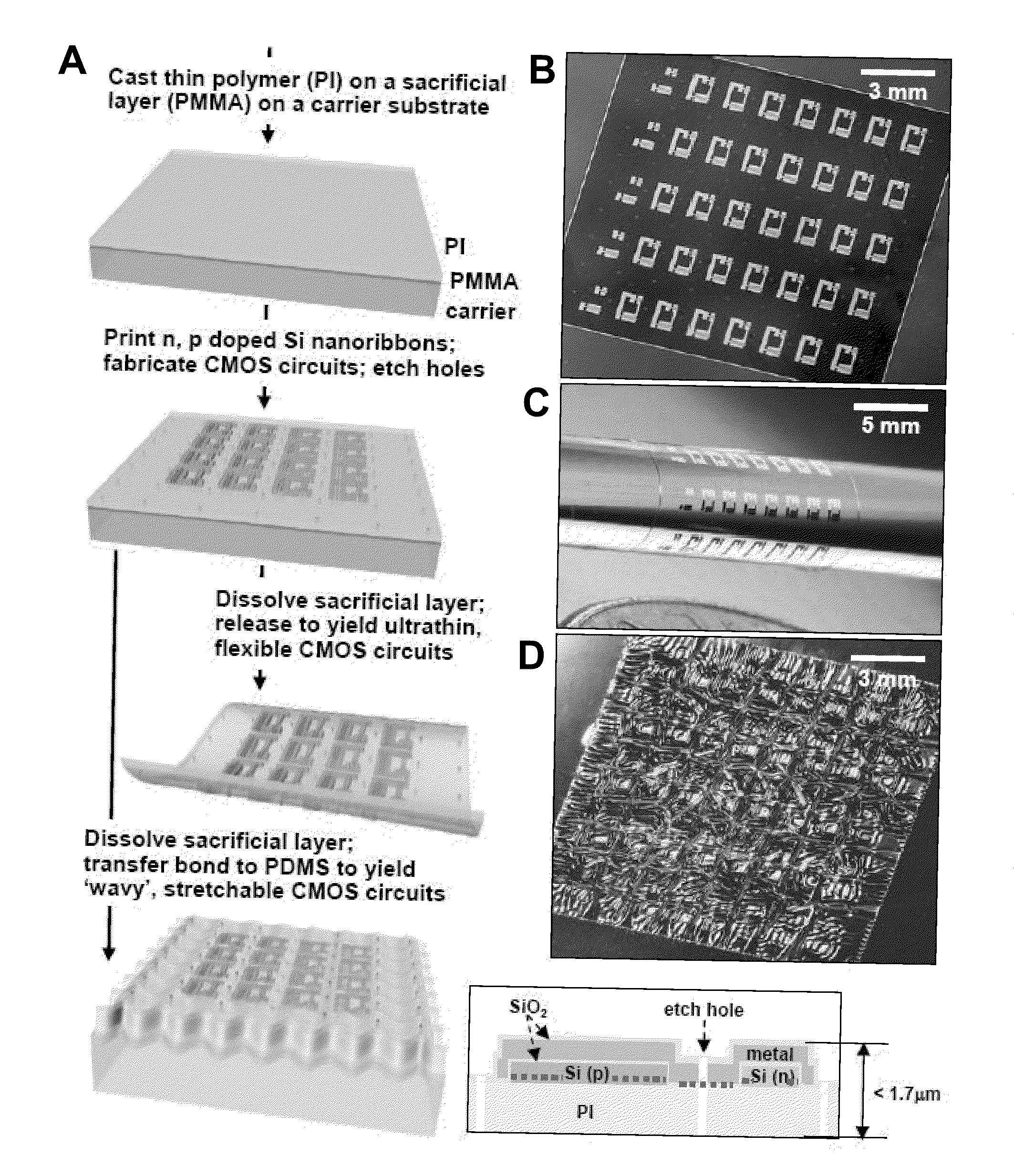

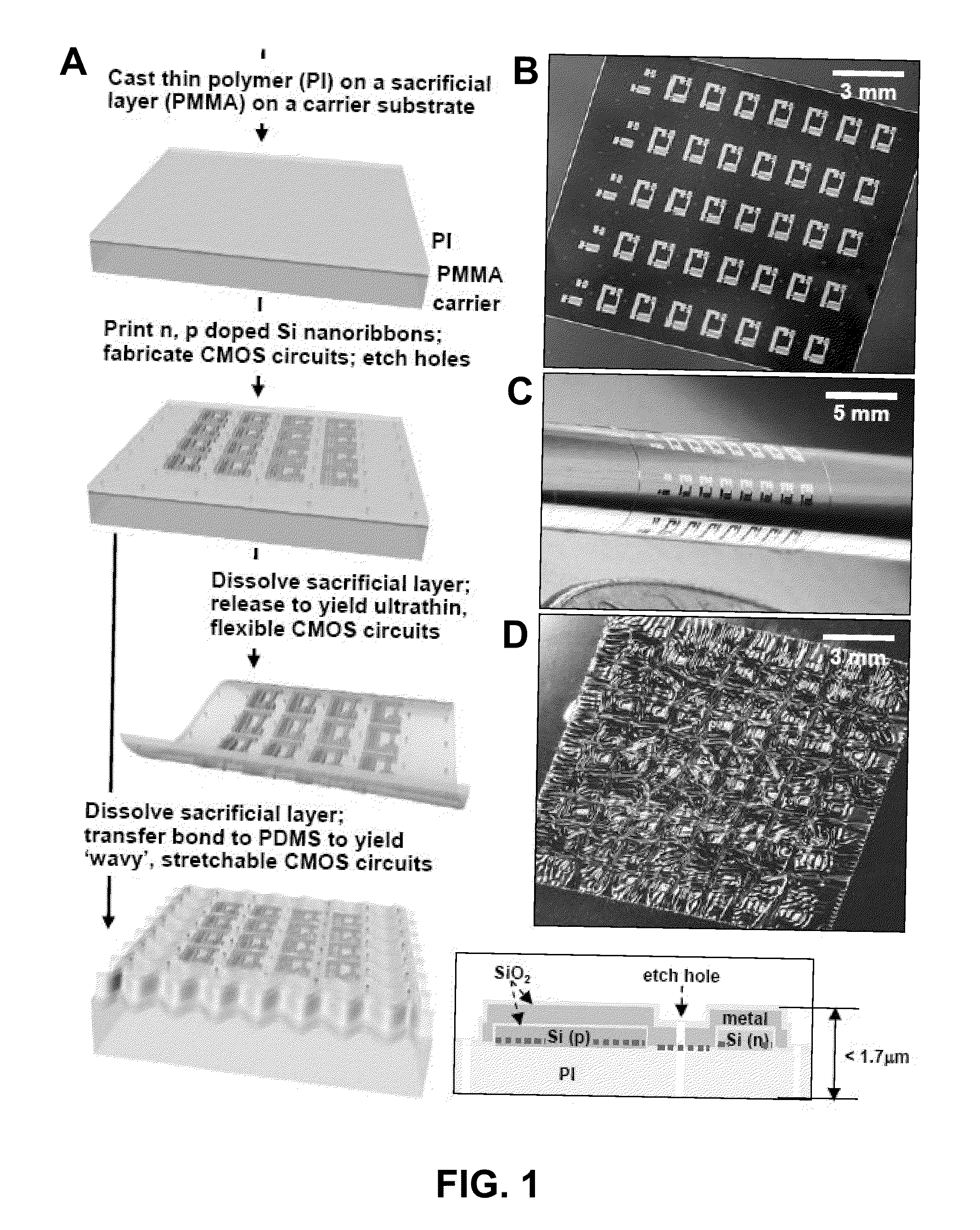

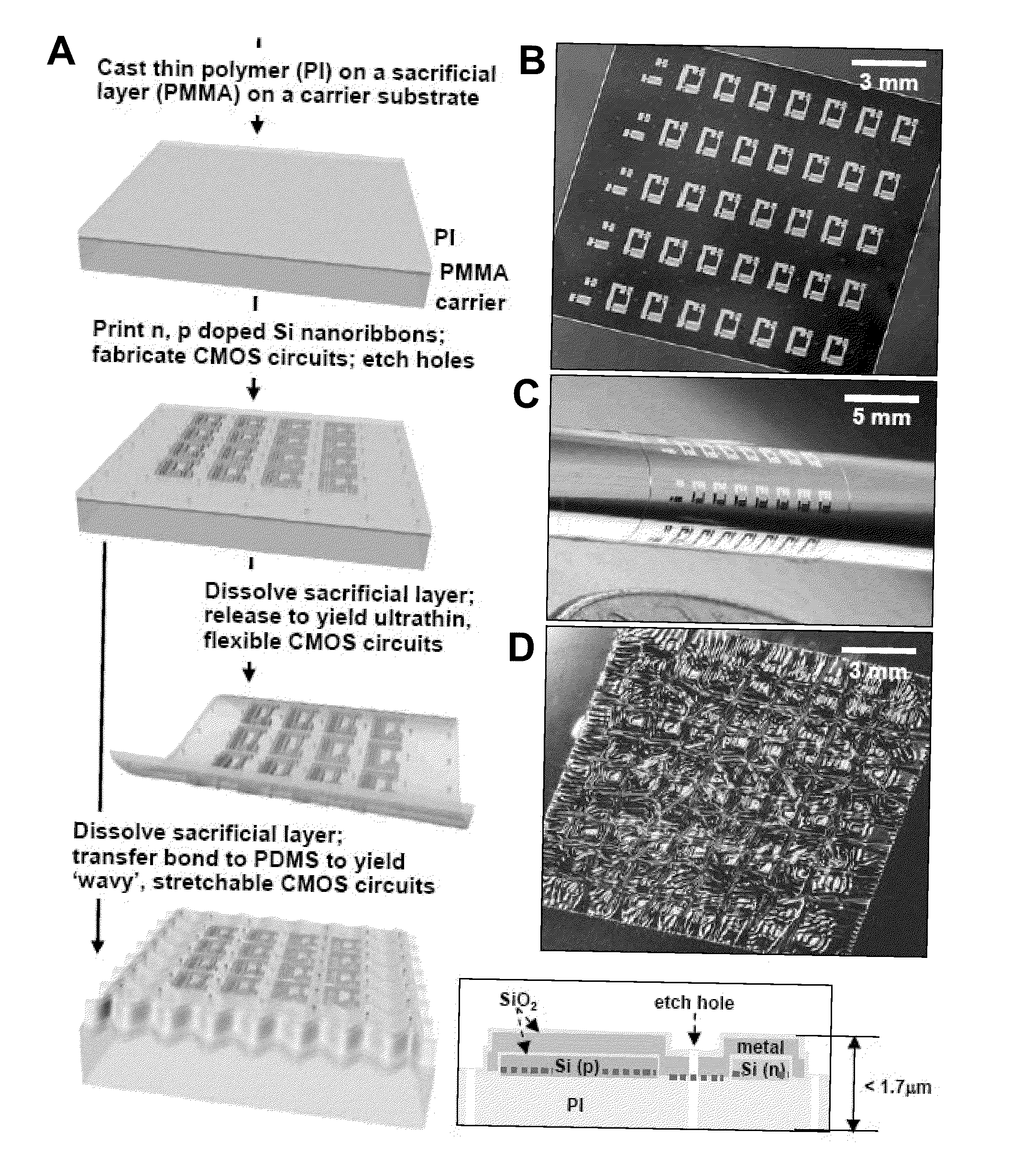

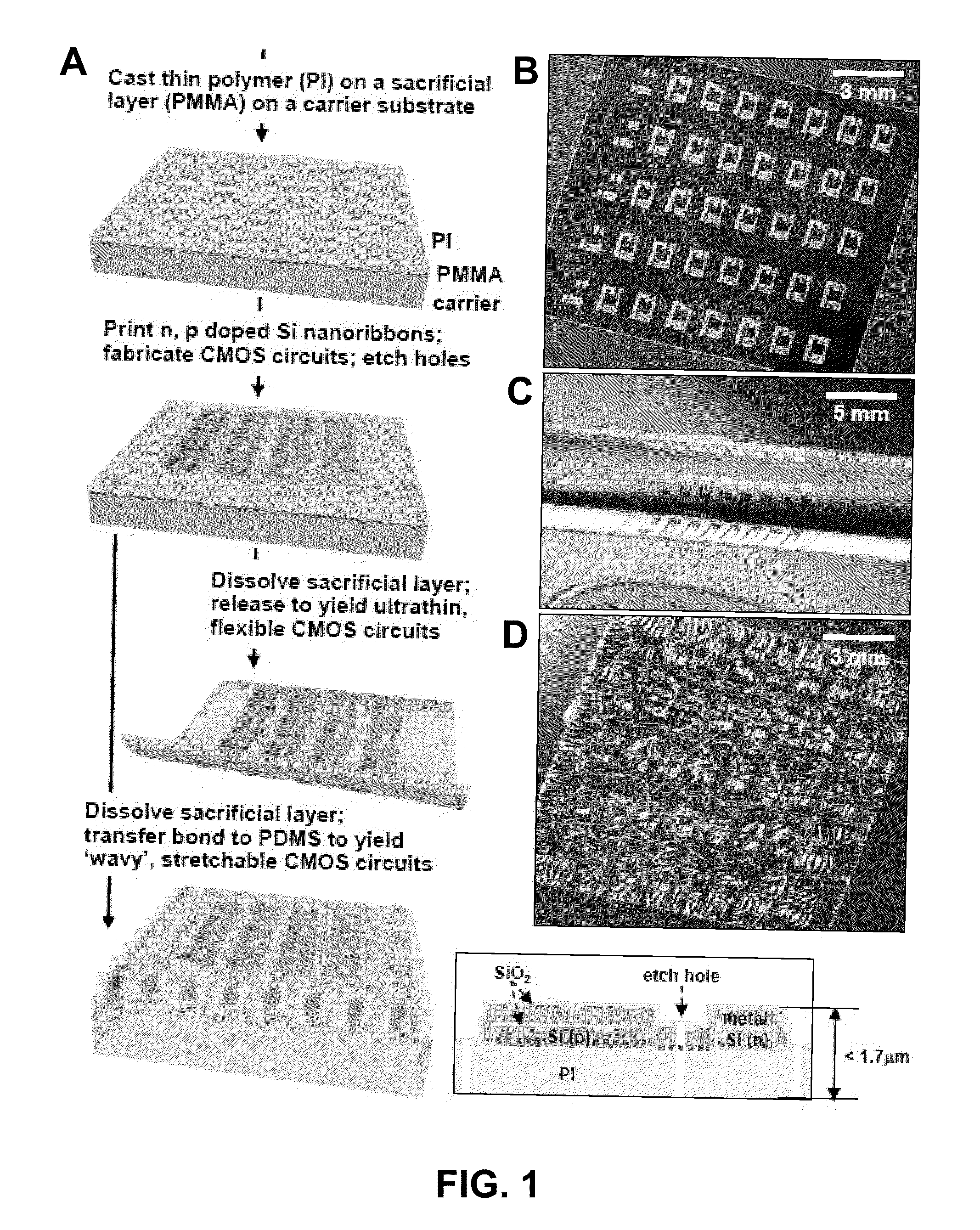

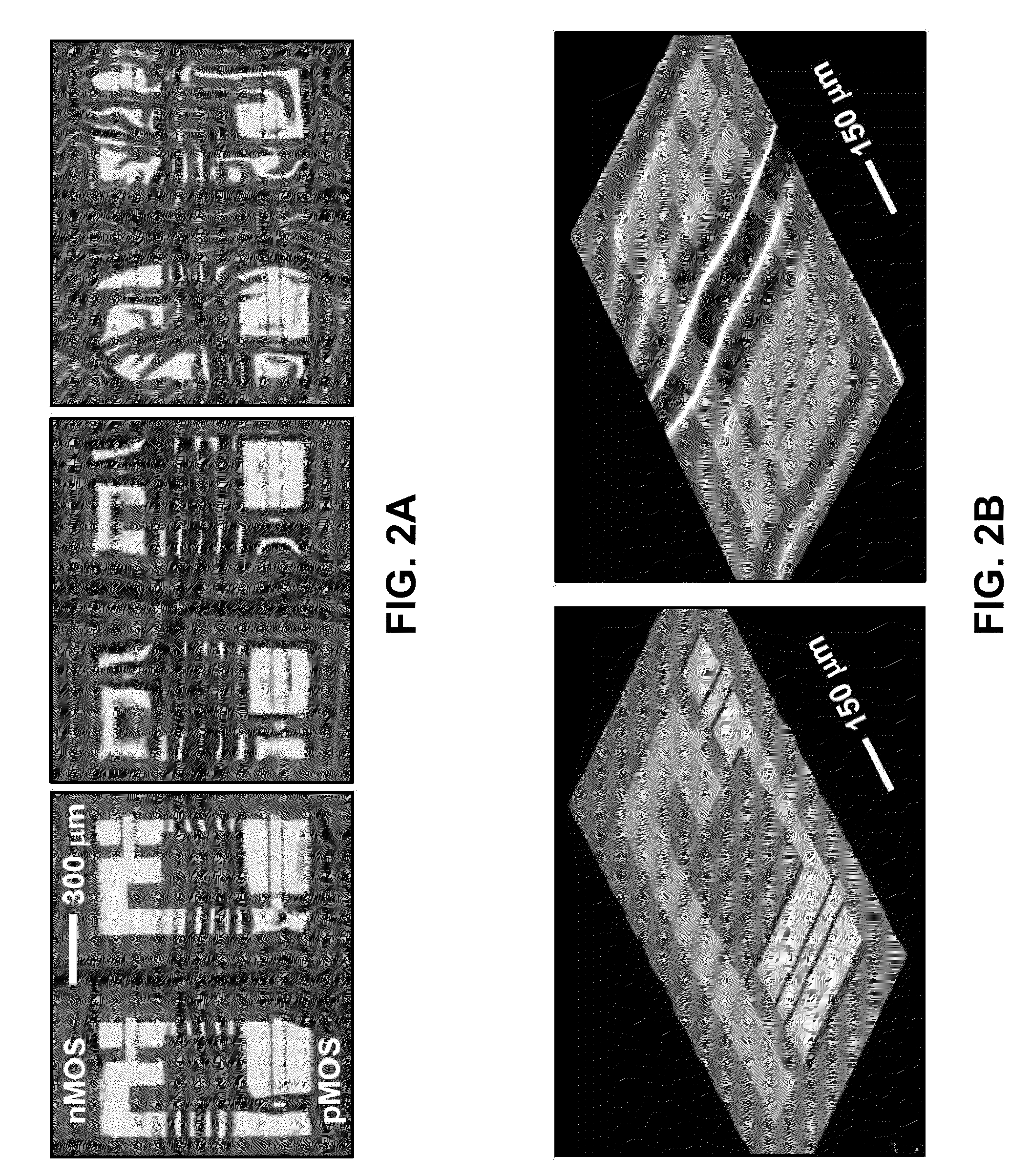

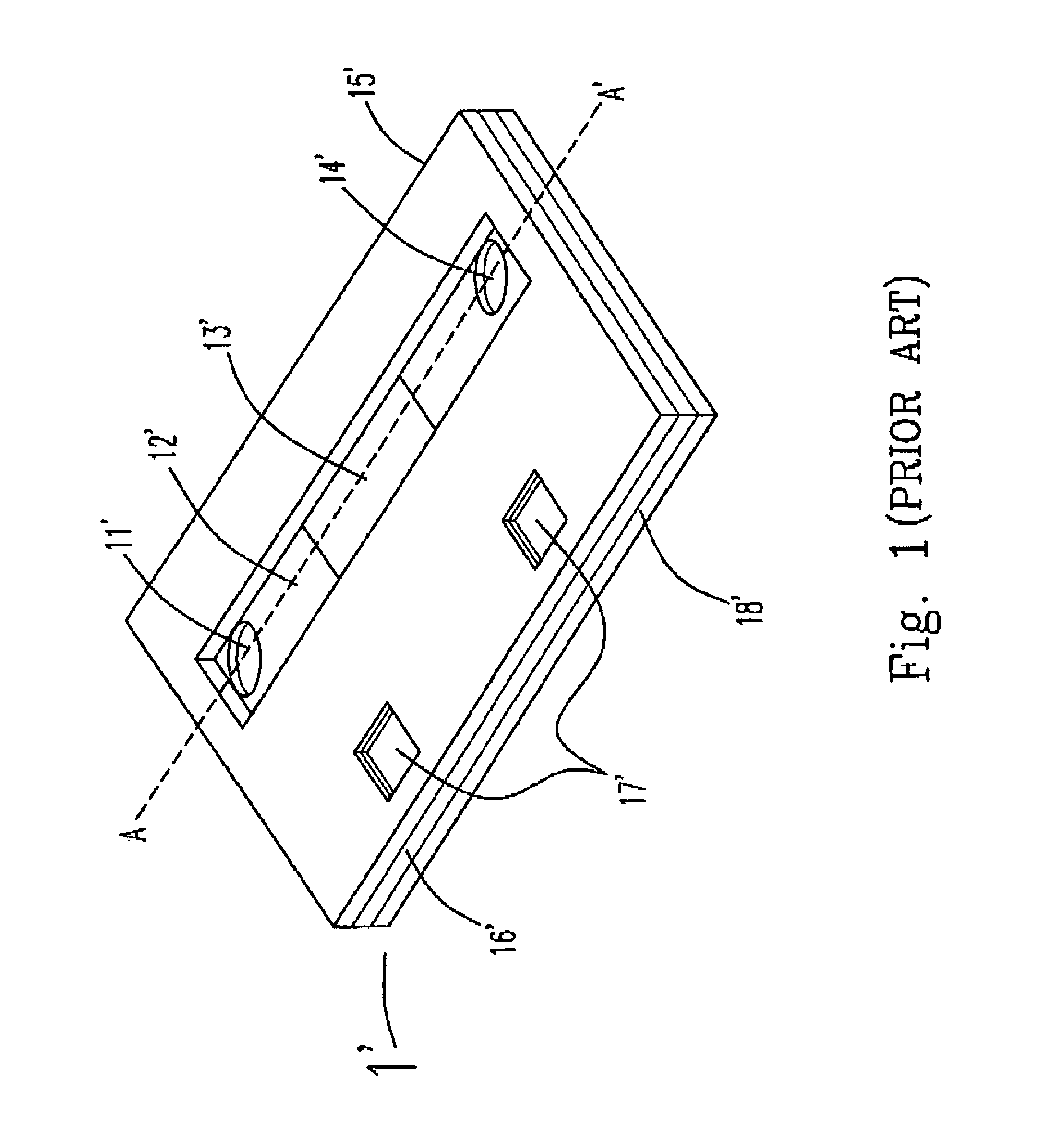

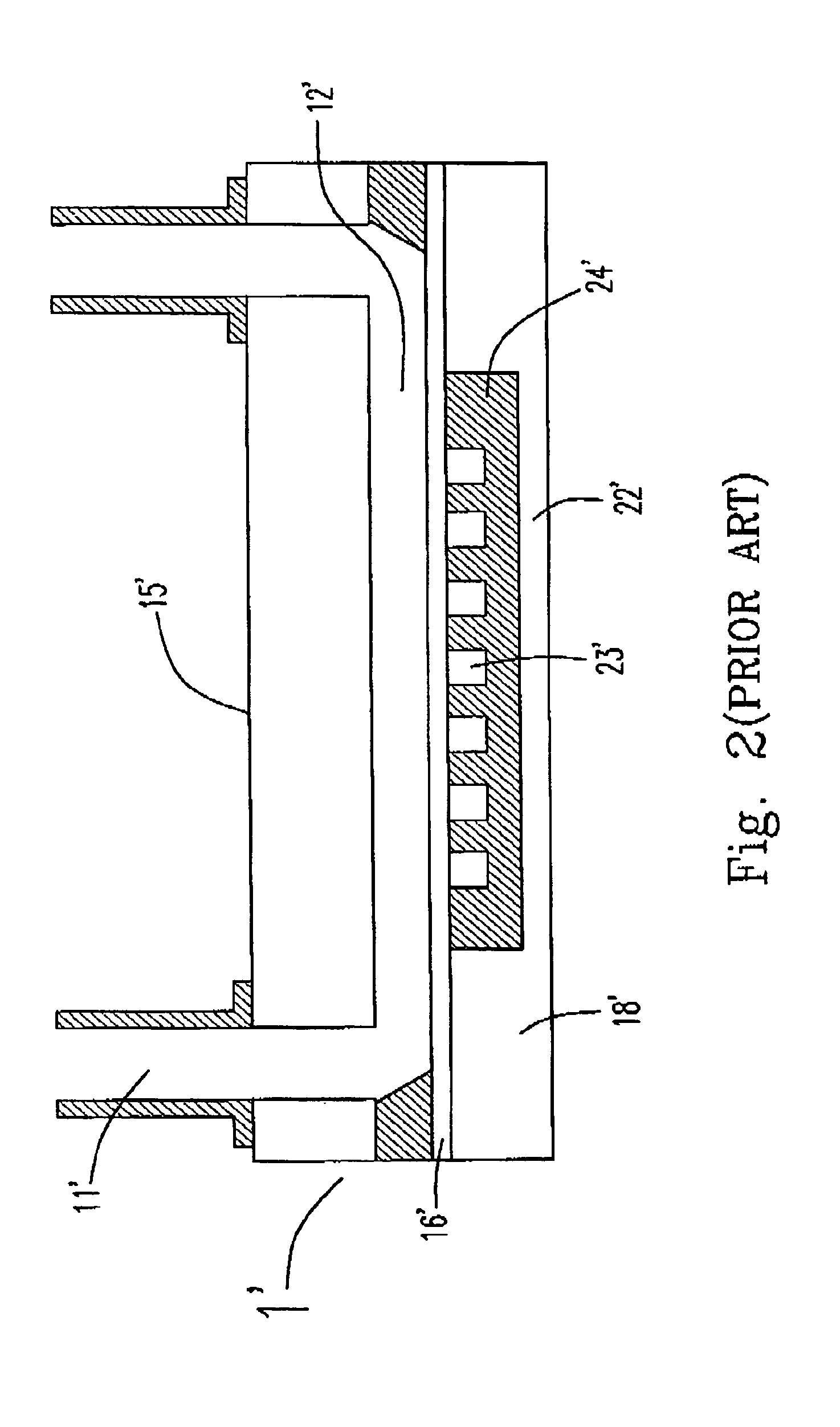

Stretchable and Foldable Electronic Devices

ActiveUS20100002402A1Easy to useQuality improvementWave amplification devicesSemiconductor/solid-state device detailsIsolation layerEngineering

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

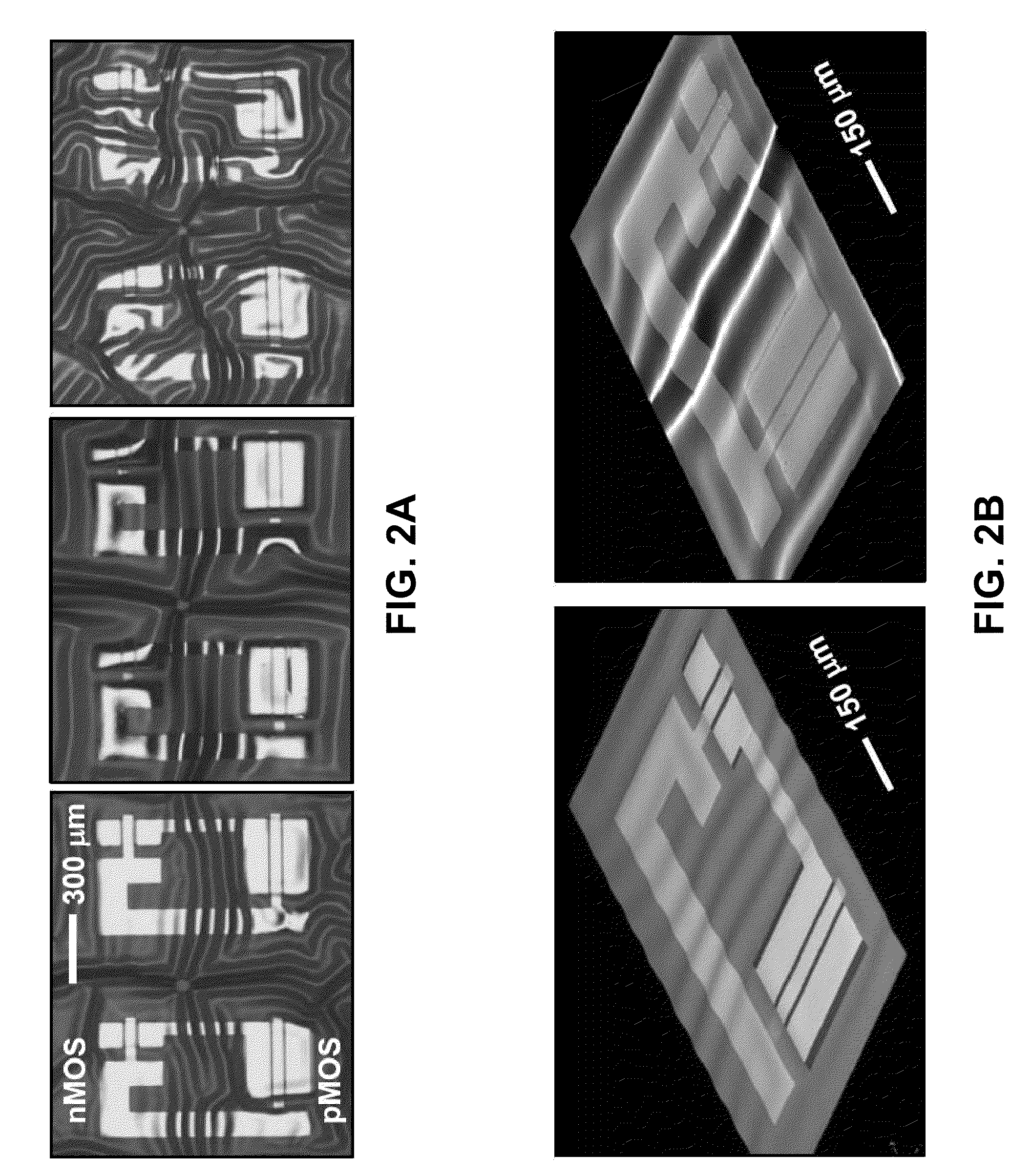

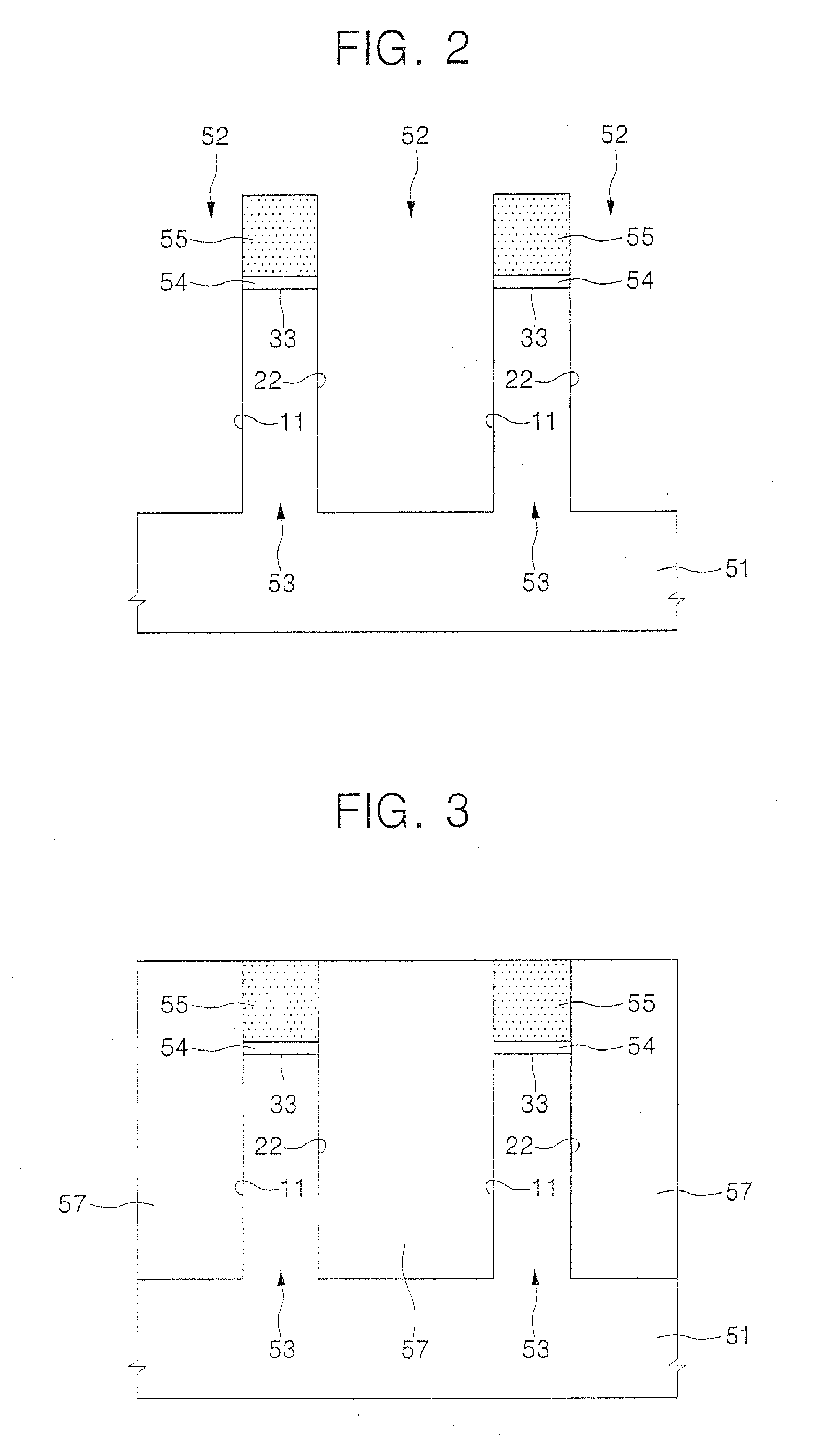

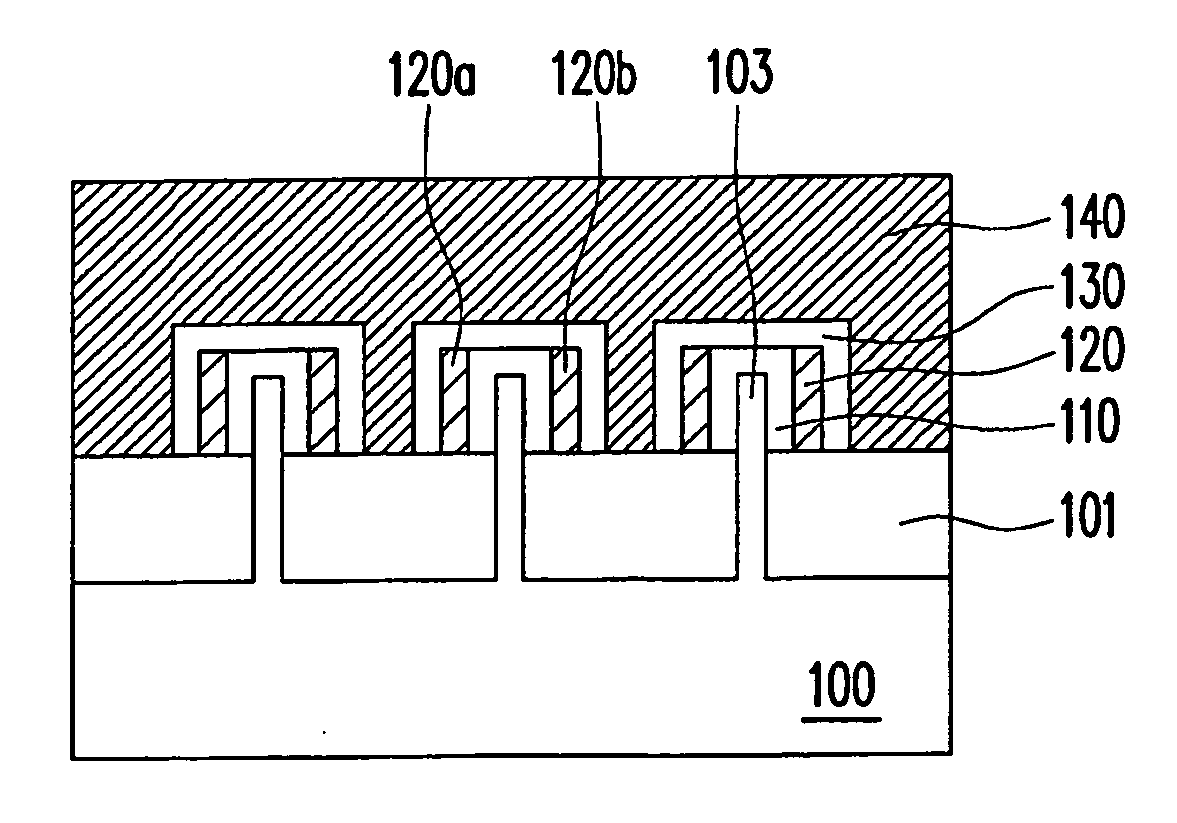

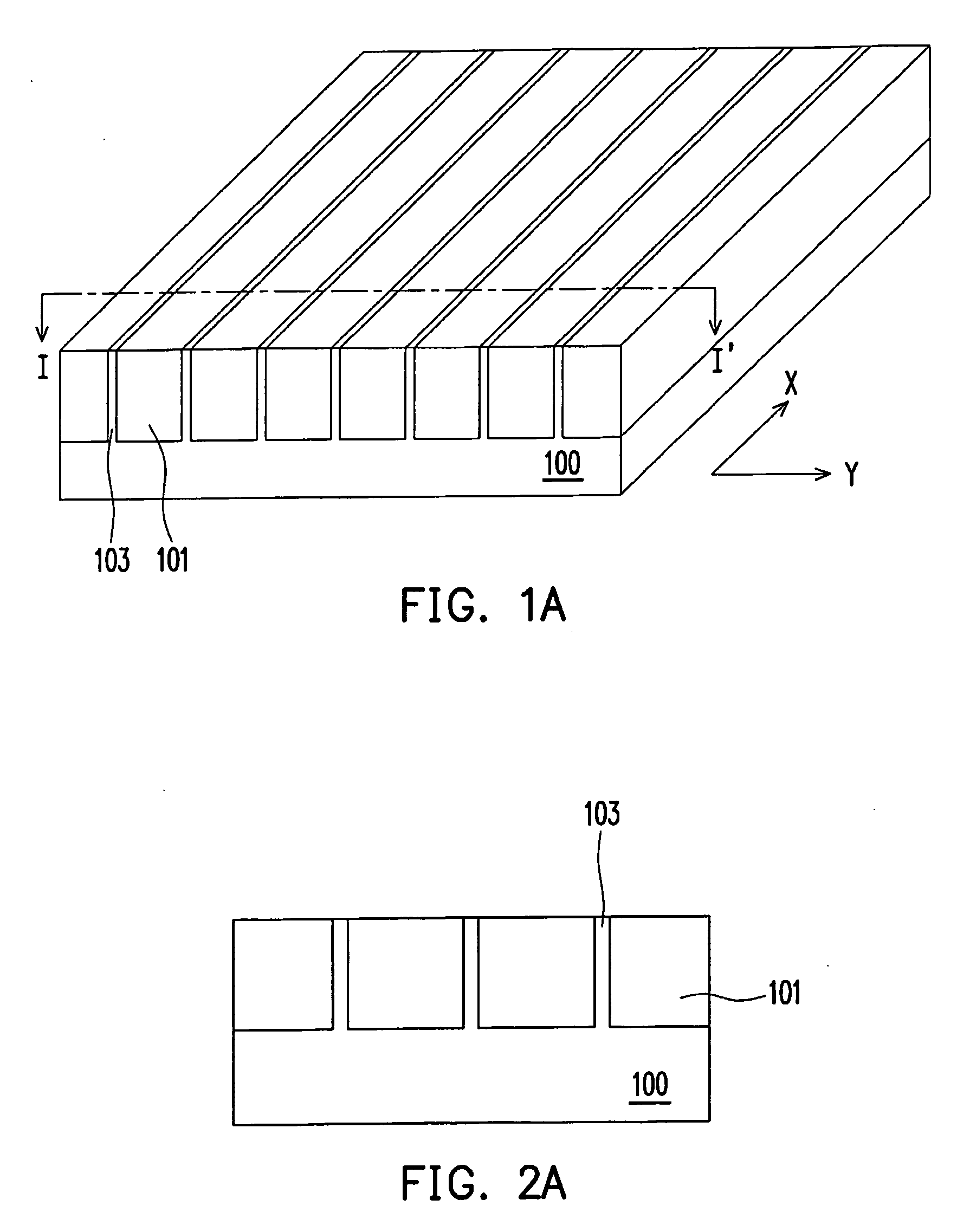

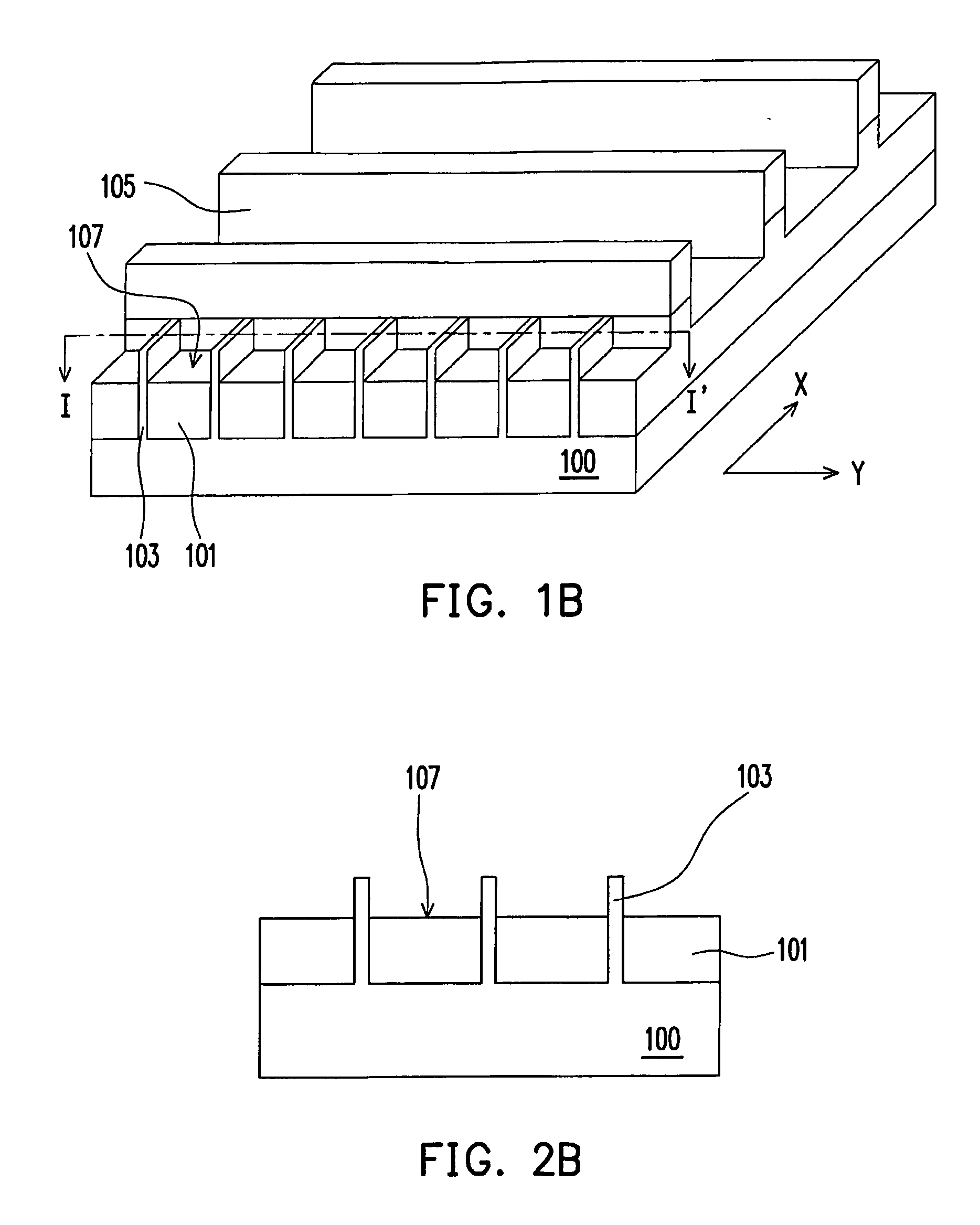

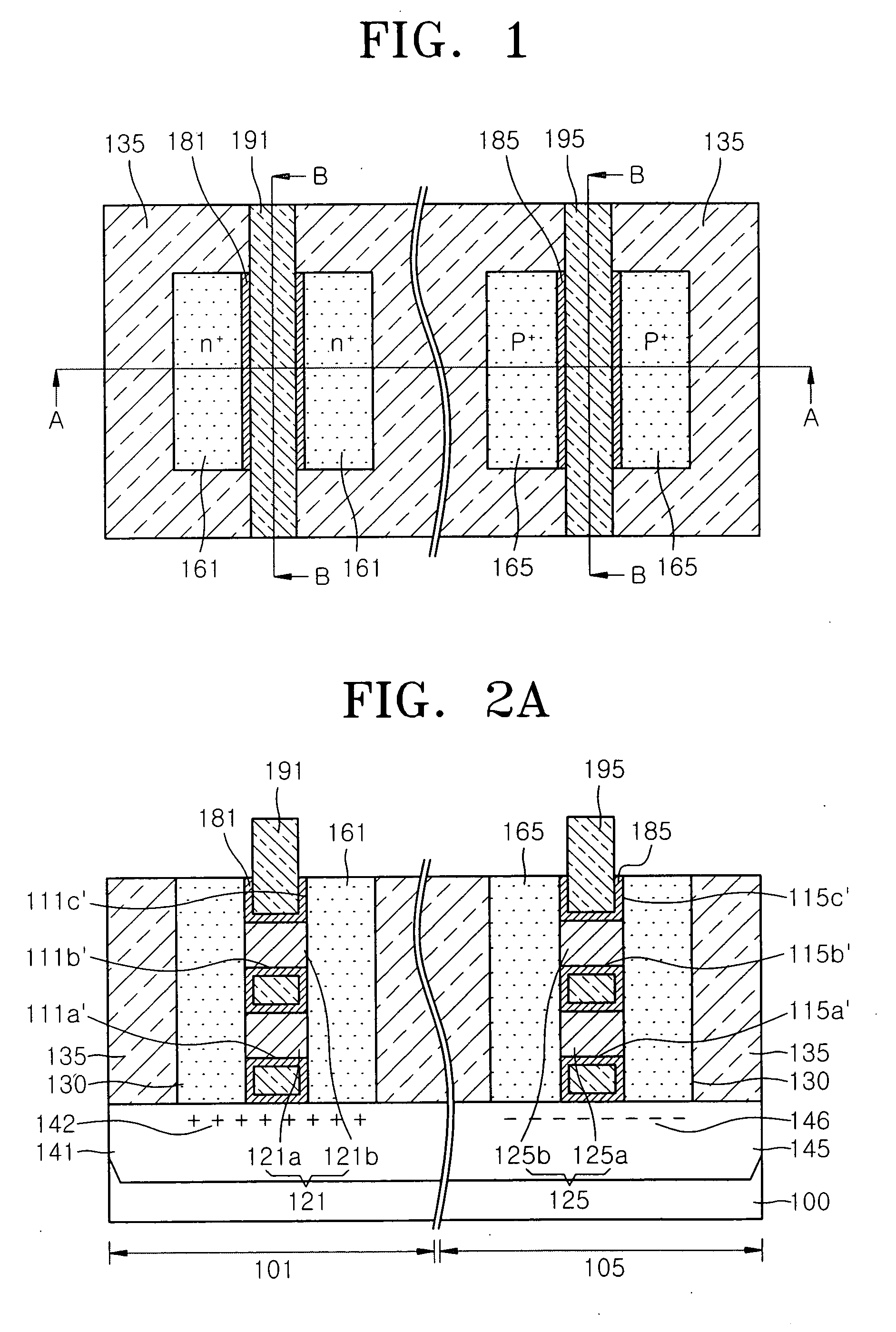

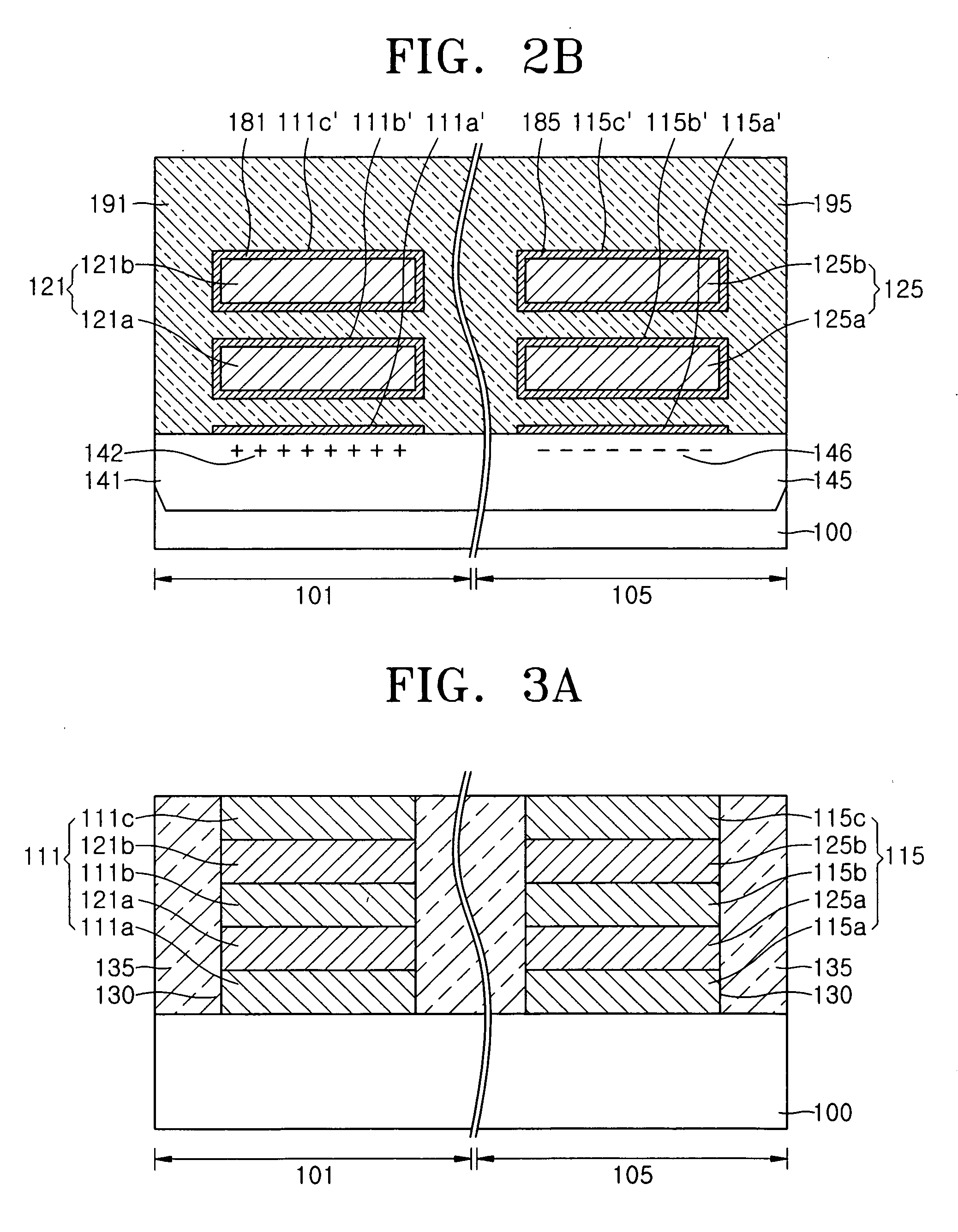

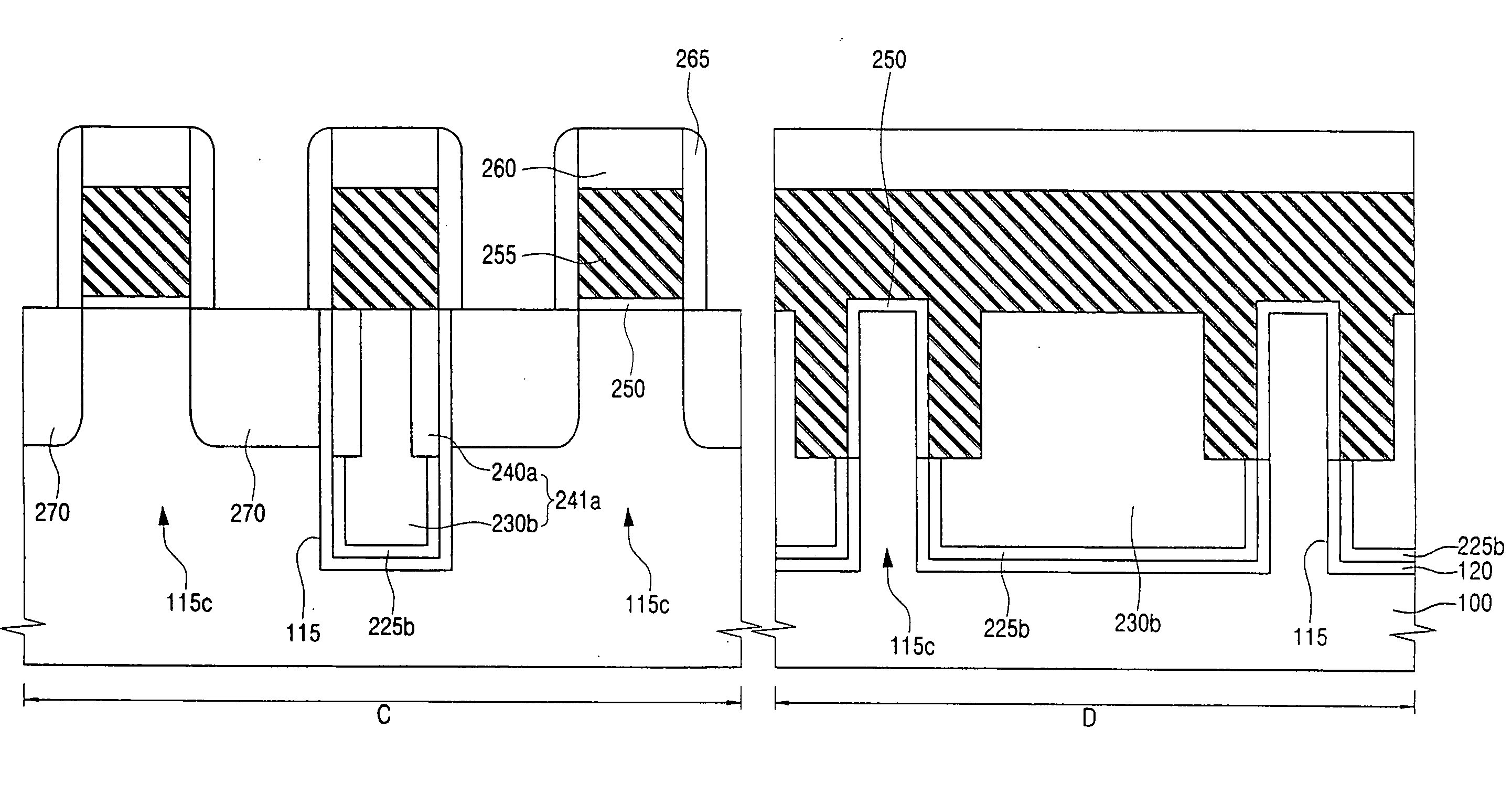

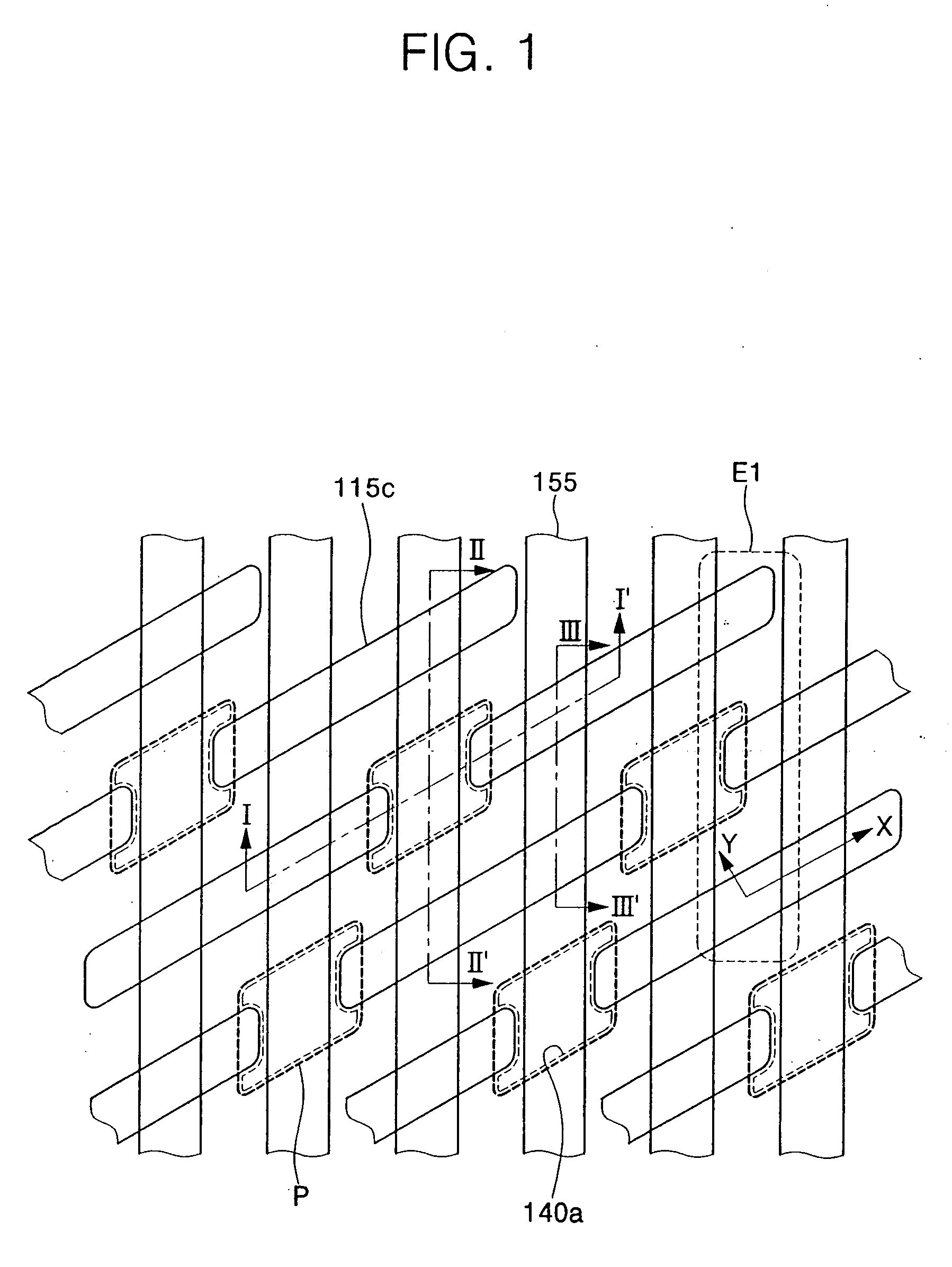

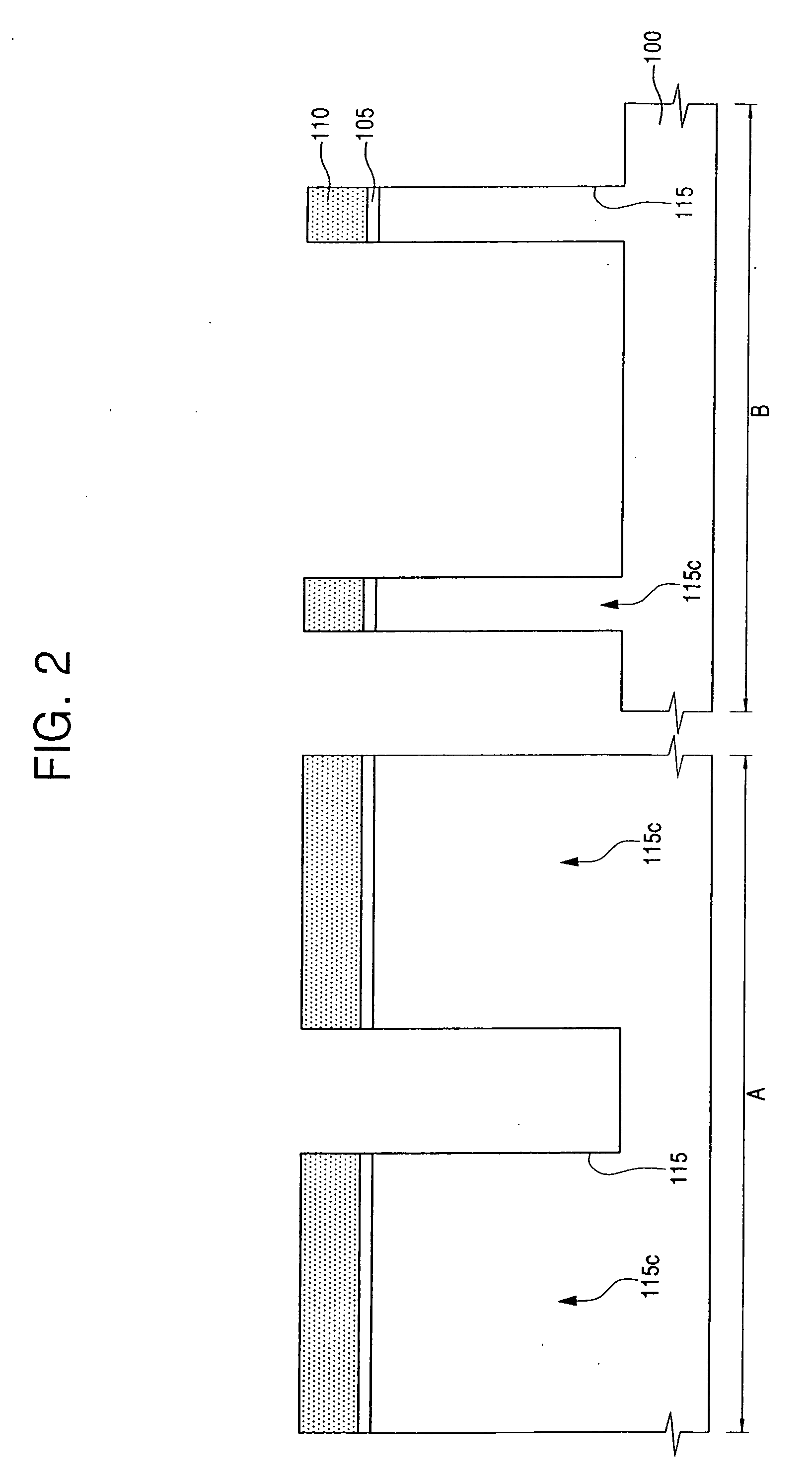

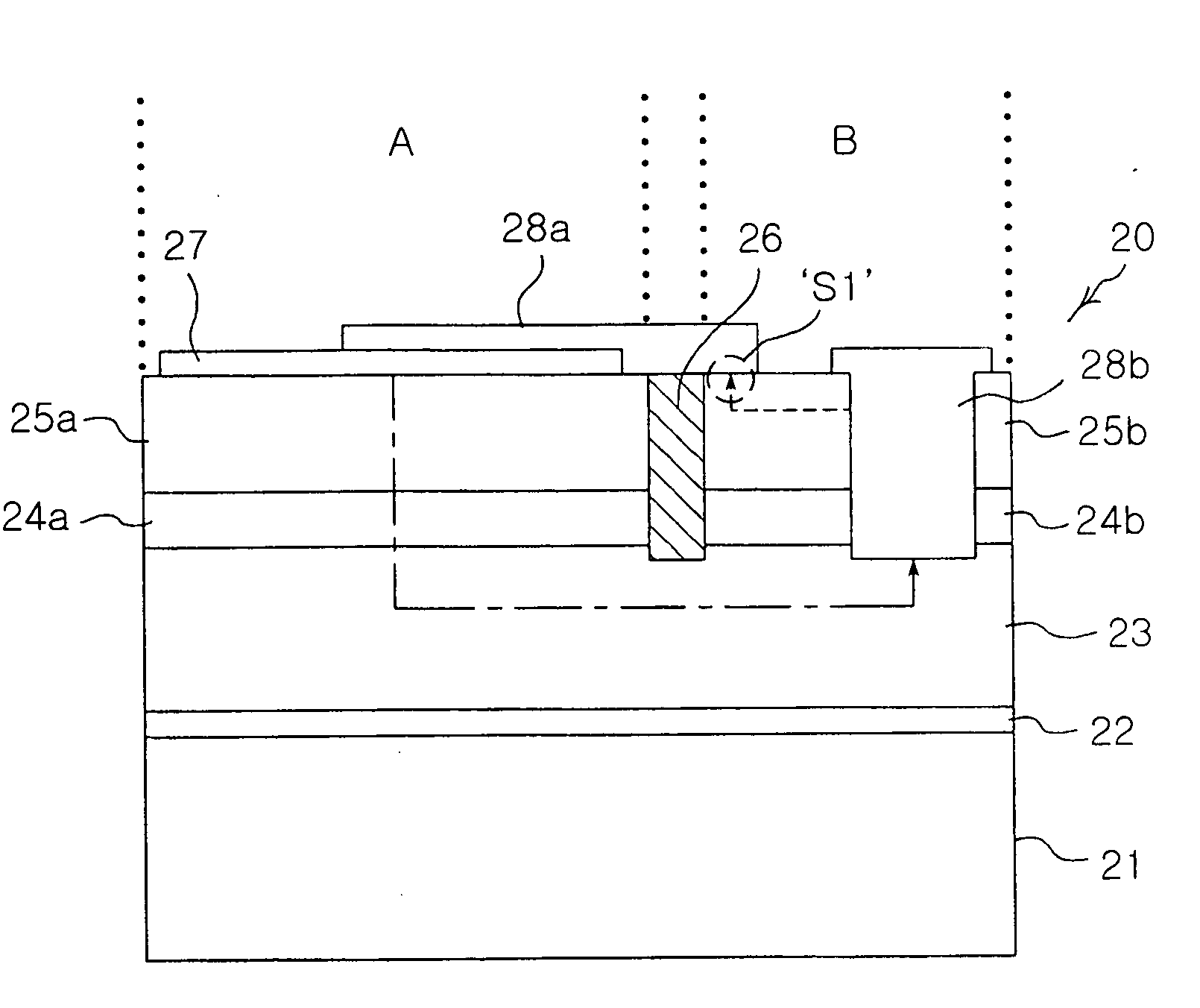

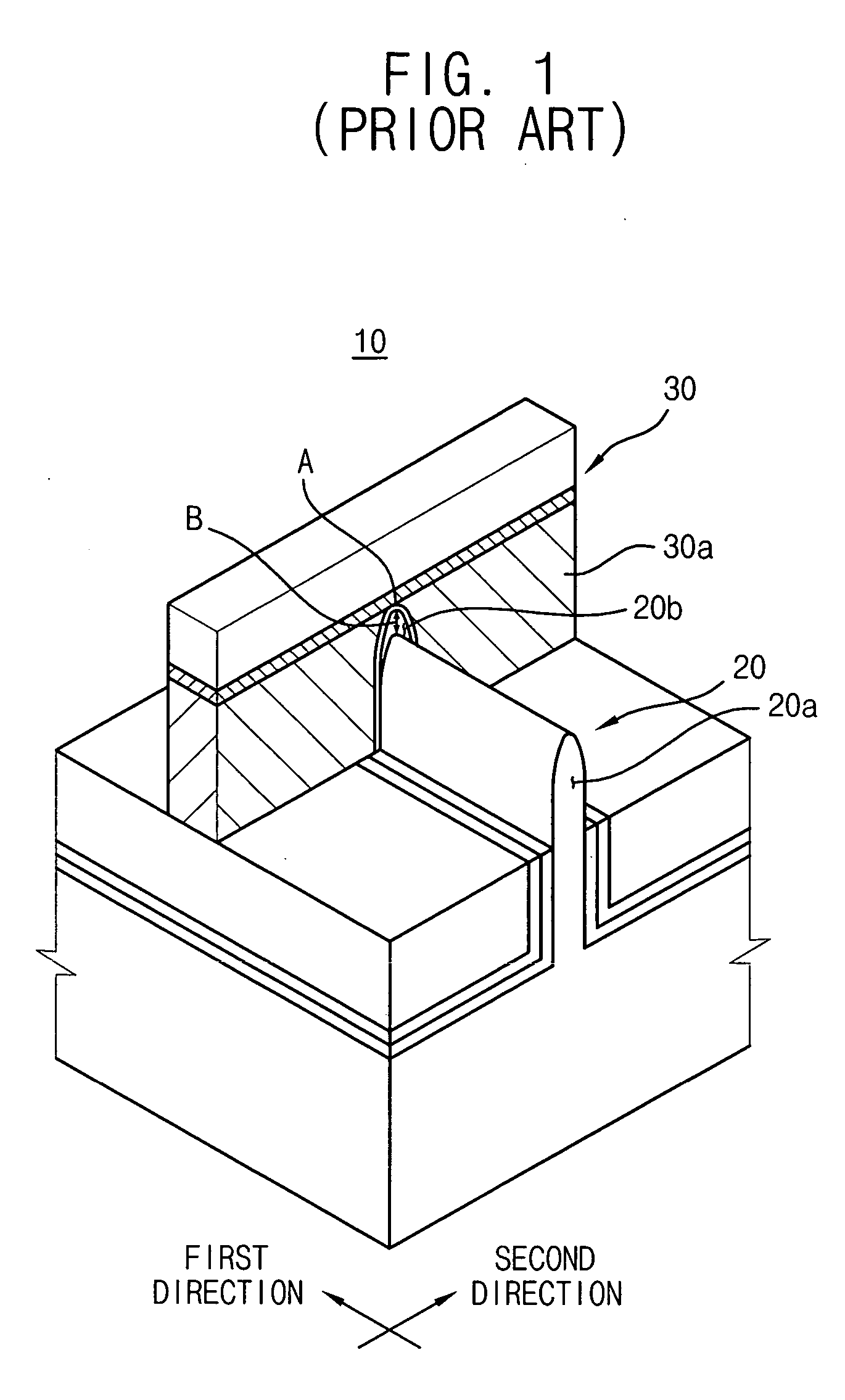

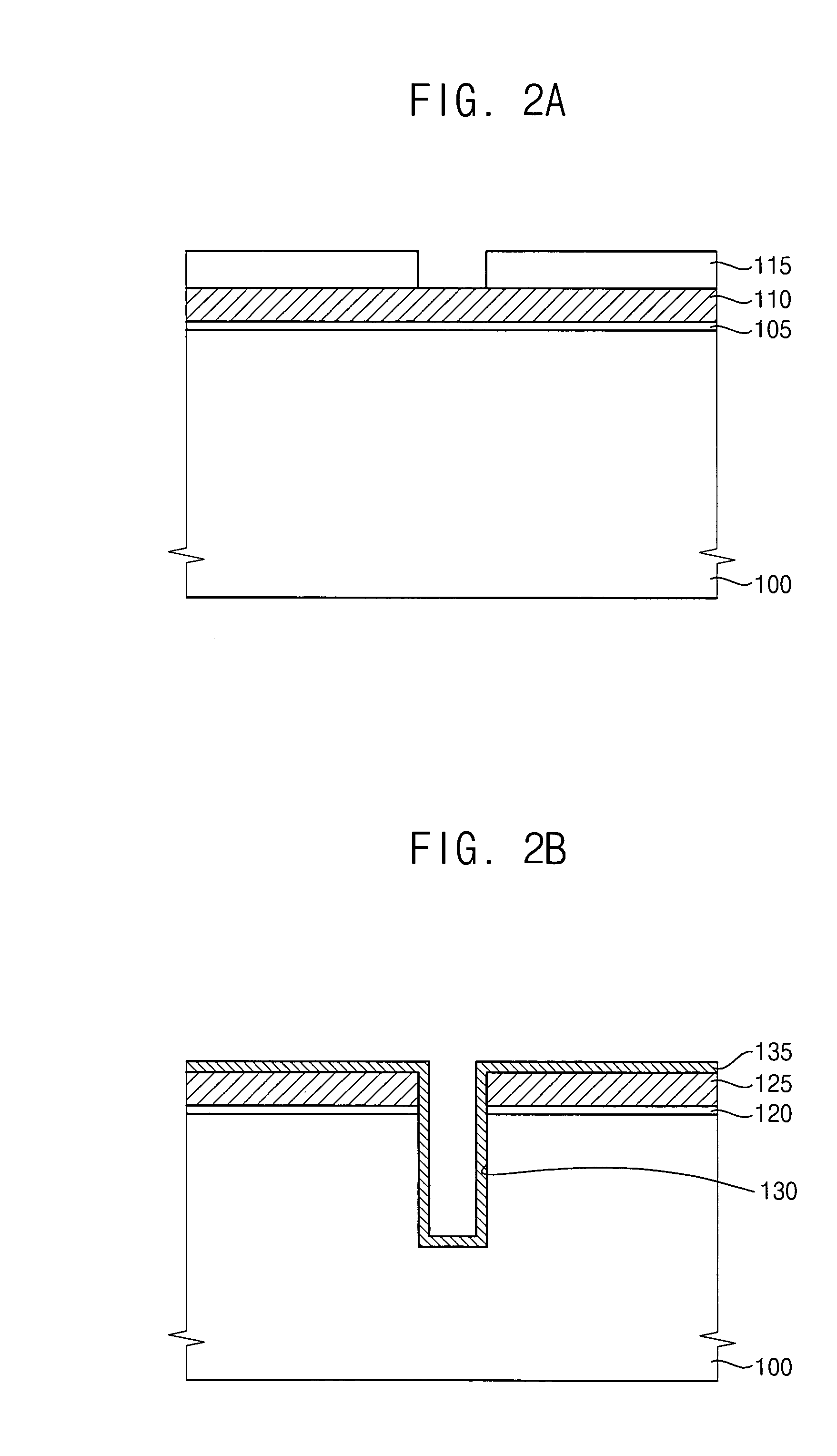

Method of fabricating a semiconductor device having self-aligned floating gate and related device

ActiveUS20070090443A1Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIsolation layer

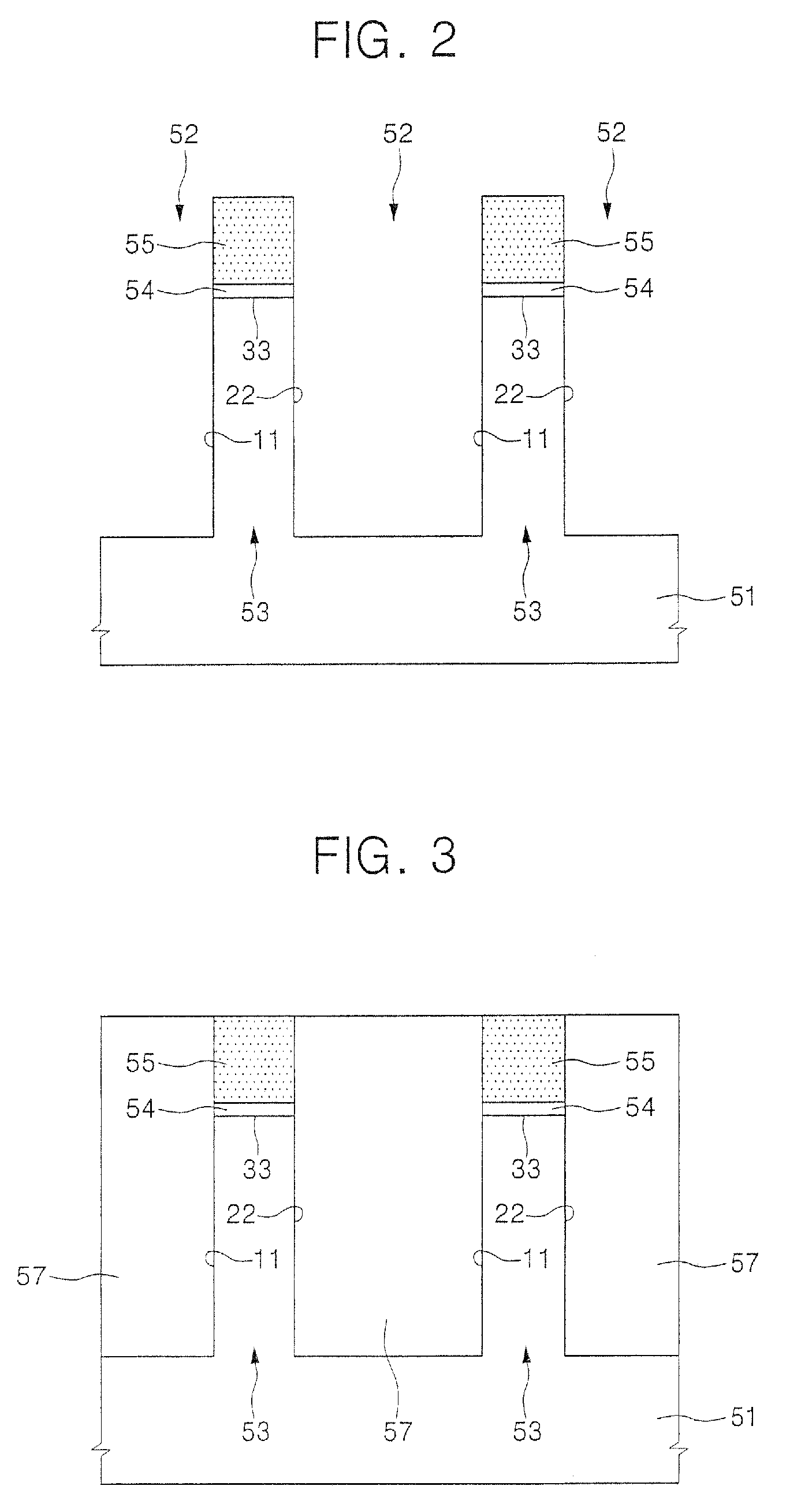

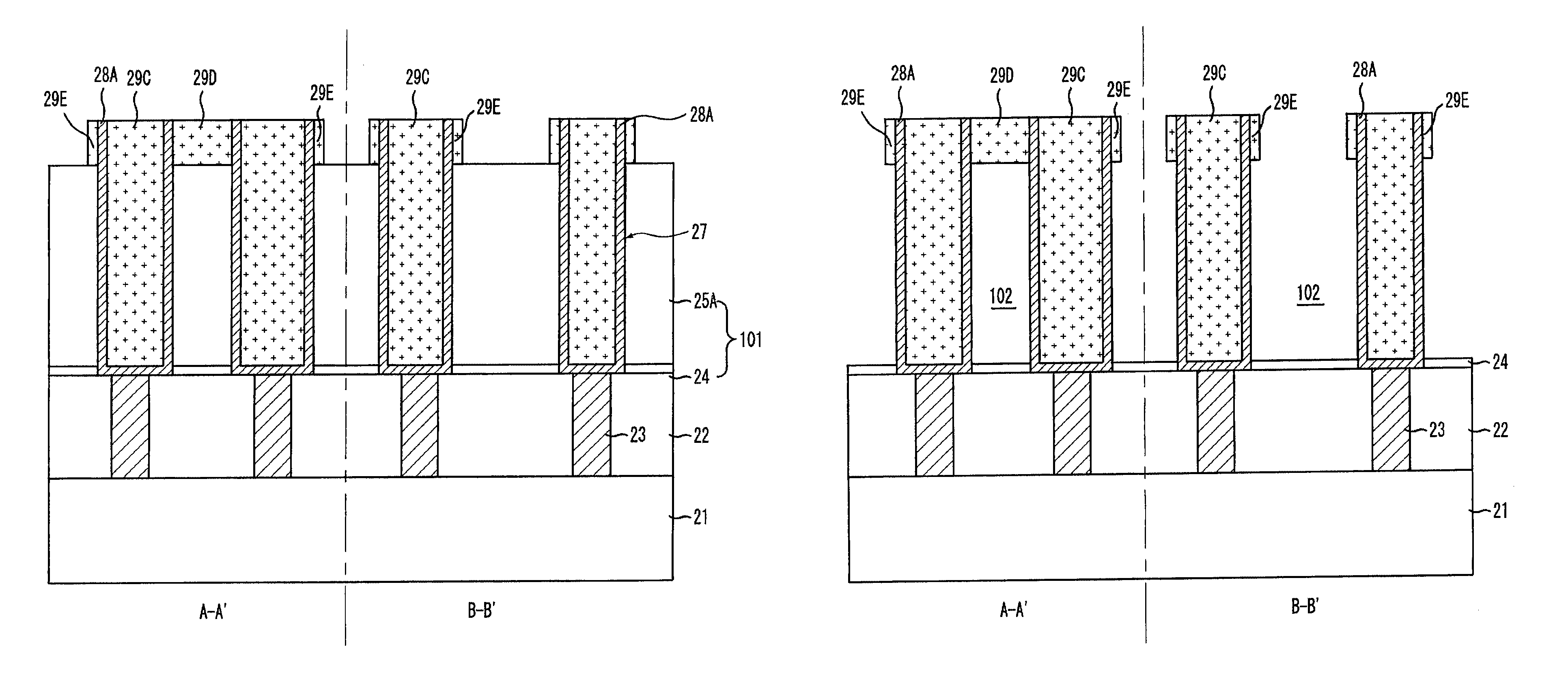

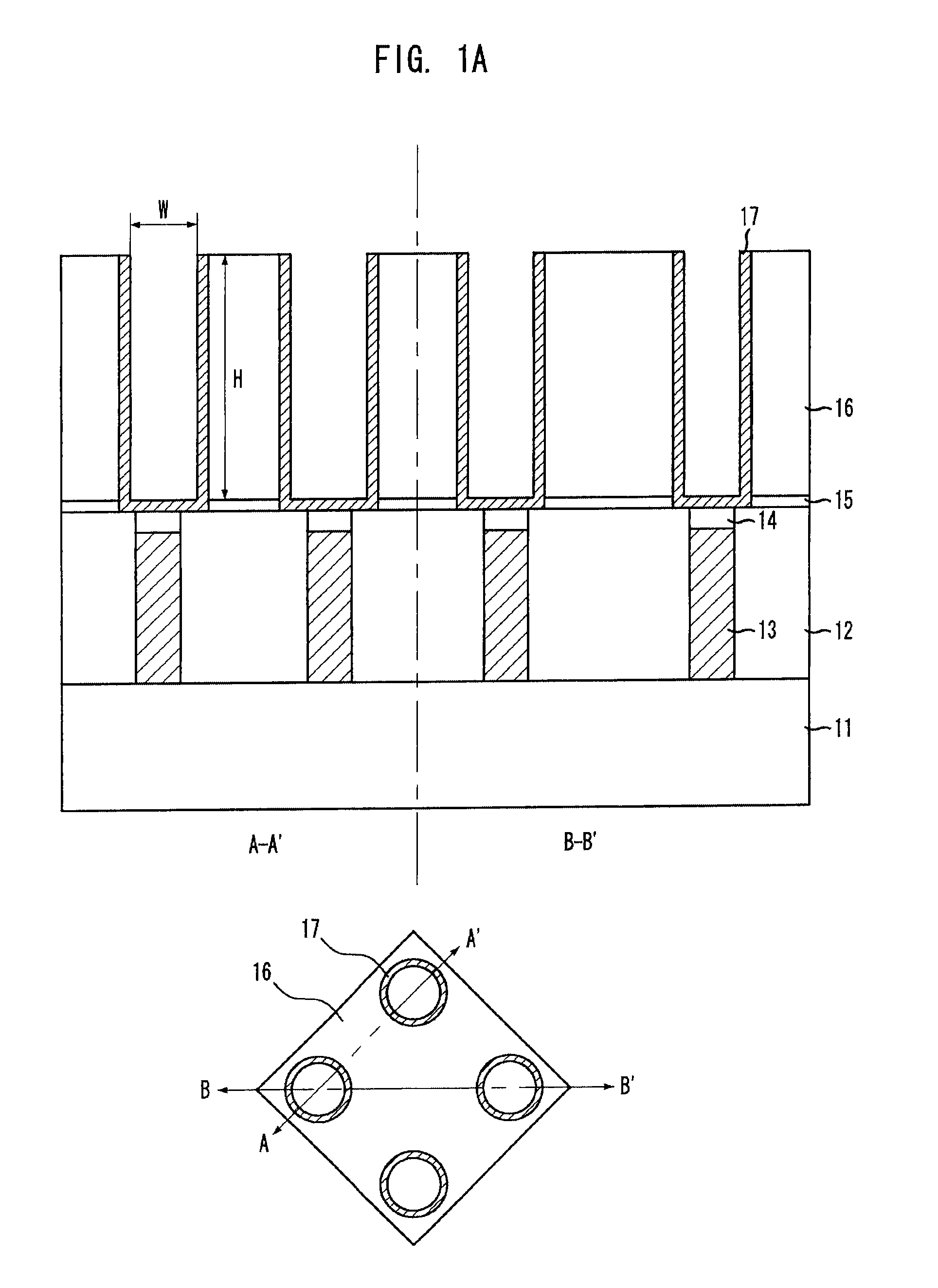

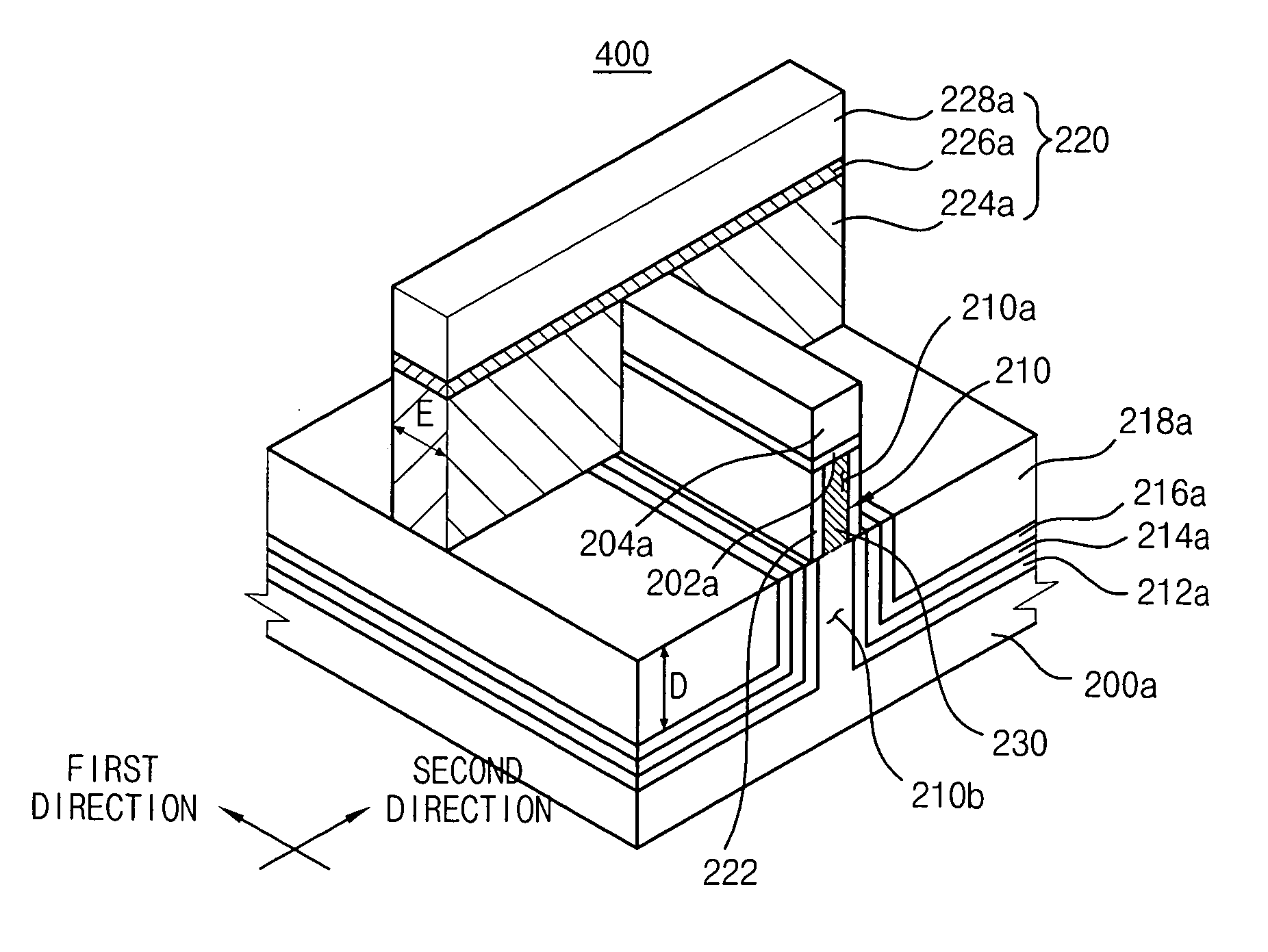

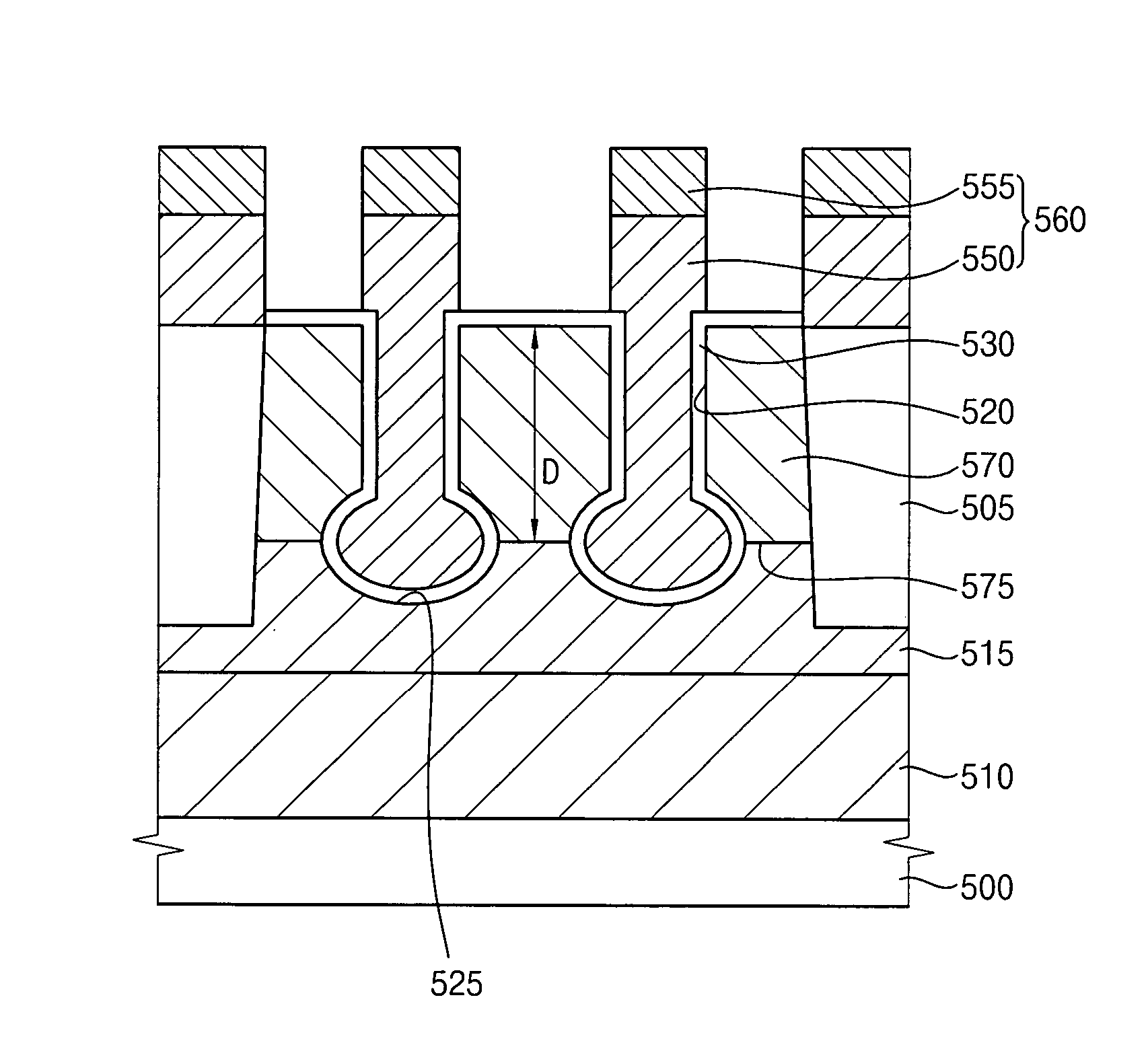

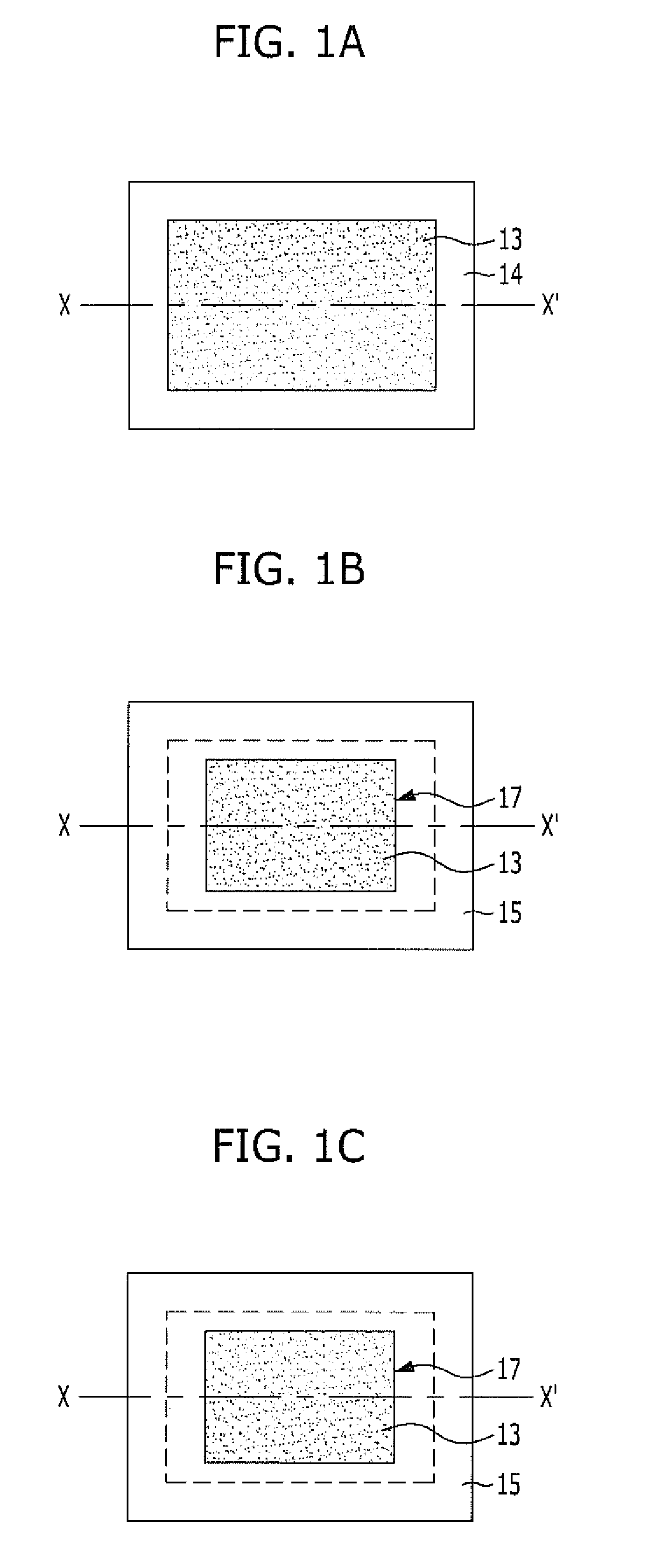

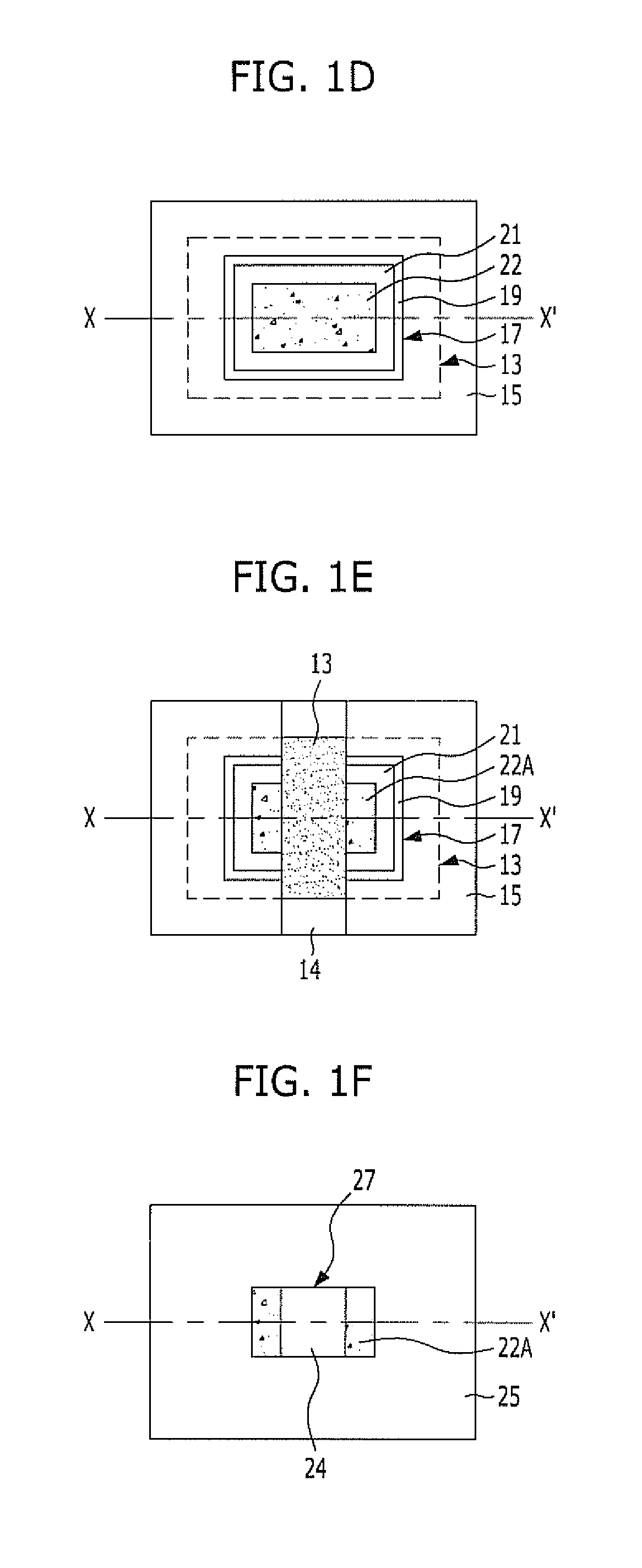

A semiconductor device such as a flash memory device having a self-aligned floating gate and a method of fabricating the same is provided. An embodiment of the device includes an isolation layer defining a fin body is formed in a semiconductor substrate. The fin body has a portion protruding above the isolation layer. A sacrificial pattern is formed on the isolation layer. The sacrificial pattern has an opening self-aligned with the protruding portion of the fin body. The protruding fin body is exposed in the opening. An insulated floating gate pattern is formed to fill the opening. The sacrificial pattern is then removed. An inter-gate dielectric layer covering the floating gate pattern is formed. A control gate conductive layer is formed over the inter-gate dielectric layer. The control gate conductive layer, the inter-gate dielectric layer, and the floating gate pattern are patterned to form a control gate electrode crossing the fin body as well as the insulated floating gate interposed between the control gate electrode and the fin body.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of fabricating a semiconductor device having self-aligned floating gate and related device

ActiveUS7329580B2Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricDevice material

A semiconductor device such as a flash memory device having a self-aligned floating gate and a method of fabricating the same is provided. An embodiment of the device includes an isolation layer defining a fin body is formed in a semiconductor substrate. The fin body has a portion protruding above the isolation layer. A sacrificial pattern is formed on the isolation layer. The sacrificial pattern has an opening self-aligned with the protruding portion of the fin body. The protruding fin body is exposed in the opening. An insulated floating gate pattern is formed to fill the opening. The sacrificial pattern is then removed. An inter-gate dielectric layer covering the floating gate pattern is formed. A control gate conductive layer is formed over the inter-gate dielectric layer. The control gate conductive layer, the inter-gate dielectric layer, and the floating gate pattern are patterned to form a control gate electrode crossing the fin body as well as the insulated floating gate interposed between the control gate electrode and the fin body.

Owner:SAMSUNG ELECTRONICS CO LTD

Stretchable and foldable electronic devices

ActiveUS8552299B2Easy to useQuality improvementWave amplification devicesSemiconductor/solid-state device detailsIsolation layerSemiconductor

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

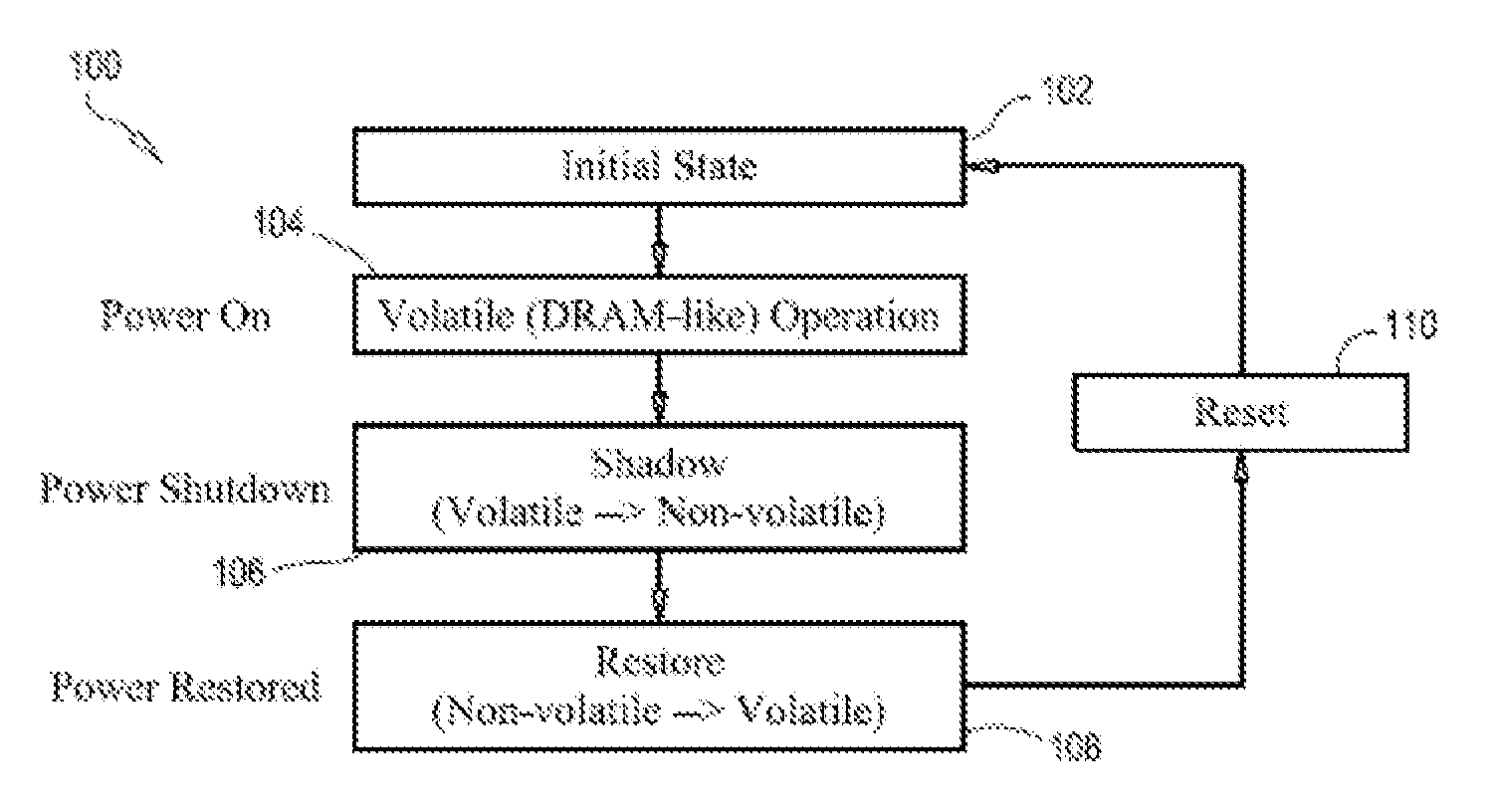

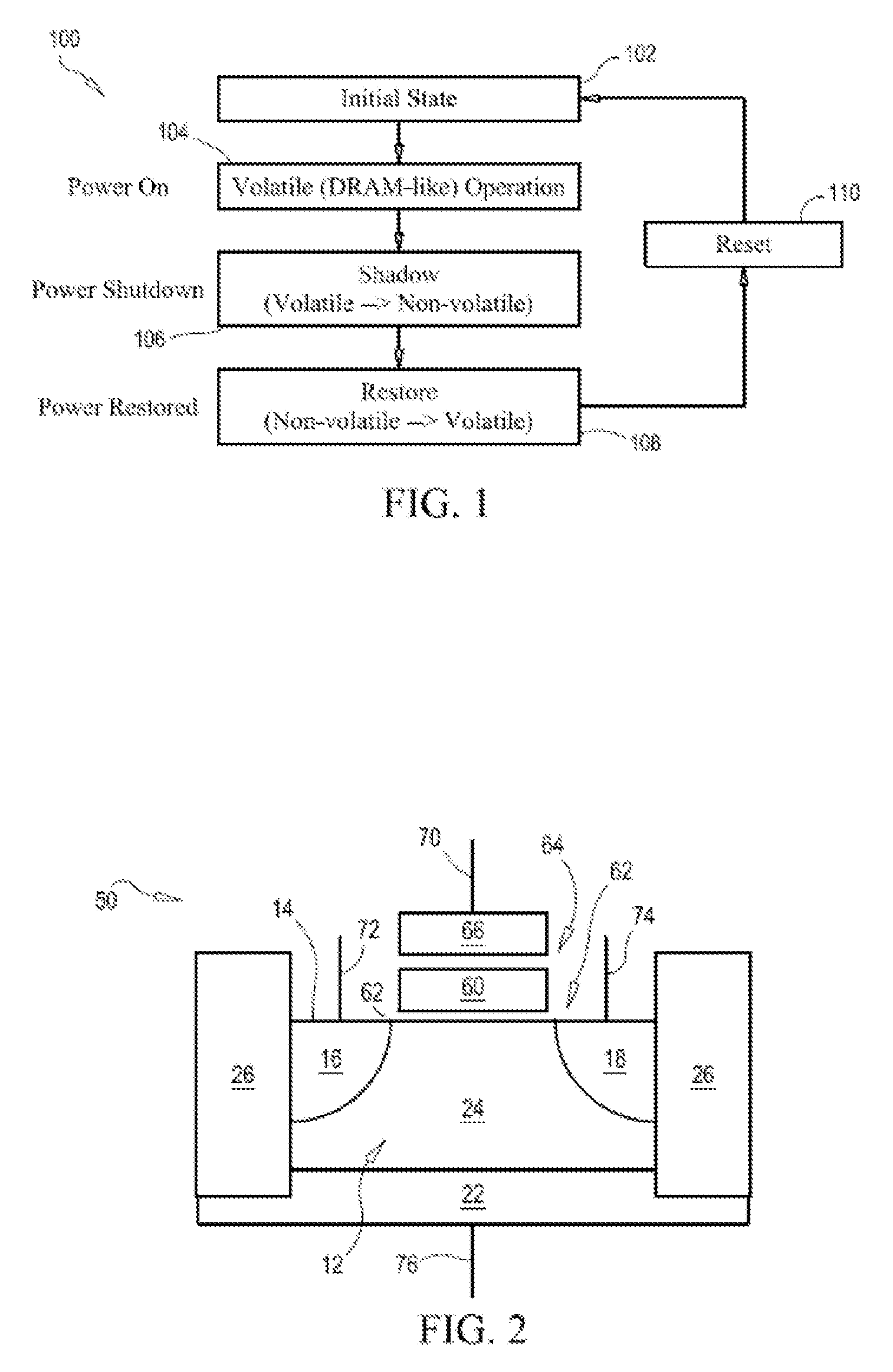

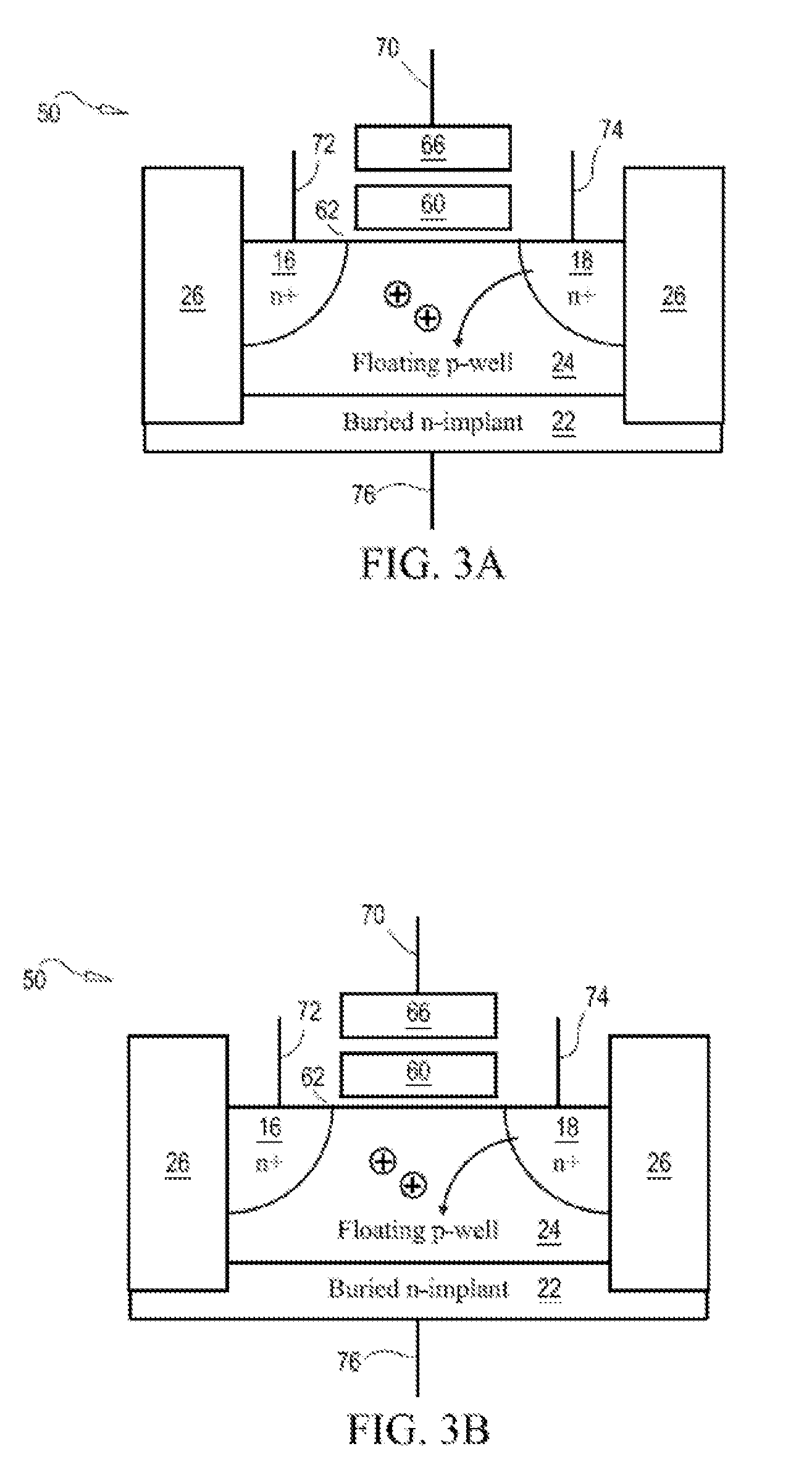

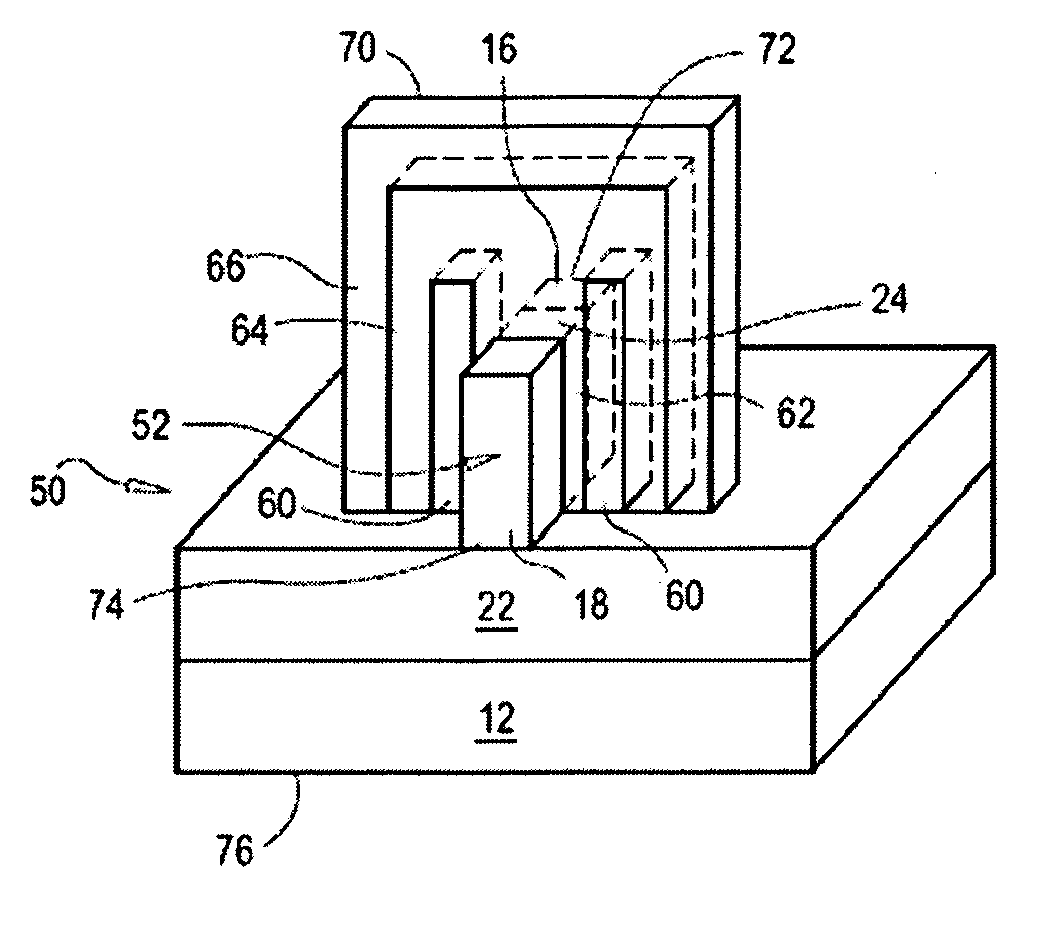

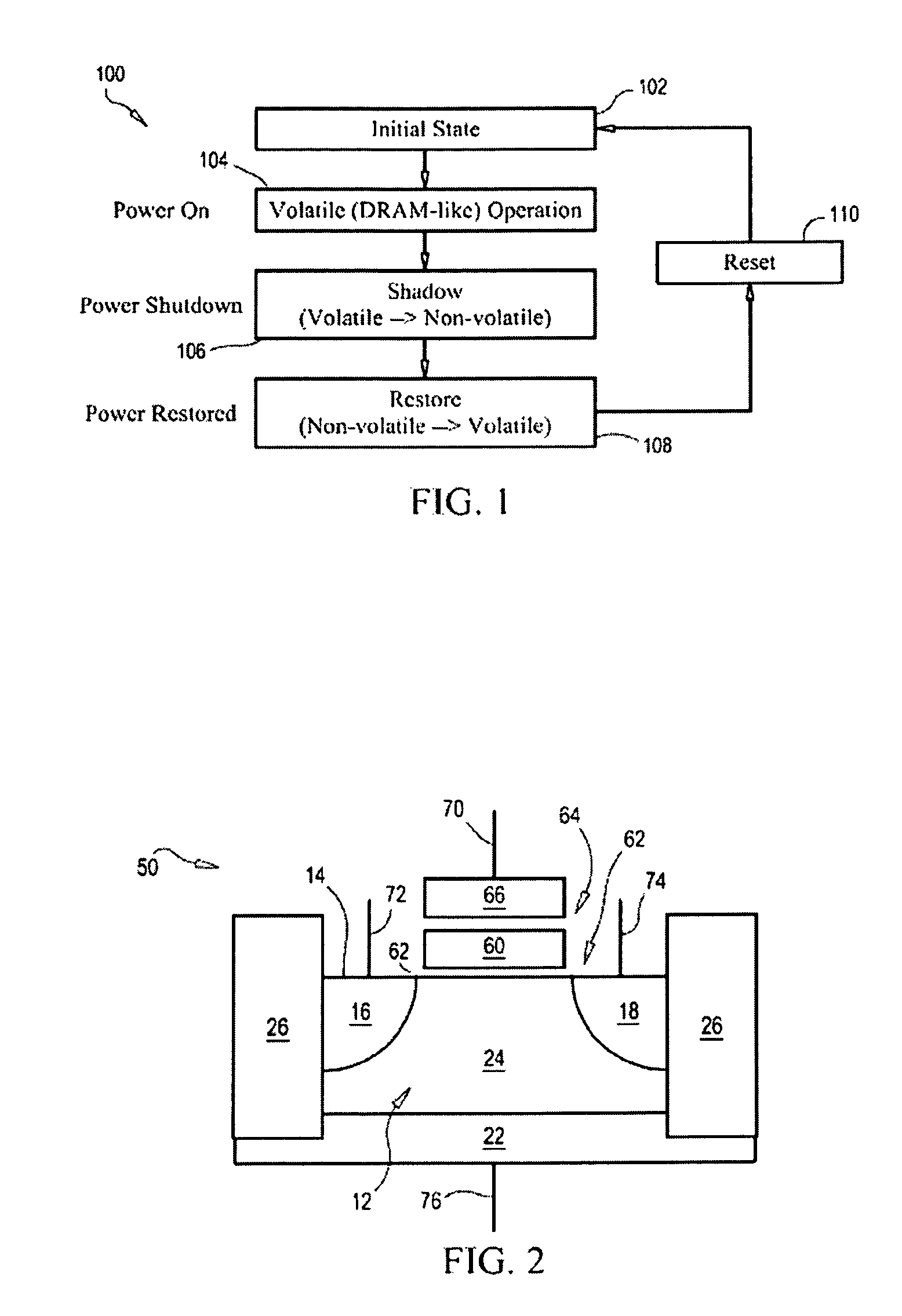

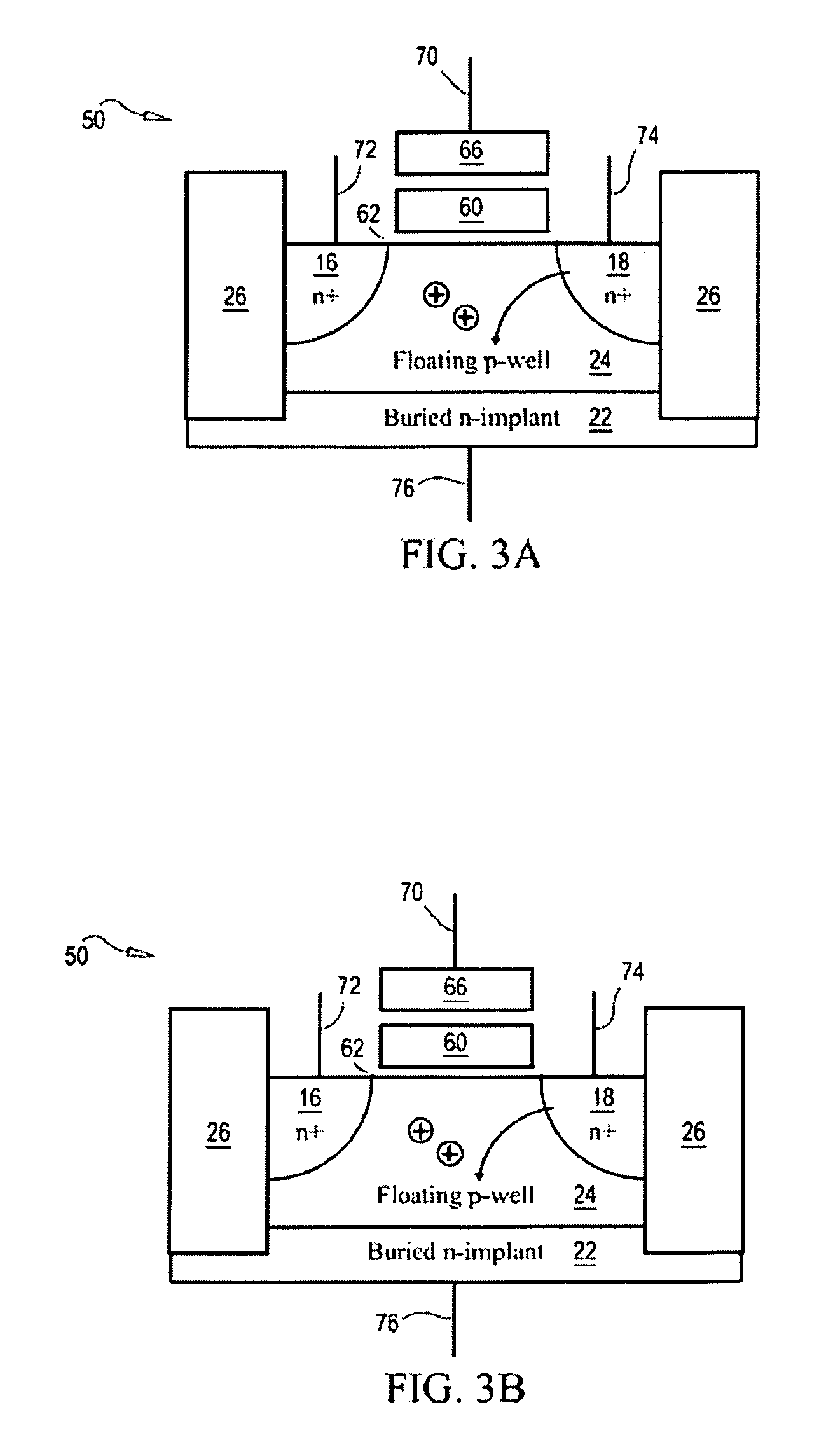

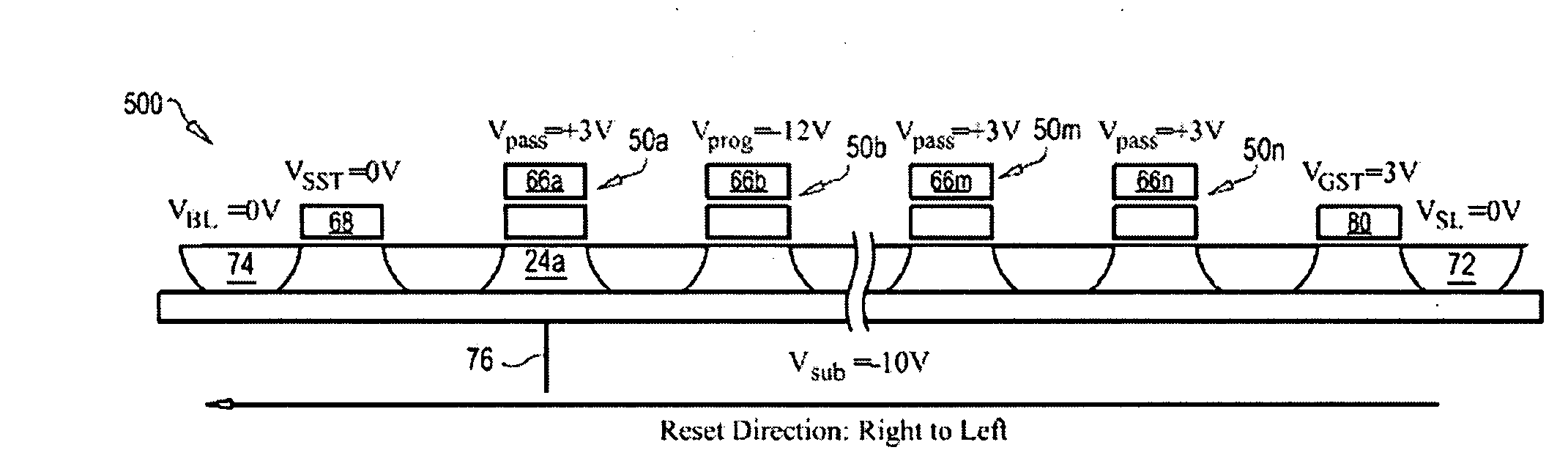

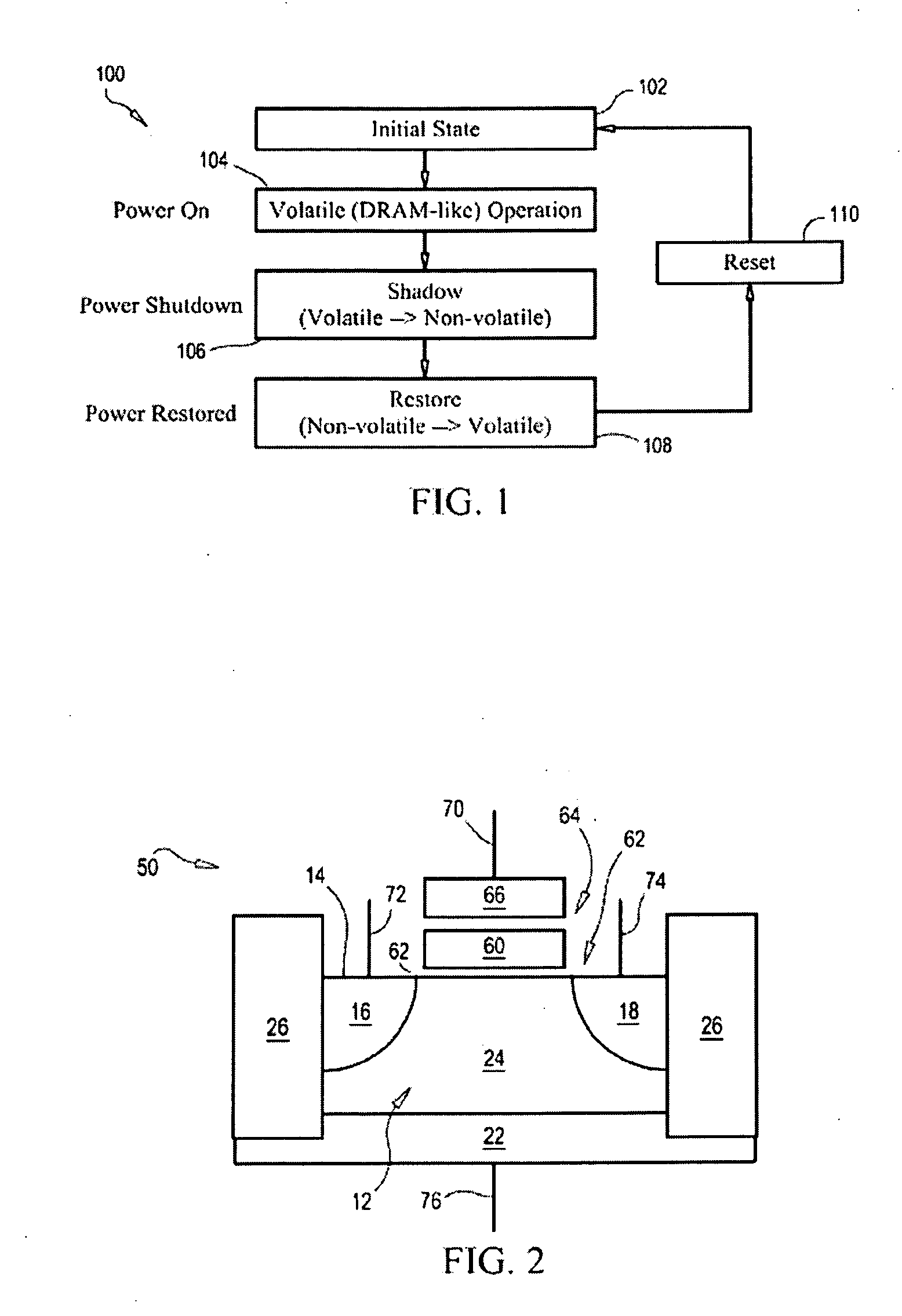

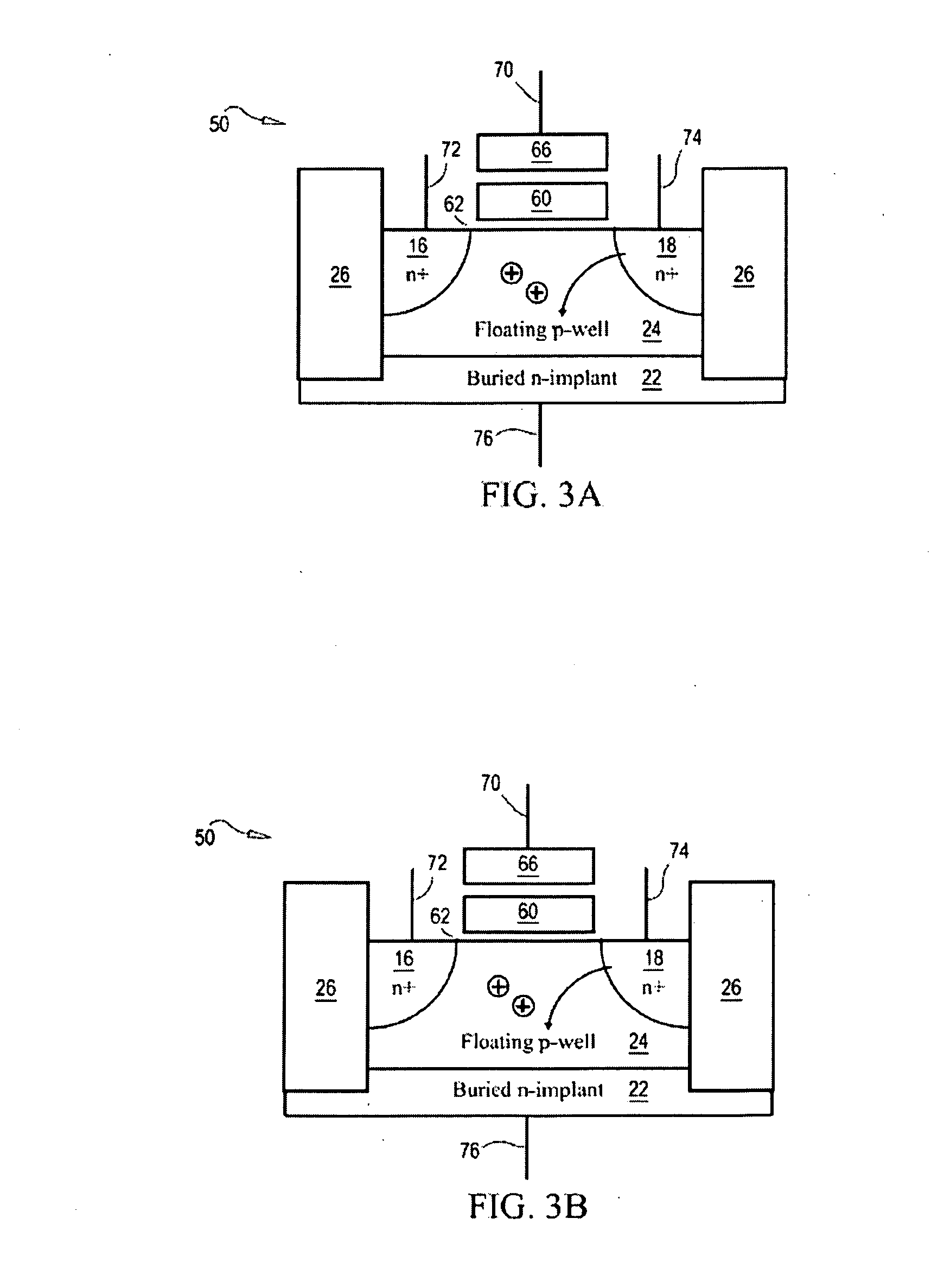

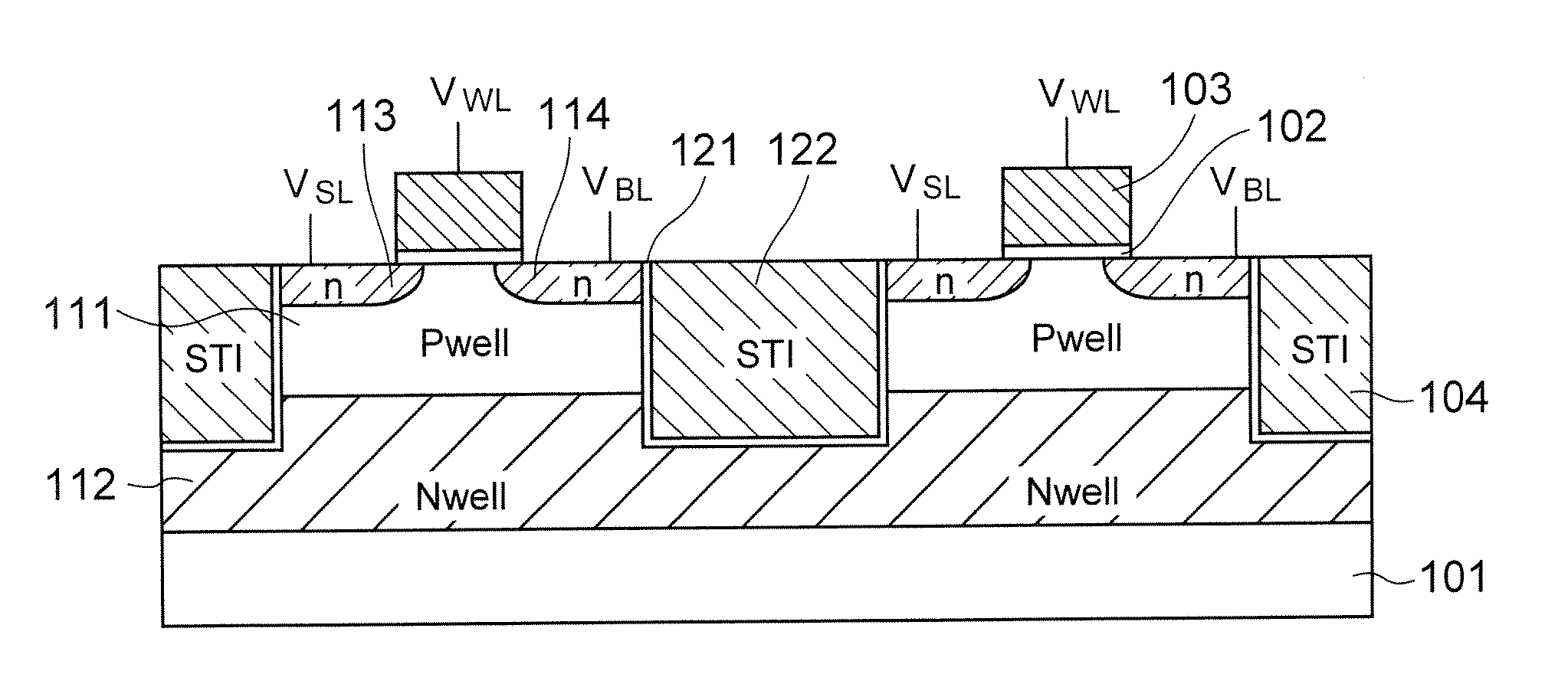

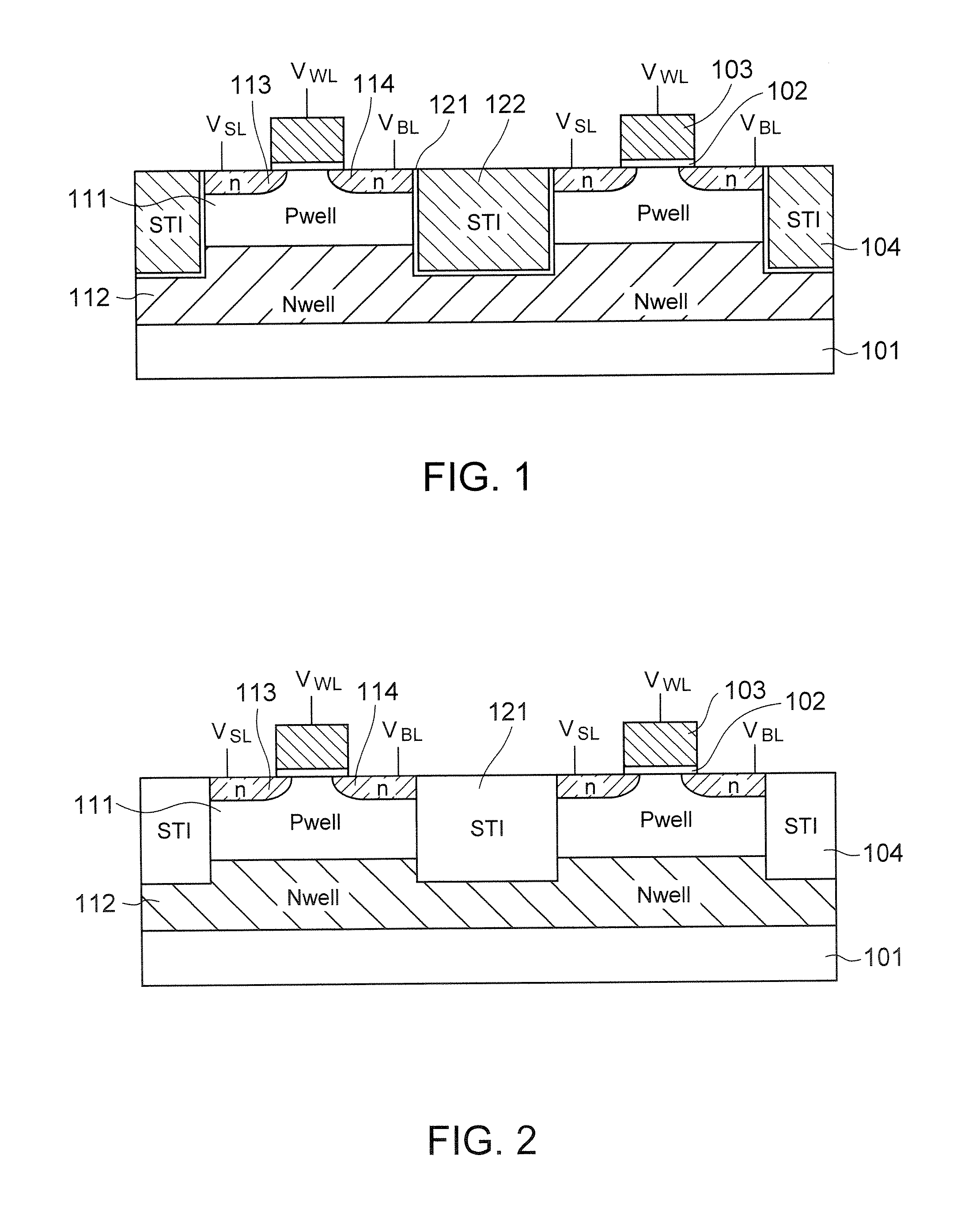

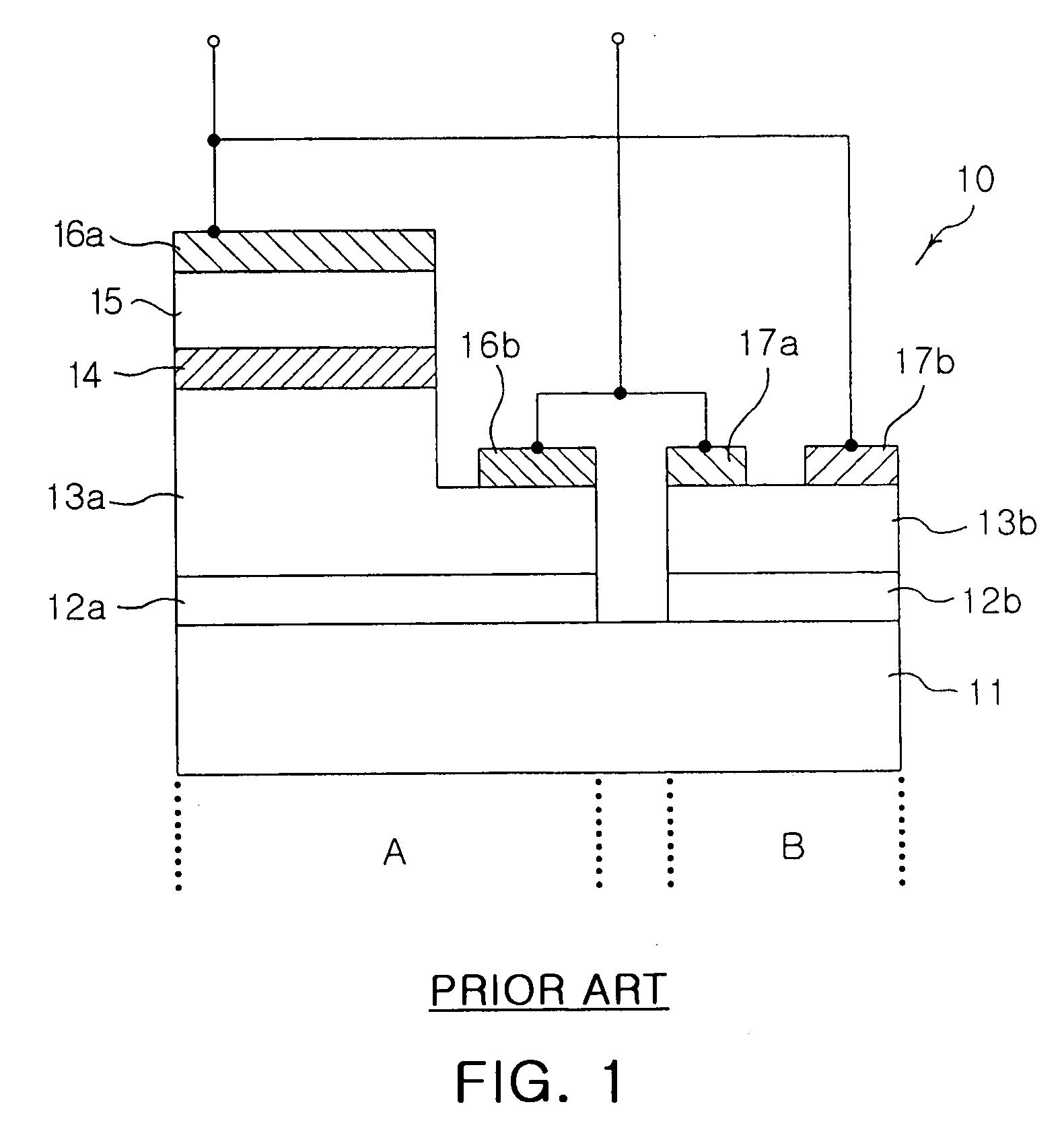

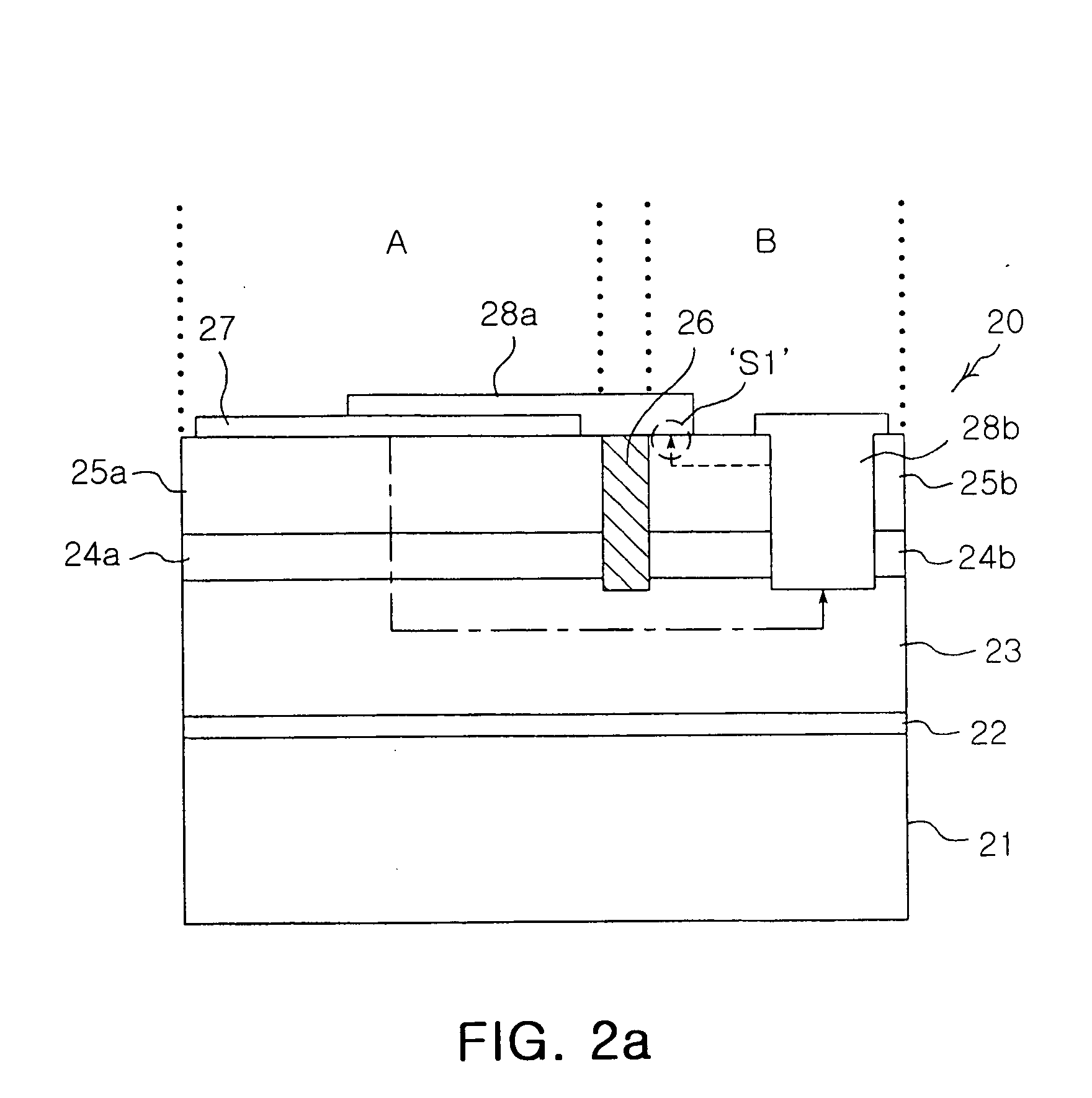

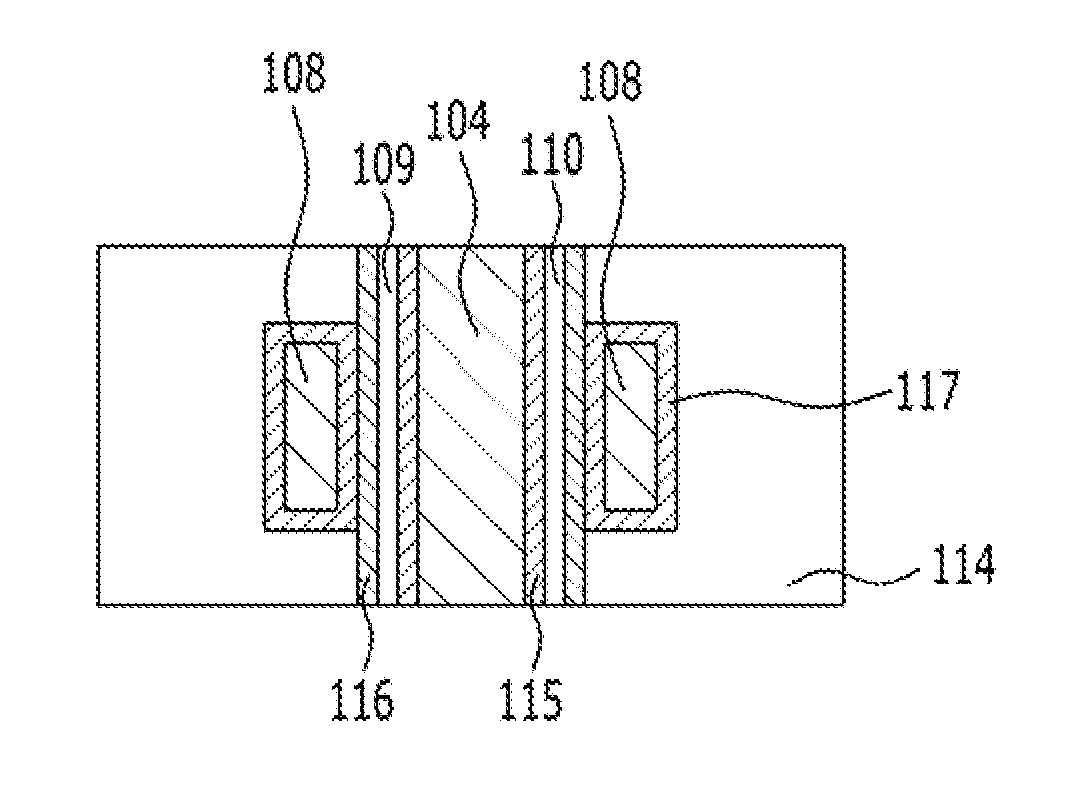

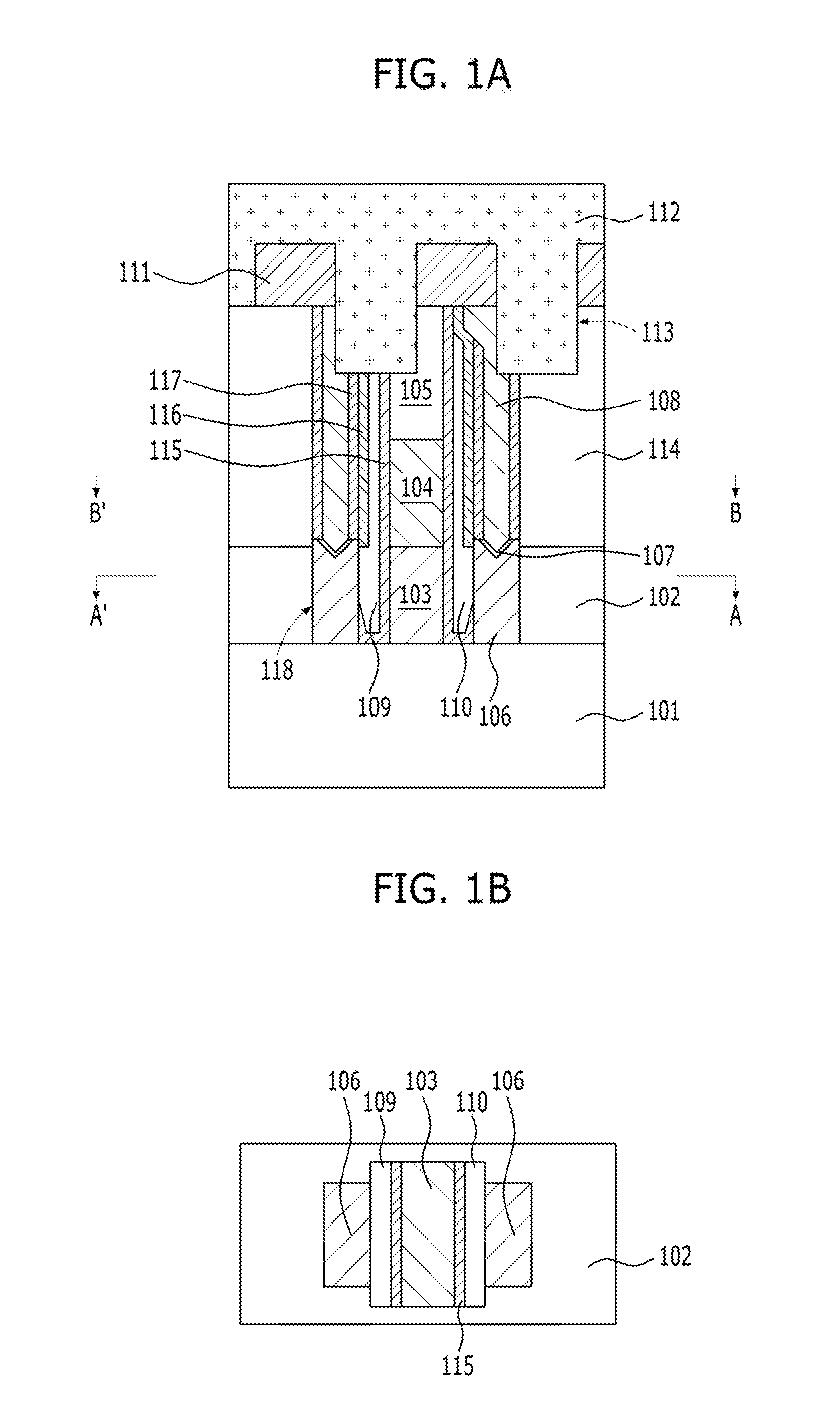

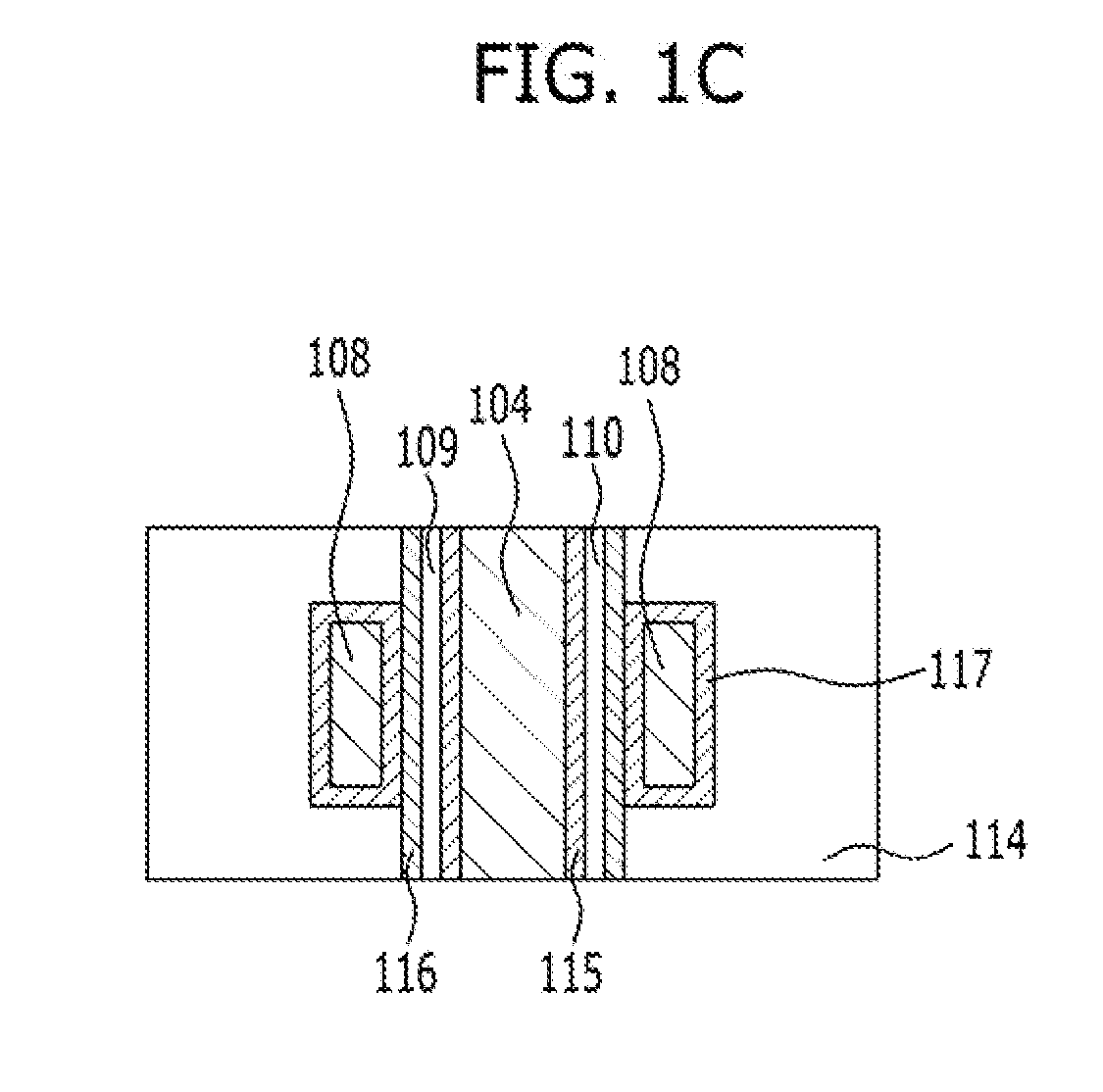

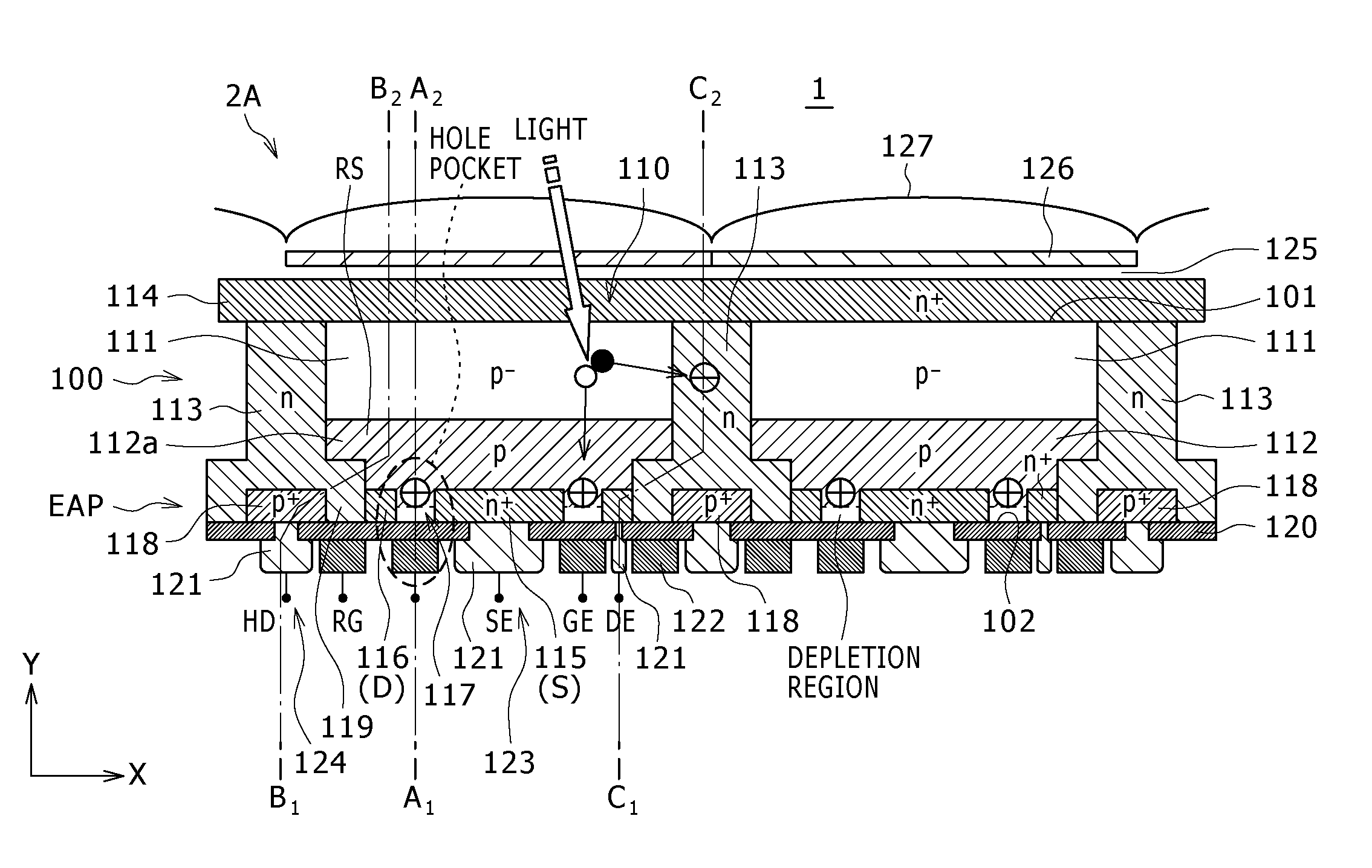

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

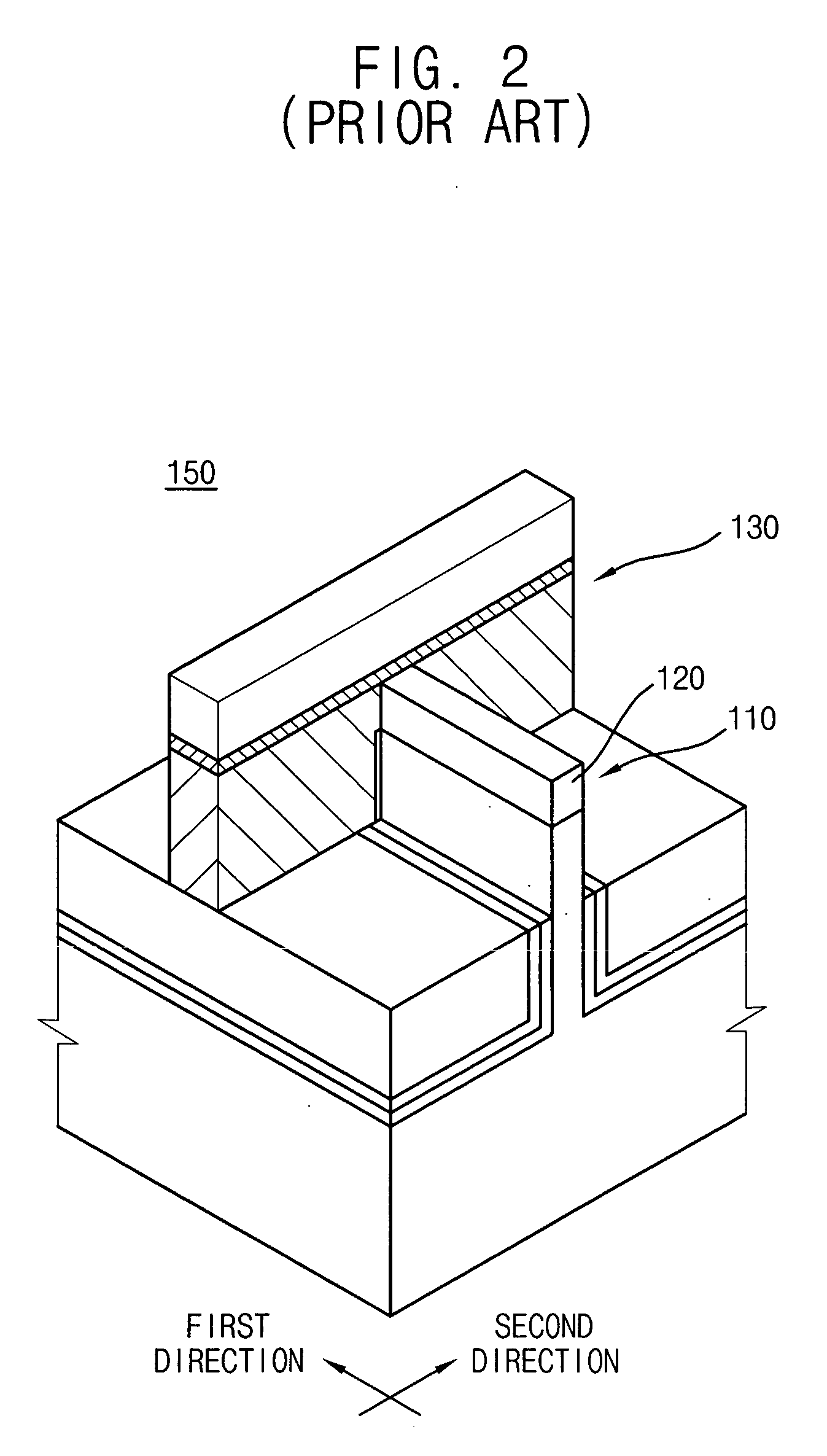

Non-volatile memory

InactiveUS20080224202A1Improve stability and reliabilityLow working voltageTransistorSolid-state devicesIsolation layerEngineering

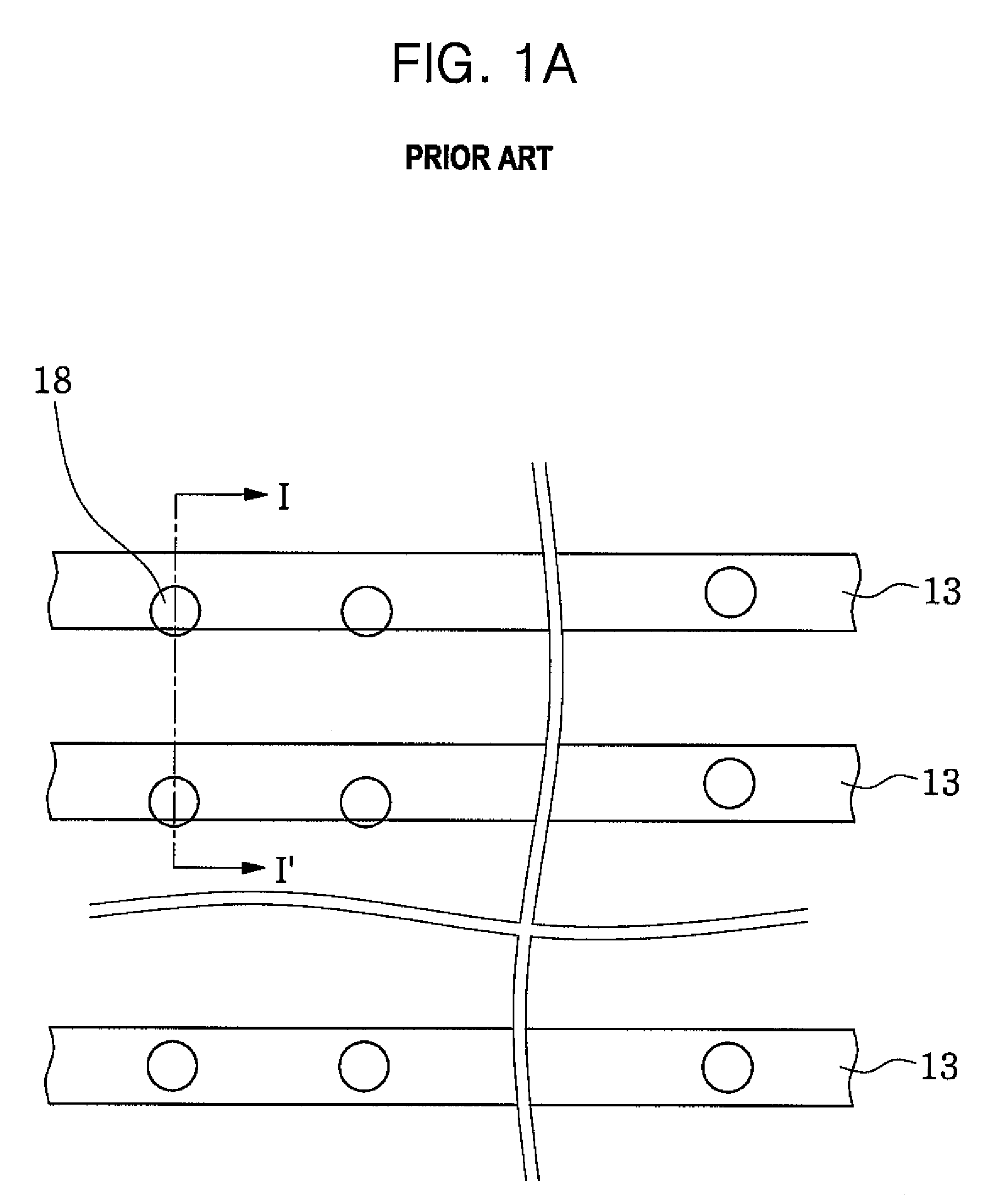

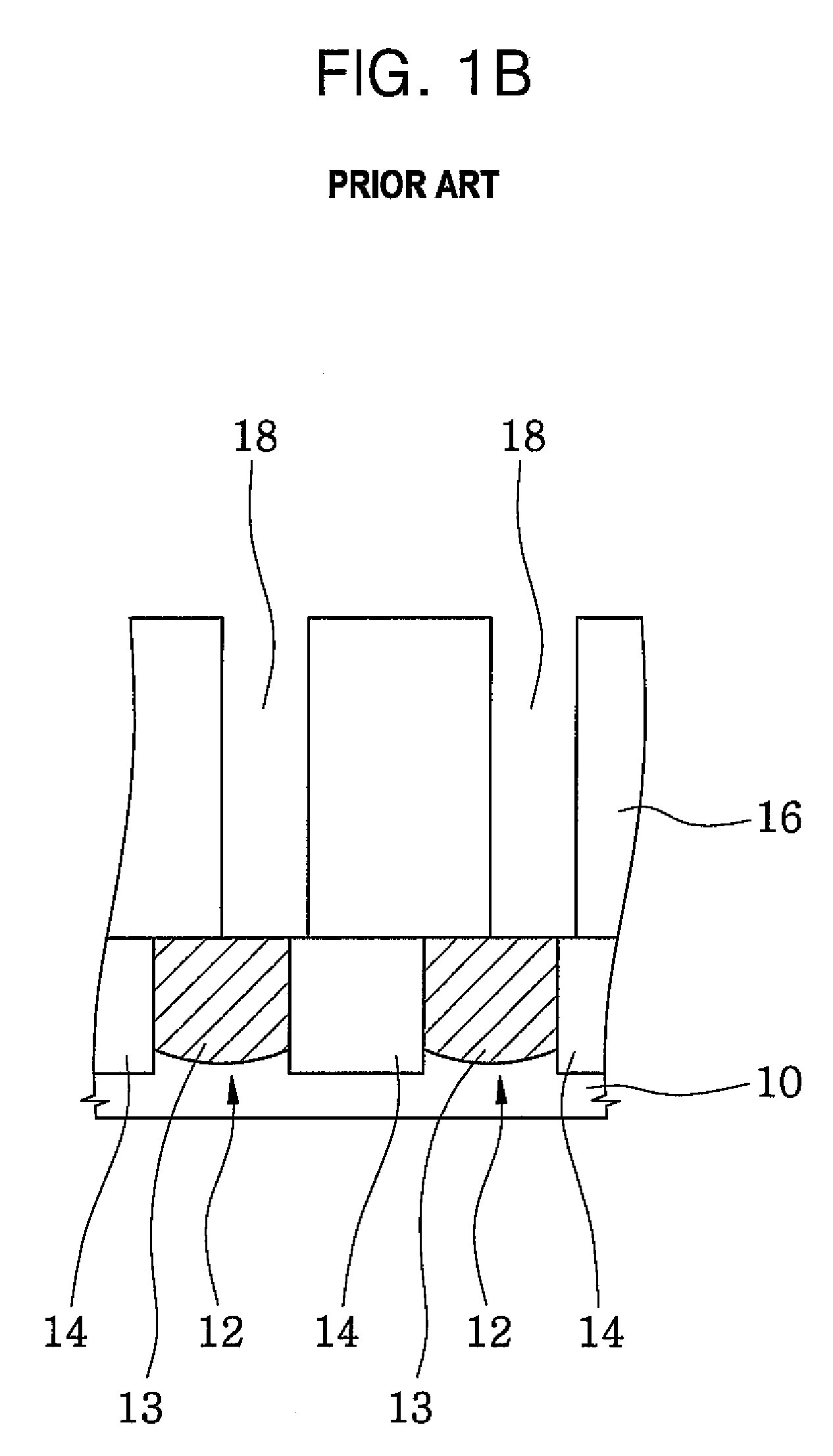

A non-volatile memory includes a substrate, a number of isolation layers, a number of active layers, a number of floating gates, a number of control gates and a number of doped regions. The active layers are disposed in the substrate between the isolation layers, and the top surface of the active layer is higher than that of the isolation layer. The active layers and the isolation layers are arranged in parallel to each other and extend in the first direction. The control gates are disposed in the substrate. The control gates are arranged in parallel and extend in the second direction which crosses the first direction. The floating gates are disposed between the active layers and the control gates. The doped regions are disposed in the active layers between the control gates.

Owner:POWERCHIP SEMICON CORP

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

Method for fabricating a cylinder-type capacitor utilizing a connected ring structure

InactiveUS7910452B2Reduce tiltSolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerEngineering

A method for fabricating a capacitor includes forming an isolation layer over a substrate. The isolation layer forms a plurality of open regions. Storage nodes are formed on surfaces of the open regions. An upper portion of the isolation layer is etched to expose upper outer walls of the storage nodes. A sacrificial layer is formed over the isolation layer to enclose the upper outer walls of the storage nodes. The isolation layer and the sacrificial layer are then removed.

Owner:SK HYNIX INC

Multi-channel semiconductor device and method of manufacturing the same

Provided are a multi-channel semiconductor device and a method for manufacturing the semiconductor device through a simplified process. A sacrificial layer and a channel layer are alternately stacked on a semiconductor substrate. Thereafter, the sacrificial layer and the channel layer are etched to form a separated active pattern, and a device isolation layer is formed to cover sidewalls of the active pattern. Dopant ions are implanted into the entire semiconductor substrate, thereby forming a channel separation region under the active pattern. A portion of the active pattern is etched to separate the active pattern from a pair of facing sidewalls of the device separation layer, thereby forming a channel pattern having a pair of first exposed sidewalls. Source / drain semiconductor layers are formed on the first sidewalls of the channel pattern, and a part of the device isolation layer is removed to expose a pair of second sidewalls of the channel pattern contacting with the device separation layer. Thereafter, the sacrificial layer included in the channel pattern is remove, and a conductive layer for a gate electrode is formed to cover the channel layer exposed by the removing of the sacrificial layer.

Owner:SAMSUNG ELECTRONICS CO LTD

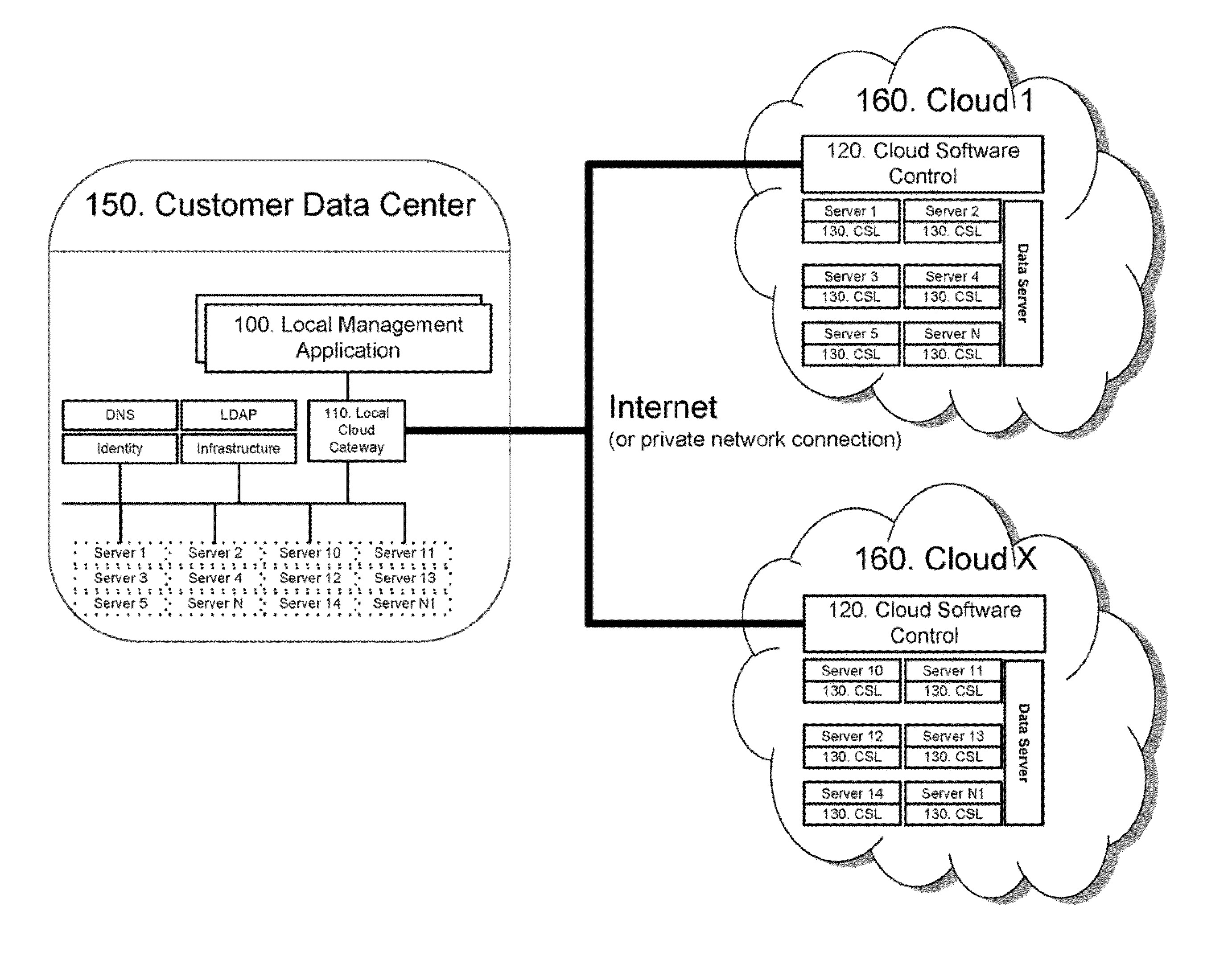

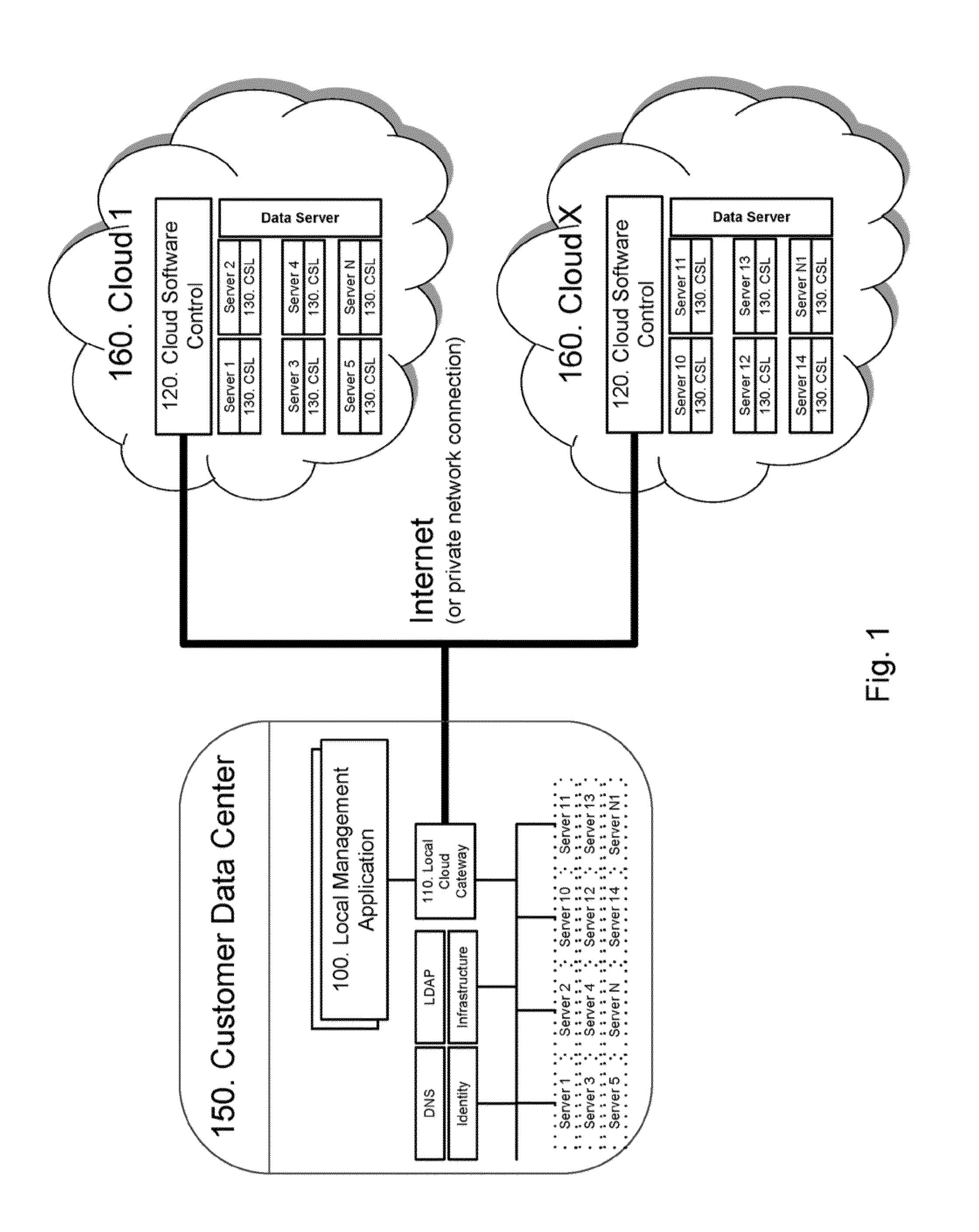

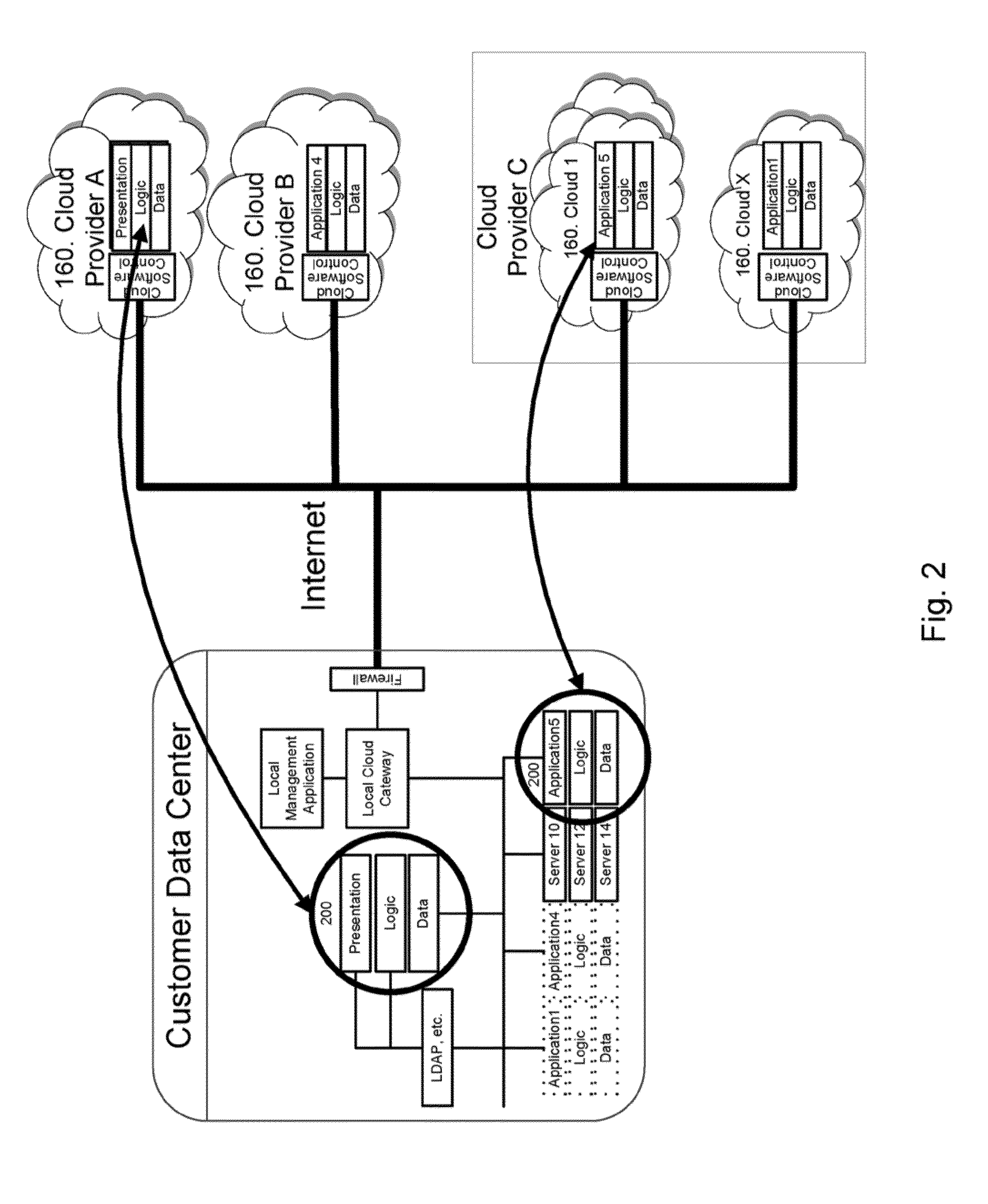

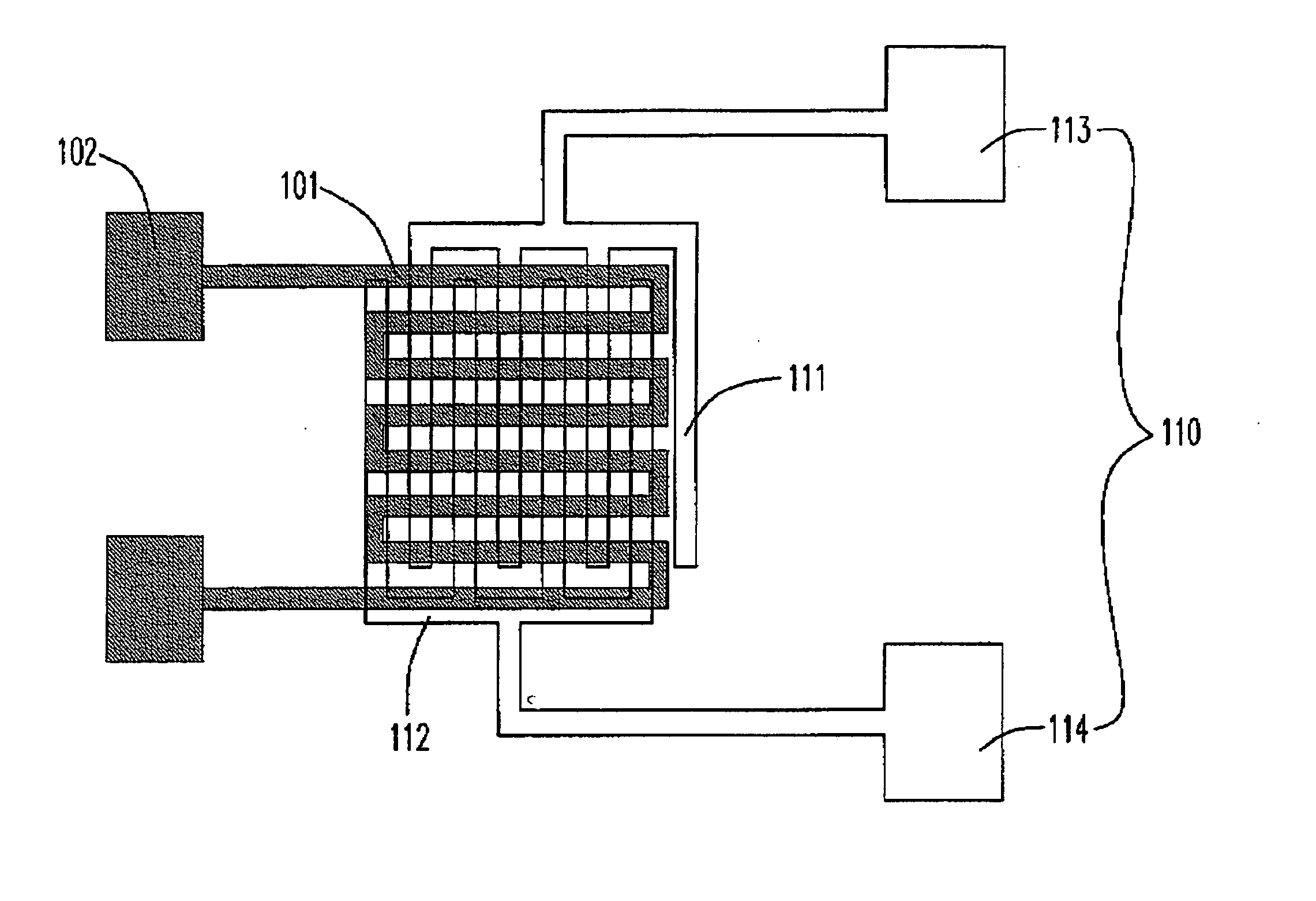

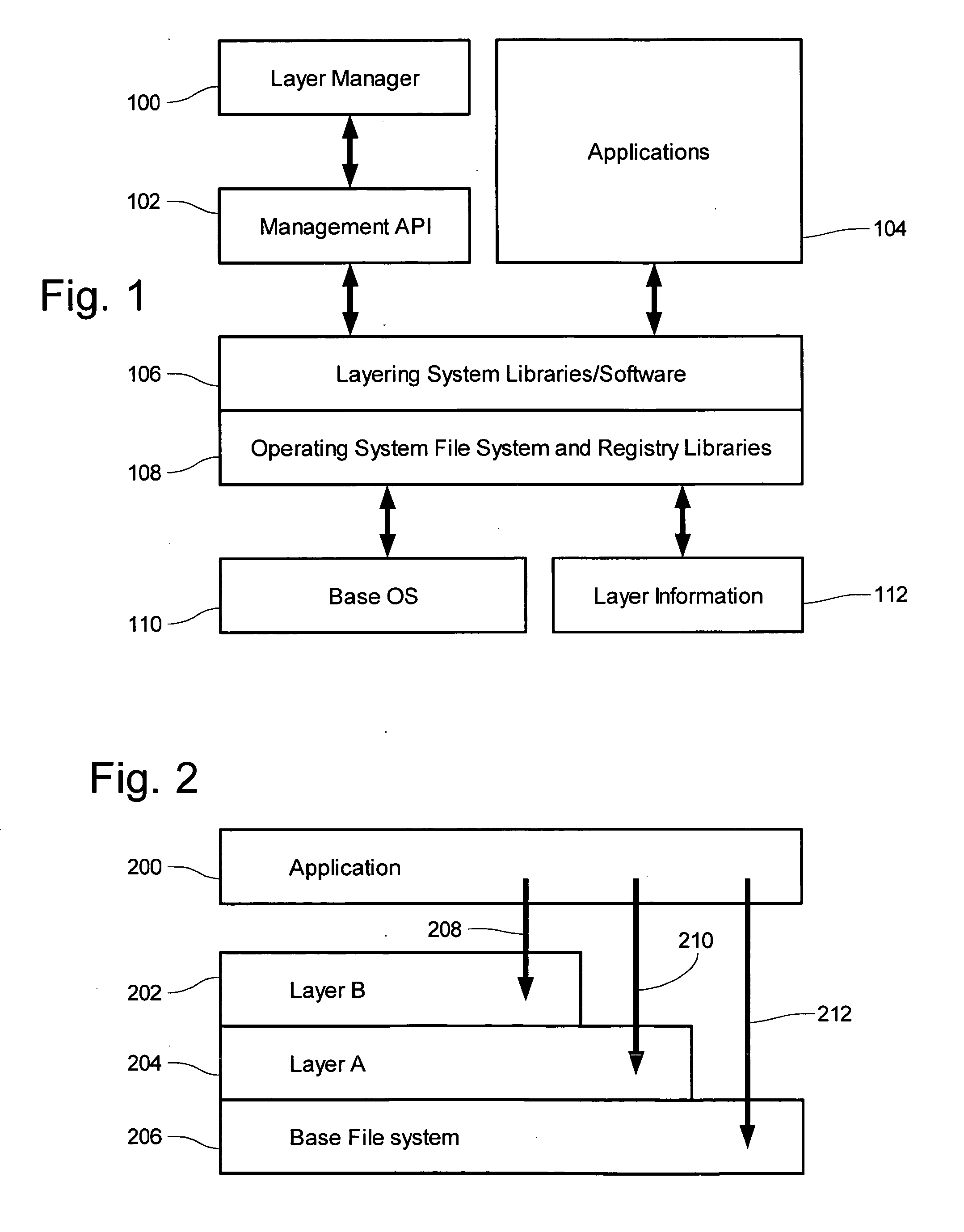

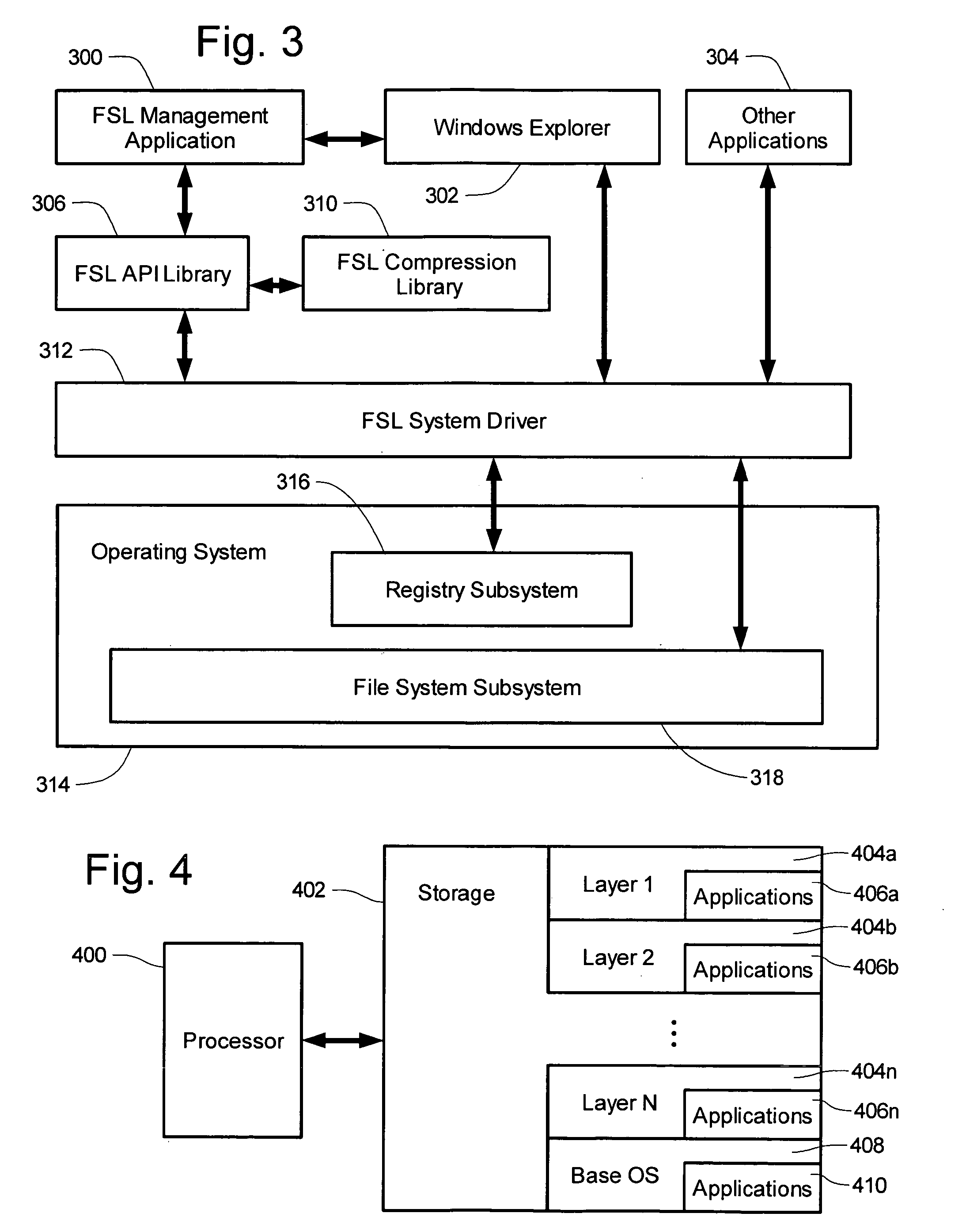

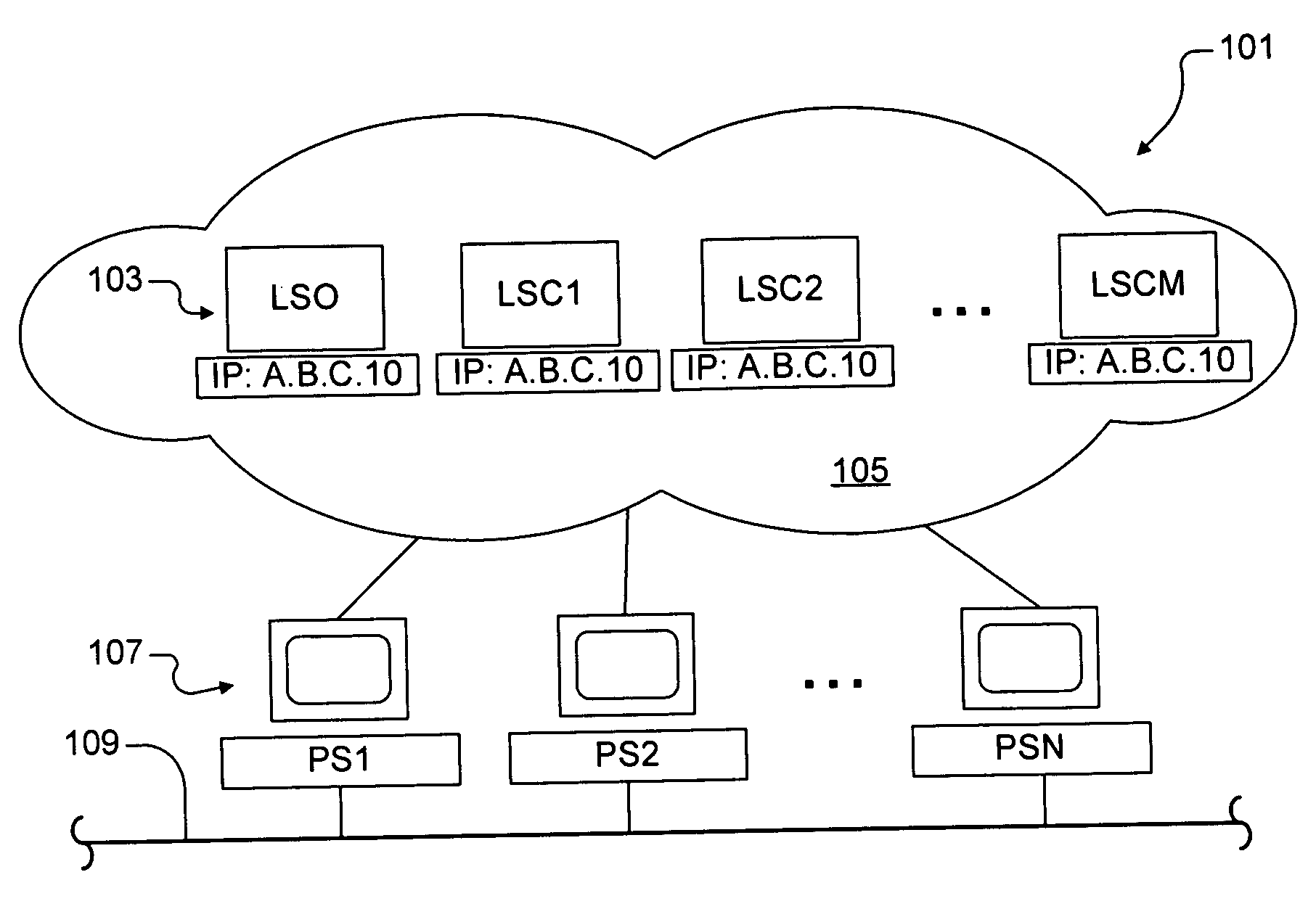

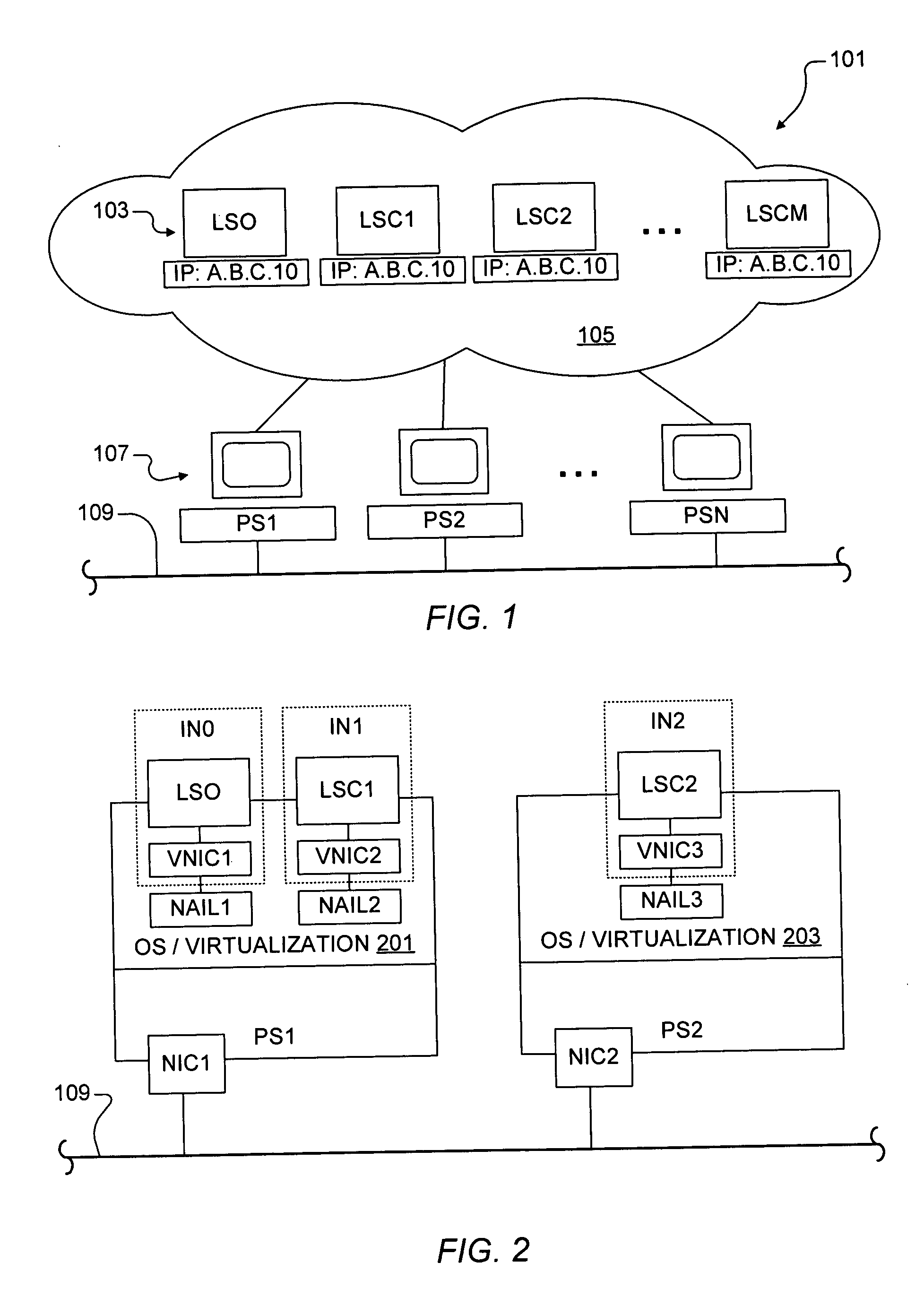

Environment preserving cloud migration and management

ActiveUS8417938B1Maximise its operationProtect environmentProgram controlTransmissionData centerIsolation layer

A system and method of operation is disclosed describing migration, management, and operation of applications and servers from customer data centers to cloud computing platforms without modification to existing environments or user access procedures. A cloud isolation layer operates as a virtual layer on the cloud platform, enabling server operation in a virtual environment that appears the same as the prior local environment. A cloud software image and a local cloud gateway act to redirect existing addressing from the local environment to the cloud implementation through secure network and data paths. A local management application provides a control interface and maps and manages the local environment and utilized cloud resources.

Owner:RAKUTEN GRP INC

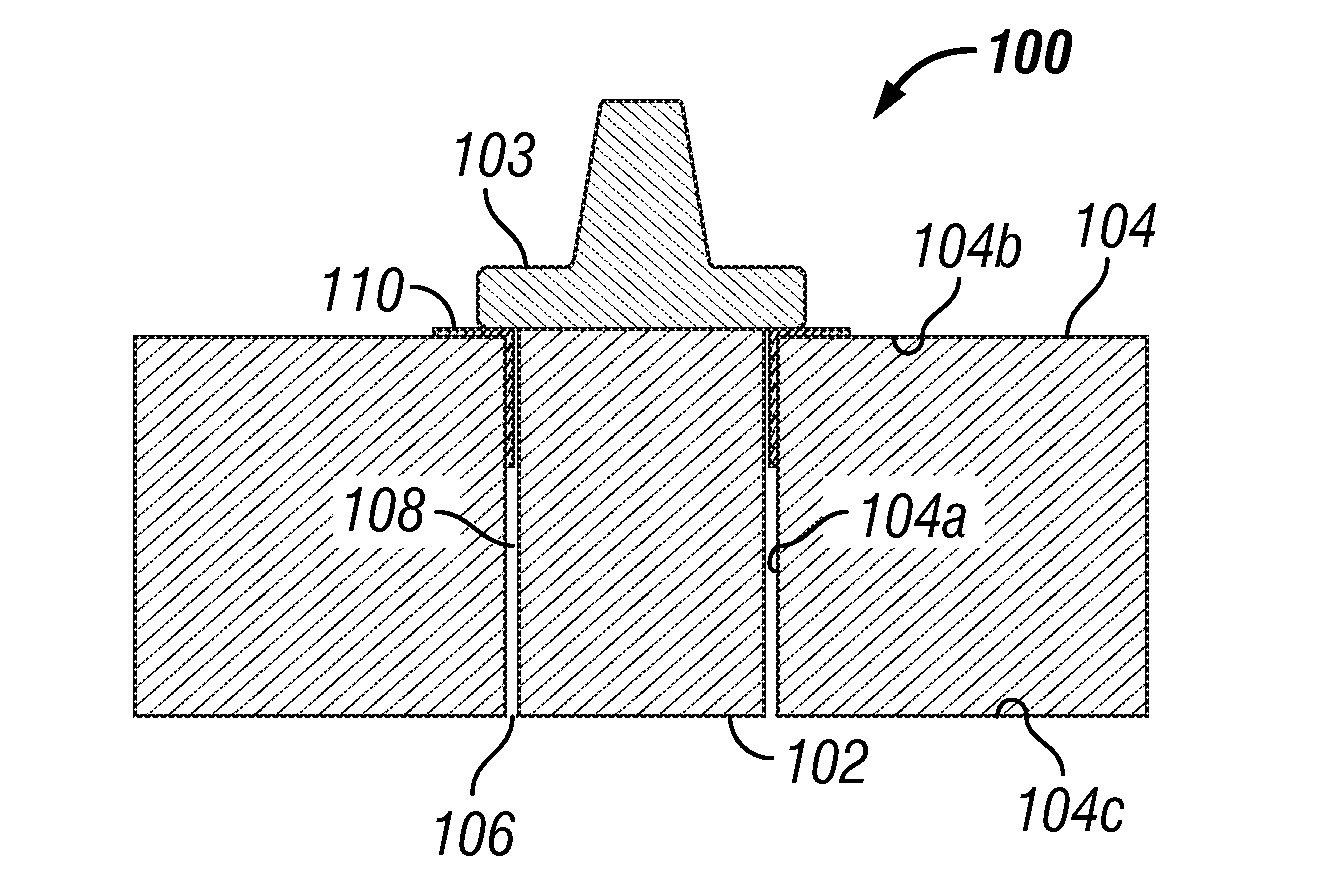

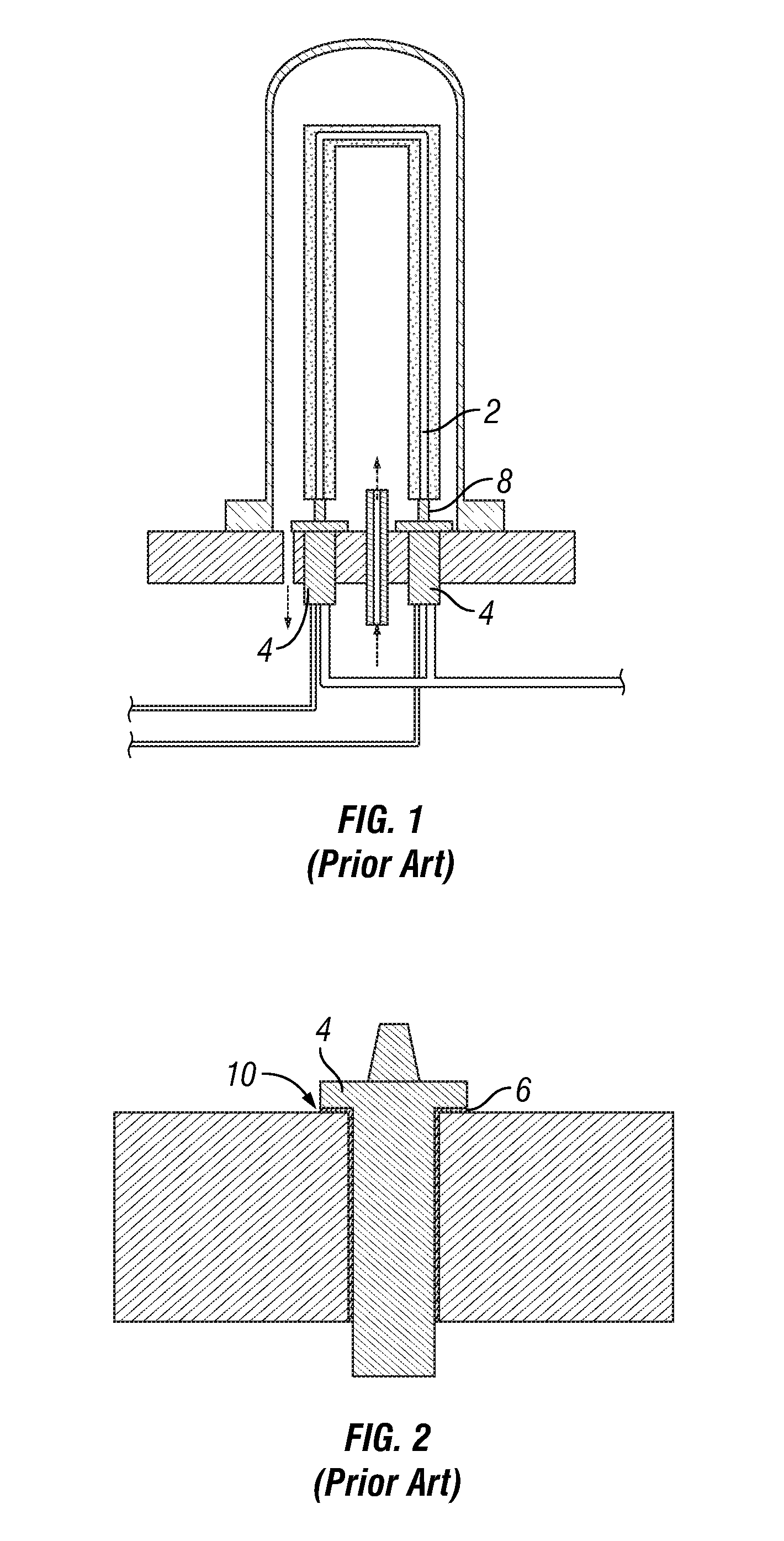

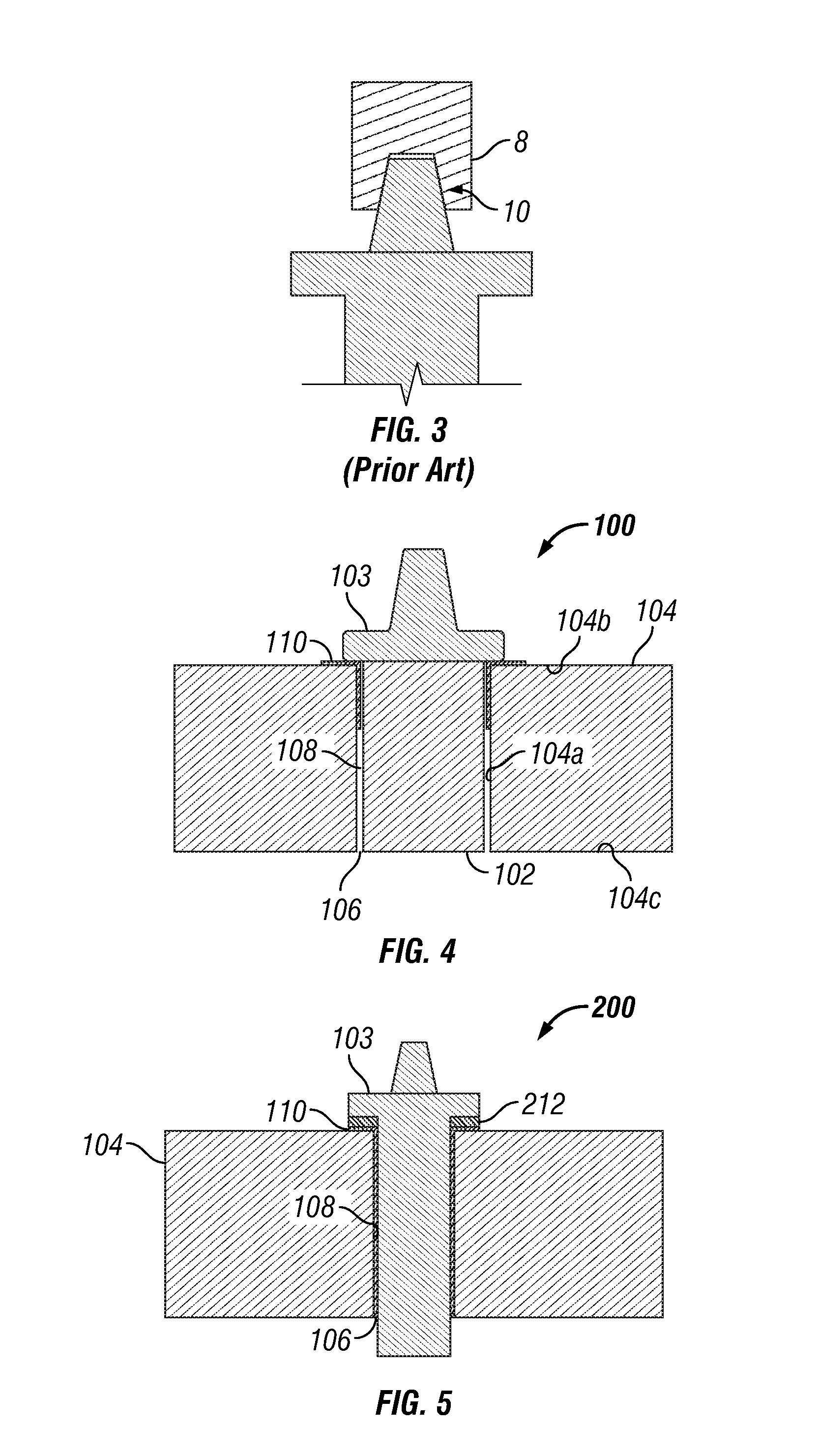

High temperature and high voltage electrode assembly design

InactiveUS20100147219A1Improve throughputHigh voltageElectric discharge tubesSilicon compoundsIsolation layerEngineering

A chemical vapor deposition apparatus is disclosed. The chemical vapor deposition apparatus comprises a chamber having a base plate, a chamber wall, a gas inlet and a gas outlet. The base plate has holes therethrough. A plurality of electrodes extend through the holes of the base plate. The plurality of electrodes are capable of being attached to a power source. At least two of the plurality of electrodes are capable of being electrically coupled to a silicon rod positioned in the chamber. An electrical isolation bushing can be positioned between each of the plurality of electrodes and the base plate. The electrical isolation bushing comprises a sleeve portion surrounding a portion of the electrodes that extends through the base plate and a collar portion surrounding the holes at a surface of the base plate. In some instances, the collar portion can comprise a different material than the sleeve portion. In some instances, an isolation layer can be employed in addition to the isolation bushing, the isolation layer surrounding the holes at the surface of the base plate. In some instances, the collar portion and the sleeve portion are both ceramic.

Owner:GTSP GLOBAL

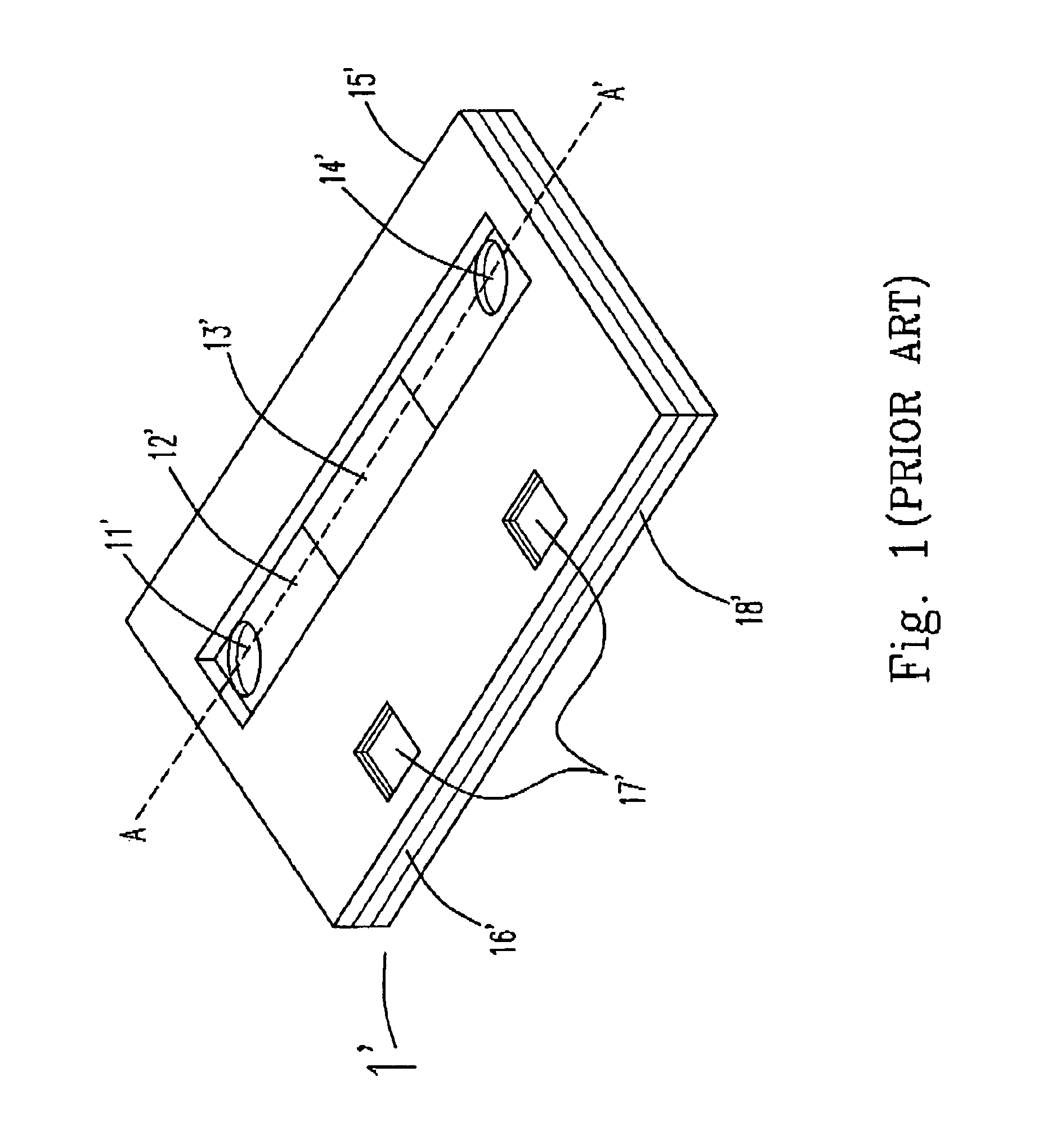

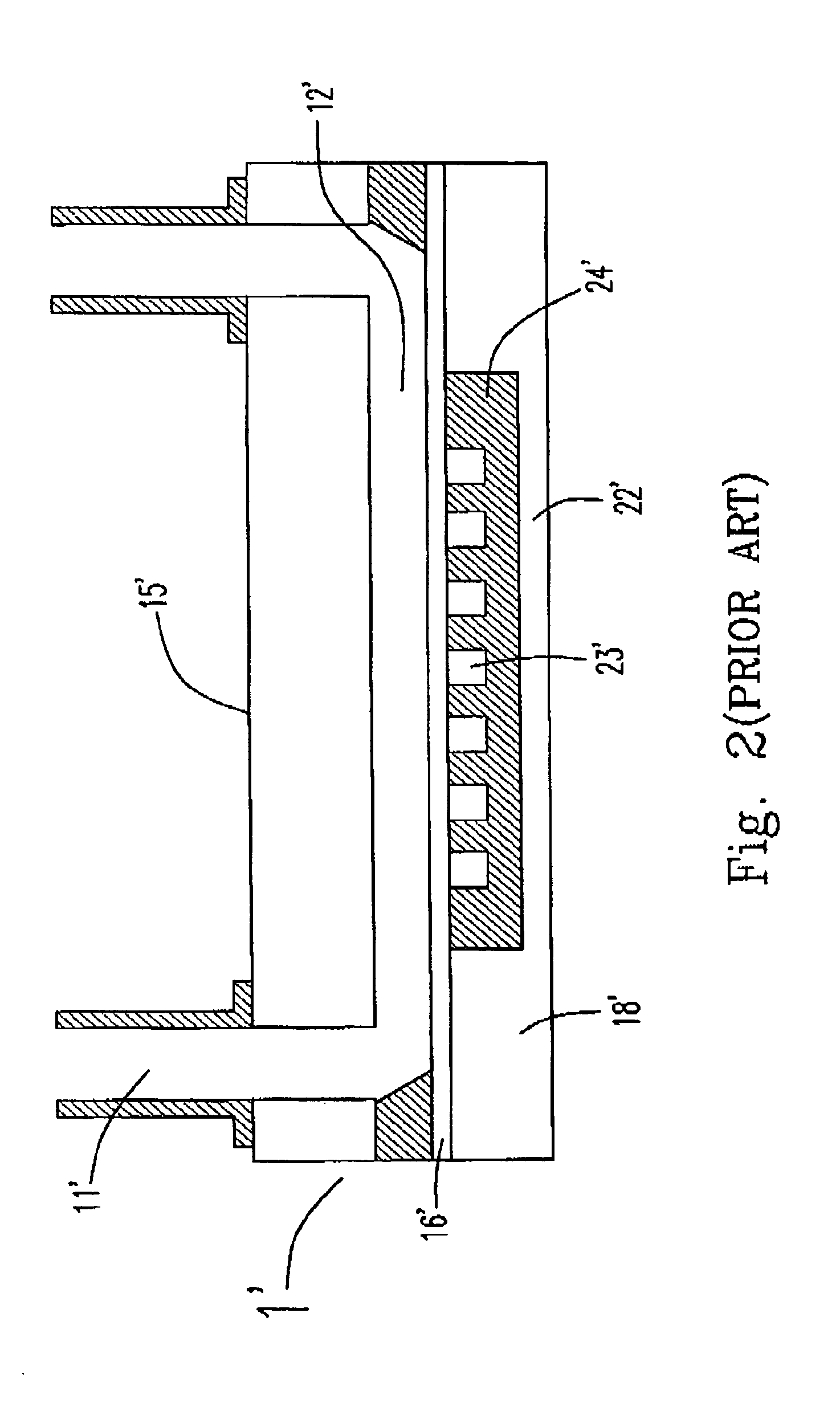

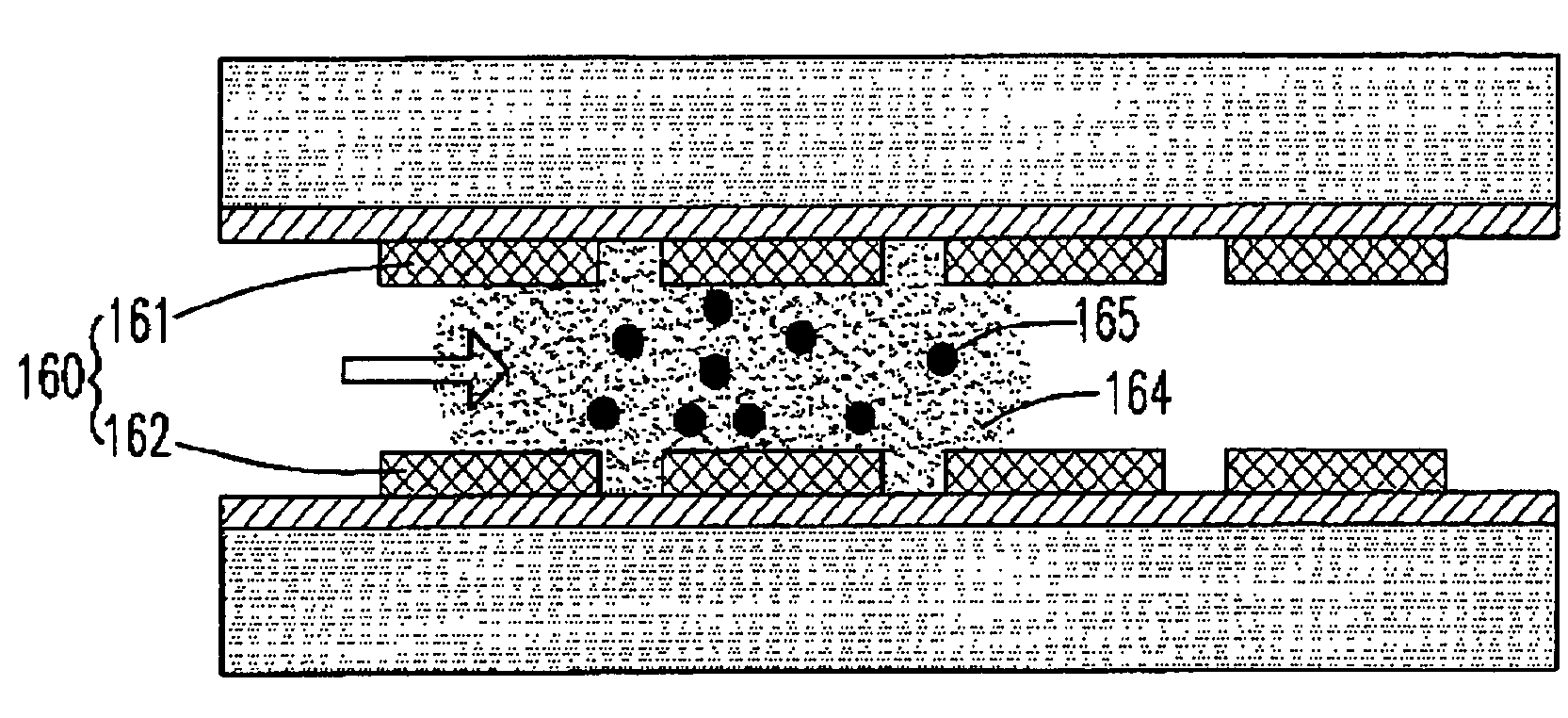

Electrowetting electrode device with electromagnetic field for actuation of magnetic-bead biochemical detection system

InactiveUS20050056569A1Reduce dissipationEnhanced magnetic forceMaterial thermal conductivityMicrobiological testing/measurementElectricityMagnetic bead

A detecting device for biochemical detections is provided. The detecting device includes a first substrate, a magnetic layer located on the first substrate, an isolation layer located on the magnetic layer, at least a first electrode located on the isolation layer, a first dielectric layer located on the first electrode, a first hydrophobic layer located on the first dielectric layer, a second substrate, at least a second electrode located on the second substrate and having a cathode and an anode, a second dielectric layer located on the second electrode and a second hydrophobic layer located on the second dielectric layer. The first electrode is zigzag-shaped, and the cathode and the anode of the second electrode are comb-shaped and interlaced with each other.

Owner:NATIONAL TSING HUA UNIVERSITY +1

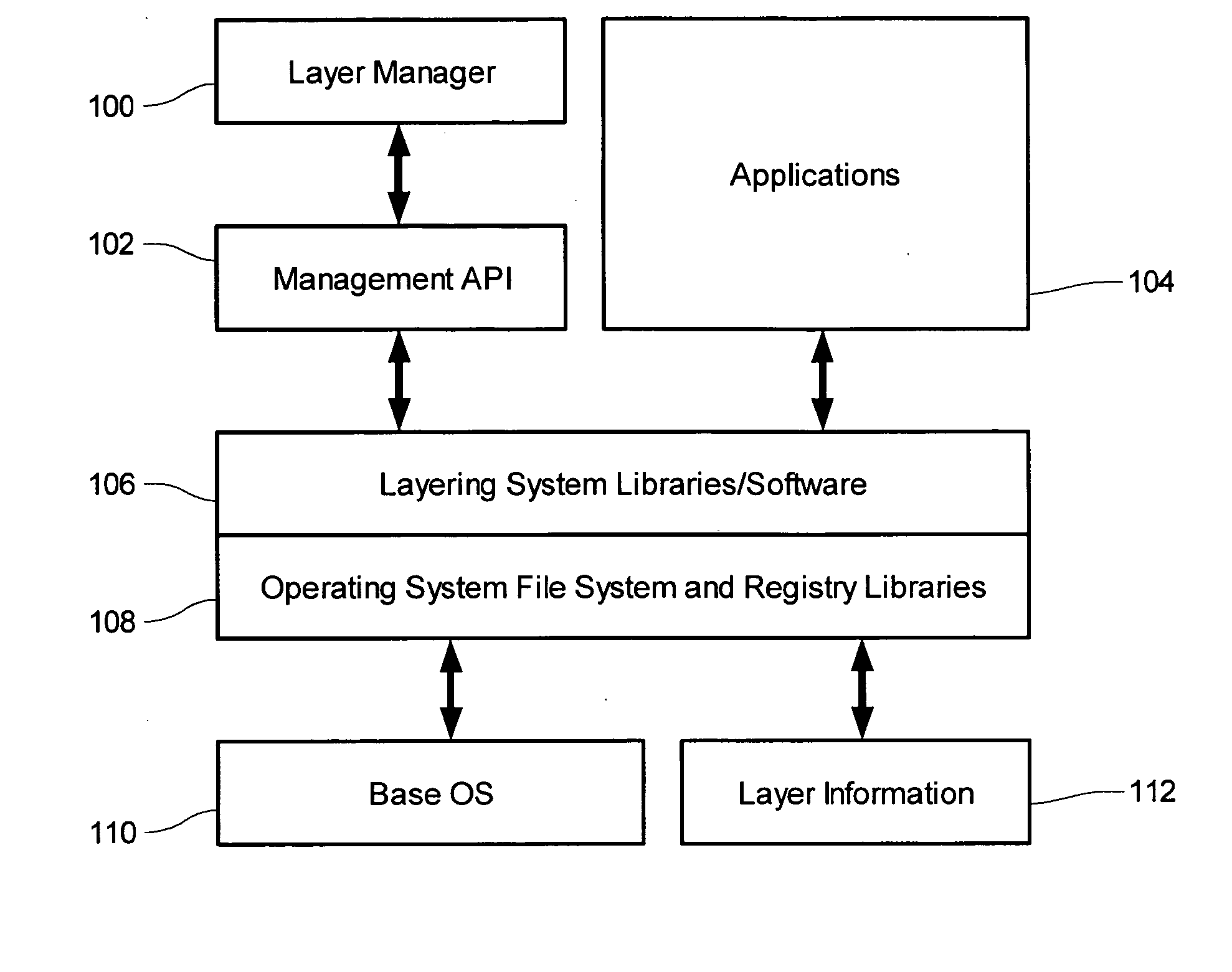

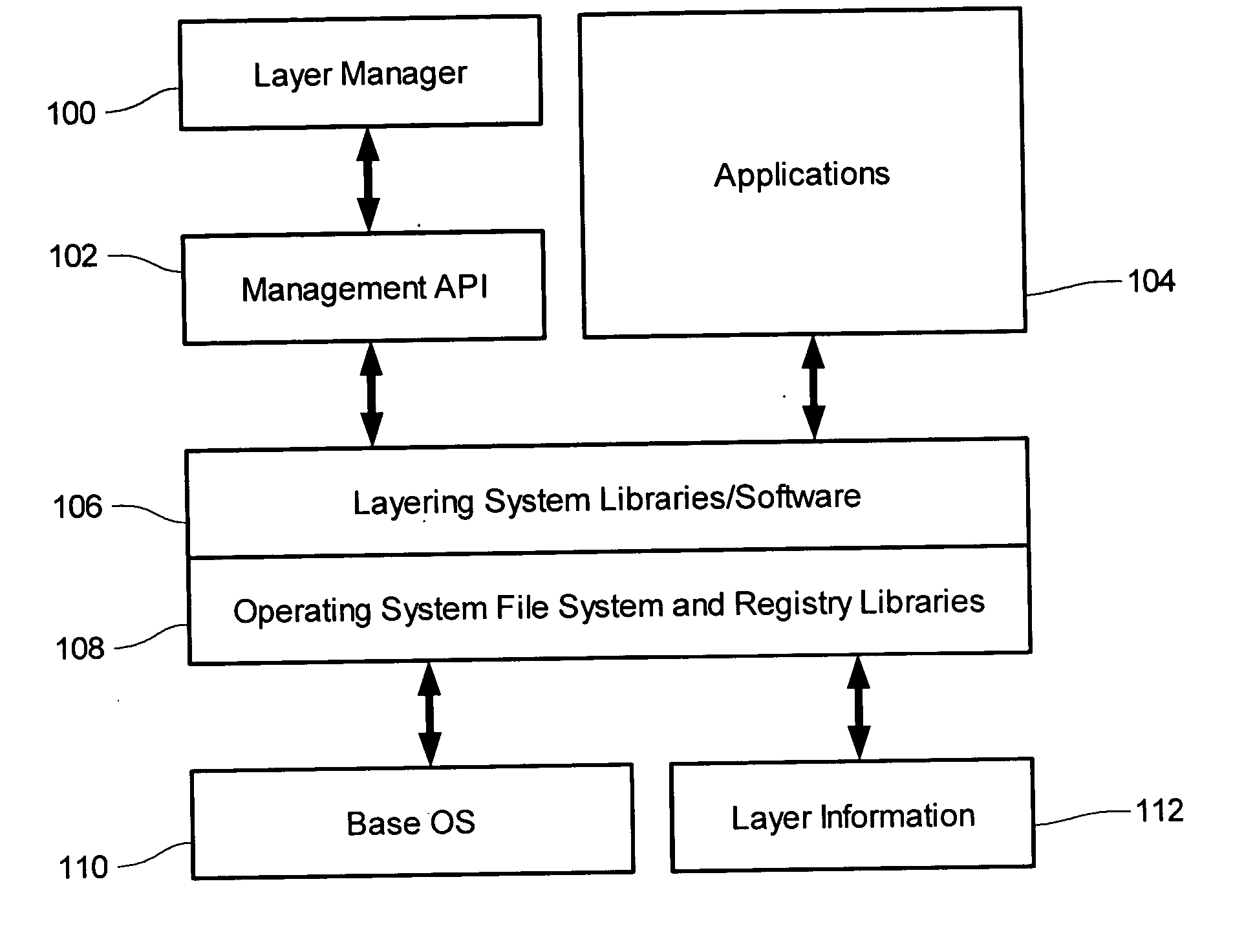

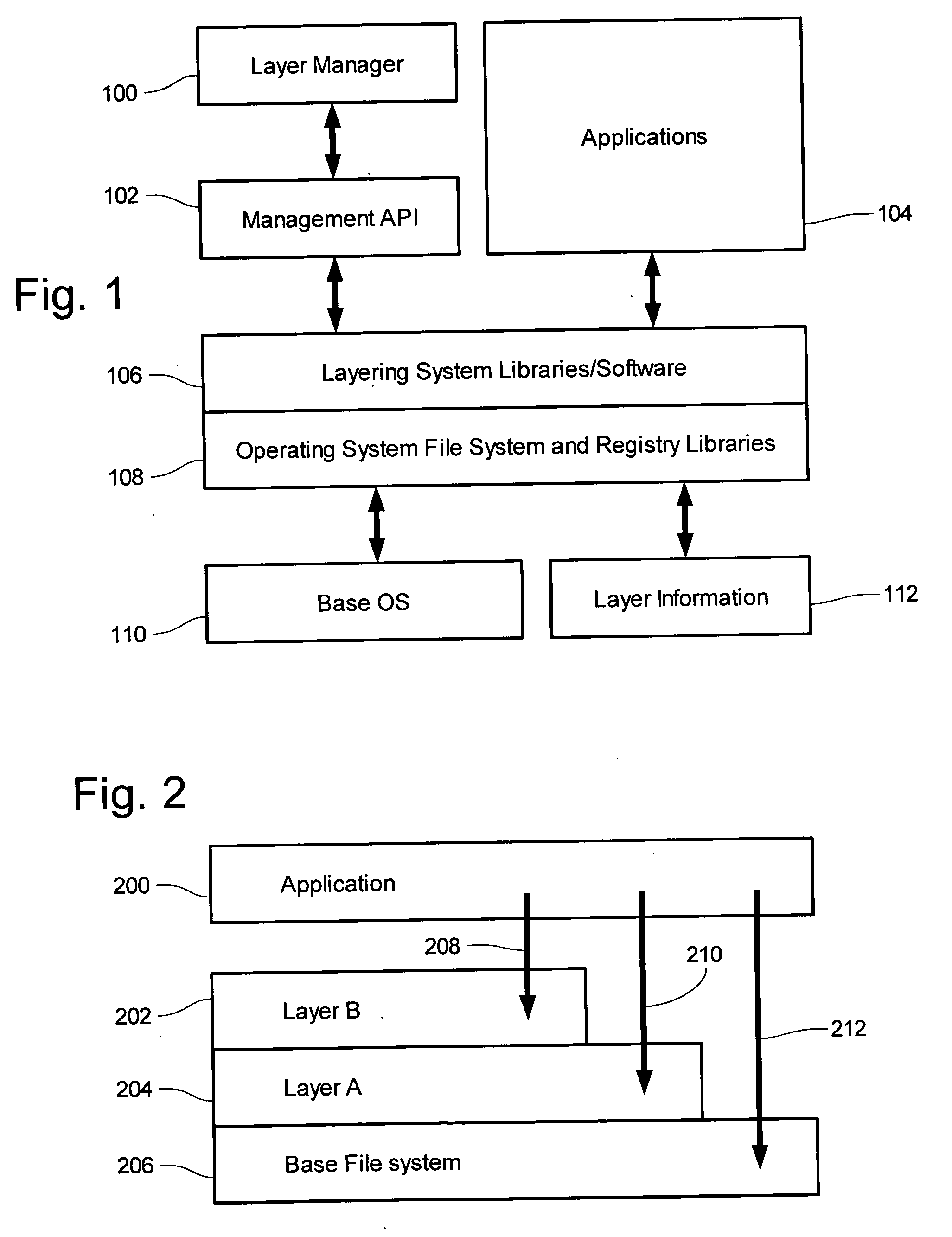

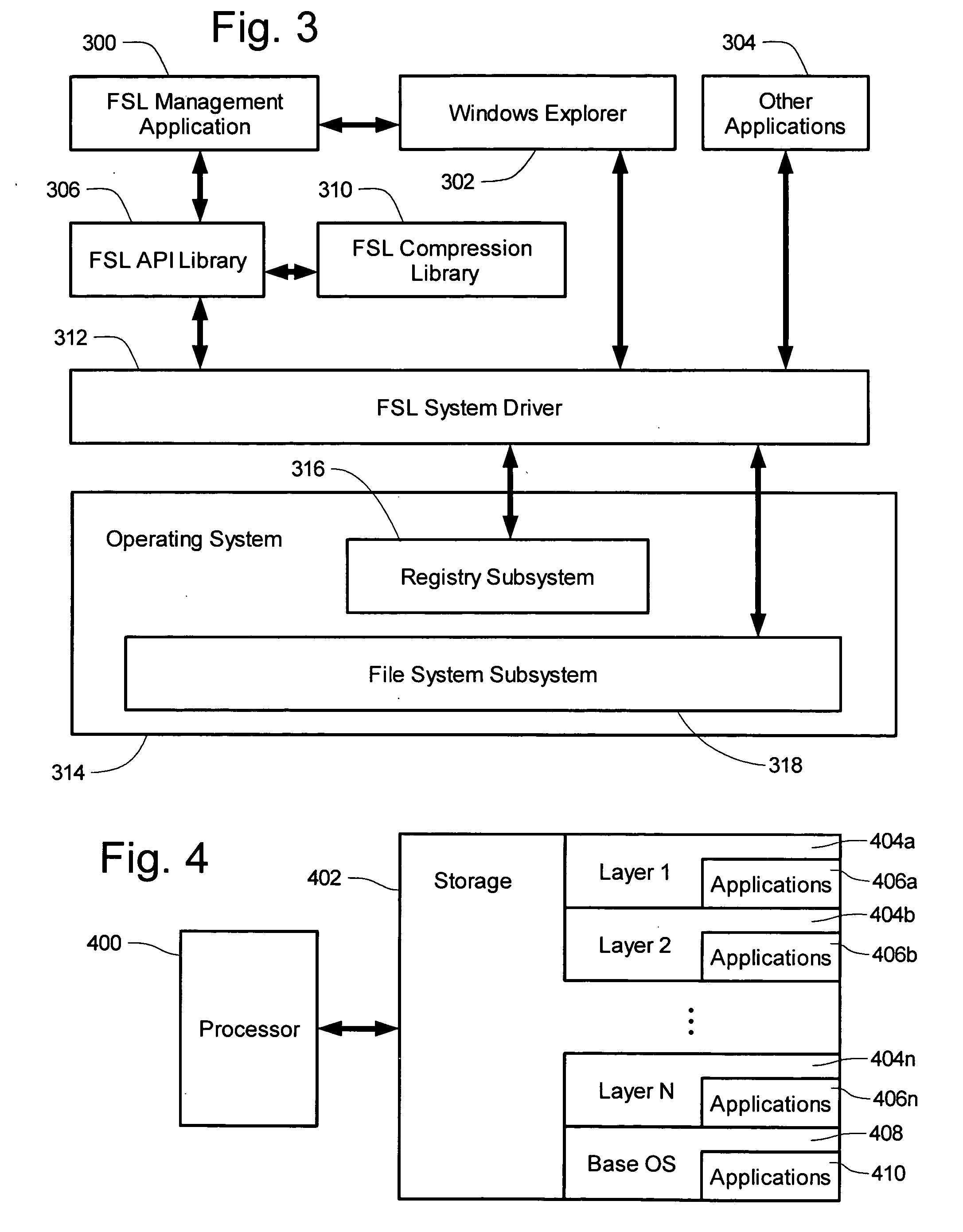

Intrusion Protection System Utilizing Layers

The inventions relate generally to protection of computing systems by isolating intrusive attacks into layers, those layers containing at least file objects and being accessible to applications, those layers further maintaining potentially intrusive file objects separately from regular file system objects such that the regular objects are protected and undisturbed. Also disclosed herein are computing systems which use layers and / or isolation layers, and various systems and methods for using those systems. Detailed information on various example embodiments of the inventions are provided in the Detailed Description below, and the inventions are defined by the appended claims.

Owner:CA TECH INC

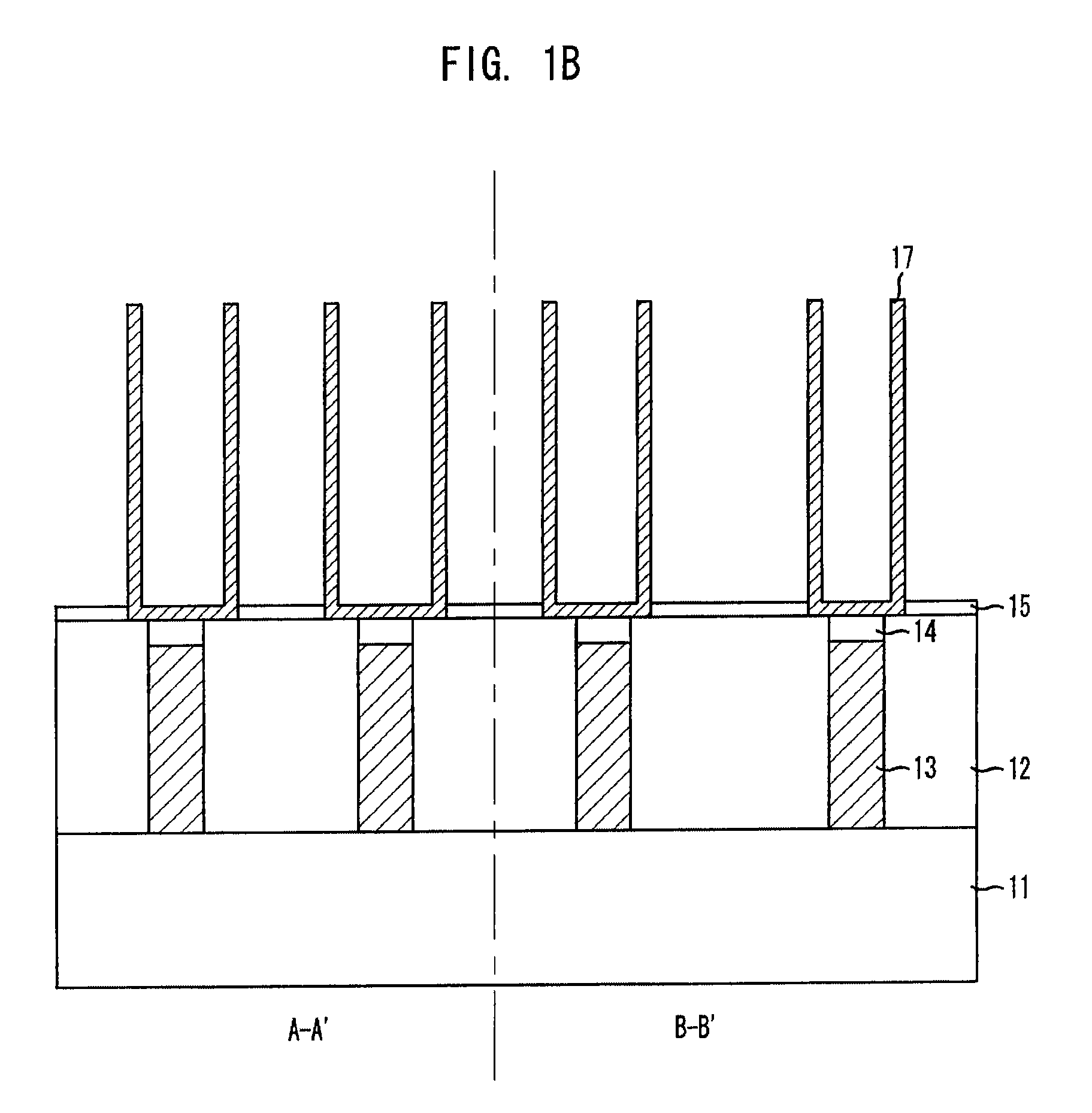

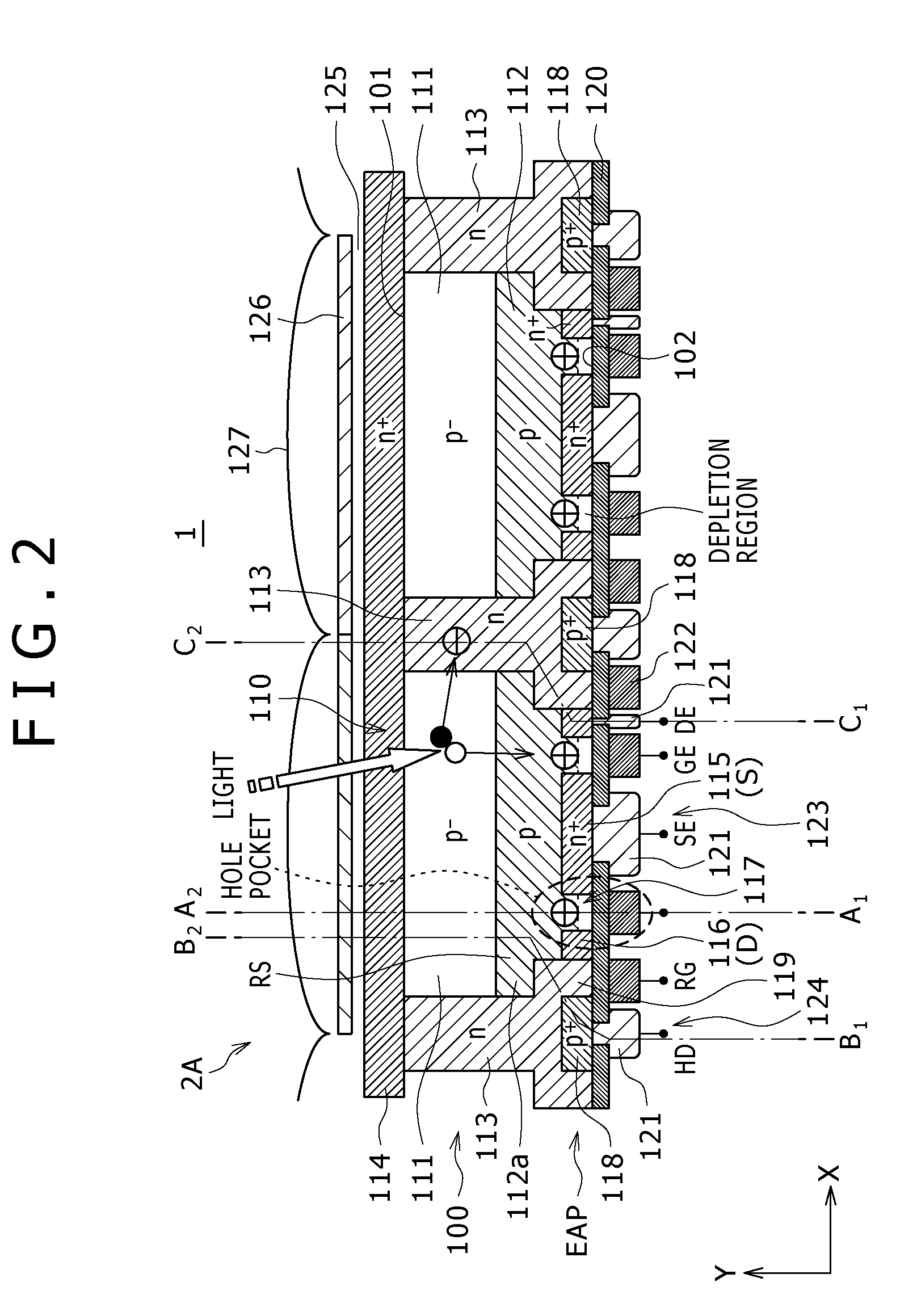

Semiconductor device and method for manufacturing the same

A semiconductor device of one embodiment of the present invention includes a substrate; isolation layers, each of which is formed in a trench formed on the substrate and has an insulating film and a conductive layer; a semiconductor layer of a first conductivity type for storing signal charges, formed between the isolation layers and isolated from the conductive layers by the insulating films; a semiconductor layer of a second conductivity type, formed under the semiconductor layer of the first conductivity type; and a transistor having a gate insulator film formed on the semiconductor layer of the first conductivity type and a gate electrode formed on the gate insulator film.

Owner:KK TOSHIBA

Intrusion protection system utilizing layers and triggers

The inventions relate generally to protection of computing systems by isolating intrusive attacks into layers, those layers containing at least file objects and being accessible to applications, those layers further maintaining potentially intrusive file objects separately from regular file system objects such that the regular objects are protected and undisturbed. Also disclosed herein are computing systems which use layers and / or isolation layers, and various systems and methods for using those systems. Detailed information on various example embodiments of the inventions are provided in the Detailed Description below, and the inventions are defined by the appended claims.

Owner:CA TECH INC

Electrowetting electrode device with electromagnetic field for actuation of magnetic-bead biochemical detection system

InactiveUS7189359B2Reduce dissipationEnhanced magnetic forceMaterial analysis by electric/magnetic meansLaboratory glasswaresElectricityMagnetic bead

A detecting device for biochemical detections is provided. The detecting device includes a first substrate, a magnetic layer located on the first substrate, an isolation layer located on the magnetic layer, at least a first electrode located on the isolation layer, a first dielectric layer located on the first electrode, a first hydrophobic layer located on the first dielectric layer, a second substrate, at least a second electrode located on the second substrate and having a cathode and an anode, a second dielectric layer located on the second electrode' and a second hydrophobic layer located on the second dielectric layer. The first electrode is zigzag-shaped, and the cathode and the anode of the second electrode are comb-shaped and interlaced with each other.

Owner:NATIONAL TSING HUA UNIVERSITY +1

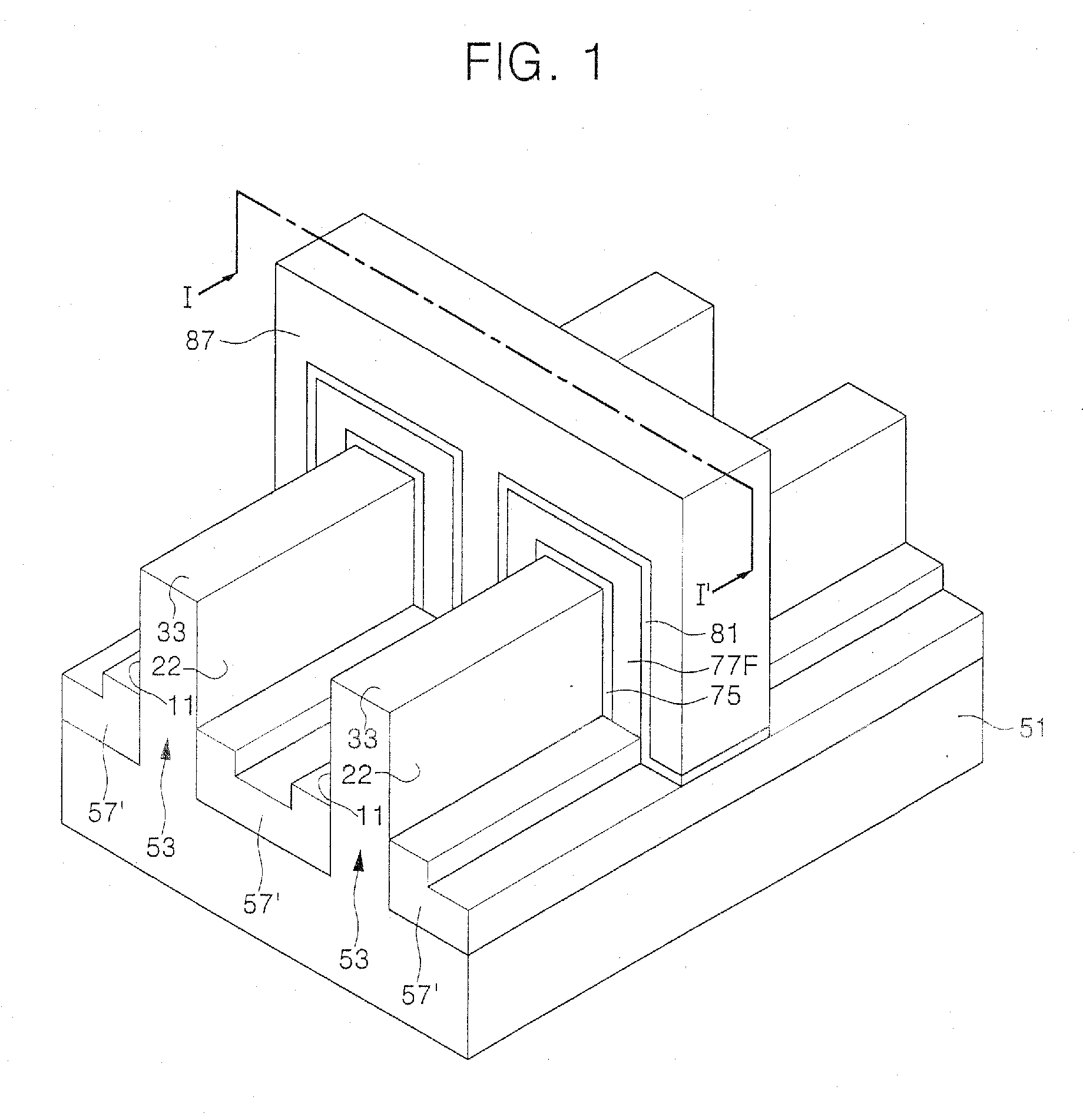

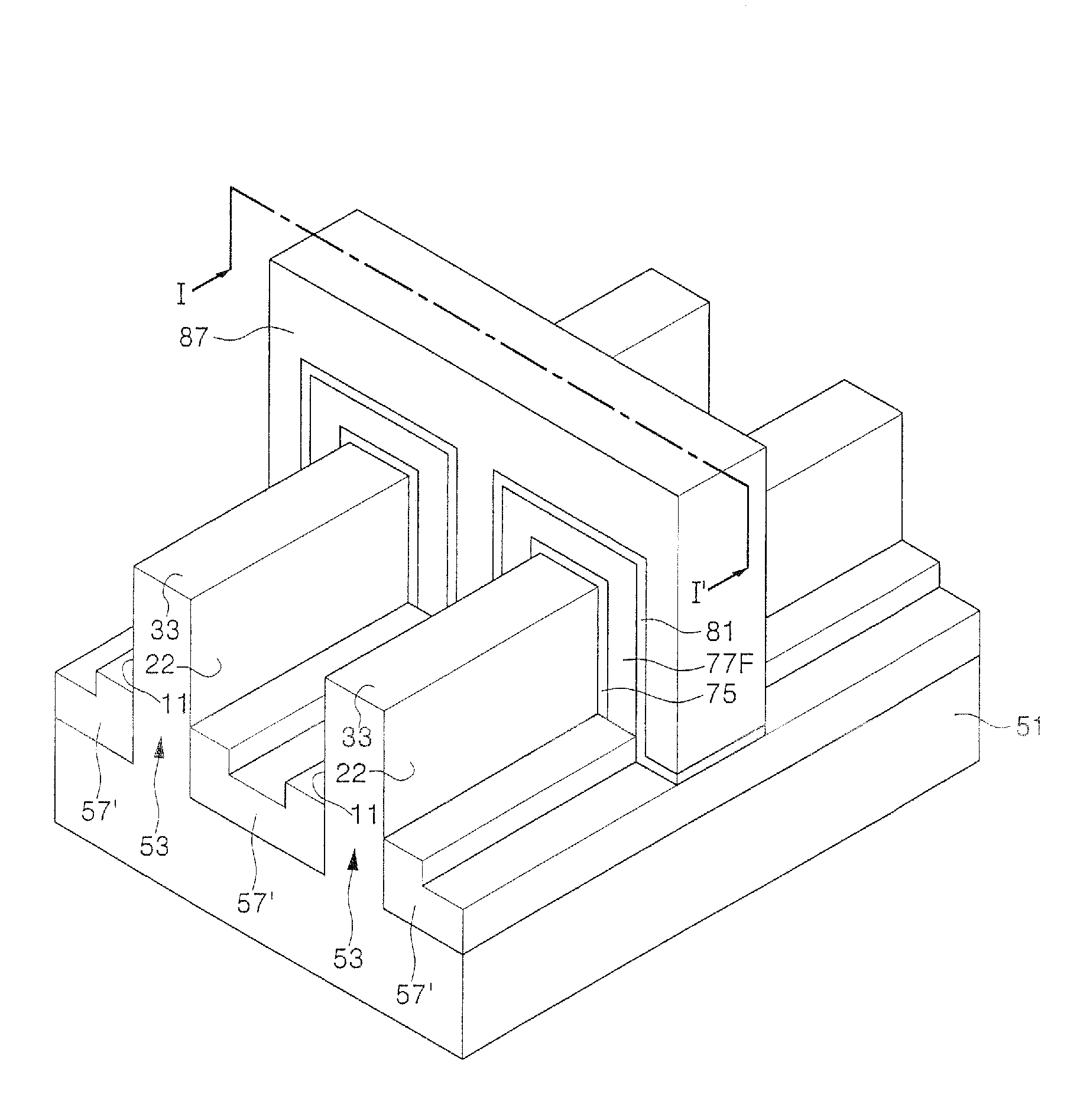

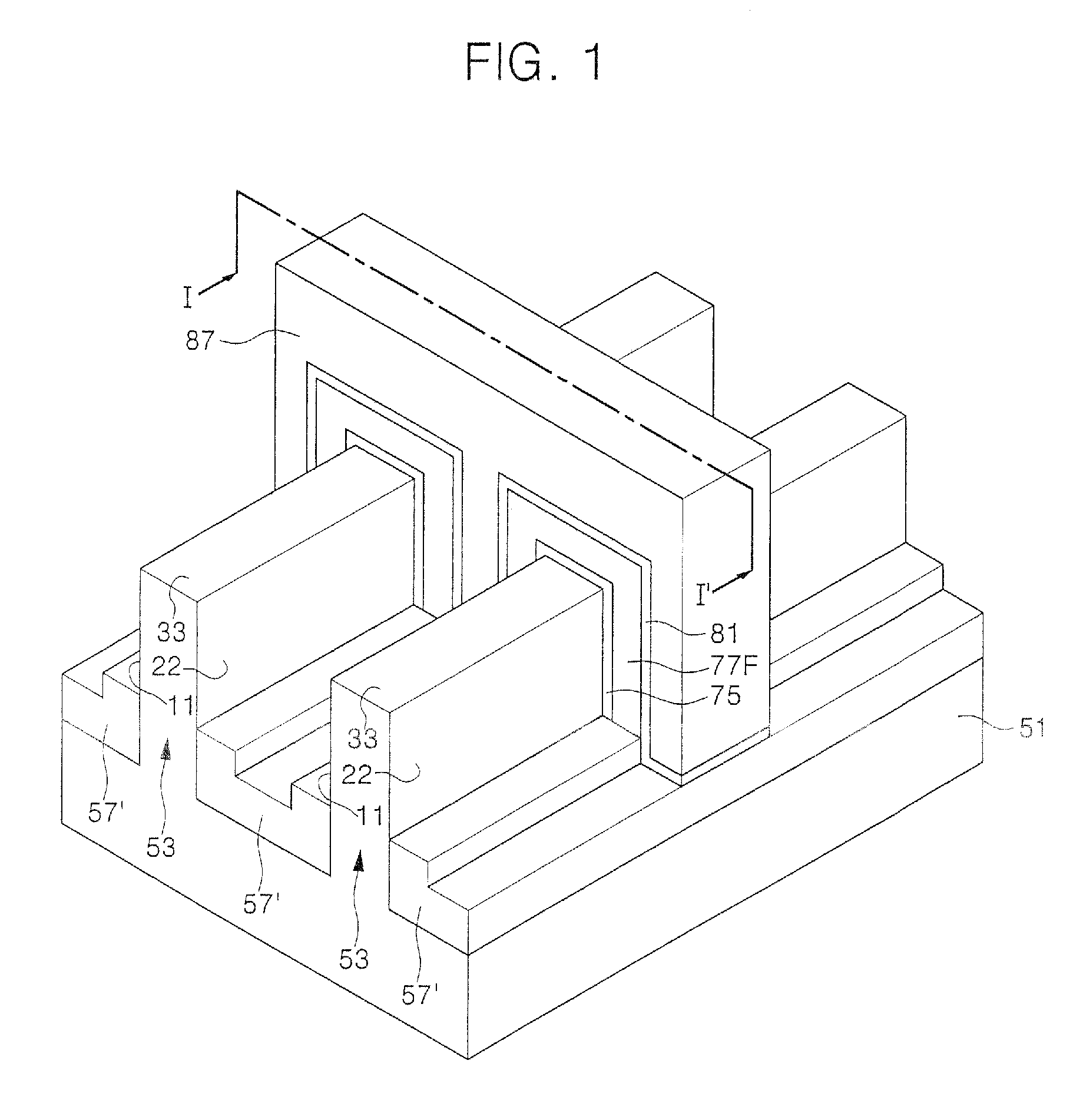

Isolation method of defining active fins, method of fabricating semiconductor device using the same and semiconductor device fabricated thereby

InactiveUS20070134884A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialIsolation layer

An isolation method of defining active fins, a method of fabricating a semiconductor device using the same, and a semiconductor device fabricated thereby are provided. The method of fabricating a semiconductor device includes: preparing a semiconductor substrate; and forming a plurality of active fins having major and minor axes and two-dimensionally arrayed on the semiconductor substrate in directions of the major and minor axes. A liner pattern is formed on lower sidewalls of the active fins. An isolation layer is formed on the semiconductor substrate having the liner pattern, and the isolation layer exposes top surfaces of the active fins and a part of the active fins' sidewalls substantially parallel to the major axis. Parallel gate lines are formed to cover the top surfaces and the exposed sidewalls of the active fins, cross over the active fins, and run on the isolation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

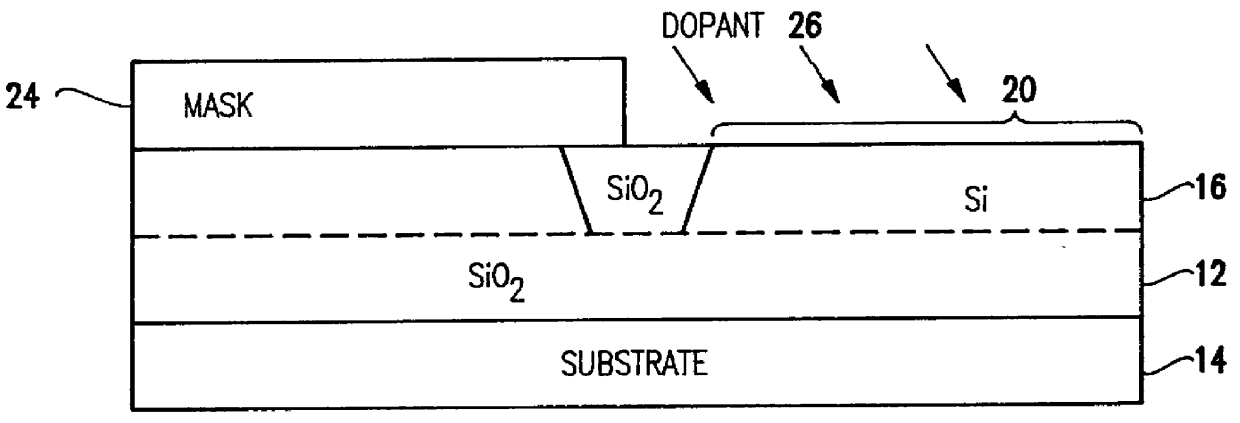

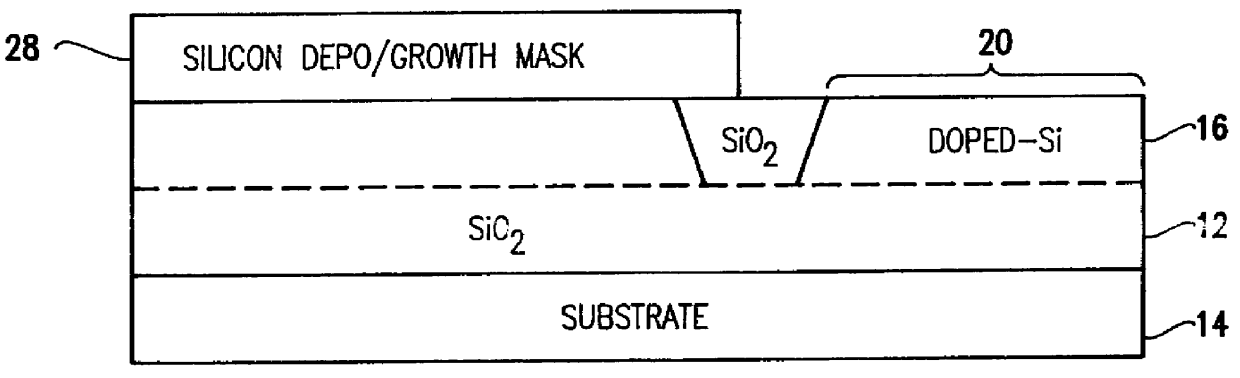

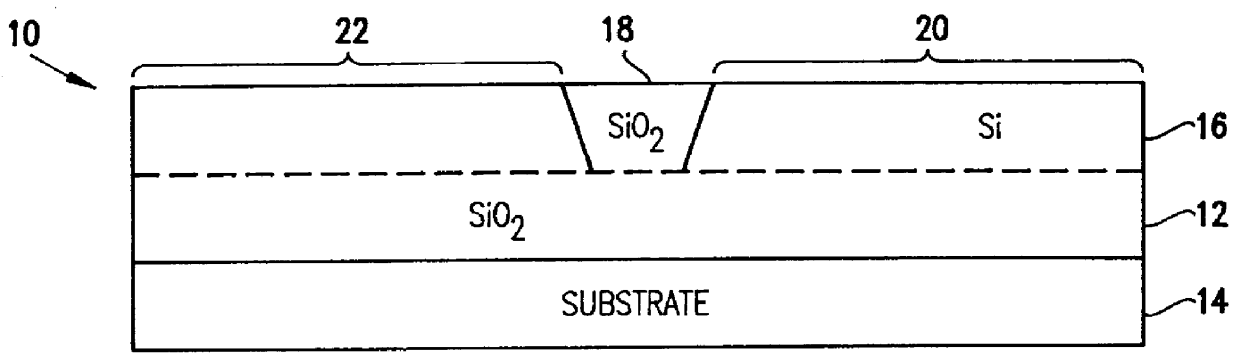

Silicon-on-insulator and CMOS-on-SOI double film fabrication process with a coplanar silicon and isolation layer and adding a second silicon layer on one region

InactiveUS6096584AHigher power-to-failure thresholdImprove protectionTransistorSolid-state devicesIsolation layerElectronic component

Silicon is formed at selected locations on a silicon-insulator (SOI) substrate during fabrication of selected electronic components, including resistors, capacitors, and diodes. The silicon location is defined using a patterned, removable mask, and the silicon may be applied by deposition or growth and may take the form of polysilicon or crystalline silicon. Electrostatic discharge (ESD) characteristics of the SOI device is significantly improved by having a thick double layer of silicon in selected regions.

Owner:GLOBALFOUNDRIES INC

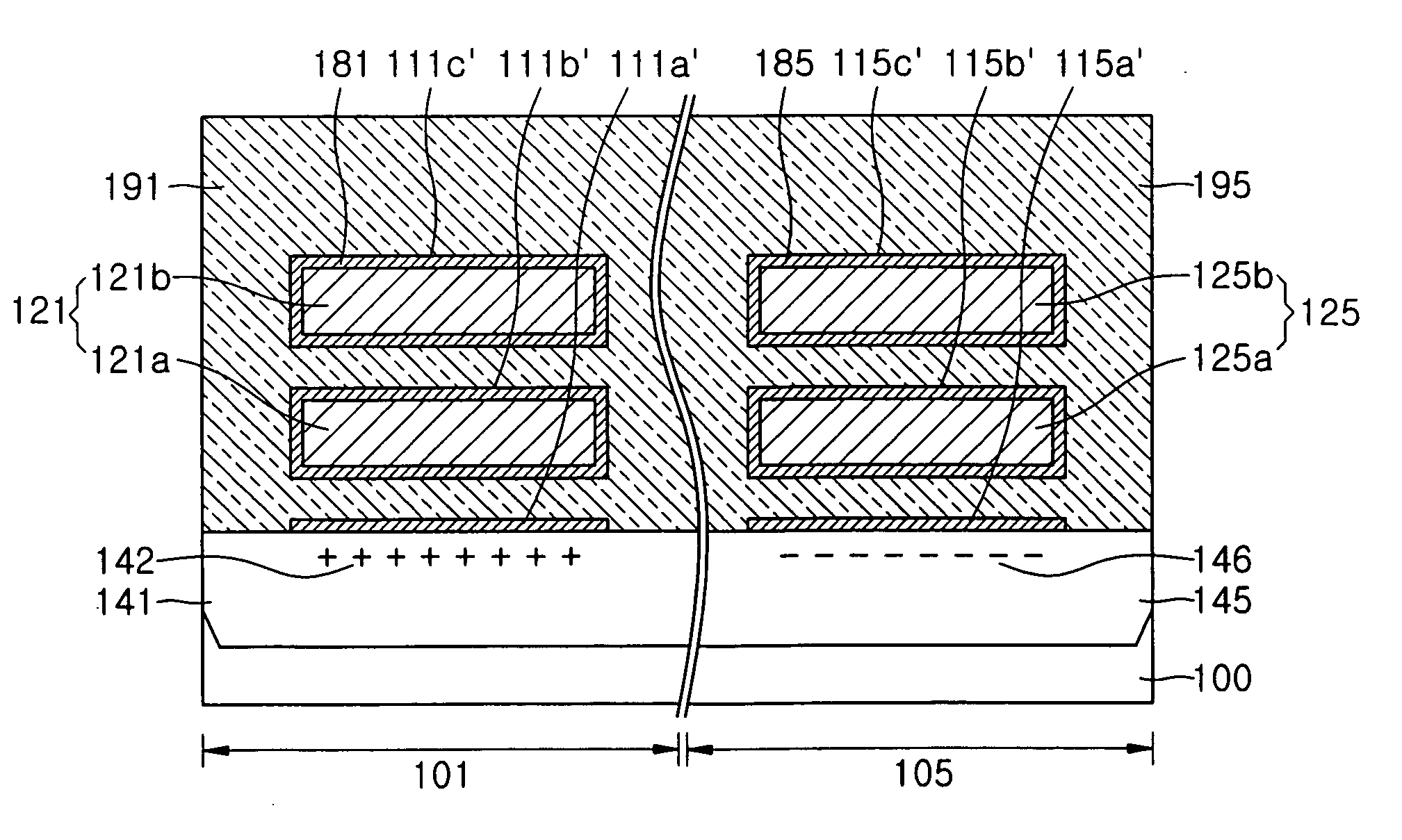

Nitride semiconductor light emitting device having electrostatic discharge(ESD) protection capacity

ActiveUS20060060880A1Increase the number ofIncrease in sizeSolid-state devicesSemiconductor devicesOhmic contactIsolation layer

A nitride semiconductor light emitting device including a light emitting diode and a diode formed on a single substrate, in which the light emitting diode and the diode use a common electrode. According to the present invention, an active layer and a p-type nitride semiconductor layer are each divided into a first region and a second region by an insulative isolation layer, and an ohmic contact layer is formed on the p-type nitride semiconductor layer contained in the first region. A p-type electrode is formed on the ohmic contact layer and is extended to the p-type nitride semiconductor layer contained in the second region. An n-type electrode is formed on the p-type nitride semiconductor layer contained in the second region, passes through the p-type nitride semiconductor layer and the active layer contained in the second region, and is connected to the first n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device including air gaps and method for fabricating the same

ActiveUS20150126013A1Reduce parasitic capacitanceTransistorSemiconductor/solid-state device detailsBit lineParasitic capacitance

Disclosed are a semiconductor device capable of reducing parasitic capacitance between adjacent conductive structures and a method for fabricating the same. The semiconductor device includes a plurality of bit line structures each comprising a first contact plug formed over a substrate and a bit line formed over the first contact plug. A spacer structure having air gaps is formed on sidewalls of the first contact plug and on sidewalls of the bit line. An plug isolation layer is formed between the plurality of bit line structures. The isolation layer includes an opening. A second contact plug is formed in the opening and a memory element is formed over the second contact plug.

Owner:SK HYNIX INC

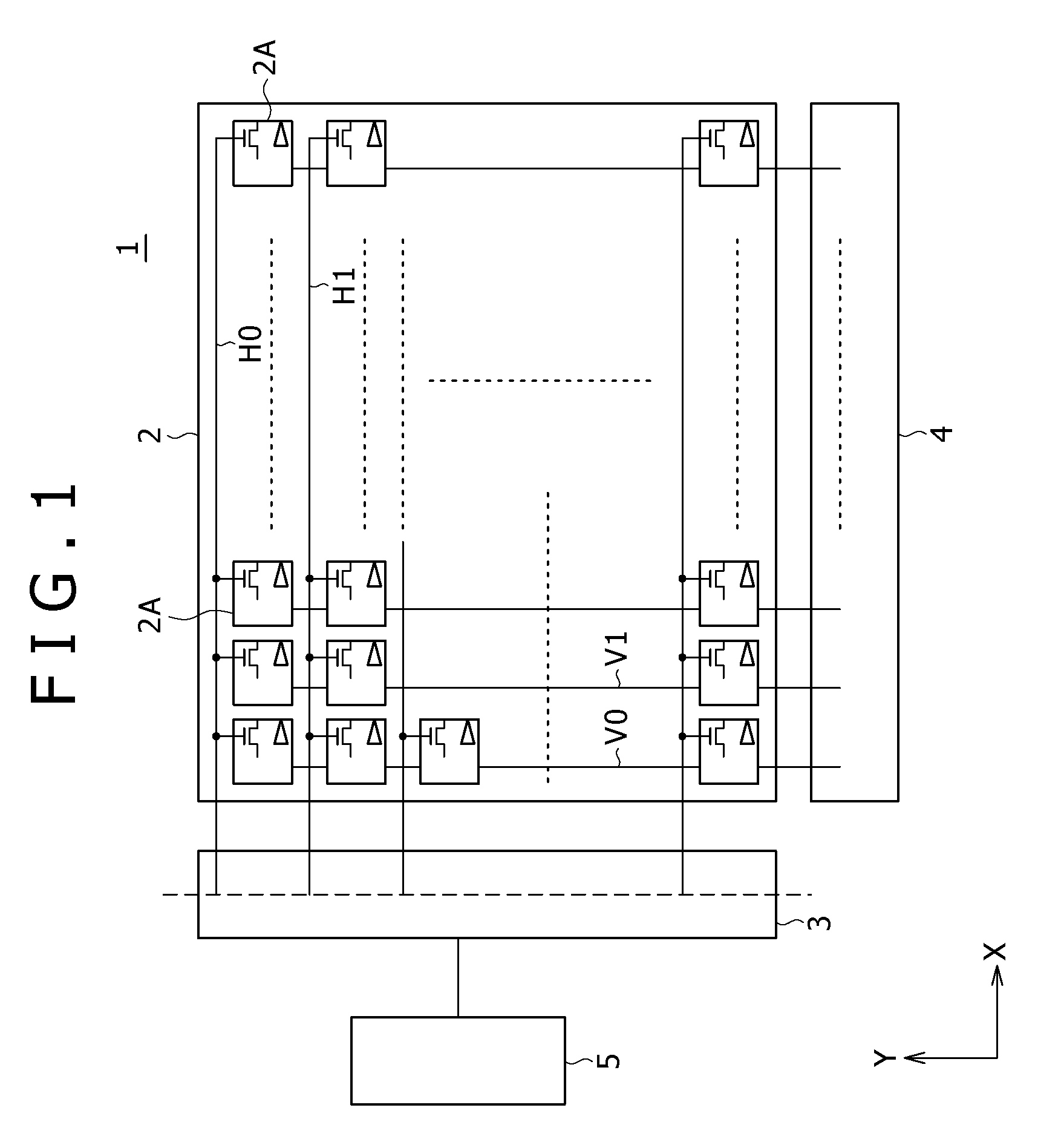

Solid-state imaging device and camera

ActiveUS20080290382A1Long distanceReduce capacityTransistorTelevision system detailsIsolation layerTransistor

A solid-state imaging device including: a substrate; a light-receiving part; a second-conductivity-type isolation layer; a detection transistor; and a reset transistor.

Owner:SONY CORP

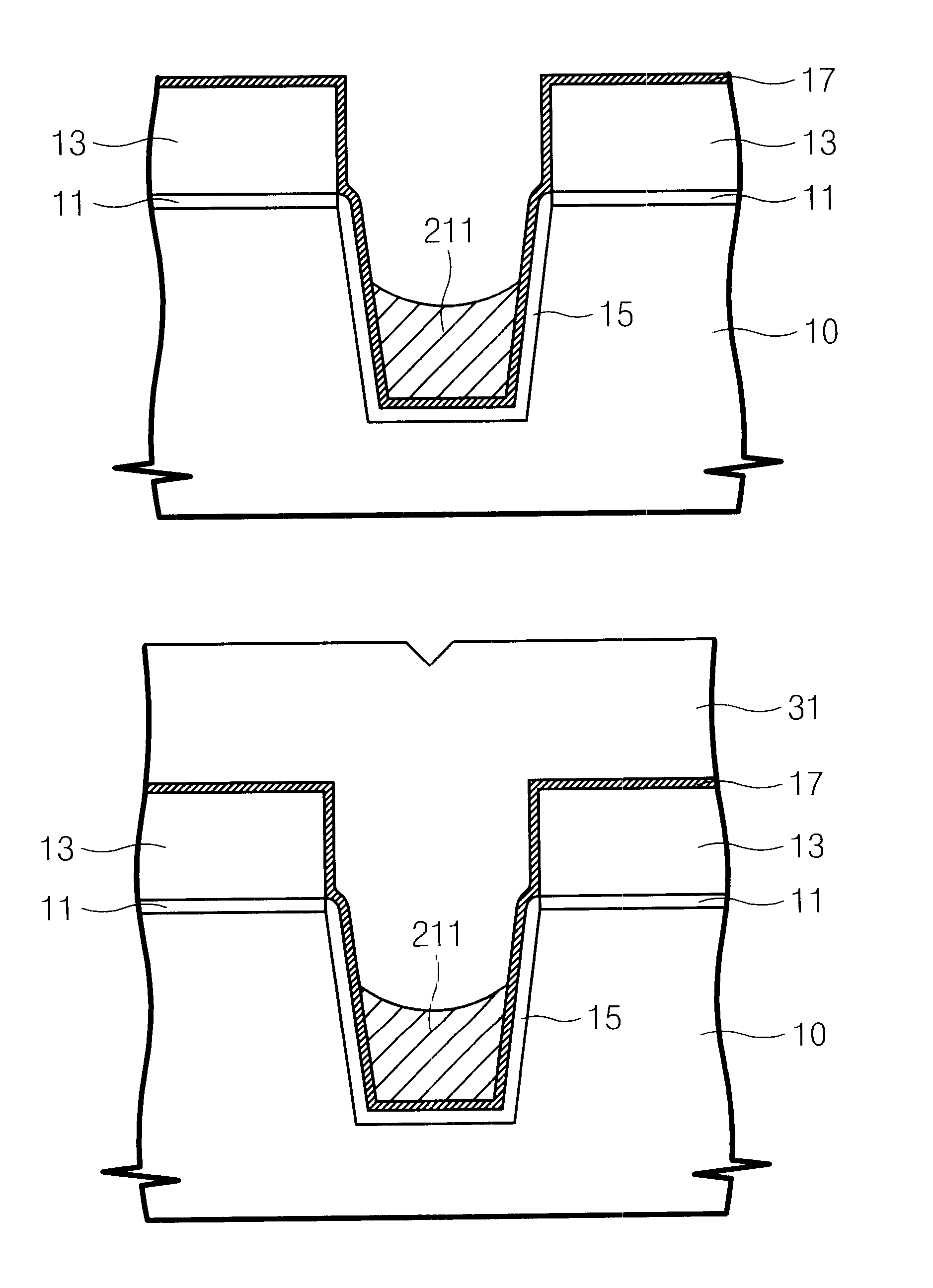

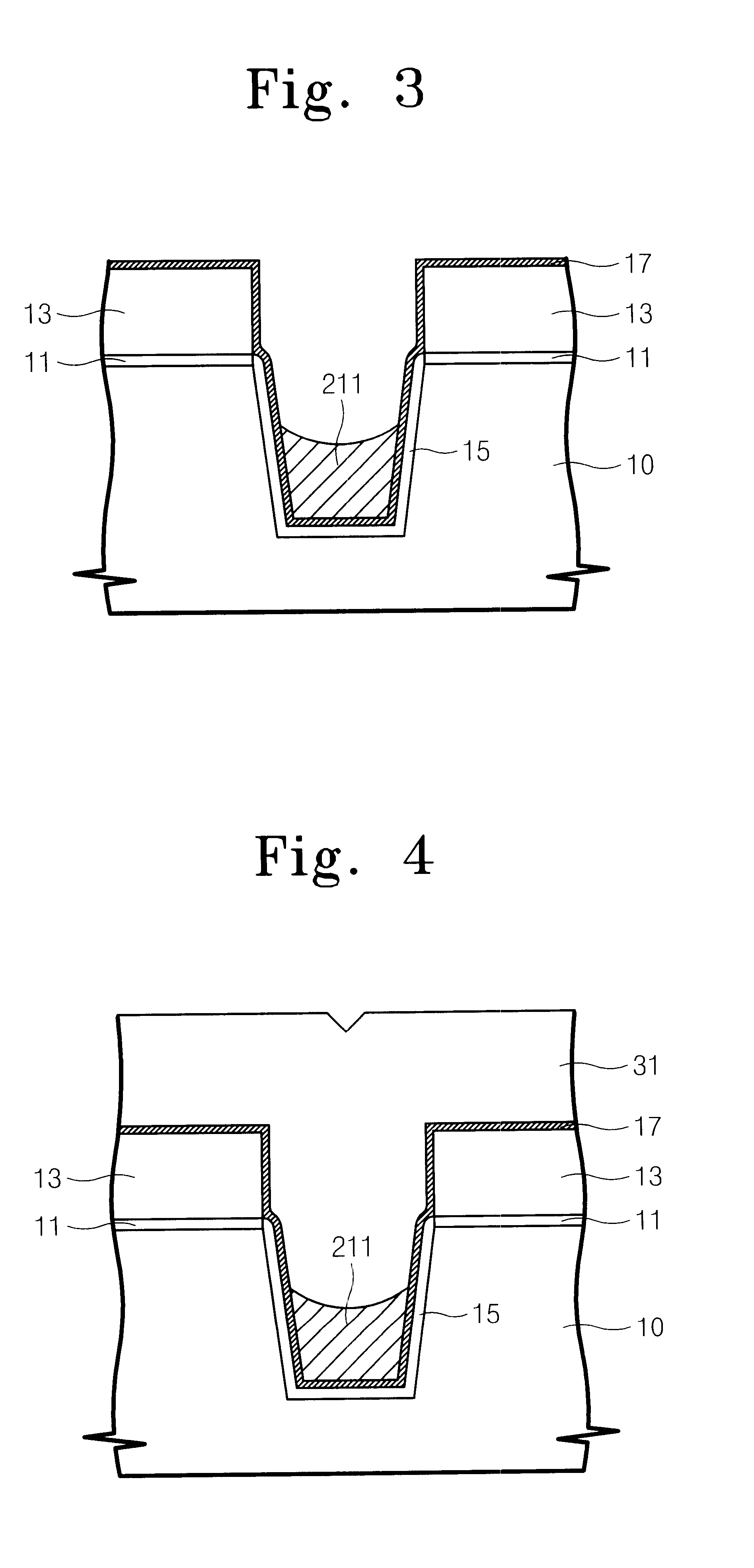

Method of forming an insulating layer in a trench isolation type semiconductor device

InactiveUS6566229B2Good shape retentionEasy annealingSemiconductor/solid-state device manufacturingDevice materialPolysilazane

A method of forming a trench-type device isolation layer in which a trench is filled through two steps, wherein a polysilazane solution is coated on a semiconductor substrate, in which a trench for device isolation layer is formed, in a spin on glass (SOG) manner to form an SOG layer filling a predetermined portion of the trench. In order to maintain a conformal coating thickness without overfilling the trench, the polysilazane solution preferably has a solid-state perhydro polysilazane ([SiH2NH]n) of between about 5 to about 15 percent by weight. Following formation of the SOG layer, a subsequent annealing process is carried out. The SOG layer is etched to make a top surface of the remaining SOG layer recessed down to a degree of about 1000 Å from an inlet of the trench, and a remaining space of the trench is filled with an ozone TEOS USG layer or an HDP CVD layer.

Owner:SAMSUNG ELECTRONICS CO LTD

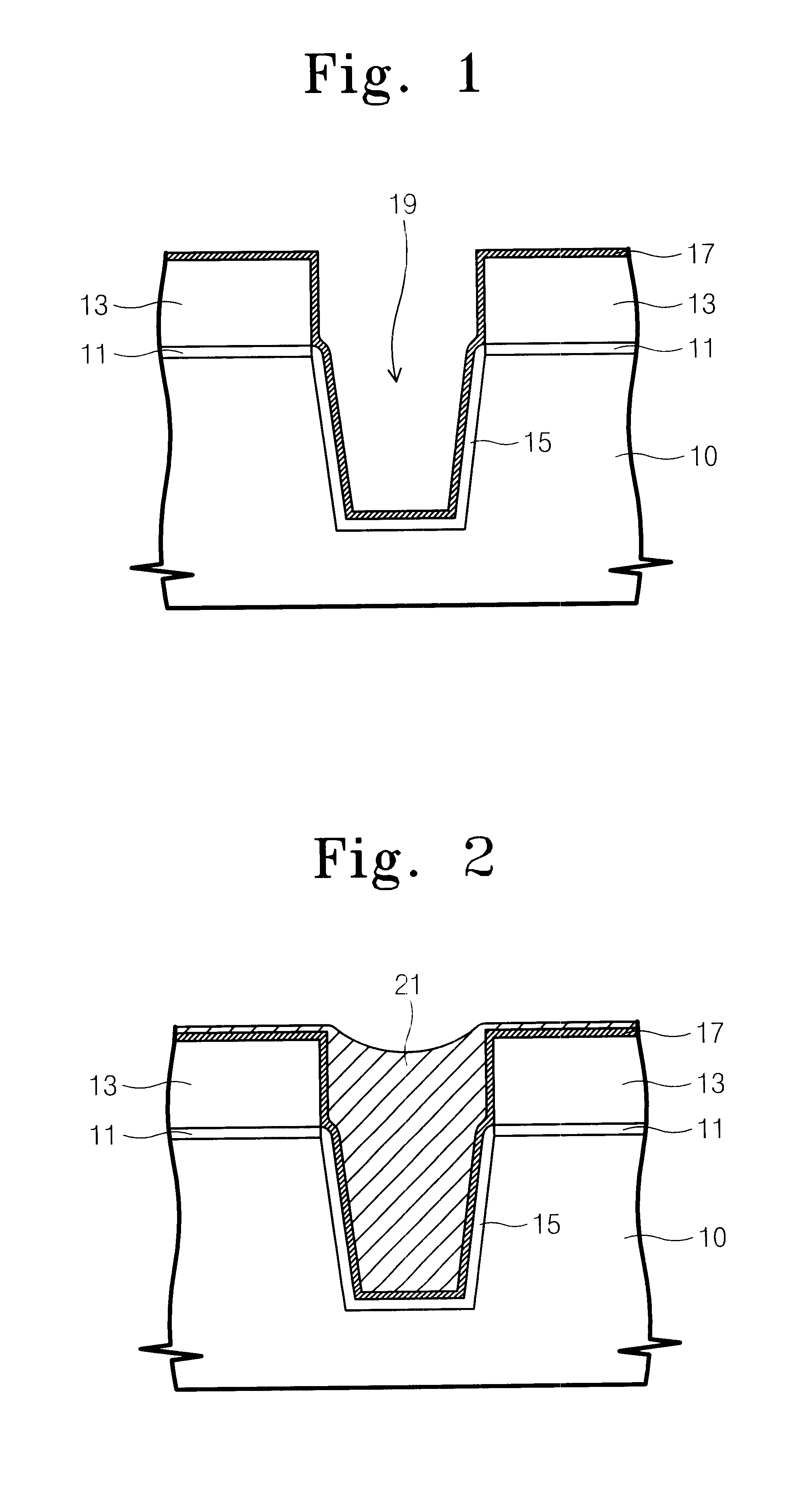

Fin field effect transistor and method of manufacturing the same

ActiveUS20060118876A1Stay in shapeAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerInternal stress

In a fin field effect transistor (FET), an active pattern protrudes in a vertical direction from a substrate and extends across the substrate in a first horizontal direction. A first silicon nitride pattern is formed on the active pattern, and a first oxide pattern and a second silicon nitride pattern are sequentially formed on the substrate and on a sidewall of a lower portion of the active pattern. A device isolation layer is formed on the second silicon nitride pattern, and a top surface of the device isolation layer is coplanar with top surfaces of the oxide pattern and the second silicon nitride pattern. A buffer pattern having an etching selectivity with respect to the second silicon nitride pattern is formed between the first oxide pattern and the second silicon nitride pattern. Internal stresses that can be generated in sidewalls of the active pattern are sufficiently released and an original shape of the first silicon nitride pattern remains unchanged, thereby improving electrical characteristics of the fin FET.

Owner:SAMSUNG ELECTRONICS CO LTD

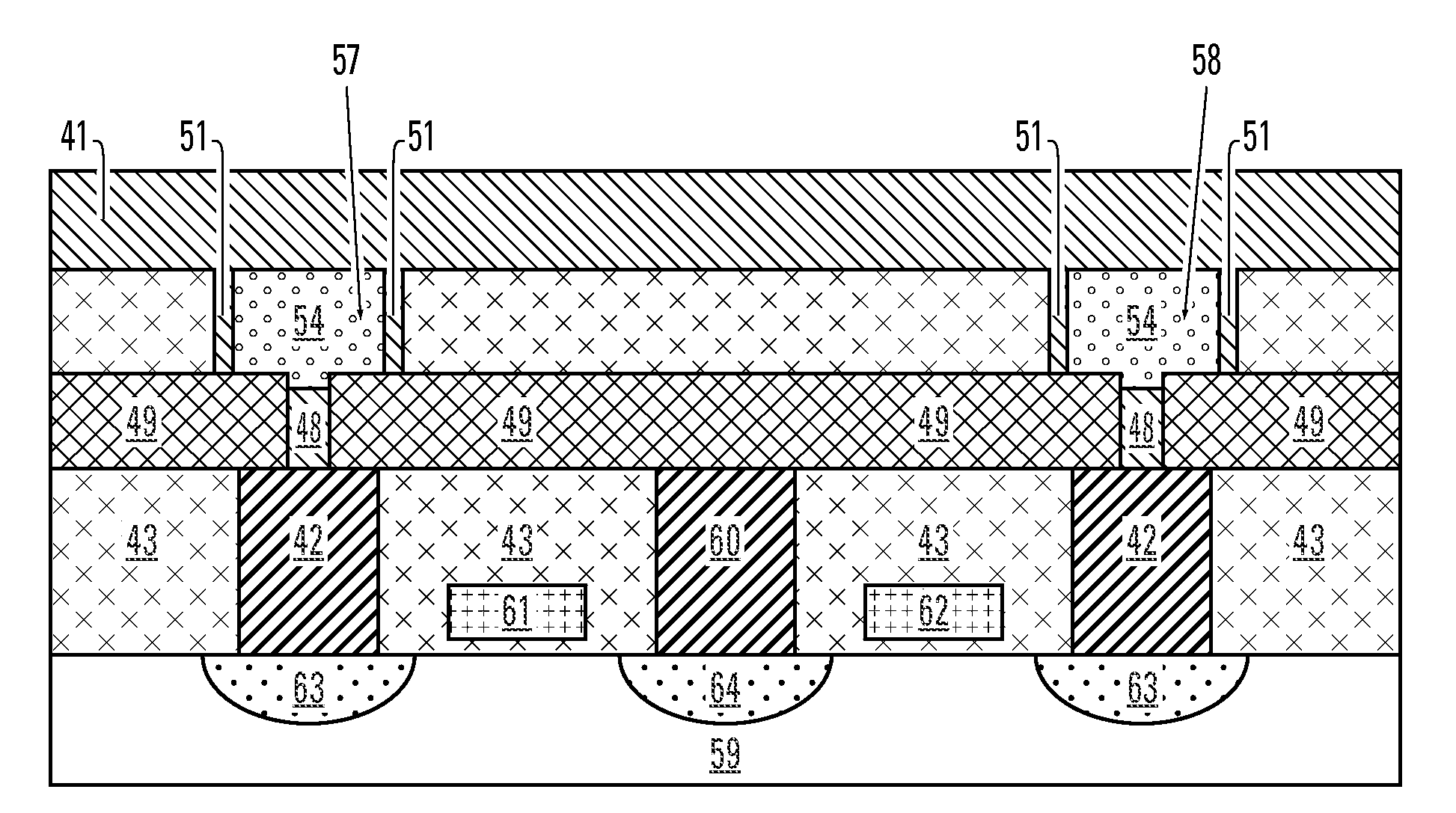

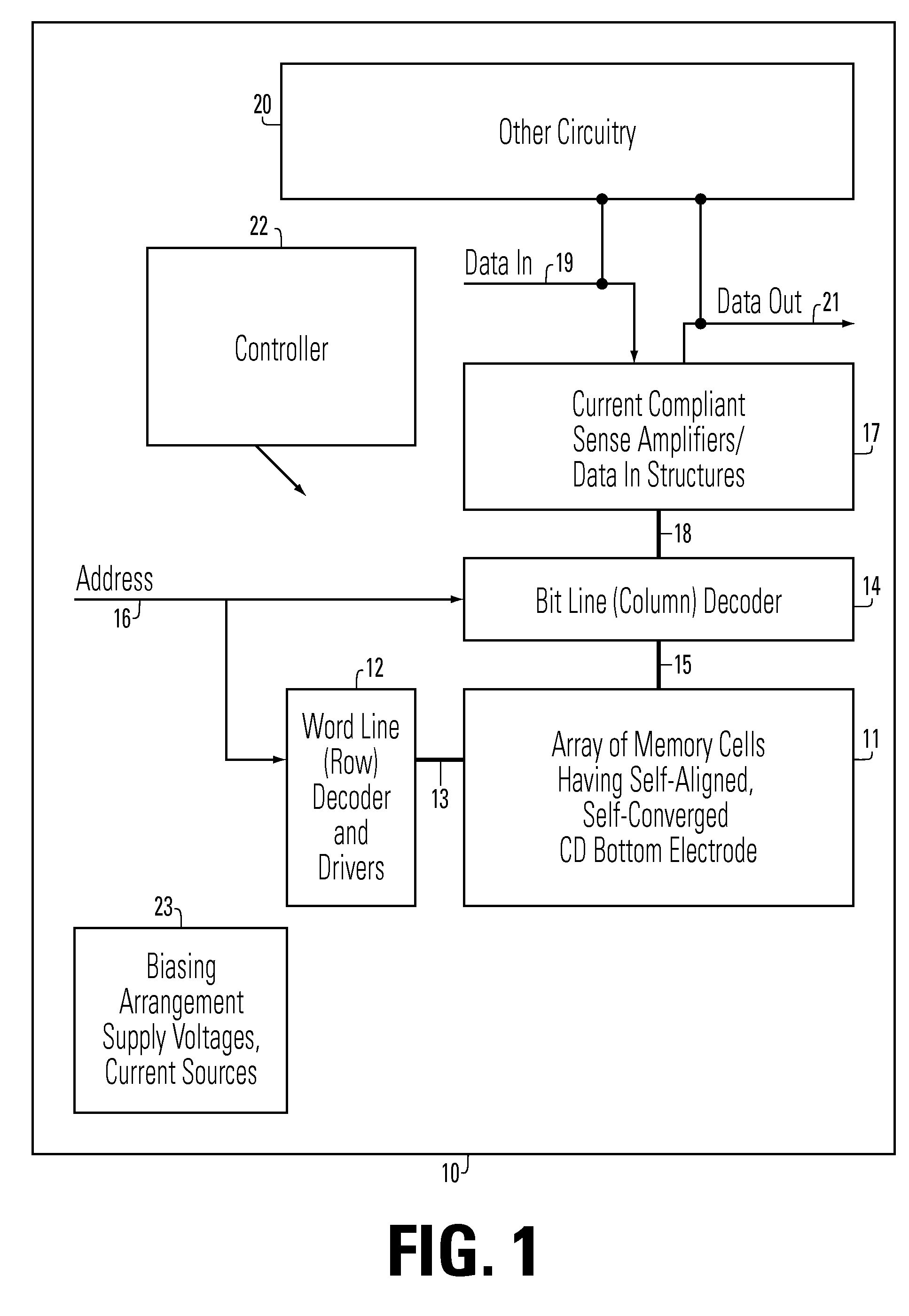

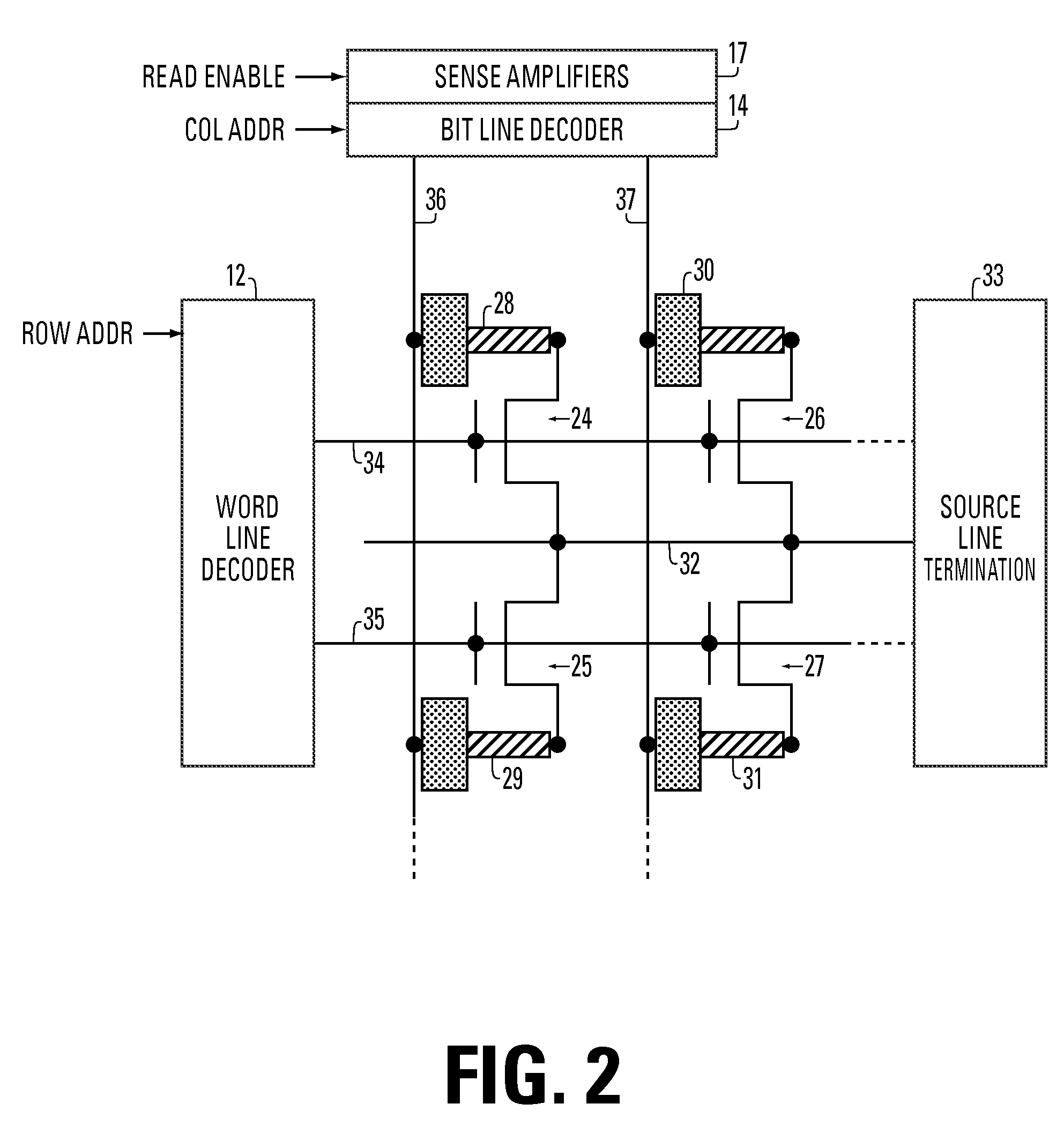

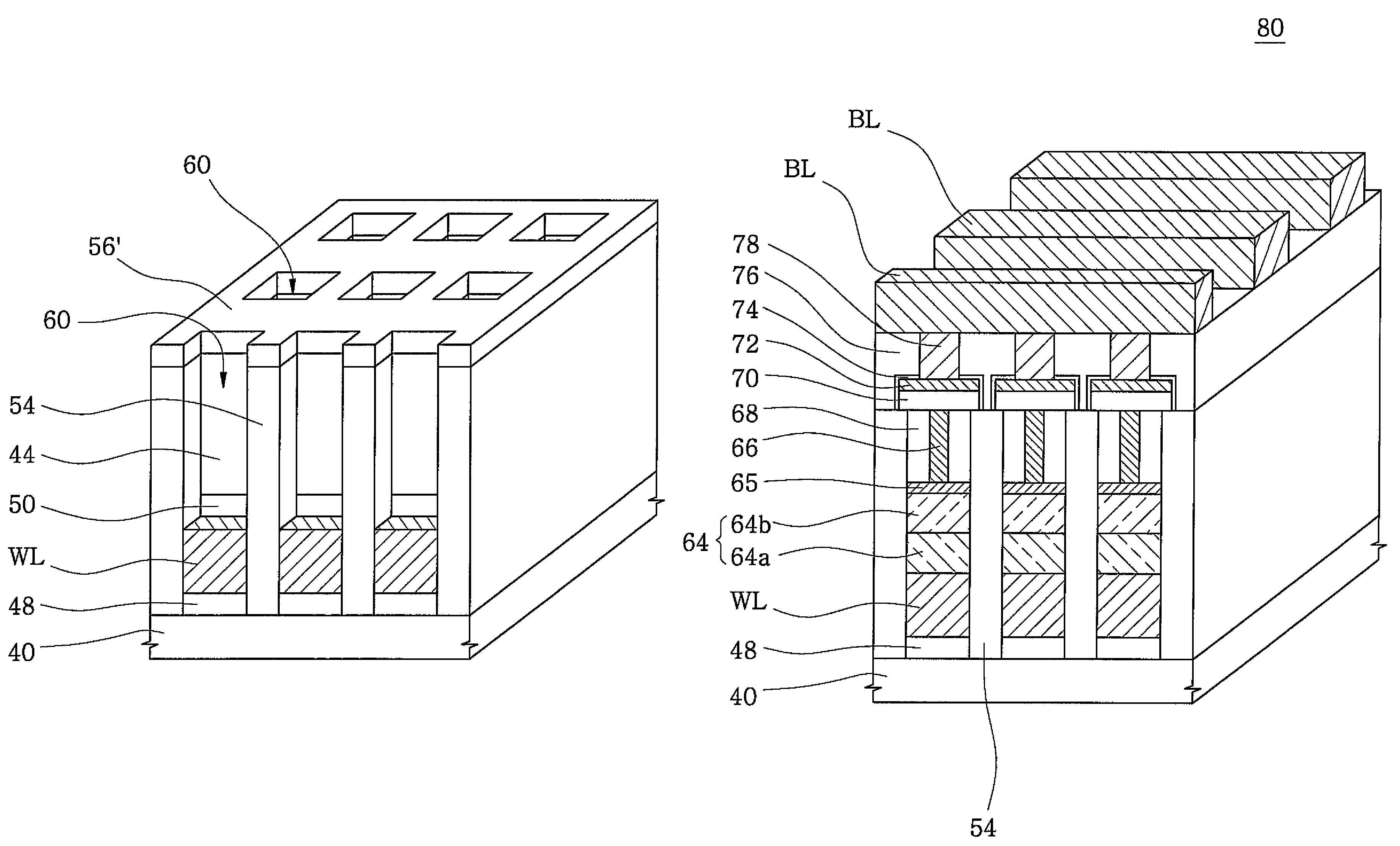

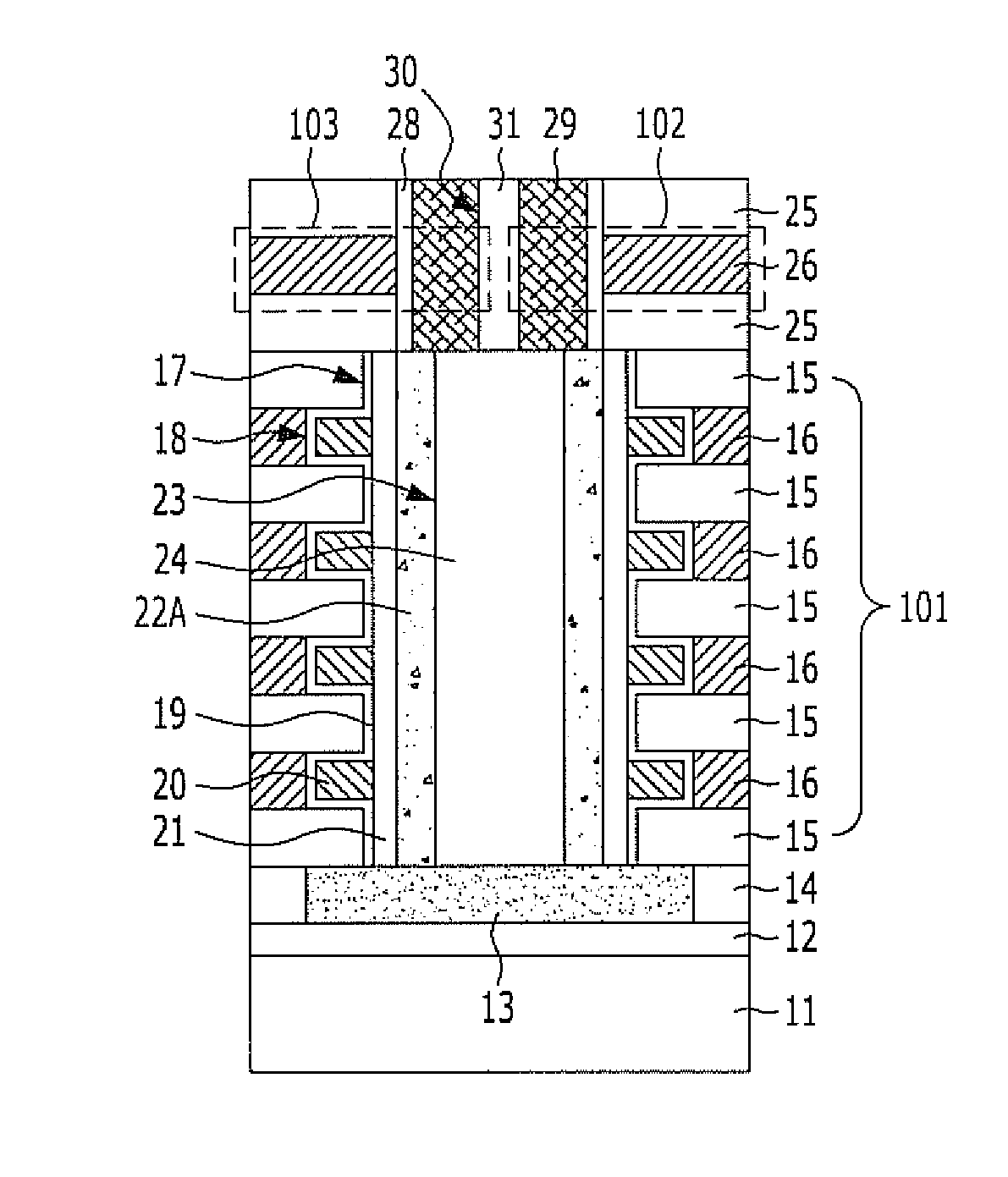

Phase change memory cell in via array with self-aligned, self-converged bottom electrode and method for manufacturing

ActiveUS20090072215A1Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryIsolation layer

An array of "mushroom" style phase change memory cells is manufactured by forming a separation layer over an array of contacts, forming an isolation layer on the separation layer and forming an array of memory element openings in the isolation layer using a lithographic process. Etch masks are formed within the memory element openings by a process that compensates for variation in the size of the memory element openings that results from the lithographic process. The etch masks are used to etch through the separation layer to define an array of electrode openings. Electrode material is deposited within the electrode openings; and memory elements are formed within the memory element openings. The memory elements and bottom electrodes are self-aligned.

Owner:MACRONIX INT CO LTD +1

Methods of fabricating a semiconductor device including a self-aligned cell diode

ActiveUS7541252B2Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialIsolation layer

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming a recess structure, recessed channel type transistor and method of manufacturing the recessed channel type transistor

InactiveUS20060113590A1Reduce widthReduce leakage currentSemiconductor devicesInsulation layerIsolation layer

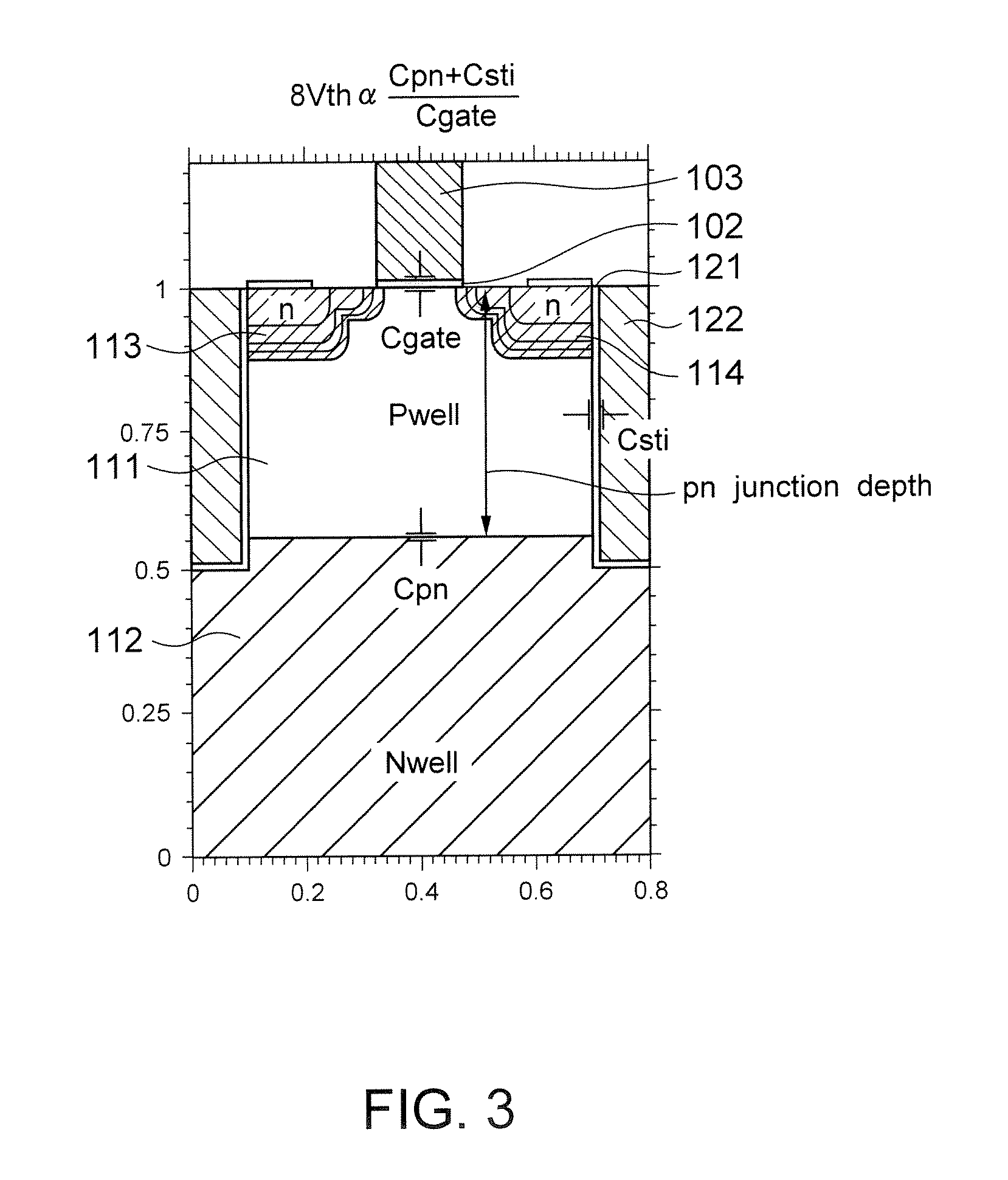

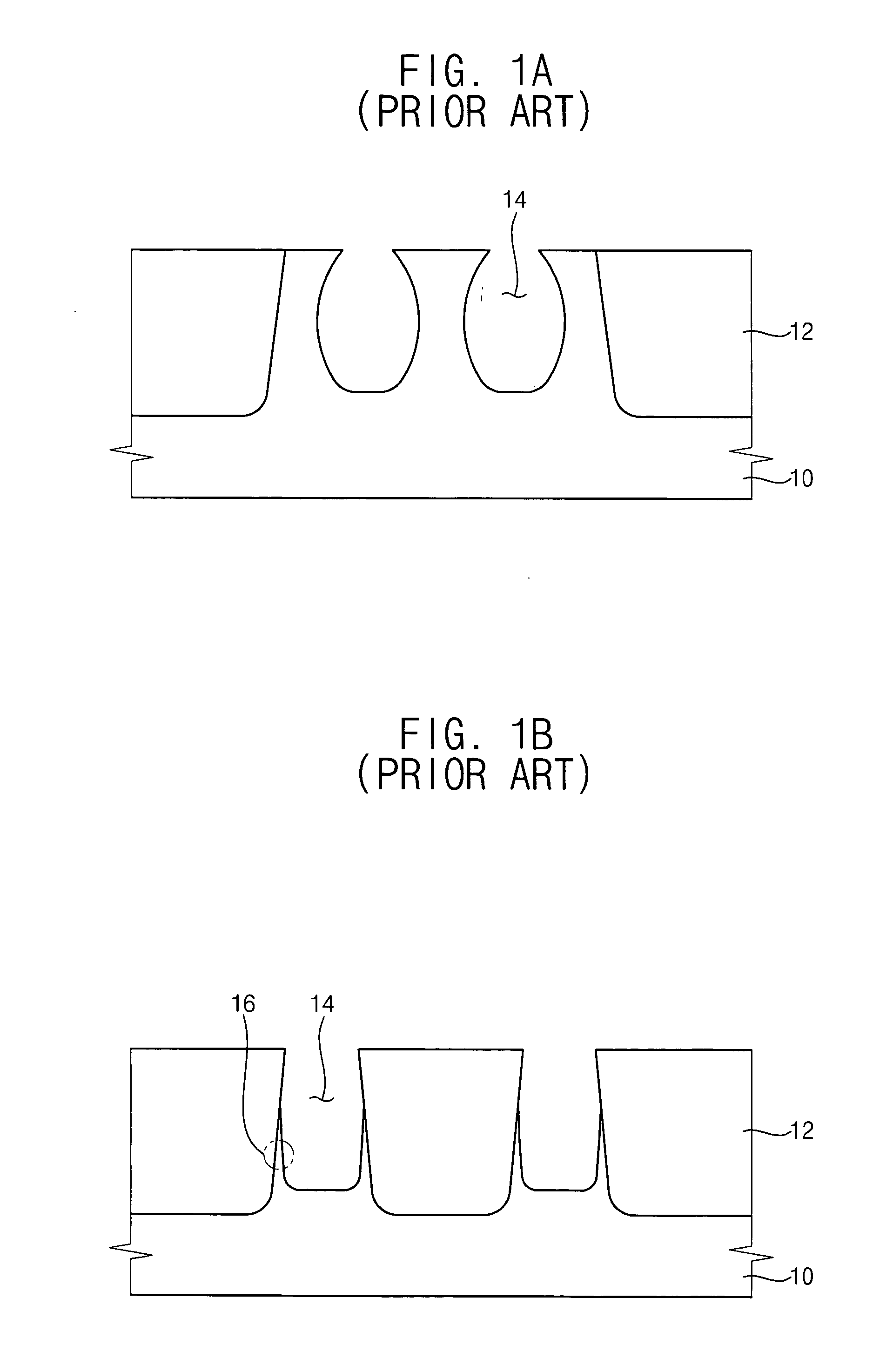

An isolation layer having a first depth is formed from an upper face of a substrate. Source / drain regions including junctions are formed in the substrate. Each of the junctions has a second depth substantially smaller than the first depth. A first recess is formed in the substrate by a first etching process. A protection layer pattern is formed on a sidewall of the first recess. A second recess is formed beneath the first recess. The second recess has a width substantially larger than that of the first recess. The second recess is formed by a second etching process using an etching gas containing an SF6 gas, a Cl2 gas and an O2 gas. A gate insulation layer is formed on surfaces of the first and the second recesses. The second recess having an enlarged shape may reduce a width of the junction between the gate electrode and the isolation layer so that a leakage current generated through the junction may decrease.

Owner:SAMSUNG ELECTRONICS CO LTD

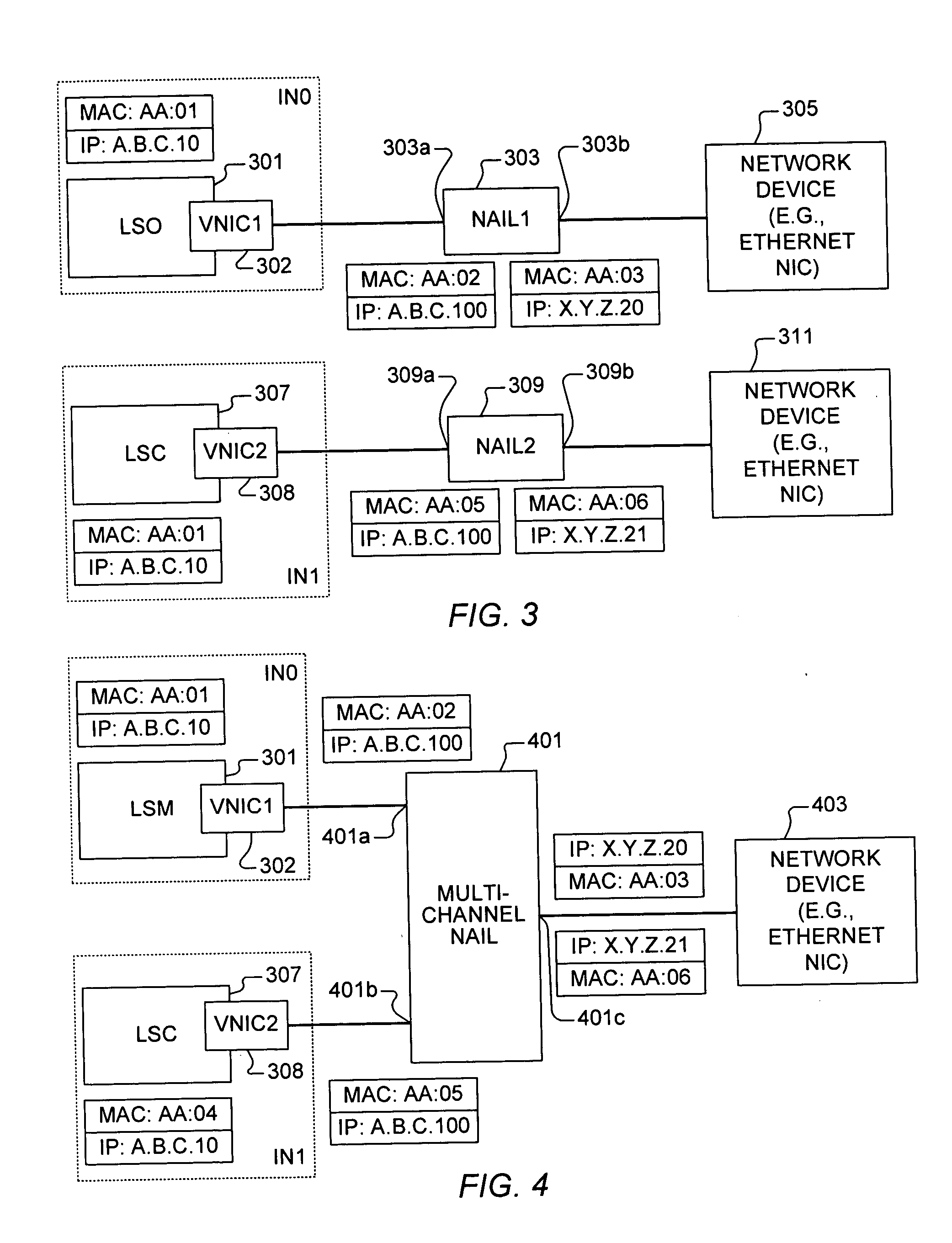

Network abstraction and isolation layer for masquerading machine identity of a computer

ActiveUS20050108407A1Data switching by path configurationMultiple digital computer combinationsIdentity transformIp address

A network abstraction and isolation layer (NAIL) for masquerading the machine identity of a computer in a network to enable the computer to communicate in the network with a different machine identity including an isolated network interface for communicating with the computer, an abstraction network interface for communicating with a network device coupled to the network, and control logic. The control logic is coupled to the isolated and abstraction network interfaces and performs machine identity translation to masquerade machine identity of the computer relative to the network. Machine identity masquerading includes selectively translating any one or more of an IP address, a MAC address, a machine name, a system identifier, and a DNS Name in the header or payload of communication packets.

Owner:QUEST SOFTWARE INC

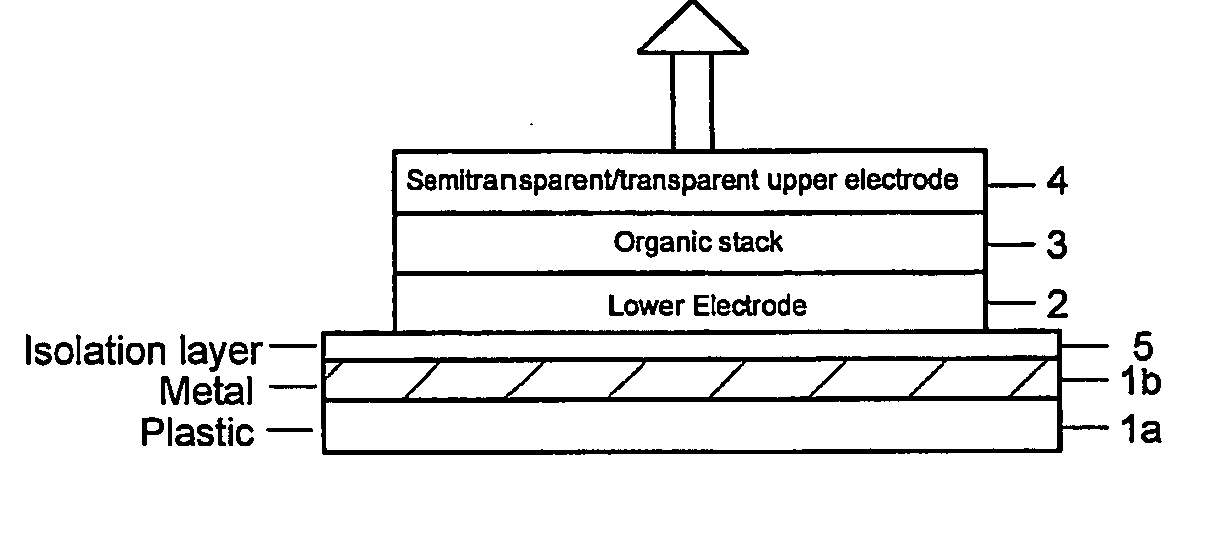

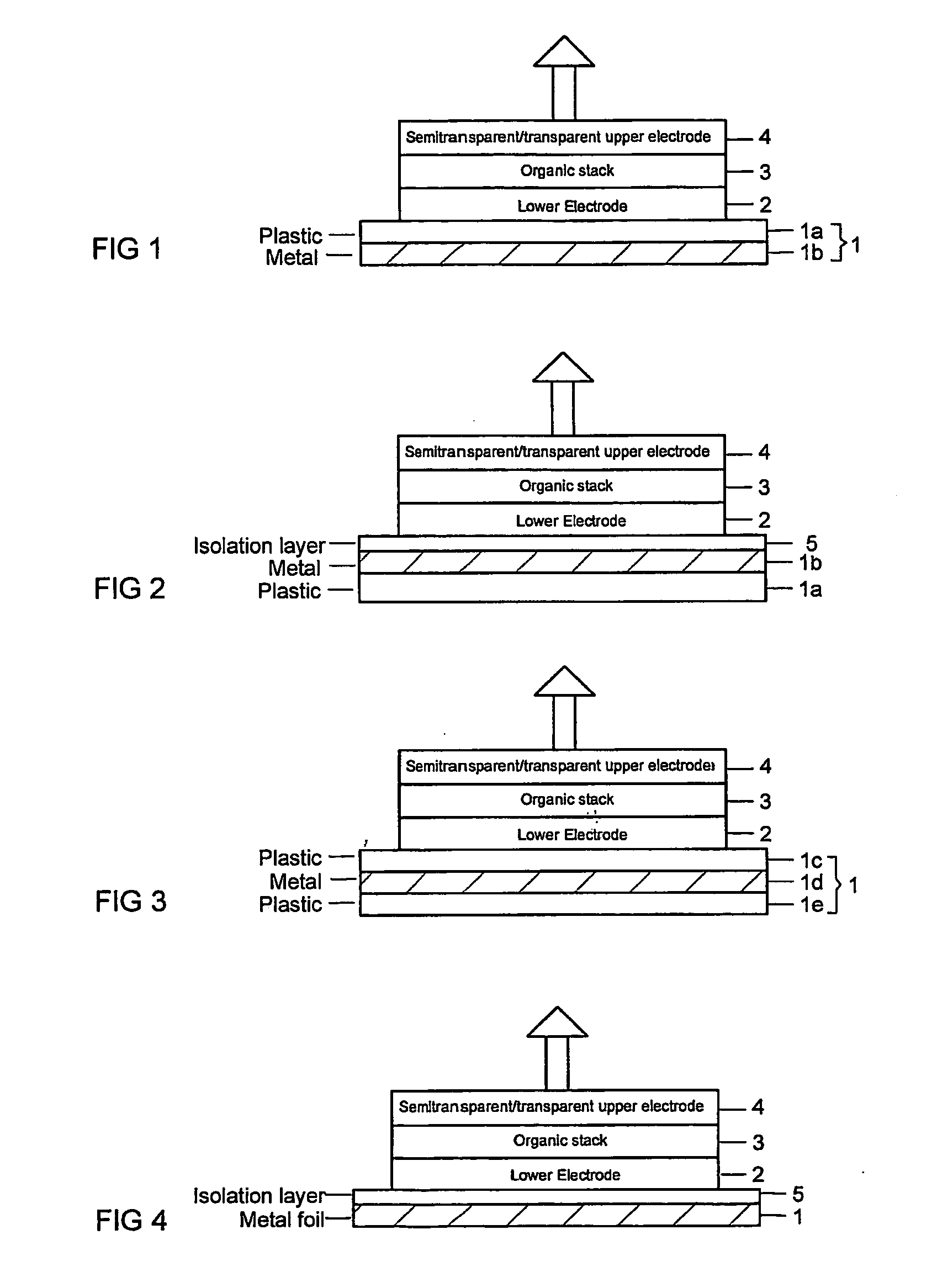

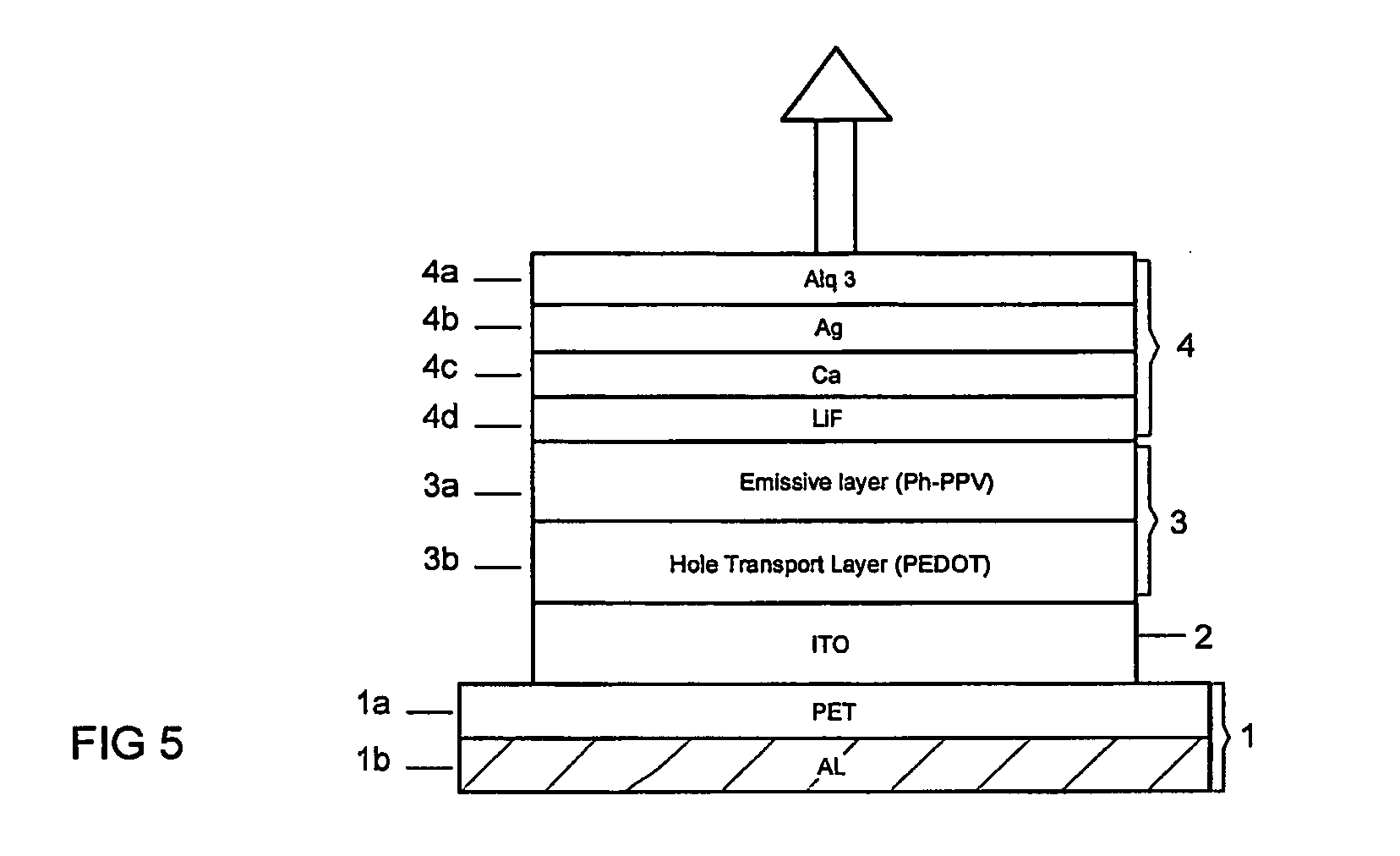

Flexible Electroluminescent Devices

InactiveUS20070222370A1Minimize permeation of oxygen and moistureImprove barrier propertiesDischarge tube luminescnet screensFinal product manufactureMetal foilIsolation layer

An organic light emitting diode (OLED) formed on an opaque flexible substrate is disclosed. The opaque flexible substrate is composed of one of the following: (i) a plastic layer laminated to or coated with a metal layer, (ii) a metal layer sandwiched between two plastic layers, or (iii) a metal foil. When the OLED is formed on a metal surface of the flexible substrate, the metal surface may be coated with an isolation layer. The isolation layer may be a spin-coated polymer layer or a dielectric layer. The metal in the flexible substrate serves as a barrier to minimize the permeation of oxygen and moisture to the OLED. In addition, the OLED is provided with a transparent or semi-transparent upper electrode so that light can emit through the upper electrode.

Owner:AGENCY FOR SCI TECH & RES

Method for fabricating 3d-nonvolatile memory device

InactiveUS20120231593A1Solid-state devicesSemiconductor/solid-state device manufacturingMain channelIsolation layer

A method for fabricating a 3D-nonvolatile memory device includes forming a sub-channel over a substrate, forming a stacked layer over the substrate, the stacked layer including a plurality of interlayer dielectric layers that are alternatively stacked with conductive layers, selectively etching the stacked layer to form a first open region exposing the sub-channel, forming a main-channel conductive layer to gap-fill the first open region, selectively etching the stacked layer and the main-channel conductive layer to form a second open region defining a plurality of main channels, and forming an isolation layer to gap-fill the second open region.

Owner:SK HYNIX INC