Patents

Literature

1018 results about "Gate insulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

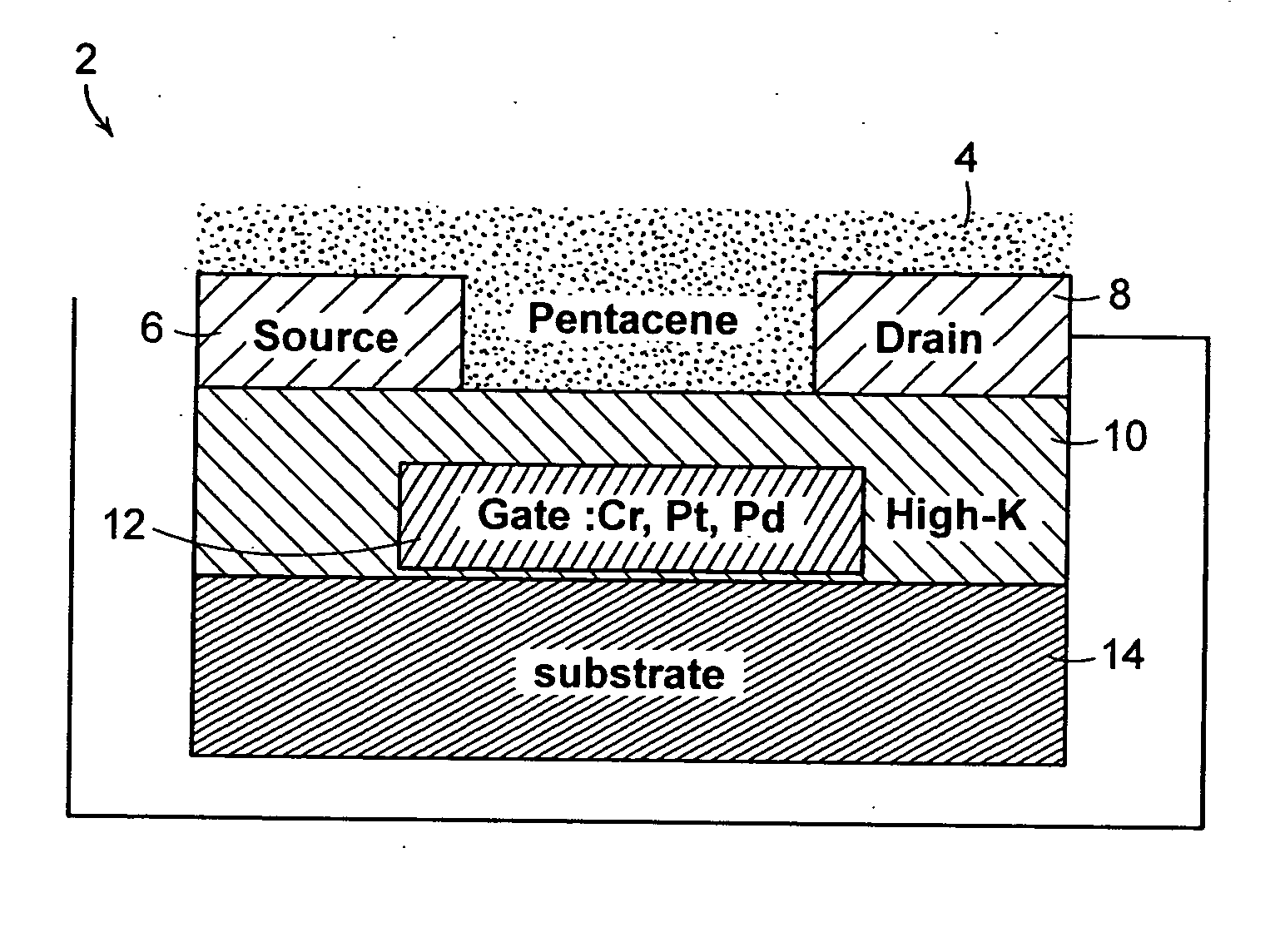

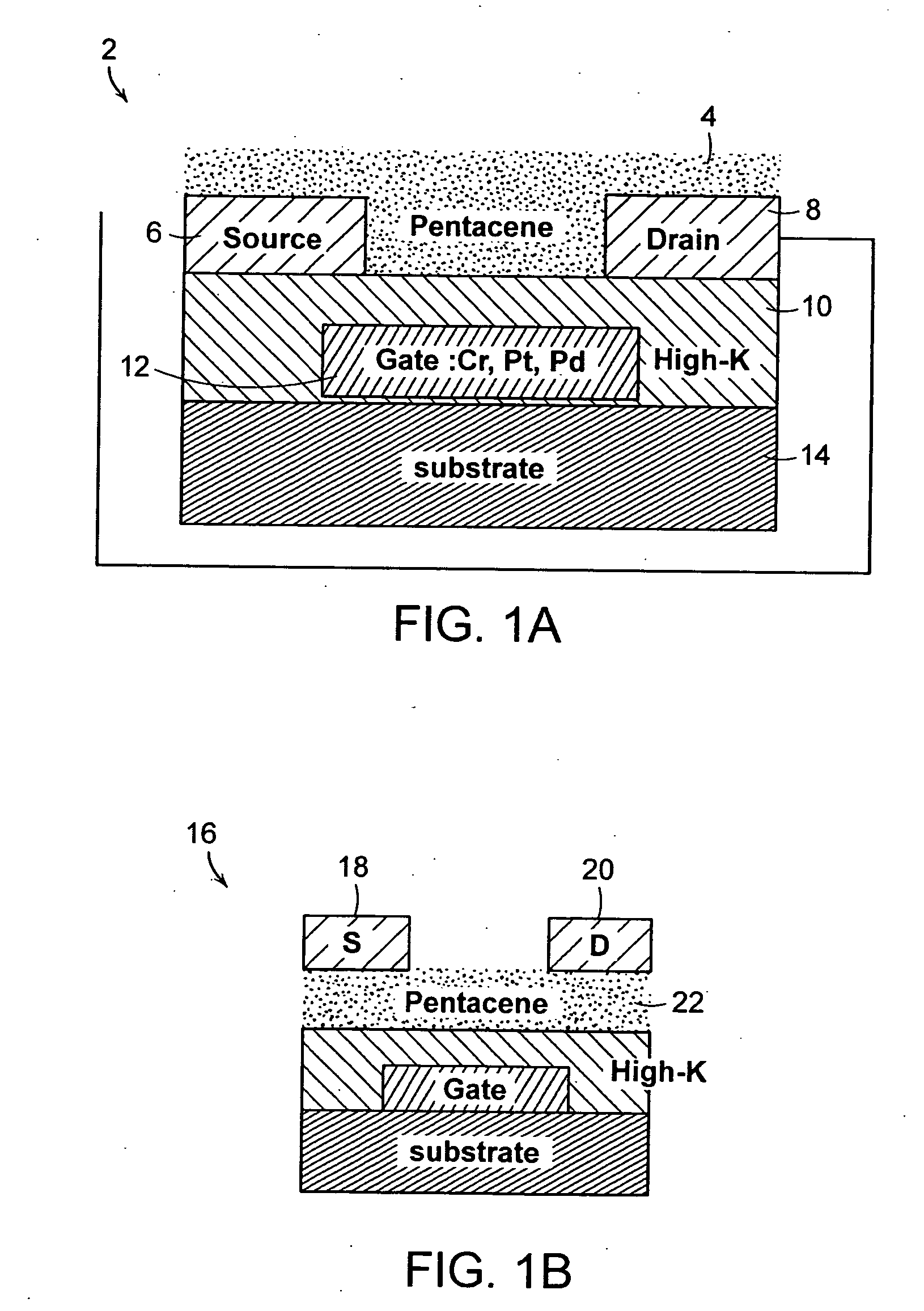

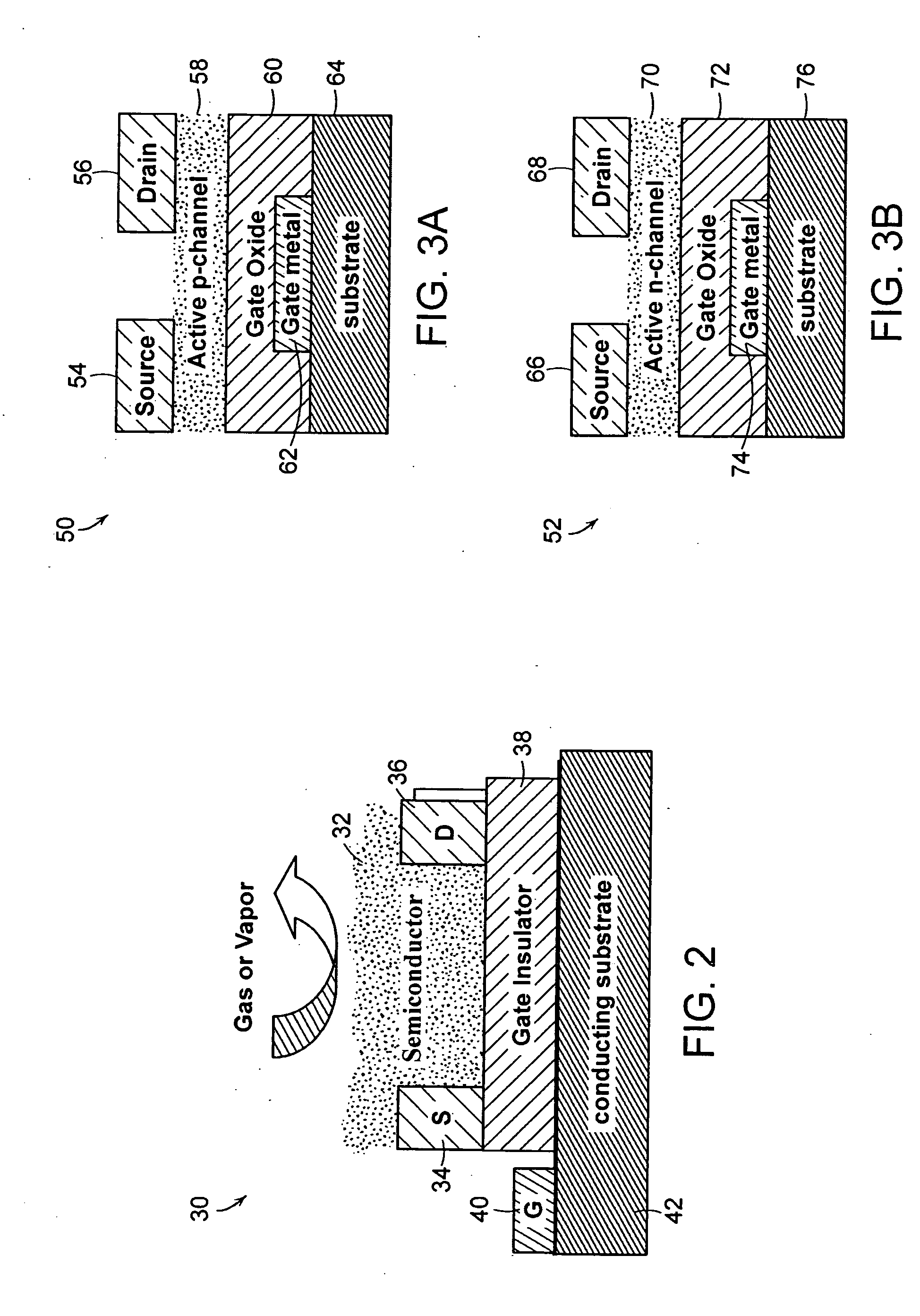

Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications

A thin film transistor (TFT) includes a source electrode, a drain electrode, and a gate electrode. A gate insulator is coupled to the source electrode, drain electrode, and gate electrode. The gate insulator includes room temperature deposited high-K materials so as to allow said thin film transistor to operate at low operating voltage.

Owner:MASSACHUSETTS INST OF TECH

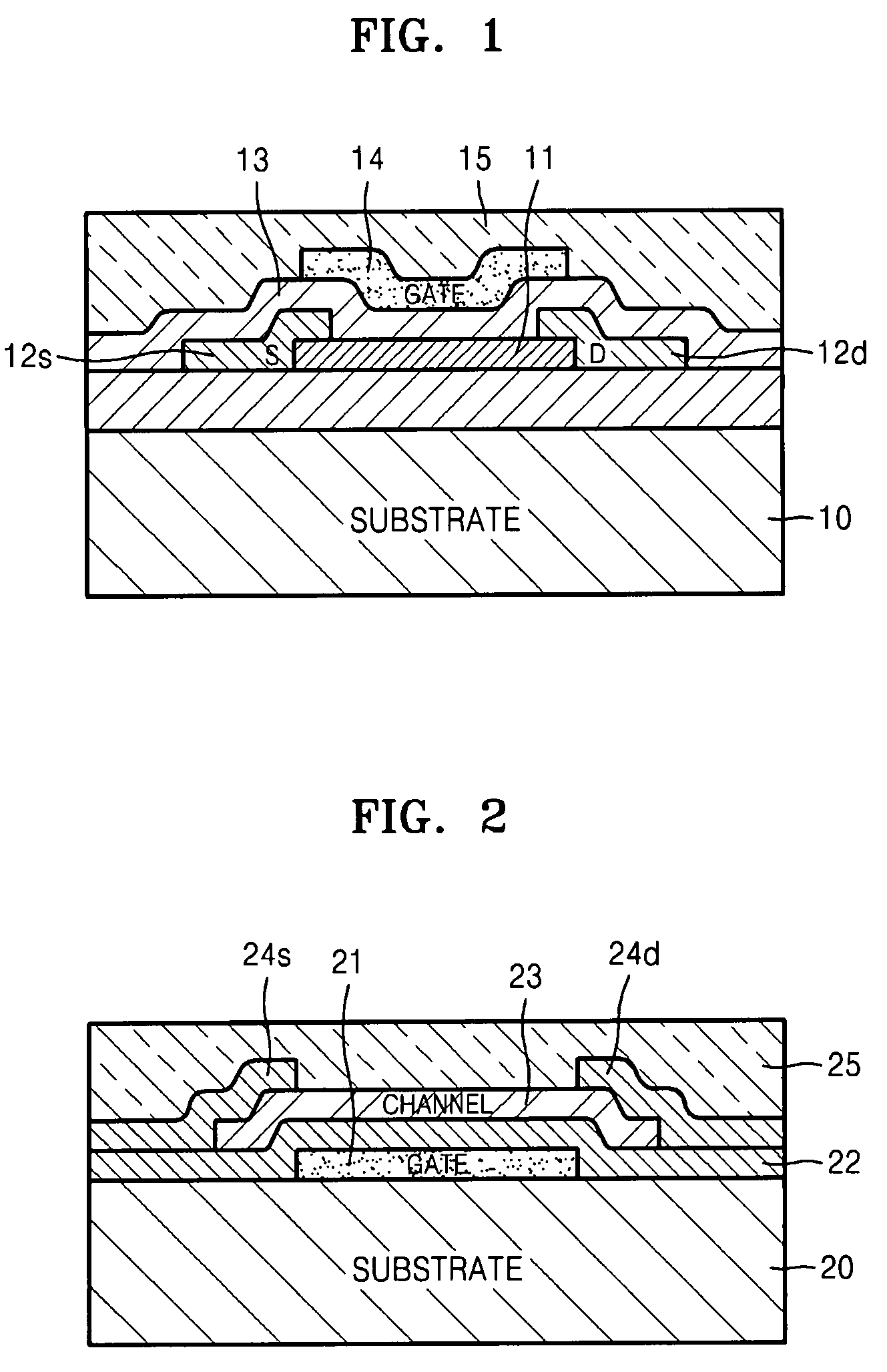

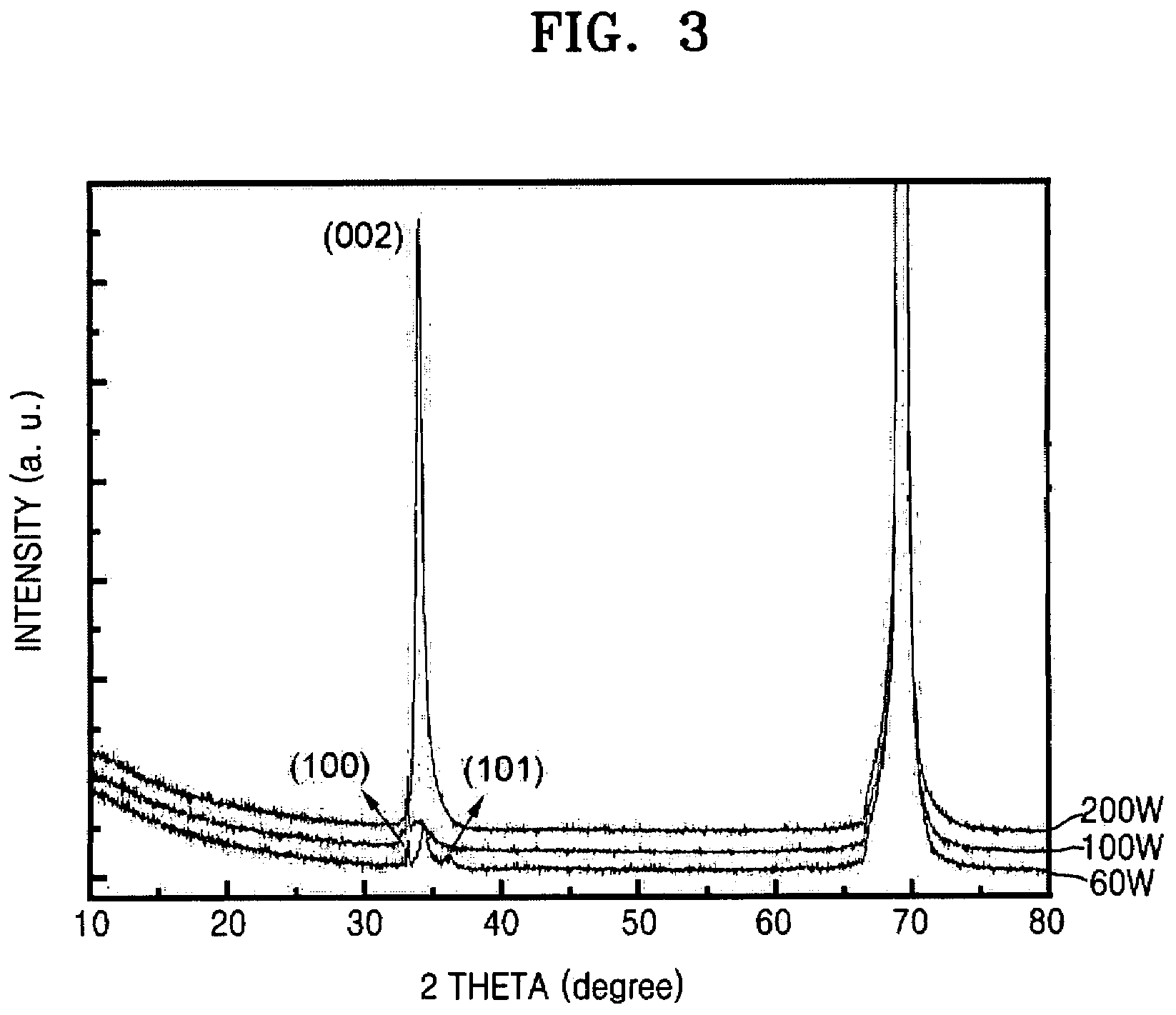

ZnO thin film transistor and method of forming the same

InactiveUS20070272922A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate insulatorEngineering

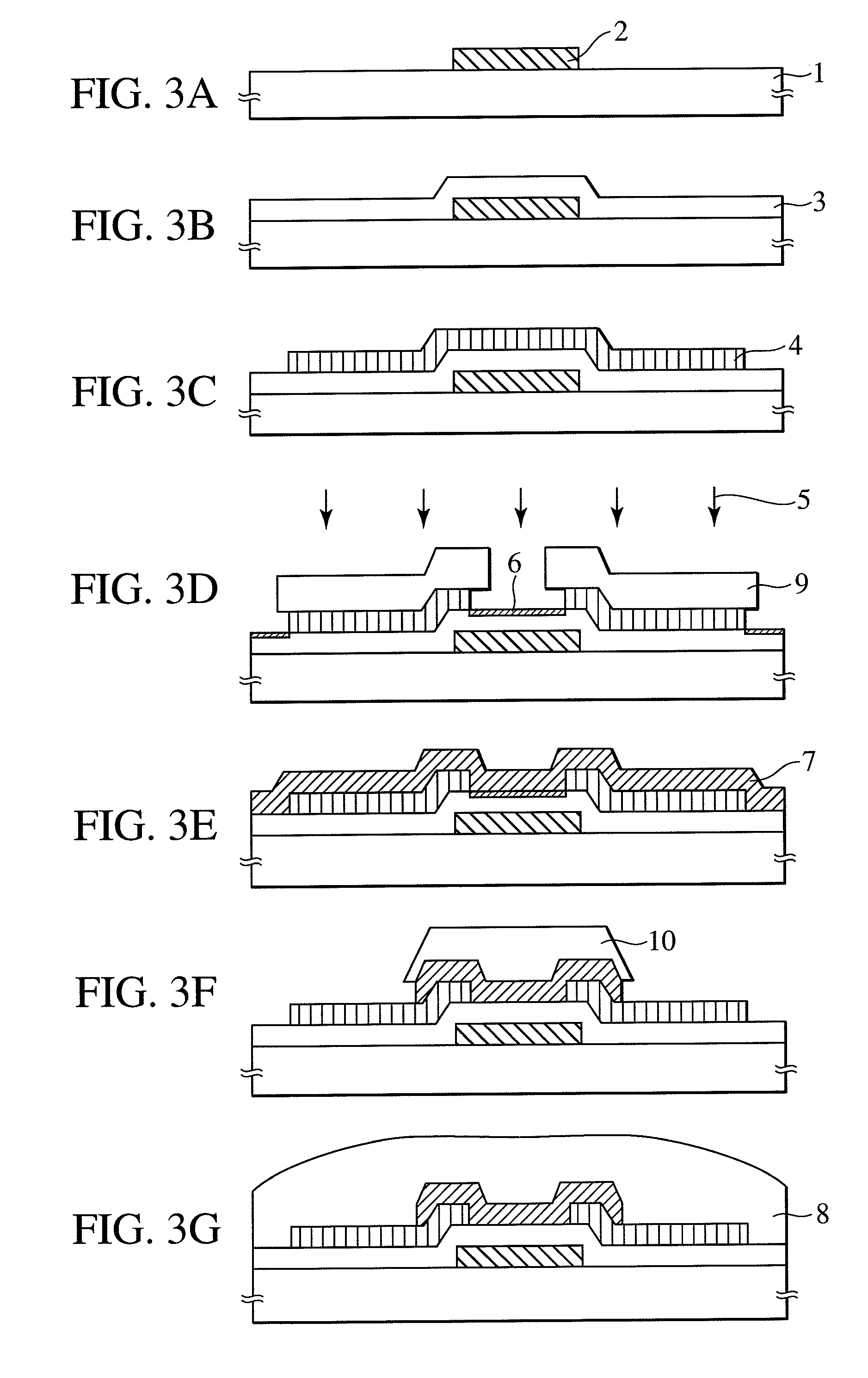

A zinc oxide (ZnO) thin film transistor (TFT) and method of forming the same are provided. The ZnO may include a ZnO semiconductor channel, a conductive ZnO gate forming an electric field around the ZnO semiconductor channel, an ZnO gate insulator interposed between the conductive ZnO gate and the ZnO semiconductor channel and an insulating ZnO passivation layer on the ZnO semiconductor channel, the conductive ZnO gate and the ZnO gate insulator to protect the ZnO semiconductor channel, the conductive ZnO gate, and the ZnO gate insulator. A thin film transistor (TFT) may be formed by forming a semiconductor channel, forming a conductive gate having an electric field around the semiconductor channel, forming a gate insulator between the conductive gate and the semiconductor channel, and forming an insulating passivation layer on the semiconductor channel, the conductive gate and the gate insulator.

Owner:SAMSUNG ELECTRONICS CO LTD

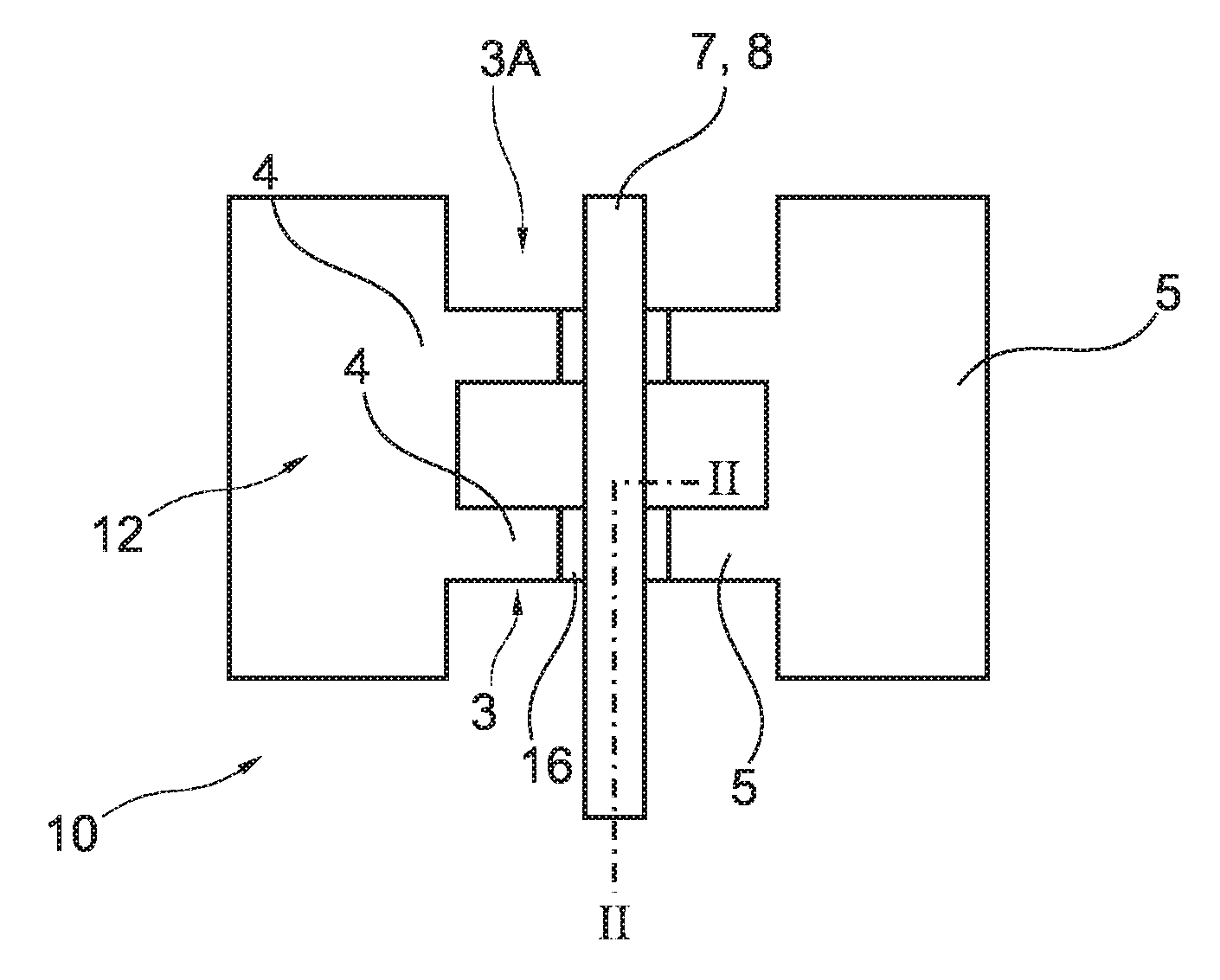

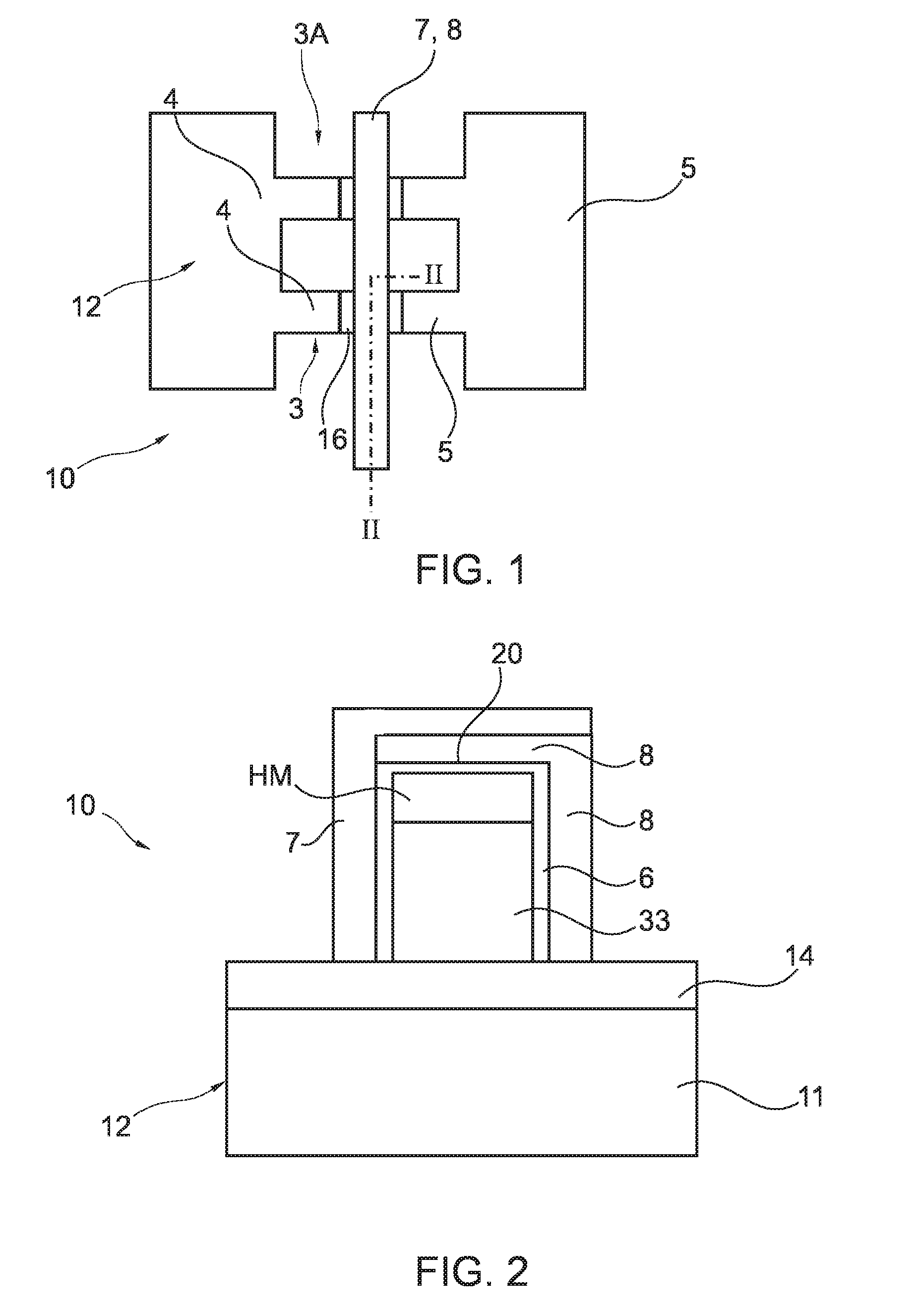

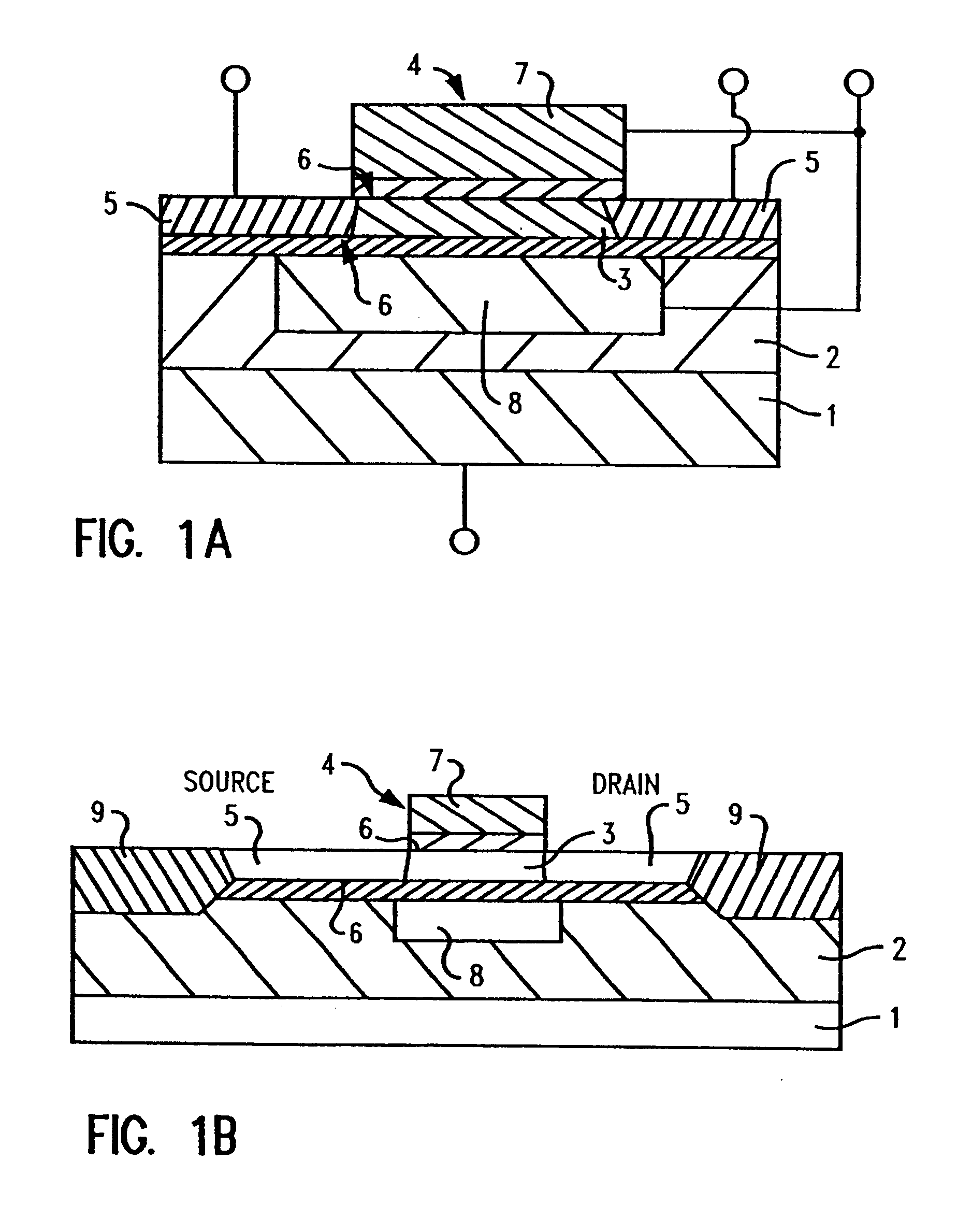

Transistor device and method of manufacturing such a transistor device

ActiveUS20100025766A1Suitable for high-scale integrationImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate insulatorEngineering

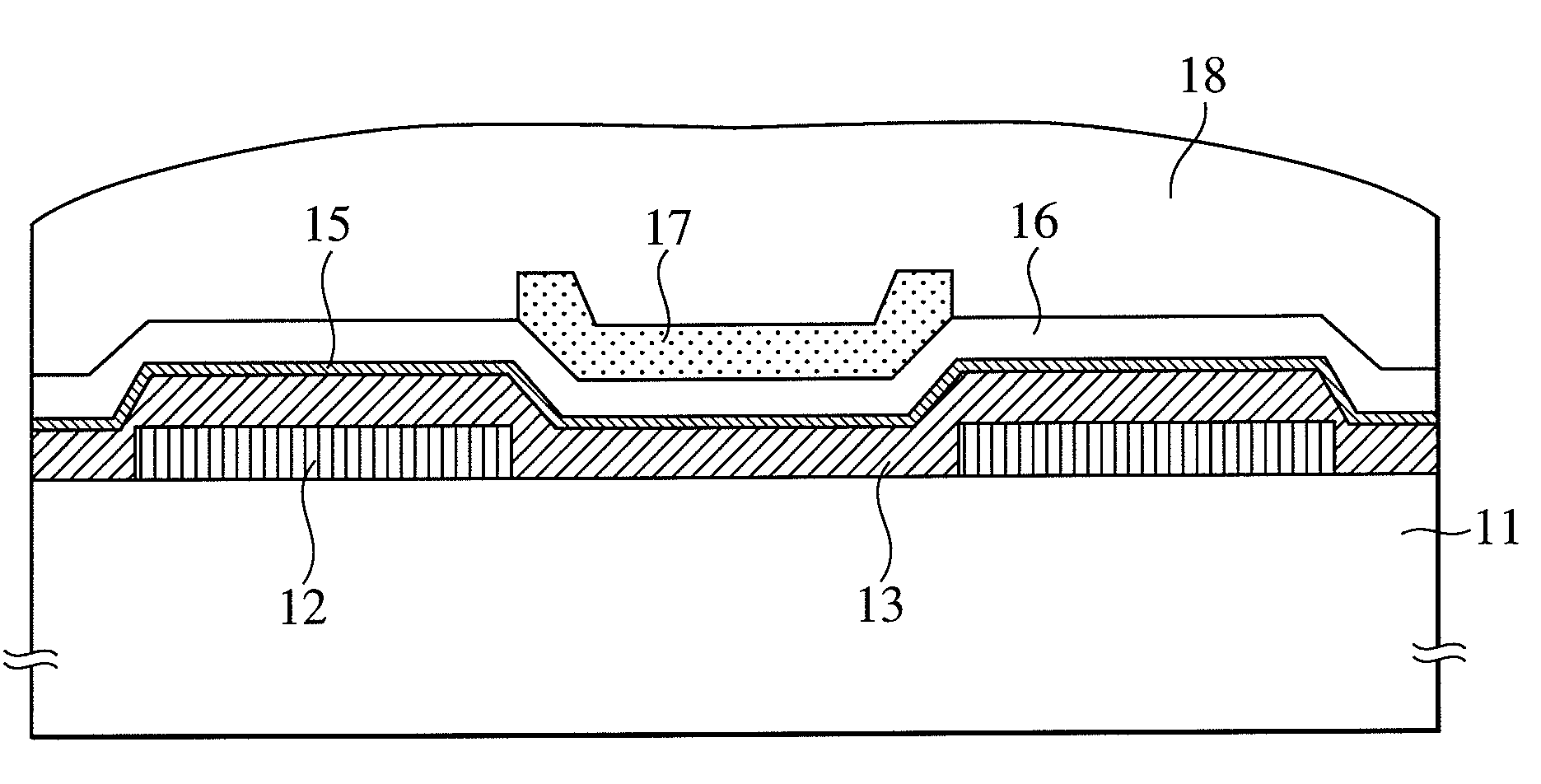

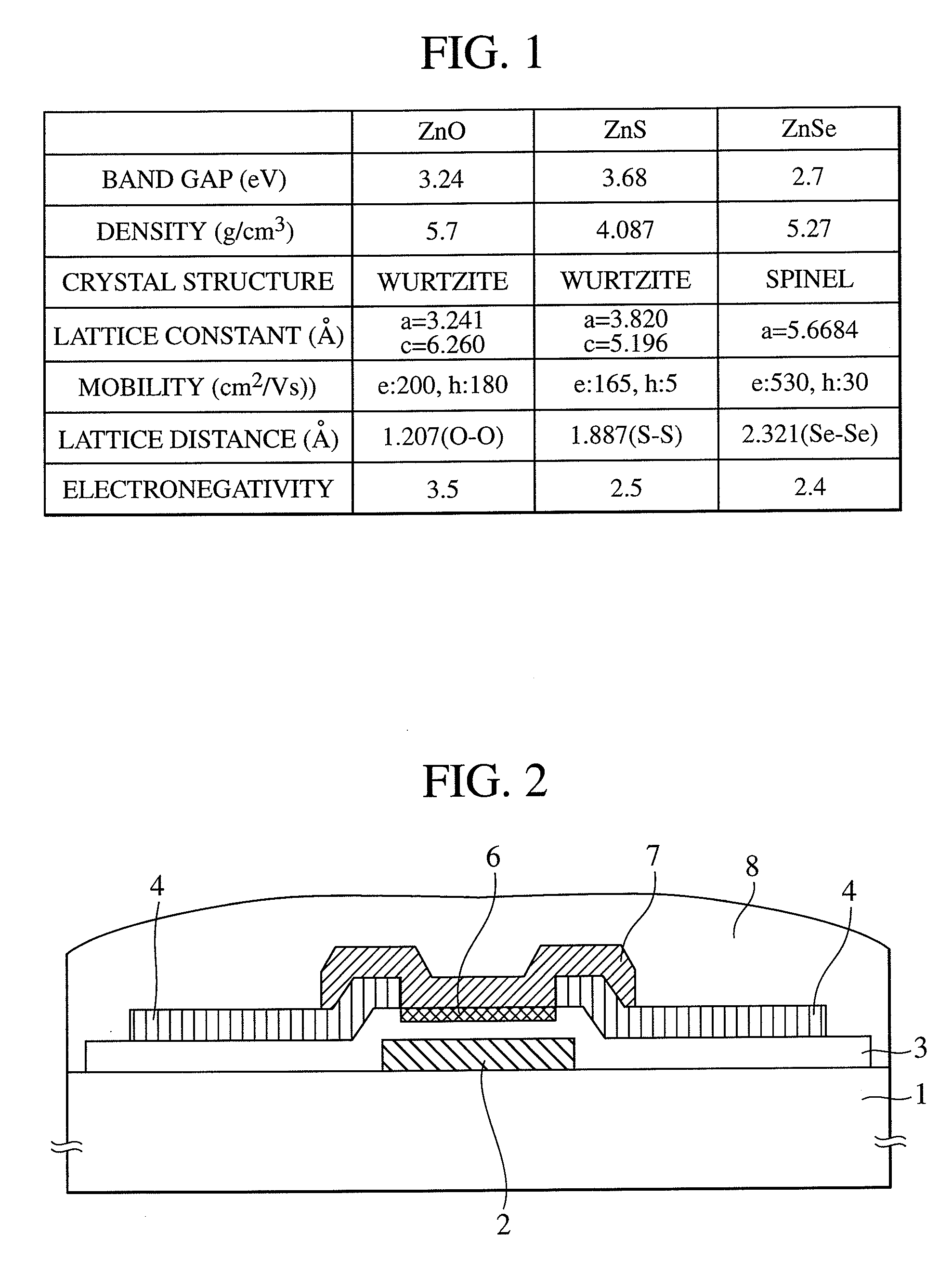

A transistor device (10), the transistor device (10) comprising a substrate (11, 14), a fin (3, 3A) aligned along a horizontal direction on the substrate (11, 14), a first source / drain region (4) of a first type of conductivity in the fin (3, 3A), a second source / drain region (5) of a second type of conductivity in the fin (3, 3A), wherein the first type of conductivity differs from the second type of conductivity, a channel region (33) in the fin (3, 3A) between the first source / drain region (4) and the second source / drain region (5), a gate insulator (6) on the channel region (33), and a gate structure (7, 8) on the gate insulator (6), wherein the sequence of the first source / drain region (4), the channel region (33) and the second source / drain region (5) is aligned along the horizontal direction.

Owner:UNITED MICROELECTRONICS CORP

Oxide semiconductor device and surface treatment method of oxide semiconductor

InactiveUS20090166616A1Effectively suppressing the threshold potential shift and occurrence of leak currentPhysical property is lessSolid-state devicesSemiconductor/solid-state device manufacturingGas phaseThreshold potential

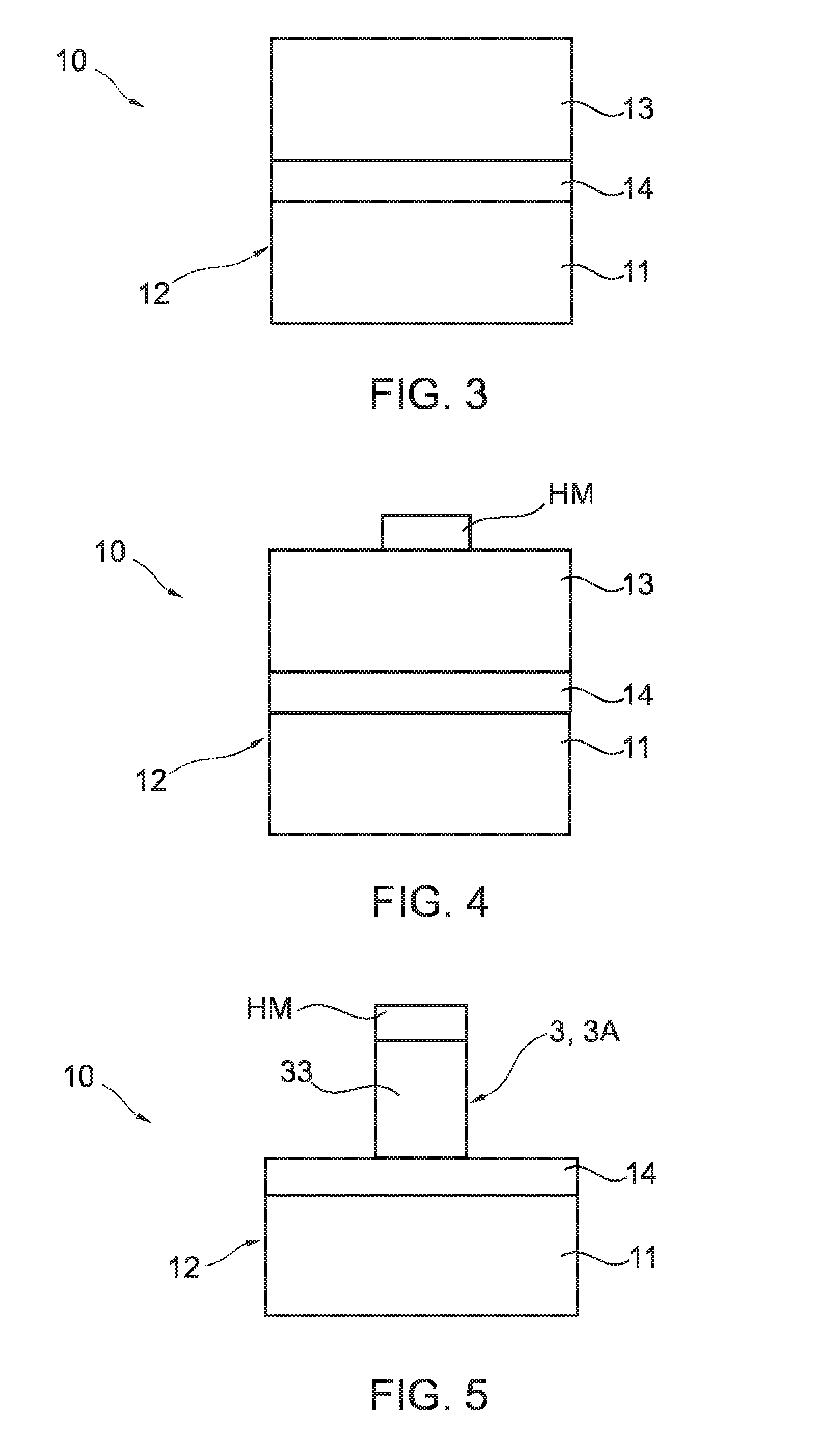

Oxygen defects formed at the boundary between the zinc oxide type oxide semiconductor and the gate insulator are terminated by a surface treatment using sulfur or selenium as an oxygen group element or a compound thereof, the oxygen group element scarcely occurring physical property value change. Sulfur or selenium atoms effectively substitute oxygen defects to prevent occurrence of electron supplemental sites by merely applying a gas phase or liquid phase treatment to an oxide semiconductor or gate insulator with no remarkable change on the manufacturing process. As a result, this can attain the suppression of the threshold potential shift and the leak current in the characteristics of a thin film transistor.

Owner:HITACHI LTD

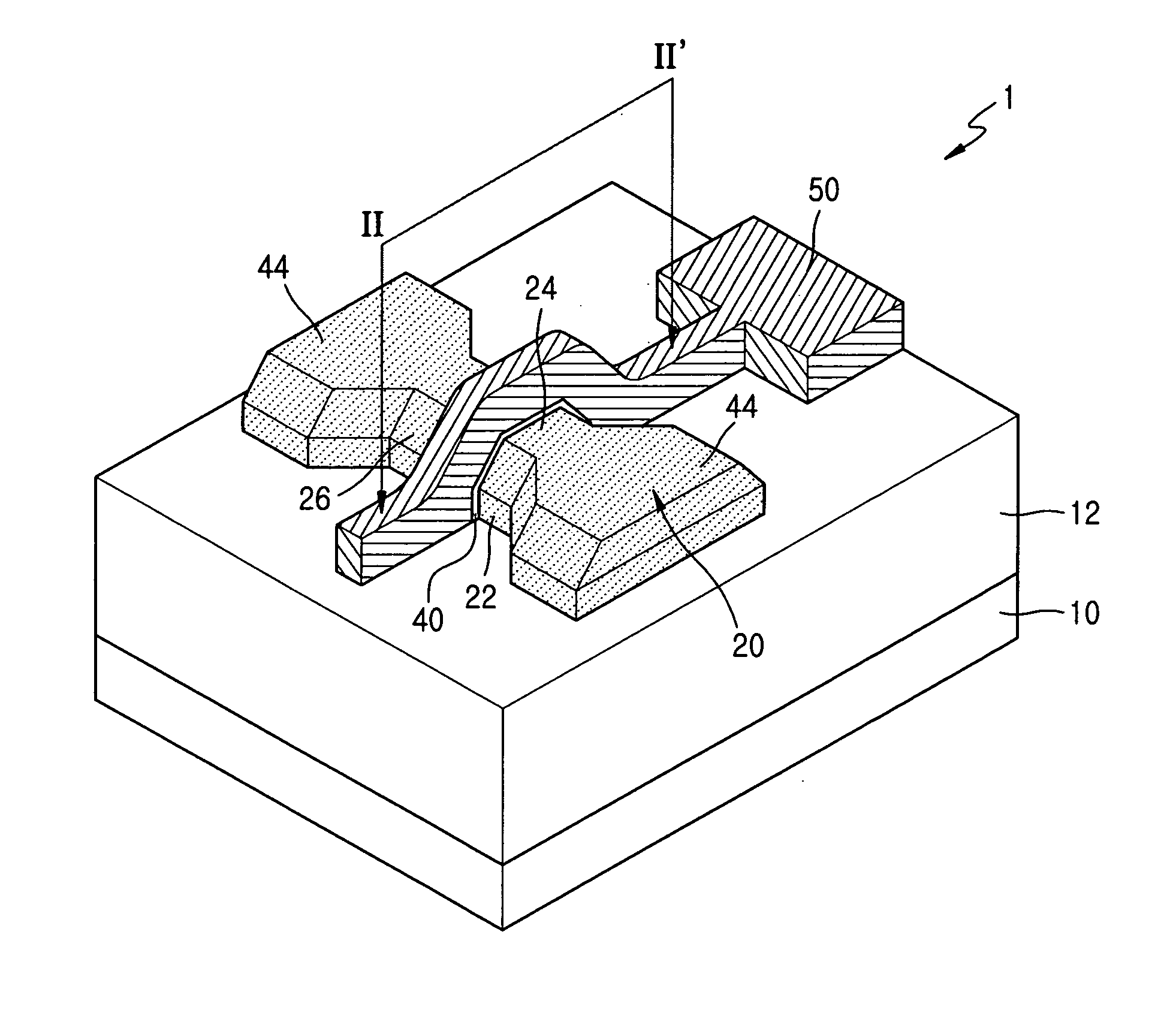

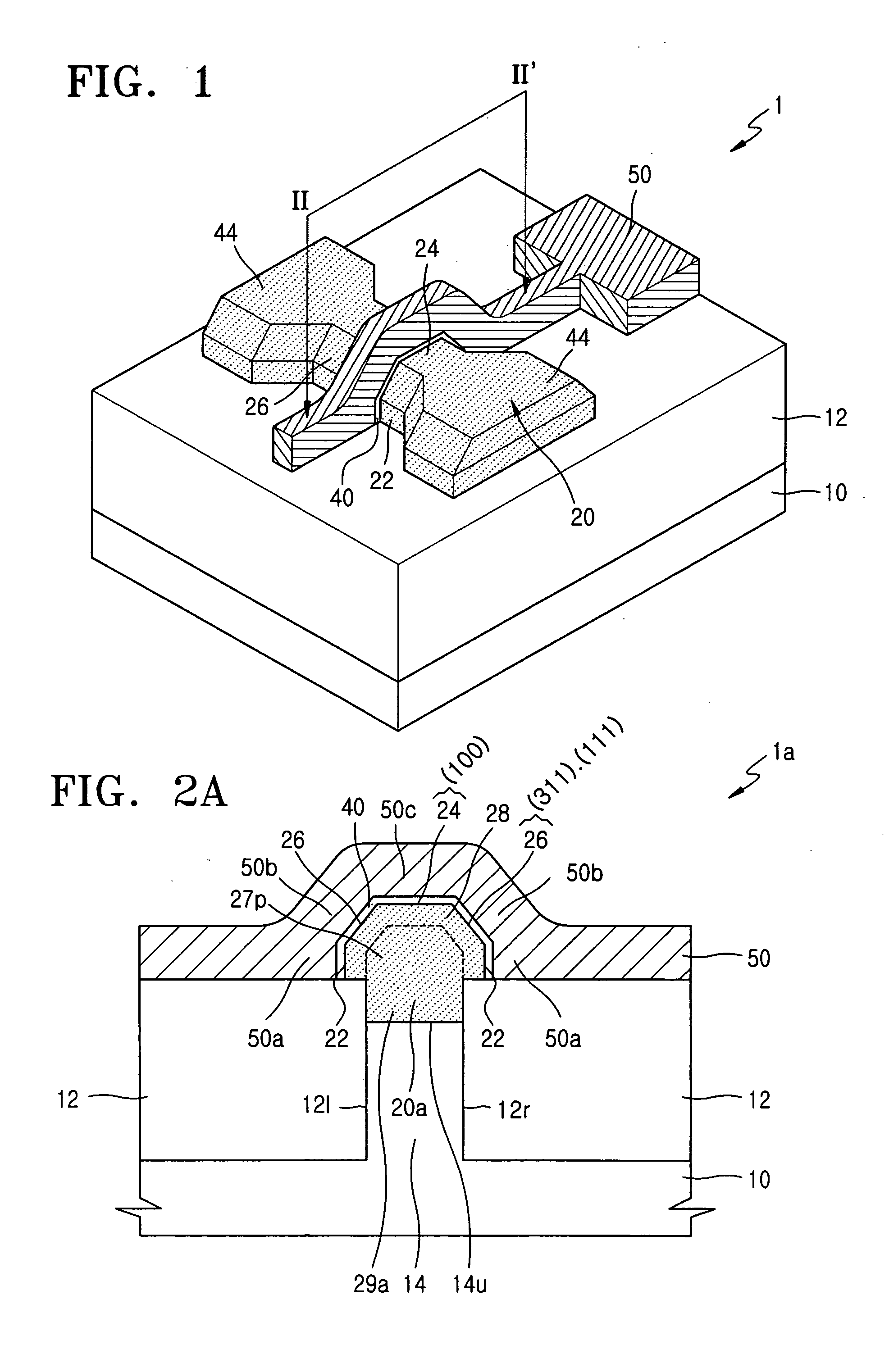

At least penta-sided-channel type of FinFET transistor

ActiveUS20050156202A1TransistorSemiconductor/solid-state device manufacturingGate insulatorChannel types

An at least penta-sided-channel type of FinFET transistor may include: a base; a semiconductor body formed on the base, the body being arranged in a long dimension to have source / drain regions sandwiching a channel region, at least the channel, in cross-section transverse to the long dimension, having at least five planar surfaces above the base; a gate insulator on the channel region of the body; and a gate electrode formed on the gate insulator.

Owner:SAMSUNG ELECTRONICS CO LTD

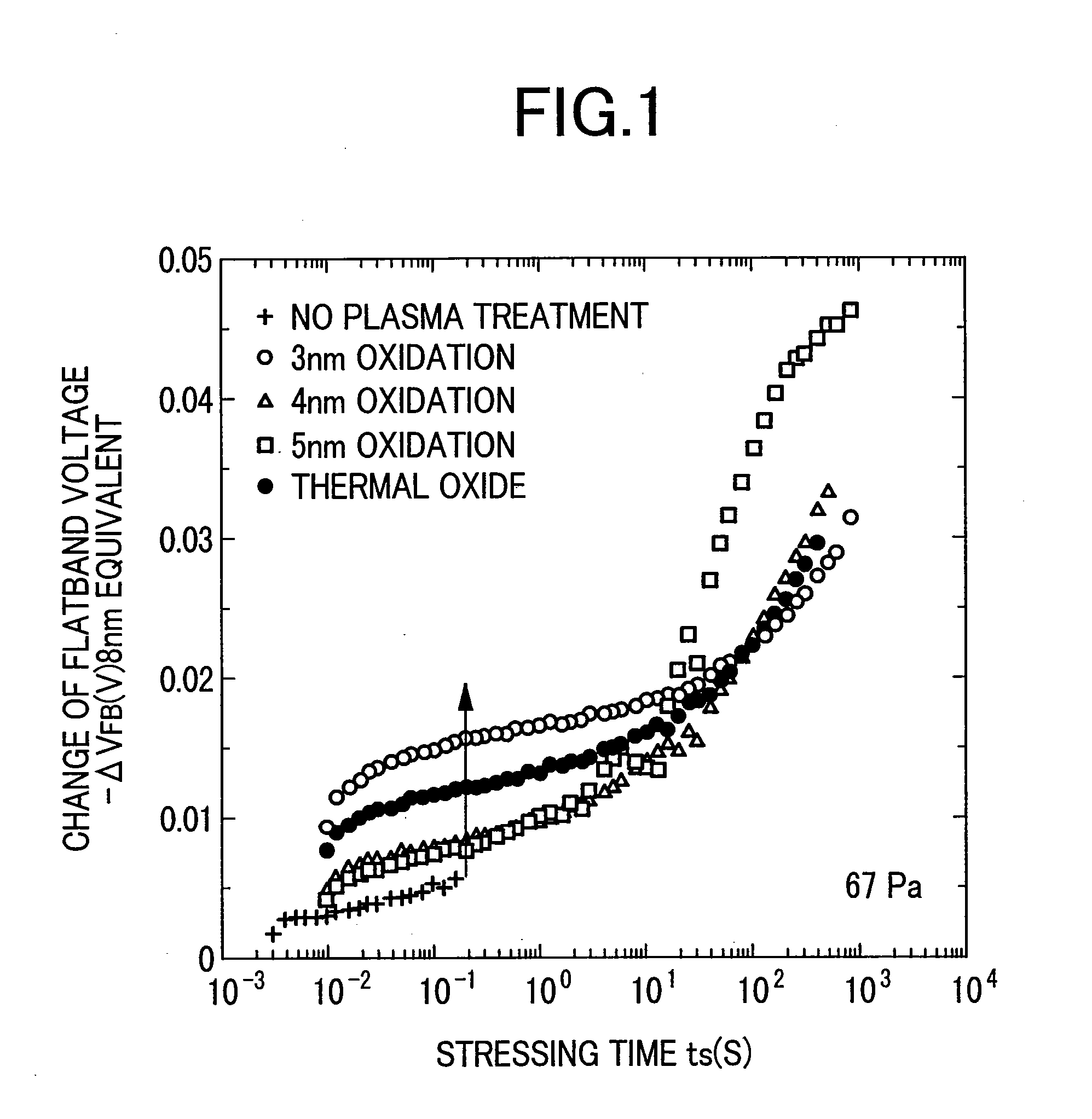

Method for fabricating semiconductor devices

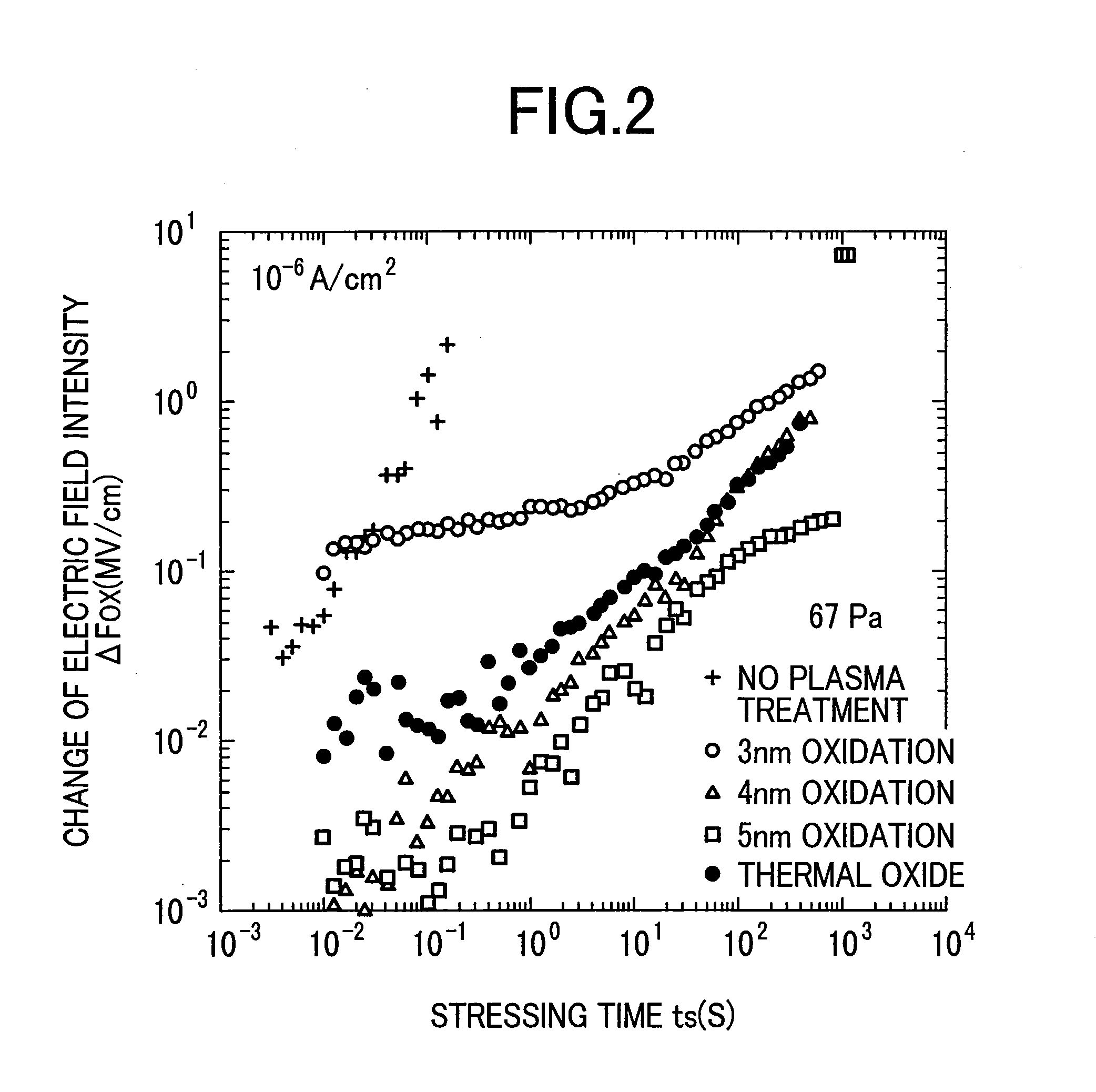

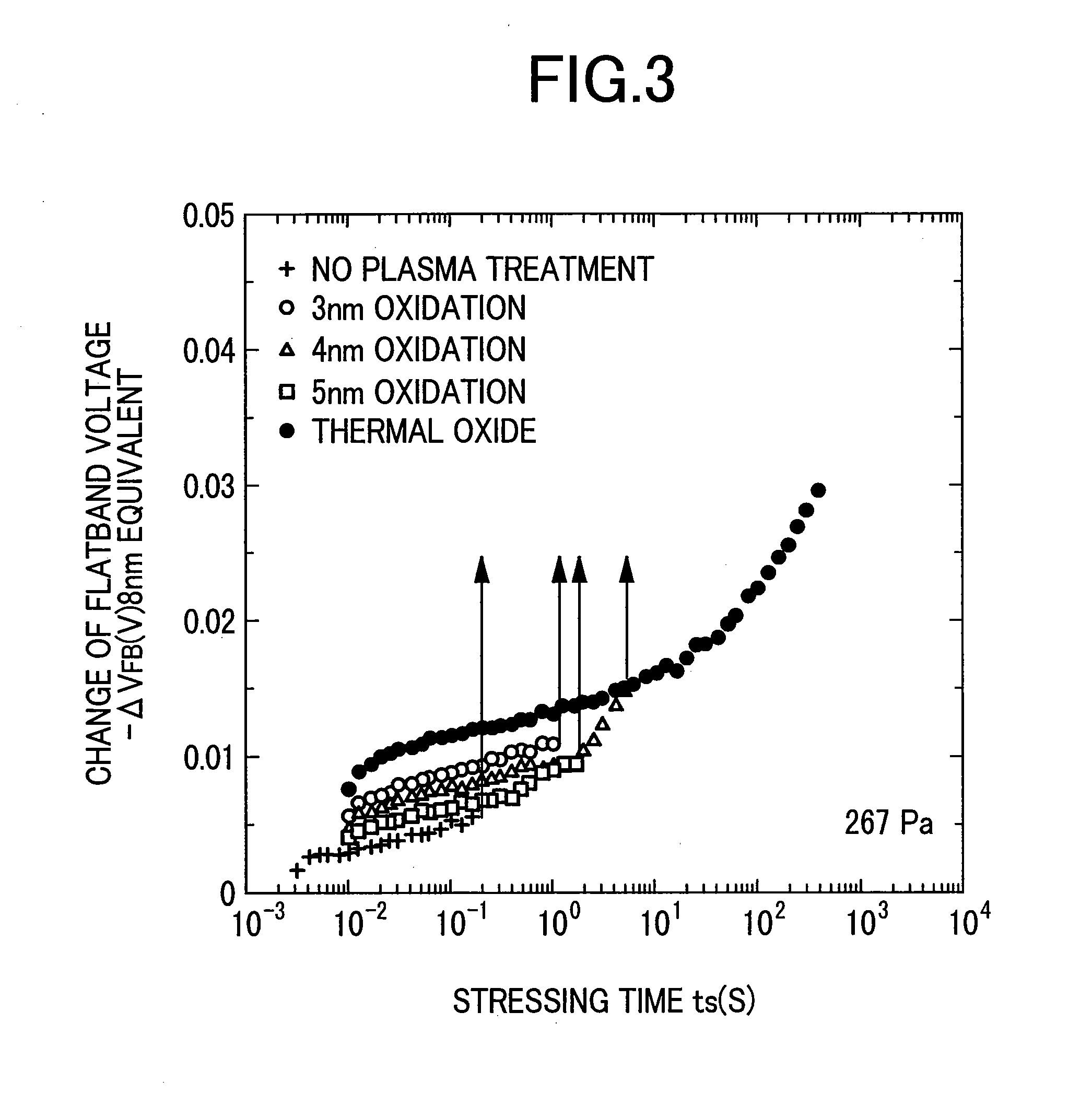

InactiveUS20070190744A1TransistorSemiconductor/solid-state device detailsOxygen plasmaGate insulator

Owner:RENESAS ELECTRONICS CORP

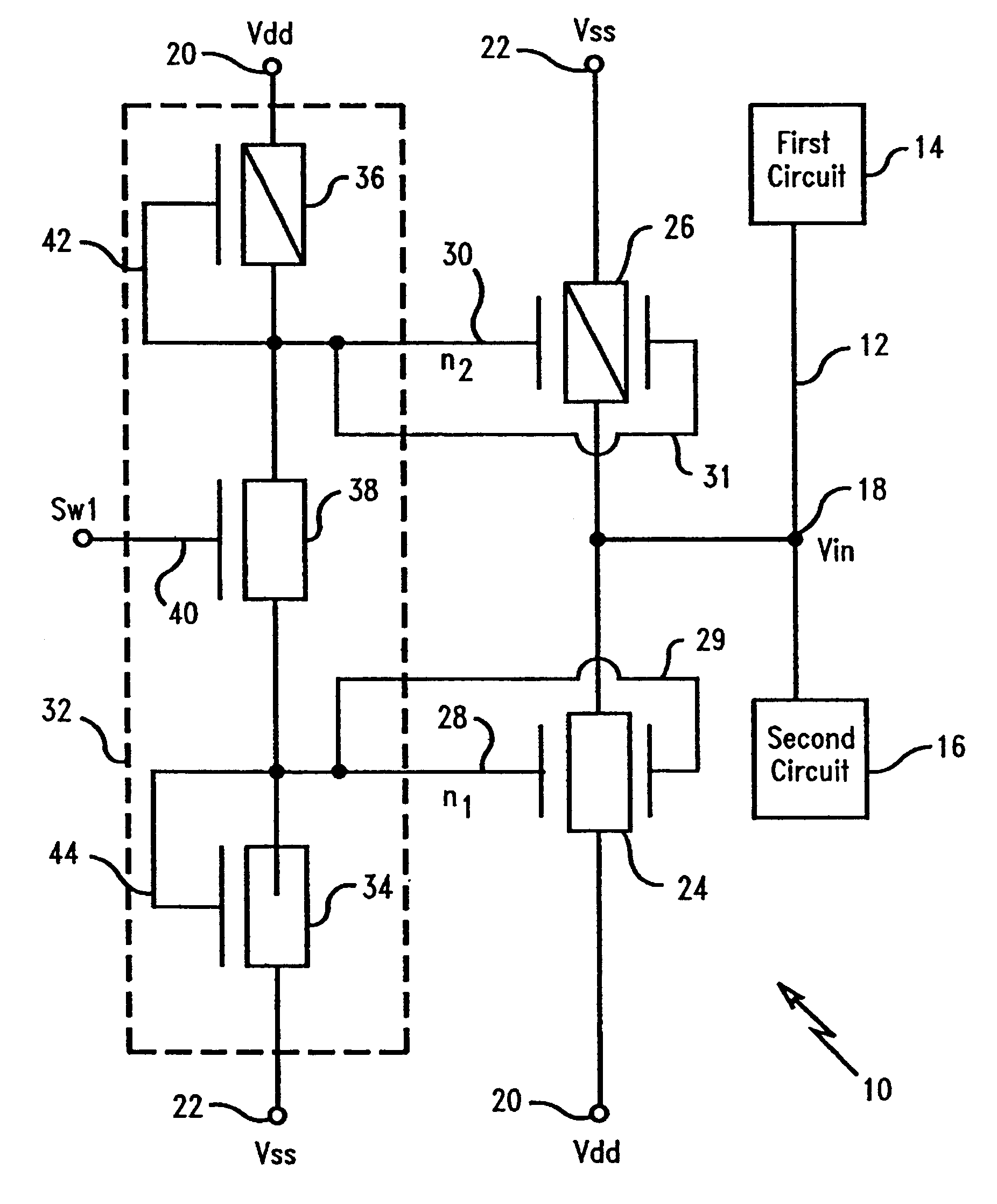

Double-gate low power SOI active clamp network for single power supply and multiple power supply applications

InactiveUS6433609B1Improve performanceReduce power consumptionTransistorPulse automatic controlActive clampLow voltage

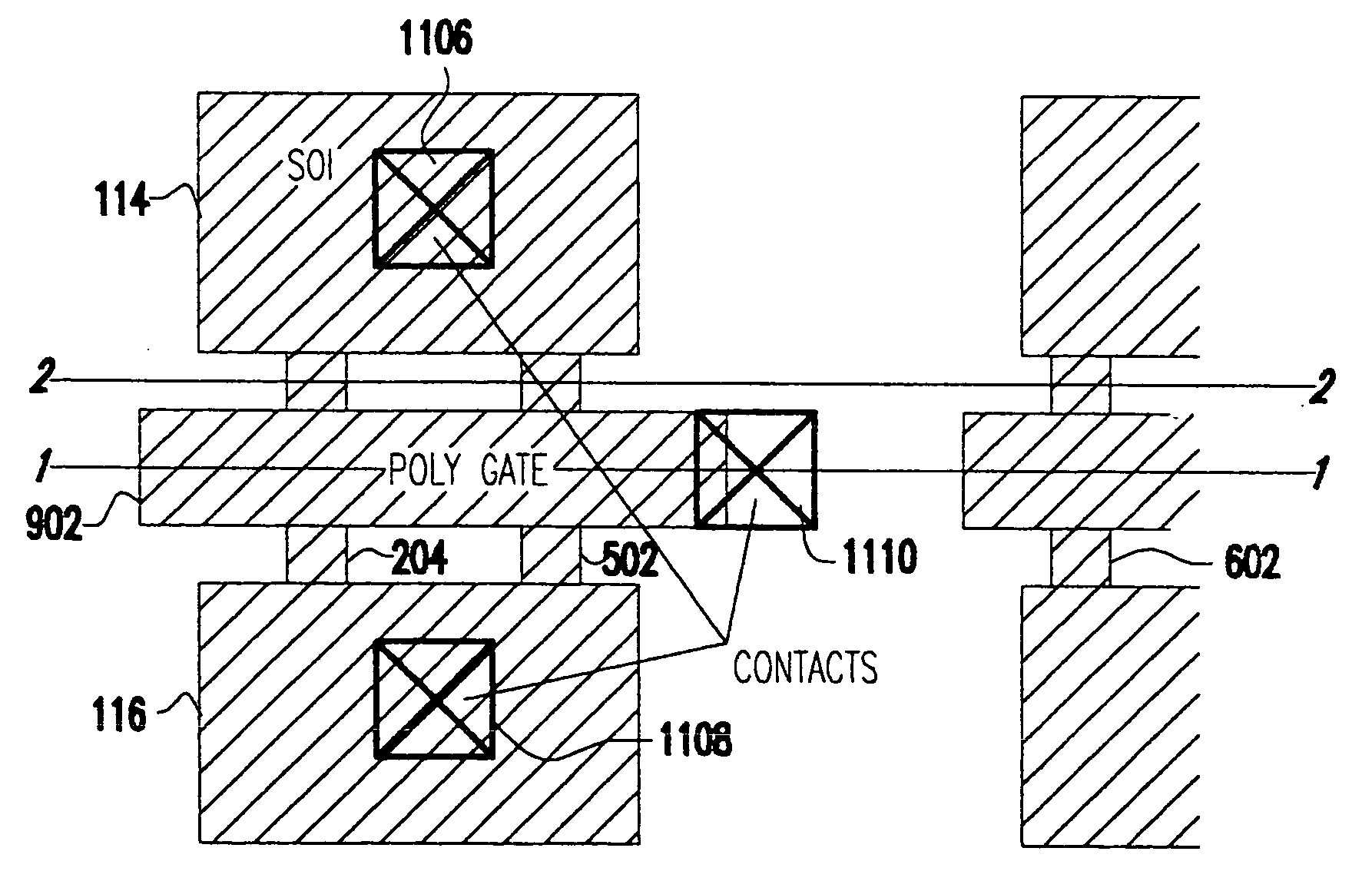

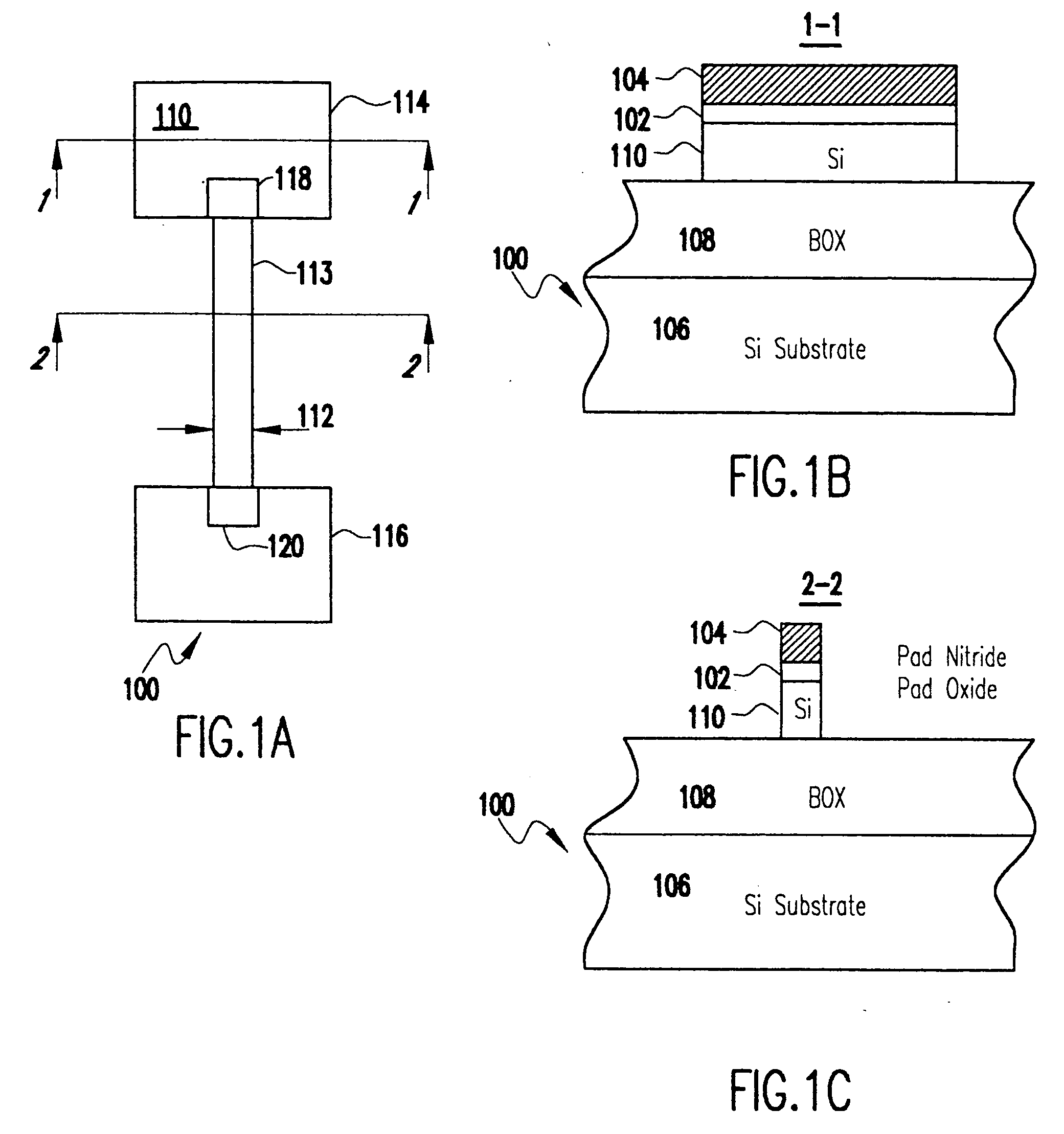

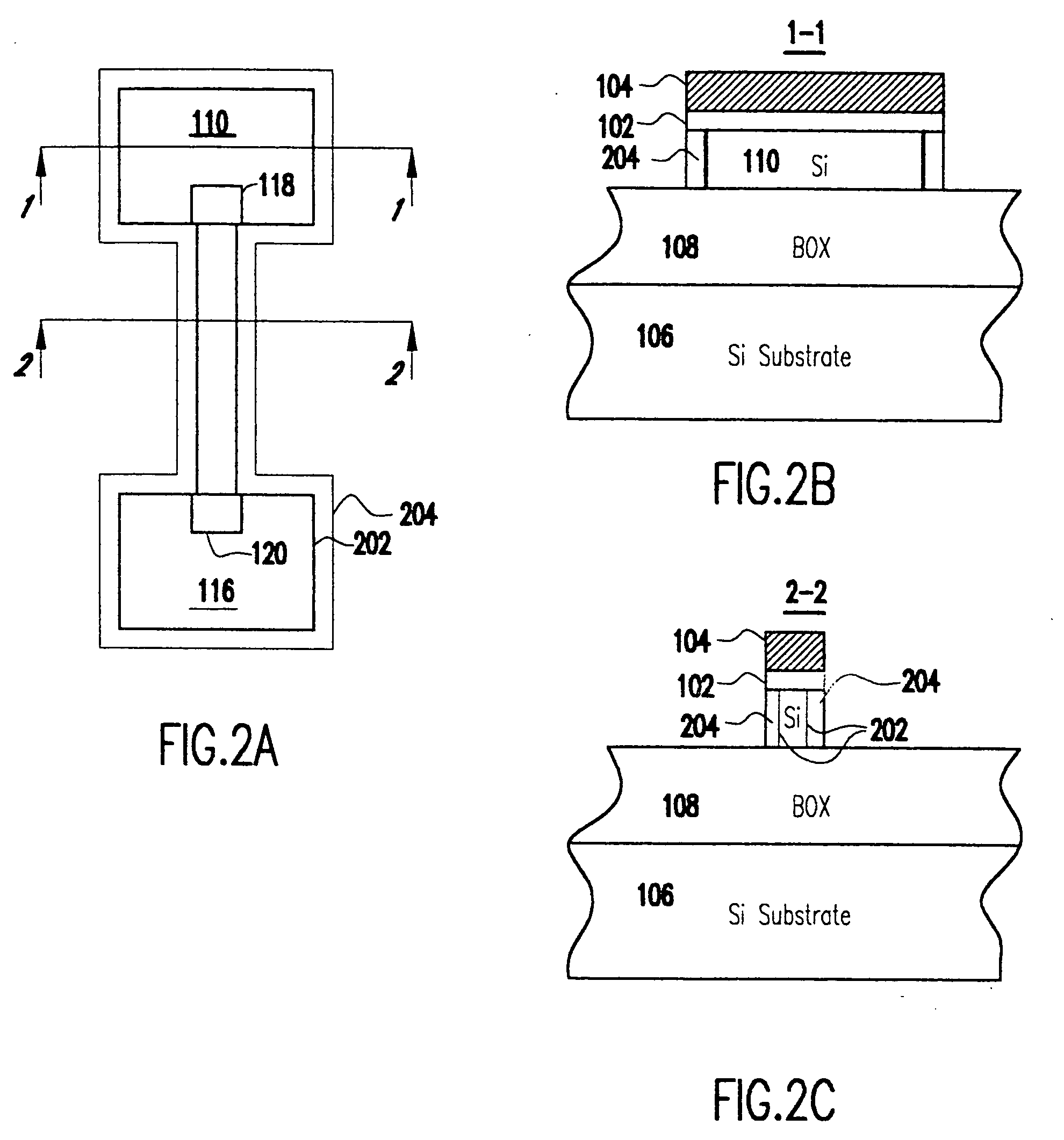

A double-gated low power active clamp circuit for digital circuits includes a first double-gated MOSFET serially connected between an upper power supply voltage and an input terminal to be clamped, and a second double-gated MOSFET serially connected between a lower voltage power supply and the input terminal. The voltages at the gates of the first and second double-gated MOSFETs are held at constant reference voltages by a single or double reference circuits. The clamping action can be switched on or off. The double-gated active clamping network can be implemented with a single power supply voltage, or with multiple power supply voltages. The use of the back gates of the double-gated active clamping network enables additional clamping and ESD protection for smaller generations of transistors, such as, those having dimensions below 0.1 micron. The device is particularly suited for use with dynamic threshold double-gated silicon-on-insulator, FINFET, and bulk triple well technologies.

Owner:GLOBALFOUNDRIES US INC

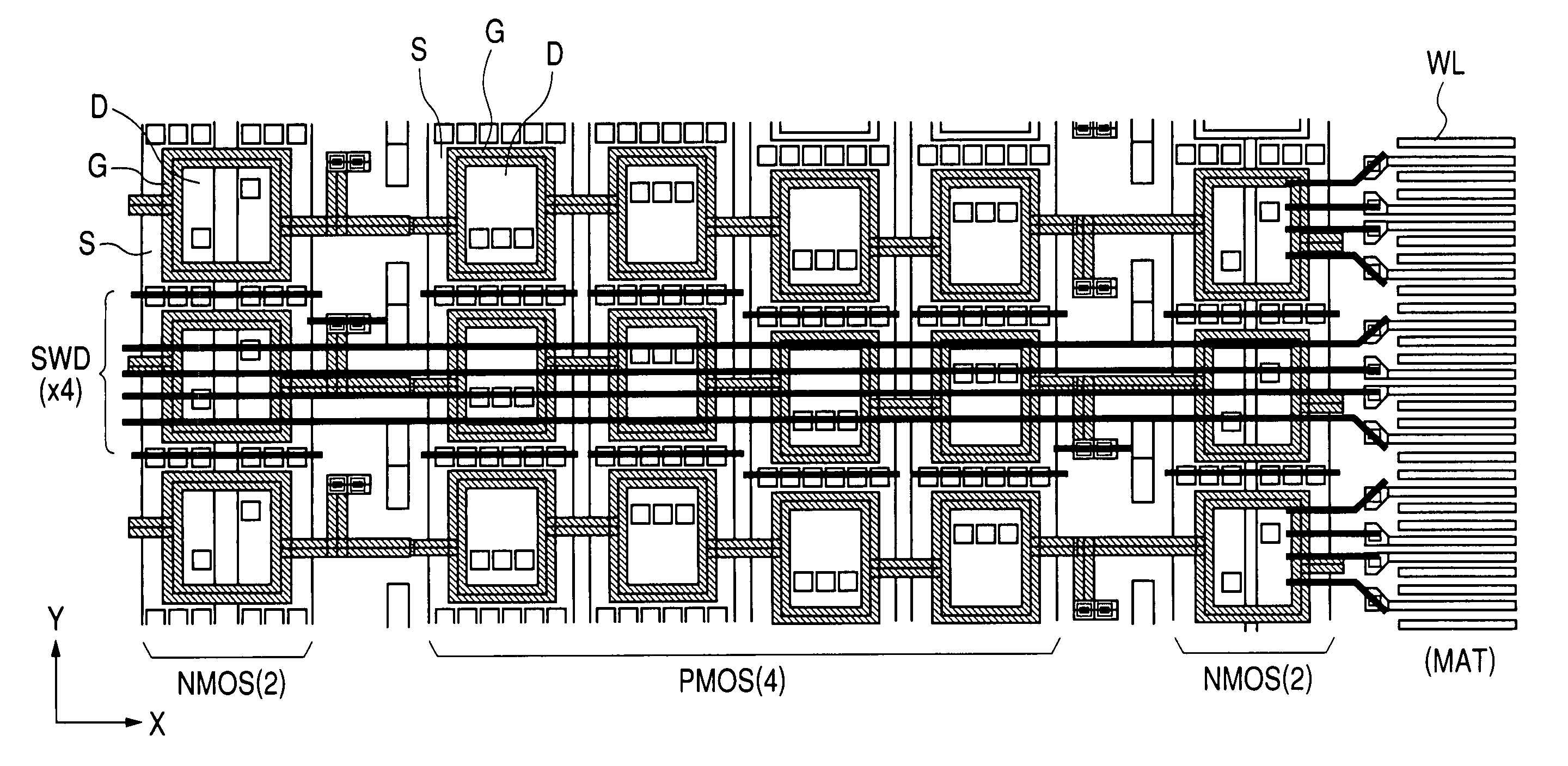

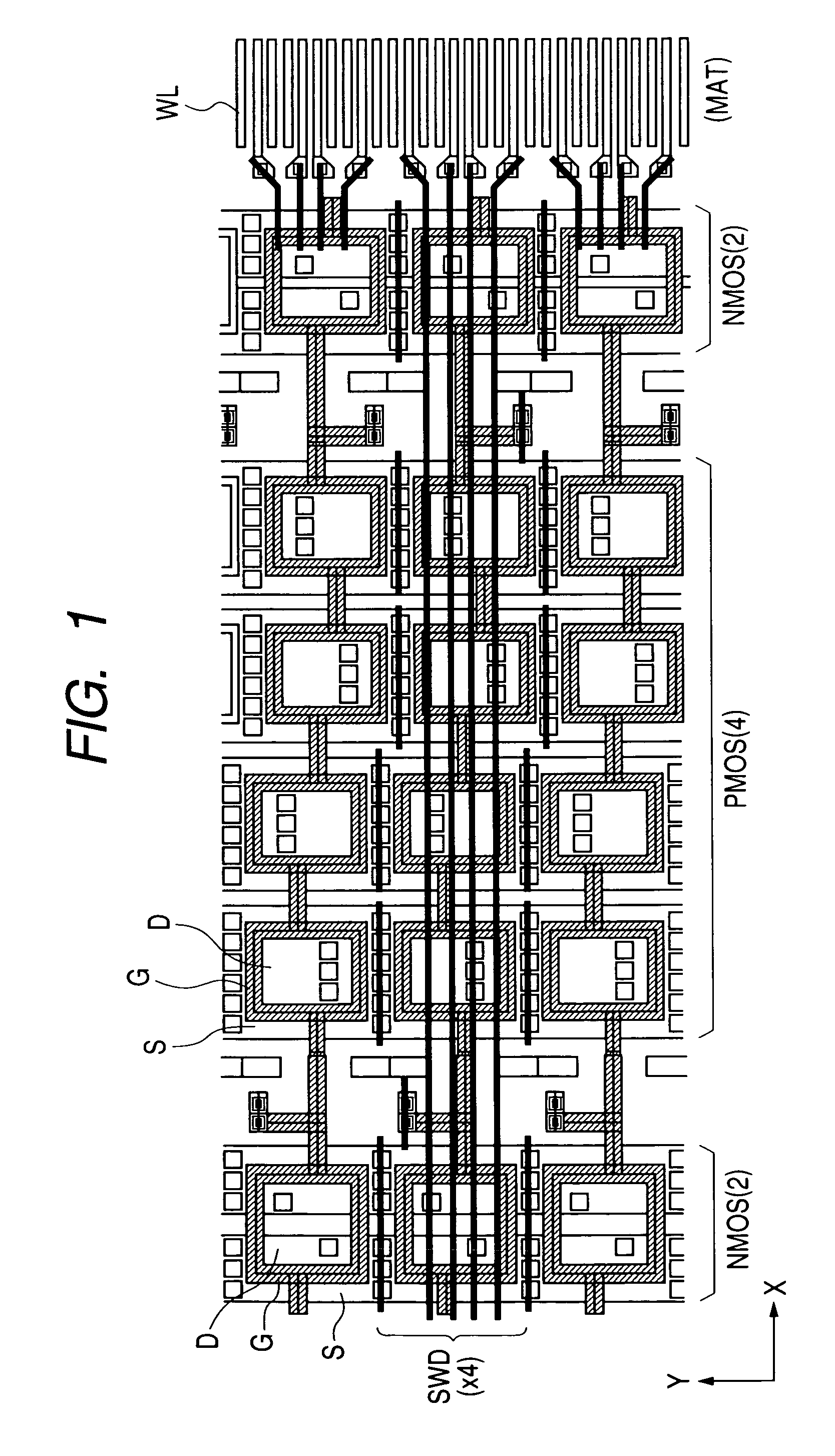

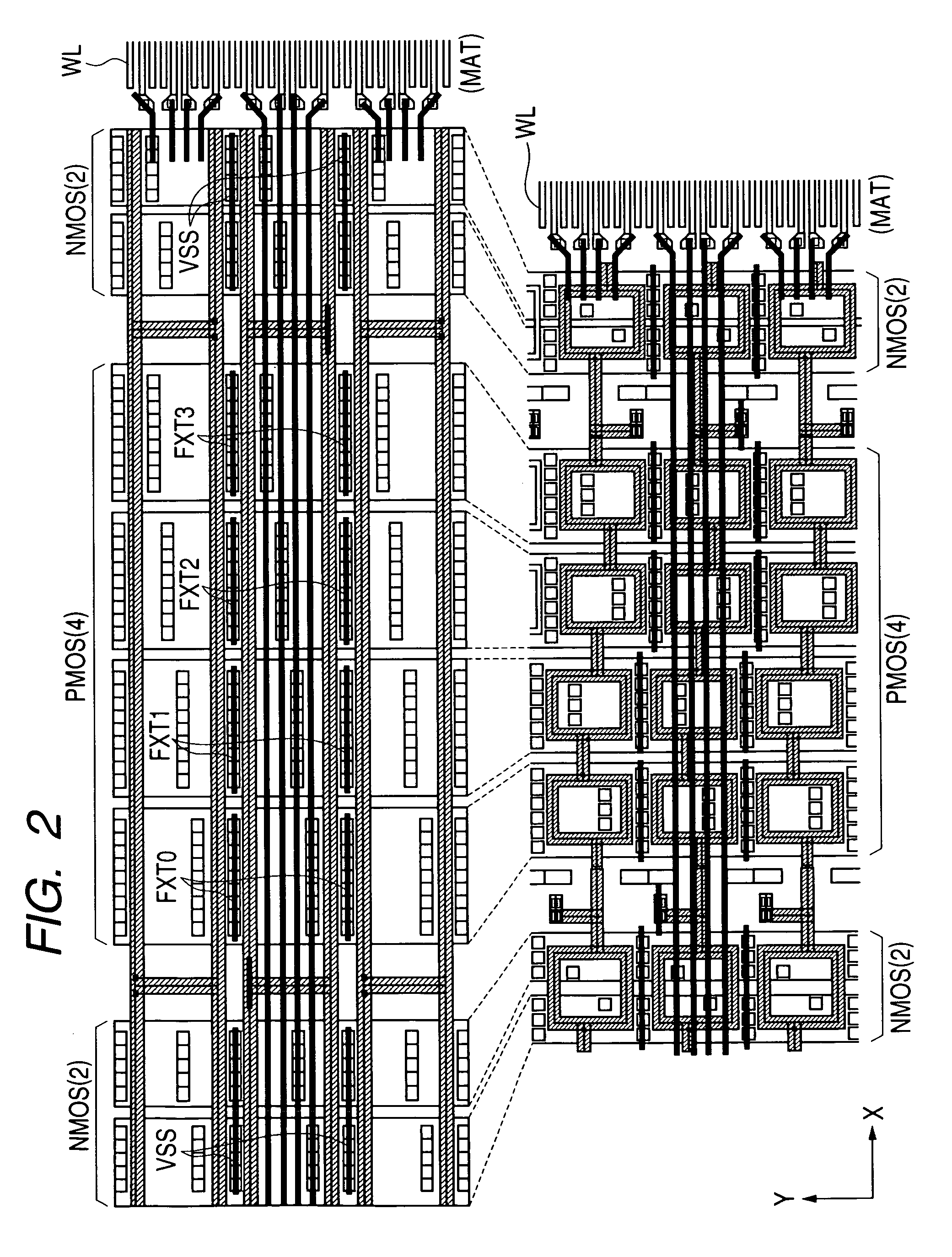

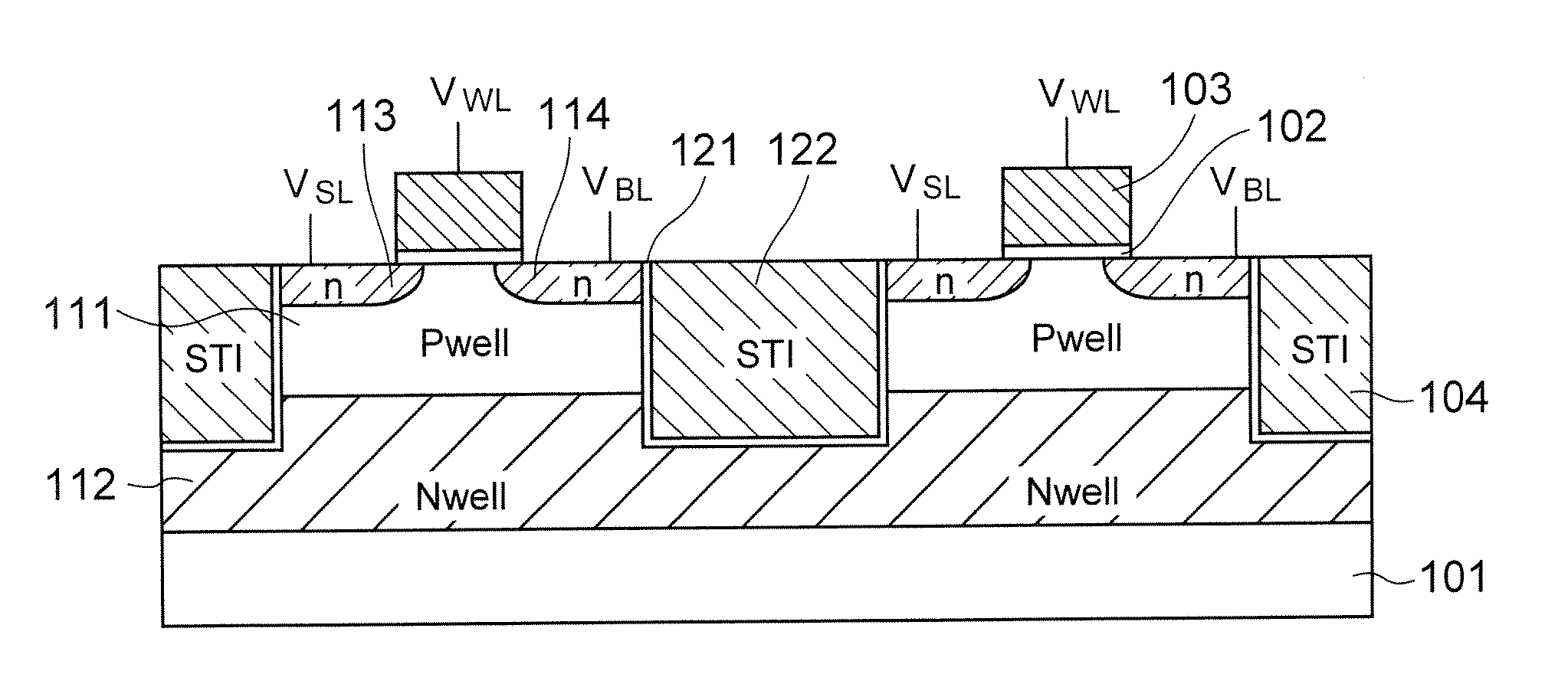

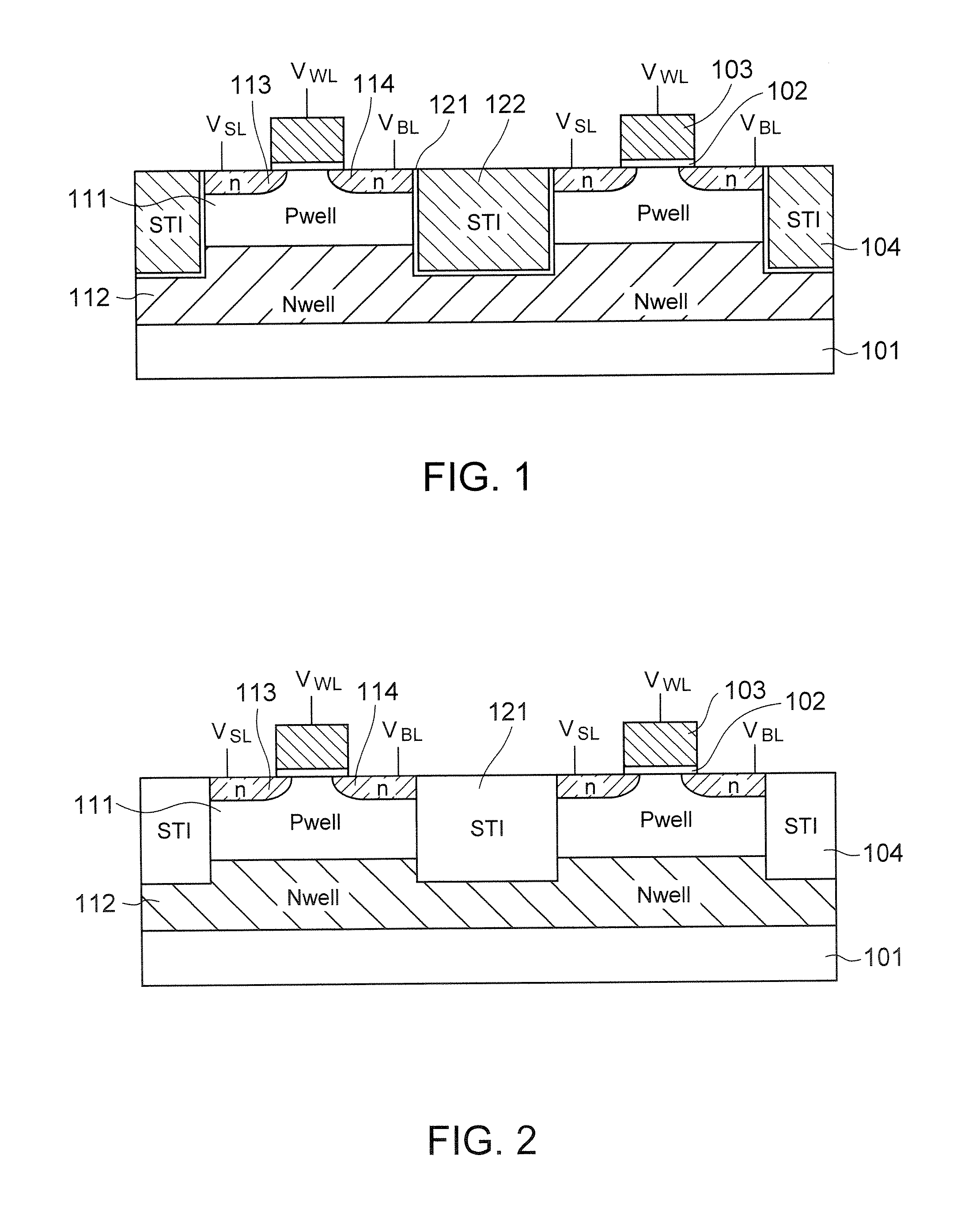

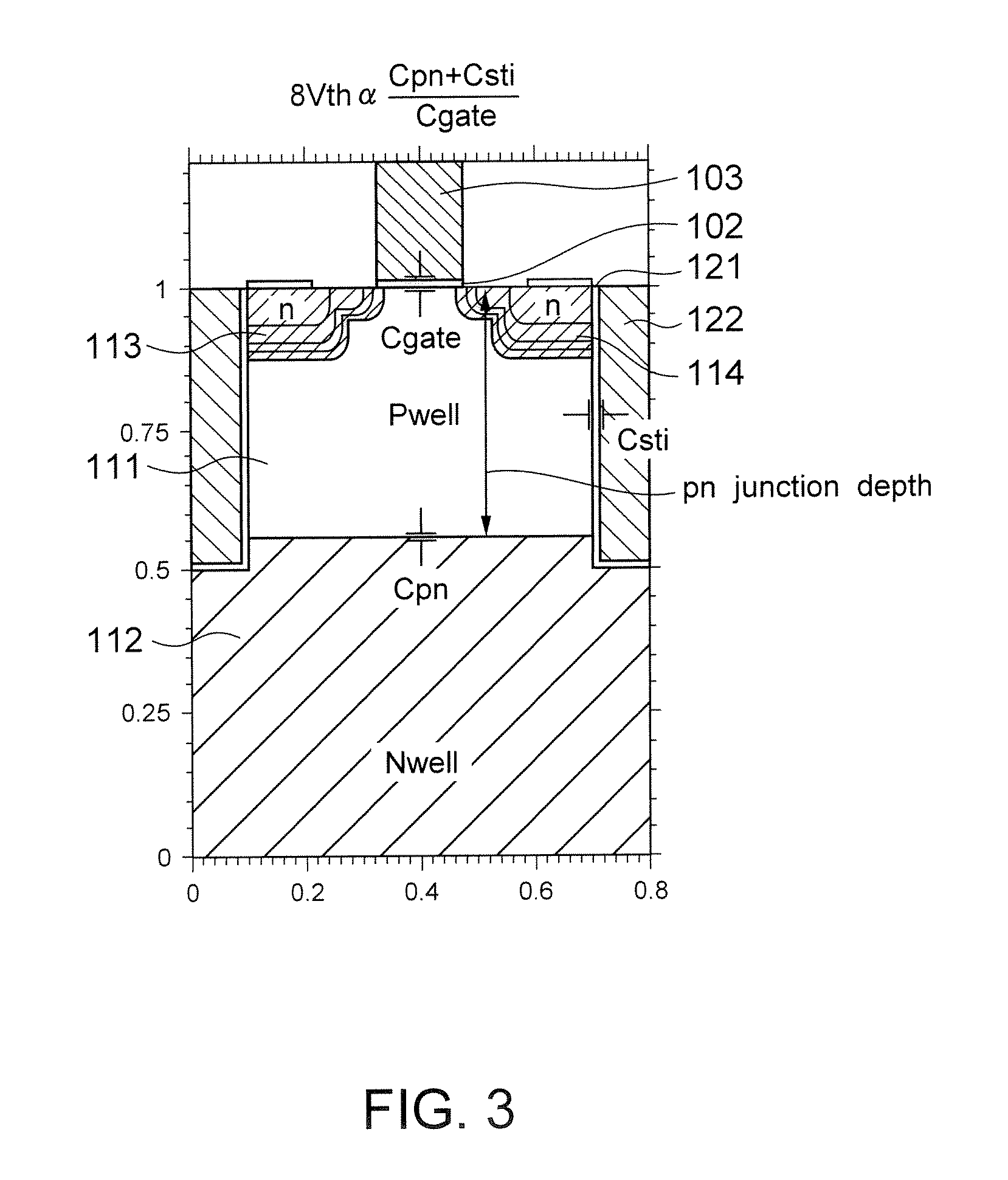

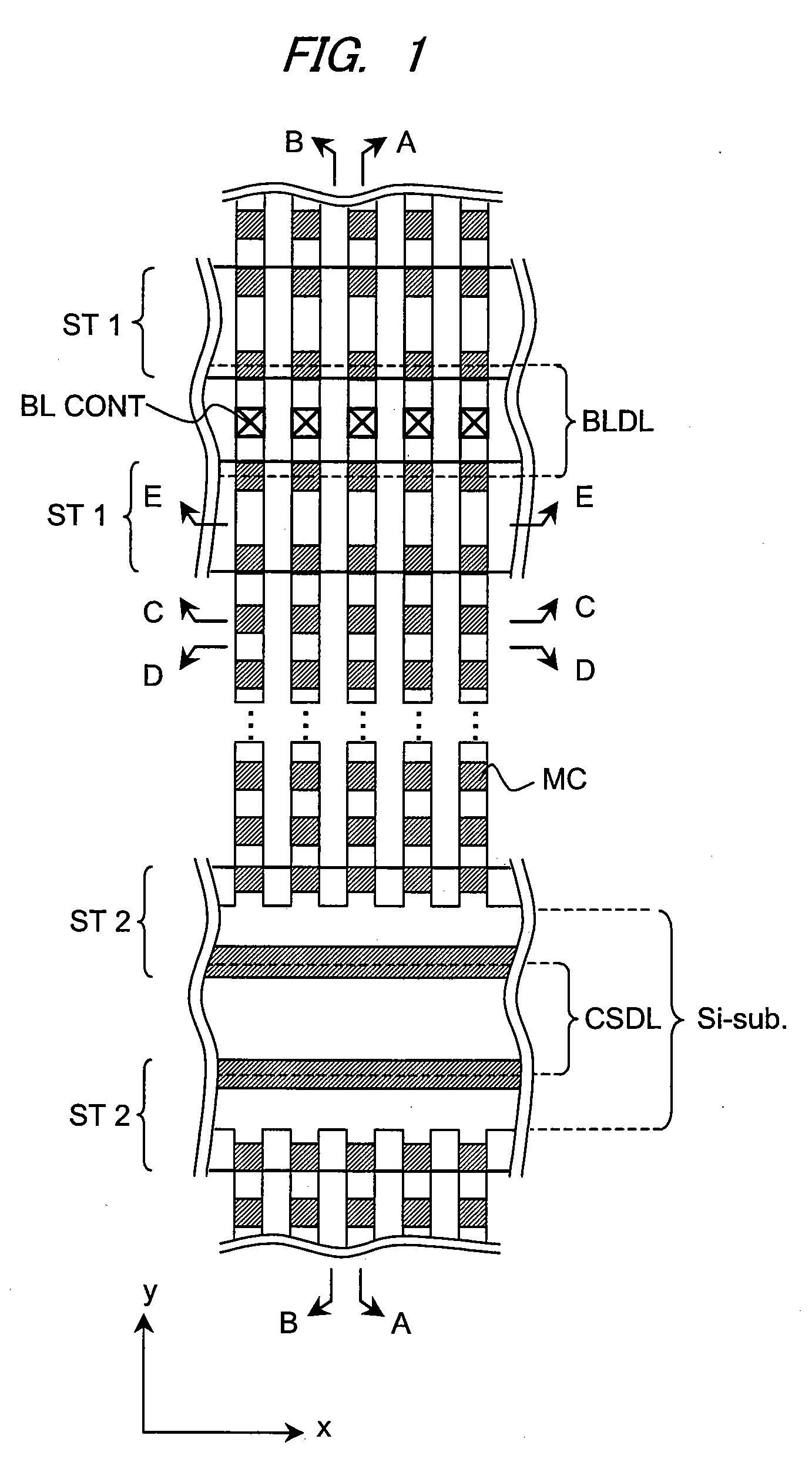

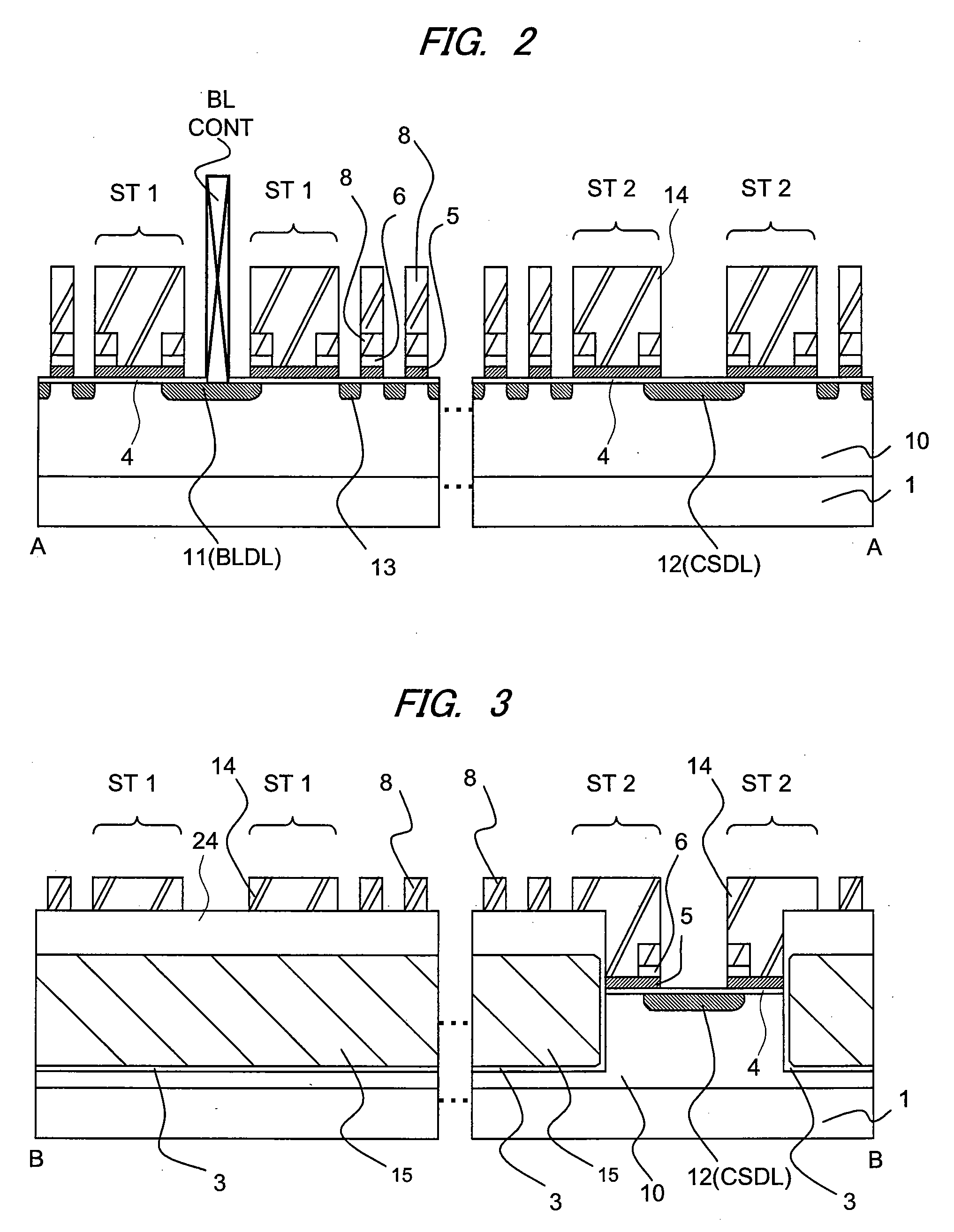

Semiconductor integrated circuit device

InactiveUS7016214B2Reduced footprintSuppress relative deviation of operation characteristicsTransistorSolid-state devicesMOSFETGate insulator

A semiconductor integrated circuit device capable of achieving higher integration and simplification of manufacturing processes is provided. Circuitry is provided which includes a first N-channel MOSFET and a first p-channel MOSFET each having a gate insulating dielectric film with a first film thickness, wherein a poly-silicon layer making up a gate electrode is doped with an N-type impurity. The circuitry also includes a second N-channel MOSFET having a gate insulator film with a second film thickness thinner than the first thickness, wherein an N-type impurity is doped into a polysilicon layer making up a gate electrode, and a second P-channel MOSFET with a P-type impurity being doped into a polysilicon layer making up a gate electrode. The gate electrodes of the first N-channel MOSFET and first P-channel MOSFET are integrally formed and mutually connected together.

Owner:HITACHI LTD

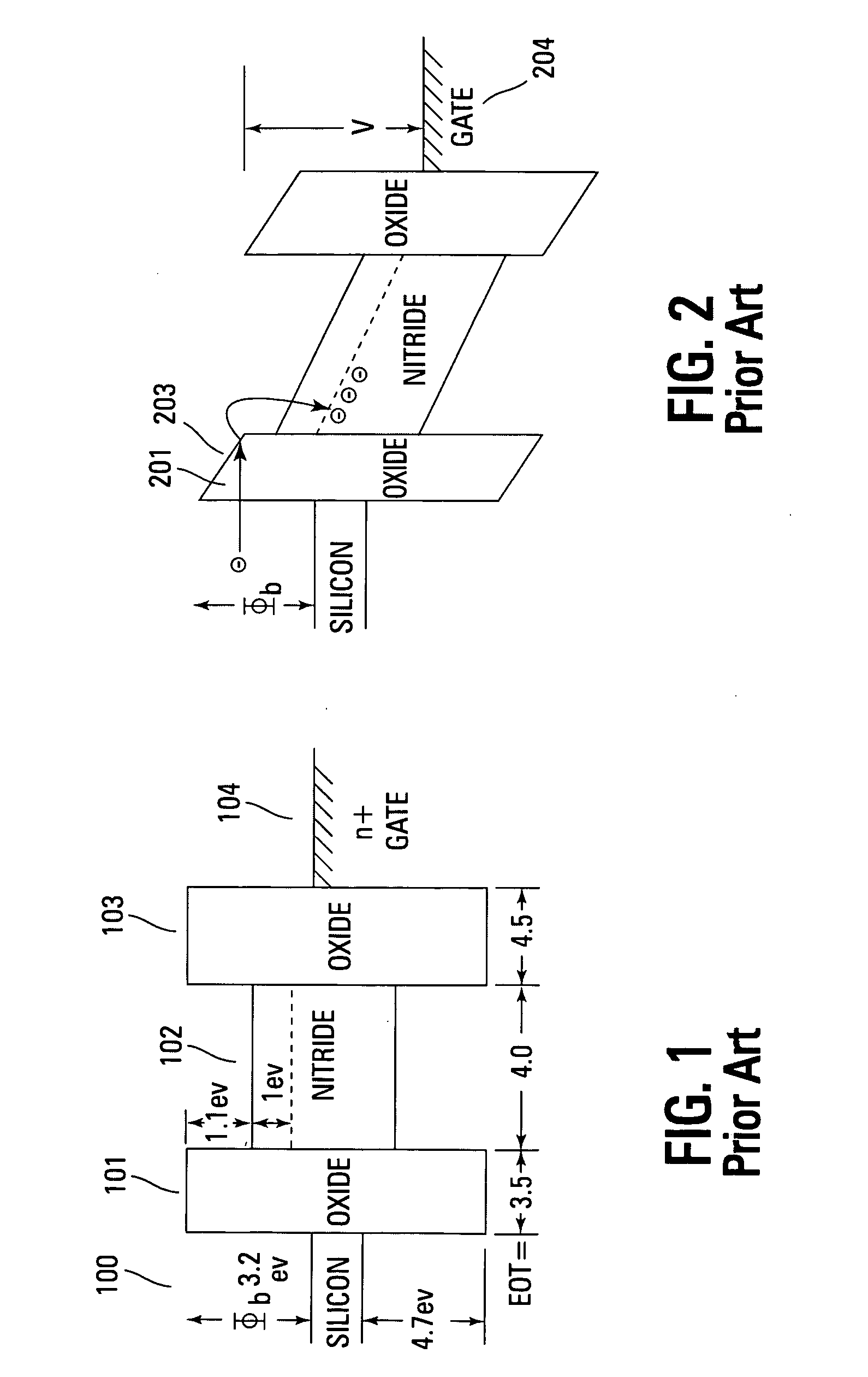

Memory utilizing oxide-nitride nanolaminates

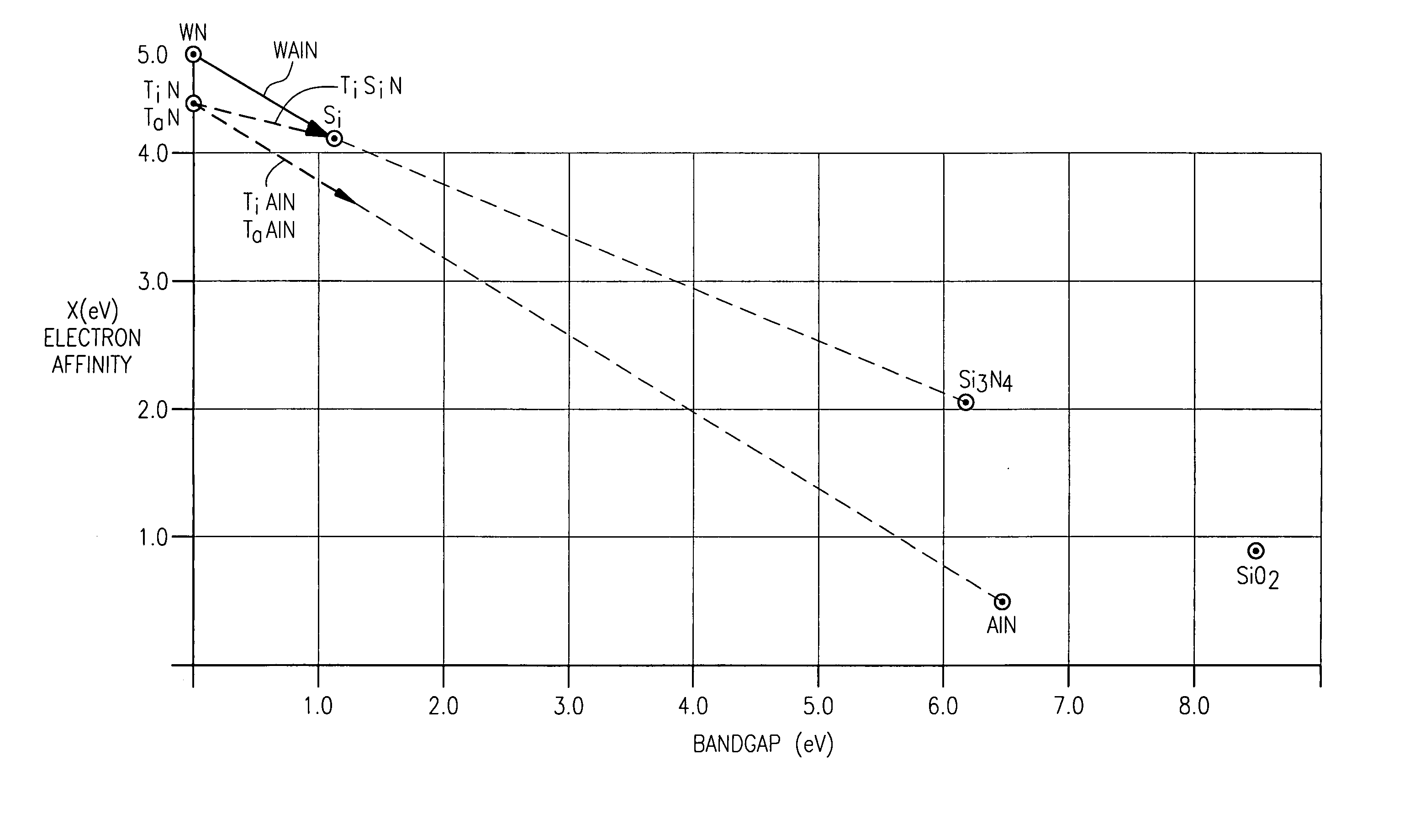

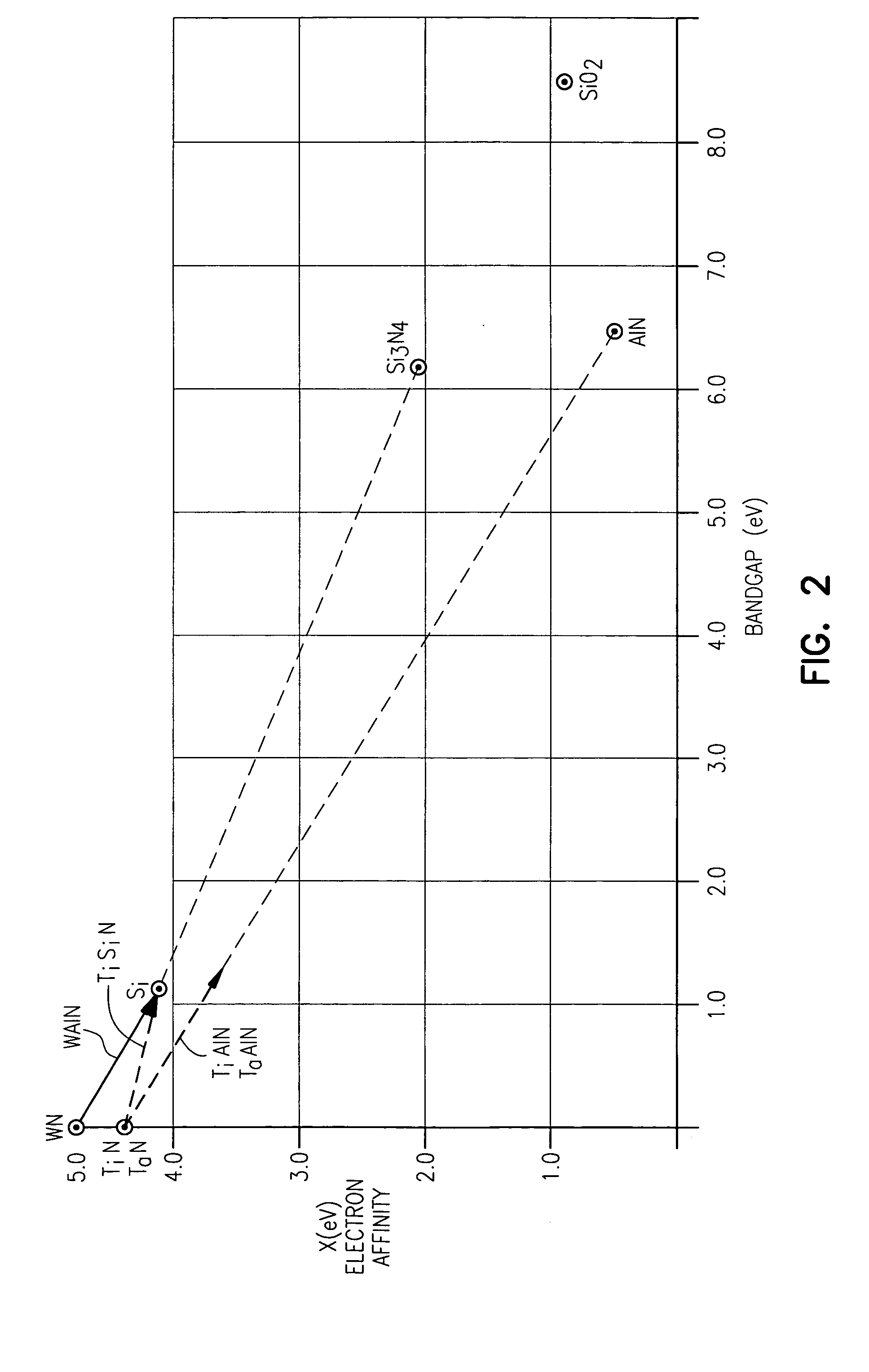

Structures, systems and methods for transistors utilizing oxide-nitride nanolaminates are provided. One transistor embodiment includes a first source / drain region, a second source / drain region, and a channel region therebetween. A gate is separated from the channel region by a gate insulator. The gate insulator includes oxide-nitride nanolaminate layers to trap charge in potential wells formed by different electron affinities of the oxide-nitride nanolaminate layers.

Owner:MICRON TECH INC

Enhanced electroless deposition of dielectric precursor materials for use in in-laid gate MOS transistors

InactiveUS6465334B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectroless depositionOxygen

High quality dielectric layers, e.g., high-k dielectric layers comprised of at least one refractory or lanthanum series transition metal oxide or silicate, for use as gate insulator layers in in-laid metal gate MOS transistors and CMOS devices, are fabricated by forming an ultra-thin catalytic metal layer, e.g., a monolayer thick layer of Pd or Pd, on a Si-based semiconductor substrate, electrolessly plating on the catalytic layer comprising at least one refractory or lanthanum series transition metal or metal-based dielectric precursor layer, such as of Zr and / or Hf, and then reacting the precursor layer with oxygen or with oxygen and the semiconductor substrate to form the at least one high-k metal oxide or silicate. The inventive methodology prevents, or at least substantially reduces, oxygen access to the substrate surface during at least the initial stage(s) of formation of the gate insulator layer, thereby minimizing deleterious formation of oxygen-induced surface states at the semiconductor substrate / gate insulator interface.

Owner:GLOBALFOUNDRIES US INC

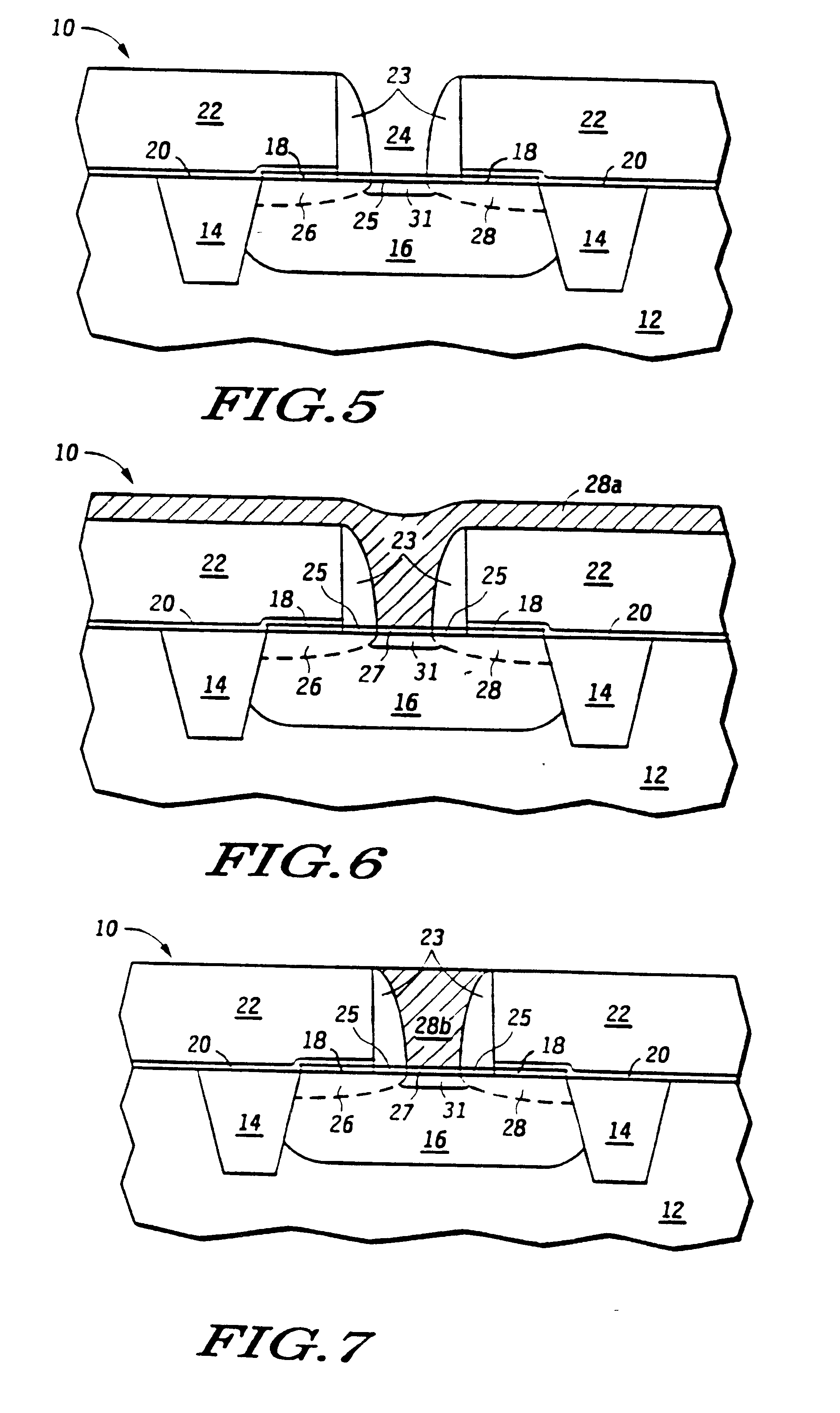

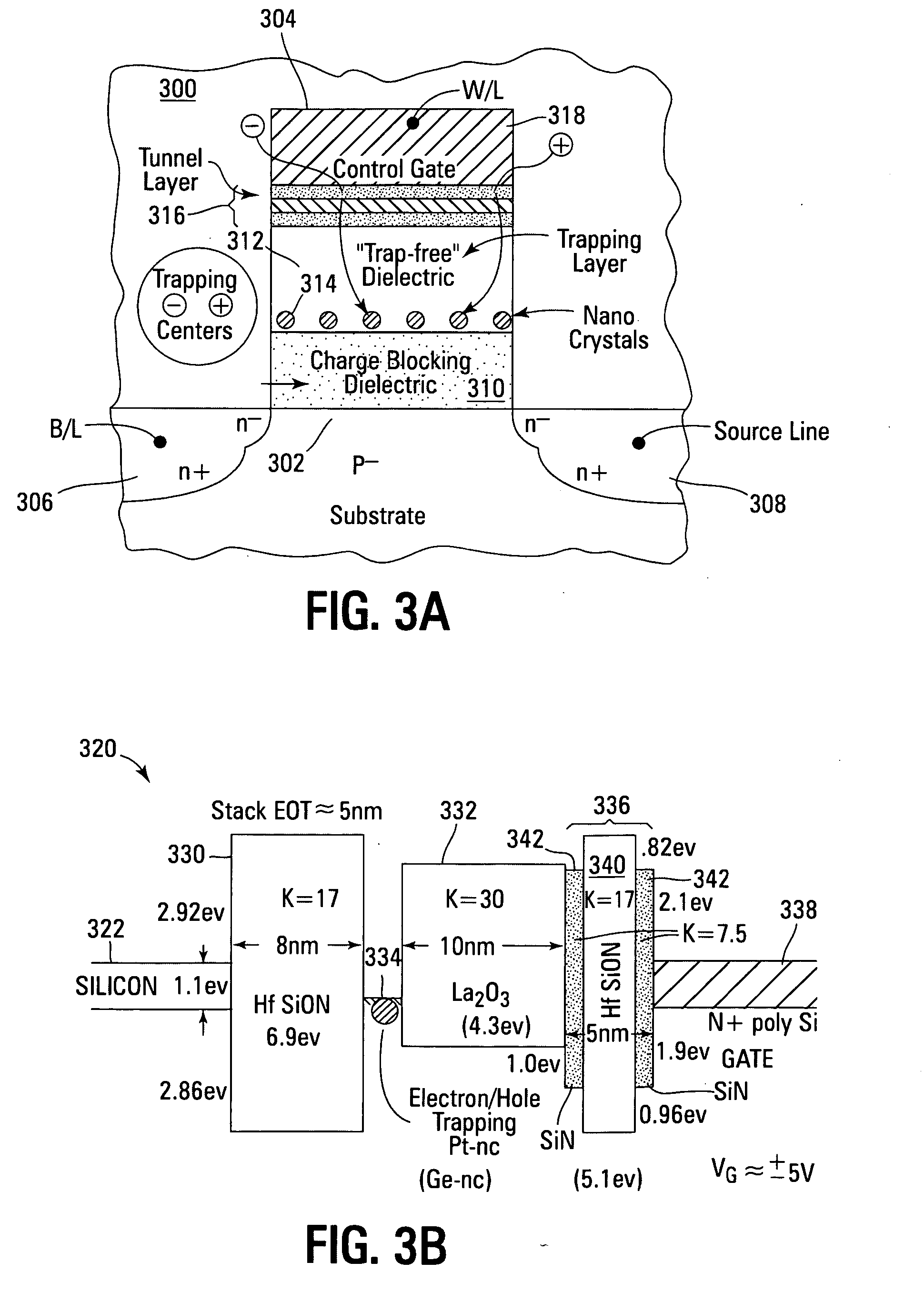

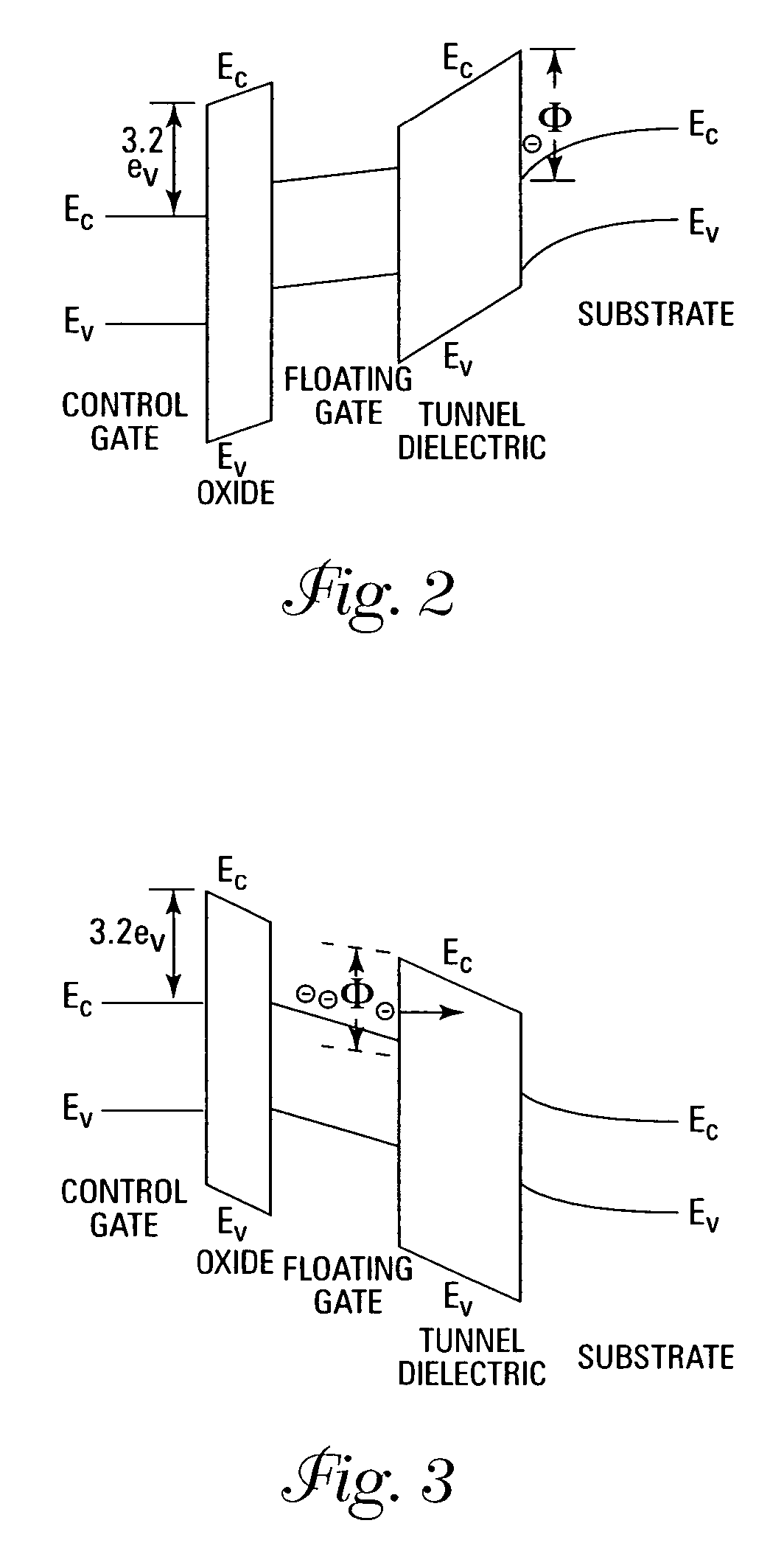

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

Semiconductor device and method for manufacturing the same

A semiconductor device of one embodiment of the present invention includes a substrate; isolation layers, each of which is formed in a trench formed on the substrate and has an insulating film and a conductive layer; a semiconductor layer of a first conductivity type for storing signal charges, formed between the isolation layers and isolated from the conductive layers by the insulating films; a semiconductor layer of a second conductivity type, formed under the semiconductor layer of the first conductivity type; and a transistor having a gate insulator film formed on the semiconductor layer of the first conductivity type and a gate electrode formed on the gate insulator film.

Owner:KK TOSHIBA

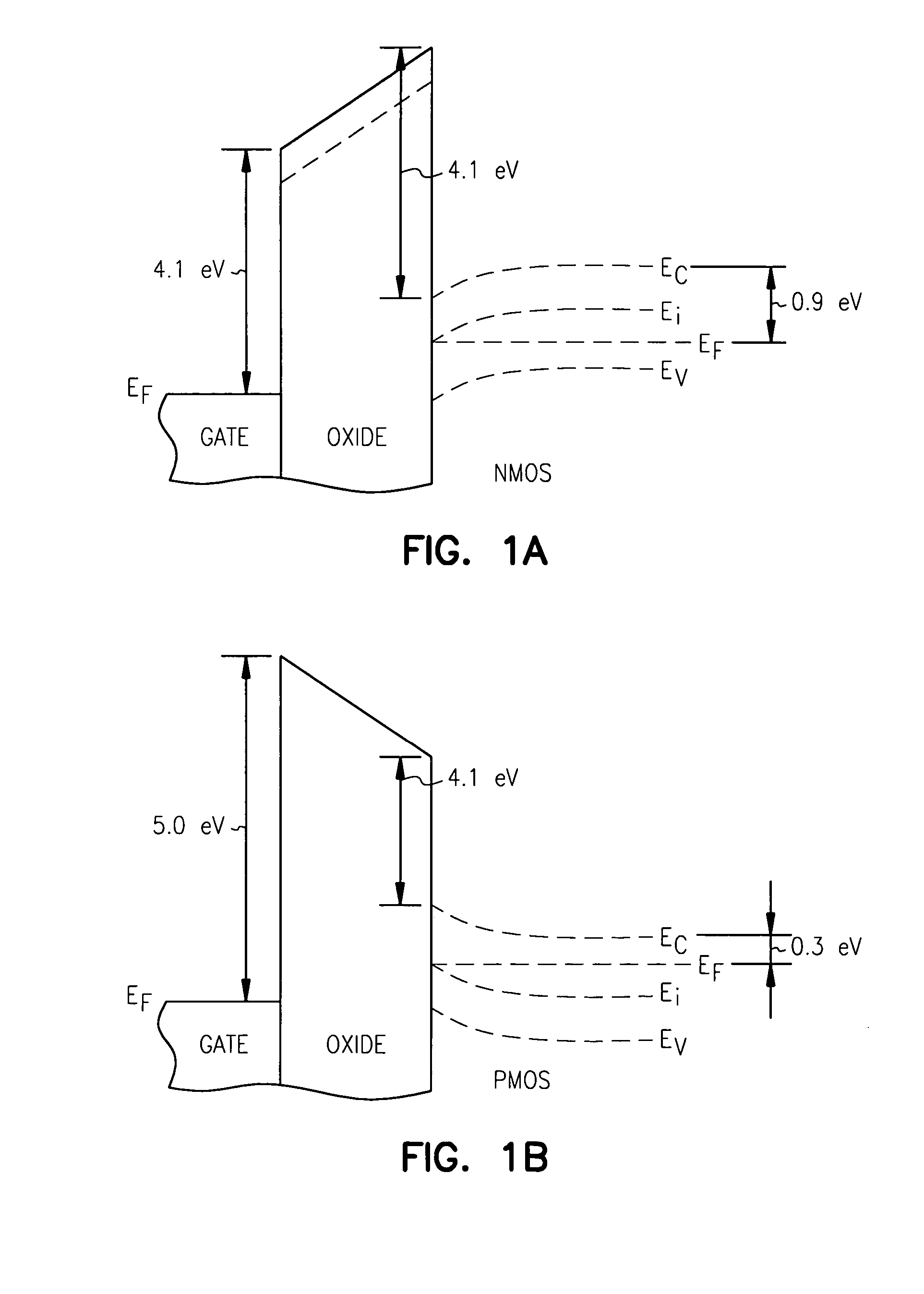

Metal gated ultra short MOSFET devices

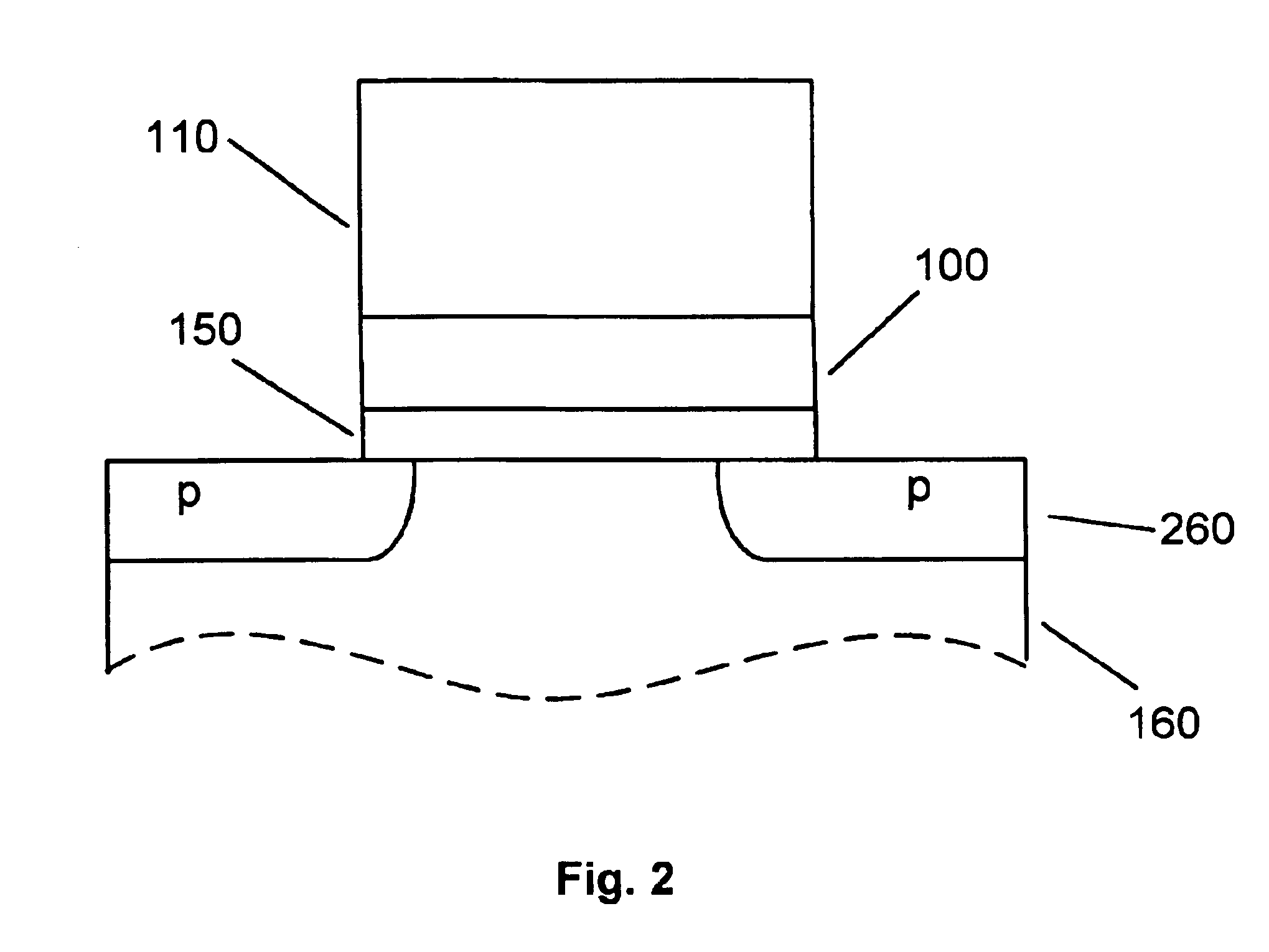

MOSFET devices suitable for operation at gate lengths less than about 40 nm, and methods of their fabrication is being presented. The MOSFET devices include a ground plane formed of a monocrystalline Si based material. A Si based body layer is epitaxially disposed over the ground plane. The body layer is doped with impurities of opposite type than the ground plane. The gate has a metal with a mid-gap workfunction directly contacting a gate insulator layer. The gate is patterned to a length of less than about 40 nm, and possibly less than 20 nm. The source and the drain of the MOSFET are doped with the same type of dopant as the body layer. In CMOS embodiments of the invention the metal in the gate of the NMOS and the PMOS devices may be the same metal.

Owner:GLOBALFOUNDRIES INC

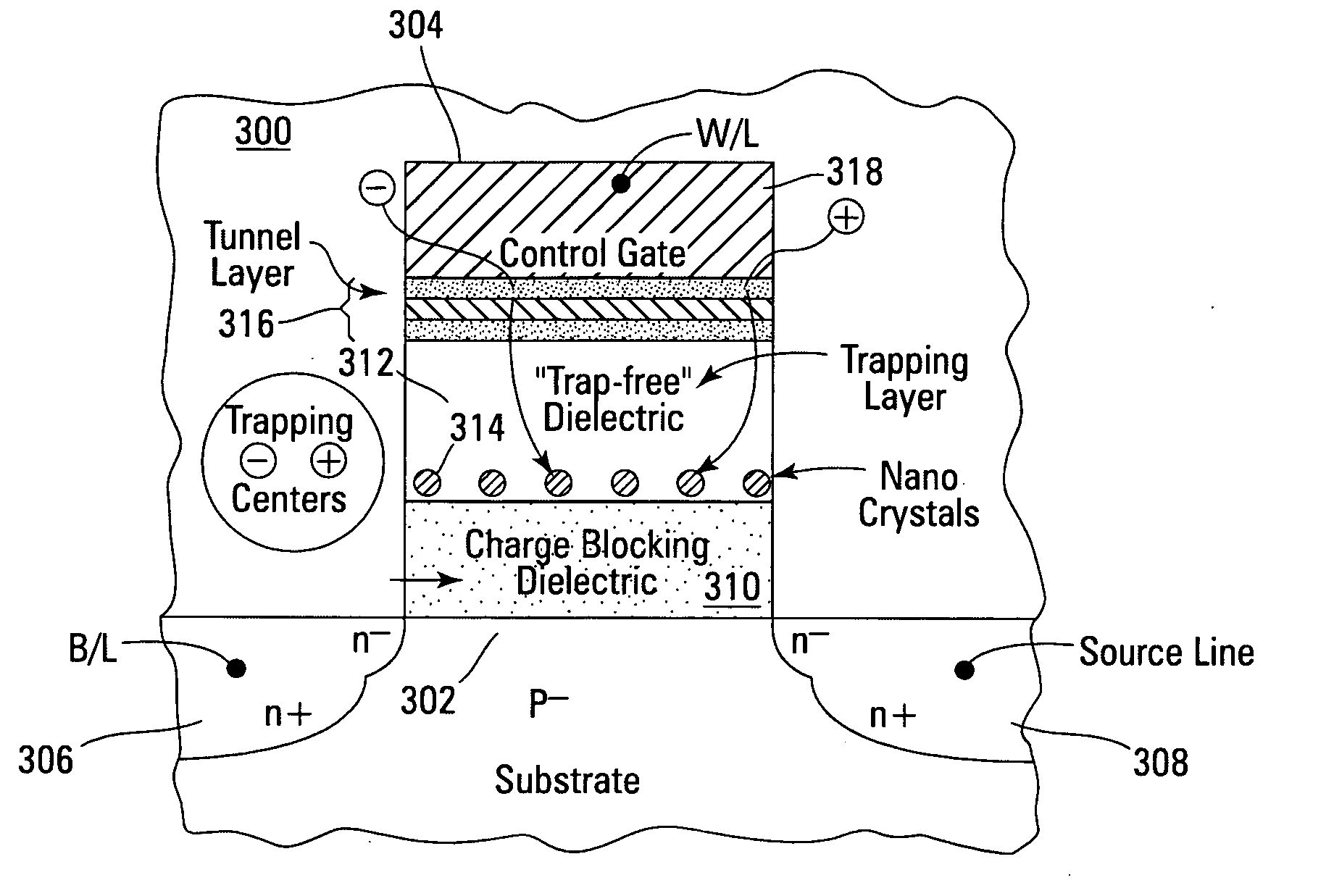

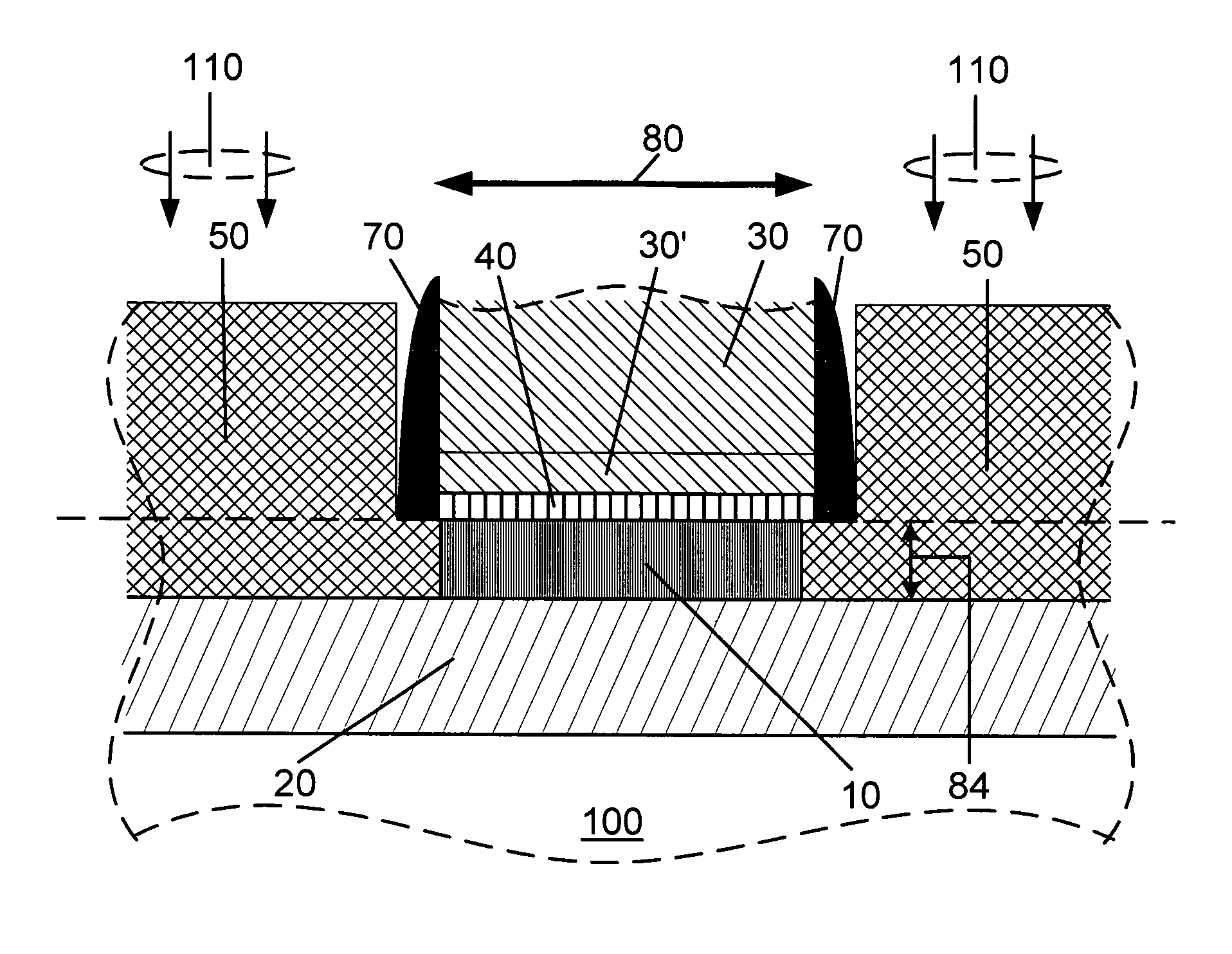

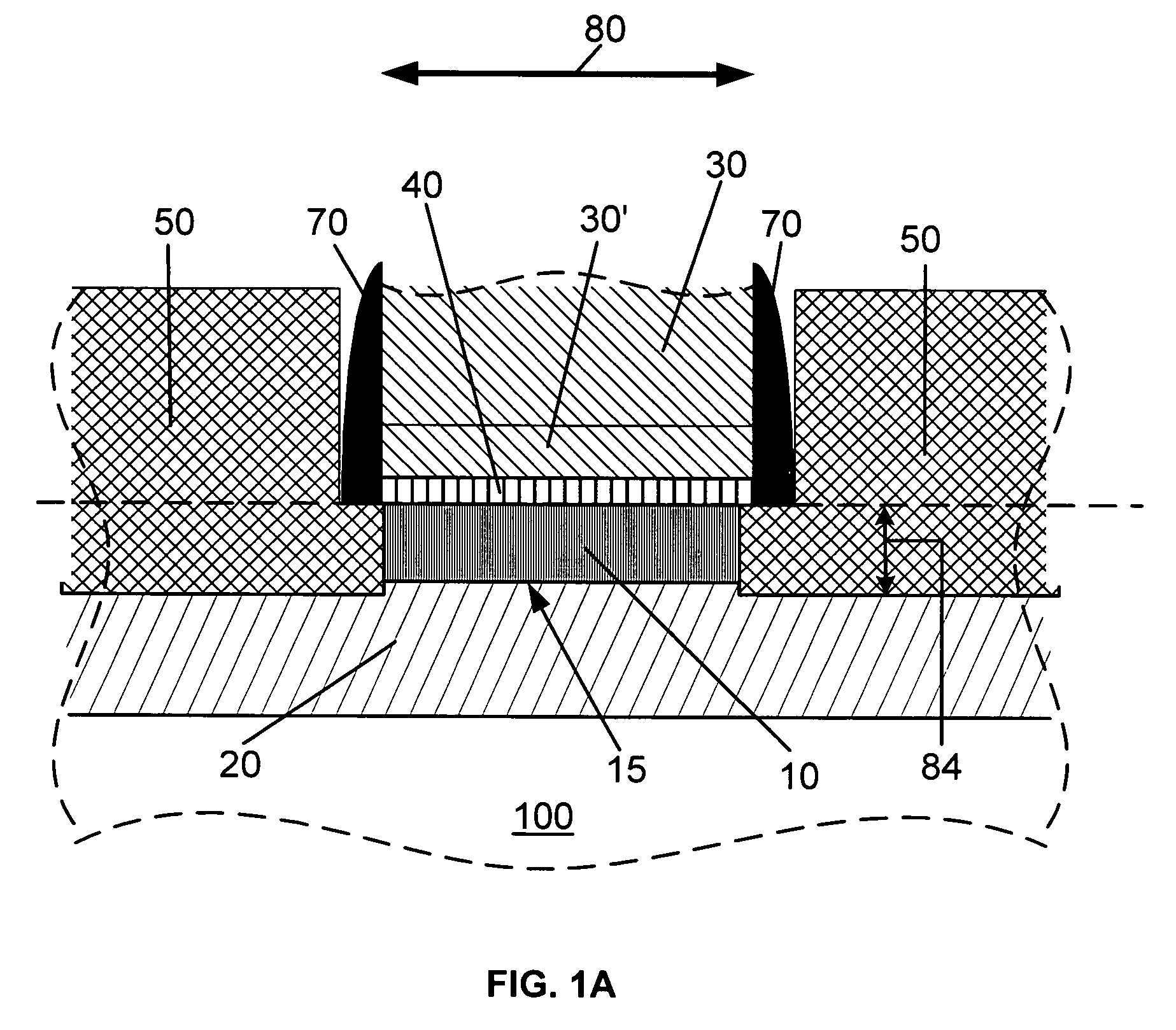

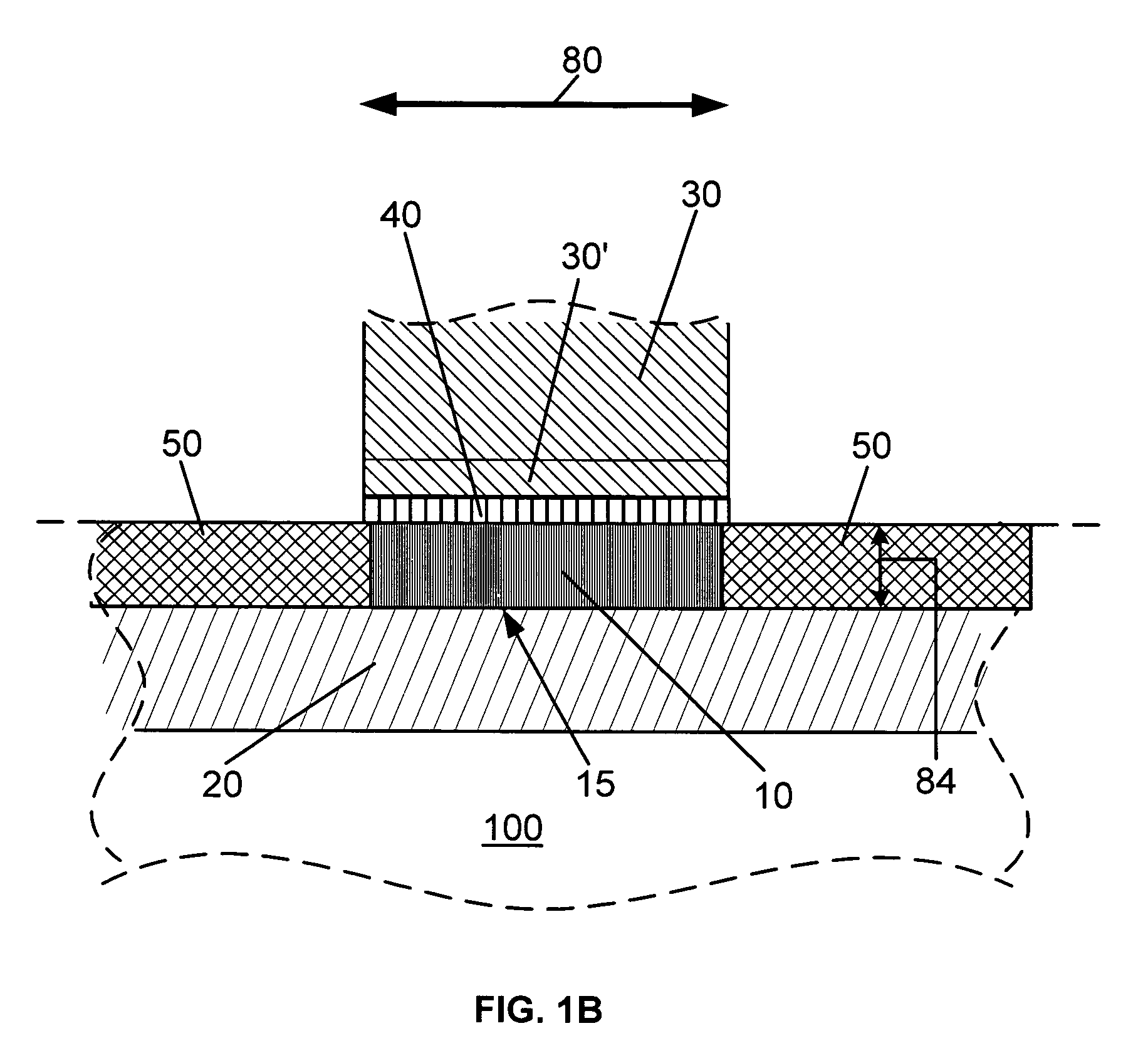

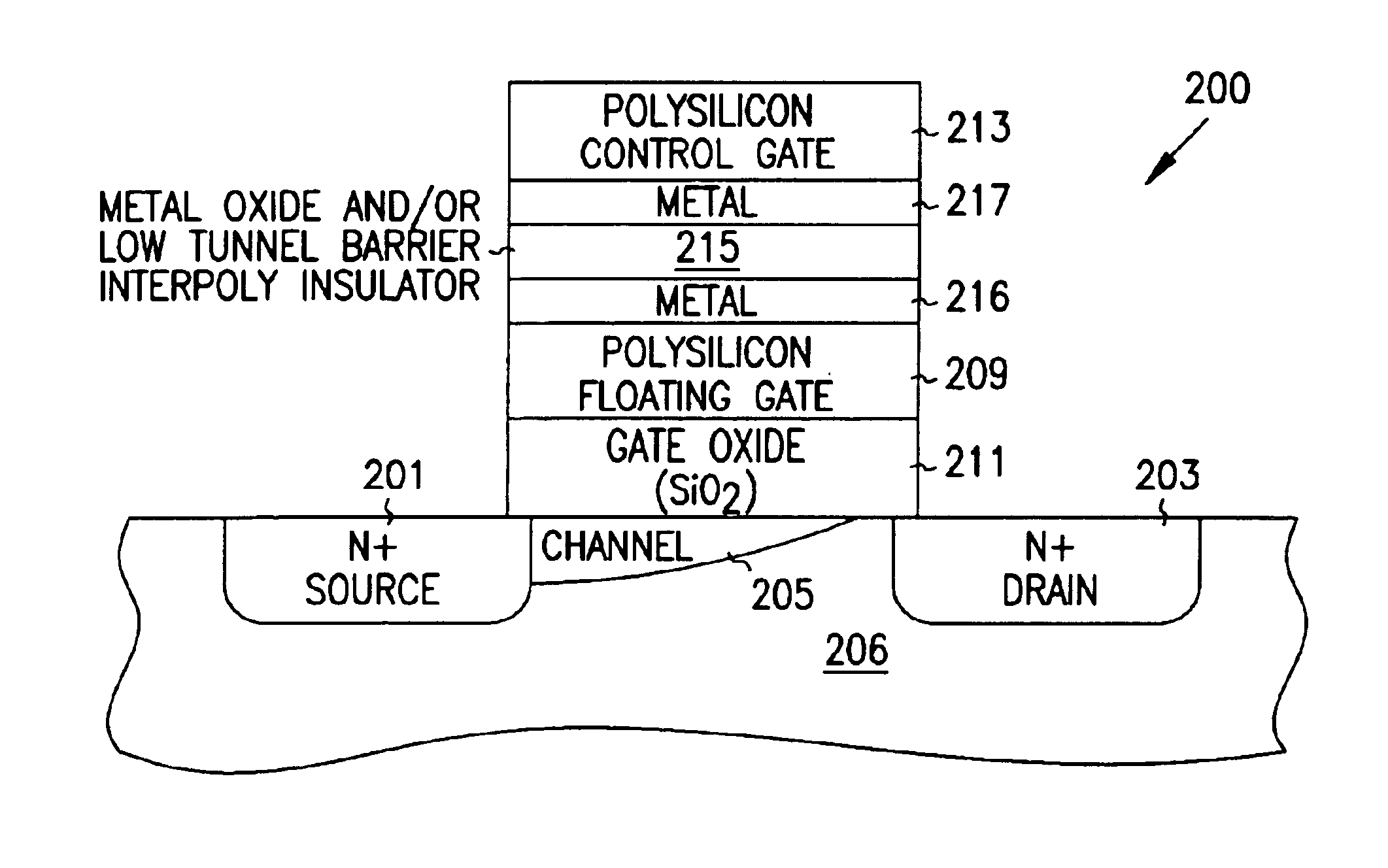

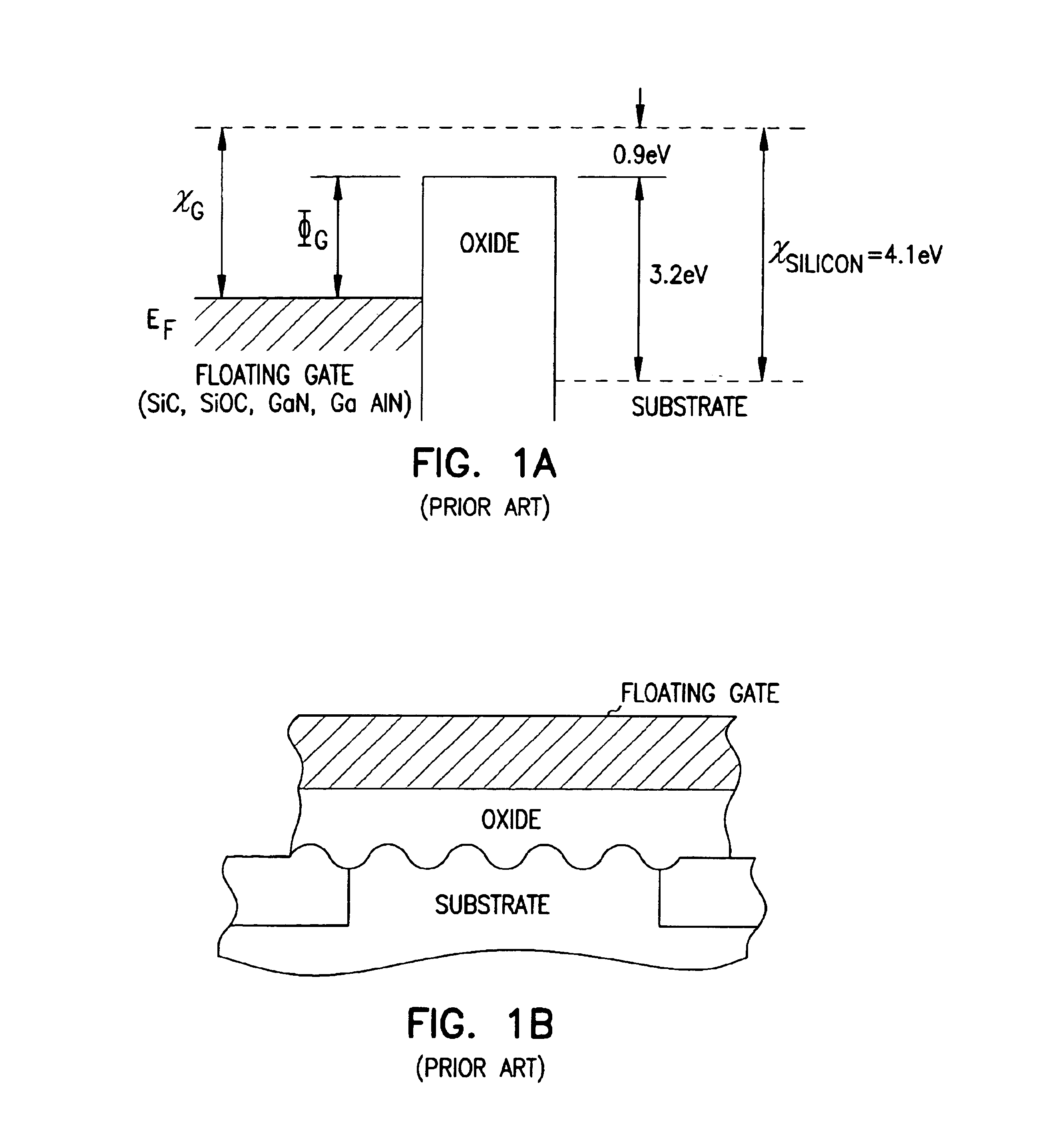

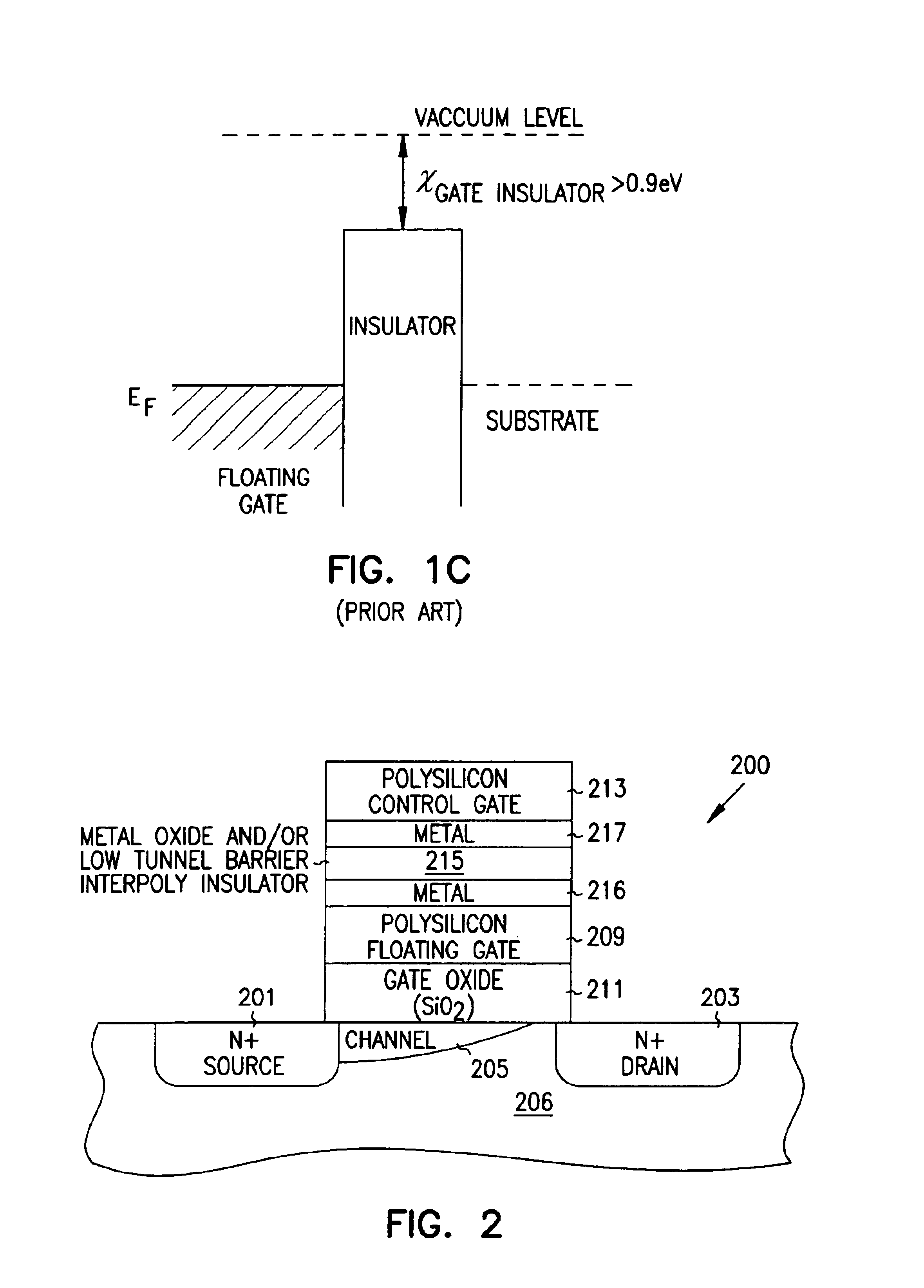

Programmable array logic or memory devices with asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, Zro2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

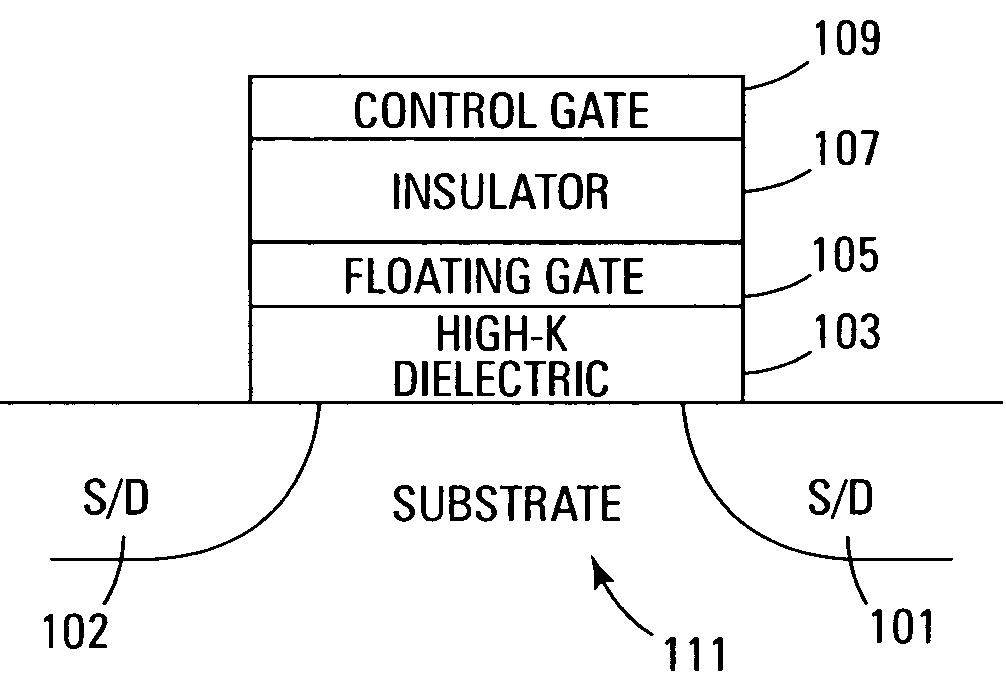

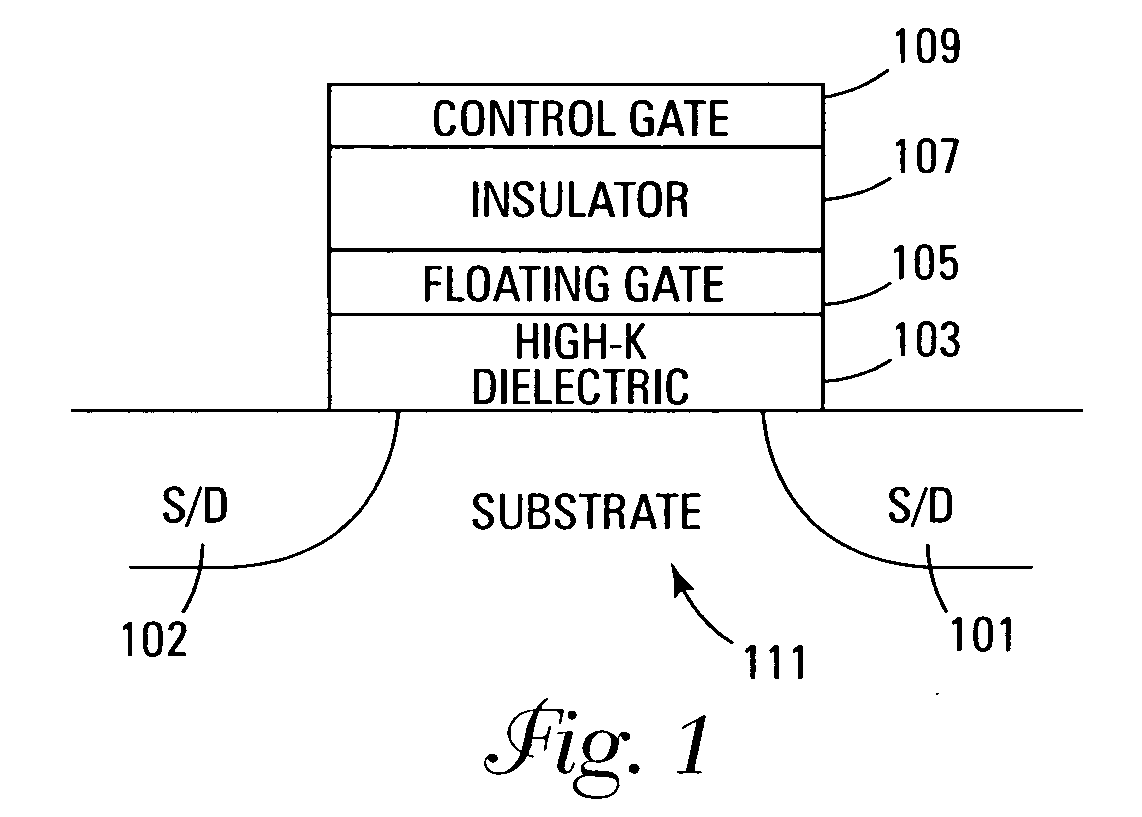

Flash memory having a high-permittivity tunnel dielectric

A high permittivity tunneling dielectric is used in a flash memory cell to provide greater tunneling current into the floating gate with smaller gate voltages. The flash memory cell has a substrate with source / drain regions. The high-k tunneling dielectric is formed above the substrate. The high-k tunneling dielectric can be deposited using evaporation techniques or atomic layer deposition techniques. The floating gate is formed on top of the high-k dielectric layer with an oxide gate insulator on top of that. A polysilicon control gate is formed on the top gate insulator.

Owner:MICRON TECH INC

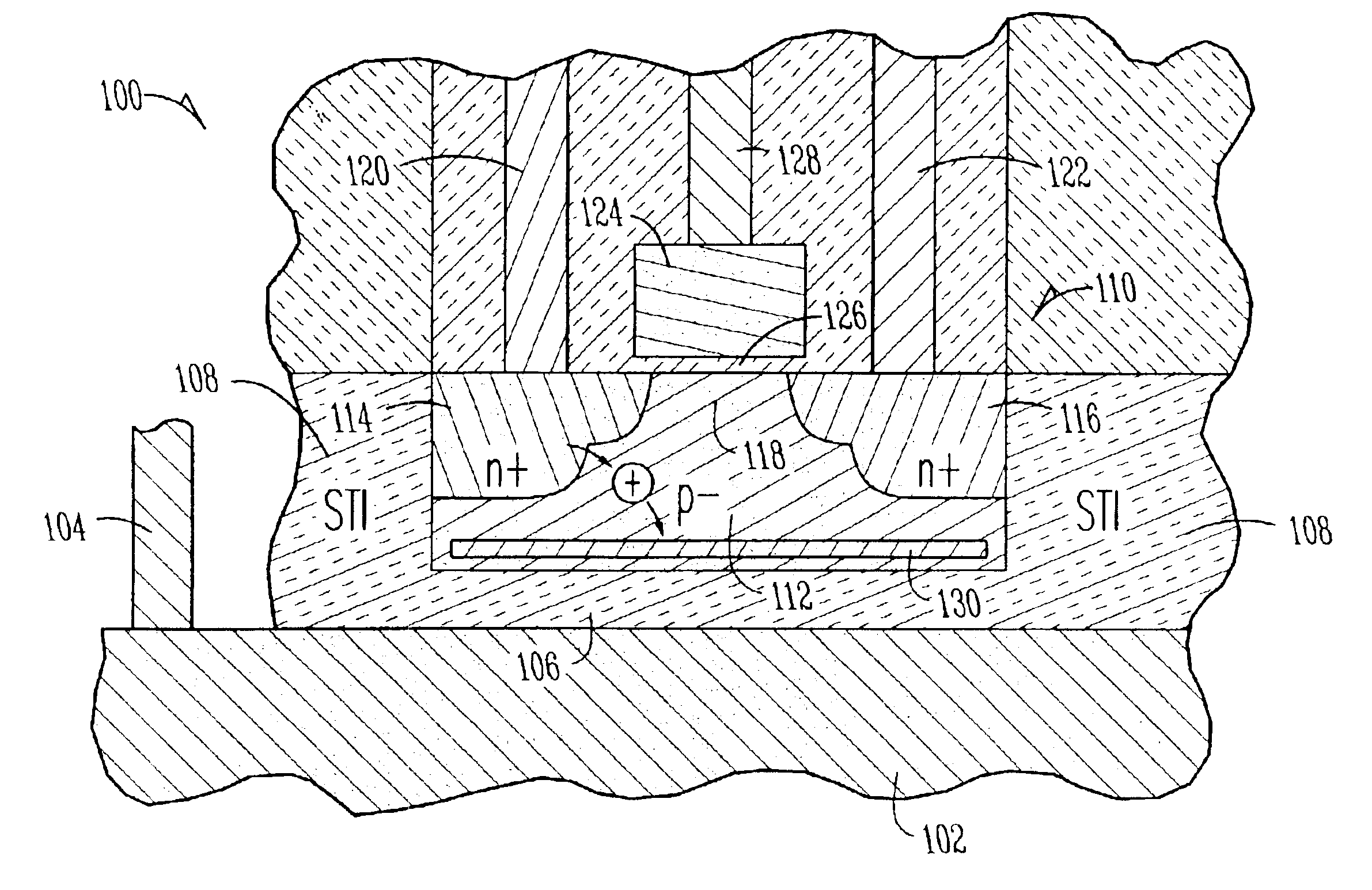

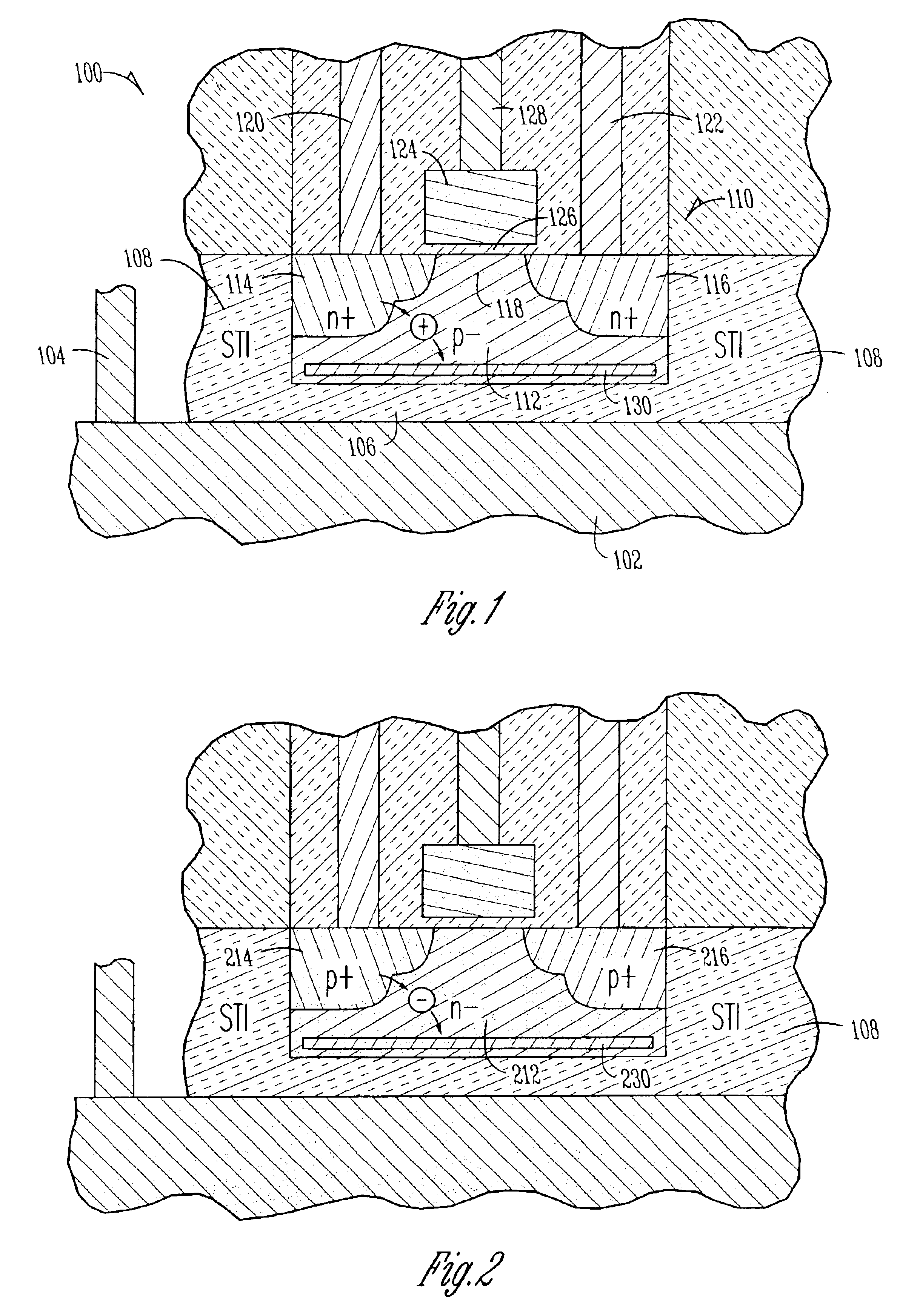

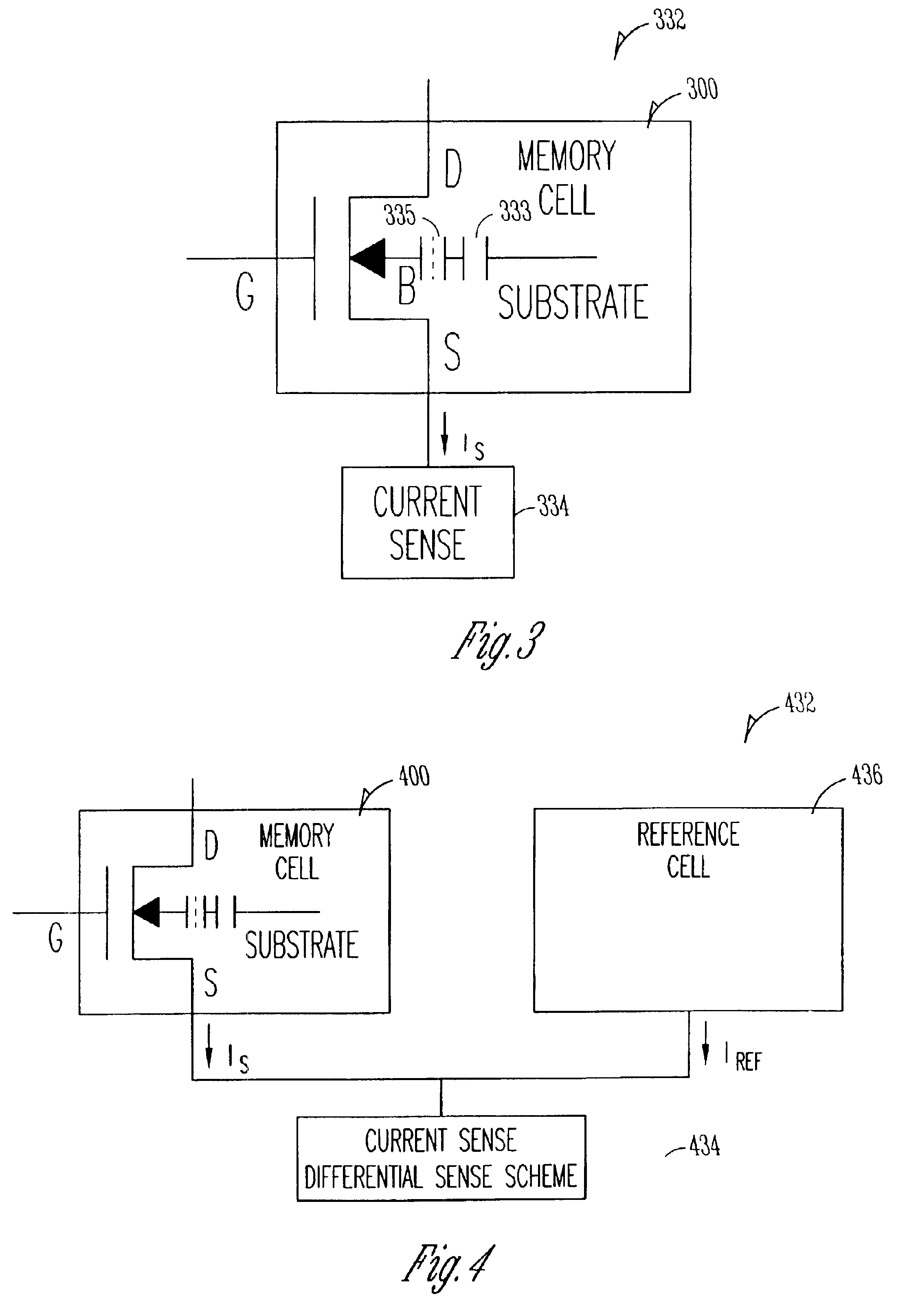

One transistor SOI non-volatile random access memory cell

InactiveUS6888200B2Long charge retention and non-volatilityHigh densityTransistorSolid-state devicesTrappingRandom access memory

One aspect of the present subject matter relates to a memory cell, or more specifically, to a one-transistor SOI non-volatile memory cell. In various embodiments, the memory cell includes a substrate, a buried insulator layer formed on the substrate, and a transistor formed on the buried insulator layer. The transistor includes a floating body region that includes a charge trapping material. A memory state of the memory cell is determined by trapped charges or neutralized charges in the charge trapping material. The transistor further includes a first diffusion region and a second diffusion region to provide a channel region in the body region between the first diffusion region and the second diffusion region. The transistor further includes a gate insulator layer formed over the channel region, and a gate formed over the gate insulator layer. Other aspects are provided herein.

Owner:MICRON TECH INC

Atomic layer deposition of CMOS gates with variable work functions

Structures, systems and methods for transistors having gates with variable work functions formed by atomic layer deposition are provided. One transistor embodiment includes a first source / drain region, a second source / drain region, and a channel region therebetween. A gate is separated from the channel region by a gate insulator. The gate includes a ternary metallic conductor formed by atomic layer deposition.

Owner:ROUND ROCK RES LLC

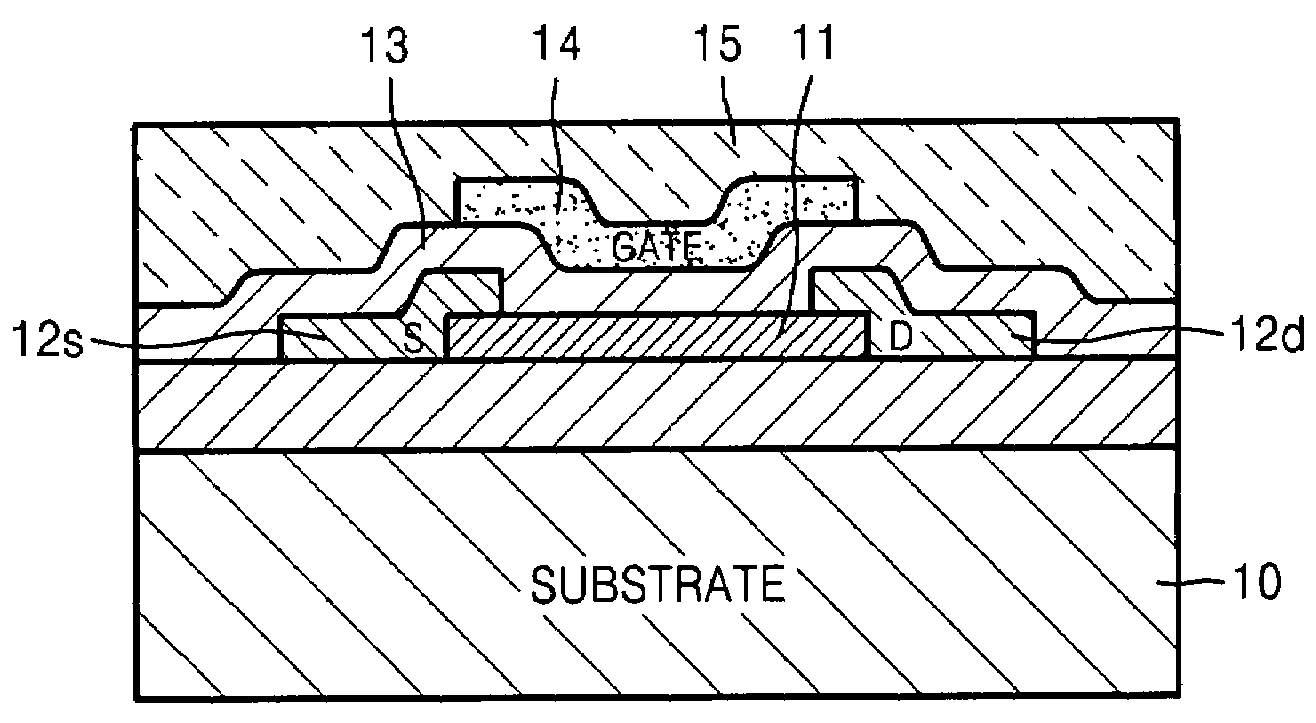

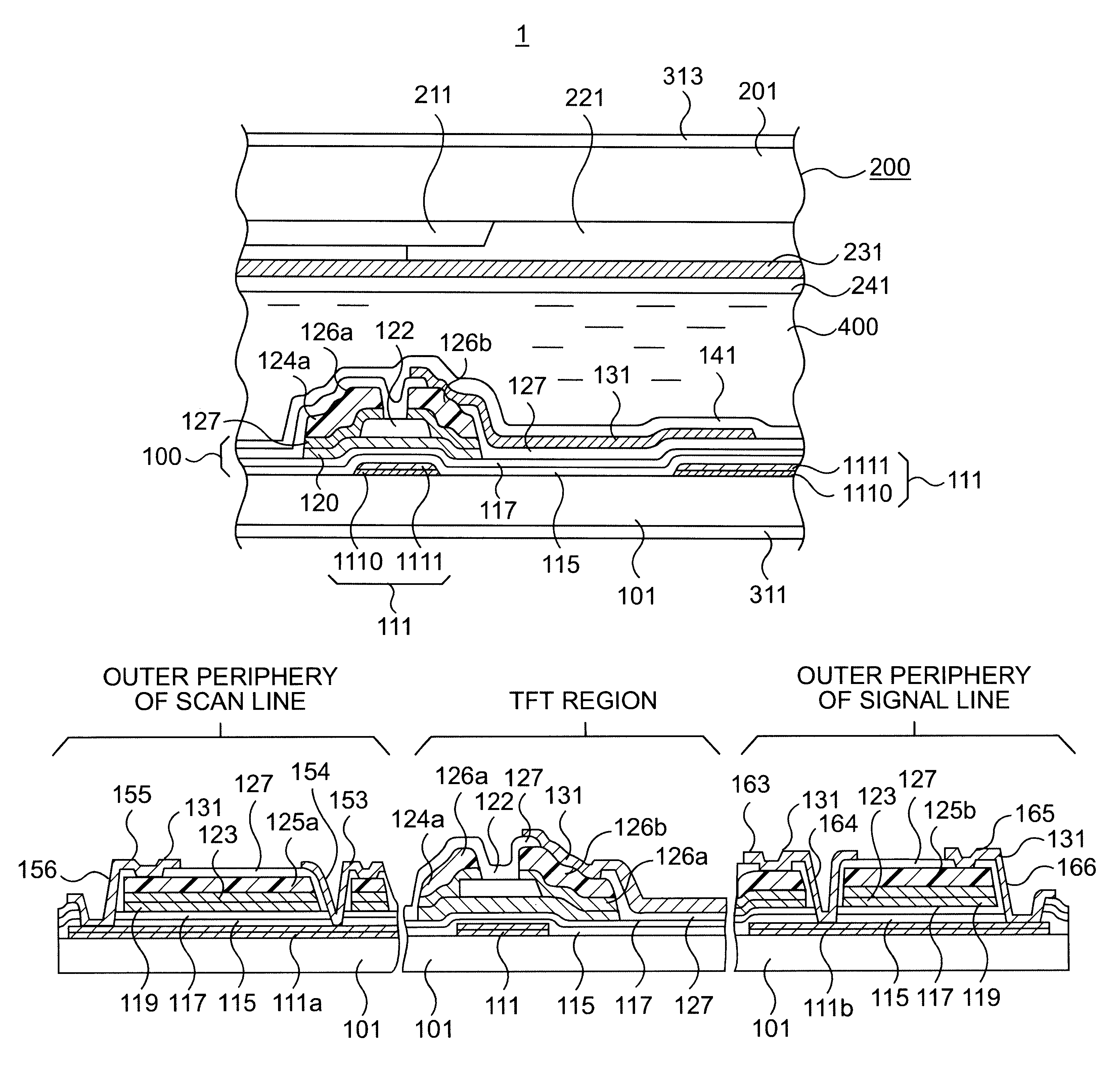

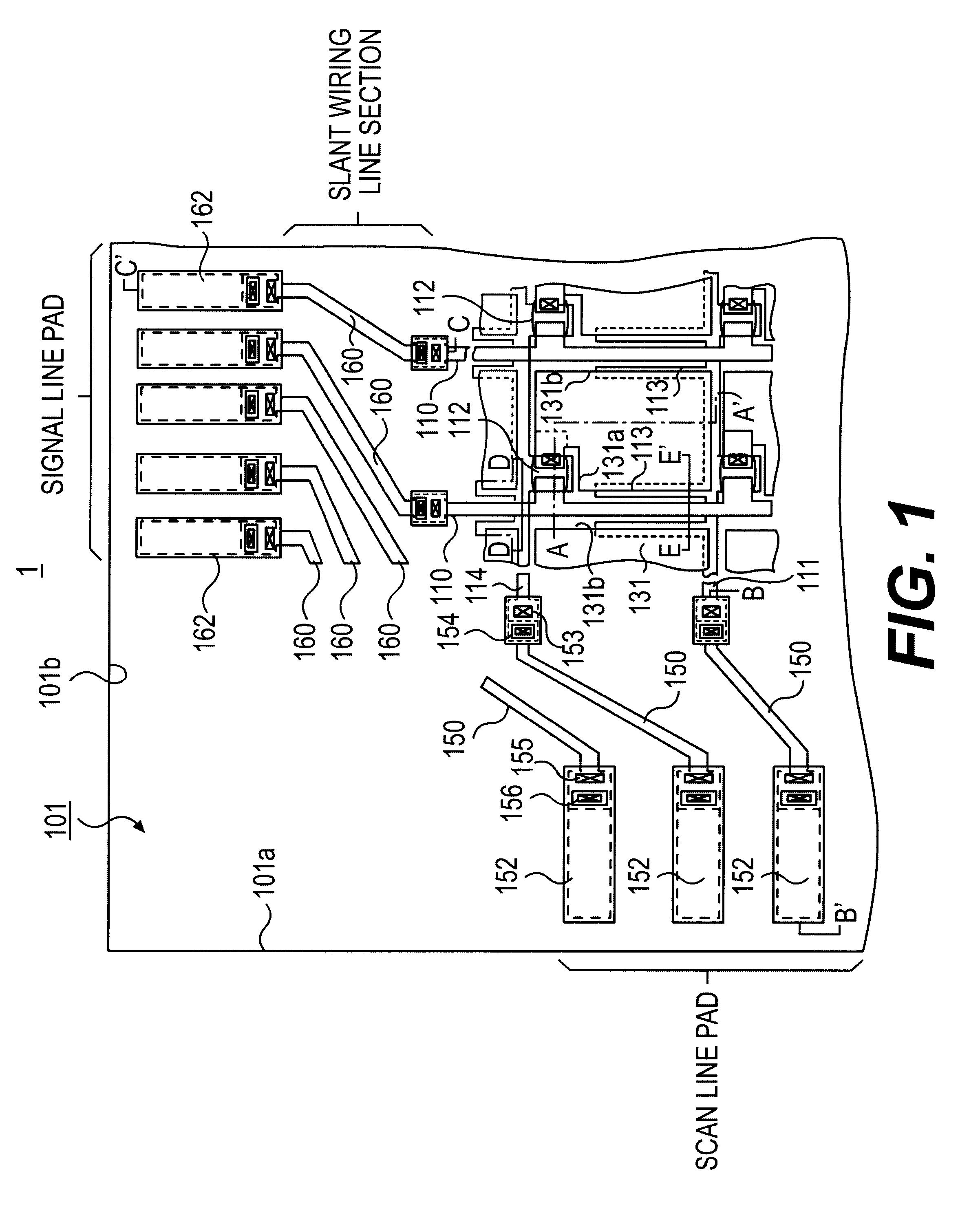

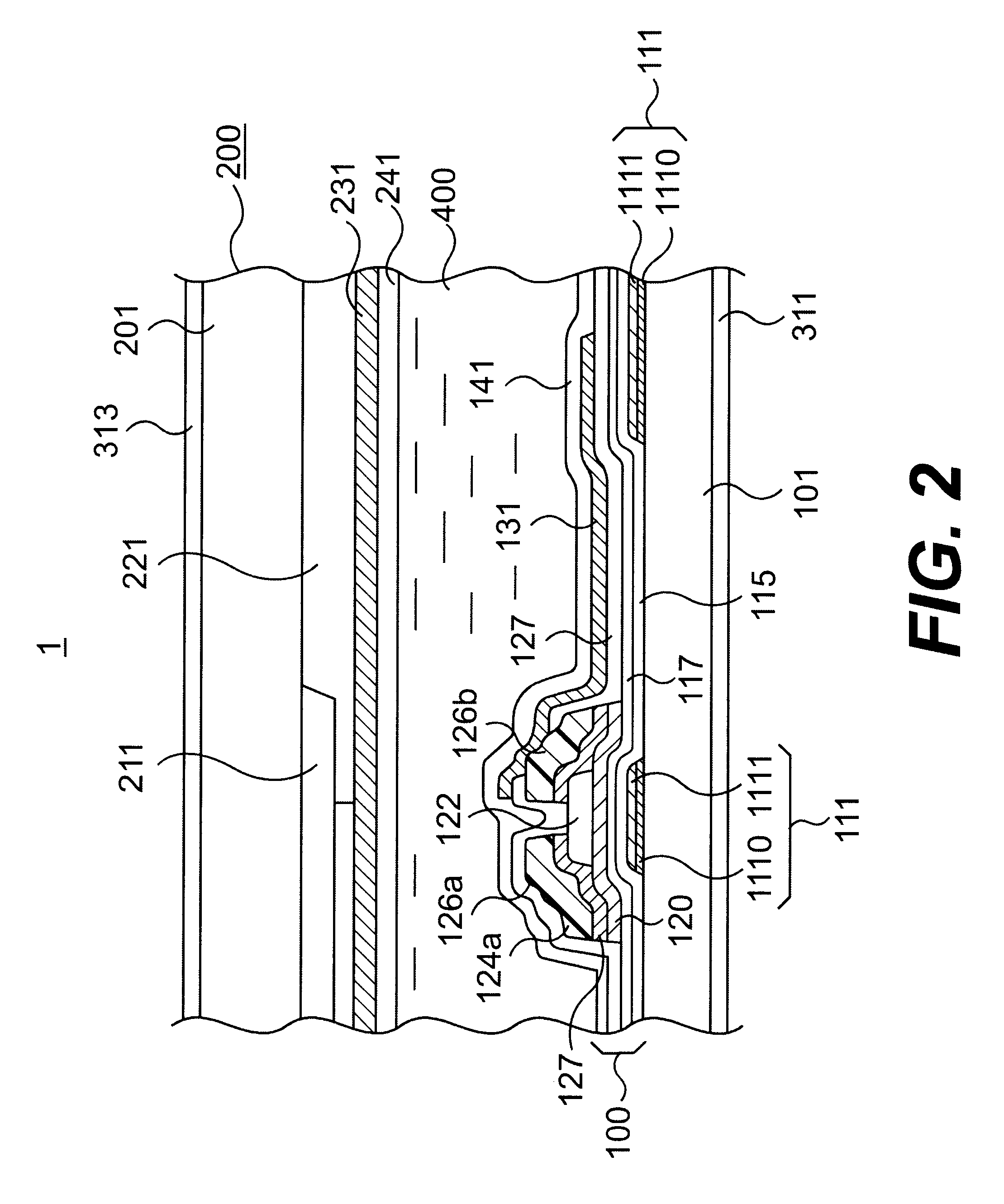

Method of manufacturing array substrate

InactiveUS6528357B2Reduce productionSolid-state devicesSemiconductor/solid-state device manufacturingOXALIC ACID DIHYDRATEDielectric

In the manufacturing method of array substrates for use in flat panel display devices including liquid crystal display (LCD) devices, it is aimed to prevent failure of interlayer dielectric film due to wiring deformation or the like while reducing the resistivity of wiring. It is also aimed to prevent corrosion of a metal wiring layer at the etching process and to thereby prevent deterioration of production yield due to corrosion. According to the method of the invention, to form scanning lines (111), an aluminum-neodymium alloy (Al-Nd) film (1110) is deposited in 300 nm thickness on the first hand, and then 50 nm thick Mo film (1110) is deposited thereon. Subsequently, gate insulator films (115 and 117) are formed by CVD processes at a substrate temperature of 350° C. Further, an etching process for forming pixel electrode (131) is carried out by HBr, HI, Oxalic acid or a mixture liquid containing at least one of these acids.

Owner:KK TOSHIBA

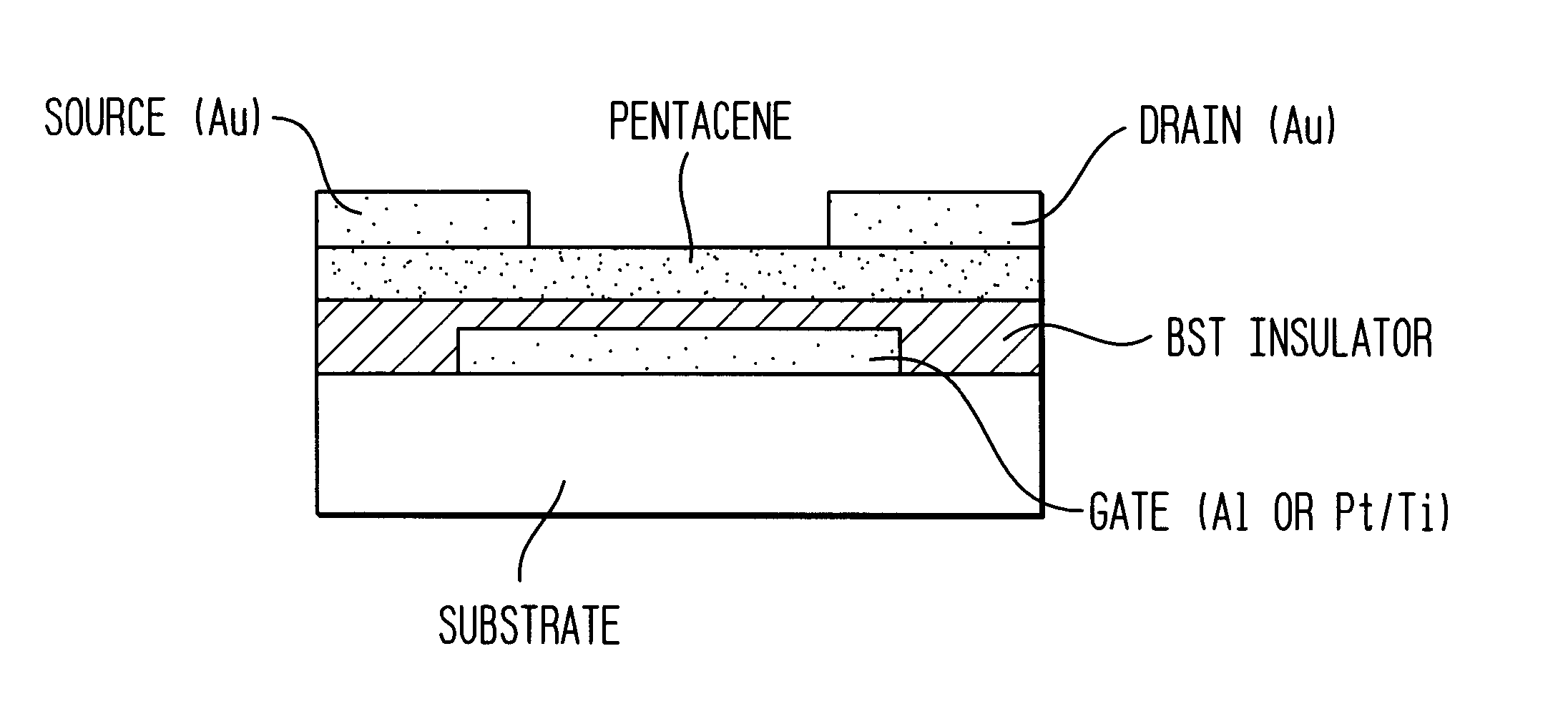

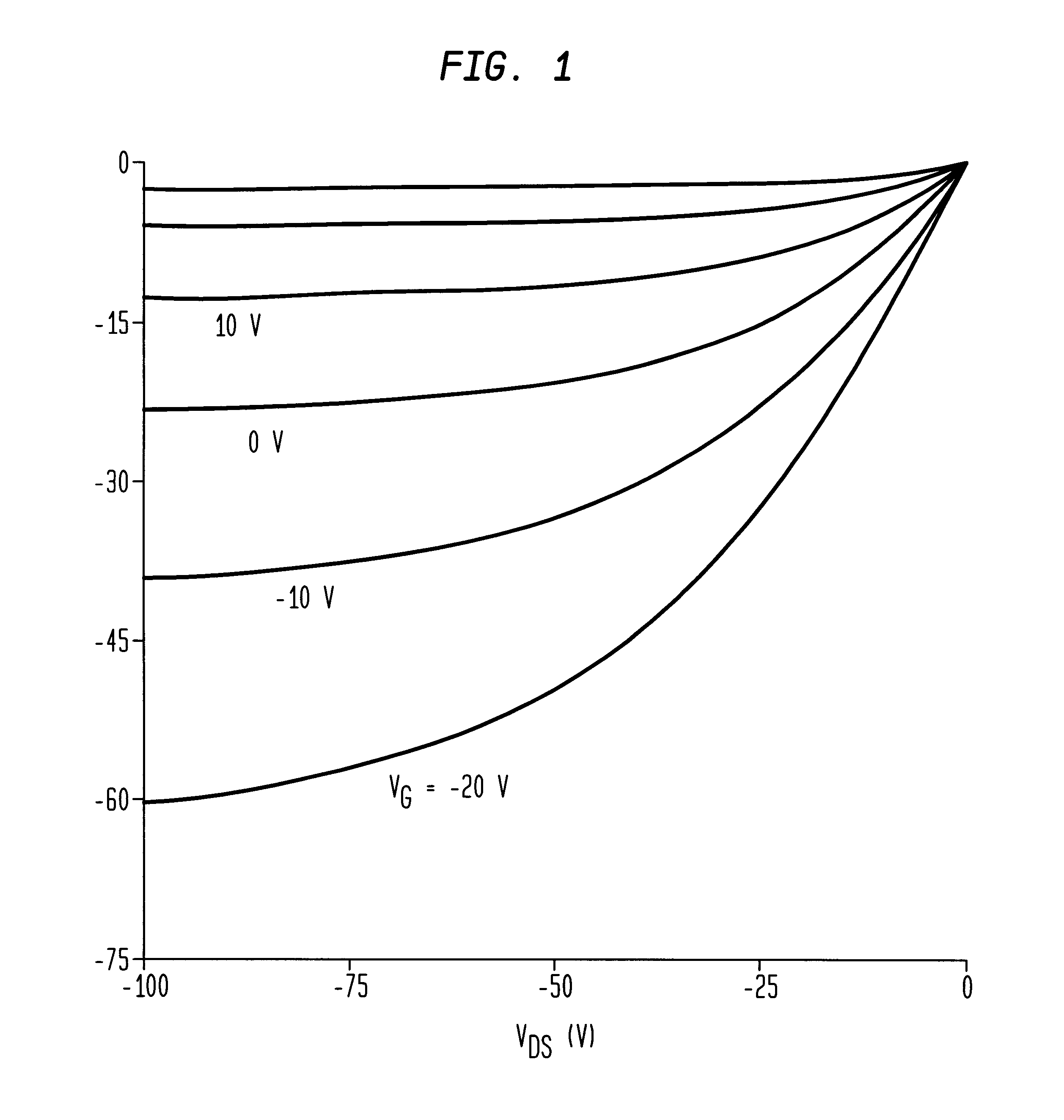

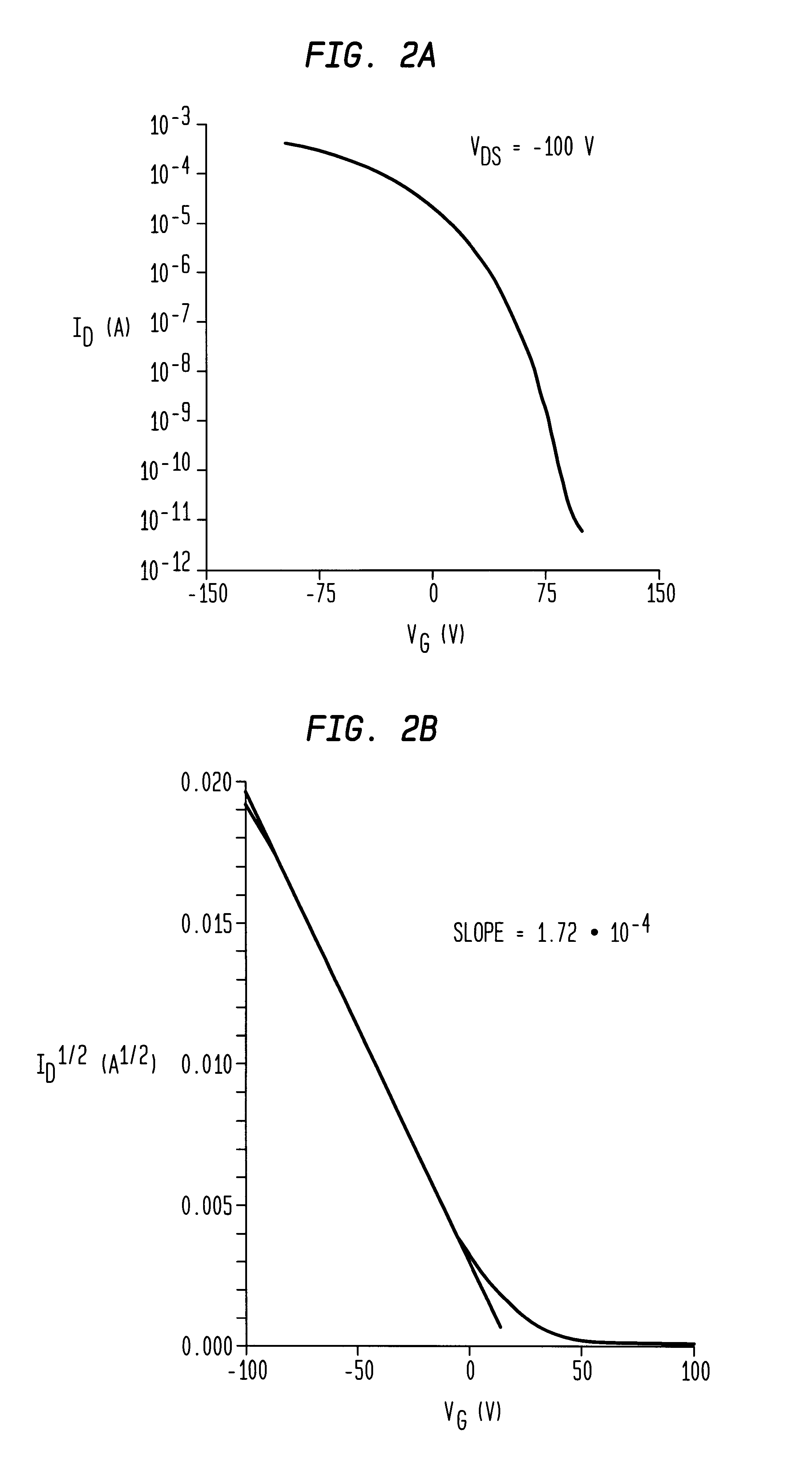

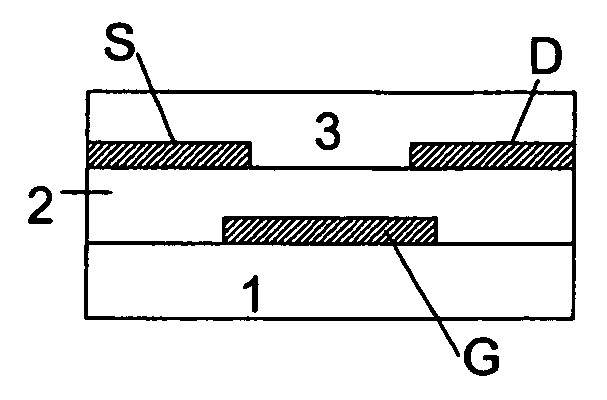

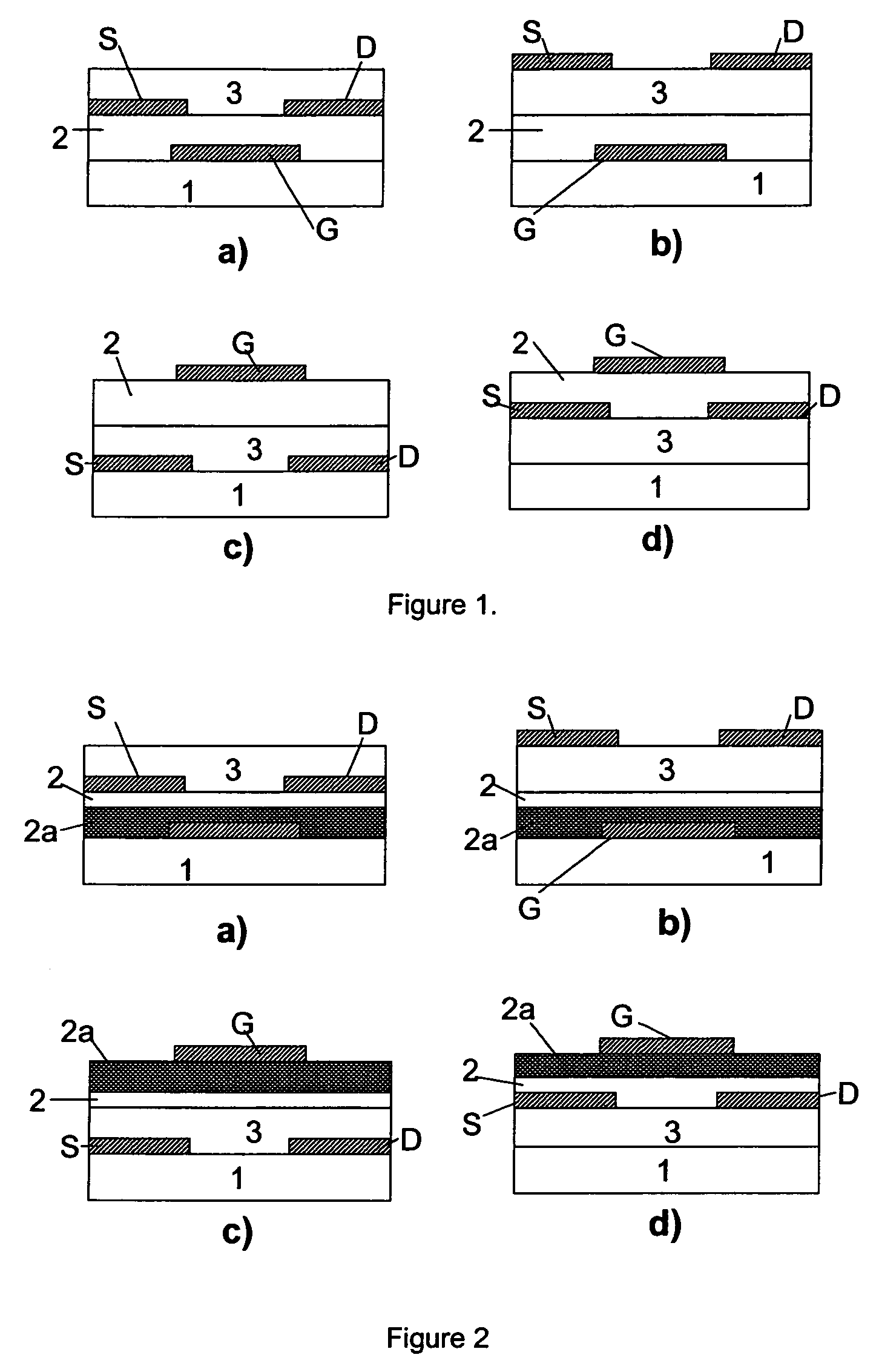

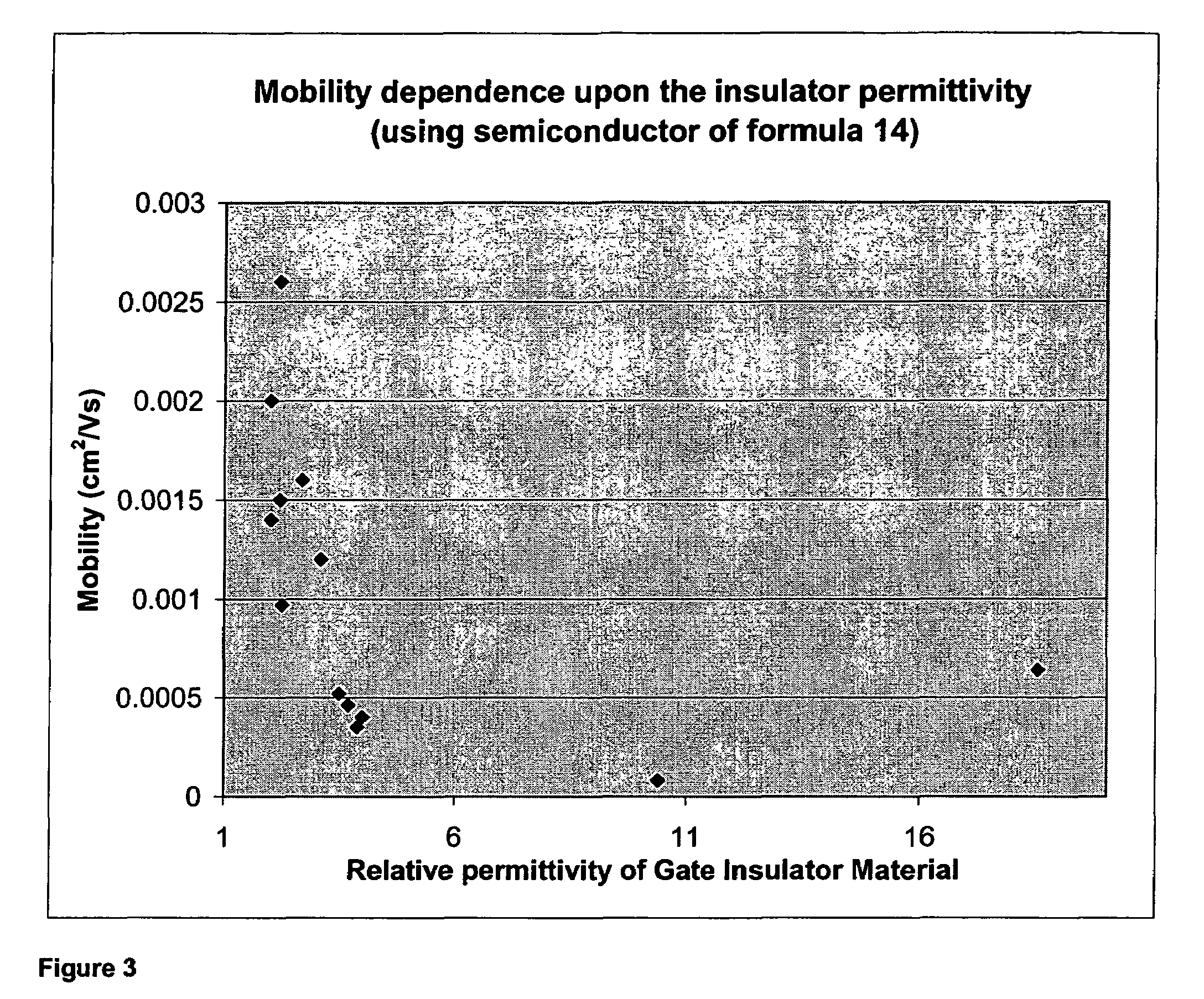

Thin-film field-effect transistor with organic semiconductor requiring low operating voltages

InactiveUS6344660B1Reduce thicknessImprove mobilityTransistorSolid-state devicesDisplay deviceFlat panel display

A thin film transistor (TFT) device structure based on an organic semiconductor material, that exhibits a high field effect mobility, high current modulation and a low sub-threshold slope at lower operating voltages than the current state of the art organic TFT devices. The structure comprises a suitable substrate disposed with he following sequence of features: a set of conducting gate electrodes covered with a high dielectric constant insulator, a layer of the organic semiconductor, sets of electrically conducting source and drain electrodes corresponding to each of the gate lines, and an optional passivation layer that can overcoat and protect the device structure. Use of high dielectric constant gate insulators exploits the unexpected gate voltage dependence of the organic semiconductor to achieve high field effect mobility levels at very low operating voltages. Judicious combinations of the choice of this insulator material and the means to integrate it into the TFT structure are taught that would enable easy fabrication on glass or plastic substrates and the use of such devices in flat panel display applications.

Owner:GLOBALFOUNDRIES INC

Electrolytic deposition of dielectric precursor materials for use in in-laid gate MOS transistors

InactiveUS6300203B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrolysisOxygen

High quality dielectric layers, e.g., high-k dielectric layers comprised of at least one refractory or lanthanum series transition metal oxide or silicate, for use as gate insulator layers in in-laid metal gate MOS transistors and CMOS devices, are formed by electrolytically plating a metal or metal-based dielectric precursor layer comprising at least one refractory or lanthanum series transition metal, on a semiconductor substrate, typically a silicon-based substrate, and then reacting the precursor layer with oxygen or with oxygen and the semiconductor substrate to form the at least one refractory or lanthanum series transition metal oxide or silicate. The inventive methodology prevents, or at least substantially reduces, oxygen access to the substrate surface during at least the initial stage(s) of formation of the gate insulator layer, thereby minimizing deleterious formation of oxygen-induced surface states at the semiconductor substrate / gate insulator interface.

Owner:GLOBALFOUNDRIES US INC

Organic field effect transistor with an organic dielectric

InactiveUS7029945B2Improve performancePreventing modulationTransistorSolid-state devicesOrganic field-effect transistorGate insulator

A process of manufacturing an organic field effect device is provided comprising the steps of (a) depositing from a solution an organic semiconductor layer; and (b) depositing from a solution a layer of low permittivity insulating material forming at least a part of a gate insulator, such that the low permittivity insulating material is in contact with the organic semiconductor layer, wherein the low permittivity insulating material is of relative permittivity from 1.1 to below 3.0. In addition, an organic field effect device manufactured by the process is provided.

Owner:MERCK PATENT GMBH

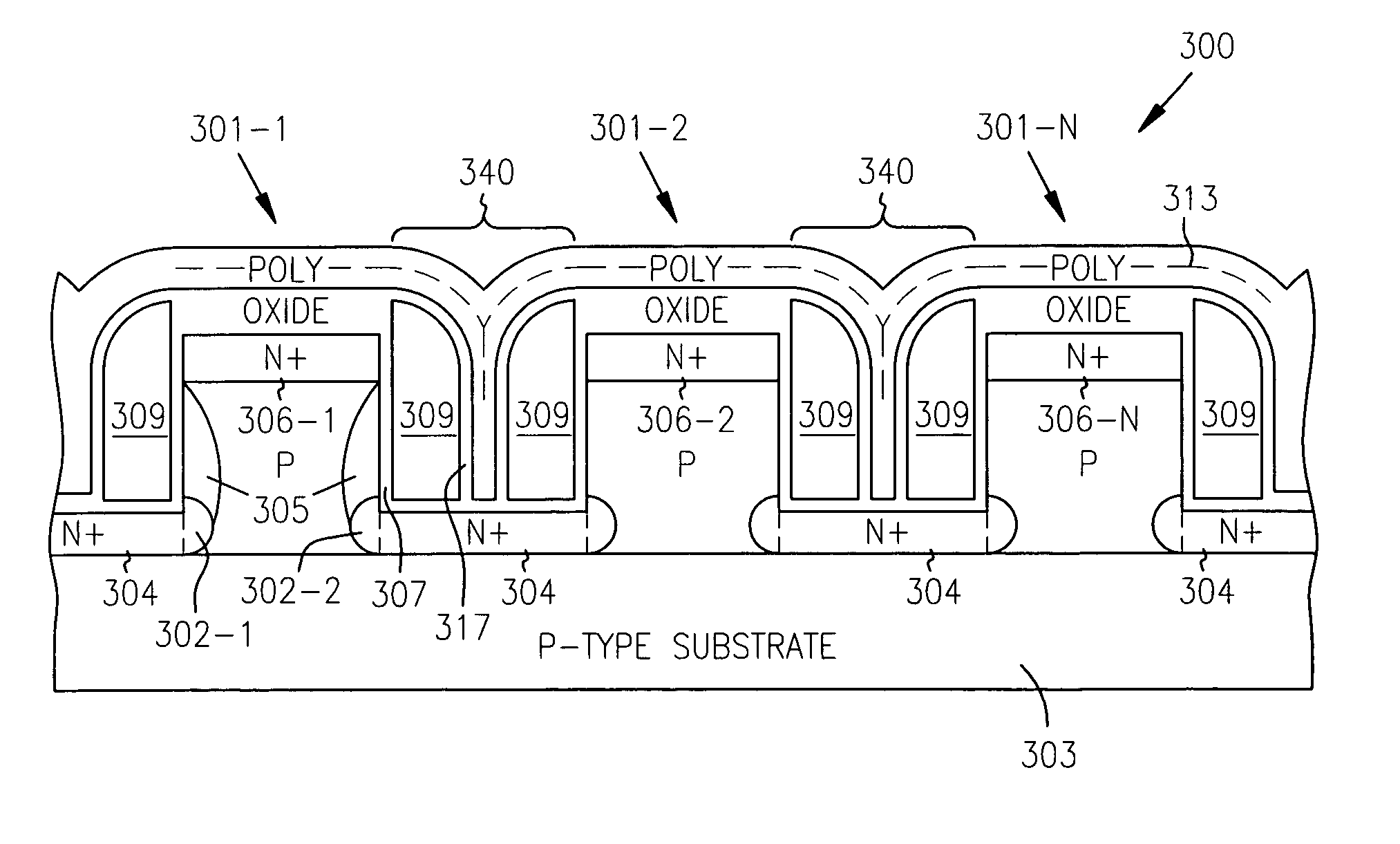

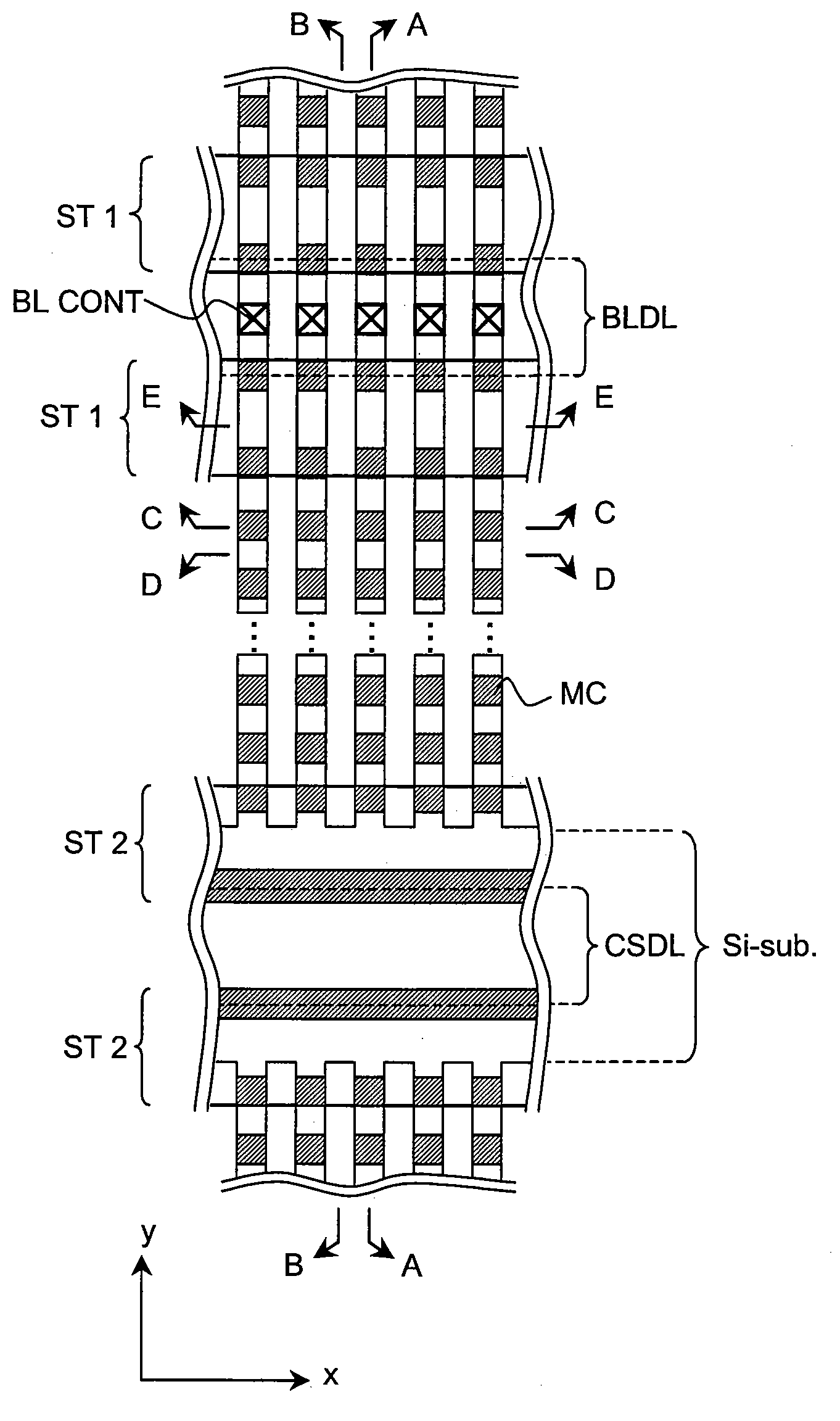

Nonvolatile semiconductor memory device and manufacturing method thereof

InactiveUS20070257305A1Improve reliability of flashDecreasing threshold voltage changeTransistorSolid-state devicesPotential changeGate insulator

By decreasing the threshold voltage shift due to the potential change of the cells adjacent in a word line direction, the reliability of a flash memory can be enhanced. Memory cells of a flash memory are formed in p-type wells of a semiconductor substrate and include gate insulator films, floating gates, high-K insulator films, and control gates (word lines). The floating gates and control gates (word lines) are isolated by high-K insulator films. The plurality of memory cells arrayed in row a direction are isolated by isolation trenches extending in a column direction. In the isolation trenches, a silicon oxide film is embedded. In the silicon oxide film, an air gap is provided. A lower end of the air gap extends near to the bottom of the isolation trench, and its upper end extends further above the upper surface of the high-K insulator film covering the floating gate.

Owner:RENESAS TECH CORP

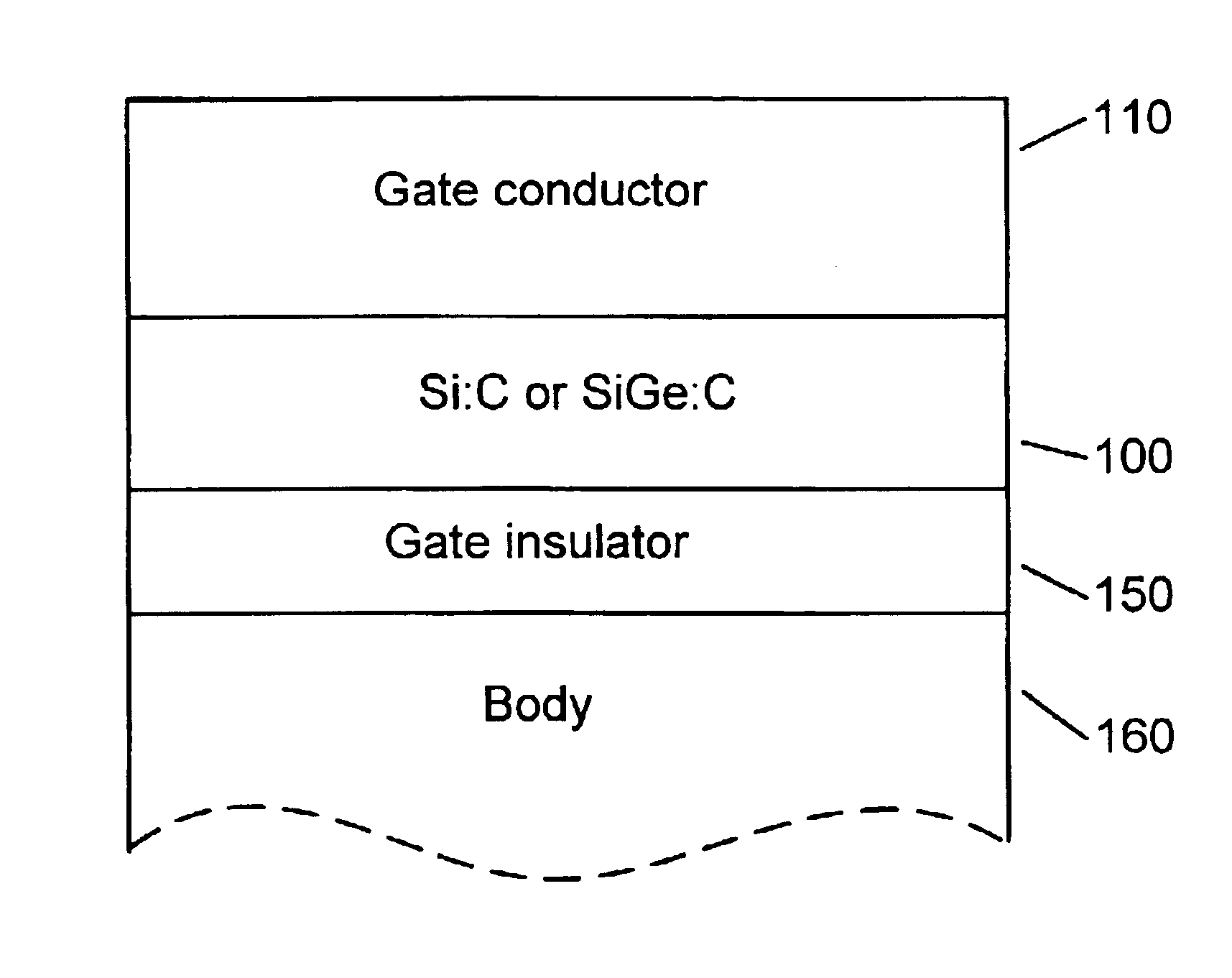

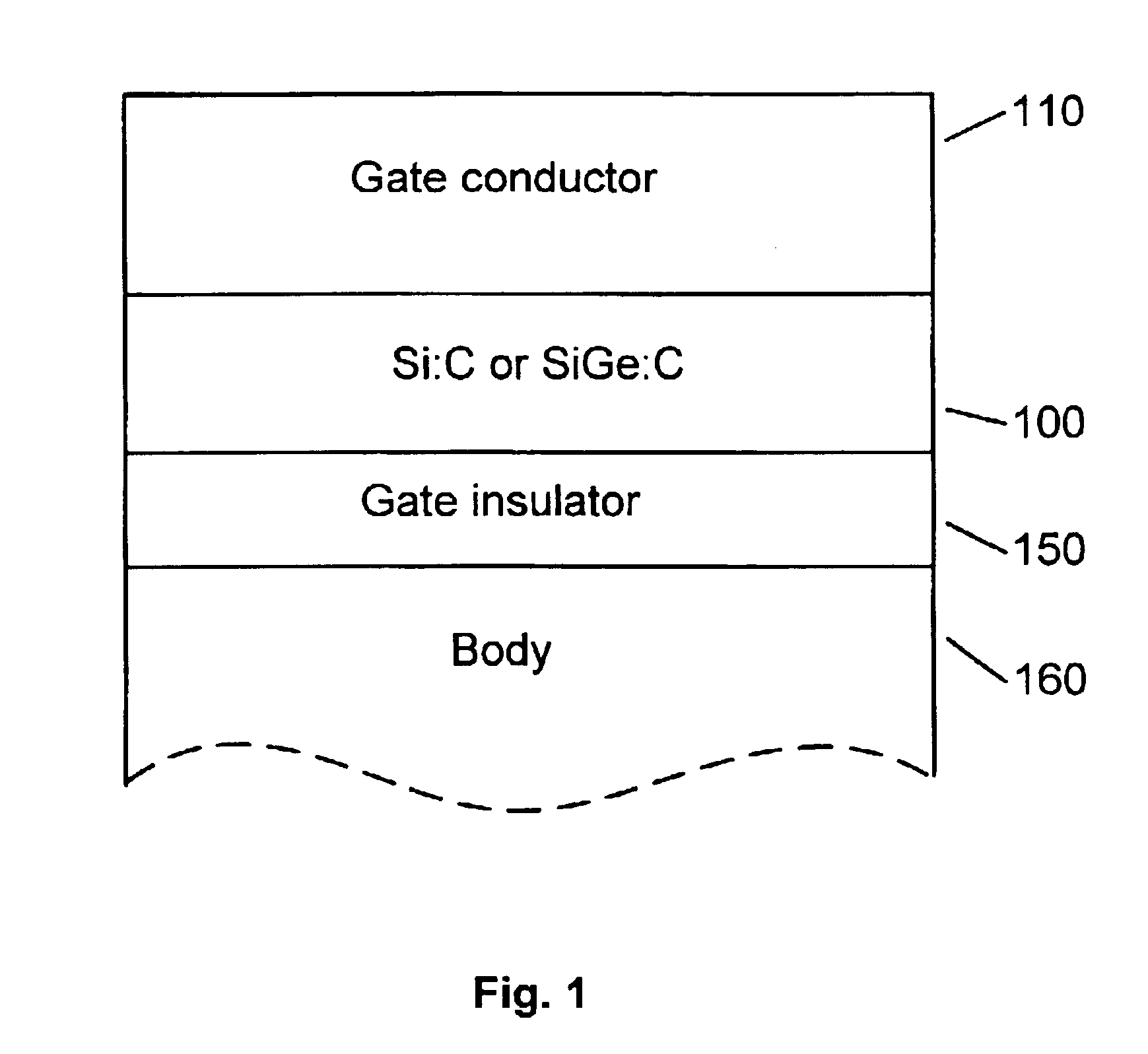

High performance FET devices and methods therefor

InactiveUS6909186B2Suitable for low temperature operationIncrease the areaTransistorSemiconductor/solid-state device detailsDopantGate insulator

Structure and methods of fabrication are disclosed for an enhanced FET devices in which dopant impurities are prevented from diffusing through the gate insulator. The structure comprises a Si:C, or SiGe:C, layer which is sandwiched between the gate insulator and a layer which is doped with impurities in order to provide a preselected workfunction. It is further disclosed how this, and further improvements for FET devices, such as raised source / drain and multifaceted gate on insulator, MODFET on insulator are integrated with strained Si based layer on insulator technology.

Owner:IBM CORP

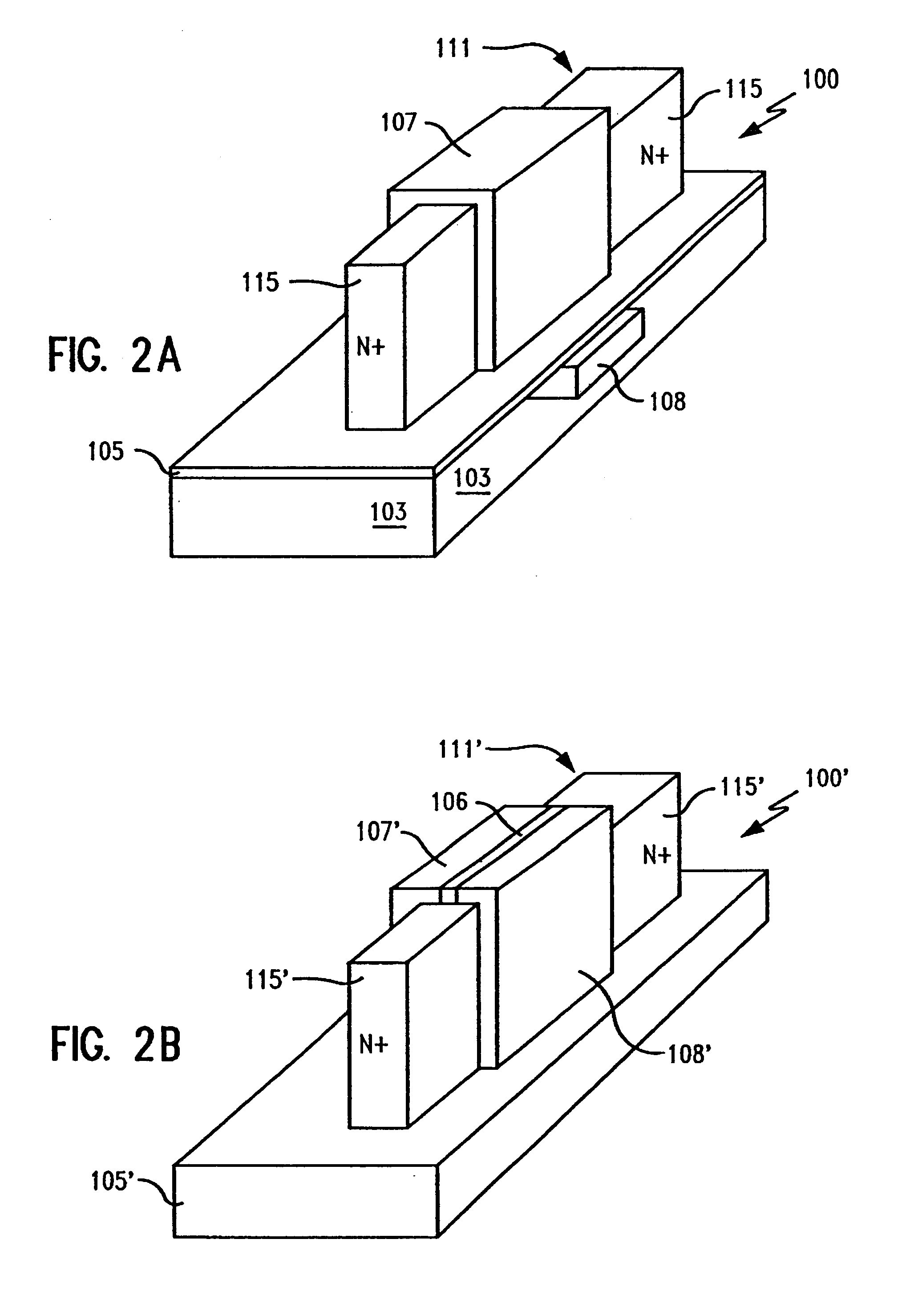

Method of fabricating semiconductor side wall fin

InactiveUS20050001216A1Tolerance channel thicknessGrowth is not complicatedTransistorSolid-state devicesGate insulatorEngineering

Owner:GLOBALFOUNDRIES INC

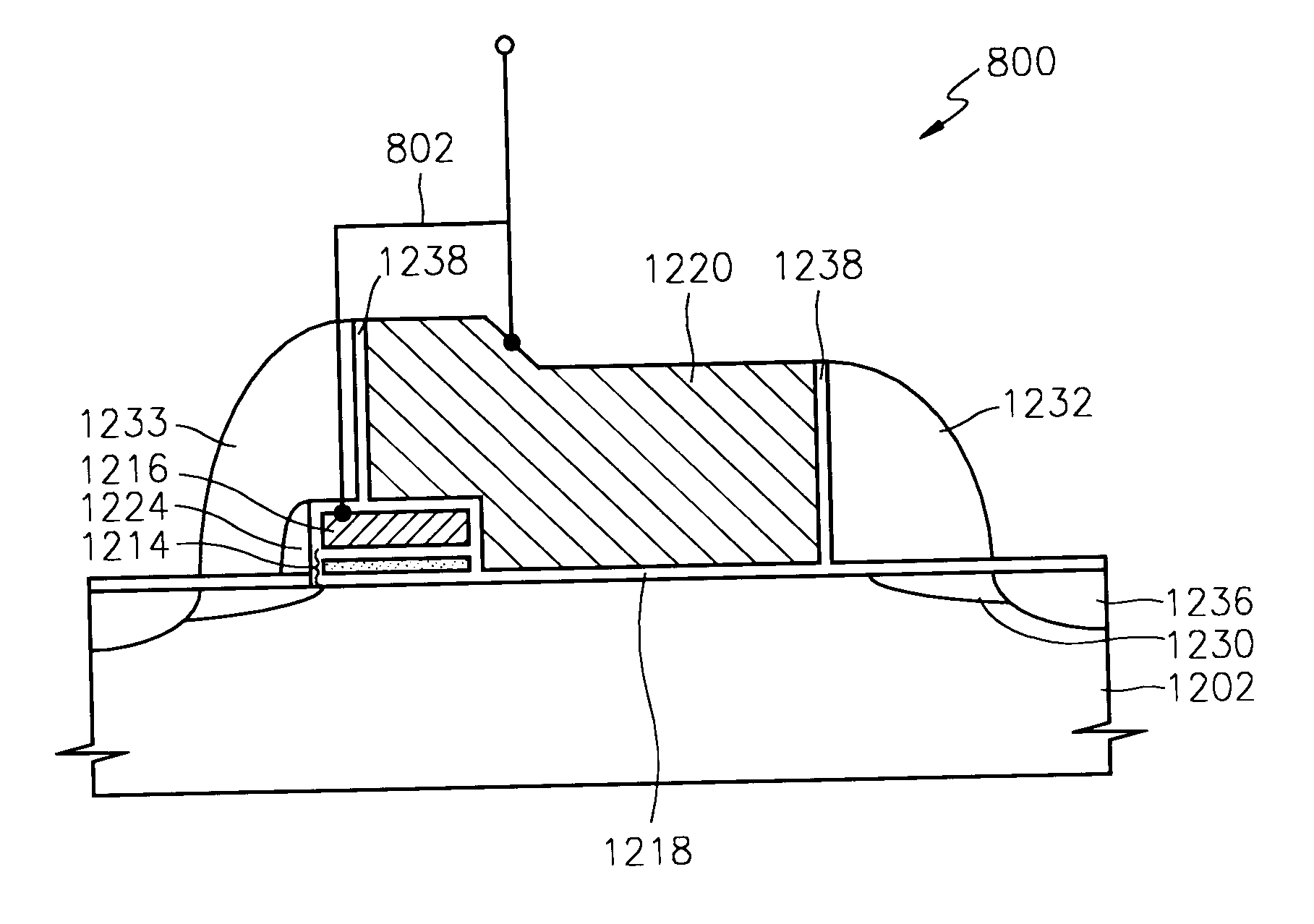

Scalable integrated logic and non-volatile memory

ActiveUS20060110870A1Improve performanceNanoinformaticsSemiconductor/solid-state device manufacturingGate insulatorGate stack

A scalable, logic transistor has a pair of doped regions for the drain and source. A gate insulator layer is formed over the substrate and between the drain and source regions. A gate stack is formed of a gate layer, such as polysilicon or metal, between two metal nitride layers. A compatible non-volatile memory transistor can be formed from this basic structure by adding a high-K dielectric constant film with an embedded metal nano-dot layer between the tunnel insulator and the gate stack.

Owner:MICRON TECH INC

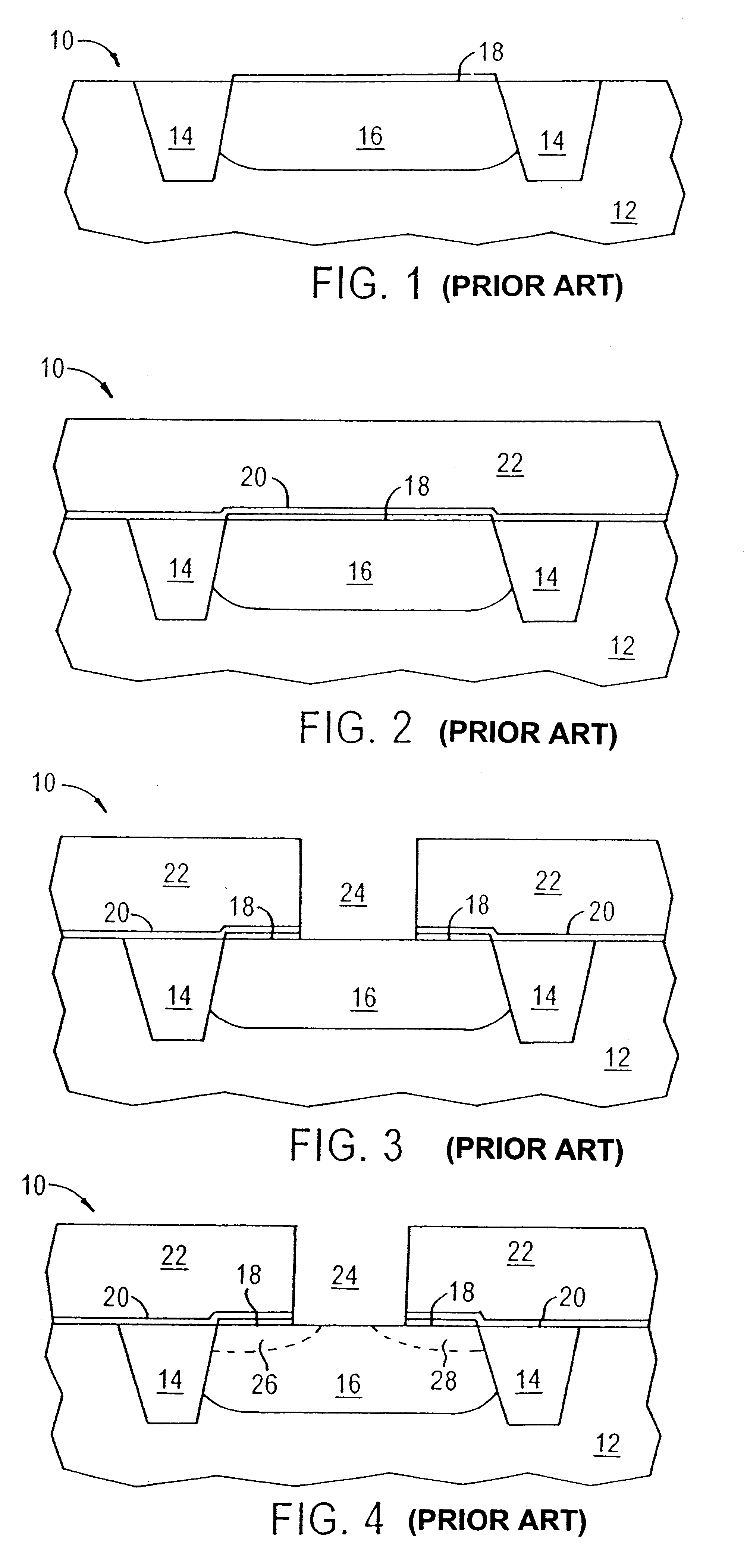

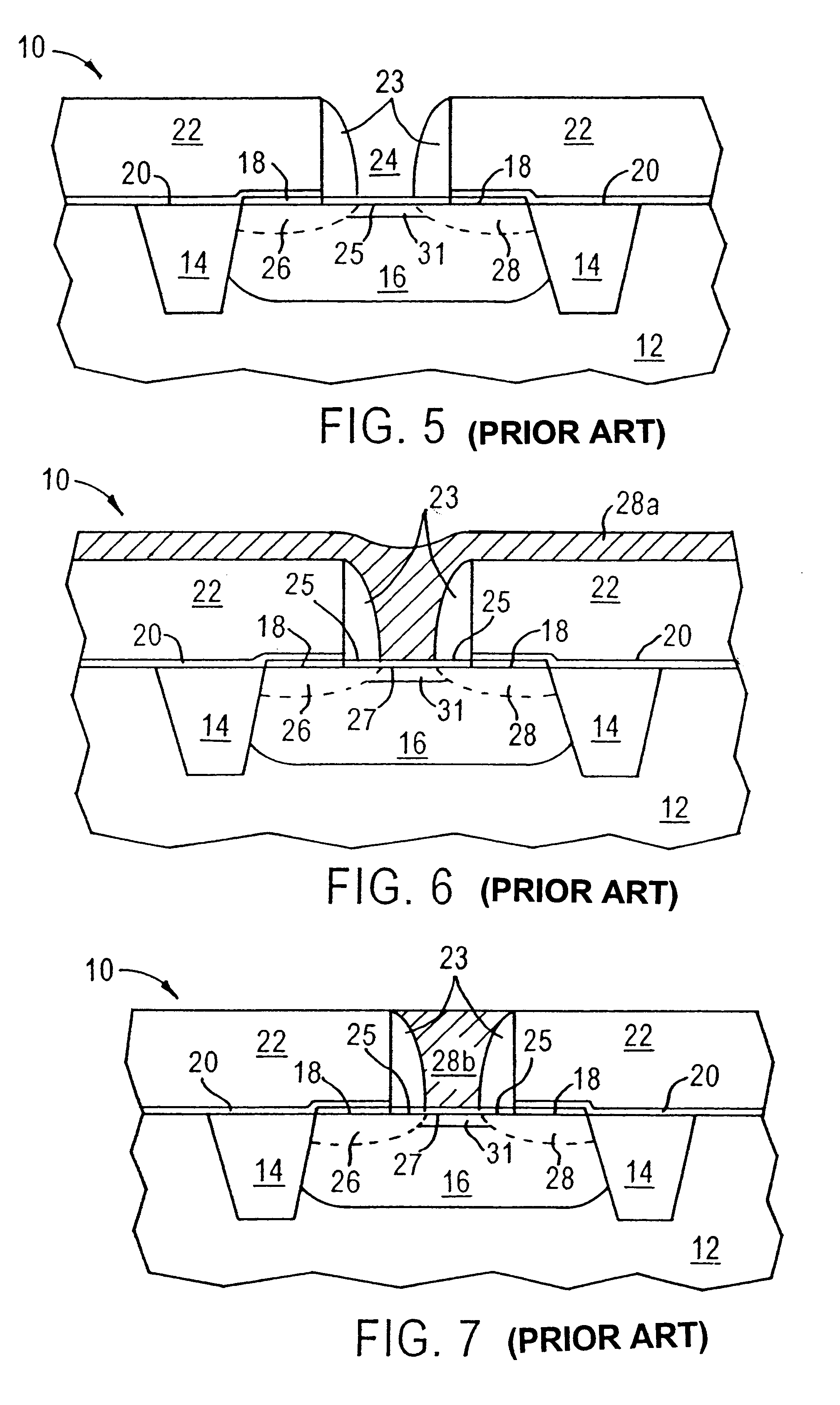

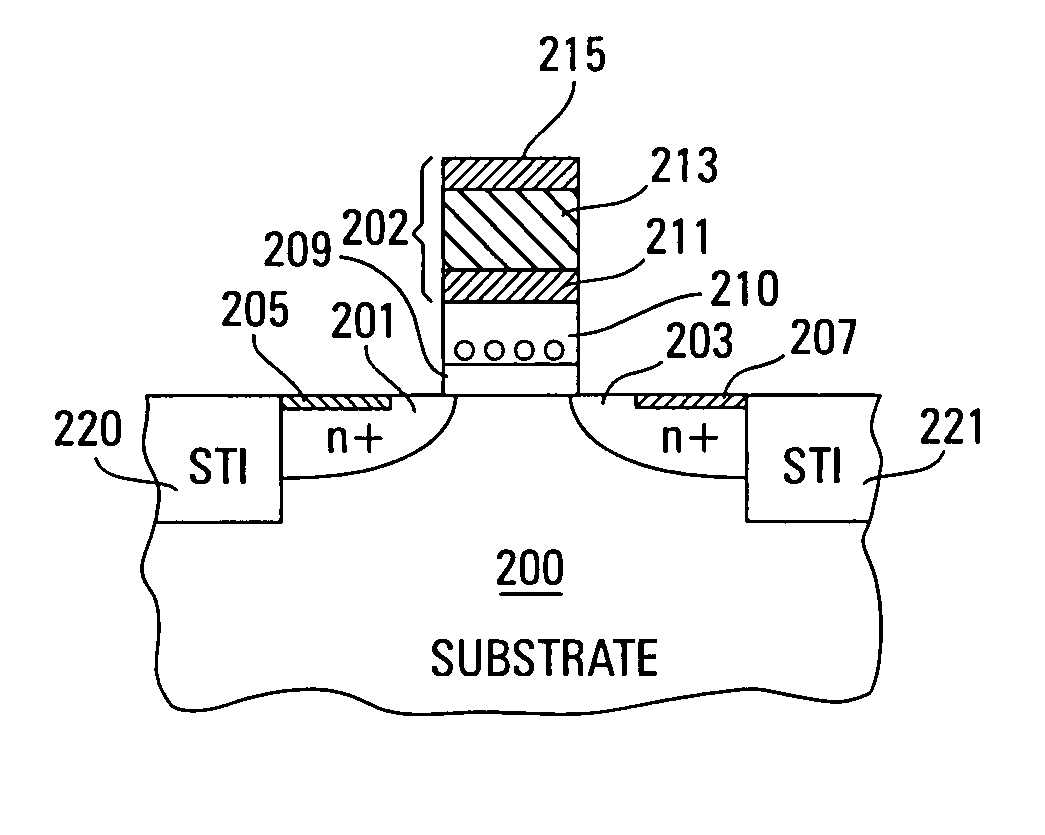

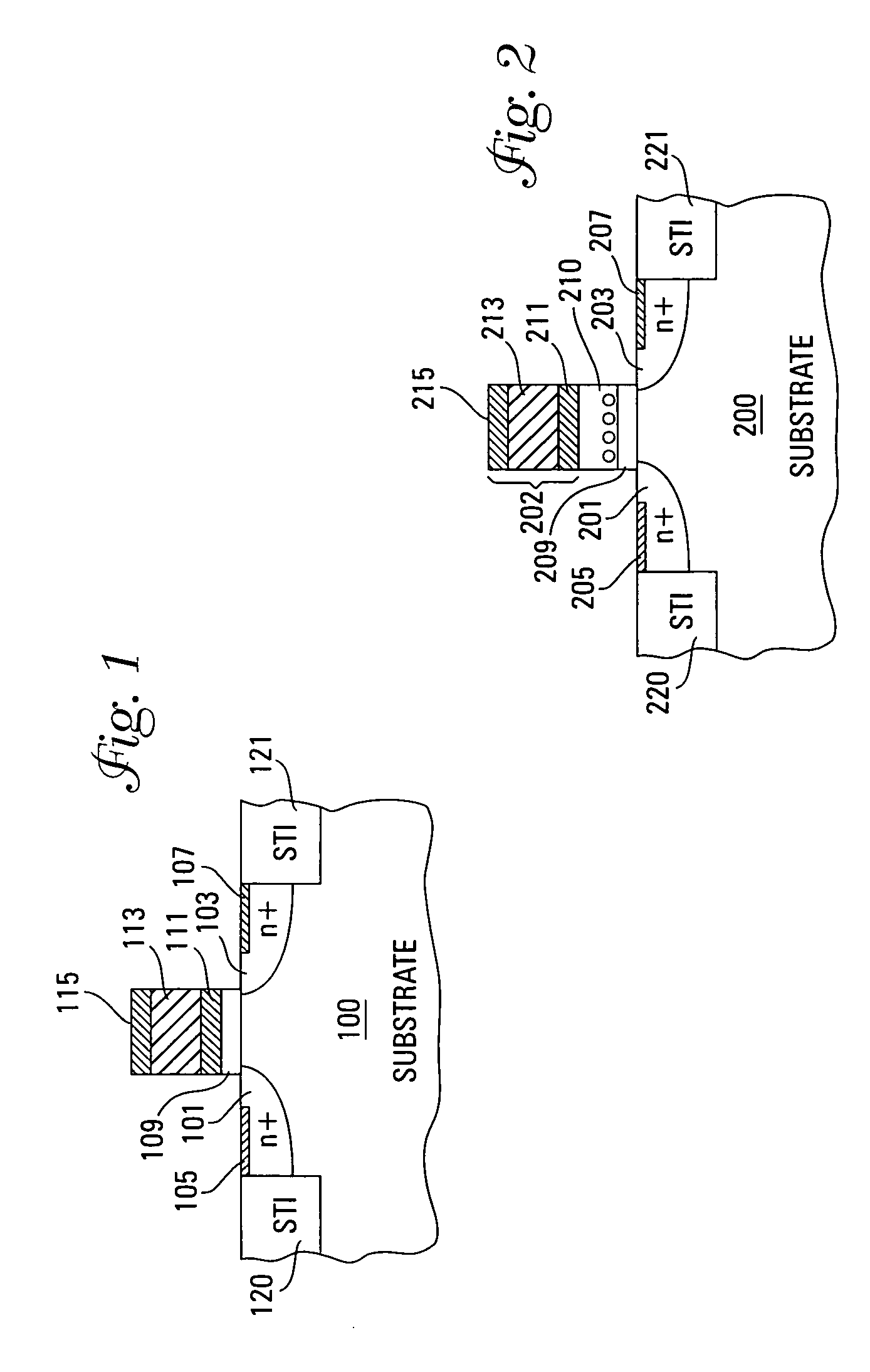

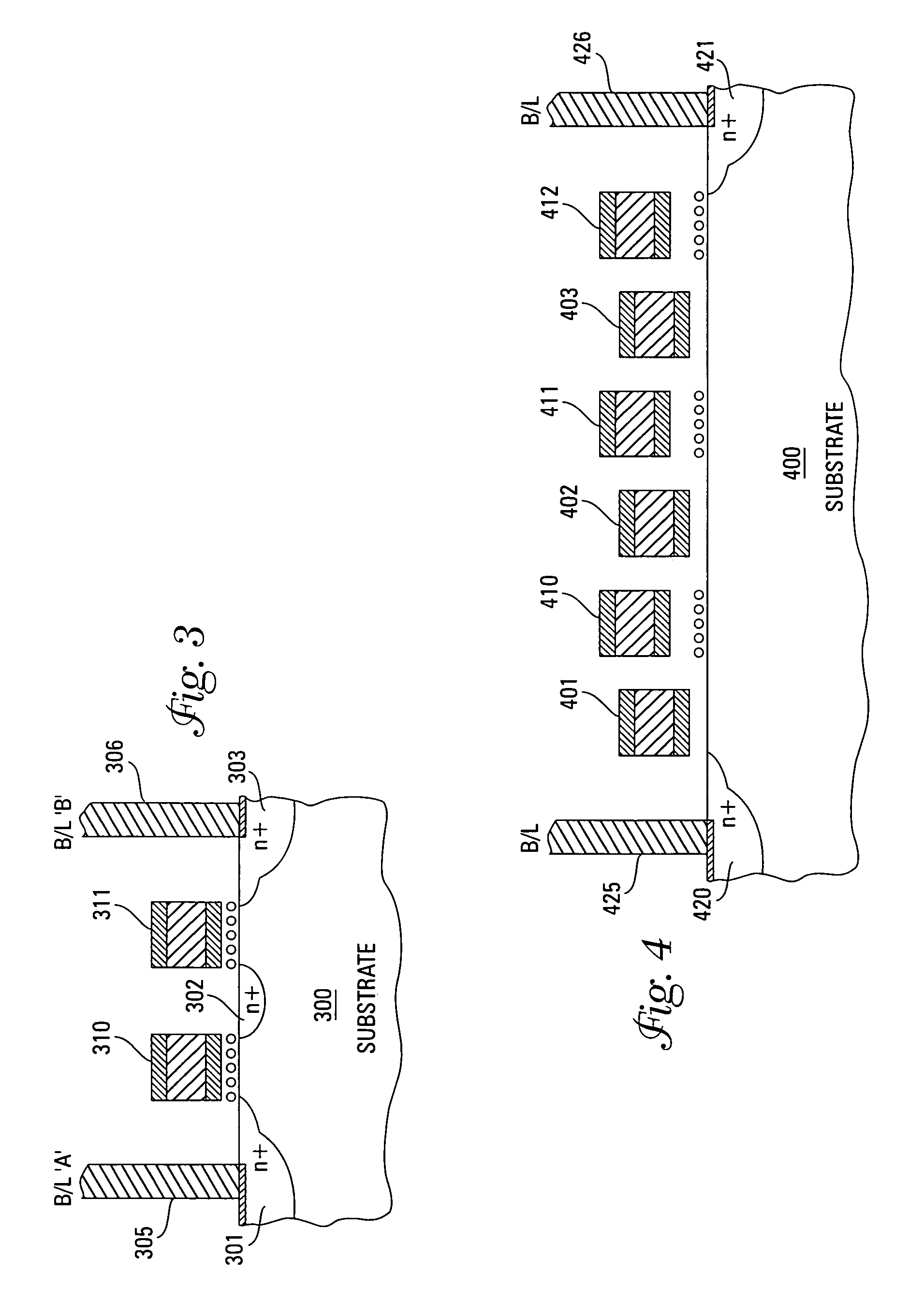

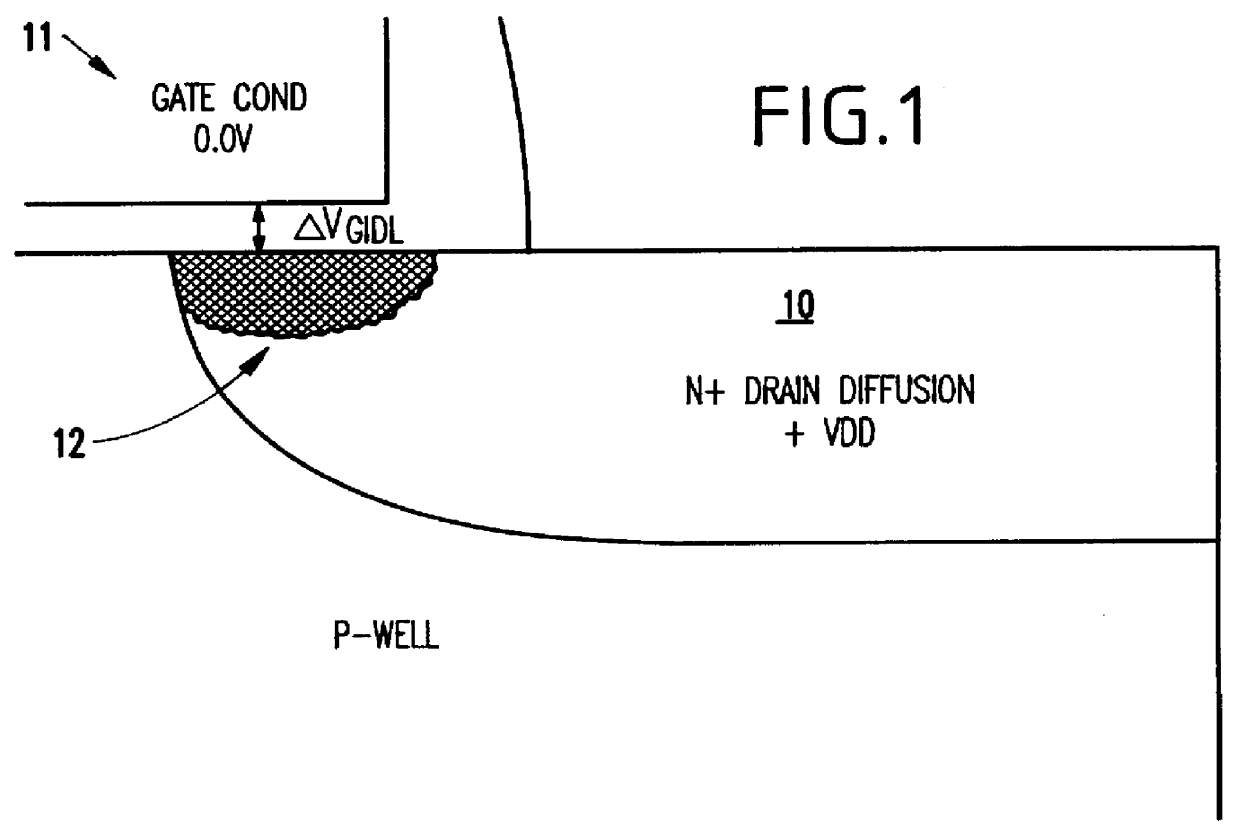

MOSFET structure and process for low gate induced drain leakage (GILD)

InactiveUS6097070ASemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical conductor

A structure and method for forming a metal oxide semiconductor field effect transistor structure comprises, a substrate having a gate-channel region and source and drain regions adjacent the gate-channel region, a gate insulator over the substrate, a central gate conductor positioned above the gate-channel region and over the gate insulator and outer gate conductors over the gate insulator and adjacent the central gate conductor, wherein the gate insulator has a first thickness under the central gate conductor and a second thickness greater than the first thickness under the outer gate conductors. The center and outer gate conductors may consist of different material types (i.e., different work functions). The polarity of the source-drain doping is independent of the polarity of the central or outer gate conductors.

Owner:GLOBALFOUNDRIES INC

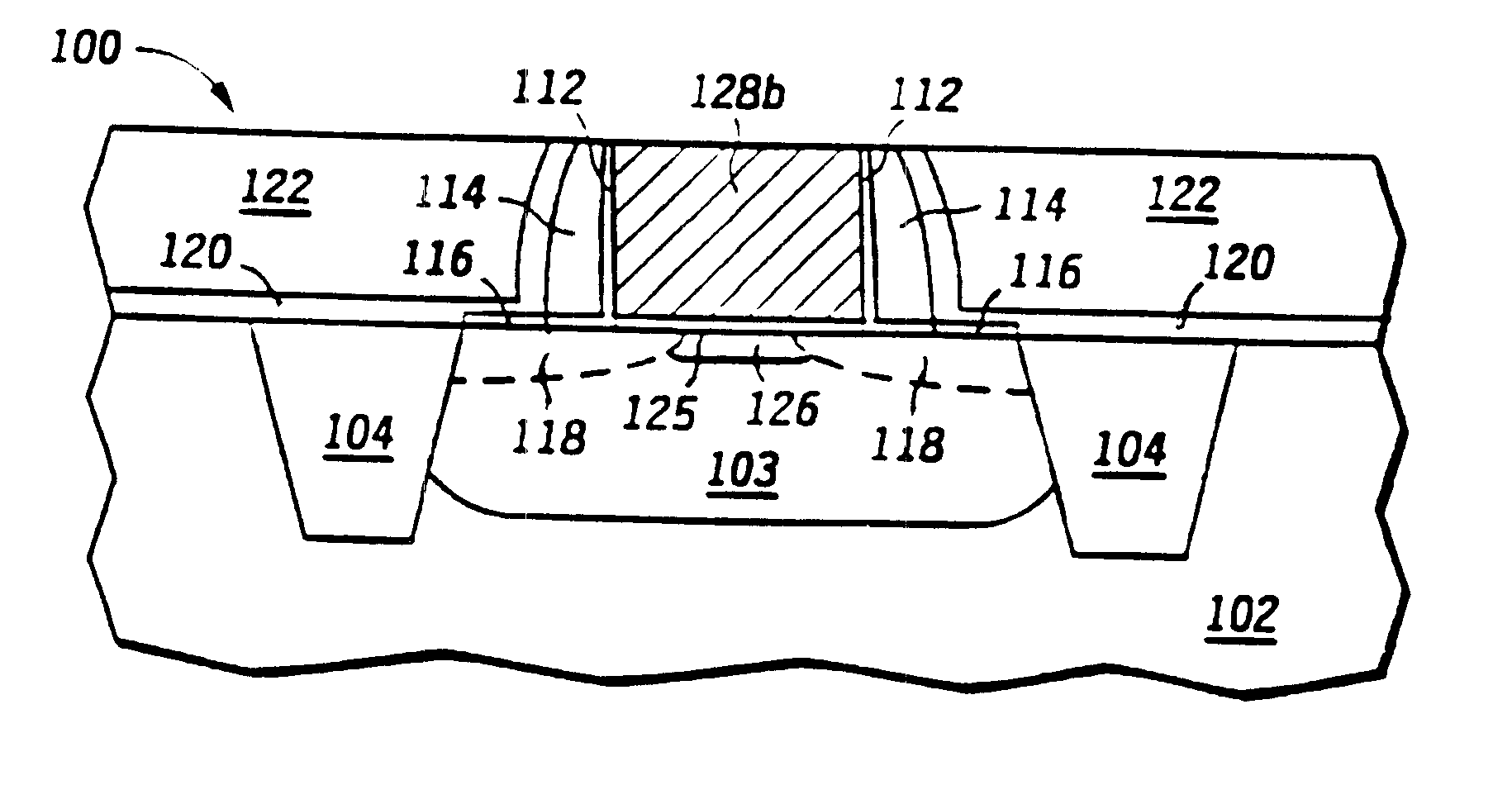

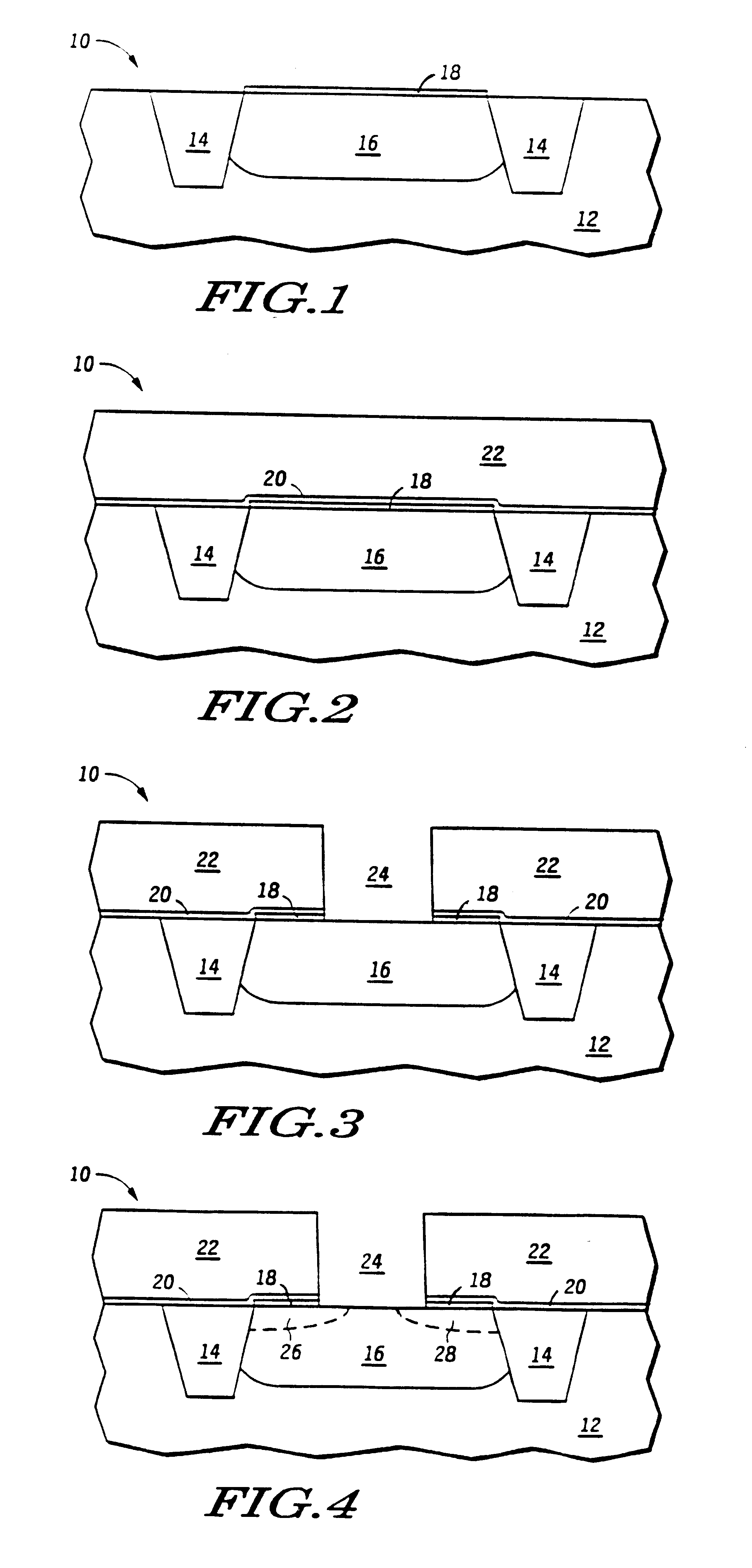

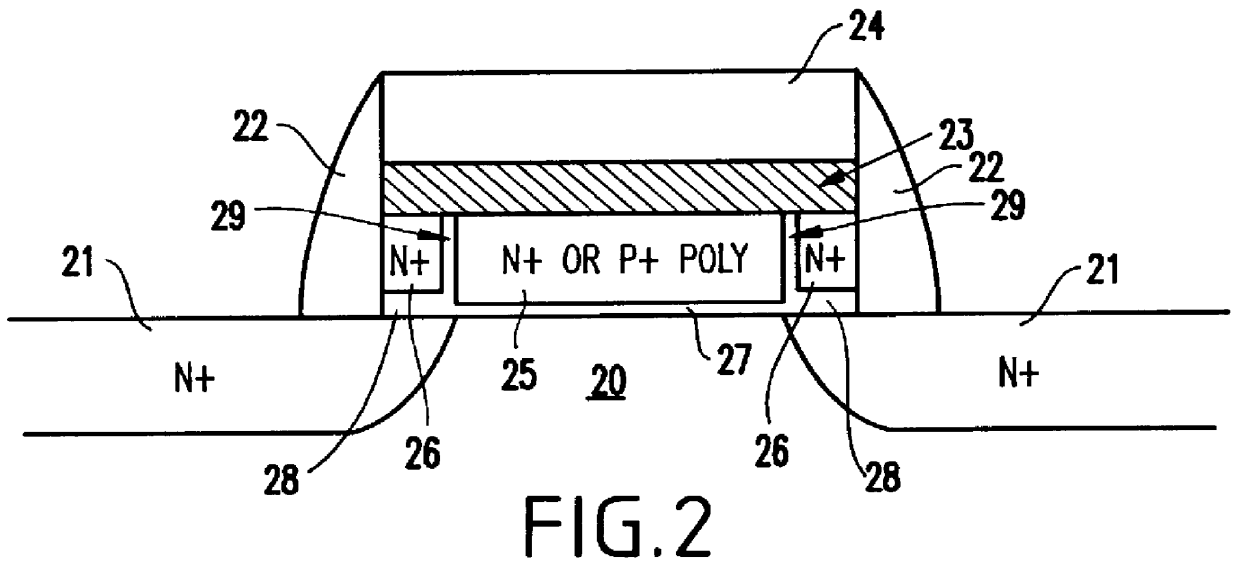

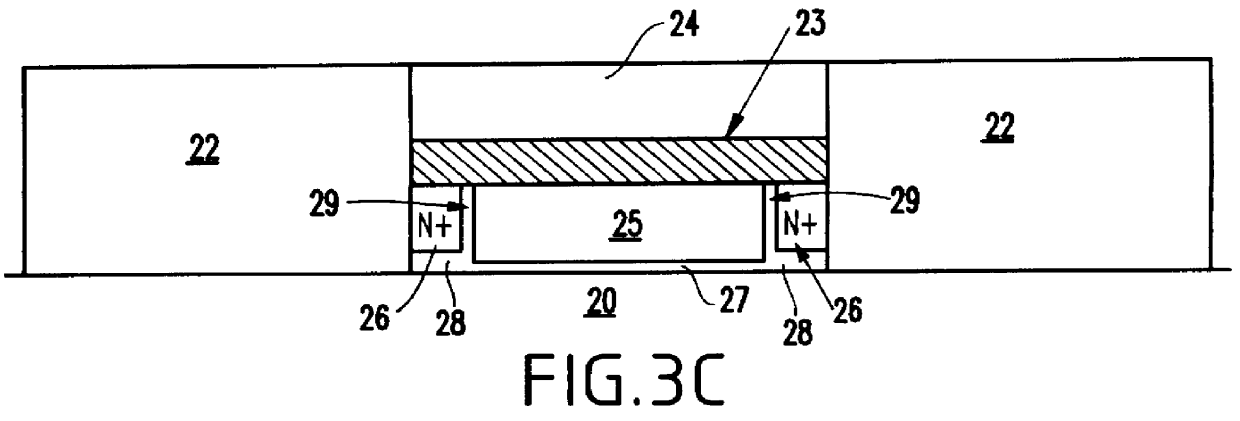

Local sonos-type structure having two-piece gate and self-aligned ono and method for manufacturing the same

A local SONOS structure having a two-piece gate and a self-aligned ONO structure includes: a substrate; an ONO structure on the substrate; a first gate layer on and aligned with the ONO structure; a gate insulator on the substrate aside the ONO structure; and a second gate layer on the first gate layer and on the gate insulator. The first and second gate layers are electrically connected together. Together, the ONO structure and first and second gate layers define at least a 1-bit local SONOS structure. A corresponding method of manufacture includes: providing a substrate; forming an ONO structure on the substrate; forming a first gate layer on and aligned with the ONO structure; forming a gate insulator on the substrate aside the ONO structure; forming a second gate layer on the first gate layer and on the gate insulator; and electrically connecting the first and second gate layers.

Owner:SAMSUNG ELECTRONICS CO LTD

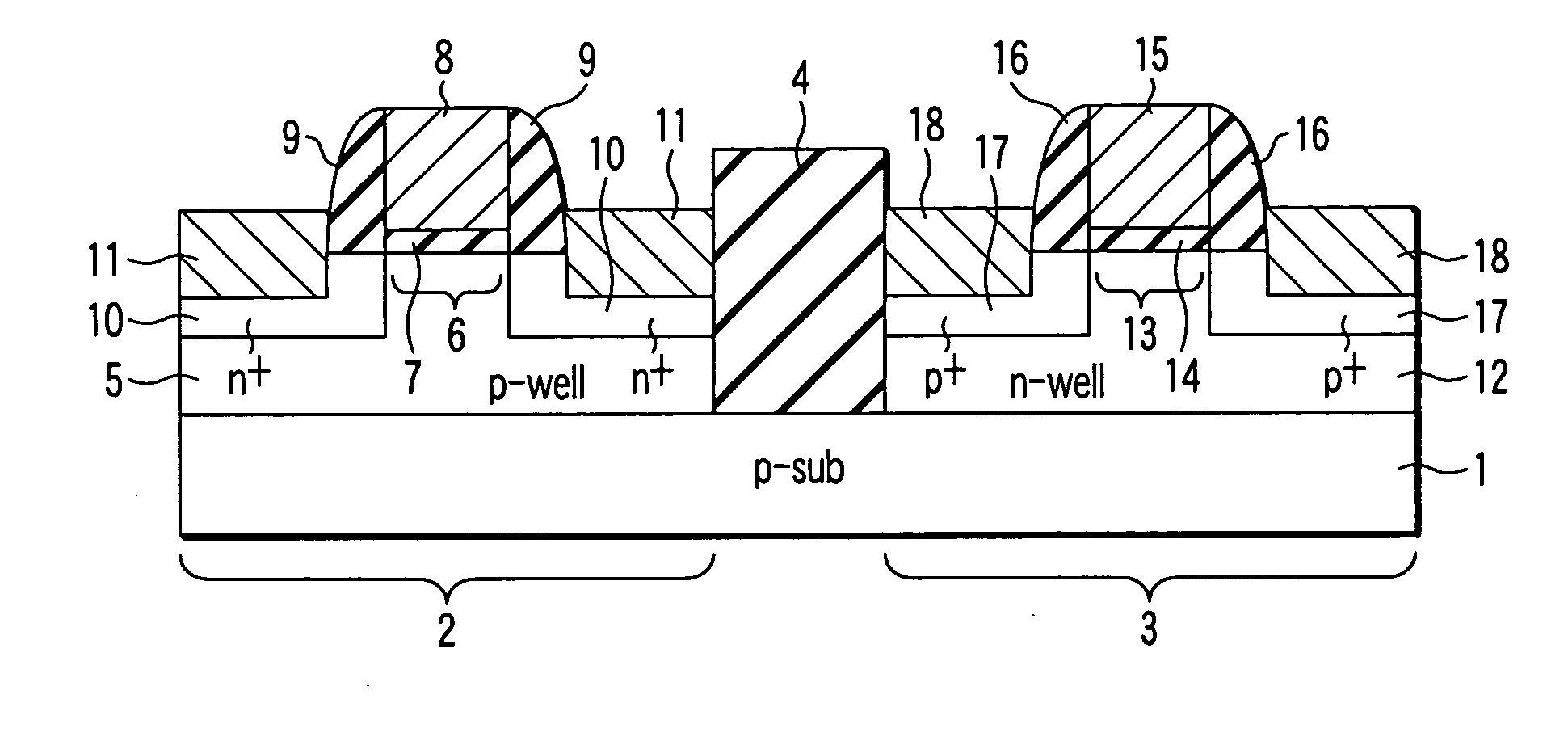

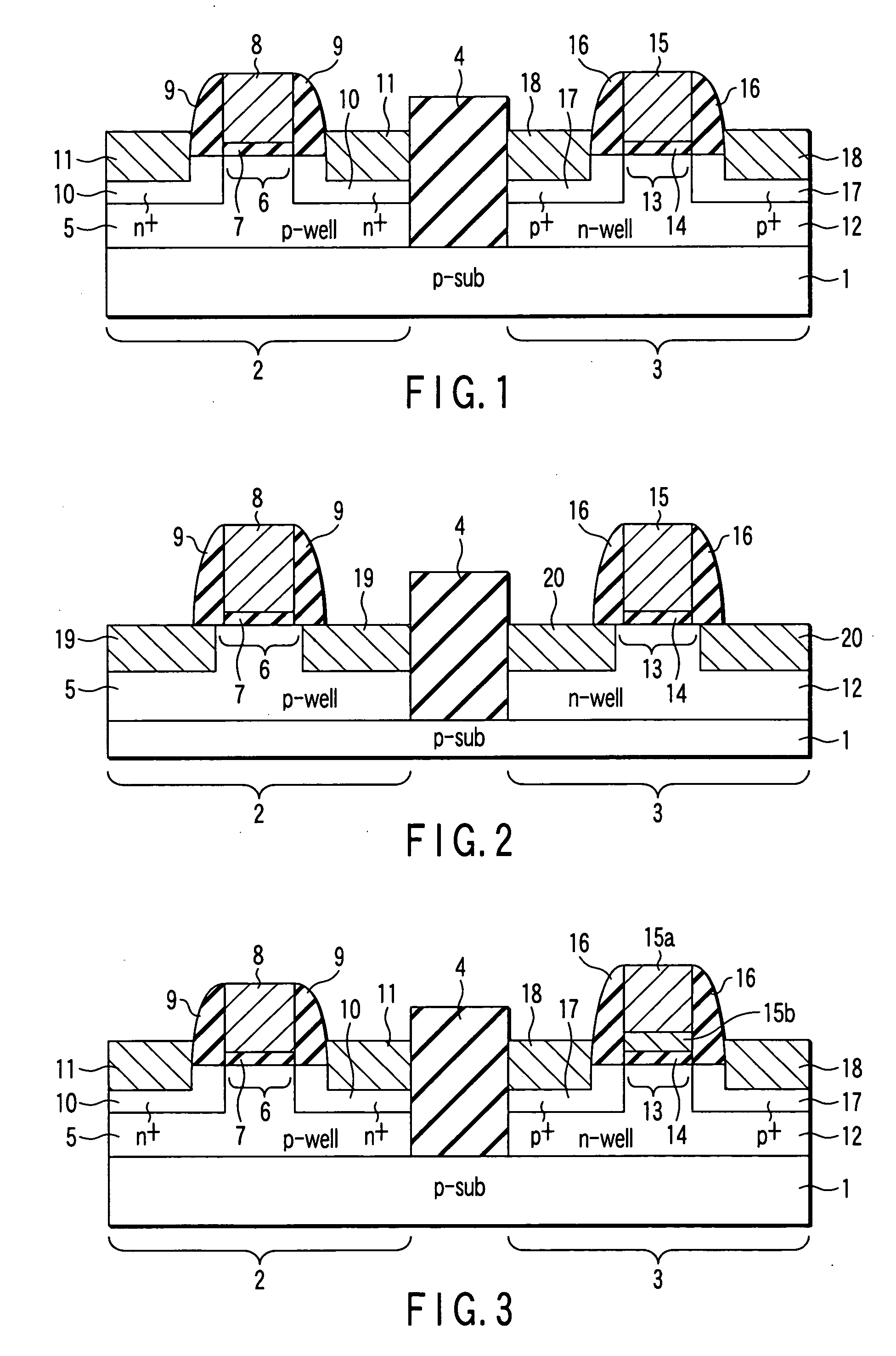

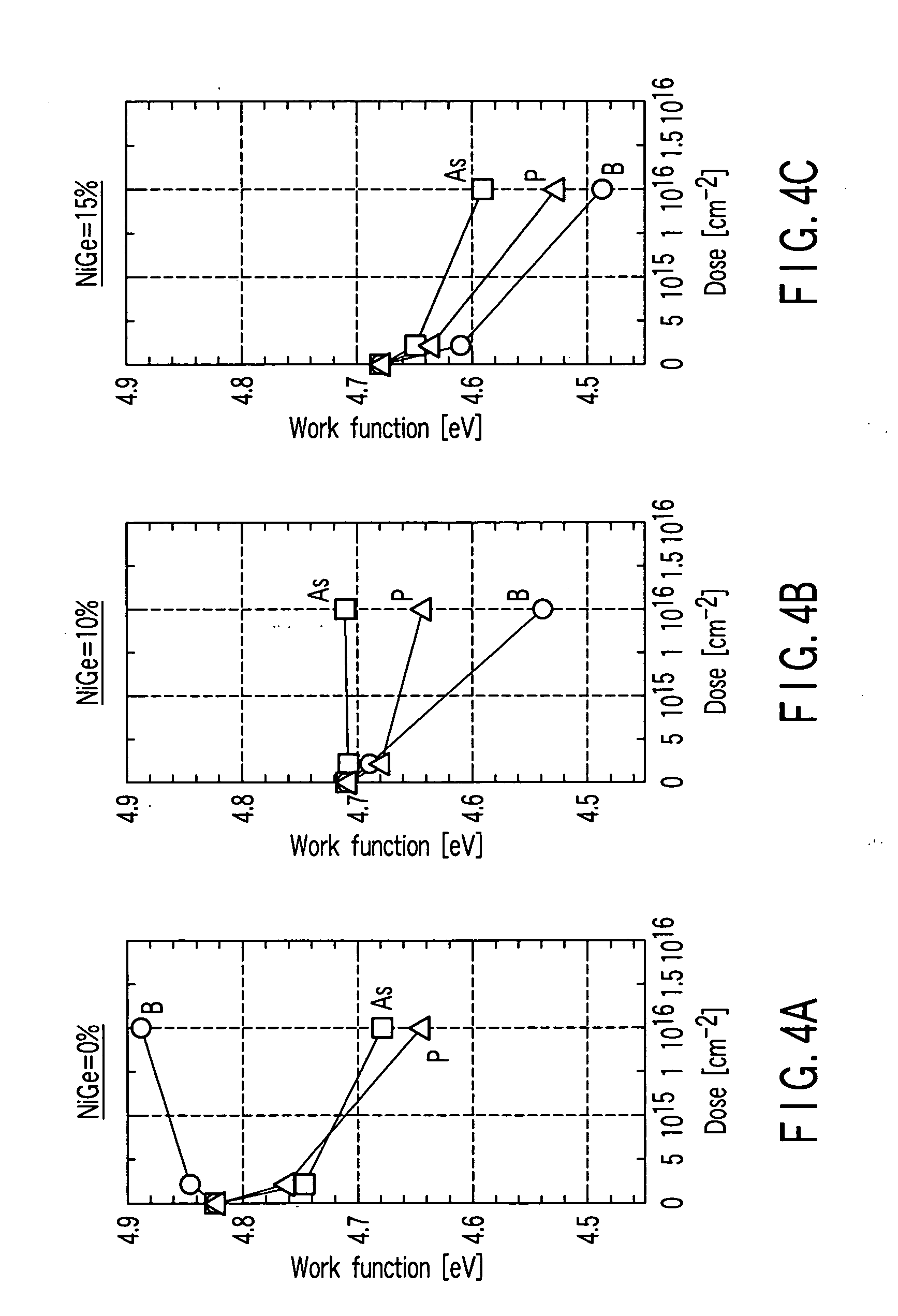

Method of making semiconductor device and semiconductor device

InactiveUS20080179752A1Lower junction resistanceTransistorSemiconductor/solid-state device detailsDevice materialGate insulator

A metal insulator semiconductor field effect transistor (MISFET) having a strained channel region is disclosed. Also disclosed is a method of fabricating a semiconductor device having a low-resistance junction interface. This fabrication method includes the step of forming a gate electrode above a silicon substrate with a gate insulator film being sandwiched therebetween. Then, form a pair of heavily-doped p (p+) type diffusion layers in or on the substrate surface at both sides of the gate electrode to a concentration of 5×1019 atoms / cm3 or more and yet less than or equal to 1×1021 atoms / cm3. Next, silicidize the p+-type layers by reaction with a metal in the state that each layer is applied a compressive strain.

Owner:KK TOSHIBA

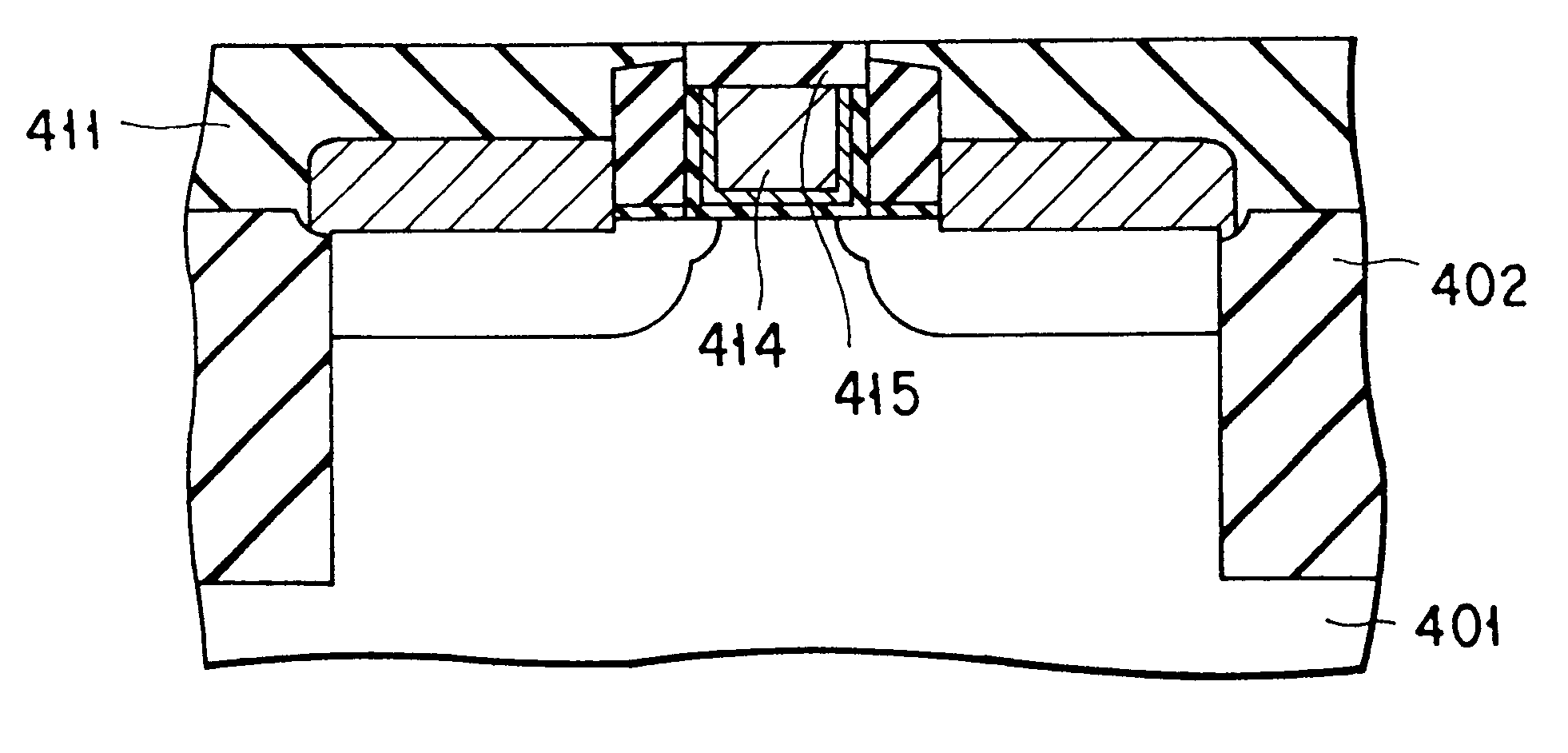

Semiconductor device

A semiconductor device comprises n-type and p-type semiconductor devices formed on the substrate, the n-type device including an n-channel region formed on the substrate, n-type source and drain regions formed opposite to each other interposing the n-channel region therebetween, a first gate insulator formed on the n-channel region, and a first gate electrode formed on the first gate insulator and including a compound of a metal M and a first group-IV elements Si1−a Gea (0≦a≦1), the p-type device including a p-channel region formed on the substrate, p-type source and drain regions formed opposite to each other interposing the p-channel region therebetween, a second gate insulator formed on the p-channel region, and a second gate electrode formed on the second gate insulator, and including a compound of the metal M and a second group-IV element Si1−c Gec (0≦c≦1, a≠c).

Owner:KK TOSHIBA

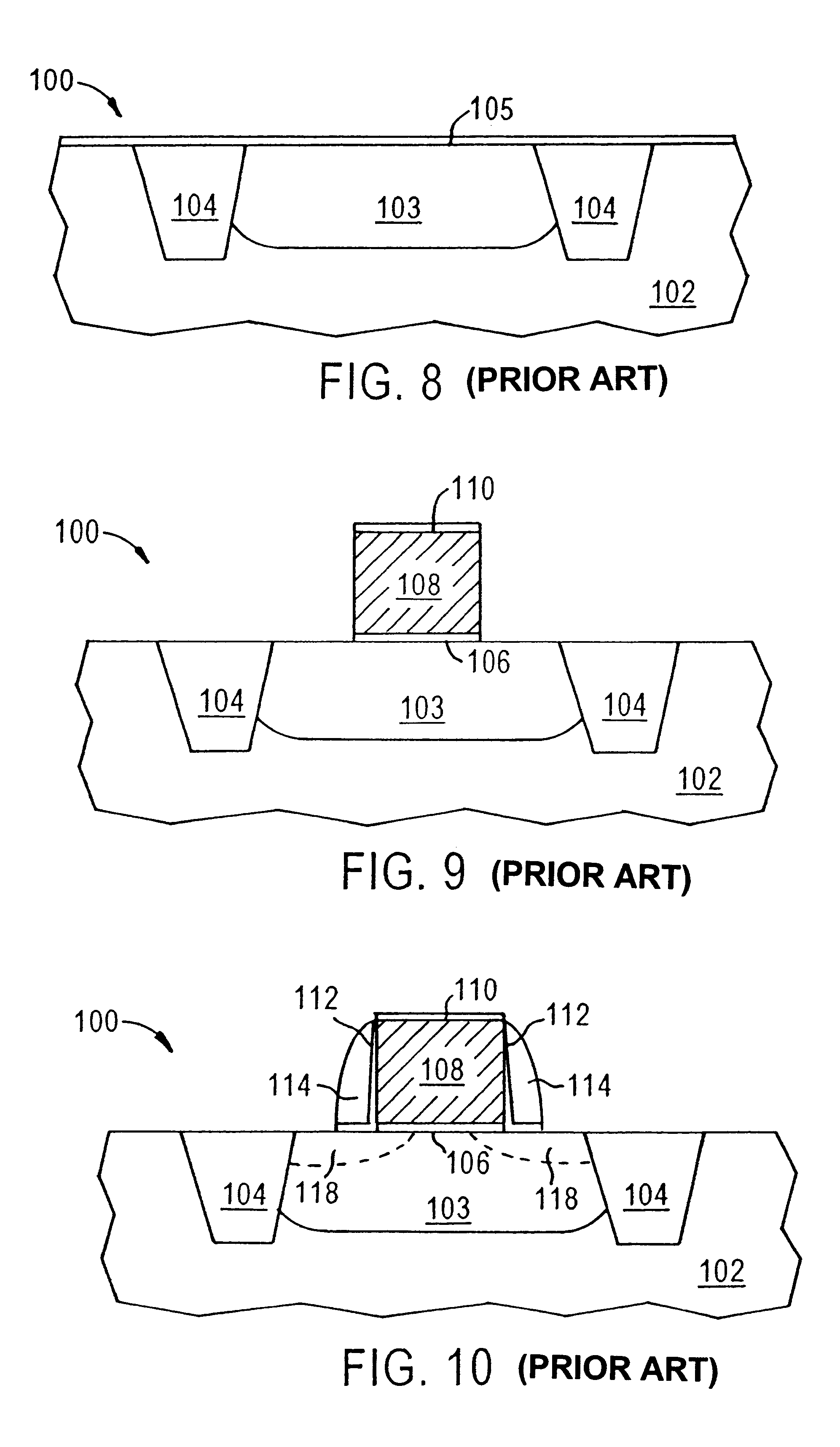

Semiconductor device and manufacturing method therefor

InactiveUS6515338B1Inhibit deteriorationHigh yieldTransistorSolid-state devicesGate insulatorSemiconductor

A method of manufacturing semiconductor device comprises the steps of forming a first film and a second film on a semiconductor substrate, selectively removing the second film, the first film and a top portion of the semiconductor substrate to form a first groove, burying a first insulator film in the first groove to form an isolation region, patterning the second film surrounded by the isolation region to form a dummy gate layer, doping the semiconductor substrate with an impurity using the dummy gate layer as a mask, forming a second insulator film on the semiconductor substrate surrounded by the dummy gate layer and the first insulator film, removing the dummy gate layer and the first film to form a second groove, forming a gate insulator film on the semiconductor substrate in the second groove, and forming a gate electrode on the gate insulator film in the second groove.

Owner:KK TOSHIBA