Patents

Literature

2901 results about "Doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In semiconductor production, doping is the intentional introduction of impurities into an intrinsic semiconductor for the purpose of modulating its electrical, optical and structural properties. The doped material is referred to as an extrinsic semiconductor. A semiconductor doped to such high levels that it acts more like a conductor than a semiconductor is referred to as a degenerate semiconductor.

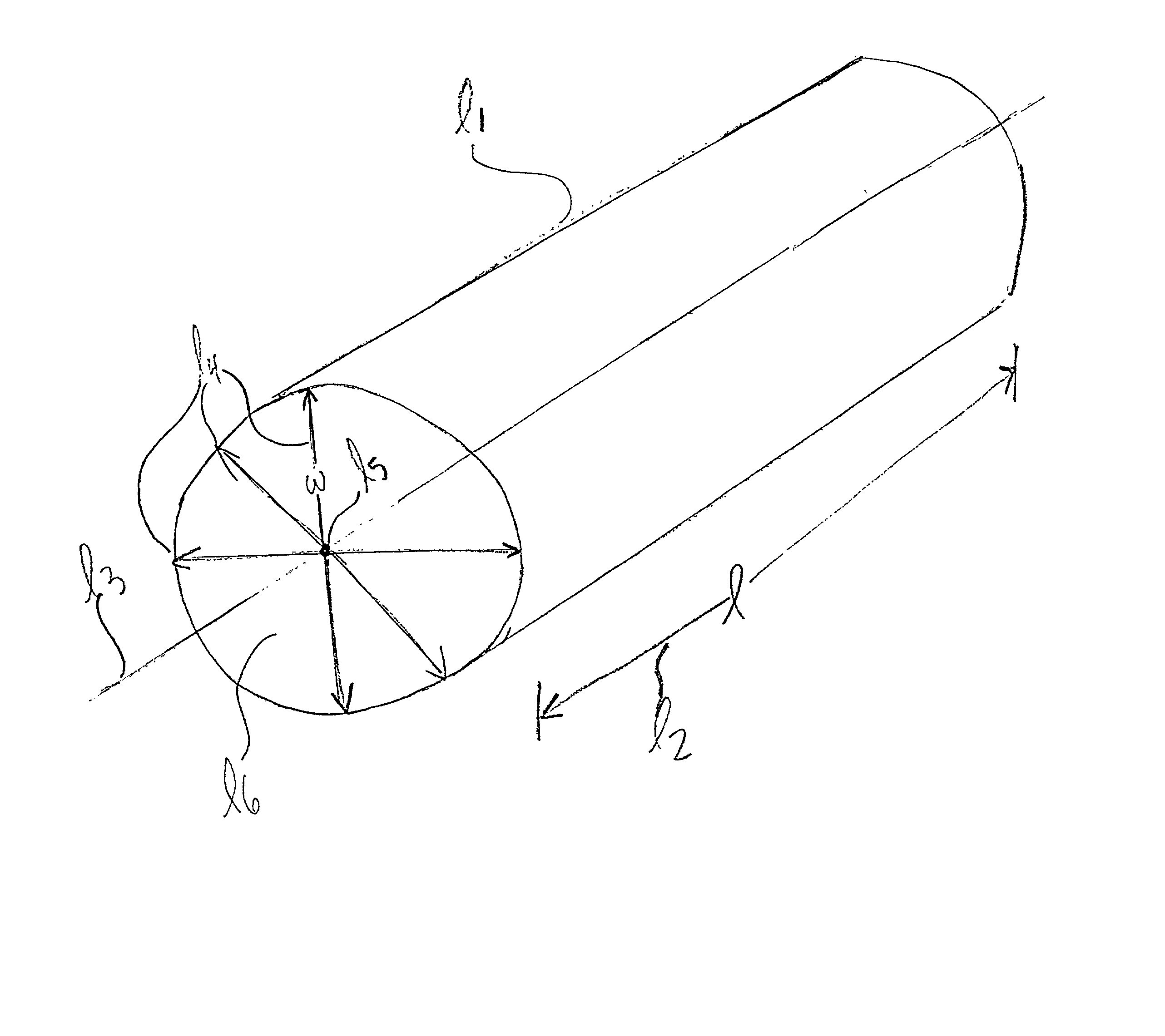

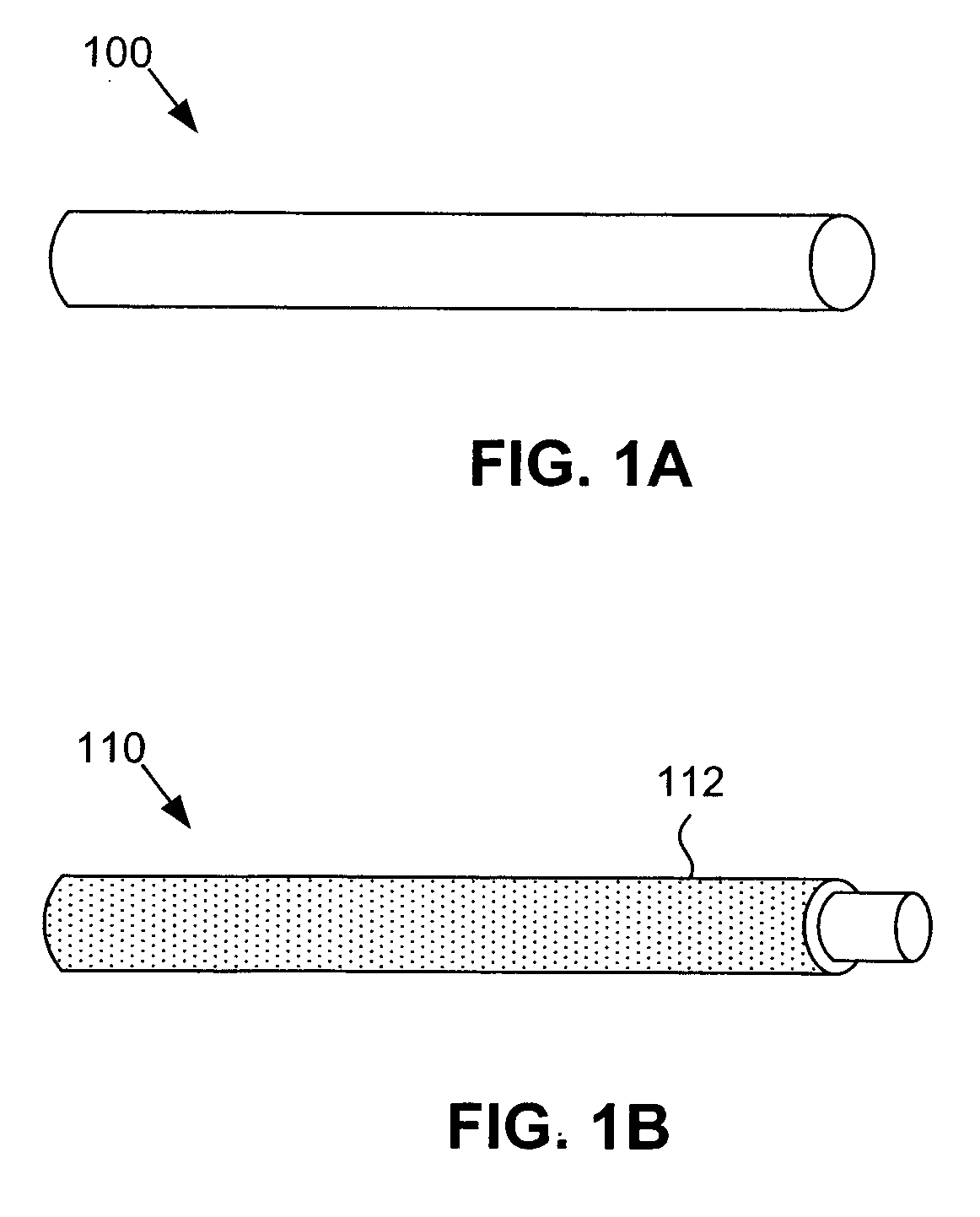

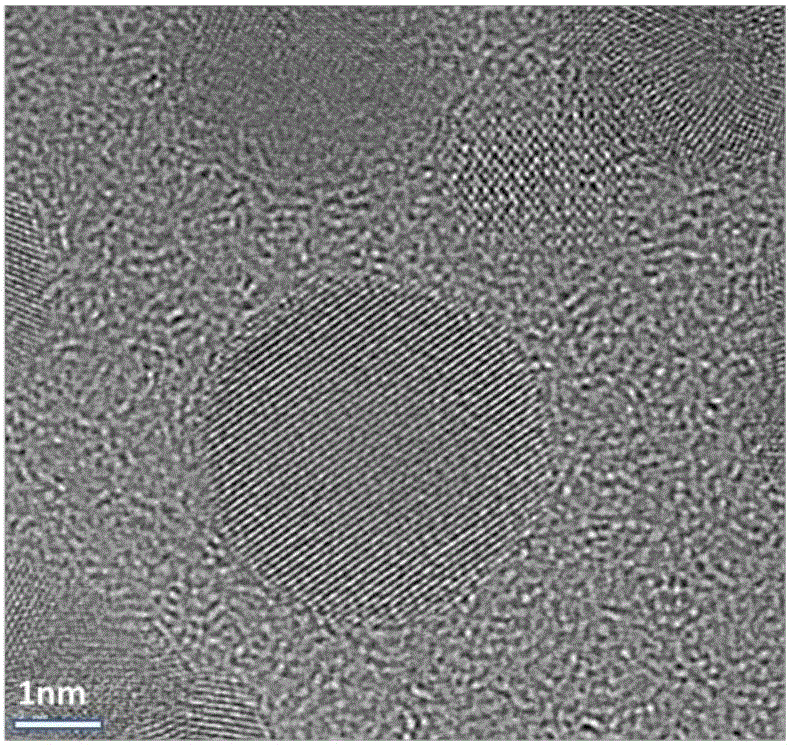

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

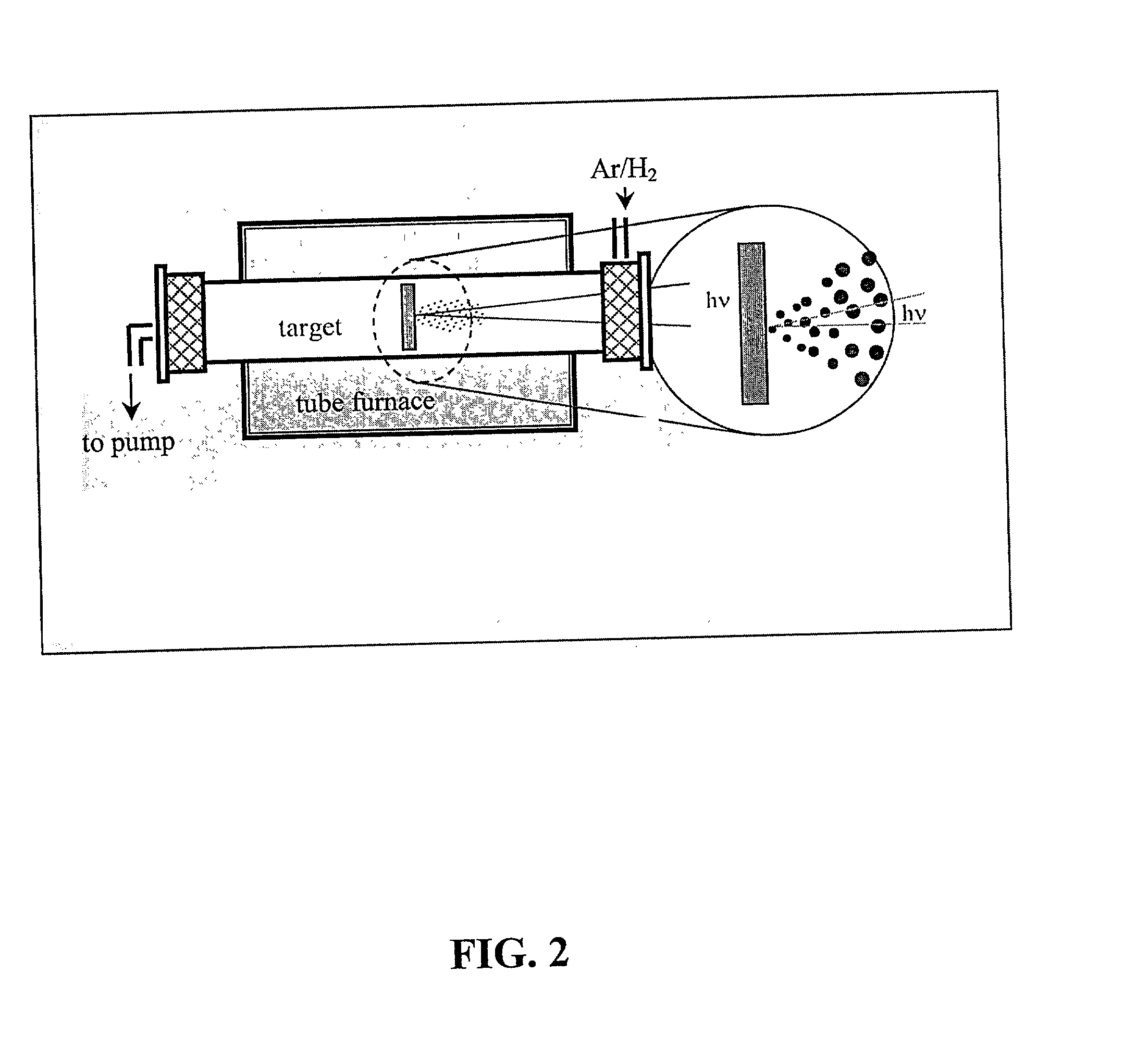

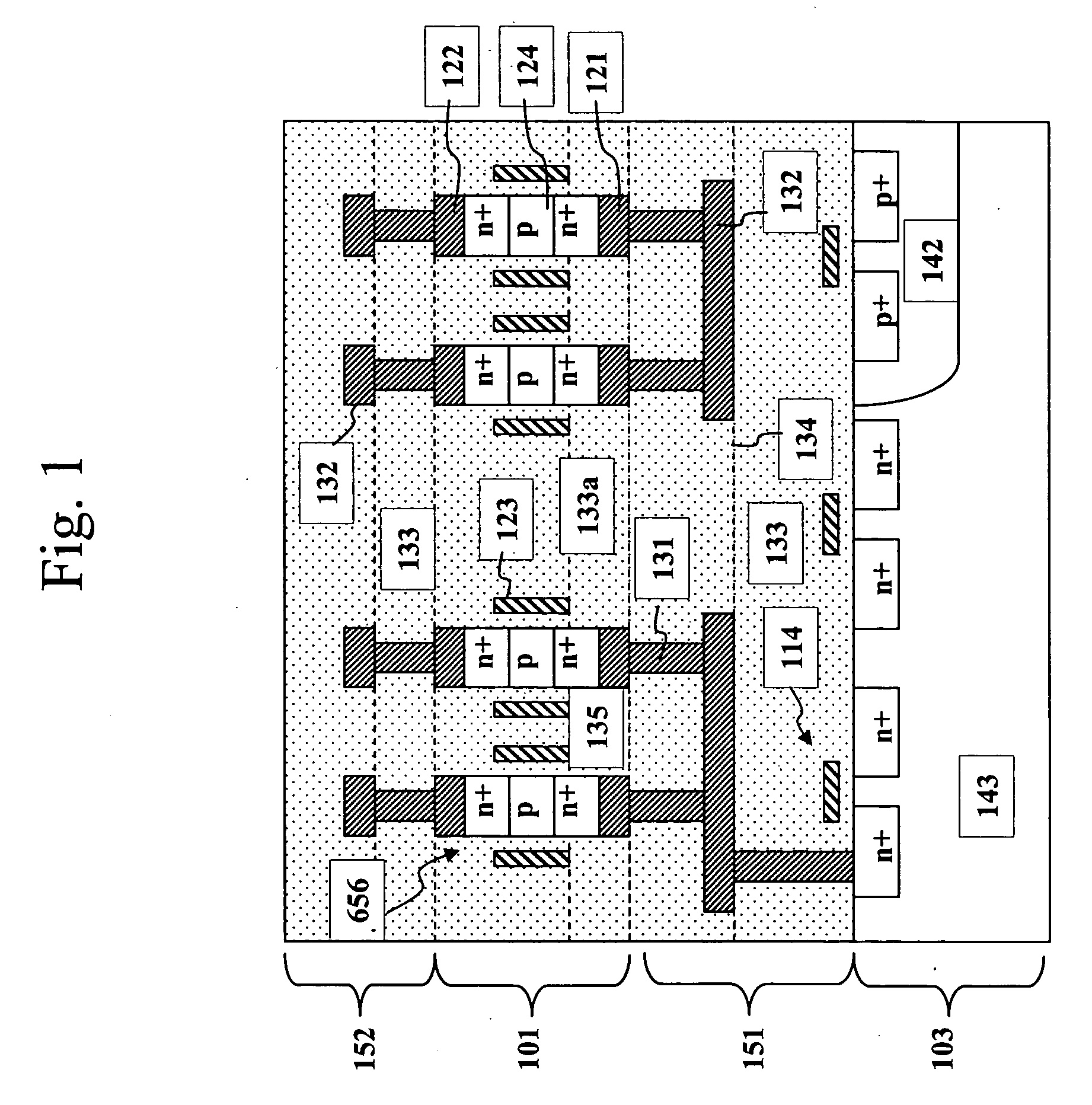

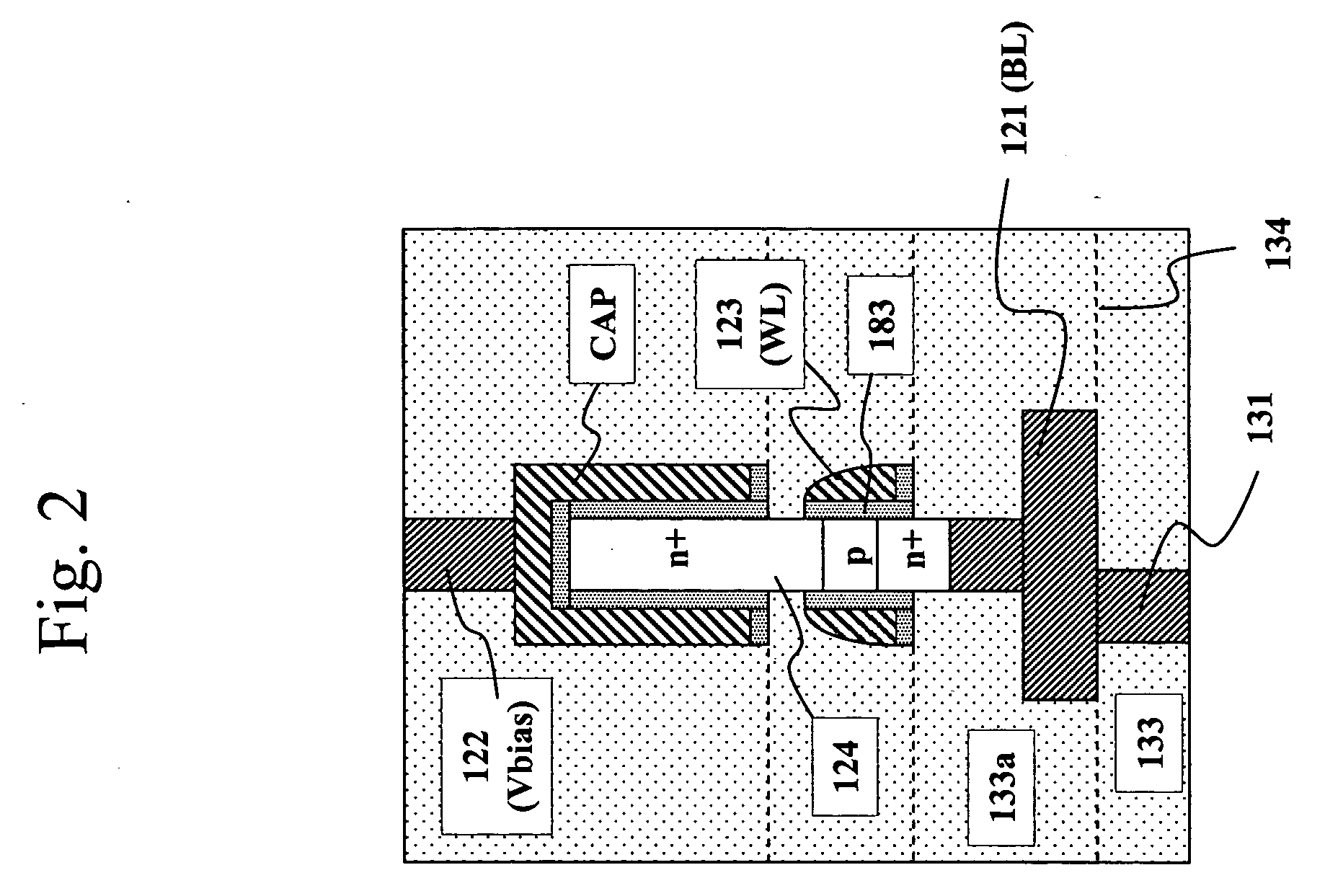

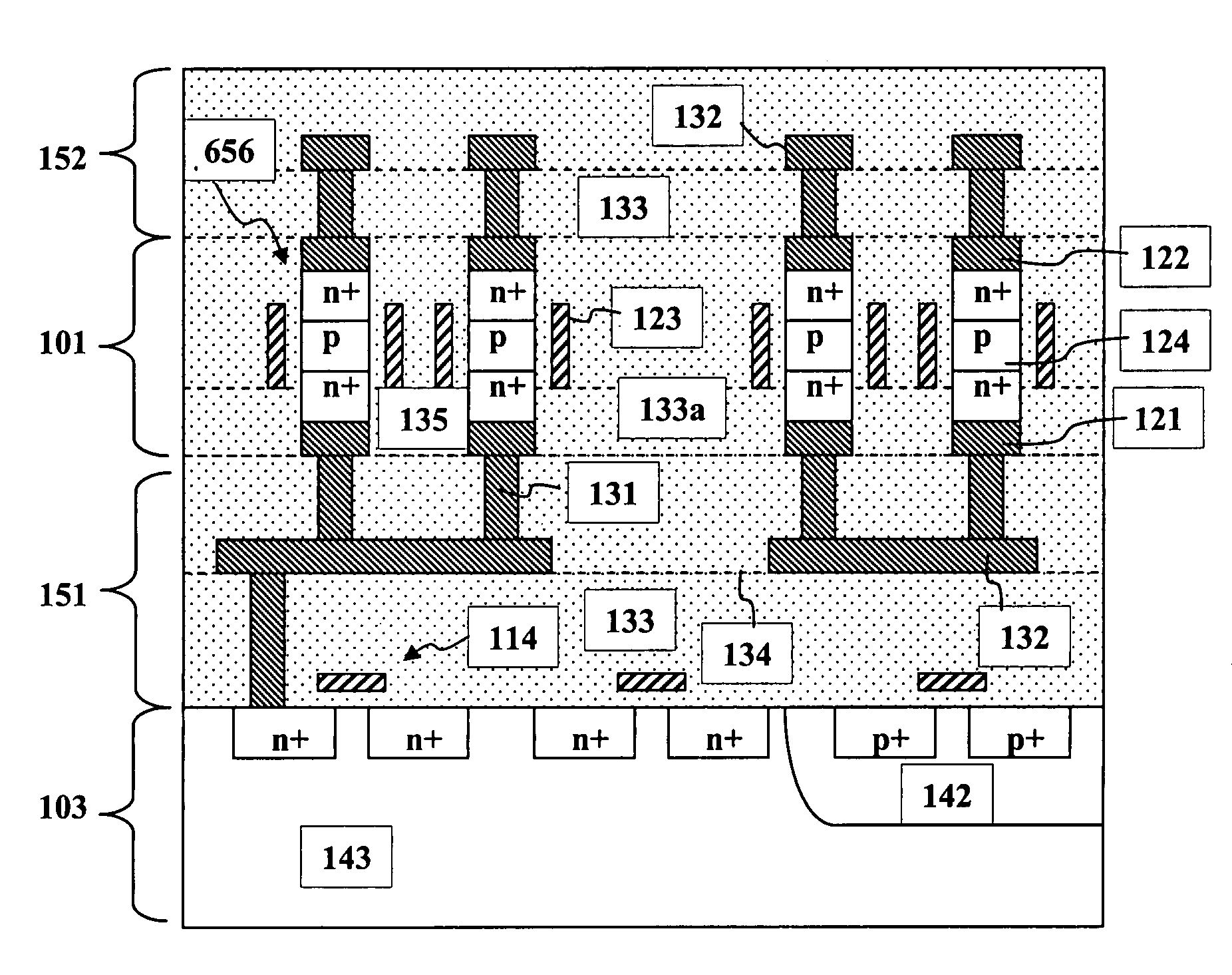

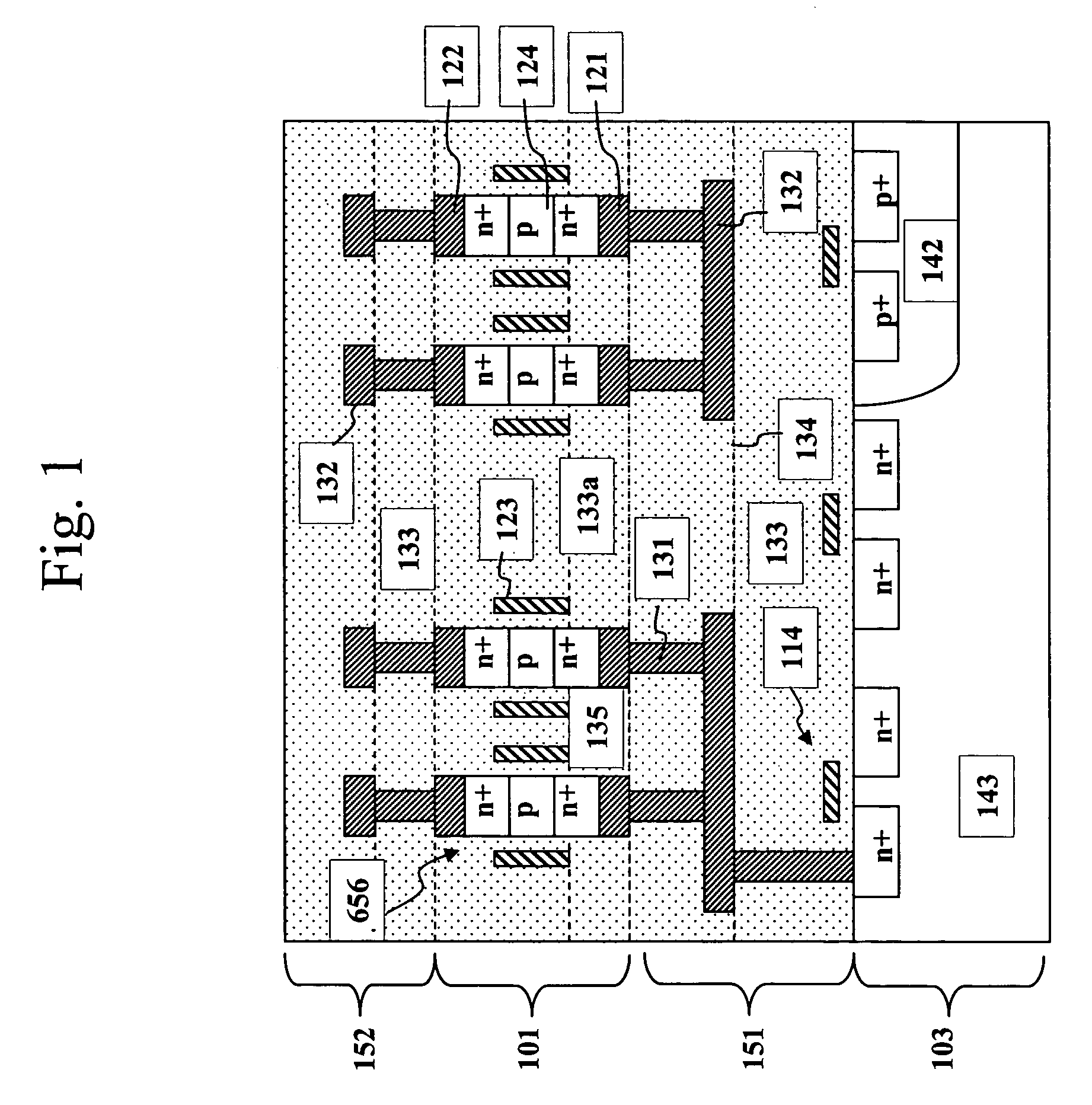

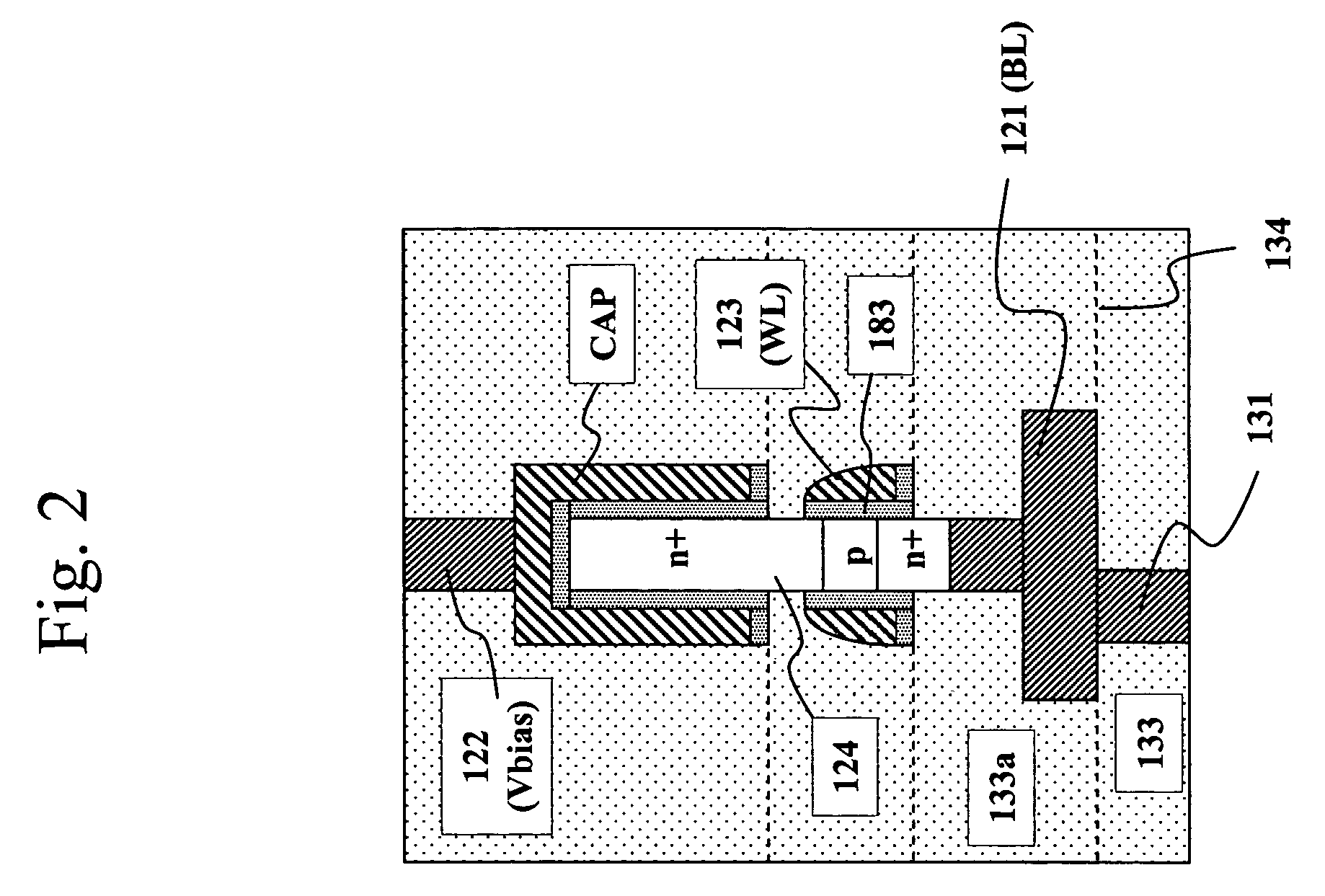

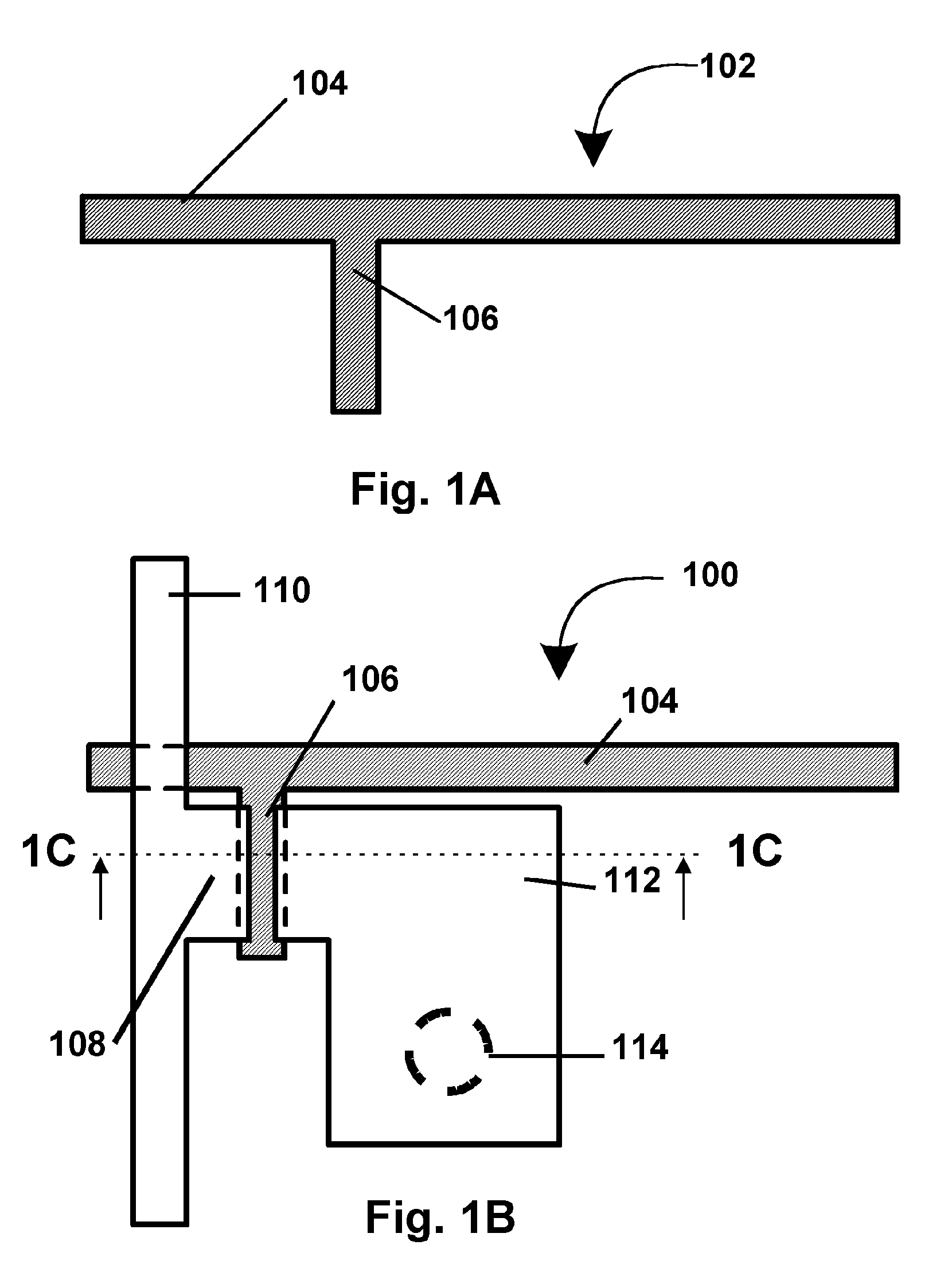

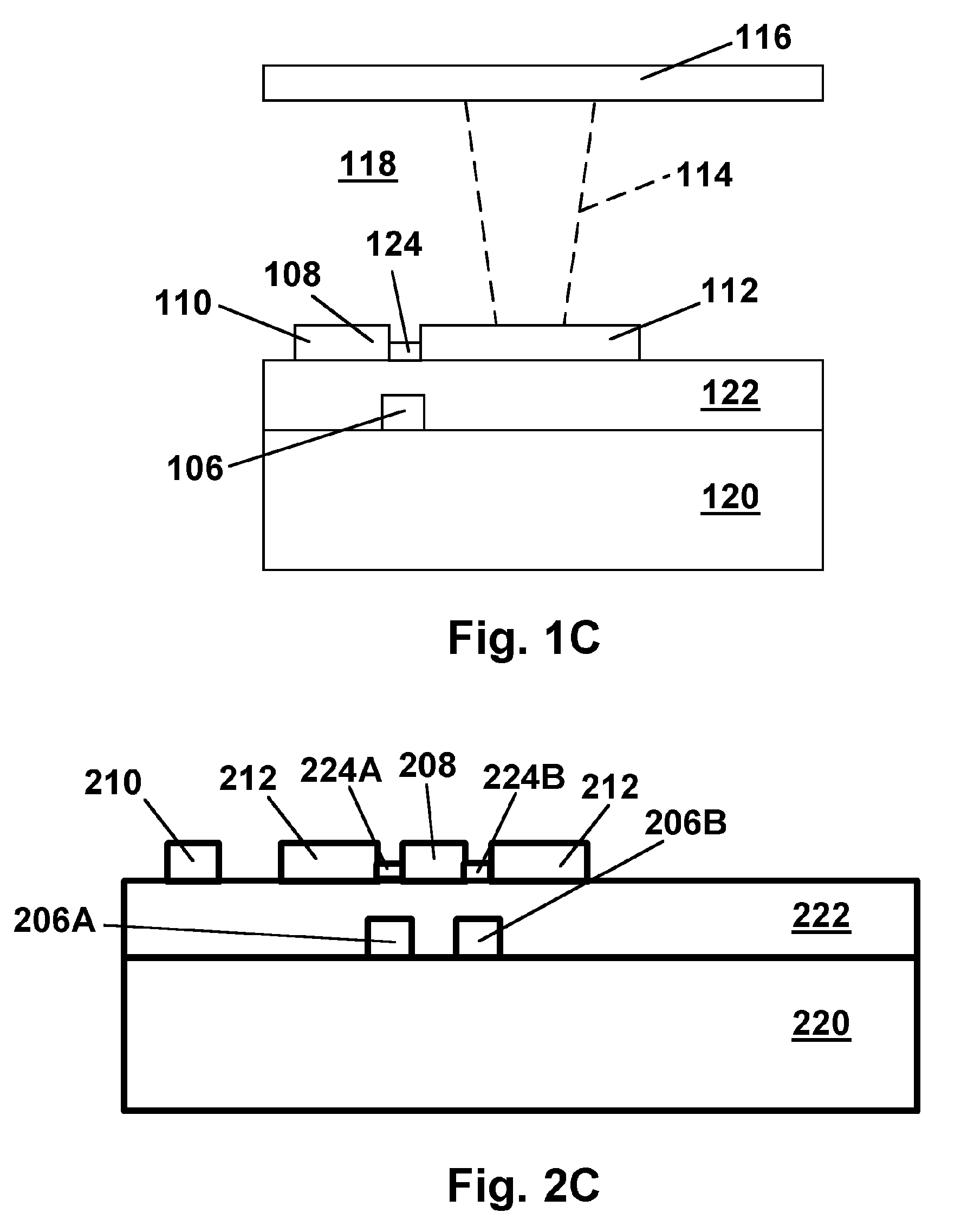

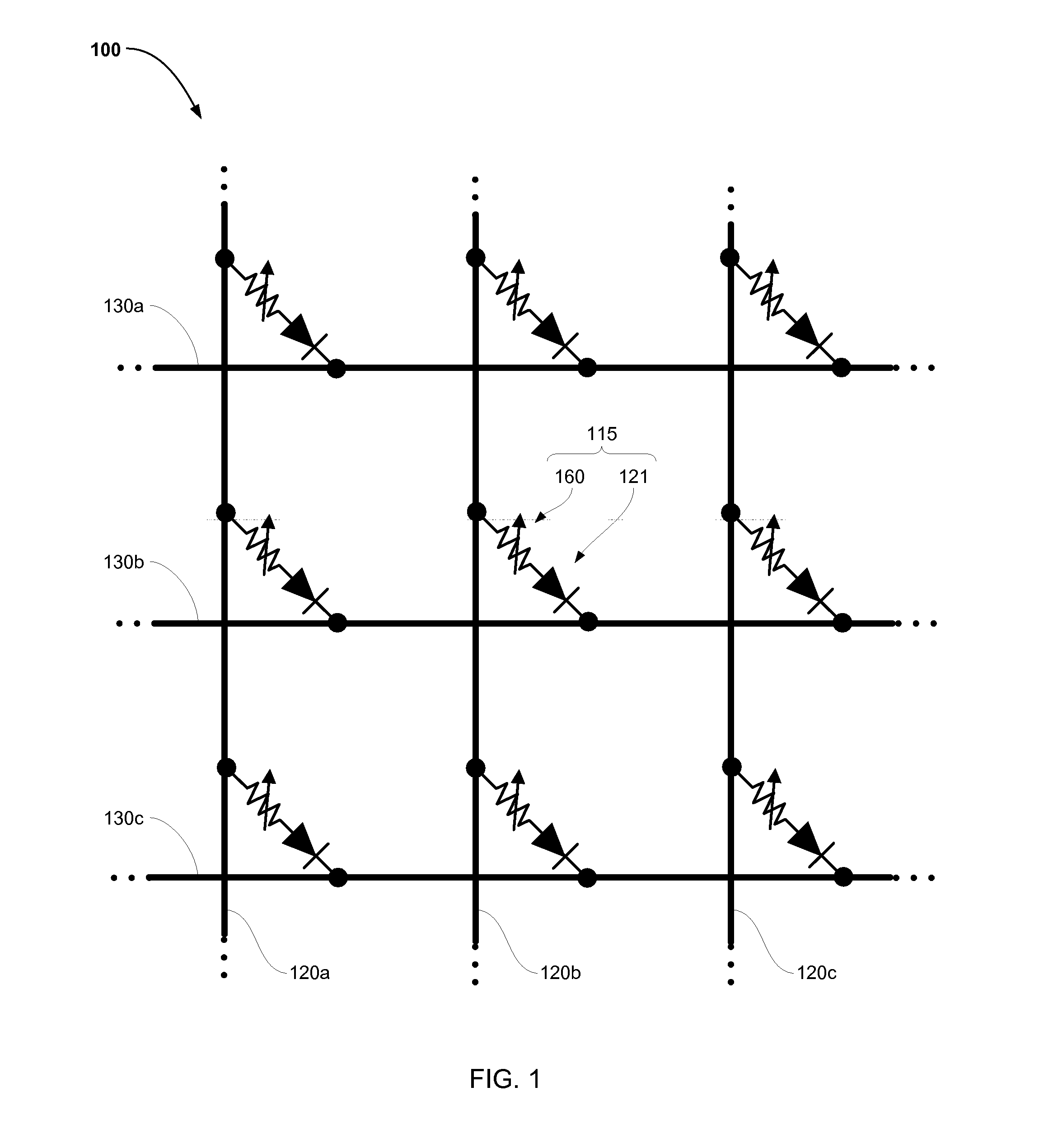

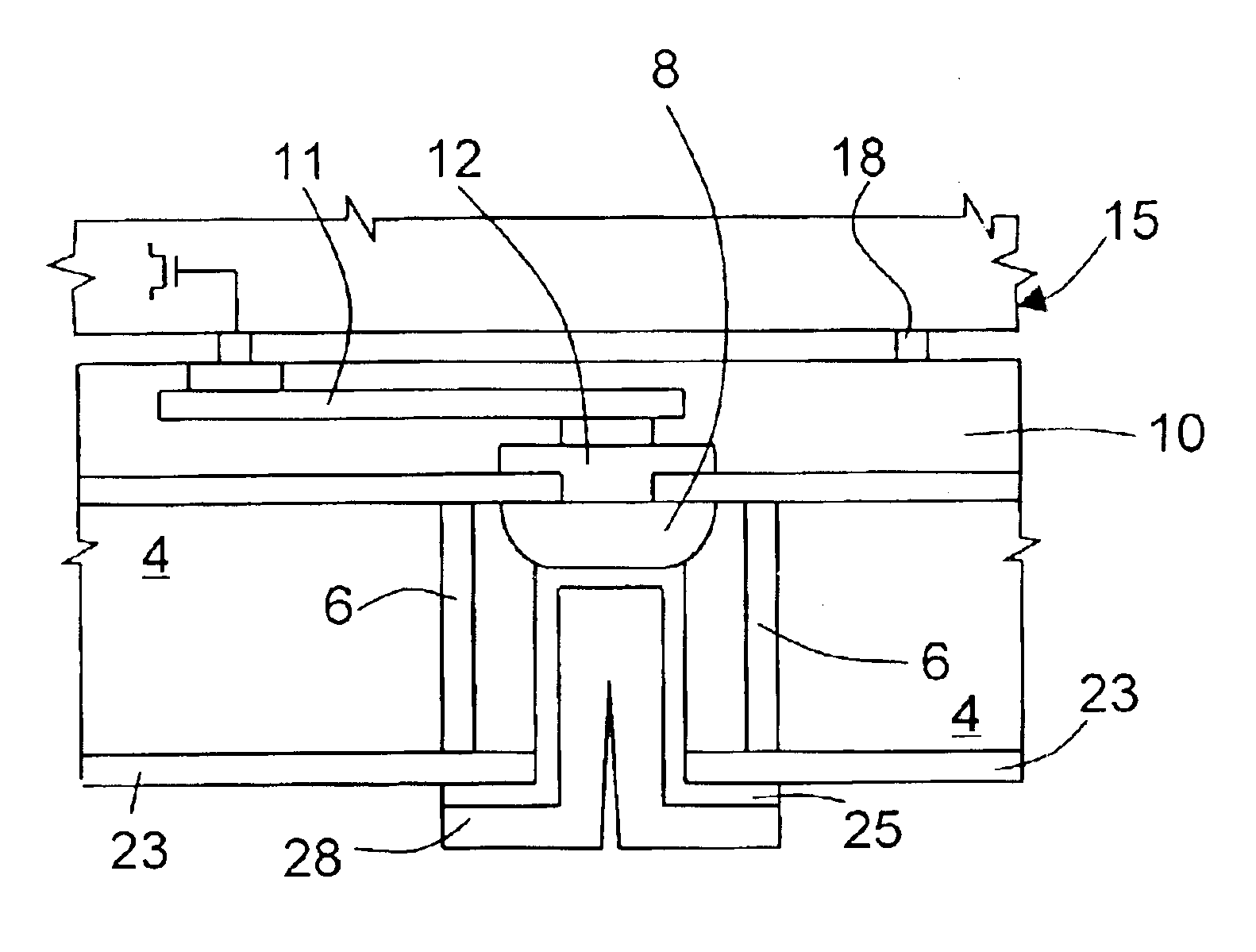

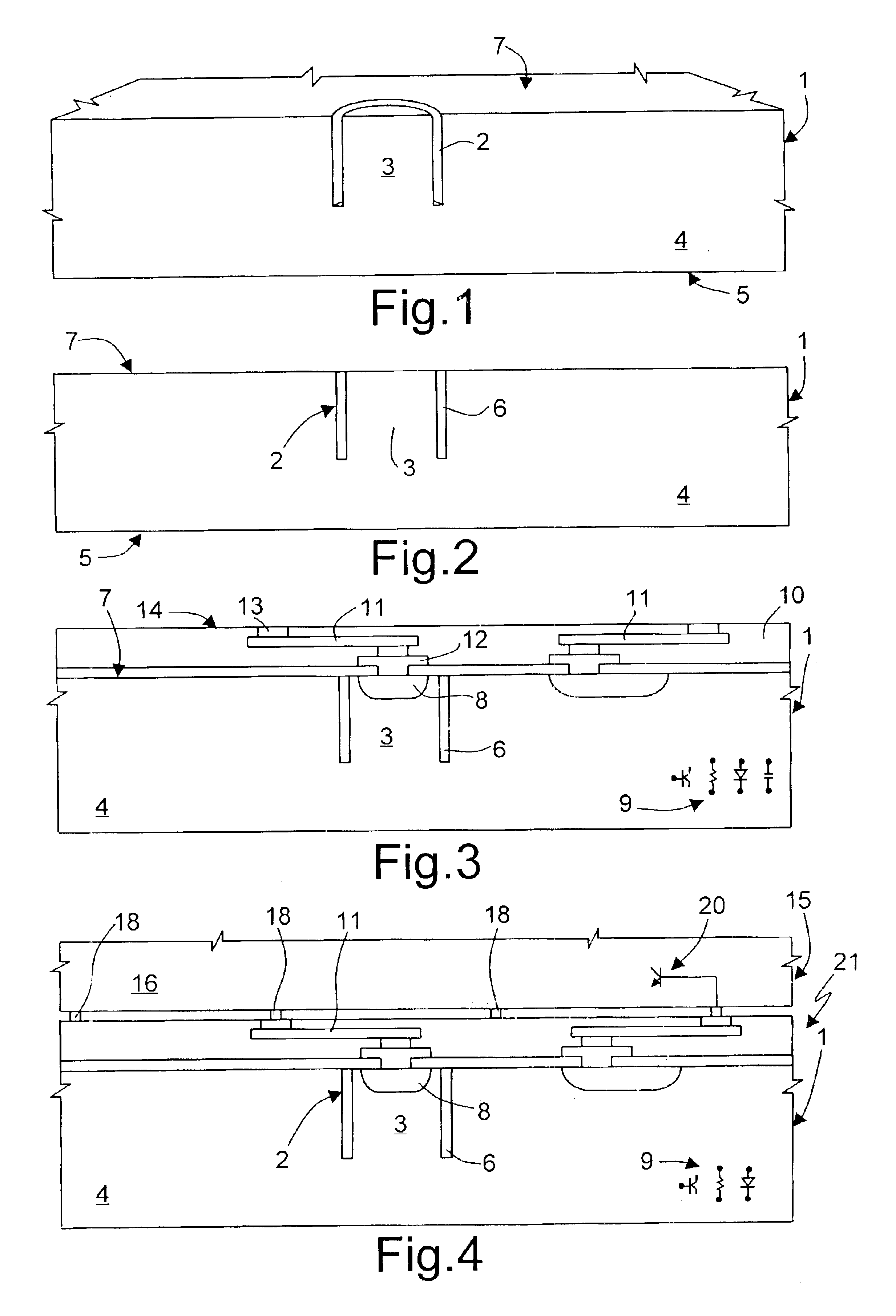

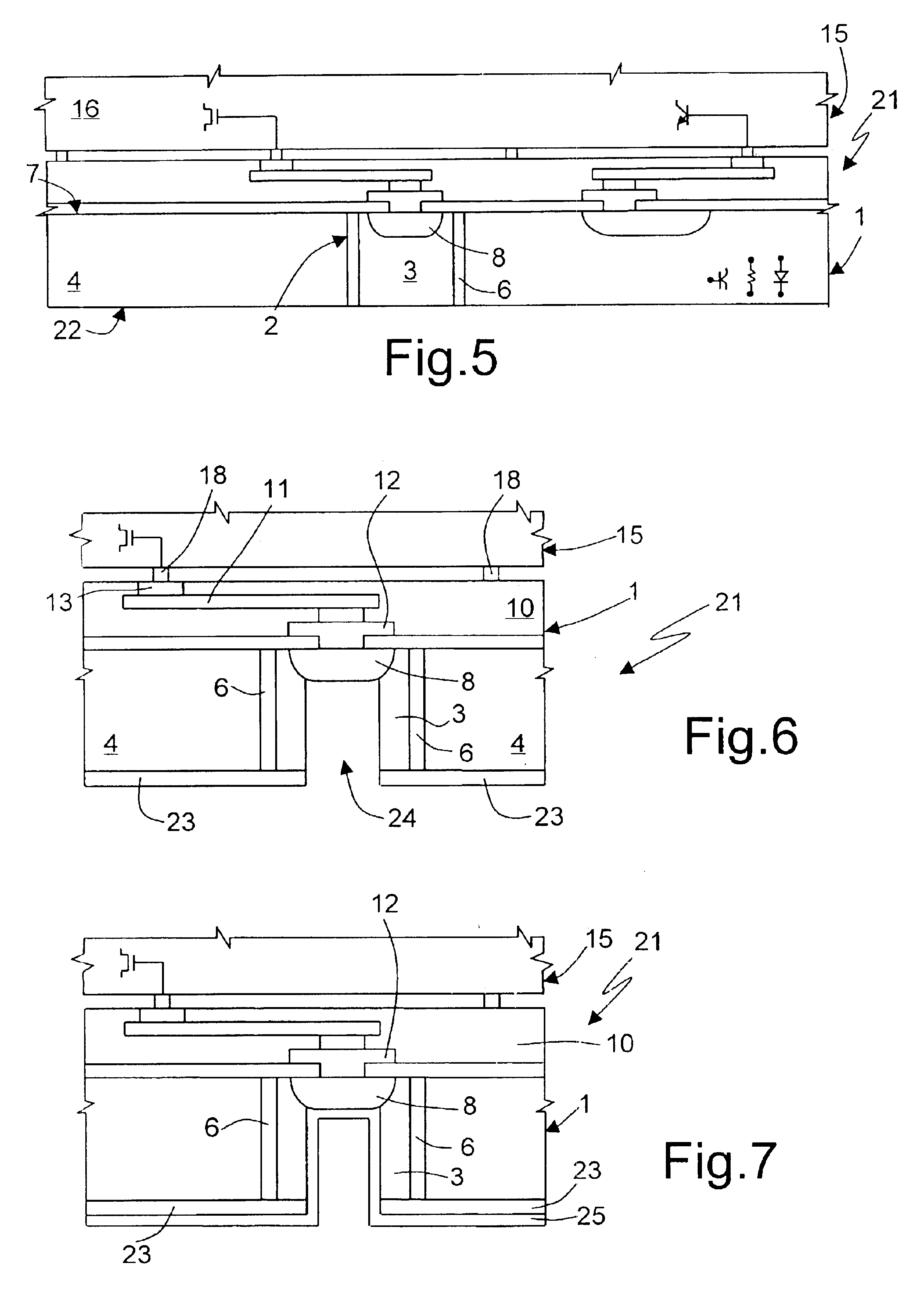

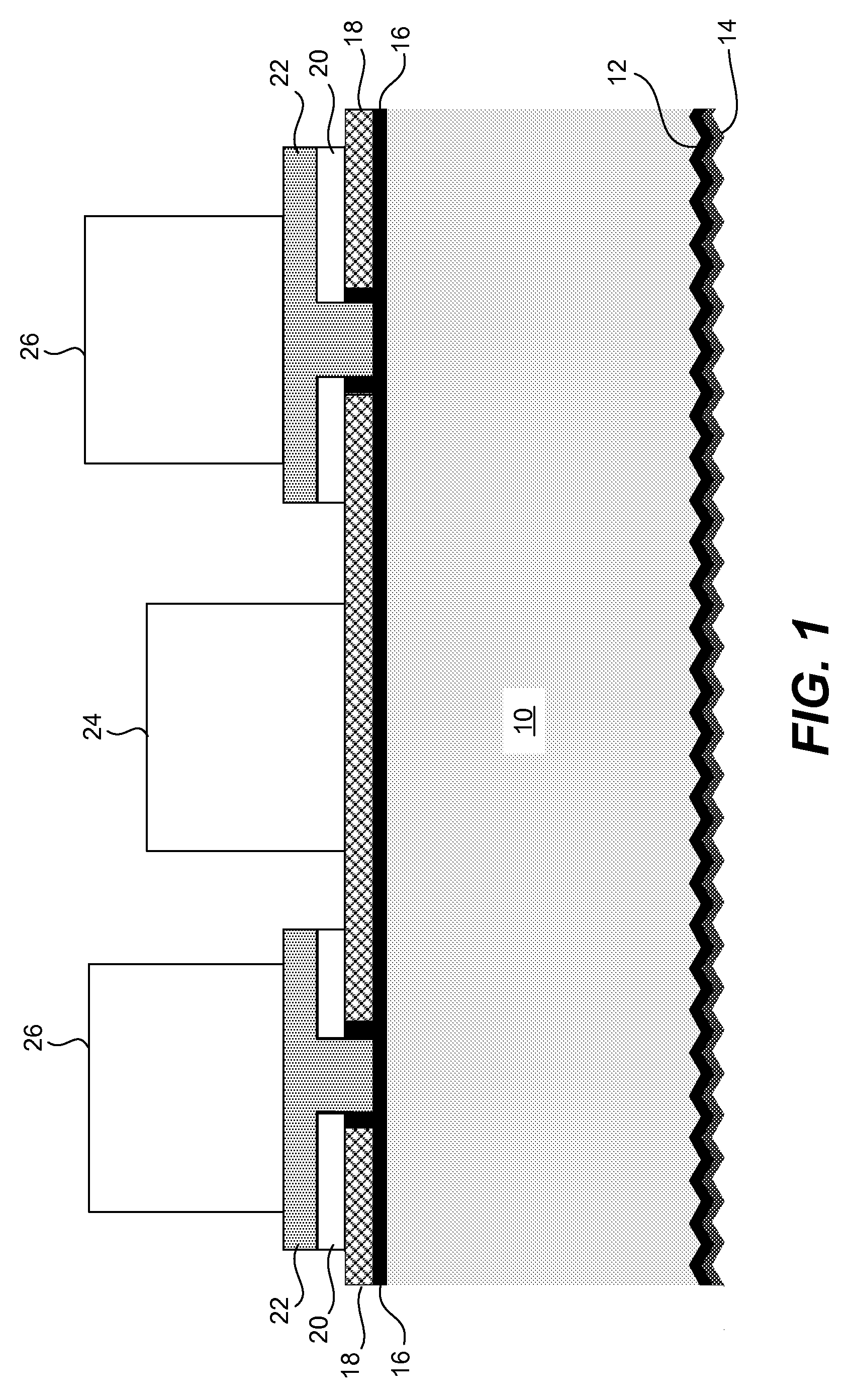

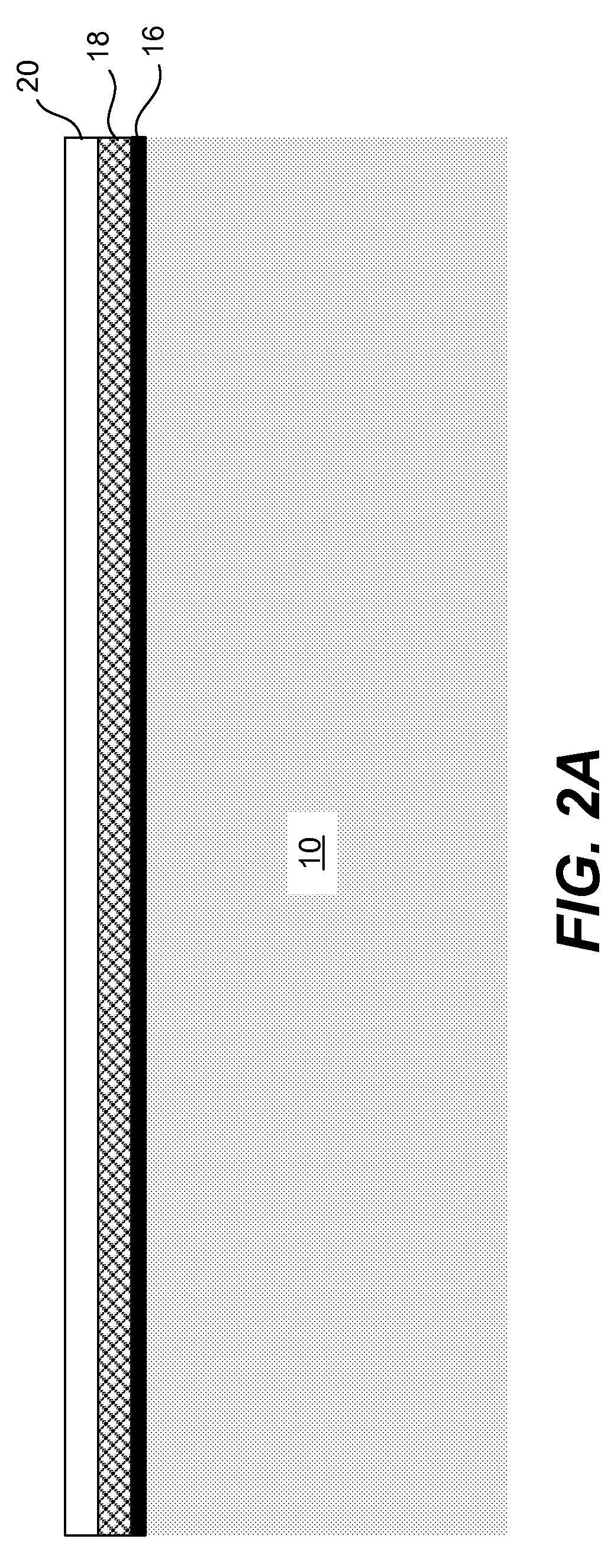

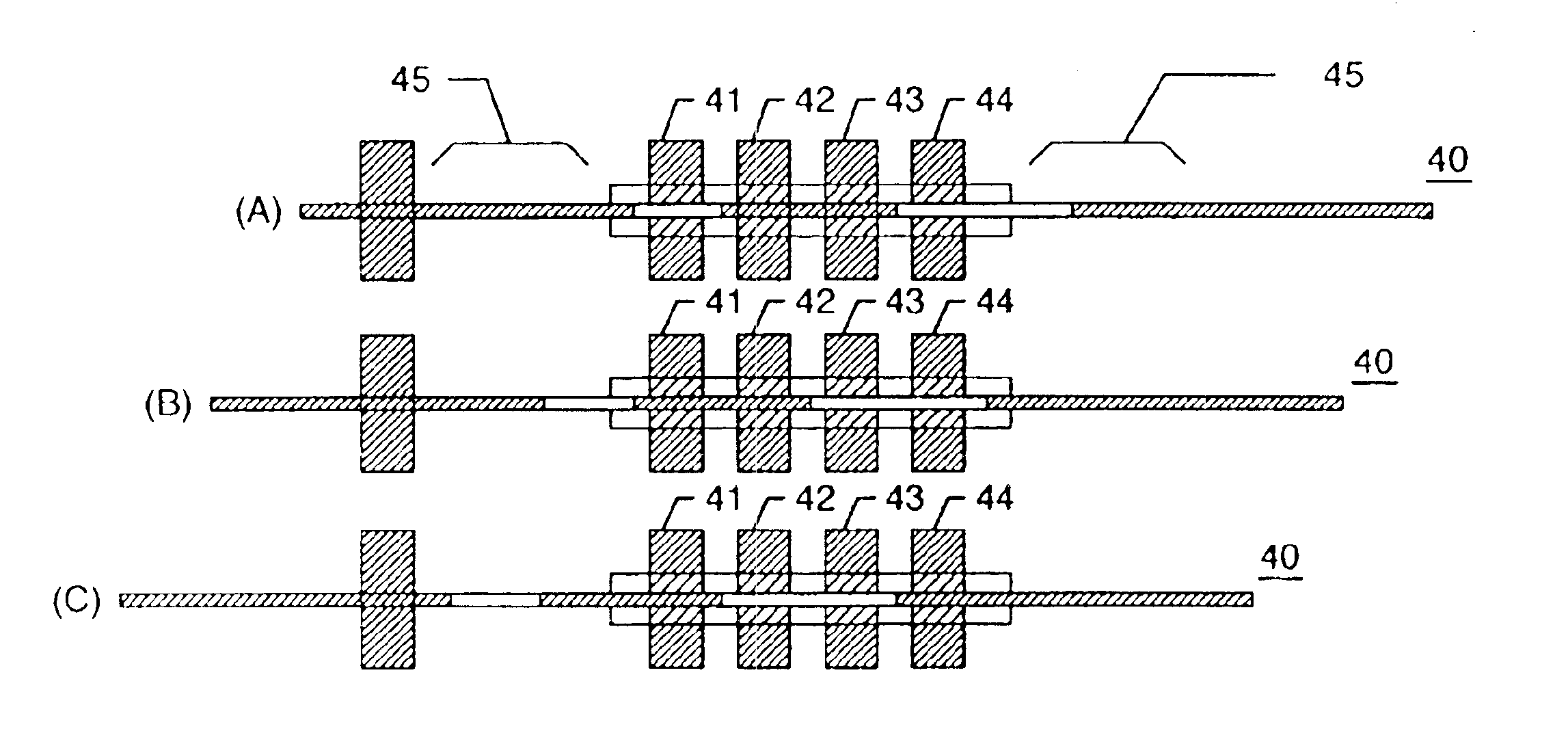

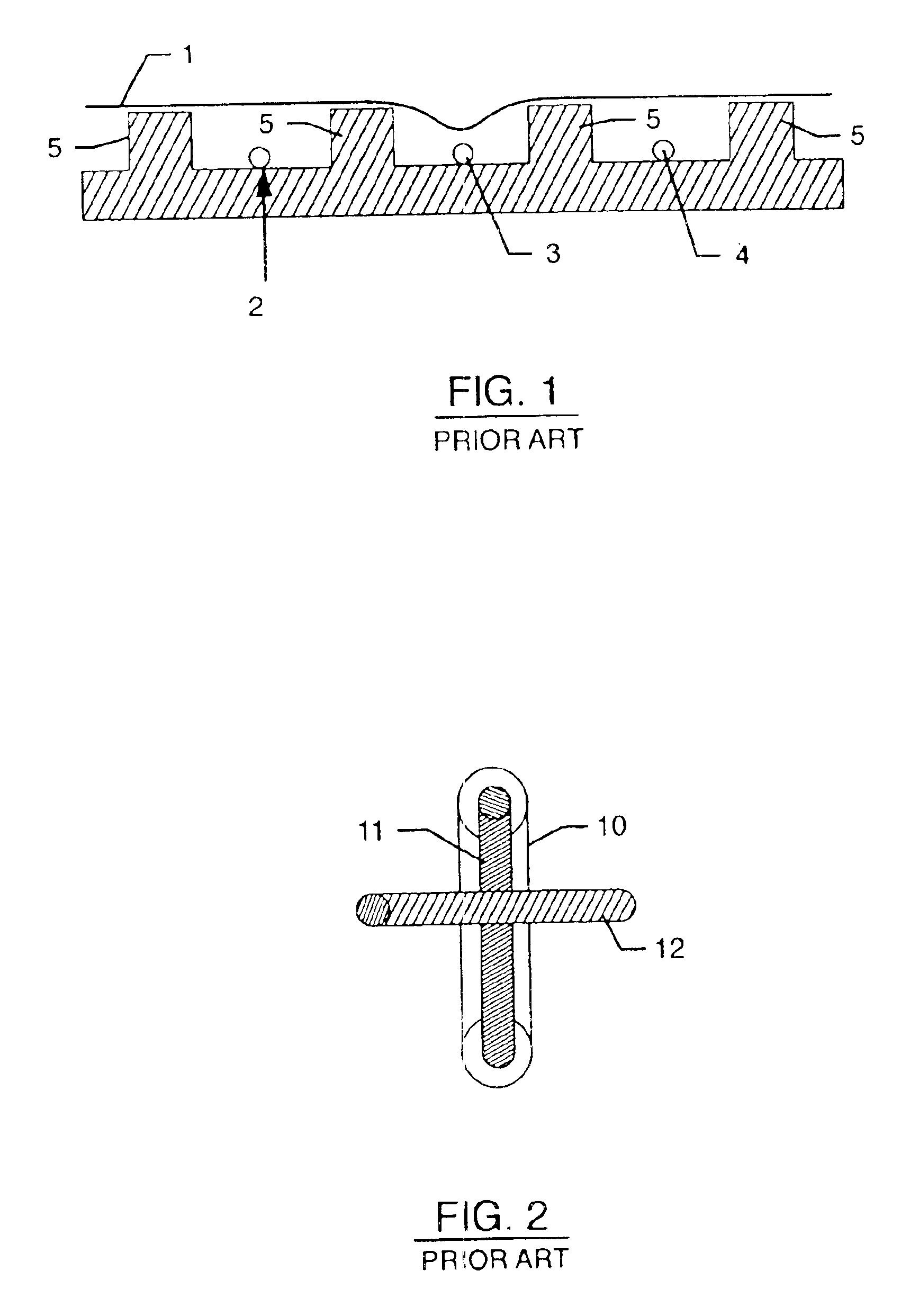

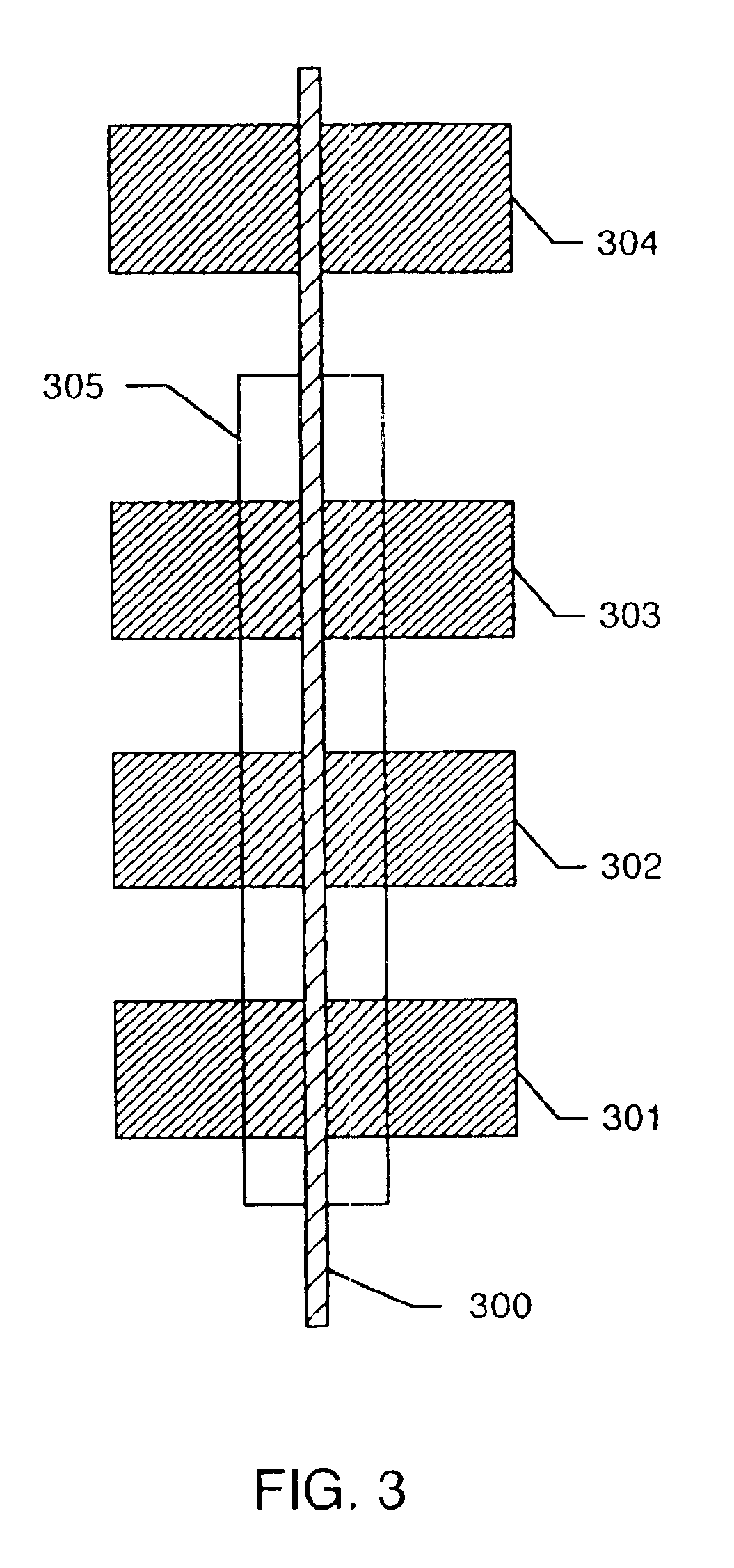

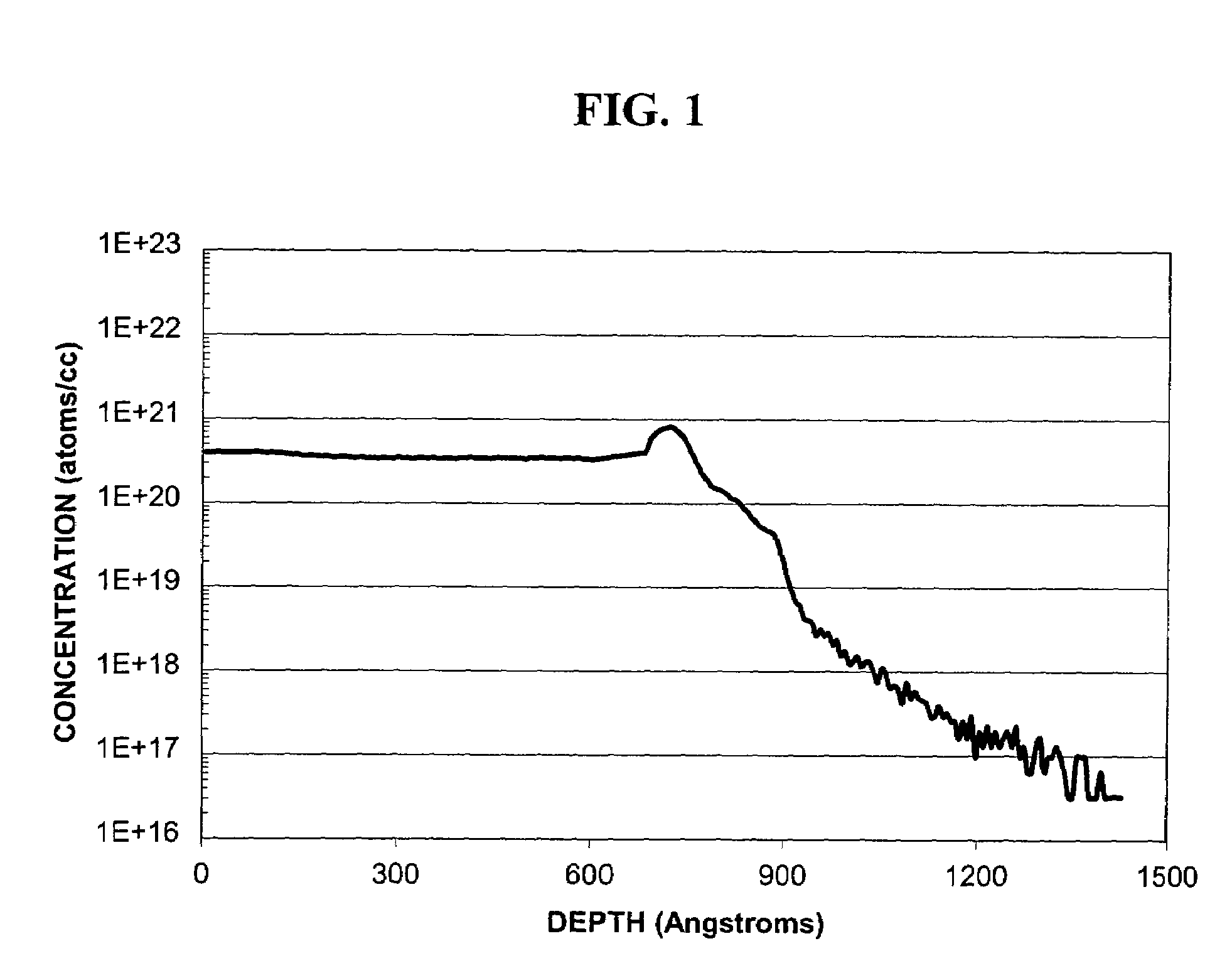

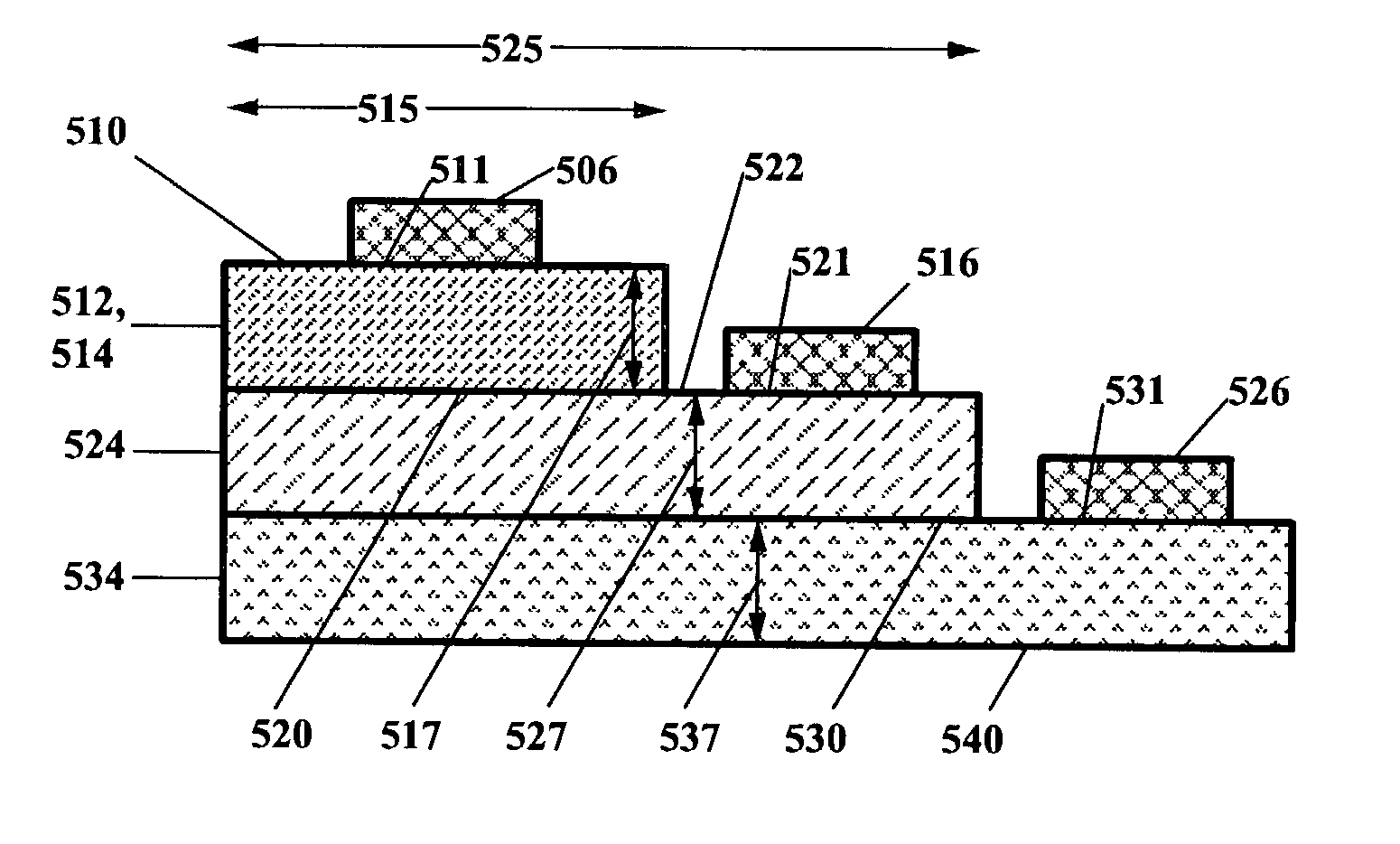

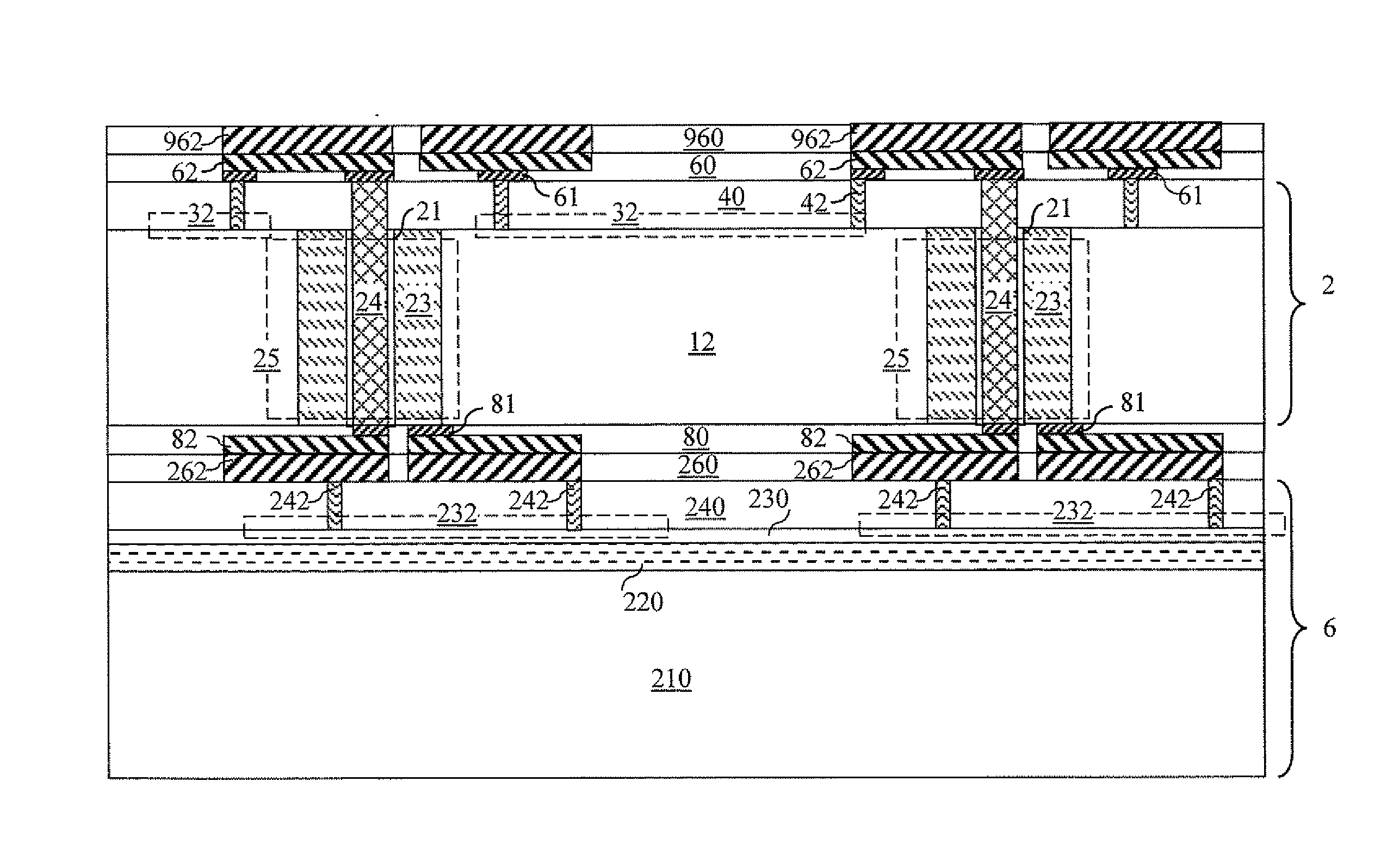

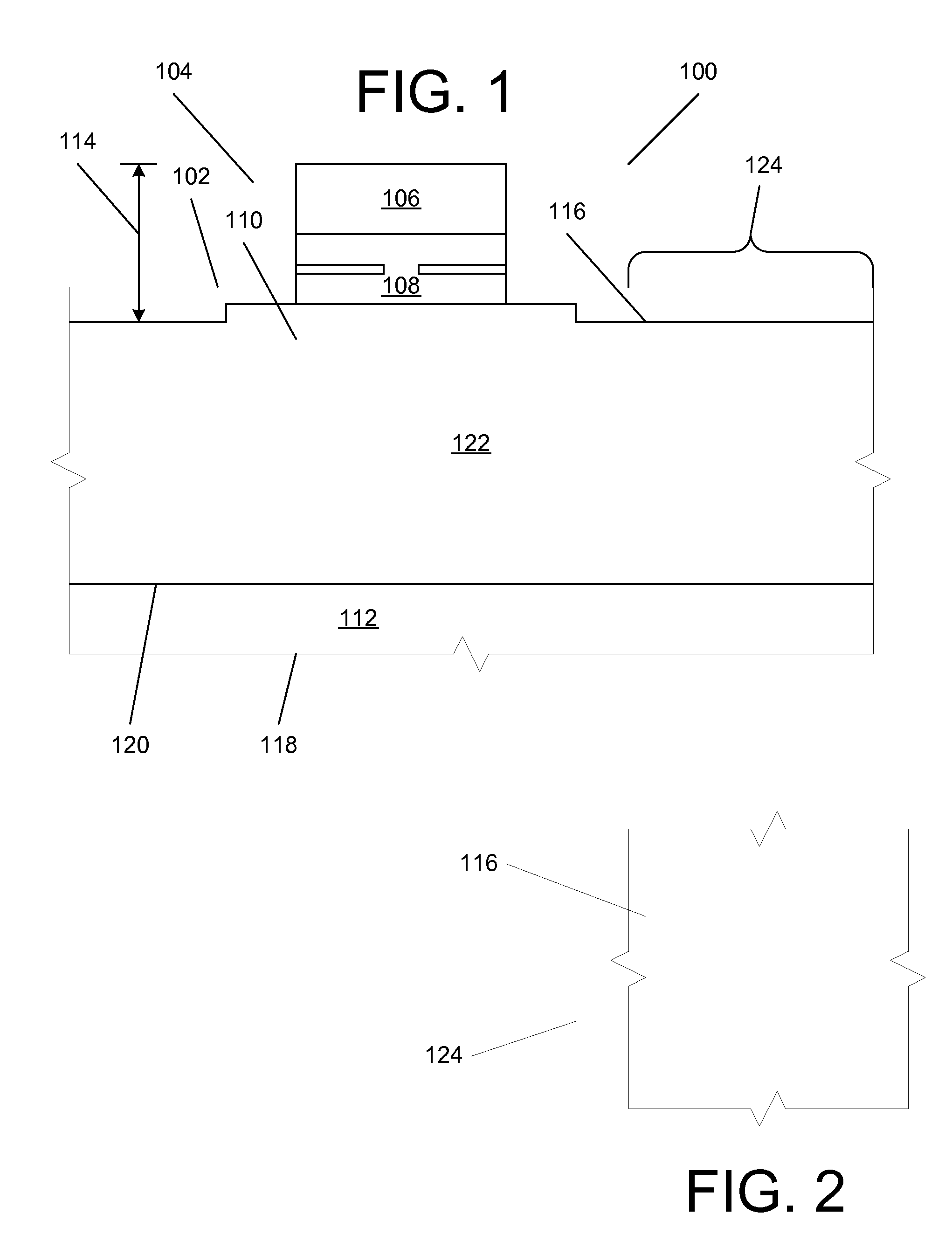

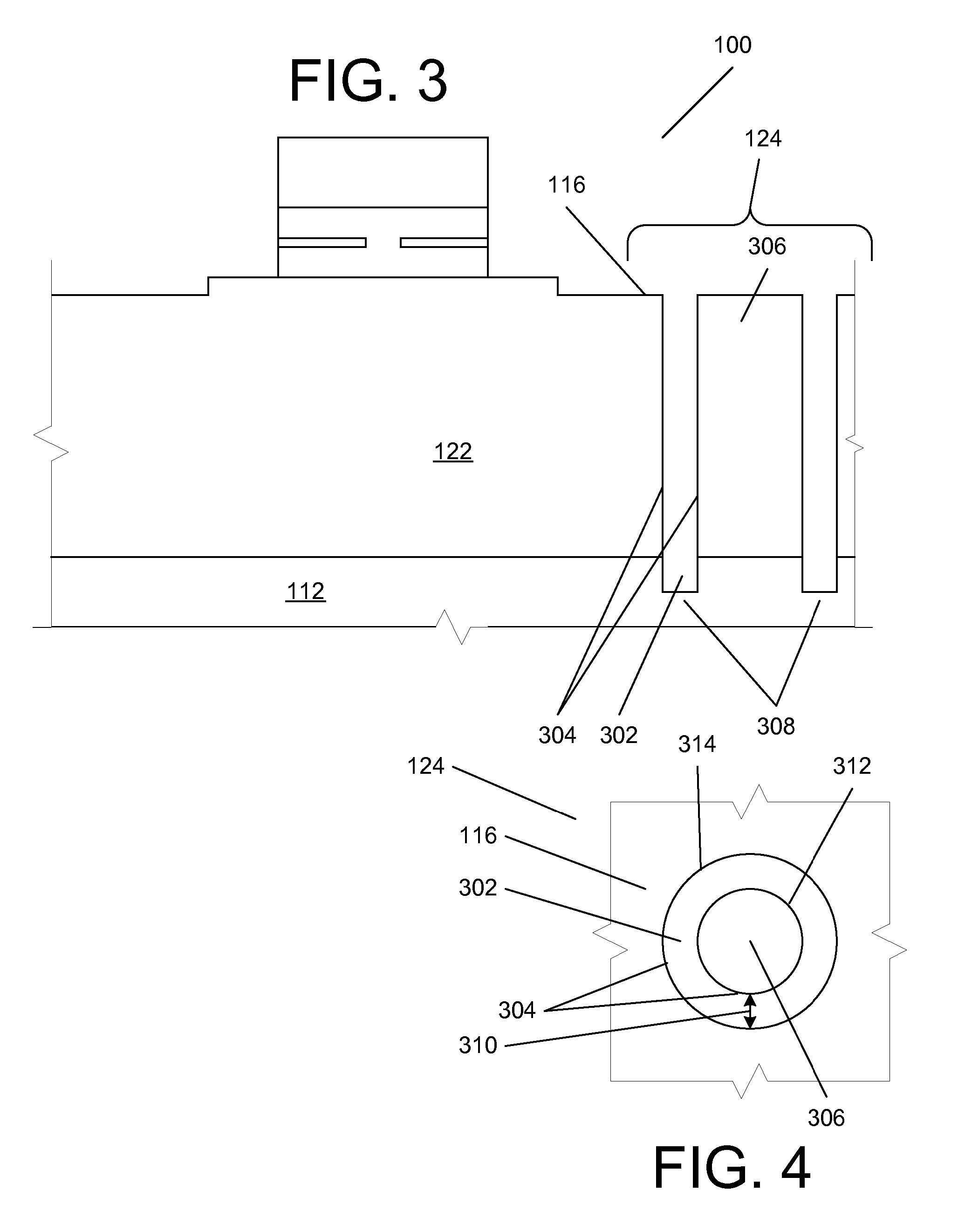

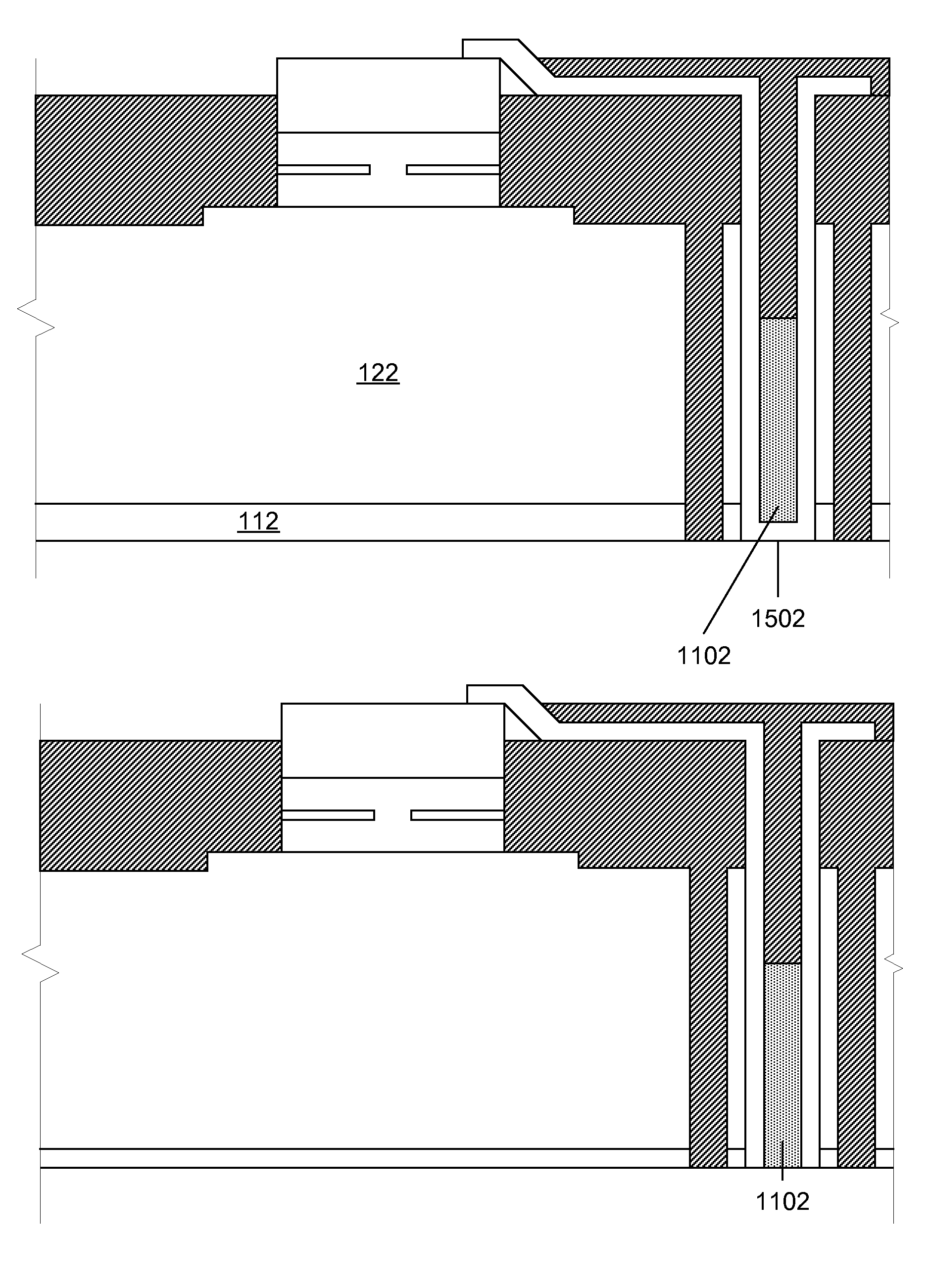

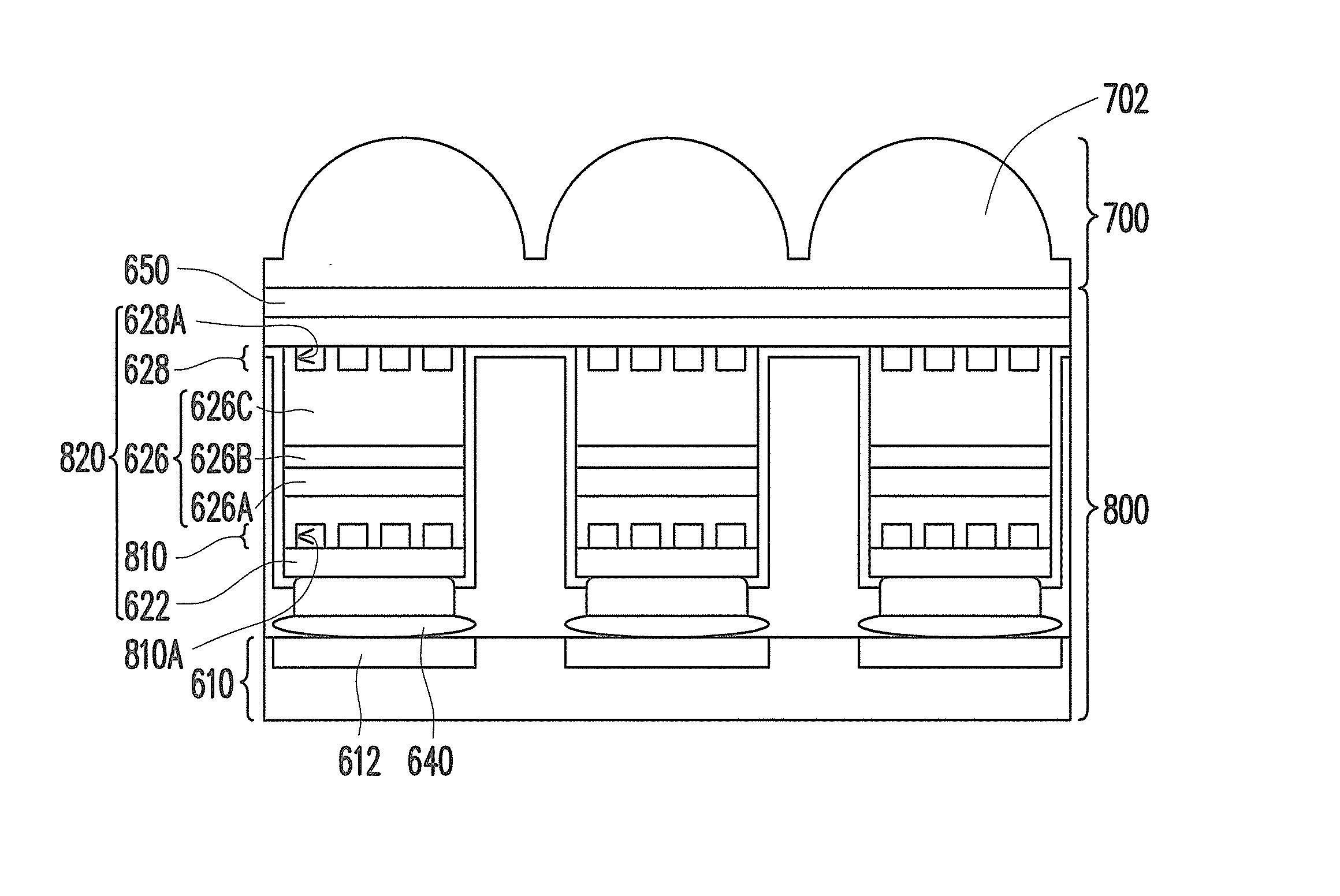

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

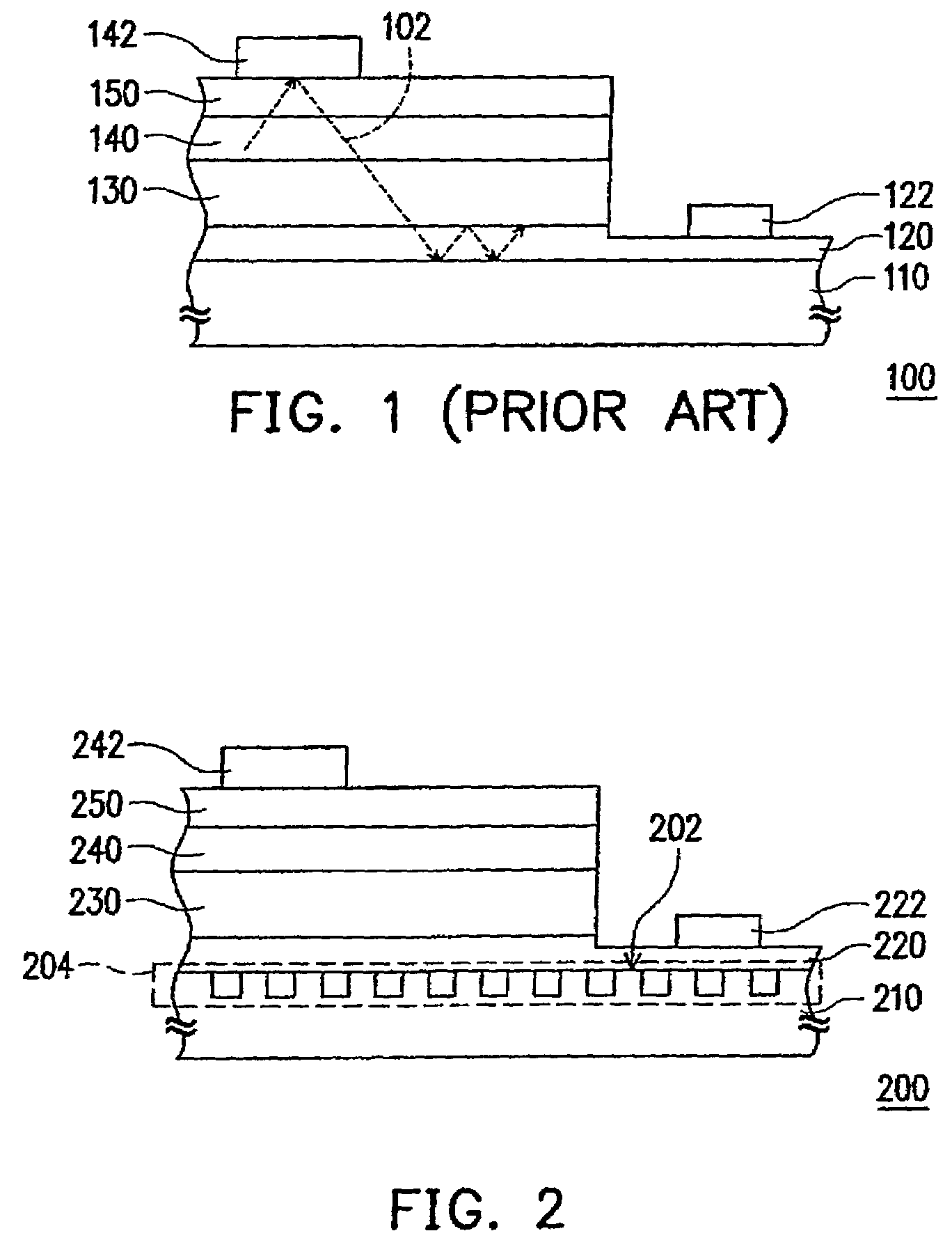

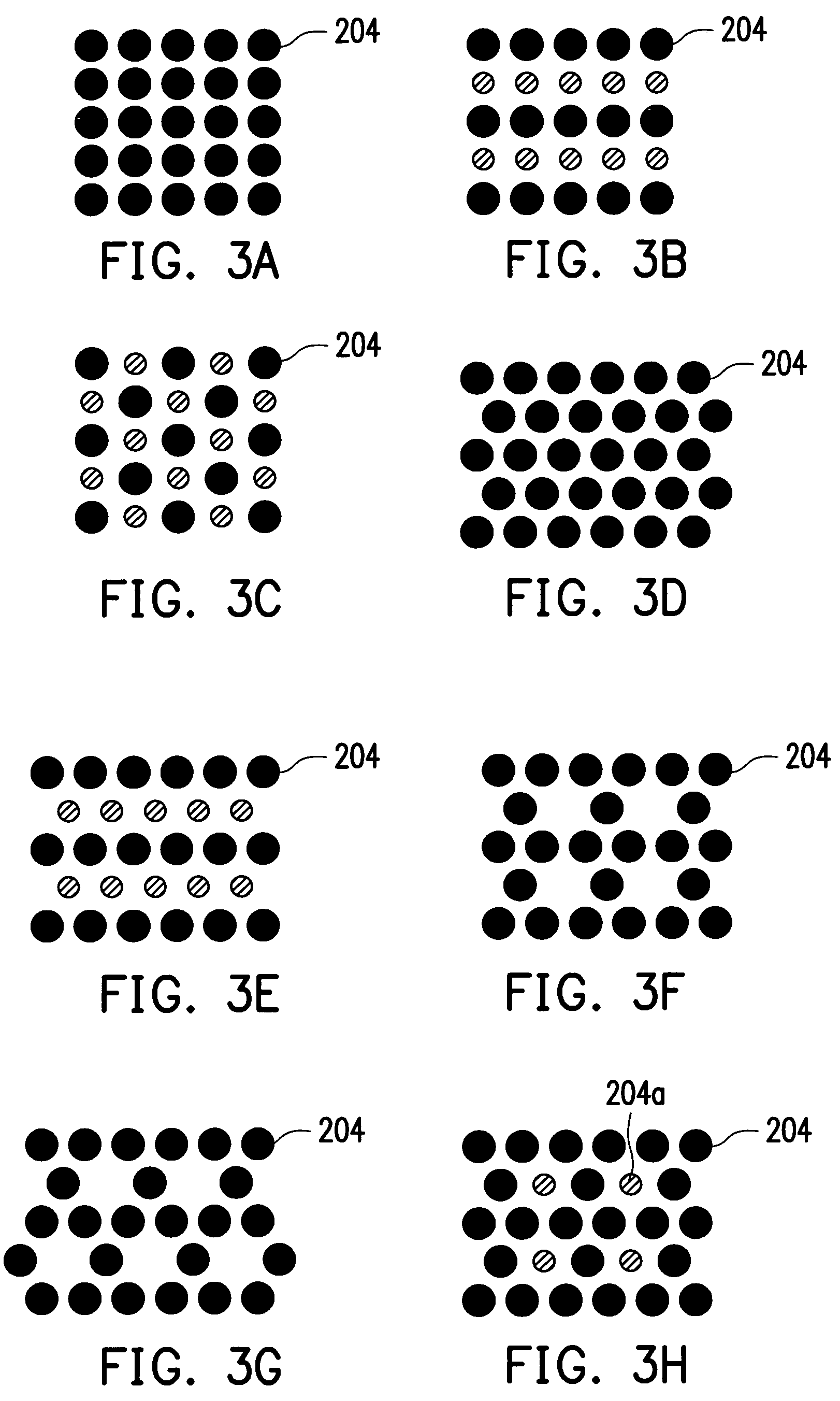

Power IC having SOI structure

The present invention relates in general to power ICs, etc. having the SOI structure, and more specifically to the structure in which an SOI substrate comprises a base substrate, an SOI oxide film formed on the base substrate, and active layers formed on the SOI oxide film, and also integrates on itself power devices and the corresponding control elements monolithically. Between this base substrate and this SOI oxide film is formed heavily-doped semiconductor regions having a conductivity type opposite to that of this base substrate. Hence, the junction capacitance between the base substrate and the heavily-doped semiconductor regions decreases an actual capacitance between the base substrate and the active layer so that to inhibit or prevent inversion layers from being formed at the bottom of the active layers.

Owner:KK TOSHIBA

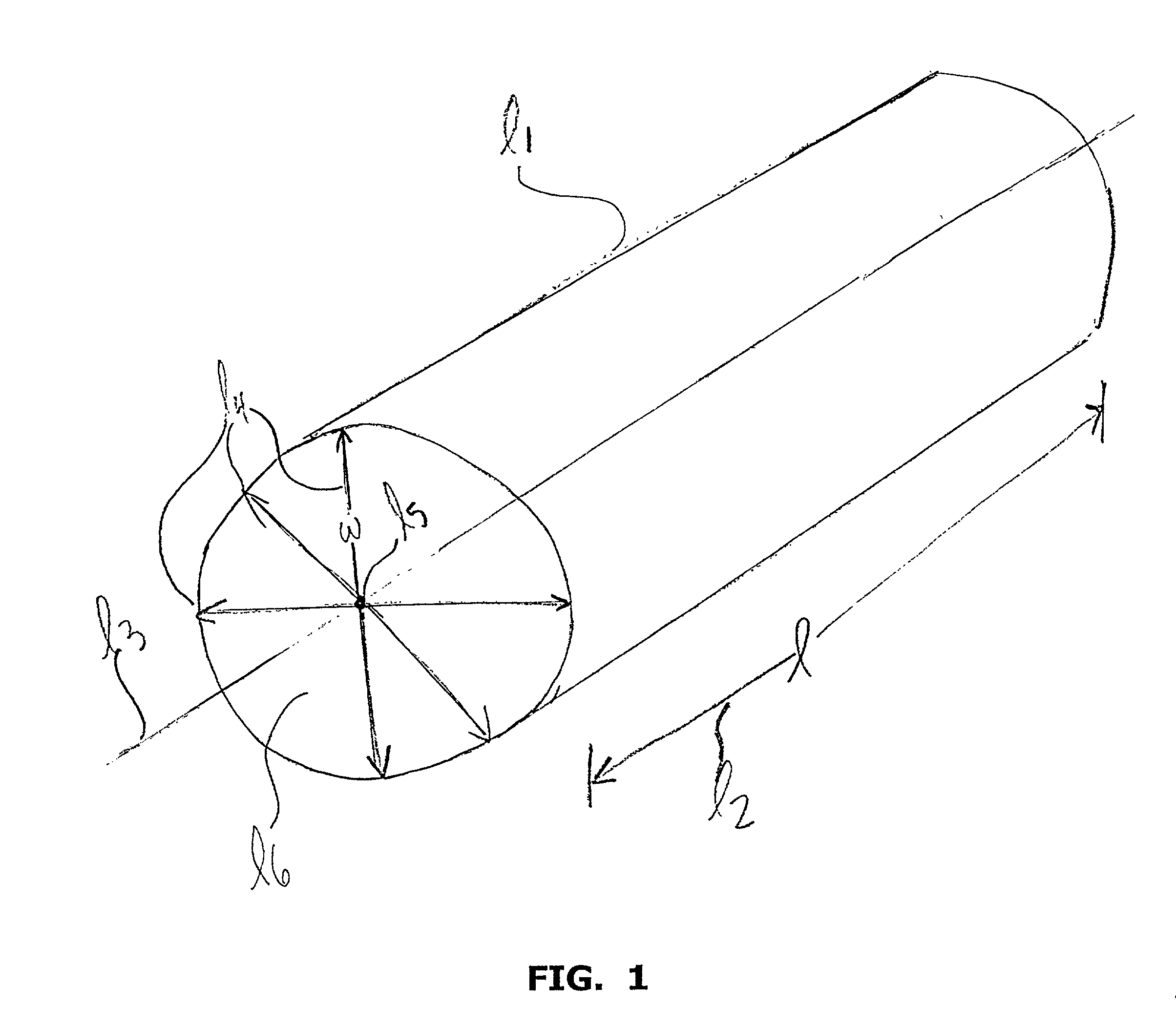

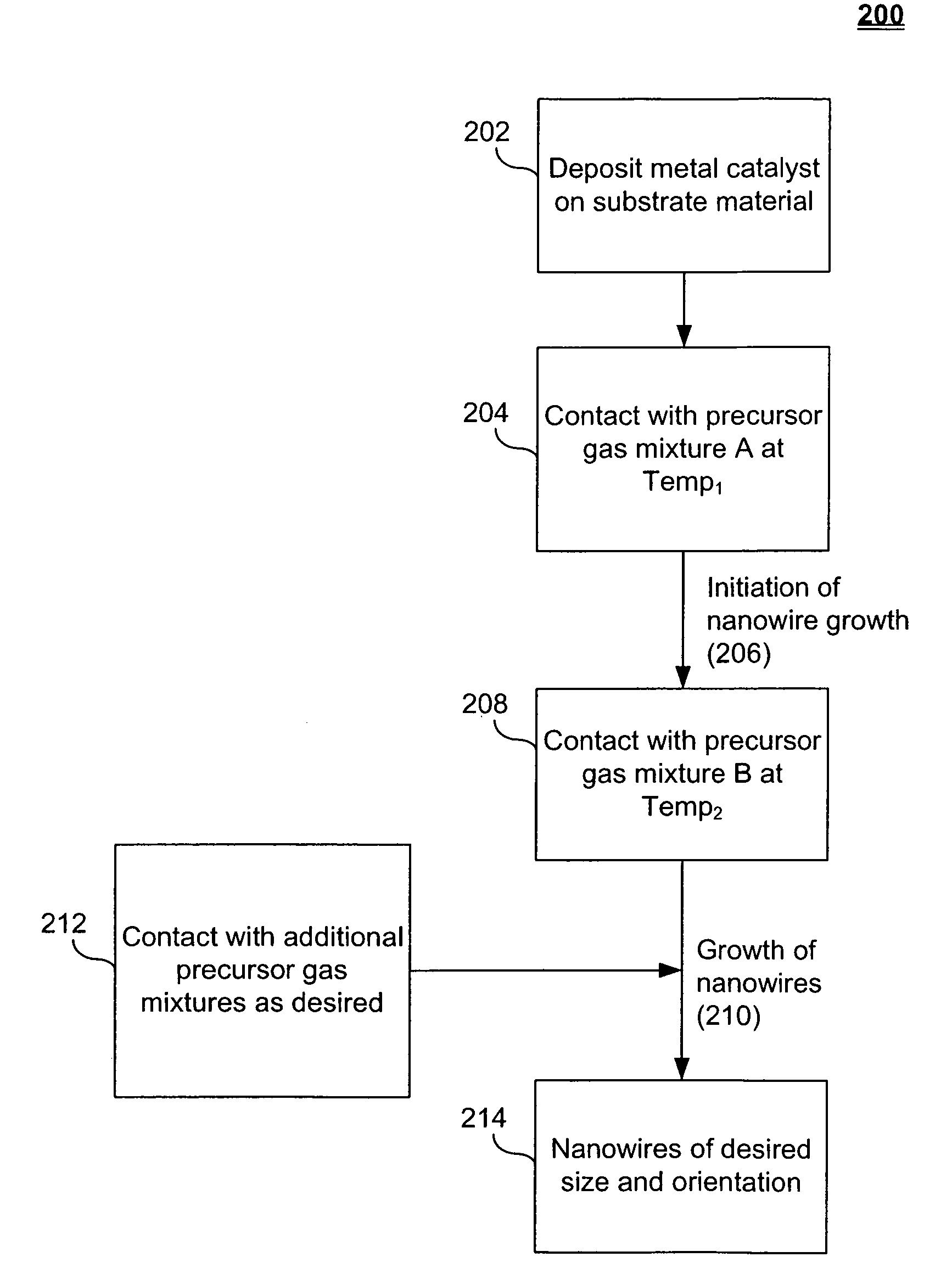

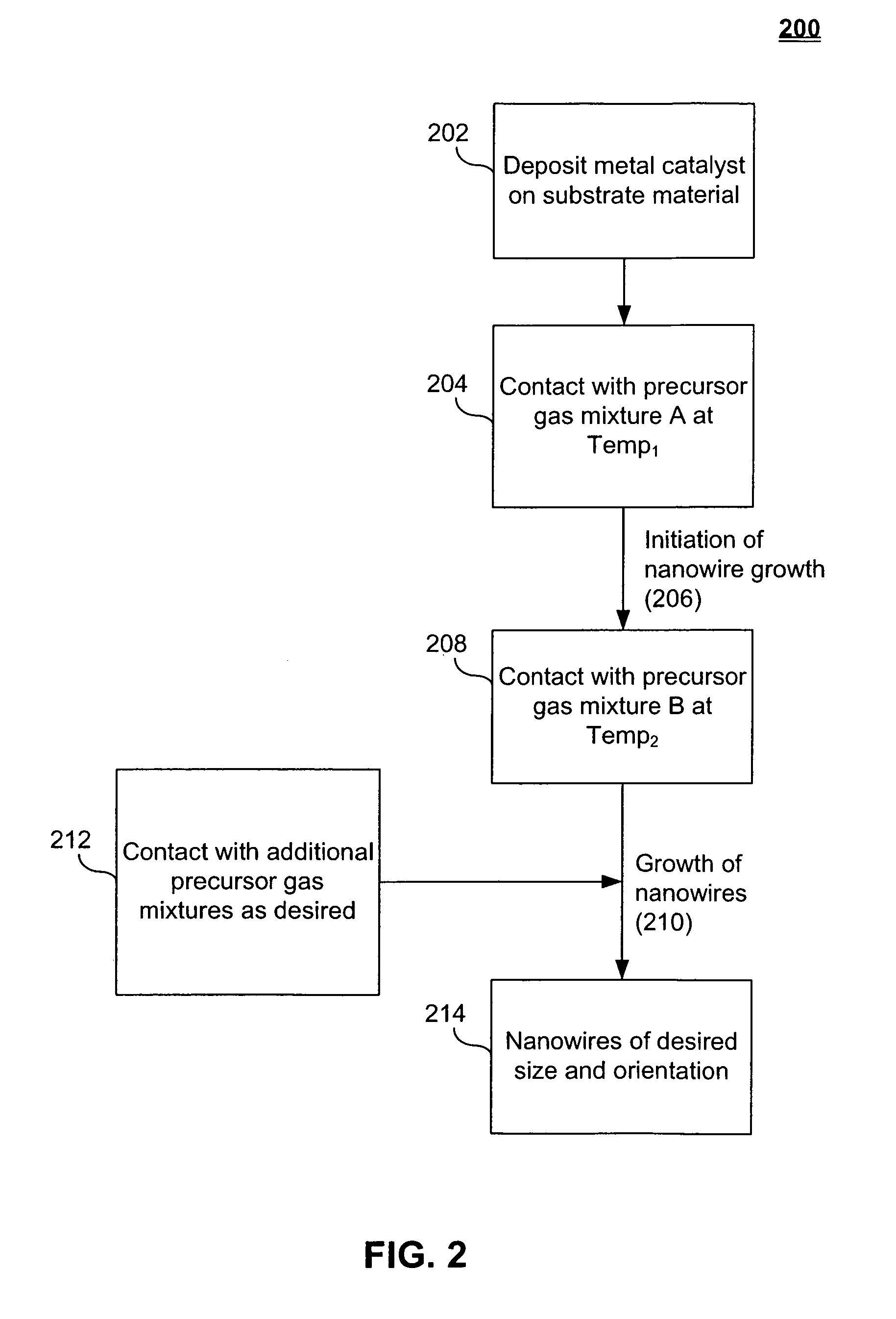

Systems and methods for nanowire growth and harvesting

ActiveUS7105428B2Minimize diffusionIncrease depositionMaterial nanotechnologyNanostructure manufactureNanowireSilicon

Owner:ONED MATERIAL INC

Chalcogenide memory device with multiple bits per cell

InactiveUS6838692B1Reduce energy inputSave energySolid-state devicesDigital storagePhase-change materialSemiconductor

A memory device with multiple bits per-cell. The memory device includes a side electrode; a doped semiconductor region disposed laterally in contact with a sidewall of the side electrode, such that the doped semiconductor region forms a diode, or the junction between the side electrode and the doped semiconductor region forms a diode; a layer of phase-changing material disposed laterally in contact with a sidewall of the doped semiconductor region, such that the doped semiconductor region is disposed between the layer of phase-changing material and the side electrode; and an upper electrode disposed on the layer of phase-changing material. Many storage regions can be stacked vertically, and multiple bits can be stored in one cell. Also, the contact area is reduced to a minimum dimension below the photolithographic limit.

Owner:MACRONIX INT CO LTD

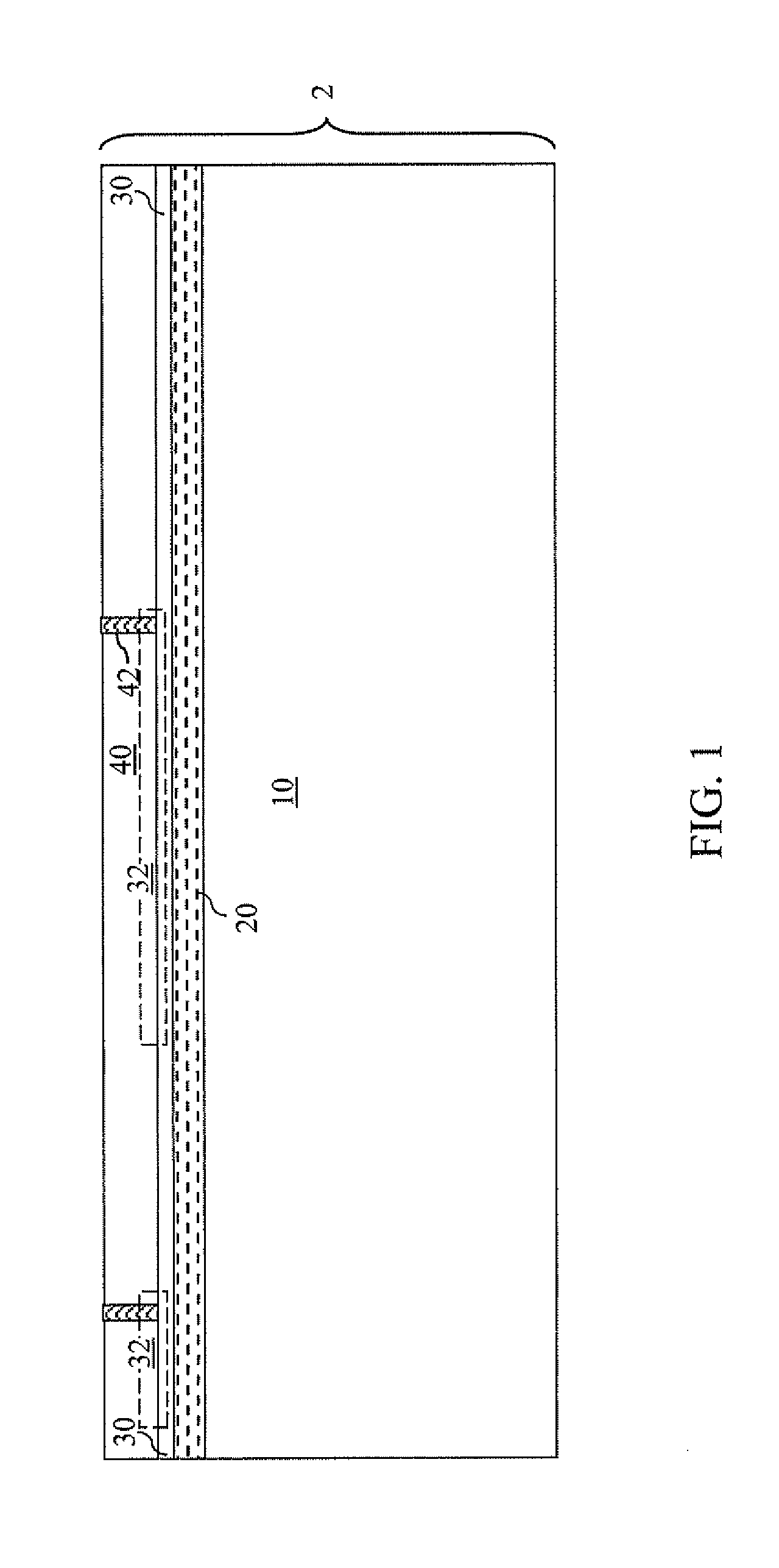

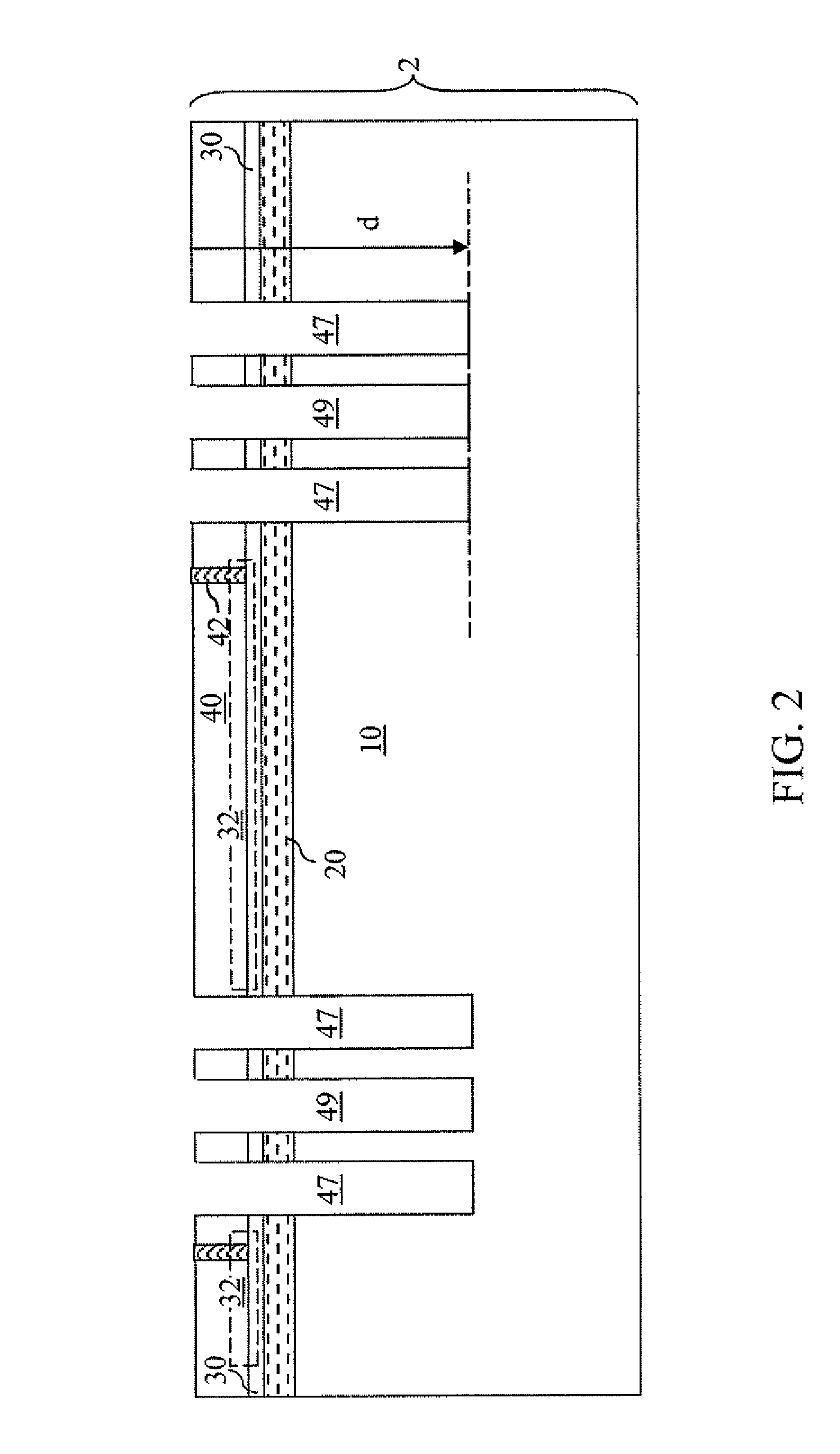

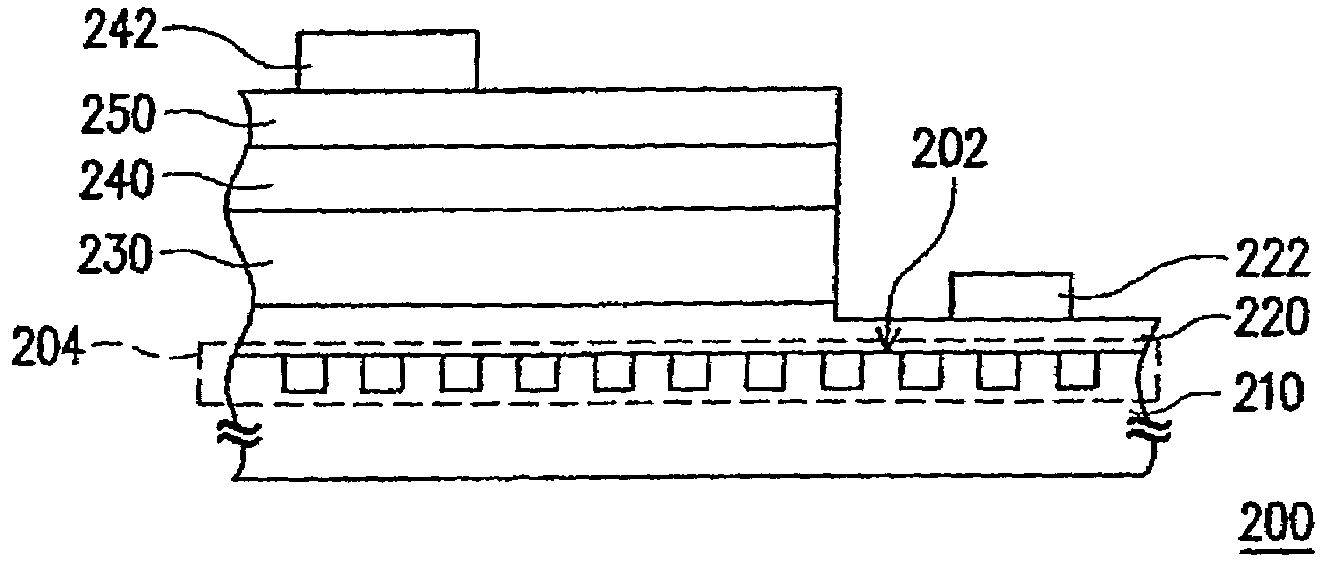

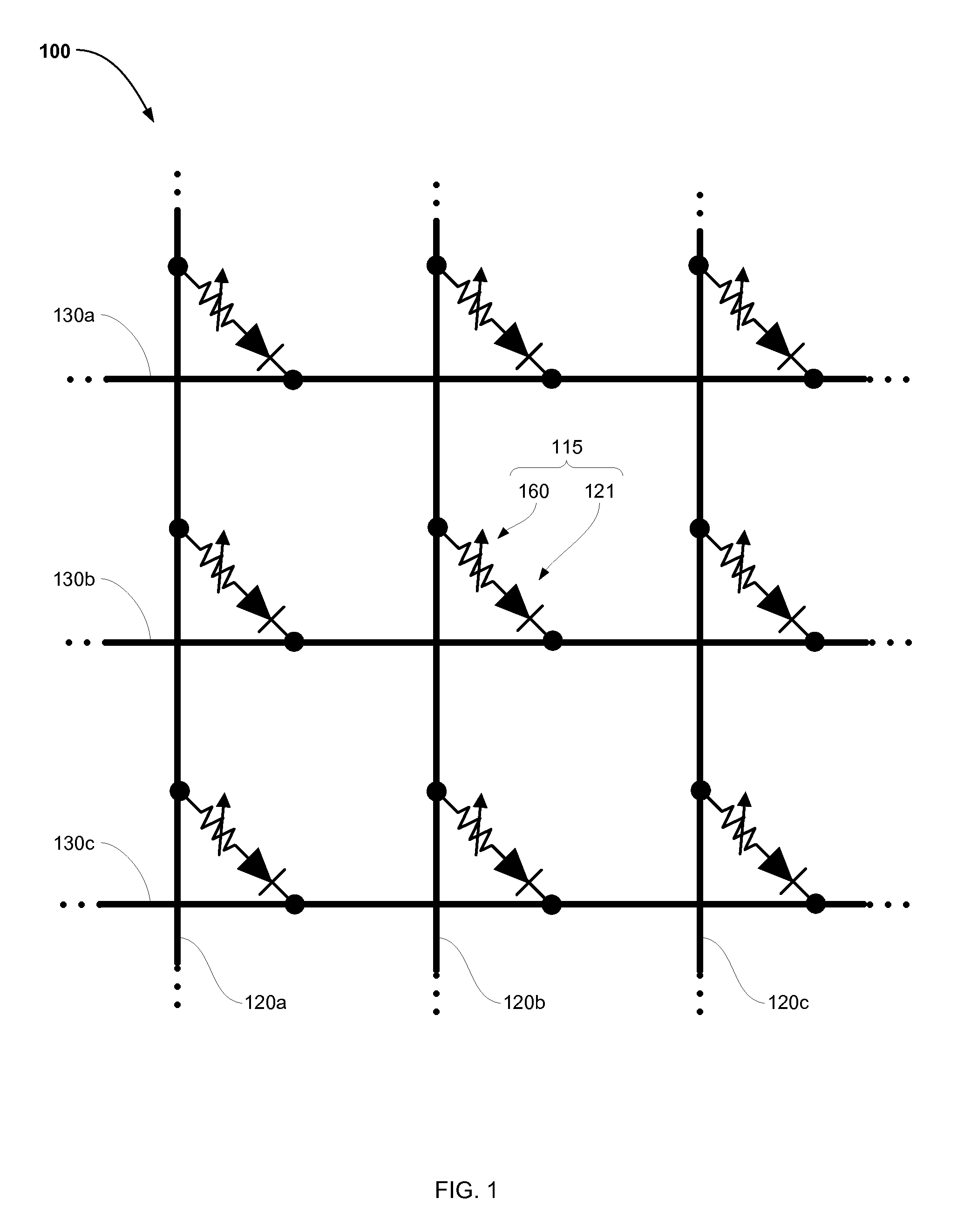

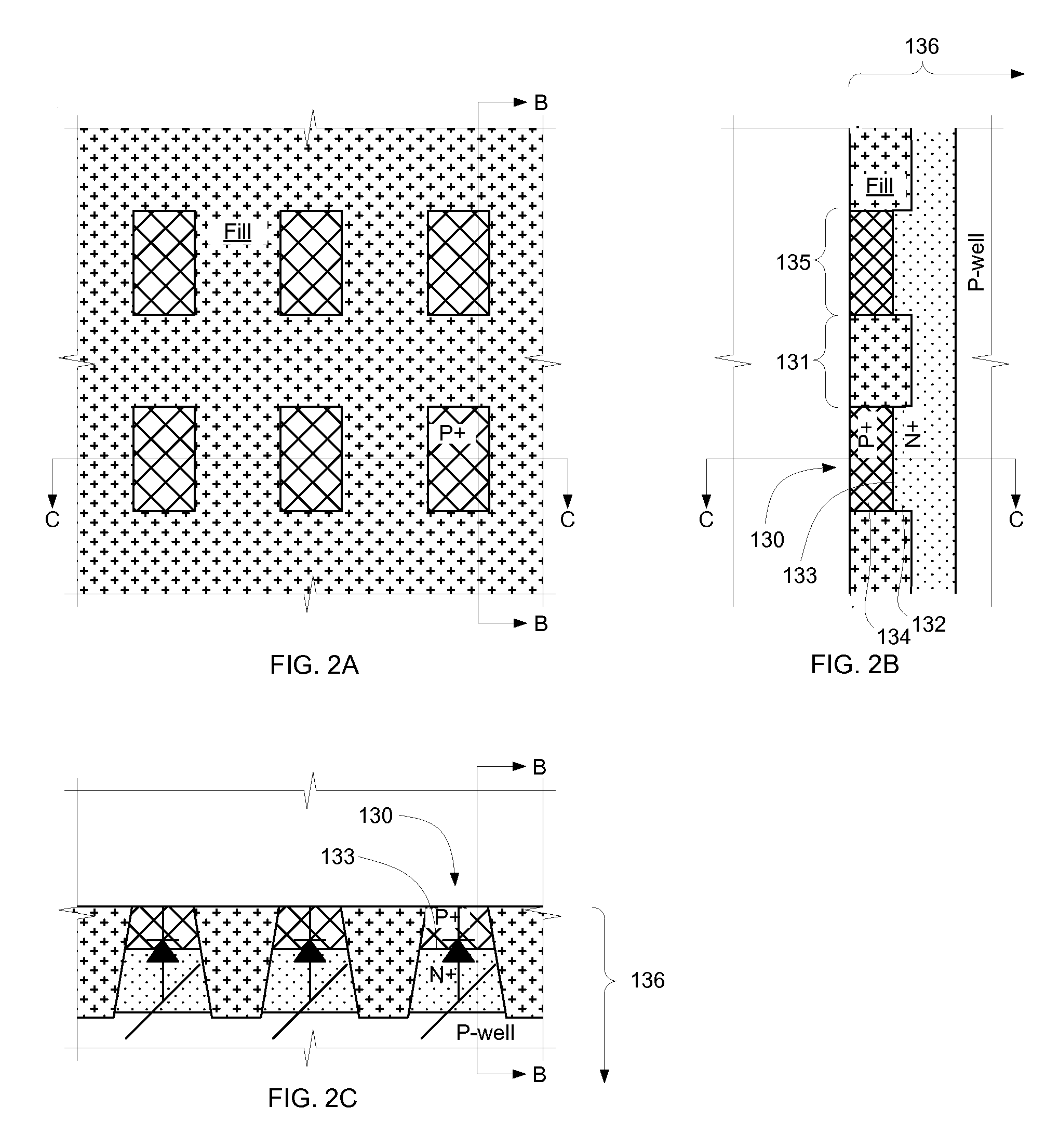

Backplanes for display applications, and components for use therein

InactiveUS7605799B2Slow changeLow cost manufacturingTransistorStatic indicating devicesCapacitanceDisplay device

A thin-film transistor includes a gate electrode having first and second gate electrode edges on opposed sides, and a drain electrode having a first edge that overlaps the first gate electrode edge, and a second edge that overlaps the second gate electrode edge. A diode array is fabricated by successive deposition of a conductive layer, a doped semiconductor layer and an undoped semiconductor layer adjacent to the substrate. A display pixel unit provides reduced capacitative coupling between a pixel electrode and a source line. The source line includes an extension that provides a source for the transistor. A patterned conductive portion is disposed adjacent to the source line. Another display pixel unit provides reduced pixel electrode voltage shifts using a source line and a balance line.

Owner:E INK CORPORATION

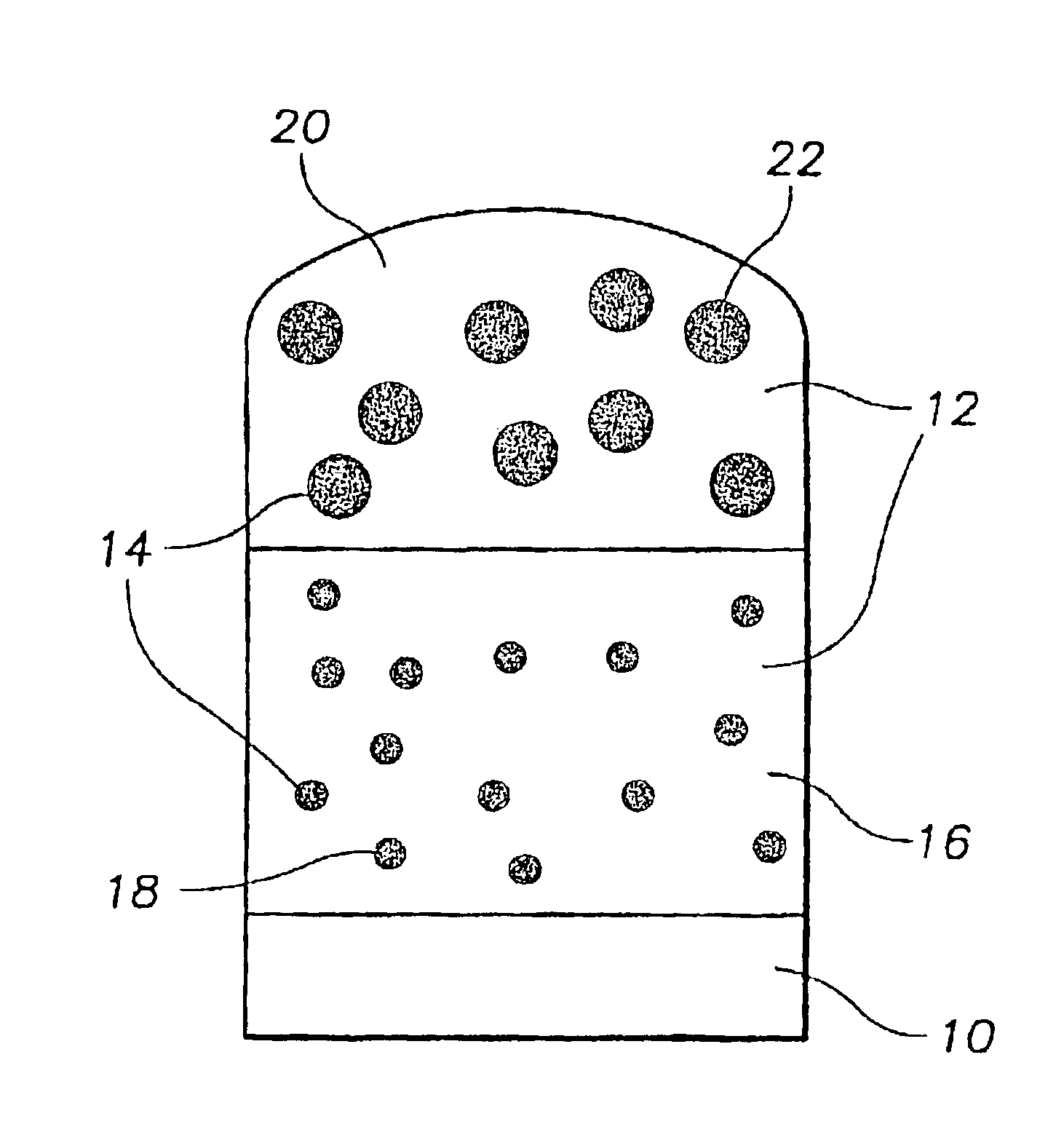

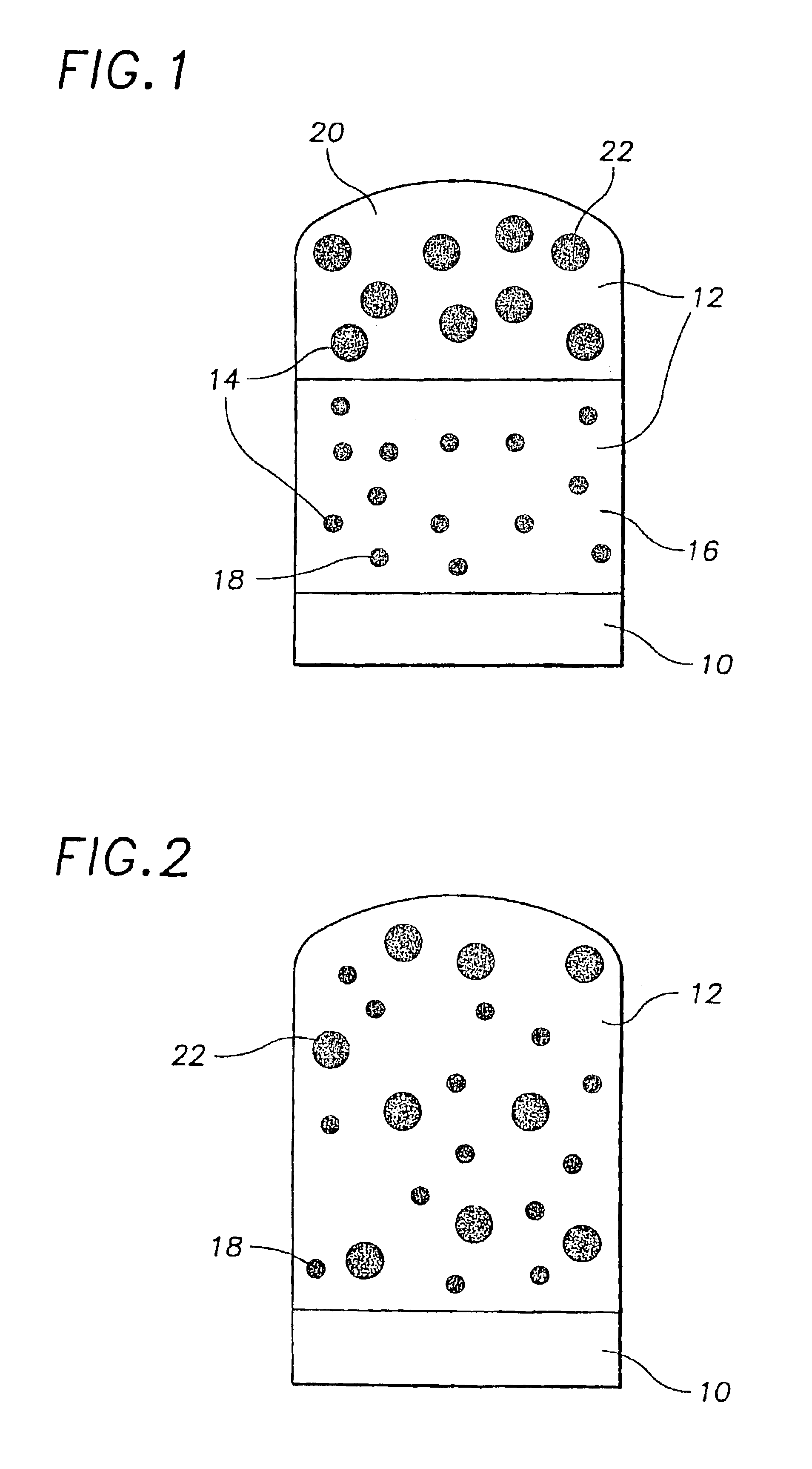

Quantum dot white and colored light emitting diodes

InactiveUS6890777B2Manufacturing flexibilityDesired colorLaser detailsNanoinformaticsPhotoluminescenceColored light

An electronic device comprising a population of quantum dots embedded in a host matrix and a primary light source which causes the dots to emit secondary light of a selected color, and a method of making such a device. The size distribution of the quantum dots is chosen to allow light of a particular color to be emitted therefrom. The light emitted from the device may be of either a pure (monochromatic) color, or a mixed (polychromatic) color, and may consist solely of light emitted from the dots themselves, or of a mixture of light emitted from the dots and light emitted from the primary source. The dots desirably are composed of an undoped semiconductor such as CdSe, and may optionally be overcoated to increase photoluminescence.

Owner:LUMILEDS

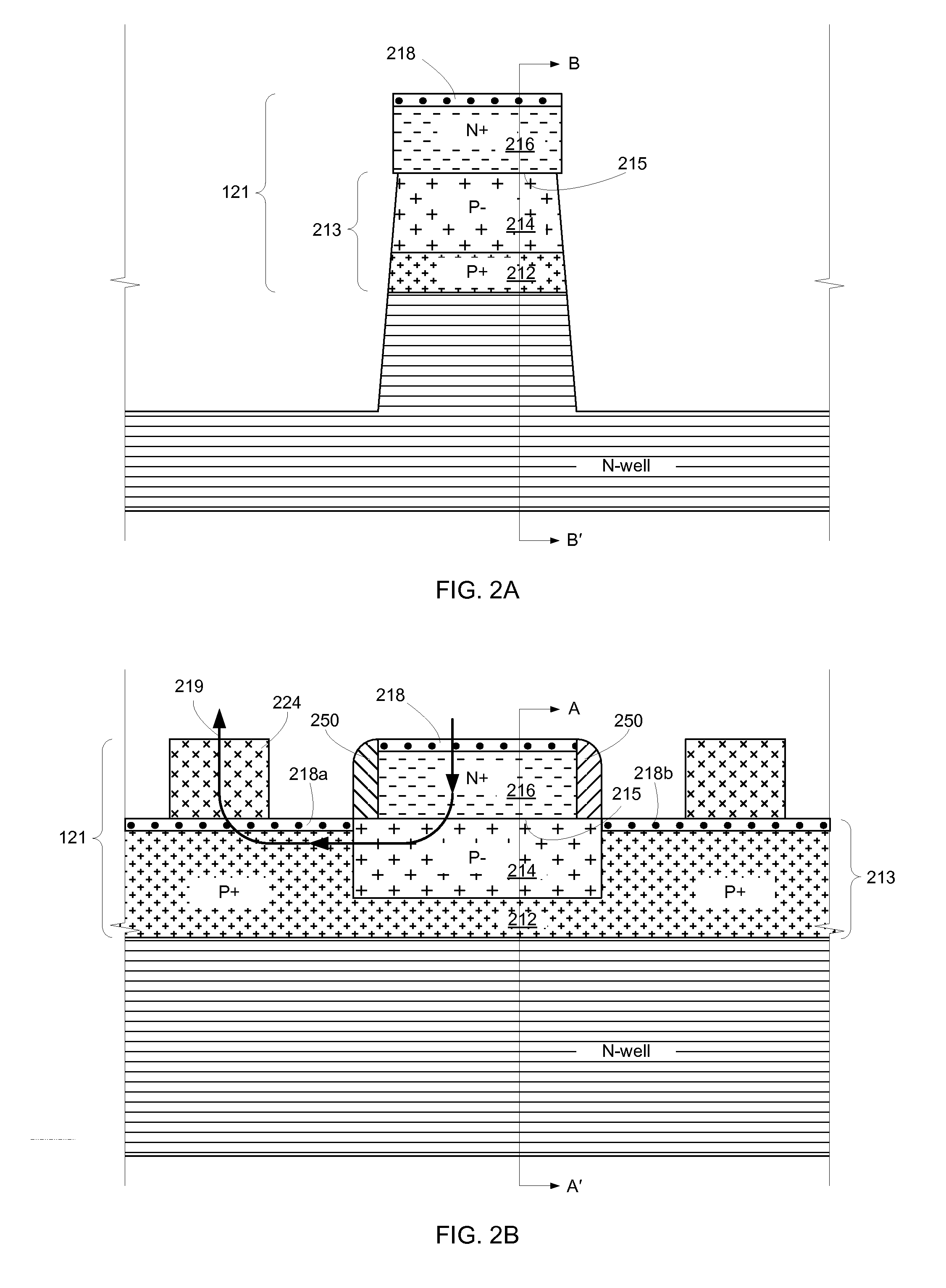

Memory cell access device having a pn-junction with polycrystalline and single-crystal semiconductor regions

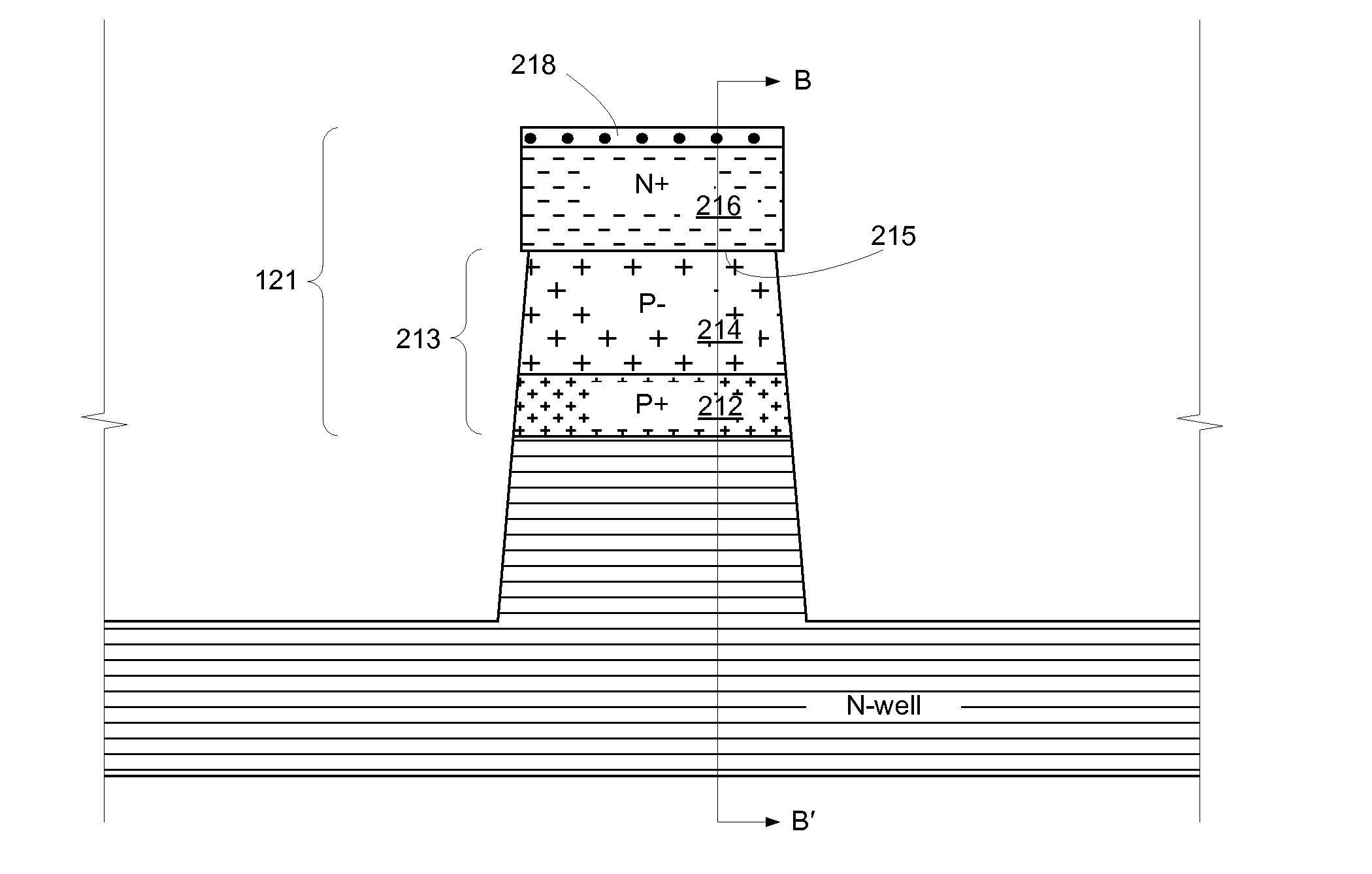

ActiveUS20100117048A1Inhibited DiffusionImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalP–n junction

A memory device includes a driver comprising a pn-junction in the form of a multilayer stack including a first doped semiconductor region having a first conductivity type, and a second doped semiconductor region having a second conductivity type opposite the first conductivity type, the first and second doped semiconductors defining a pn-junction therebetween, in which the first doped semiconductor region is formed in a single-crystalline semiconductor, and the second doped semiconductor region includes a polycrystalline semiconductor. Also, a method for making a memory device includes forming a first doped semiconductor region of a first conductivity type in a single-crystal semiconductor, such as on a semiconductor wafer; and forming a second doped polycrystalline semiconductor region of a second conductivity type opposite the first conductivity type, defining a pn-junction between the first and second regions.

Owner:MACRONIX INT CO LTD

Process for manufacturing a through insulated interconnection in a body of semiconductor material

InactiveUS6838362B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsInterconnection

The process for manufacturing a through insulated interconnection is performed by forming, in a body of semiconductor material, a trench extending from the front (of the body for a thickness portion thereof; filling the trench with dielectric material; thinning the body starting from the rear until the trench, so as to form an insulated region surrounded by dielectric material; and forming a conductive region extending inside said insulated region between the front and the rear of the body and having a higher conductivity than the first body. The conductive region includes a metal region extending in an opening formed inside the insulated region or of a heavily doped semiconductor region, made prior to filling of the trench.

Owner:STMICROELECTRONICS SRL +1

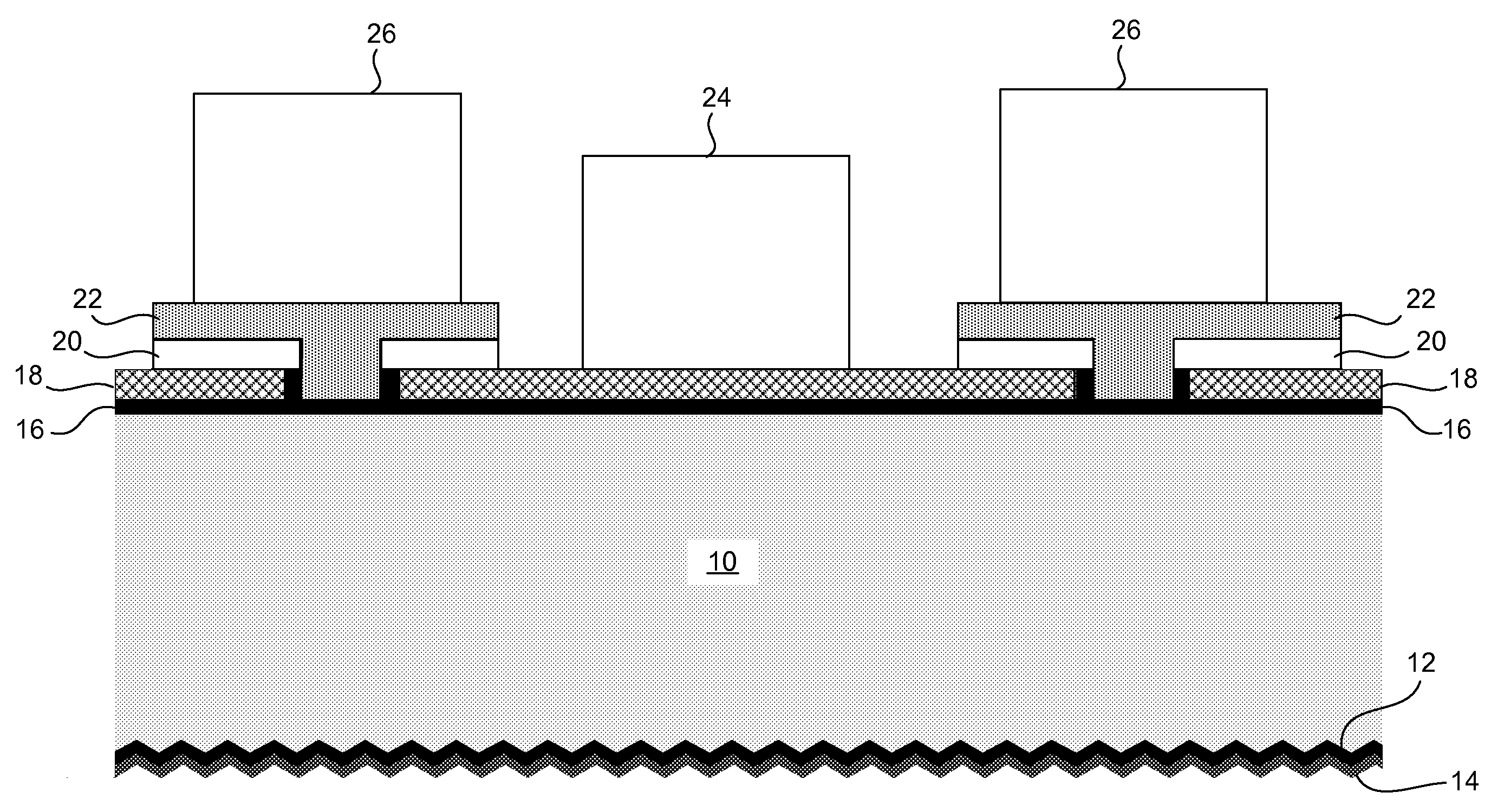

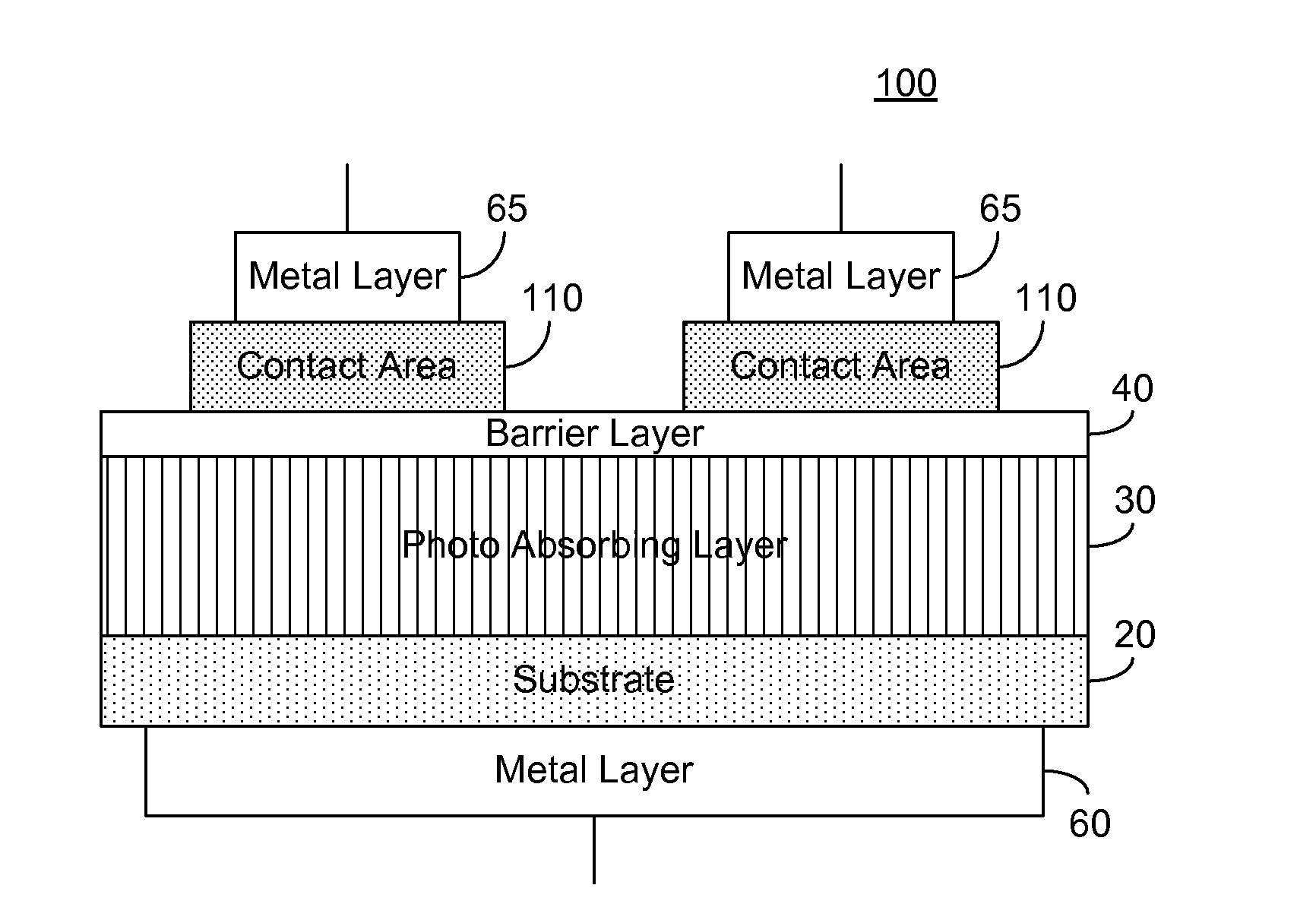

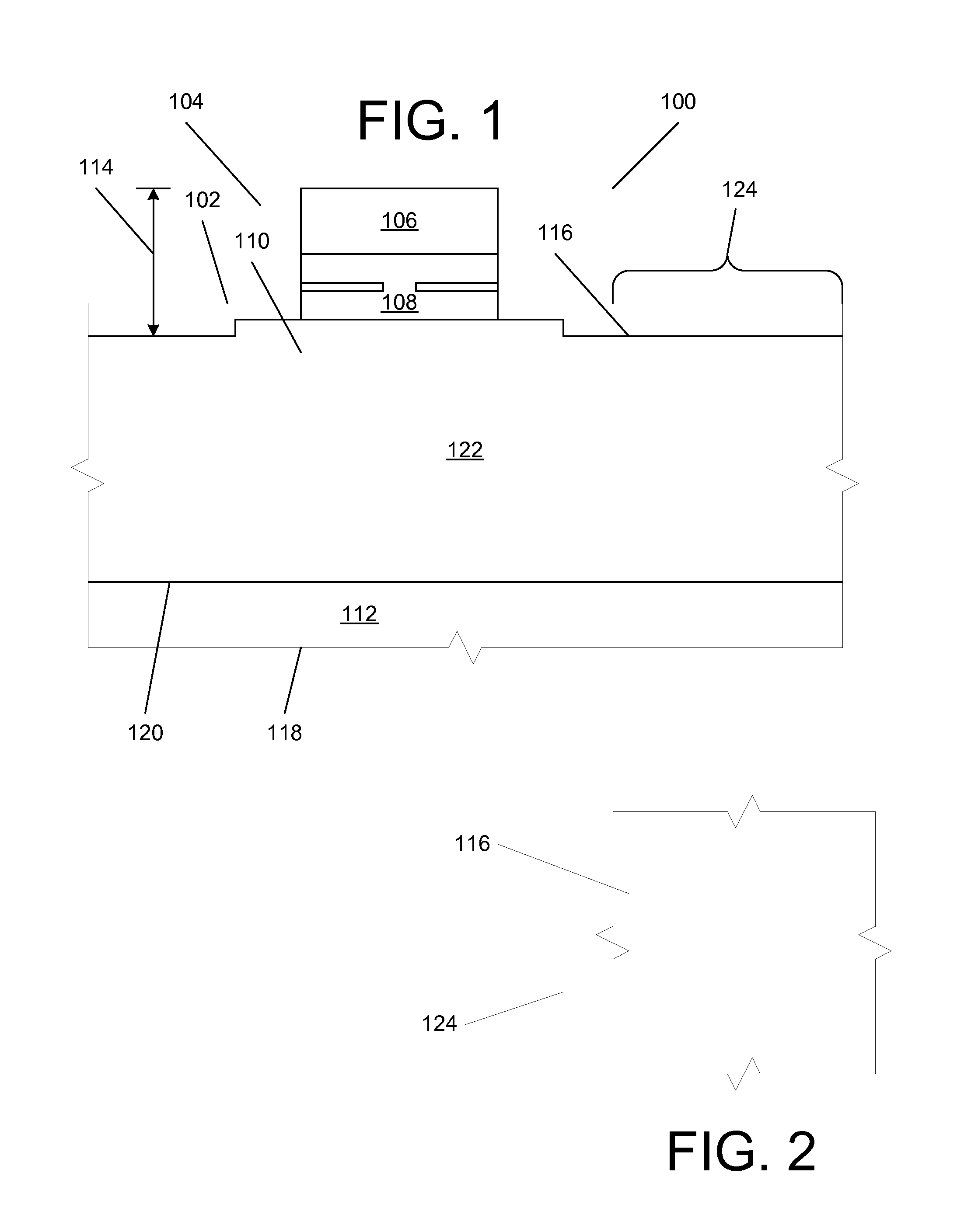

Solar cell having doped semiconductor heterojunction contacts

A silicon solar cell has doped amorphous silicon contacts formed on a tunnel silicon oxide layer on a surface of a silicon substrate. High temperature processing is unnecessary in fabricating the solar cell.

Owner:MAXEON SOLAR PTE LTD

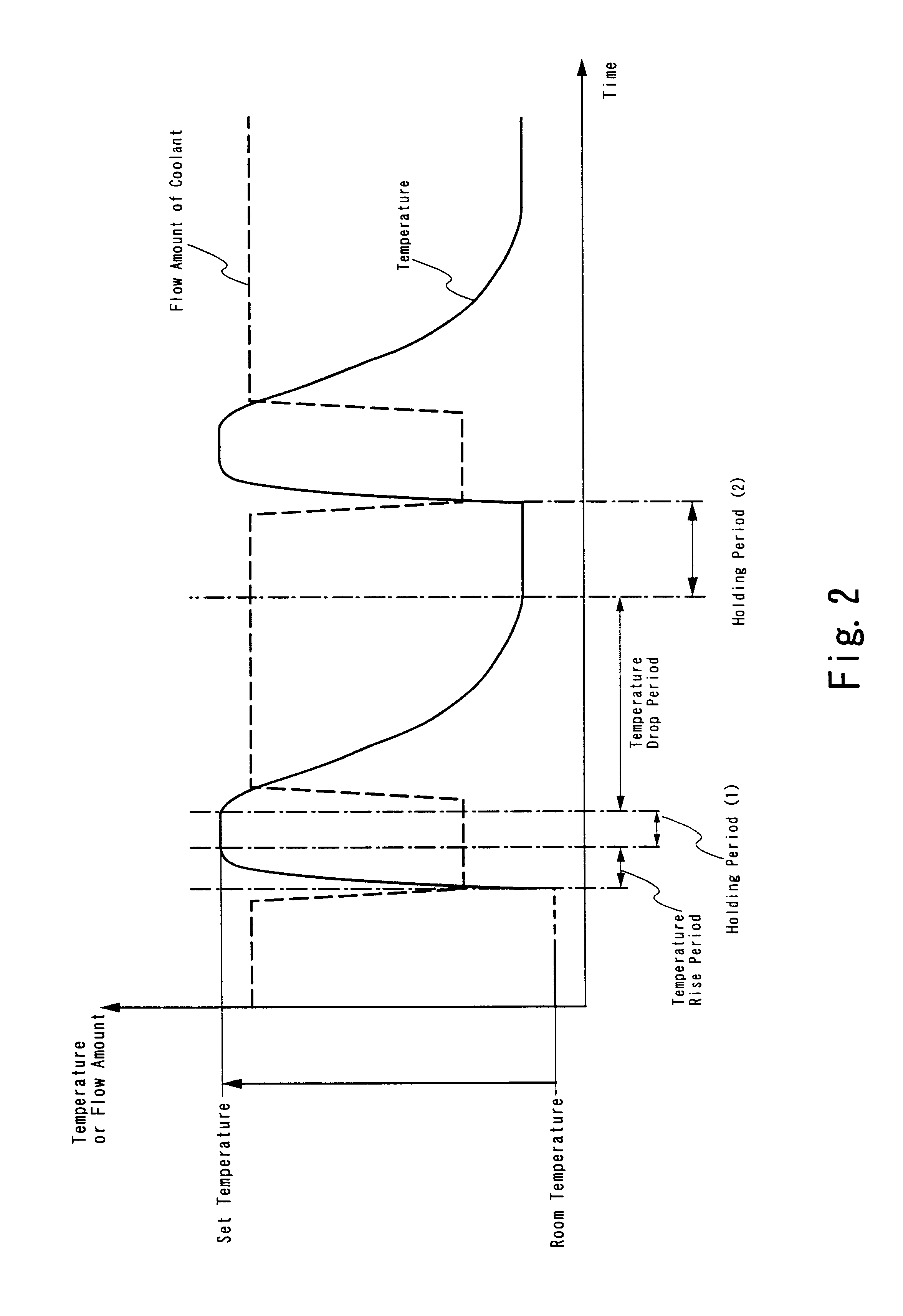

Semiconductor device manufacturing method, heat treatment apparatus, and heat treatment method

For manufacture of a semiconductor device using a low heat resistant substrate such as a glass substrate, a method of heat treatment for activating an impurity element that is used to dope a semiconductor film and for performing gettering on the semiconductor film in a short period of time without deforming the substrate, is provided. Also provided is a heat treatment apparatus for carrying out the above heat treatment. The heat treatment method of the present invention involves irradiating an object with light emitted from a lamp light source, and is characterized in that the lamp light source emits light for 0.1 to 20 seconds at a time and that light from the lamp light source irradiates the object several times. The method is also characterized in that the irradiated region is subjected to pulsating light from the lamp light source such that the irradiated region holds the temperature to its highest for 0.5 to 5 seconds. The method is also characterized in that the amount of coolant to be supplied is increased or reduced in accordance with blinking of the lamp light source to enhance the effect of the heat treatment on the semiconductor film and to prevent a heat-induced damage to the substrate.

Owner:SEMICON ENERGY LAB CO LTD

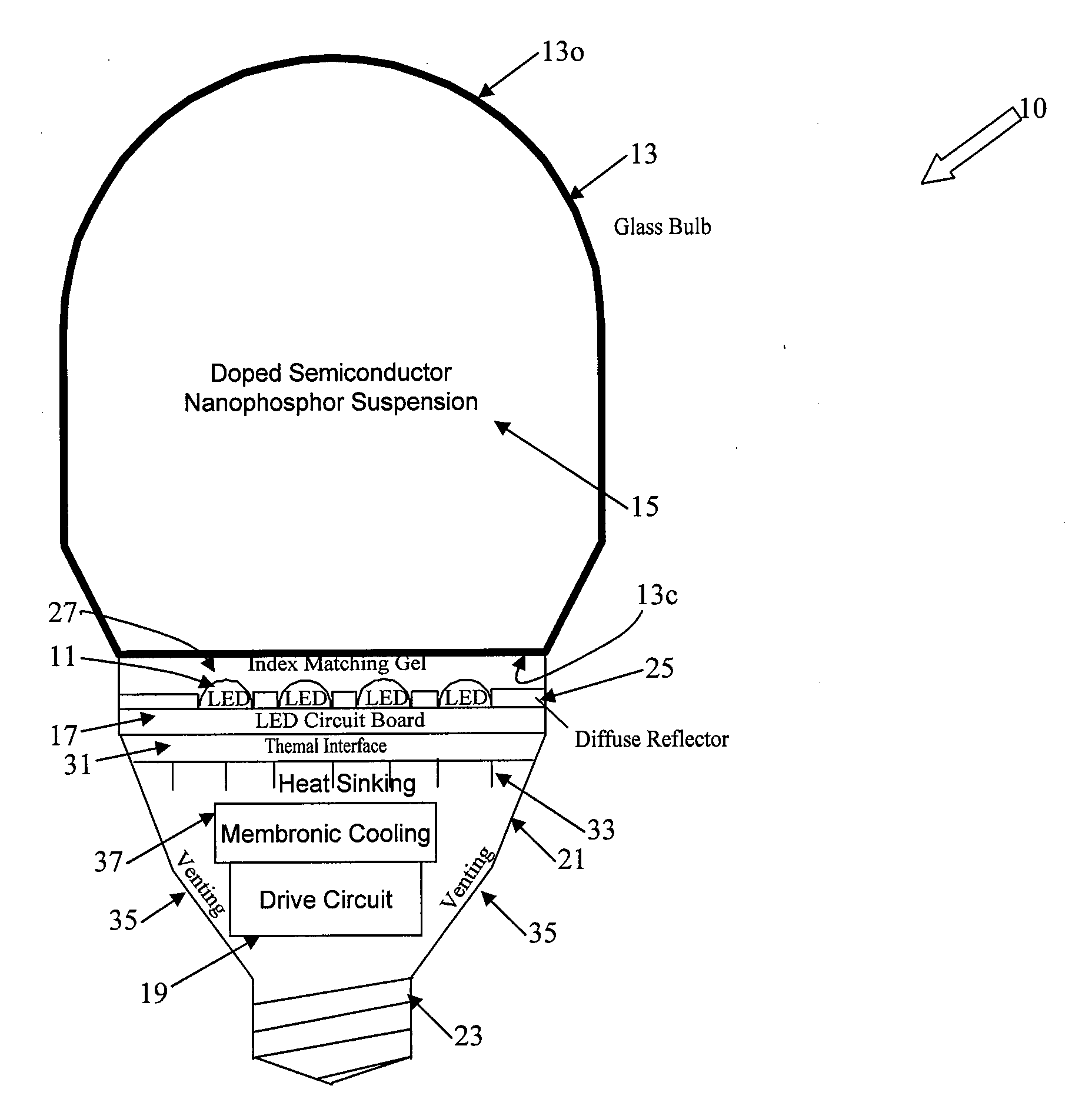

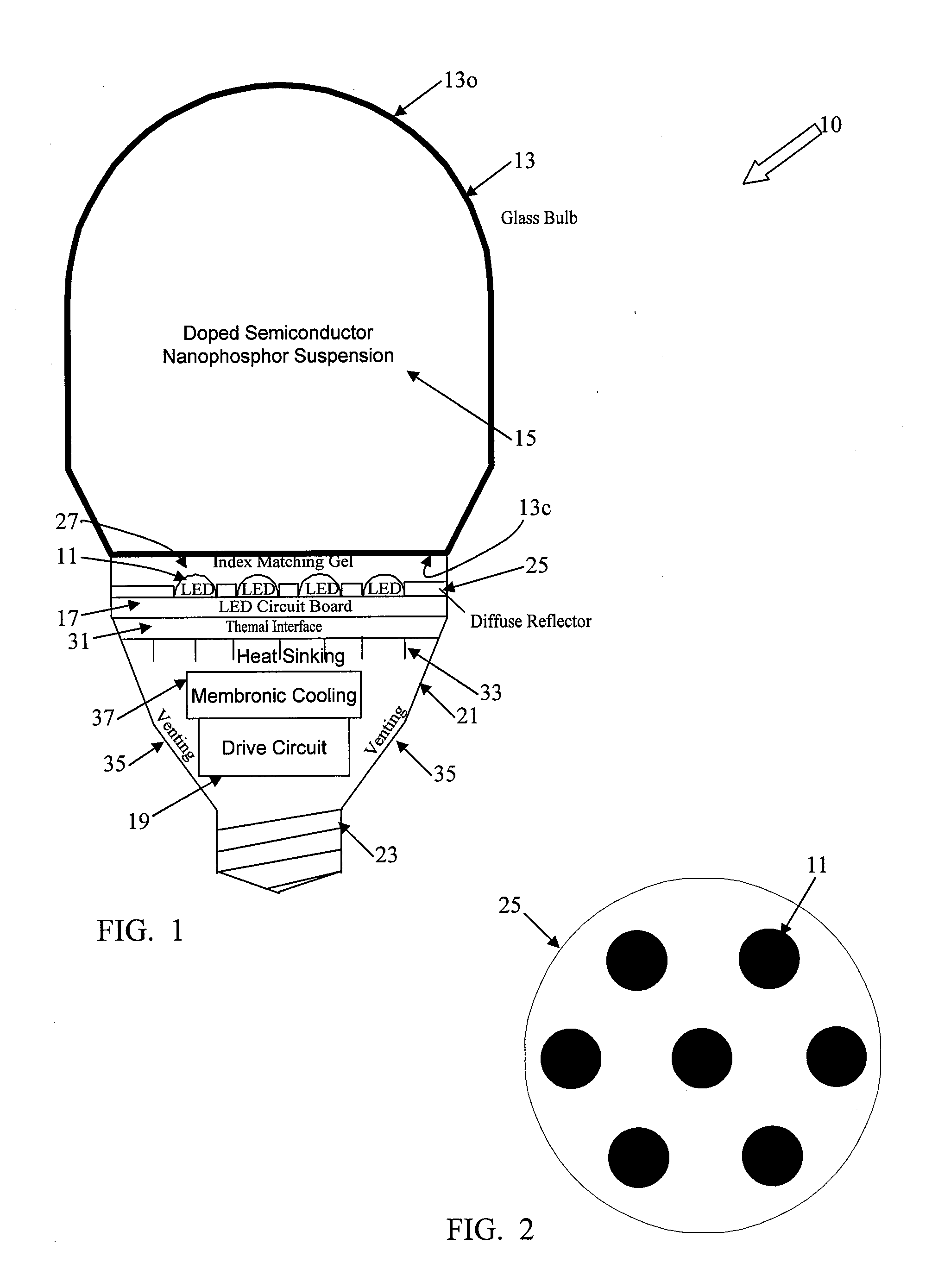

Lamp using solid state source and doped semiconductor nanophosphor

ActiveUS20110175528A1Easy to useHighly desirable characteristicPoint-like light sourceElectric circuit arrangementsElectricityEffect light

A lamp uses a solid state source to pump one or more doped semiconductor nanophosphors to produce a light output of a desired characteristic. The nanophosphor(s) is dispersed in a material, examples of which include liquids and gases. Various nanophosphors are discussed. In the examples, the material with the doped semiconductor nanophosphor(s) dispersed therein appears at least substantially clear when the lamp is off. The exemplary lamp also includes circuitry for driving the solid state source and a housing that at least encloses the drive circuitry. The lamp has a lighting industry standard lamp base mechanically connected to the housing and electrically connected to provide electricity to the circuitry for driving the solid state source.

Owner:ABL IP HLDG

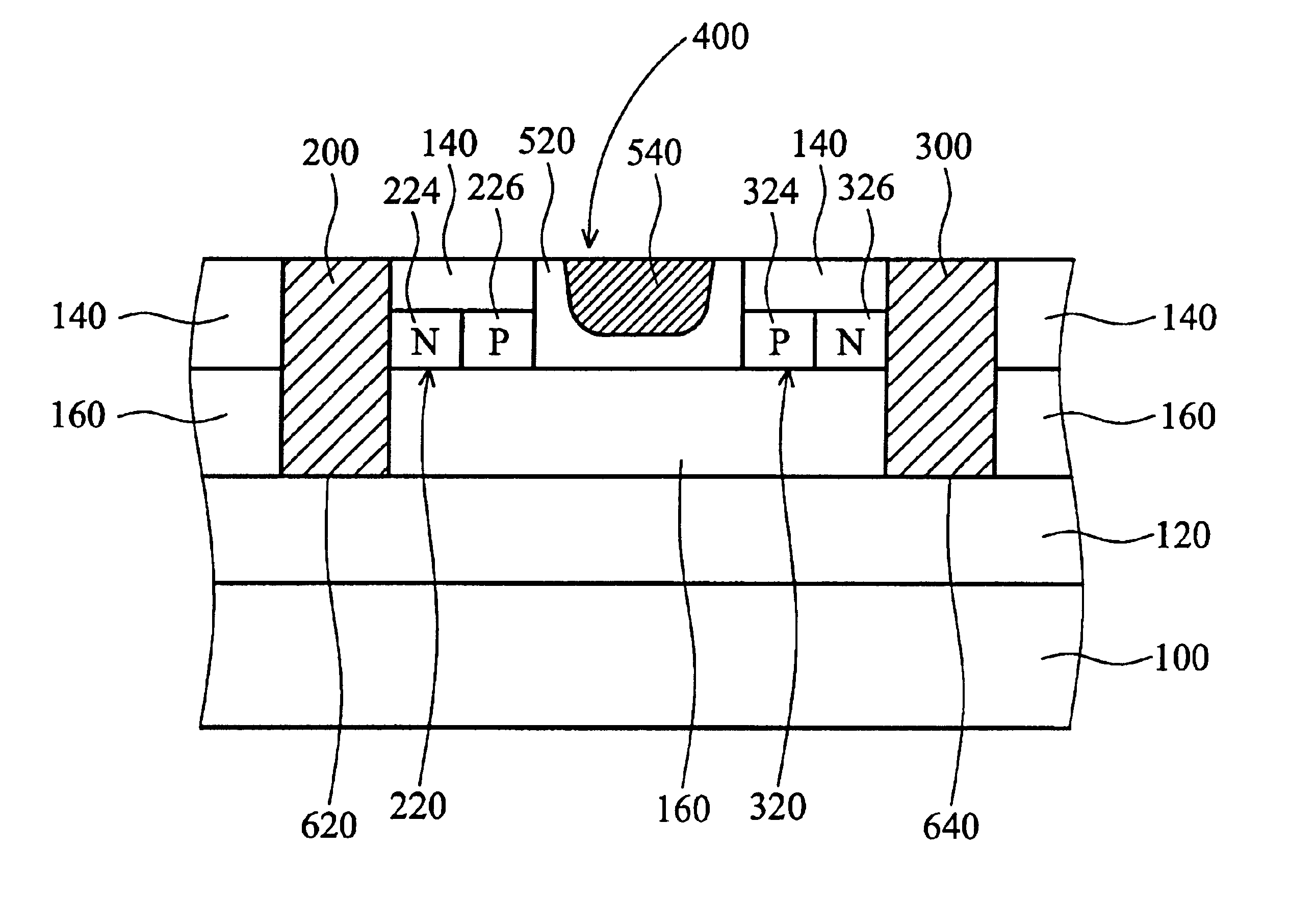

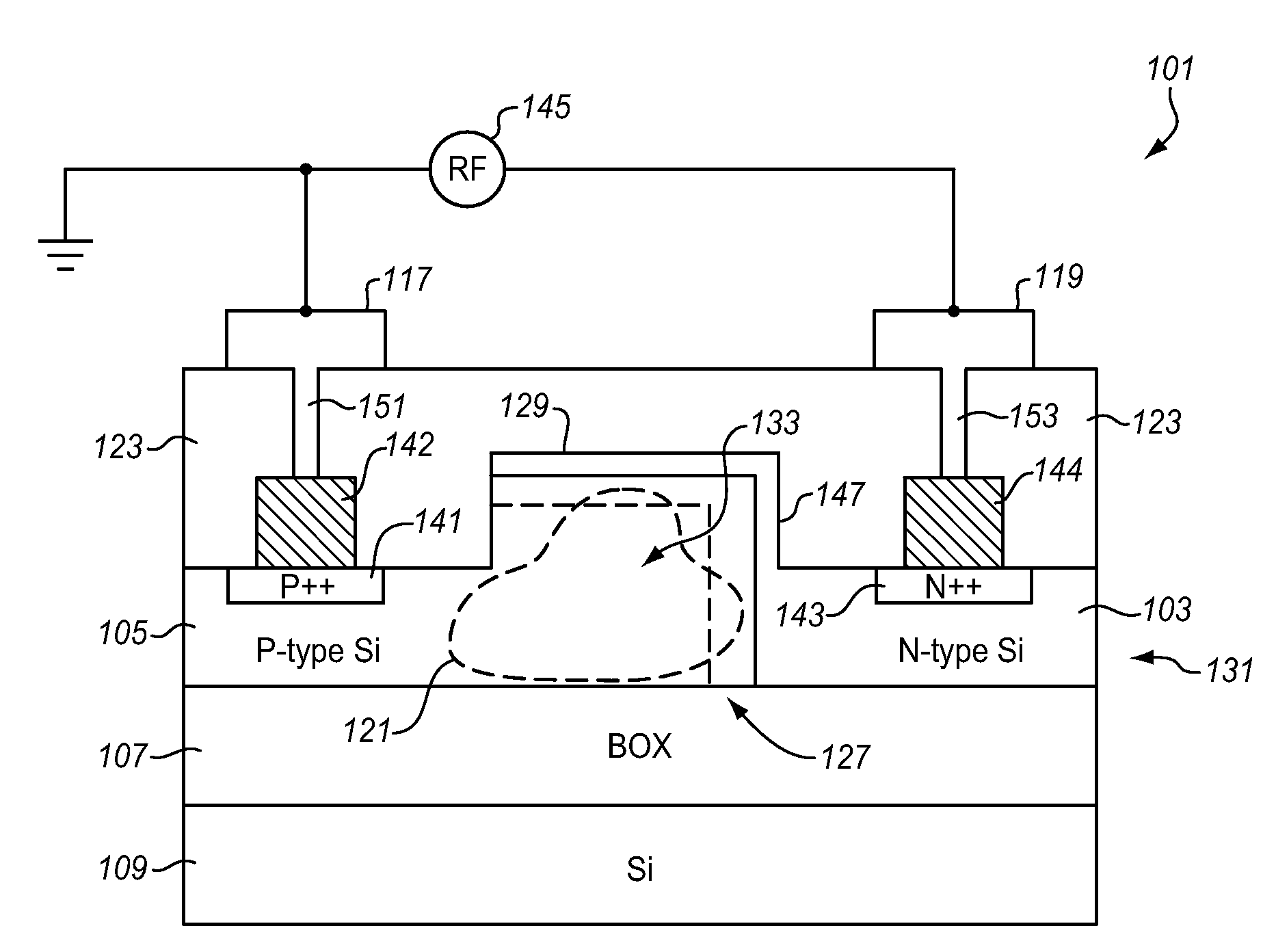

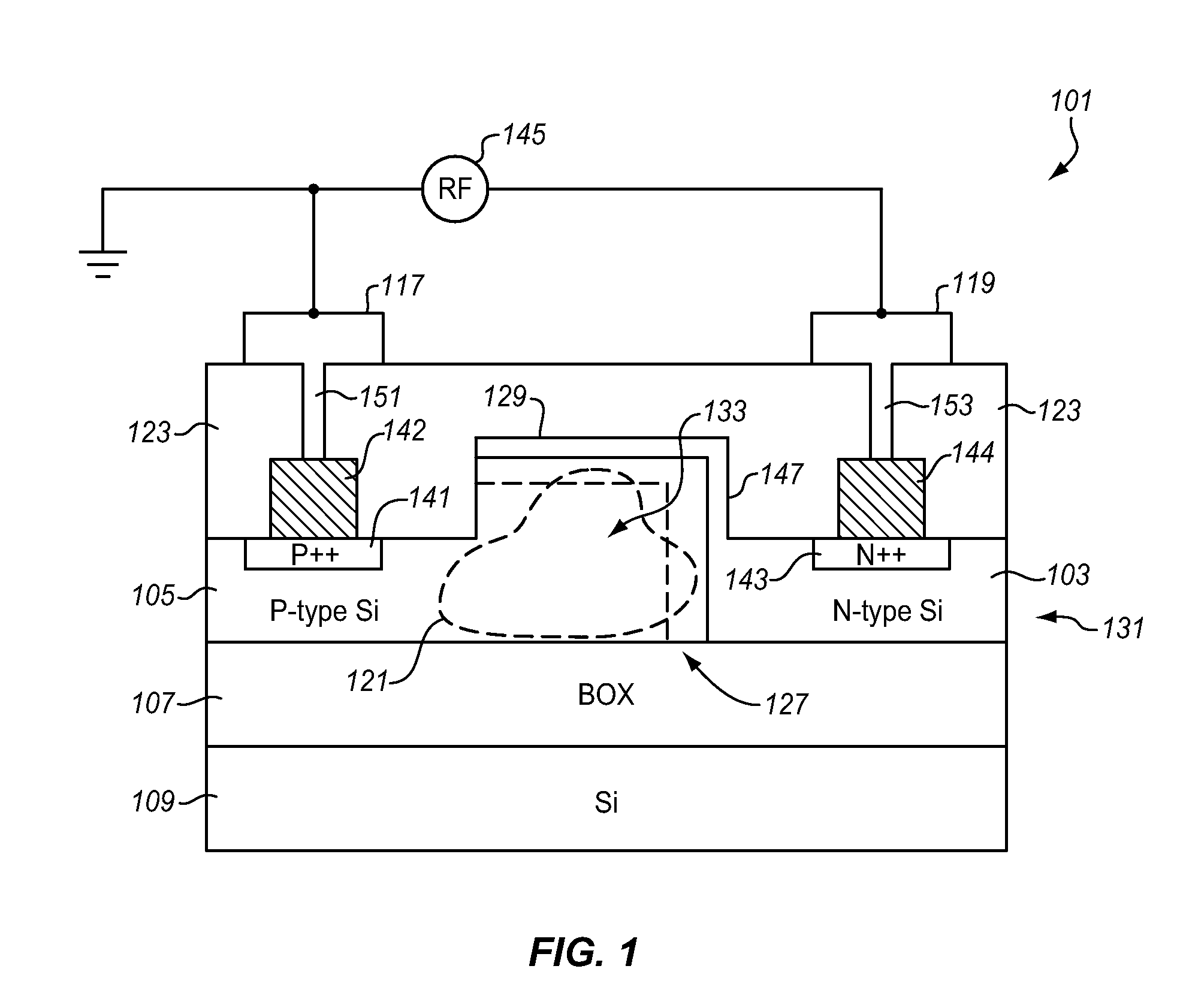

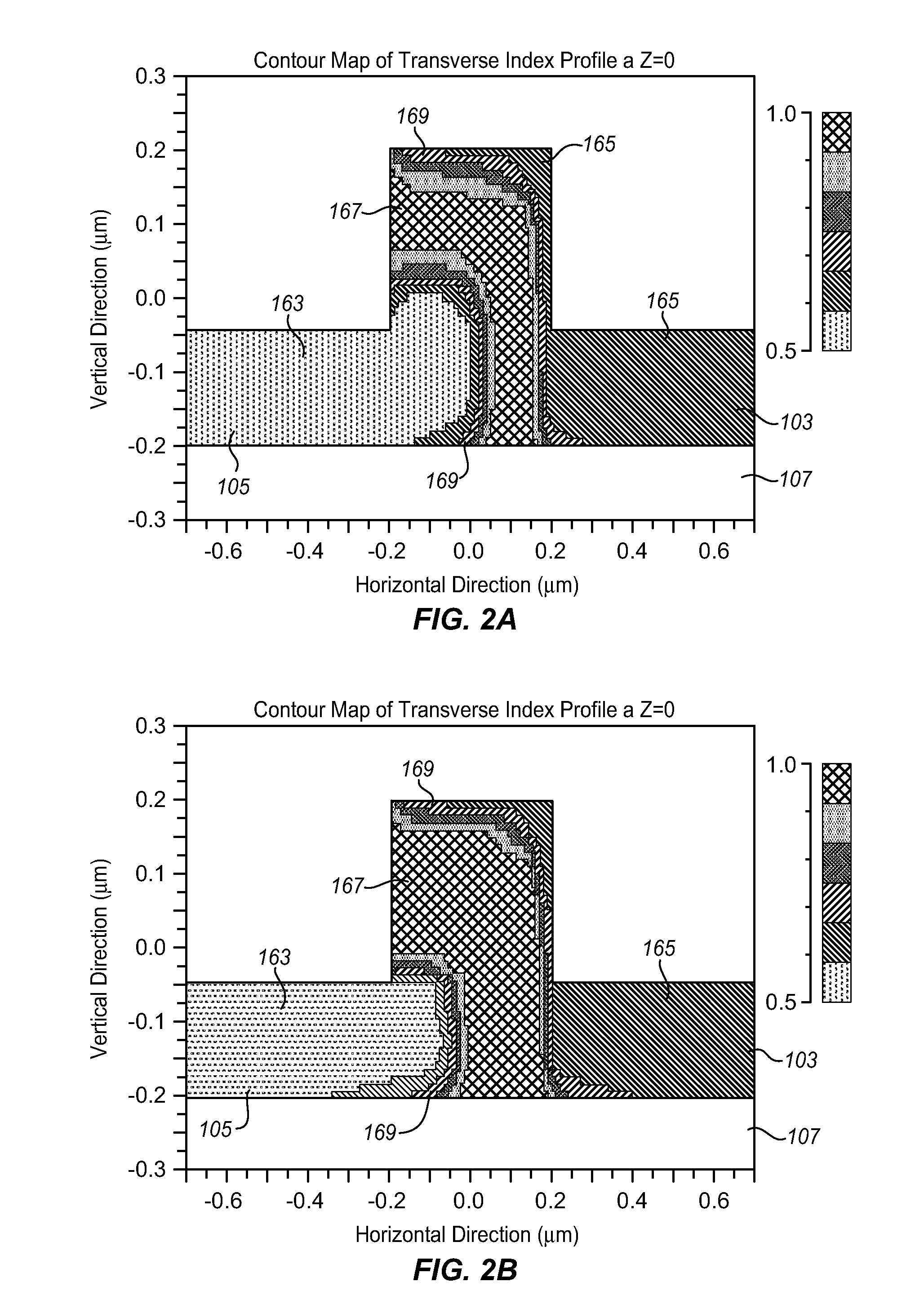

Method and Apparatus for High Speed Silicon Optical Modulation Using PN Diode

InactiveUS20100080504A1Coupling light guidesOptical waveguide light guideWaveguidePerpendicular direction

A method and apparatus for high speed silicon optical modulation is described using a PN diode. In one example, an optical waveguide has adjoining first and second doped semiconductor regions. The first and second regions have opposite doping types and the first doped region extends in two perpendicular directions through the waveguide.

Owner:INTEL CORP

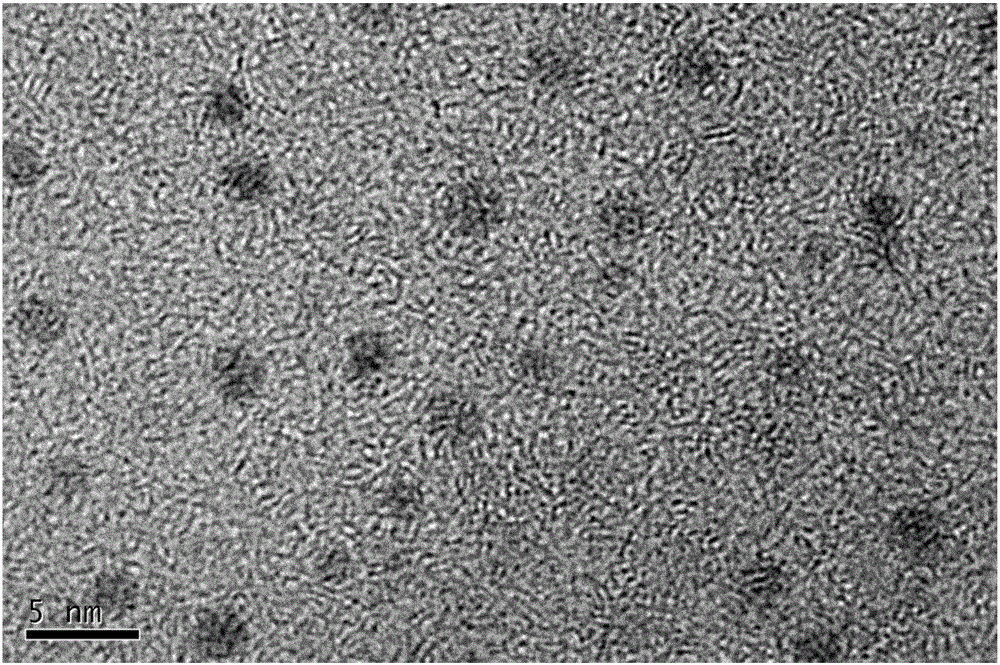

Stochastic assembly of sublithographic nanoscale interfaces

InactiveUS6900479B2Tighter address encodingReasonable efficiencySemiconductor/solid-state device detailsNanoinformaticsWire rodEngineering

A method for controlling electric conduction on nanoscale wires is disclosed. The nanoscale wires are provided with controllable regions axially and / or radially distributed. Controlling those regions by means of microscale wires or additional nanoscale wires allows or prevents electric conduction on the controlled nanoscale wires. The controllable regions are of two different types. For example, a first type of controllable region can exhibit a different doping from a second type of controllable region. The method allows one or more of a set of nanoscale wires, packed at sublithographic pitch, to be independently selected.

Owner:CALIFORNIA INST OF TECH +3

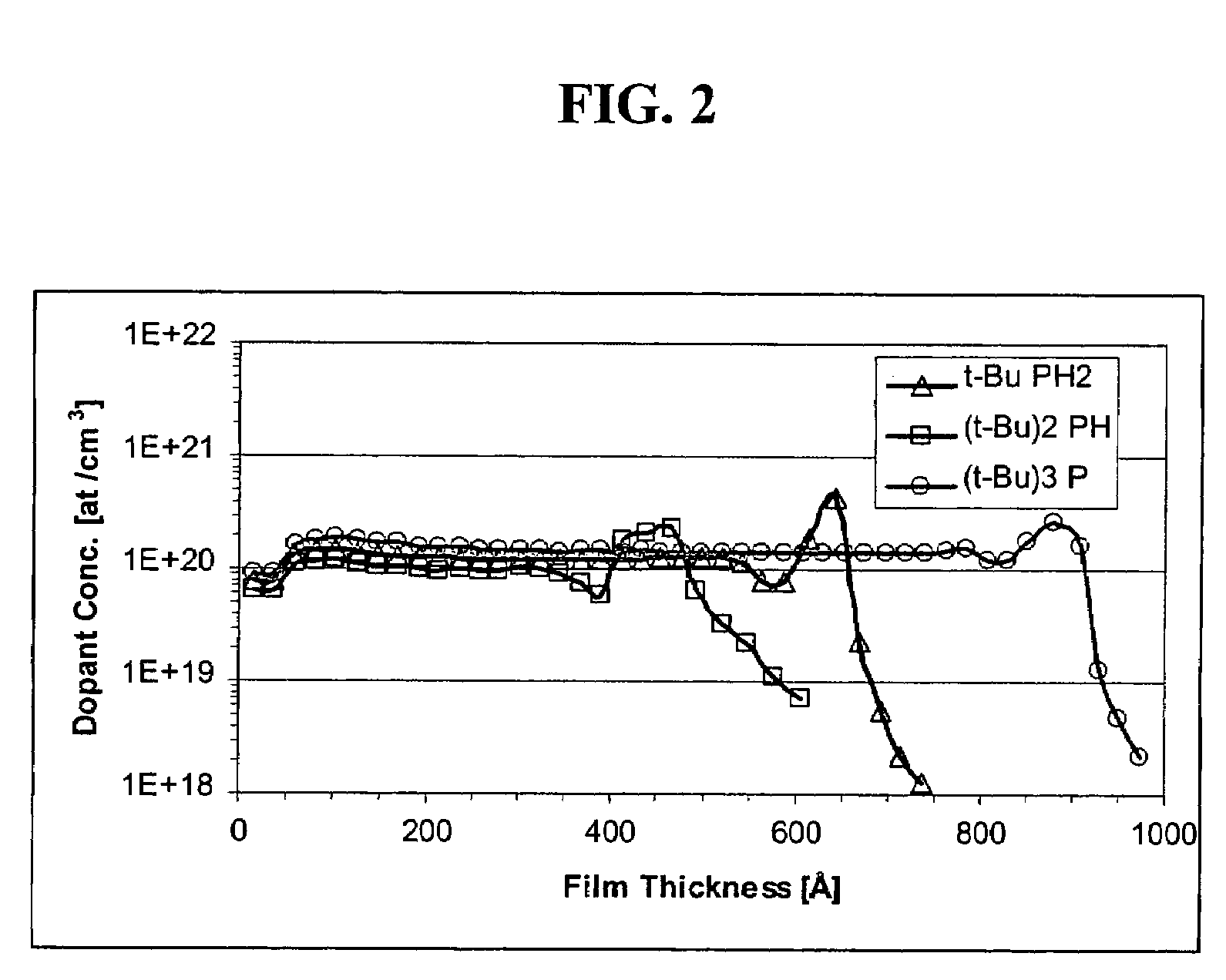

Methods of forming a doped semiconductor thin film, doped semiconductor thin film structures, doped silane compositions, and methods of making such compositions

ActiveUS7314513B1Reduce volatilityHigh molecular weightOther chemical processesSemiconductor/solid-state device manufacturingIsomerizationElectron

Methods for forming doped silane and / or semiconductor thin films, doped liquid phase silane compositions useful in such methods, and doped semiconductor thin films and structures. The composition is generally liquid at ambient temperatures and includes a Group IVA atom source and a dopant source. By irradiating a doped liquid silane during at least part of its deposition, a thin, substantially uniform doped oligomerized / polymerized silane film may be formed on a substrate. Such irradiation is believed to convert the doped silane film into a relatively high-molecular weight species with relatively high viscosity and relatively low volatility, typically by cross-linking, isomerization, oligomerization and / or polymerization. A film formed by the irradiation of doped liquid silanes can later be converted (generally by heating and annealing / recrystallization) into a doped, hydrogenated, amorphous silicon film or a doped, at least partially polycrystalline silicon film suitable for electronic devices. Thus, the present invention enables use of high throughput, low cost equipment and techniques for making doped semiconductor films of commercial quality and quantity from doped “liquid silicon.”

Owner:ENSURGE MICROPOWER ASA

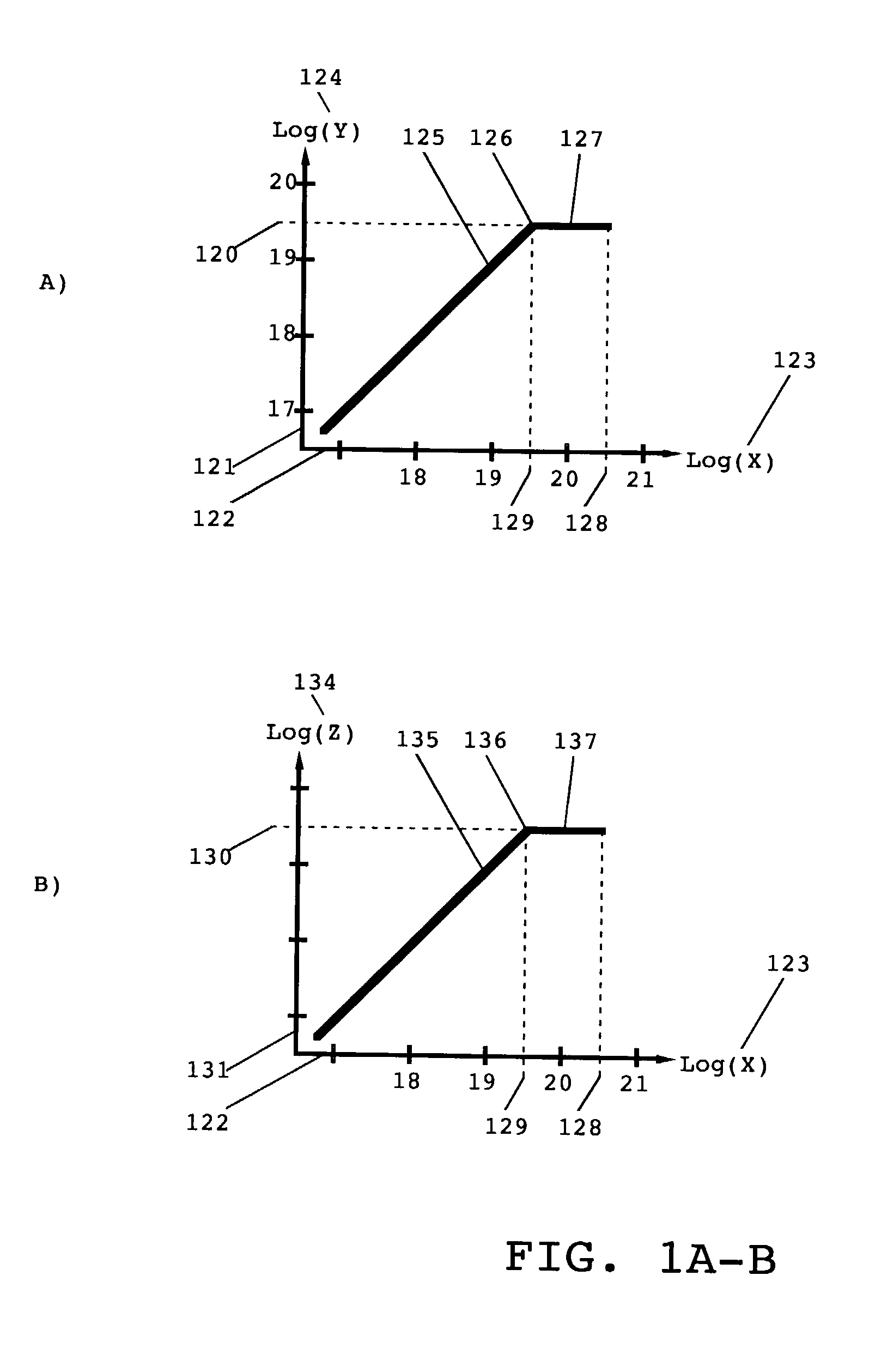

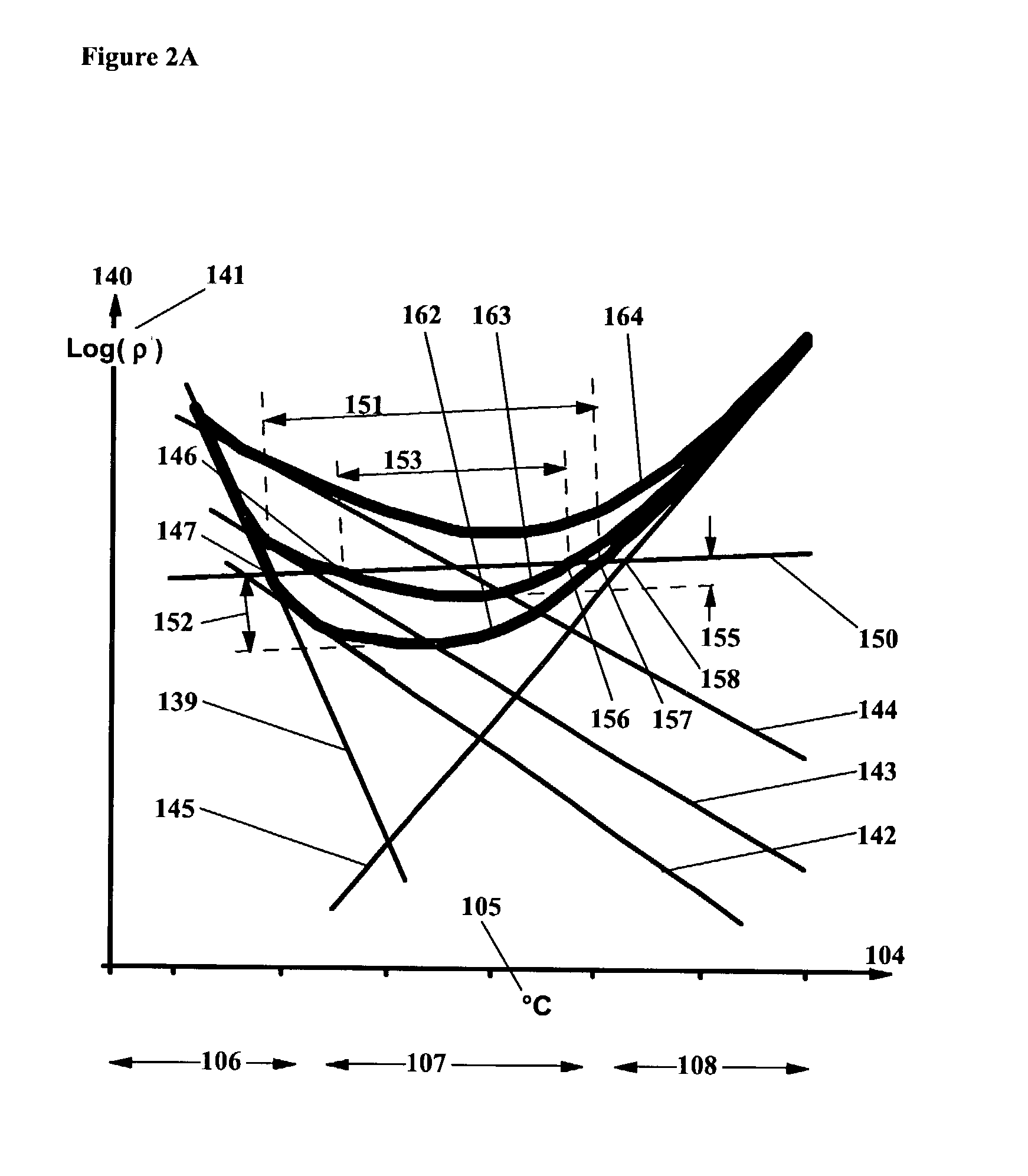

Methods of hyperdoping semiconductor materials and hyperdoped semiconductor materials and devices

InactiveUS20030121468A1Avoiding and mitigating formationEasy to operateTransistorPolycrystalline material growthSide effectSemiconductor materials

Methods are disclosed for producing highly doped semiconductor materials. Using the invention, one can achieve doping densities that exceed traditional, established carrier saturation limits without deleterious side effects. Additionally, highly doped semiconductor materials are disclosed, as well as improved electronic and optoelectronic devices / components using said materials. The innovative materials and processes enabled by the invention yield significant performance improvements and / or cost reductions for a wide variety of semiconductor-based microelectronic and optoelectronic devices / systems. Materials are grown in an anion-rich environment, which, in the preferred embodiment, are produced by moderate substrate temperatures during growth in an oxygen-poor environment. The materials exhibit fewer non-radiative recombination centers at higher doping concentrations than prior art materials, and the highly doped state of matter can exhibit a minority carrier lifetime dominated by radiative recombination at higher doping levels and higher majority carrier concentrations than achieved in prior art materials. Important applications enabled by these novel materials include high performance electronic or optoelectronic devices, which can be smaller and faster, yet still capture or emit light efficiently, and high performance electronics, such as transistors, which can be smaller and faster, yet cooler.

Owner:YALE UNIV

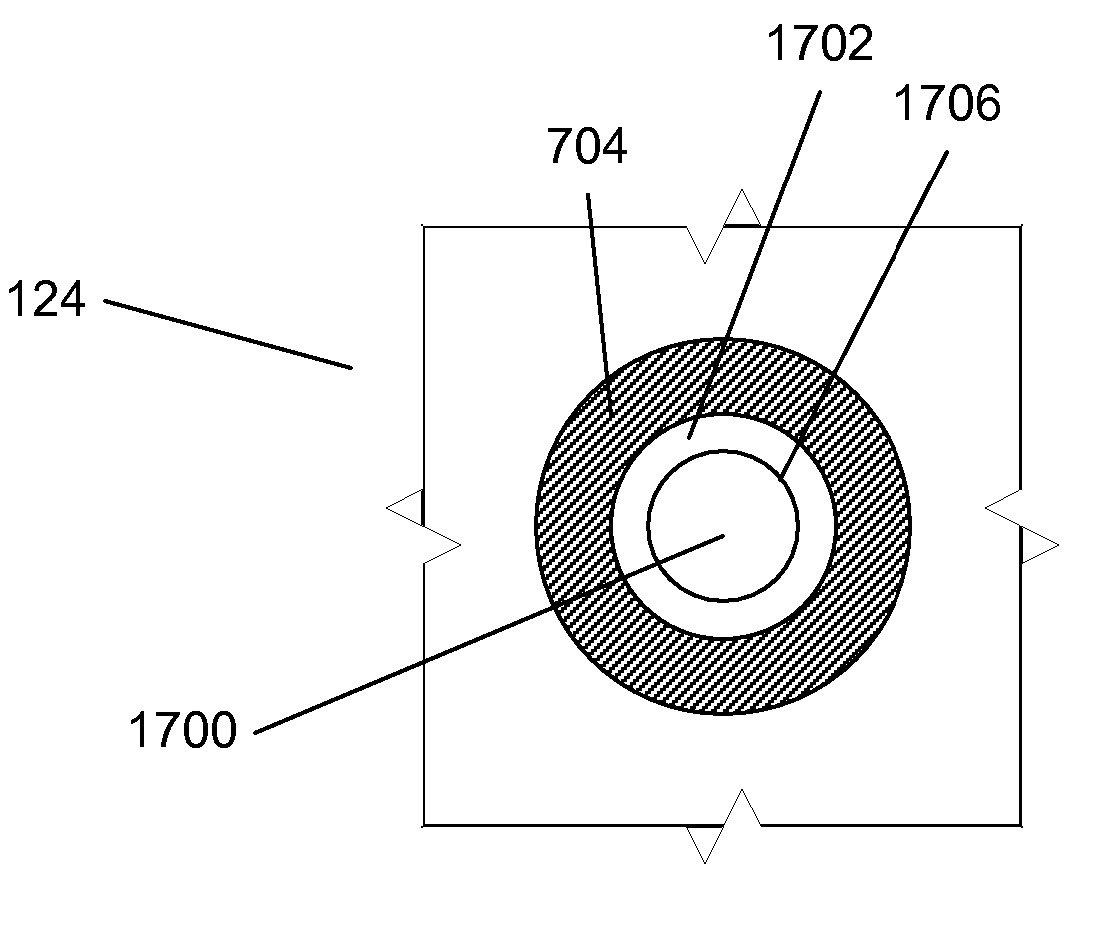

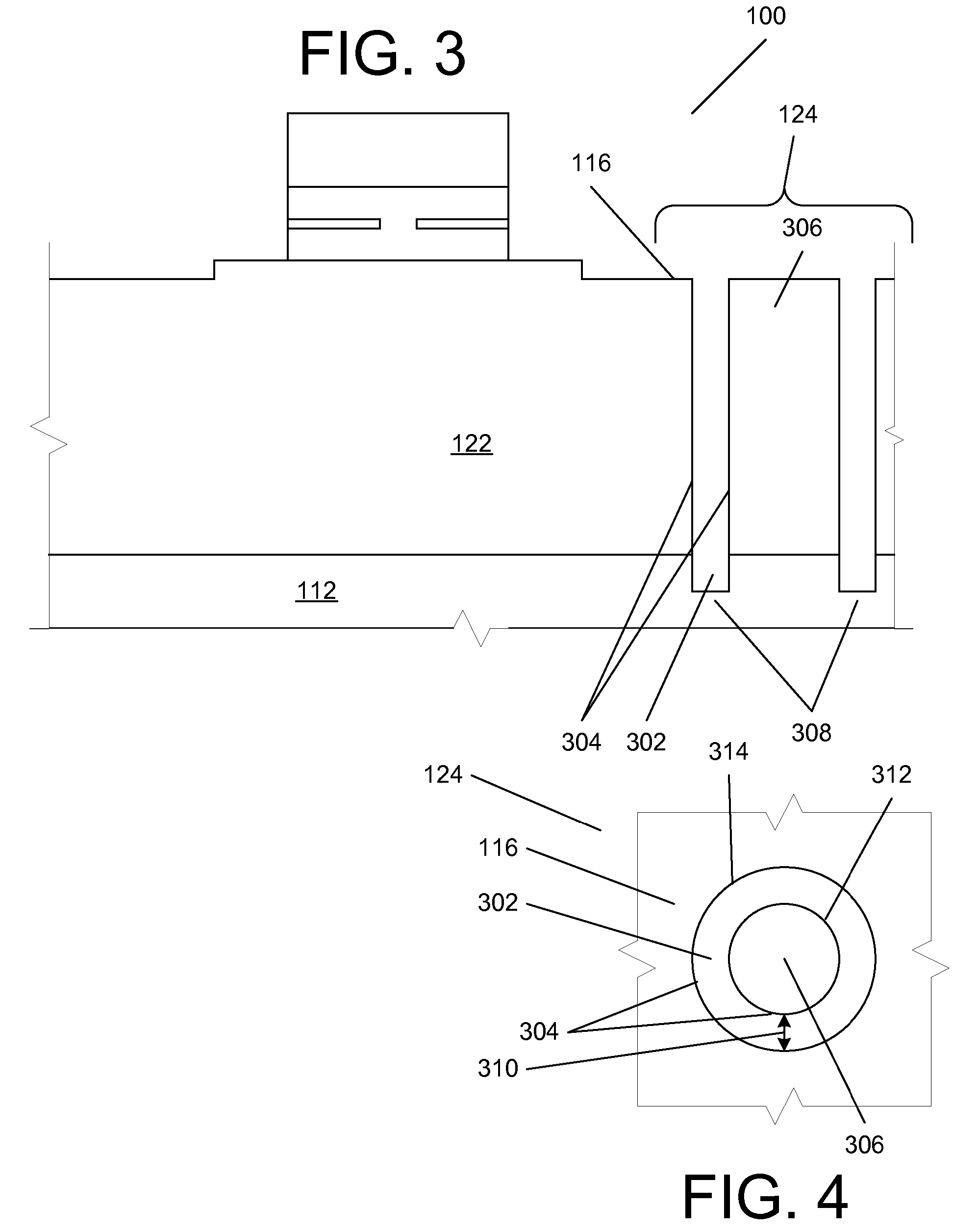

Signal shielding through-substrate vias for 3D integration

InactiveUS20110241185A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsConductive materials

A shielded through-substrate via (TSV) structure includes a first through-substrate via configured to transmit a signal at least from a top surface of a semiconductor device layer in a substrate to a bottommost surface of the substrate. The shielded TSV structure includes at least one second TSV located on the outside of the first TSV and configured to laterally shield the first TSV from external electrical signals. The at least one second TSV can be a unitary cylindrical structure including the first TSV therein, or a plurality of discrete structures configured to laterally shield the first TSV with gaps thereamongst. The at least one second TSV can include a conductive material that is different from the material of the substrate, or the at least one TSV can include a doped semiconductor material that is derived from the semiconductor material within the substrate.

Owner:GLOBALFOUNDRIES INC

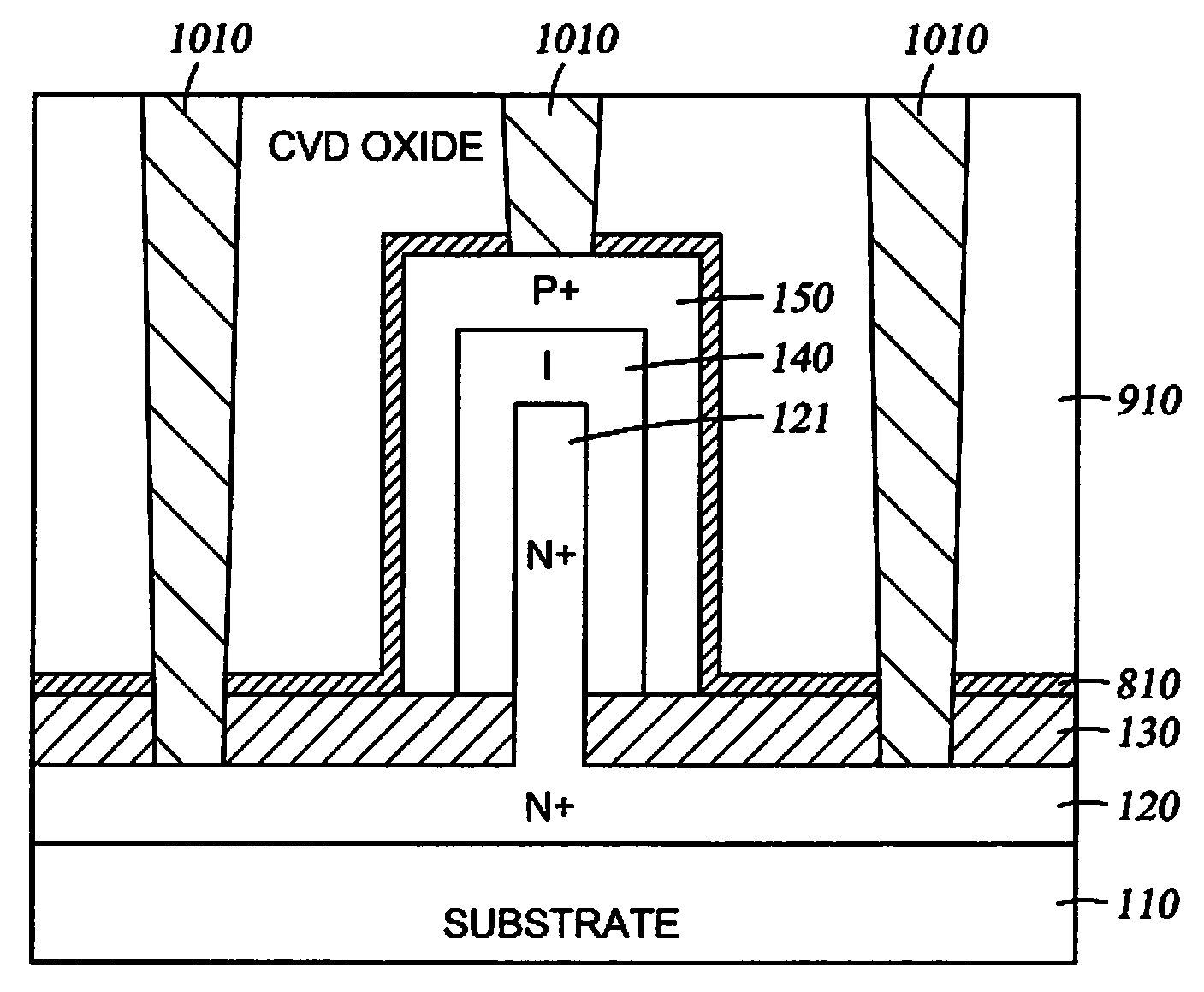

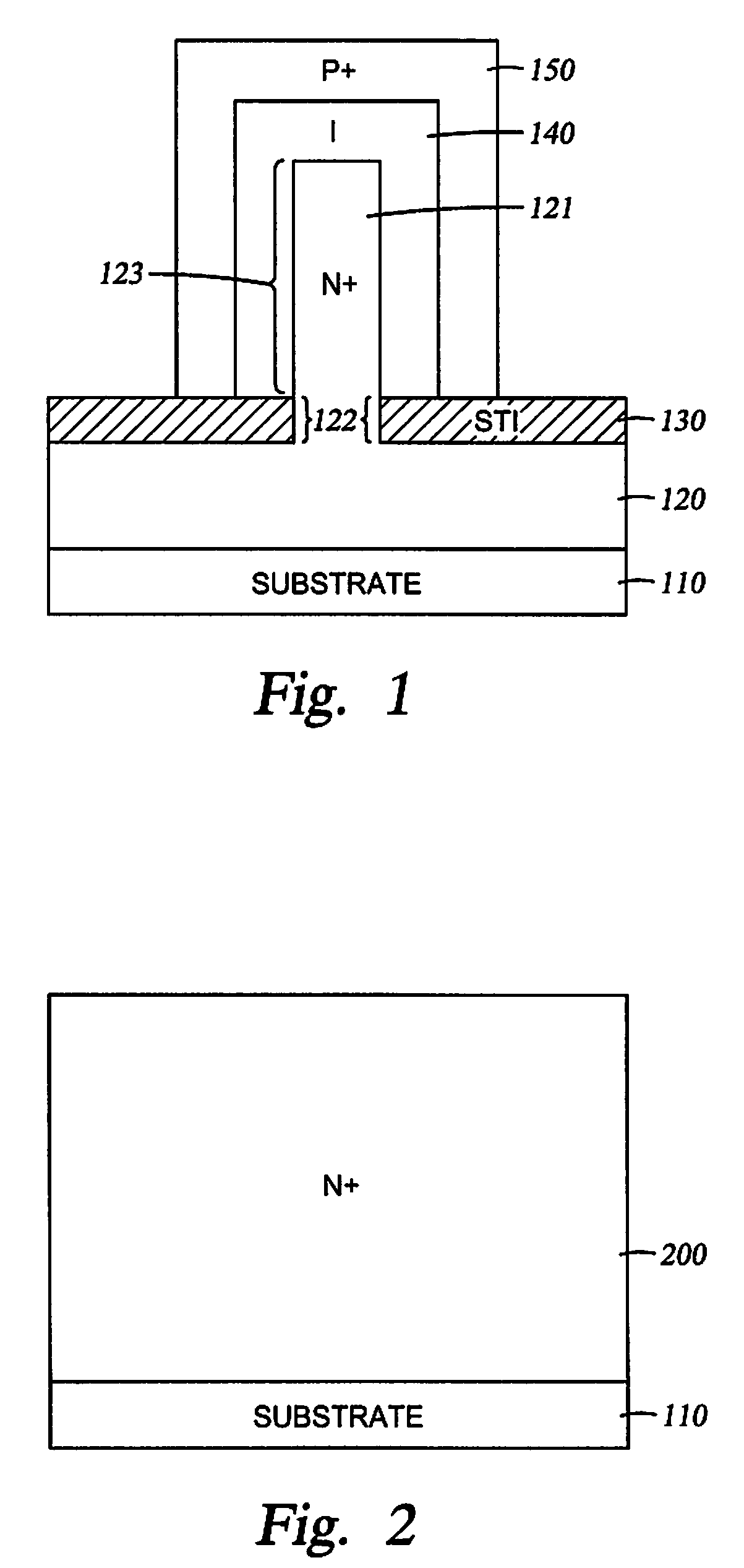

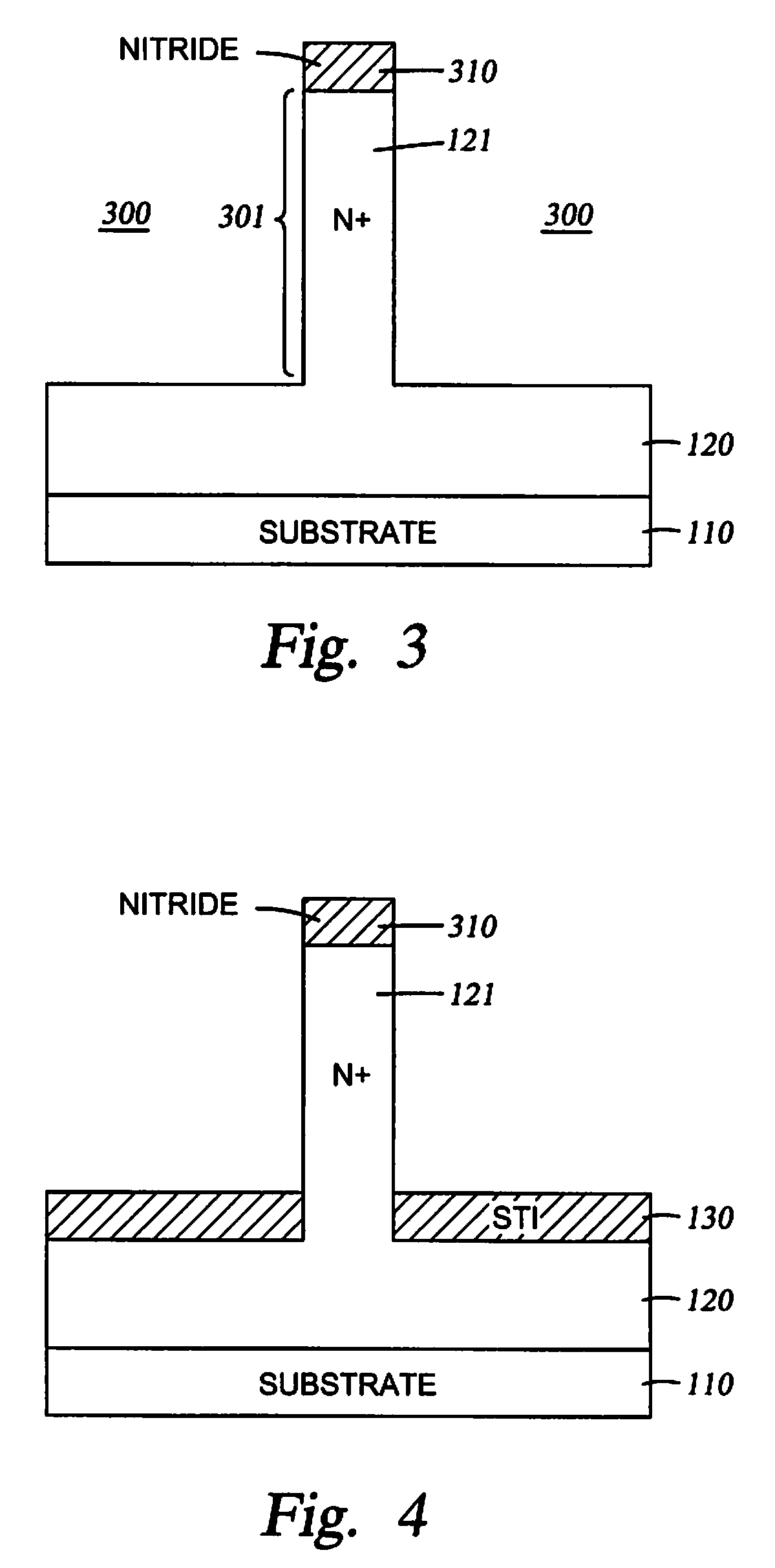

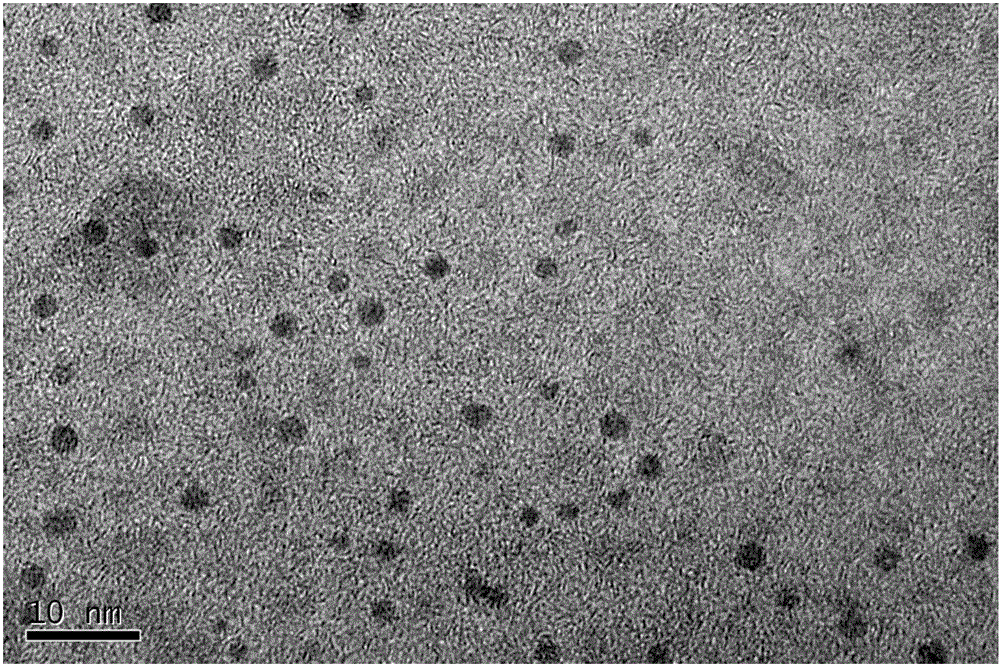

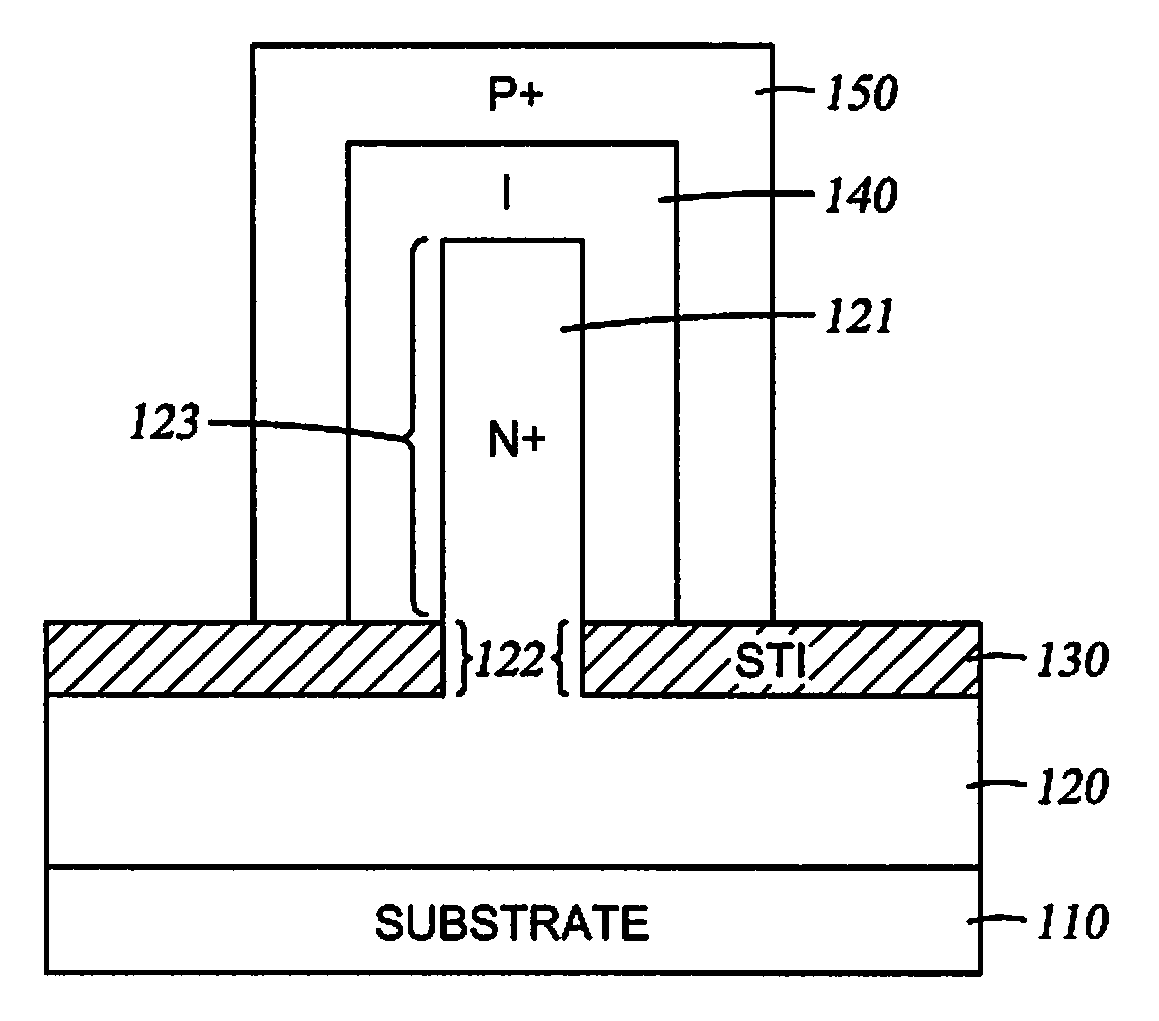

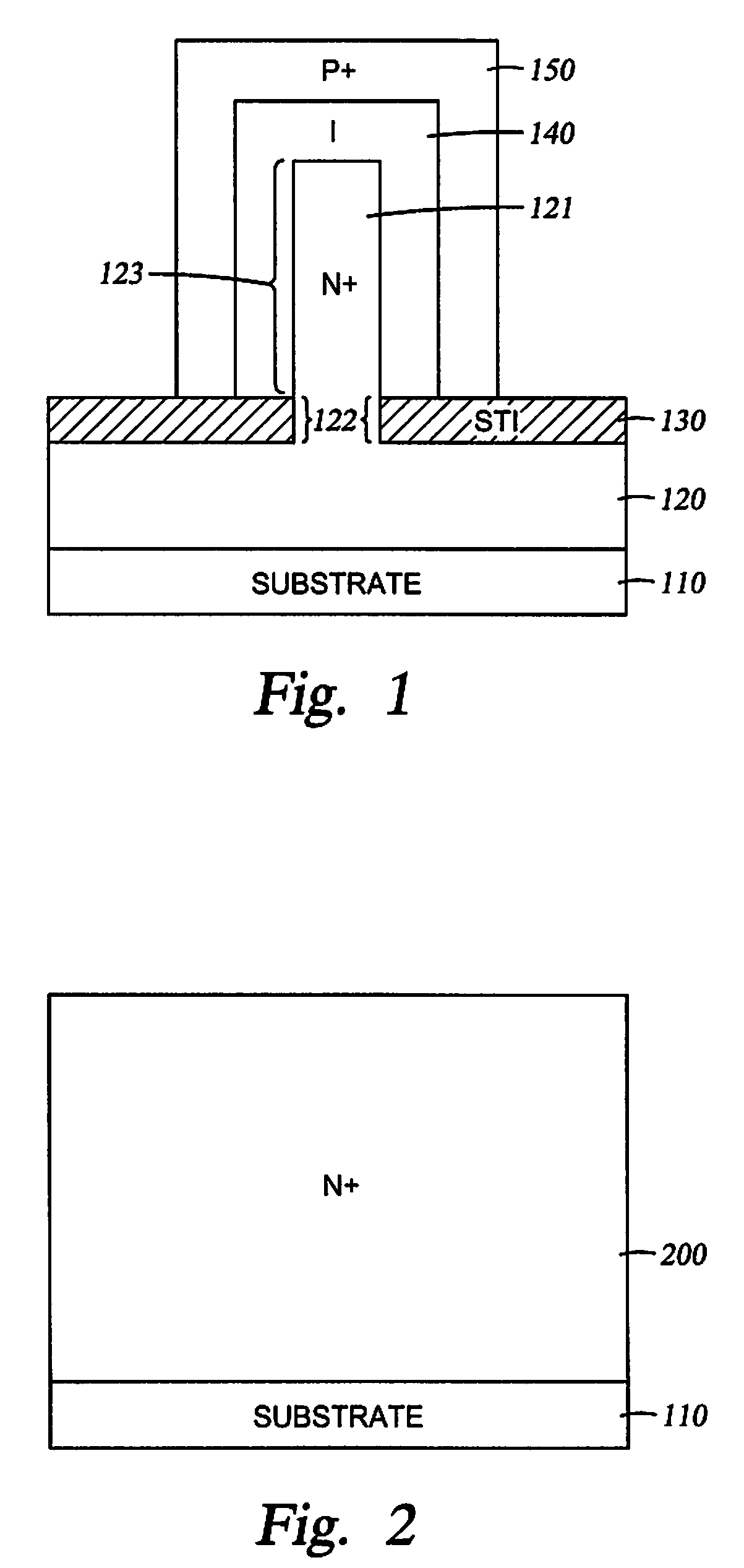

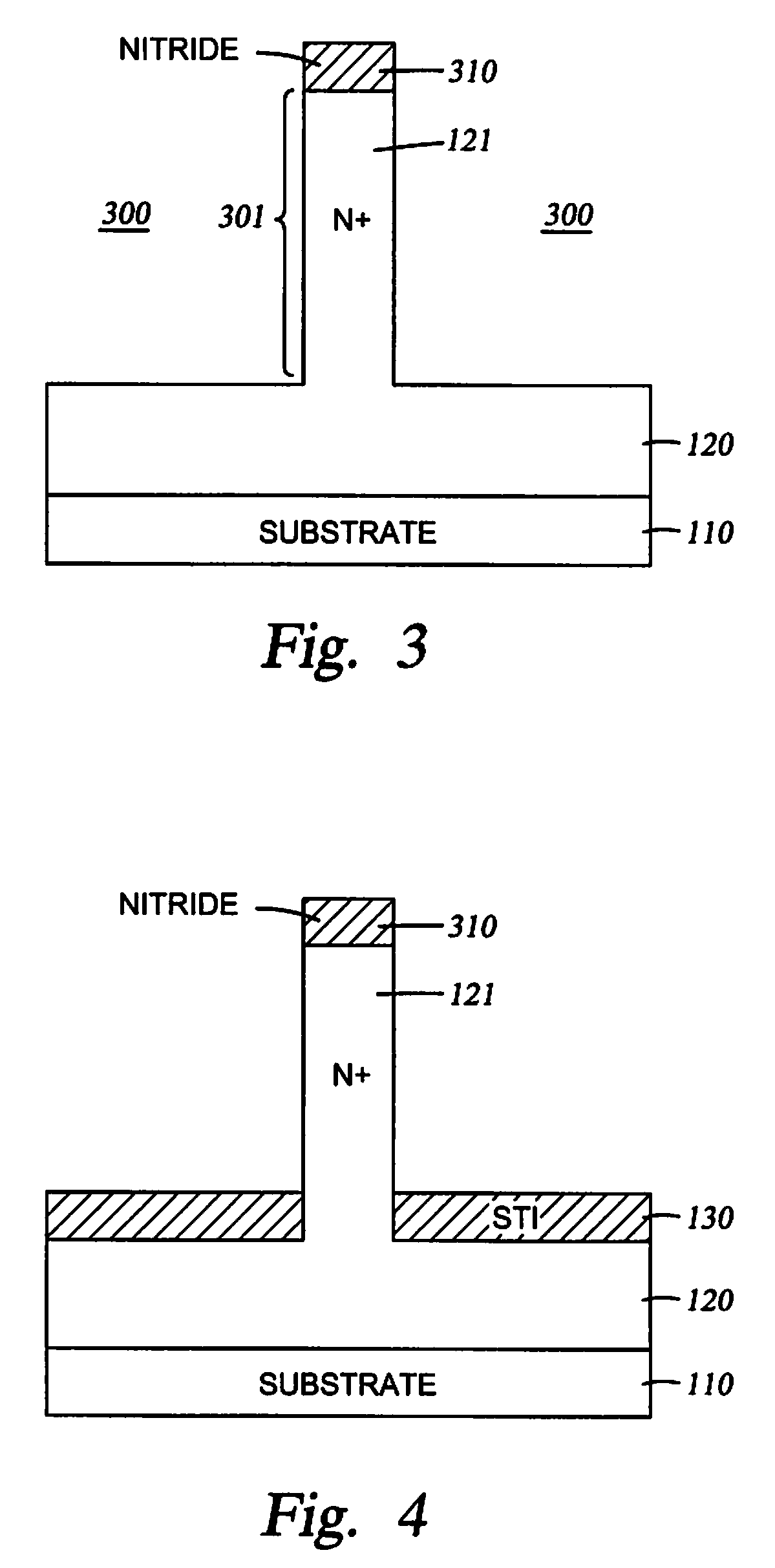

Fin PIN diode

Embodiments of the invention generally relate to the field of semiconductor devices, and more specifically to fin-based junction diodes. A portion of a doped semiconductor fin may protrude through a first doped layer. An intrinsic layer may be disposed on the protruding semiconductor fin. A second semiconductor layer may be disposed on the intrinsic layer, thereby forming a PIN diode compatible with FinFET technology and having increased junction area.

Owner:INT BUSINESS MASCH CORP

Nitrogen, phosphorus and sulphur doping or co-doping carbon dot and batch controllable preparing method and application thereof

InactiveCN104987863ASimple processShort synthesis timeNanoopticsFluorescence/phosphorescenceAir atmosphereSilica gel

The invention provides a nitrogen, phosphorus and sulphur doping or co-doping carbon dot and a batch controllable preparing method and application thereof. The method comprises the steps that a carbon source, a nitrogen source, a phosphorus source and a sulphur source are evenly mixed, and a mixture is obtained, wherein the molar ratio of C to N to P to S in the mixture is 1 to 0-0.8 to 0-0.4 to 0-0.4, and the contents of N, P and S are prevented from being zero at the same time; in the air, the mixture is heated to be fused, the reaction is carried out for 3 min to 60 min, natural cooling is carried out till the indoor temperature is reached, a reaction product is separated by a silicagel column, raw materials which do not react are removed, and the nitrogen, phosphorus and sulphur doping or co-doping carbon dot is obtained. According to the method, the technology is simple, the compound time is short, batch producing can be achieved, the doping amount can be adjusted and controlled accurately, the fluorescence color of the prepared carbon dot ranges from blue to green, the application can be achieved on bioluminescence marking and cell imaging aspects, and the good economic benefit and the application prospect are achieved.

Owner:XI AN JIAOTONG UNIV

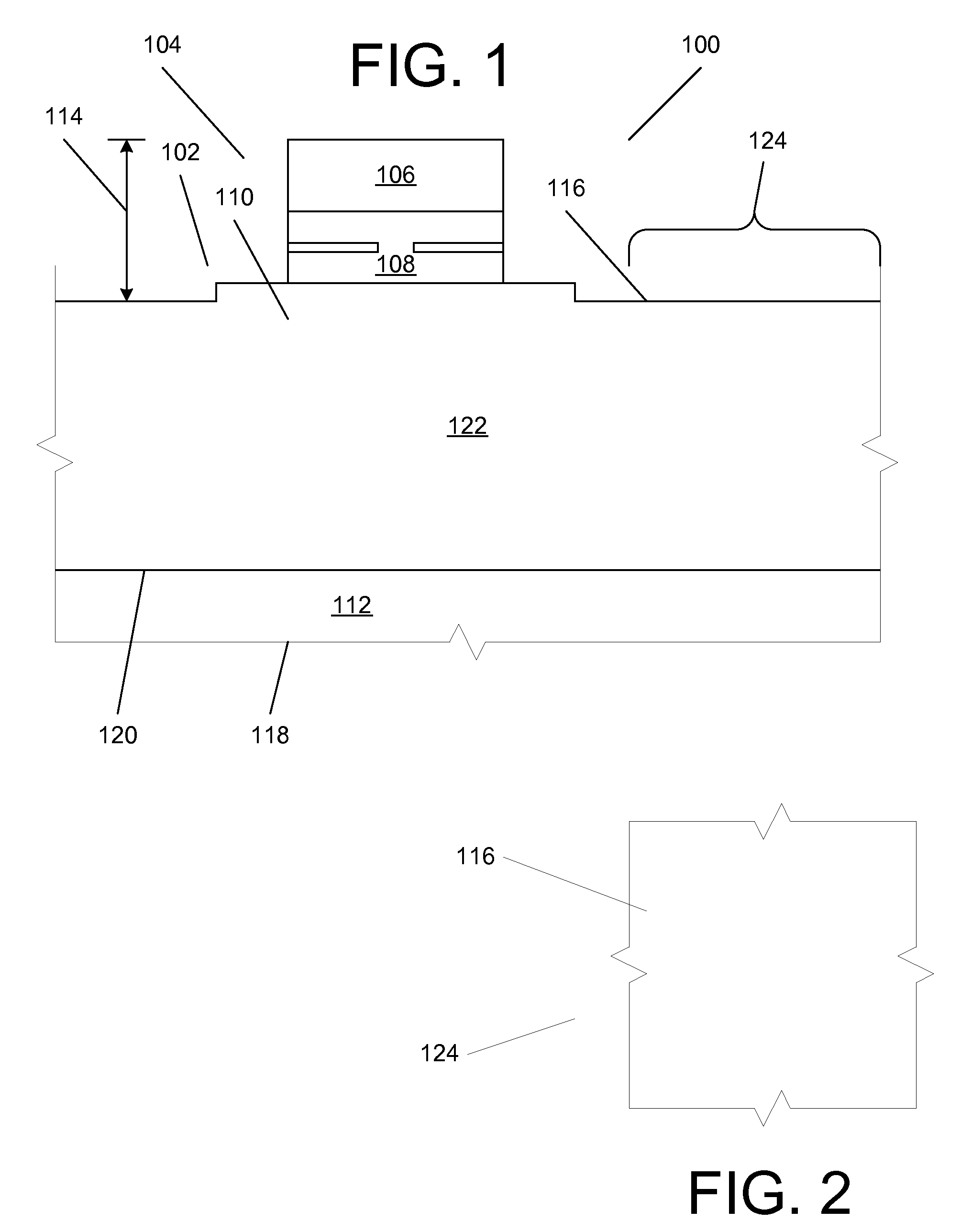

Back-to-front via process

ActiveUS20070161235A1Easy to shapeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsSemiconductor chip

A method performed on a semiconductor chip having a doped semiconductor material abutting a substrate involves creating a first via through at least a portion of the substrate extending from an outer side of the substrate towards the doped semiconductor material, the first via having a wall surface and a bottom, introducing a first electrically conductive material into the first via so as to create an electrically conductive path, creating a second via, aligned with the first via, extending from an outer surface of the doped portion of the semiconductor chip to the bottom, and introducing a second electrically conductive material into the second via so as to create an electrically conductive path.

Owner:CUFER ASSET LTD LLC

Fin Pin Diode

Embodiments of the invention generally relate to the field of semiconductor devices, and more specifically to fin-based junction diodes. A portion of a doped semiconductor fin may protrude through a first doped layer. An intrinsic layer may be disposed on the protruding semiconductor fin. A second semiconductor layer may be disposed on the intrinsic layer, thereby forming a PIN diode compatible with FinFET technology and having increased junction area.

Owner:IBM CORP

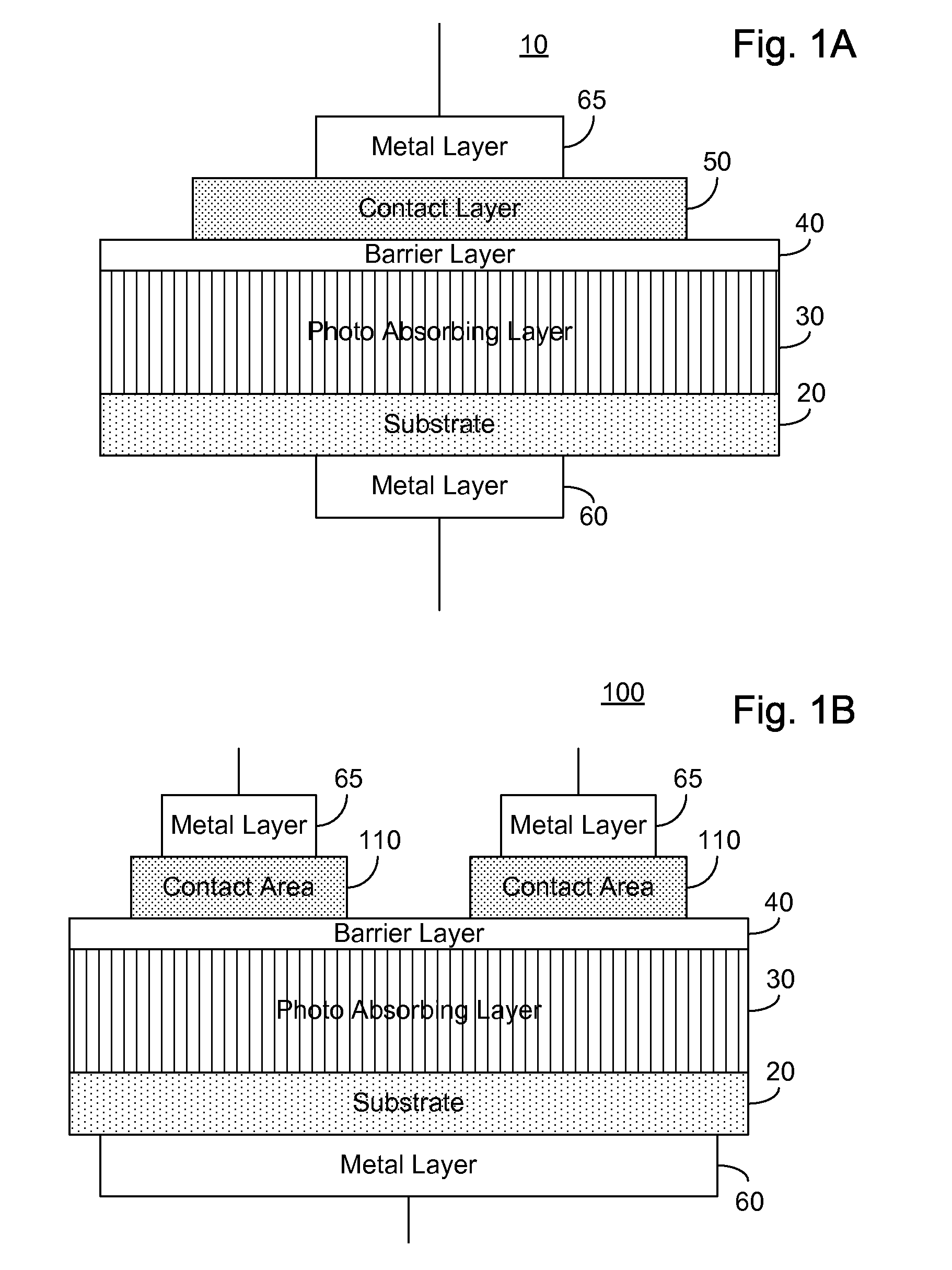

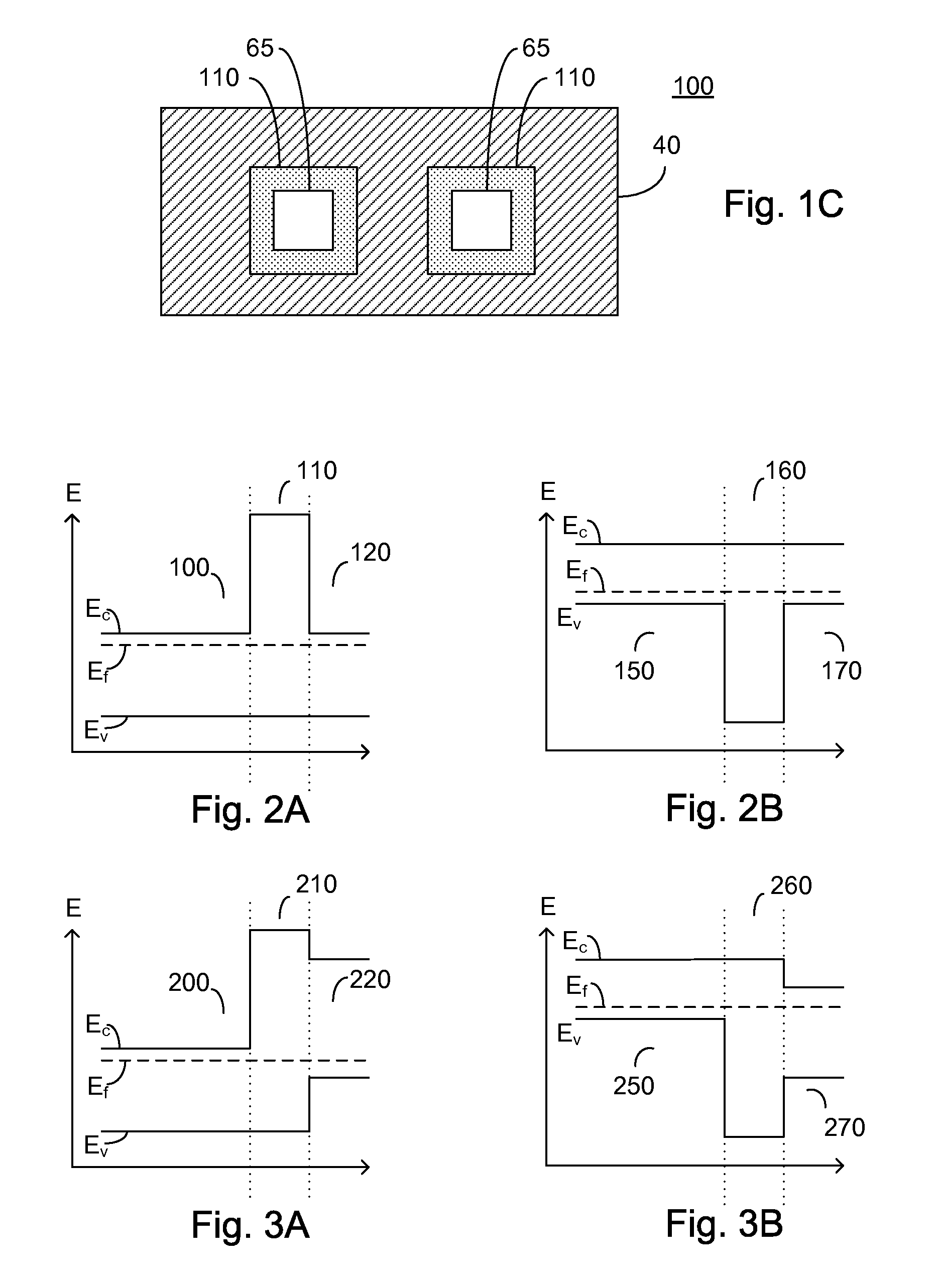

Reduced dark current photodetector

ActiveUS7687871B2Total current dropAvoid tunnelingFinal product manufactureSemiconductor/solid-state device manufacturingValence bandPhotodetector

Owner:MAIMON SHIMON

Back-to-front via process

ActiveUS7534722B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsSemiconductor chip

A method performed on a semiconductor chip having a doped semiconductor material abutting a substrate involves creating a first via through at least a portion of the substrate extending from an outer side of the substrate towards the doped semiconductor material, the first via having a wall surface and a bottom, introducing a first electrically conductive material into the first via so as to create an electrically conductive path, creating a second via, aligned with the first via, extending from an outer surface of the doped portion of the semiconductor chip to the bottom, and introducing a second electrically conductive material into the second via so as to create an electrically conductive path.

Owner:CUFER ASSET LTD LLC

Diffusion layer for semiconductor devices

ActiveUS20070190731A1Improve equipment reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor alloysAlloy

A diffusion layer for semiconductor devices is provided. In accordance with embodiments of the present invention, a semiconductor device, such as a transistor, comprises doped regions surrounded by a diffusion barrier. The diffusion barrier may be formed by recessing regions of the substrate and implanting fluorine or carbon ions. A silicon layer may be epitaxially grown over the diffusion barrier in the recessed regions. Thereafter, the recessed regions may be filled and doped with a semiconductor or semiconductor alloy material. In an embodiment, a semiconductor alloy material, such as silicon carbon, is selected to induce a tensile stress in the channel region for an NMOS device, and a semiconductor alloy material, such as silicon germanium, is selected to induce a compressive stress in the channel region for a PMOS device.

Owner:TAIWAN SEMICON MFG CO LTD

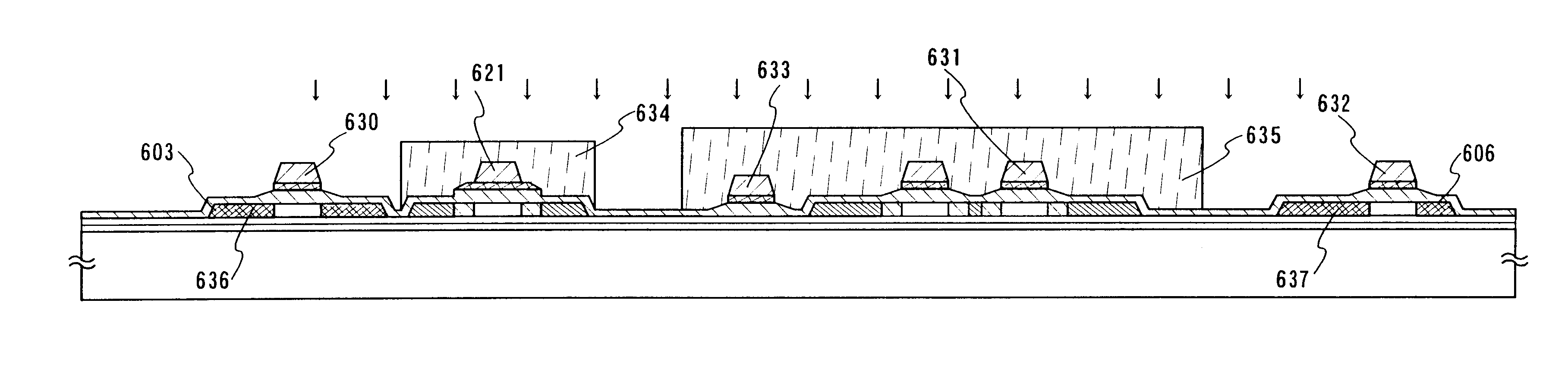

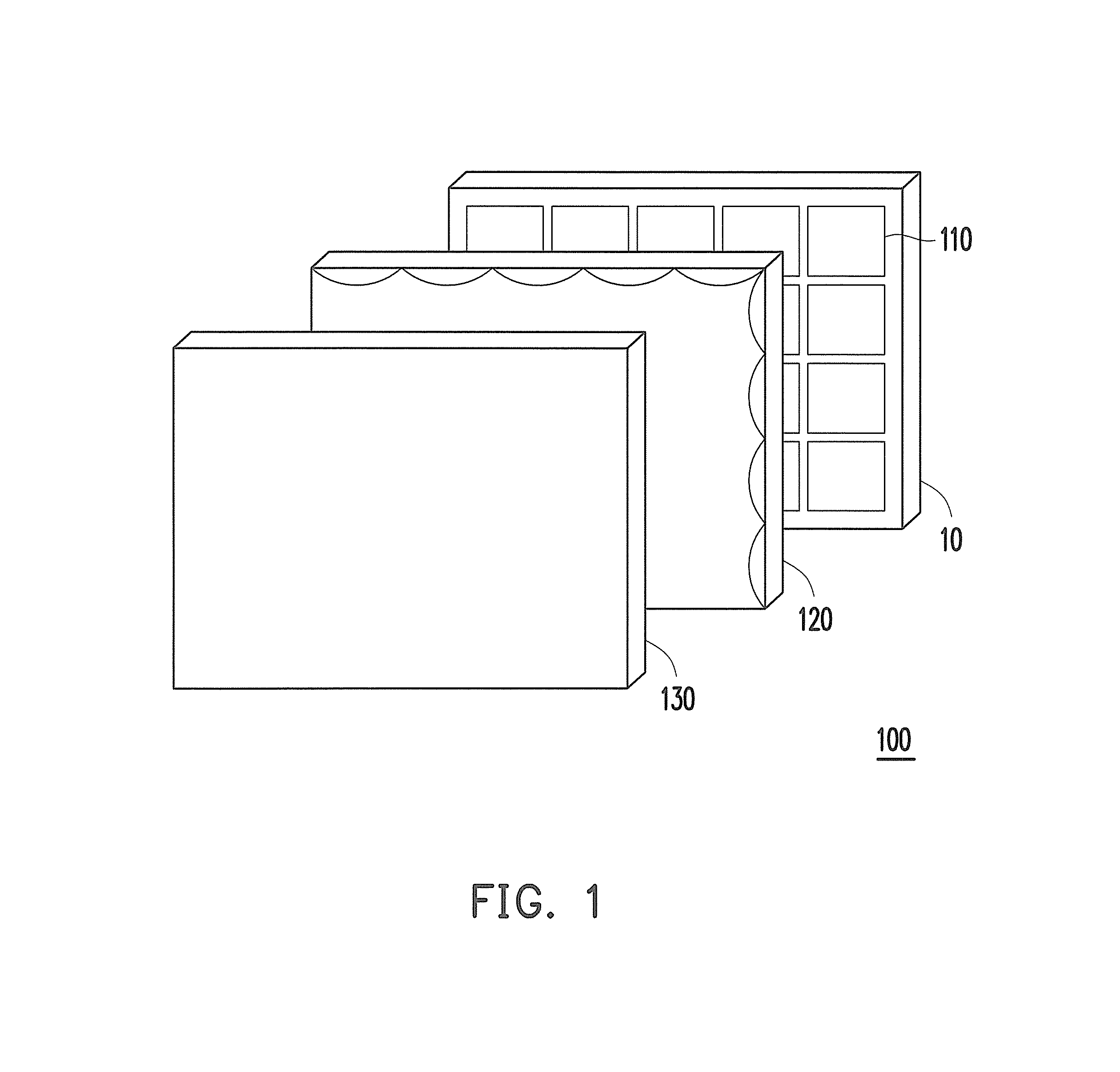

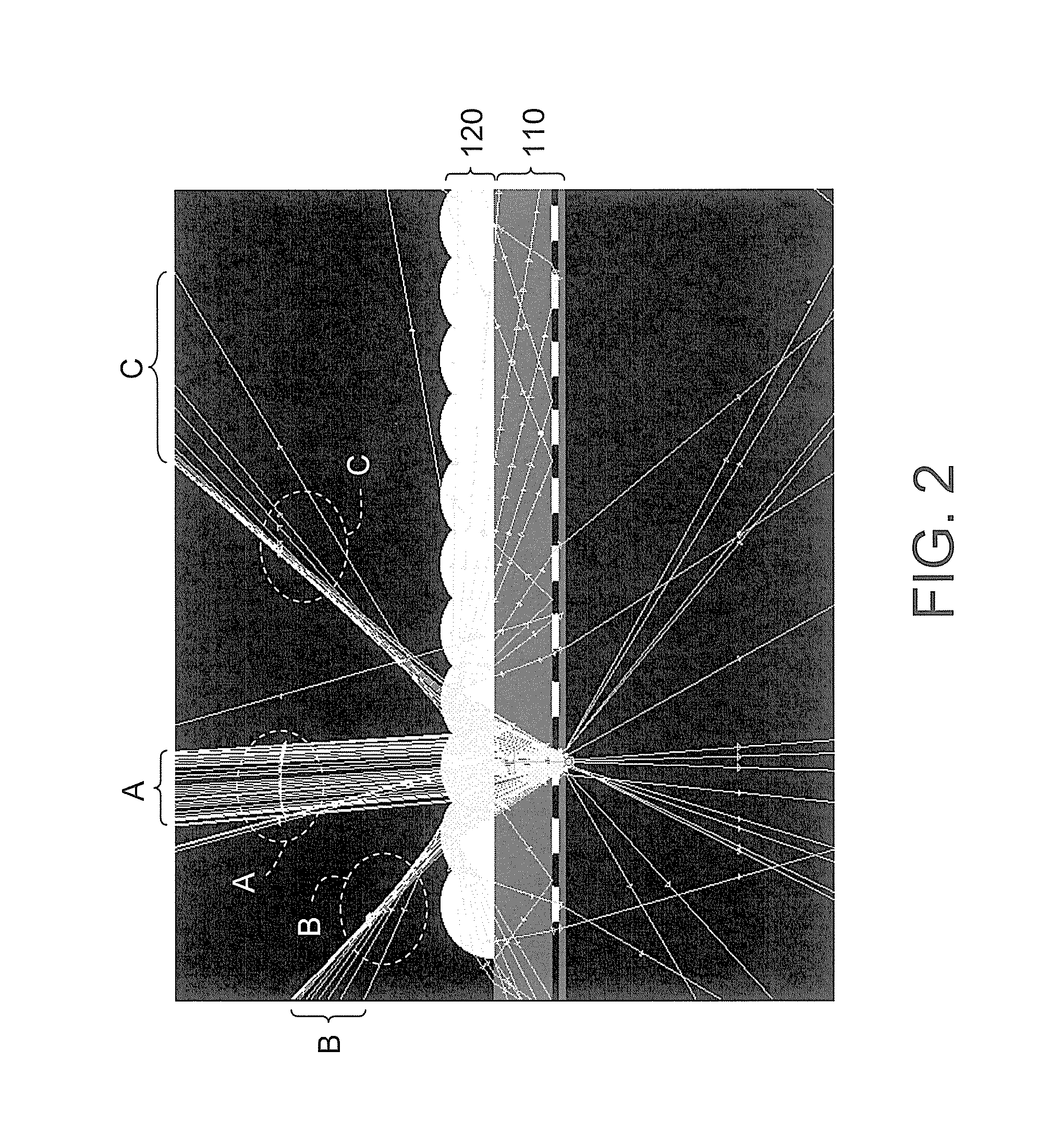

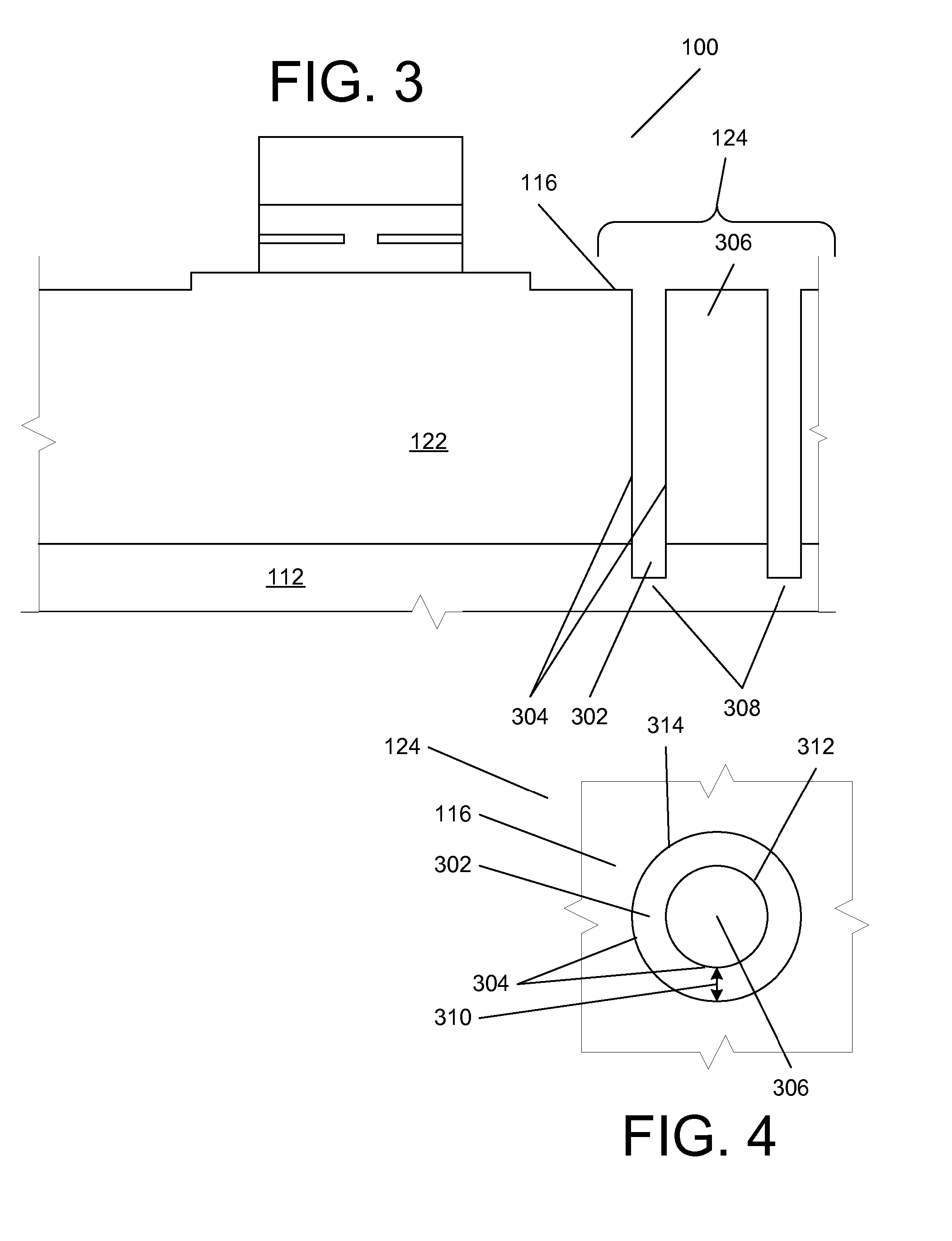

Light emitting unit array and projection system

A light emitting unit array including a plurality of micro-light emitting diodes (μ-LEDs) is provided. The micro-light emitting diodes are arranged in an array on a substrate, and each of the micro-light emitting diodes includes a reflection layer, a light emitting structure, and a light collimation structure. The light emitting structure is disposed on the reflection layer, and includes a first type doped semiconductor layer, an active layer, and a second type doped semiconductor layer that are stacked sequentially. At least a portion of the first type doped semiconductor layer, the active layer, and the second type doped semiconductor layer are sandwiched between the reflection layer and the light collimation structure.

Owner:IND TECH RES INST

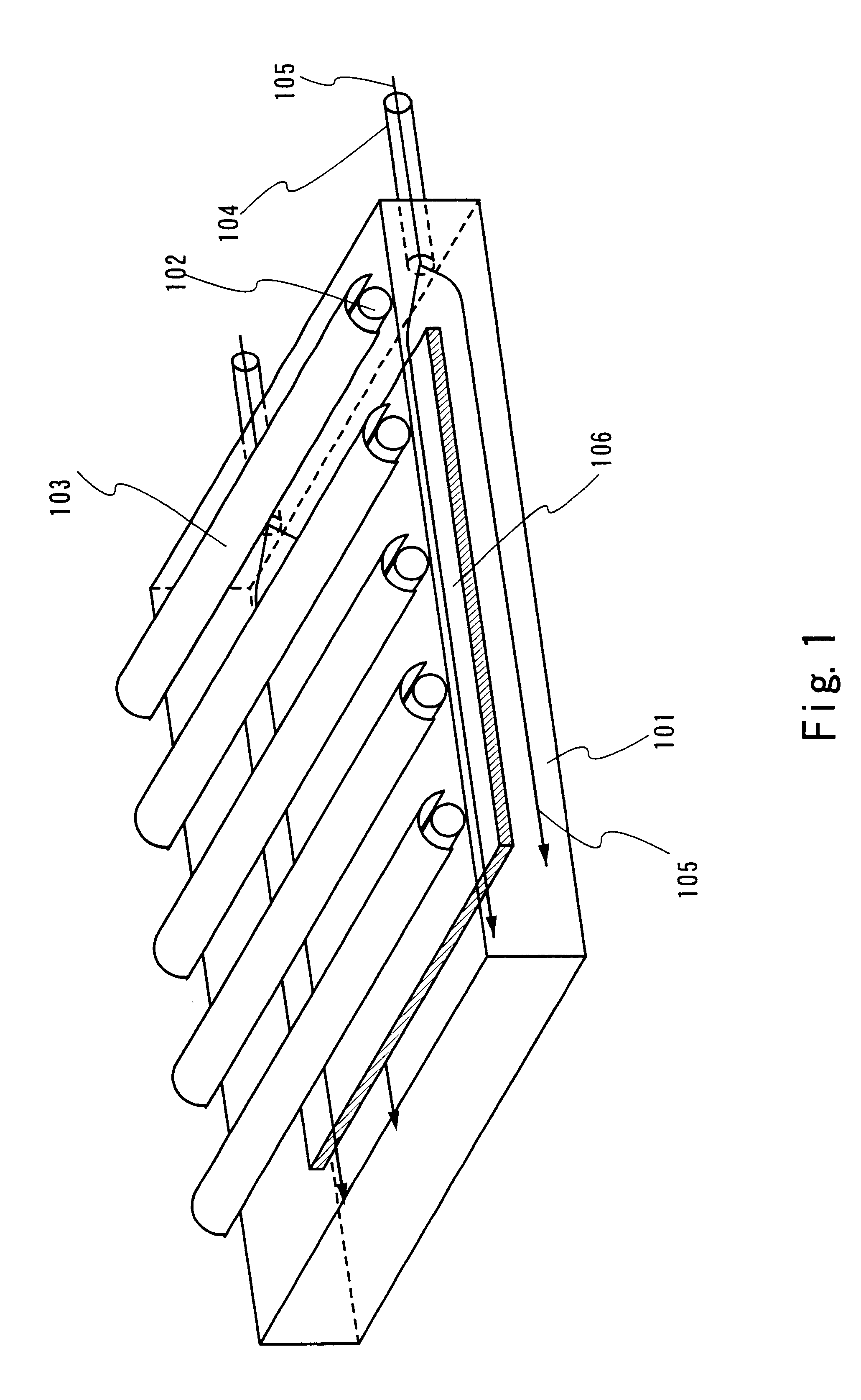

Light emitting diode structure having photonic crystals

ActiveUS7173289B1Improve epitaxy qualitySurface lightSolid-state devicesSemiconductor devicesPhotonic crystalPhotonics

A light emitting diode (LED) structure includes a substrate with a surface and cylindrical photonic crystals, a first type doping semiconductor layer, a first electrode, a light emitting layer, a second type doping semiconductor layer and a second electrode. The first type doping semiconductor layer is formed on the substrate to cover the photonic crystals. The light emitting layer, the second type doping semiconductor layer and the second electrode are sequentially formed on a portion of the first type doping semiconductor layer. The first electrode is formed on the other portion of the first type doping semiconductor layer without being covered by the light emitting layer. Because the substrate with photonic crystals can improve the epitaxial quality of the first type doping semiconductor layer and increase the energy of the light forwardly emitting out of the LED, the light emitting efficiency of the LED is effectively enhanced.

Owner:FORMOSA EPITAXY INCORPORATION +1

Chip capacitive coupling

ActiveUS7786592B2Semiconductor/solid-state device detailsSolid-state devicesCapacitanceSemiconductor materials

A method of creating a semiconductor chip having a substrate, a doped semiconductor material abutting the substrate and a device pad at an outer side of the doped semiconductor material involves creating a via through at least a portion of the substrate, the via having a periphery and a bottom at a location and depth sufficient to bring the via into proximity with the device pad but be physically spaced apart from the device pad, introducing an electrically conductive material into the via, and connecting the electrically conductive material to a signal source so the signal will deliberately be propagated from the electrically conductive material to the device pad without any direct electrical connection existing between the electrically conductive material and the device pad.

Owner:CUFER ASSET LTD LLC

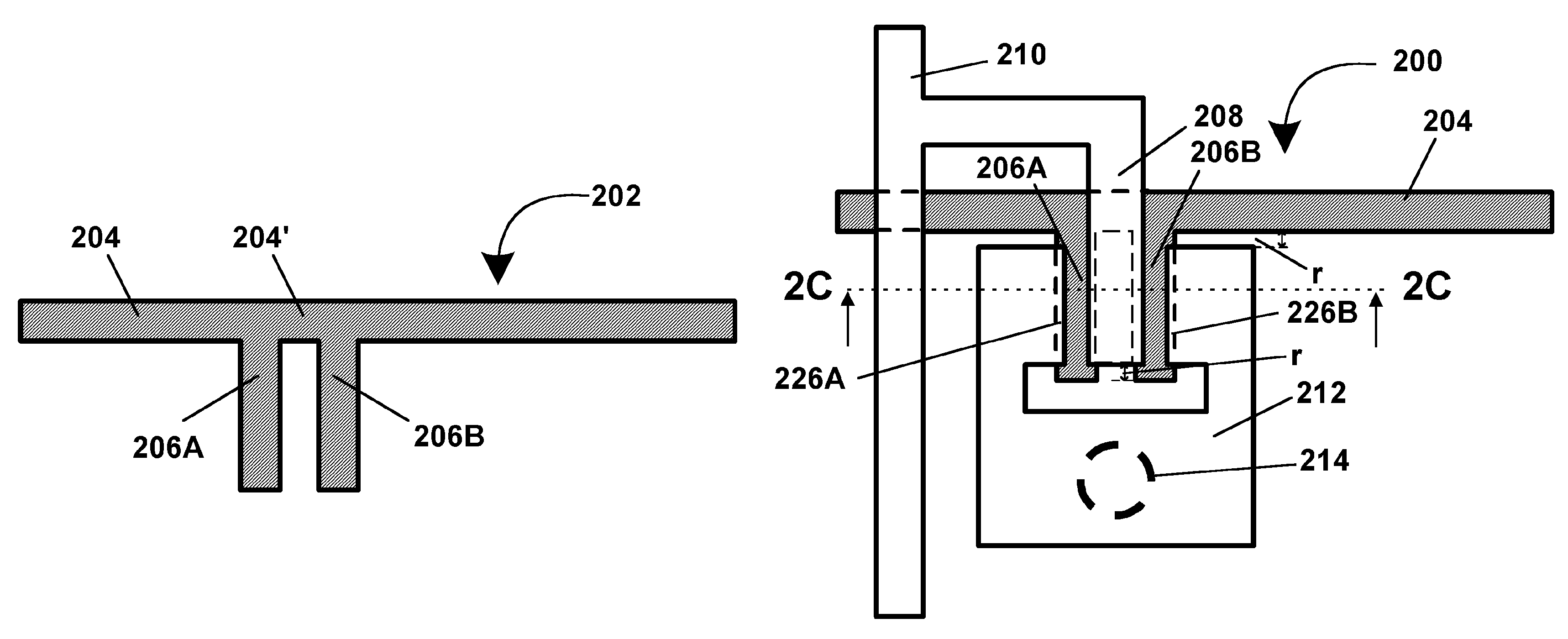

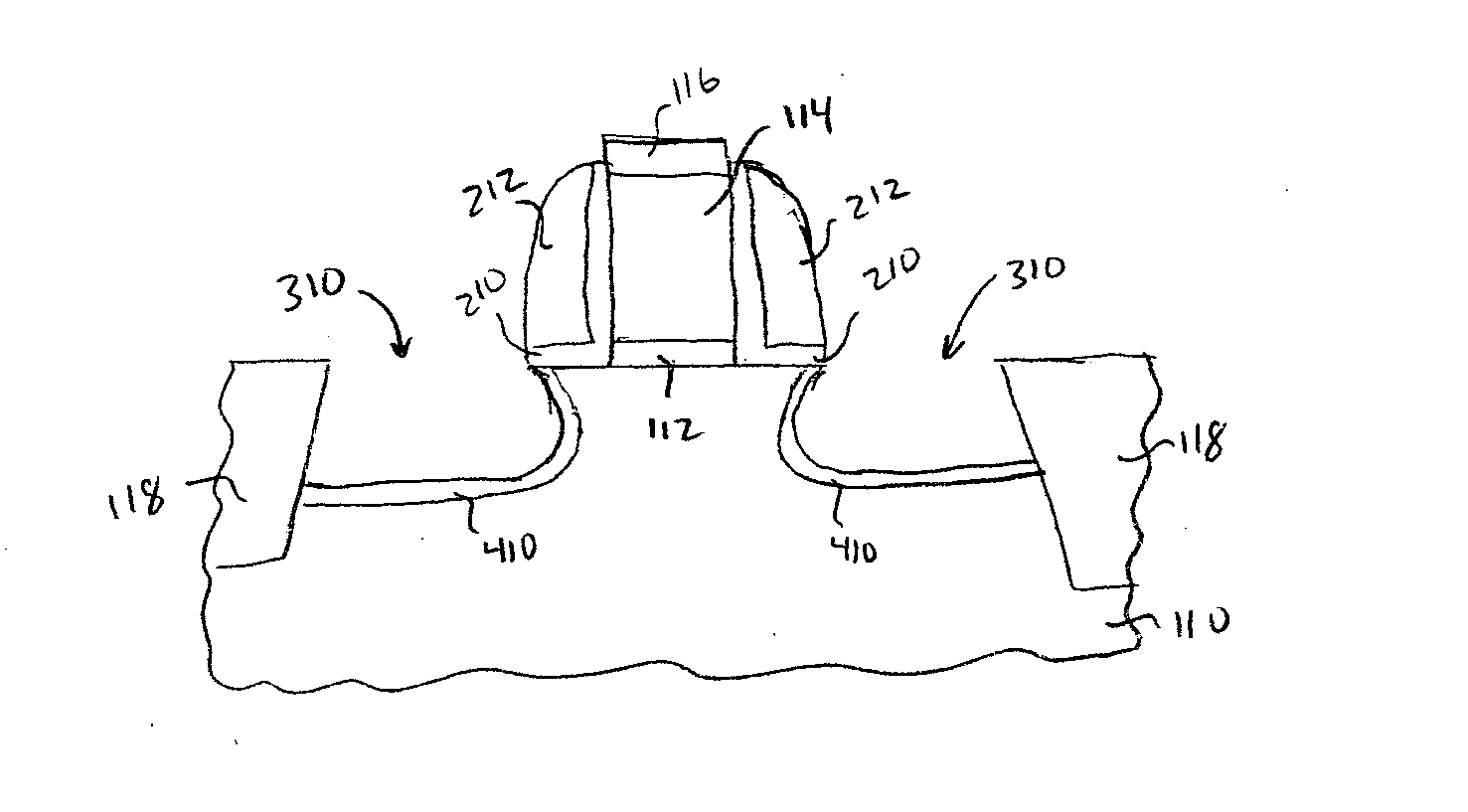

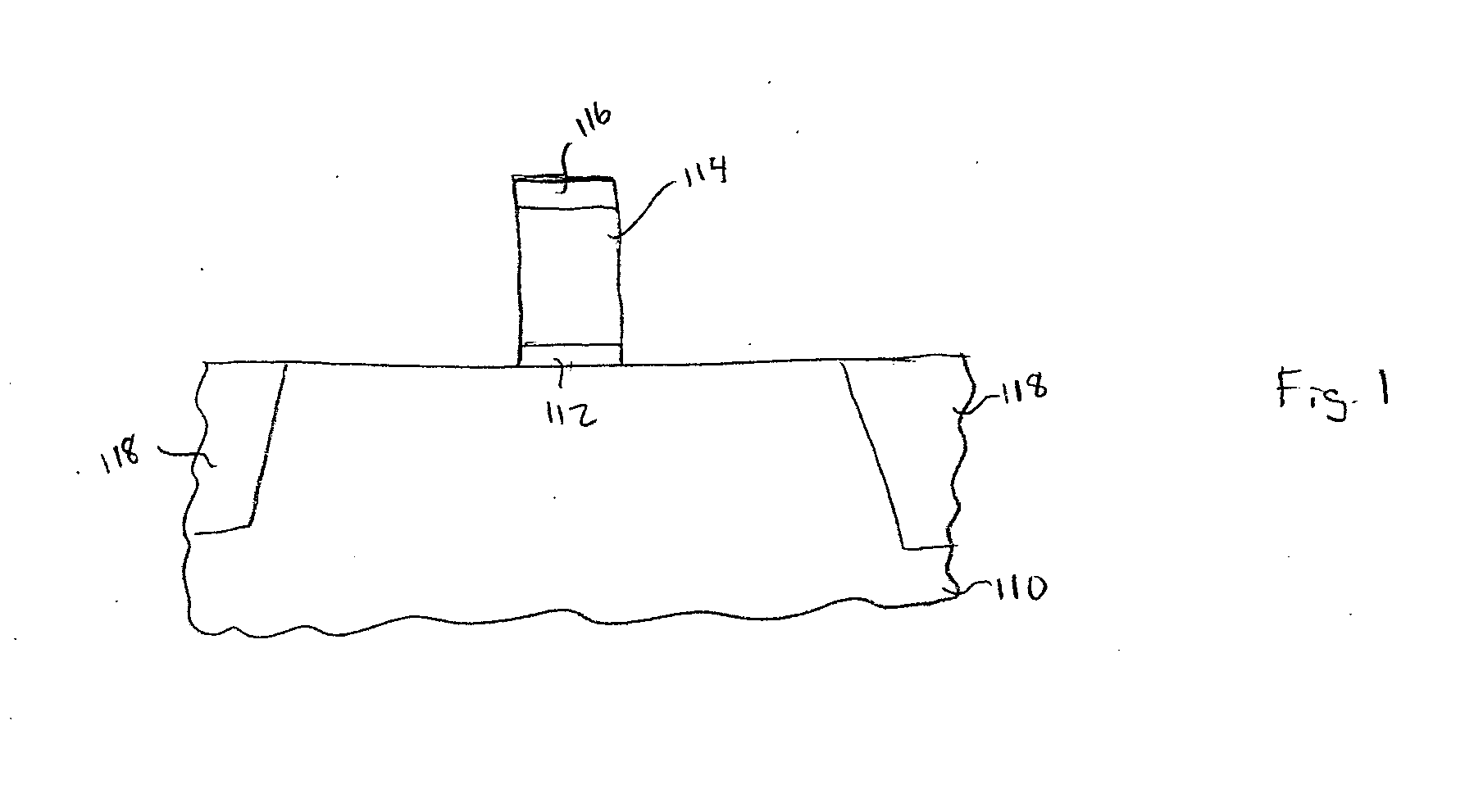

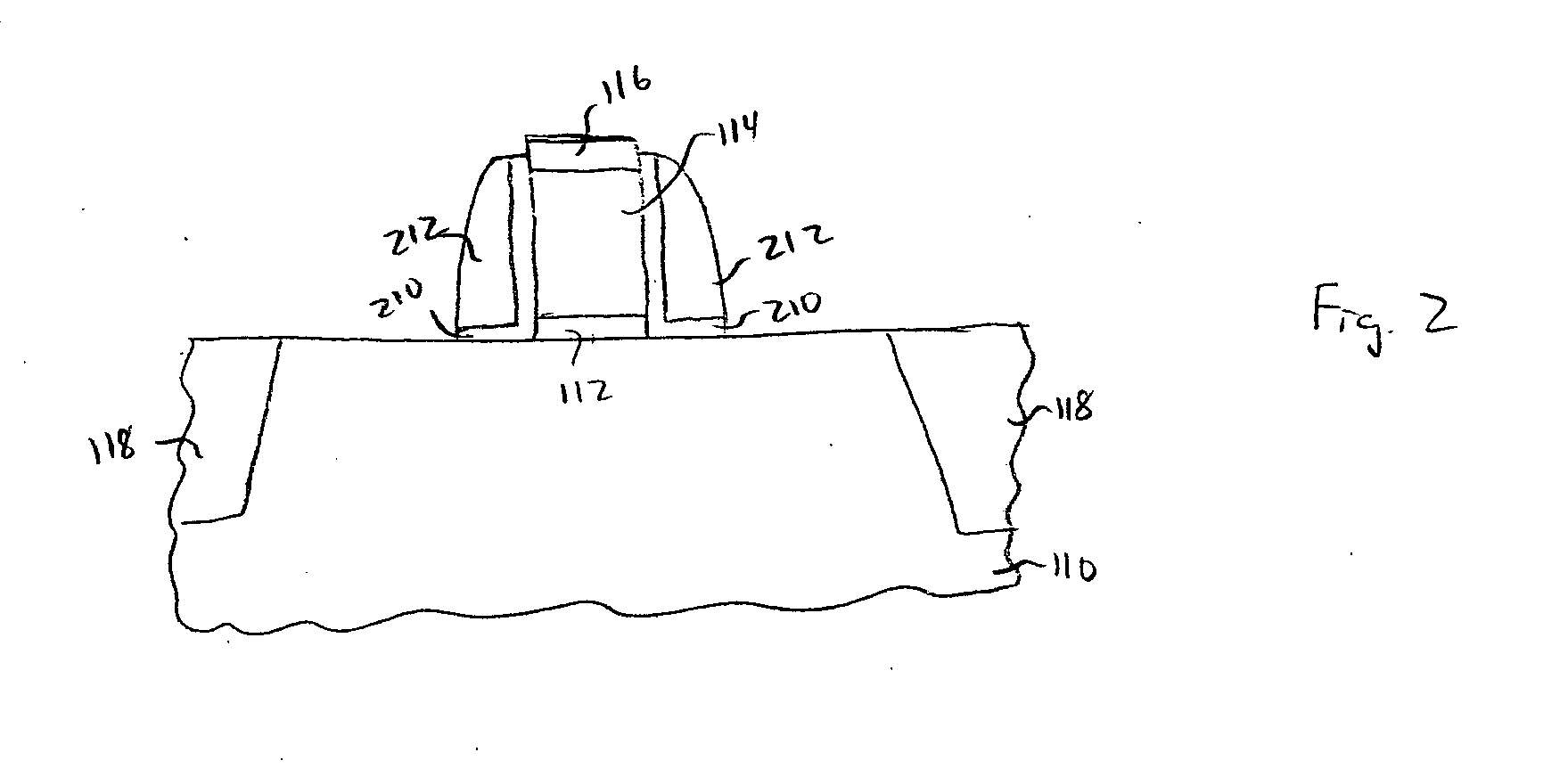

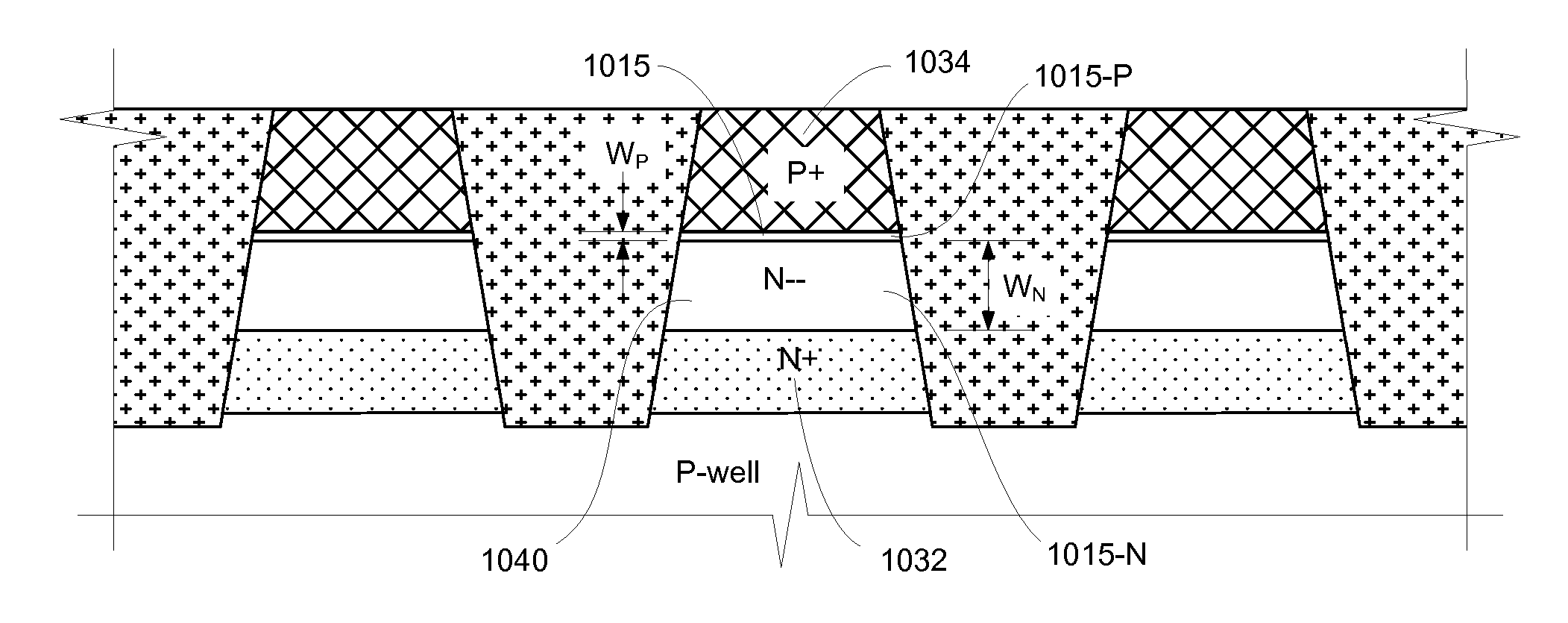

Method of forming memory cell access device

ActiveUS20120326265A1Solve the large leakage currentImproved memory operationSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalP–n junction

A memory device includes an access device including a first doped semiconductor region having a first conductivity type, and a second doped semiconductor region having a second conductivity type opposite the first conductivity type. Both the first and the second doped semiconductor regions are formed in a single-crystalline semiconductor body, and define a p-n junction between them. The first and second doped semiconductor regions are implemented in isolated parallel ridges formed in the single-crystal semiconductor body. Each ridge is crenellated, and the crenellations define semiconductor islands; the first doped semiconductor region occupies a lower portion of the islands and an upper part of the ridge, and the second doped semiconductor region occupies an upper portion of the islands, so that the p-n junctions are defined within the islands.

Owner:IBM CORP +1

Method for preparing high-performance doped diamond-like film

InactiveCN101748381AImprove overall performanceImprove performanceChemical vapor deposition coatingIon beam depositionPhysics

The invention discloses a method for preparing a high-performance doped diamond-like film. The method is characterized by comprising the following steps: firstly, utilizing ultrasonic cleaning technology to remove a polluted layer on the surface of a substrate; utilizing ion beam assisted deposition technology to prepare a gradient transition layer; and finally utilizing ion beam deposition and magnetron sputtering to synthesize a multi-element doped DLC film, wherein except any one of carbonaceous gases, such as methane, acetylene, benzene, ethanol, acetone and the like, any gas containing non-carbon elements, such as silicon hydride, boron hydride, phosphorane, carbon tetrafluoride and the like, is simultaneously introduced, and a metal sputtering source is opened for the doping of metal elements. The method has the advantages of synthesizing the multi-element doped DLC film which is simultaneously doped with the metal elements and the nonmetal elements, fully developing the complementary advantages of the doped metal elements and the doped nonmetal elements and remarkably improving the combination properties of the DLC film.

Owner:CHINA UNIV OF GEOSCIENCES (BEIJING)