Patents

Literature

73results about How to "Improve epitaxy quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

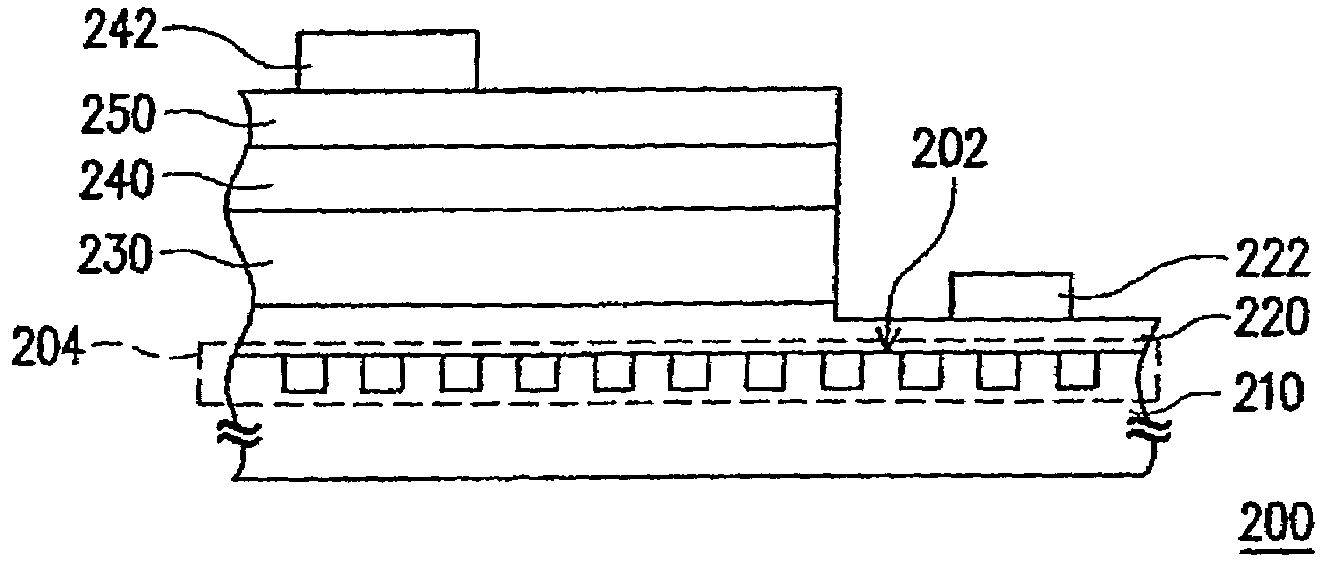

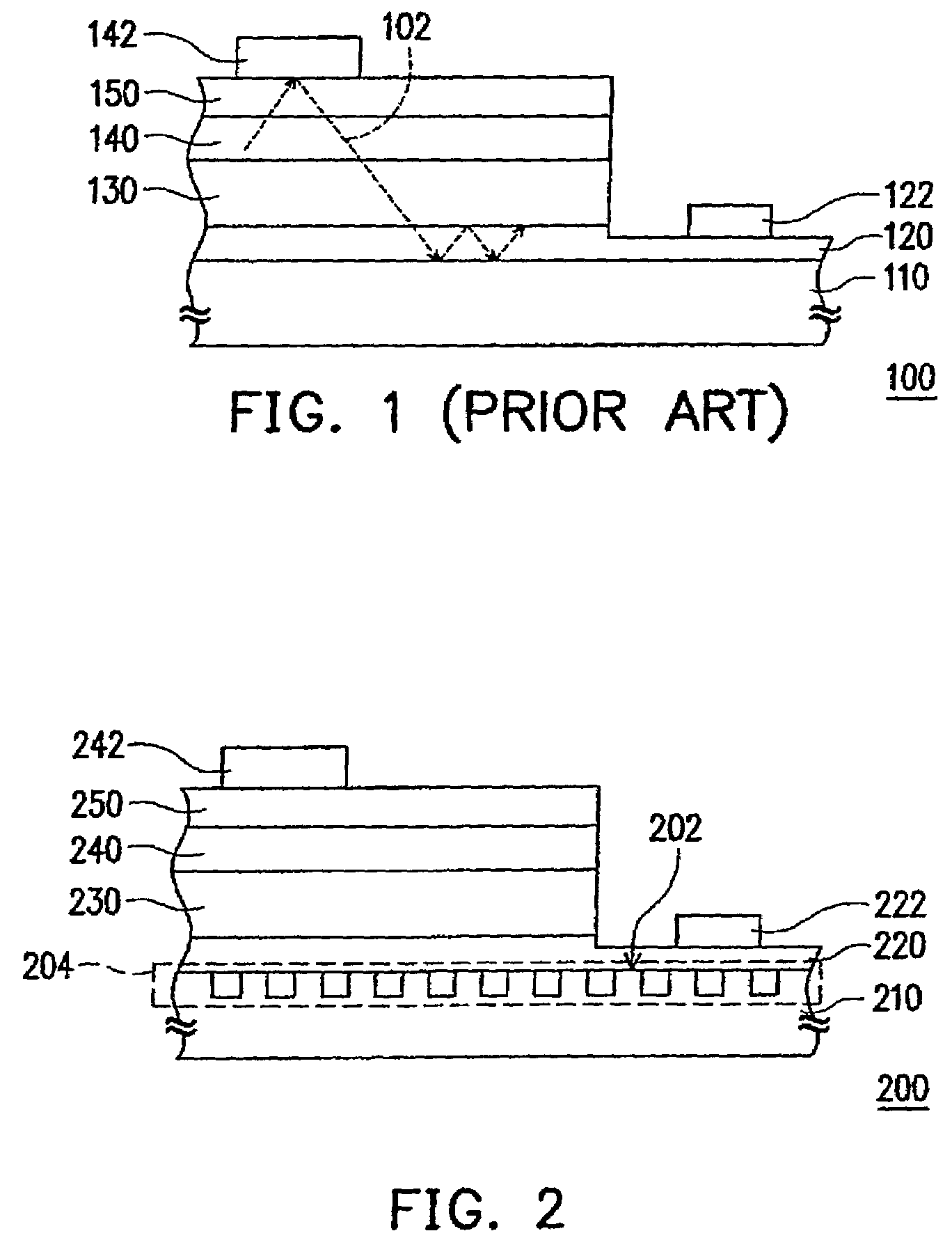

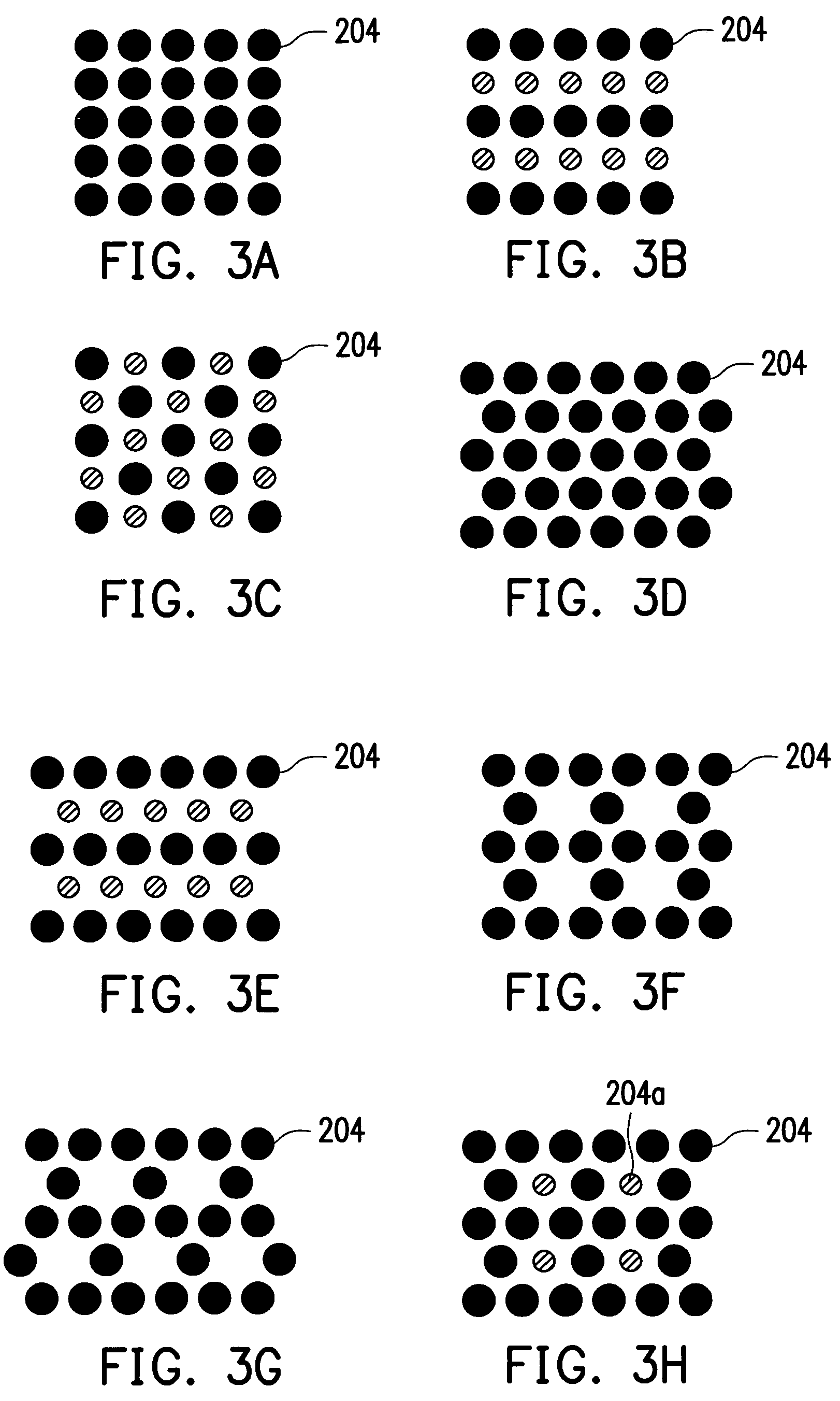

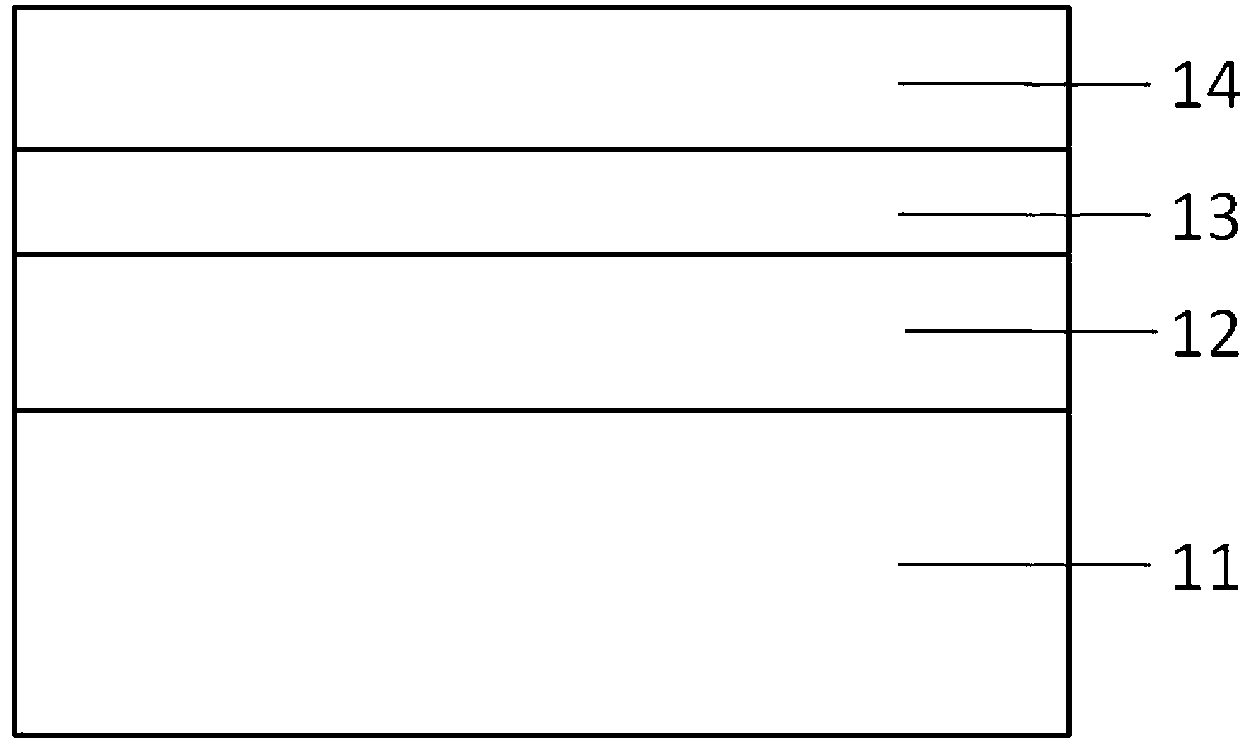

Light emitting diode structure having photonic crystals

ActiveUS7173289B1Improve epitaxy qualitySurface lightSolid-state devicesSemiconductor devicesPhotonic crystalPhotonics

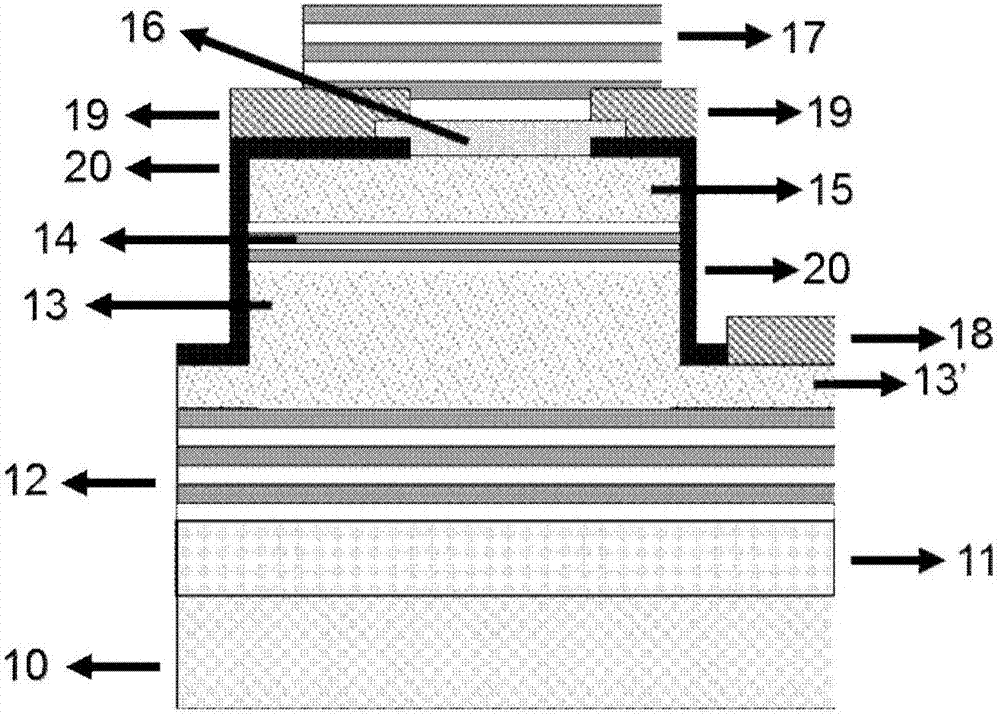

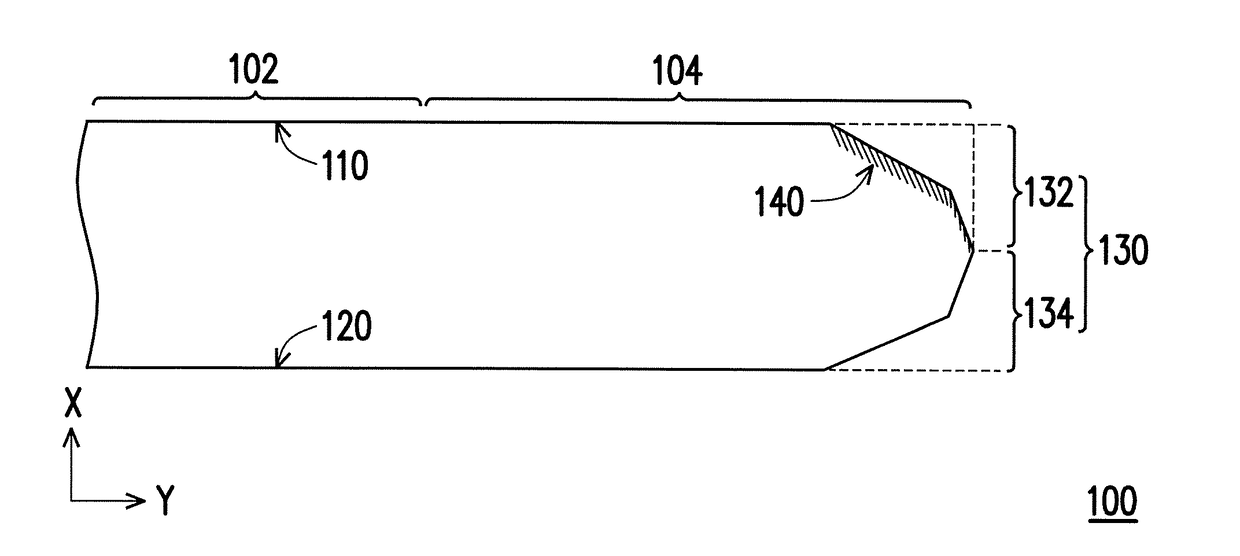

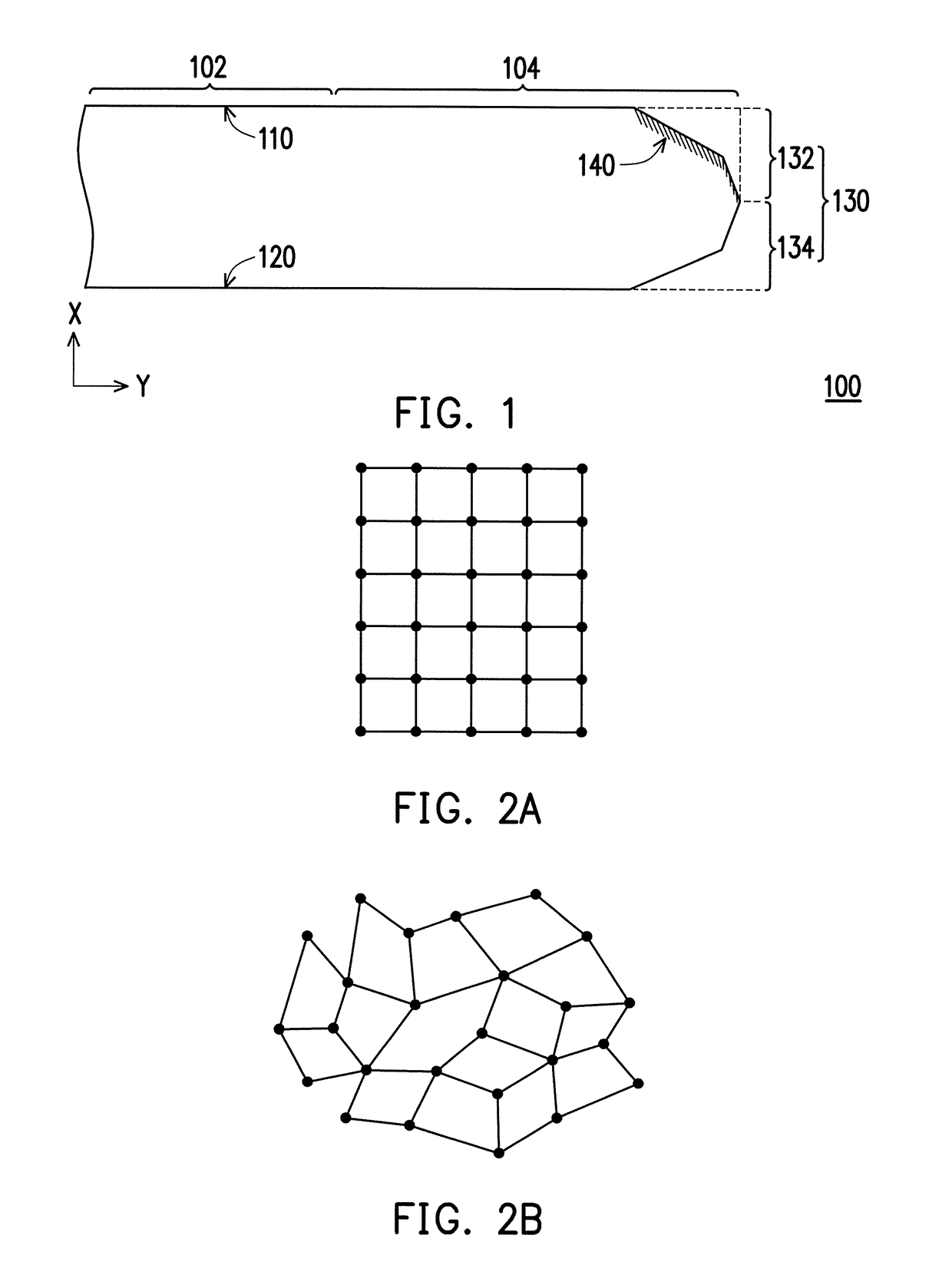

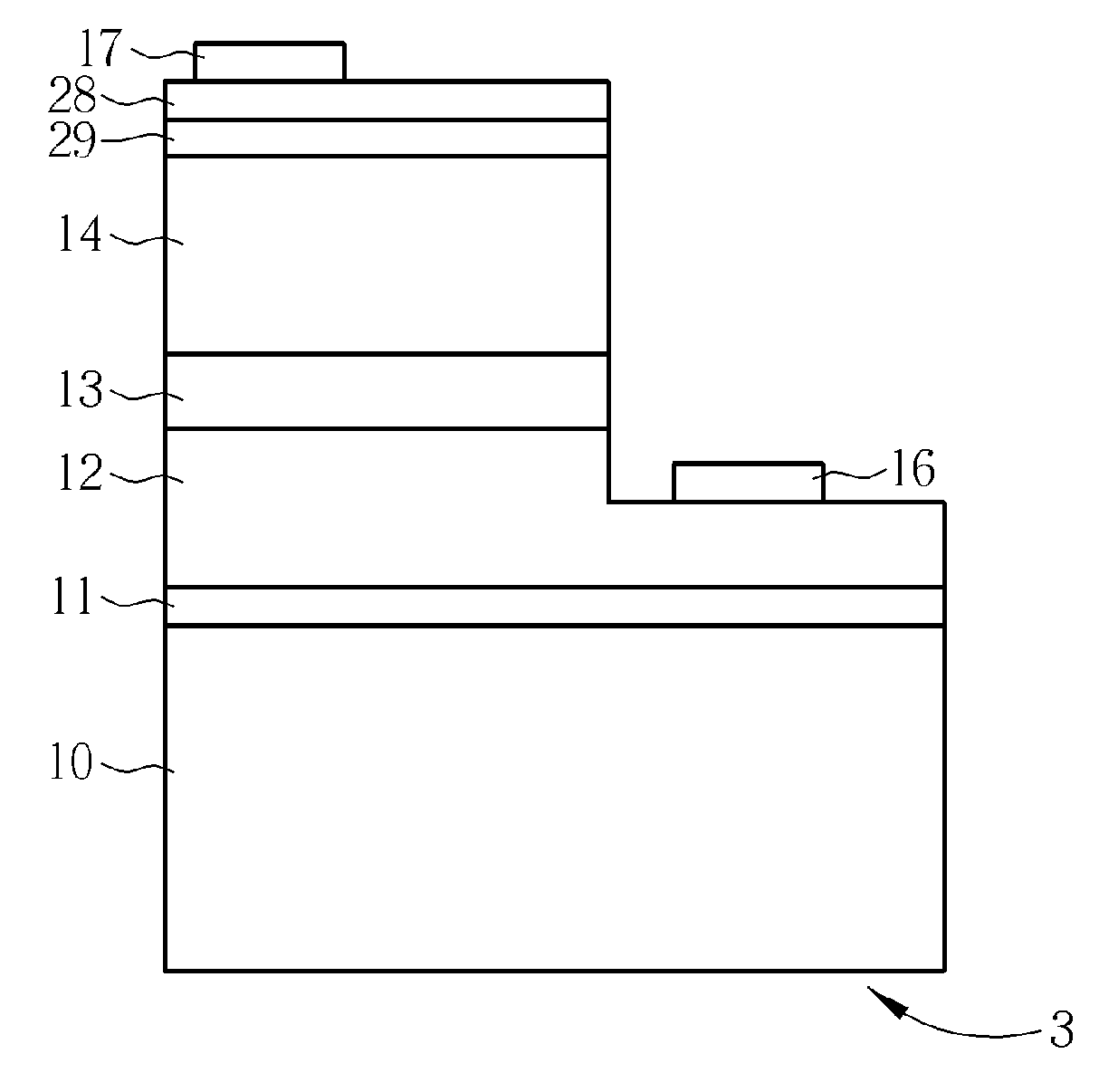

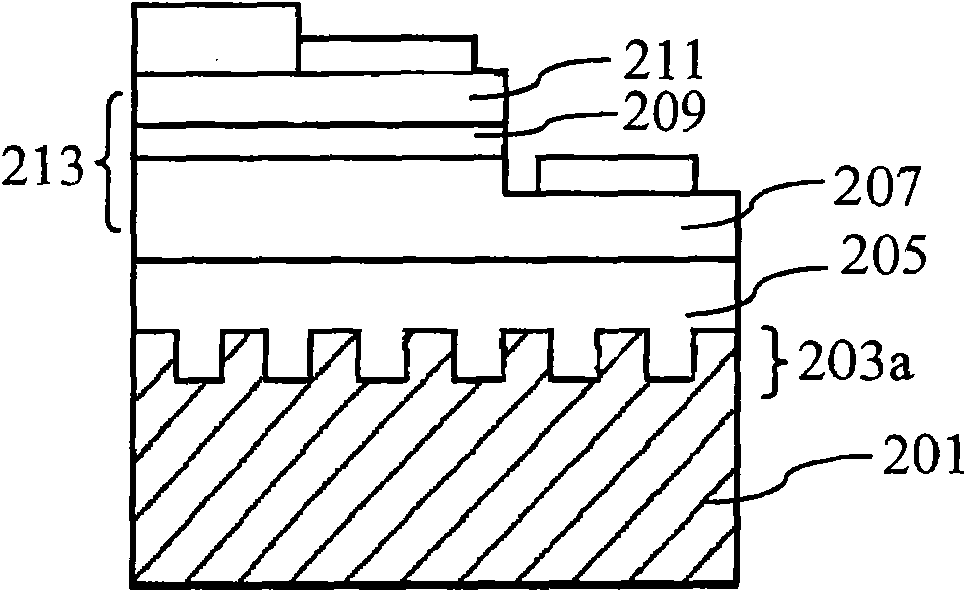

A light emitting diode (LED) structure includes a substrate with a surface and cylindrical photonic crystals, a first type doping semiconductor layer, a first electrode, a light emitting layer, a second type doping semiconductor layer and a second electrode. The first type doping semiconductor layer is formed on the substrate to cover the photonic crystals. The light emitting layer, the second type doping semiconductor layer and the second electrode are sequentially formed on a portion of the first type doping semiconductor layer. The first electrode is formed on the other portion of the first type doping semiconductor layer without being covered by the light emitting layer. Because the substrate with photonic crystals can improve the epitaxial quality of the first type doping semiconductor layer and increase the energy of the light forwardly emitting out of the LED, the light emitting efficiency of the LED is effectively enhanced.

Owner:FORMOSA EPITAXY INCORPORATION +1

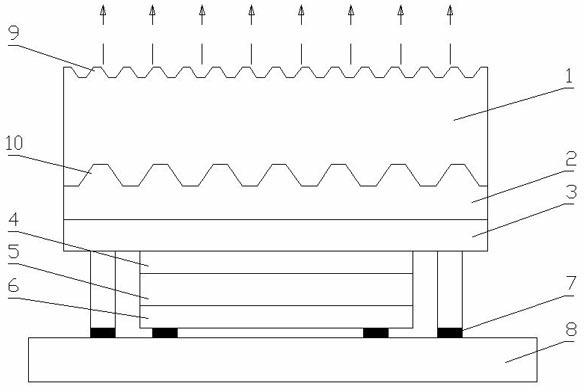

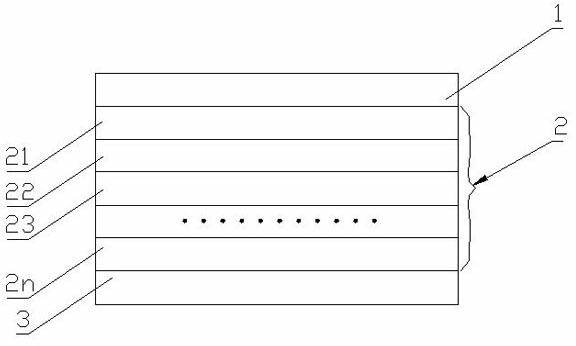

Inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer

InactiveCN102157654AImprove radiative recombination luminous efficiencyReduce defect densitySemiconductor devicesQuantum efficiencyQuantum well

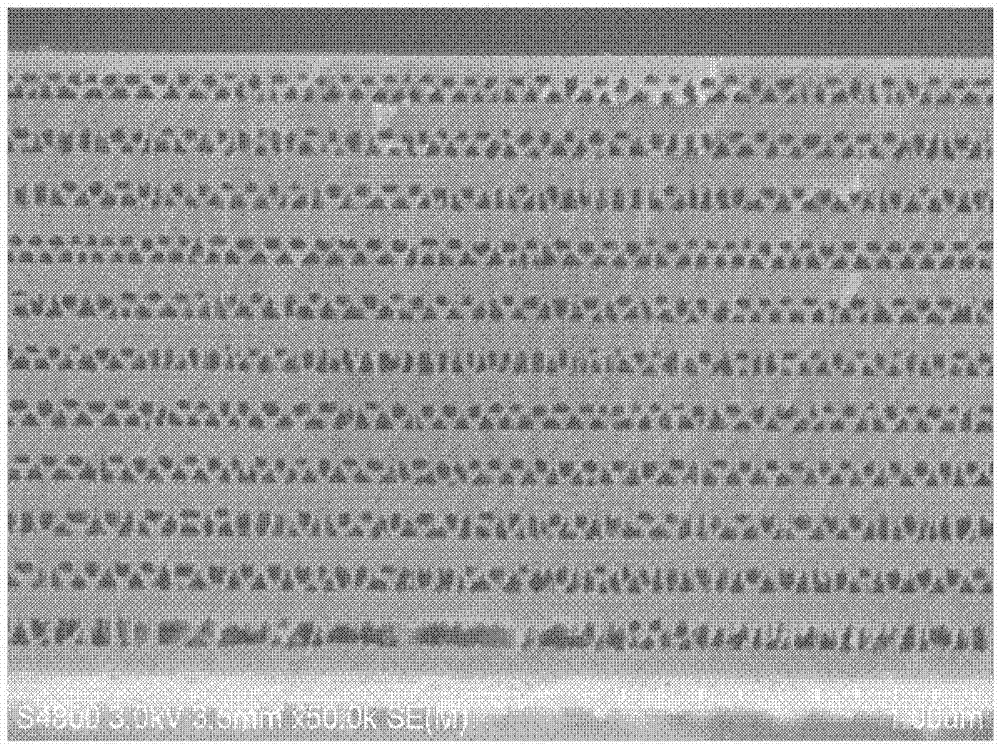

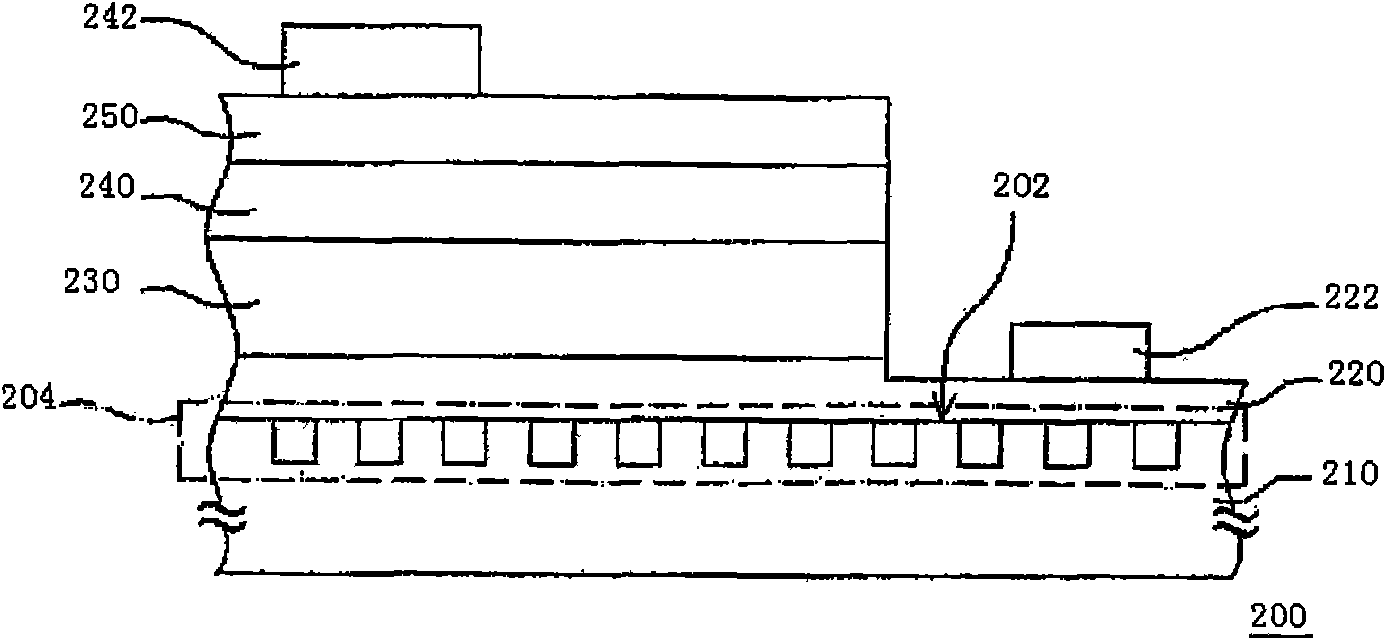

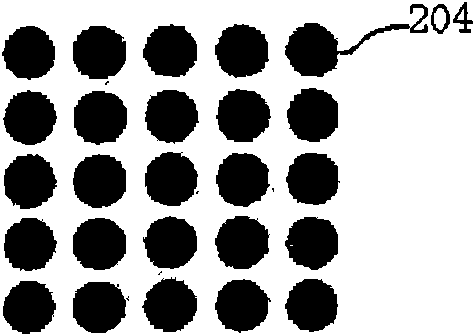

The invention discloses an inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer, wherein the chip comprises a sapphire substrate distributed with 102-104 shrinkage pools at upper and lower surfaces, an AlxGa1-xN component gradual change buffer layer composed of an unit layer formed by k non-doping AlxGa1-xN epitaxial materials, a n-type GaN epitaxial layer, an InGaN / GaN multi-quantum well, a p-type GaN layer, a transparent ITO (indium tin oxide) conductive film, an inverted mounting welding electrode and a silicon substrate from upper to lower. The LED chip disclosed by the invention uses the shrinkage pool structure for improving the emergent probability of LED emergent lights, and increasing the heat radiation area and growth stress acting range of the substrate, so that the GaB epitaxial quality and the radiation composite luminous efficiency are improved; the buffer layer of the n-type GaN epitaxial layer is manufactured by the AlxGa1-xN with gradually reduced Al component, so that the light-emitting efficiency and the internal quantum efficiency of the LED are improved, and a relatively high light output power is obtained.

Owner:CHONGQING UNIV

Preparation method of low stress state composite substrate for GaN growth

ActiveCN105514224AReduced stress stateImproving epitaxial growth qualitySemiconductor devicesComposite substrateDielectric layer

The invention discloses a preparation method of a low stress state composite substrate for GaN growth. The preparation method comprises that a GaN monocrystal epitaxial layer is prepared on a sapphire substrate; a stress compensation layer is deposited at the back side of a thermally and electrically conductive transfer substrate of high welding point; bonding dielectric layers of high welding point are prepared at the surfaces of a GaN epitaxial wafer and the transfer substrate respectively; the GaN epitaxial wafer is bonded to the thermally and electrically conductive substrate by the high-temperature diffusion bonding technology; and the composite substrate with high temperature stability and low stress state for GaN growth is obtained. According to the composite substrate of the invention, homoepitaxy can be realized and a vertical structural device can be directly prepared as a traditional composite substrate, the low stress state and high-temperature stability can be also realized, and the quality of subsequent GaN epitaxial growth and chip preparation can be effectively improved.

Owner:SINO NITRIDE SEMICON

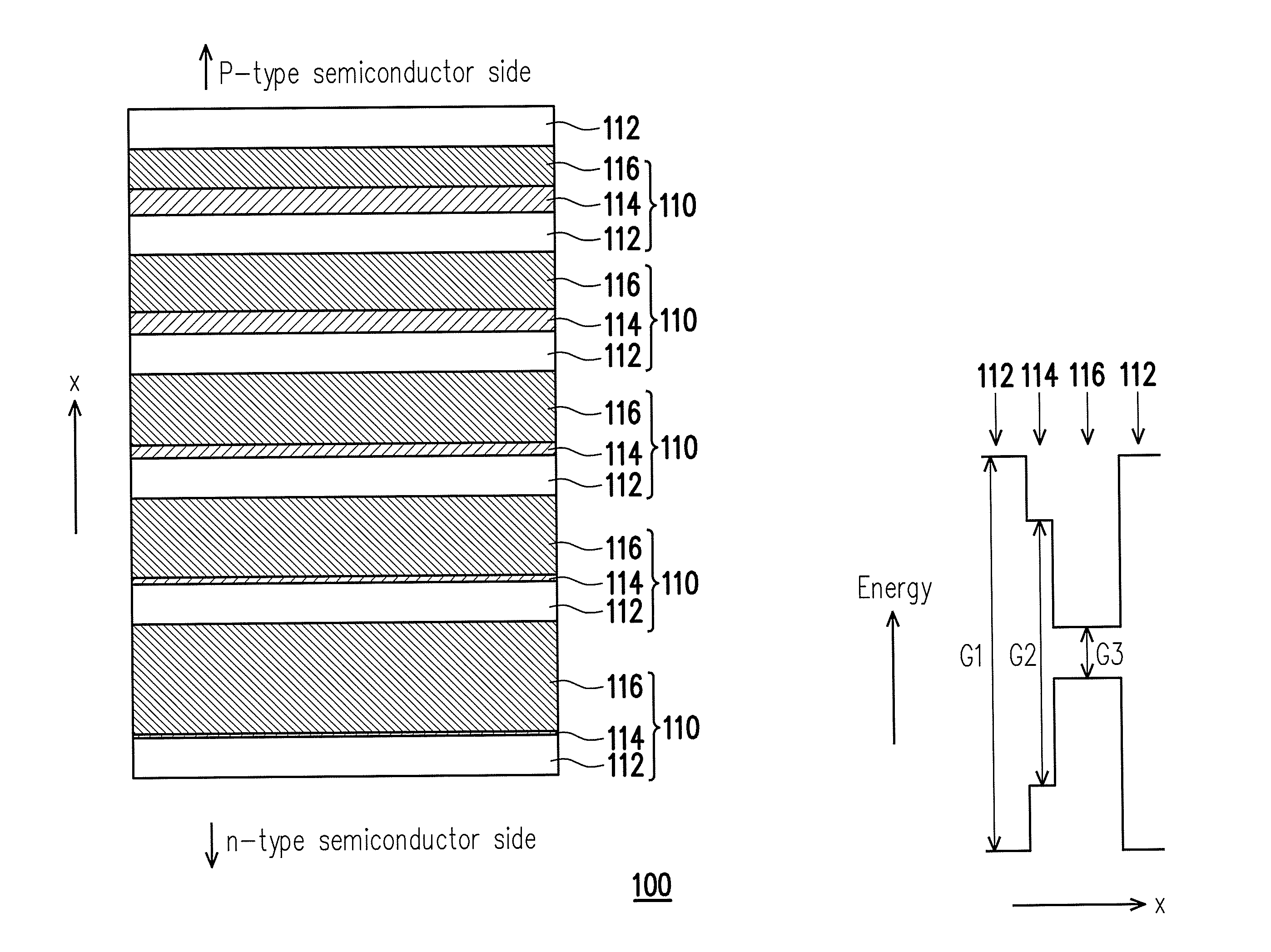

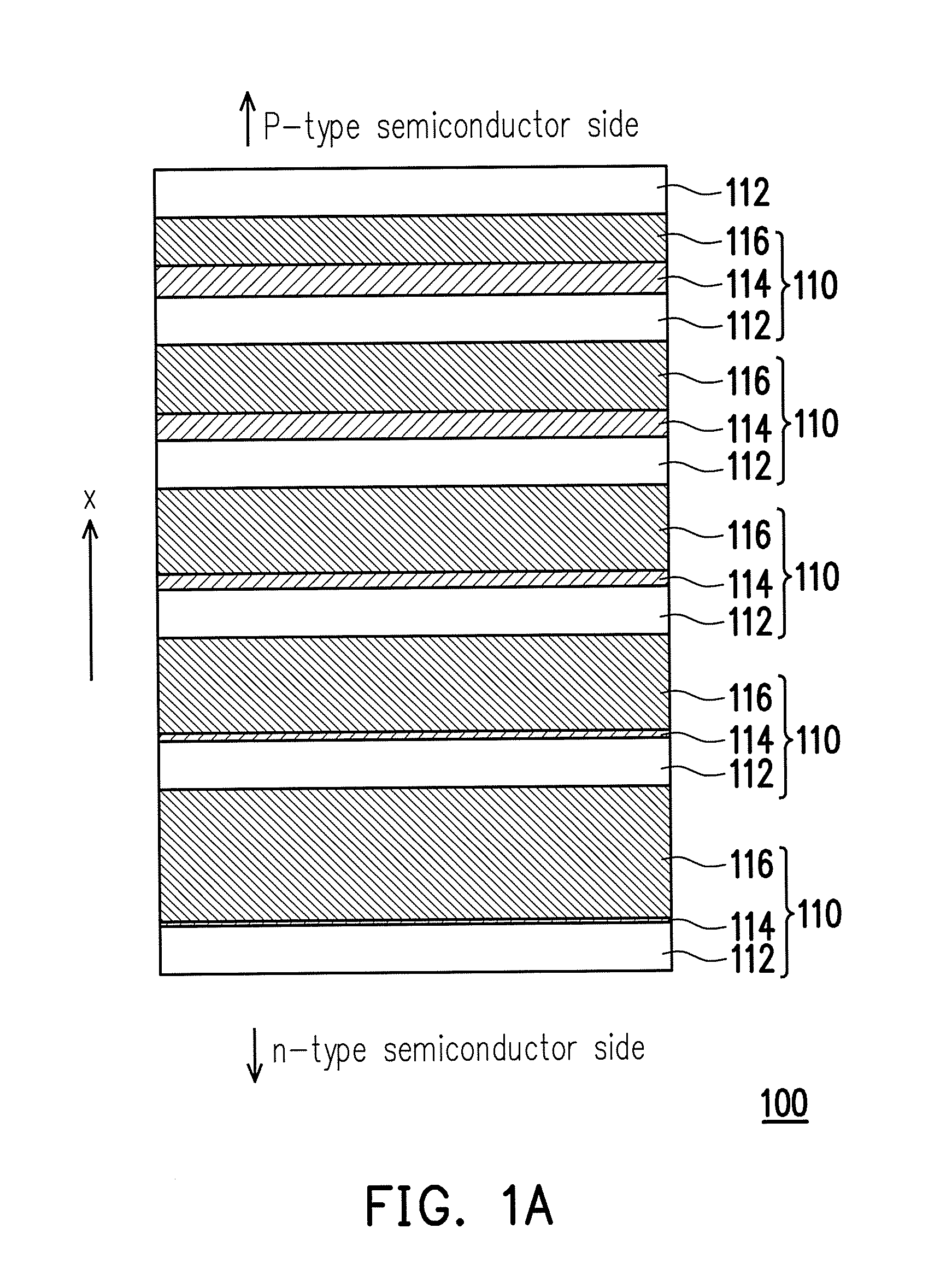

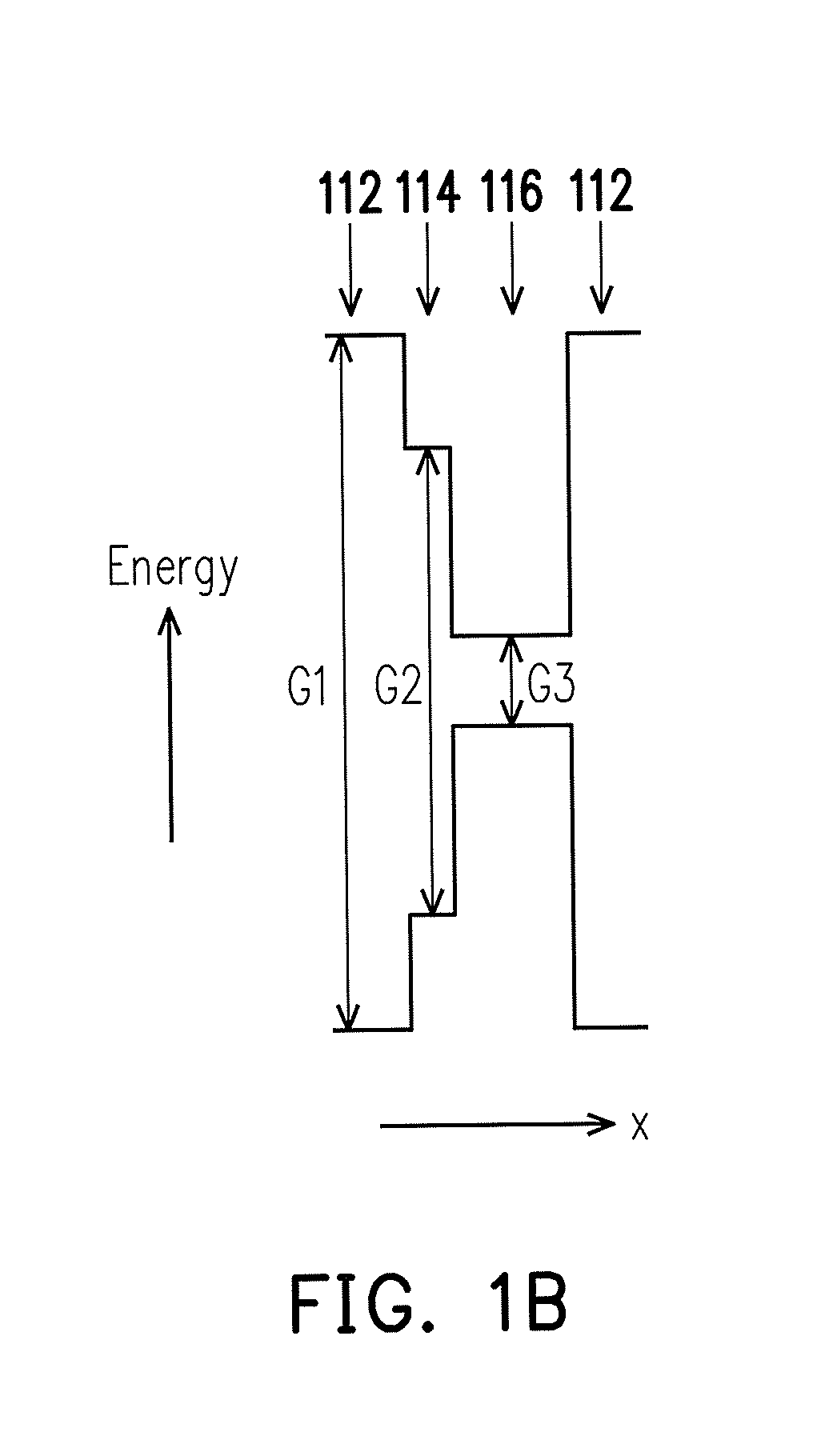

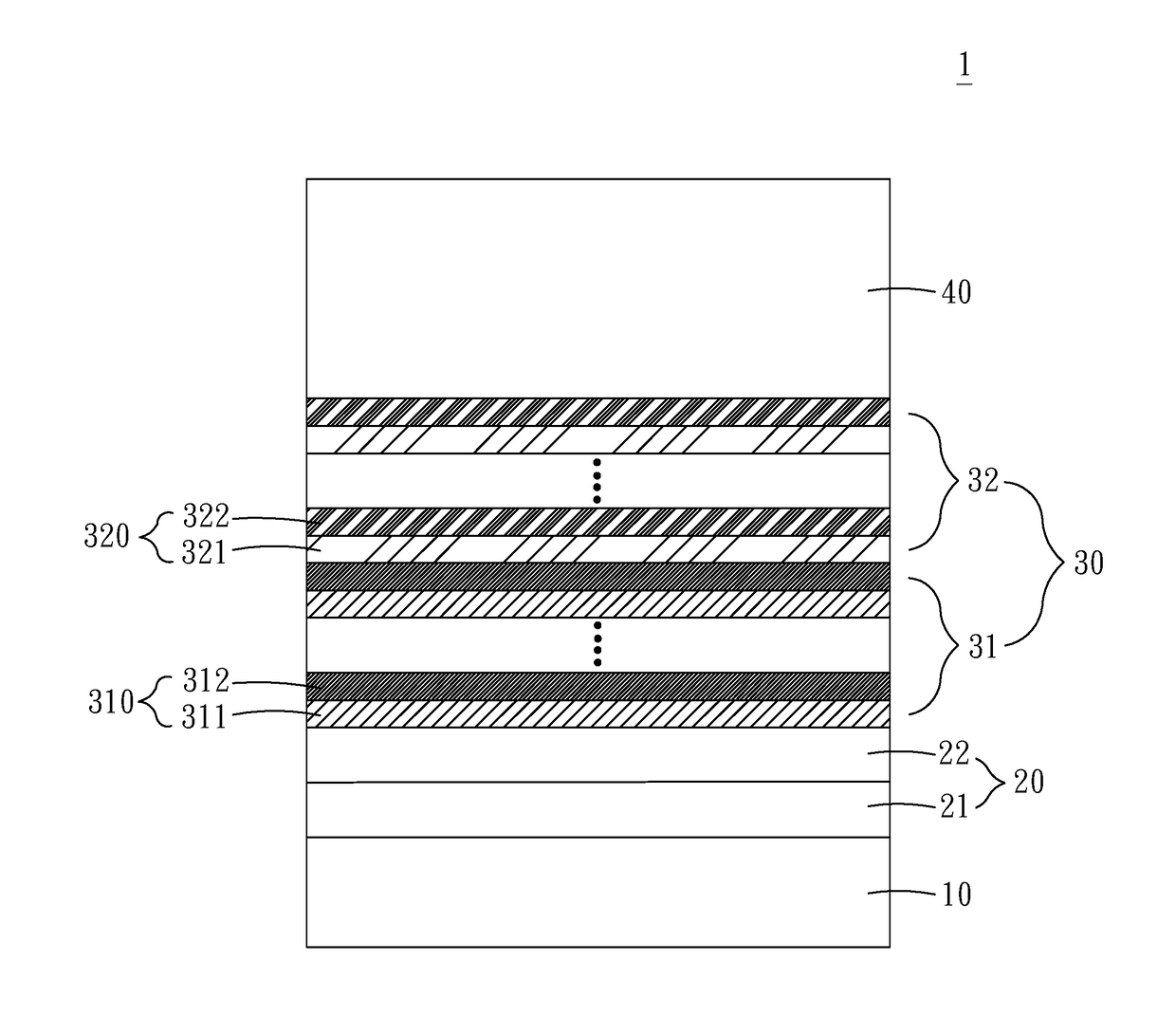

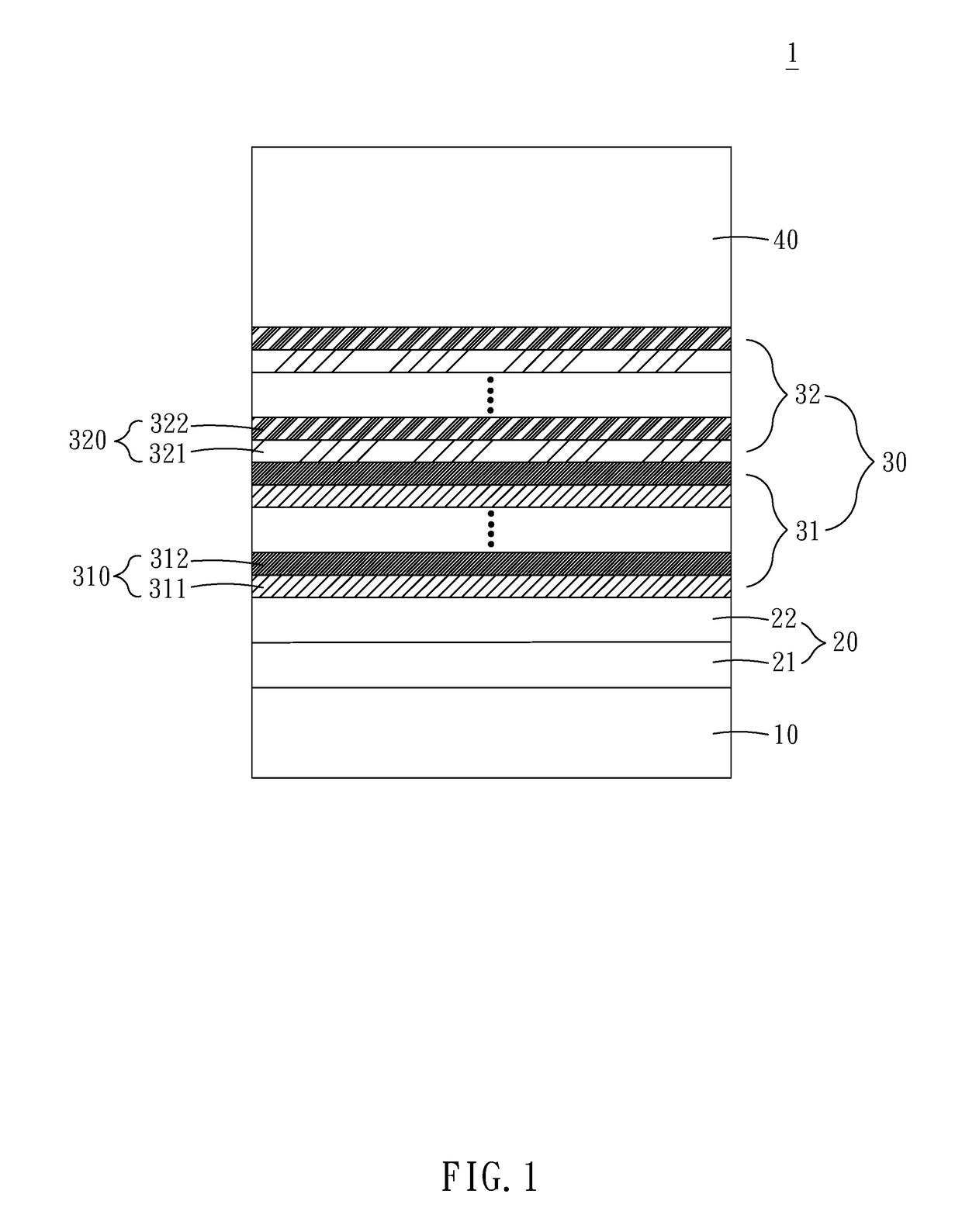

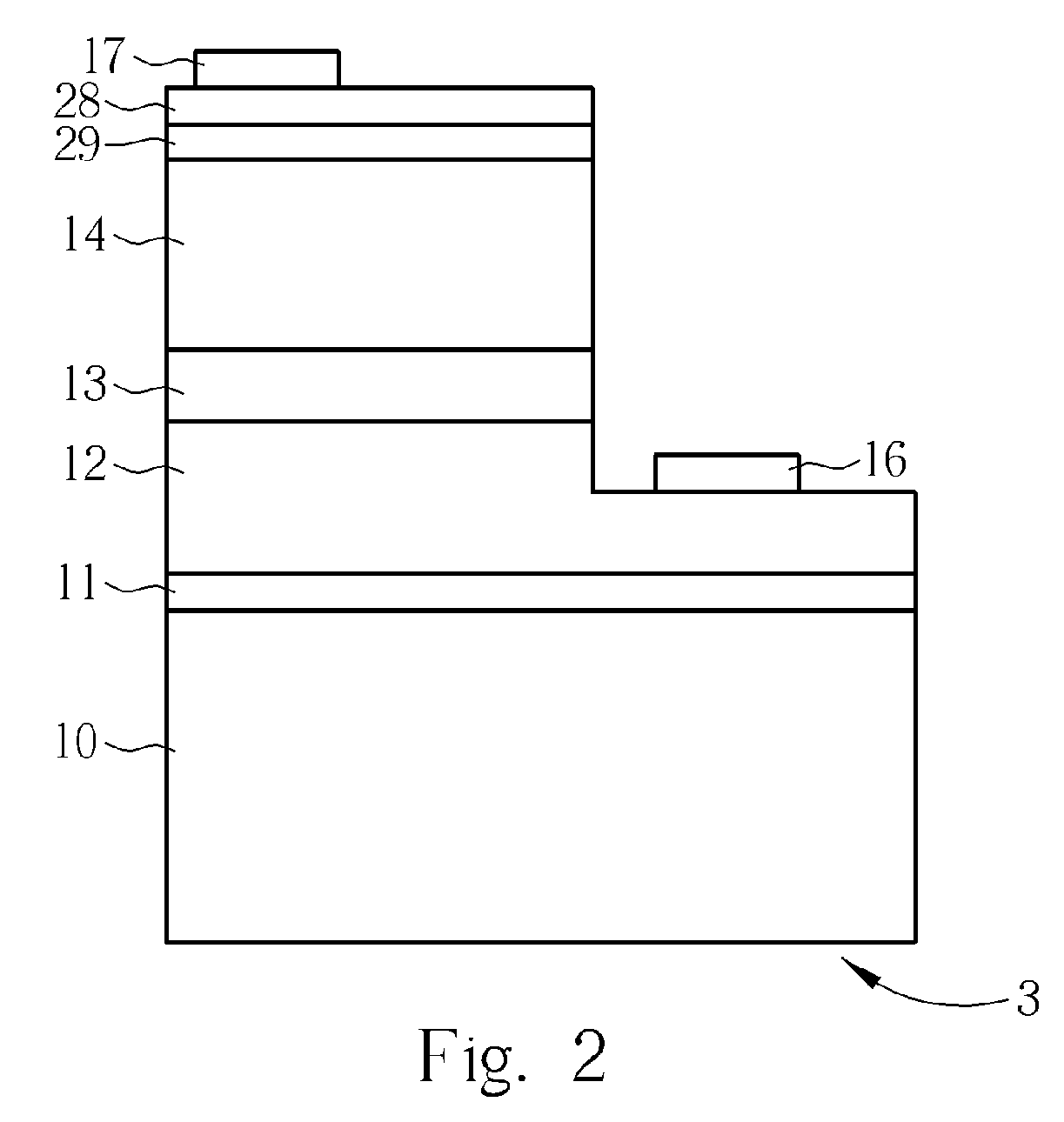

Multiple quantum well structure and method for manufacturing the same

ActiveUS20170033260A1Good optical performanceImprove epitaxy qualitySemiconductor devicesOptoelectronicsIntermediate level

A multiple quantum well structure includes a plurality of well-barrier sets arranged along a direction. Each of the well-barrier sets includes a barrier layer, at least one intermediate level layer, and a well layer. A bandgap of the barrier layer is greater than an average bandgap of the intermediate level layer, and the average bandgap of the intermediate level layer is greater than a bandgap of the well layer. The barrier layers, the intermediate level layers, and the well layers of the well-barrier sets are stacked by turns. Thicknesses of at least parts of the well layers in the direction gradually decrease along the direction, and thicknesses of at least parts of the intermediate level layers in the direction gradually increase along the direction. A method for manufacturing a multiple quantum well structure is also provided.

Owner:GENESIS PHOTONICS

Patterned opto-electrical substrate and method for manufacturing the same

ActiveCN104465917AImprove light extraction efficiencyImprove luminous brightnessSemiconductor/solid-state device manufacturingSemiconductor devicesMicron scaleEngineering

Owner:KINIK

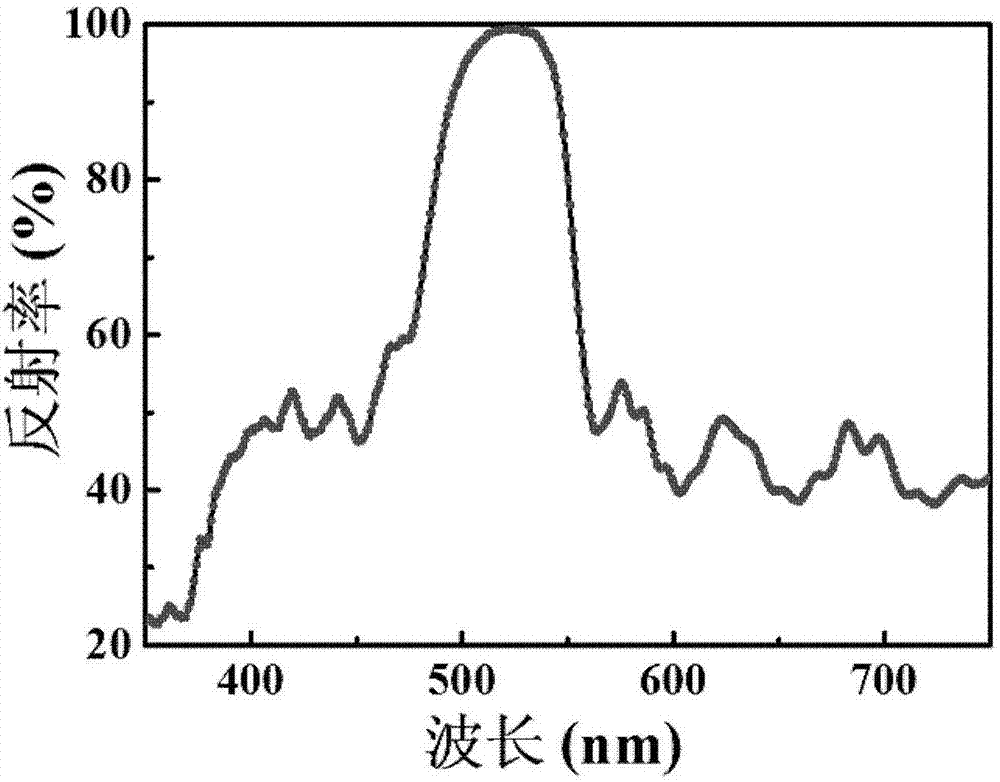

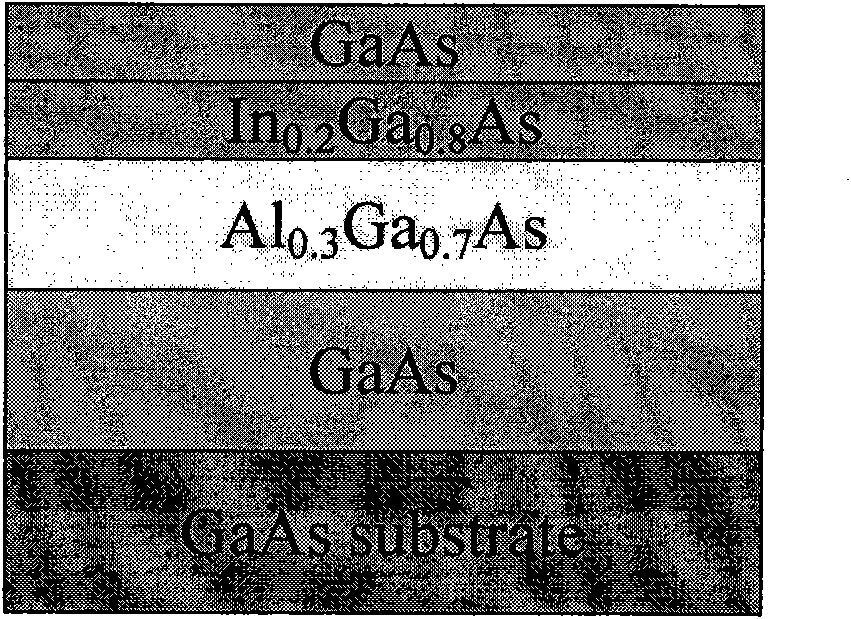

Porous-DBR-based InGaN-based resonant cavity enhanced detector chip

InactiveCN107046071AImprove epitaxy qualityThe epitaxy process is simple and controllableSemiconductor devicesPhysicsResonant cavity

The invention relates to a porous-DBR-based InGaN-based resonant cavity enhanced detector chip comprising a substrate, a buffer layer formed on the substrate, a bottom porous DBR layer formed on the buffer layer, an n type GaN layer formed on the bottom porous DBR layer, an active region formed on the n type GaN layer, a p type GaN layer formed in the active region, a side wall passivation layer, a transparent conductive layer, an n electrode, a p electrode, and a top dielectric DBR layer. The one side of the n type GaN layer is formed downwardly to form a table board and a protrusion is formed at the other side of the n type GaN layer. The side wall passivation layer is formed at the upper surface of the p type GaN layer and the side walls of the protruding n type GaN layer, the active region, and the p type GaN layer; and a window is formed in the middle of the side wall passivation layer formed at the upper surface of the p type GaN layer. The transparent conductive layer is formed at the upper surfaces of the side wall passivation layer and the p type GaN layer at the window. The n electrode is formed on the table board of the n type GaN layer. The p electrode is manufactured around the upper surface of the side wall passivation layer. And the top dielectric DBR layer is formed on the transparent conductive layer and the p electrode.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

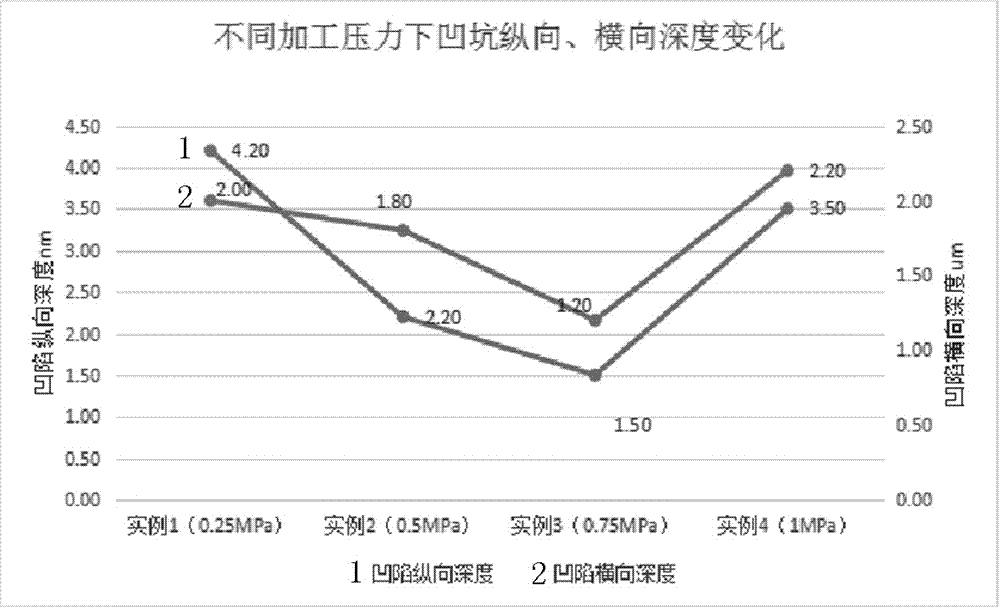

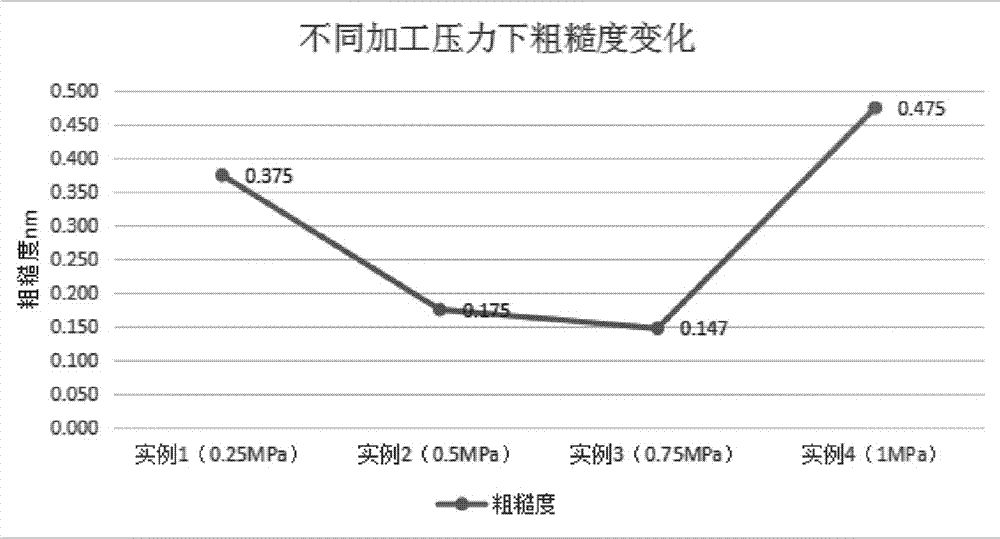

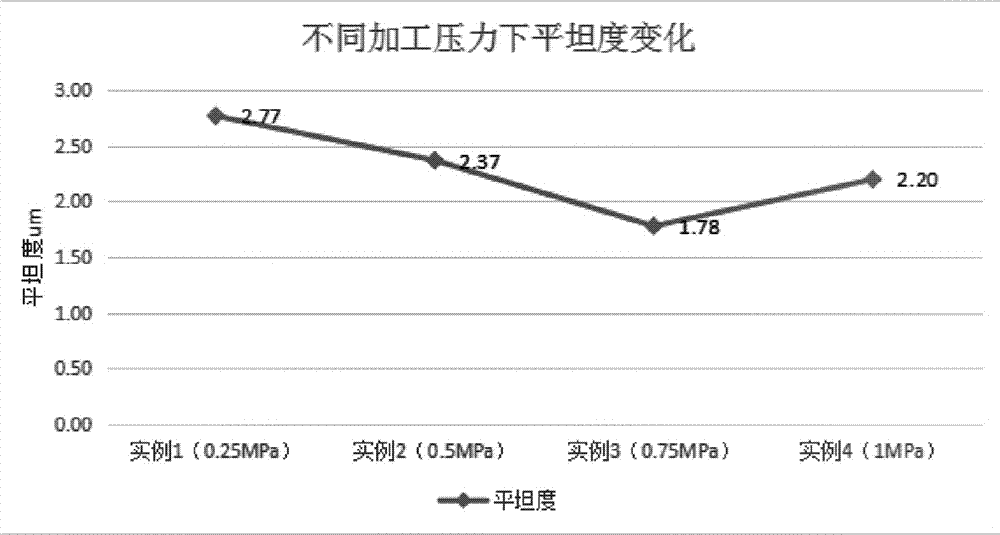

Polishing method for lithium tantalate substrate

The invention discloses a polishing method for a lithium tantalate substrate. The method includes the steps of 1, grinding a cut tantalate lithium wafer with an abrasive material with the particle size of 5-20 microns, and obtaining a lithium tantalate grinding sheet with the surface of a rough structure; 2, directly conducting chemical corrosion on the lithium tantalate grinding sheet in a sealed container filled with the mixed acid of nitric acid and hydrofluoric acid, wherein the roughness of the tantalate lithium wafer is smaller than 200 nm, and the flatness is smaller than 5 microns; obtaining a lithium tantalate corrosion sheet with the surface of a random disordered pit structure; 3, conducting single-side polishing on the lithium tantalate corrosion sheet with a single-polishing machine and a polishing liquid, wherein the polishing pressure is 0.005-1 MPa, the roughness of the tantalate lithium wafer is smaller than 0.5 nm, and the flatness is smaller than 3 microns; obtaining a lithium tantalite polishing sheet. The polishing method has the advantages of one-time polishing, batch production and high polishing efficiency, and the produced lithium tantalate substrate has high surface flatness which determines that the lithium tantalate substrate is not easily broken in the application of devices; the material utilization is high, and the processing yield is high.

Owner:TDG HLDG CO LTD

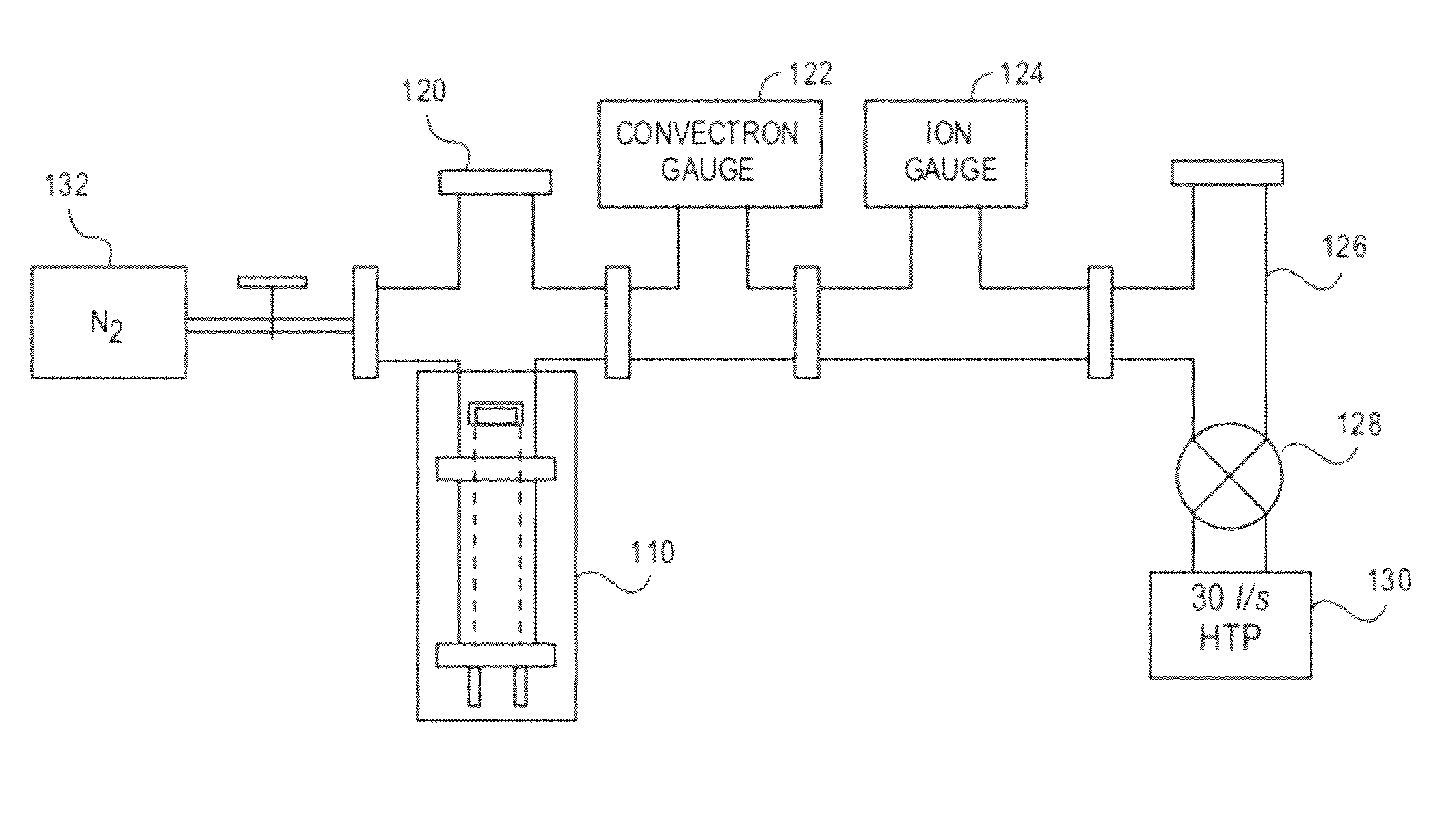

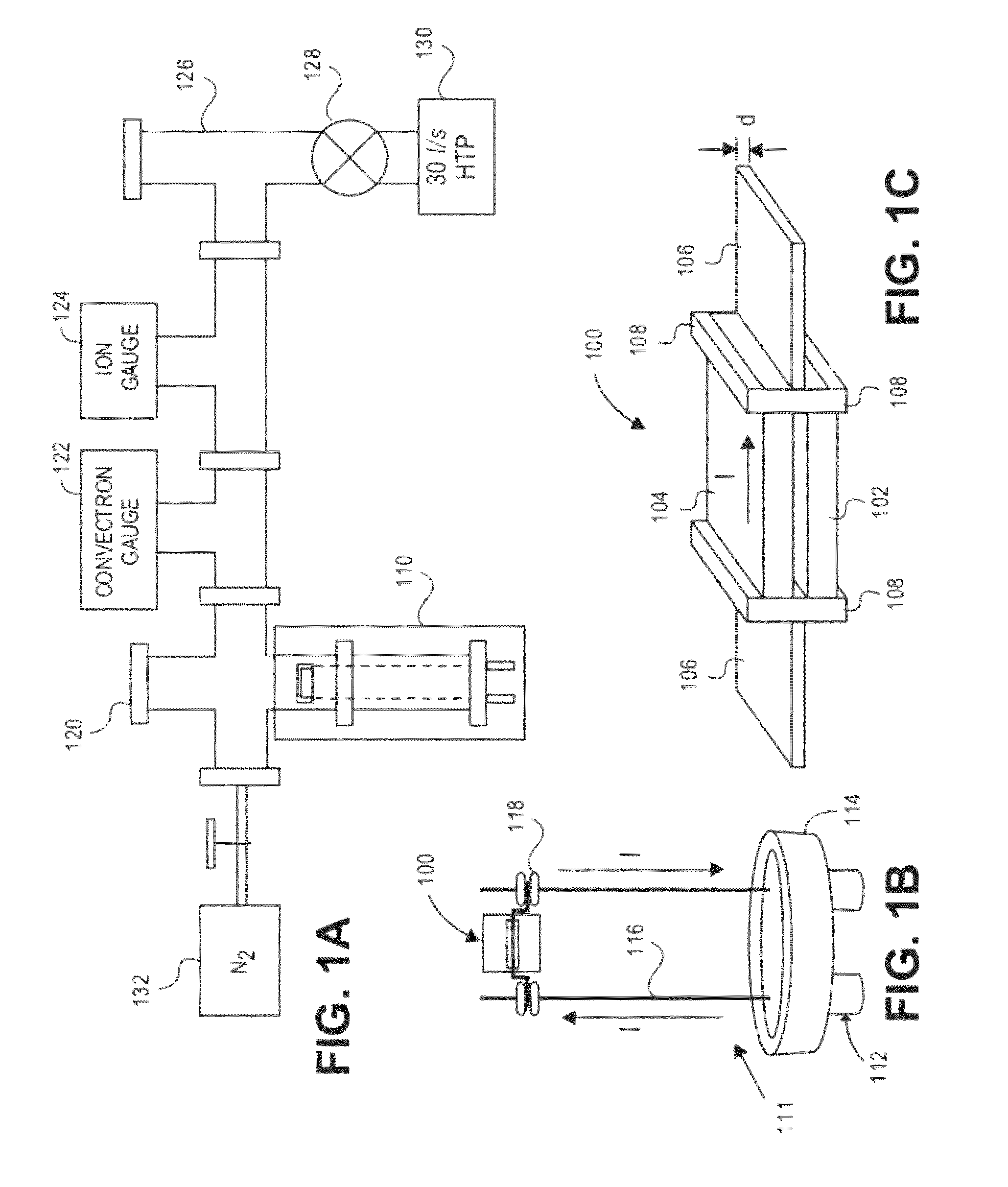

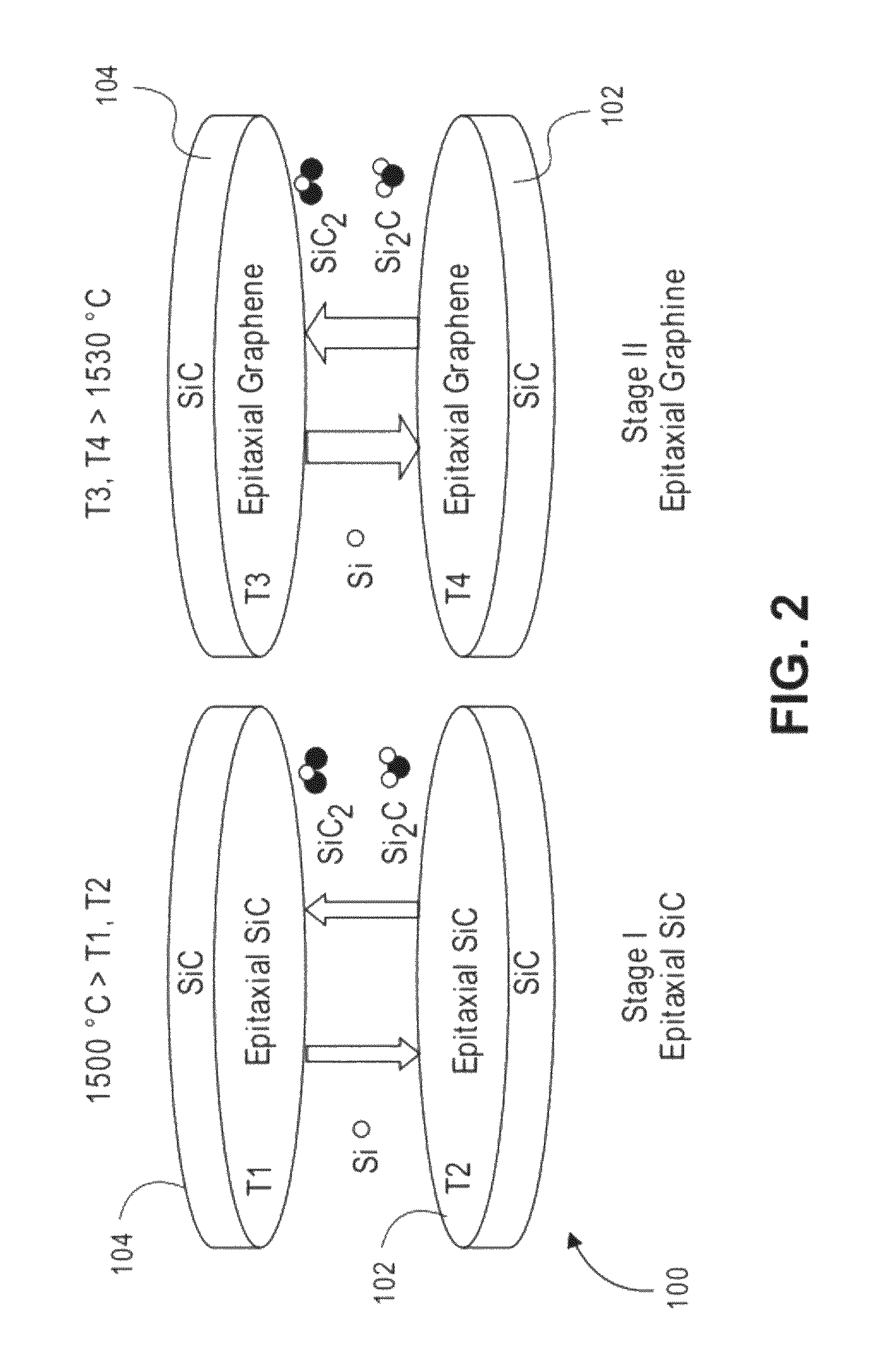

Method for synthesis of high quality graphene

ActiveUS8142754B2Improve epitaxy qualitySmall sizeMaterial nanotechnologyGrapheneWaferingEvaporation

A method is described herein for the providing of high quality graphene layers on silicon carbide wafers in a thermal process. With two wafers facing each other in close proximity, in a first vacuum heating stage, while maintained at a vacuum of around 10−6 Torr, the wafer temperature is raised to about 1500° C., whereby silicon evaporates from the wafer leaving a carbon rich surface, the evaporated silicon trapped in the gap between the wafers, such that the higher vapor pressure of silicon above each of the wafers suppresses further silicon evaporation. As the temperature of the wafers is raised to about 1530° C. or more, the carbon atoms self assemble themselves into graphene.

Owner:RGT UNIV OF CALIFORNIA

Gallium nitride-based light emitting device with roughened surface and fabricating method thereof

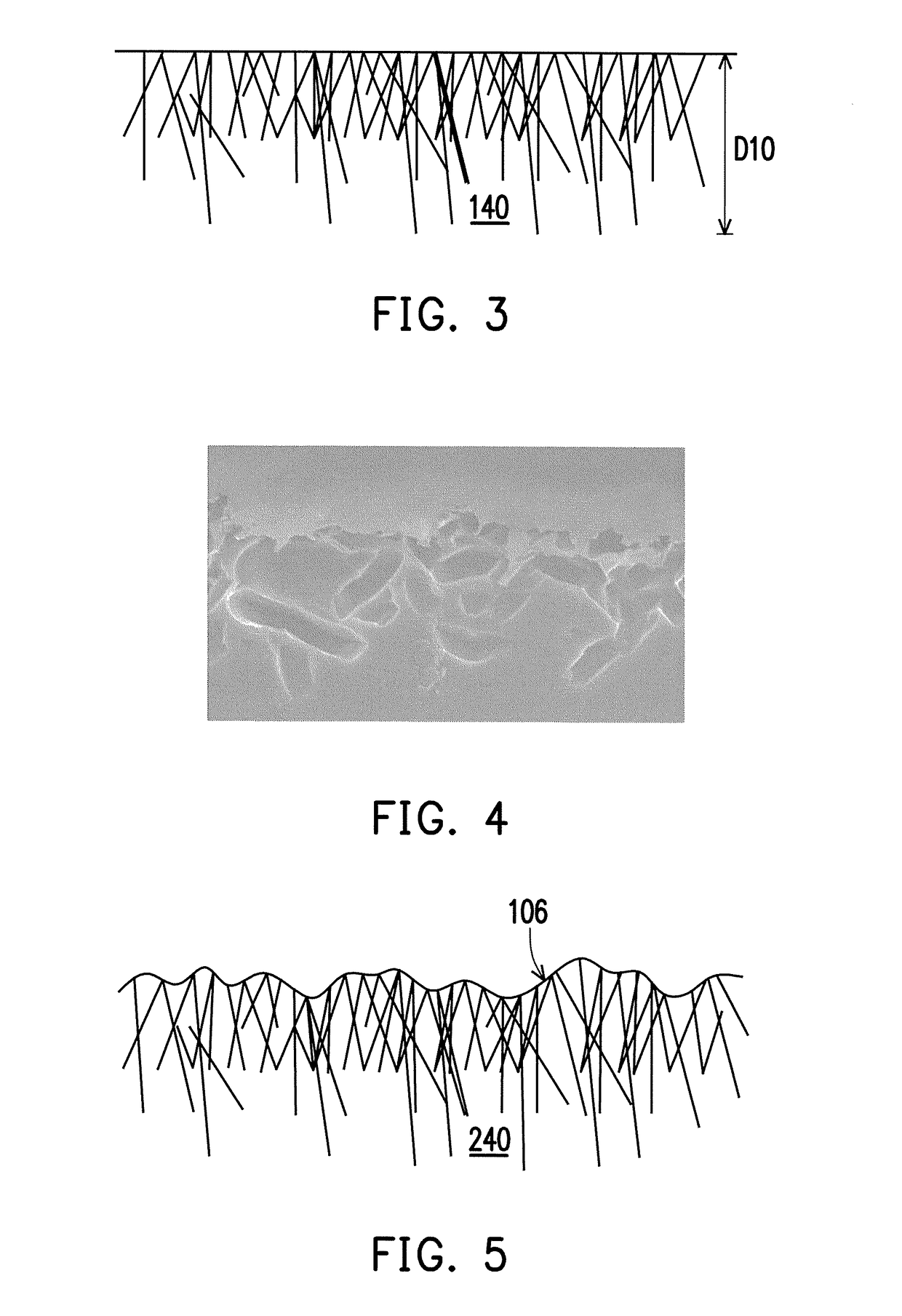

InactiveUS20090321780A1Improve epitaxy qualityOperating characteristics of the device will not be affectedSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideRough surface

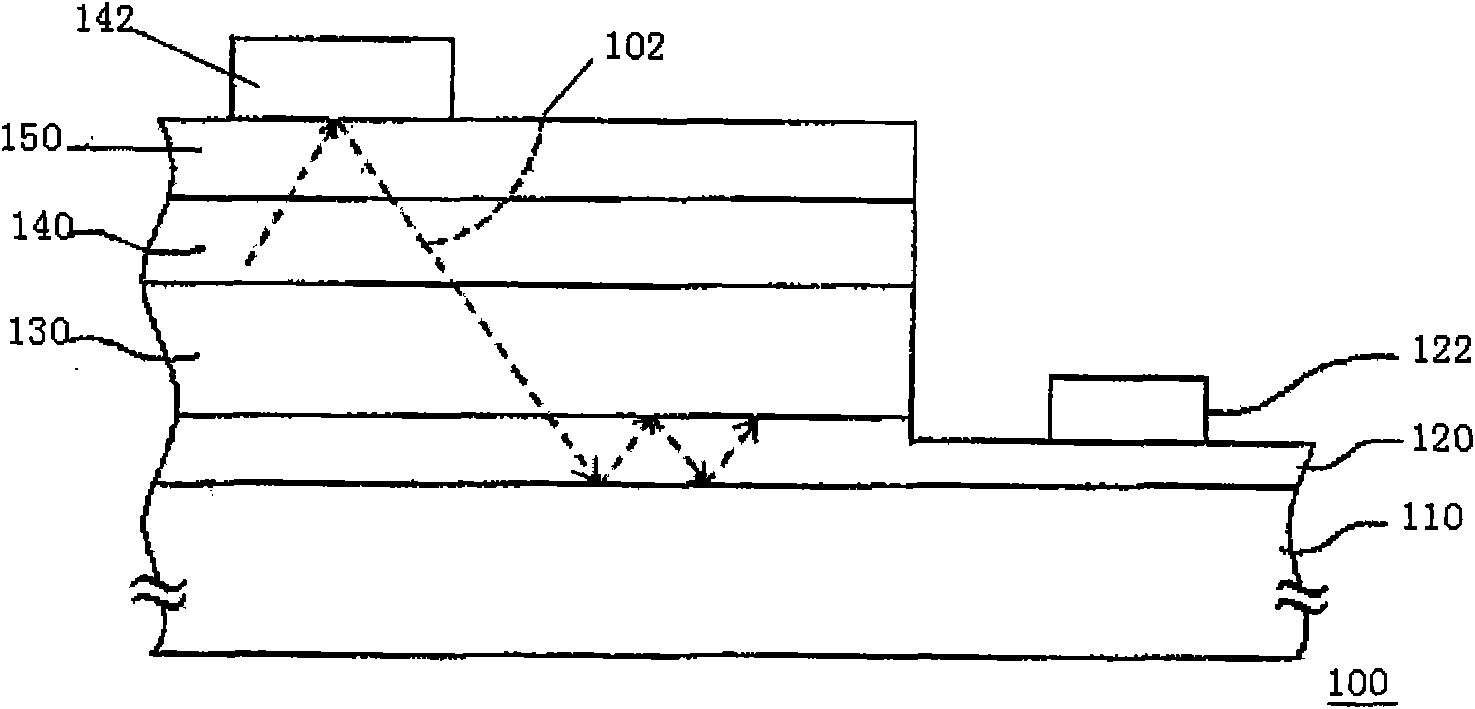

A gallium nitride-based light emitting device with a roughened surface is described. The light emitting device comprises a substrate, a buffer layer grown on the substrate, an n-type III-nitride semiconductor layer grown on the buffer layer, a III-nitride semiconductor active layer grown on the n-type III-nitride semiconductor layer, a first p-type III-nitride semiconductor layer grown on the III-nitride semiconductor active layer, a heavily doped p-type III semiconductor layer grown on the first p-type III-nitride semiconductor, and a roughened second p-type III-nitride semiconductor layer grown on the heavily doped p-type III semiconductor layer.

Owner:ADVANCED OPTOELECTRONICS TECH

Method for preparing III-V compound semiconductor nanotube structure material by GSMBE

ActiveCN101591811AImprove epitaxy qualityPrecise growth controlPolycrystalline material growthSemiconductor/solid-state device manufacturingDecompositionPre treatment

The invention relates to a method for preparing III-V compound semiconductor nanotube structure material by GSMBE, which comprises the following steps: pretreating a substrate in a GSMBE system; using As2 obtained by arsine decomposition as an As source, adjusting the pressure PV of AsH3 in an air source furnace to 450 to 700 Torr, and controlling the intensity of molecular flows; transferring the substrate to a GSMBE growth chamber for epitaxial growth; and making patterns by using a semiconductor etching process, and making the III-V compound semiconductor nanotube structure material after etching. The III-V compound semiconductor material system is highly selective, convenient in resource as well as capable of doping nanotube interior and exterior wall materials. The preparation method is simple in operation, low in cost and suitable for large-scale production.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Sapphire substrate and polishing method and application thereof

ActiveCN101604666AImprove adhesionAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsProcessing cost

The invention relates to the field of semiconductor materials and discloses a sapphire substrate and a polishing method and an application thereof. The surface of the sapphire substrate is polished, and the polished surface has random sunken patterns. The surface of the sapphire substrate is partially planarized. Therefore the processing cost for the sapphire substrate is greatly reduced and the polishing efficiency is increased.

Owner:SHANGHAI XINANNA ELECTRONICS TECH

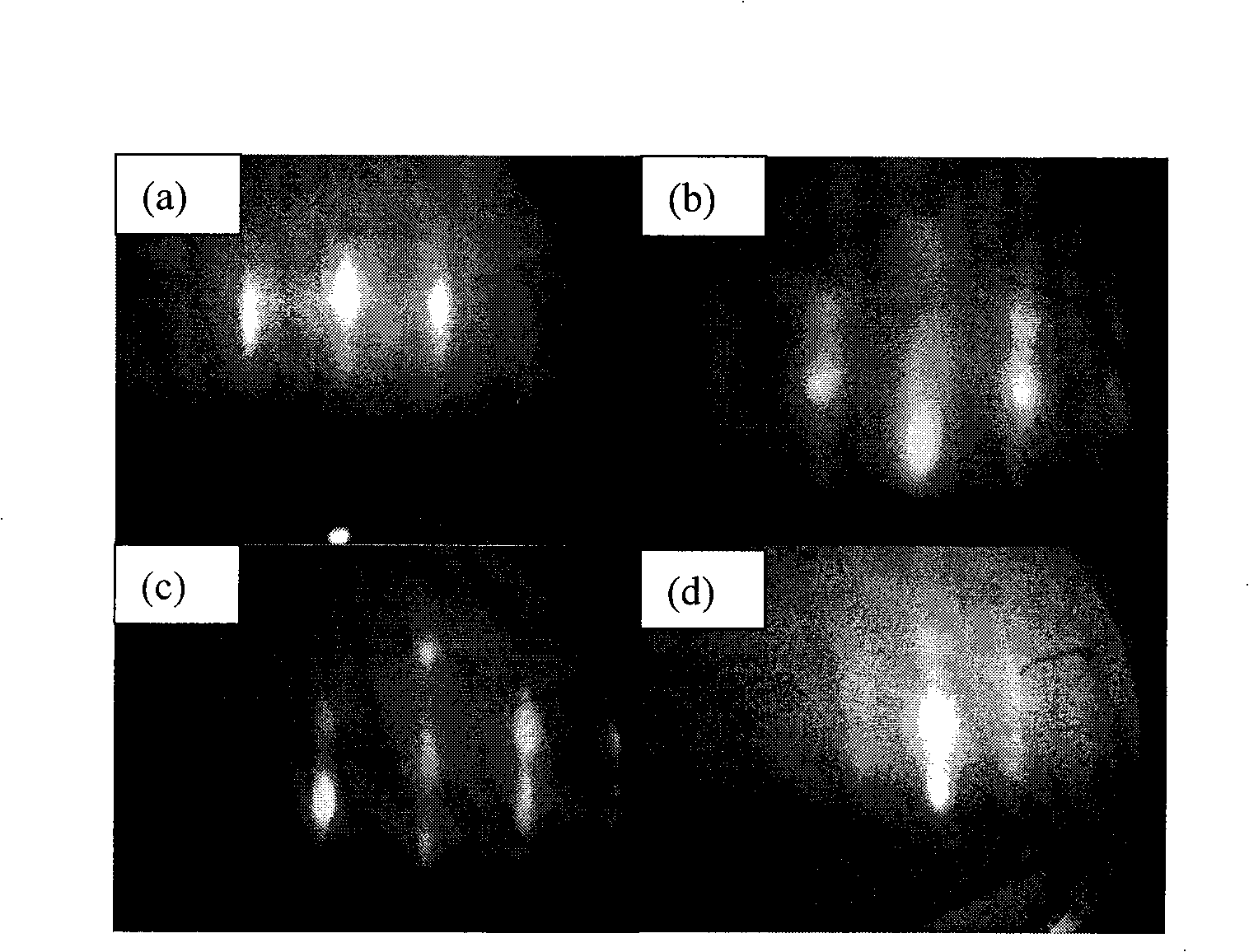

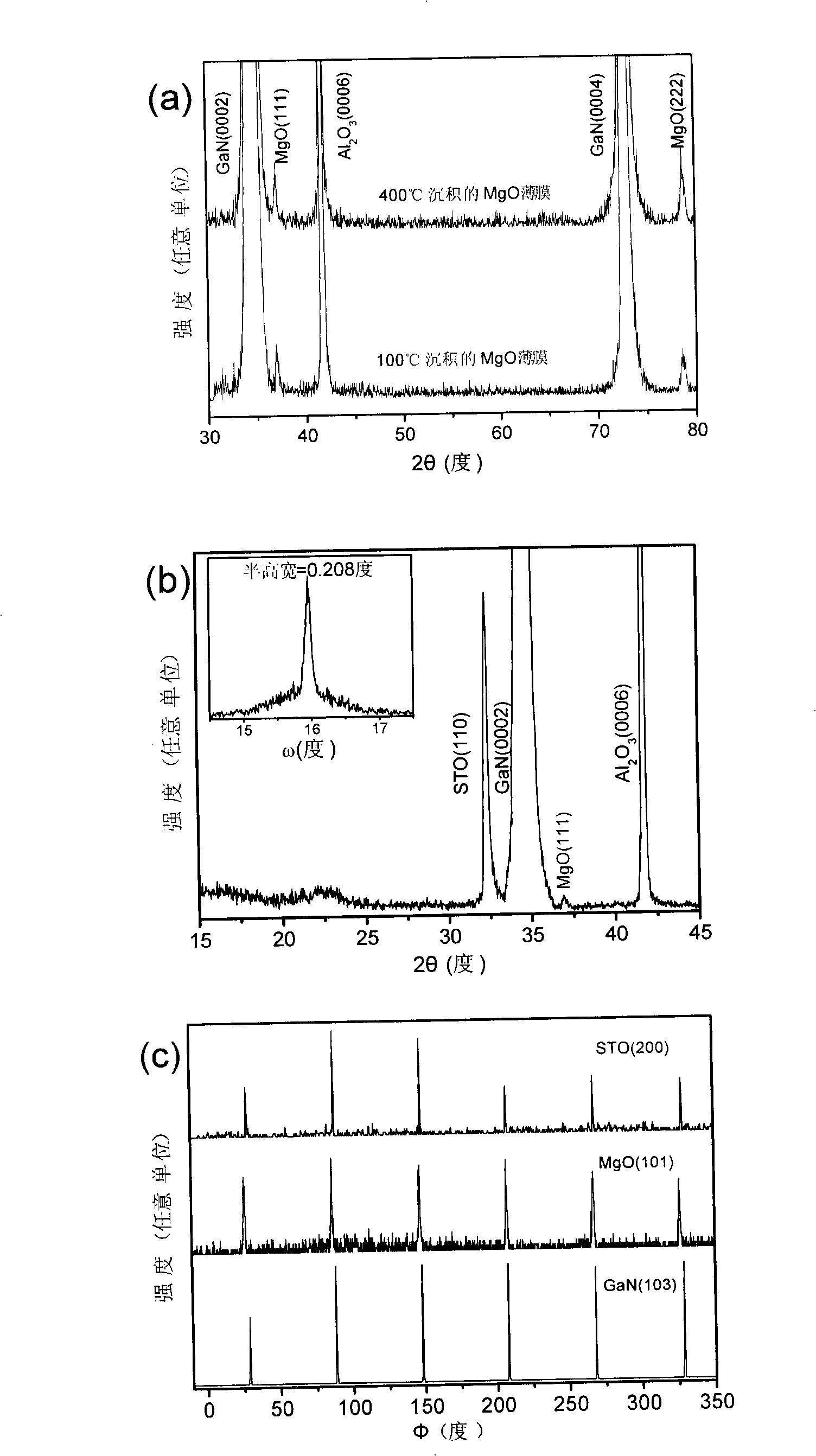

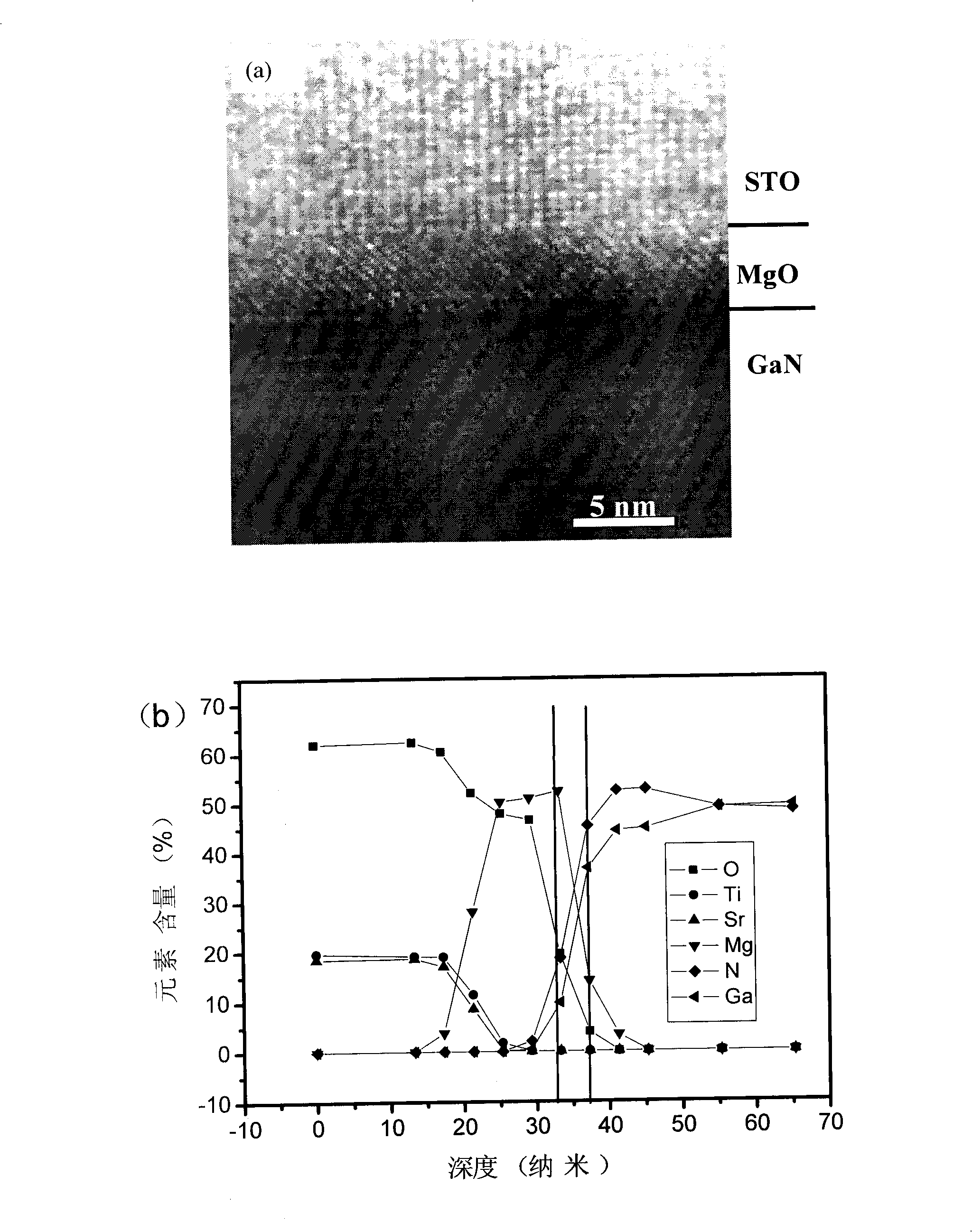

ABO3/MgO/GaN heterojunction structure and preparation method thereof

InactiveCN101527314AImprove epitaxy qualityReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMaterial Design

The invention discloses ABO3 / MgO / GaN heterojunction structure and a preparation method thereof, and relates to the field of microelectronic material. The ABO3 / MgO / GaN heterojunction structure comprises a substrate and ABO3, wherein, an MgO nano buffer layer film is arranged between the substrate and the ABO3, the substrate is GaN epitaxial slice, and the ABO3 is oxide film material with calcium-state structure. The MgO film has good thermal stability and can be combined with oxygen stably, so as to be an effective blocking layer for preventing oxygen atoms from spreading towards the semiconductor substrate; meanwhile, MgO has the cubic symmetry crystalline structure with the crystallographic lattice constant approaching to most of ferroelectric oxide; the MgO film with nano thickness leads a ferroelectric film with the ABO3 structure which grows subsequently can grow on the GaN in an oriented way. The ABO3 / MgO / GaN heterojunction structure prepared by the invention has clear interlayer interfaces, thus providing a feasible material design and growing method for realizing oxide / semiconductor integrated devices.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

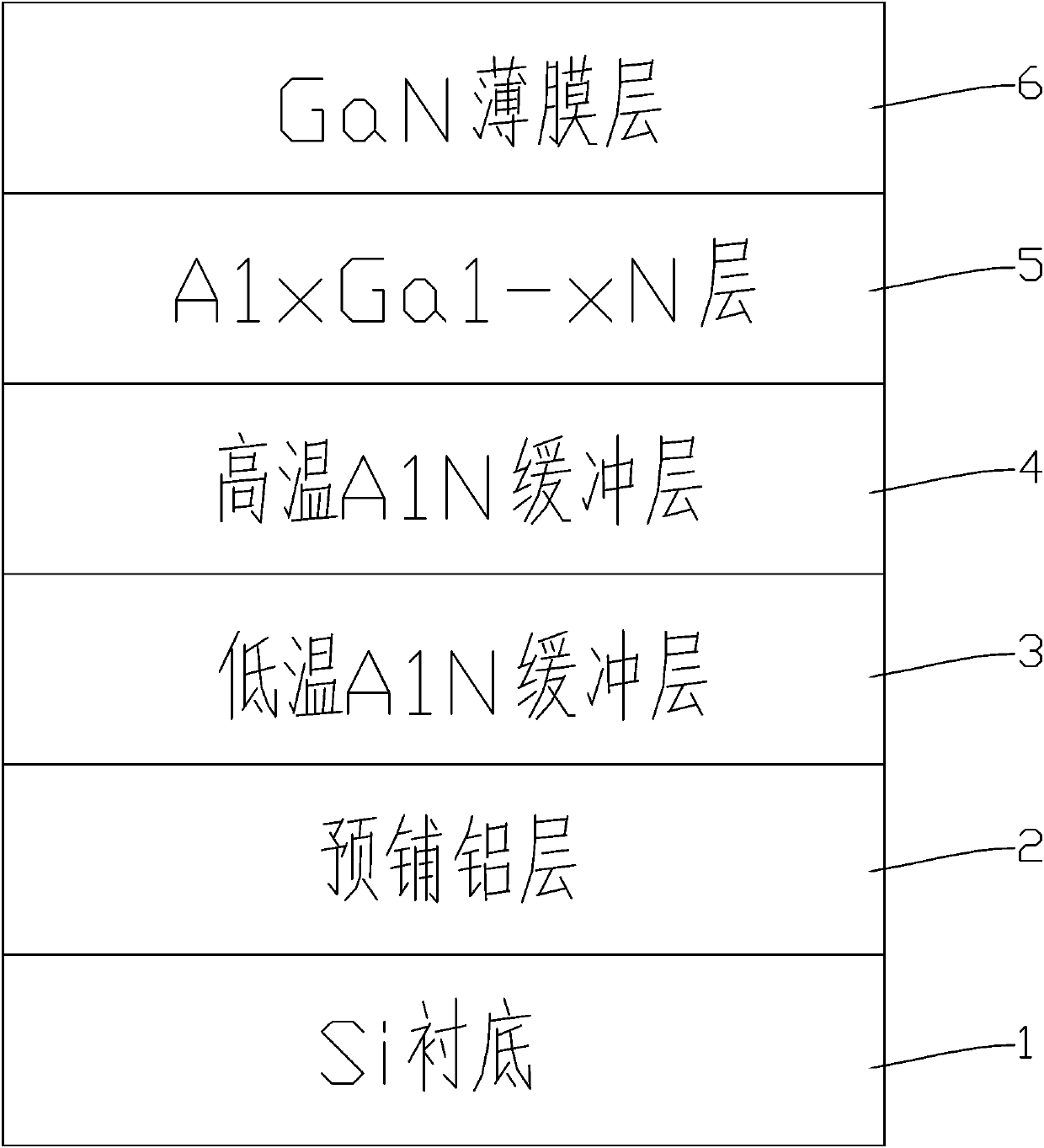

Method for epitaxial growth of gallium nitride (GaN) thin film on Si substrate

InactiveCN110541157ASolve crackingSolve for uniformitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingStress reliefGallium nitride

The invention relates to a method for epitaxial growth of a gallium nitride (GaN) thin film on a Si substrate, the crack growth of GaN epitaxial thin films is limited, the surface topography is uniform, the process is relatively easy, and the method is easy to realize. According to the technical scheme, the method includes the steps that a metal-organic chemical vapor deposition (MOCVD) system isadopted for epitaxial growth and the epitaxial growth of the GaN thin film is conducted on the Si substrate. The method is characterized in that the epitaxial structure of the GaN thin film sequentially comprises the Si substrate, a pre-buried aluminum layer, a low temperature aluminum nitride (AlN) buffer layer, a high temperature aluminum nitride (AlN) buffer layer, a gallium nitride aluminum (AlxGal-xN) layer and the GaN thin film layer, wherein the low temperature AlN buffer layer is a low temperature AlN three-dimensional nucleating layer, the high temperature AlN buffer layer is a high temperature AlN three-dimensional nucleating layer, the AlxGal-xN layer is an AlxGal-xN stress relief layer, and the GaN thin film layer is a final growth layer.

Owner:WENZHOU UNIVERSITY +1

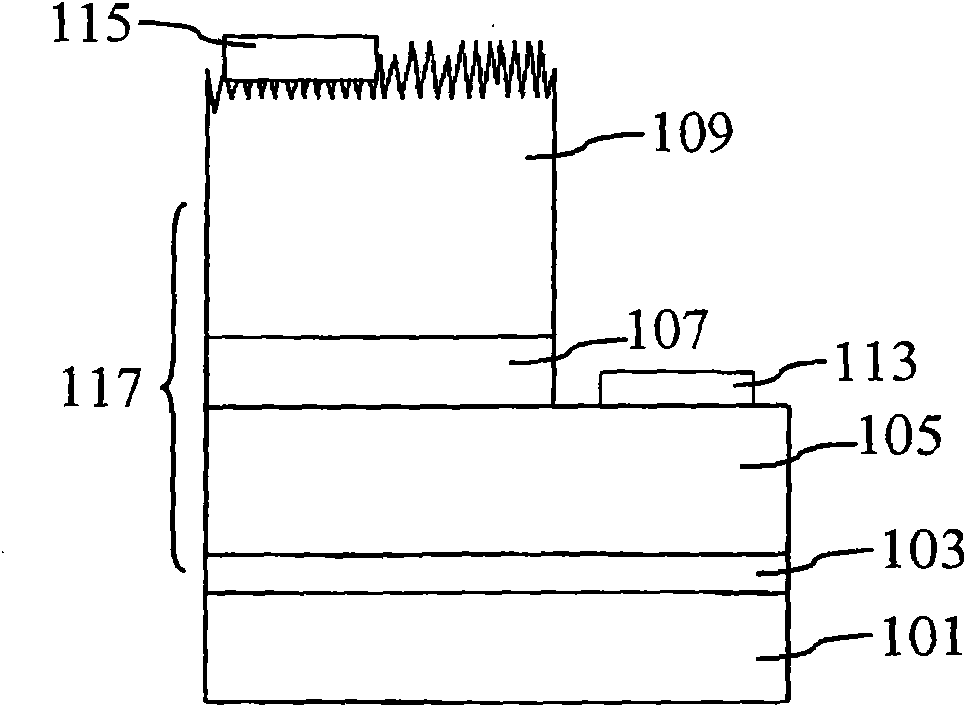

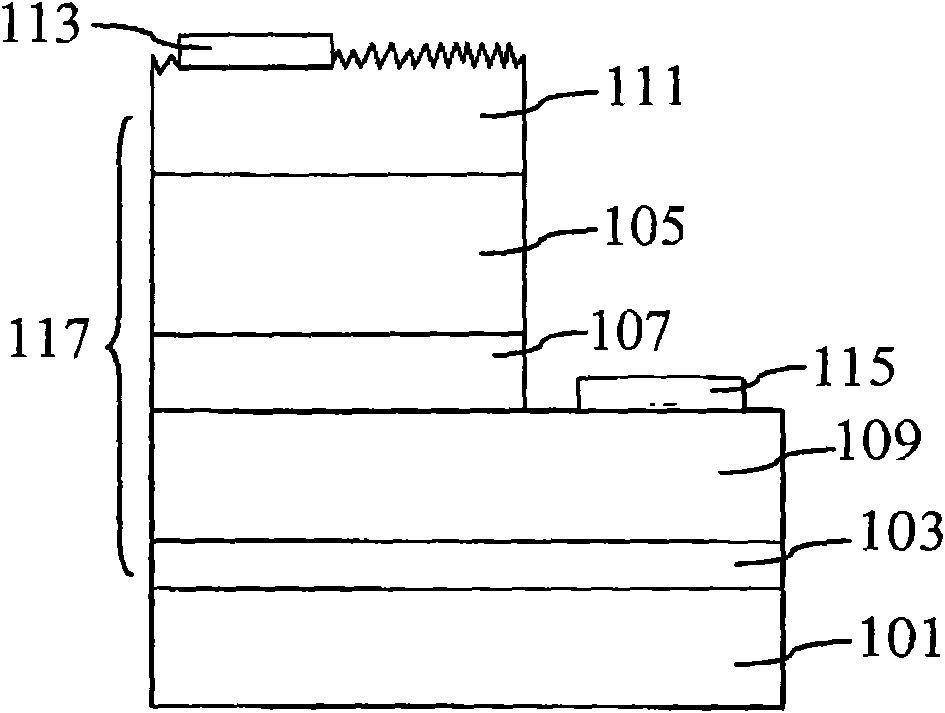

Light-emitting diode device and method for manufacturing the same

InactiveCN102683529ASolve the problem of uneven current distributionAvoid the efficiency dip effectSolid-state devicesSemiconductor devicesActive layerLight-emitting diode

The invention discloses a light-emitting diode device and a method for manufacturing the same. An undoped semiconductor layer and a current blocking structure of the light-emitting diode device are disposed on a substrate in sequence. Light-emitting structures of the light-emitting diode device are separately disposed on the current blocking structure. Each of the light-emitting structures has a first conductivity type semiconductor layer, an active layer and a second conductivity type semiconductor layer arranged on the first conductivity type semiconductor layer in sequence, and a first electrode and a second electrode, respectively located on the other part of the first conductivity type semiconductor layer and the second conductivity type semiconductor layer. The first conductivity type semiconductor layer and the second conductivity type semiconductor layer have different conductivity types. Insulating spacers of the light-emitting diode device are respectively located between the adjacent light-emitting structures. Conductive wires of the light-emitting diode device respectively connect the first electrode of one of the adjacent light-emitting structures and the second electrode of the other light-emitting structure in sequence.

Owner:CHI MEI LIGHTING TECH +1

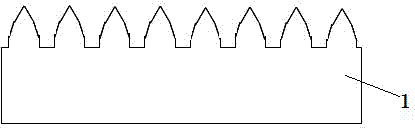

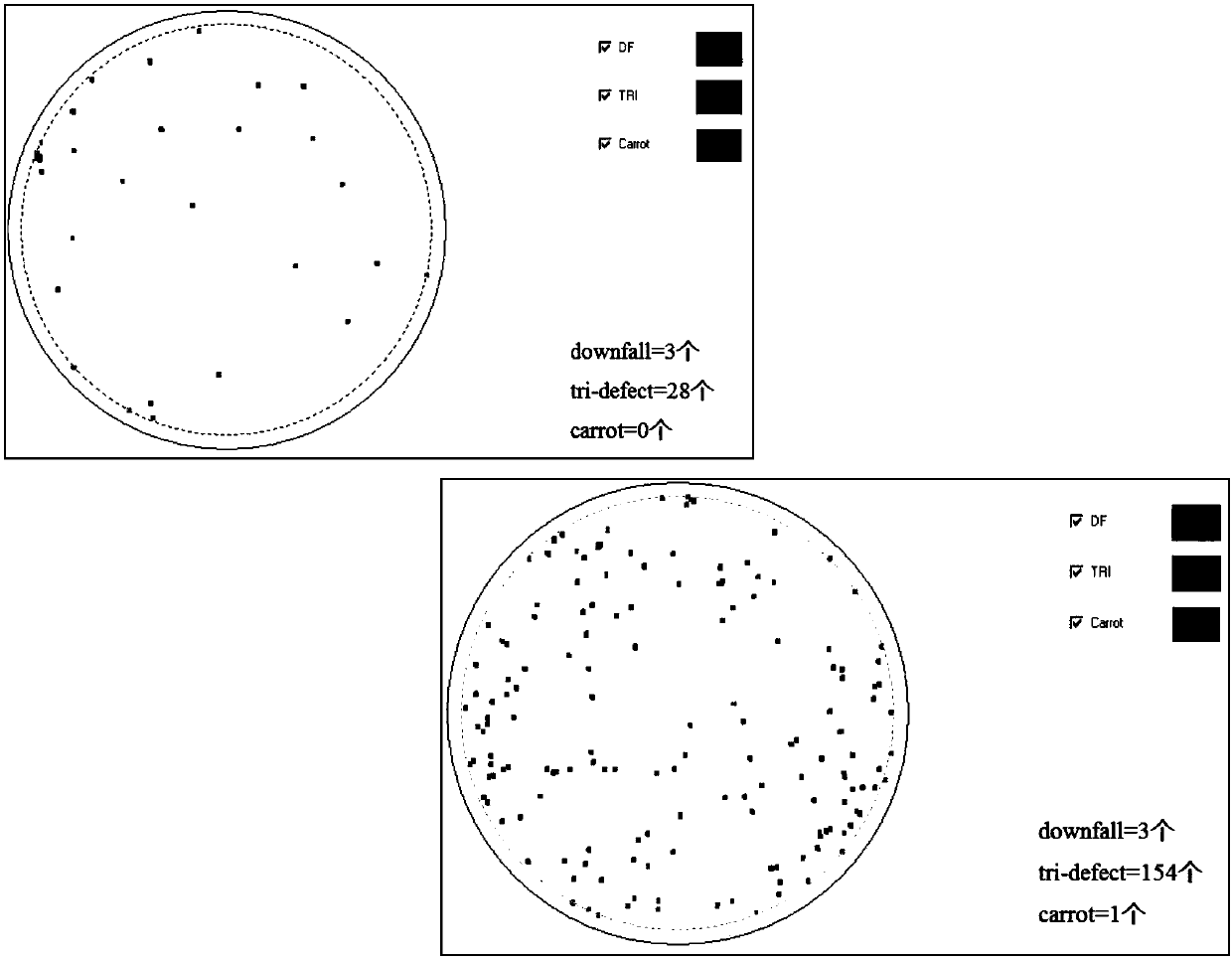

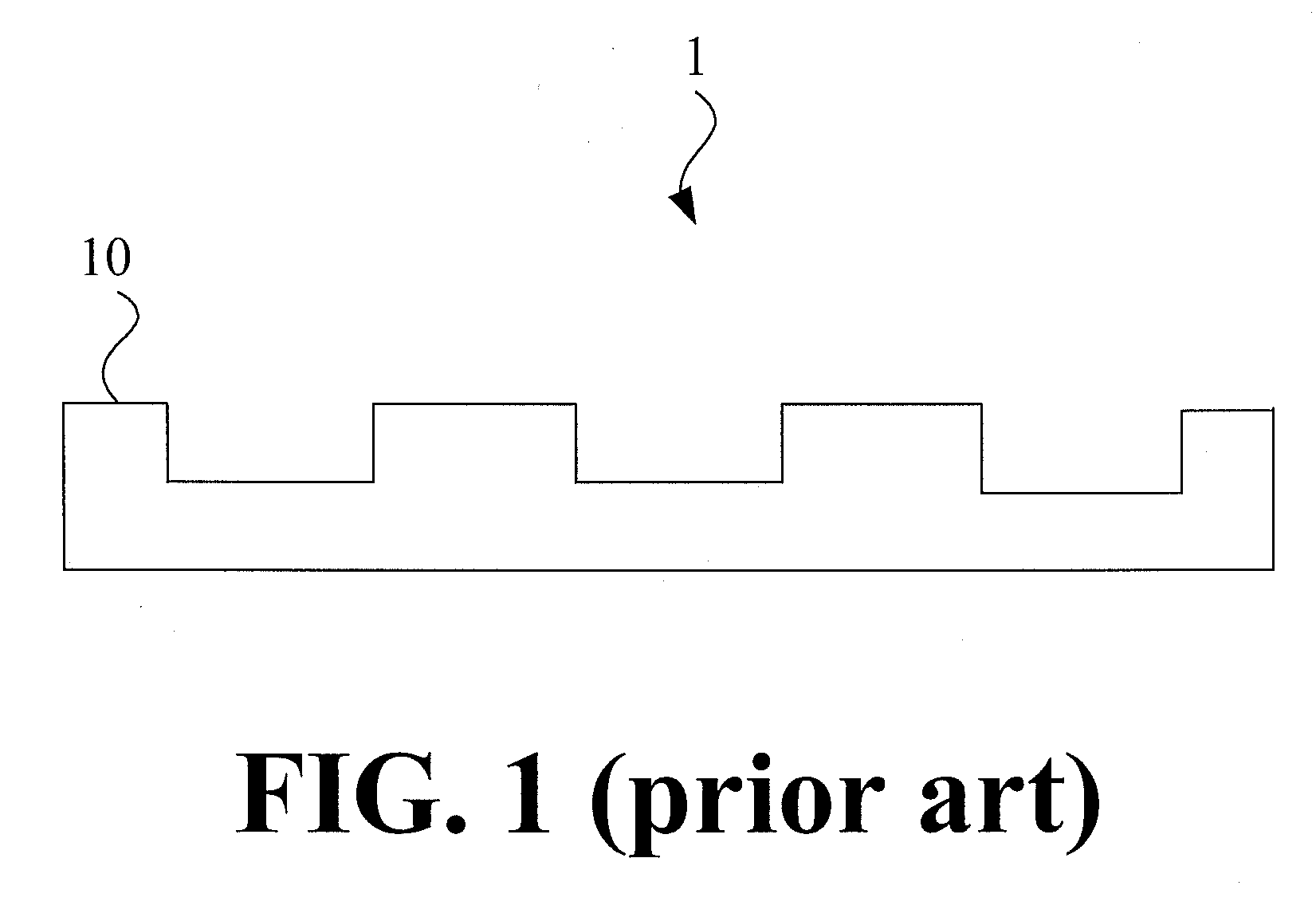

Graphical silicon carbide (SiC) substrate

InactiveCN102925969AReduced linear dislocation densityImprove epitaxy qualityFrom chemically reactive gasesSingle crystalGallium nitride

The invention relates to a graphical silicon carbide (SiC) substrate. The surface of the graphical SiC substrate comprises periodized protrusions or concave images which are formed by means of plasma etching or wet etching, wherein the periodized protrusions or the concave images are any one of multilateral cones, multilateral cylinders, multi-rowed frustums, trapezoid multilateral frustums, trapezoid round pedestals, hemispheres or spherical crowns. Periodic images are combination of any two or more than two of the multilateral cones, the multilateral cylinders, the multi-rowed frustums, the trapezoid multilateral frustums, the trapezoid round pedestals, the hemispheres or the spherical crowns. The graphical SiC substrate can improve epitaxy quality of heteroepitaxy of gallium nitride (GaN) and homoepitaxy of 3C-SiC which take SiC as the substrate, and improves performance and stability of elements prepared by epitaxial wafers.

Owner:SHANGHAI INST OF TECH

Ultraviolet light-emitting diode

InactiveUS20170141263A1Quality improvementImprove electrical performanceSemiconductor devicesSecondary layerAluminium

The present invention relates to an ultraviolet light-emitting diode (LED), which includes a gradual superlattice layer. The gradual superlattice layer comprises a first superlattice layer and a second superlattice layer. The first superlattice layer includes a multi-layer structure having repetitive stacks of a unit formed by a first layer and a second layer. The second superlattice layer includes a multi-layer structure having repetitive stacks of a unit formed by a third layer and a fourth layer. The concentrations of aluminum in the first, second, third, and fourth layers decrease sequentially. By disposing the gradual superlattice layer, the quality of the epitaxial structure may be improved apparently.

Owner:LEXTAR ELECTRONICS CORP

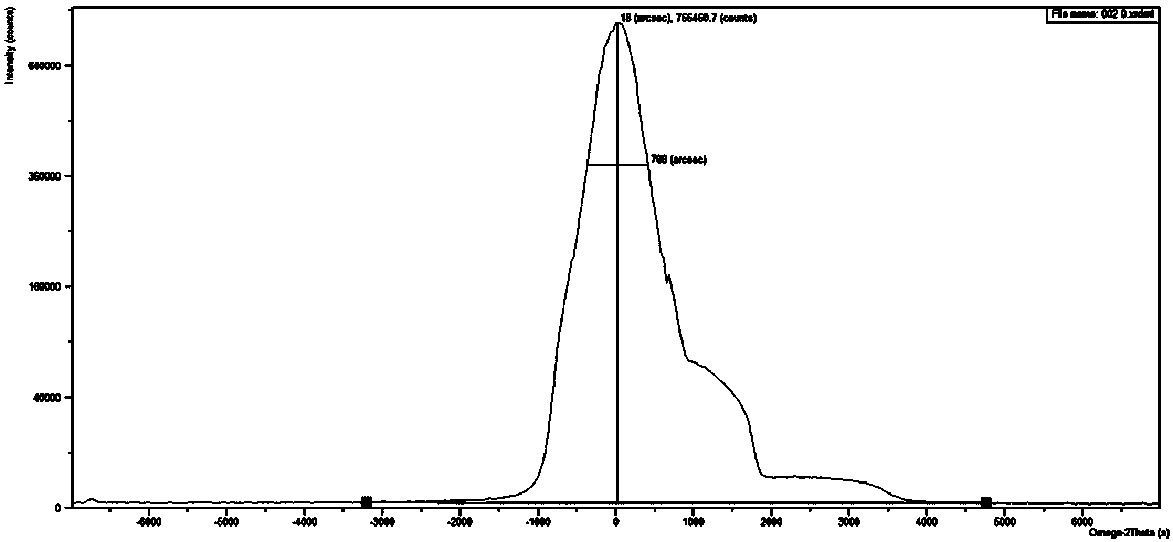

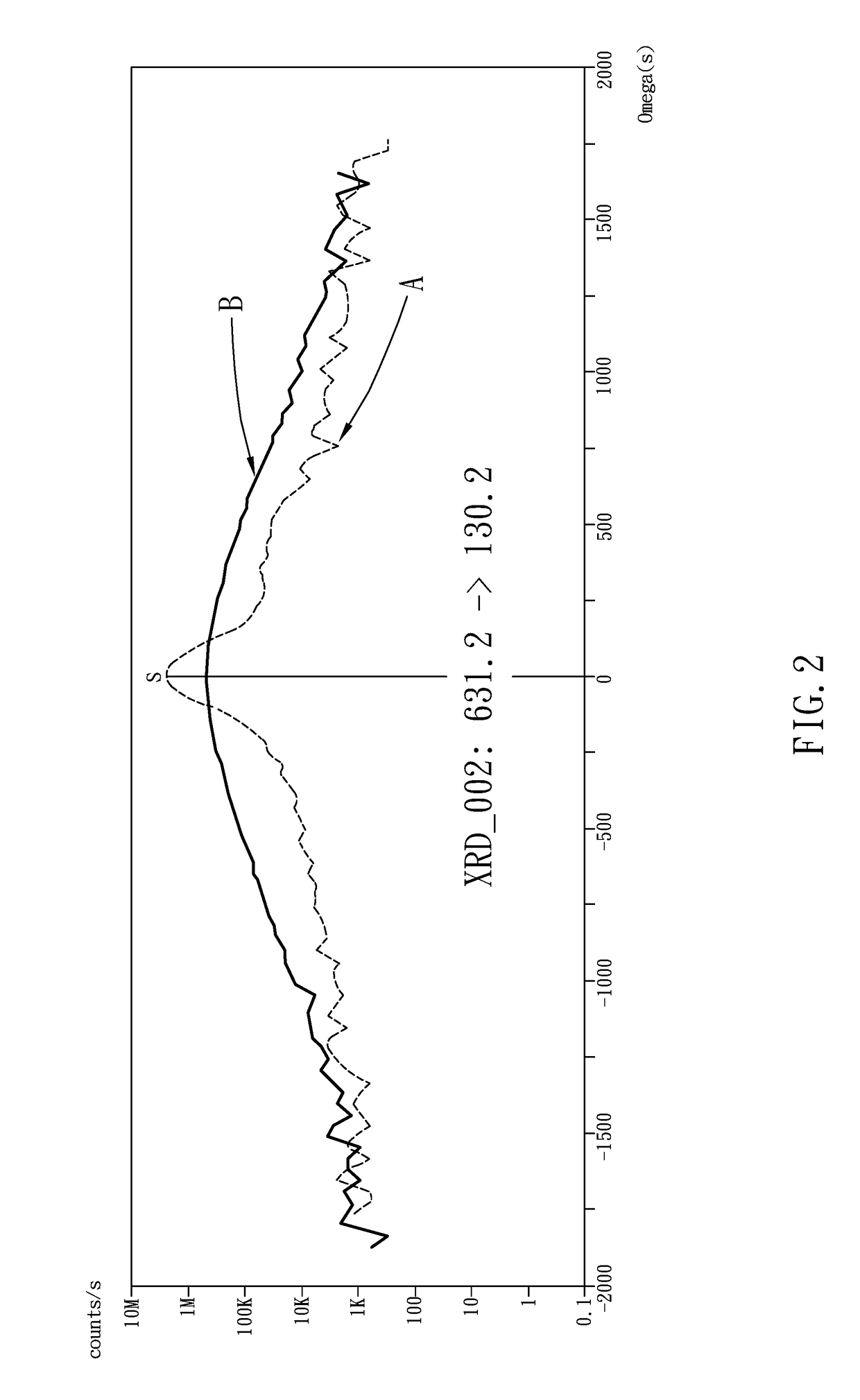

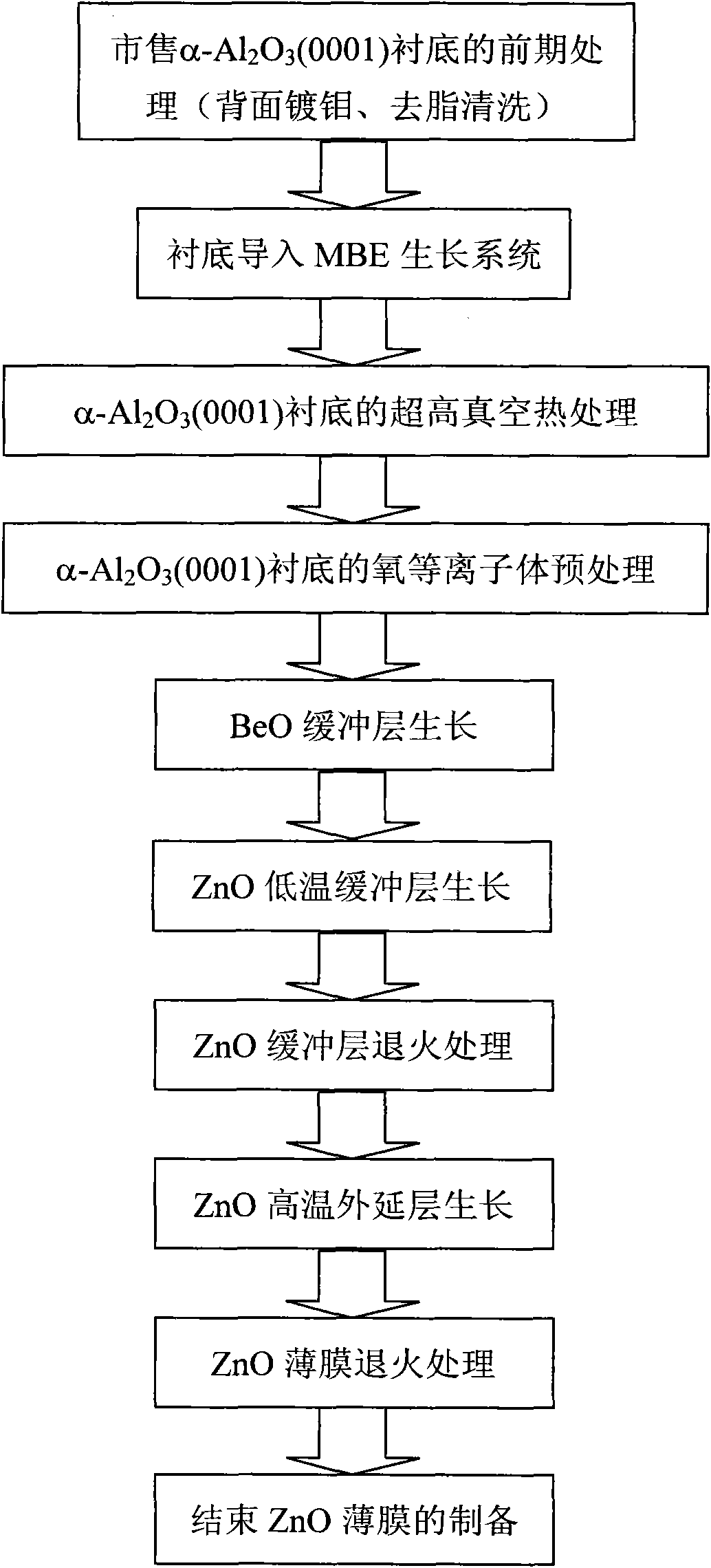

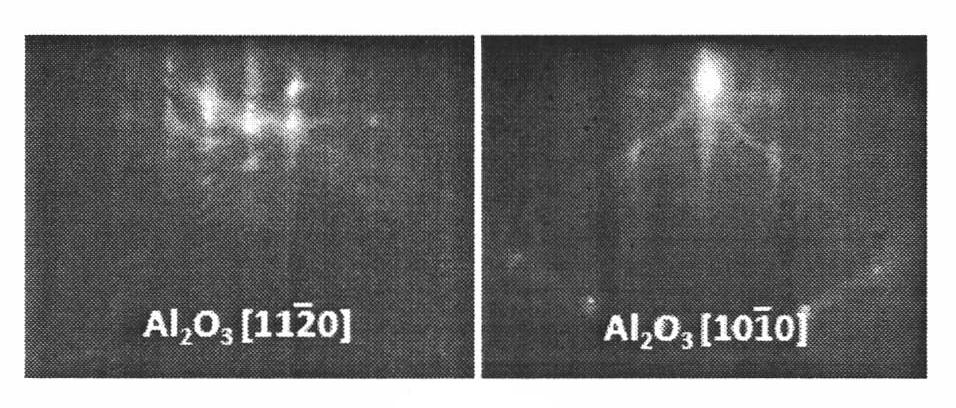

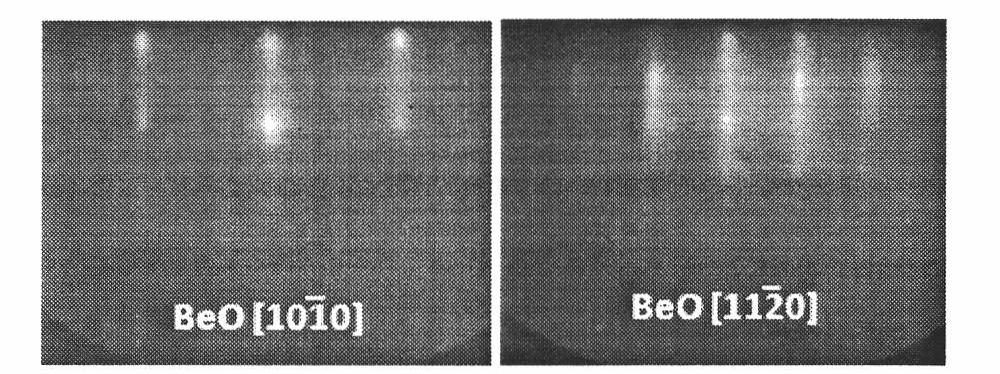

Method for preparing high-quality ZnO monocrystal film on sapphire substrate

InactiveCN101834127AEpitaxial growth is easyImprove epitaxy qualitySemiconductor/solid-state device manufacturingUltraviolet detectorsOxygen plasma

The invention discloses a method for preparing a high-quality ZnO monocrystal film on a sapphire substrate, which is the method for preparing the high-quality ZnO monocrystal film on the sapphire substrate by a surface, interface and buffer layer combined growth method and comprises the following concrete steps of: carrying out ultrahigh vacuum heat processing combined with oxygen plasma preprocessing on the surface of the sapphire (0001) substrate; then depositing a BeO buffer layer to supply an ideal template for the epitaxial growth of ZnO, and then preparing the high-quality ZnO film by a publicly known two-step growth method. The ZnO monocrystal film prepared according to the method has very good crystallization performance and is applicable for the manufacture of high-performance photoelectronic devices such as an ultraviolet detector and the like.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

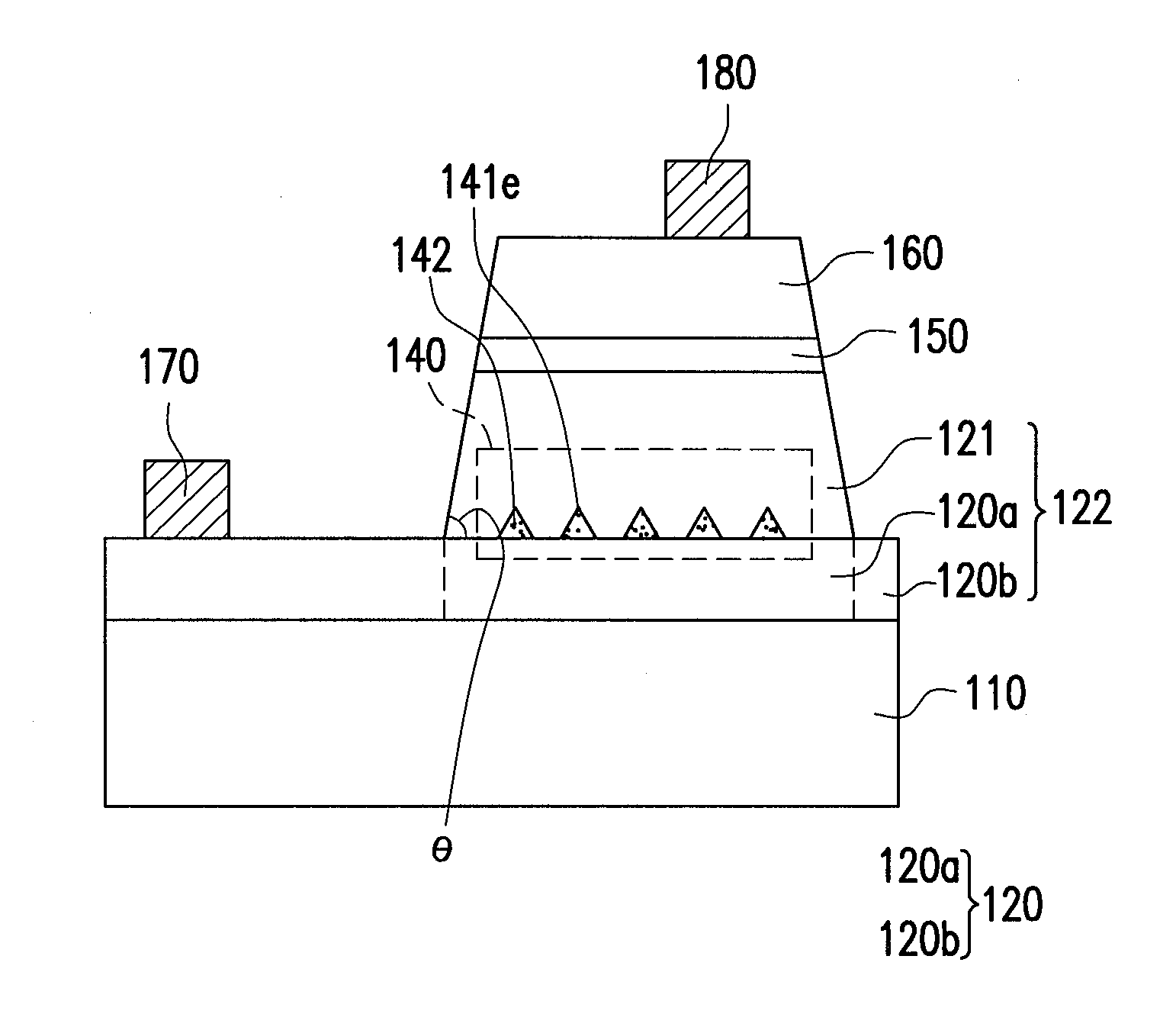

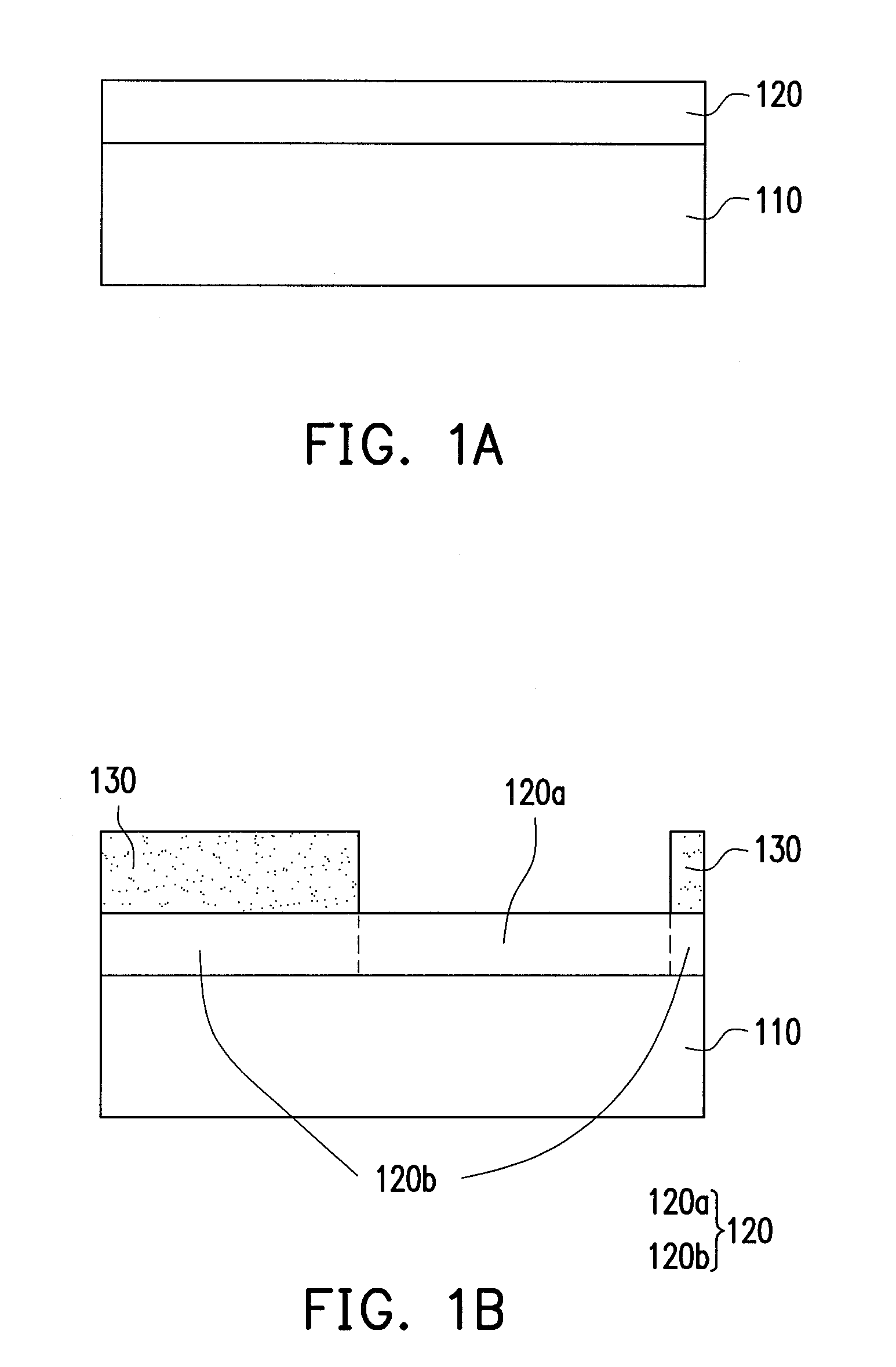

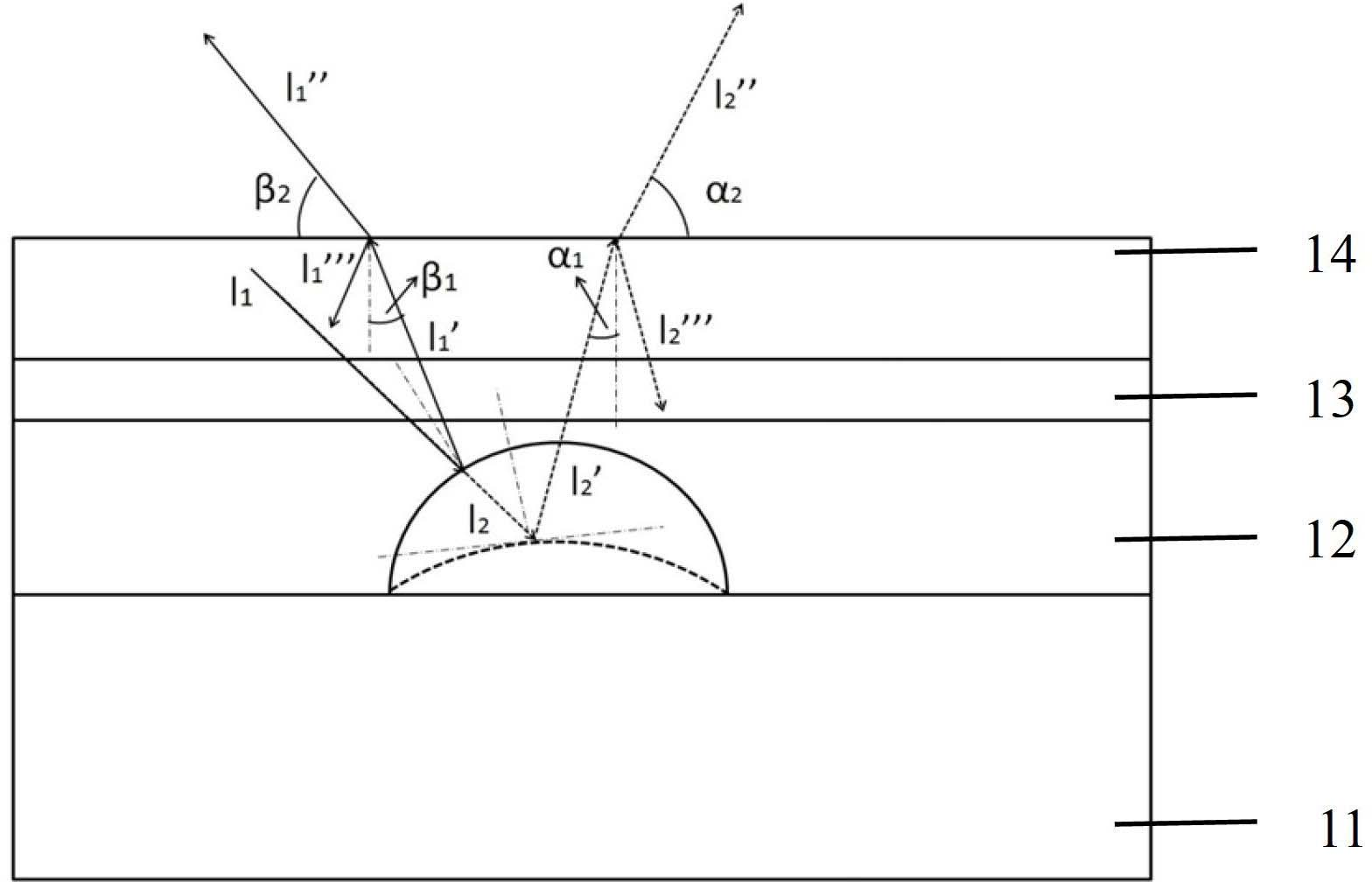

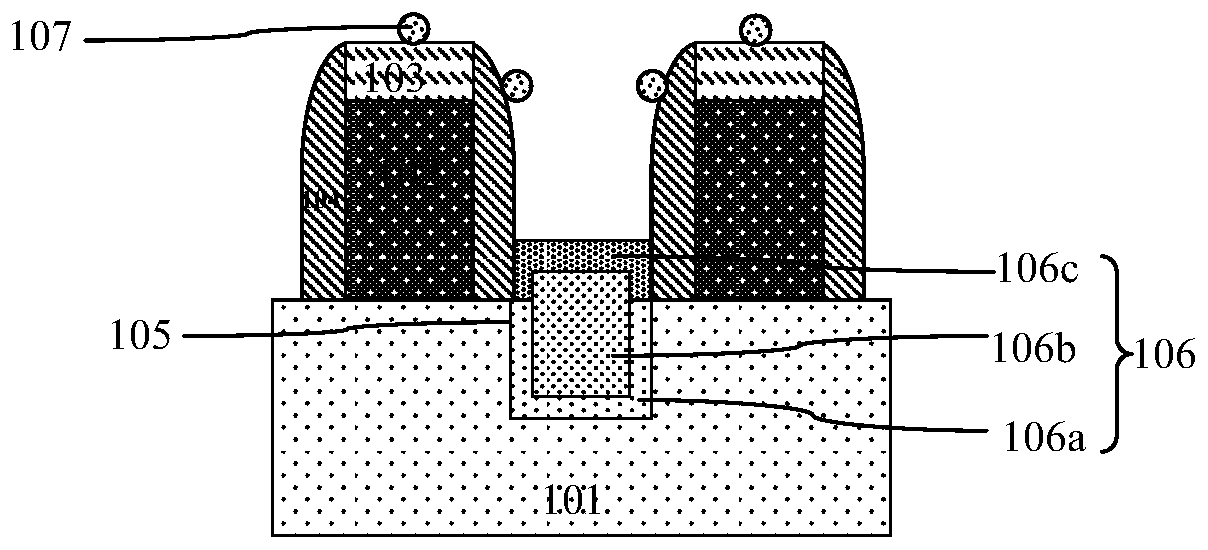

Semiconductor light-emitting device and manufacturing method thereof

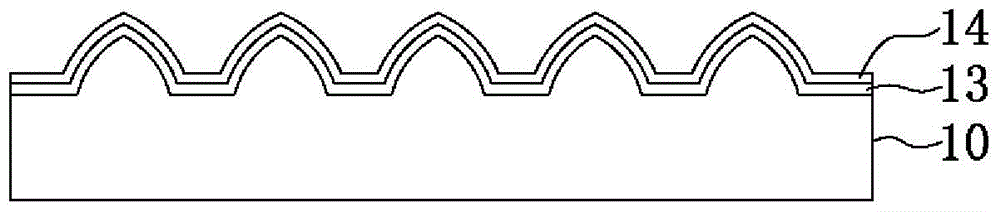

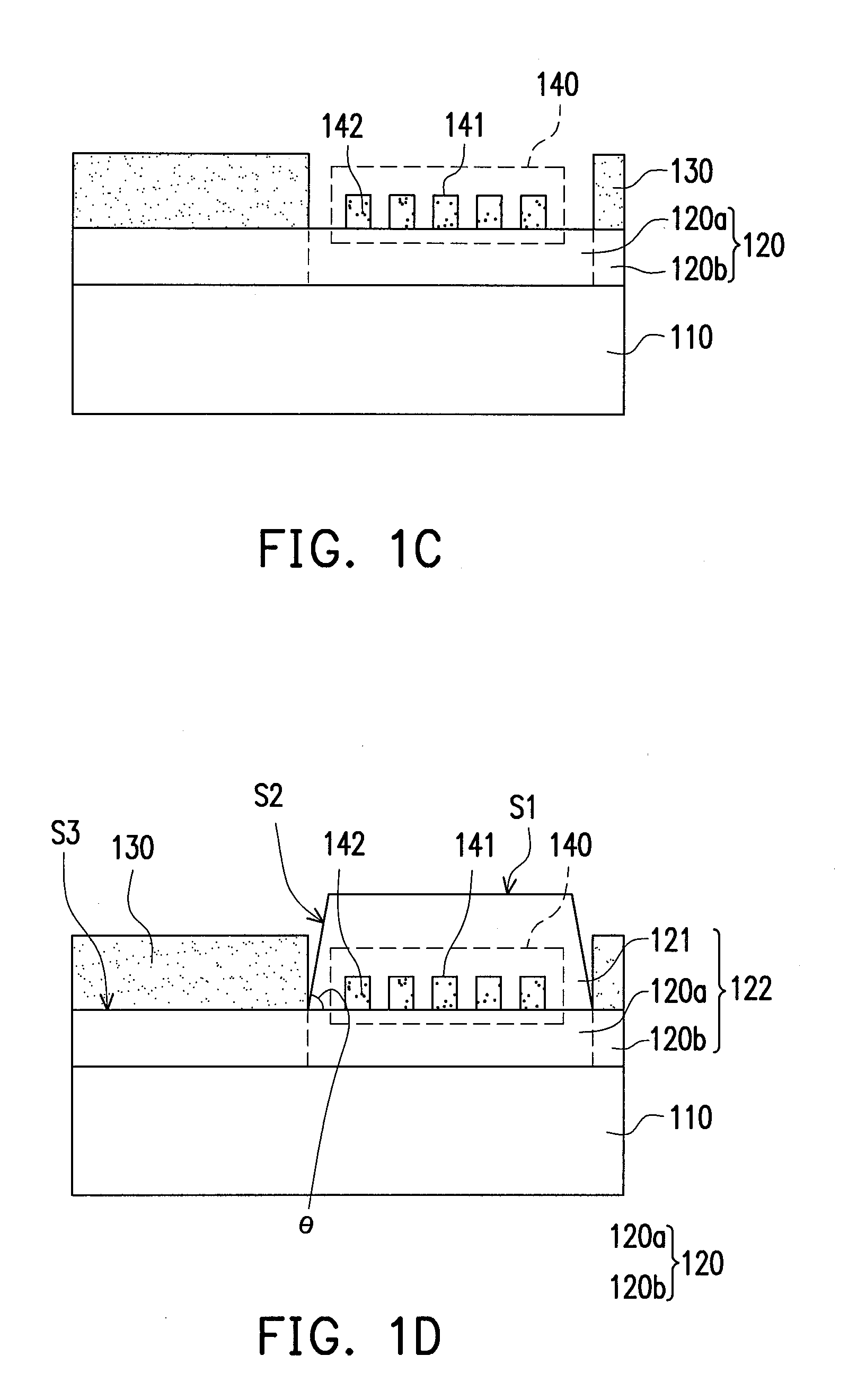

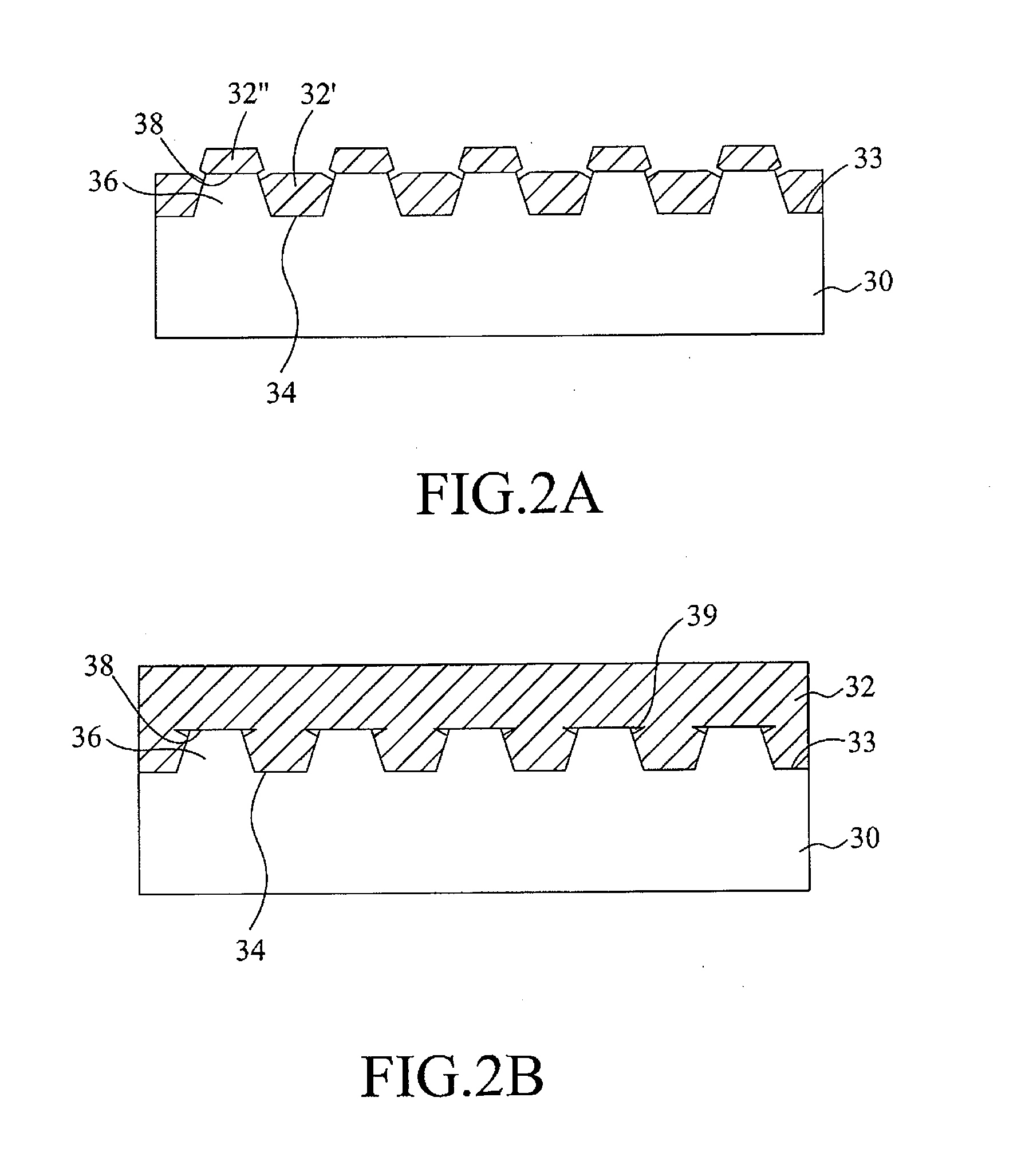

InactiveUS20130240932A1Improve light extraction efficiencyImprove extraction efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorMaterials science

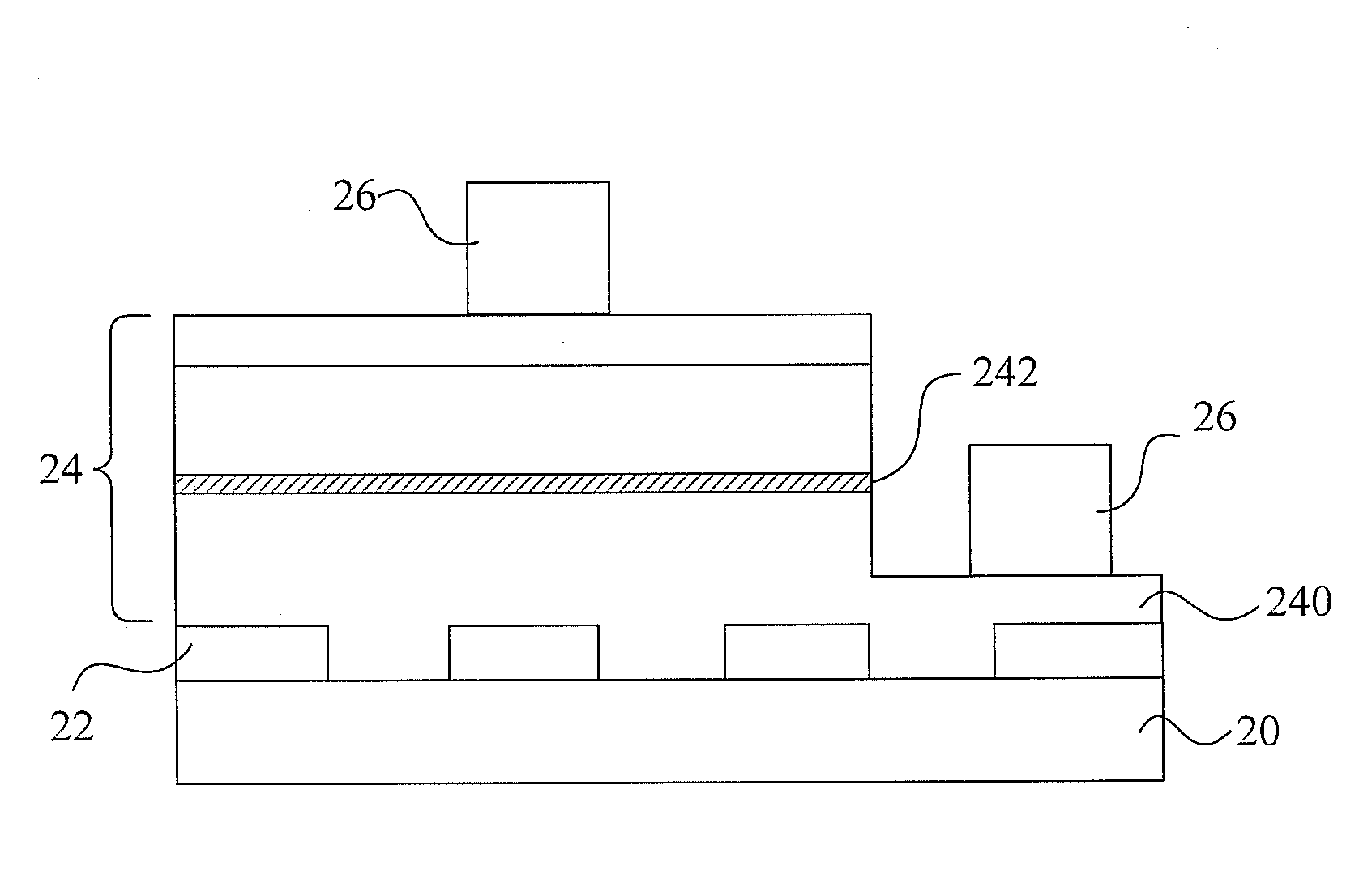

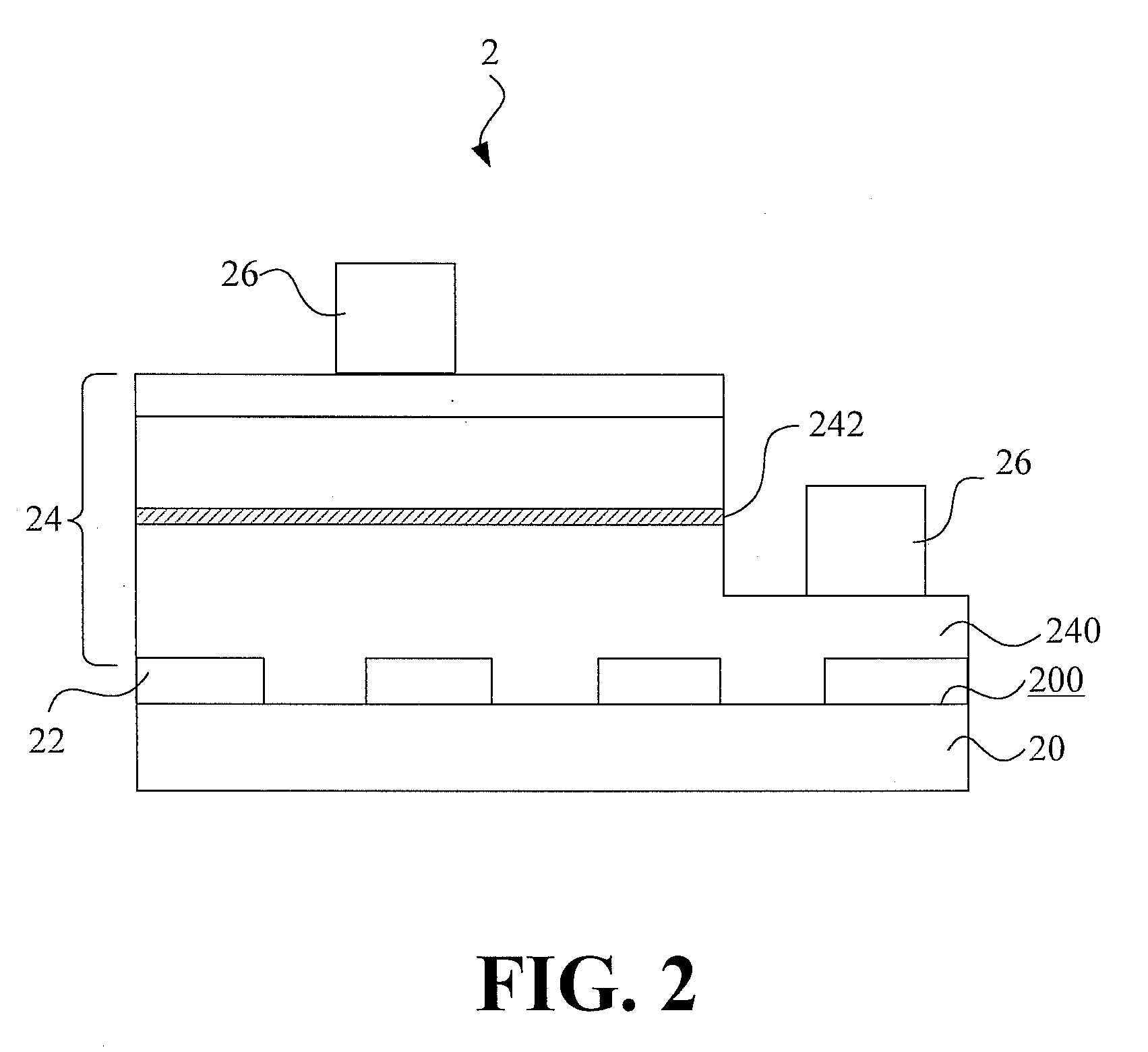

A semiconductor light-emitting device and a manufacturing method thereof are provided, wherein the semiconductor light-emitting device includes a substrate, a first type doped semiconductor layer, a light-emitting layer, a second type doped semiconductor layer and an optical micro-structure layer. The first type doped semiconductor layer is disposed on the substrate and includes a base portion and a mesa portion. The base portion has a top surface, and the mesa portion is disposed on the top surface of the base portion. The light-emitting layer is disposed on the first type doped semiconductor layer. The second type doped semiconductor layer is disposed on the light-emitting layer. The optical micro-structure layer is embedded in the first type doped semiconductor layer.

Owner:GENESIS PHOTONICS

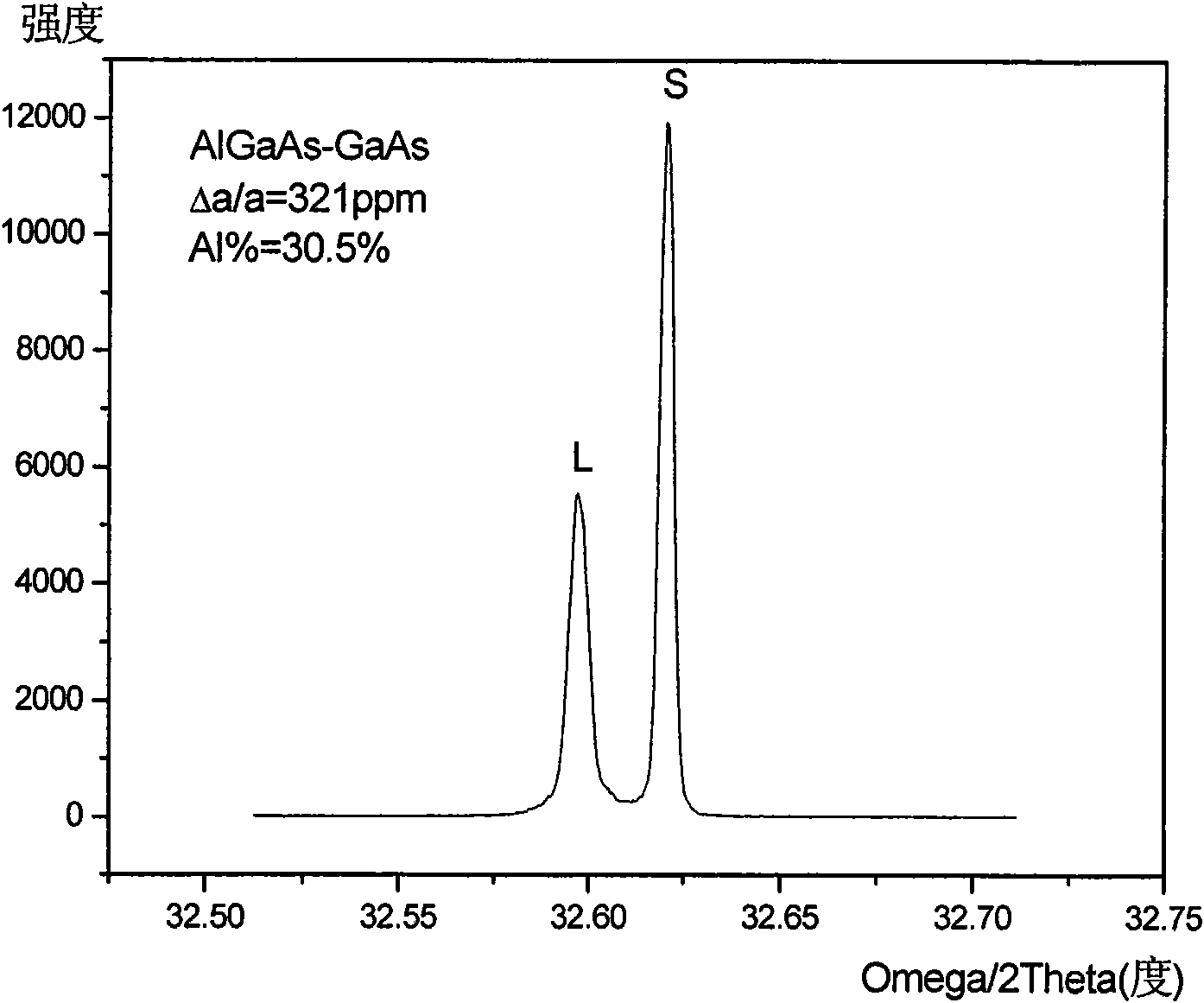

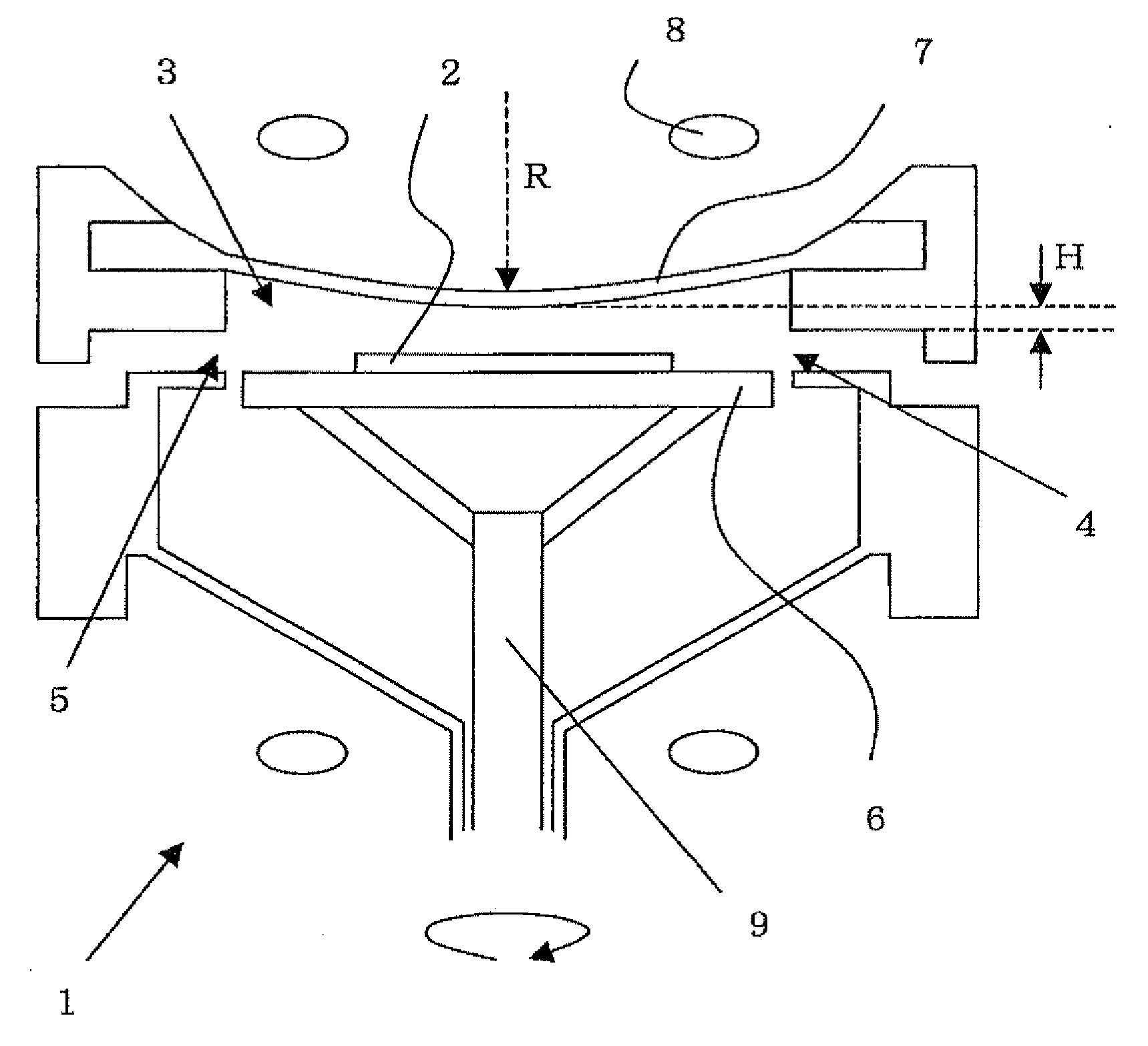

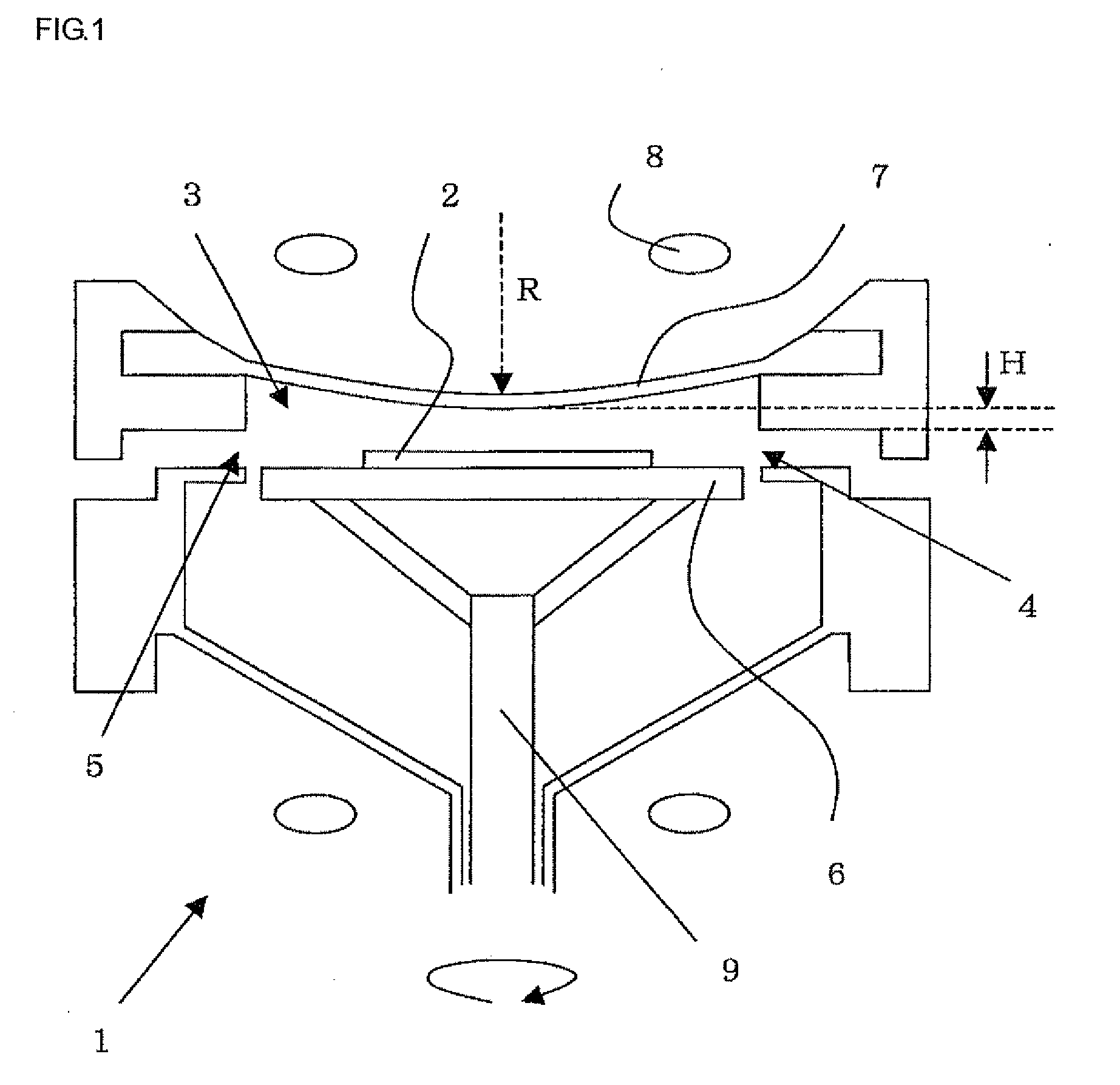

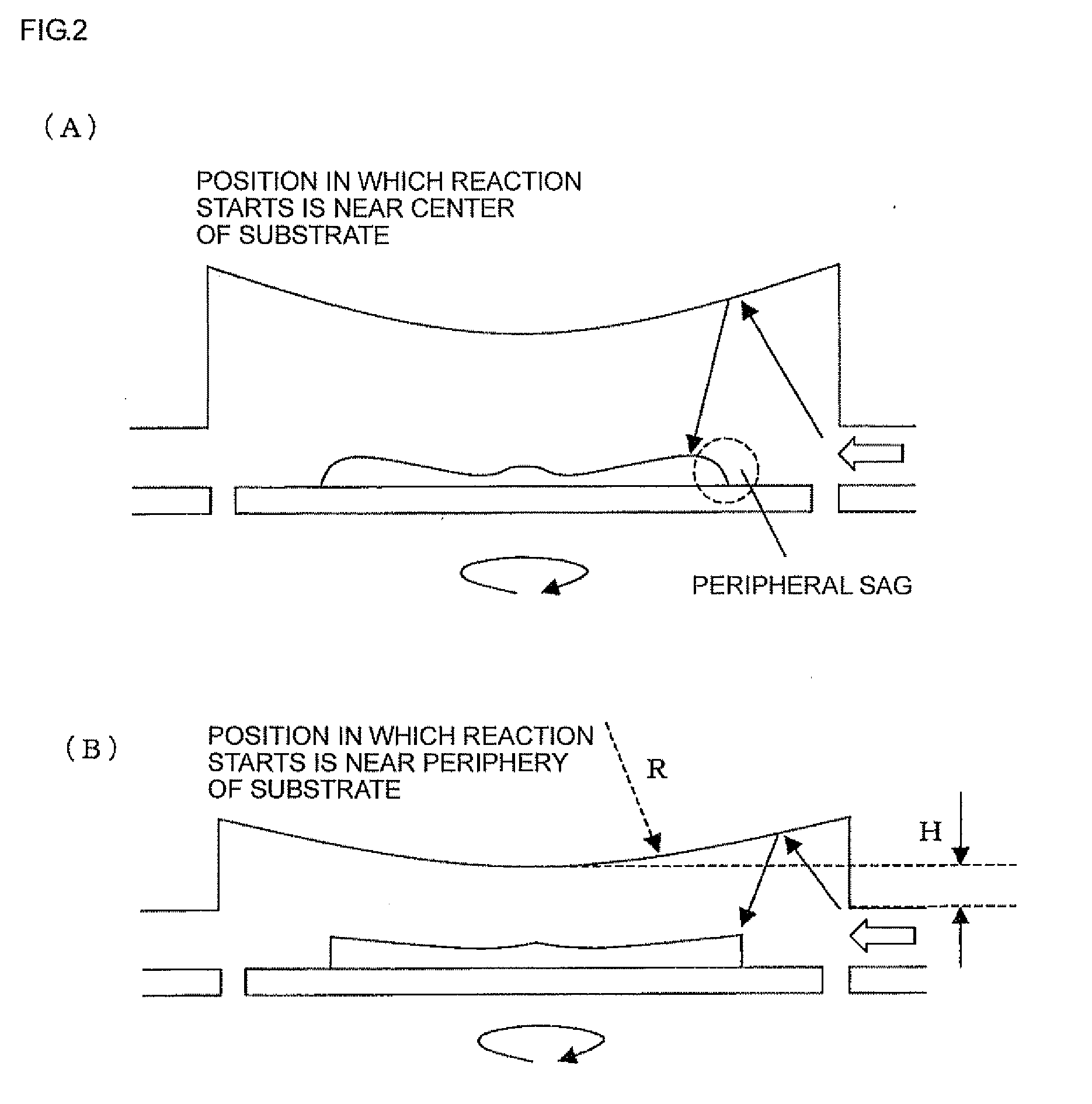

Epitaxial growth method

ActiveUS20100251958A1Improve epitaxy qualityImprove productivityPolycrystalline material growthFrom chemically reactive gasesProduction rateSingle crystal substrate

The invention provides an epitaxial growth method which is a single wafer processing epitaxial growth method by which at least a single crystal substrate is placed in a reaction chamber with an upper wall having a downward convexity and an epitaxial layer is deposited on the single crystal substrate by introducing raw material gas and carrier gas into the reaction chamber through a gas feed port, in which, after any one of the radius of curvature of the upper wall of the reaction chamber and a difference between an upper end of the gas feed port and a lower end of the upper wall of the reaction chamber in the height direction or both are adjusted in accordance with the flow rate of the carrier gas which is introduced into the reaction chamber through the gas feed port, an epitaxial layer is deposited on the single crystal substrate. As a result, a single wafer processing epitaxial growth method is provided that can obtain the effects, such as an increase in the quality of an epitaxial wafer and an increase in productivity, which are produced by the degree of the flow rate of carrier gas, and deposit an epitaxial layer on a single crystal substrate without deforming the film thickness shape.

Owner:SHIN-ETSU HANDOTAI CO LTD

Semiconductor substrate and manufacturing method thereof

ActiveUS20180019115A1Improve epitaxy qualityGrowth inhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorEpitaxy

A semiconductor substrate and a manufacturing method thereof are provided. The semiconductor substrate has an epitaxy region located at a central portion of a main plane of the semiconductor substrate, a periphery region surrounding the epitaxy region and an injured region distributed inside the periphery region.

Owner:GLOBALWAFERS CO LTD

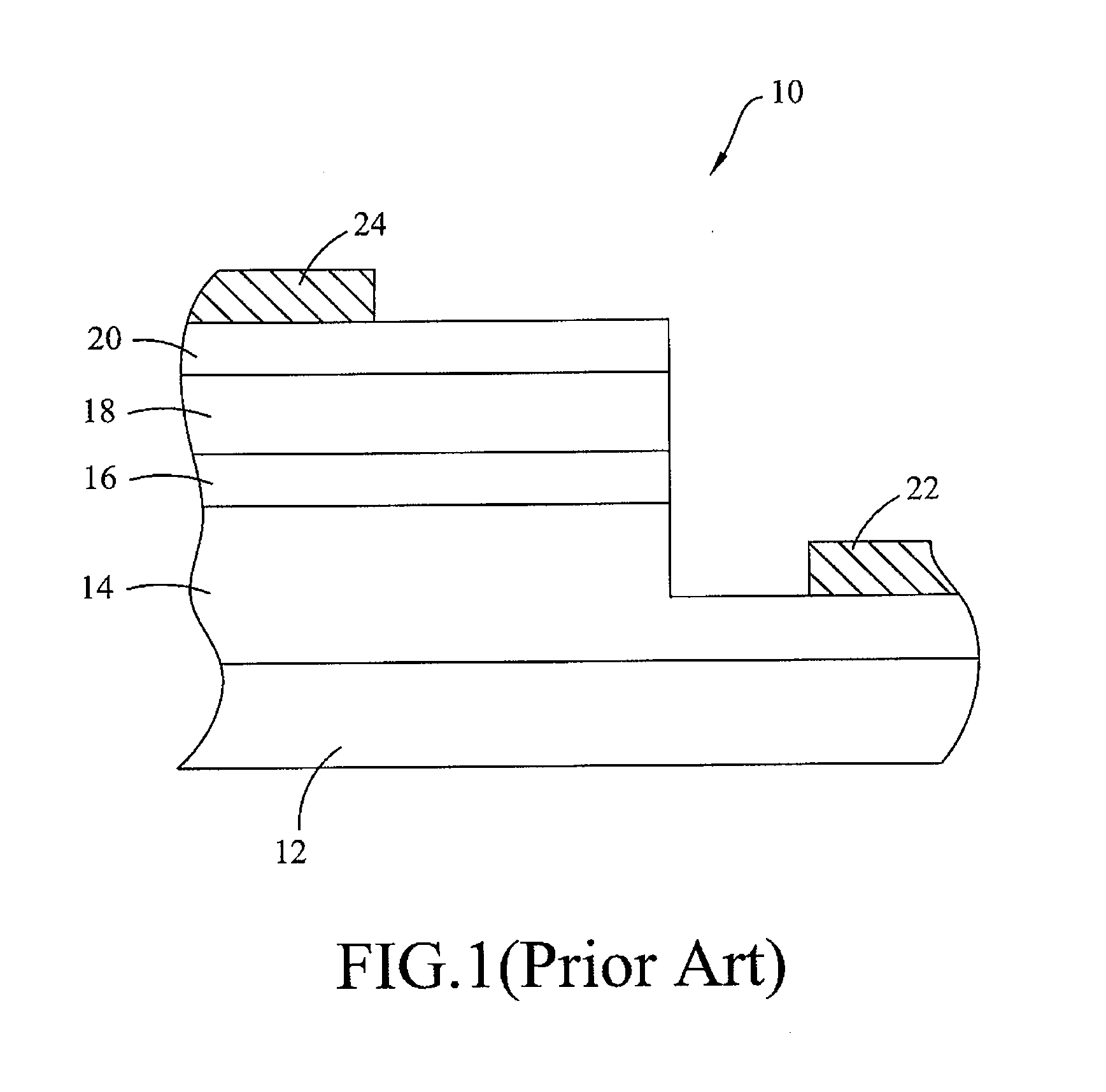

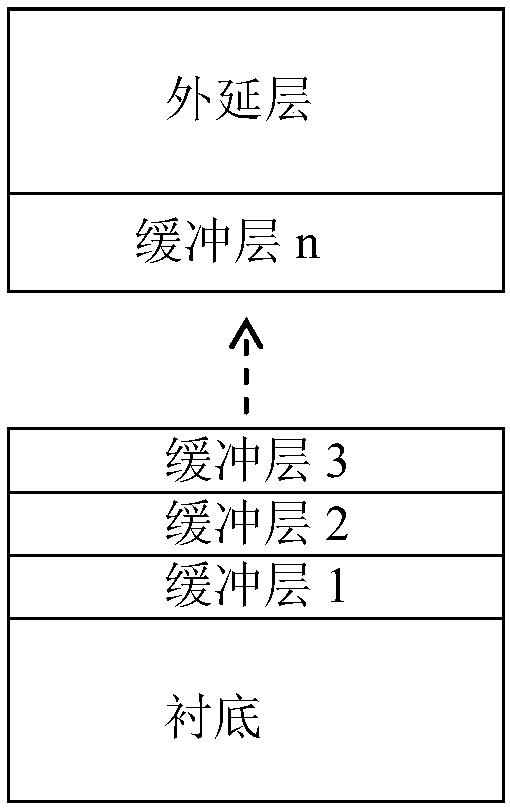

Ternary nitride-based buffer layer of a nitride-based light-emitting device and a method for manufacturing the same

ActiveUS7497905B2Simplify the complex and difficult production processShorten the construction periodPolycrystalline material growthSemiconductor/solid-state device manufacturingNitrogenLight emitting device

Ternary nitride-based buffer layer of a nitride-based light-emitting device and related manufacturing method. The device includes a substrate and a plurality of layers formed over the substrate in the following sequence: a ternary nitride-based buffer layer, a first conductivity type nitride-based semiconductor layer, a light-emitting layer, and a second conductivity type nitride-based semiconductor layer. The manufacturing method includes introducing a first reaction source containing a first group III element into a chamber at a first temperature that is subsequently deposited on the surface of the substrate, the melting point of said element being lower than the first temperature. Introducing a second reaction source containing a second group III element and a third reaction source containing a nitrogen element into the chamber at a second temperature, no lower than the melting point of the first group III element, for forming a ternary nitride-based buffer layer with the first group III element.

Owner:EPISTAR CORP

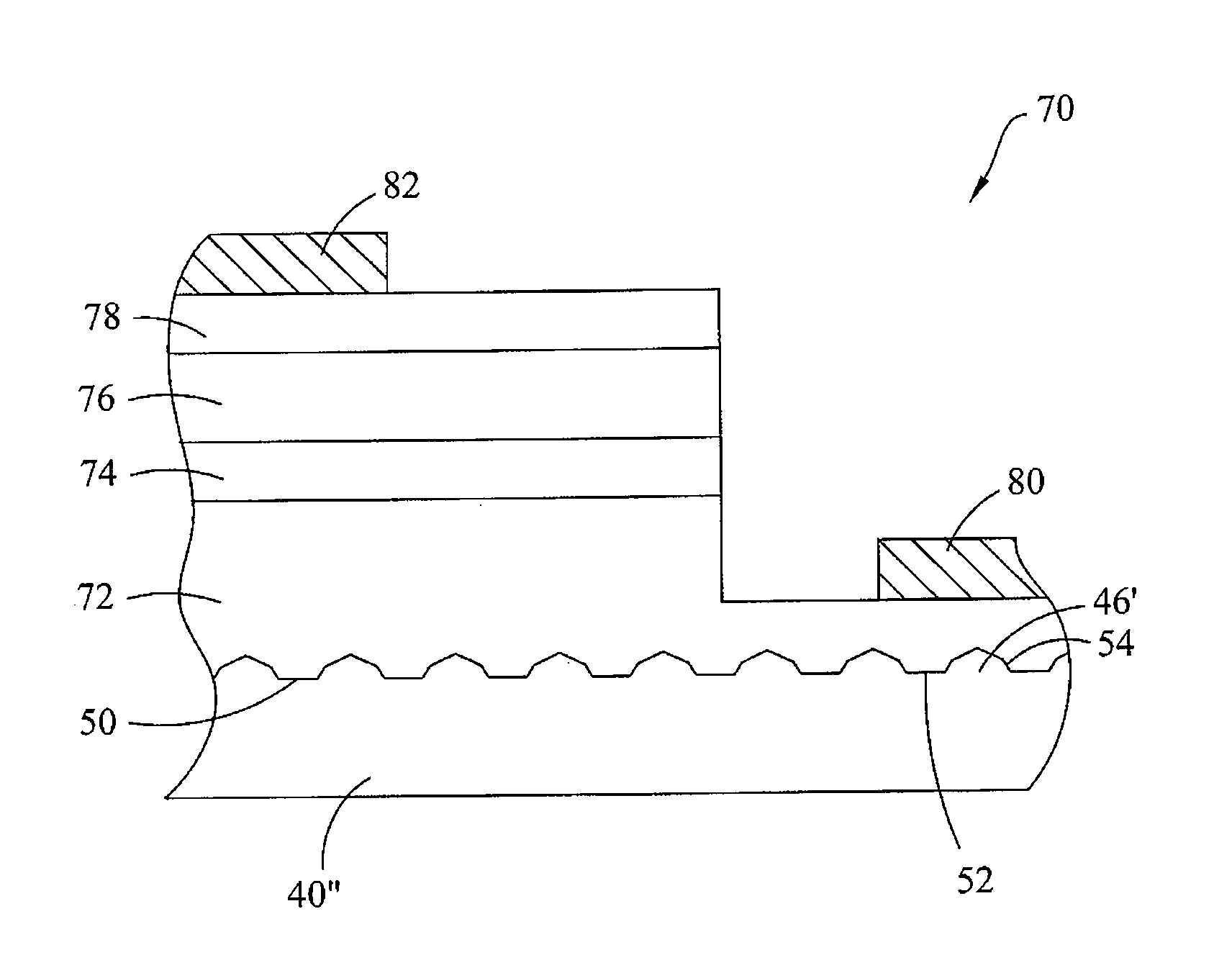

Light-emitting semiconductor device

InactiveUS20110284895A1Improve epitaxial qualityImprove epitaxy qualitySemiconductor devicesCrystallizationSemiconductor device

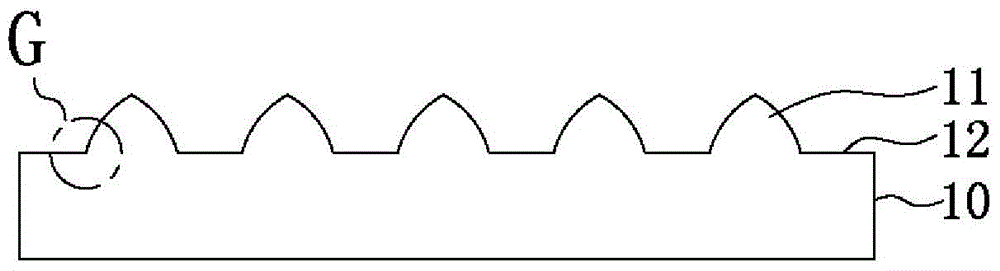

The present invention provides a light-emitting semiconductor device, which comprises a substrate having a surface formed with a plane and a plurality of protrusions out of the plane. The plane is on a crystalline orientation. The protrusion is provided with an outer surface consisting of a plurality of sidewall surfaces. The sidewall surfaces are substantially not on the crystalline orientation. The protrusion is formed with an outline edge extended from the bottom to the top of the protrusion from a side view. The outline edge comprises at least one turning point. A first conductive type semiconductor layer is above the surface of the substrate, an active layer is above the first conductive type semiconductor layer, and a second conductive type semiconductor layer is above the active layer.

Owner:EPISTAR CORP

patterned sic substrate

InactiveCN102925969BReduced linear dislocation densityImprove epitaxy qualityFrom chemically reactive gasesSingle crystalGallium nitride

The invention relates to a graphical silicon carbide (SiC) substrate. The surface of the graphical SiC substrate comprises periodized protrusions or concave images which are formed by means of plasma etching or wet etching, wherein the periodized protrusions or the concave images are any one of multilateral cones, multilateral cylinders, multi-rowed frustums, trapezoid multilateral frustums, trapezoid round pedestals, hemispheres or spherical crowns. Periodic images are combination of any two or more than two of the multilateral cones, the multilateral cylinders, the multi-rowed frustums, the trapezoid multilateral frustums, the trapezoid round pedestals, the hemispheres or the spherical crowns. The graphical SiC substrate can improve epitaxy quality of heteroepitaxy of gallium nitride (GaN) and homoepitaxy of 3C-SiC which take SiC as the substrate, and improves performance and stability of elements prepared by epitaxial wafers.

Owner:SHANGHAI INST OF TECH

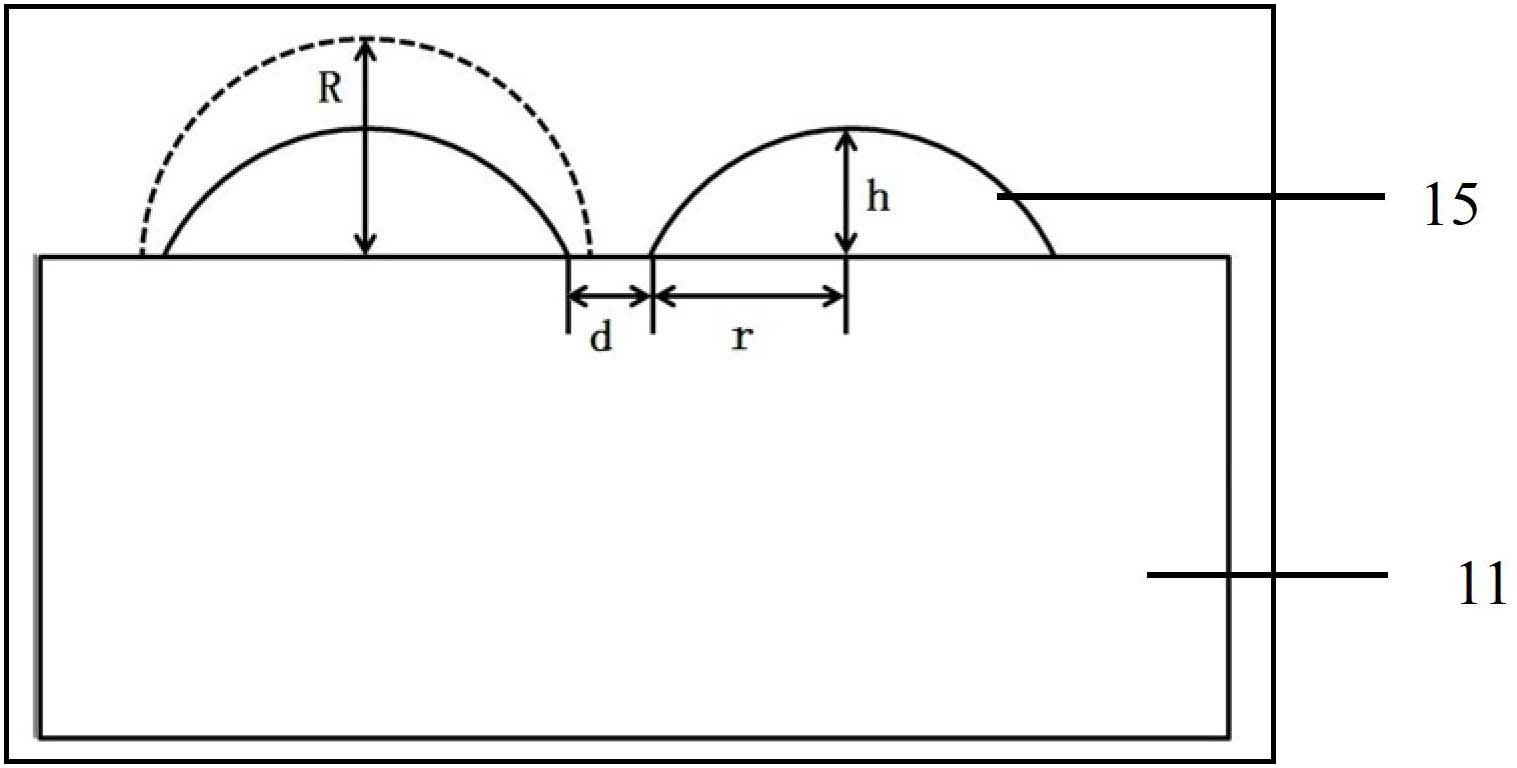

Patterned substrate of LED chip and LED chip

InactiveCN102694086AIncreased Scatter ChanceImprove light extraction efficiencySemiconductor devicesOptoelectronicsPatterned substrate

The invention discloses a patterned substrate of an LED chip and an LED chip. Patterns of the substrate consist of a plurality of identically-shaped spherical caps arranged on the surface of the substrate, the height h of each spherical cap is 75-85 percent of the radius R of the sphere corresponding to the spherical cap, and the distance d between the edges of the adjacent spherical caps is 30-50 percent of the radius r of the bottom surface of the spherical caps. Compared with the prior art, the patterned substrate has better light extraction efficiency than a substrate with hemispherical patterns with the same bottom surface radius, is simpler in actual processing and facilitates popularized application.

Owner:SOUTH CHINA UNIV OF TECH

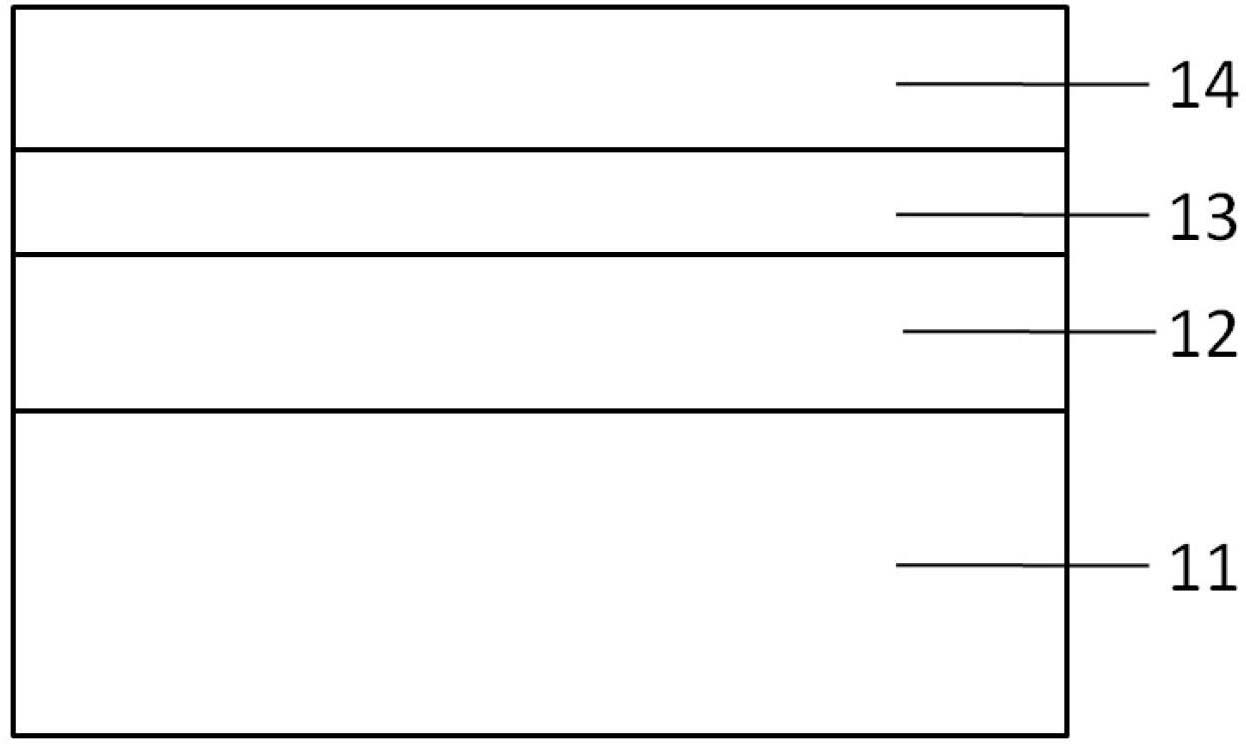

High-quality silicon carbide epitaxial growth technology

InactiveCN107829135AReduce the number of defectsImprove featuresPolycrystalline material growthFrom chemically reactive gasesWaferingGas phase

The invention discloses a high-quality silicon carbide epitaxial growth technology. A plurality of silicon carbide buffer layers are sequentially homogeneously grown on a silicon carbide substrate bya chemical vapor deposition process, and a silicon carbide epitaxial layer is grown on the uppermost buffer layer, wherein the growth rate of all the buffer layers increases stepwise from bottom to top, and the growth rate of the top buffer layer is not higher than the growth rate of the epitaxial layer. Multiple buffer layers are formed through the stepped control of the growth rate, and a plurality of interfaces formed by the brief growth interruption among the buffer layers sequentially reduce the propagation of defects, so the extended propagation of the defects of the substrate to the epitaxial layer is blocked, the number of the defects in the epitaxial layer is reduced, the epitaxial quality is improved, and the characteristics and the yield of functional devices manufactured basedon above obtained epitaxial wafers are improved.

Owner:EPIWORLD INT

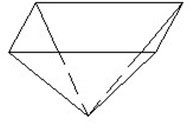

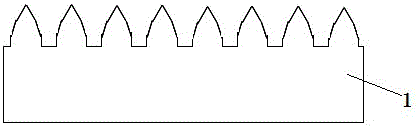

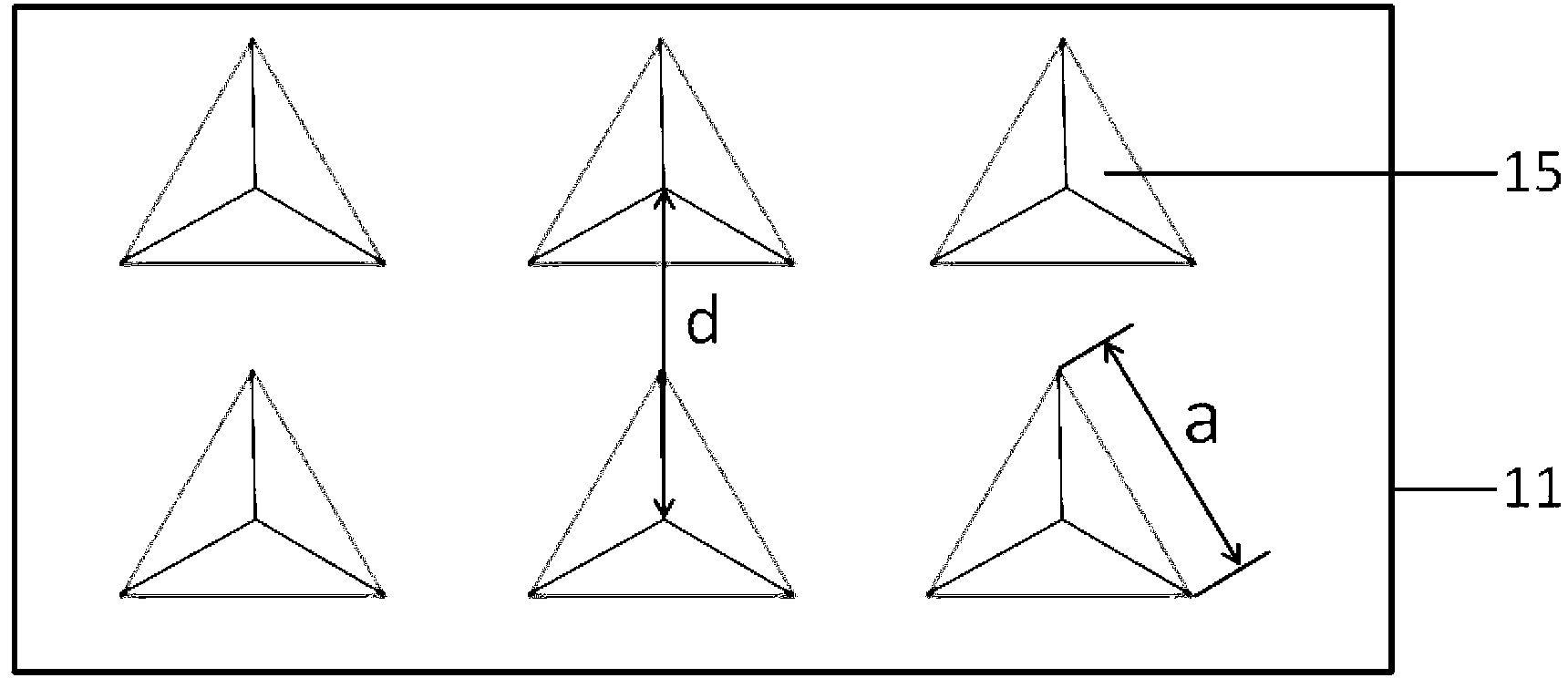

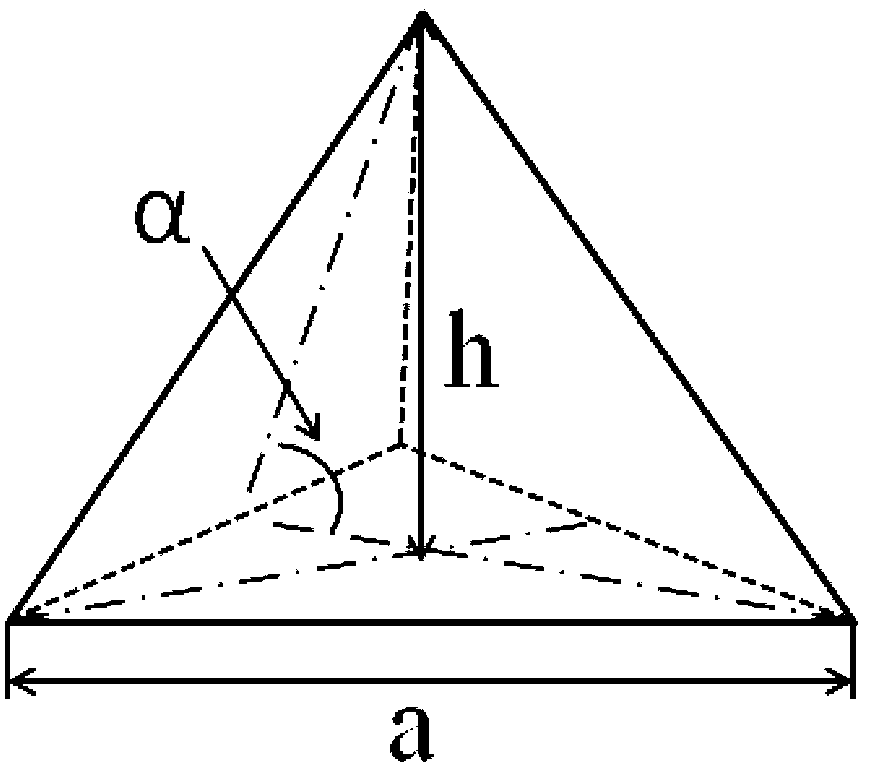

Patterned substrate of pattern improved LED chip and LED chip containing the same

InactiveCN103022302AImproved ability to reach the top of the LED chipImprove light extraction efficiencySemiconductor devicesState of artOptoelectronics

The invention discloses a patterned substrate of pattern improved LED chip. The pattern of the substrate is composed of a plurality of regular triangular pyramids with the same shape which are arranged on the surface of the substrate, and the inclination angle alpha of the regular triangular pyramids is 60 DEG to 65 DEG. The space D of the adjacent regular triangular pyramids is 1 to 1.4 times the length A of the side of the regular triangular pyramids. The invention further discloses a LED chip containing the patterned substrate of pattern improved LED chip. Compared with the prior art, the LED chip containing the patterned substrate of pattern improved LED chip has better extraction efficiency than a LED chip with a common substrate, and is convenient in popularization and application. According to the patterned substrate of pattern improved LED chip and LED chip containing the same, the regular triangular pyramids graph accords with the crystal lattice structure of GaN, and the target pattern can be easily obtained in practical processing.

Owner:SOUTH CHINA UNIV OF TECH

Semiconductor light-emitting device with selectively formed buffer layer on substrate

InactiveUS20090050914A1Reduce reflectionImprove external quantum efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesLight emitting deviceSemiconductor

The invention discloses a semiconductor light-emitting device and a method of fabricating the same. The semiconductor light-emitting device according to the invention includes a substrate, a buffer layer, a multi-layer structure, and an ohmic electrode structure. The buffer layer is selectively formed on an upper surface of the substrate such that the upper surface of the substrate is partially exposed. The multi-layer structure is formed to overlay the buffer layer and the exposed upper surface of the substrate. The multi-layer structure includes a light-emitting region. The buffer layer assists a bottom-most layer of the multi-layer structure in lateral and vertical epitaxial growth. The ohmic electrode structure is formed on the multi-layer structure.

Owner:SINO AMERICAN SILICON PROD +1

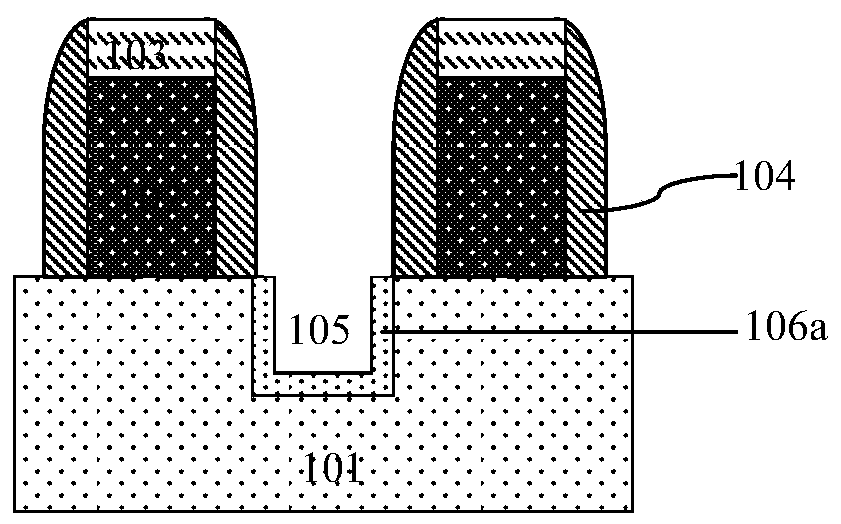

Manufacturing method of embedded epitaxial layer

PendingCN111599764ASimple processLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEngineering

The invention discloses a manufacturing method of an embedded epitaxial layer. The method comprises the steps of 1, forming a U-shaped groove in a silicon substrate by adopting a dry etching process;and 2, filling an embedded epitaxial layer in the groove, wherein the step 2 comprises the sub-steps of 21, carrying out epitaxial growth to form a buffer layer; 22, carrying out epitaxial growth to form a main body layer, and forming particle defects in the growth process of the main body layer; 23, introducing an etching gas into the same epitaxial growth cavity to perform back etching so as toremove particle defects; and 24, carrying out epitaxial growth to form a cap layer. According to the invention, the particle defects generated in the epitaxial growth process of the embedded epitaxiallayer can be eliminated, so that the yield of products can be improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Semiconductor photoelectric structure for improving light extraction efficiency and manufacturing method thereof

InactiveCN101964382BImprove light extraction efficiencyReduce defect densitySemiconductor devicesElectrical conductorSemiconductor package

Owner:ZHANJING TECH SHENZHEN +1

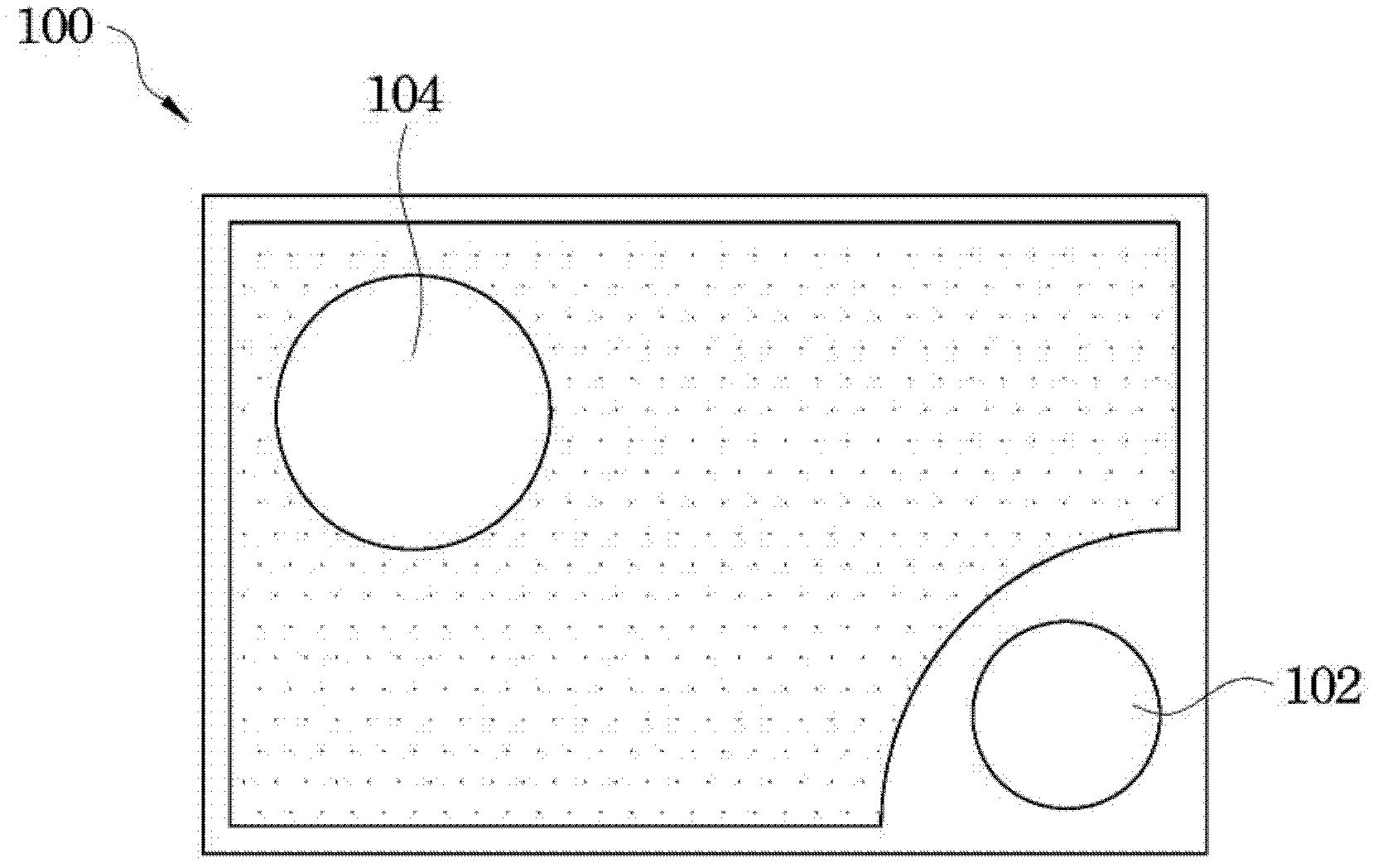

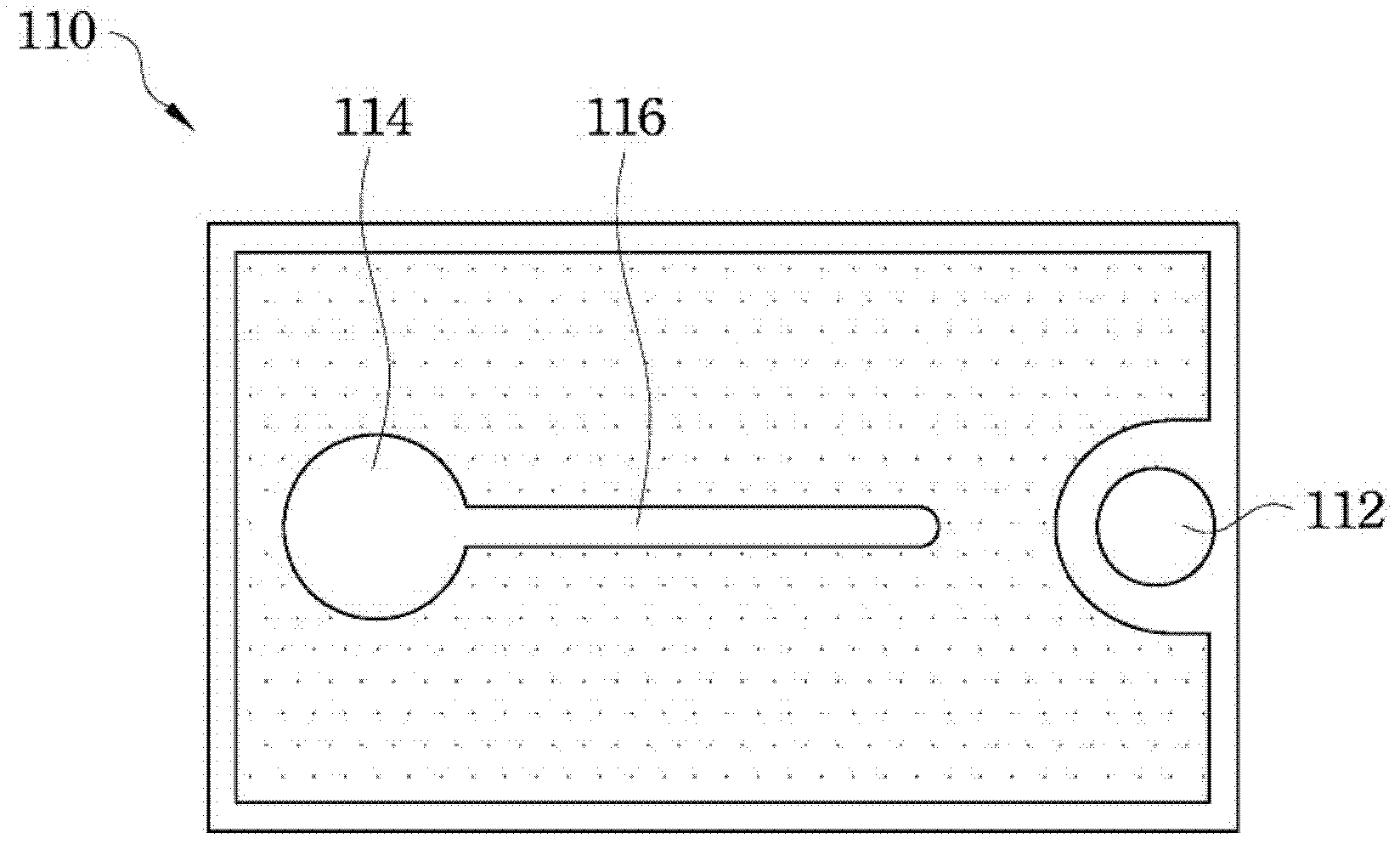

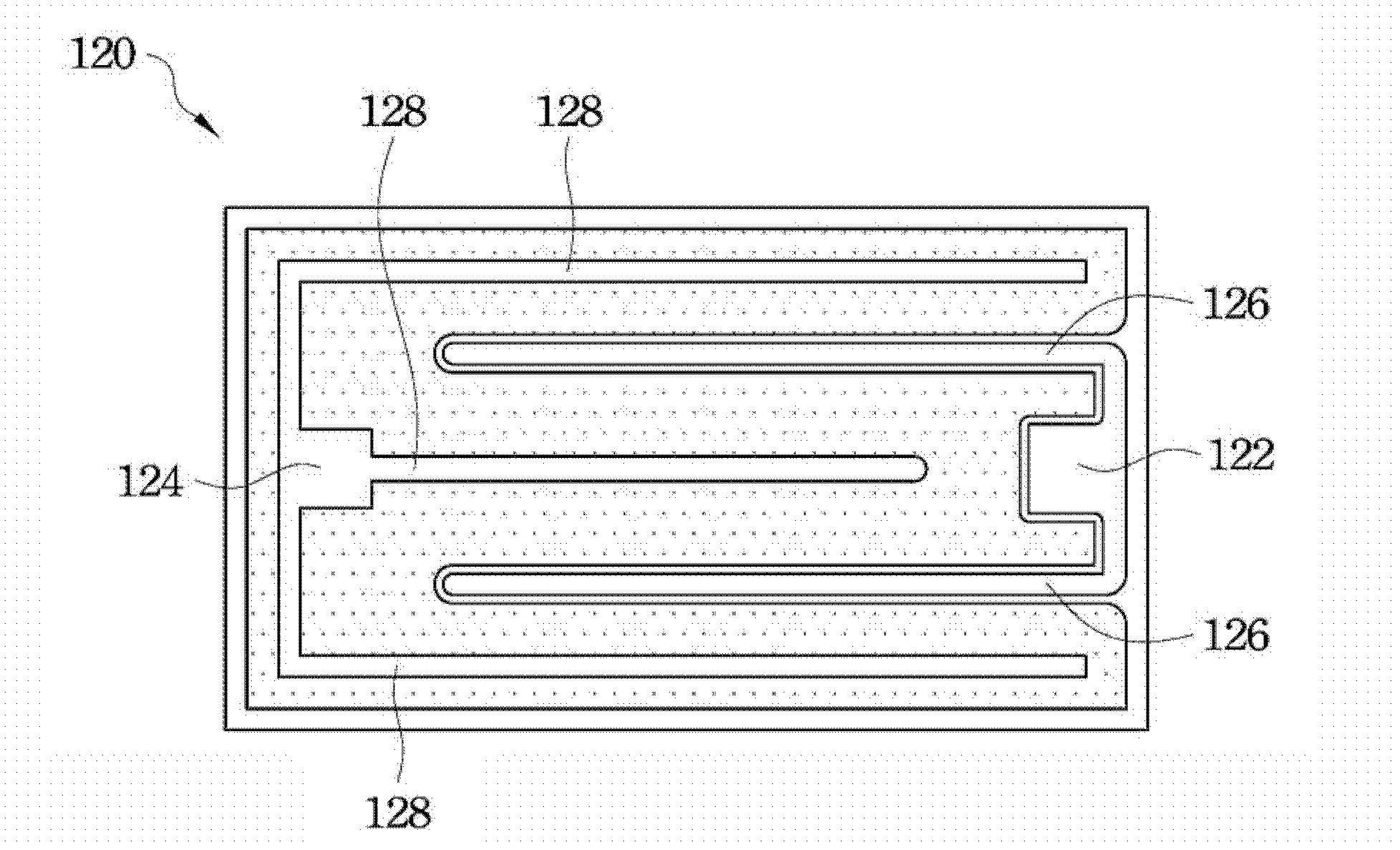

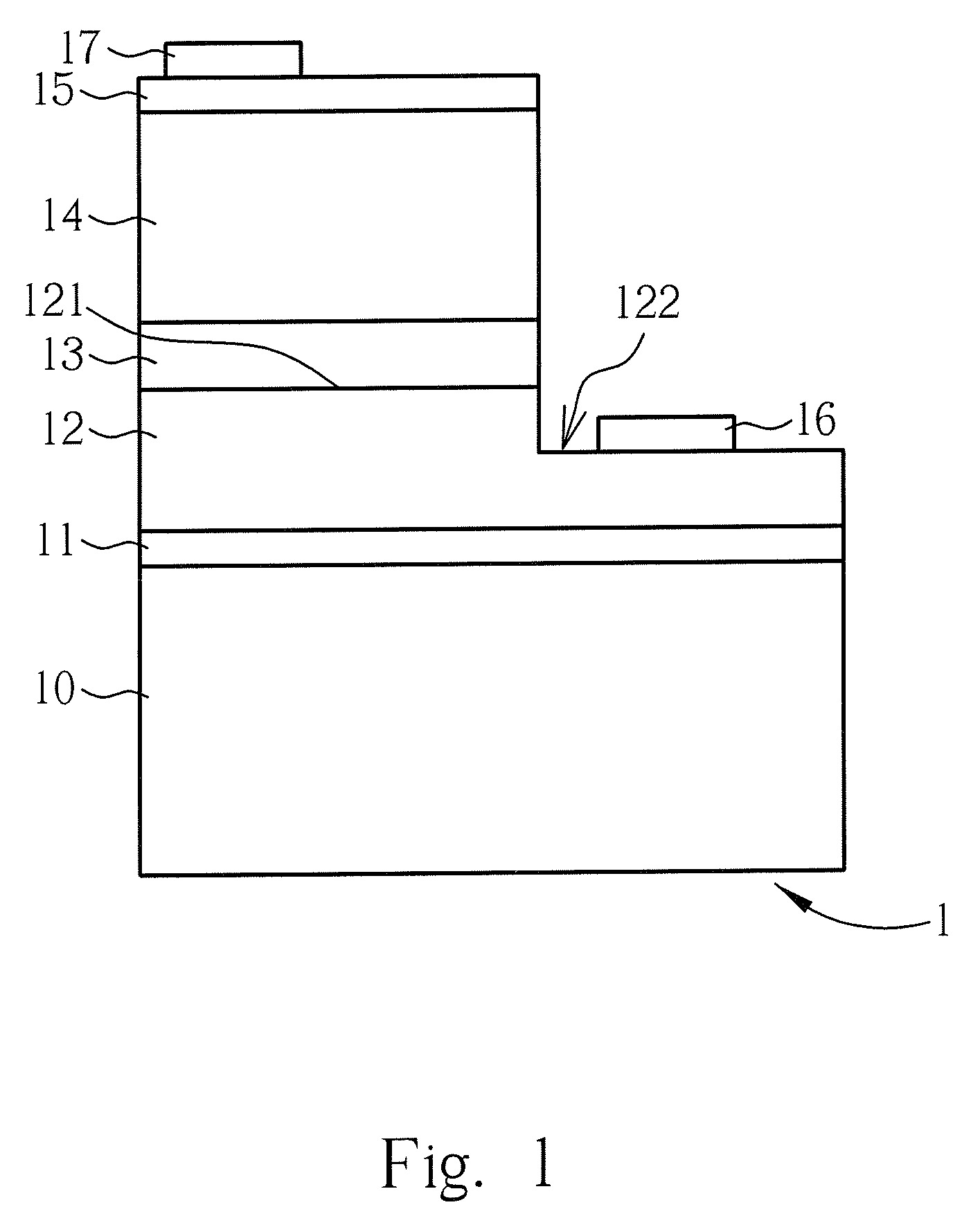

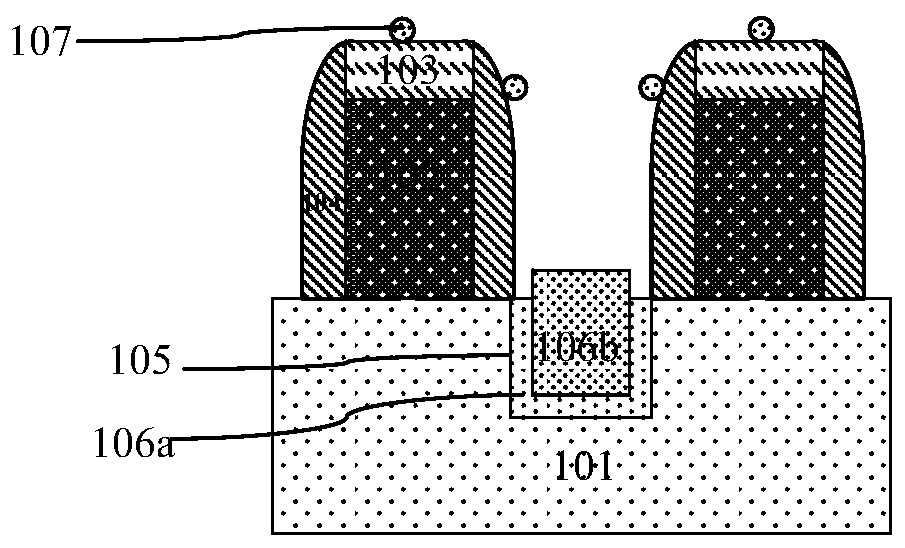

Light-emitting diode (LED) structure

InactiveCN101859840AImprove epitaxy qualityImprove internal quantum efficiencySemiconductor devicesDopingLead structure

The invention discloses a light-emitting diode (LED) structure which comprises a substrate, a first doped semiconductor layer, a first electrode, a light-emitting layer, a second doped semiconductor layer and a second electrode, wherein the substrate is provided with a surface and a plurality of cylindrical photon crystals positioned on the surface; the first doped semiconductor layer is arranged on the substrate to cover the photon crystals; the light-emitting layer, the second doped semiconductor layer and the second electrode are sequentially arranged on part of the first doped semiconductor layer; and the first electrode is arranged on part of the first doped semiconductor layer on which the light-emitting layer is not covered. Because the substrate provided with the photon crystals can improve the epitaxial quality of the first doped semiconductor layer and increase the light energy of the forward ejected LED structure, the light-emitting efficiency of the LED structure can be effectively improved.

Owner:江苏璨扬光电有限公司