Manufacturing method of embedded epitaxial layer

A manufacturing method and epitaxial layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of increasing particle defect size, and achieve the effect of low cost and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

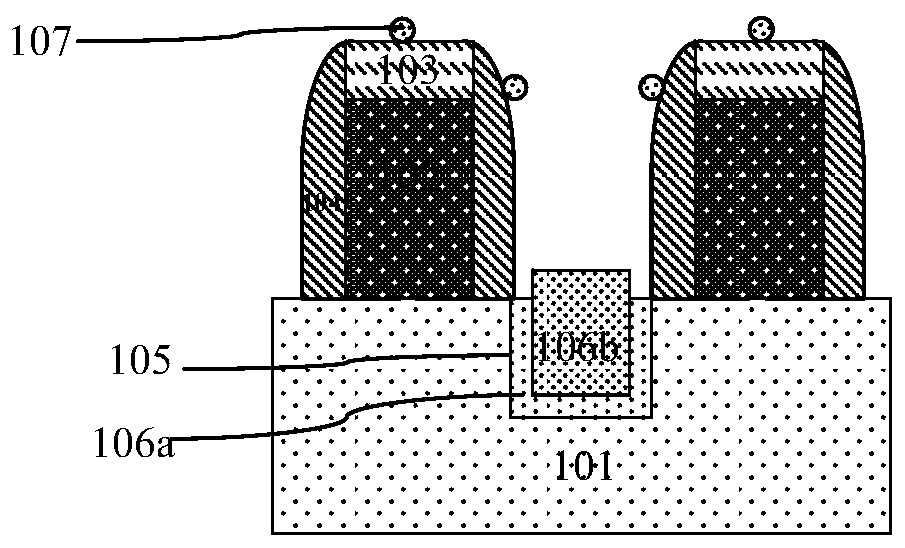

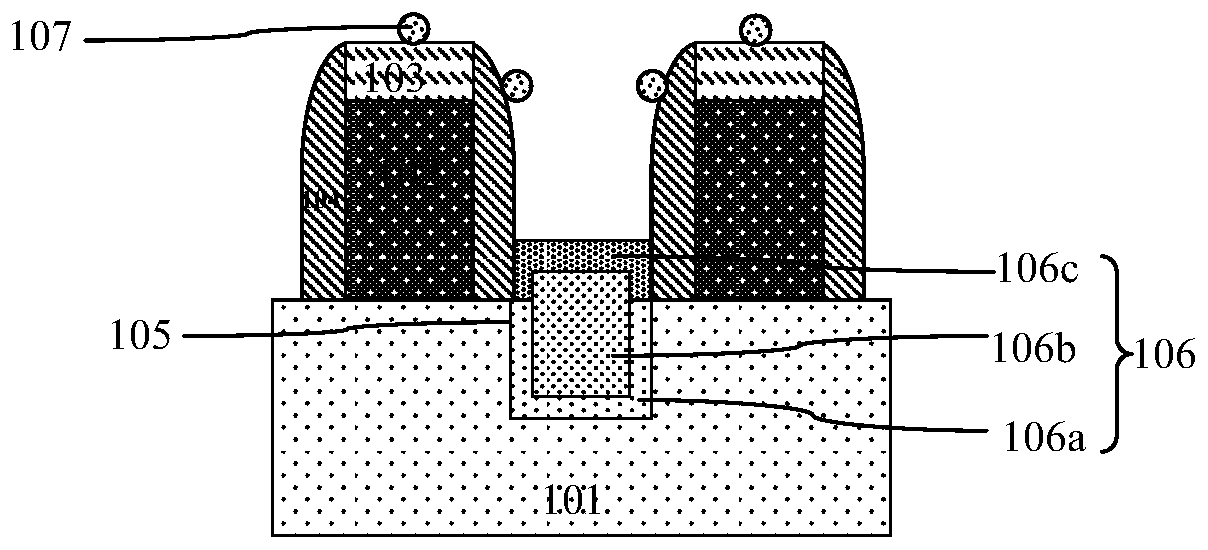

[0066] Such as figure 2 Shown is the flow chart of the epitaxial process method of the embodiment of the present invention; as Figure 3A to Figure 3D As shown, it is a schematic diagram of the device structure in each step of the manufacturing method of the embedded epitaxial layer 6 in the embodiment of the present invention; the manufacturing method of the embedded epitaxial layer 6 in the embodiment of the present invention includes the following steps:

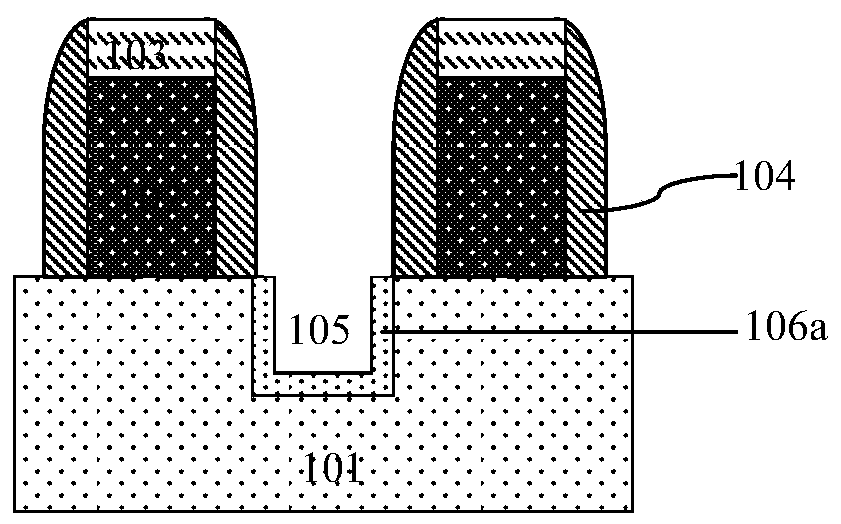

[0067] Step 1, such as Figure 3A As shown, a groove 5 is formed in the silicon substrate by a dry etching process, and the cross section of the groove 5 is a U-shaped structure.

[0068] In the embodiment of the present invention, a gate structure is formed on the silicon substrate, and the grooves 5 are self-aligned and formed in the grooves 5 on both sides of the gate structure;

[0069] The gate structure includes a gate dielectric layer and a polysilicon gate 2 stacked in sequence;

[0070] The top of the polysil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More