Patents

Literature

5612 results about "Secondary layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Field effect transistor

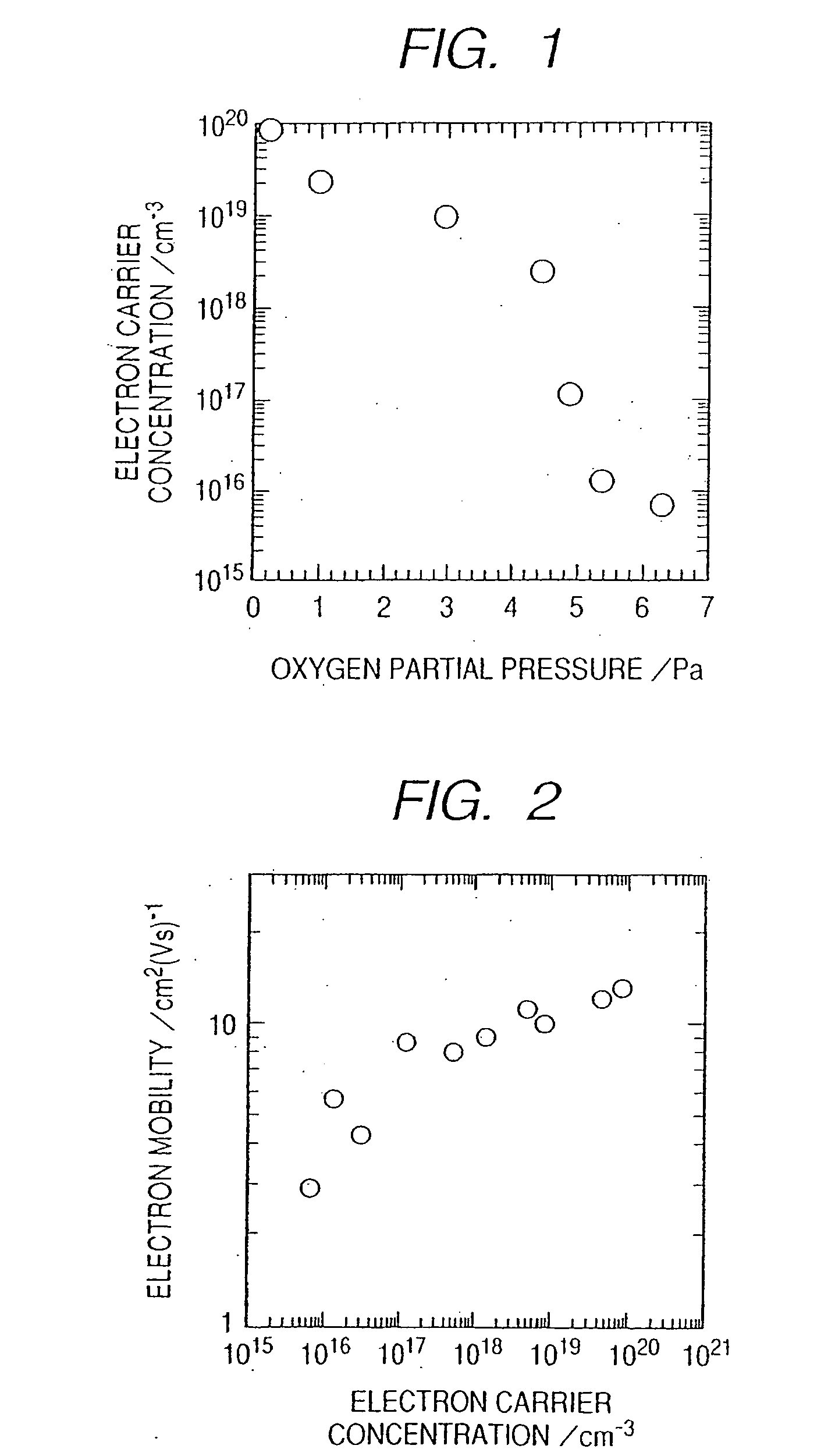

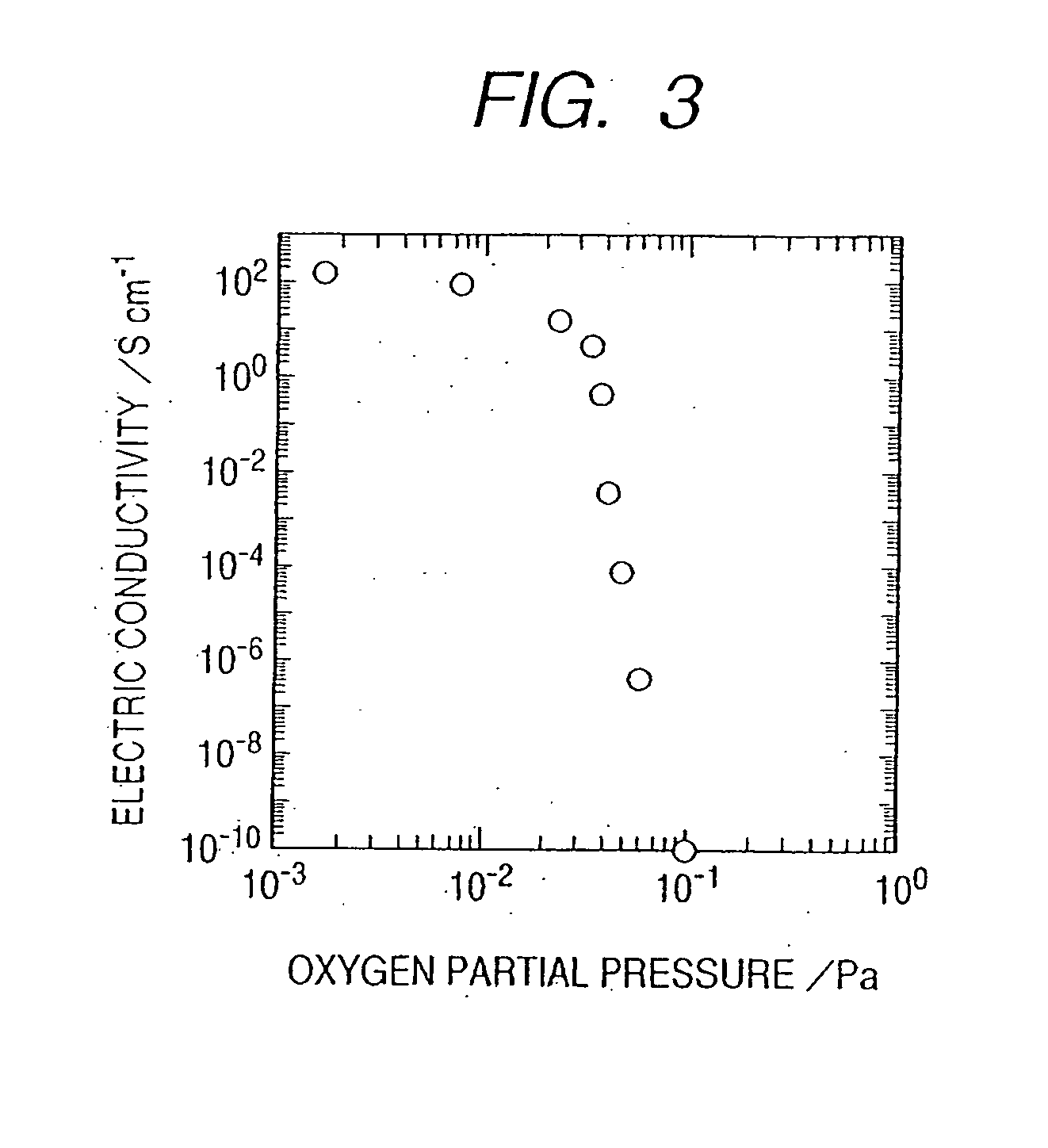

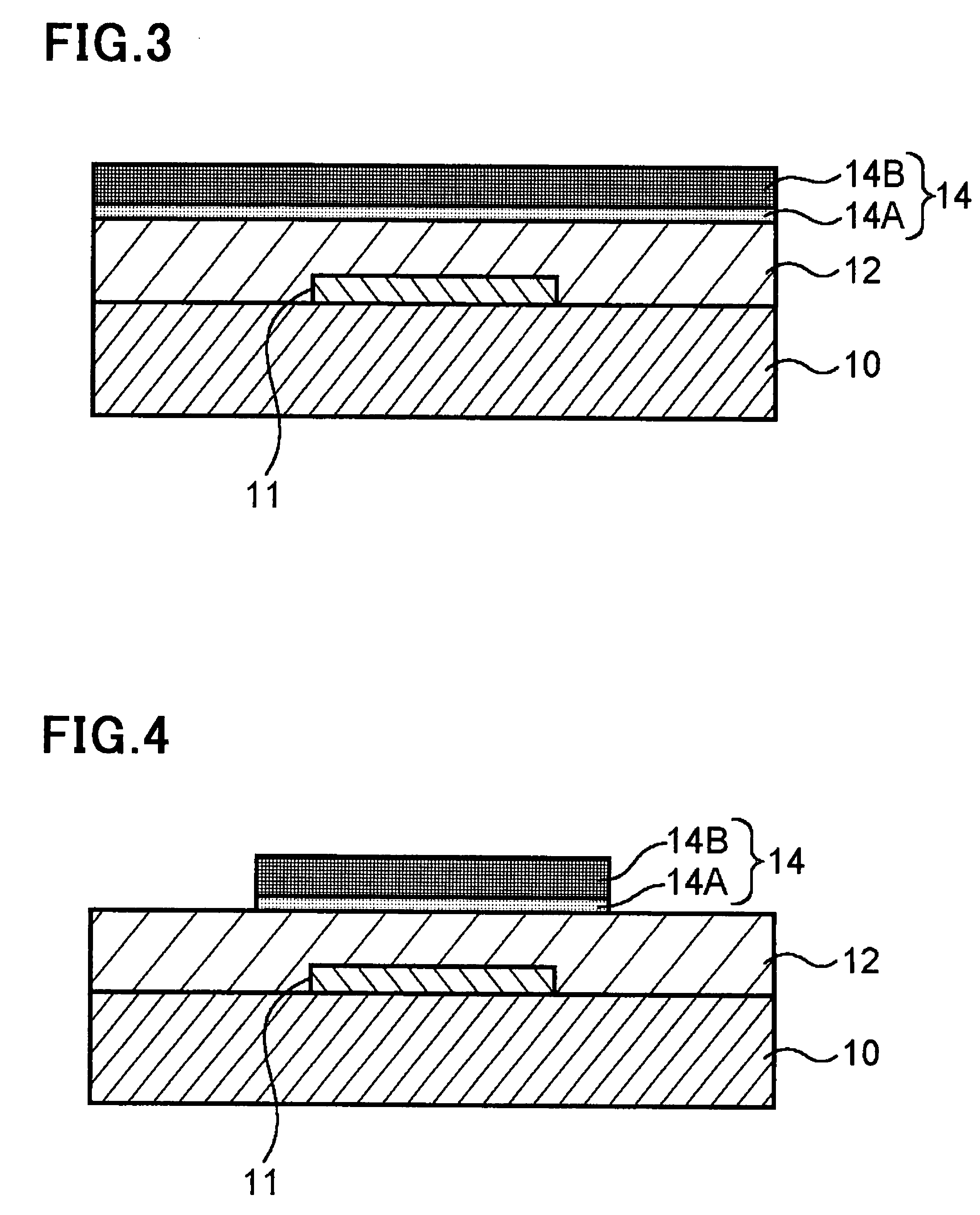

ActiveUS20060113539A1Inhibit currentMaintain good propertiesSolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorElectron

A novel field-effect transistor is provided which employs an amorphous oxide. In an embodiment of the present invention, the transistor comprises an amorphous oxide layer containing electron carrier at a concentration less than 1×10−18 / cm3, and the gate-insulating layer is comprised of a first layer being in contact with the amorphous oxide and a second layer different from the first layer.

Owner:CANON KK +2

Subcutaneous glucose electrode

InactiveUS6881551B2Reduce transportationAccurate measurementBioreactor/fermenter combinationsBiological substance pretreatmentsConcentrations glucosePolyamide

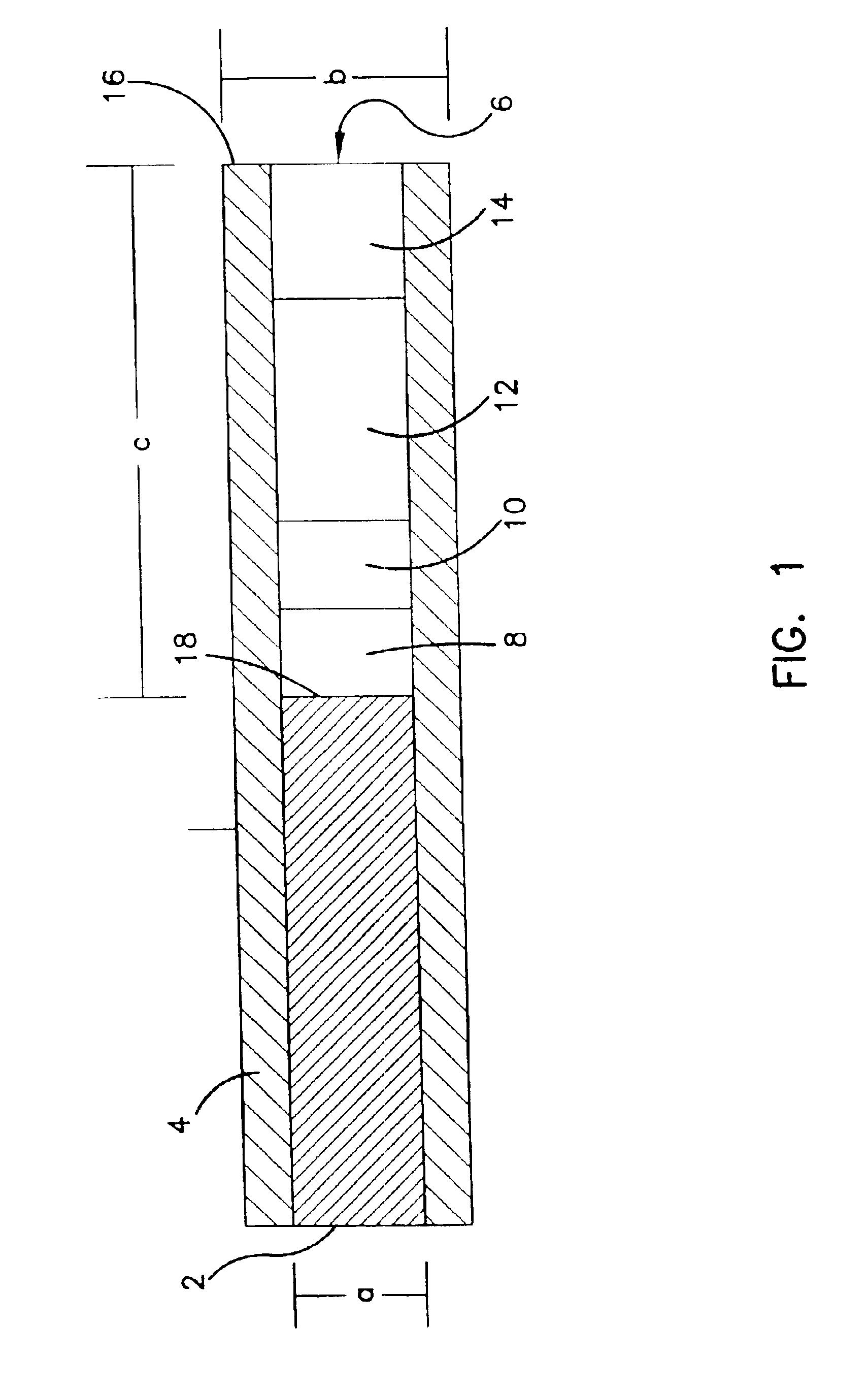

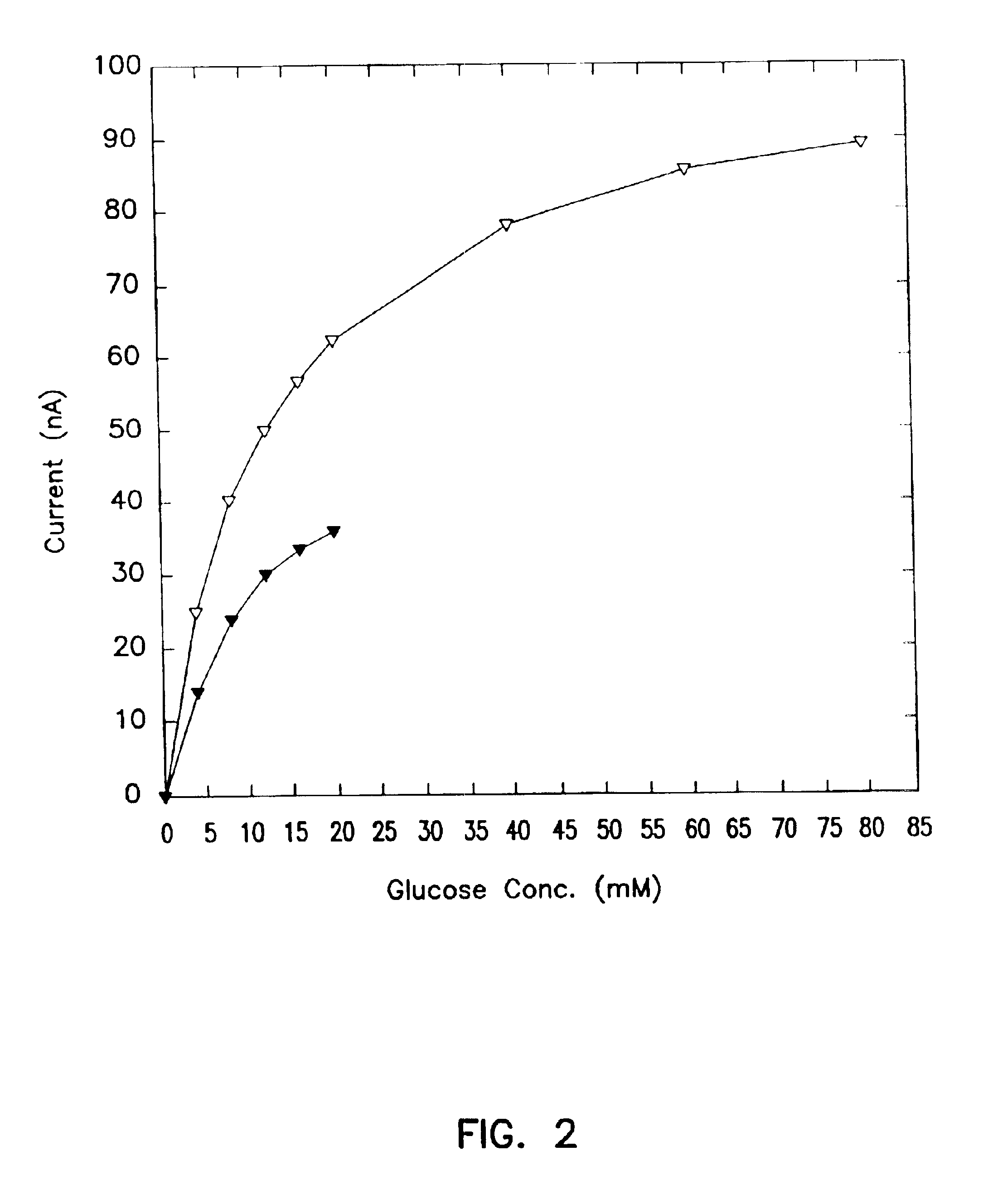

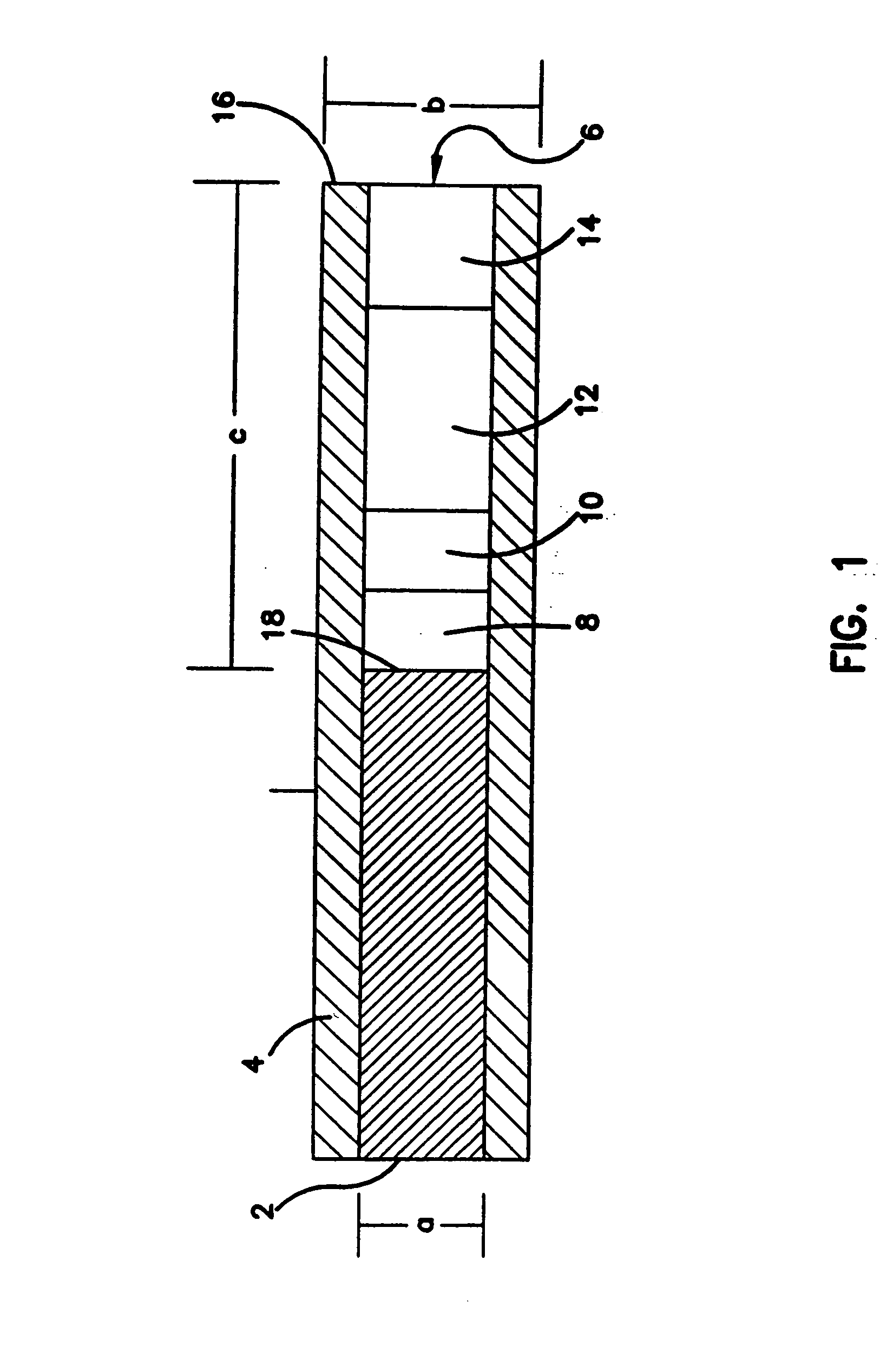

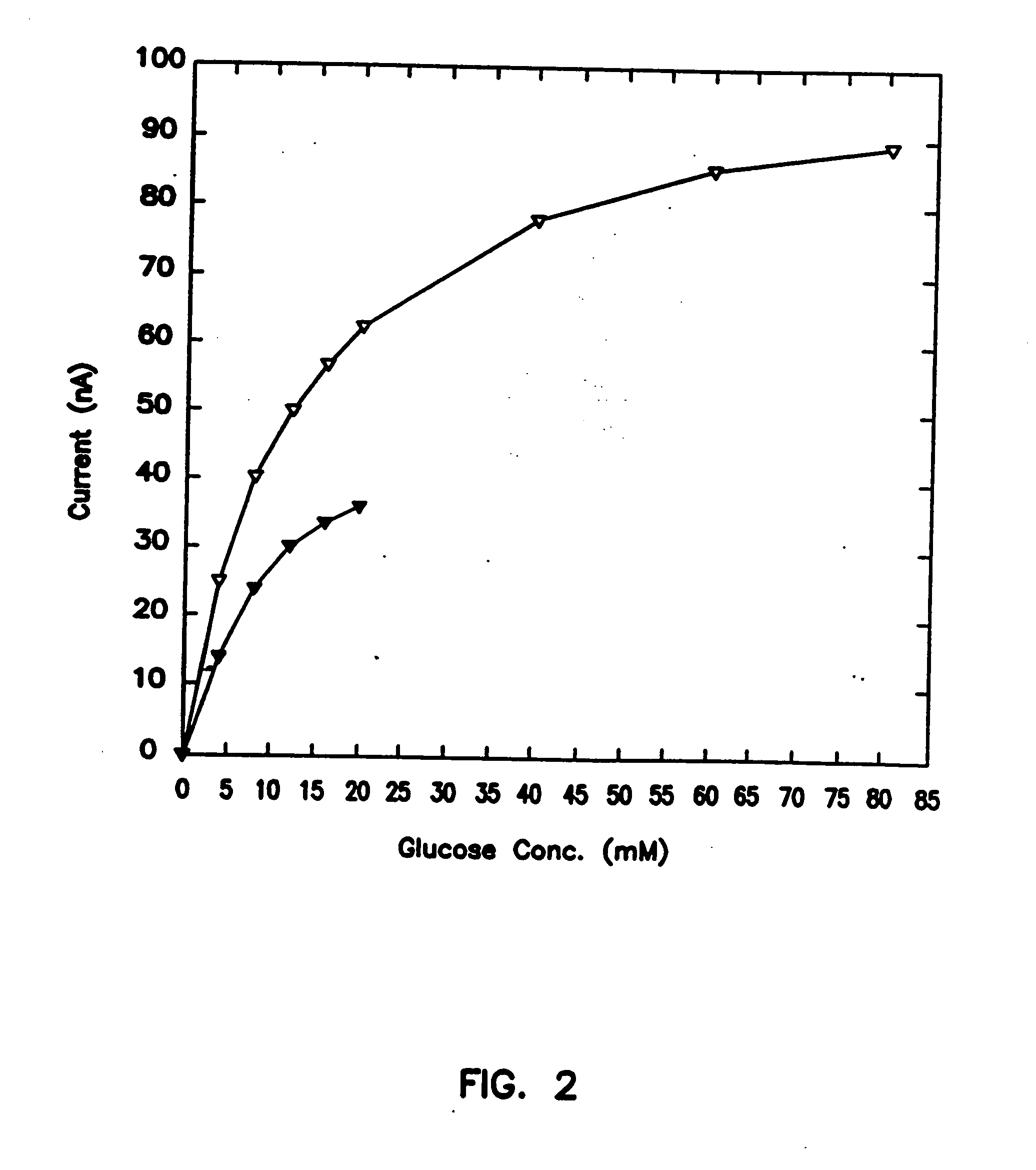

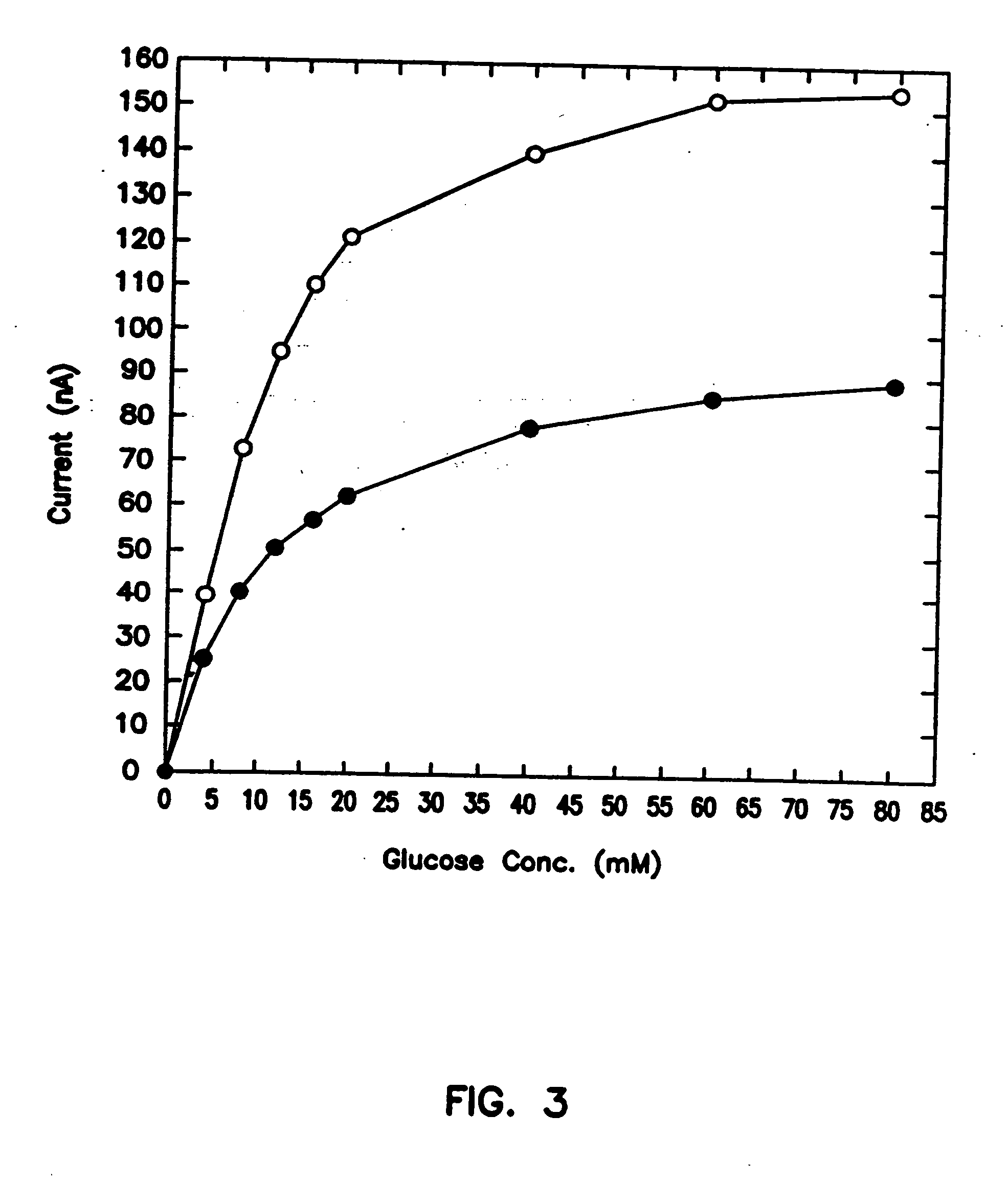

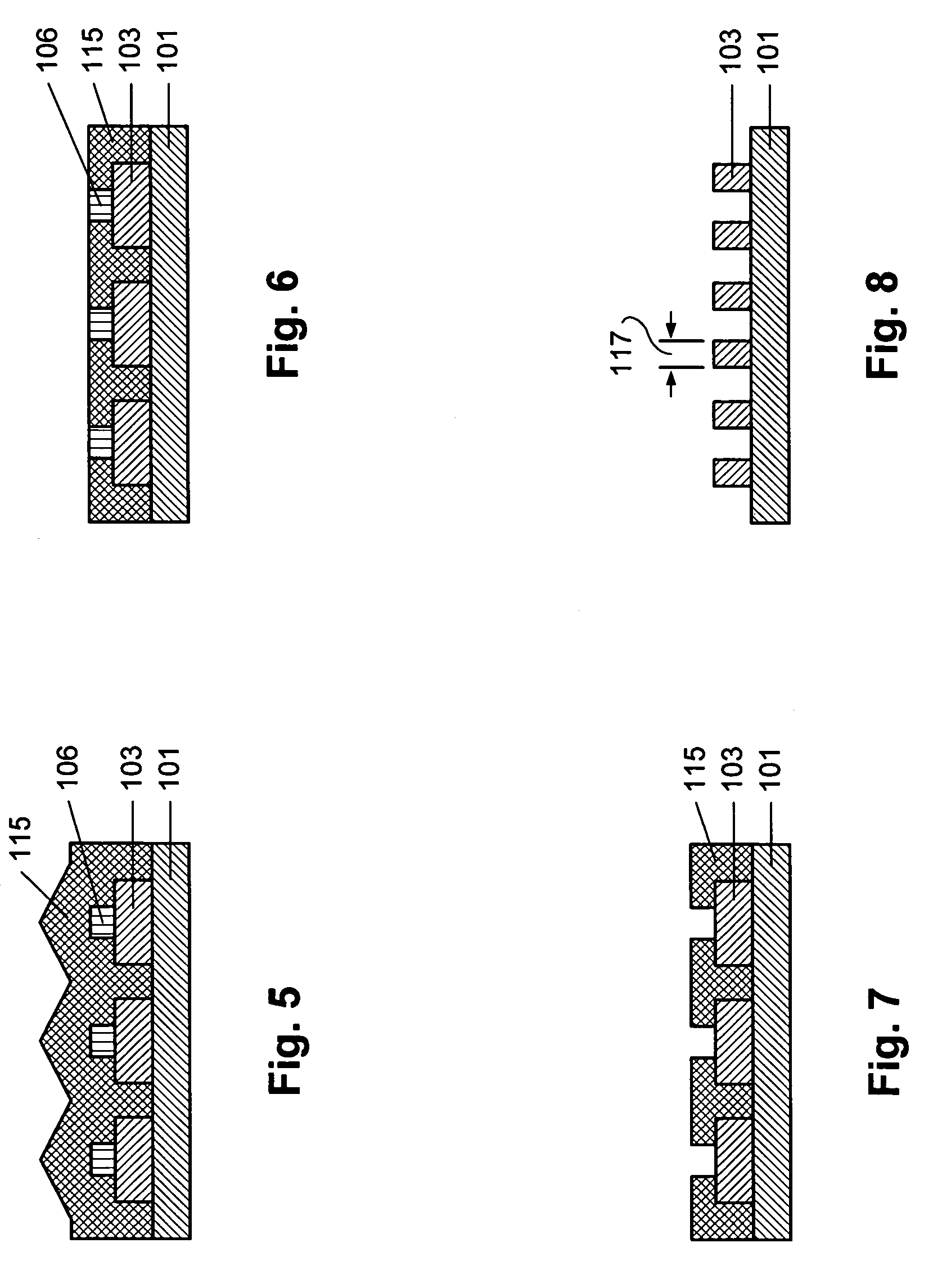

A small diameter flexible electrode designed for subcutaneous in vivo amperometric monitoring of glucose is described. The electrode is designed to allow “one-point” in vivo calibration, i.e., to have zero output current at zero glucose concentration, even in the presence of other electroreactive species of serum or blood. The electrode is preferably three or four-layered, with the layers serially deposited within a recess upon the tip of a polyamide insulated gold wire. A first glucose concentration-to-current transducing layer is overcoated with an electrically insulating and glucose flux limiting layer (second layer) on which, optionally, an immobilized interference-eliminating horseradish peroxidase based film is deposited (third layer). An outer (fourth) layer is biocompatible.

Owner:THERASENSE

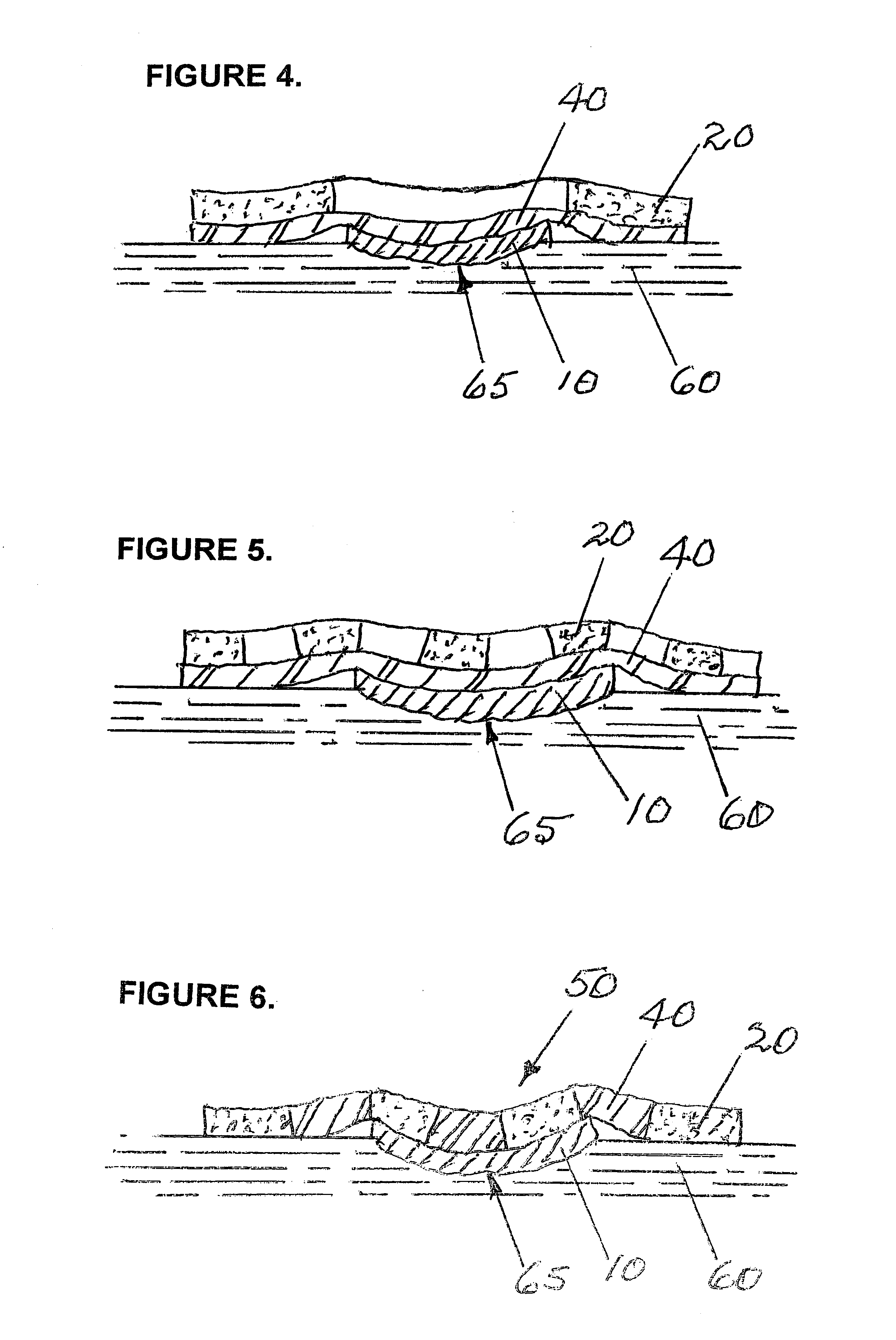

Bioabsorbable wound dressing

ActiveUS7041868B2Promote wound healingEasy to useAdhesive dressingsNon-surgical orthopedic devicesCell adhesionAdhesion process

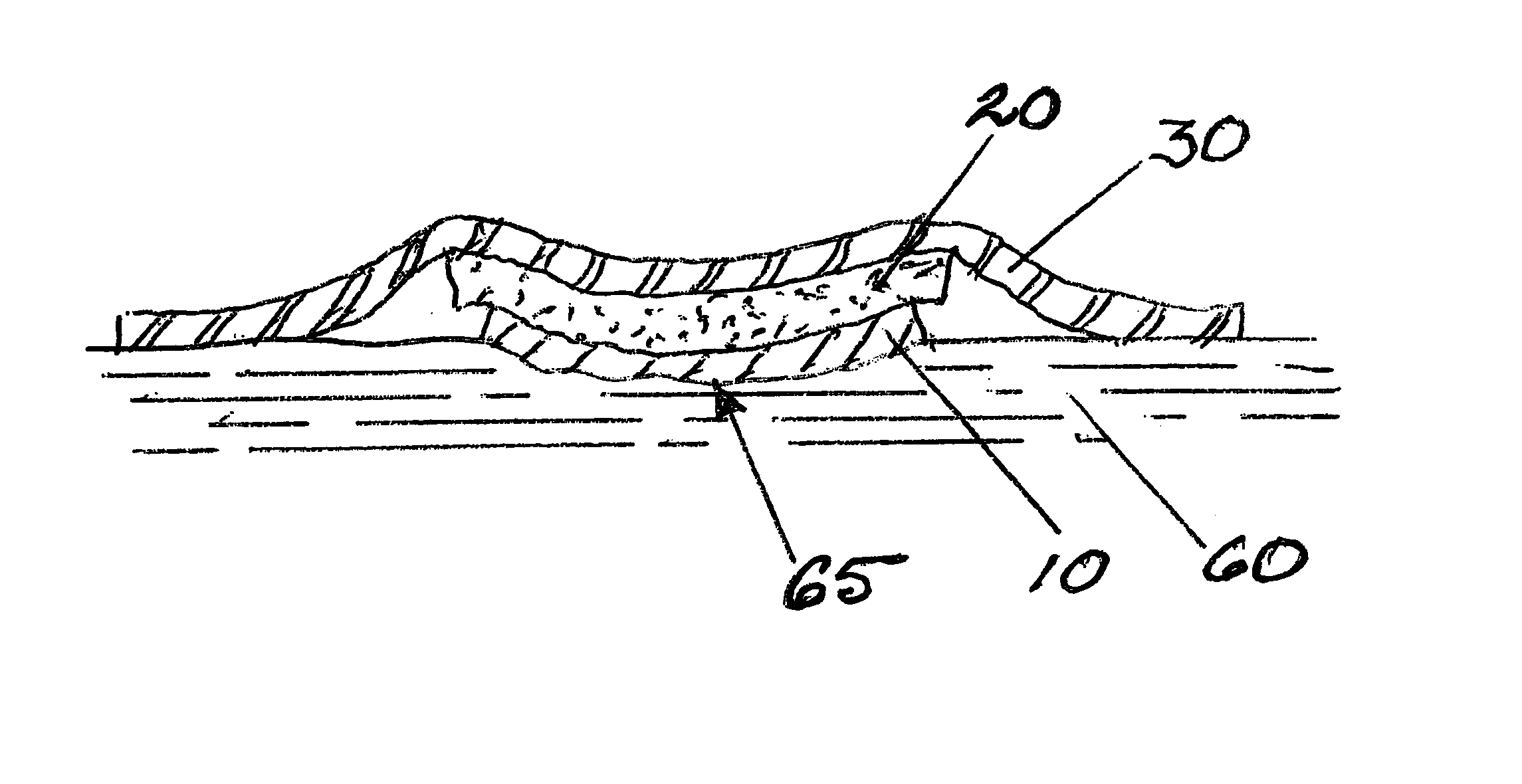

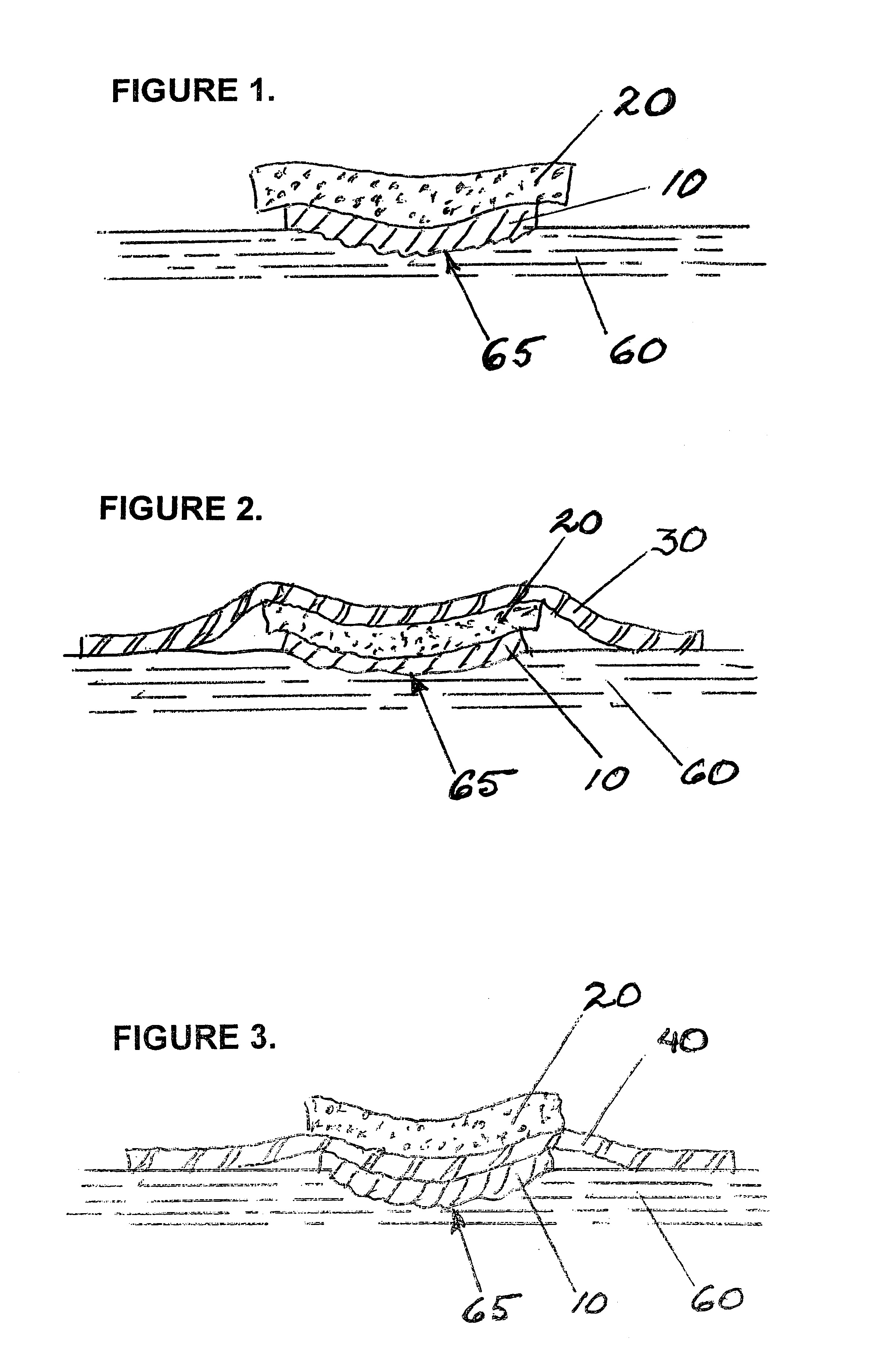

A wound dressing includes a first layer located adjacent the wound and which comprises a material that is bioabsorbable, porous and adapted for serving as a scaffold for cell attachment and proliferation; and a second layer which is in contact with the first layer and which comprises an absorbent, gel forming material adapted for serving as a barrier to cell adhesion and penetration. A method of treating a wound with the dressing is also disclosed.

Owner:AVENT INC

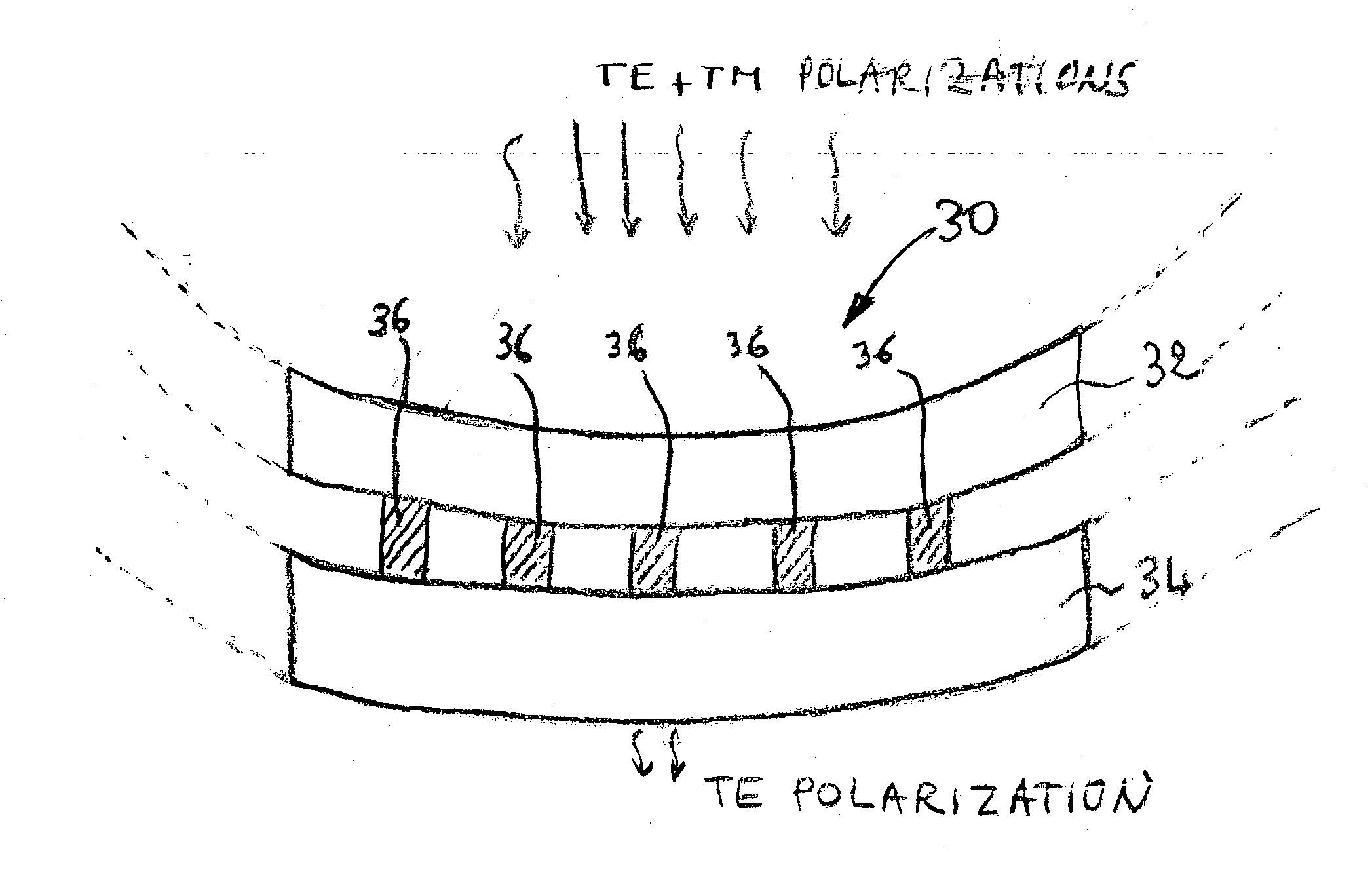

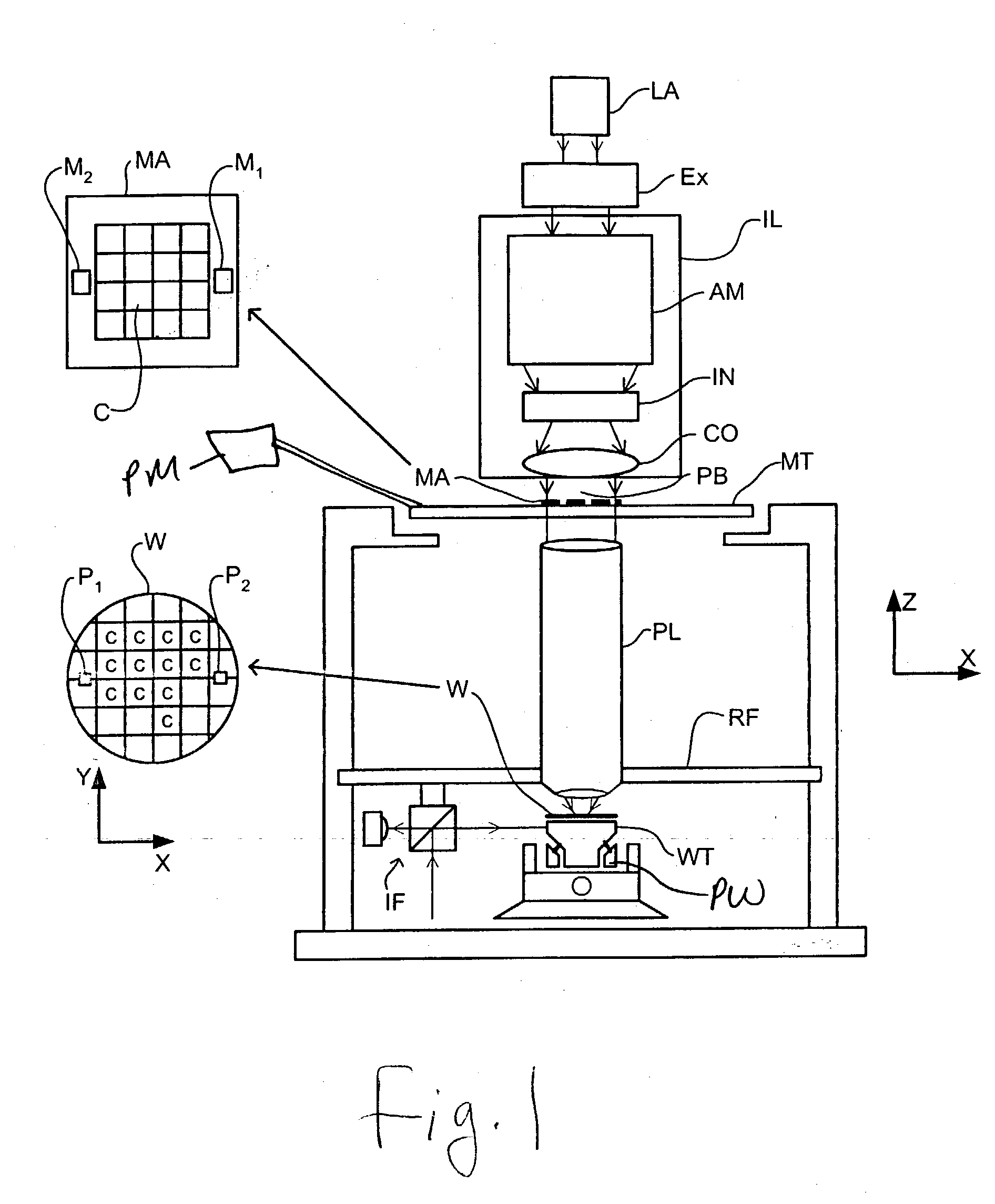

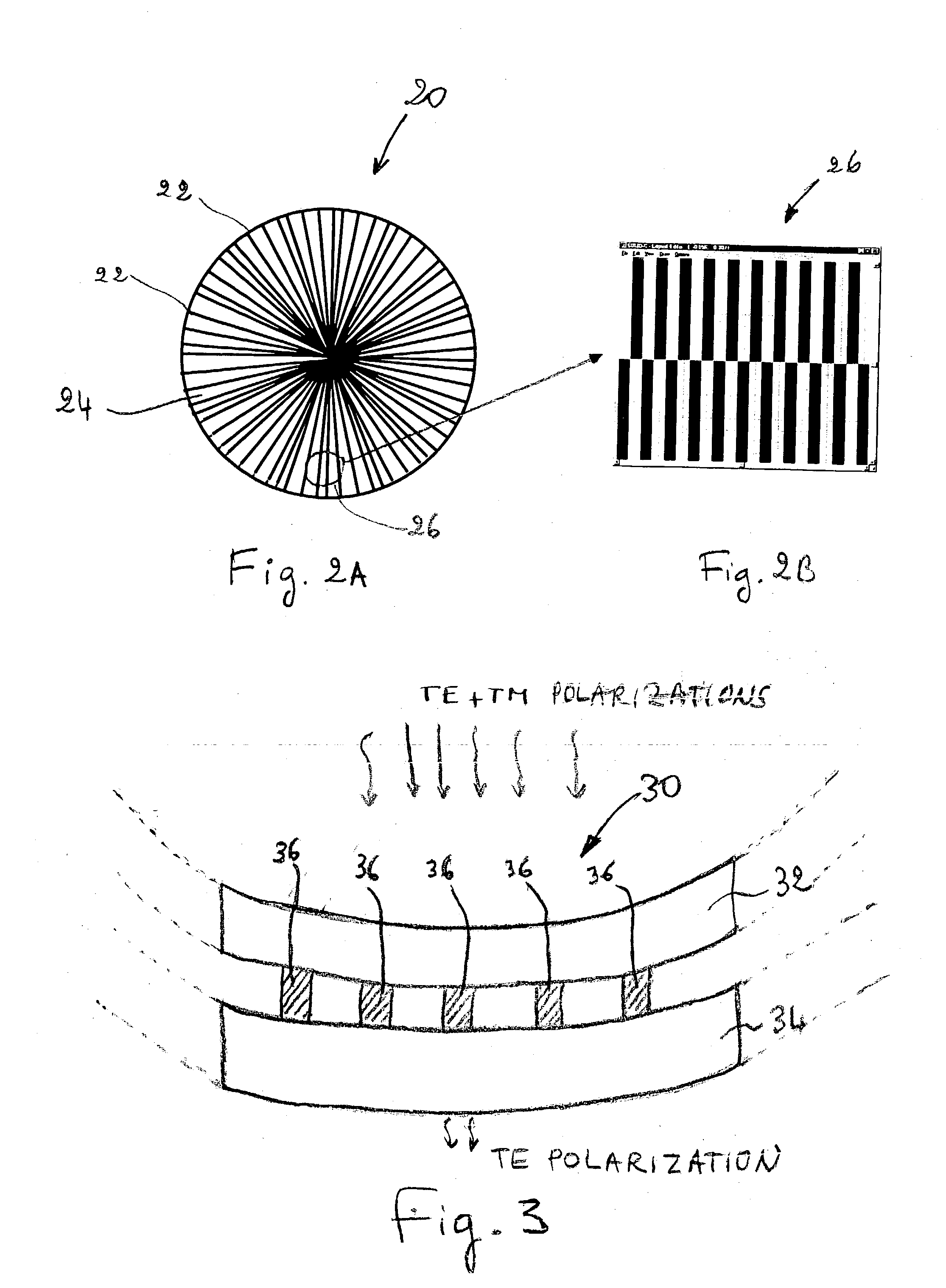

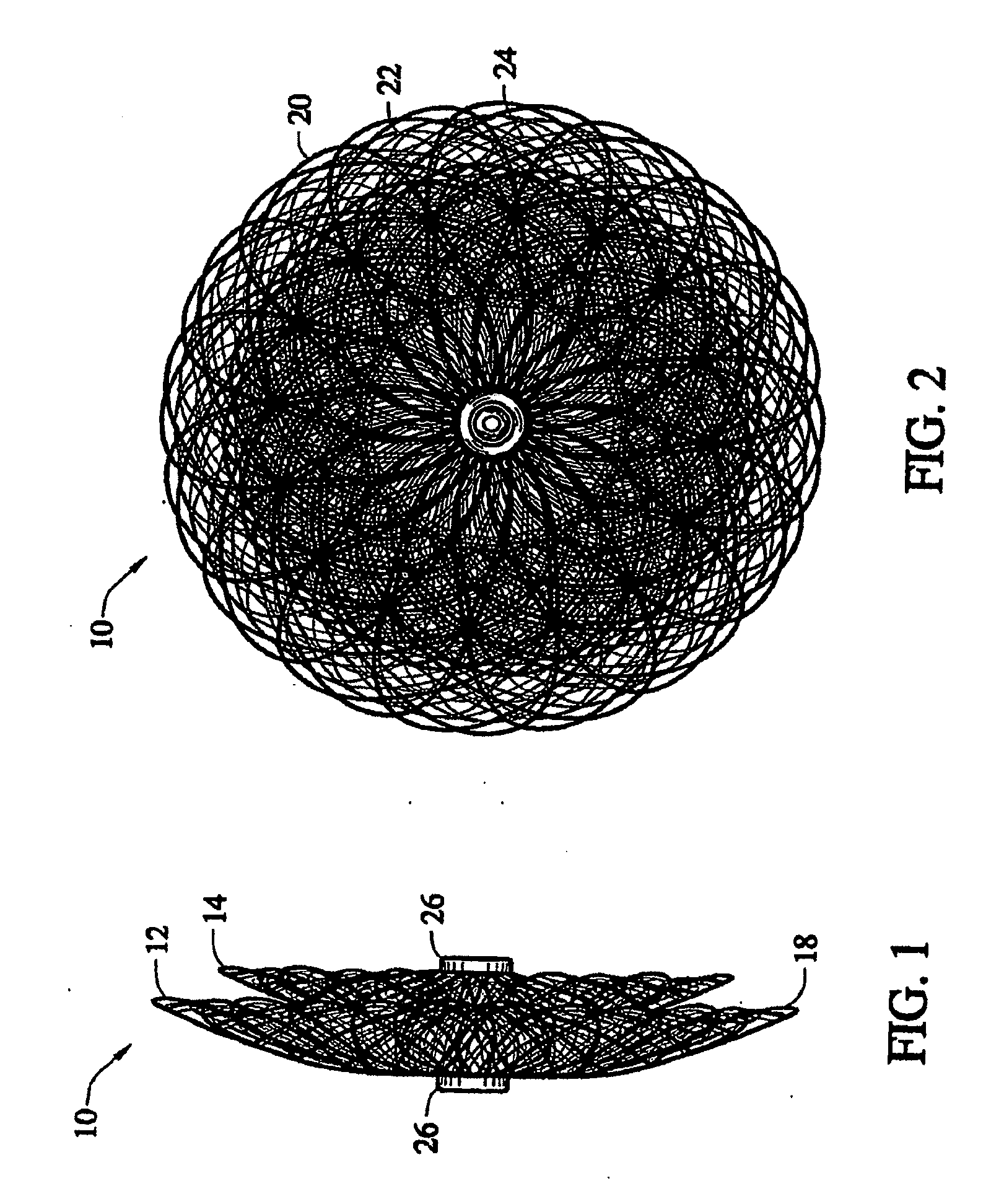

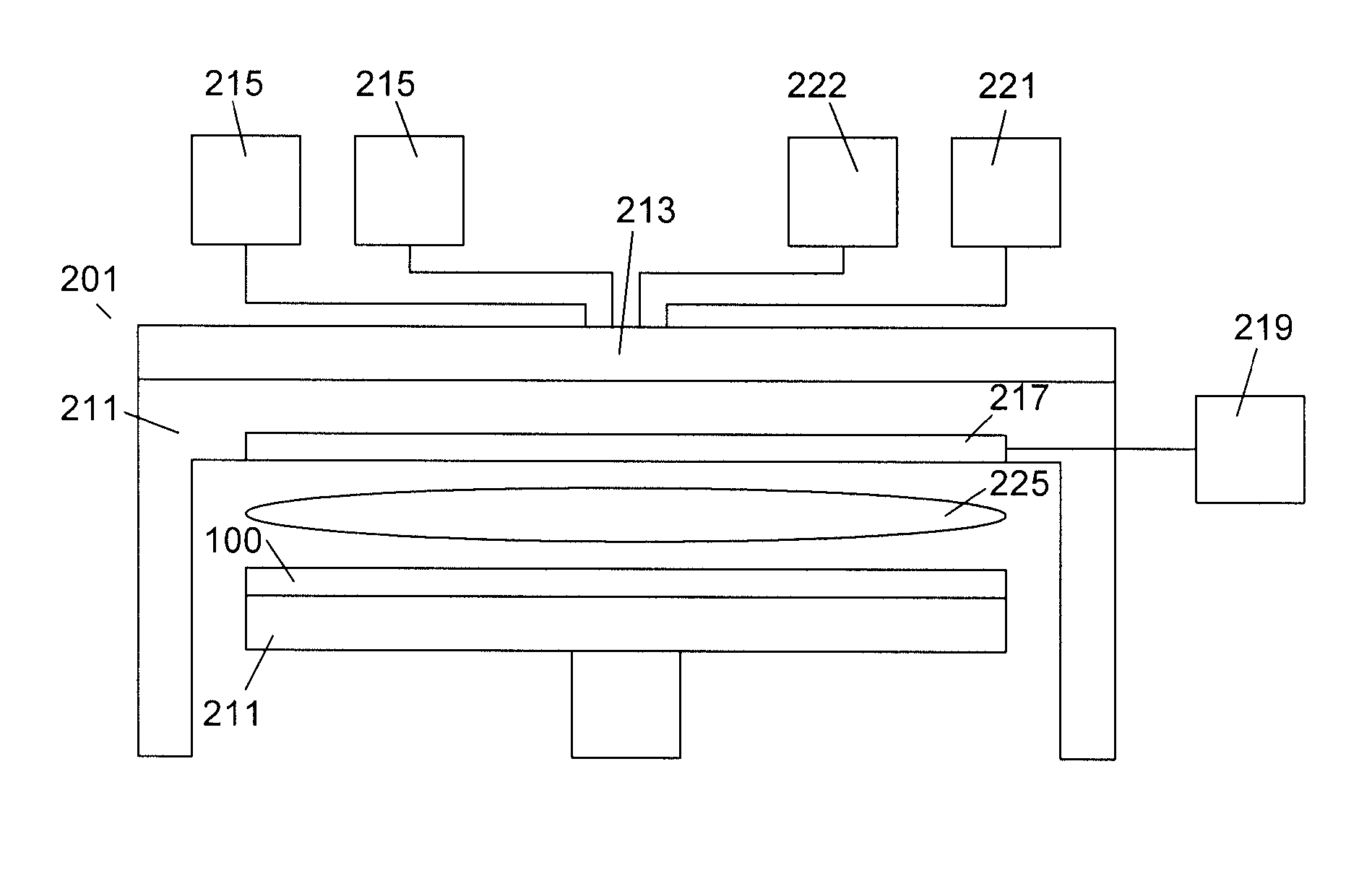

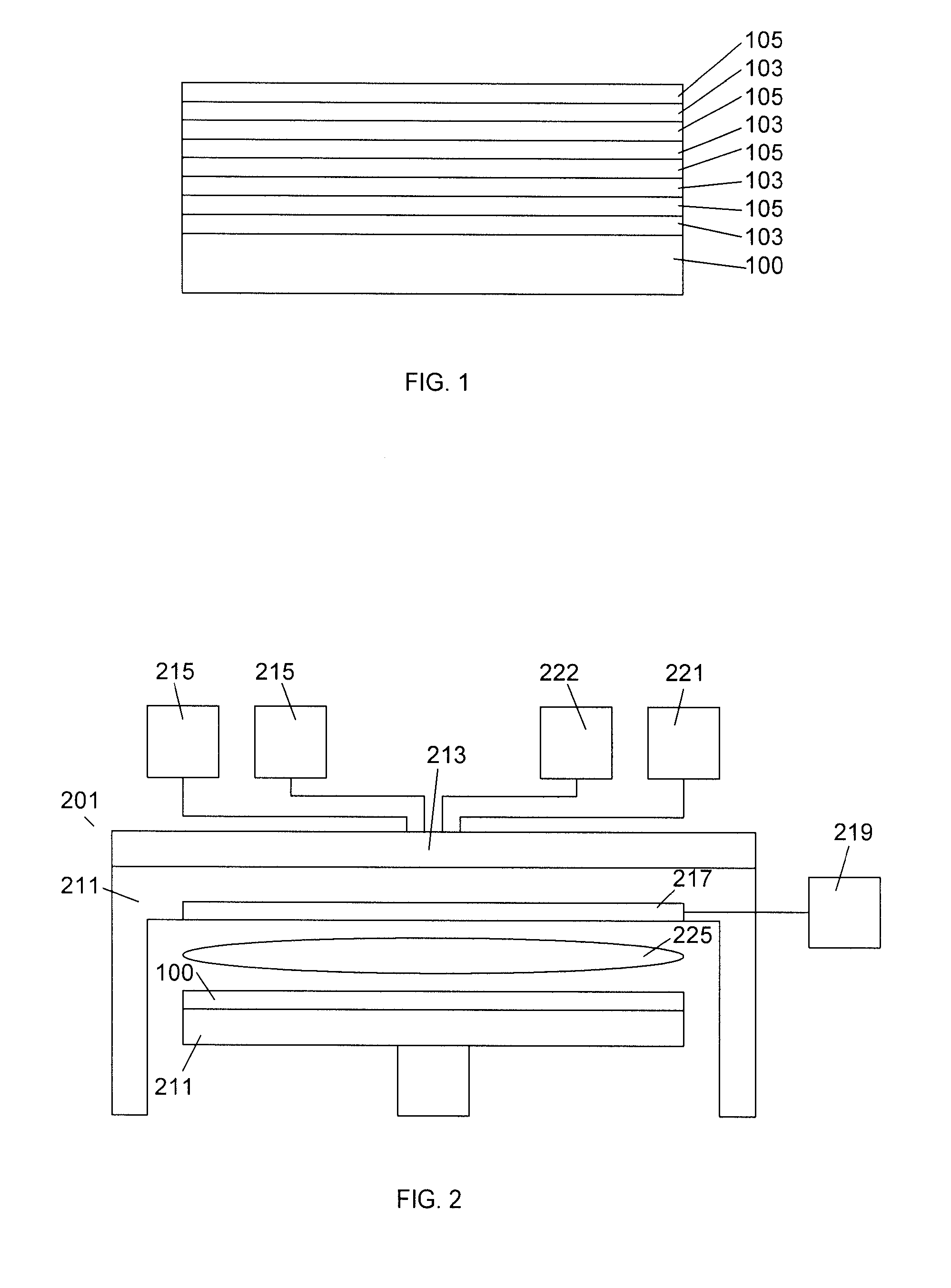

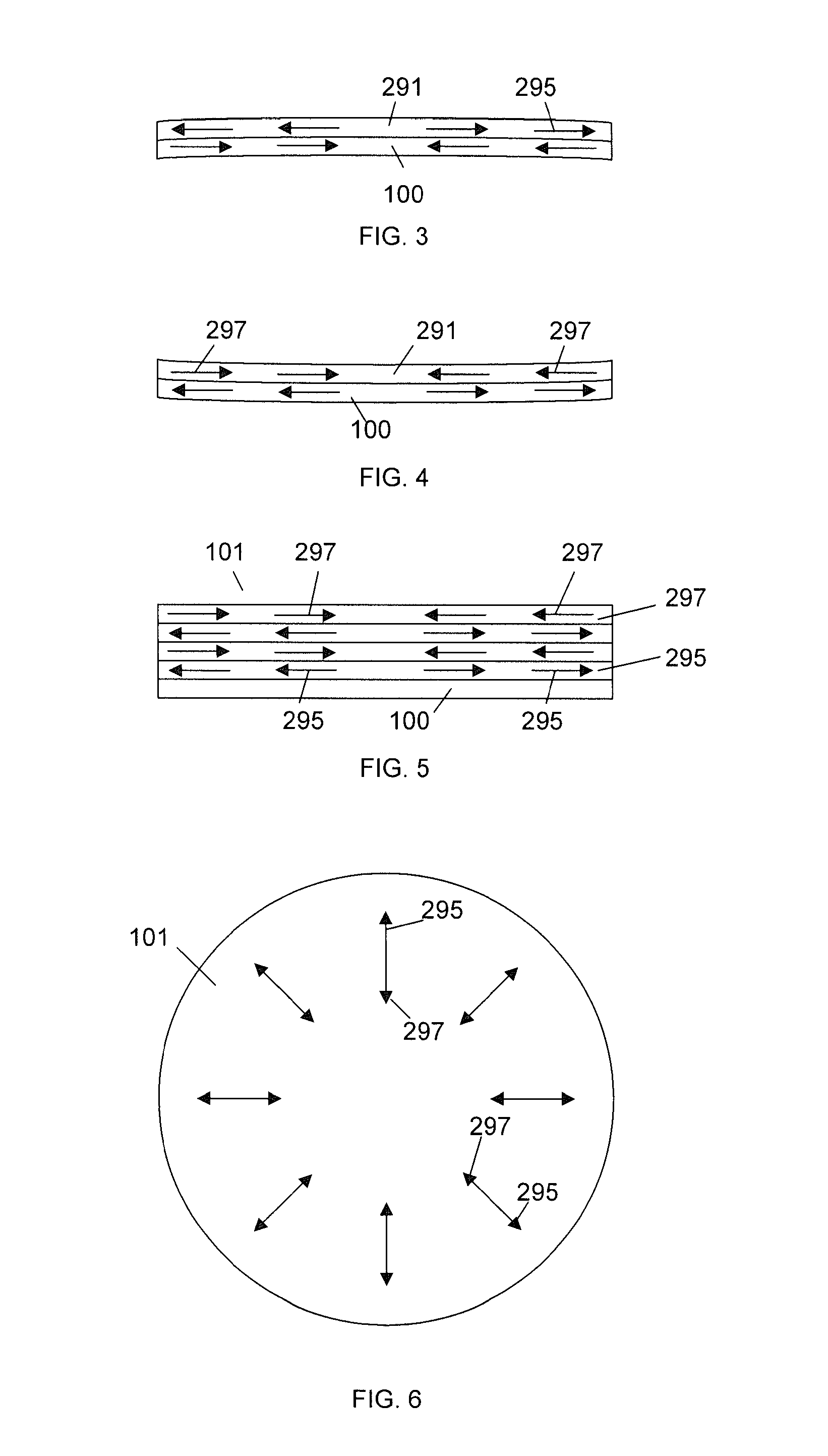

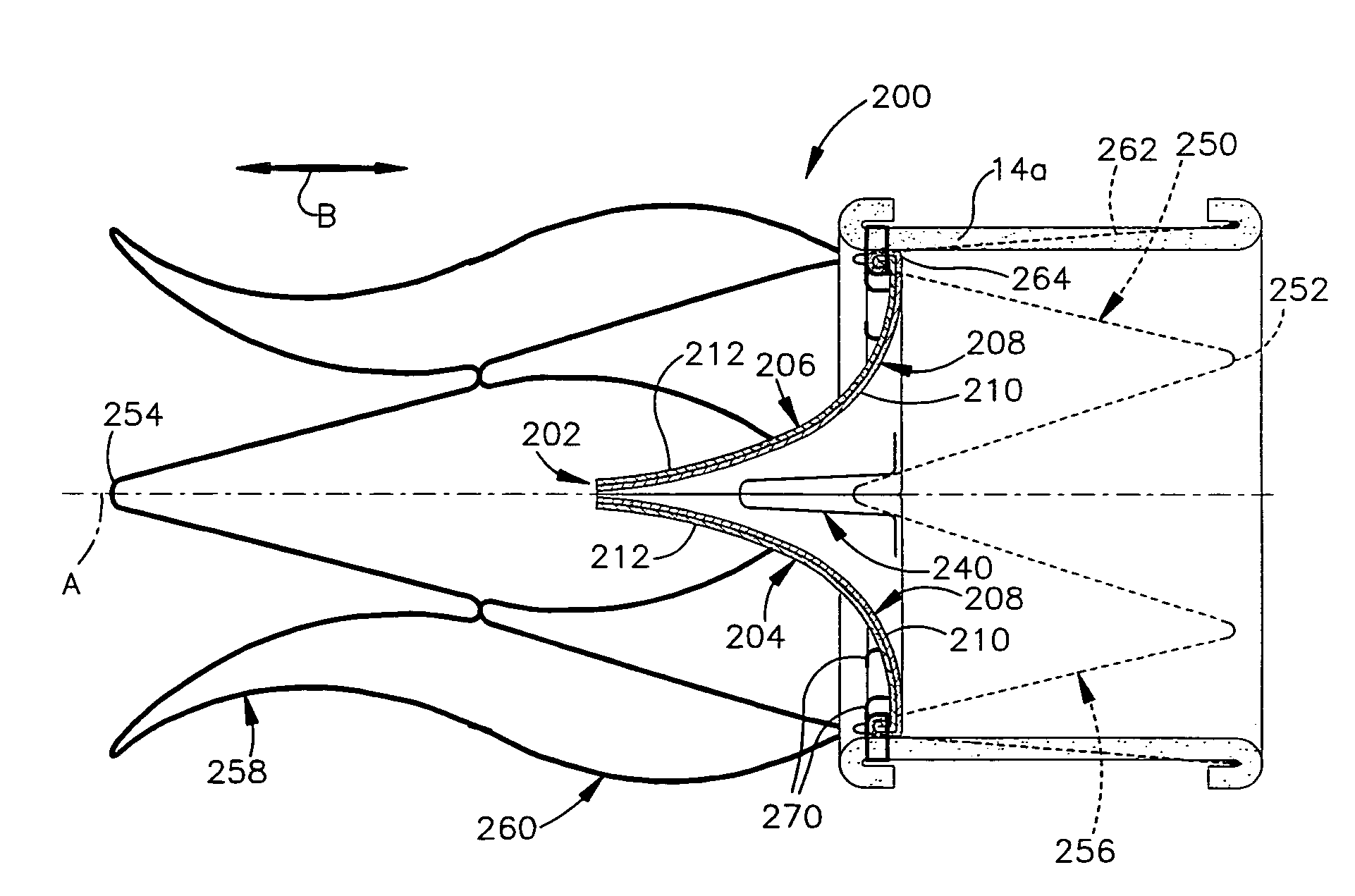

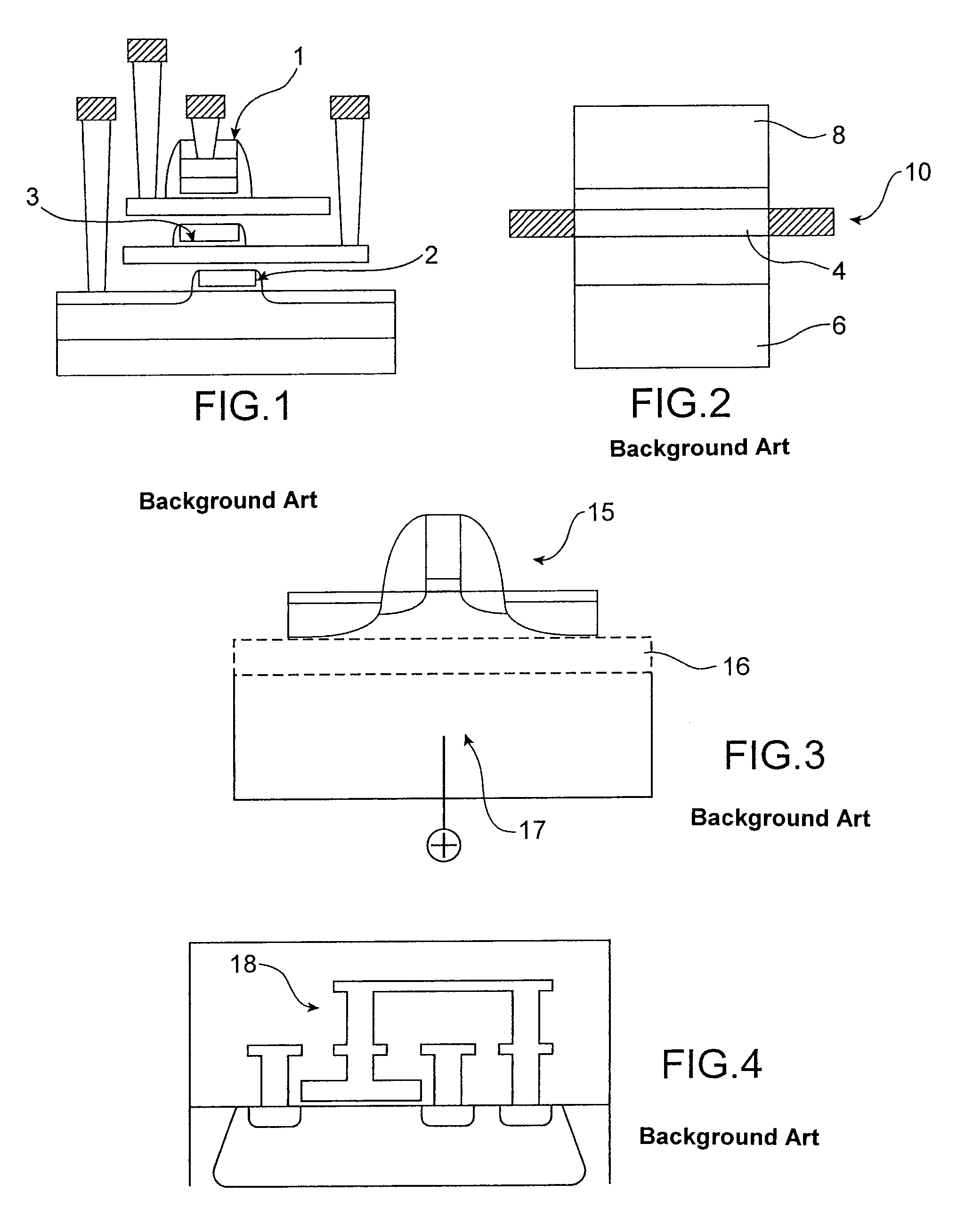

Stationary and dynamic radial transverse electric polarizer for high numerical aperture systems

InactiveUS20040169924A1Polarising elementsSemiconductor/solid-state device manufacturingHigh numerical apertureClassical mechanics

A radial transverse electric polarizer device is provided. The device includes a first layer of material having a first refractive index, a second layer of material having a second refractive index, and a plurality of elongated elements azimuthally and periodically spaced apart, and disposed between the first layer and the second layer. The plurality of elongated elements interact with electromagnetic waves of radiation to transmit transverse electric polarization of electromagnetic waves of radiation. One aspect of the invention is, for example, to use such polarizer device in a lithographic projection apparatus to increase imaging resolution. Another aspect is to provide a device manufacturing method including polarizing a beam of radiation in a transverse electric polarization.

Owner:ASML NETHERLANDS BV

Method of determining analyte level using subcutaneous electrode

InactiveUS20050287620A1Reduce transportationAccurate measurementMicrobiological testing/measurementMaterial analysis by electric/magnetic meansConcentrations glucosePeroxidase

A small diameter flexible electrode designed for subcutaneous in vivo amperometric monitoring of glucose is described. The electrode is designed to allow “one-point” in vivo calibration, i.e., to have zero output current at zero glucose concentration, even in the presence of other electroreactive species of serum or blood. The electrode is preferably three or four-layered, with the layers serially deposited within a recess upon the tip of a polyamide insulated gold wire. A first glucose concentration-to-current transducing layer is overcoated with an electrically insulating and glucose flux limiting layer (second layer) on which, optionally, an immobilized interference-eliminating horseradish peroxidase based film is deposited (third layer). An outer (fourth) layer is biocompatible.

Owner:THERASENSE

Biocompatible implant and use of the same

InactiveUS20060252981A1Good biological affinityStrong enoughImpression capsEye implantsRough surfaceBiological body

The present invention provides an implant capable of being cellularized in treatment of an injured organ or tissue in organisms. The present inventors found that a biocompatible implant comprising a biological molecule and a support is capable of being cellularized. The implant can be used instead of conventional implants which essentially comprise cells. The present invention provides a biocompatible implant comprising A) a biological molecule and B) a support. The present invention also provides A) a first layer having a rough surface, B) a rough surface; B) a second layer having a strength which allows the support to resist in vivo shock. The first layer is attached to the second layer via at least one point.

Owner:CARDIO

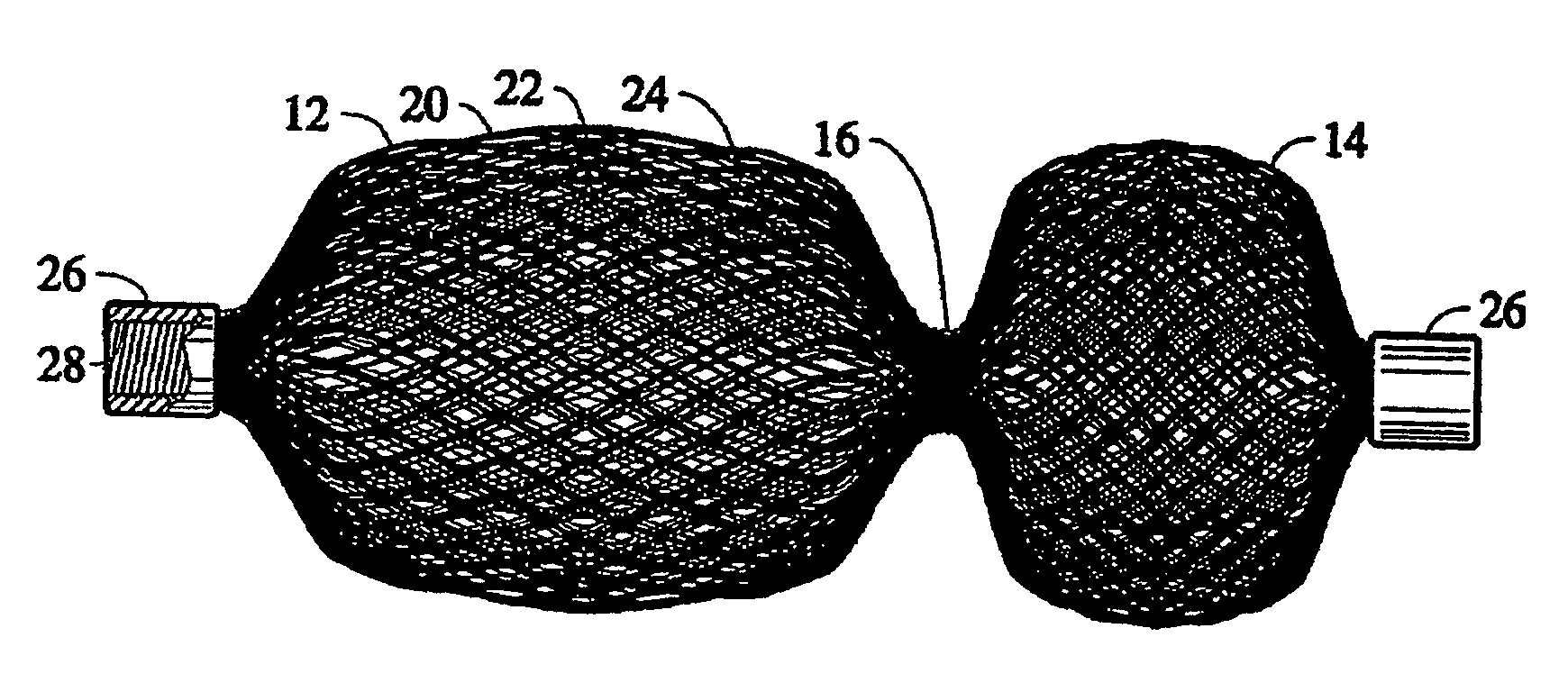

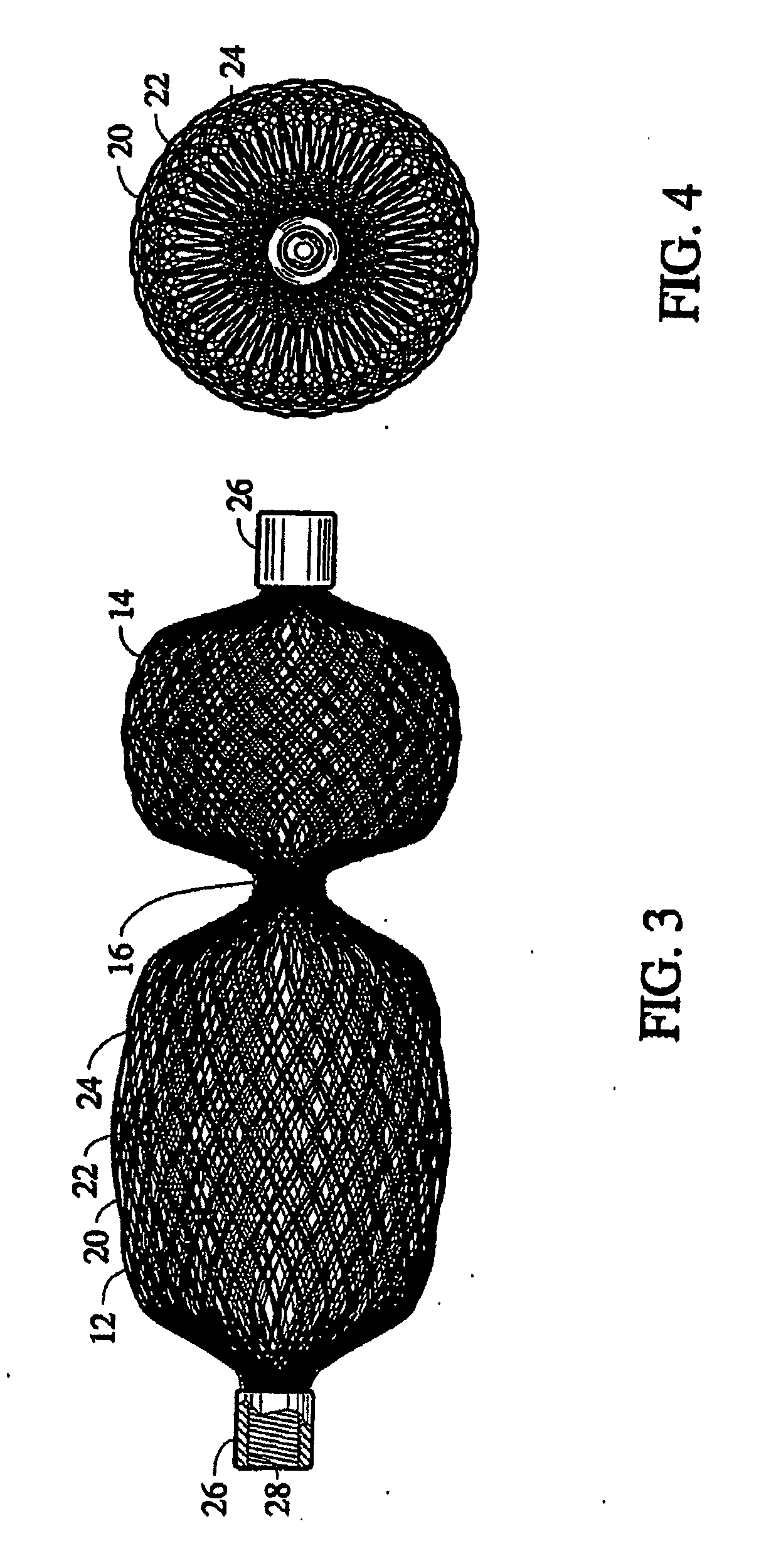

Device for occluding vascular defects

A multi-layer occluder for treating a target site within the body is provided. The occluder may include first and second layers. For example, the first layer may include braided strands of metallic material, and the second layer may include braided strands of polymeric material. At least one of the first or second layers may be configured to facilitate thrombosis.

Owner:ST JUDE MEDICAL CARDILOGY DIV INC

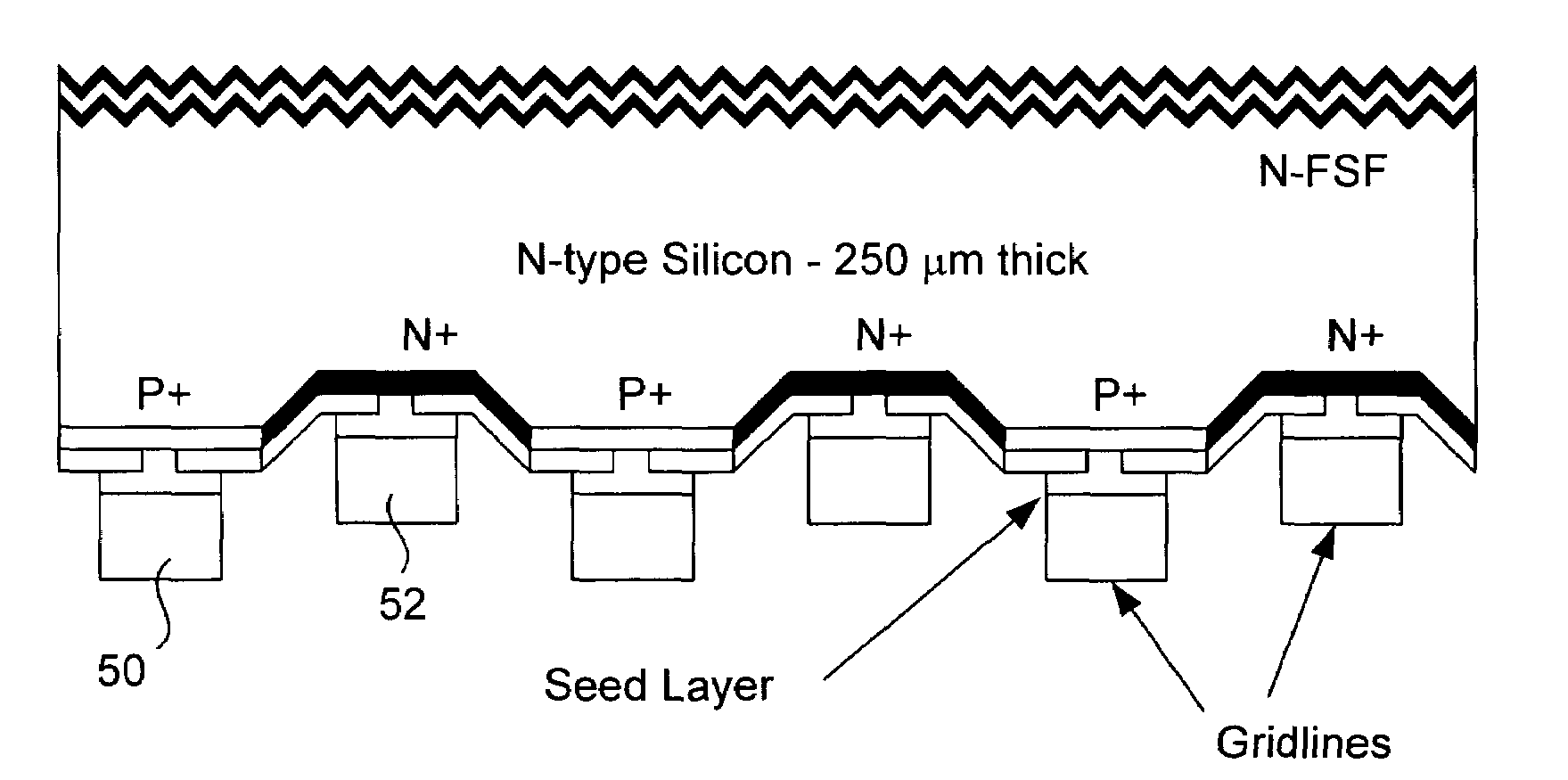

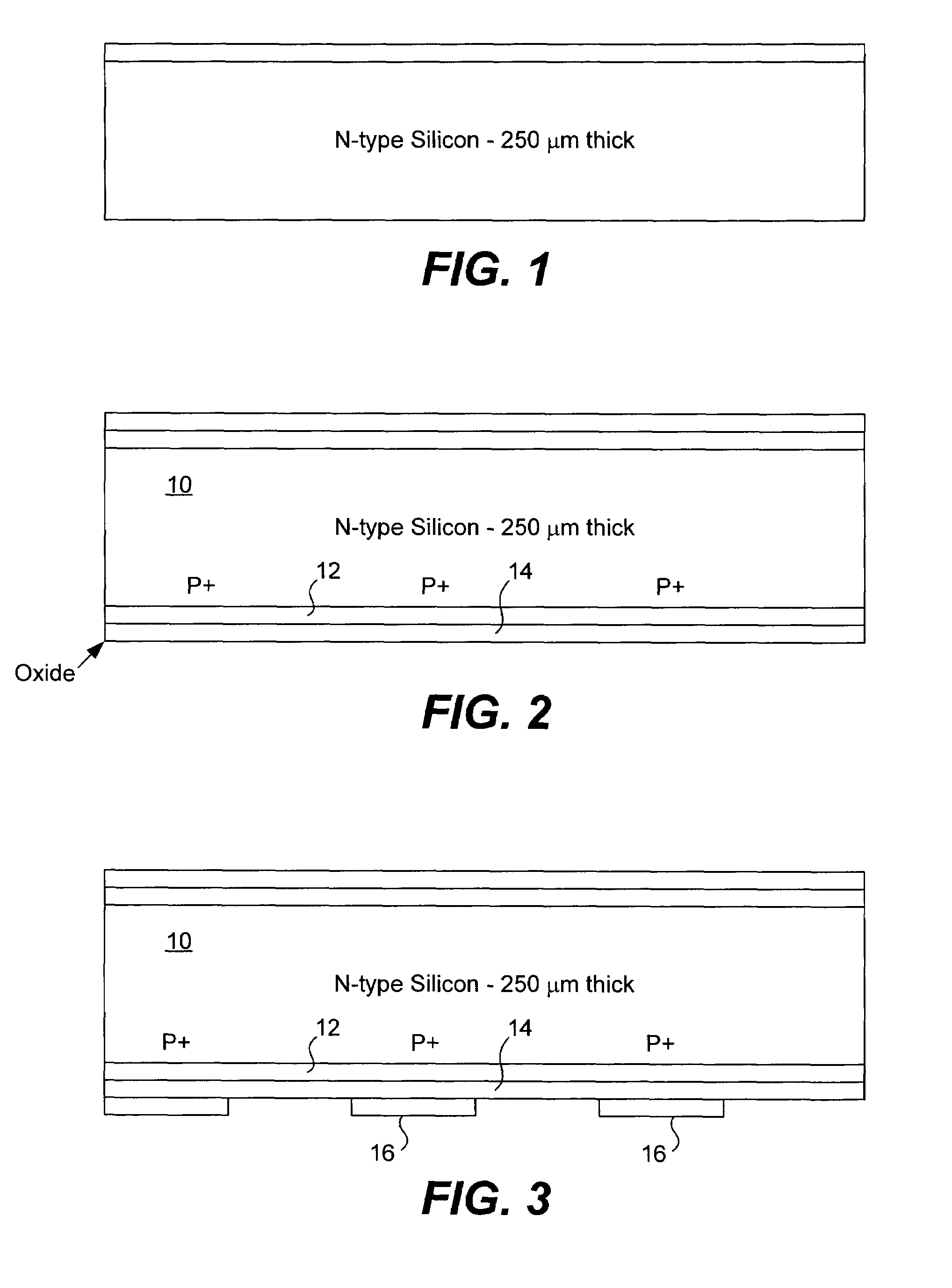

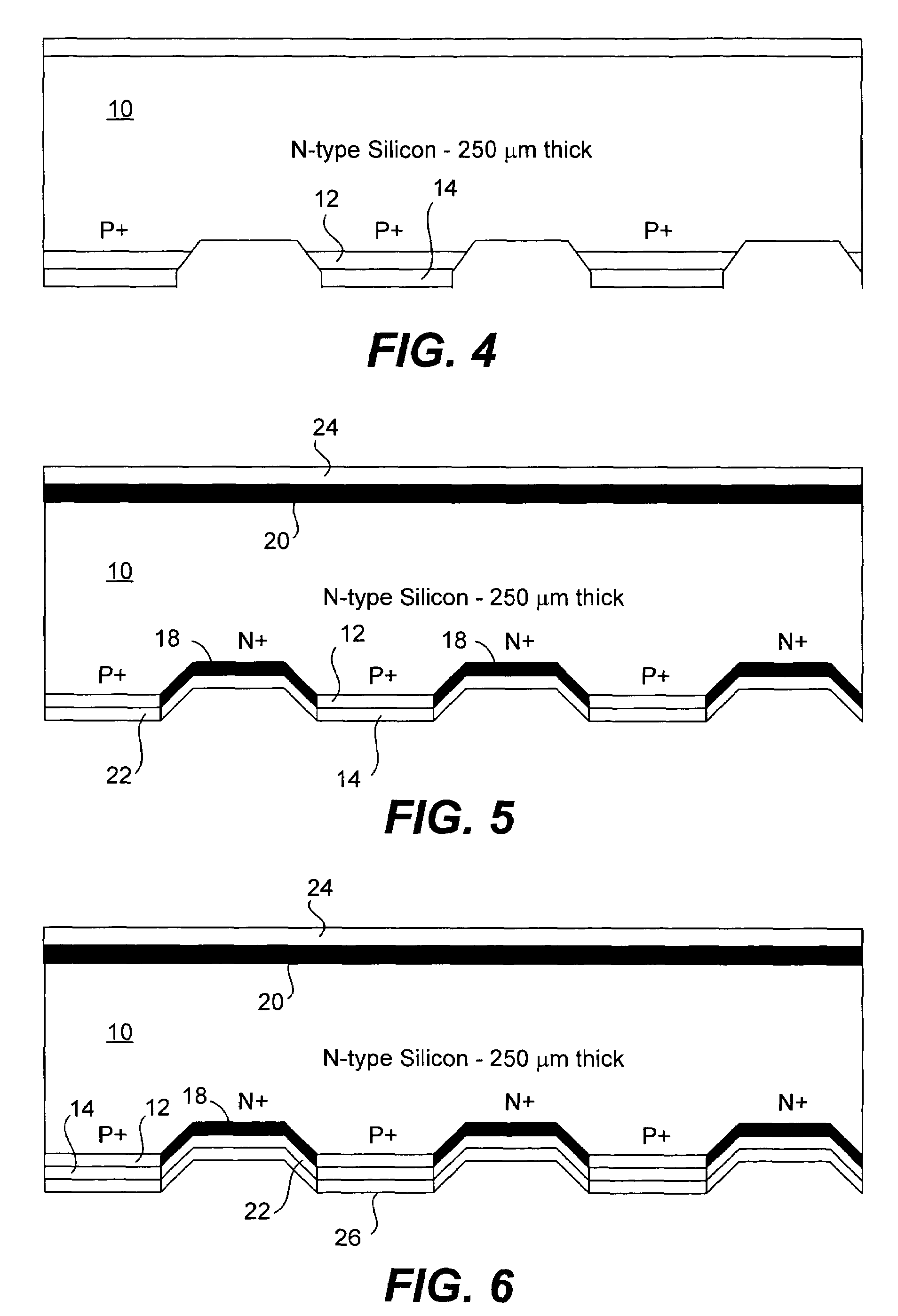

Solar cell and method of manufacture

ActiveUS7339110B1Easy to manufactureLess expensiveFinal product manufacturePhotovoltaic energy generationEngineeringSilicon oxide

A solar cell that is readily manufactured using processing techniques which are less expensive than microelectronic circuit processing. In preferred embodiments, printing techniques are utilized in selectively forming masks for use in etching of silicon oxide and diffusing dopants and in forming metal contacts to diffused regions. In a preferred embodiment, p-doped regions and n-doped regions are alternately formed in a surface of the wafer in offset levels through use of masking and etching techniques. Metal contacts are made to the p-regions and n-regions by first forming a seed layer stack that comprises a first layer such as aluminum that contacts silicon and functions as an infrared reflector, second layer such titanium tungsten that acts as diffusion barrier, and a third layer functions as a plating base. A thick conductive layer such as copper is then plated over the seed layer, and the seed layer between plated lines is removed. A front surface of the wafer is preferably textured by etching or mechanical abrasion with an antireflection layer provided over the textured surface. A field layer can be provided in the textured surface with the combined effect being a very low surface recombination velocity.

Owner:MAXEON SOLAR PTE LTD +1

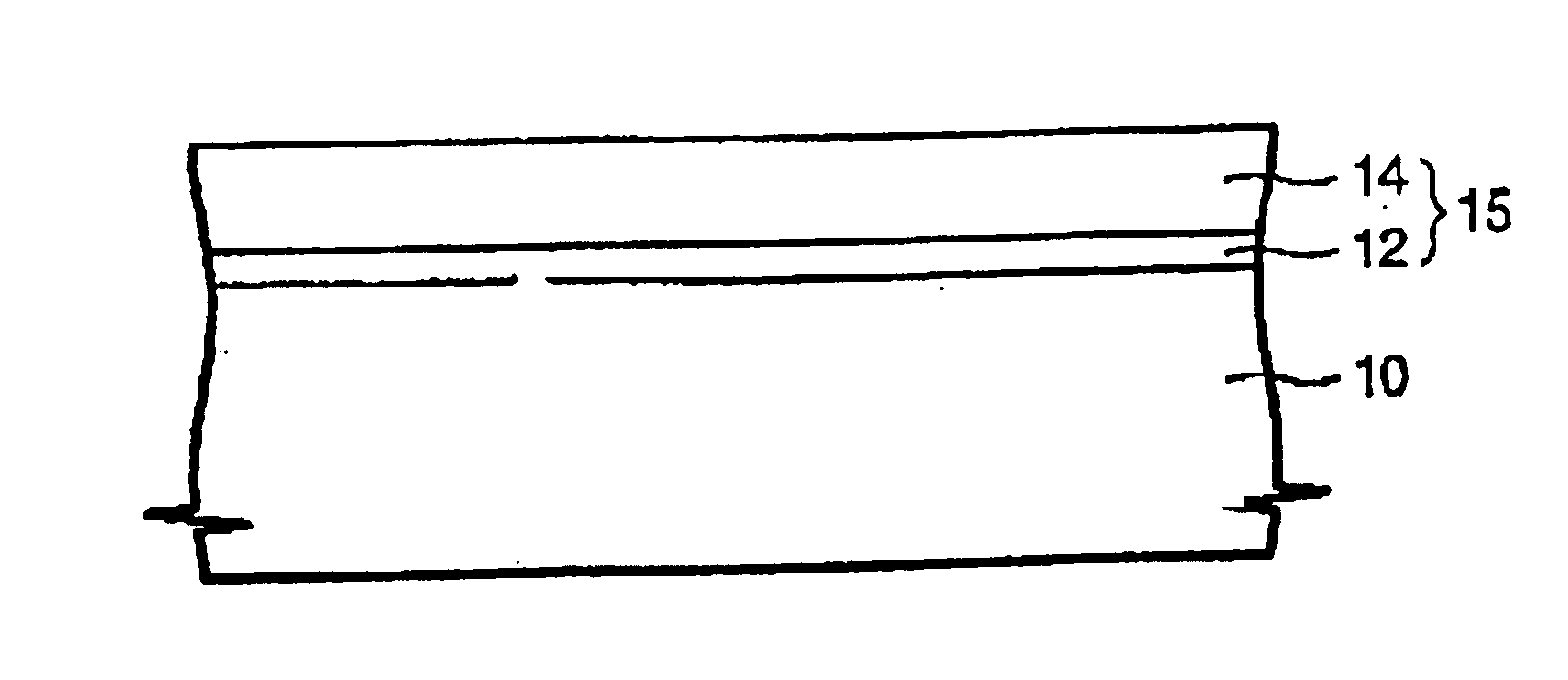

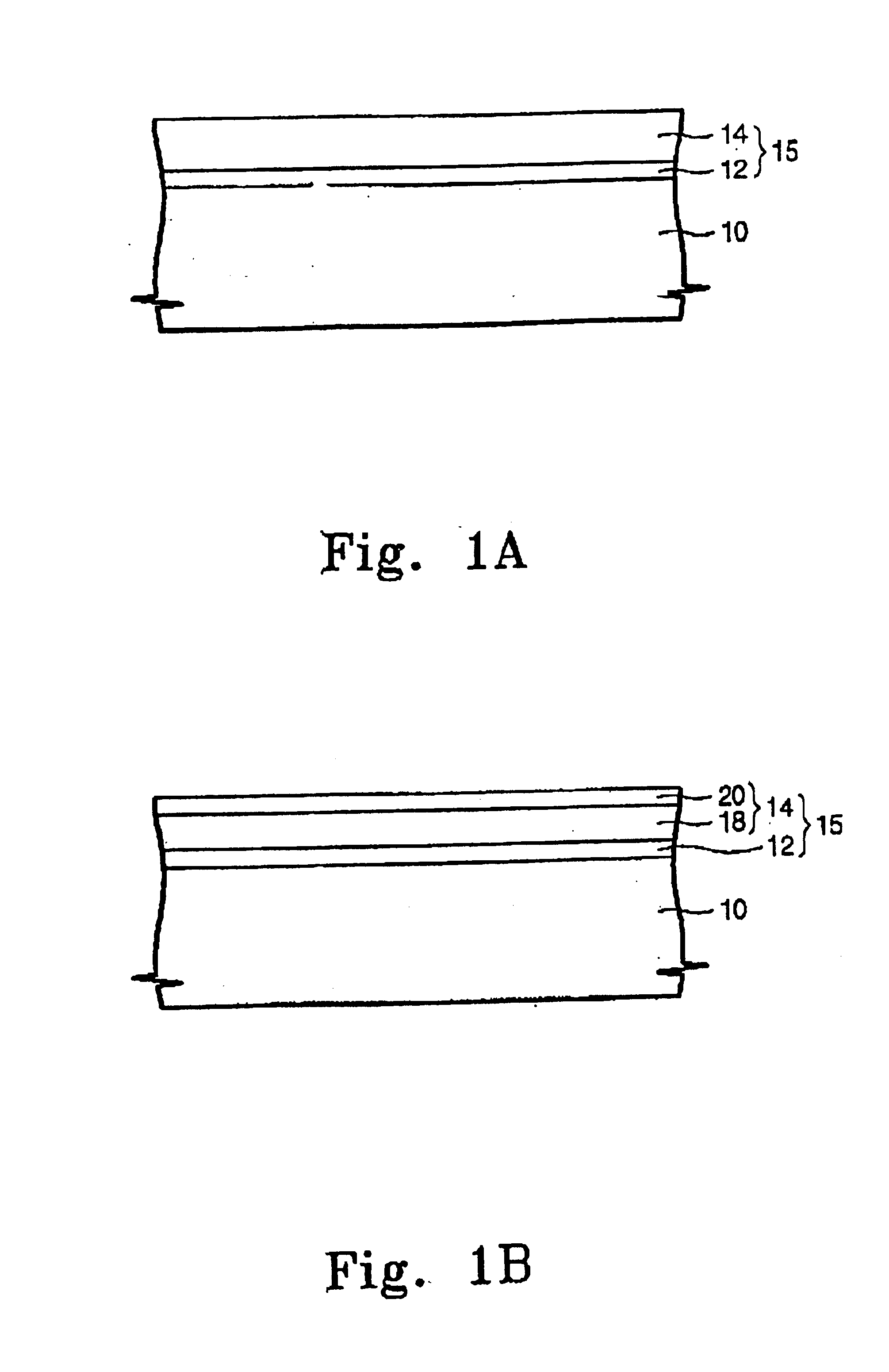

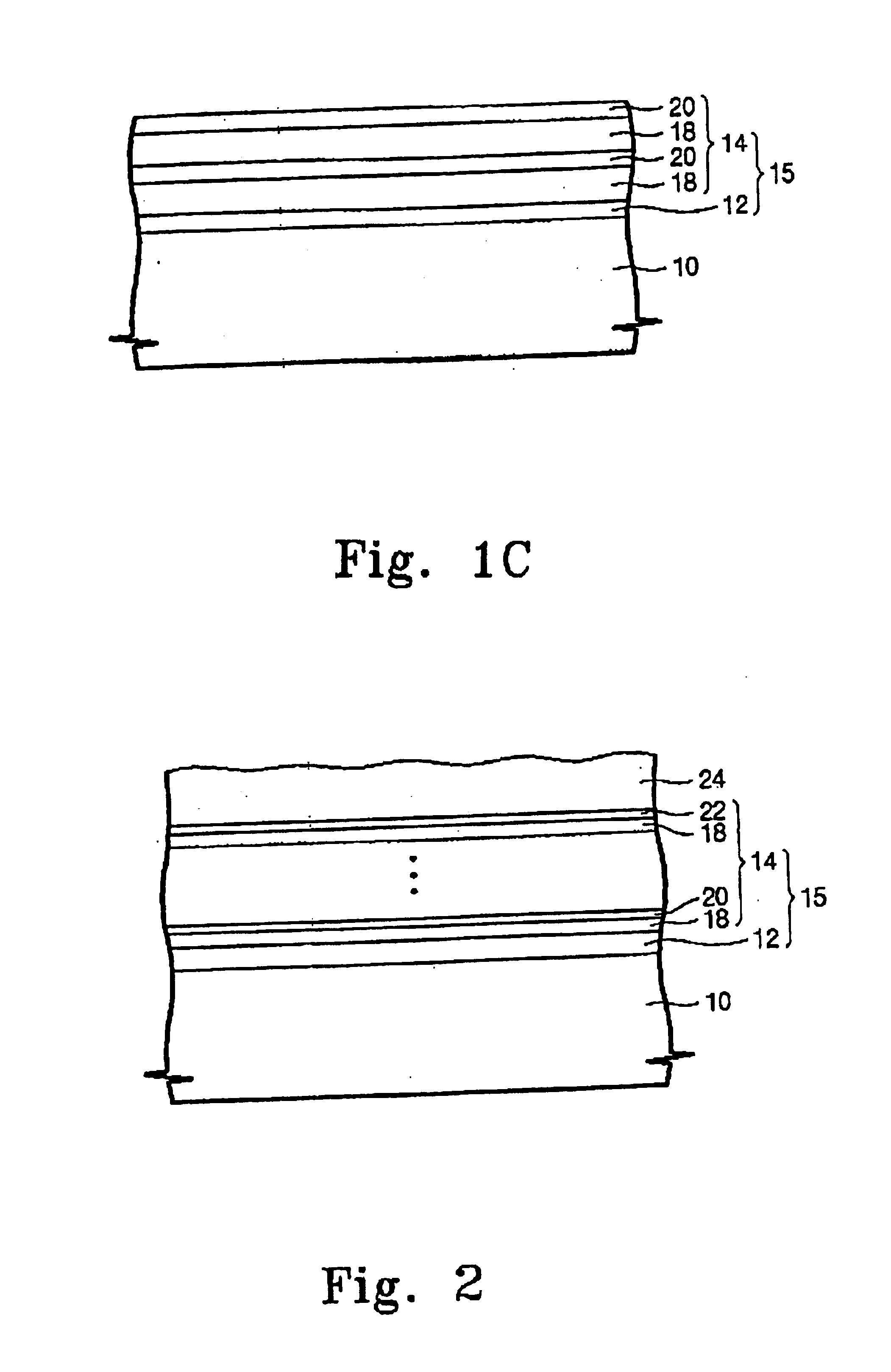

Method for forming layer constituted by repeated stacked layers

ActiveUS9018093B2High wet etching selectivityUniform film qualitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneSecondary layer

A method for forming a layer constituted by repeated stacked layers includes: forming a first layer and a second layer on a substrate under different deposition conditions to form a stacked layer, wherein the film stresses of the first and second layers are tensile or compressive and opposite to each other, and the wet etch rates of the first and second layers are at least 50 times different from each other; and repeating the above step to form a layer constituted by repeated stacked layers, wherein the deposition conditions for forming at least one stacked layer are different from those for forming another stacked layer.

Owner:ASM IP HLDG BV

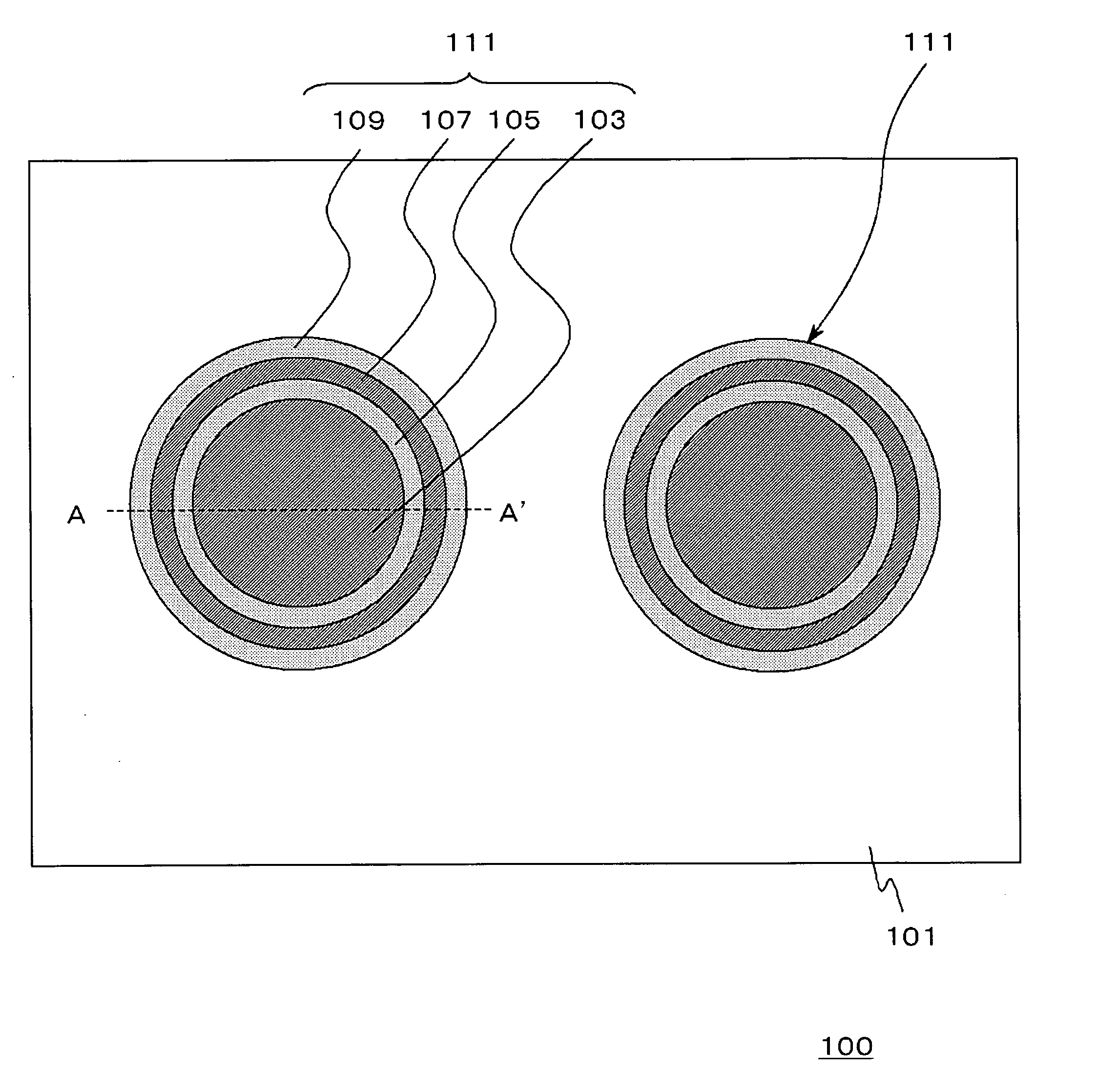

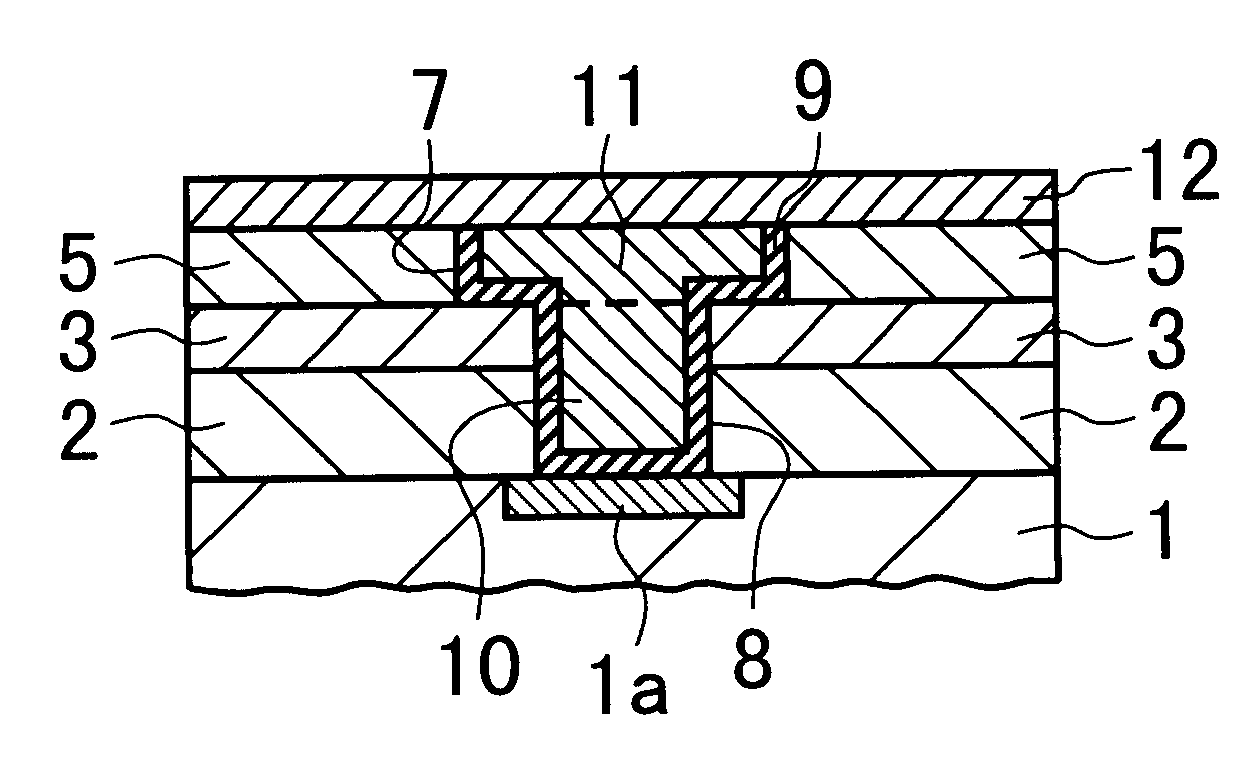

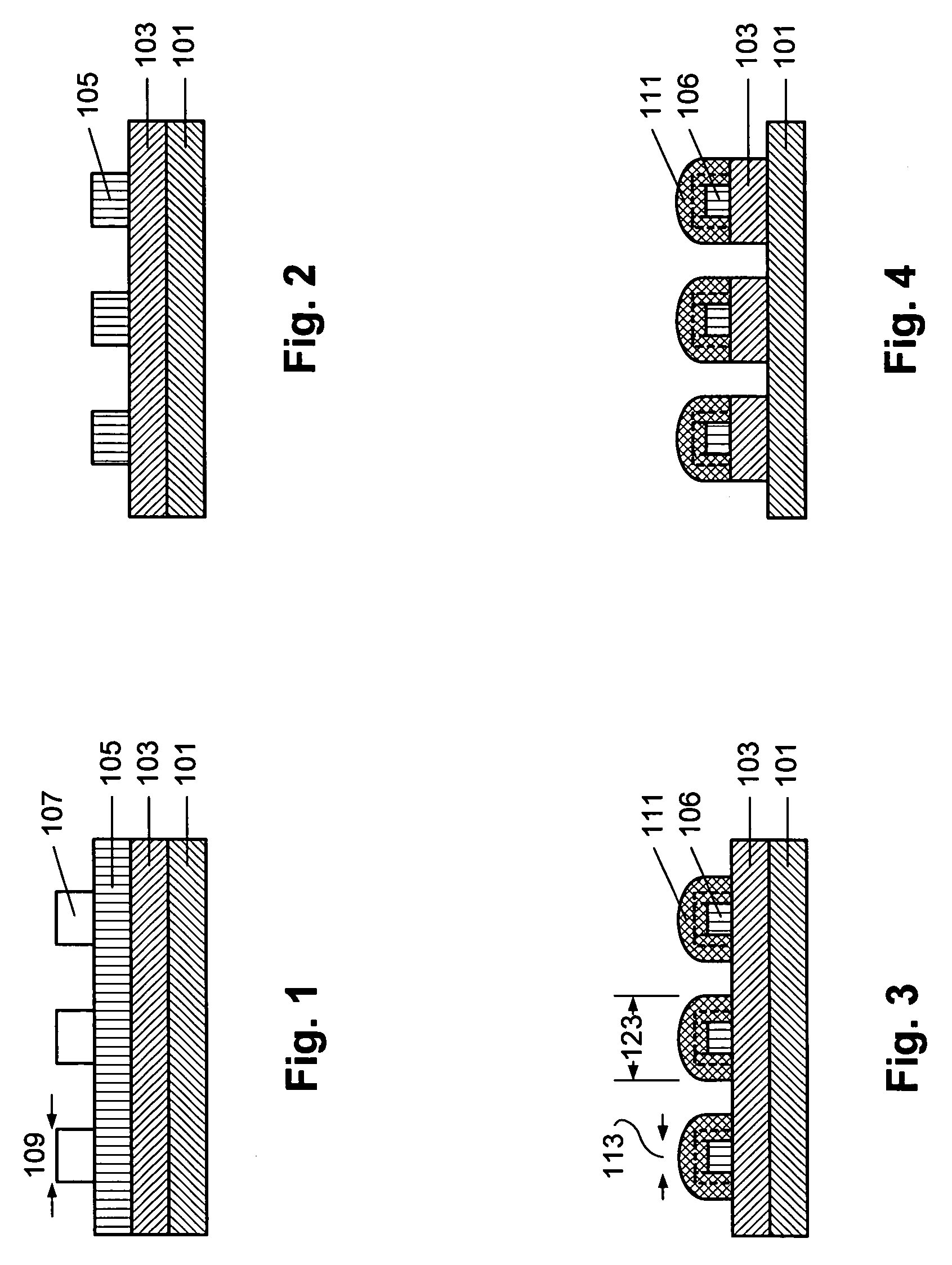

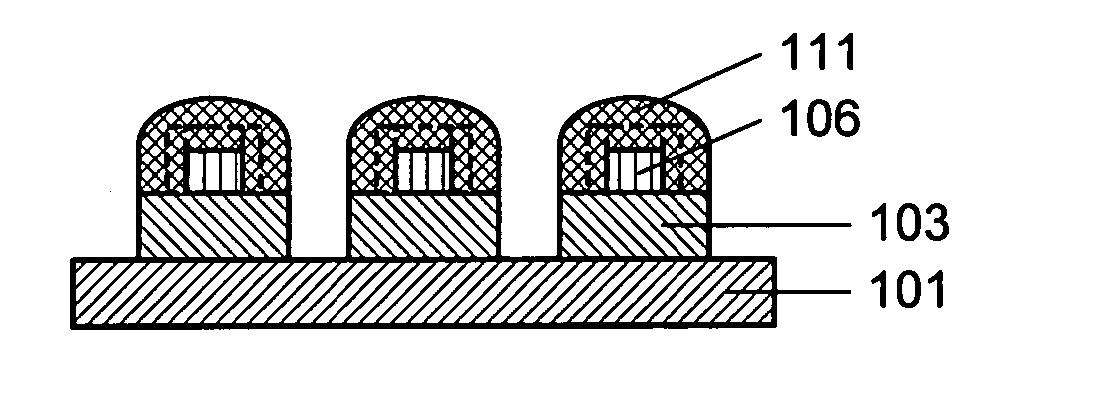

Semiconductor device and method for manufacturing the same

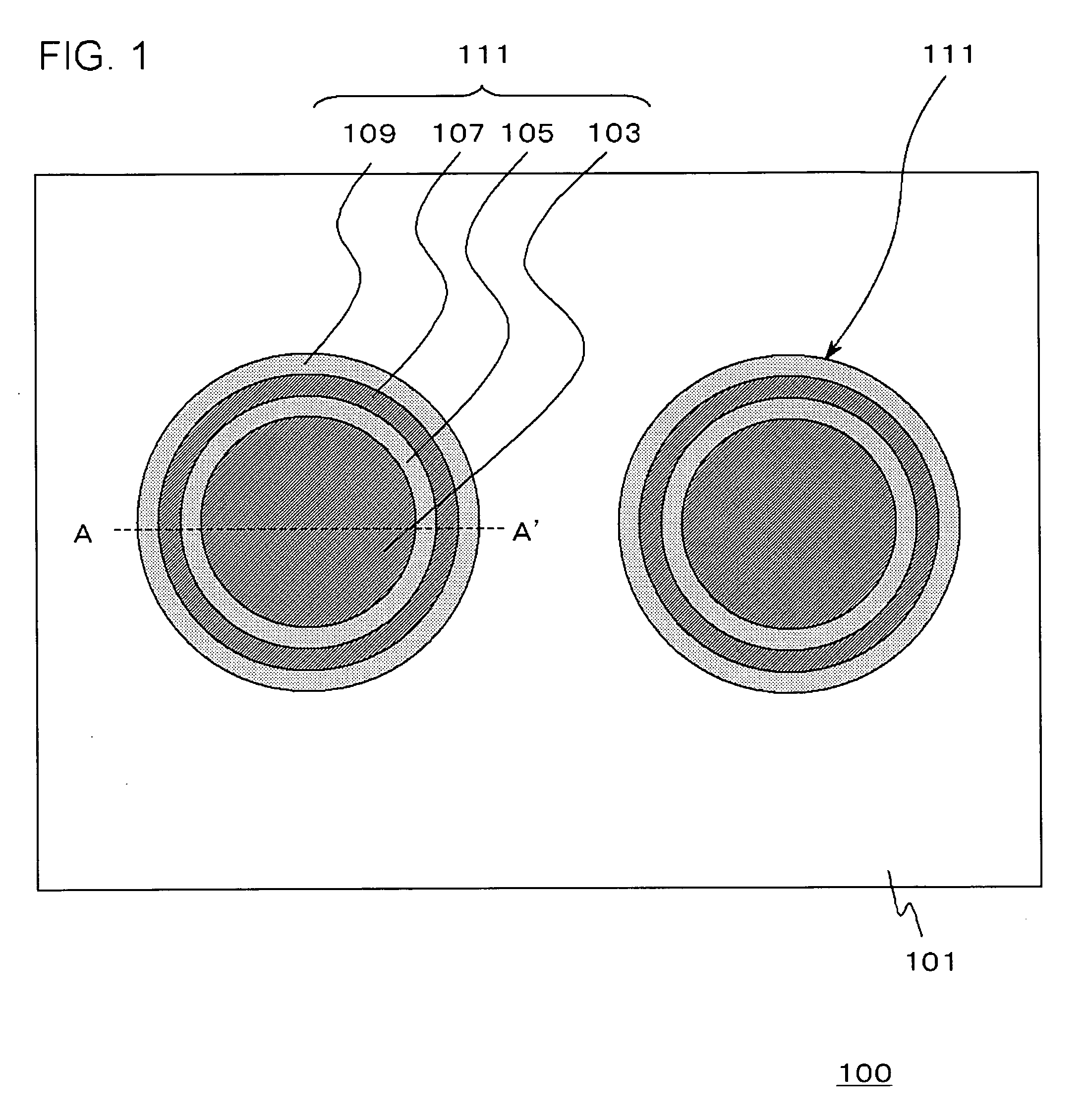

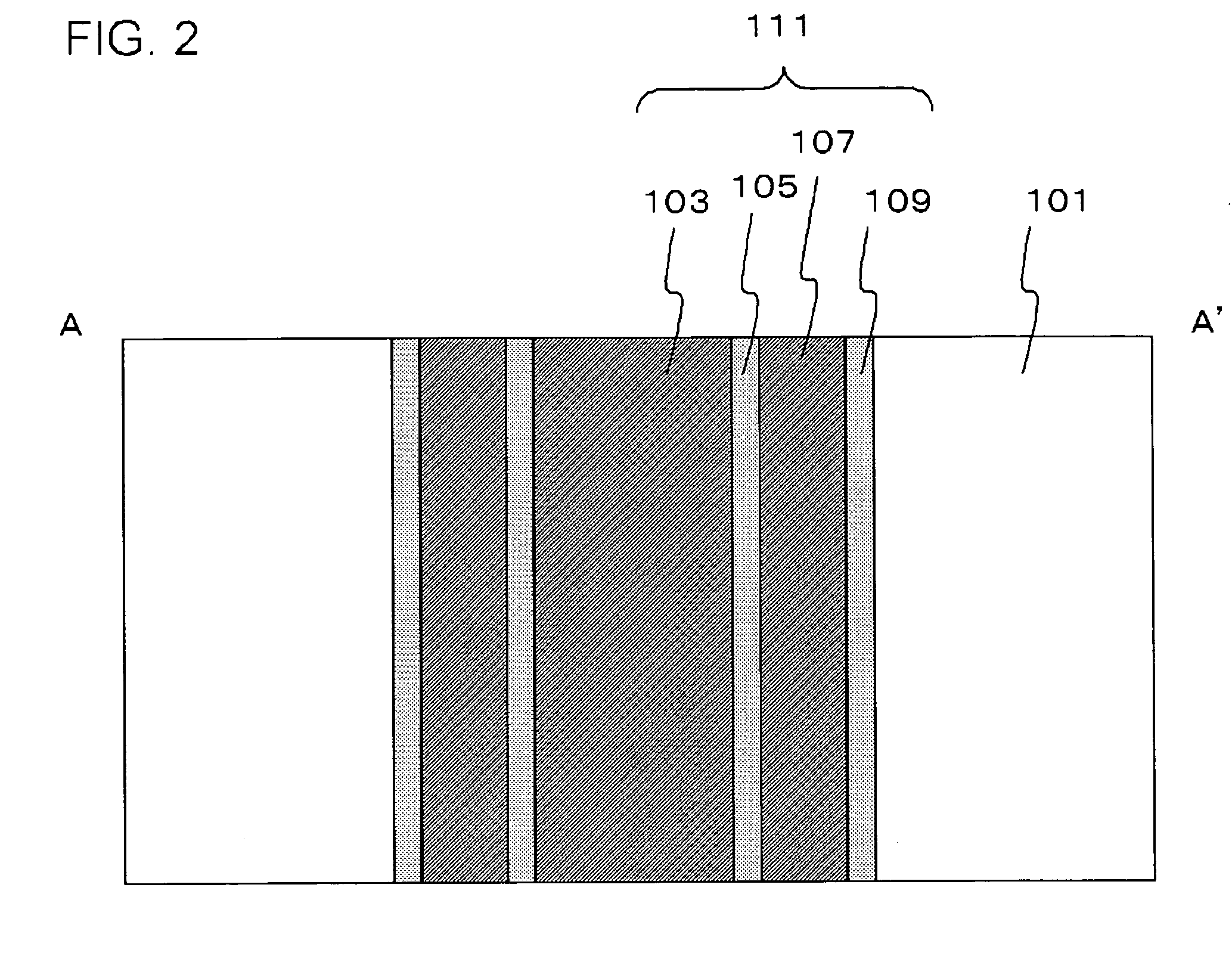

ActiveUS20060001174A1Stable productionSimple processSemiconductor/solid-state device detailsSolid-state devicesSecondary layerEngineering

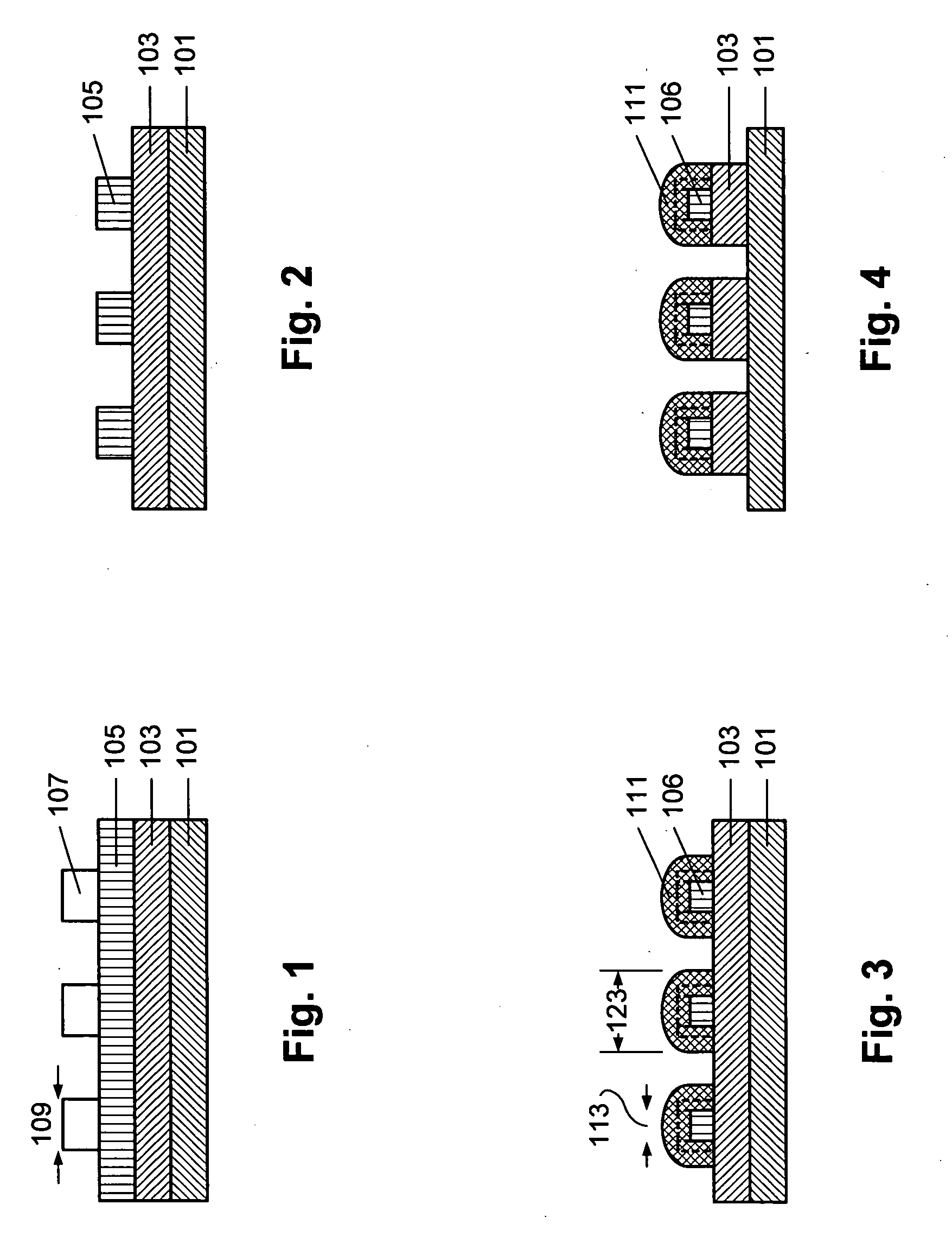

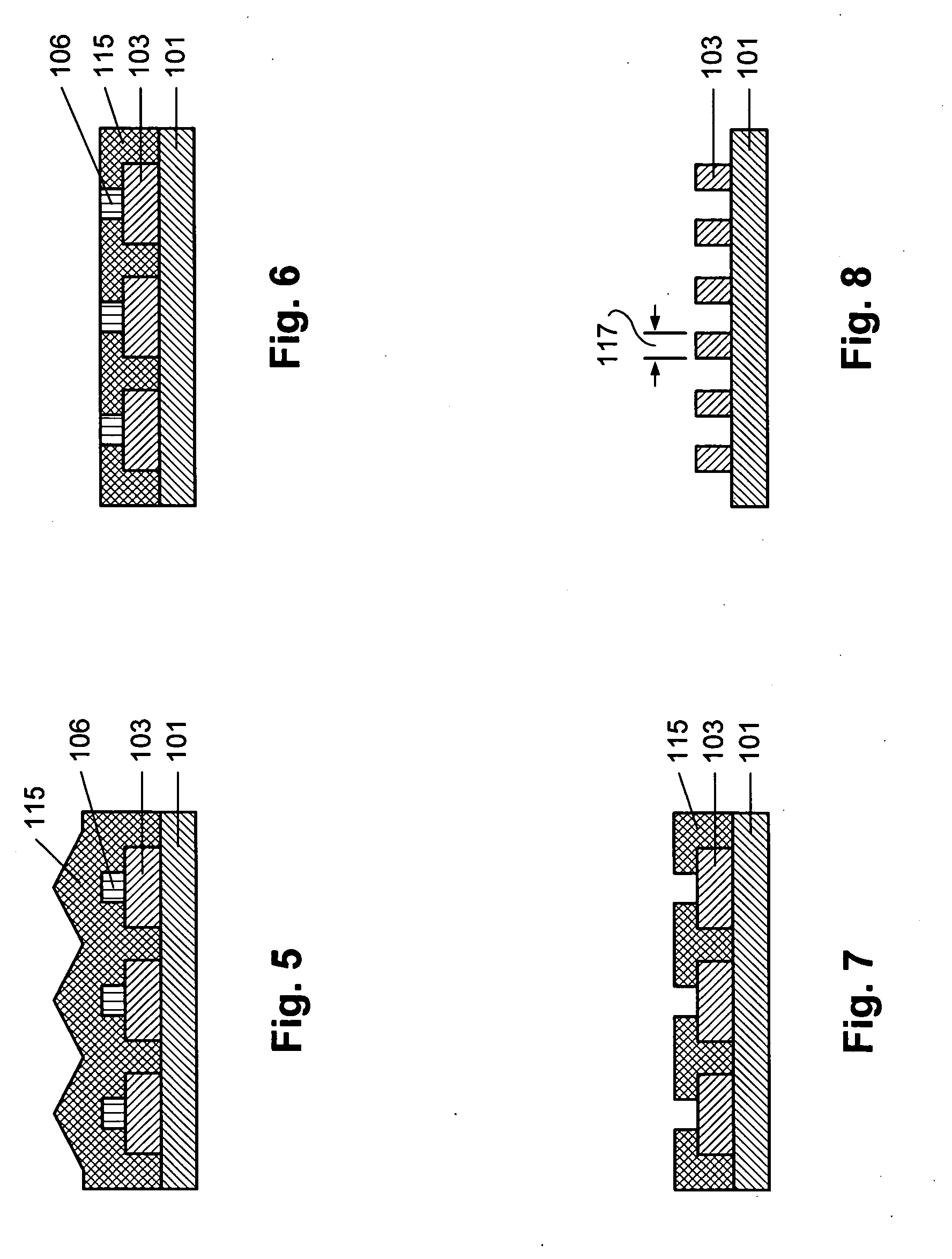

A semiconductor device 100 is provided with a multiplex through plug 111 that fills an opening extending through the silicon substrate 101. The multiplex through plugs 111 comprises a column-shaped and solid first through electrode 103, a first insulating film 105 that covers the cylindrical face of the first through electrode 103, a second through electrode 107 that covers the cylindrical face of the first insulating film 105 and a second insulating film 109 that covers the cylindrical face of the second through electrode 107, and these have a common central axis. The upper cross sections of the first insulating film 105, the second through electrode 107 and the second insulating film 109 are annular-shaped.

Owner:TESSERA ADVANCED TECH

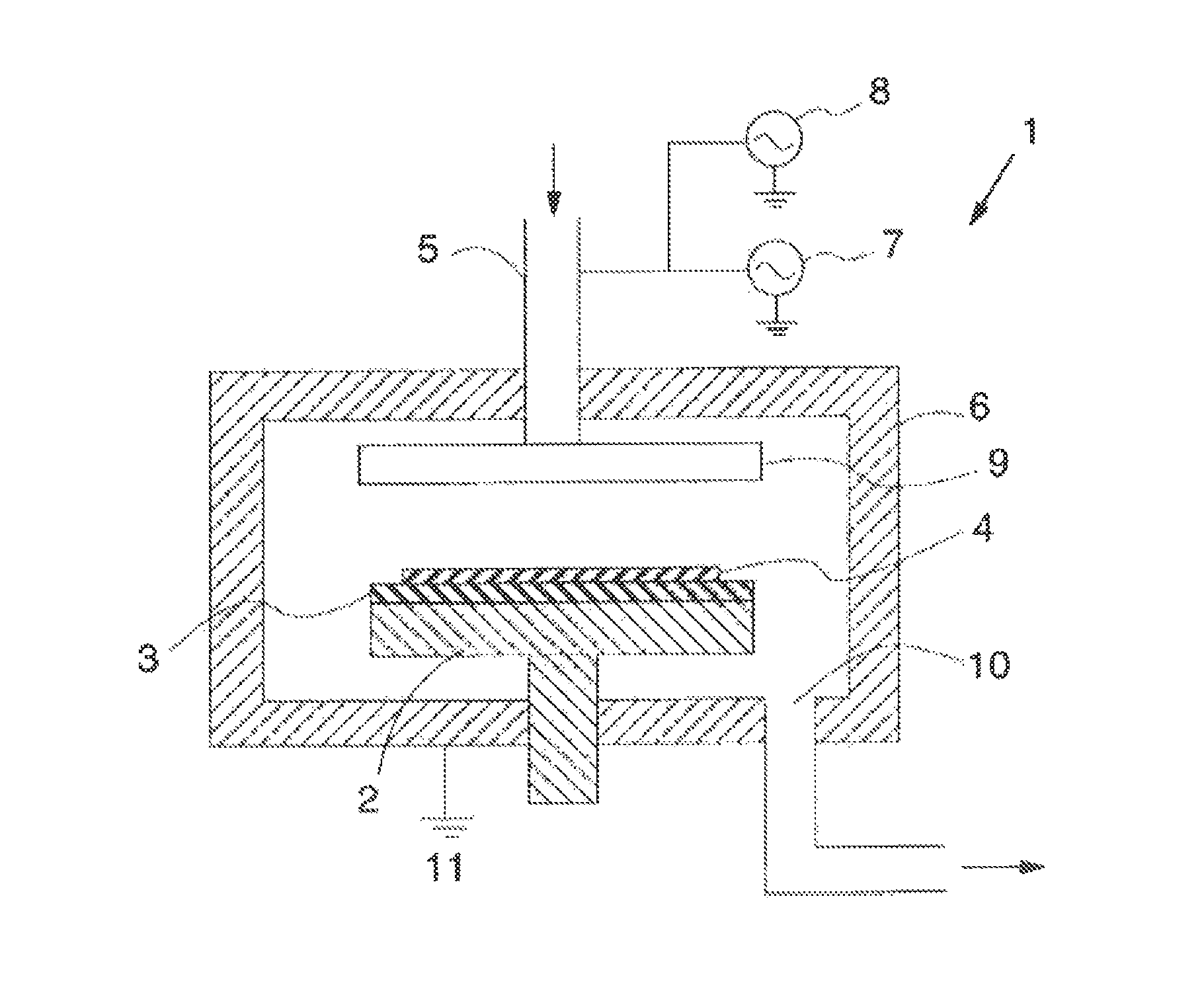

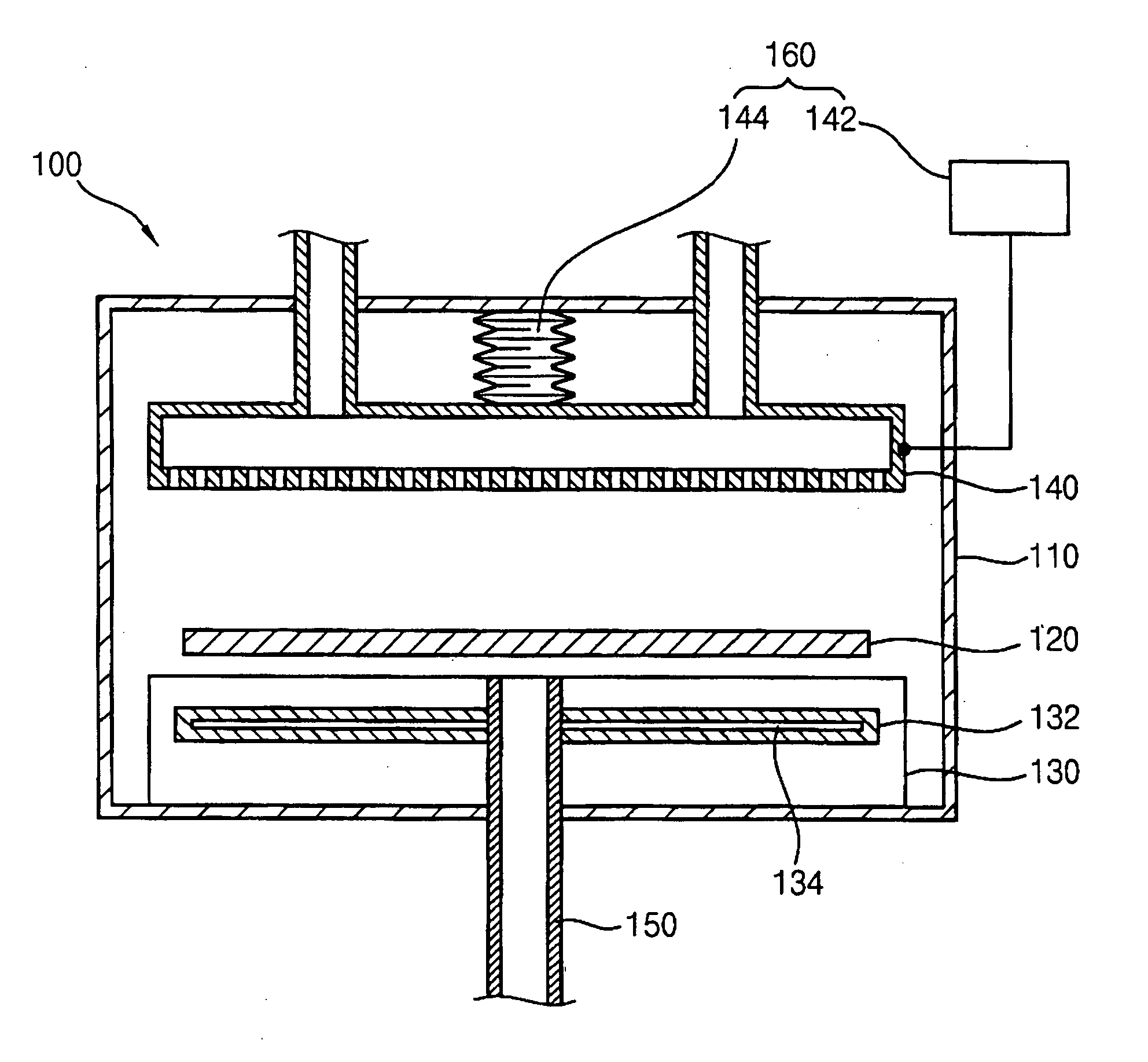

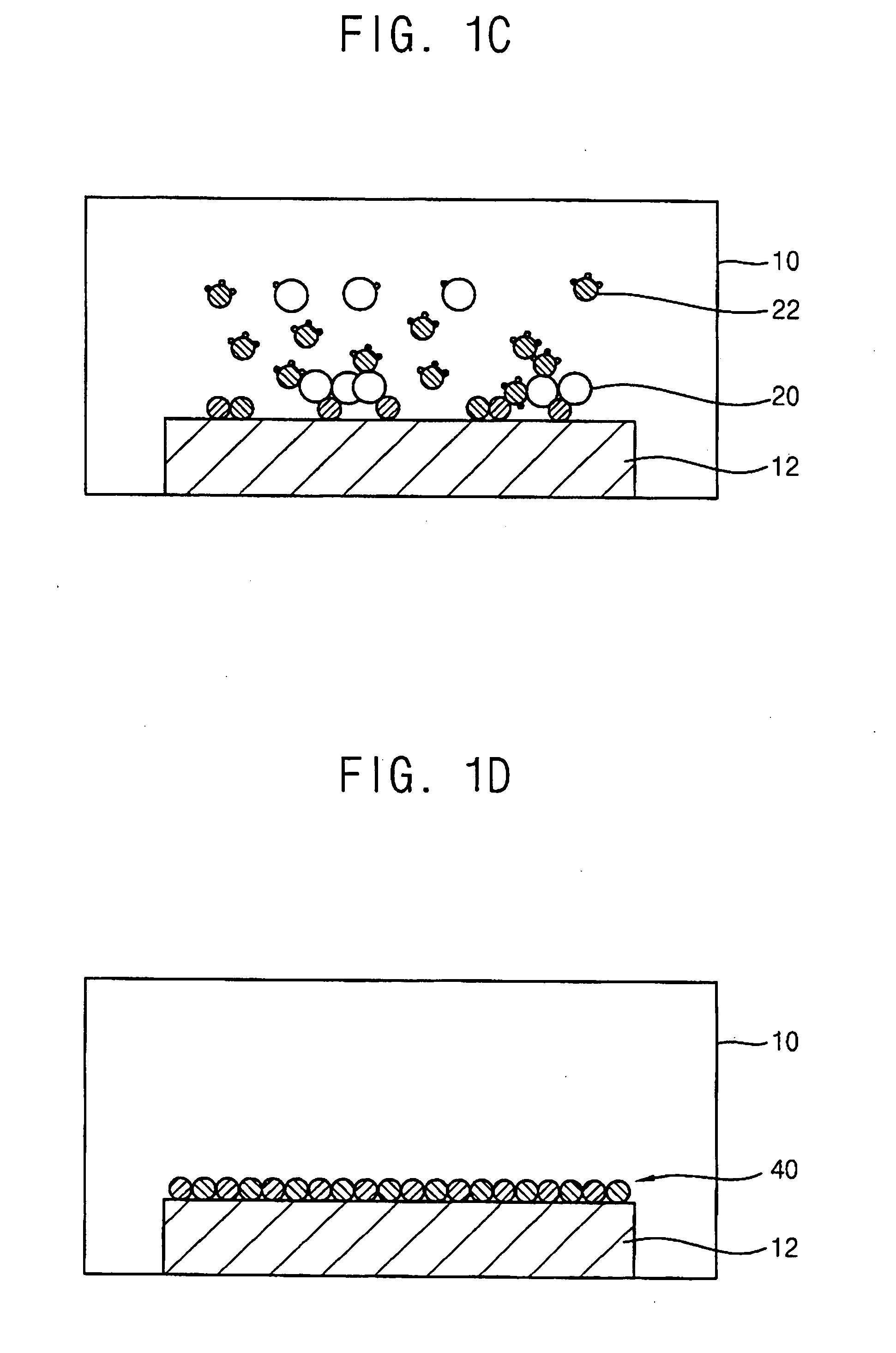

Method of forming a layer on a semiconductor substrate and apparatus for performing the same

InactiveUS20060000411A1Preventing deterioration of layerIncrease total manufacturing throughputSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialThin layer

In a method of forming a thin layer for a semiconductor device through an ALD process and a CVD process in the same chamber, a semiconductor substrate is introduced into a processing chamber, and an interval between a showerhead and the substrate is adjusted to a first gap distance. A first layer is formed on the substrate at a first temperature through an ALD process. The interval between the showerhead and the substrate is additionally adjusted to a second gap distance, and a second layer is formed on the first layer at a second temperature through a CVD process. Accordingly, the thin layer has good current characteristics, and the manufacturing throughput of a semiconductor device is improved.

Owner:SAMSUNG ELECTRONICS CO LTD

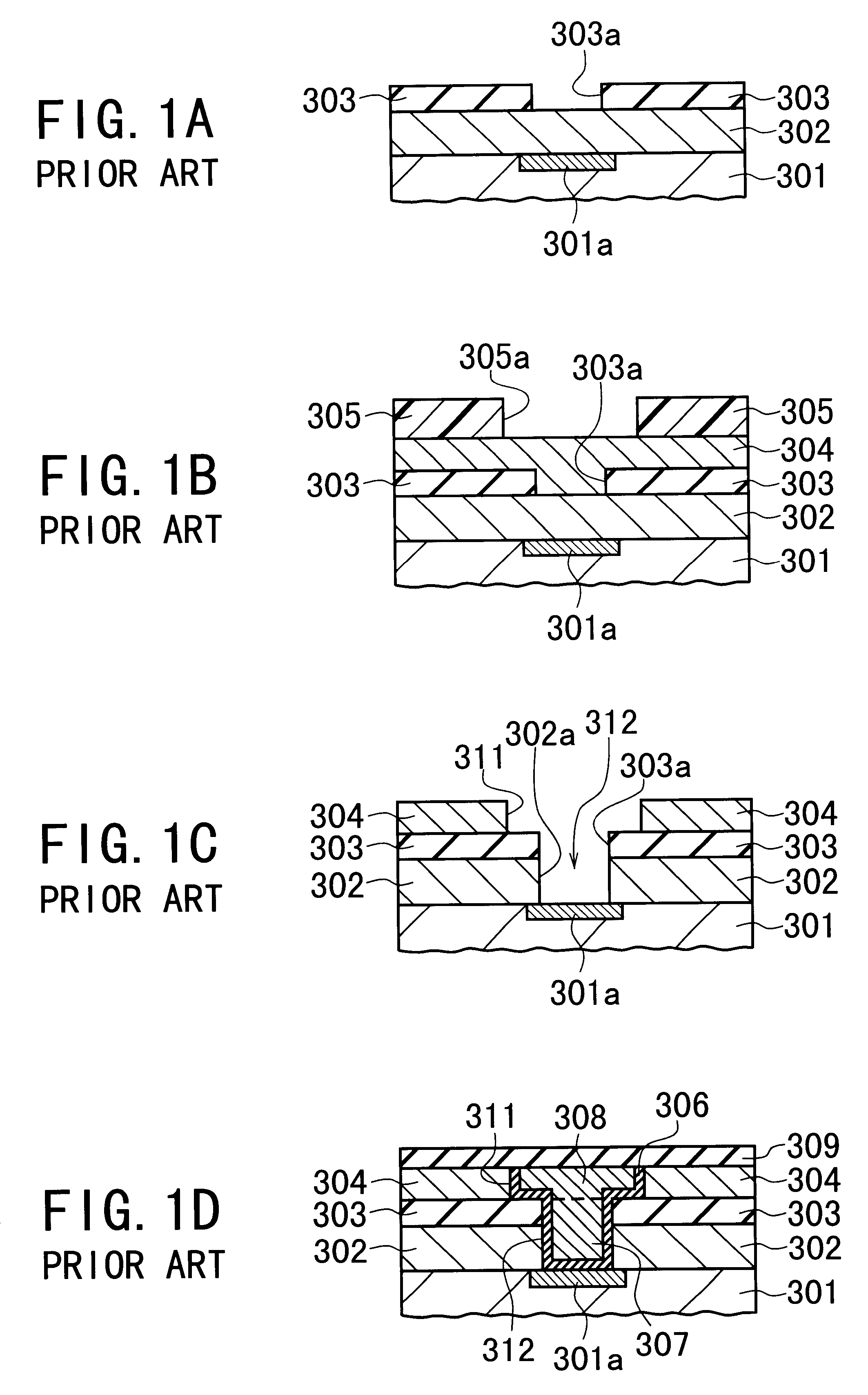

Semiconductor device and method of fabricating the same

InactiveUS6245665B1Semiconductor/solid-state device detailsSolid-state devicesPropagation delayElectronic component

A semiconductor device equipped with the dual damascene structure that is provided, which suppresses the propagation delay of signals effectively without using any complicated processes. The device is comprised of (i) a semiconductor substrate having a lower wiring layer and electronic elements; (ii) a first interlayer dielectric layer formed on the substrate; (iii) a second interlayer dielectric layer formed on the first interlayer dielectric layer, the second interlayer dielectric layer being made of carbon-containing SiO2; (iv) a third interlayer dielectric layer formed on the second interlayer dielectric layer; (v) a fourth interlayer dielectric layer formed on the third interlayer dielectric layer, the fourth interlayer dielectric layer being made of carbon-containing SiO2; (vi) the first and second interlayer dielectric layers having a via hole penetrating therethrough; (vii) the third interlayer dielectric layer having a recess overlapping with the via hole, the recess being formed to communicate with the via hole; (viii) a metal plug formed in the via hole to be contacted with the lower wiring layer or the electronic elements in the substrate; (ix) a metal wiring layer formed in the recess; and (x) a fourth interlayer dielectric layer formed on the third interlayer dielectric layer to cover the metal wiring layer.

Owner:NEC CORP

Methods of Forming Nonvolatile Memory Devices Using Nonselective and Selective Etching Techniques to Define Vertically Stacked Word Lines

InactiveUS20120003831A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSecondary layer

Methods of forming nonvolatile memory devices include forming a stack of layers of different materials on a substrate. This stack includes a plurality of first layers of a first material and a plurality of second layers of a second material arranged in an alternating sequence of first and second layers. A selected first portion of the stack of layers is isotropically etched for a sufficient duration to define a first trench therein that exposes sidewalls of the alternating sequence of first and second layers. The sidewalls of each of the plurality of first layers are selectively etched relative to sidewalls of adjacent ones of the plurality of second layers. Another etching step is then performed to recess sidewalls of the plurality of second layers and thereby expose portions of upper surfaces of the plurality of first layers. These exposed portions of the upper surfaces of the plurality of first layers, which may act as word lines of a memory device, are displaced laterally relative to each other.

Owner:SAMSUNG ELECTRONICS CO LTD

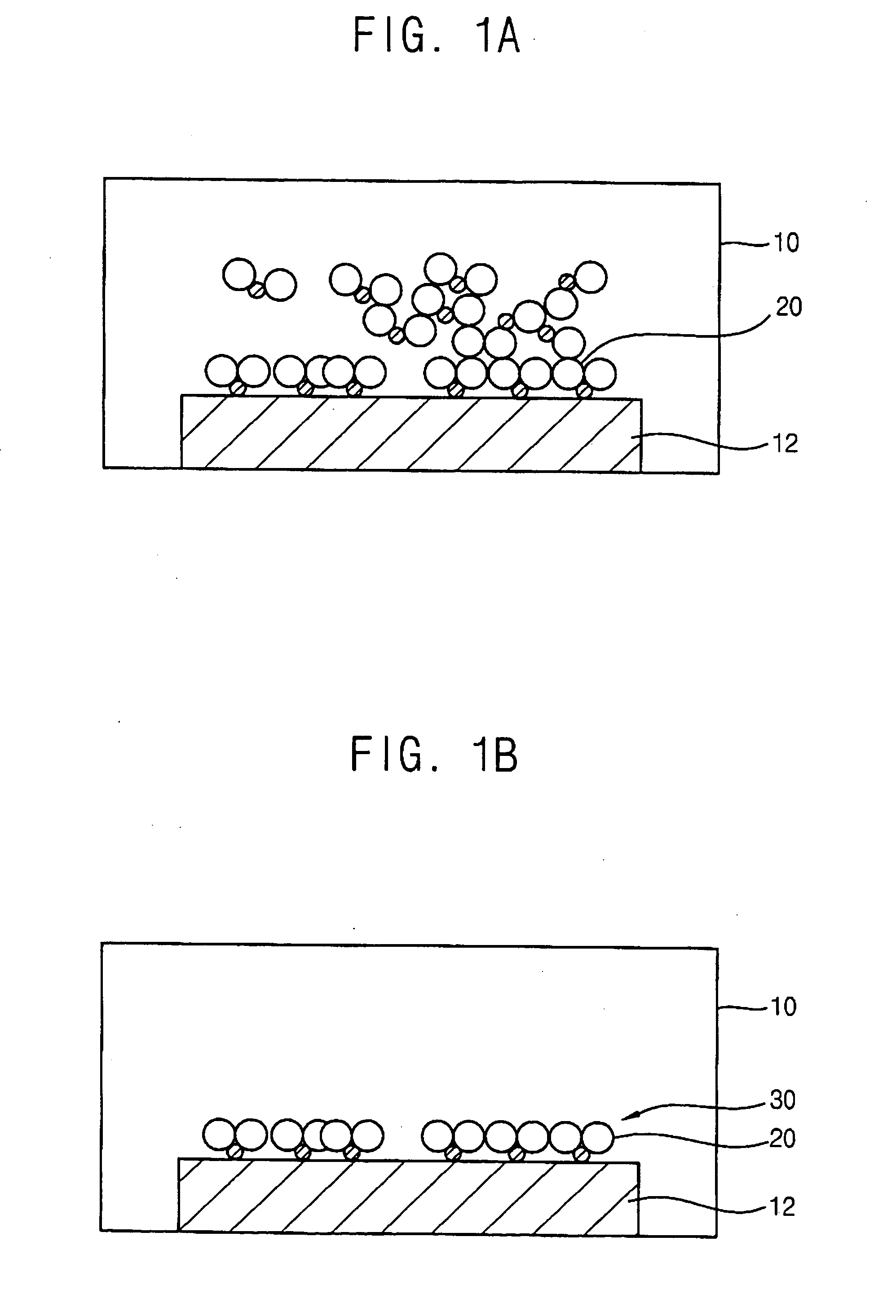

PECVD oxide-nitride and oxide-silicon stacks for 3D memory application

ActiveUS8076250B1Improve bonding interfaceAvoid layeringSemiconductor/solid-state device detailsSolid-state devicesMaterials science3d memory

A layer stack of different materials is deposited on a substrate in a single plasma enhanced chemical vapor deposition processing chamber while maintaining a vacuum. A substrate is placed in the processing chamber and a first processing gas is used to form a first layer of a first material on the substrate. A plasma purge and gas purge are performed before a second processing gas is used to form a second layer of a second material on the substrate. The plasma purge and gas purge are repeated and the additional layers of first and second materials are deposited on the layer stack.

Owner:APPLIED MATERIALS INC

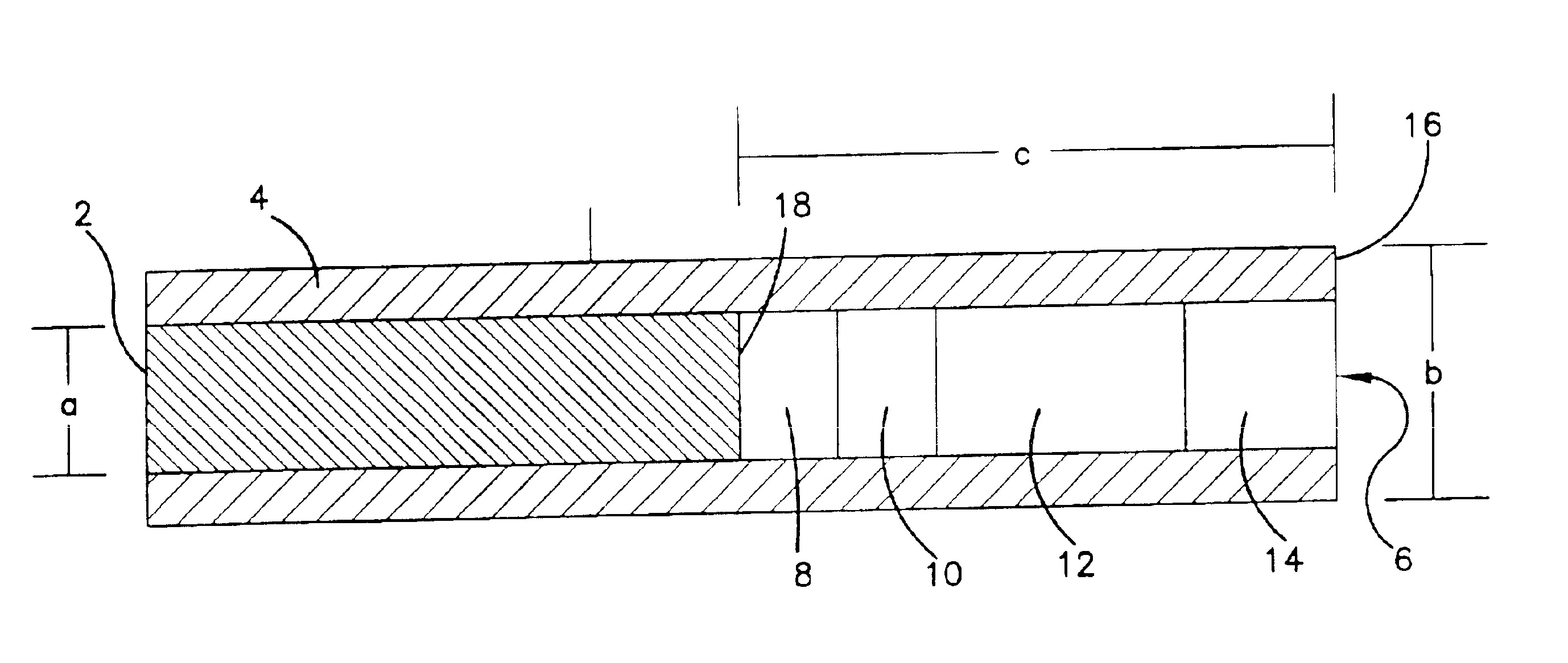

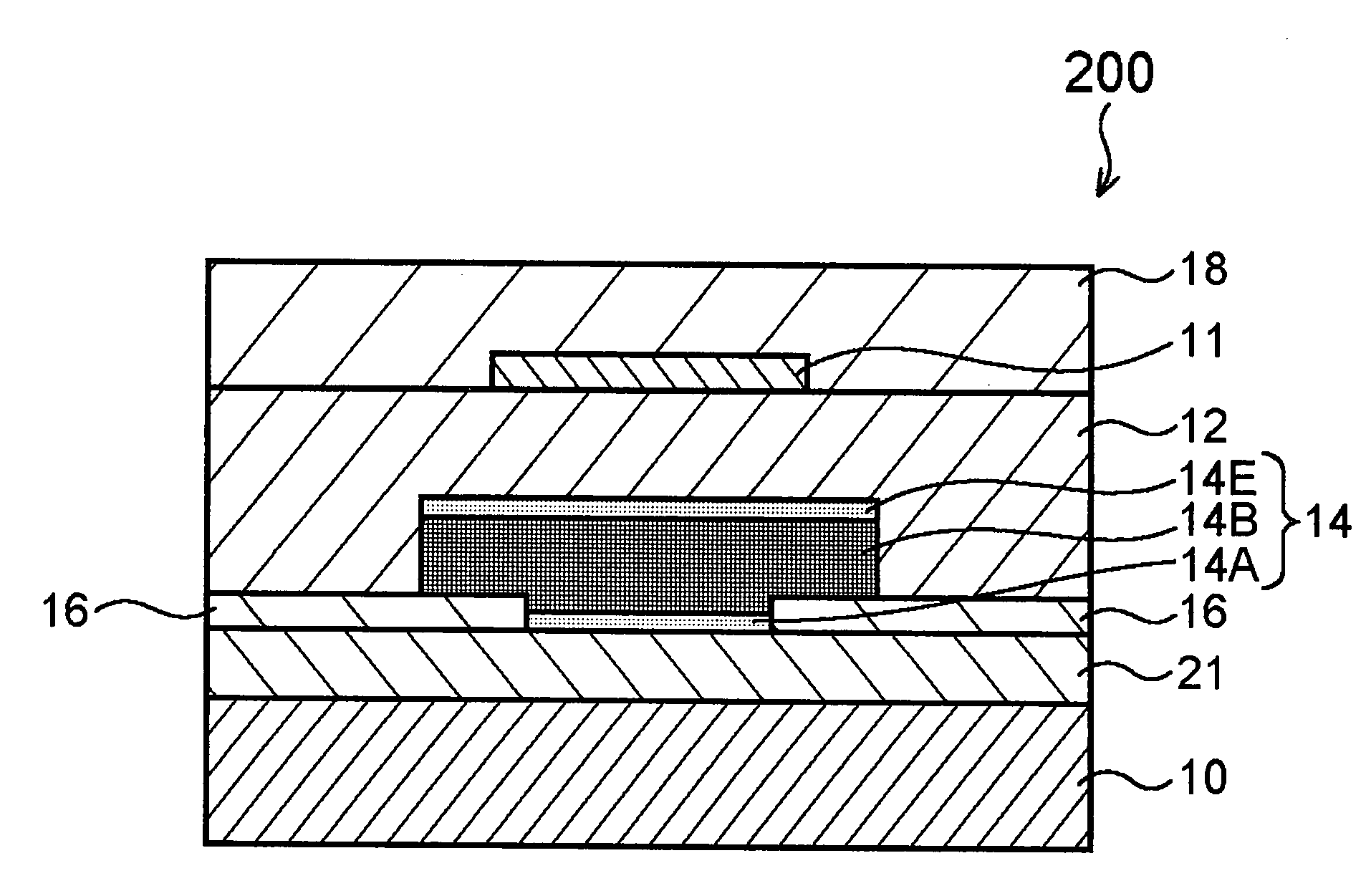

Thin-film device and method of fabricating the same

ActiveUS7884360B2Good reproducibilityImprove yieldSemiconductor/solid-state device manufacturingSemiconductor devicesInterface layerEngineering

A thin-film device includes a first electrical insulator, an oxide-semiconductor film formed on the first electrical insulator, and a second electrical insulator formed on the oxide-semiconductor film, the oxide-semiconductor film defining an active layer. The oxide-semiconductor film is comprised of a first interface layer located at an interface with the first electrical insulating insulator, a second interface layer located at an interface with the second electrical insulator, and a bulk layer other than the first and second interface layers. A density of oxygen holes in at least one of the first and second interlayer layers is smaller than a density of oxygen holes in the bulk layer.

Owner:NEC LCD TECH CORP

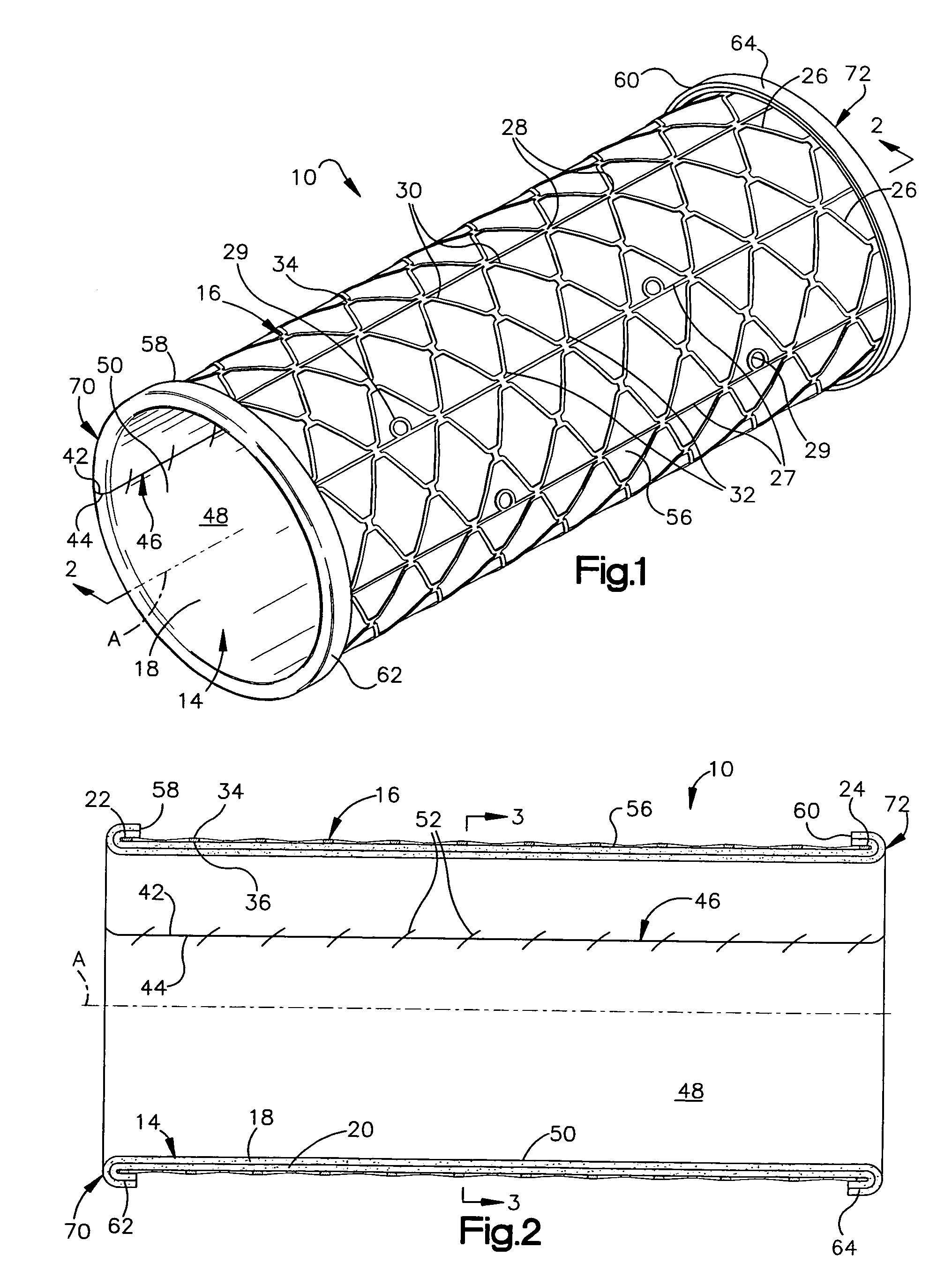

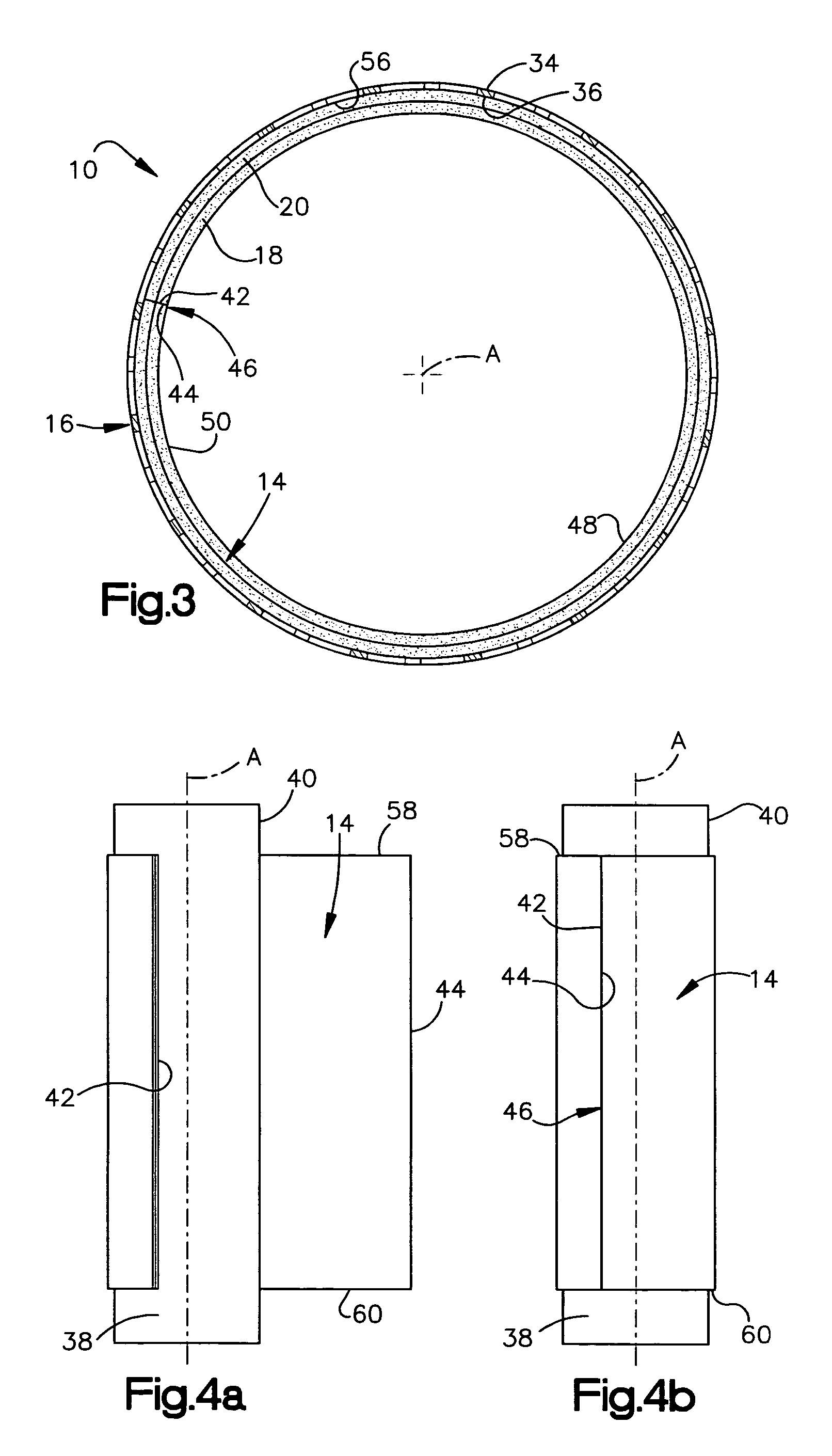

Prosthetic cardiac value and method for making same

A prosthetic valve for replacing a cardiac valve includes an expandable support member and at least two valve leaflets made of a first layer of biological material selected from peritoneal tissue, pleural tissue or pericardial tissue. A second layer of biological material is attached to the support member. The second layer is also made from peritoneal tissue, pleural tissue or pericardial tissue. The second layer includes a radially inwardly facing surface that defines a conduit for directing blood flow. The valve leaflets extend across the conduit to permit unidirectional flow of blood through the conduit. Methods for making and implanting the prosthetic valve are also provided.

Owner:THE CLEVELAND CLINIC FOUND

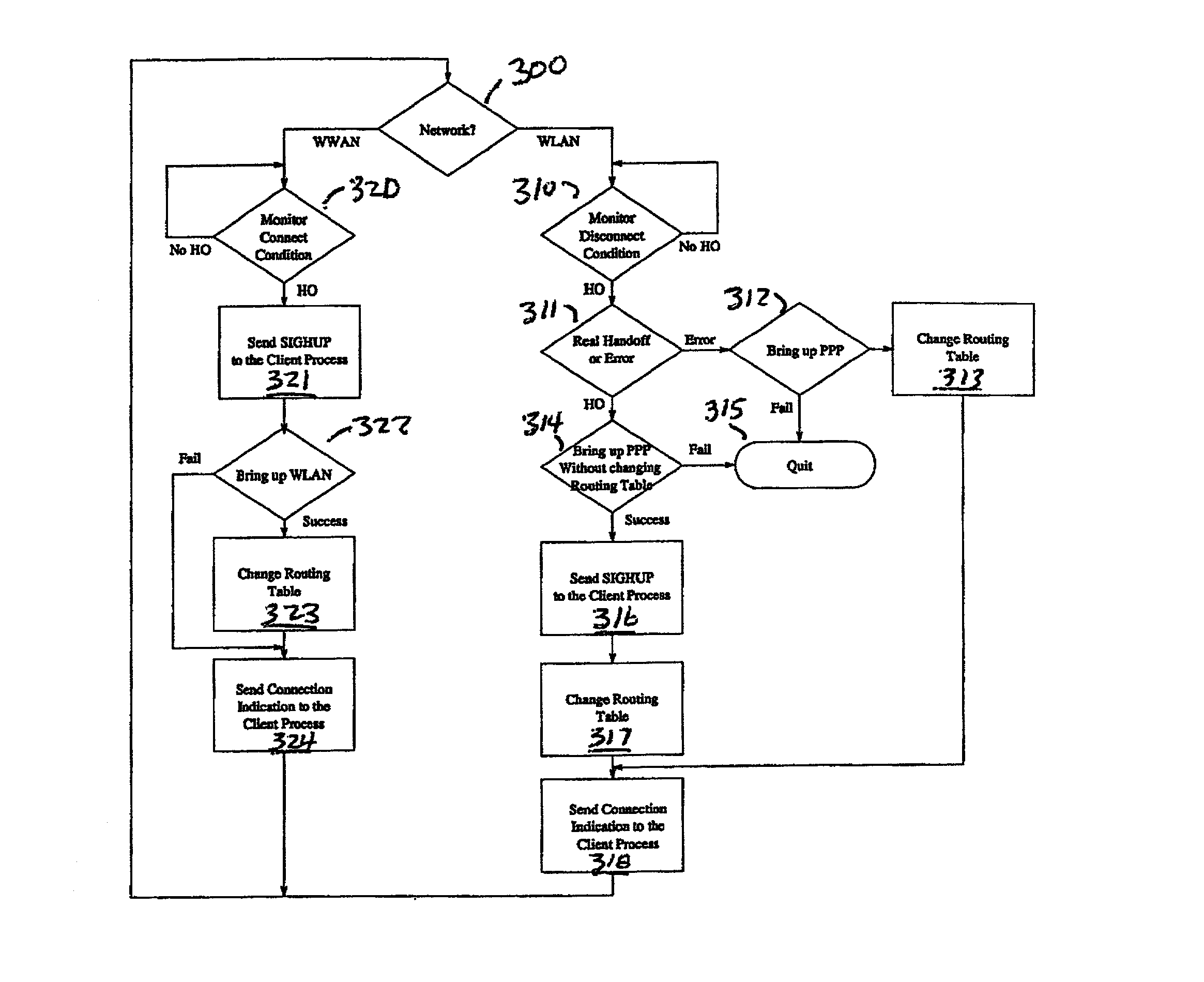

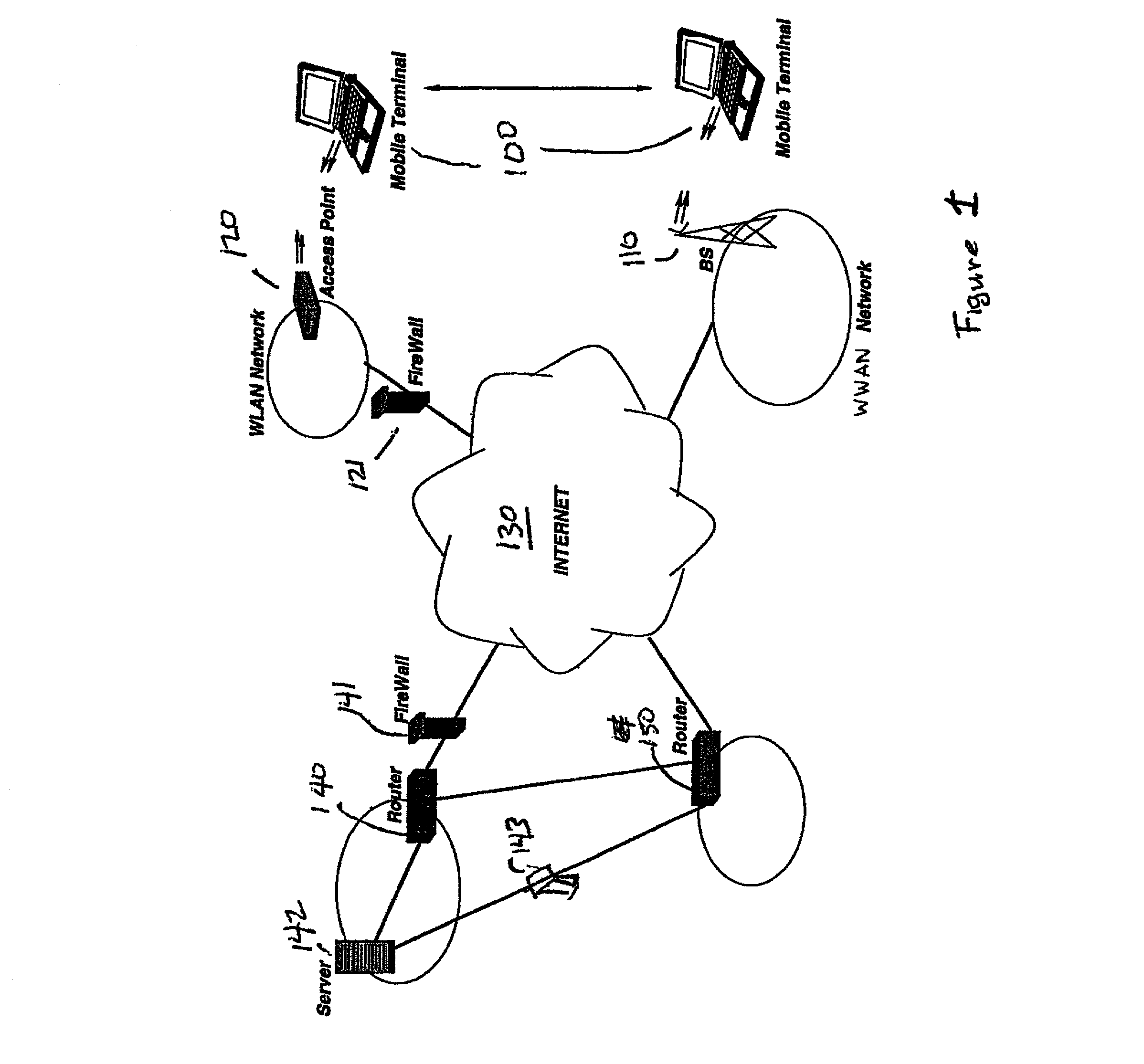

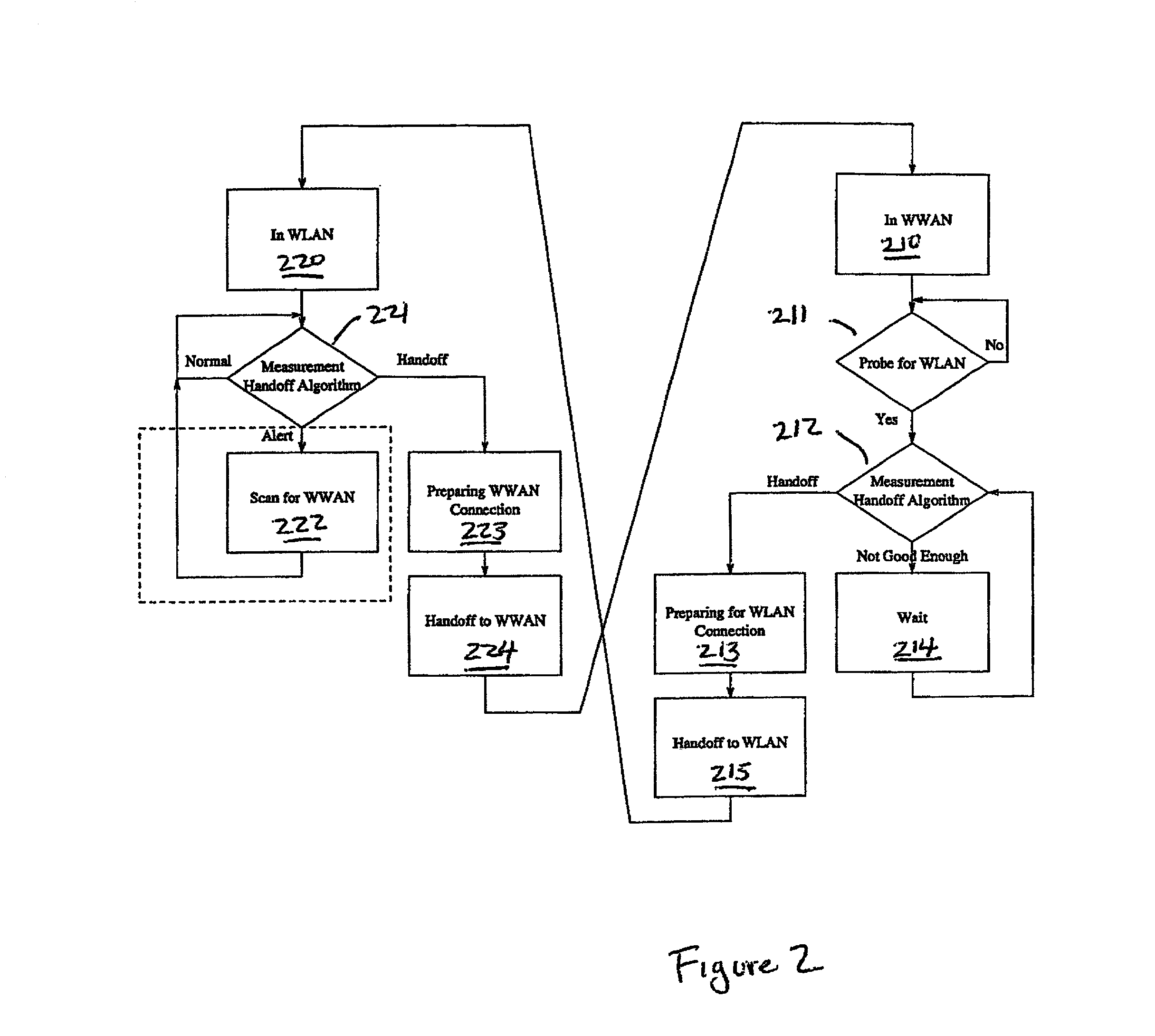

Method and apparatus for seamless mobility with layer two assistance

ActiveUS7009952B1Wireless network protocolsRadio/inductive link selection arrangementsQuality of serviceAccess technology

One aspect of the present invention includes a method of handing off a network session between two different access technologies, in response to a quality of service metric, while maintaining the session. Additional aspects of the present invention are described in the claims, specification and drawings.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

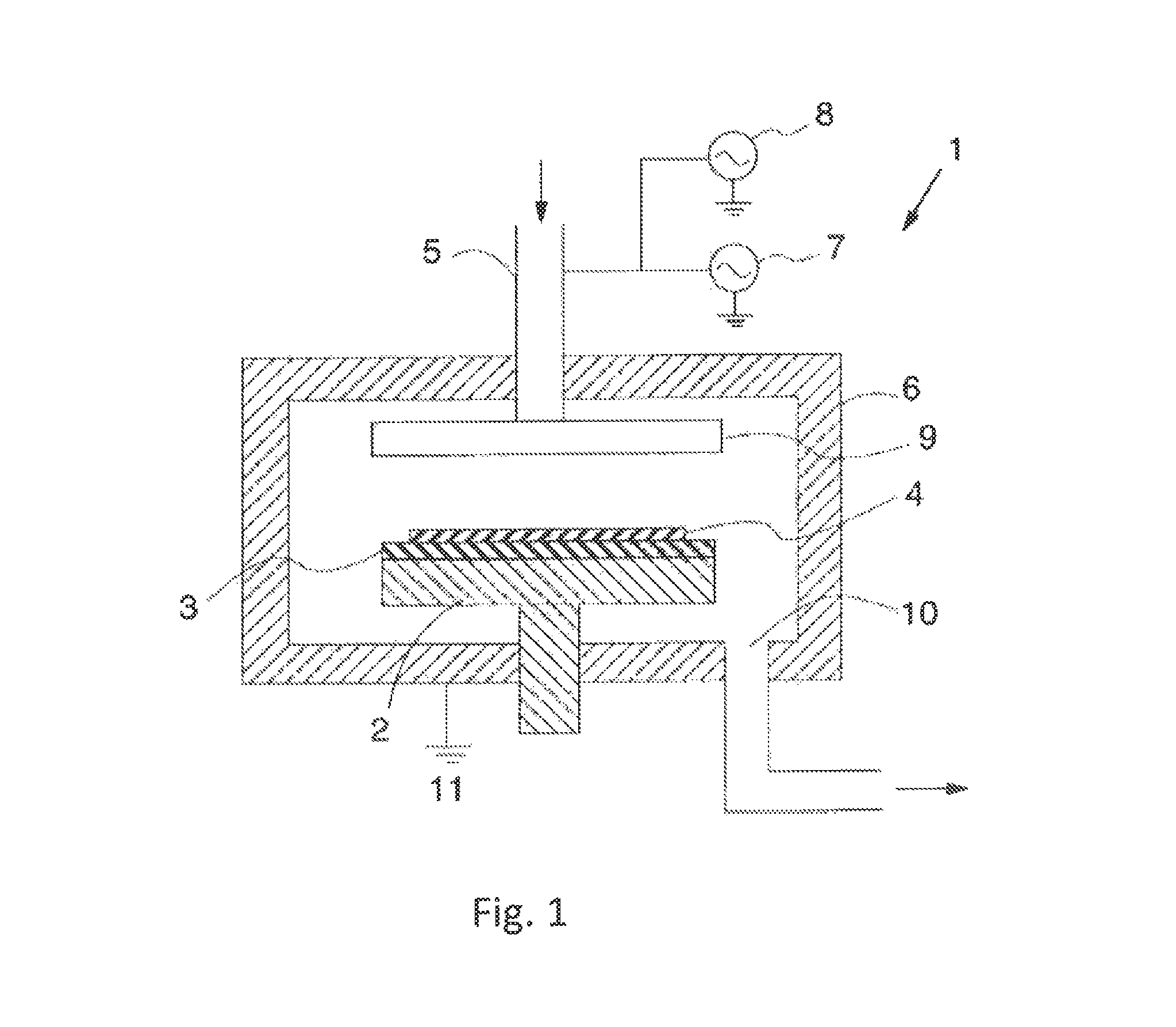

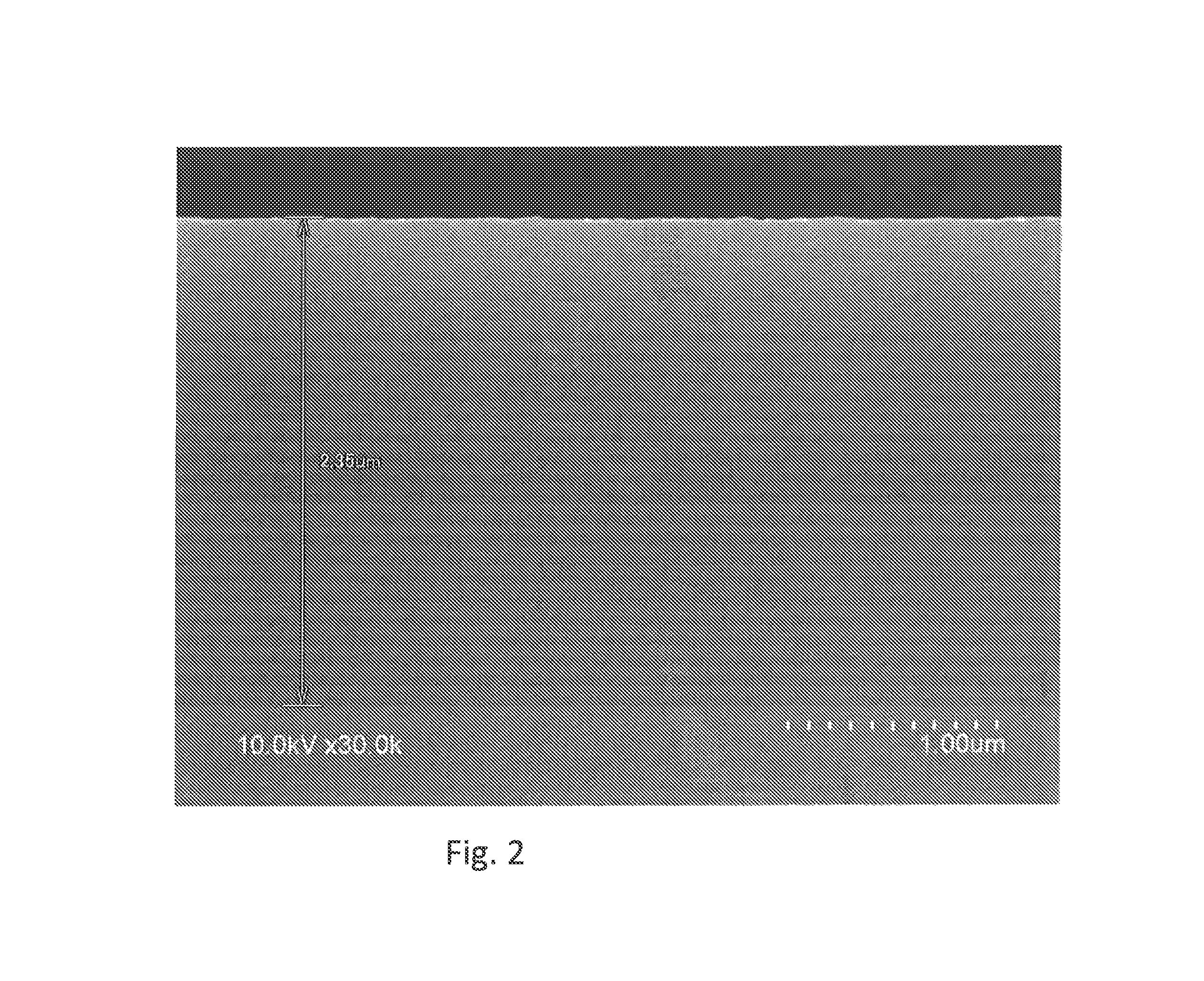

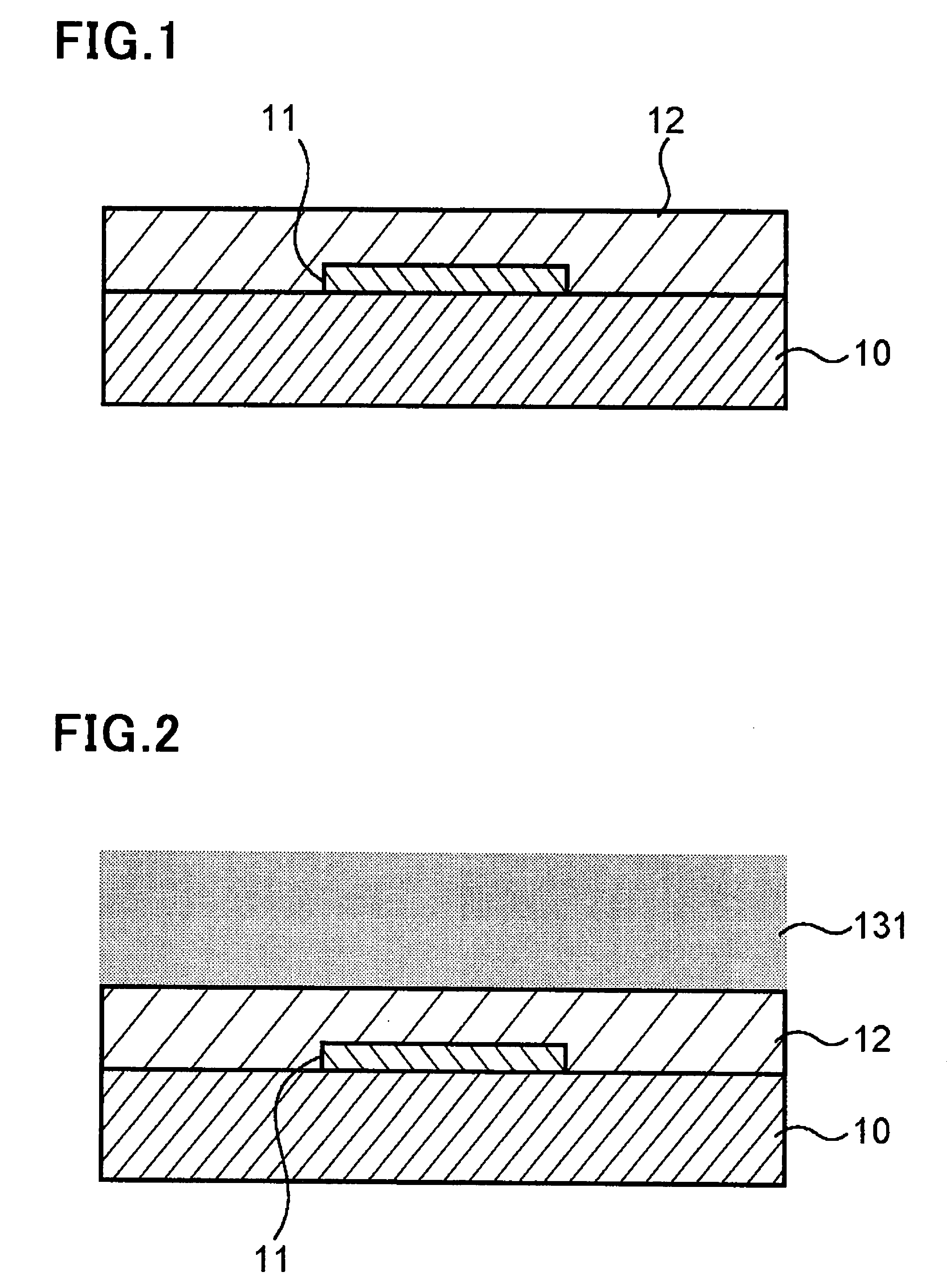

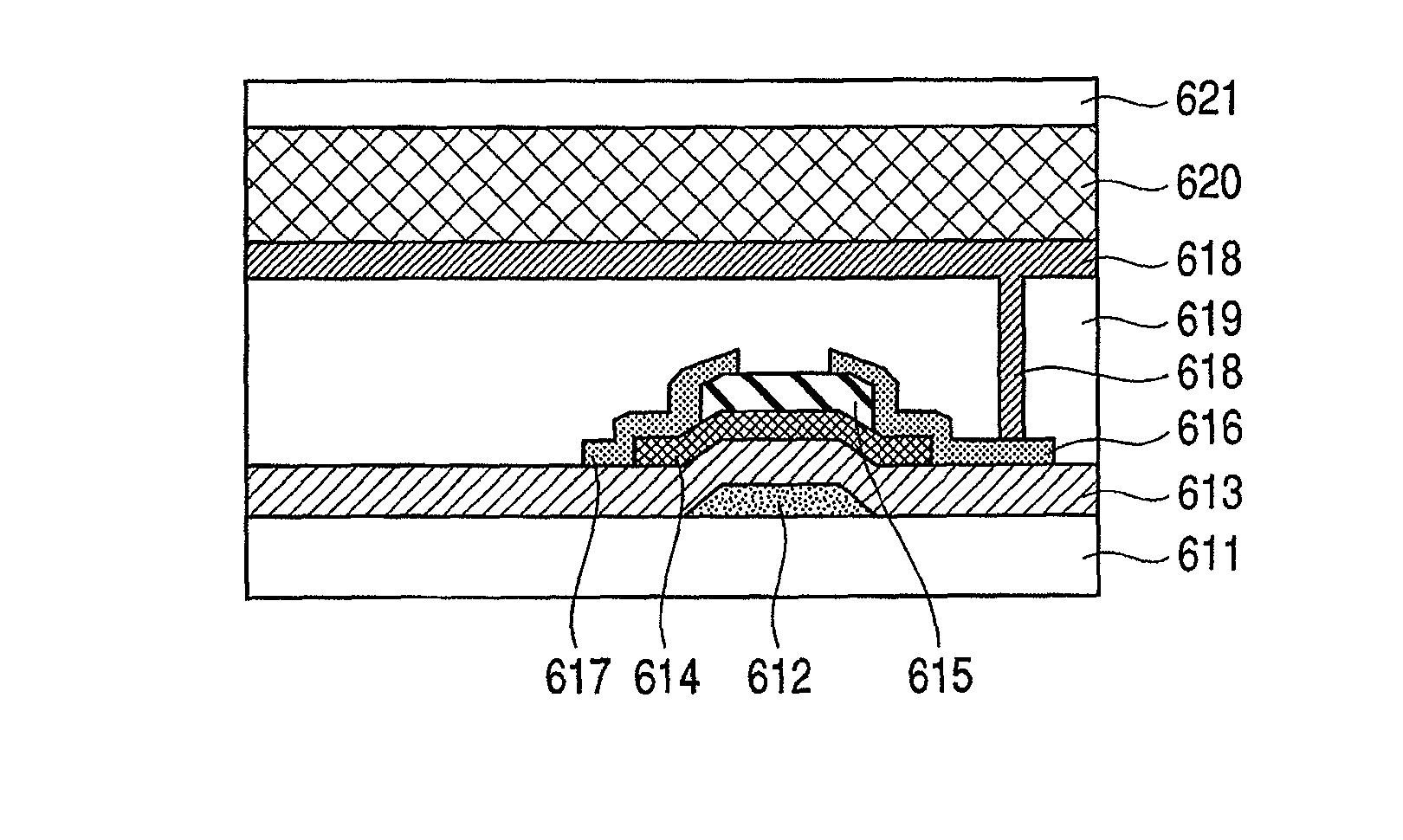

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

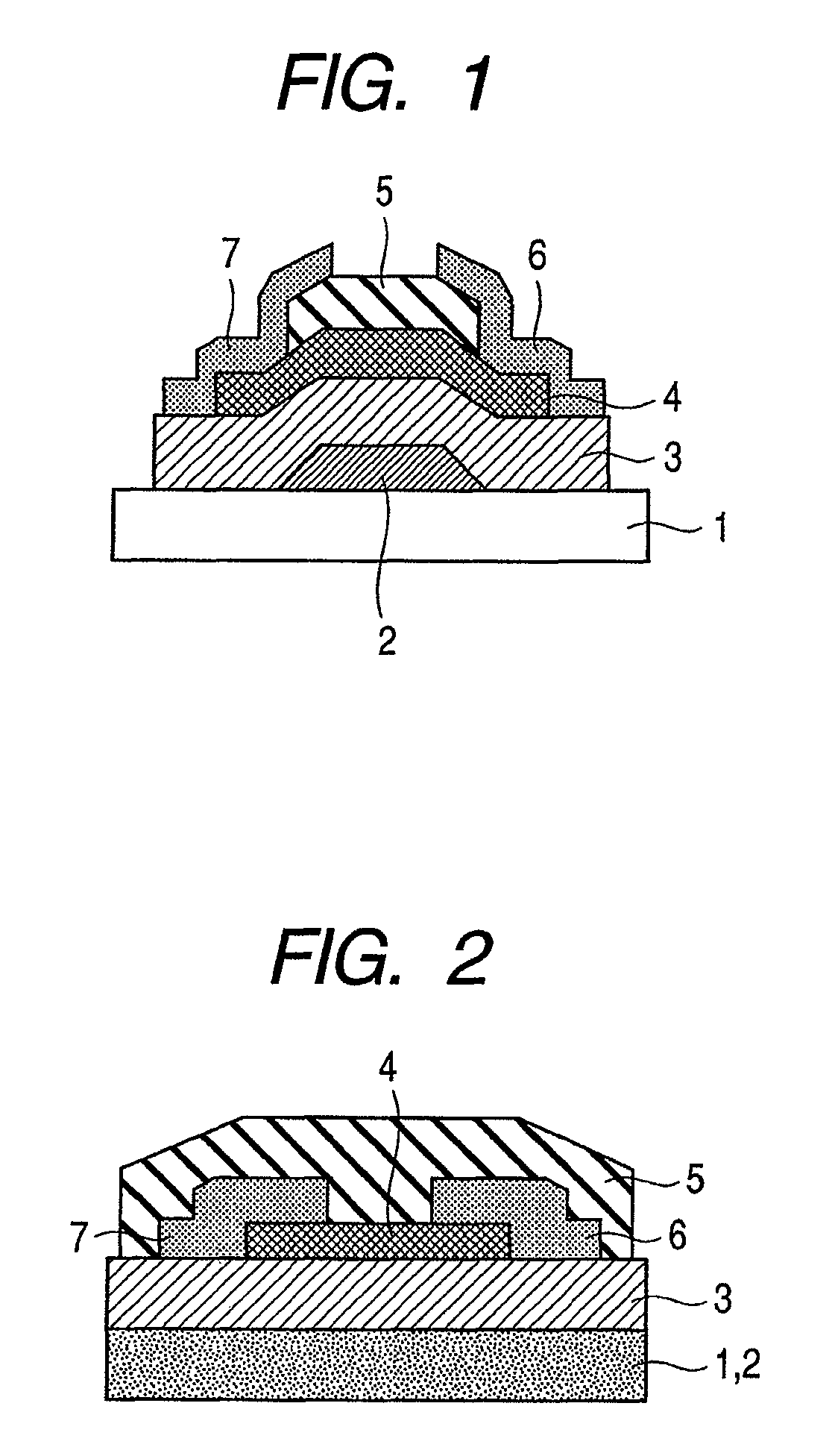

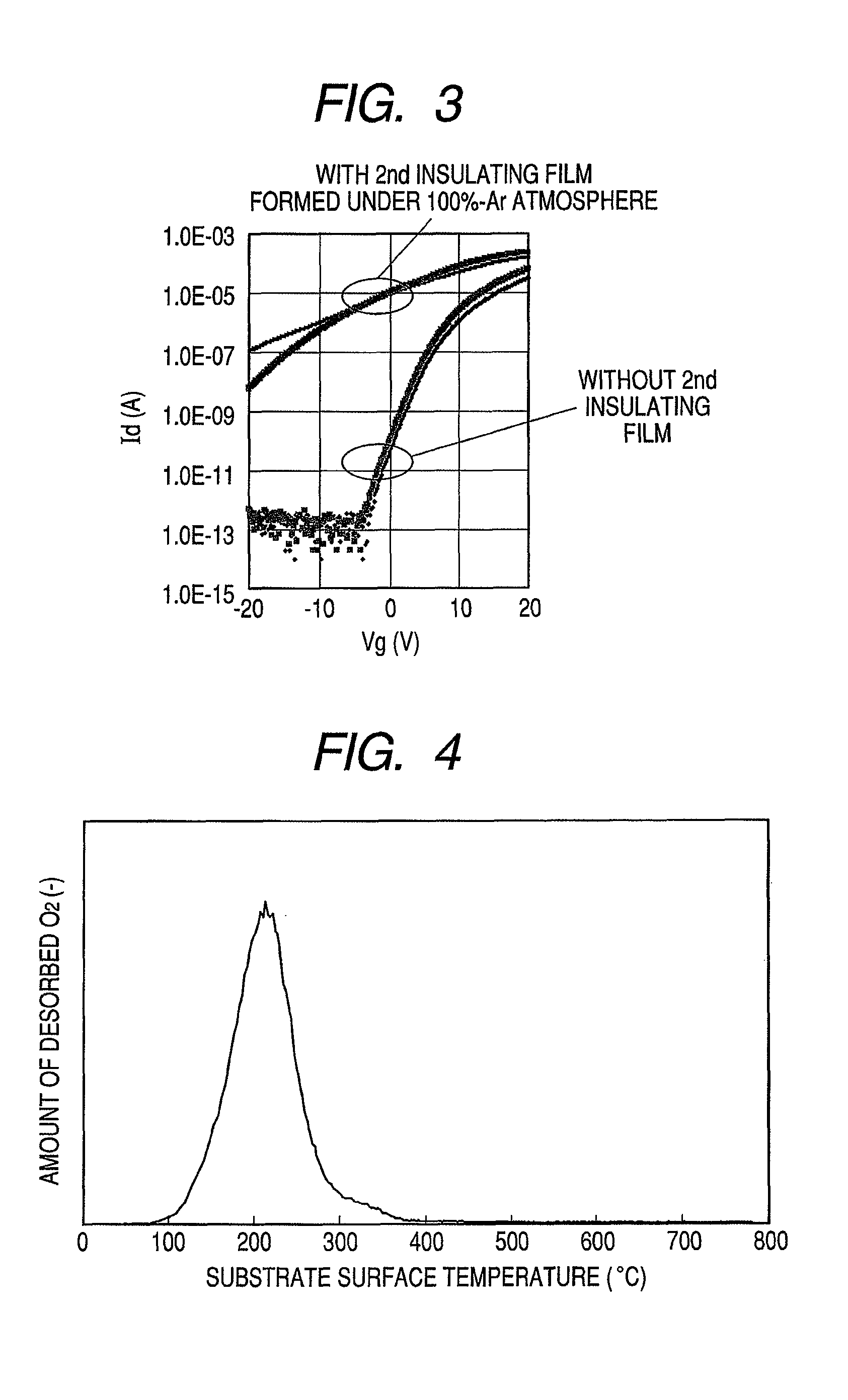

InactiveUS8148721B2Optimise total massImprove batch productivityTransistorElectroluminescent light sourcesDesorptionBottom gate

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

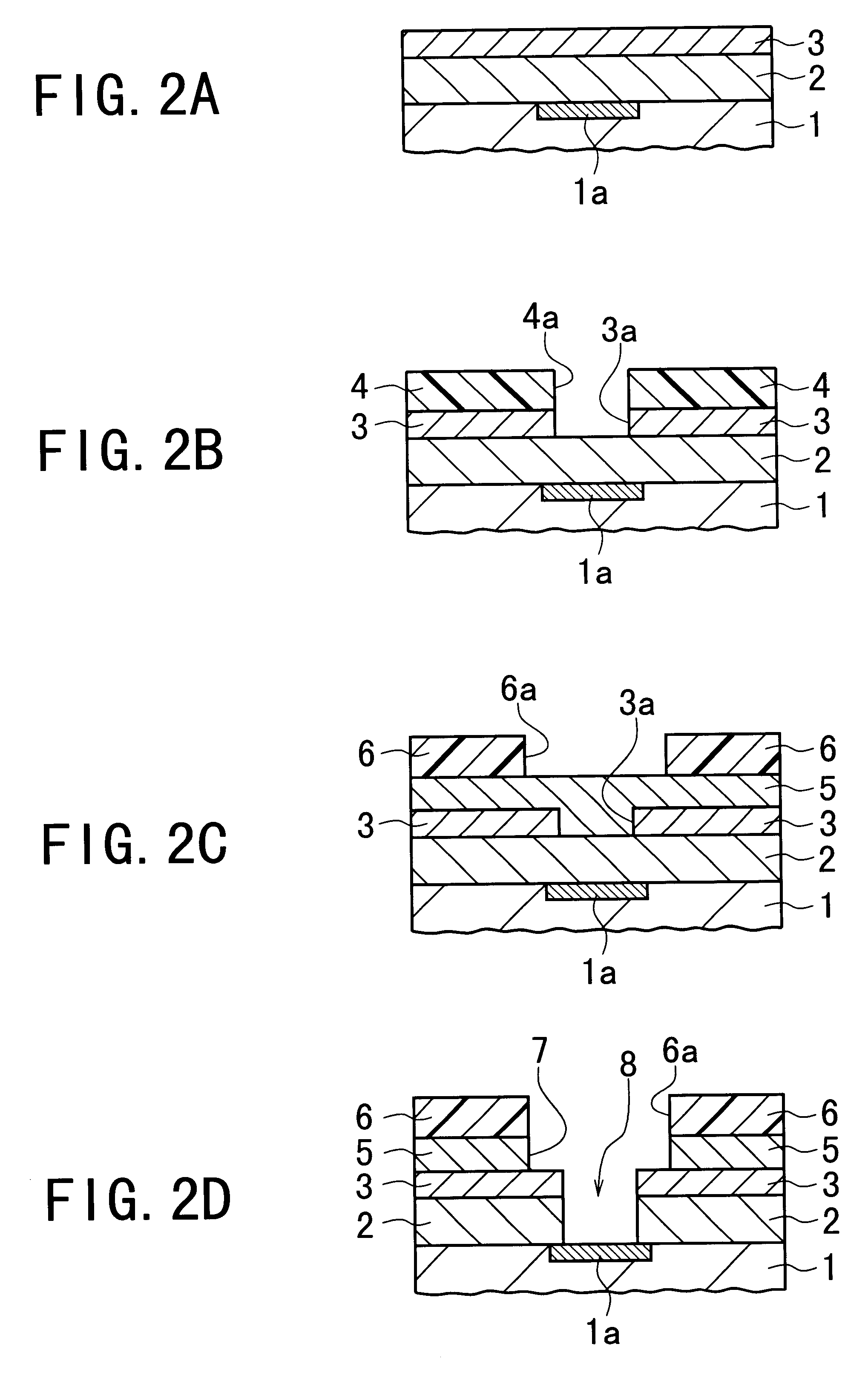

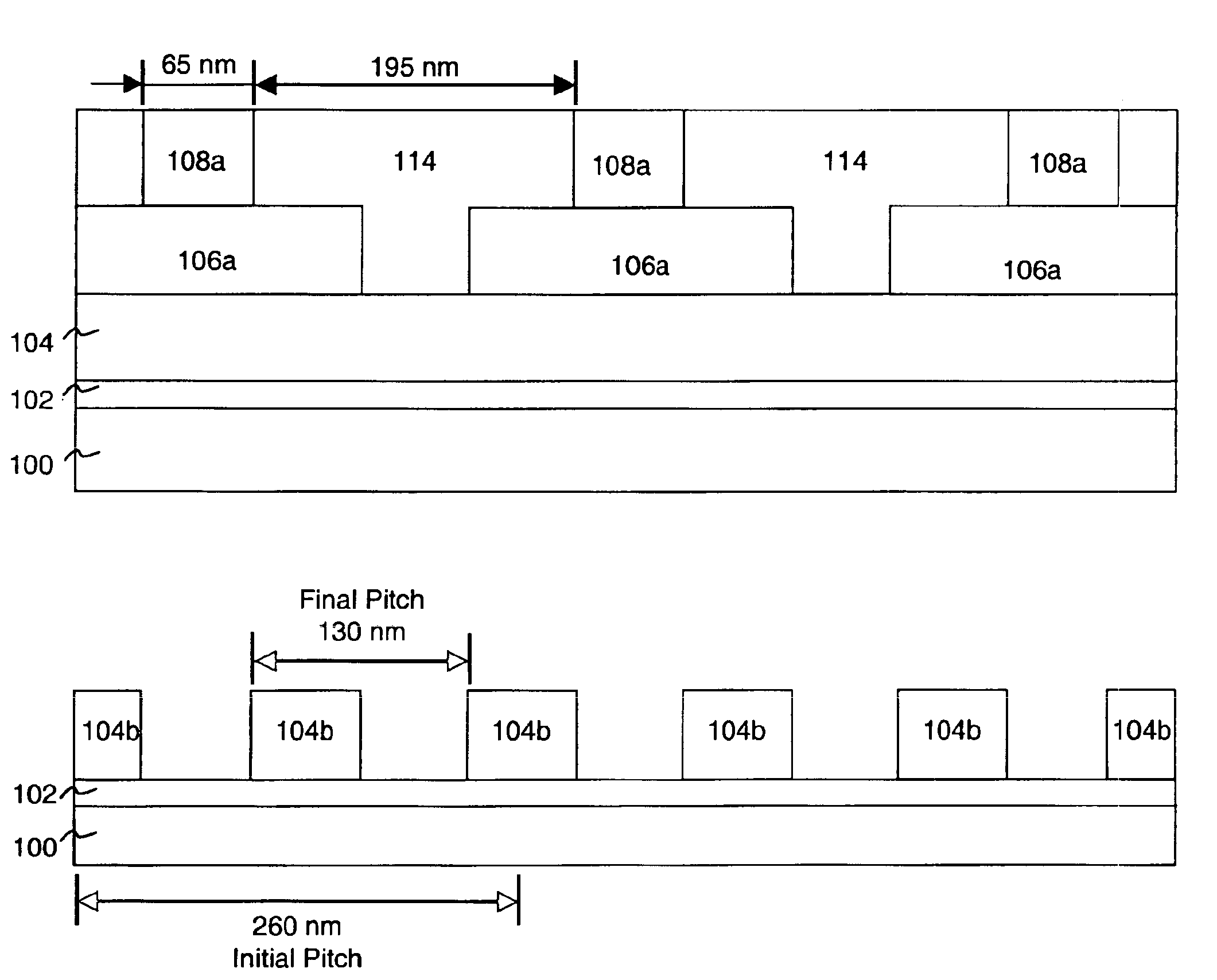

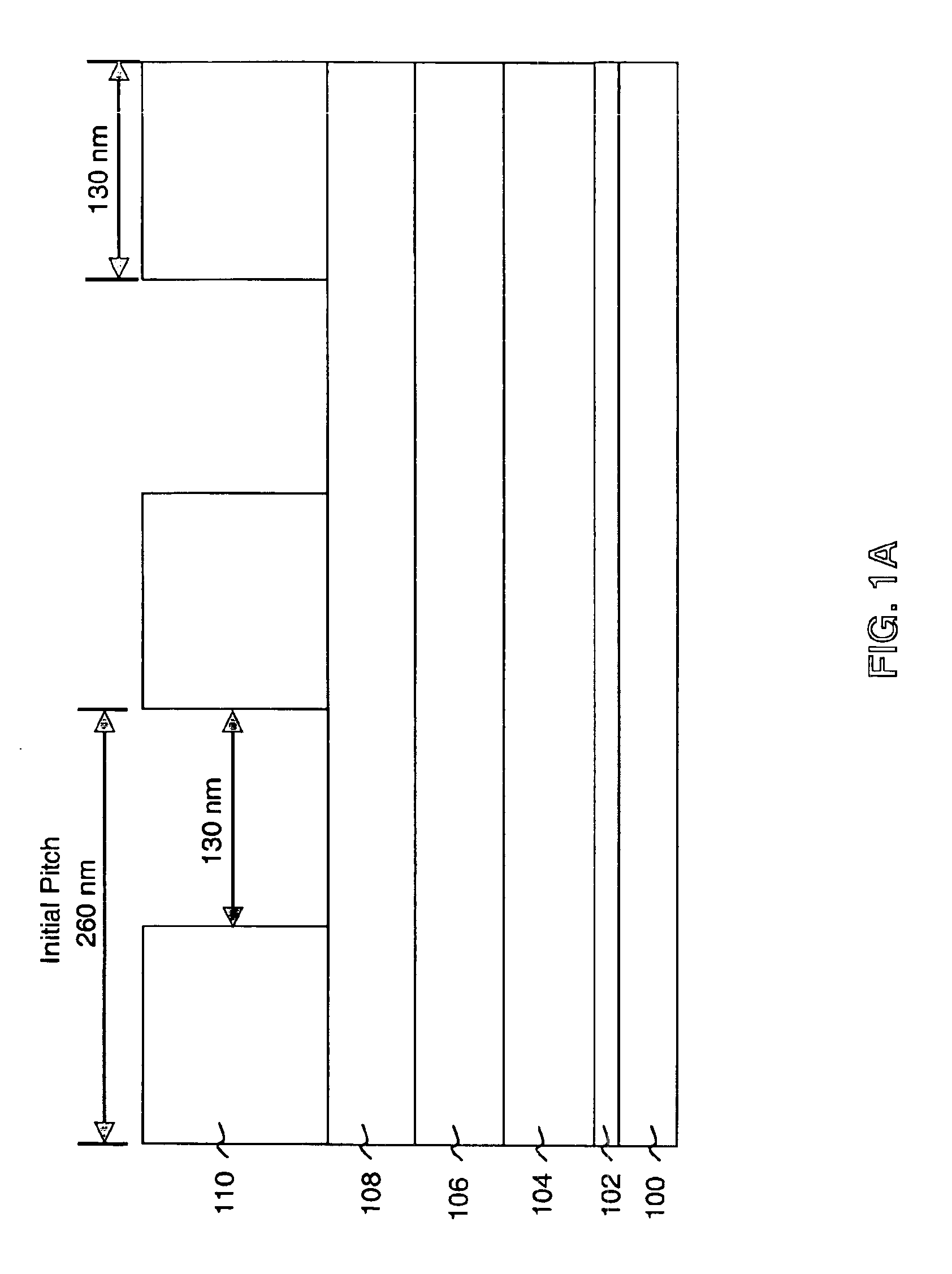

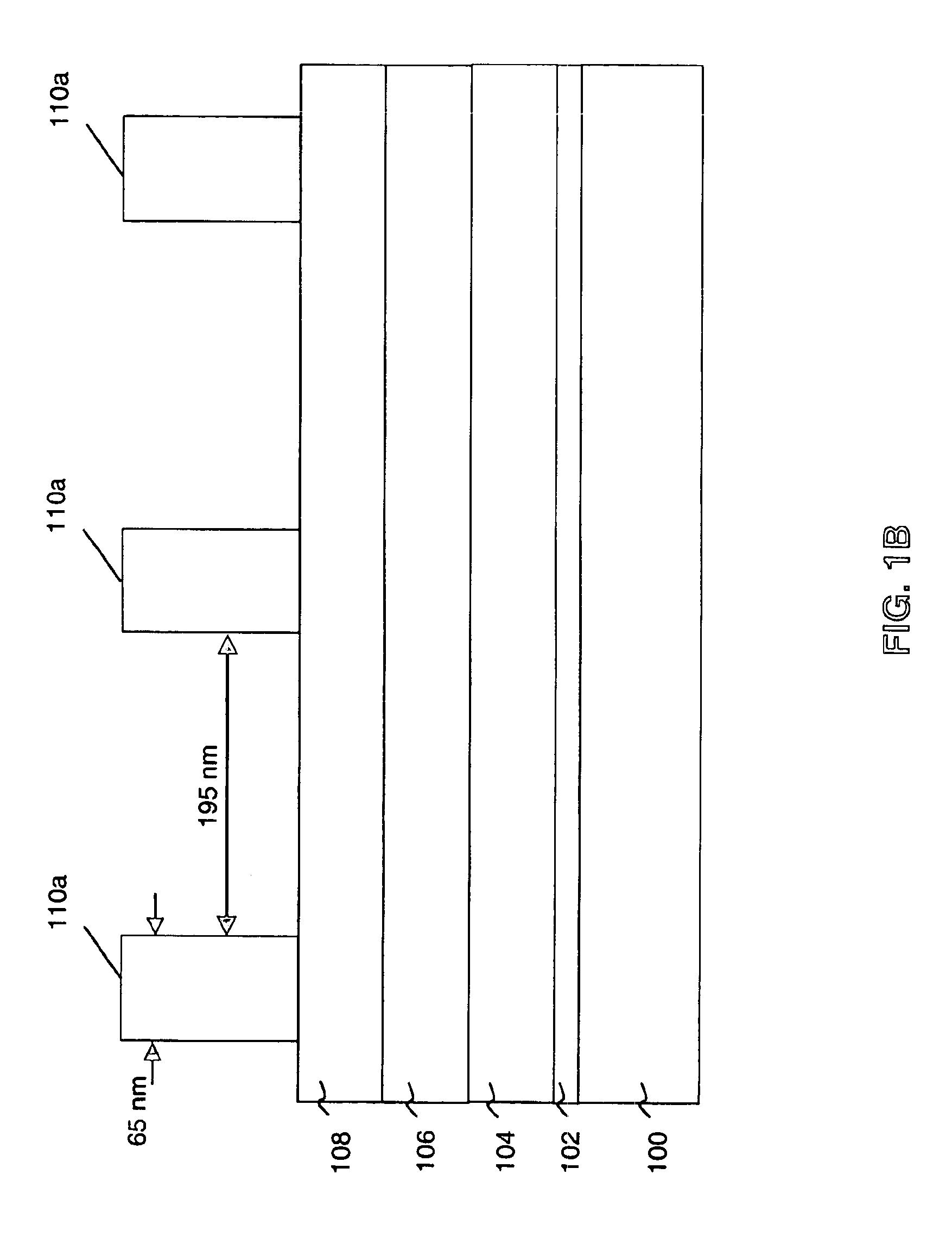

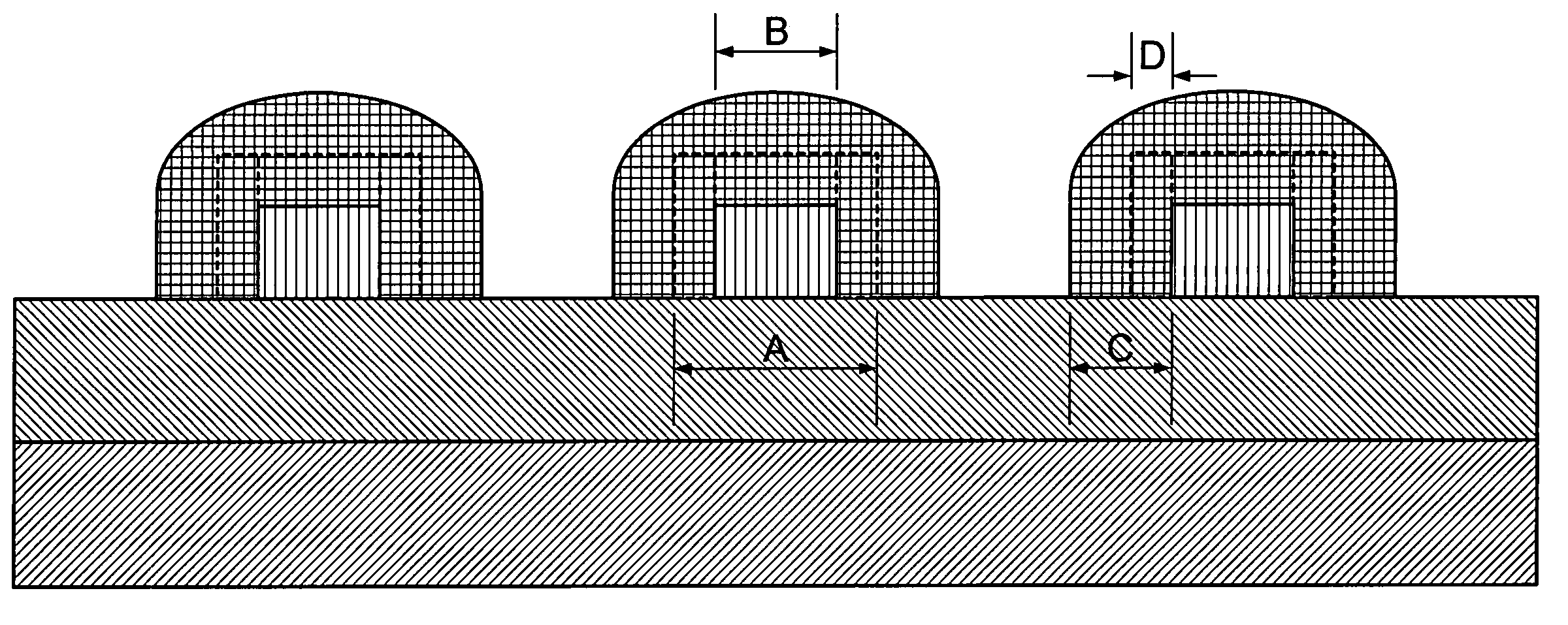

Fabrication method of sub-resolution pitch for integrated circuits

ActiveUS6867116B1Reduce spacingCost-effectiveSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotonic integrated circuit

A method of manufacturing a semiconductor device using a scanner, wherein the scanner is capable of realizing a minimum pitch, wherein the minimum pitch is the smallest possible pitch for the scanner, the method including providing a semiconductor substrate, forming a first layer over the semiconductor substrate, forming a second layer over the first layer, patterning the second layer to form a plurality of second layer patterns, patterning the first layer to form a plurality of first layer patterns, performing a tone reversal to form a reversed tone for the second layer patterns, and etching the first layer patterns using the reversed tone as a mask, wherein the etched first layer patterns have a final pitch size, and wherein the final pitch is smaller than the minimum pitch.

Owner:MACRONIX INT CO LTD

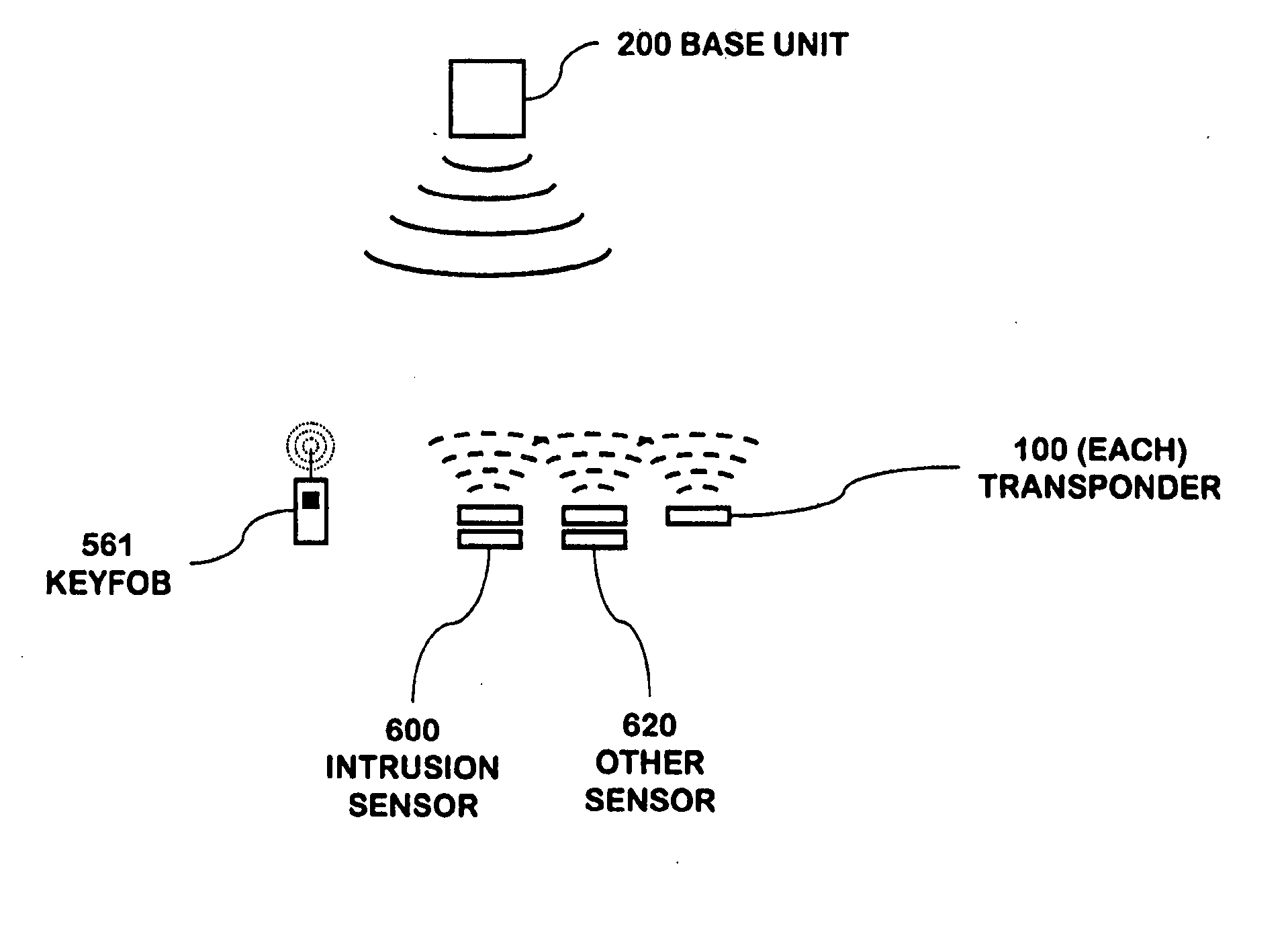

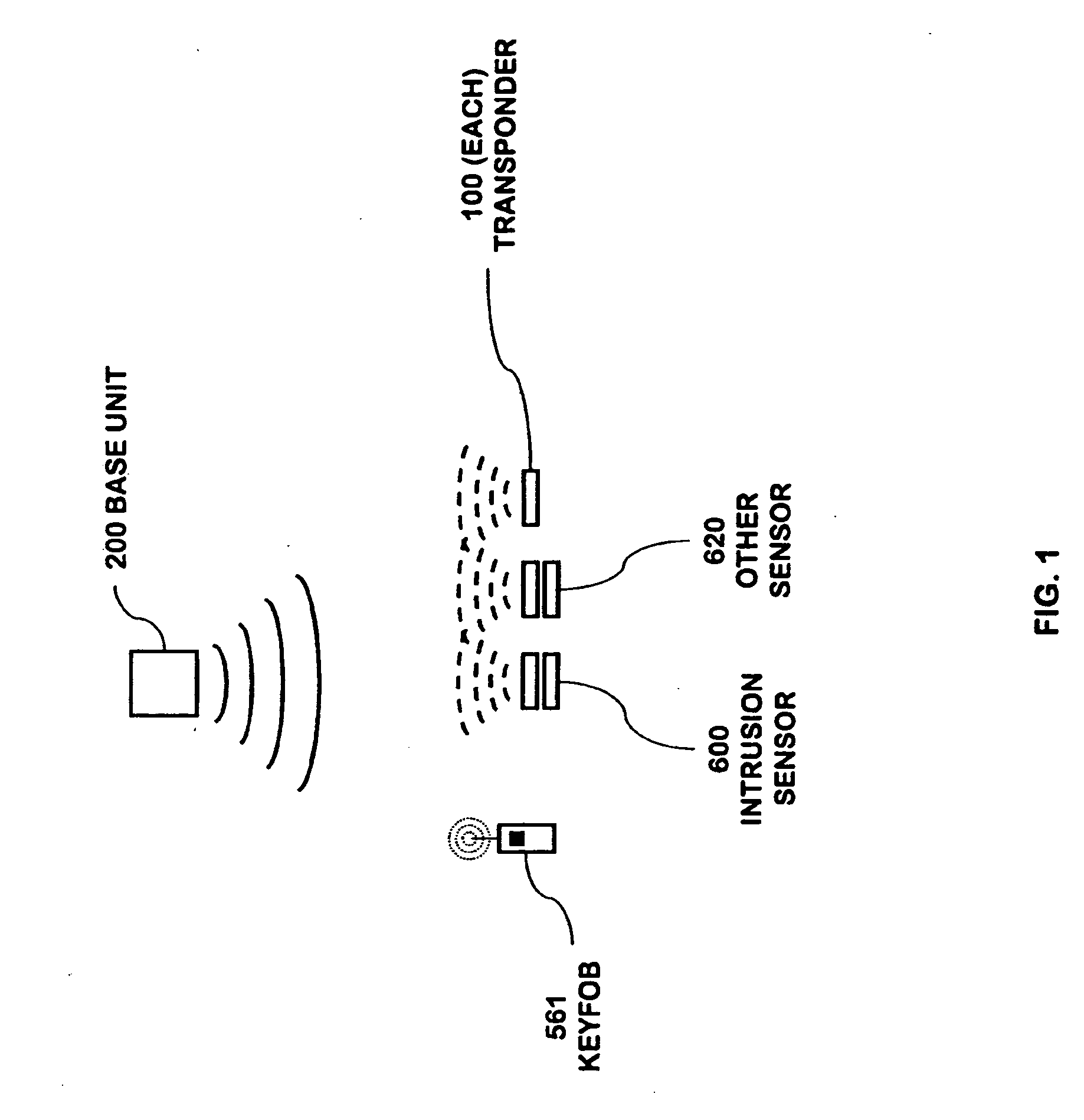

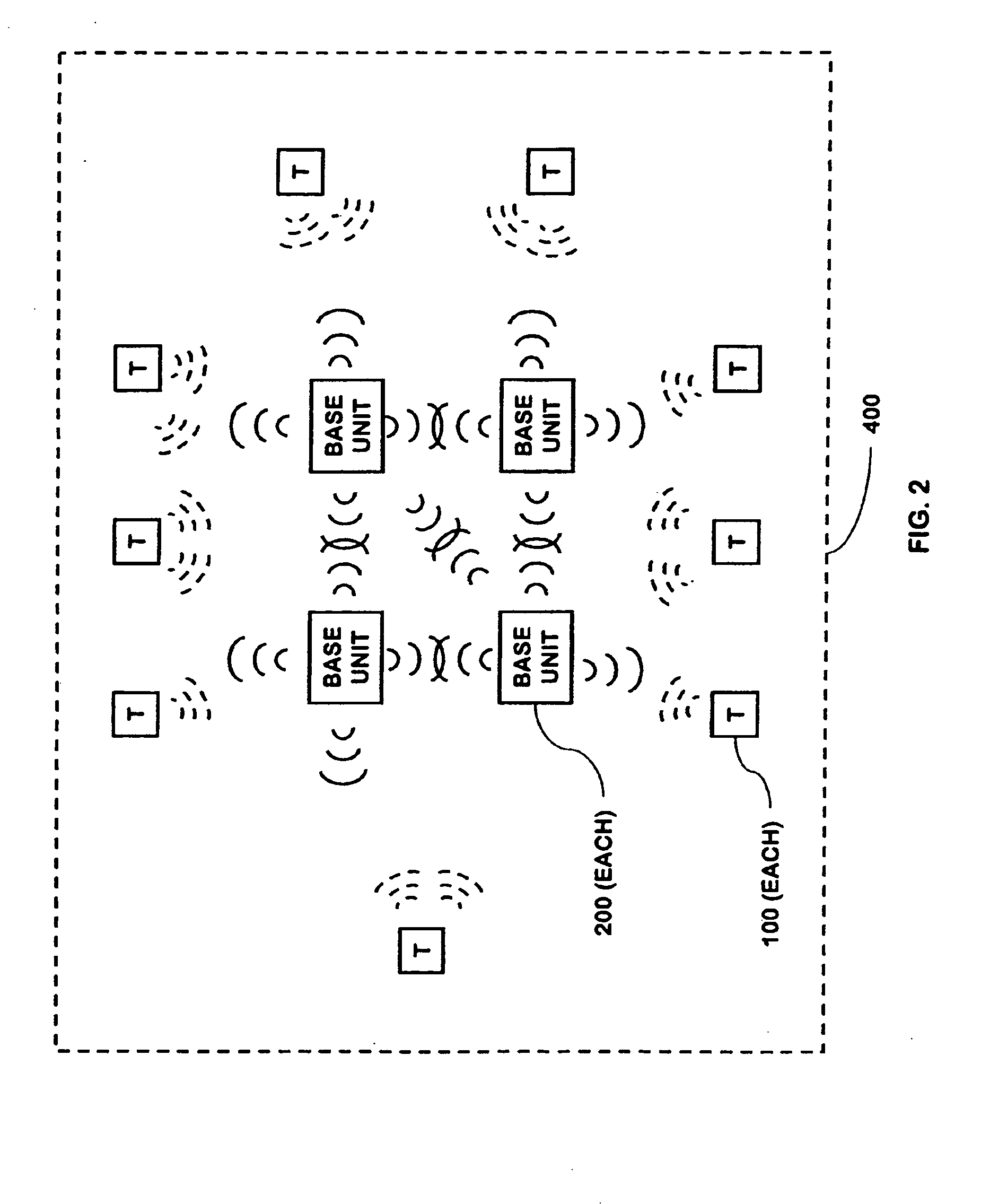

Multi-level meshed security network

InactiveUS20060145842A1Improve reliabilityLow costSafety arrangmentsComputer controlEngineeringSecondary layer

Owner:ADT US HLDG INC

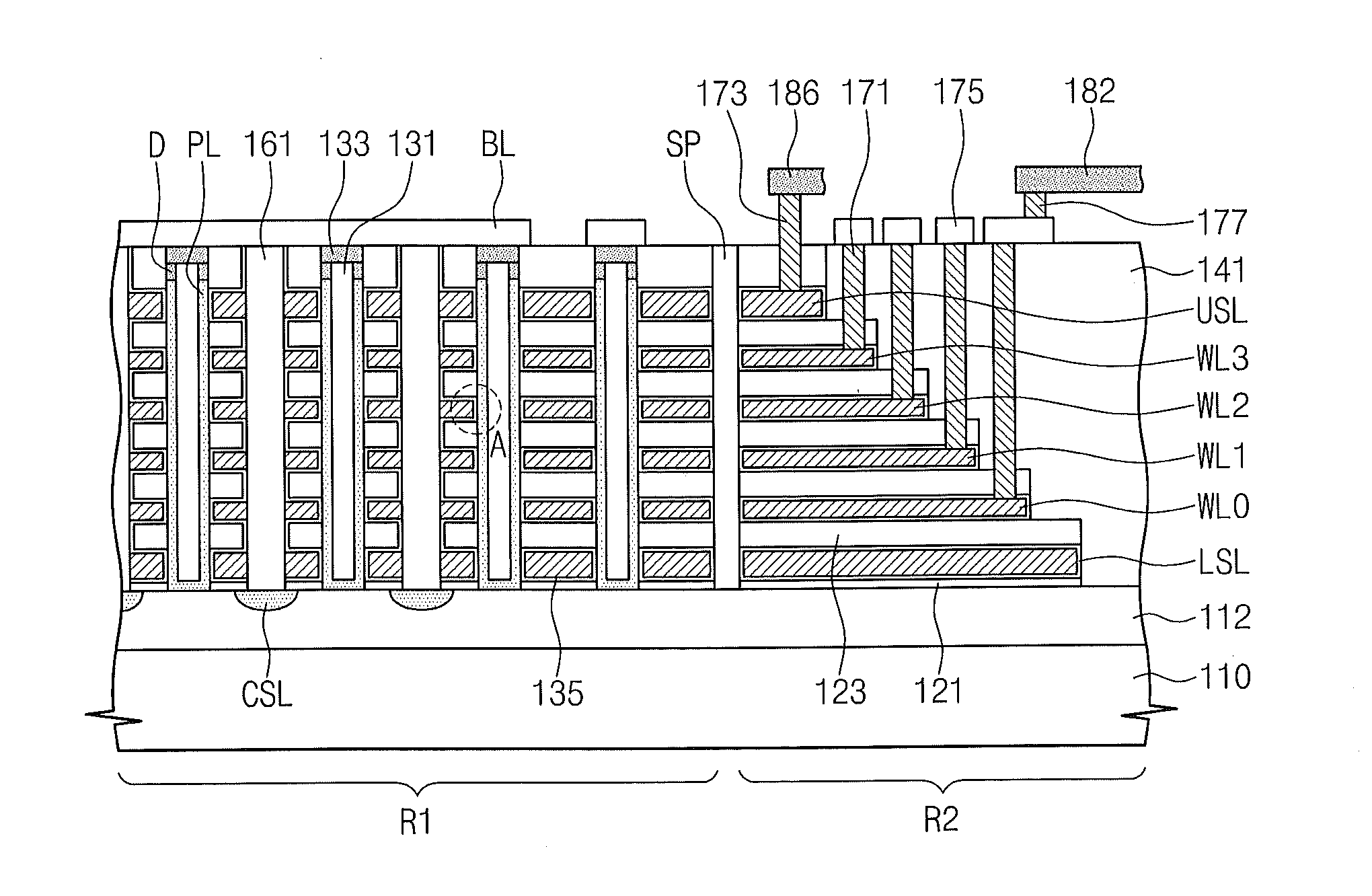

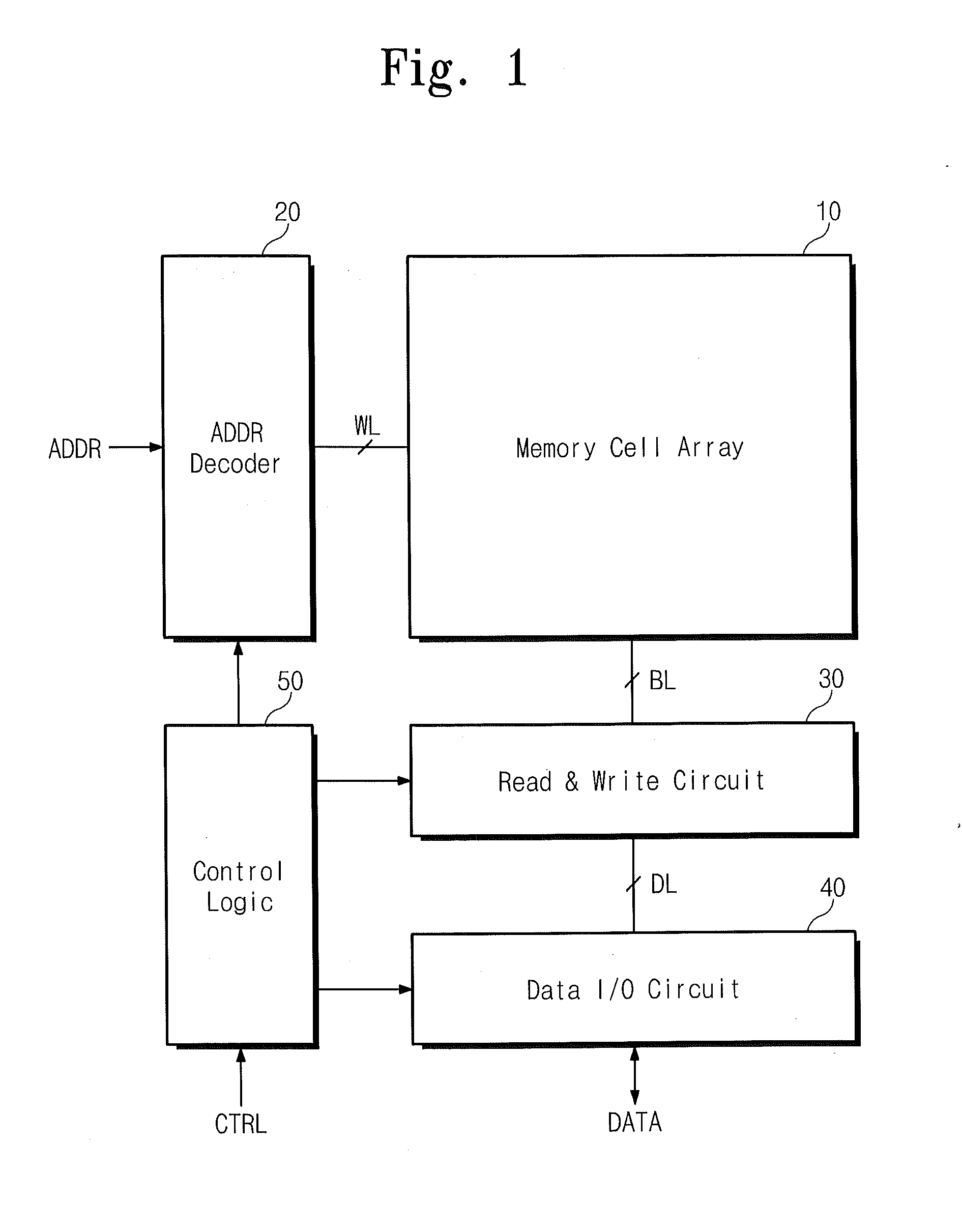

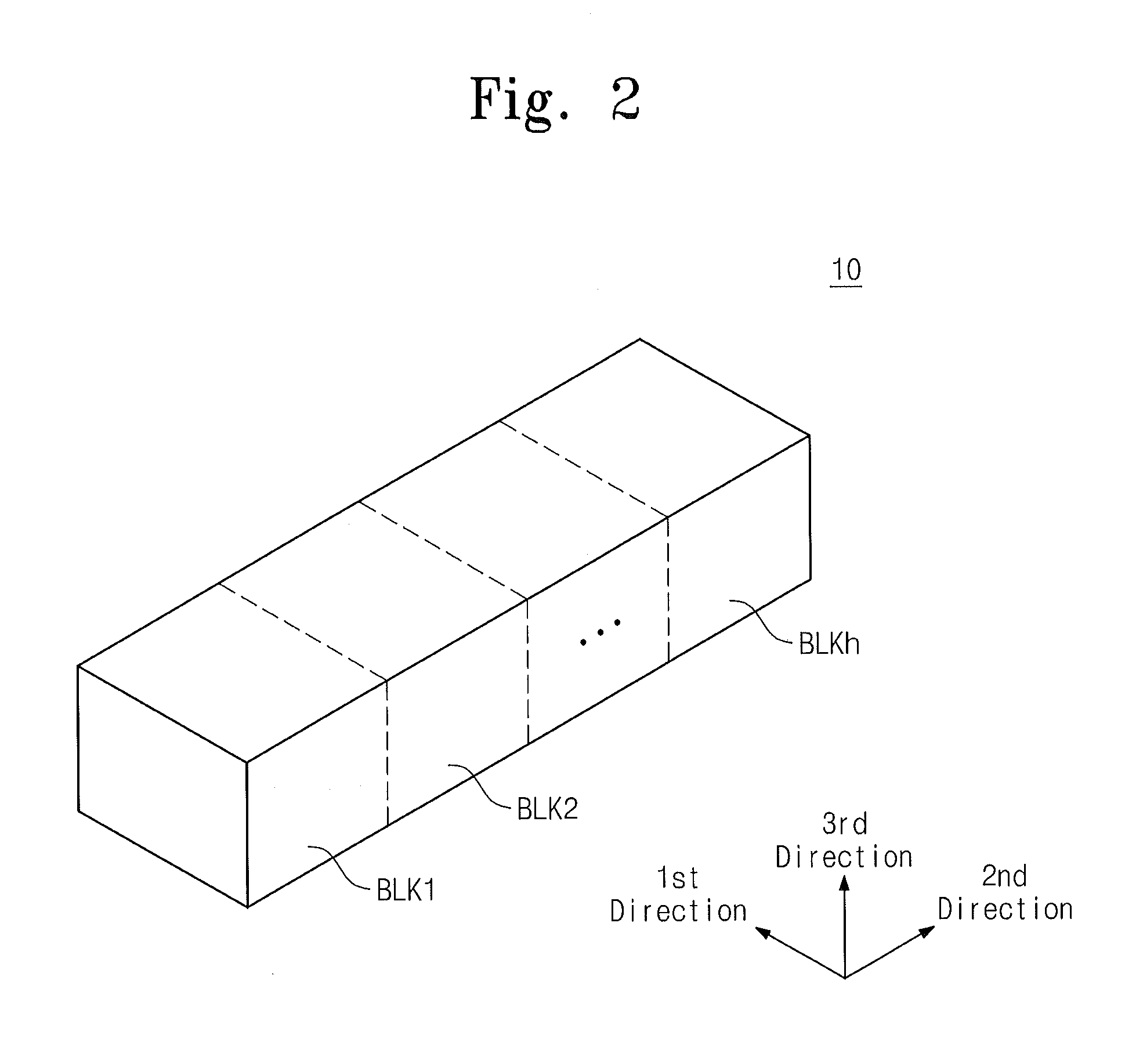

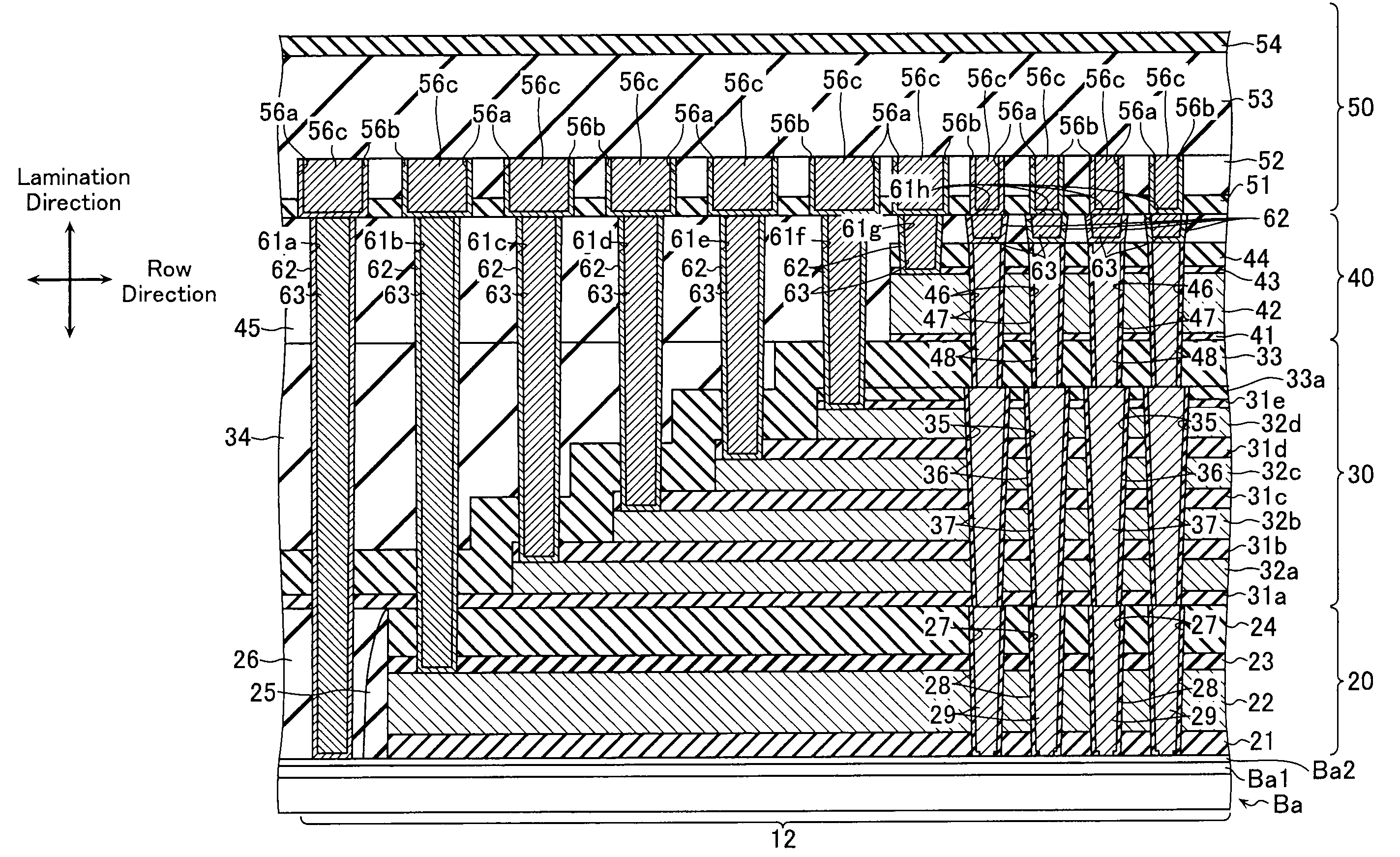

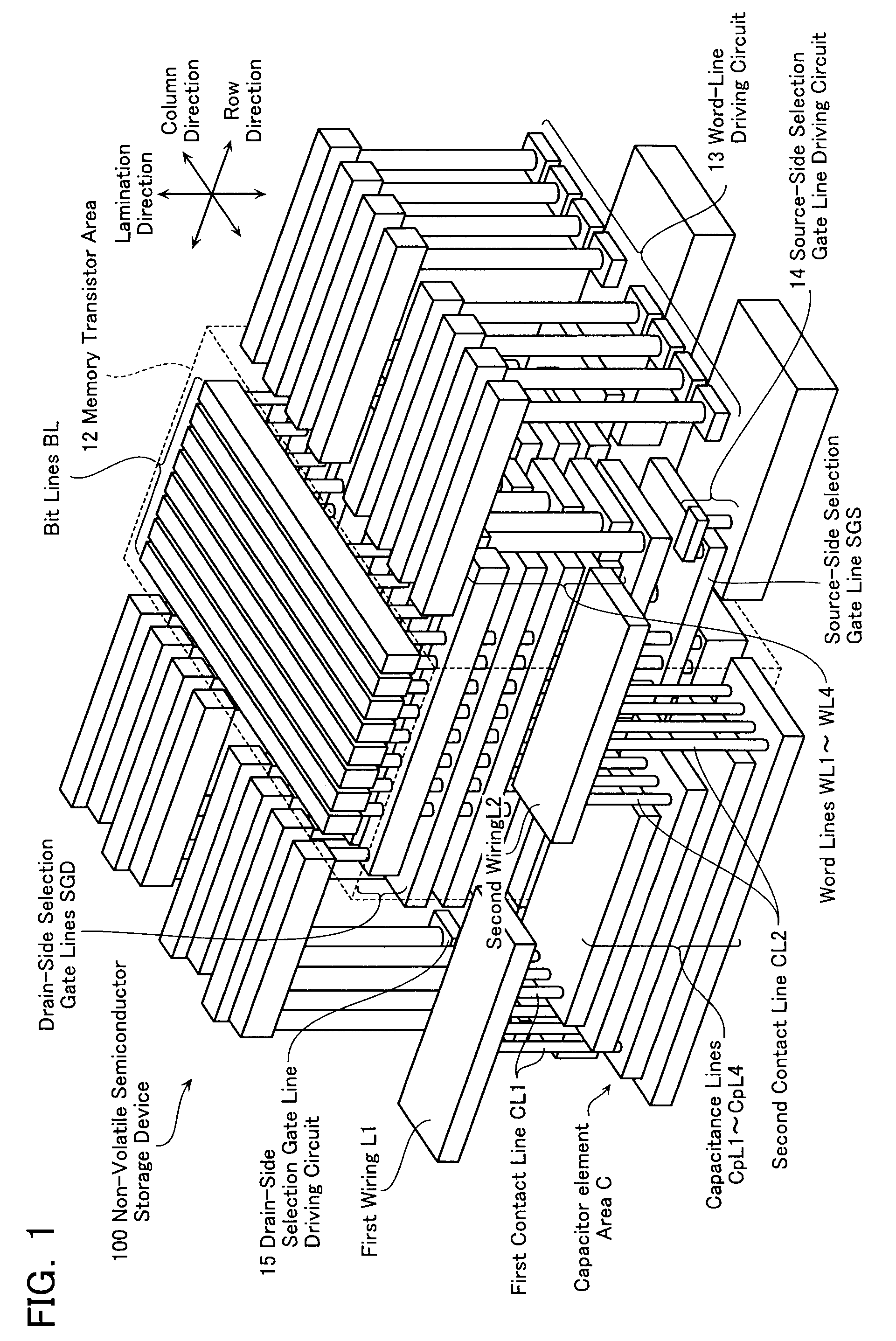

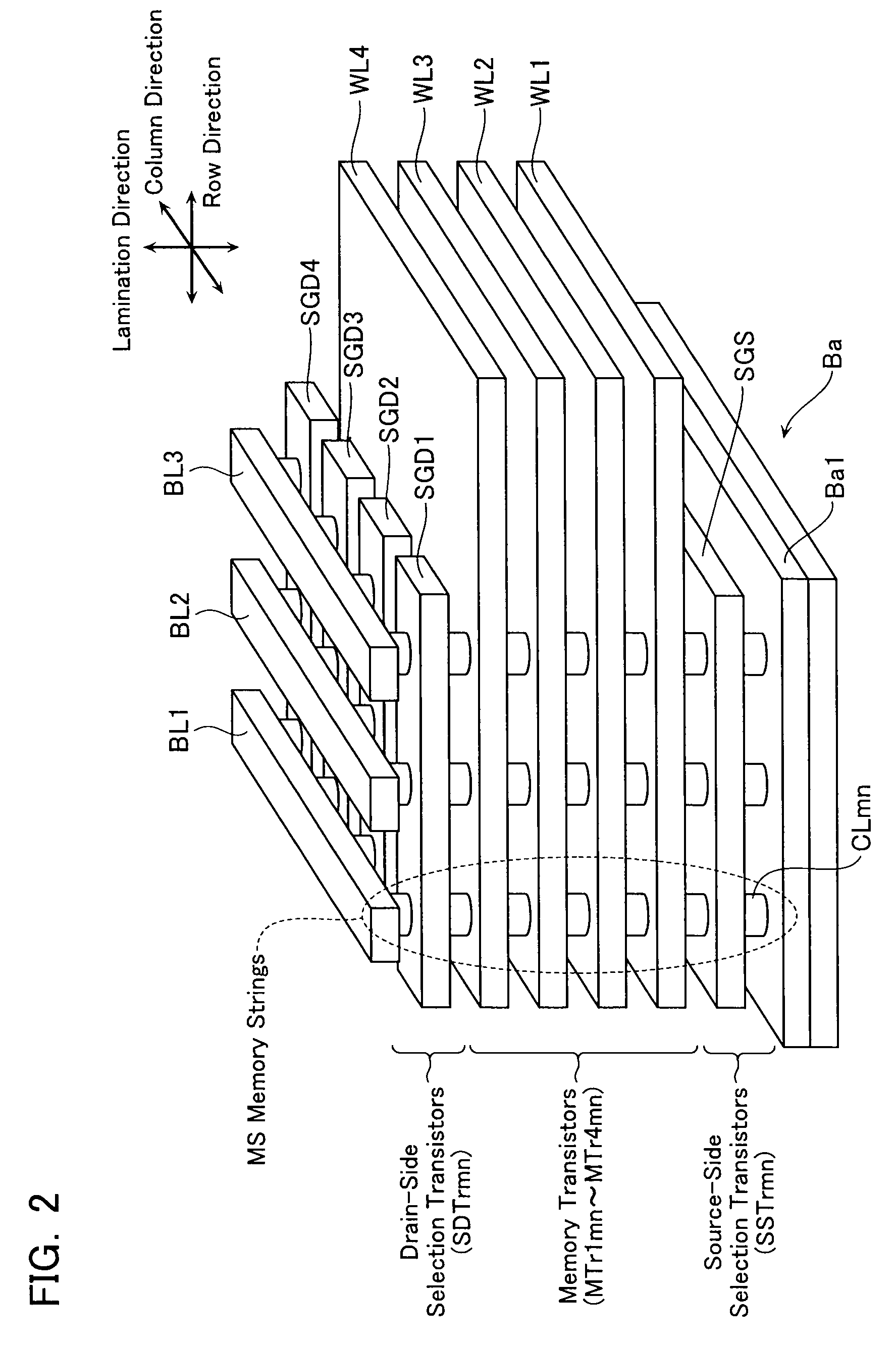

Semiconductor storage device

A non-volatile semiconductor storage device has: a plurality of memory strings with a plurality of electrically rewritable memory cells connected in series; and a capacitor element area including capacitor elements. Each of the memory strings includes: a plurality of first conductive layers laminated on a substrate; and a plurality of first interlayer insulation layers formed between the plurality of first conductive layers. The capacitor element area includes: a plurality of second conductive layers laminated on a substrate and formed in the same layer as the first conductive layers; and a plurality of second interlayer insulation layers formed between the plurality of second conductive layers and formed in the same layer as the first interlayer insulation layers. A group of the adjacently-laminated second conductive layers is connected to a first potential, while another group thereof is connected to a second potential.

Owner:KK TOSHIBA

Coated tablet formulation and method

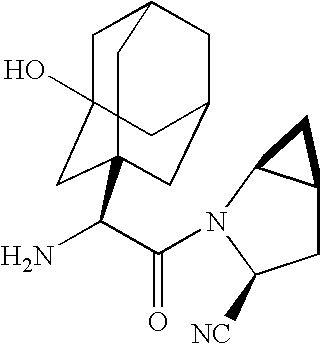

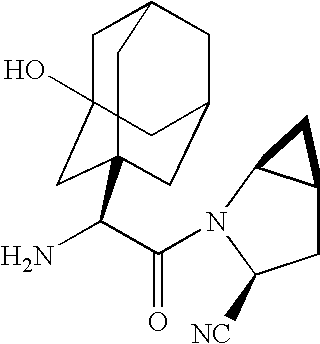

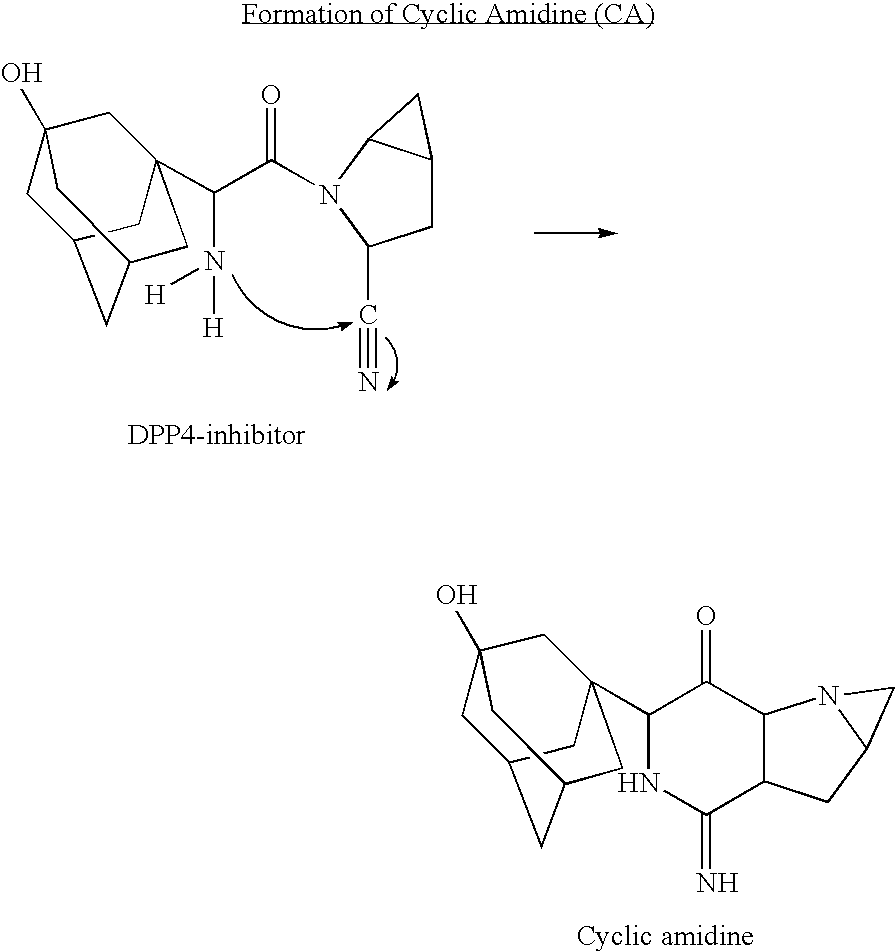

ActiveUS20050266080A1Good chemical stabilityEasy to prepareBiocideMetabolism disorderCoated tabletsExcipient

A coated tablet formulation is provided which includes a medicament such as the DPP4-inhibitor, saxaglipitin or its HCl salt, which is subject to intra-molecular cyclization, which formulation includes a tablet core containing one or more fillers, and other conventional excipients, which tablet core includes a coating thereon which may include two or more layers, at least one layer of which is an inner seal coat layer which is formed of one or more coating polymers, a second layer of which is formed of medicament which is the DPP4-inhibitor and one or more coating polymers, and an optional, but preferable third outer protective layer which is formed of one or more coating polymers. A method for forming the coated tablet is also provided.

Owner:ASTRAZENECA AB

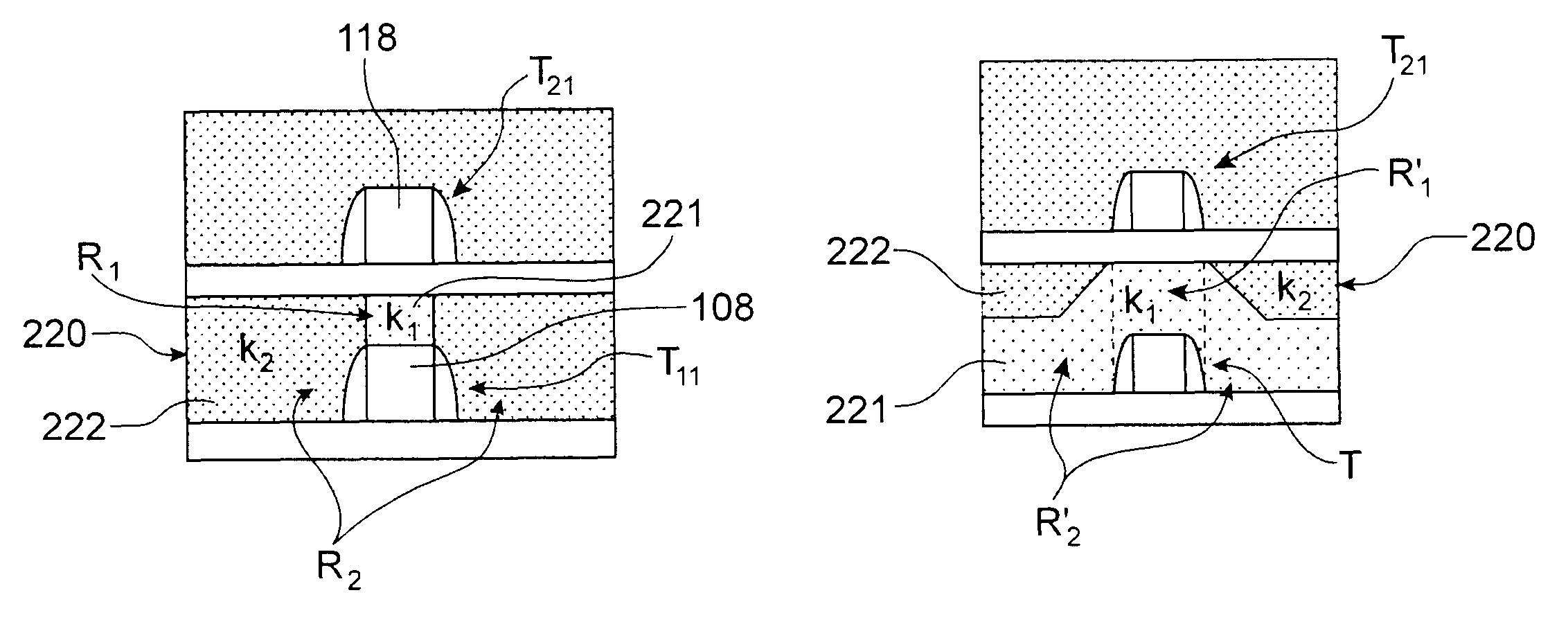

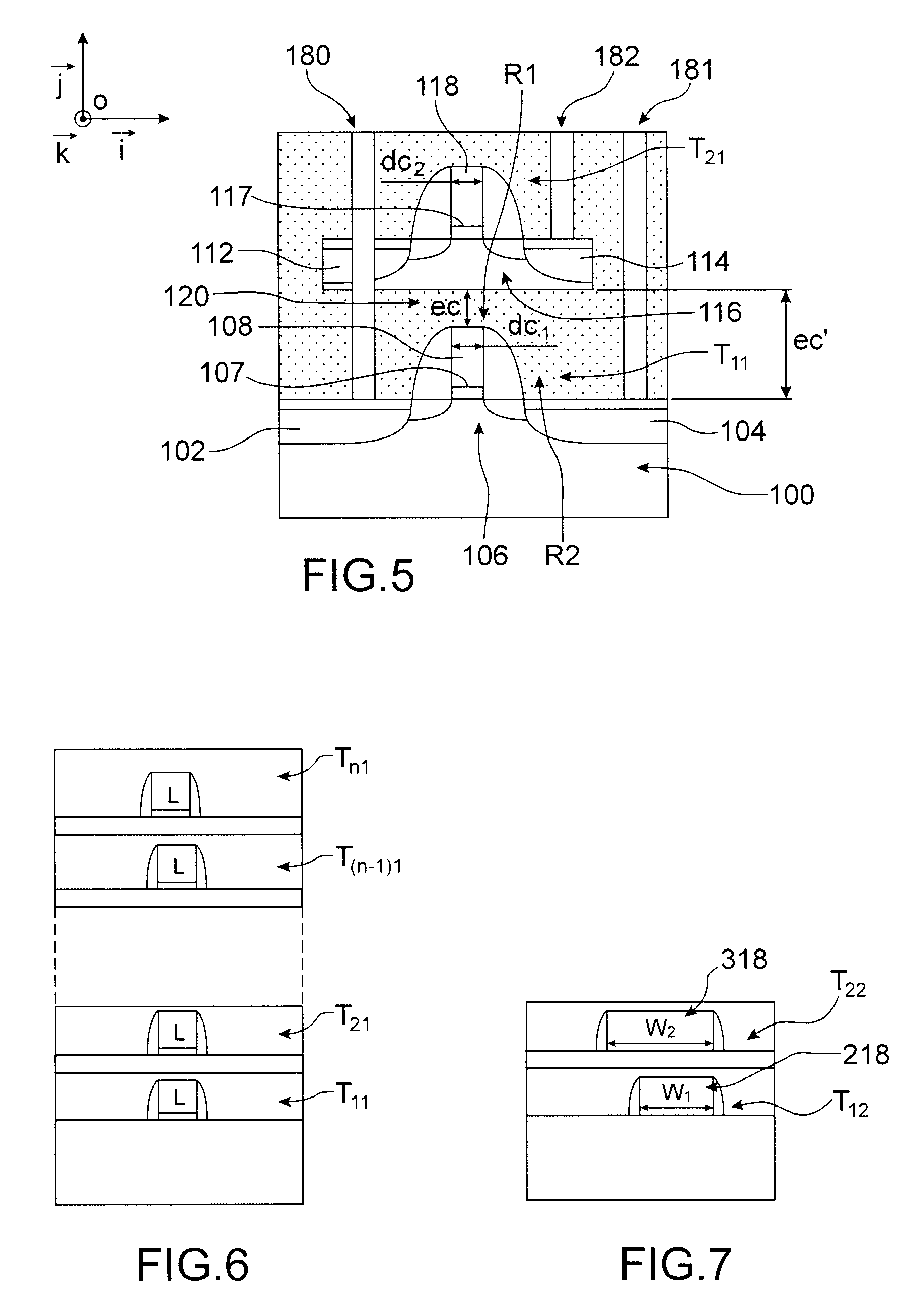

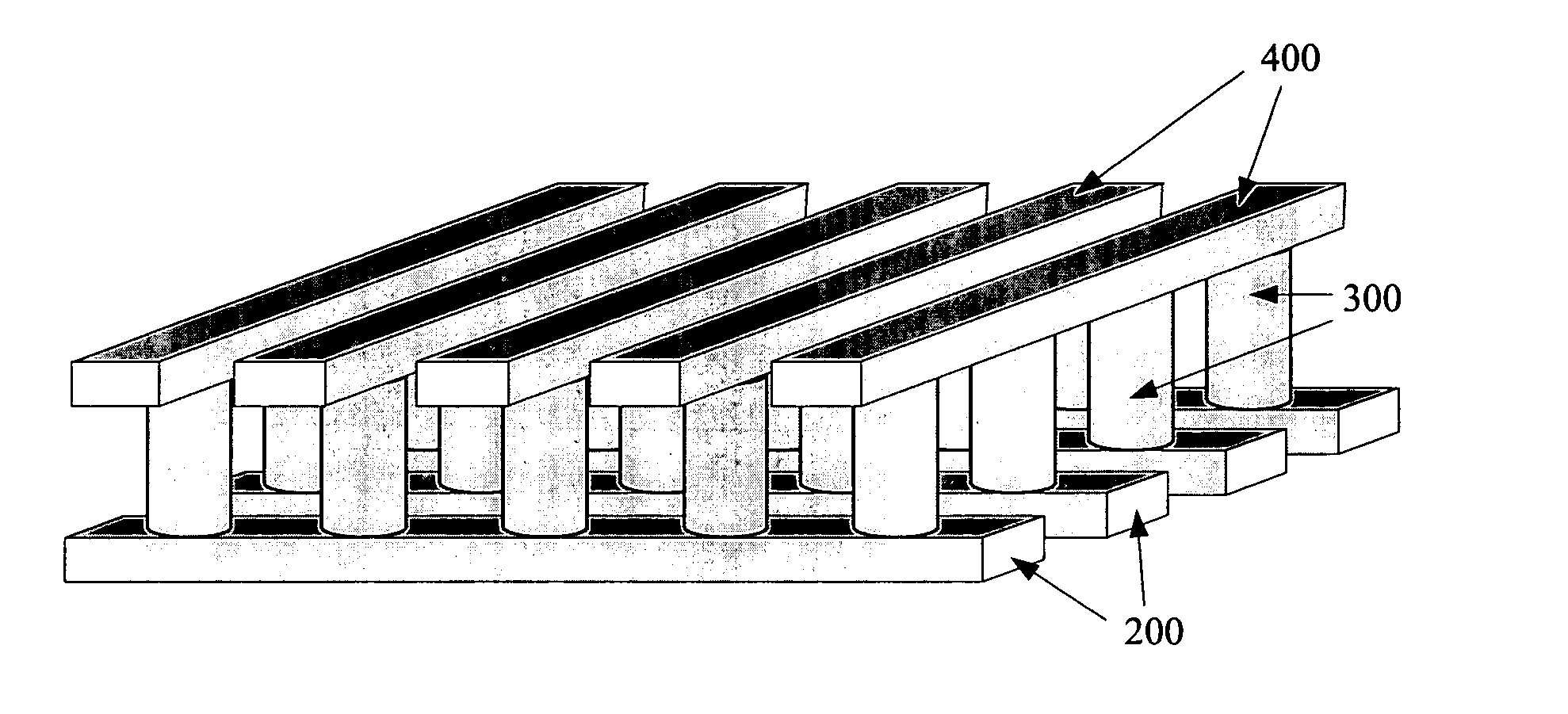

Circuit with transistors integrated in three dimensions and having a dynamically adjustable threshold voltage VT

ActiveUS8183630B2Avoid couplingReduced topographyTransistorSolid-state devicesHemt circuitsThreshold voltage

A microelectronic device including: a substrate surmounted by a stack of layers, at least one first transistor situated at a given level of said stack, at least one second transistor situated at a second level of said stack, above said given level, the first transistor including a gate electrode situated opposite a channel zone of the second transistor, the first transistor and the second transistor being separated by an insulating zone, and said insulating zone being constituted of several different dielectric materials include a first dielectric material and a second dielectric material.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

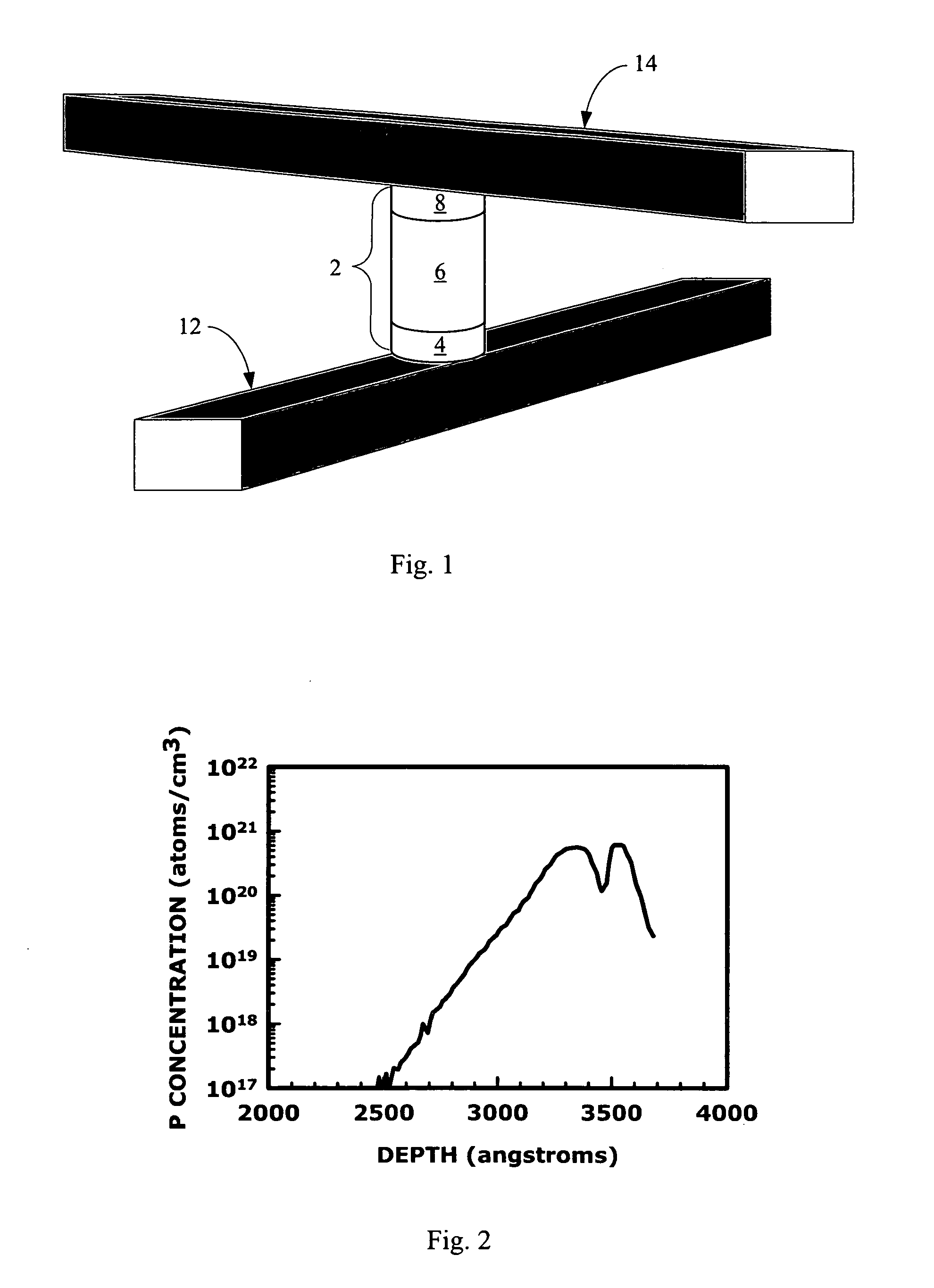

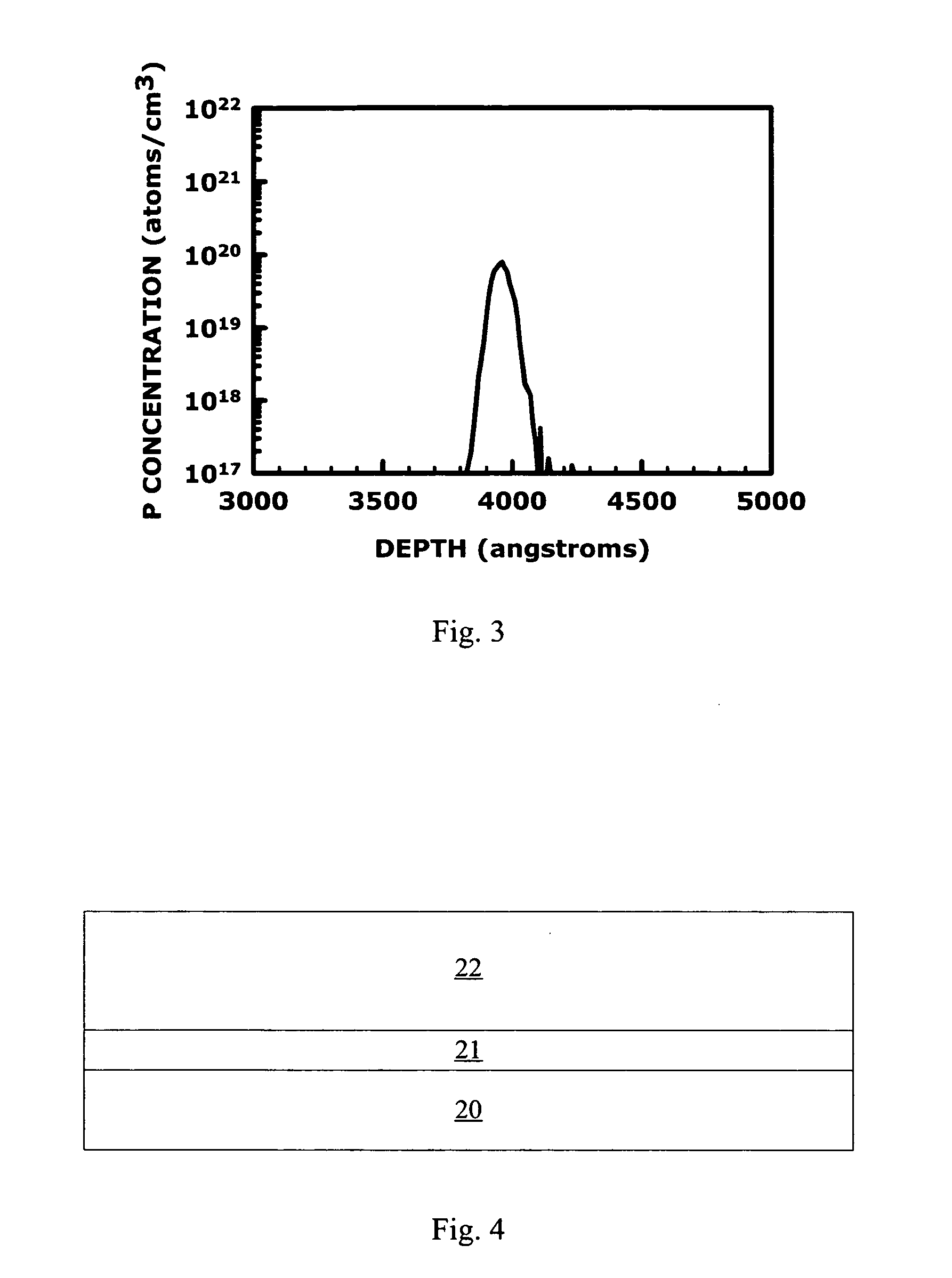

Deposited semiconductor structure to minimize N-type dopant diffusion and method of making

ActiveUS20060087005A1Solid-state devicesSemiconductor/solid-state device manufacturingDopantSemiconductor structure

In deposited silicon, n-type dopants such as phosphorus and arsenic tend to seek the surface of the silicon, rising as the layer is deposited. When a second undoped or p-doped silicon layer is deposited on n-doped silicon with no n-type dopant provided, a first thickness of this second silicon layer nonetheless tends to include unwanted n-type dopant which has diffused up from lower levels. This surface-seeking behavior diminishes when germanium is alloyed with the silicon. In some devices, it may not be advantageous for the second layer to have significant germanium content. In the present invention, a first heavily n-doped semiconductor layer (preferably at least 10 at % germanium) is deposited, followed by a silicon-germanium capping layer with little or no n-type dopant, followed by a layer with little or no n-type dopant and less than 10 at % germanium. The germanium in the first layer and the capping layer minimizes diffusion of n-type dopant into the germanium-poor layer above.

Owner:SANDISK TECH LLC

Dielectric layer for semiconductor device and method of manufacturing the same

InactiveUS6844604B2Improving interface characteristicReduce maintenanceTransistorSolid-state devicesDevice materialInterface layer

A multi-layer dielectric layer structure for a semiconductor device. The multi-layer dielectric layer structure comprises a silicate interface layer having a dielectric constant greater than that of silicon nitride and a high-k dielectric layer overlying the silicate interface layer. The high-k dielectric layer comprises one or more ordered pairs of first and second layers. With the present invention, the dielectric constant of the high-k dielectric layer can be optimized while improving interface characteristics. With a higher crystallization temperature realized by forming the multi-layer structure, each of whose layers is not more than the critical thickness, leakage current can be reduced, thereby improving device performance.

Owner:SAMSUNG ELECTRONICS CO LTD

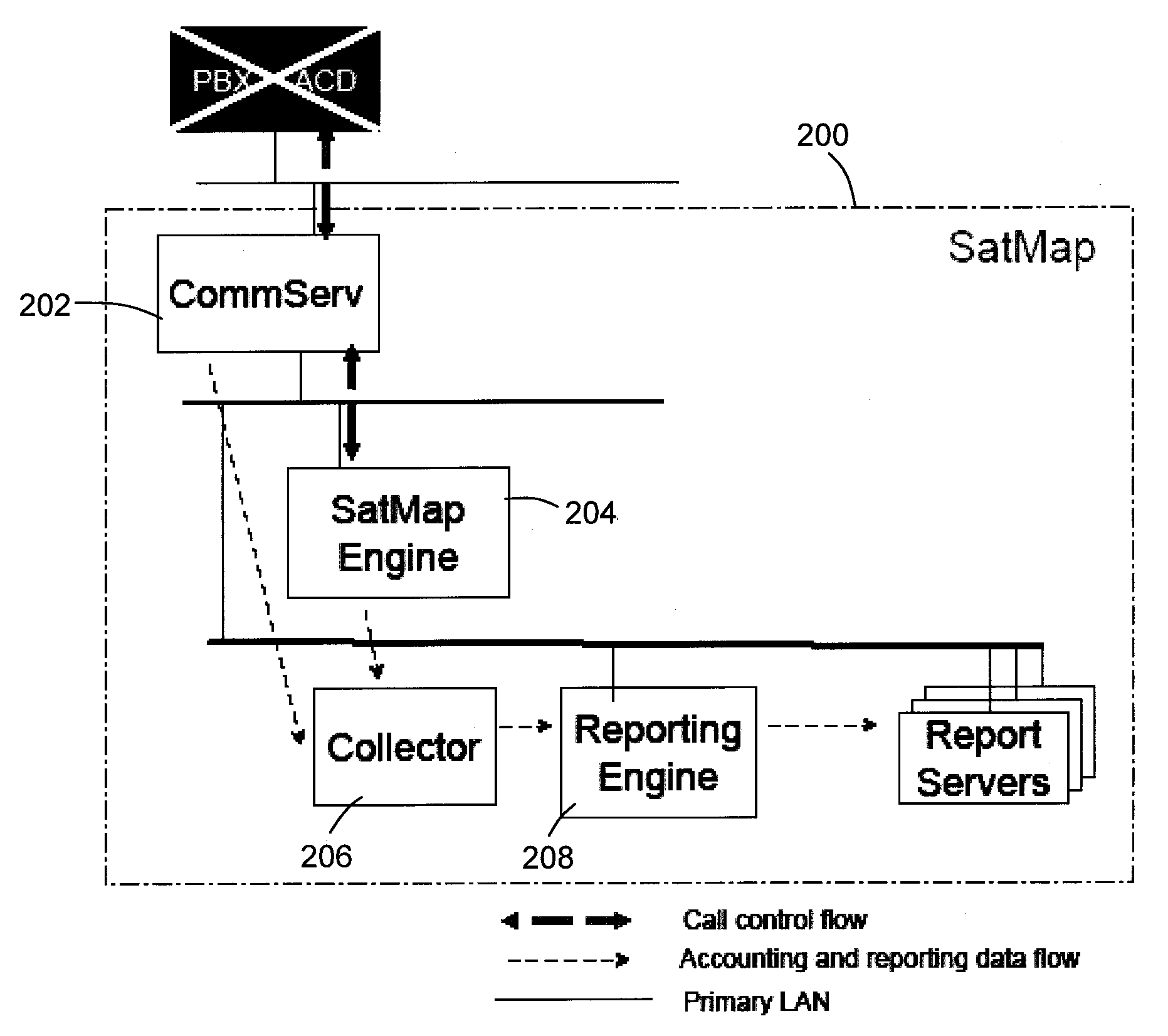

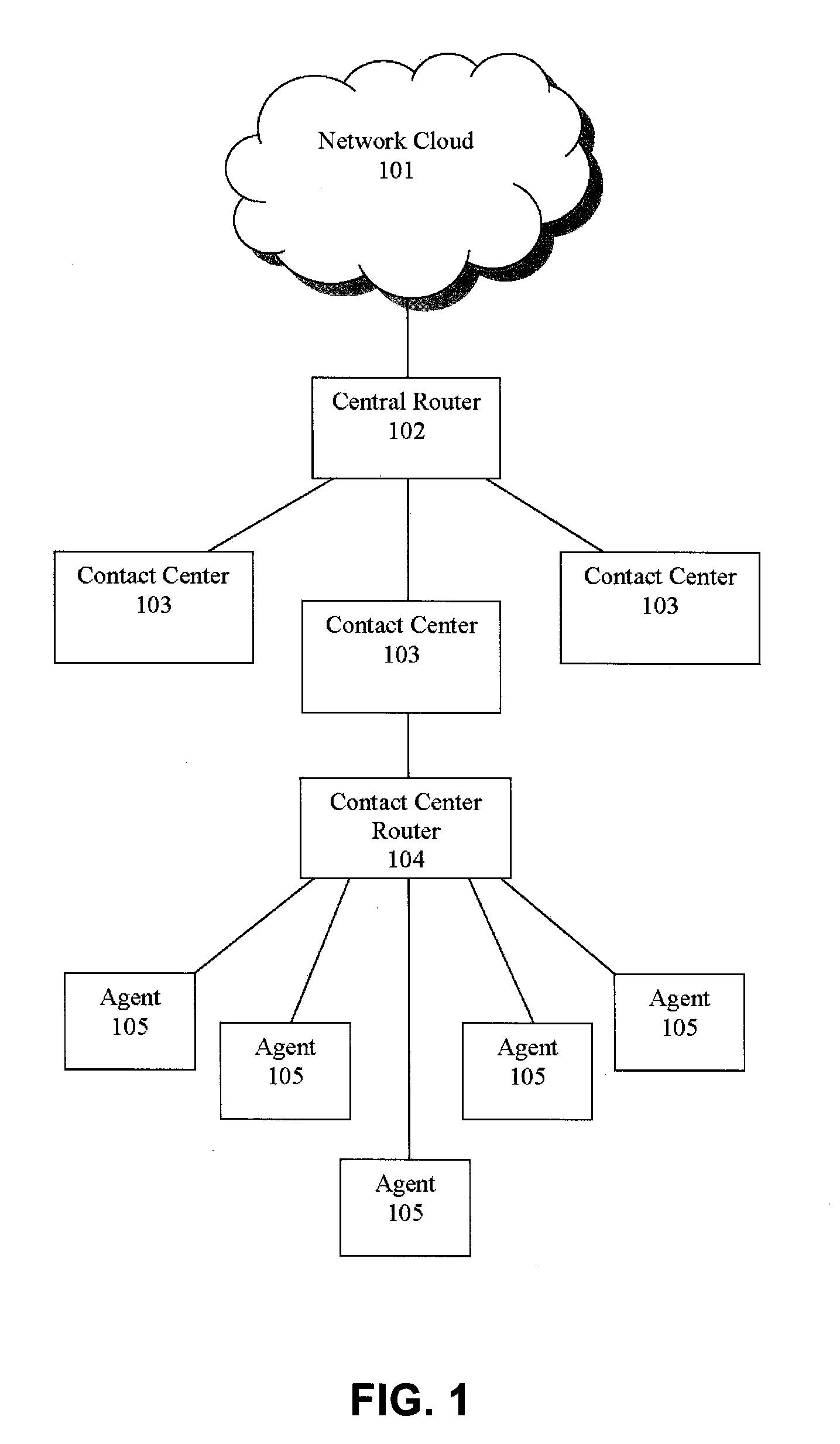

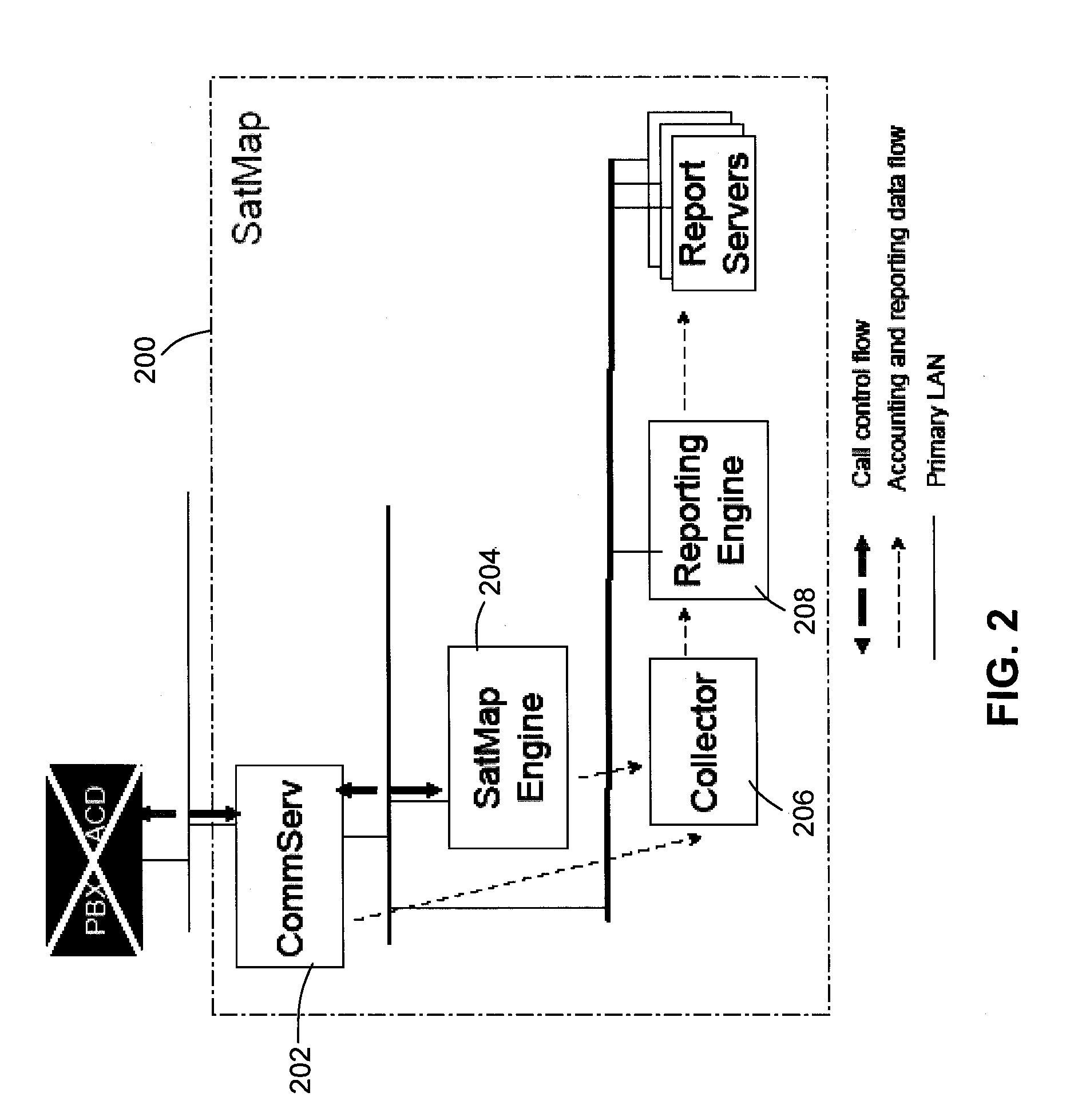

Balancing multiple computer models in a call center routing system

ActiveUS20100111285A1Adjust balanceDigital computer detailsBiological neural network modelsPattern matchingParallel computing

Systems and methods are disclosed for routing callers to agents in a contact center utilizing a multi-layer processing approach to matching a caller to an agent. A first layer of processing may include two or more different computer models or methods for scoring or determining caller-agent pairs in a routing center. The output of the first layer may be received by a second layer of processing for balancing or weighting the outputs and selecting a final caller-agent match. The two or more methods may include conventional queue based routing, performance based routing, pattern matching algorithms, affinity matching, and the like. The output or scores of the two or more methods may be processed be the second layer of processing to select a caller-agent pair and cause the caller to be routed to a particular agent.

Owner:AFINITI LTD

Method of pitch dimension shrinkage

ActiveUS7183205B2Dimension can be narrowedAvoid disadvantagesPhotomechanical apparatusSemiconductor/solid-state device manufacturingSecondary layerPhysics

Roughly described, a patterned first layer is provided over a second layer which is formed over a substrate. In a conversion process, first layer material is consumed at feature sidewalls to form third layer material at the feature sidewalls. The width of third layer material at each of the sidewalls is greater than the width of first layer material consumed at the respective sidewall in the conversion process. The second layer is patterned using the third layer material as mask. A fourth layer of material is formed over the substrate, and planarized or otherwise partially removed so as to expose the top surfaces of the features in the first layer through the fourth layer. The exposed first layer material is removed to expose portions of the second layer through the fourth layer, and the second layer is further patterned using the fourth layer material as a mask.

Owner:MACRONIX INT CO LTD

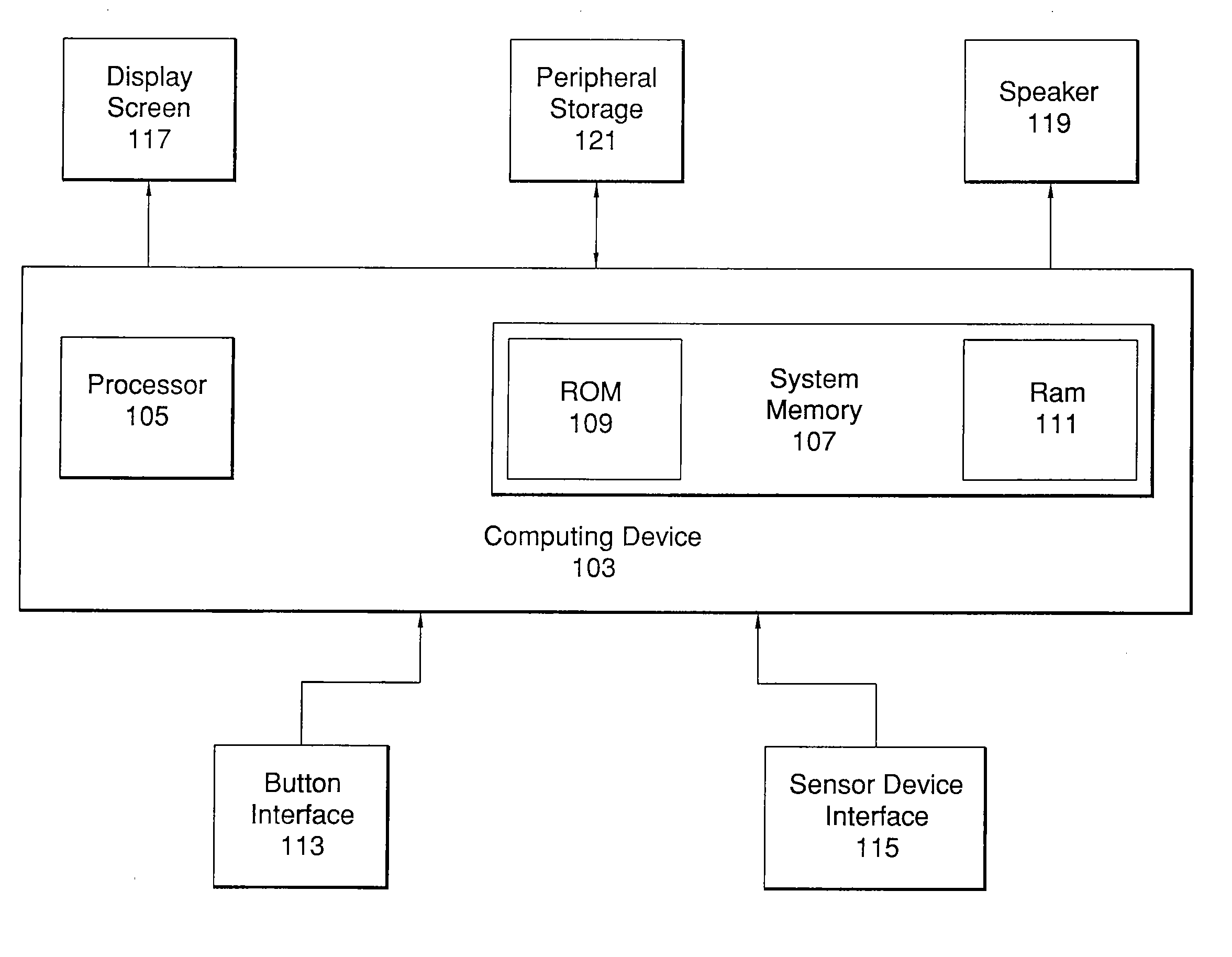

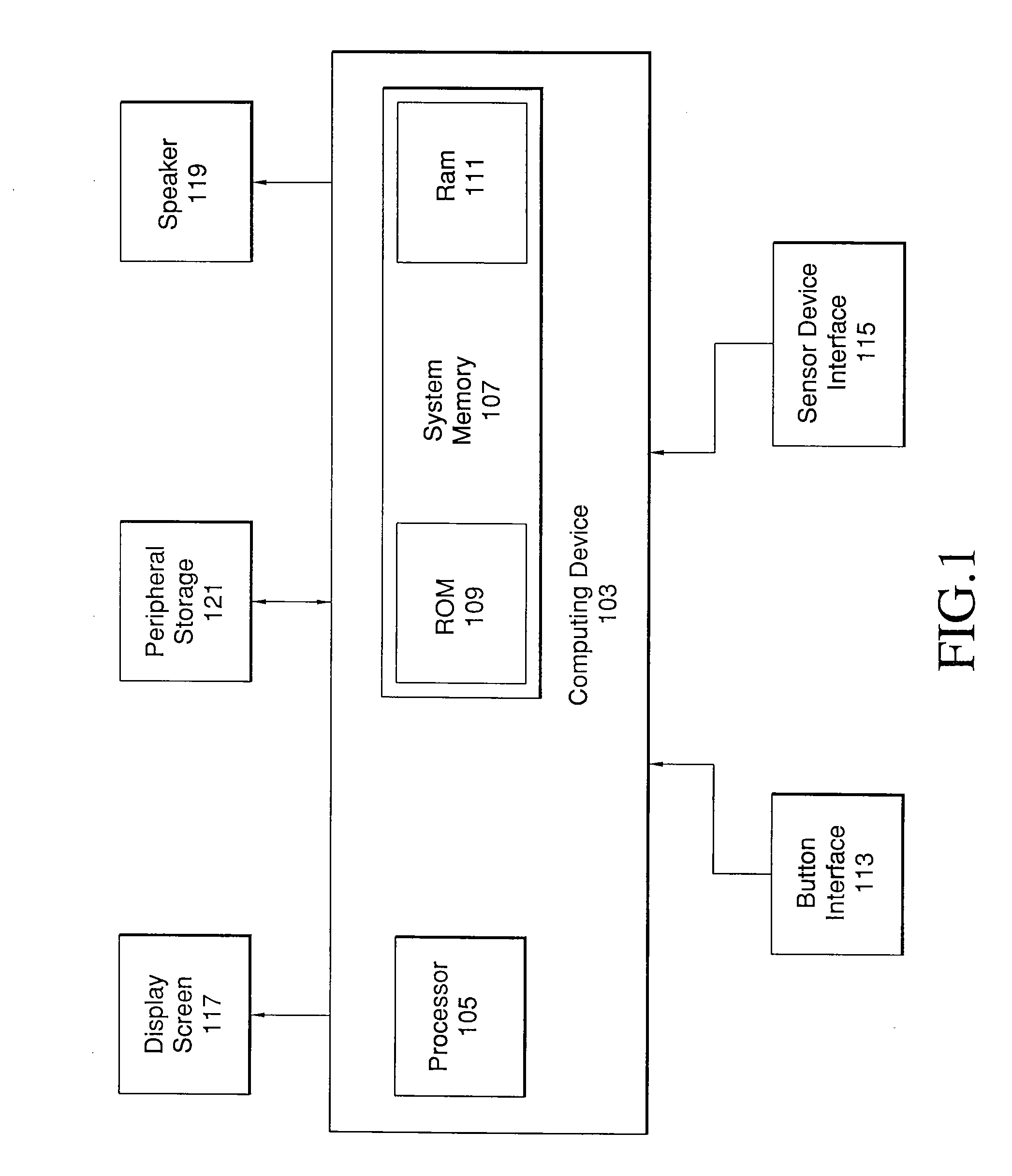

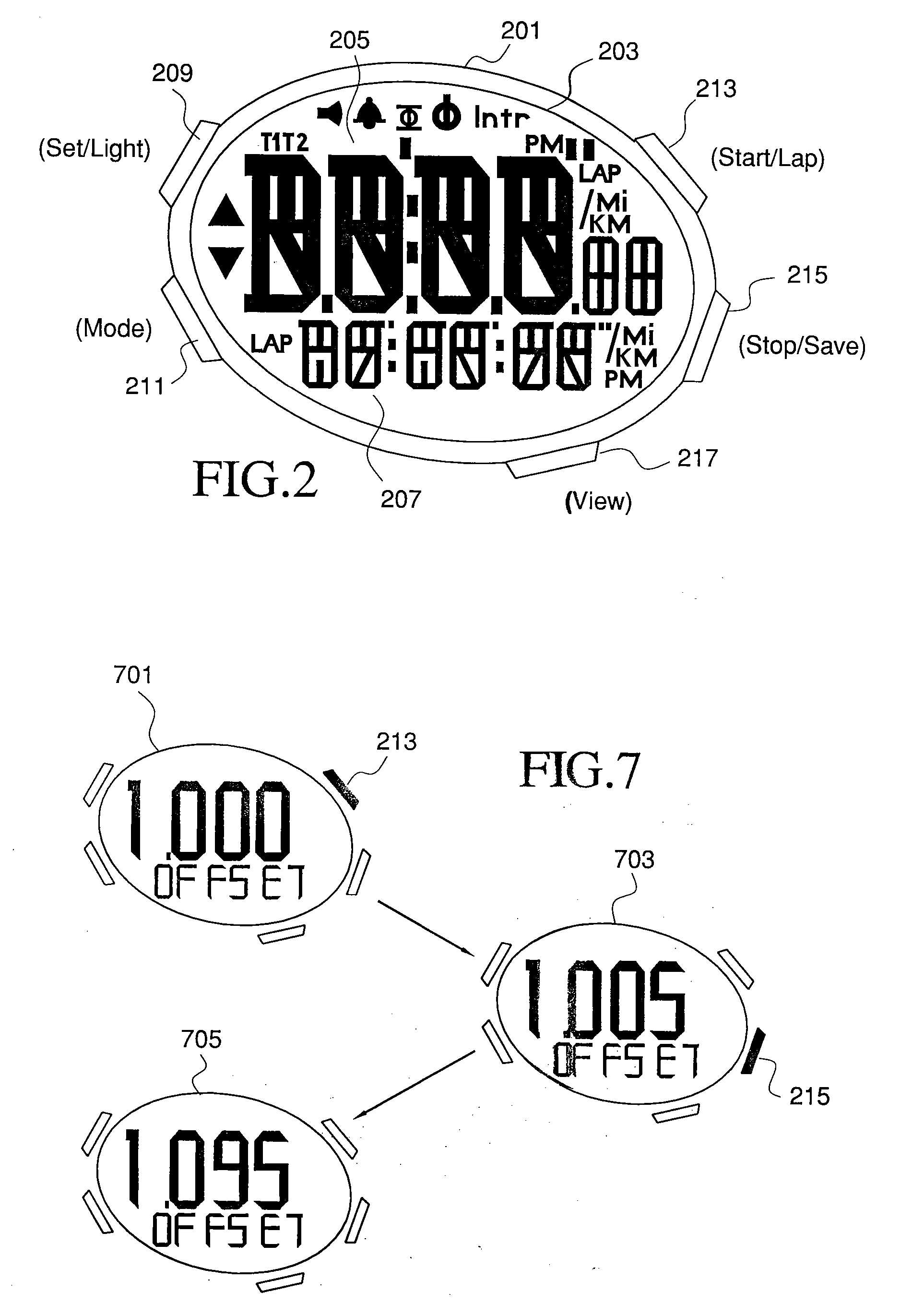

Adaptive Watch

InactiveUS20070159926A1Easy to controlPhysical therapies and activitiesMechanical clocksSpecific functionBroad category

A watch or other type of portable electronic console that employs a number of different functions in order to improve its usability. The watch may, for example, allow a user to connect the watch to one or more remote electronic devices, such as an electronic performance sensor or MP3 player. The watch then displays information related to the connected electronic devices. Still further, the watch may allow a user to control the operation of one or more connected remote electronic devices. Thus, if the watch is connected to a remote speed / distance monitor employing a calibration variable, then the watch may allow the user to adjust the calibration variable. The watch also provides a multi-tiered menu for accessing its various functions. Each operational mode in the first tier relates to a broad category of different functions of the watch, and contains one or more operational submodes in a second tier. The submodes in the second tier are for performing specific functions related to the generic category of functions identified by the first-tier operational mode. Still further, the watch allows a user to conveniently select how the information provided by the watch is displayed. Moreover, the watch includes a power save function that reduces the power consumption of the watch when it is not in use.

Owner:NIKE INC

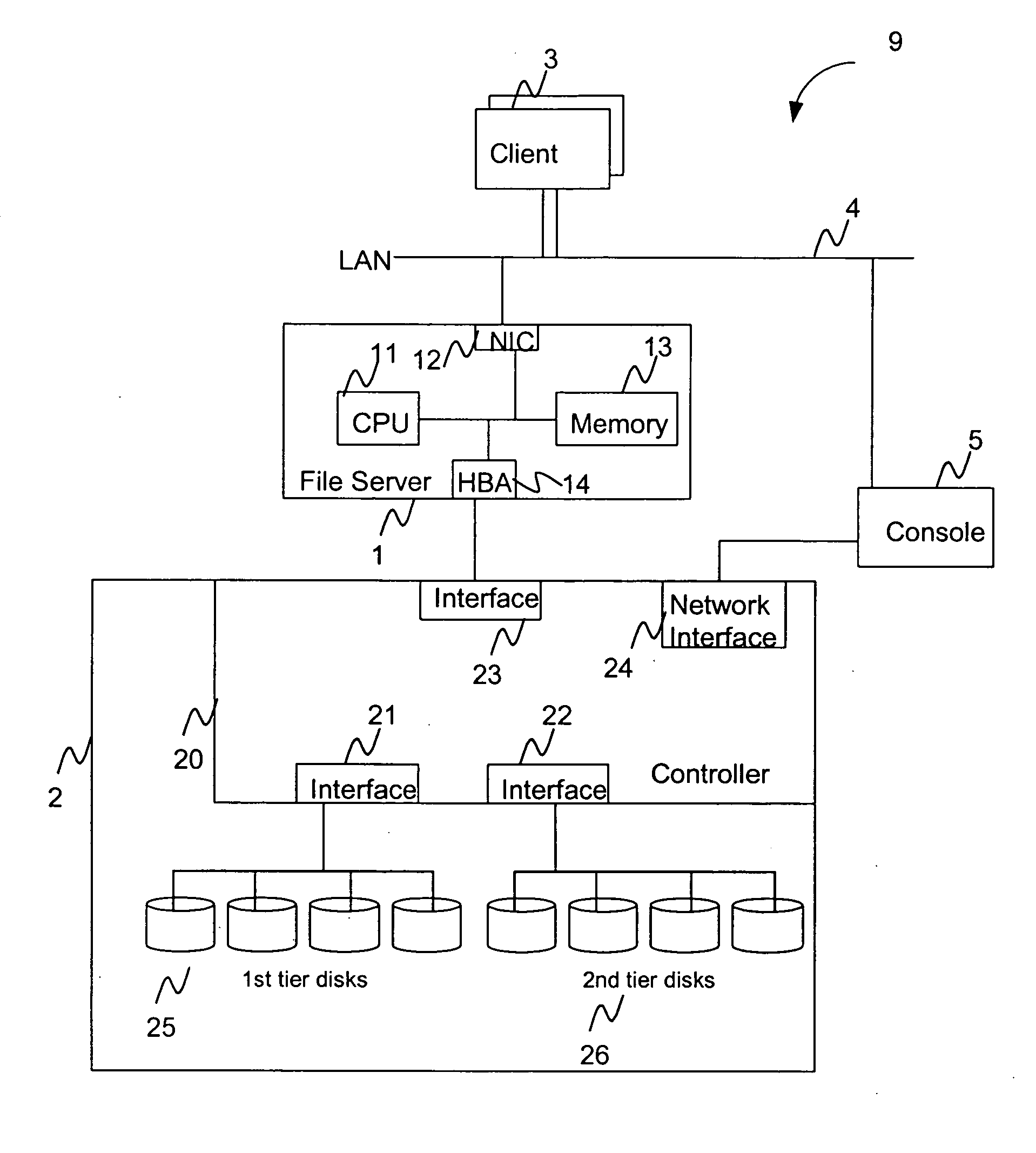

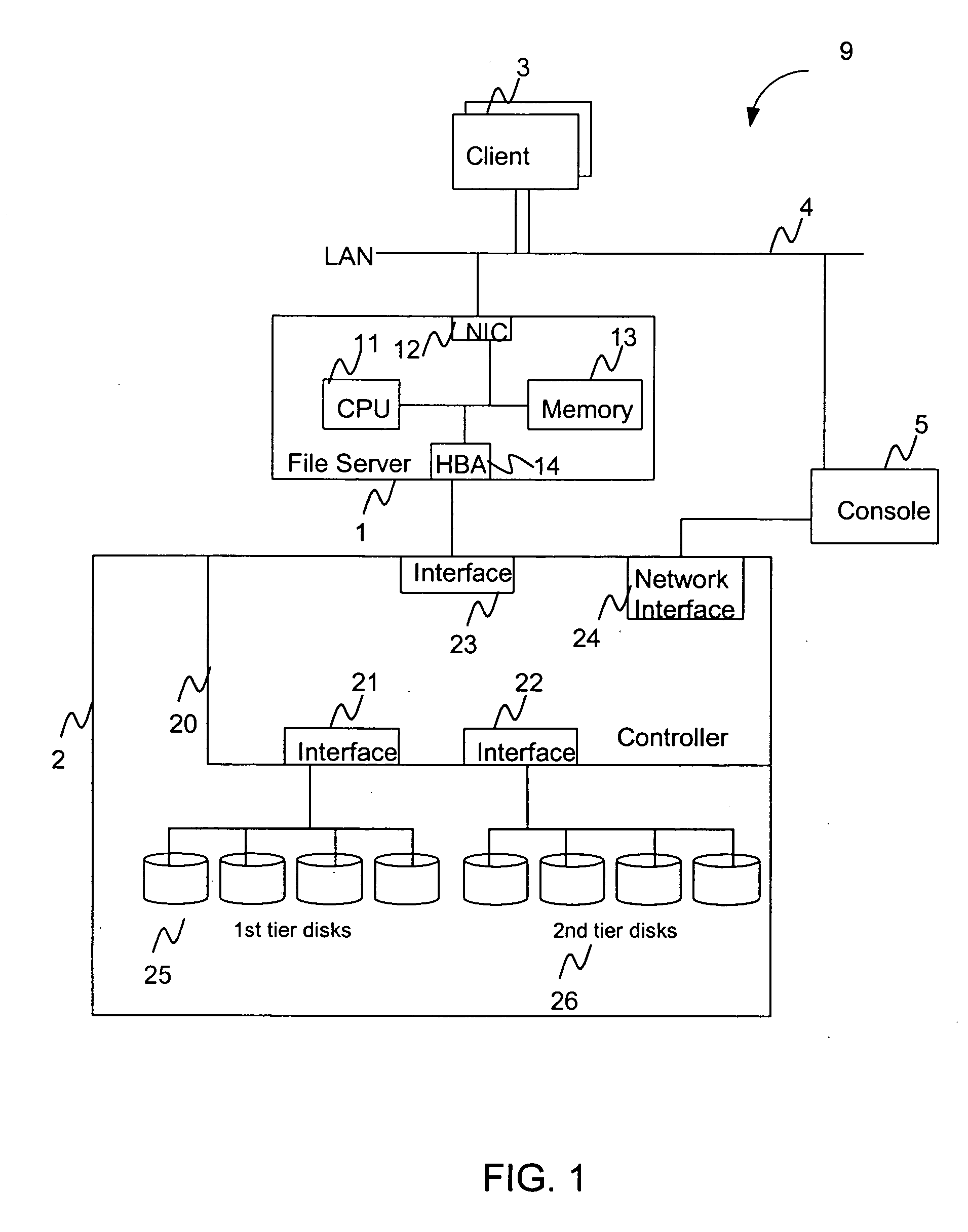

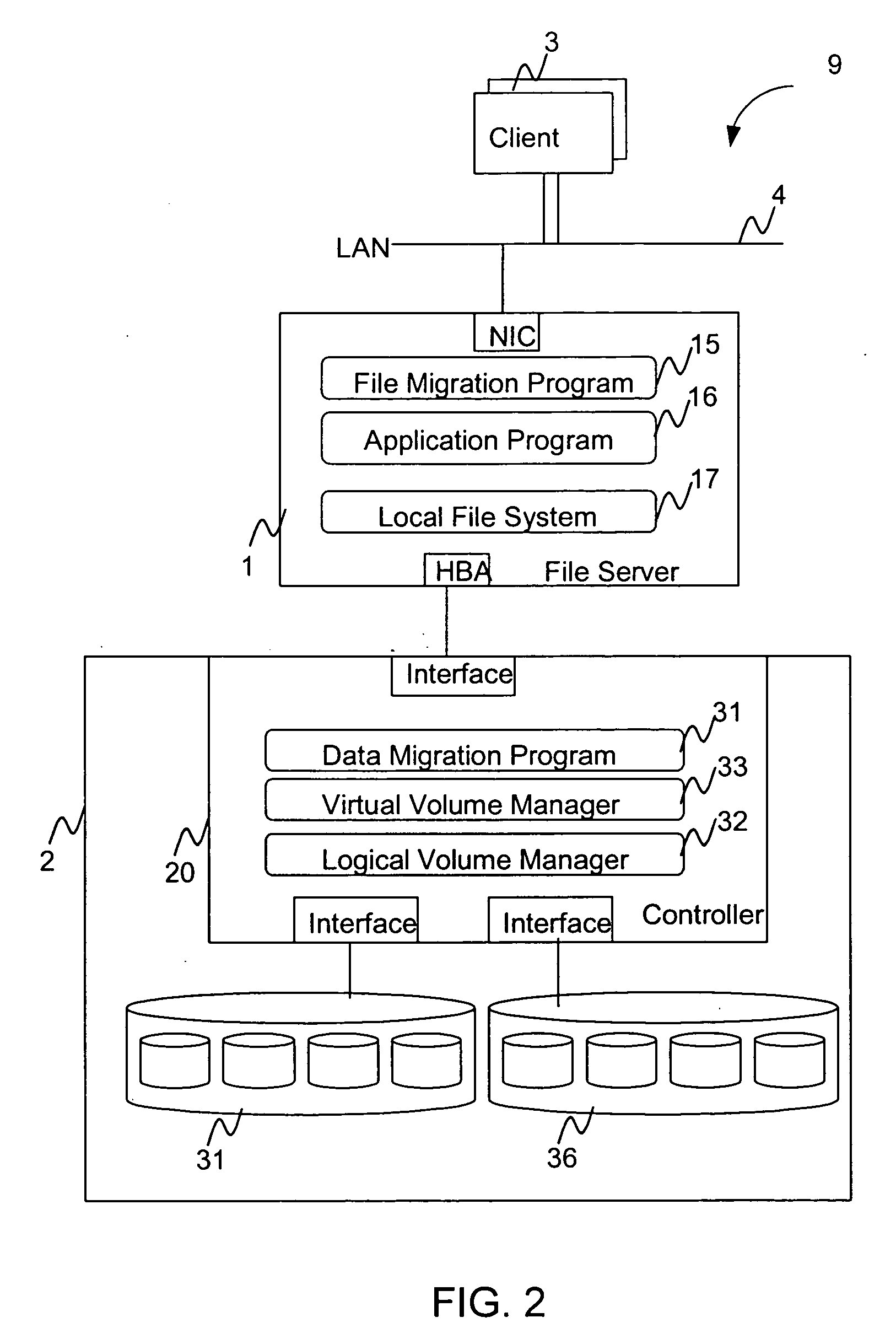

Hierarchical storage management system

InactiveUS20060010169A1Digital data information retrievalSpecial data processing applicationsFile systemSecondary layer

A hierarchical storage system comprises a host computer and a storage system. The storage system comprises at lease two kinds of storage devices, a first tier storage and a second tier storage. The first tier storage is a high performance (or high cost) storage device, and the second tier storage is a lower performance (or lower cost) storage device. The storage system creates a virtual volume based on the first and second tier storages, and enables the host computer to access the virtual volume. A file system in the host computer knows which region of the virtual volume corresponds to the first tier storage and which region of the virtual volume corresponds to the second tier storage. When the file system receives a command to migrate a file from the first tier to the second tier storage, e.g., from a user, the file system examines the address information of the virtual volume where the file resides, and instructs the storage system to migrate the blocks of the designated addresses.

Owner:HITACHI LTD

Method of pitch dimension shrinkage

ActiveUS20050272259A1Avoid disadvantagesDimension can be narrowedPhotomechanical apparatusSemiconductor/solid-state device manufacturingSecondary layerPhysics

Roughly described, a patterned first layer is provided over a second layer which is formed over a substrate. In a conversion process, first layer material is consumed at feature sidewalls to form third layer material at the feature sidewalls. The width of third layer material at each of the sidewalls is greater than the width of first layer material consumed at the respective sidewall in the conversion process. The second layer is patterned using the third layer material as mask. A fourth layer of material is formed over the substrate, and planarized or otherwise partially removed so as to expose the top surfaces of the features in the first layer through the fourth layer. The exposed first layer material is removed to expose portions of the second layer through the fourth layer, and the second layer is further patterned using the fourth layer material as a mask.

Owner:MACRONIX INT CO LTD