Patents

Literature

48309 results about "Dielectric layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

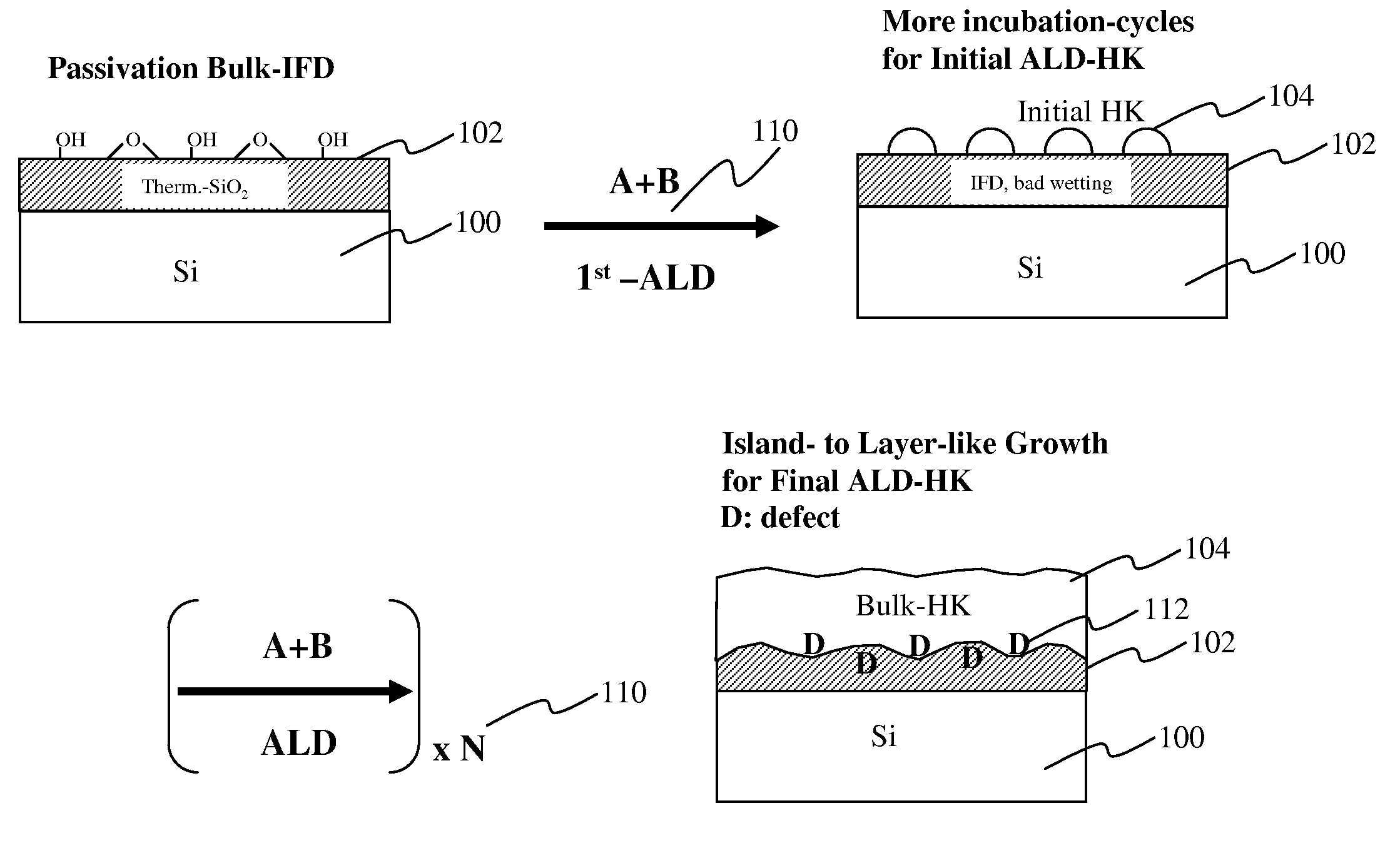

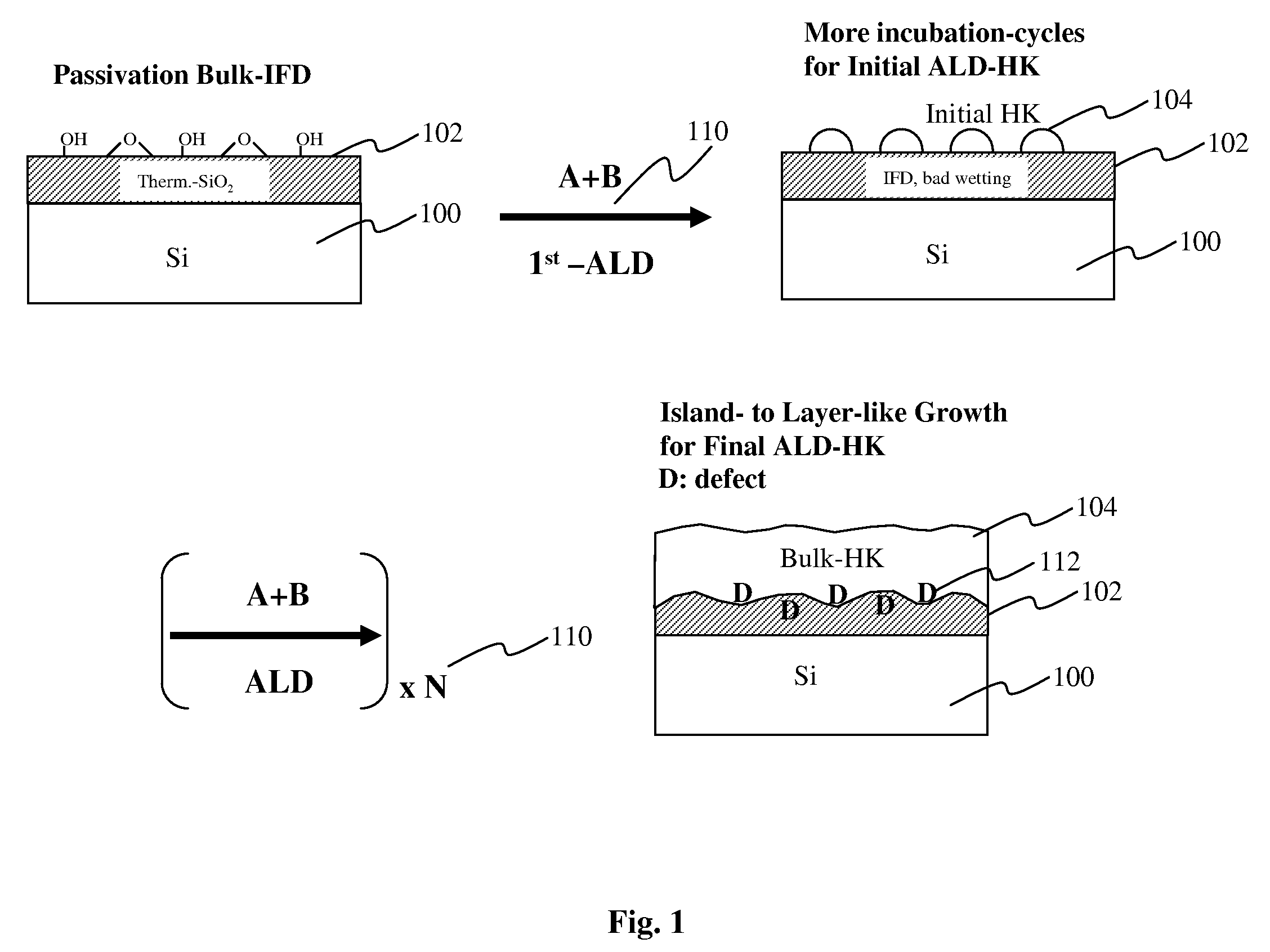

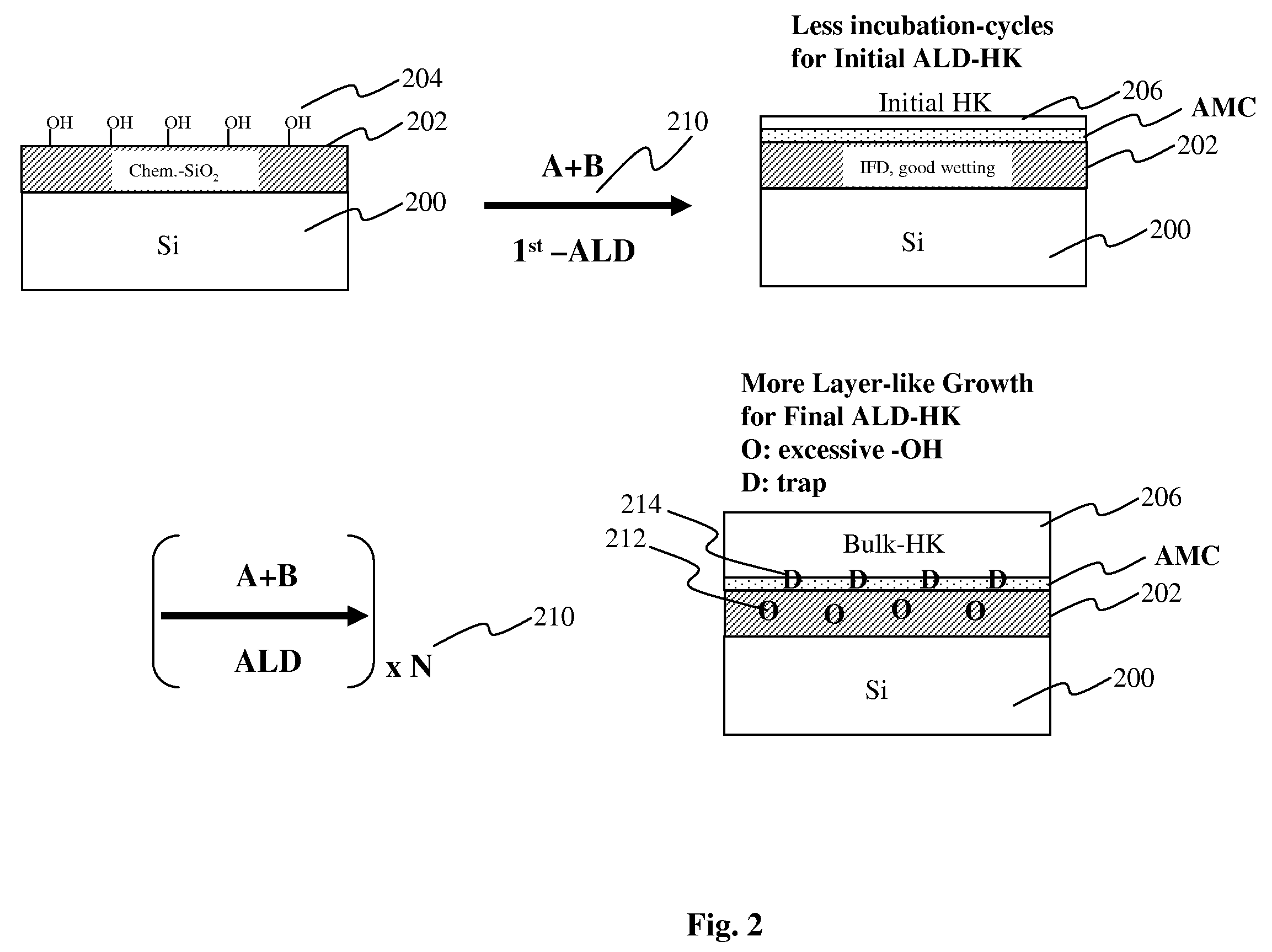

In an embodiment, a dielectric layer is graded with respect to a crystalline structure profile across the dielectric layer. In an embodiment, a dielectric layer is formed by atomic layer deposition incorporating sequencing techniques to generate a doped dielectric material.

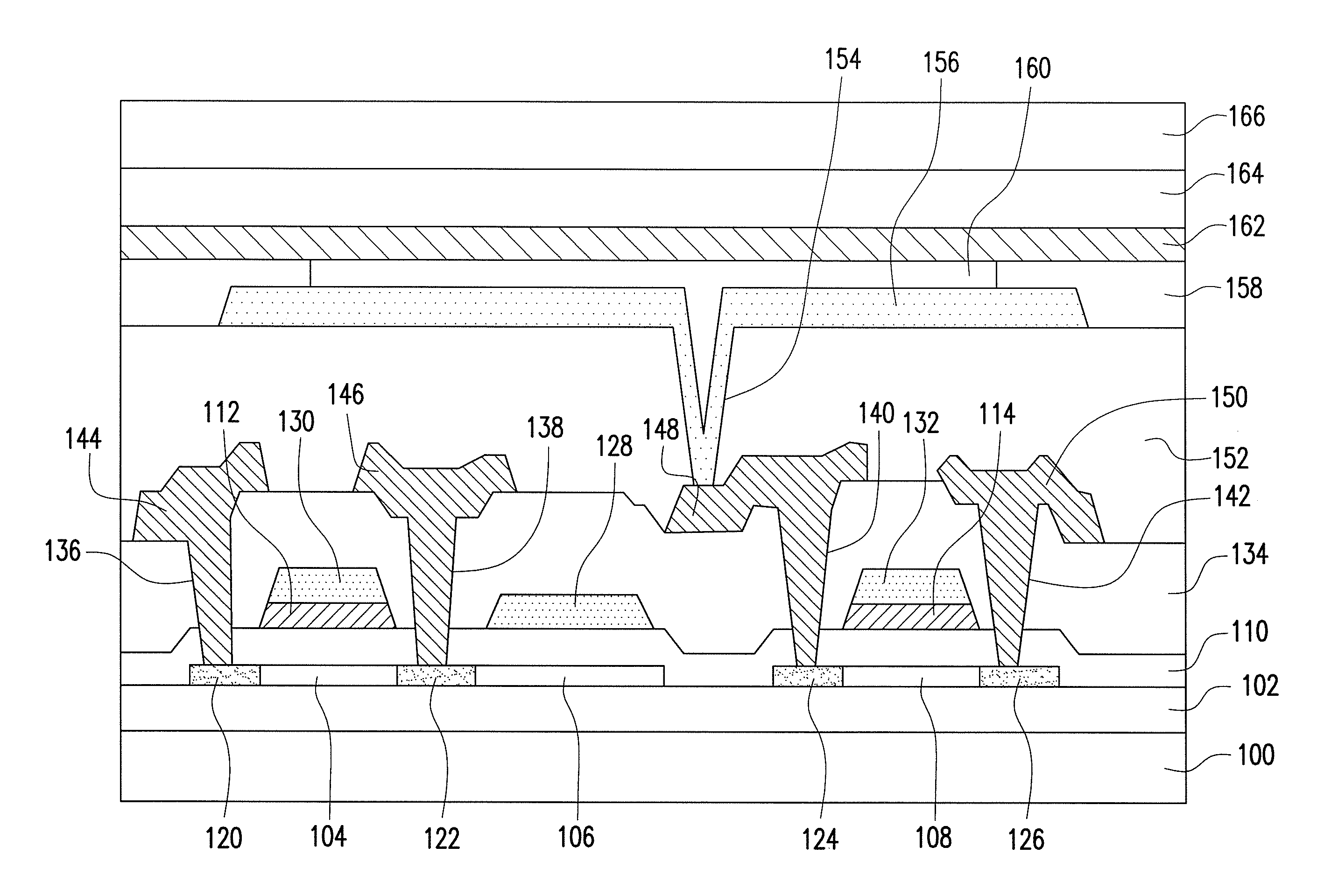

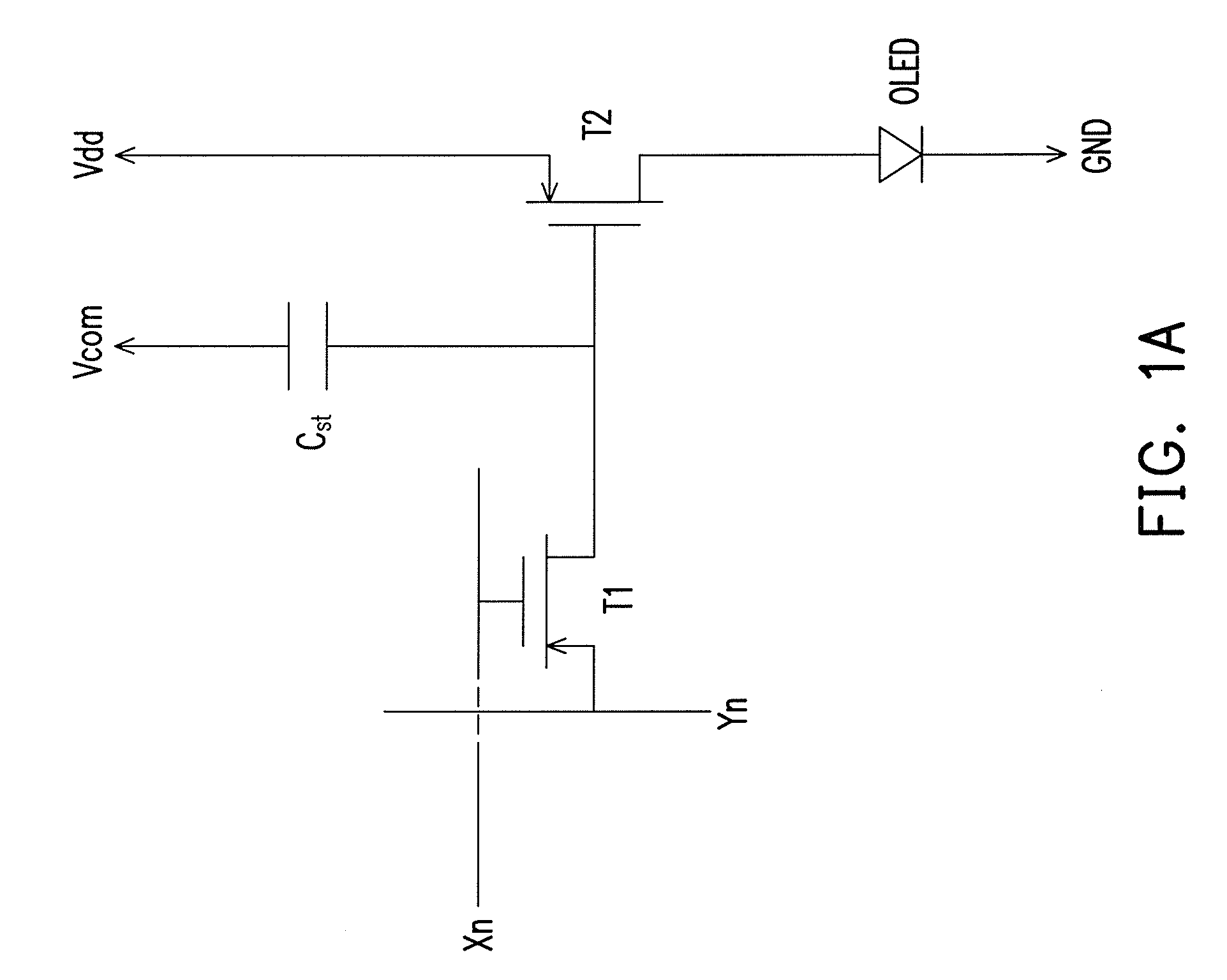

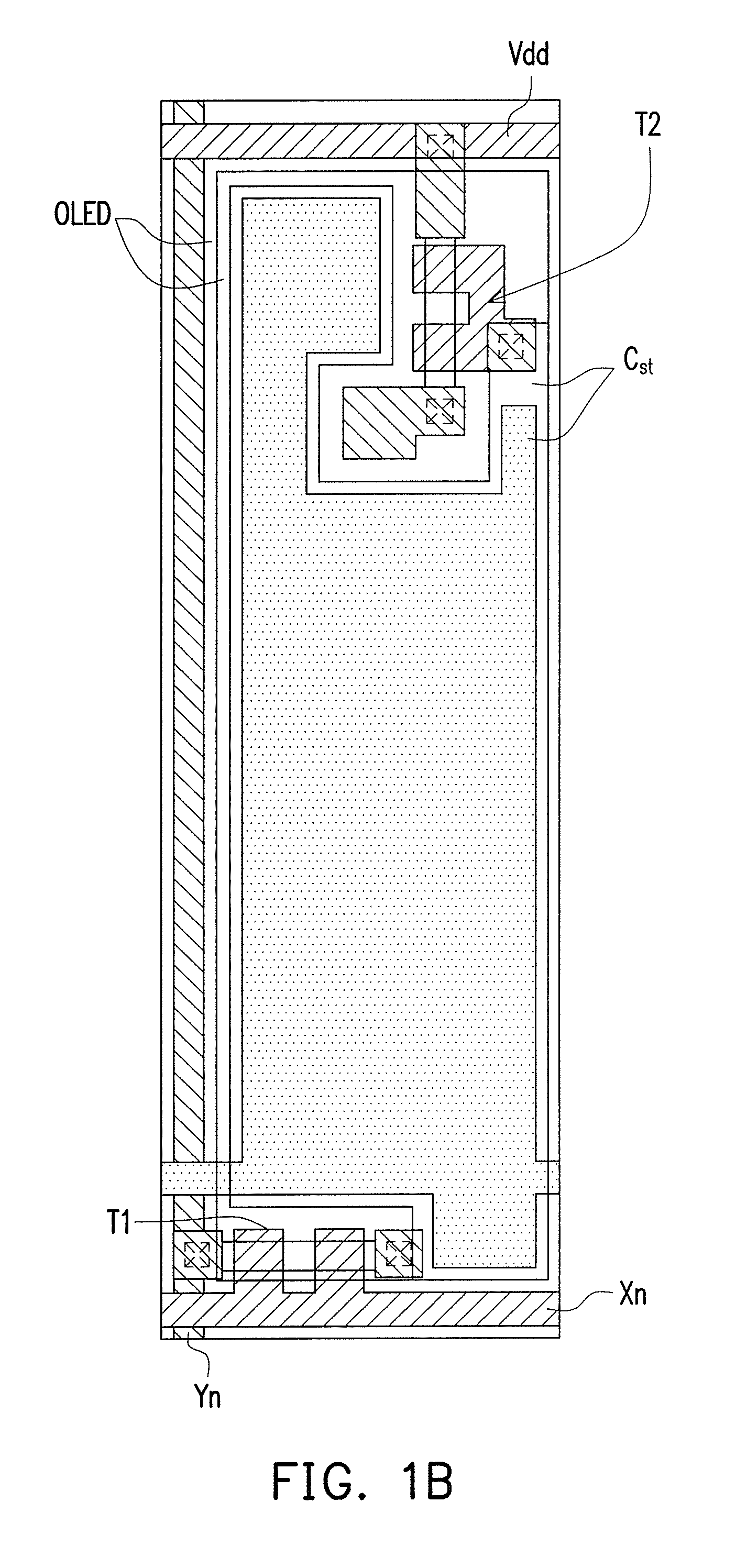

Method for fabricating pixel structure of active matrix organic light-emitting diode

ActiveUS20090068773A1Improve pixel aperture ratioIncrease the aperture ratioSolid-state devicesSemiconductor/solid-state device manufacturingActive matrixScan line

Owner:IND TECH RES INST

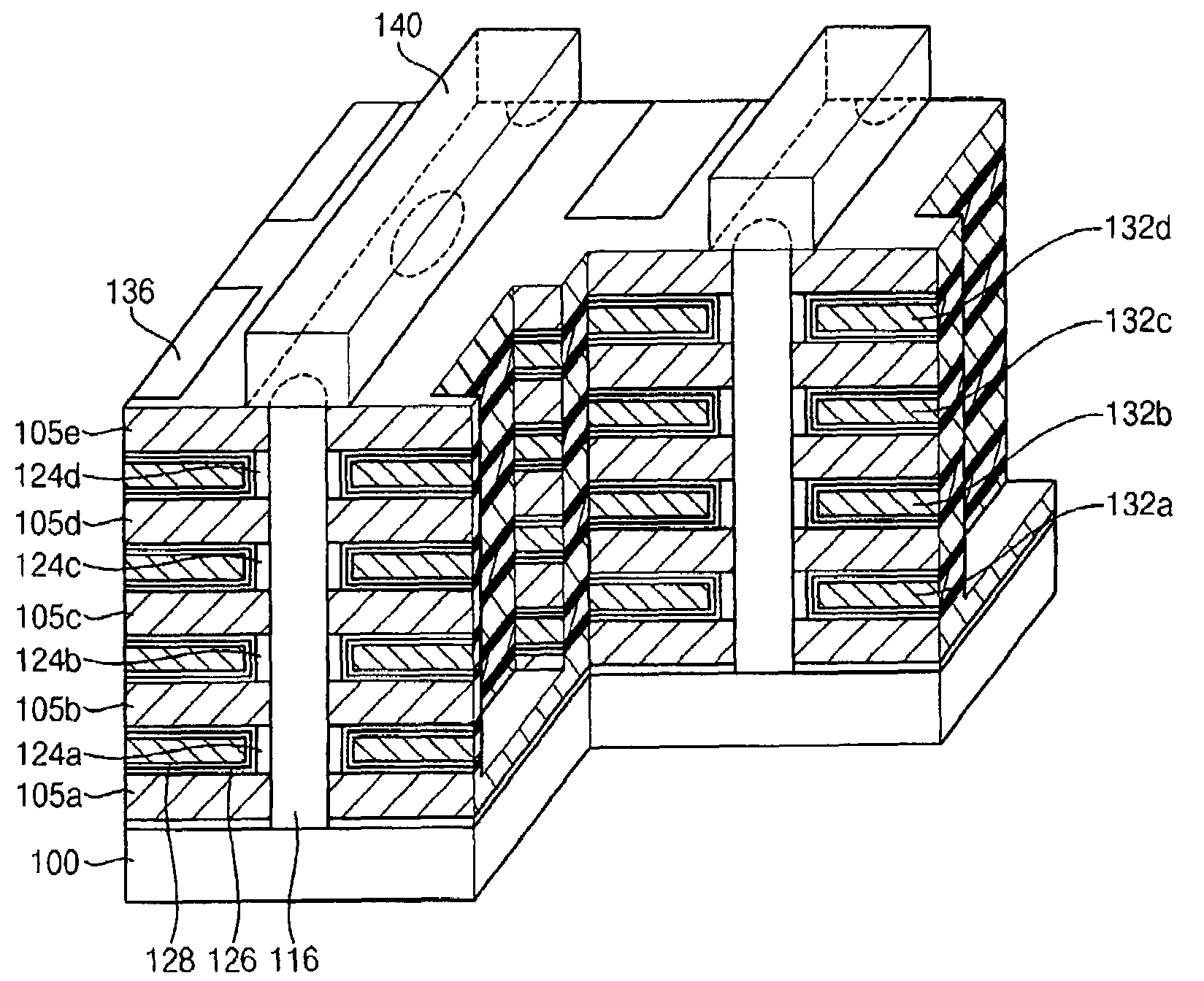

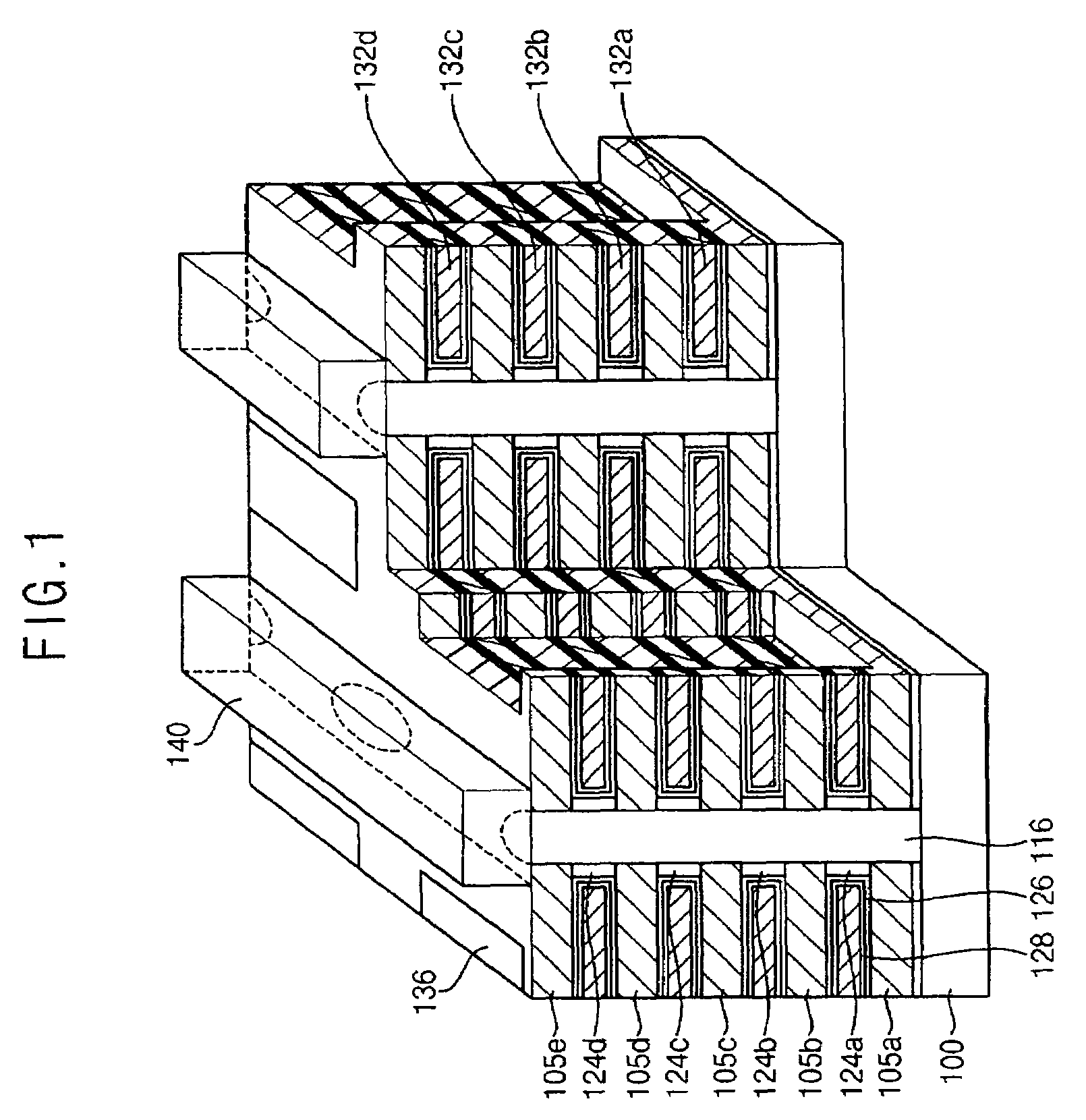

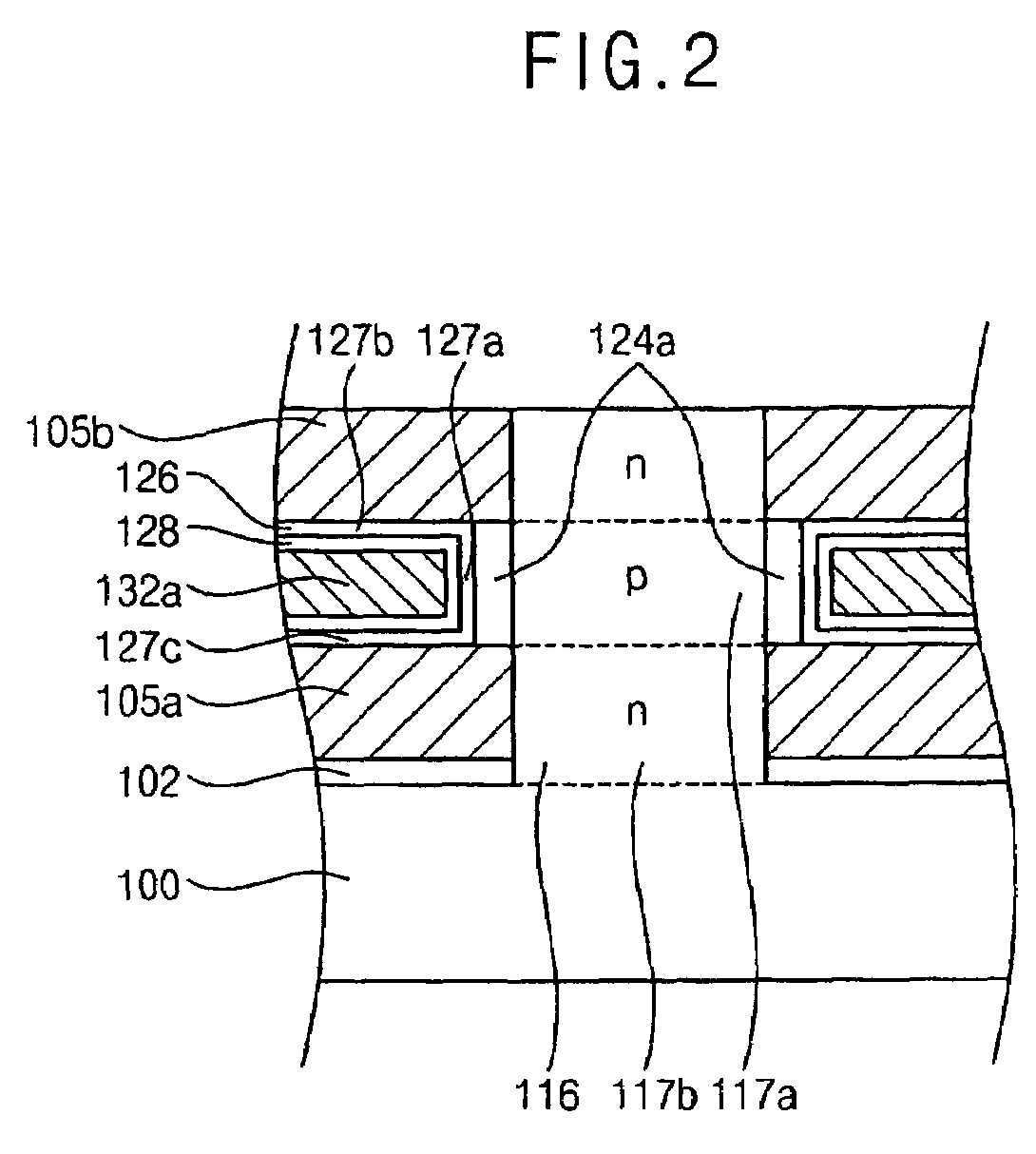

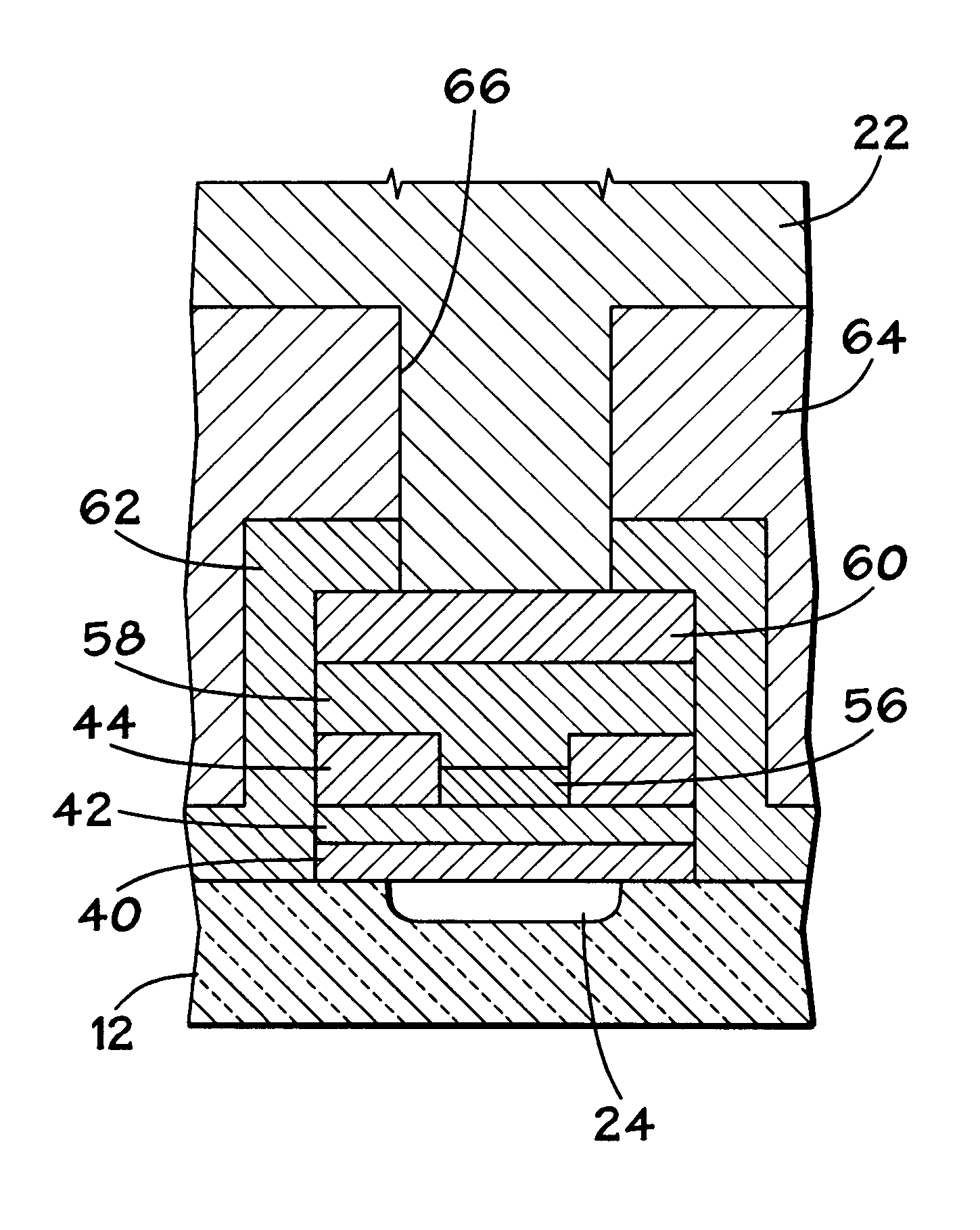

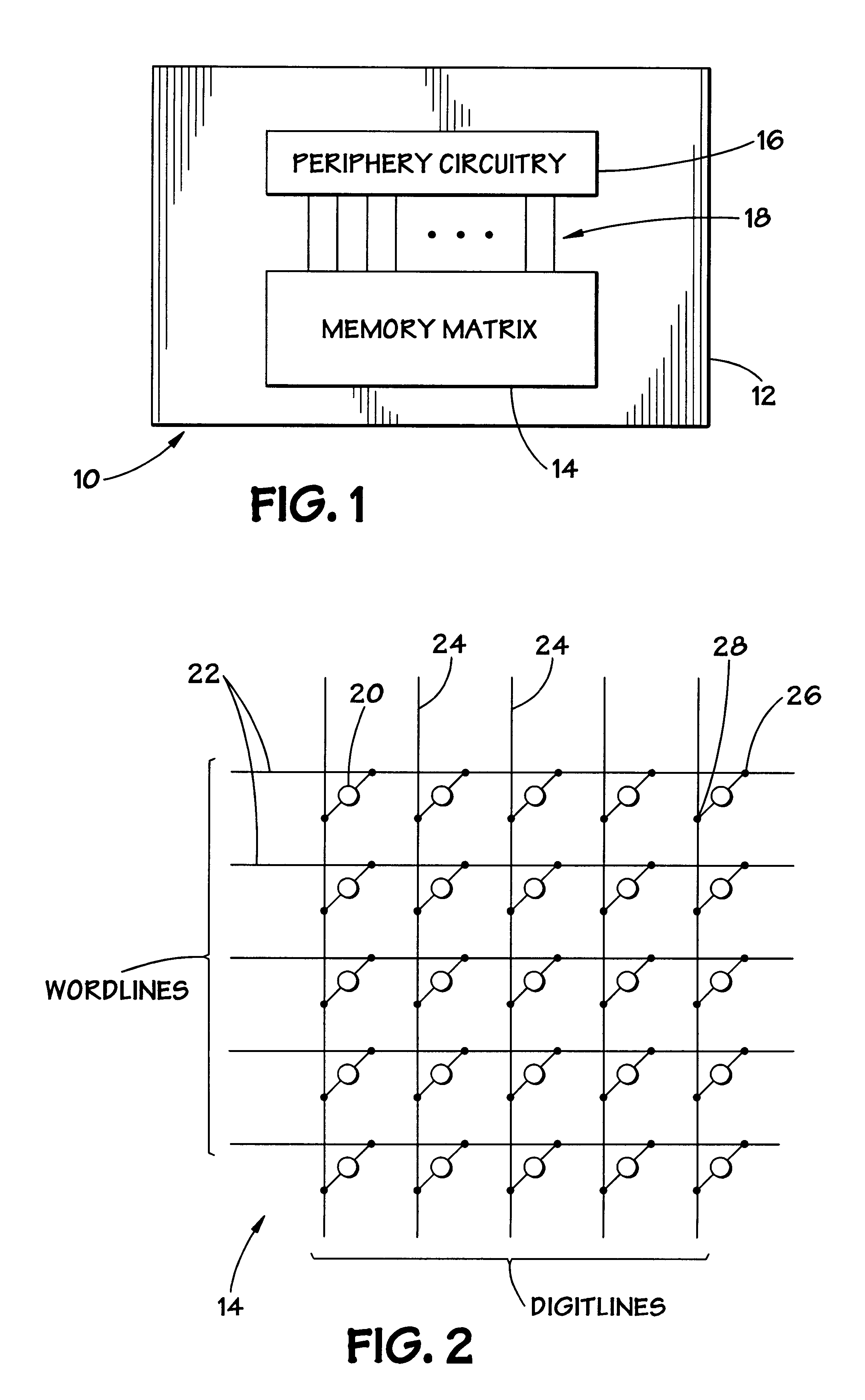

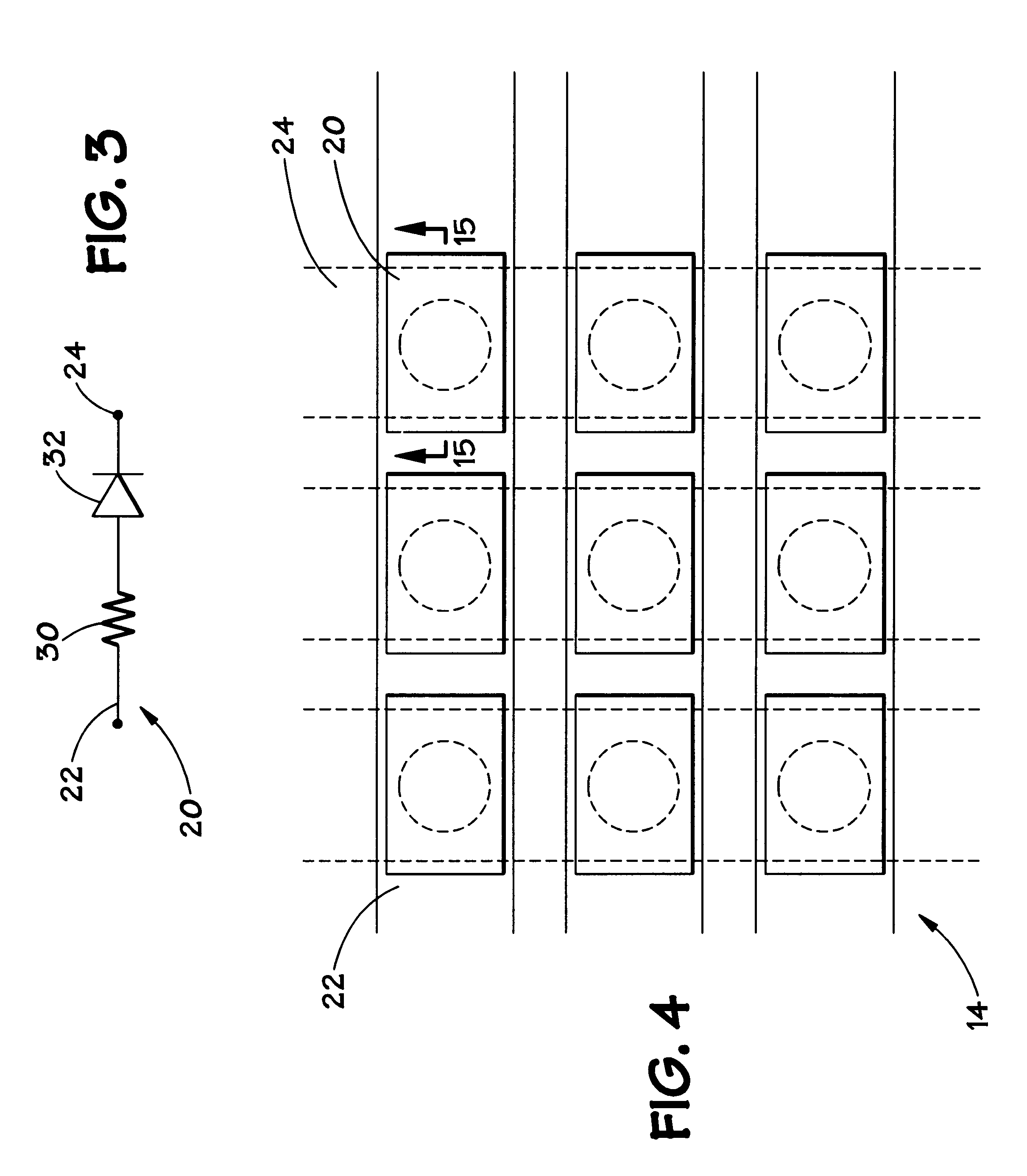

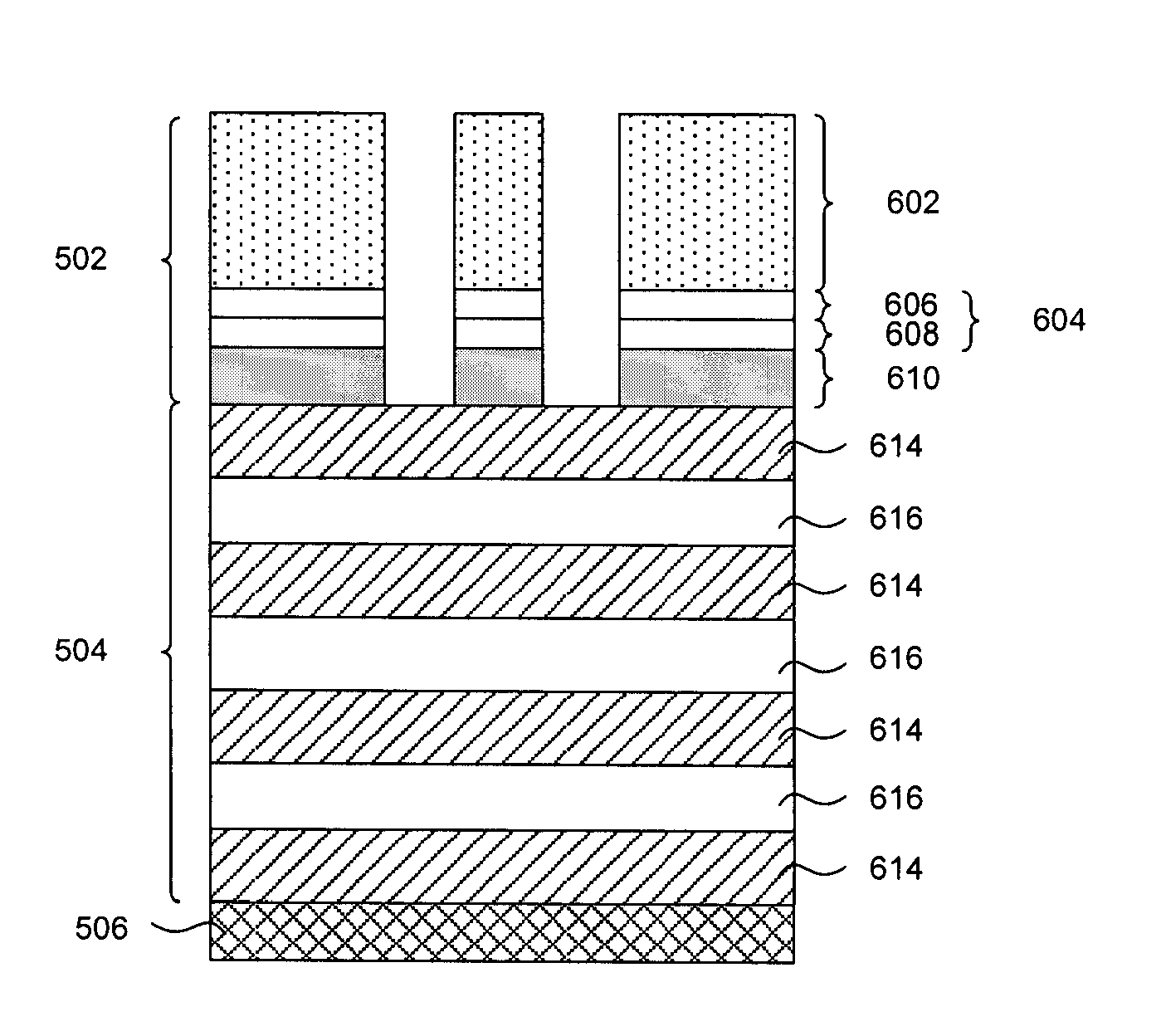

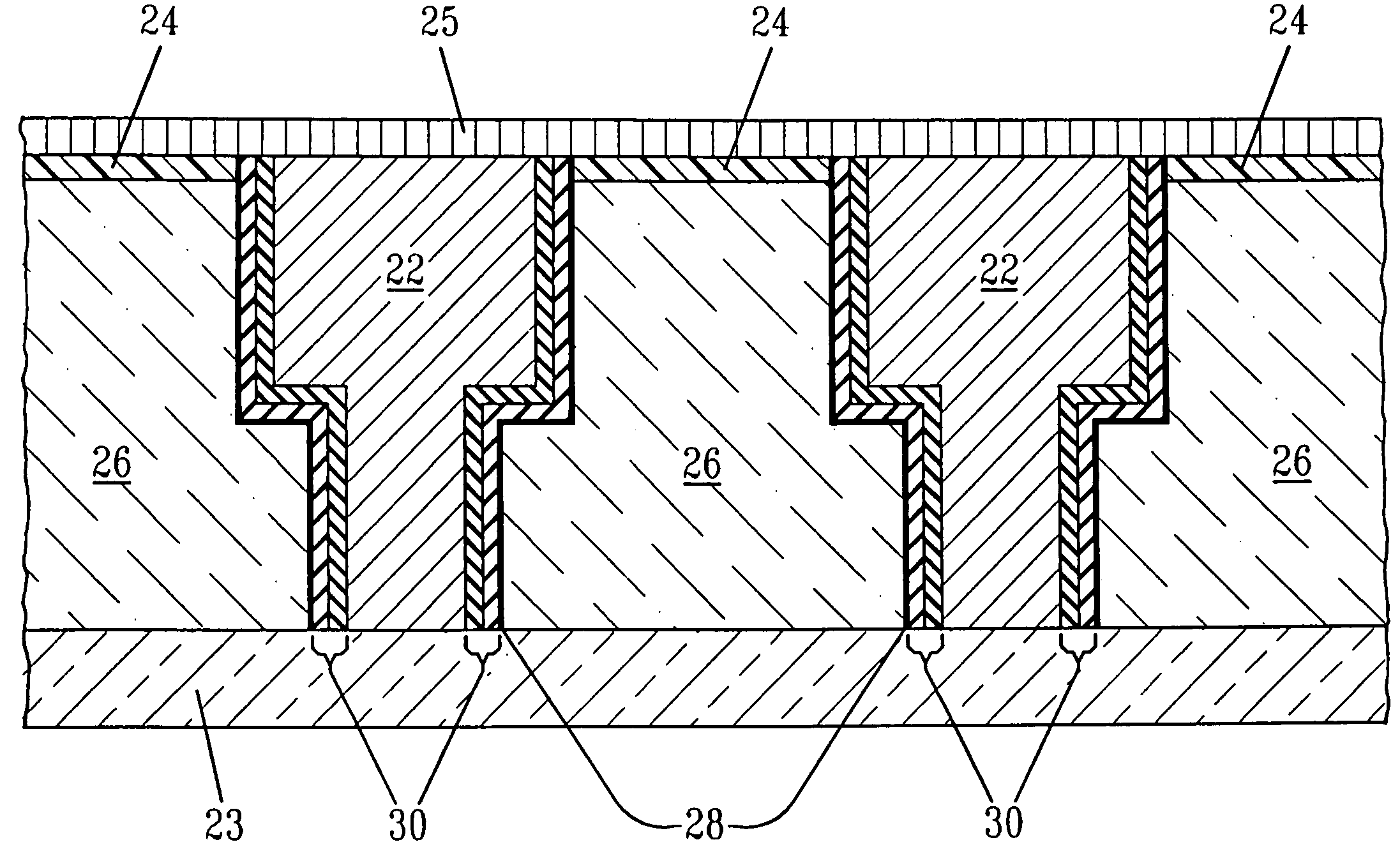

Vertical-type non-volatile memory devices

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

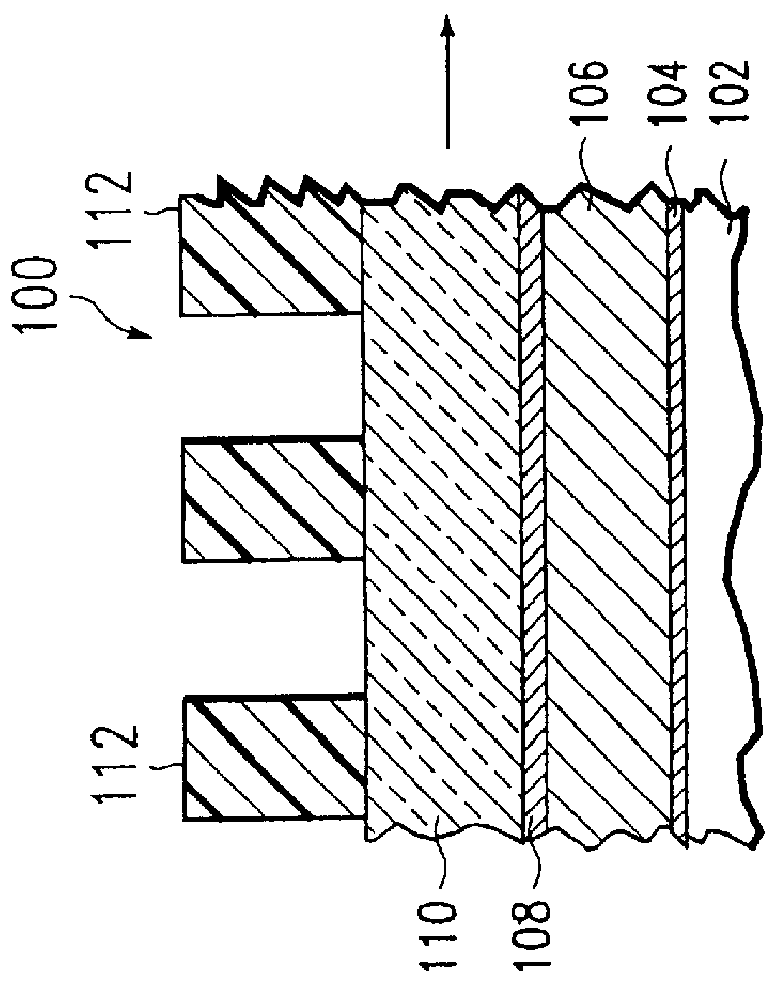

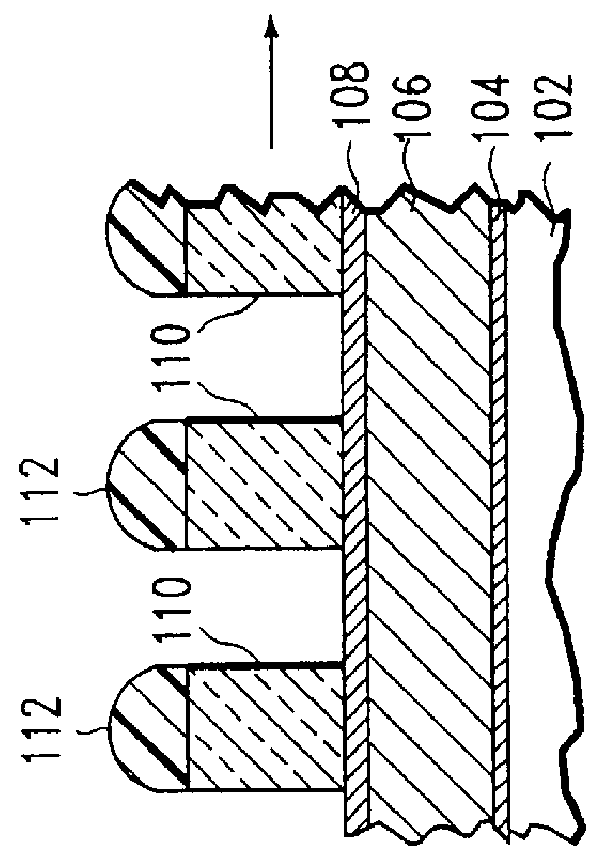

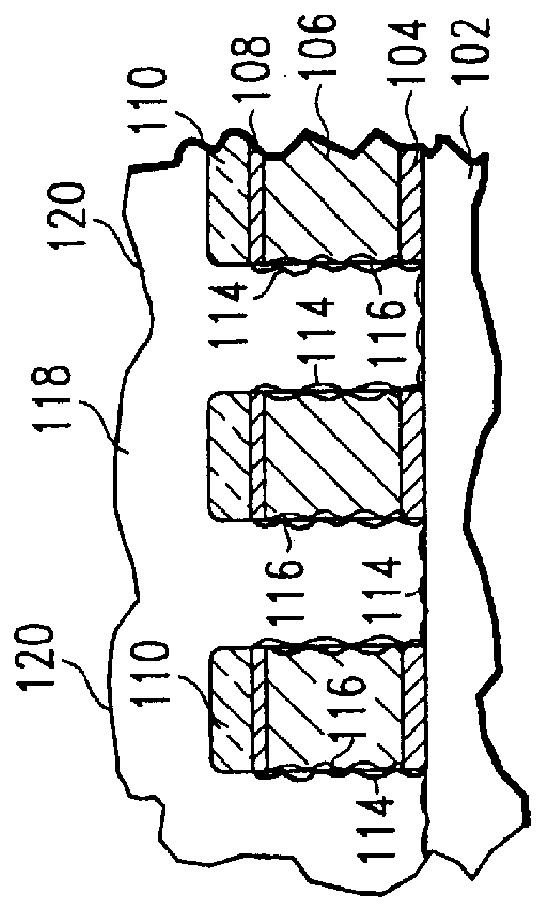

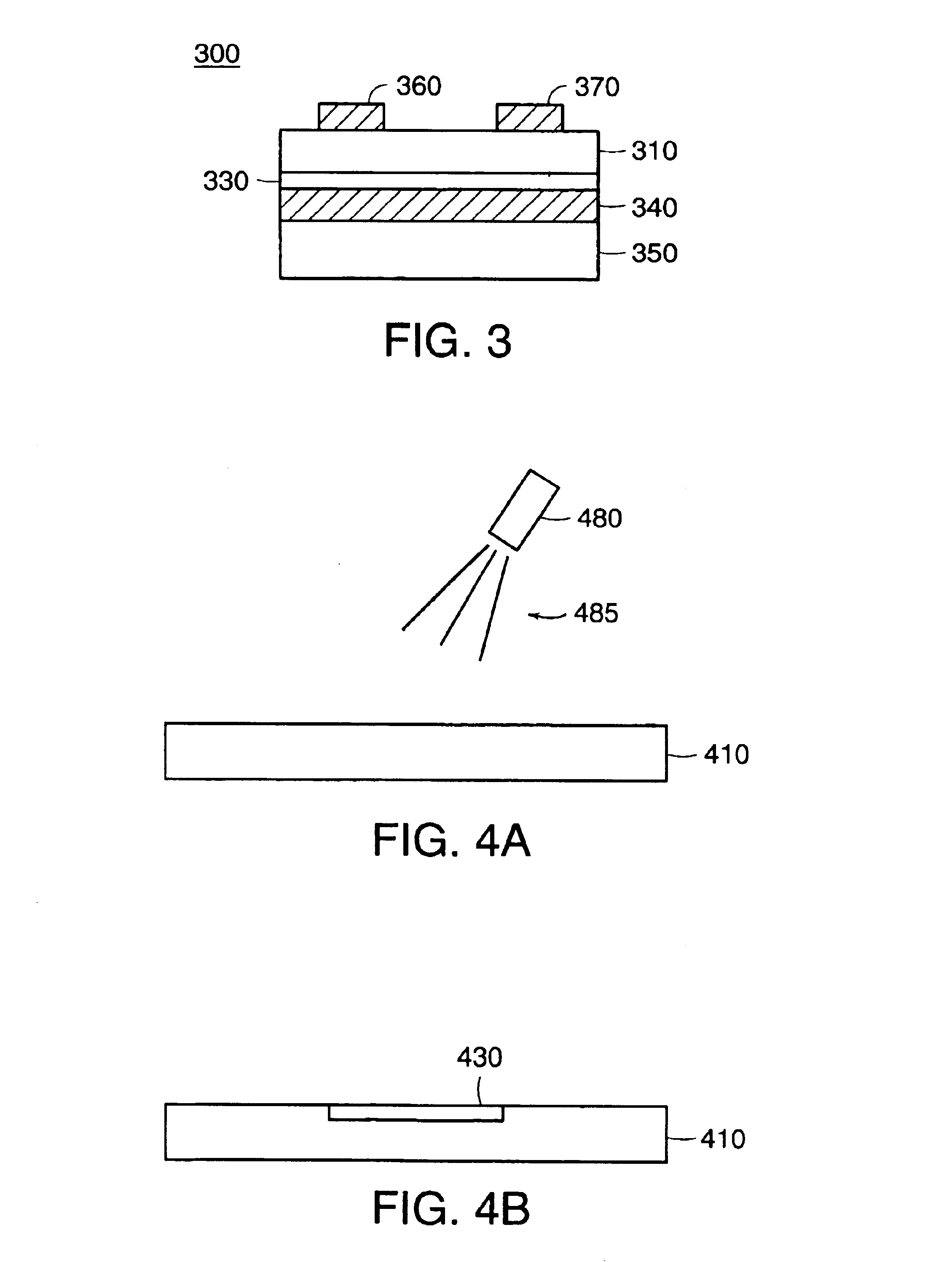

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

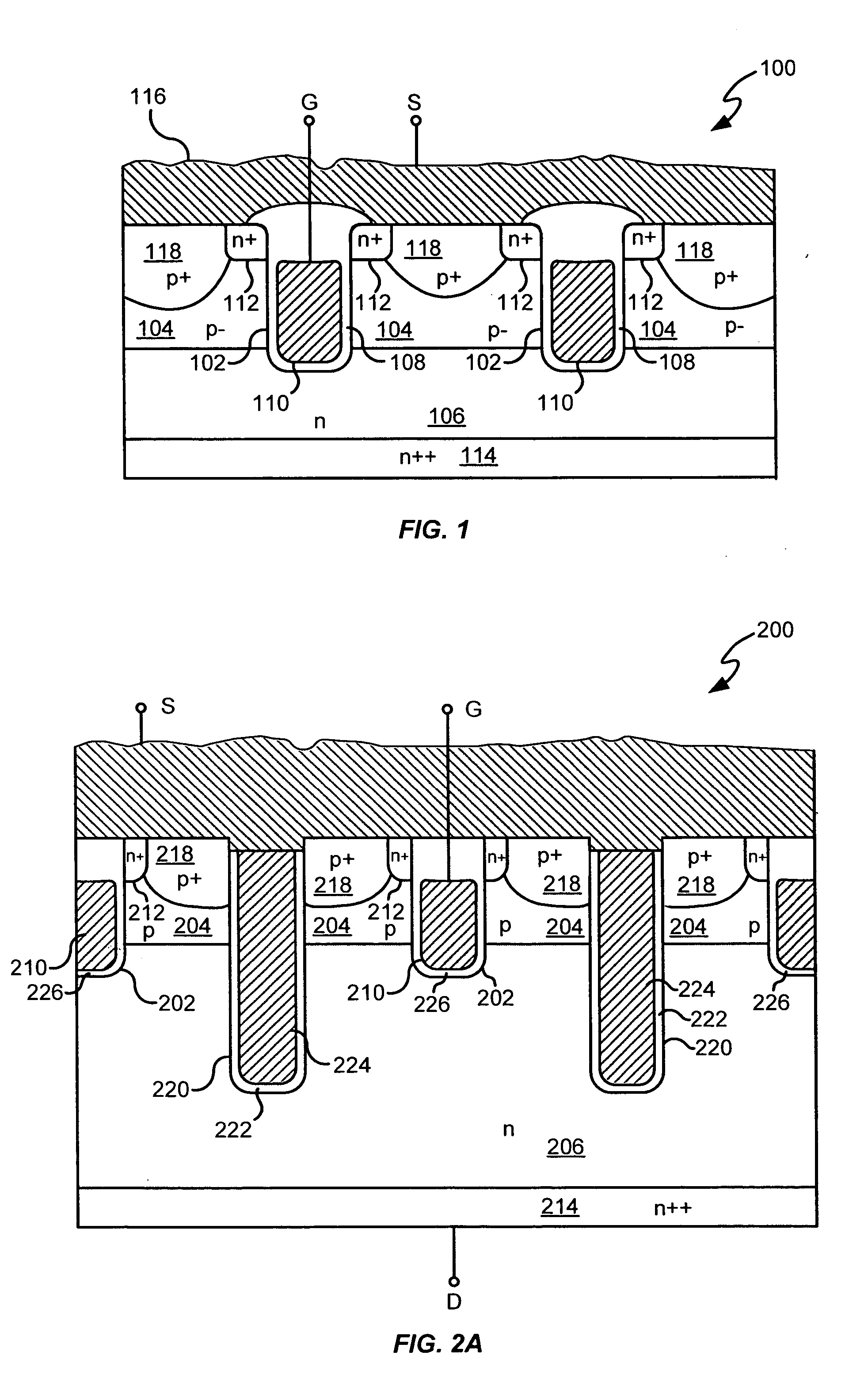

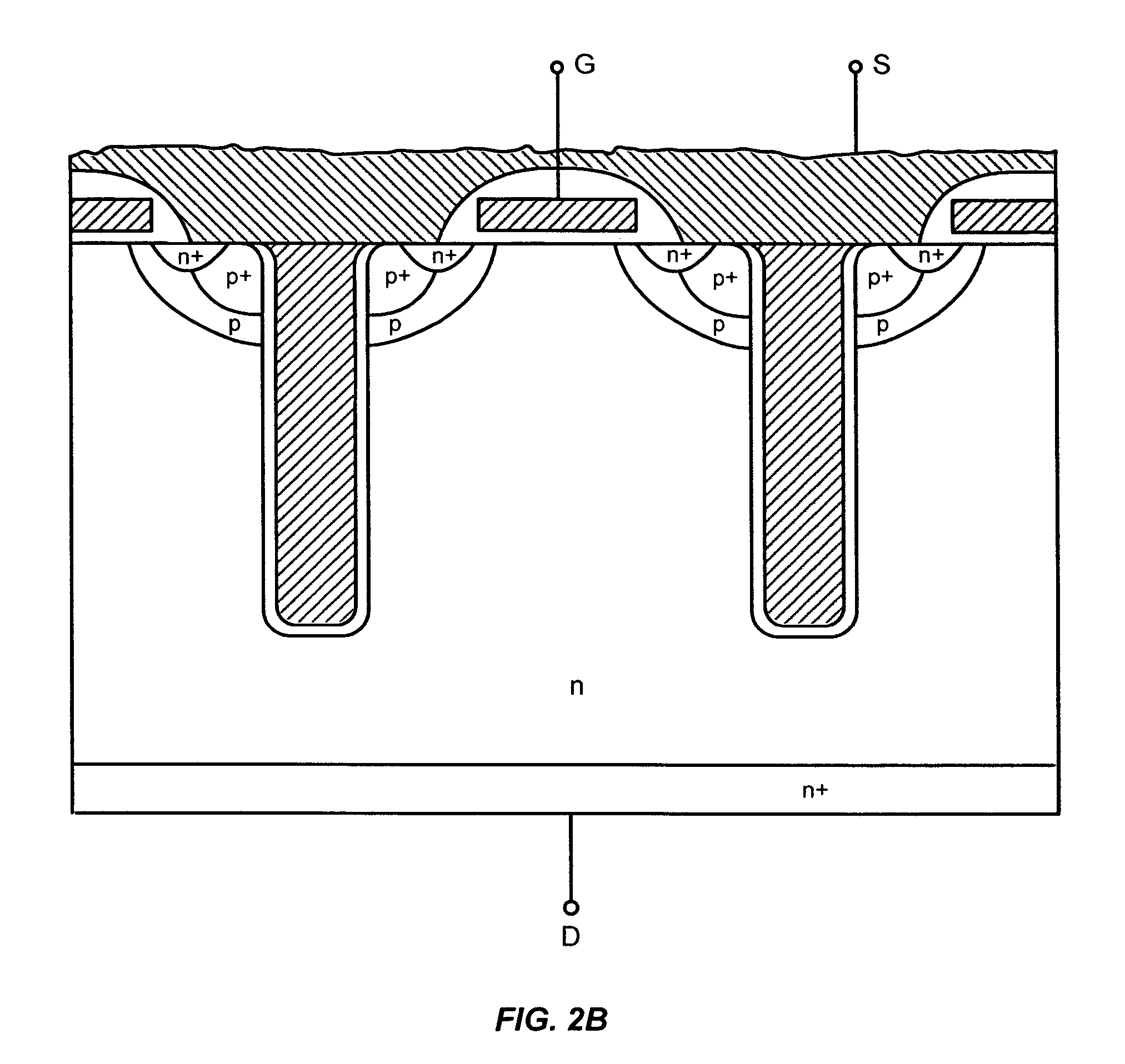

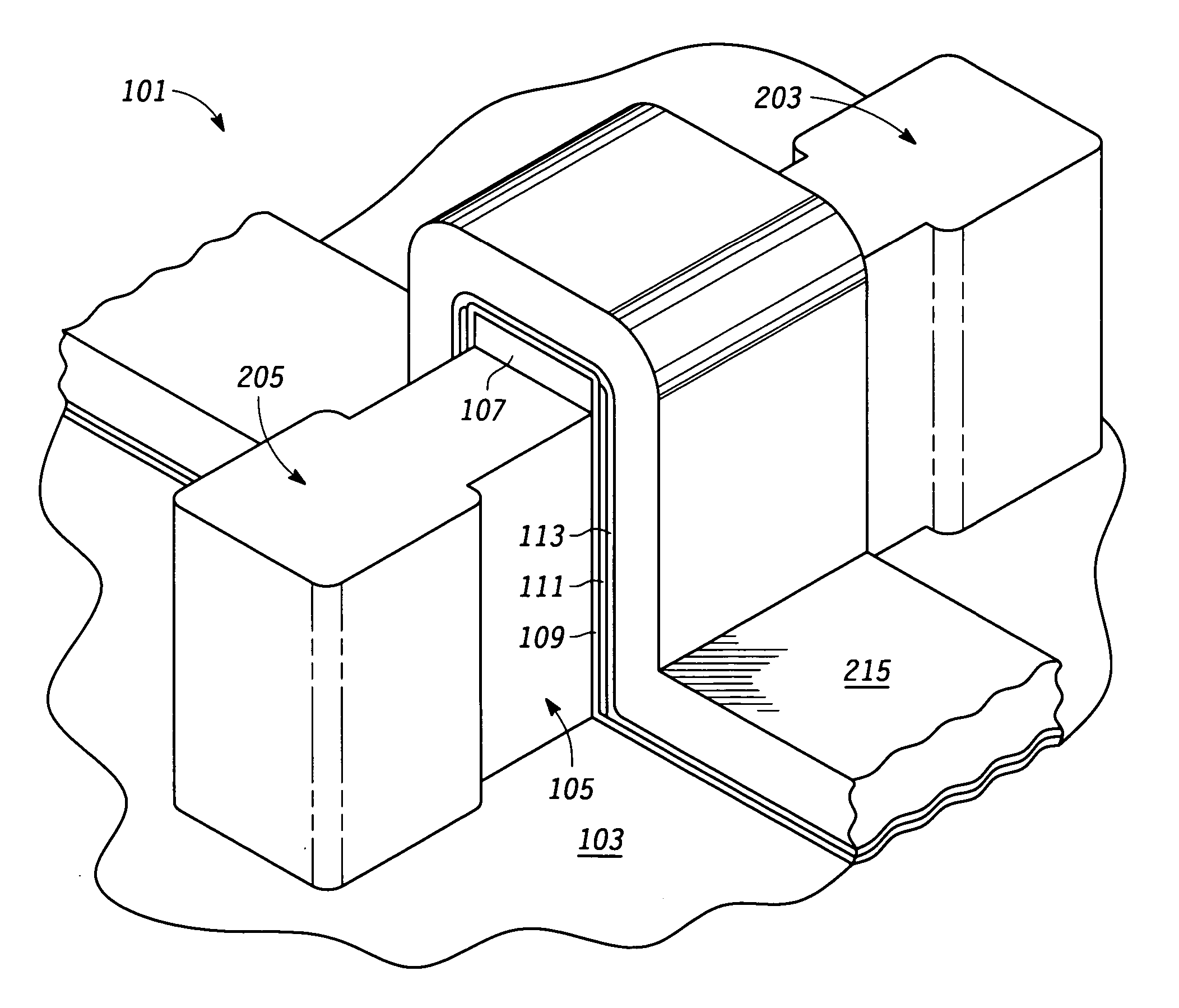

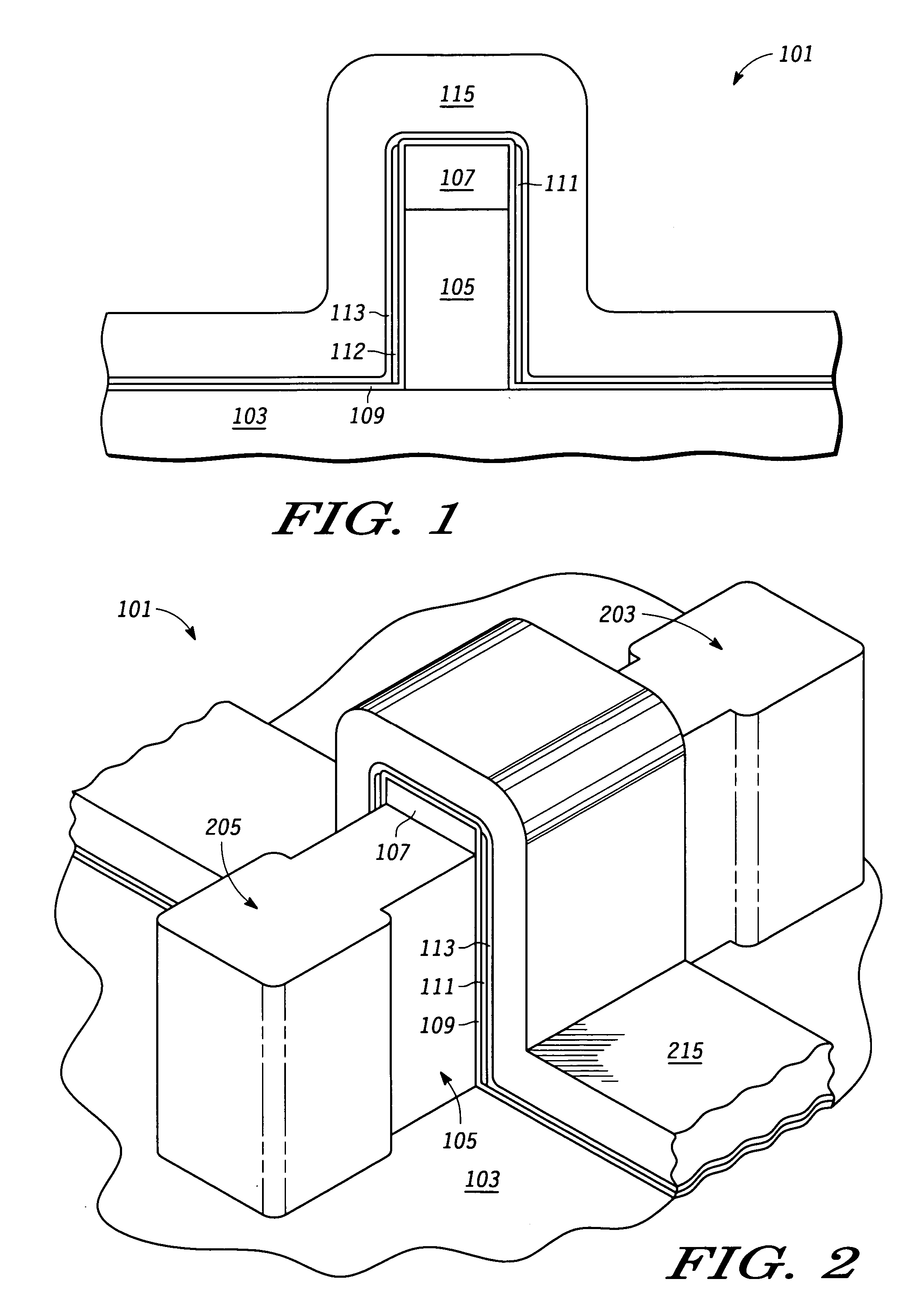

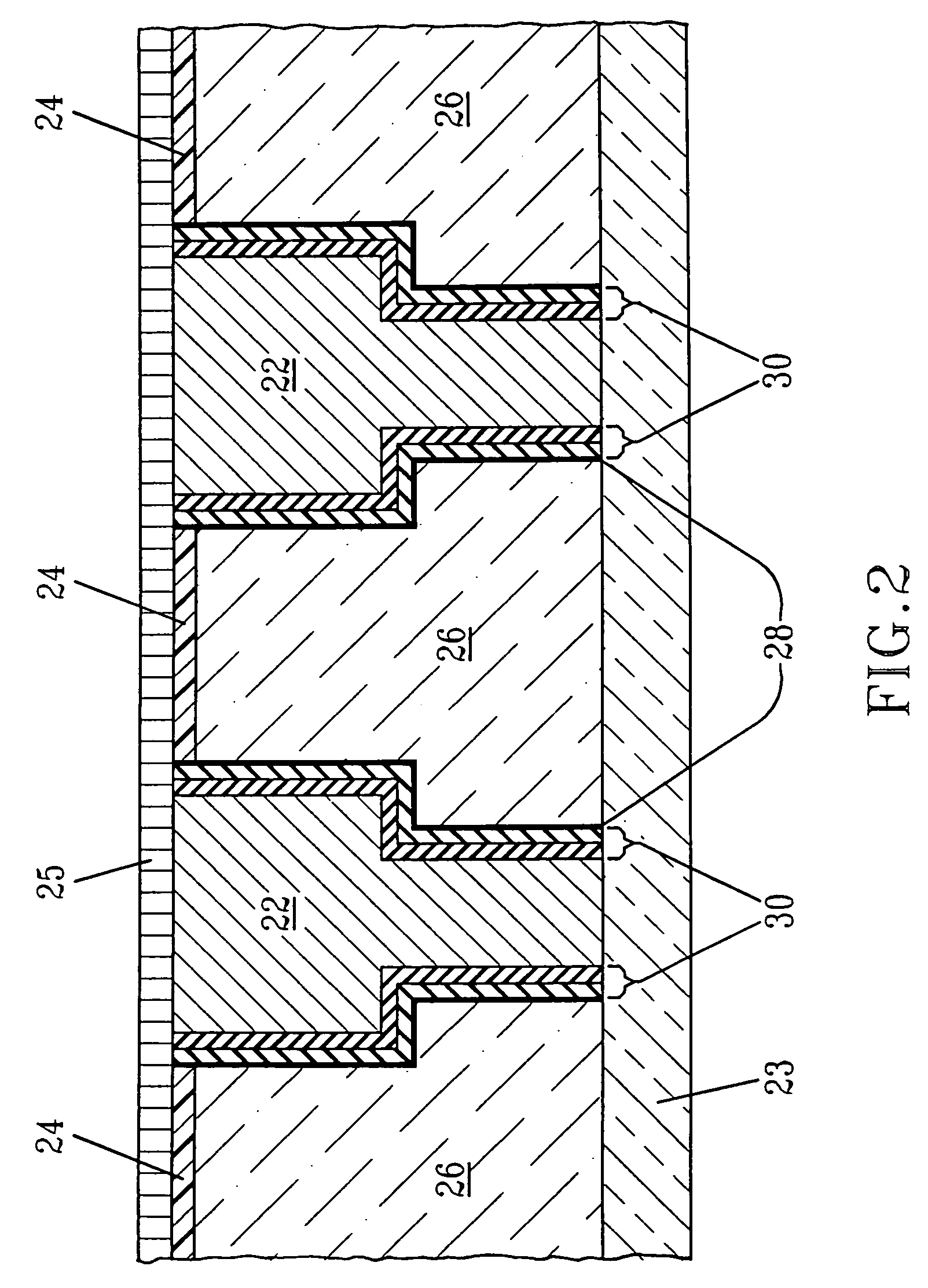

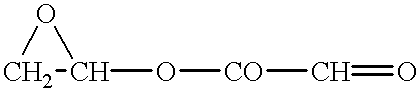

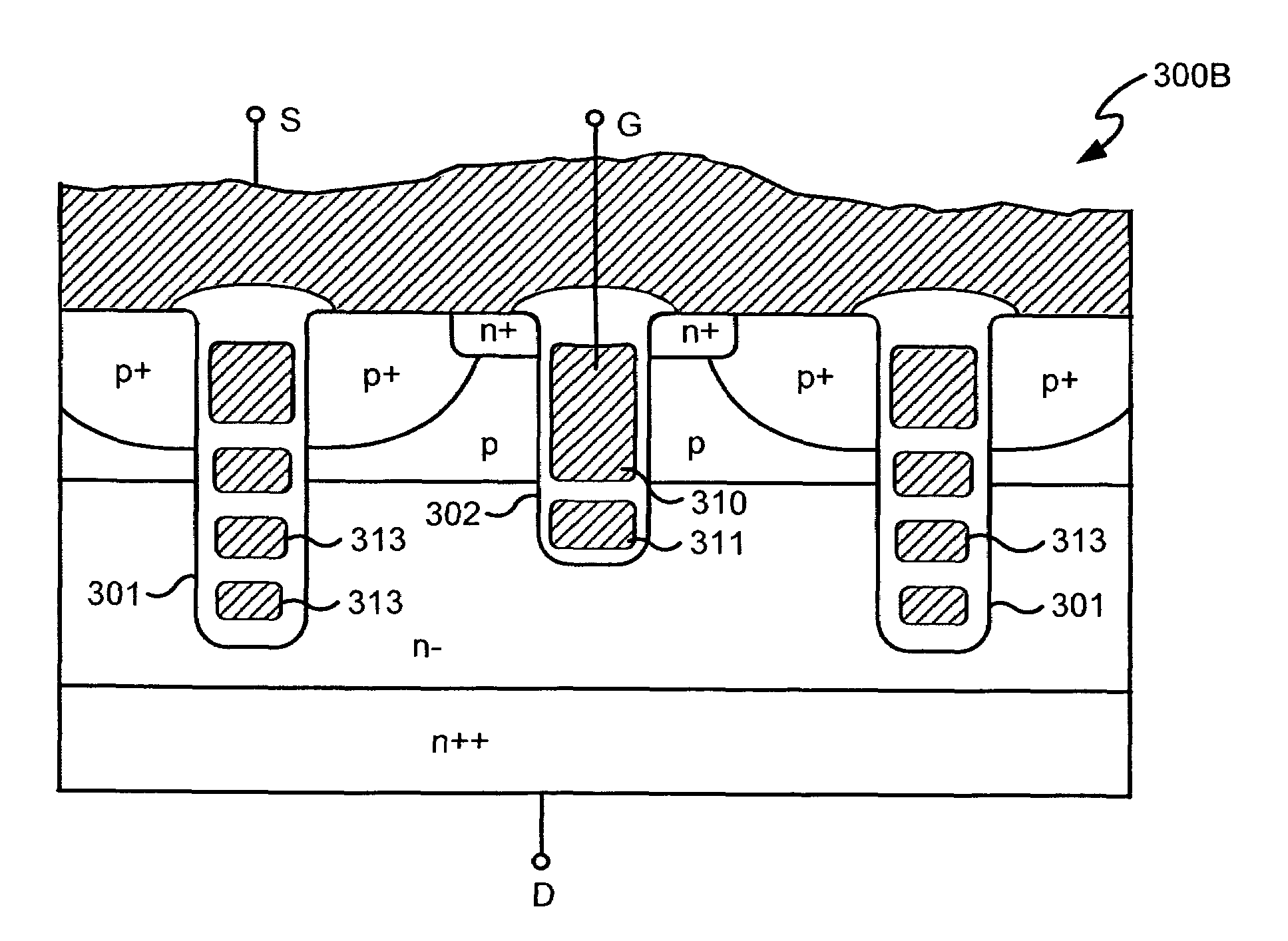

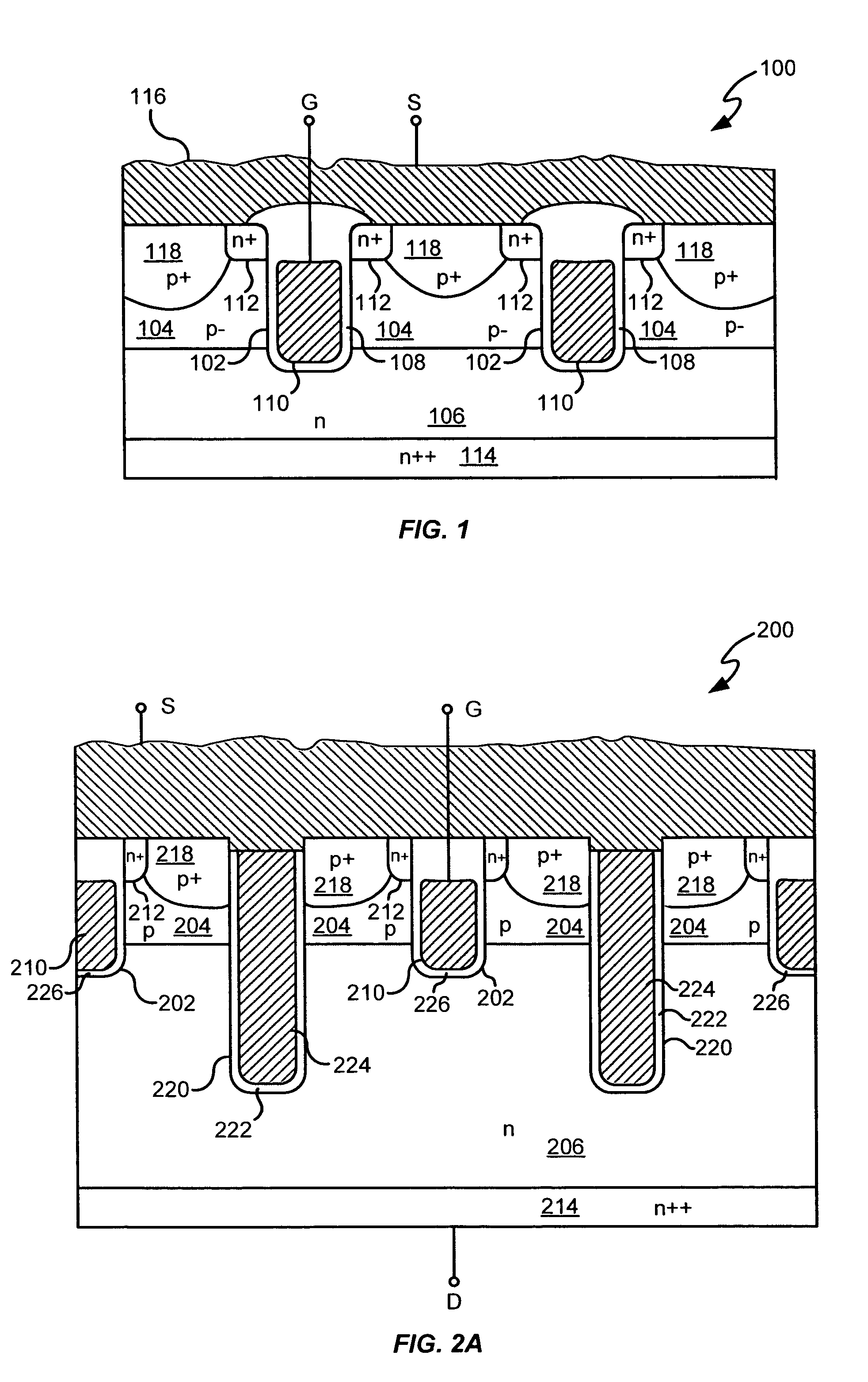

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

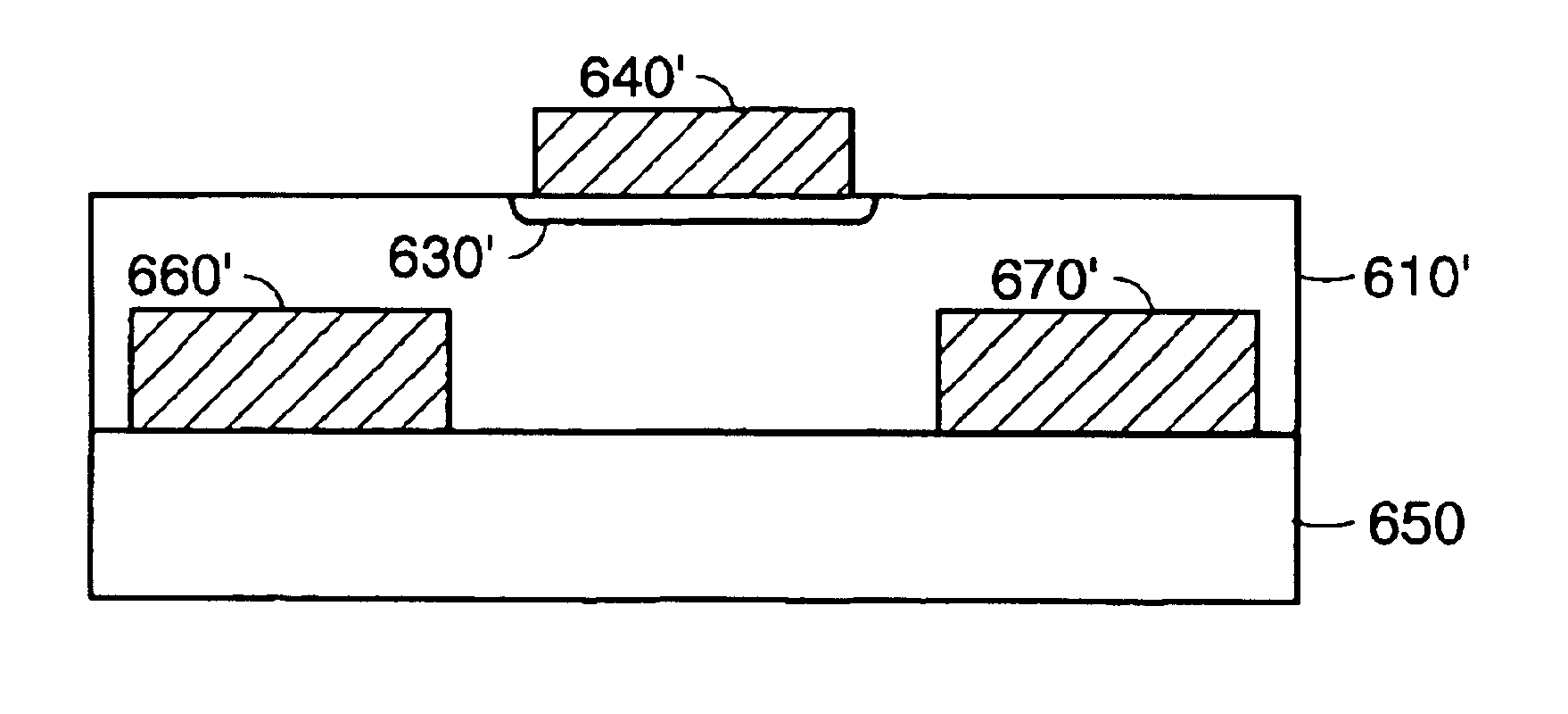

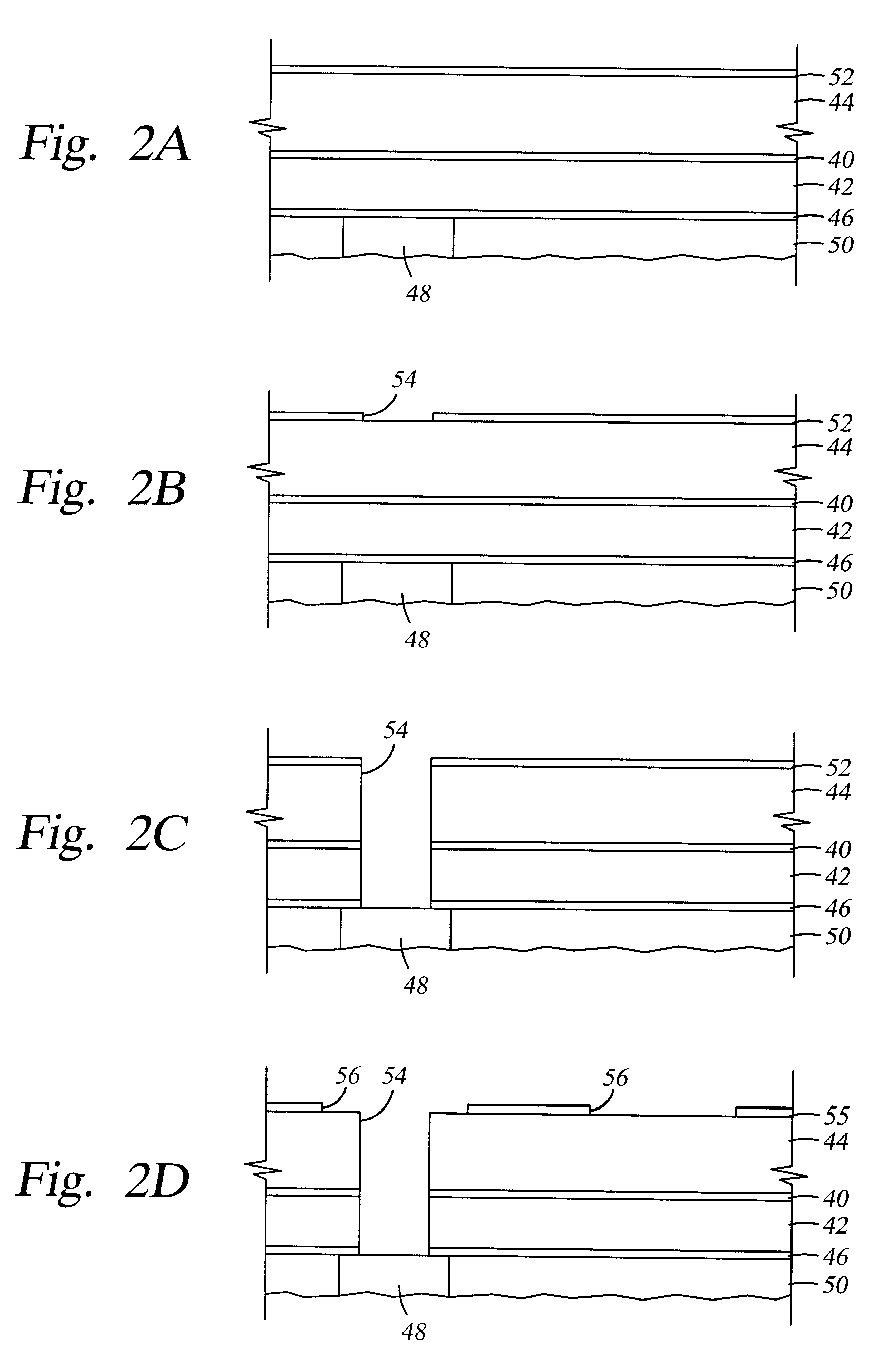

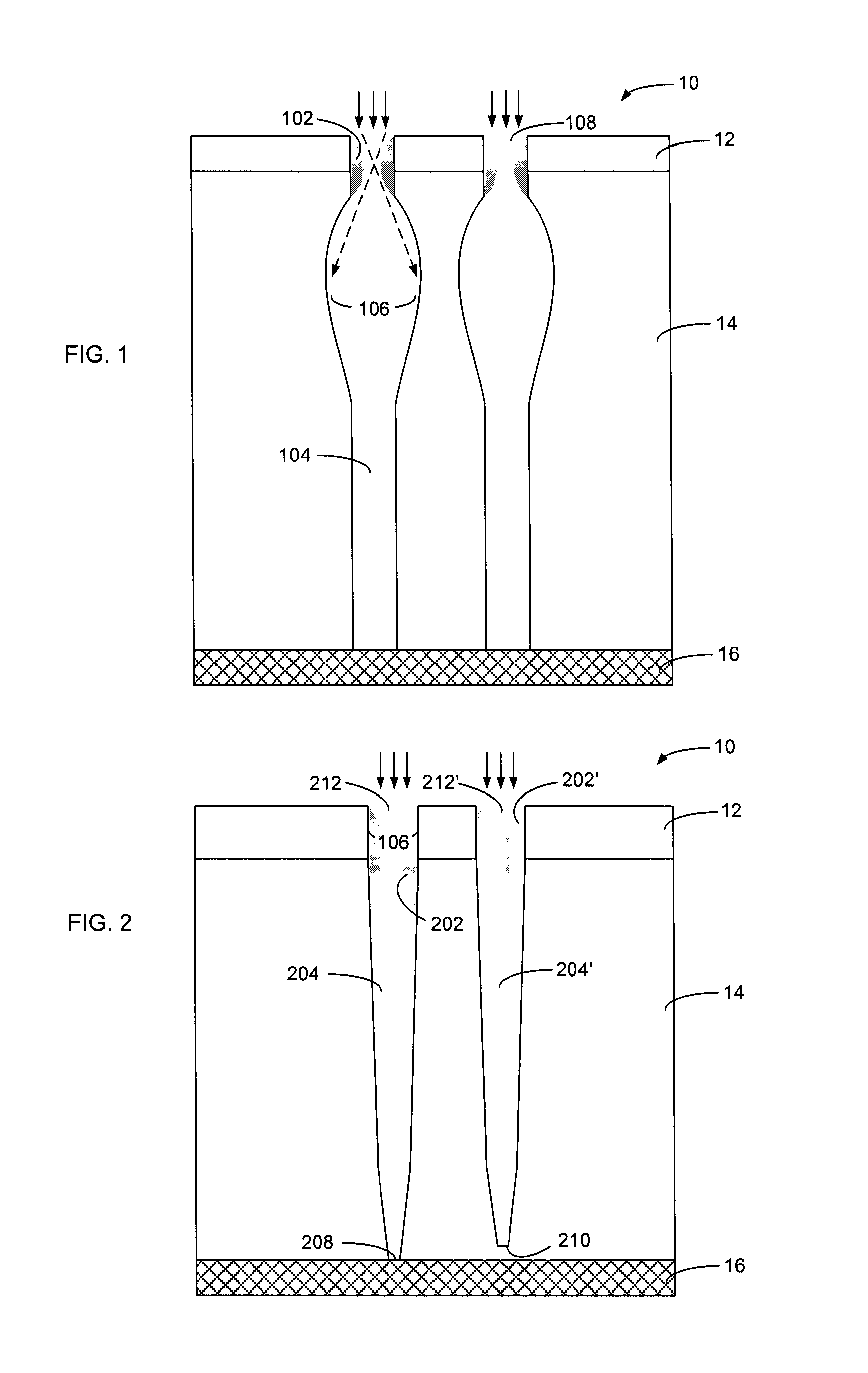

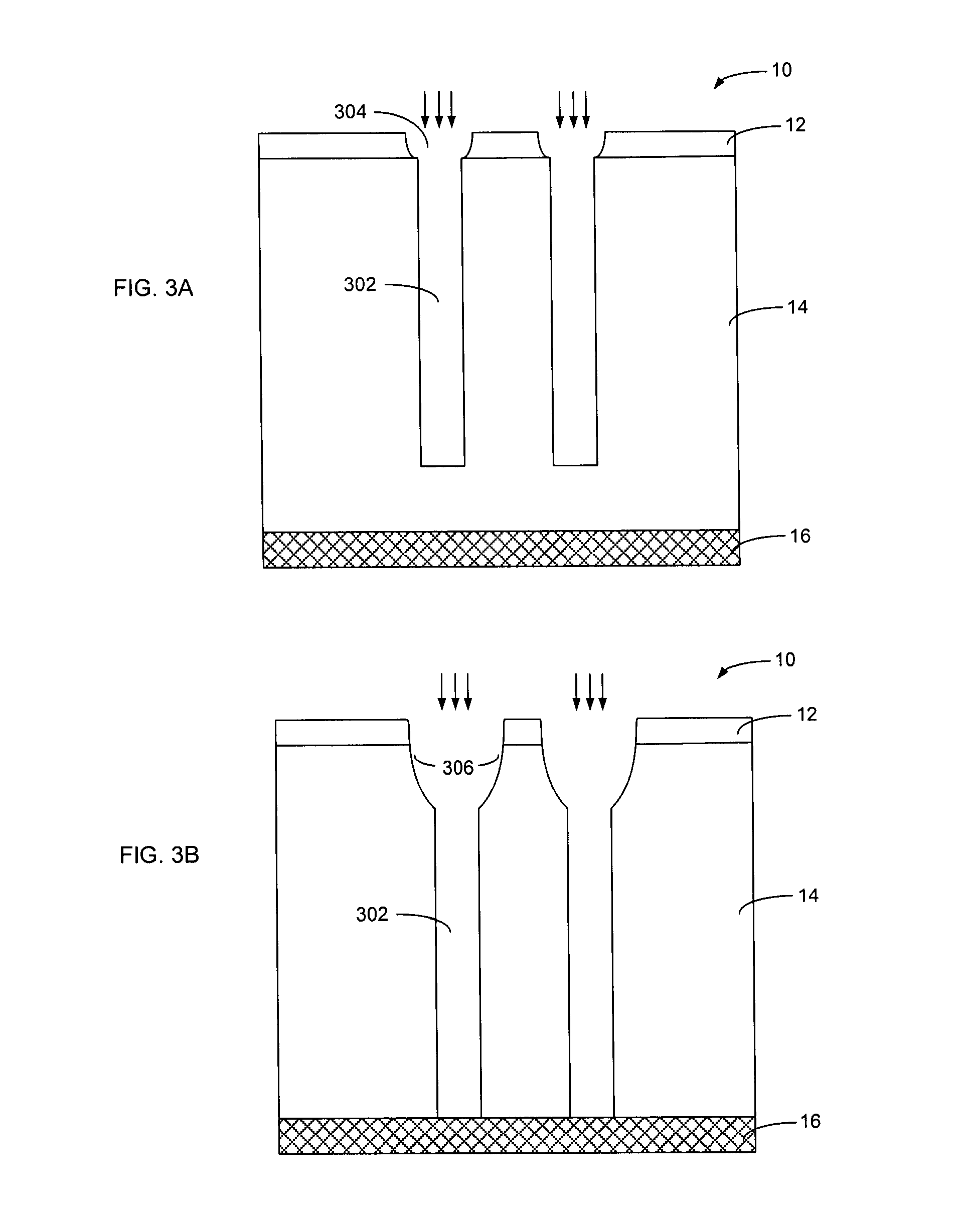

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

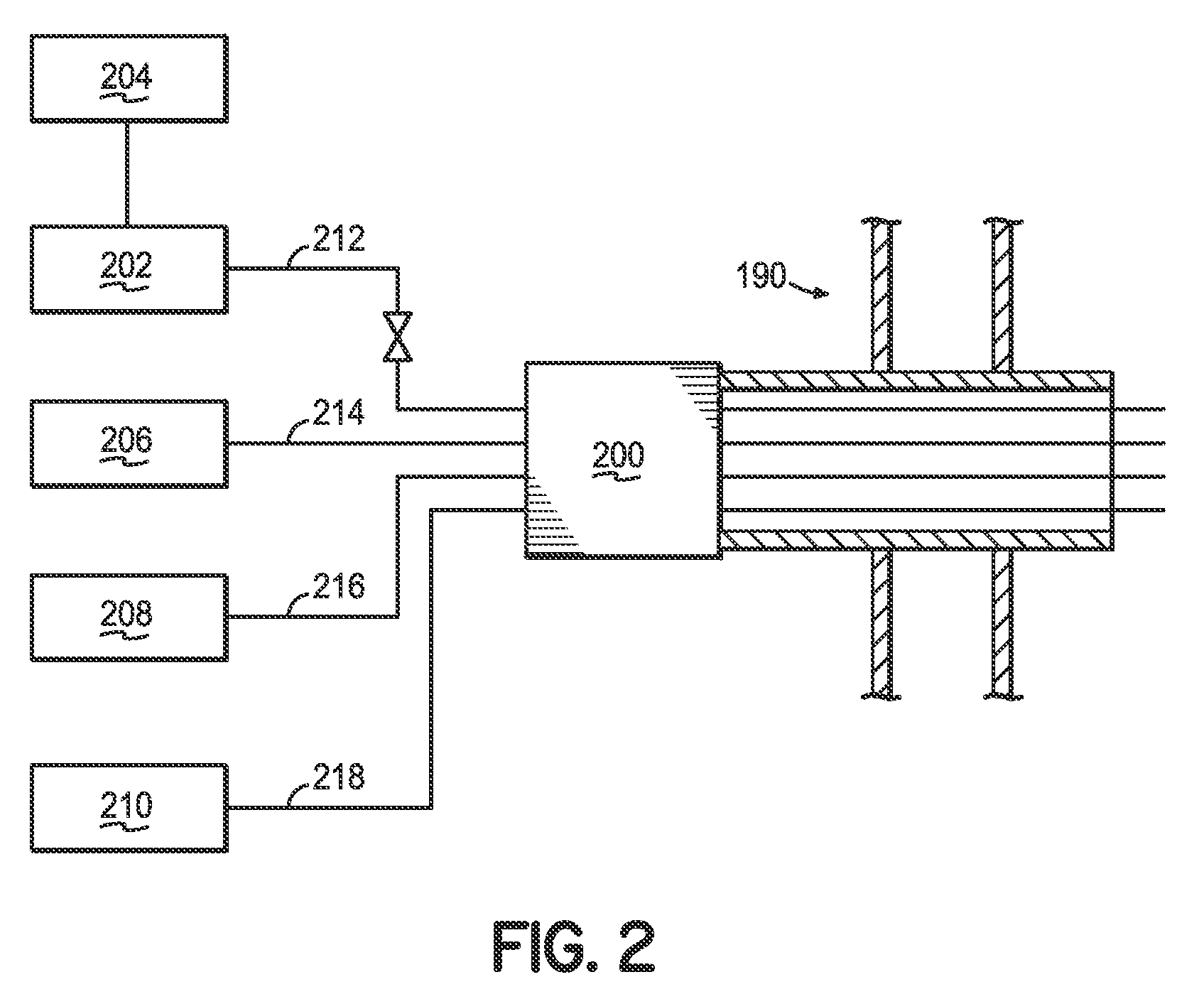

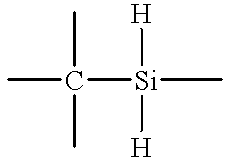

Method of depositing a low k dielectric with organo silane

InactiveUS6054379ASemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilane compoundsSilanes

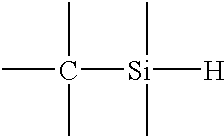

A method and apparatus for depositing a low dielectric constant film by reaction of an organo silane compound and an oxidizing gas. The oxidized organo silane film has excellent barrier properties for use as a liner or cap layer adjacent other dielectric layers. The oxidized organo silane film can also be used as an etch stop or an intermetal dielectric layer for fabricating dual damascene structures. The oxidized organo silane films also provide excellent adhesion between different dielectric layers. A preferred oxidized organo silane film is produced by reaction of methyl silane, CH3SiH3, and N2O.

Owner:APPLIED MATERIALS INC

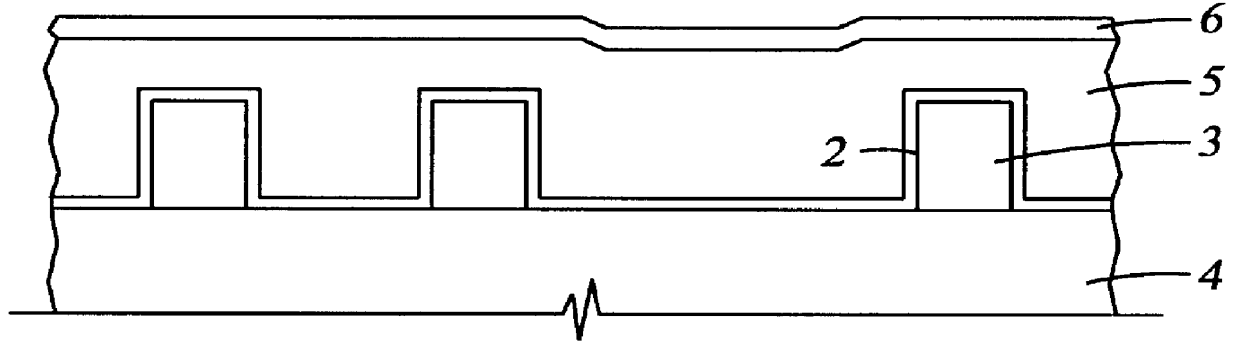

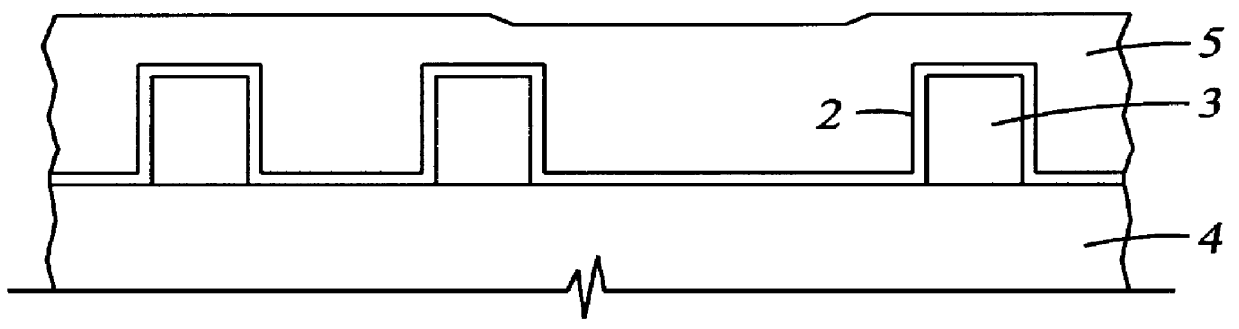

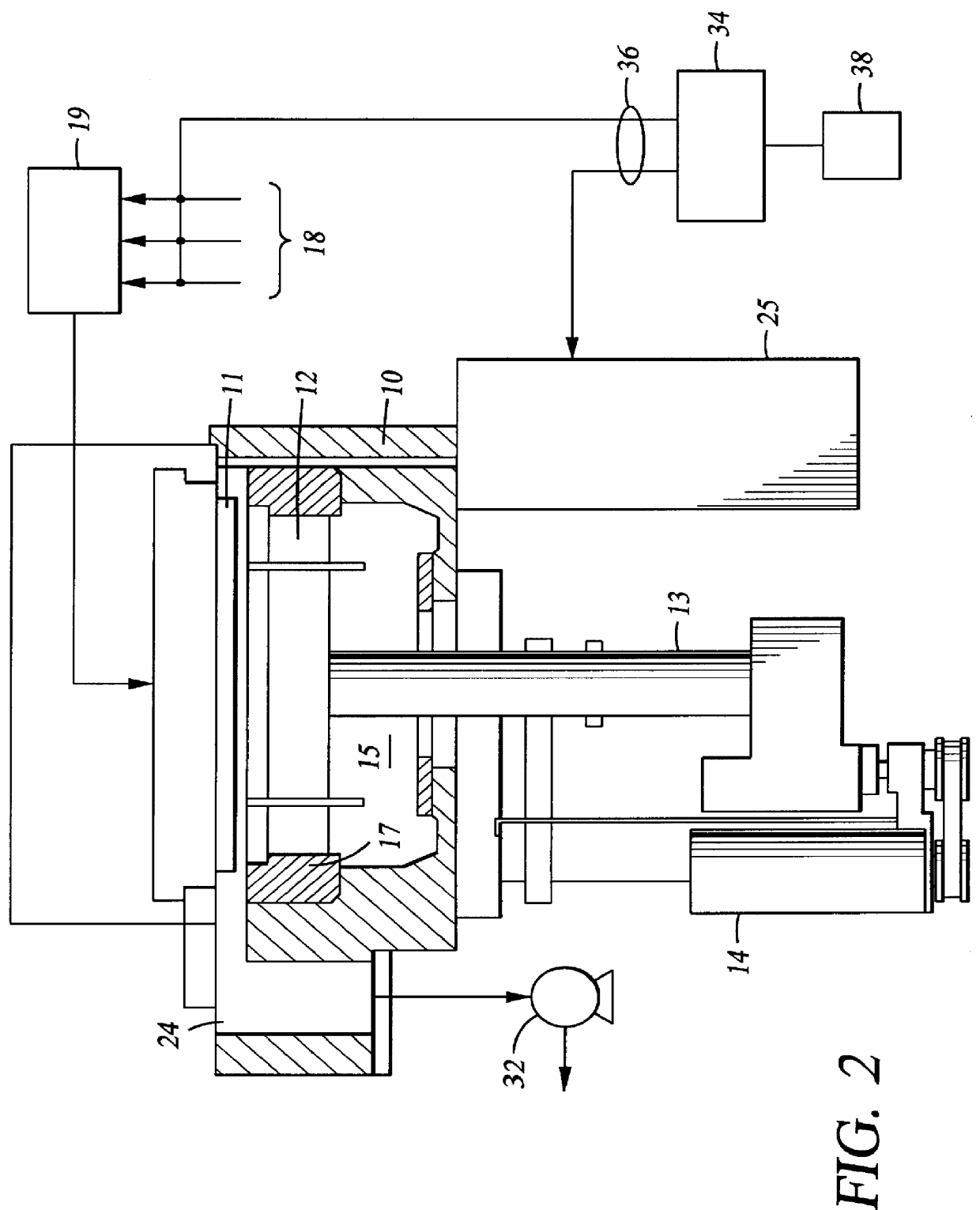

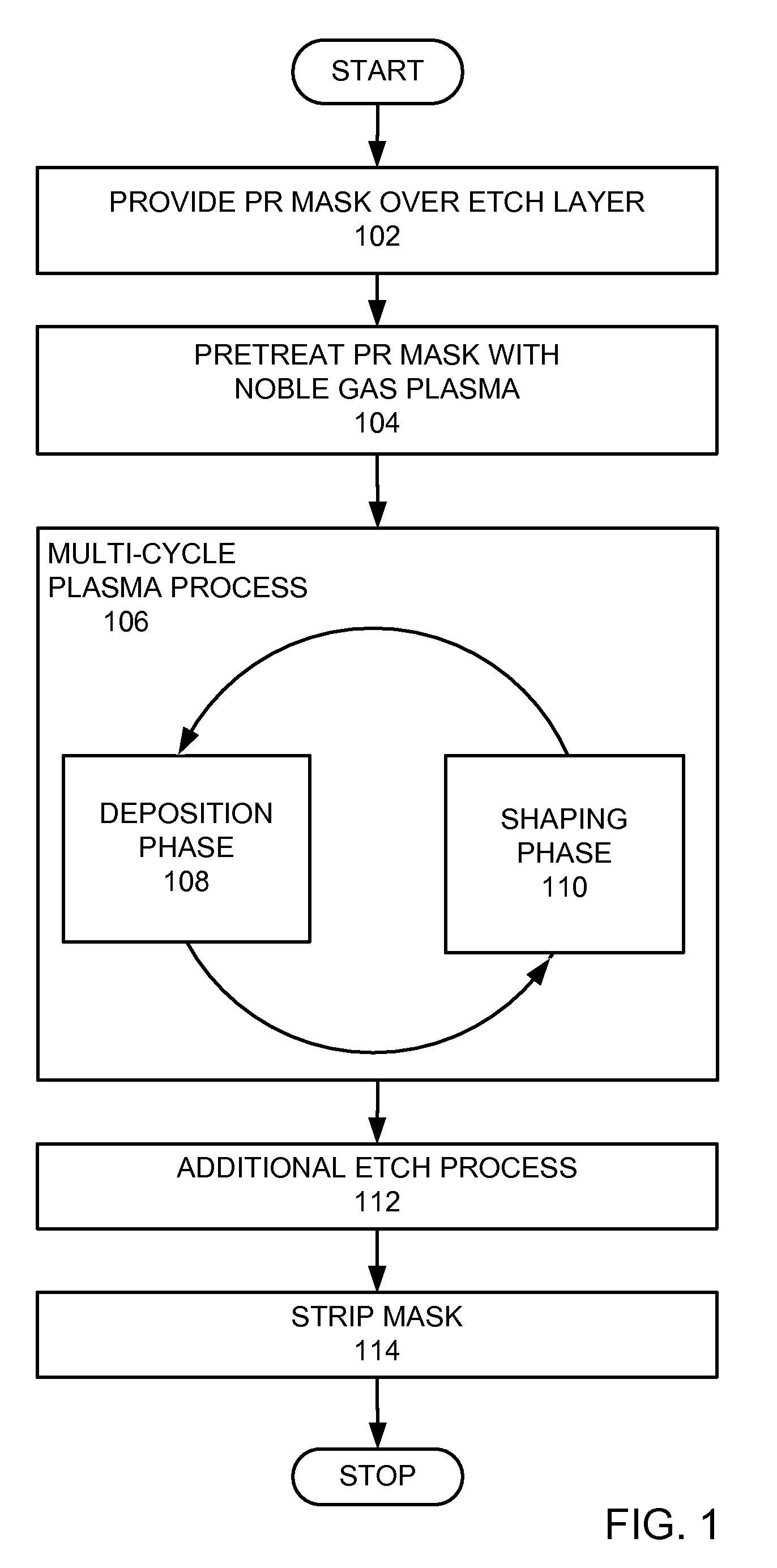

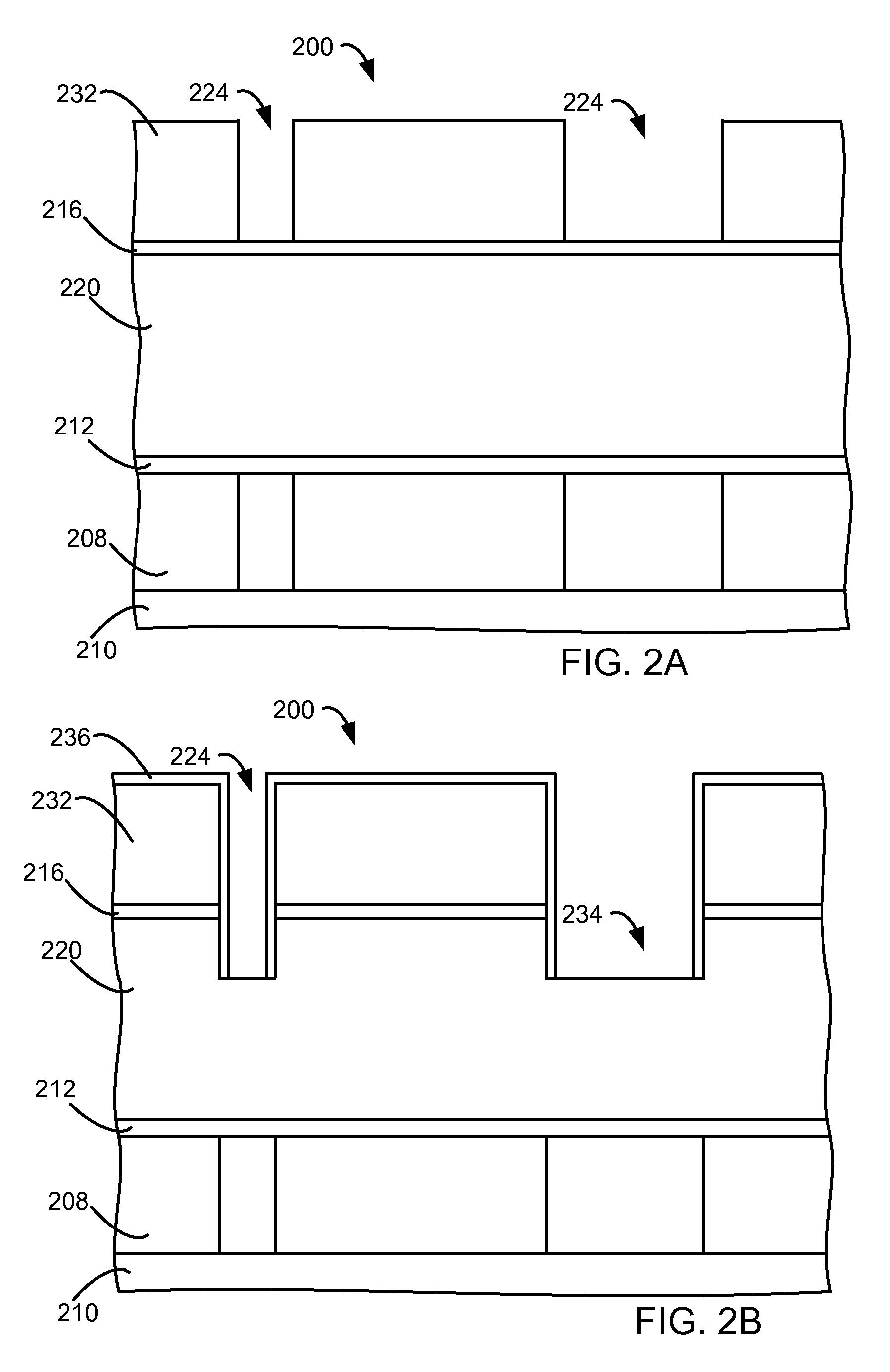

Plasma process with photoresist mask pretreatment

InactiveUS20090286400A1Decorative surface effectsSemiconductor/solid-state device manufacturingNoble gasLaser light

A method for etching features in a dielectric layer through a photoresist (PR) mask is provided. The PR mask is patterned using laser light having a wavelength not more than 193 nm. The PR mask is pre-treated with a noble gas plasma, and then a plurality of cycles of a plasma process is provided. Each cycle includes a deposition phase that deposits a deposition layer over the PR mask, the deposition layer covering a top and sidewalls of mask features of the PR mask, and a shaping phase that shapes the deposition layer deposited over the PR mask.

Owner:LAM RES CORP

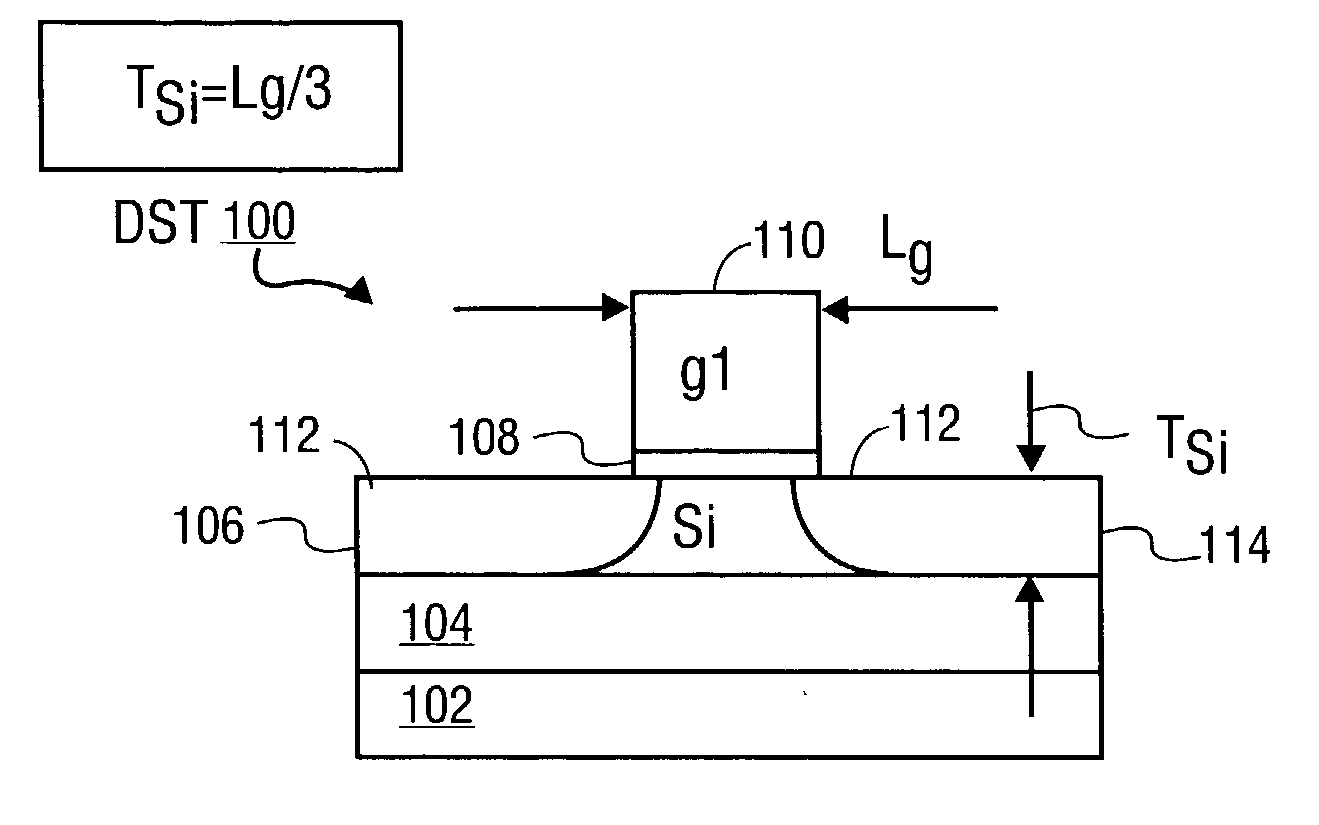

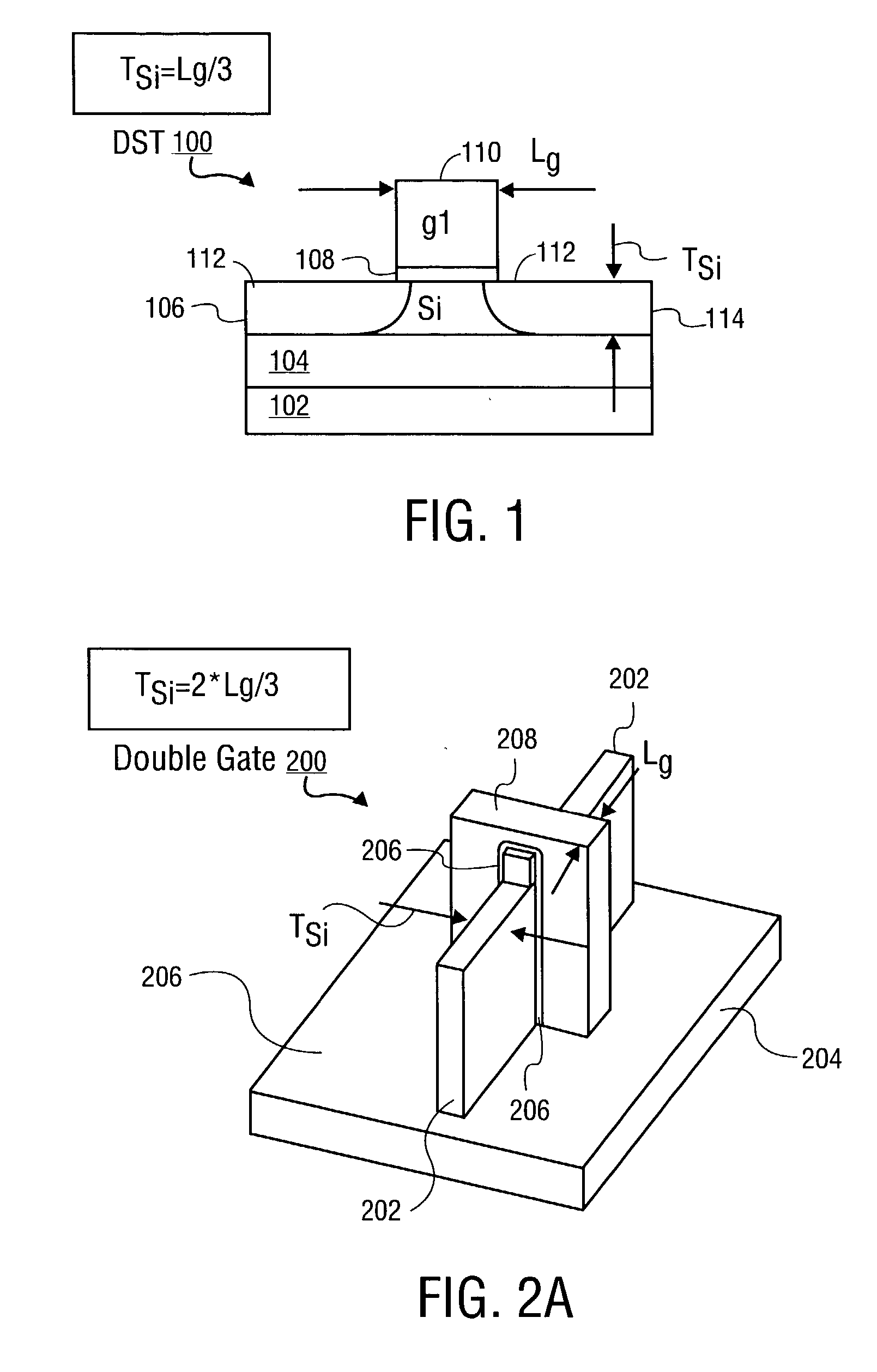

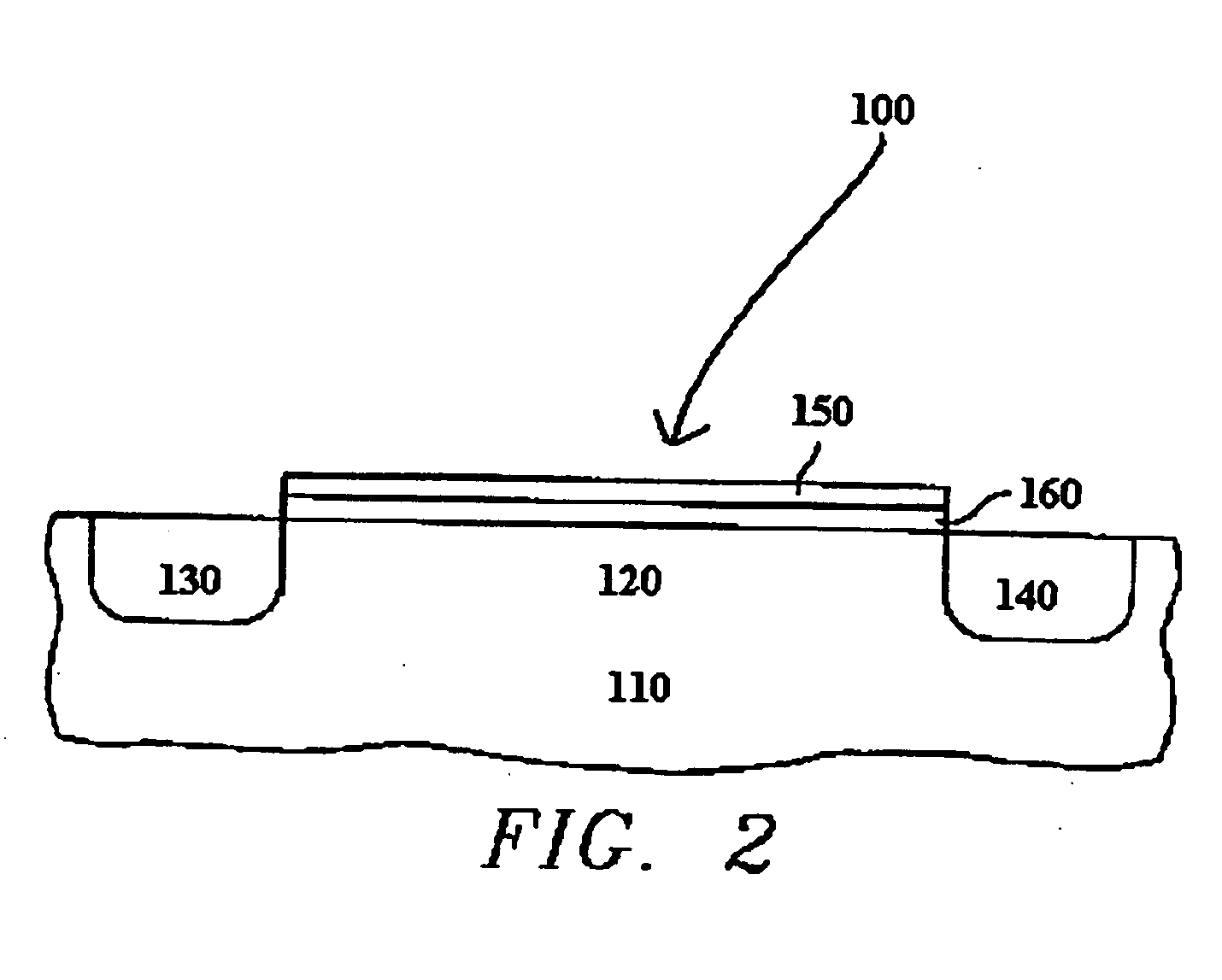

Tri-gate devices and methods of fabrication

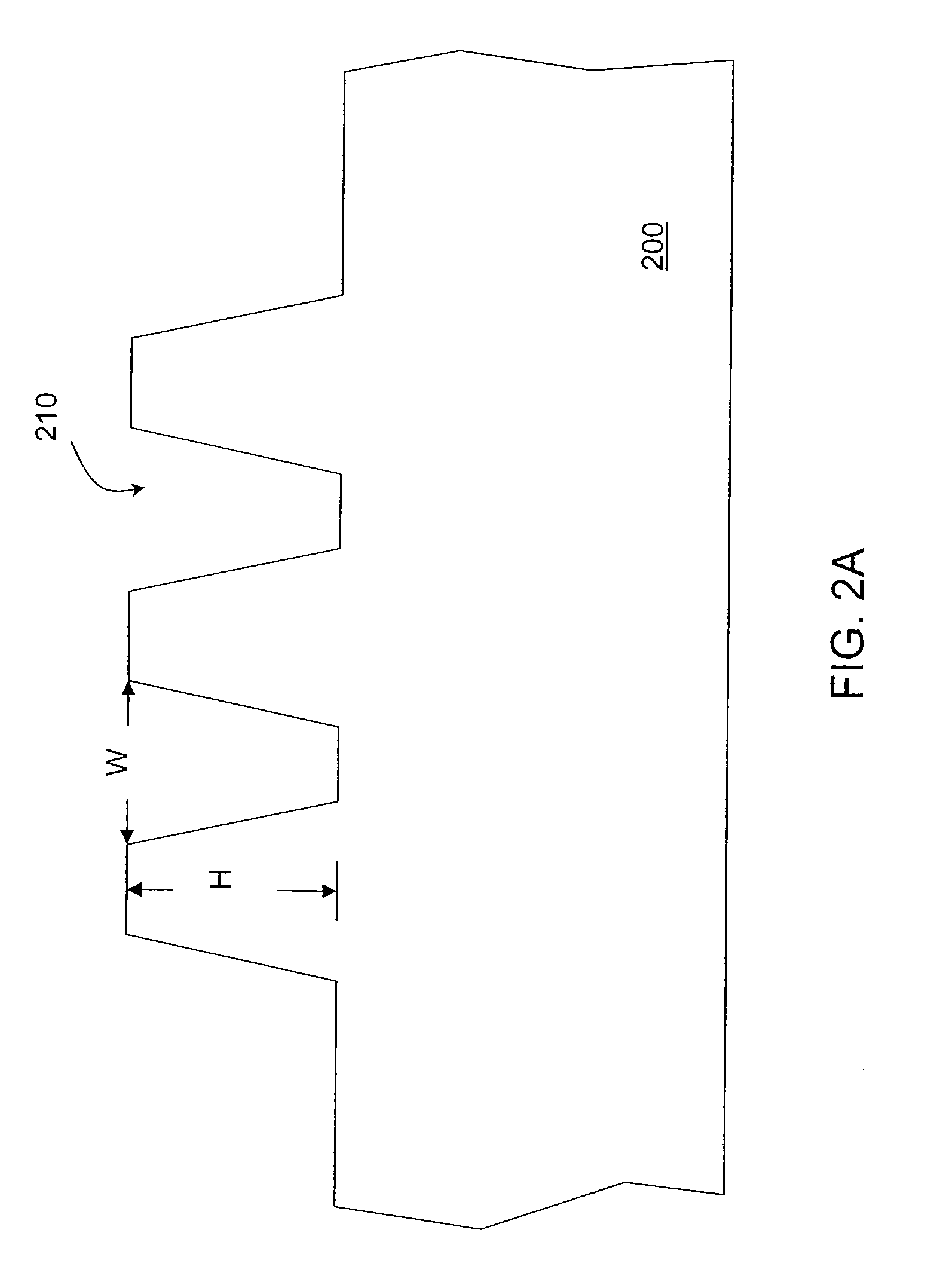

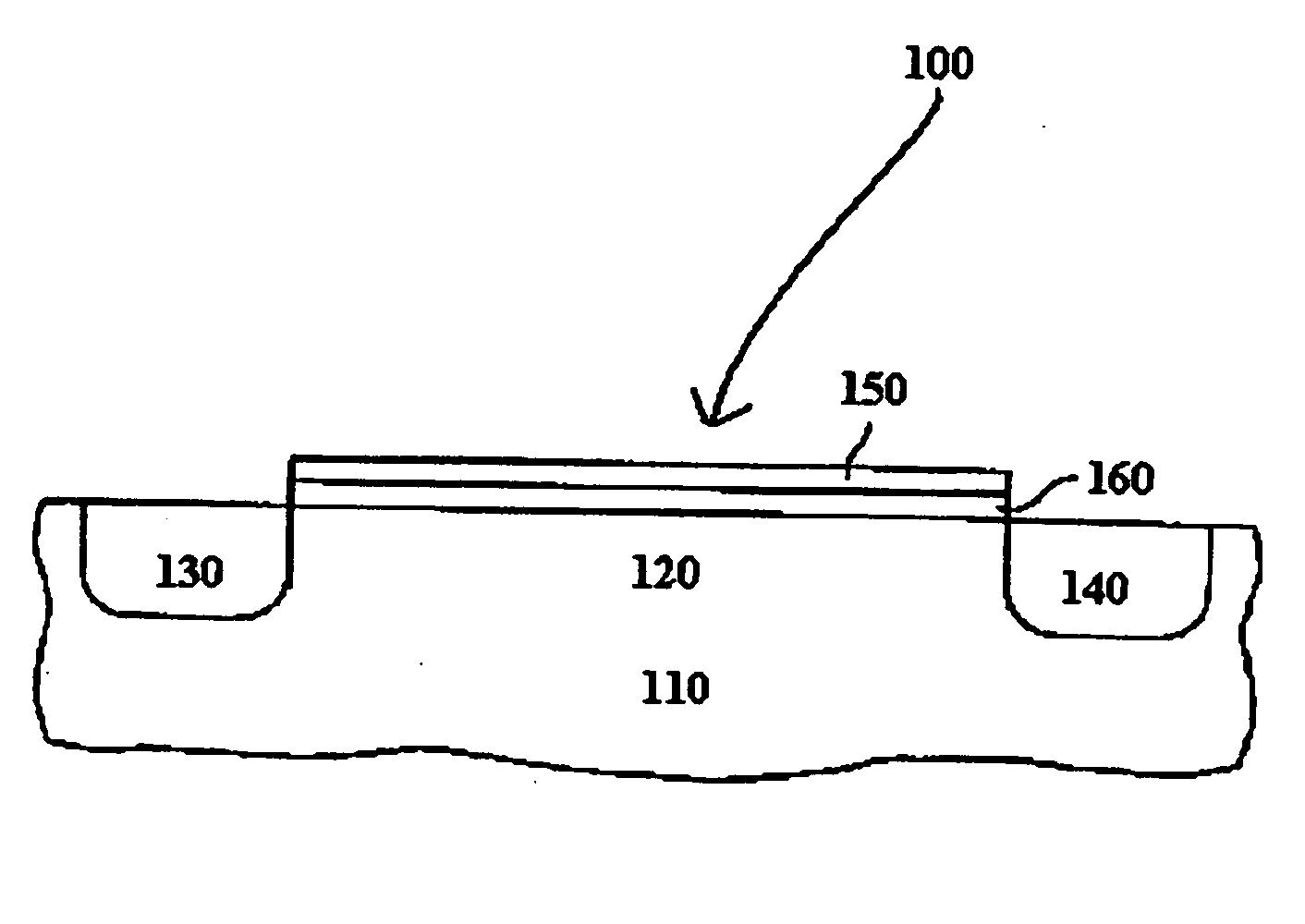

The present invention is a semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls formed on a substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body.

Owner:INTEL CORP

Method of etching patterned layers useful as masking during subsequent etching or for damascene structures

InactiveUS6080529APhotomechanical apparatusSemiconductor/solid-state device manufacturingConductive polymerOrganic base

A first embodiment of the present invention pertains to a method of patterning a semiconductor device conductive feature while permitting easy removal of any residual masking layer which remains after completion of the etching process. A multi-layered masking structure is used which includes a layer of high-temperature organic-based masking material overlaid by either a patterned layer of inorganic masking material or by a layer of patterned high-temperature imageable organic masking material. The inorganic masking material is used to transfer a pattern to the high-temperature organic-based masking material and is then removed. The high-temperature organic-based masking material is used to transfer the pattern and then may be removed if desired. This method is also useful in the pattern etching of aluminum, even though aluminum can be etched at lower temperatures. A second embodiment of the present invention pertains to a specialized etch chemistry useful in the patterning of organic polymeric layers such as low k dielectrics, or other organic polymeric interfacial layers. This etch chemistry is useful for mask opening during the etch of a conductive layer or is useful in etching damascene structures where a metal fill layer is applied over the surface of a patterned organic-based dielectric layer. The etch chemistry provides for the use of etchant plasma species which minimize oxygen, fluorine, chlorine, and bromine content.

Owner:APPLIED MATERIALS INC

Reactive formation of dielectric layers and protection of organic layers in organic semiconductor device fabrication

InactiveUS6842657B1Use is harmfulDamage is causedSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerOrganic semiconductor

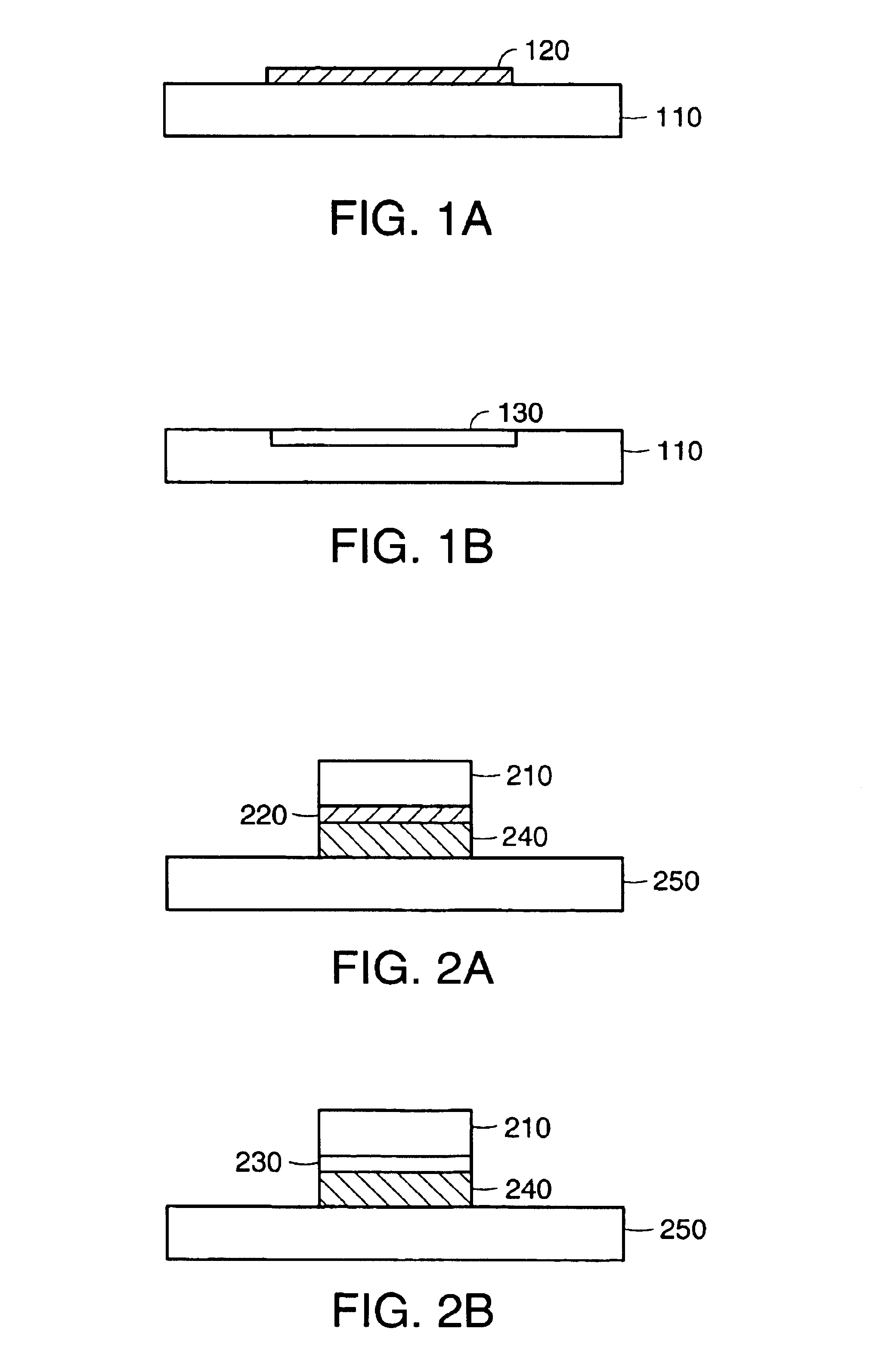

In one embodiment of the invention, a method of manufacturing a semiconductor device comprises the steps of: a) providing an organic semiconductor layer; b) depositing a reactive species on a portion of the organic semiconductor layer; and c) reacting the reactive species with the portion of the organic layer to form a dielectric layer.

Owner:E INK CORPORATION

Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound

InactiveUS6413583B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

A method for depositing silicon oxide layers having a low dielectric constant by reaction of an organosilicon compound and a hydroxyl forming compound at a substrate temperature less than about 400° C. The low dielectric constant films contain residual carbon and are useful for gap fill layers, pre-metal dielectric layers, inter-metal dielectric layers, and shallow trench isolation dielectric layers in sub-micron devices. The hydroxyl compound can be prepared prior to deposition from water or an organic compound. The silicon oxide layers are preferably deposited at a substrate temperature less than about 40° C. onto a liner layer produced from the organosilicon compound to provide gap fill layers having a dielectric constant less than about 3.0.

Owner:APPLIED MATERIALS INC

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

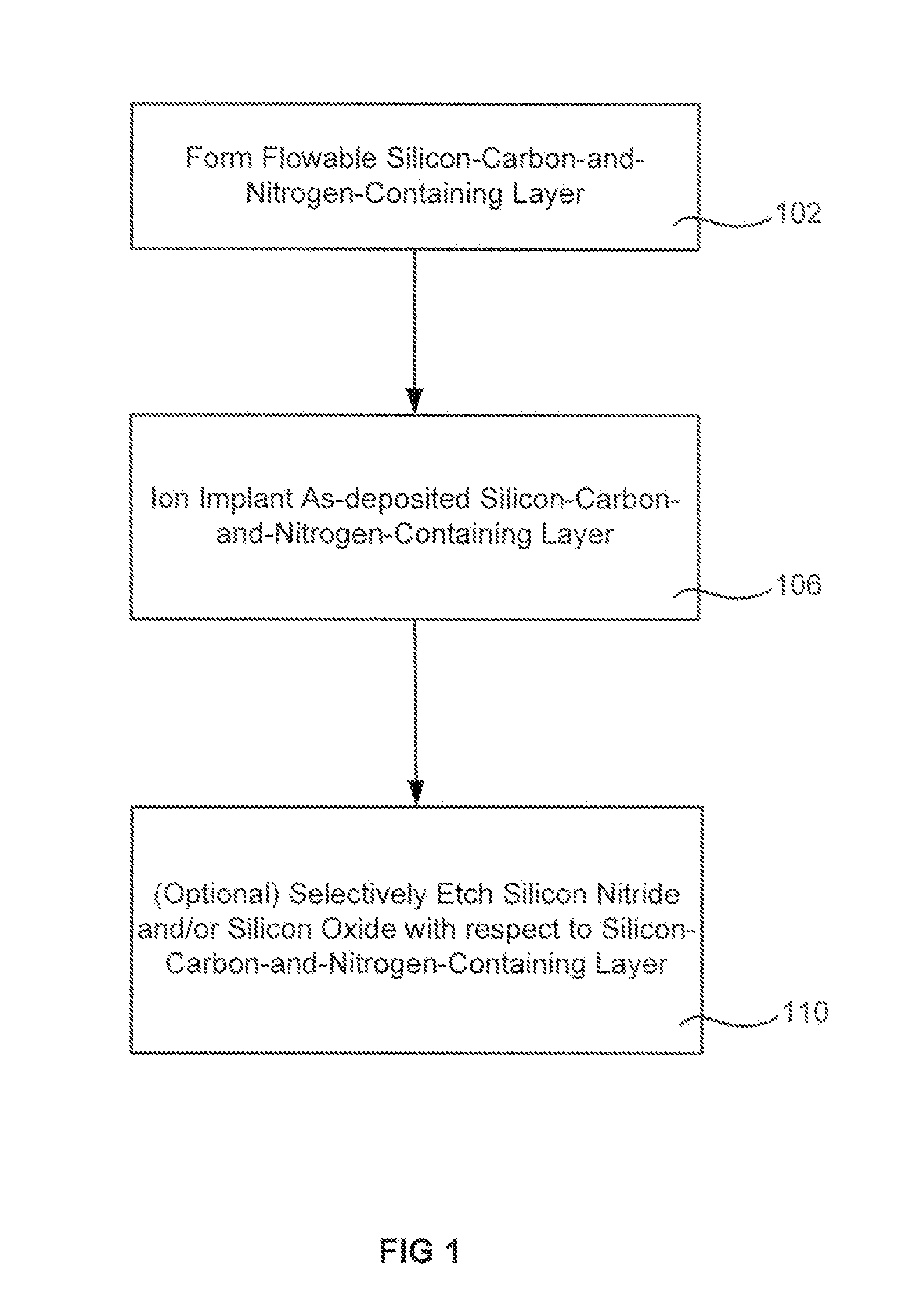

Doping of dielectric layers

InactiveUS20130217243A1Increase etch tolerancePrevent shrinkageSemiconductor/solid-state device manufacturingDeposition temperaturePhysical chemistry

Methods are described for forming and treating a flowable silicon-carbon-and-nitrogen-containing layer on a semiconductor substrate. The silicon and carbon constituents may come from a silicon-and-carbon-containing precursor while the nitrogen may come from a nitrogen-containing precursor that has been activated to speed the reaction of the nitrogen with the silicon-and-carbon-containing precursor at lower deposition temperatures. The initially-flowable silicon-carbon-and-nitrogen-containing layer is ion implanted to increase etch tolerance, prevent shrinkage, adjust film tension and / or adjust electrical characteristics. Ion implantation may also remove components which enabled the flowability, but are no longer needed after deposition. Some treatments using ion implantation have been found to decrease the evolution of properties of the film upon exposure to atmosphere.

Owner:APPLIED MATERIALS INC

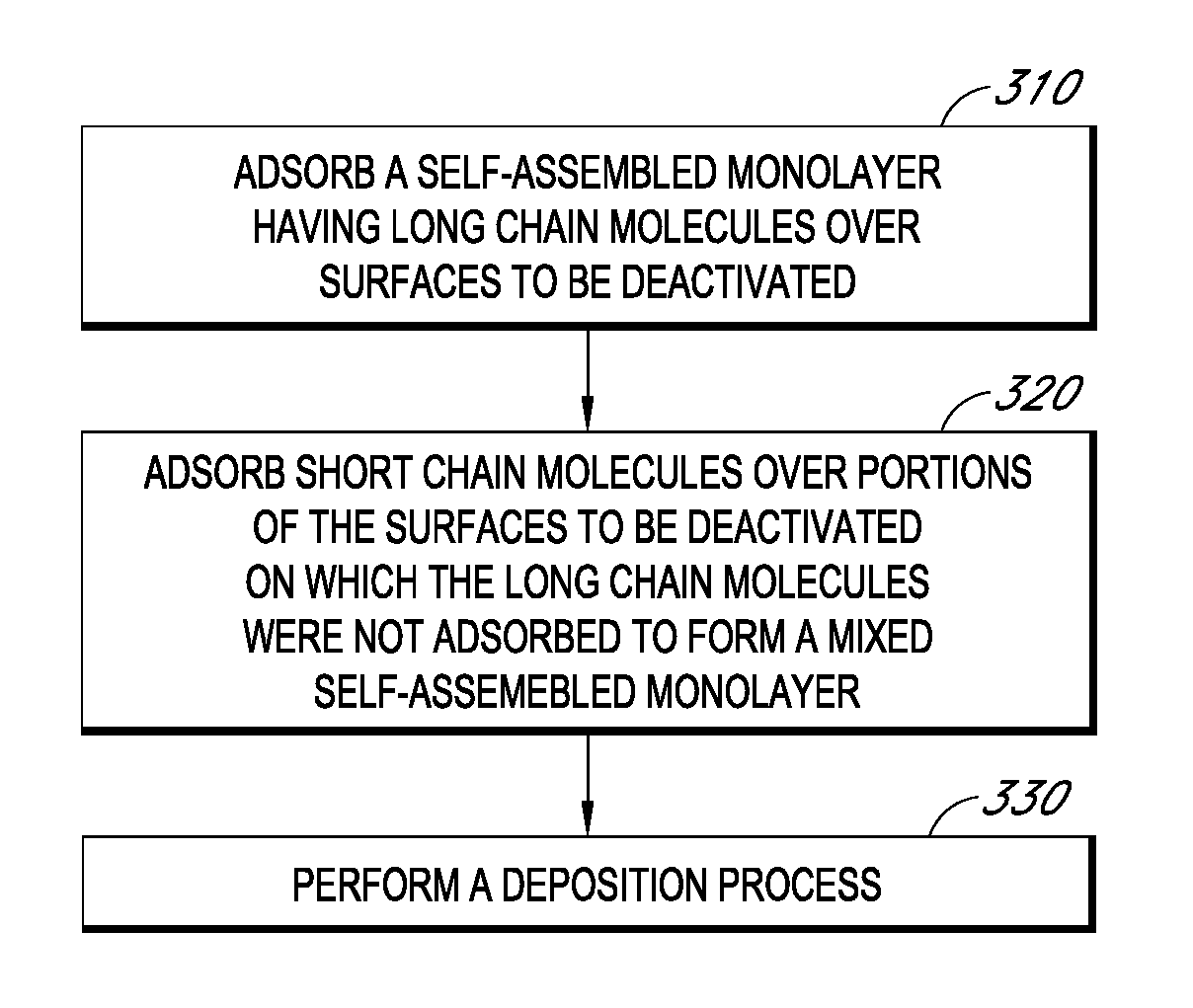

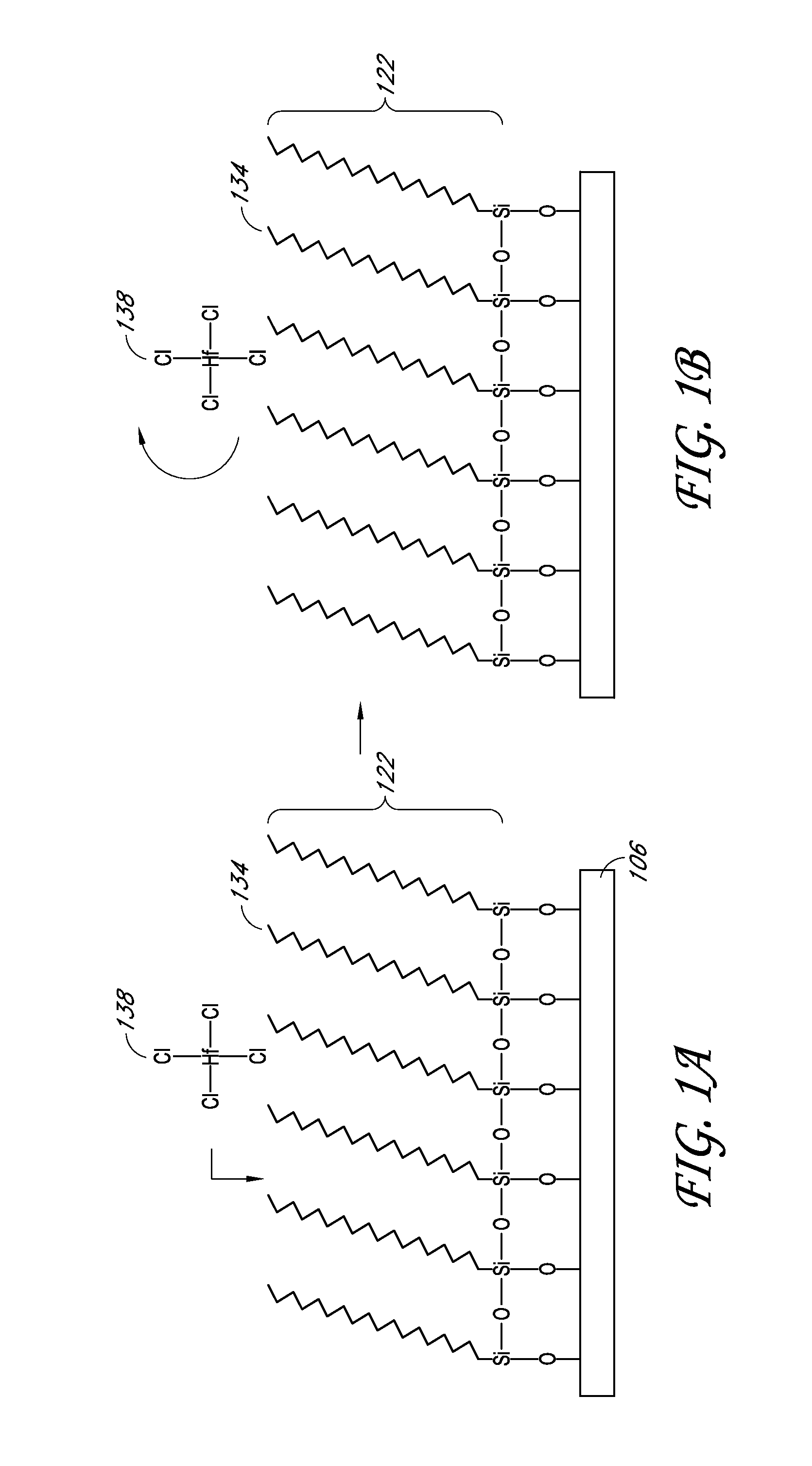

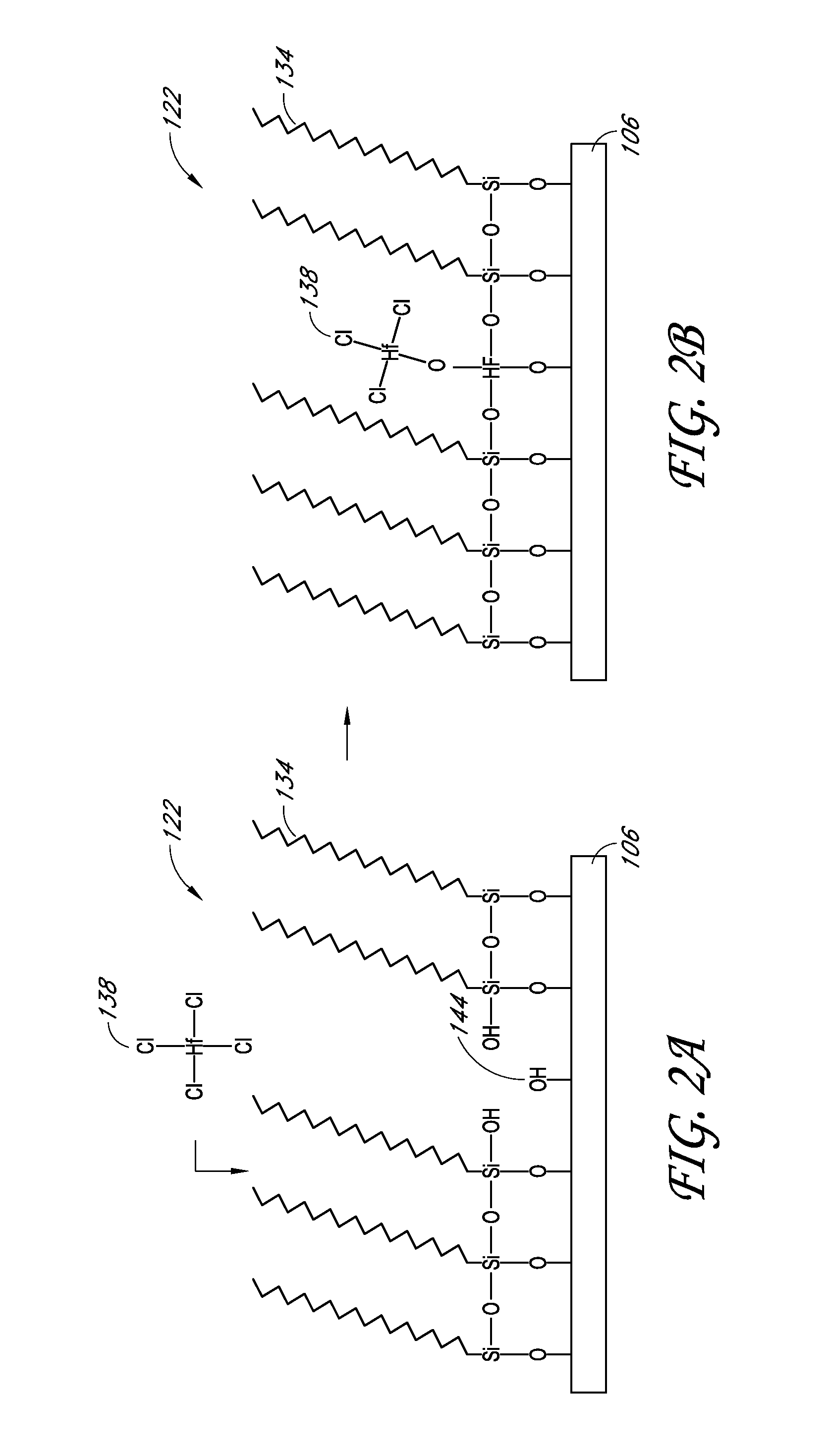

Reactive site deactivation against vapor deposition

Methods and structures relating to the formation of mixed SAMs for preventing undesirable growth or nucleation on exposed surfaces inside a reactor are described. A mixed SAM can be formed on surfaces for which nucleation is not desired by introducing a first SAM precursor having molecules of a first length and a second SAM precursor having molecules of a second length shorter than the first. Examples of exposed surfaces for which a mixed SAM can be provided over include reactor surfaces and select surfaces of integrated circuit structures, such as insulator and dielectric layers.

Owner:ASM IP HLDG BV

Activated Chemical Process for Enhancing Material Properties of Dielectric Films

ActiveUS20080199977A1High dielectric constantLow dielectric constantSemiconductor/solid-state device manufacturingFluid pressure measurement by mechanical elementsDielectric layerElectron

A method for restoring a dielectric constant of a layer of a silicon-containing dielectric material having a first dielectric constant and at least one surface, wherein the first dielectric constant of the layer of silicon-containing dielectric material has increased to a second dielectric constant, the method comprising the steps of: contacting the at least one surface of the layer of silicon-containing dielectric material with a silicon-containing fluid; and exposing the at least one surface of the layer of silicon-containing dielectric material to an energy source selected from the group consisting of: UV radiation, heat, and an electron beam, wherein the layer of silicon-containing dielectric material has a third dielectric constant that is lower than the second dielectric constant after exposing the layer of silicon-containing dielectric material to the energy source.

Owner:VERSUM MATERIALS US LLC

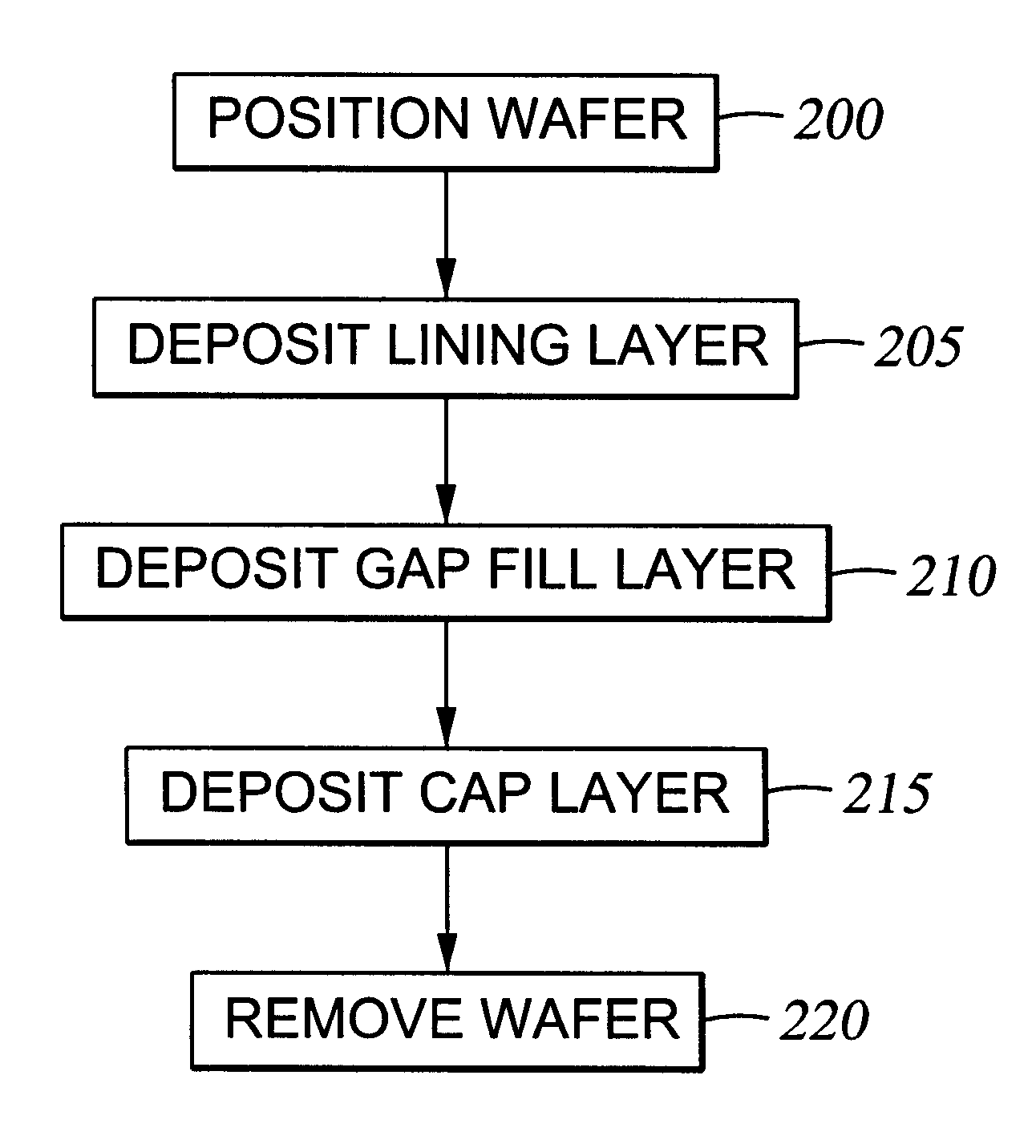

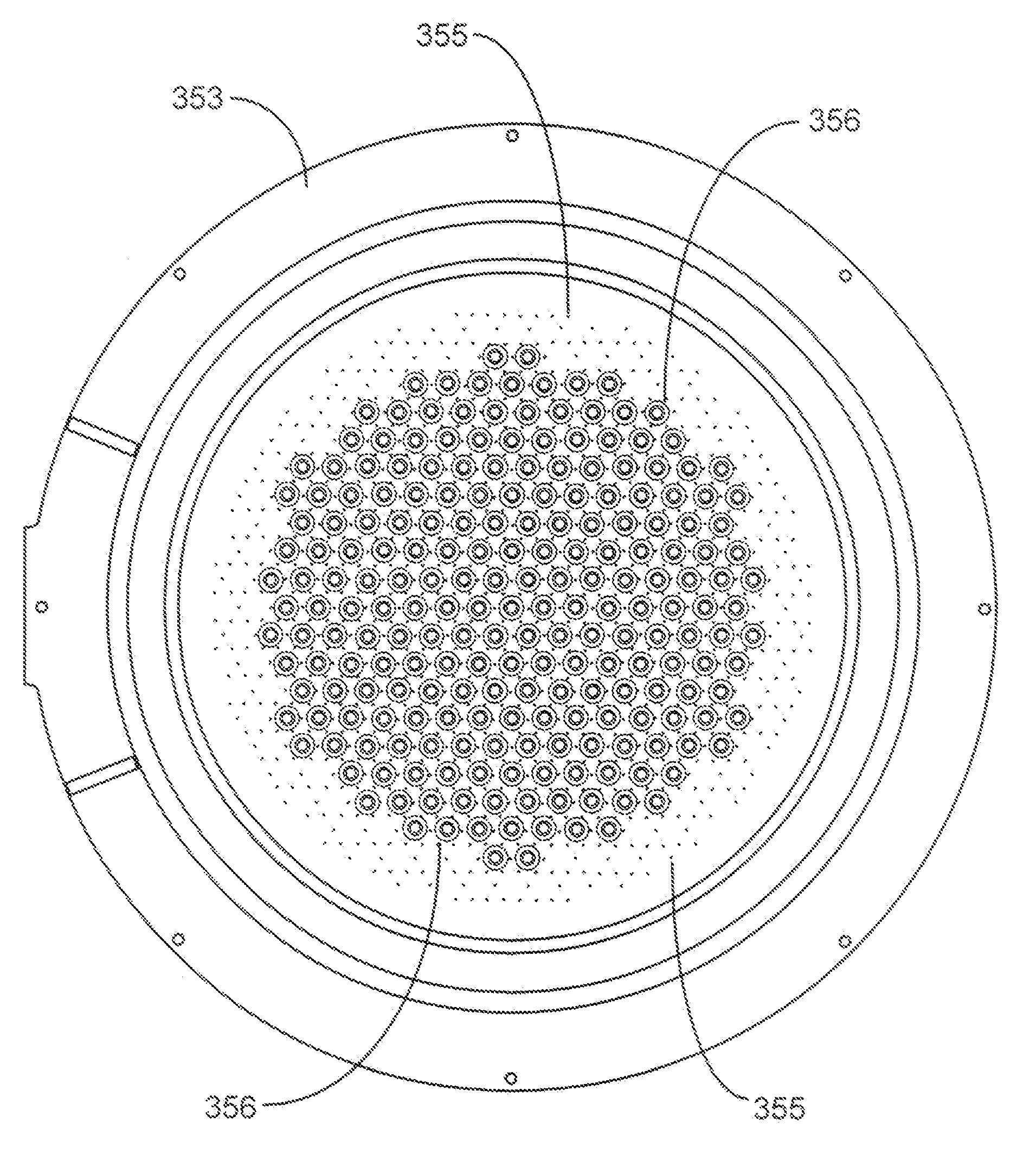

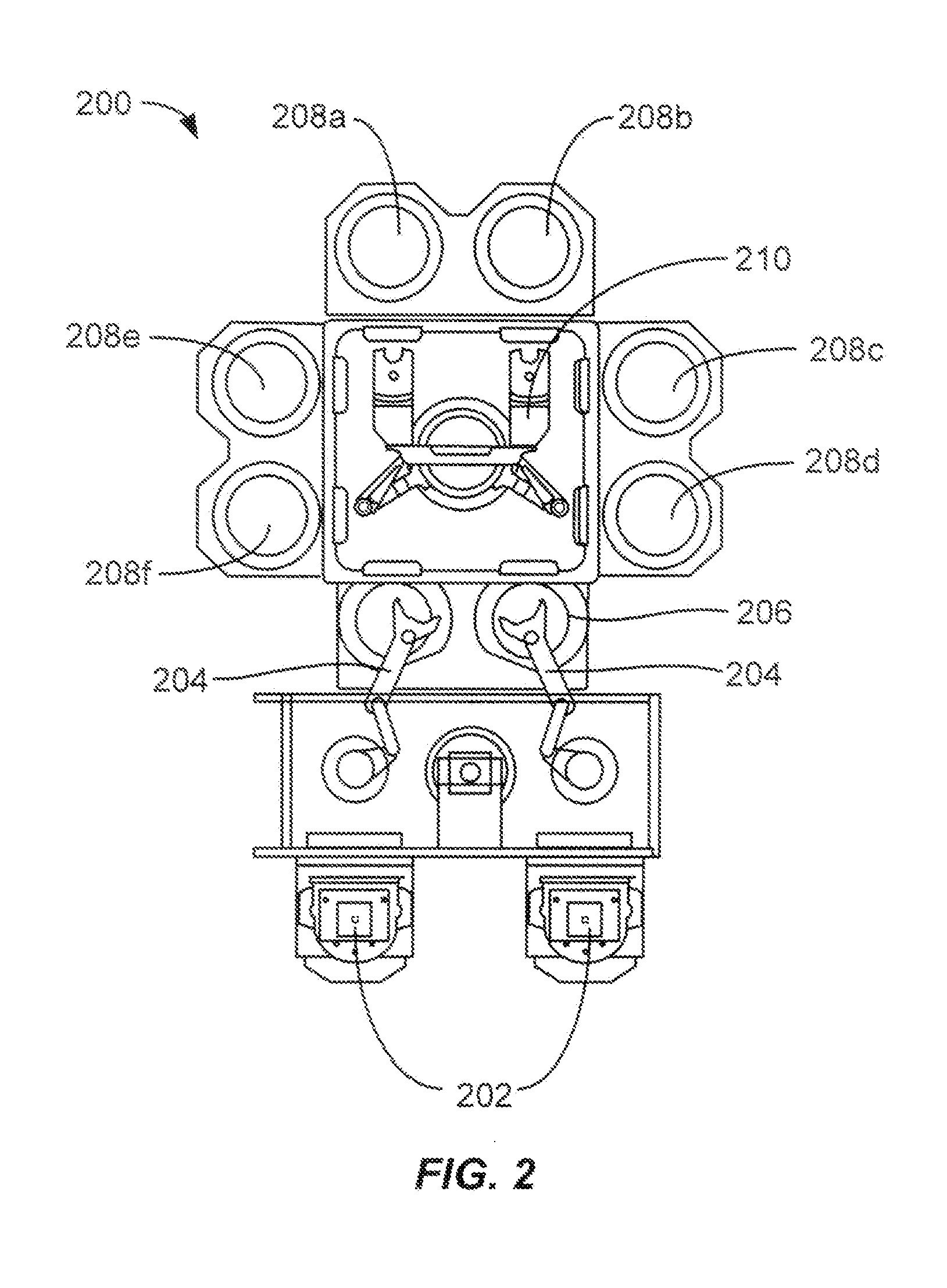

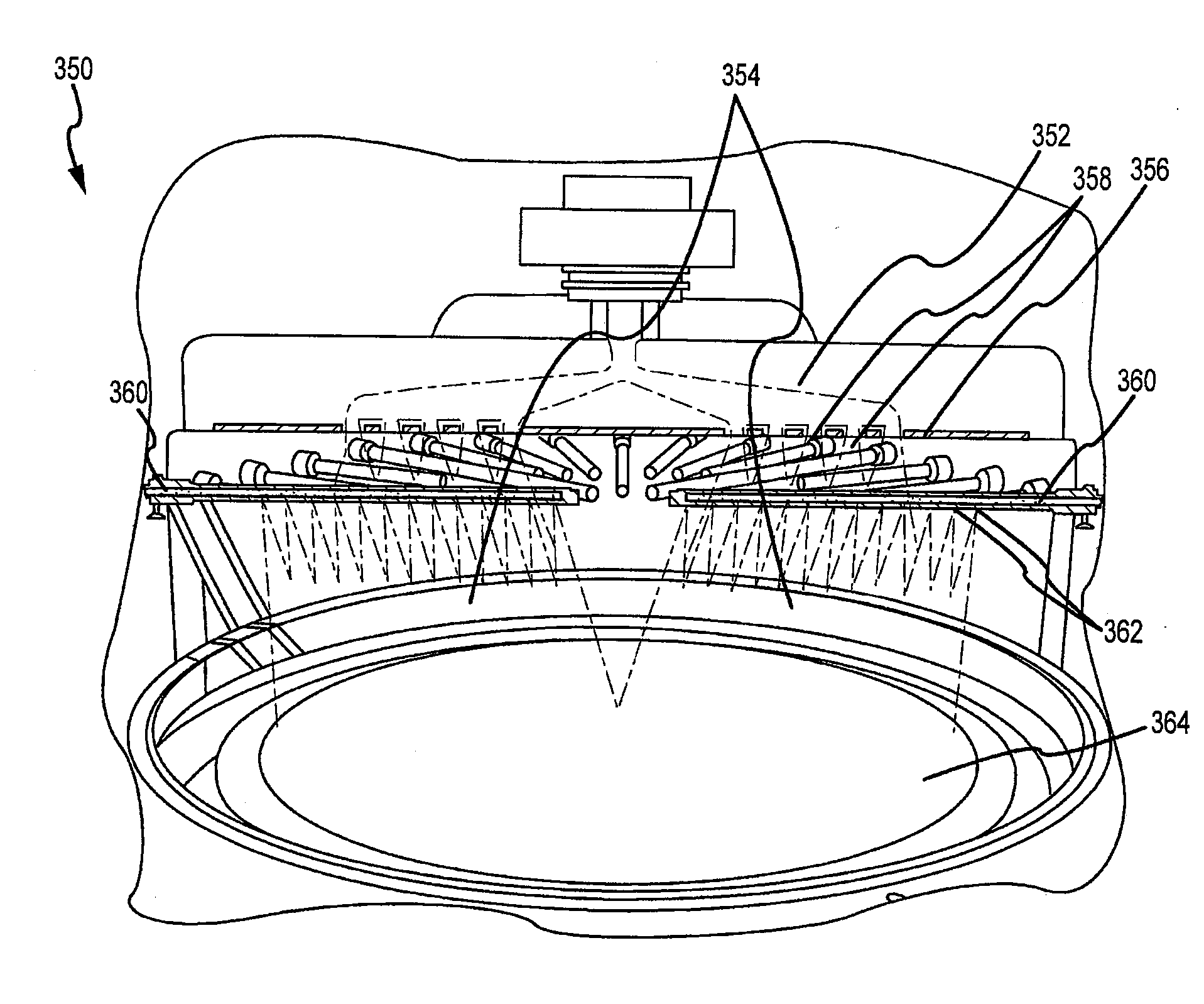

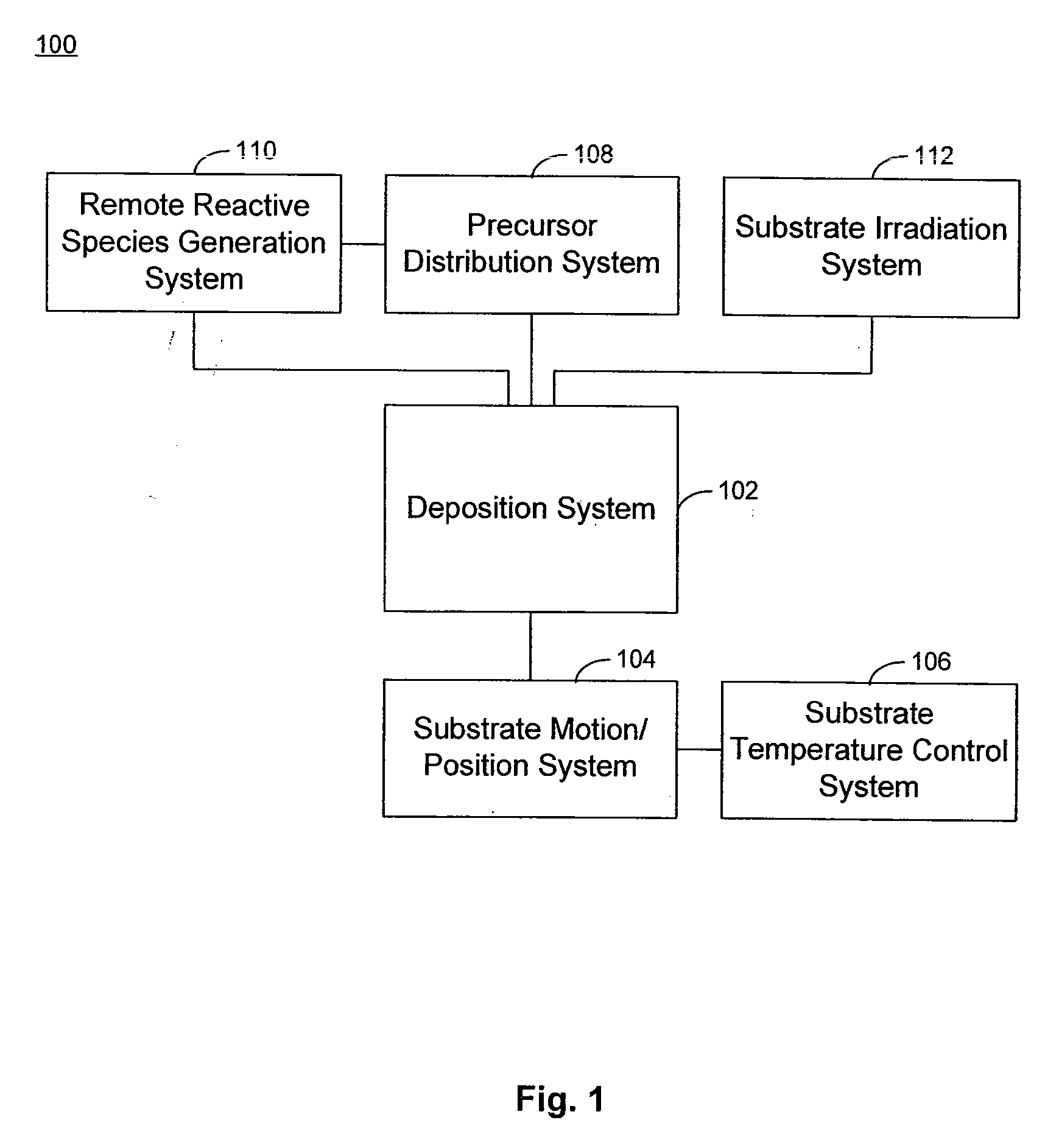

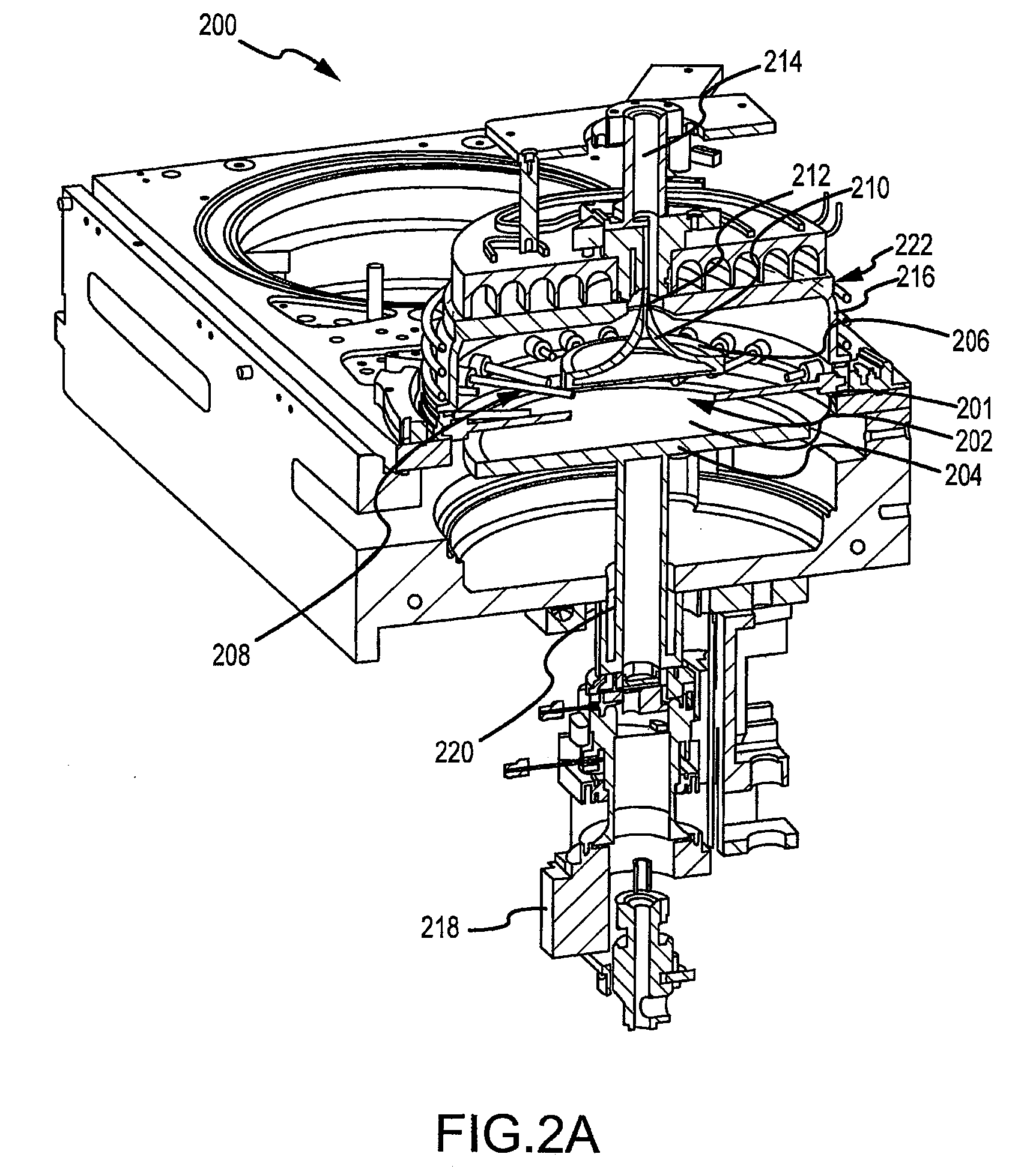

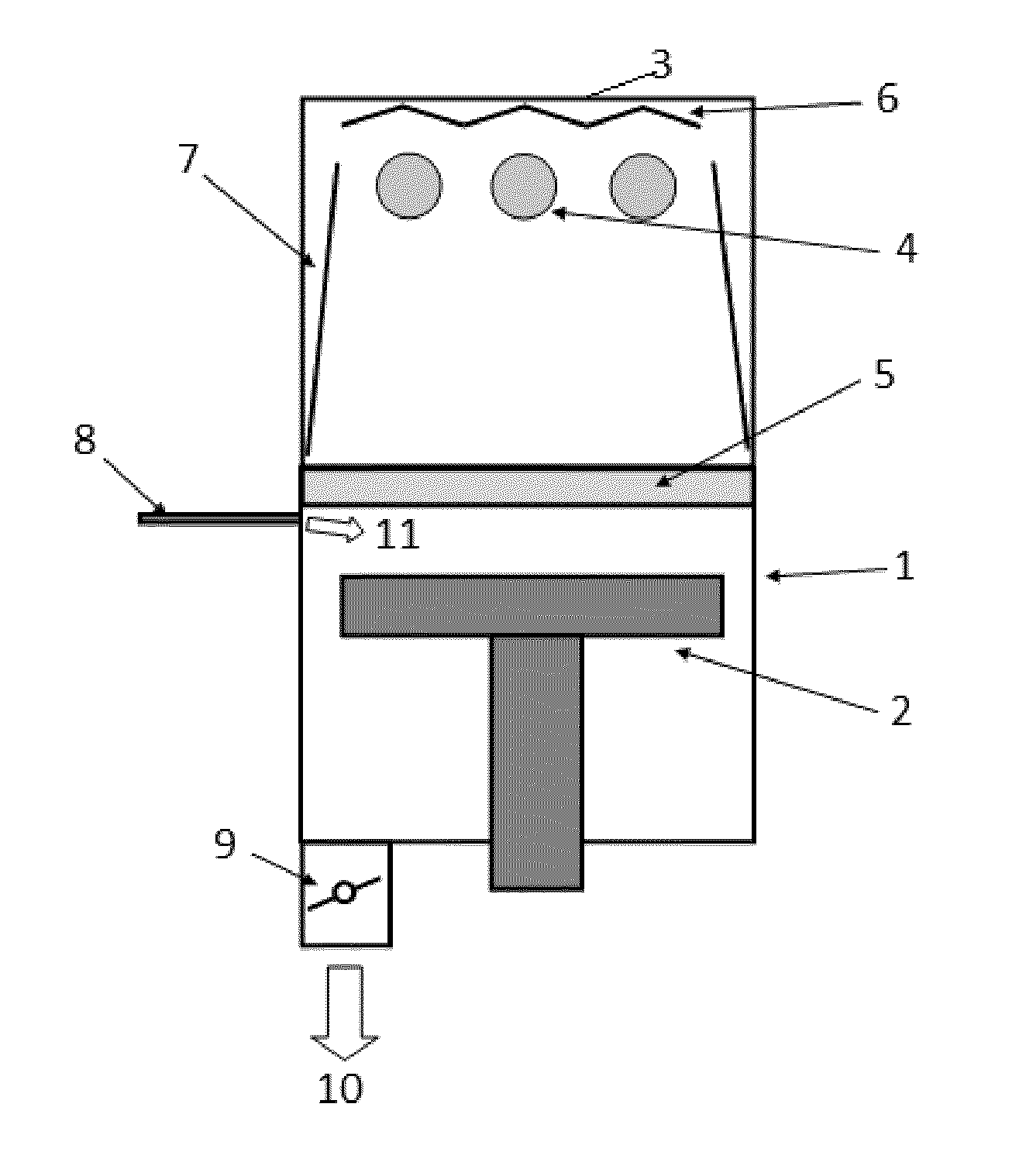

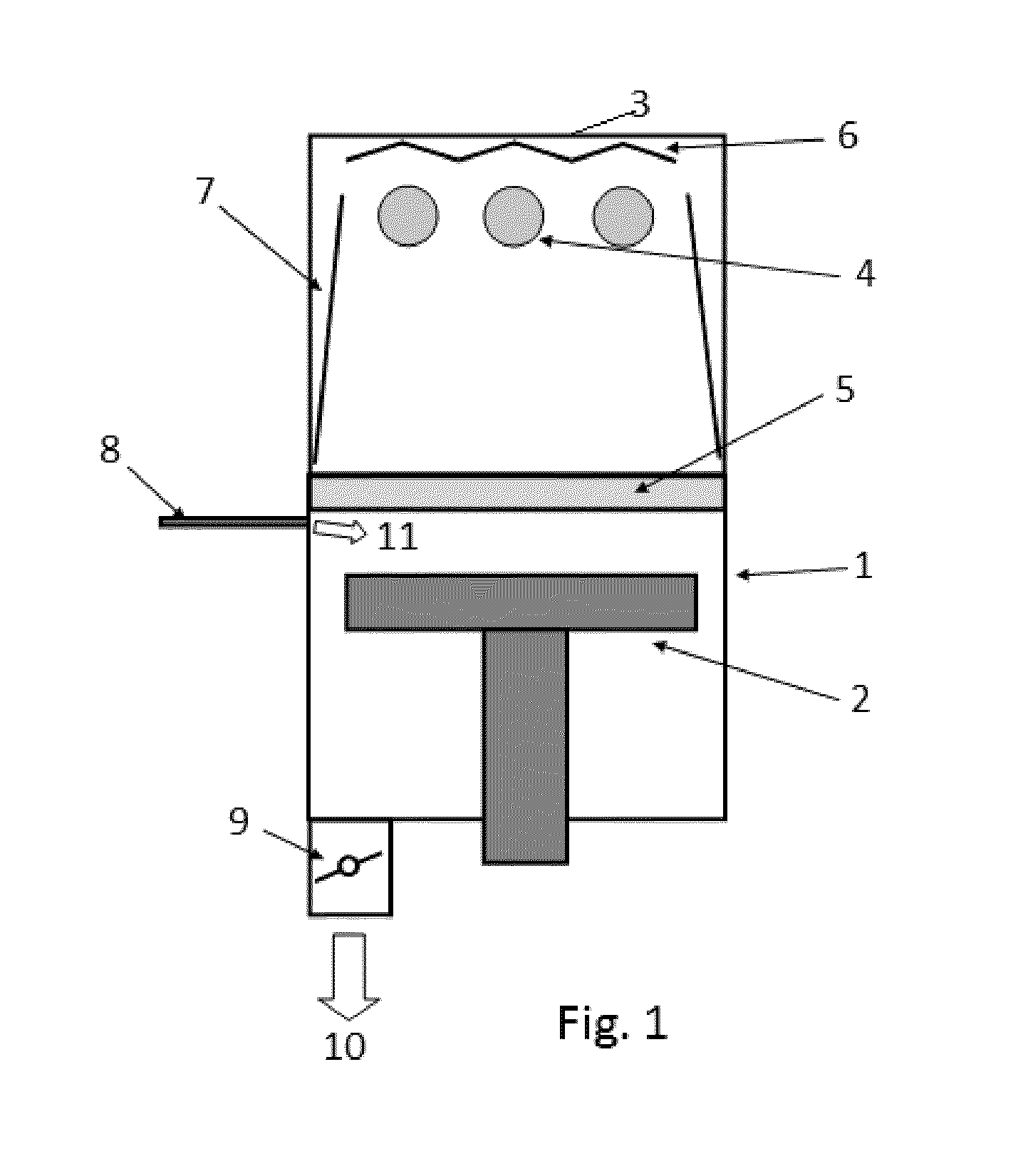

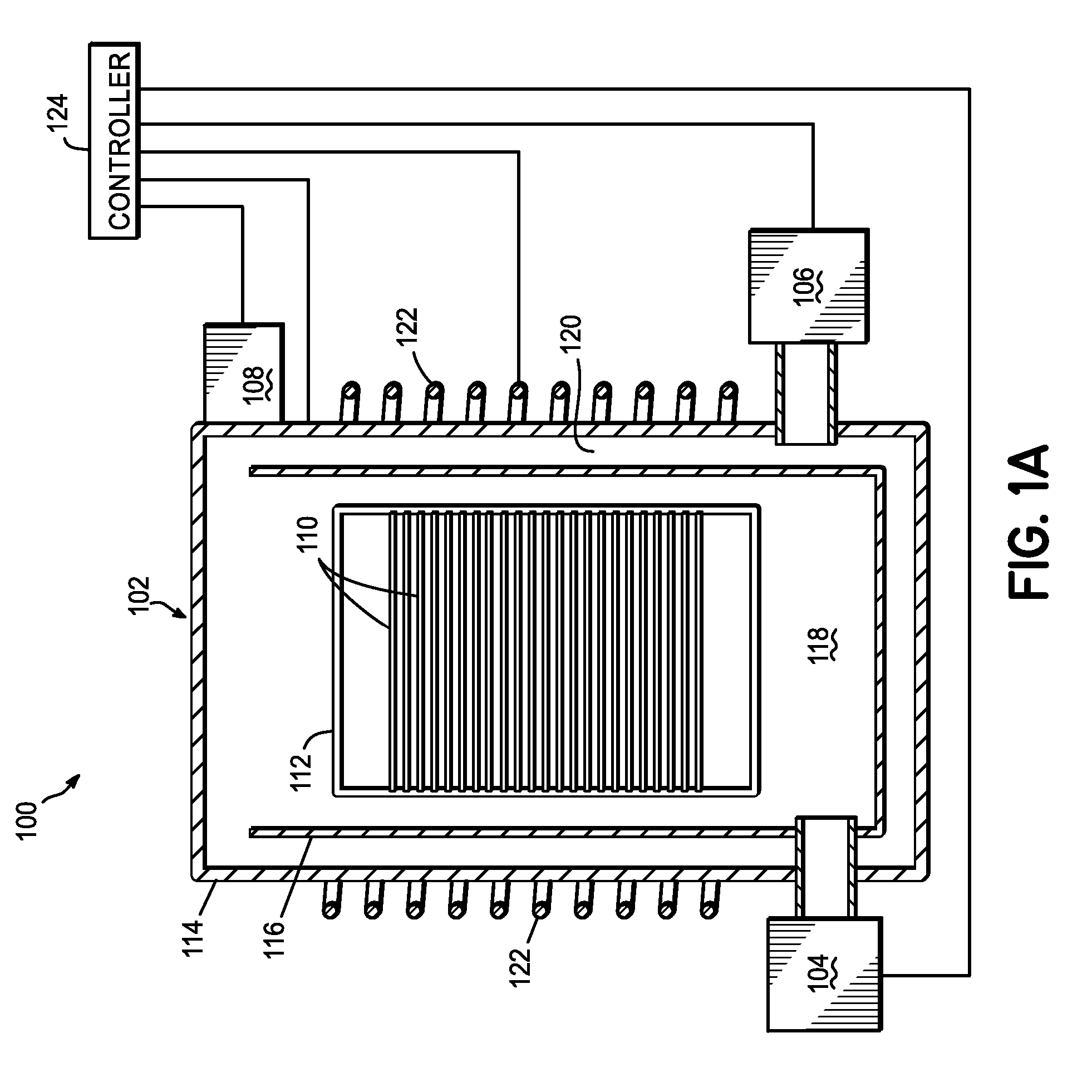

Process chamber for dielectric gapfill

InactiveUS20070281106A1Electric discharge tubesSemiconductor/solid-state device manufacturingRemote plasmaDistribution system

A system to form a dielectric layer on a substrate from a plasma of dielectric precursors is described. The system may include a deposition chamber, a substrate stage in the deposition chamber to hold the substrate, and a remote plasma generating system coupled to the deposition chamber, where the plasma generating system is used to generate a dielectric precursor having one or more reactive radicals. The system may also include a precursor distribution system that includes at least one top inlet and a plurality of side inlets. The top inlet may be positioned above the substrate stage and the side inlets may be radially distributed around the substrate stage. The reactive radical precursor may be supplied to the deposition chamber through the top inlet. An in-situ plasma generating system may also be included to generate the plasma in the deposition chamber from the dielectric precursors supplied to the deposition chamber.

Owner:APPLIED MATERIALS INC

Small electrode for a chalcogenide switching device and method for fabricating same

InactiveUS6189582B1Solid-state devicesSemiconductor/solid-state device manufacturingDielectric layerElectrode material

A memory cell and a method of fabricating the memory cell having a small active area. By forming a spacer in a window that is sized at the photolithographic limit, a pore may be formed in dielectric layer which is smaller than the photolithographic limit. Electrode material is deposited into the pore, and a layer of structure changing material, such as chalcogenide, is deposited onto the lower electrode, thus creating a memory element having an extremely small and reproducible active area.

Owner:ROUND ROCK RES LLC

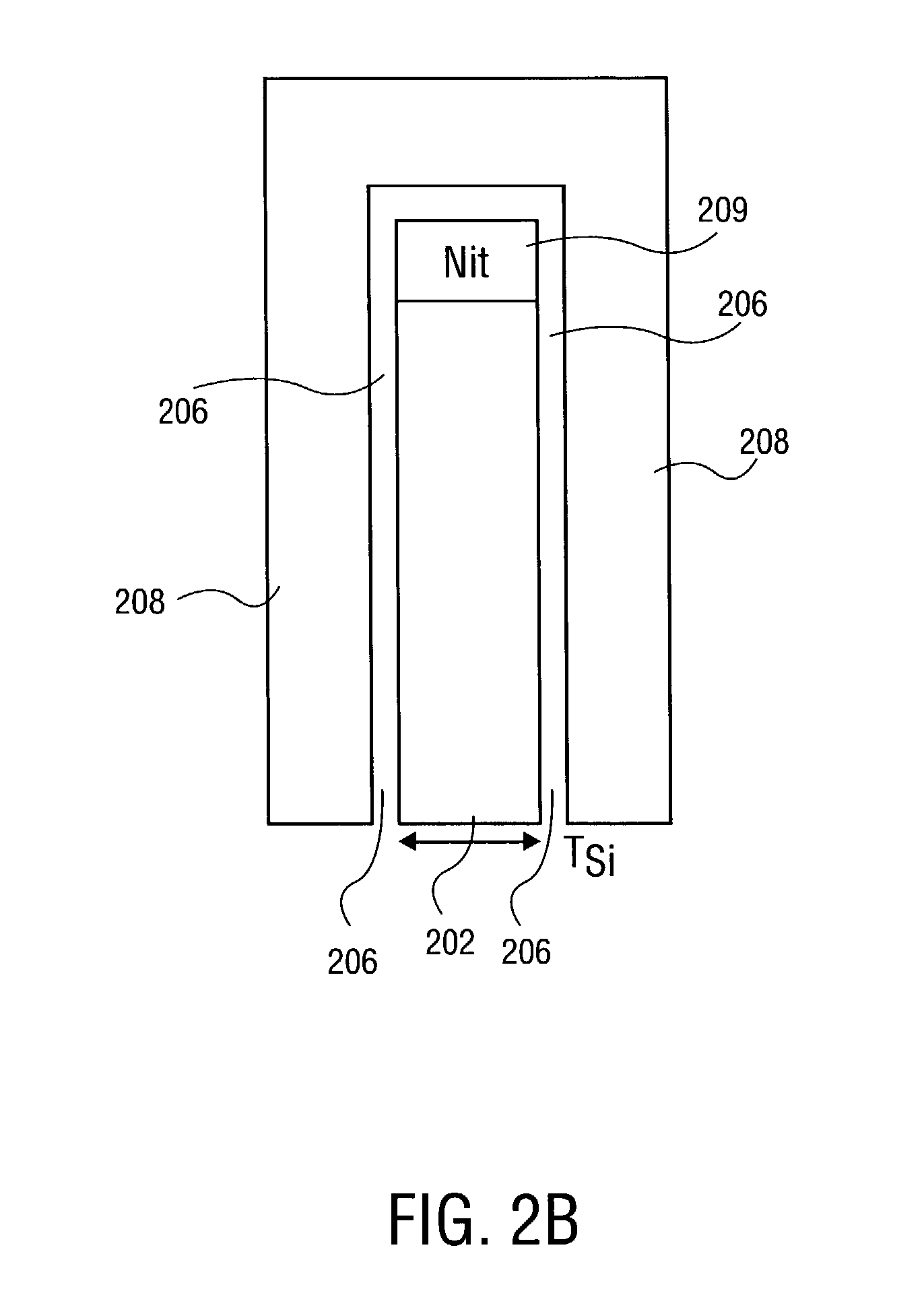

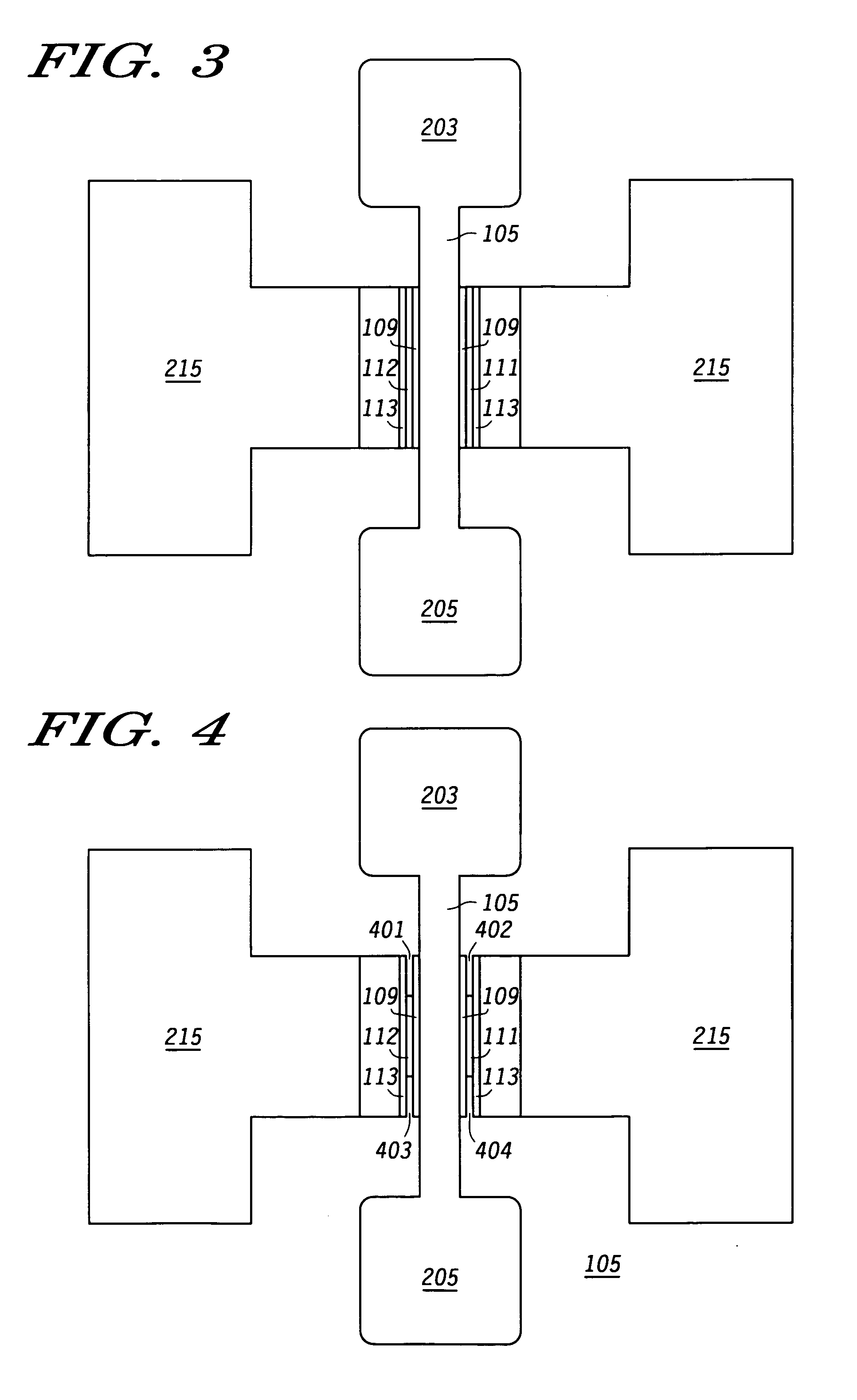

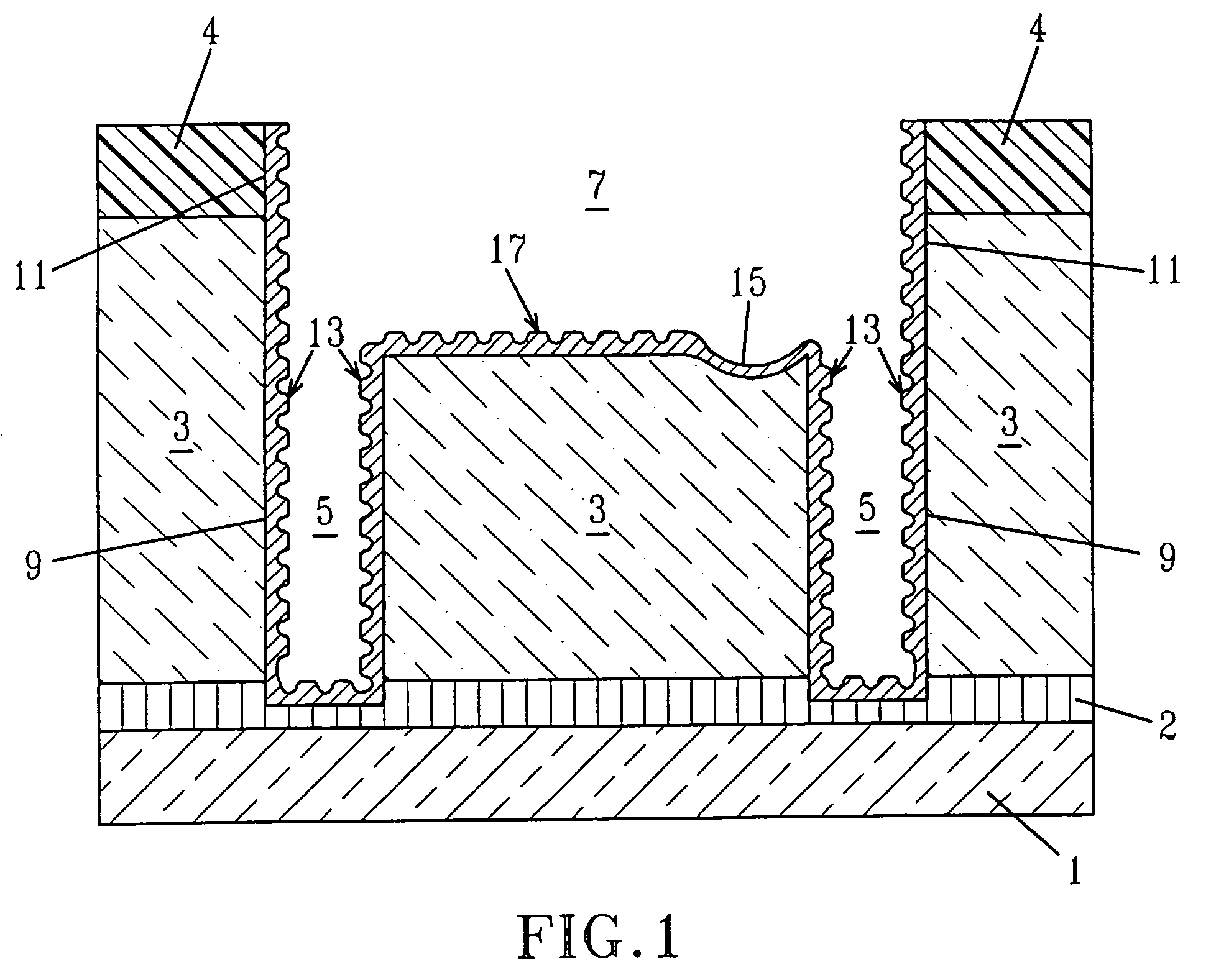

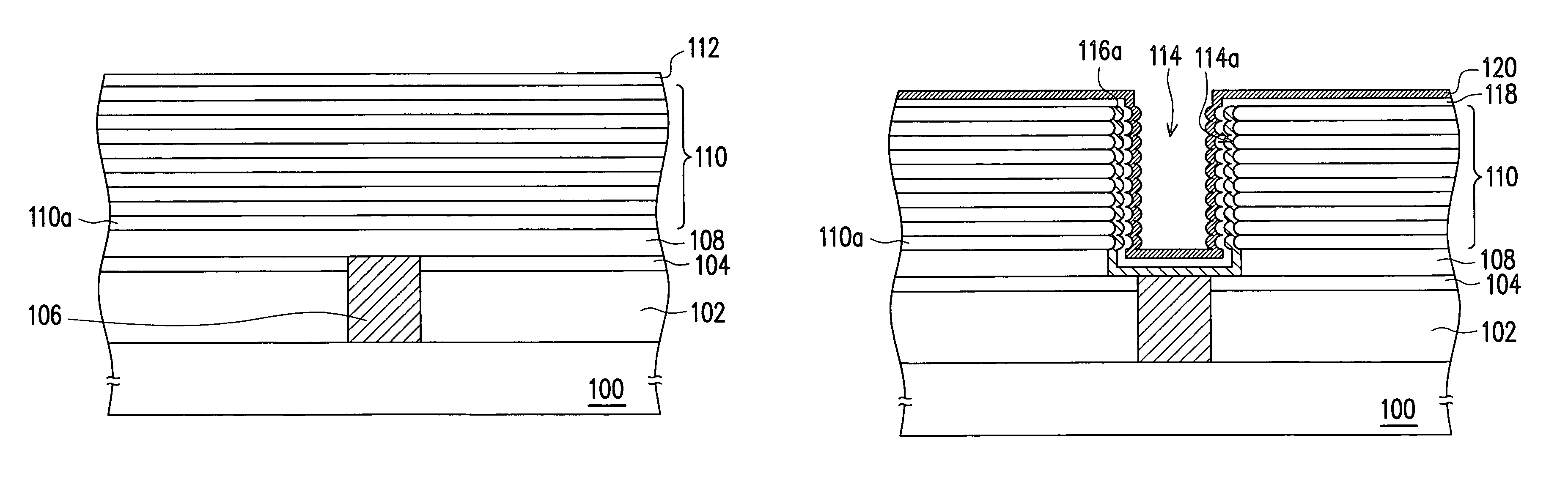

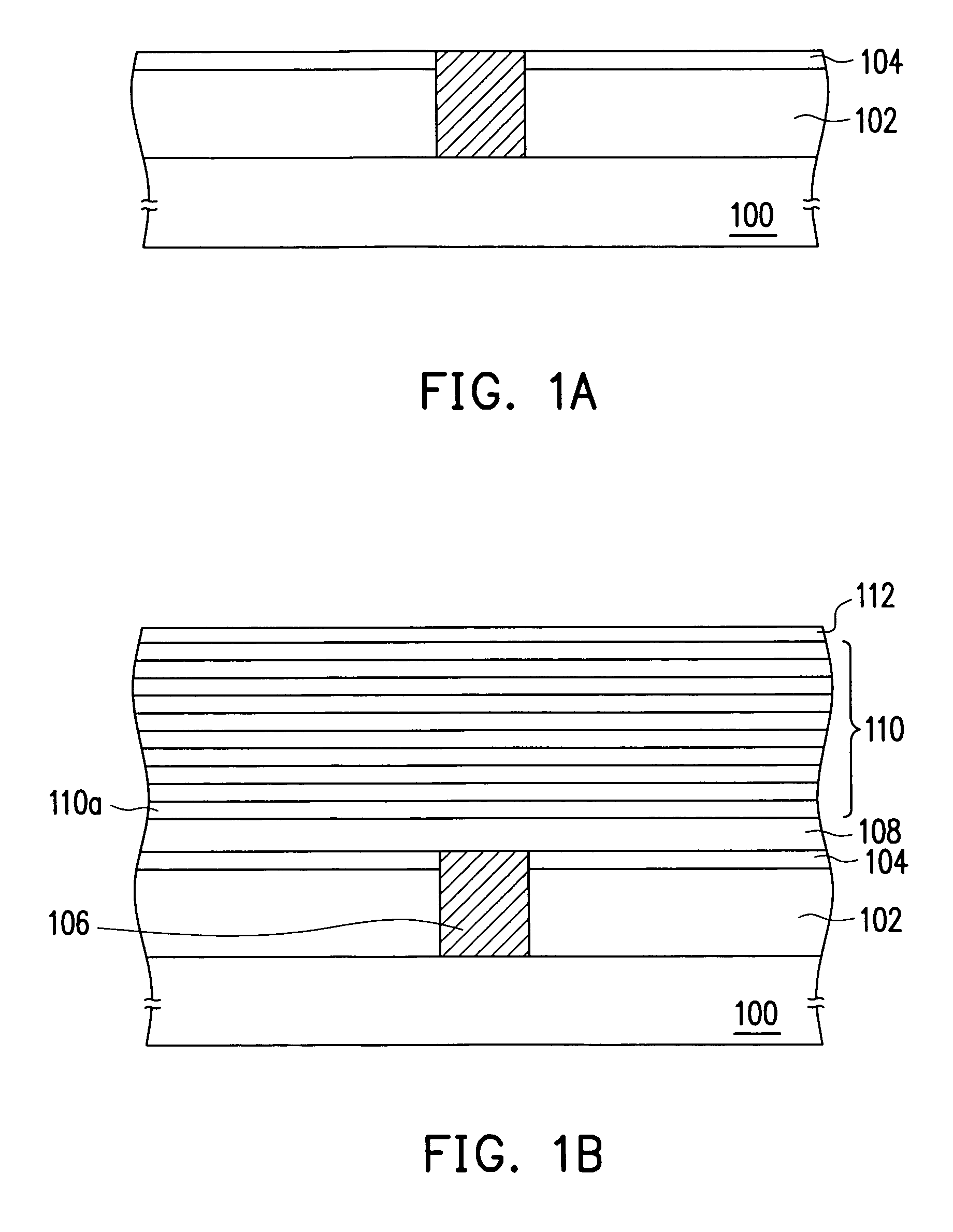

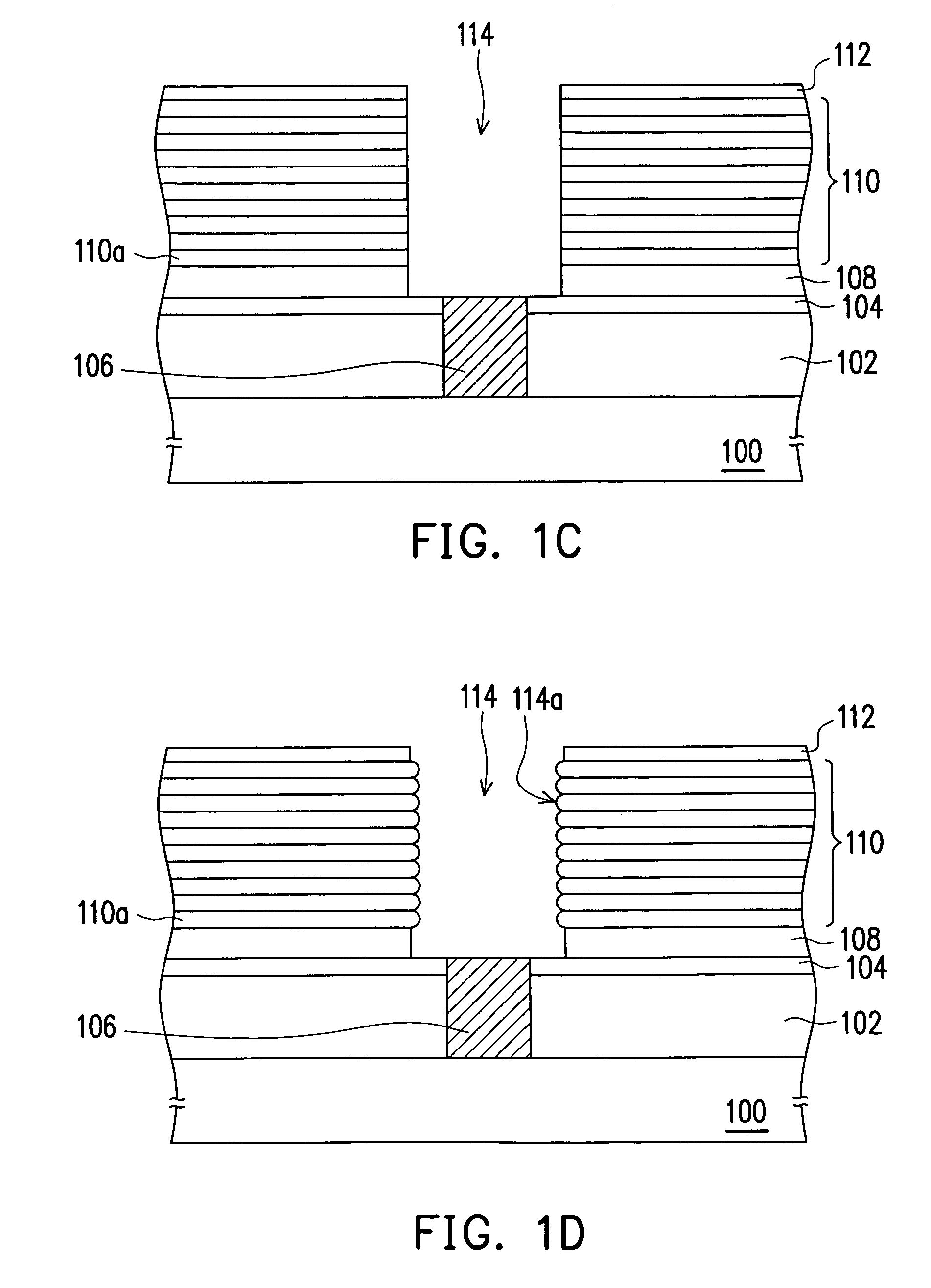

Charge storage structure formation in transistor with vertical channel region

A semiconductor device includes a semiconductor structure having a first sidewall. A vertical channel region is formed in the semiconductor structure along the first sidewall between a first current electrode region and a second current electrode region. First and second charge storage structures are formed adjacent to the first sidewall in openings of a dielectric layer. The first and second charge storage structures are electrically isolated from each other and from the semiconductor structure. A control electrode is formed adjacent to the first sidewall. In another embodiment, third and fourth charge storage structures may be formed adjacent to a second sidewall of the semiconductor structure in openings of a dielectric layer.

Owner:NXP USA INC

Formation of well-controlled thin SiO, SiN, SiN, SiON layer for multilayer high-K dielectric applications

A process for fabricating a semiconductor device having a high-K dielectric layer over a silicon substrate, including steps of growing on the silicon substrate an interfacial layer of a silicon-containing dielectric material; and depositing on the interfacial layer a layer comprising at least one high-K dielectric material, in which the interfacial layer is grown by laser excitation of the silicon substrate in the presence of oxygen, nitrous oxide, nitric oxide, ammonia or a mixture of two or more thereof. In one embodiment, the silicon-containing material is silicon dioxide, silicon nitride, silicon oxynitride or a mixture thereof.

Owner:ADVANCED MICRO DEVICES INC

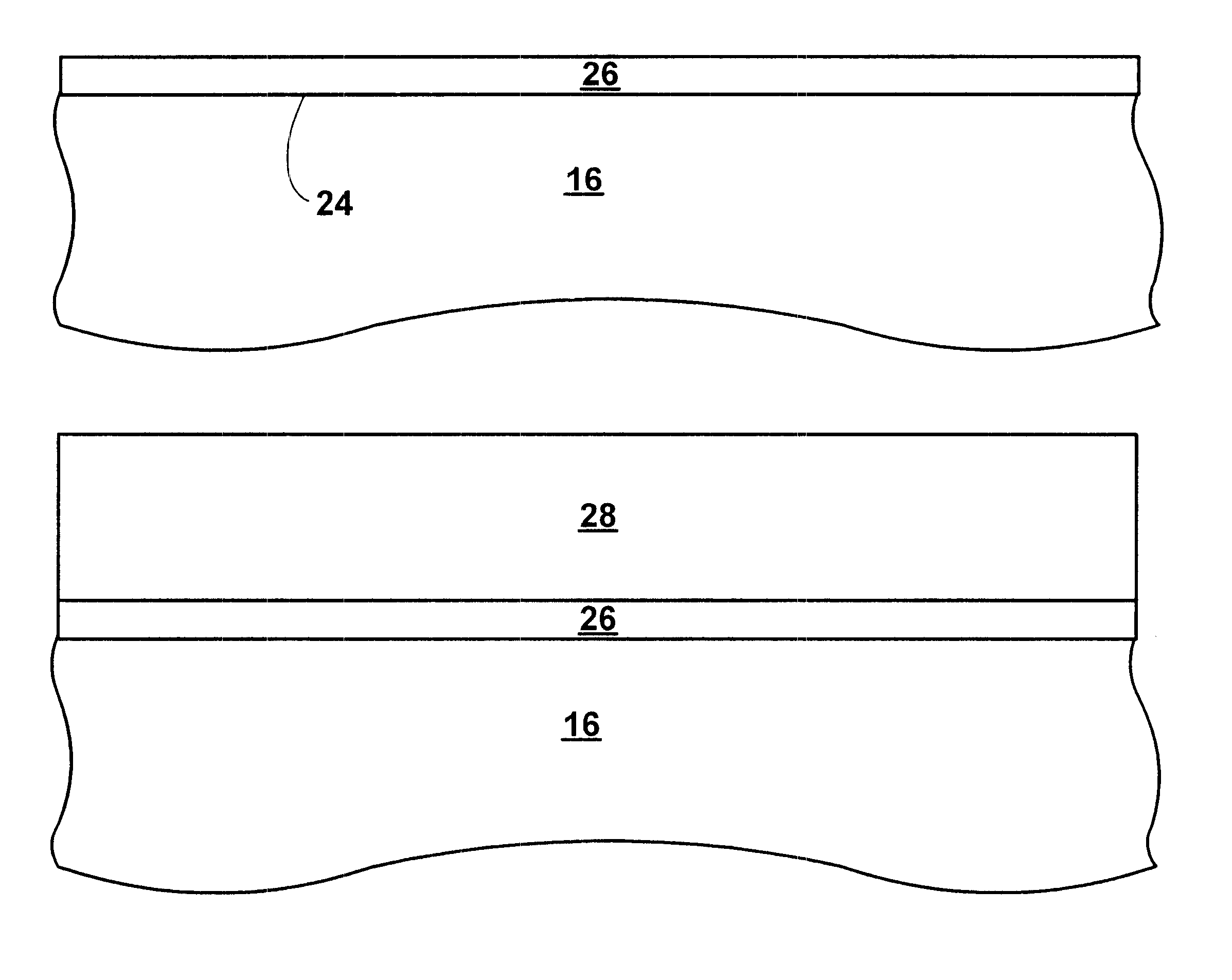

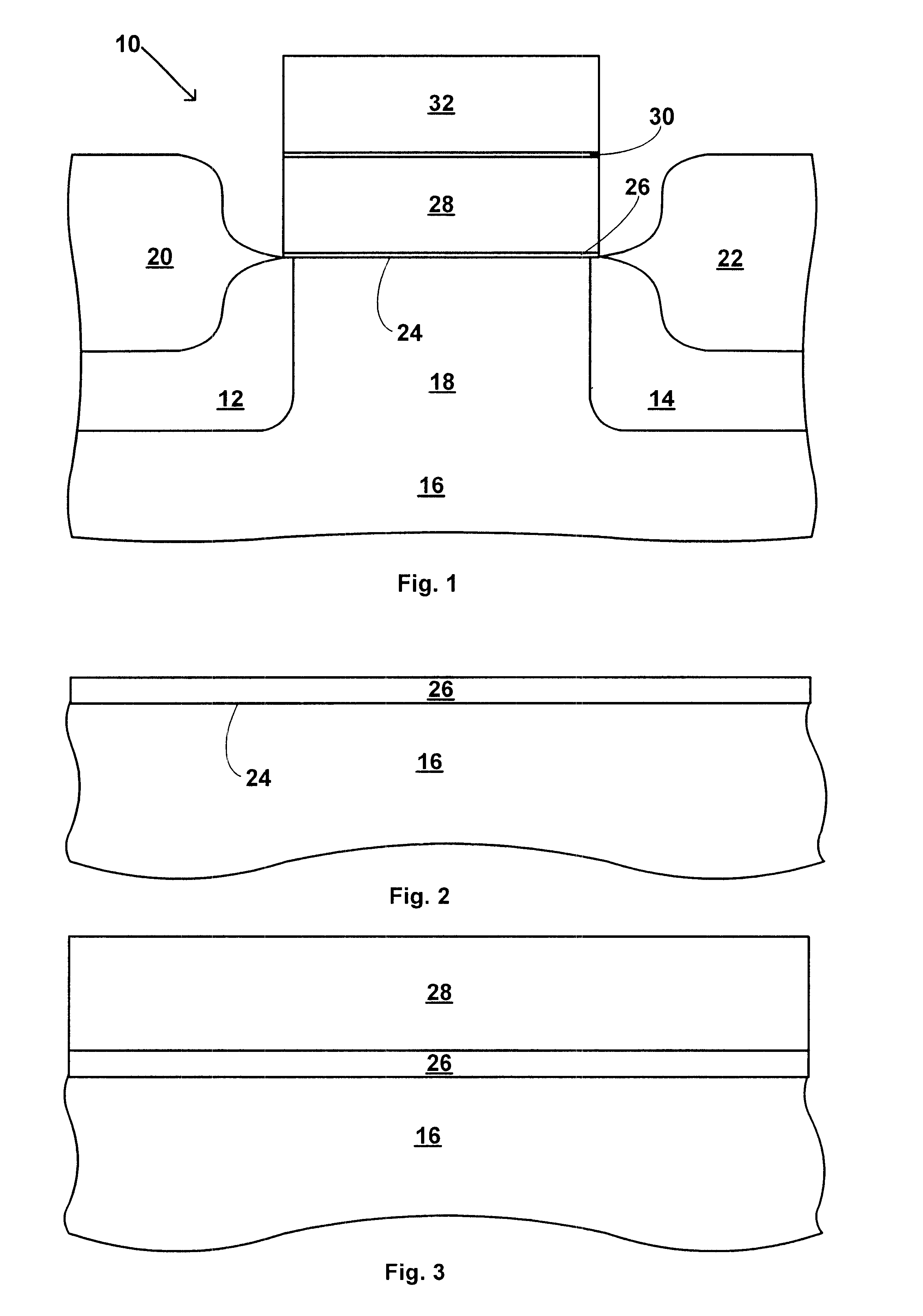

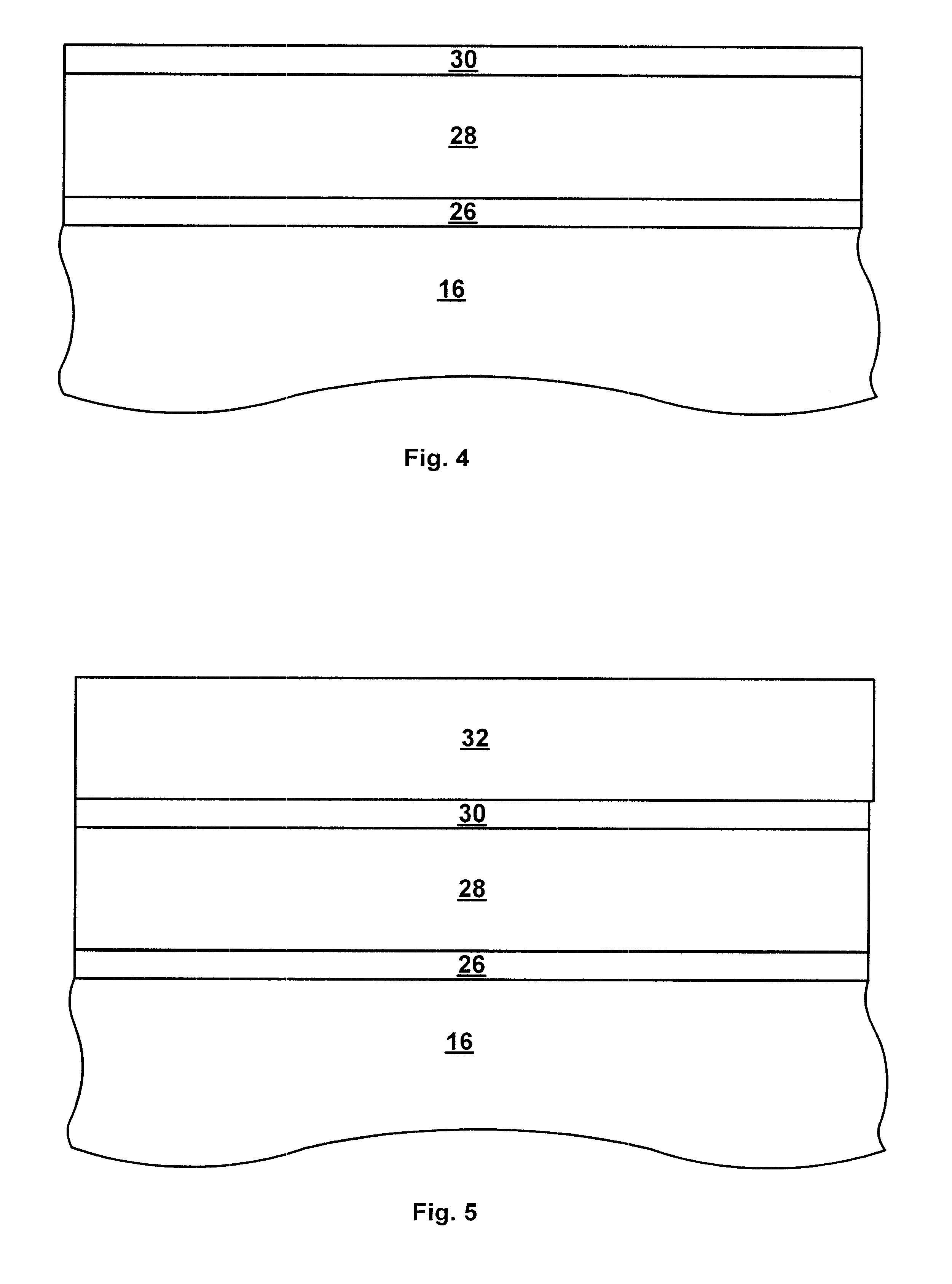

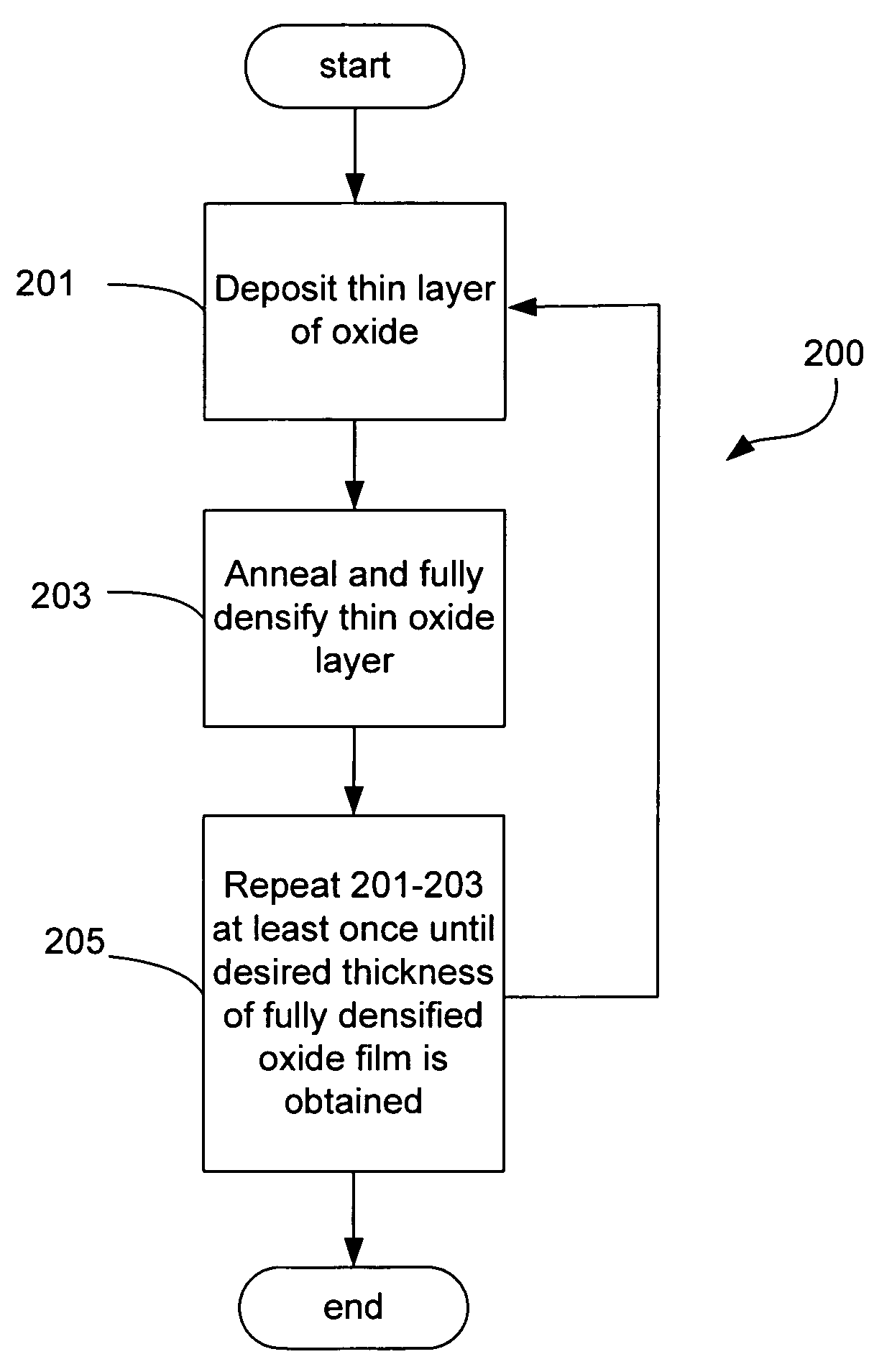

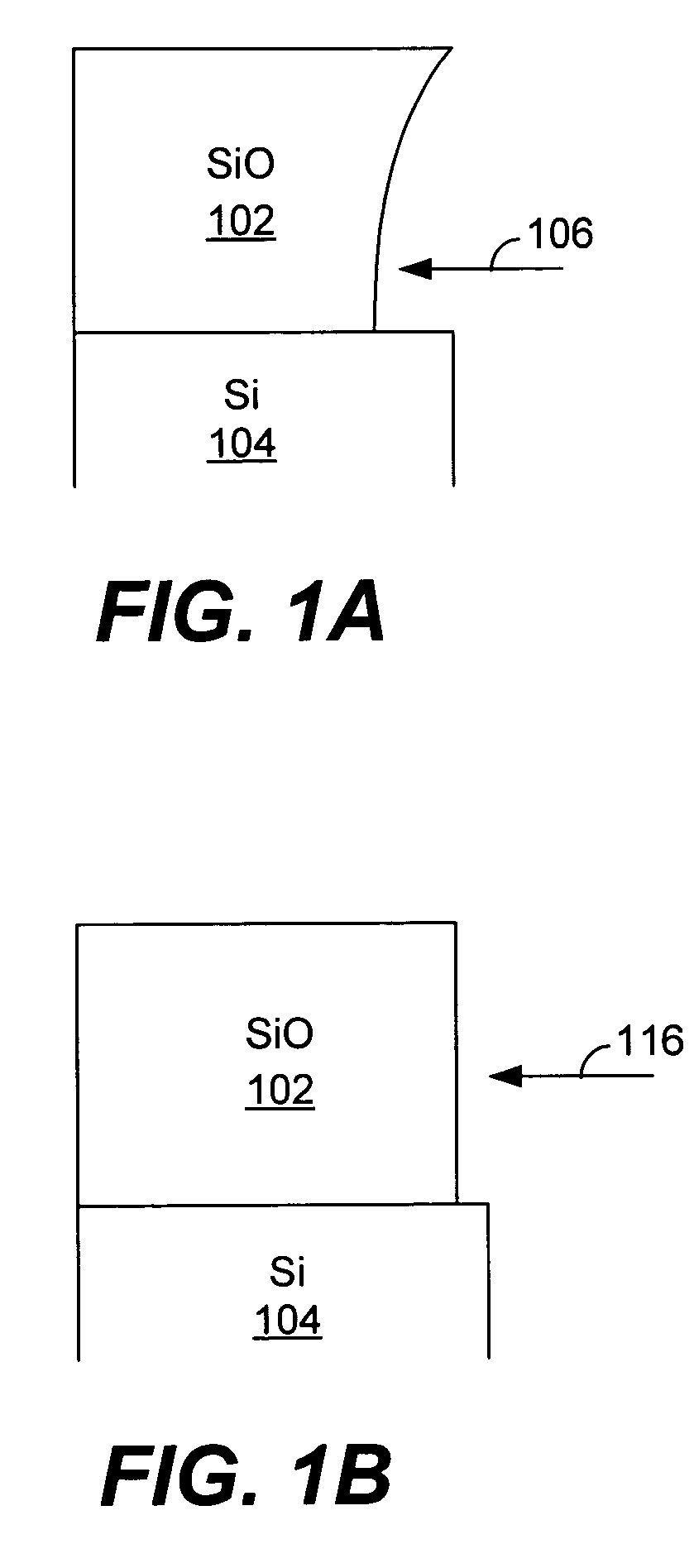

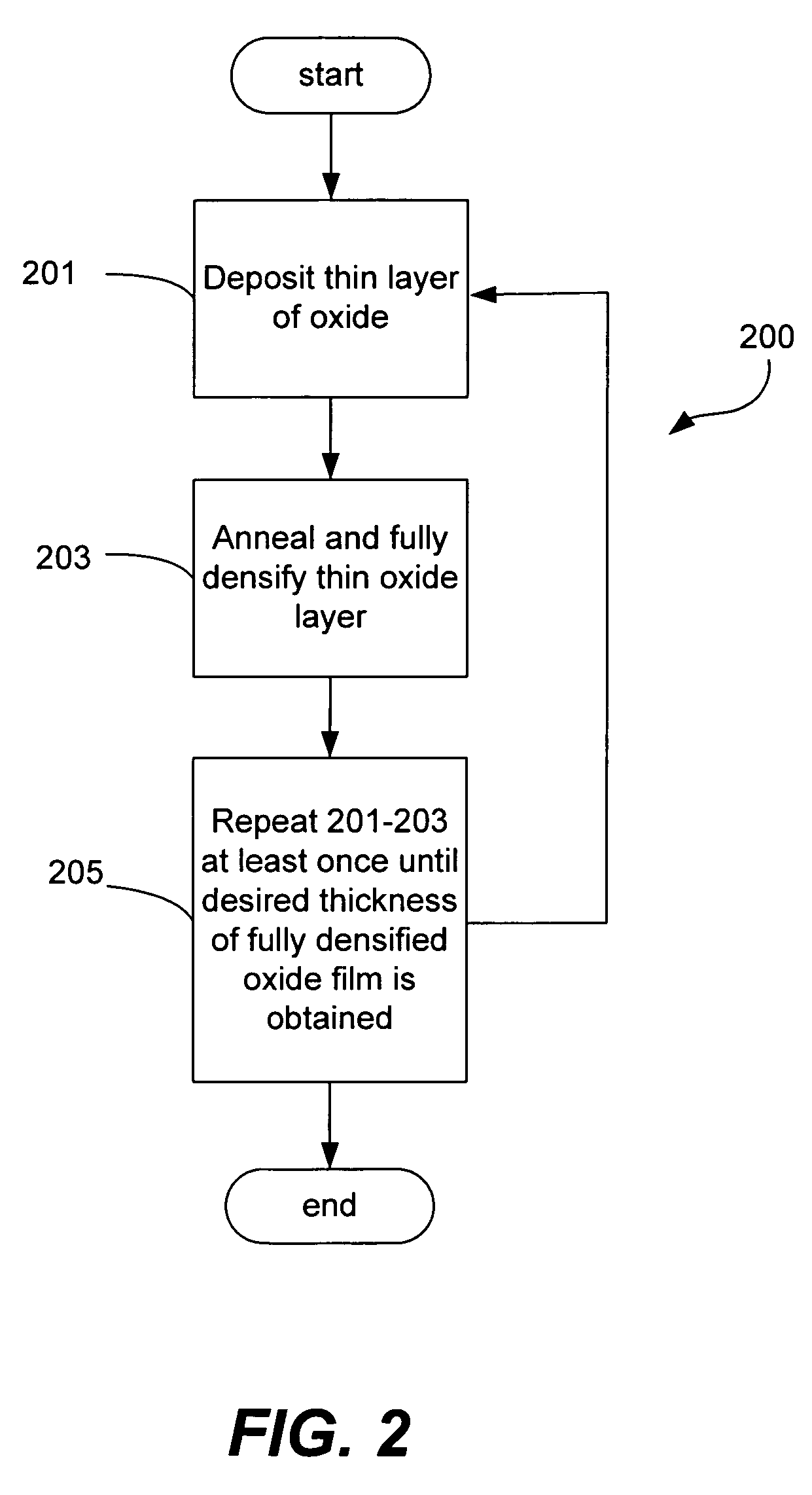

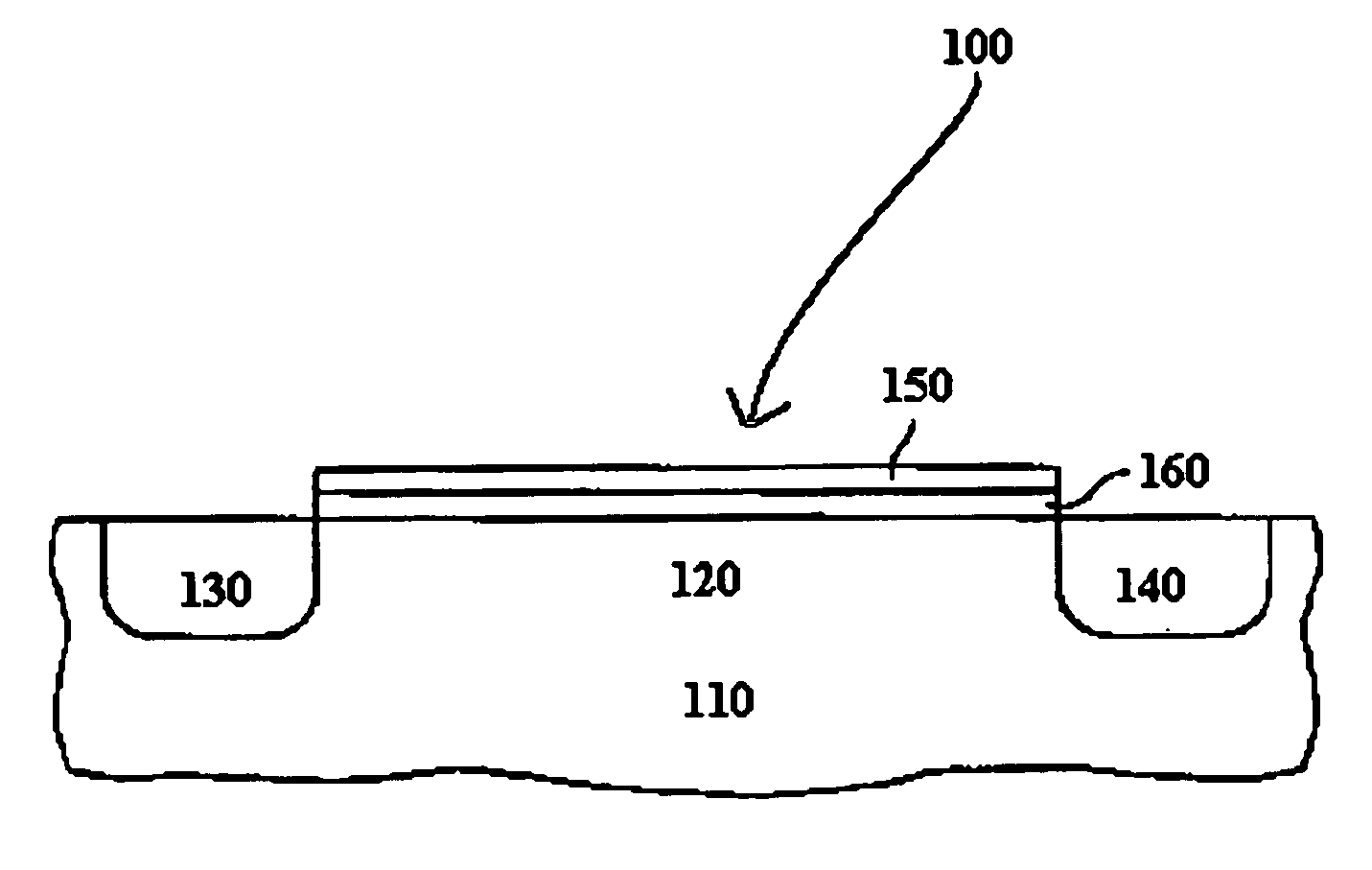

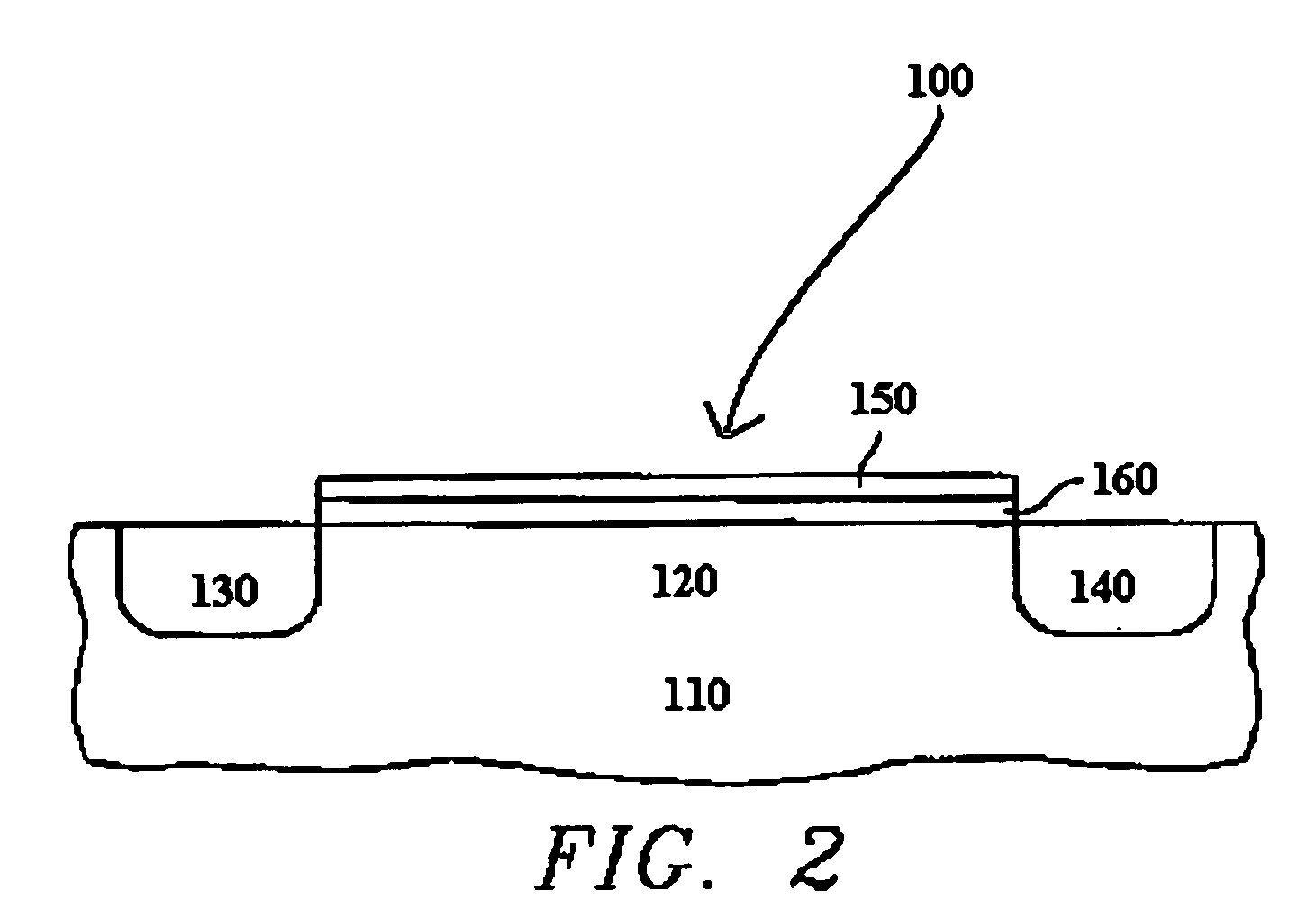

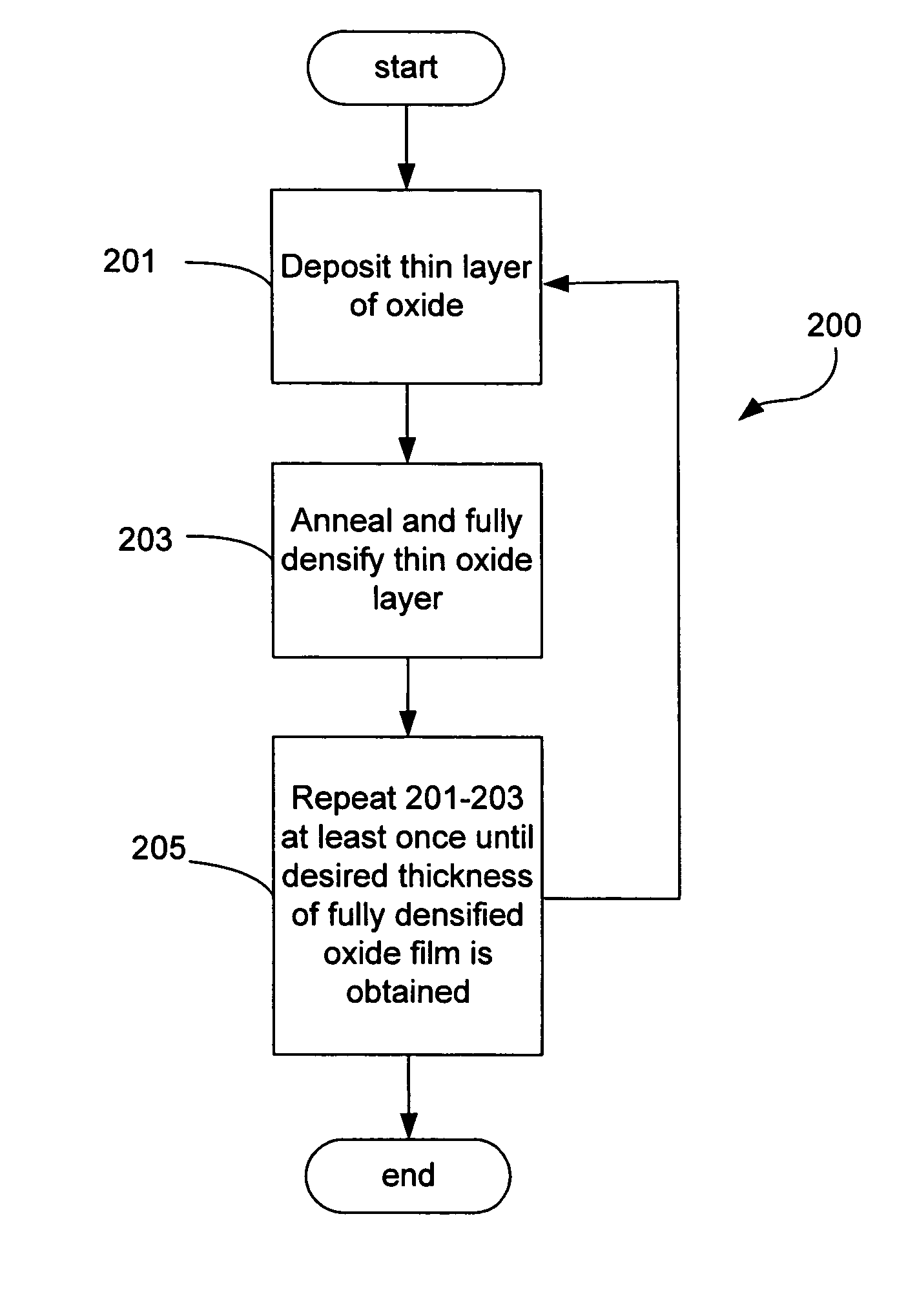

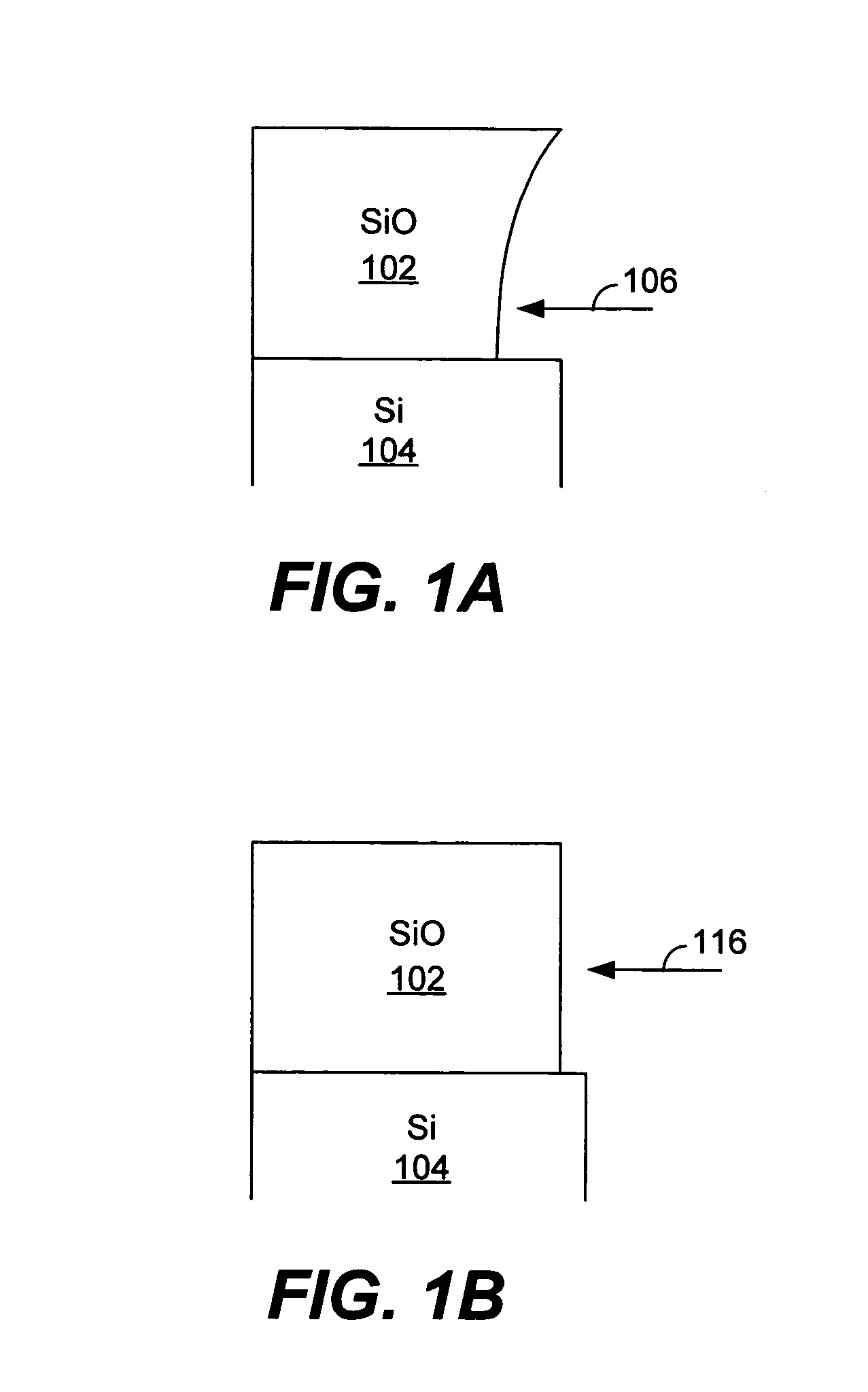

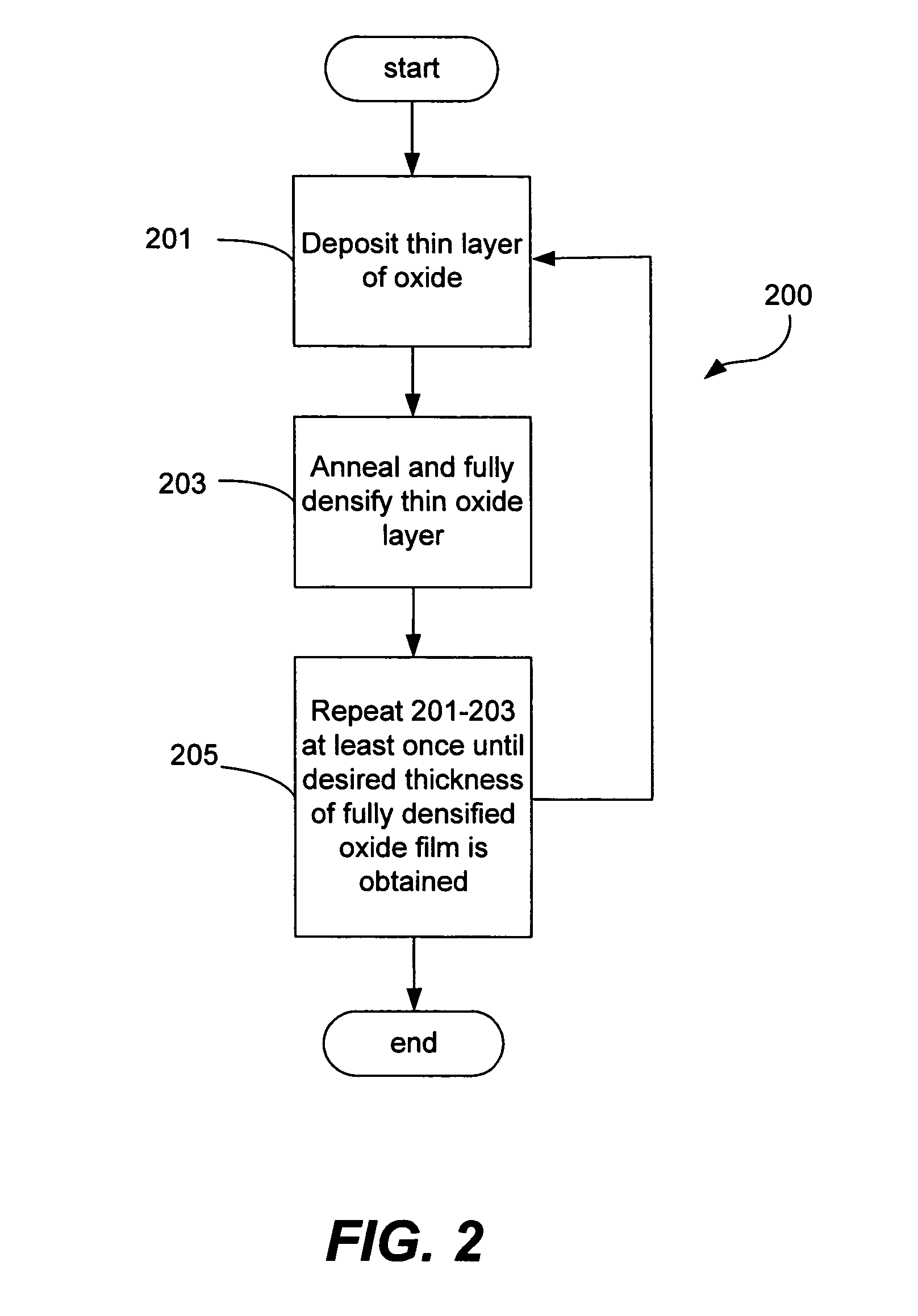

Sequential deposition/anneal film densification method

ActiveUS7790633B1Maintaining film propertyMaintain propertiesSemiconductor/solid-state device manufacturingProcedure AgentsOptoelectronics

A silicon dioxide-based dielectric layer is formed on a substrate surface by a sequential deposition / anneal technique. The deposited layer thickness is insufficient to prevent substantially complete penetration of annealing process agents into the layer and migration of water out of the layer. The dielectric layer is then annealed, ideally at a moderate temperature, to remove water and thereby fully densify the film. The deposition and anneal processes are then repeated until a desired dielectric film thickness is achieved.

Owner:NOVELLUS SYSTEMS

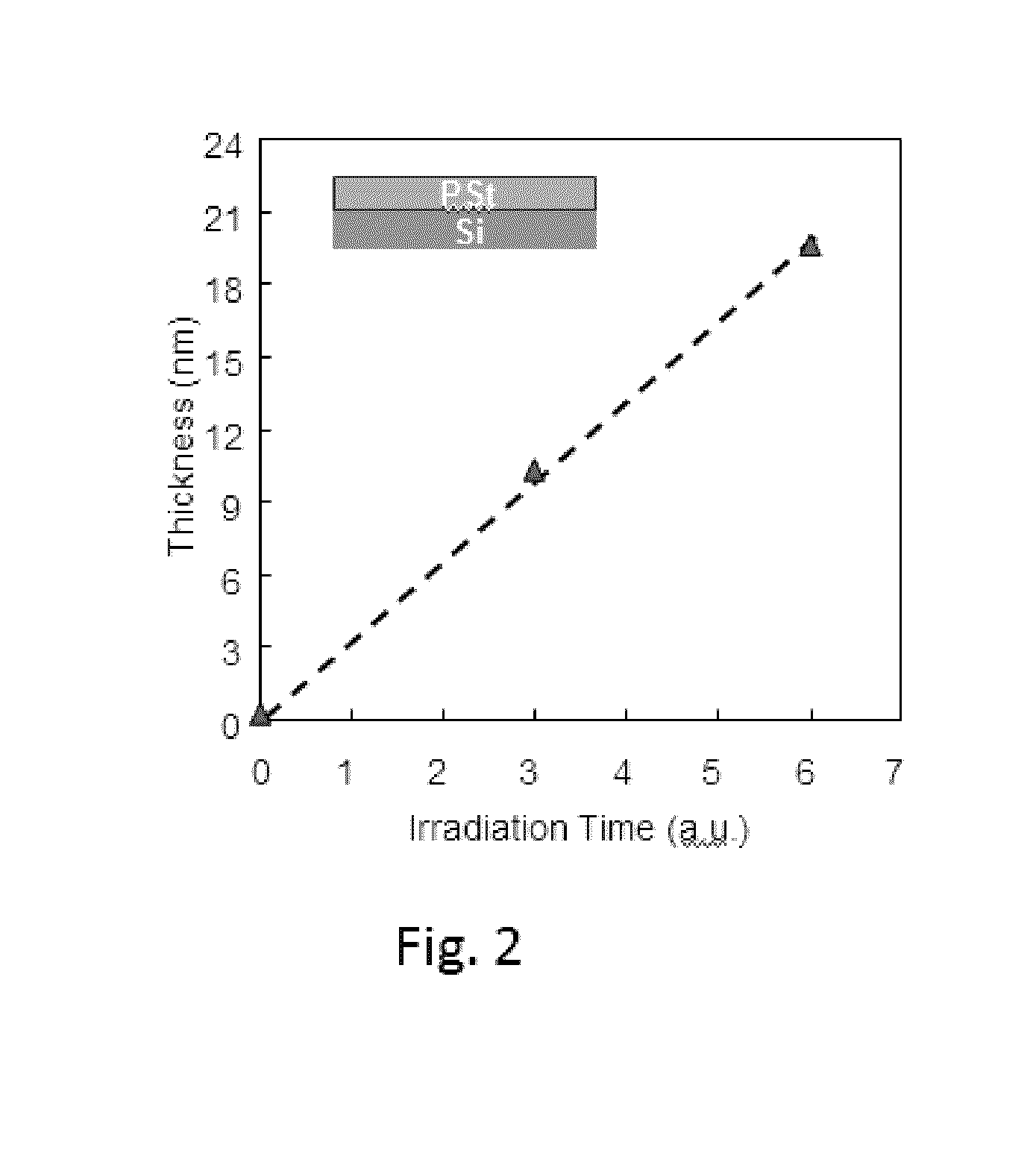

Method for Sealing Pores at Surface of Dielectric Layer by UV Light-Assisted CVD

InactiveUS20110159202A1Improve controllabilityReduce throughputPretreated surfacesSemiconductor/solid-state device manufacturingOptoelectronicsIrradiation

A method for sealing pores at a surface of a dielectric layer formed on a substrate, includes: providing a substrate on which a dielectric layer having a porous surface is formed as an outermost layer; placing the substrate in an evacuatable chamber; irradiating the substrate with UV light in an atmosphere of hydrocarbon and / or oxy-hydrocarbon gas; sealing pores at the porous surface of the dielectric layer as a result of the irradiation; and continuously irradiating the substrate with UV light in the atmosphere of hydrocarbon and / or oxy-hydrocarbon gas until a protective film having a desired thickness is formed on the dielectric layer as a result of the irradiation.

Owner:ASM JAPAN

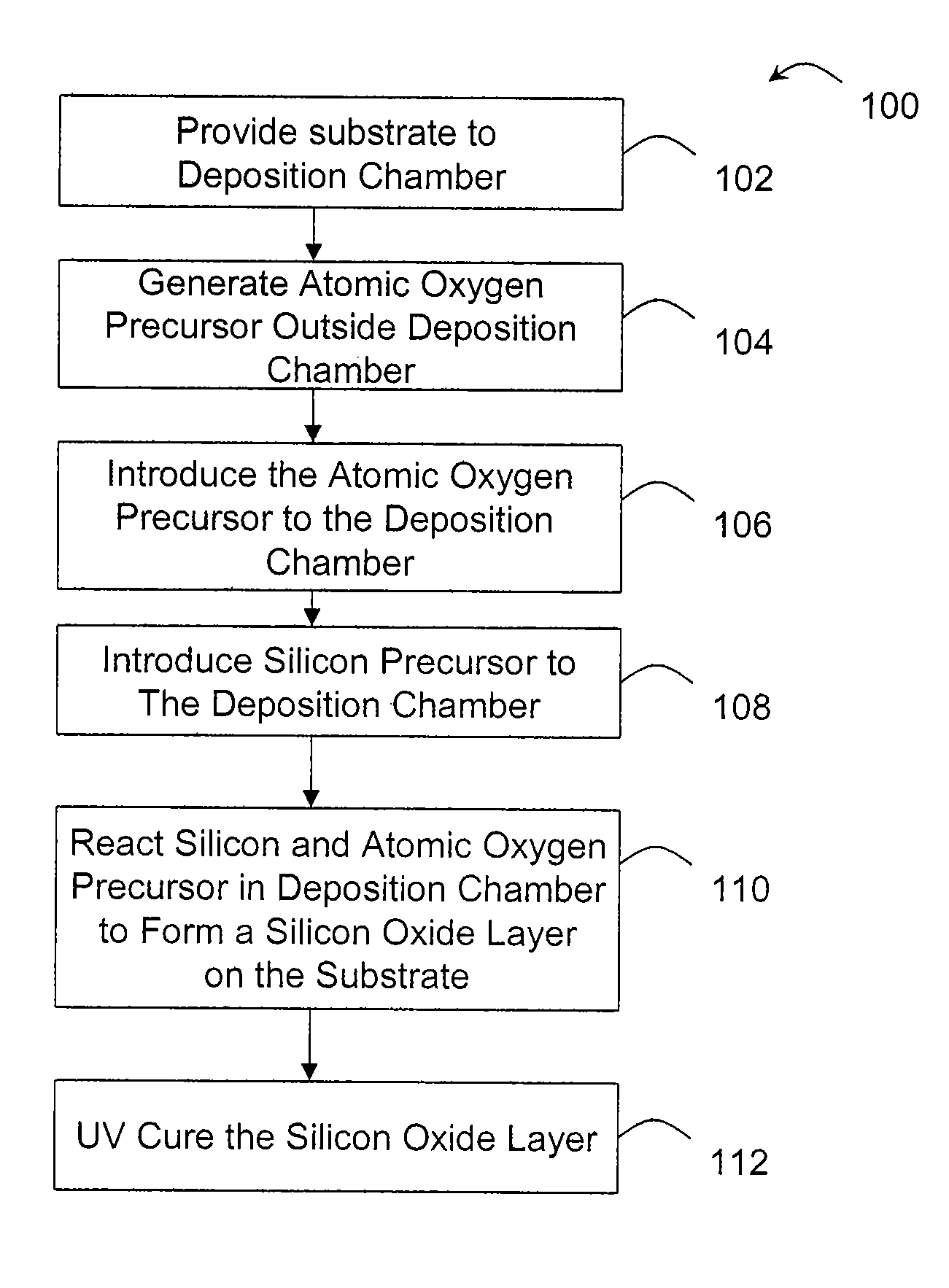

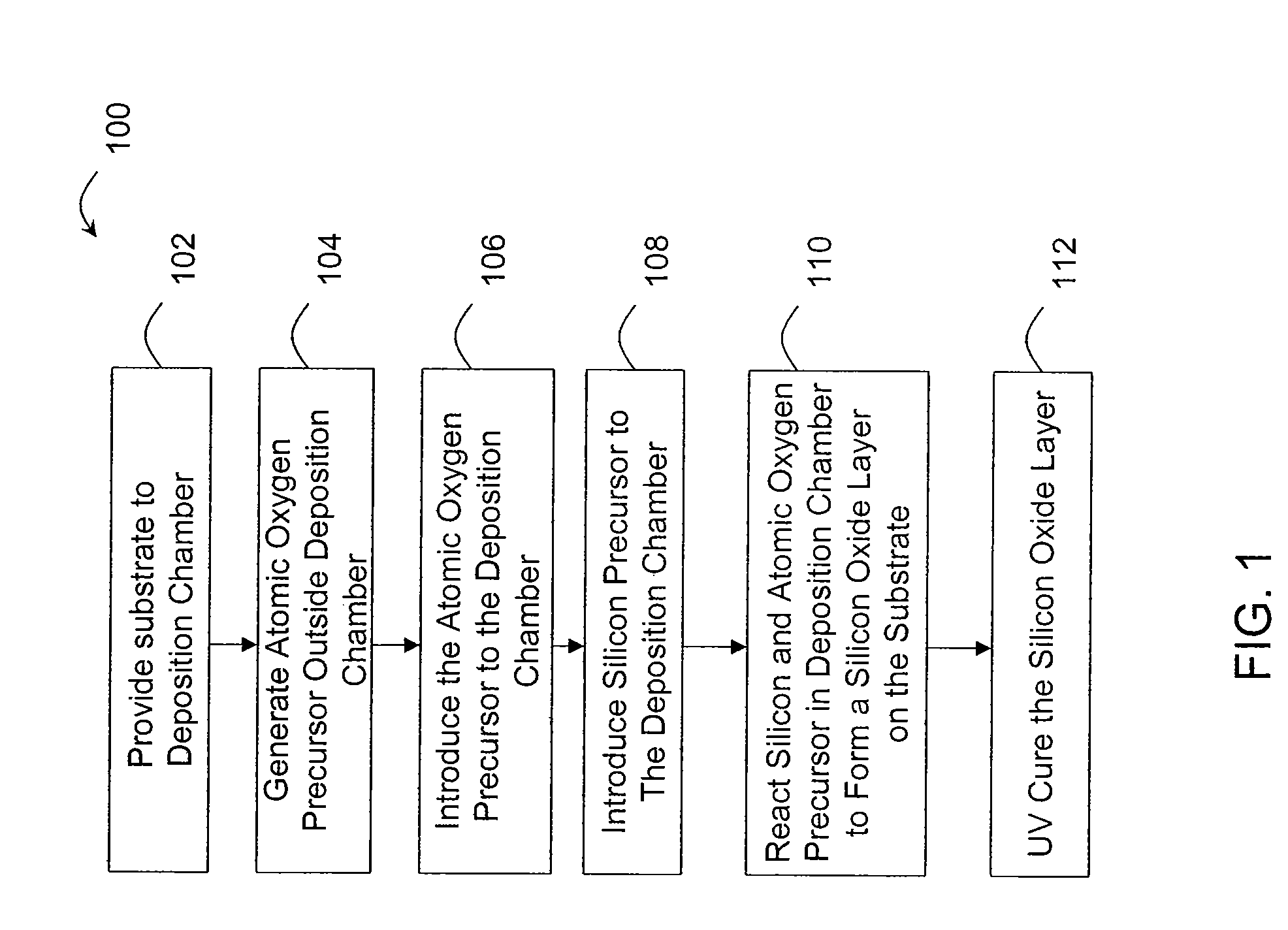

Methods for forming a dielectric layer within trenches

ActiveUS7803722B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductor structureUltraviolet

A method for forming a semiconductor structure includes reacting a silicon precursor and an atomic oxygen or nitrogen precursor at a processing temperature of about 150° C. or less to form a silicon oxide or silicon-nitrogen containing layer over a substrate. The silicon oxide or silicon-nitrogen containing layer is ultra-violet (UV) cured within an oxygen-containing environment.

Owner:APPLIED MATERIALS INC

Method of Fabricating a Gate Dielectric for High-K Metal Gate Devices

ActiveUS20100075507A1Facilitate formation of the high-k dielectric layerImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricSulfur

The present disclosure provides a method of fabricating a semiconductor device. The method includes providing a substrate, forming an interfacial layer on the substrate by treating the substrate with radicals, and forming a high-k dielectric layer on the interfacial layer. The radicals are selected from the group consisting of hydrous radicals, nitrogen / hydrogen radicals, and sulfur / hydrogen radicals.

Owner:TAIWAN SEMICON MFG CO LTD

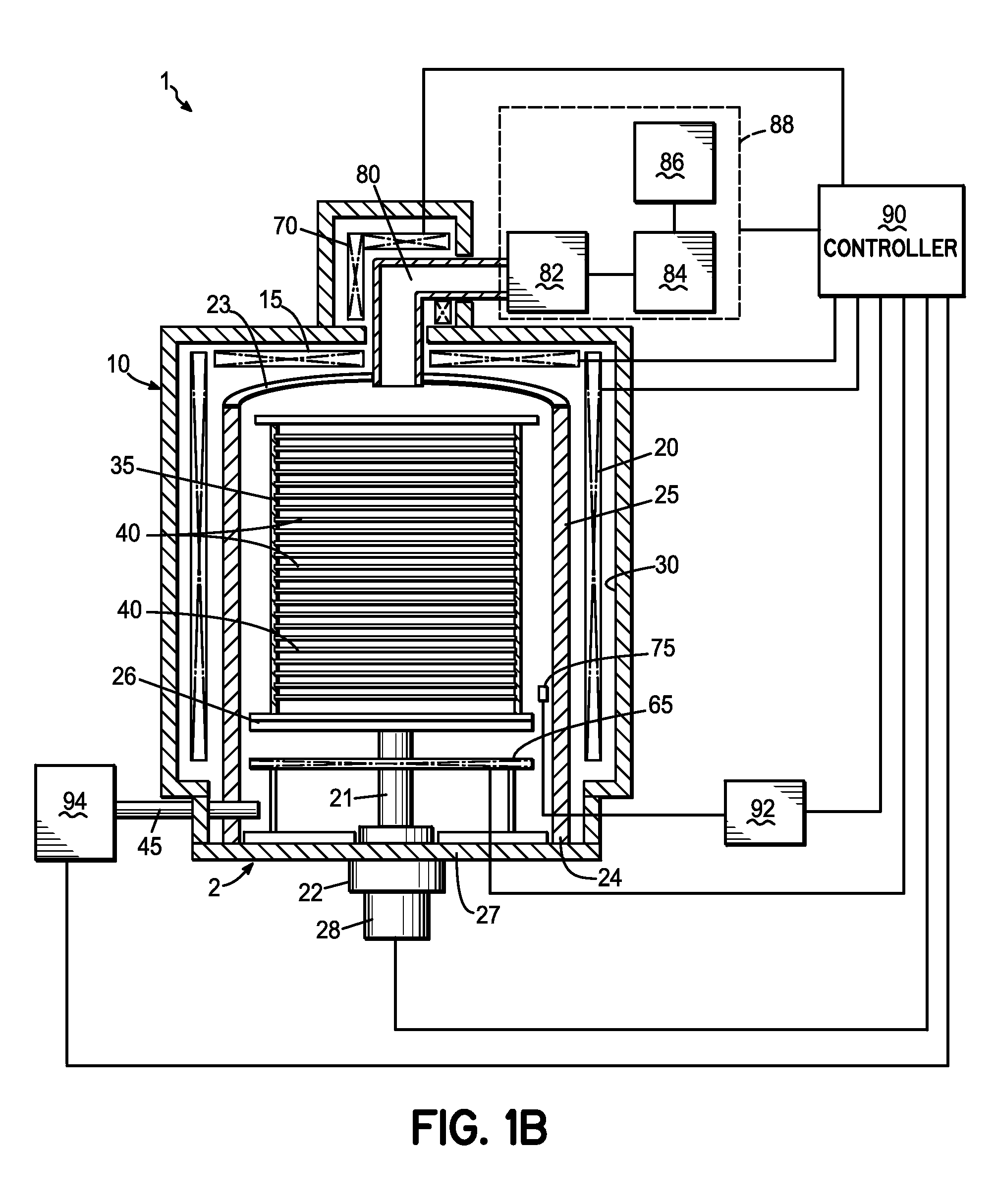

In-situ atomic layer deposition

InactiveUS20070037412A1Improve uniformityImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingWaferingHafnium

An in situ method for forming a HfO2 high-k dielectric layer in a batch wafer processing system. The method comprises first loading a plurality of wafers into a process chamber, and then pre-treating the plurality of wafers in the process chamber with a first oxidizer. After pre-treating the wafers, and without removing the wafers from the process chamber, the method then comprises depositing HfO2 on the plurality of wafers by atomic layer deposition, which comprises a plurality of deposition cycles, each cycle comprising alternating exposure of the plurality of wafers in the process chamber to a second oxidizer and a hafnium precursor. The hafnium precursor is selected from hafnium tert-butoxide (HTB) or hafnium tetra-diethylamide (TDEAH).

Owner:TOKYO ELECTRON LTD

Method of etching high aspect ratio features in a dielectric layer

Methods of etching HAR features in a dielectric layer are described. In one embodiment, a substrate is provided into an etch chamber. The substrate has a patterned mask disposed on a dielectric layer formed thereon where the patterned mask has openings. A gas mixture is provided into the etch chamber, the gas mixture includes CO, O2, a fluorocarbon gas, and an optional inert gas. A plasma is formed from the gas mixture. Features are etched in the dielectric layer through the openings in the presence of the plasma

Owner:APPLIED MATERIALS INC

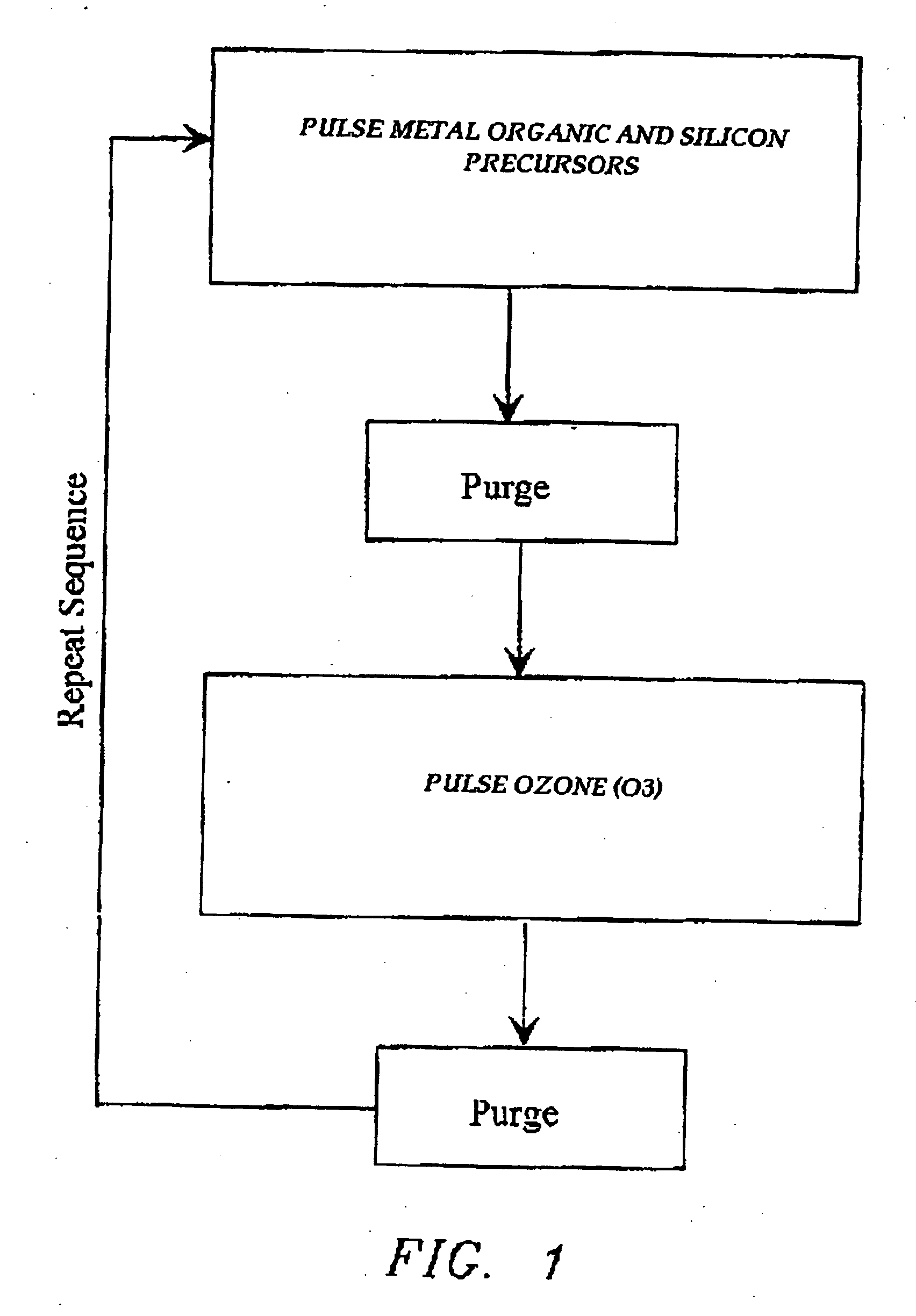

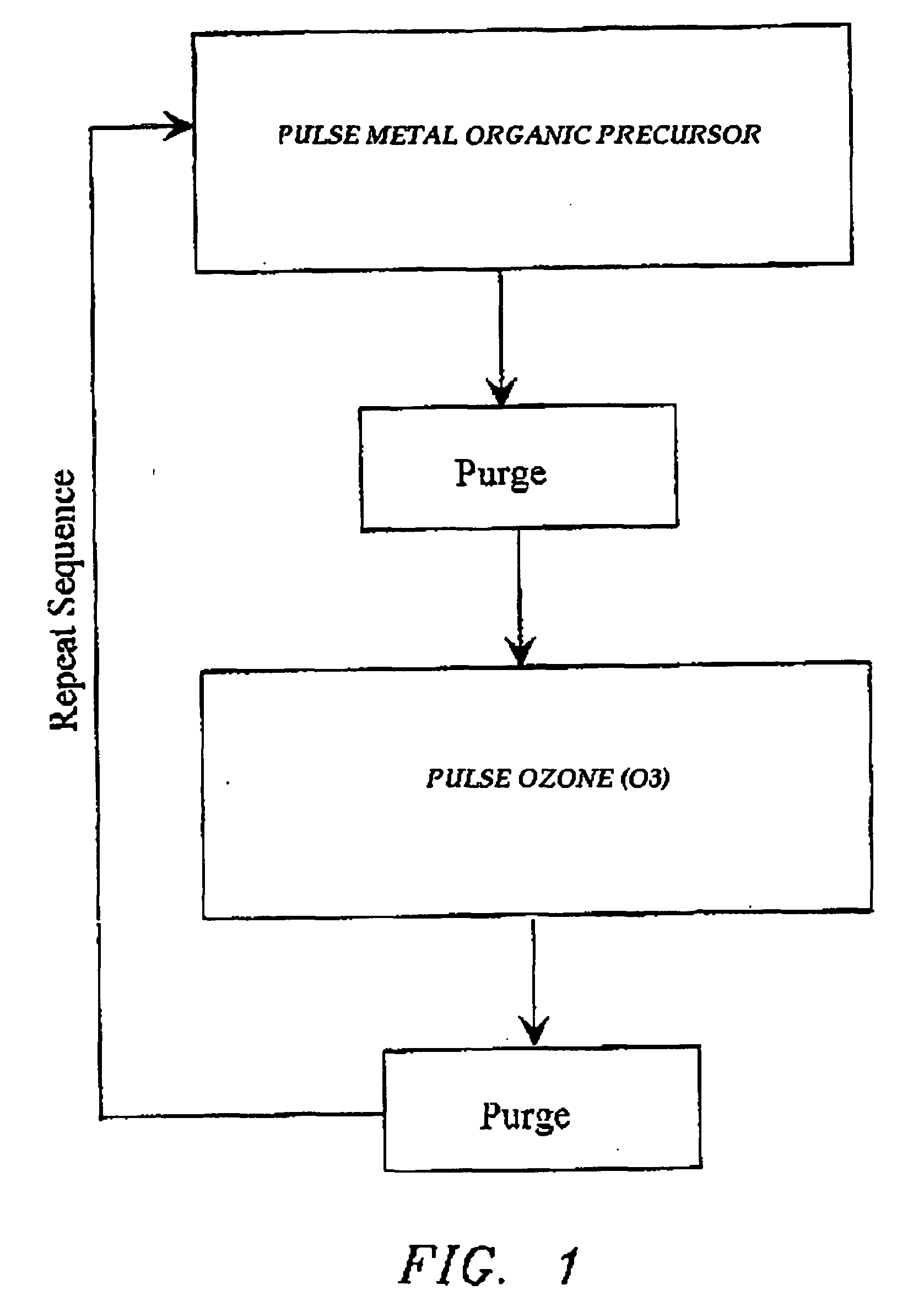

Atomic layer deposition of high k metal silicates

InactiveUS20060228888A1Reduce carbon pollutionReduce stepsSolid-state devicesSemiconductor/solid-state device manufacturingHafniumAtomic layer deposition

The present invention relates to the atomic layer deposition (“ALD”) of high k dielectric layers of metal silicates, including hafnium silicate. More particularly, the present invention relates to the ALD formation of metal silicates using metal organic precursors, silicon organic precursors and ozone. Preferably, the metal organic precursor is a metal alkyl amide and the silicon organic precursor is a silicon alkyl amide.

Owner:AVIZA TECHNOLOGY INC +1

Structures and methods for integration of ultralow-k dielectrics with improved reliability

ActiveUS7088003B2Semiconductor/solid-state device detailsSolid-state devicesBiological activationDielectric layer

An improved back end of the line (BEOL) interconnect structure comprising an ultralow k (ULK) dielectric is provided. The structure may be of the single or dual damascene type and comprises a dense thin dielectric layer (TDL) between a metal barrier layer and the ULK dielectric. Disclosed are also methods of fabrication of BEOL interconnect structures, including (i) methods in which a dense TDL is provided on etched opening of a ULK dielectric and (ii) methods in which a ULK dielectric is placed in a process chamber on a cold chuck, a sealing agent is added to the process chamber, and an activation step is performed.

Owner:GLOBALFOUNDRIES U S INC

Method of manufacturing charge storage device

InactiveUS7405166B2Increase electrode areaEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceHydrogen fluoride

Owner:IND TECH RES INST

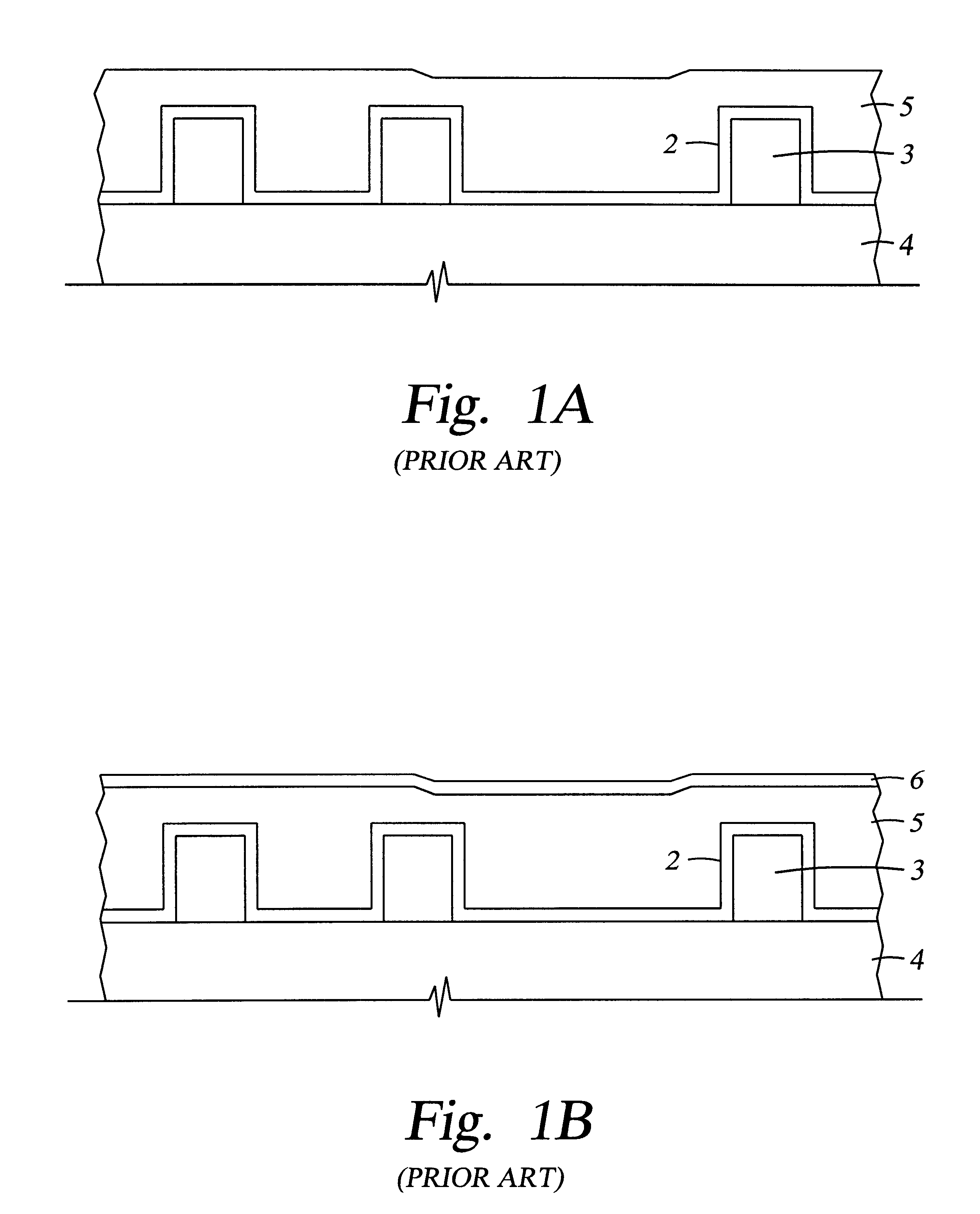

CVD nanoporous silica low dielectric constant films

InactiveUS6171945B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideGradual increase

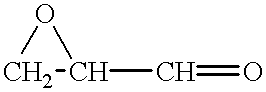

A method and apparatus for depositing nano-porous low dielectric constant films by reaction of a silicon hydride containing compound or mixture optionally having thermally labile organic groups with a peroxide compound on the surface of a substrate. The deposited silicon oxide based film is annealed to form dispersed microscopic voids that remain in a nano-porous silicon oxide based film having a foam structure. The nano-porous silicon oxide based films are useful for filling gaps between metal lines with or without liner or cap layers. The nano-porous silicon oxide based films may also be used as an intermetal dielectric layer for fabricating dual damascene structures. Preferred nano-porous silicon oxide based films are produced by reaction of 1,3,5-trisilanacyclohexane, bis(formyloxysilano)methane, or bis(glyoxylylsilano)methane and hydrogen peroxide followed by a cure / anneal that includes a gradual increase in temperature.

Owner:APPLIED MATERIALS INC

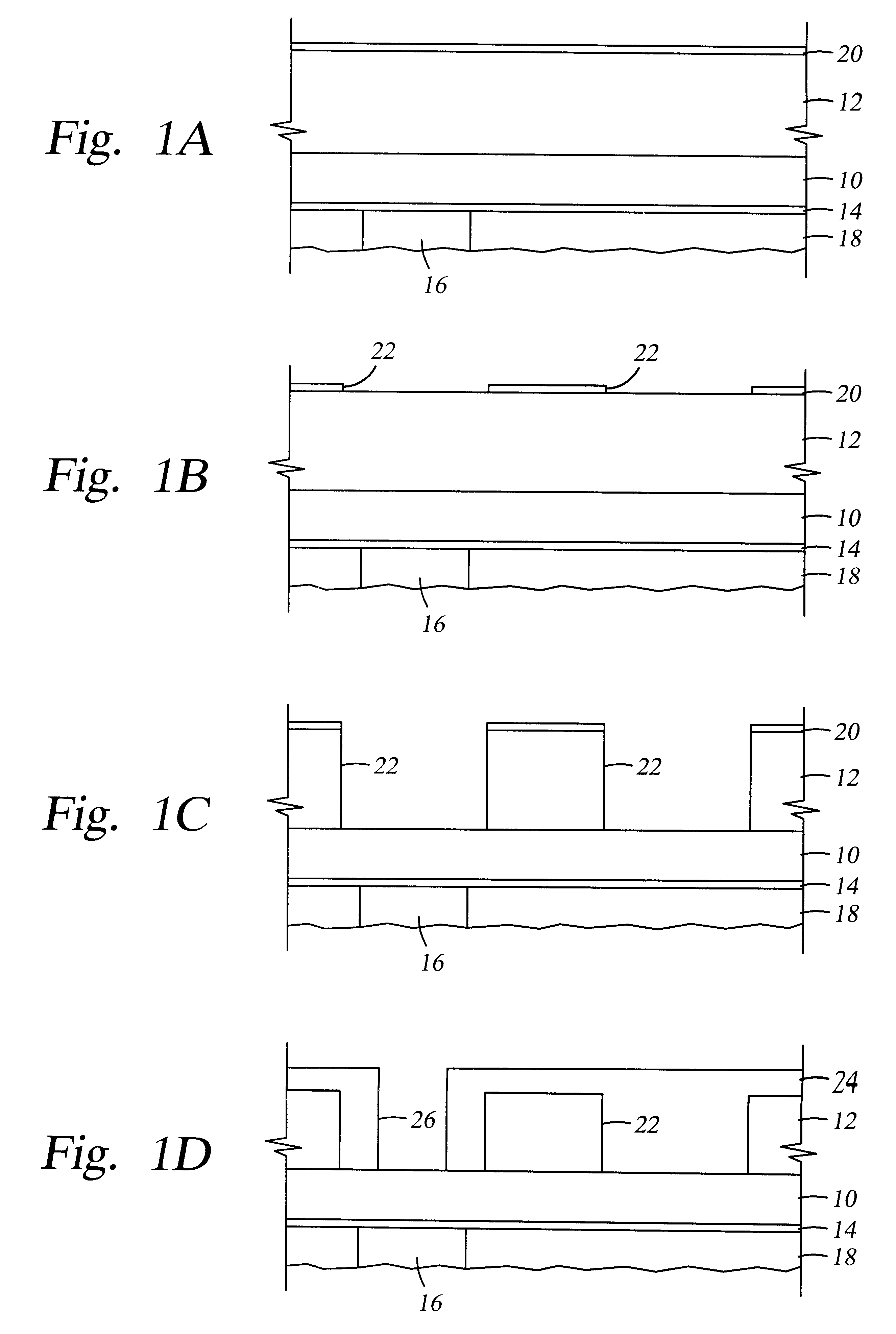

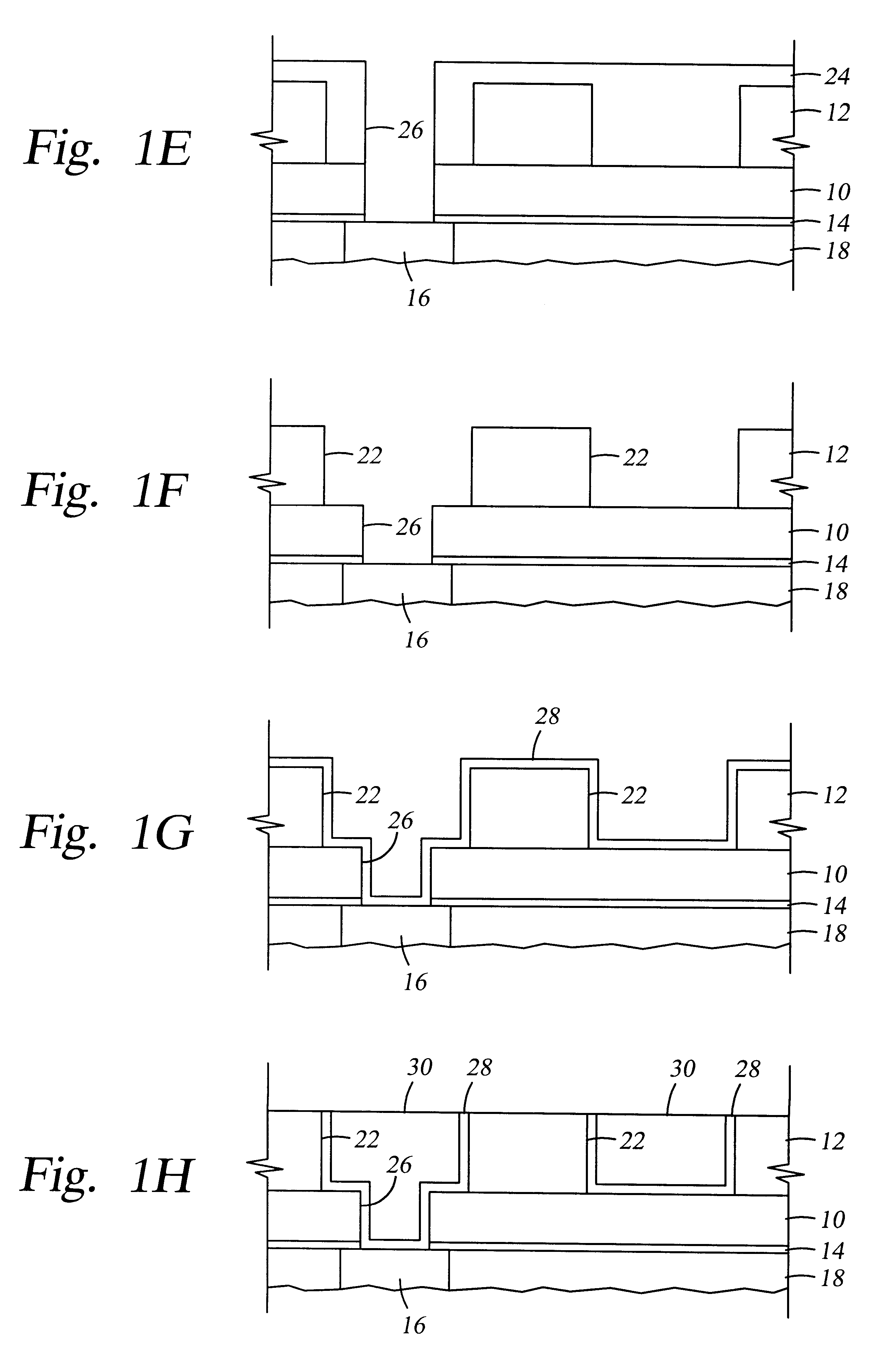

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Atomic layer deposition of high-k metal oxides

InactiveUS20060258078A1Improve thermal stabilityLess growthSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerTitanium oxide

The present invention relates to the atomic layer deposition (“ALD”) of high k dielectric layers of metal oxides containing Group 4 metals, including hafnium oxide, zirconium oxide, and titanium oxide. More particularly, the present invention relates to the ALD formation of Group 4 metal oxide films using an metal alkyl amide as a metal organic precursor and ozone as a co-reactant.

Owner:AVIZA TECHNOLOGY INC +1

Sequential deposition/anneal film densification method

ActiveUS7148155B1Maintaining film propertyMaintain propertiesSemiconductor/solid-state device manufacturingDielectric membraneThin membrane

A silicon dioxide-based dielectric layer is formed on a substrate surface by a sequential deposition / anneal technique. The deposited layer thickness is insufficient to prevent substantially complete penetration of annealing process agents into the layer and migration of water out of the layer. The dielectric layer is then annealed, ideally at a moderate temperature, to remove water and thereby fully densify the film. The deposition and anneal processes are then repeated until a desired dielectric film thickness is achieved.

Owner:NOVELLUS SYSTEMS