Patents

Literature

514 results about "Dielectric membrane" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dielectric properties the membrane, provided that the thickness of the membrane is constant. Thus, the total membrane capacitance is c =. m. C , where is the specific membrane capacitance (typically expressed in units of μF/cm ) and is the area.

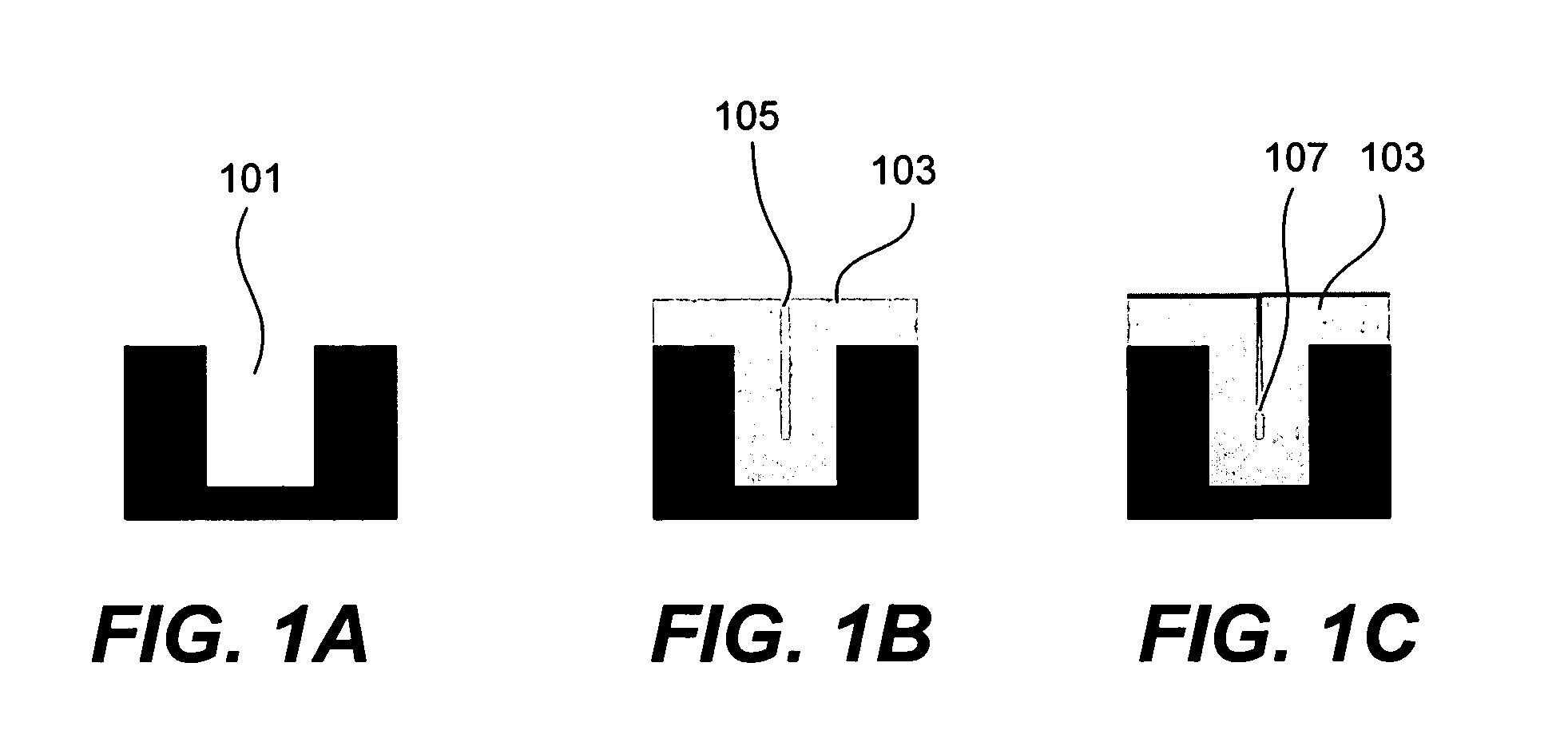

Method of selective coverage of high aspect ratio structures with a conformal film

ActiveUS7625820B1High aspect ratioVacuum evaporation coatingSputtering coatingMetallurgySilicon oxide

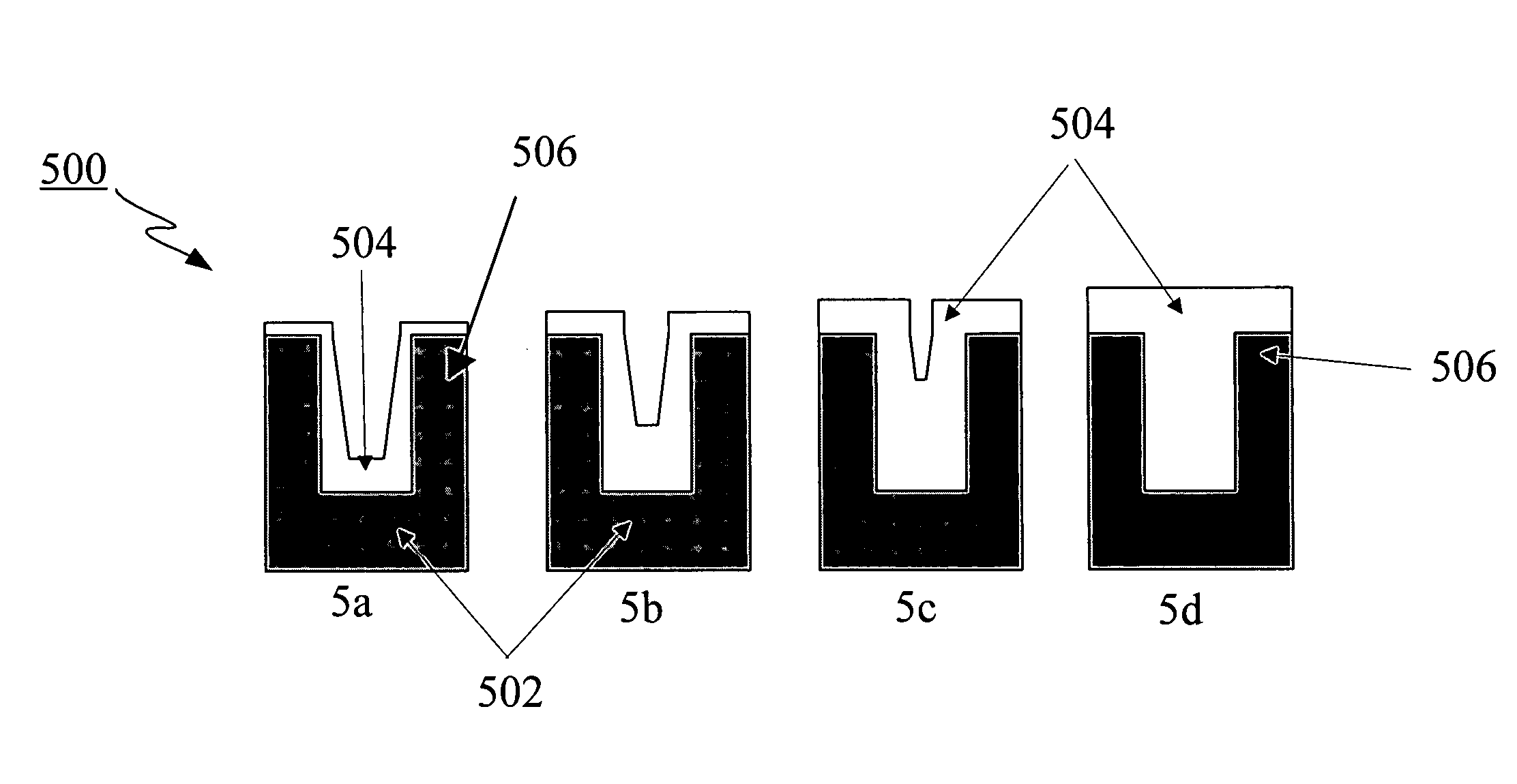

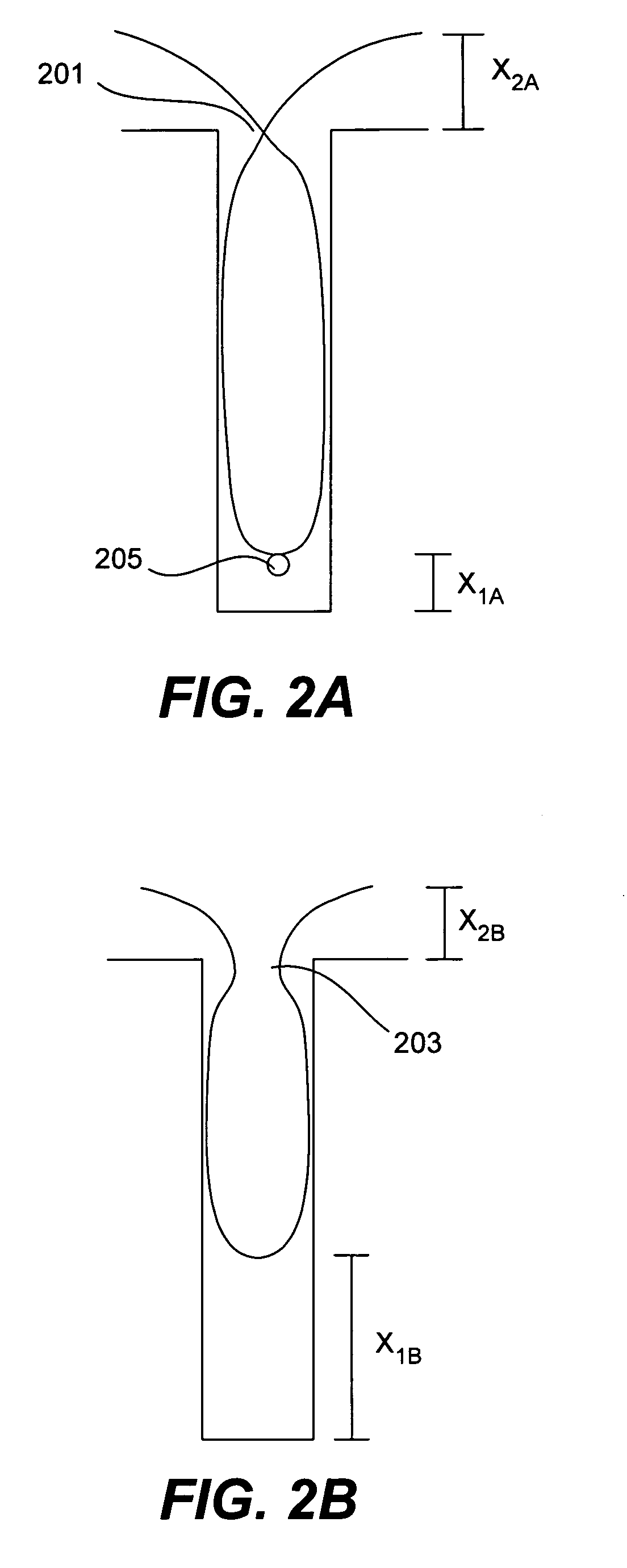

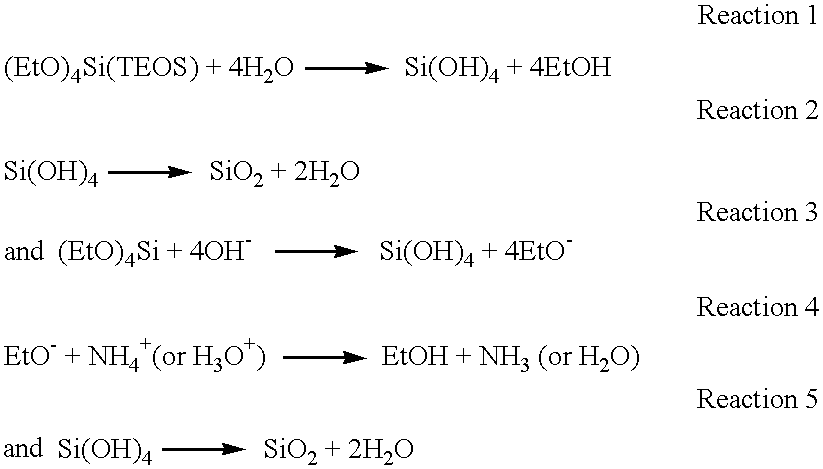

Methods for forming thin dielectric films by selectively depositing a conformal film of dielectric material on a high aspect ratio structure have uses in semiconductor processing and other applications. A method for forming a dielectric film involves providing in a deposition reaction chamber a substrate having a gap on the surface. The gap has a top opening and a surface area comprising a bottom and sidewalls running from the top to the bottom. A conformal silicon oxide-based dielectric film is selectively deposited in the gap by first preferentially applying a film formation catalyst or a catalyst precursor on a portion representing less than all of the gap surface area. The substrate surface is then exposed to a silicon-containing precursor gas such that a silicon oxide-based dielectric film layer is preferentially formed on the portion of the gap surface area. The preferential application of the catalyst or catalyst precursor may occur either at the top of the gap, for example to form a sacrificial mask, or at the bottom of the gap to create a seamless and void-free gap fill.

Owner:NOVELLUS SYSTEMS

Method for Forming Conformal Nitrided, Oxidized, or Carbonized Dielectric Film by Atomic Layer Deposition

ActiveUS20150147483A1Easy to oxidizeEasily and nitridedSpecial surfacesChemical vapor deposition coatingAtomic layer depositionSilicon

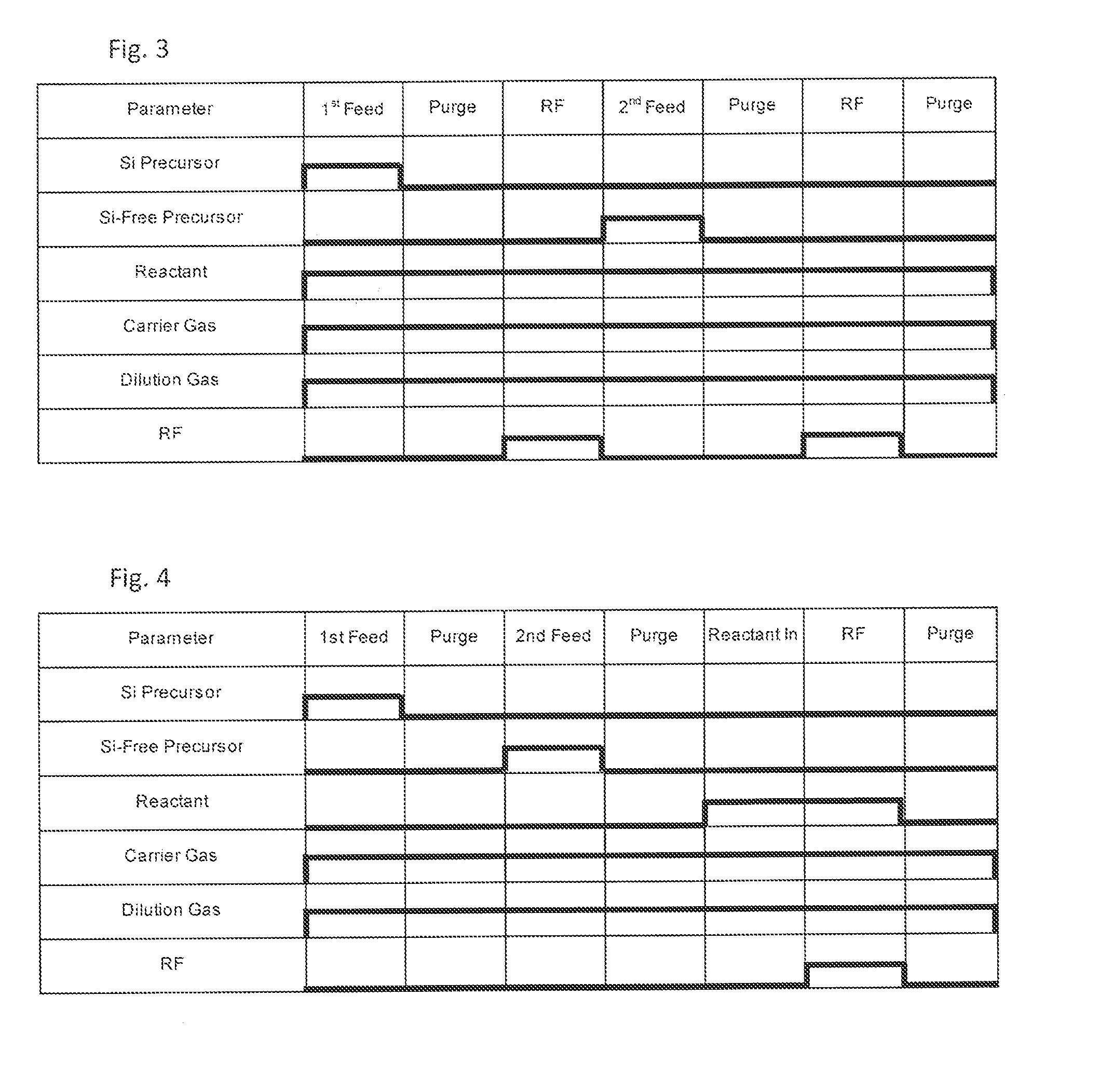

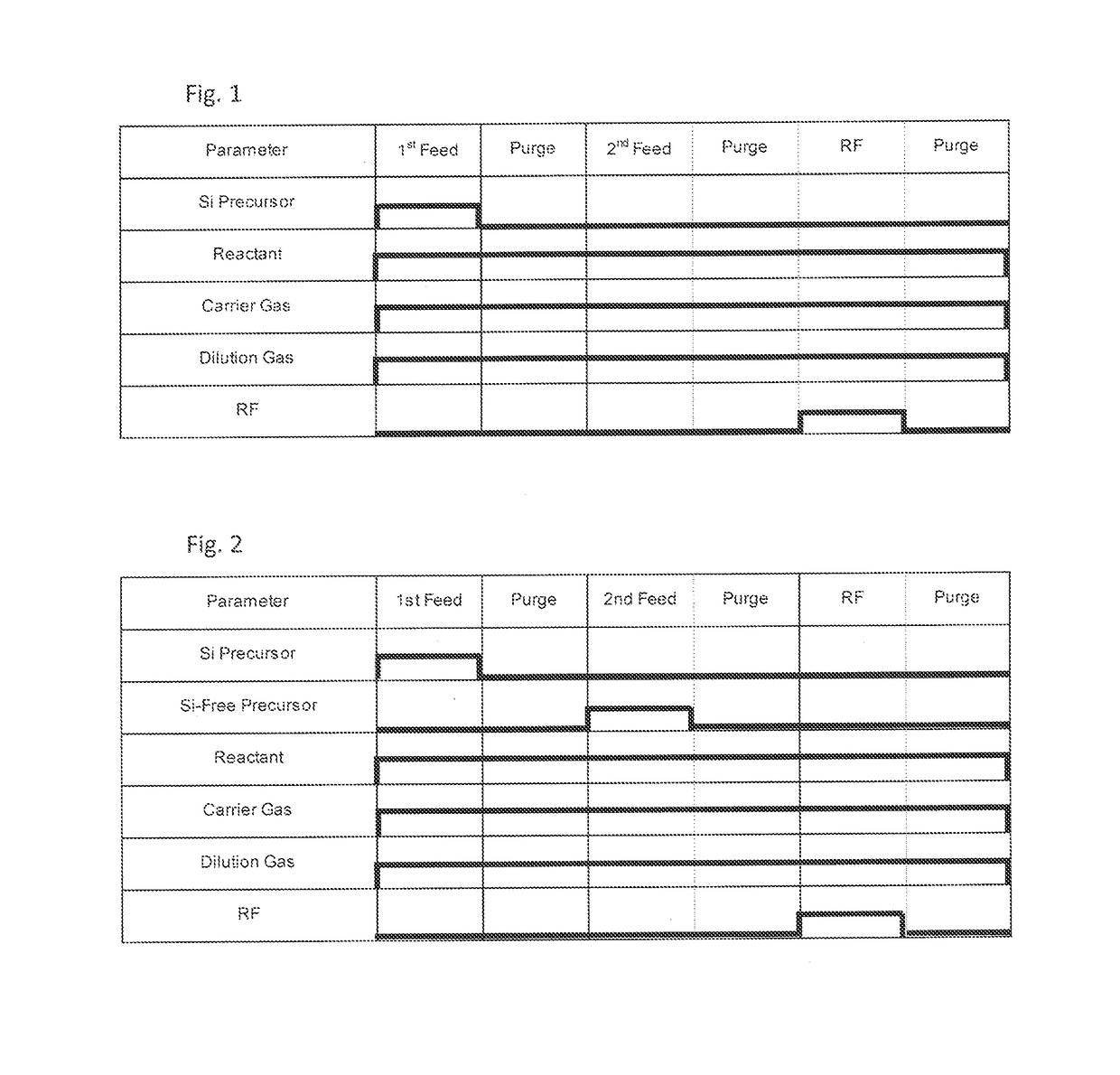

A method for forming a film on a patterned surface of a substrate by atomic layer deposition (ALD) processing includes: adsorbing onto a patterned surface a first precursor containing silicon or metal in its molecule; adsorbing onto the first-precursor-adsorbed surface a second precursor containing no silicon or metal in its molecule; exposing the second-precursor-adsorbed surface to an excited reactant to oxidize, nitride, or carbonize the precursors adsorbed on the surface of the substrate; and repeating the above cycle to form a film on the patterned surface of the substrate.

Owner:ASM IP HLDG BV

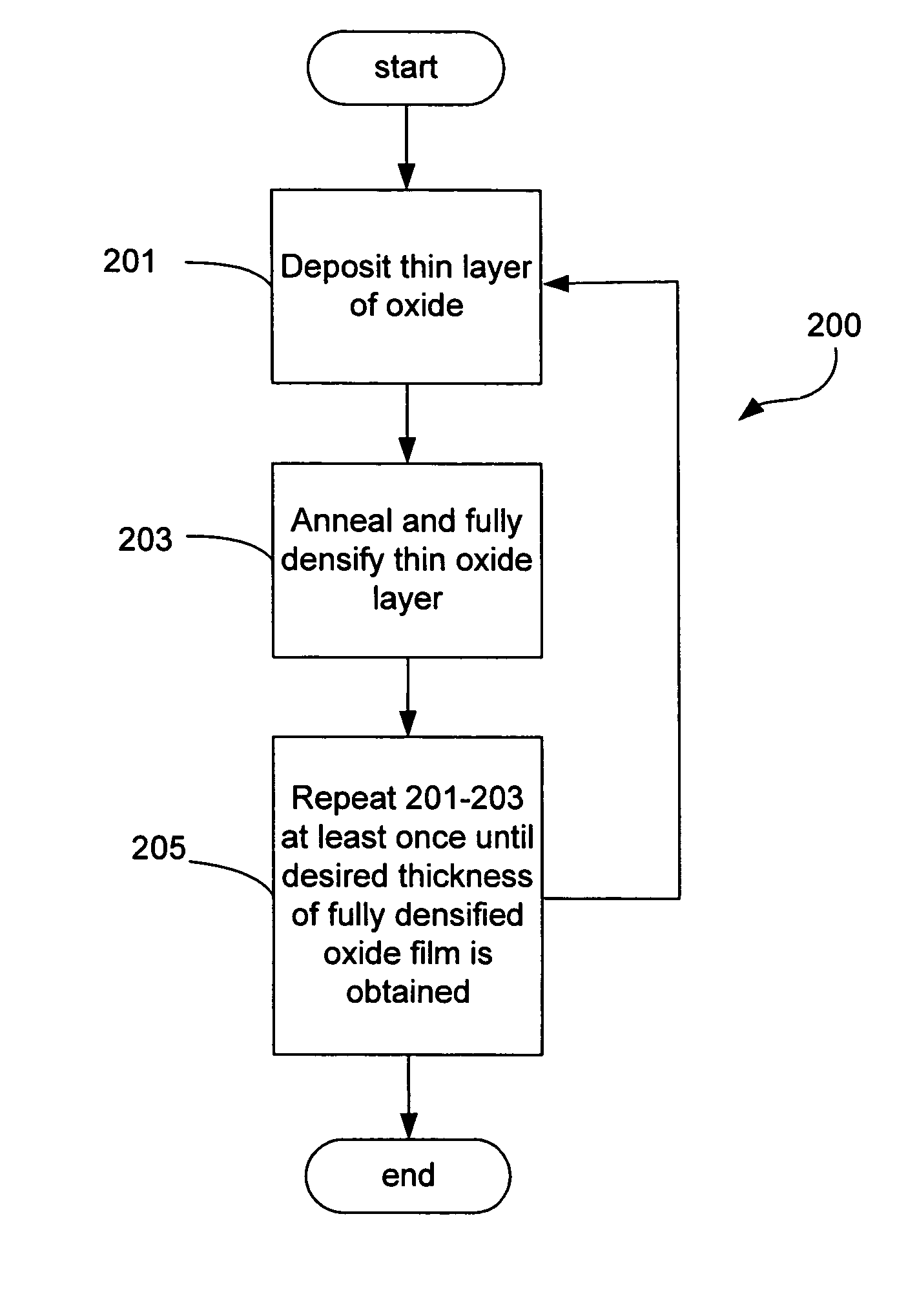

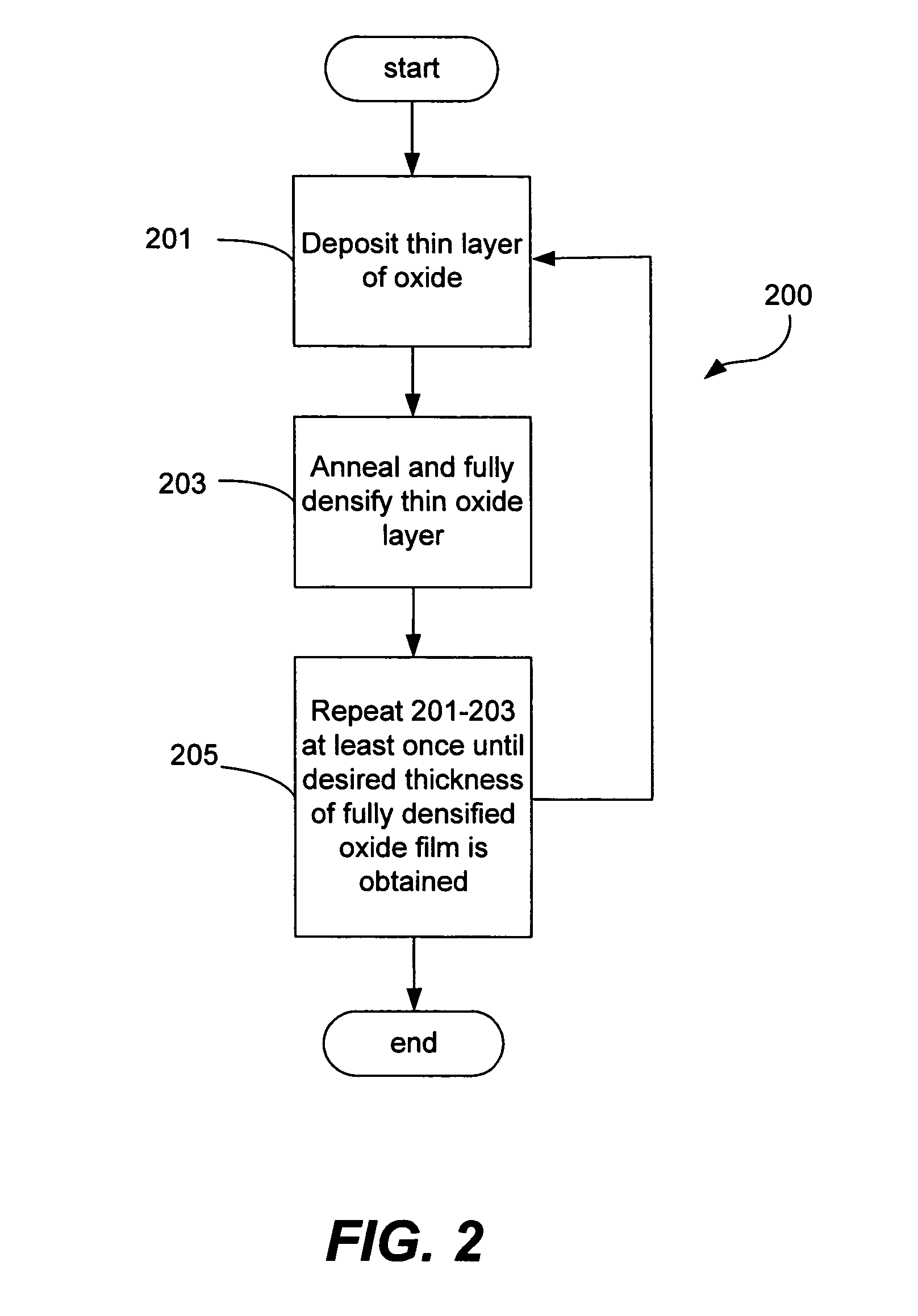

Sequential deposition/anneal film densification method

ActiveUS7148155B1Maintaining film propertyMaintain propertiesSemiconductor/solid-state device manufacturingDielectric membraneThin membrane

A silicon dioxide-based dielectric layer is formed on a substrate surface by a sequential deposition / anneal technique. The deposited layer thickness is insufficient to prevent substantially complete penetration of annealing process agents into the layer and migration of water out of the layer. The dielectric layer is then annealed, ideally at a moderate temperature, to remove water and thereby fully densify the film. The deposition and anneal processes are then repeated until a desired dielectric film thickness is achieved.

Owner:NOVELLUS SYSTEMS

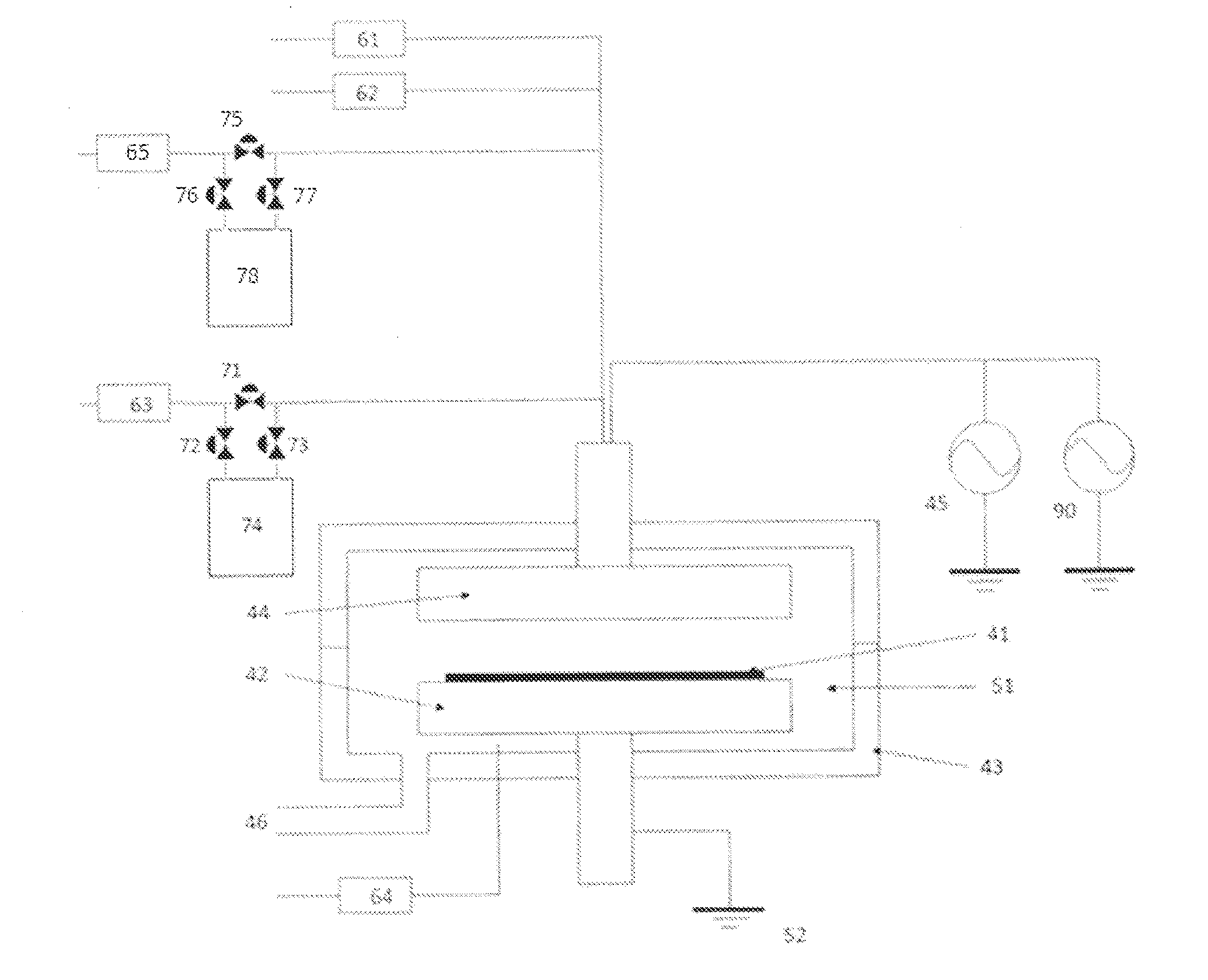

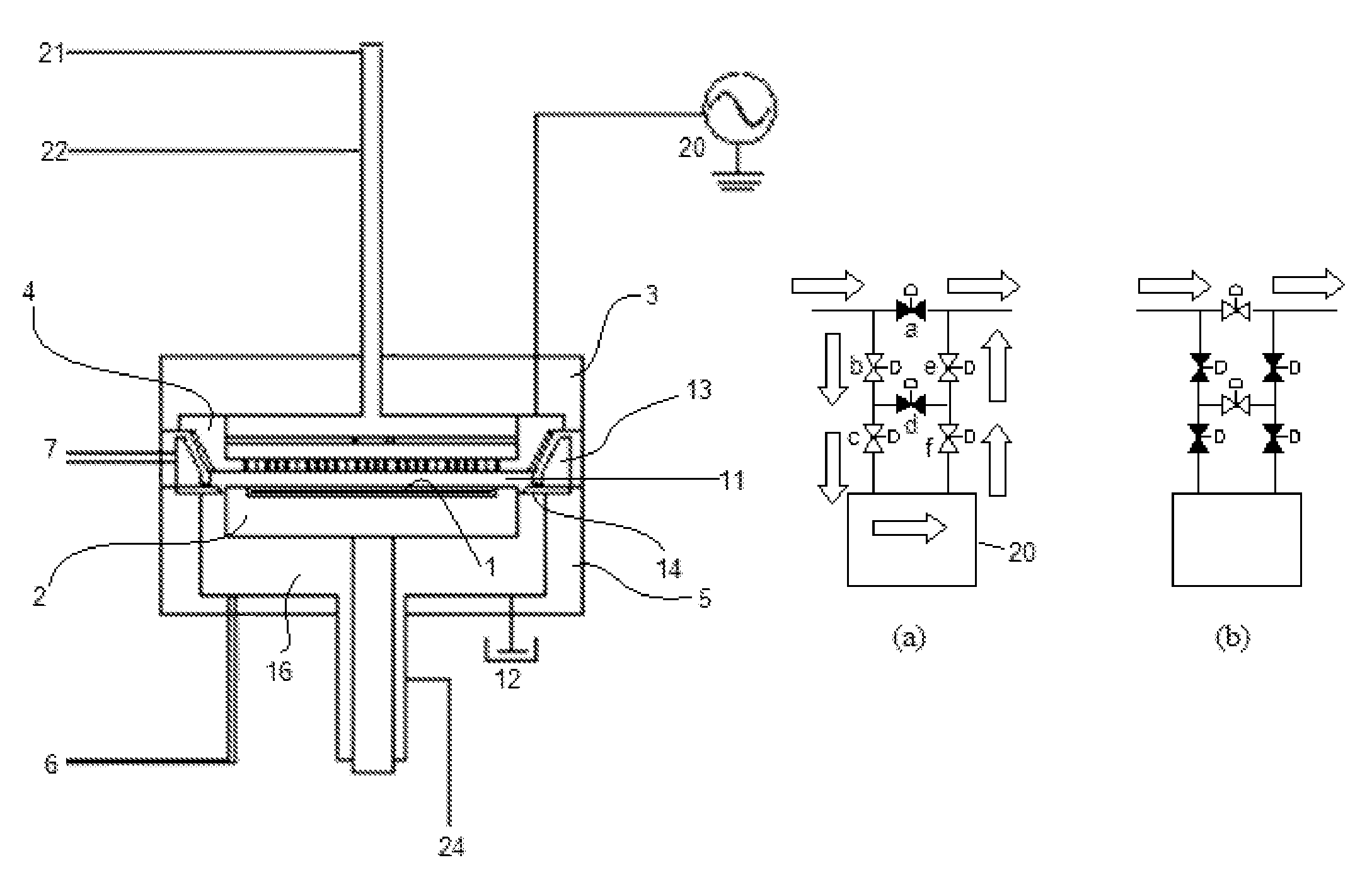

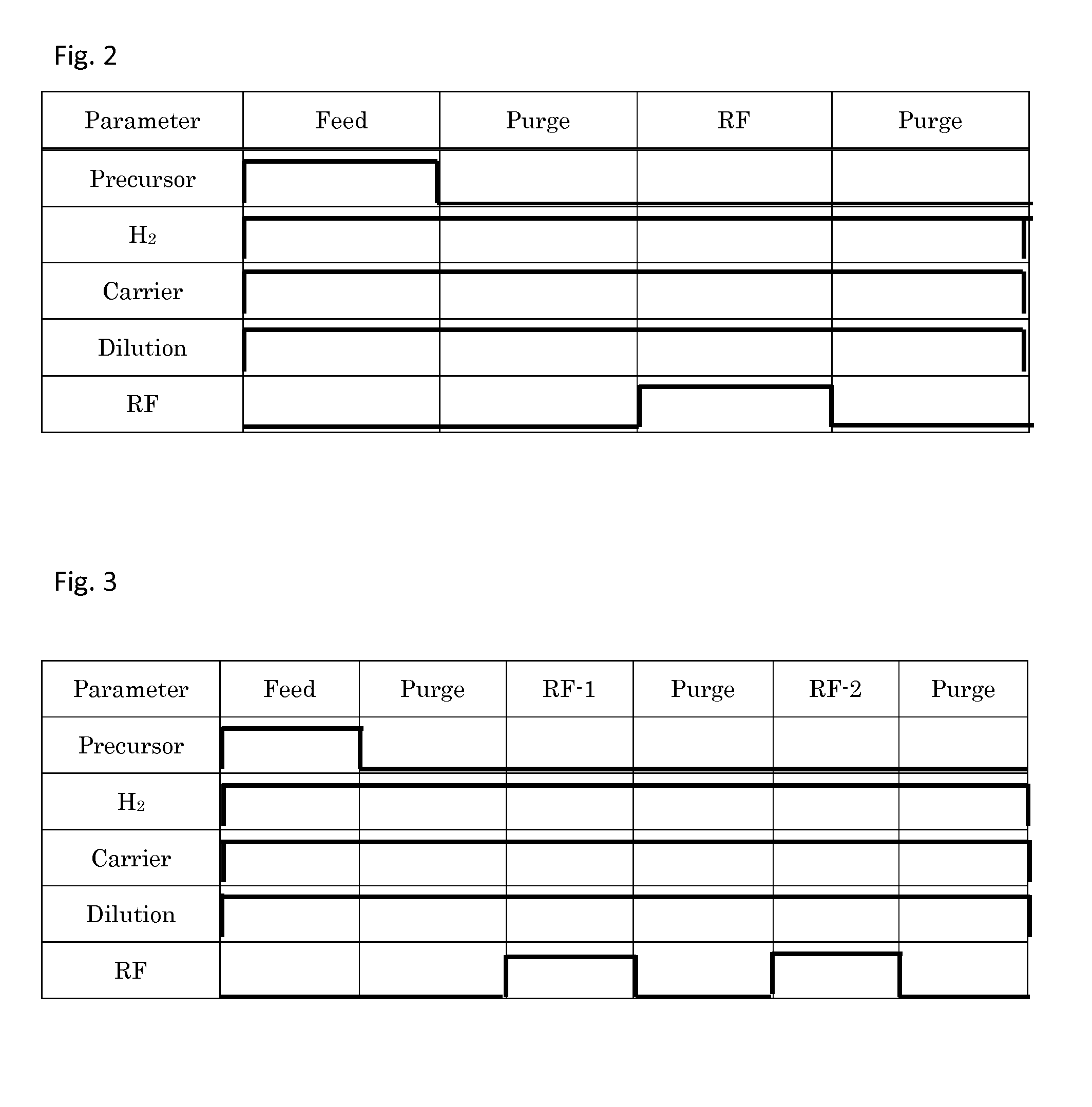

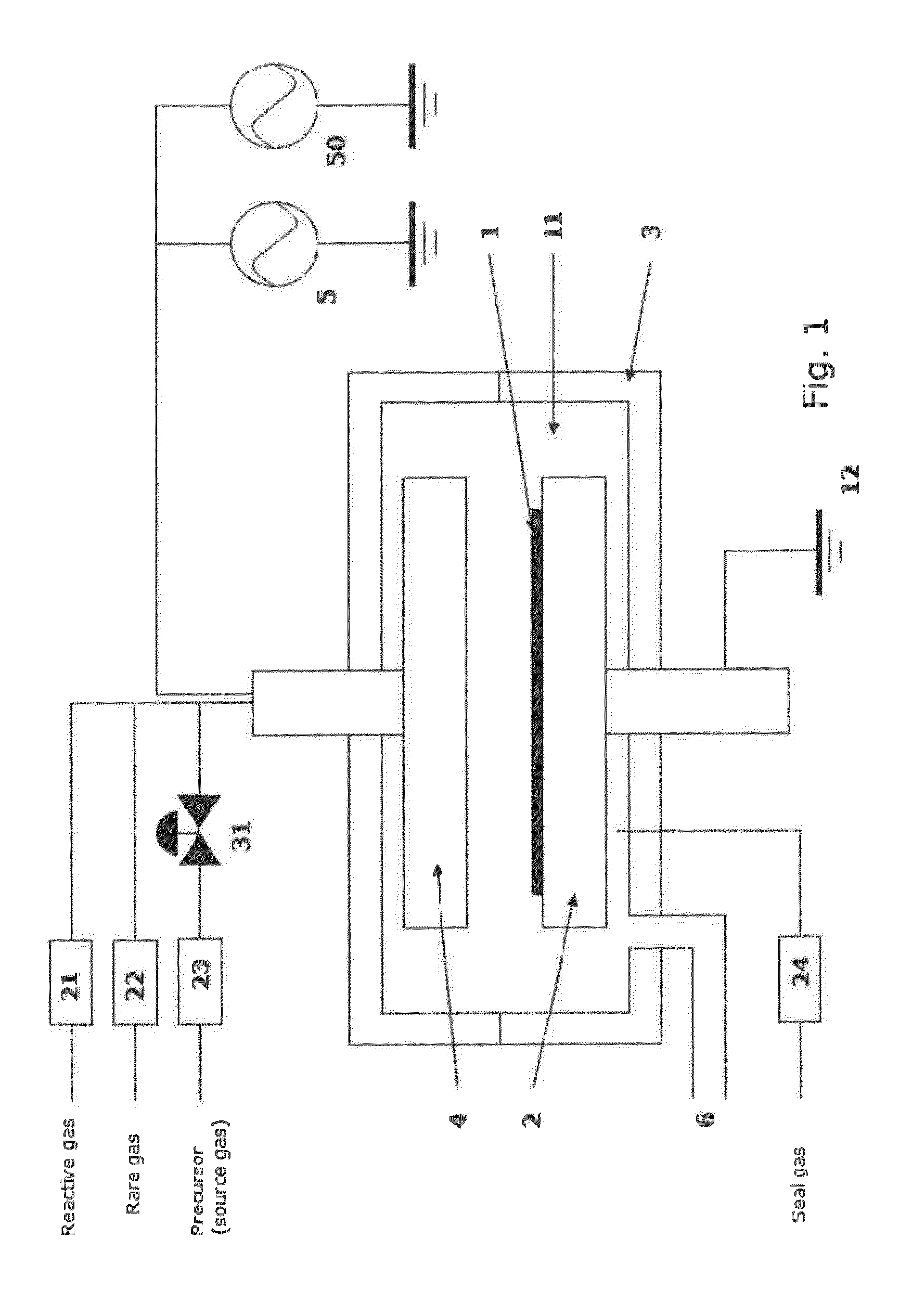

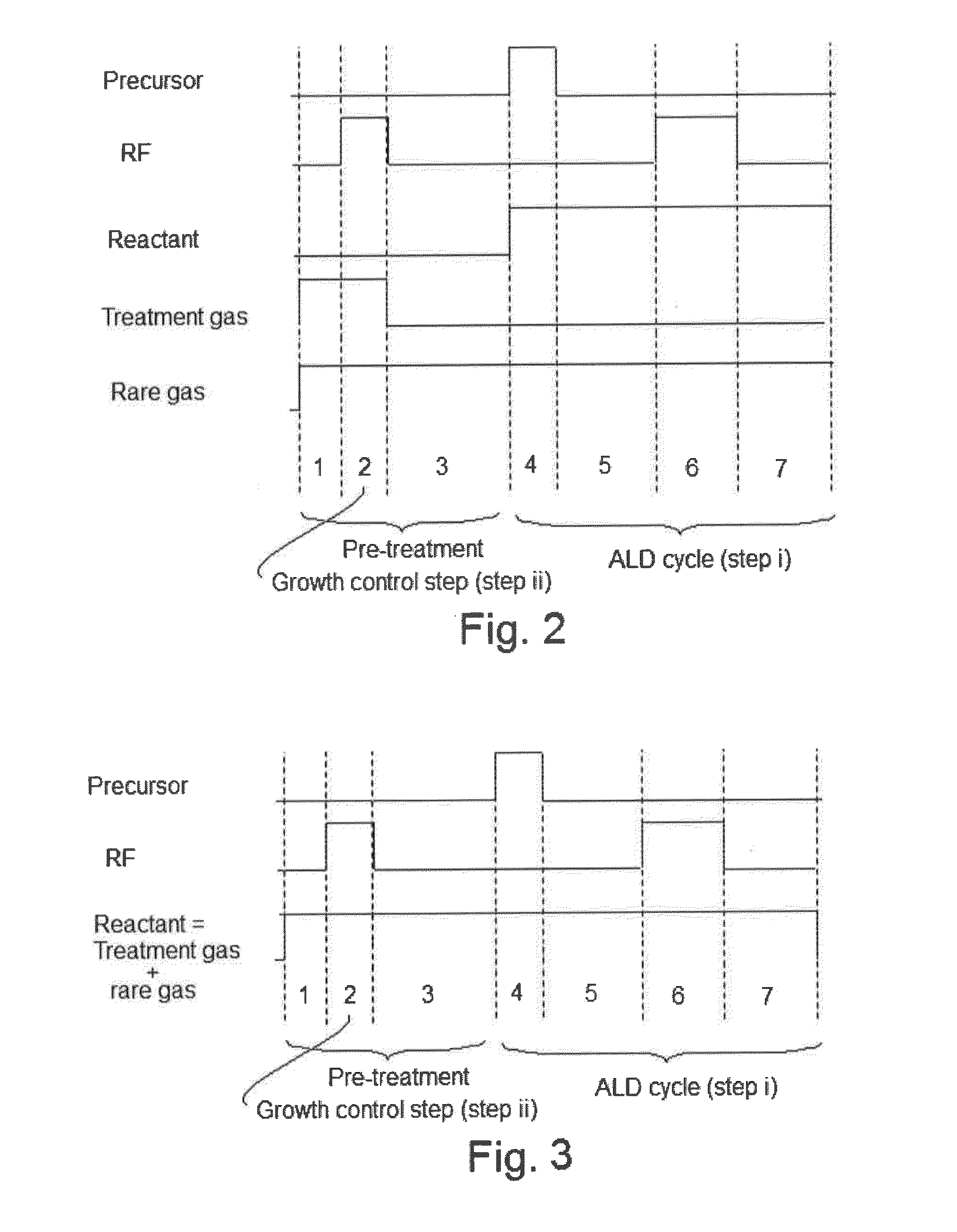

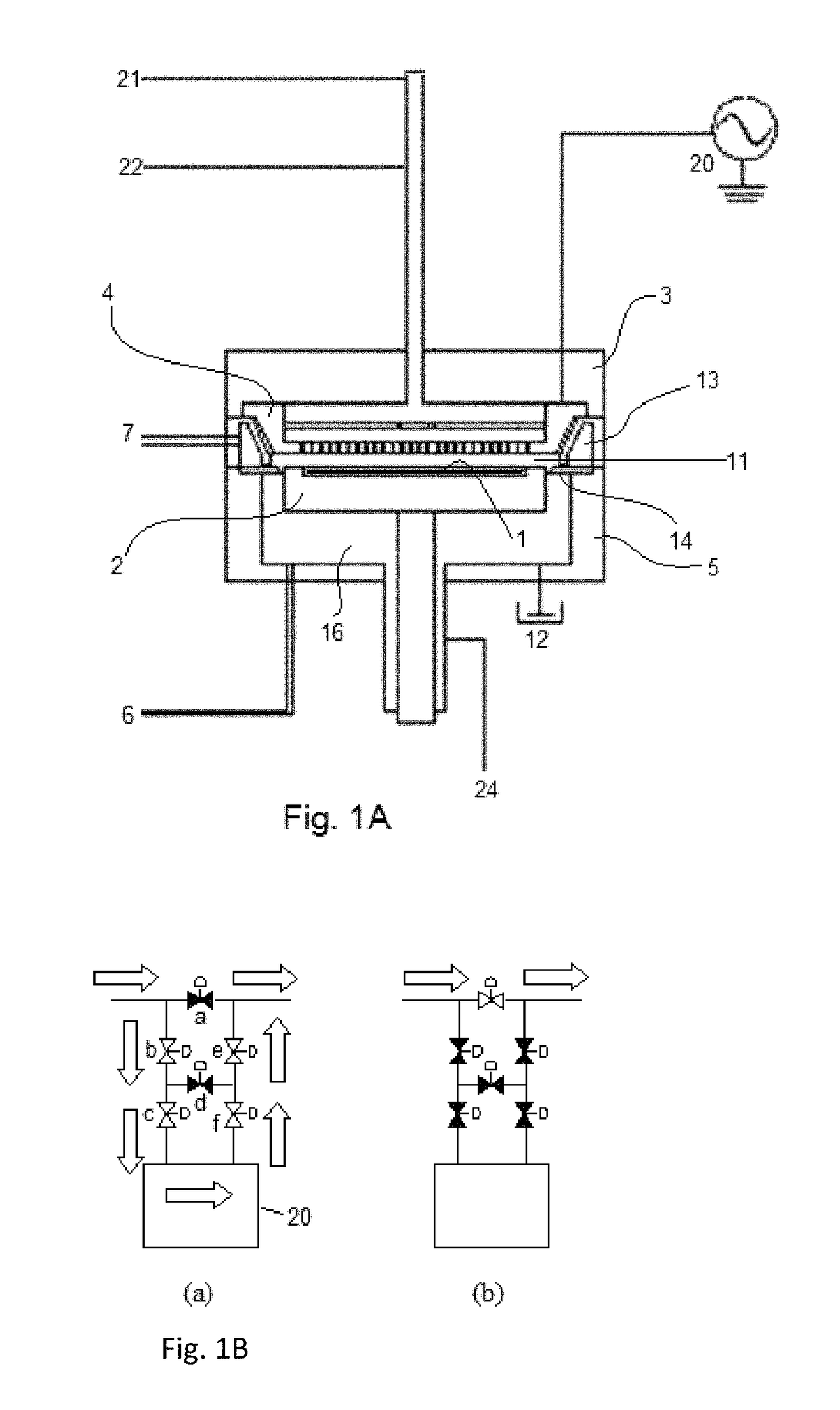

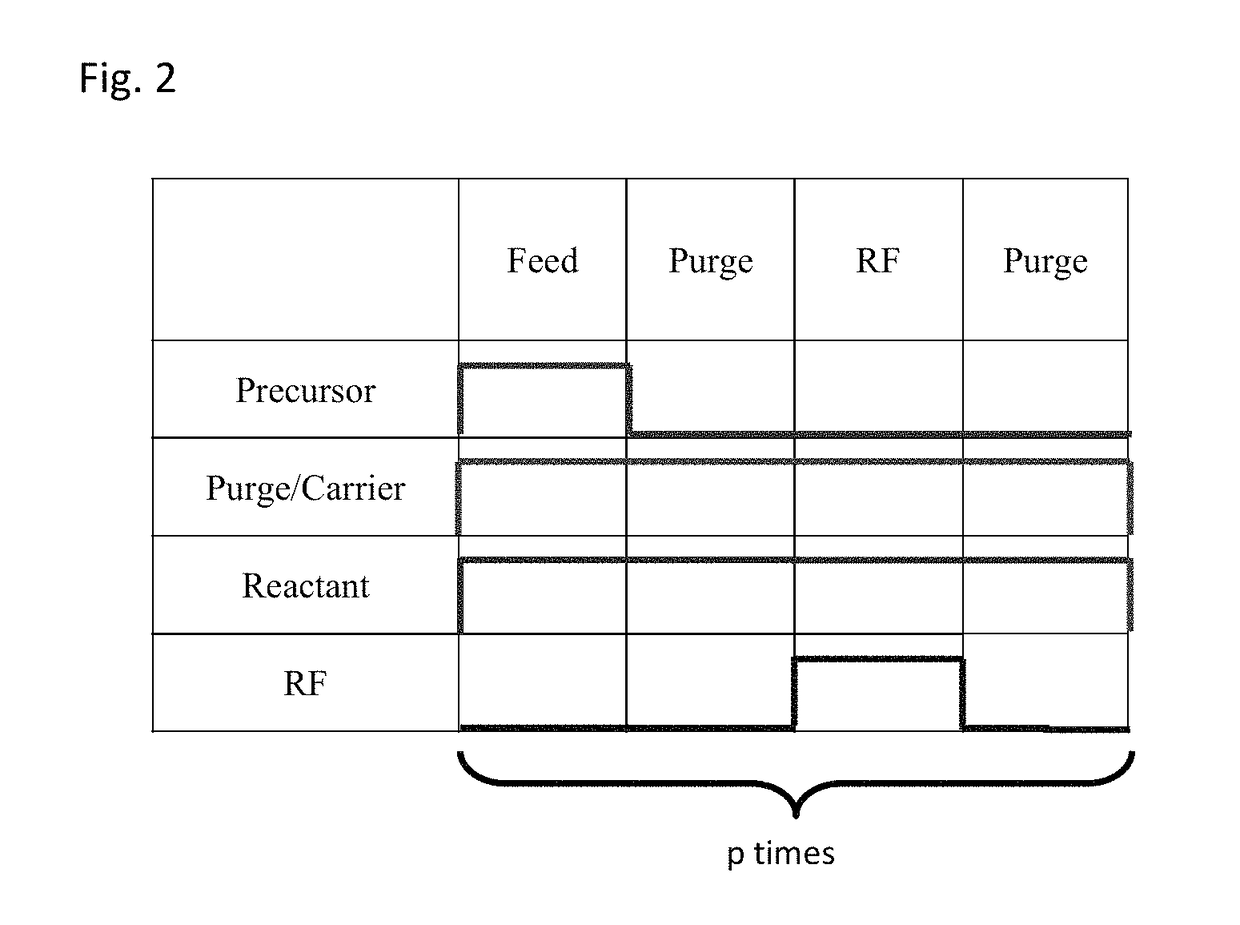

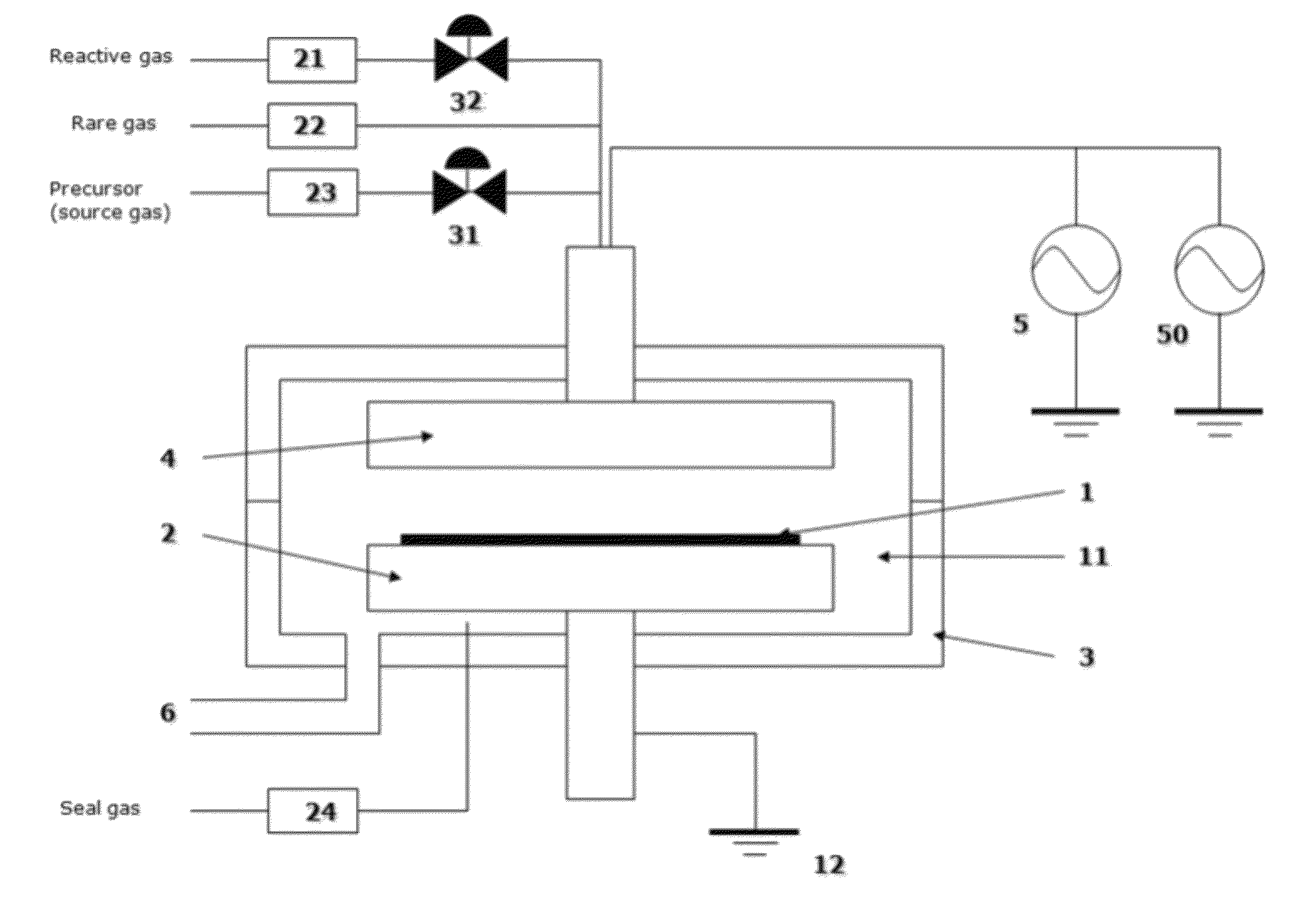

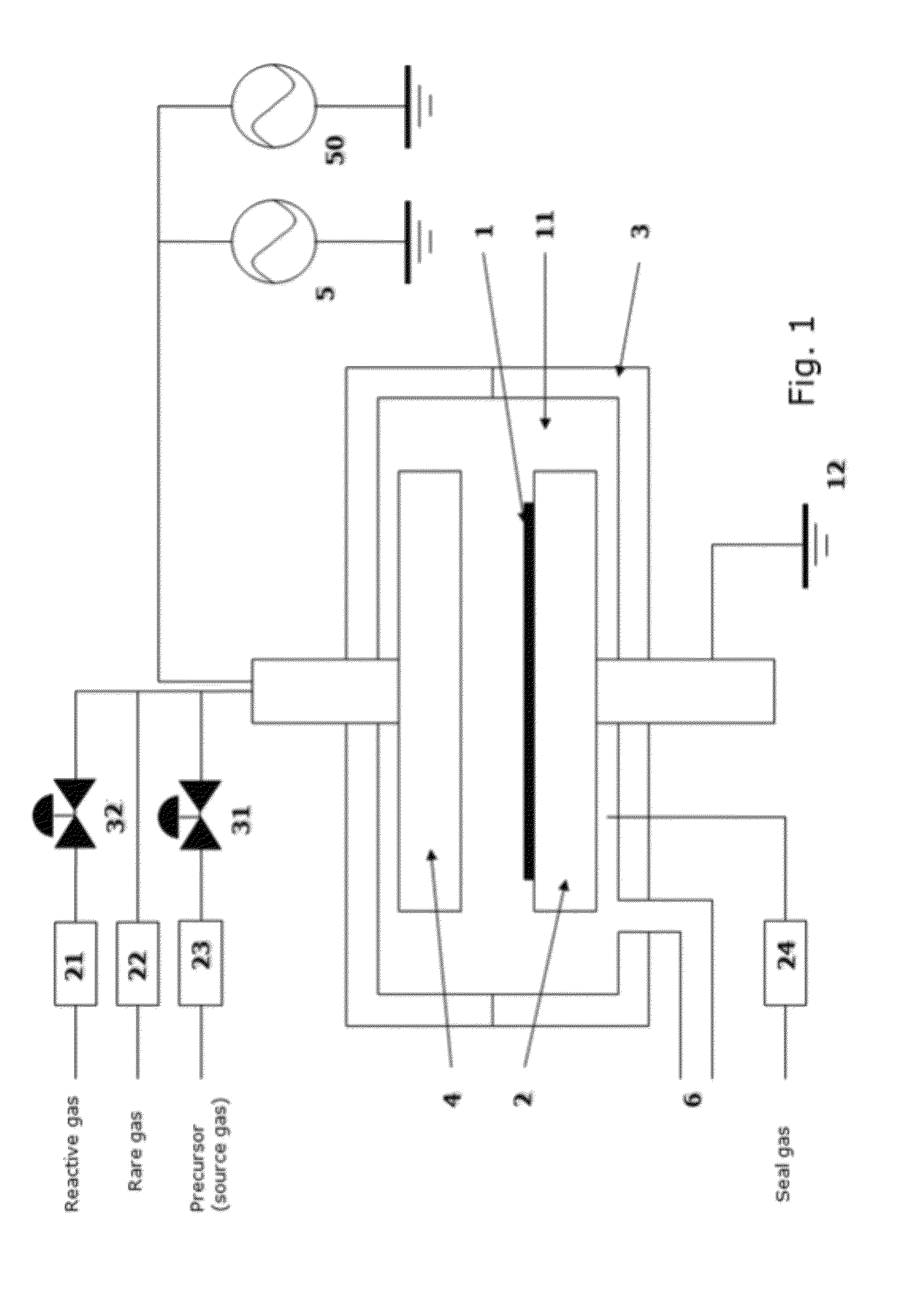

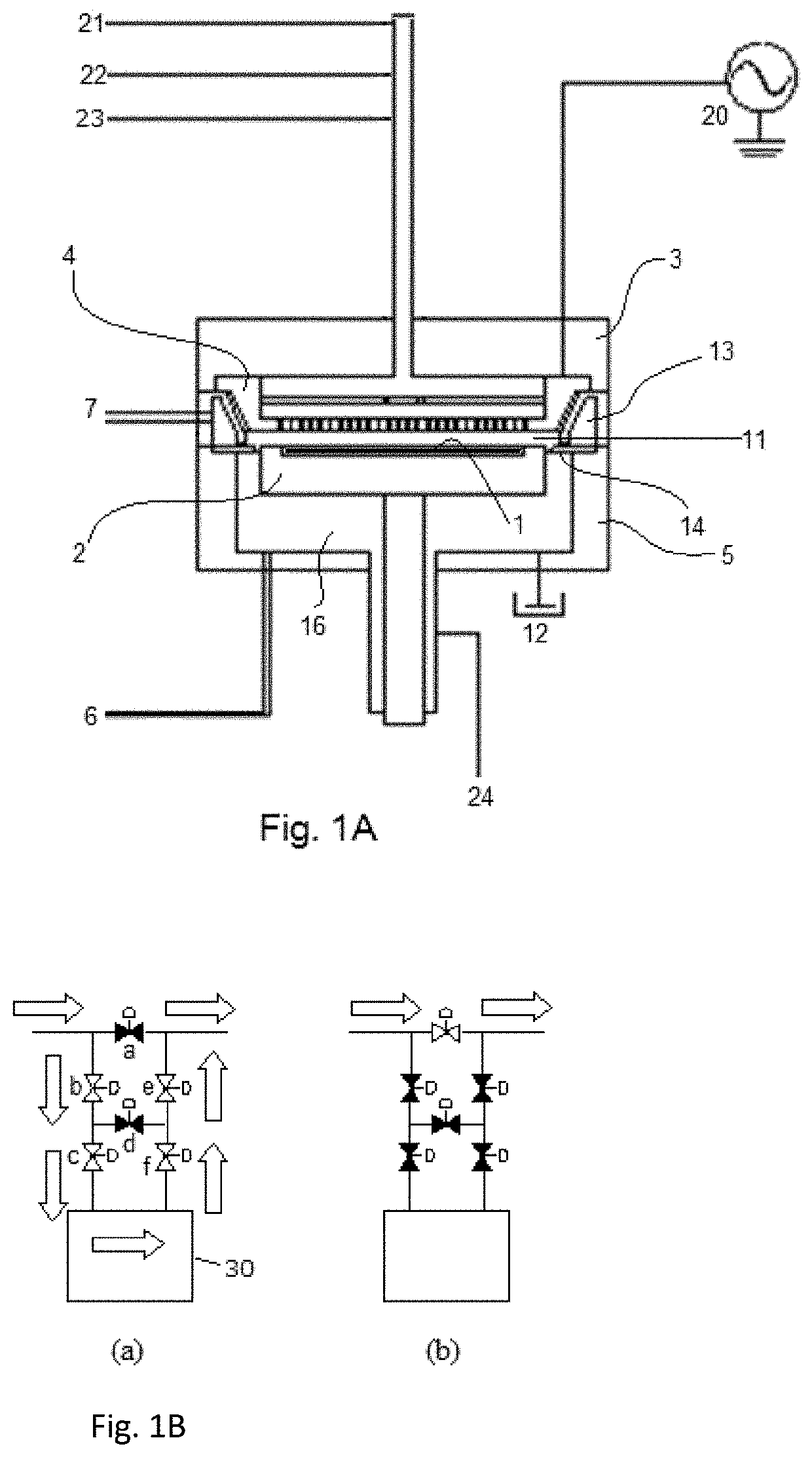

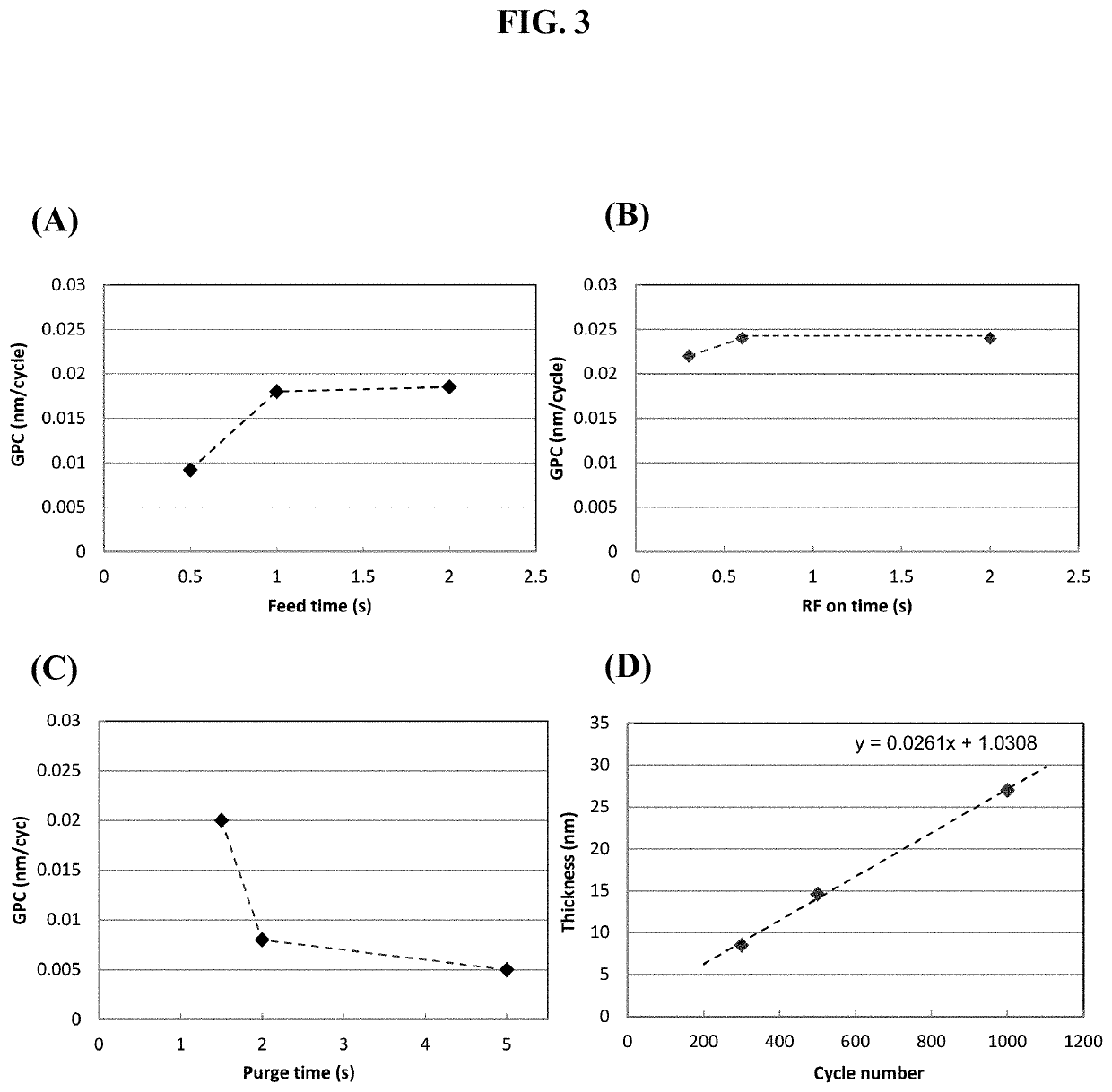

Method for forming dielectric film in trenches by PEALD using H-containing gas

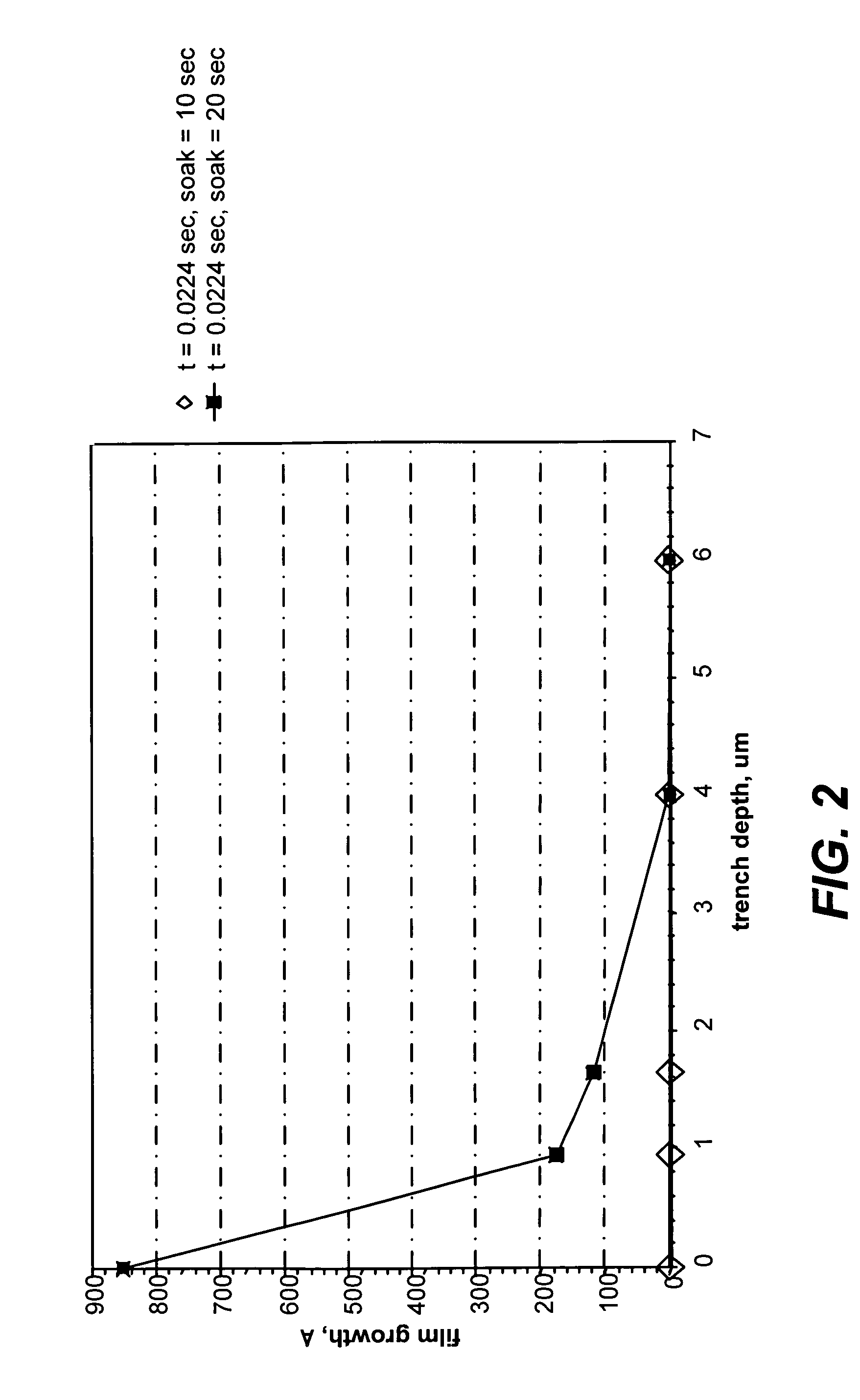

ActiveUS9455138B1Increase deposition rateHigh film thicknessSemiconductor/solid-state device manufacturingChemical physicsNoble gas

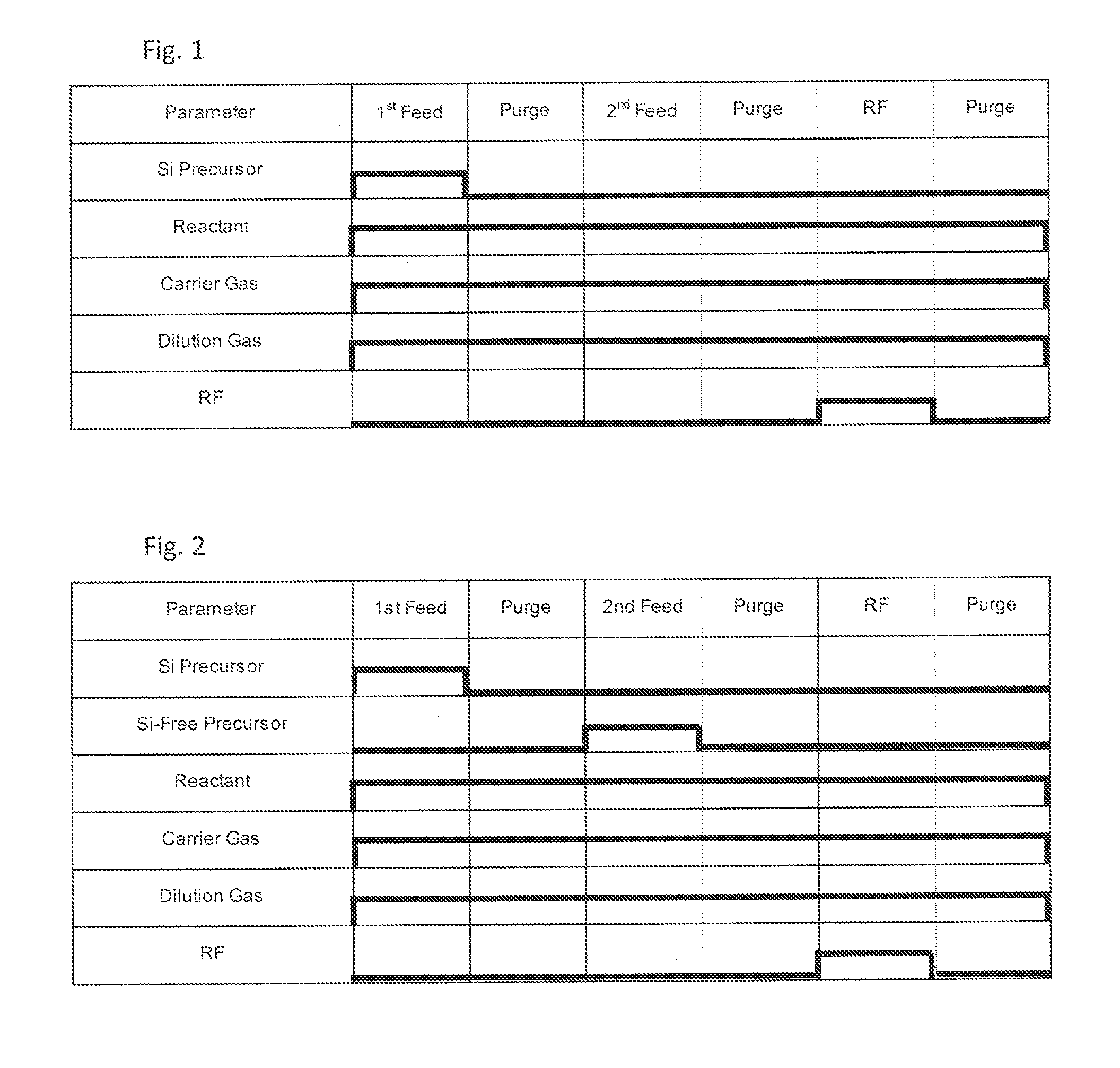

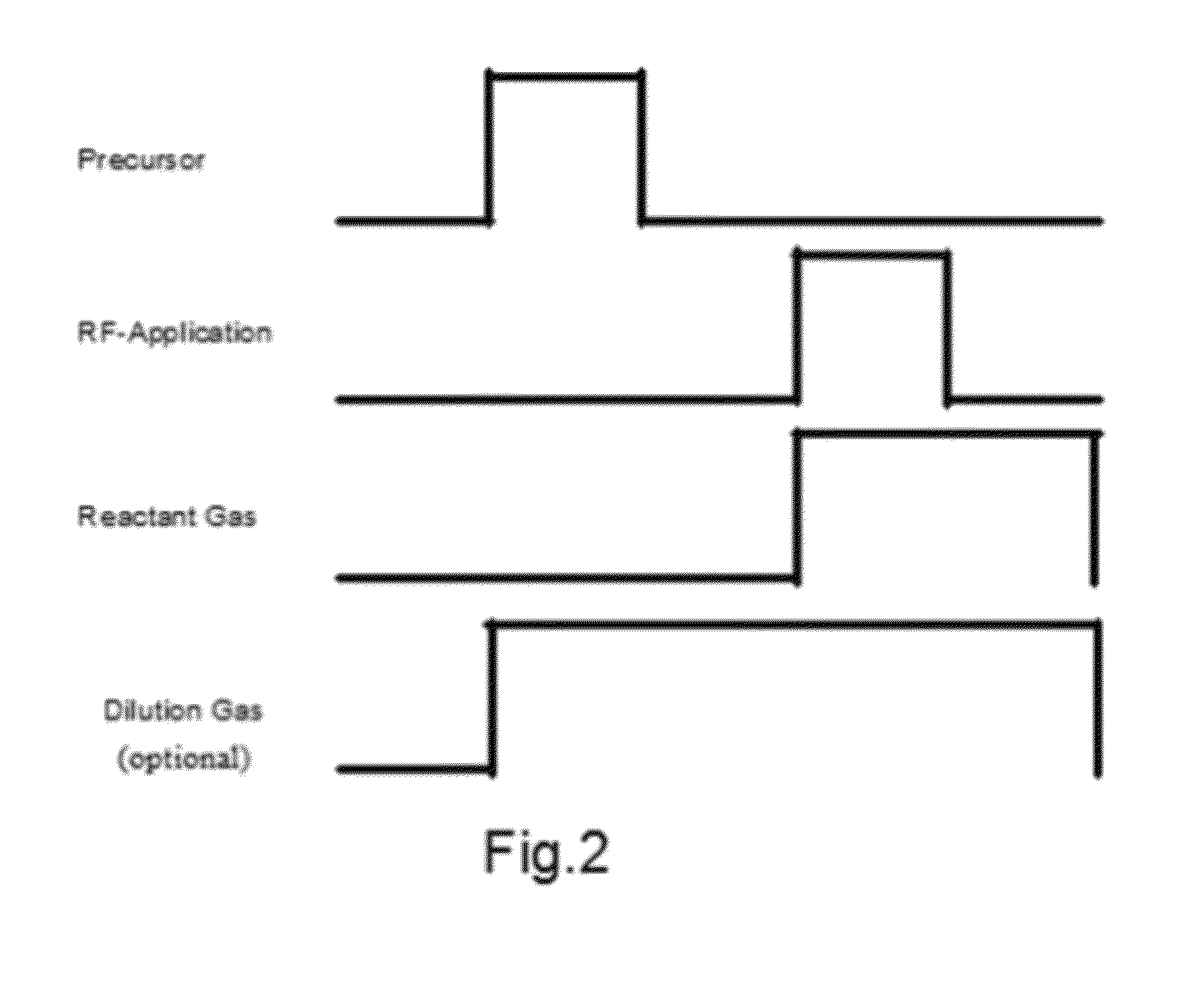

A method for forming a dielectric film in a trench on a substrate by plasma-enhanced atomic layer deposition (PEALD) performs one or more process cycles, each process cycle including: (i) feeding a silicon-containing precursor in a pulse; (ii) supplying a hydrogen-containing reactant gas at a flow rate of more than about 30 sccm but less than about 800 sccm in the absence of nitrogen-containing gas; (iii) supplying a noble gas to the reaction space; and (iv) applying RF power in the presence of the reactant gas and the noble gas and in the absence of any precursor in the reaction space, to form a monolayer constituting a dielectric film on a substrate at a growth rate of less than one atomic layer thickness per cycle.

Owner:ASM IP HLDG BV

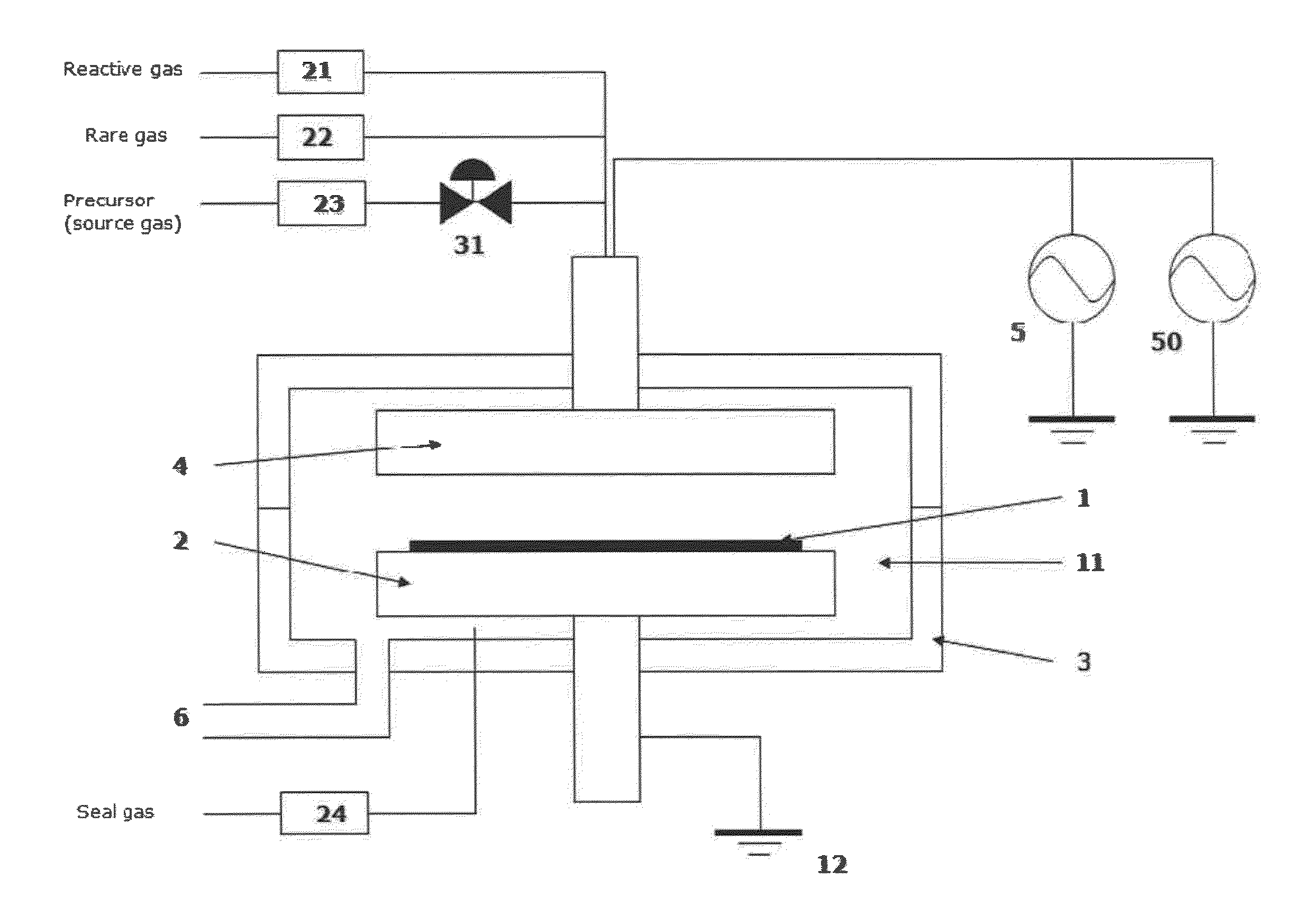

Method for Forming Silicon-Containing Dielectric Film by Cyclic Deposition with Side Wall Coverage Control

ActiveUS20130330933A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric membranePhysical chemistry

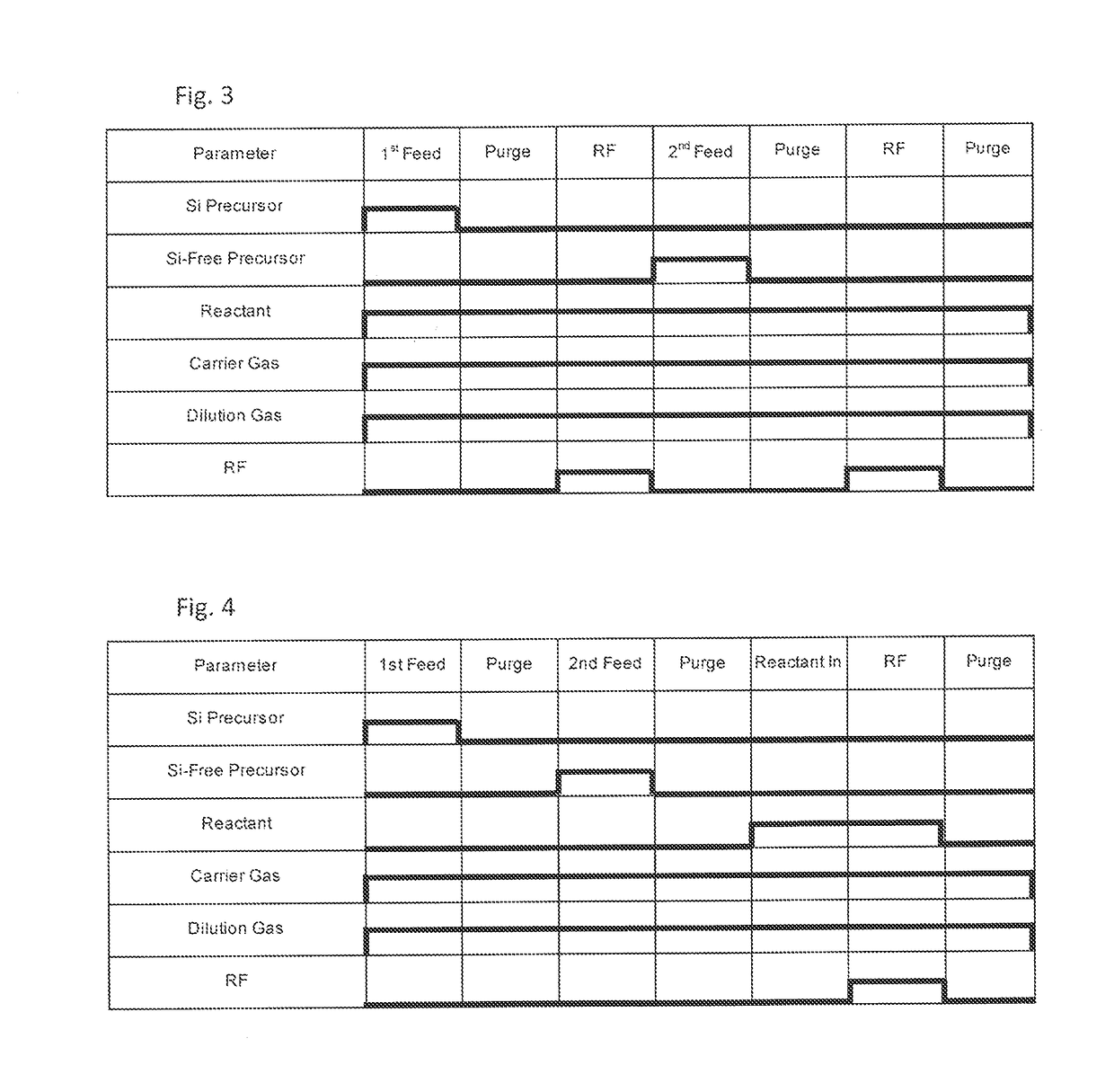

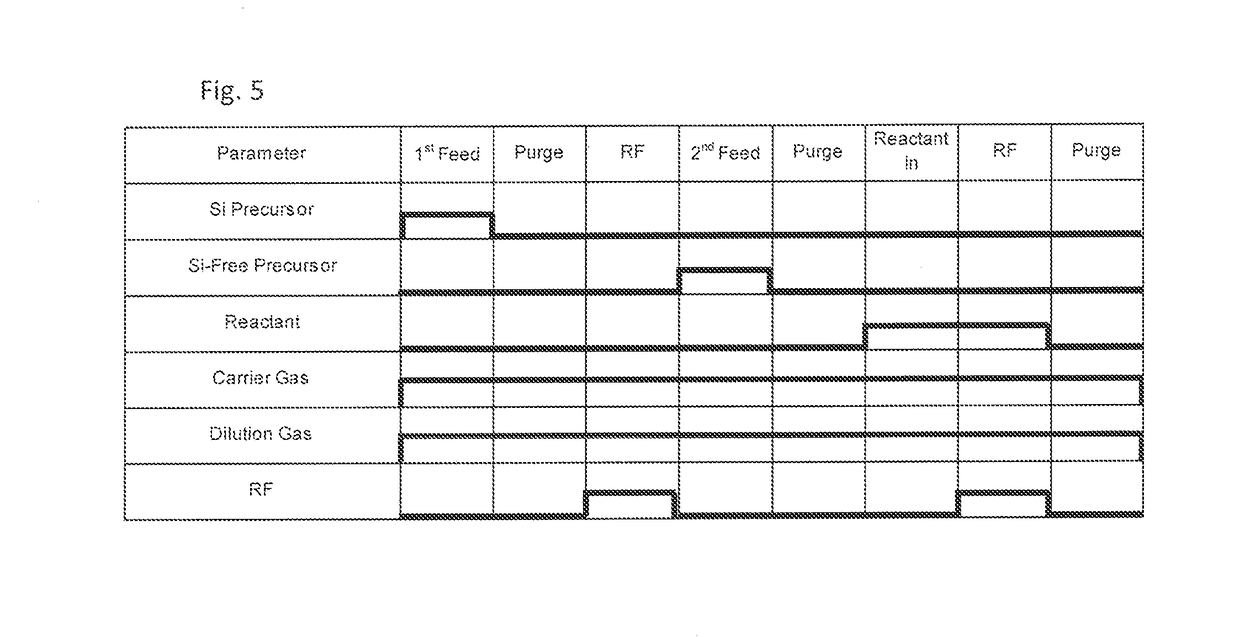

A method of forming a dielectric film having Si—C bonds and / or Si—N bonds on a semiconductor substrate by cyclic deposition, includes: (i) conducting one or more cycles of cyclic deposition in a reaction space wherein a semiconductor substrate is placed, using a Si-containing precursor and a reactant gas; and (ii) before or after step (i), applying a pulse of RF power to the reaction space while supplying a rare gas and a treatment gas without supplying a Si-containing precursor, whereby a dielectric film having Si—C bonds and / or Si—N bonds is formed on the semiconductor substrate.

Owner:ASM IP HLDG BV

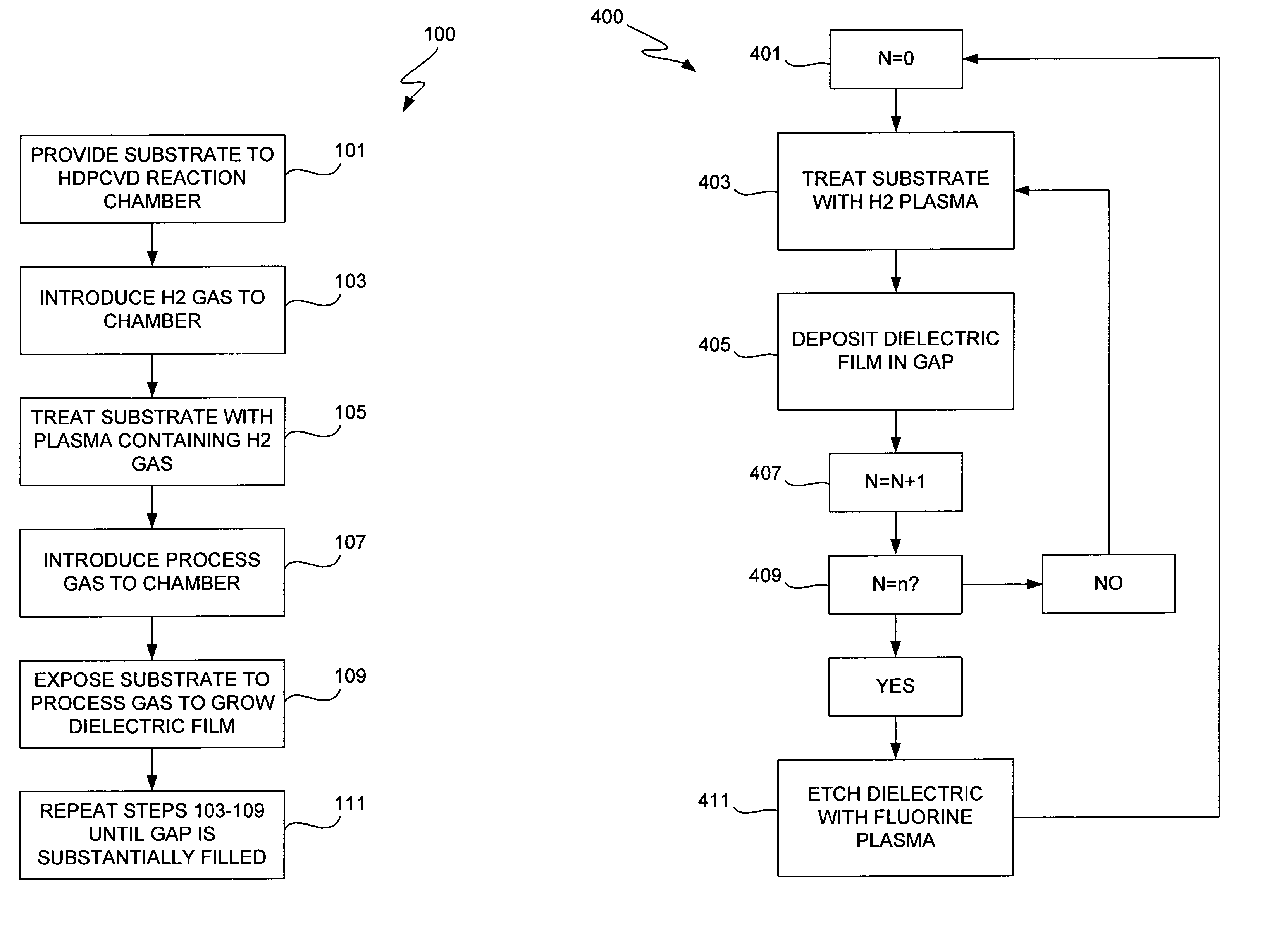

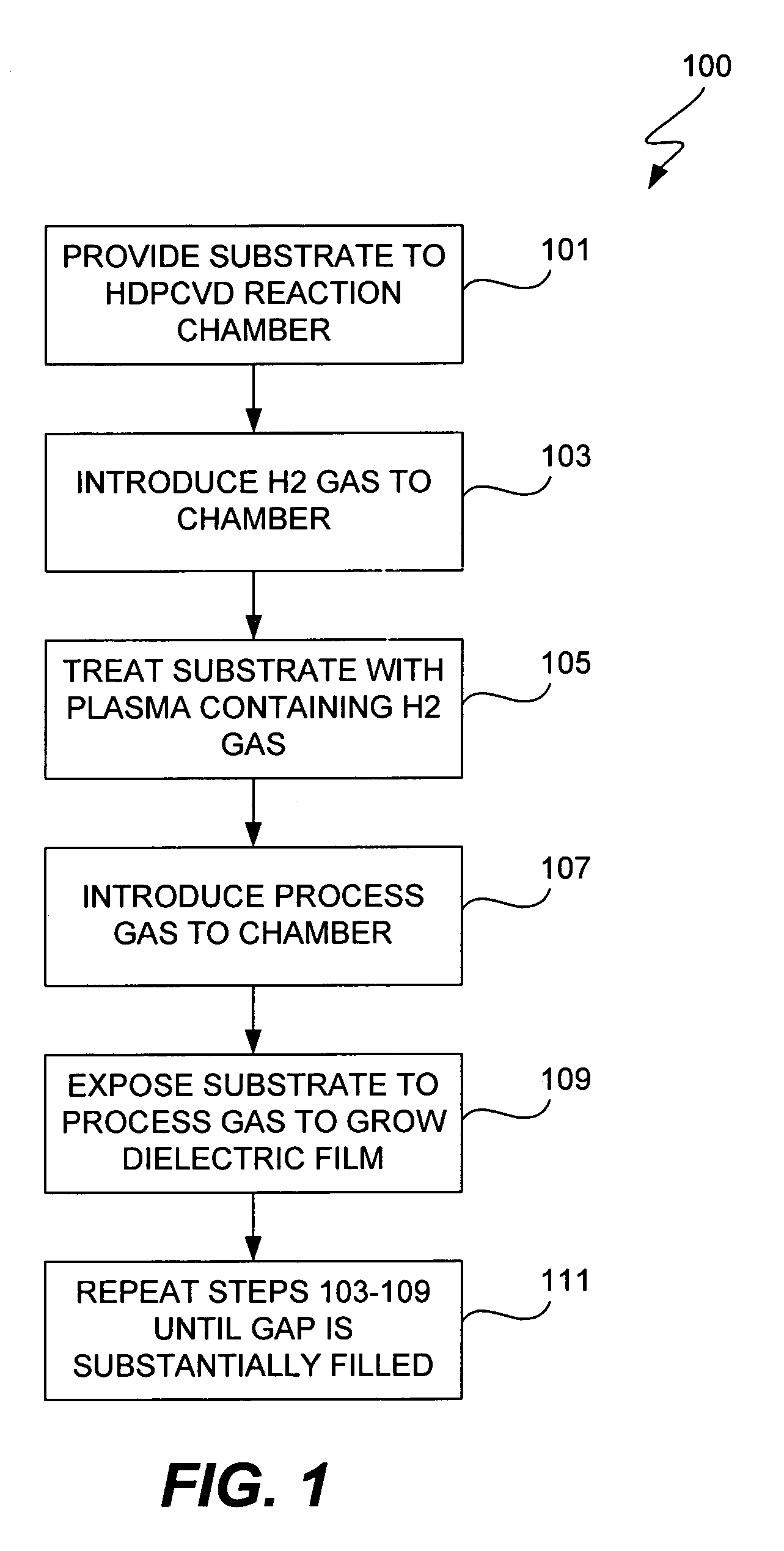

Hydrogen treatment enhanced gap fill

ActiveUS7211525B1Reduce and eliminate depositionReduce or eliminate the need for etch stepsSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric membranePhysical chemistry

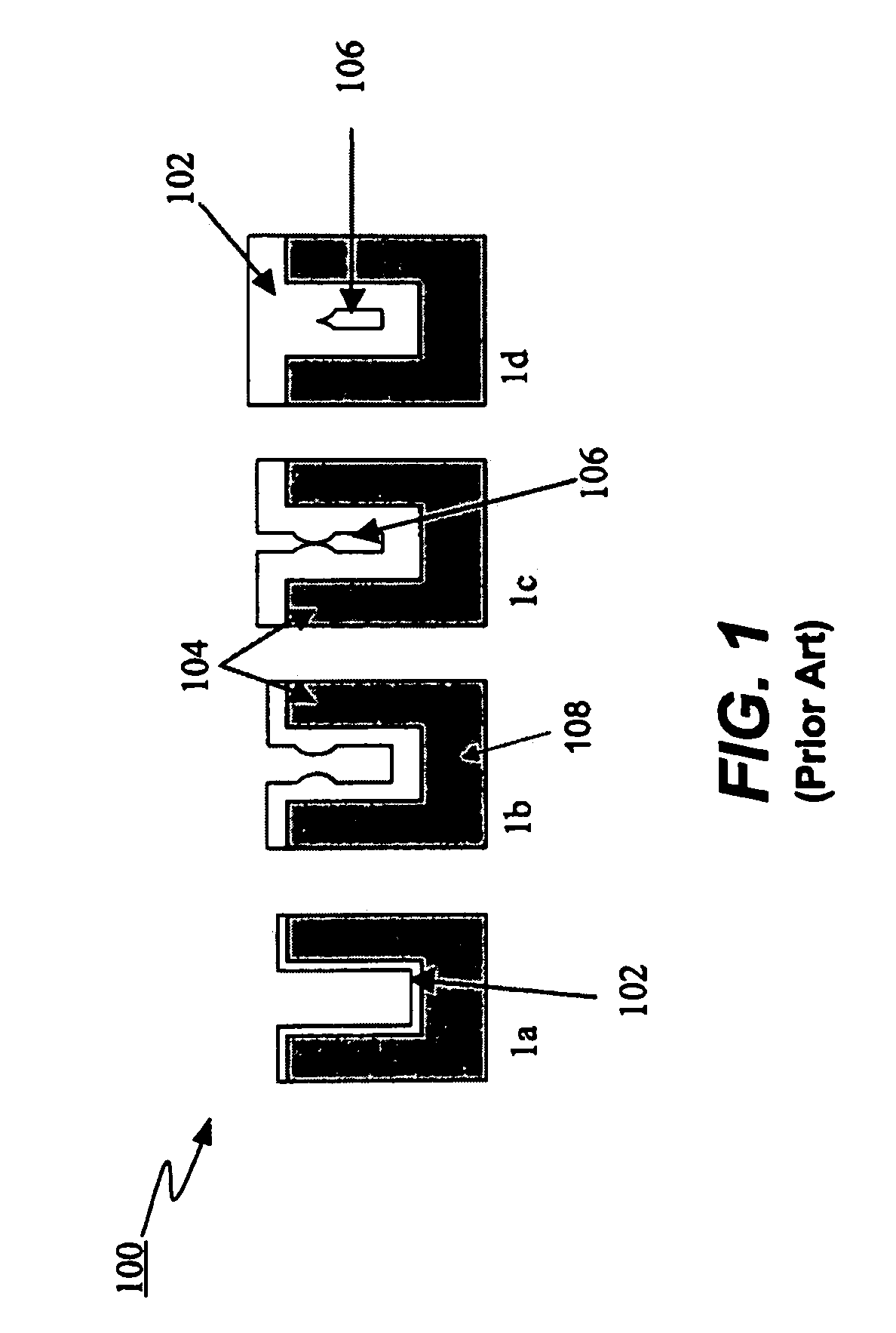

Methods of filling gaps on semiconductor substrates with dielectric film are described. The methods reduce or eliminate sidewall deposition and top-hat formation. The methods also reduce or eliminate the need for etch steps during dielectric film deposition. The methods include treating a semiconductor substrate with a hydrogen plasma before depositing dielectric film on the substrate. In some embodiments, the hydrogen treatment is used is conjunction with a high rate deposition process.

Owner:NOVELLUS SYSTEMS

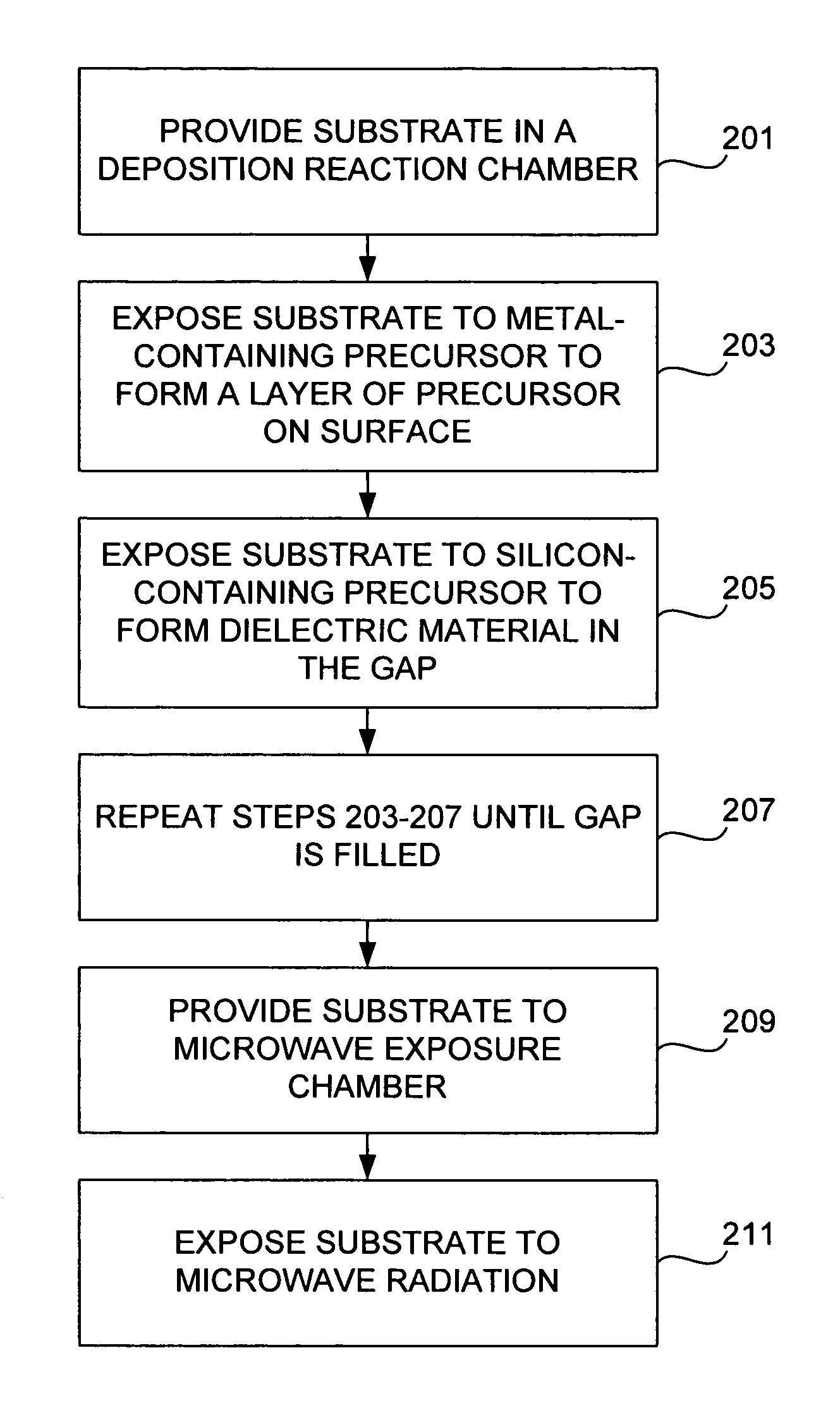

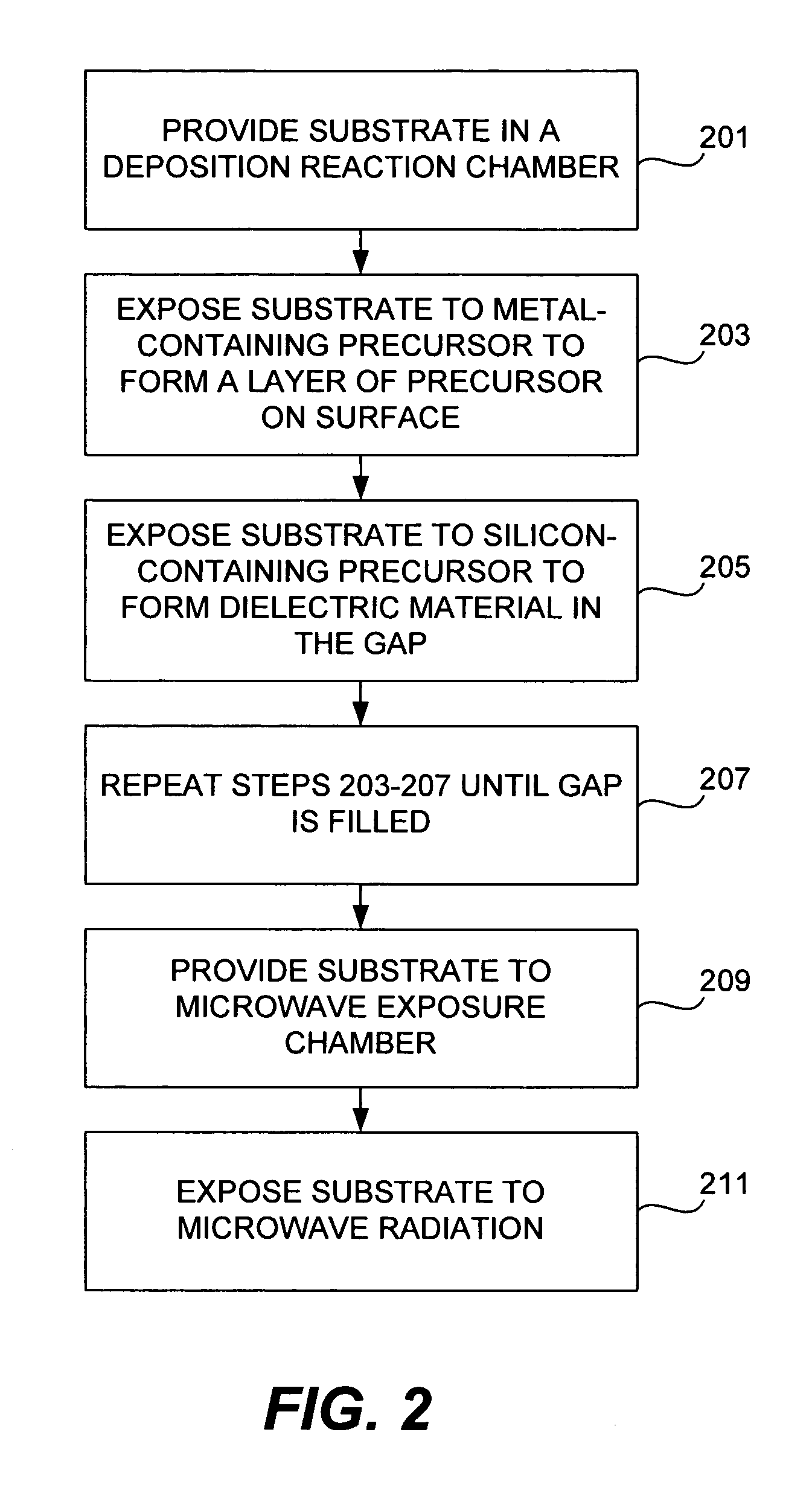

Hydroxyl bond removal and film densification method for oxide films using microwave post treatment

ActiveUS7589028B1High densityImprove film propertiesRadiation applicationsSemiconductor/solid-state device manufacturingDielectricMicrowave

Methods of forming dielectric films with increased density and improved film properties are provided. The methods involve exposing dielectric films to microwave radiation. According to various embodiments, the methods may be used to remove hydroxyl bonds, increase film density, reduce or eliminate seams and voids, and optimize film properties such as dielectric constant, refractive index and stress for particular applications. In certain embodiments, the methods are used to form conformal films deposited by a technique such as PDL. The methods may be used in applications requiring low thermal budgets.

Owner:NOVELLUS SYSTEMS

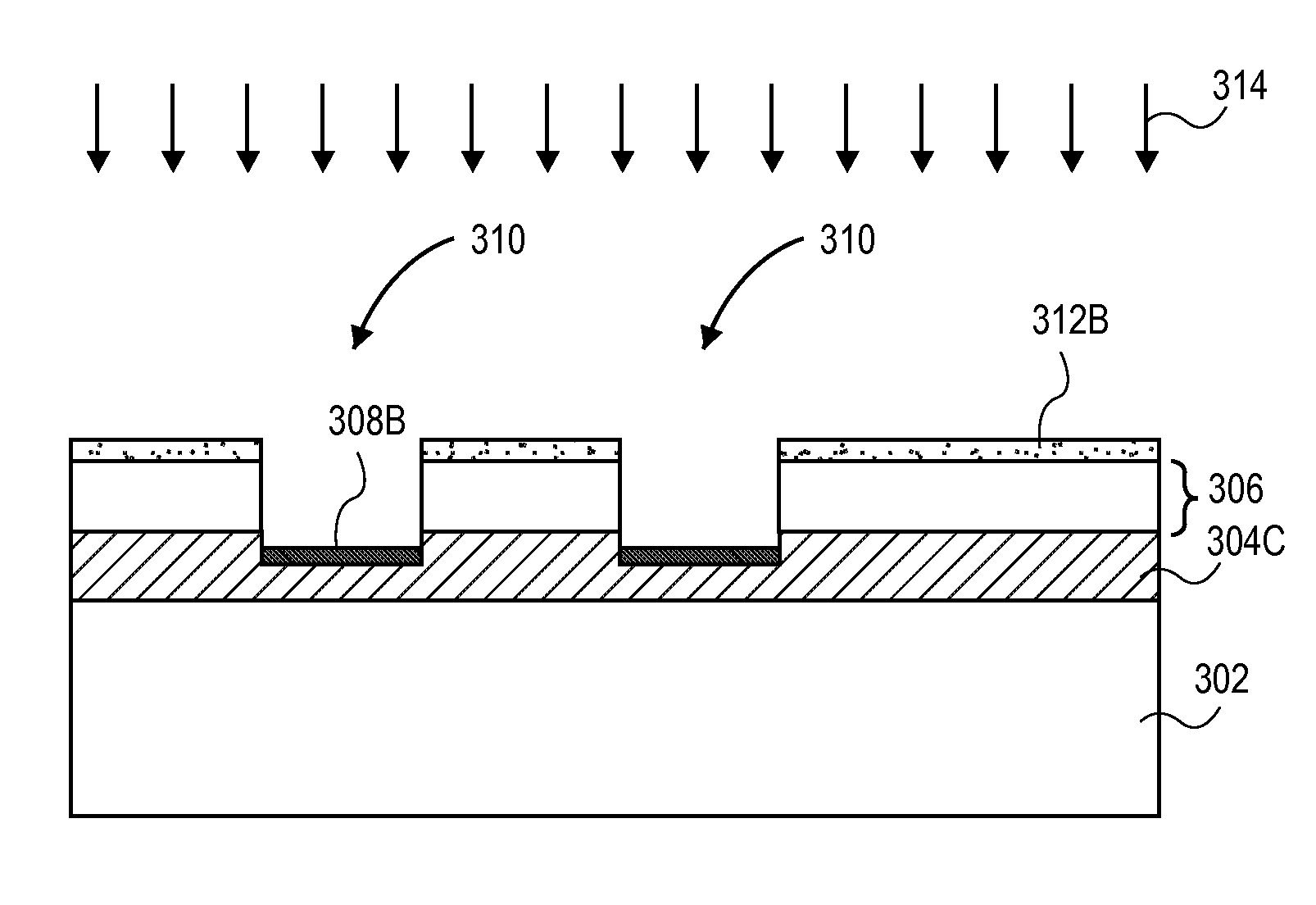

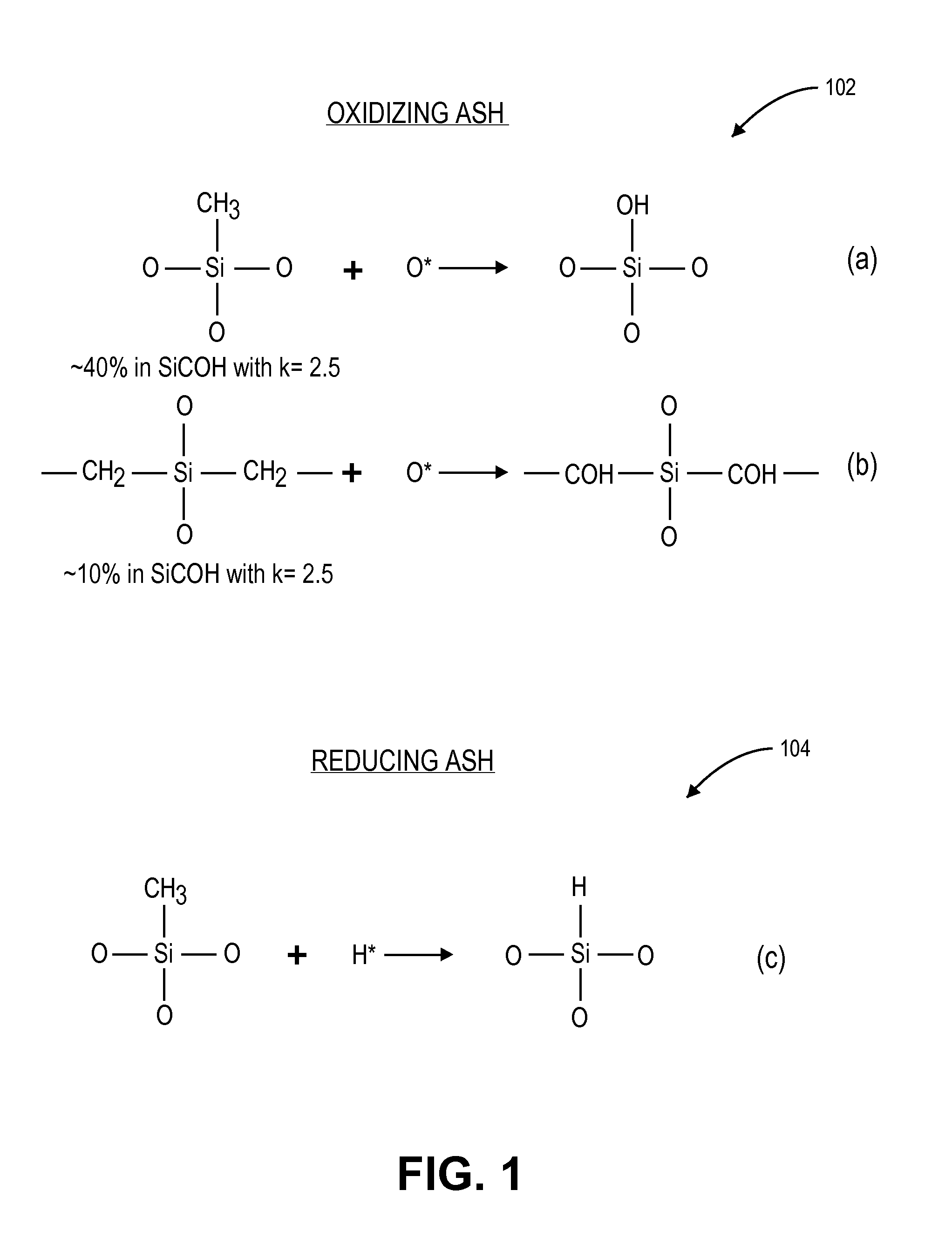

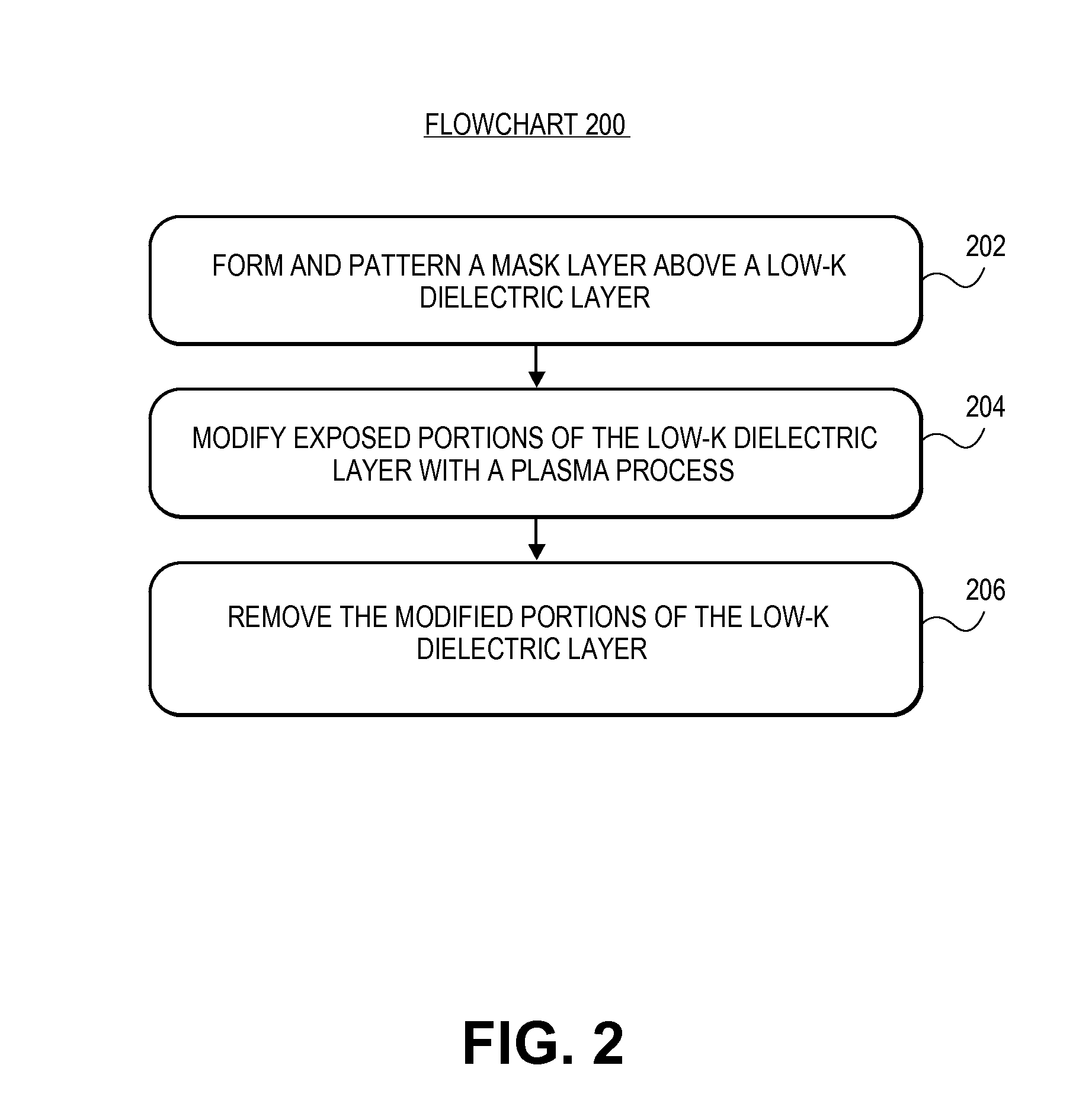

Method of patterning a low-k dielectric film

Methods of patterning low-k dielectric films are described. For example, a method includes forming and patterning a mask layer above a low-k dielectric layer, the low-k dielectric layer disposed above a substrate. Exposed portions of the low-k dielectric layer are modified with a plasma process. The modified portions of the low-k dielectric layer are removed selective to the mask layer and unmodified portions of the low-k dielectric layer.

Owner:APPLIED MATERIALS INC

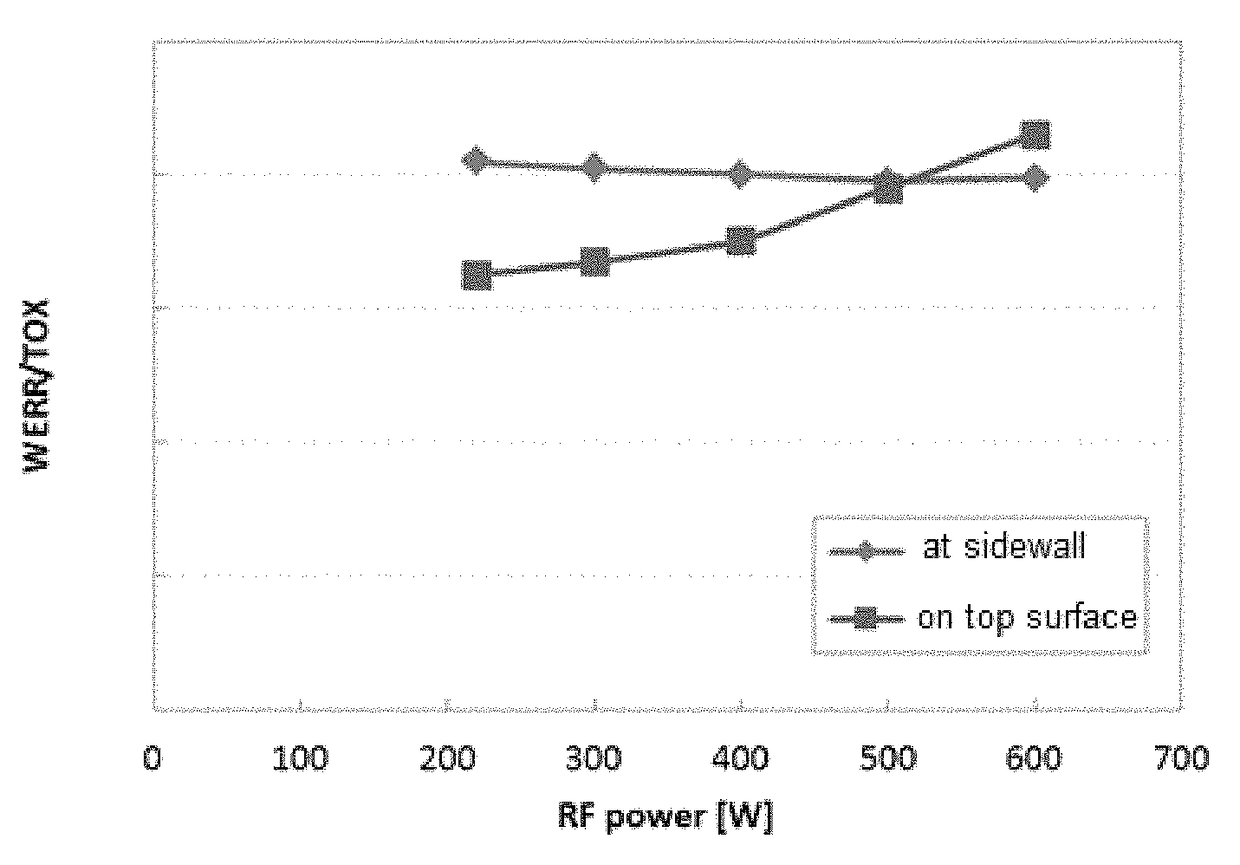

Method for depositing dielectric film in trenches by PEALD

ActiveUS9909214B2Quality improvementReduce the differenceElectric discharge tubesDecorative surface effectsDielectric membraneThin membrane

A method for depositing a dielectric film in a trench by plasma-enhanced atomic layer deposition (PEALD) includes depositing a dielectric film in a trench of a substrate by PEALD under conditions wherein the wet etch rate of the depositing film on a top surface of the substrate is substantially equivalent to or higher than the wet etch rate of the depositing film at a sidewall of the trench, wherein a precursor fed into the reaction space has —N(CH3)2 as a functional group.

Owner:ASM IP HLDG BV

Method of Depositing Dielectric Film by ALD Using Precursor Containing Silicon, Hydrocarbon, and Halogen

ActiveUS20120295449A1Accelerates the carbonization processHigh conformalitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricHalogen

A method of forming a dielectric film having at least Si—N, Si—C, or Si—B bonds on a semiconductor substrate by atomic layer deposition (ALD), includes: supplying a precursor in a pulse to adsorb the precursor on a surface of a substrate; supplying a reactant gas in a pulse over the surface without overlapping the supply of the precursor; reacting the precursor and the reactant gas on the surface; and repeating the above steps to form a dielectric film having at least Si—N, Si—C, or Si—B bonds on the substrate. The precursor has at least one Si—C or Si—N bond, at least one hydrocarbon, and at least two halogens attached to silicon in its molecule.

Owner:ASM JAPAN

Method for forming conformal nitrided, oxidized, or carbonized dielectric film by atomic layer deposition

ActiveUS10179947B2Easy to oxidizeEasily and nitridedChemical vapor deposition coatingPlasma techniqueDielectric membraneThin membrane

A method for forming a film on a patterned surface of a substrate by atomic layer deposition (ALD) processing includes: adsorbing onto a patterned surface a first precursor containing silicon or metal in its molecule; adsorbing onto the first-precursor-adsorbed surface a second precursor containing no silicon or metal in its molecule; exposing the second-precursor-adsorbed surface to an excited reactant to oxidize, nitride, or carbonize the precursors adsorbed on the surface of the substrate; and repeating the above cycle to form a film on the patterned surface of the substrate.

Owner:ASM IP HLDG BV

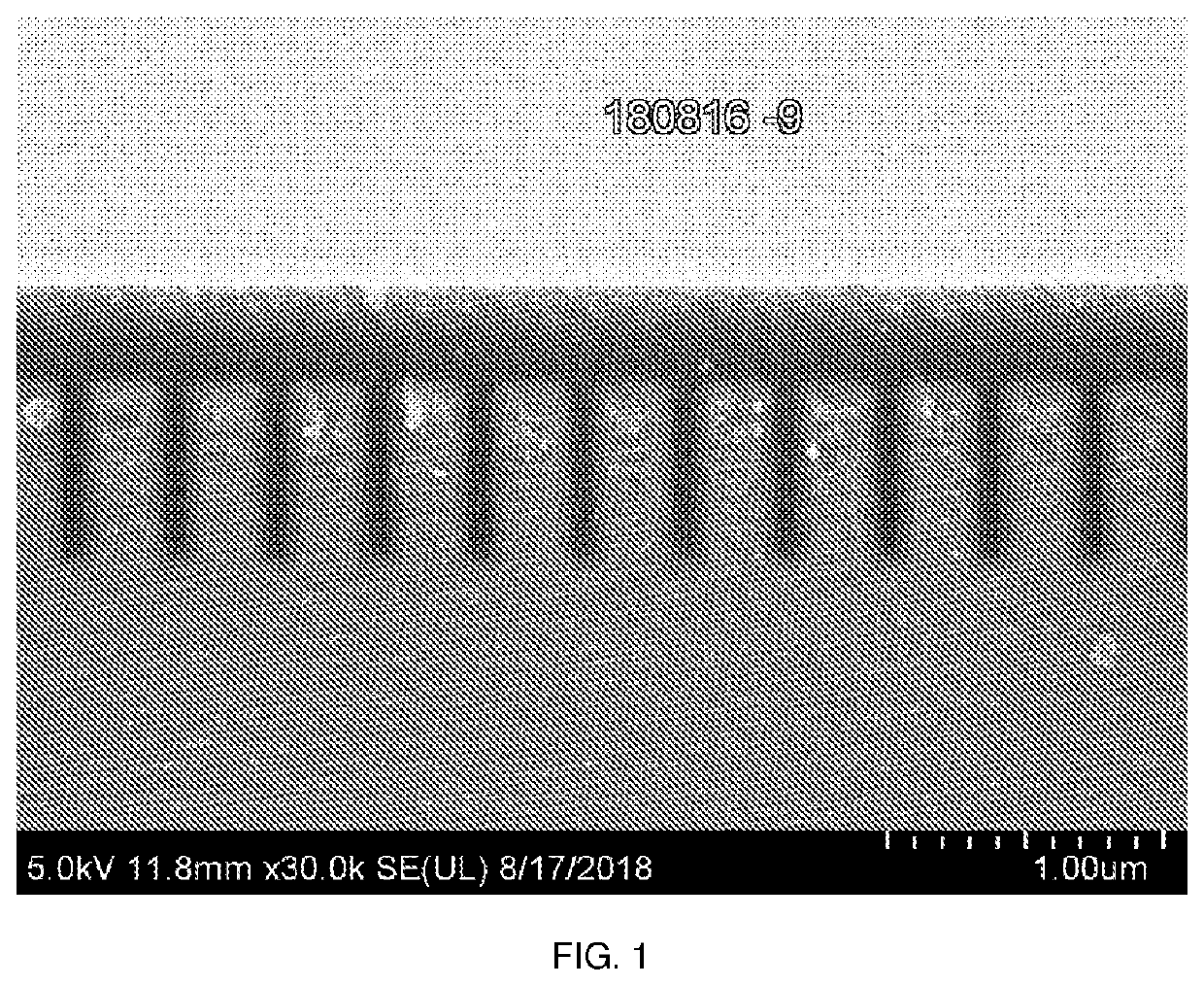

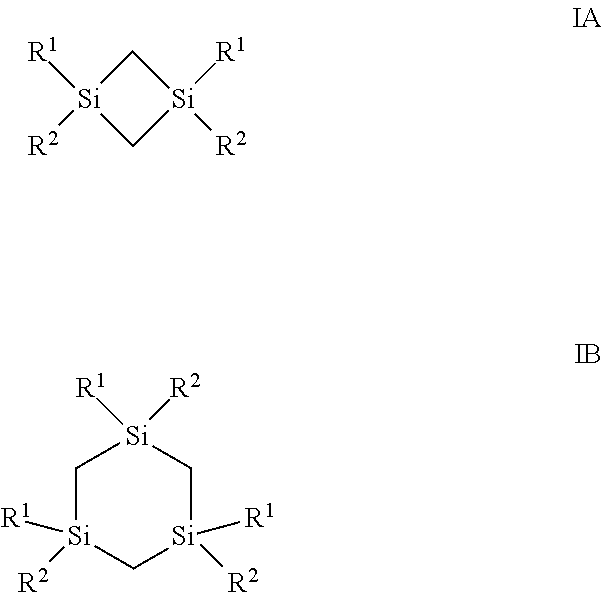

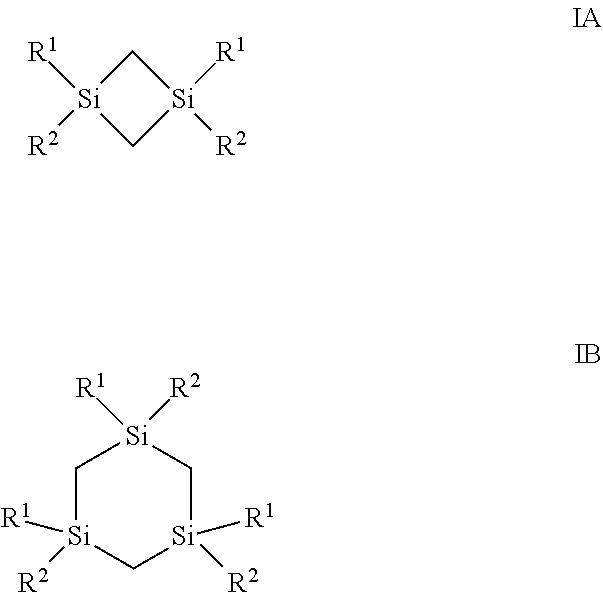

Compositions and methods for depositing silicon-containing films

PendingUS20200270749A1Group 4/14 element organic compoundsSemiconductor/solid-state device manufacturingDielectric membranePhysical chemistry

Described herein are compositions and methods of forming a dielectric film comprising silicon and carbon onto at least a surface of a substrate, the method comprising introducing into a reactor at least one silacycloalkane precursor selected from the group consisting of compounds represented by the structure of Formula IA and compounds represented by the structure of Formula IB: as defined herein.

Owner:VERSUM MATERIALS US LLC

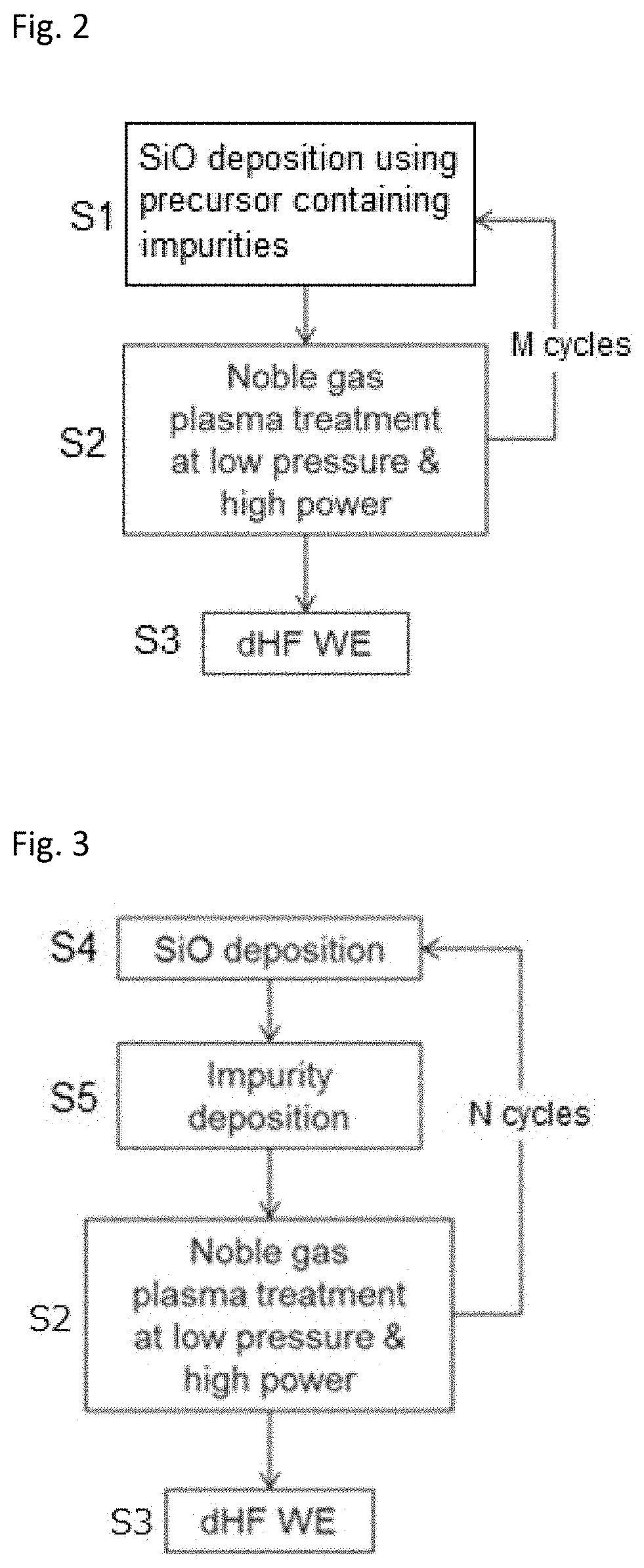

Method of topology-selective film formation of silicon oxide

ActiveUS20200251328A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric membraneSilicon oxide

A method for forming a dielectric film containing a Si—O bond a trench formed in an upper surface of a substrate, includes: designing a topology of a final dielectric film containing a Si—O bond formed in the trench by preselecting a target portion to be selectively removed relative to a non-target portion of an initial dielectric film resulting in the final dielectric film; conformally depositing the initial dielectric film on the upper surface and in the trench; and relatively increasing an amount of impurities contained in the target portion of the initial dielectric film relative to an amount of impurities contained in the non-target portion of the initial dielectric film to obtain a treated dielectric film, thereby giving the target portion and the non-target portion different chemical resistance properties when subjected to etching.

Owner:ASM IP HLDG BV

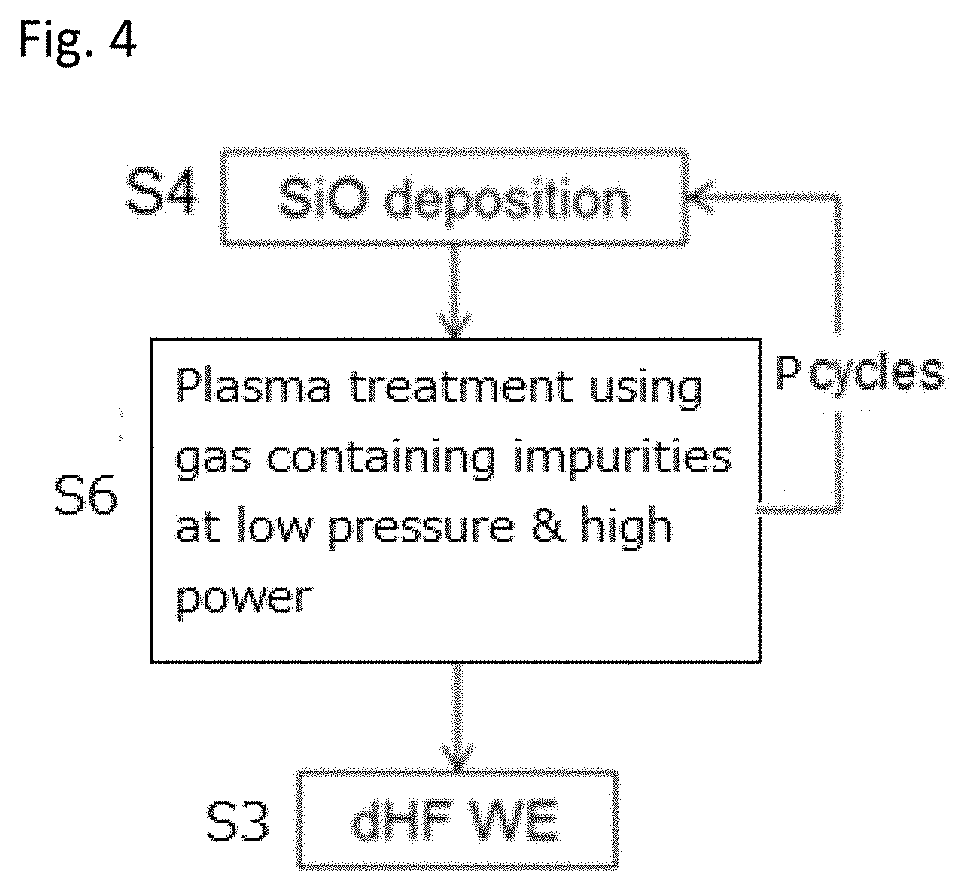

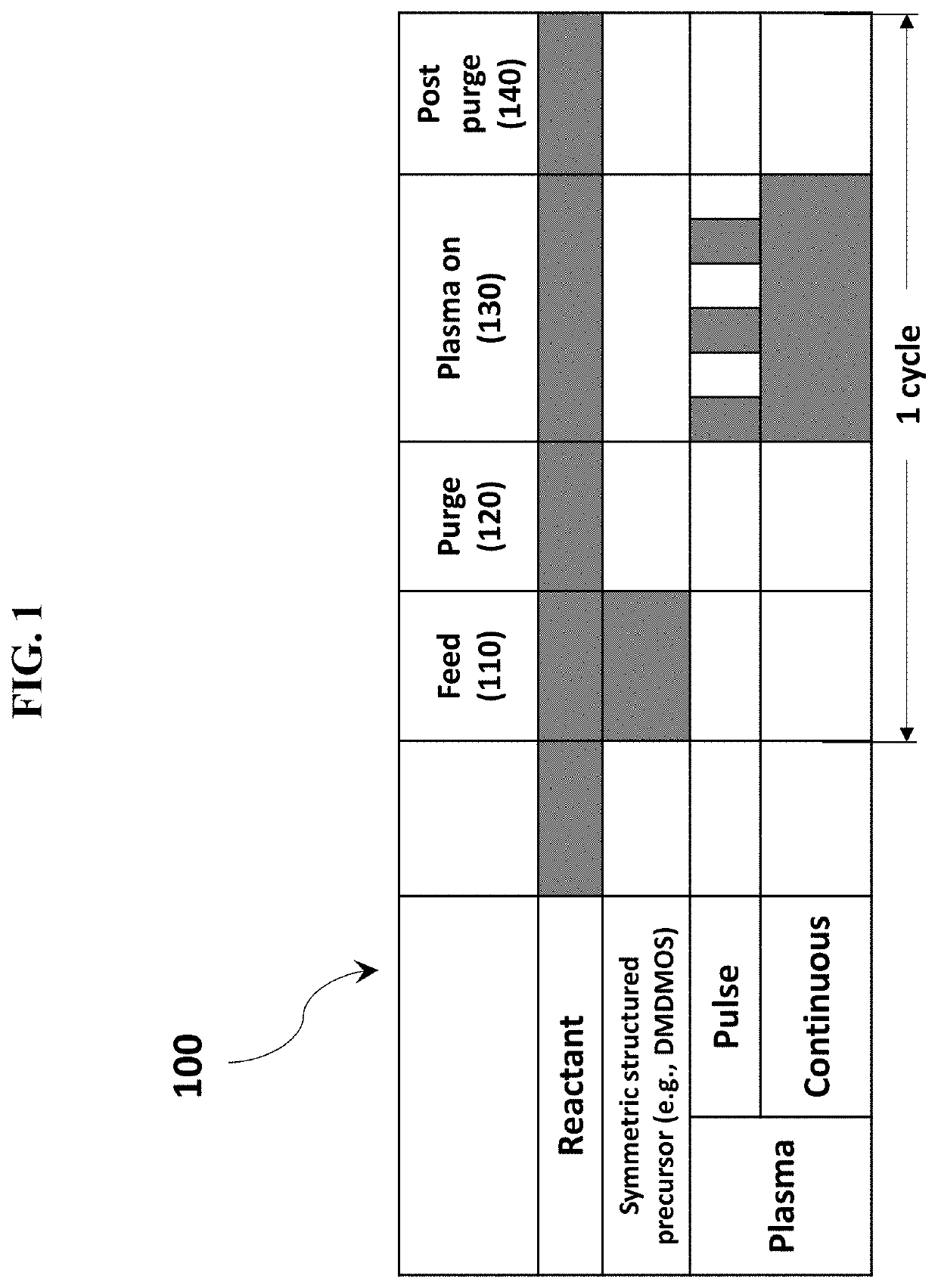

Structures including dielectric layers and methods of forming same

PendingUS20210066075A1Readily apparentSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric membraneDeposition process

Methods of forming structures having dielectric films with improved properties, such as, for example, improved elastic modulus and / or dielectric constant are disclosed. Exemplary films can be formed using a cyclic deposition process. Exemplary methods use activated species to cleave (e.g., symmetric-structured) precursor molecules to form the high quality dielectric layers.

Owner:ASM IP HLDG BV

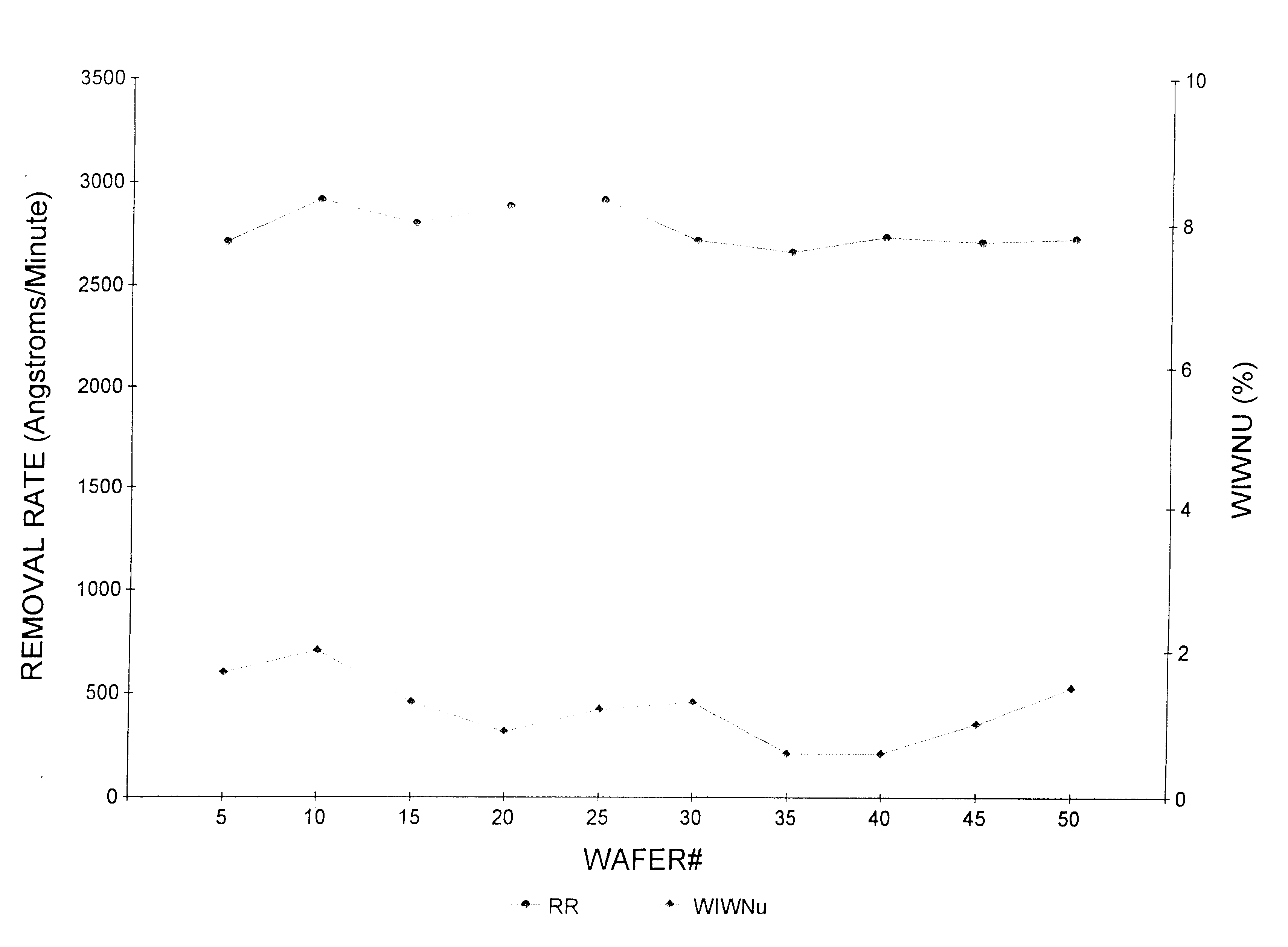

Planarization compositions and methods for removing interlayer dielectric films

InactiveUS6322600B1Improve planarization qualityQuality improvementPigmenting treatmentOther chemical processesThinningDielectric thin films

A planarization composition is set forth for chemical mechanical planarization of dielectric layers for semiconductor manufacture. The composition comprises spherical silica particles having an average diameter of from 30 nm to about 400 nm, and a narrow range of particle sizes, wherein about 90% of the particles is within 20% of the average particle diameter. The composition includes a liquid carrier comprising up to about 9% alcohol and an amine hydroxide in the amount of about 0.2 to about 9% by weight. The pH of the composition is in the range of about 9 to about 11.5, and the remainder of the solution is water. The composition has low amounts of metal ions, and the composition is used for thinning, polishing and planarizing interlayer dielectric thin films, shallow trench isolation structures, and isolation of gate structures. The invention also comprises methods for using the planarization composition in the manufacture of semiconductor devices.

Owner:ADVANCED TECH MATERIALS INC

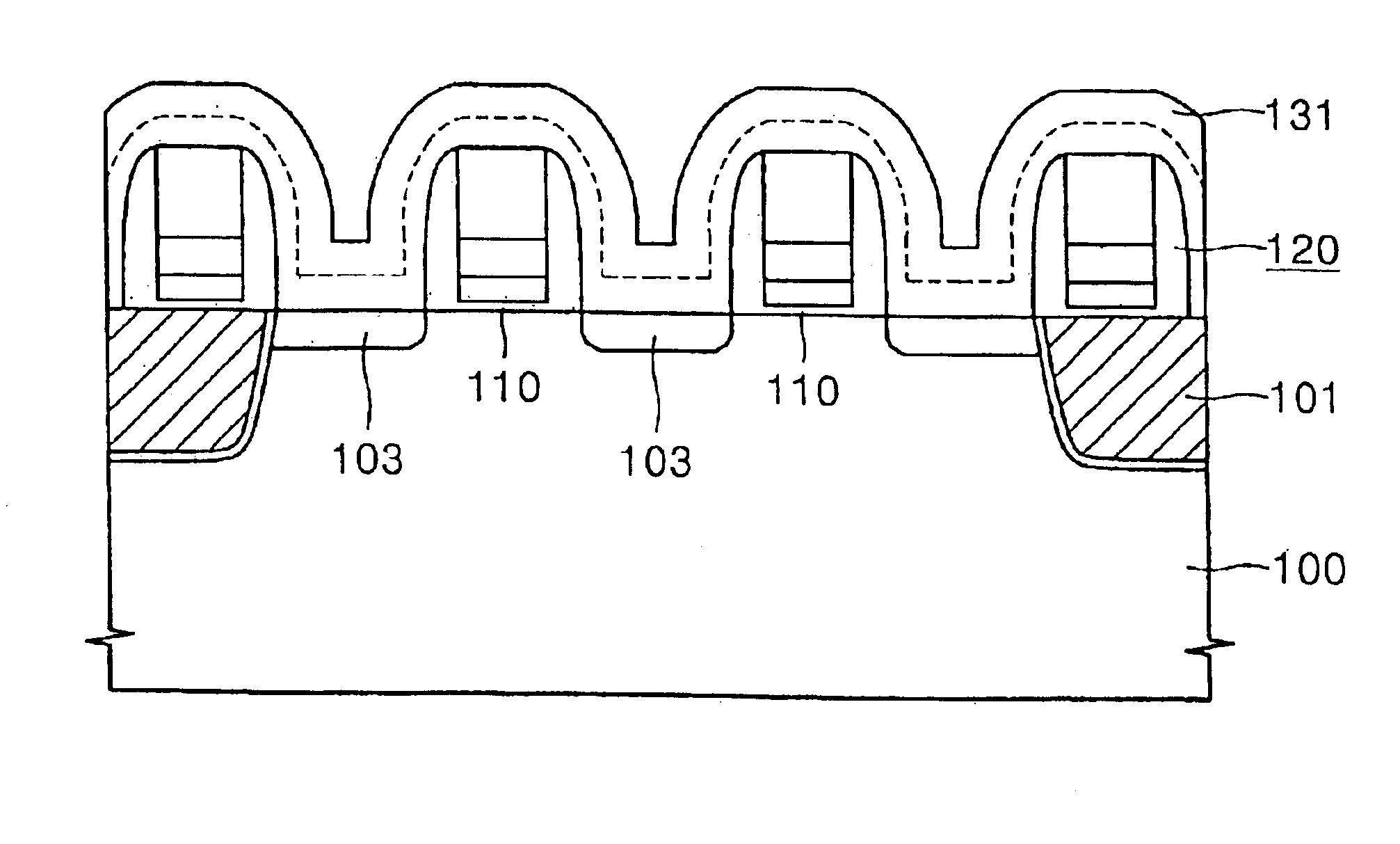

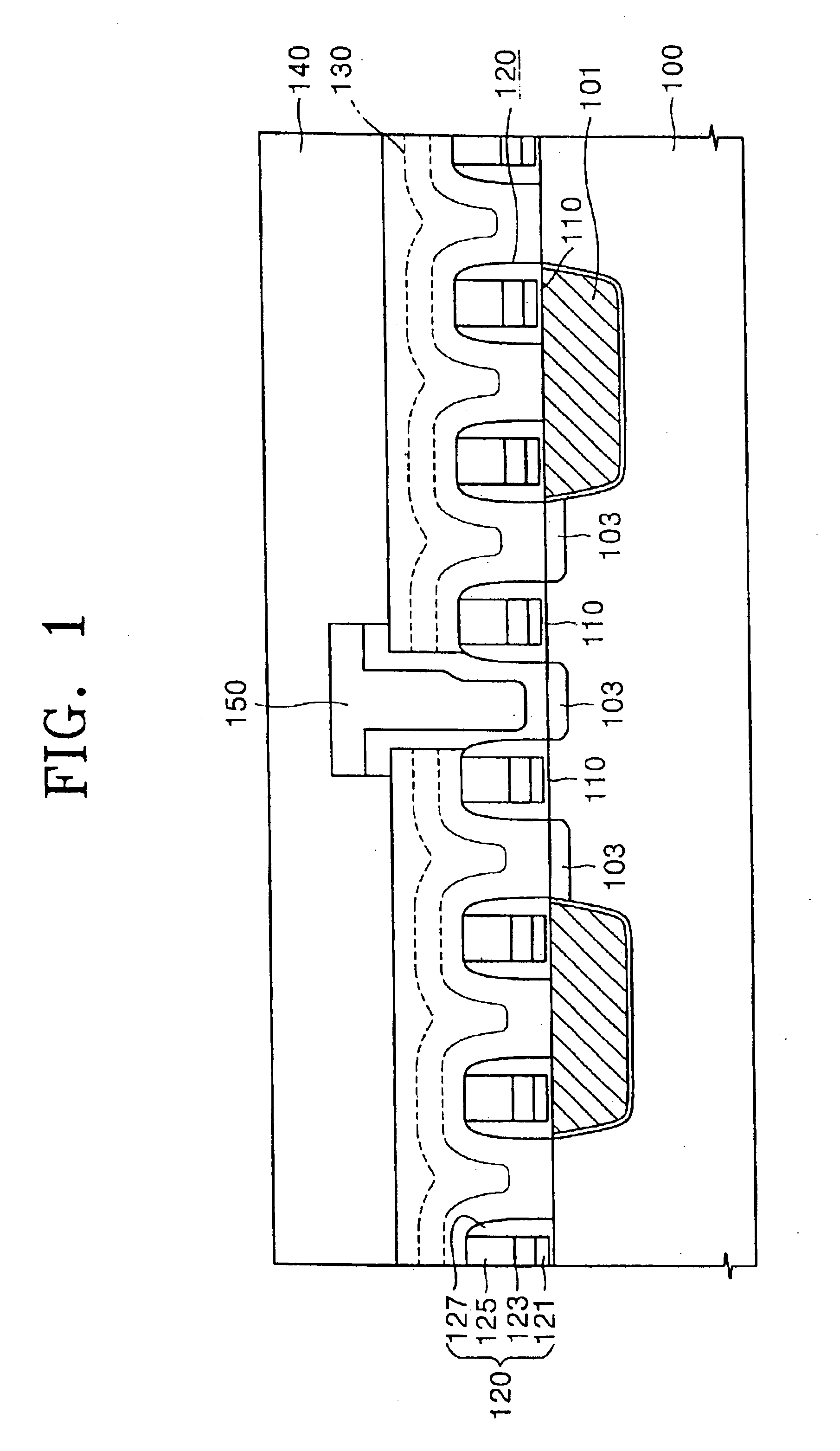

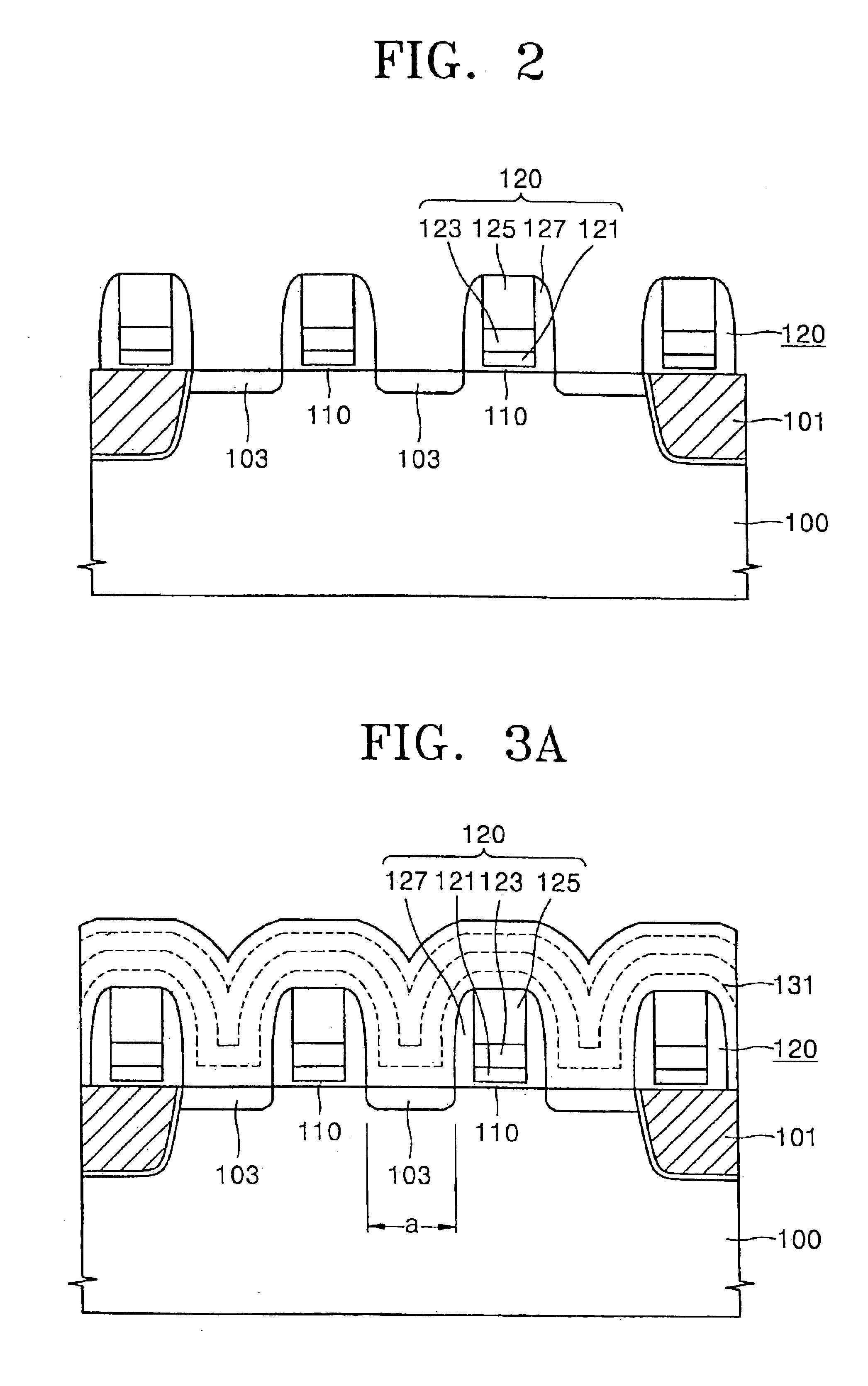

Method for fabricating semiconductor device and forming interlayer dielectric film using high-density plasma

InactiveUS6867141B2Simple processGood step coverageTransistorSemiconductor/solid-state device detailsDielectricHigh density

A method for fabricating a semiconductor device and forming an insulating film used therein, includes forming an isolation insulating film on a semiconductor wafer and forming gates, separated by gaps having a predetermined distance, on an active region. Next, a first interlayer dielectric film is deposited to a predetermined thickness on the semiconductor wafer having the gates, so that the gaps between the gates are not completely filled. Then, a sputtering etch is performed entirely on a surface of the first interlayer dielectric film. Thereafter, the first interlayer dielectric film is partially removed through isotropic etching. Next, a second interlayer dielectric film is deposited on the first interlayer dielectric film so that the gaps between the gates are completely filled. According to the above method, a gap between gate patterns can be completely filled without a void by performing sputtering etch on interlayer dielectric films formed on gate patterns, thereby enhancing the reliability of a semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

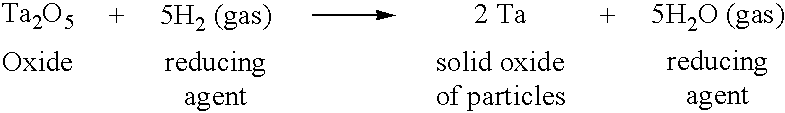

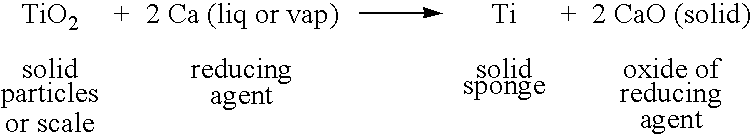

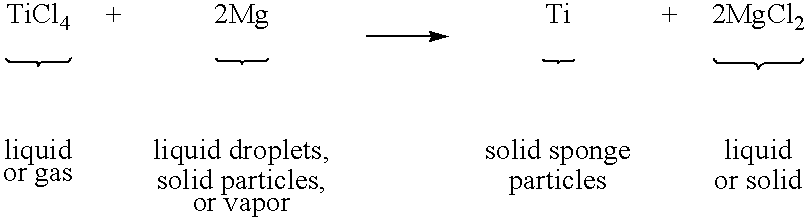

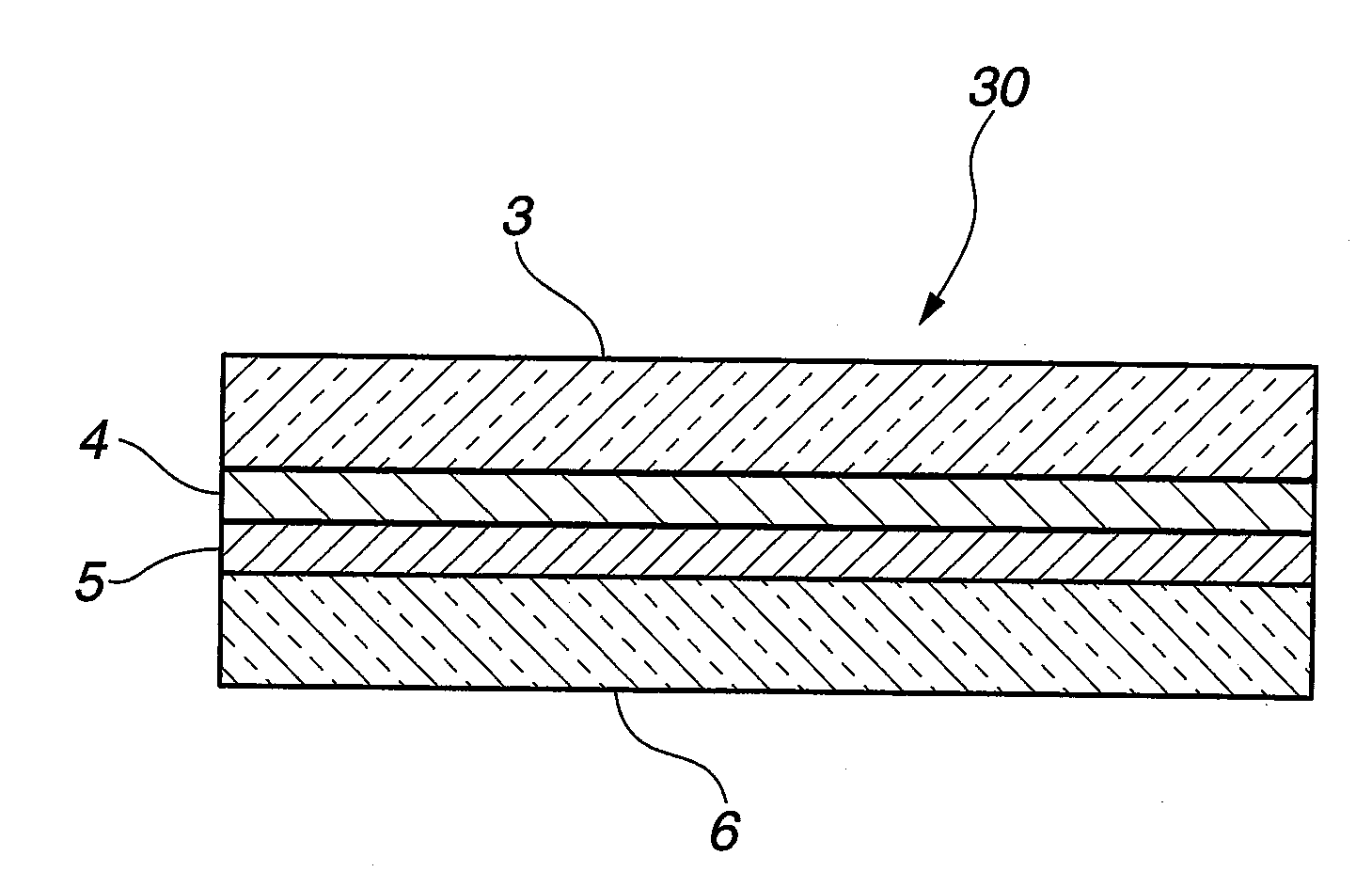

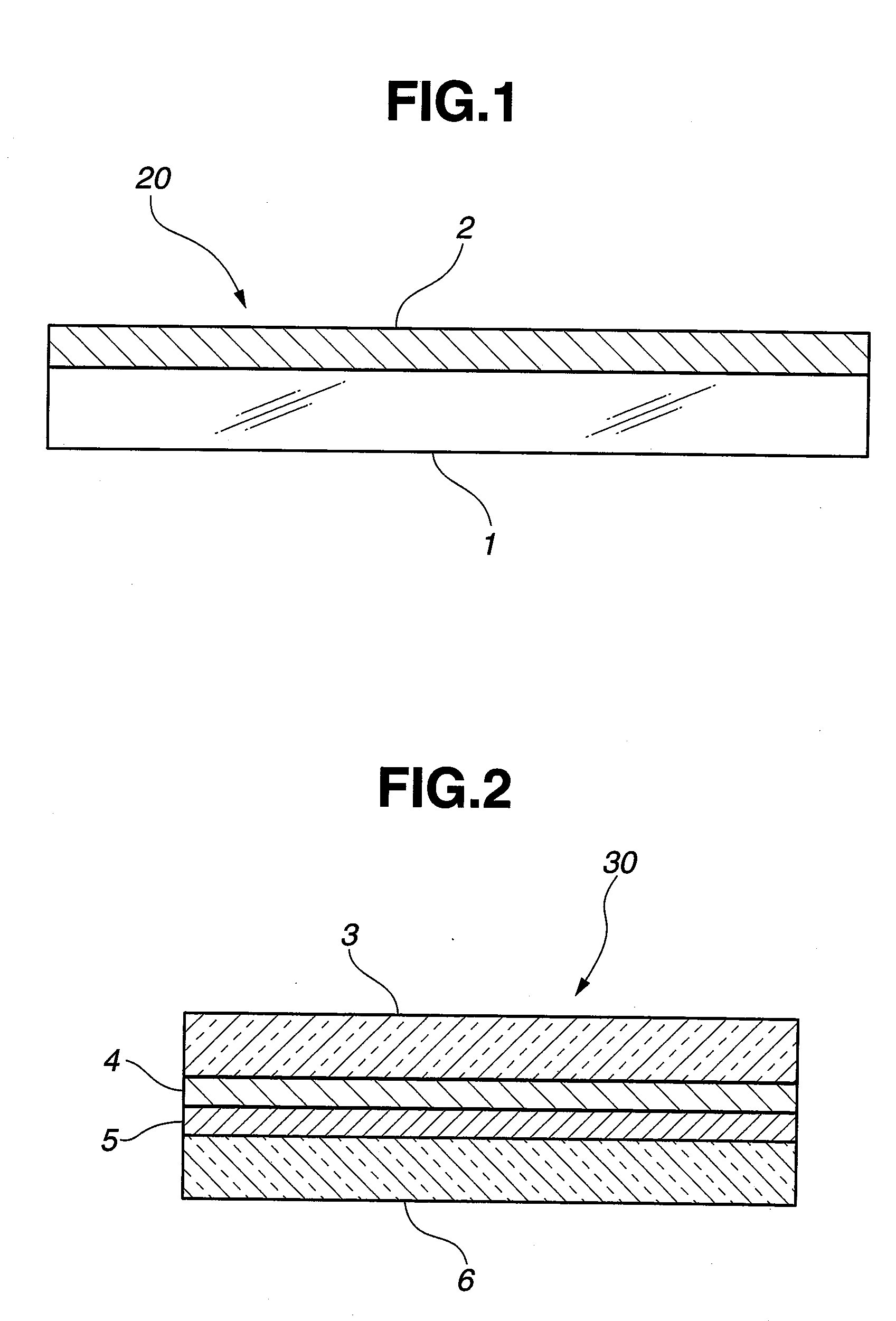

High power capacitors from thin layers of metal powder or metal sponge particles

InactiveUS20030169560A1Increase surface areaSmall sizeFixed capacitor dielectricSolid-state devicesDielectric strengthHigh surface area

An anode (14, 208, 410) and / or cathode (12, 212, 420) of a capacitor has a large surface area. The high surface area of the anode is provided by forming the anode from a thin, electrically conductive layer (16) formed from metal particles (18) or an electrically conductive metallic sponge (416). These materials provide a porous structure with a large surface area of high accessibility. The particles are preferably directional or non-directional sponge particles of a metal, such as titanium. The conductive layer hasa dielectric film (36, 236, 414) on its surface, formed by anodizing the particle surfaces. The dielectric film has a combination of high dielectric constant and high dielectric strength. The cathode (12, 212, 420) of the capacitor is either a conventional solid material or, more preferably, has a large surface provided by forming the surface from a sponge or particles analogously to the anode. The high dielectric strengths obtainable from the capacitor allow for extreme miniaturization, making the capacitor particularly suited for integrated circuit applications.

Owner:TITANIUM POWER TECH

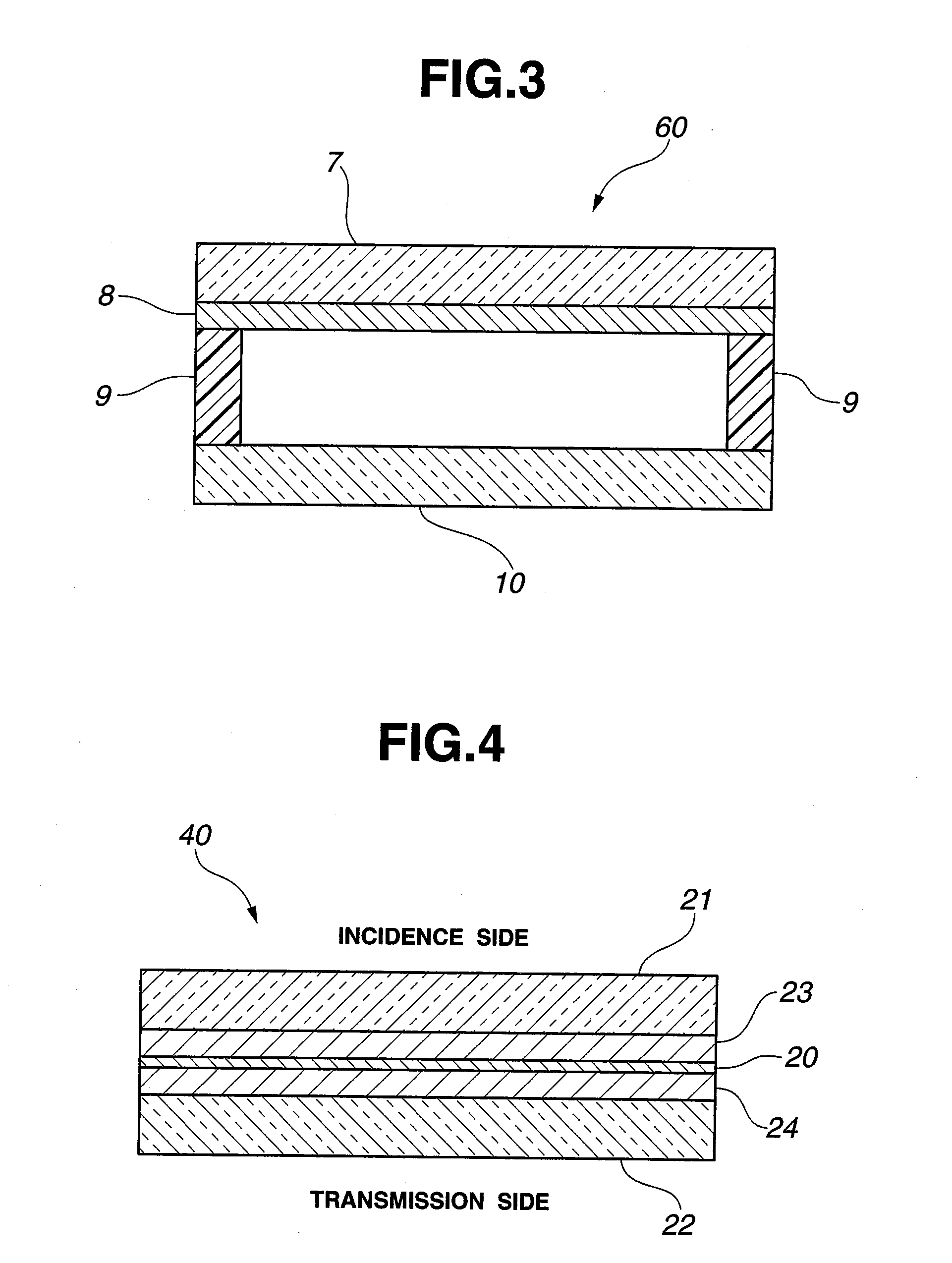

Near Infrared Ray Reflective Substrate And Near Infrared Ray Reflective Laminated Glass Employing That Substrate, Near Infrared Ray Reflective Double Layer Glass

InactiveUS20090237782A1High visible lightImprove insulation effectMirrorsOptical filtersInfraredRefractive index

In a near-infrared reflective substrate prepared by forming on a transparent substrate a near-infrared reflective film prepared by alternate deposition of low-refractive-index dielectric films and high-refractive-index dielectric films, there is provided a near-infrared reflective substrate characterized in that the transparent substrate is a plate glass or polymer resin sheet, that it is 70% or greater in visible light transmittance defined in JIS R3106-1998, and that it has a maximum value of reflection that exceeds 50% in a wavelength region of 900 nm to 1400 nm.

Owner:CENT GLASS CO LTD

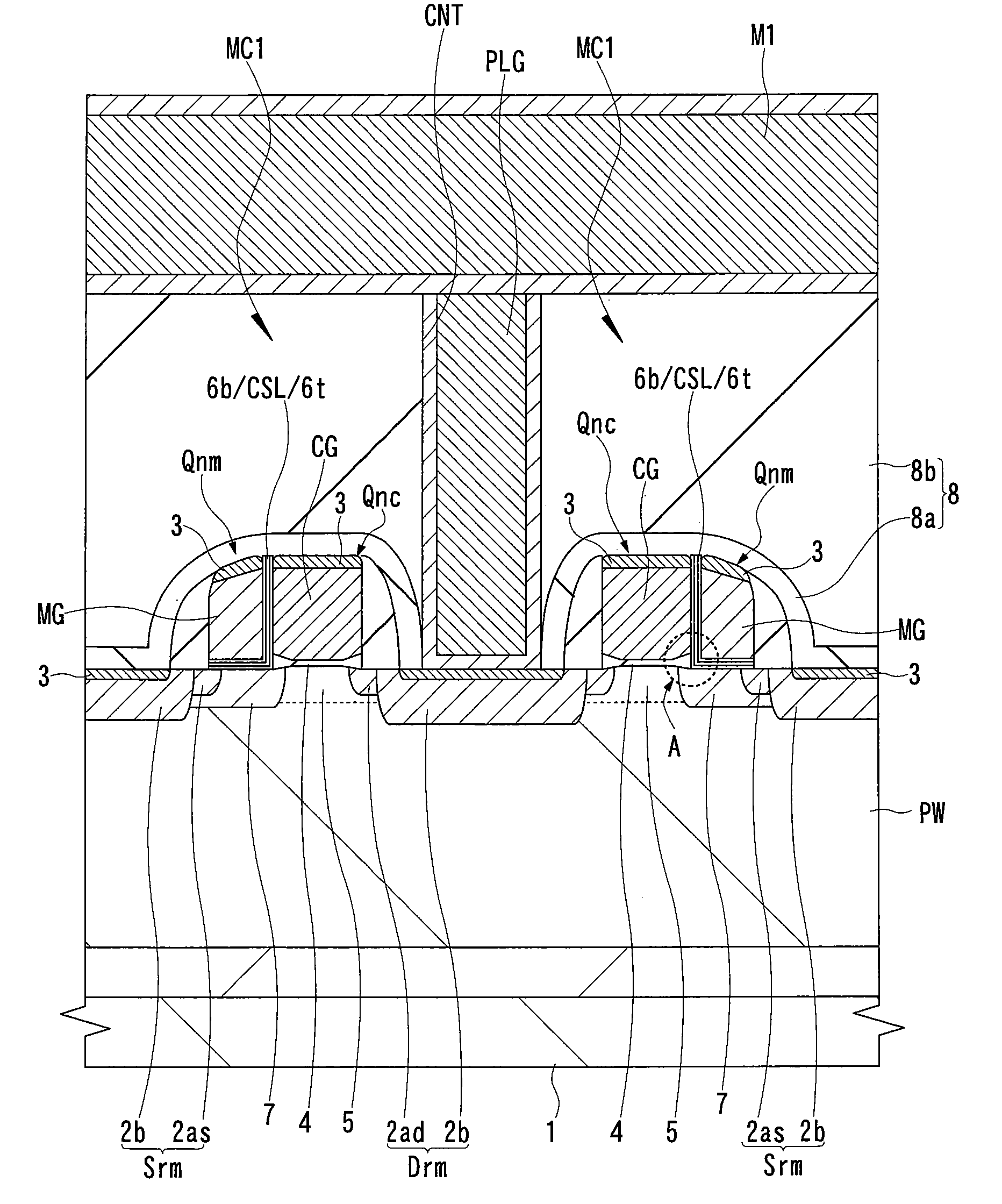

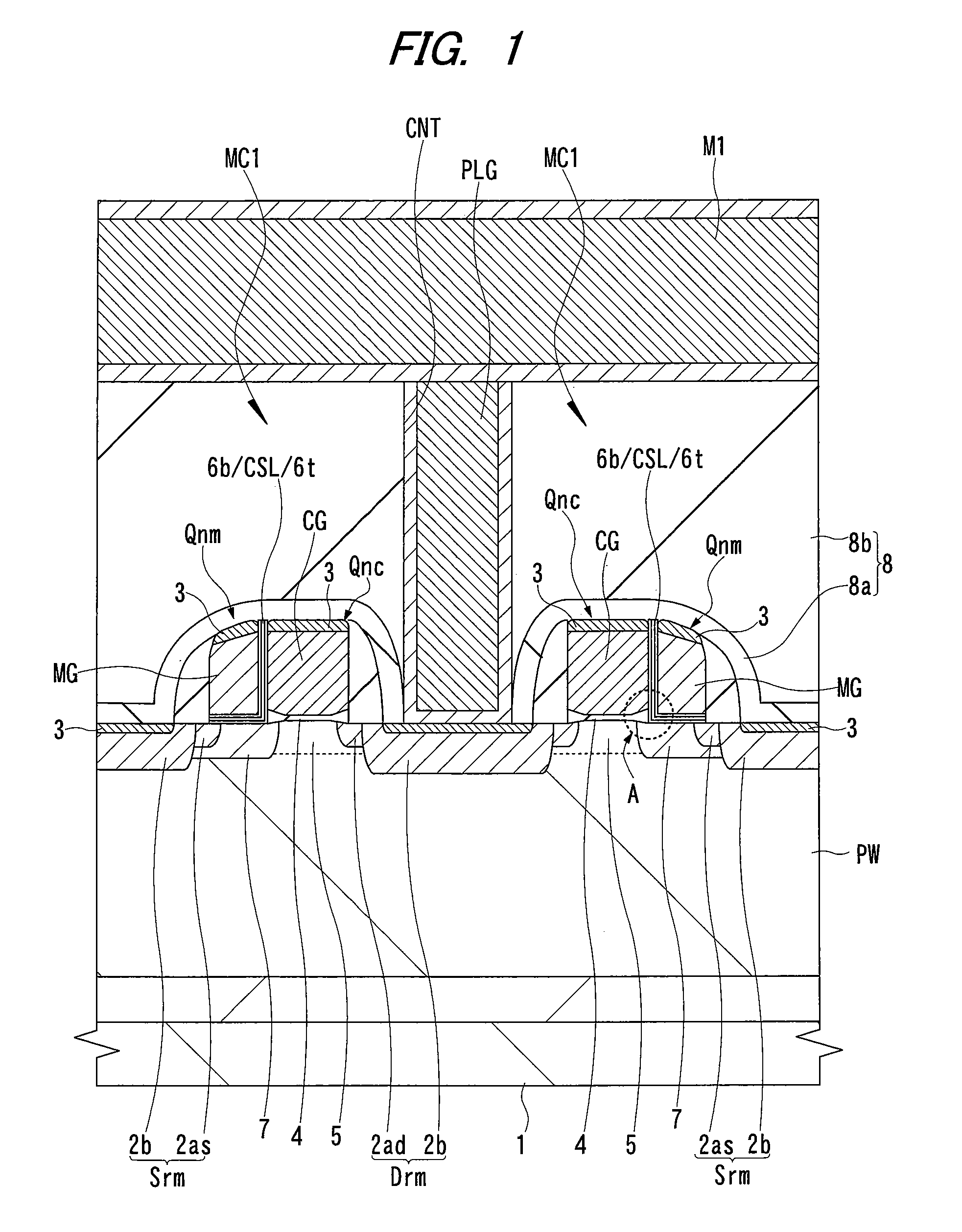

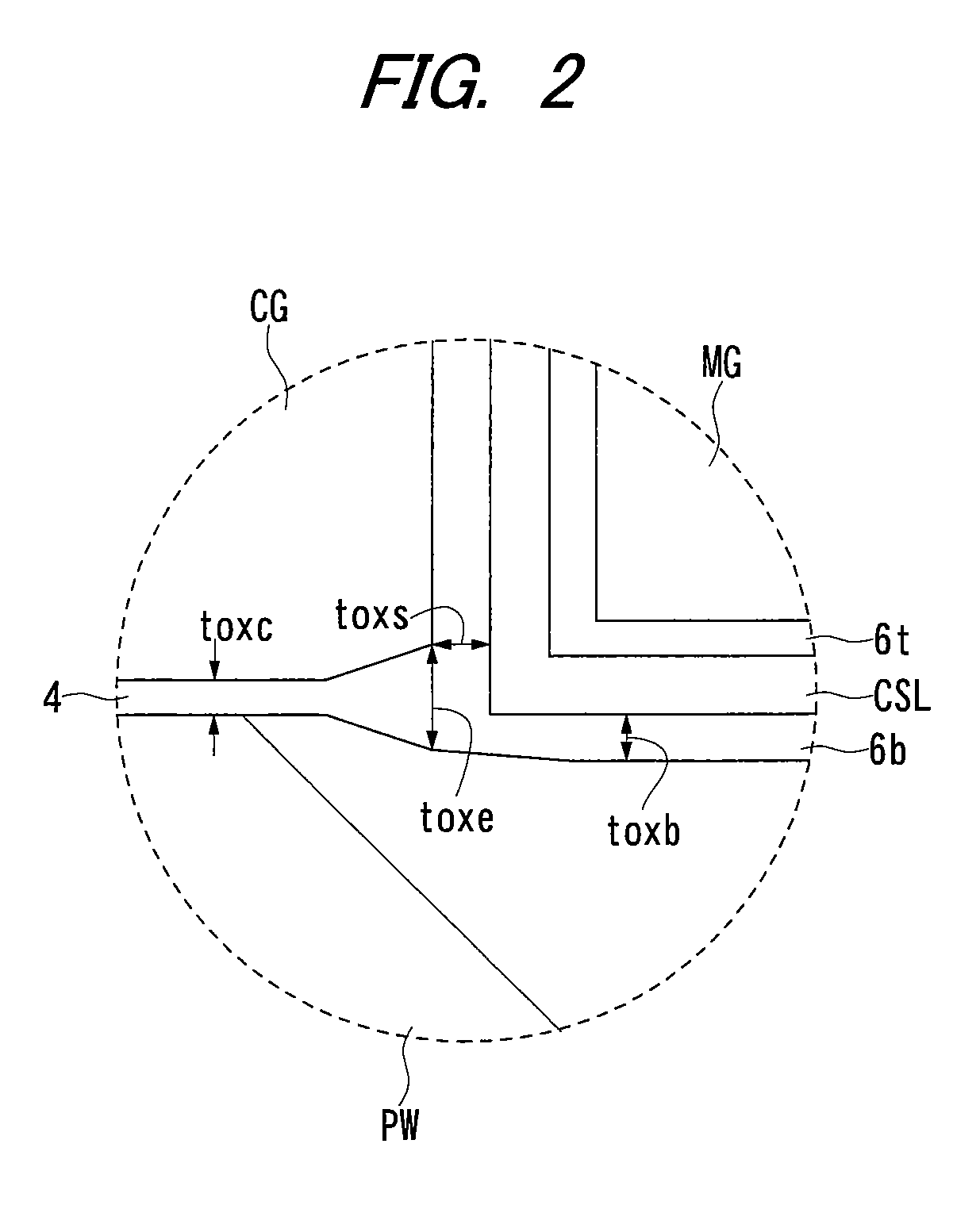

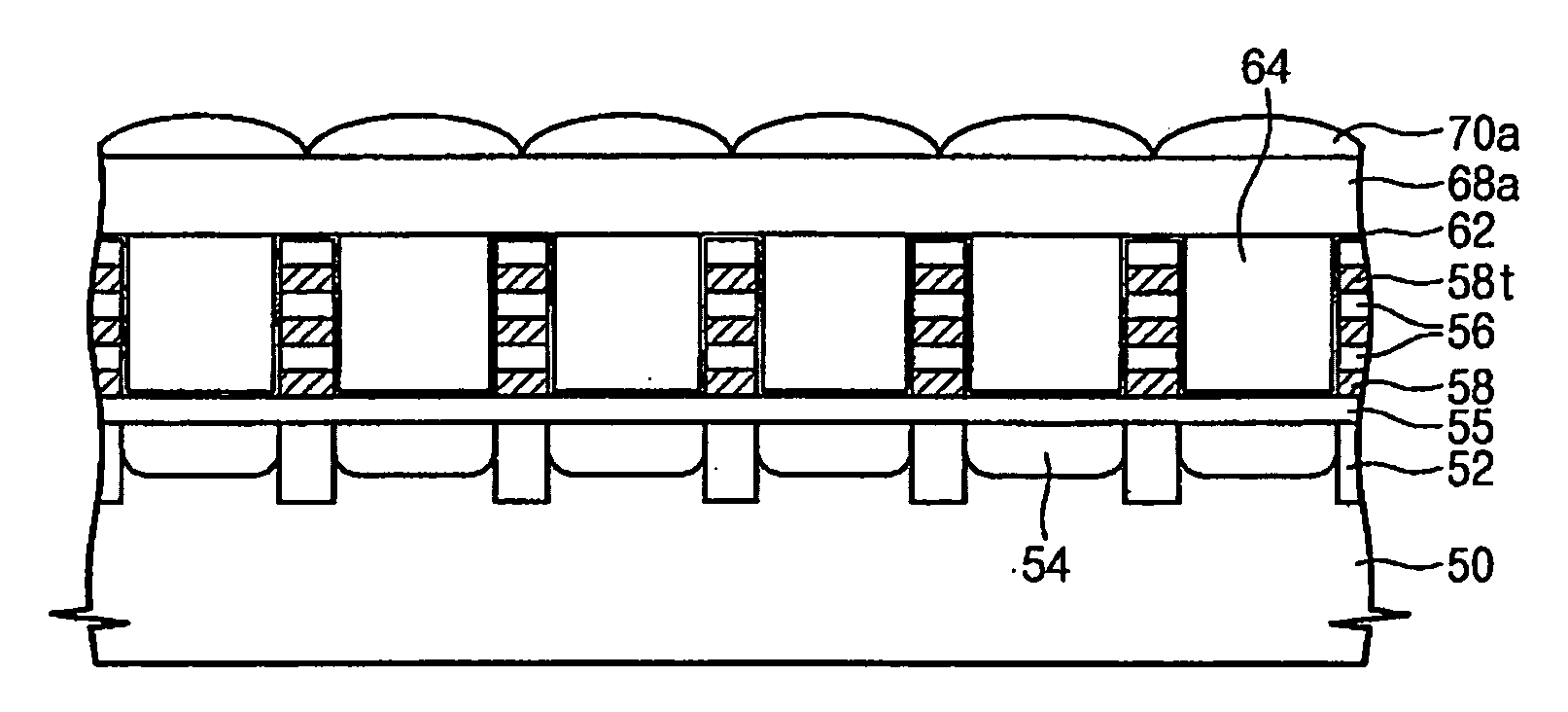

Semiconductor memory device and method of manufacturing the same

InactiveUS20090050956A1Total current dropReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

In a memory cell including an nMIS for memory formed on the sides of an nMIS for select and an nMIS for select via dielectric films and a charge storage layer, the thickness of a gate dielectric under the gate longitudinal direction end of a select gate electrode is formed thicker than that of the gate dielectric under the gate longitudinal direction center and the thickness of the lower layer dielectric film that is positioned between the select gate electrode and the charge storage layer and is nearest to a semiconductor substrate is formed 1.5 times or below of the thickness of the lower layer dielectric film positioned between the semiconductor substrate and the charge storage layer.

Owner:RENESAS TECH CORP

Shippable heat-treatable sputter coated article and zinc cathode sputtering target containing low amounts of tin

InactiveUS6899953B1Improve chemical durabilityReduced hazeVacuum evaporation coatingSputtering coatingMetal PrimerLow emissivity

Tin is added to a zinc cathode target to enhance the sputter efficiency of the target. Films deposited using the cathode, e.g., greater than zero but less than 10 weight percent tin and greater than 90 but less than 100 weight percent zinc improve the chemical durability of a high transmittance, low emissivity coating stack over coating stacks having zinc oxides without tin oxide. High transmittance, low emissivity coating stacks are heated with the heated coating having reduced haze by selecting the thickness of metal primer layer between an infrared reflective film, e.g. a silver film and a dielectric film, e.g., a 52-48 zinc stannate, zinc oxide, tin oxide film or a zinc oxide film. Also disclosed are enhancing films that lower the resistivity of silver films deposited thereon and improve chemical durability of the coating stack.

Owner:VITRO FLAT GLASS LLC

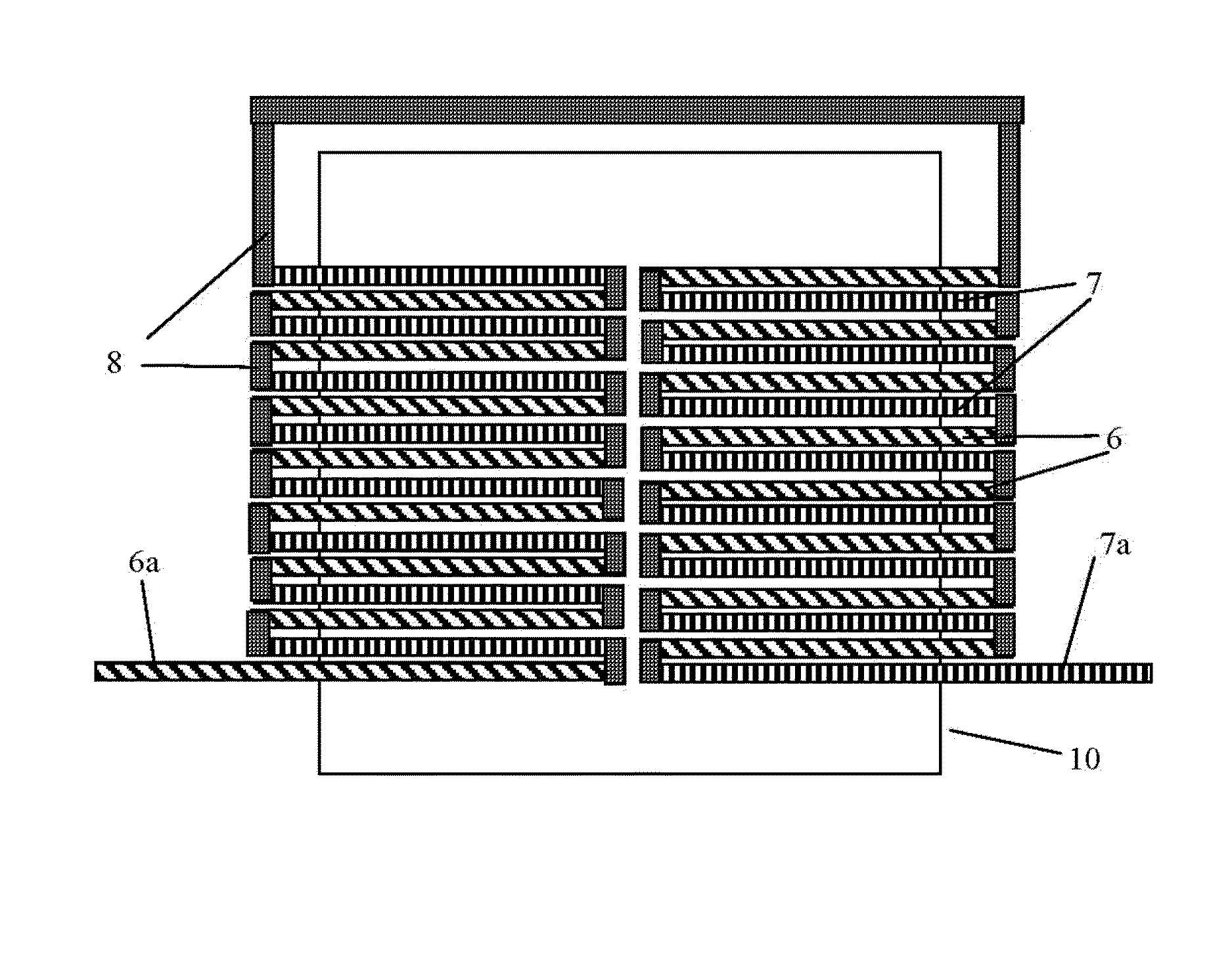

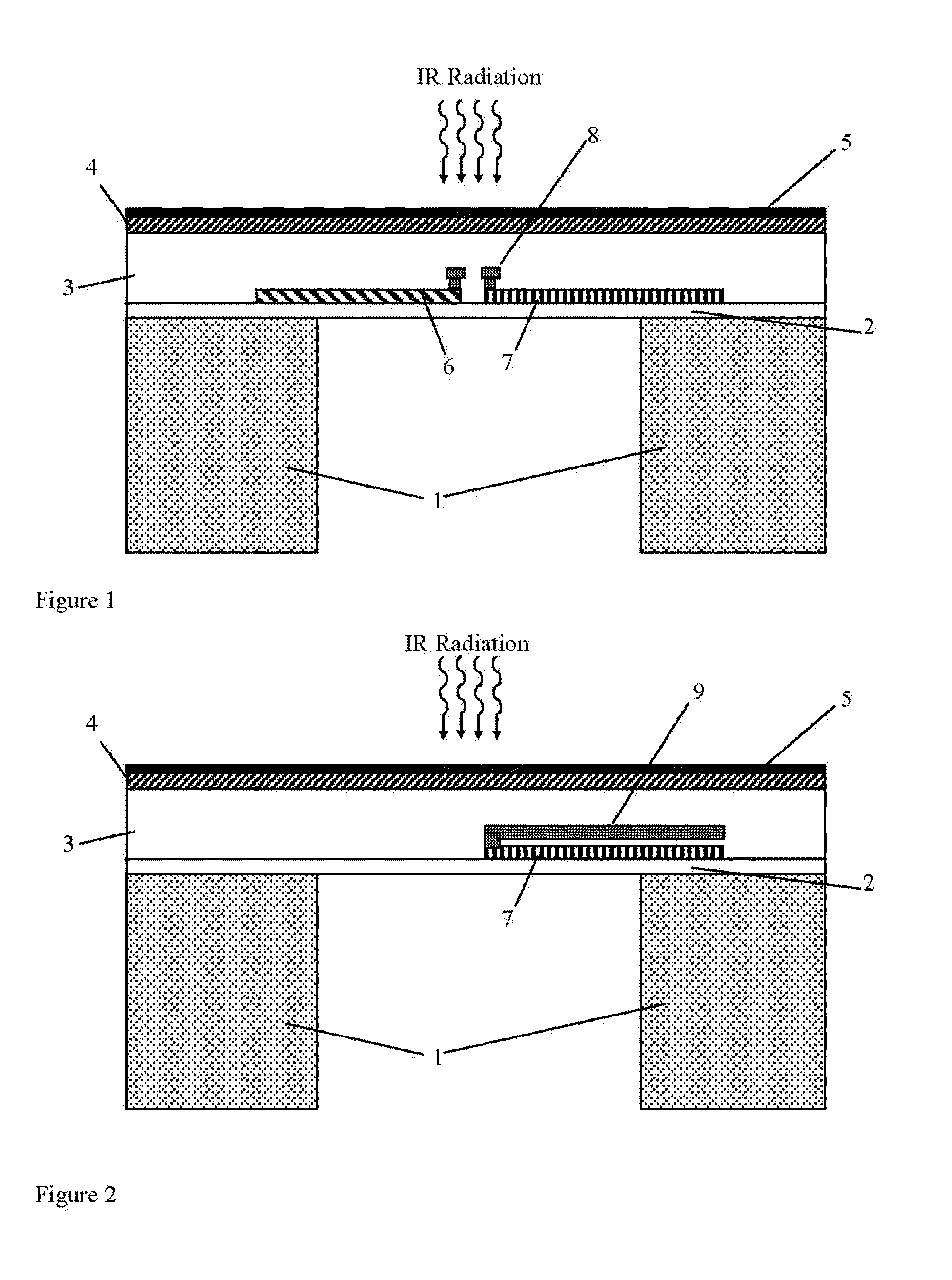

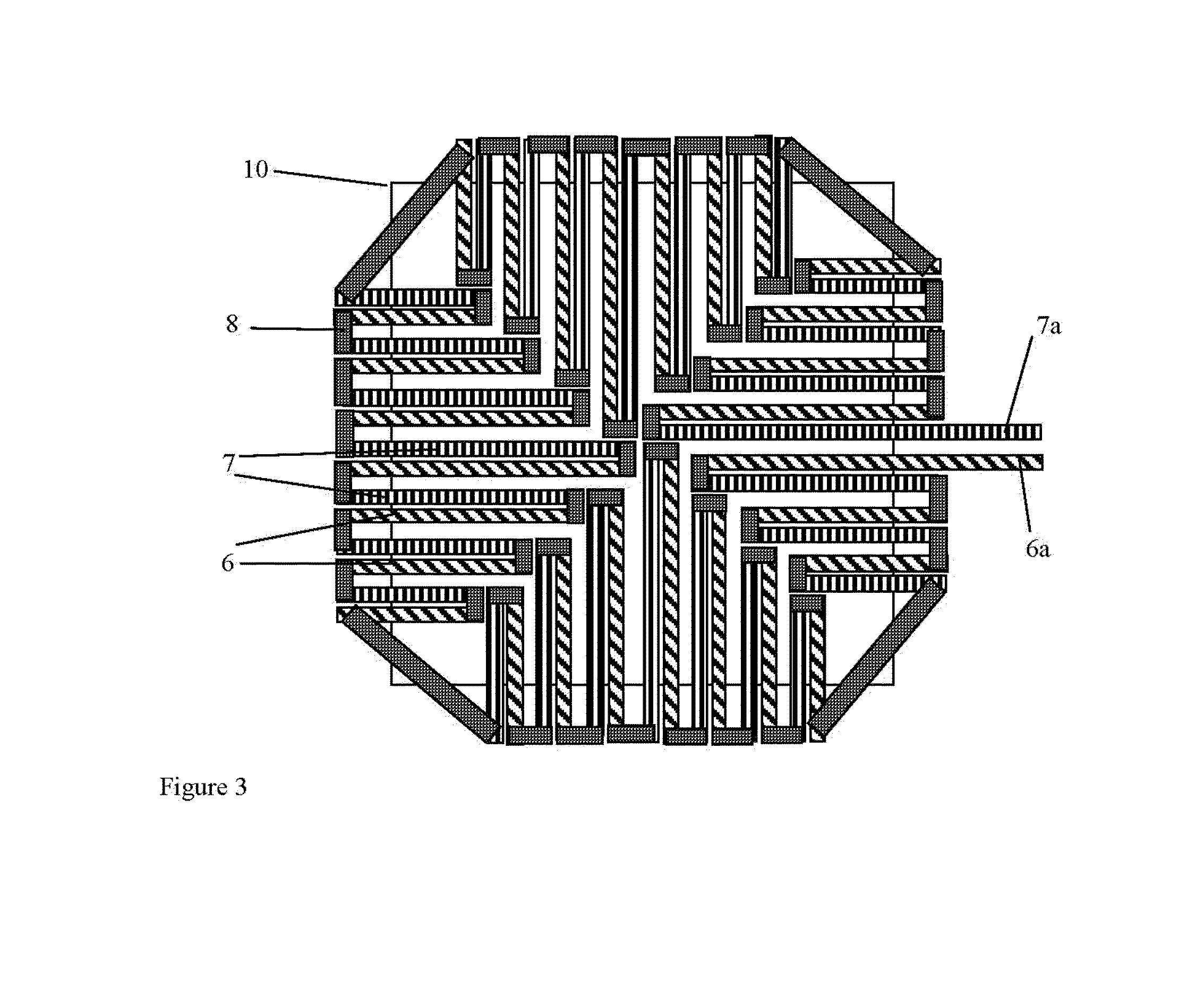

IR detector

ActiveUS8552380B1Improve performanceHigh emissivitySolid-state devicesMaterial analysis by optical meansDielectric membraneThermopile

An IR detector in the form of a thermopile including one or more thermocouples on a dielectric membrane supported by a silicon substrate. Each thermocouple is composed of two materials, at least one of which is p-doped or n-doped single crystal silicon. The device is formed in an SOI process. The device is advantageous as the use of single crystal silicon reduces the noise in the output signal, allows higher reproducibility of the geometrical and physical properties of the layer and in addition, the use of an SOI process allows a temperature sensor, as well as circuitry to be fabricated on the same chip. The detector can also have an IR filter wafer bonded onto it and / or have arrays of thermopiles to increase the sensitivity. The devices can also be integrated with an IR source on the same silicon chip and packaged to form a complete and miniaturised NDIR sensor.

Owner:AMS SENSORS UK LTD

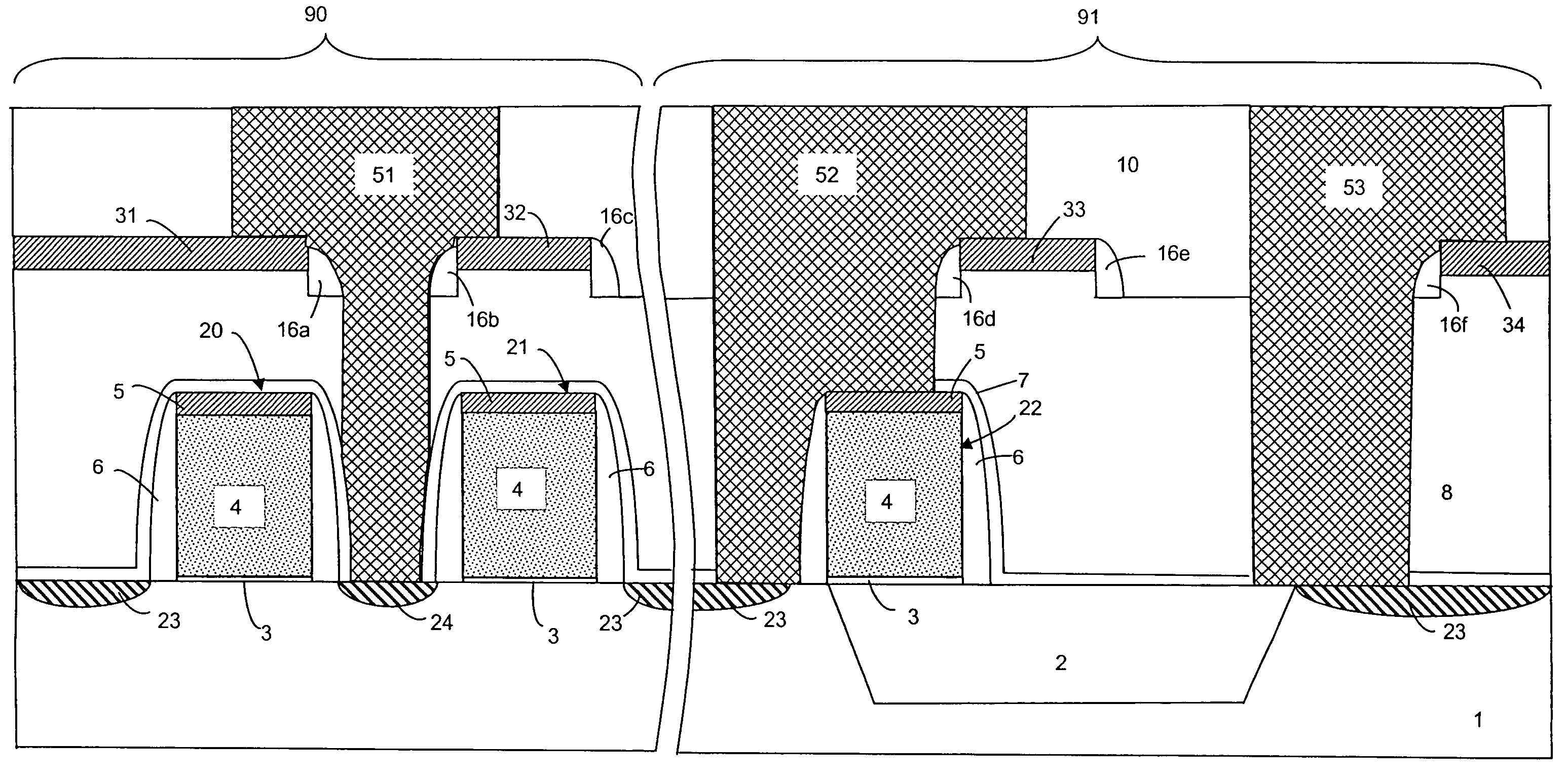

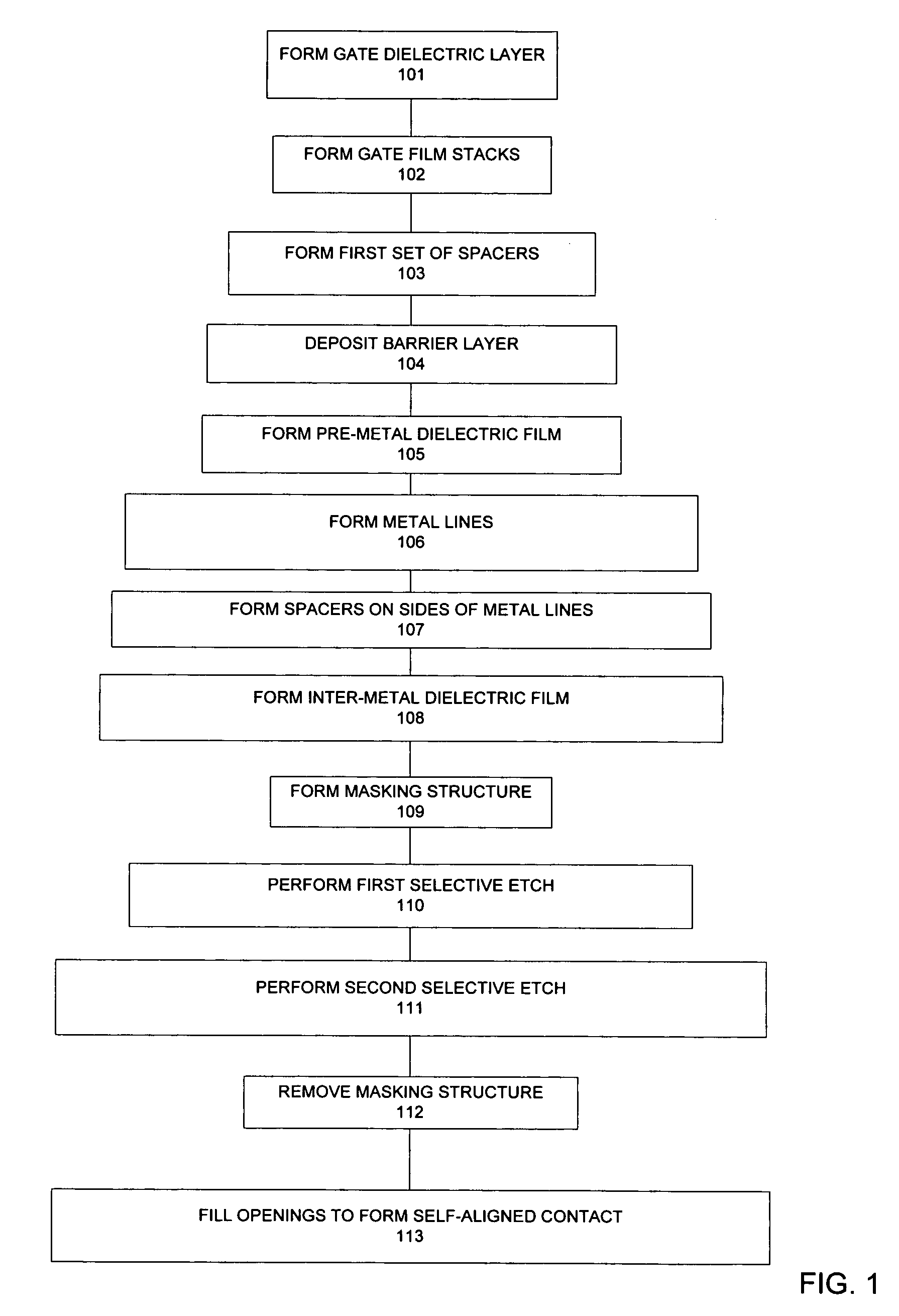

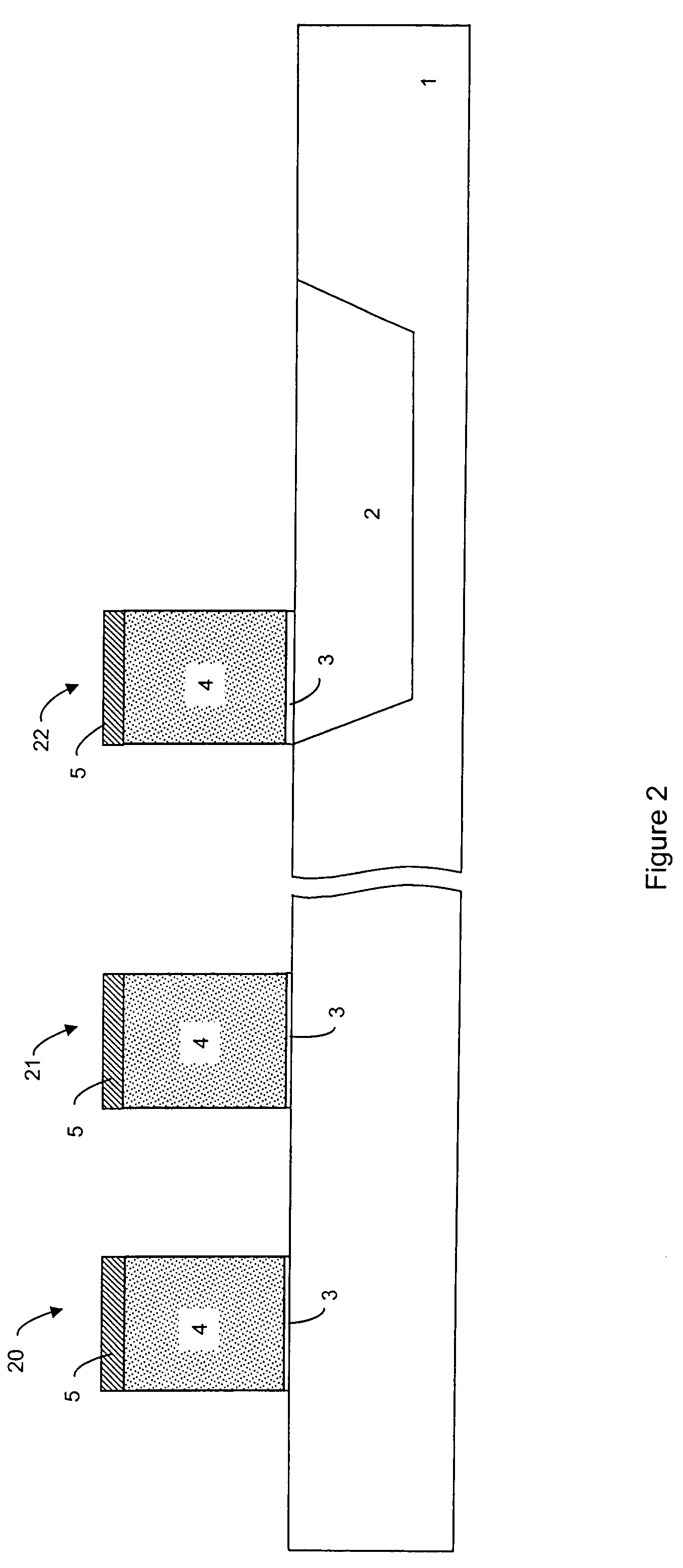

Self-aligned contact structure and process for forming self-aligned contact structure

ActiveUS7037774B1Reduce the overall heightExcellent gap fillingSemiconductor/solid-state device manufacturingCMOSDielectric

A CMOS structure and a process for forming CMOS devices are disclosed in which gate film stacks are formed over a semiconductor substrate. A barrier layer and a first dielectric film are formed such that they extend over the gate film stacks. Metal lines are formed over the pre-metal dielectric film and spacers are formed that extend on opposite sides of the metal lines. A second dielectric film is formed that extends over the metal lines. A masking structure is formed that defines a contact opening. Selective etch processes are performed to form a self-aligned contact opening, with the adjacent metal lines and spacers aligning the self-aligned contact opening between adjacent gate film stacks. A metal layer is then deposited and planarized to form a self-aligned contact. The masking structure can also define additional contact openings, which are simultaneously etched and filled with metal to form borderless, strapped and shared contacts. These borderless contacts, contacts and shared contacts can either be aligned on one side or can be positioned using only the masking structure.

Owner:INTEGRATED DEVICE TECH INC

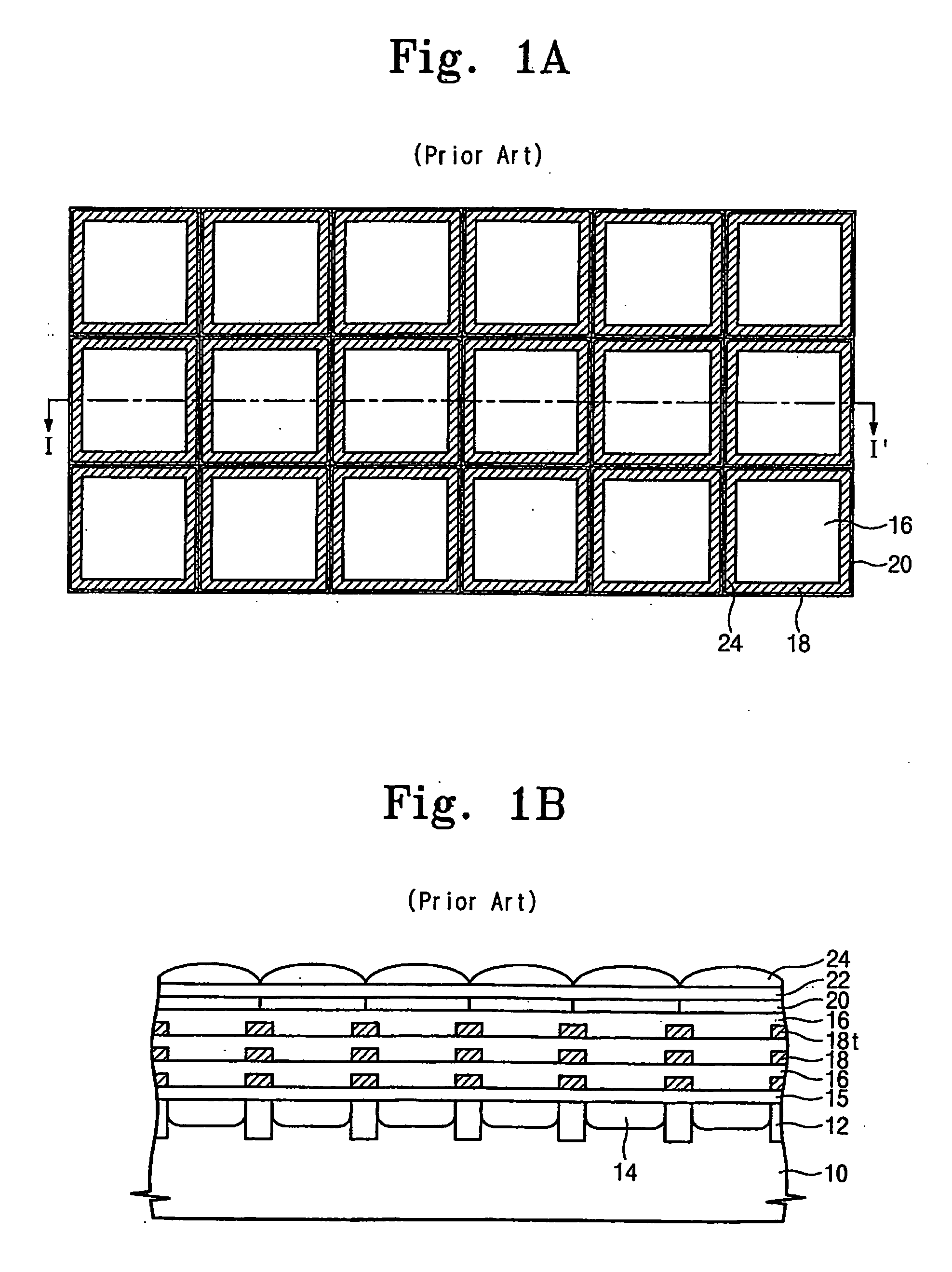

Image sensor and method of fabrication

InactiveUS20080251697A1Reduce light lossIncrease the number ofRadiation pyrometrySolid-state devicesDielectric membranePhotoelectric conversion

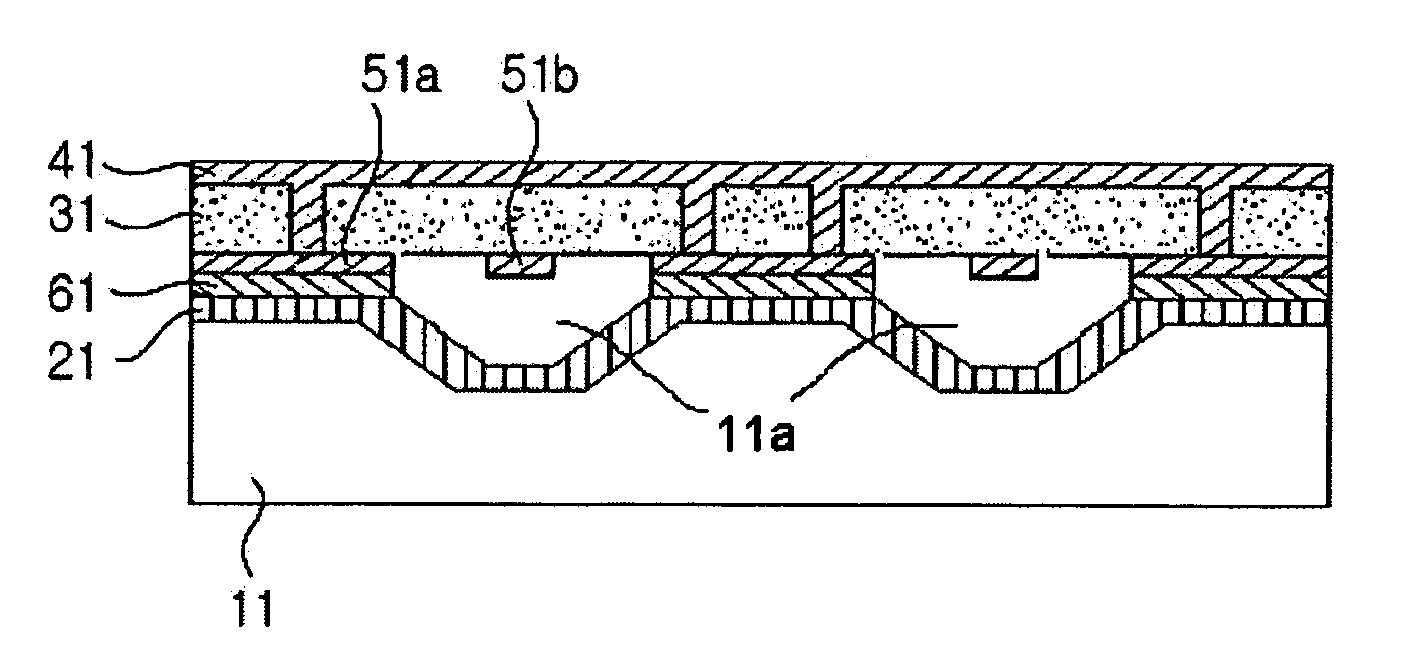

Disclosed is an image sensor and method of fabricating the same. The image sensor includes a photoelectric transformation region formed in a semiconductor substrate, and pluralities of interlayer dielectric films formed over the photoelectric transformation regions. The interlayer dielectric films contain multilevel interconnection layers. A color filter layer is disposed in a well region formed in the interlayer dielectric films over the photoelectric transformation region. A passivation layer is interposed between the color filter layer and the interlayer dielectric films.

Owner:SAMSUNG ELECTRONICS CO LTD

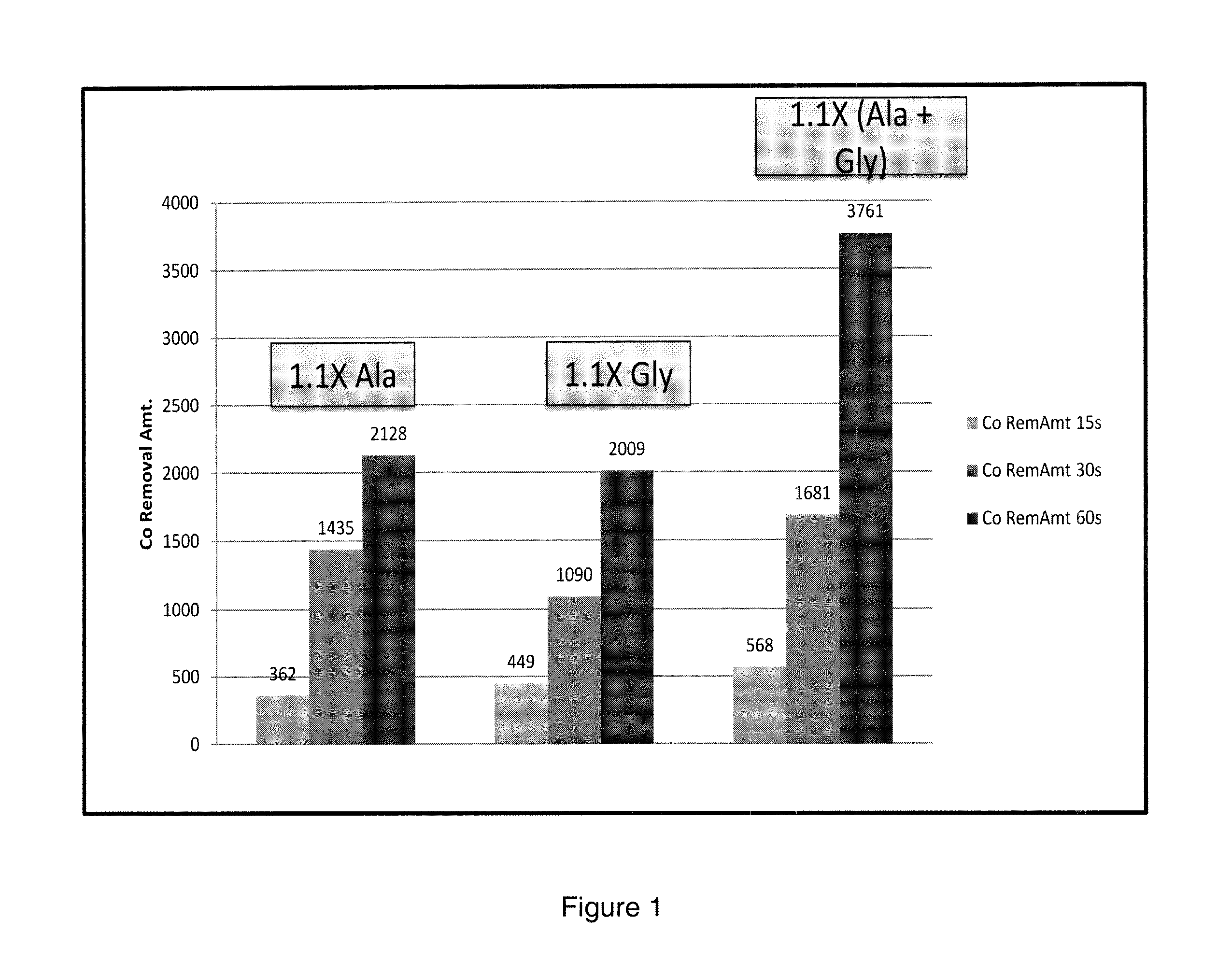

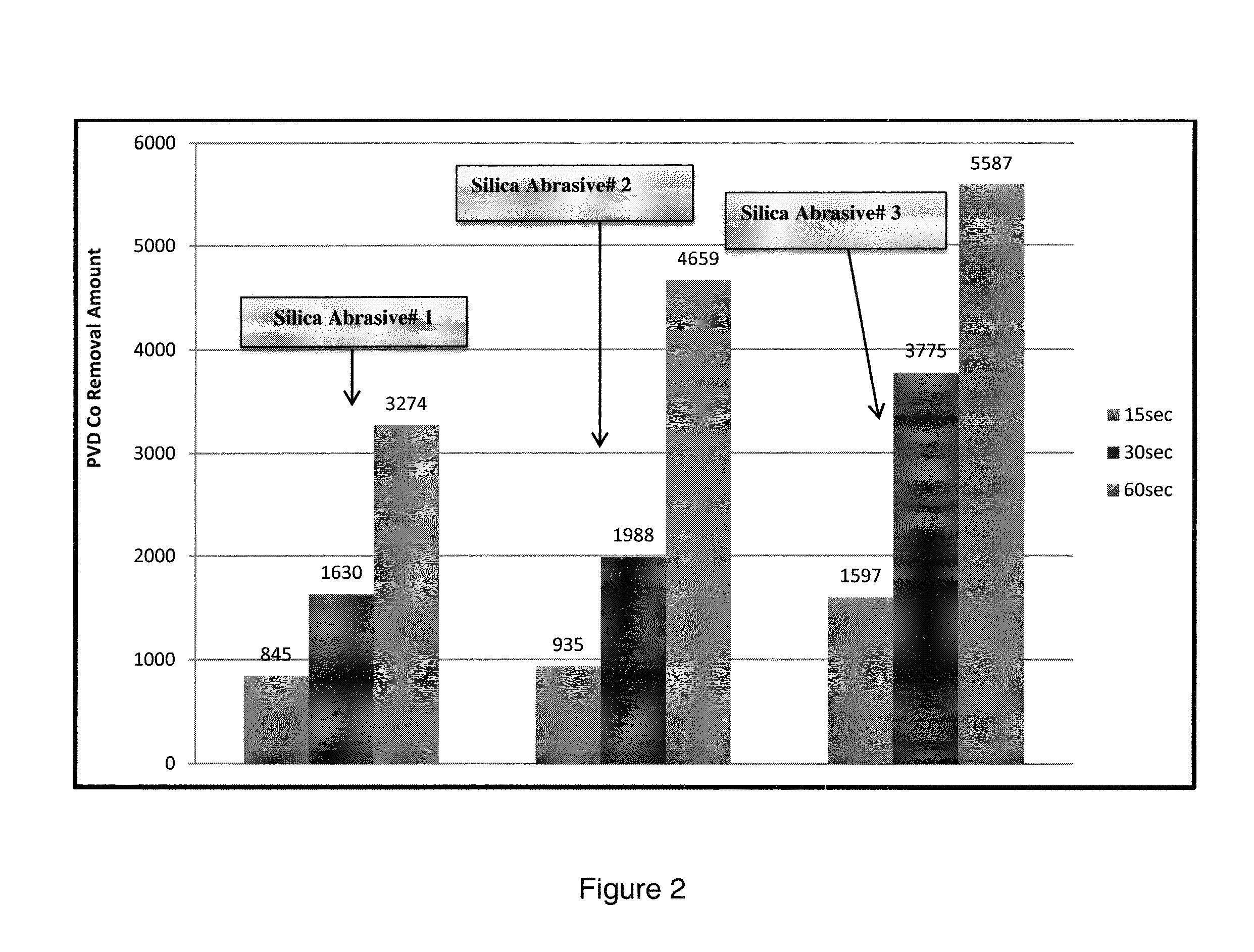

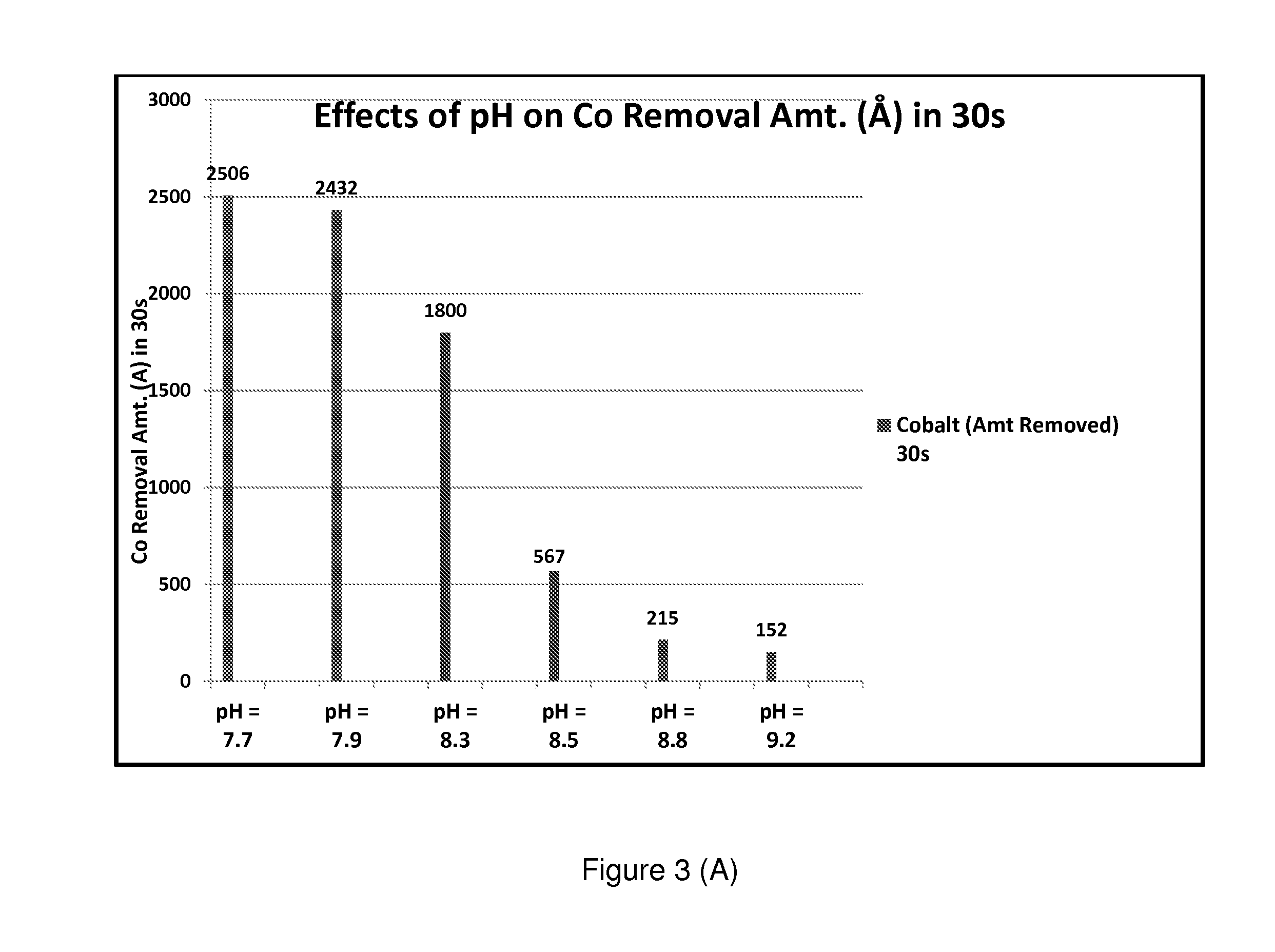

Chemical Mechanical Polishing (CMP) of Colbalt-Containing Substrate

ActiveUS20160027657A1High removal rateHigh and tunable Co film removal rateSemiconductor/solid-state device manufacturingSurface treatment compositionsCobaltHigh selectivity

Chemical mechanical polishing (CMP) compositions, methods and systems for polish cobalt or cobalt-containing substrates are provided. Dual, or at least two chelators were used in the CMP polishing compositions as complexing agents for achieving the unique synergetic effects to afford high, tunable Co removal rates and with low static etch rates on Co film surface for the efficient Co corrosion protection during CMP process. The cobalt chemical mechanical polishing compositions also provide very high selectivity of Co film vs. other barrier layers, such as Ta, TaN, Ti, and TiN, and dielectric film, such as TEOS, SiNx, low-k, and ultra low-k films.

Owner:VERSUM MATERIALS US LLC

Method of forming insulating film and method of producing semiconductor device

InactiveUS20030092238A1Low reliabilityHigh-speed operation characteristicTransistorSemiconductor/solid-state device manufacturingHigh dielectric permittivitySemiconductor

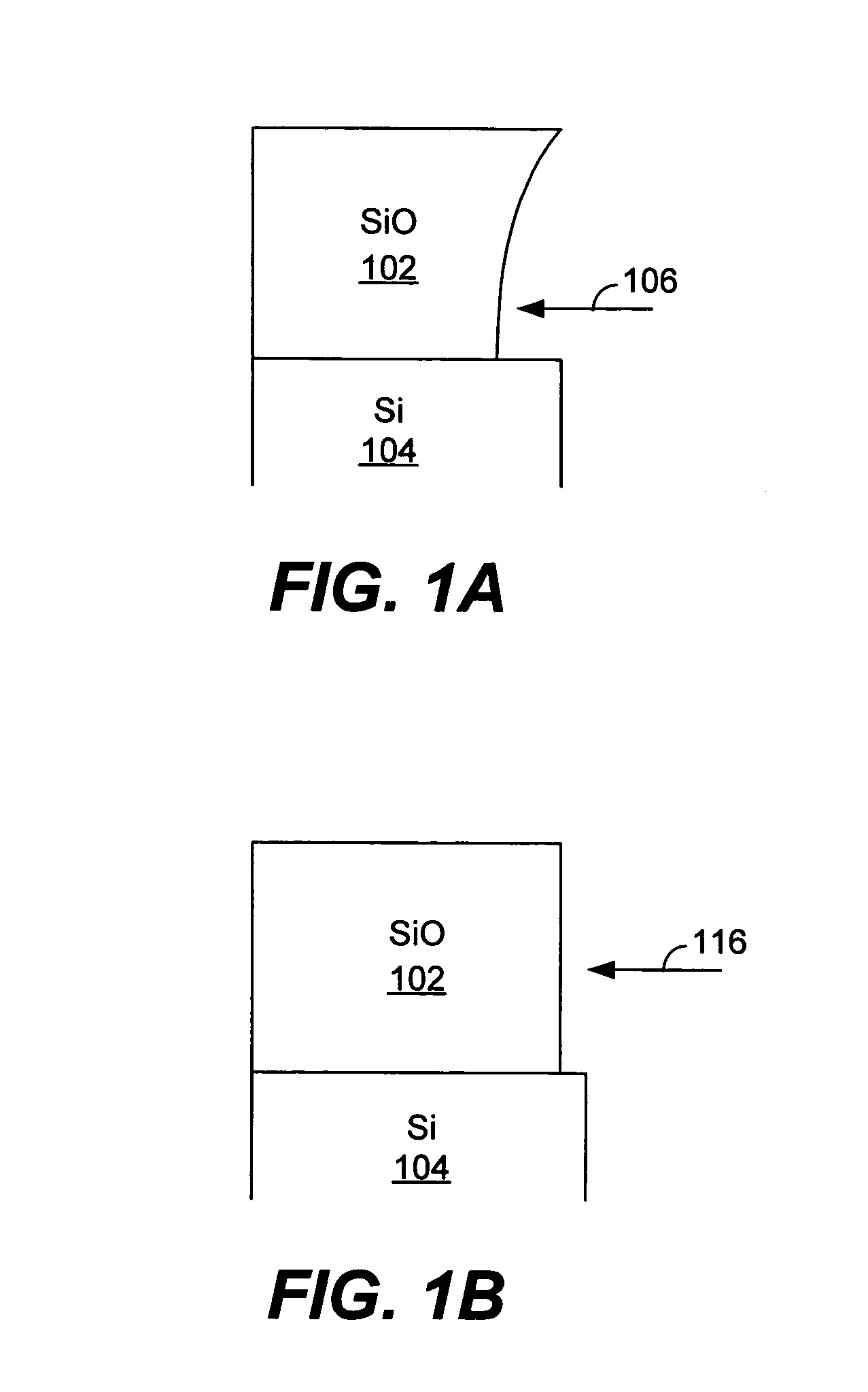

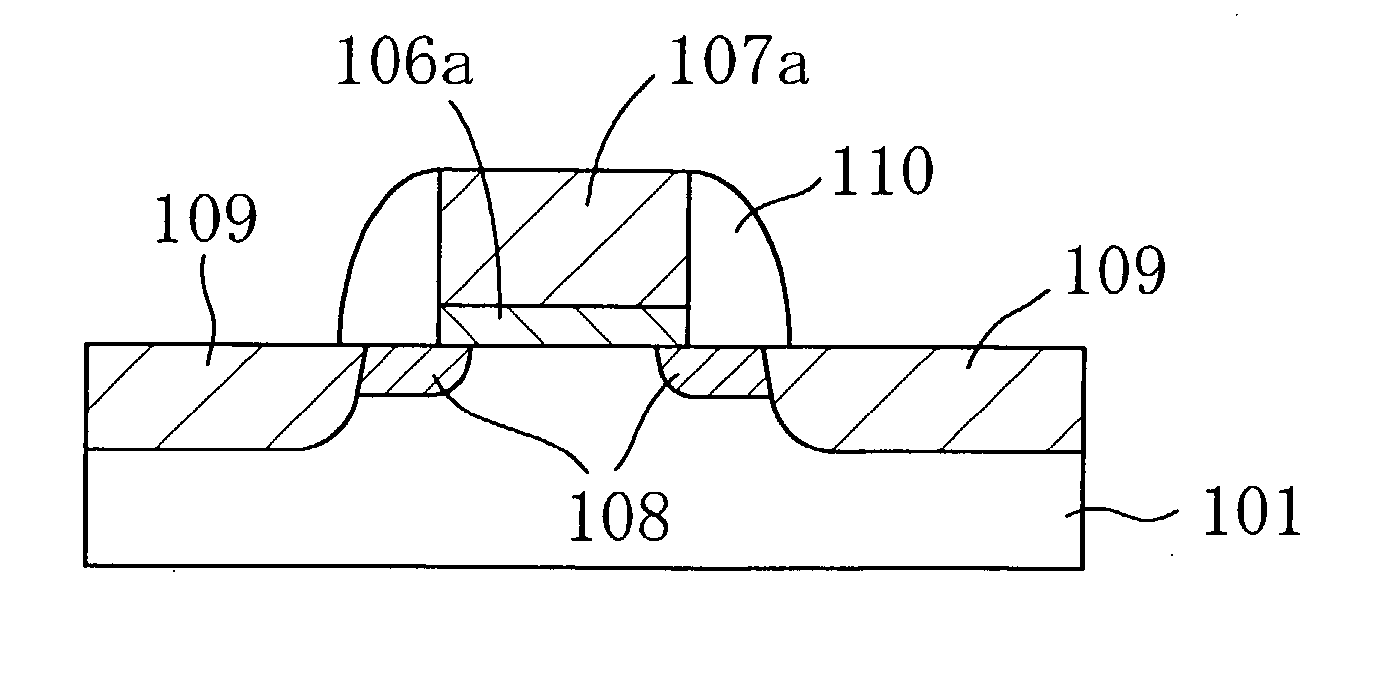

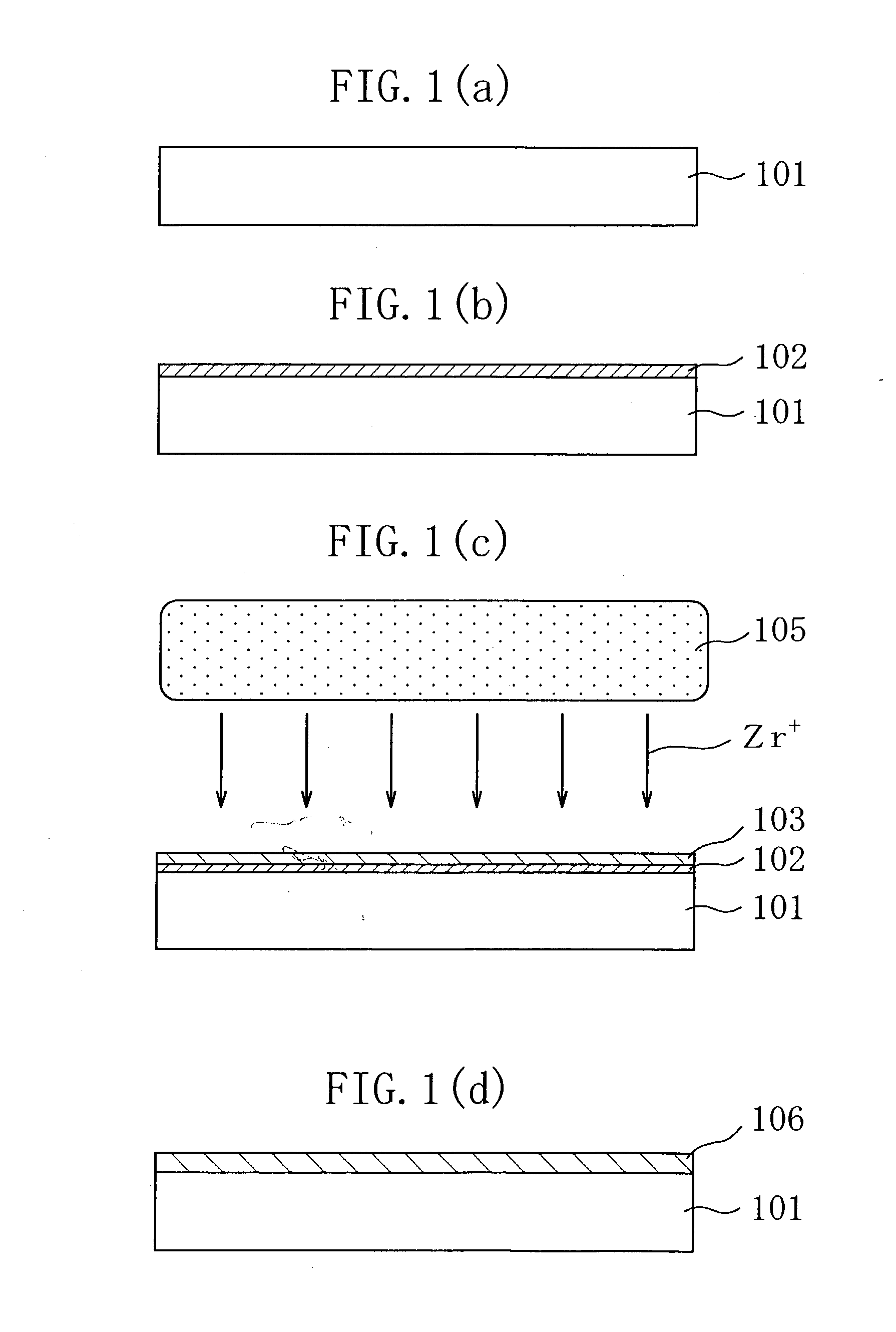

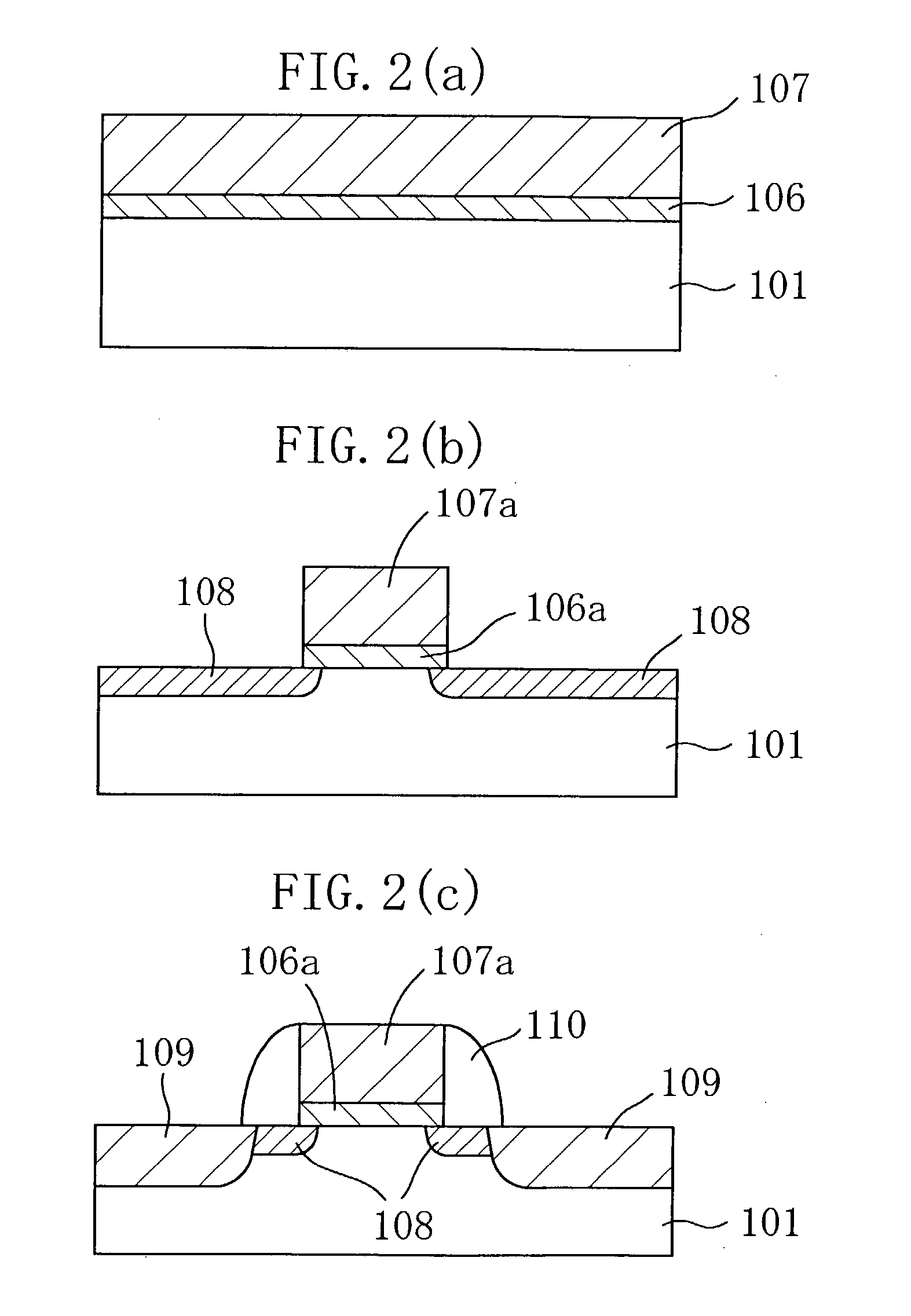

A high dielectric film is formed by utilizing atom injection into a film through ion implantation or the like, and heat treatment. For example, an SiO2 film 102 which is a thermal oxide film is formed on a silicon substrate 101, and then Zr ions (Zr+) are injected from a plasma 105 into the SiO2 film 102. Thereafter, by annealing the SiO2 film 102 and a Zr injected layer 103, injected Zr is diffused in the Zr injected layer 103 and then the SiO2 film 102 and the Zr injected layer 103 are as a whole changed into a high dielectric film 106 of a high dielectric constant formed of Zr-Si-O (silicate). By using the high dielectric film 106 as an insulating film for an MISFET, an MISFET having excellent gate leakage properties can be achieved.

Owner:PANNOVA SEMIC

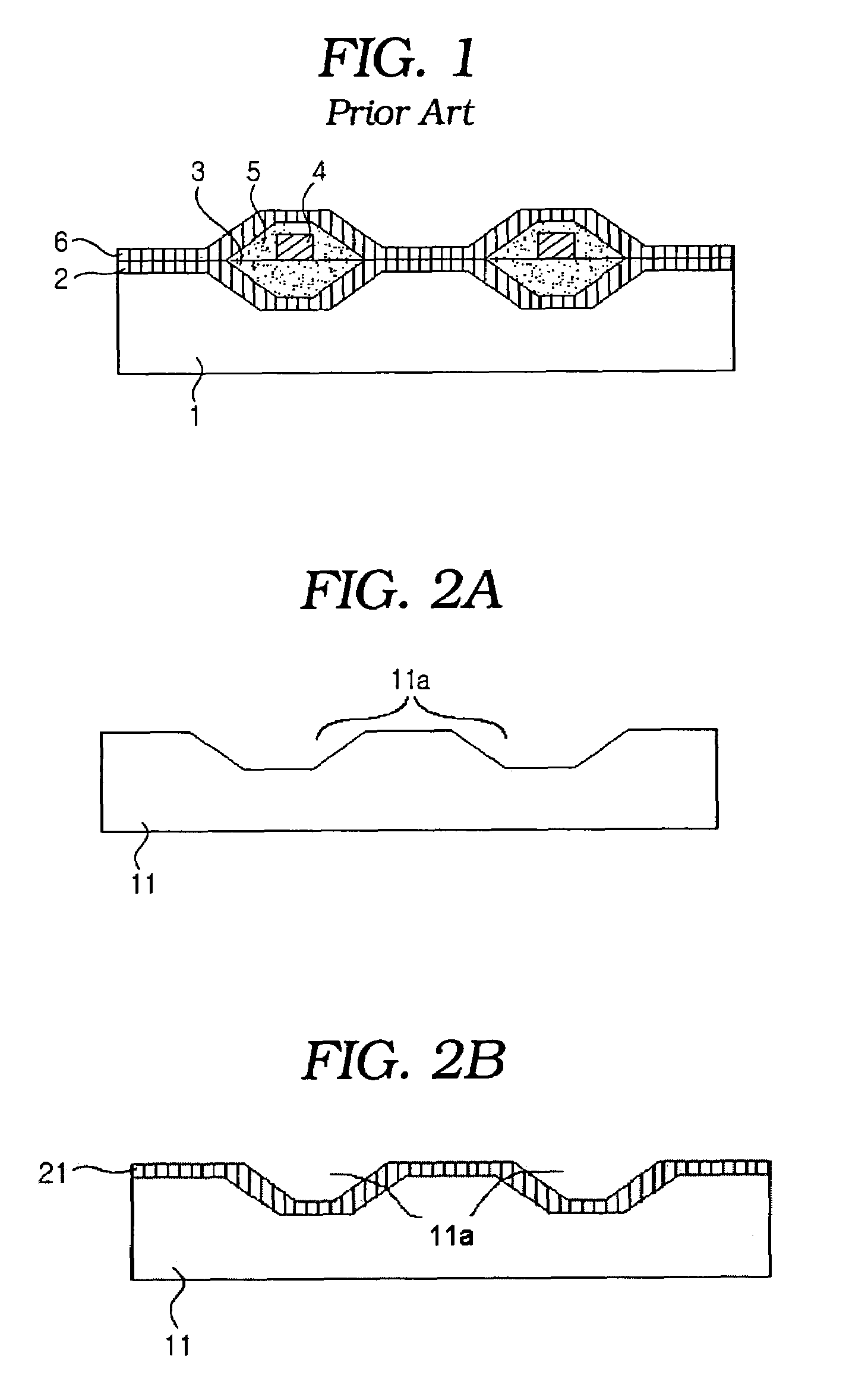

Grooved coaxial-type transmission line, manufacturing method and packaging method thereof

InactiveUS7400222B2Avoid signal lossReduced dimensionPrinted circuit aspectsSolid-state devicesEpoxyTransfer procedure

Disclosed herein are a transmission line of coaxial type and a manufacturing method thereof, capable of preventing a radiative signal loss of signal lines during transmission of an RF signal and removing signal interference between adjacent signal lines, thus allowing signal lines to be compactly arrayed during a manufacture of IC, and reducing a dimension of the IC. The transmission line of coaxial type includes grooves provided on a semiconductor substrate, a first ground layer, an electrically conductive epoxy coated on a flat part of the first ground layer except the grooves, second ground layers provided on the electrically conductive epoxy, a dielectric film provided at a position above the grooves and the second ground layers, a third ground layer provided on an upper surface of the dielectric film, and signal lines placed in spaces defined by the grooves and a lower surface of the dielectric film. In this case, the electrically conductive epoxy is coated on only contact surfaces of the first and second ground layers, and the signal lines are attached to the lower surface of the dielectric film.

Owner:KOREA ADVANCED INST OF SCI & TECH

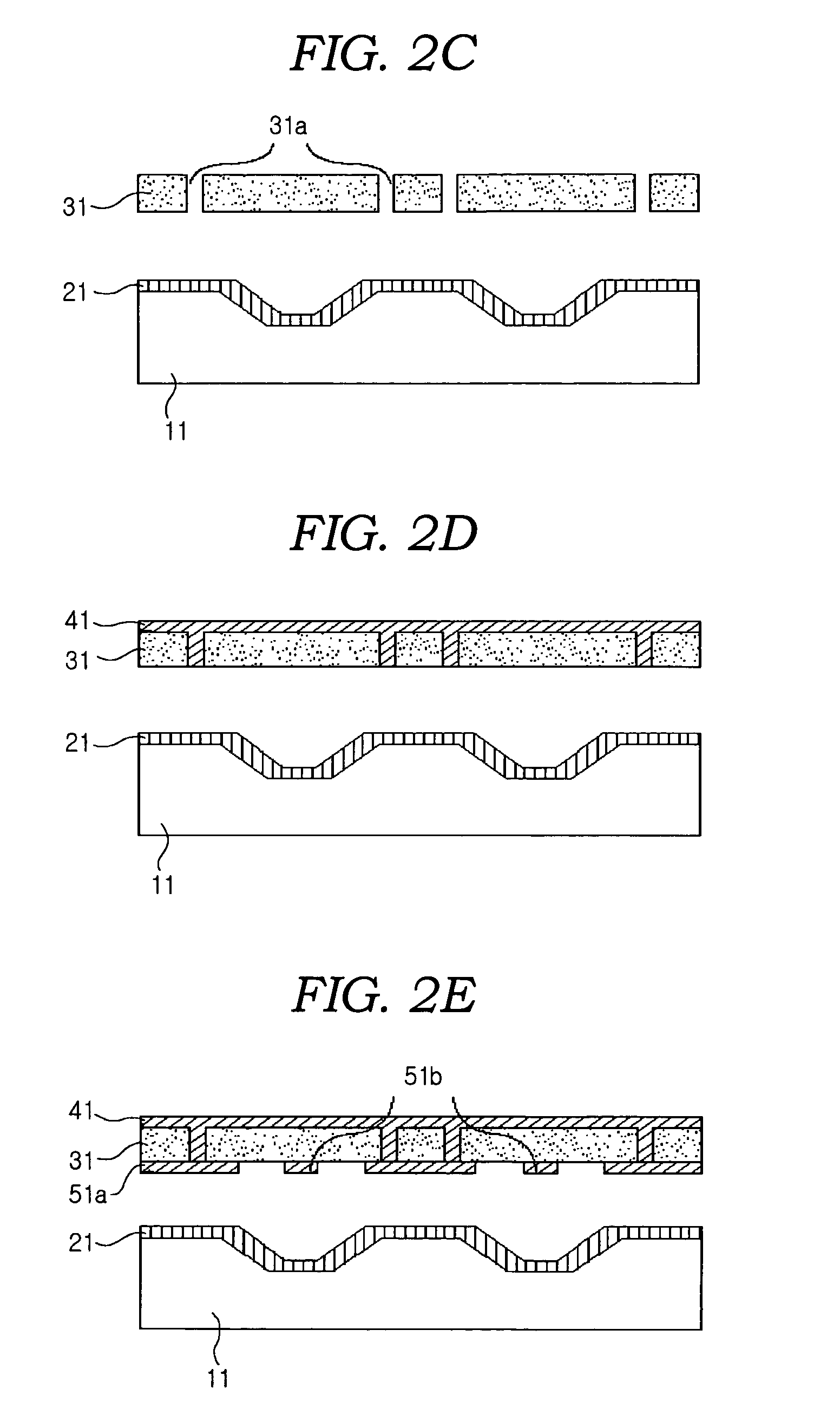

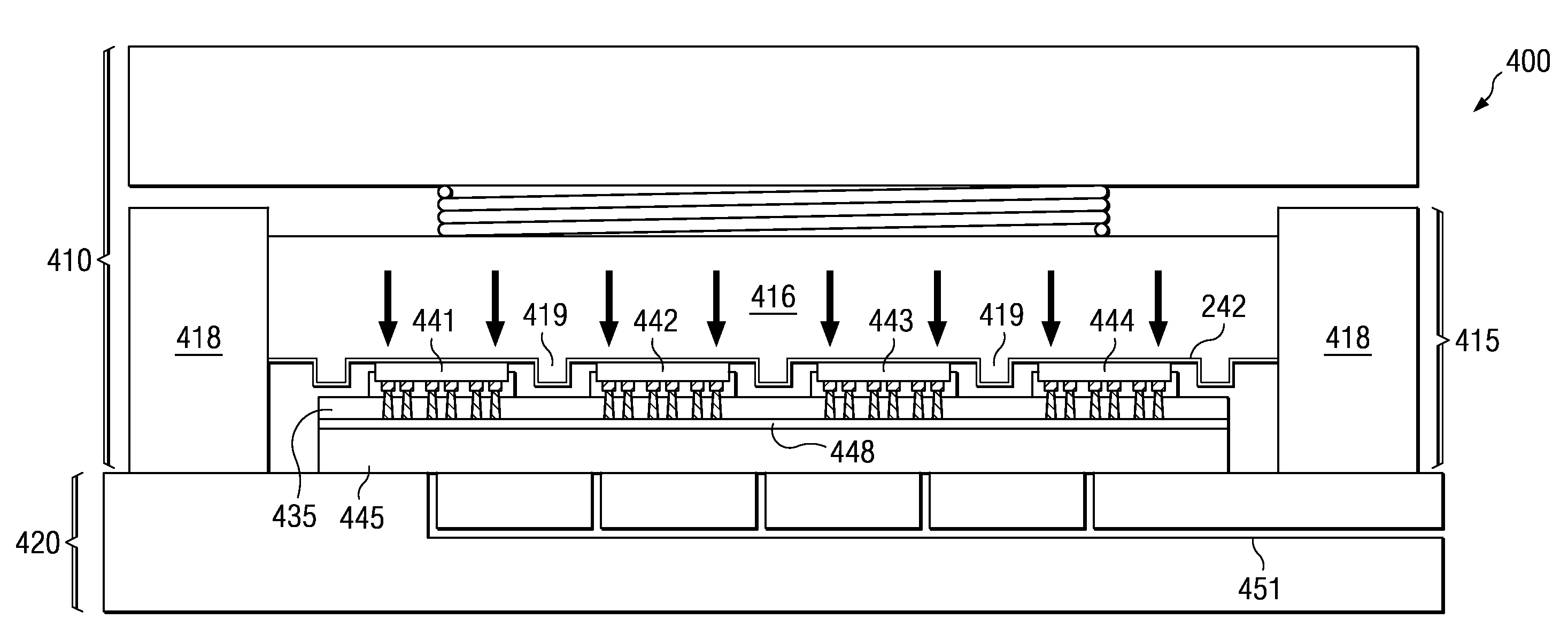

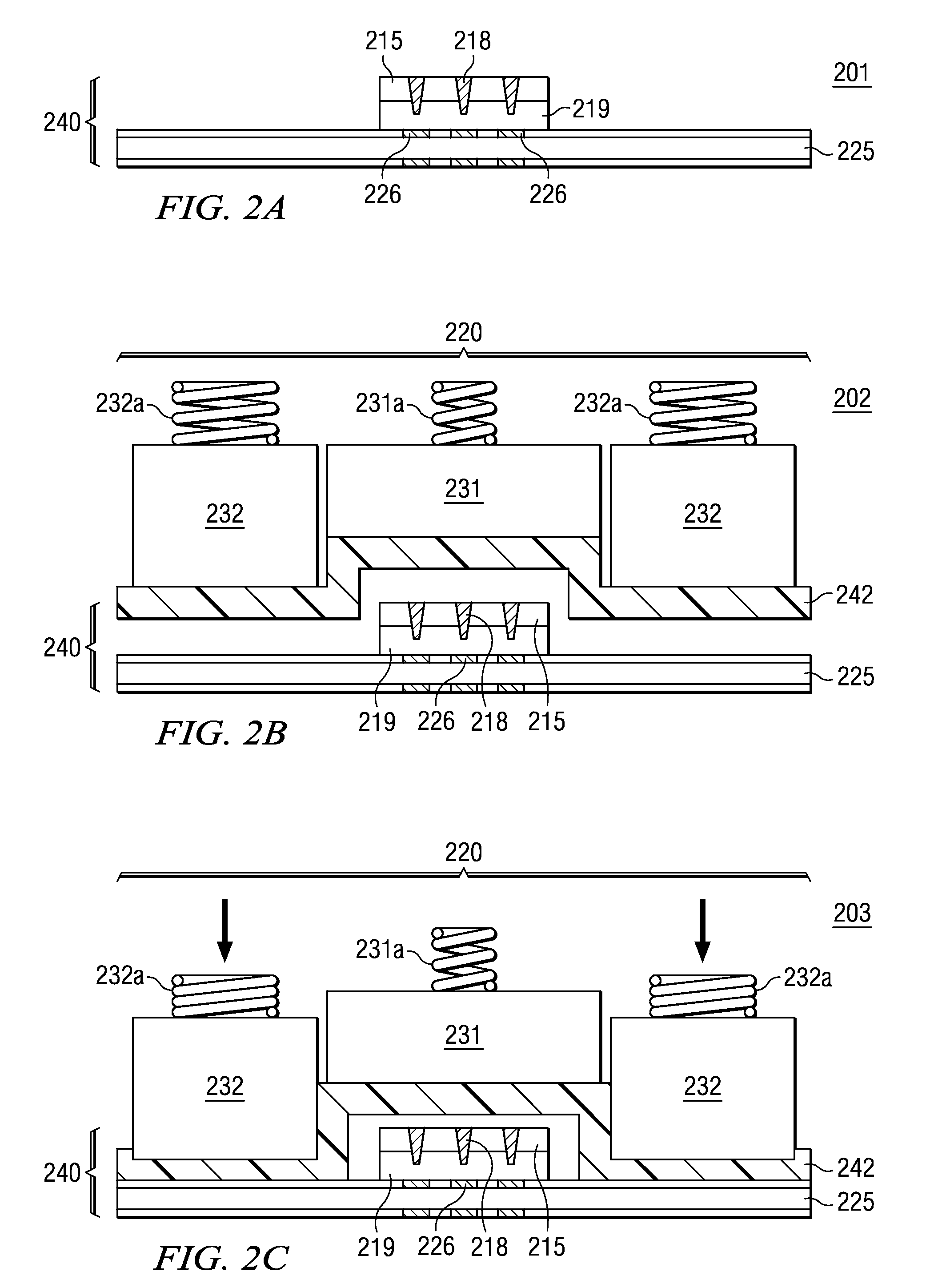

Combined metallic bonding and molding for electronic assemblies including void-reduced underfill

ActiveUS20090291524A1Small sizeReducing joint misalignmentCasting safety devicesSolid-state devicesElectrical conductorDielectric membrane

A method for forming electronic assemblies includes providing a plurality of IC die each having IC bonding conductors and a workpiece having workpiece bonding conductors. A curable dielectric film is applied to the IC bonding conductors or the workpiece surface. The plurality of IC die are placed on the workpiece surface so that the plurality of IC bonding conductors are aligned to and face the plurality of workpiece bonding conductors to provide a first bonding. The placing is performed at a vacuum level corresponding to a pressure <1 kPa, and at a temperature sufficient to provide tackiness to the curable dielectric film. The plurality of IC die are then pressed to provide a second bonding. A temperature during pressing cures the curable dielectric film to provide an underfill and forms metallic joints between the plurality of IC bonding conductors and the plurality of workpiece bonding conductors.

Owner:TEXAS INSTR INC

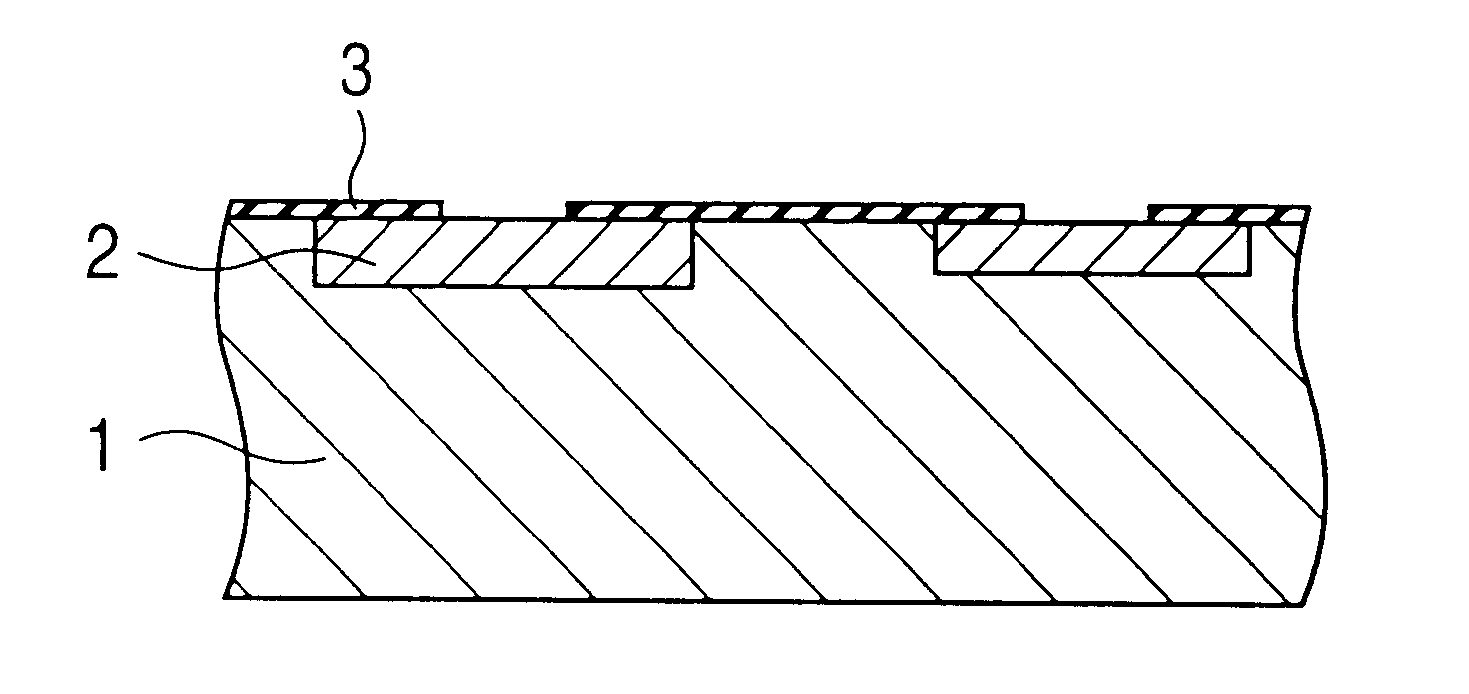

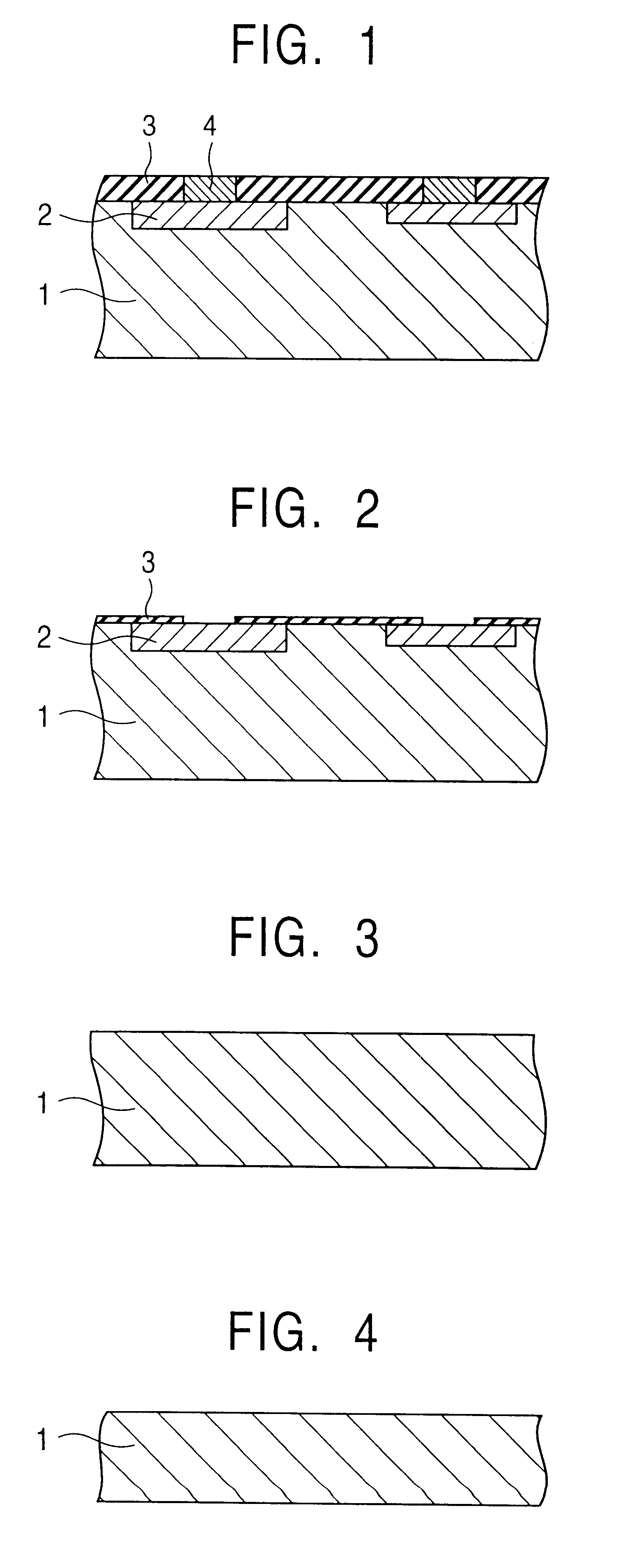

Method for reclaiming wafer substrate and polishing solution compositions therefor

InactiveUS6451696B1Extension of timeReduce thicknessSemiconductor/solid-state device manufacturingDielectric layerMetal

A method for reclaiming a wafer substrate material having a metallic film and a dielectric film includes a step for removing the entire metallic film and a part of the dielectric film with a chemical etching agent so as not to substantially dissolve the wafer substrate material itself, a step for removing the residual dielectric layer and the degenerated zone beneath the surface of the substrate by chemical-mechanical polishing, and a step for polishing at least one surface of the substrate.

Owner:KOBE STEEL LTD

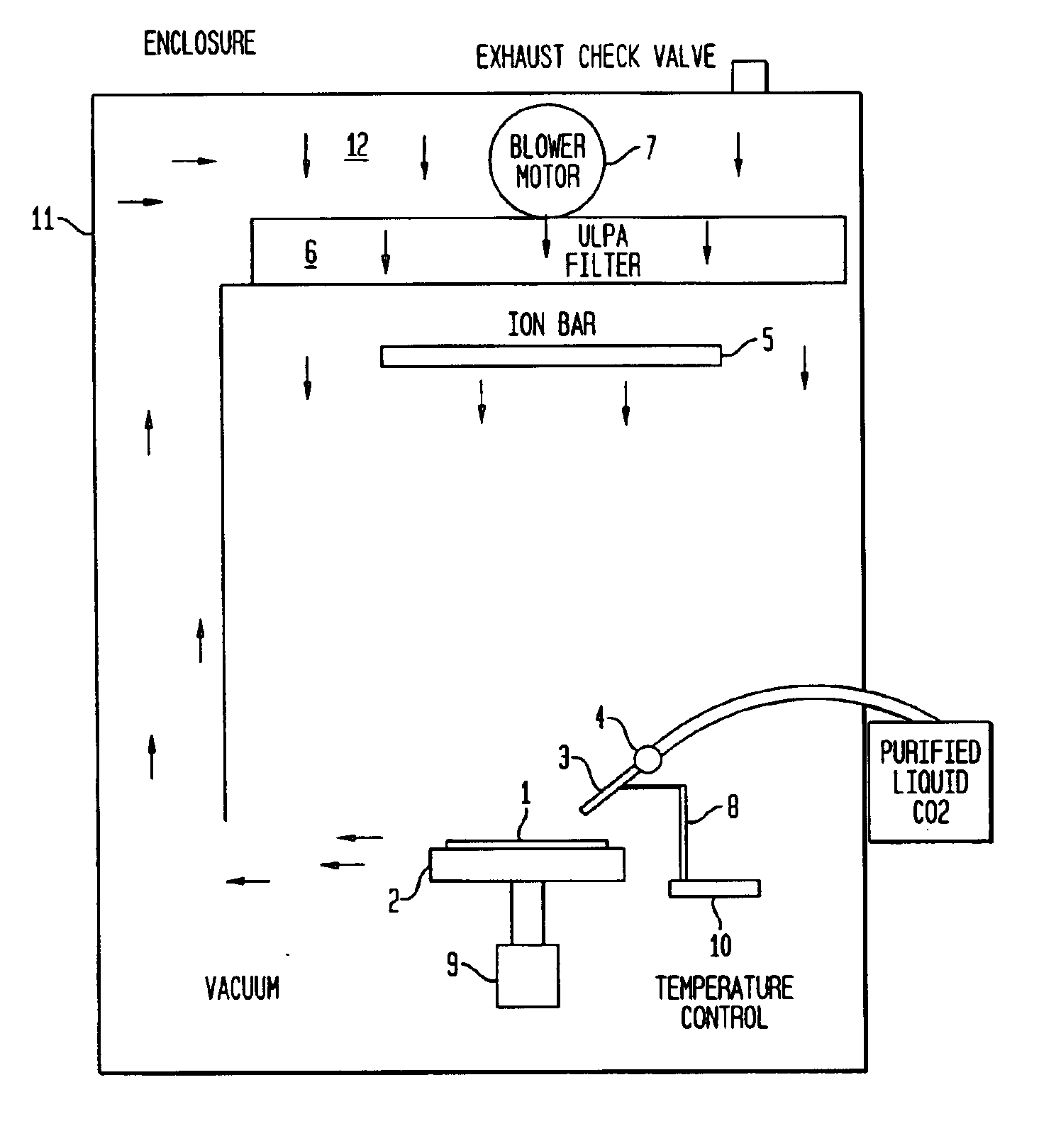

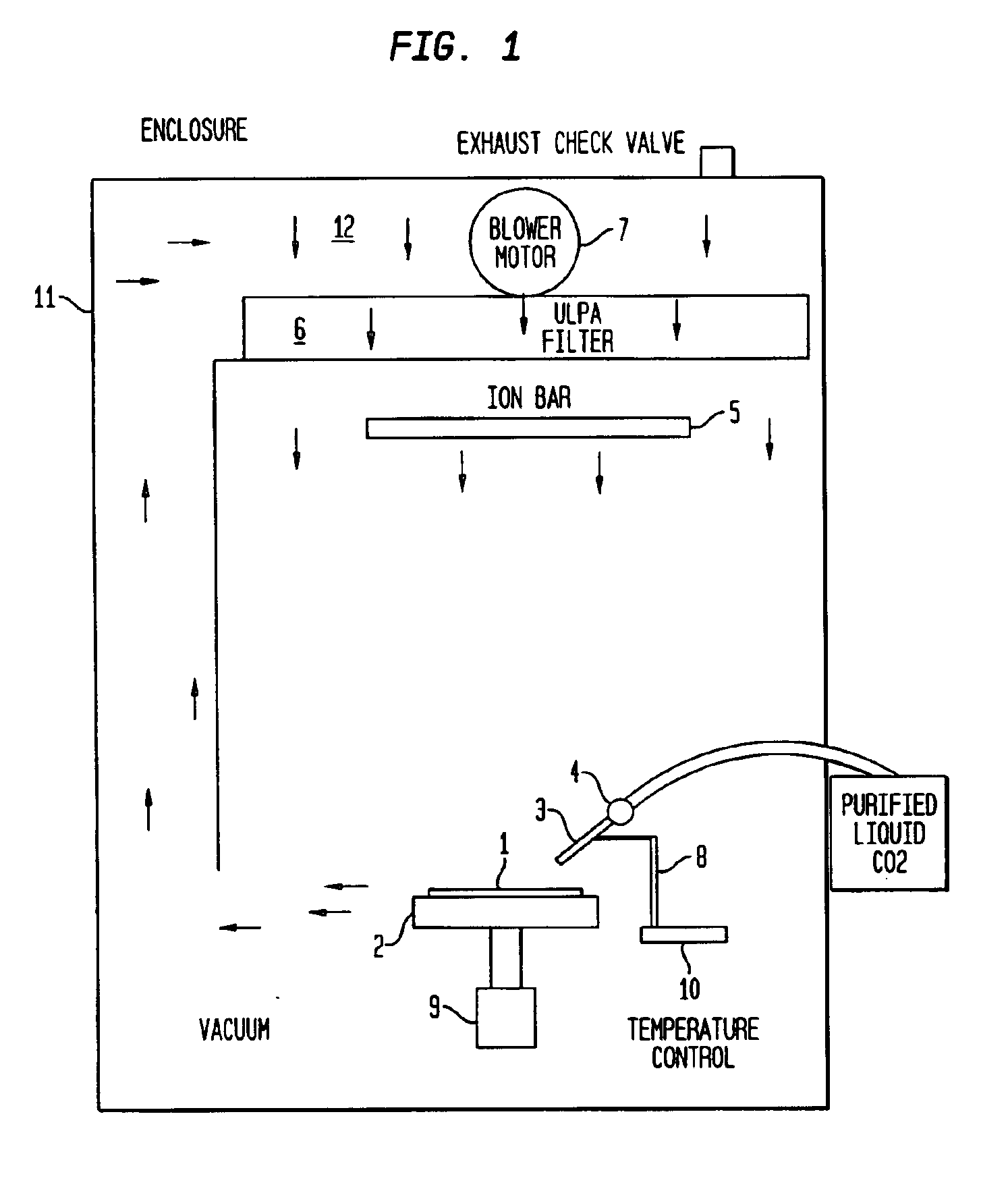

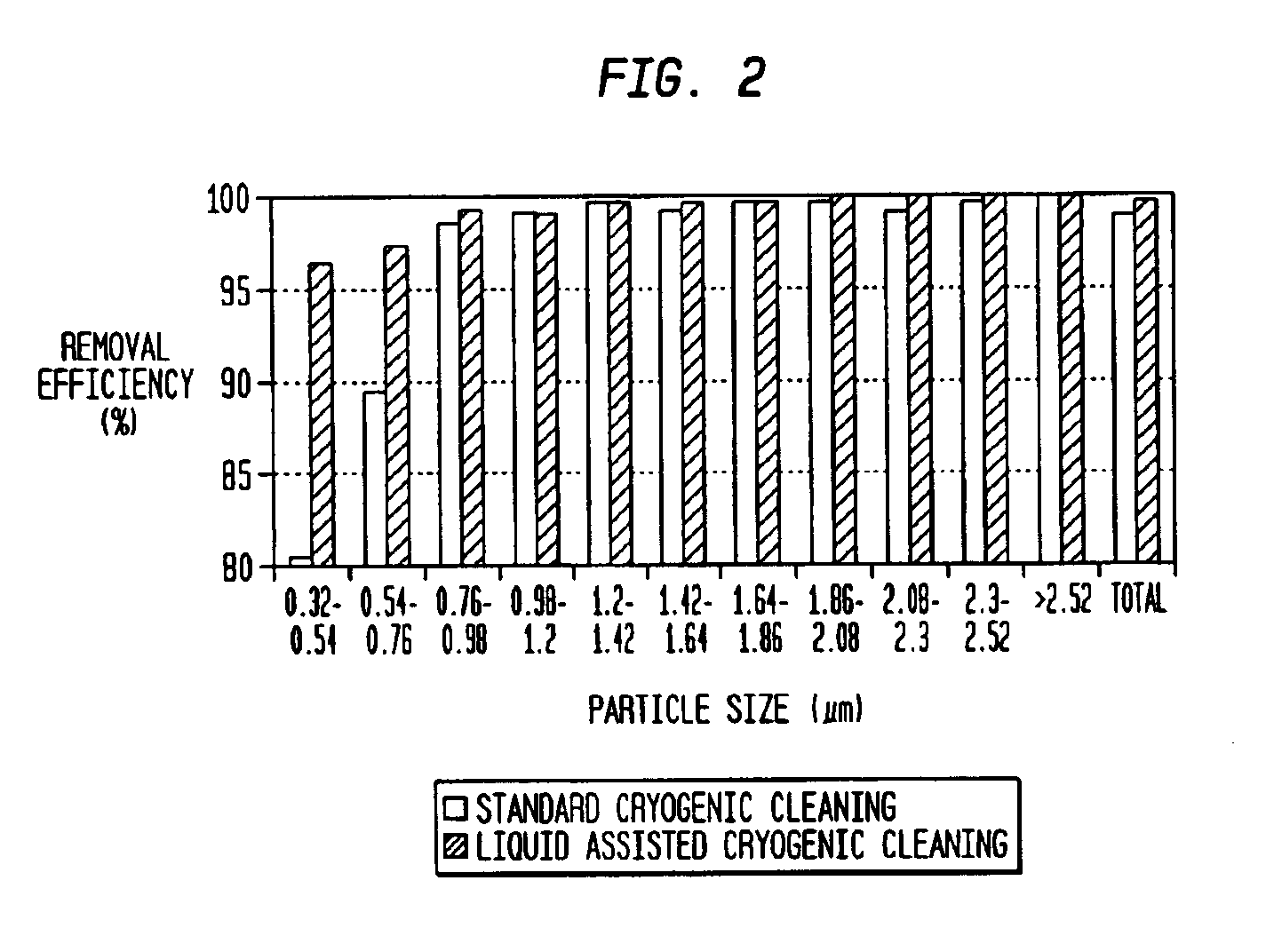

Liquid-assisted cryogenic cleaning

InactiveUS6852173B2Reduce van der Waals forcesPromote sheddingSemiconductor/solid-state device manufacturingCleaning using liquidsDielectric membraneEngineering

The present invention is directed to the use of a high vapor pressure liquid prior to or simultaneous with cryogenic cleaning to remove contaminants from the surface of substrates requiring precision cleaning such as semiconductors, metal films, or dielectric films. A liquid suitable for use in the present invention preferably has a vapor pressure above 5 kPa and a freezing point below −50° C.

Owner:BOC INC +1

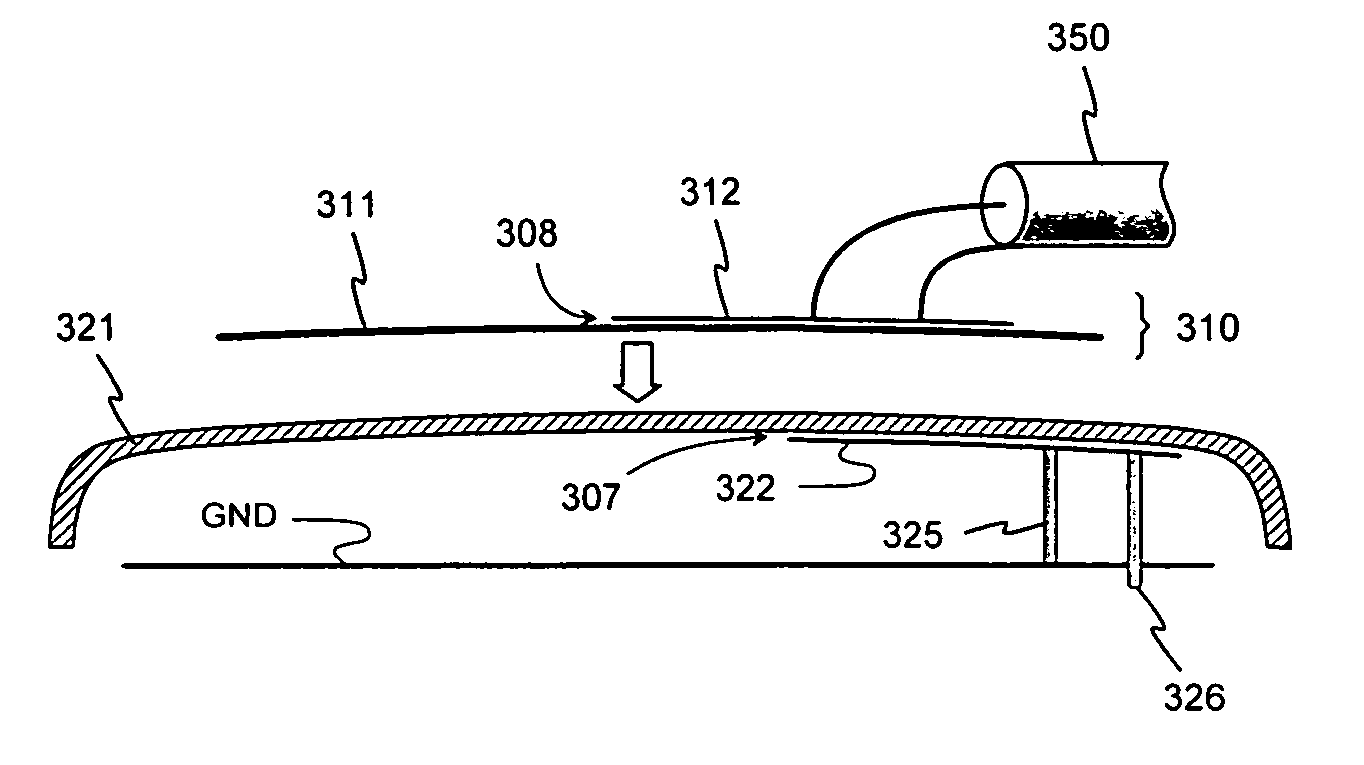

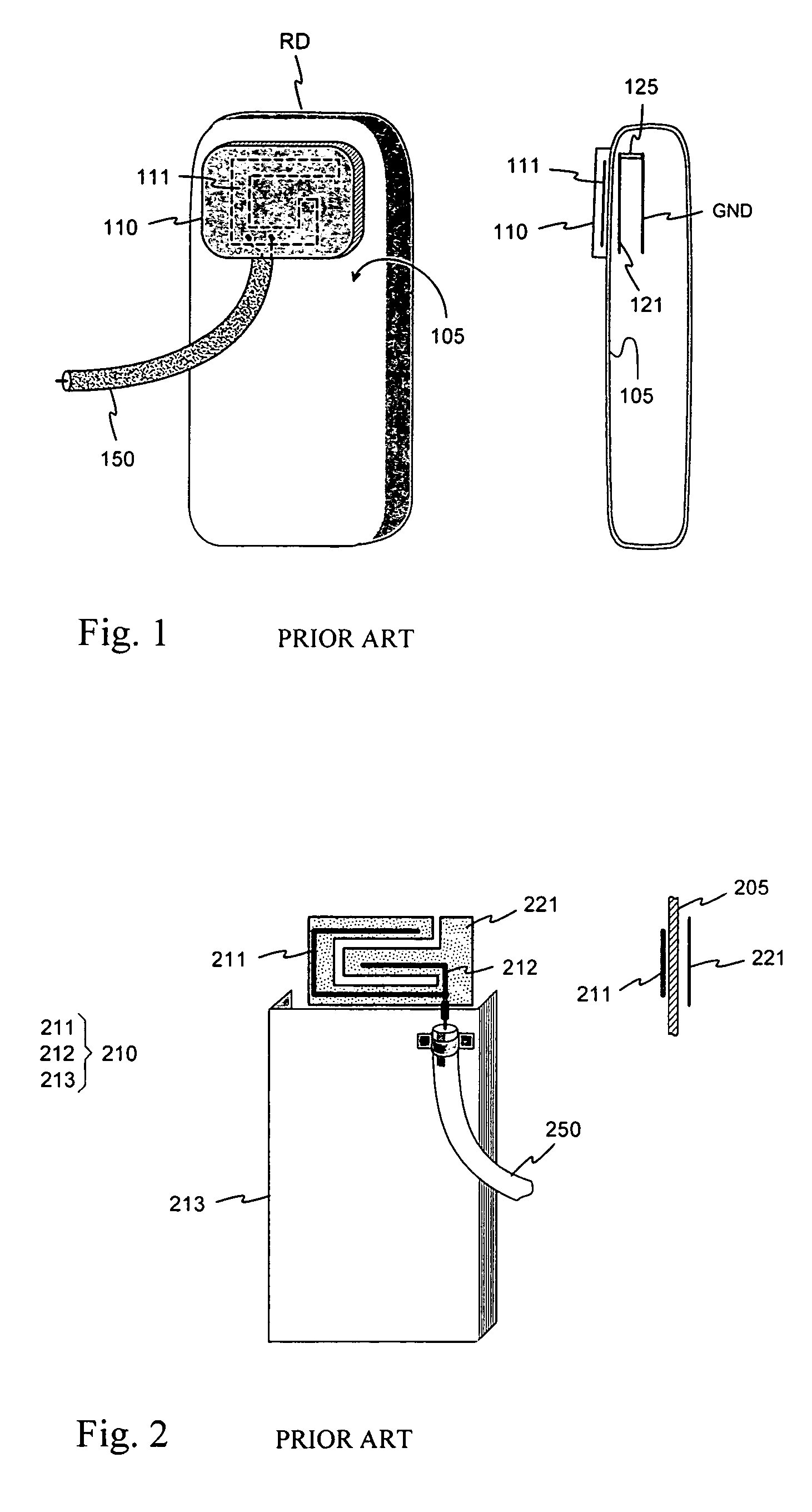

Antenna arrangement for connecting an external device to a radio device

InactiveUS7405702B2Small distanceAntenna supports/mountingsAntenna adaptation in movable bodiesElectromagnetic couplingUltrasound attenuation

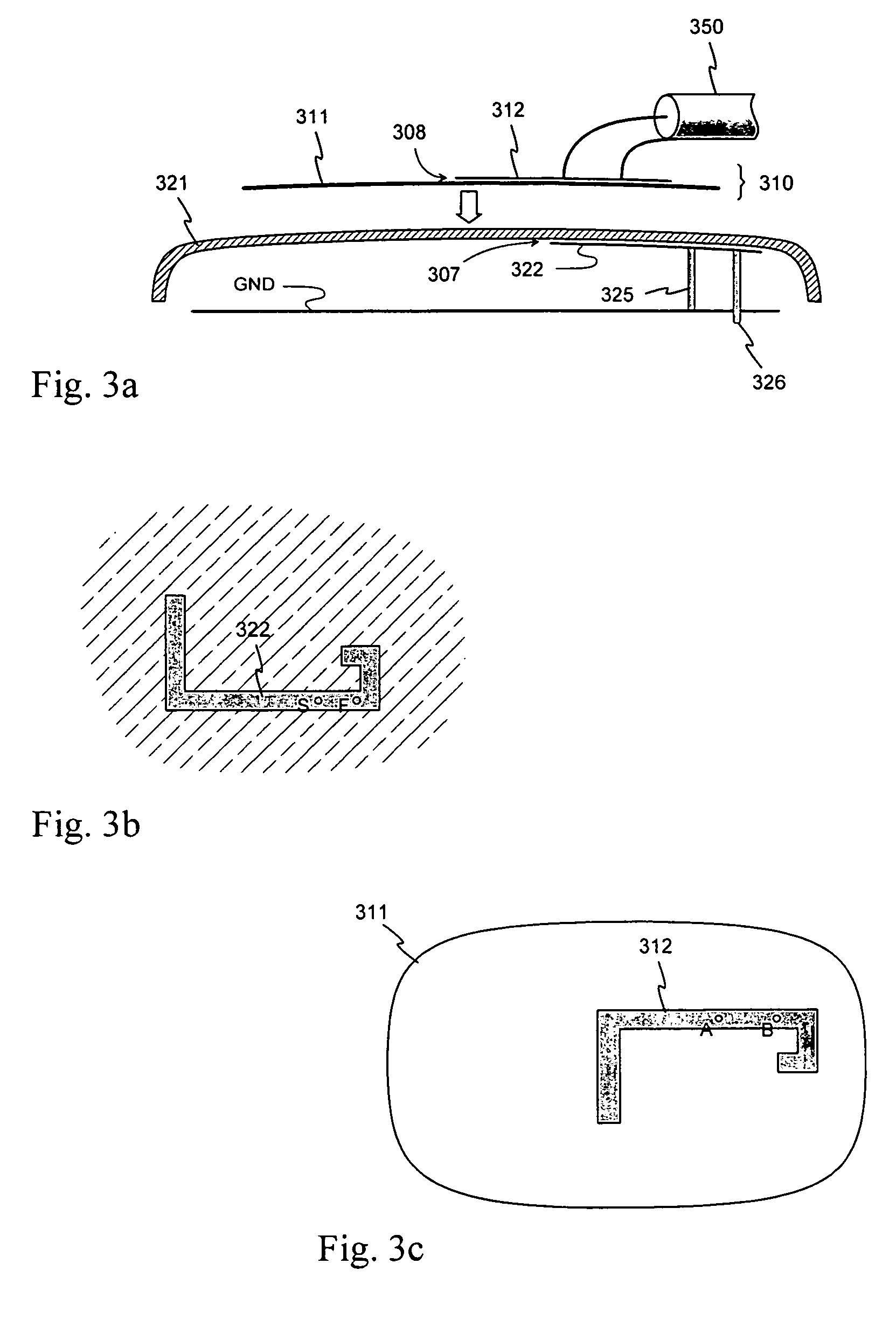

An arrangement by which an external device is connected to a radio device via its antenna without modifying the radio device mechanically. The radiating element (311) of the antenna of the radio device is a conductive part of its casing, which is fed electromagnetically by means of a feed element (322). The connecting is implemented by a coupler (310) to be placed at the antenna on top of the casing, from which coupler there is an intermediate cable (350) to the external device. The coupler includes a coupling element (311), from which there is electromagnetic coupling to the radiating element (321) through a thin dielectric membrane, or direct galvanic coupling. From the coupling element to the jumper cable there is electromagnetic coupling through an intermediate element (312), or direct galvanic coupling. Because the radiating plane is located on the outer surface of the radio device, its distance to the coupling element can be made very small. Thus the attenuation caused by the coupler on the transfer path from the antenna port of the radio device to the external device is lower than in the known arrangements.

Owner:CANTOR FITZGERALD SECURITIES