Patents

Literature

10622 results about "Silicon chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

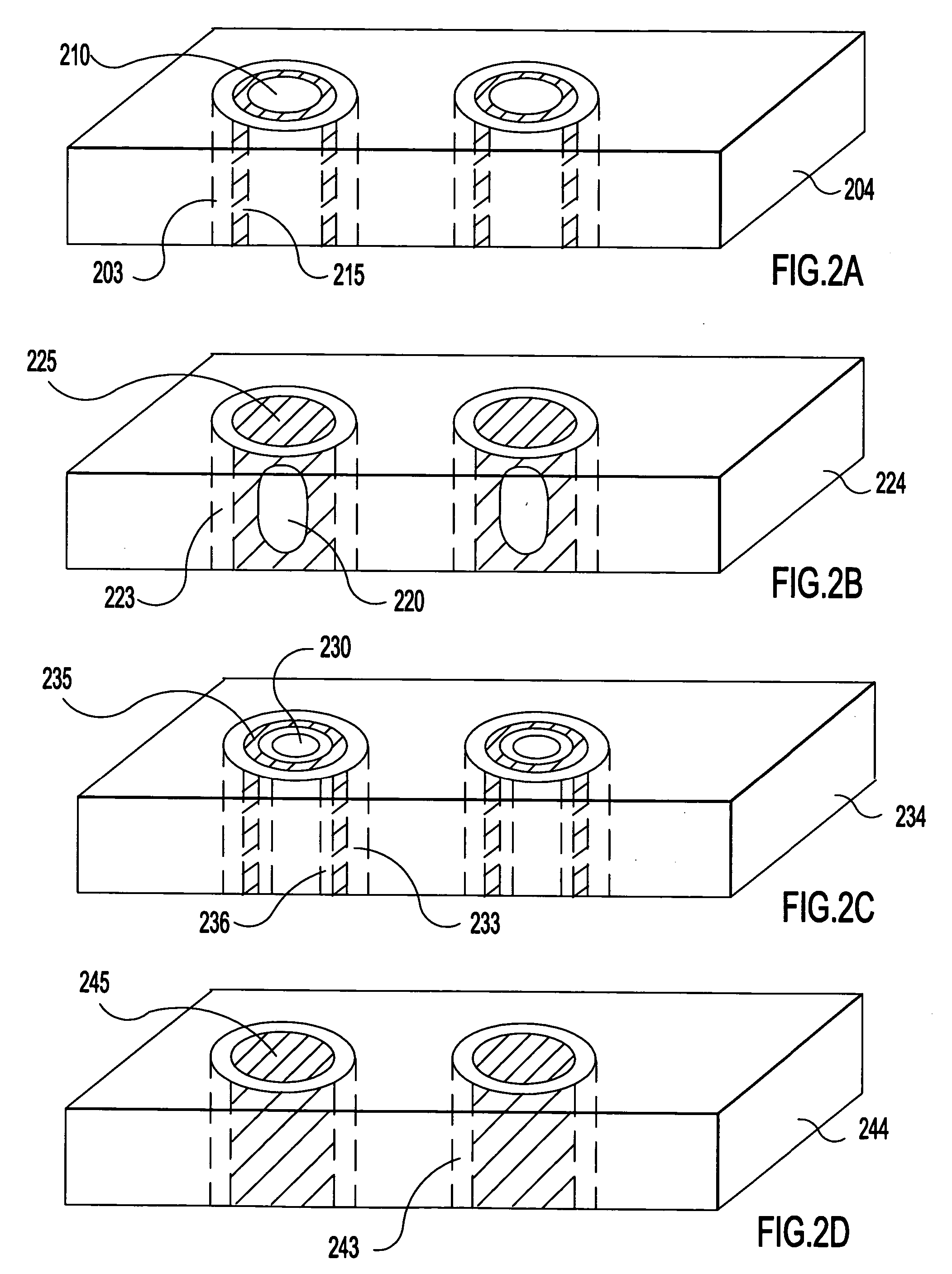

Silicon chip carrier with conductive through-vias and method for fabricating same

InactiveUS20050121768A1Effective modulusSemiconductor/solid-state device detailsSolid-state devicesSilicon chipElastic modulus

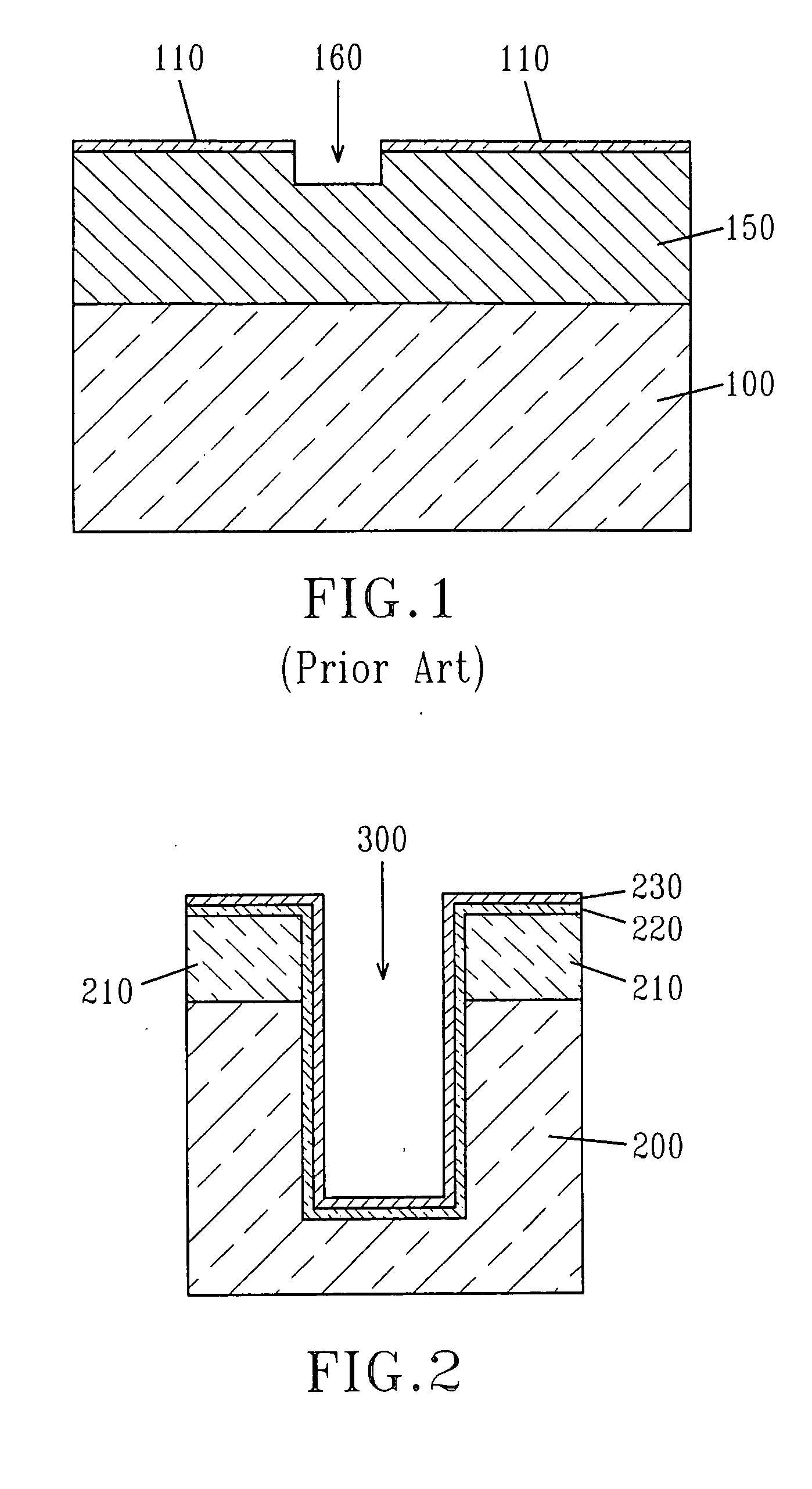

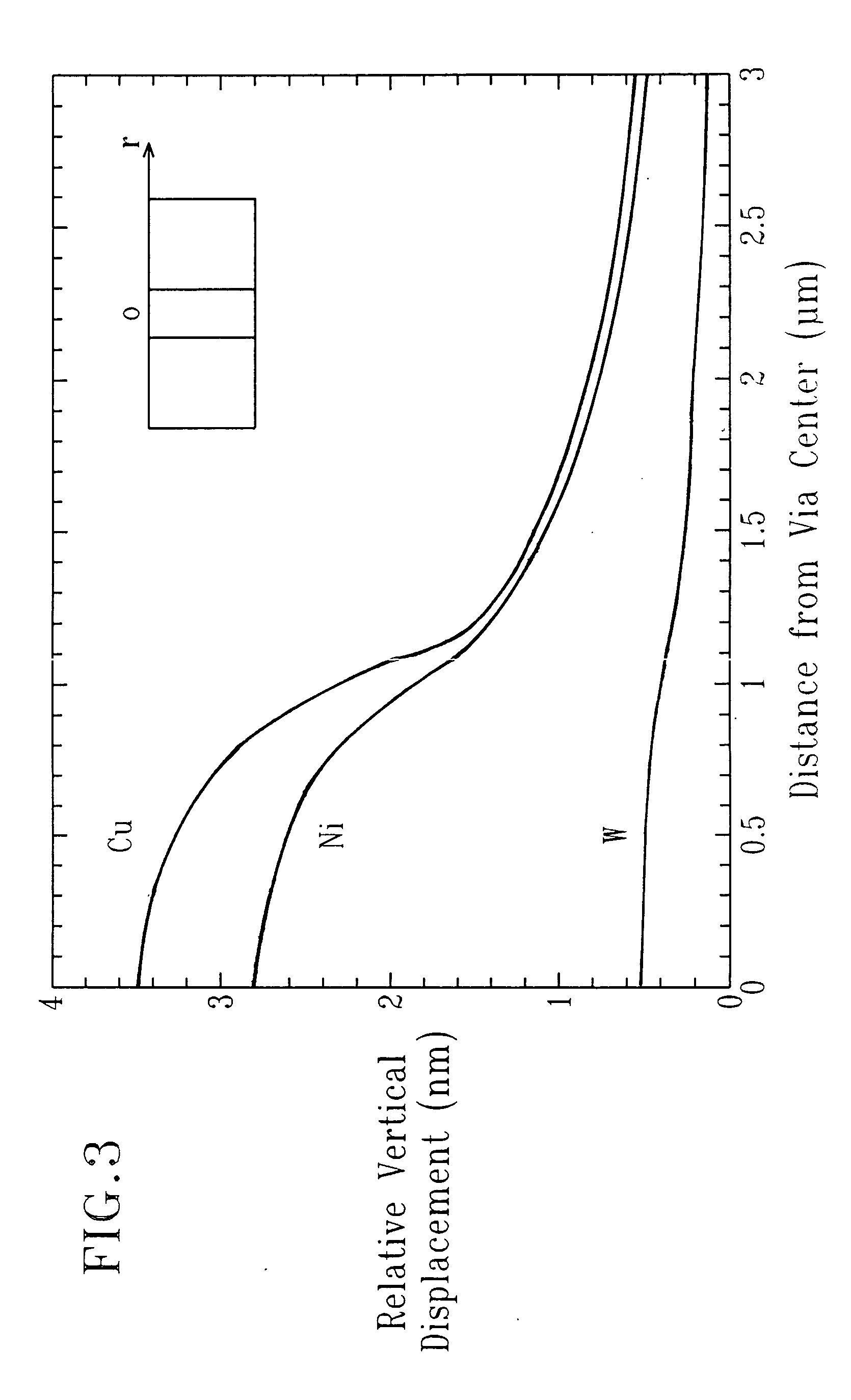

A carrier structure and method for fabricating a carrier structure with through-vias each having a conductive structure with an effective coefficient of thermal expansion which is less than or closely matched to that of the substrate, and having an effective elastic modulus value which is less than or closely matches that of the substrate. The conductive structure may include concentric via fill areas having differing materials disposed concentrically therein, a core of the substrate material surrounded by an annular ring of conductive material, a core of CTE-matched non-conductive material surrounded by an annular ring of conductive material, a conductive via having an inner void with low CTE, or a full fill of a conductive composite material such as a metal-ceramic paste which has been sintered or fused.

Owner:GLOBALFOUNDRIES INC

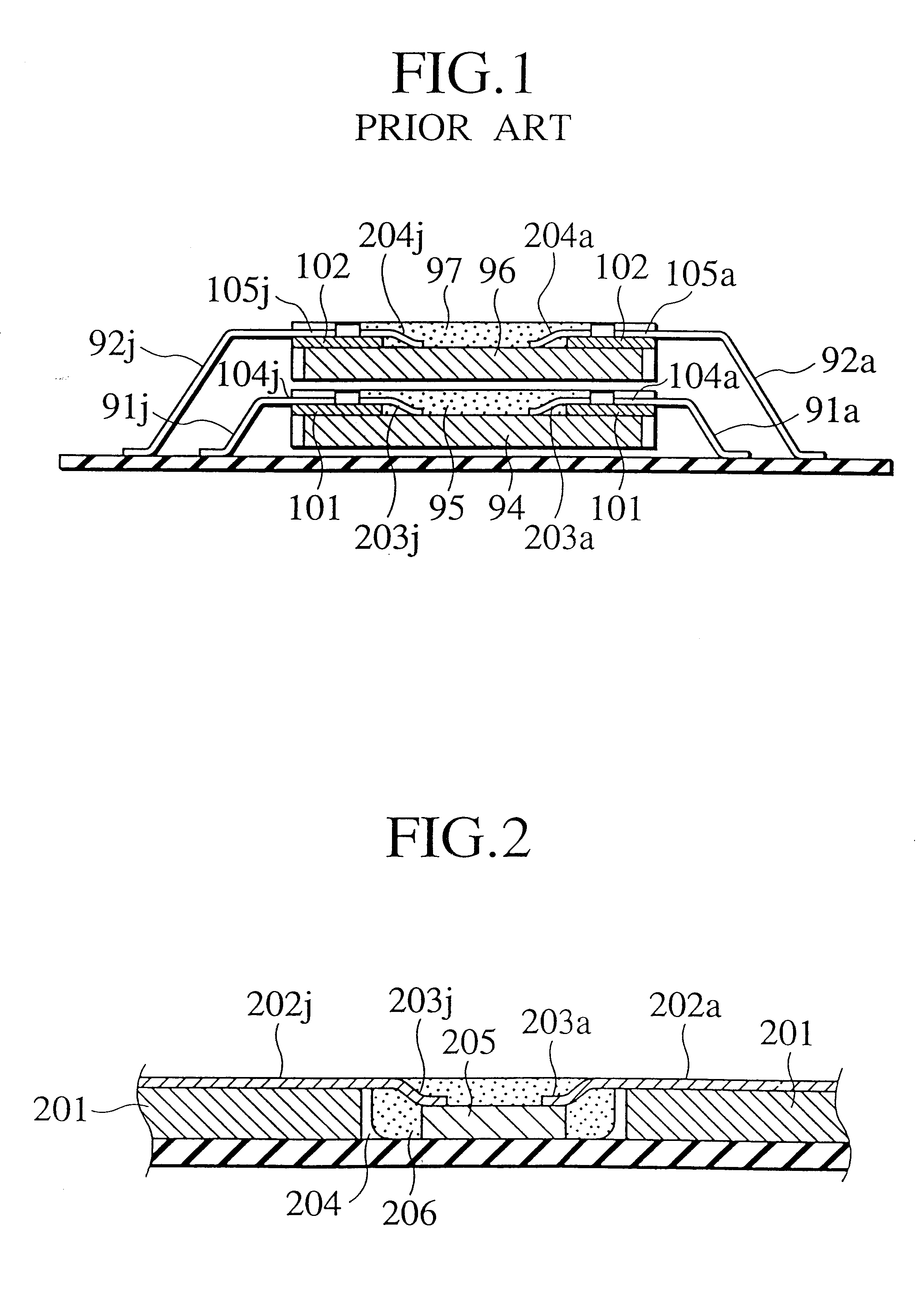

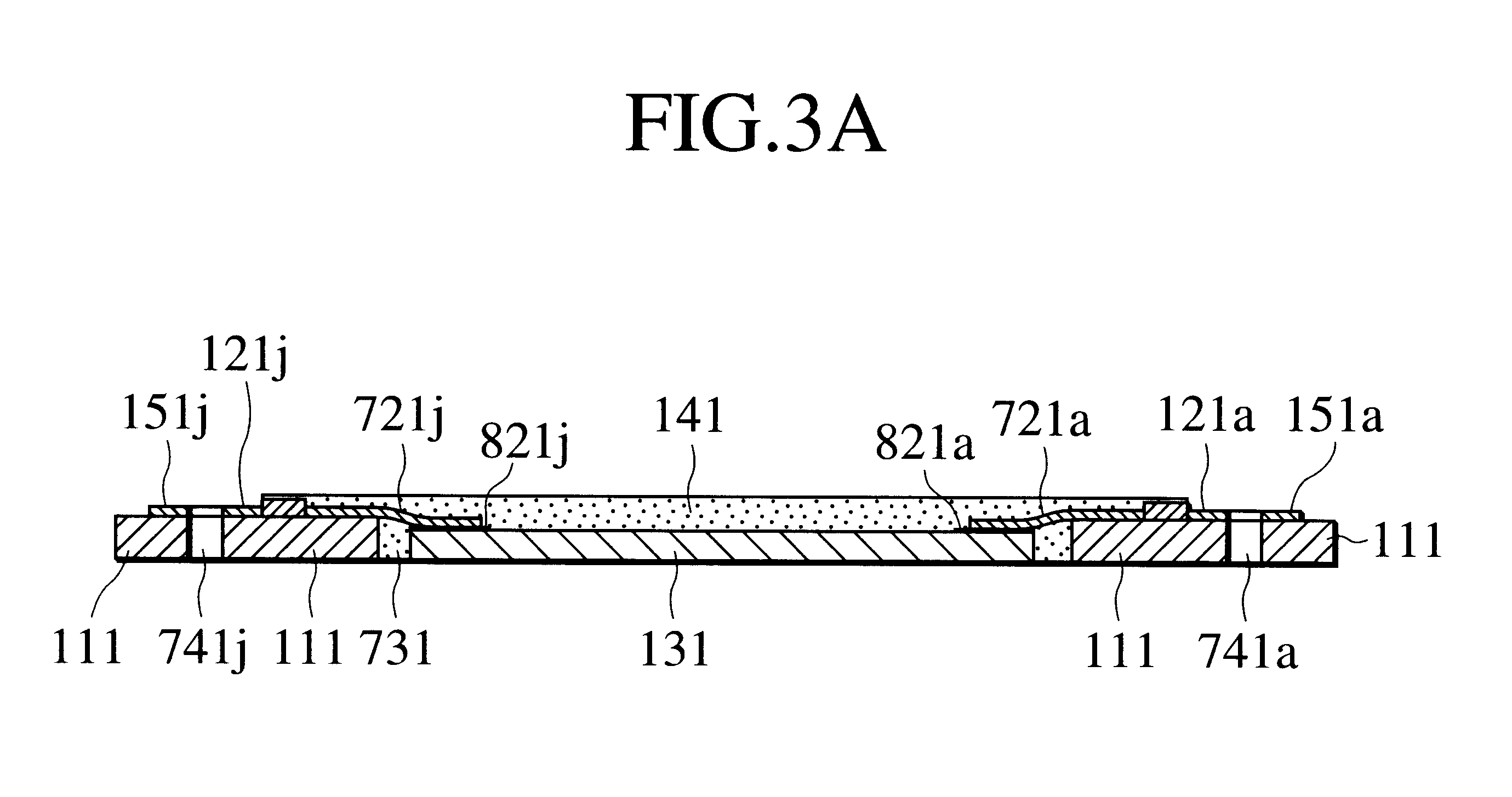

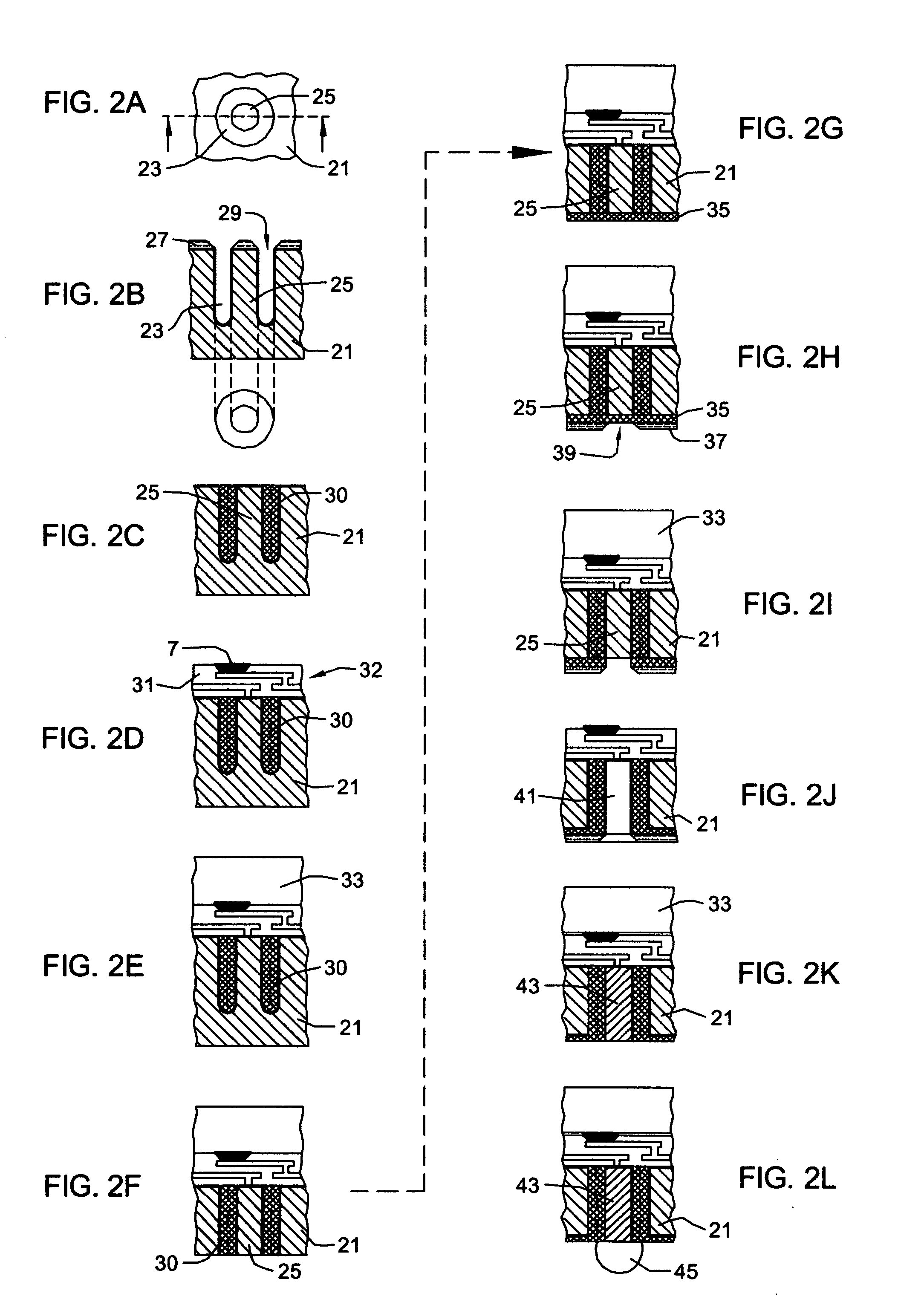

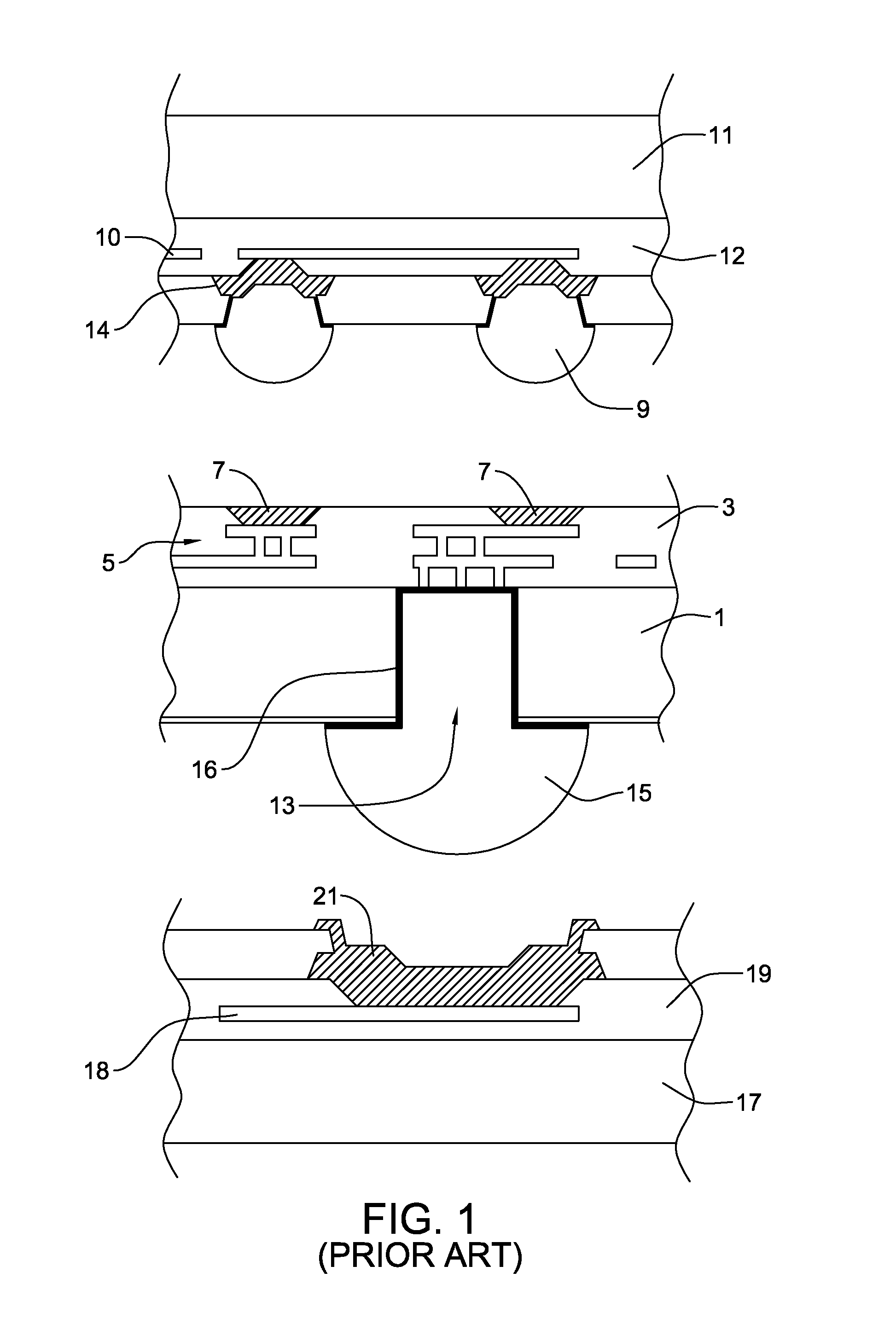

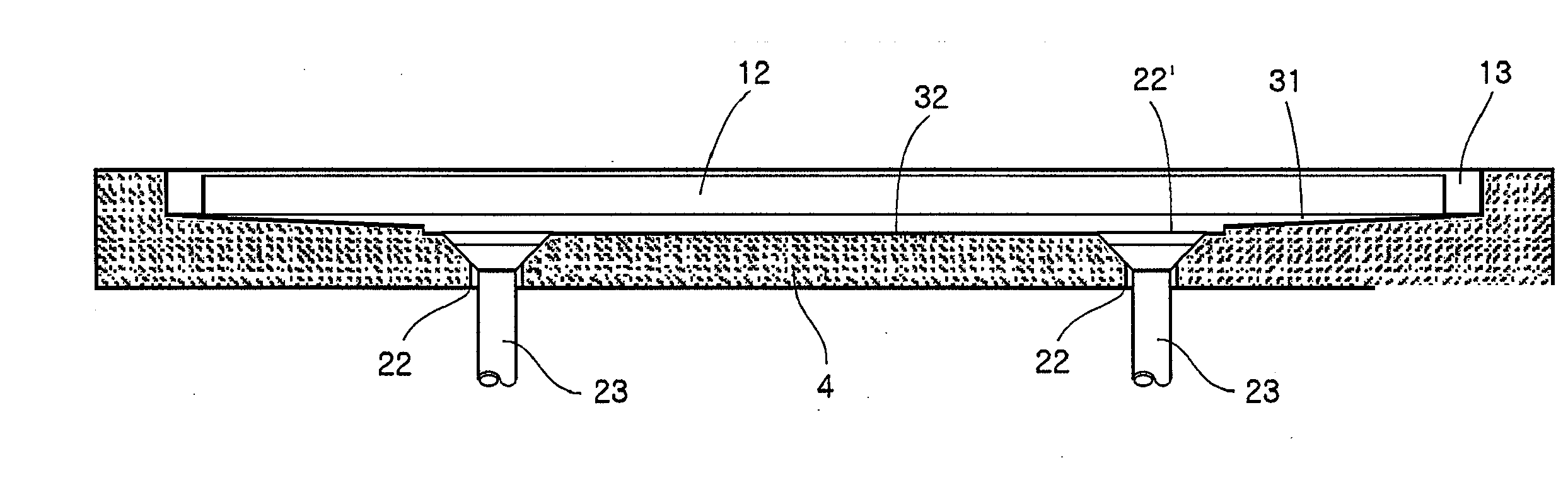

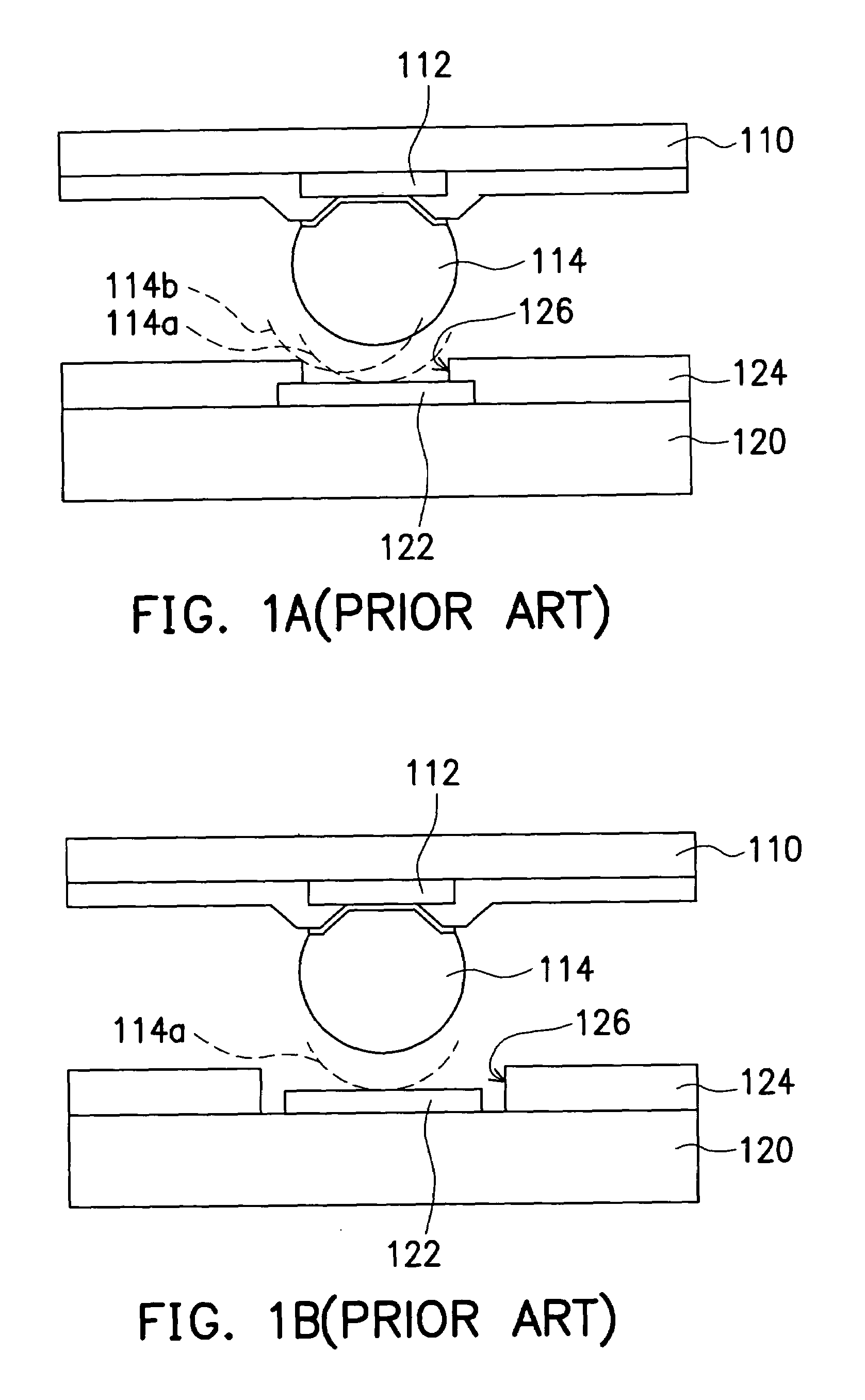

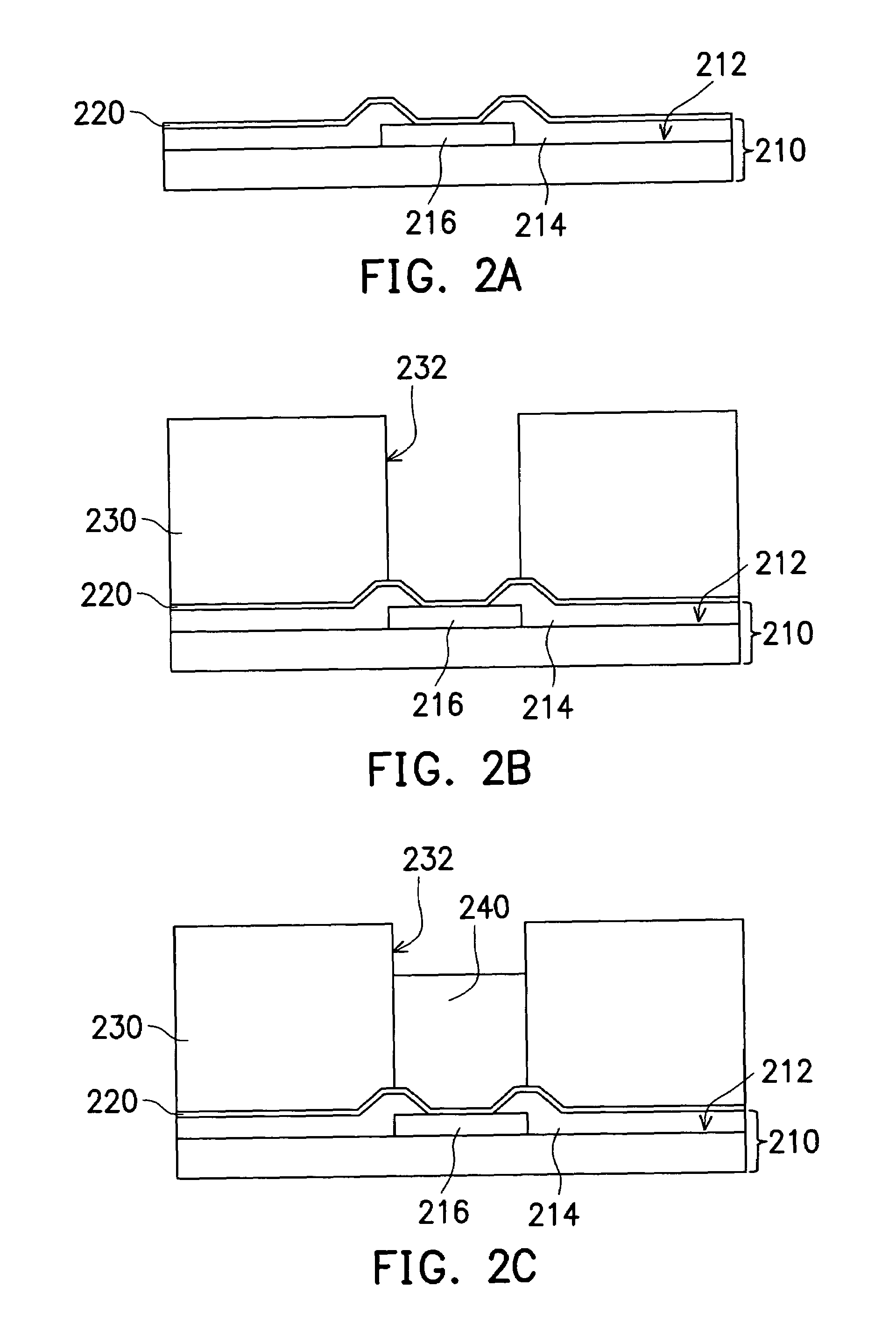

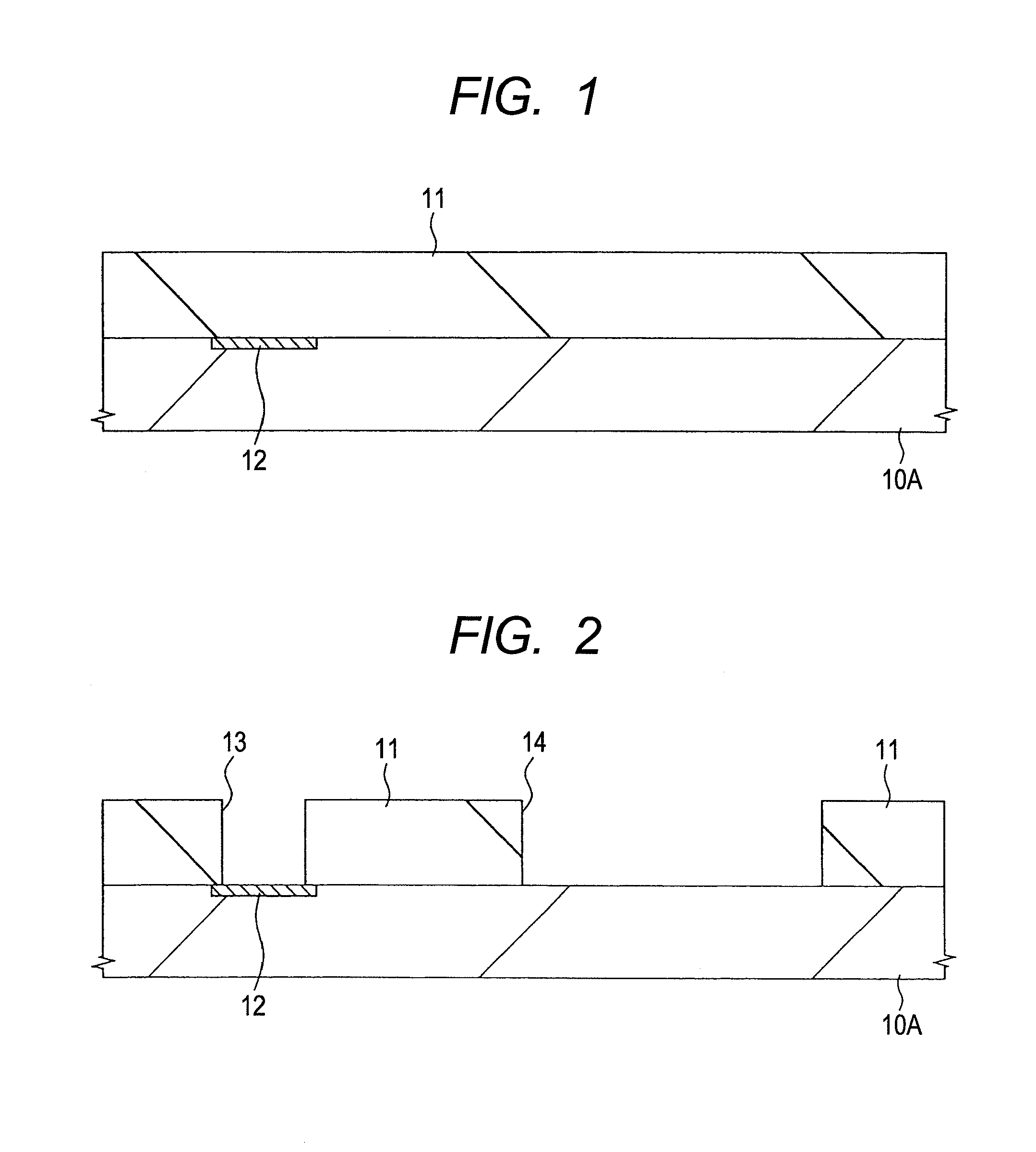

Package having very thin semiconductor chip, multichip module assembled by the package, and method for manufacturing the same

InactiveUS6239496B1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor package

A semiconductor package of this invention has an insulating substrates, wiring layers disposed on the surface of the insulating substrate, a semiconductor chip disposed in a device hole provided in the insulating substrate, inner-joint-conductors for connecting at least part of the bonding pads on the surface of the semiconductor chip to the corresponding inner-joint-conductors and connection lands connected to the wiring layers. The device hole is provided so that it goes through the center of the insulating substrate. The semiconductor chip is thinner than the insulating substrate. Then, this semiconductor chip is disposed in the device hole such that a bottom thereof is flush with a bottom plane of the insulating substrate. Further, this invention provides a MCM in which plural pieces of the thin semiconductor packages are laminated. In the MCM, the semiconductor packages are laminated such that top and bottom faces of the thin silicon chip are inverted. Predetermined connection lands are electrically connected to each other through a connecting conductor. This MCM has a high mechanical strength in its stacked structure and there is a low possibility that crack may occur in the package due to stress in the bending direction.

Owner:KK TOSHIBA

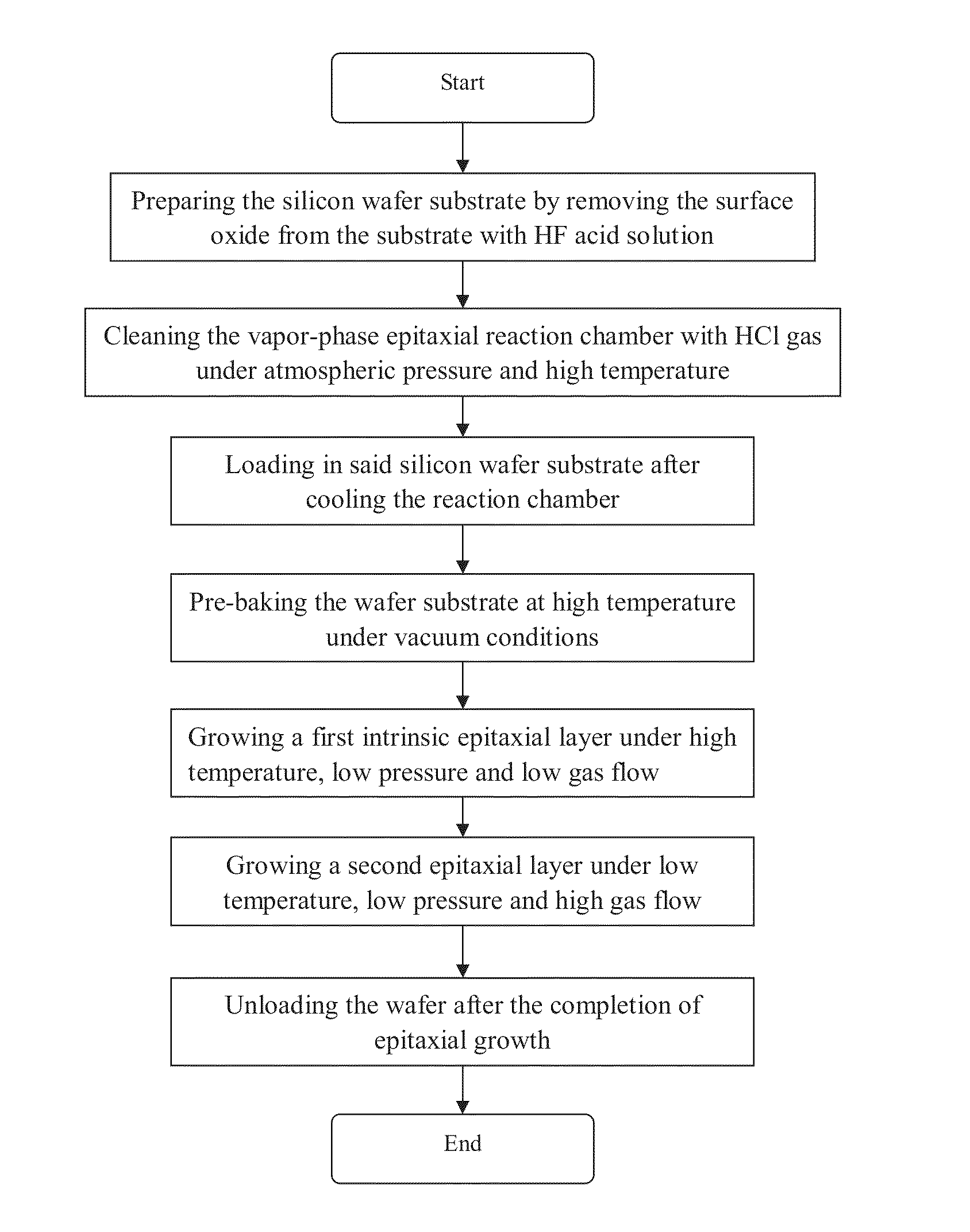

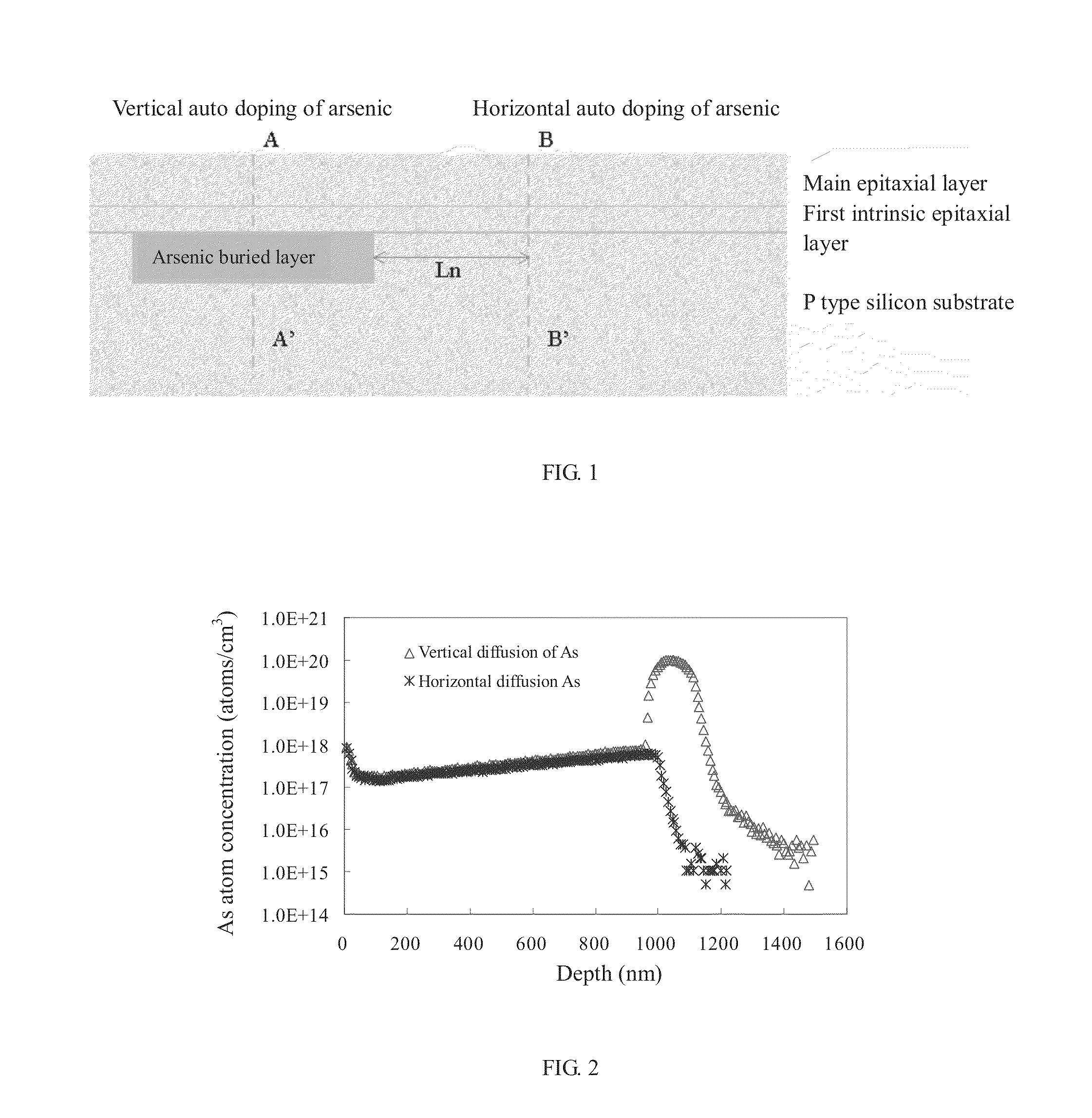

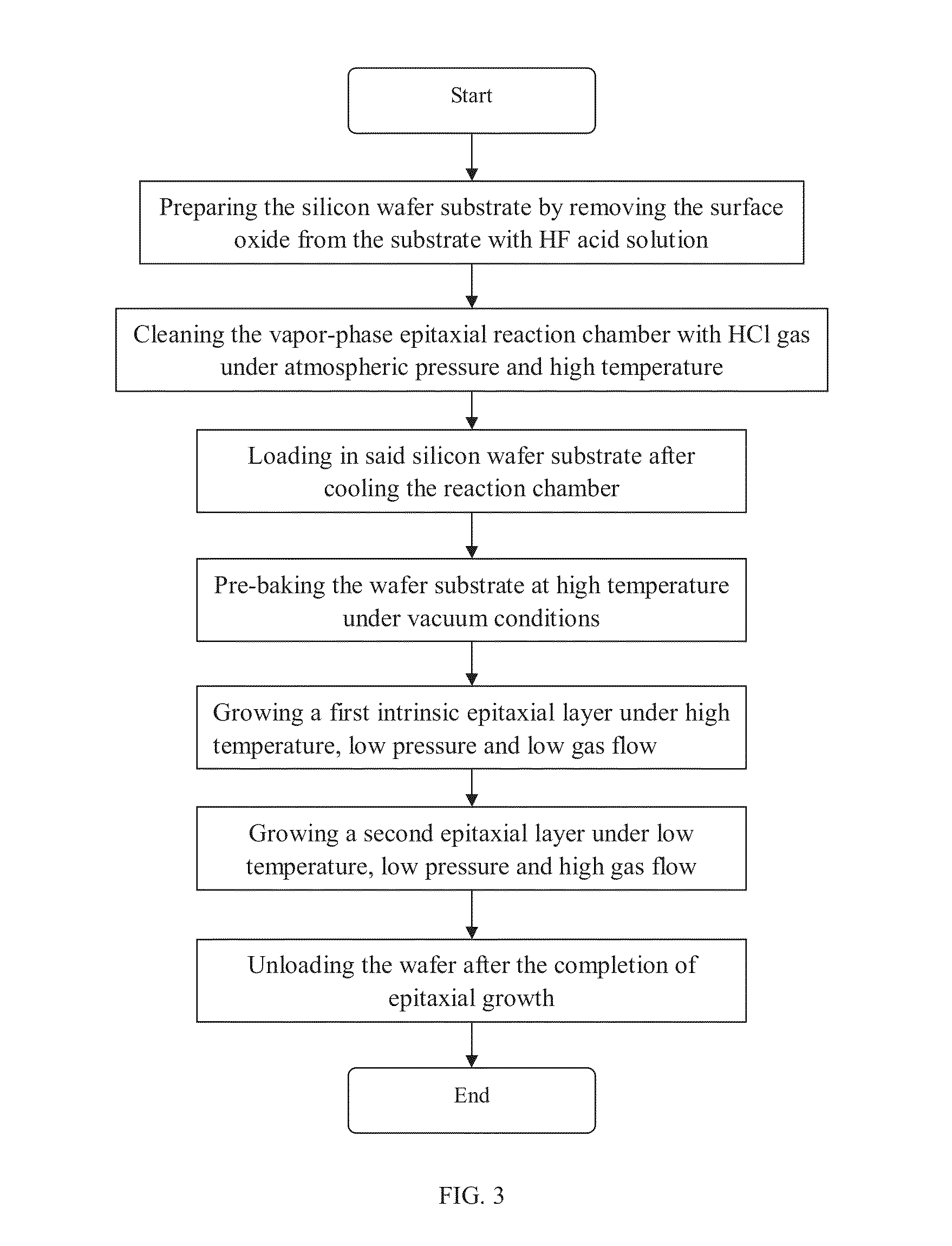

Method of epitaxial growth effectively preventing auto-doping effect

ActiveUS20130145984A1Improve equipment reliabilityInhibited DiffusionPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantMoisture

This invention relates to a method of epitaxial growth effectively preventing auto-doping effect. This method starts with the removal of impurities from the semiconductor substrate having heavily-doped buried layer region and from the inner wall of reaction chamber to be used. Then the semiconductor substrate is loaded in the cleaned reaction chamber to be pre-baked under vacuum conditions so as to remove moisture and oxide from the surface of said semiconductor substrate before the extraction of the dopant atoms desorbed from the surface of the semiconductor substrate. Next, under high temperature and low gas flow conditions, a first intrinsic epitaxial layer is formed on the surface of said semiconductor substrate where the dopant atoms have been extracted out. Following this, under low temperature and high gas flow conditions, a second epitaxial layer of required thickness is formed on the structural surface of the grown intrinsic epitaxial layer. Last, silicon wafer is unloaded after cooling. This method can prevent auto-doping effect during the epitaxial growth on semiconductor substrate and thus ensure the performance and enhance the reliability of the devices in peripheral circuit region.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

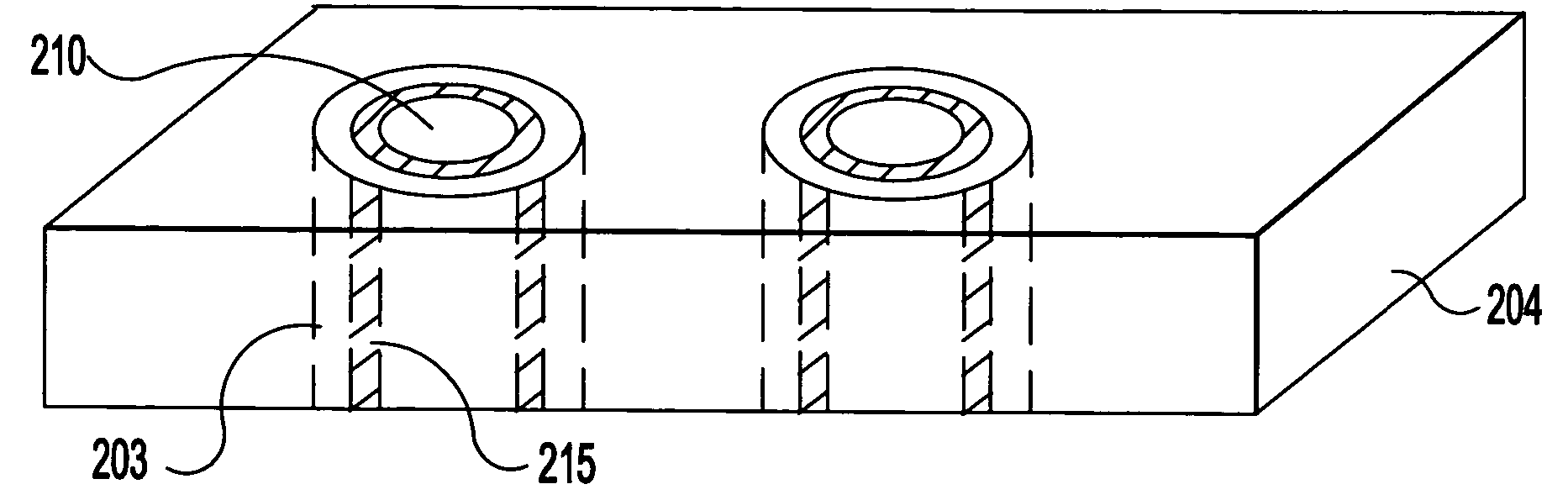

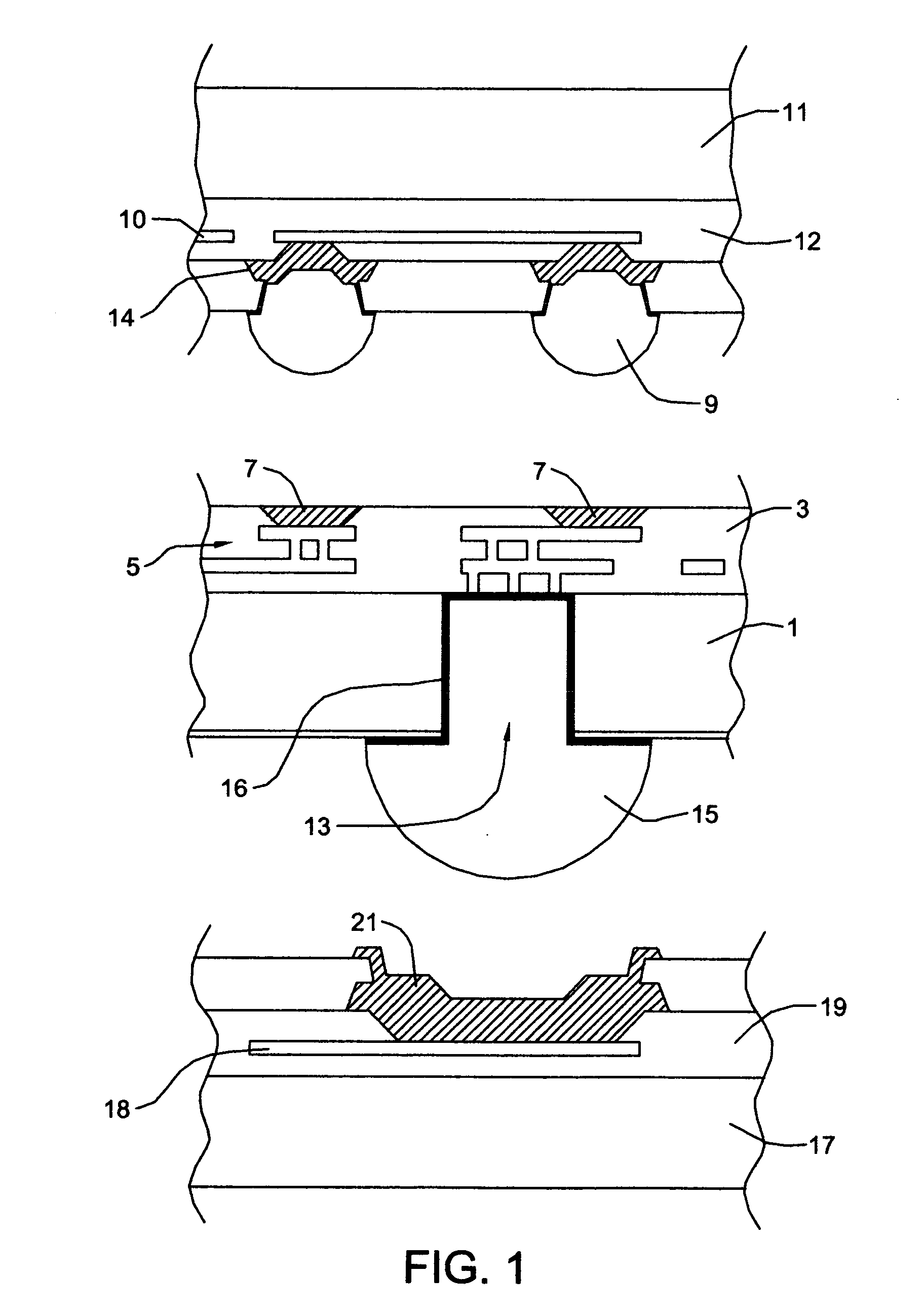

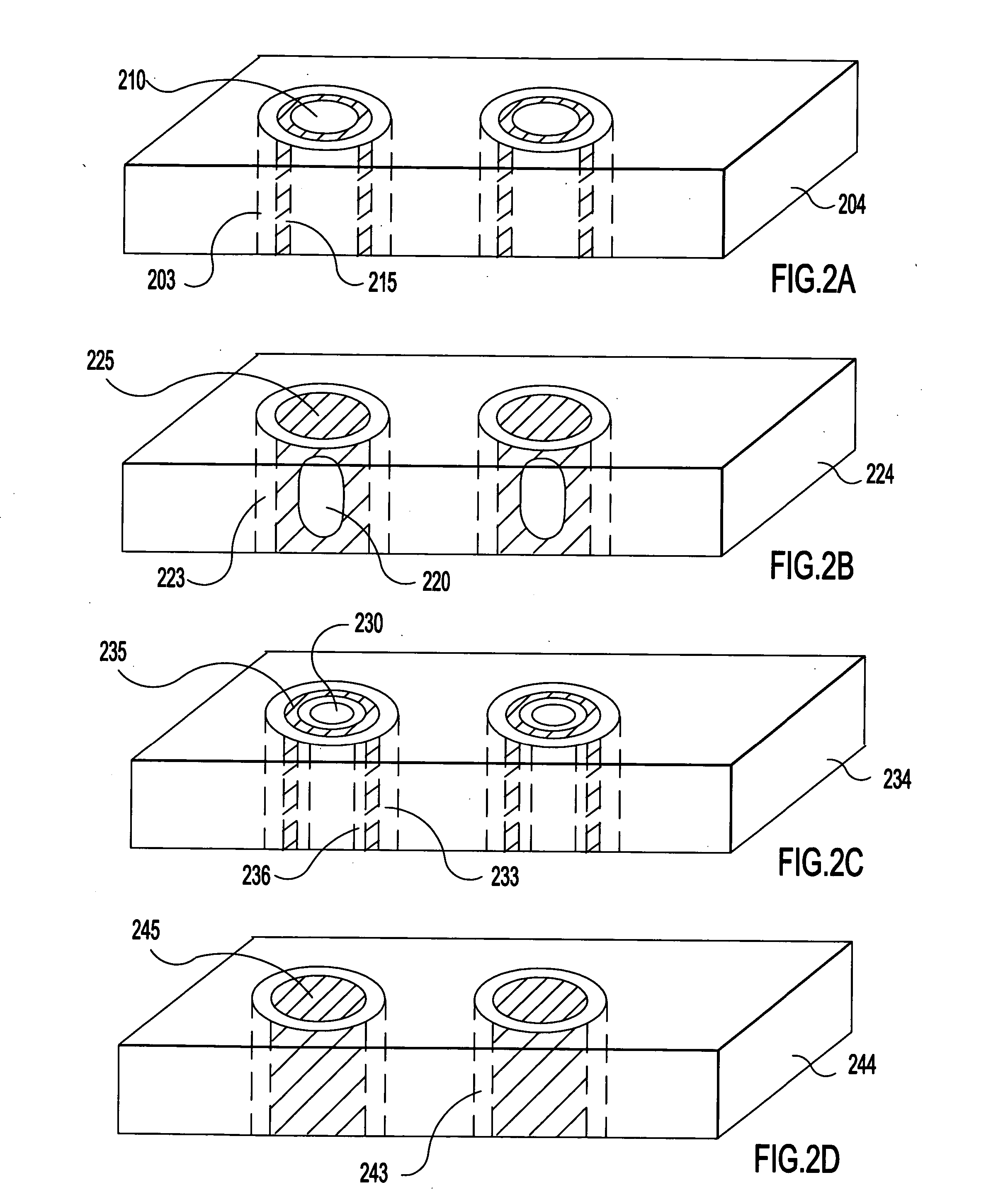

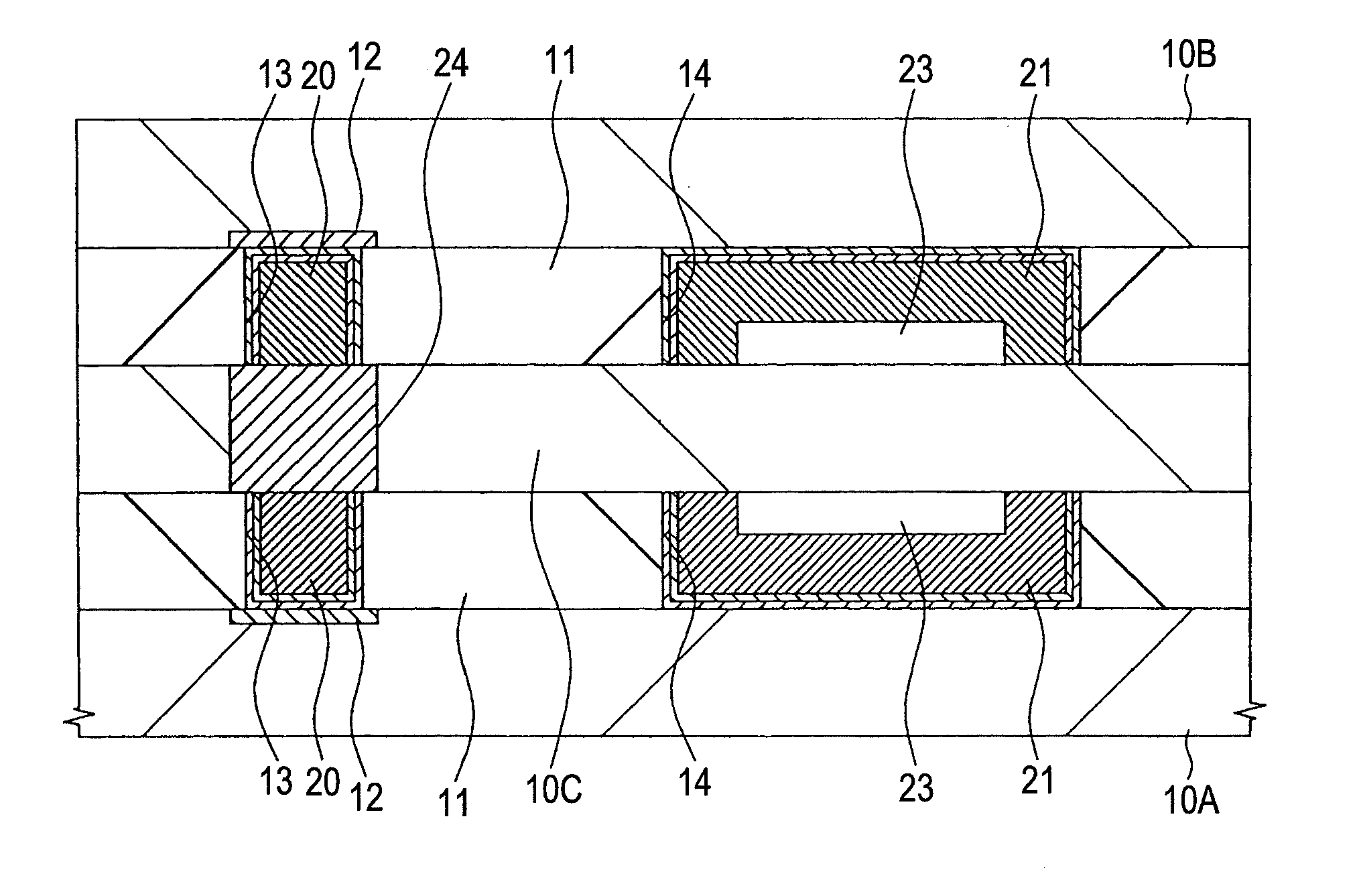

Conductive through via structure and process for electronic device carriers

ActiveUS20070048896A1Improve methodSimple structureCoupling device connectionsSemiconductor/solid-state device detailsDistal portionConductive materials

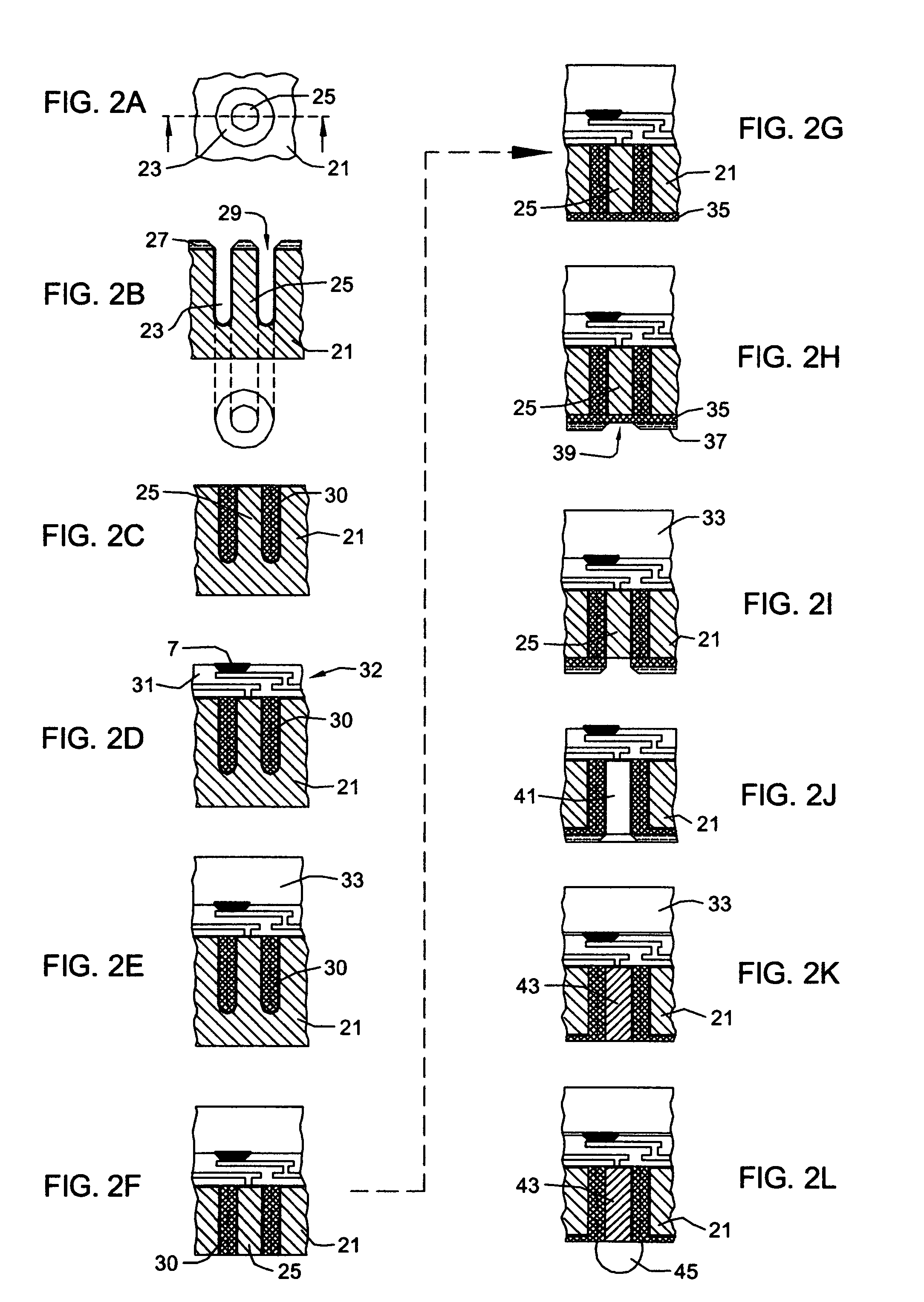

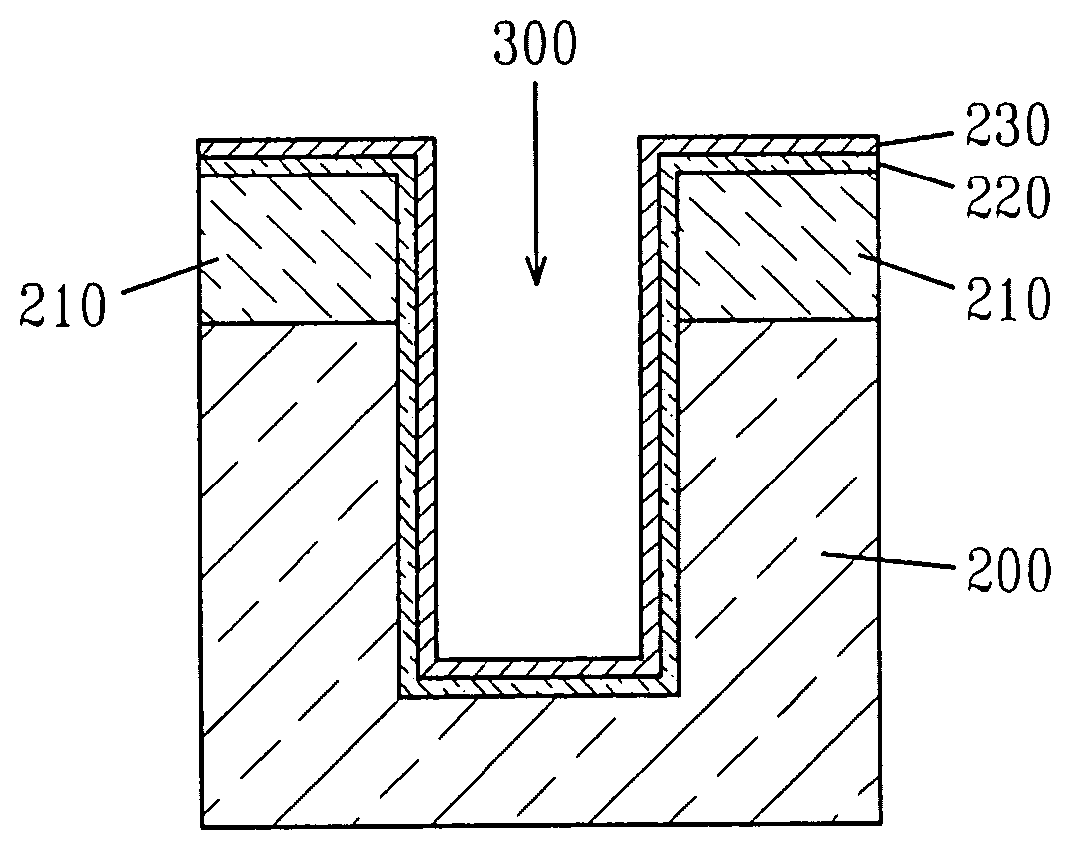

Conductive through vias are formed in electronic devices and electronic device carrier, such as, a silicon chip carrier. An annulus cavity is etched into the silicon carrier from the top side of the carrier and the cavity is filled with insulating material to form an isolation collar around a silicon core region. An insulating layer with at least one wiring level, having a portion in contact with the silicon core region, is formed on the top side of the carrier. Silicon is removed from the back side of the carrier sufficient to expose the distal portion of the isolation collar. The core region is etched out to expose the portion of the wiring level in contact with the silicon core region to form an empty via. The via is filled with conductive material in contact with the exposed portion of the wiring level to form a conductive through via to the wiring level. A solder bump formed, for example, from low melt C4 solder, is formed on the conductive via exposed on the carrier back side. The process acts to make the conductive via fill step independent of the via isolation step.

Owner:IBM CORP

Silicon chip carrier with conductive through-vias and method for fabricating same

InactiveUS20060027934A1Semiconductor/solid-state device detailsSolid-state devicesOptoelectronicsThermal expansion

A carrier structure and method for fabricating a carrier structure with through-vias each having a conductive structure with an effective coefficient of thermal expansion which is less than or closely matched to that of the substrate, and having an effective elastic modulus value which is less than or closely matches that of the substrate. The conductive structure may include concentric via fill areas having differing materials disposed concentrically therein, a core of the substrate material surrounded by an annular ring of conductive material, a core of CTE-matched non-conductive material surrounded by an annular ring of conductive material, a conductive via having an inner void with low CTE, or a full fill of a conductive composite material such as a metal-ceramic paste which has been sintered or fused.

Owner:GLOBALFOUNDRIES INC

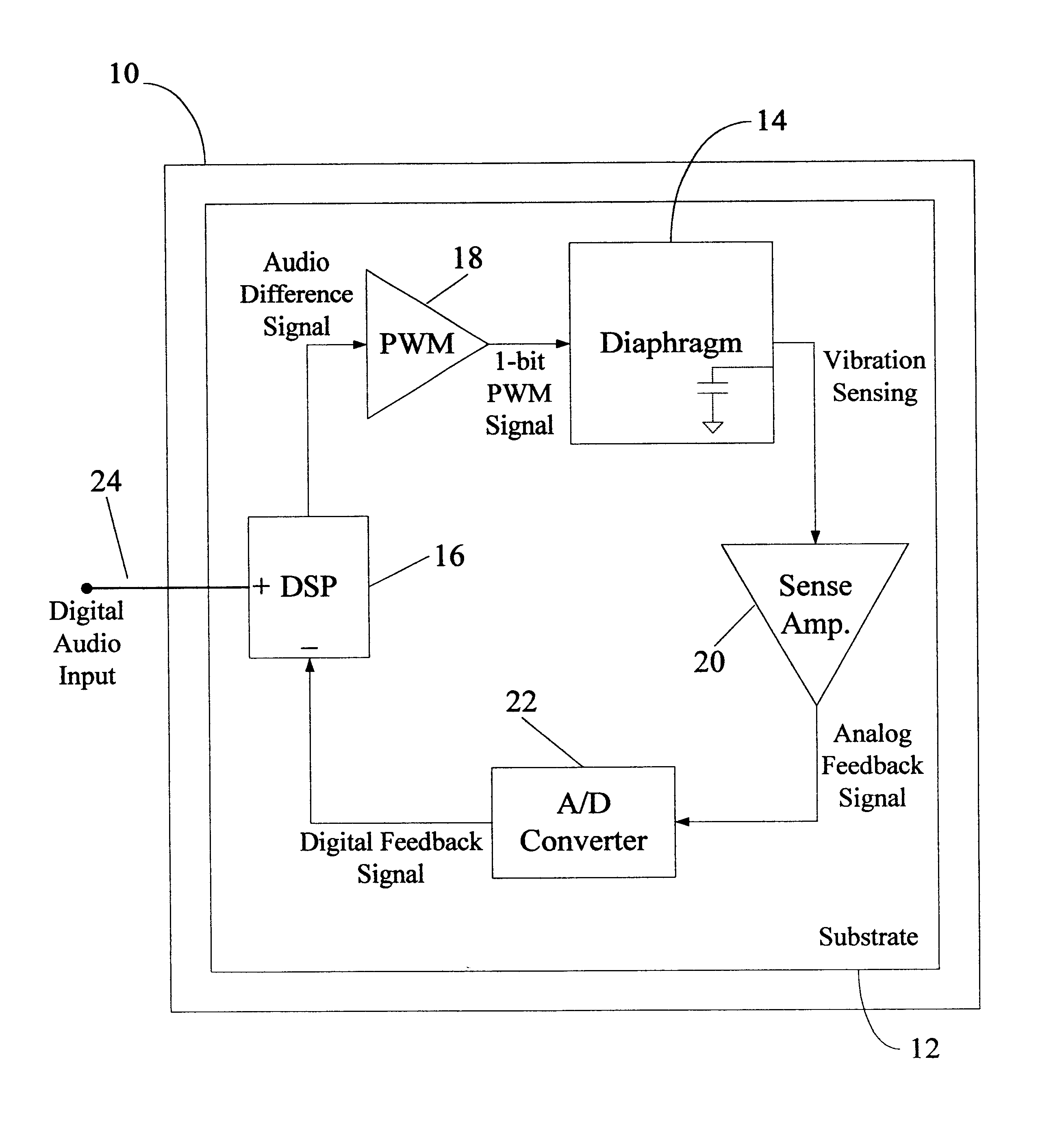

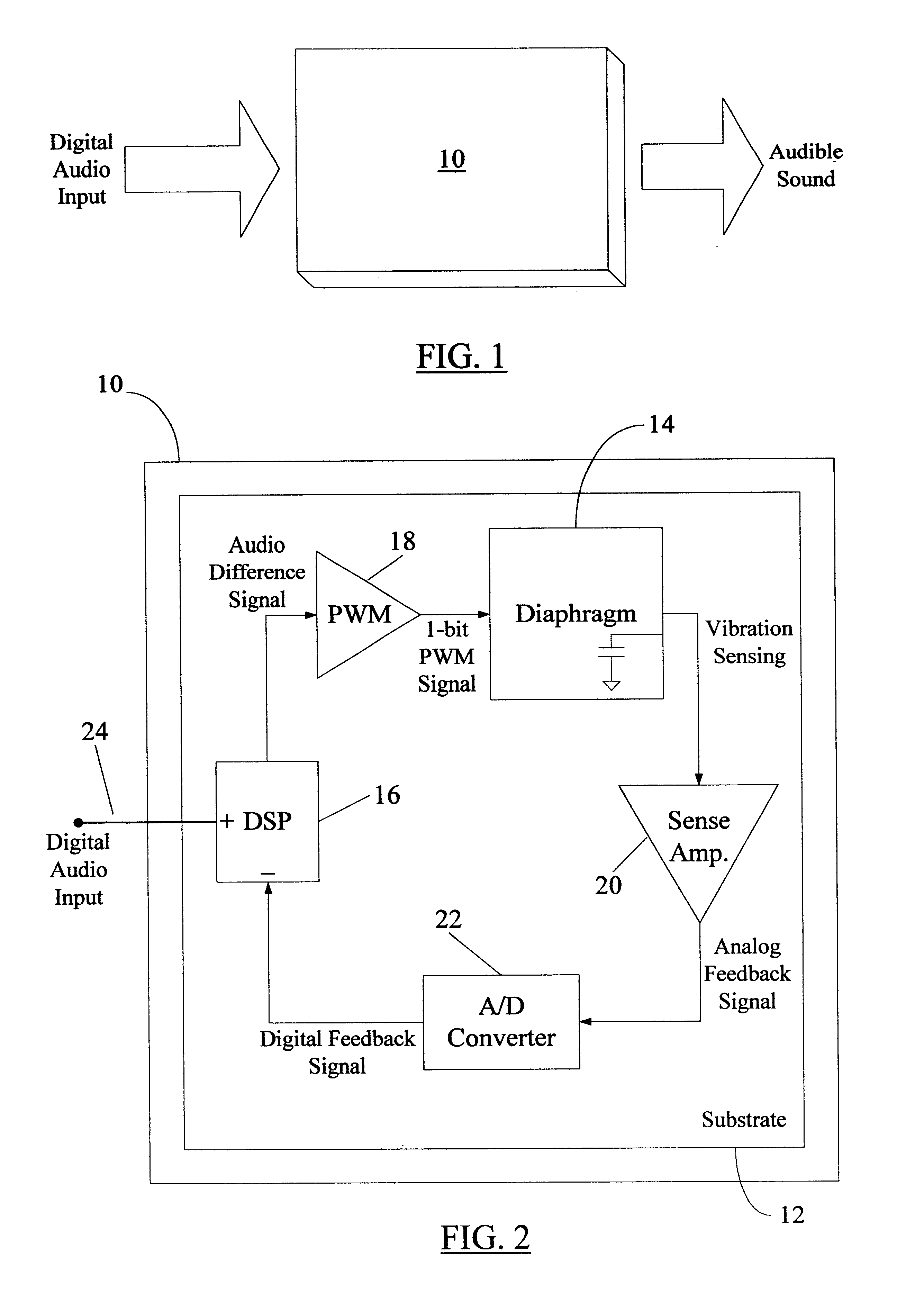

MEMS digital-to-acoustic transducer with error cancellation

InactiveUS6829131B1Low production costHigh quality audio reproductionCircuit-breaking switches for excess currentsTelevision system detailsTransducerEngineering

An acoustic transducer comprising a substrate; and a diaphragm formed by depositing a micromachined membrane onto the substrate. The diaphragm is formed as a single silicon chip using a CMOS MEMS (microelectromechanical systems) semiconductor fabrication process. The curling of the diaphragm during fabrication is reduced by depositing the micromachined membrane for the diaphragm in a serpentine-spring configuration with alternating longer and shorter arms. As a microspeaker, the acoustic transducer of the present invention converts a digital audio input signal directly into a sound wave, resulting in a very high quality sound reproduction at a lower cost of production in comparison to conventional acoustic transducers. The micromachined diaphragm may also be used in microphone applications.

Owner:CARNEGIE MELLON UNIV

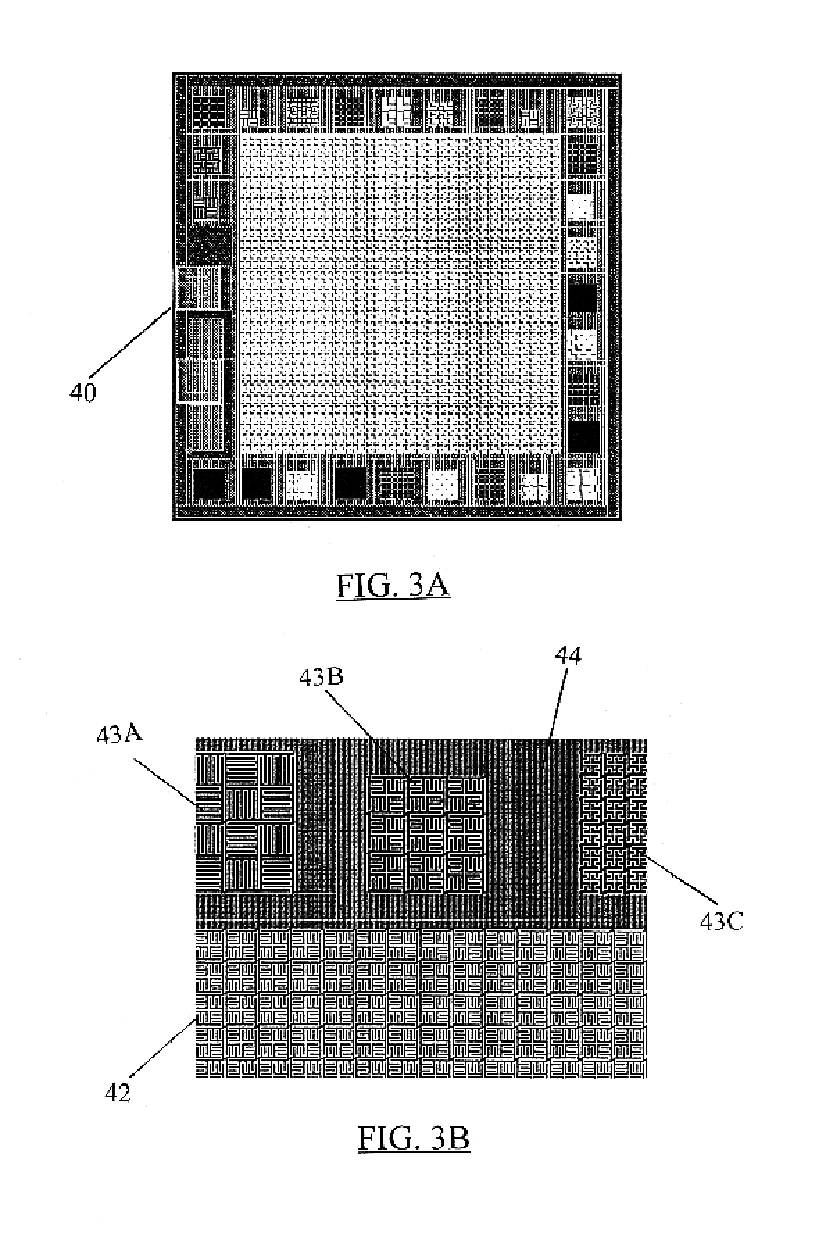

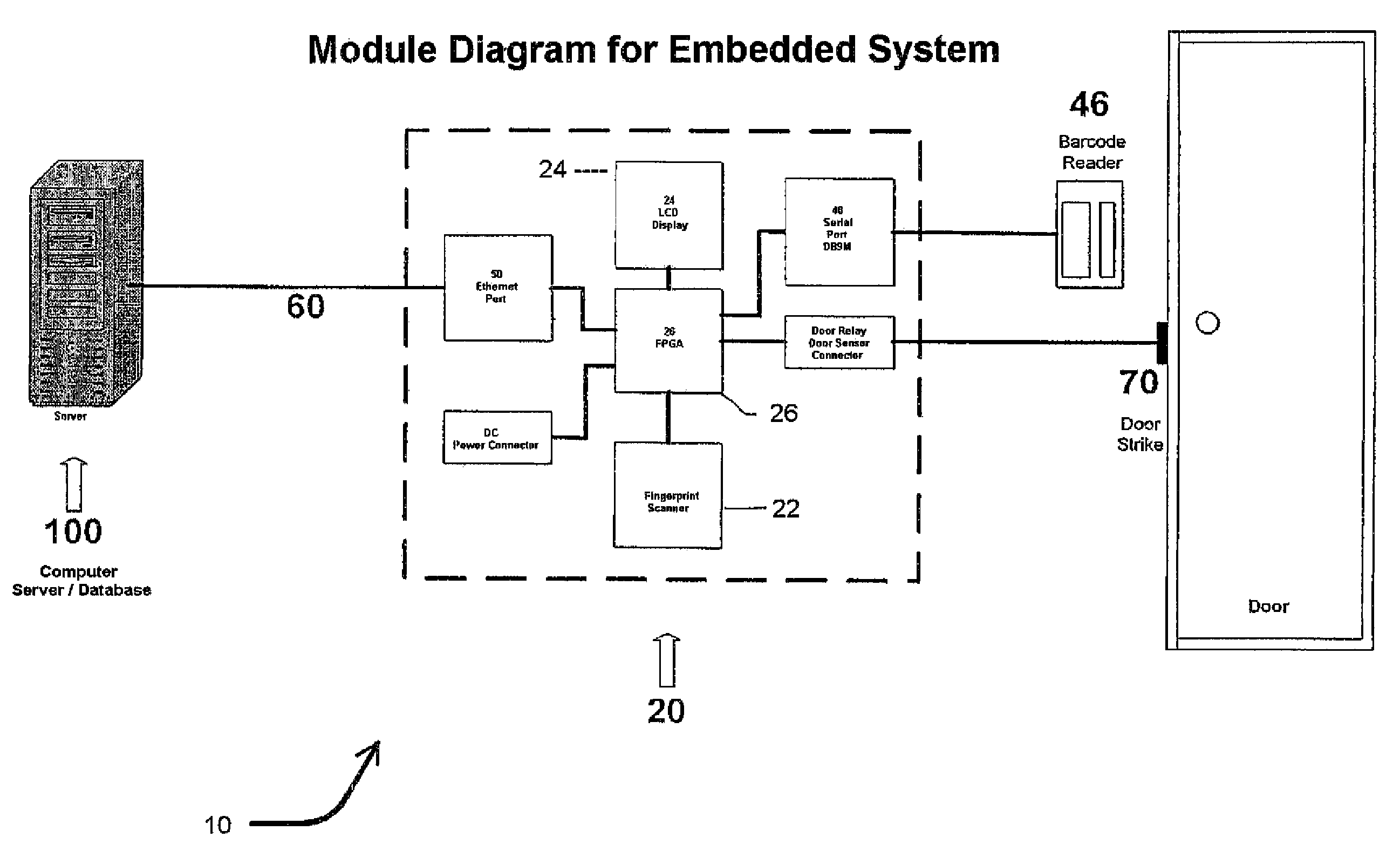

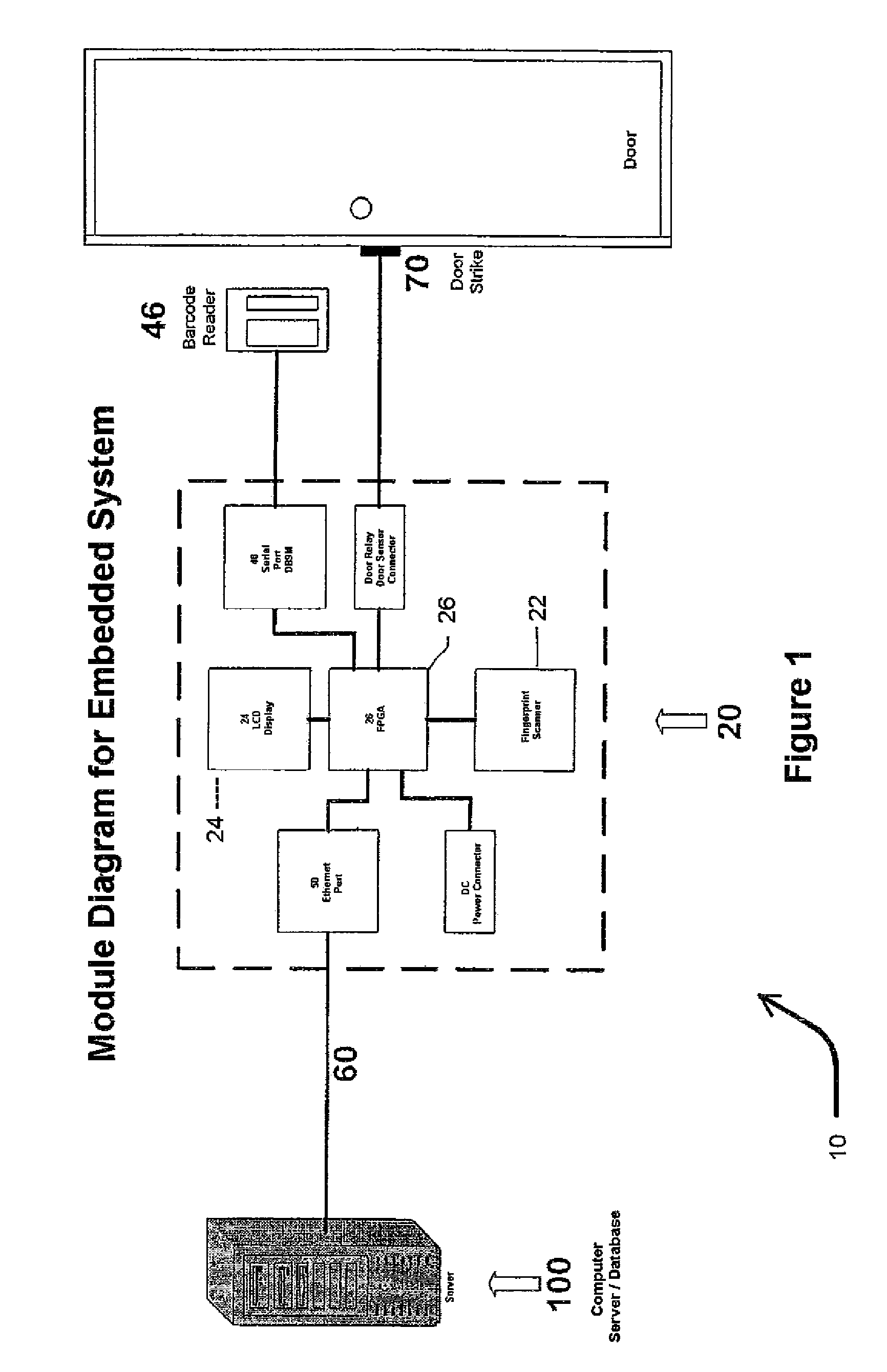

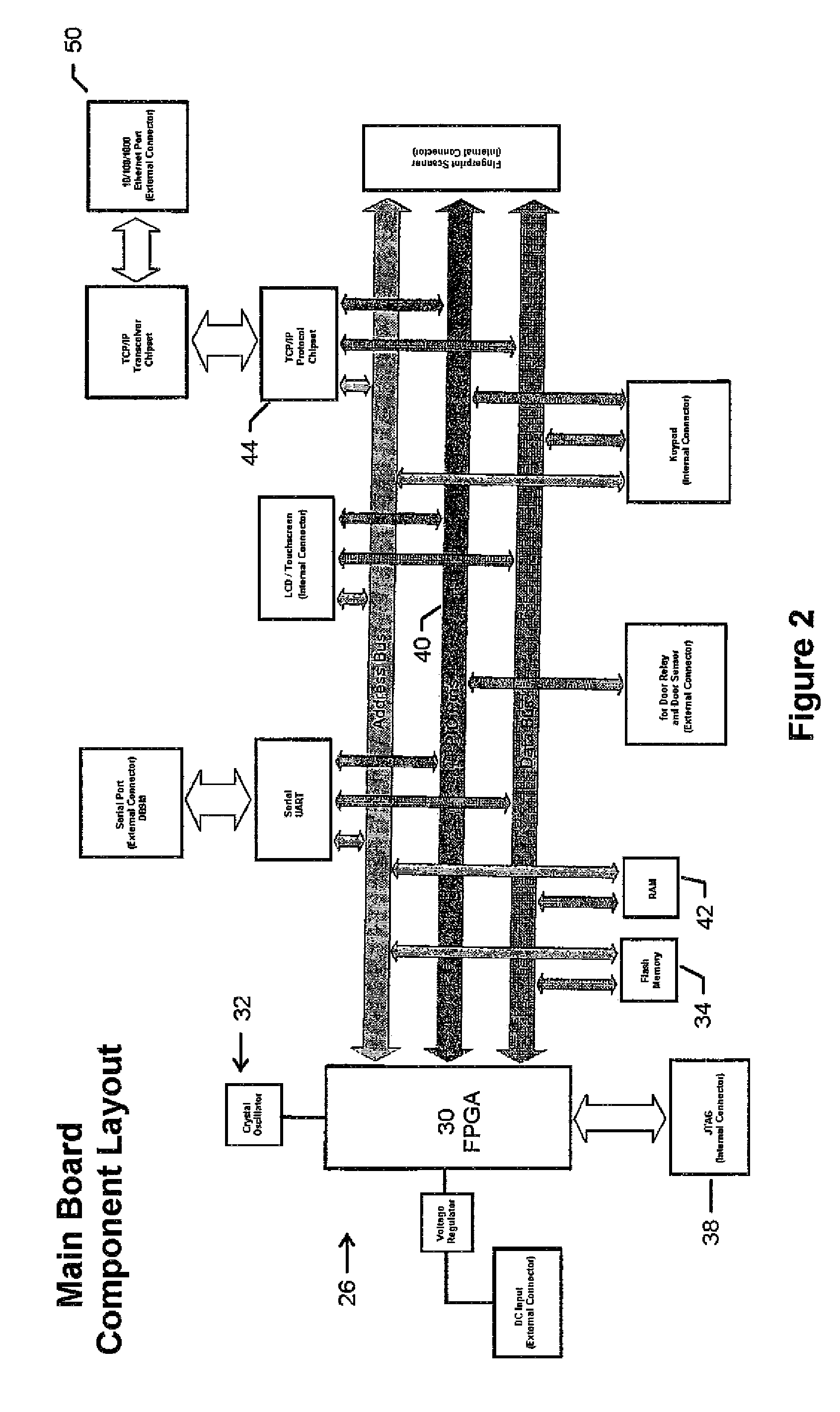

Biometric access control and time and attendance network including configurable system-on-chip (CSOC) processors with embedded programmable logic

ActiveUS7424618B2Compact efficient designCost efficient designElectric signal transmission systemsDigital data processing detailsHard disc driveHuman interaction

A biometric access control and time and attendance system comprises an integrated network including one or more remote access devices in electronic communication with a computer database. Each remote access device comprises a silicon chip based system and preferably includes a biometric input device, a liquid crystal display (LCD), computer processing capabilities based on embedded system architecture with configurable system-on-chip (CSOC) technology, and an electrical output for controlling a door lock or the like. The use of CSOC architecture in lieu of conventional personal computer technology (e.g. mother boards, hard drives, video controllers and the like) allows for a more compact and cost efficient design. A plurality of remote access devices is configured for communication with a primary computer database wherein data corresponding to biometric samples for all authorized users is stored. In an embodiment wherein the biometric input devices comprise fingerprint scanners, the devices are configured to facilitate fingerprint identification by incorporating an auto-targeting capability that enables the user to simply place his or her finger on the fingerprint scanner whereafter the system adjusts the scanned image by automatically shifting the scanned image data to a properly targeted position thereby enabling the system compare the scanned print to the biometric samples in the system's data storage memory. Auto-targeting capability eliminates the requirement for manual targeting present in systems of the background art thereby improving system performance and minimizing reliance on human interaction. The present invention contemplates the use of auto-targeting with other biometric systems, such as facial recognition and / or retinal scanning systems, or any other biometric identification technology.

Owner:PROFILE SOLUTIONS

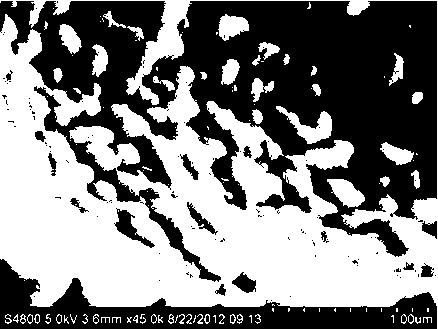

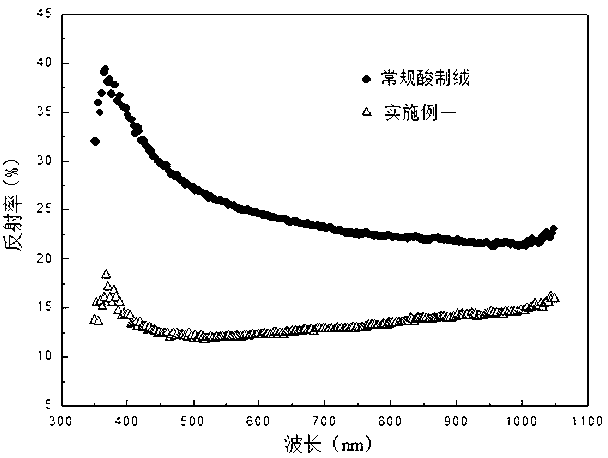

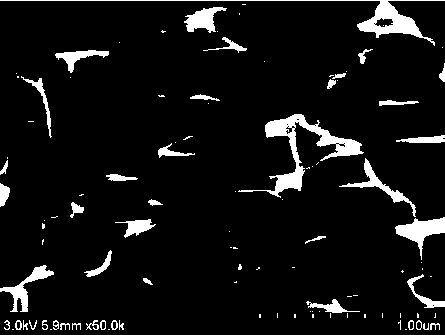

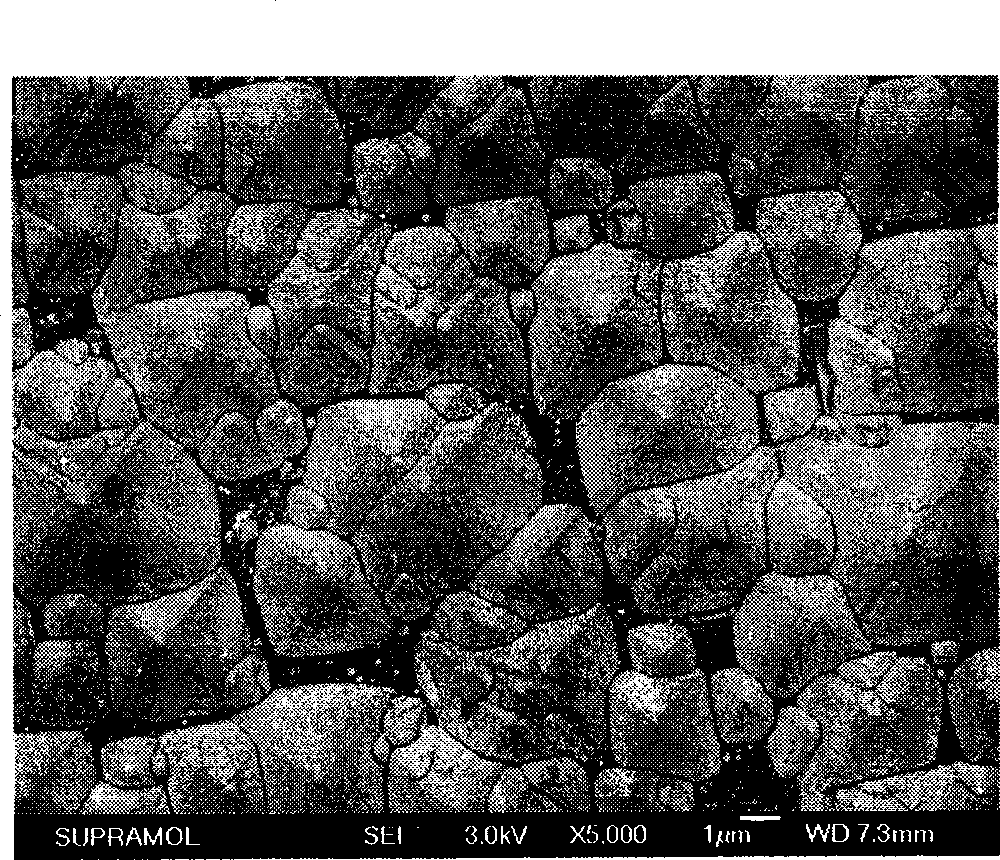

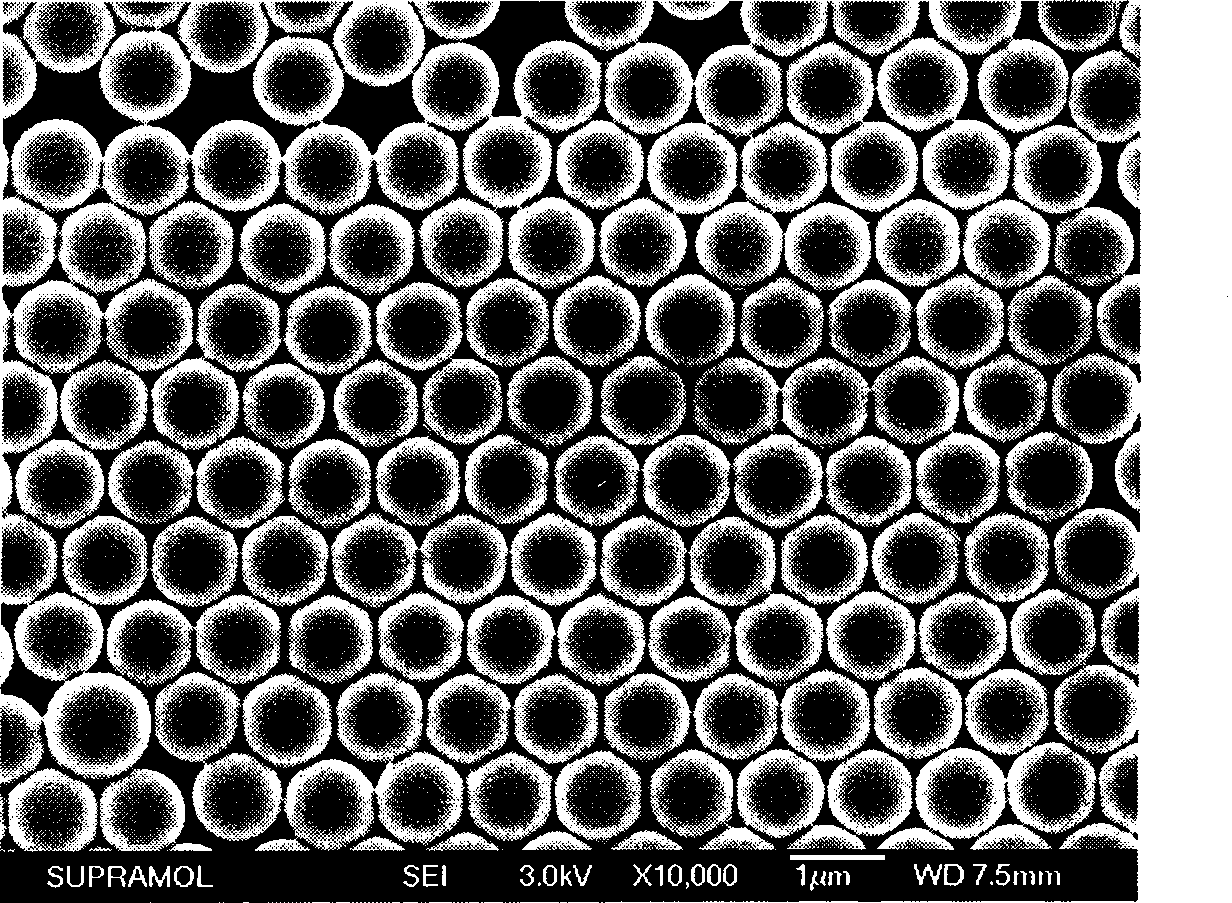

Textured structure of crystalline silicon solar cell and preparation method thereof

ActiveCN103219428AImprove conversion efficiencySimple manufacturing methodPhotovoltaic energy generationSemiconductor devicesMicrometerSpins

The invention discloses a preparation method of a textured structure of a crystalline silicon solar cell. The method includes the steps of (1) cleaning and texture preparation, (2) soaking a silicon wafer in a solution containing metal ions to enable the surface of the silicon wafer to be coated with a layer of metal nanometer particles, (3) corroding the surface of the silicon wafer to form a nanometer-grade texture, (4) cleaning to remove the metal particles, (5) carrying out microstructure amendment etching in second chemical corrosive liquid, and (6) cleaning and spin-drying. As is proved by a test, the size of the textured structure is between 100nm-500nm; the textured structure is of a nanopore shape with a large hole diameter and a small depth, or a nanometer pyramid with edge angles, or of a nanometer pit shape structure with an edge angle nanometer cone body or with an edge angle; and compared with a nanometer-micrometer composite textured structure disclosed in CN102610692A, the textured structure enables conversion efficiency of a cell piece to be improved by about 0.2%-0.5%, and an unexpected effect is achieved.

Owner:SUZHOU UNIV +1

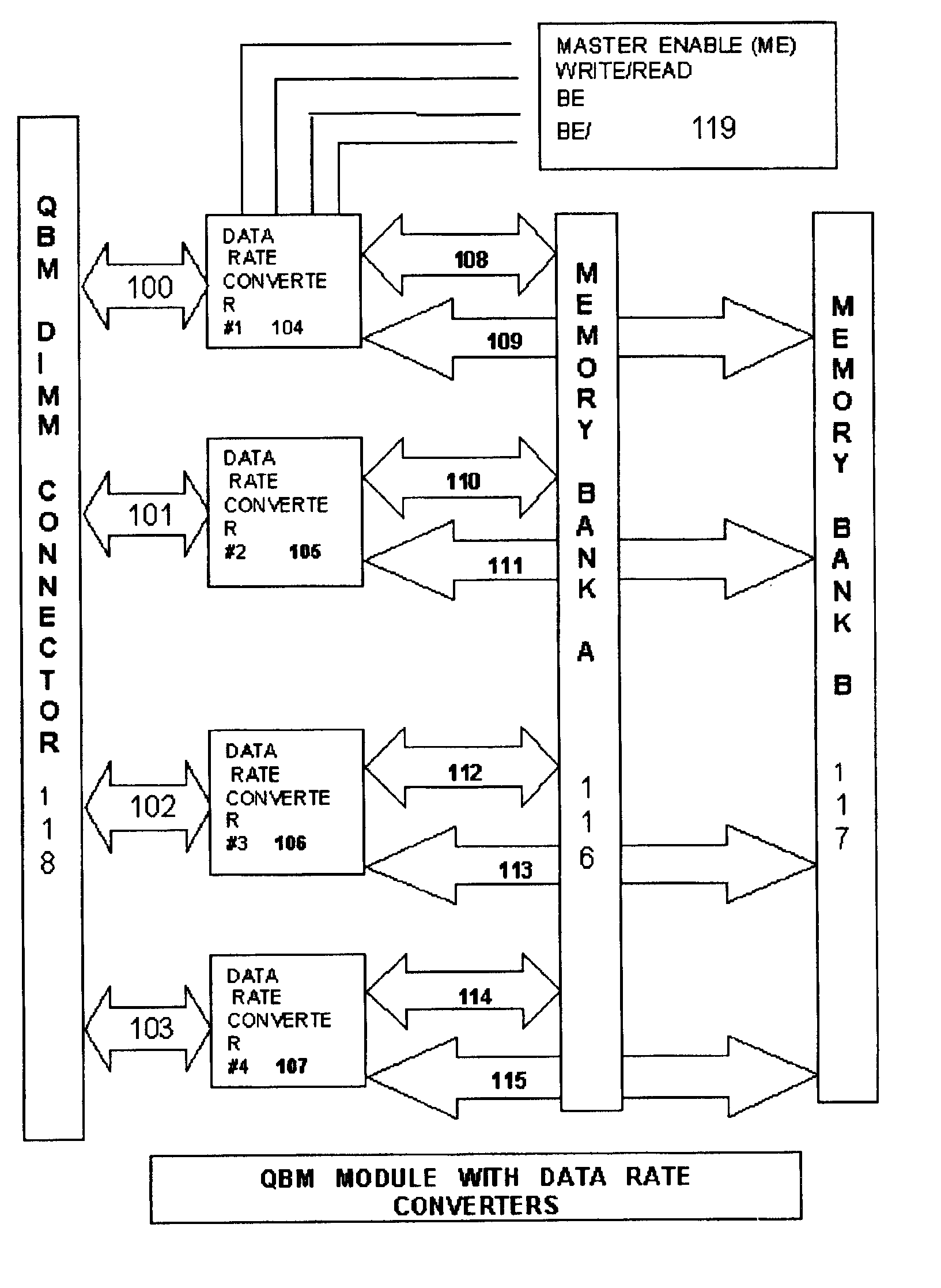

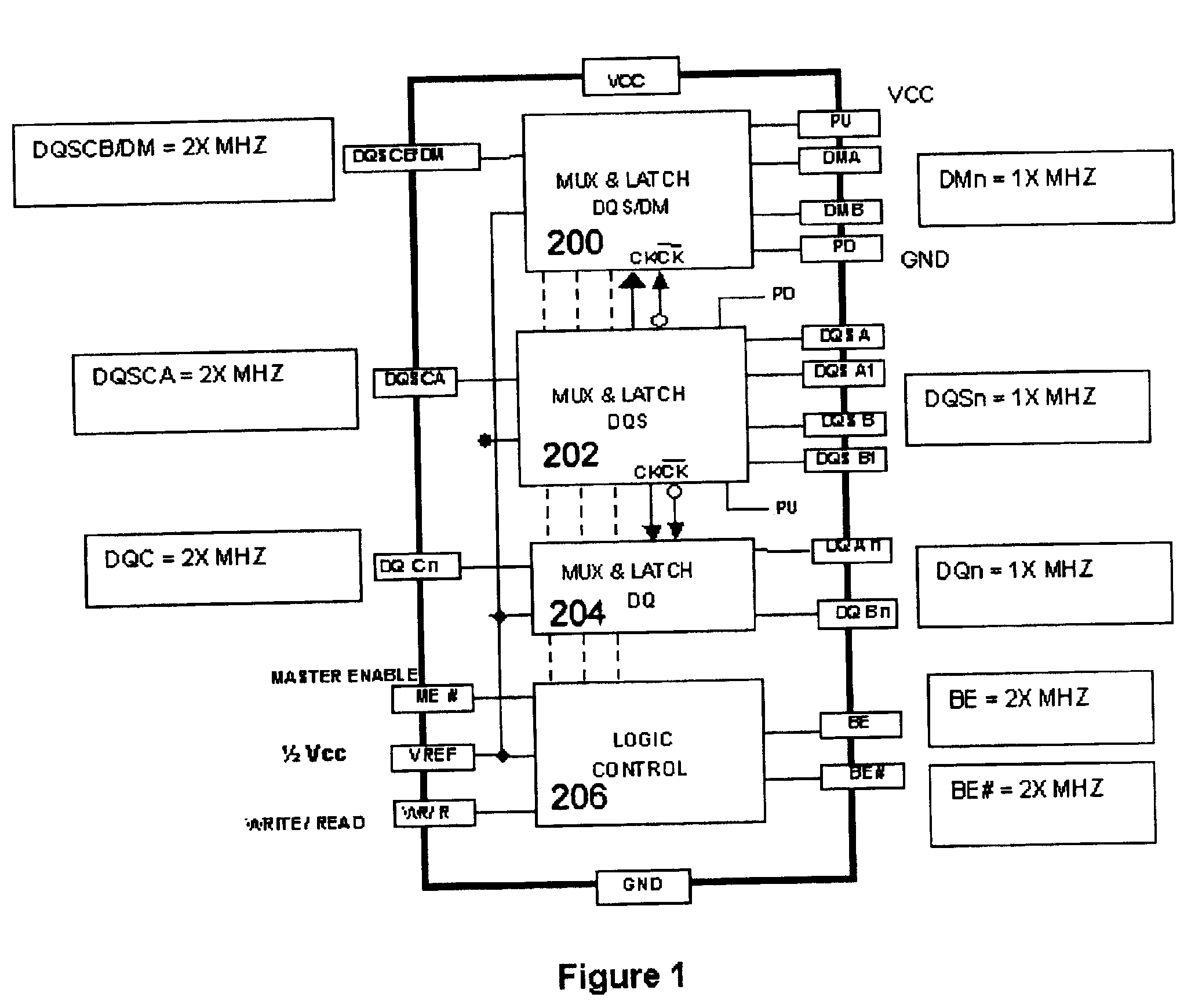

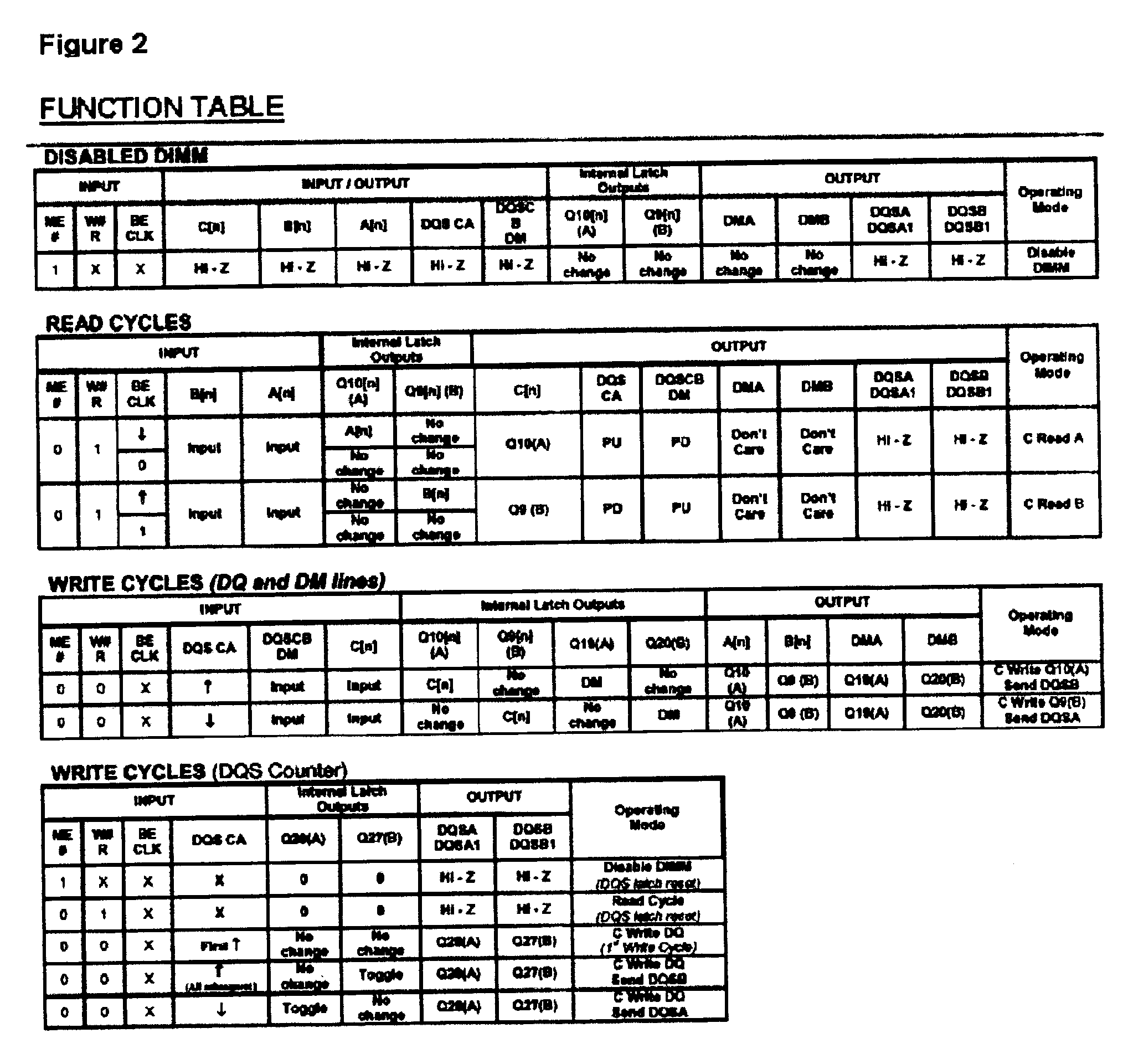

High-speed data-rate converting and switching circuit

InactiveUS6854042B1Extended durationMemory adressing/allocation/relocationDigital storageSignal onMemory bus

A high speed bidirectional data rate conversion circuit converts 1× data rate signals from attached devices on port A and port B to 2× data rate signals on bus C and further converts 2× high speed data rate signals on bus C to 1× data rate signals on ports A and B for memory devices attached to ports A and B. The usage of pass gate switches and combination of latches and counters is used to permit proper synchronization of the data signals, and to further generate strobe signals at both system bus and memory bus sides, and to further generate data mask signals for writing to the memory bus side of the circuit. The collection of such switching elements and latches are provided on a single silicon chip which includes of the functions of the invention.

Owner:URENSCHI ASSETAB LIABILITY

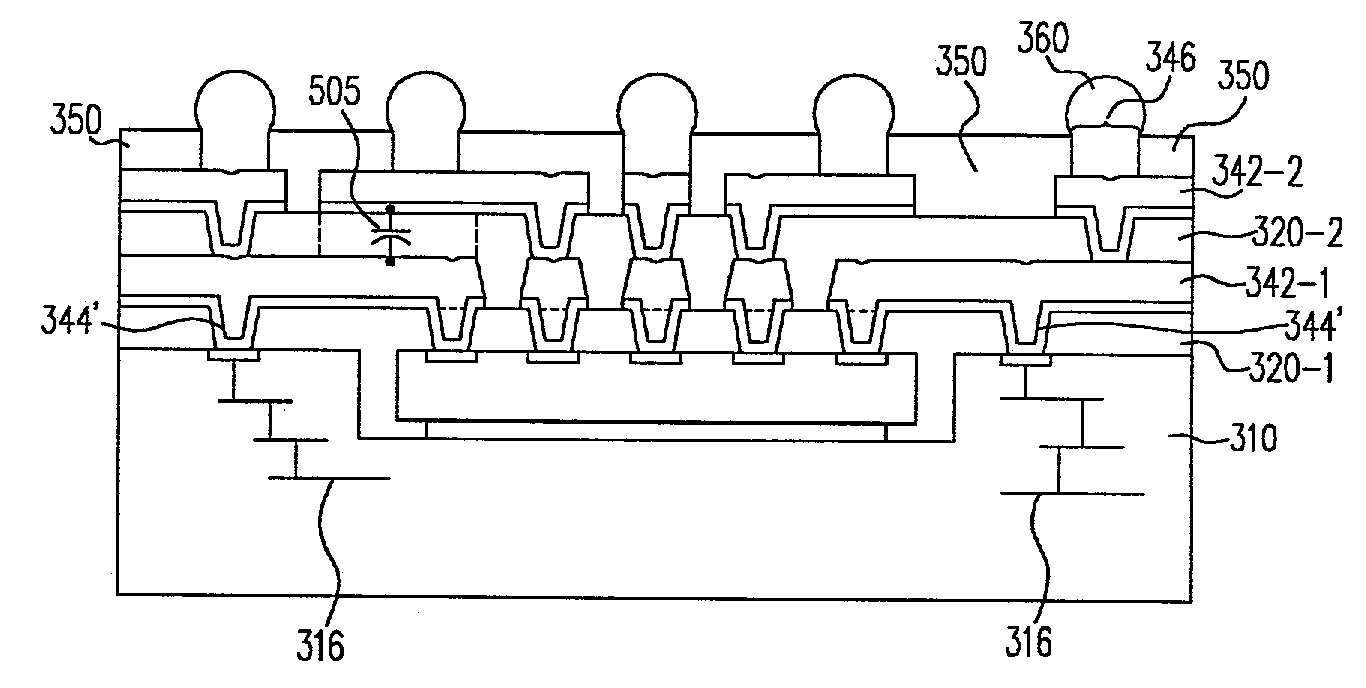

Conductive through via process for electronic device carriers

ActiveUS7488680B2Improve methodSimple structureCoupling device connectionsSemiconductor/solid-state device detailsEngineeringConductive materials

Conductive through vias are formed in electronic devices and electronic device carrier, such as, a silicon chip carrier. An annulus cavity is etched into the silicon carrier from the top side of the carrier and the cavity is filled with insulating material to form an isolation collar around a silicon core region. An insulating layer with at least one wiring level, having a portion in contact with the silicon core region, is formed on the top side of the carrier. Silicon is removed from the back side of the carrier sufficient to expose the distal portion of the isolation collar. The core region is etched out to expose the portion of the wiring level in contact with the silicon core region to form an empty via. The via is filled with conductive material in contact with the exposed portion of the wiring level to form a conductive through via to the wiring level. A solder bump formed, for example, from low melt C4 solder, is formed on the conductive via exposed on the carrier back side. The process acts to make the conductive via fill step independent of the via isolation step.

Owner:INT BUSINESS MASCH CORP

Silicon chip carrier with through-vias using laser assisted chemical vapor deposition of conductor

ActiveUS20050082676A1High aspect ratioSemiconductor/solid-state device detailsSolid-state devicesControl mannerGas phase

This disclosure teaches a method of filling deep vias or capping deep conducting paste filled vias in silicon or glass substrate using laser assisted chemical vapor deposition of metals. This method uses a continuous wave or pulsed laser to heat the via bottom and the growing metal fill selectively by selecting the laser wavelength such that silicon and / or glass do not absorb the energy of the laser in any appreciable manner to cause deposition in the field. Alternatively holographic mask or an array of micro lenses may be used to focus the laser beams to the vias to fill them with metal. The substrate is moved in a controlled manner in the z-direction away from the laser at about the rate of deposition thus causing the laser heating to be focused on the surface region of the growing metal fill.

Owner:ELPIS TECH INC

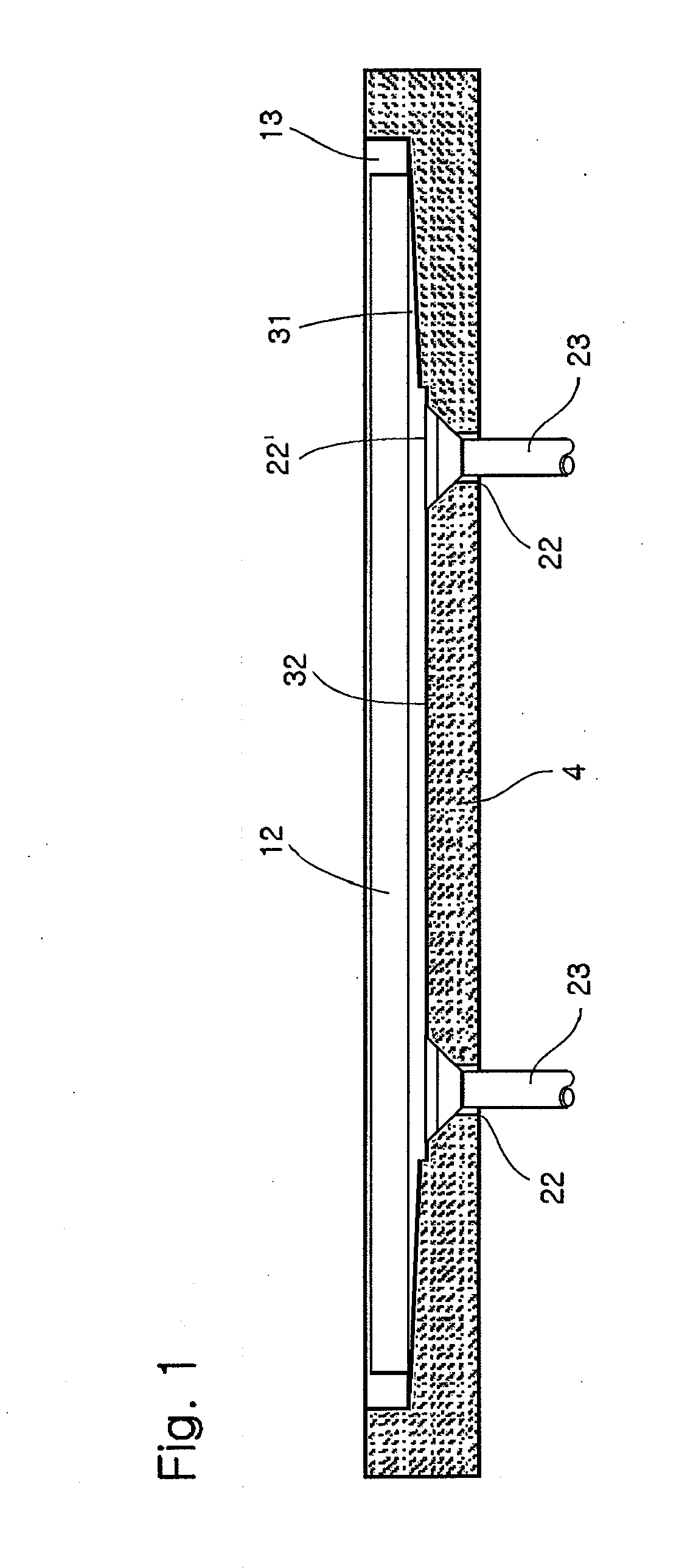

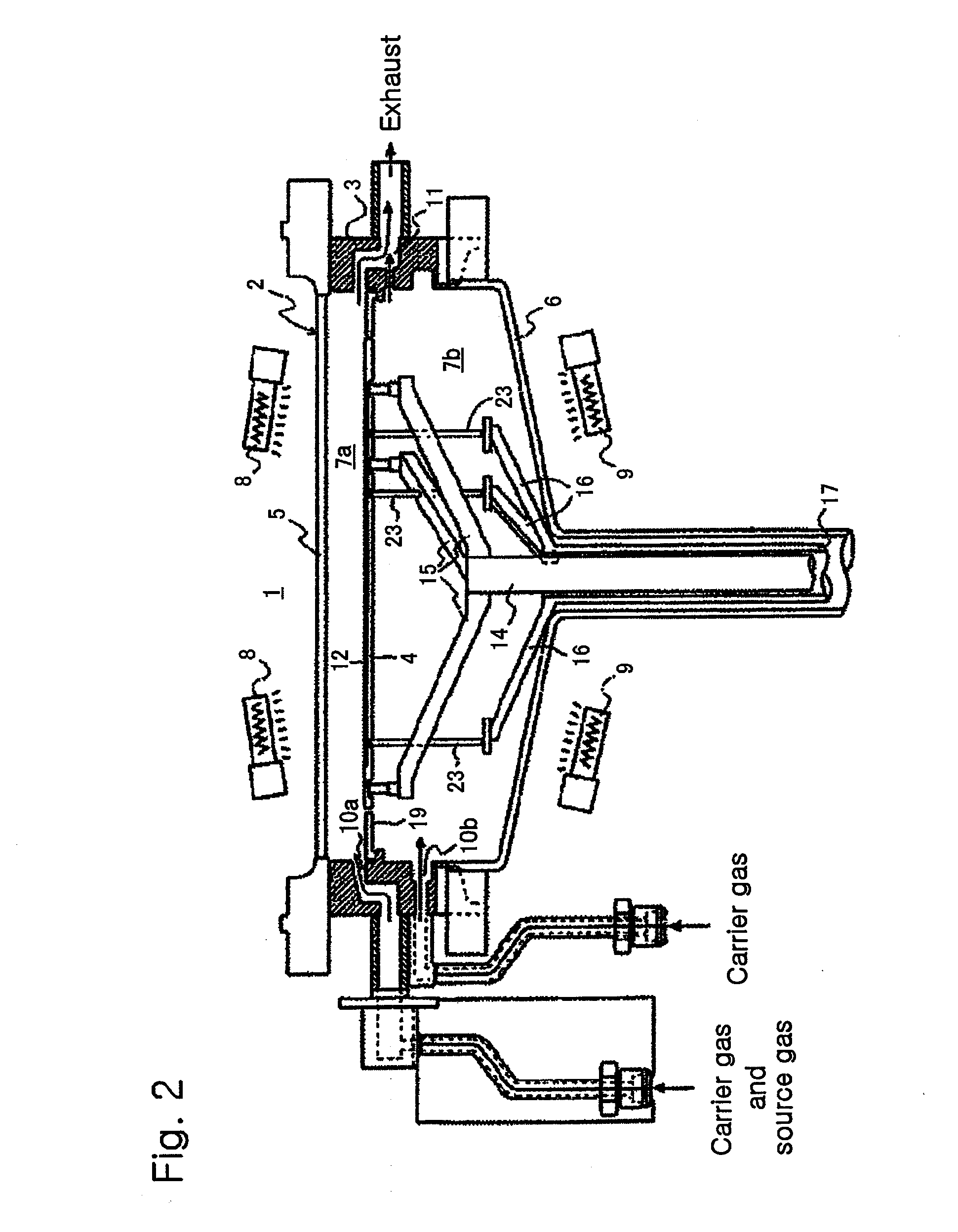

Method of manufacturing epitaxial silicon wafer and apparatus thereof

ActiveUS20070227441A1Improve uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingSusceptorWafering

A method of forming an epitaxial layer to increase flatness of an epitaxial silicon wafer is provided. In particular, a method of controlling the epitaxial layer thickness in a peripheral part of the wafer is provided. An apparatus for manufacturing an epitaxial wafer by growing an epitaxial layer with reaction of a semiconductor wafer and a source gas in a reaction furnace comprising: a pocket in which the semiconductor wafer is placed; a susceptor fixing the semiconductor; orientation-dependent control means dependent on a crystal orientation of the semiconductor wafer and / or orientation-independent control means independent from the crystal orientation of the semiconductor wafer, wherein the apparatus may improve flatness in a peripheral part of the epitaxial layer.

Owner:SUMCO TECHXIV

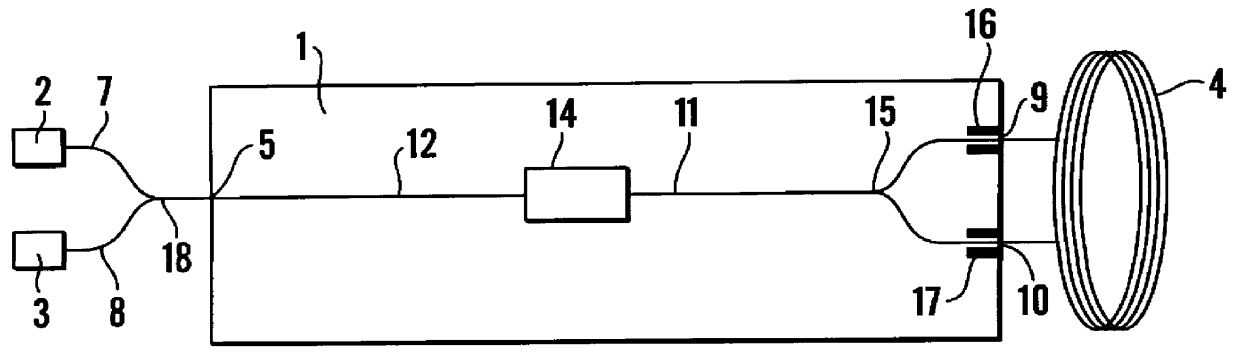

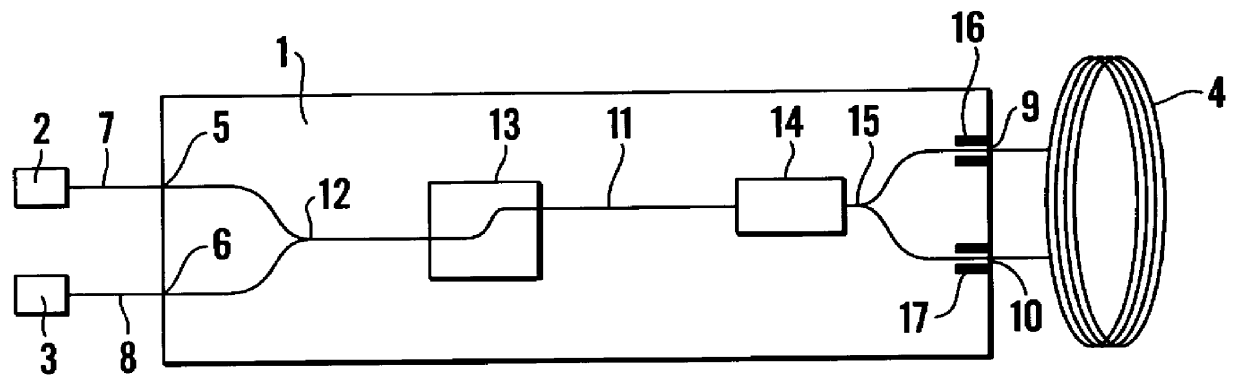

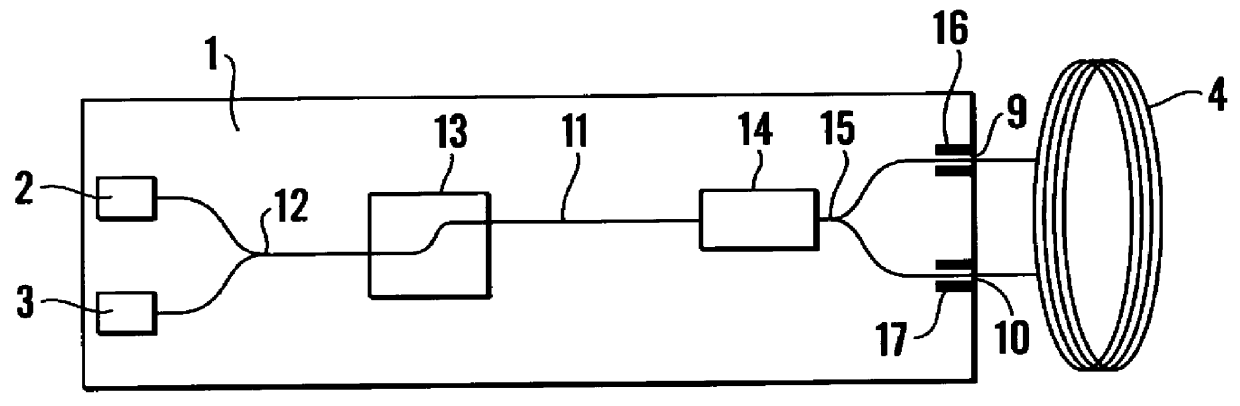

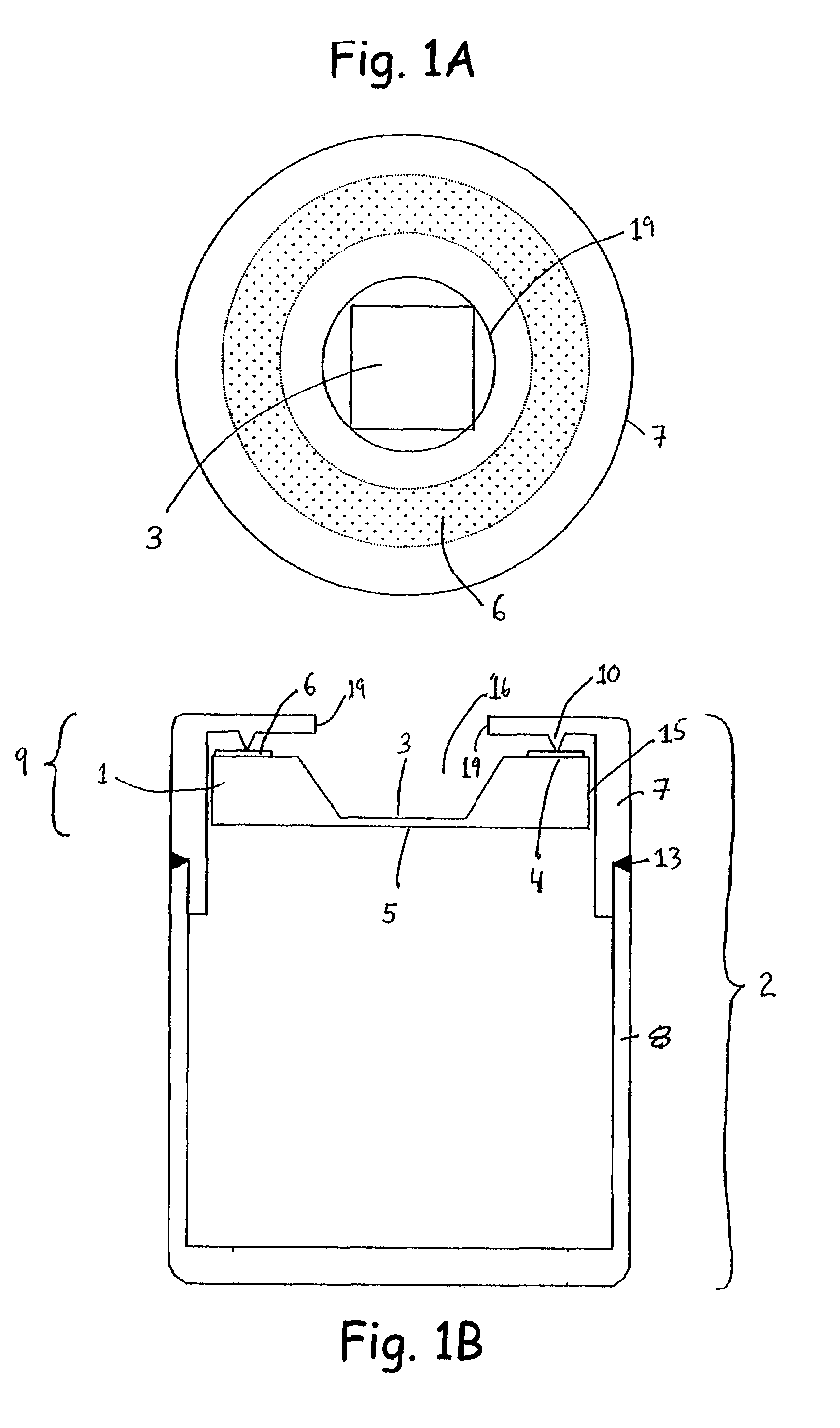

Integrated optical circuit

InactiveUS6163632ASagnac effect gyrometersSpeed measurement using gyroscopic effectsFiberPhase shifted

An integrated optical circuit for use in a fibre optic gyroscope which senses rotation rates by determining a phase shift due to the Sagnac Effect between light beams travelling around an optical fibre sensing loop (4) in opposite directions, the circuit being provided on a silicon-on-insulator chip comprising a layer of silicon separated from a substrate by an insulating layer, the circuit comprising: rib waveguides (11) formed in the silicon layer for receiving light from a light source (2) and transmitting light to a light detector (3), fibre optic connectors (9) in the form of grooves etched in the silicon layer for receiving the respective ends of the optical fibre sensing loop (4); rib waveguides (11) formed in the silicon layer for transmitting light to and from said fibre optic connectors (9) so as to direct light beams in opposite directions around the sensing loop (4) and receive light beams returning therefrom, phase determining means and (13,17,31) integrated in silicon layer for determining a phase shift between the light beams returning from the sensing loop (4).

Owner:BOOKHAM TECH

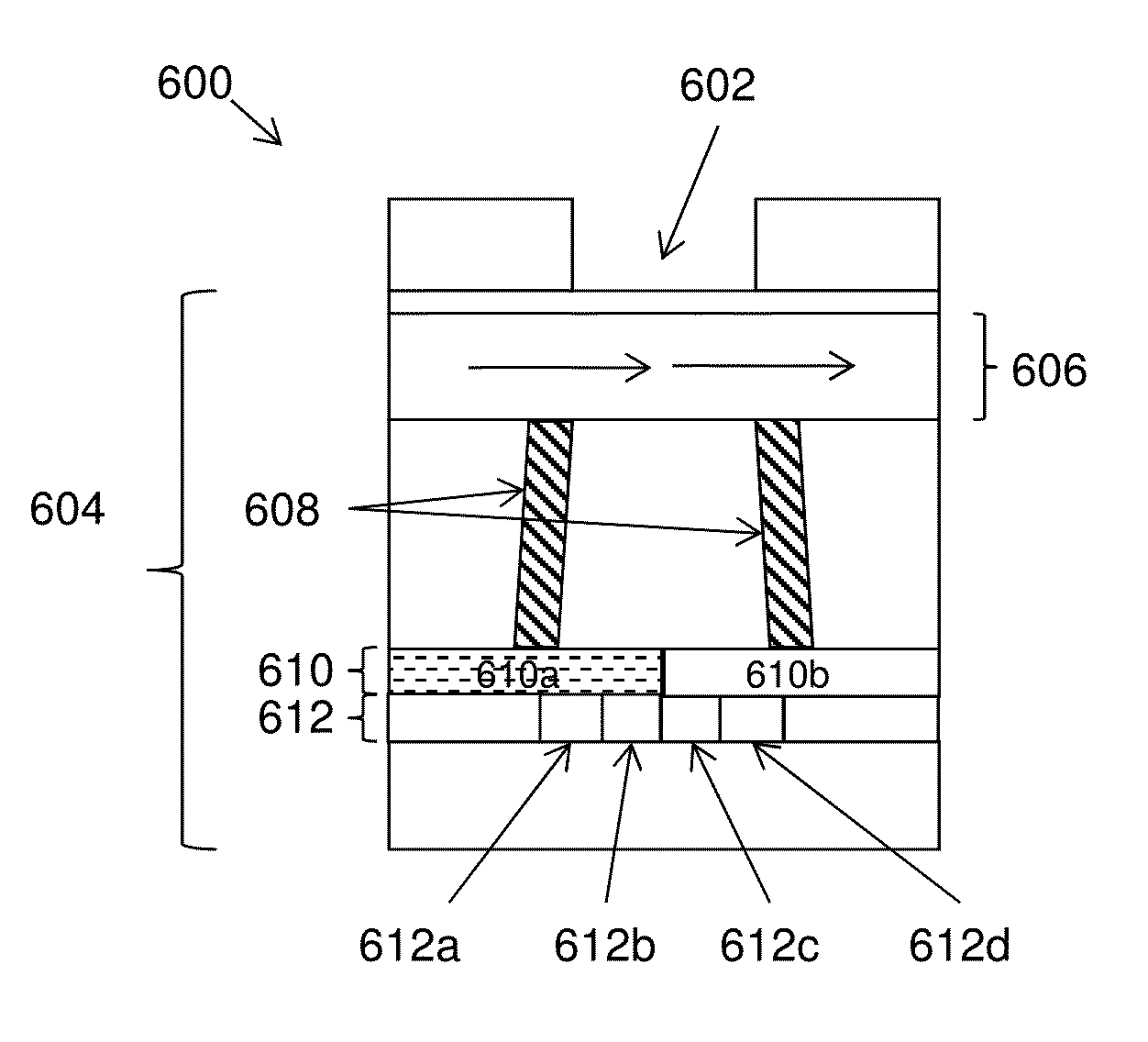

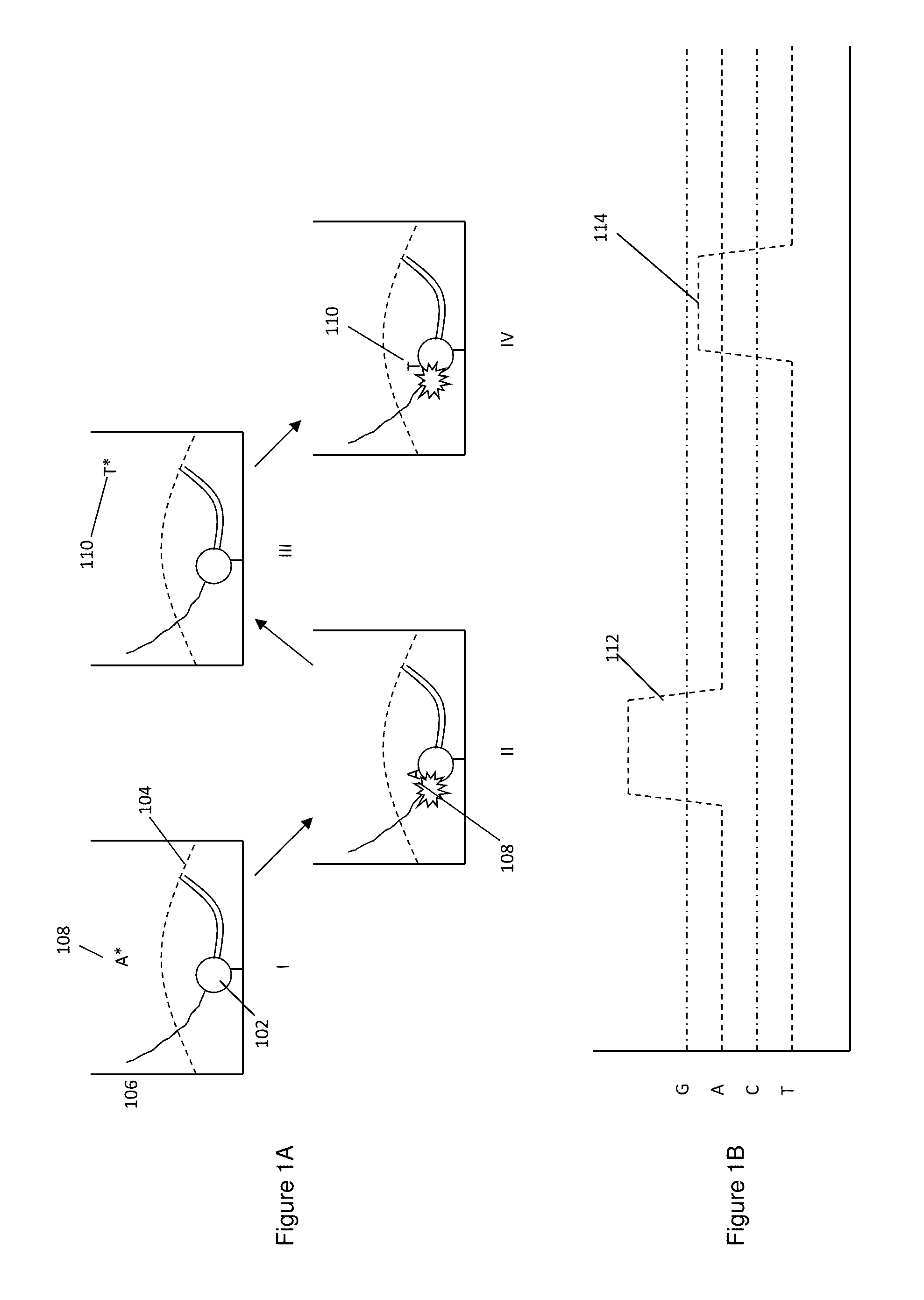

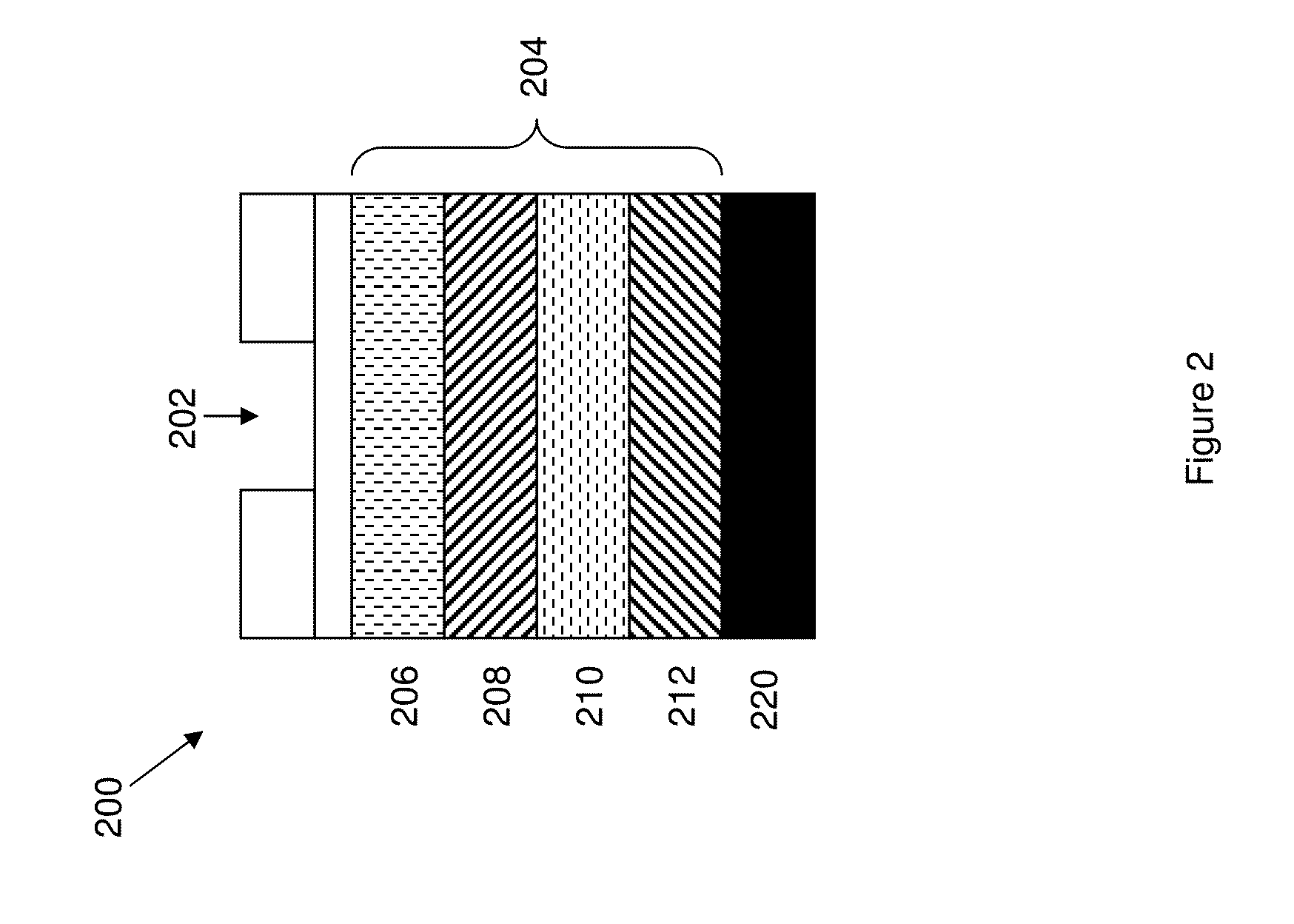

Arrays of integrated analytical devices and methods for production

Arrays of integrated analytical devices and their methods for production are provided. The arrays are useful in the analysis of highly multiplexed optical reactions in large numbers at high densities, including biochemical reactions, such as nucleic acid sequencing reactions. The integrated devices allow the highly sensitive discrimination of optical signals using features such as spectra, amplitude, and time resolution, or combinations thereof. The arrays and methods of the invention make use of silicon chip fabrication and manufacturing techniques developed for the electronics industry and highly suited for miniaturization and high throughput.

Owner:PACIFIC BIOSCIENCES

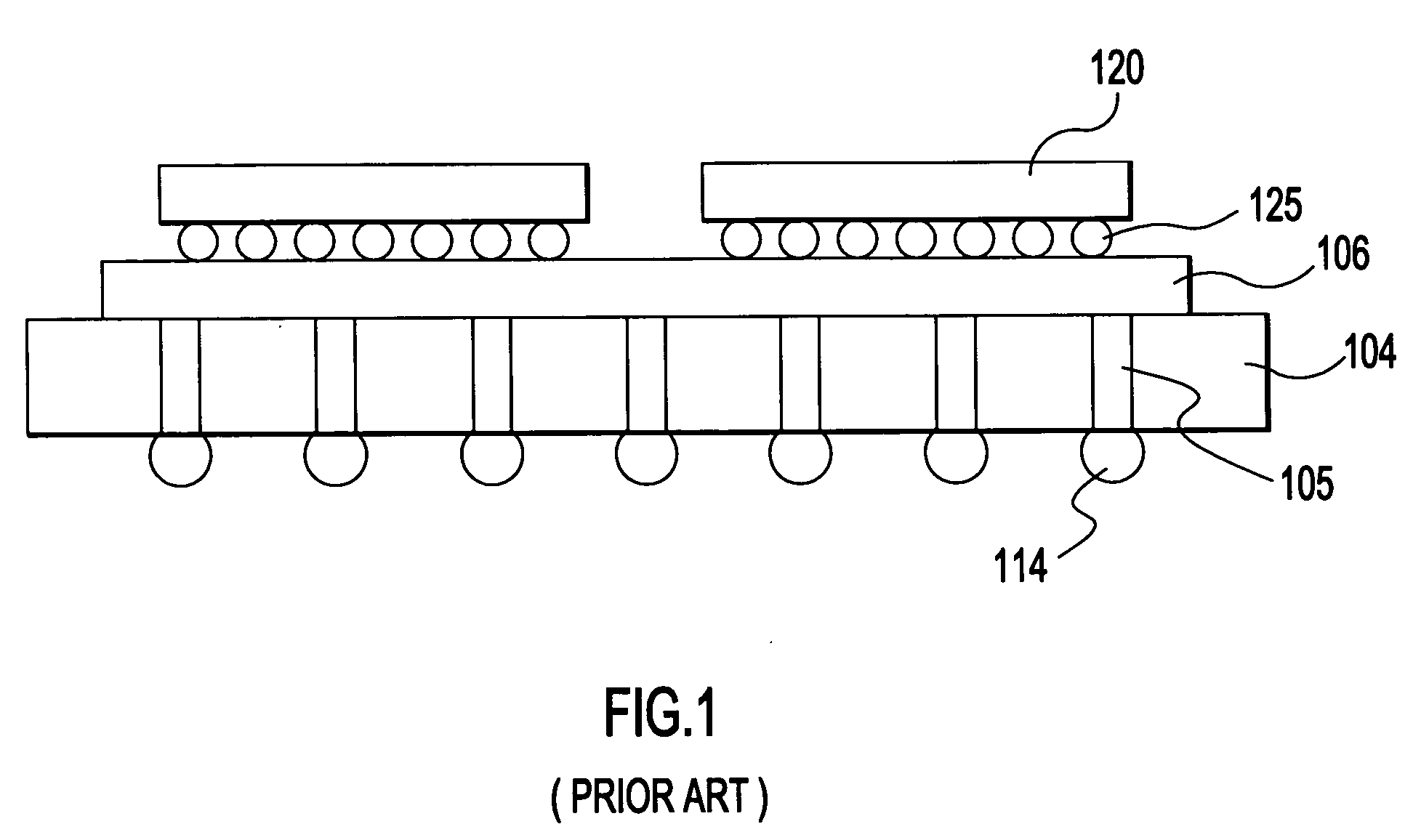

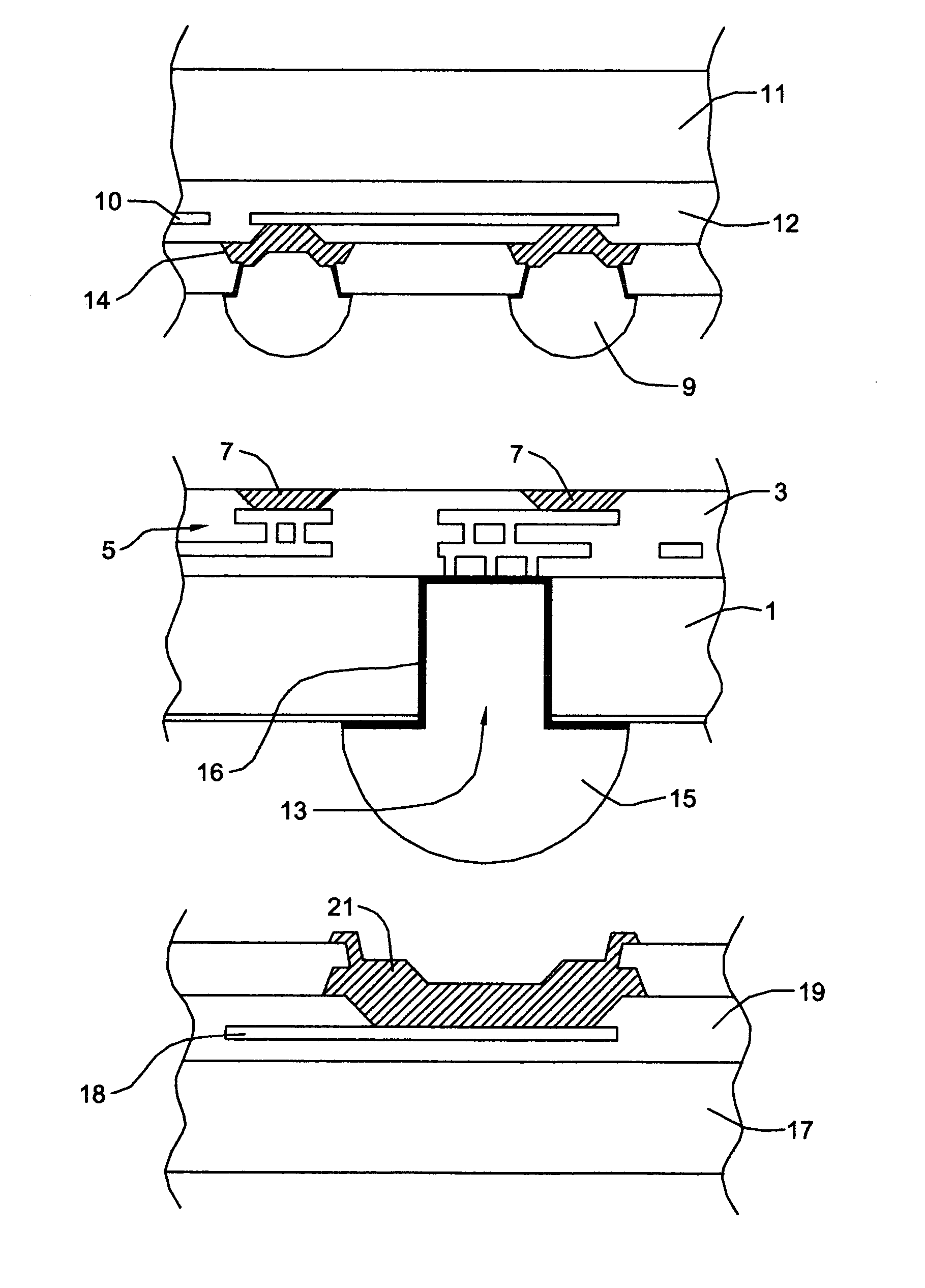

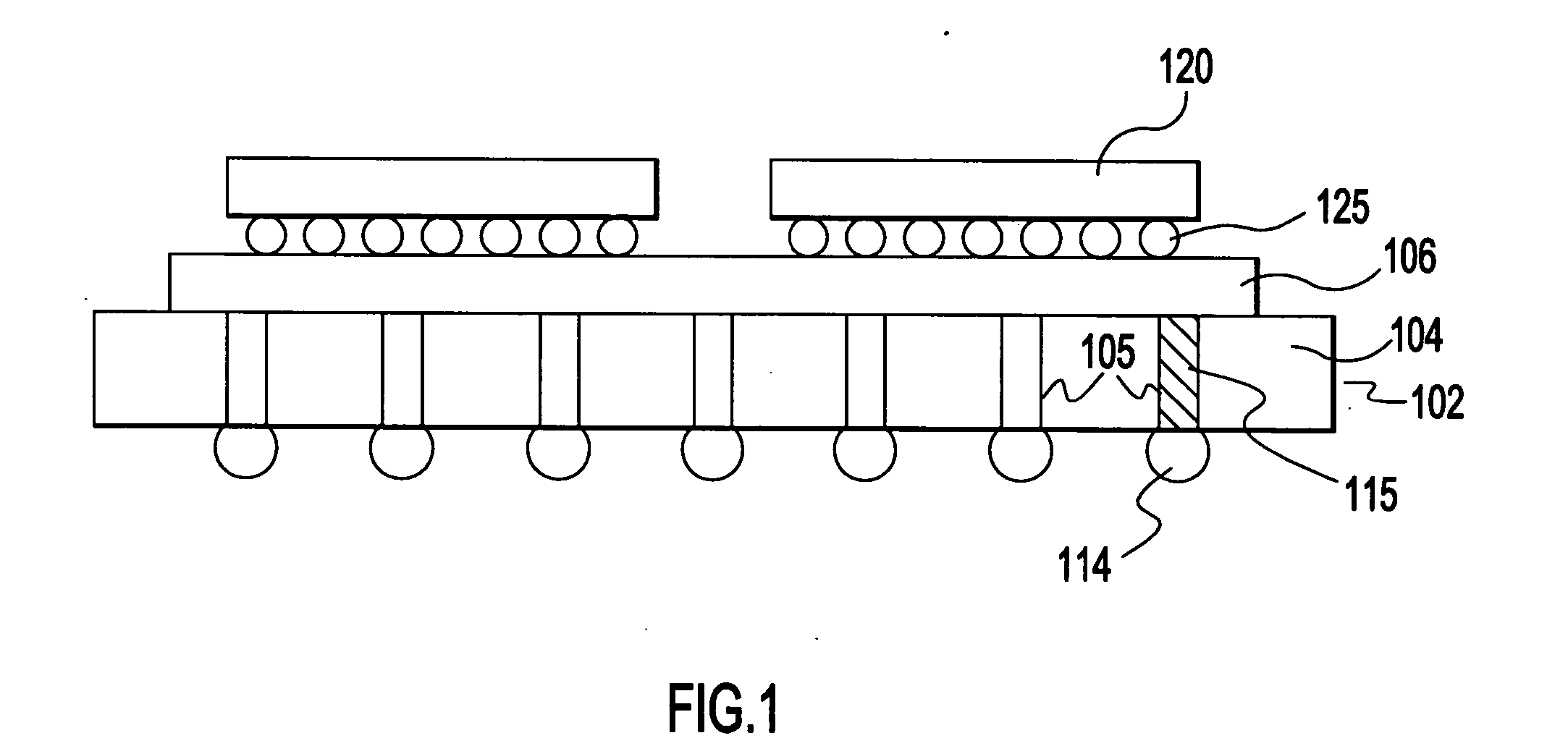

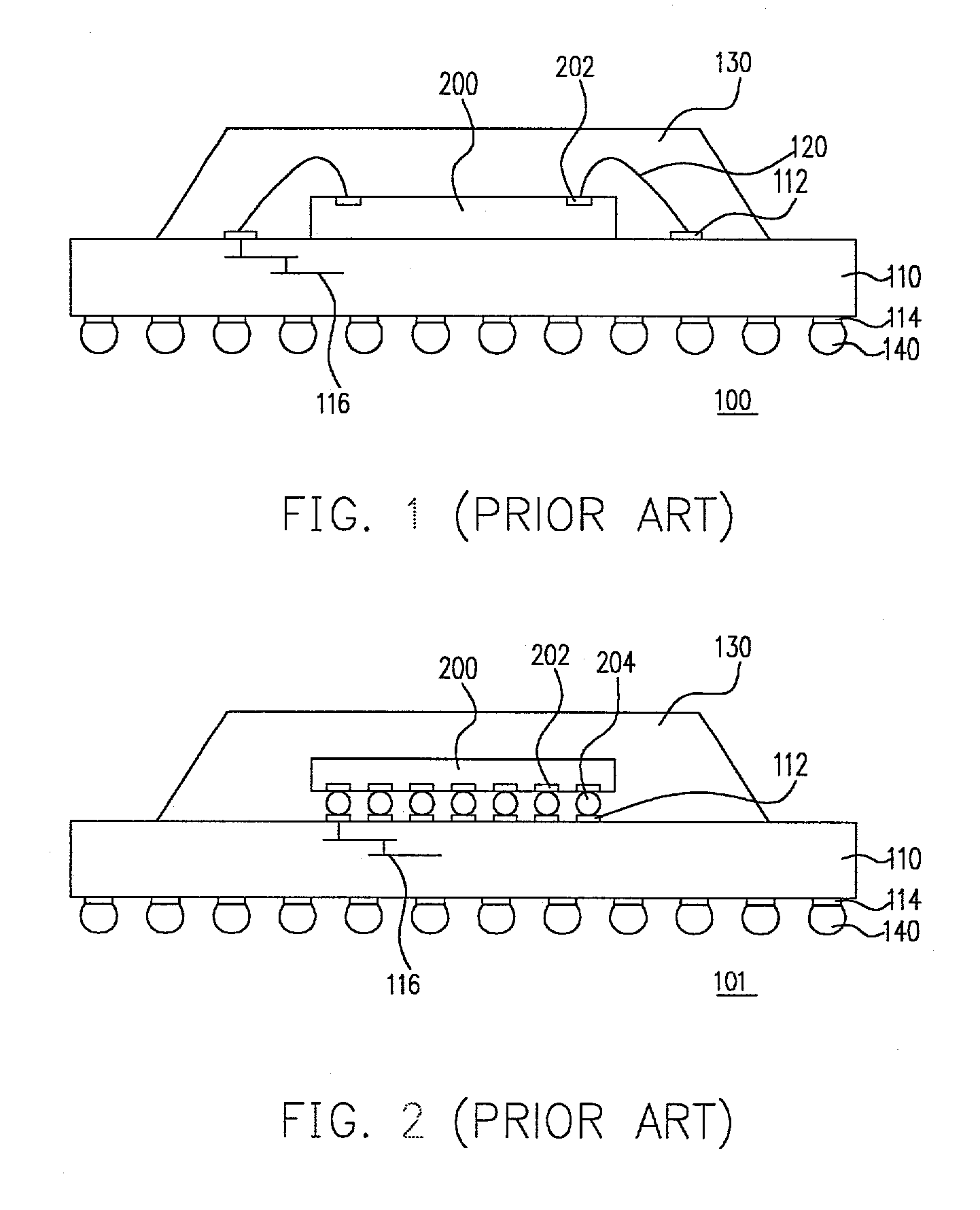

Integrated circuit package and method of manufacture

InactiveUS7087991B2Eliminates connective requirementImprove cooling effectPrinted circuit assemblingSemiconductor/solid-state device detailsInsulation layerSolder ball

An integrated circuit package and a method of manufacturing the package. A silicon chip is attached to the surface of a substrate or attached to the bottom surface of a cavity in the substrate so that the active surface of the chip is exposed. One or more build-up circuit structures are formed over the substrate. Each build-up circuit structure has at least one insulation layer, at least one patterned circuit layer and a plurality of via openings with conductive material therein so that bonding pads on the active surface of the chip connect electrically with the patterned circuit layer through the vias. To form a ball grid array package, solder balls may also be attached to the solder ball pads on the patterned circuit layer so that the bonding pads on the chip are electrically connected to an external circuit through the build-up circuit structure and the solder balls.

Owner:VIA TECH INC

Preparation method of graphene-carbon nanotube compound film based on three-dimensional network appearance

InactiveCN102417176AImprove uniformityReduce surface resistanceNanotechnologyPolyethylene terephthalate glycolMeth-

The invention discloses a preparation method of a graphene-carbon nanotube compound film based on a three-dimensional network appearance. The method comprises the step of: transferring and stamping graphene and a carbon nanotube onto glass, a tantalum sheet, a silicon chip, a stainless steel plate or a polyethylene glycol terephthalate substrate in the mass ratio (1-10):1 through spraying deposition or vacuum suction filtration, wherein the grapheme is graphene oxide prepared by using an improved Hummers method; and a preparation method of a carbon nanotube solution comprises the following steps of: mixing acids; dispersing surfactants such as sodium lauryl sulfate, sodium dodecyl benzene sulfonate and hexadecyl trimethyl ammonium bromide in an auxiliary way, and the like. The graphene-carbon nanotube compound film prepared by adopting the method has the advantages of adjustable transmission and surface resistance, high uniformity, high stability, simple preparation method process and the like, and can be loaded on a rigid substrate as well as a flexible substrate.

Owner:TIANJIN UNIV

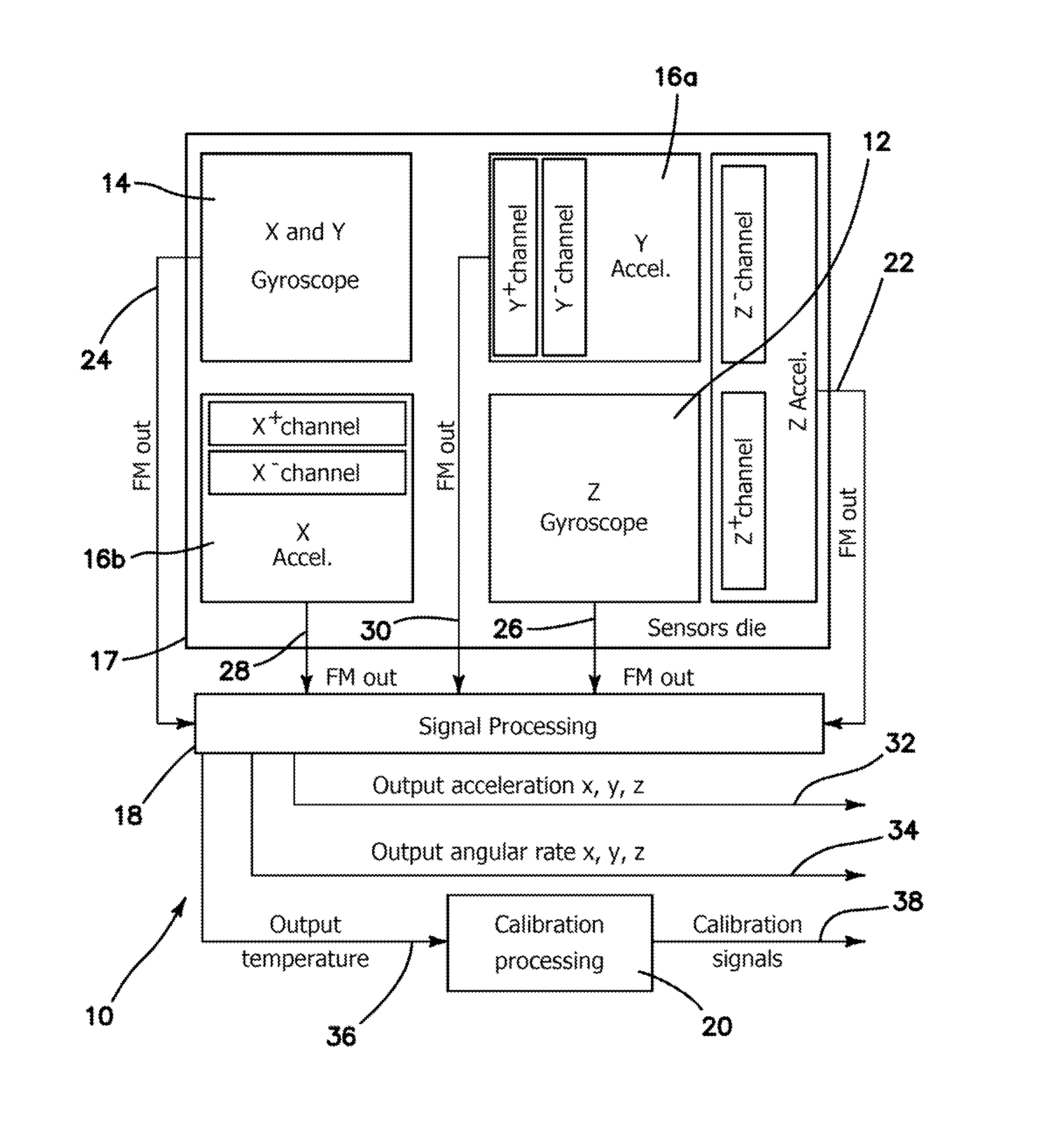

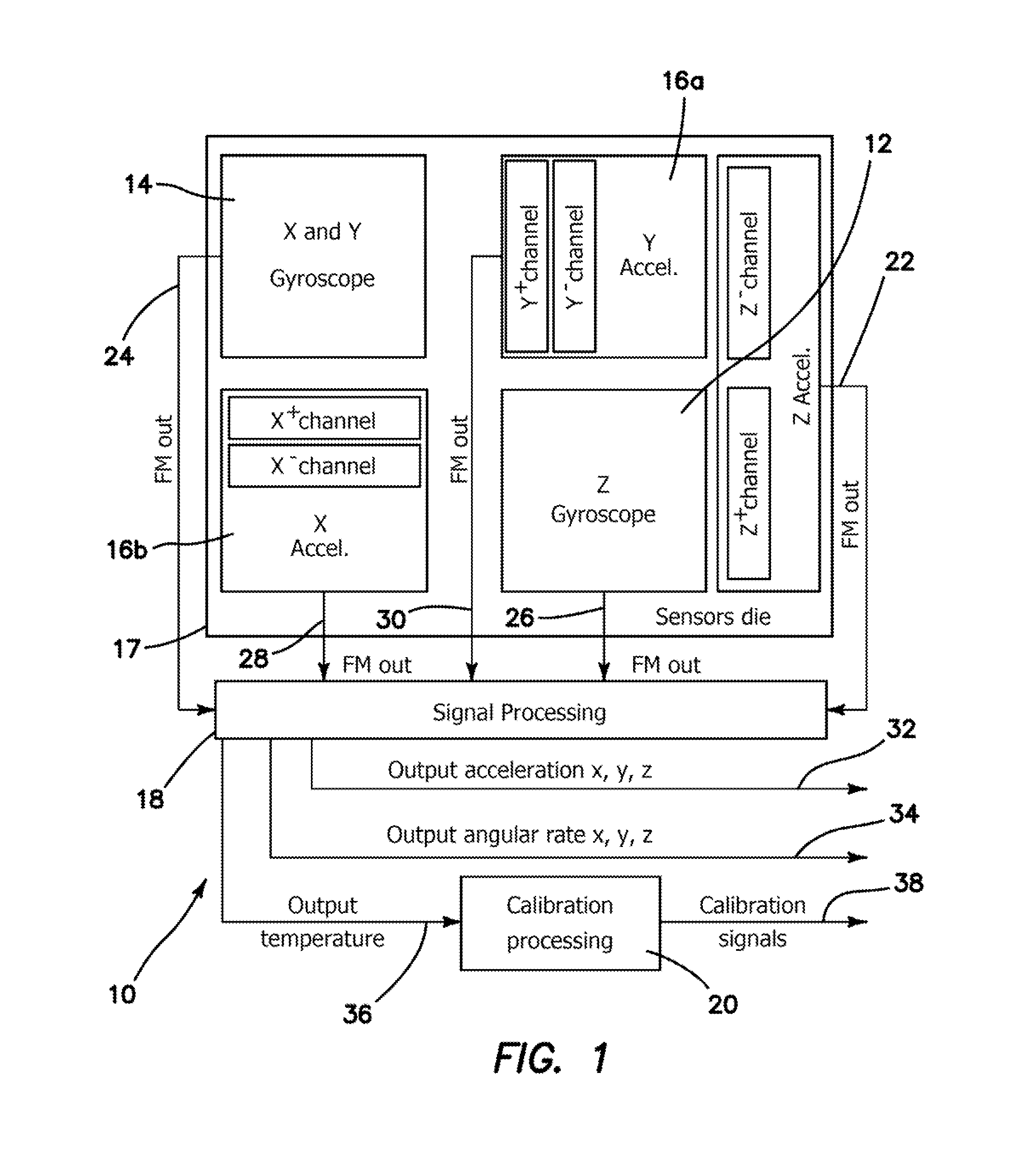

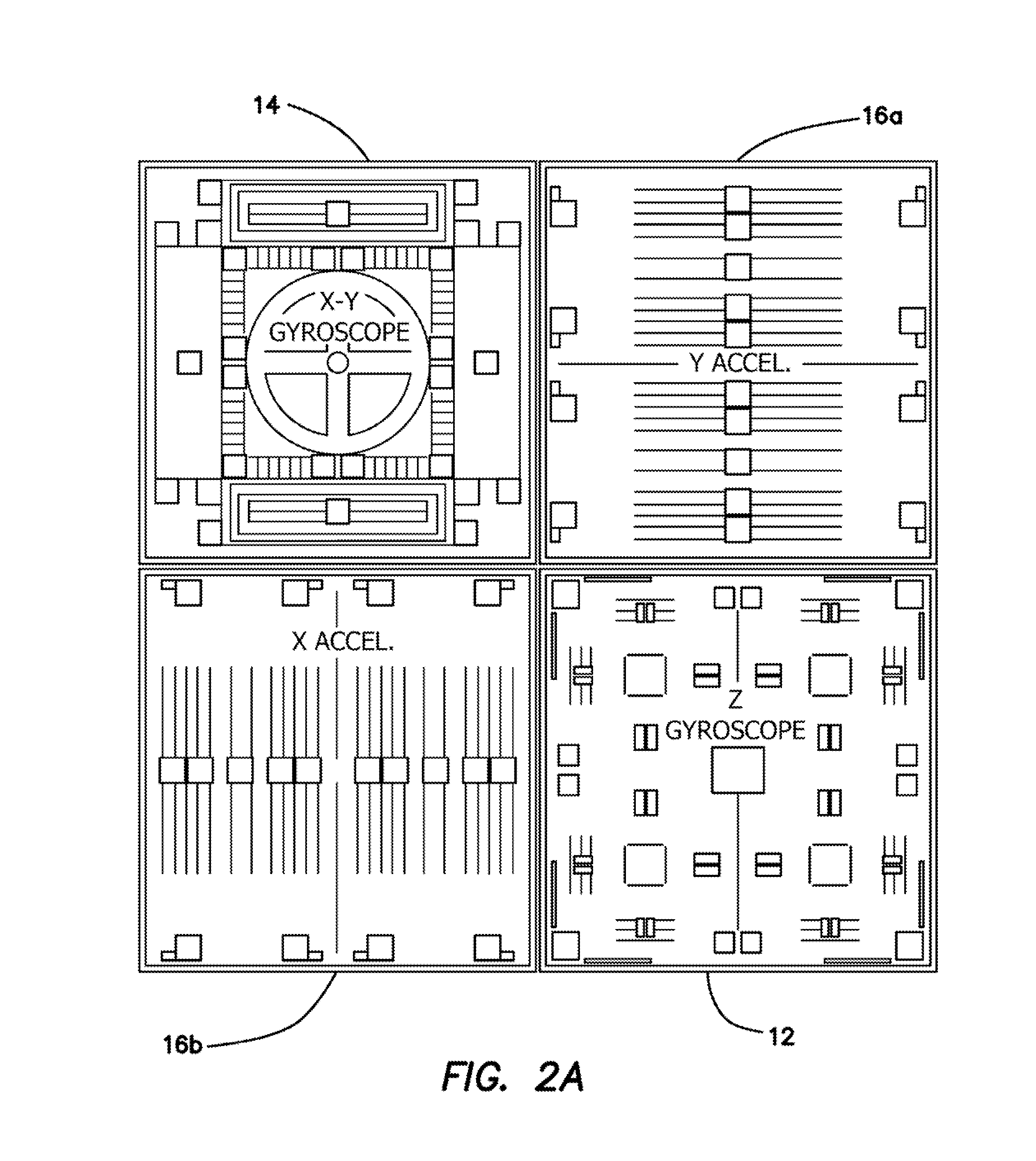

Multi-Axis Chip-Scale MEMS Inertial Measurement Unit (IMU) Based on Frequency Modulation

ActiveUS20140208823A1Ultra-high precisionUltra-high stabilityTesting/calibration of speed/acceleration/shock measurement devicesGyroscopes/turn-sensitive devicesGyroscopeAccelerometer

A multi-axis microelectromechanical-systems (MEMS) inertial measurement unit (IMU) is fabricated in a vacuum sealed single packaged device. An FM vibratory gyroscope and an FM resonant accelerometer both for generating FM output signals is fabricated in the silicon chip using MEMS. A signal processor is coupled to the an FM vibratory gyroscope and to the FM resonant accelerometer for receiving the FM gyroscopic output signals and the FM accelerometer output signals. The signal processor generates simultaneous and decoupled measurement of input acceleration, in put rotation rate, and temperature and / or temperature distribution within the IMU, self-calibration of the biases and scale factors of the IMU and its support electronics against temperature variations and other common mode errors, and reduction of the cross axis sensitivity by reducing acceleration errors in the gyroscope and rotation errors in the accelerometer.

Owner:RGT UNIV OF CALIFORNIA

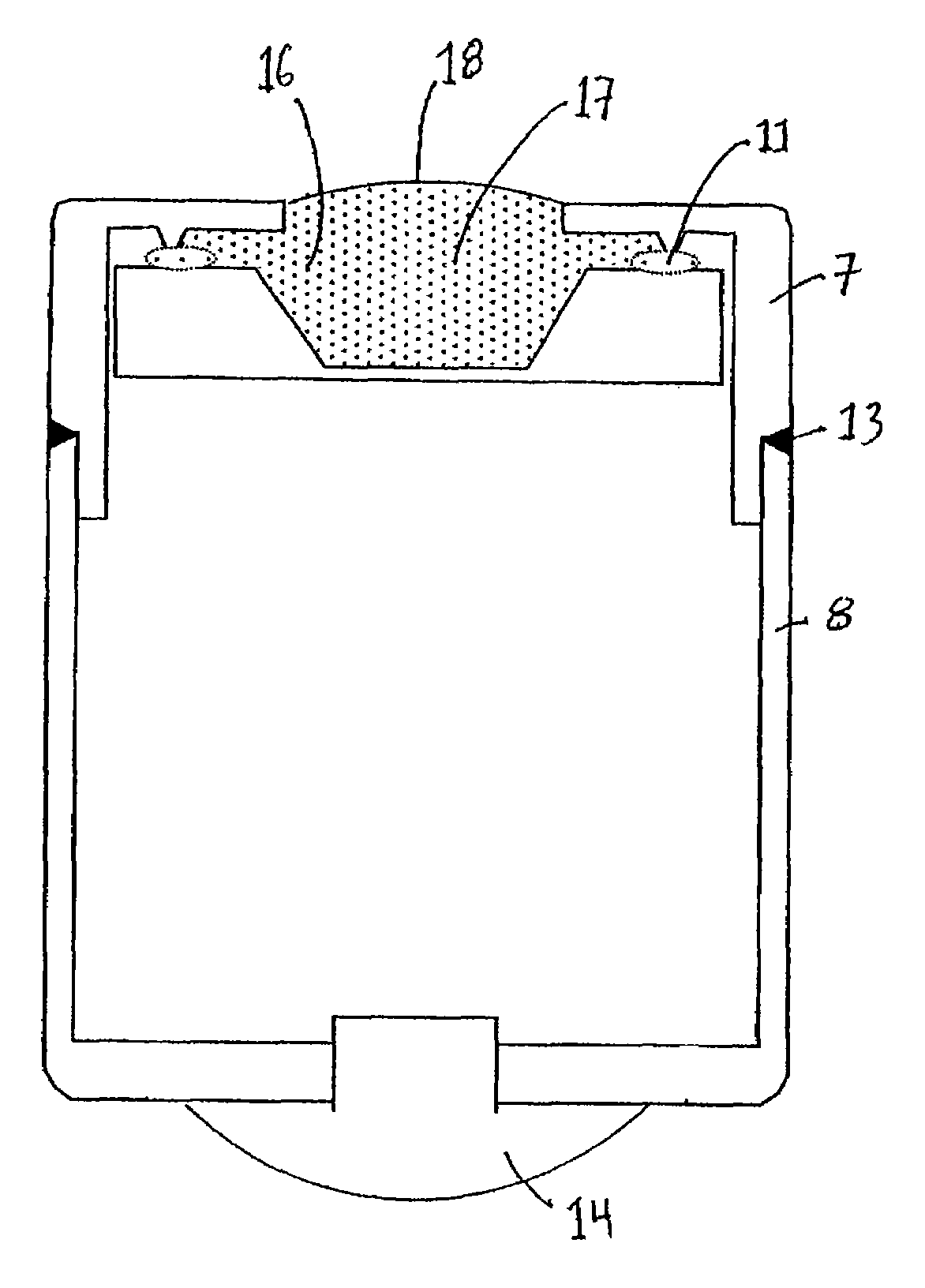

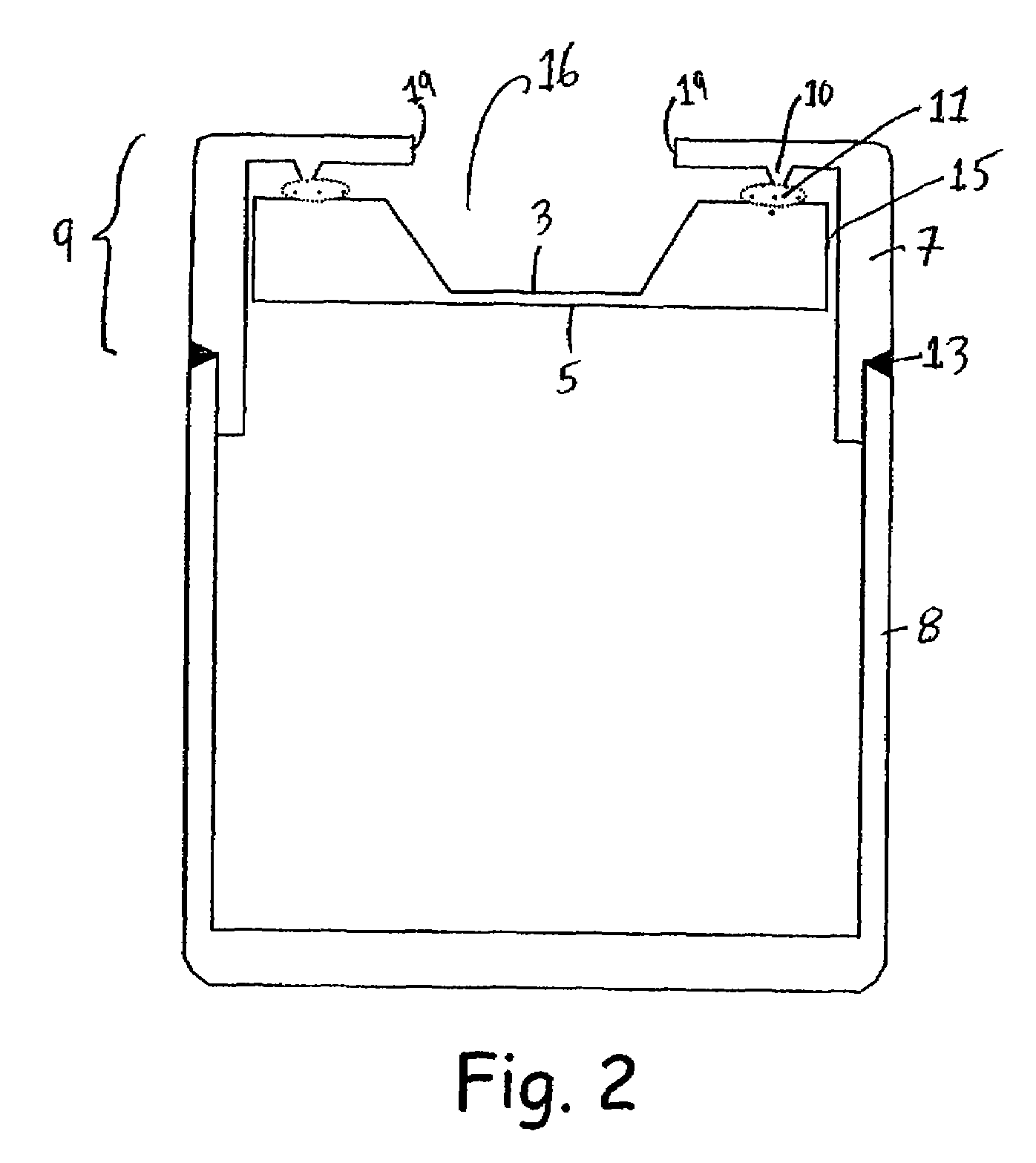

Hermetically sealable silicon system and method of making same

InactiveUS7402899B1Efficient workSemiconductor/solid-state device detailsSolid-state devicesHermetic sealSilicon alloy

A device and method for hermetically sealing a medical device is provided. In one aspect, a silicon device is coupled to a sensor, such as a pressure transducer, which benefits from having direct contact with its environment, which in many cases, is the human body. Thus, a method to hermetically seal the non-sensing portion of a silicon device while allowing the sensing portion (e.g. the pressure transducer) to have direct contact with the body is provided. In one aspect, a silicon chip, a gold preform and a metallic housing are each primed for sealing and are assembled. The assembly is then heated to react the gold preform to the silicon chip and to form a molten gold-silicon alloy in-situ to bind the metallic housing to the non-sensing portion of the silicon chip. In this way, the non-sensing portion of the silicon chip is hermetically sealed and protected from exposure, while still permitting exposure of the sensing portion to the environment.

Owner:PACESETTER INC

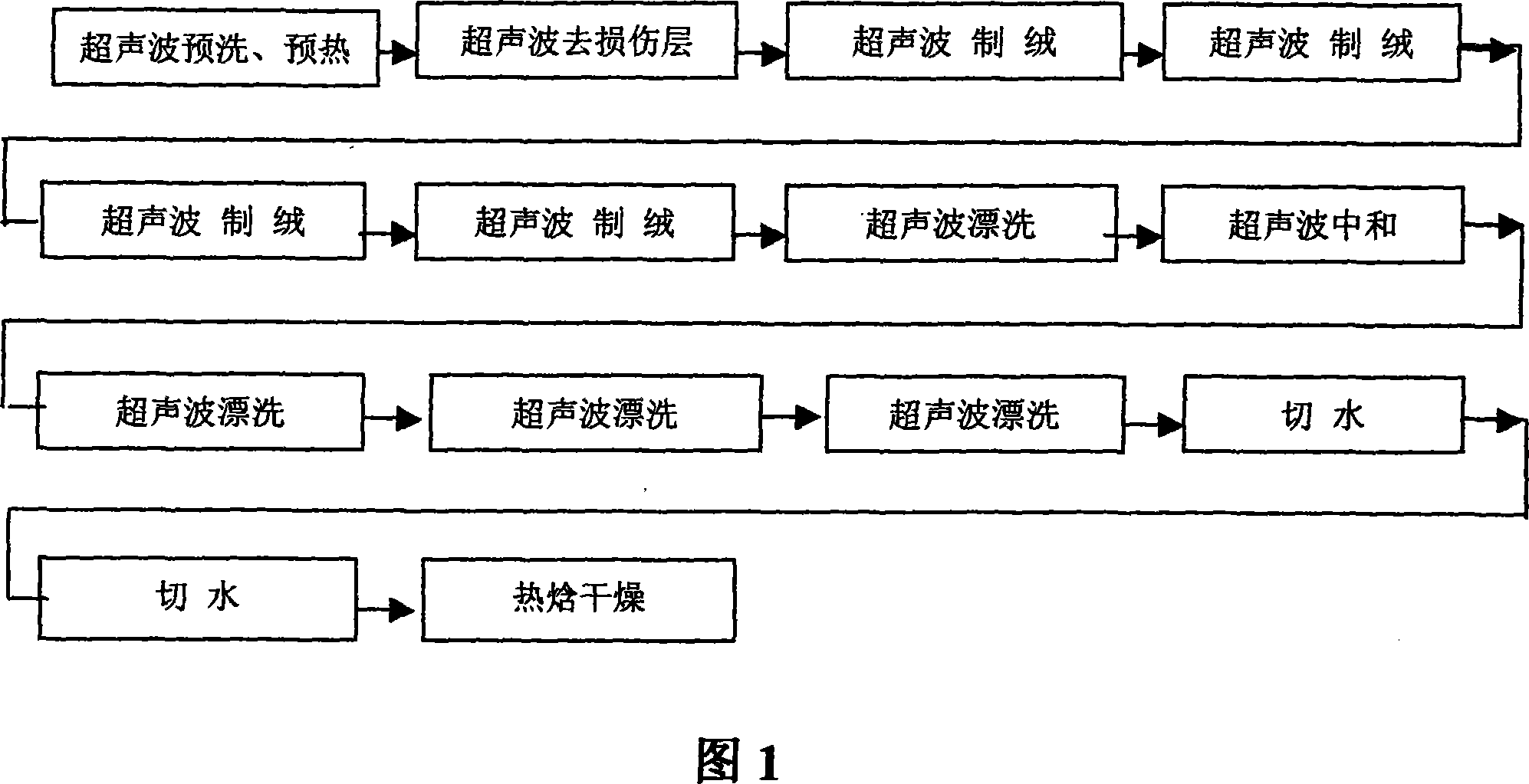

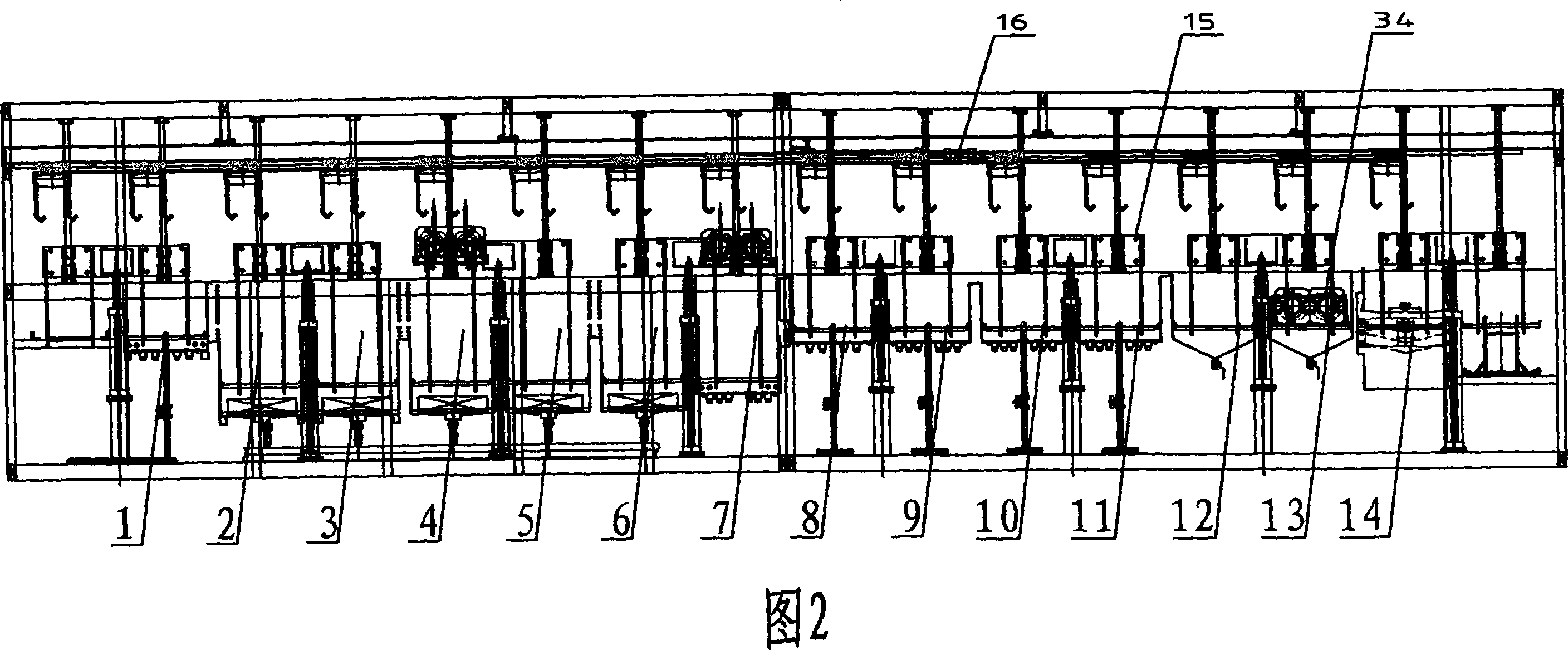

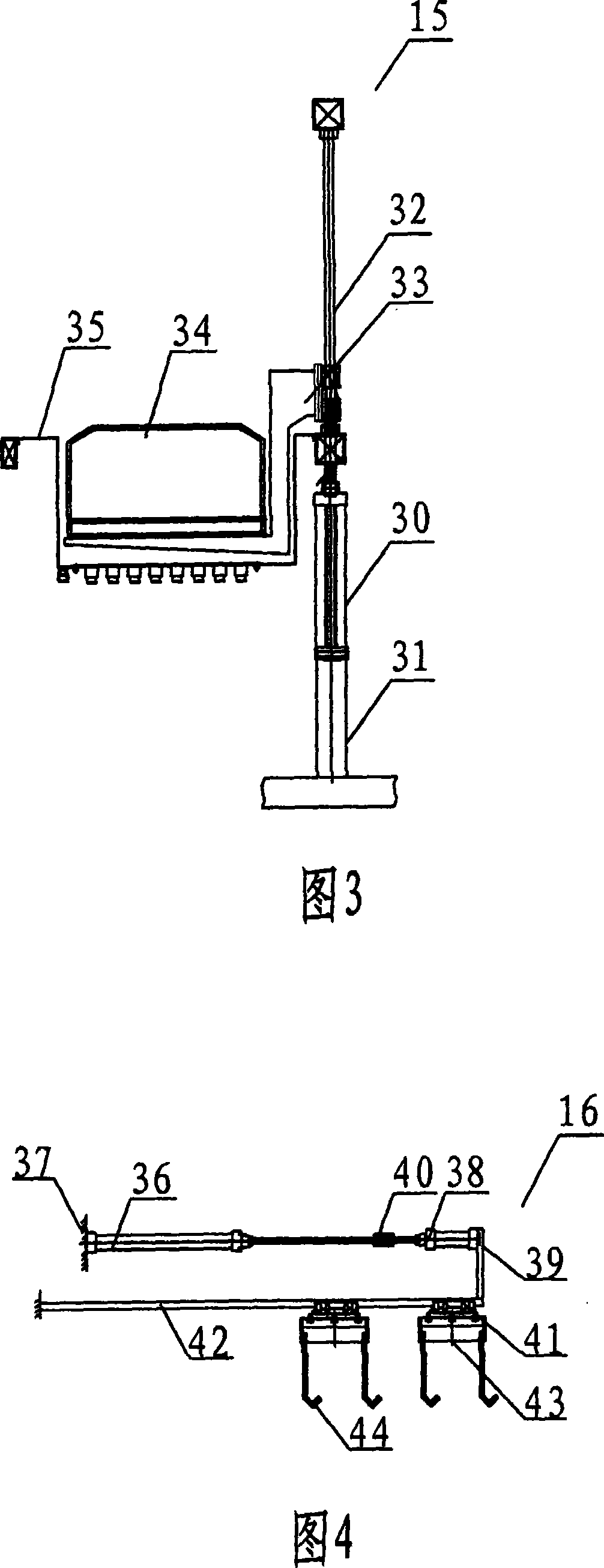

Chemical etching, cleaning and drying method of single-crystal silicon solar battery and integrated processing machine

InactiveCN101087007AImprove reflective effectAvoid secondary pollutionFinal product manufactureSemiconductor devicesEtchingWater source

Monocrystalline silicon solaode chemical etching, washing, drying method and integral processor belong to technique field of chemical etching technique and washing. It characterized in that it not only includes water, acid, alkali, but also ultrasonic participates in etching and washing course: it includes following steps: (1) ultrasonic washes and heats in advance, (2) ultrasonic removes damnification layer, (3) ultrasonic makes herbs into wool, (4) ultrasonic rinses, (5) washing with acid to counteract, (6) ultrasonic rinses, (7) cutting water, (8) hot enthalpy to dry. Positive effects of the invention are: adopting ultrasonic to etch and wash, liquid of making wool can be acted with silicon piece, similar coarseness degree can be generated on surface, perfect pyramid pattern can be obtained; it also eliminates kalium, natrium ion from alkalescent solution, and extends service life of silicon piece; pollution can be decreased, energy consumption and water source can be saved greatly, it is a practical invention.

Owner:SHANGHAI MINGXING KAICHENG ULTRASONIC TECH +2

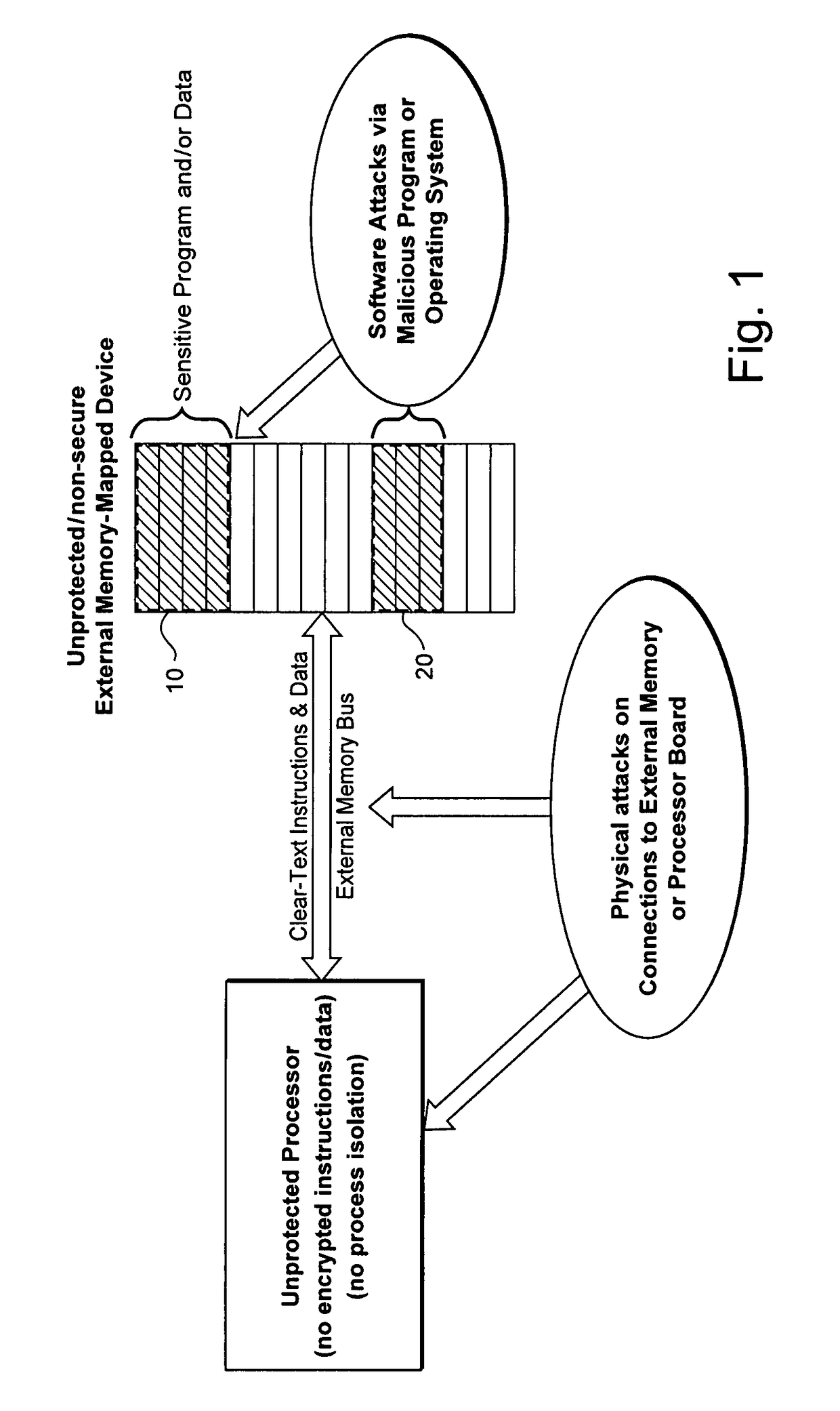

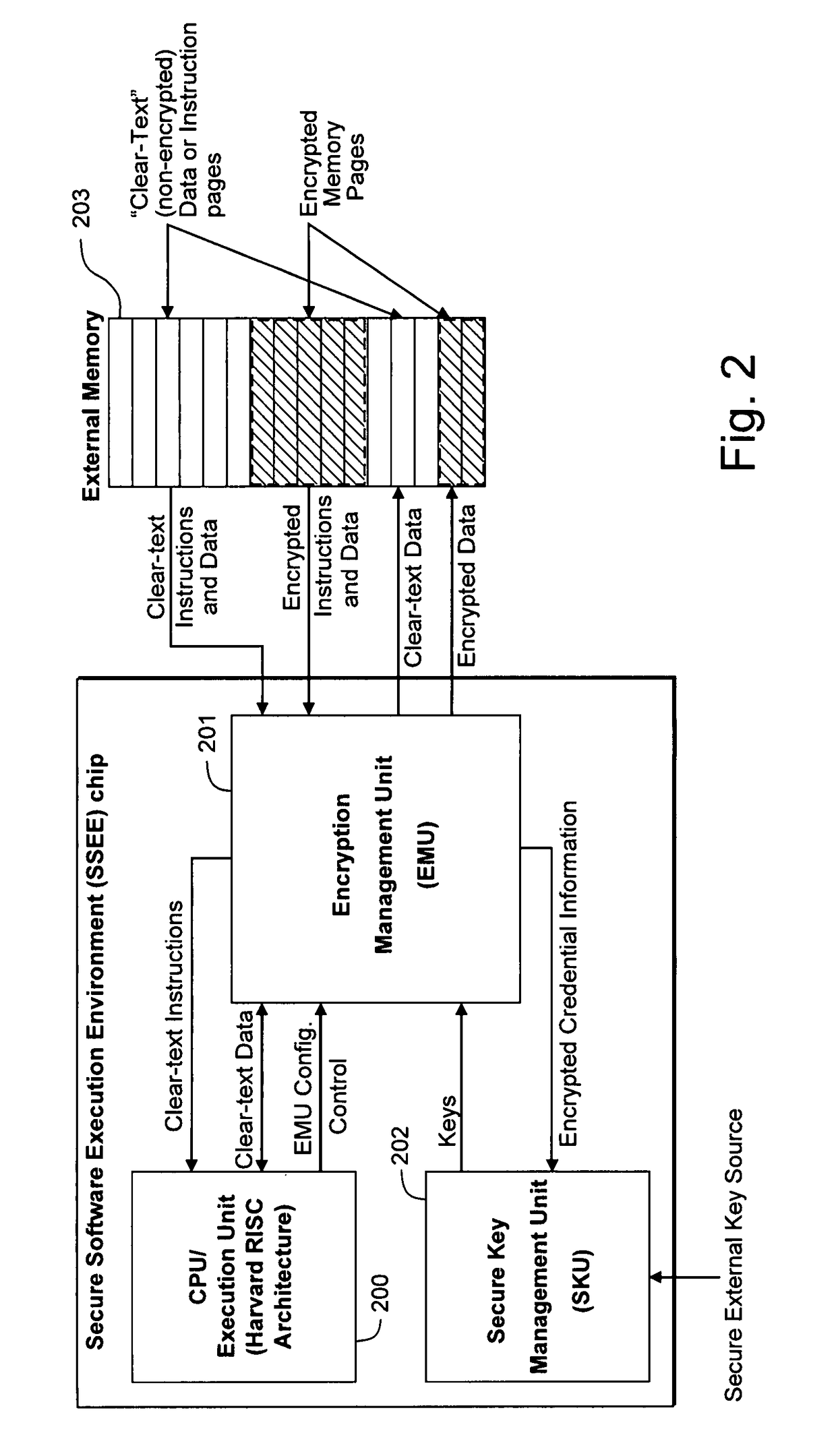

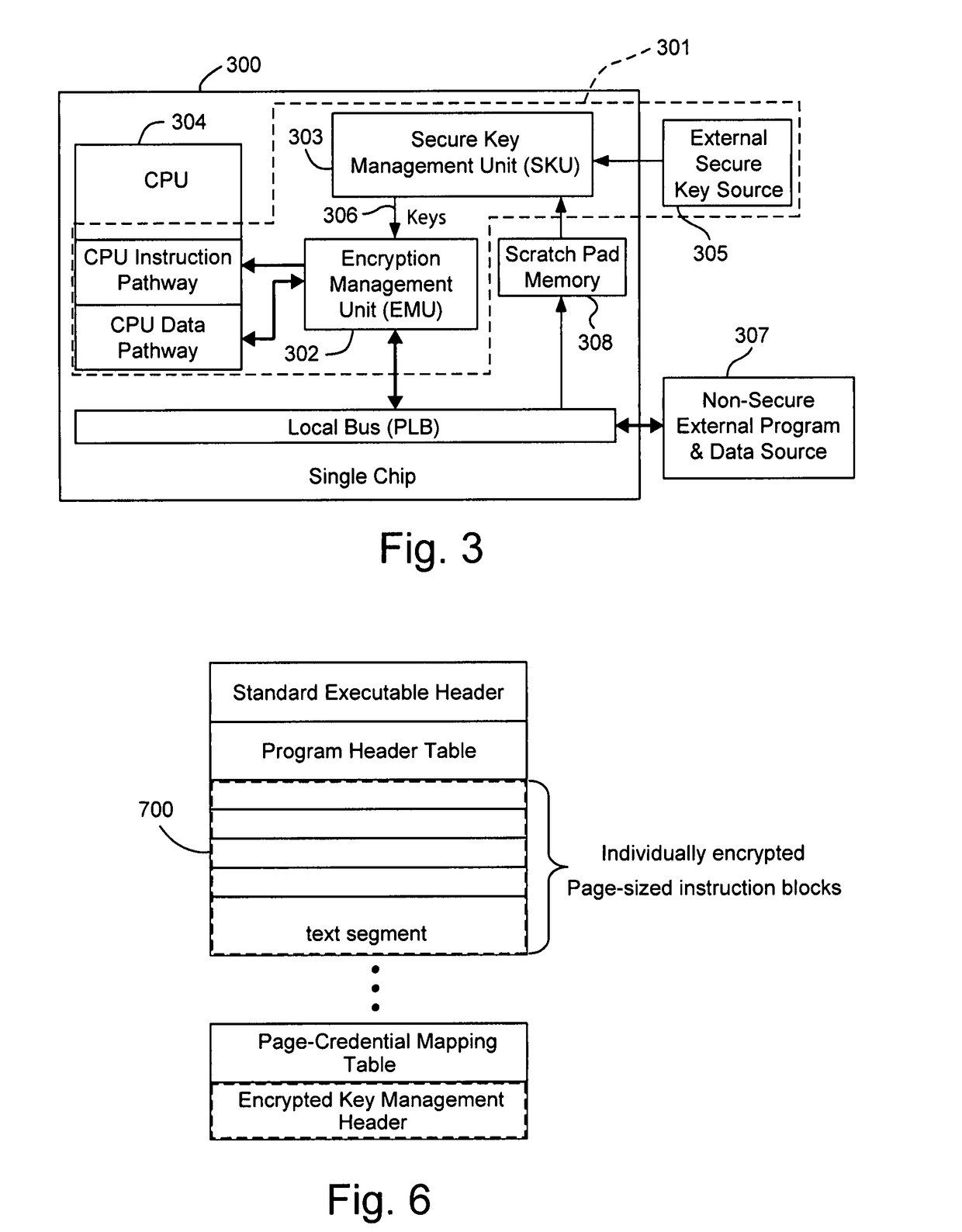

Hardware-facilitated secure software execution environment

InactiveUS8473754B2Avoid unwanted disclosureProvide confidentialityUser identity/authority verificationUnauthorized memory use protectionConfidentialityKey management

A hardware-facilitated secure software execution environment provides protection of both program instructions and data against unauthorized access and / or execution to maintain confidentiality and integrity of the software or the data during distribution, in external memories, and during execution. The secure computing environment is achieved by using a hardware-based security method and apparatus to provide protection against software privacy and tampering. A Harvard architecture CPU core is instantiated on the same silicon chip along with encryption management unit (EMU) circuitry and secure key management unit (SKU) circuitry. Credential information acquired from one or more sources is combined by the SKU circuitry to generate one or more security keys provided to the EMU for use in decrypting encrypted program instructions and / or data that is obtained from a non-secure, off-chip source such as an external RAM, an information storage device or other network source. In a non-limiting illustrative example implementation, the EMU decrypts a single memory page of encrypted instructions or data per a corresponding encryption key provided by the SKU. Although instantiated on the same chip, the CPU core does not have direct access to the SKU circuitry or to encryption key information generated by the SKU.

Owner:MACAULAY BROWN +1

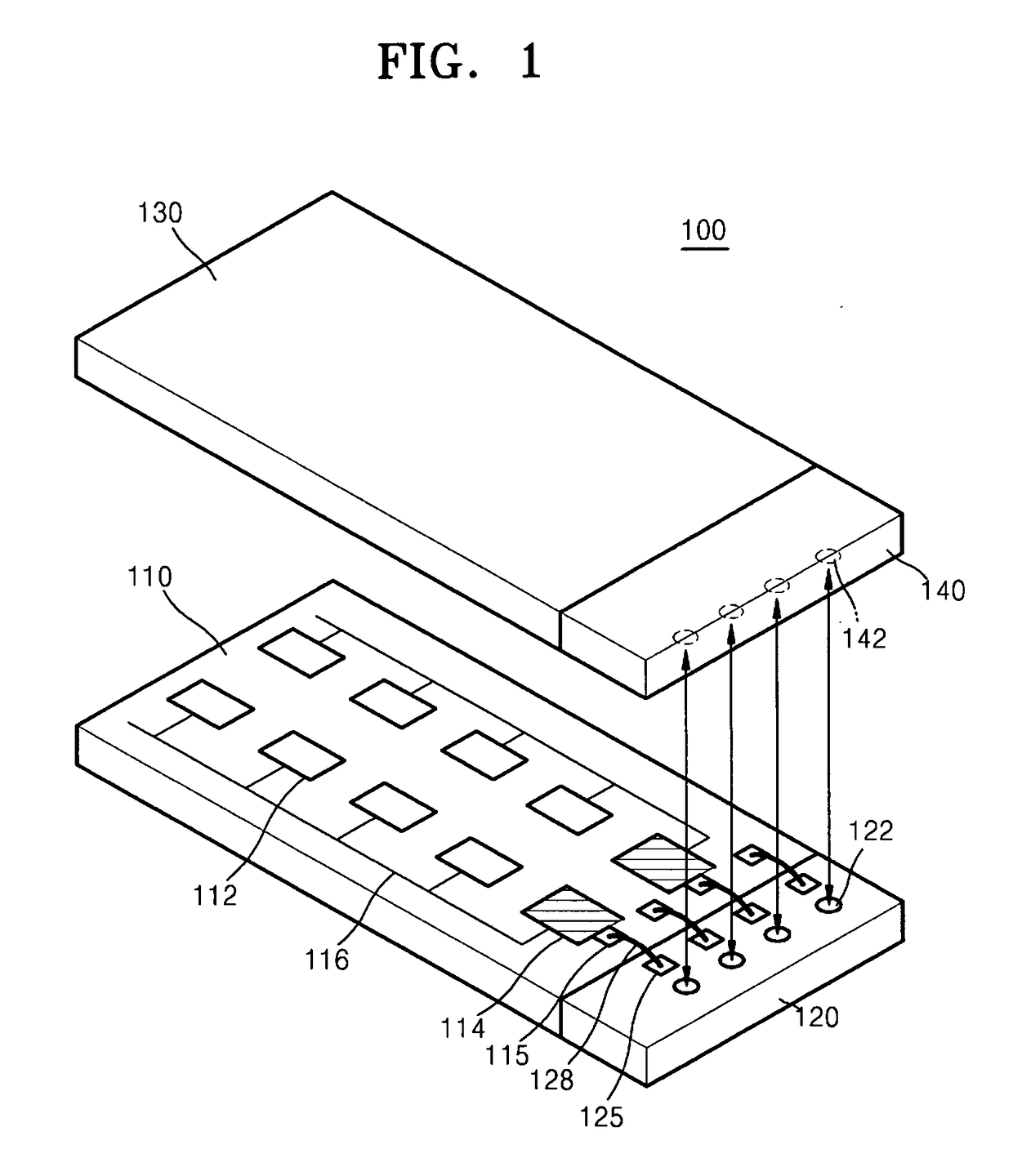

Multi-chips with an optical interconnection unit

A multi-chip having an optical interconnection unit is provided. The multi-chip having an optical interconnection unit includes a plurality of silicon chips sequentially stacked, a plurality of optical device arrays on a side of each of the plurality of the silicon chips such that the optical device arrays correspond to each other and a wiring electrically connecting the silicon chip and the optical device array attached to a side of the silicon chip, wherein the corresponding optical device arrays forms an optical connection unit by transmitting and receiving an optical signal between the corresponding optical device arrays in different layers. Each of the optical device arrays includes at least one of a light emitting device and a light receiving device.

Owner:SAMSUNG ELECTRONICS CO LTD

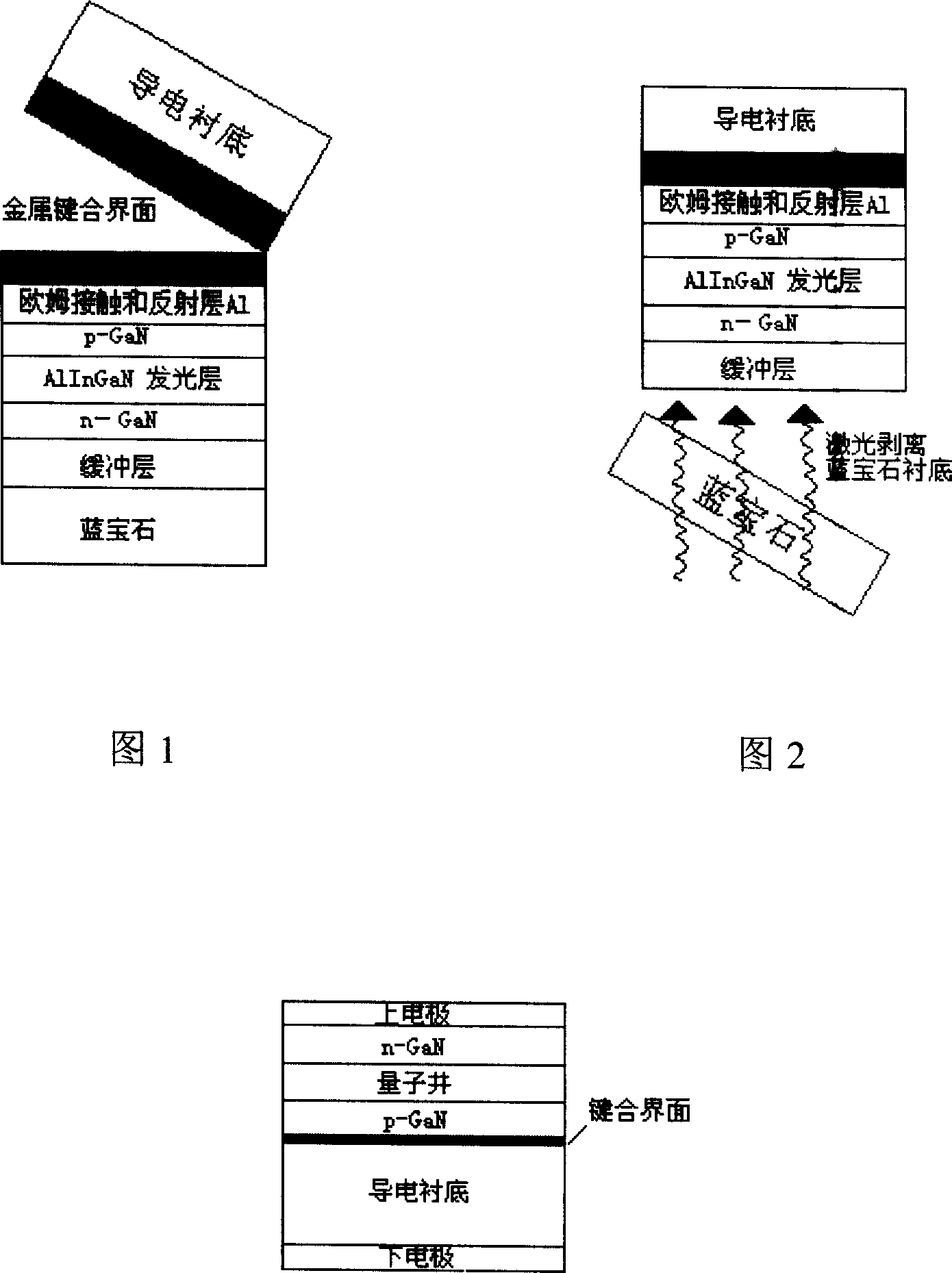

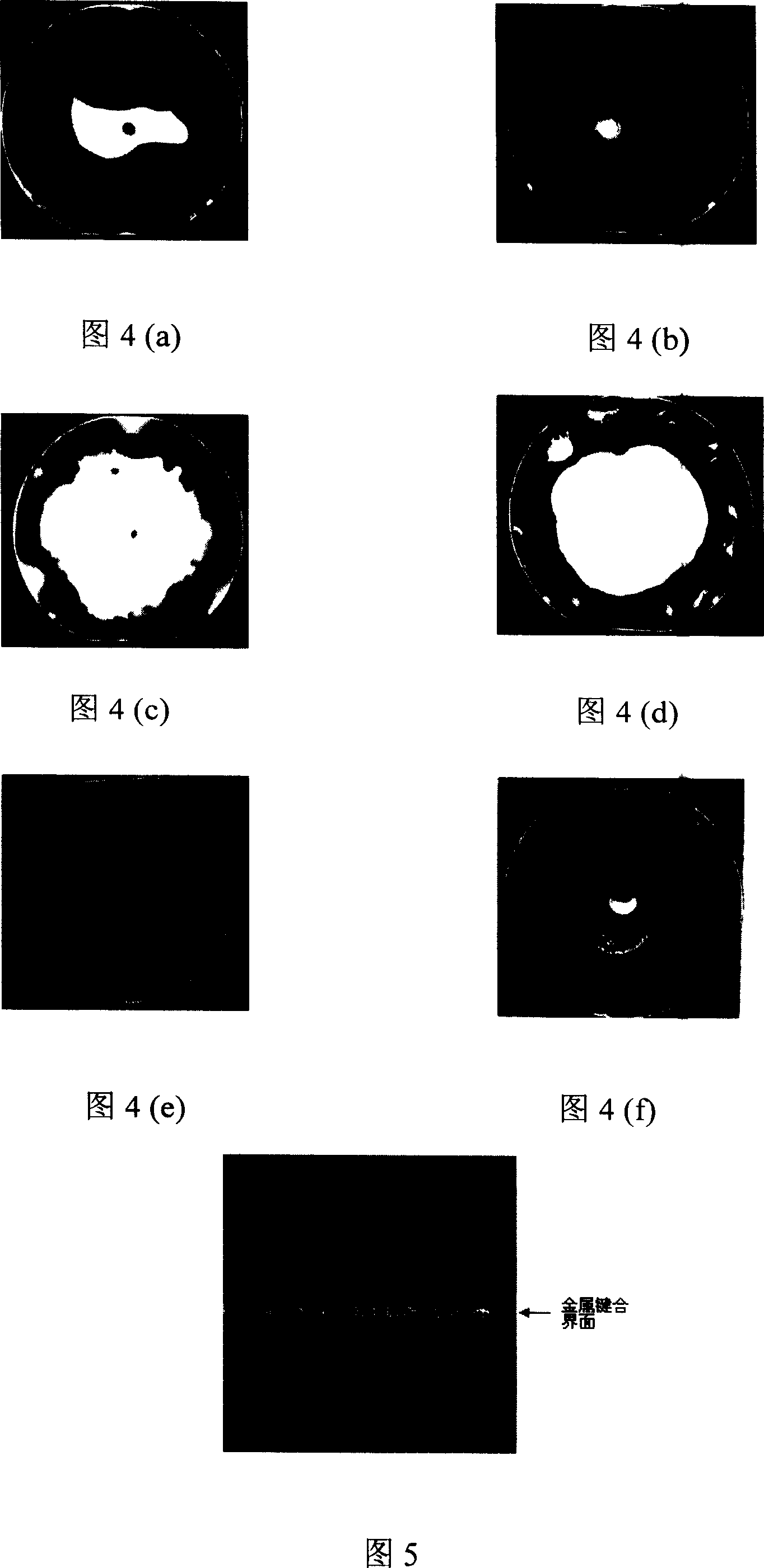

Method for realizing gallium nitride ELD vertical structure using metal bounding process

InactiveCN101005110AImprove yieldAchieve preparationSemiconductor devicesOhmic contactGallium nitride

Using metal bonding technique in diffusion bonding form, the method bonds gallium nitride LED developed and prepared on sapphire and silicon chip in low resistance together, and realizes ohmic contact. Advantages are: stable bonding technique, high ratio of good produced parts, small area, using material of luminous layer fully, as well as good conductivity and heat conductivity of substrate.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

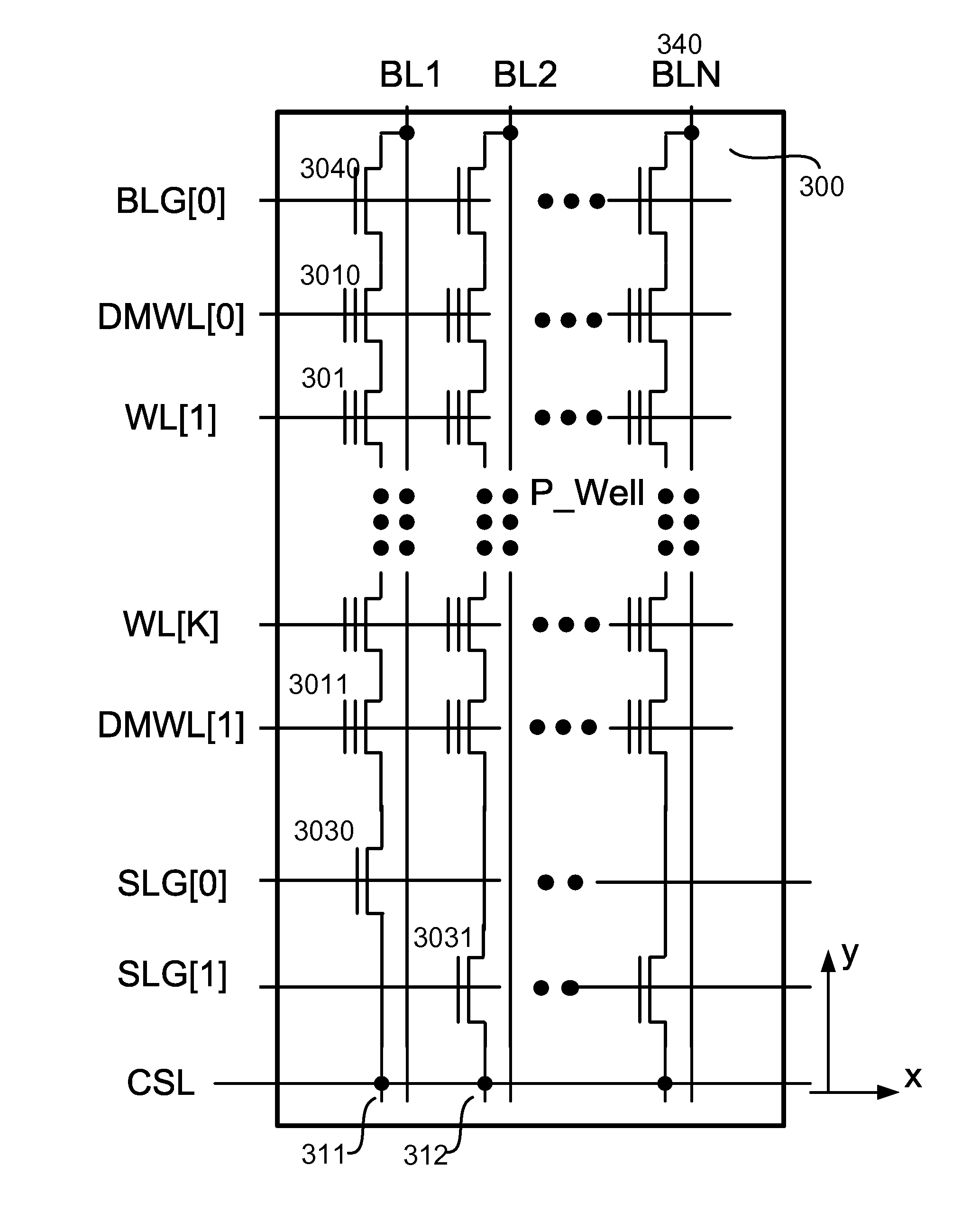

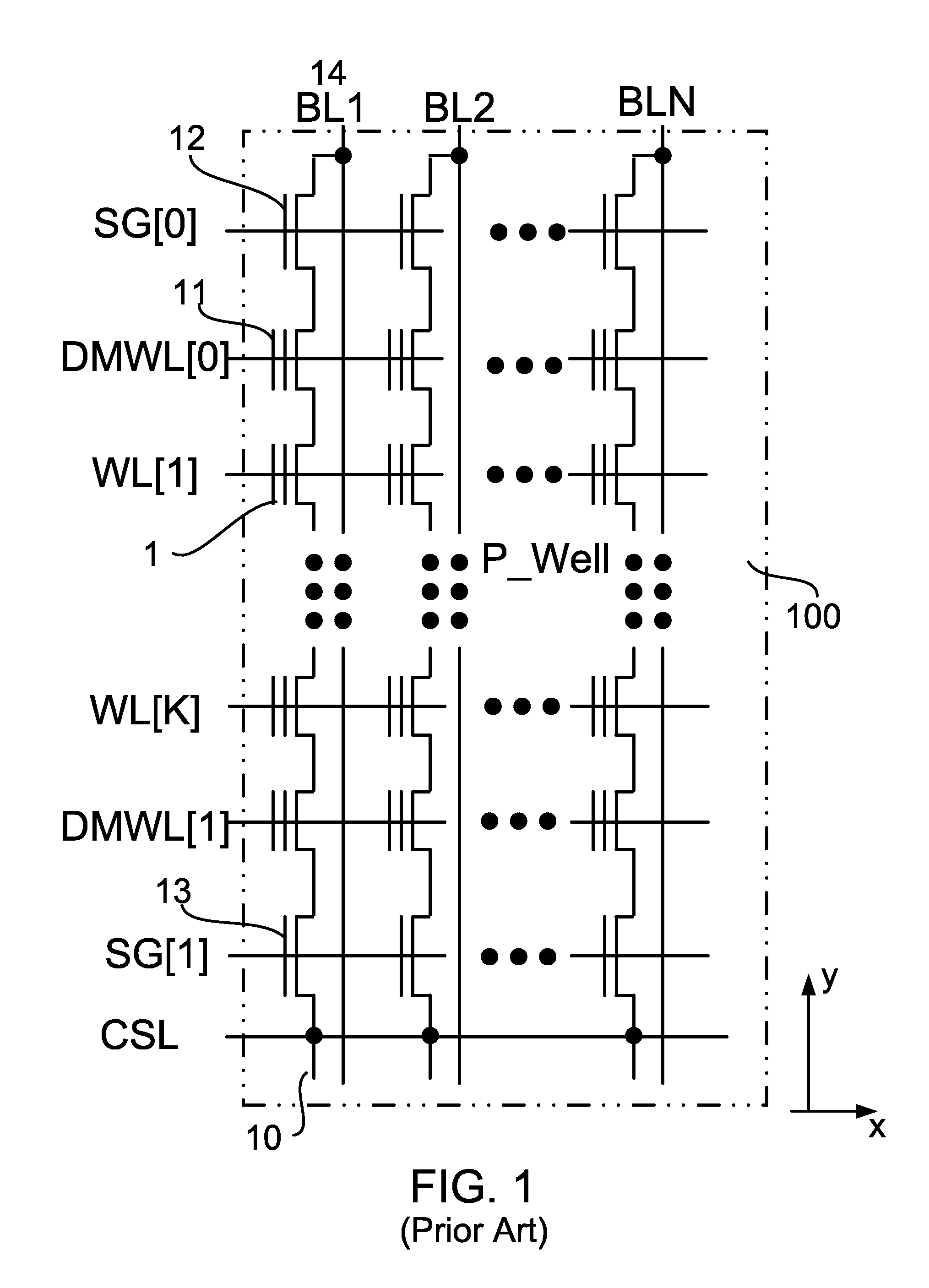

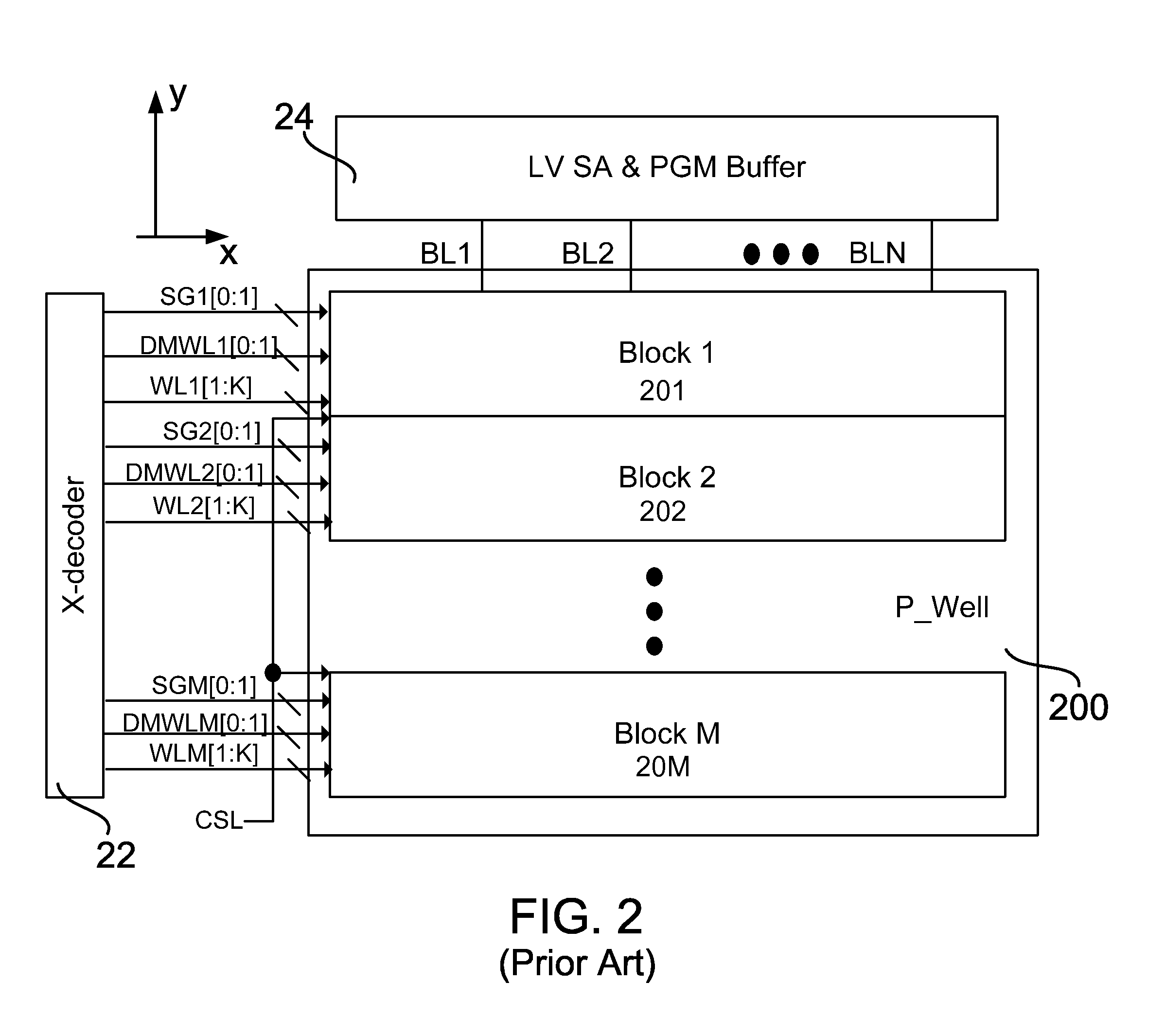

Non-boosting program inhibit scheme in NAND design

InactiveUS20130272067A1Save power consumptionReduced operating requirementsRead-only memoriesDigital storageComputer hardwareComputer architecture

A low-current FN channel scheme for erase, program, program-inhibit and read operations is disclosed for NAND NVM memories. This invention discloses a block array architecture and 3-step half-page program algorithm to achieve less error rate of NAND cell threshold voltage level. Thus, the error correction code capability requirement can be reduced, thus the program yield can be increased to reduce the overall NAND die cost at advanced nodes below 20 nm. As a result, this NAND array can still use the LV, compact PGM buffer for saving in the silicon area and power consumption. In addition, the simpler on-chip state-machine design can be achieved with the superior quality of less program errors.

Owner:APLUS FLASH TECH

Method for manufacturing and integrating multichannel high-sensitive biosensor

InactiveCN101592627AHigh sensitivityExtend your lifeSemi-permeable membranesNanostructure manufactureField-effect transistorMicrofluidic channel

The invention provides a method for manufacturing and integrating a multichannel high-sensitive biosensor. The method comprises the following steps: firstly, based on an SOI silicon chip, adopting a top-down method to manufacture an FET field effect transistor of a silicon nanometer wire; secondly, utilizing polydimethylsiloxane (PDMS) to manufacture a plurality of microfluid channels; and finally, modifying the silicon nanometer wires in different microfluid channels to allow the silicon nanometer wire to be modified with different detecting antibodies and small molecules for detecting different target molecules. The sensor manufacture by the method can be used for simultaneously detecting relevant factors (such as DNA, RNA, protein and the like) or virus of different types of diseases and has the characteristics of high sensitivity, stability, easy integration and the like.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

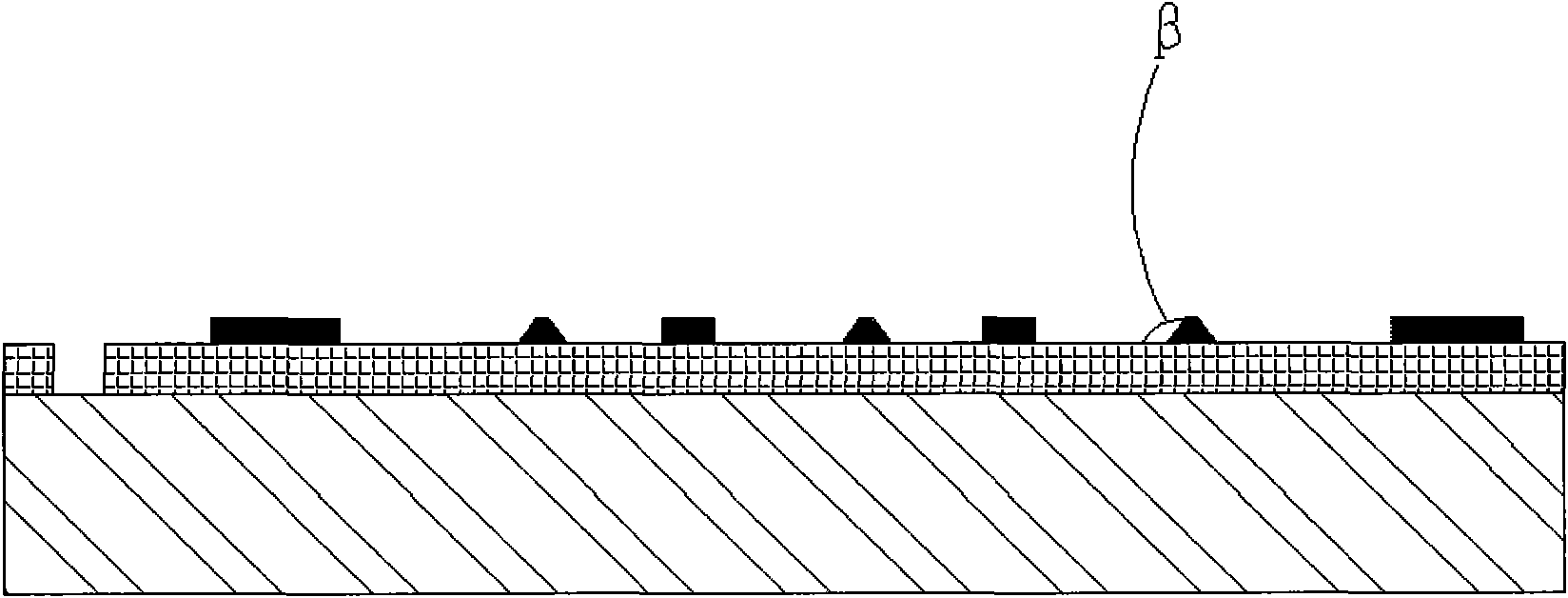

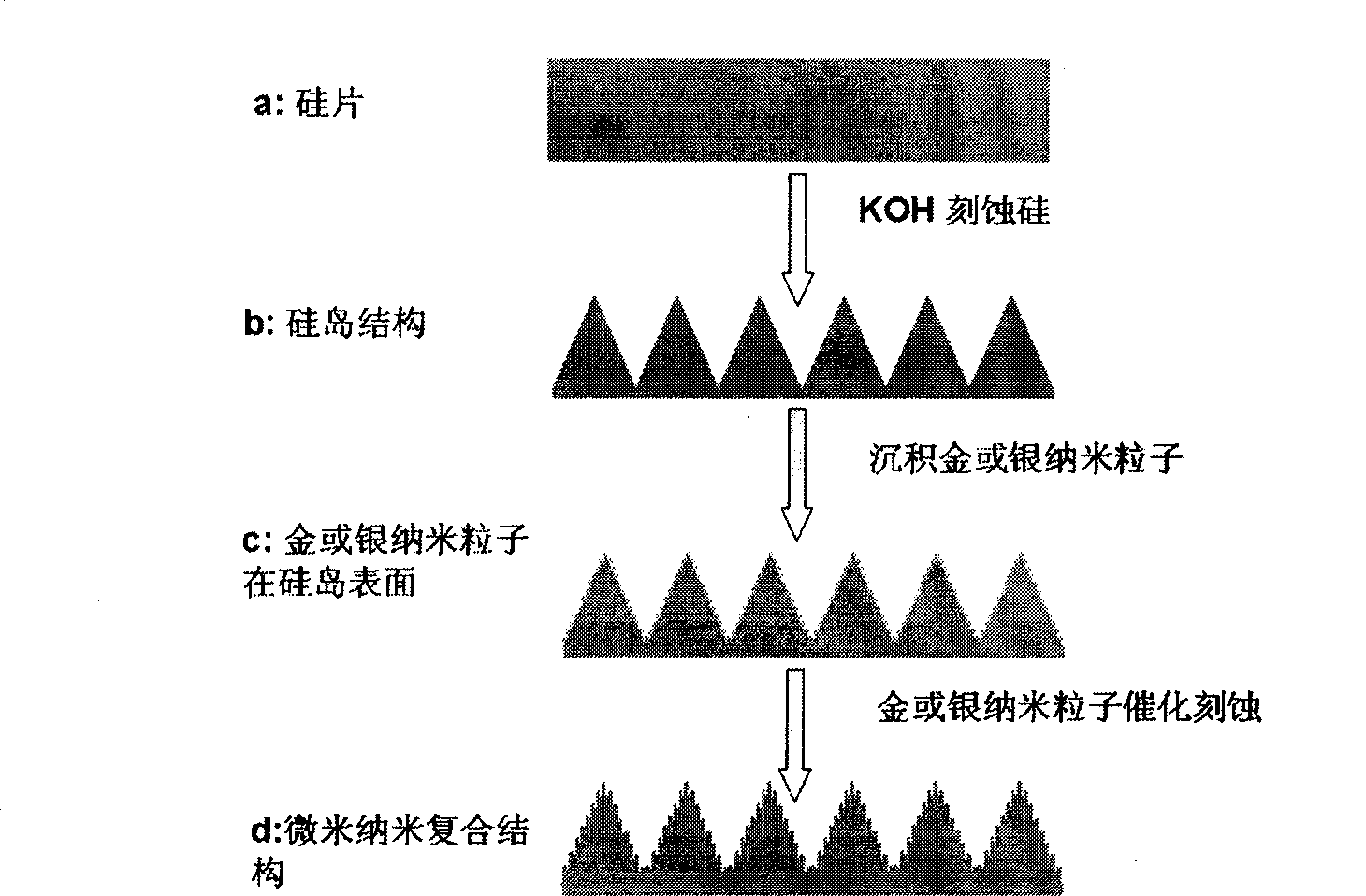

Method for preparing super-hydrophobic antireflex micron and nano composite structure surface

The invention belongs to the technical field of preparing the surface of a composite structure, and in particular relates to a method for preparing super-hydrophobic antireflective silicon surface with a micron and nanometer composite structure. The method comprises the following steps: cleaning a silicon chip; preparing a micron-level silicon island and a gridding structure on the surface of the silicon chip; carrying out catalytic etching taking silver or aurum nanoparticles as blockage; obtaining the surface of the micron and nanometer composite structure; and carrying out chemical modification of the surface of the composite structure. A static contact angle between the super-hydrophobic antireflective material surface prepared by the method and water is more than 150 degrees, and a static rolling angle of water is less than 3 degrees. The surface has superior antireflective performance, and in particular, the light reflectivity within the wavelength range between 800 and 1,100 nm is less than 3 percent. With application of the method, the super-hydrophobic antireflective silicon surface of the micron and nanometer composite structure can be produced on scale, can be widely applied to a solar cell, a microfluidic chip, a photoelectric device, and the like, and has good industrial application prospect.

Owner:JILIN UNIV

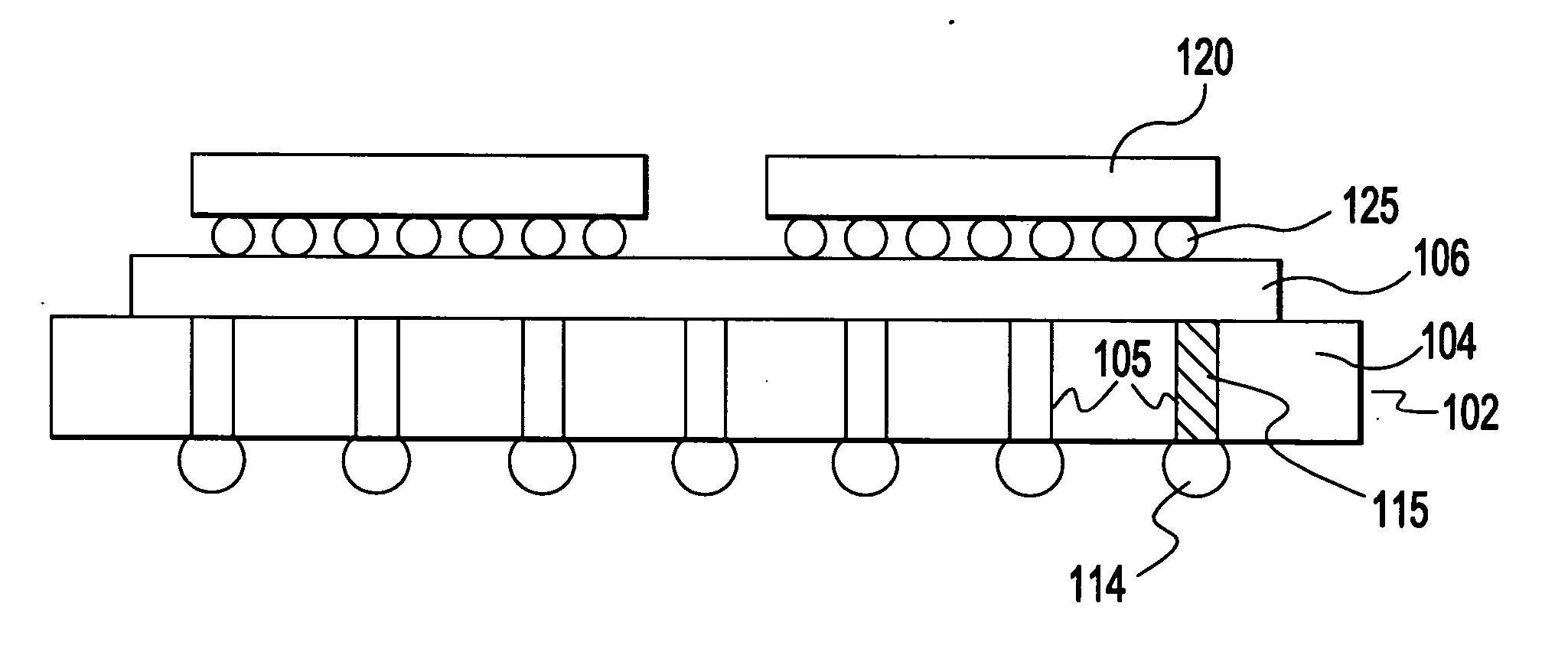

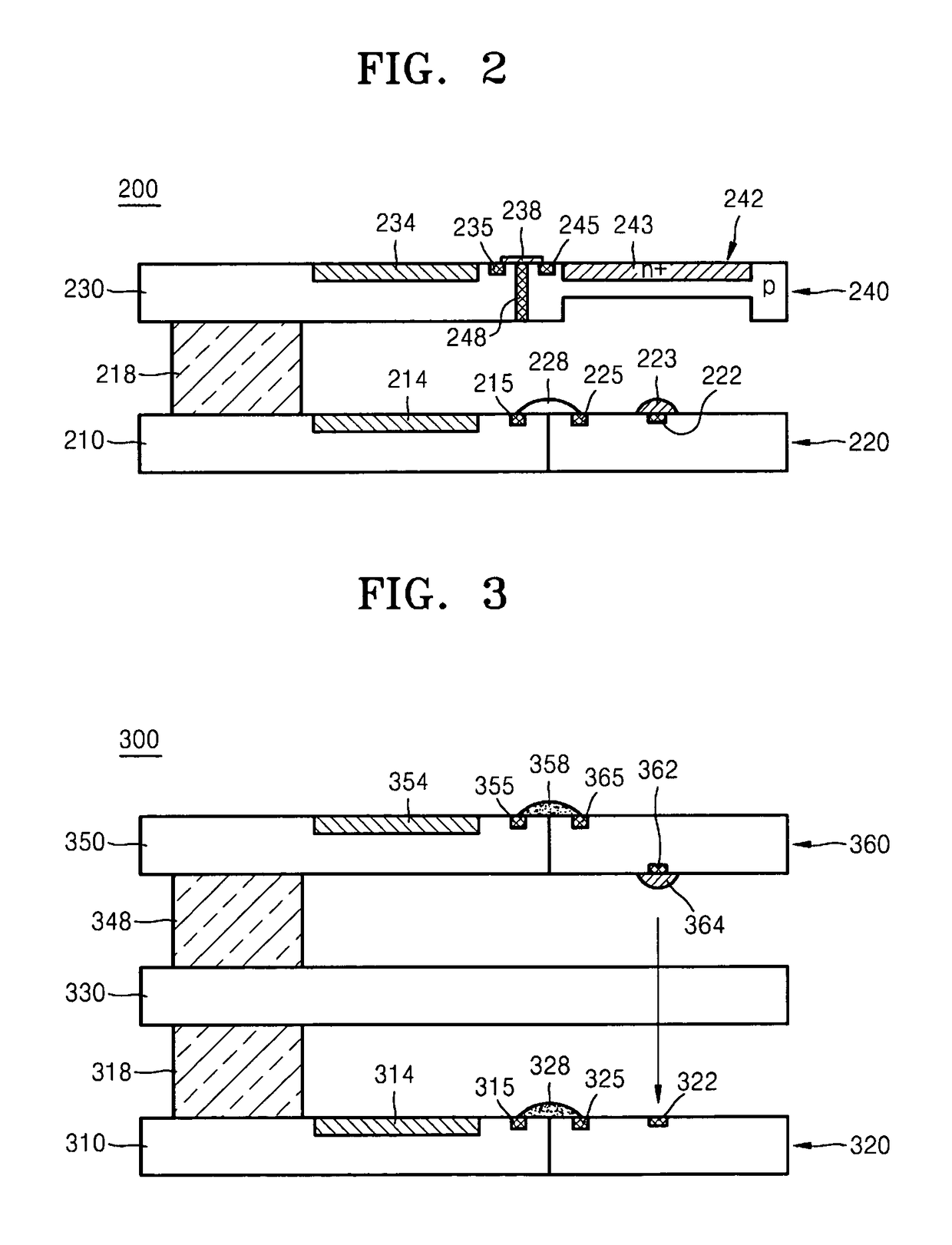

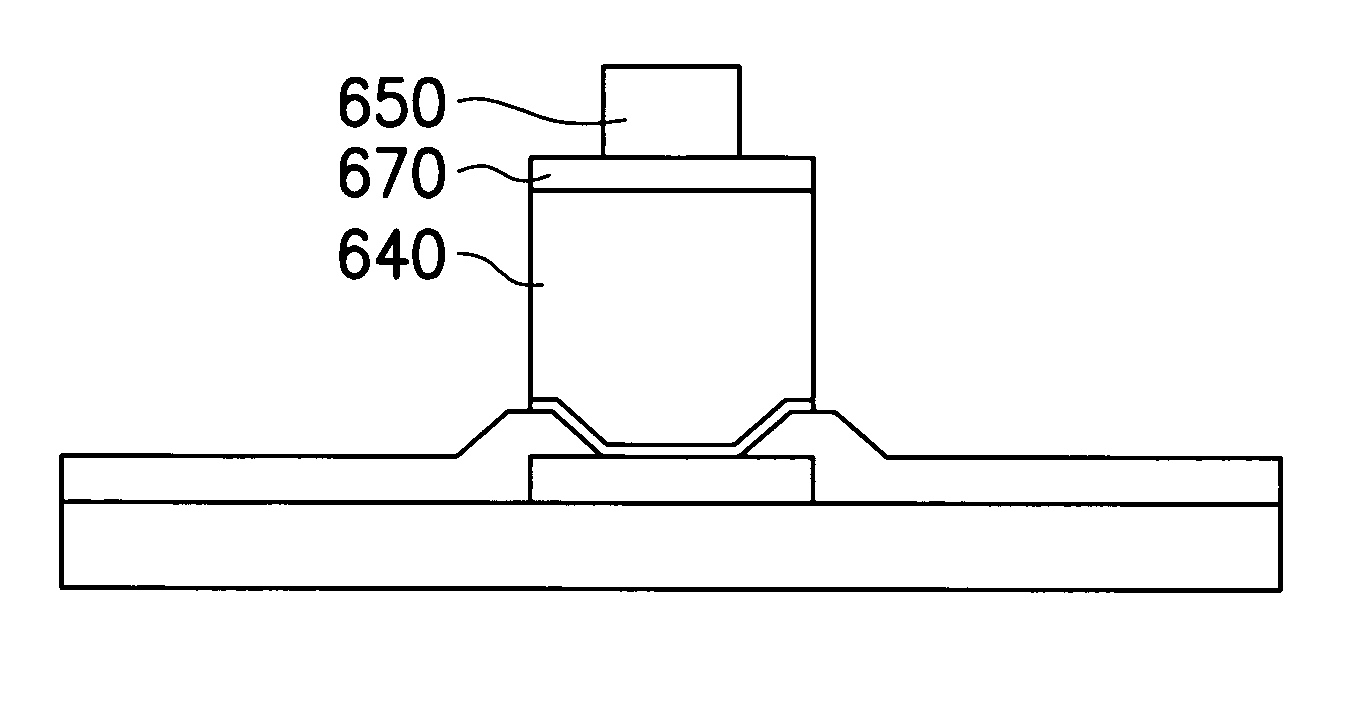

Bonding structure with pillar and cap

InactiveUS7208834B2Easy to separateIncrease the separation distanceSemiconductor/solid-state device detailsSolid-state devicesConductive materialsEngineering

Owner:QUALCOMM INC

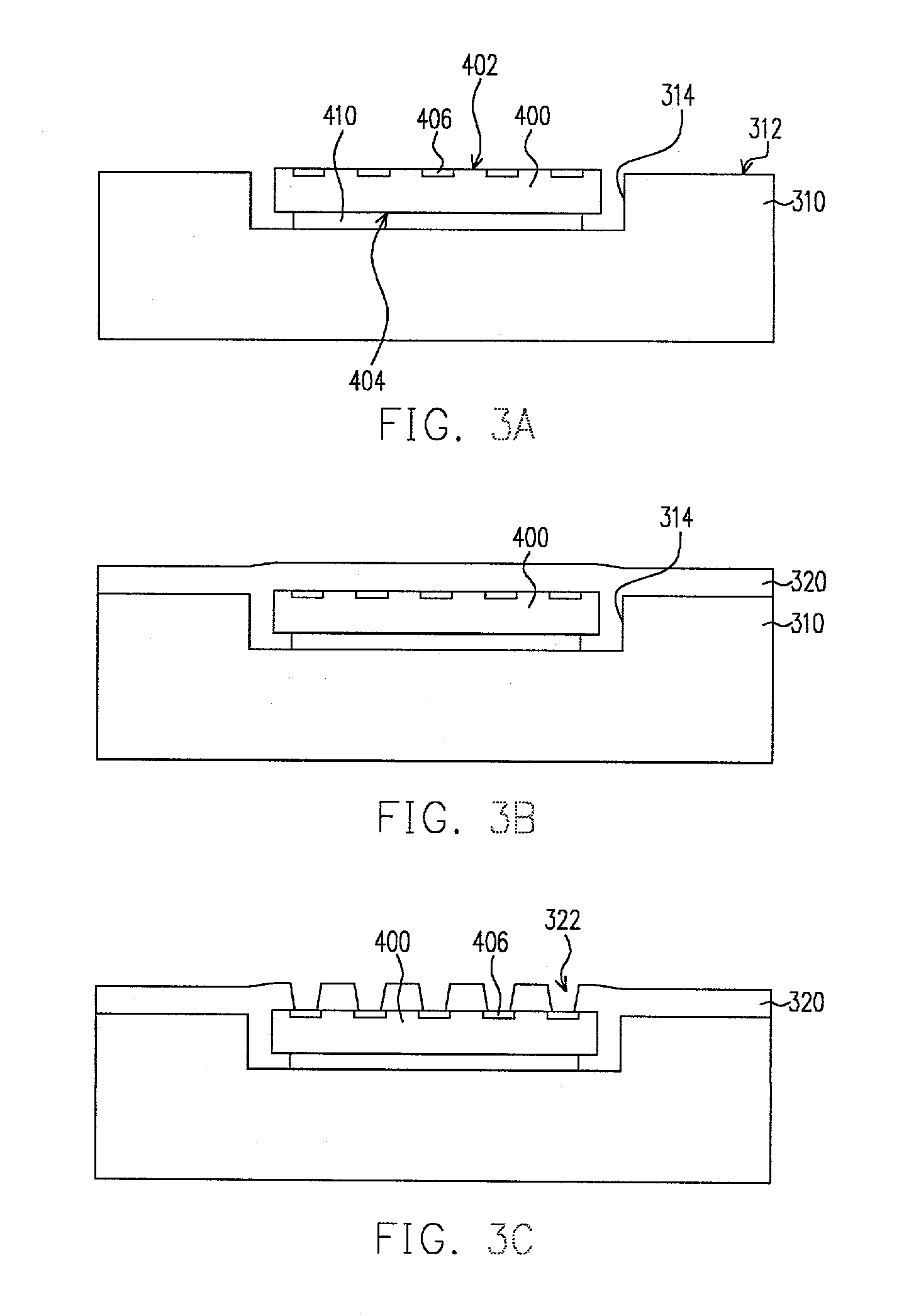

Semiconductor device and method for manufacturing the same

InactiveUS20120068355A1Reduce the likelihood of occurrenceReduce generationSemiconductor/solid-state device detailsSolid-state devicesWafer stackingSilicon

A semiconductor device including two silicon wafers stacked and bonded together with bumps of one wafer electrically coupled with those of the other wafer, in which generation of voids on the junction surface between the silicon wafers is suppressed. Due to a recess made in the surface of a buried conductive film, a cavity is formed in the junction surface between the silicon wafers. The ends of the cavity extend to the periphery of the junction surface between the silicon wafers. This allows the air trapped on the junction surface between the silicon wafers to get out through the cavity, thereby reducing the possibility of generation of voids on the junction surface.

Owner:HITACHI LTD

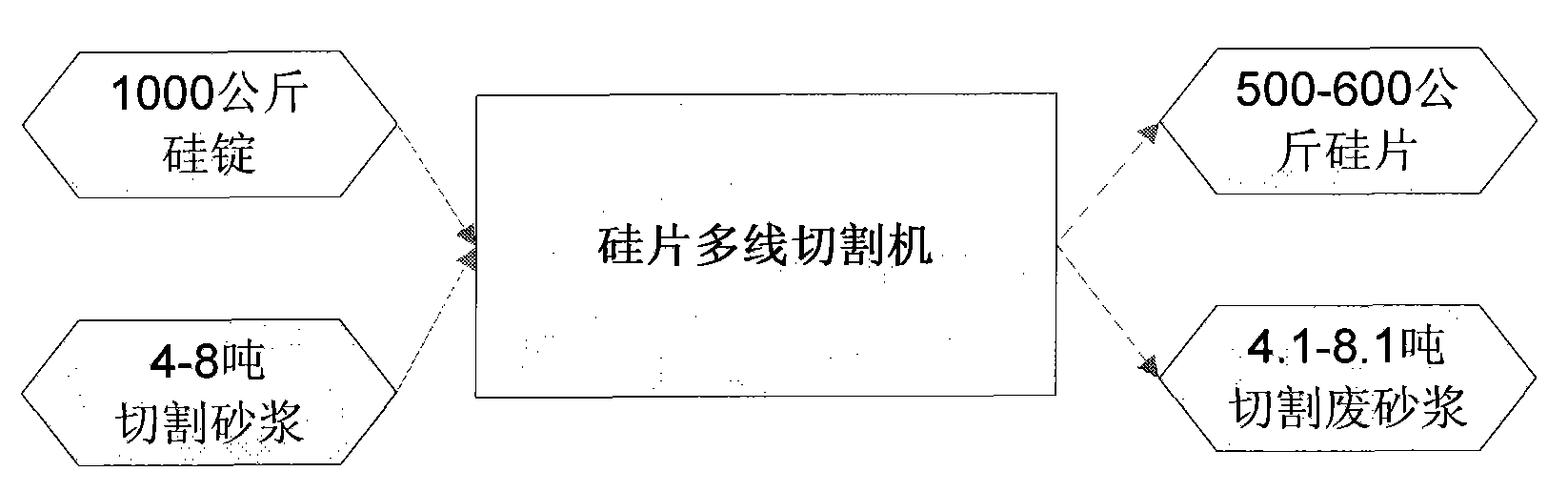

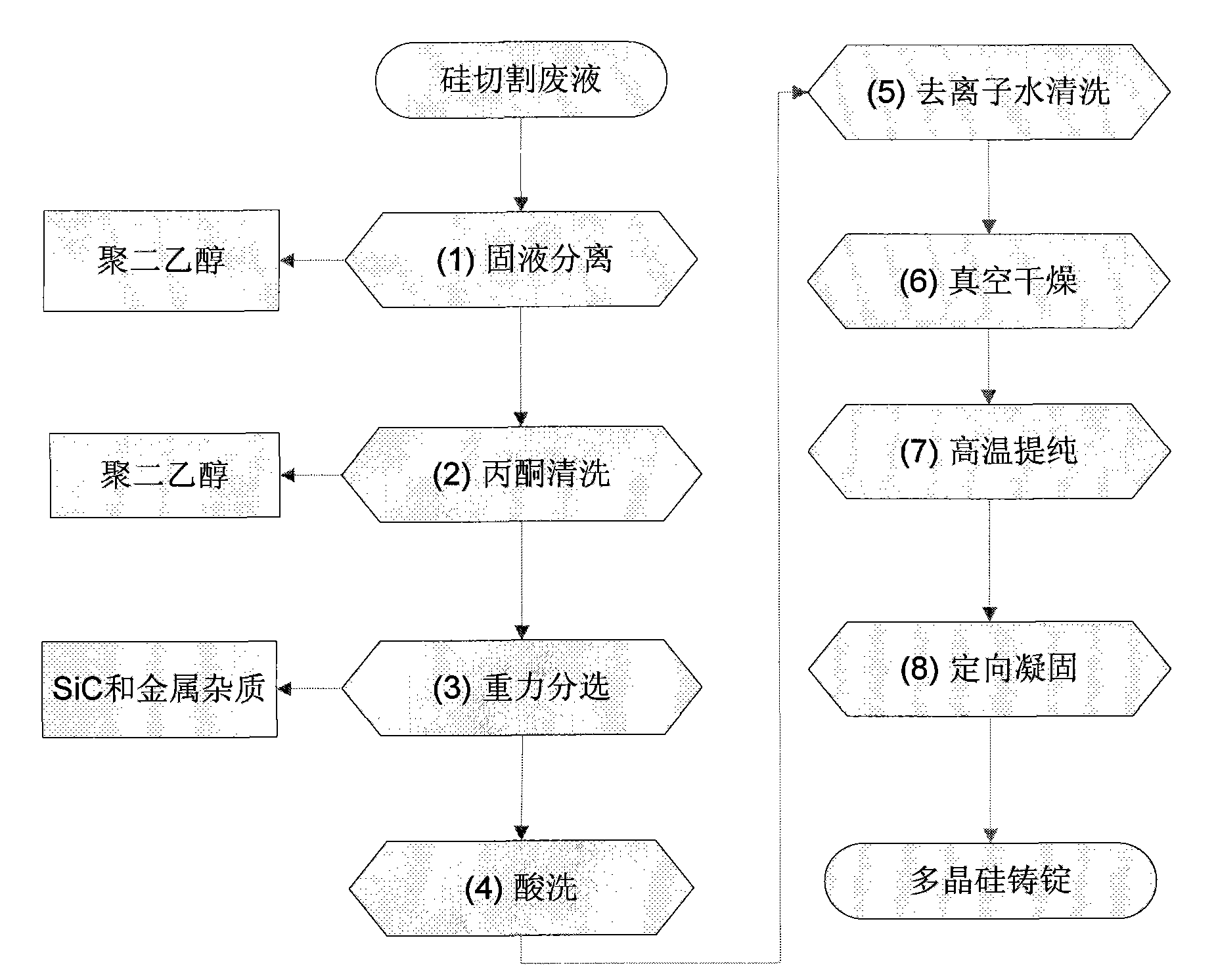

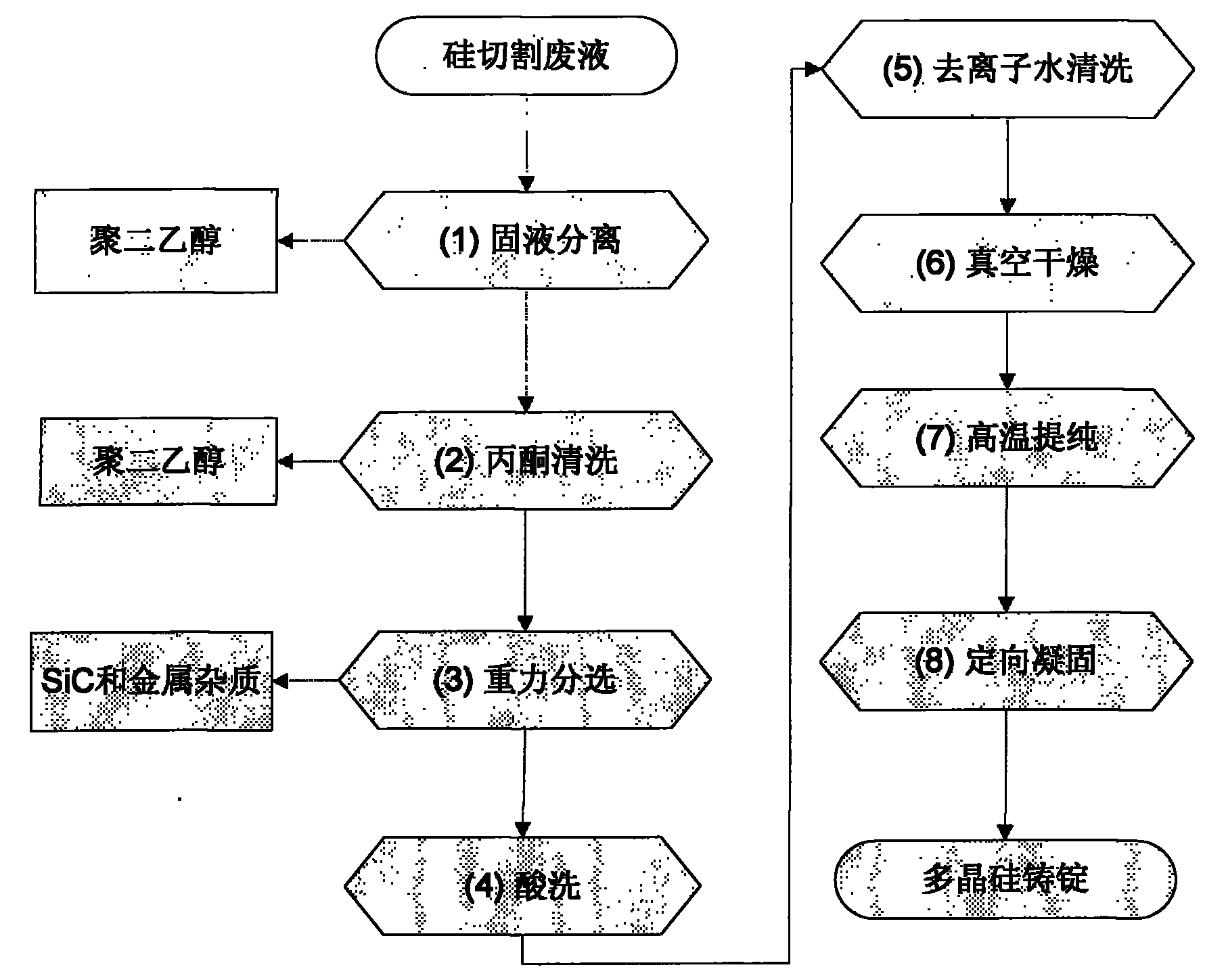

Method for recovering polysilicon ingots, carborundum powder and polyethylene glycol from cutting waste mortar

InactiveCN101792142AHigh yieldMultistage water/sewage treatmentSilicon compoundsPotassiumPolyethylene glycol

The invention discloses a method for recovering polysilicon ingots, carborundum powder and polyethylene glycol from cutting waste mortar. The recovering method comprises the following steps shown as an attached diagram, wherein the high temperature purification comprises the following steps of: mixing the prepared silicon micro powder with a fluxing agent according to the weight ratio of 1: 0.5-5 into lumps, carrying out high temperature treatment in a high temperature vacuum furnace with the treatment temperature range of 1450-1800 DEG C and the treatment time range of 1-10h; and then carrying out directional solidification on melting-state high purity silicon subjected to the high temperature treatment to obtain the polysilicon ingots; wherein the fluxing agent is selected from one or any mixture of silica, alumina, calcium oxide, magnesium oxide, potassium oxide, sodium oxide, calcium fluoride, magnesium fluoride, sodium fluoride, sodium chloride, potassium chloride and calcium chloride. The invention has the advantages that: the yields of carborundum and polyethylene glycol are high and can reach more than 70-80 percent; and the recovered polysilicon ingots reach the purity of 6-7N and completely satisfy of the requirement for preparing silicon slices of silicon solar cell.

Owner:唐康宁

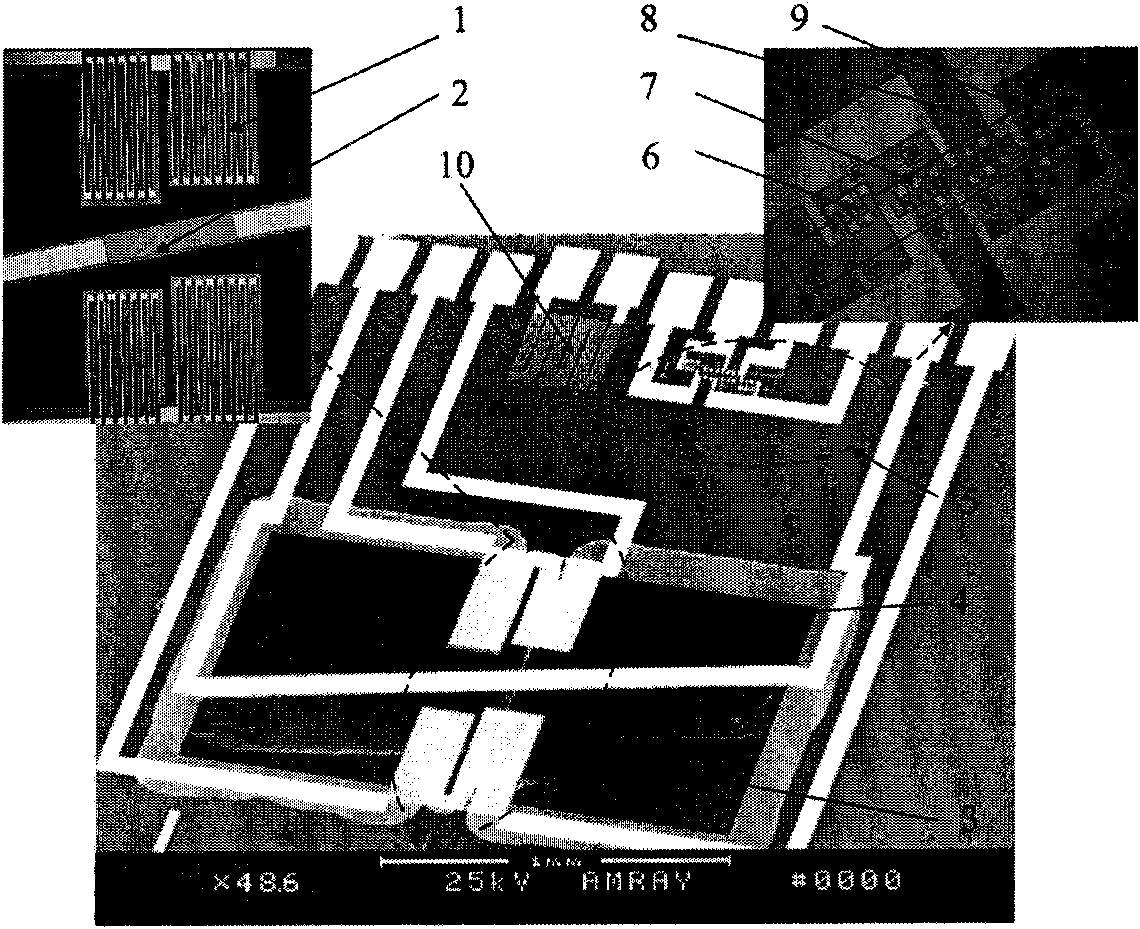

Integrated silicon chip for testing acceleration, pressure and temperature, and manufacturing method thereof

ActiveCN101551403AHigh sensitivityImprove stabilityFluid pressure measurement using ohmic-resistance variationDecorative surface effectsAccelerometerThermopile

The invention relates to an integrated silicon chip for testing acceleration, pressure and temperature, and the manufacturing method thereof. The invention is characterized in manufacturing the pressure sensor, temperature sensor and accelerometers of thermoelectric pile on to one chip by the same micro processing technology. The acceleration is detected by adopting thermal convection type accelerometers, using polysilicon resistor as heater, using a thermoelectric pile composed of two pairs of metals (such as aluminium and tungsten-titanium) and P type or N type polysilicon to detect the temperature difference in the sealed cavity caused by acceleration. The high accurate absolute pressure sensor is manufactured by using silicon nitride film with low stress as the core structure layer of the pressure sensor chip, and forming force sensitive resistor track by polysilicon film, forming vacuum reference cavity by TEOS bolt in LPCVD furnace. At the same time, the temperature sensor is composed by using polysilicon thermistor to detect temperature change. The integrated chip achieves the advantages of microminiaturization, low cost, high precision, high reliability and high stability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

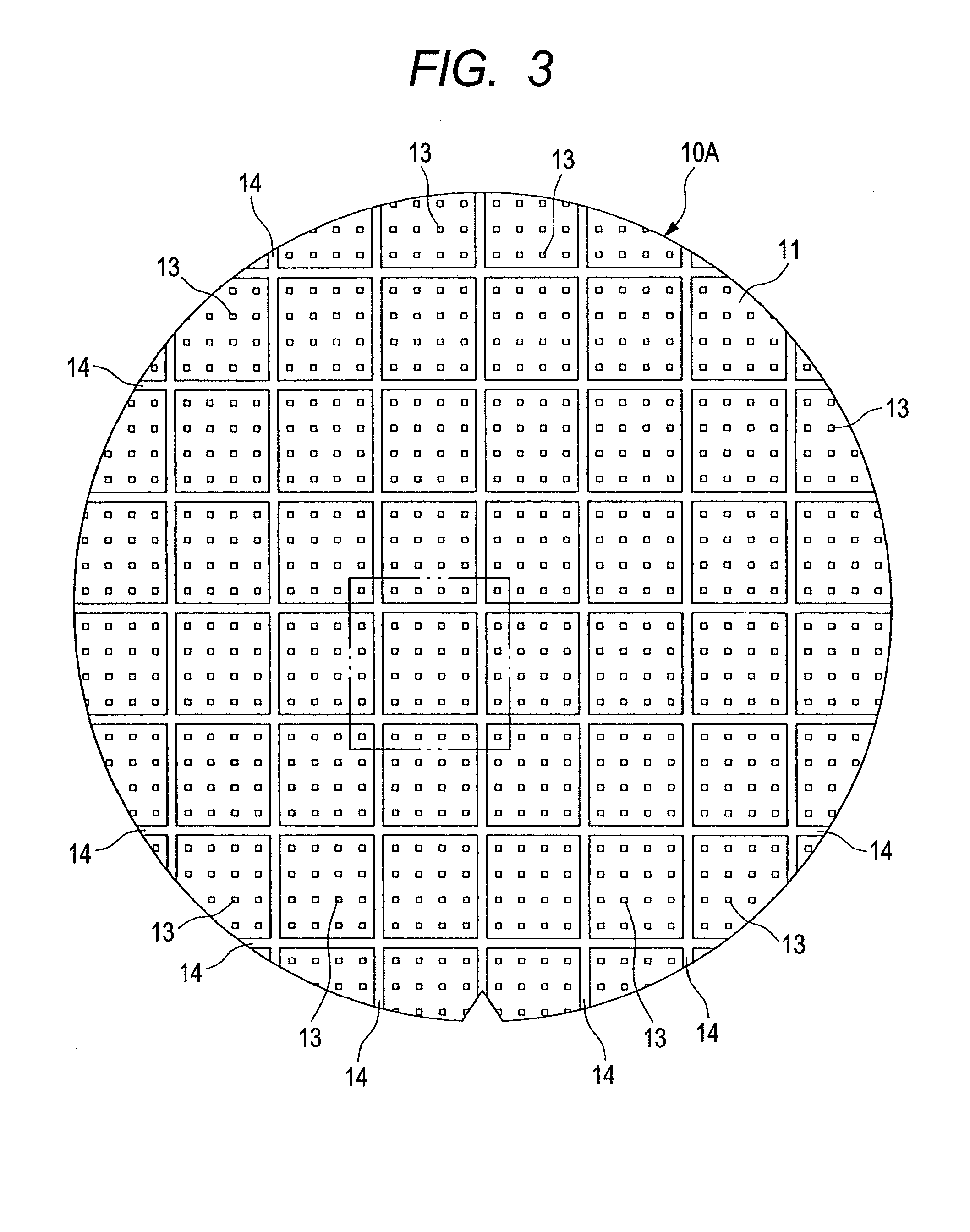

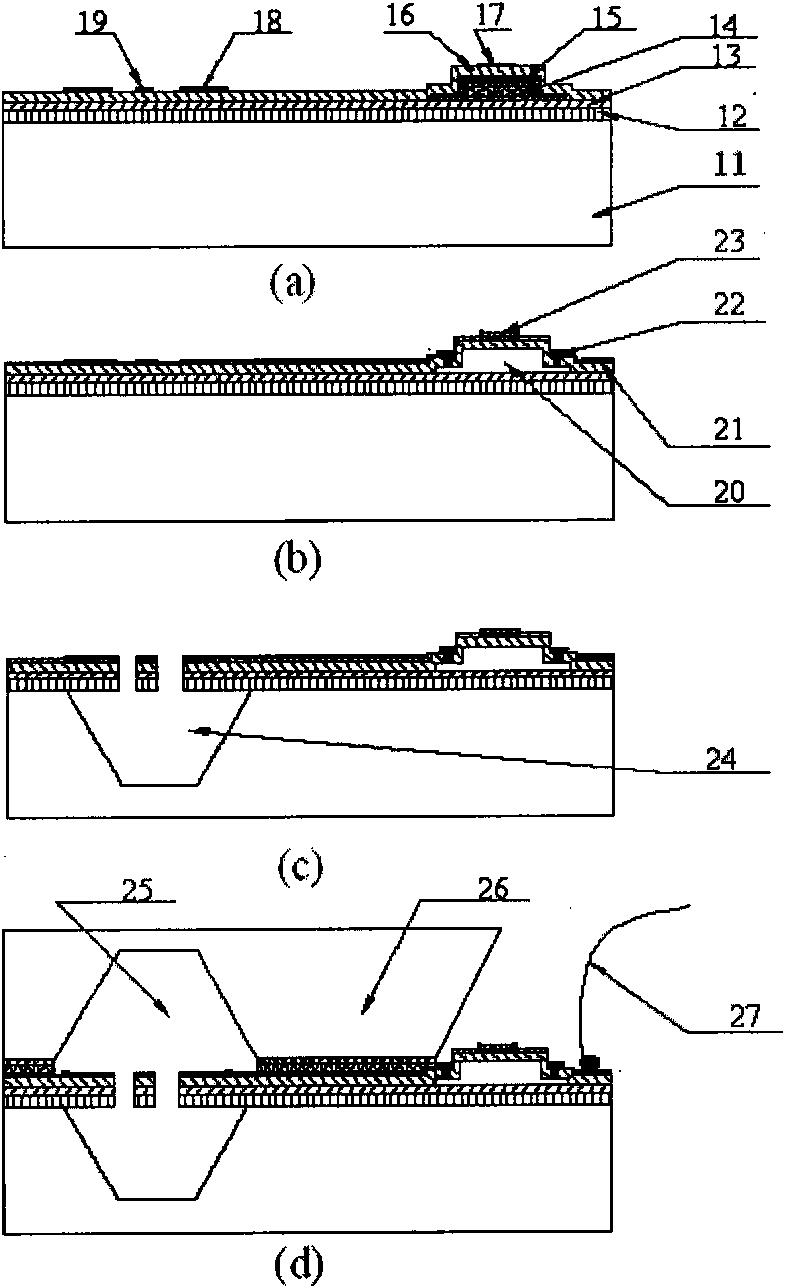

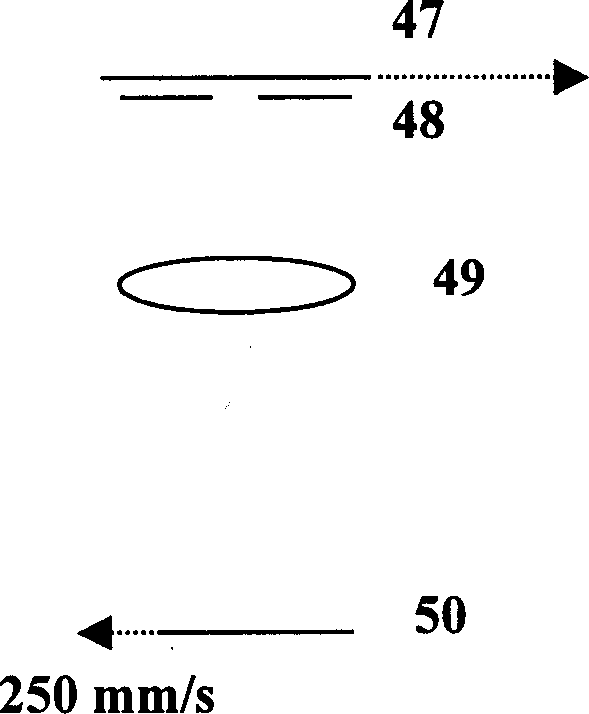

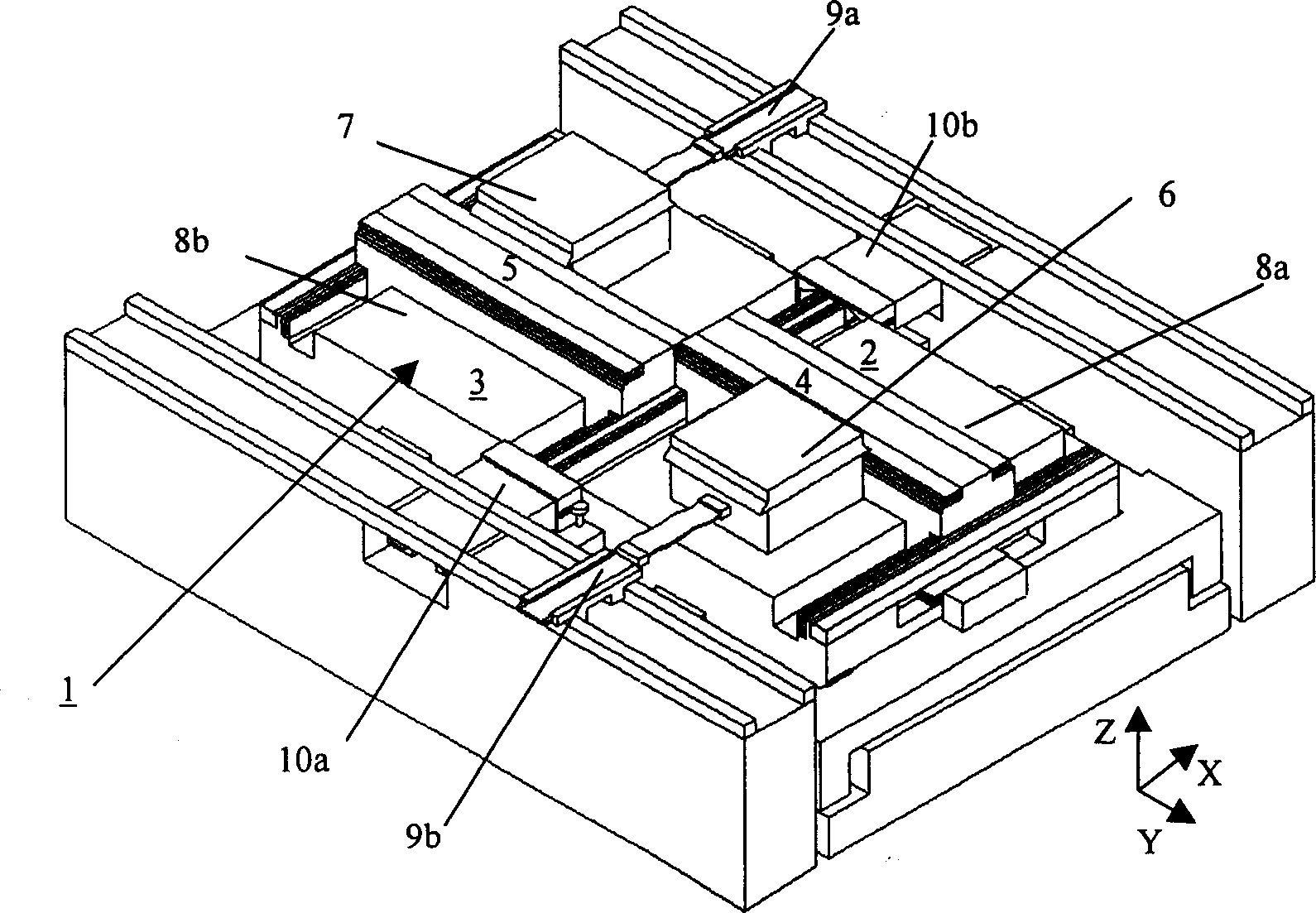

Step-by-step projection photo-etching machine double set shifting exposure ultra-sophisticated positioning silicon chip bench system

ActiveCN1485694AImprove exposure efficiencyReduce complexitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringSilicon chip

A step-by-step projection photo-etching machine double shift exposure ultra precise positioning silicon chip bench system, comprising a silicon chip bench positioning unit operating in the exposure station, and a silicon chip bench positioning unit operating in the preliminary treatment station, each positioning unit includes a silicon chip carrying device. The system can increase the exposure efficiency without the problem of overlapping and interference in the working space. It also realizes simplified structure, and high reliability and positioning precision.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD +1