Patents

Literature

224results about How to "Reduce the likelihood of occurrence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

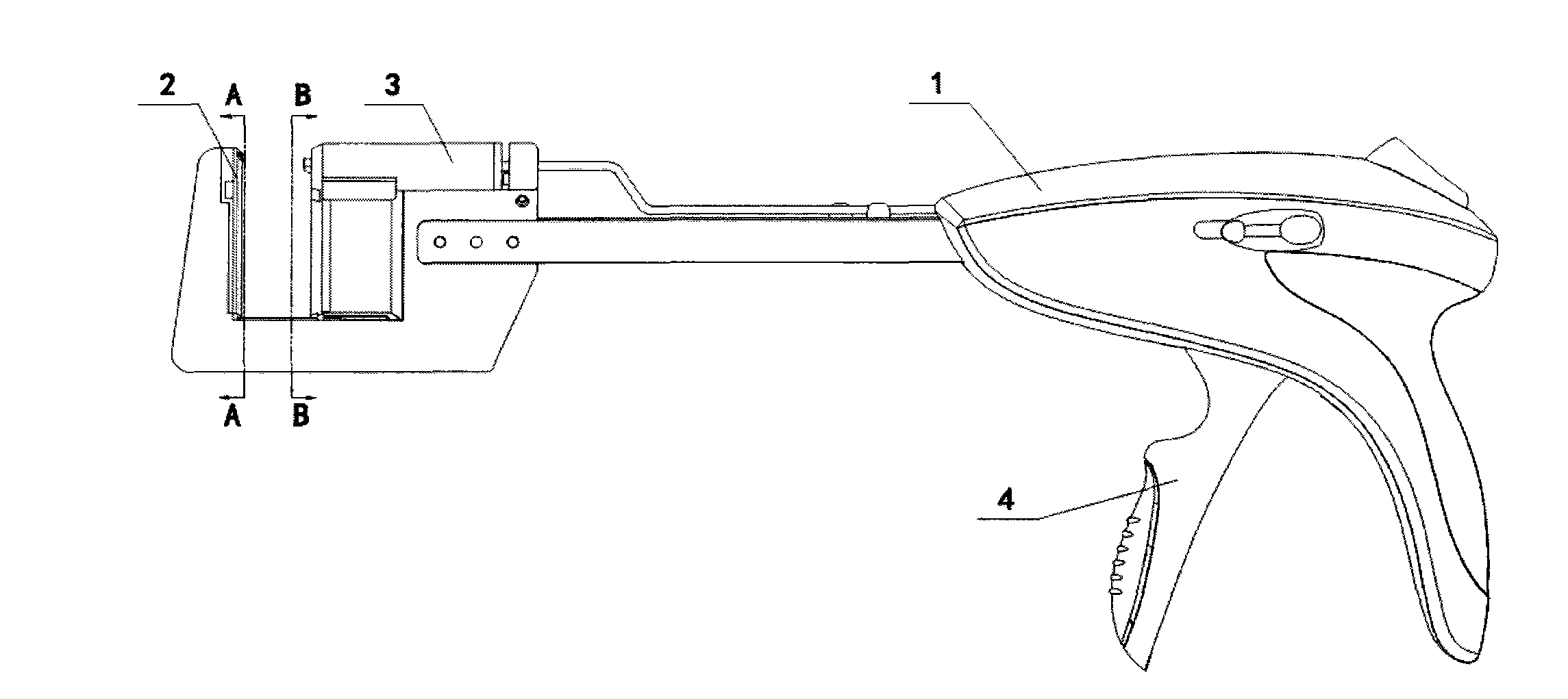

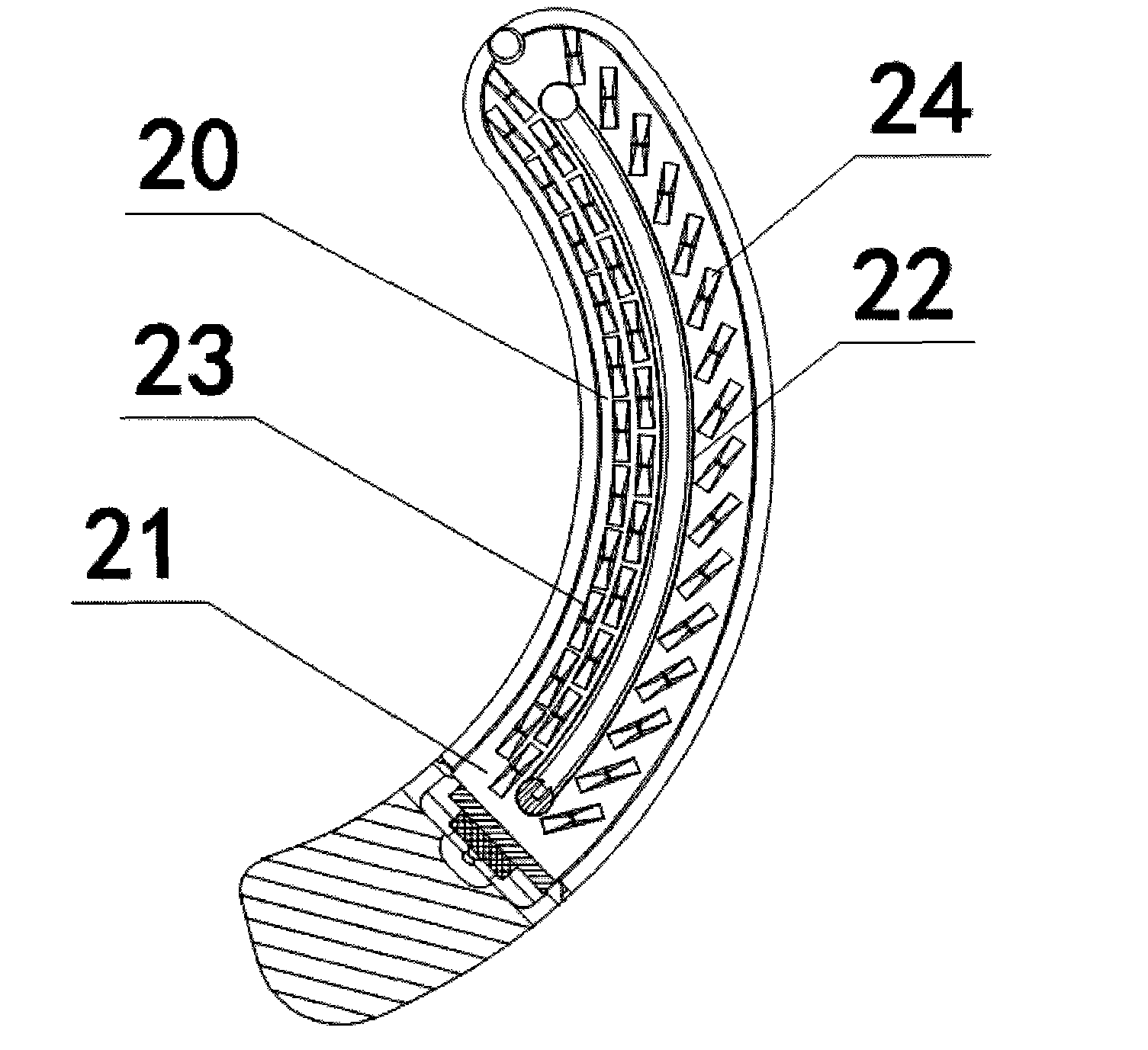

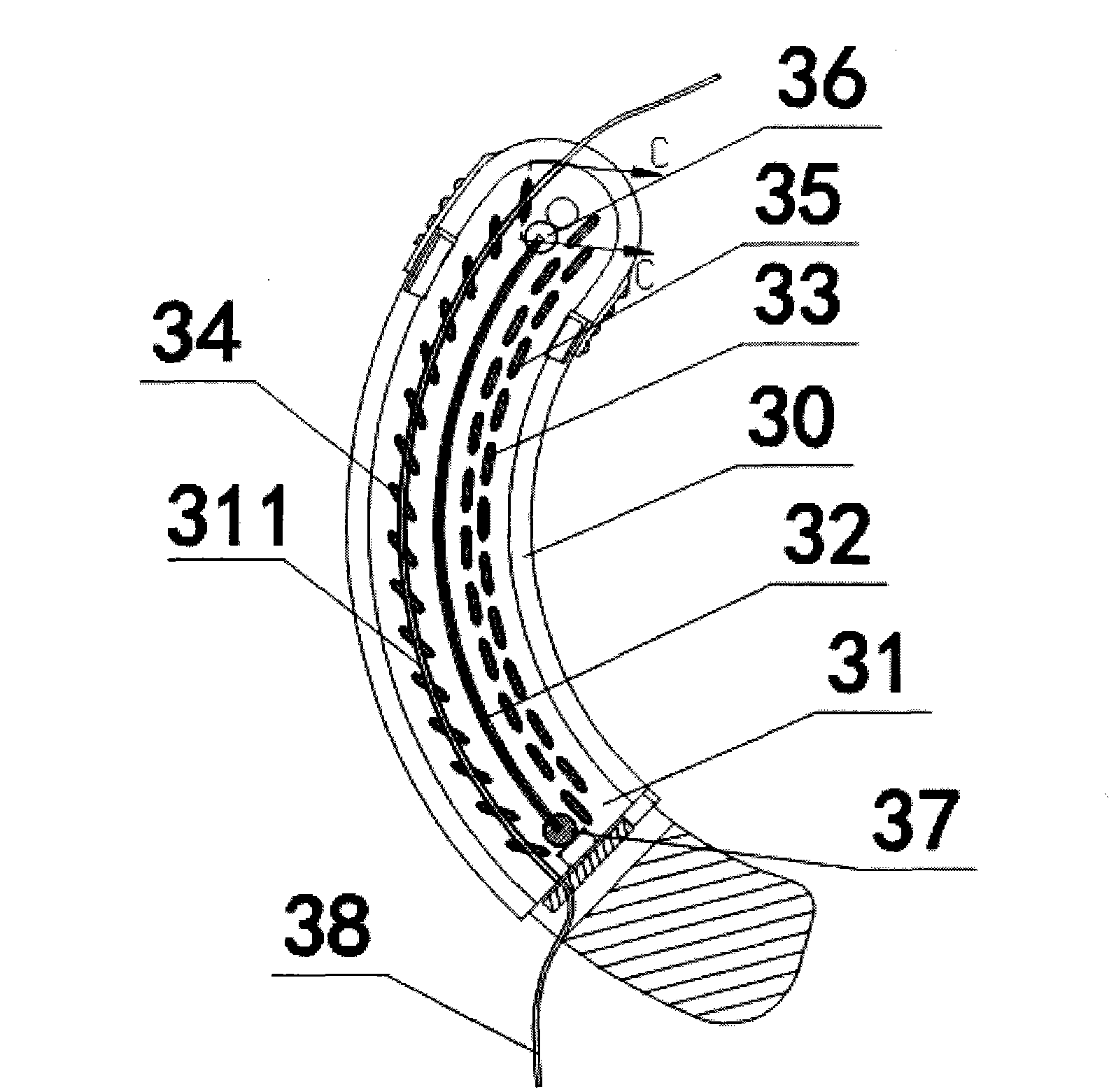

Surgical operating instrument

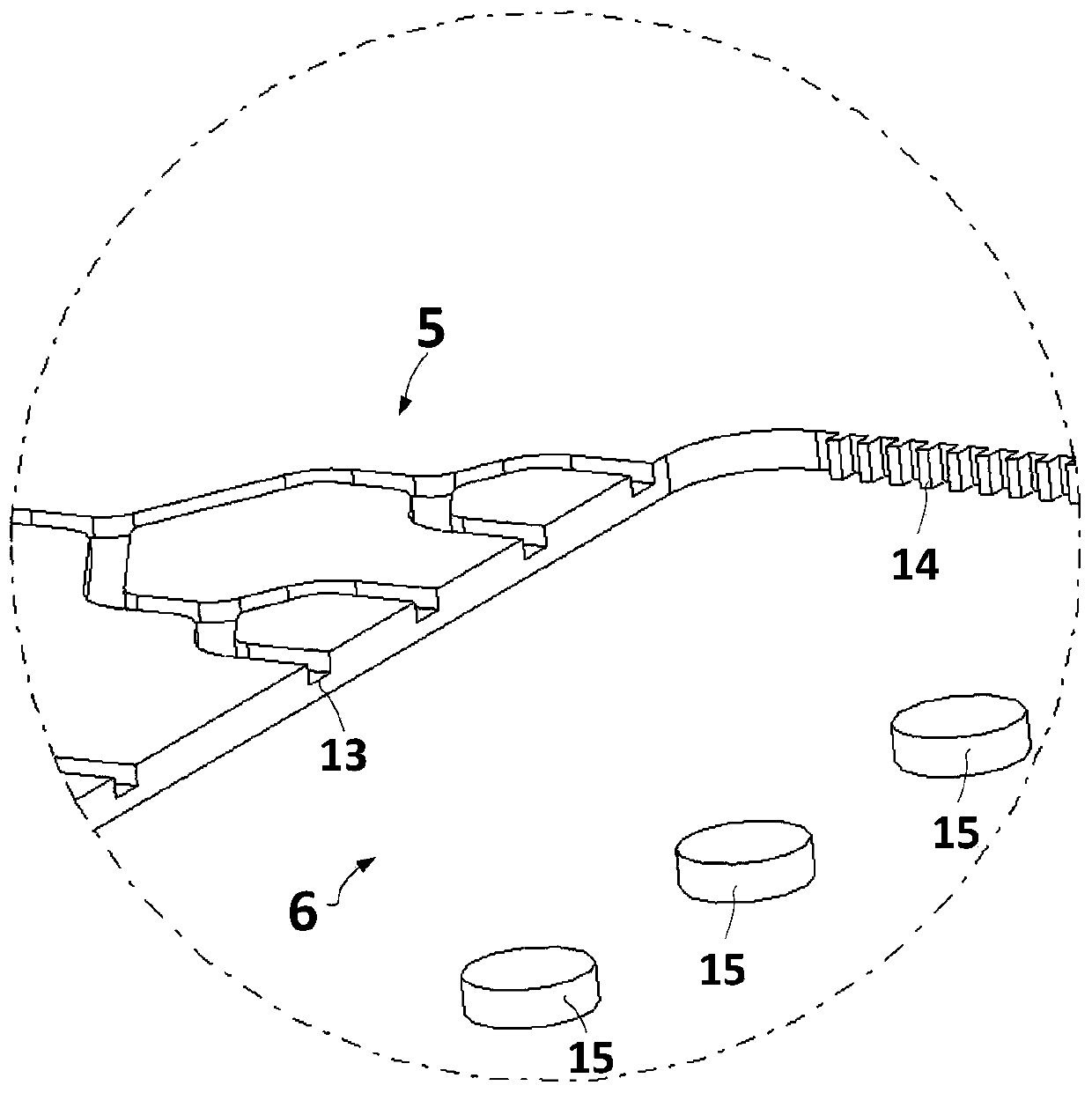

InactiveCN103908313AEfficient resectionReduce the likelihood of occurrenceSurgical staplesButt jointLow rectal cancer

The invention discloses a surgical operating instrument. The surgical operating instrument comprises a body, a nail cartridge, a nail anvil and a handle arranged on the body through a pivot, wherein the nail cartridge and the nail anvil are arranged at the far end of the body, the nail cartridge comprises a nail cartridge body, and the nail cartridge body comprises a knife slot, suturing nail placing holes and pocket nail placing holes. Nail pushing pieces and suturing nails which are in butt joint are arranged in the suturing nail placing holes. Nail pushing pieces and suturing nails which are in butt joint are arranged in the pocket nail placing holes. A line accommodating groove is further formed in the nail cartridge face and communicated with at least one part of pocket nail placing holes to form a certain angle, and a pocket line is arranged in the line accommodating groove and located between two nail feet of at least one part of pocket nails. The surgical operating instrument has the advantages that the surgical operating instrument is suitable for a low rectal cancer resection, can effectively and completely excise left diseased tissue ends and greatly reduces the occurrence possibility of medical negligence.

Owner:TOUCHSTONE INTERNATIONAL MEDICAL SCIENCE CO LTD

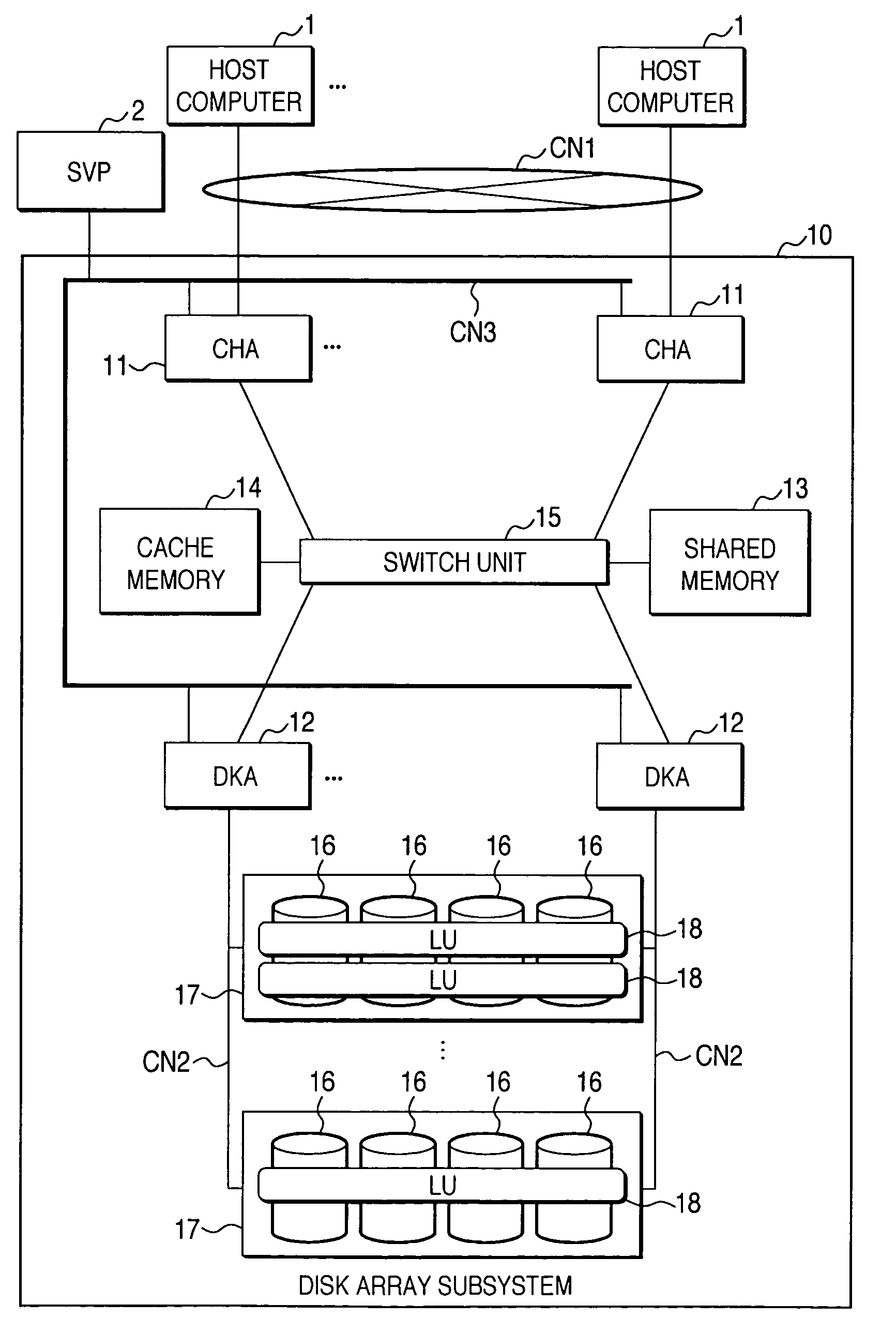

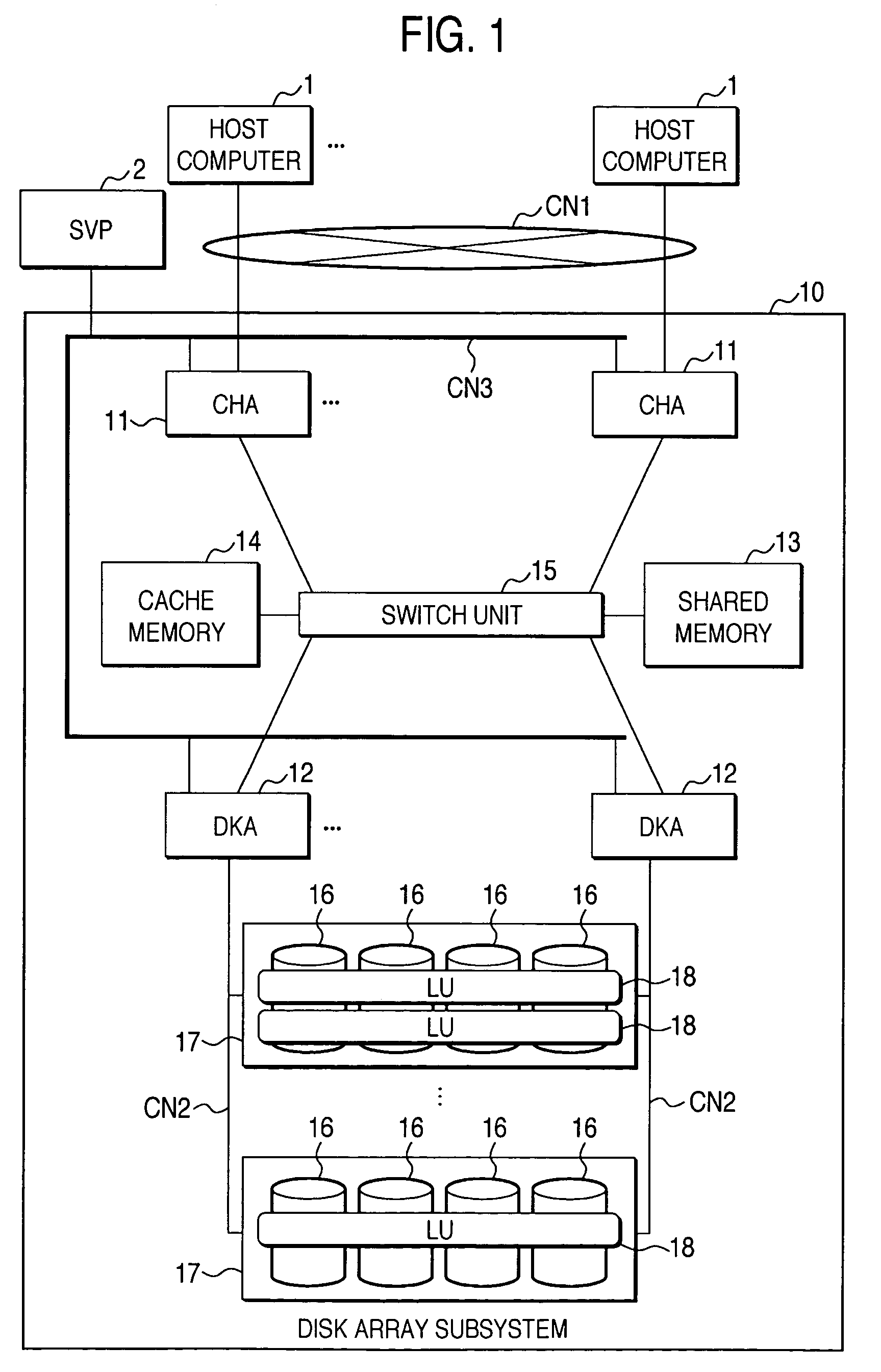

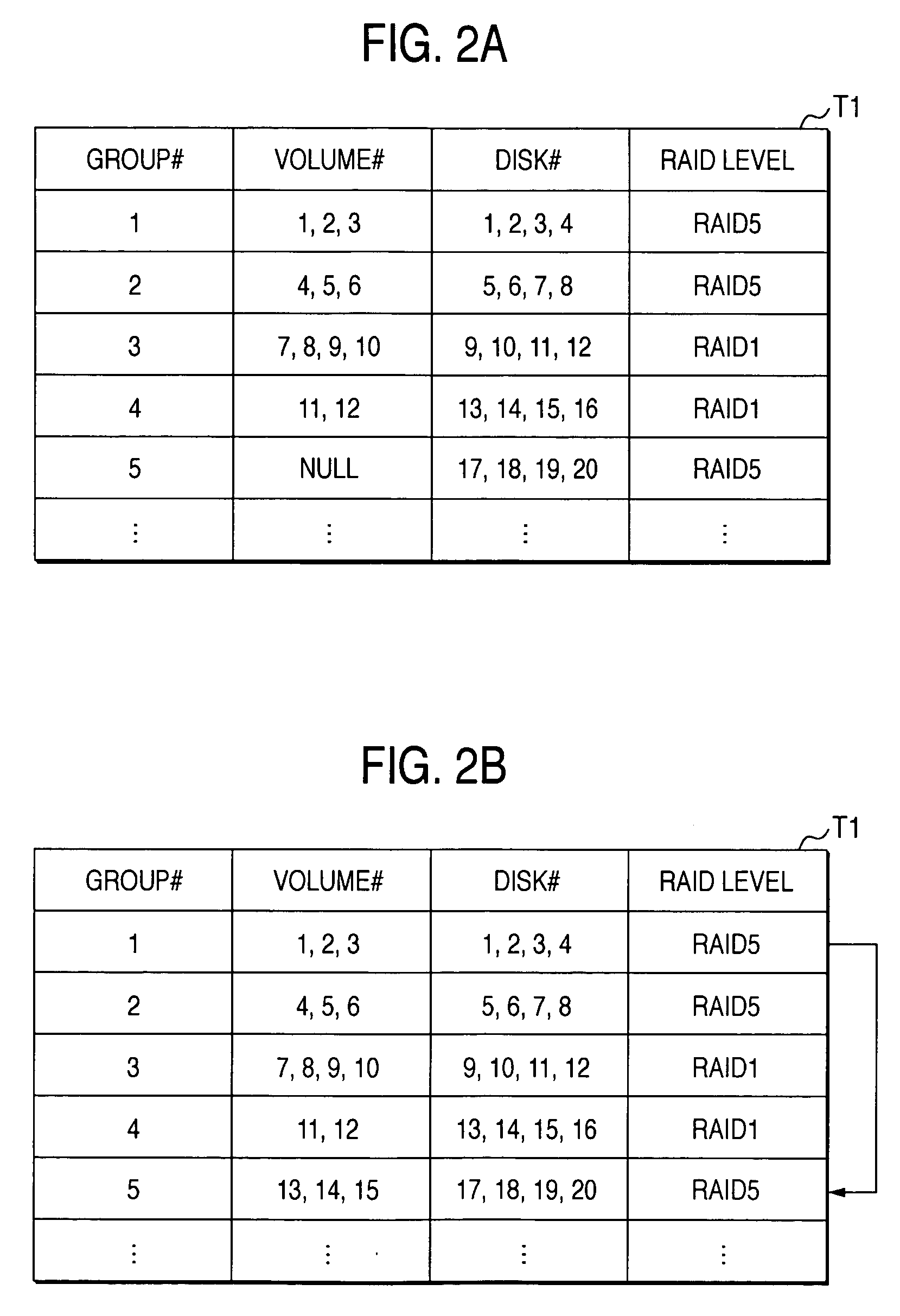

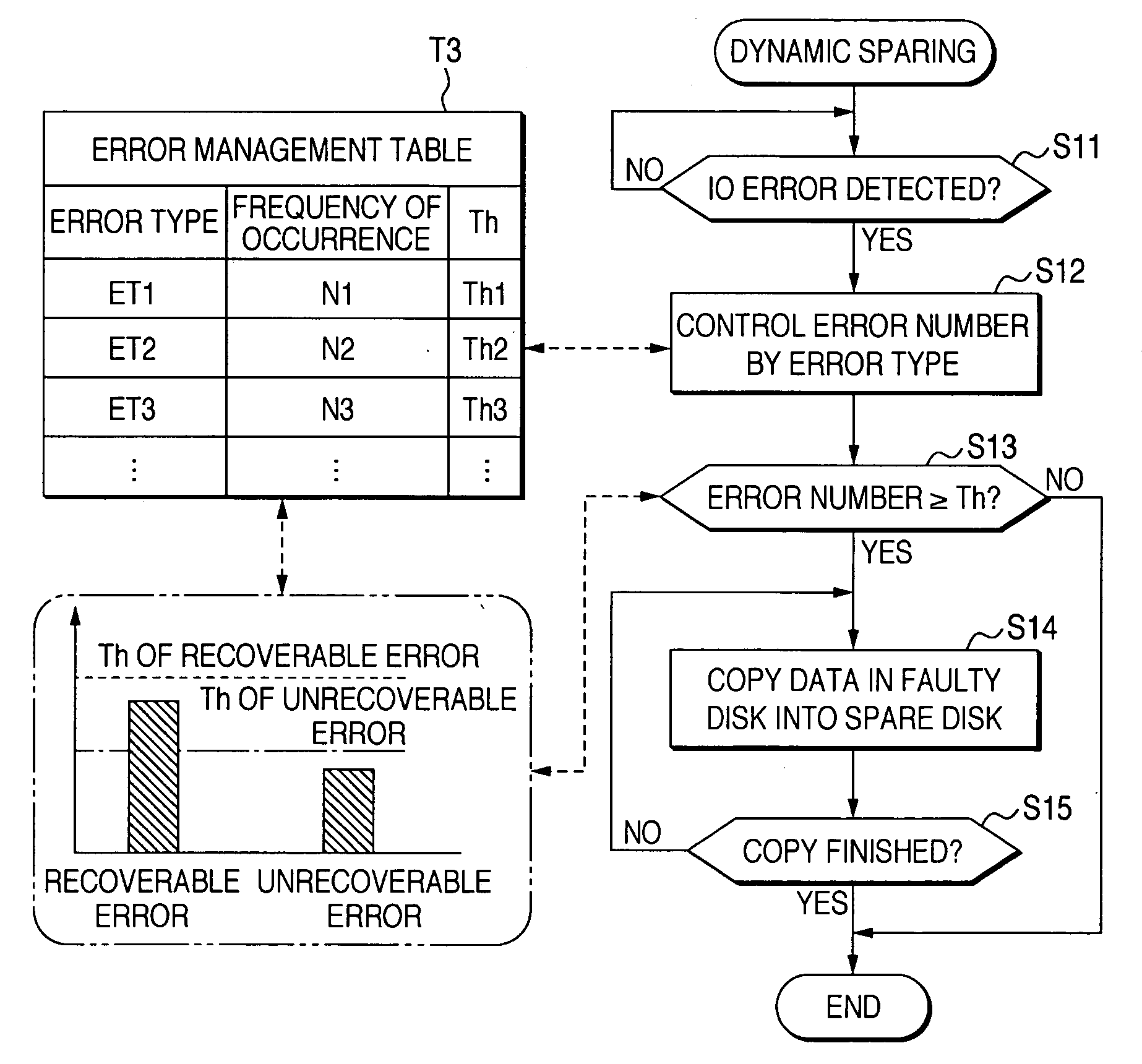

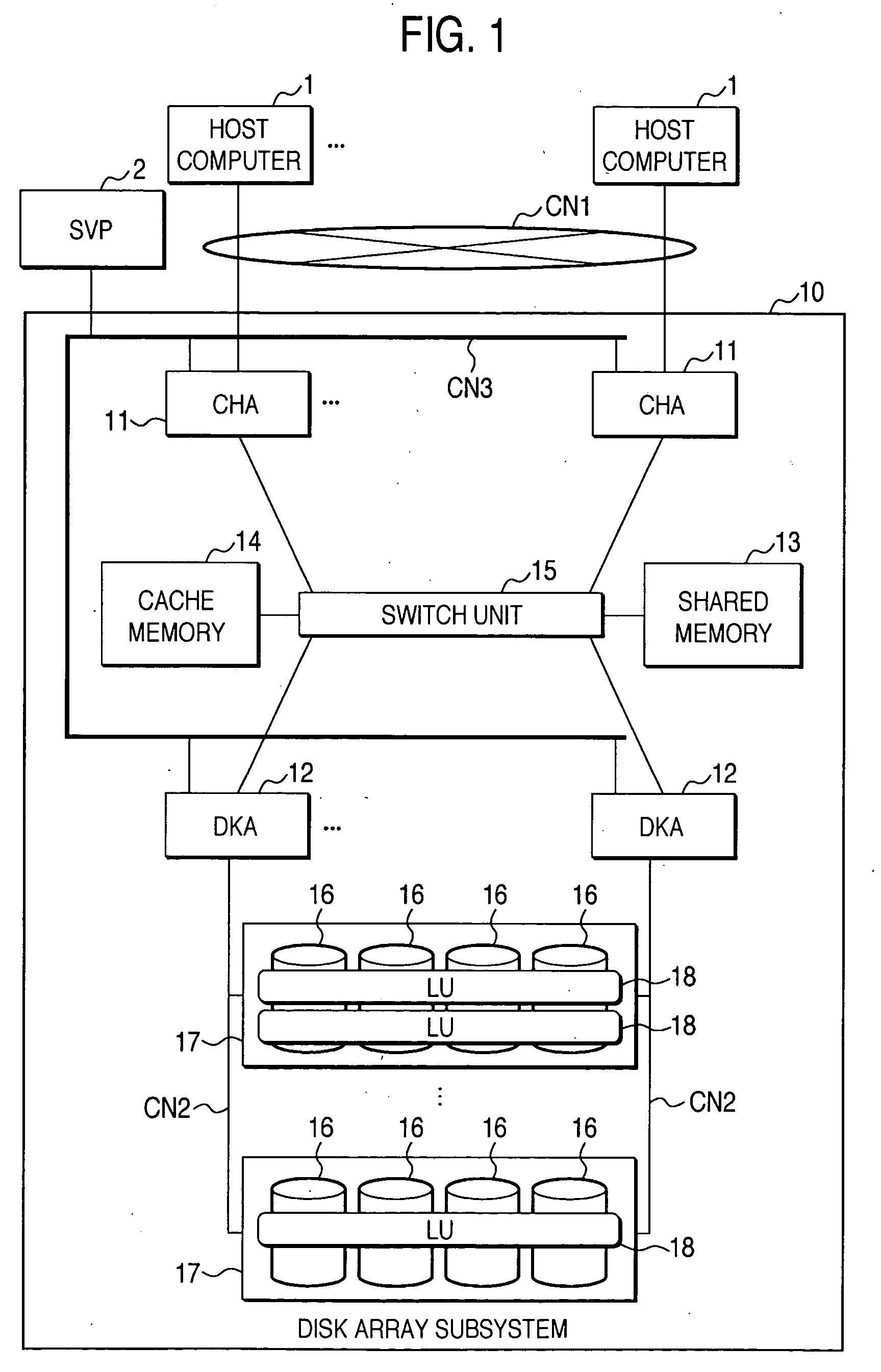

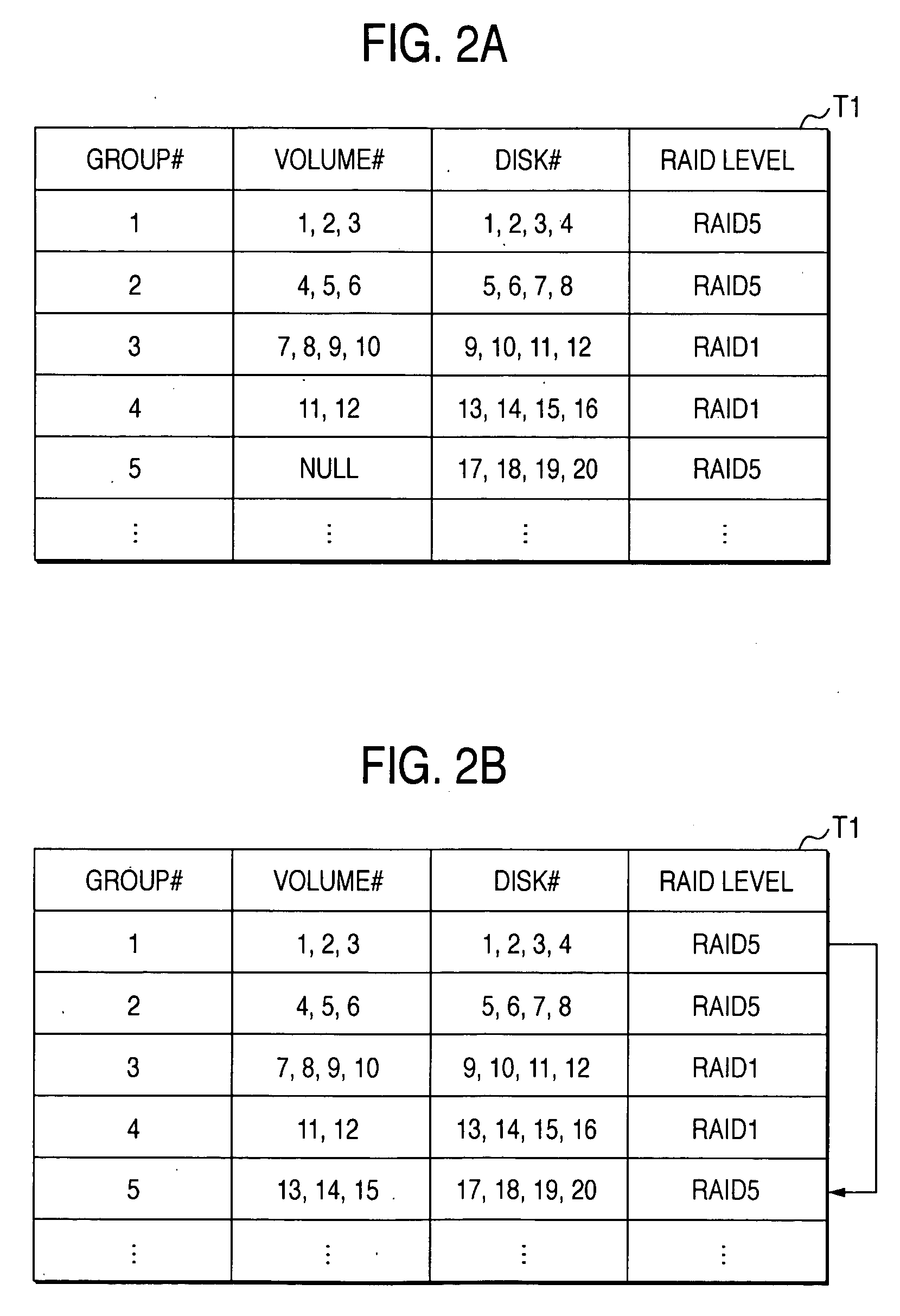

Disk array system and a method of avoiding failure of the disk array system

ActiveUS7028216B2Avoid failureReduce the likelihood of occurrenceInput/output to record carriersMemory loss protectionRAIDDisk array

The invention is intended to reduce disk access during data transfer from a disk in which occurrence of failure is anticipated to a spare disk as much as possible so that occurrence of double-failure is prevented in advance. When occurrence of failure in a disk which configures a RAID group, contents stored in the disk is copied to the spared disk. Simultaneously, another RAID group is paired with the above described RAID group and a secondary volume is provided therein. A write request is directed to the secondary volume. A differential bitmap controls a update data. Data which is not updated is read out from the primary volume, and data which is already updated is read from the secondary volume. When data transfer is completed, contents stored in the secondary volume are copied to the primary volume.

Owner:GOOGLE LLC

Disk array system and a method of avoiding failure of the disk array system

ActiveUS20050114728A1Avoid failureReduce the likelihood of occurrenceInput/output to record carriersMemory loss protectionRAIDDisk array

The invention is intended to reduce disk access during data transfer from a disk in which occurrence of failure is anticipated to a spare disk as much as possible so that occurrence of double-failure is prevented in advance. When occurrence of failure in a disk which configures a RAID group, contents stored in the disk is copied to the spared disk. Simultaneously, another RAID group is paired with the above described RAID group and a secondary volume is provided therein. A write request is directed to the secondary volume. A differential bitmap controls a update data. Data which is not updated is read out from the primary volume, and data which is already updated is read from the secondary volume. When data transfer is completed, contents stored in the secondary volume are copied to the primary volume.

Owner:GOOGLE LLC

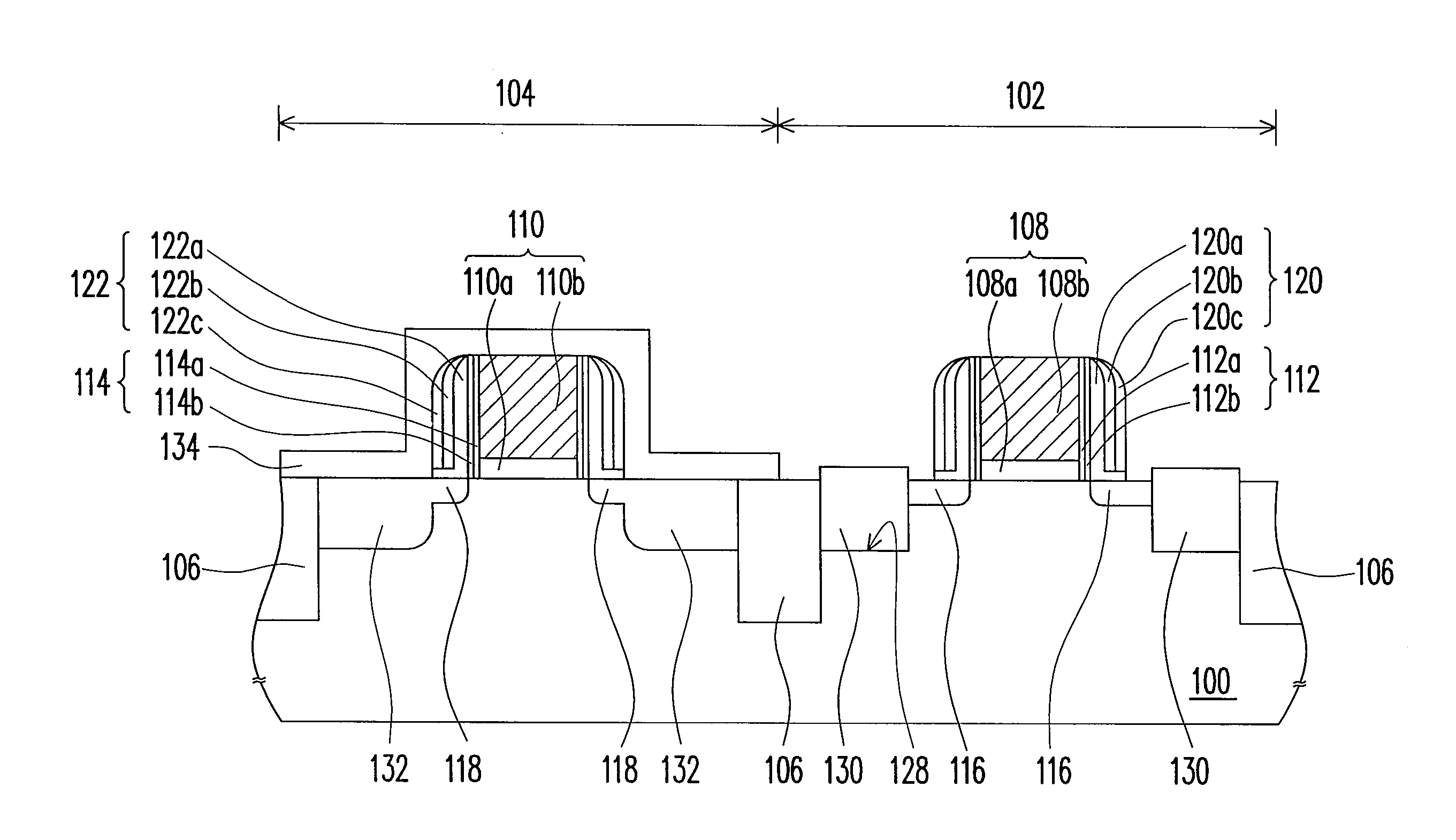

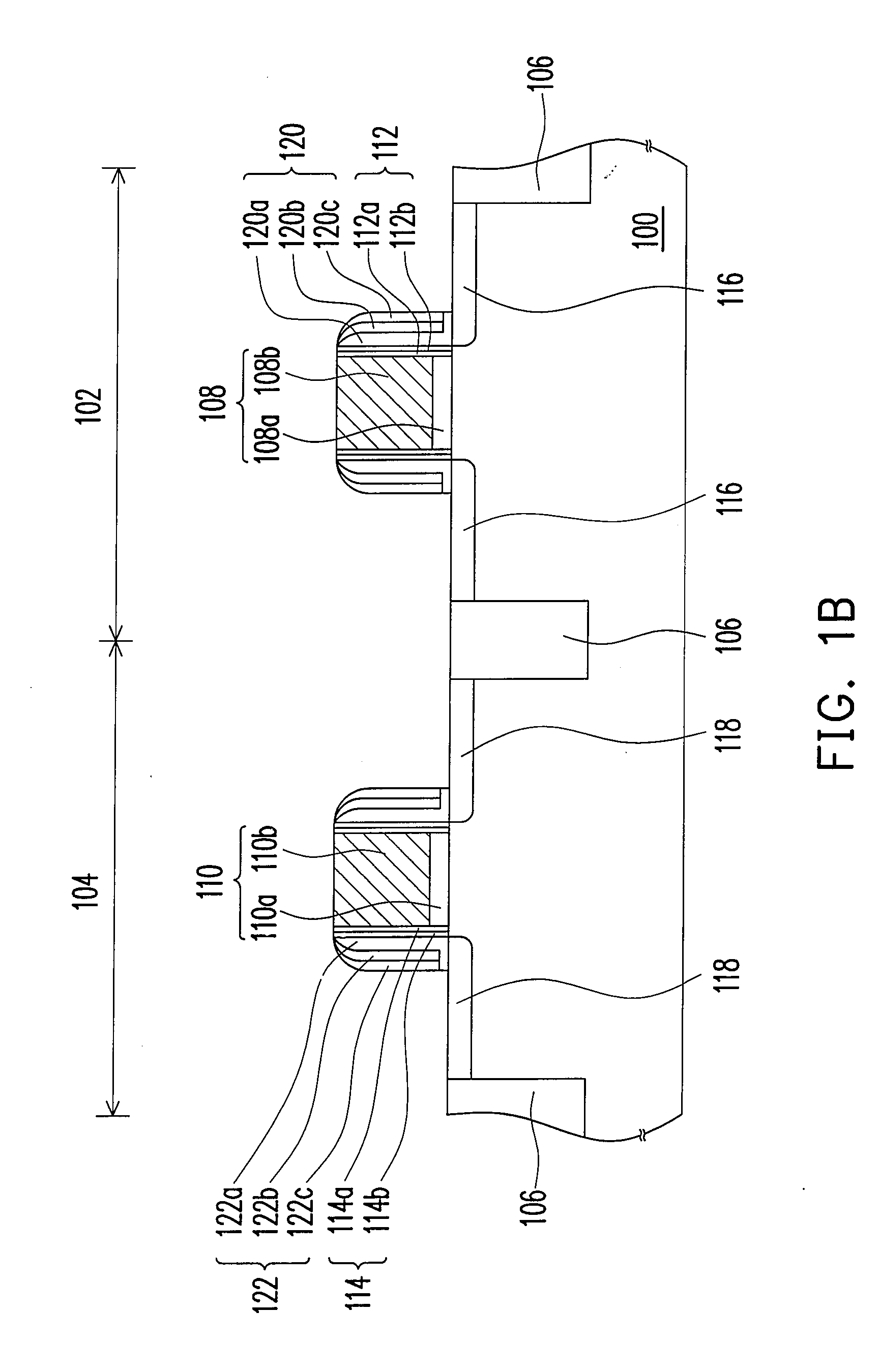

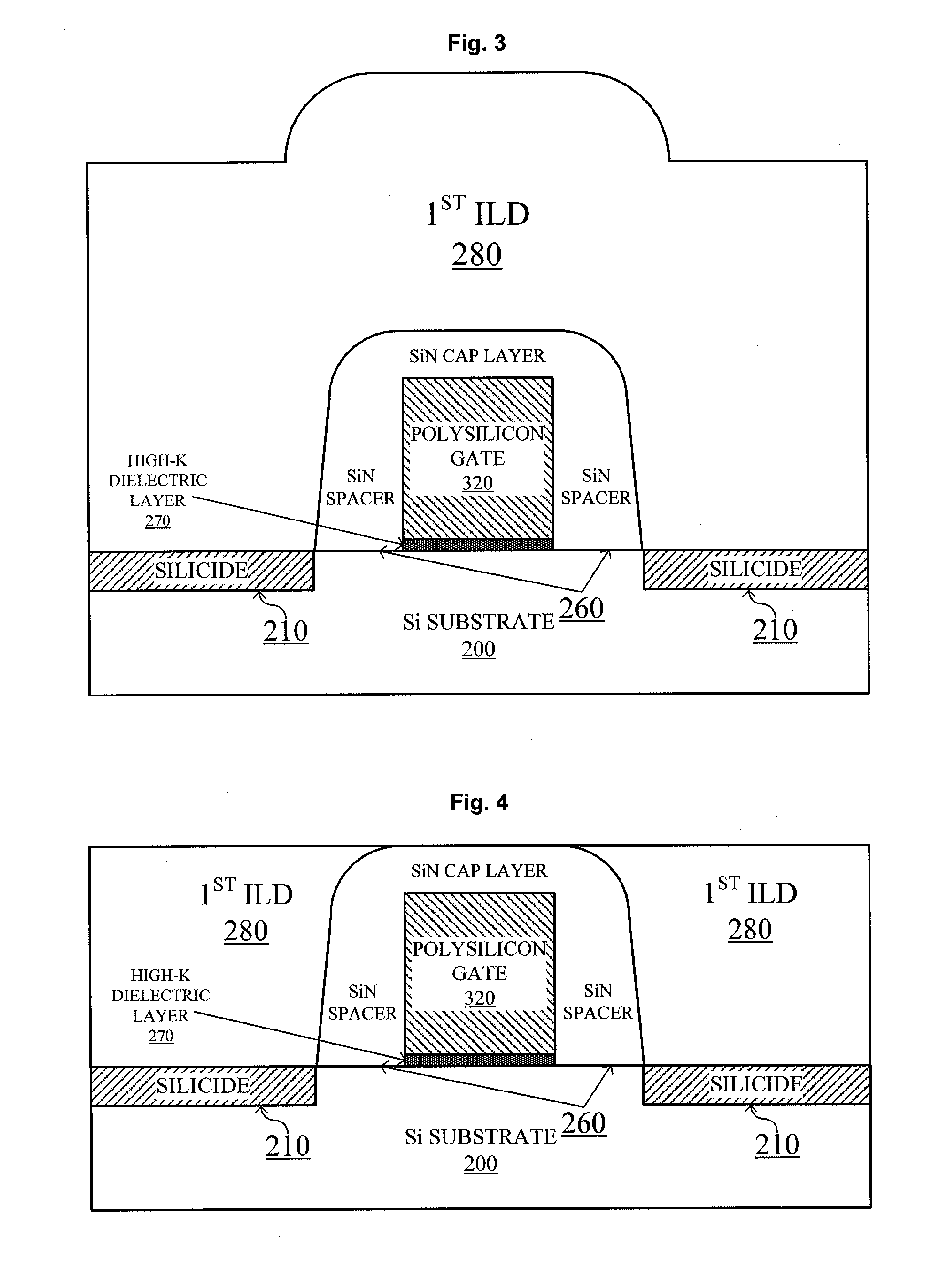

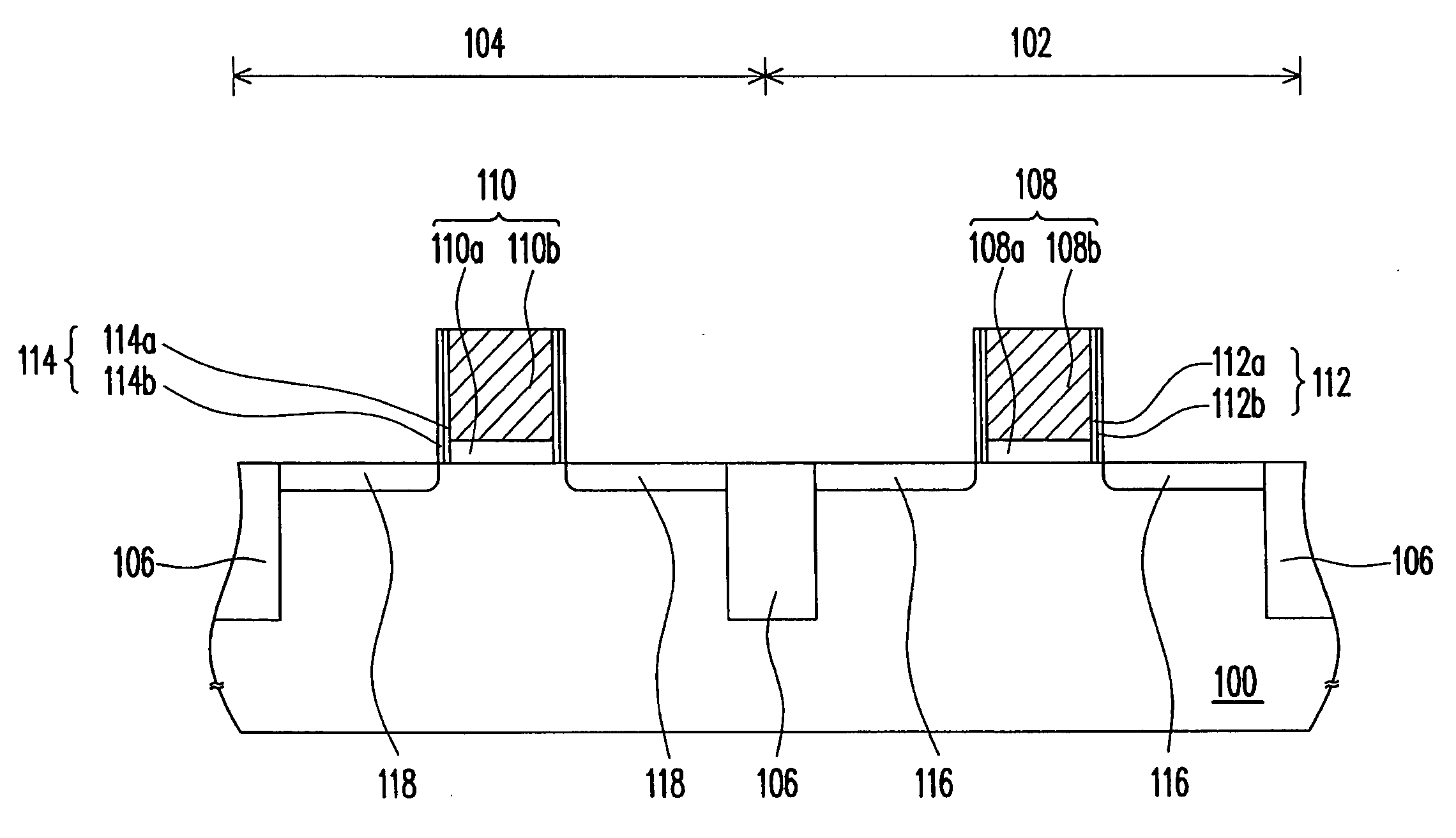

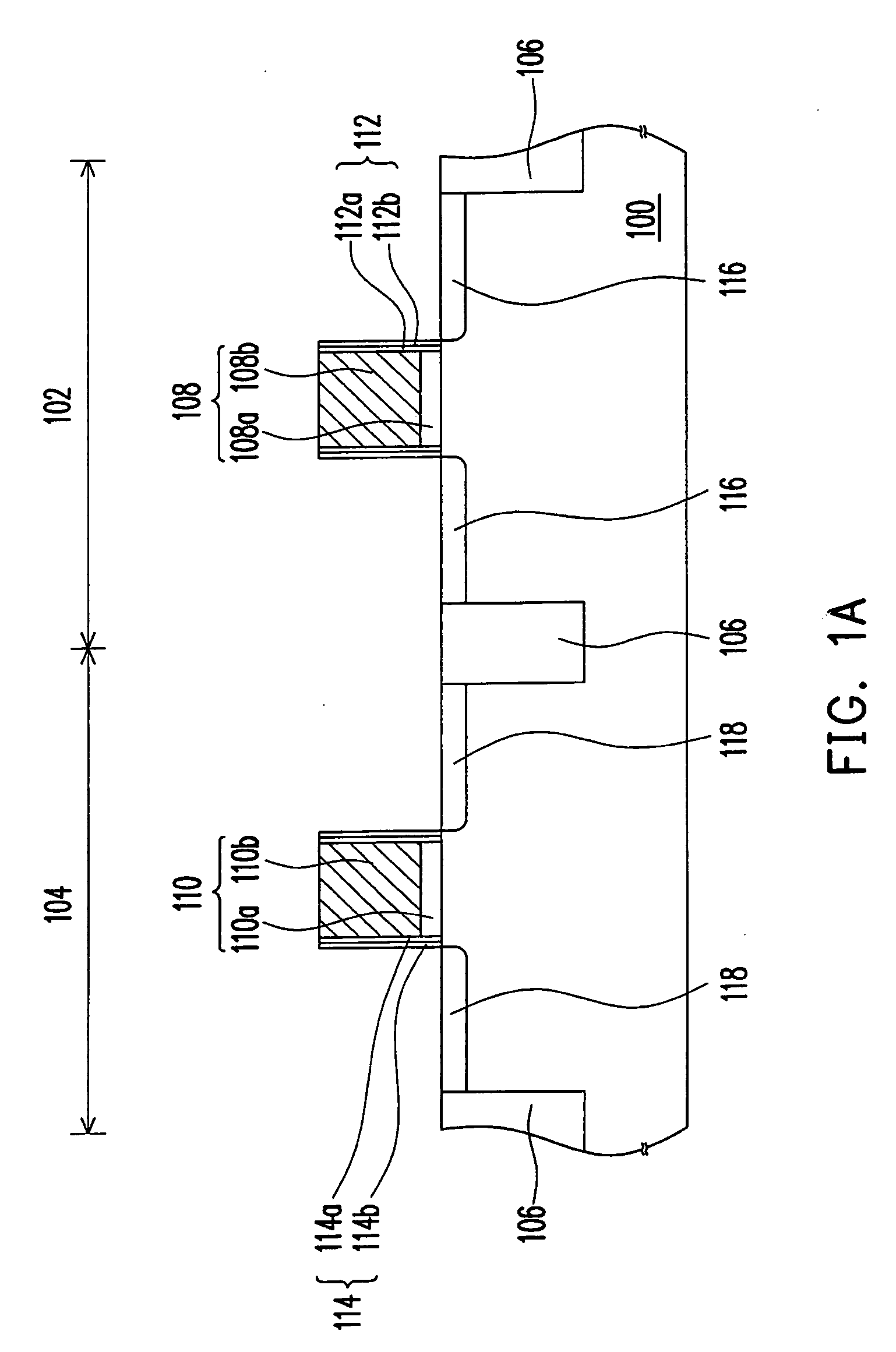

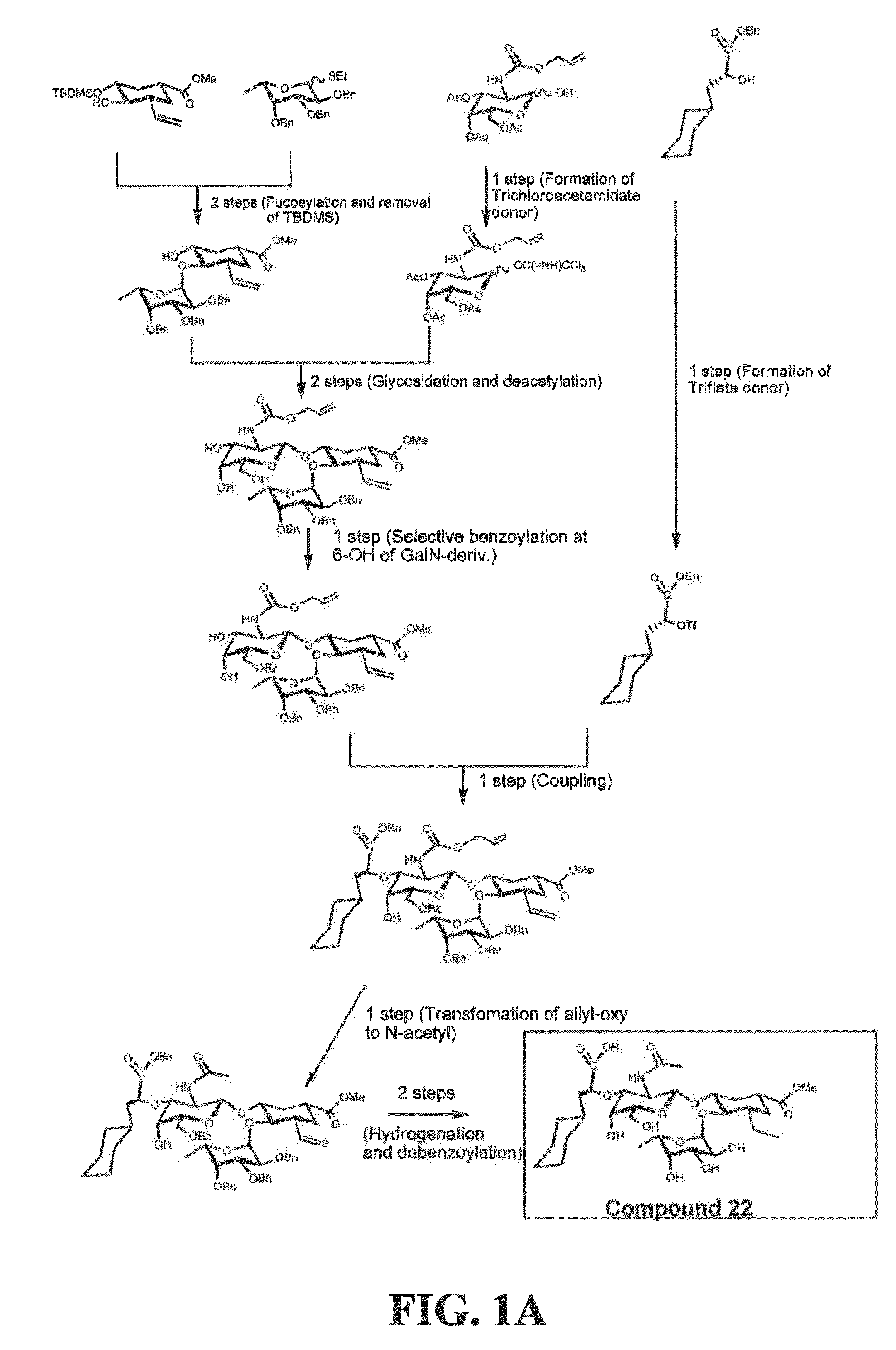

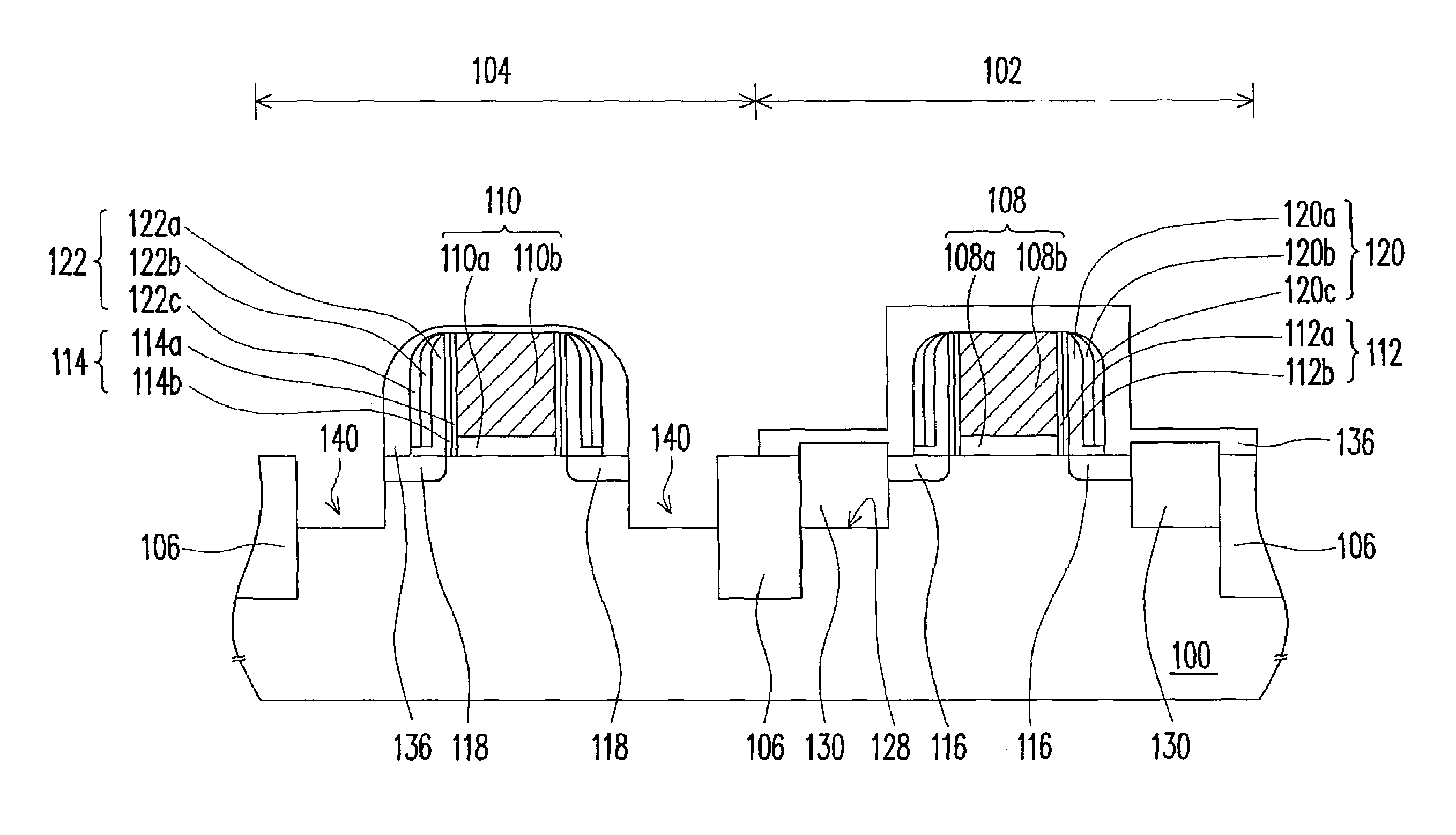

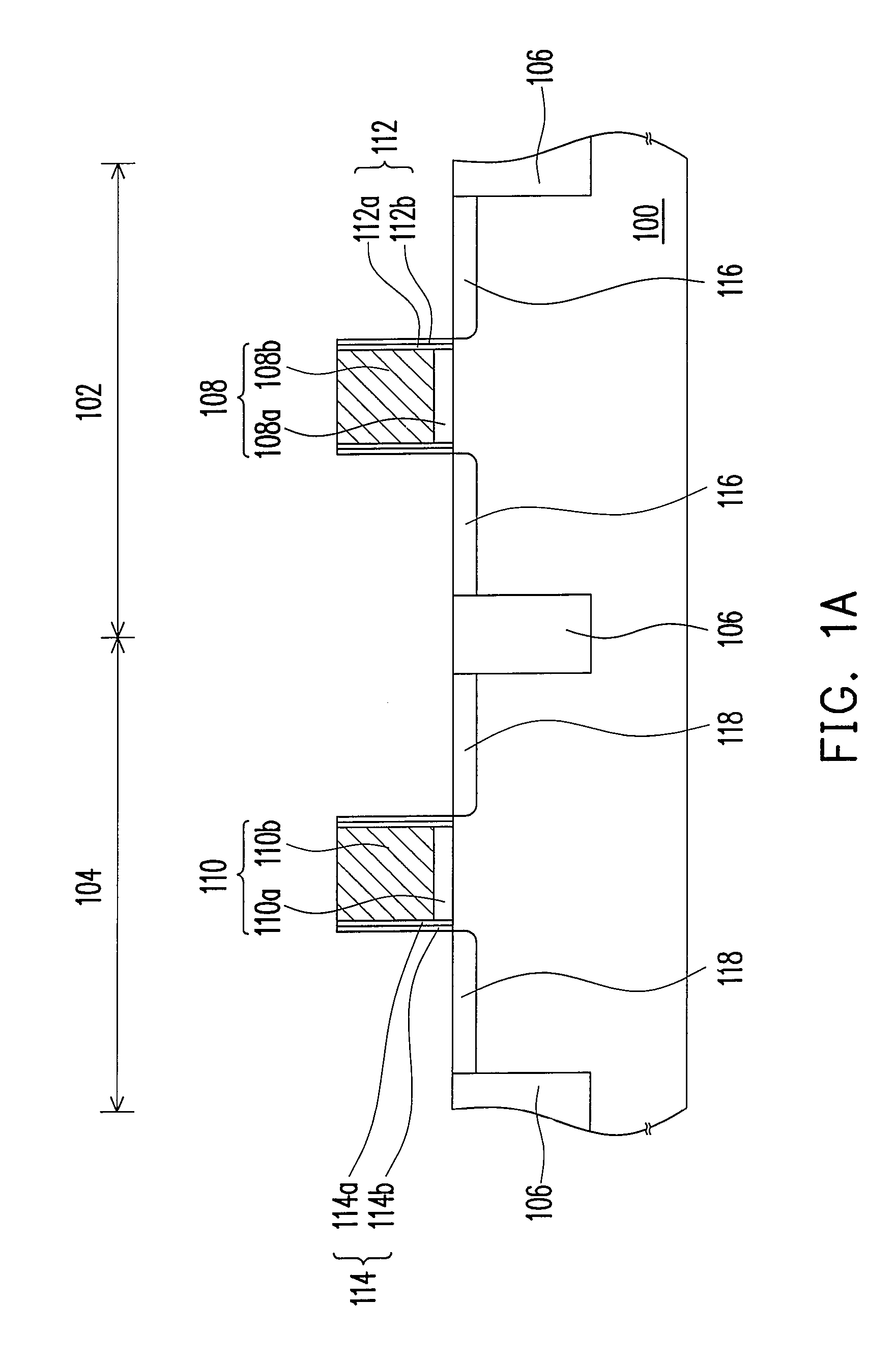

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS20080061366A1Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

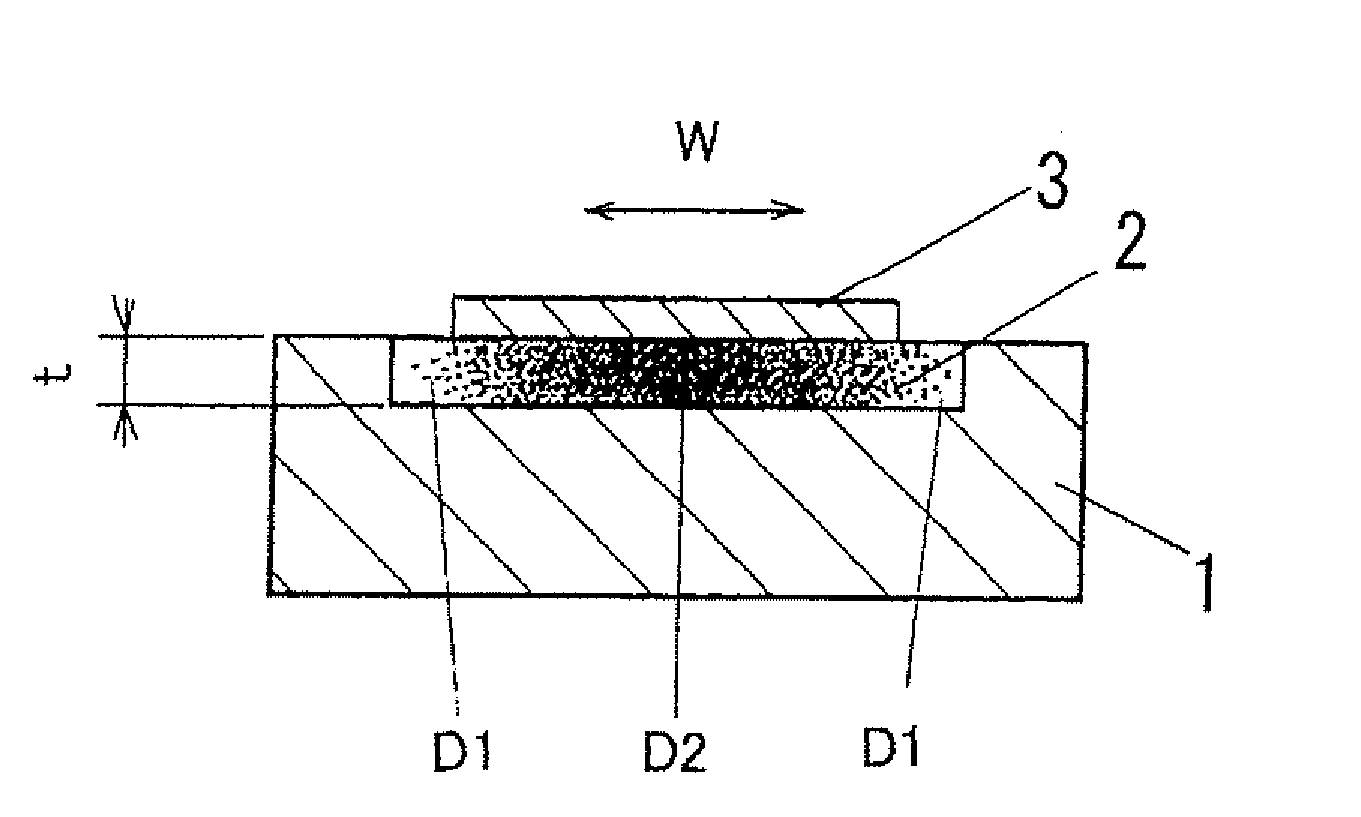

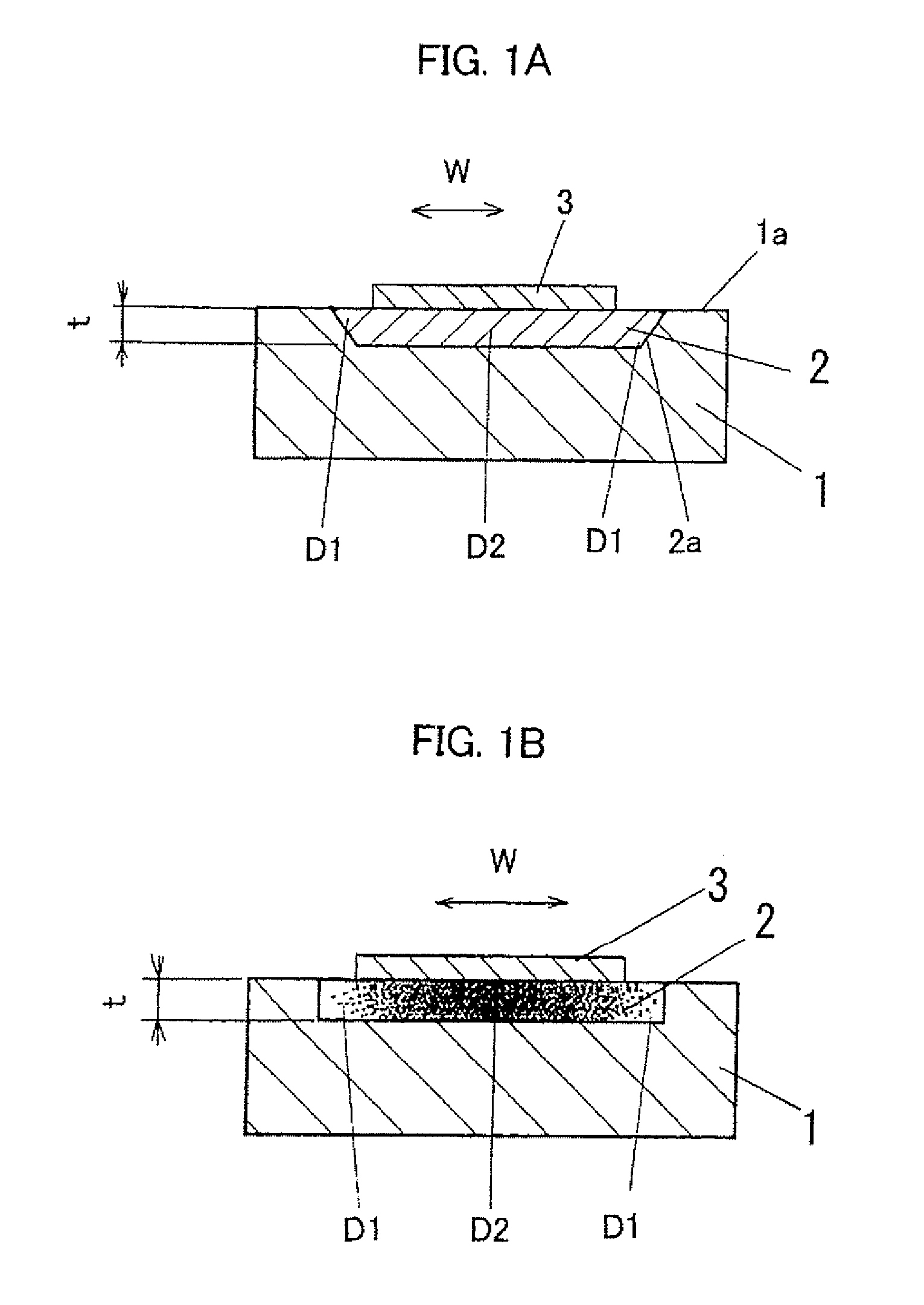

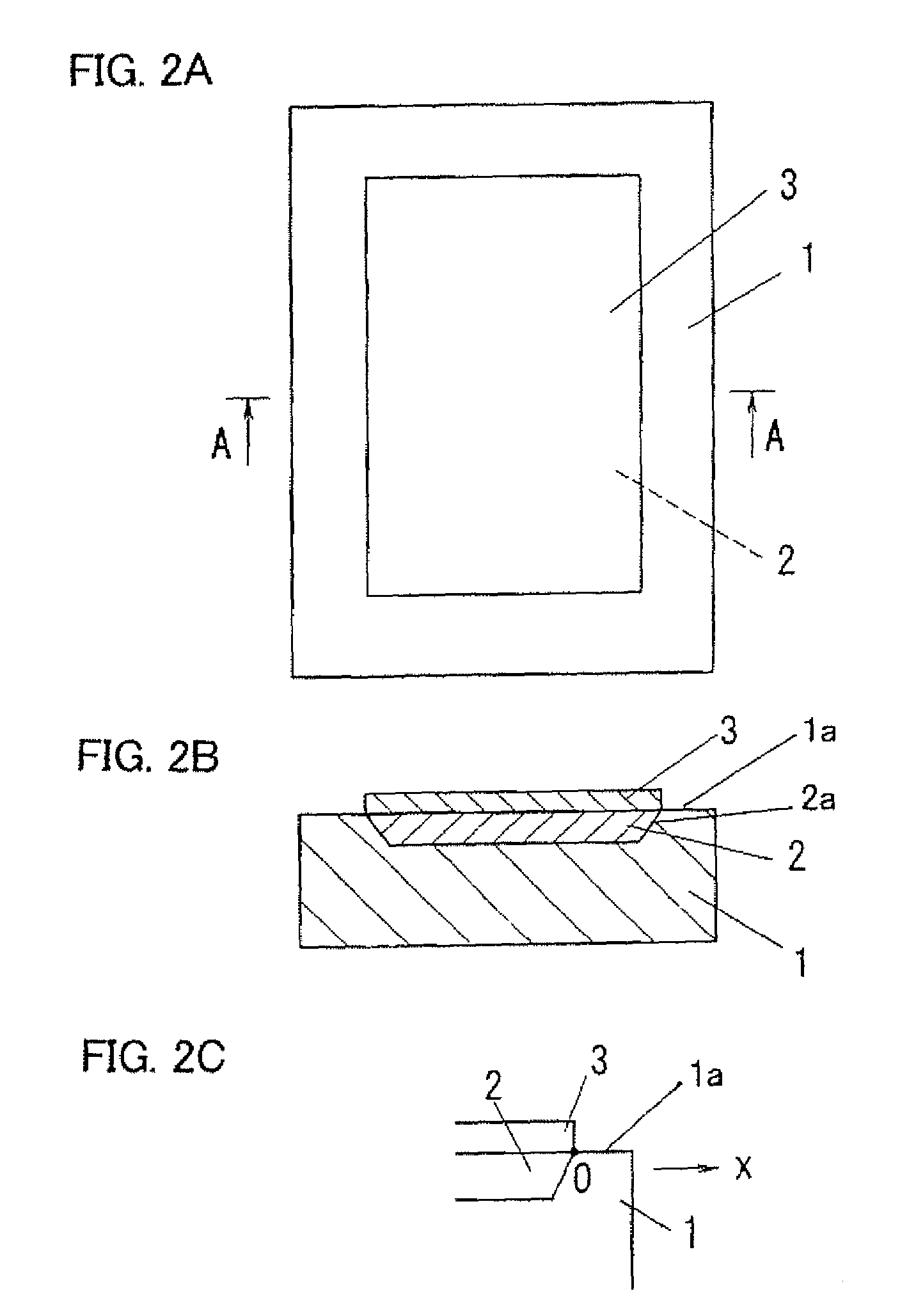

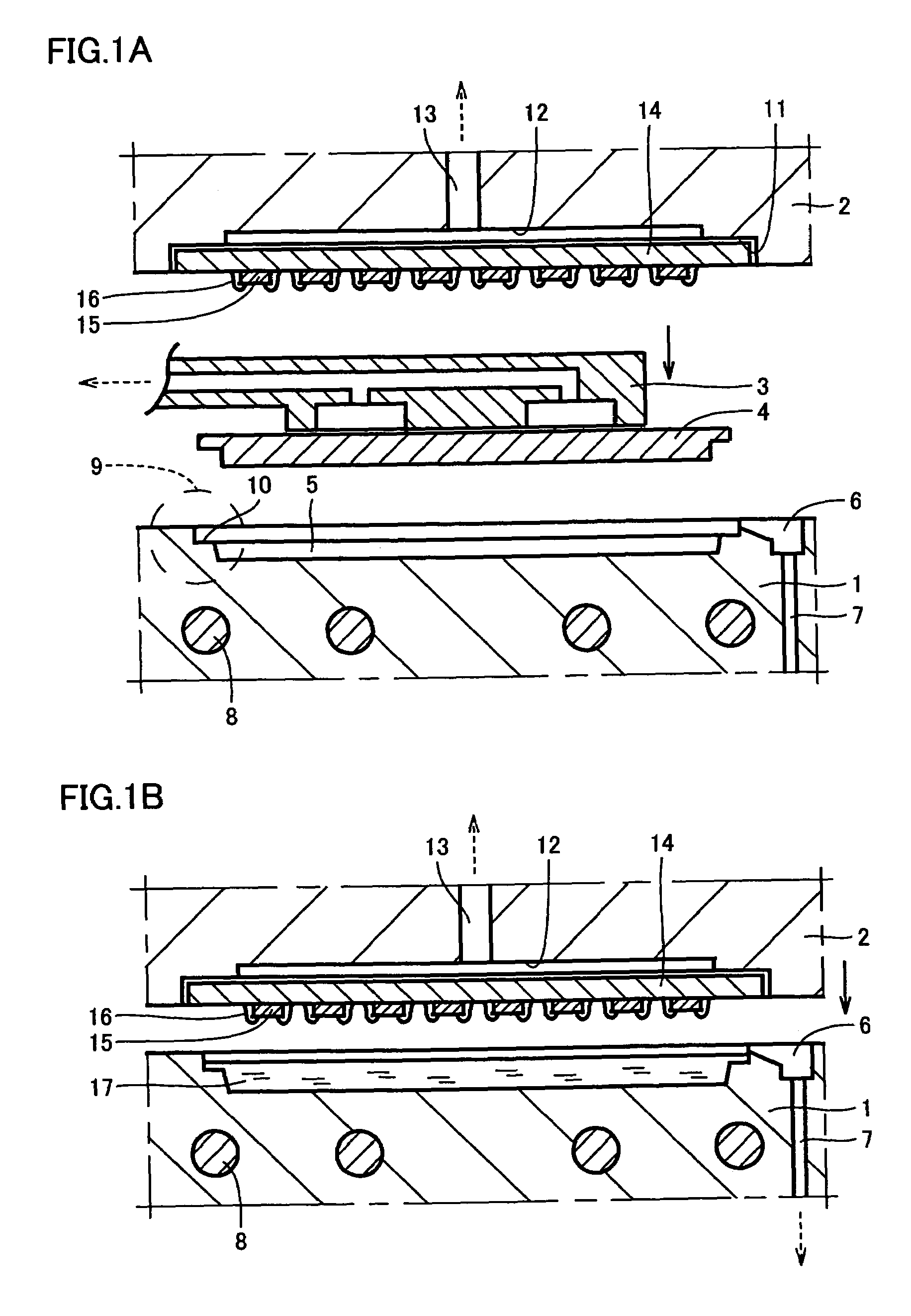

Pressure wave generator and process for manufacturing the same

InactiveUS7474590B2Reduce the likelihood of occurrenceMade smallMicrophonesElectrothermic-effect transistorPorosityElectrical conductor

Even when compression stress is generated because a volume of a thermal insulation layer 2 is expanded due to oxidized by oxygen in the air, occurrence of cracks and fractures of the thermal insulation layer and a heating conductor 3 caused by the cracks are prevented by dispersing the compression stress. A pressure wave generator comprises a substrate 1, the thermal insulation layer 2 of porous material which is formed on a surface of the substrate 1 in thickness direction, and the heating conductor 3 of thin film formed on the thermal insulation layer 2, and generates pressure waves by heat exchange between the heating conductor 3 and a medium. When a thickness at the center of the thermal insulation layer 2 in width direction W is used as a reference thickness, and it is assumed that distribution of thickness of thermal insulation layer in the width direction is averaged with the reference thickness, porosity in an outer peripheral portion of the thermal insulation layer is made smaller than porosity in the center portion. By making the porosity in the outer peripheral portion of the thermal insulation layer 2 smaller, a number of immovable points on the outer periphery of the thermal insulation layer 2 restricted by the substrate 1 is increased and the positions of them are dispersed, so that the compression stress compressed in the outer peripheral portion of the thermal insulation layer 2 can be dispersed.

Owner:MATSUSHITA ELECTRIC WORKS LTD

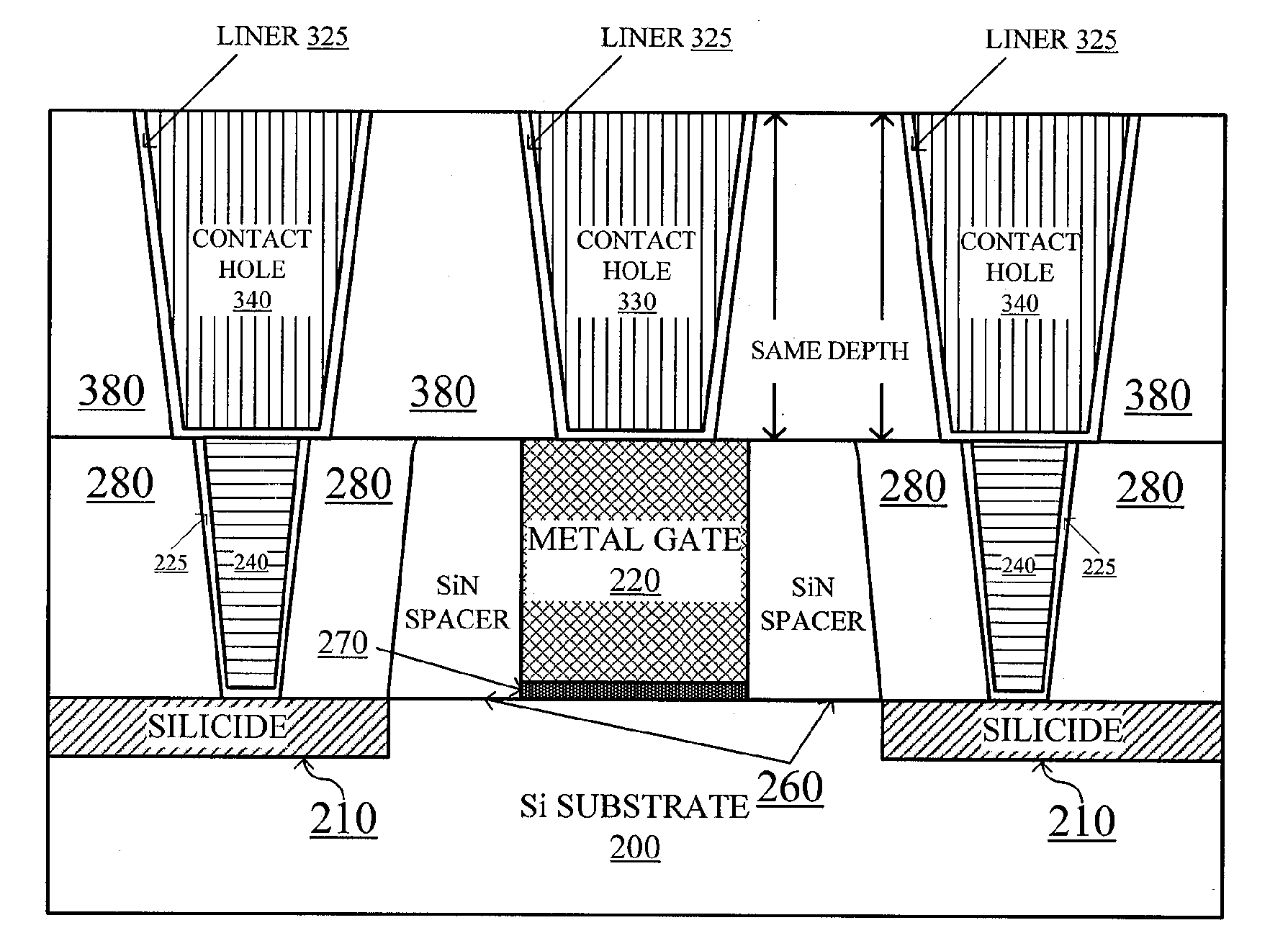

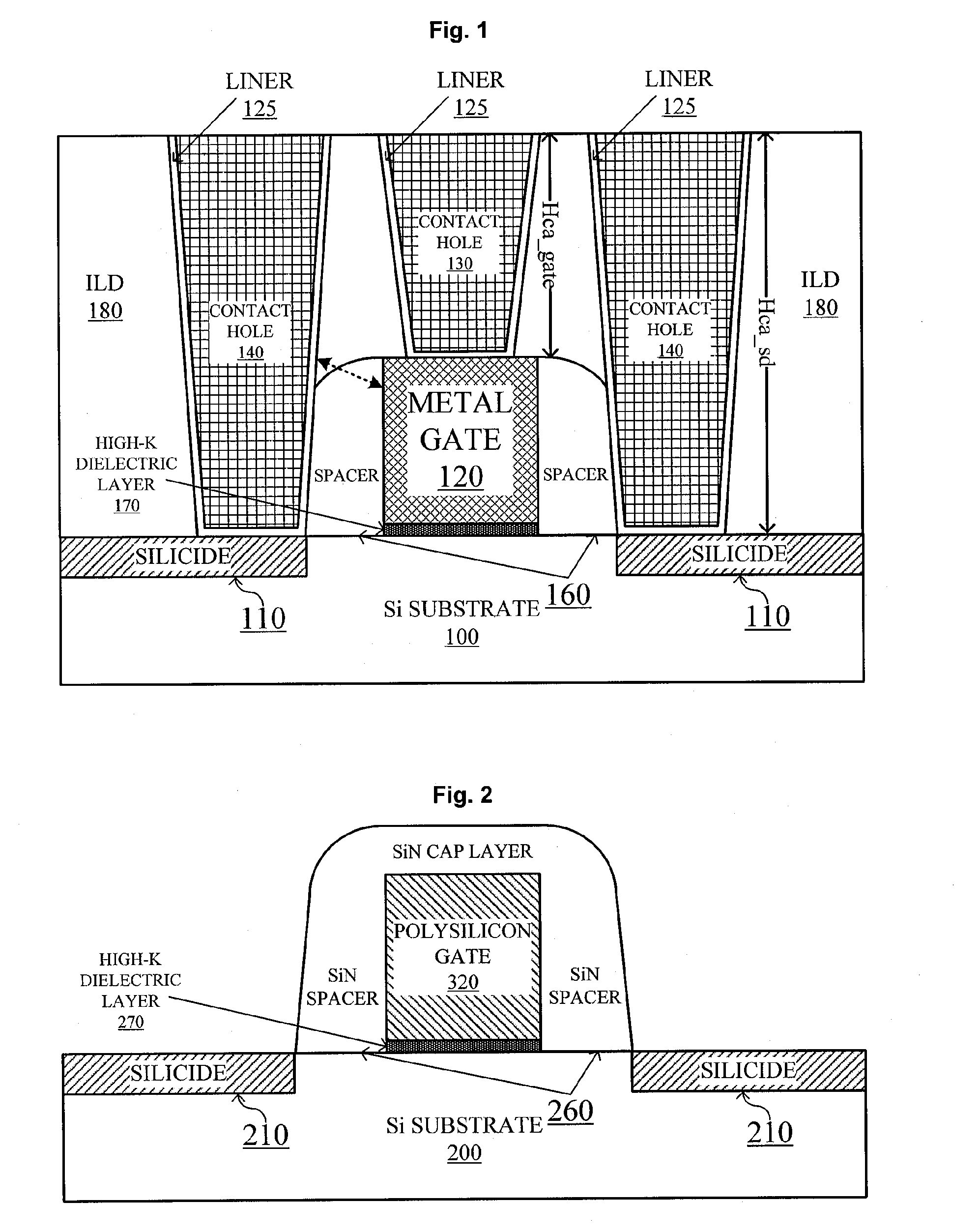

Semiconductor device and method for manufacturing the same

ActiveUS20110062502A1Reduce the possibilityReduce the likelihood of occurrenceSemiconductor/solid-state device detailsSolid-state devicesInter layerDielectric layer

The present invention proposes a method of forming a dual contact hole, comprising steps of: forming a source / drain region and a replacement gate structure on a semiconductor substrate, the replacement gate structure including a replacement gate; depositing a first inter-layer dielectric layer; planarizing the first inter-layer dielectric layer to expose the replacement gate in the replacement gate structure; removing the replacement gate and depositing to form a metal gate; etching to form a first source / drain contact opening in the first inter-layer dielectric layer; sequentially depositing a liner and filling conductive metal in the first source / drain contact opening to form a first source / drain contact hole; depositing a second inter-layer dielectric layer on the first inter-layer dielectric layer; etching to form a second source / drain contact opening and a gate contact opening in the second inter-layer dielectric layer; and sequentially depositing a liner and filling conductive metal in the second source / drain contact opening and the gate contact opening to form a second source / drain contact hole and a gate contact hole. The present invention also proposes a semiconductor device manufactured by the above process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

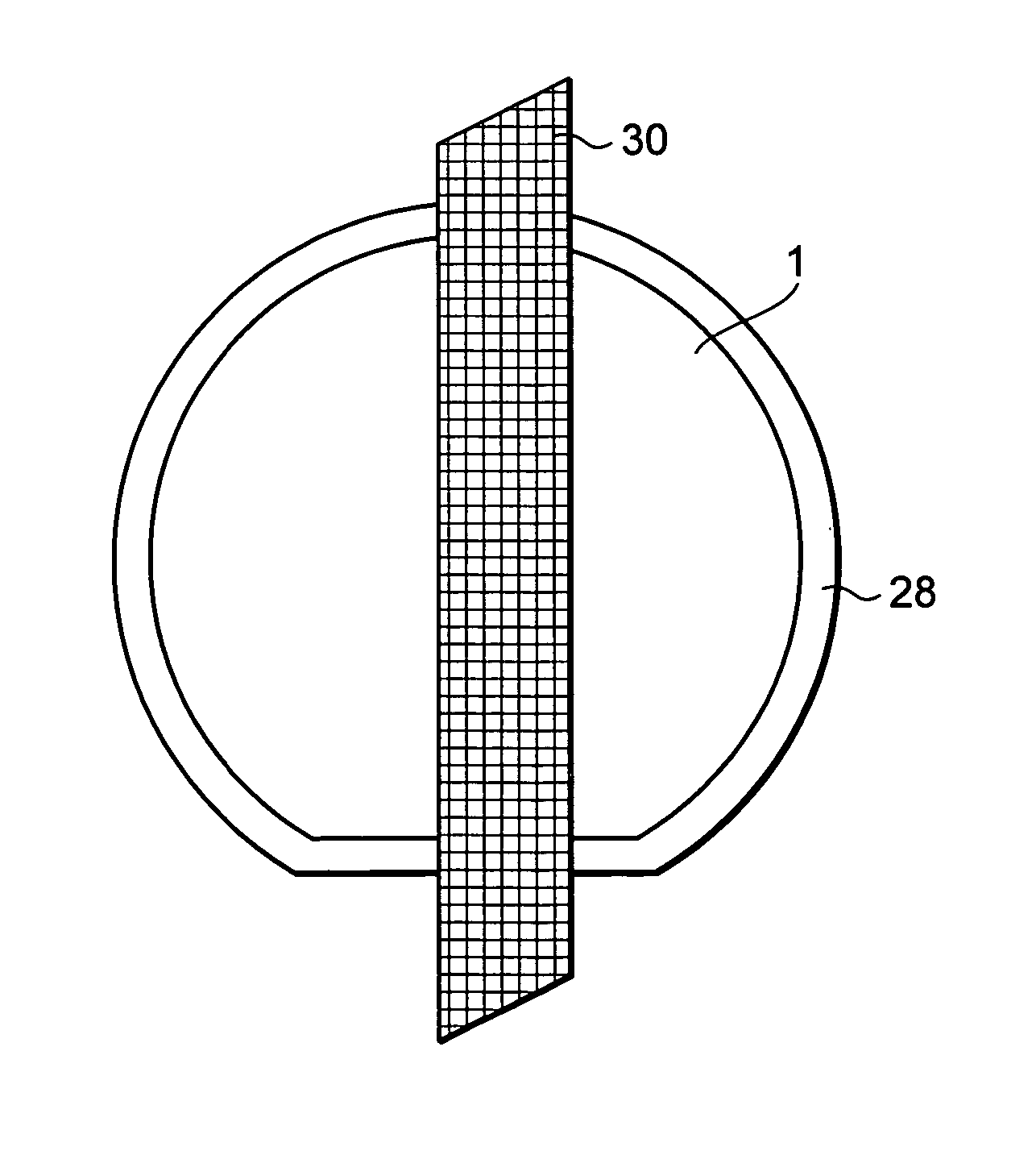

Semiconductor device and method for manufacturing the same

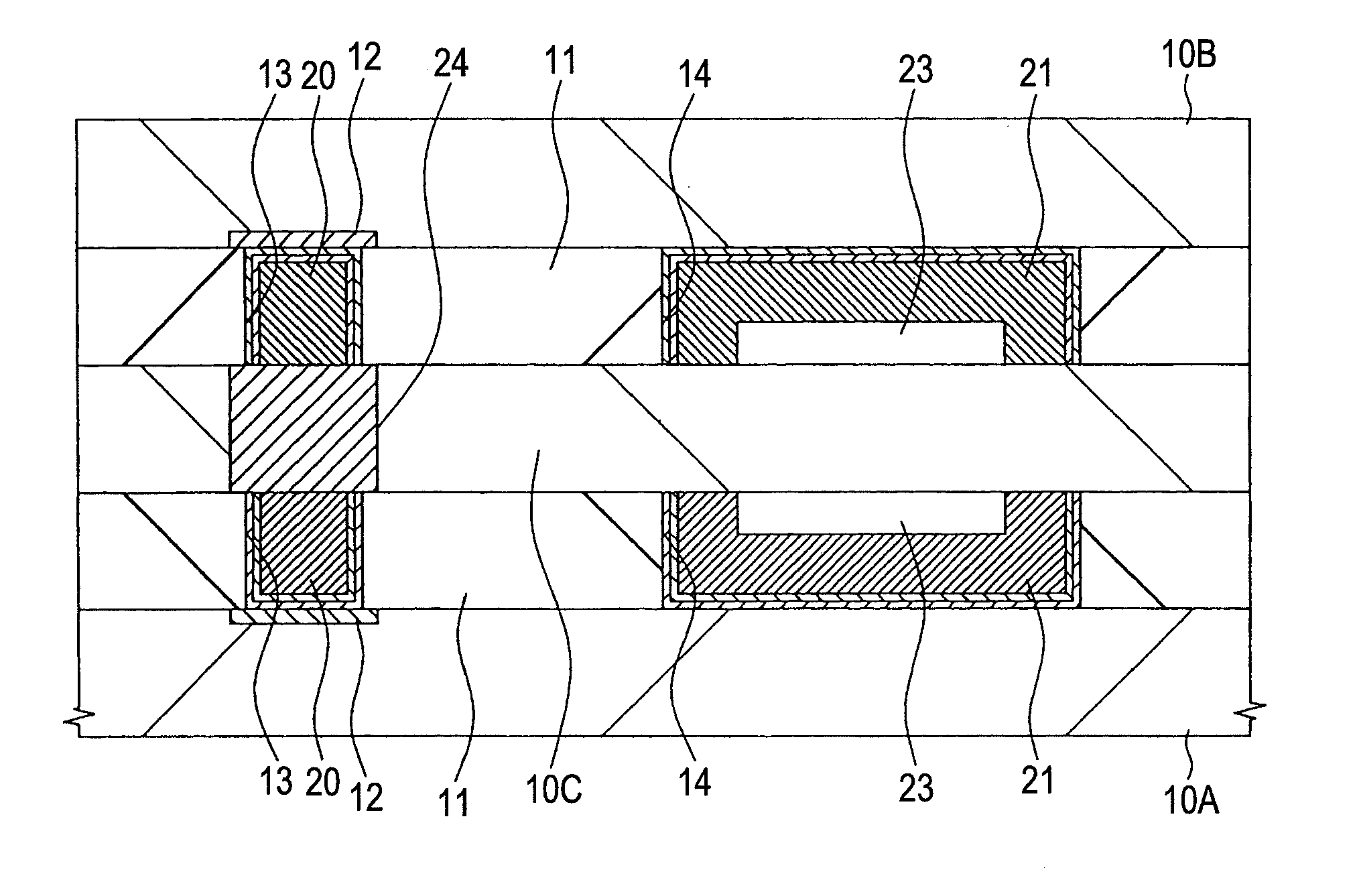

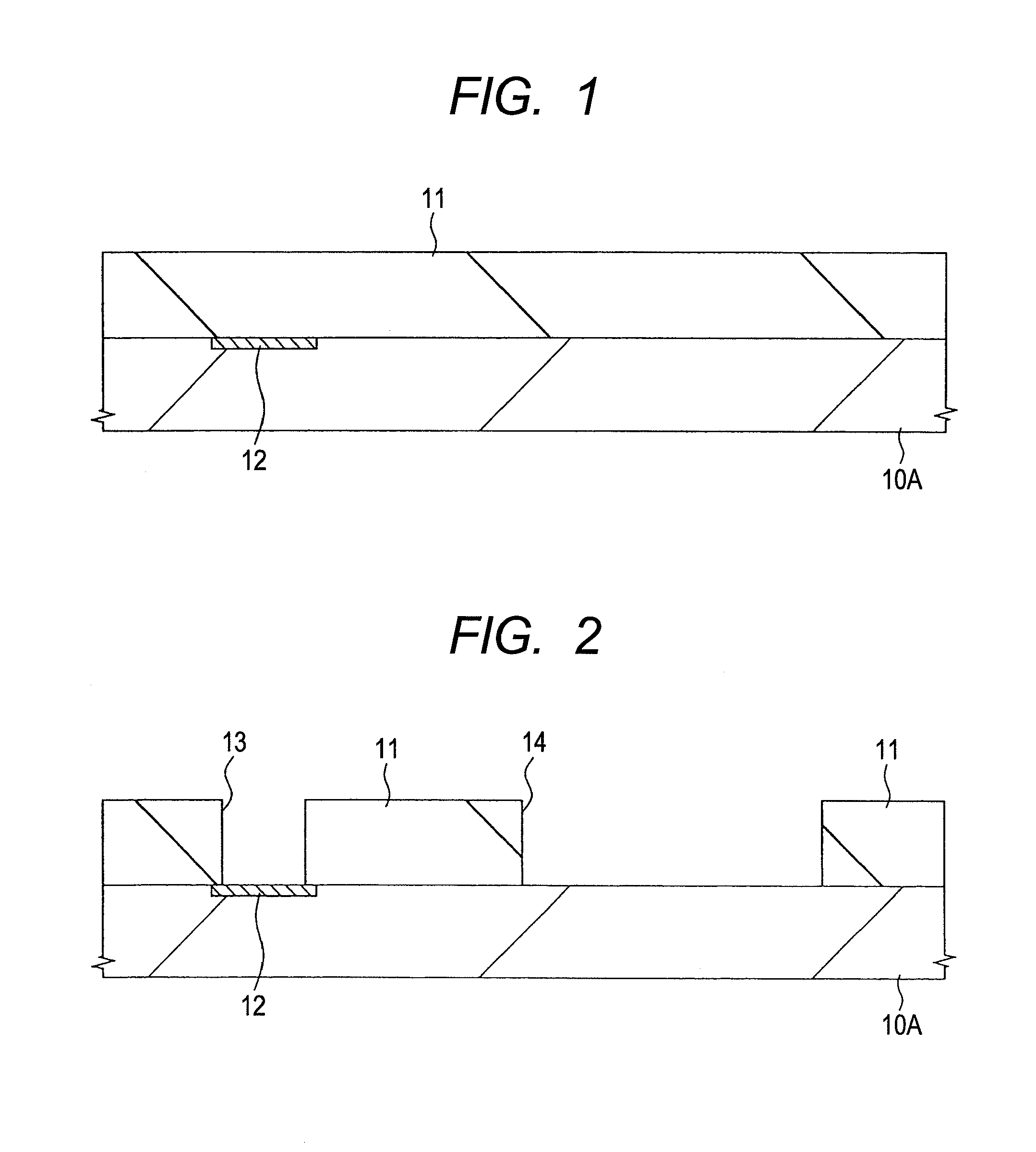

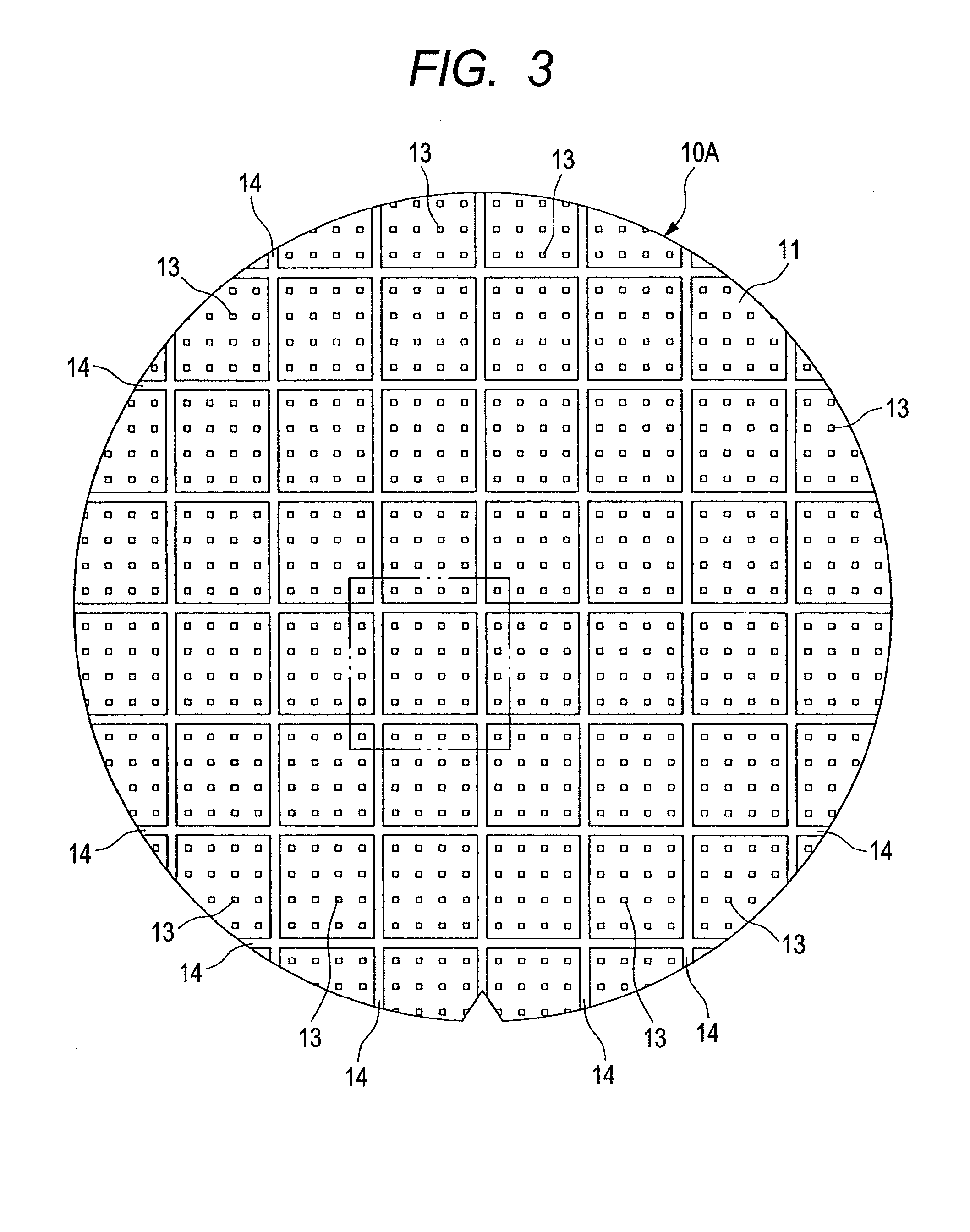

InactiveUS20120068355A1Reduce the likelihood of occurrenceReduce generationSemiconductor/solid-state device detailsSolid-state devicesWafer stackingSilicon

A semiconductor device including two silicon wafers stacked and bonded together with bumps of one wafer electrically coupled with those of the other wafer, in which generation of voids on the junction surface between the silicon wafers is suppressed. Due to a recess made in the surface of a buried conductive film, a cavity is formed in the junction surface between the silicon wafers. The ends of the cavity extend to the periphery of the junction surface between the silicon wafers. This allows the air trapped on the junction surface between the silicon wafers to get out through the cavity, thereby reducing the possibility of generation of voids on the junction surface.

Owner:HITACHI LTD

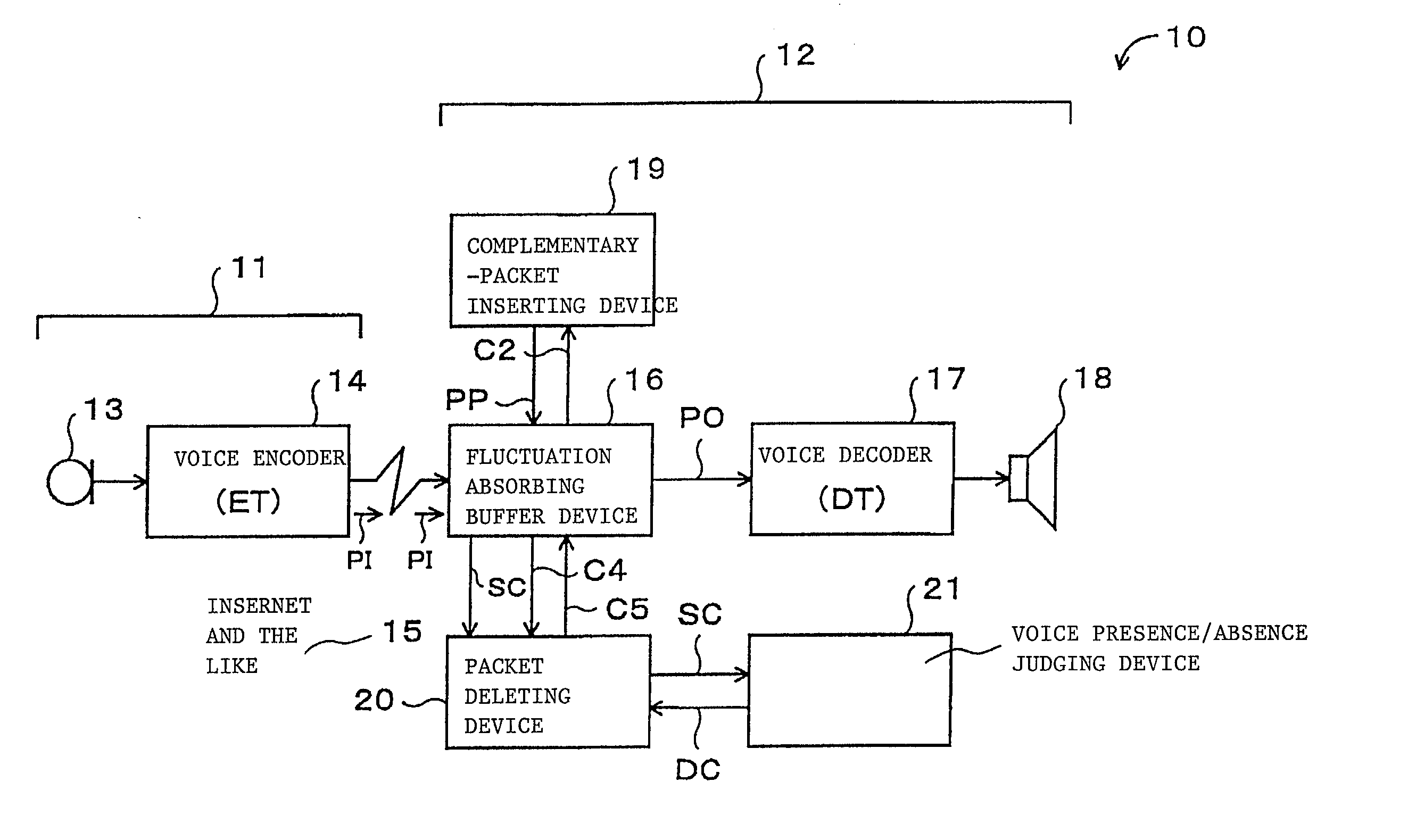

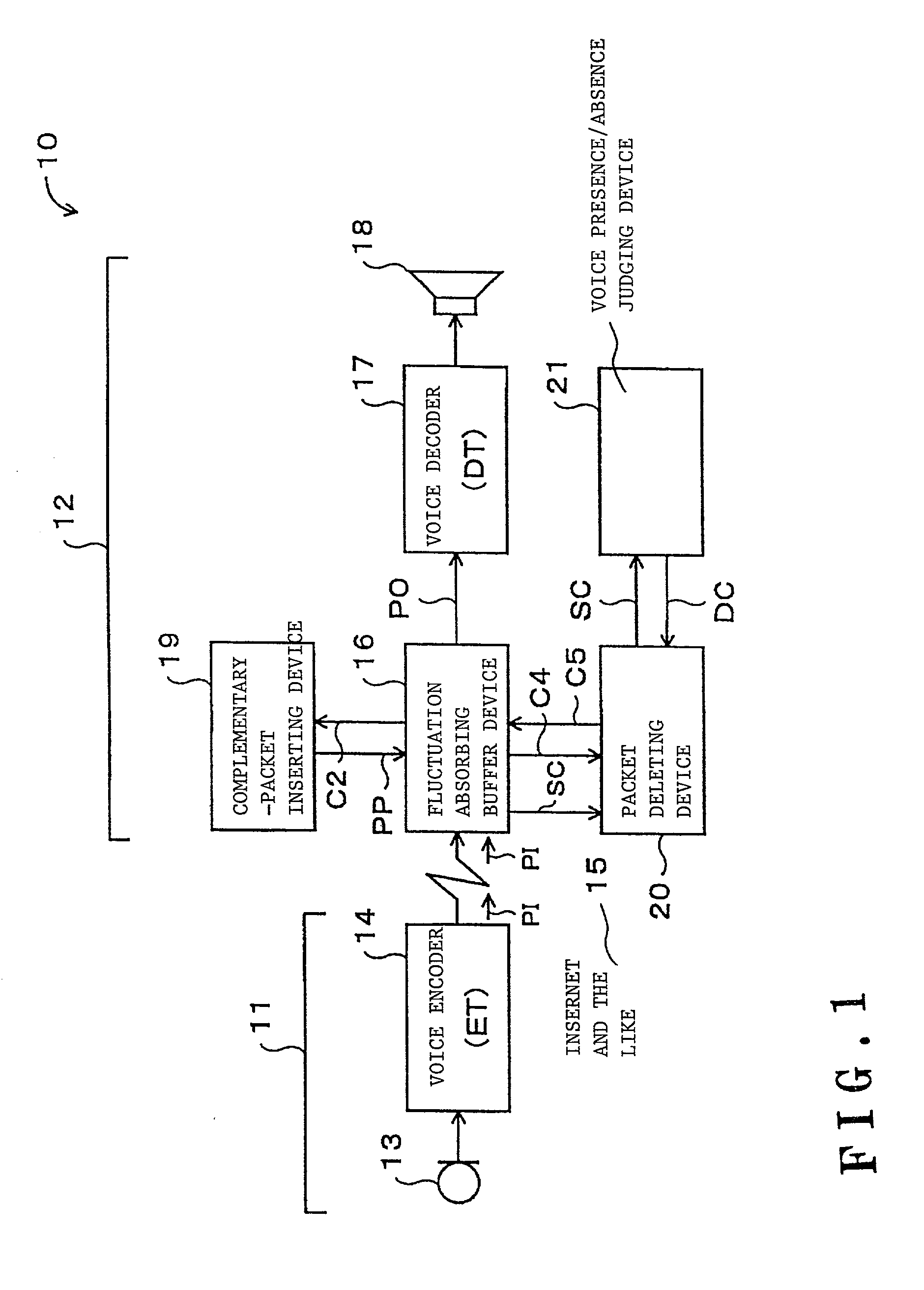

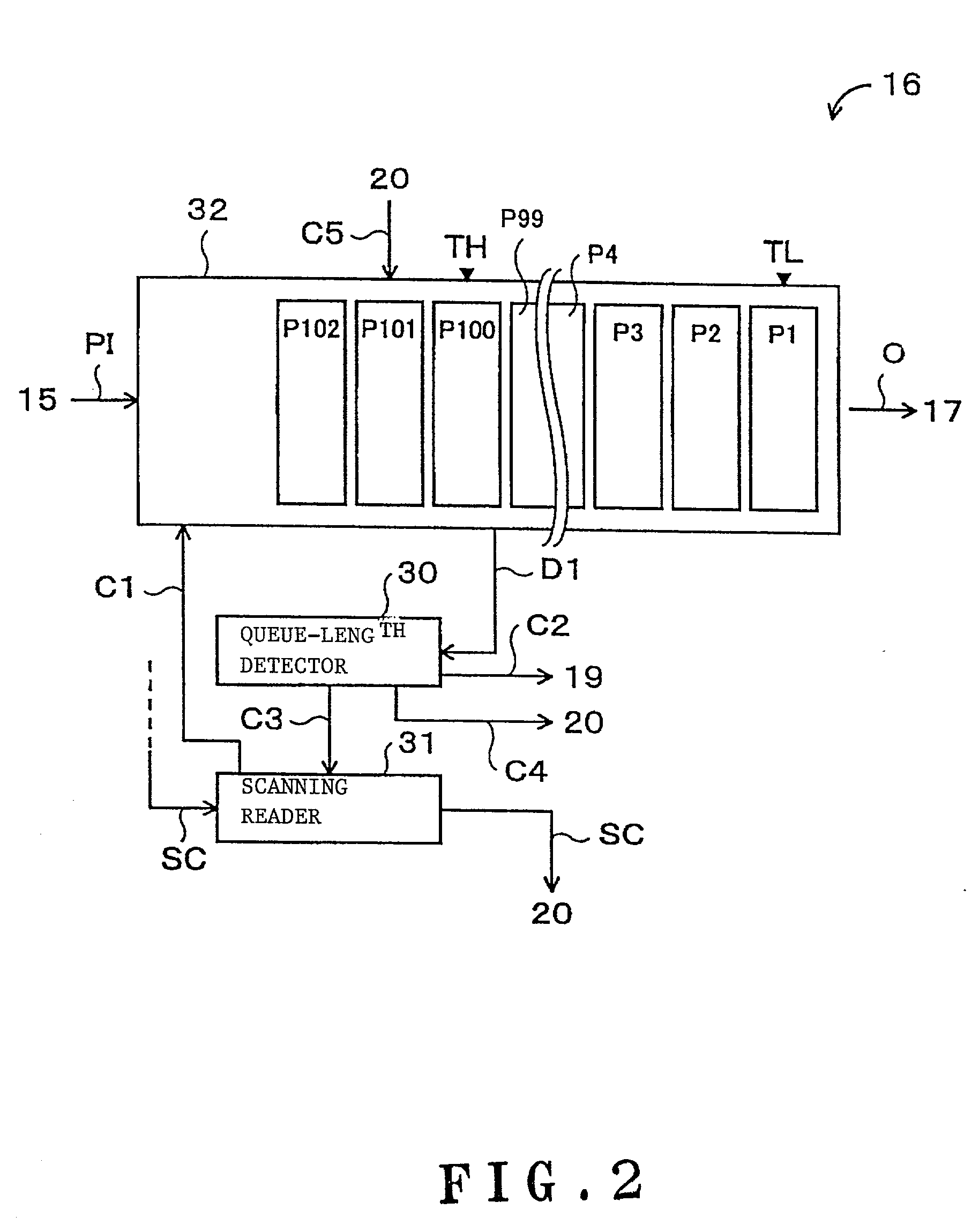

Quality control device for voice packet communications

InactiveUS20020064158A1Improve responsivenessReduce data sizeError preventionFrequency-division multiplex detailsPacket communicationControl signal

A quality control device which improves the quality of voice packet communication. The quality control device used for voice packet communications for transmitting voice packets through a quality non-assurance type network includes a buffer memory for temporarily storing voice packets received through the network and forming a queue of the received voice packets, a queue operating device for operating the queue in accordance with an operation control signal to be supplied, a sequence examining device for examining vocal properties of a sequence of voice information contained in a plurality of voice packets that constitute the queue stored in the buffer memory, and an operation control device for changing the operation control signal in accordance with an examination result of the sequence examining means.

Owner:OKI ELECTRIC IND CO LTD

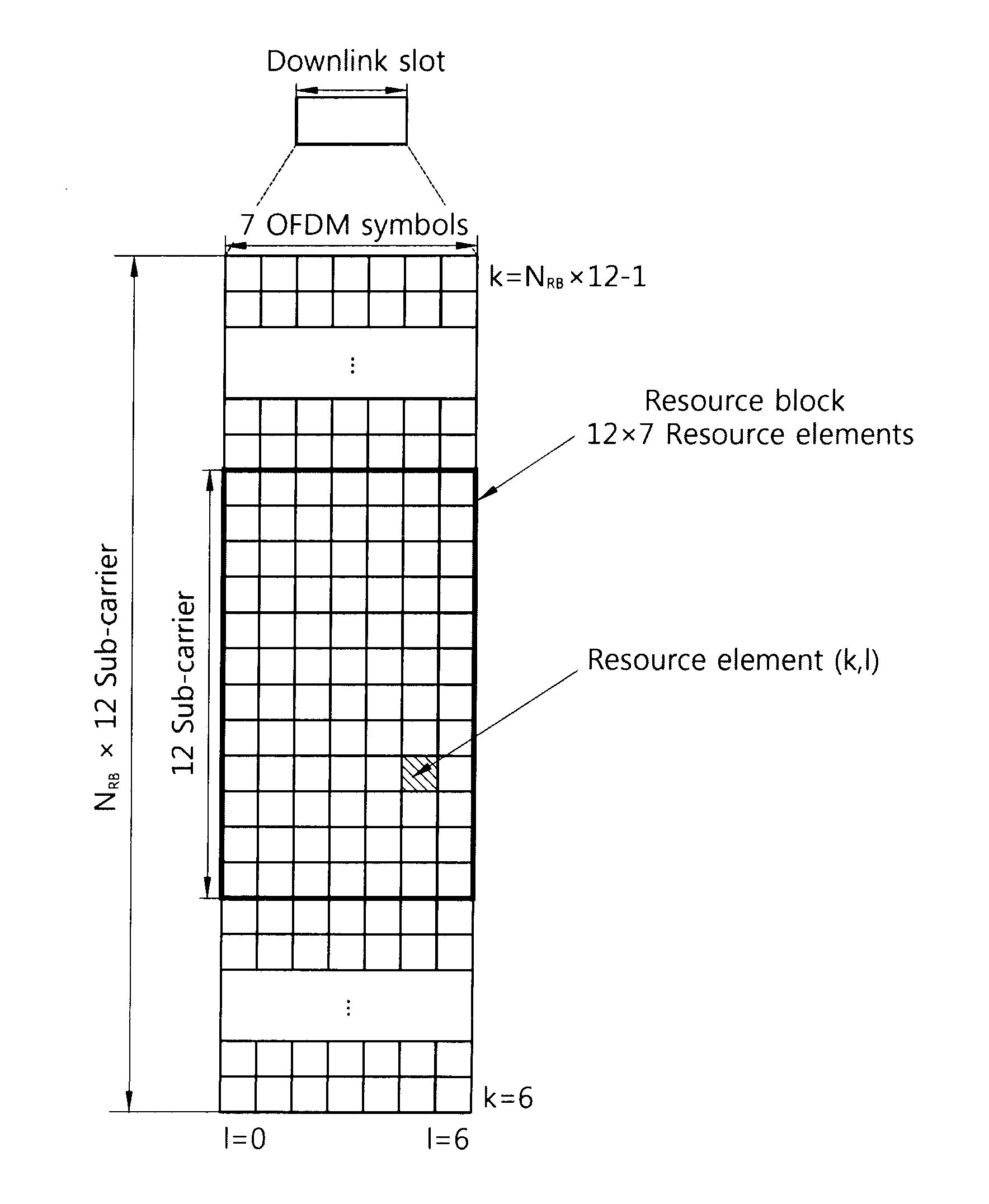

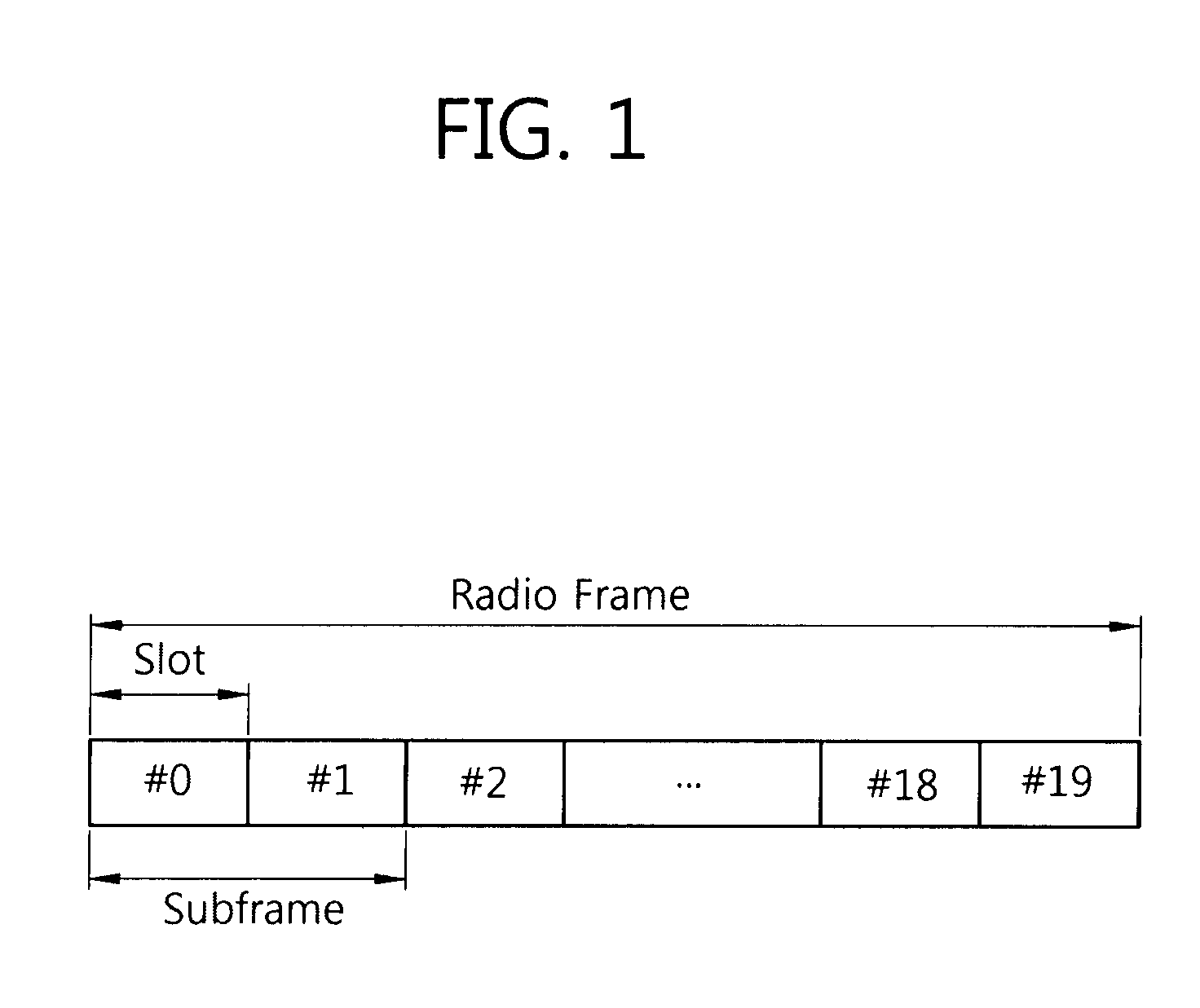

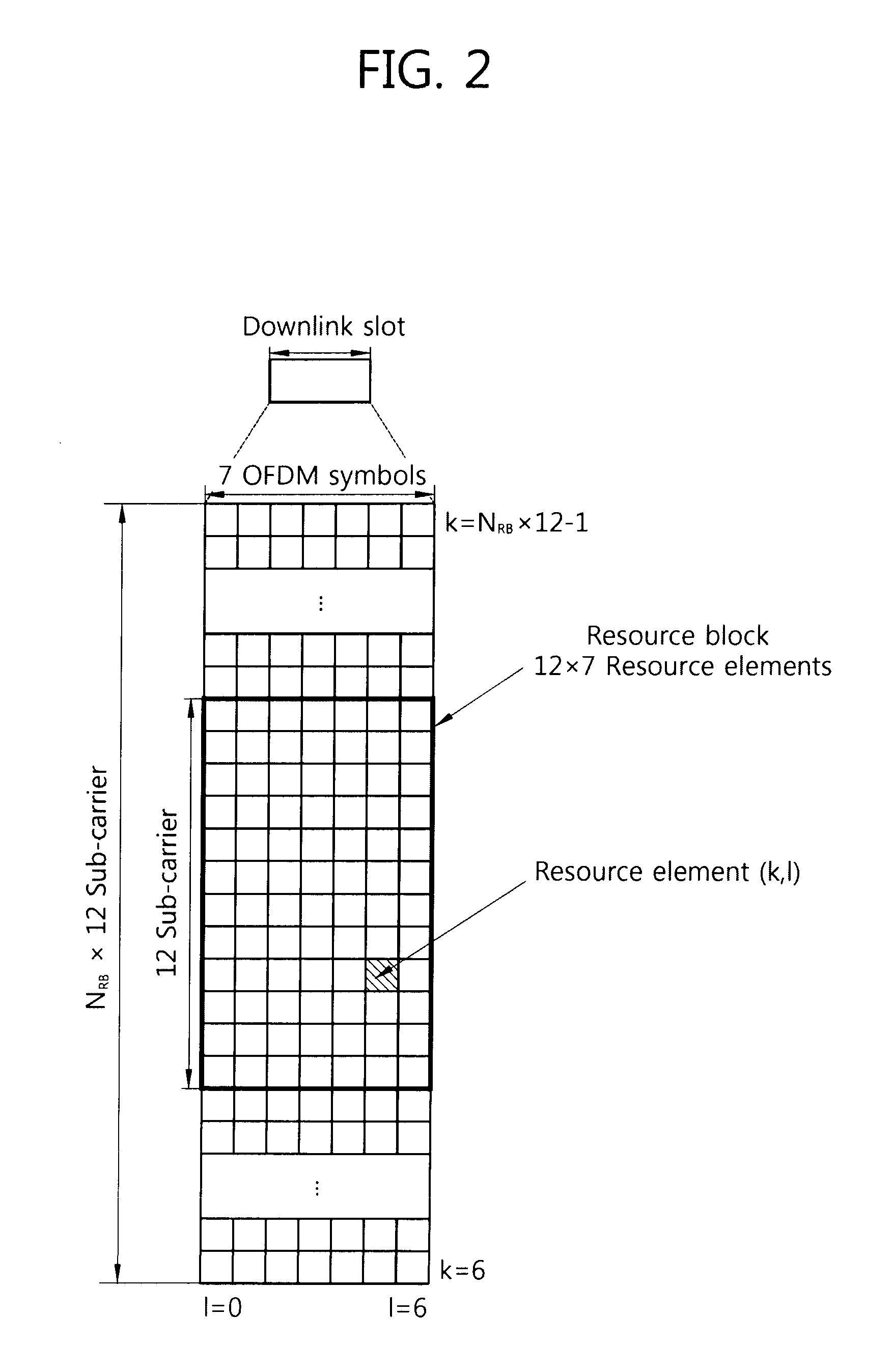

Method for setting starting position of data channel in wireless communication system and device using method

ActiveUS20140301359A1Reduce the likelihood of occurrenceImprove system efficiencyTransmission path divisionSignal allocationTime domainCommunications system

Provided are a method for setting a starting position in a time domain of a data channel in a wireless communication system and a device using the method therof. The method comprises the steps of: receiving position information notifying the position at which data channels start in a plurality of subframes; receiving a control channel in a first downlink subframe; and receiving at least one data channel scheduled by the control channel in the plurality of the downlink subframes, wherein the position at which the data channel starts in the plurality of the downlink subframes is determined on the basis of the position information.

Owner:LG ELECTRONICS INC

Complementary metal-oxide-semiconductor device

InactiveUS20080116525A1Improve device performanceReliability performance be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

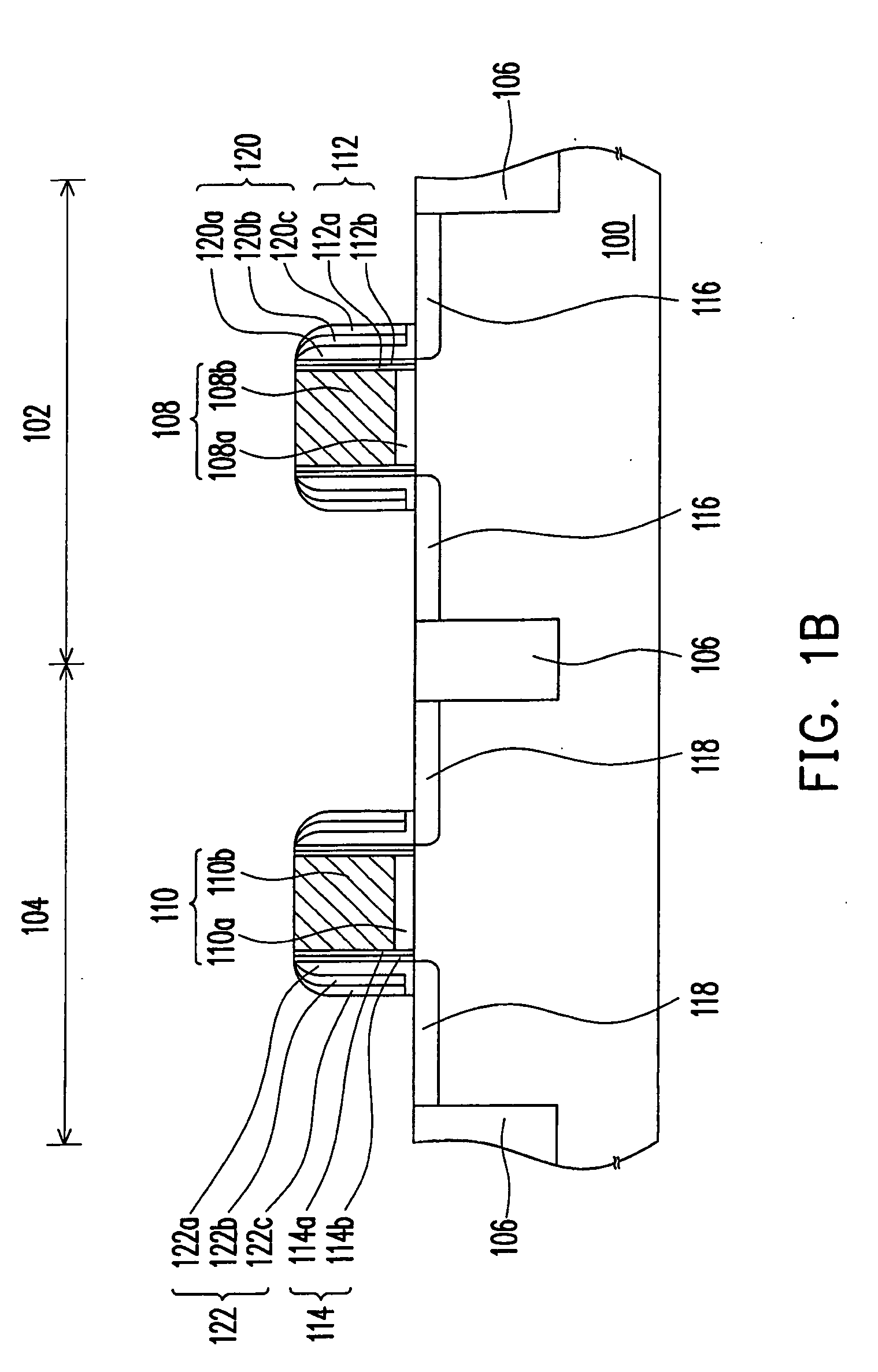

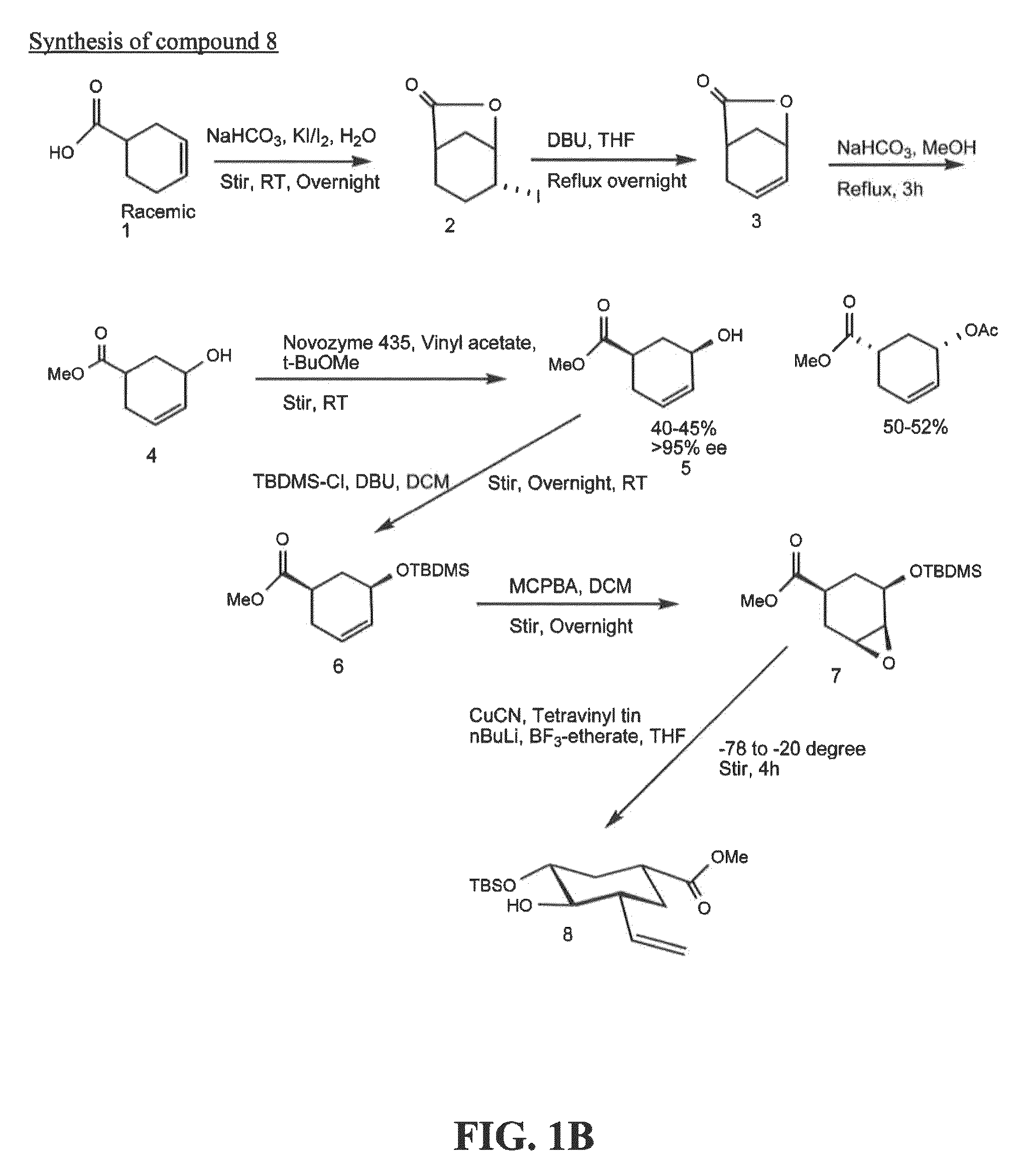

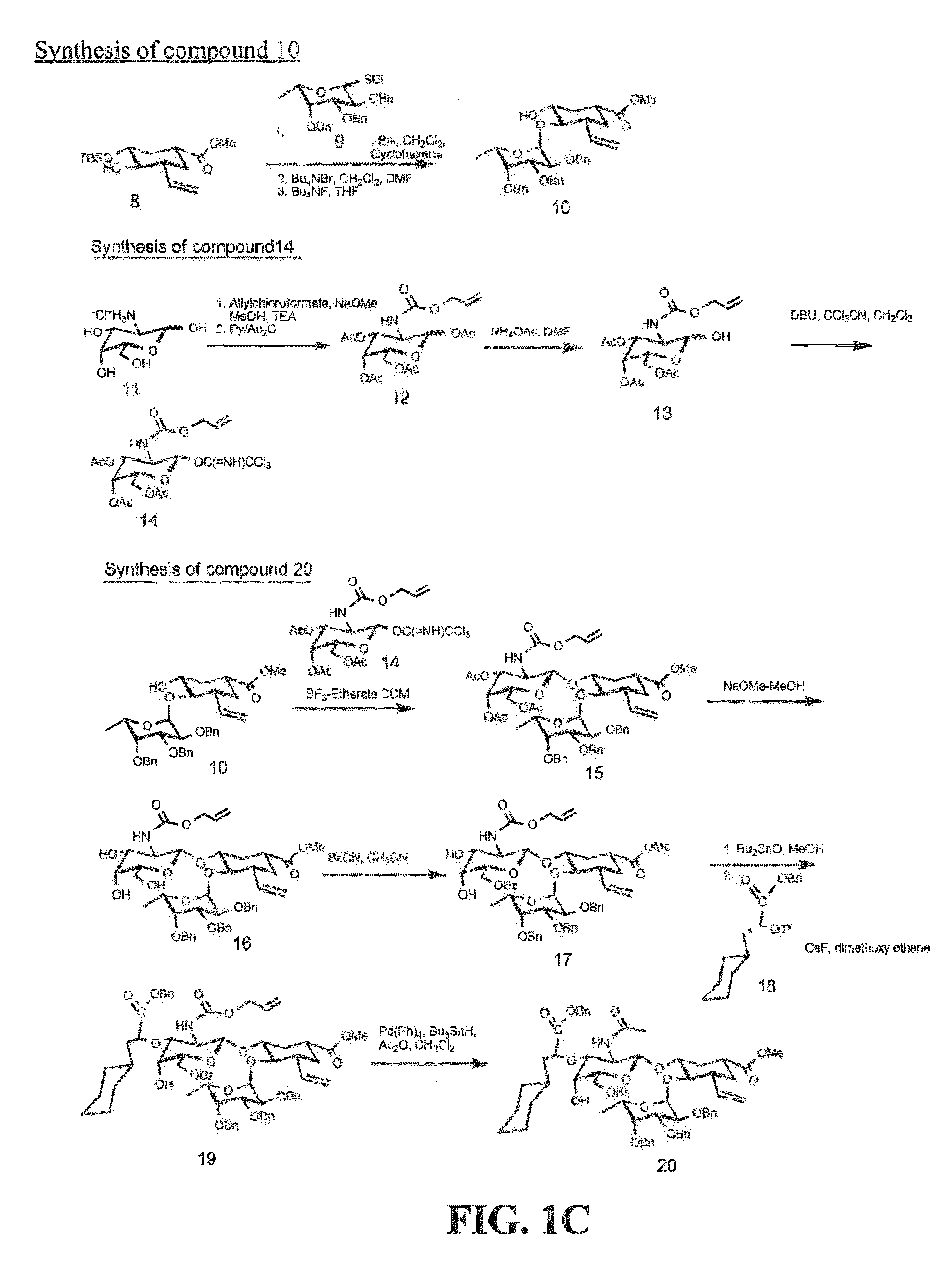

E-selectin antagonist compounds, compositions, and methods of use

ActiveUS9109002B2Enhancing hematopoietic stem cell survivalReduce the likelihood of occurrenceEsterified saccharide compoundsOrganic active ingredientsAptamerDisease

Methods and compositions using E-selectin antagonists are provided for the treatment and prevention of diseases and disorders treatable by inhibiting binding of E-selectin to an E-selectin ligand. Described herein are E-selectin antagonists including, for example, glycomimetic compounds, antibodies, aptamers and peptides that are useful in methods for treatment of cancers, and treatment and prevention of metastasis, inhibiting infiltration of the cancer cells into bone marrow, reducing or inhibiting adhesion of the cancer cells to endothelial cells including cells in bone marrow, and inhibiting thrombus formation.

Owner:GLYCOMIMETICS

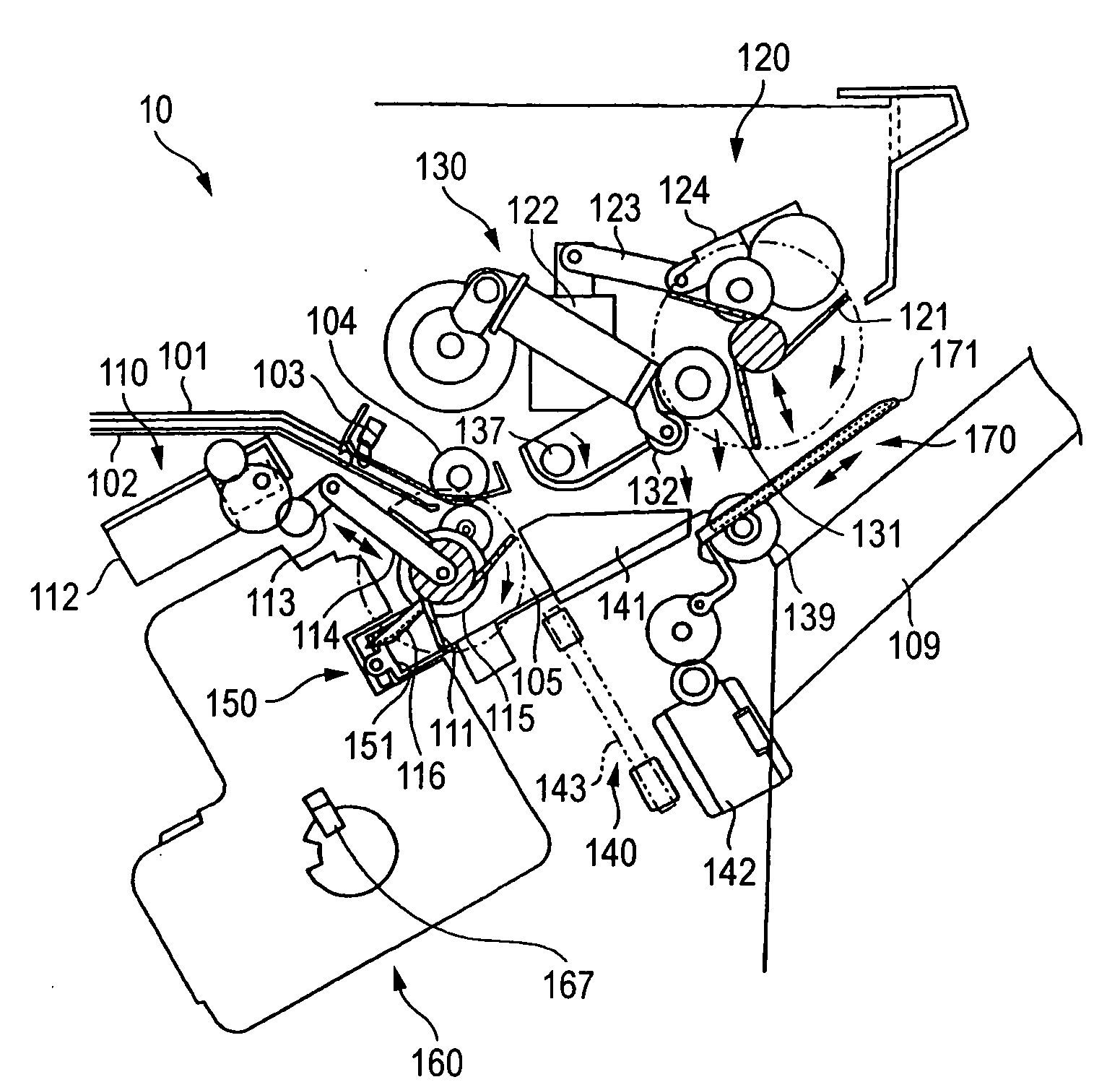

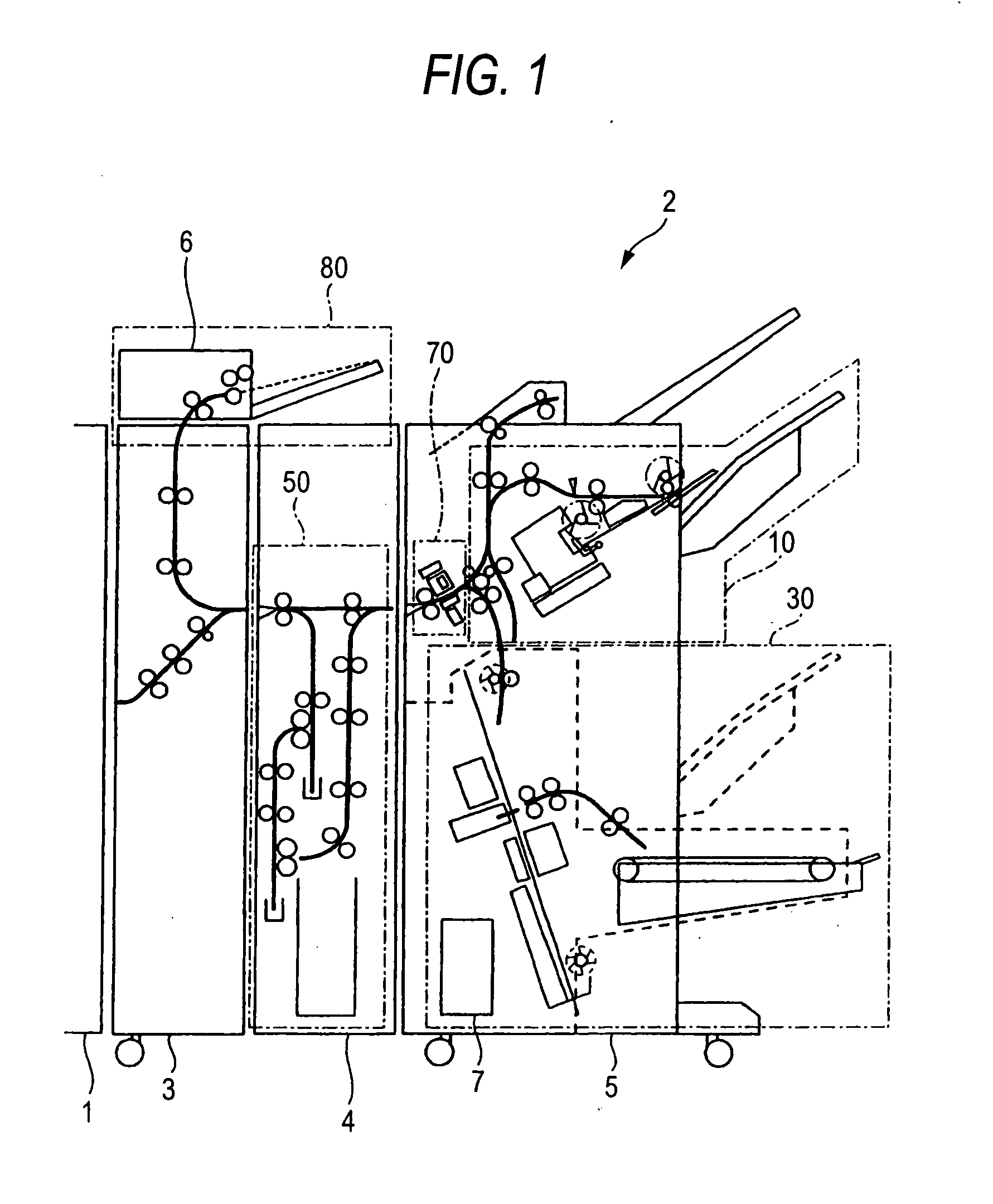

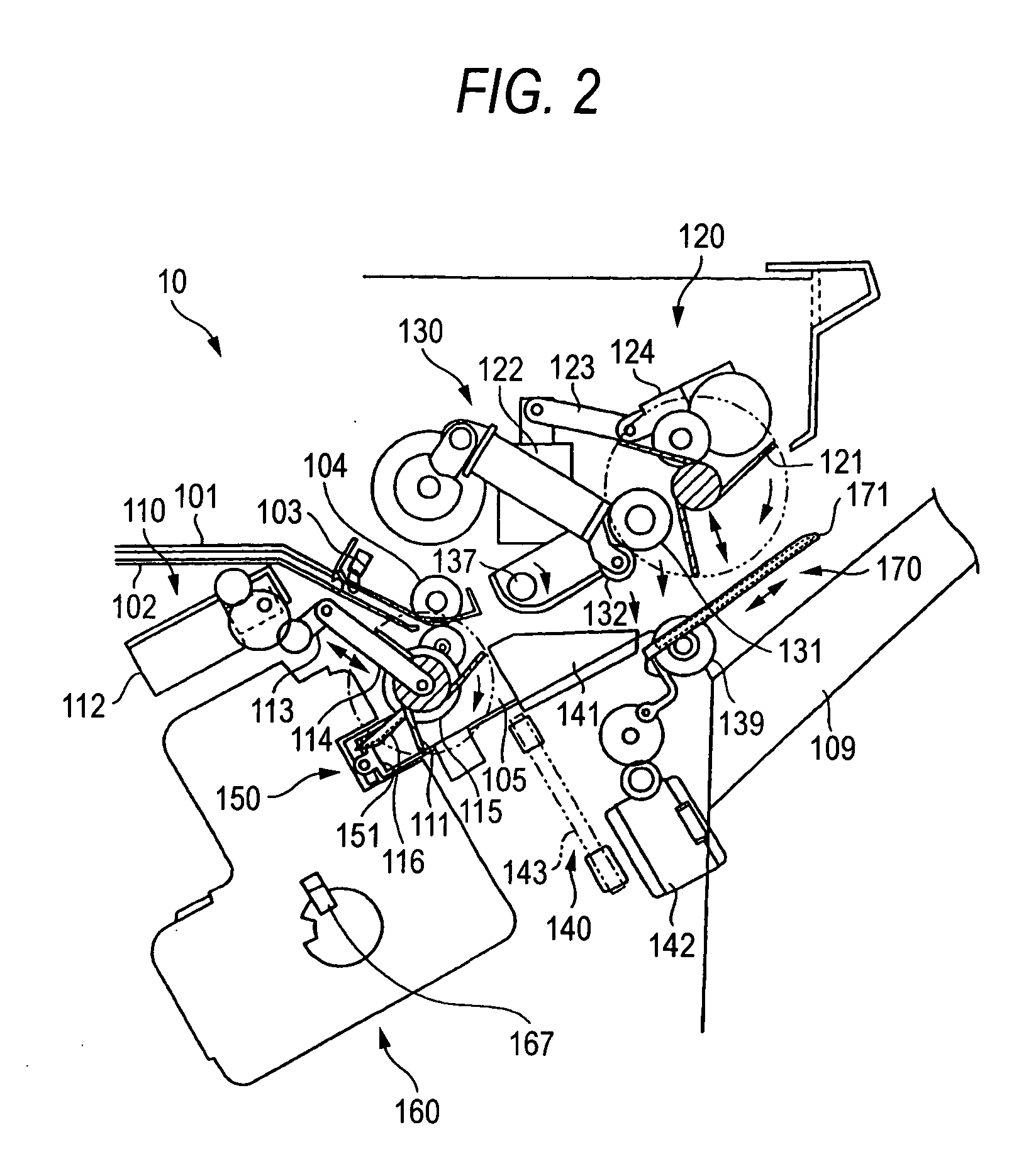

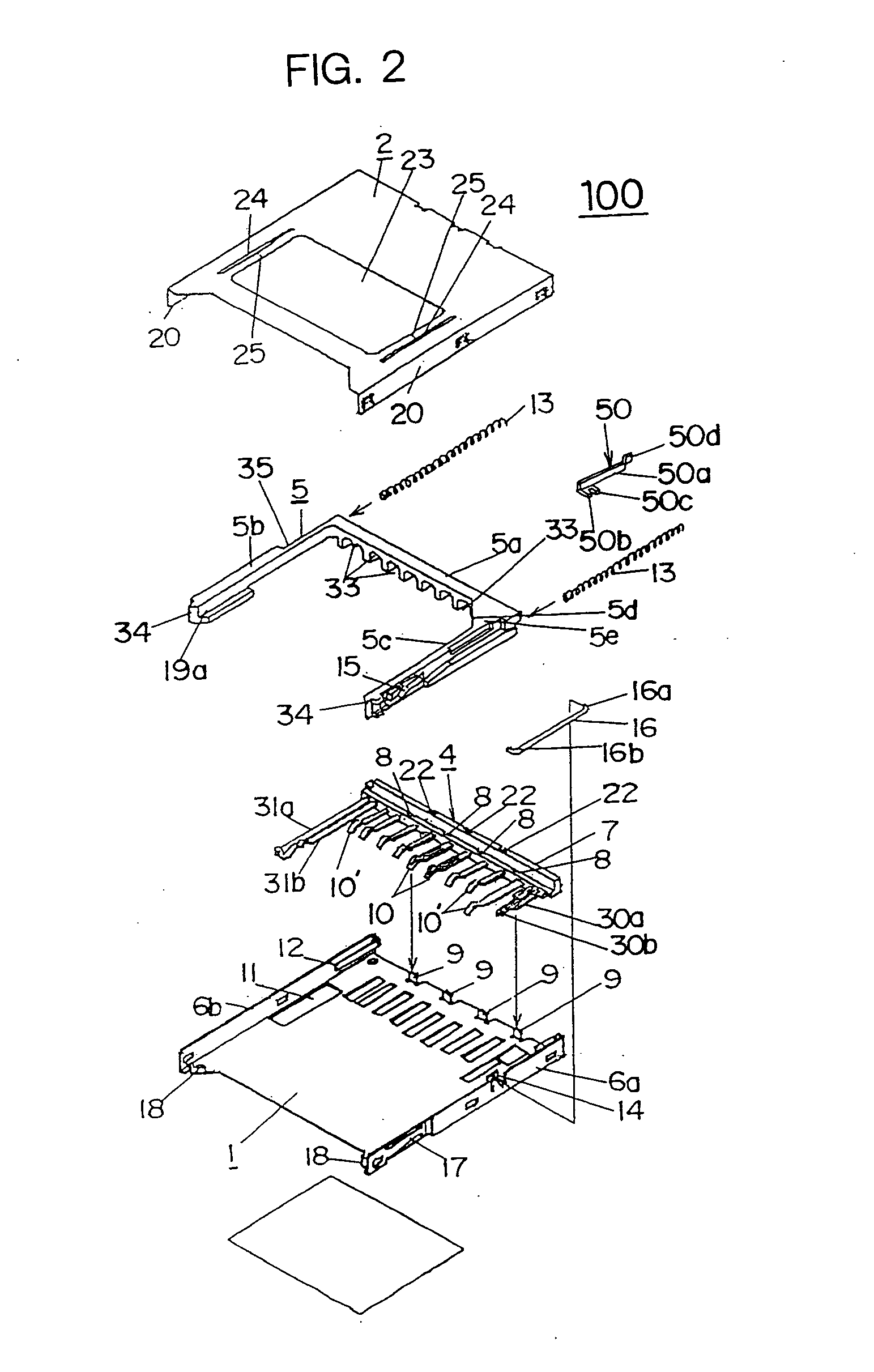

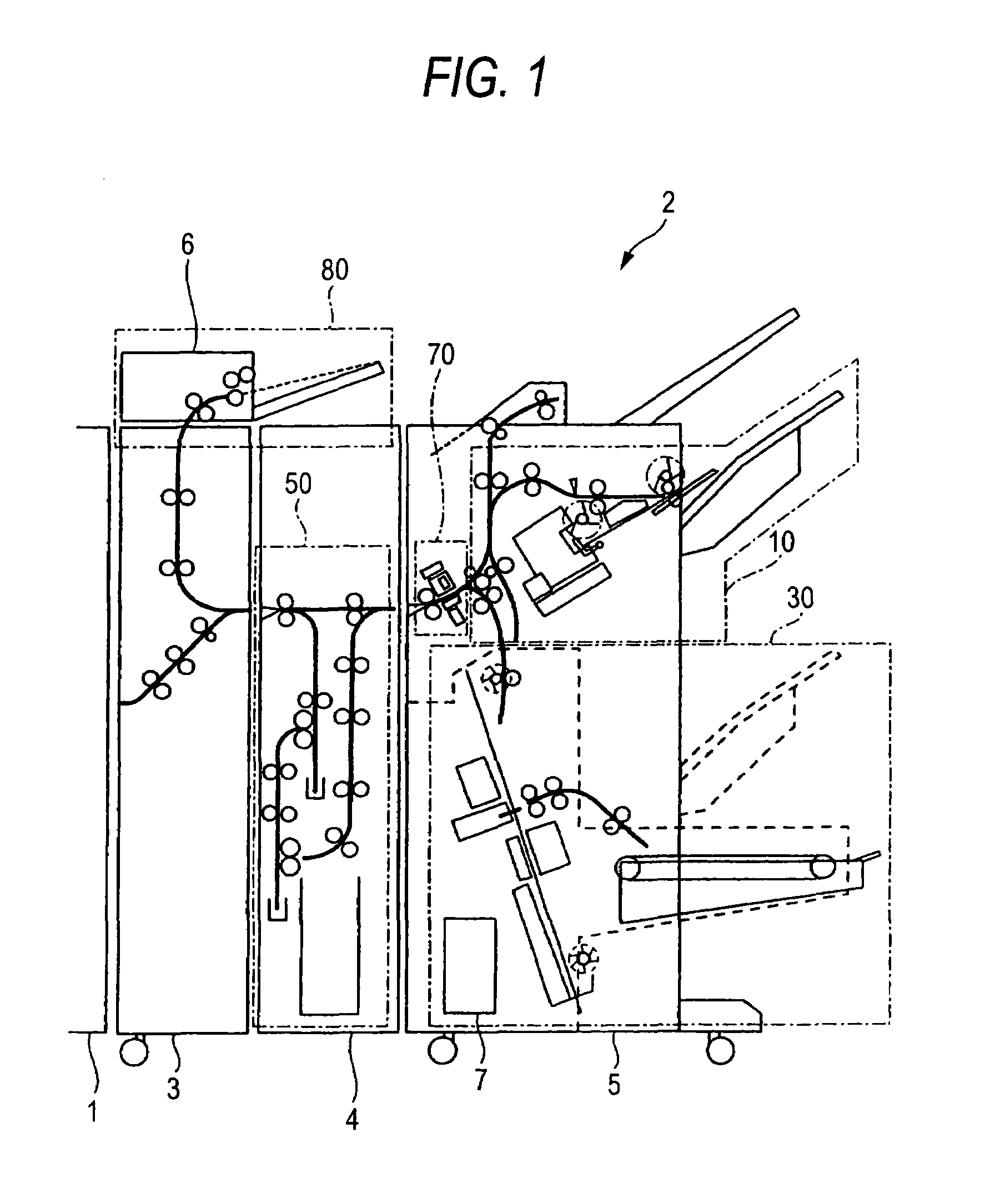

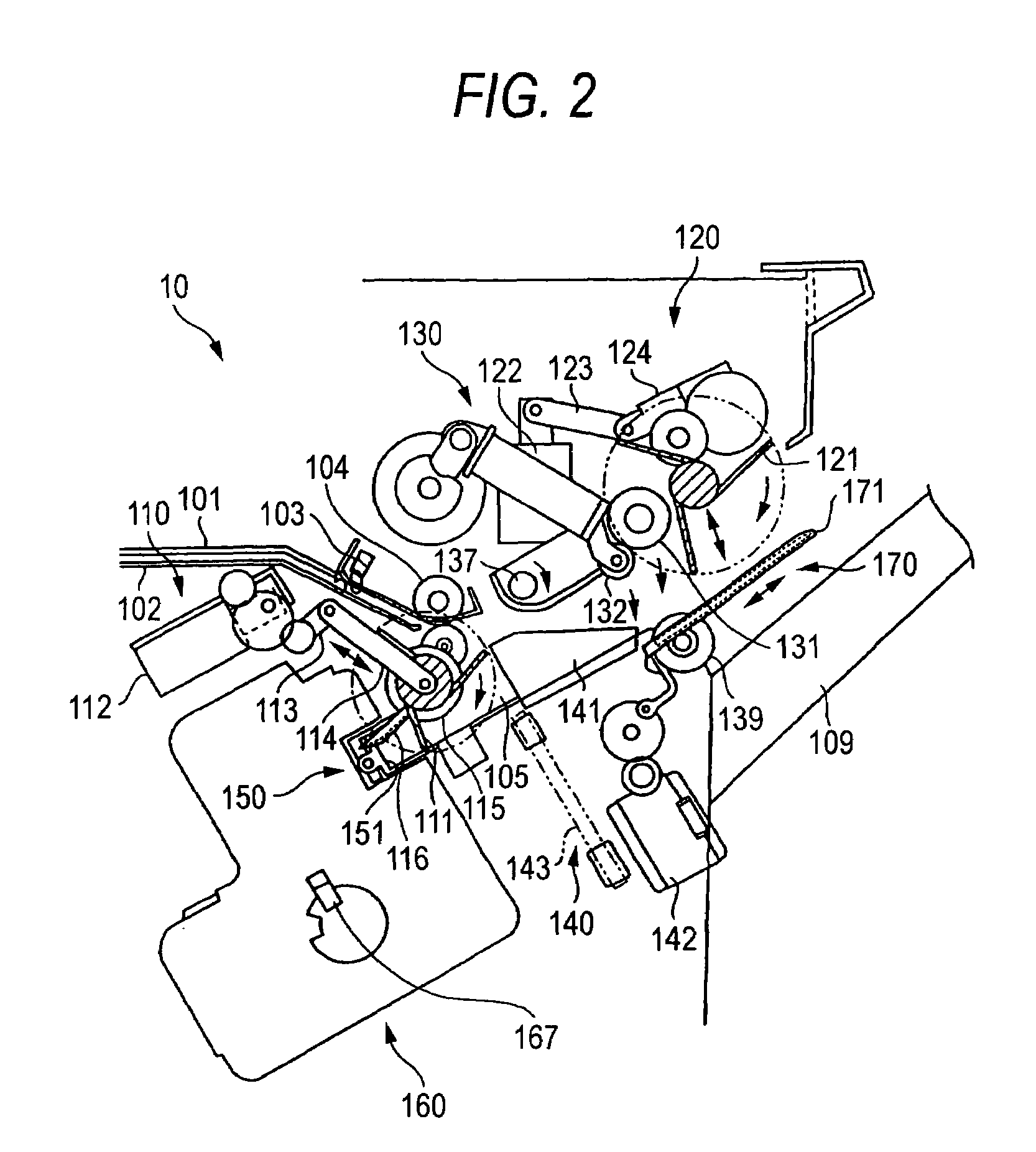

Stapling device

ActiveUS20060017210A1Reduce the likelihood of occurrenceProductivity is deterioratedStapling toolsNailingEngineeringElectrical and Electronics engineering

A stapler unit has a staple section, a cutter section, and a receiving section. A stapling device further includes a staple recovery box which is disposed at a staple discarding position and which recovers the tip ends to be discarded from the receiving section; and a staple discarding mechanism which delivers the tip ends received in the receiving section of the stapler unit to the staple recovery box. One of the plural stapling positions is identical with the staple discarding position.

Owner:FUJIFILM BUSINESS INNOVATION CORP

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS7402496B2Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

Owner:UNITED MICROELECTRONICS CORP

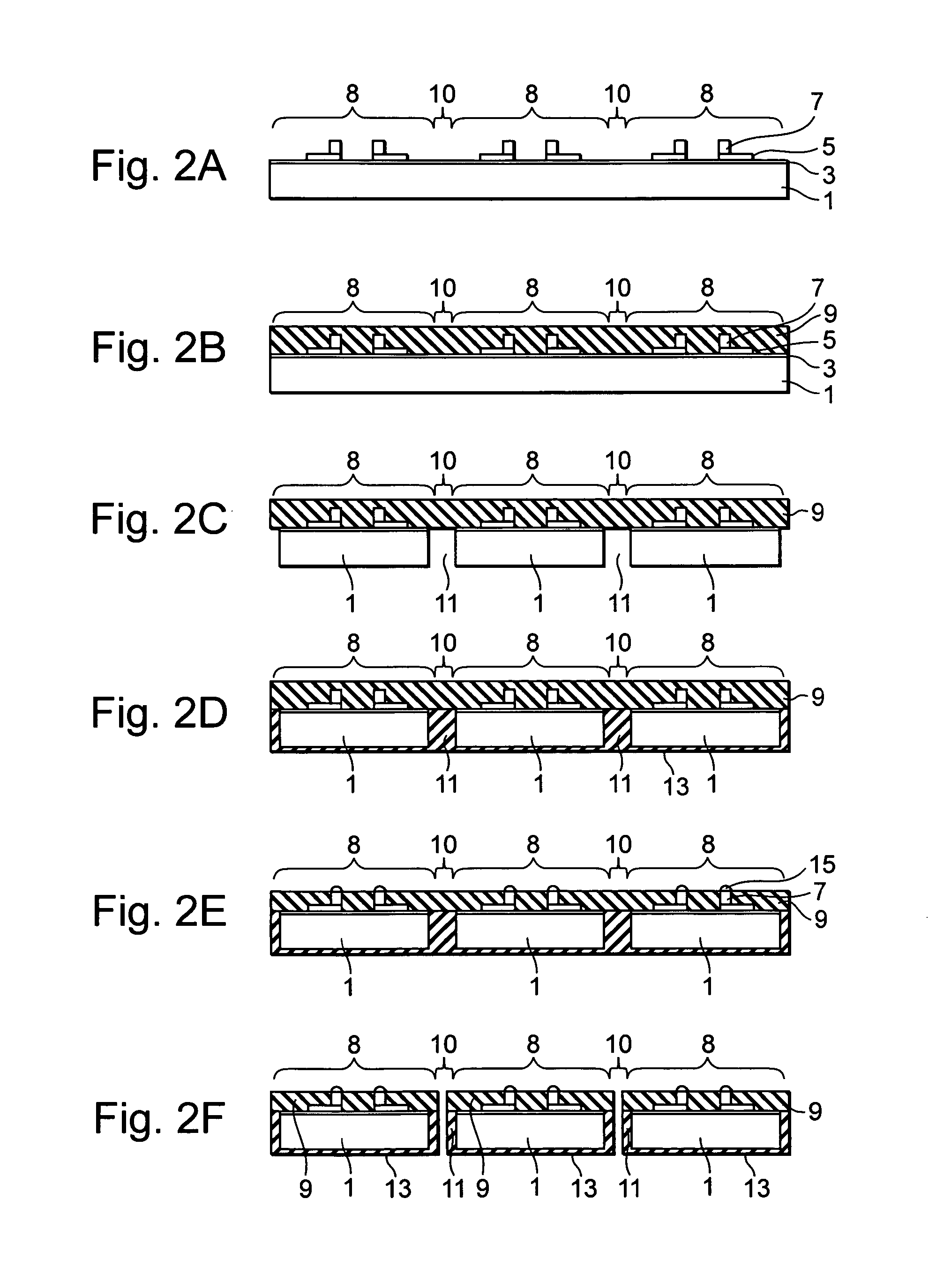

Method for manufacturing semiconductor device

InactiveUS20060154447A1Reduce debrisReduce the likelihood of occurrenceSolid-state devicesSemiconductor/solid-state device manufacturingBoundary regionSemiconductor

A method for manufacturing a semiconductor device comprises the steps of forming protruded electrodes on a plurality chip areas of a semiconductor wafer having the plurality of chip areas and boundary regions formed among the chip areas, both being provided in a surface of the semiconductor wafer, forming a surface-side protective member so as to cover the surface of the semiconductor wafer and the protruded electrodes, removing the semiconductor wafer corresponding to the boundary regions and forming trenches which expose the surface-side protective member, forming a back-side protective member with which the trenches are filled and which covers the back of the semiconductor wafer, and dividing the semiconductor wafer in the boundary regions with widths thinner than those of the trenches in such a manner that the surface-side protective member and the back-side protective member charged into the trenches are left in cut sections.

Owner:LAPIS SEMICON CO LTD

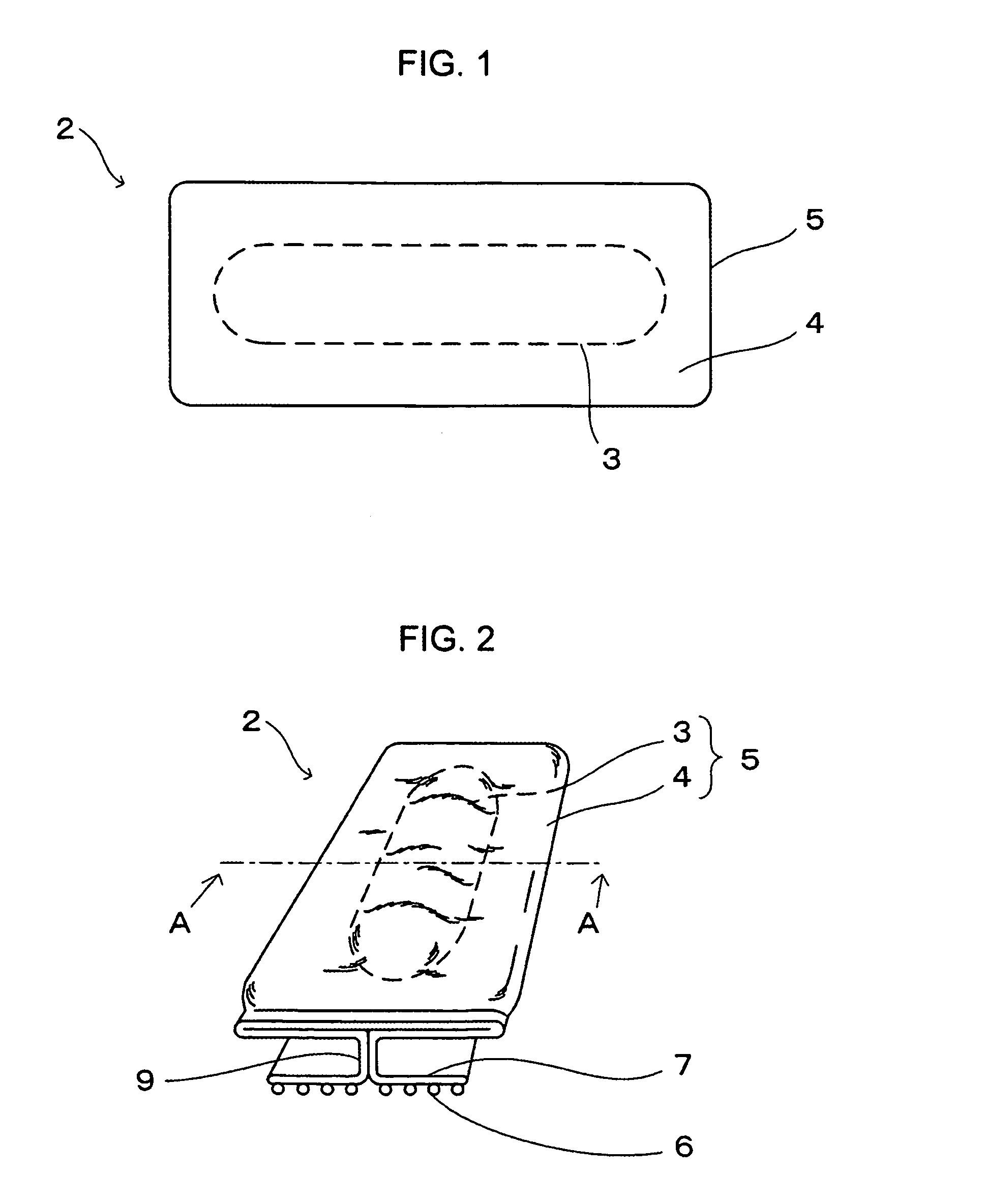

Auxiliary pad for mounting absorbable article

The present invention concerns an auxiliary pad for absorbent article that can prevent body fluid from leaking along with the dislocation of an absorbent article such as sanitary napkin, and provides a hygienic article that can reduce the occurrence of body fluid leak, even when the dislocation of fitting happens, all the way securing a sufficient adhesion to the inside of the thigh.An auxiliary pad for absorbent article (2), comprising an absorbent sheet body (5) adhered to the inside of the thigh of the wearer for absorbing body fluid, a linkage stem body (9) for linking the absorbent sheet body and an junction sheet body (7), and the junction sheet body (7) to which an adhesive (6) is applied, is attached to a sanitary napkin (10) to constitute a sanitary article (1).

Owner:UNI CHARM CORP

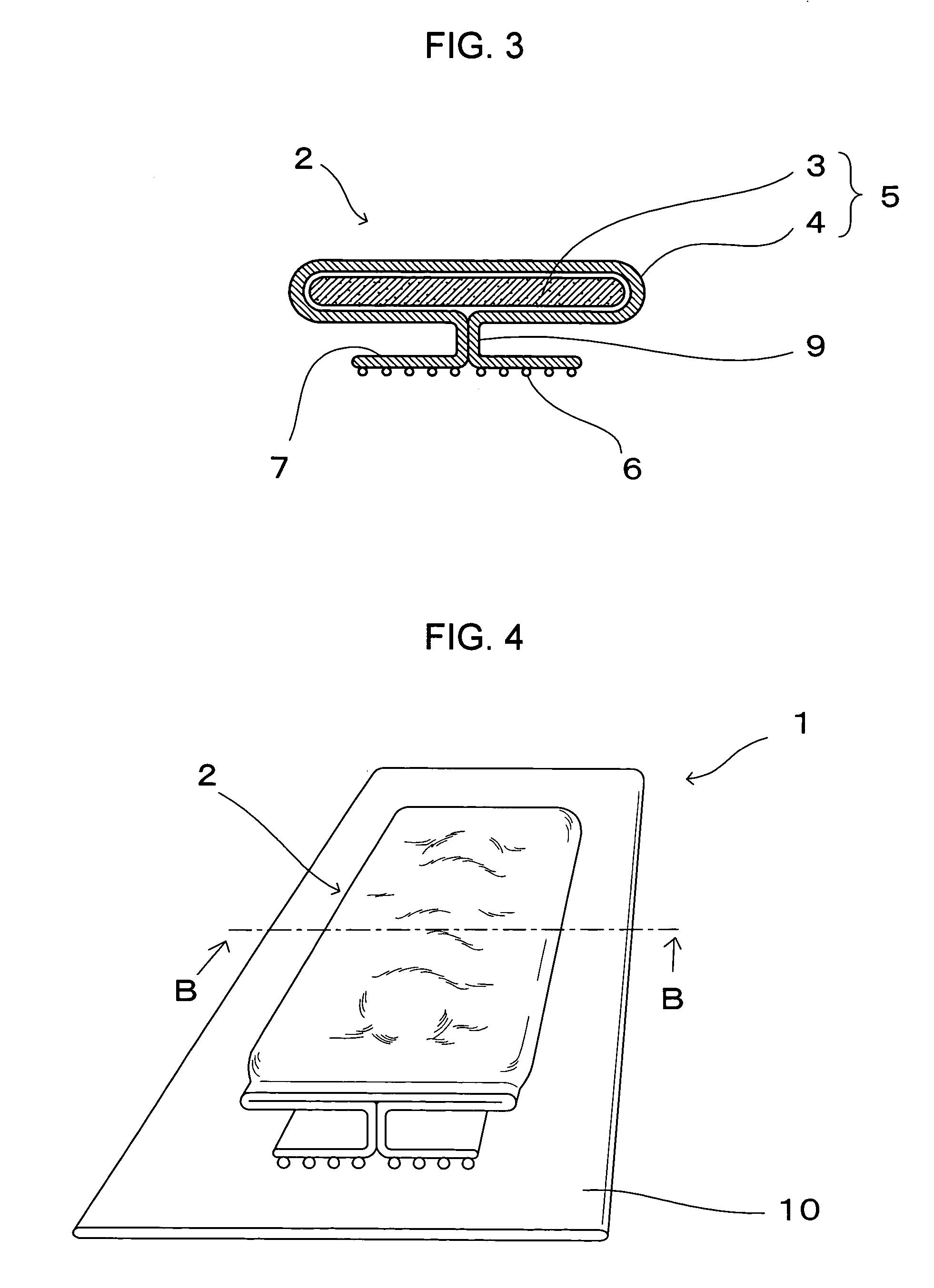

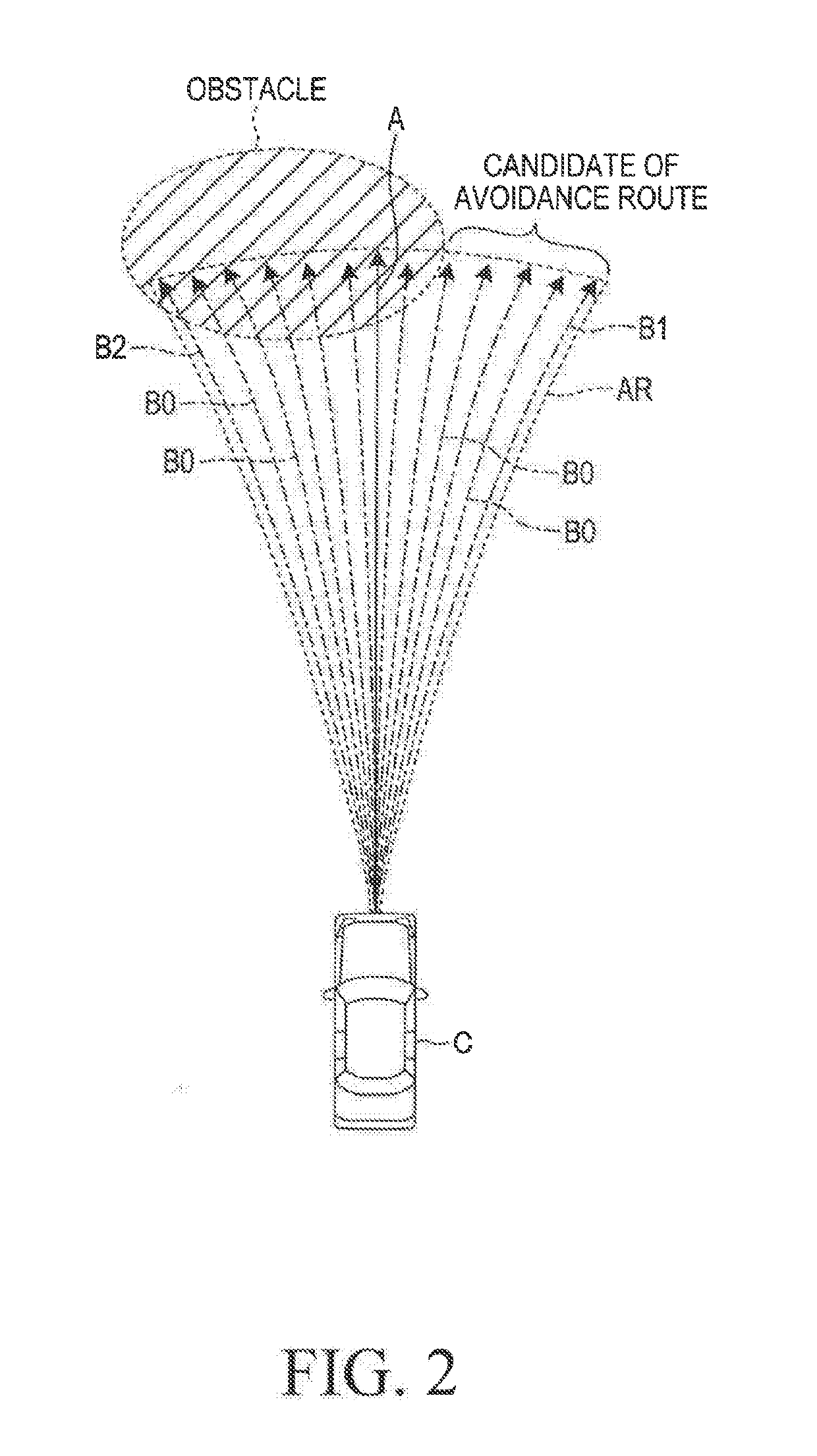

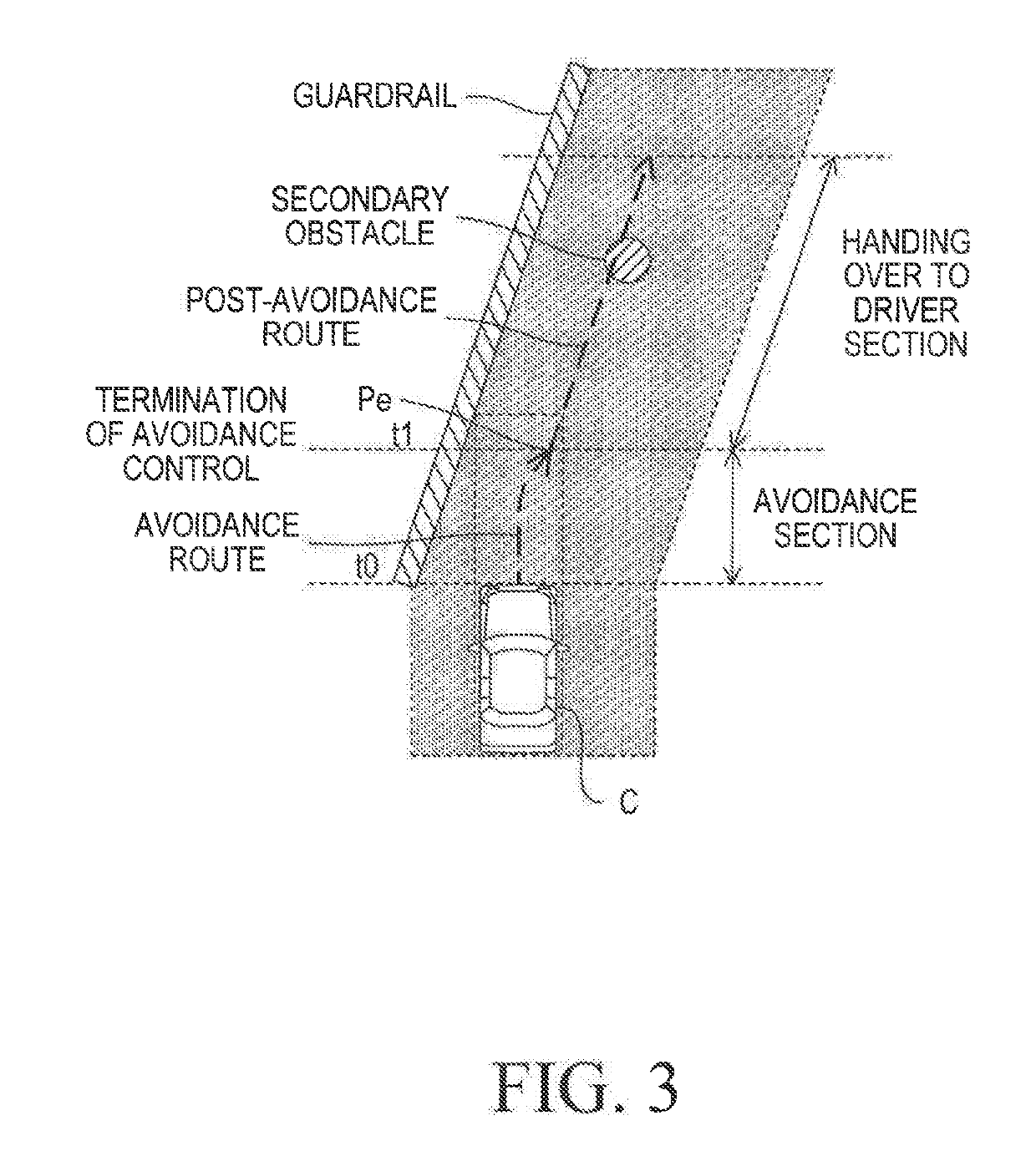

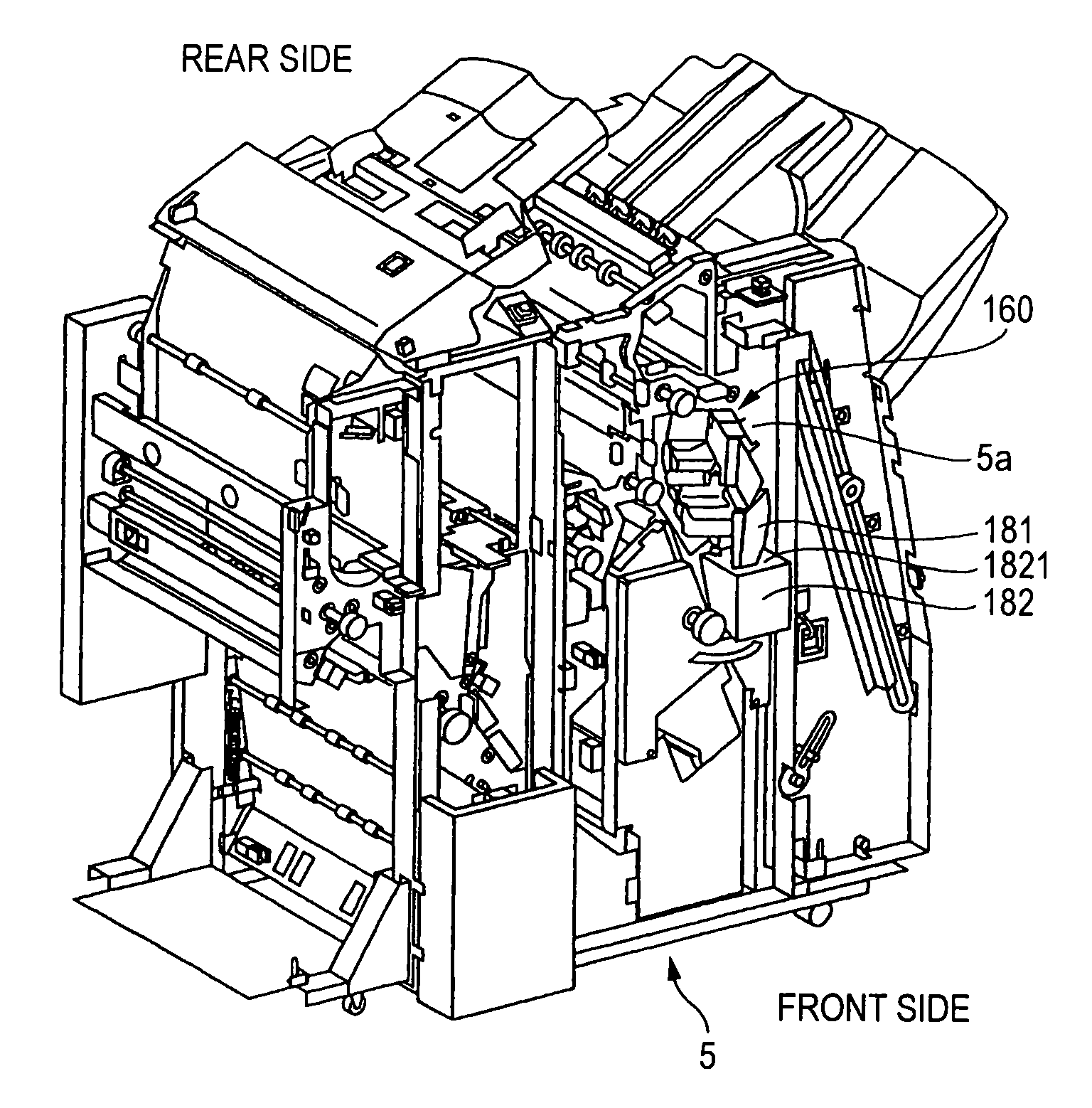

Collision avoidance assist apparatus

ActiveUS20190100197A1Reduces possibility of occurrenceReduce the likelihood of occurrenceNavigational calculation instrumentsRoad vehicles traffic controlAutomatic steeringAutomatic braking

An avoidance route calculation part calculates an avoidance route for avoiding a collision between an own vehicle and an obstacle through a collision avoidance assist control (an automatic brake control and an automatic steering control). A post-avoidance route calculation part calculates a post-avoidance route. A post-avoidance route collision determination part determinates whether a secondary obstacle is present on the post-avoidance route. When the secondary obstacle is determined to be present, the automatic steering control is prohibited from being performed.

Owner:TOYOTA JIDOSHA KK

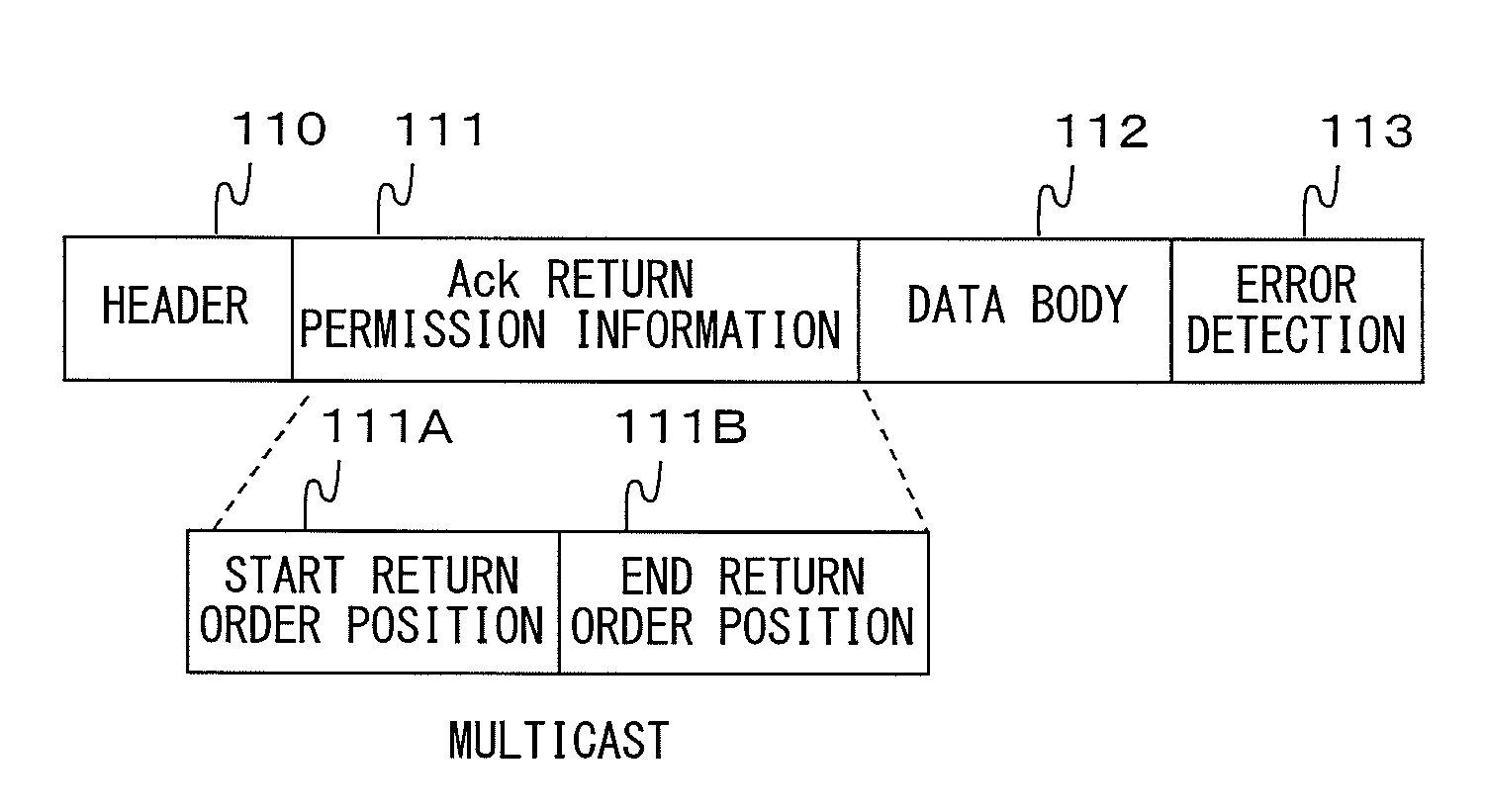

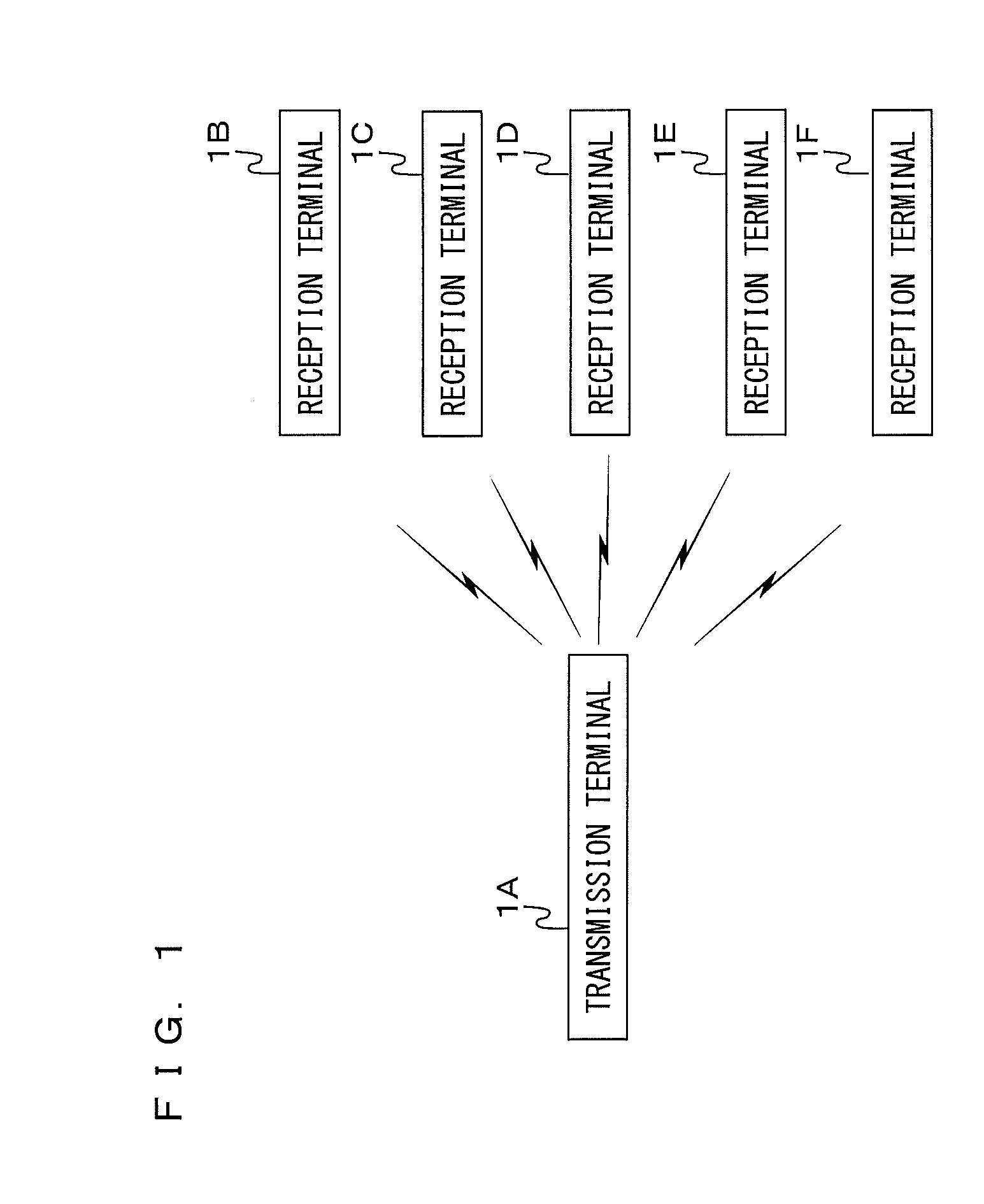

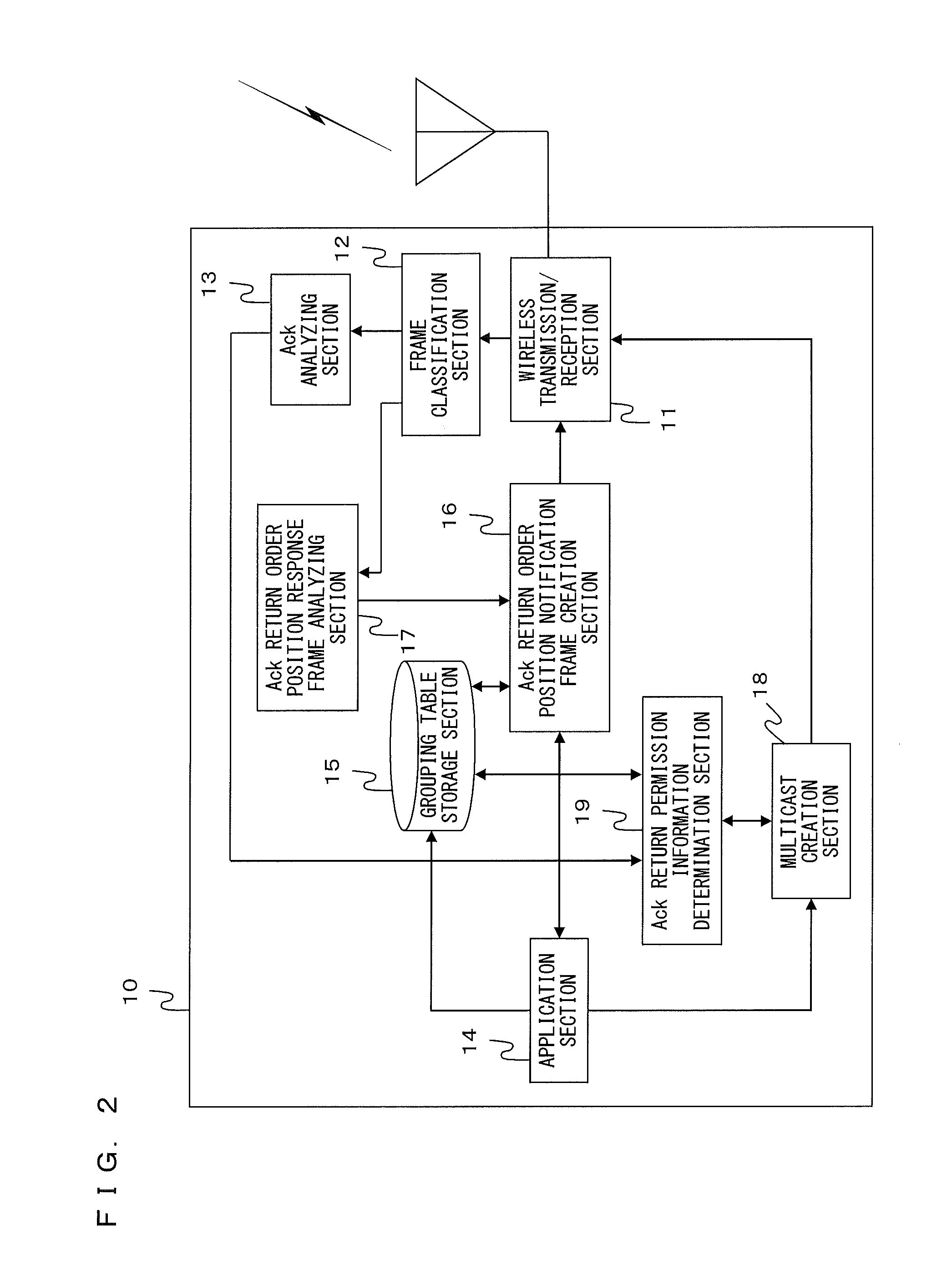

Communication method

InactiveUS20120106427A1Reduction of Ack return permission information setEasy to useTransmission control/equalisingBroadcast transmission systemsCommunication qualityComputer terminal

Provided is a communication method for improving the communication quality of multicast transmission. A grouping table storage section stores a grouping table in which Ack return order positions indicating priority orders of the reception terminals which each return an Ack, and addresses of the reception terminals are set. An Ack return order position notification frame creation section notifies each reception terminal of a corresponding Ack return order position based on the grouping table. An Ack return permission information determination section refers to the grouping table, determines the number of reception terminal that are to be permitted to return an Ack, and creates Ack return permission information in which information about the reception terminals that are to be permitted to return an Ack is set, based on the determined number of reception terminals. A multicast creation section creates a multicast containing the Ack return permission information and transmission data.

Owner:PANASONIC CORP

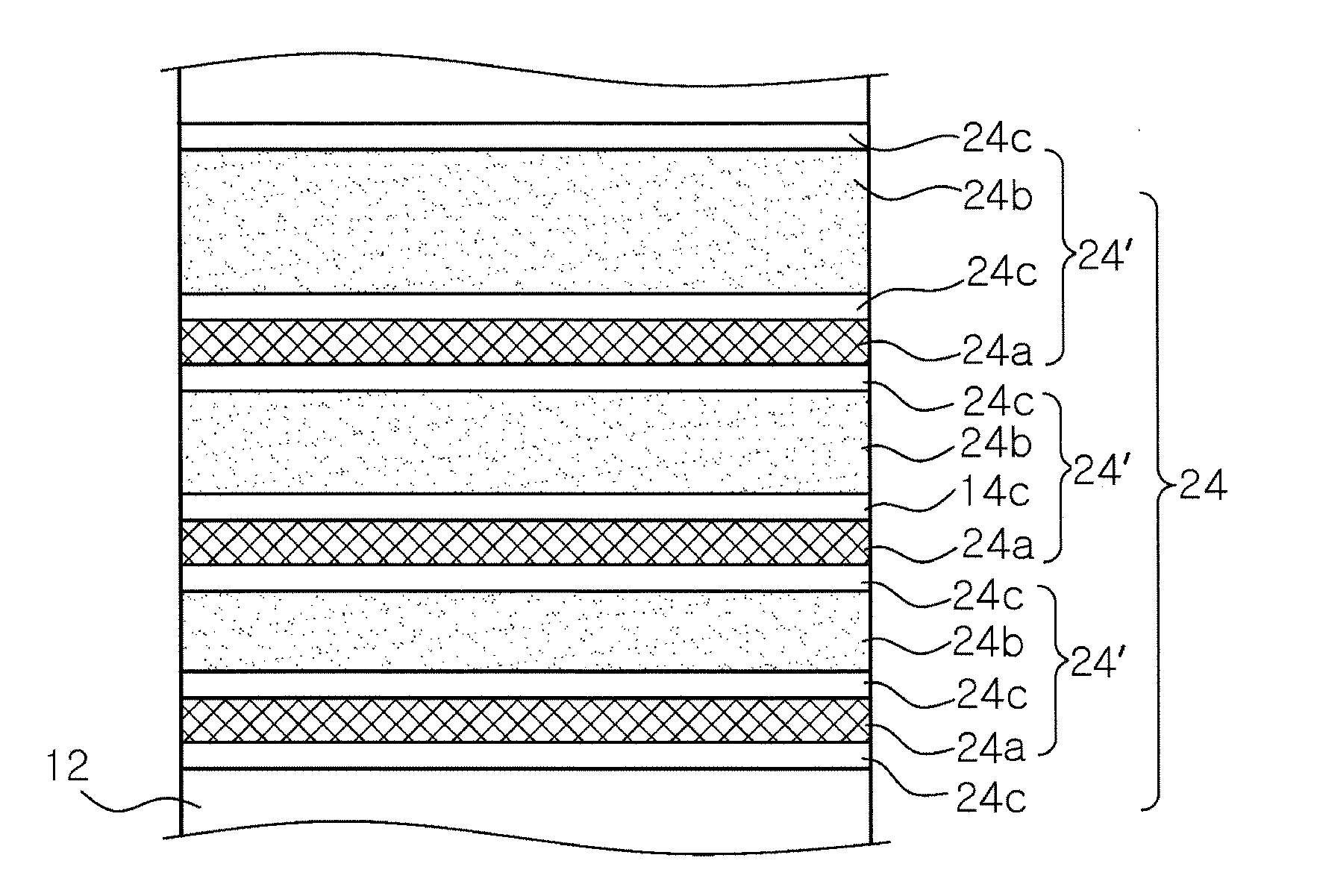

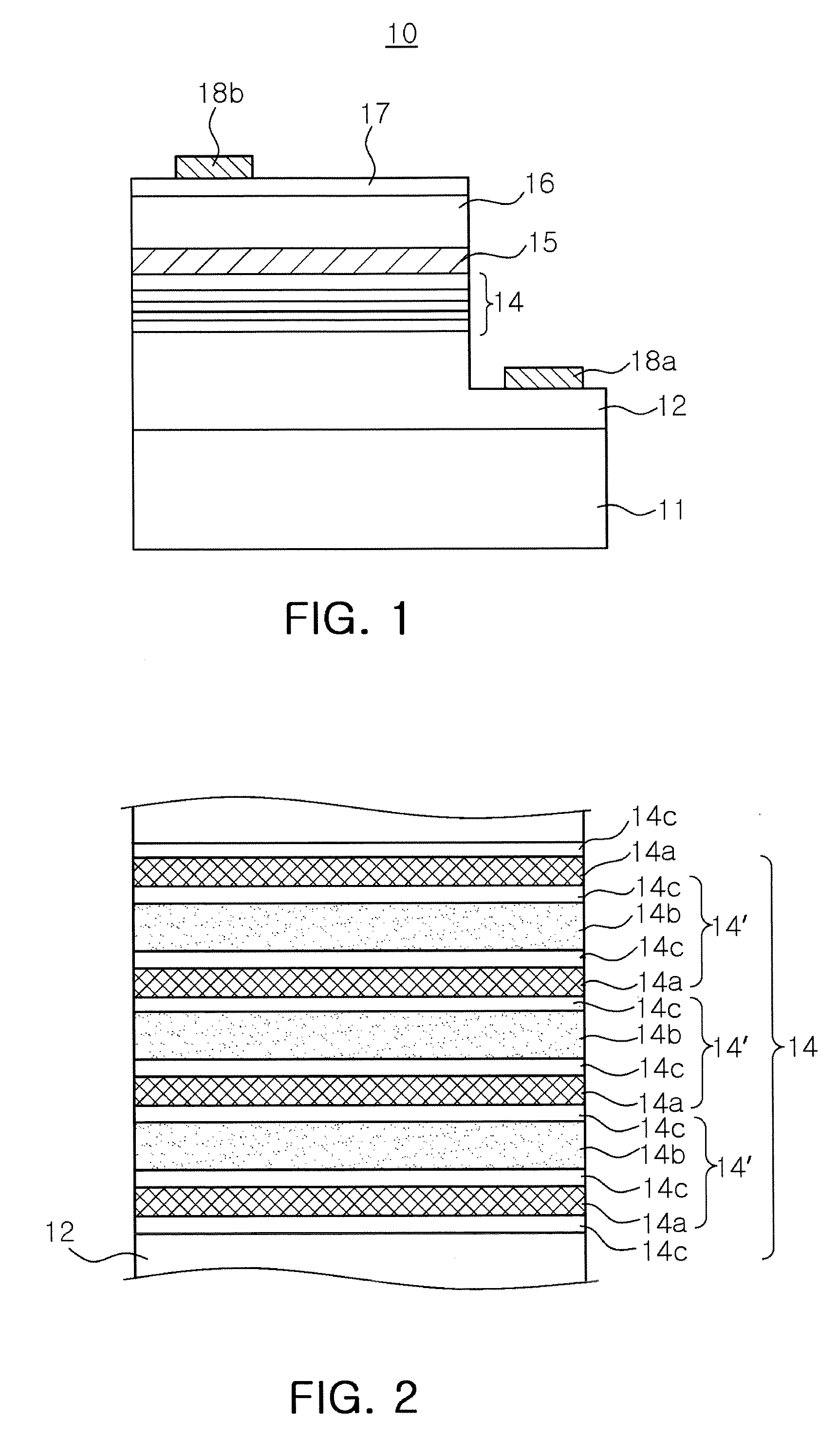

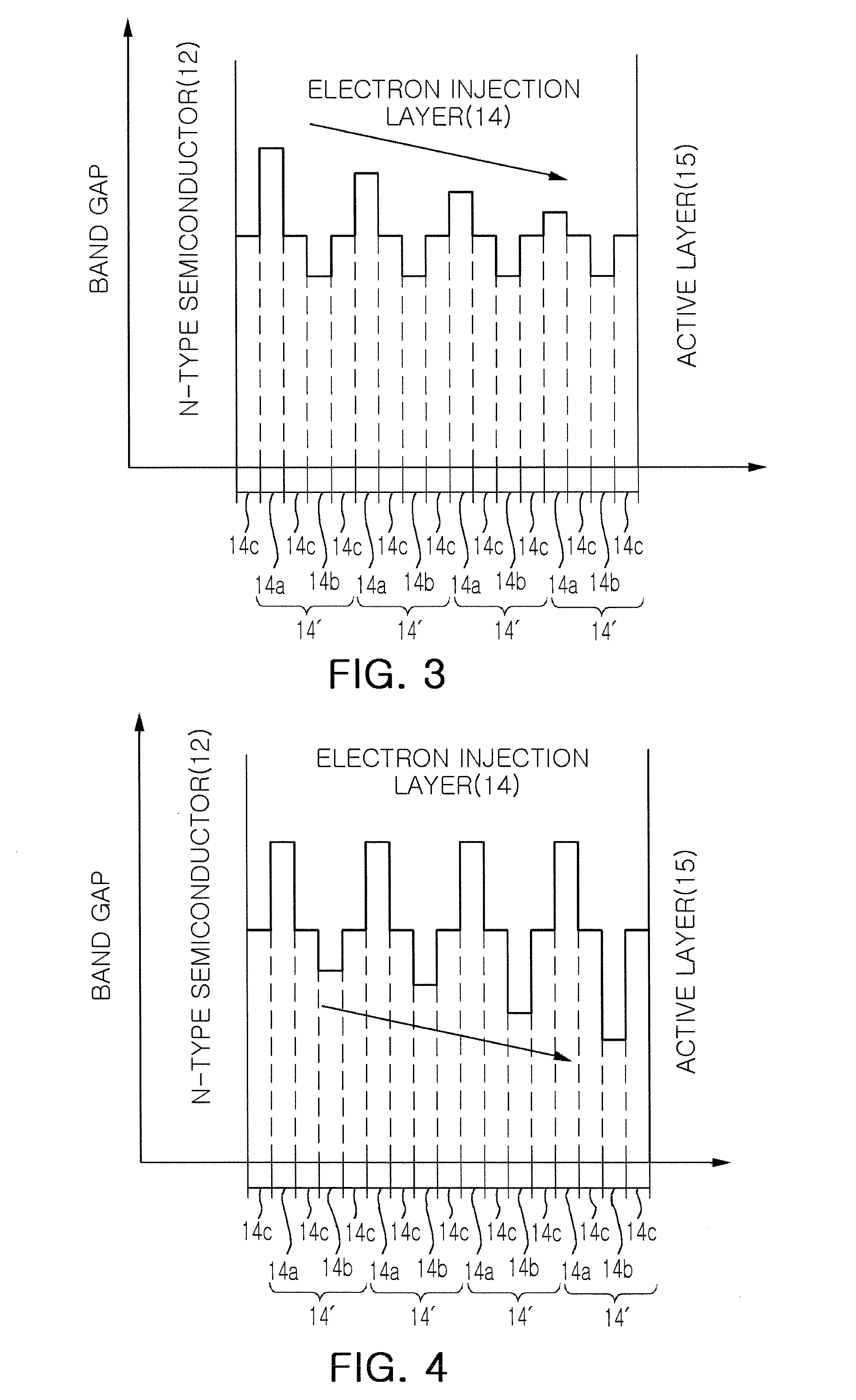

Nitride semiconductor light emitting device

ActiveUS20120261687A1Improved in current distributionGood effectSemiconductor devicesActive layerLight emitting device

There is provided a nitride semiconductor light emitting device including: n-type and p-type nitride semiconductor layers; an active layer disposed between the n-type and p-type nitride semiconductor layers; and an electron injection layer disposed between the n-type nitride semiconductor layer and the active layer. The electron injection layer has a multilayer structure, in which three or more layers having different energy band gaps are stacked, and the multilayer structure is repetitively stacked at least twice. At least one layer among the three or more layers has a reduced energy band gap in individual multilayer structures in a direction toward the active layer, and the layer having the lowest energy band gap has an increased thickness in individual multilayer structures in a direction toward the active layer.

Owner:SAMSUNG ELECTRONICS CO LTD

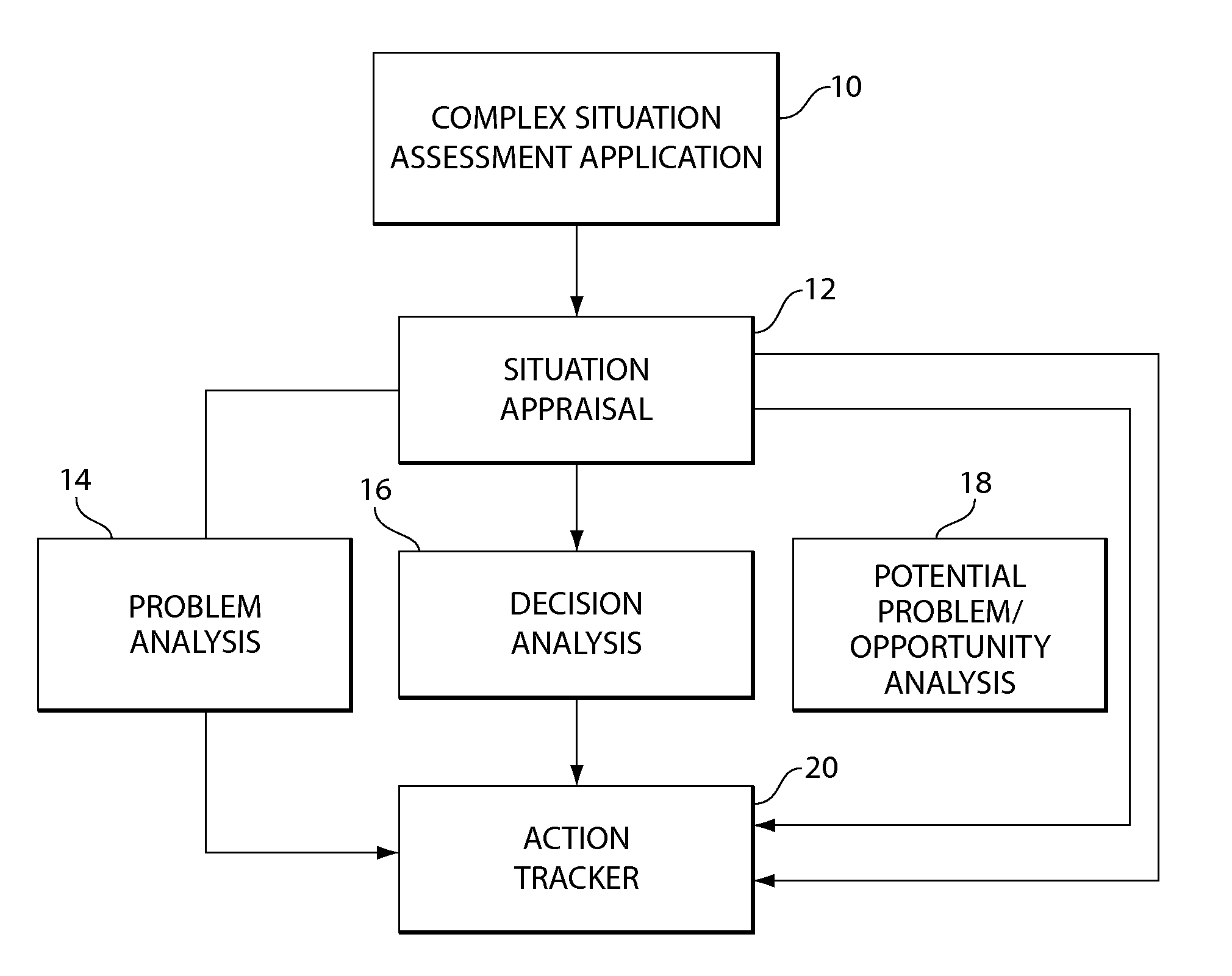

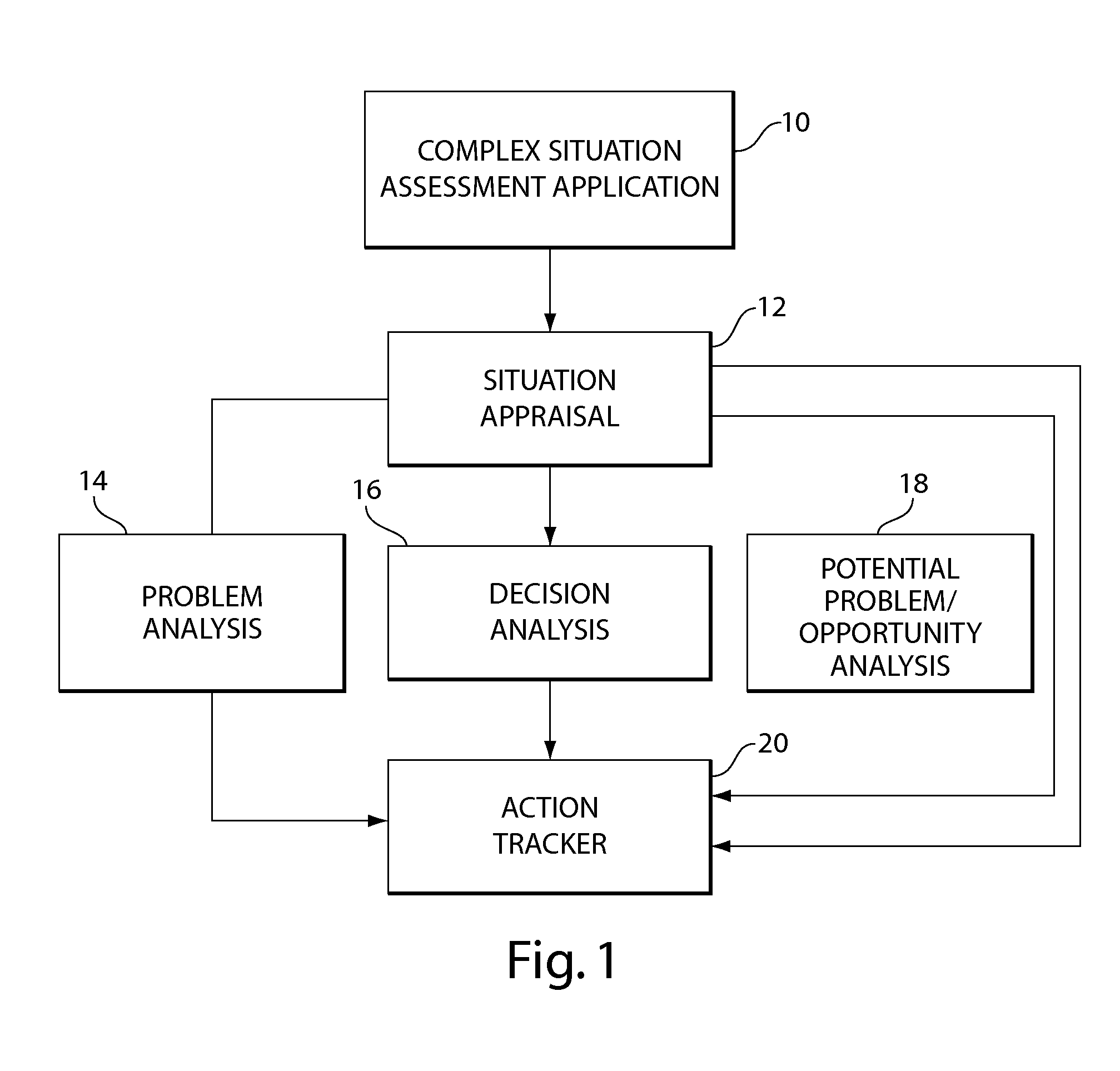

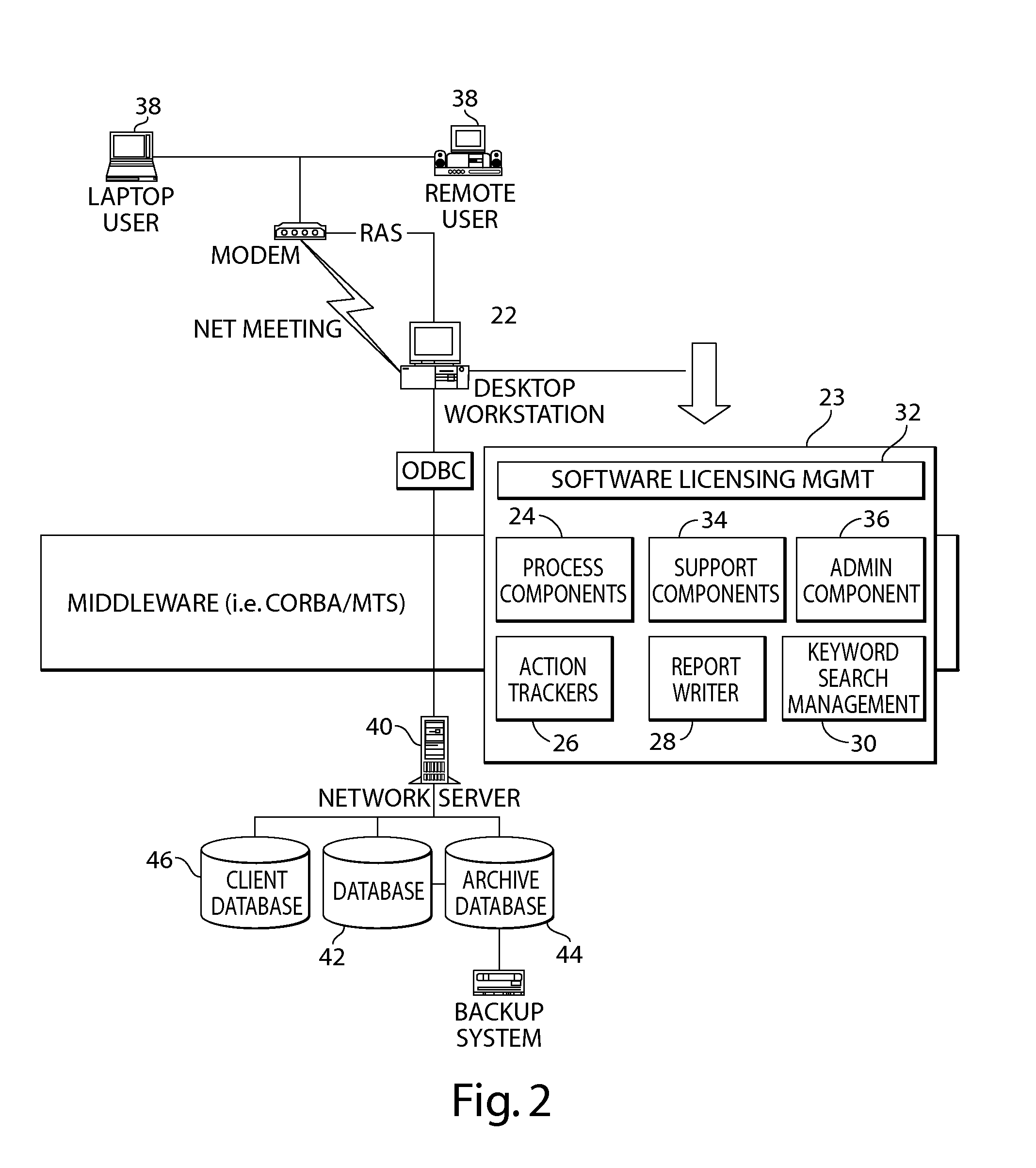

Method and apparatus for problem solving, decision making and storing, analyzing, and retrieving enterprisewide knowledge and conclusive data

InactiveUS7096188B1Preserving enterprisewide knowledgePreserving expertiseResourcesSpecific program execution arrangementsGraphical user interfaceBusiness enterprise

A computer software application, graphical user interface, and method for entering information concerning a complex business situation, refining such information in a stepwise manner through the interface, generating a list of effective actions for addressing such a business situation, and storing such information in a knowledge base adapted for future query and reporting use of such a complex business situations is provided.

Owner:WELLS FARGO BUSINESS CREDEIT INC

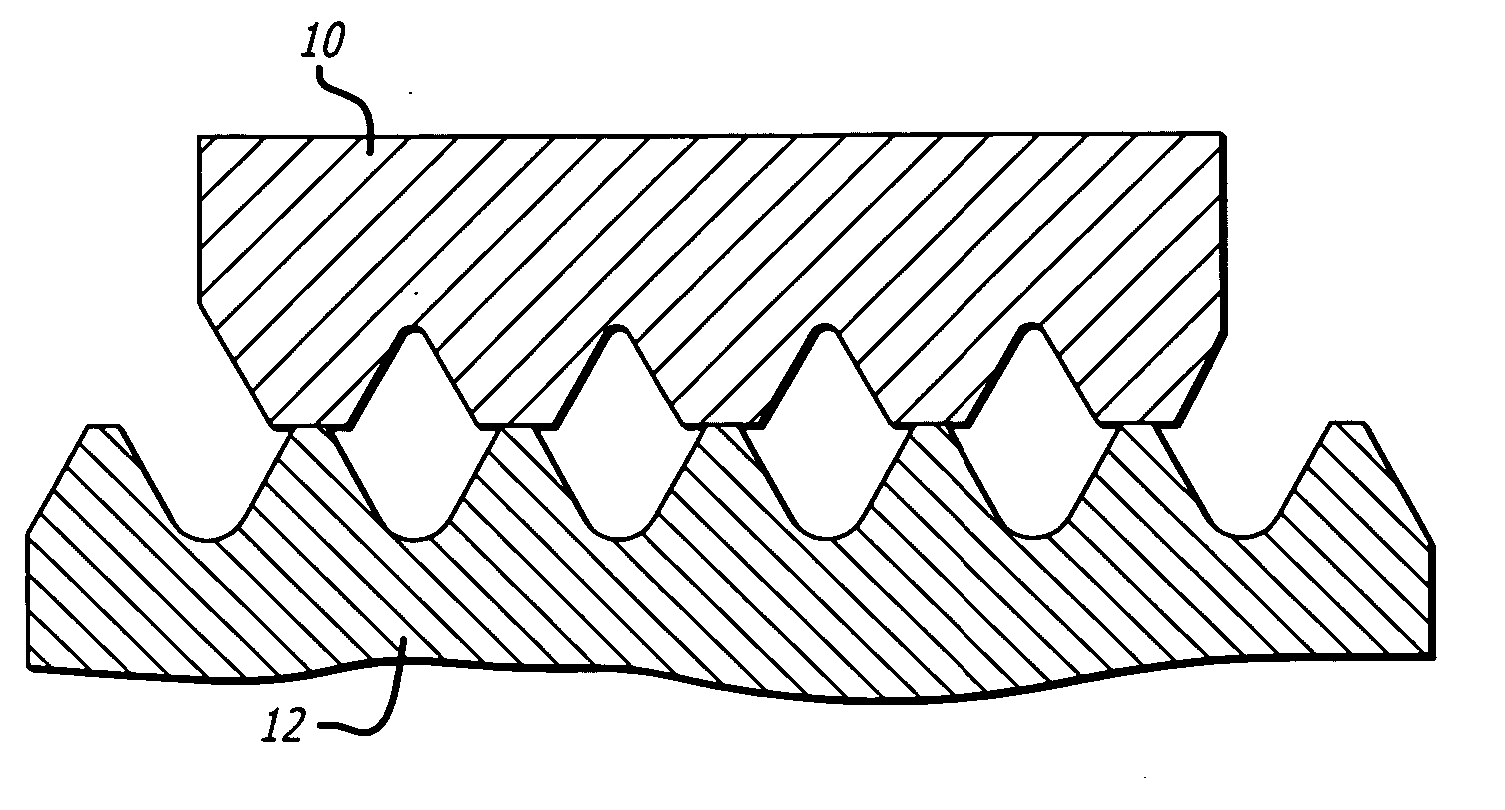

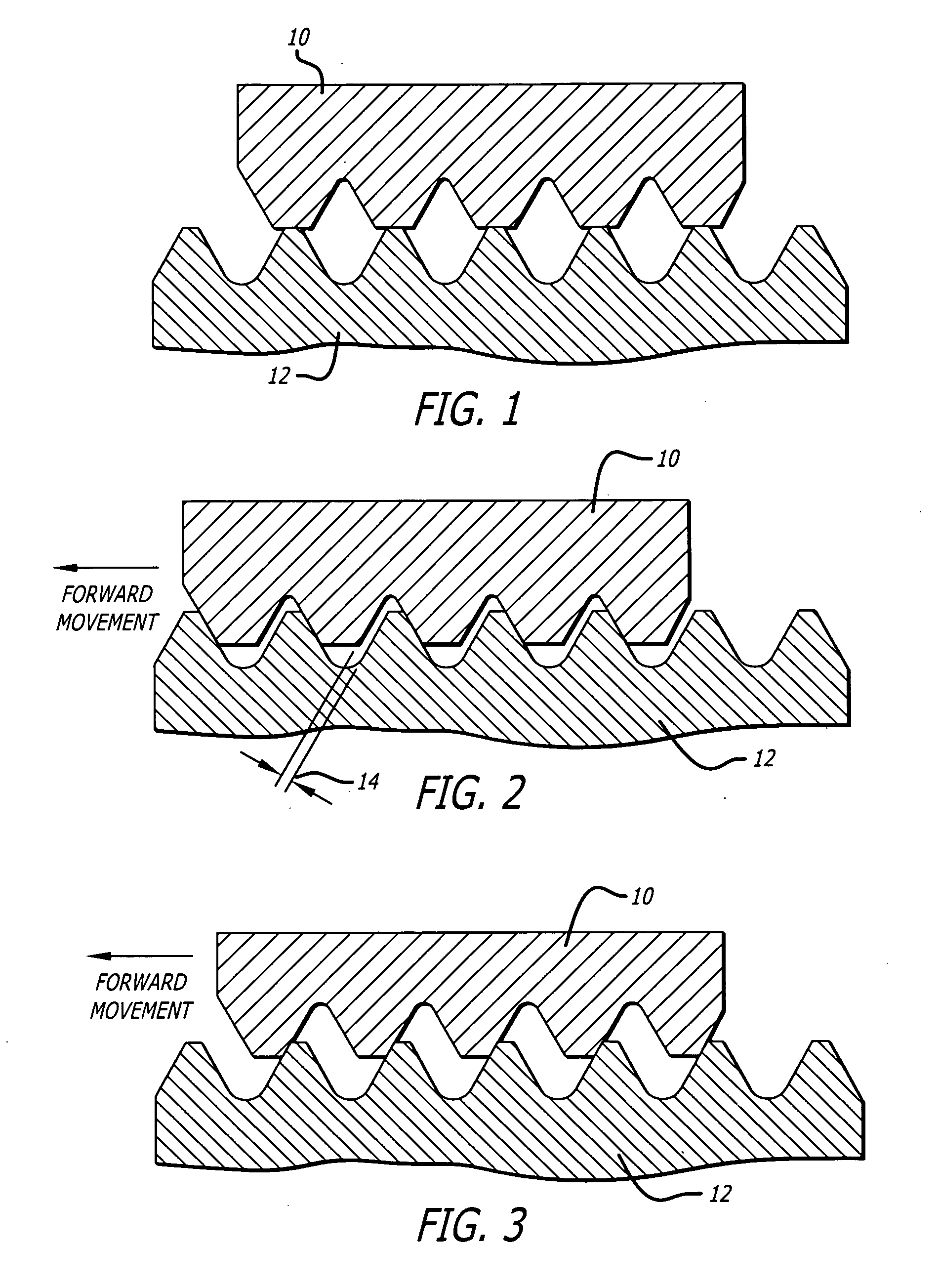

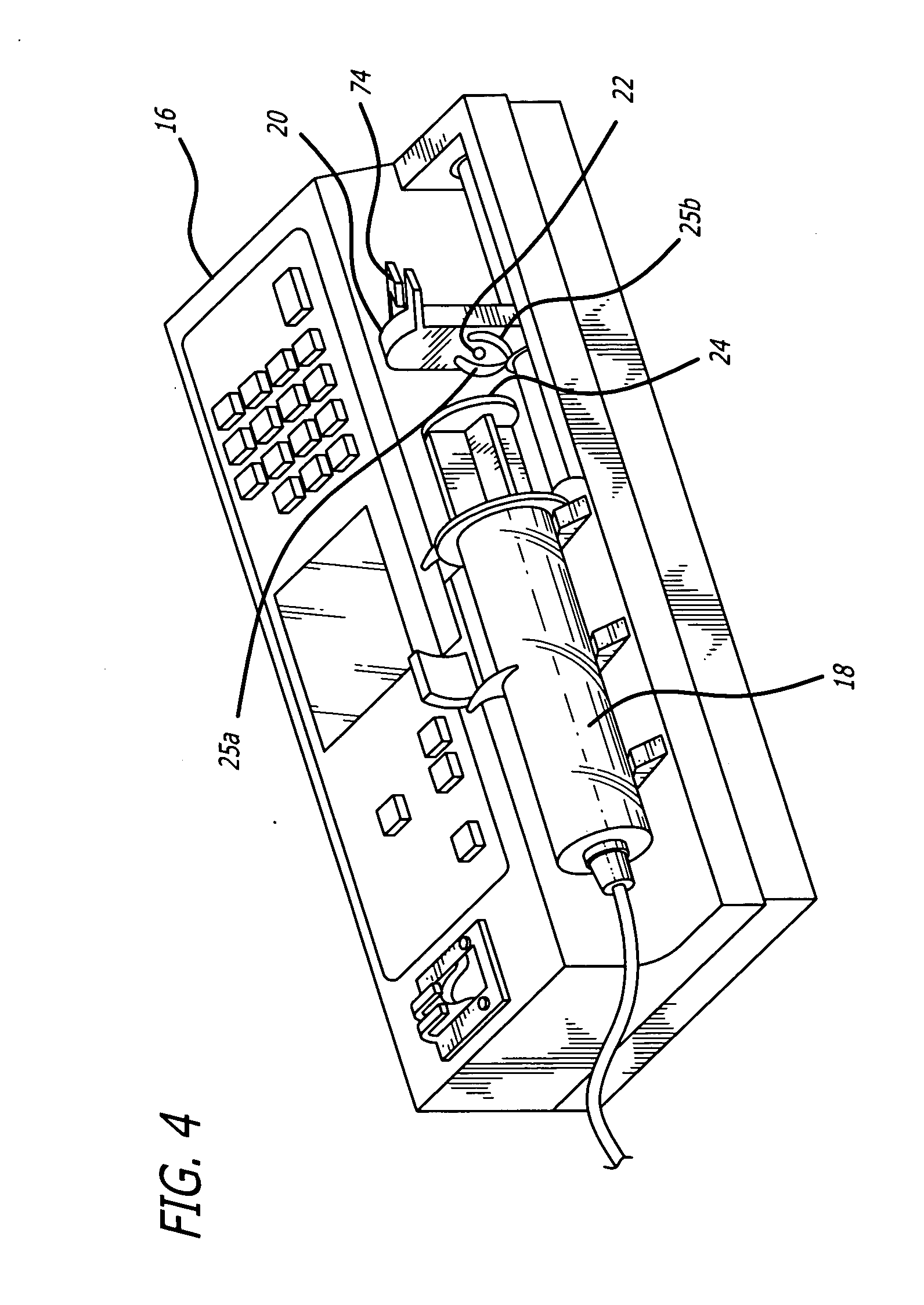

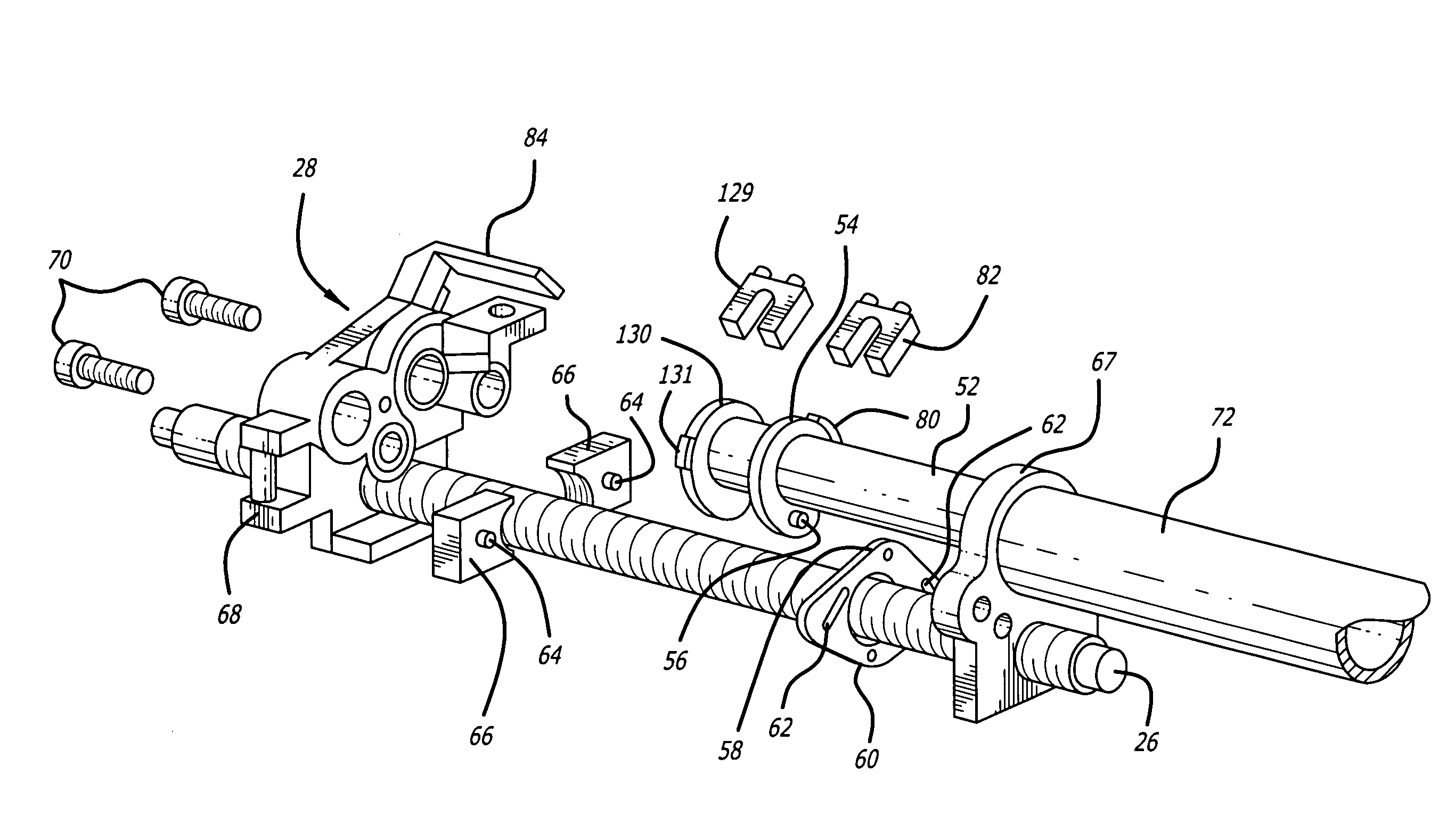

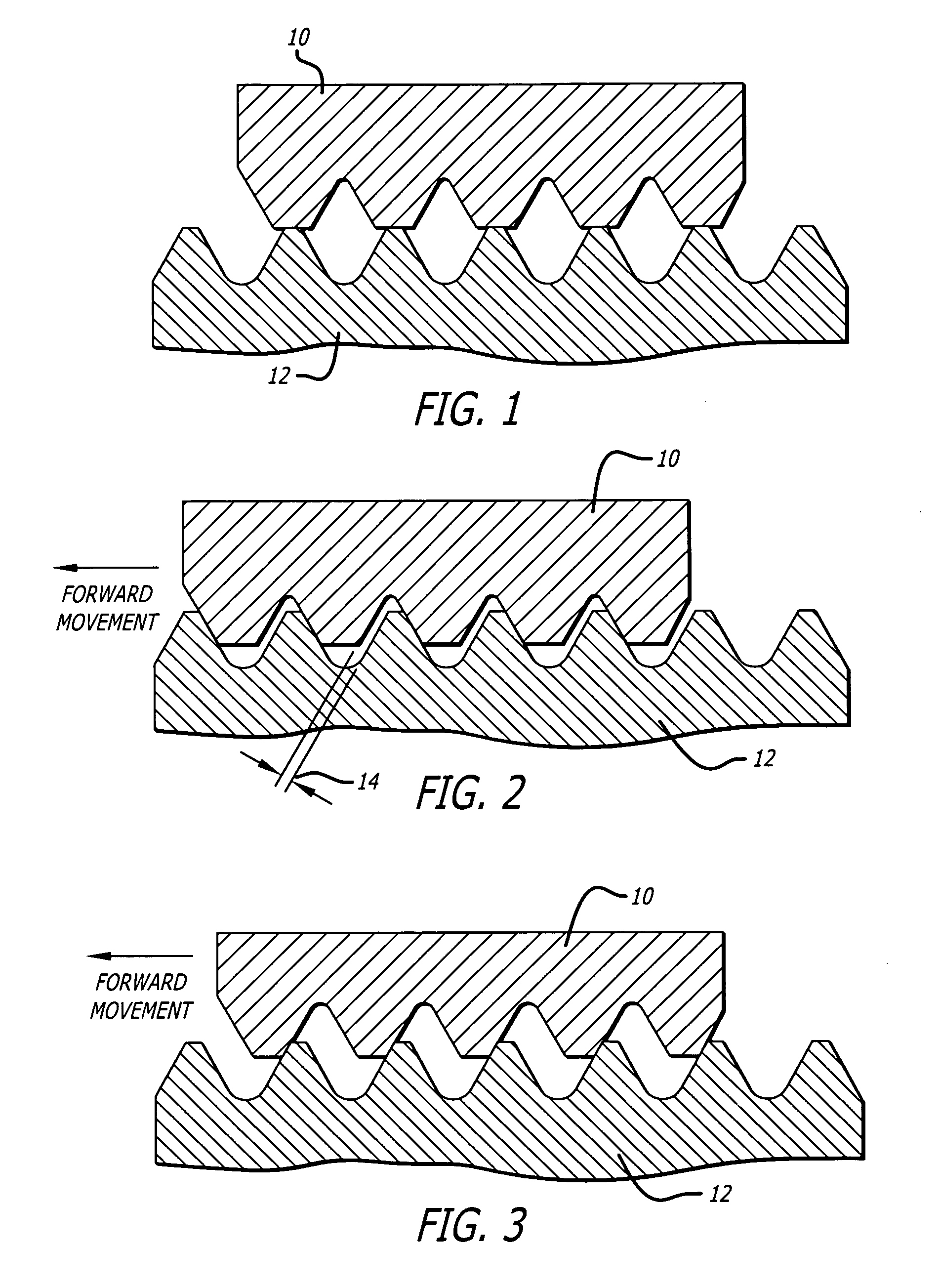

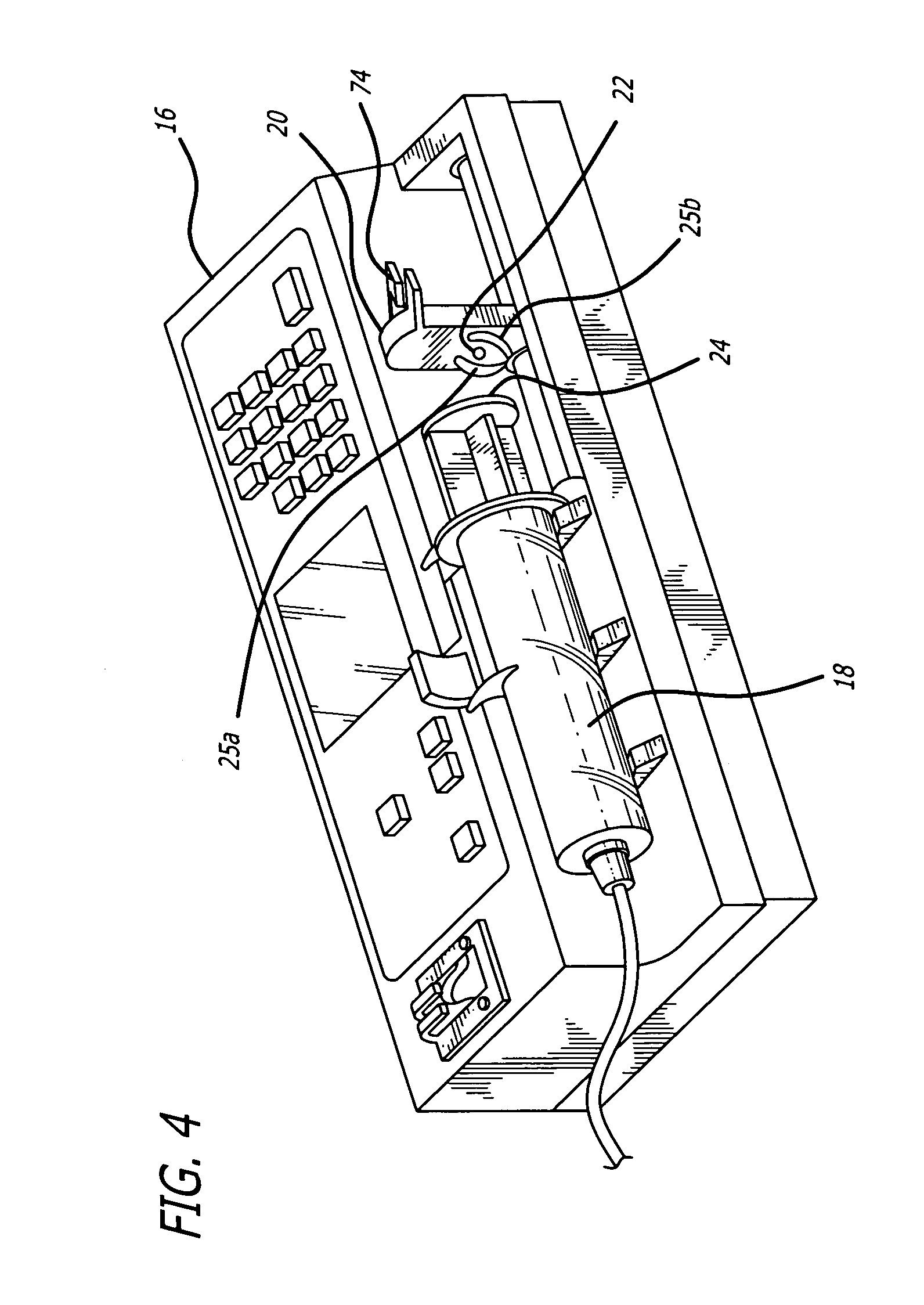

Dynamic lead screw thread engagement system and method

ActiveUS20070074596A1Precise and accurate controlReduce the possibilityPrecision positioning equipmentPortable liftingLinear motionConversion factor

A system and method for automatically aligning the threads of a lead screw with the threads of a screw drive mechanism, the screw drive mechanism operating to translate the rotational motion of the lead screw into linear motion to expel the contents of a mounted syringe. The system comprises a driver position sensor for determining the position of the screw drive mechanism along the lead screw and a processor for receiving position signals from the driver position sensor, for determining a requisite rotation of the lead screw to ensure alignment of the two sets of threads, and for effectuating the requisite rotation of the lead screw to achieve that alignment. An automatic calibration routine is included that checks for variances in calibration of the system and if found, updates a conversion factor to restore accuracy. Various sensors are used to monitor the operation of components.

Owner:CAREFUSION 303 INC

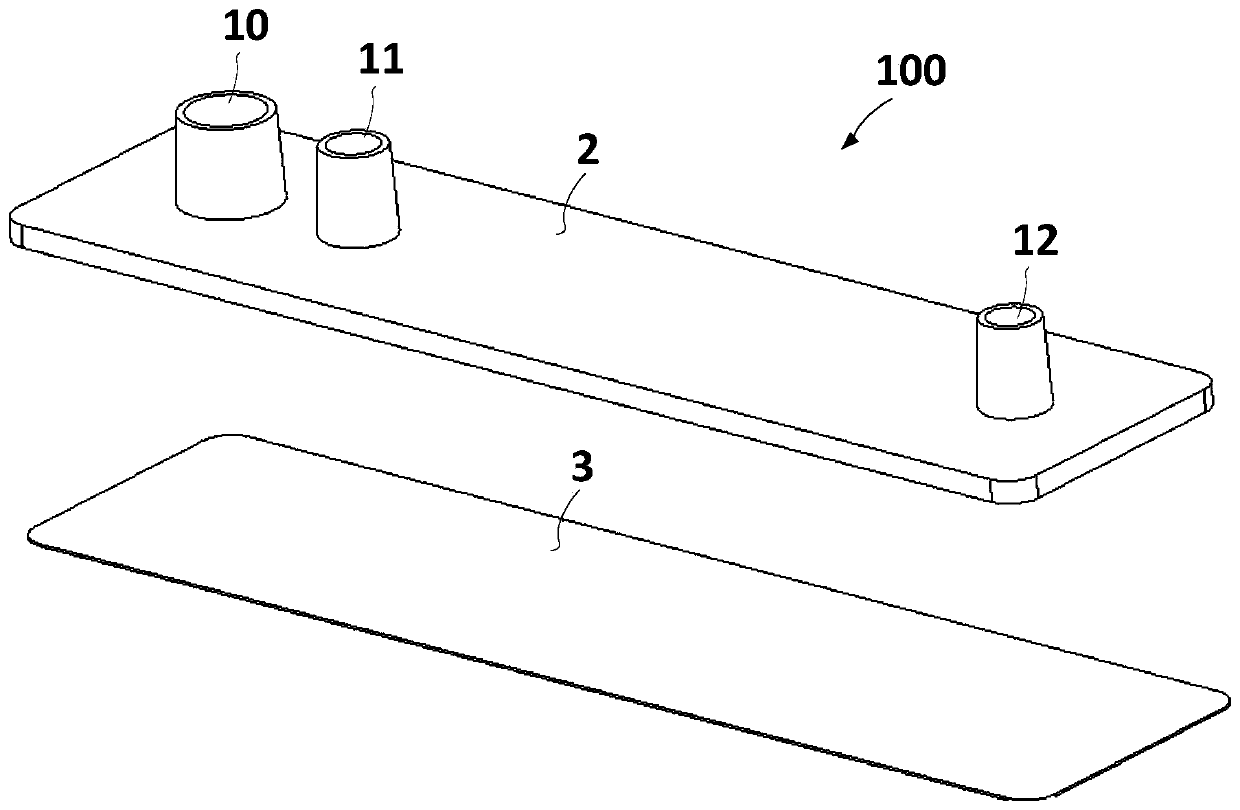

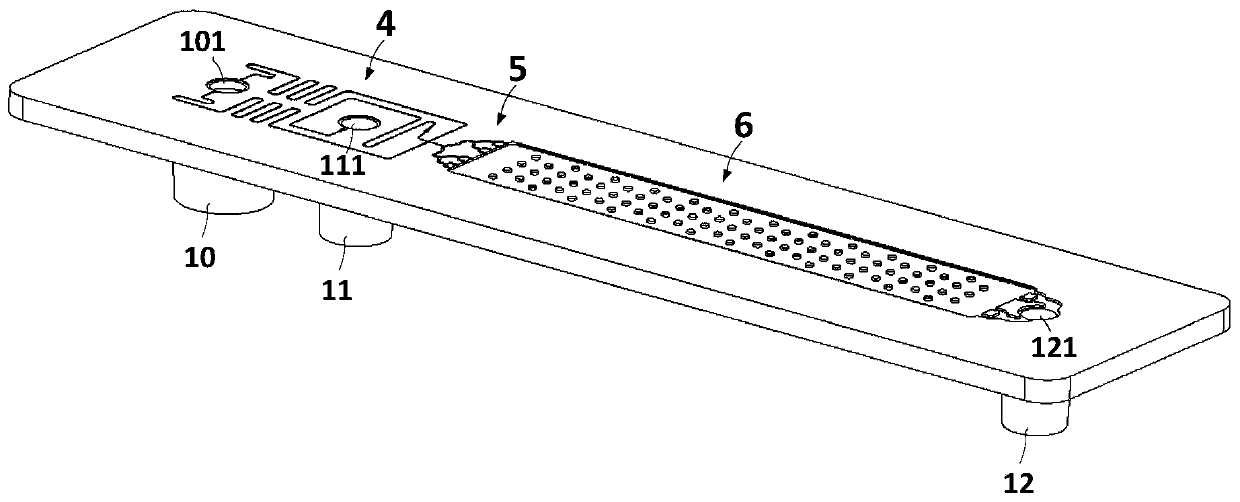

Integrated droplet microfluidic chip structure, preparation method and microfluidic chip assembly

PendingCN109825426AHighly integratedHigh degree of automationBioreactor/fermenter combinationsBiological substance pretreatmentsPositive pressureFluorescence

The invention provides an integrated droplet microfluidic chip structure. All functional modules of droplet generation, amplification and detection are integrated on the same microfluidic chip to achieve the whole enclosed process from the droplet generation to fluorescence detection. The invention also relates to an integrated droplet microfluidic chip structure preparation method and a microfluidic chip assembly. The structure is compatible with the positive pressure or negative pressure drive mode, the pressure response time is short, the rapid droplet generation can be achieved, and the sample preparation time is greatly reduced. Droplet generation oil is not required to be filled in advance, the operation is simple, and popularization and application in the technical field of digitalPCR are facilitated.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

Dynamic lead screw thread engagement system and method

ActiveUS7543516B2Reduce the likelihood of occurrencePrecise and accurate controlMedical devicesPortable liftingLinear motionConversion factor

A system and method for automatically aligning the threads of a lead screw with the threads of a screw drive mechanism, the screw drive mechanism operating to translate the rotational motion of the lead screw into linear motion to expel the contents of a mounted syringe. The system comprises a driver position sensor for determining the position of the screw drive mechanism along the lead screw and a processor for receiving position signals from the driver position sensor, for determining a requisite rotation of the lead screw to ensure alignment of the two sets of threads, and for effectuating the requisite rotation of the lead screw to achieve that alignment. An automatic calibration routine is included that checks for variances in calibration of the system and if found, updates a conversion factor to restore accuracy. Various sensors are used to monitor the operation of components.

Owner:CAREFUSION 303 INC

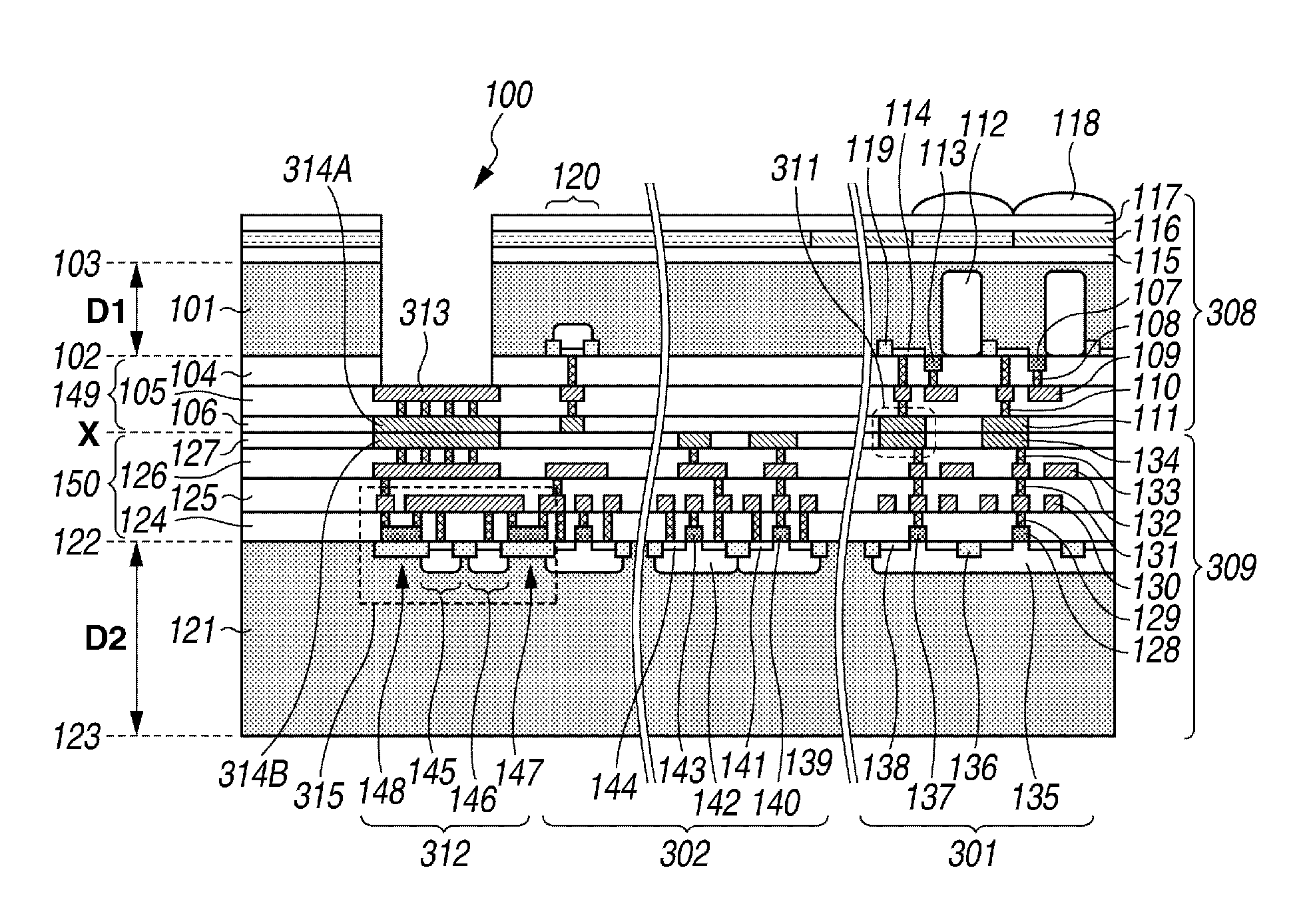

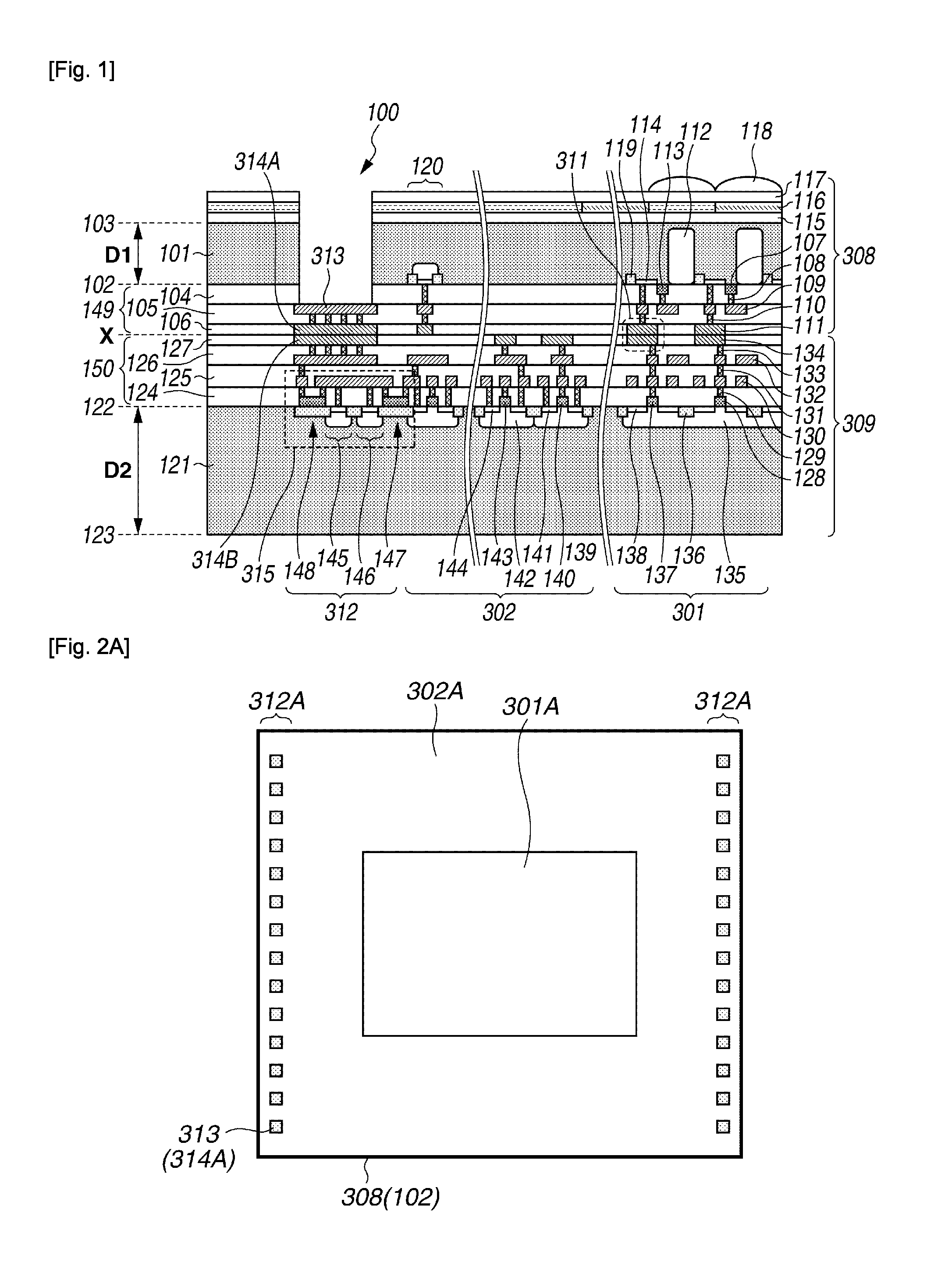

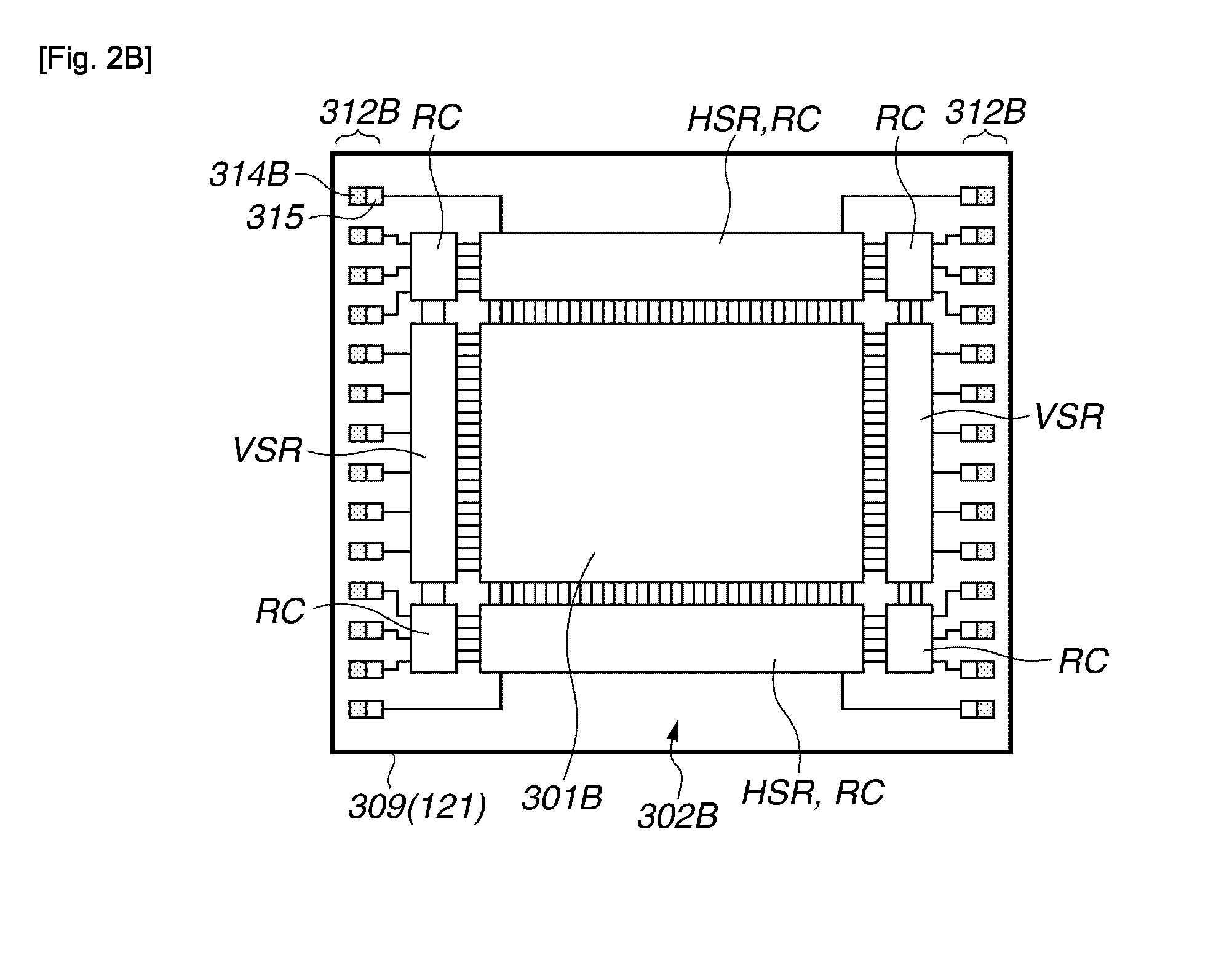

Solid-state imaging device, members for the same, and imaging system

ActiveUS20130099098A1Reduce the likelihood of occurrenceAvoid it happening againSemiconductor/solid-state device detailsSolid-state devicesEngineeringPhotoelectric conversion

The present invention provides a solid-state imaging device including a pad capable of reducing inferior connection with an external terminal. The solid-state imaging device includes a first substrate provided, on its front face, with photoelectric conversion elements, a first wiring structure, a second substrate provided, on its front face, with at least a part of peripheral circuits, and a second wiring structure. The first substrate, the first wiring structure, the second wiring structure, and the second substrate are provided in this order. The first wiring structure includes a wiring layer including wirings made mainly of copper. The second wiring structure includes a wiring layer including wirings made mainly of copper. Wirings made mainly of copper in the wiring layer in the first wiring structure are bonded with wirings made mainly of copper in the wiring layer in the second wiring structure. The solid-state imaging device includes a pad formed of a conductive element made mainly of aluminum.

Owner:CANON KK

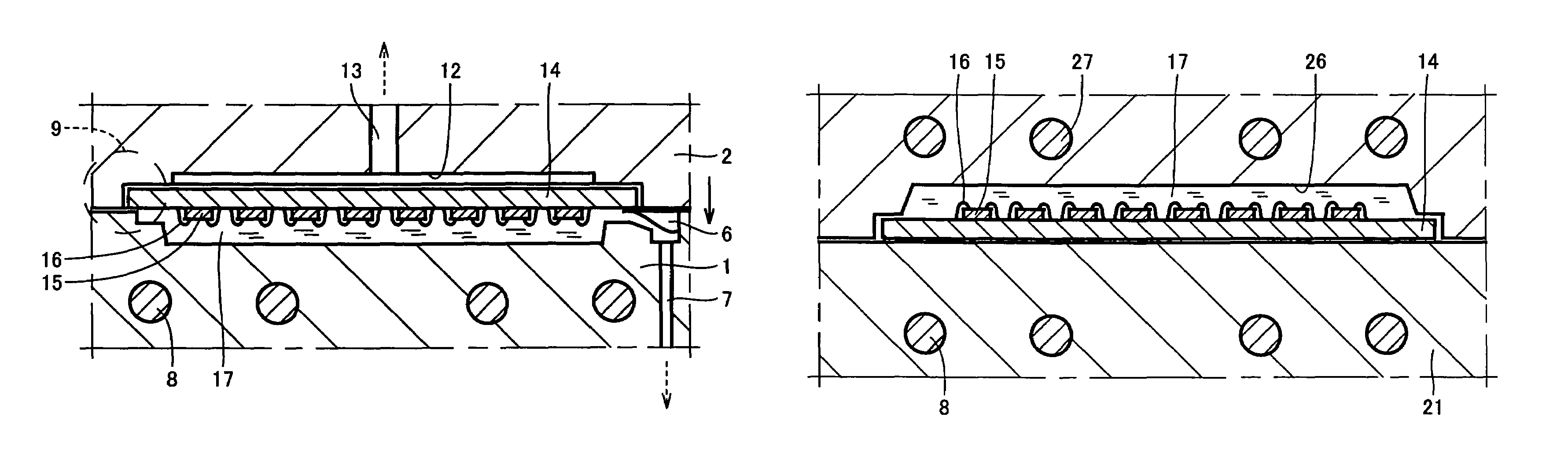

Method of resin encapsulation, apparatus for resin encapsulation, method of manufacturing semiconductor device, semiconductor device and resin material

ActiveUS7056770B2Reduce the likelihood of occurrenceEasy to useSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device fabrication

Owner:SOCIONEXT INC +1

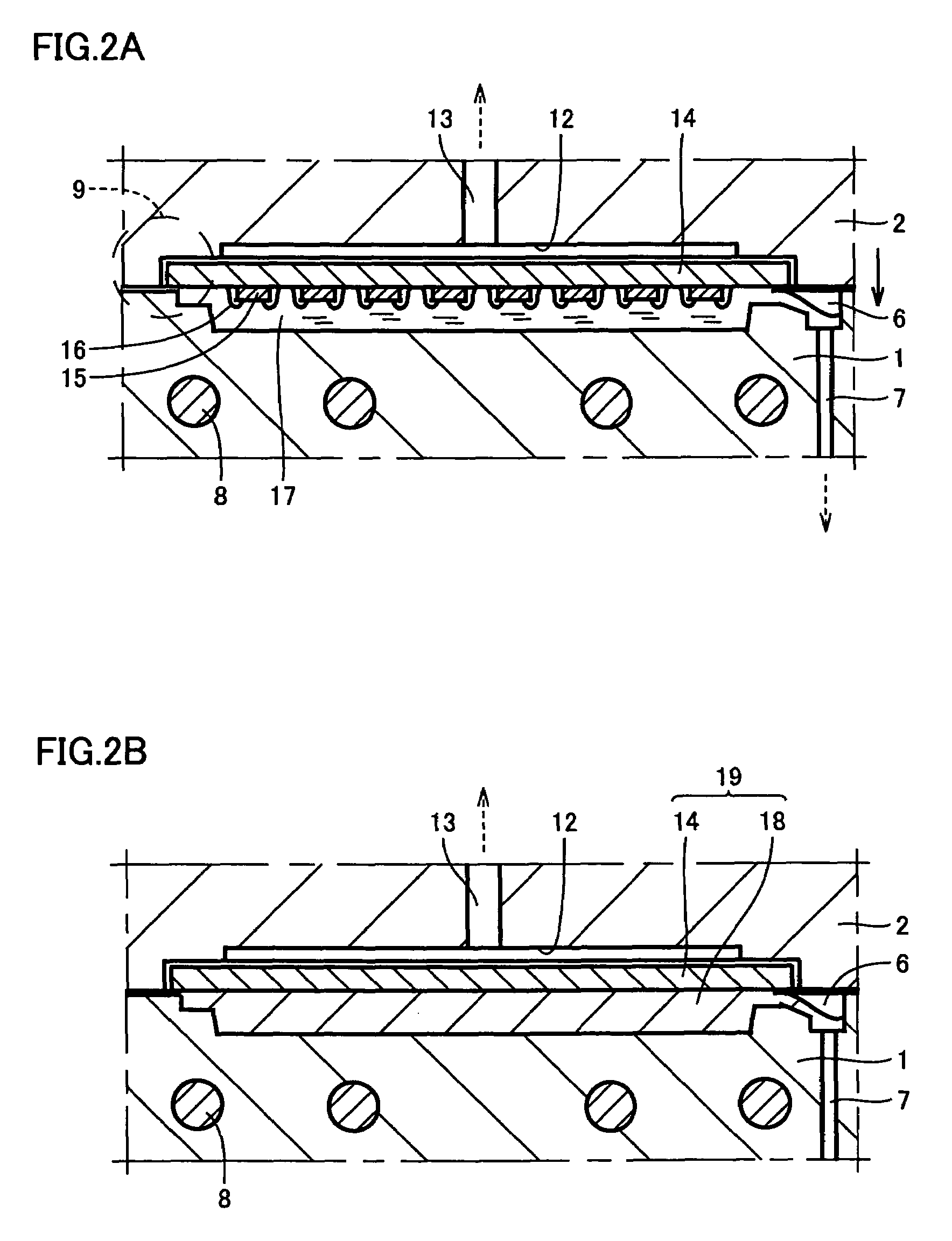

Method and apparatus for detection and treatment of autonomic system imbalance

InactiveUS20090318983A1Preventing heart rhythm disturbanceReduce likelihood of occurrenceElectrocardiographyMedical devicesCardiologyElectrical impulse

Owner:ARMOUNDAS ANTONIS A +1

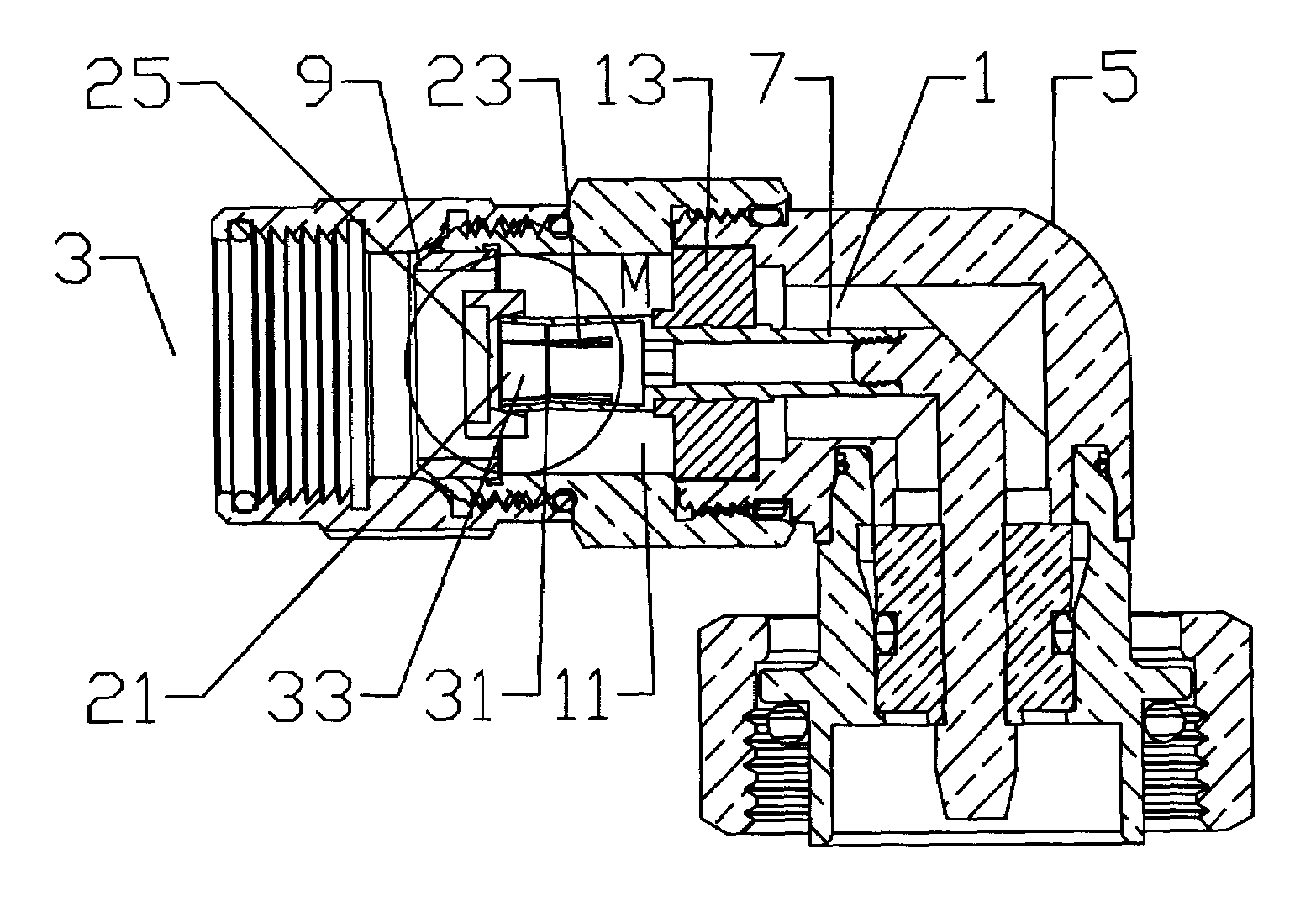

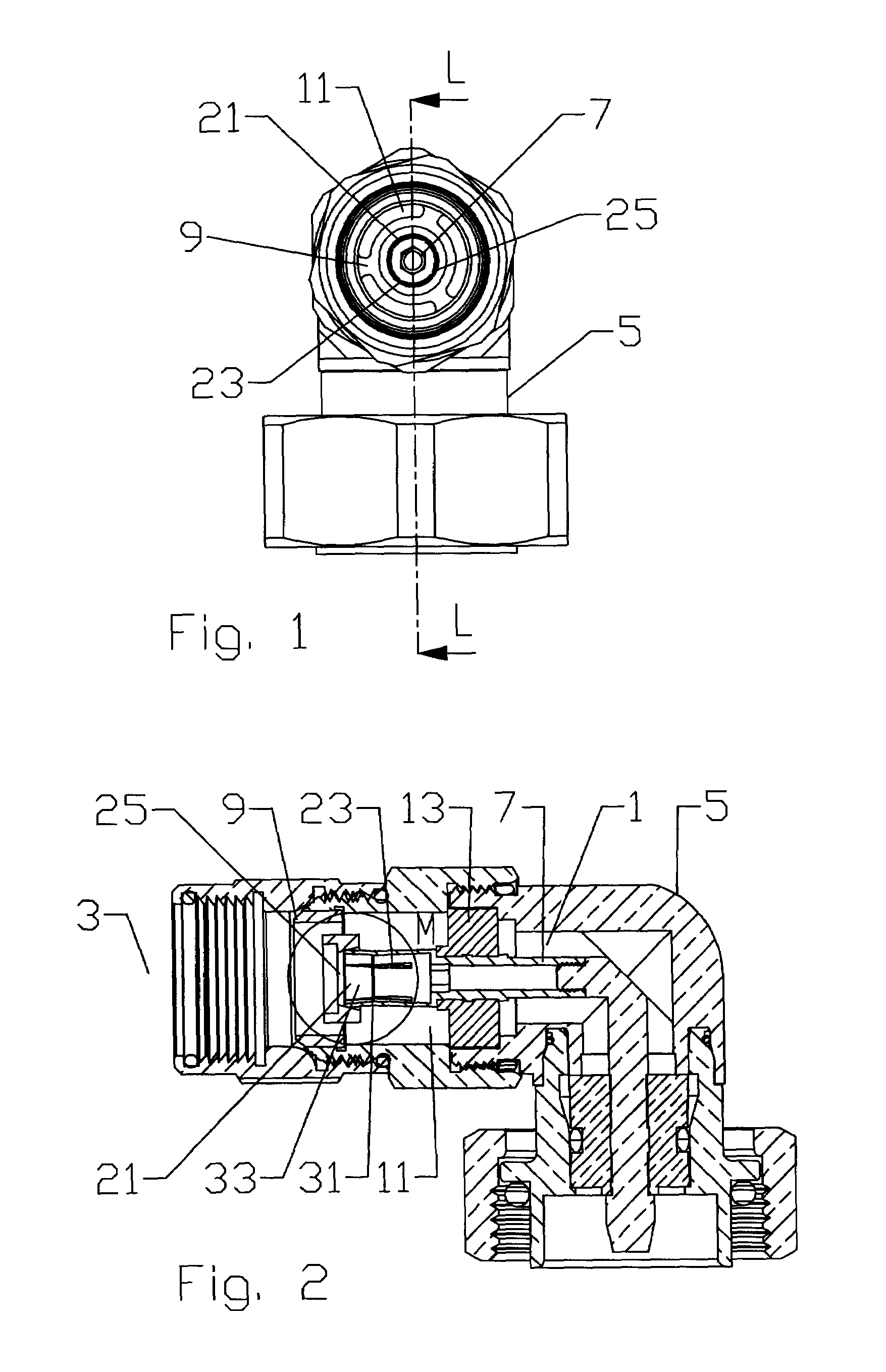

Coaxial connector inner contact arrangement

InactiveUS7621778B1Reduce the likelihood of occurrenceSimple requirementsElectrically conductive connectionsTwo pole connectionsCoaxial cableMechanical engineering

An inner contact arrangement for a coaxial cable connector. The inner contact supported coaxially within a connector bore of the connector by a support insulator. A plurality of tines extending from a central portion of the inner contact, the tines may be angled outward from a longitudinal axis of the inner contact and or provided with a shoulder. A bias insulator with a ramp bore, the bias insulator retained within the connector bore and contacting the cable end of the tines.

Owner:COMMSCOPE INC

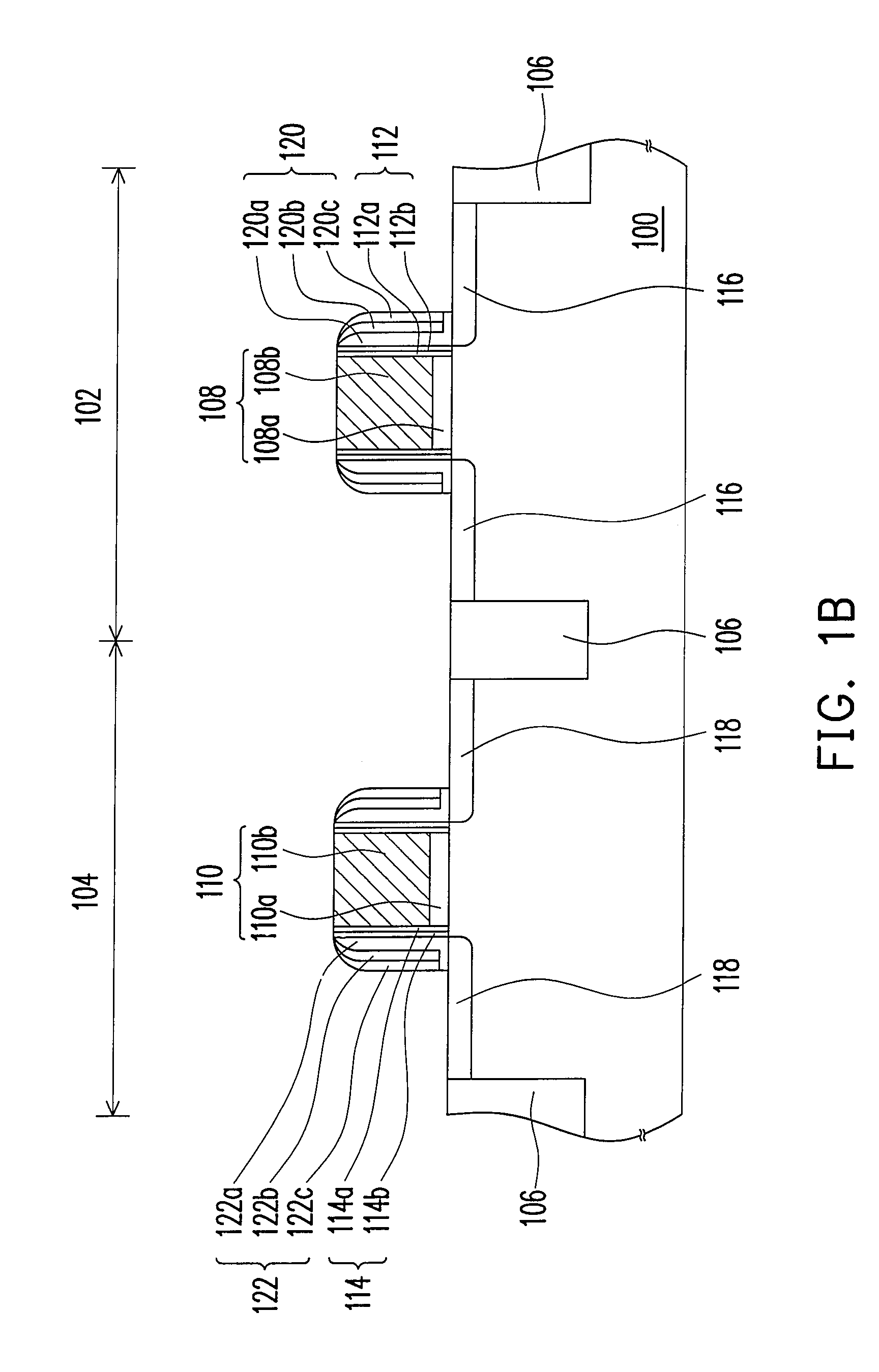

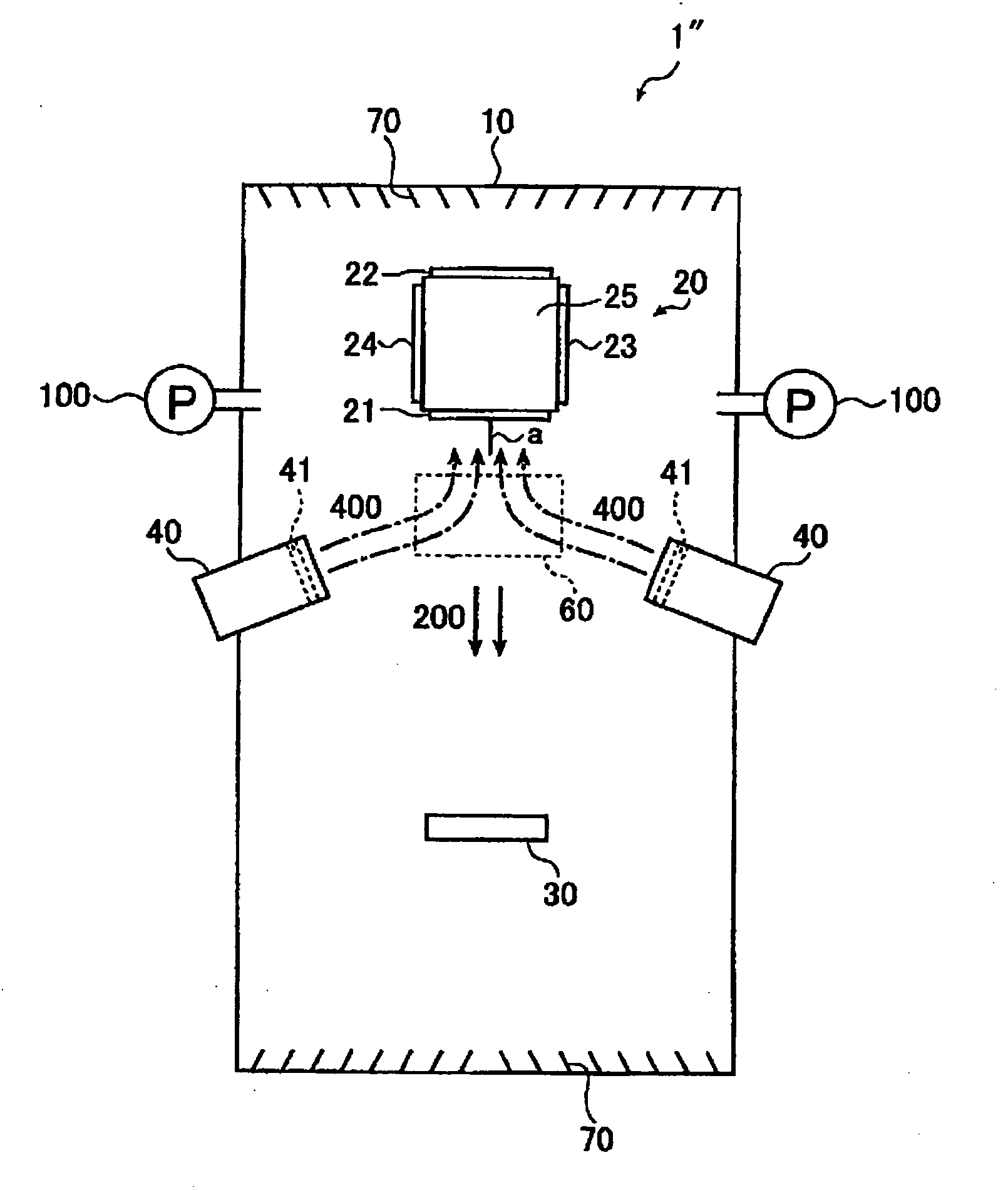

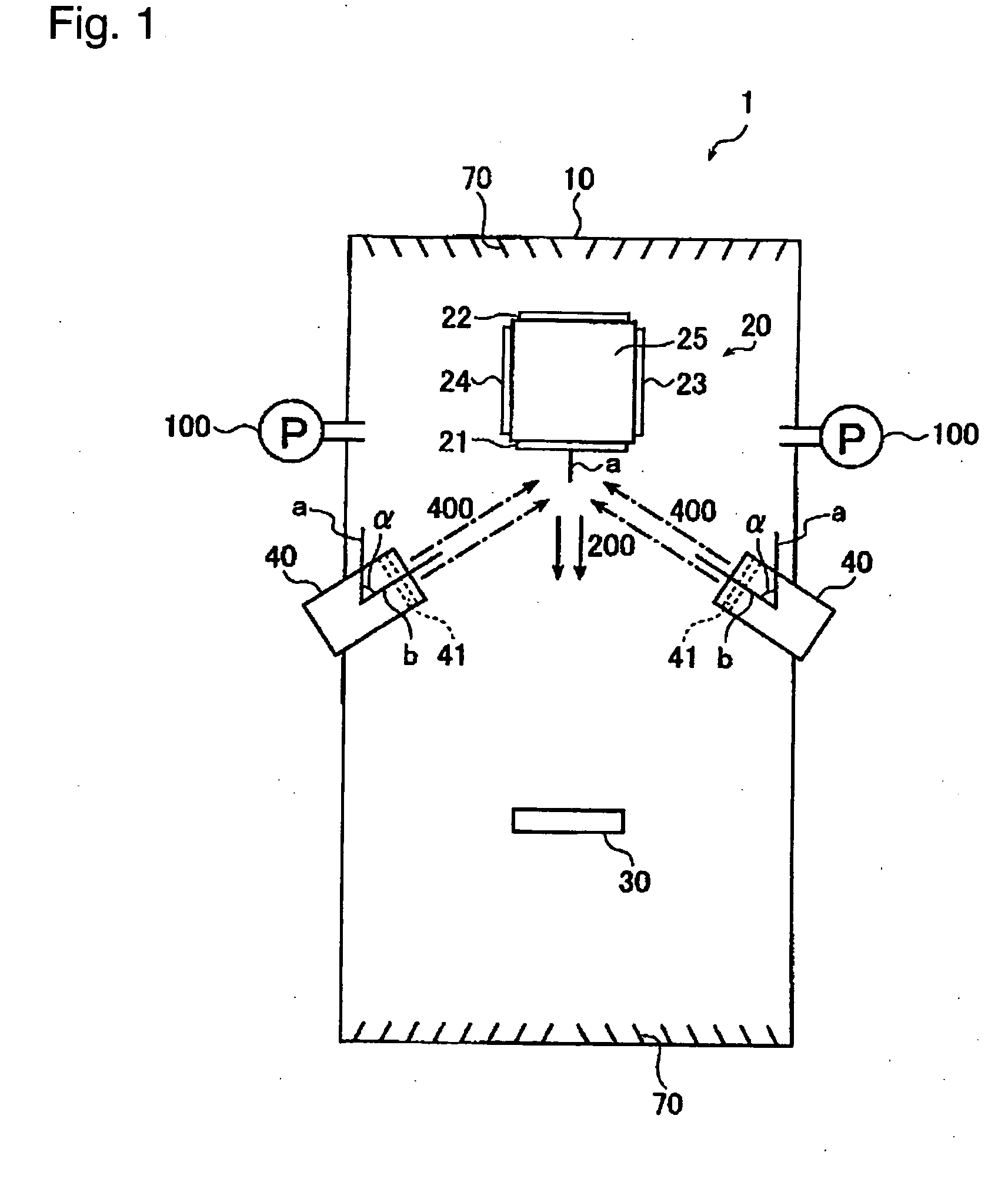

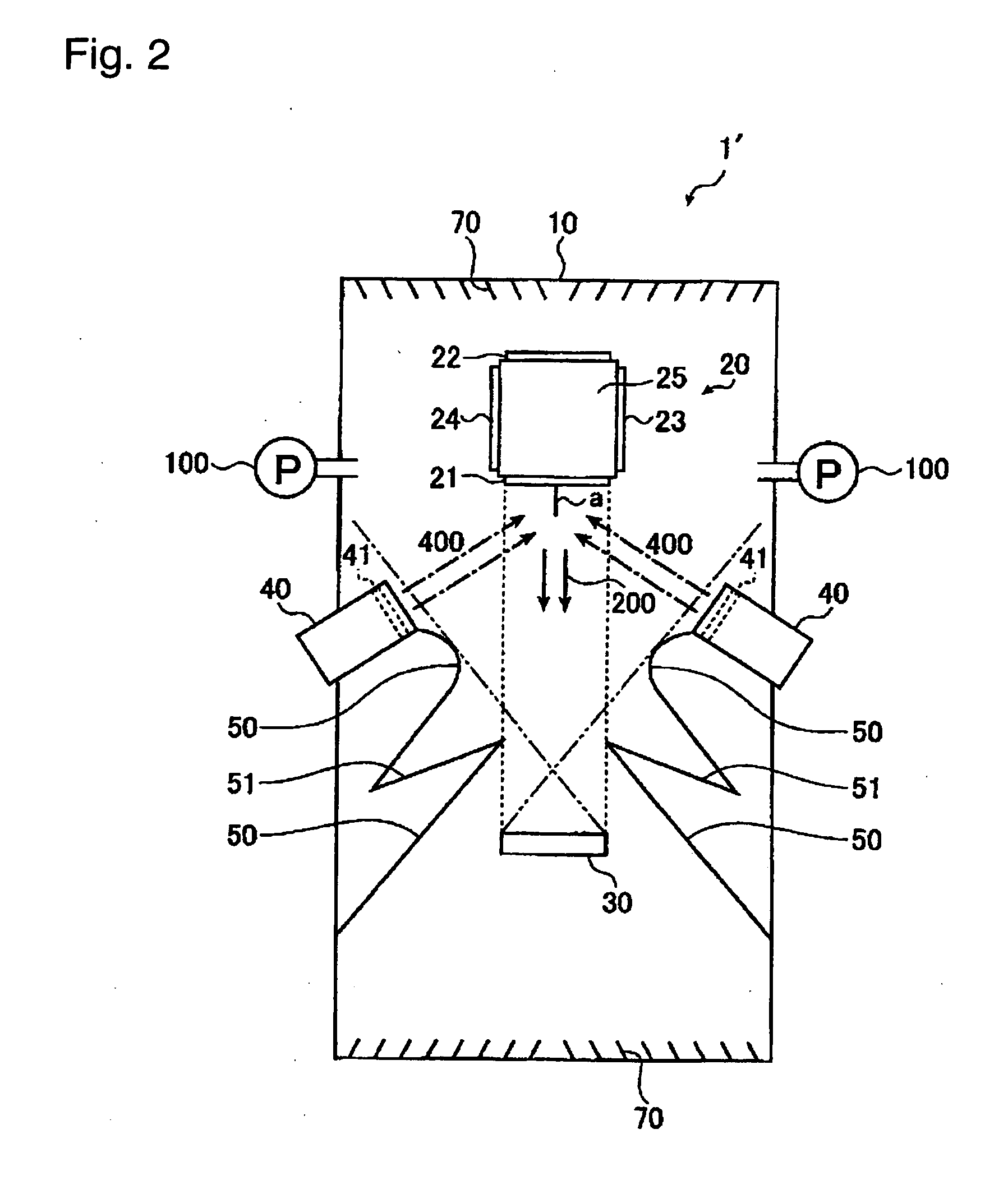

Ion beam sputtering apparatus and film deposition method for a multilayer for a reflective-type mask blank for EUV lithography

InactiveUS20070087578A1Reduce the likelihood of occurrenceReduce the possibilityNanoinformaticsVacuum evaporation coatingLithographic artistIon beam

A film deposition method for a multilayer for a EUV mask blank by which a defect caused by the mixing of a particle in the layer during film formation can be prevented and an ion beam sputtering apparatus suitable for the method are presented. A film deposition method for forming a multilayer for a reflective-type mask blank for EUV lithography on a film deposition substrate by using an ion beam sputtering method, the film deposition method being characterized in that a sputtering target and a film deposition substrate are disposed at opposed positions with a predetermined space, and ion beams are injected to the sputtering target from an ion source which is disposed at a position out of the region where particles move linearly from the film deposition substrate toward the sputtering target.

Owner:ASAHI GLASS CO LTD

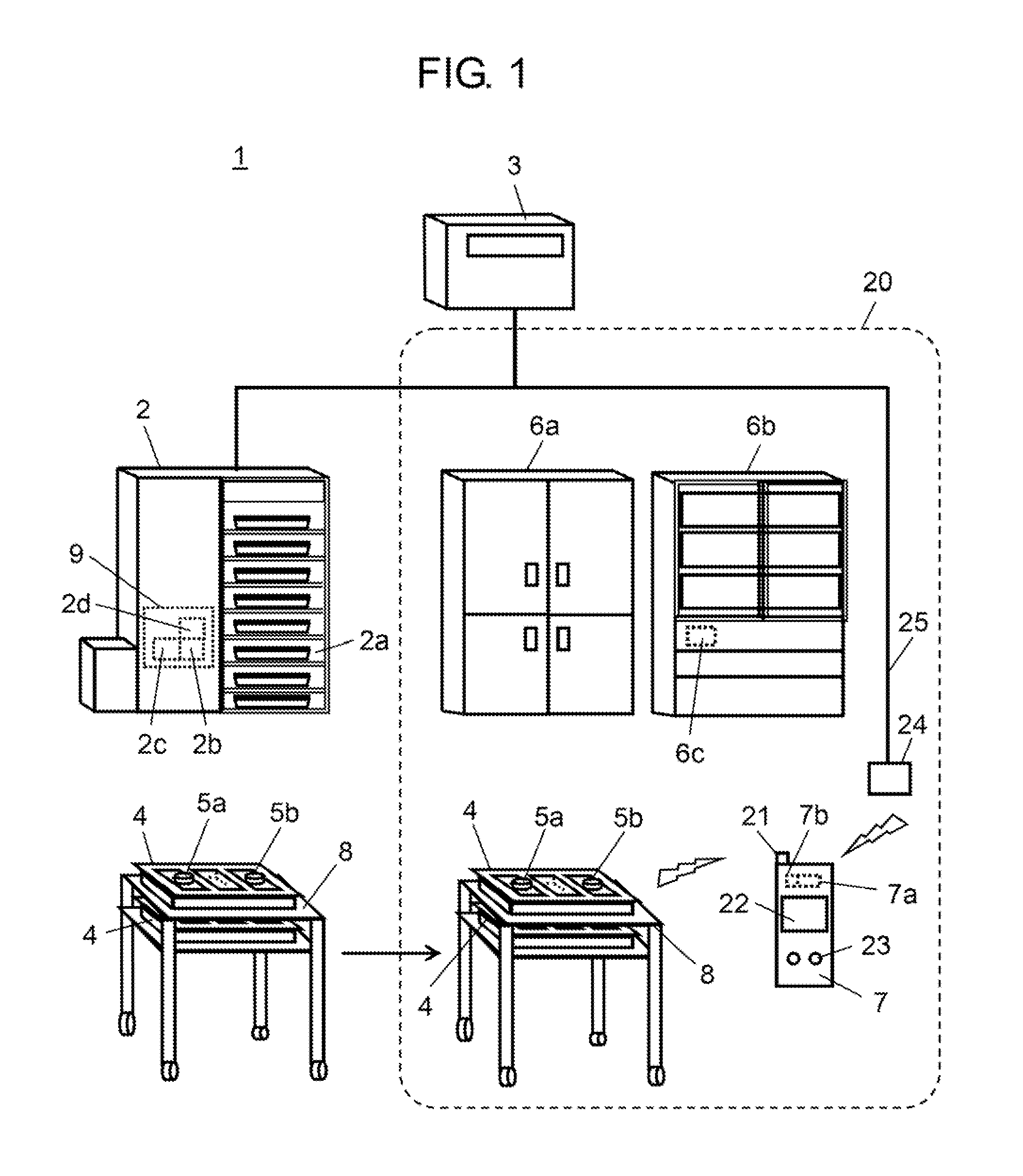

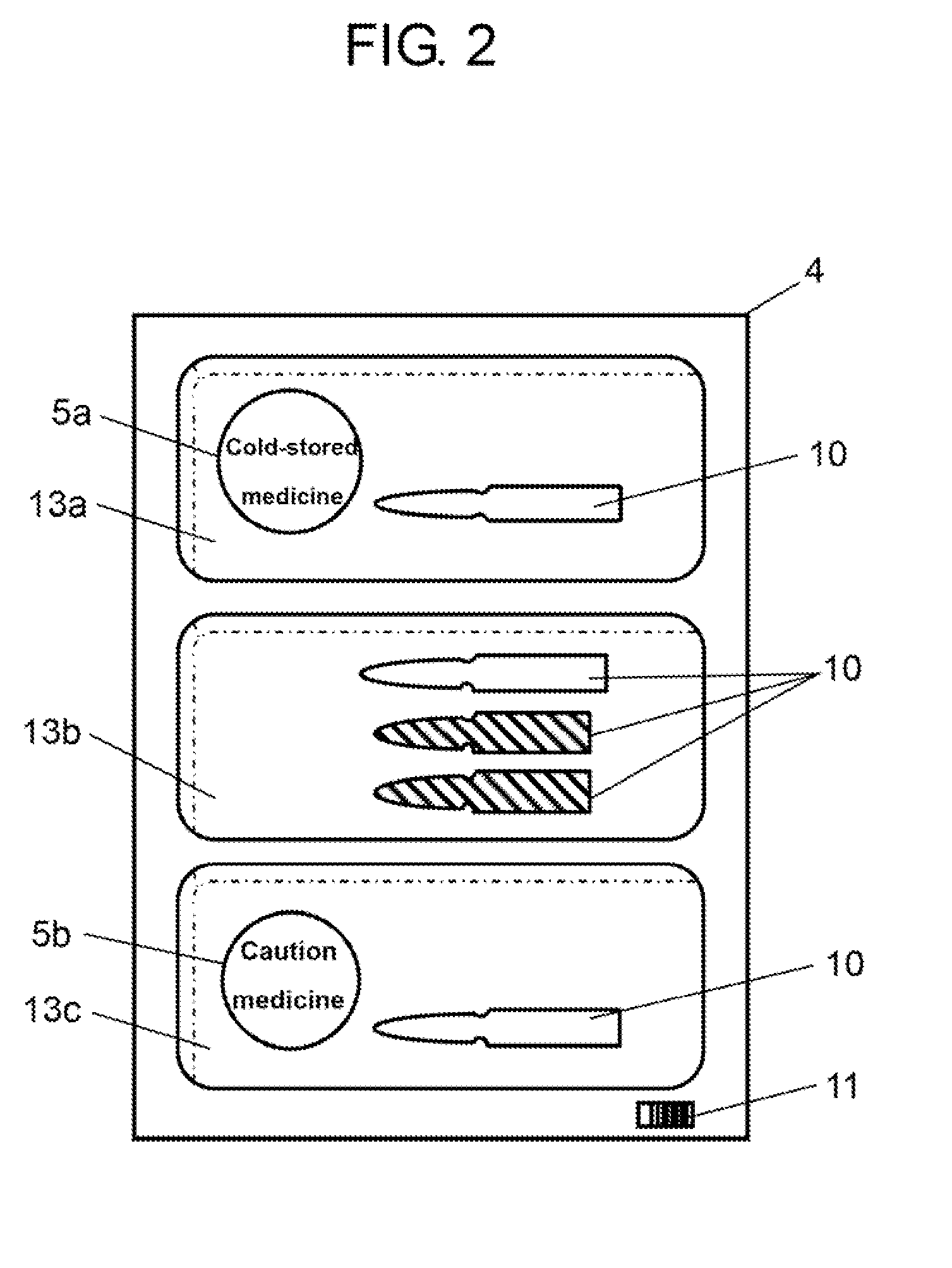

Medicine selection support system, medicine selection support method, medicine dispensing device, and dummy body

InactiveUS20110112682A1Reduce the possibilityReduce the likelihood of occurrenceDigital data processing detailsCoin-freed apparatus detailsSupporting systemPharmacy

A medicine selection support system of the invention includes an automatic dispensing device for dispensing a general medicine and a dummy body for a managed medicine based on the pharmacy information, a management terminal for reading medicine information of the managed medicine from the dummy body, and an exchange support section for supporting exchange between the managed medicine and the dummy body from the medicine information read by the terminal. With the automatic dispensing device, a dummy body corresponding to the managed medicine can be dispensed at the same timing as that of a general medicine.

Owner:PANASONIC CORP

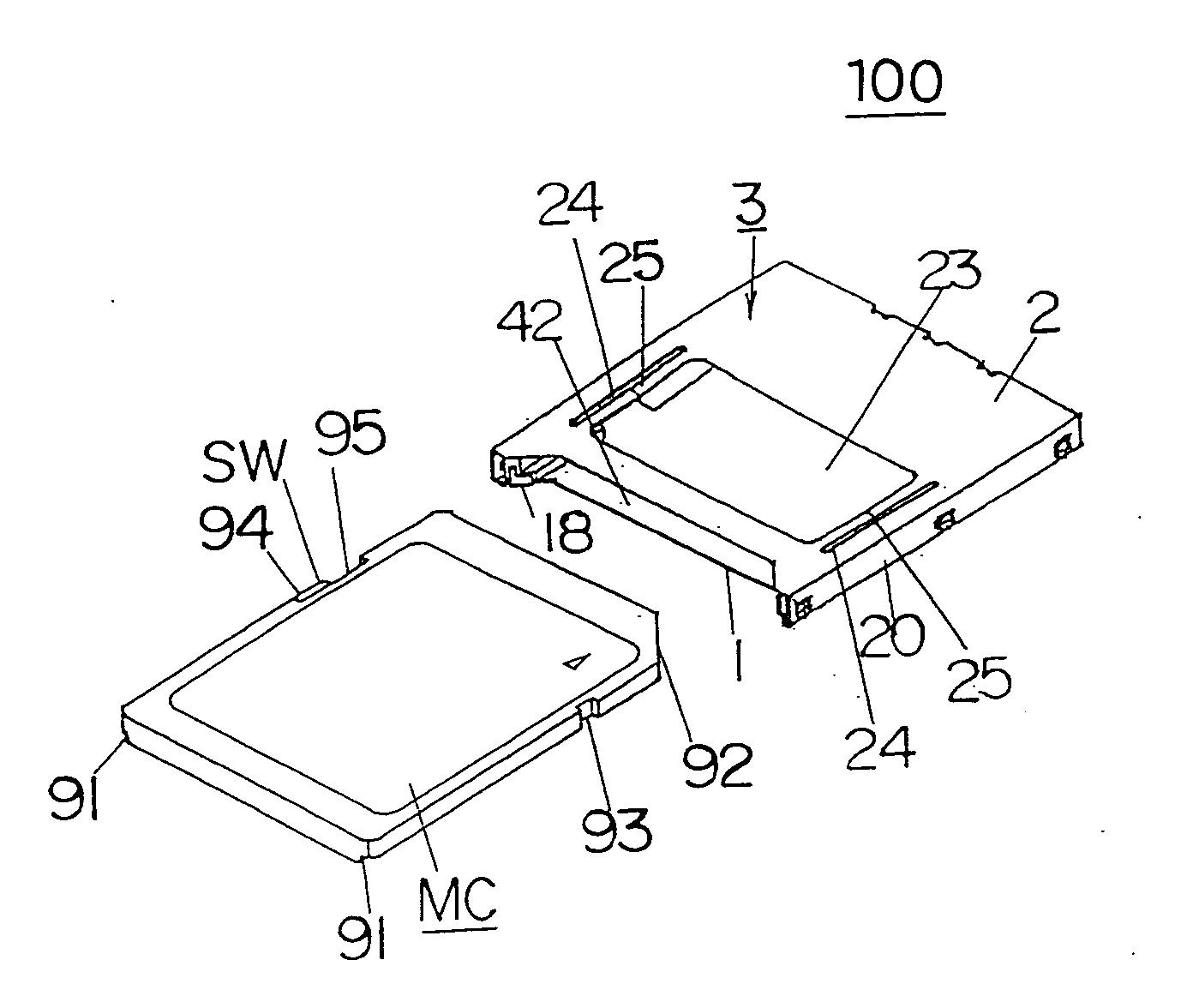

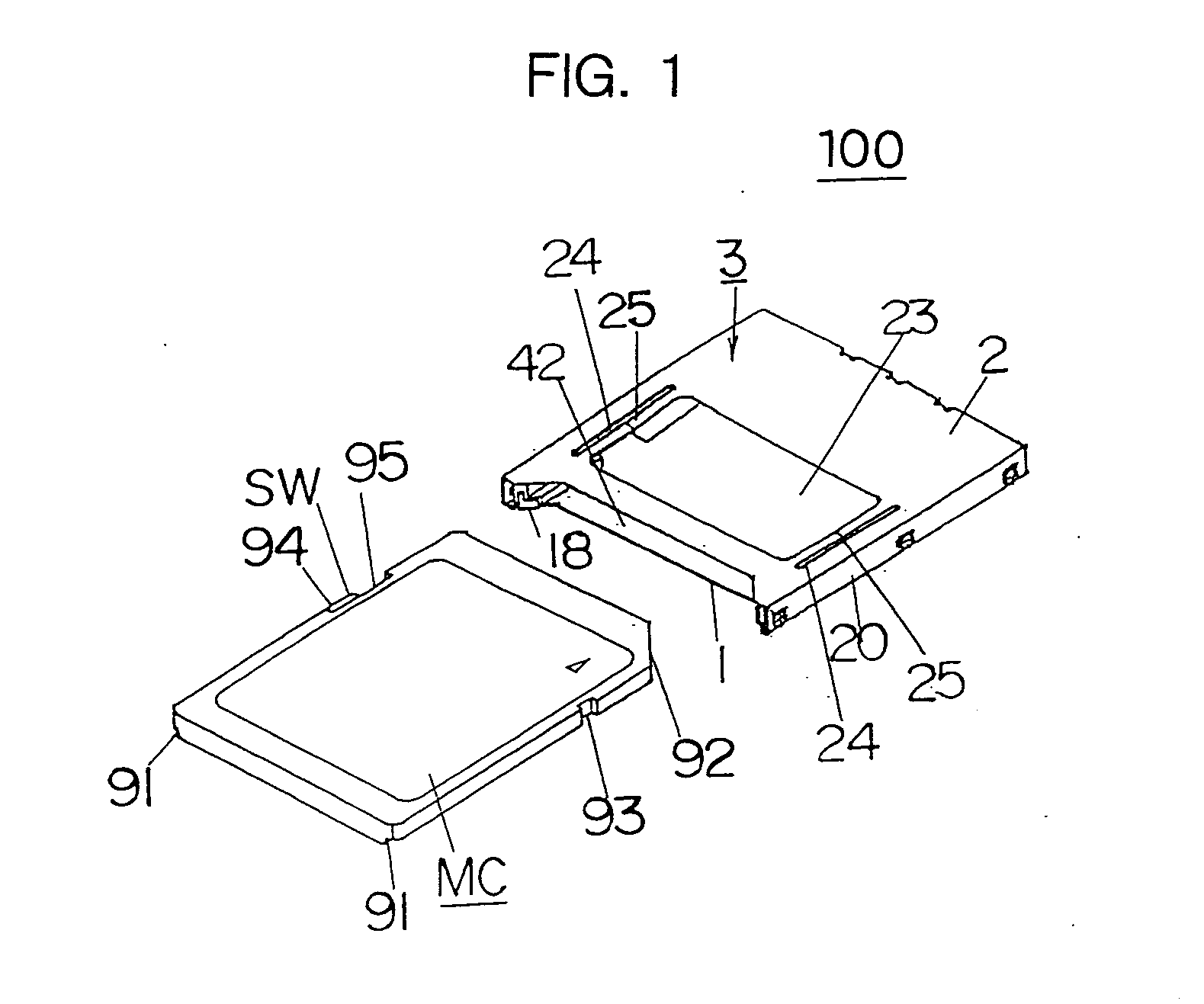

Connector and contact for the connector

InactiveUS20050020137A1Reduce the possibilityShorten the time periodCoupling contact membersCo-operative working arrangementsEngineeringElectric power

In a connector used for recording and reproducing apparatus of a memory card, it is aimed to prevent an instantaneous make break phenomenon, in which a contact portion of a contact and a terminal of a memory card is instantaneously opened and suppliance of electric power to the memory card is instantaneously stopped when an impact is applied to the connector, and a deformation of the contact due to the impact. Three plate spring portions arranged in parallel with each other and three contact portions respectively provided in the vicinities of front ends of the plate spring portions are formed in the vicinity of a front end of the contact. Two plate spring portions among three plate spring portions, for example, the plate spring portions disposed at both sides are integrally combined at the front end portions of them. A length of another plate spring portion, for example disposed at the center is made shorter than the lengths of the others. Thus, a number of contact portions can be increased without reducing mechanical strength of the front end portion of the contact.

Owner:MATSUSHITA ELECTRIC WORKS LTD

Stapling device

ActiveUS7396008B2Reduce the likelihood of occurrenceProductivity is deterioratedStapling toolsNailingElectrical and Electronics engineeringEngineering

A stapler unit has a staple section, a cutter section, and a receiving section. A stapling device further includes a staple recovery box which is disposed at a staple discarding position and which recovers the tip ends to be discarded from the receiving section; and a staple discarding mechanism which delivers the tip ends received in the receiving section of the stapler unit to the staple recovery box. One of the plural stapling positions is identical with the staple discarding position.

Owner:FUJIFILM BUSINESS INNOVATION CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com