Patents

Literature

634 results about "Epitaxial material" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

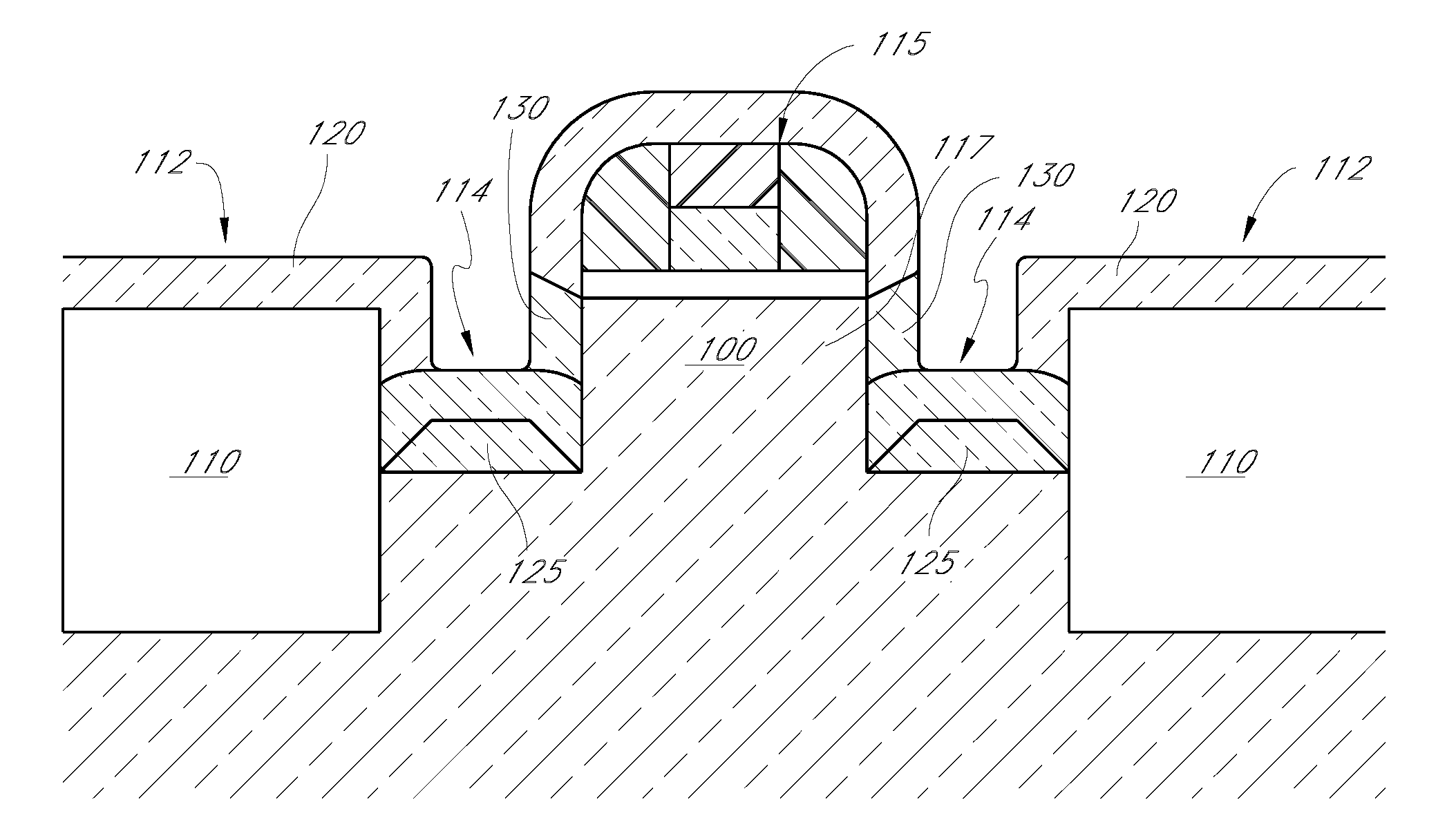

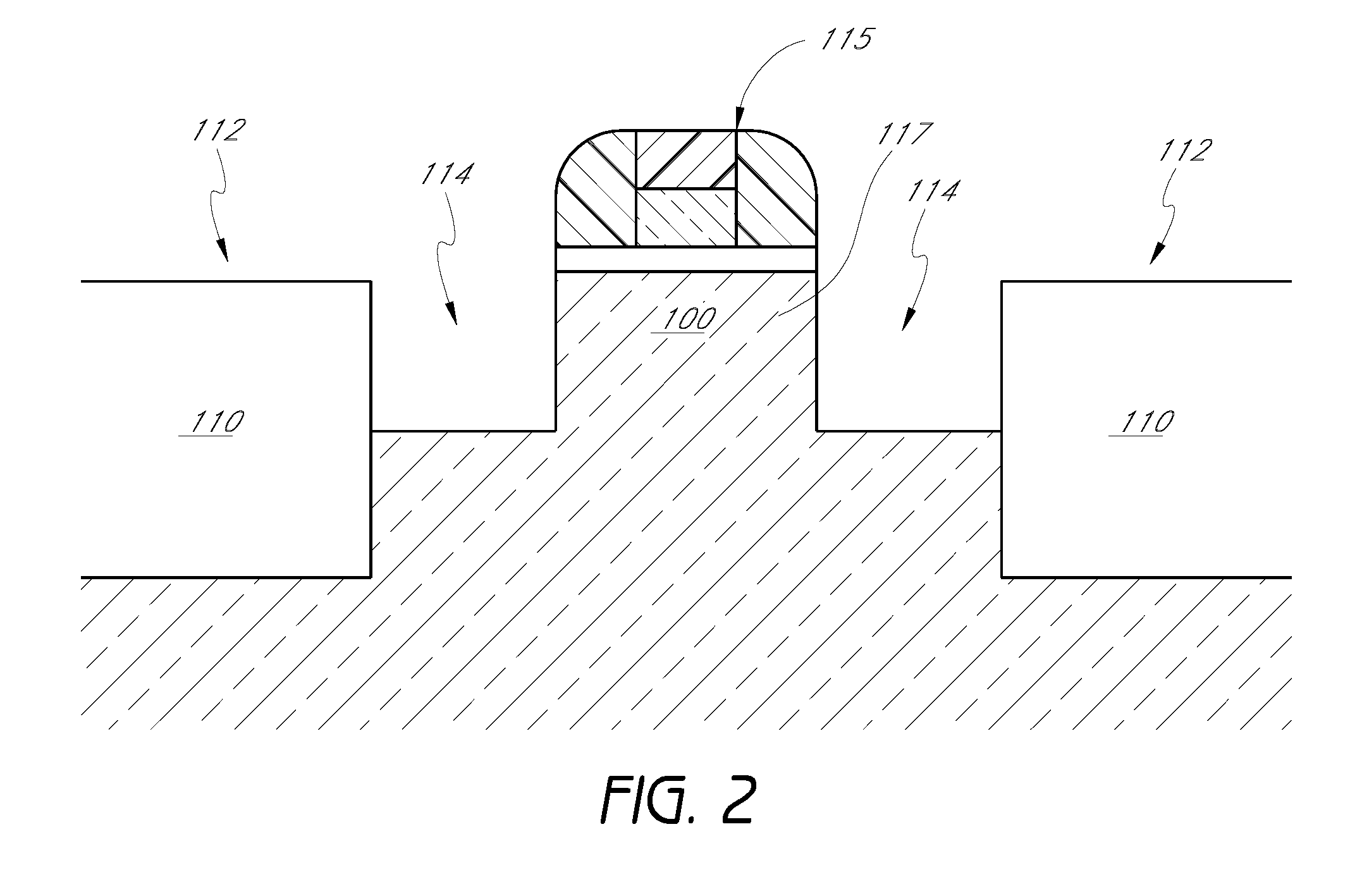

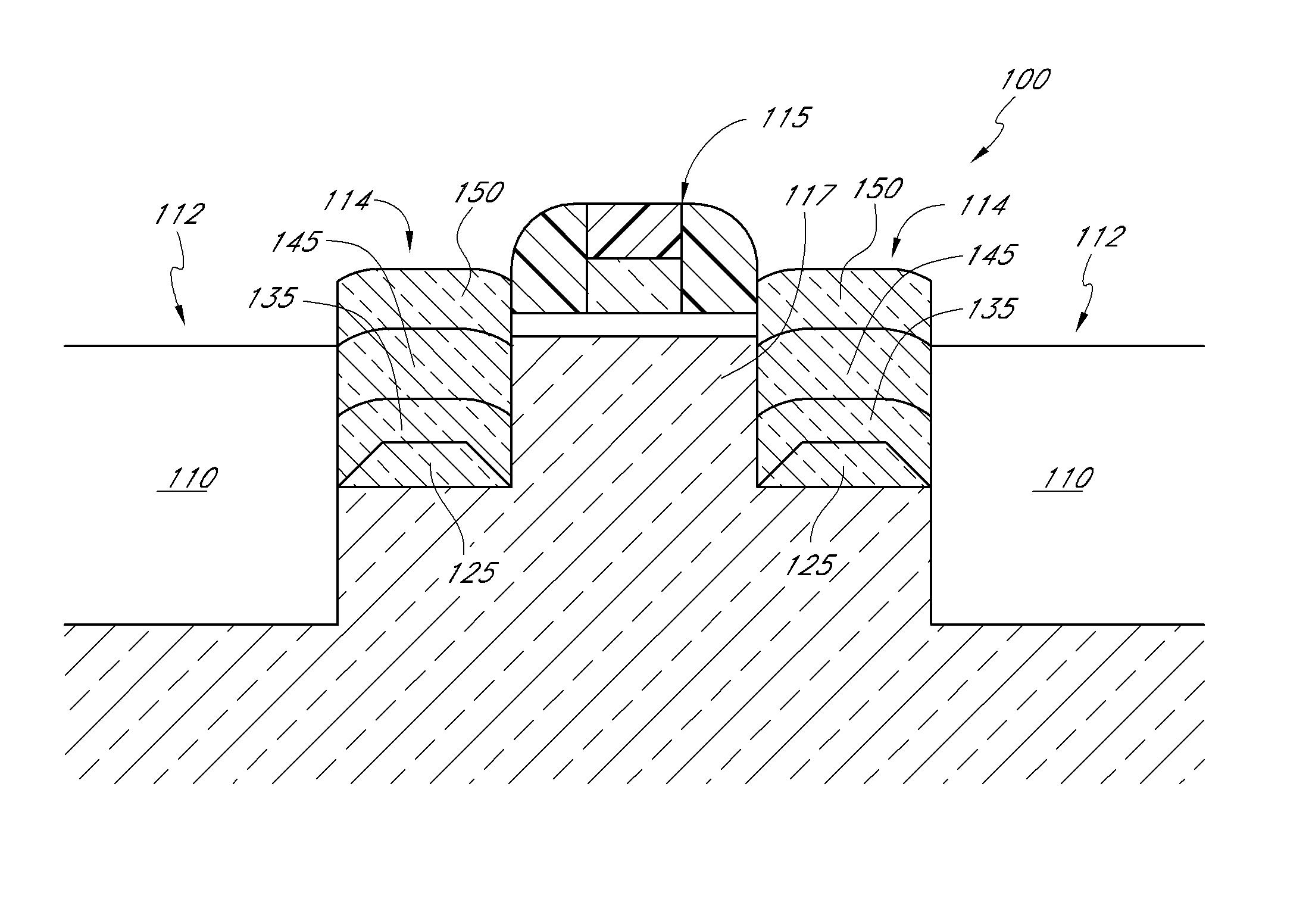

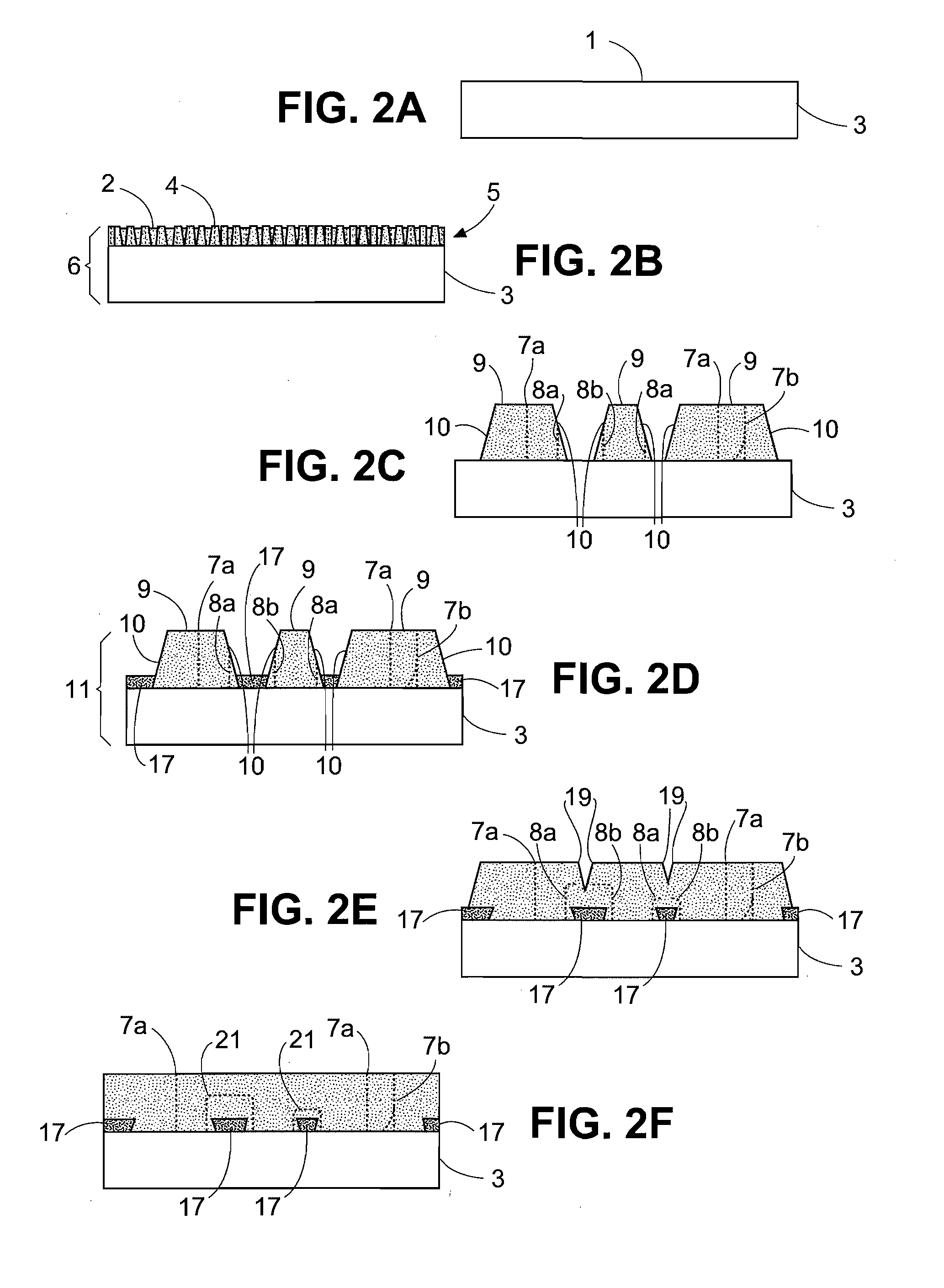

Selective epitaxial formation of semiconductor films

ActiveUS8278176B2Semiconductor/solid-state device manufacturingSemiconductor devicesCyclic processMetallurgy

Epitaxial layers are selectively formed in semiconductor windows by a cyclical process of repeated blanket deposition and selective etching. The blanket deposition phases leave non-epitaxial material over insulating regions, such as field oxide, and the selective etch phases preferentially remove non-epitaxial material while deposited epitaxial material builds up cycle-by-cycle. Quality of the epitaxial material improves relative to selective processes where no deposition occurs on insulators. Use of a germanium catalyst during the etch phases of the process aid etch rates and facilitate economical maintenance of isothermal and / or isobaric conditions throughout the cycles. Throughput and quality are improved by use of trisilane, formation of amorphous material over the insulating regions and minimizing the thickness ratio of amorphous:epitaxial material in each deposition phase.

Owner:ASM IP HLDG BV

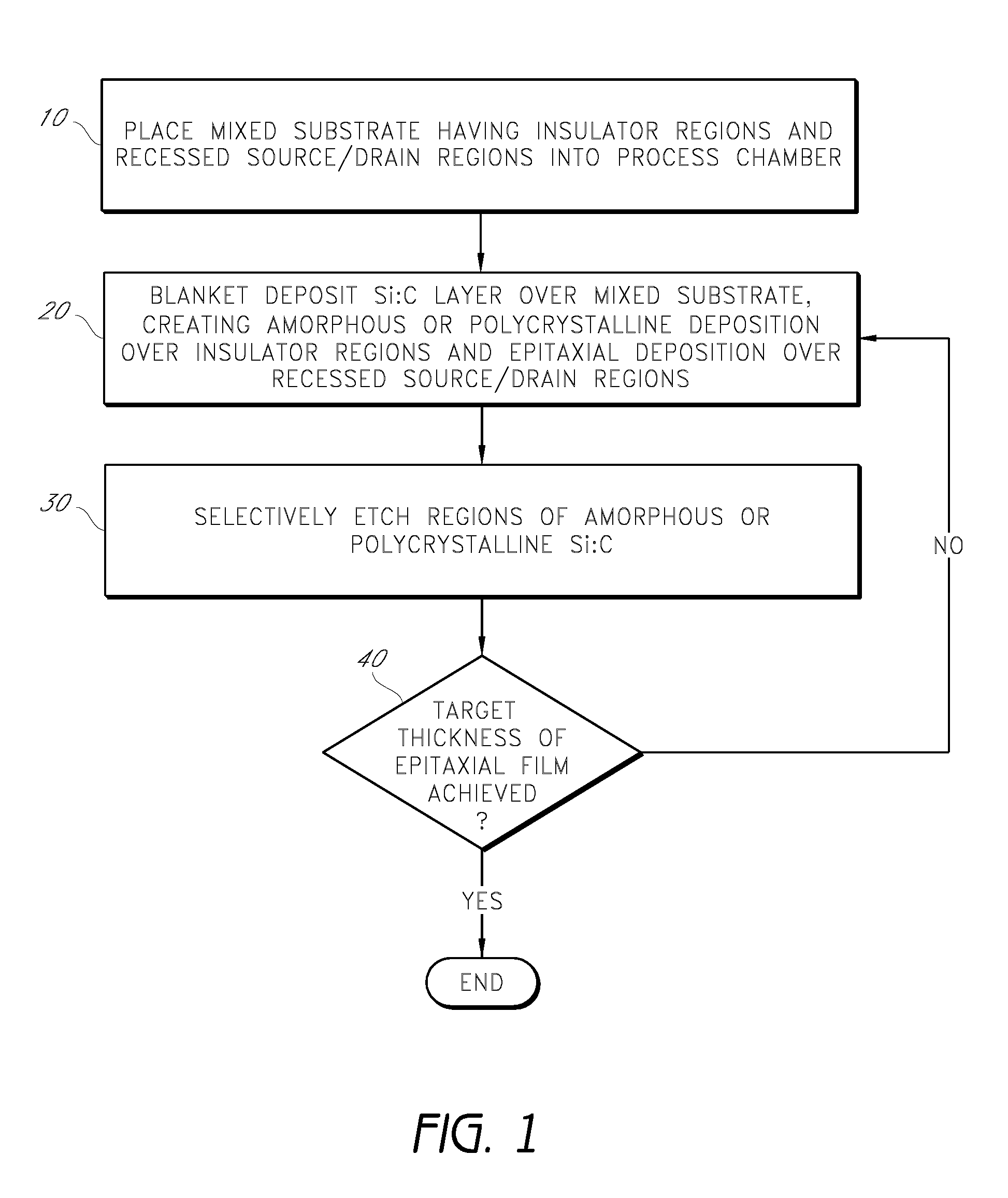

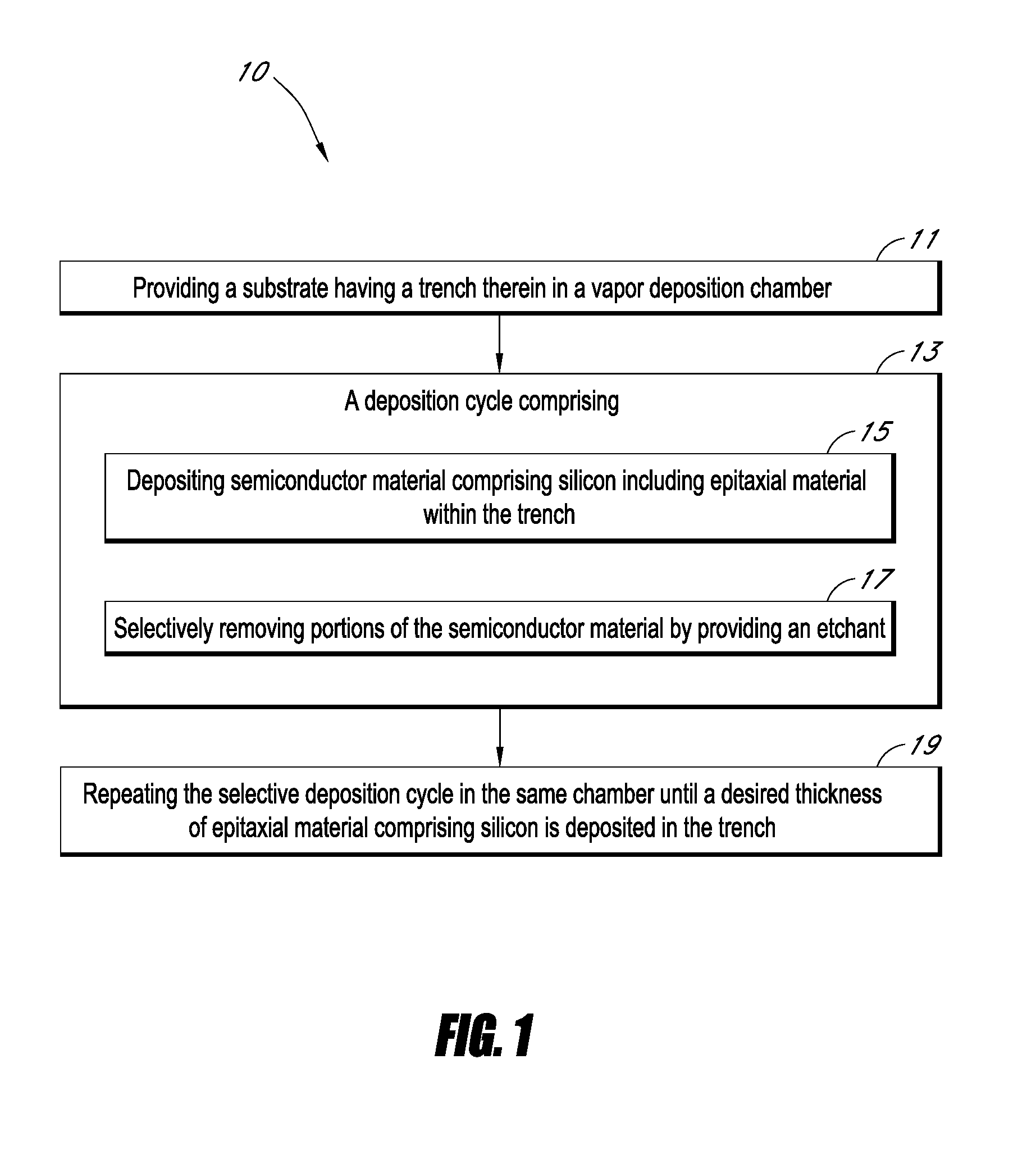

Cyclical epitaxial deposition and etch

ActiveUS8367528B2Semiconductor/solid-state device manufacturingSemiconductor devicesEpitaxial materialSemiconductor

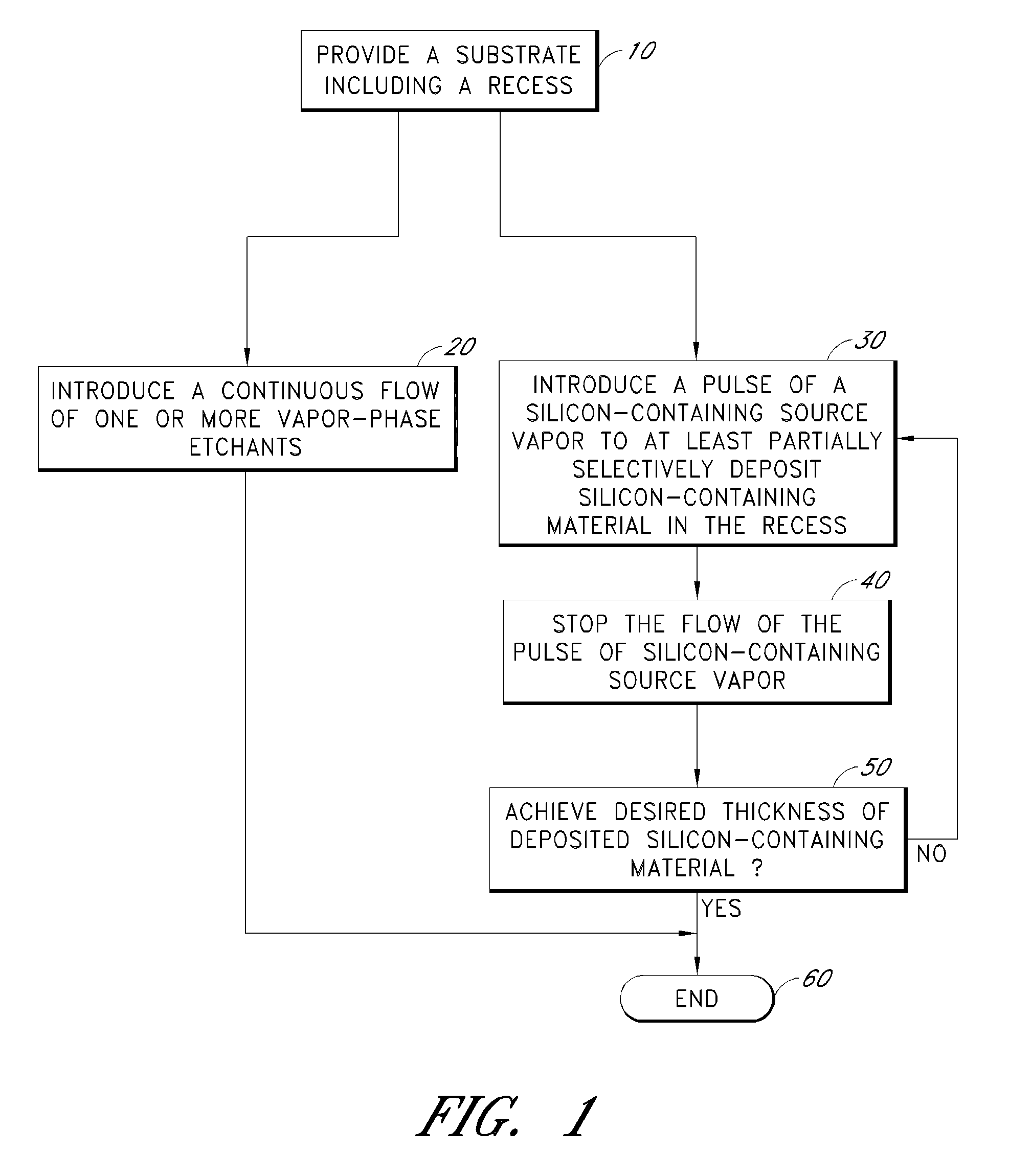

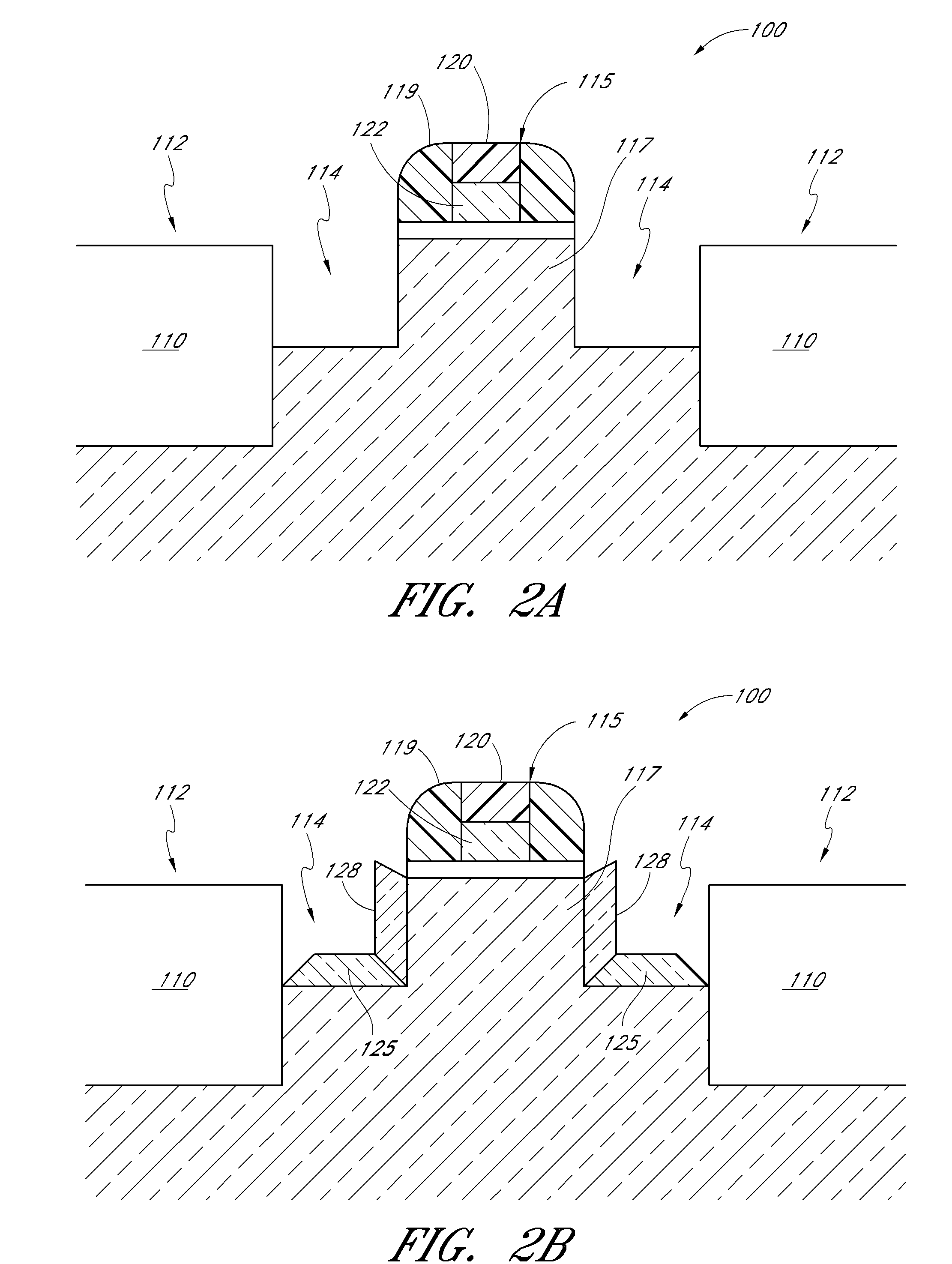

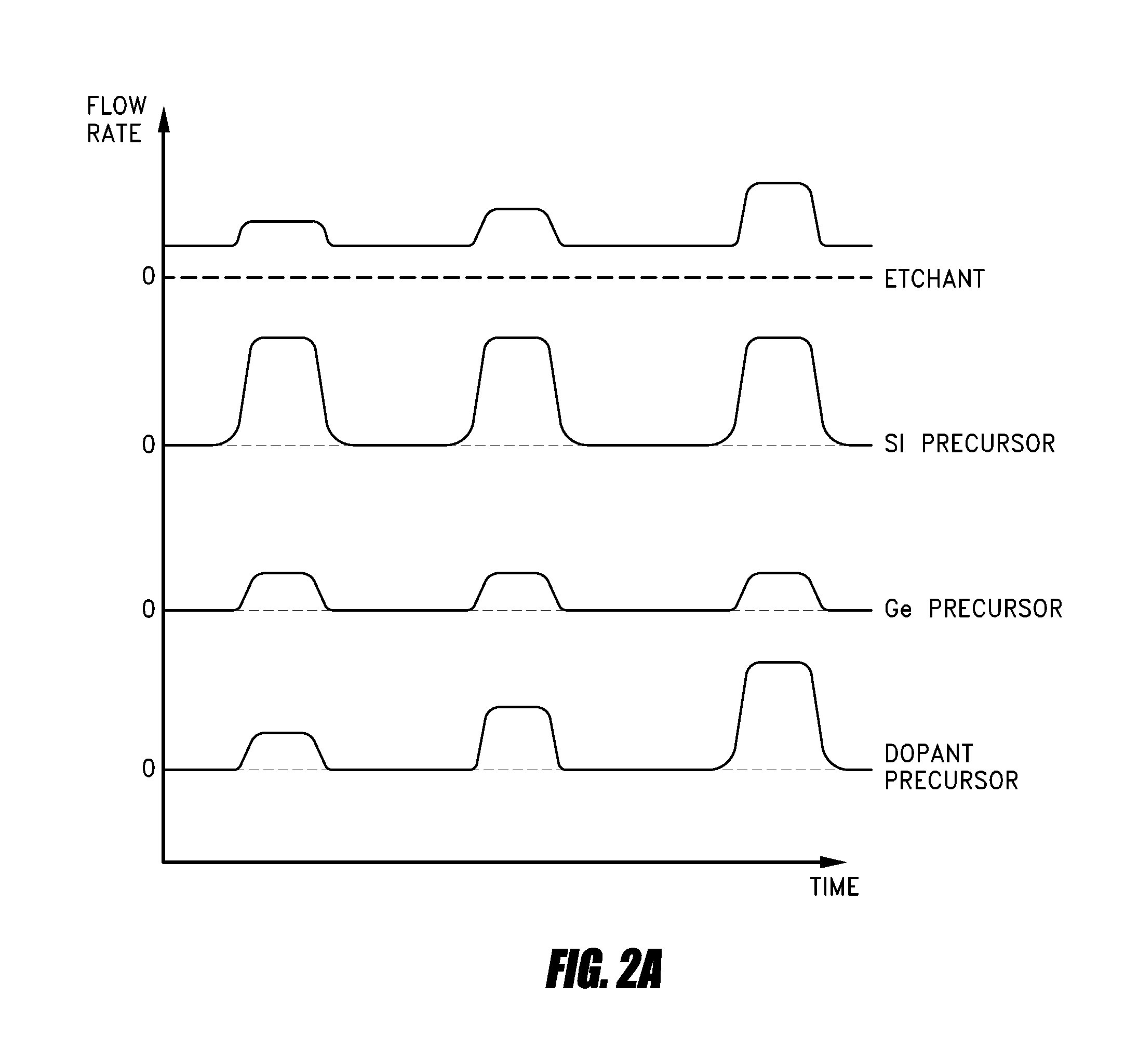

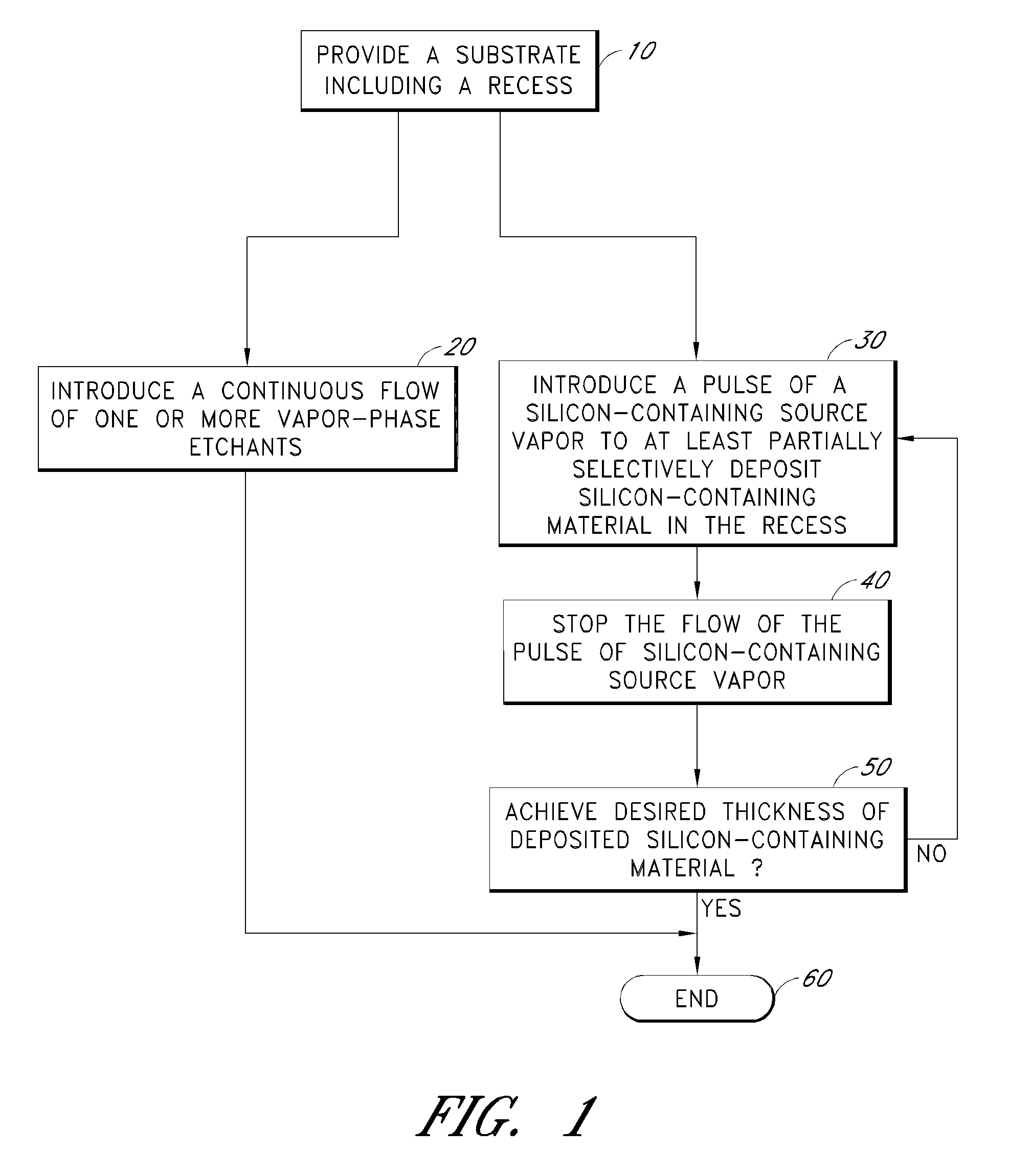

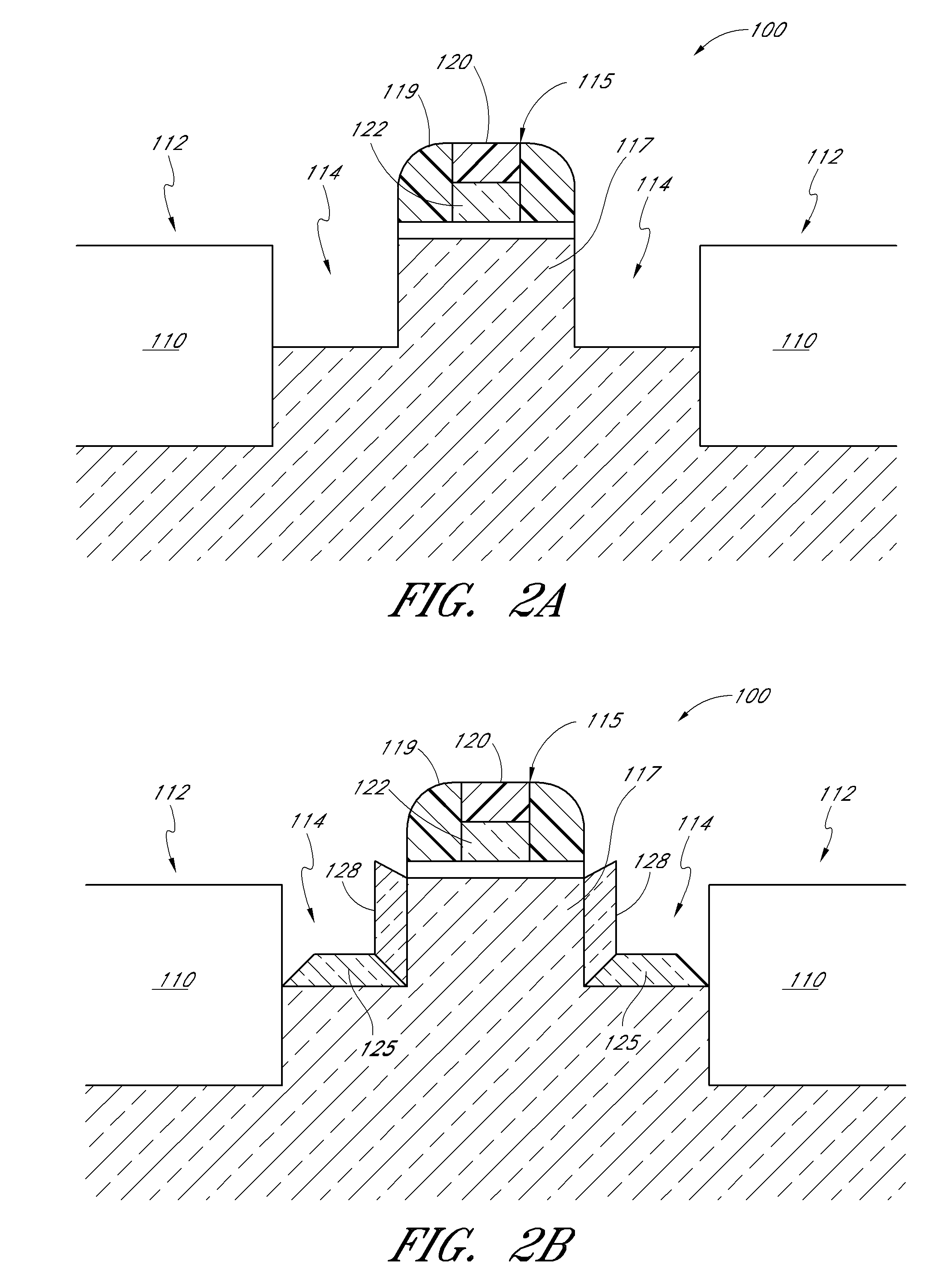

Methods for selectively depositing high quality epitaxial material include introducing pulses of a silicon-source containing vapor while maintaining a continuous etchant flow. Epitaxial material is deposited on areas of a substrate, such as source and drain recesses. Between pulses, the etchant flow continues such that lower quality epitaxial material may be removed, as well as any non-epitaxial material that may have been deposited. The pulse of silicon-source containing vapor may be repeated until a desired thickness of epitaxial material is selectively achieved in semiconductor windows, such as recessed source / drain regions.

Owner:ASM IP HLDG BV

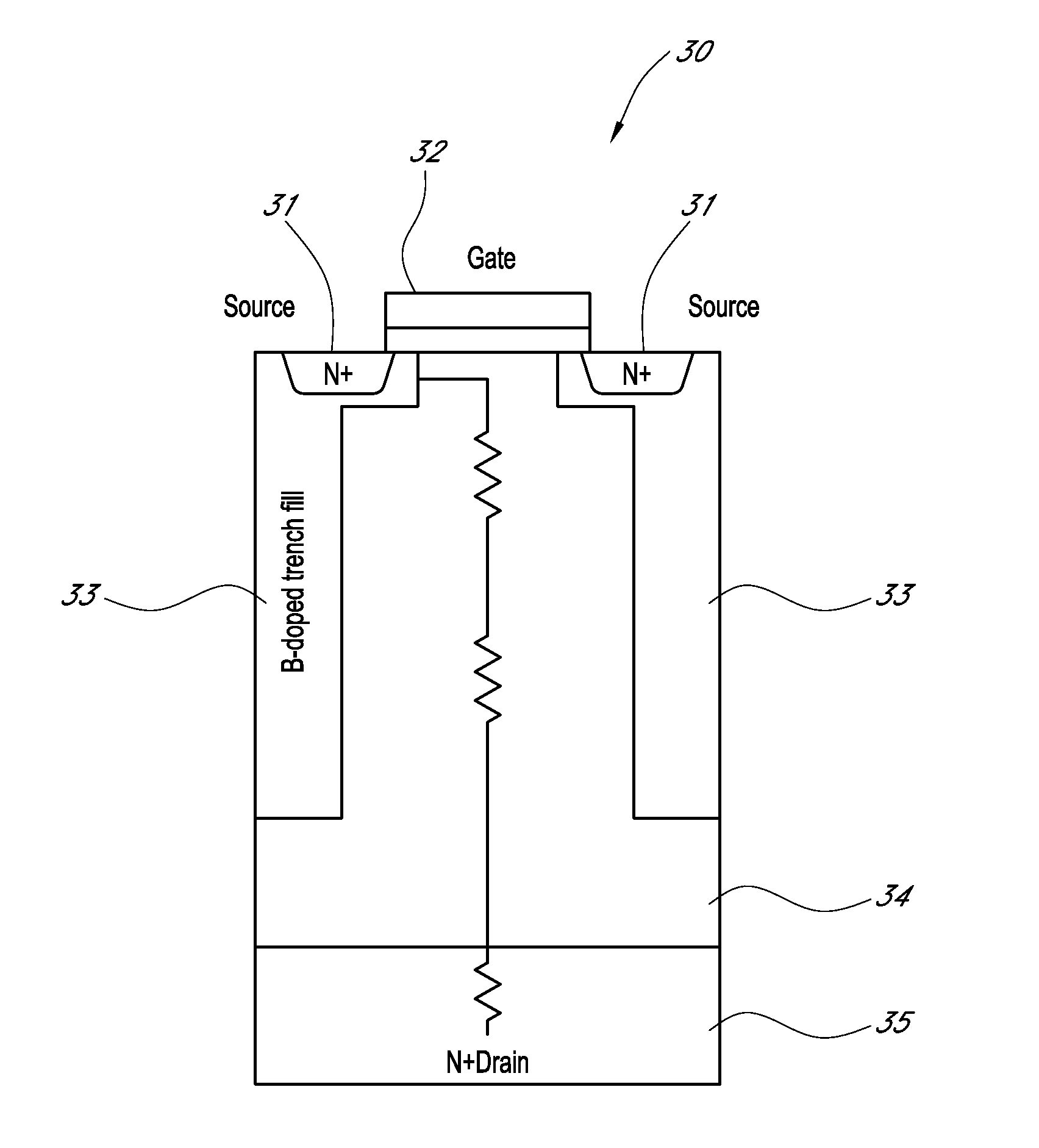

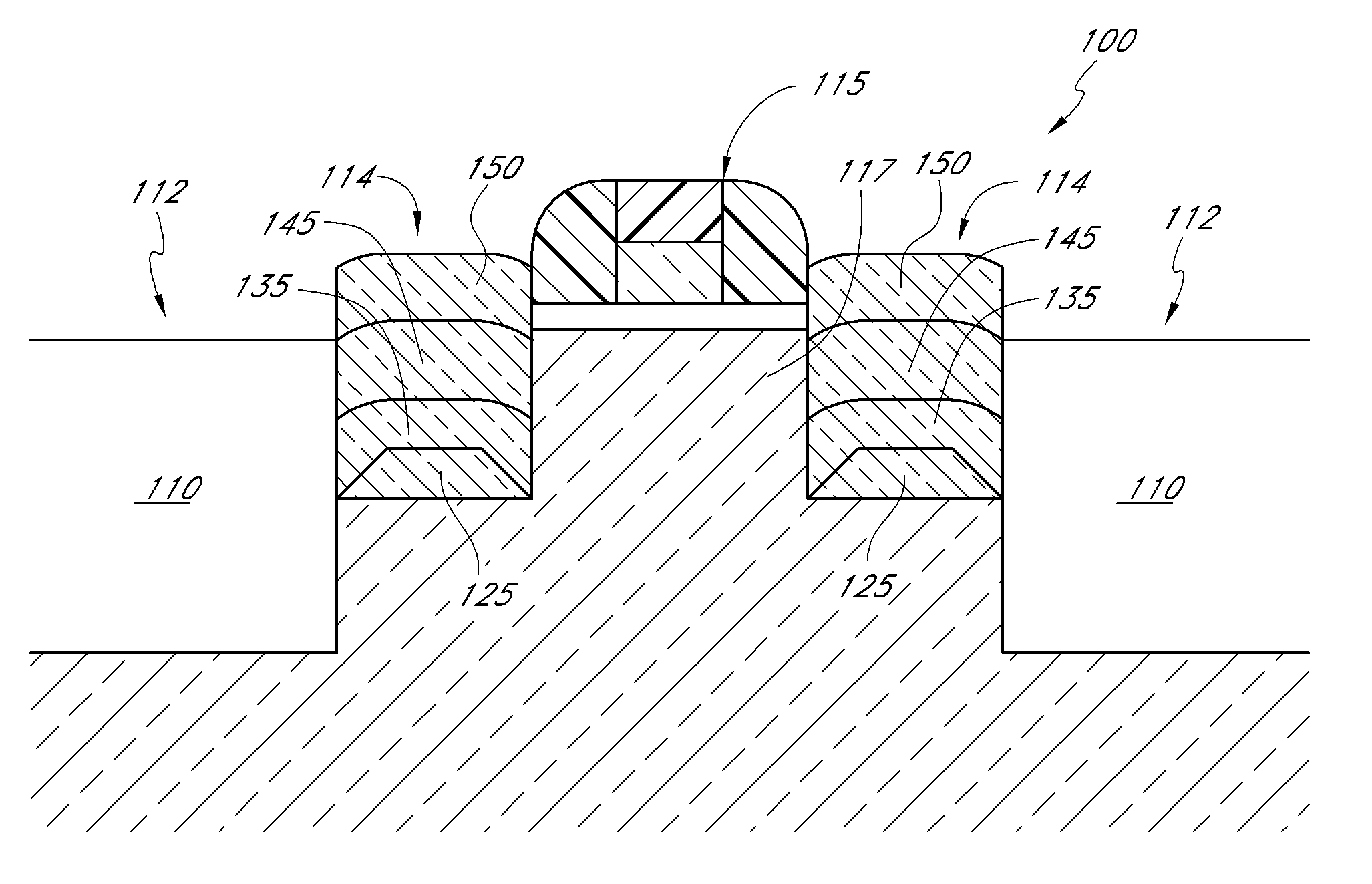

Processes and structures for dopant profile control in epitaxial trench fill

InactiveUS20130320429A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantEpitaxial material

Methods of depositing epitaxial material using a repeated deposition and etch process. The deposition and etch processes can be repeated until a desired thickness of silicon-containing material is achieved. During the deposition process, a doped silicon film can be deposited. The doped silicon film can be selectively deposited in a trench on a substrate. The trench can have a liner comprising silicon and carbon prior to depositing the doped silicon film. The doped silicon film may also contain germanium. Germanium can promote uniform dopant distribution within the doped silicon film.

Owner:ASM IP HLDG BV

Cyclical epitaxial deposition and etch

ActiveUS20110117732A1Quality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesEpitaxial materialSemiconductor

Methods for selectively depositing high quality epitaxial material include introducing pulses of a silicon-source containing vapor while maintaining a continuous etchant flow. Epitaxial material is deposited on areas of a substrate, such as source and drain recesses. Between pulses, the etchant flow continues such that lower quality epitaxial material may be removed, as well as any non-epitaxial material that may have been deposited. The pulse of silicon-source containing vapor may be repeated until a desired thickness of epitaxial material is selectively achieved in semiconductor windows, such as recessed source / drain regions.

Owner:ASM IP HLDG BV

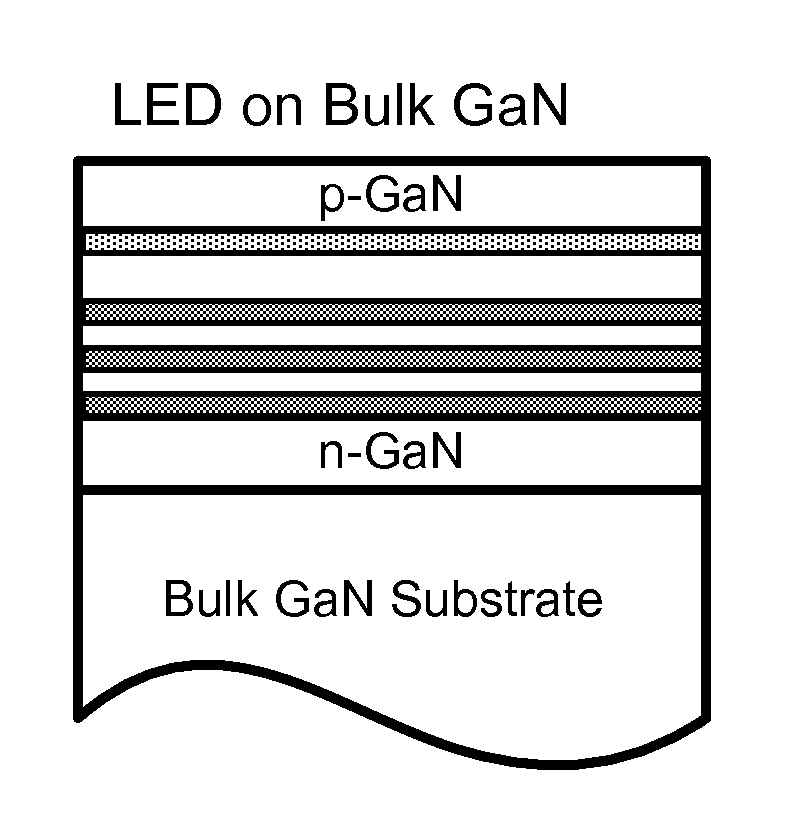

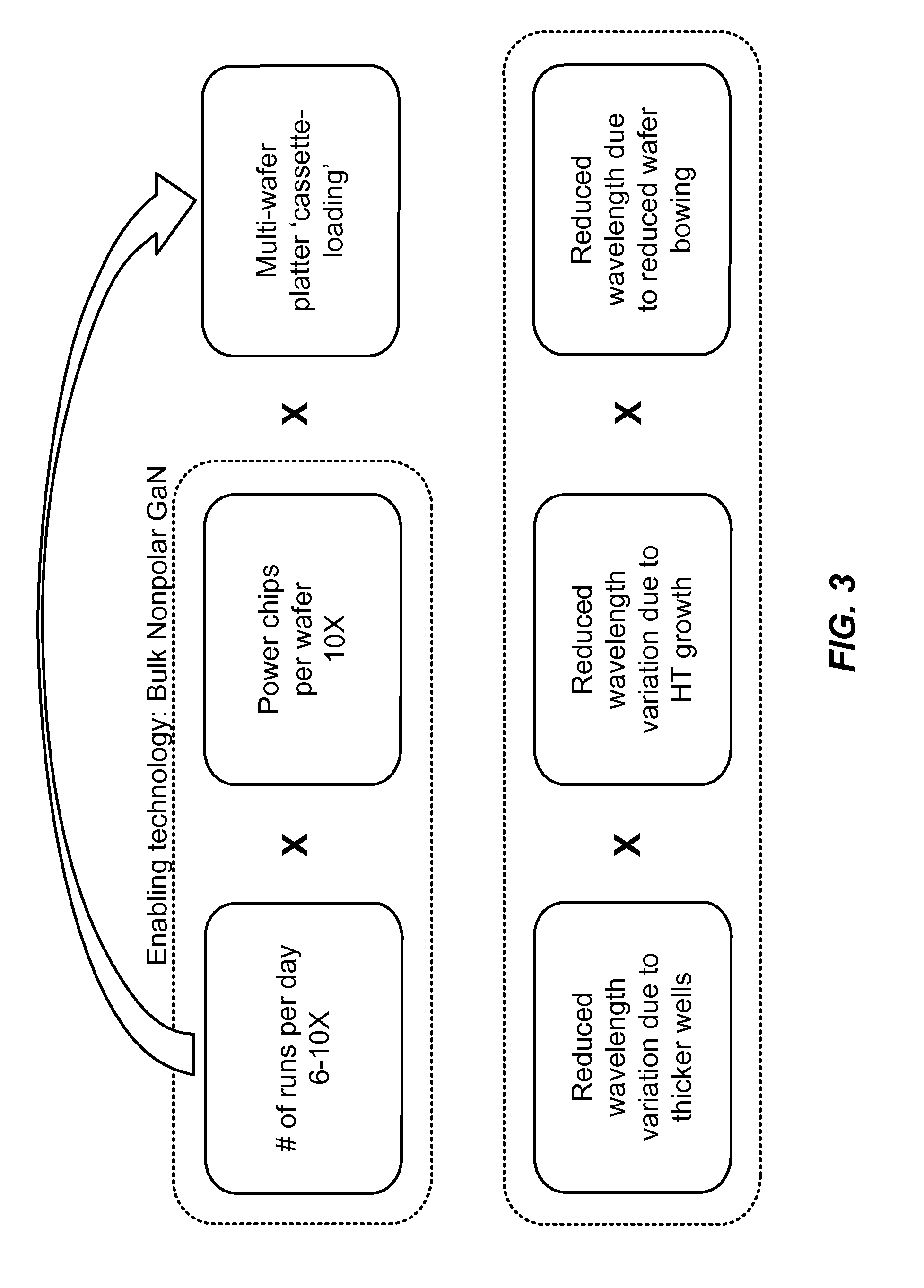

Rapid Growth Method and Structures for Gallium and Nitrogen Containing Ultra-Thin Epitaxial Structures for Devices

InactiveUS20110056429A1Quick upgradeReduce processing timePolycrystalline material growthSemiconductor/solid-state device manufacturingEpitaxial materialNitrogen

A method for rapid growth of gallium and nitrogen containing material is described. The method includes providing a bulk gallium and nitrogen containing substrate. A first epitaxial material of first thickness is formed over the substrate, preferably with a pseudomorphical process. The method also forms a second epitaxial layer over the first to create a stacked structure. The stacked structure consists of a total thickness of less than about 2 microns.

Owner:SORAA

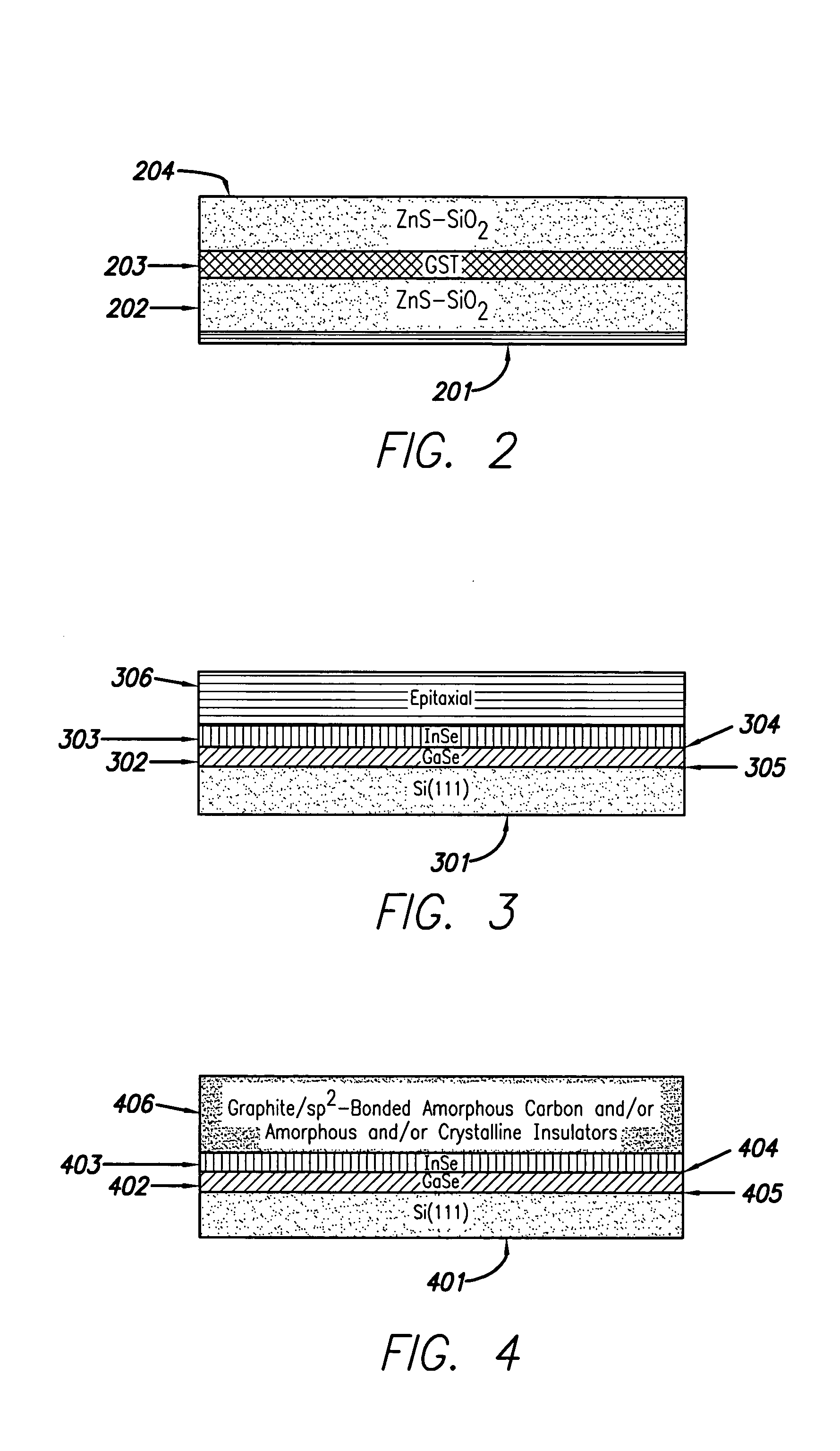

Capping layer for enhanced performance media

InactiveUS20050074576A1High materialElectrostatic charge injection carrier recordingElectron beam carrier recordingEpitaxial materialConductive materials

A media storage device and method for fabricating said device is provided. The device comprises a data layer capable of storing and erasing data via application of an energy beam, such as a near field optical non diffraction limited beam or electron beam. A separate capping layer is deposited on the data layer. The separate capping layer is relatively transparent to the energy beam and may be formed from various materials, including but not limited to an epitaxial material, a conducting material, and a robust high melting point material, such as Molybdenum.

Owner:HEWLETT PACKARD DEV CO LP

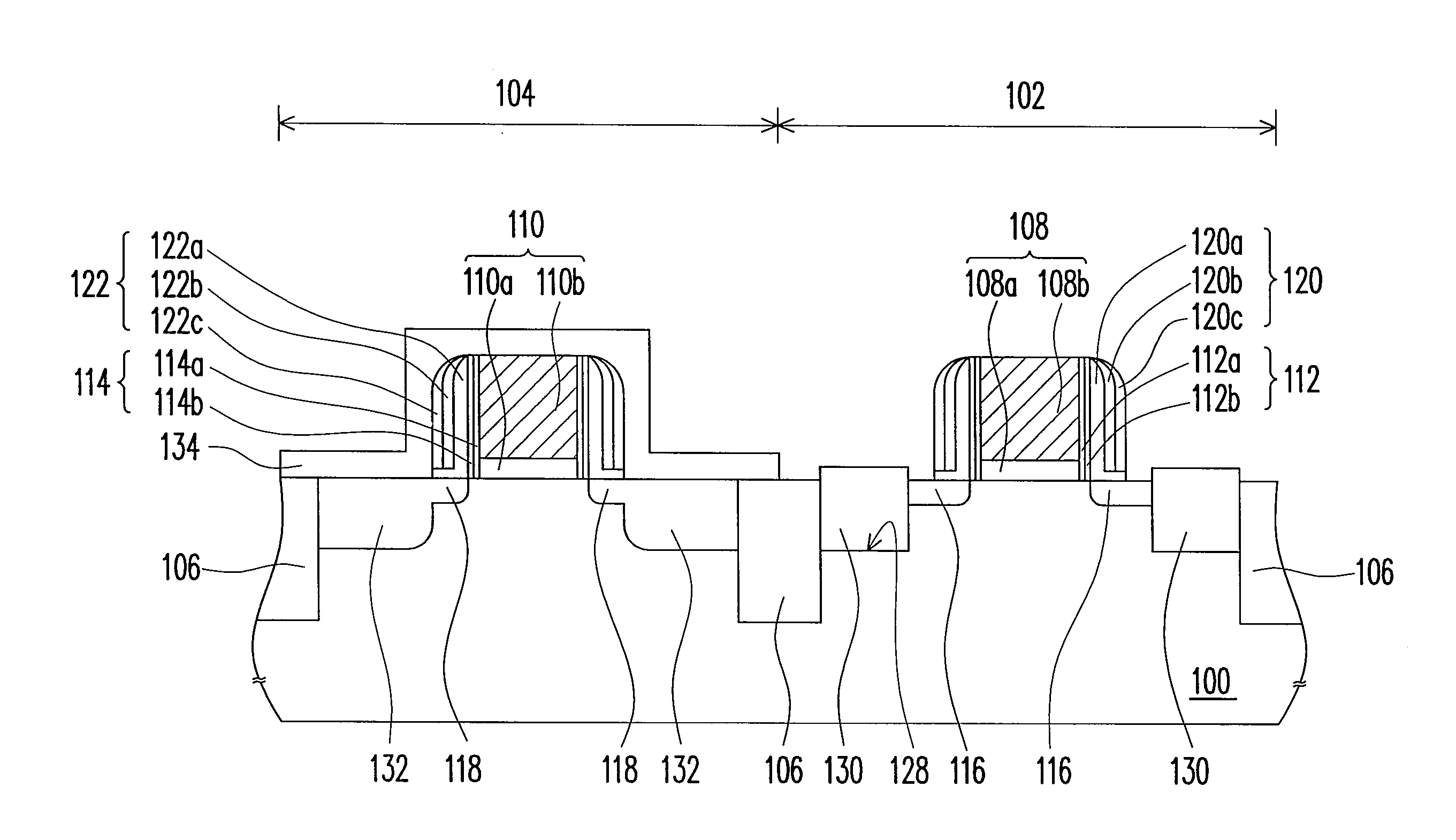

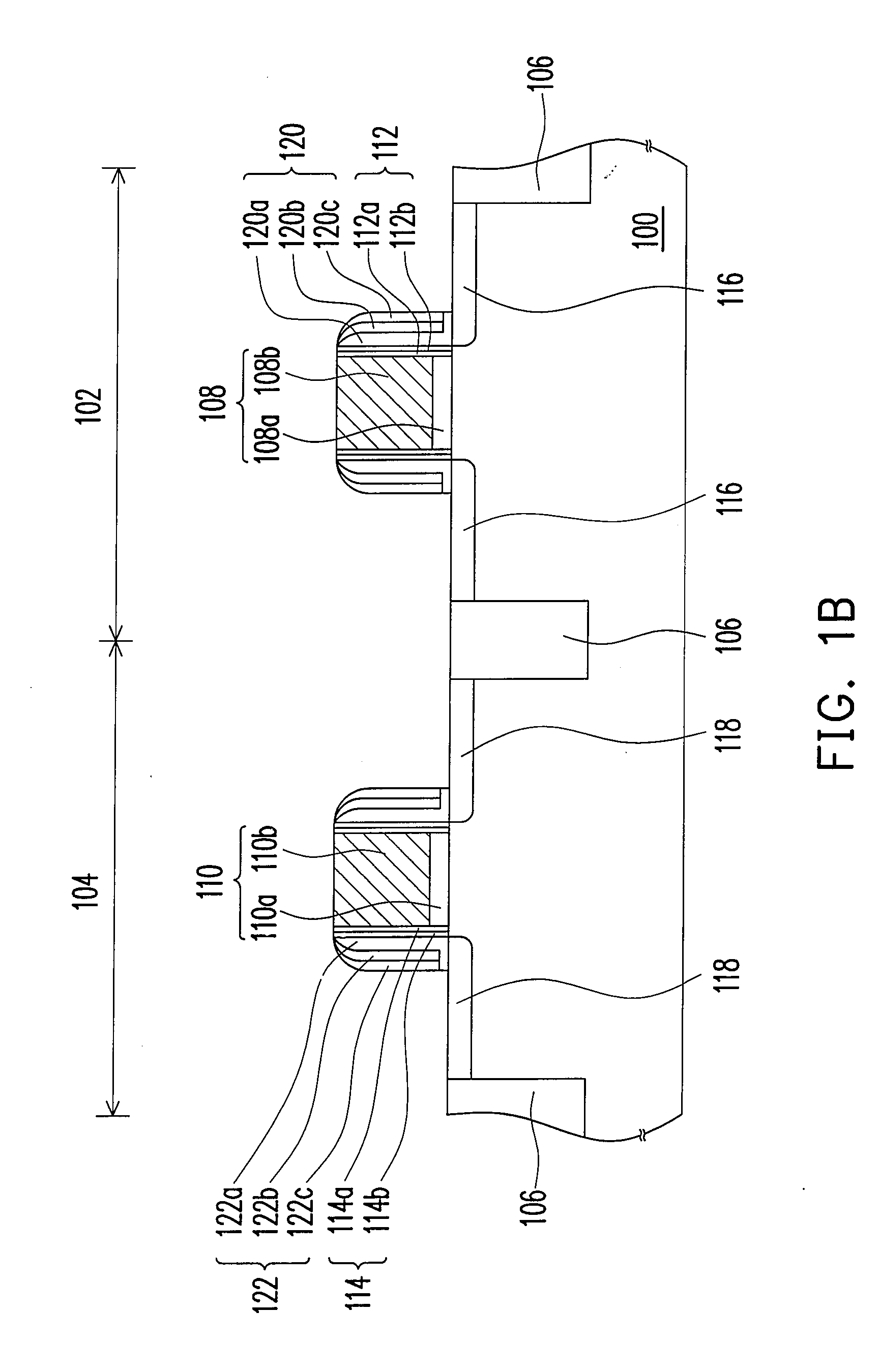

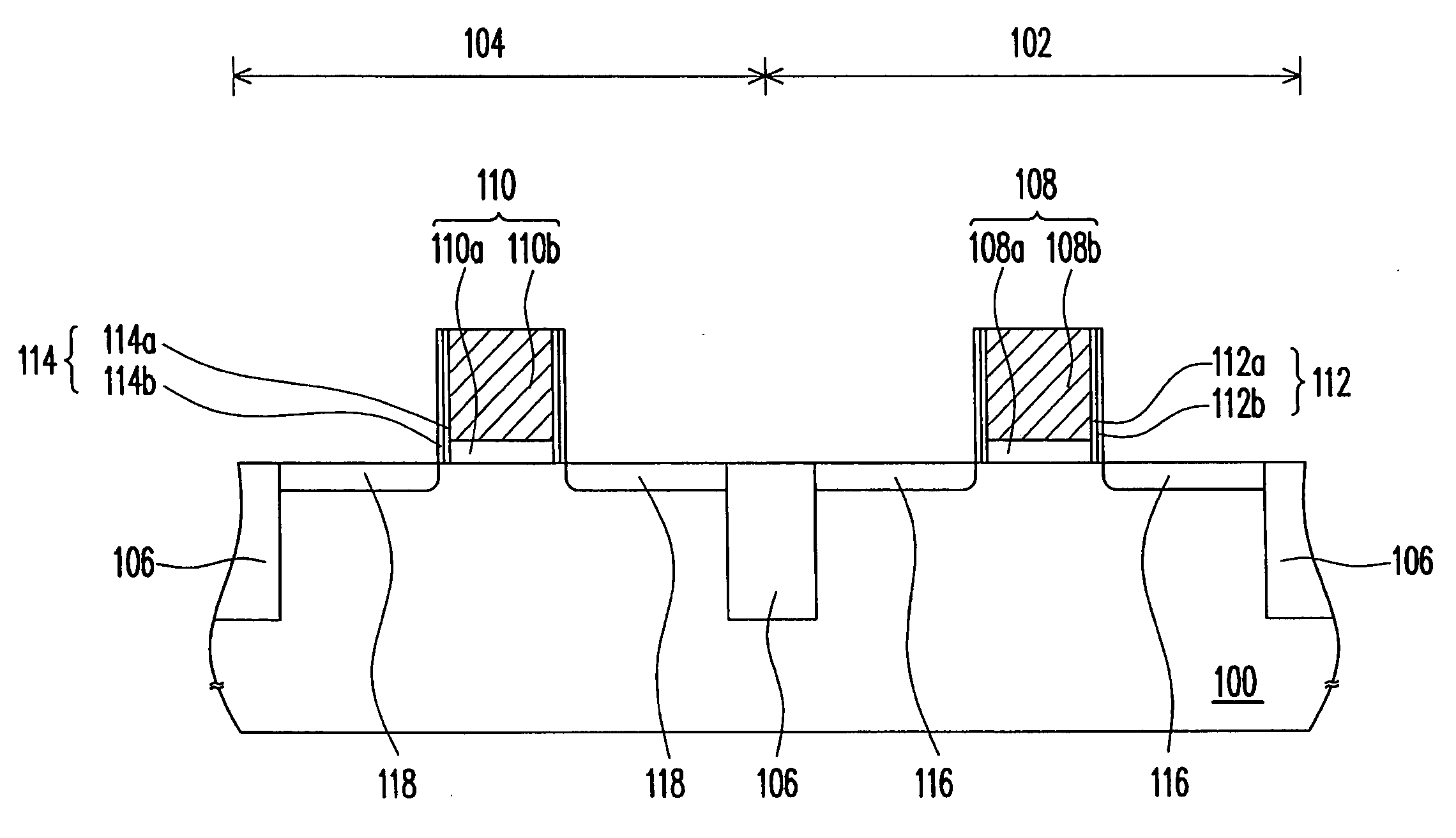

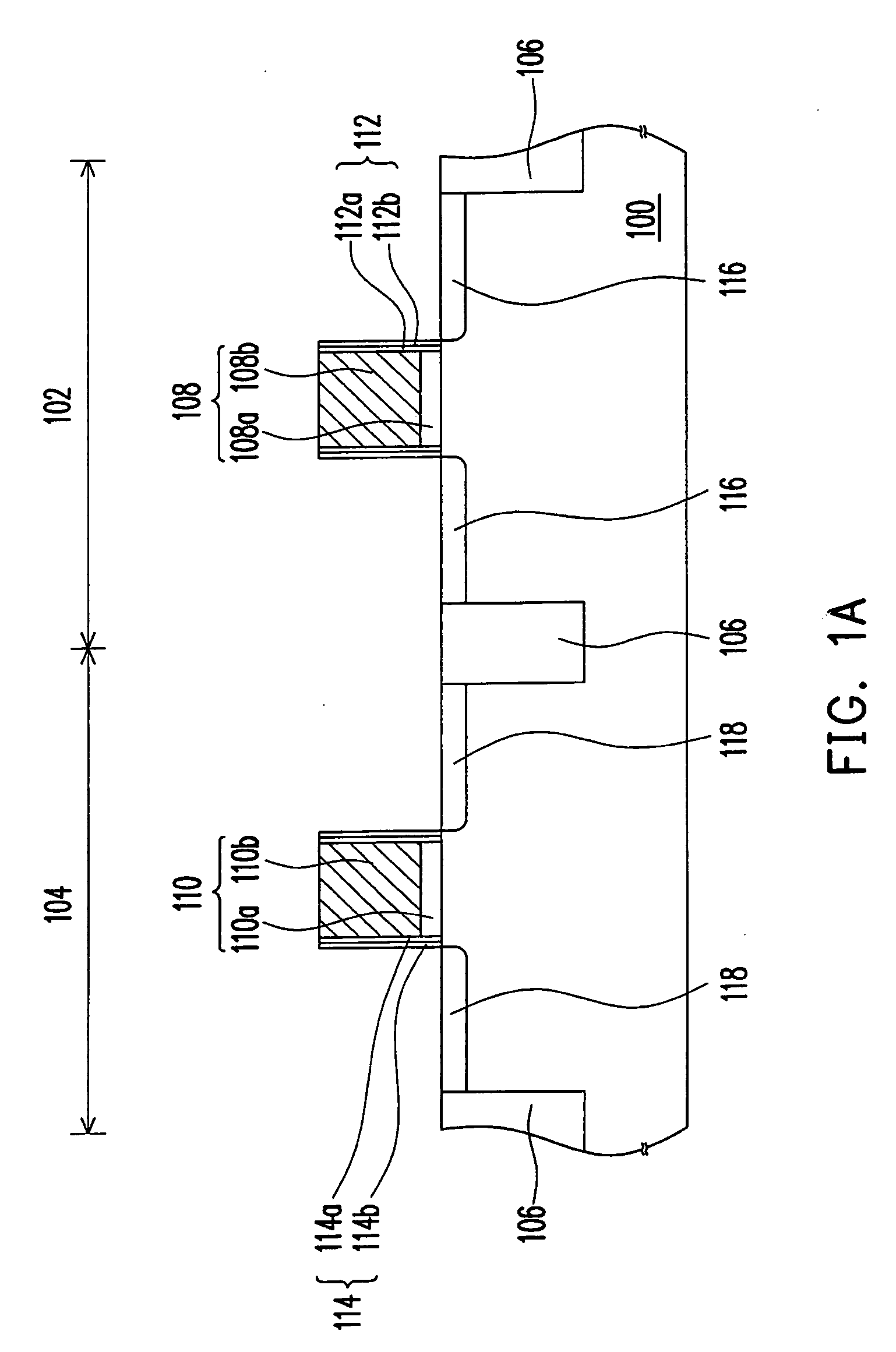

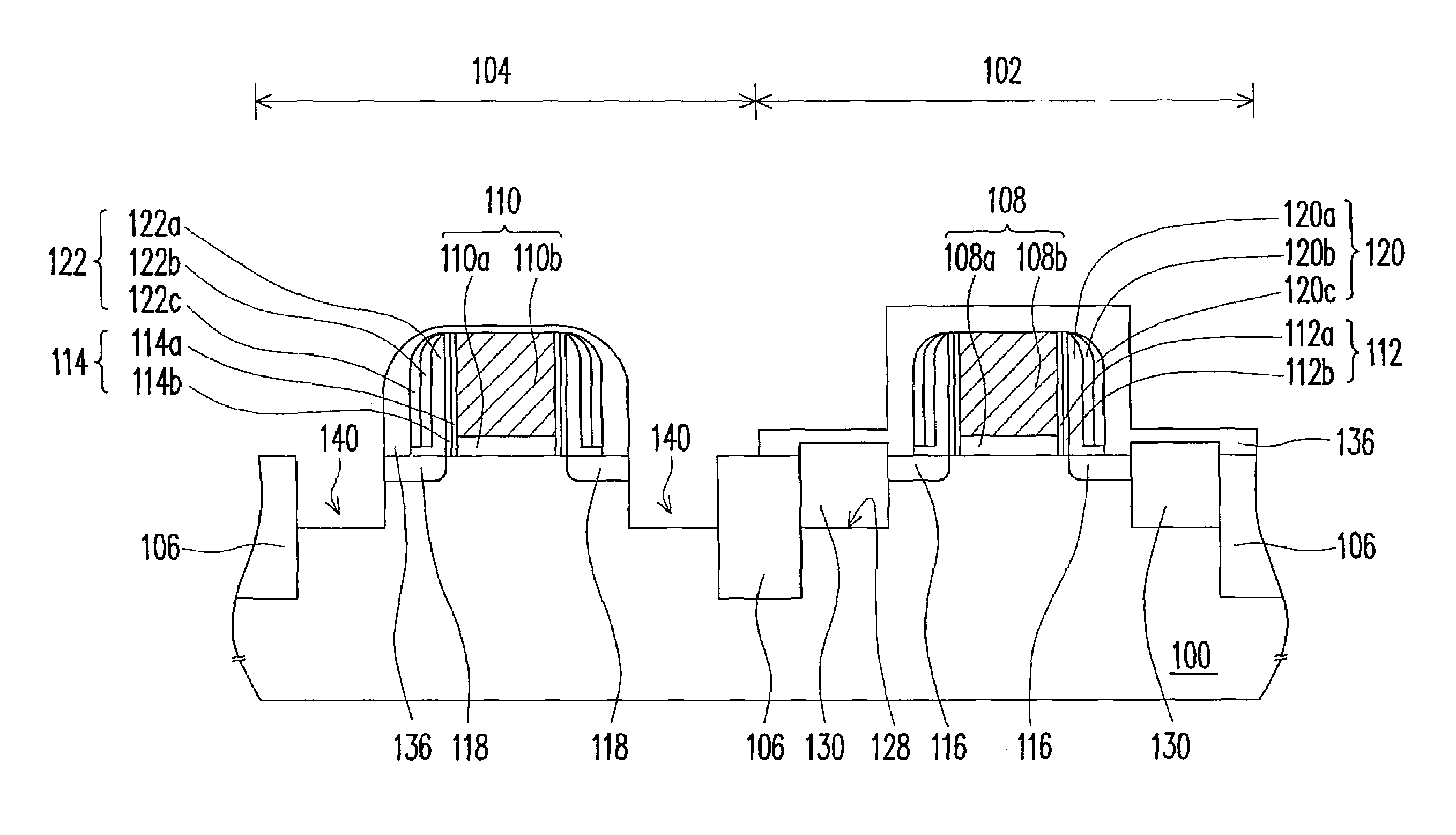

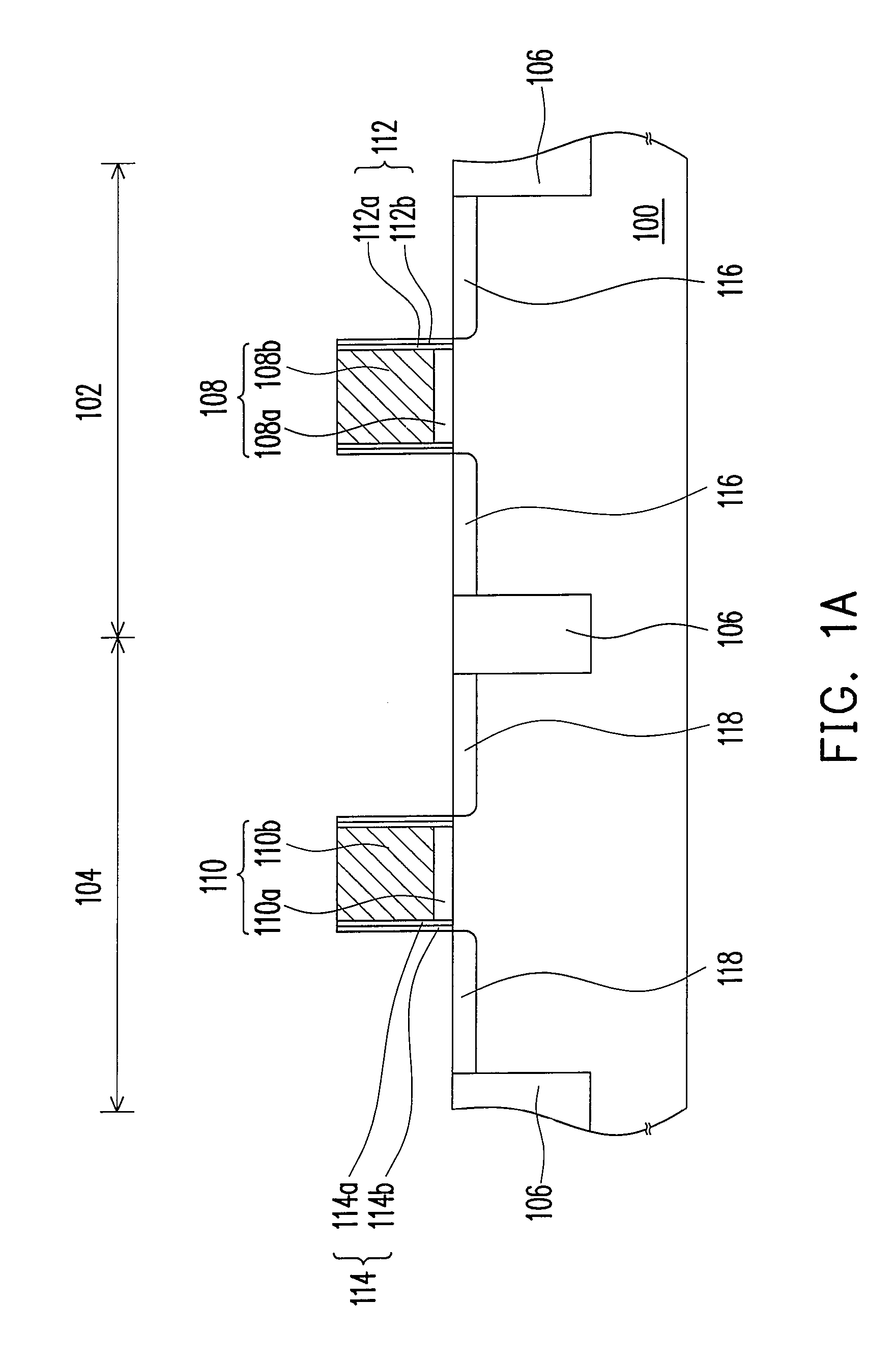

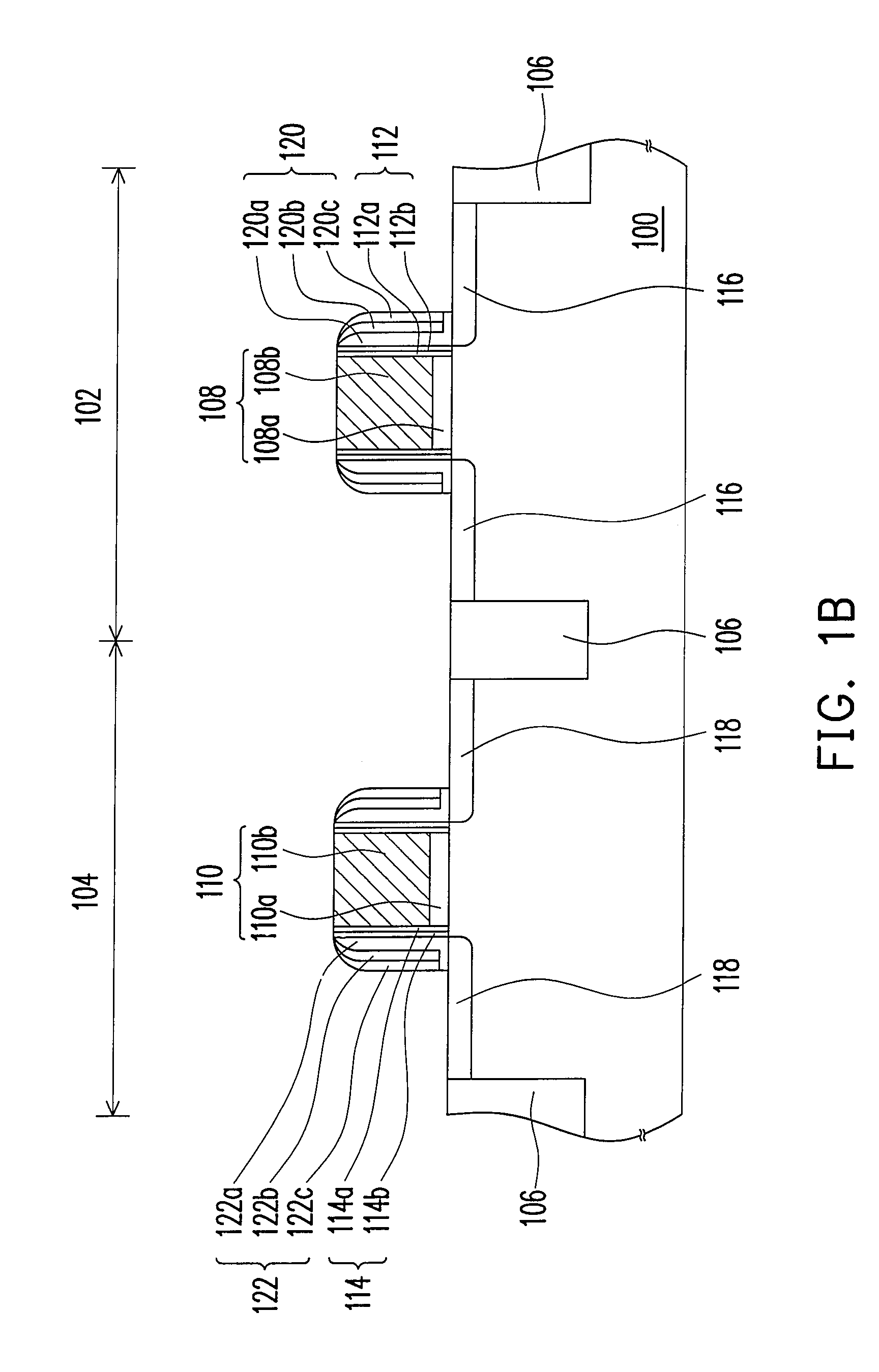

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS20080061366A1Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

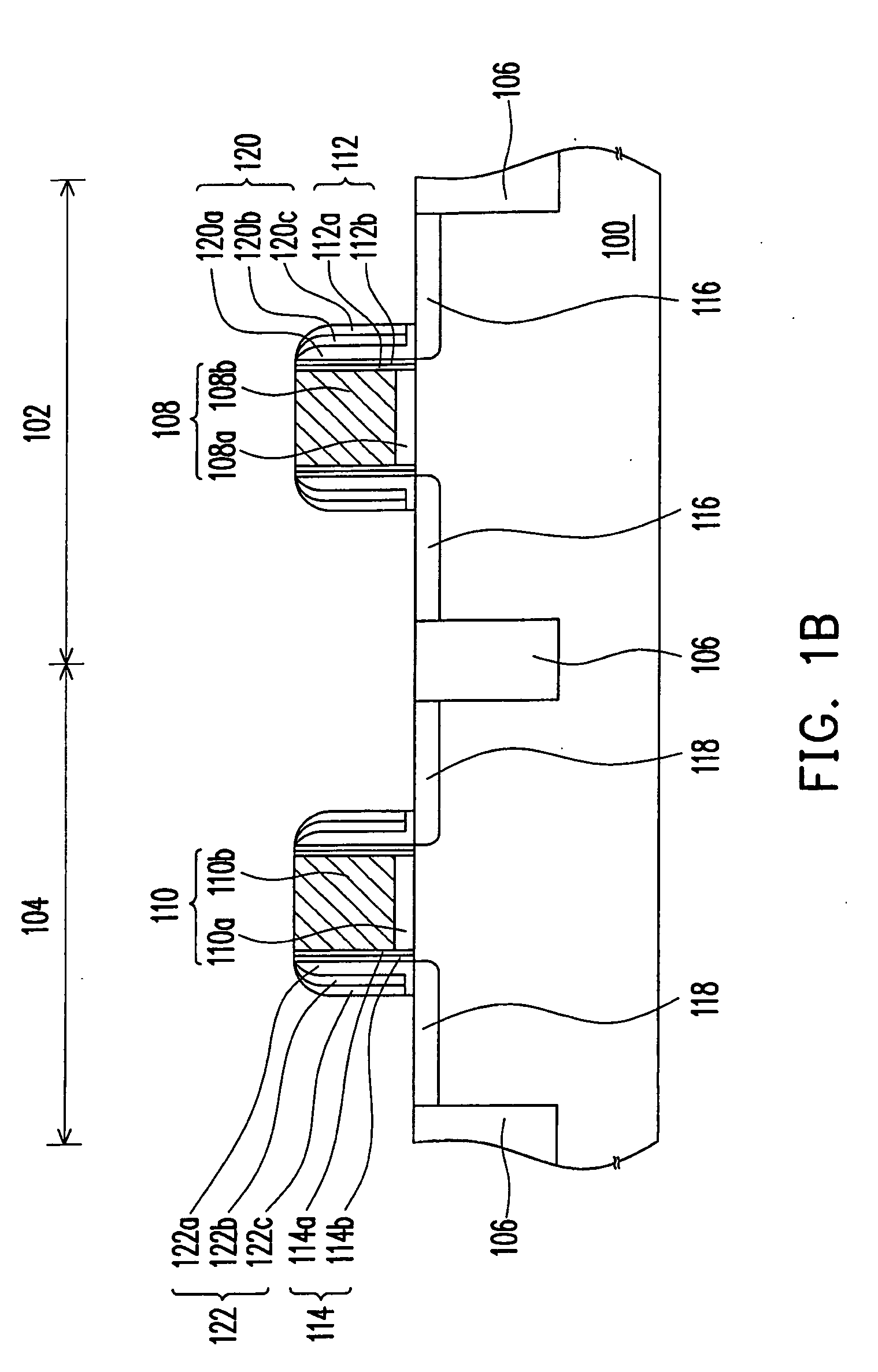

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

III-V Nitride homoepitaxial material of improved MOVPE epitaxial quality (surface texture and defect density) formed on free-standing (Al,In,Ga)N substrates, and opto-electronic and electronic devices comprising same

InactiveUS20030213964A1Improve material qualityReduce dislocation densityPolycrystalline material growthAfter-treatment detailsCelsius DegreeSource material

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer of improved epitaxial quality deposited on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 10<5>, nitrogen source material partial pressure in a range of from about 1 to about 10<3 >torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 10<2 >microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

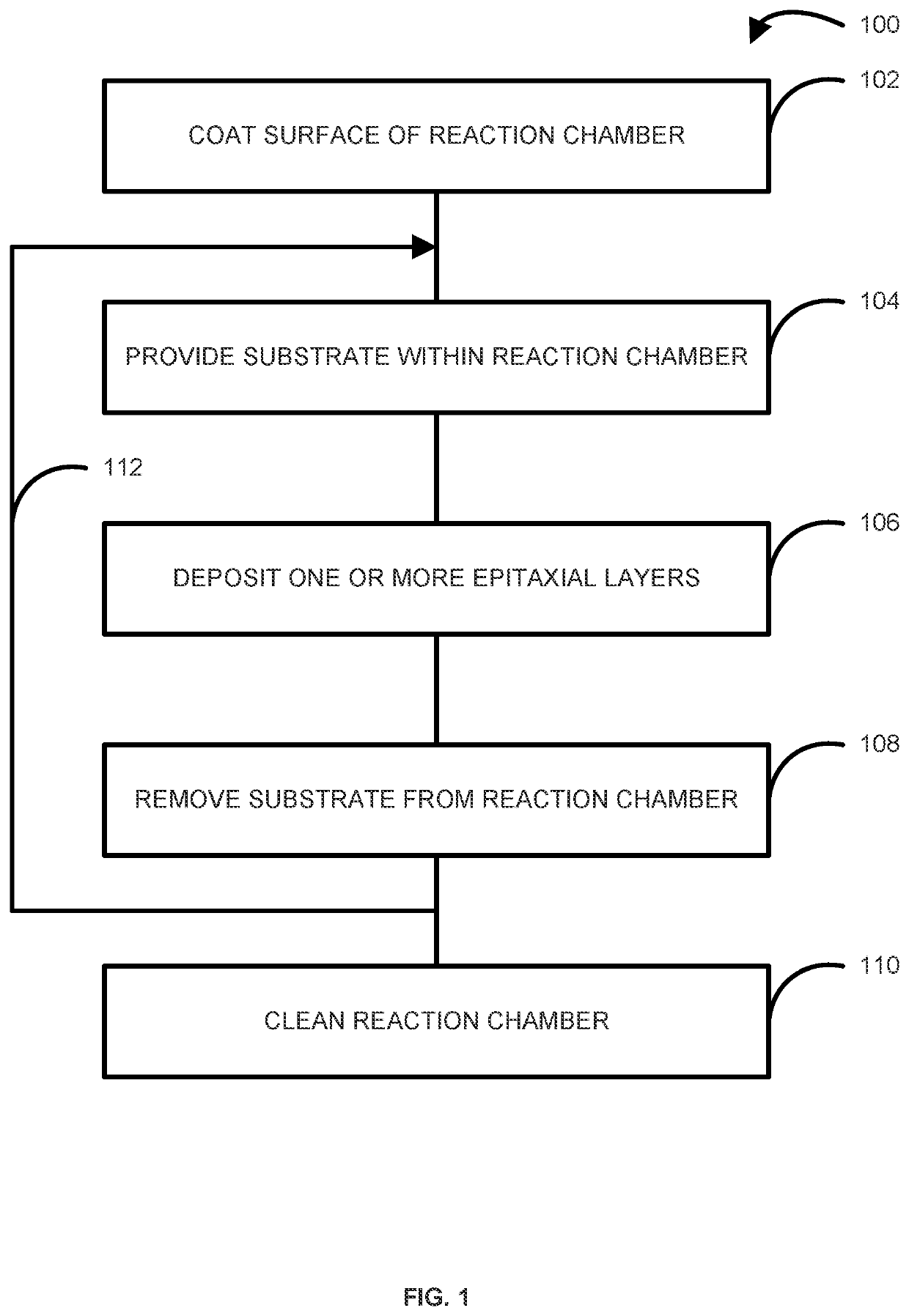

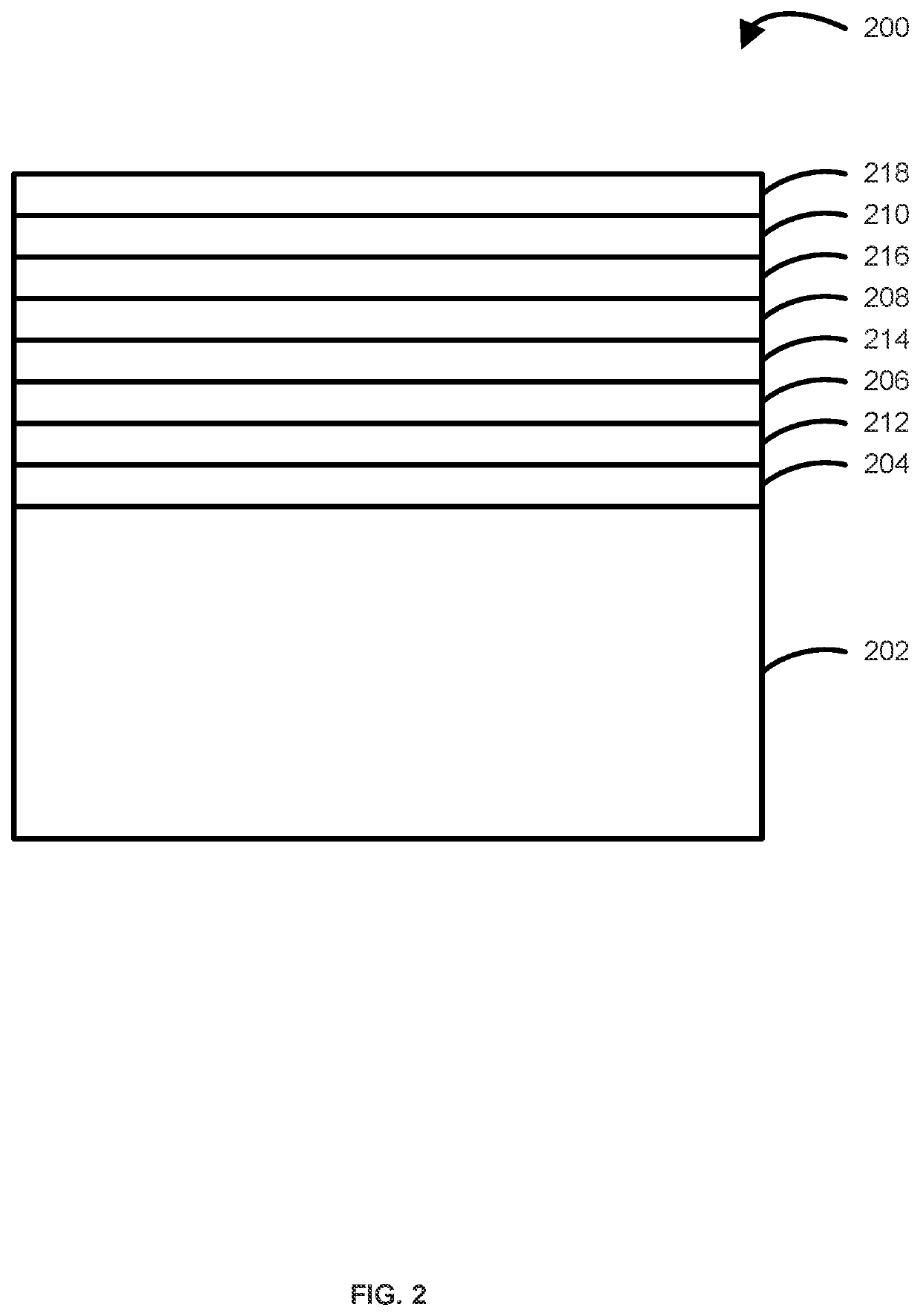

Method of depositing epitaxial material, structure formed using the method, and system for performing the method

PendingUS20210292902A1Improve throughputThe material is lowPolycrystalline material growthSemiconductor/solid-state device manufacturingEpitaxial materialEngineering

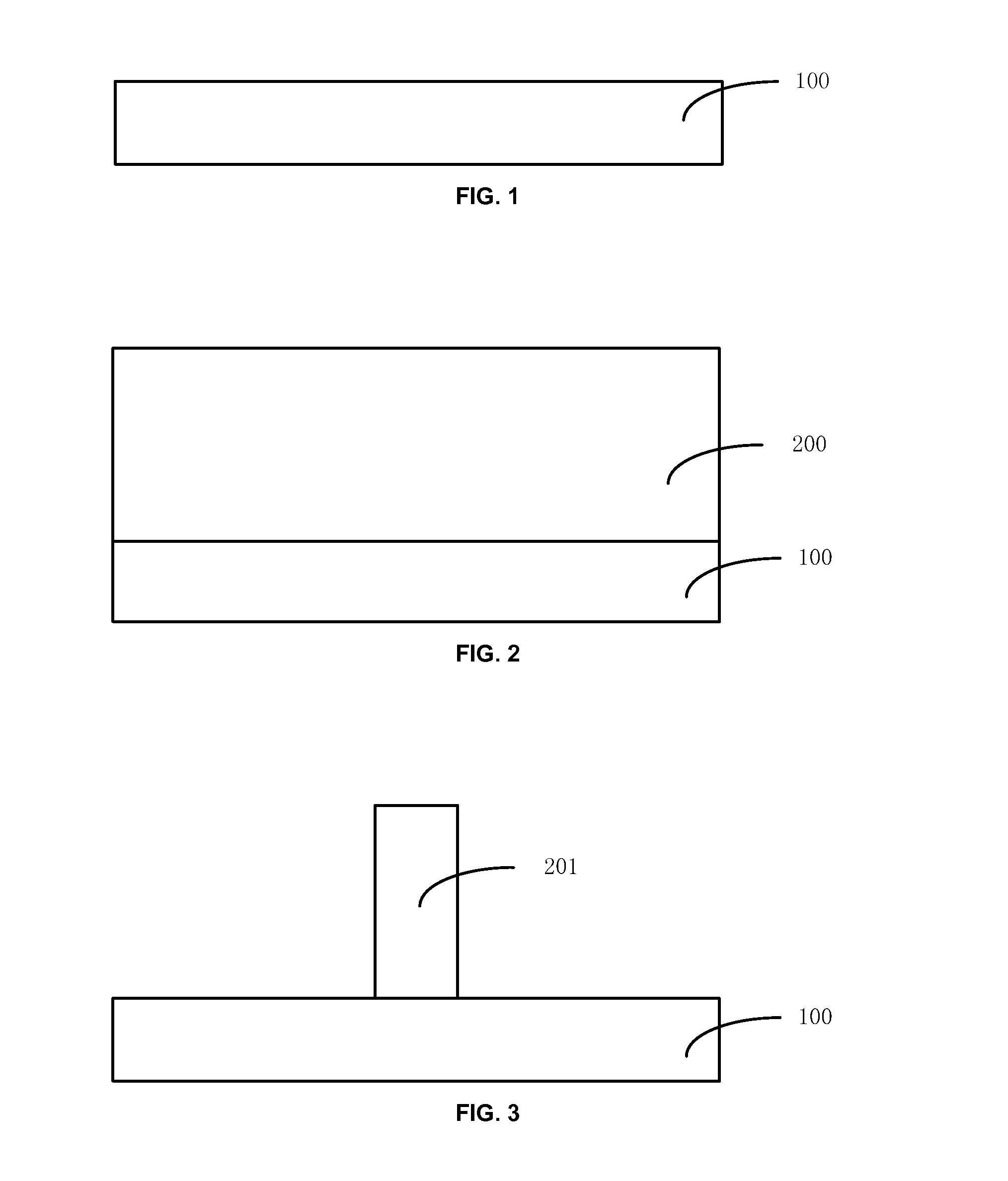

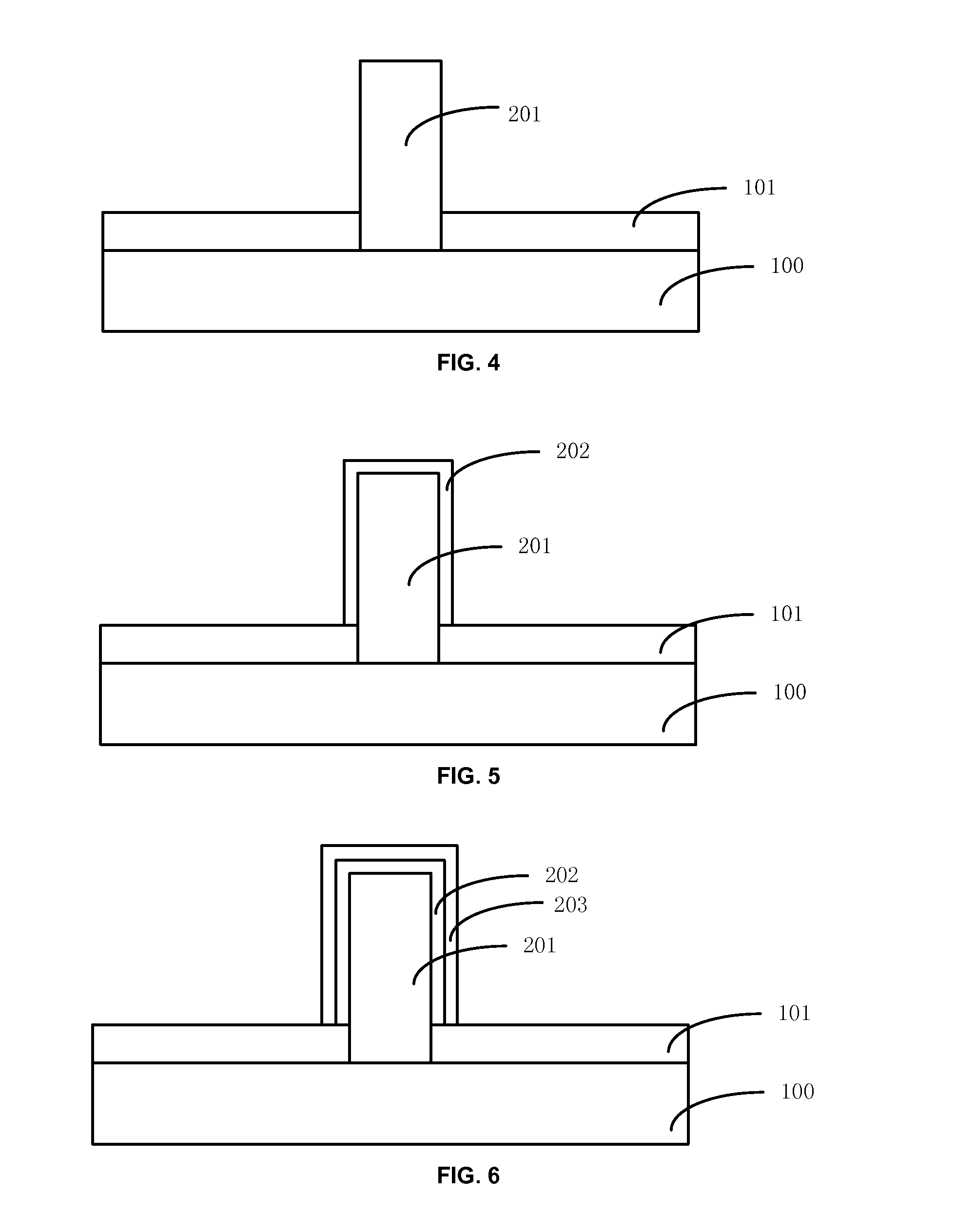

A method of depositing one or more epitaxial material layers, a device structure formed using the method and a system for performing the method are disclosed. Exemplary methods include coating a surface of a reaction chamber with a precoat material, processing a number of substrates, and then cleaning the reaction chamber.

Owner:ASM IP HLDG BV

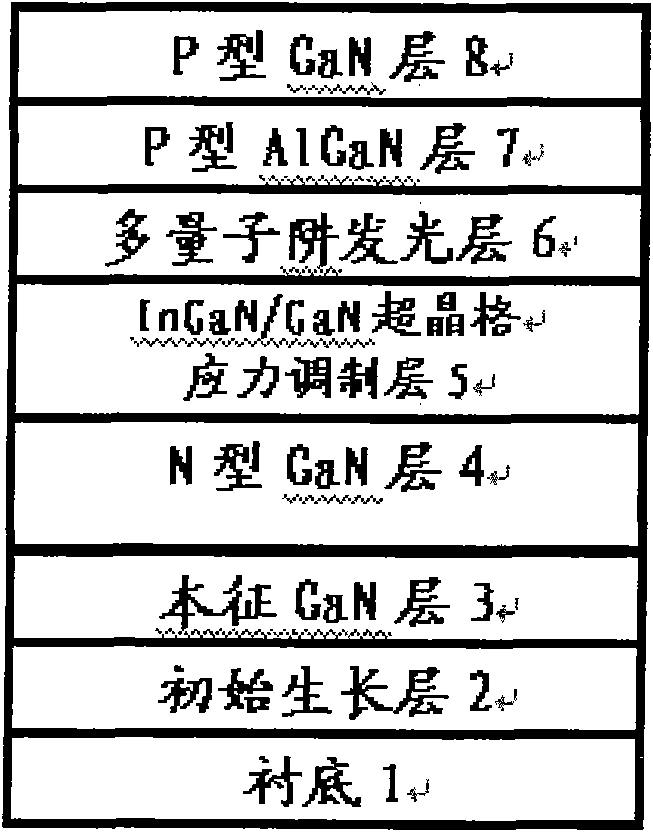

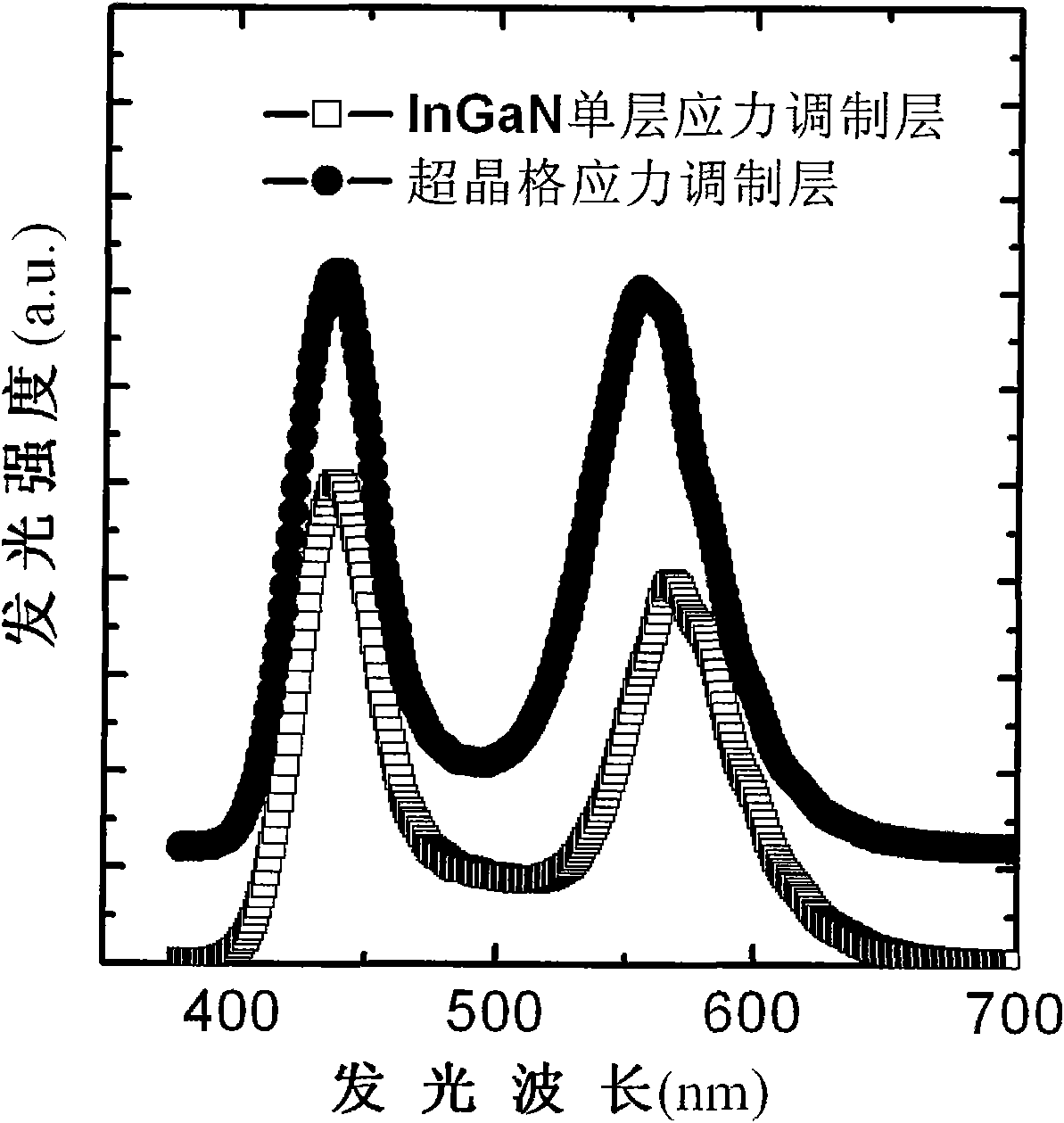

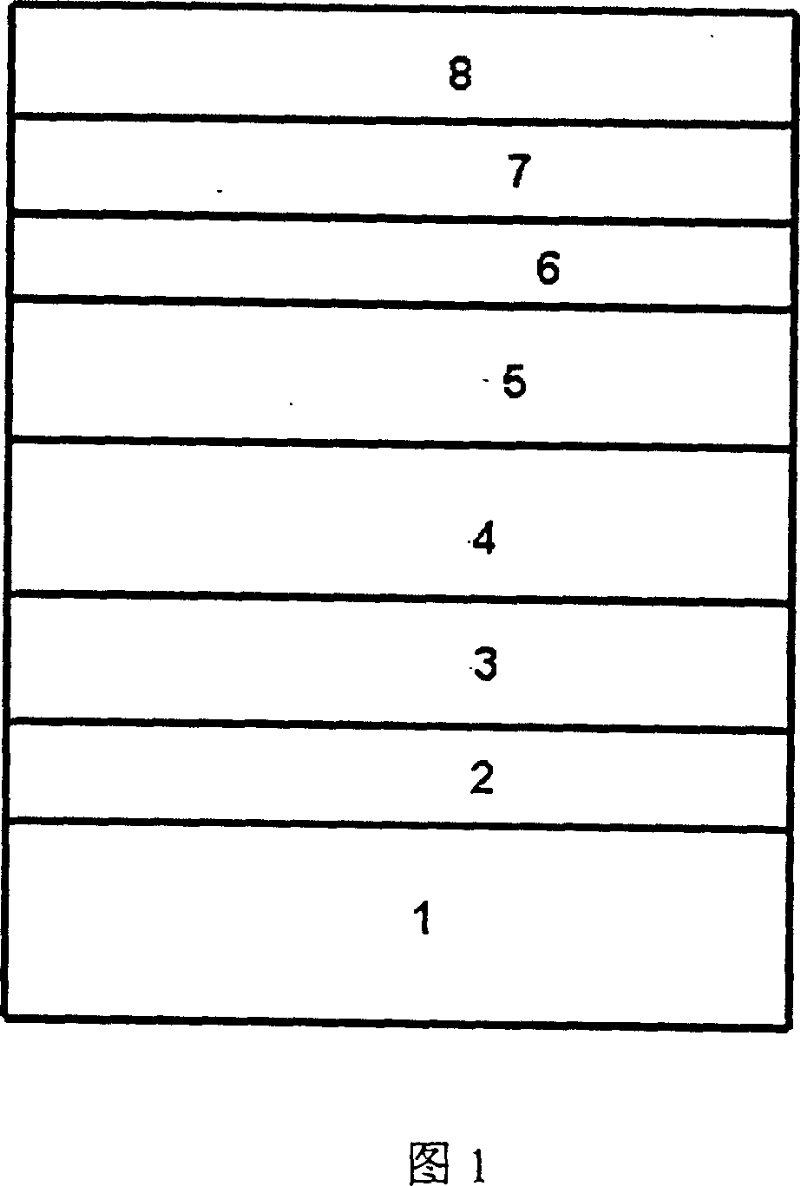

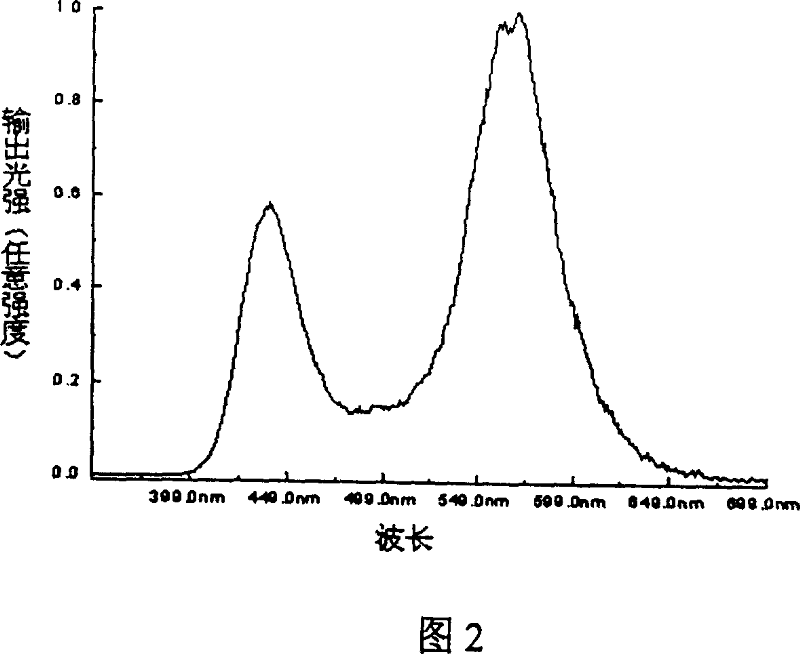

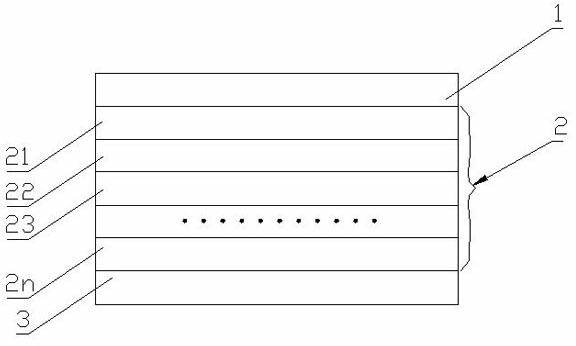

GaN-based Single chip white light emitting diode epitaxial material

InactiveCN101685844AReduce dislocationImprove luminous efficiencySemiconductor devicesStress relaxationWavelength

The invention relates to GaN-based Single chip white light emitting diode epitaxial material comprising a substrate and also comprising an initial growth layer, an intrinsic GaN buffer layer, an n-type GaN layer, a stress relaxation layer, an InGaN multiple quantum well structure light emitting layer, a p-type AlGaN sandwich layer and a p-type GaN layer which grow in sequence on the substrate. Thestress relaxation layer is an InGaN / GaN superlattice stress modulation layer which comprises InGaN layers and GaN layers, which are grown alternatively; the InGaN layers and GaN layers have the growth cycle of 6-500 and the corresponding thickness of 10 nm to 3 Mum; and the In components in the InGaN layers are in the range of 1-35 percent. Because the stress-relaxed InGaN / GaN superlattice stressmodulation layer is added between the n-type GaN layer and a multiple quantum light emitting layer, the In segregation effect is strengthened, InGaN quantum dots with different components are formed,and the mixing of different-wave light emitted by the InGaN quantum dots realizes the white light emitting. The cost of the white light emitting diode is reduced radically, the light emitting efficiency and the light using efficiency are increased and the integral performance of the white light emitting diode is improved.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

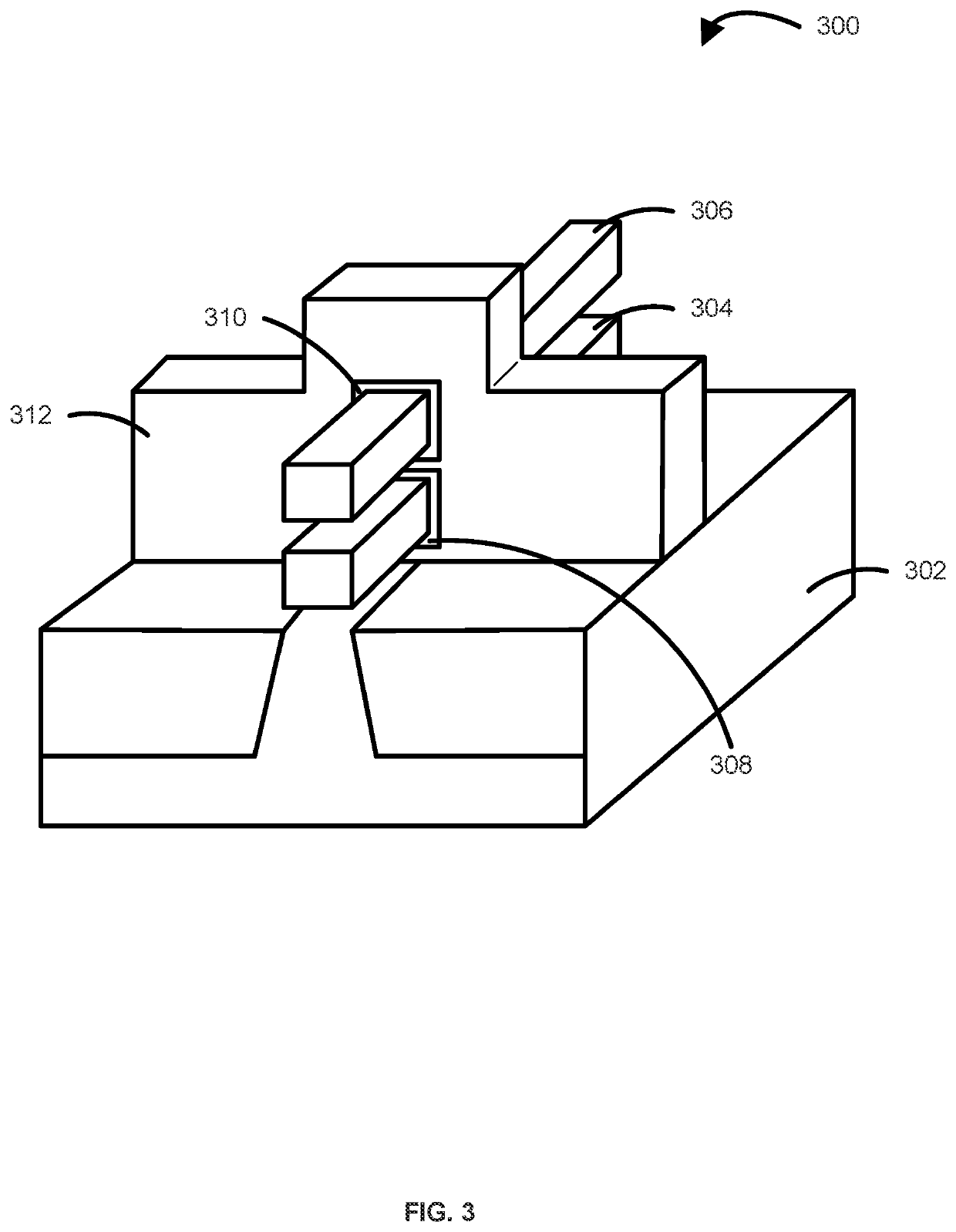

Multi-gate device and method of fabrication thereof

A method of semiconductor device fabrication is described that includes forming a first fin extending from a substrate. The first fin has a source / drain region and a channel region and the first fin is formed of a first stack of epitaxial layers that includes first epitaxial layers having a first composition interposed by second epitaxial layers having a second composition. The method also includes removing the second epitaxial layers from the source / drain region of the first fin to form first gaps, covering a portion of the first epitaxial layers with a dielectric layer and filling the first gaps with the dielectric material and growing another epitaxial material on at least two surfaces of each of the first epitaxial layers to form a first source / drain feature while the dielectric material fills the first gaps.

Owner:TAIWAN SEMICON MFG CO LTD

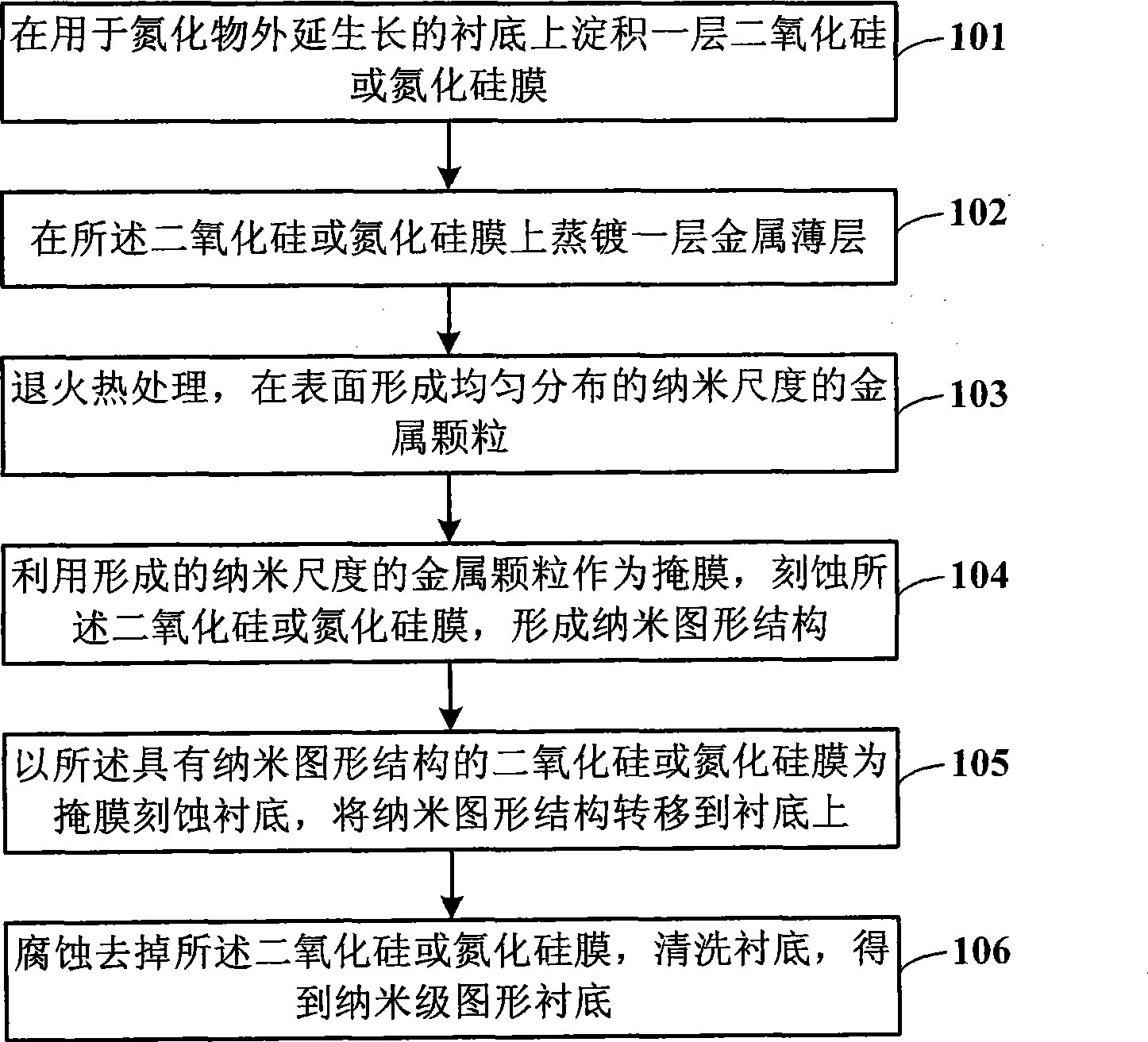

Method for preparing nano-scale pattern substrate for nitride epitaxial growth

InactiveCN101373714AReduce dislocation densityImprove crystal qualitySemiconductor/solid-state device manufacturingThin metalEpitaxial material

The invention relates to the semiconductor technical field and discloses a method for manufacturing a nanometer pattern substrate used for the epitaxial growth of a nitride. The method comprises the followings steps: settling a layer of silicon dioxide or silicon nitride film on a substrate used for the epitaxial growth of the nitride; the silicon dioxide or silicon nitride film is coated with a layer of thin metal layer through vapor deposition; conducting the annealing heat treatment, and forming uniformly distributed nano-scaled metal particles; utilizing the formed nano-scaled metal particles as masks to etch the silicon dioxide or silicon nitride film so as to form a nanometer pattern structure; using the silicon dioxide or silicon nitride film with the nanometer pattern structure as a mask etching substrate to transfer the nanometer pattern structure of the substrate; and etching to remove the silicon dioxide or silicon nitride film, cleaning the substrate, and obtaining the nanometer pattern substrate. The invention can reduce the dislocation density in the epitaxial layer of the nitride, improve the crystal quality of epitaxial materials, improve the performance of devices and help to realize the scaled and large area manufacture.

Owner:UNILUMIN GRP

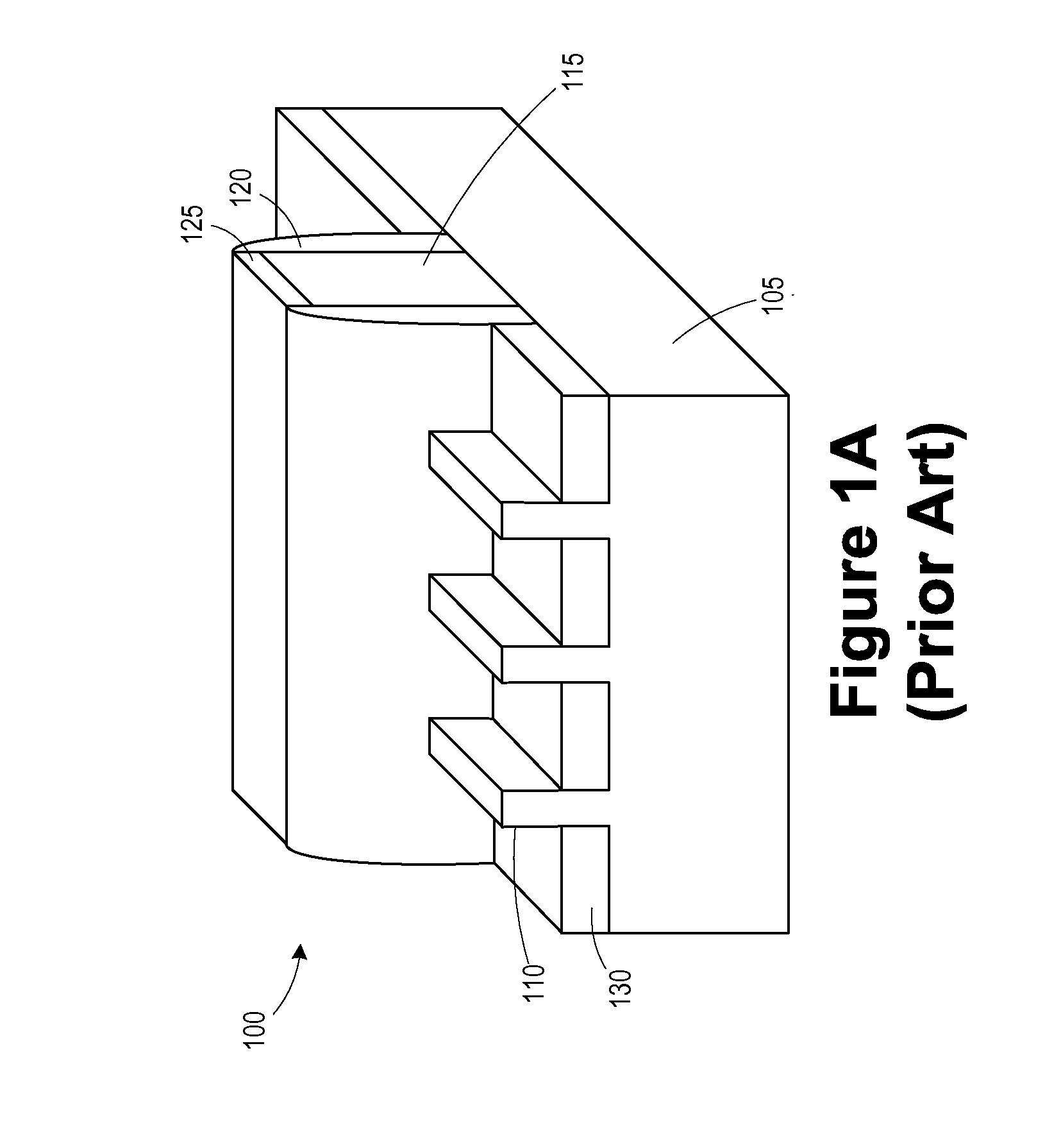

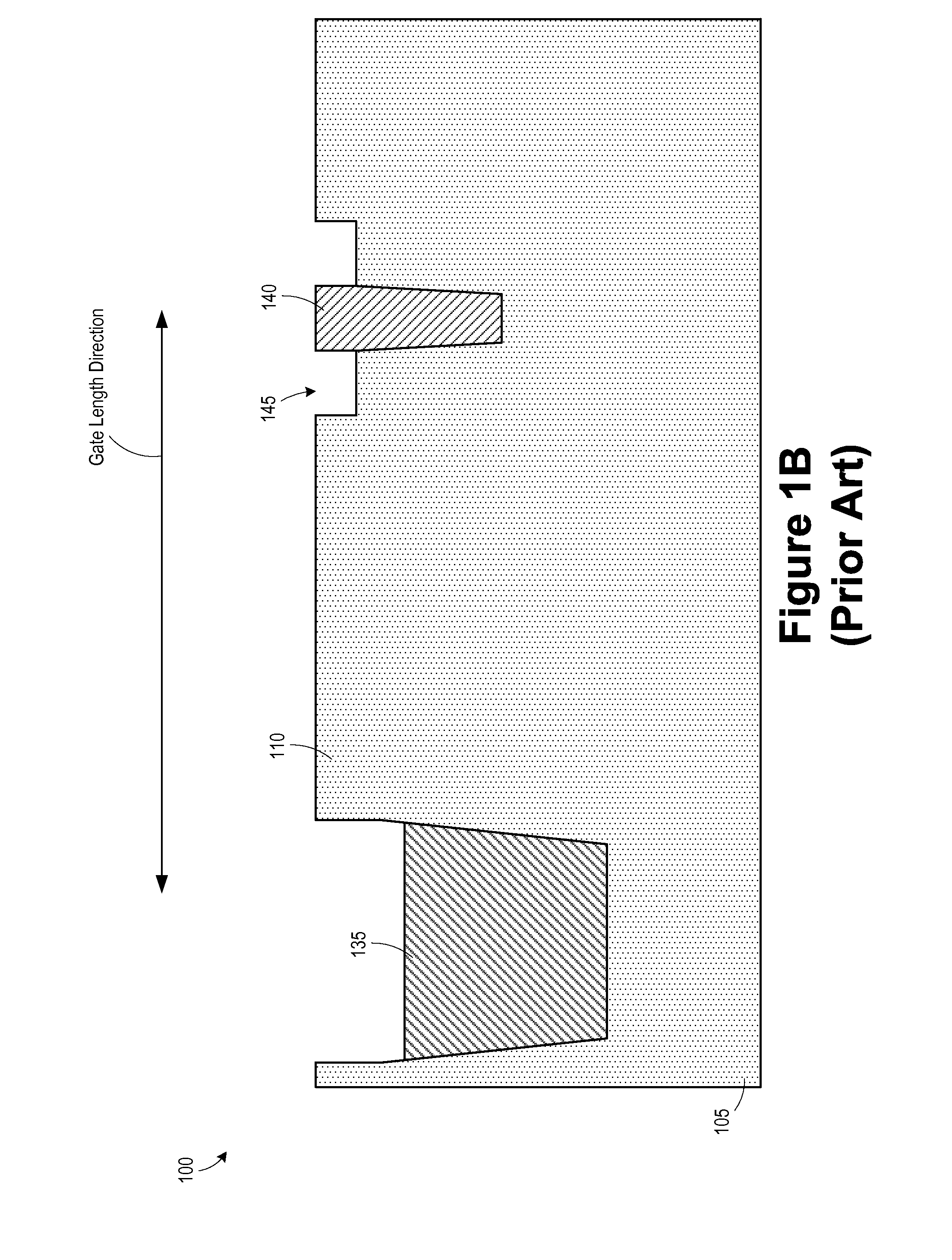

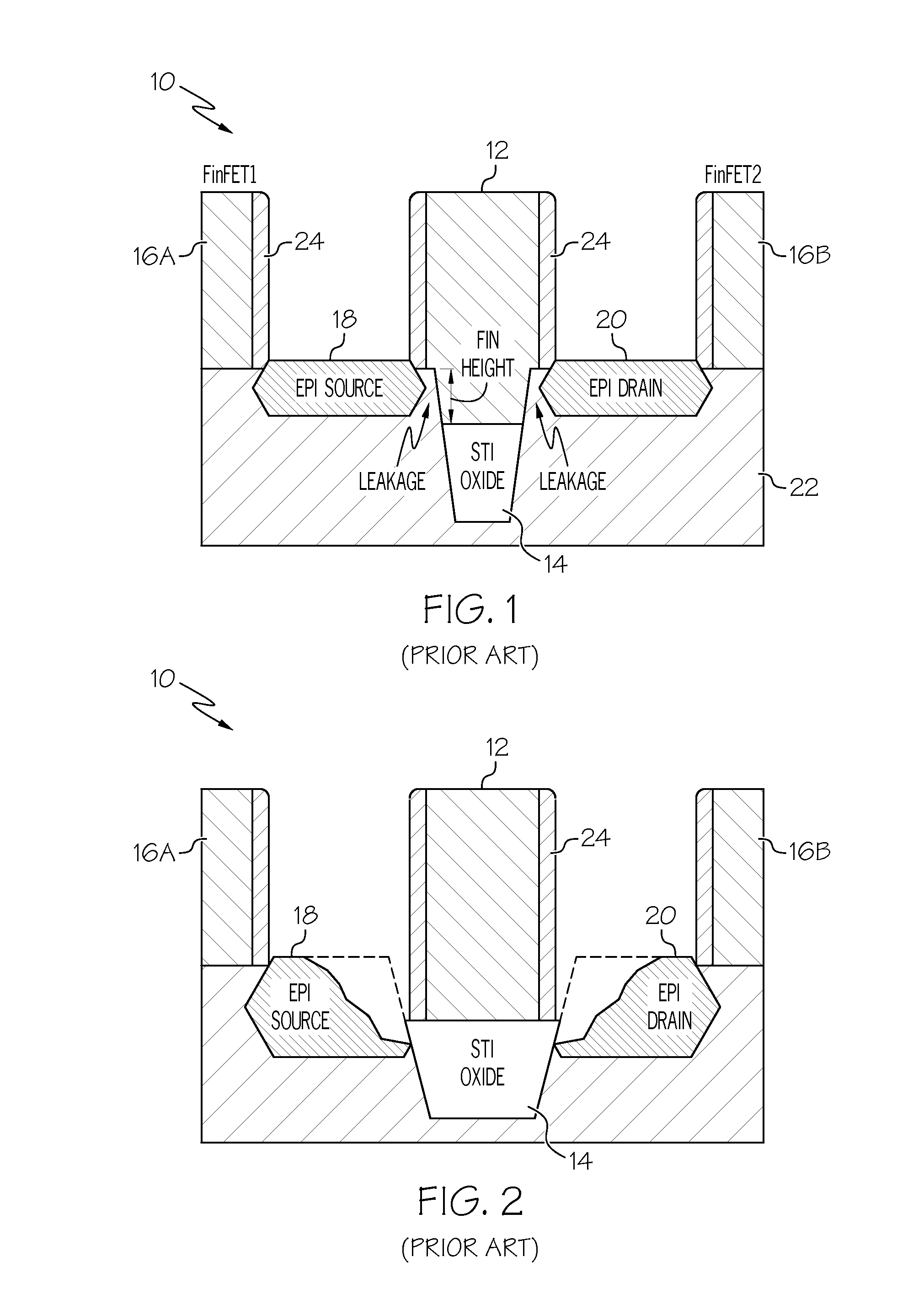

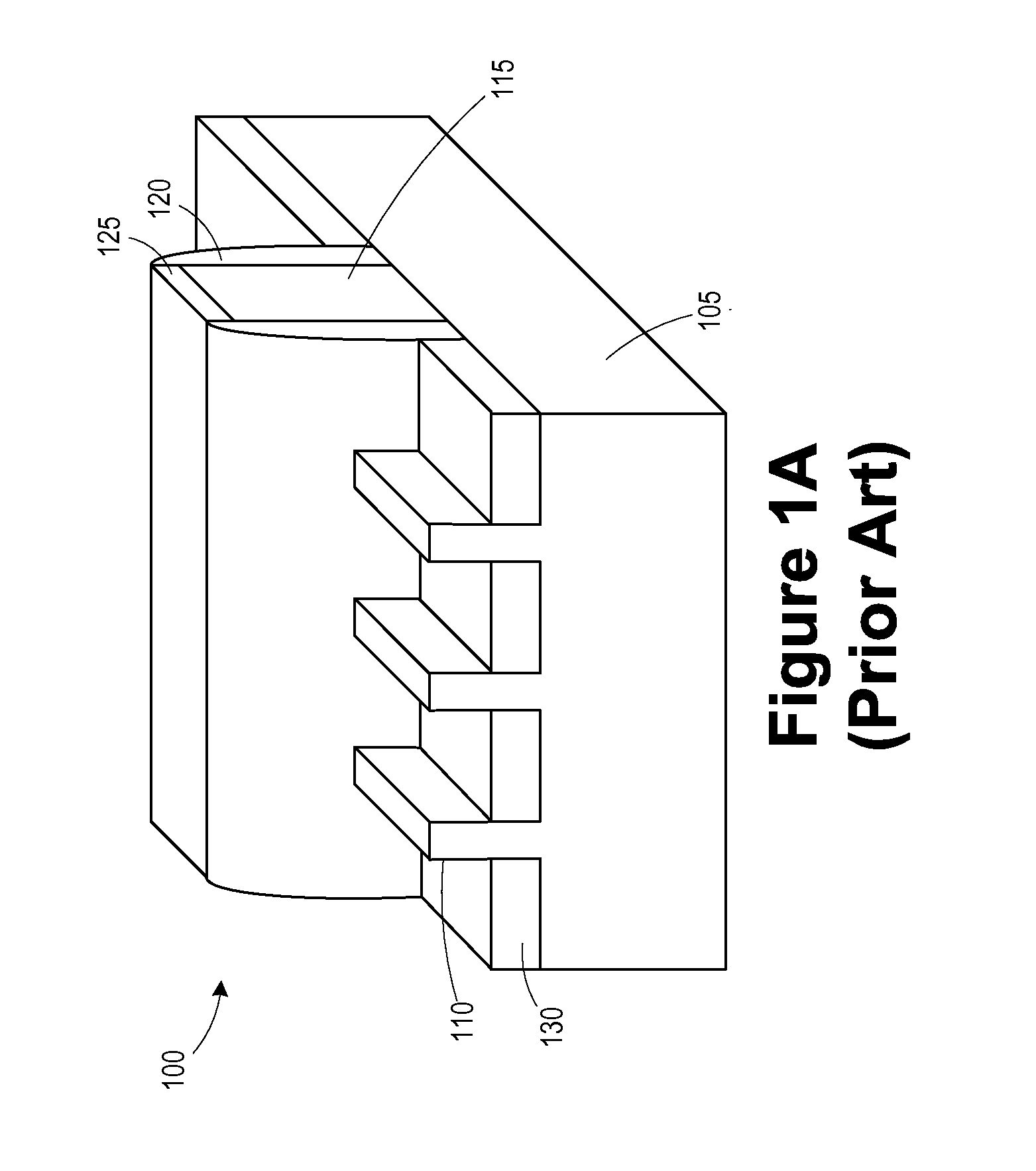

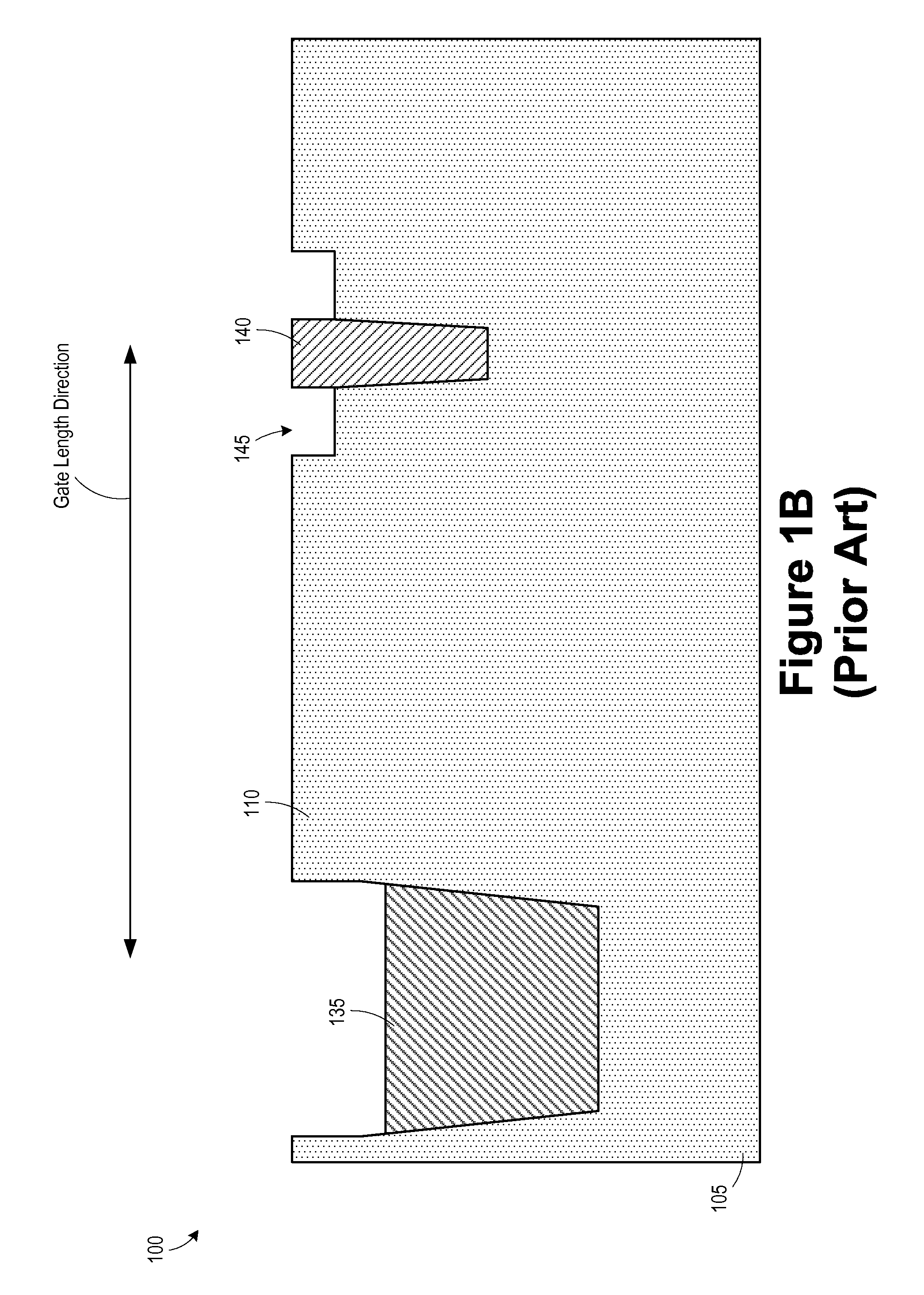

Method for forming single diffusion breaks between finfet devices and the resulting devices

A method includes forming a fin in a semiconductor substrate. A plurality of sacrificial gate structures are formed above the fin. A selected one of the sacrificial gate structures is removed to define a first opening that exposes a portion of the fin. An etch process is performed through the first opening on the exposed portion of the fin to define a first recess in the fin. The first recess is filled with a dielectric material to define a diffusion break in the fin. A device includes a fin defined in a substrate, a plurality of gates formed above the fin, a plurality of recesses filled with epitaxial material defined in the fin, and a diffusion break defined at least partially in the fin between two of the recesses filled with epitaxial material and extending above the fin.

Owner:GLOBALFOUNDRIES US INC

Low Resistance Source Drain Contact Formation

ActiveUS20170213889A1Reduce contact resistanceIncrease volumeSemiconductor/solid-state device manufacturingSemiconductor devicesContact formationDielectric

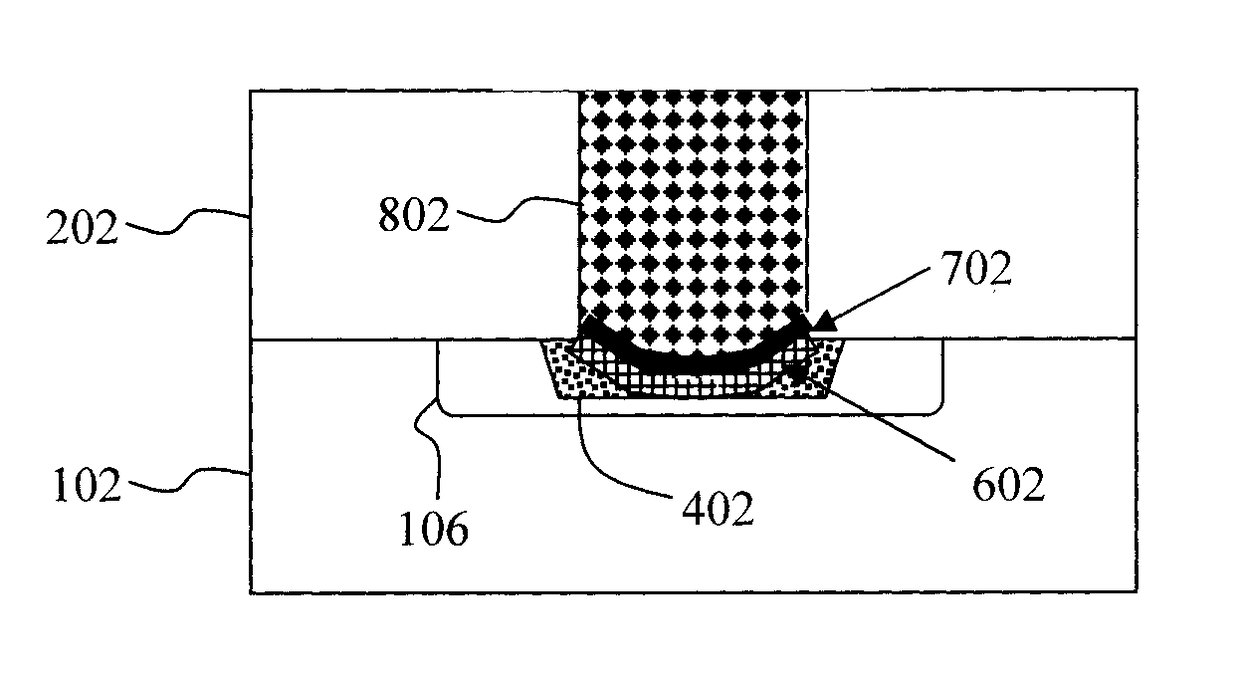

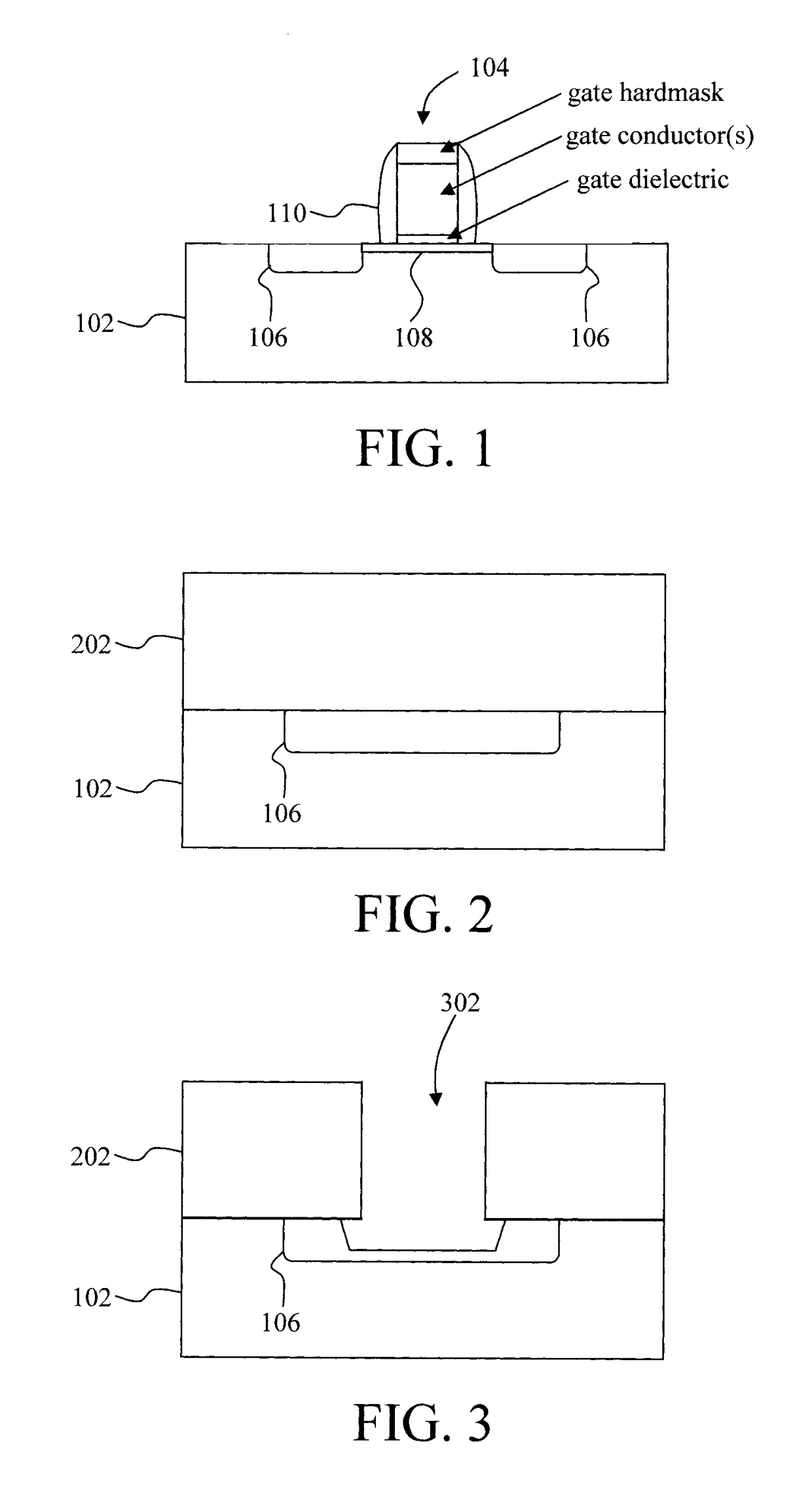

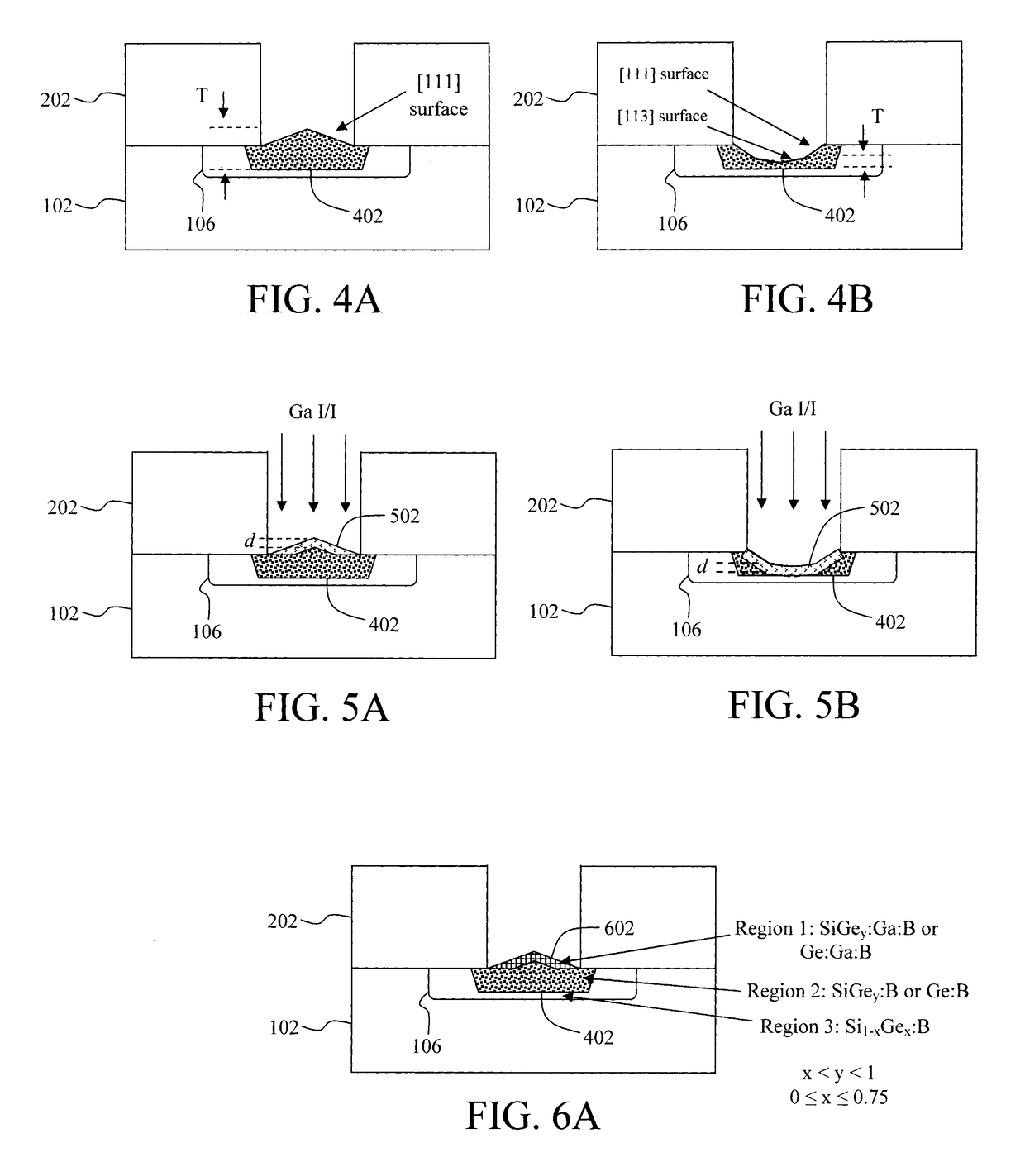

Techniques for forming Ga-doped source drain contacts in Ge-based transistors are provided. In one aspect, a method for forming Ga-doped source and drain contacts includes the steps of: depositing a dielectric over a transistor; depositing a dielectric over the transistor; forming contact trenches in the dielectric over, and extending down to, source and drain regions of the transistor; depositing an epitaxial material into the contact trenches; implanting gallium ions into the epitaxial material to form an amorphous gallium-doped layer; and annealing the amorphous gallium-doped layer under conditions sufficient to form a crystalline gallium-doped layer having a homogenous gallium concentration of greater than about 5×1020 at. / cm3. Transistor devices are also provided utilizing the present Ga-doped source and drain contacts.

Owner:IBM CORP +1

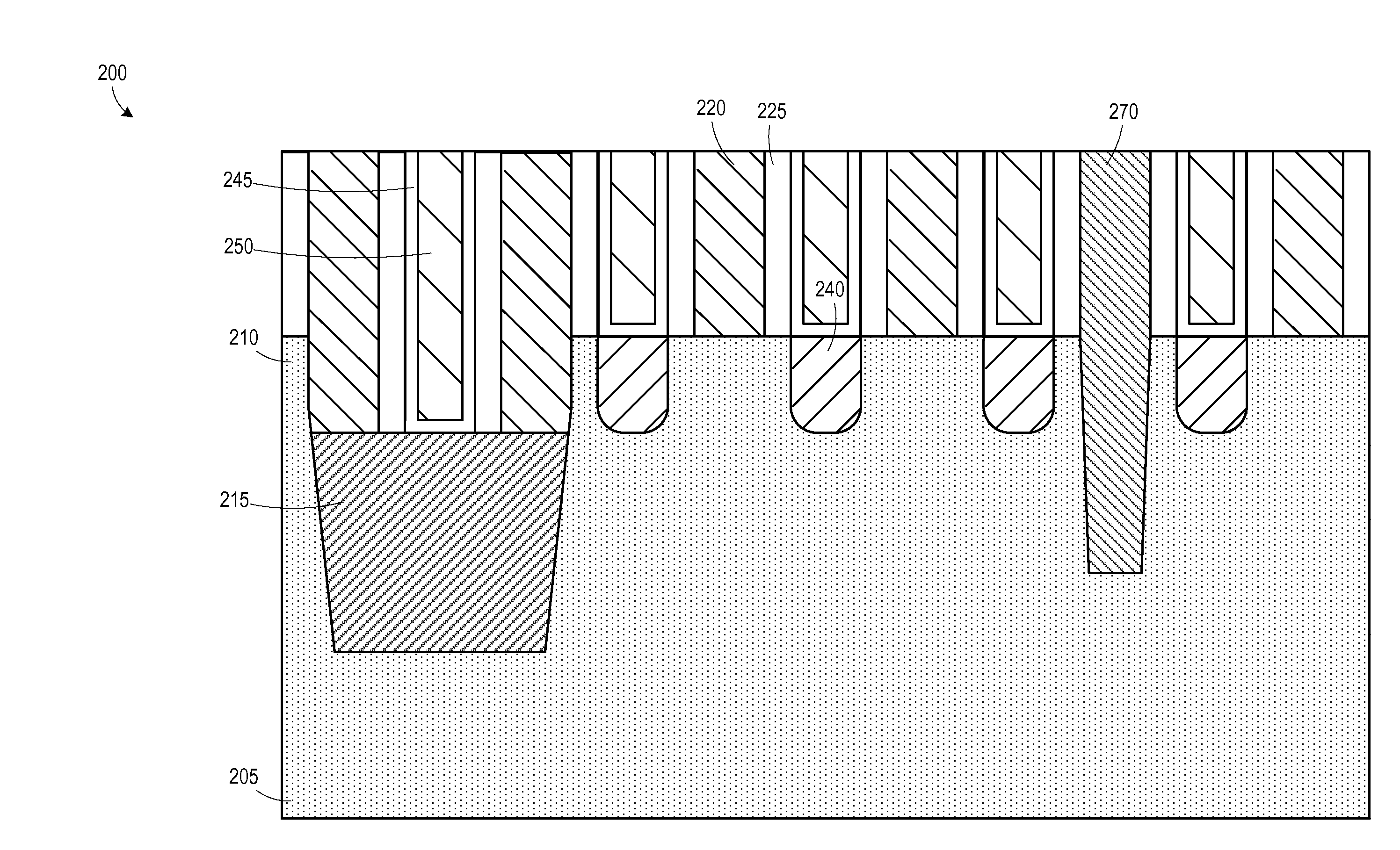

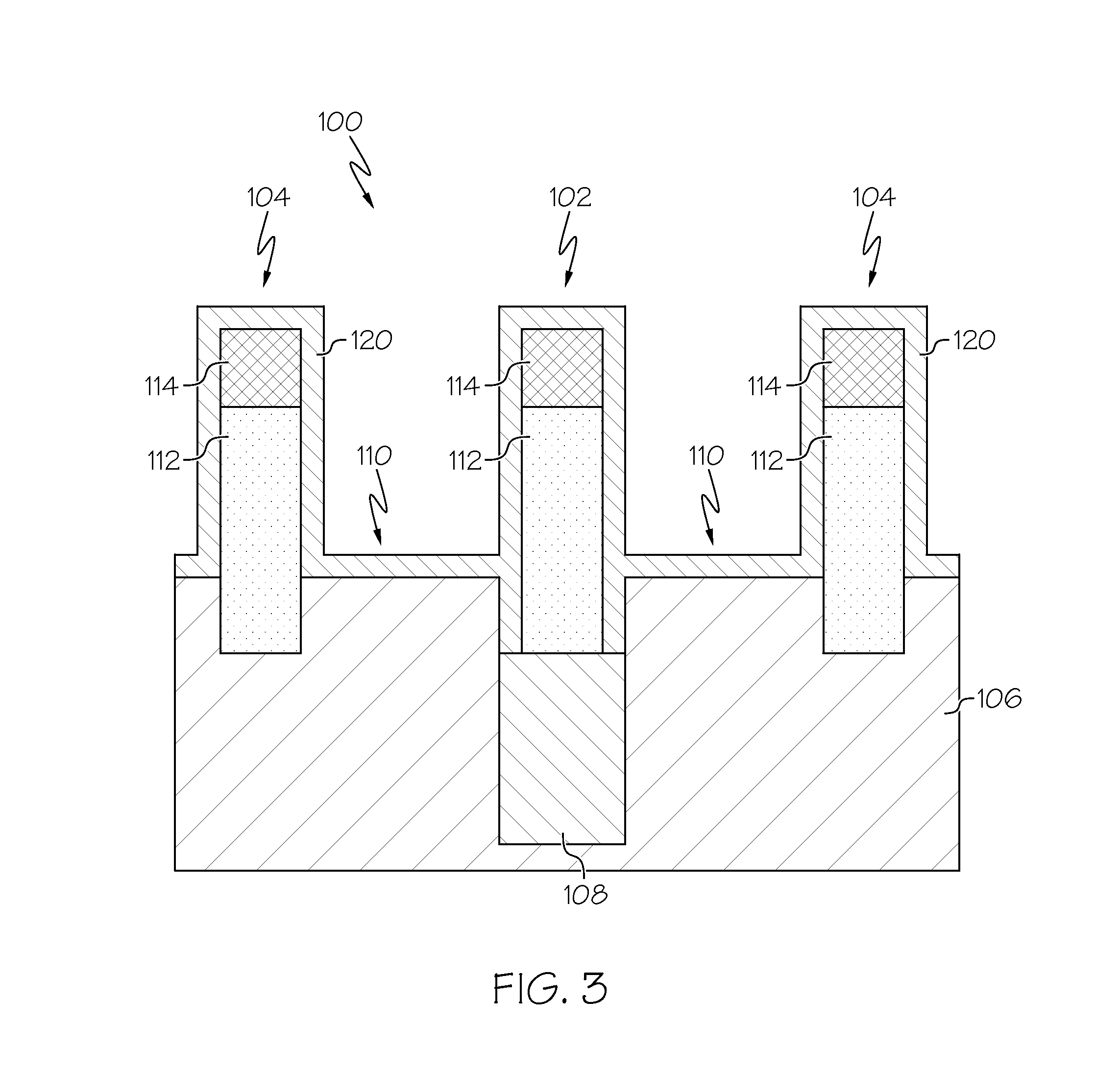

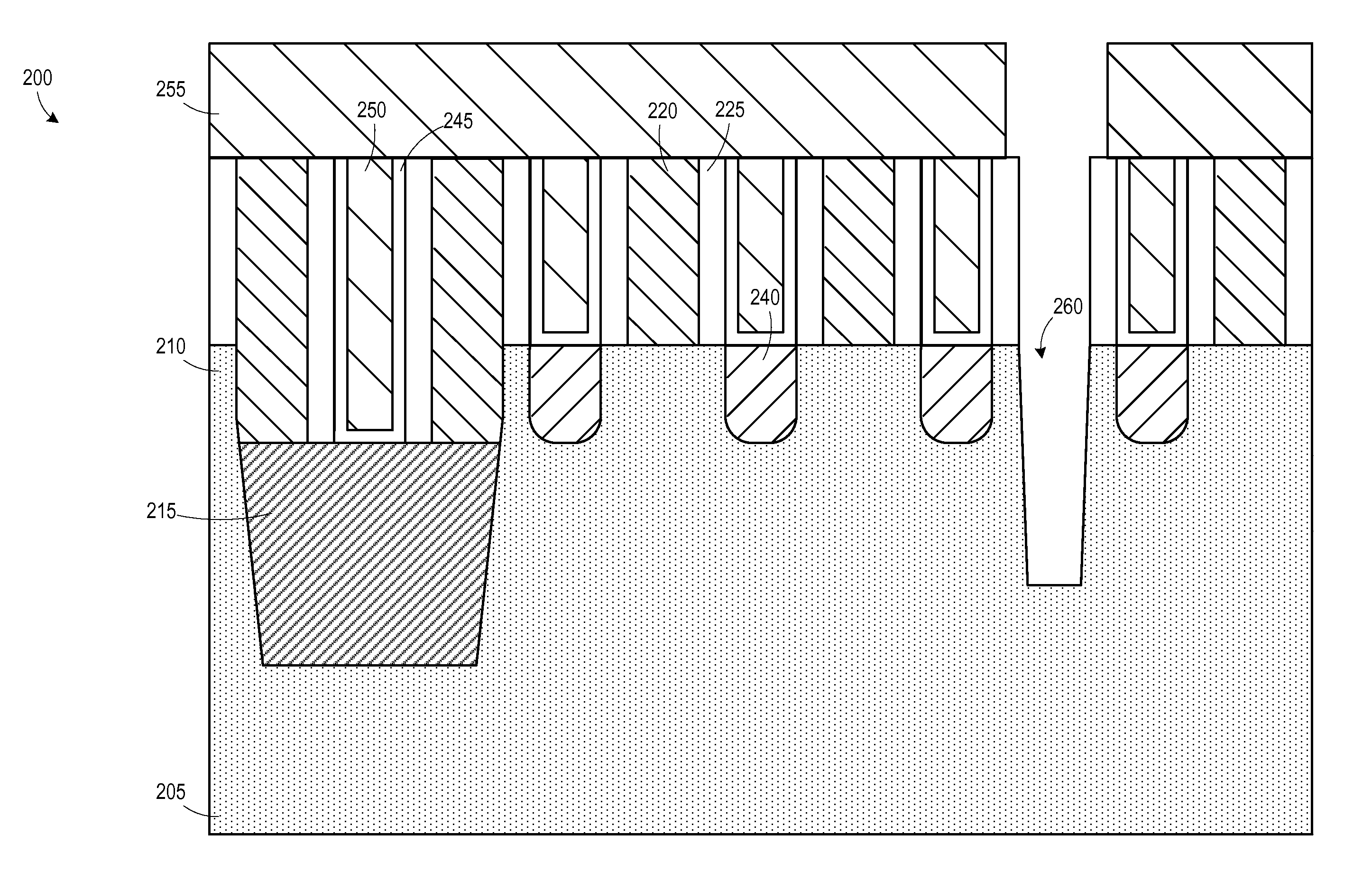

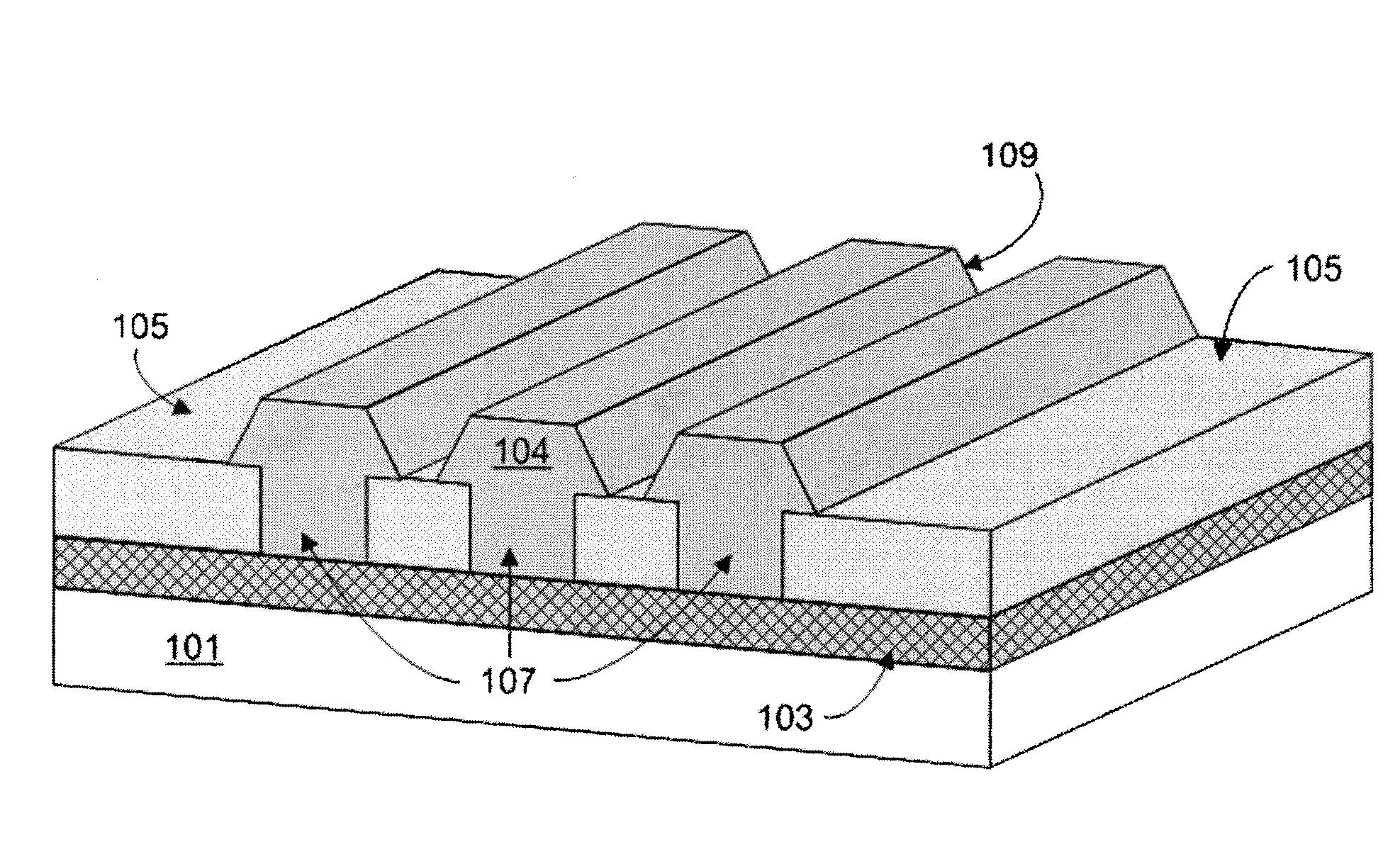

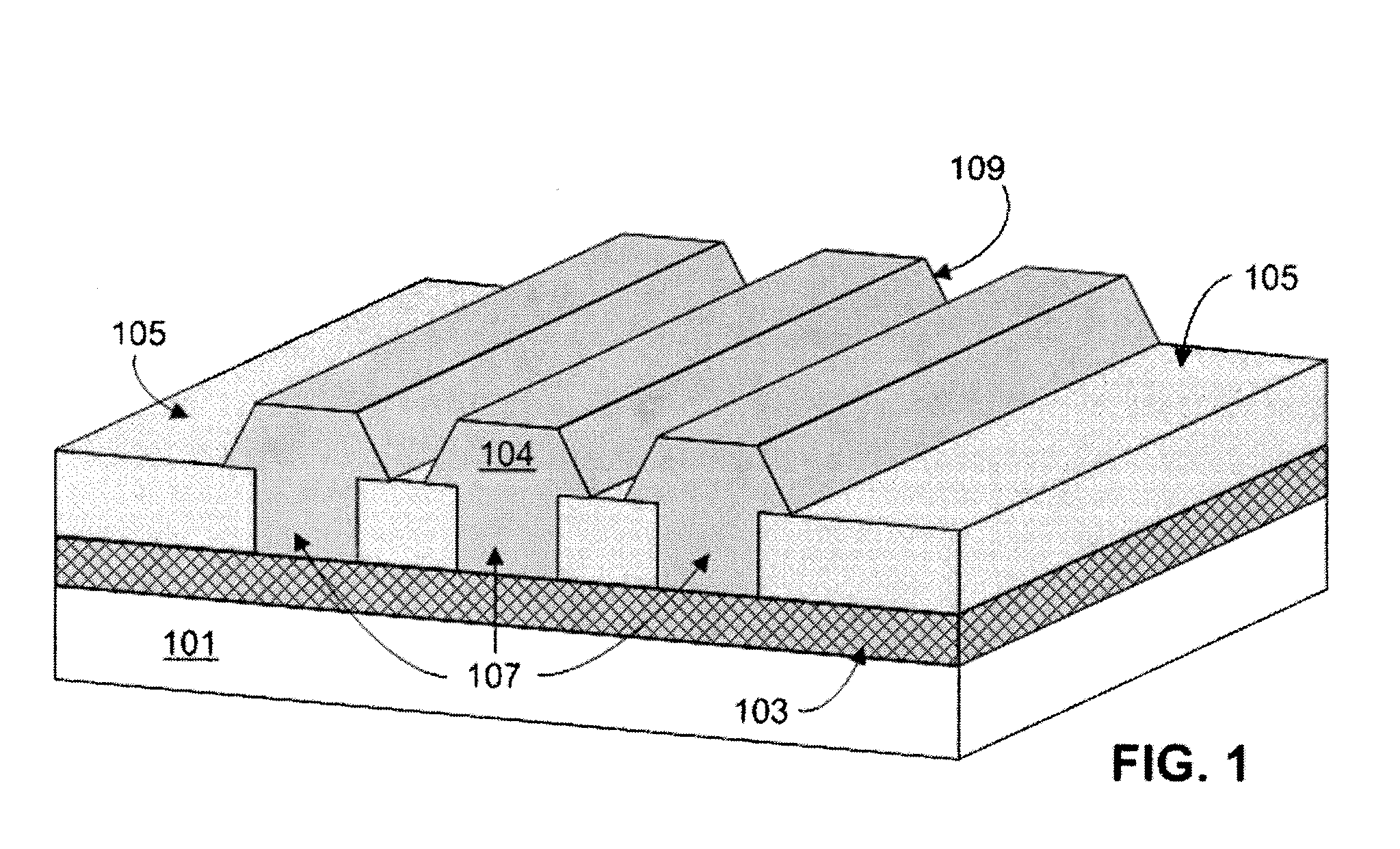

Epitaxial block layer for a fin field effect transistor device

ActiveUS20150021695A1Uniform growthSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEpitaxial material

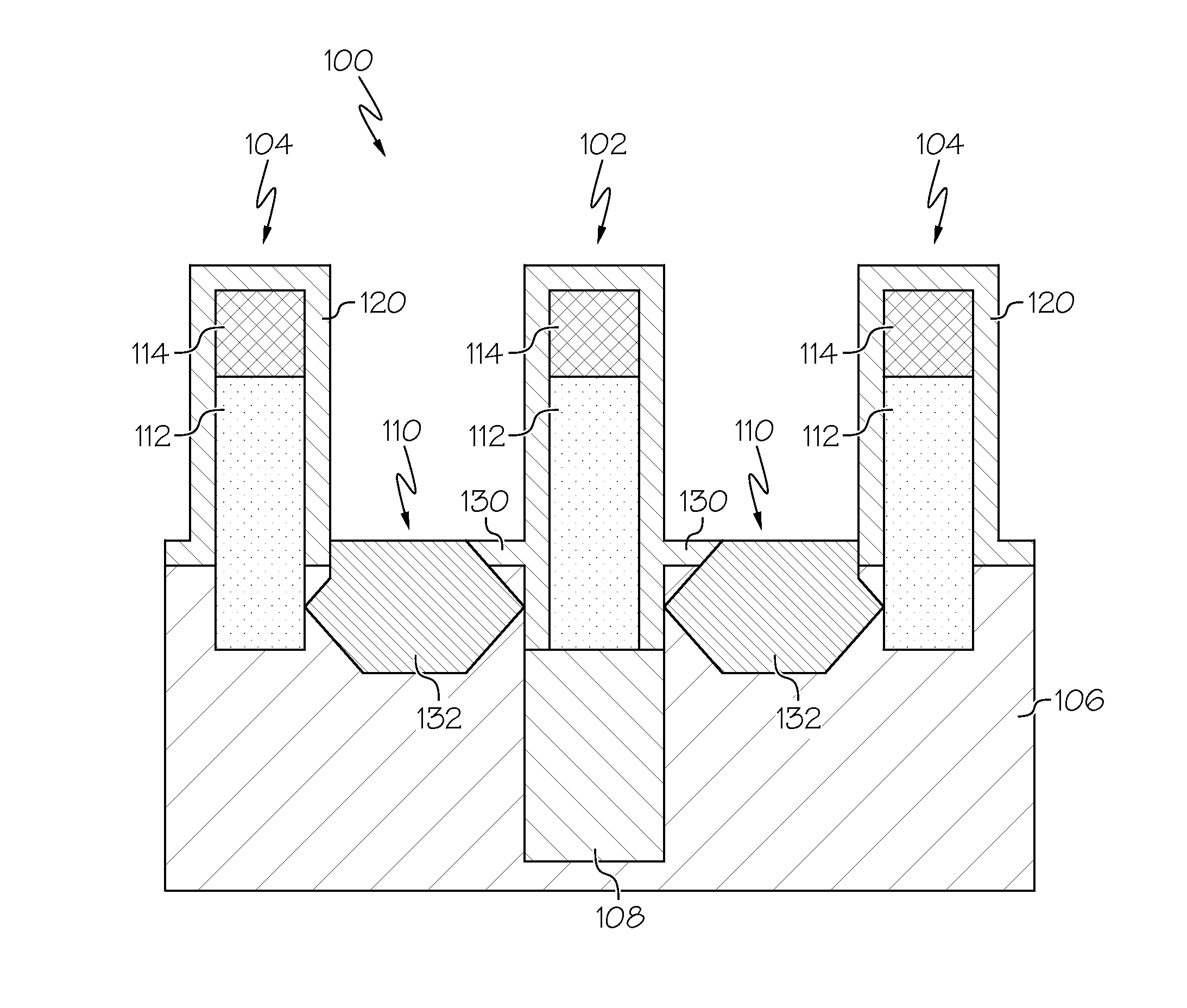

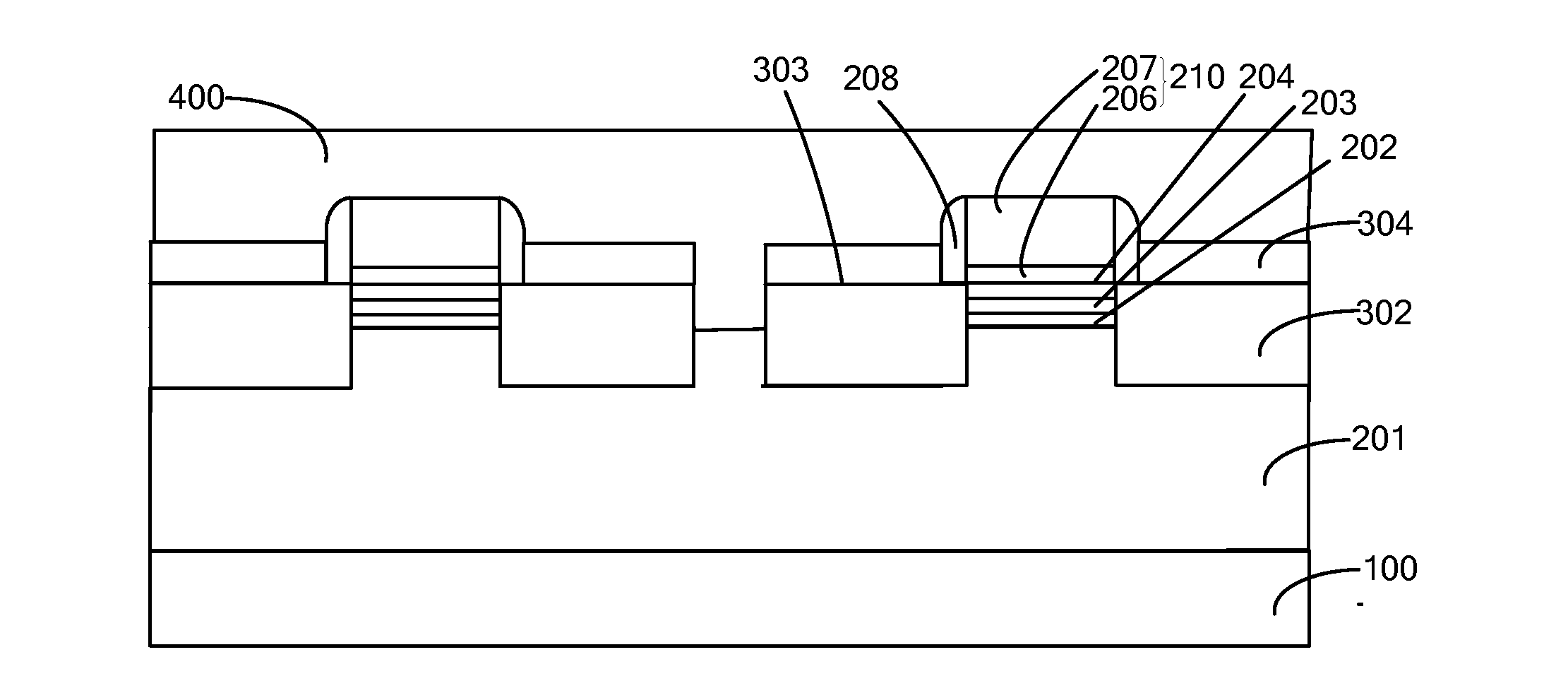

Approaches for enabling uniform epitaxial (epi) growth in an epi junction area of a semiconductor device (e.g., a fin field effect transistor device) are provided. Specifically, a semiconductor device is provided including a dummy gate and a set of fin field effect transistors (FinFETs) formed over a substrate; a spacer layer formed over the dummy gate and each of the set of FinFETs; and an epi material formed within a set of recesses in the substrate, the set of recesses formed prior to removal of an epi block layer over the dummy gate.

Owner:GLOBALFOUNDRIES US INC

Complementary metal-oxide-semiconductor device

InactiveUS20080116525A1Improve device performanceReliability performance be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

Three-dimensional quantum well transistor and fabrication method

ActiveUS20140203243A1Reduce resistanceImprove thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesQuantum wellEpitaxial material

Three dimensional quantum well transistors and fabrication methods are provided. A quantum well layer, a barrier layer, and a gate structure can be sequentially formed on an insulating surface of a fin part. The gate structure can be formed over the barrier layer and across the fin part. The QW layer and the barrier layer can form a hetero-junction of the transistor. A recess can be formed in the fin part on both sides of the gate structure to suspend a sidewall spacer. A source and a drain can be formed by growing an epitaxial material in the recess and the sidewall spacer formed on both sidewalls of the gate electrode can be positioned on surface of the source and the drain.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for forming single diffusion breaks between finFET devices and the resulting devices

A method includes forming a fin in a semiconductor substrate. A plurality of sacrificial gate structures are formed above the fin. A selected one of the sacrificial gate structures is removed to define a first opening that exposes a portion of the fin. An etch process is performed through the first opening on the exposed portion of the fin to define a first recess in the fin. The first recess is filled with a dielectric material to define a diffusion break in the fin. A device includes a fin defined in a substrate, a plurality of gates formed above the fin, a plurality of recesses filled with epitaxial material defined in the fin, and a diffusion break defined at least partially in the fin between two of the recesses filled with epitaxial material and extending above the fin.

Owner:GLOBALFOUNDRIES U S INC

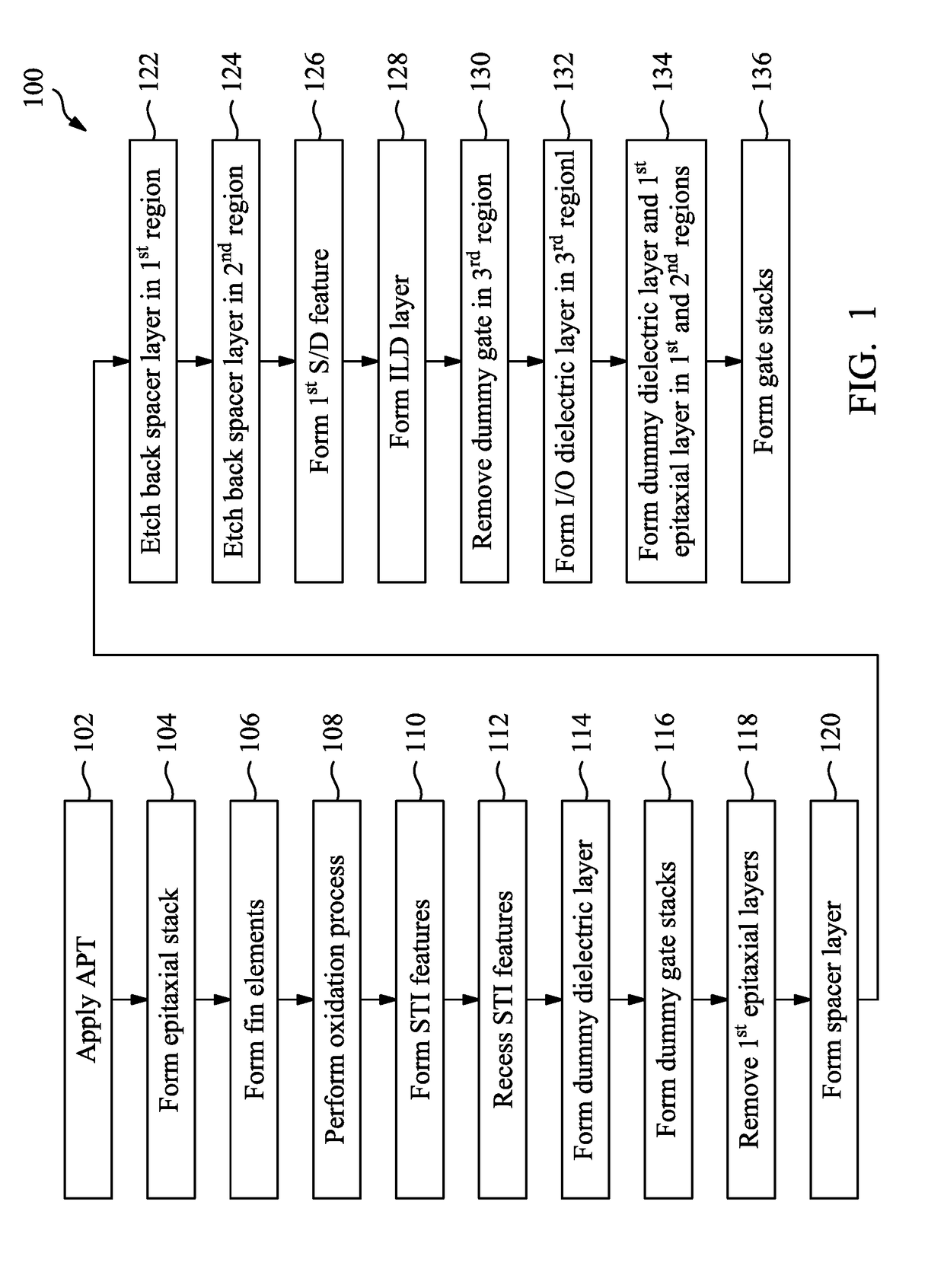

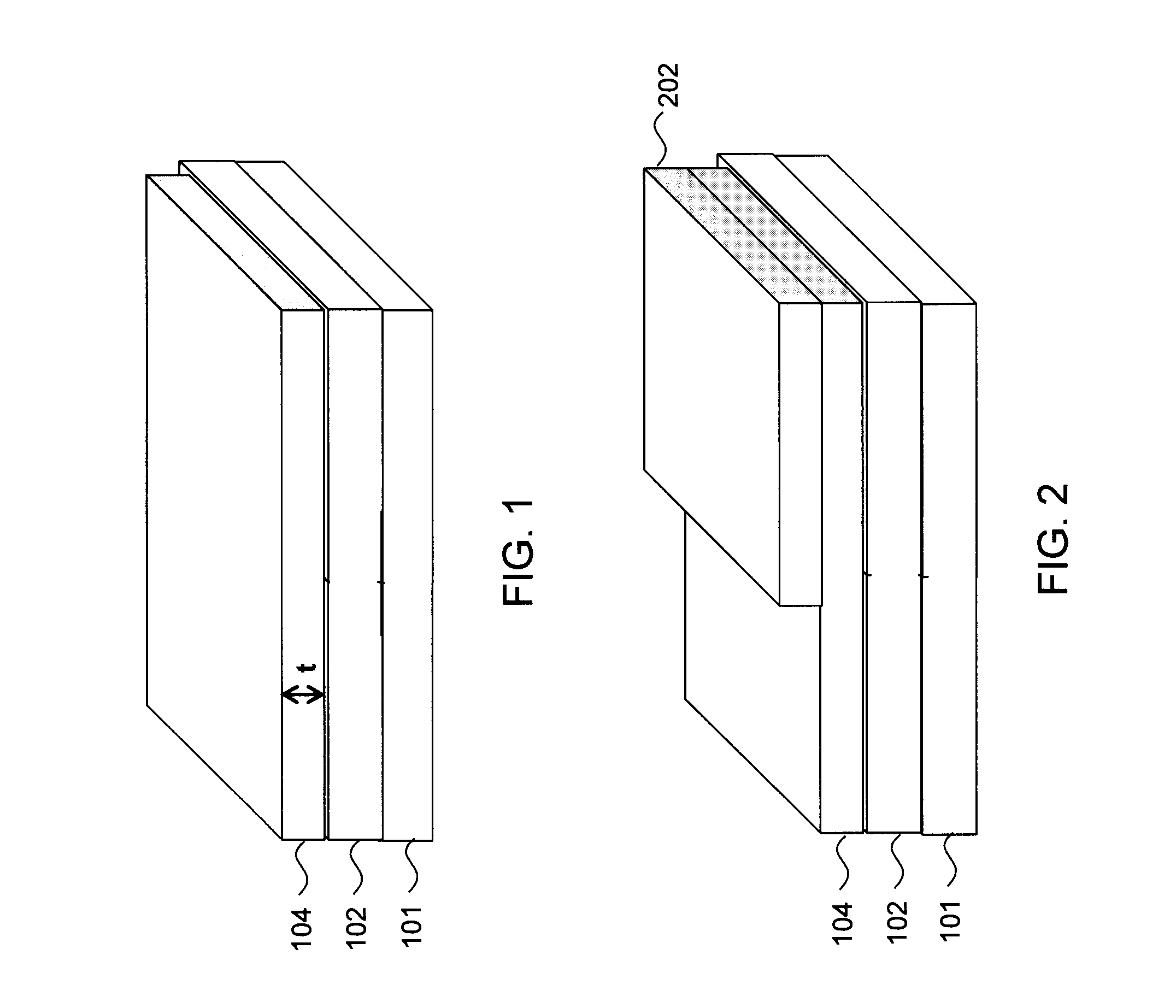

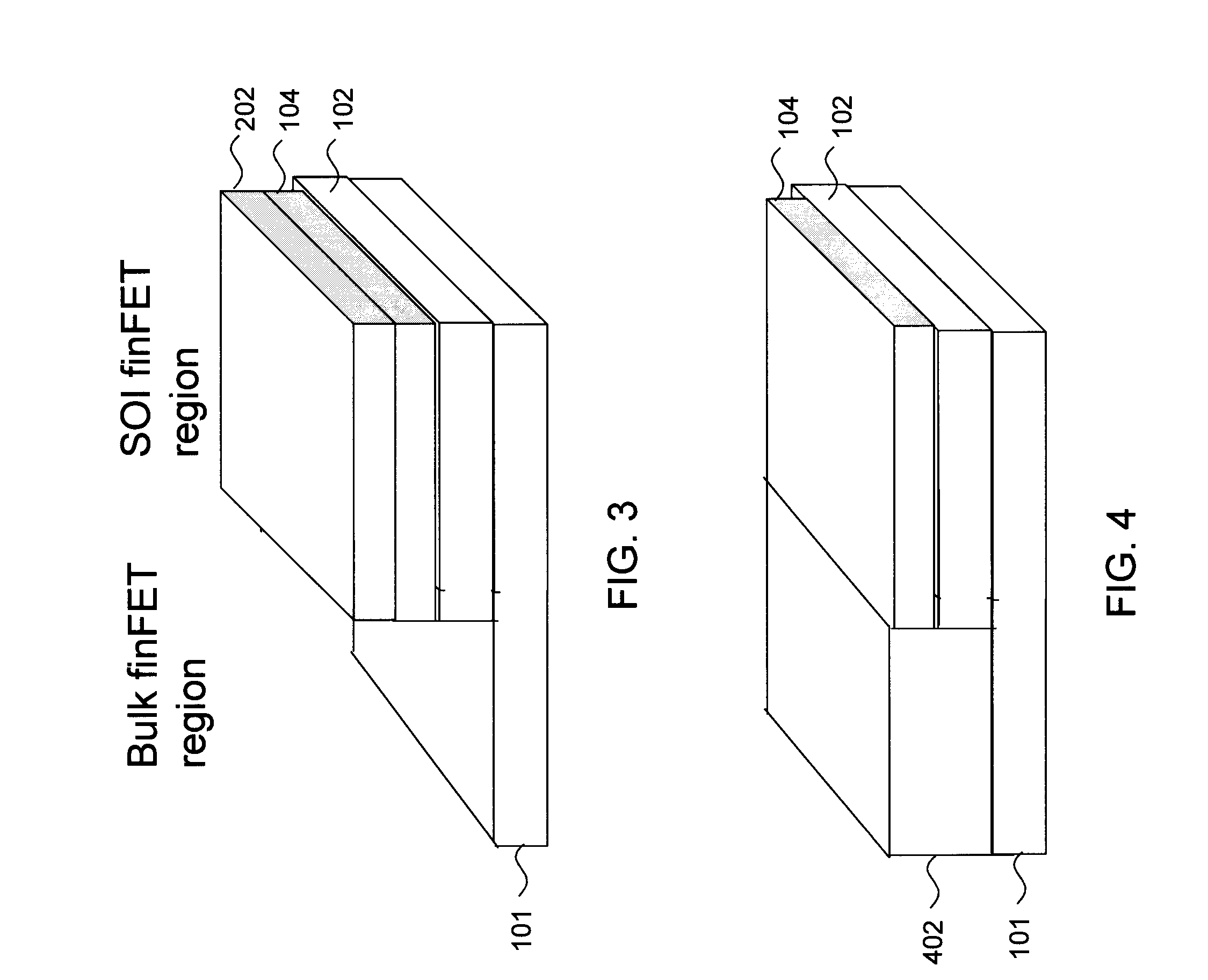

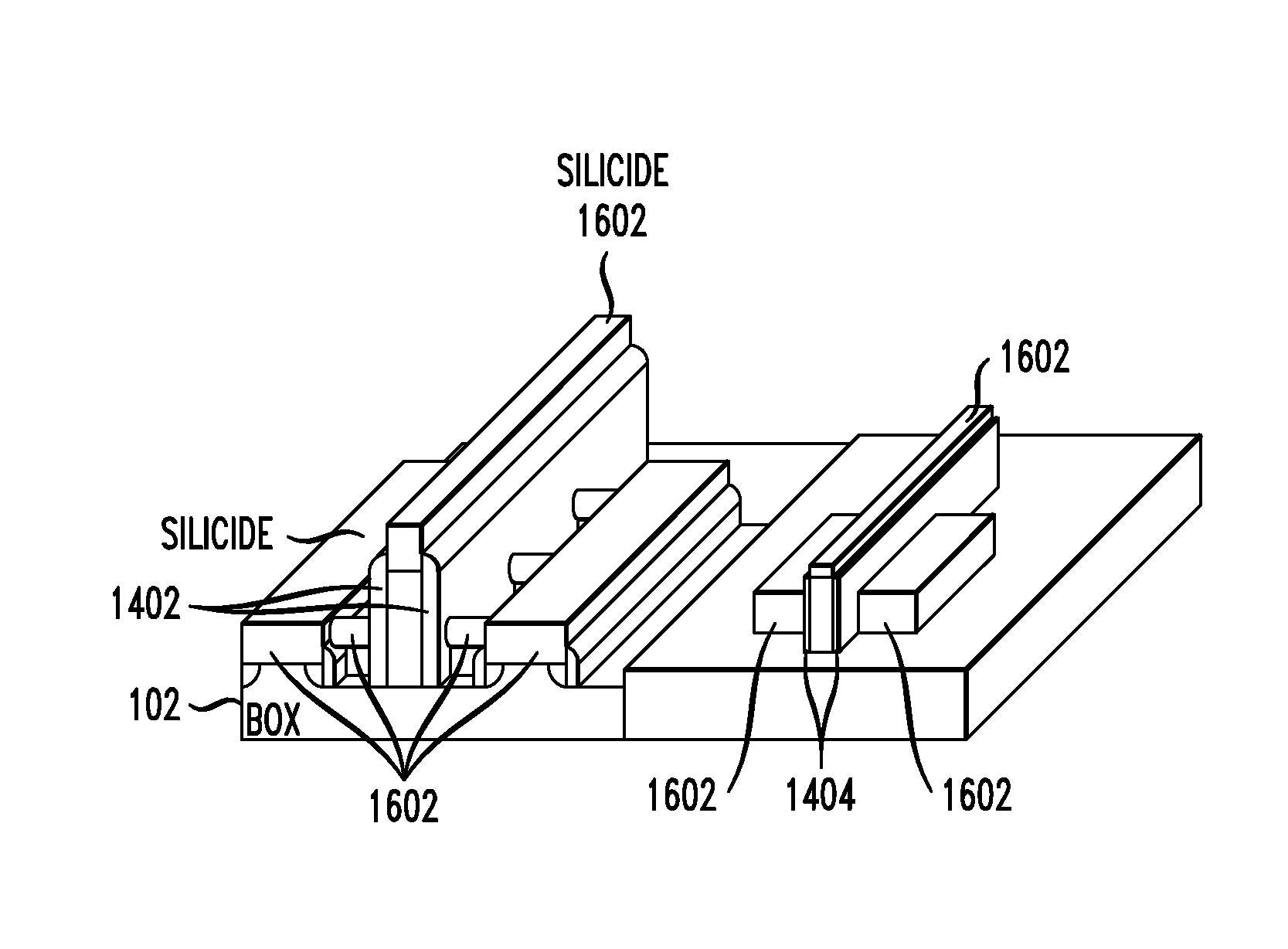

Bulk FinFET and SOI FinFET hybrid technology

InactiveUS8466012B1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSLithographic artist

Hybrid bulk finFET and SOI finFET devices and methods for fabrication thereof are provided. In one aspect, a method for fabricating a CMOS circuit having SOI finFET and bulk finFET devices includes the following steps. A wafer is provided having an active layer separated from a substrate by a BOX. Portions of the active layer and BOX are removed in a second region of the wafer so as to expose the substrate. An epitaxial material is grown in the second region of the wafer templated from the substrate. Fins are etched in the active layer and in the epitaxial material using fin lithography hardmasks. Gate stacks are formed covering portions of the fins which serve as channel regions of the SOI finFET / bulk finFET devices. An epitaxial material is grown on exposed portions of the fins which serves as source and drain regions of the SOI finFET / bulk finFET devices.

Owner:GLOBALFOUNDRIES INC

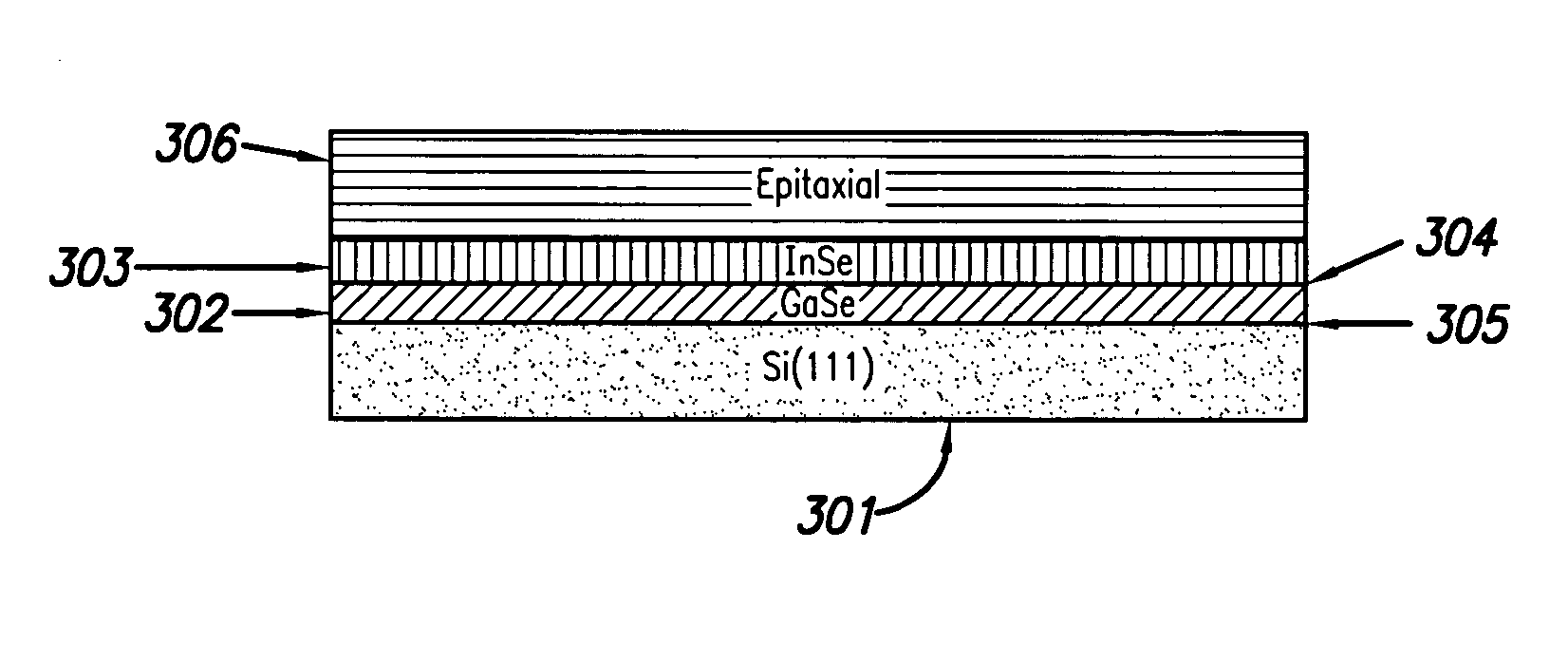

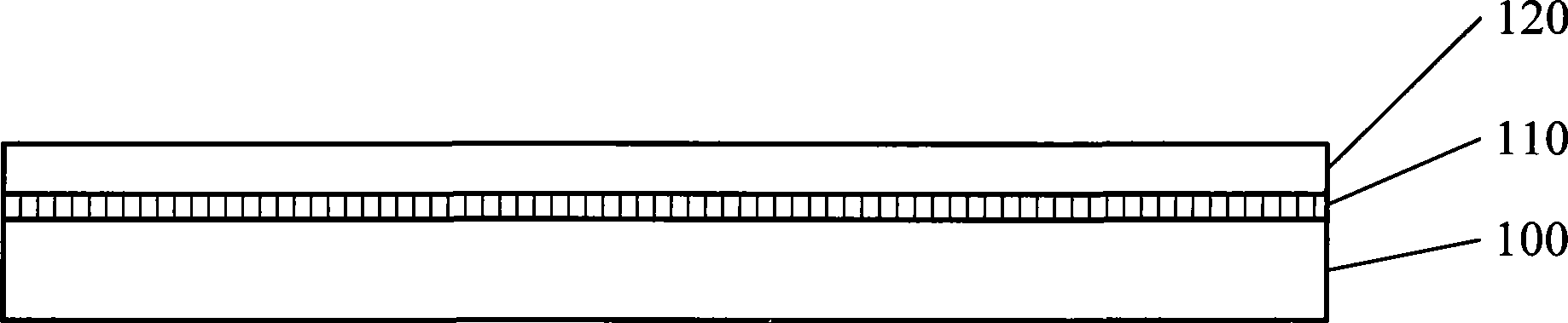

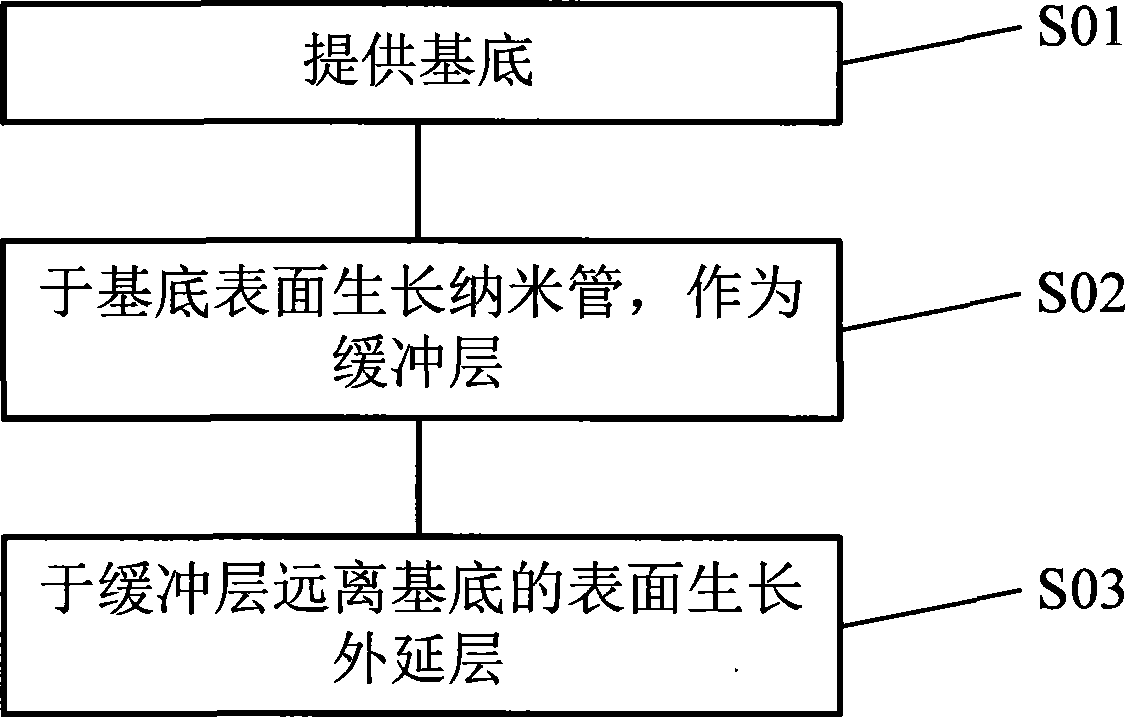

Semiconductor foreign substrate and growing method thereof

InactiveCN101378104AReduce stressImprove crystal qualitySemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchEpitaxial material

The invention provides a foreign substrate of the semiconductor, comprising a substrate layer, an epitaxial layer and a buffer layer with nanotube materials between the substrate layer and the epitaxial layer. The invention also provides a growth method for the foreign substrate of the semiconductor. The invention has the advantages that: by adopting the buffer layer with nanotube materials and making use of the properties of the flexible linkage of the nanotube, the lattice mismatch and thermal mismatch between the epitaxial layer and the substrate layer are eliminated, so as to reduce the stress in the epitaxial layer; as to the provided growth method, during the growth process of the epitaxial layer on the surface of the nanotube, the nanotube as a nucleation center during the epitaxial process of the epitaxial materials is used for forming high-quality crystal nucleus at the initial epitaxial stage, thus being beneficial to improving the crystal quality of the epitaxial layer.

Owner:SUZHOU NANOWIN SCI & TECH

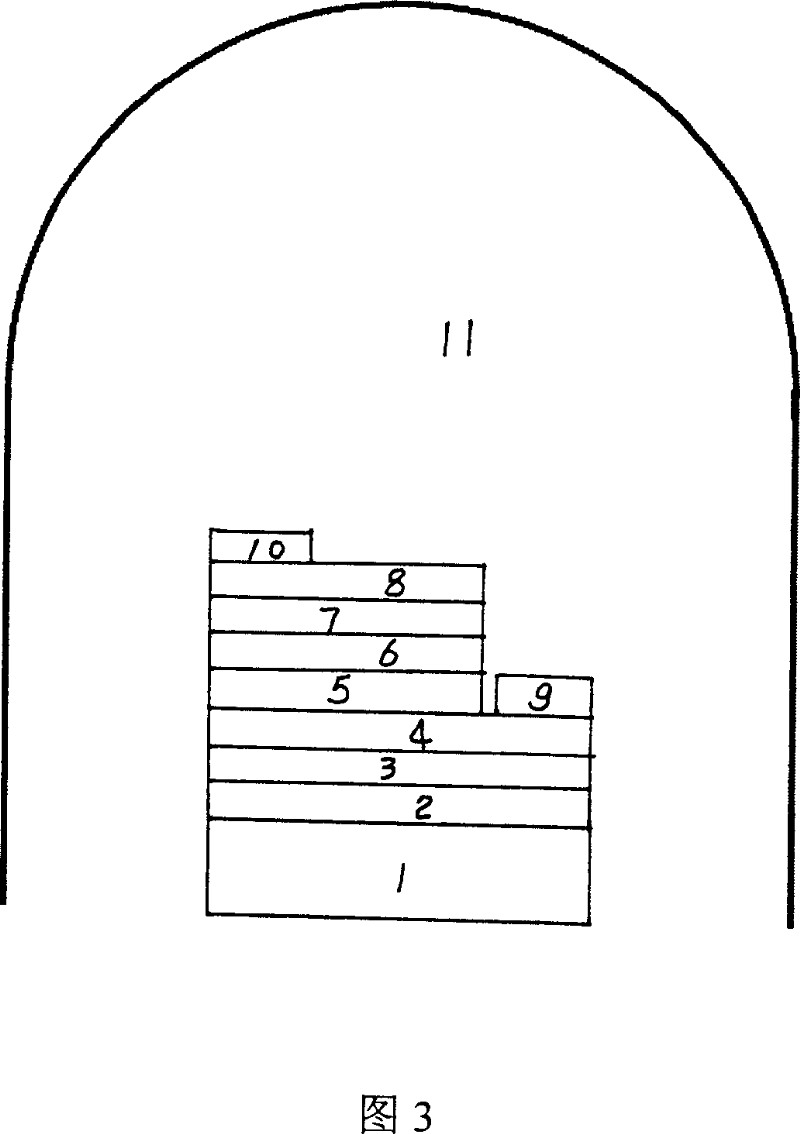

White light GaN LED epitaxial material without fluorescent powder conversion and method for making the same

InactiveCN101038947AThe production process is simpleLow costSemiconductor devicesPhosphorQuantum dot

The invention relates to epitaxial material of white light GaN light emitting diode which requires no phosphor for conversion and manufacturing method thereof, i.e. employing conventional semiconductor device deposition technique to orderly deposit an initial growth layer, an intrinsic GaN buffer layer, a n-type GaN layer, a InGaN relaxation layer, an InGaN luminescent layer of multi quantum structure, a p-type AlGaN interlayer and a p-type GaN layer; and employing the epitaxial material to make single chip white light light emitting diode; the method preserves the manufacturing techniques for making current normal monochromatic light light emitting diode device, and only improves the growth process of the GaN based luminescent material, thus, the In component achieves the level to form In quantum dot, and a stress releasing layer is added. In this manner, in the precondition of not increasing the complexity of the device, the production cost for making white light light emitting diode can be basically reduced, and the light emitting efficiency and utilization can be increased, and the weakness of the white light light emitting diode which employs phosphor for conversion can be overcome, and the whole performance of white light light emitting diode can be improved.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

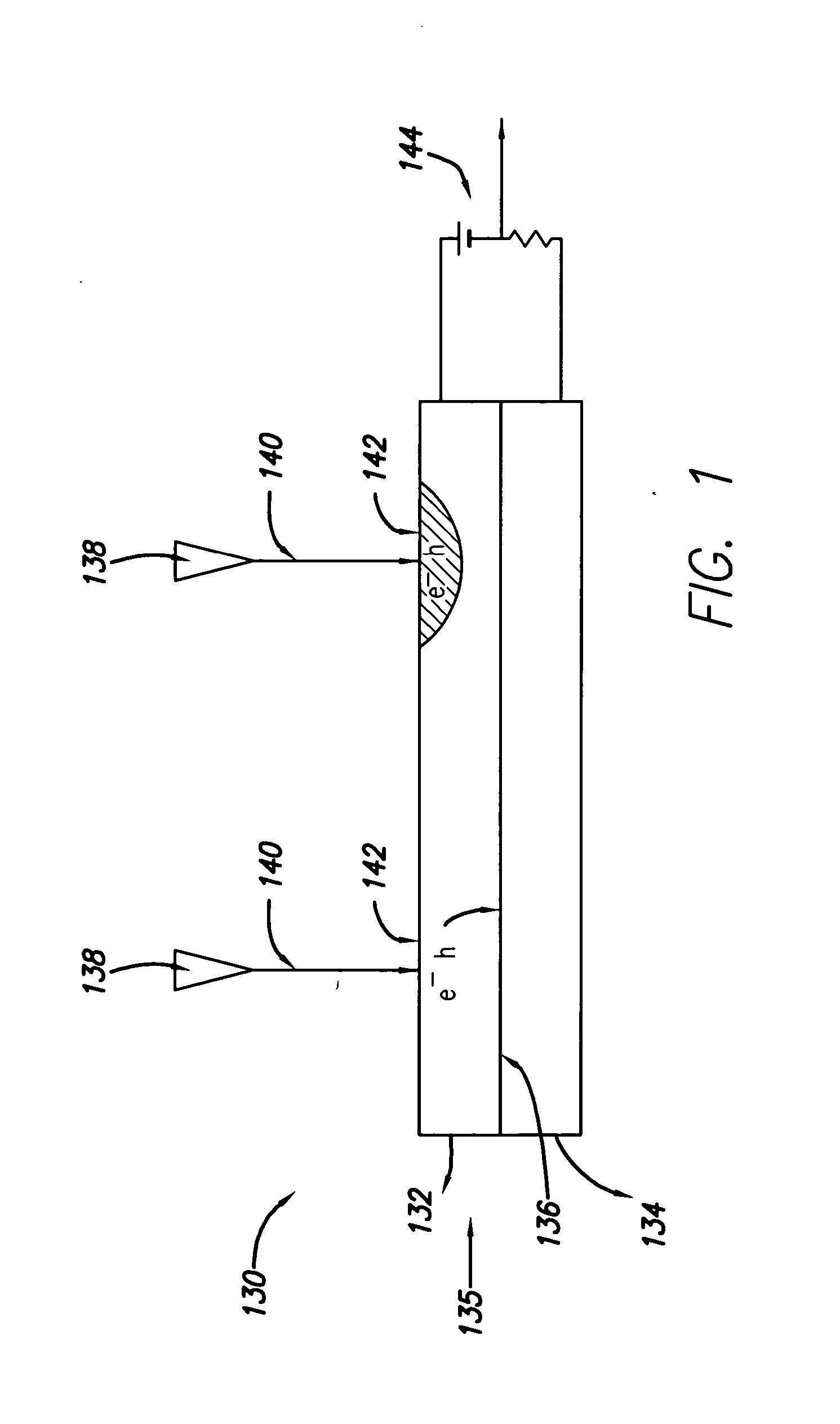

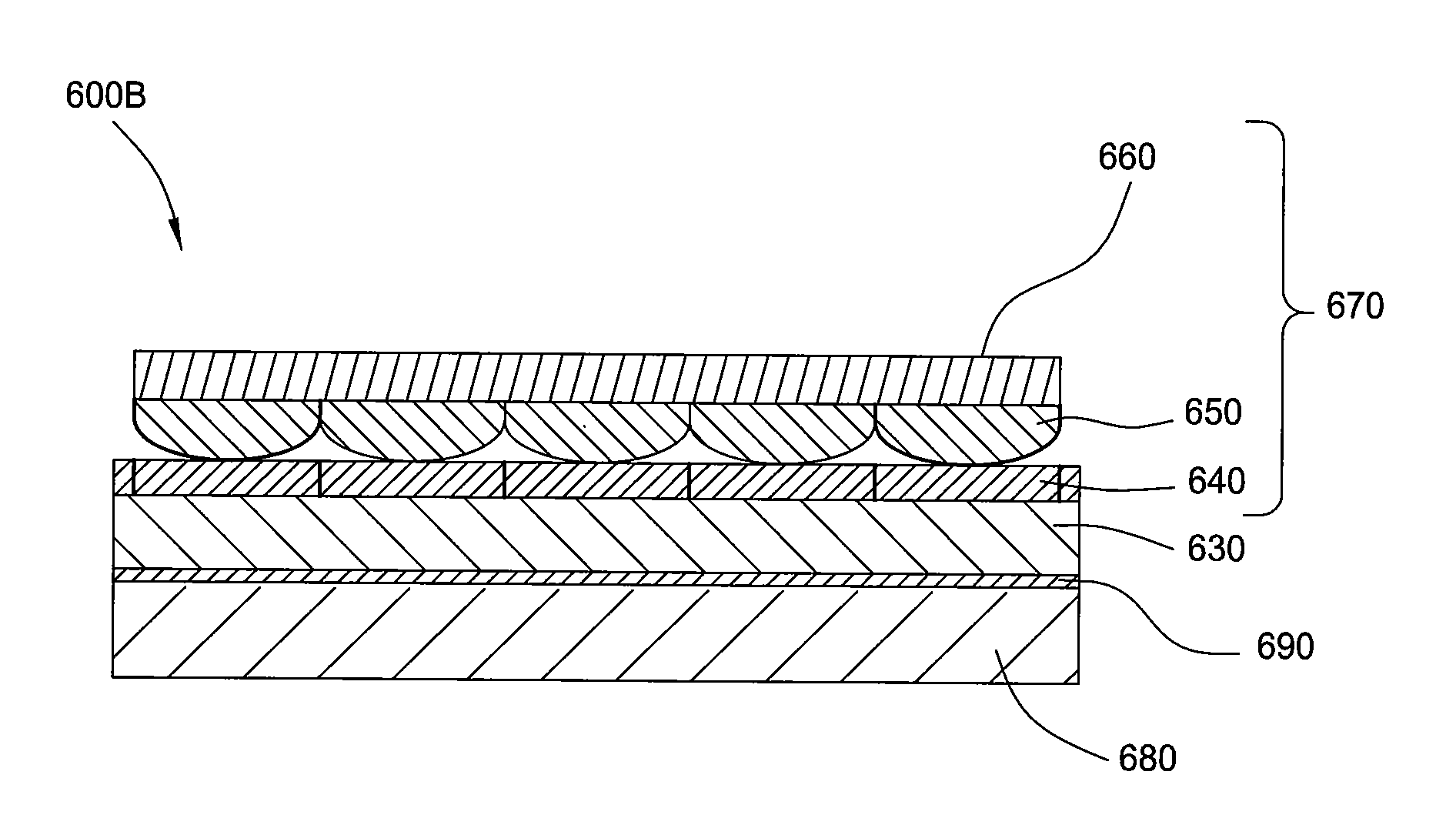

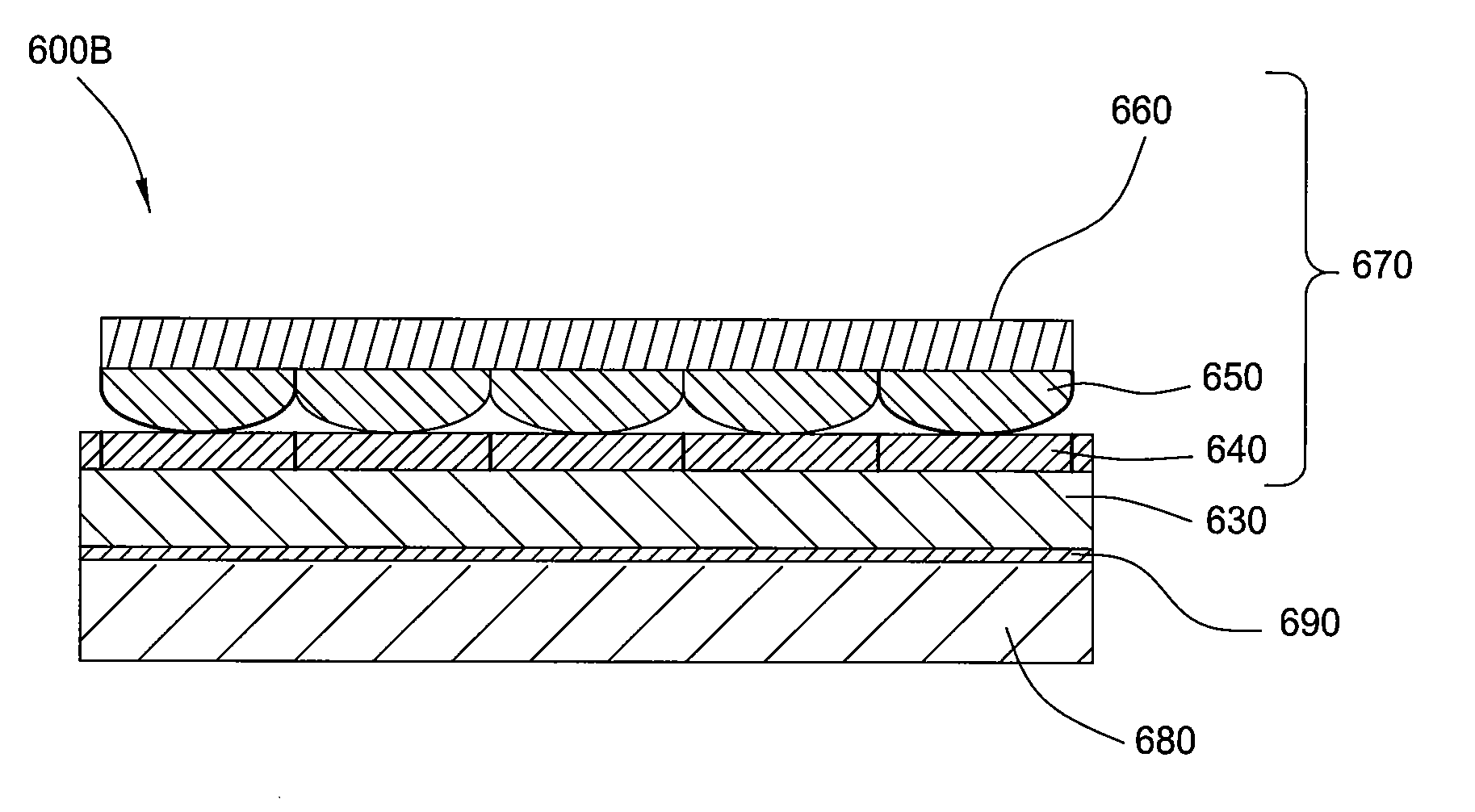

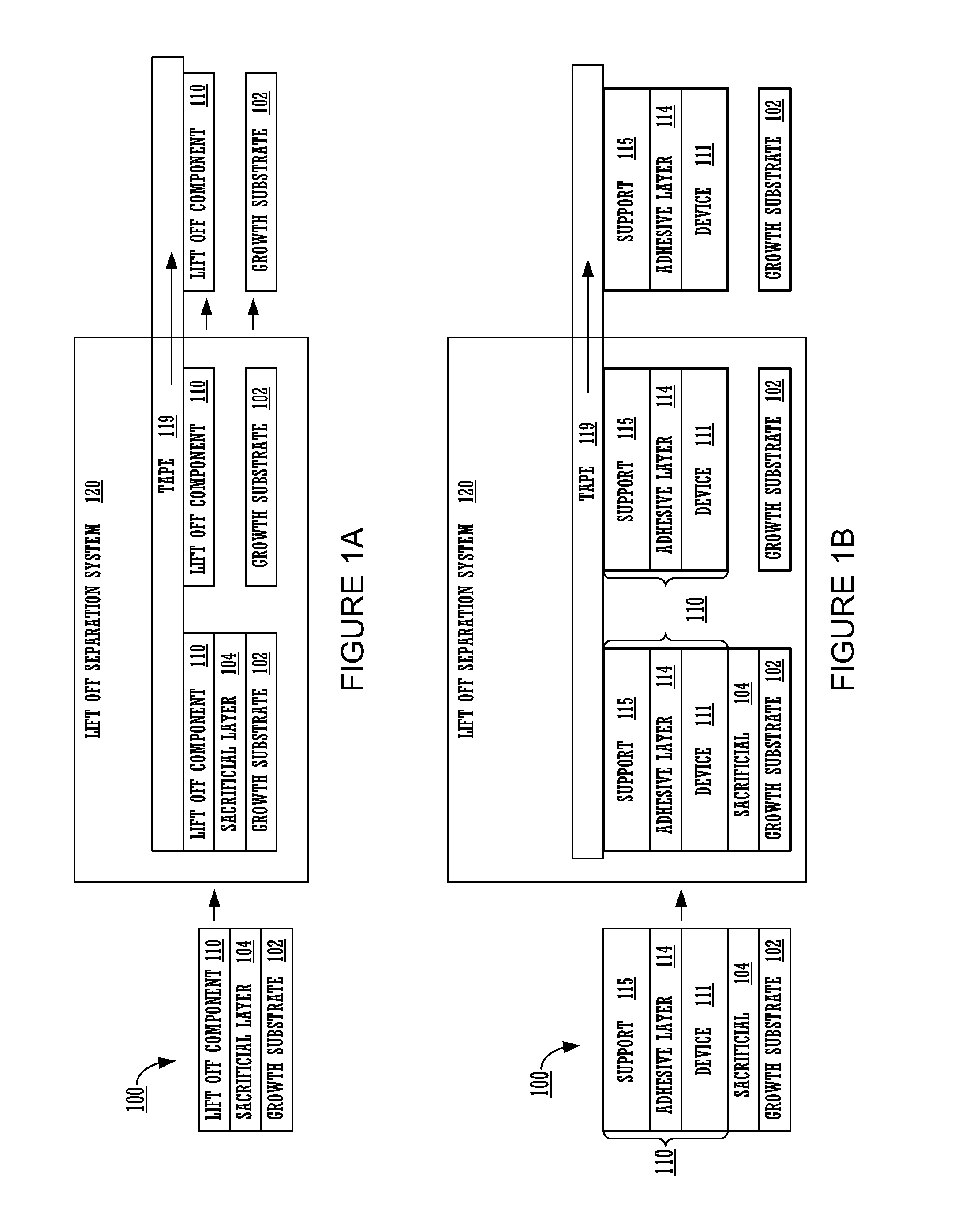

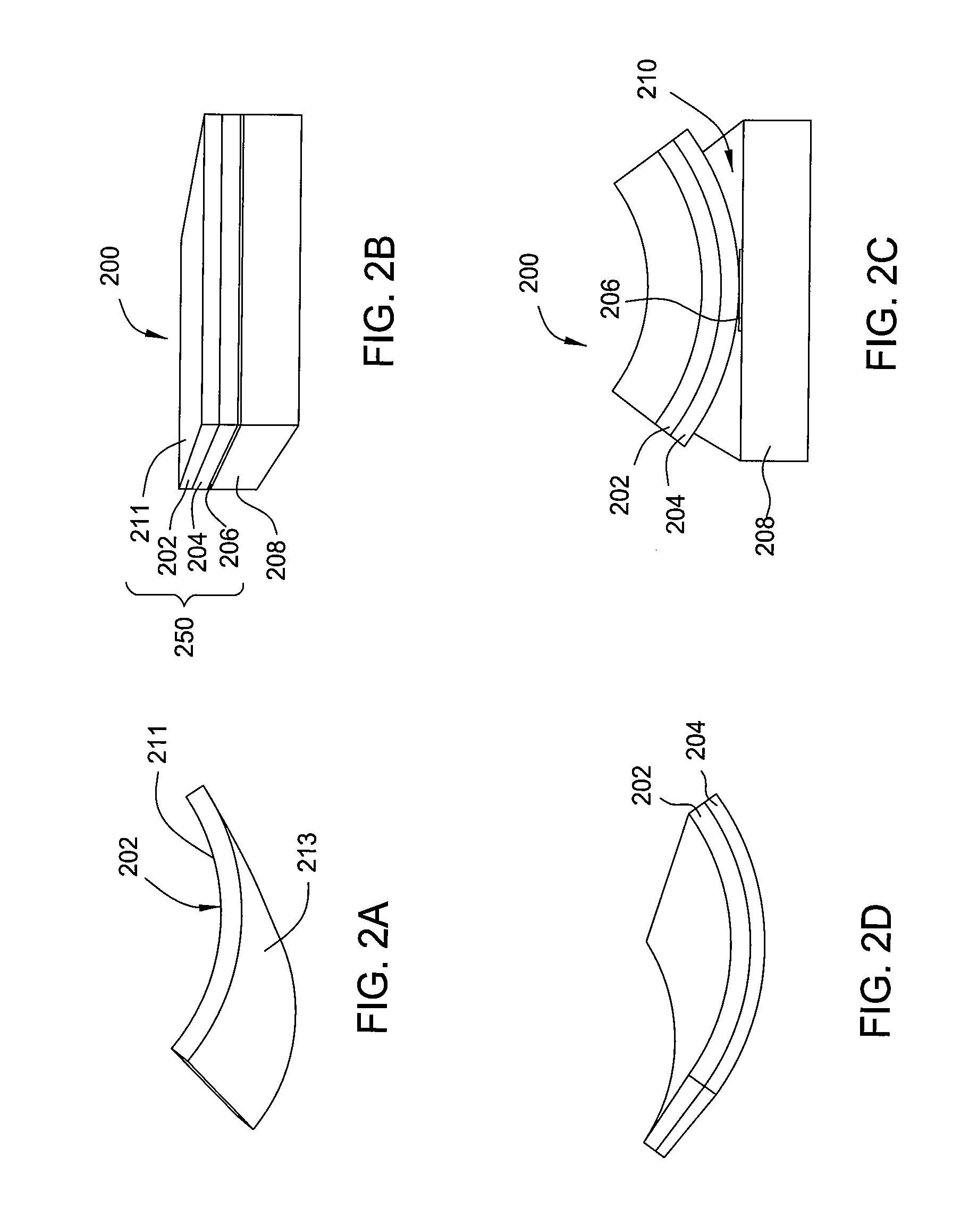

Epitaxial lift off stack having a multi-layered handle and methods thereof

ActiveUS20100001374A1Solid-state devicesSemiconductor/solid-state device manufacturingEpitaxial materialOptoelectronics

Embodiments of the invention generally relate to epitaxial lift off (ELO) thin films and devices and methods for forming such films and devices. In one embodiment, a method for forming an ELO thin film includes depositing an epitaxial material over a sacrificial layer on a substrate, adhering a multi-layered support handle onto the epitaxial material, and removing the sacrificial layer during an etching process. The etching process further includes peeling the epitaxial material from the substrate and forming an etch crevice therebetween while maintaining compression in the epitaxial material. The method further provides that the multi-layered support handle contains a stiff support layer adhered to the epitaxial material, a soft support layer adhered to the stiff support layer, and a handle plate adhered to the soft support layer. In one example, the stiff support layer may contain multiple inorganic layers, such as metal layers, dielectric layers, or combinations thereof.

Owner:ALTA DEVICES INC

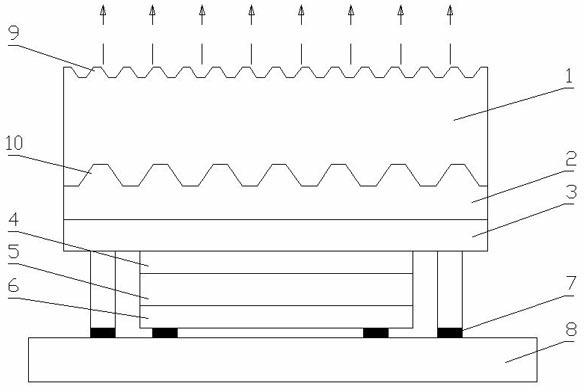

Inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer

InactiveCN102157654AImprove radiative recombination luminous efficiencyReduce defect densitySemiconductor devicesQuantum efficiencyQuantum well

The invention discloses an inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer, wherein the chip comprises a sapphire substrate distributed with 102-104 shrinkage pools at upper and lower surfaces, an AlxGa1-xN component gradual change buffer layer composed of an unit layer formed by k non-doping AlxGa1-xN epitaxial materials, a n-type GaN epitaxial layer, an InGaN / GaN multi-quantum well, a p-type GaN layer, a transparent ITO (indium tin oxide) conductive film, an inverted mounting welding electrode and a silicon substrate from upper to lower. The LED chip disclosed by the invention uses the shrinkage pool structure for improving the emergent probability of LED emergent lights, and increasing the heat radiation area and growth stress acting range of the substrate, so that the GaB epitaxial quality and the radiation composite luminous efficiency are improved; the buffer layer of the n-type GaN epitaxial layer is manufactured by the AlxGa1-xN with gradually reduced Al component, so that the light-emitting efficiency and the internal quantum efficiency of the LED are improved, and a relatively high light output power is obtained.

Owner:CHONGQING UNIV

Methods for producing improved epitaxial materials

ActiveUS20090091002A1Low densityQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor structure

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES +1

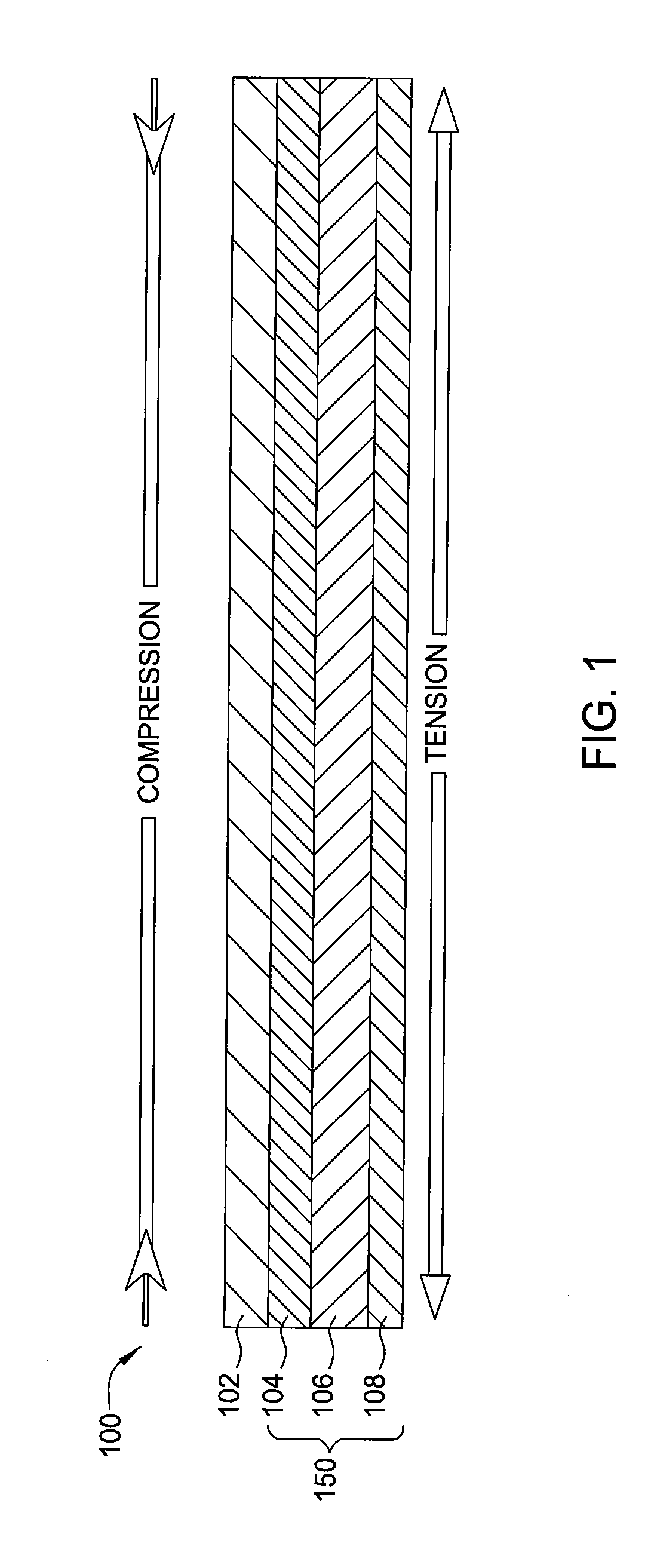

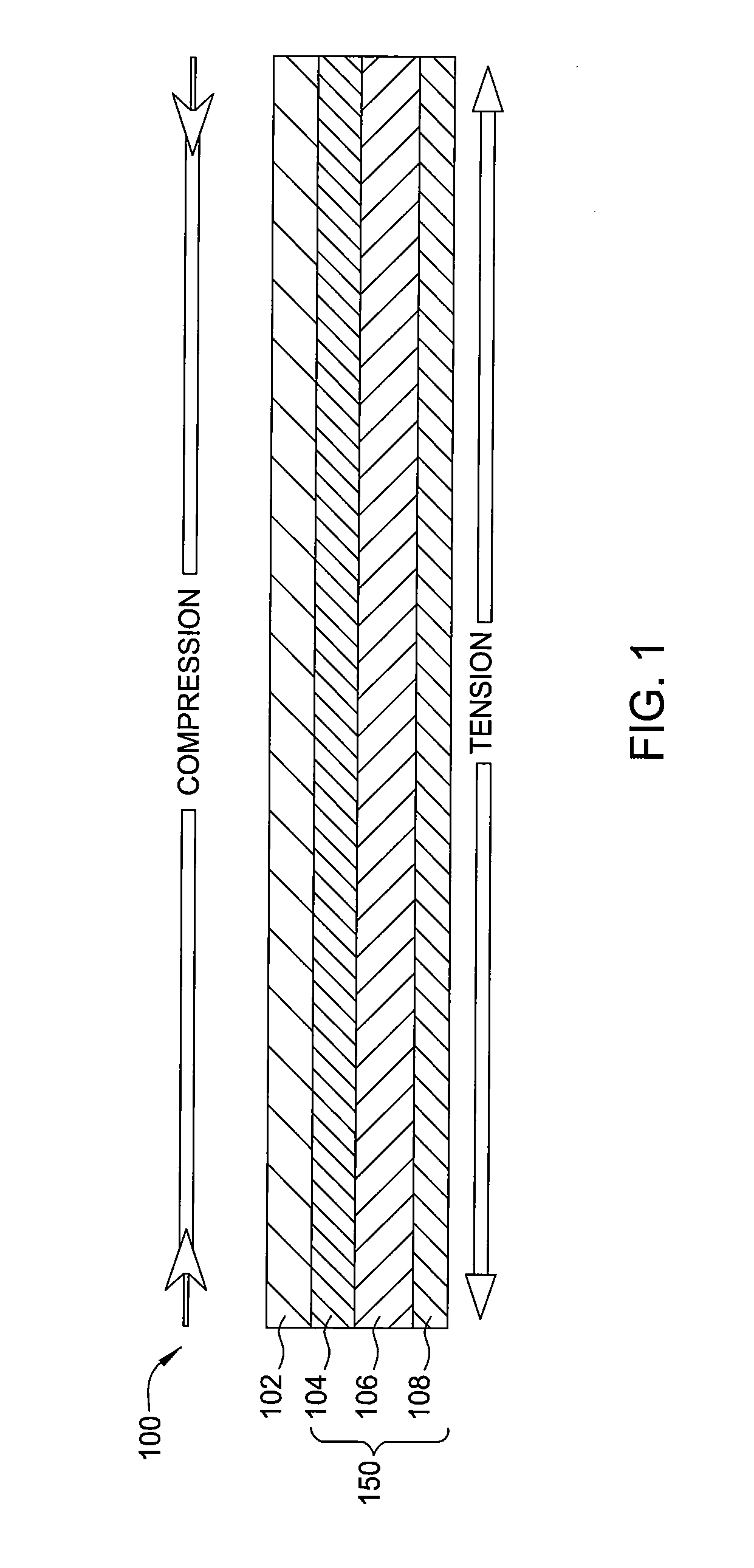

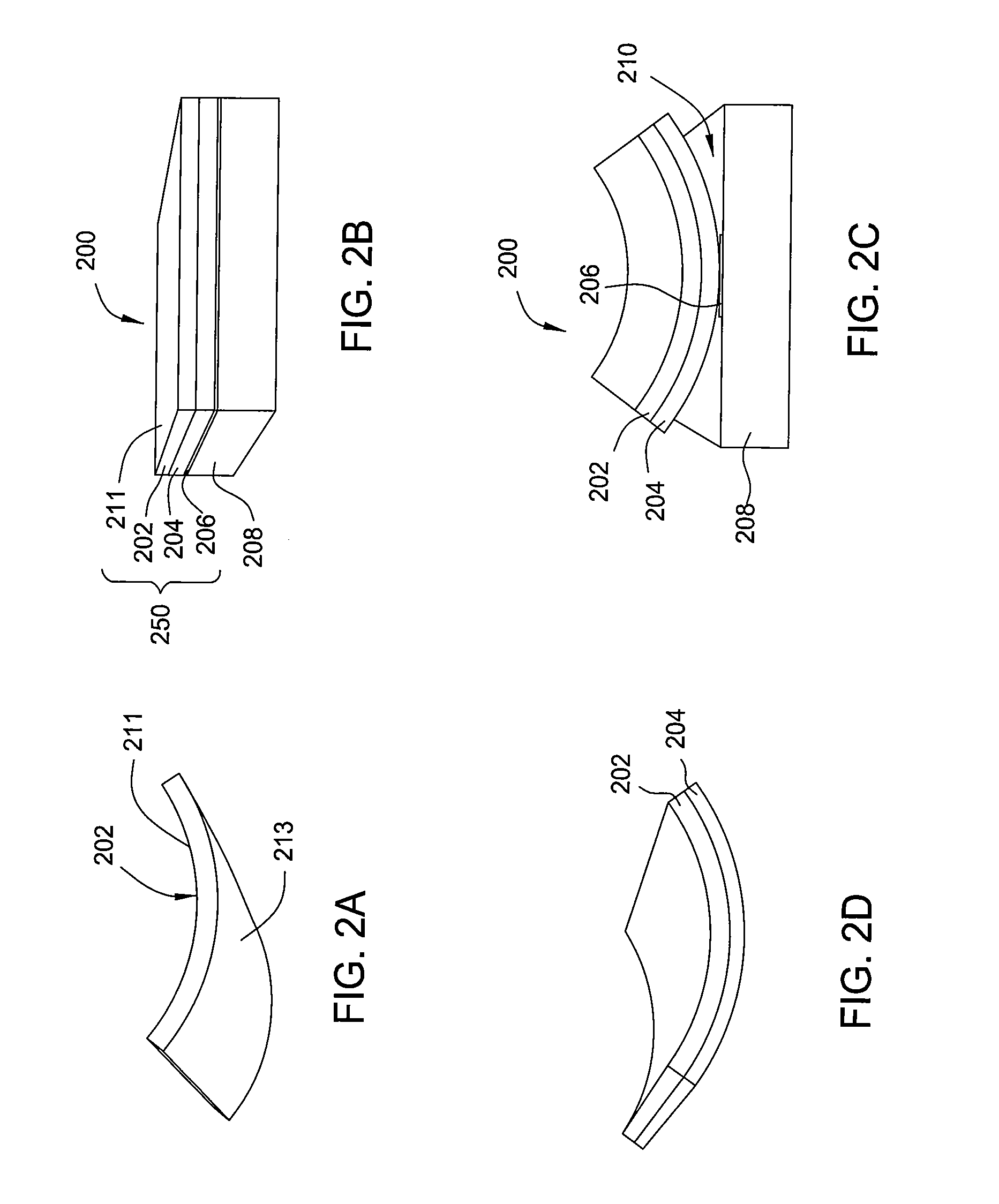

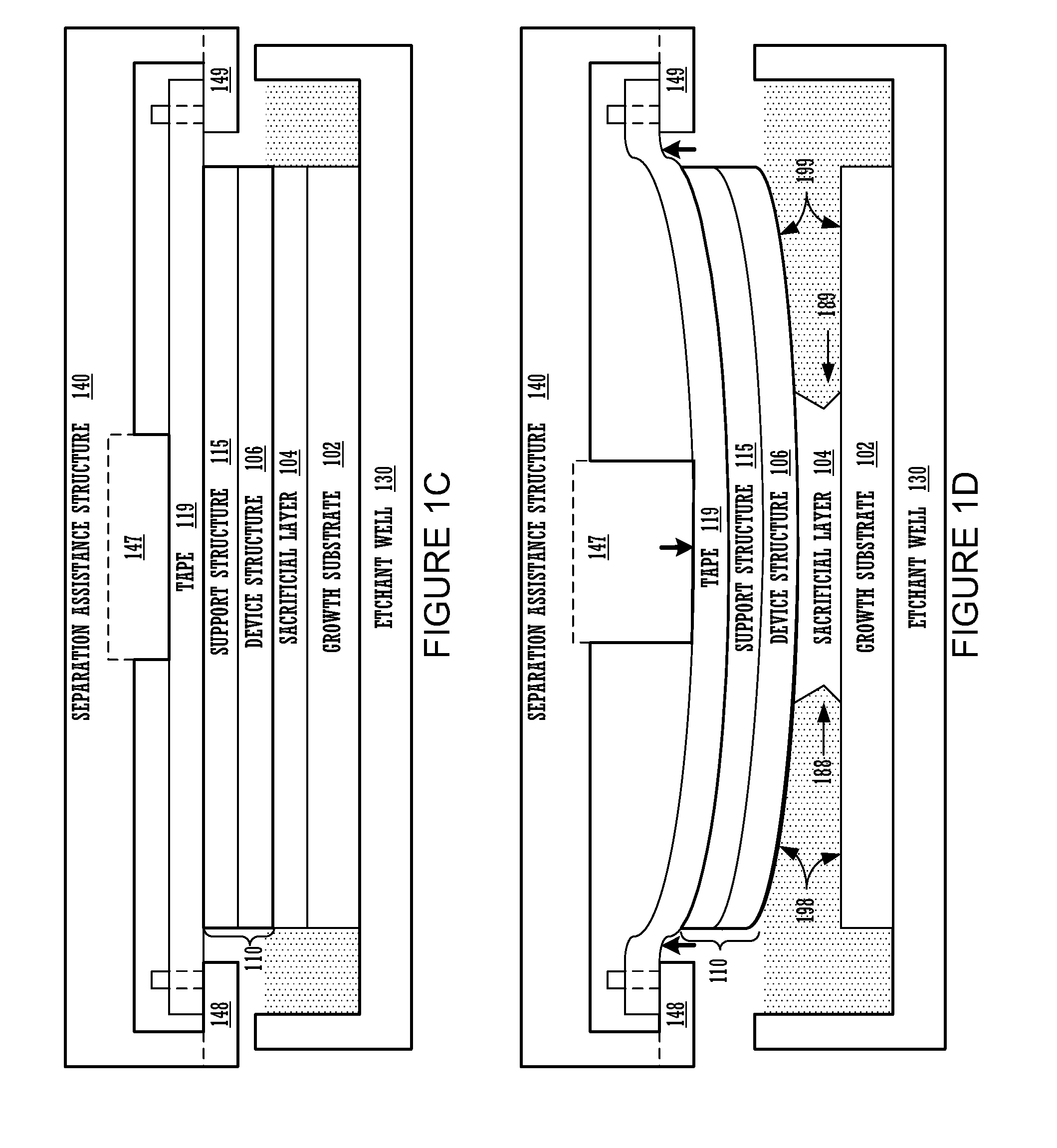

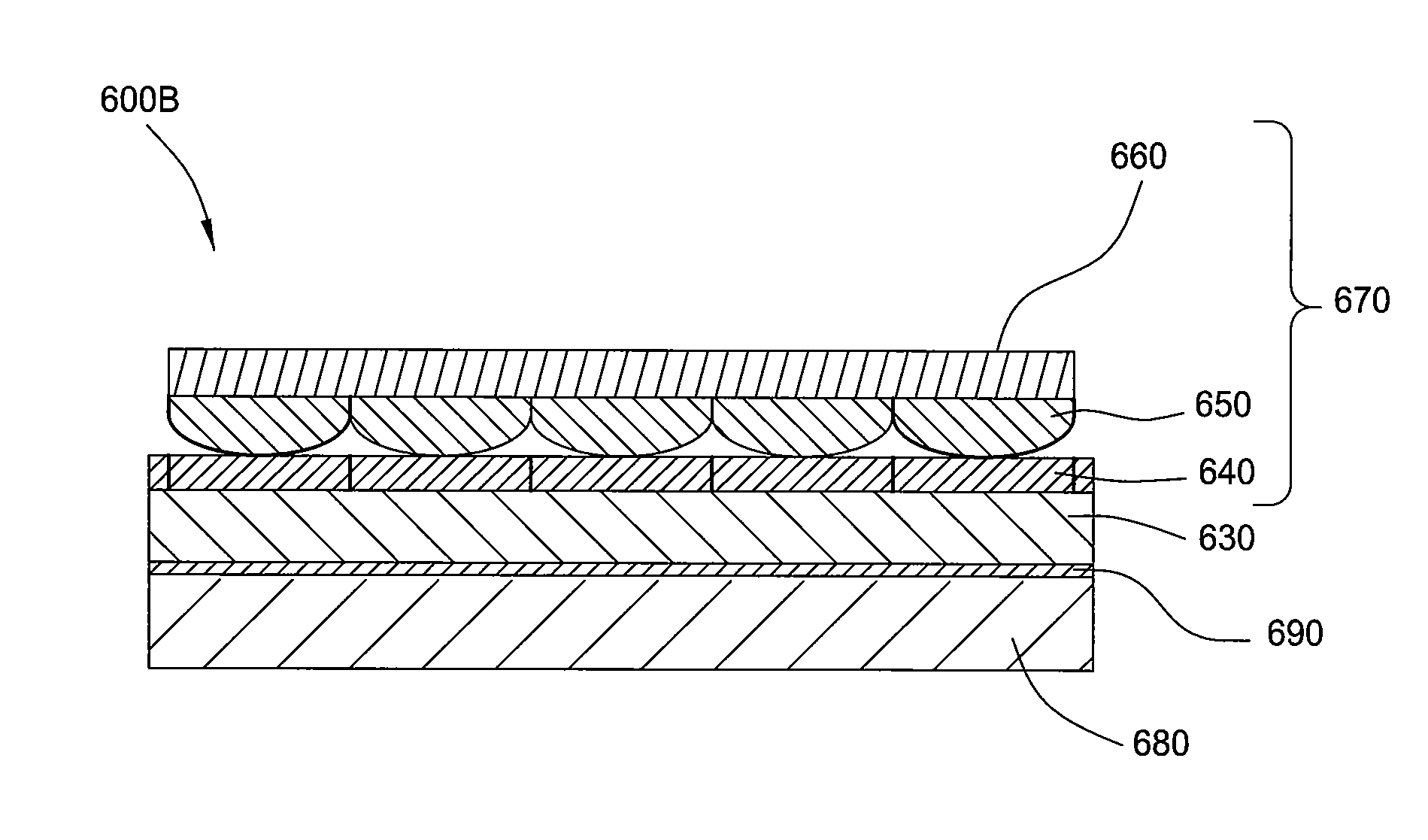

Epitaxial lift off stack having a unidirectionally shrunk handle and methods thereof

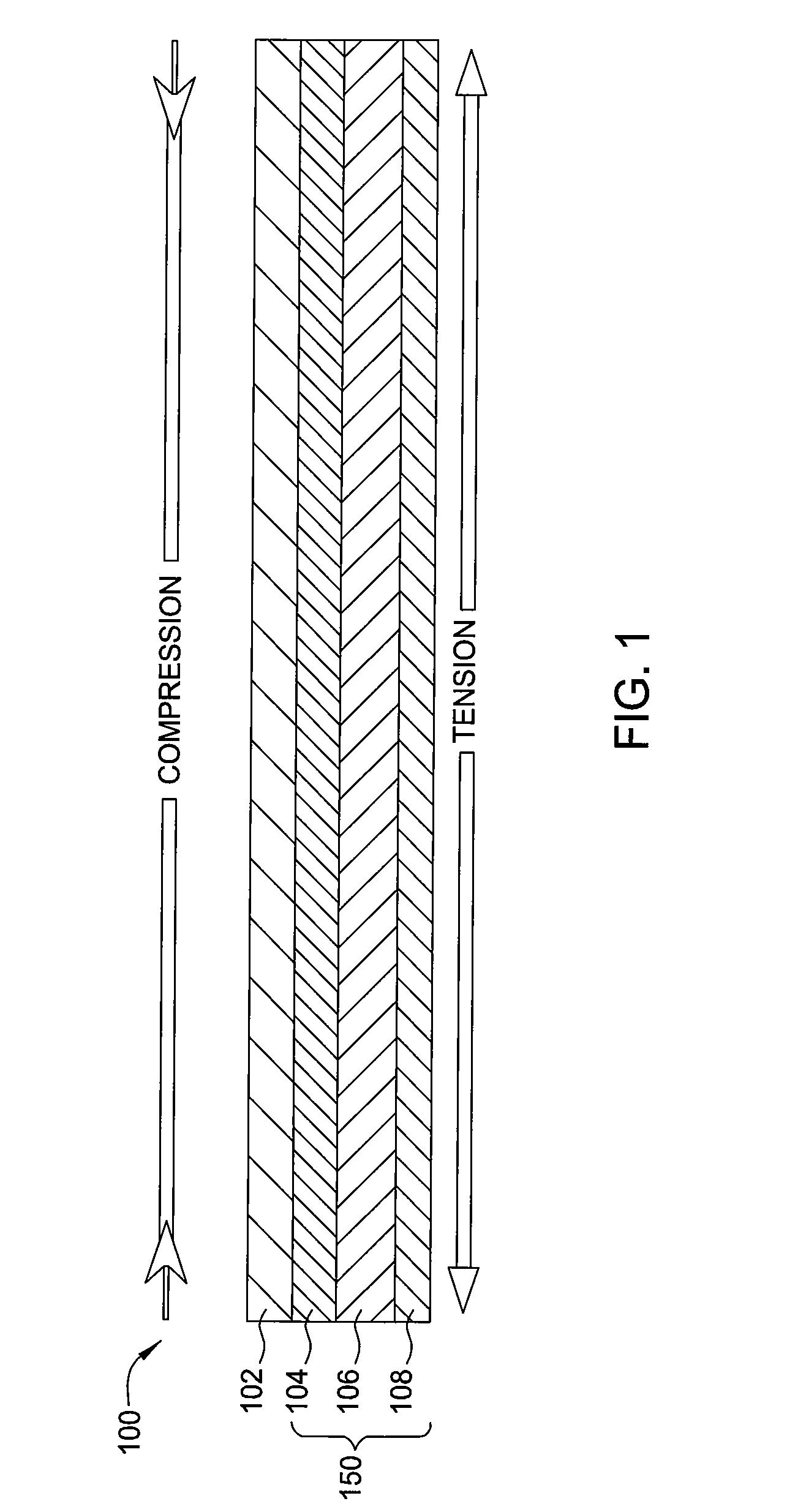

ActiveUS20090321886A1High-strength polymericNegative coefficientSolid-state devicesSemiconductor/solid-state device manufacturingFiberEpitaxial material

Embodiments of the invention generally relate to epitaxial lift off (ELO) thin films and devices and methods used to form such films and devices. In one embodiment, a method for forming an ELO thin film is provided which includes depositing an epitaxial material over a sacrificial layer on a substrate, adhering a unidirectionally induced-shrinkage support handle onto the epitaxial material, and shrinking the support handle tangential to reinforcement fibers therein to form tension in the support handle and compression in the epitaxial material during the shrinking process. The unidirectionally induced-shrinkage support handle contains a shrinkable material and reinforcement fibers extending unidirectional throughout the shrinkable material. The method further includes removing the sacrificial layer during an etching process, peeling the epitaxial material from the substrate while forming an etch crevice therebetween, and bending the support handle to have substantial curvature.

Owner:ALTA DEVICES INC

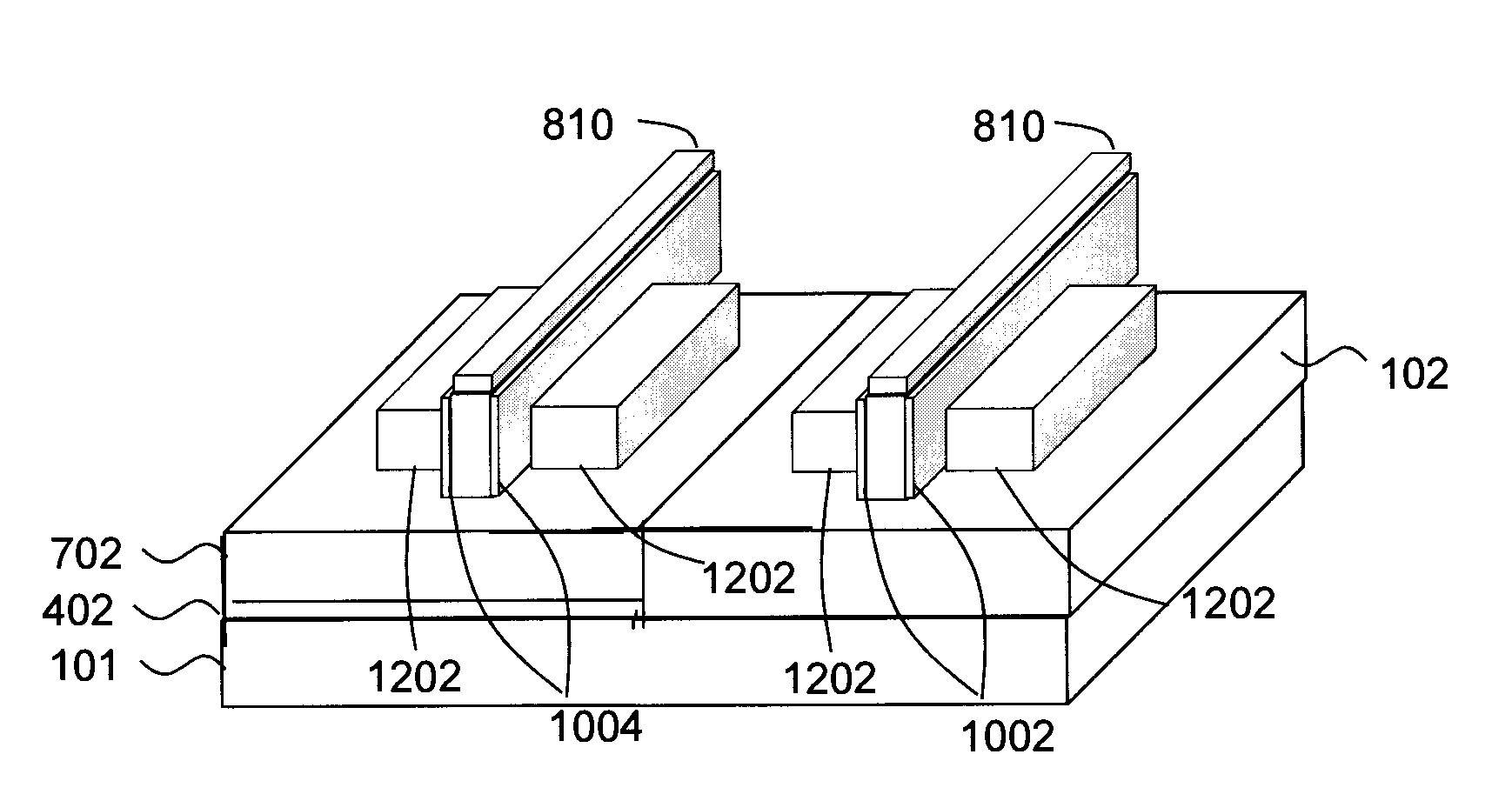

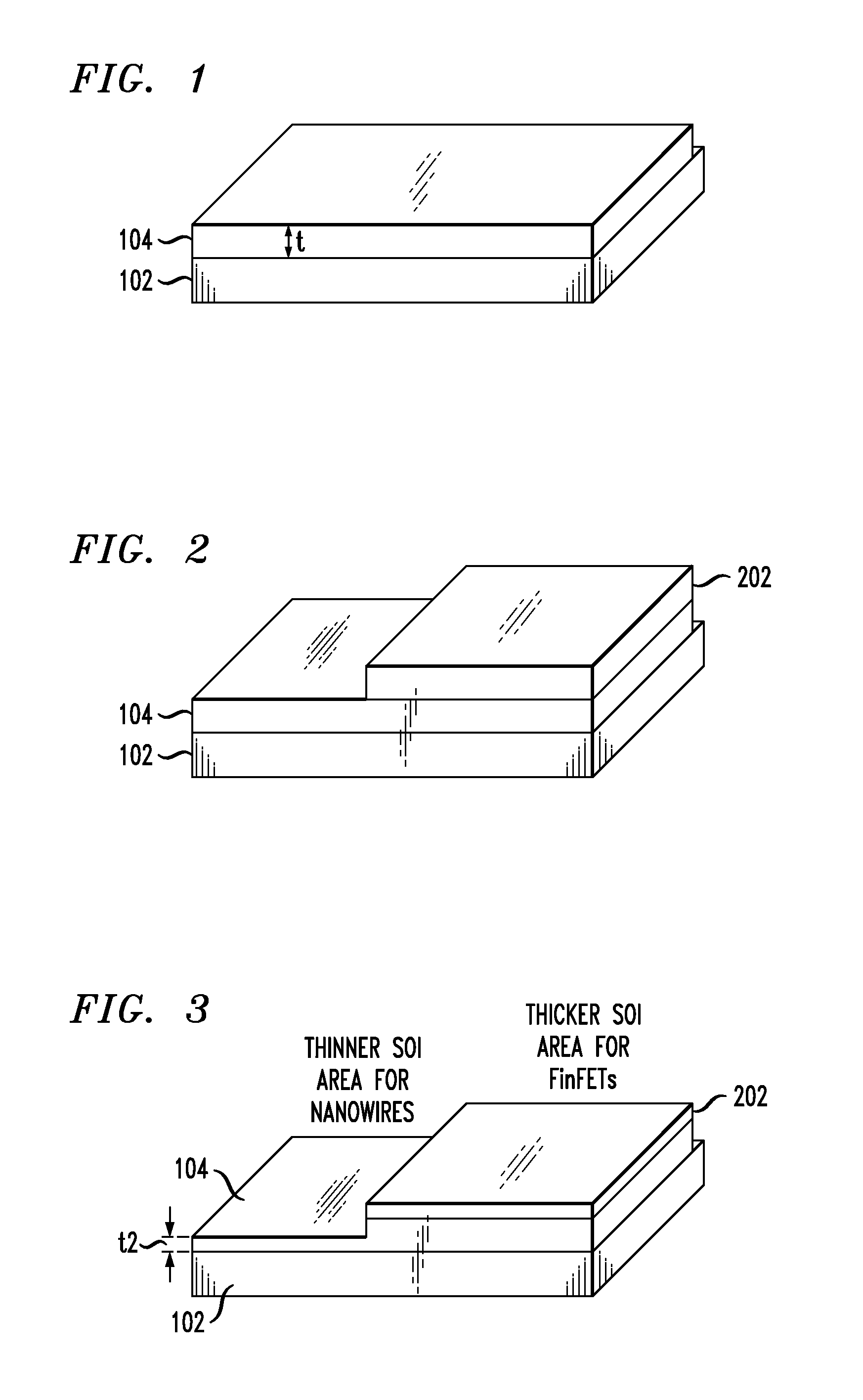

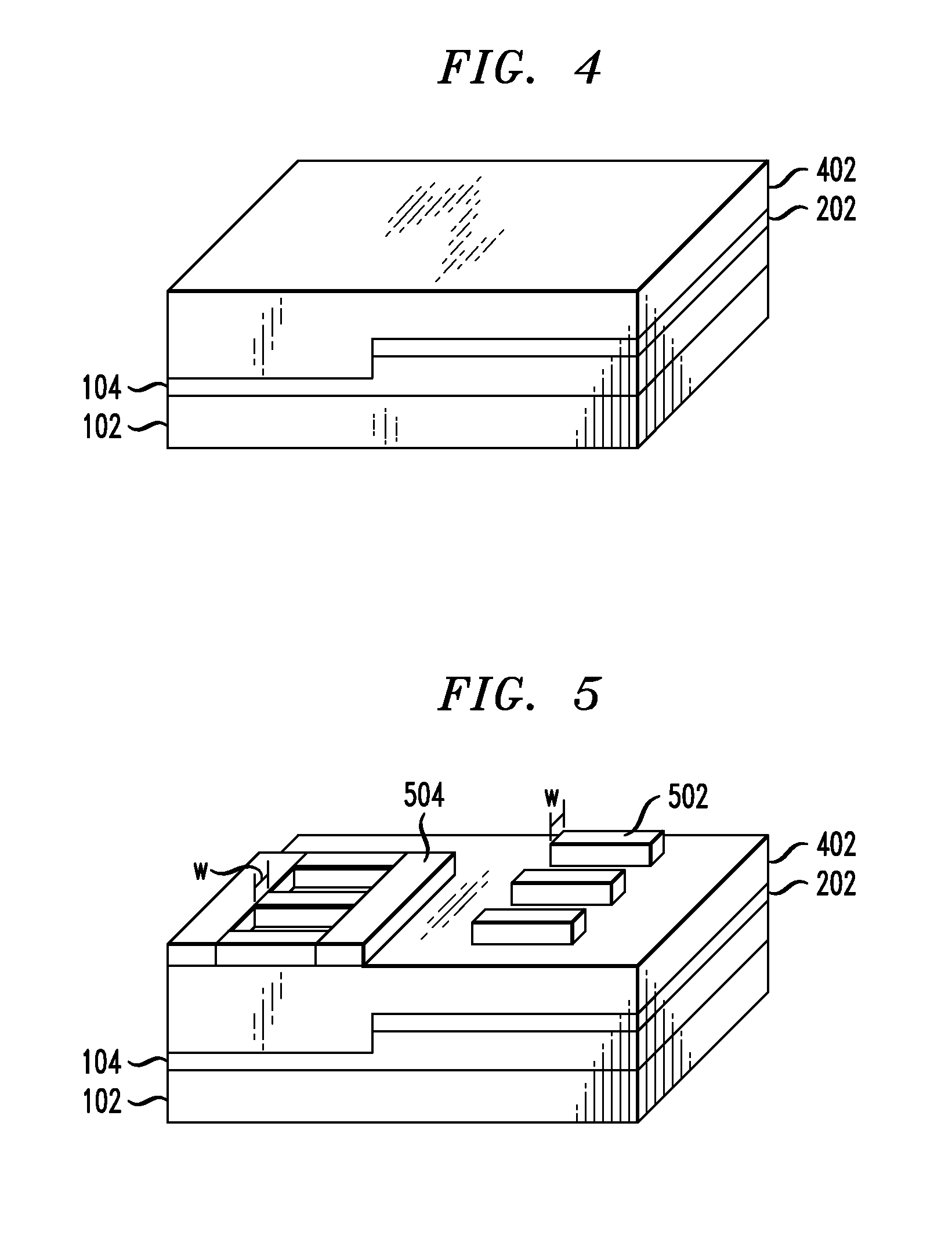

Nanowire FET and finFET hybrid technology

Hybrid nanowire FET and FinFET devices and methods for fabrication thereof are provided. In one aspect, a method for fabricating a CMOS circuit having a nanowire FET and a finFET includes the following steps. A wafer is provided having an active layer over a BOX. A first region of the active layer is thinned. An organic planarizing layer is deposited on the active layer. Nanowires and pads are etched in the first region of the active layer using a first hardmask. The nanowires are suspended over the BOX. Fins are etched in the second region of the active layer using a second hardmask. A first gate stack is formed that surrounds at least a portion of each of the nanowires. A second gate stack is formed covering at least a portion of each of the fins. An epitaxial material is grown on exposed portions of the nanowires, pads and fins.

Owner:INT BUSINESS MASCH CORP

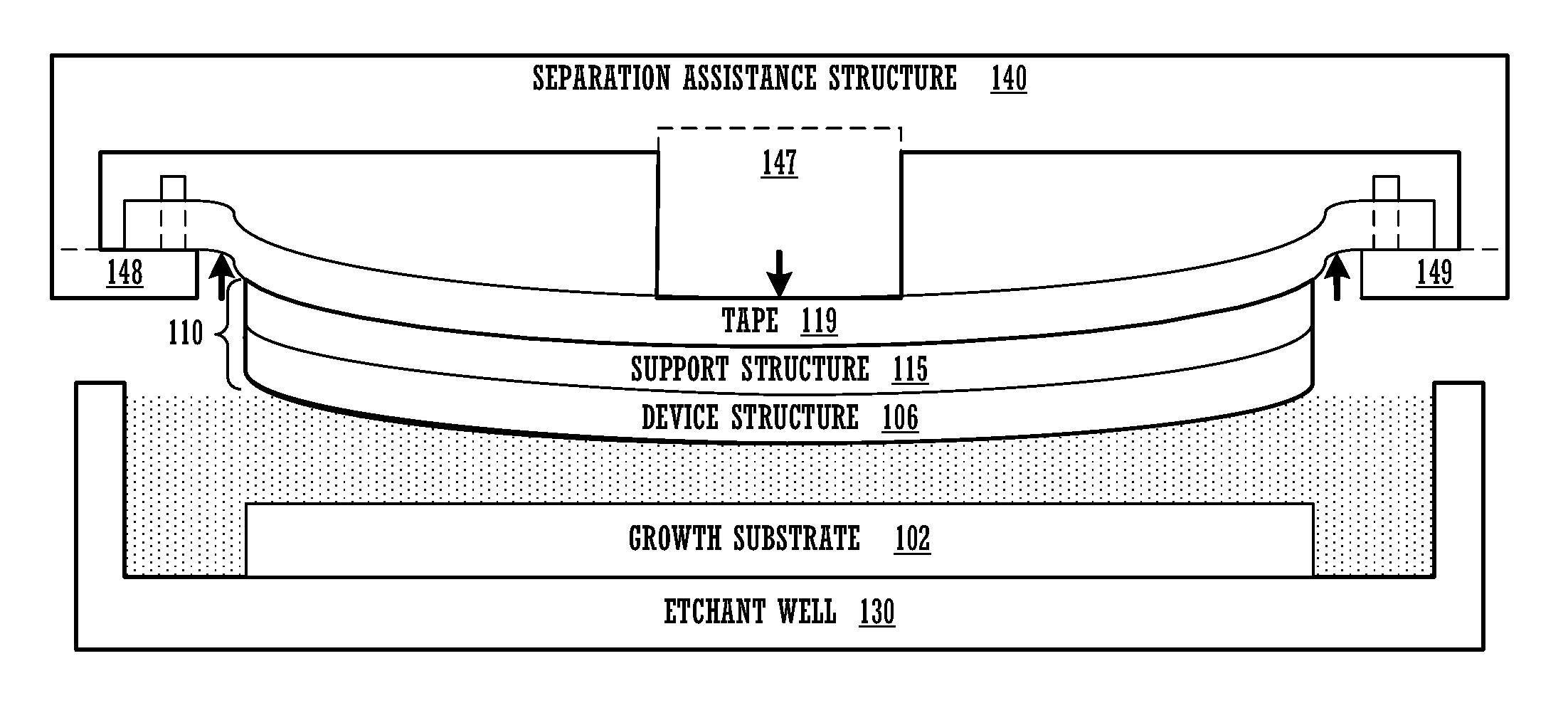

Epitaxial Lift Off Systems and Methods

ActiveUS20110214805A1Expand accessIncrease the gapMechanical working/deformationLamination ancillary operationsEpitaxial materialEngineering

Epitaxial lift off systems and methods are presented. In one embodiment a tape is disposed on the opposite side of the epitaxial material than the substrate is used to hold the epitaxial material during the etching and removal steps of the ELO process. In various embodiments, the apparatus for removing the ELO film from the substrates without damaging the ELO film may include an etchant reservoir, substrate handling and tape handling mechanisms, including mechanisms to manipulate (e.g., cause tension, peel, widen the etch gap, etc.) the lift off component during the lift off process.

Owner:ALTA DEVICES INC

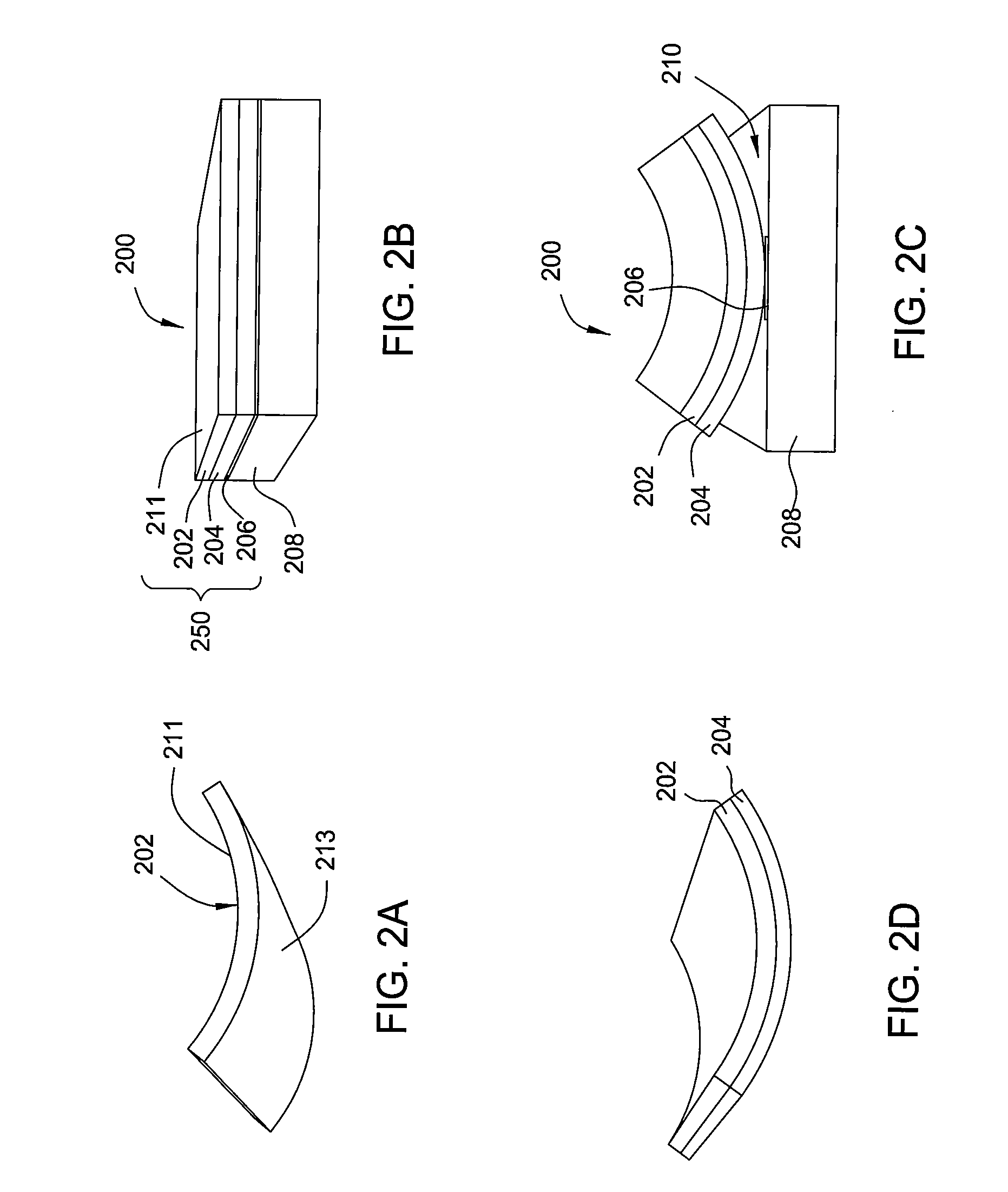

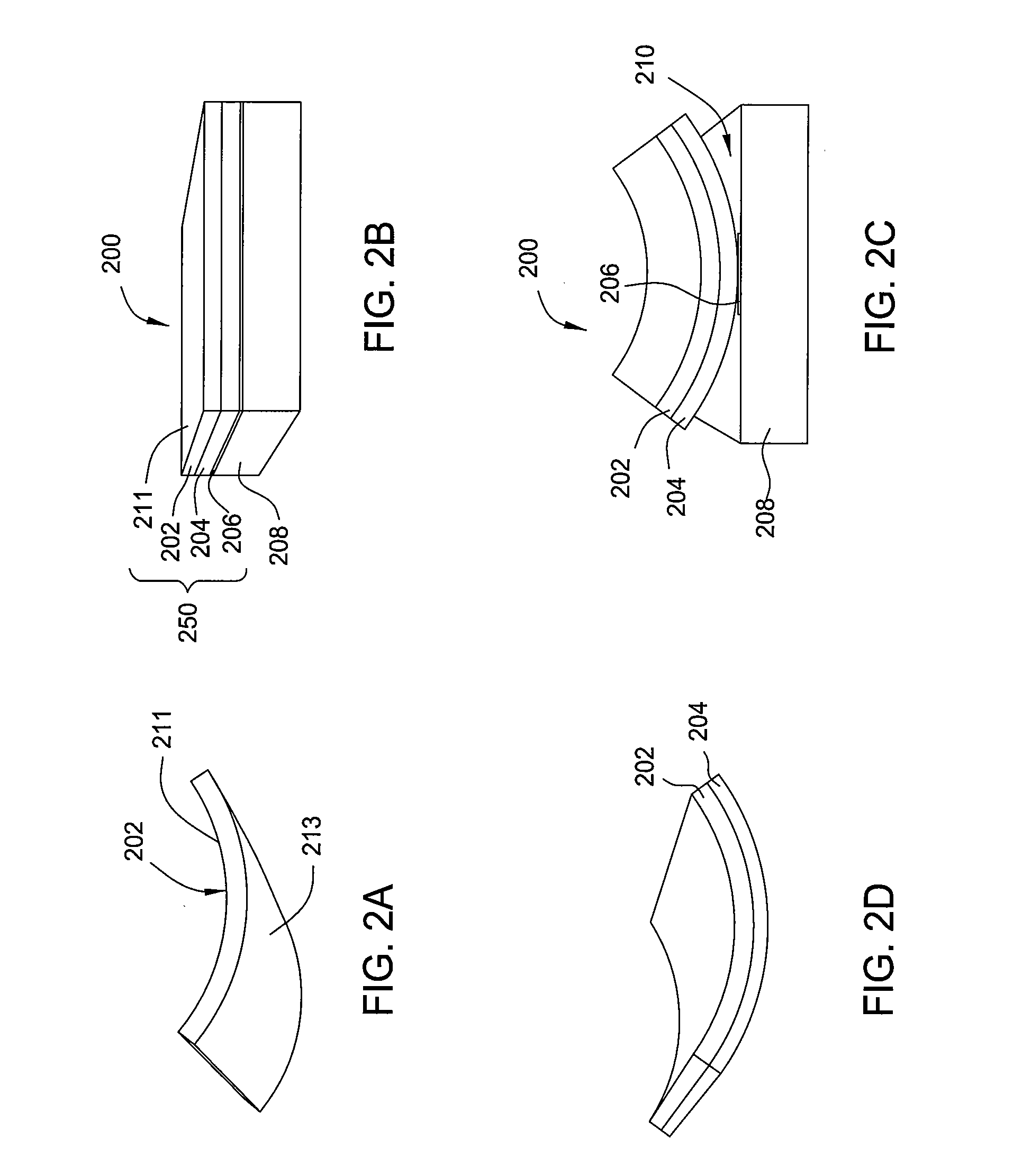

Epitaxial lift off stack having a pre-curved handle and methods thereof

ActiveUS20090321881A1High-strength polymericNegative coefficientSolid-state devicesSemiconductor/solid-state device manufacturingEpitaxial materialEngineering

Embodiments of the invention generally relate to epitaxial lift off (ELO) thin films and devices and methods used to form such films and devices. In one embodiment, a method for forming an ELO thin film is provided which includes depositing an epitaxial material over a sacrificial layer on a substrate, adhering a flattened, pre-curved support handle onto the epitaxial material, and removing the sacrificial layer during an etching process. The etching process includes bending the pre-curved support handle to have substantial curvature while peeling the epitaxial material from the substrate and forming an etch crevice therebetween. Compression is maintained within the epitaxial material during the etching process. The flattened, pre-curved support handle may be formed by flattening a pre-curved support material.

Owner:ALTA DEVICES INC

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS7402496B2Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

Owner:UNITED MICROELECTRONICS CORP

Epitaxial lift off stack having a non-uniform handle and methods thereof

ActiveUS20100001316A1Solid-state devicesSemiconductor/solid-state device manufacturingWaxEpitaxial material

Embodiments of the invention generally relate to epitaxial lift off (ELO) thin films and devices and methods used to form such films and devices. In one embodiment, a method for forming a thin film material during an epitaxial lift off process is provided which includes forming an epitaxial material over a sacrificial layer on a substrate, adhering a non-uniform support handle onto the epitaxial material, and removing the sacrificial layer during an etching process. The etching process further includes peeling the epitaxial material from the substrate while forming an etch crevice therebetween and bending the support handle to form compression in the epitaxial material during the etching process. In one example, the non-uniform support handle contains a wax film having a varying thickness.

Owner:ALTA DEVICES INC