Patents

Literature

357results about How to "Reduce dislocation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

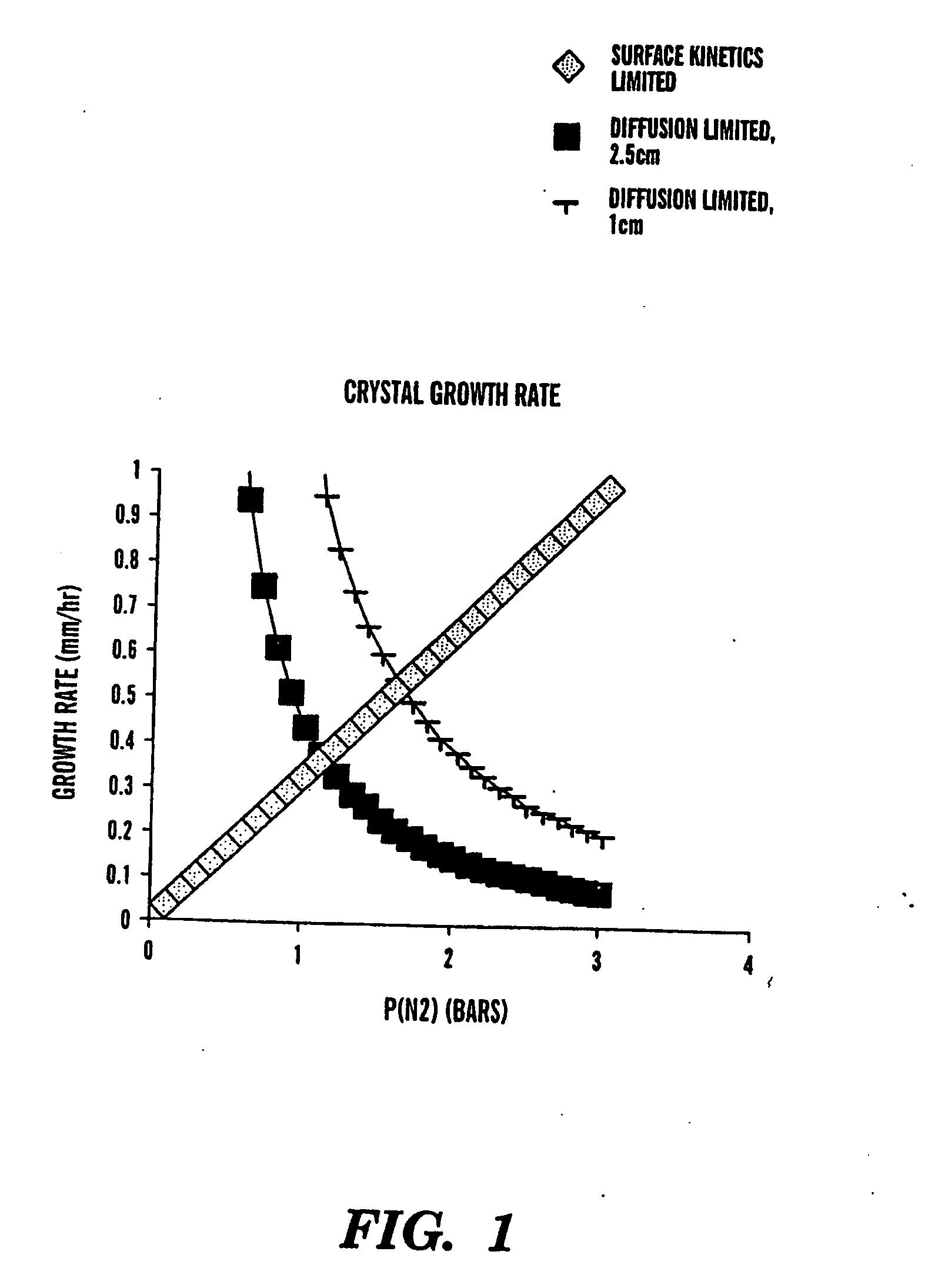

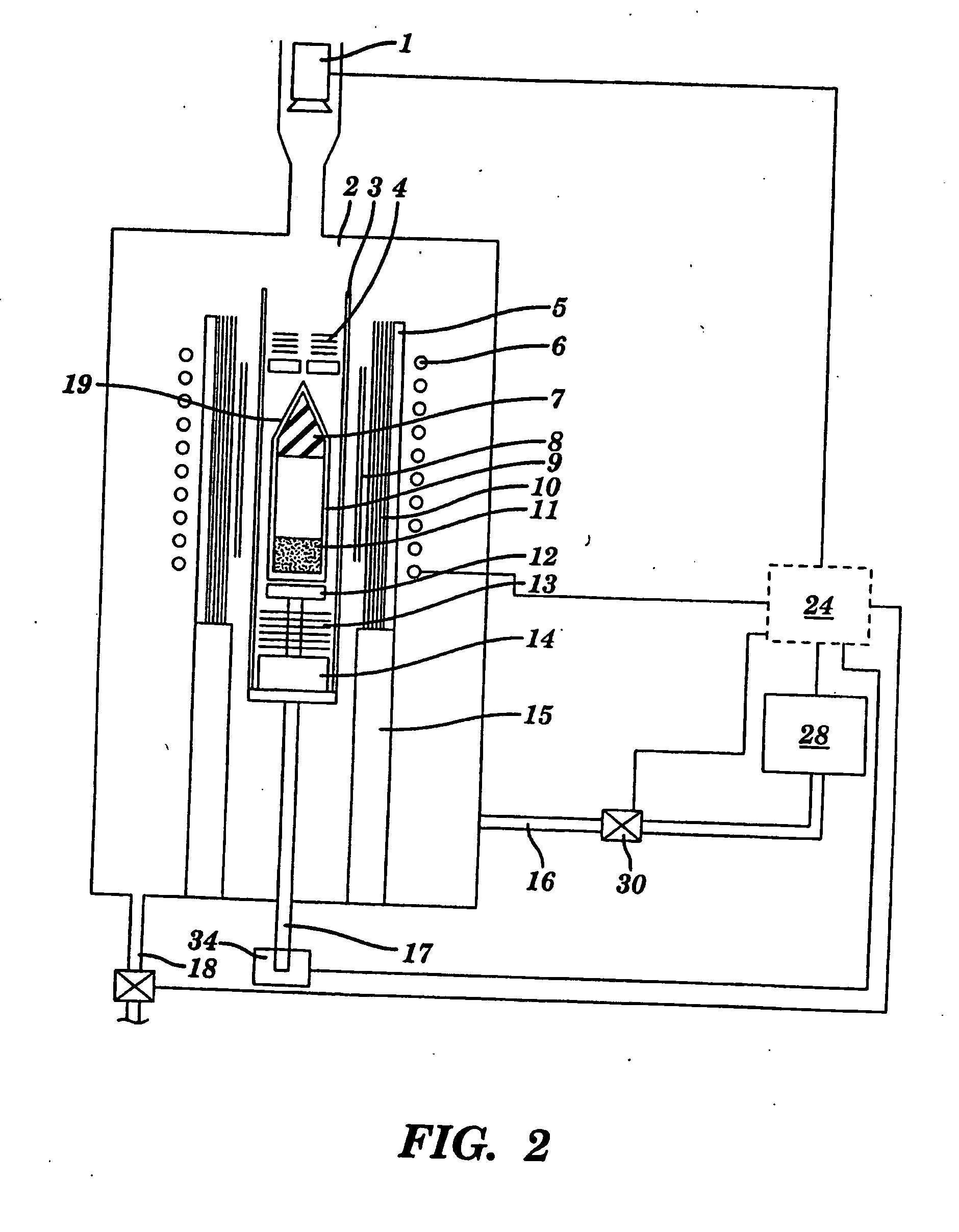

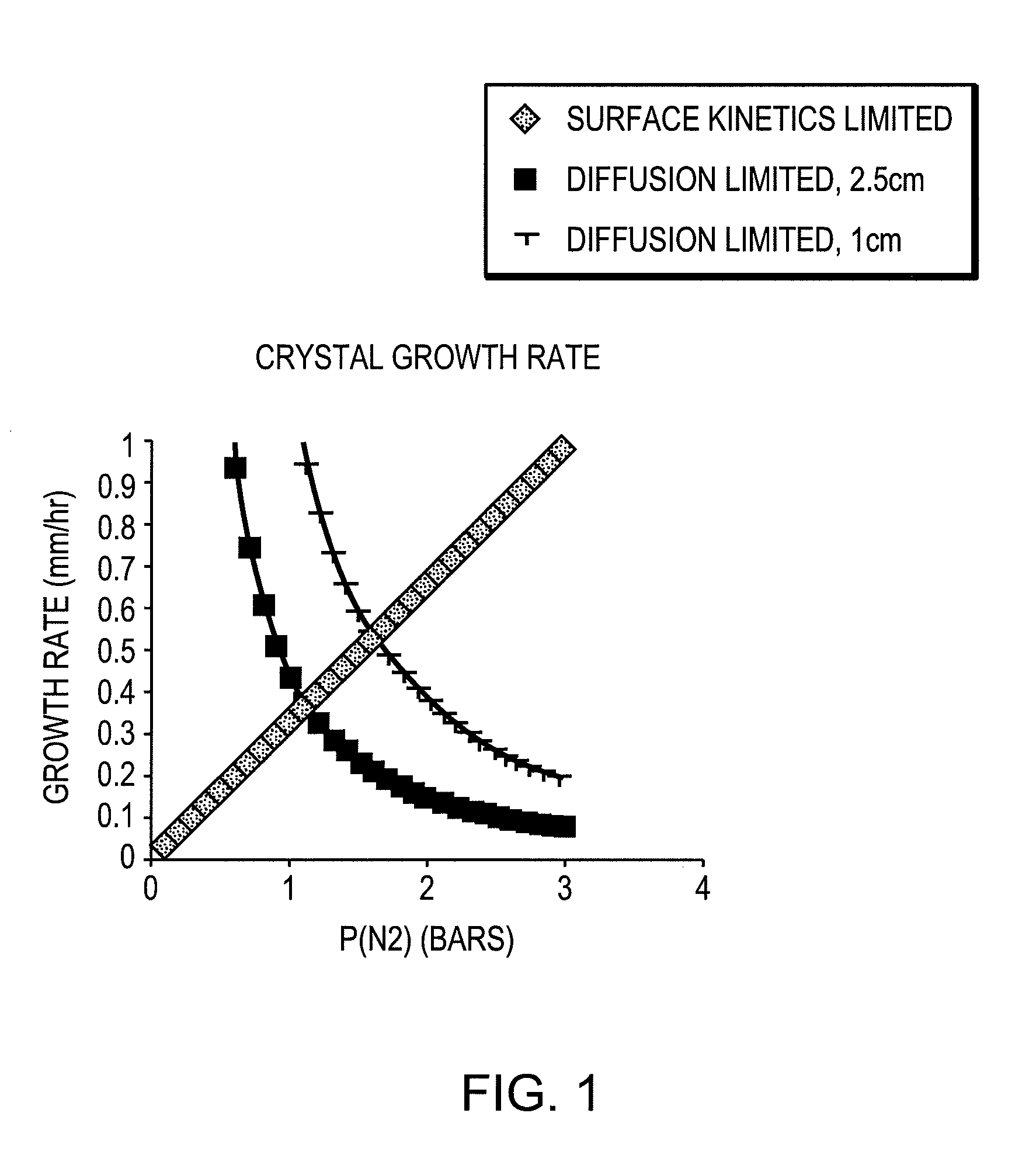

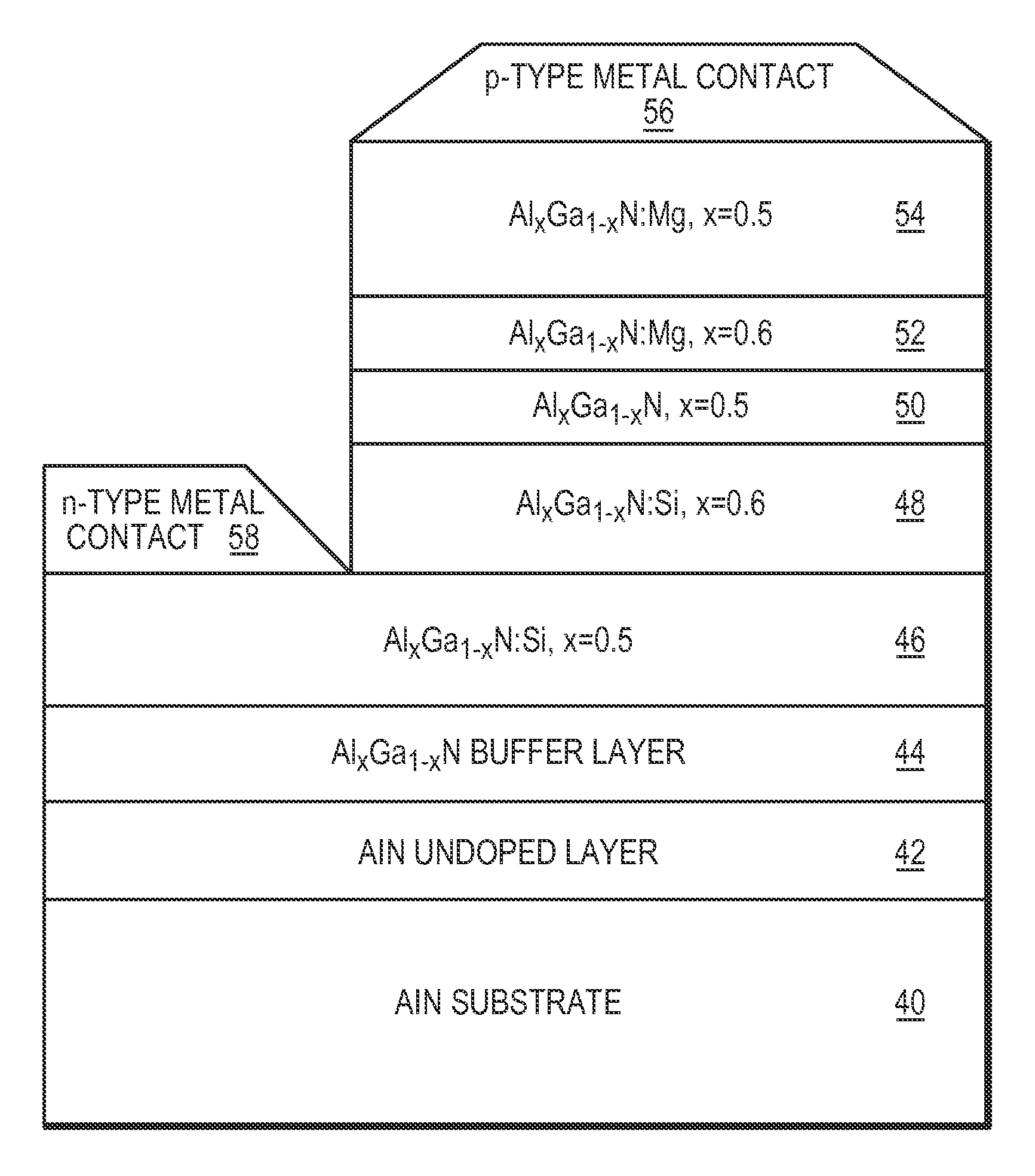

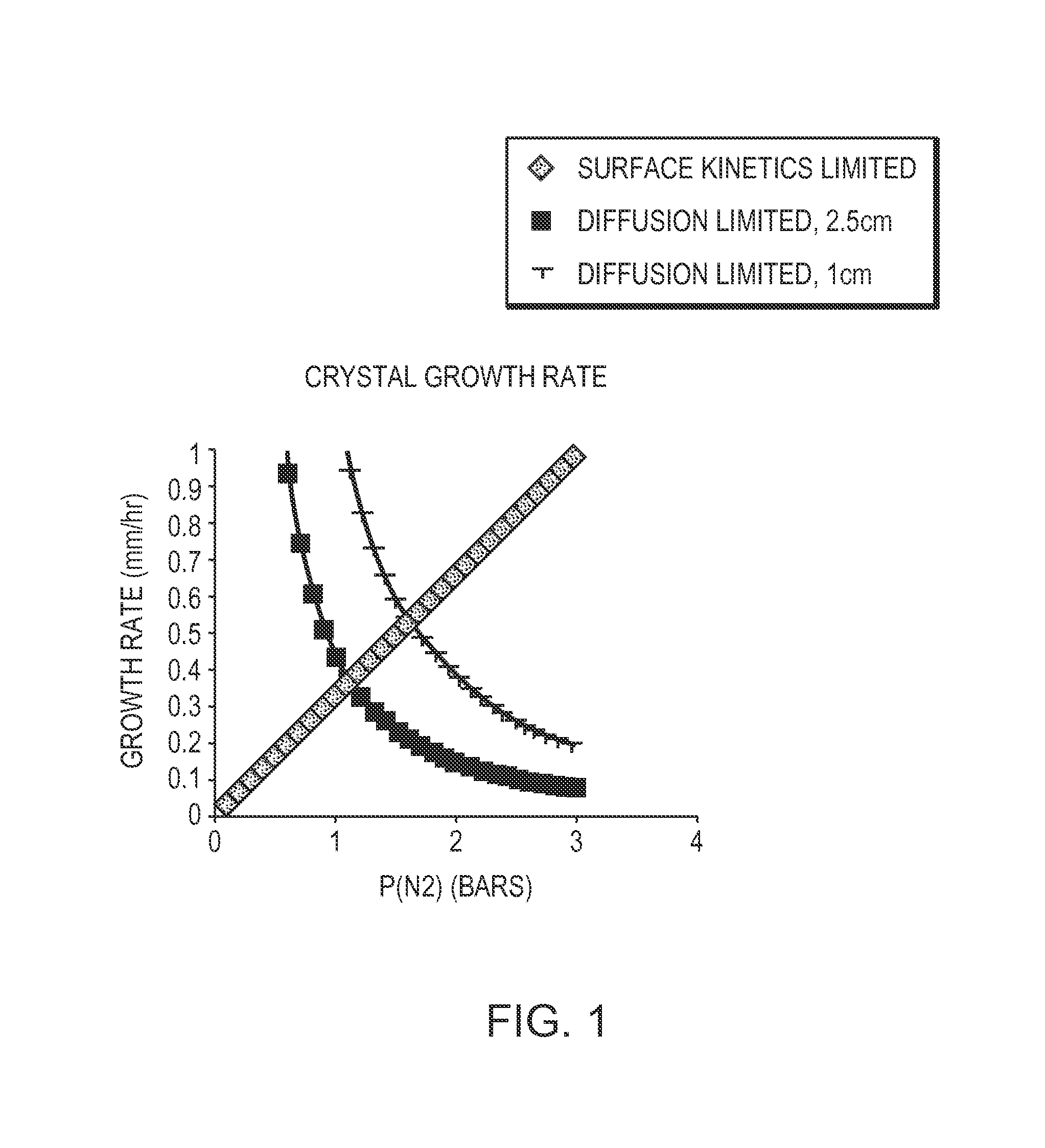

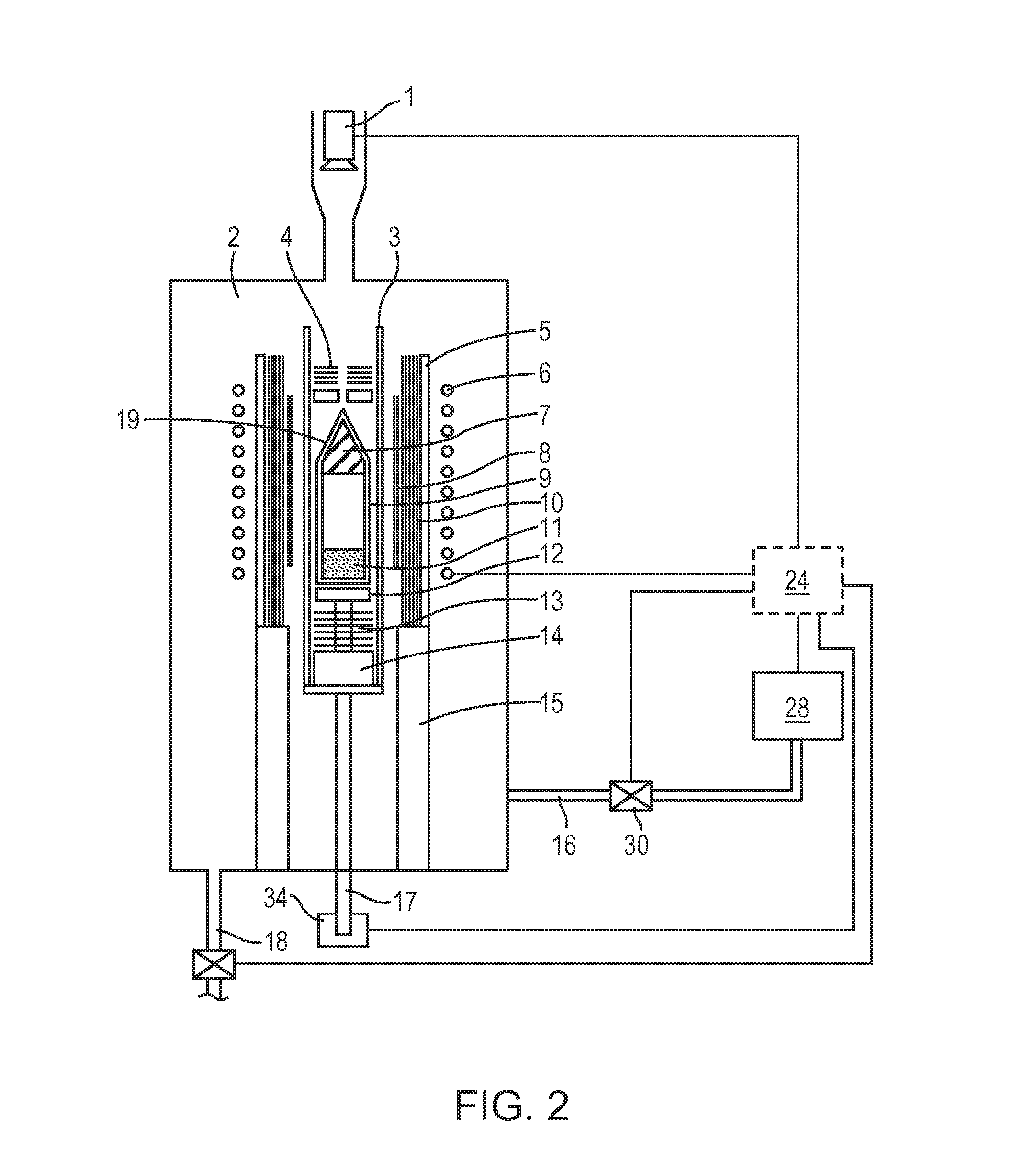

Method and apparatus for producing large, single-crystals of aluminum nitride

ActiveUS20070101932A1Facilitate productionEasy to manufacturePolycrystalline material growthSolid-state devicesDislocationBulk crystal

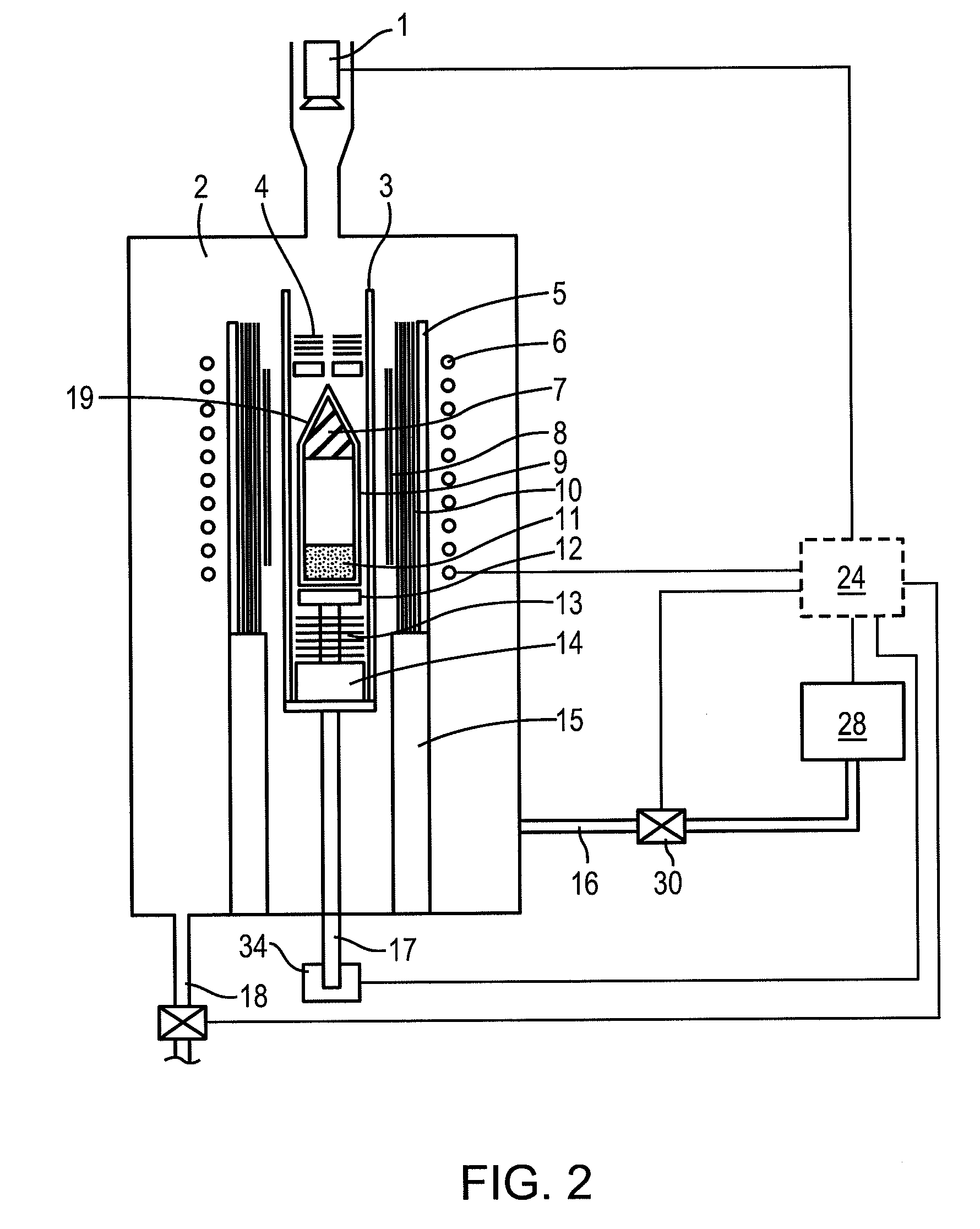

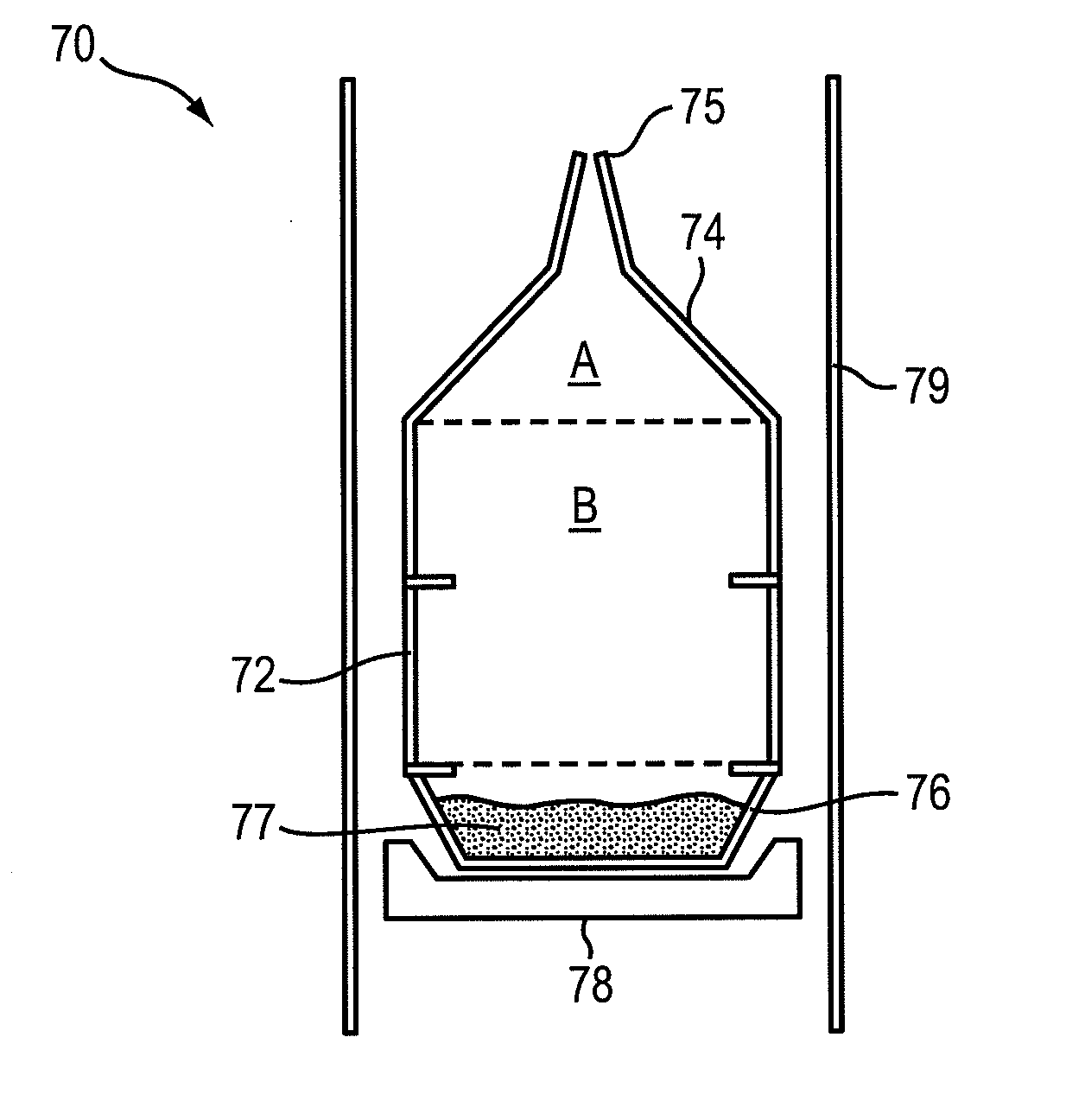

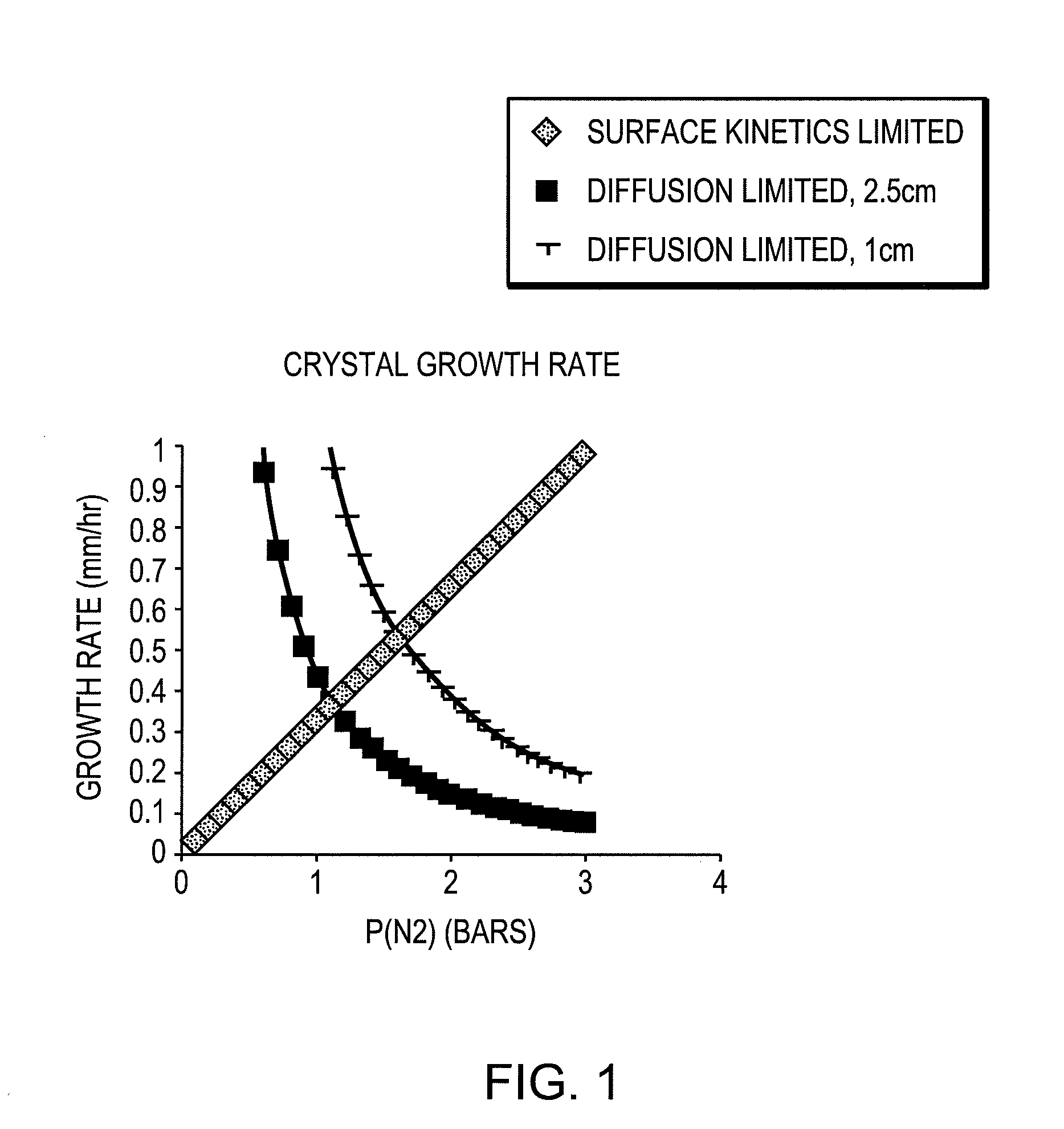

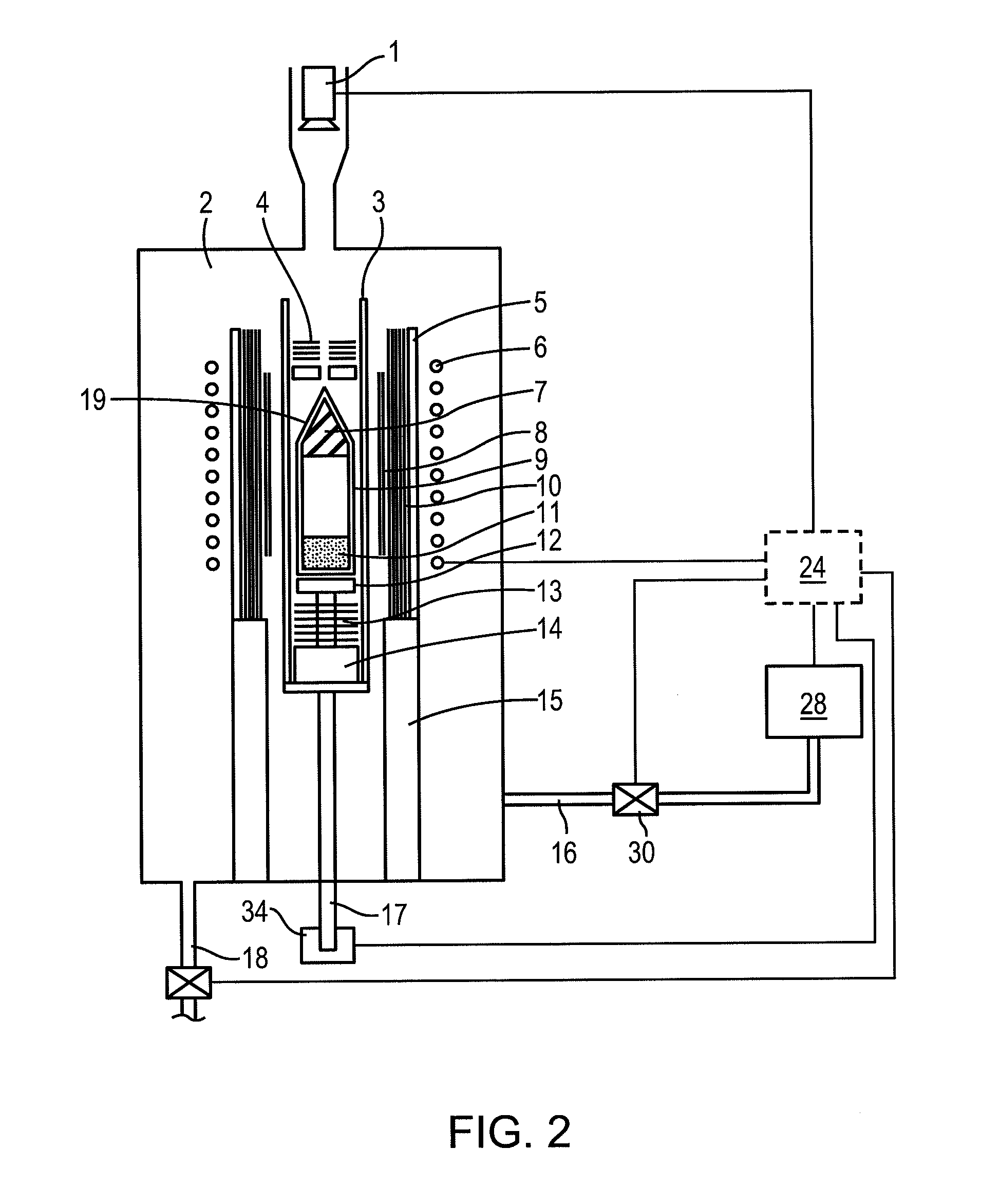

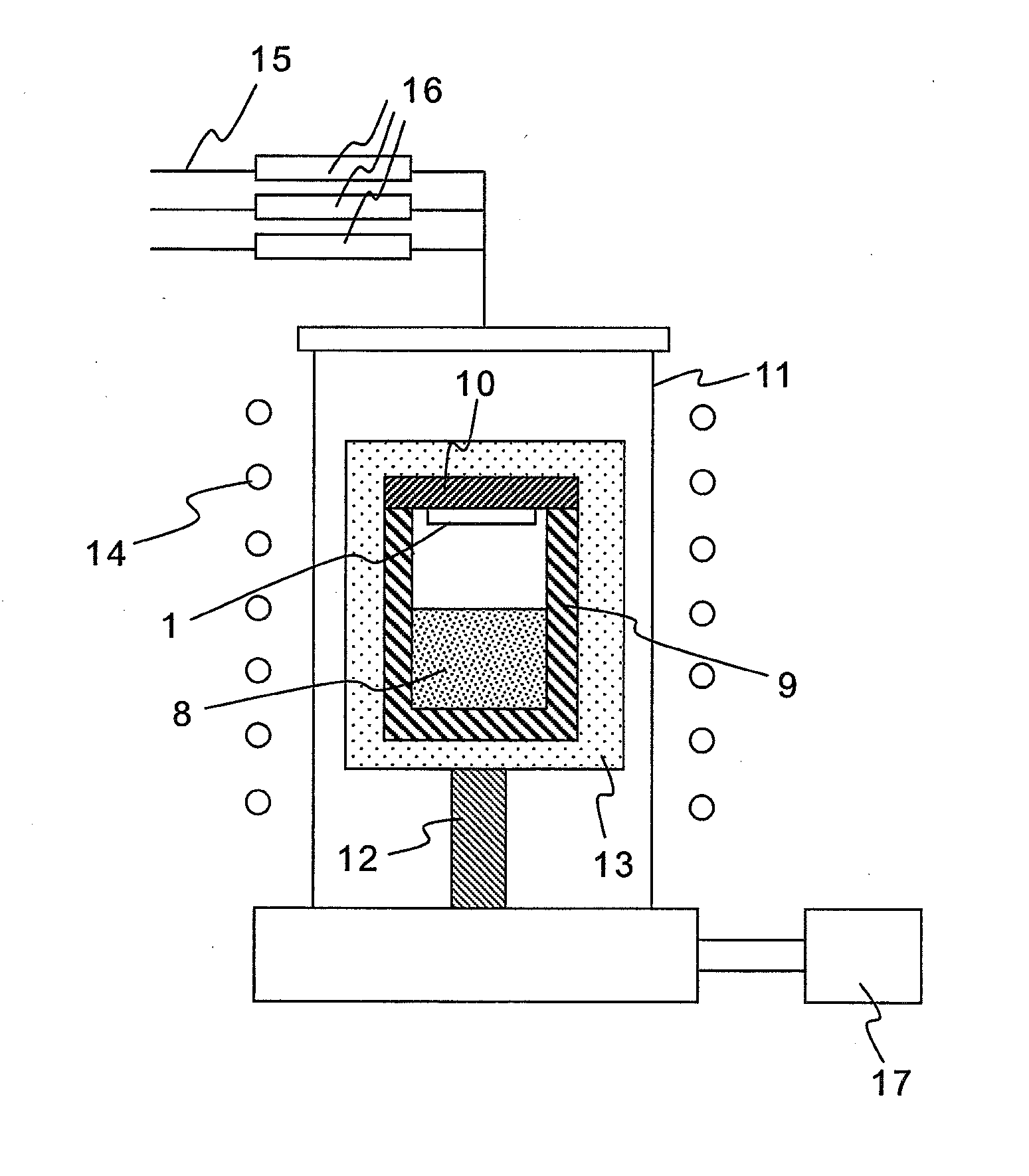

Bulk single crystals of AlN having a diameter greater than about 25 mm and dislocation densities of about 10,000 cm−2 or less and high-quality AlN substrates having surfaces of any desired crystallographic orientation fabricated from these bulk crystals.

Owner:CRYSTAL

Methods for nanoscale structures from optical lithography and subsequent lateral growth

InactiveUS20070029643A1Reduce defect densityReduce dislocationMaterial nanotechnologyDecorative surface effectsLithographic artistPhotonics

Methods, and structures formed thereby, are disclosed for forming laterally grown structures with nanoscale dimensions from nanoscale arrays which can be patterned from nanoscale lithography. The structures and methods disclosed herein have applications with electronic, photonic, molecular electronic, spintronic, microfluidic or nano-mechanical (NEMS) technologies. The spacing between laterally grown structures can be a nanoscale measurement, for example with a spacing distance which can be approximately 1-50 nm, and more particularly can be from approximately 3-5 nm. This spacing is appropriate for integration of molecular electronic devices. The pitch between posts can be less than the average distance characteristic between dislocation defects for example in GaN (ρ=1010 / cm2→d=0.1 μm) resulting an overall reduction in defect density. Large-scale integration of nanoscale devices can be achieved using lithographic equipment that is orders of magnitude less expensive that that used for advanced lithographic techniques, such as electron beam lithography.

Owner:NORTH CAROLINA STATE UNIV

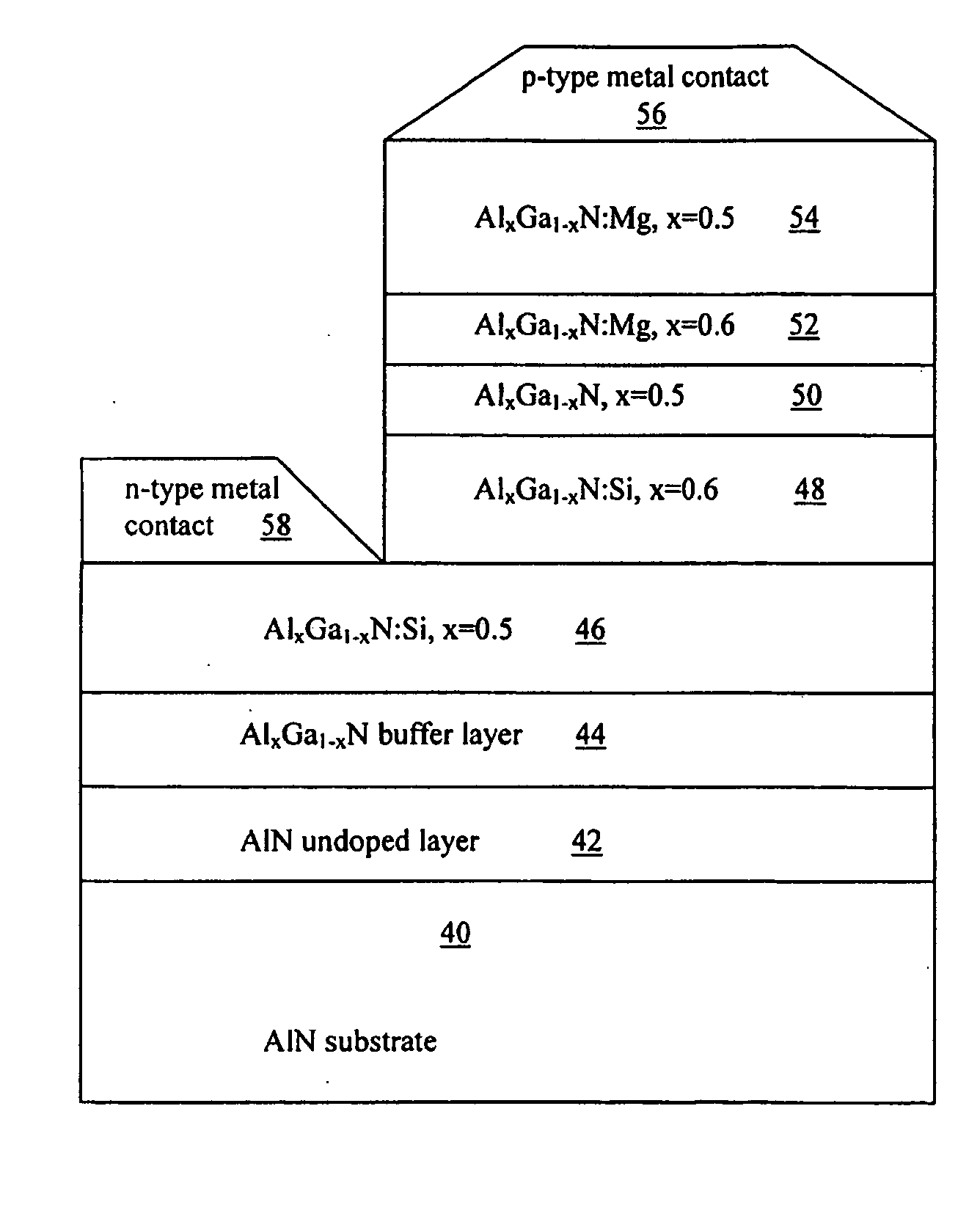

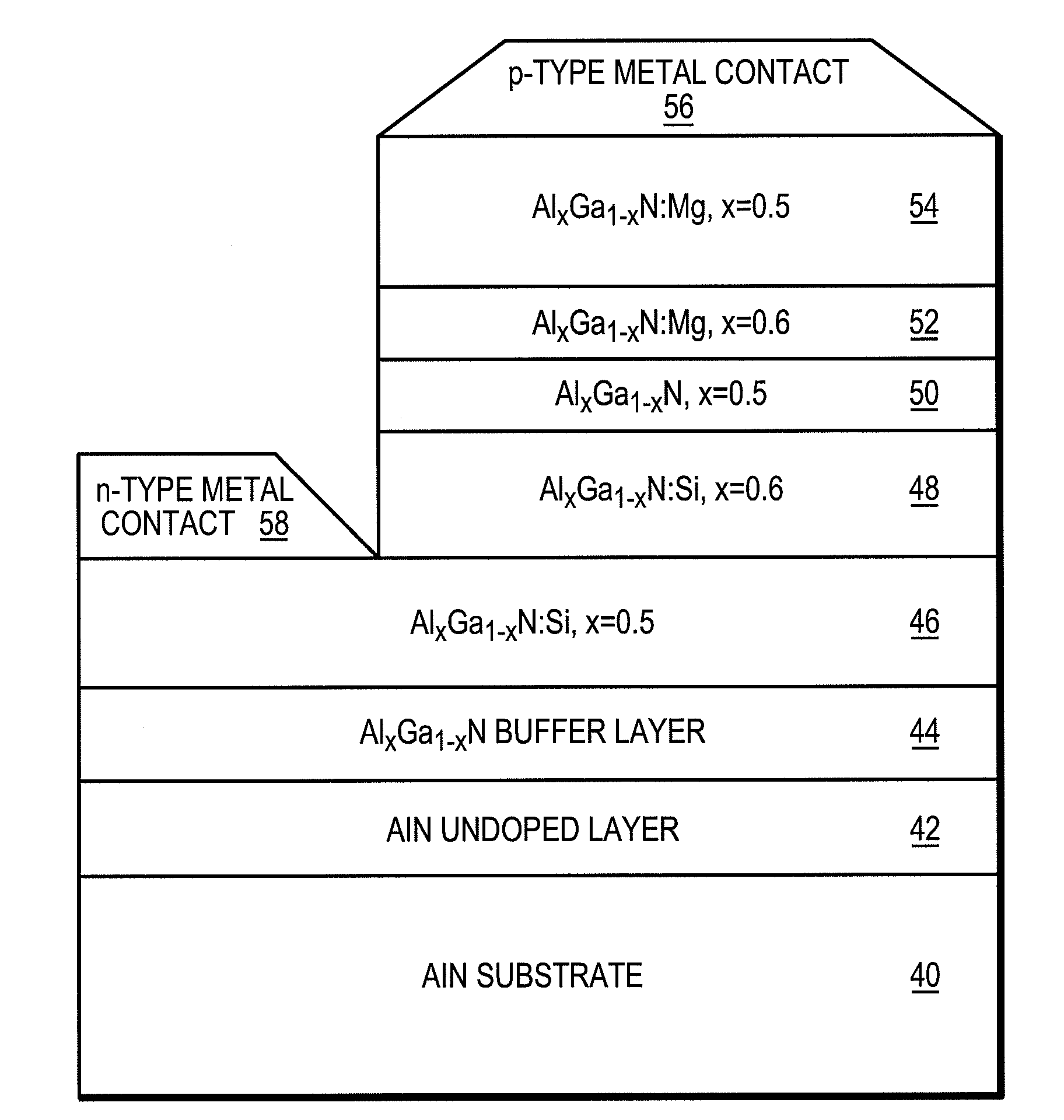

Nitride semiconductor heterostructures and related methods

InactiveUS20090283028A1Easy to manufactureGood chemical compatibilityFrom gel statePolycrystalline material growthSemiconductor structureSemiconductor heterostructures

Semiconductor structures and devices based thereon include an aluminum nitride single-crystal substrate and at least one layer epitaxially grown thereover. The epitaxial layer may comprise at least one of AlN, GaN, InN, or any binary or tertiary alloy combination thereof, and have an average dislocation density within the semiconductor heterostructure is less than about 106 cm−2.

Owner:CRYSTAL

Nitride semiconductor heterostructures and related methods

InactiveUS7638346B2Easy to manufactureReduce dislocationFrom gel statePolycrystalline material growthSemiconductor structureSemiconductor heterostructures

Owner:CRYSTAL

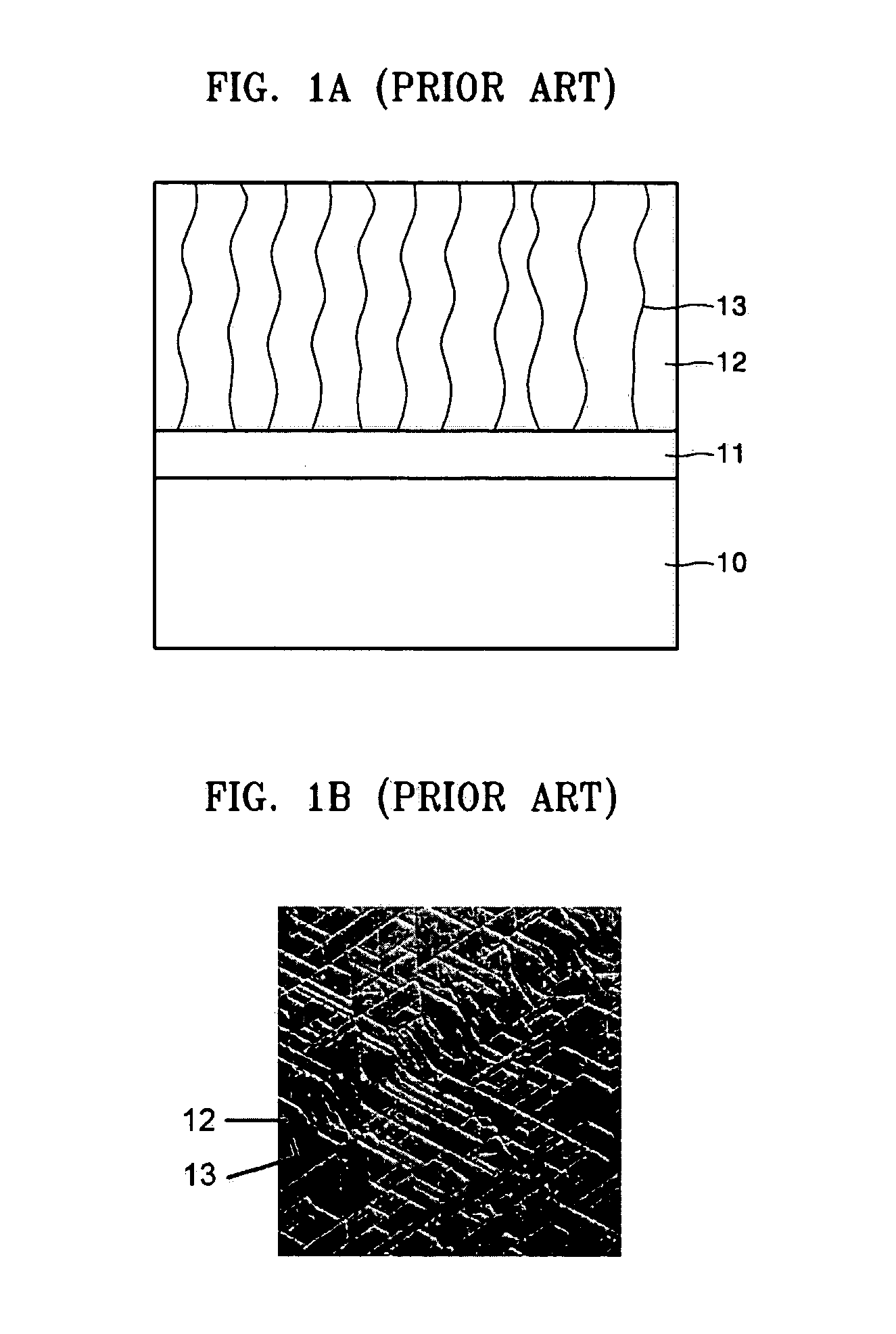

Nitride semiconductors on silicon substrate and method of manufacturing the same

InactiveUS20050077512A1Reduce crackingReduce creationPolycrystalline material growthSolid-state devicesCrystallographic defectDislocation

Provided is a nitride semiconductor formed on a Si substrate and a method of manufacturing the same. A buffer layer is formed on the silicon substrate, and an intermediate layer having voids is formed on the buffer layer. A planarizing layer is formed on the intermediate layer, and a nitride semiconductor layer is formed on the planarizing layer. Therefore, a nitride semiconductor in which the creation of crystal defects, dislocation or cracks is substantially decreased can be produced on a large scale at a low cost.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

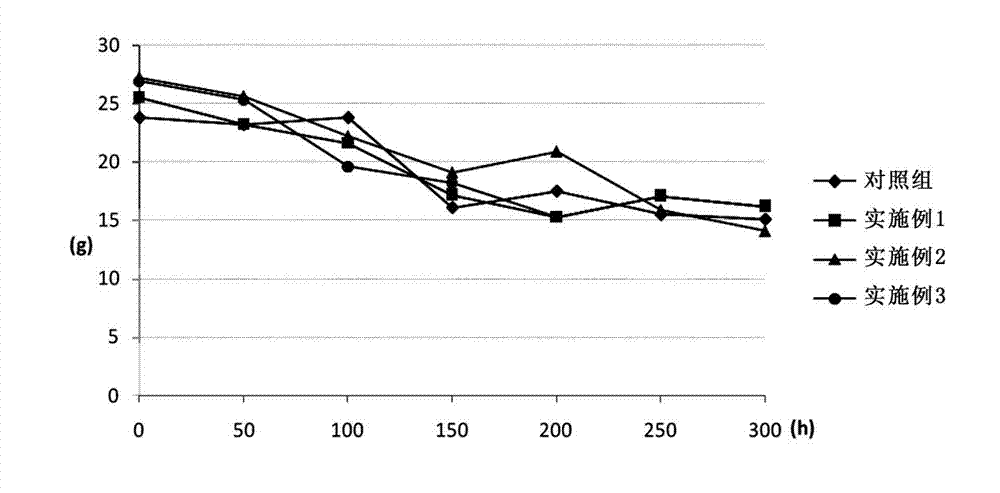

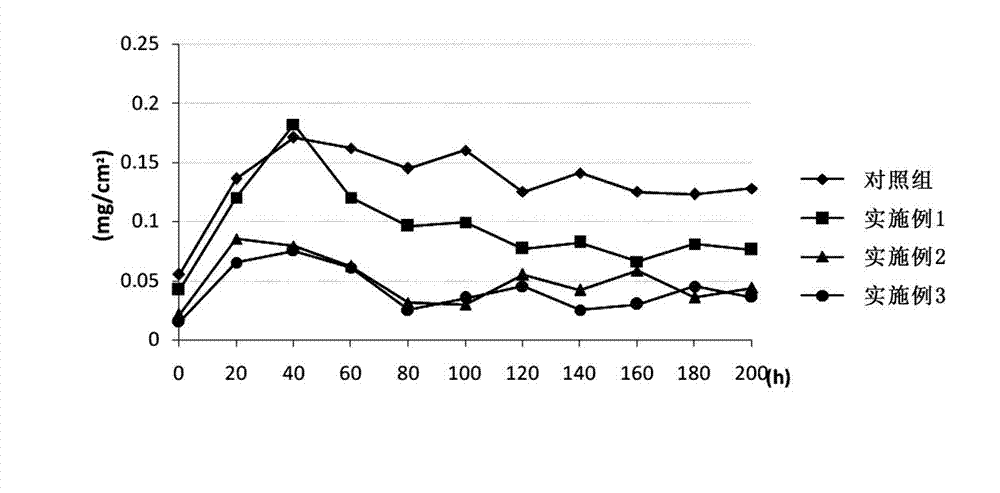

Silver alloy wire and preparation method thereof

The invention relates to a silver alloy wire and a preparation method thereof. The silver alloy wire is prepared from the following components of 0.5-10 percent of Au, 0-1 percent of Pt, 1-6 percent of Pd, 0-1 percent of Rh, 0-1 percent of Cu, 0-500ppm of Ln, 0-200ppm of Ce, 0-0.5 percent of Al, 0.7-3 percent of Ti, 0-0.2 percent of Si, 0-0.3 percent of Zn, 0-1 percent of Sn, 0-10 percent of Be and the balance of Ag. A directional continuous casting process is adopted. The prepared silver alloy wire overcomes the problem that the bonded silver wire is easily subjected to sulfur corrosion in the prior art, and has a series of other excellent characteristics.

Owner:YANTAI YINUO SEMICON MATERIAL CO LTD

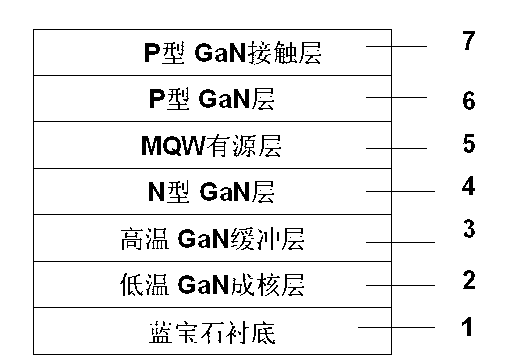

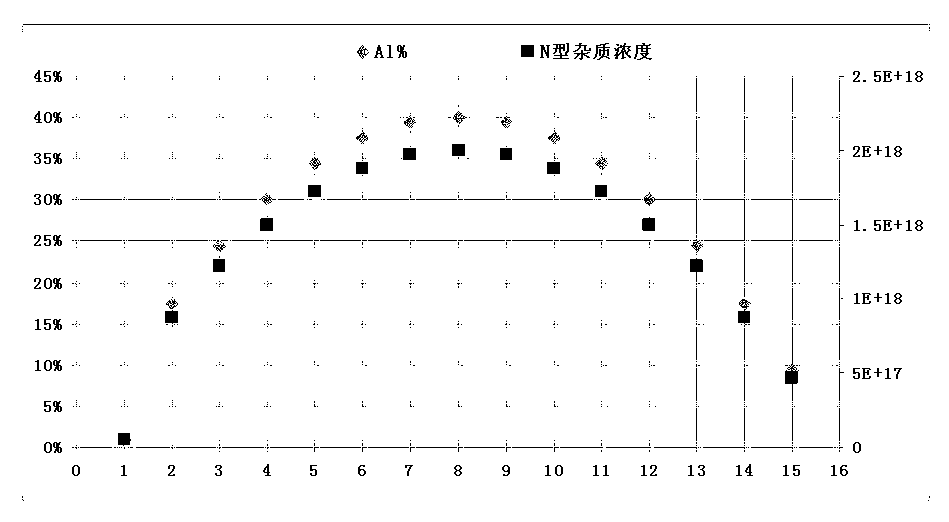

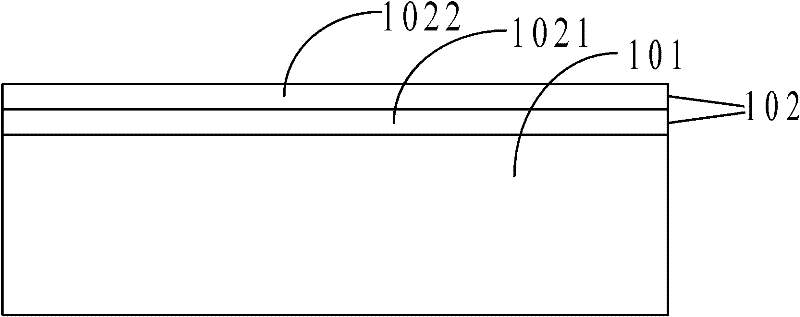

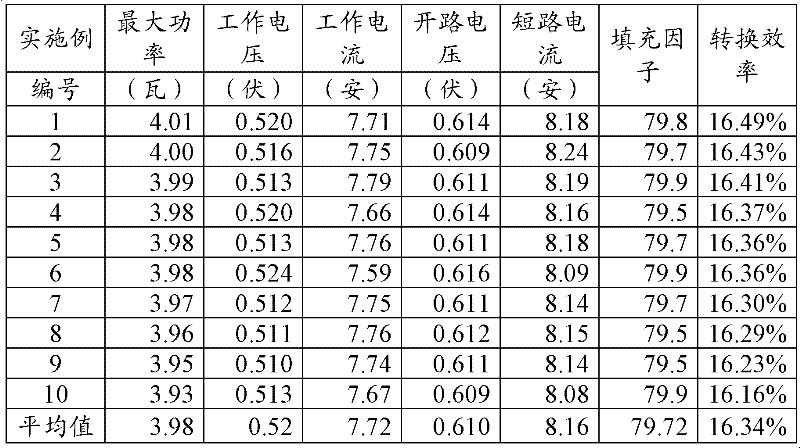

LED (light emitting diode) epitaxy structure and preparation method thereof

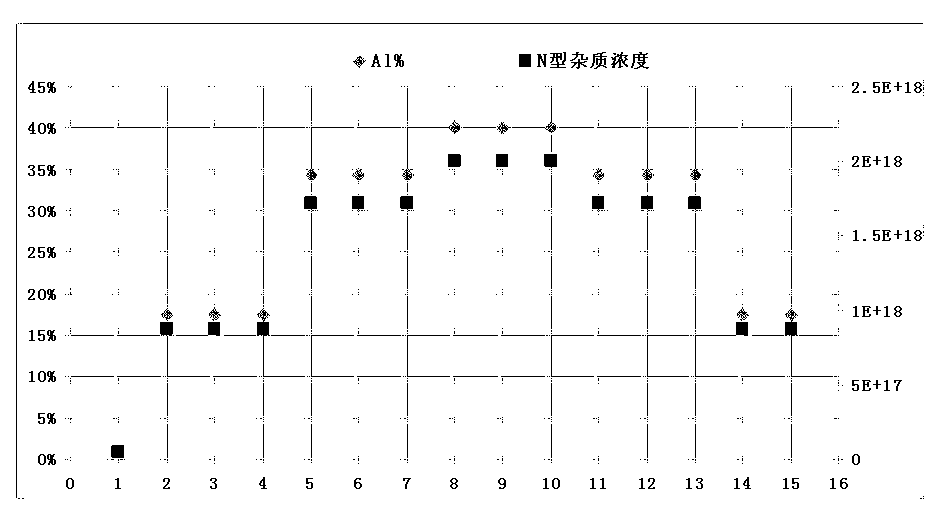

ActiveCN103236477AReduce dislocationAvoid warping effectSemiconductor devicesSemiconductor/solid-state device manufacturingCrystallographyLattice mismatch

The invention discloses an LED (light emitting diode) epitaxy structure and a preparation method thereof. The LED epitaxy structure successively comprises a substrate, a GaN nucleating layer, multiple pairs of superlattice buffer layers, an n-GaN layer, an MQW luminescent layer, a p-GaN layer and a p-type contact layer from bottom to top, wherein each superlattice buffer layer is formed by an AlGaN / n-GaN alternately stacked structure. The LED epitaxy structure is characterized in that Al(n) is defined to represent an Al component value in the nth pair of AlGaN / n-GaN superlattice buffer layer; N(n) represents the n-type impurity concentration value in the nth pair of AlGaN / n-GaN superlattice buffer layer; the variation trend of Al(n) is gradually lowered after being gradually raised; and the variation trend of N(n) is gradually lowered after being gradually raised. According to the LED epitaxy structure provided by the invention, lattice stress caused by lattice mismatch due to that a sapphire substrate and the GaN lattice are not matched can be effectively and fully released on a bottom layer growth section so as to greatly lower the warping of an epitaxial wafer in the whole high-temperature growth process and improve the wavelength concentricity and yield of the epitaxial wafer. Meanwhile, the GaN lattice quality is effectively improved, the lattice dislocation density is reduced, and the optical-electrical characteristic of the device is more stable.

Owner:ANHUI SANAN OPTOELECTRONICS CO LTD

Structure using graphite alkene as buffer layer epitaxy GaN (gallium nitride) and preparation method of structure

InactiveCN102769081AReduce stressQuality improvementPolycrystalline material growthFrom chemically reactive gasesLattice mismatchThin layer

The invention relates to a structure using graphite alkene as buffer layer epitaxy GaN (gallium nitride) and a preparation method of the structure. The method comprises the following steps of: adopting a graphite alkene layer as a buffer layer between the substrate and a gallium nitride epitaxy layer; and inserting a nitride thin layer between the graphite alkene layer and a GaN layer so as to obtain a gallium nitride epitaxy layer with low stress and high quality. The defective rate of LED (light emitting diode) devices is reduced, the quality of the LED devices is increased, and the life cycle is prolonged. The problem of lattice mismatch and thermal expansion coefficient mismatch between the substrate and the gallium nitride are solved effectively.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

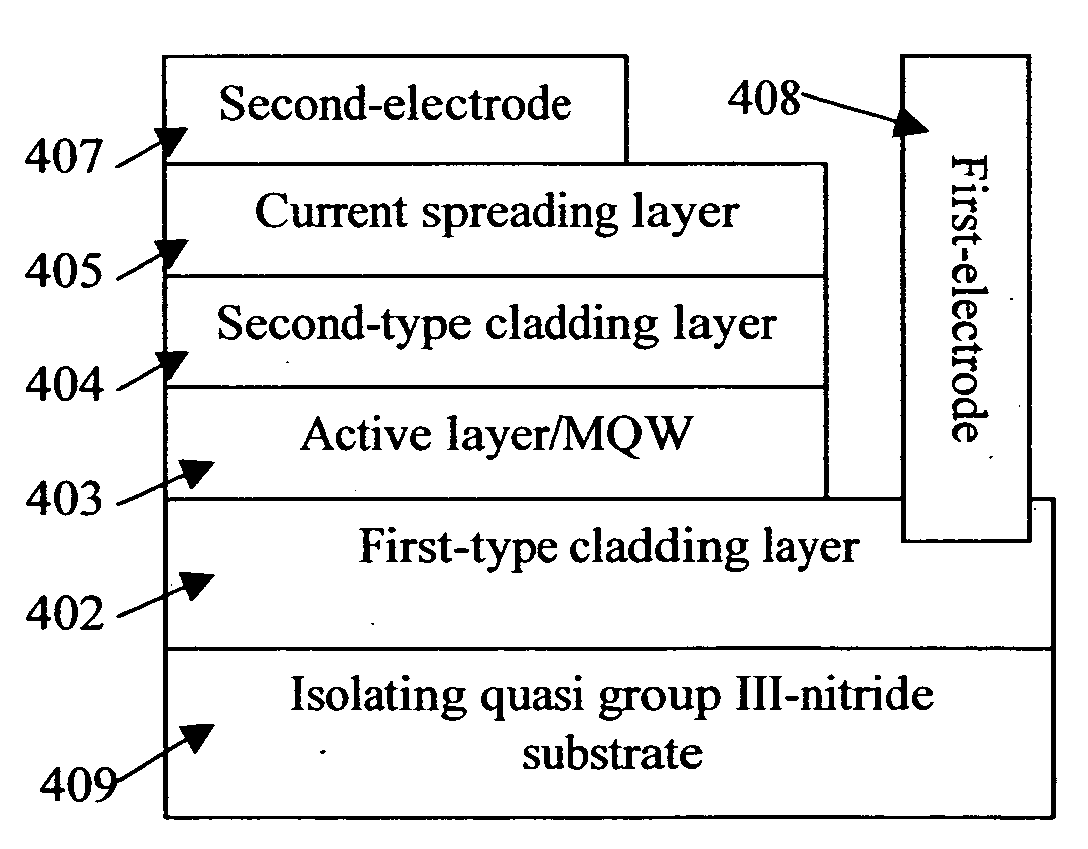

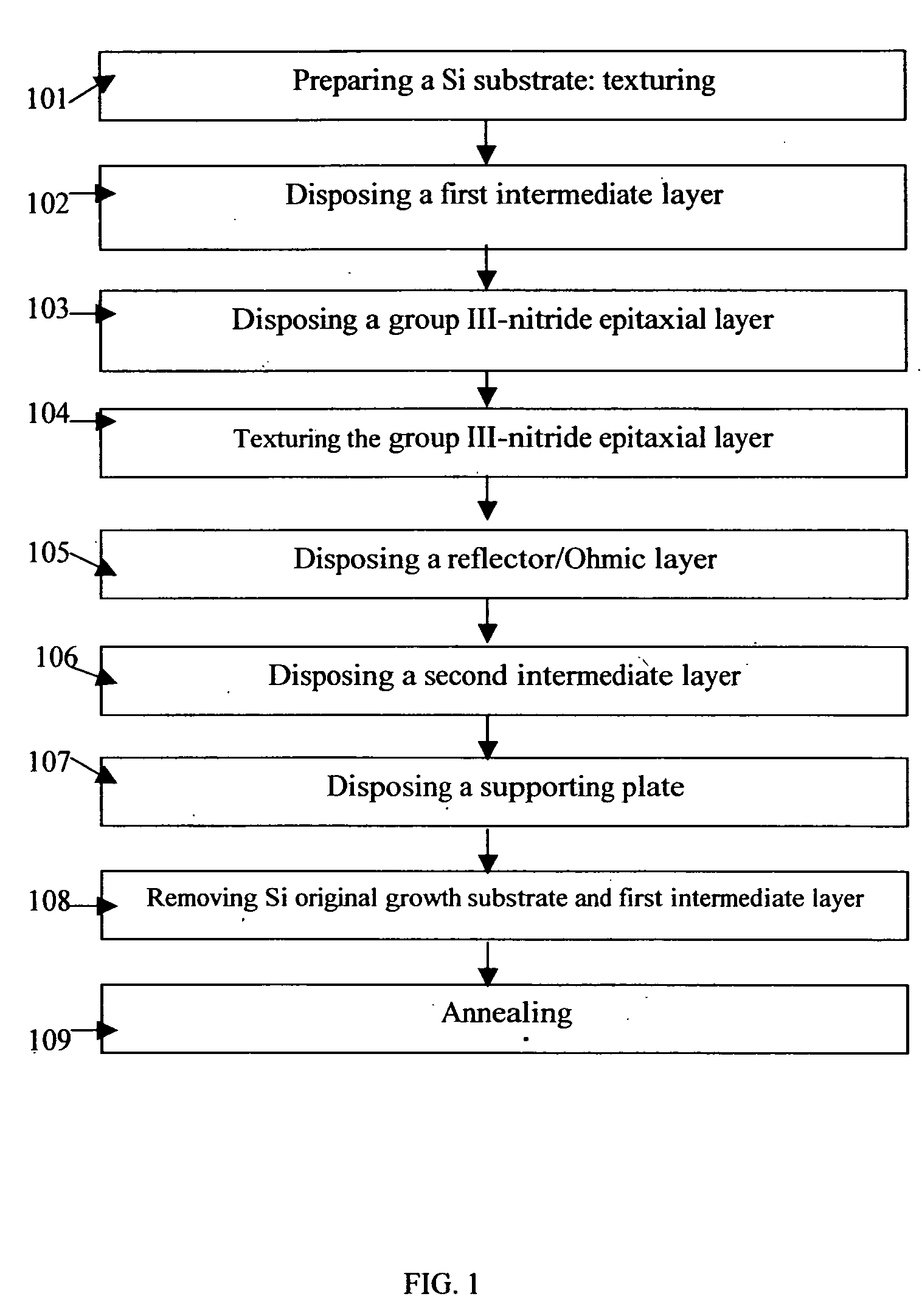

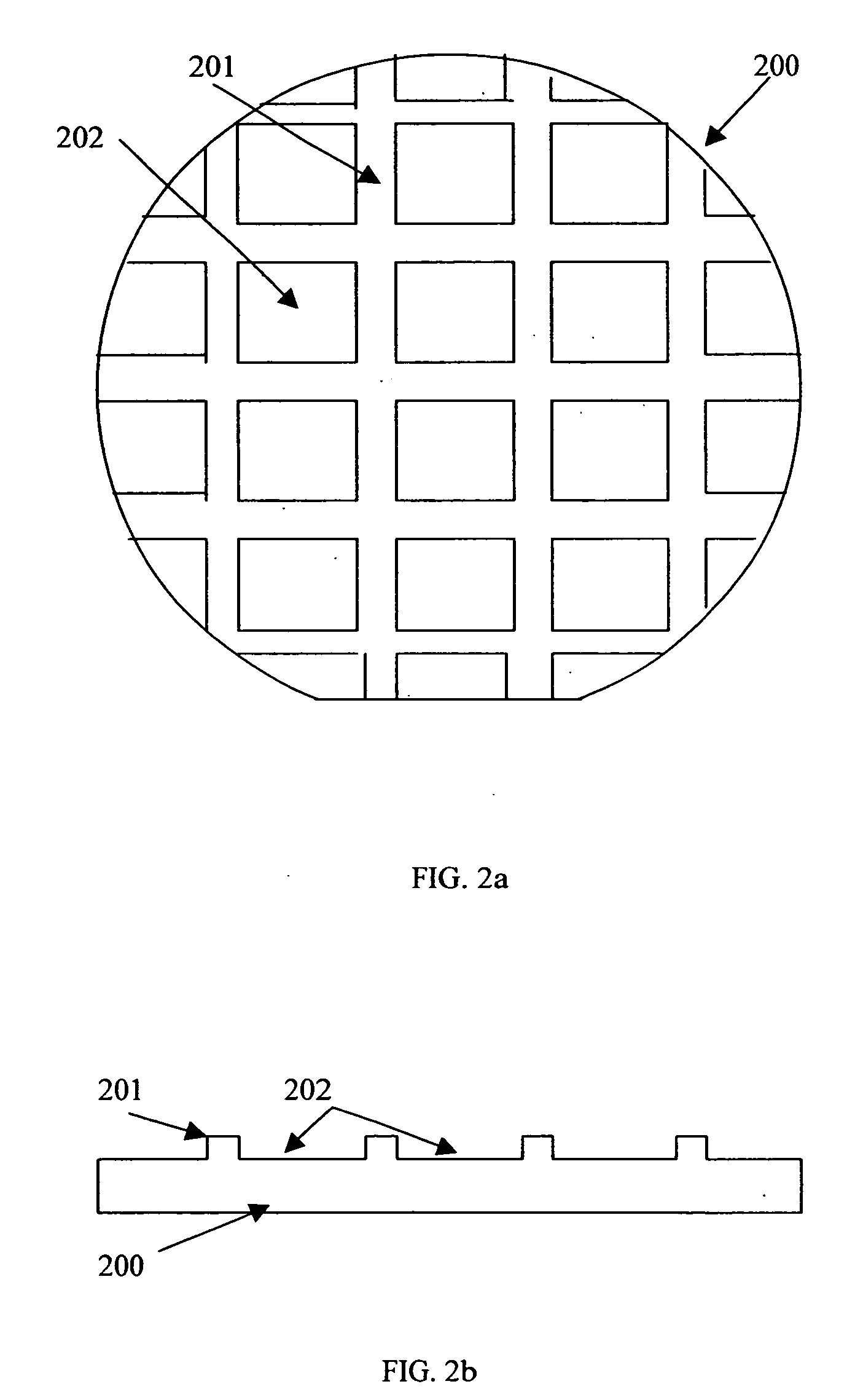

Quasi group III-nitride substrates and methods of mass production of the same

InactiveUS20060124956A1Low costHigh qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingElectrically conductiveNitride

The present invention discloses the large area high quality quasi group III-nitride substrates comprising two categories: electrically conductive and isolating. The methods manufacturing the same comprise the following process steps in the order presented: disposing a first intermediate layer on a large area silicon (Si) original growth substrate, disposing a group III-nitride epitaxial layer including a n- or p-type epitaxial layer, disposing a reflector / Ohmic layer, disposing a second intermediate layer, disposing a supporting plate, removing the silicon original growth substrate and the first intermediate layer, then the group III-nitride epitaxial layer exposed. Vertical and lateral GaN based LEDs growing on electrically conductive and isolating quasi group III-nitride substrates respectively are disclosed.

Owner:PENG HUI

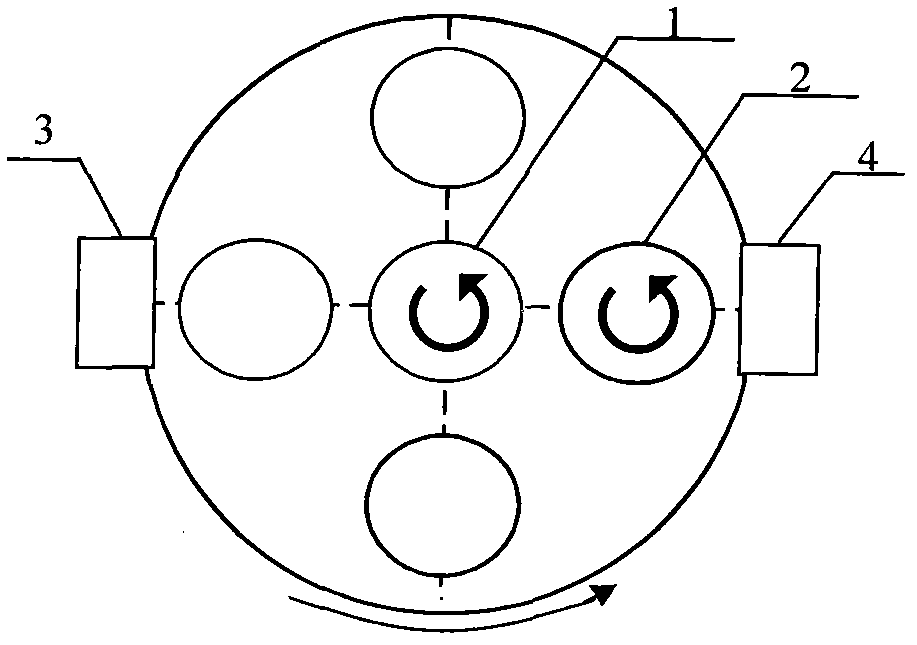

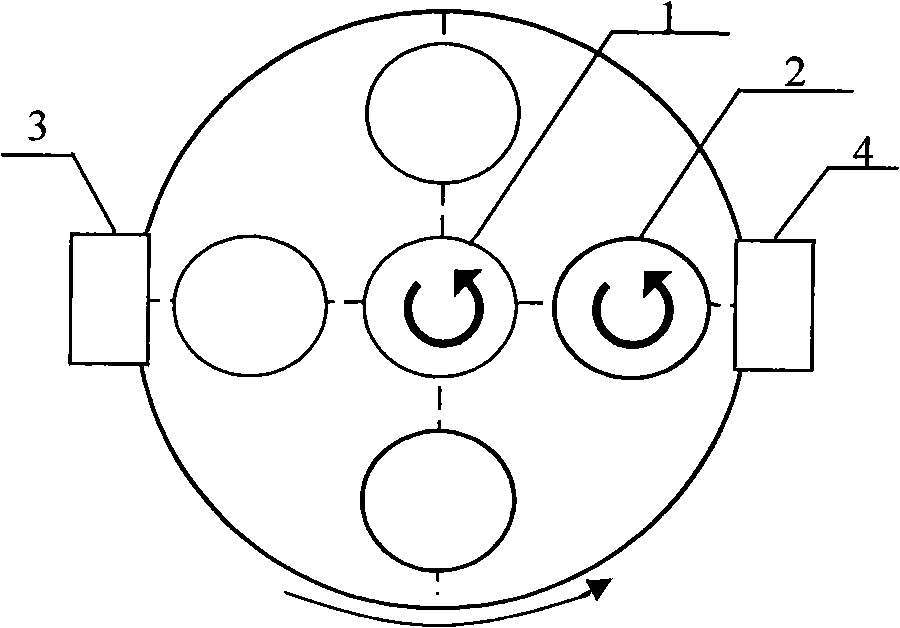

TiAlN/TiAlCN multilayer coating of substrate surface and preparing method thereof

ActiveCN102011090AMitigate defectsAlleviate dislocationVacuum evaporation coatingSputtering coatingSputteringHardness

The present invention discloses a TiAlN / TiAlCN multilayer coating of substrate surface and preparing method thereof, wherein a transitional layer is between a substrate and a TiAlN / TiAlCN multilayer coating; the multilayer coating is formed by alternating periodic arrangement of TiAlN films and TiAlCN films; in a period, the thickness sum of the TiAlN films and the TiAlCN films is 1-20 nano; the percentage by weight of C atom in the TiAlCN films is 0.1-5%. The multilayer coating of the present invention has the advantages of high hardness, low internal stress and high tenacity; the cutting efficiency and corrosion resistance of the substrate can be improved, and the service life of the substrate can be prolonged. In the present invention, the multilayer coating is deposited by high power pulse magnetron sputtering technique; the problems that cathode arc ion plating and depositing speed is too fast to prepare a nano epitaxial film and that target poisoning is caused during the procedure for preparing films by DC magnetron sputtering are solved; the nano modulation period is controlled via adjusting the autorotation and revolution speeds of the substrate and adjusting the quantity of targets.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

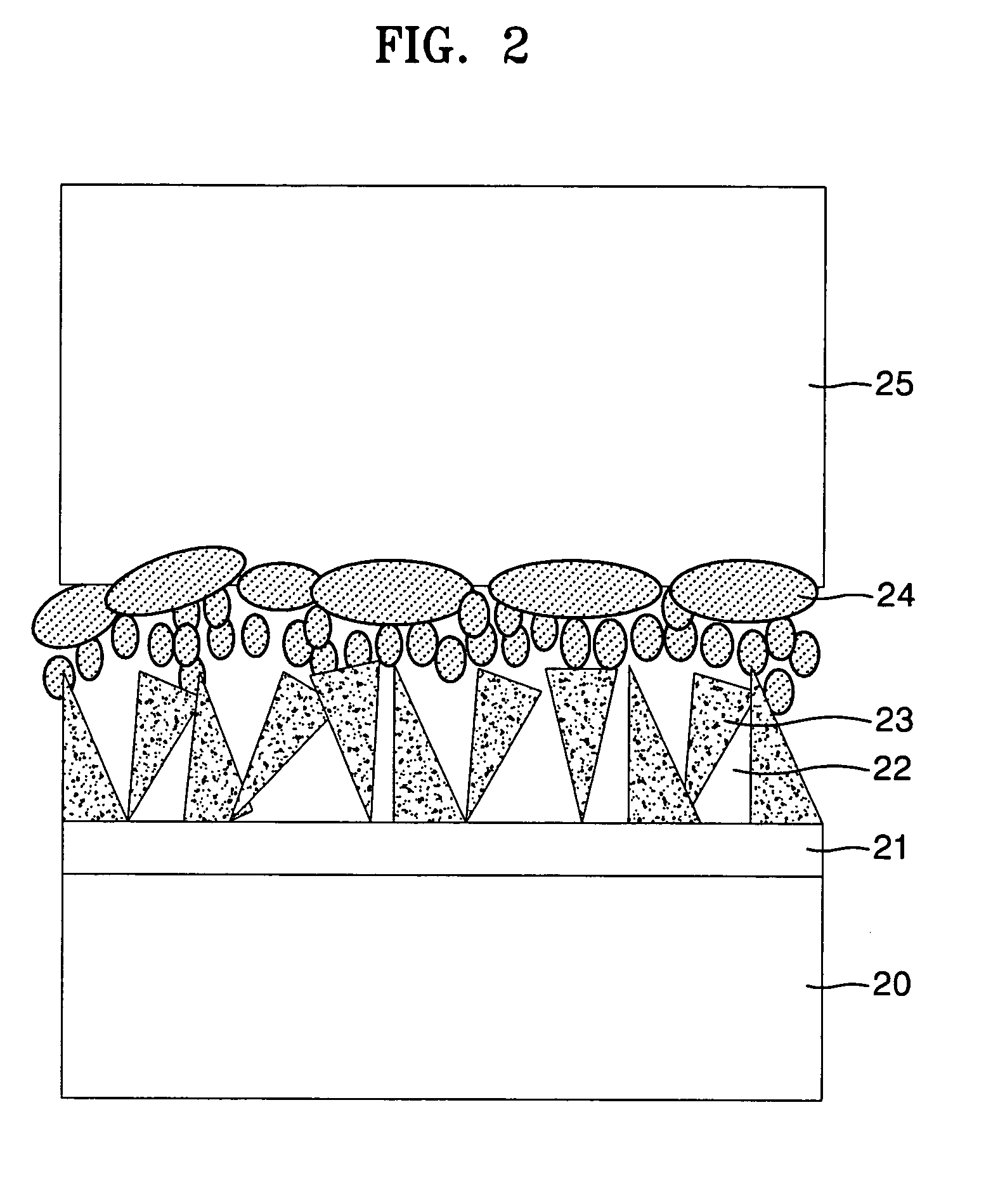

Epitaxially grown nitride-based compound semiconductor crystal substrate structure with low dislocation density

InactiveUS7196399B2Reduced dislocation and defectLow densityPolycrystalline material growthLaser detailsNitrideDislocation

A metal layer is formed directly on a nitride-based compound semiconductor base layer over a substrate body. The metal layer includes at least one metal exhibiting an atomic interaction, with assistance of a heat treatment, to atoms constituting the base layer to promote removal of constitutional atoms from the base layer, whereby pores penetrating the metal layer are formed, while many voids are formed in the nitride-based compound semiconductor base layer. An epitaxial growth of a nitride-based compound semiconductor crystal is made with an initial transient epitaxial growth, which fills the voids, and a subsequent main epitaxial growth over the porous metal layer.

Owner:SUMITOMO CHEM CO LTD

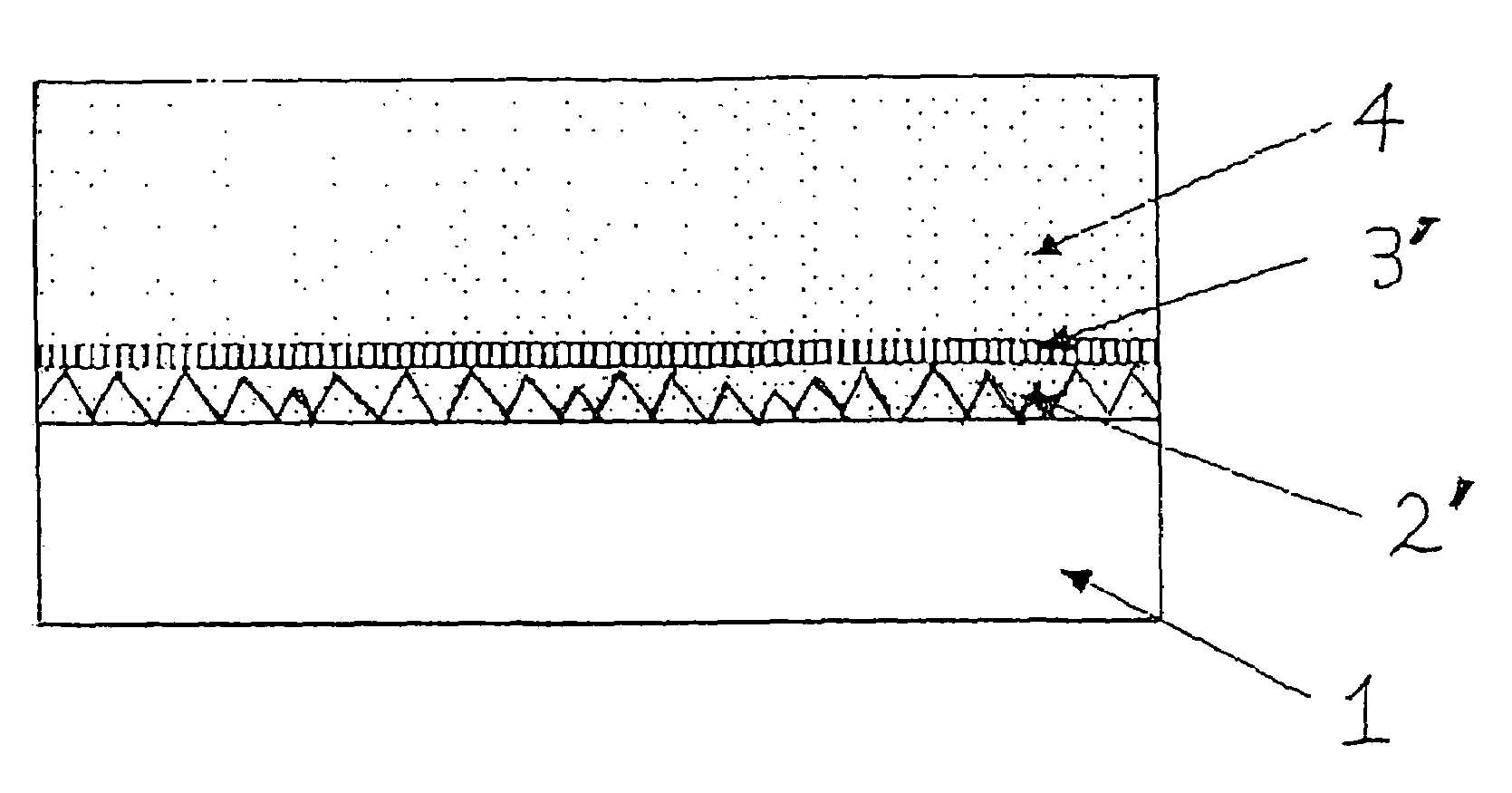

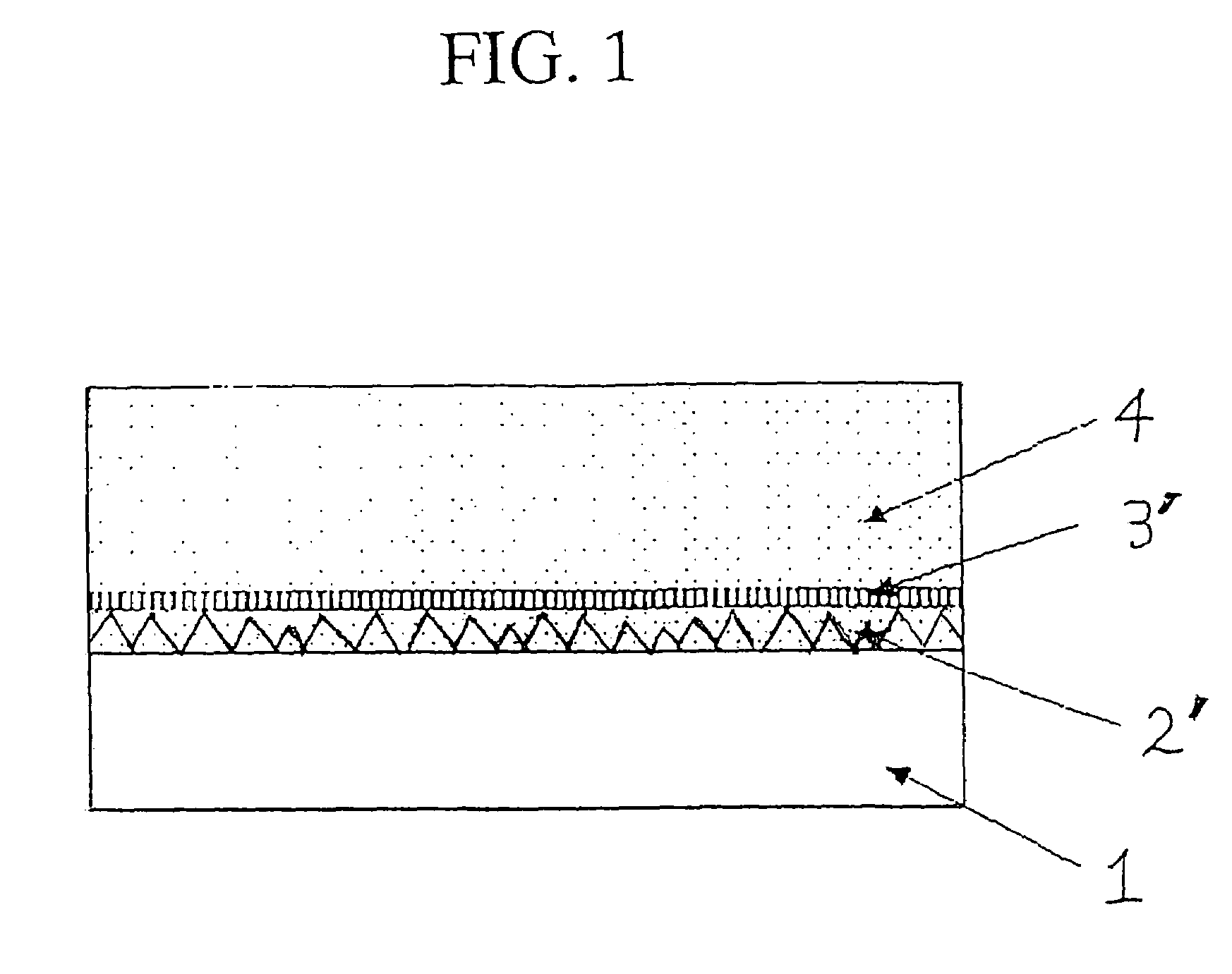

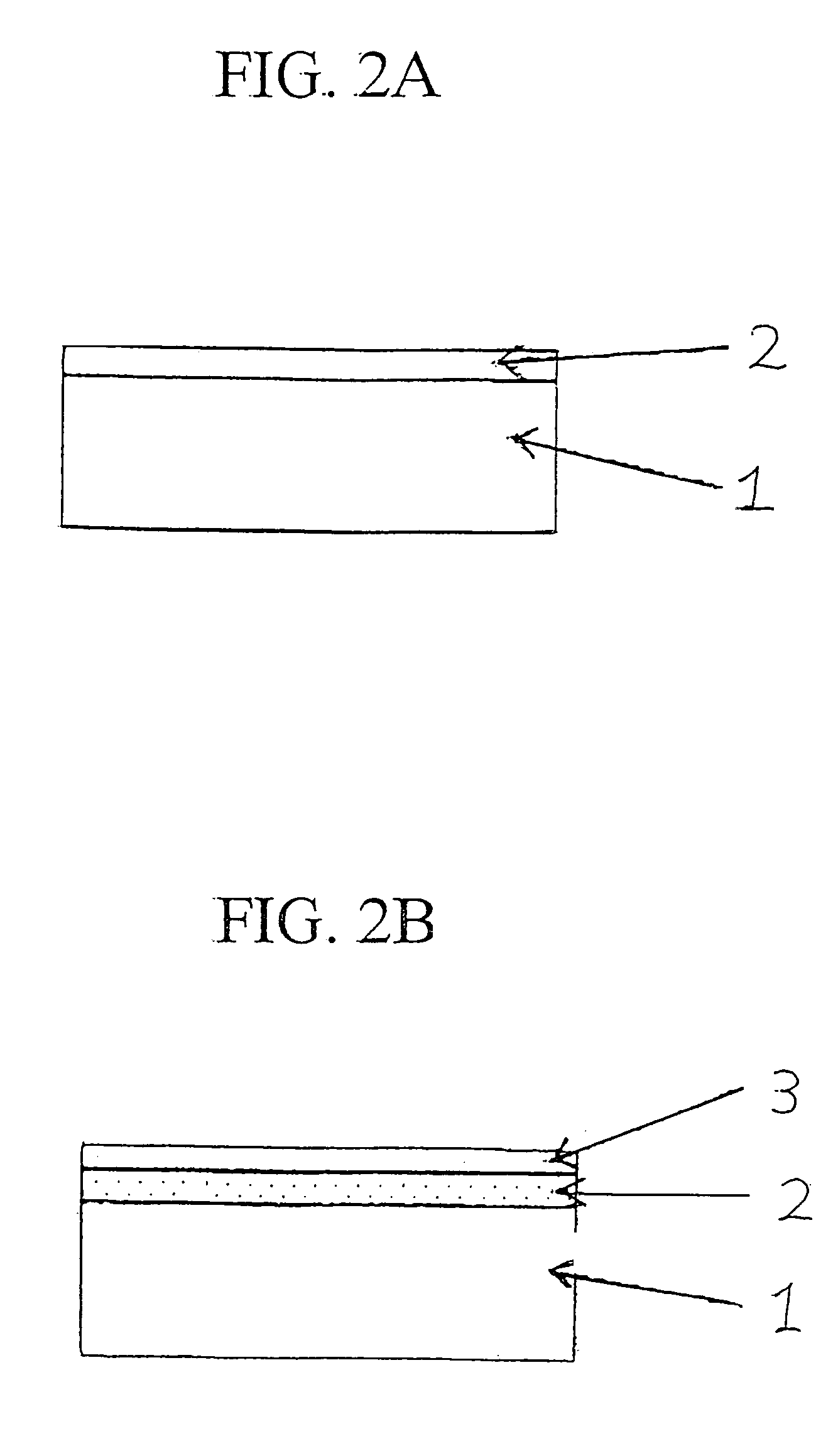

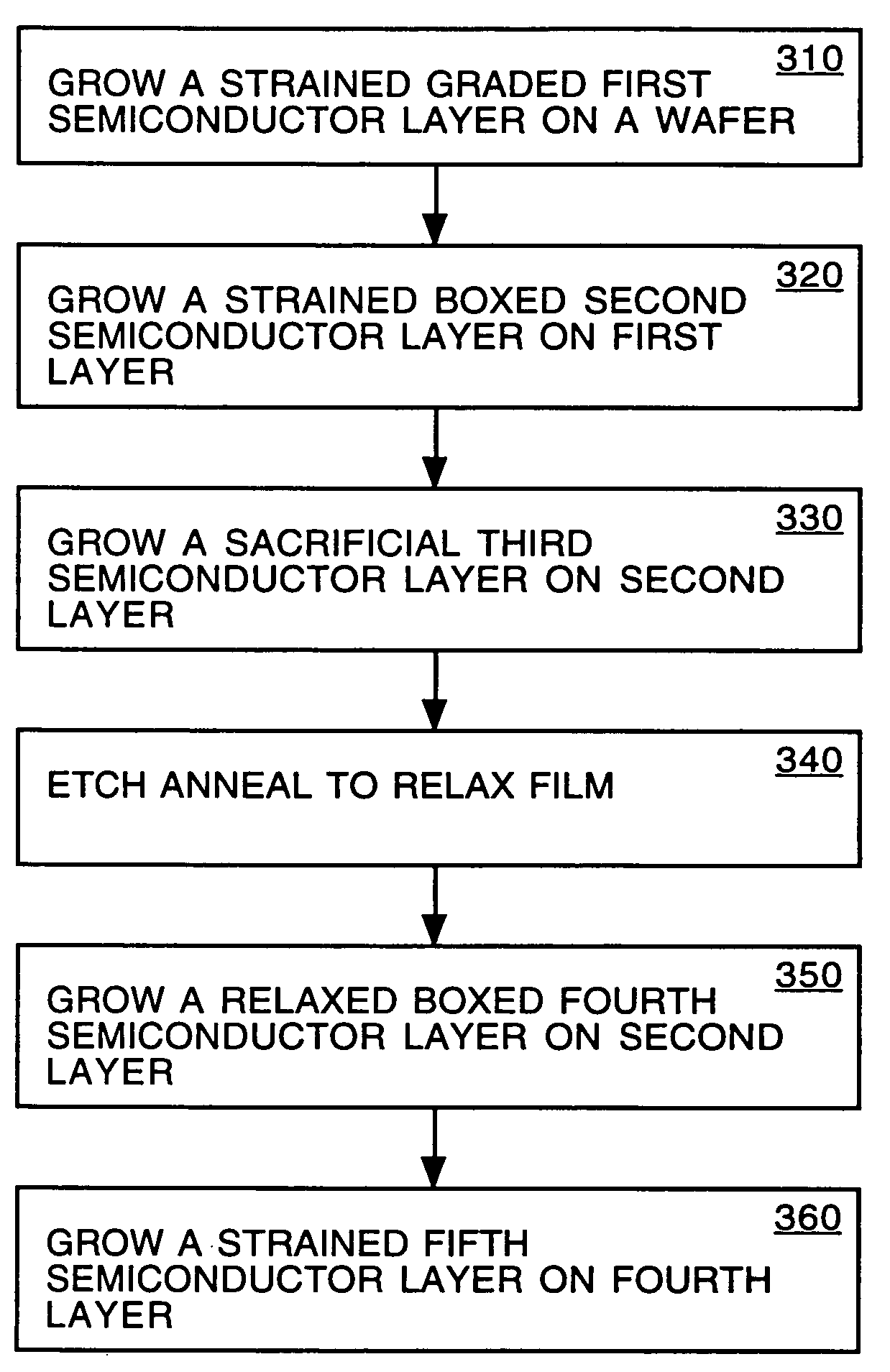

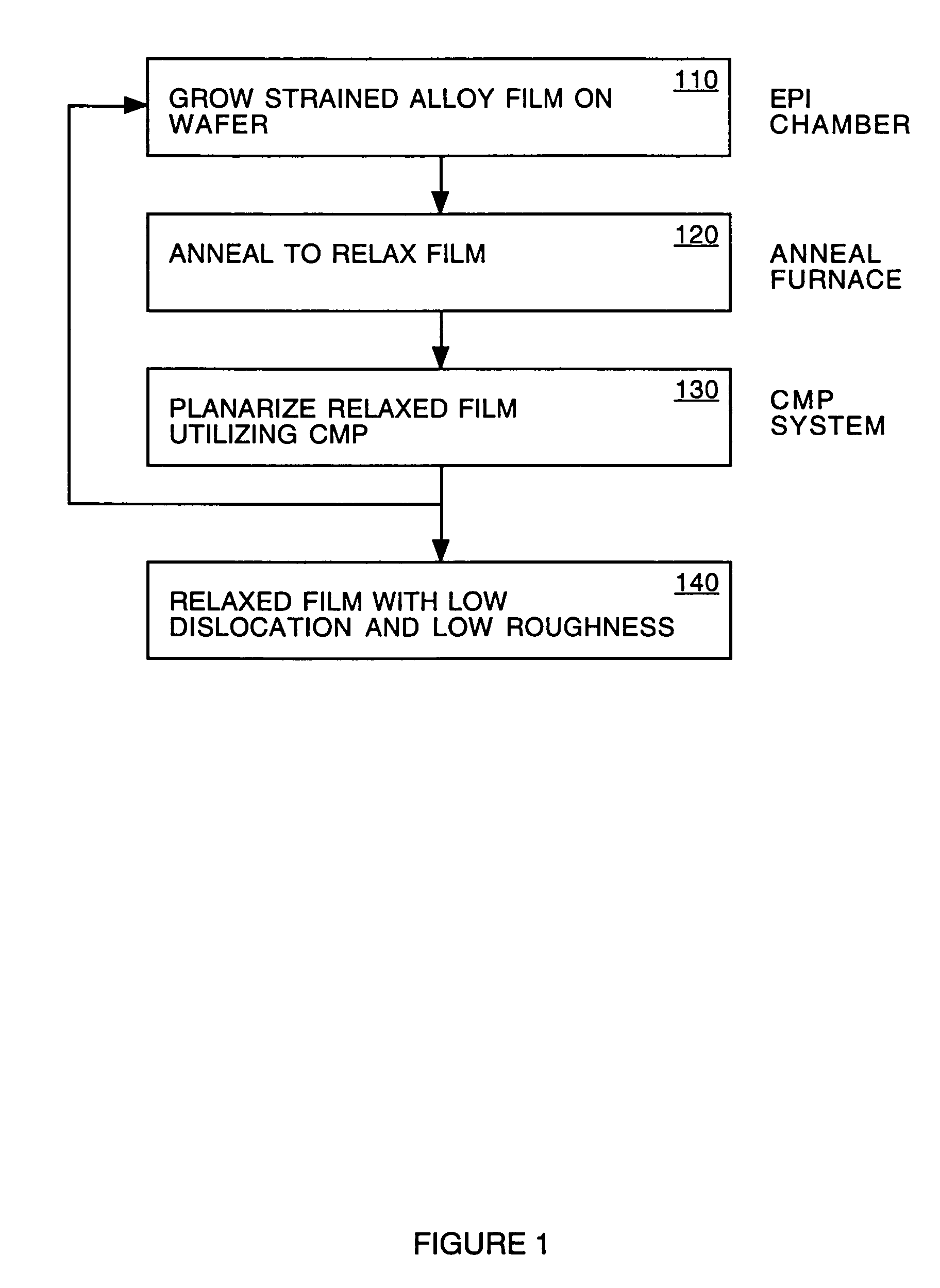

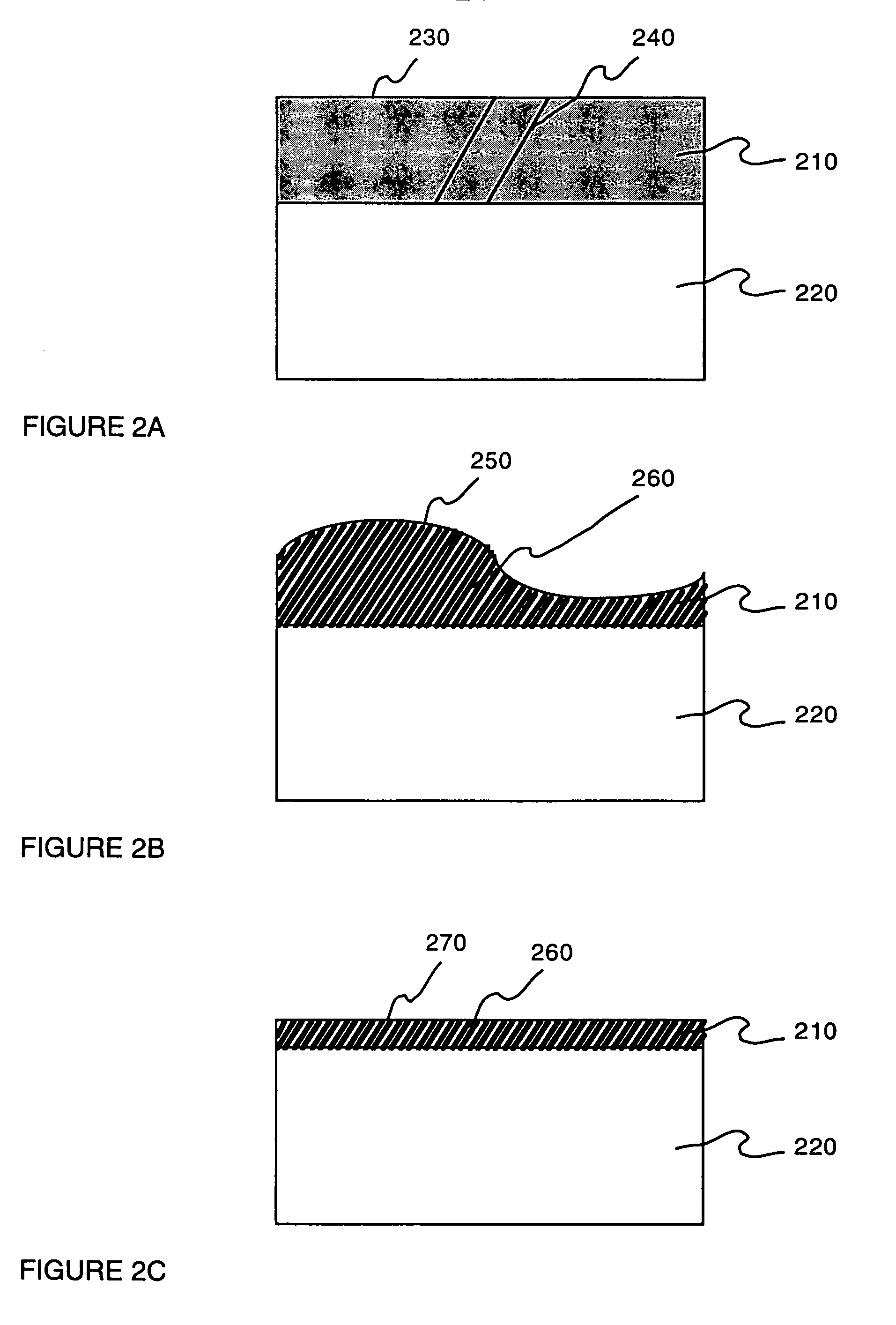

Non-contact etch annealing of strained layers

InactiveUS7147709B1Reduce dislocationReduce dislocation densityFrom gel statePolycrystalline material growthDislocationUNEXPECTED BENEFIT

The present invention provides a method of forming a strained semiconductor layer. The method comprises growing a strained first semiconductor layer, having a graded dopant profile, on a wafer, having a first lattice constant. The dopant imparts a second lattice constant to the first semiconductor layer. The method further comprises growing a strained boxed second semiconductor layer having the second lattice constant on the first semiconductor layer and growing a sacrificial third semiconductor layer having the first lattice constant on the second semiconductor layer. The method further comprises etch annealing the third and second semiconductor layer, wherein the third semiconductor layer is removed and the second semiconductor layer is relaxed. The method may further comprises growing a fourth semiconductor layer having the second lattice constant on the second semiconductor layer, wherein the fourth semiconductor layer is relaxed, and growing a strained fifth semiconductor layer having the first semiconductor lattice constant on the fourth semiconductor layer. The method controls the surface roughness of the semiconductor layers. The method also has the unexpected benefit of reducing dislocations in the semiconductor layers.

Owner:SILICON GENERAL CORPORATION

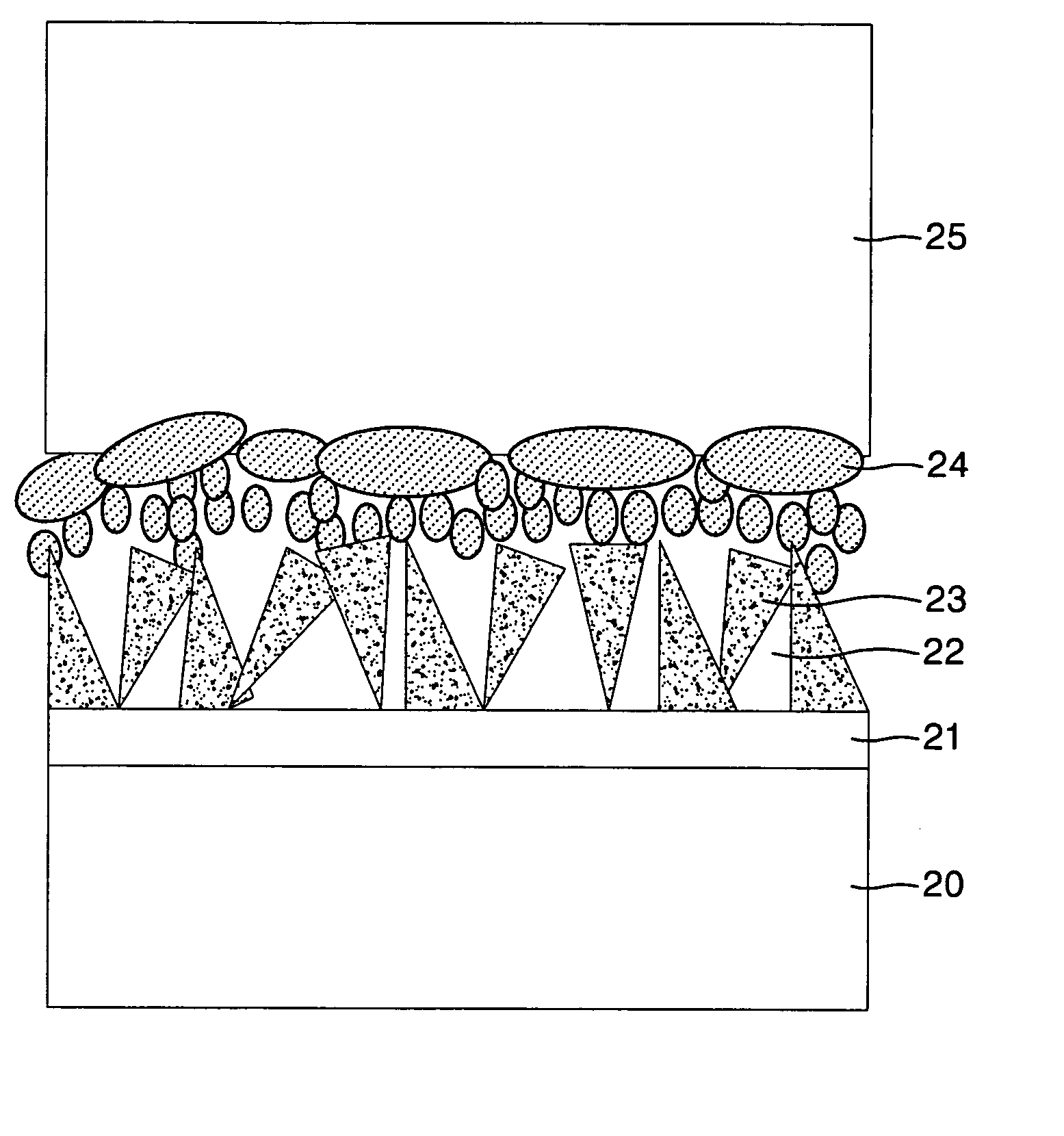

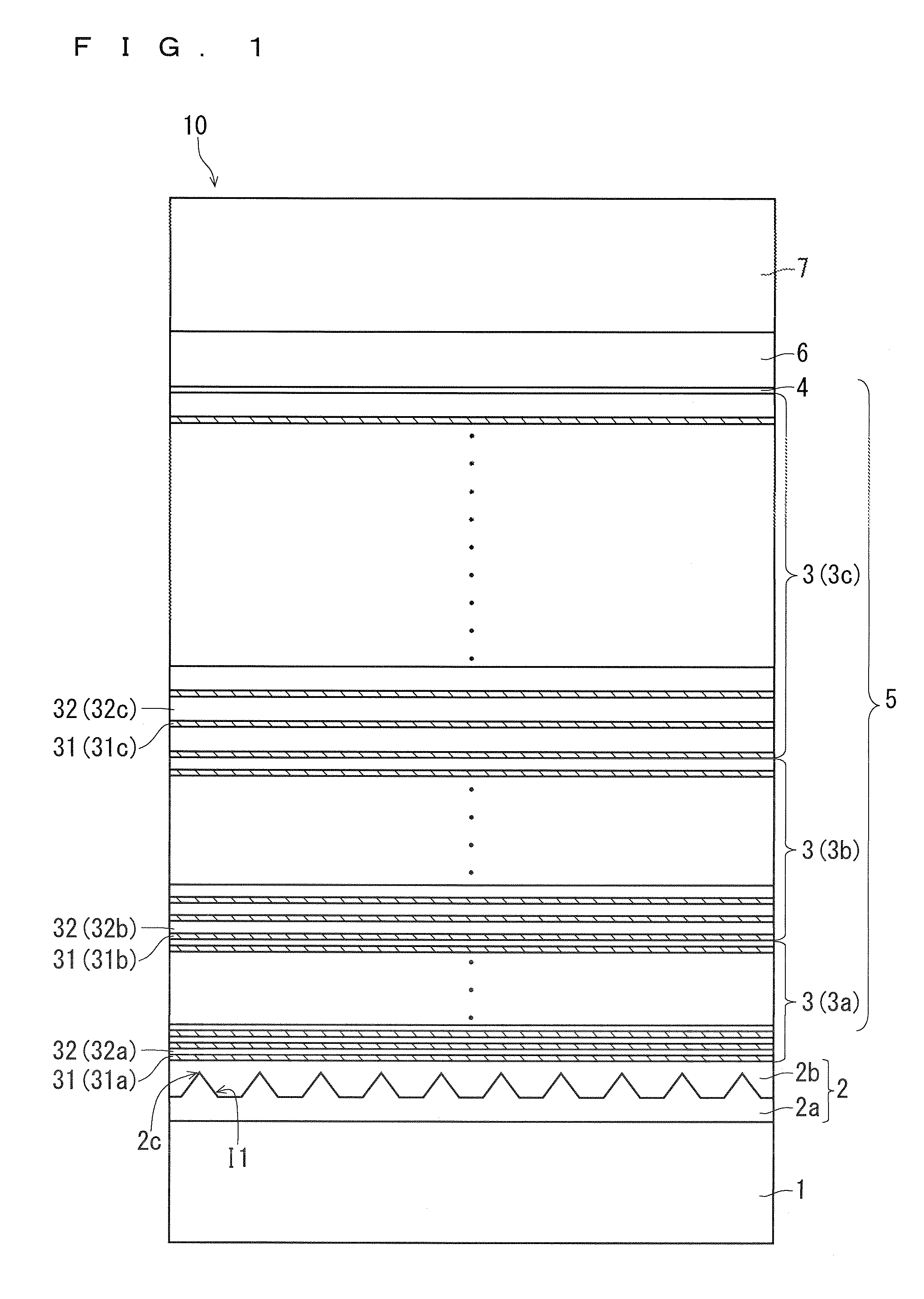

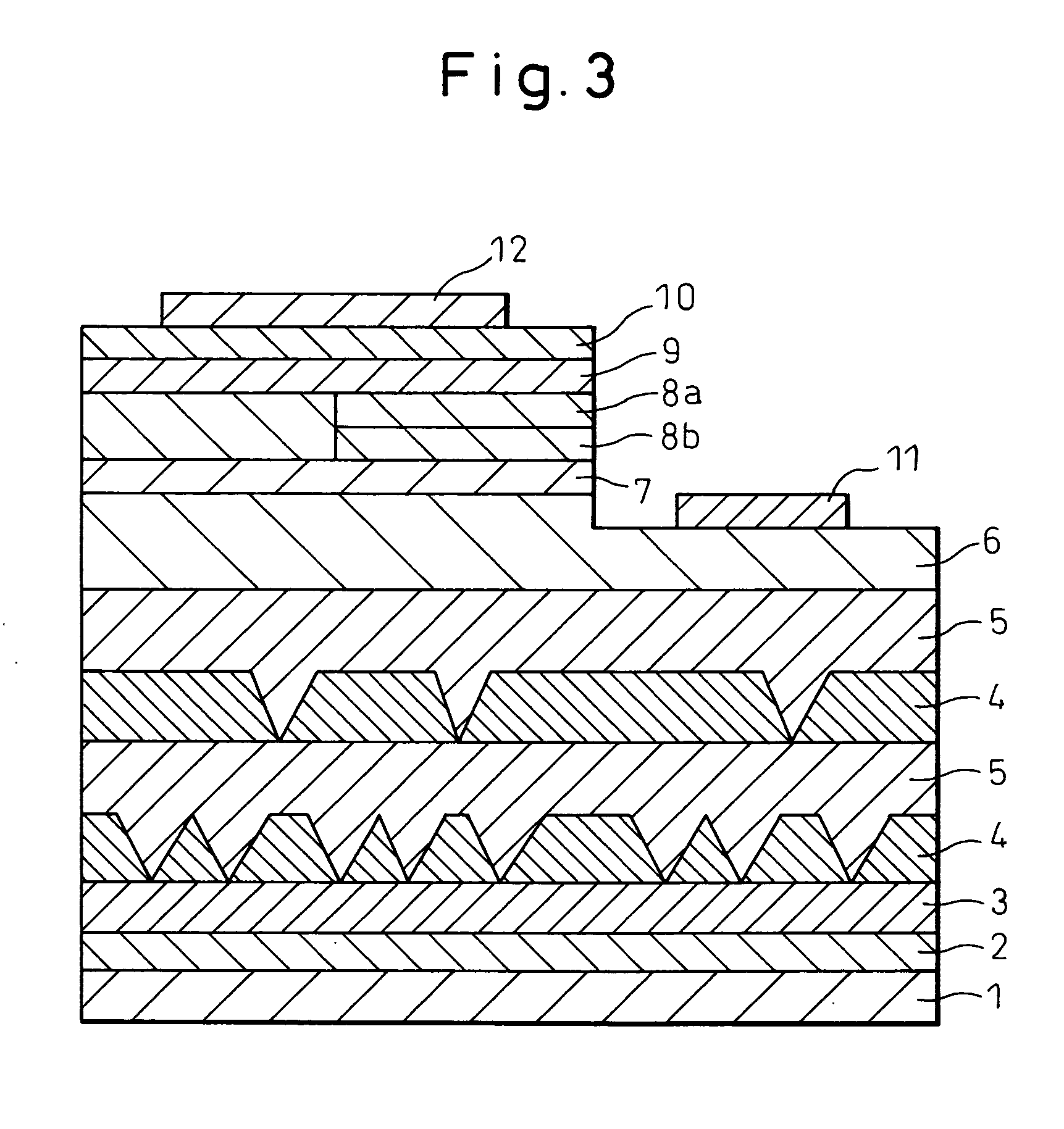

Epitaxial substrate and method for manufacturing epitaxial substrate

ActiveUS20130032781A1Reduce warpageImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingCrack freeSingle crystal

Provided is a crack-free epitaxial substrate with reduced warping, in which a silicon substrate is used as a base substrate. The epitaxial substrate includes a (111) single crystal Si substrate, a superlattice layer group in which a plurality of superlattice layers are laminated, and a crystal layer. The superlattice layer is formed of a first unit layer and a second unit layer made of group-III nitrides having different compositions being alternately and repeatedly laminated. The crystal layer is made of a group-III nitride and formed above the base substrate so as to be positioned at an upper side of the superlattice layer group relative to the base substrate. The superlattice layer group has a compressive strain contained therein. In the superlattice layer group, the more distant the superlattice layer is from the base substrate, the greater the compressive strain becomes.

Owner:NGK INSULATORS LTD

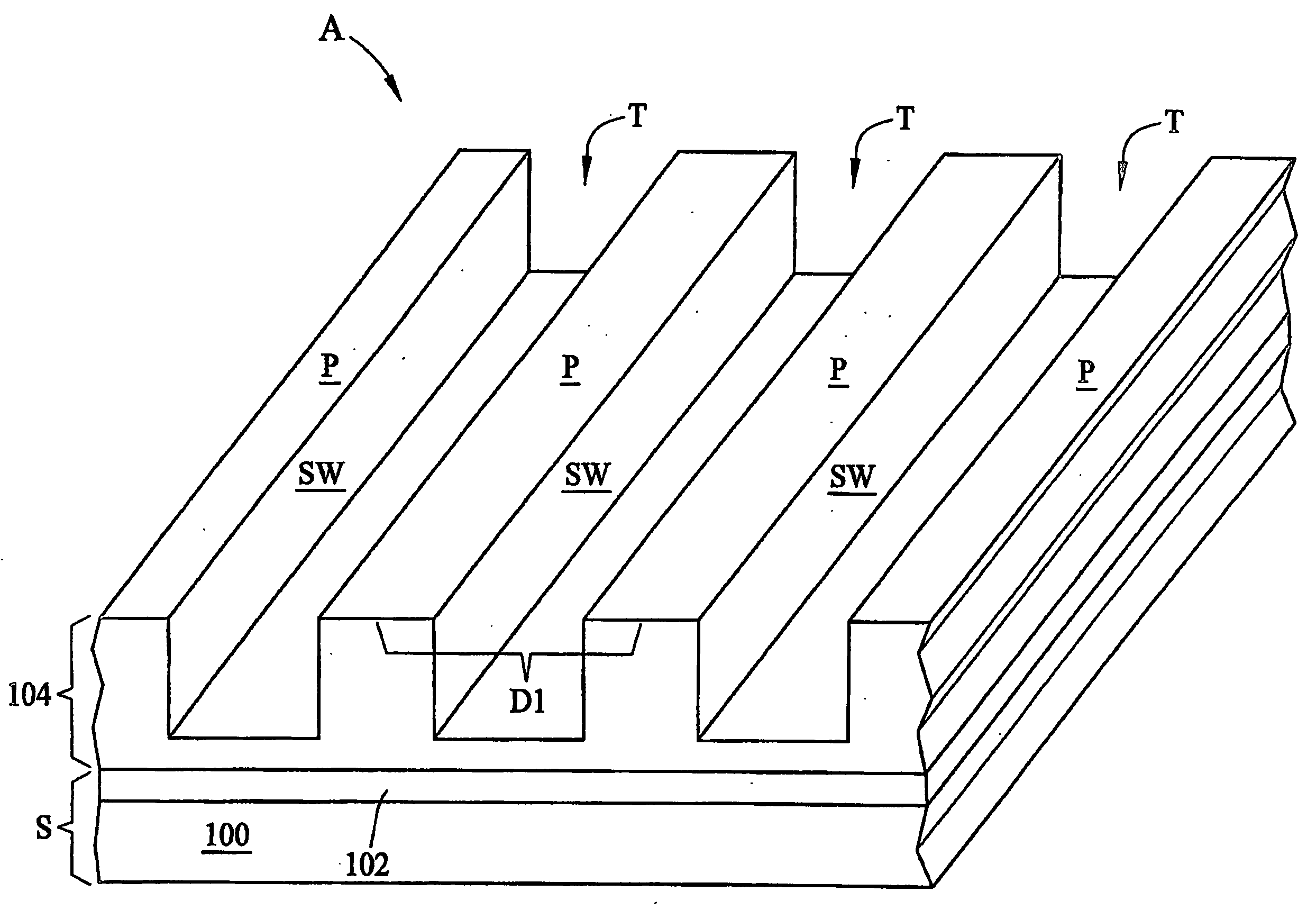

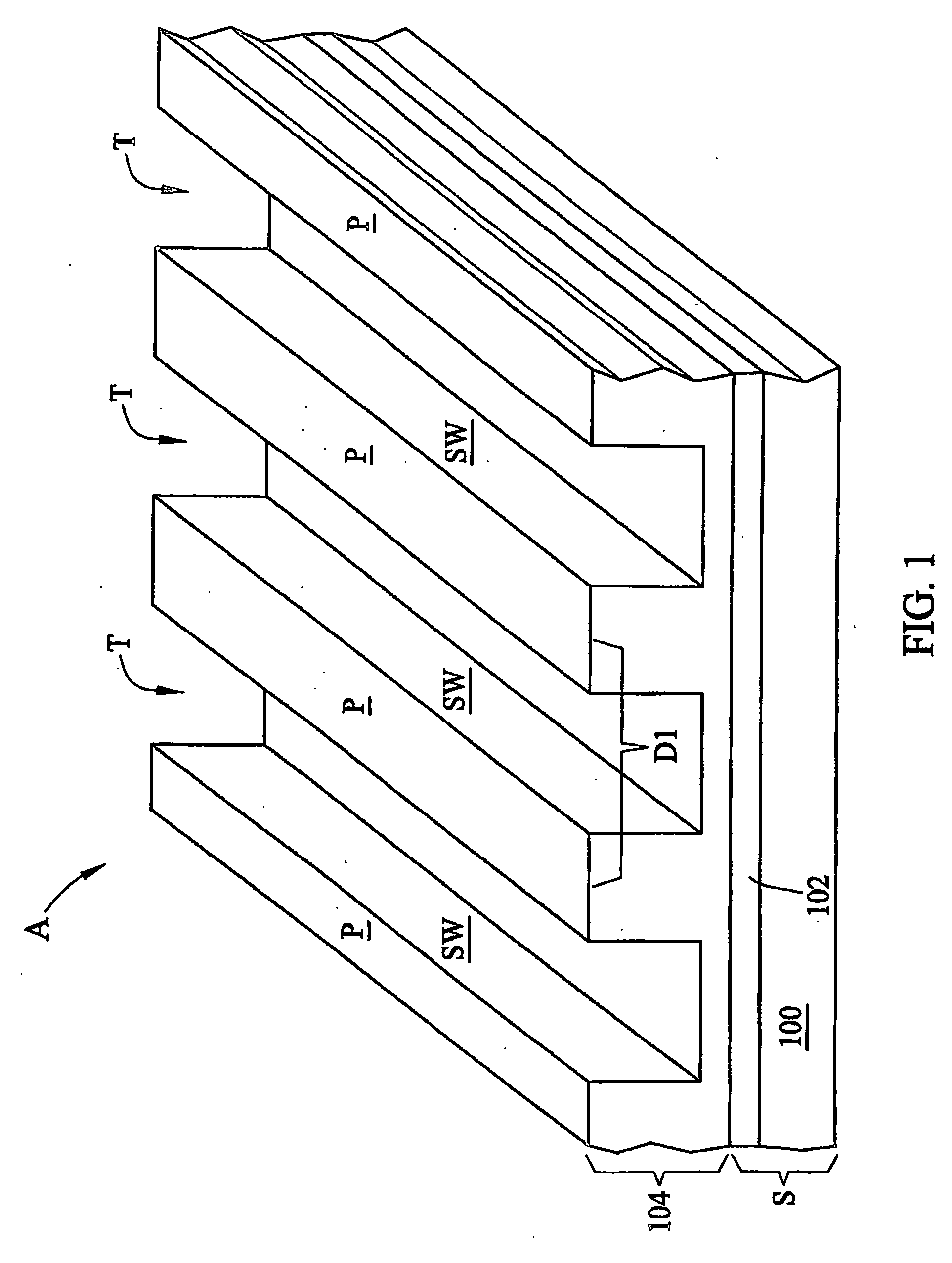

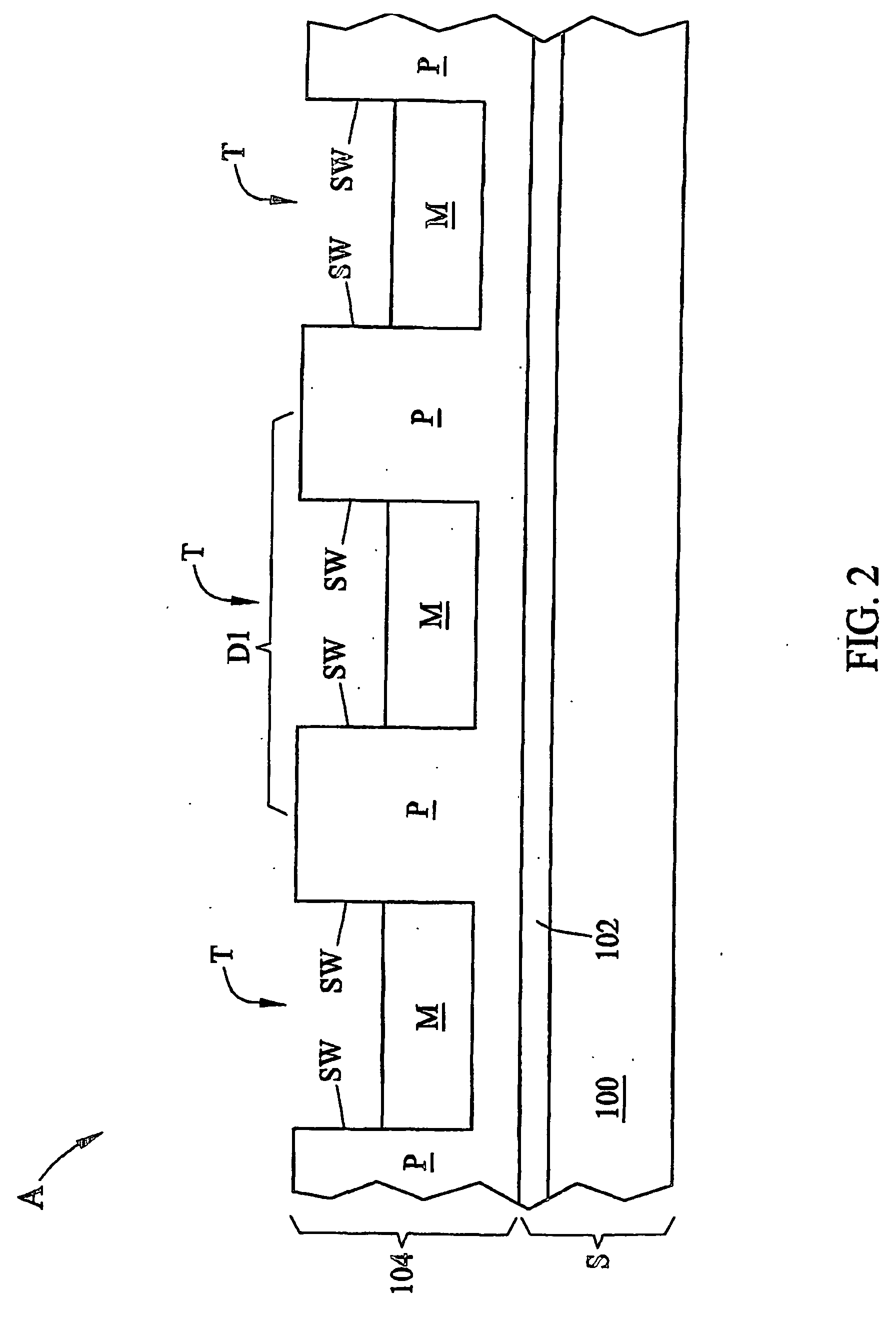

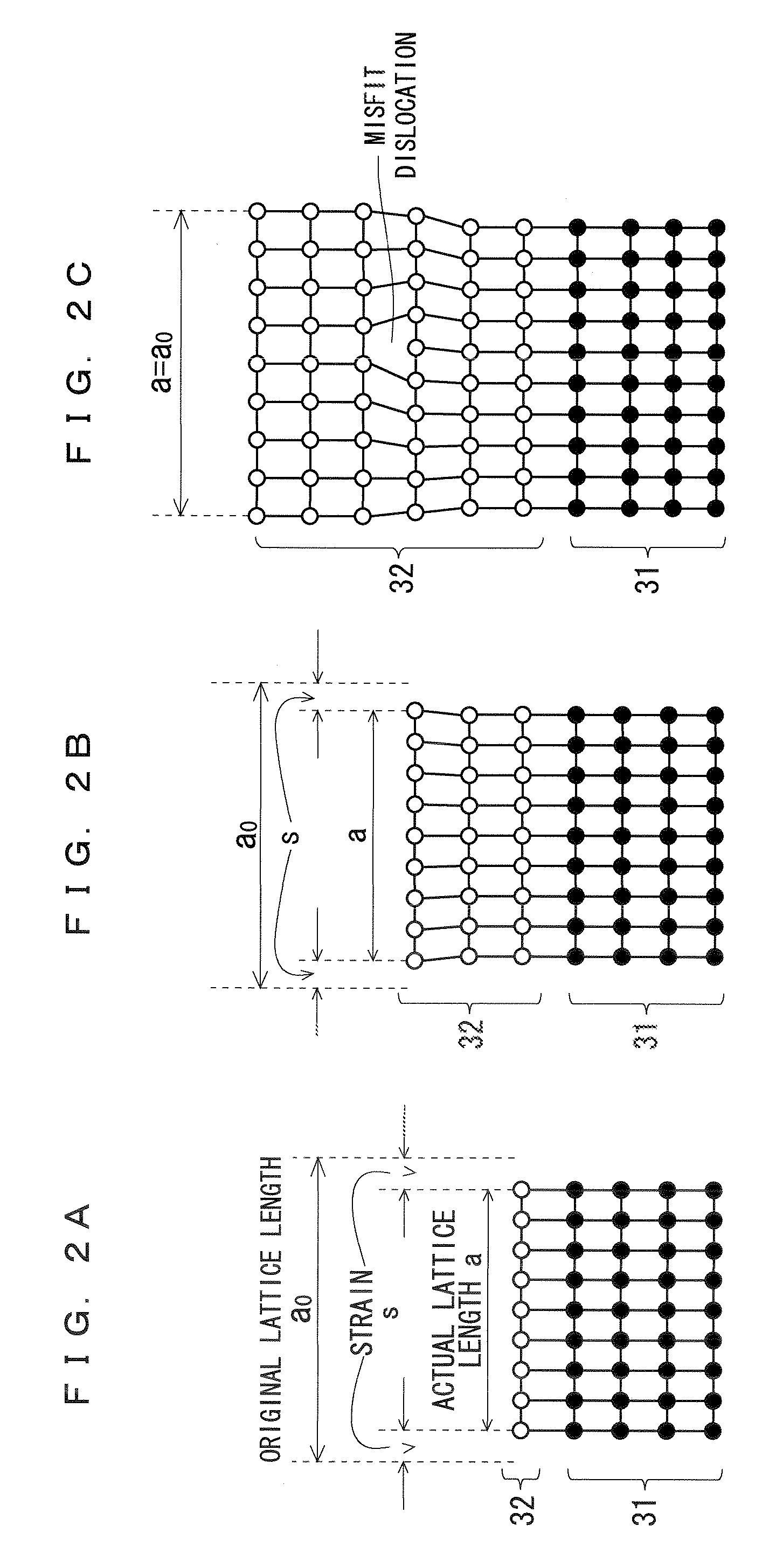

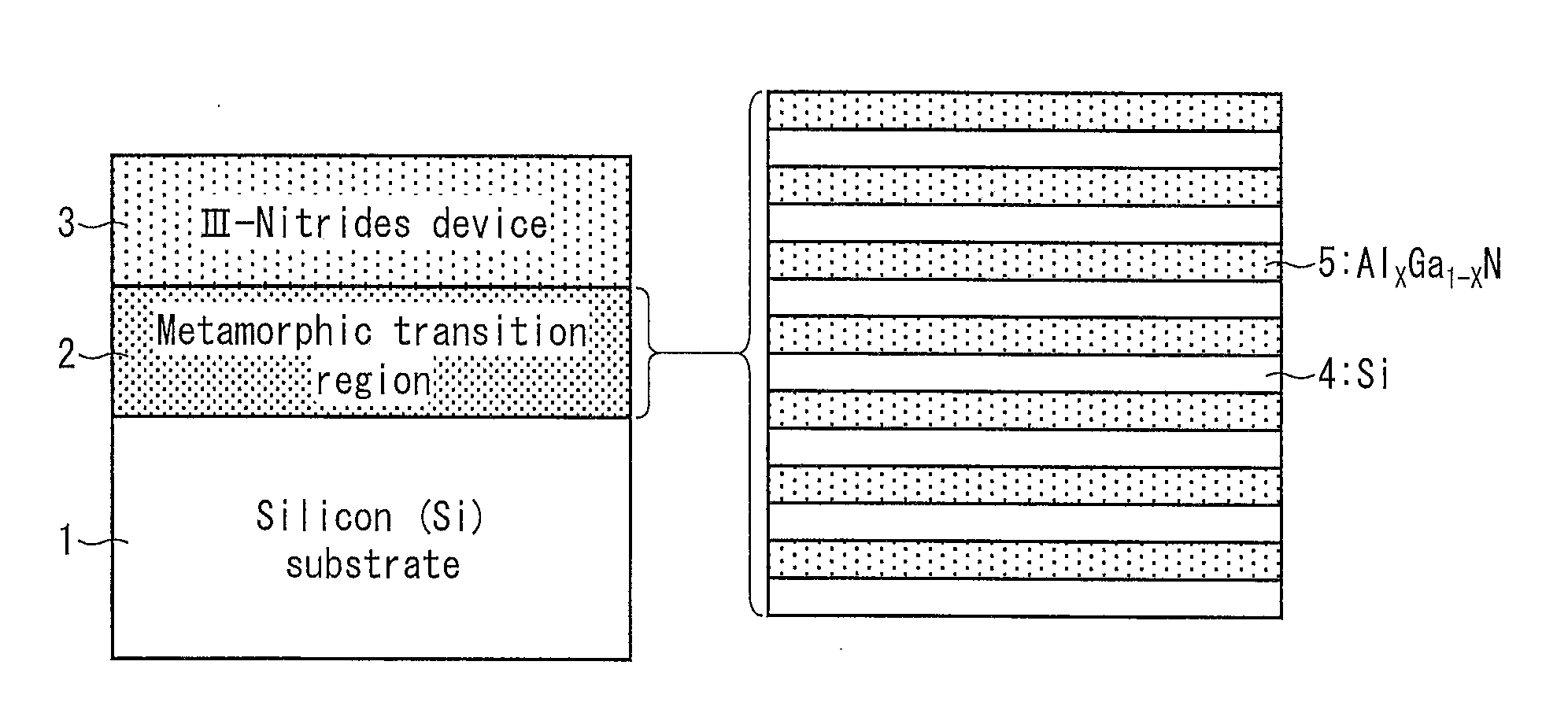

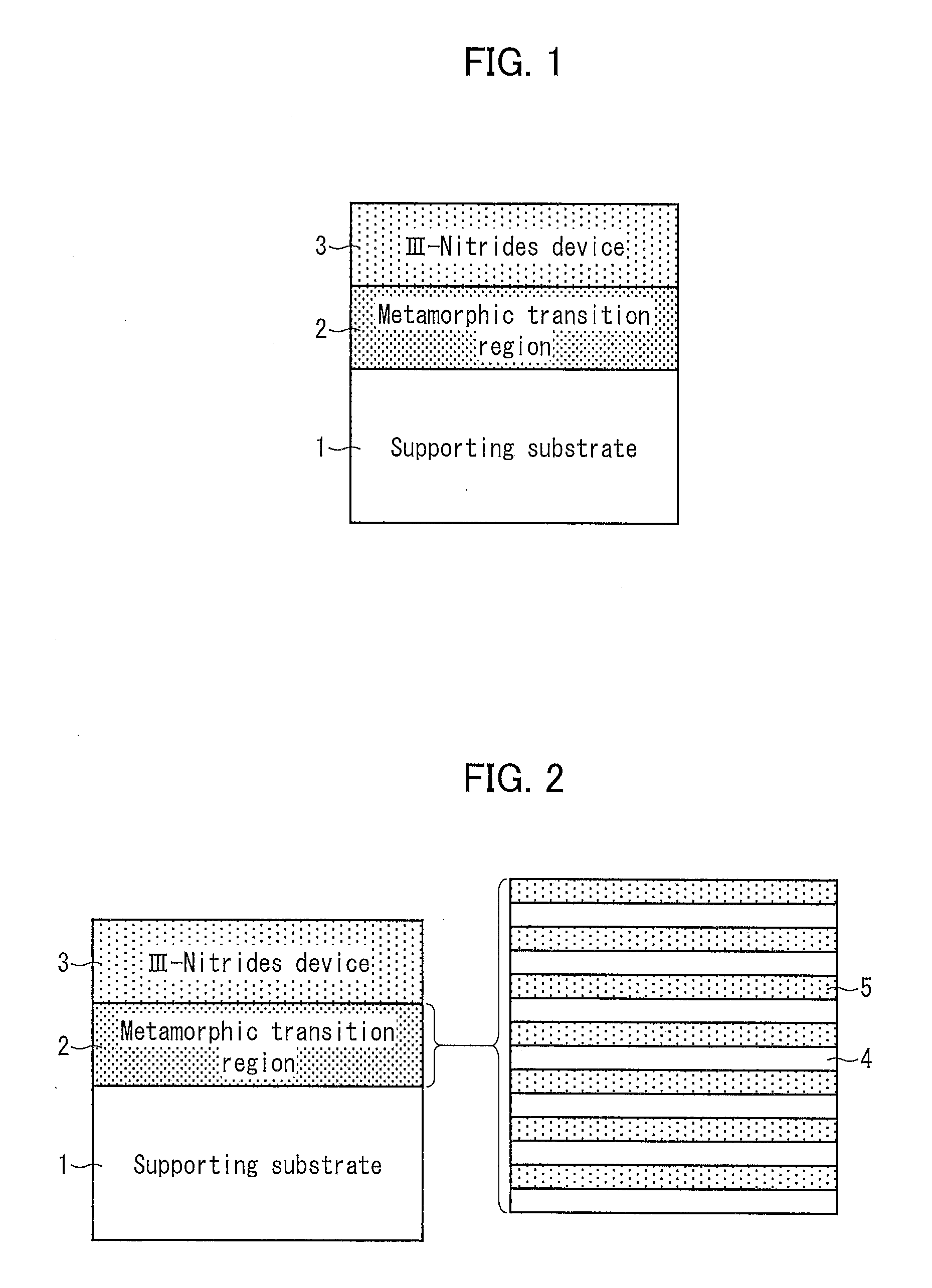

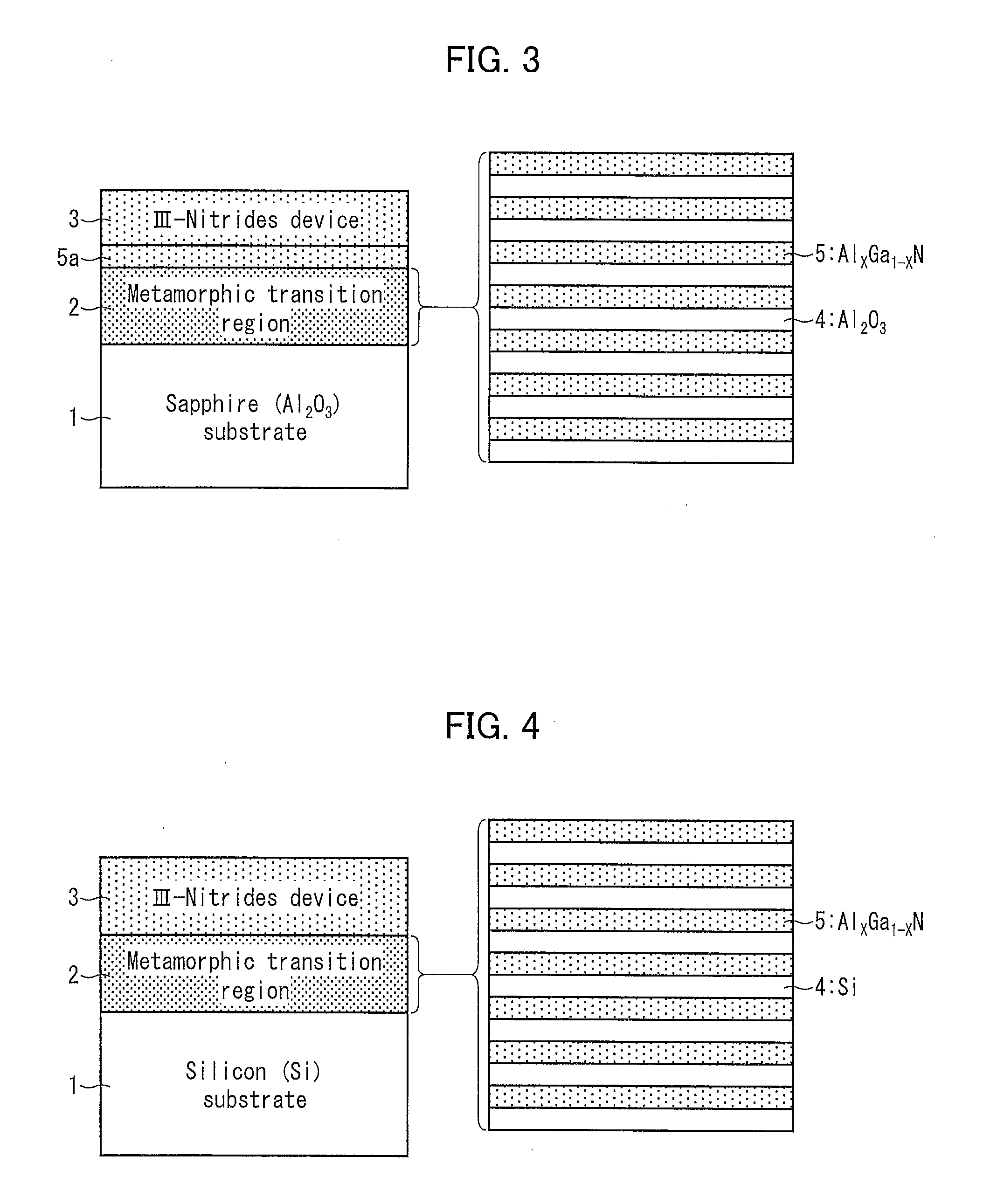

Metamorphic substrate system, method of manufacture of same, and iii-nitrides semiconductor device

InactiveUS20120187540A1Quality improvementReduce the number densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceChemical composition

A laminated substrate system containing a metamorphic transition region (2) made from multiple and alternating layers of AlxGa1-xN (5) and the supporting substrate material (4) (or a material having the same general chemical composition thereto). A III-Nitrides semiconductor device (2) with a low dislocation density is formed on top of the laminated substrate system. The multiple layers (4,5) of the metamorphic transition region form a superlattice structure whose lattice constant and structure changes along its growth direction from that of the supporting substrate (1) (in the vicinity of the supporting substrate) to that of the device (3) (in the vicinity of the device).

Owner:SHARP KK

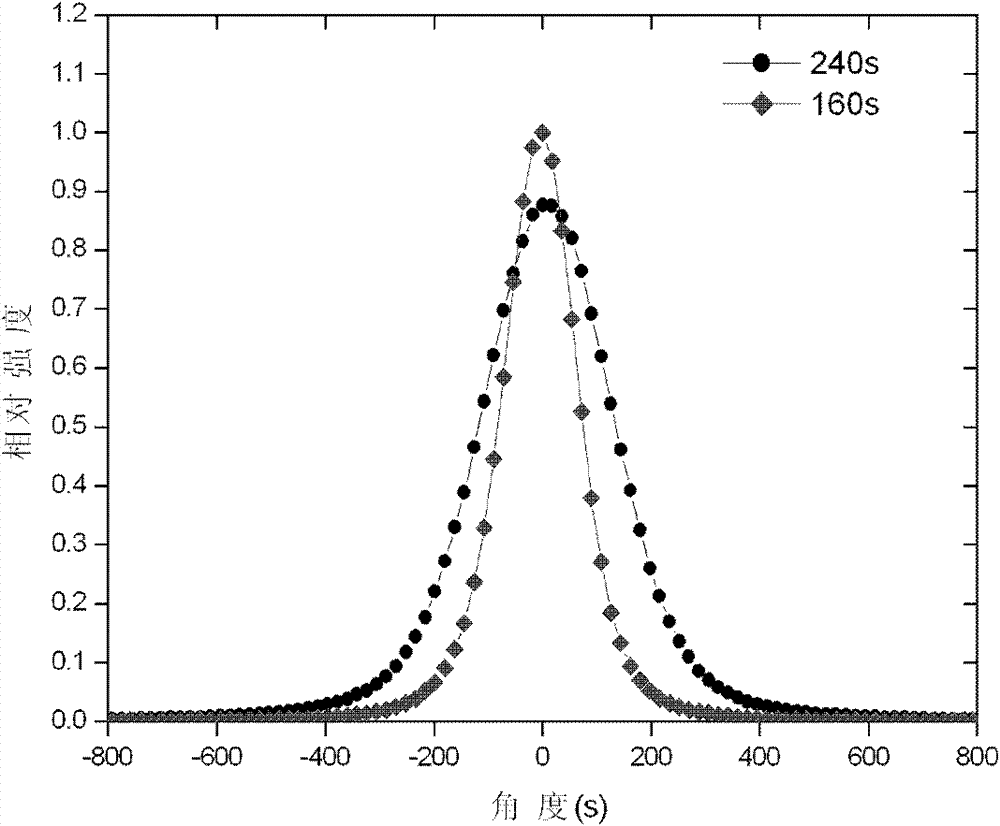

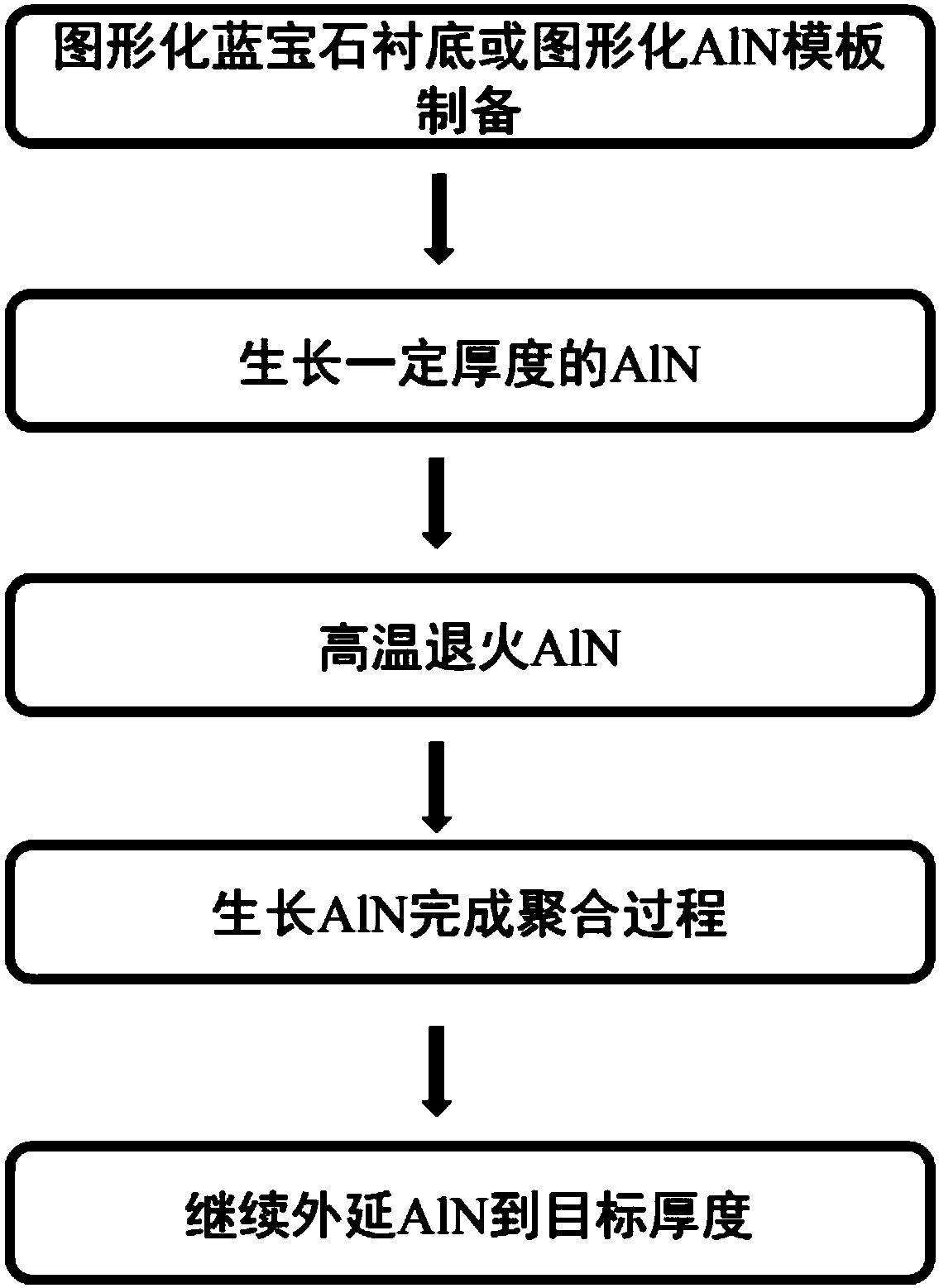

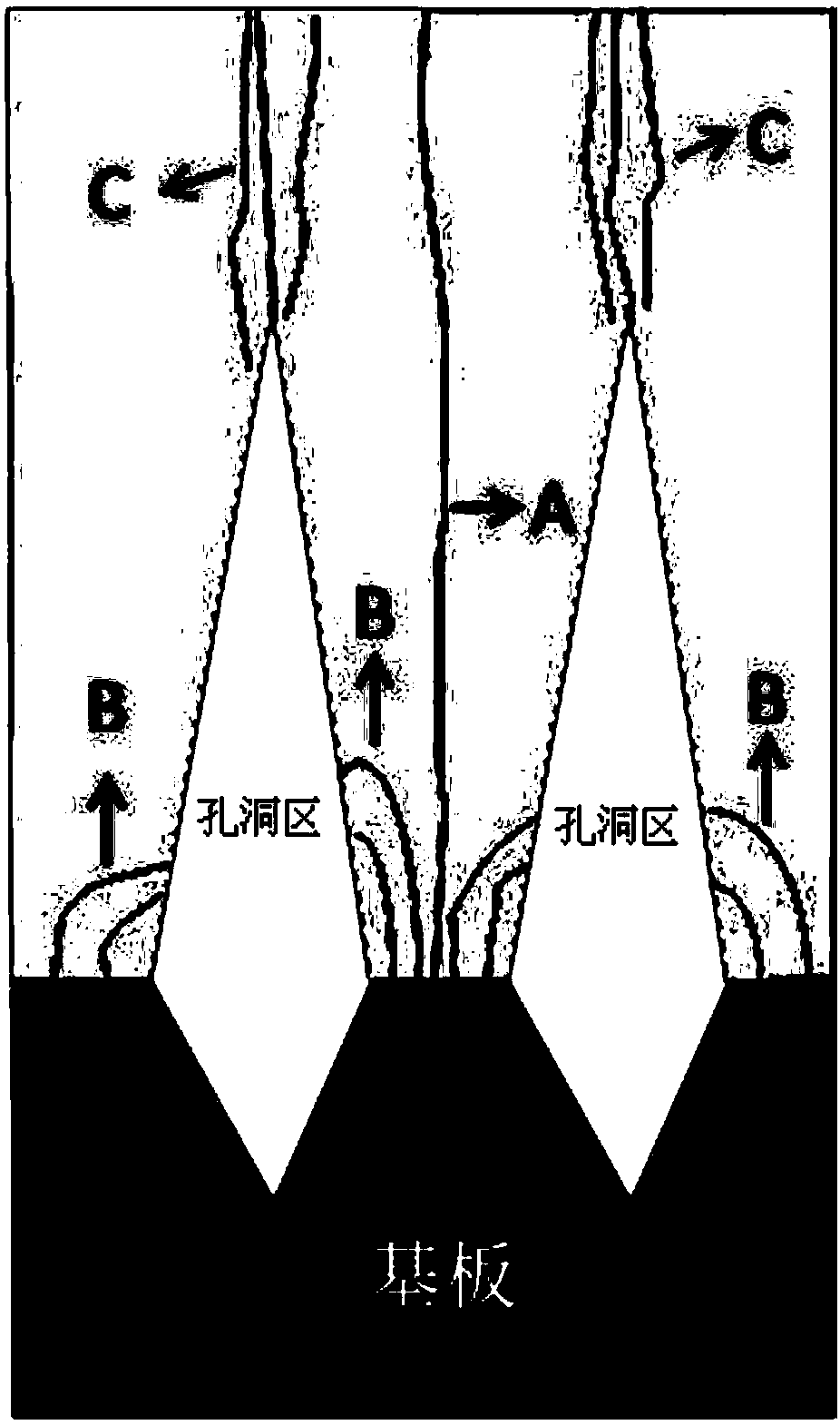

High-quality AlN epitaxial film, preparation method of high-quality AlN epitaxial film and application of high-quality AlN epitaxial film

InactiveCN108155090AReduce dislocation densityEliminate cracksFinal product manufactureSemiconductor/solid-state device manufacturingOptoelectronicsDislocation

The invention relates to a high-quality AlN epitaxial film, a preparation method of the high-quality AlN epitaxial film and the application of the high-quality AlN epitaxial film. According to the invention, the two core links of imaging a sapphire substrate / AlN template and carrying out the high-temperature annealing are combined. The approach of effectively reducing the residual stress is realized through the lateral epitaxy process and the high-temperature annealing process. In this way, an AlN epitaxial film, which is free of cracks, flat in atom level and low in dislocation density, is obtained. As a result, the invention has important significance for realizing the industrial application of AlGaN-based deep ultraviolet high-performance light-emitting and detecting instruments.

Owner:北京中博芯半导体科技有限公司

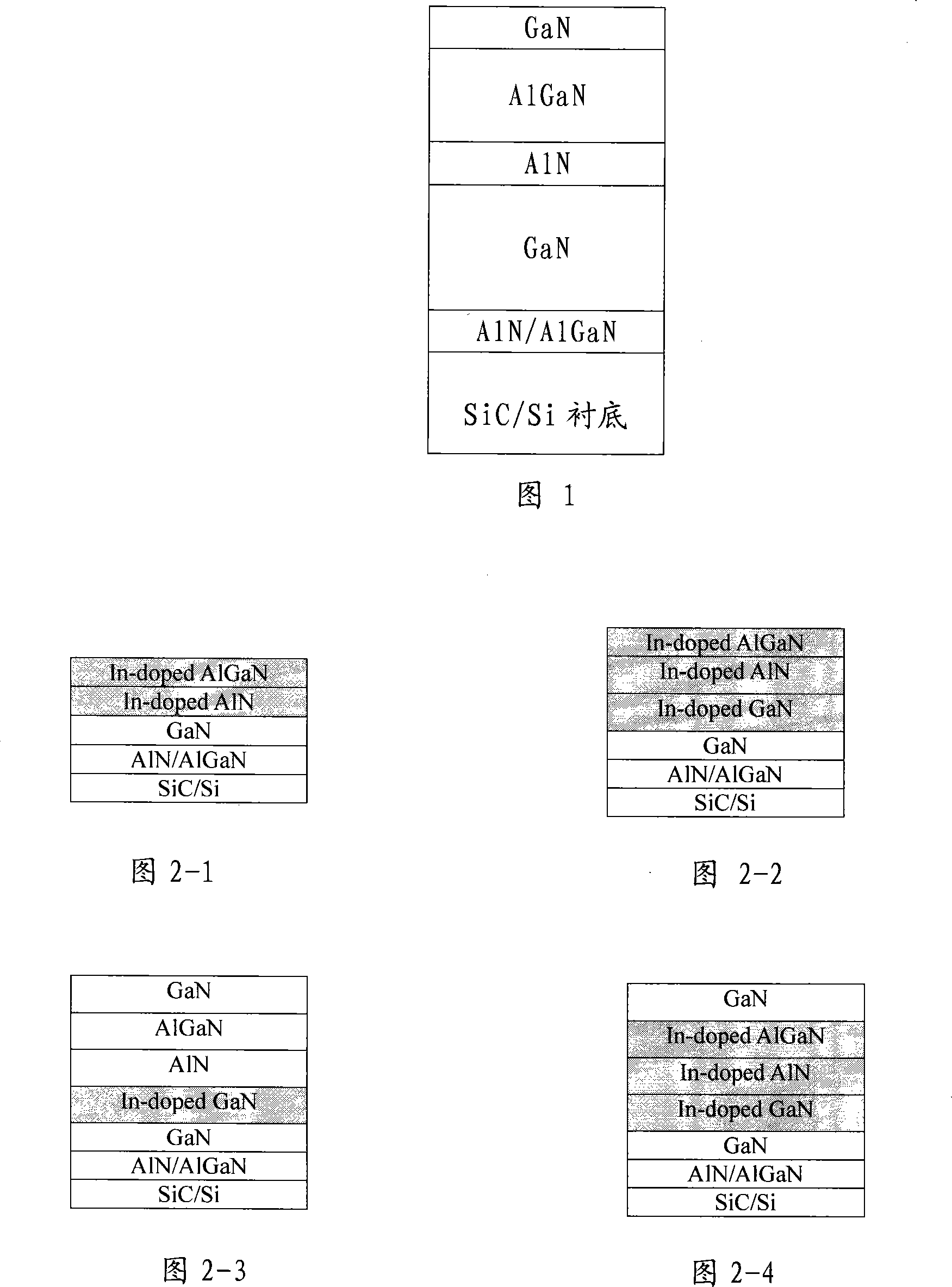

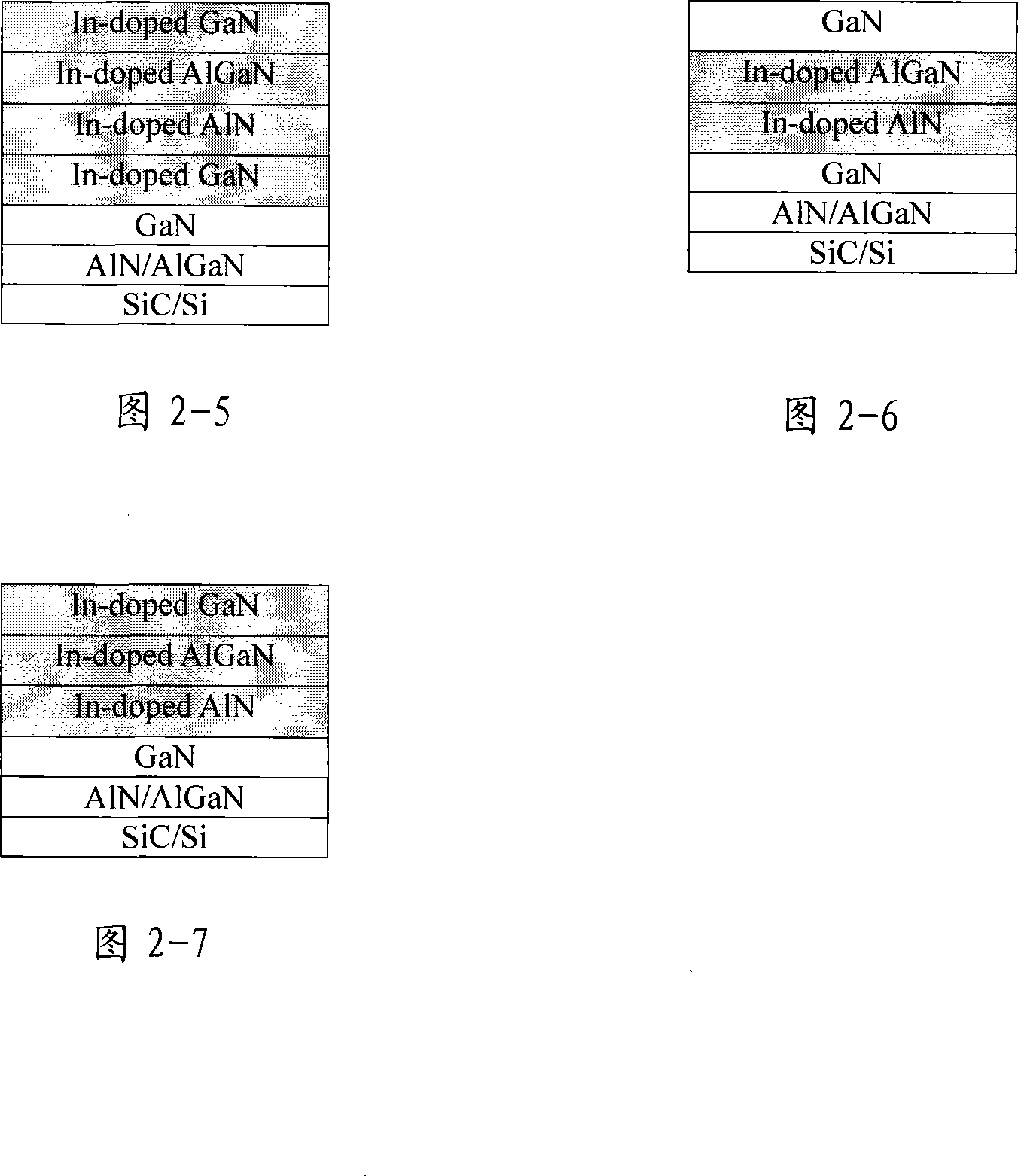

Method for improving gallium nitride based transistor material and device performance using indium doping

ActiveCN101114594AFree diffusionIncrease the diffusion distanceSemiconductor/solid-state device manufacturingGas phaseSingle crystal

The invention discloses a method of increasing the properties of the gallium nitride-based transistor material and device with indium doping and applies in the field of making gallium nitride-based HEMT or HFET materials and devices. The method and process is to form the gallium nitride-based high electron mobility transistor or heterostructure field effect transistor materials on SiC or Si single crystal substrate grown by metal-organic chemical vapor deposition epitaxial growth system. After the AlN or AlGaN nucleating layer and the GaN buffer layer are grown on the SiC or Si single crystal substrate, a GaN channel layer, an AlN insert layer, an AlGaN barrier layer and a GaN capped layer are grown, and trimethyl indium is added in the growth atmosphere to do epitaxial growth with indium doping. The dislocation of the material or device made by the method of the invention is reduced greatly. The invention improves the interfacial smoothness, increases the electron mobility of the material, increases the growth window, ensures the material grow easier, improves the current collapse of the device, reduces the leakage current and increases transconductance and gain and increases the output power of microwave power devices.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

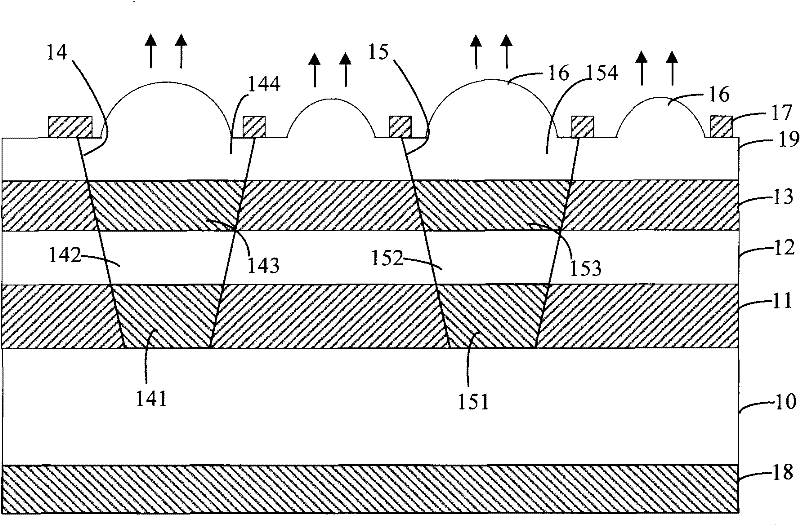

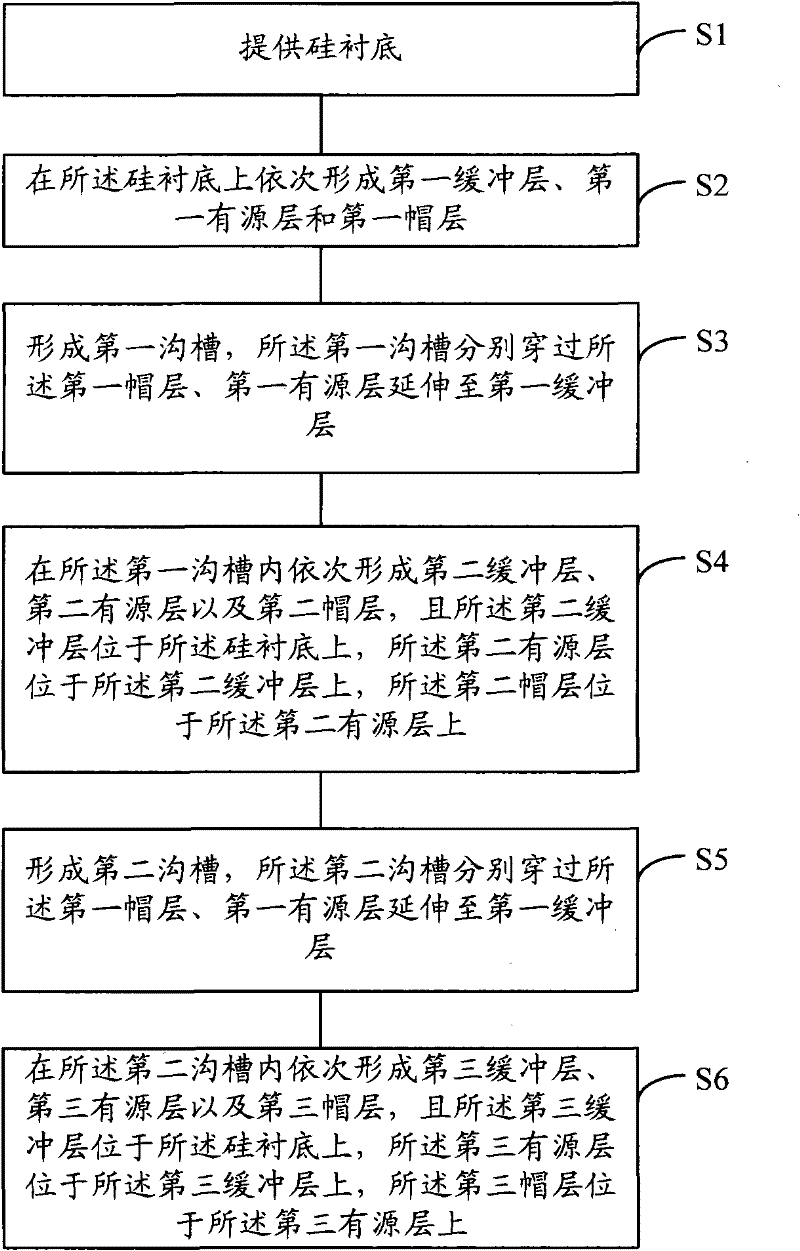

White LED chip and forming method thereof

InactiveCN102130144AEasy to controlReduce dislocationSolid-state devicesSemiconductor devicesCrystal orientationCrystal plane

The invention relates to a white light-emitting diode (LED) chip and a forming method thereof. The white LED chip comprises a silicon substrate, a first buffer layer, a first active layer, a first cap layer, a first groove and a second groove, wherein the first buffer layer, the first active layer and the first cap layer are positioned on the silicon substrate sequentially; the first groove passes through the first buffer layer and the first active layer respectively to extend to the first cap layer, and a second buffer layer, a second active layer and a second cap layer are arranged in the first groove; the second groove passes through the first buffer layer and the first active layer respectively to extend to the first cap layer, and a third buffer layer, a third active layer and a third cap layer are arranged in the second groove; and the first active layer, the second active layer and the third active layer are selected from one of a blue light active layer, a green light active layer and a red light active layer respectively and are the active layers with different colors. When used, the white LED chip can emit red light, green light and blue light simultaneously, and can emit white light after the light with three colors is mixed; and due to the adoption of the silicon substrate which deviates 1 to 9 degrees from a crystal plane (111) in the crystal orientation, dislocation between the buffer layers and the silicon substrate can be reduced.

Owner:ENRAYTEK OPTOELECTRONICS

Method of growing gallium nitride crystal and gallium nitride substrate

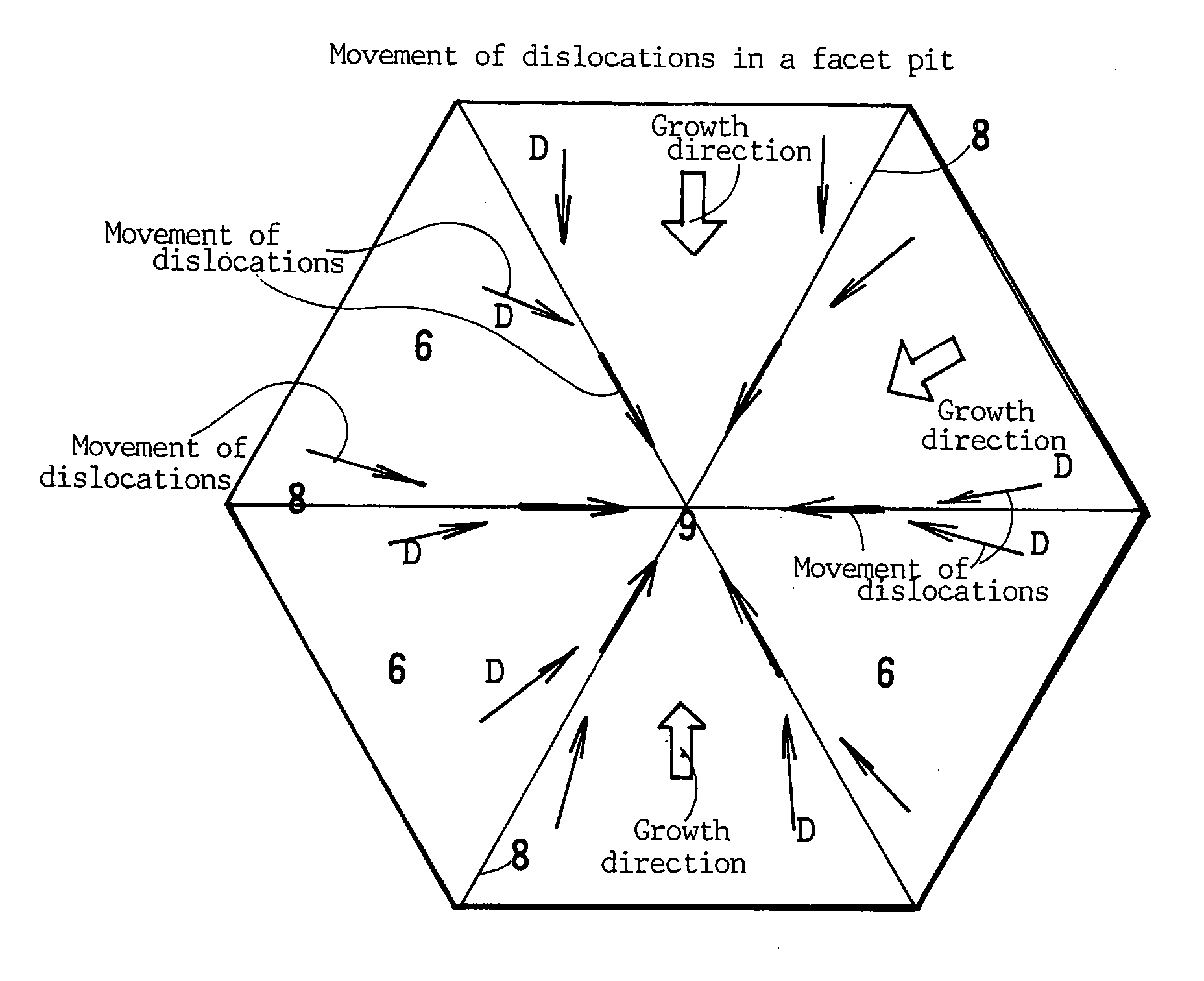

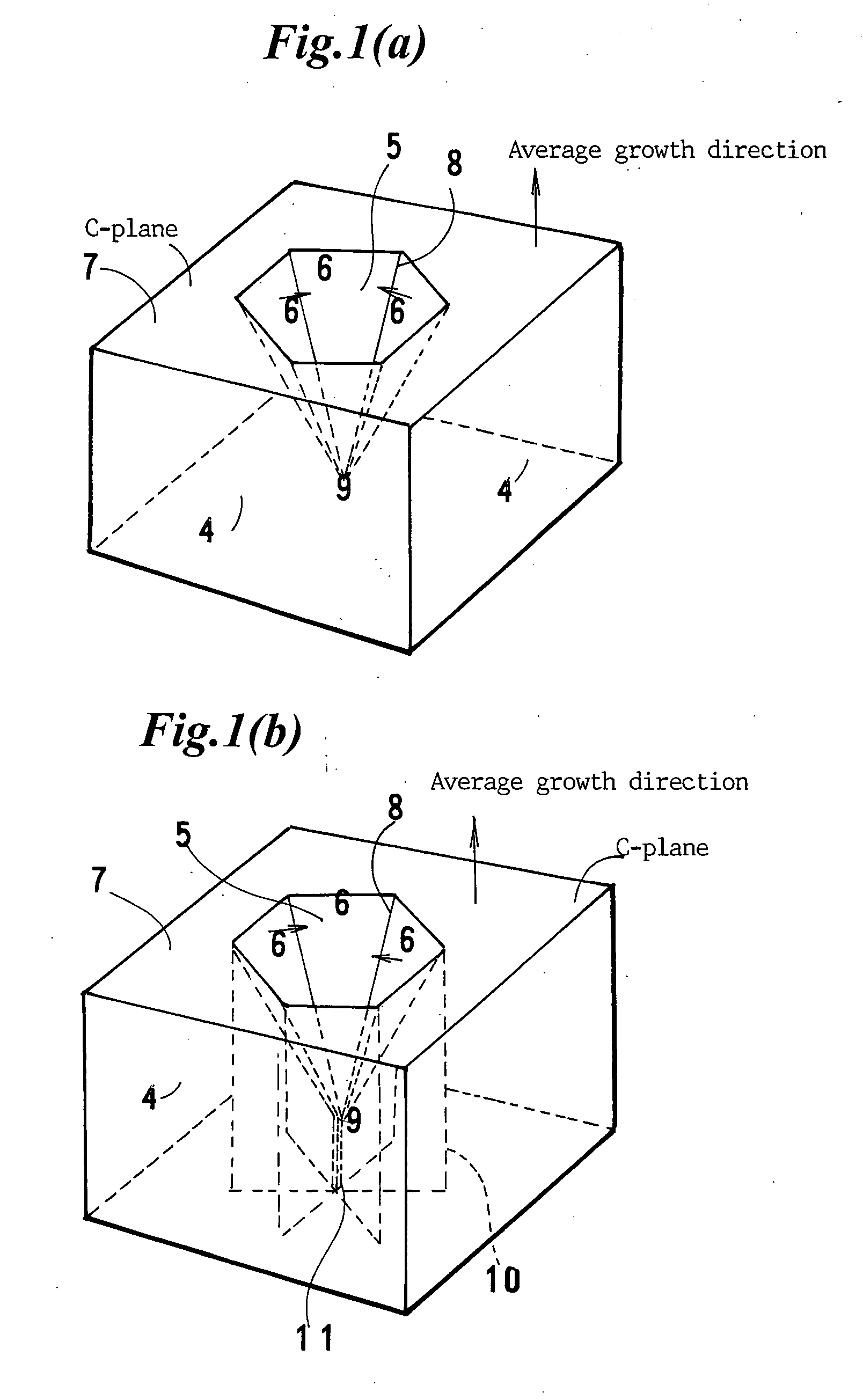

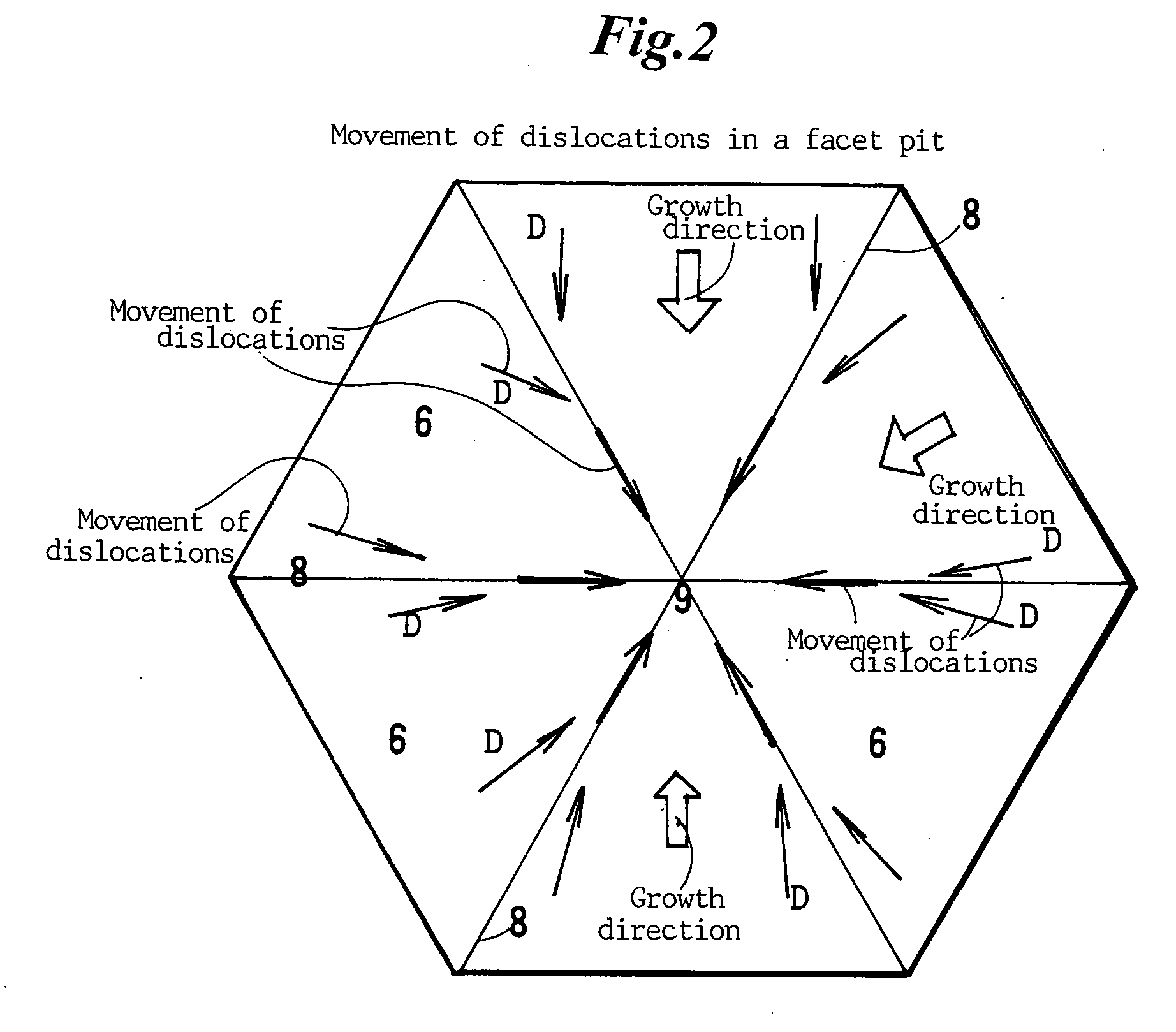

InactiveUS20070280872A1Reduce dislocationLow defect densityPolycrystalline material growthLiquid-phase epitaxial-layer growthBeak shapeGallium nitride

The GaN facet growth method produces defect accumulating regions H on masks by forming a dotmask or a stripemask on an undersubstrate, growing GaN in a reaction furnace in vapor phase, inducing GaN crystals on exposed parts without covering the masks, inviting facets starting from verges of the masks and producing defect accumulating regions H on the mask. The defect accumulating regions H have four versions, that is, non (O), polycrystal (P), c-axis inclining single crystal (A) and orientation inversion (J). The best is the orientation inversion region (J). A sign of occurrence of the orientation inversion regions (J) is beaks of inversion orientation appearing on facets. GaN is grown on a masked undersubstrate by supplying a carbon material at a hydrocarbon partial pressure of 10 Pa to 5 kPa for 0.5 hour to 2 hour by an HVPE facet growth method without burying facets.

Owner:SUMITOMO ELECTRIC IND LTD

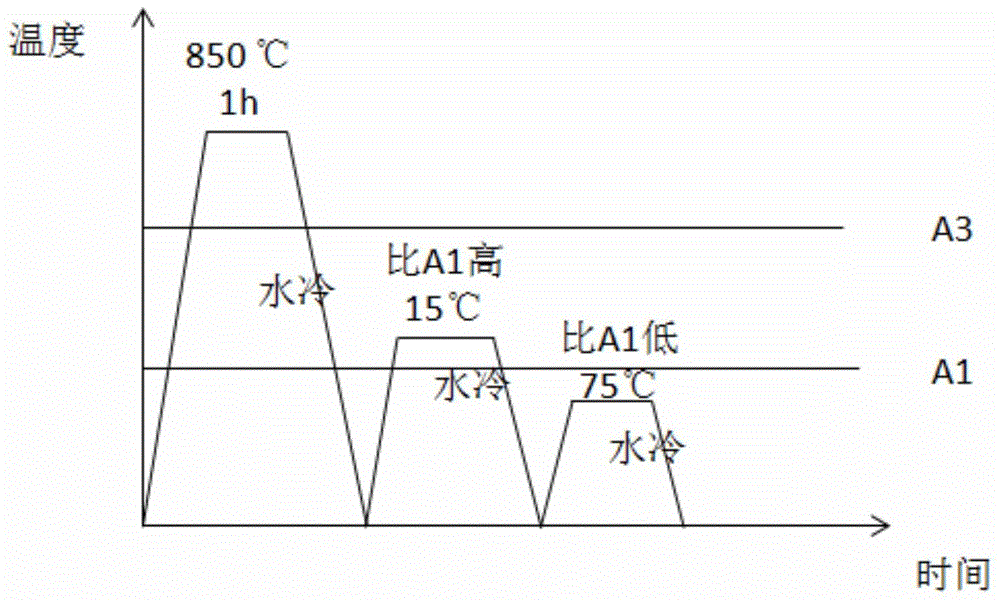

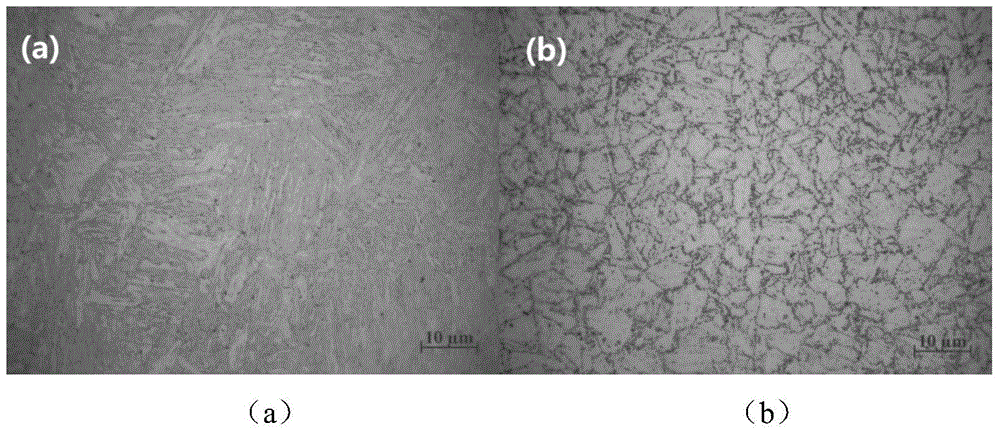

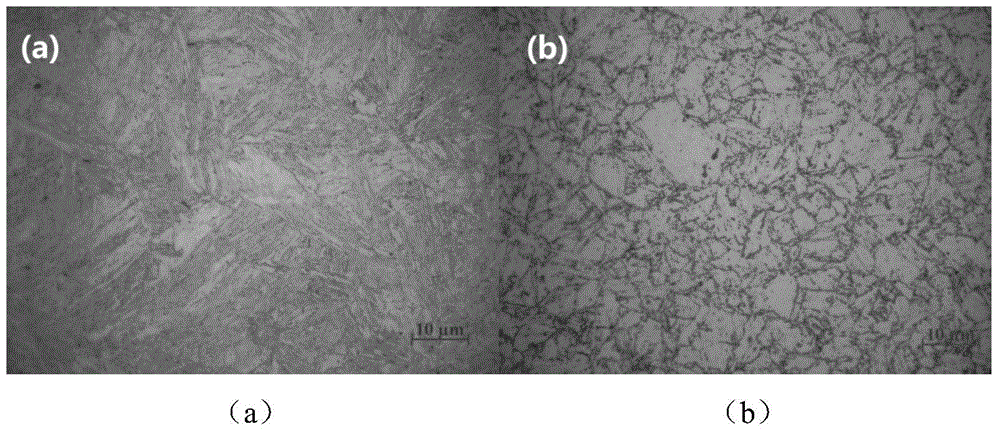

High-strength low-temperature-resistant steel and heat processing technology thereof

The invention provides high-strength low-temperature-resistant steel. The steel is composed of, by mass, 2.0-7.05% of nickel, 0.02-0.1% of carbon, 0.02-0.1% of silicon, 0.60-8.00% of manganese, 0.3-0.5% of chrome, 0.05-0.6% of molybdenum, 0.02-0.3% of copper, 0.03-2.0% of aluminum, smaller than or equal to 0.010% of phosphorus, smaller than or equal to 0.002% of sulfur, 0.004-0.010% of nitrogen, 0.0005-0.002% of oxygen, 0.0005-0.005% of calcium, and the balance iron. The invention further provides the heat processing technology and application of the high-strength low-temperature-resistant steel. By the adoption of the high-strength low-temperature-resistant steel and the heat processing technology thereof, low-temperature toughness is high, structural steel used in a low-temperature environment can be manufactured, application cost is reduced, and economical applicability is high.

Owner:SHANGHAI JIAO TONG UNIV

Method and apparatus for producing large, single-crystals of aluminum nitride

ActiveUS8545629B2Easy to manufactureReduce dislocationPolycrystalline material growthSolid-state devicesBulk crystalSingle crystal

Owner:CRYSTAL

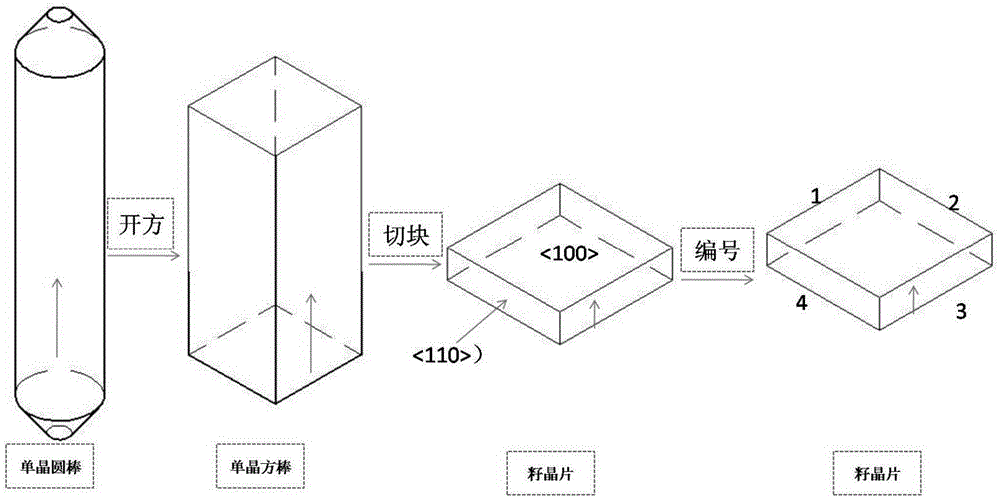

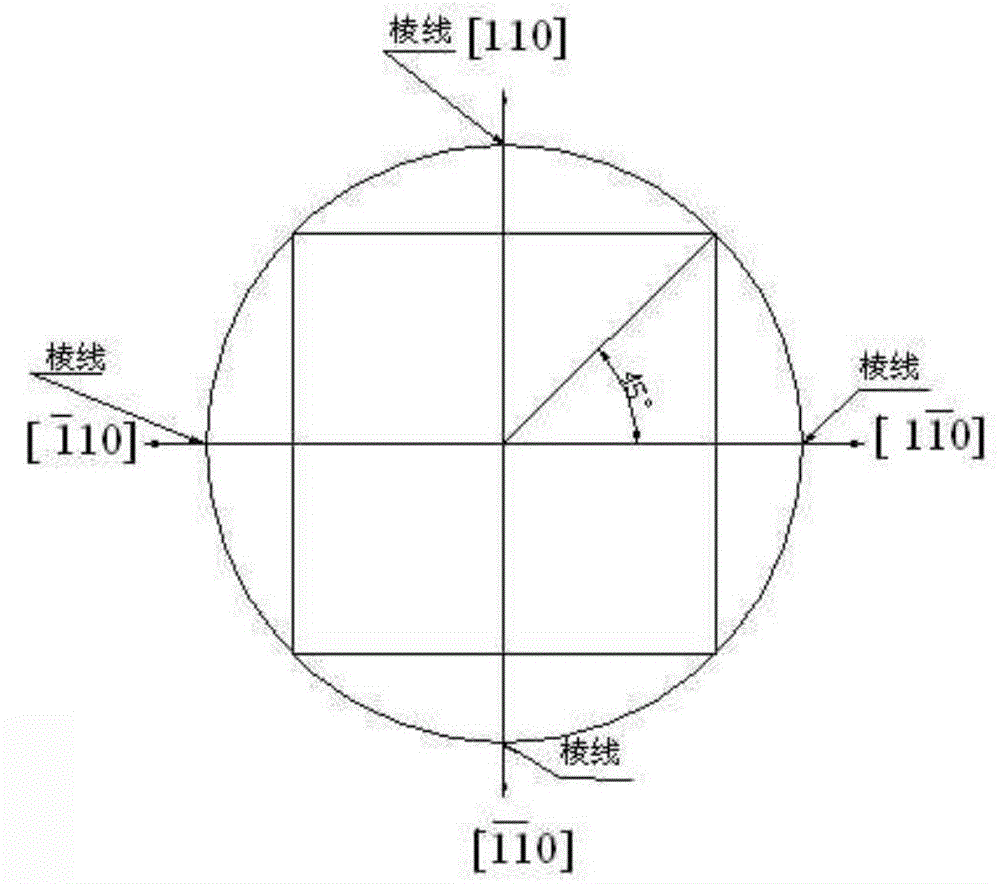

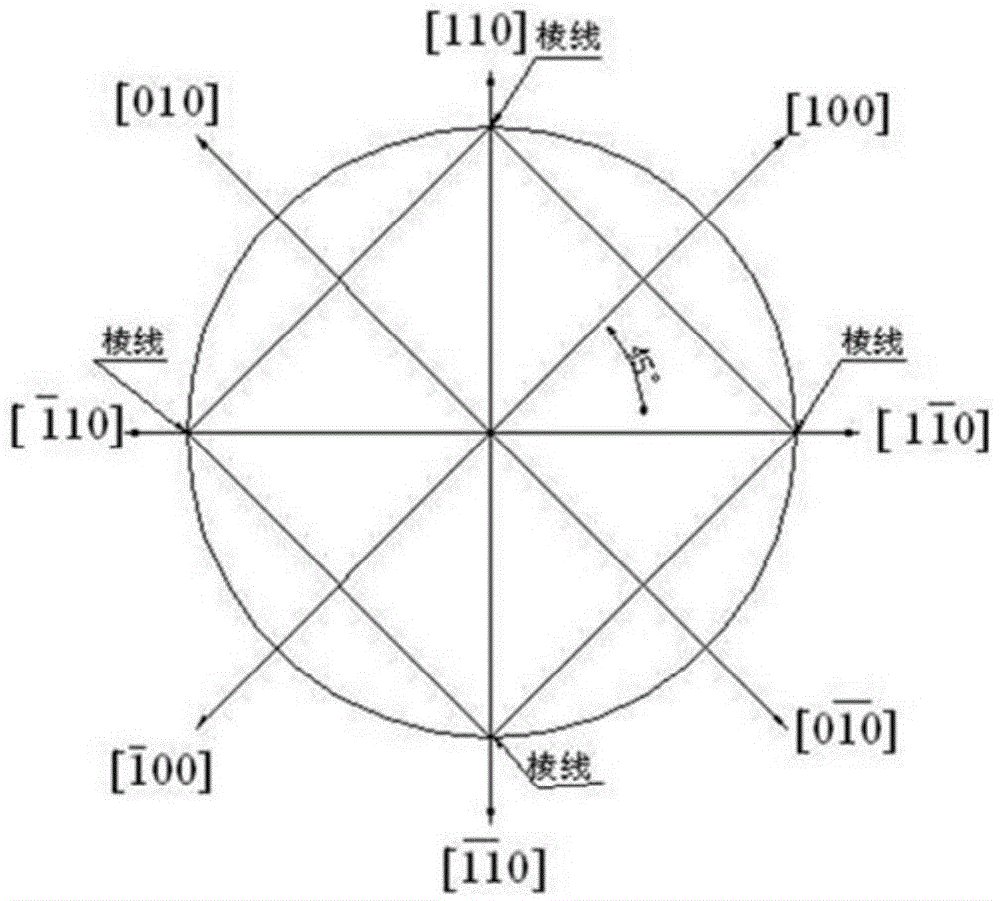

Laying method of seed crystals, preparation method of quasi-monocrystalline silicon piece and quasi-monocrystalline silicon piece

ActiveCN104911691ASimple laying methodReduce the chance of dislocationsPolycrystalline material growthFrom frozen solutionsCrucibleCrystal orientation

The invention provides a laying method of seed crystals and is used for the casting of quasi-monocrystalline silicon piece. The method comprises the steps of: seed crystals are laid on the crucible bottom, the seed crystals have a same growth surface crystal orientation of [001] or [001<->]; the seed crystals in close contact and fully cover the crucible bottom to form a seed crystal layer; the side crystal orientation of two adjacent contact the seed crystals belongs to the same crystal to the same crystal orientation family and constitute a coincidence position lattice type of grain boundary; when the side crystal orientation of the seed crystal is <110>, the crystal orientation of growth face of the adjacent seed crystals alternately splices front and back according to [001] [001<->], or one of the adjacent seed crystals rotates 90 DEG; when the side crystal orientation of the seed crystals is not <110> crystal orientation family, the crystal orientation of growth face of the adjacent seed crystals alternately splices front and back, or after the front and back alternate splicing, one of the adjacent seed crystals rotates 90 DEG. The laying of seed crystals reduces the occurrence of dislocation sources in the crystal introduction process. The invention also provides a preparation method of a quasi-monocrystalline silicon piece and the quasi-monocrystalline silicon piece.

Owner:JIANGXI SAI WEI LDK SOLAR HI TECH CO LTD

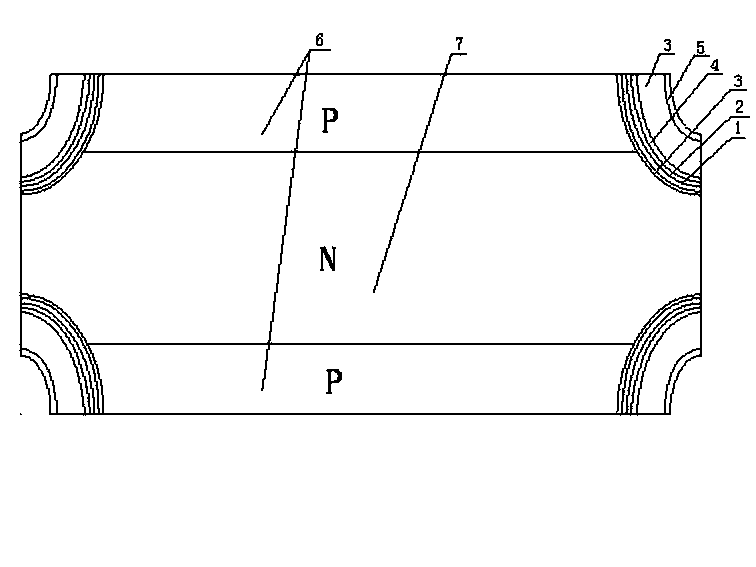

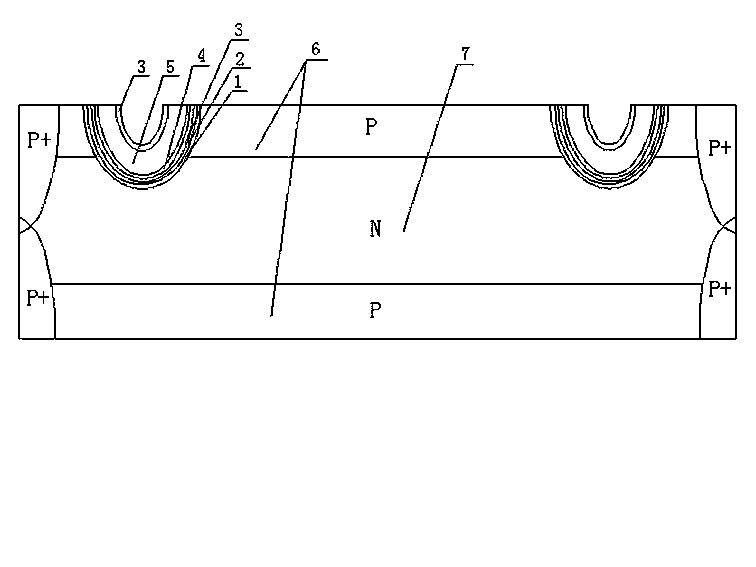

Multilayer composite membrane passivation structure of table top high-power semiconductor device and manufacturing technology of multilayer composite membrane passivation structure of table top high-power semiconductor device

ActiveCN103730430ARepair damageImprove breakdown voltagePolycrystalline material growthSemiconductor/solid-state device detailsManufacturing technologyPolycrystalline silicon

The invention discloses a multilayer composite membrane passivation structure of a table top high-power semiconductor device. The multilayer composite membrane passivation structure comprises P-type boron junction areas and an N-type phosphorus junction area, the upper end and the lower end of the N-type phosphorus junction area are provided with the P-type phosphorus areas respectively, and an alpha-polycrystalline silicon layer, a semi-insulating polycrystalline silicon thin membrane, a low-temperature heat oxidation layer, a high-temperature Si3N4 thin membrane, a negative charge glass passivation layer and a low-temperature heat oxidation layer are sequentially arranged on the surface of a PN junction of a table top of the table top high-power semiconductor device from inside to outside. A manufacturing technology of the multilayer composite membrane passivation structure of the table top high-power semiconductor device includes the following steps: a, depositing the alpha-polycrystalline silicon, b, depositing semi-insulating polycrystalline silicon, c, depositing the low-temperature heat oxidation layer, d, depositing Si3N4, e, conducting passivation on glass, and f, depositing the low-temperature heat oxidation layer in the outmost layer. The multilayer composite membrane passivation structure and the manufacturing technology have the advantages that the alpha-polycrystalline silicon layer is deposited, so that crystal lattice adaptation can be achieved, damage to crystal lattices of a silicon wafer in a groove can be repaired, leaked currents in the surfaces of junctions are reduced, and the stability and the reliability of the device at the high temperature are improved.

Owner:江苏吉莱微电子股份有限公司

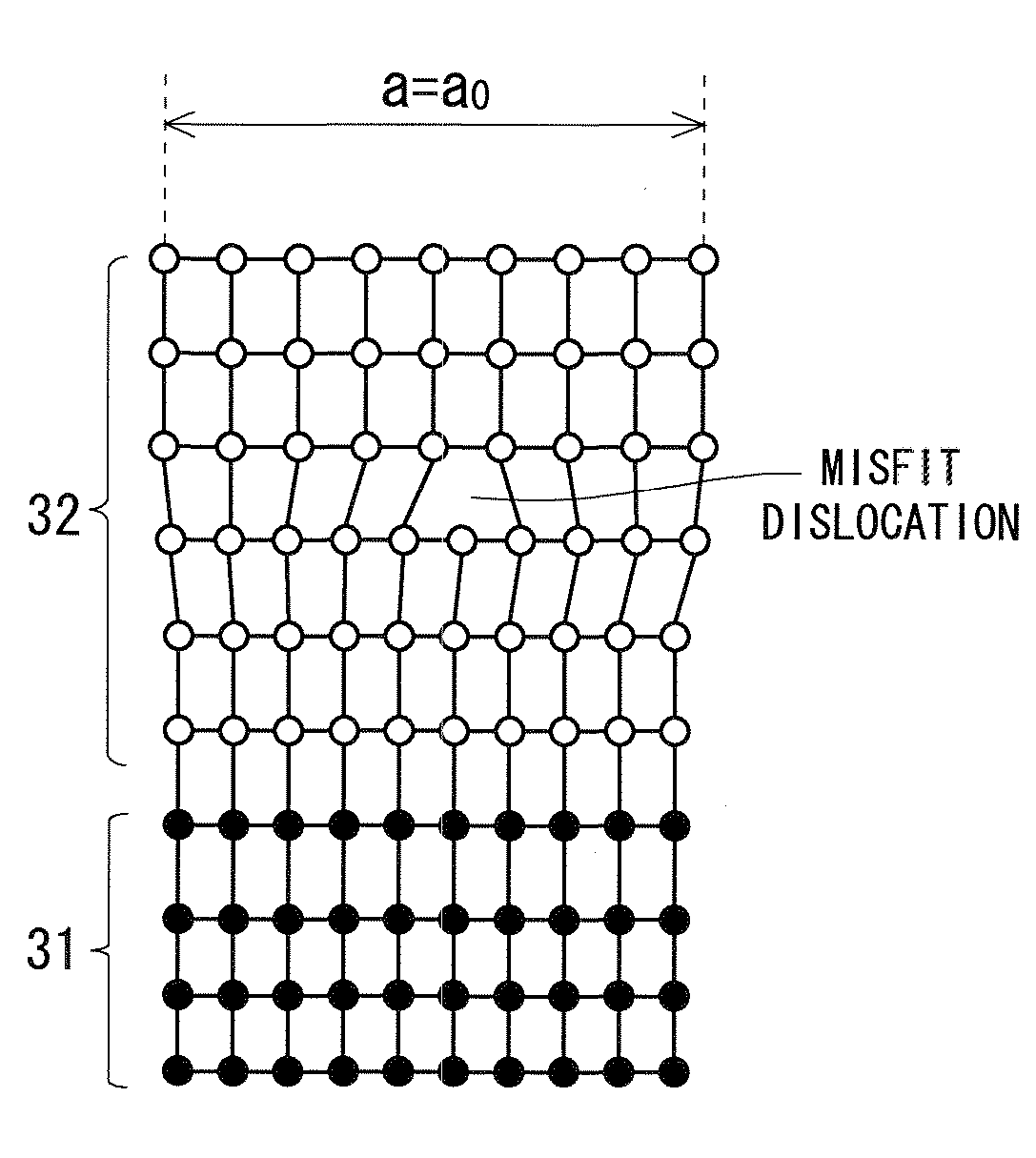

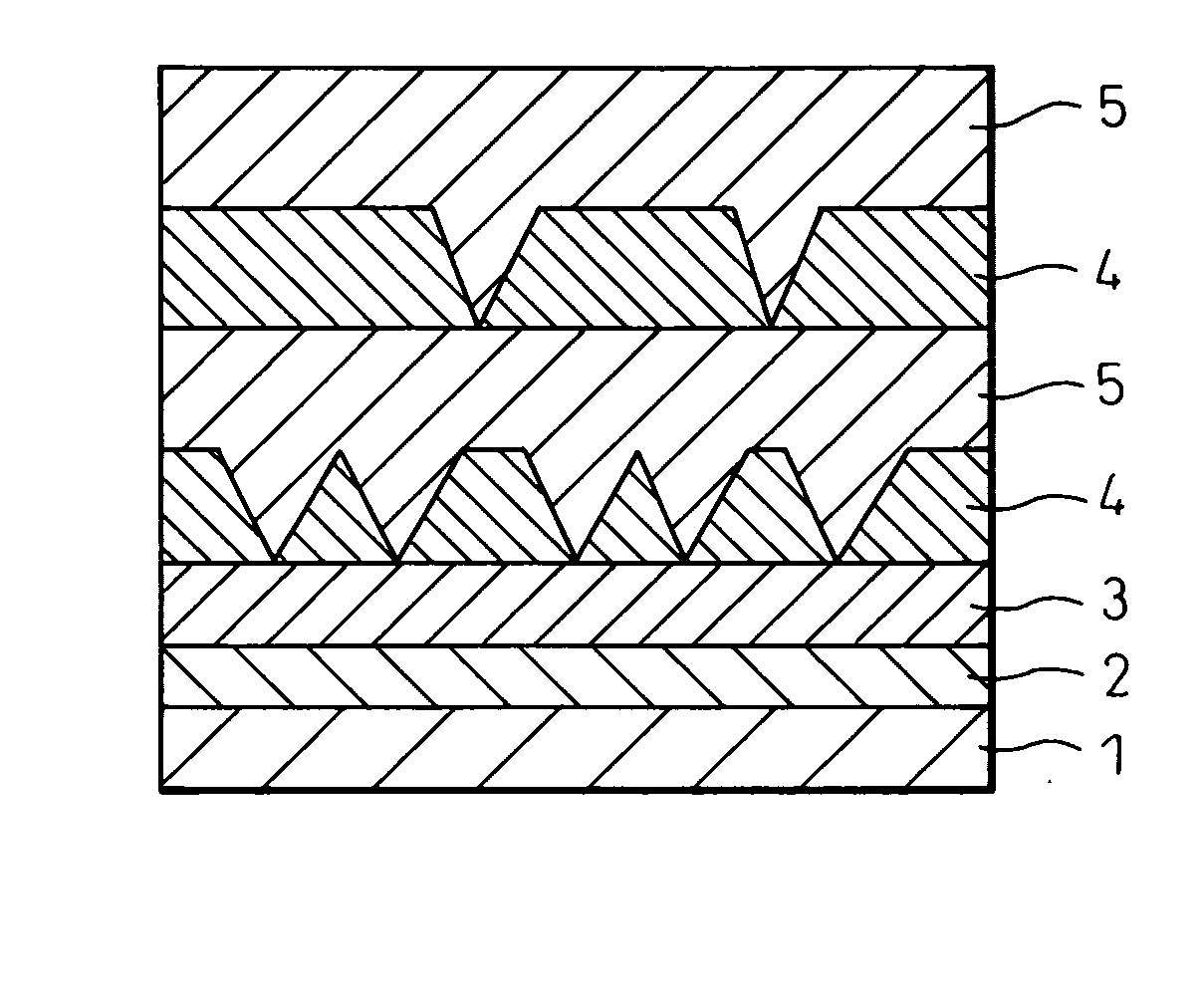

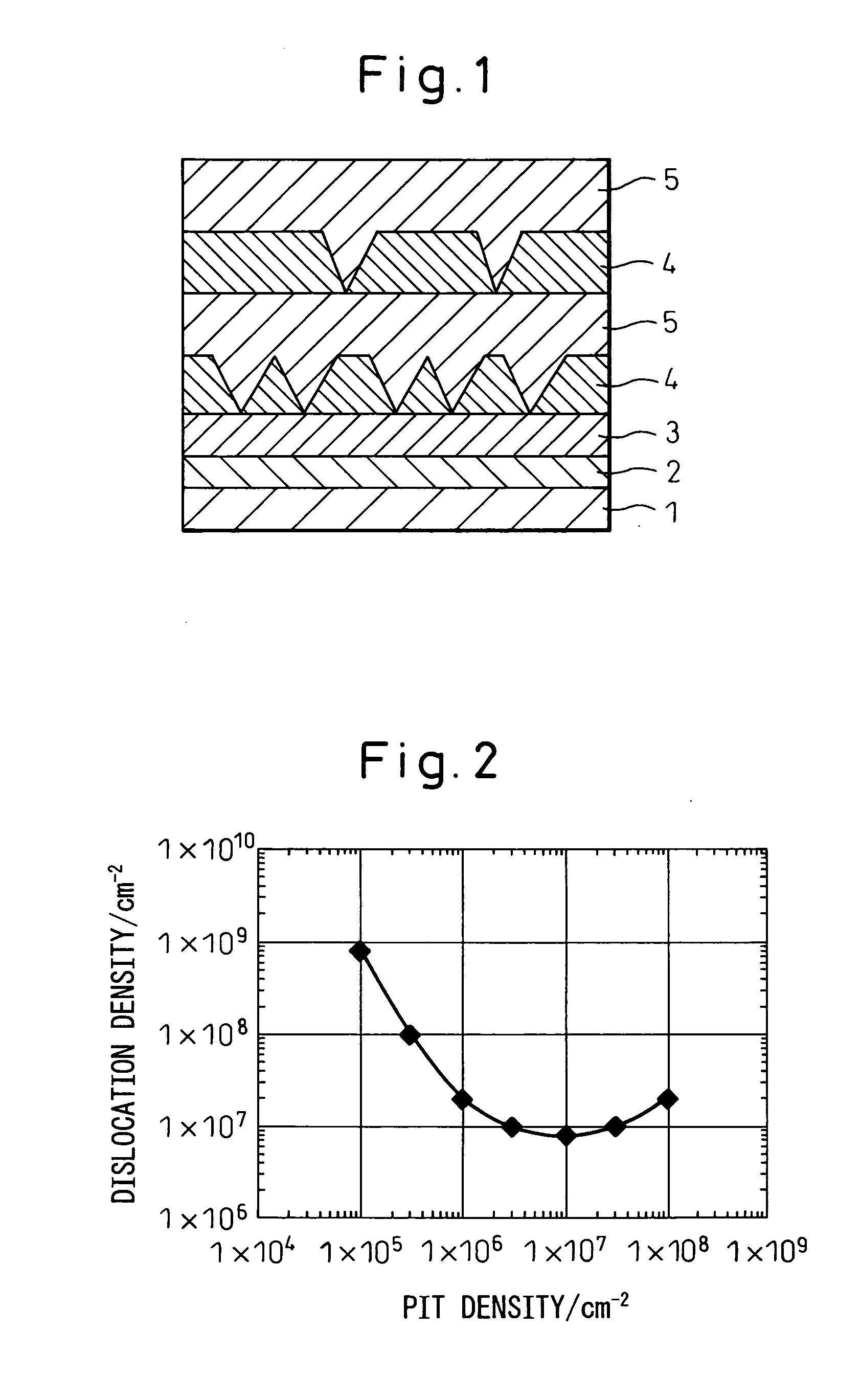

Group III nitride semiconductor stacked structure

ActiveUS20060261353A1Light emission efficiencyImproved light emissionSolid-state devicesSemiconductor devicesHigh concentrationSurface roughness

An object of the present invention is to provide a Group III nitride semiconductor stacked structure with a low dislocation density obtained by stacking only a semiconductor layer on a flat substrate by the use of a normal epitaxial growth method without processing the substrate or a deposit layer on the substrate, wherein the dislocation density is 1×107 cm−2 or less. The inventive Group III nitride semiconductor stacked structure comprises a substrate having a surface roughness (Ra) of 1 nm or less and a Group III nitride semiconductor layer directly stacked on the substrate, wherein the Group III nitride semiconductor layer comprises a plurality of layers put into contact with each other, the plurality of layers comprise a high-concentration impurity atom layer and a low-concentration impurity atom layer, and the high-concentration impurity atom layer is present on the substrate side.

Owner:TOYODA GOSEI CO LTD

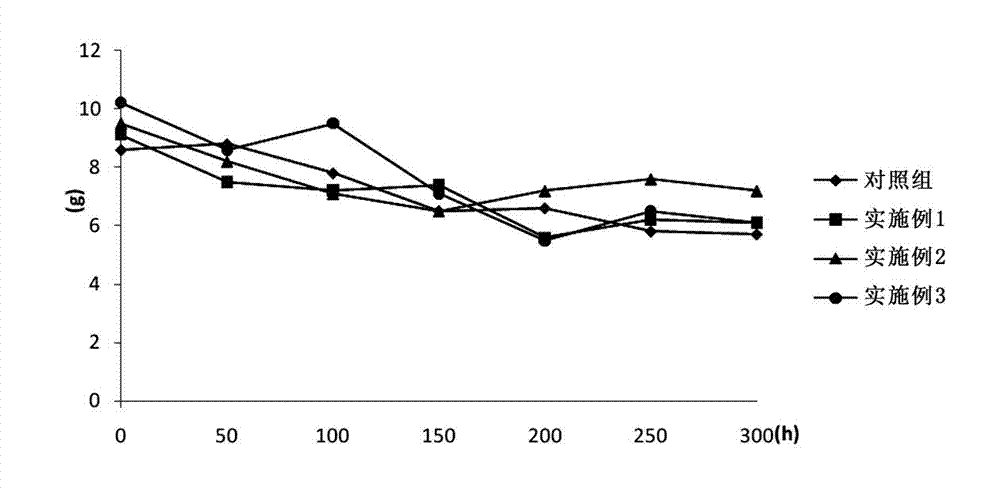

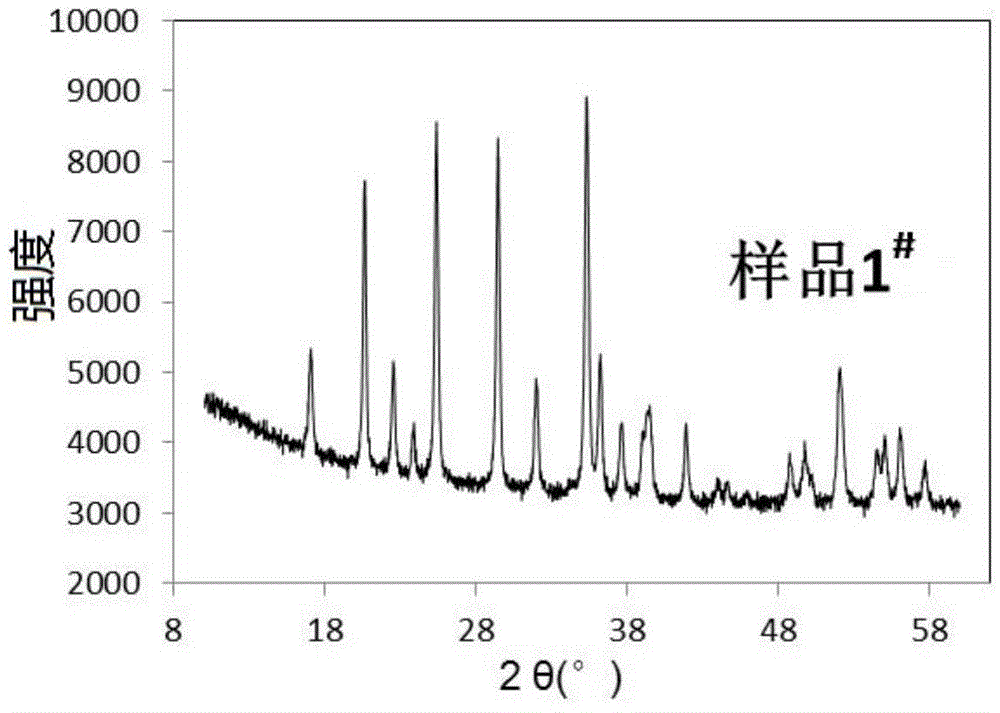

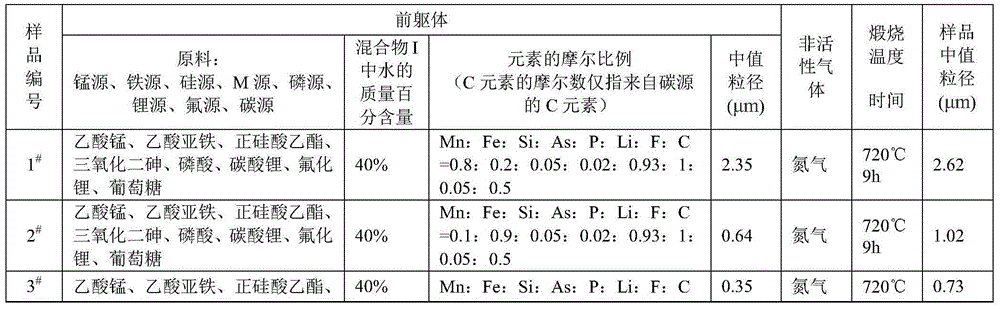

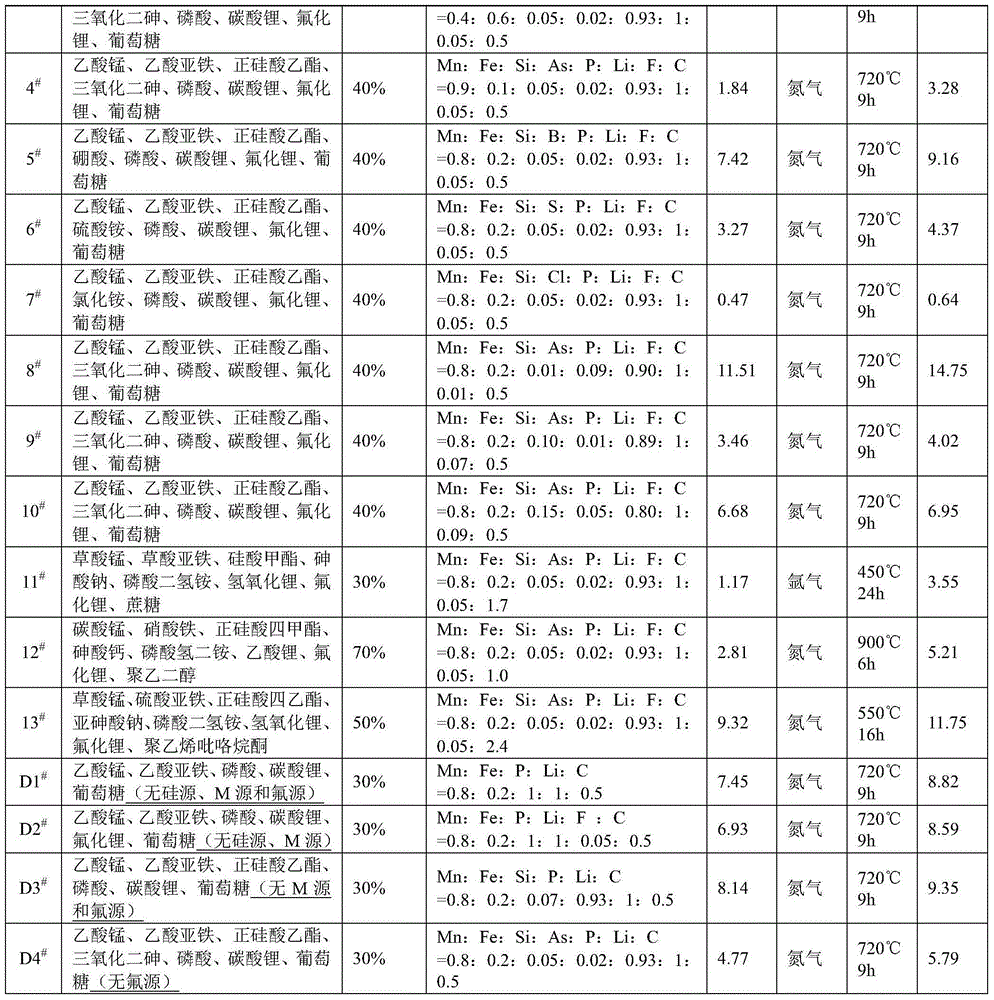

Cathode material of lithium ion battery and preparation method and application of cathode material

InactiveCN104577115AImprove cycle performanceExtend your lifeSecondary cellsPositive electrodesHigh temperature storageElectrical battery

The application discloses a cathode material of a lithium ion battery and a preparation method and application of the cathode material. Through the use of the cathode material, the change rate of the relative volume of the cathode material can be reduced under the conditions of the embedding of a lithium ion and the extraction of the lithium ion, and besides the dissolution of Mn in the cathode material is effectively restrained in a charging process and a discharging process, so that the stability of a crystal structure of the cathode material in the operating condition is improved. The lithium ion battery made from the cathode material has an excellent cycle property, an excellent safety property and an excellent high temperature storage property.

Owner:QINGHAI CONTEMPORARY AMPEREX TECH

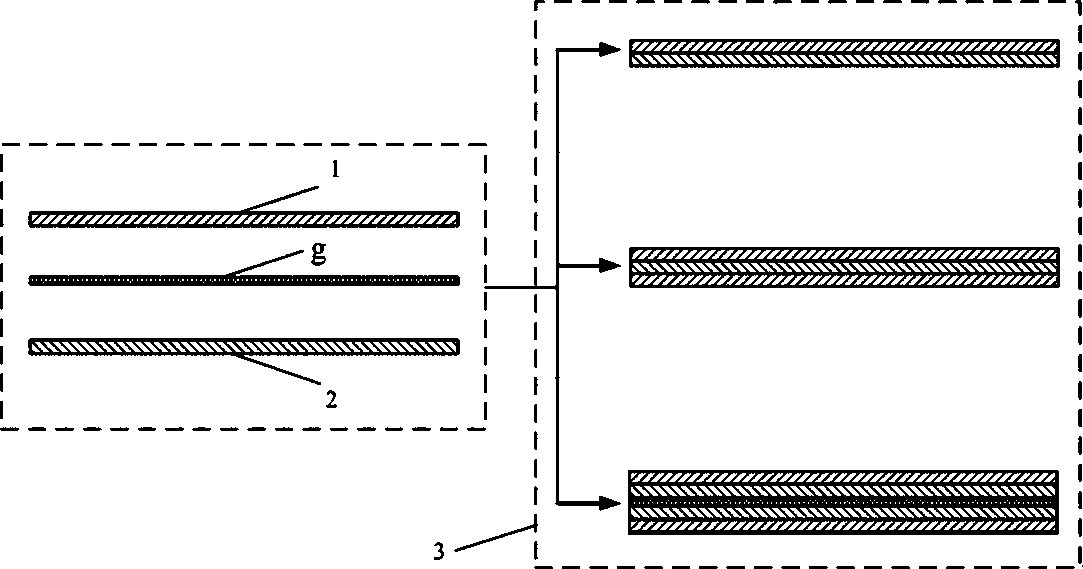

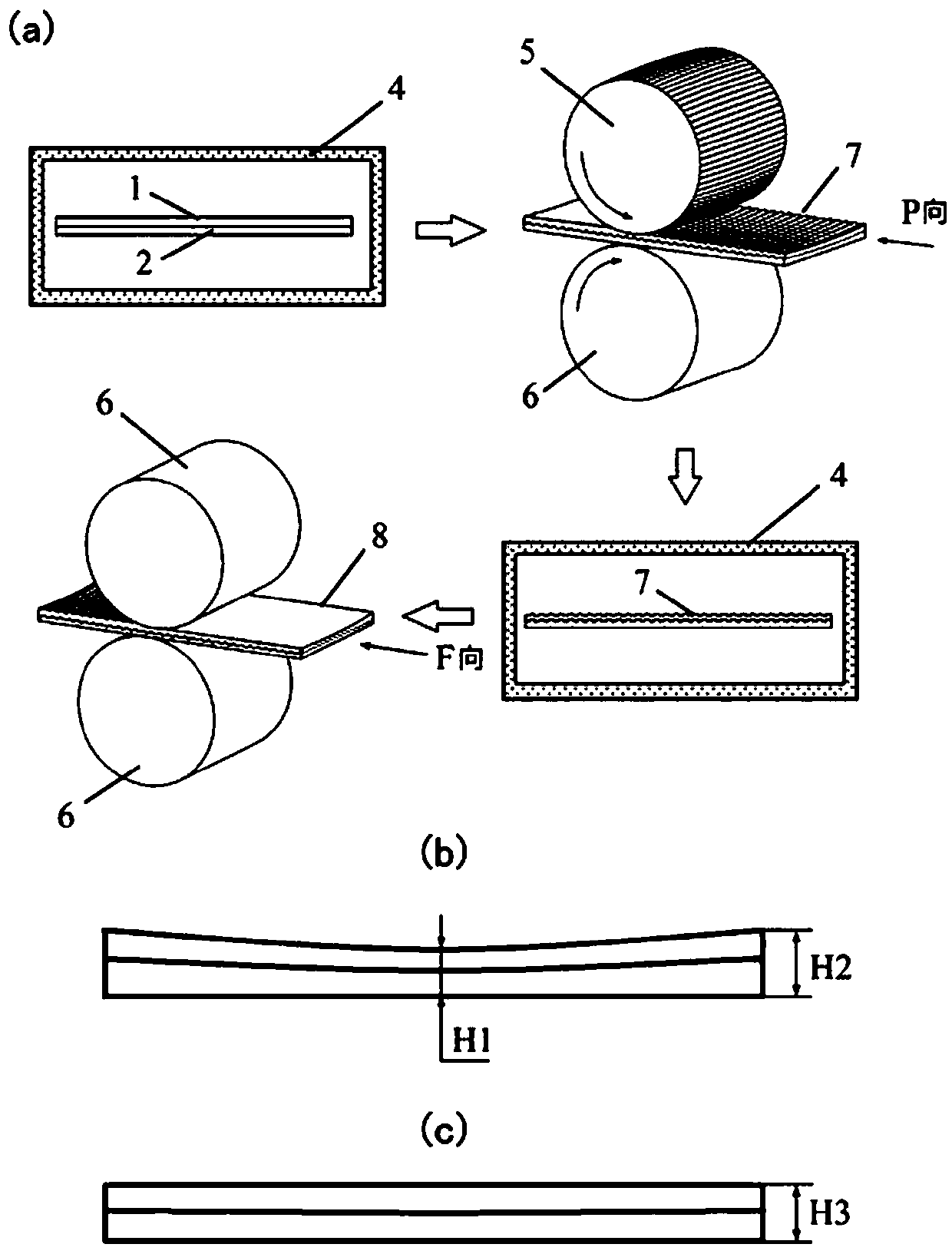

Method for rolling magnesium-aluminum layered laminated plate by drum-shaped corrugated roller

ActiveCN110722013AImprove bindingHigh bonding strengthMetal rolling arrangementsUltimate tensile strengthBonding strength

The invention relates to the field of processing of metal laminated plate belts, in particular to a method for rolling a magnesium-aluminum laminated plate by a drum-shaped corrugated roller. The method comprises the following steps of selecting a magnesium alloy plate with the same length and width as a clad plate and a pure aluminum or aluminum alloy plate as a base plate, cleaning the surface of the metal plate, buckling and assembling the ground surfaces of the base plate and the clad plate together, or buckling and stacking and assembling together. In the first pass, when the drum rolleris used for rolling the magnesium-aluminum laminated plate, a stress peak value can be formed on the lowest metal interface of the laminated plate, and the combination of the middle part of the laminated plate and the wave trough of the wave interface is promoted. In the second pass flattening process, a stress peak value is formed on the edge part of the laminated plate with poor bonding and themetal interface at the wave peak part during the first pass rolling of the plate, large plastic deformation is generated at the same time, and the bonding of the edge part of the laminated plate is promoted. According to the process, rolling is carried out twice in sequence, the bonding of the whole interface is promoted, and the bonding strength of the interface of the laminated plate is improved.

Owner:TAIYUAN UNIV OF TECH

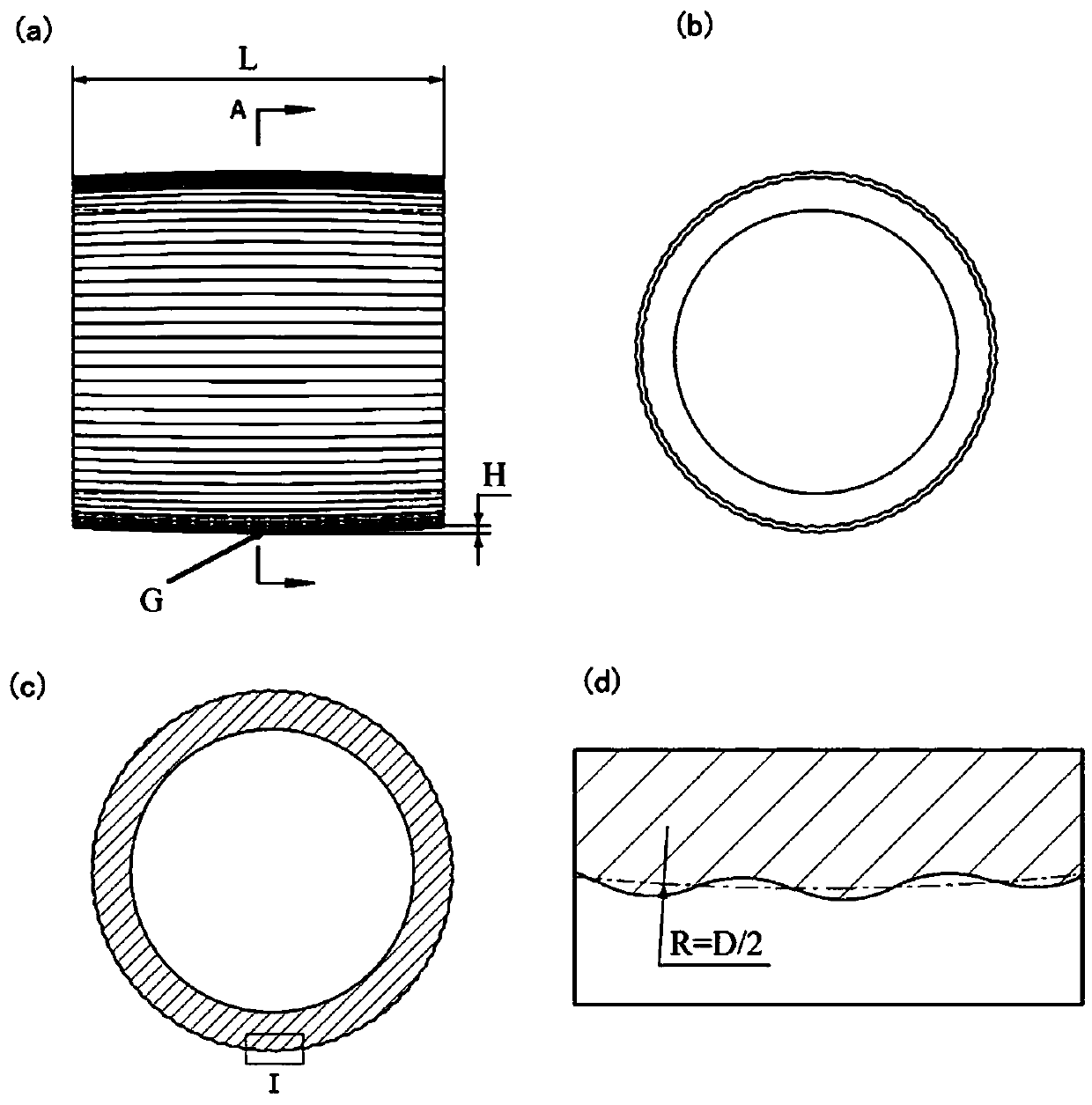

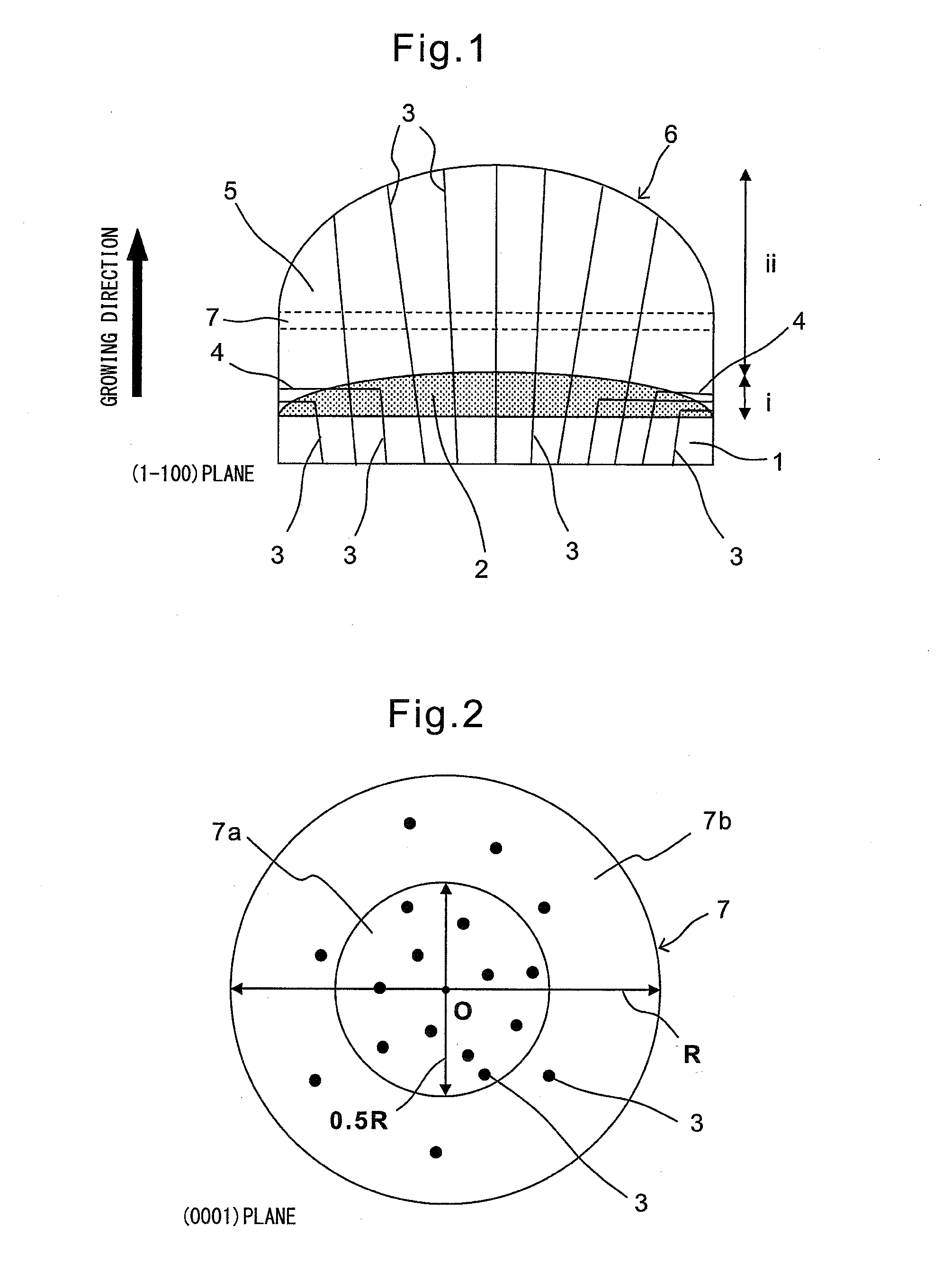

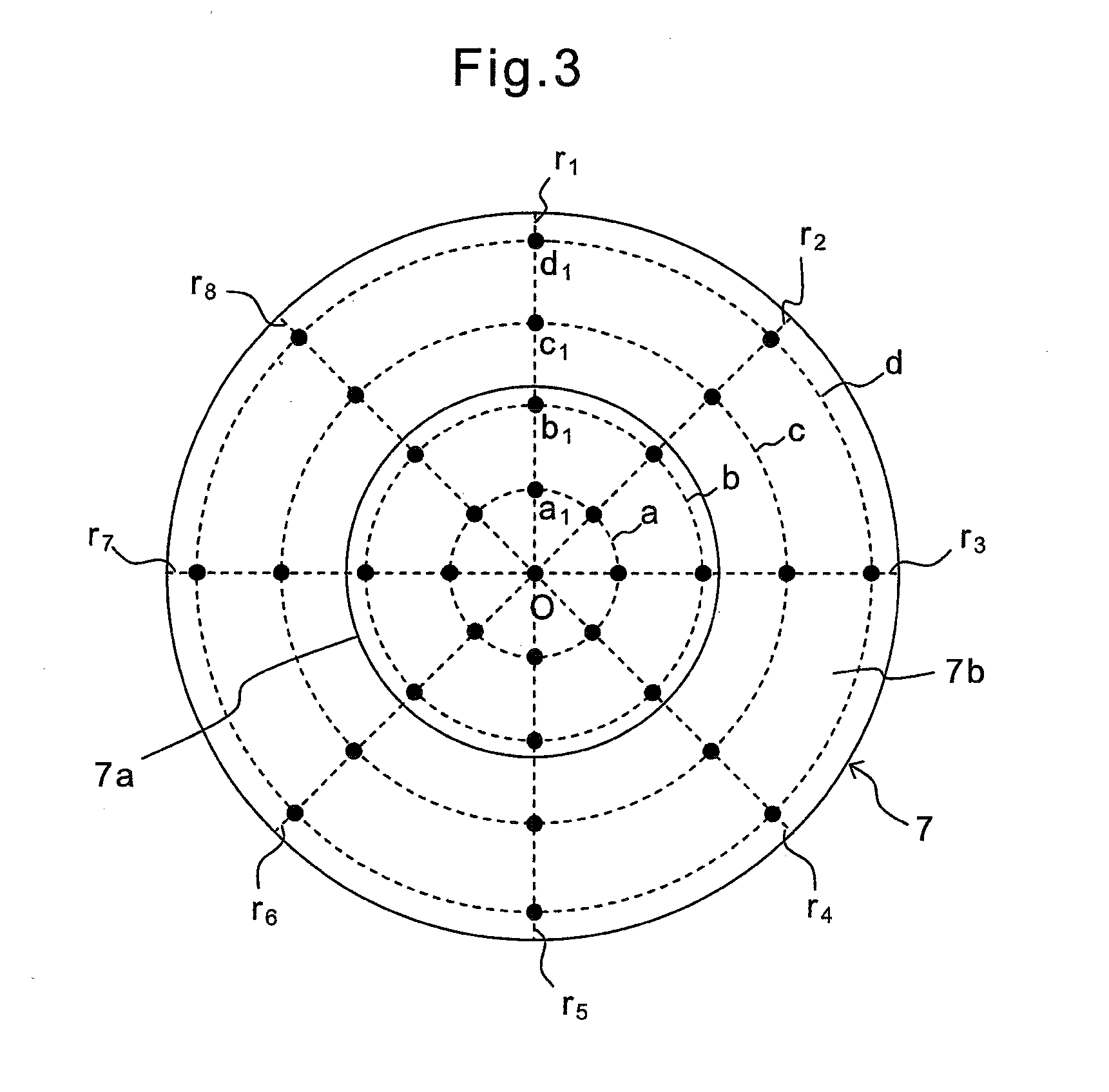

Silicon carbide single crystal wafer and manufacturing method for same

ActiveUS20140363607A1Reduce pressureReduce the temperaturePolycrystalline material growthLayered productsSingle crystal substrateOptoelectronics

Provided are a method for manufacturing a SiC single crystal having high crystal quality and, in particular, extremely low screw dislocation density and a SiC single crystal ingot obtained by the method. In particular, provided is a silicon carbide single crystal substrate that is a substrate cut from a bulk silicon carbide single crystal grown by the Physical Vapior Transport (PVT) method, in which the screw dislocation density is smaller in the peripheral region than in the center region, so that screw dislocations are partially reduced.The method is a method for manufacturing a SiC single crystal by the PVT method using a seed crystal and the ingot is a SiC single crystal ingot obtained by the method. Particularly, the silicon carbide single crystal substrate is a silicon carbide single crystal substrate in which when, by representing the diameter of the substrate as R, a center circle region having a diameter of 0.5×R centered around a center point O of the substrate and a doughnut-shaped peripheral region remaining by excluding the center circle region are defined, the average value of screw dislocation densities observed in the doughnut-shaped peripheral region is 80% or less of the average value of screw dislocation densities observed in the center circle region.

Owner:RESONAC CORP

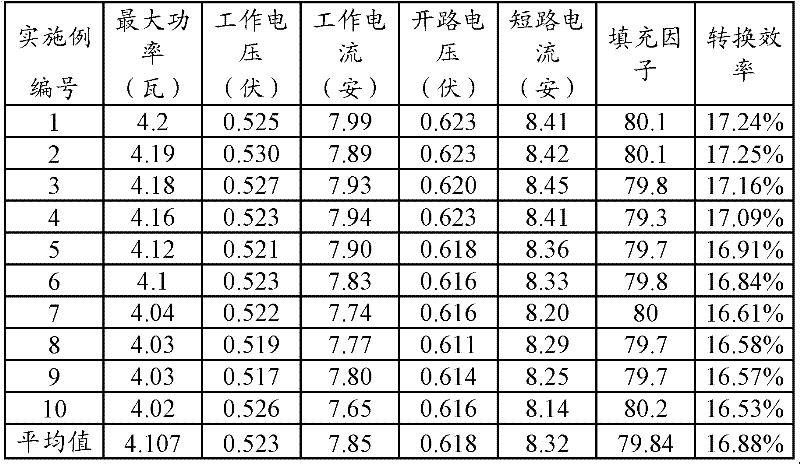

Method for preparing antireflective film of polycrystalline silicon solar cell as well as polycrystalline silicon solar cell

InactiveCN102185006AReduce dislocationExtend your lifeFinal product manufactureChemical vapor deposition coatingDislocationPolycrystalline silicon

The invention provides a method for preparing an antireflective film of a polycrystalline silicon solar cell as well as a polycrystalline silicon solar cell. The method comprises the steps of: passivation layer deposition and density layer deposition. The polycrystalline silicon solar cell comprises: a polycrystalline silicon wafer and the antireflective film located on the surface of the polycrystalline silicon wafer, wherein the antireflective film is made from silicon nitride and comprises a passivation layer and a density layer; and the passivation layer is arranged on the surface of the polycrystalline silicon wafer and the density layer is arranged on the surface of the passivation layer. In the technical scheme provided by the invention, by utilizing the passivation layer in the antireflective film, the surface of the silicon wafer and a substrate can be effectively passivated, the defects such as dislocation, crystal boundary and the like in the surface of a polycrystalline silicon material can be reduced and the carrier lifetime of the polycrystalline silicon material can be prolonged; and by utilizing the formed antireflective film, the photoelectric conversion efficiency of the polycrystalline silicon solar cell can be effectively increased and the maximum power of a cell piece is increased.

Owner:JETION SOLAR HLDG

Gallium nitride (GaN) based personal identification number (PIN) detector based on imaging sapphire substrate and preparation method

InactiveCN102593233AQuality improvementReduce defect densityFinal product manufactureSemiconductor devicesDislocationMaterial quality

The invention relates to a gallium nitride (GaN) based personal identification number (PIN) detector based on an imaging sapphire substrate and a preparation method. The structure is that a thick cushion layer grows on the imaging sapphire substrate, the thick cushion layer comprises low temperature cushion layer growing, recrystallization, three-dimensional growing and two-dimensional growing, and a GaN film material with good quality is obtained. An n+ type GaN layer, an intrinsic GaN layer and a p type GaN layer sequentially grow. A p ohmic contact electrode is deposited on the surface of a p layer, a p type film layer and an intrinsic layer are etched to an n+ type film layer, the shape of an etching table face is round, square or hexagon, an n type ohmic contact electrode is deposited on an n+ type layer, and an n type electrode is annular or square. A passivation layer grows and holes are drilled, the p electrode and the n electrode are exposed out, and a thickening electrode grows on the p electrode and the n electrode respectively. Devices prepared by using the method are high in growth material quality, small in dislocation and defect density, small in dark current and stable in performance. The dark current under reversal biasing voltage almost has no change, and quantum efficiency is substantially improved.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

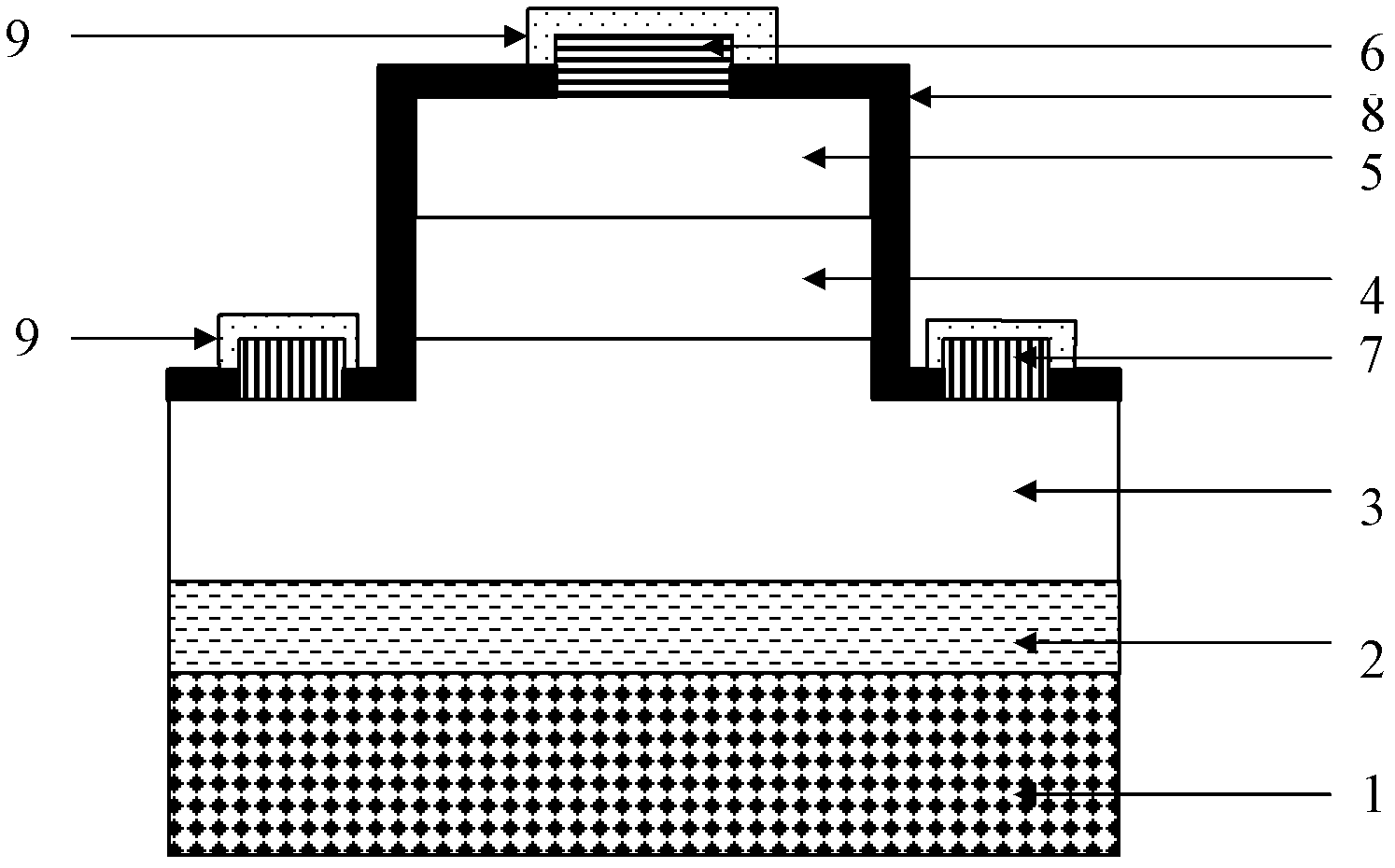

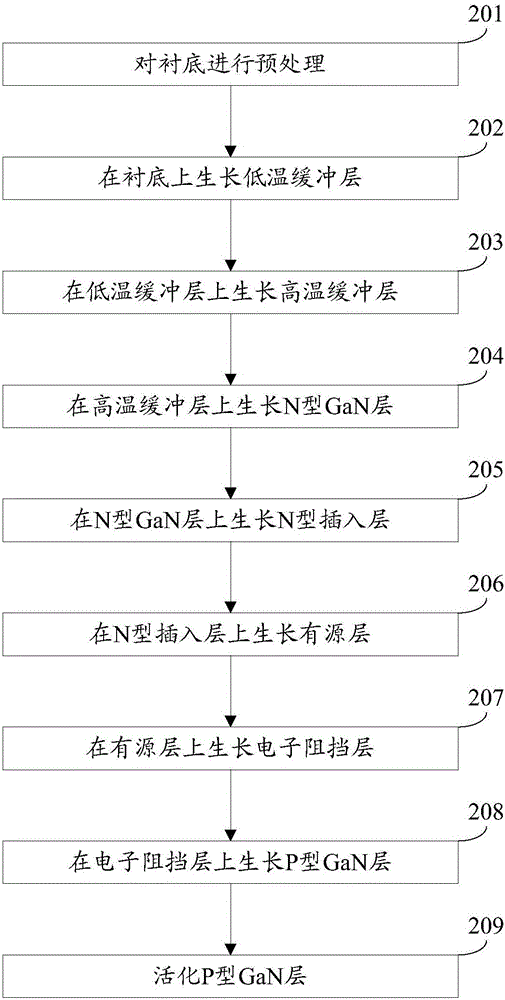

Growing method for light-emitting diode epitaxial wafer

ActiveCN106611808APromote growthReduce defect densitySemiconductor devicesDopantElectron blocking layer

The invention discloses a growing method for a light-emitting diode epitaxial wafer, and belongs to the technical field of semiconductors. The growing method comprises the following steps: growing a low-temperature buffer layer, a high-temperature buffer layer, an N-type GaN layer, an N-type inserting layer, an active layer, an electron barrier layer and a P-type GaN layer in sequence on a substrate, wherein the growth temperature of the N-type GaN layer is greater than that of the N-type inserting layer which is greater than that of the active layer; the N-type inserting layer comprises a first sublayer, a second sublayer and a third sublayer which are laminated in sequence; the first sublayer is a superlattice structure formed by alternately laminating two GaN layers in which the doping concentrations of the N-type doping agents are different, and the doping concentration of the N-type doping agent in the first sublayer is smaller than that of the N-type doping agent in the N-type GaN layer; the second sublayer is an AlGaN layer or a superlattice structure formed by alternately laminating at least three AlGaN layers and at least three GaN layers; and the third sublayer is an InGaN layer. The N-type inserting layer in the invention plays a buffer role, and is beneficial for the growth of the active layer.

Owner:HC SEMITEK ZHEJIANG CO LTD

Crystalline silicon and preparation method thereof

ActiveCN102877129AImprove battery conversion efficiencyGrow with fewer dislocationsPolycrystalline material growthFrom frozen solutionsCrucibleNucleation

The invention discloses a preparation method of crystalline silicon, which comprises the following steps: a mono-crystal silicon seed crystal is randomly paved in the center of the bottom of a crucible to form a seed crystal layer; a nucleation source is paved at the residual part of the bottom to form a nucleation source layer; a silicon material in a melting state is arranged on the seed crystal layer and the nucleation source layer to control the temperature of the bottom of the crucible so as to prevent the seed crystal layer and the nucleation source layer from being completely molten; and the temperature in the crucible is controlled to gradually increase to form temperature gradient in the direction vertical to the upward direction of the bottom of the crucible, so that the molten silicone material can form nuclear crystallization on the mono-crystal silicone seed crystal and the nucleation source and the crystalline silicon of which the center is mono-like and the periphery is high-effective polycrystal. The invention further discloses the crystalline silicon prepared by the preparation method for crystalline silicon. The preparation method for crystalline silicon reduces the consumption of the mono-crystal silicone seed crystal, saves the production cost, improves the quality of the silicon block in the area close to the side wall of the crucible; and monocrystal-like silicon and high-effective polycrystal silicone coexist in the prepared crystalline silicone, and the complementary advantages of the monocrystal-like silicone and the high-effective polycrystal silicone are realized.

Owner:JIANGXI SAI WEI LDK SOLAR HI TECH CO LTD