Patents

Literature

19905 results about "Active layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In environments containing permafrost, the active layer is the top layer of soil that thaws during the summer and freezes again during the autumn. In all climates, whether they contain permafrost or not, the temperature in the lower levels of the soil will remain more stable than that at the surface, where the influence of the ambient temperature is greatest. This means that, over many years, the influence of cooling in winter and heating in summer (in temperate climates) will decrease as depth increases.

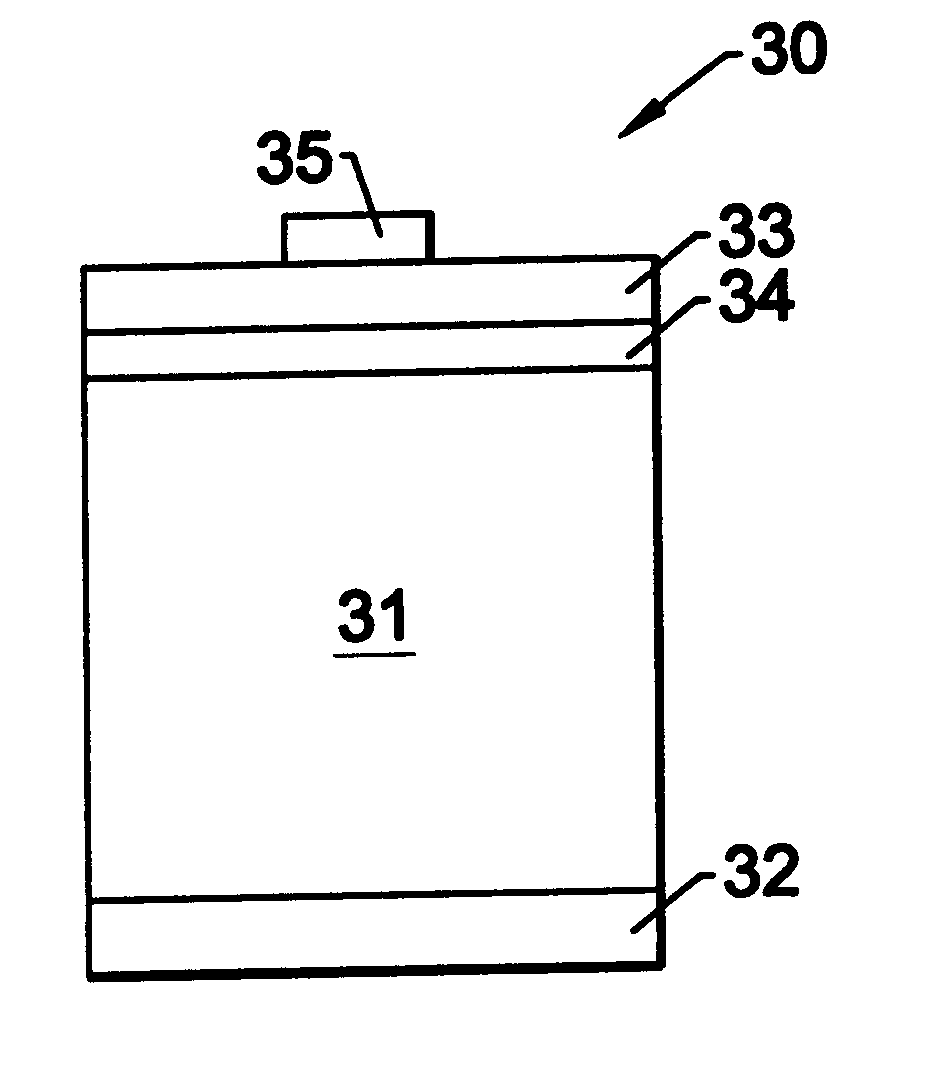

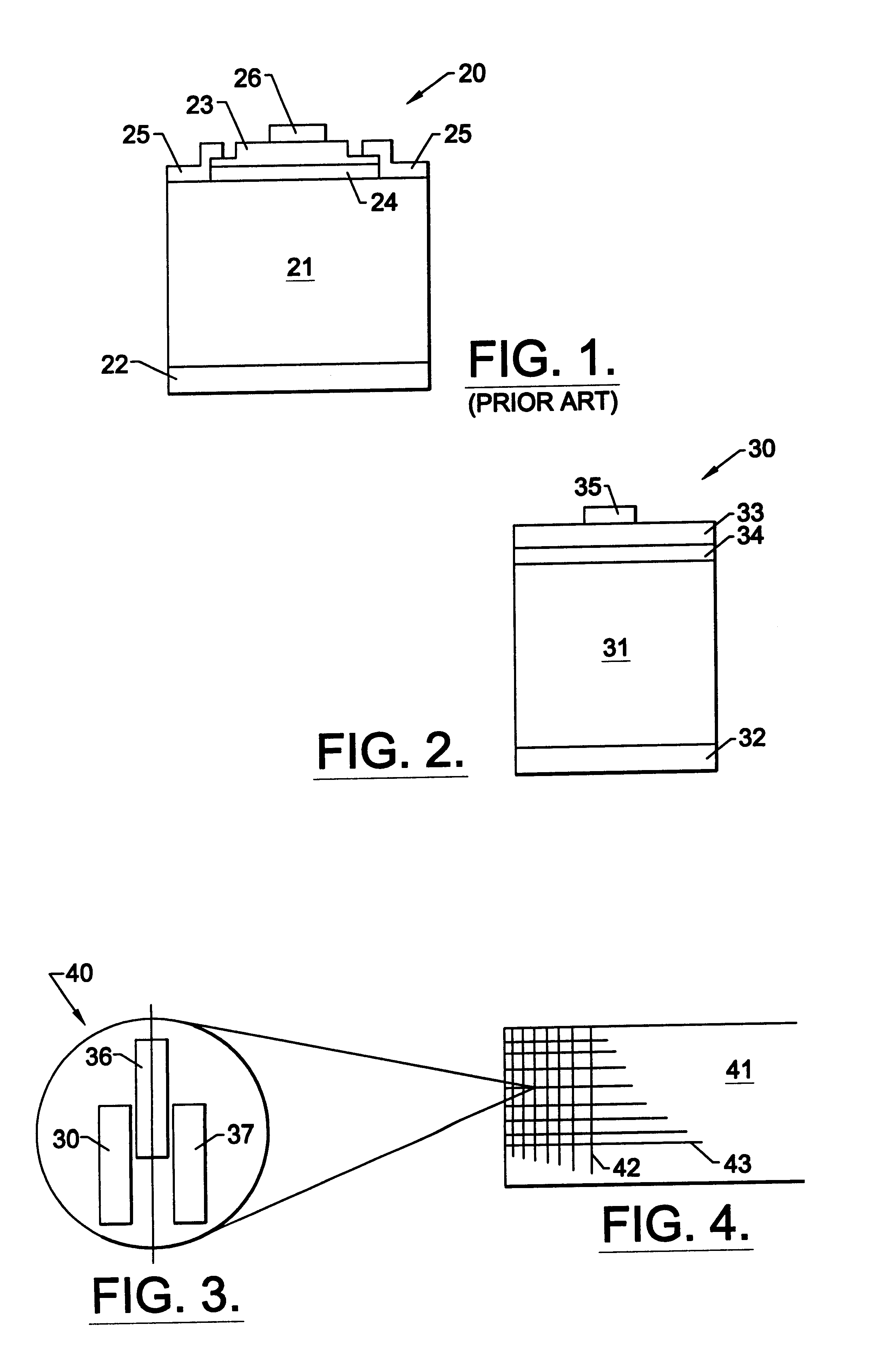

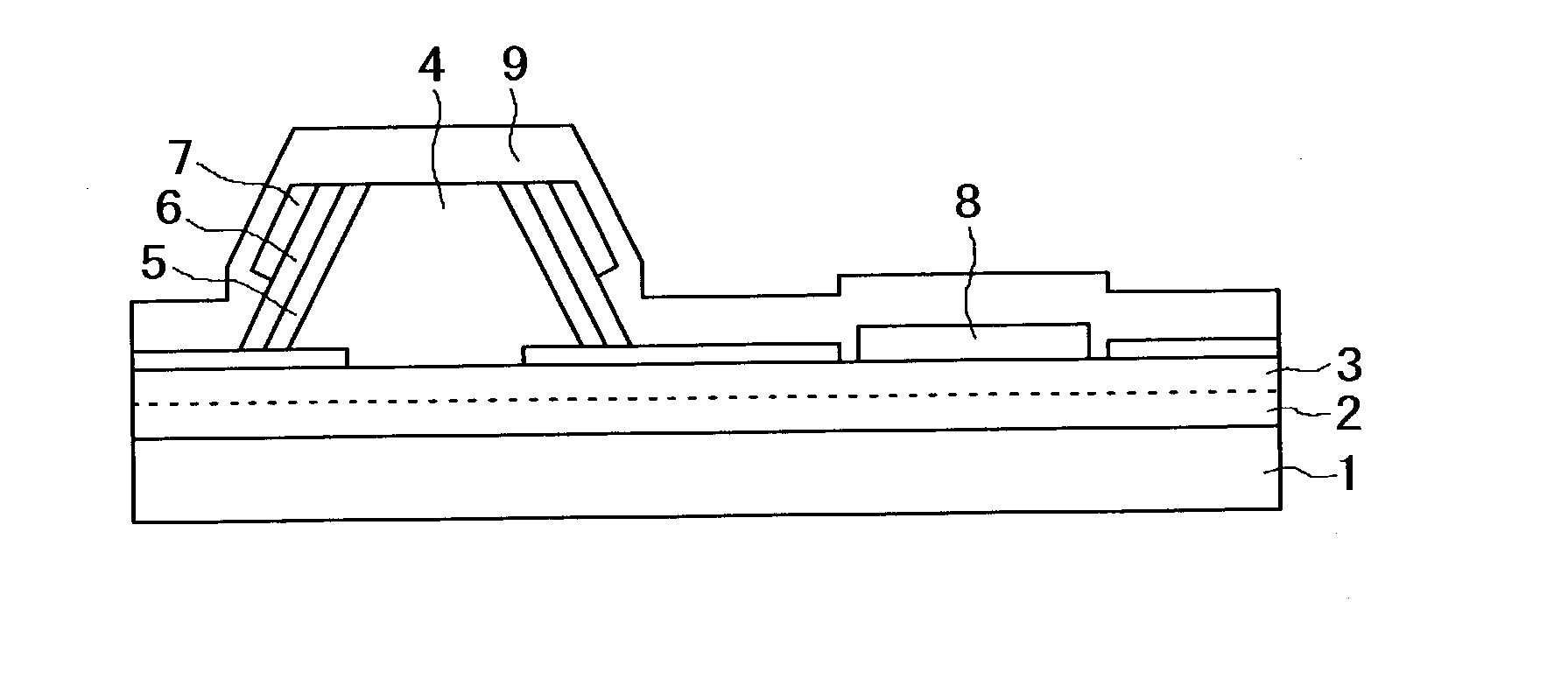

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

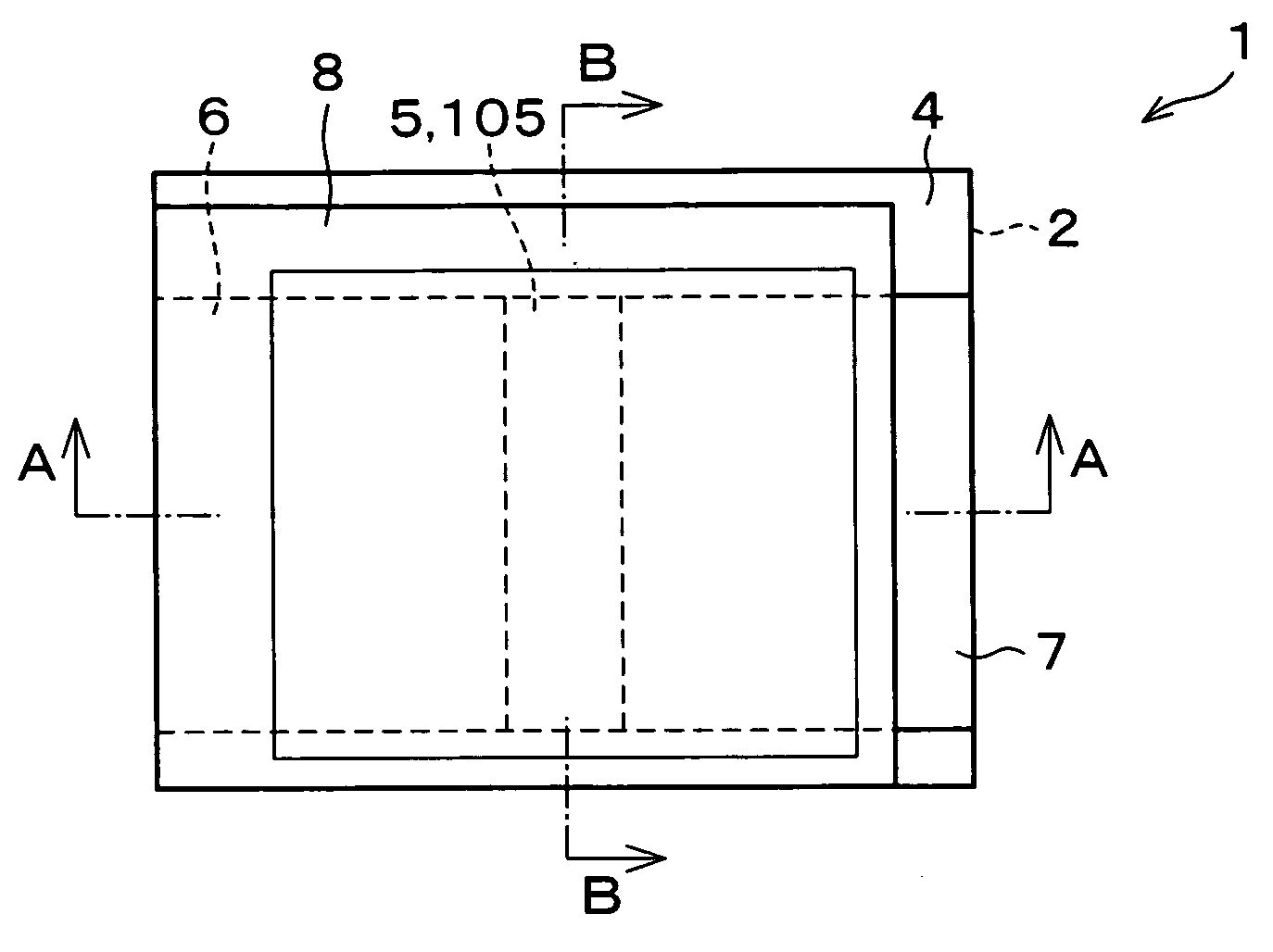

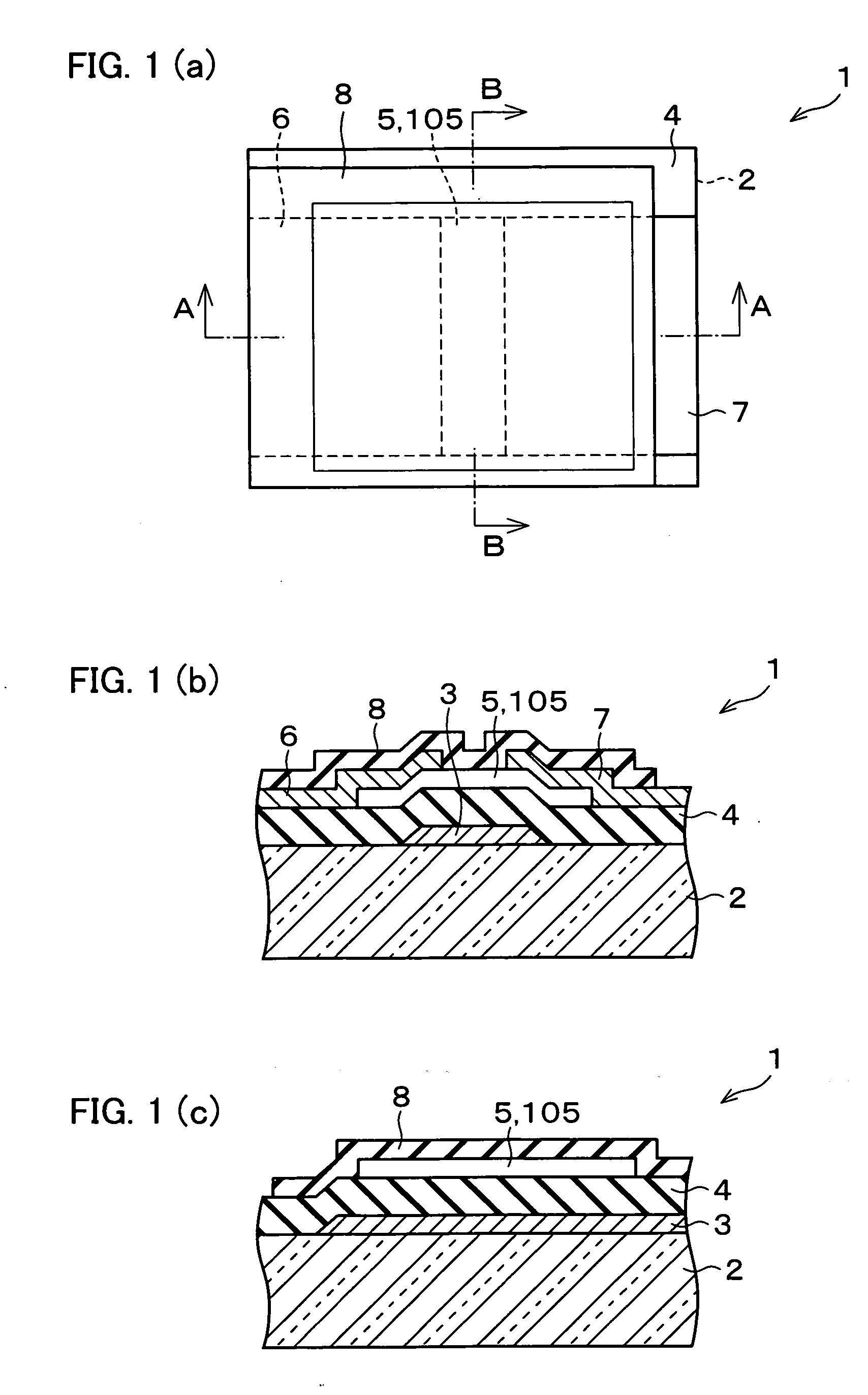

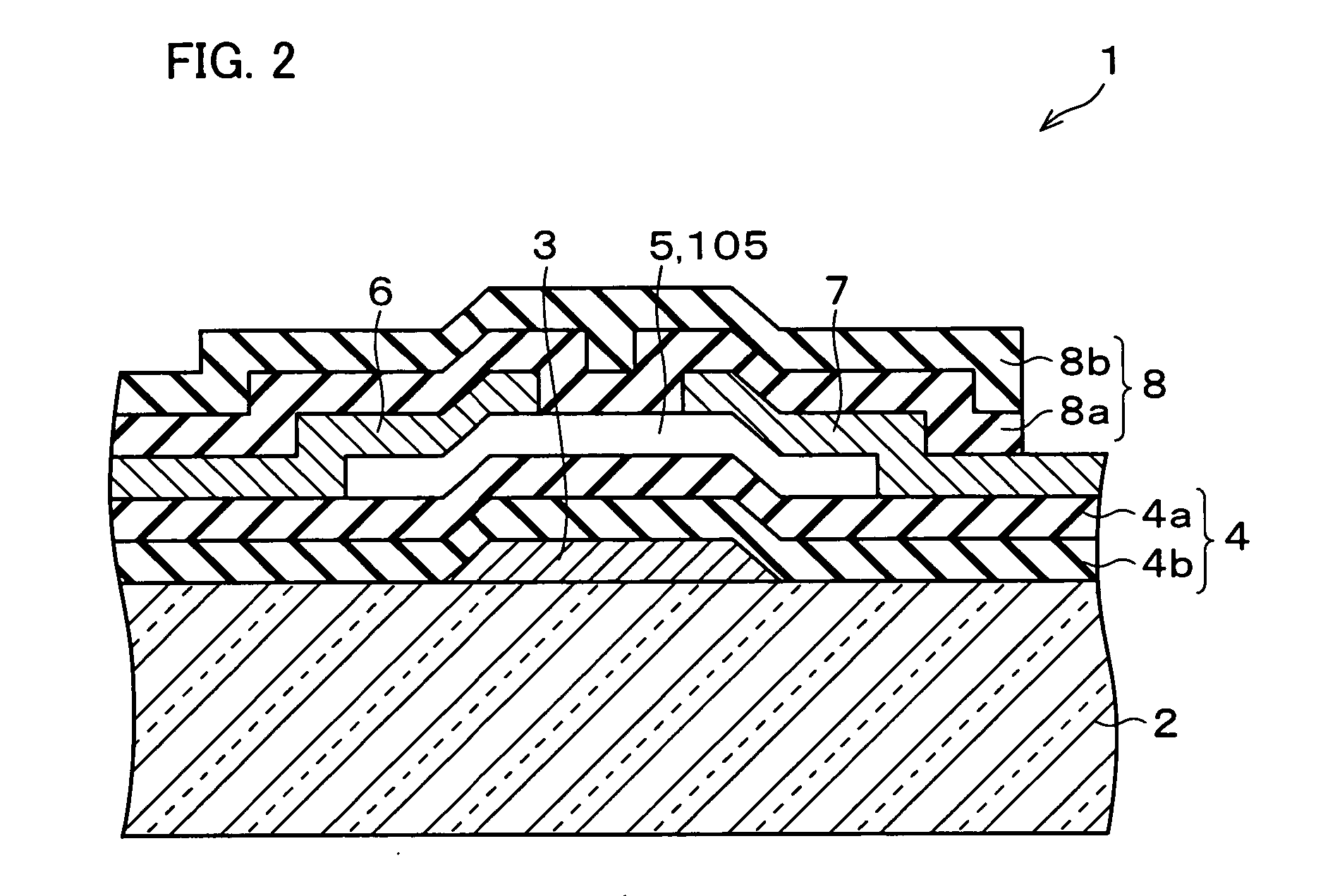

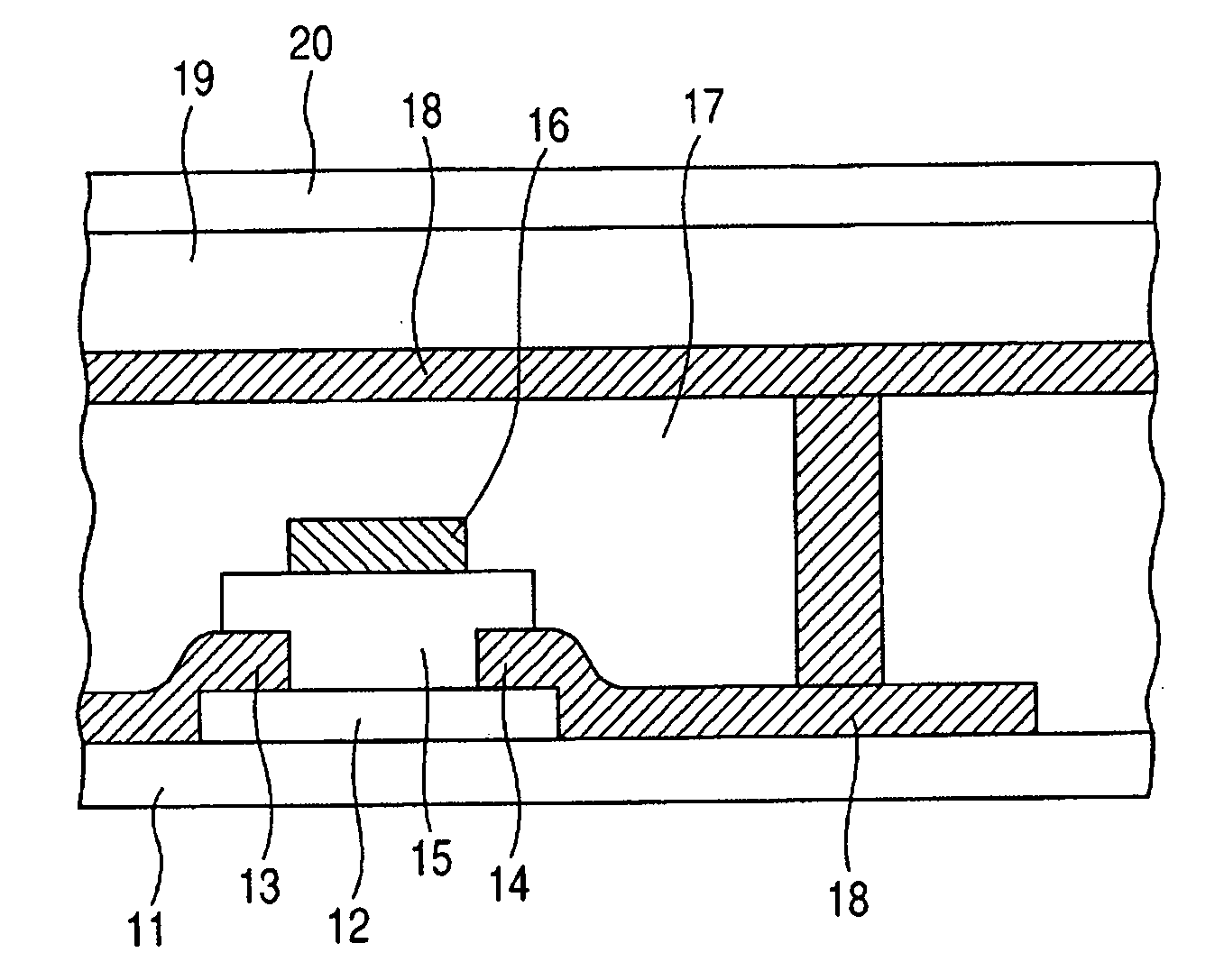

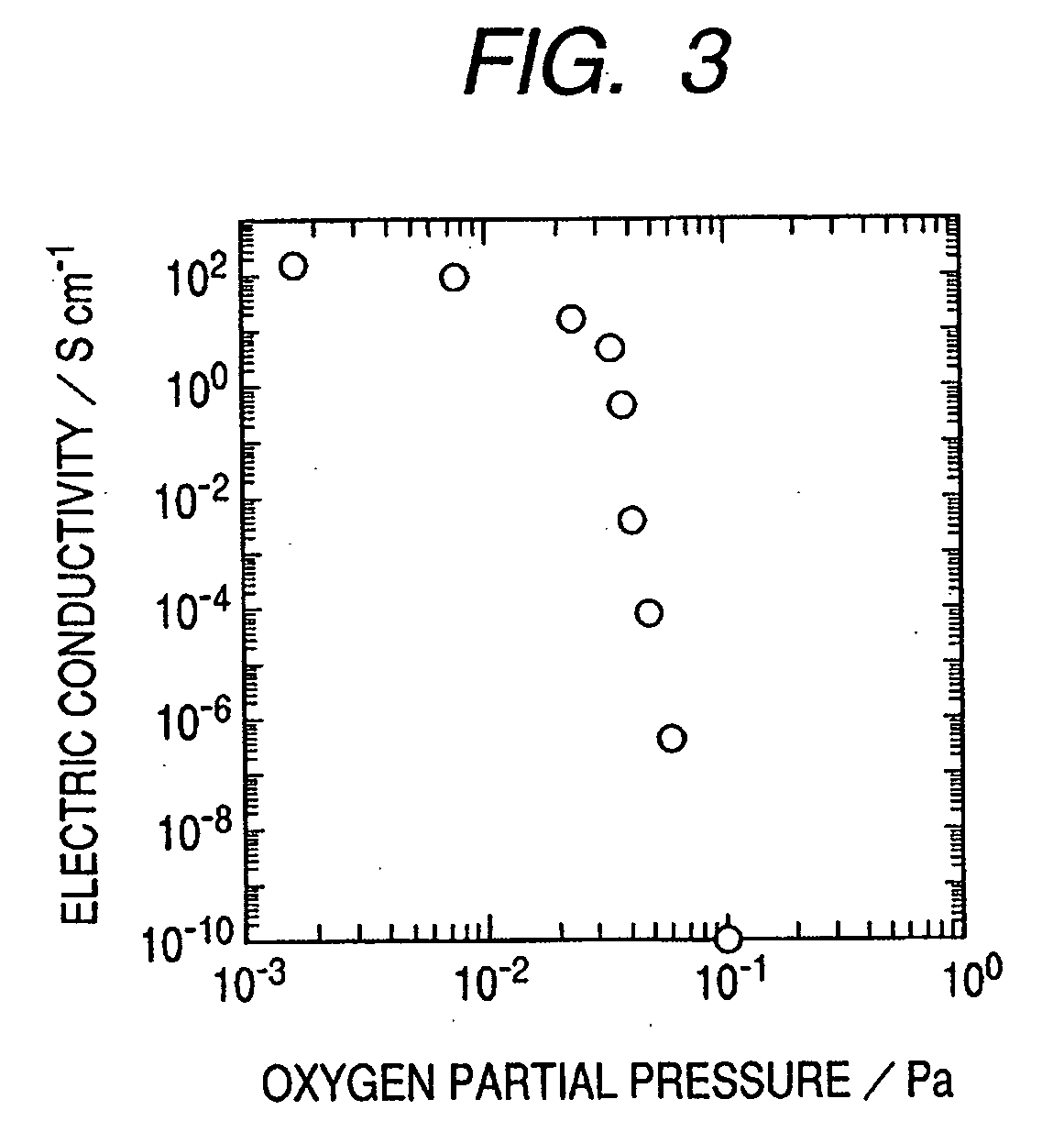

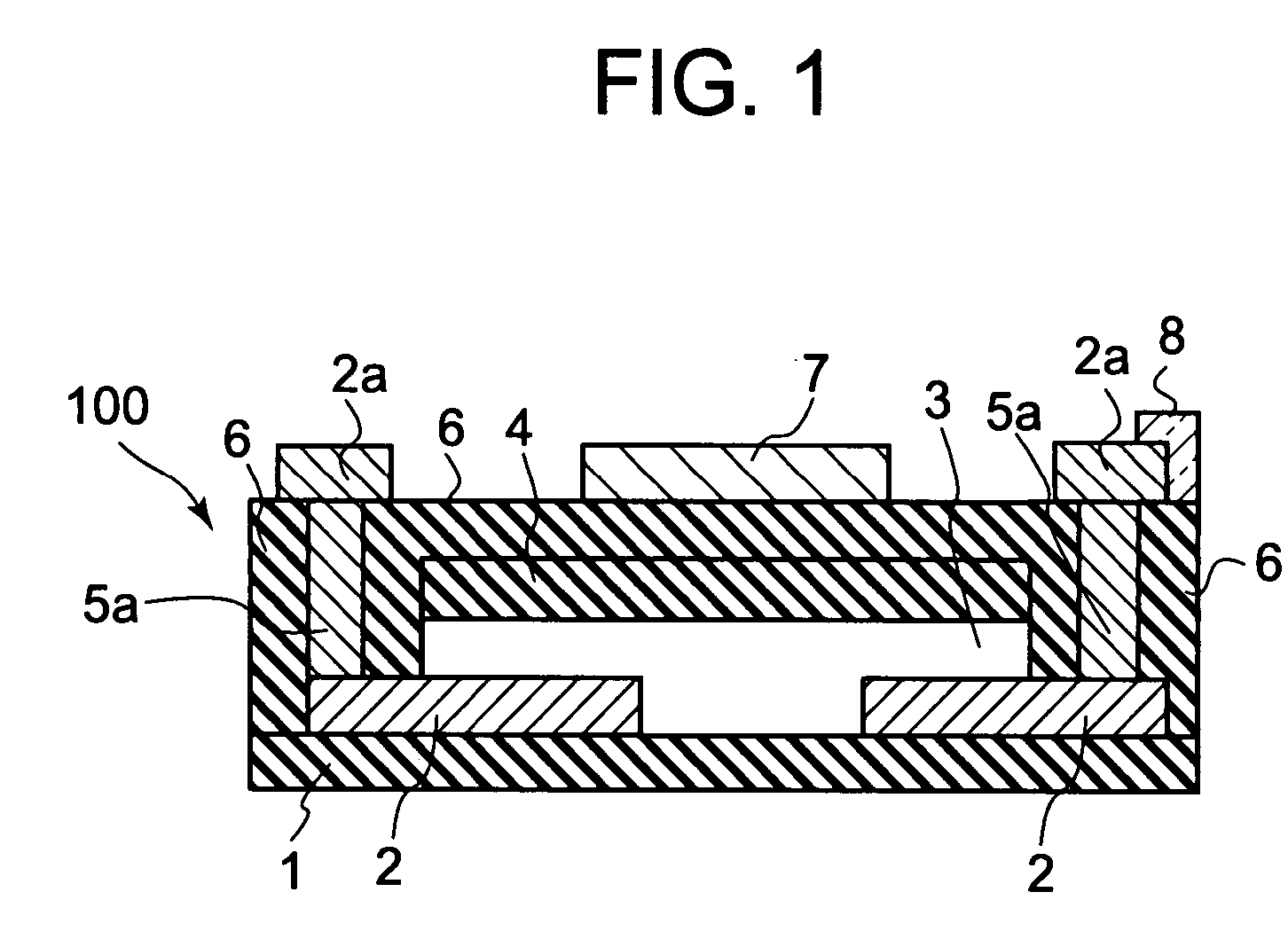

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

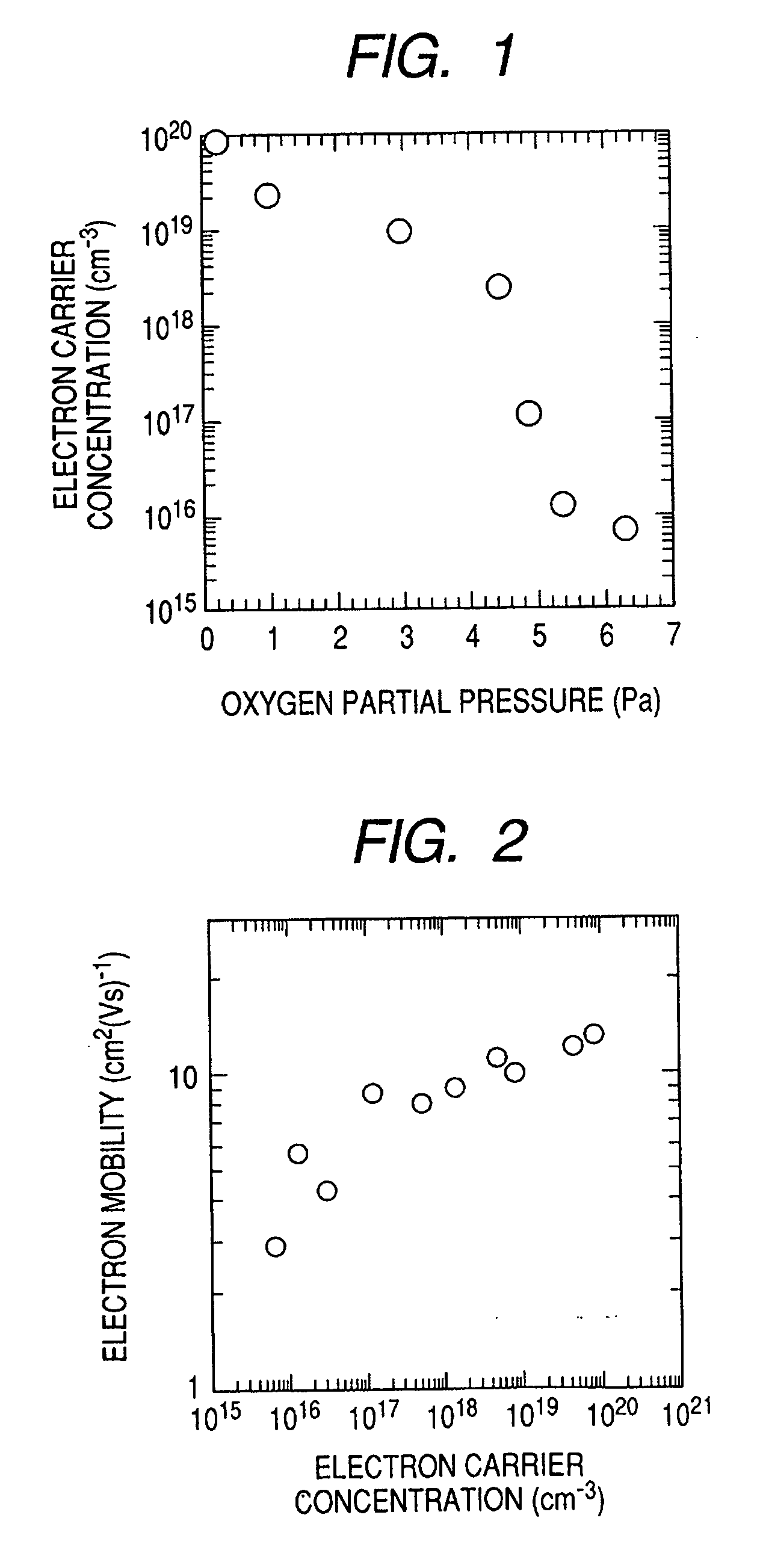

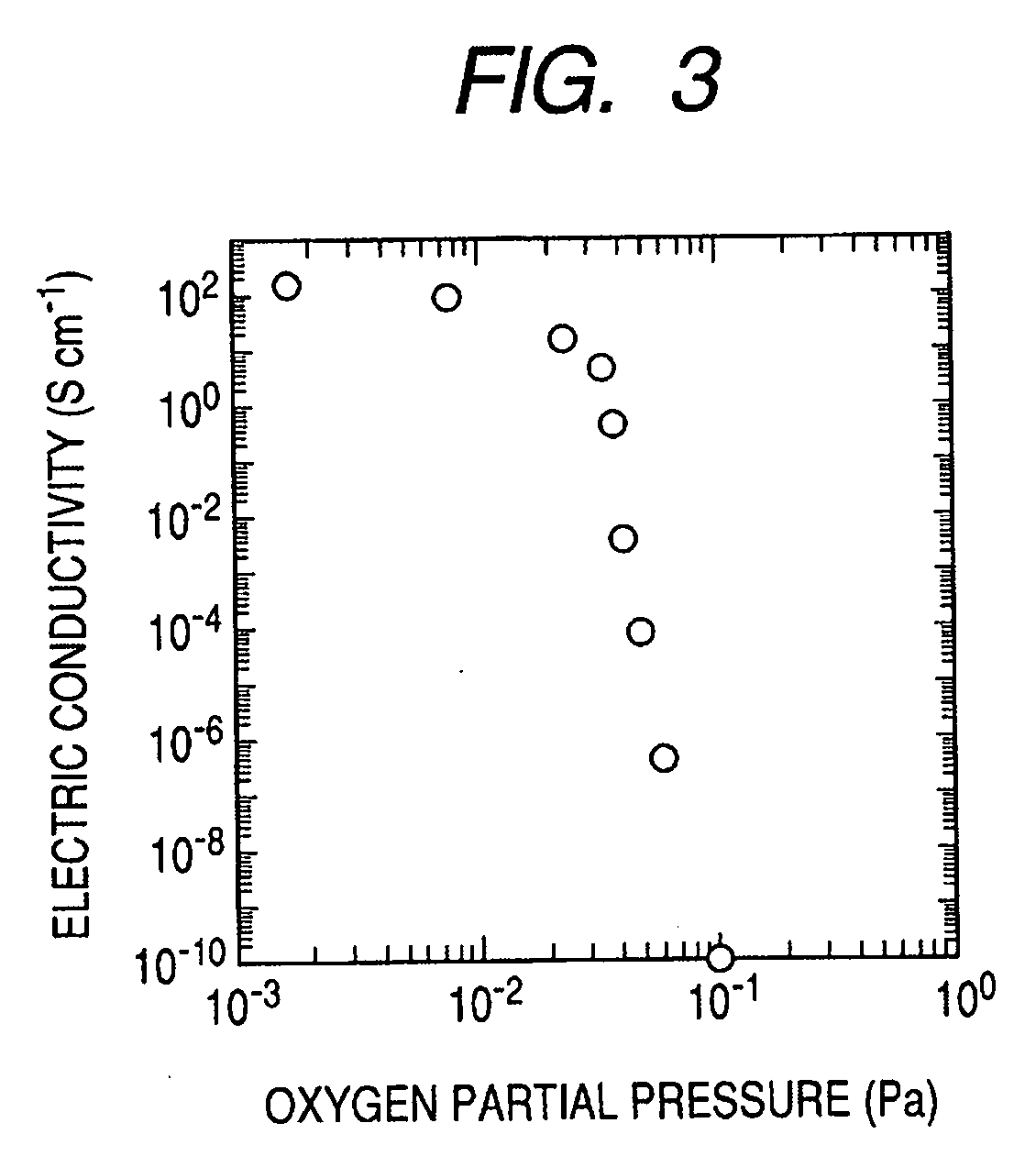

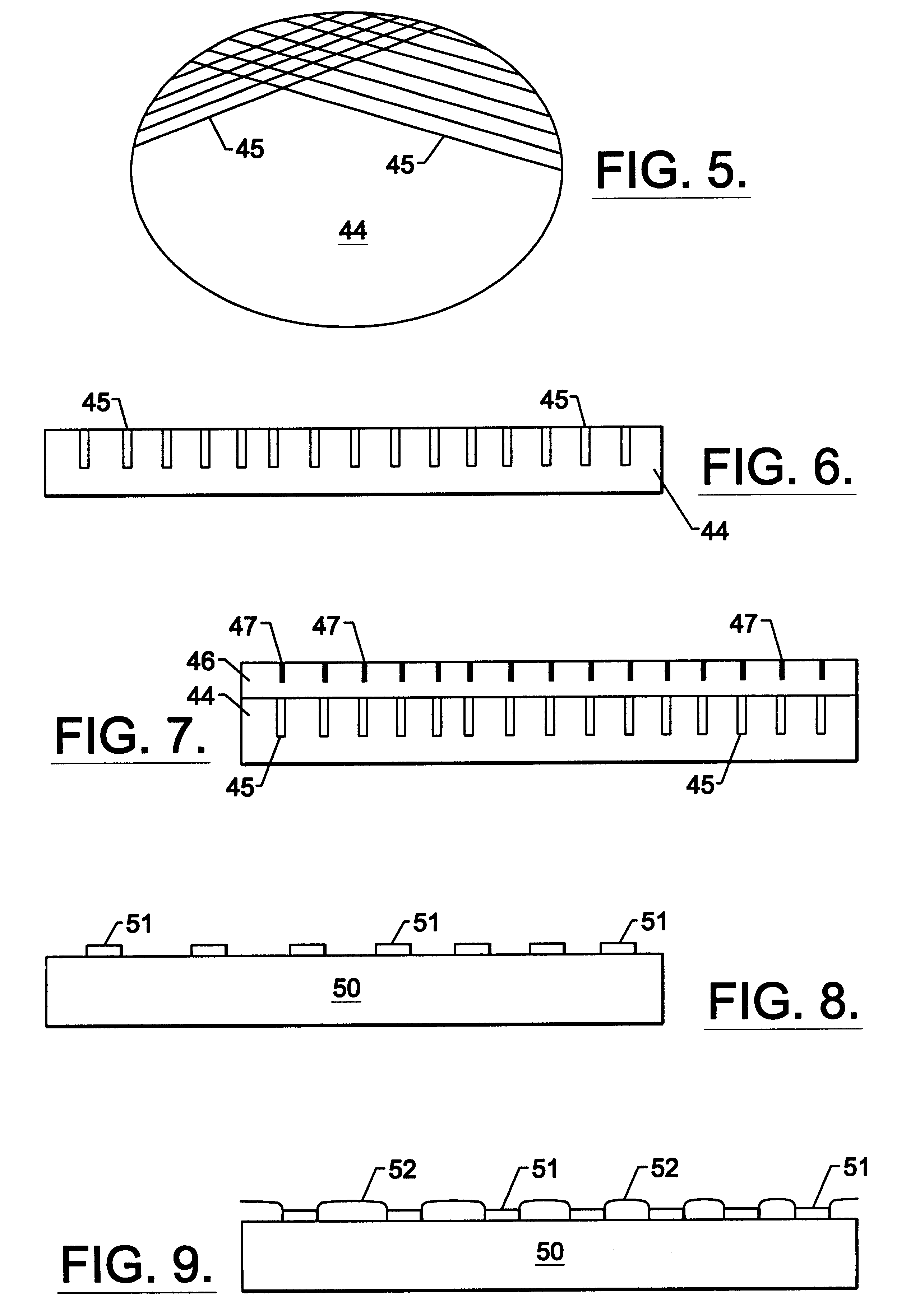

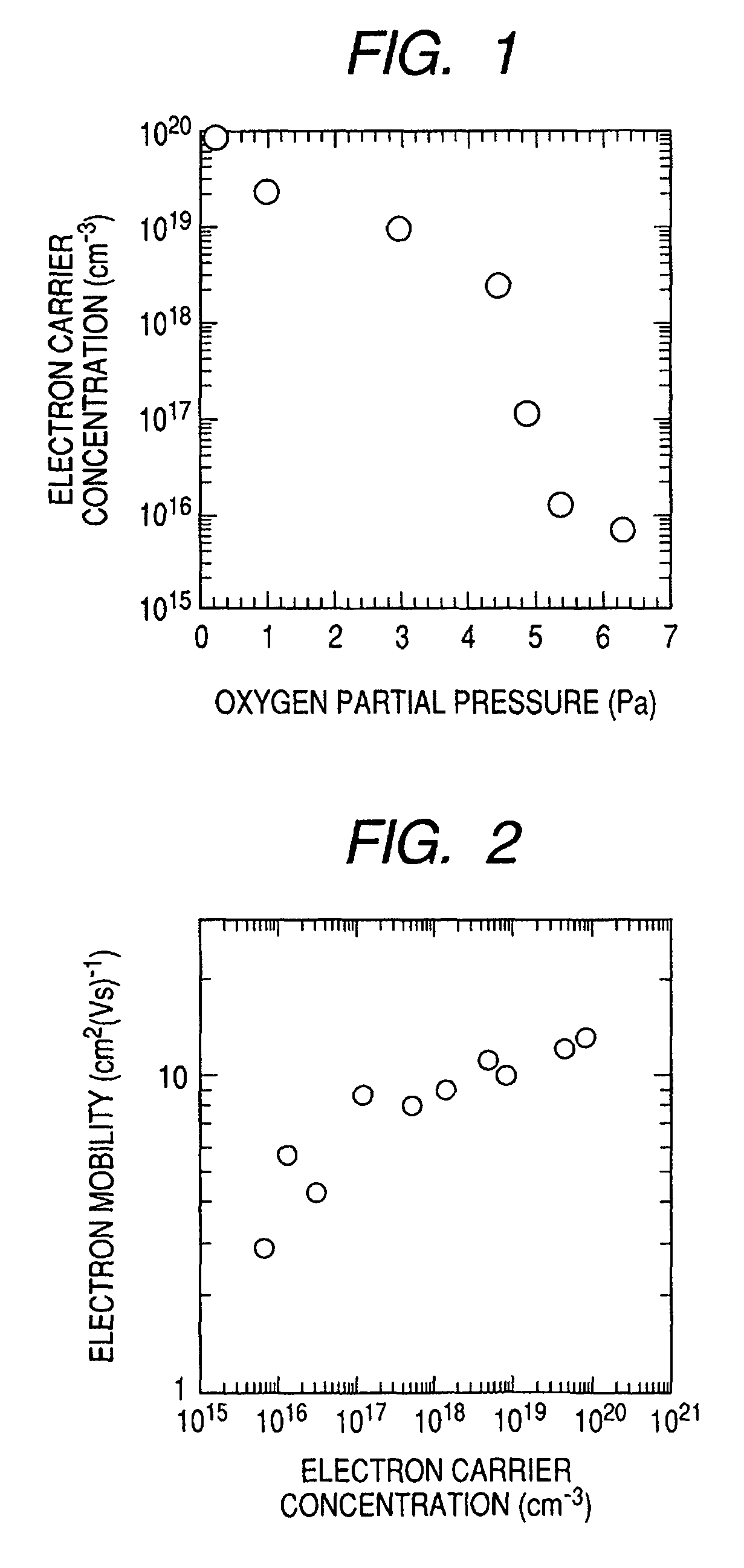

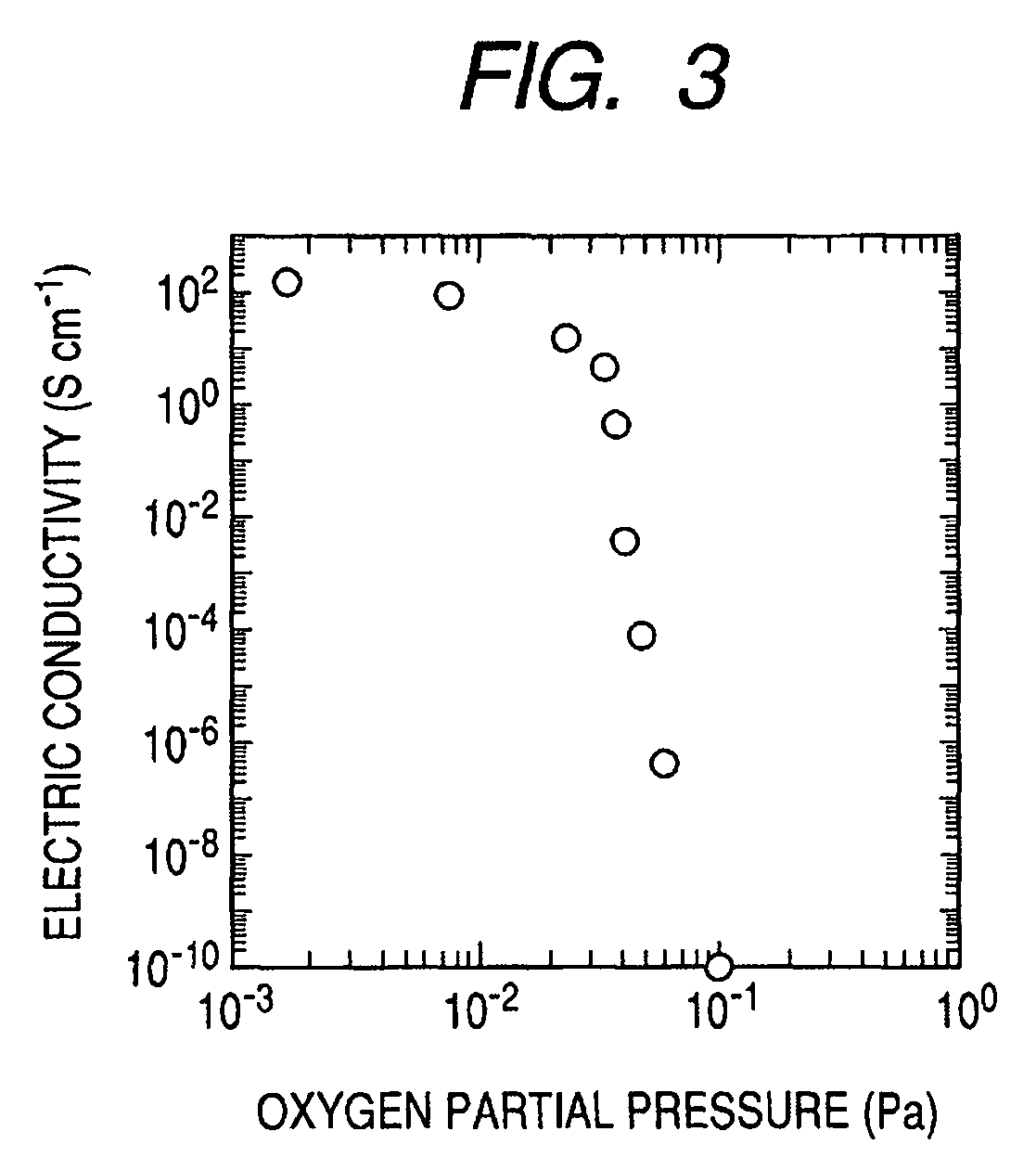

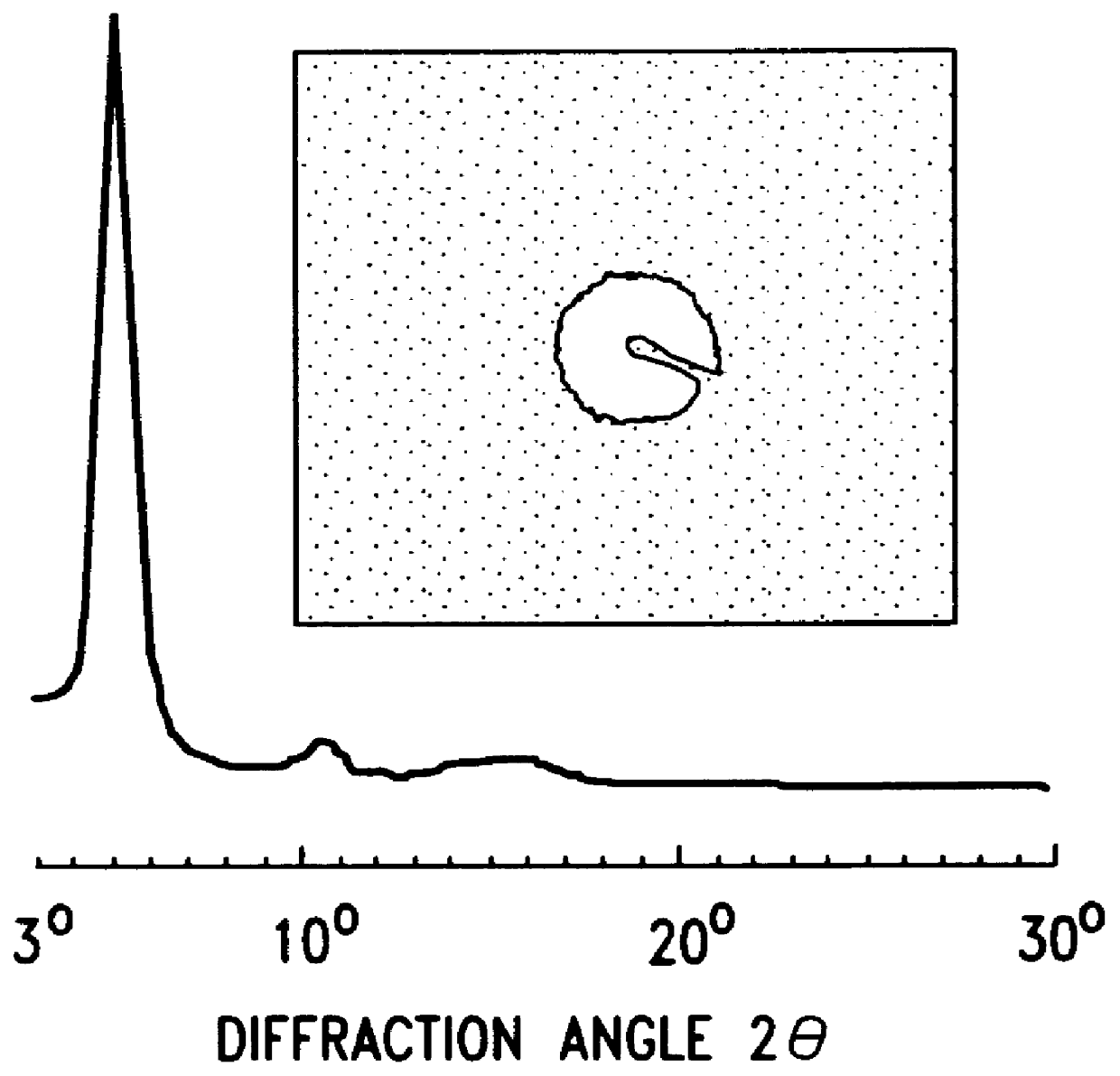

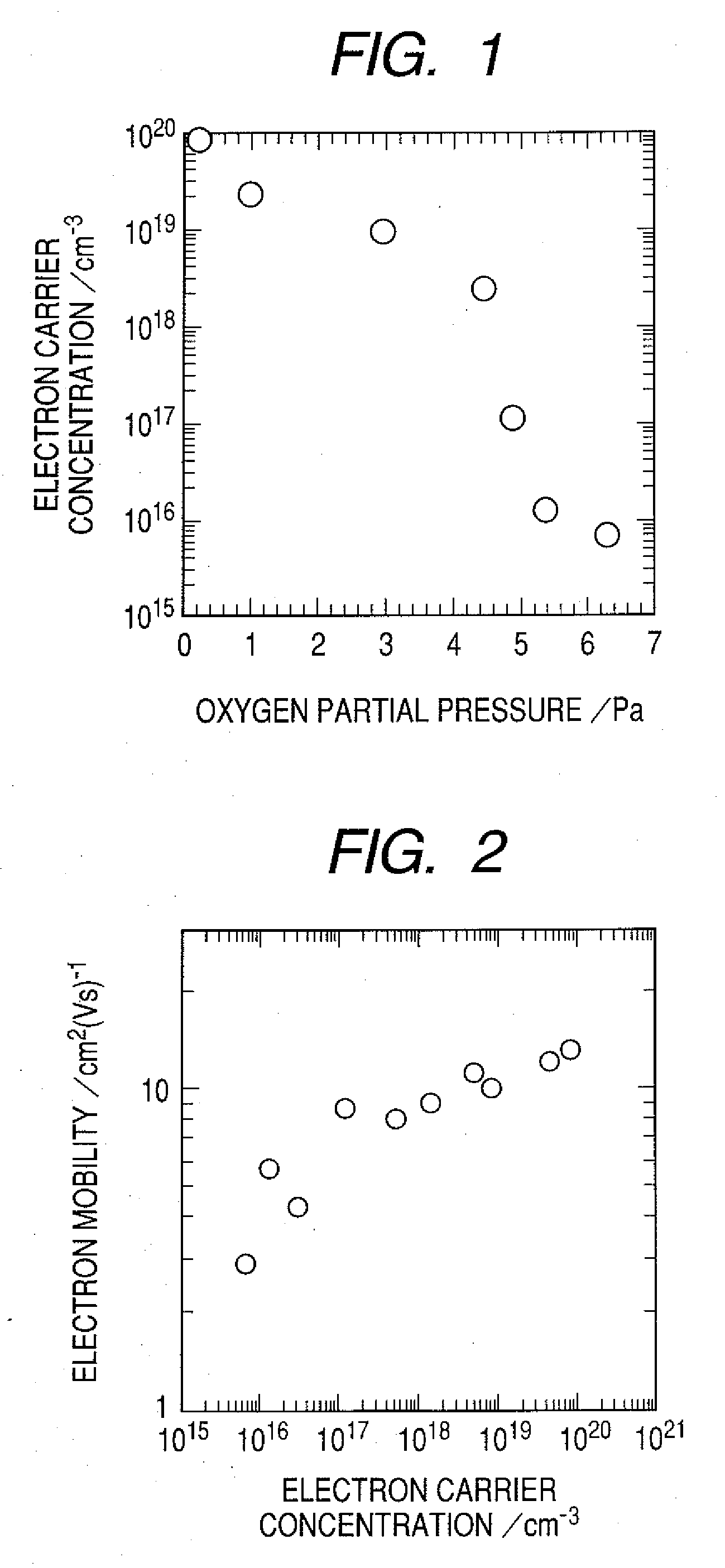

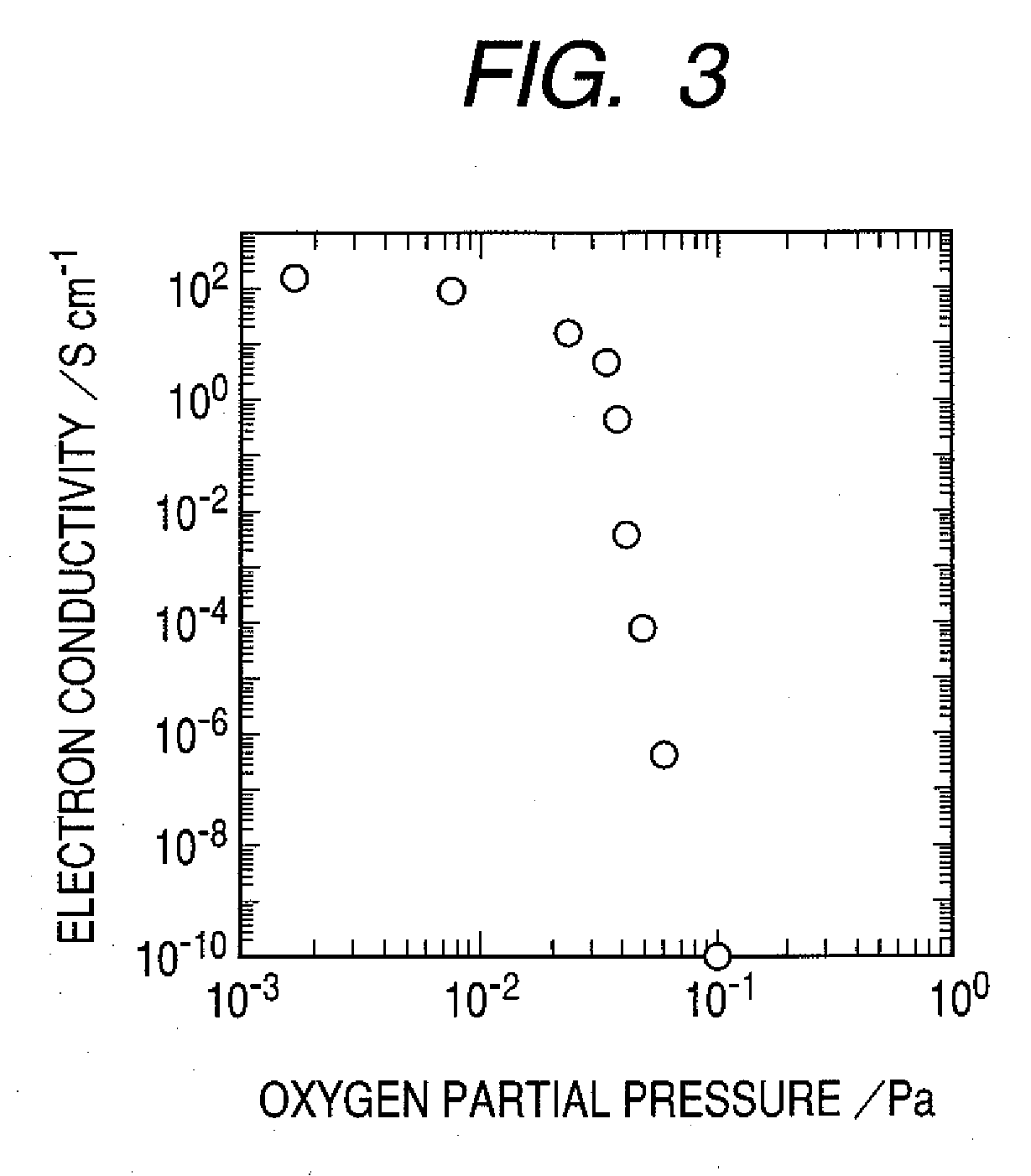

Amorphous oxide and field effect transistor

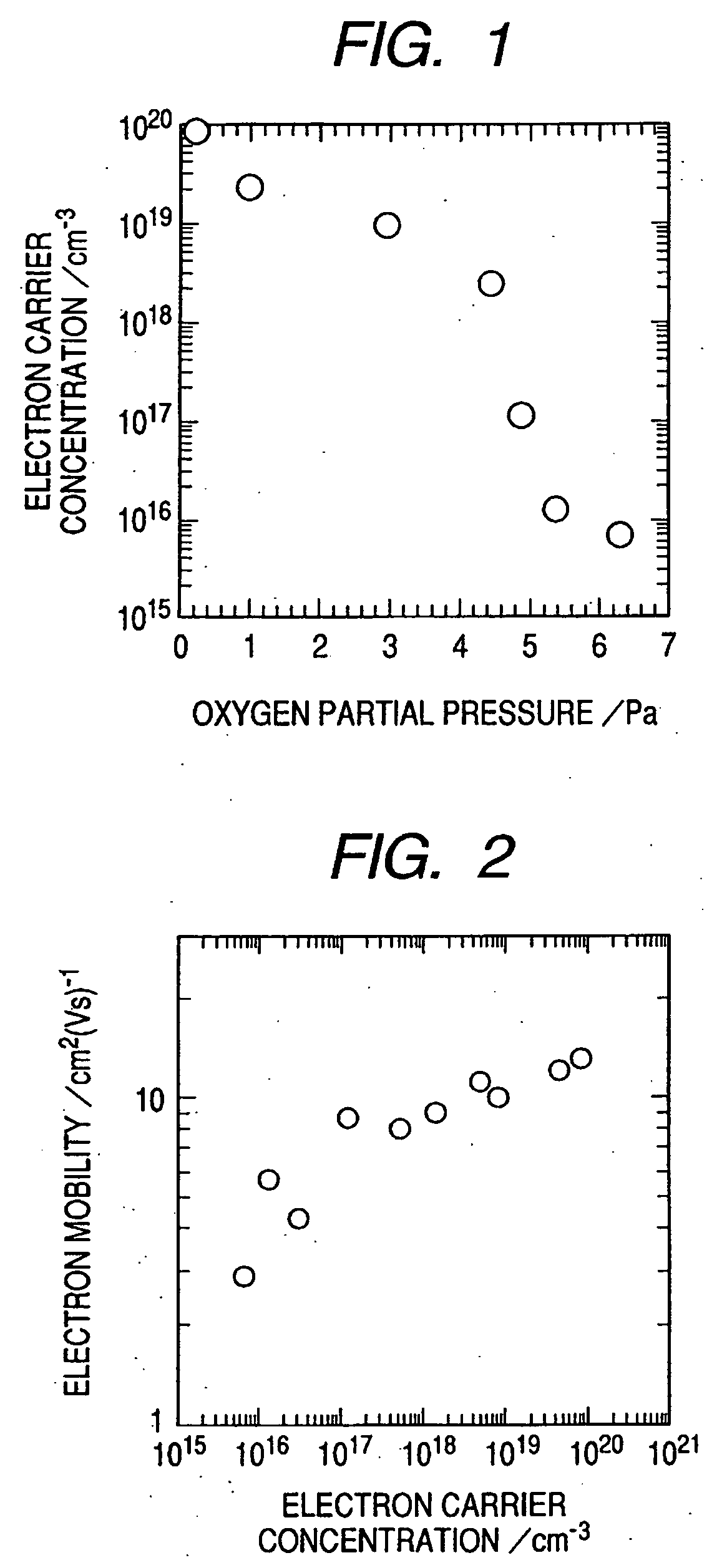

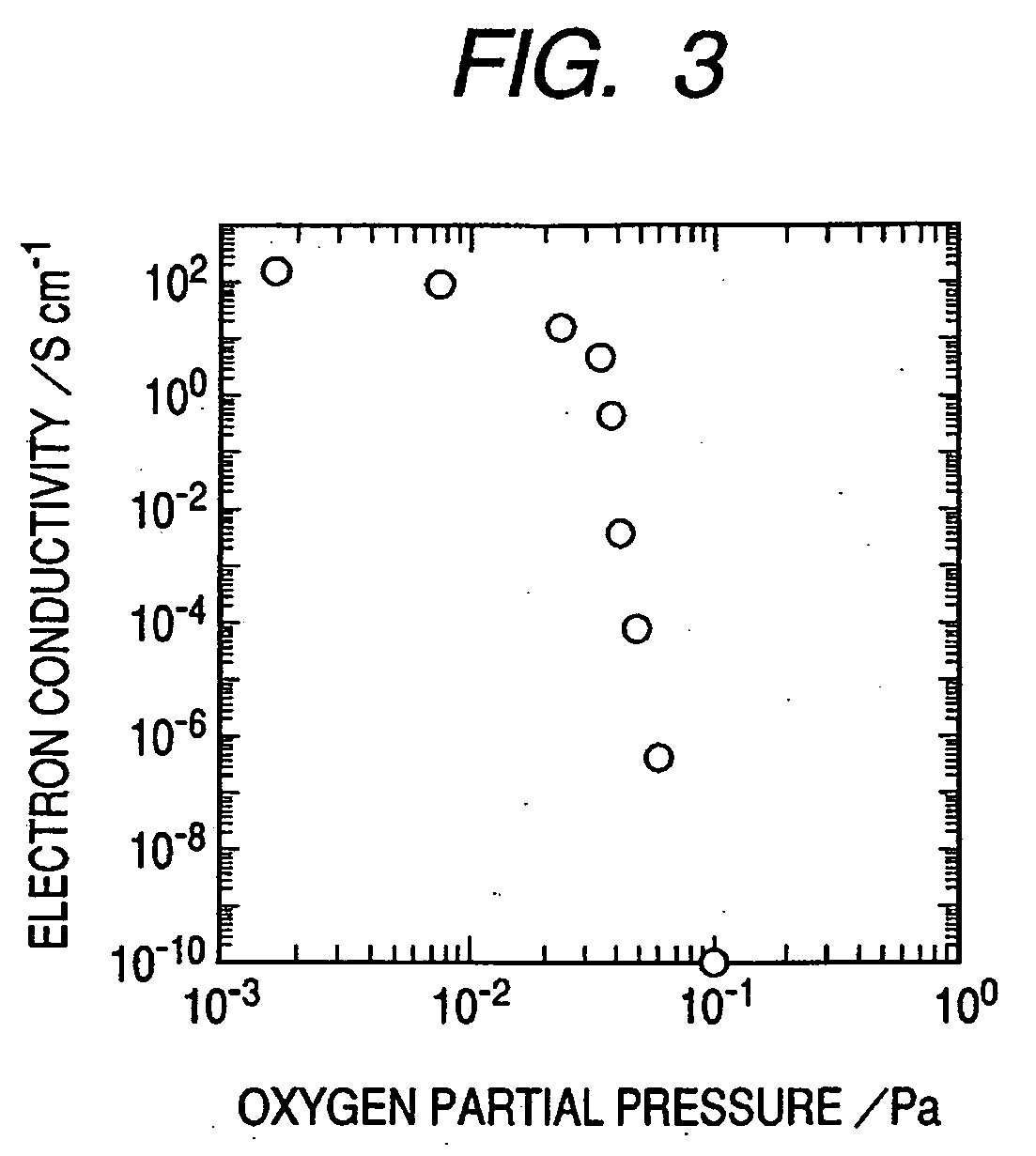

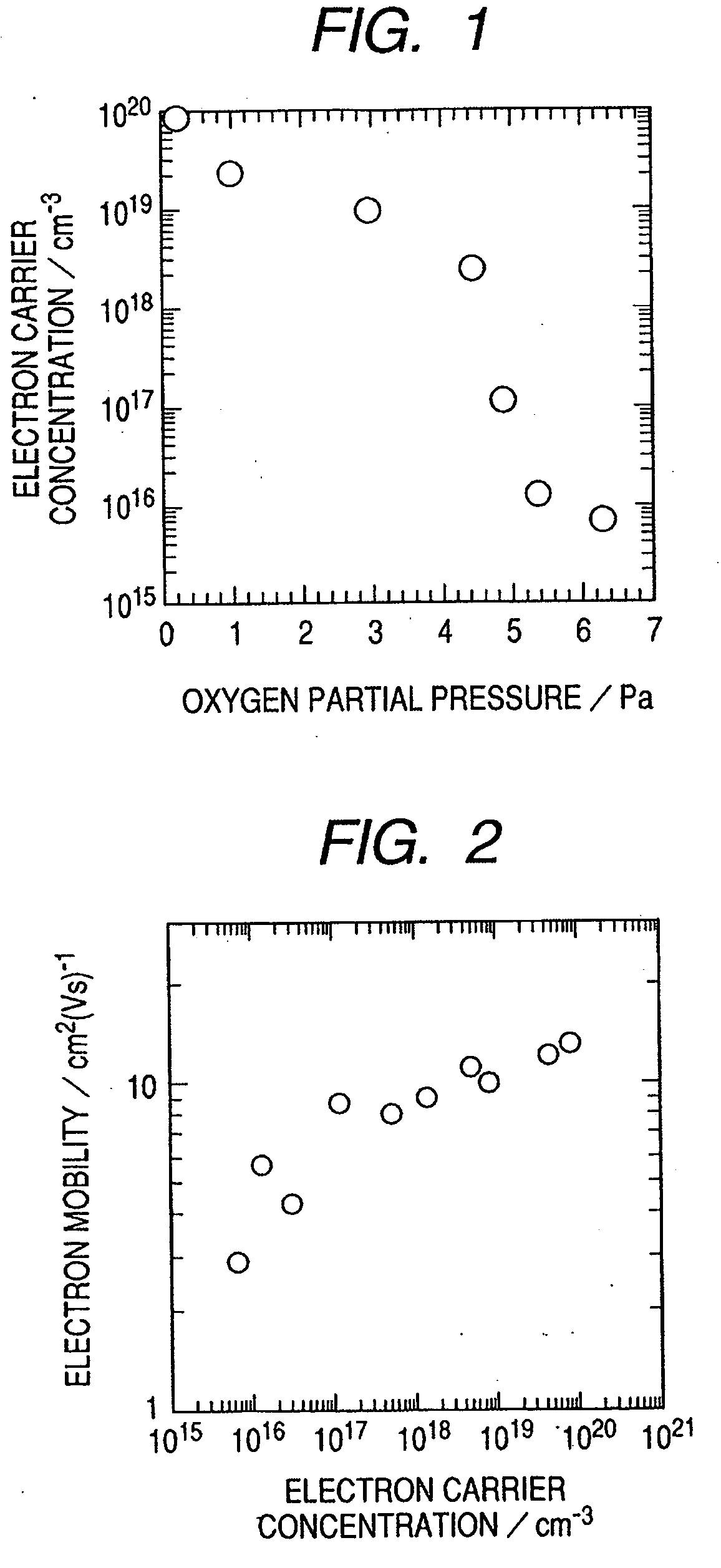

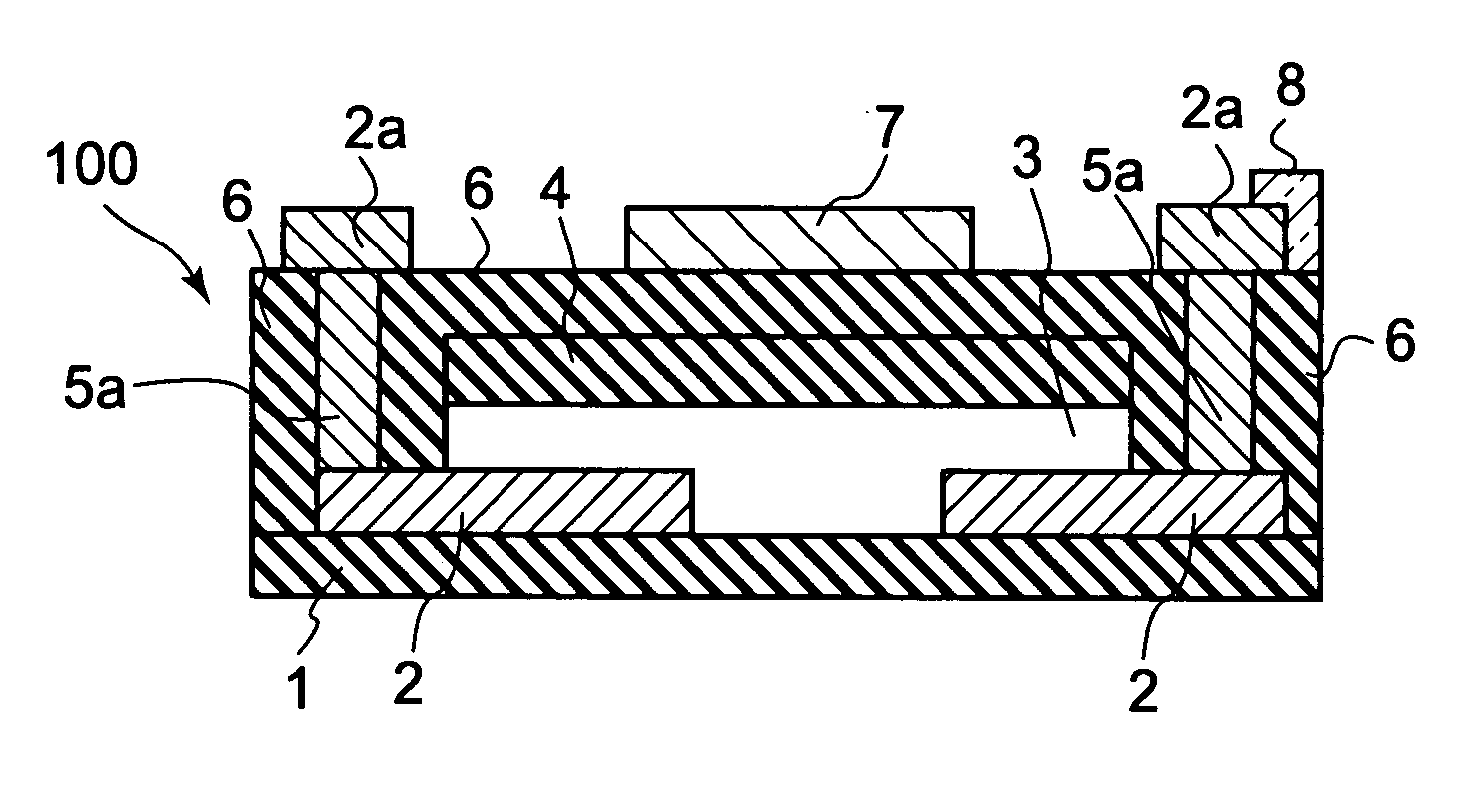

ActiveUS20060108636A1Reduced electron mobilityLow conductivitySolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorActive layer

A novel amorphous oxide applicable, for example, to an active layer of a TFT is provided. The amorphous oxide comprises microcrystals.

Owner:CANON KK +2

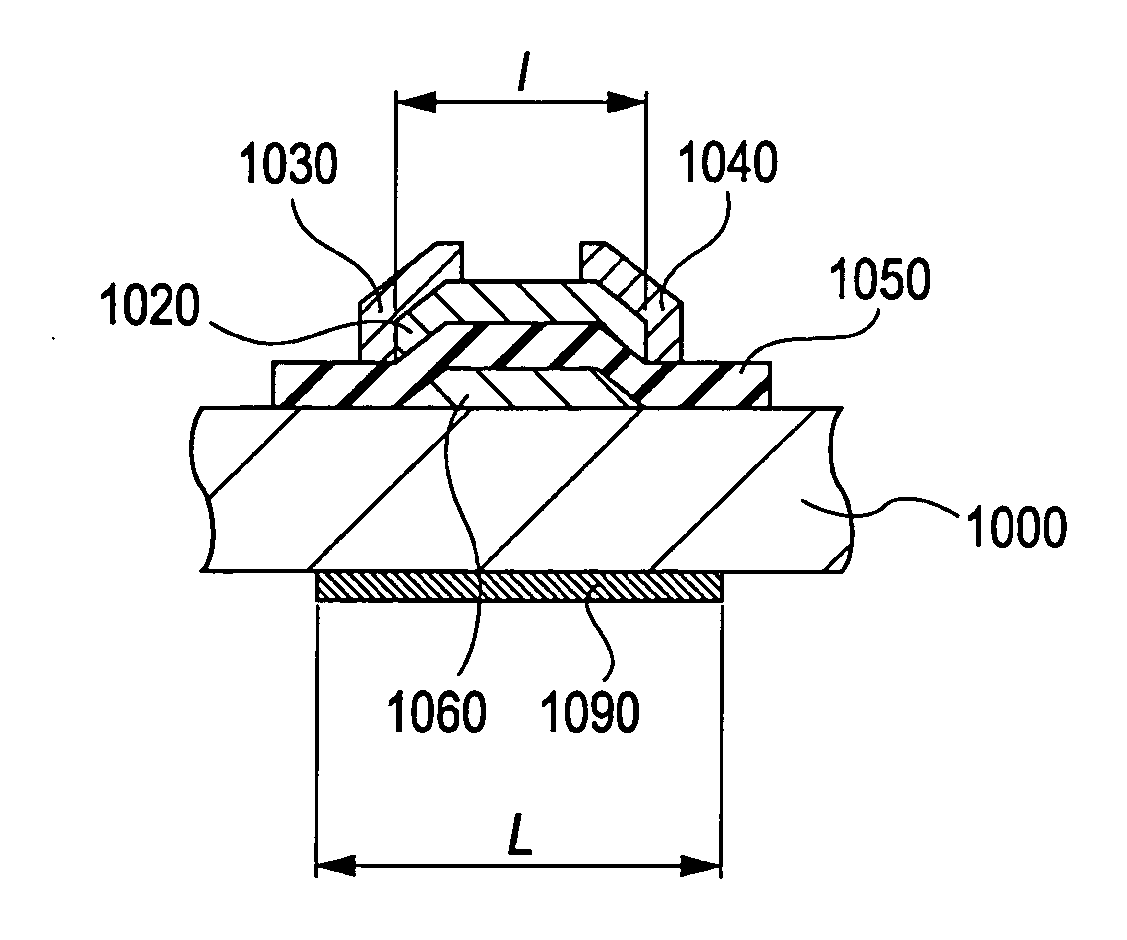

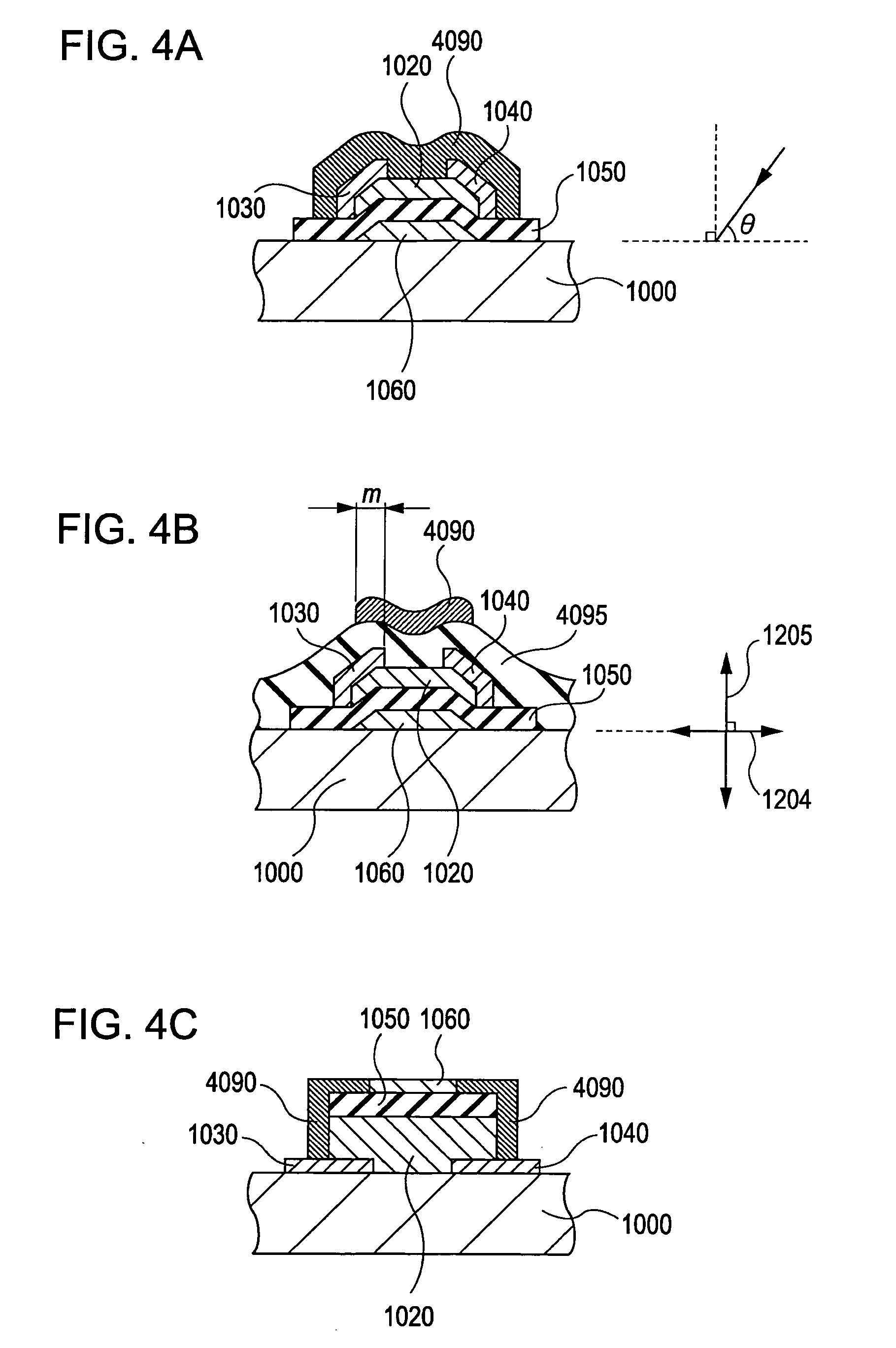

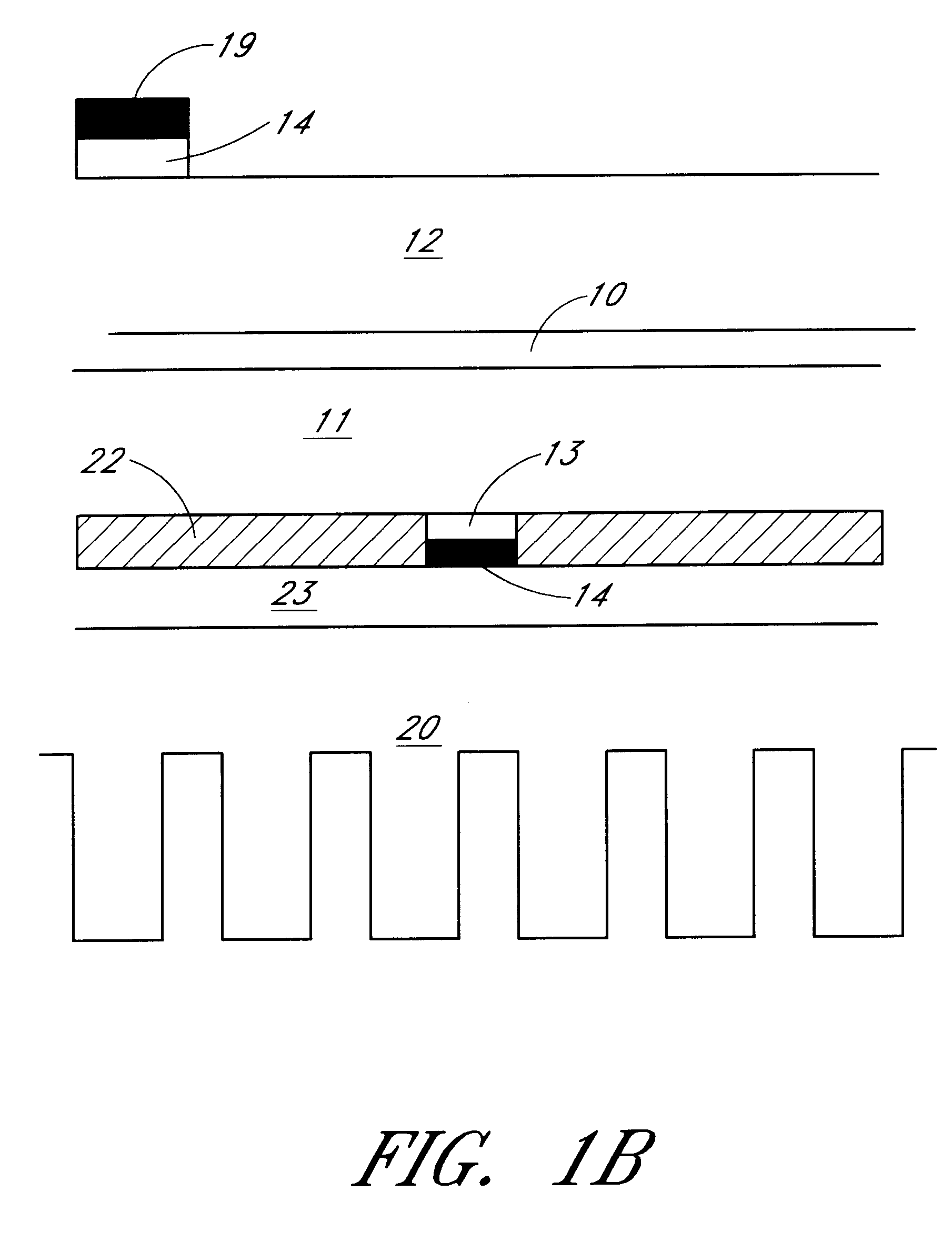

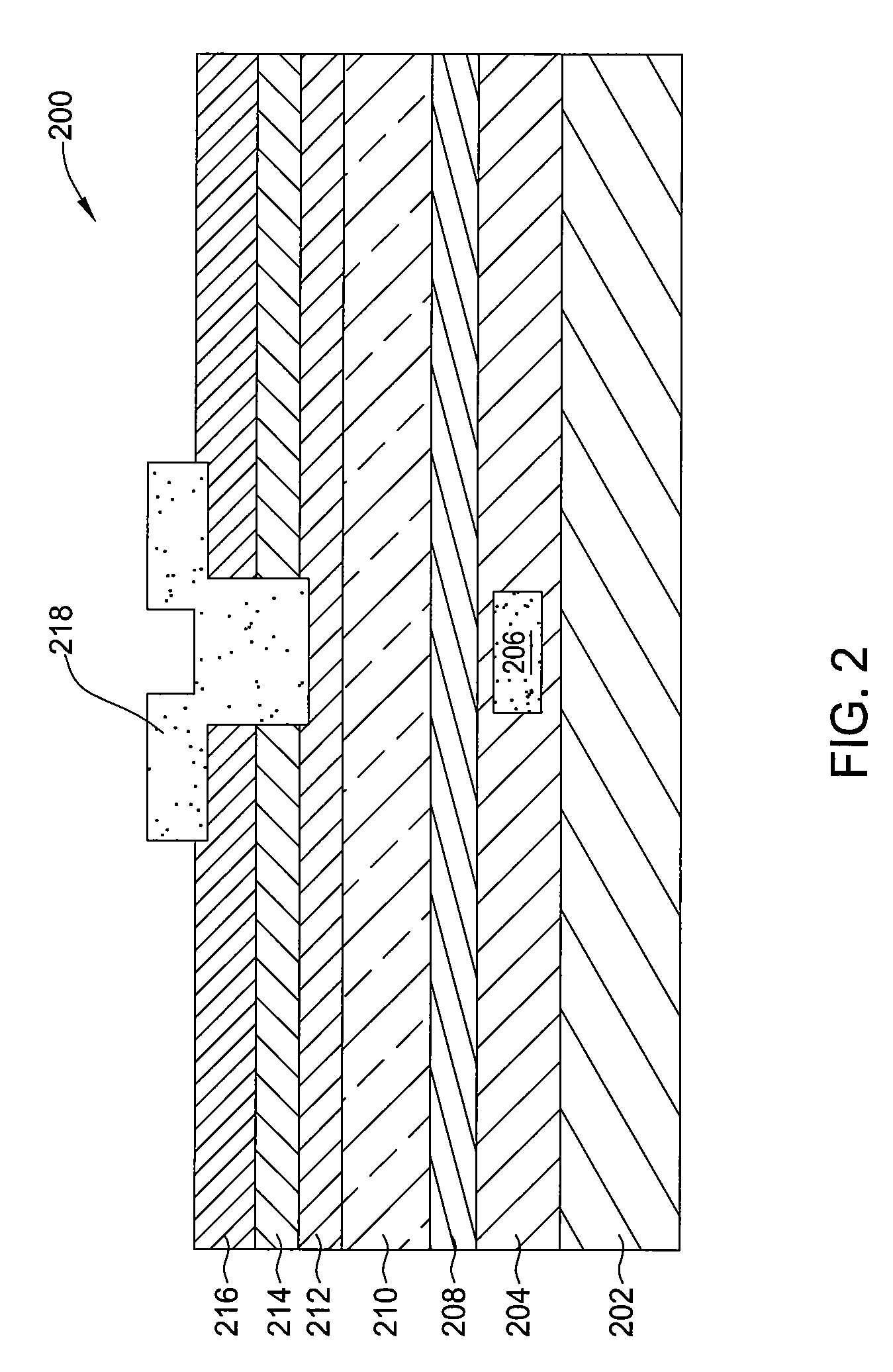

Field-effect transistor including transparent oxide and light-shielding member, and display utilizing the transistor

A field-effect transistor includes a substrate, a source electrode, a drain electrode, a gate electrode, a gate-insulating film, and an active layer. The active layer contains an oxide having a transmittance of 70% or more in the wavelength range of 400 to 800 nm. A light-shielding member is provided as a light-shielding structure for the active layer, for example, on the bottom face of the substrate.

Owner:CANON KK

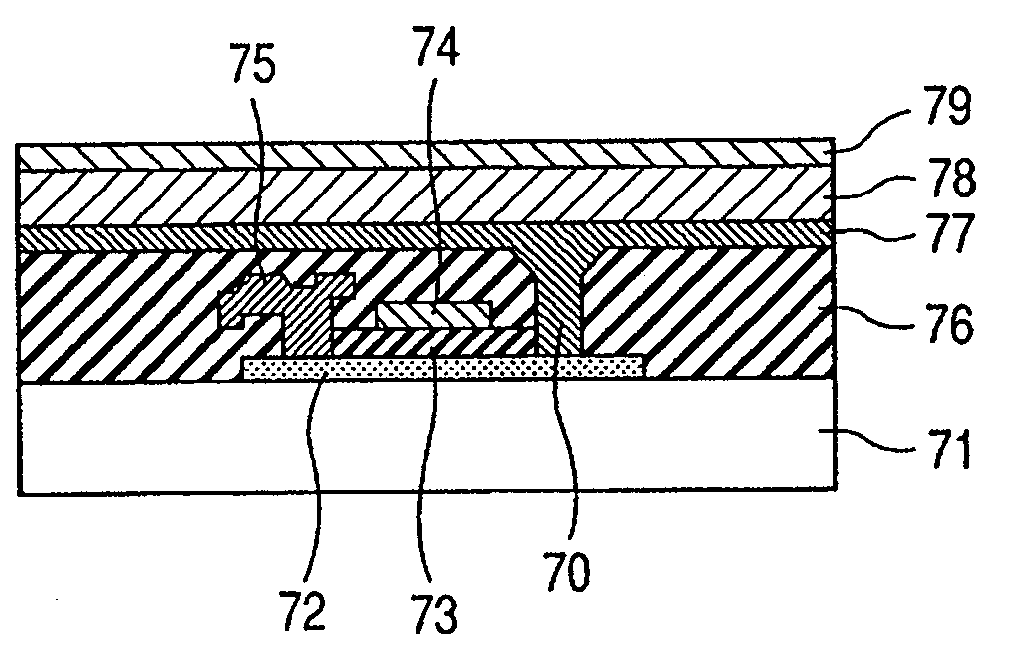

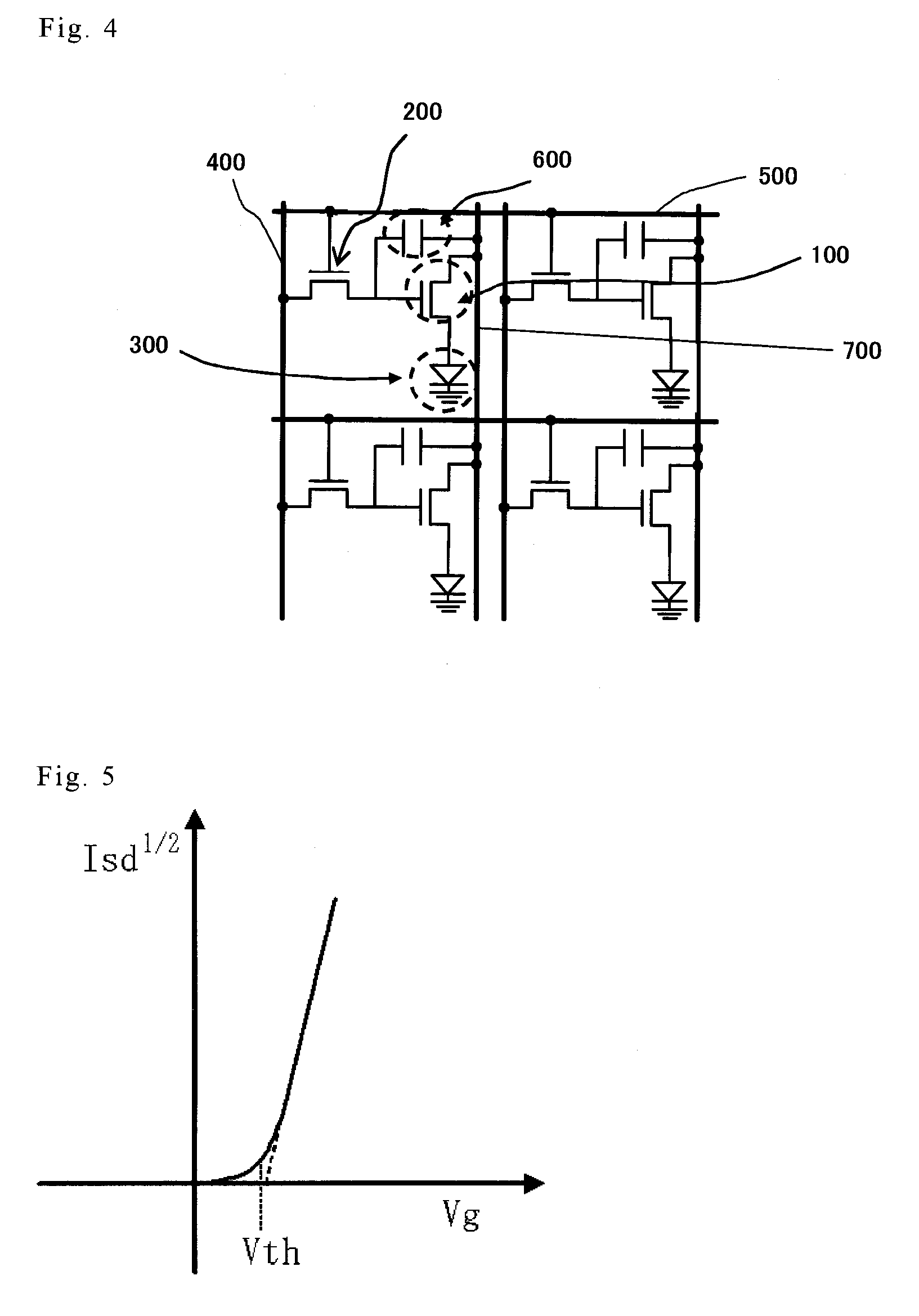

Display

An active matrix display comprising a light control device and a field effect transistor for driving the light control device. The active layer of the field effect transistor comprises an amorphous.

Owner:CANON KK +2

Light-emitting device

ActiveUS20060113549A1Desired characteristicTransistorElectroluminescent light sourcesField-effect transistorActive layer

An object of the present invention is to provide a new light-emitting device with the use of an amorphous oxide. The light-emitting device has a light-emitting layer existing between first and second electrodes and a field effect transistor, of which the active layer is an amorphous.

Owner:CANON KK +2

Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof

InactiveUS20070187678A1Improve heat resistanceImprove propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesZincActive layer

A semiconductor device includes an oxide semiconductor thin film layer primarily including zinc oxide having at least one orientation other than (002) orientation. The zinc oxide may have a mixed orientation including (002) orientation and (101) orientation. Alternatively, the zinc oxide may have a mixed orientation including (100) orientation and (101) orientation.

Owner:KOICHI IND PROMOTION CENT +1

Semiconductor device in which zinc oxide is used as a semiconductor material and method for manufacturing the semiconductor device

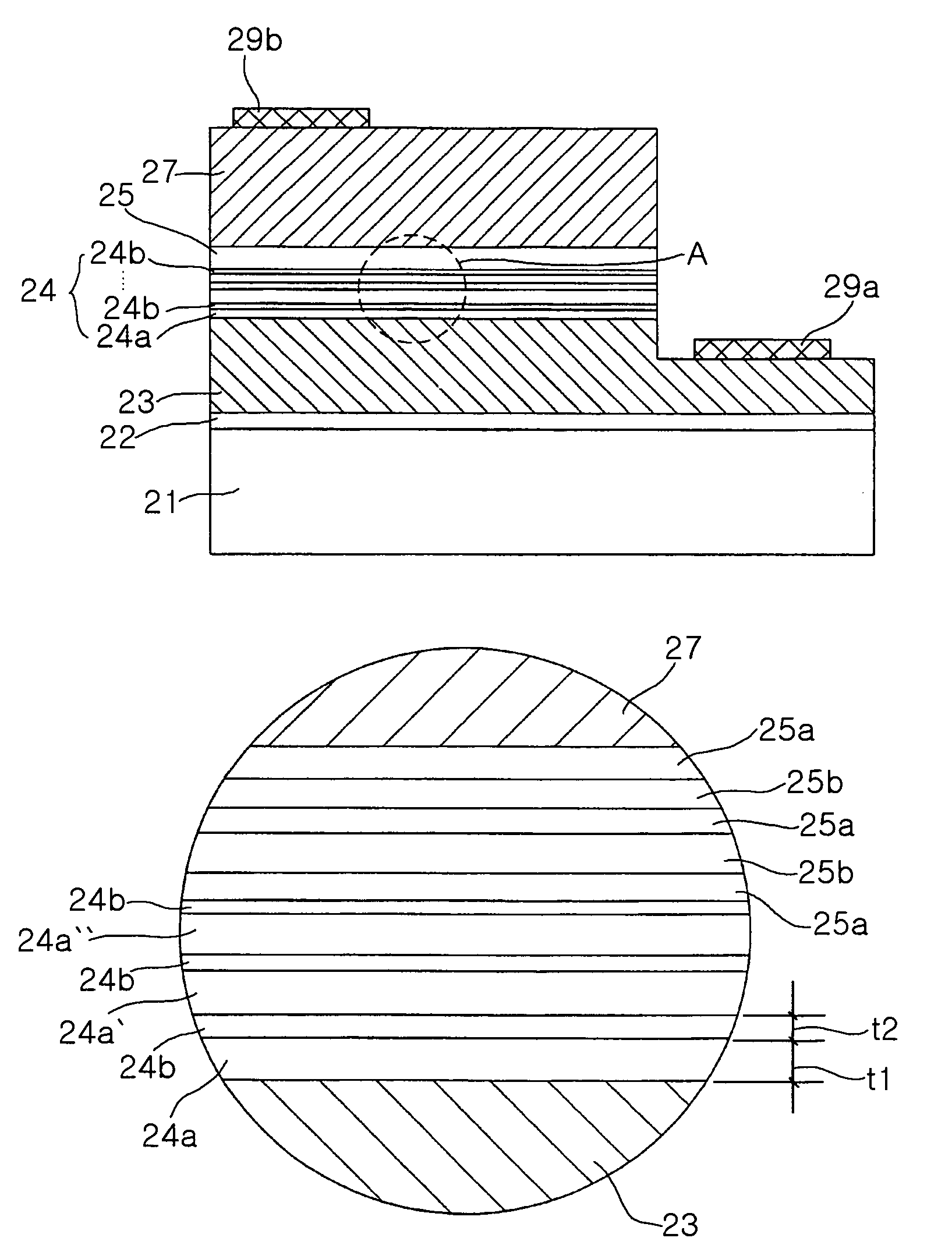

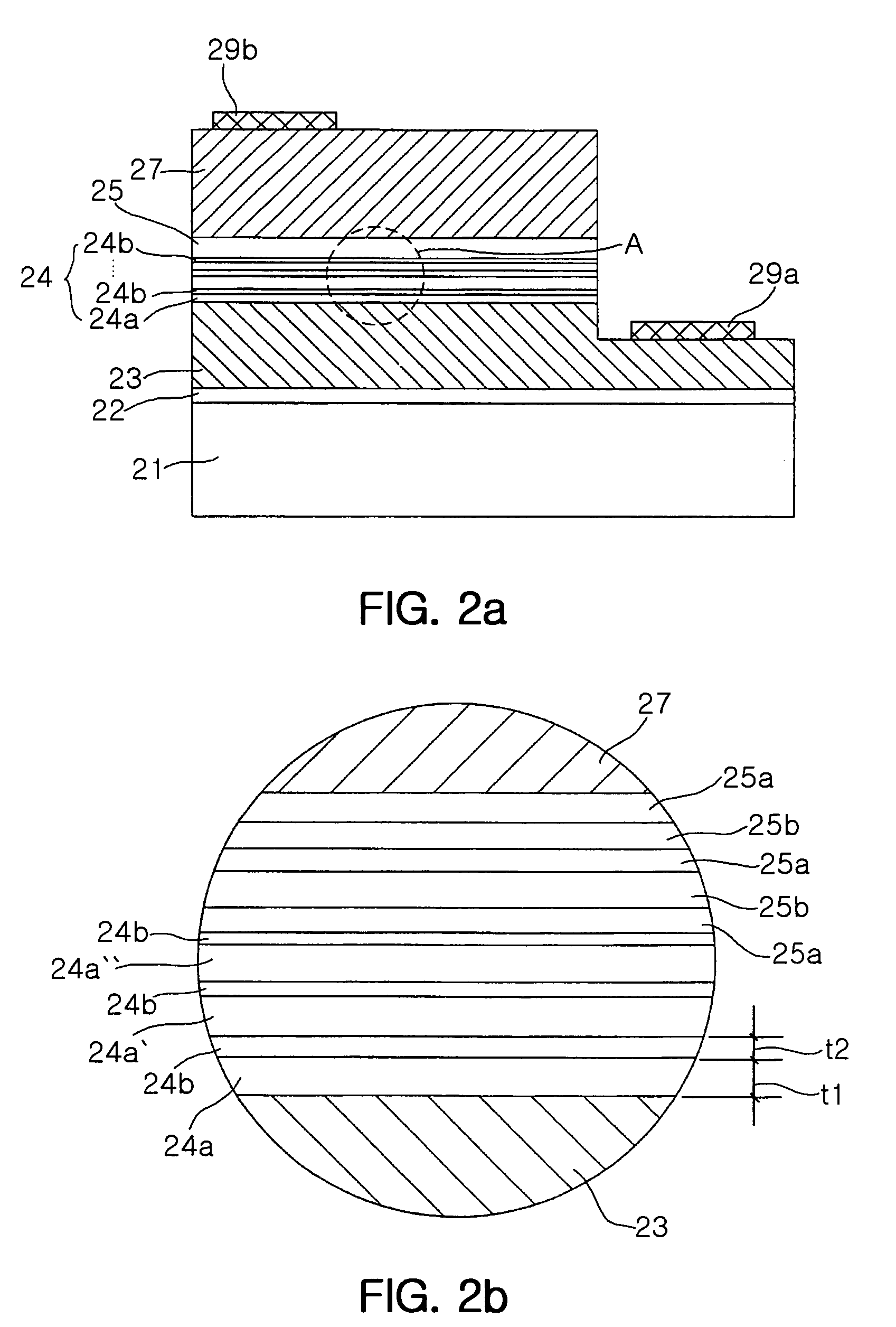

ActiveUS7501293B2Improve surface smoothnessHigh crystallinityTransistorLaser detailsSemiconductor materialsDevice material

A semiconductor device having excellent crystallinity and excellent electric characteristics includes a ZnO thin film having excellent surface smoothness. ZnO-based thin films (an n-type contact layer, an n-type clad layer, an active layer, a p-type clad layer, and a p-type contact layer) primarily including ZnO are formed sequentially by an ECR sputtering method or other suitable method on a zinc-polar surface of a ZnO substrate. A transparent electrode and a p-side electrode are formed by an evaporation method or other suitable method on a surface of the p-type contact layer, and an n-side electrode is formed on an oxygen-polar surface of the ZnO substrate.

Owner:MURATA MFG CO LTD

Light emitting semiconductor device

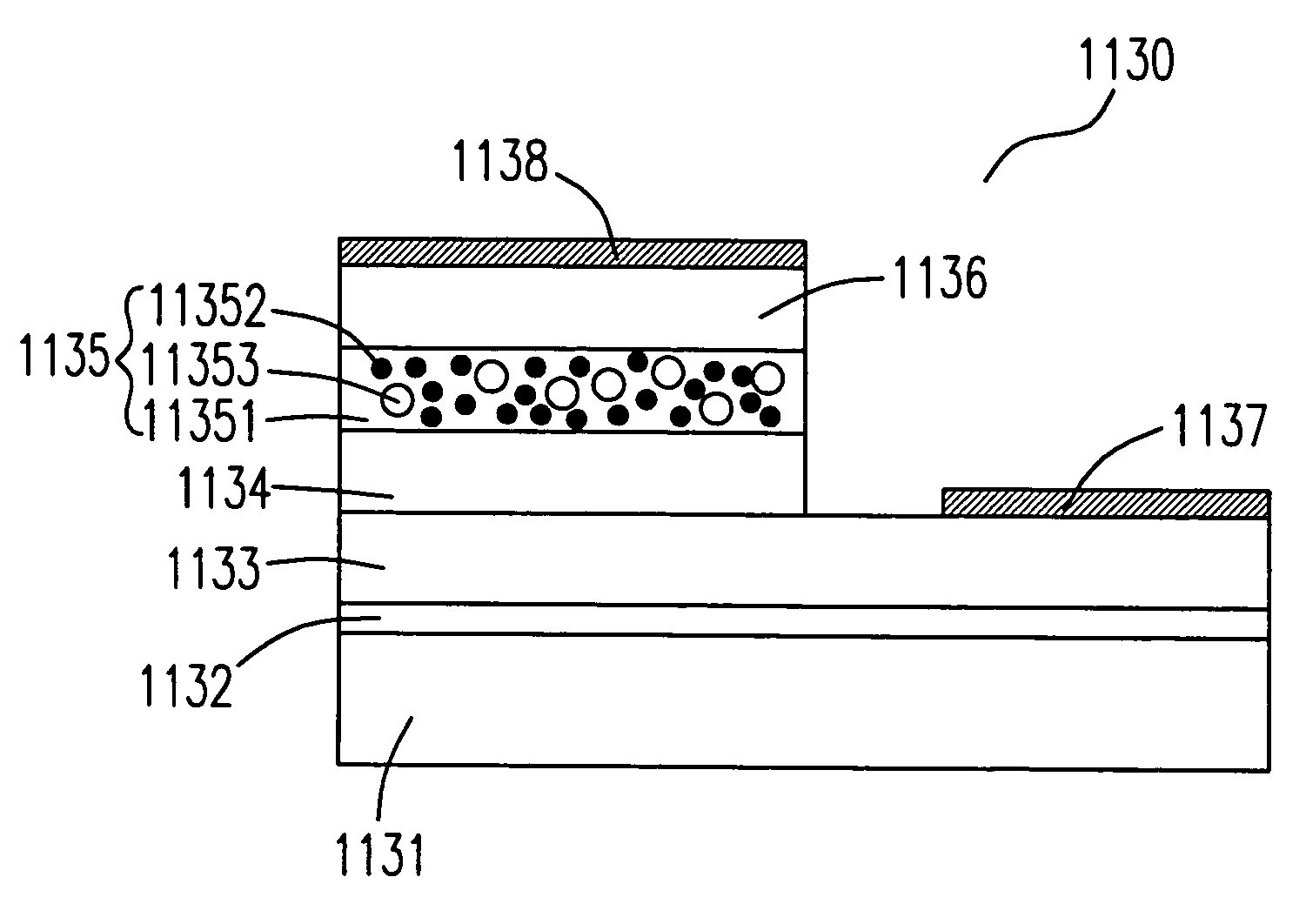

A novel NPBL and ANPL light emitting semiconductor device and a method for fabricating the same are provided. In the present invention, plural nano-particles are applied in the active layer of the light emitting semiconductor device, so that the leakage current thereof is reduced. In addition, the provided light emitting semiconductor device fabricated via a planar technology process is microscopically planar, but not planar at micro- and nano-scale. Hence the parasitic wave guiding effect, which suppresses the light extraction efficiency of the light emitting semiconductor device, is destroyed thereby.

Owner:ARIMA COMP

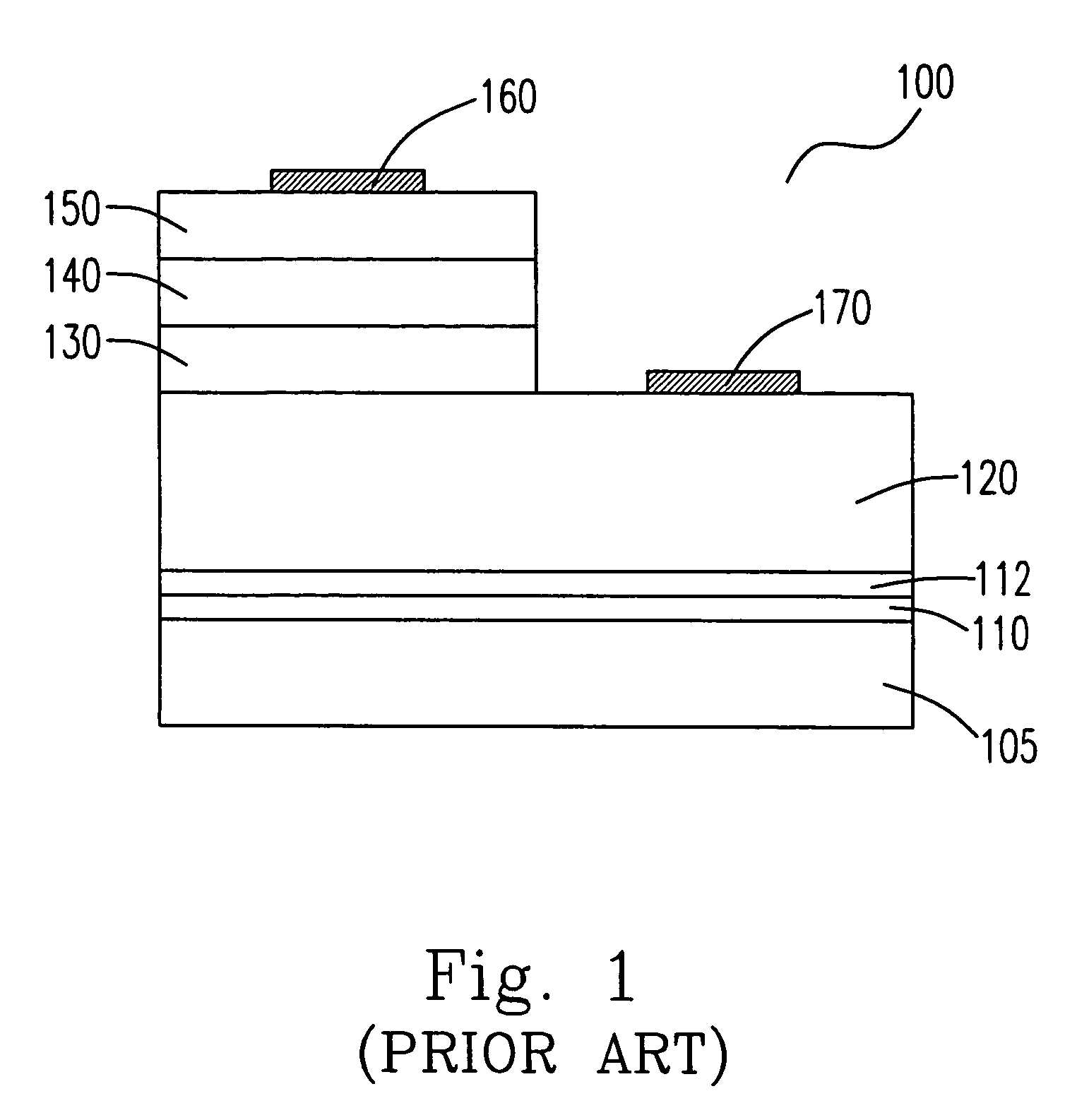

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlay structure

InactiveUS6201262B1Avoid crackingEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

Display

Owner:CANON KK +2

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlayer structure

InactiveUS6187606B1Avoid crackingMinimize and eliminate heterobarrierSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

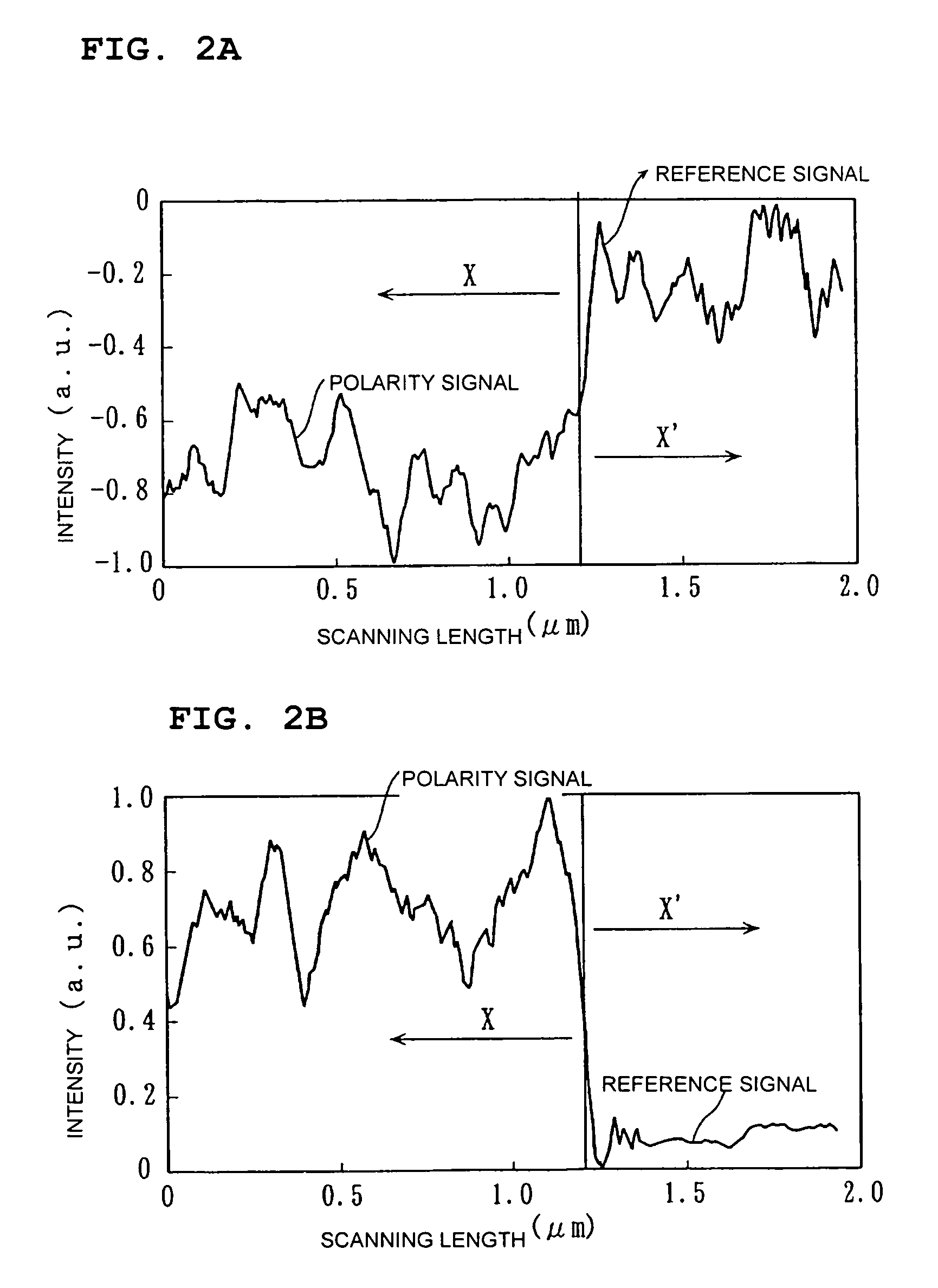

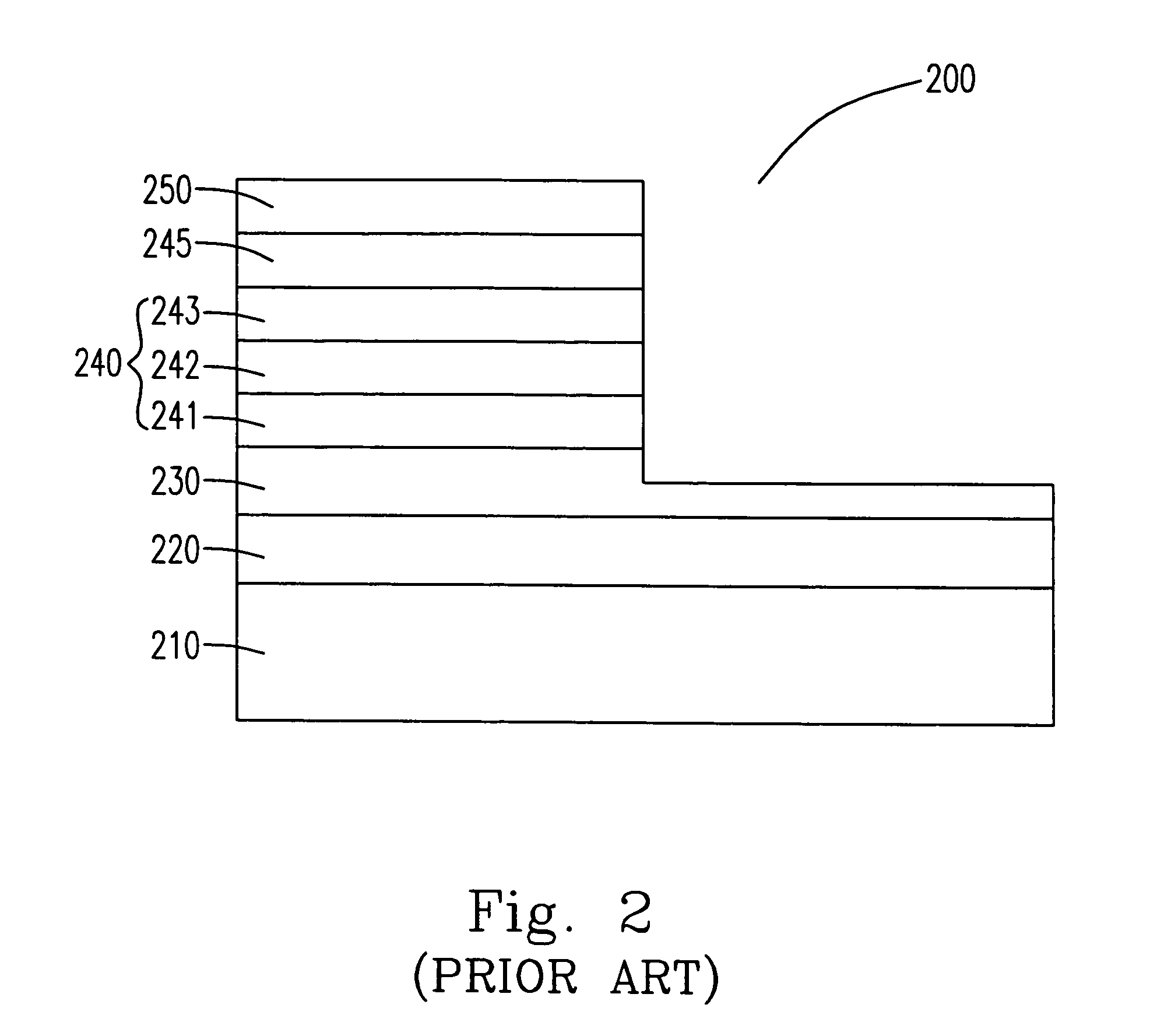

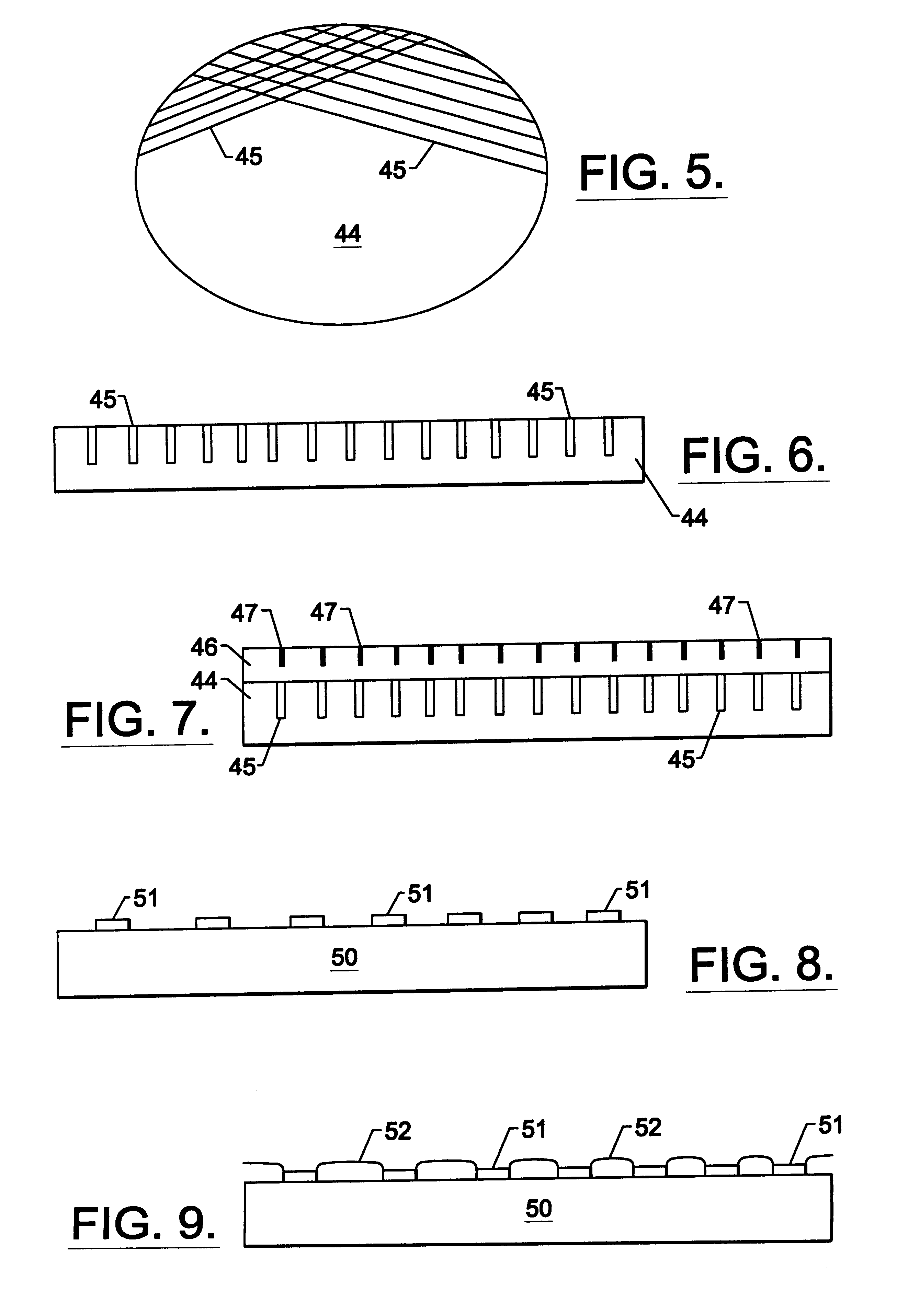

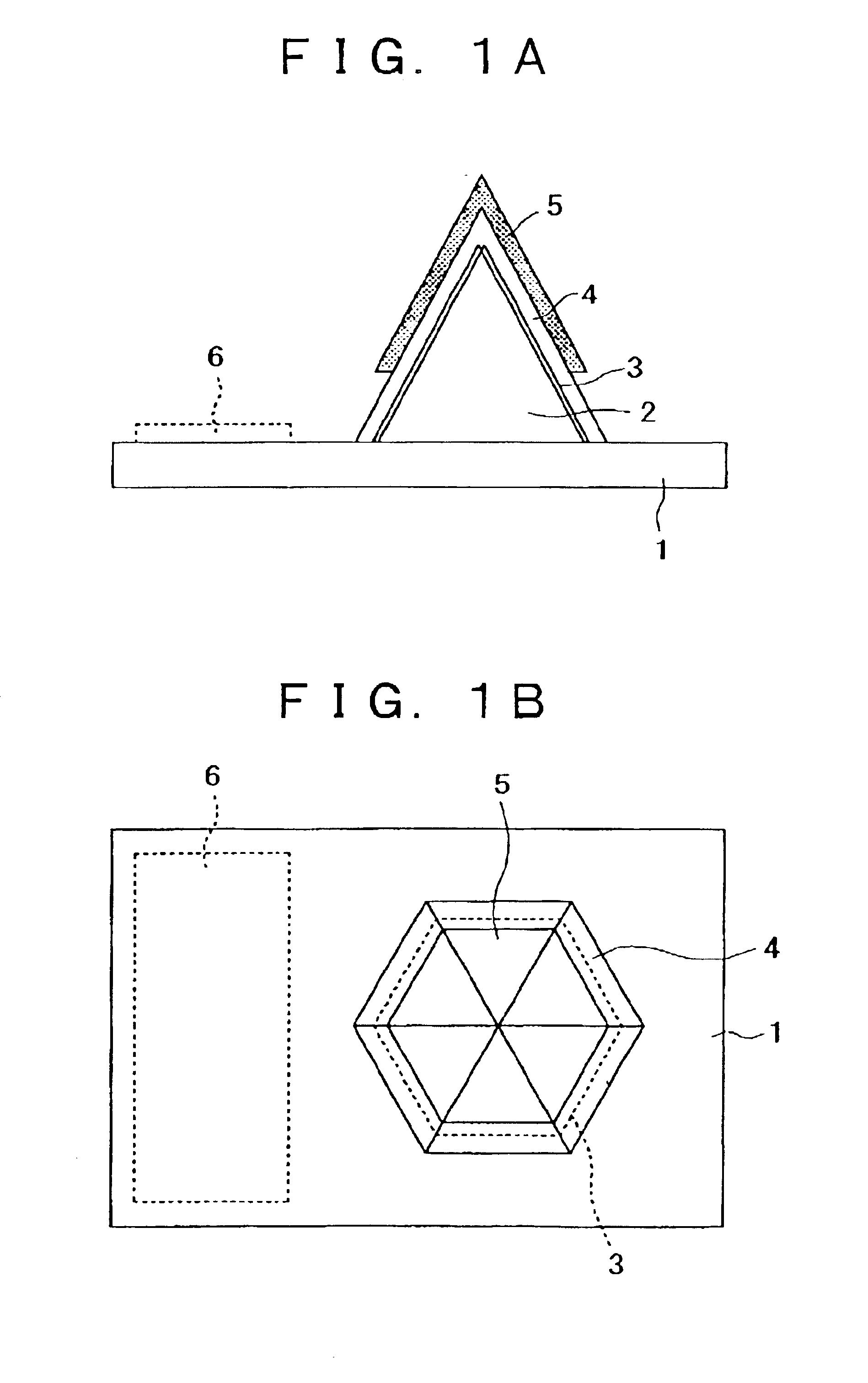

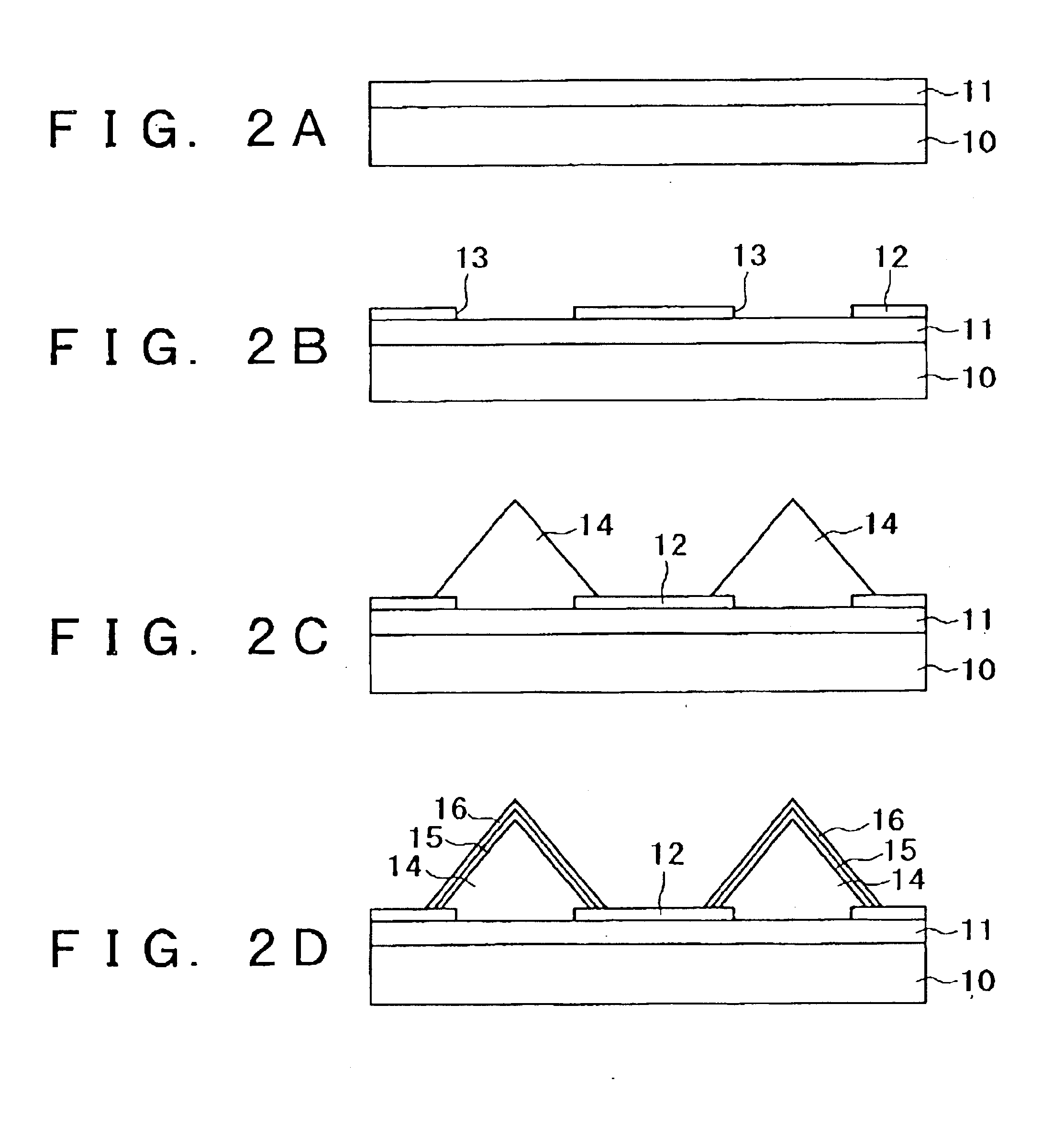

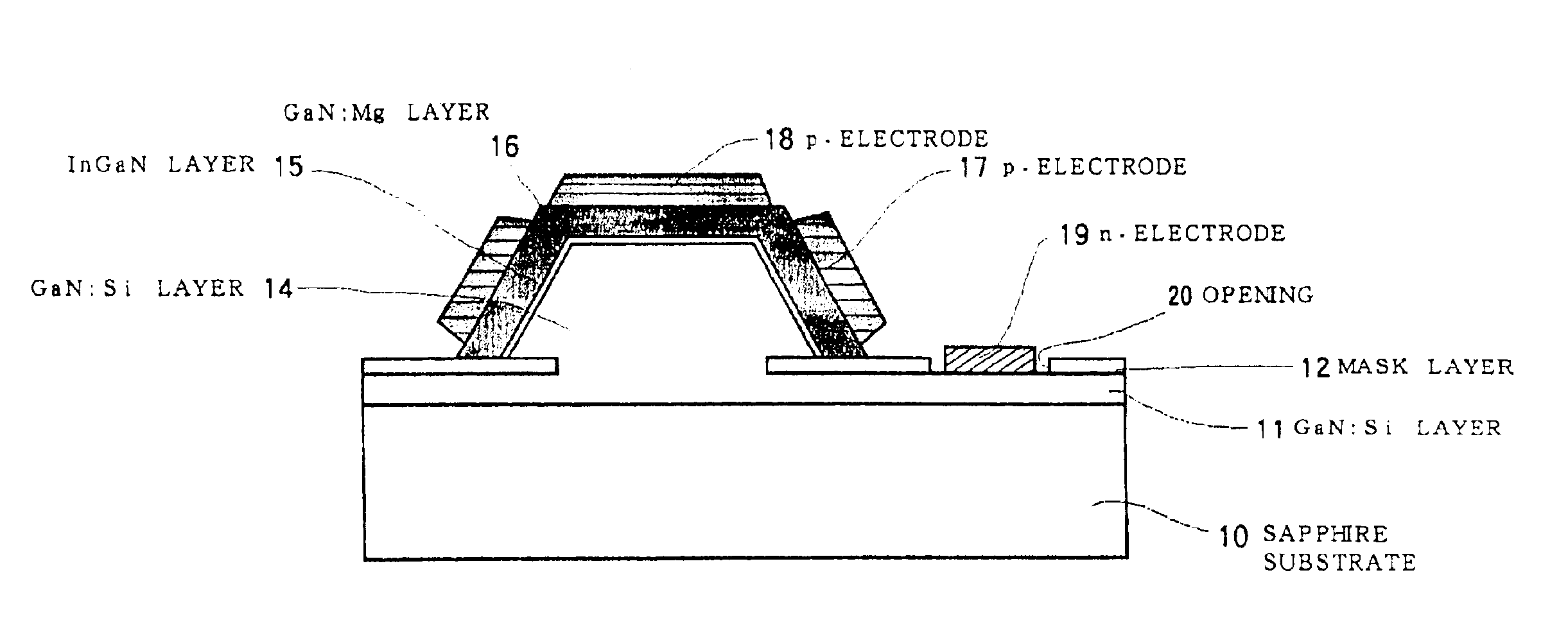

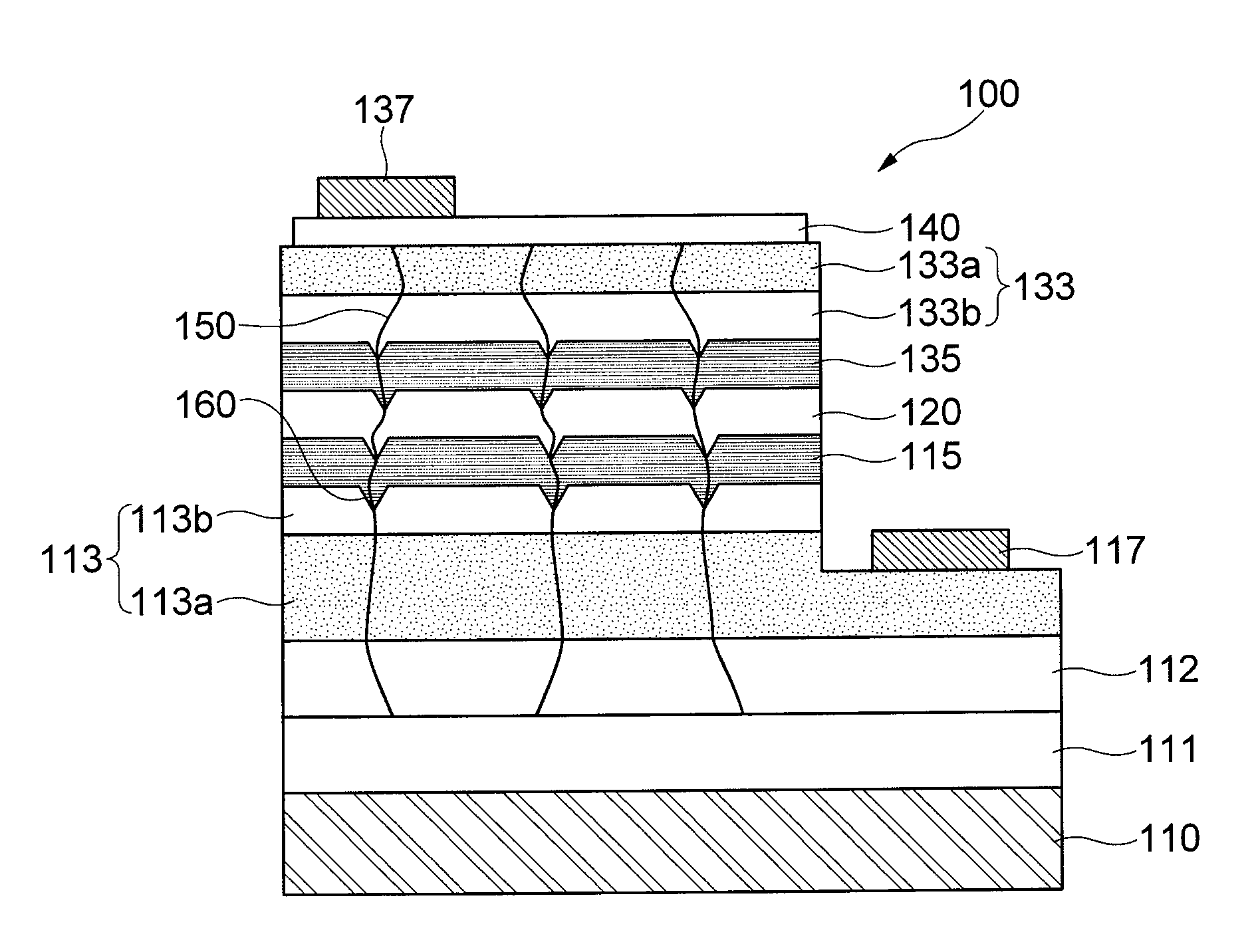

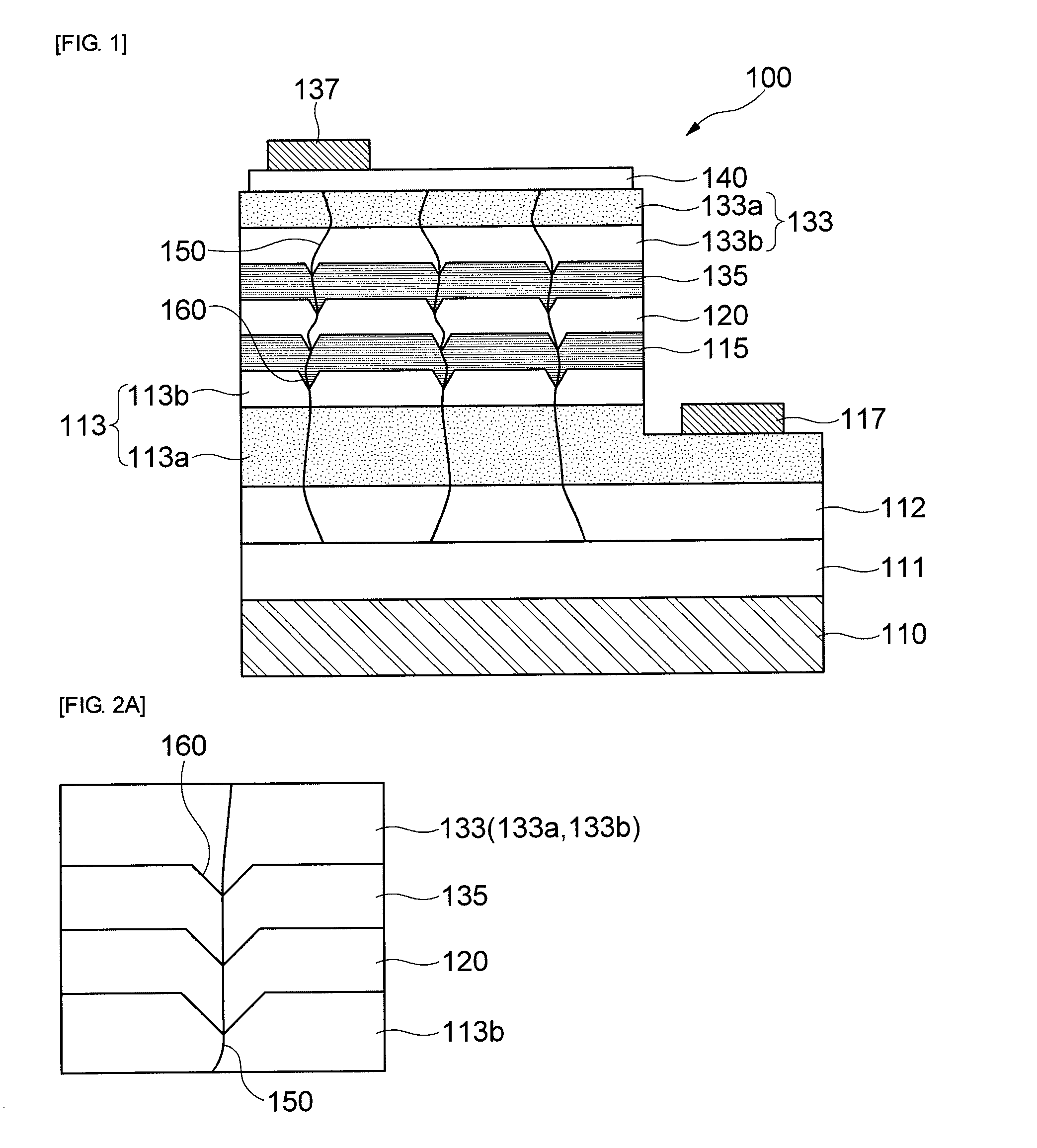

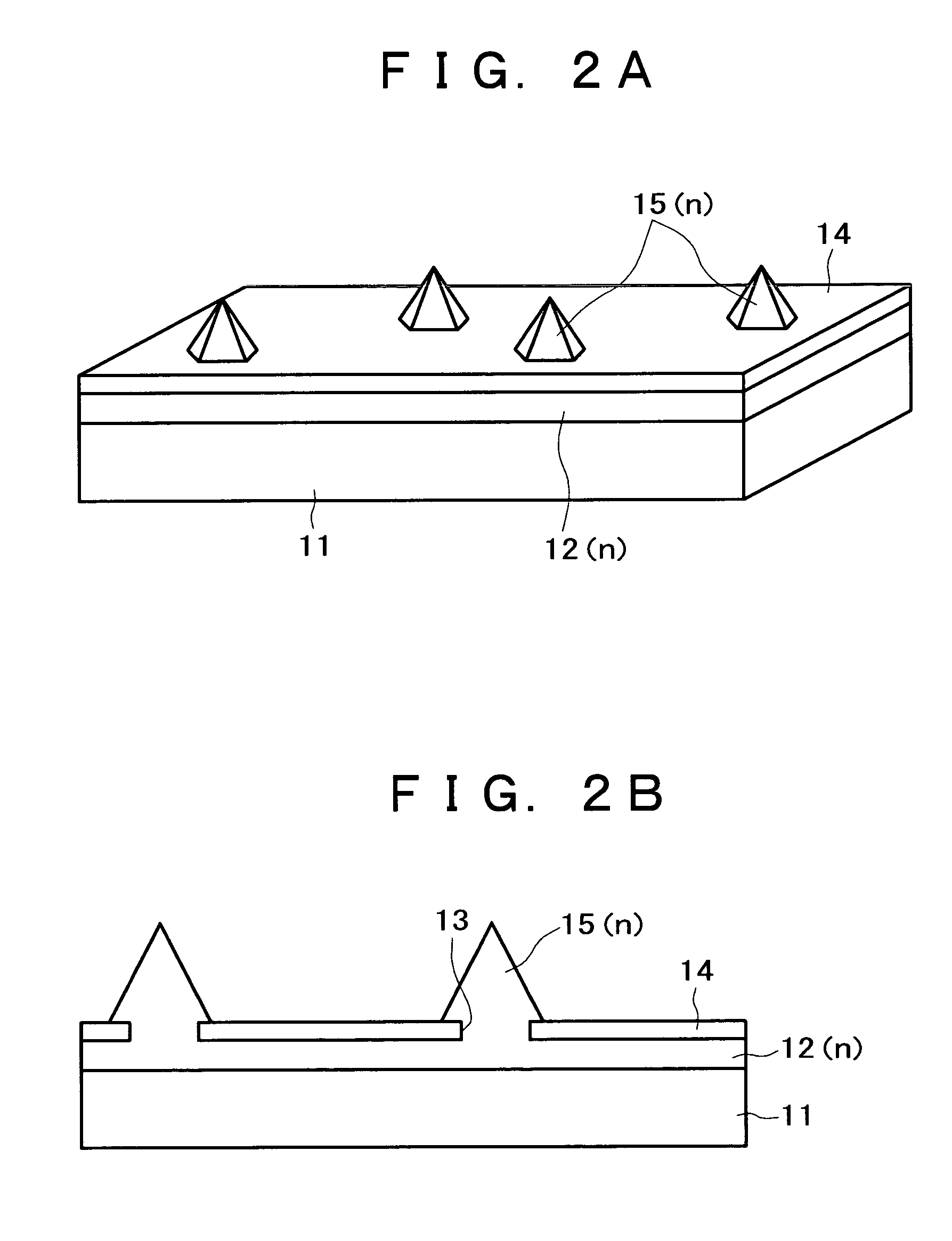

Selective growth method, and semiconductor light emitting device and fabrication method thereof

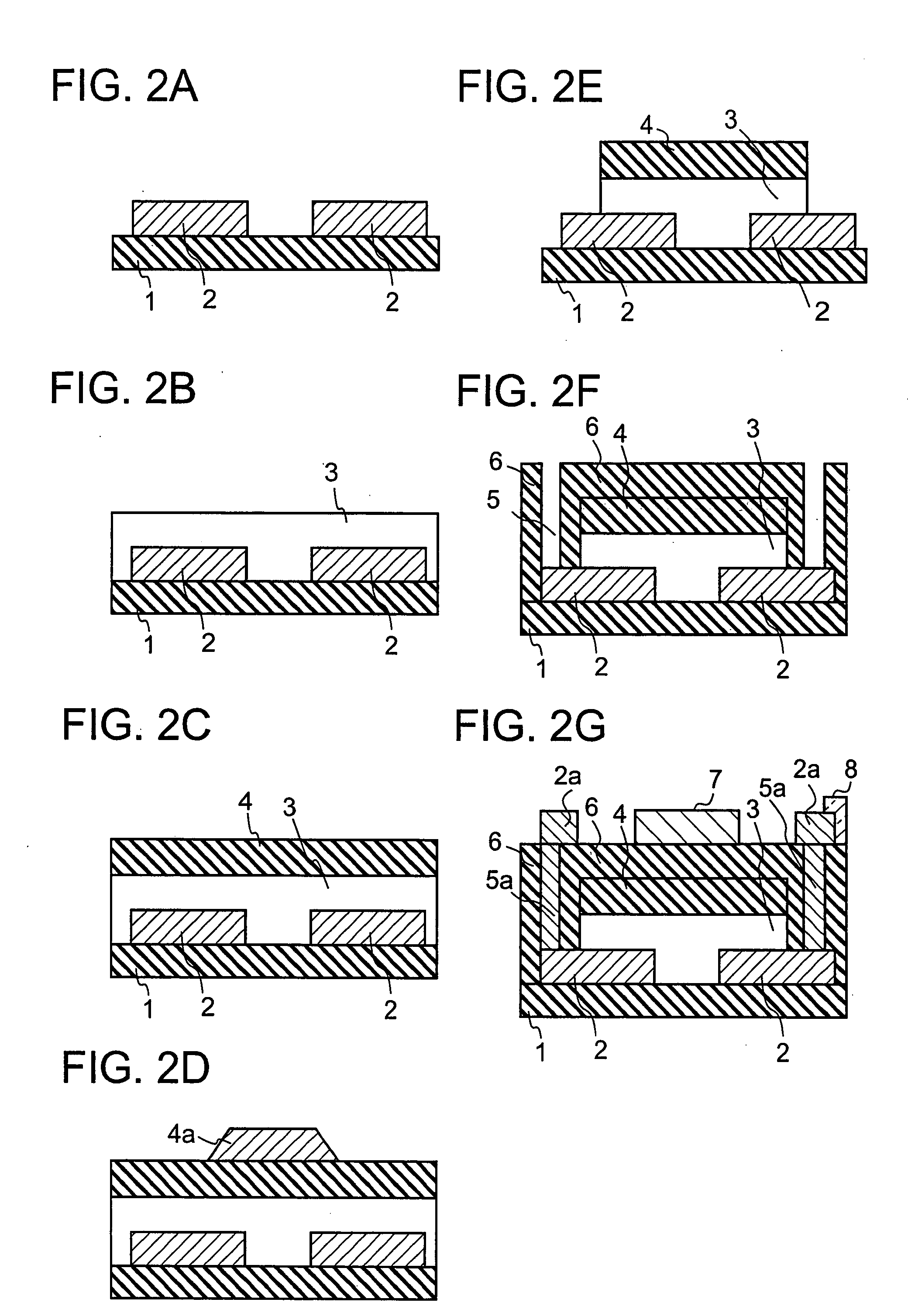

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

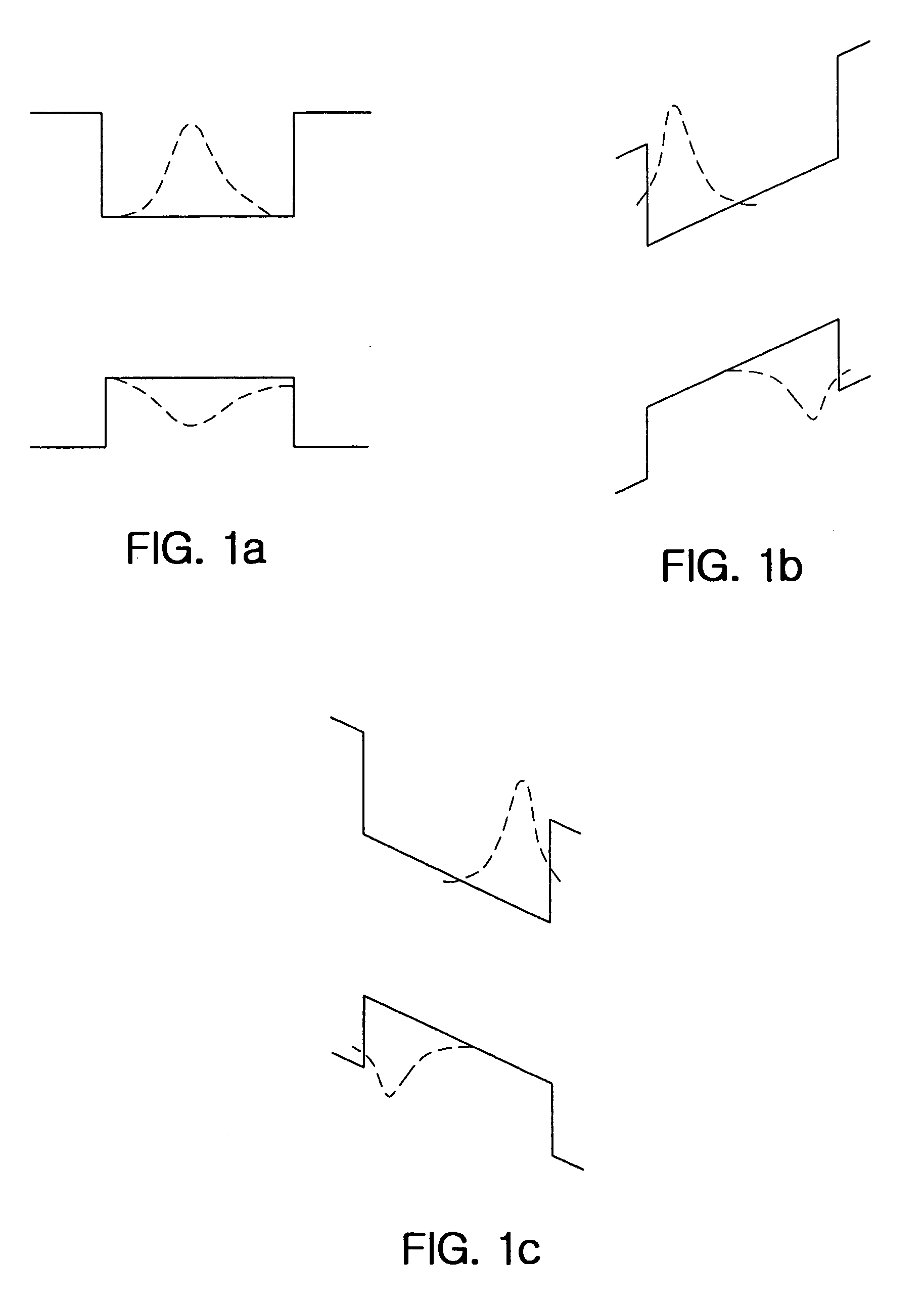

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

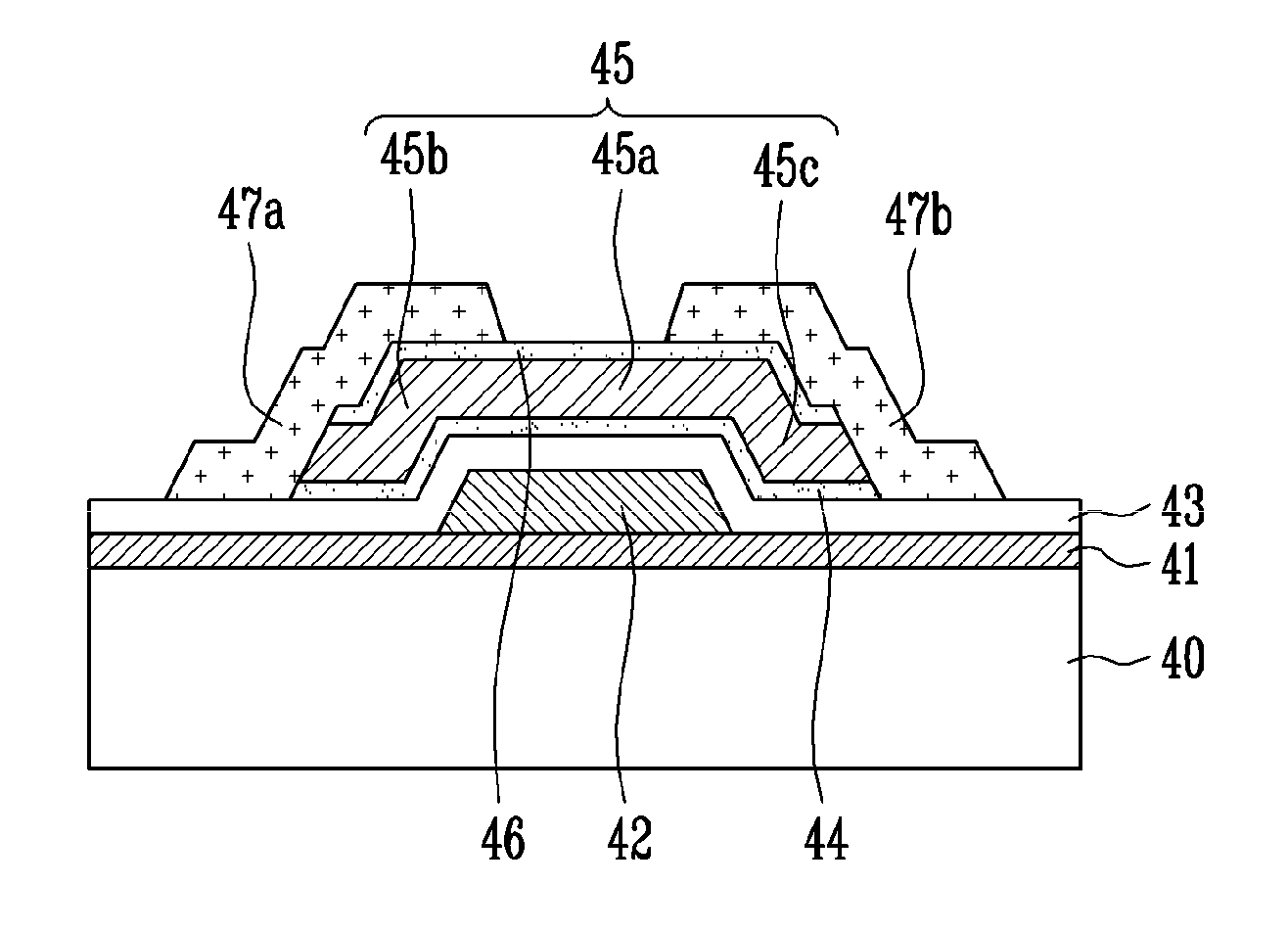

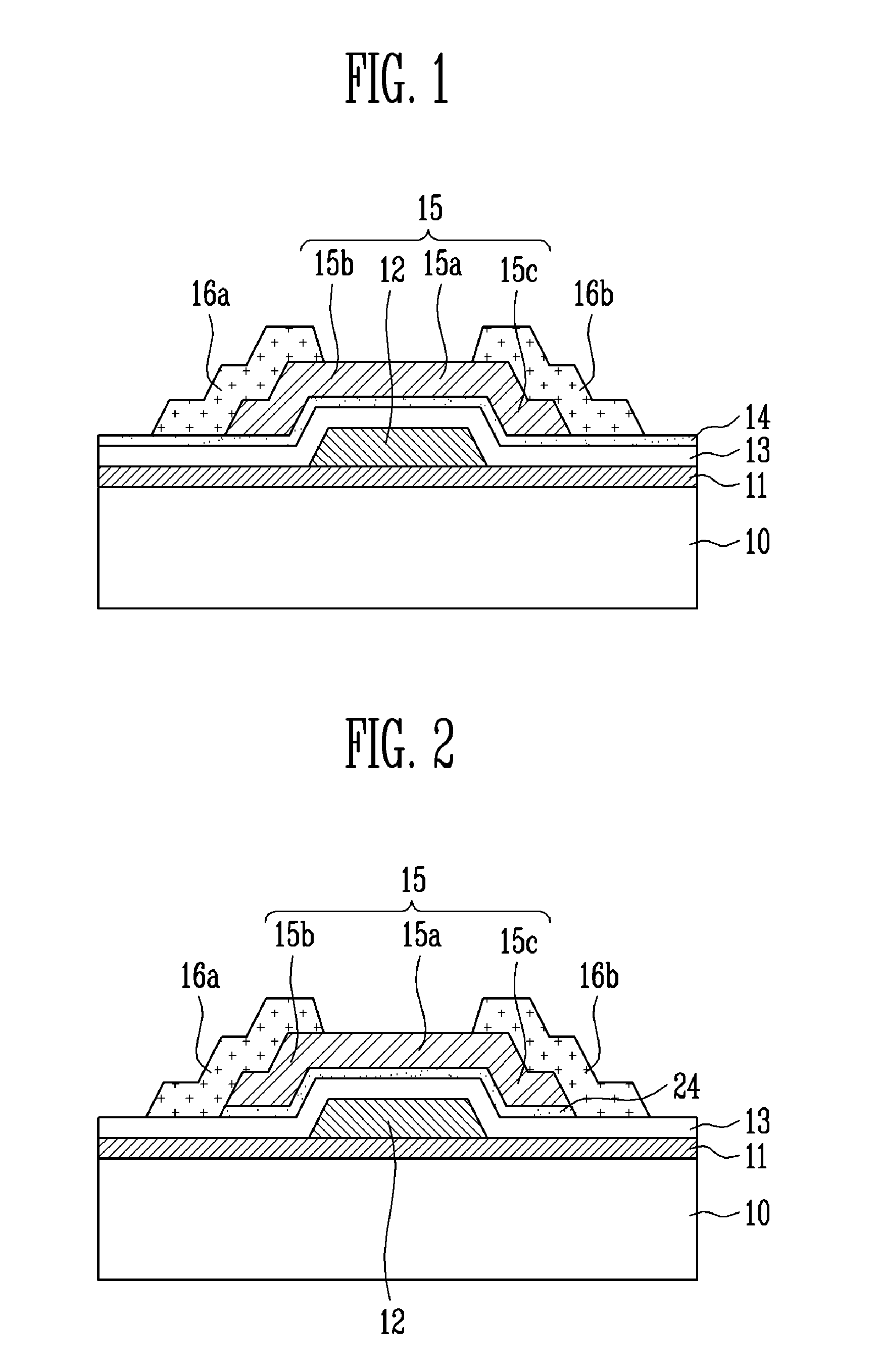

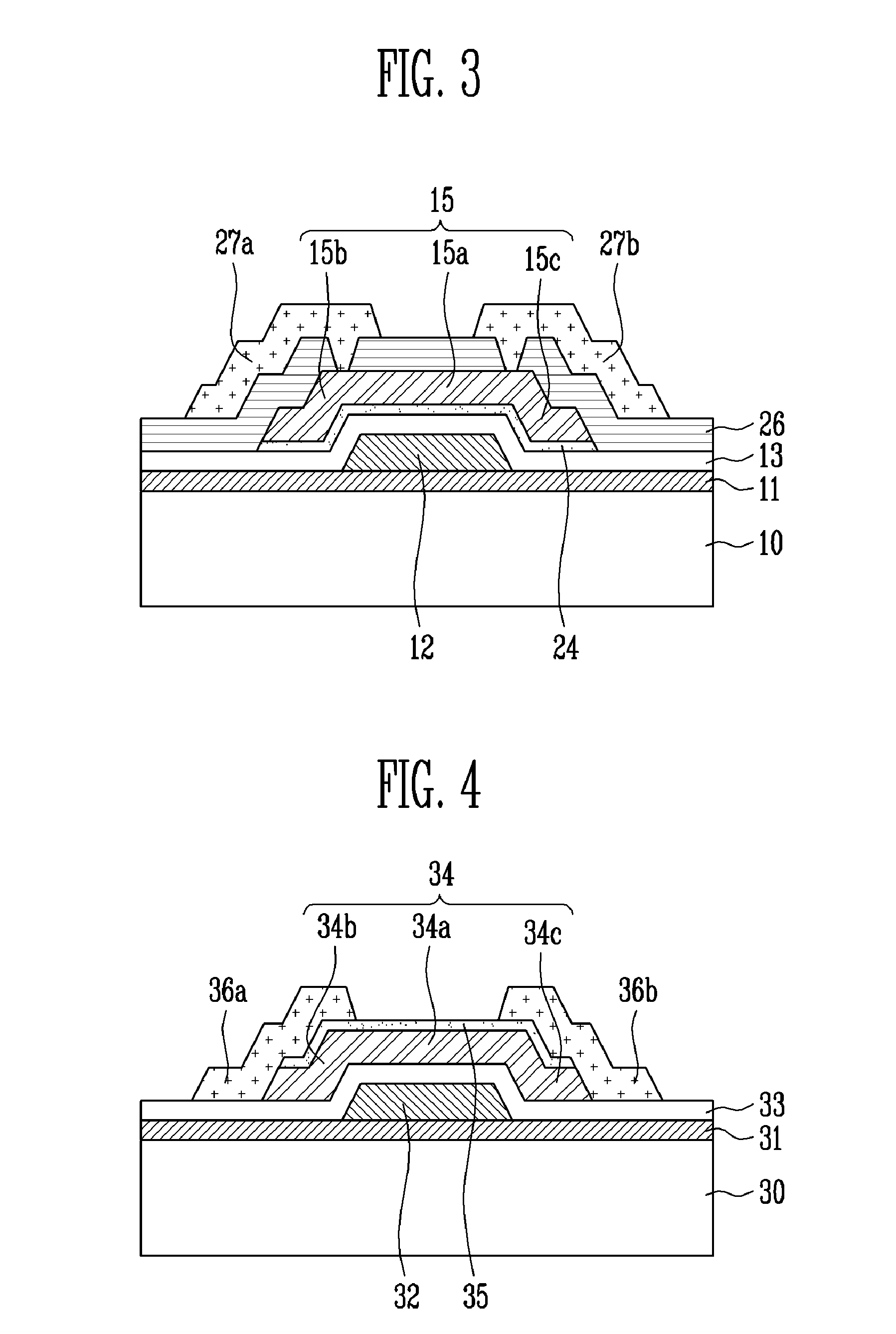

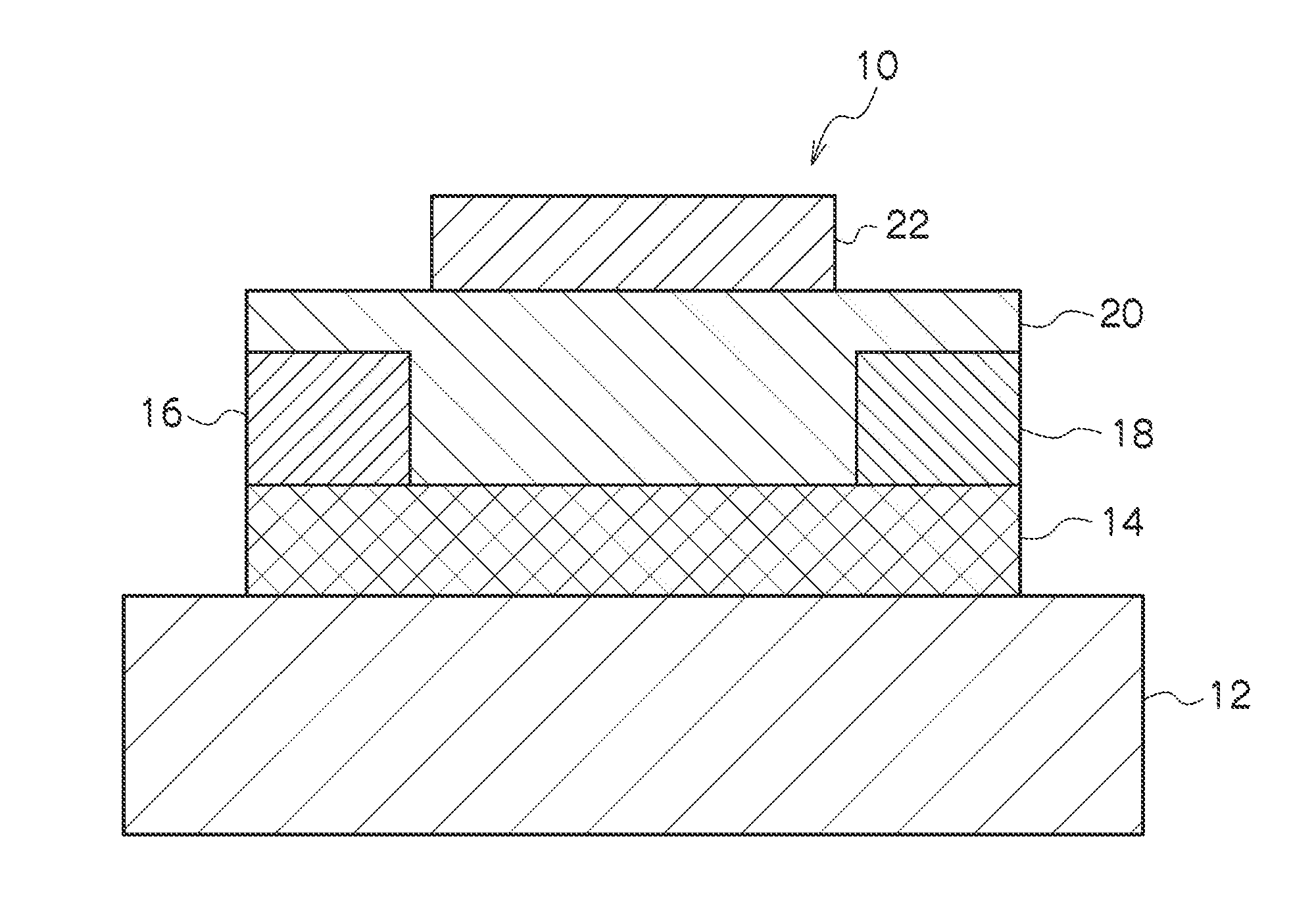

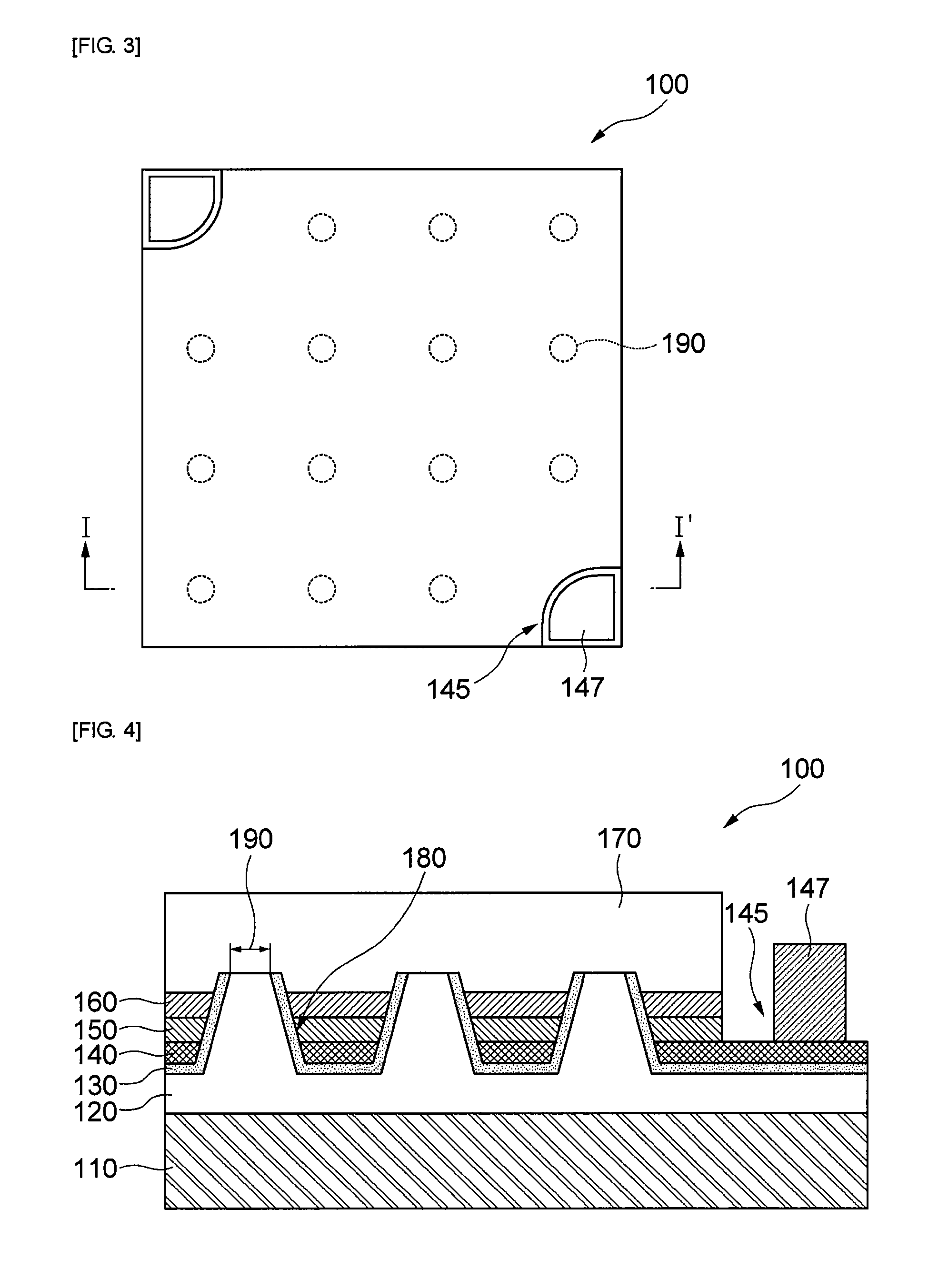

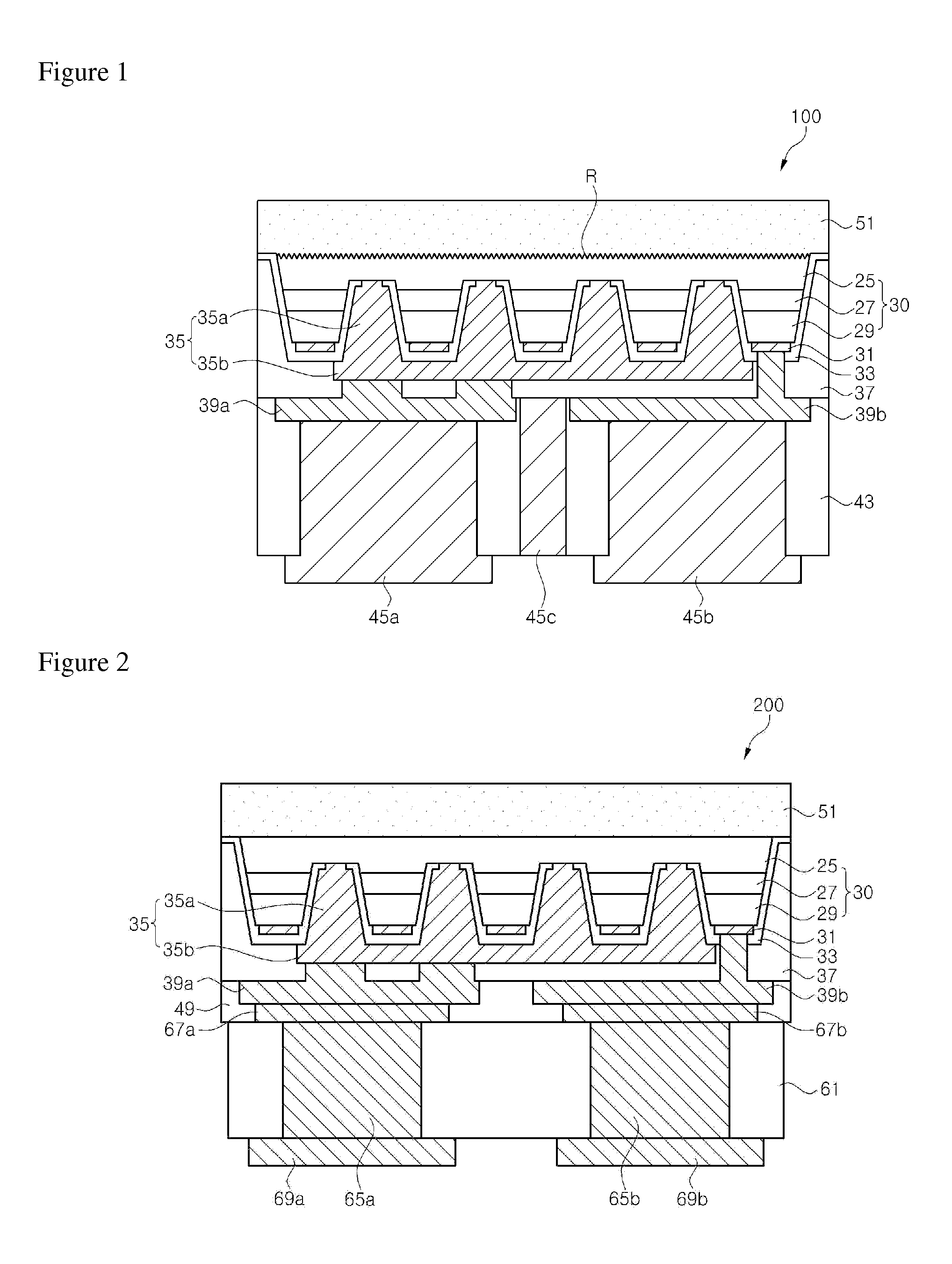

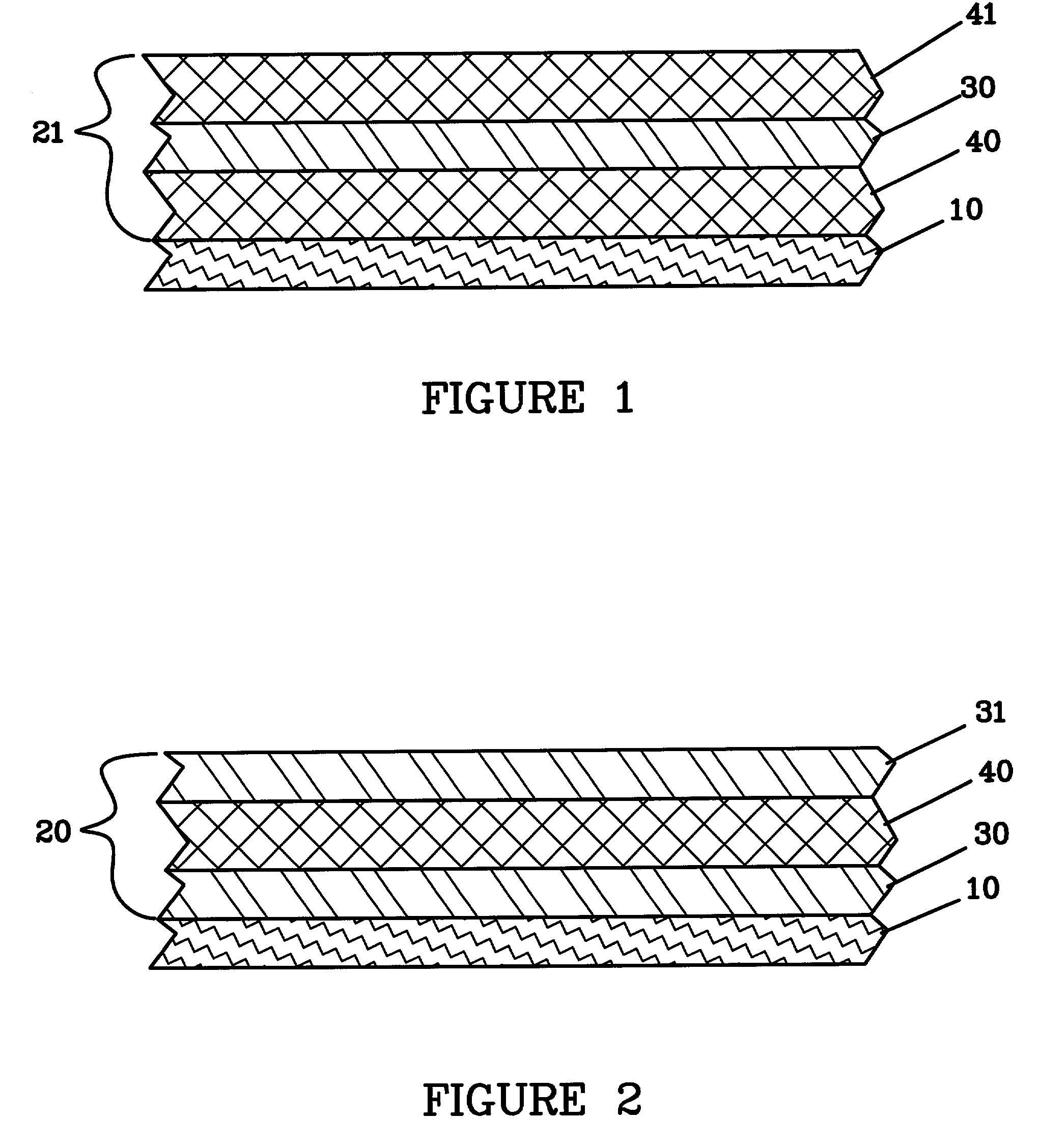

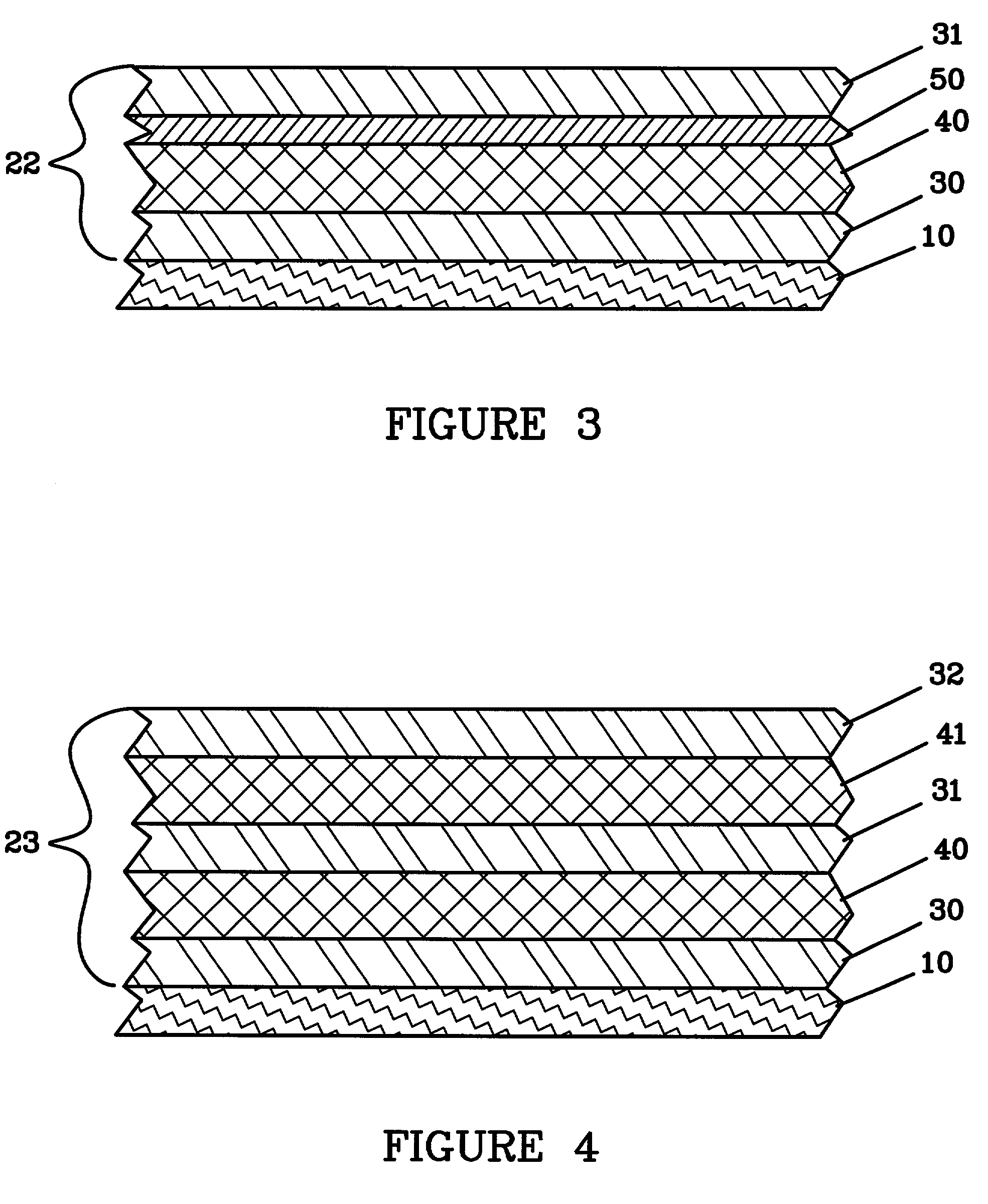

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS8148779B2Improve featuresAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

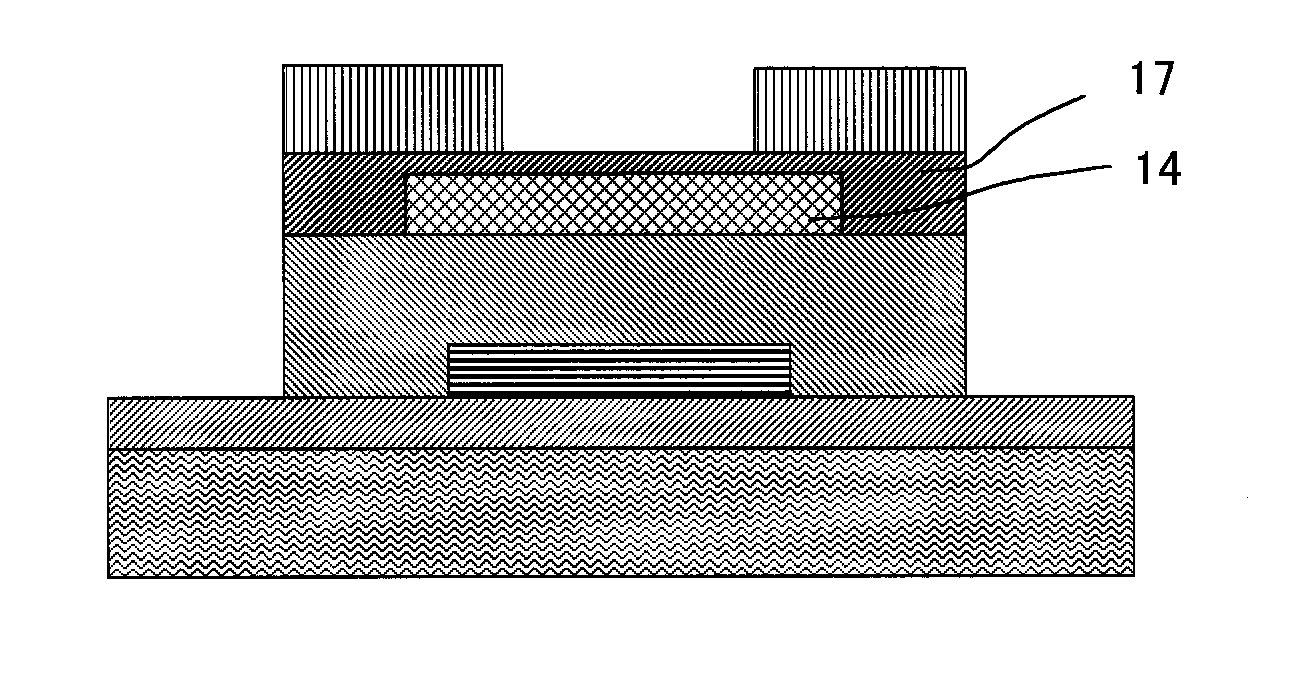

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

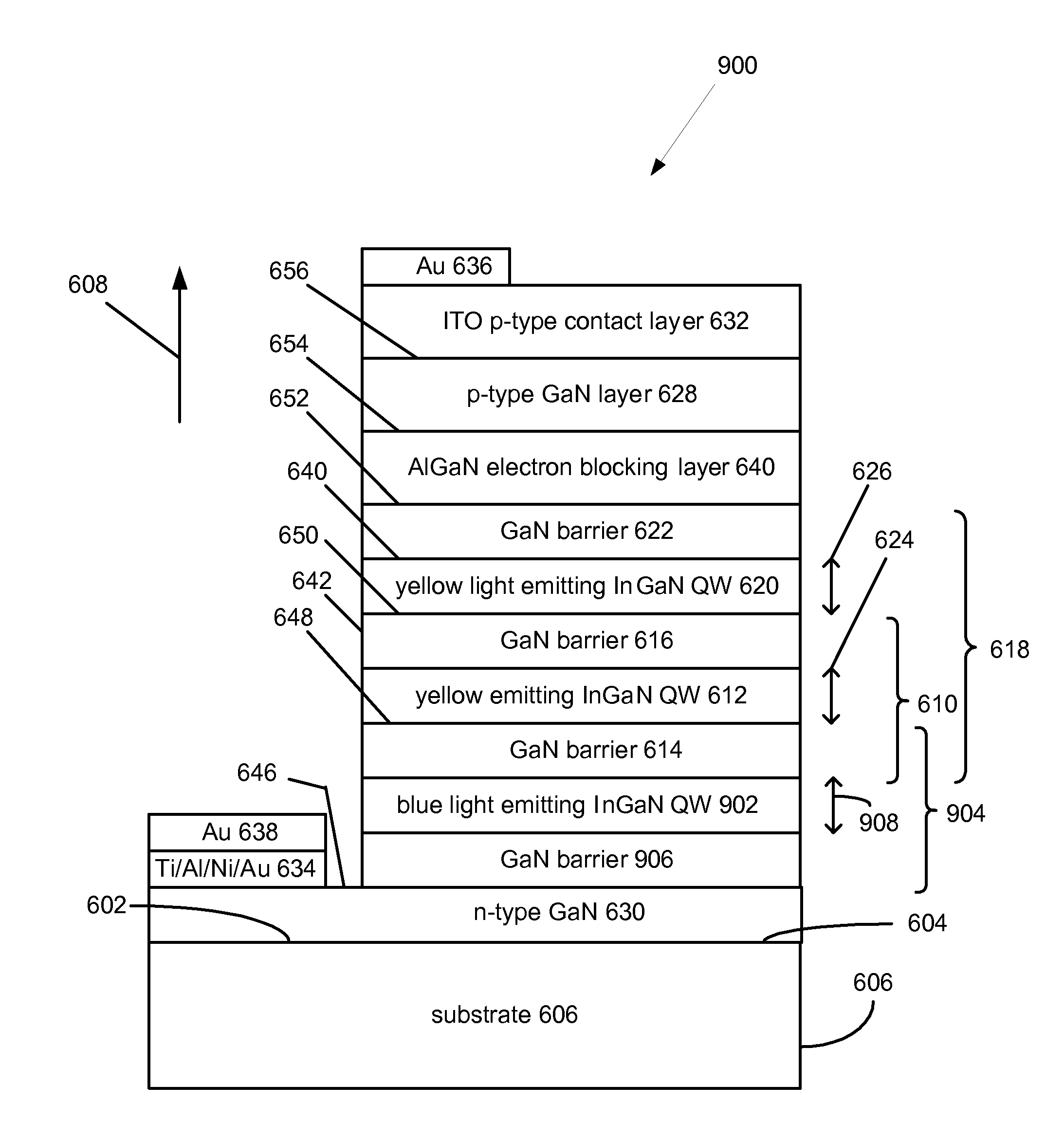

METHOD FOR FABRICATION OF SEMIPOLAR (Al, In, Ga, B)N BASED LIGHT EMITTING DIODES

A yellow Light Emitting Diode (LED) with a peak emission wavelength in the range 560-580 nm is disclosed. The LED is grown on one or more III-nitride-based semipolar planes and an active layer of the LED is composed of indium (In) containing single or multi-quantum well structures. The LED quantum wells have a thickness in the range 2-7 nm. A multi-color LED or white LED comprised of at least one semipolar yellow LED is also disclosed.

Owner:RGT UNIV OF CALIFORNIA

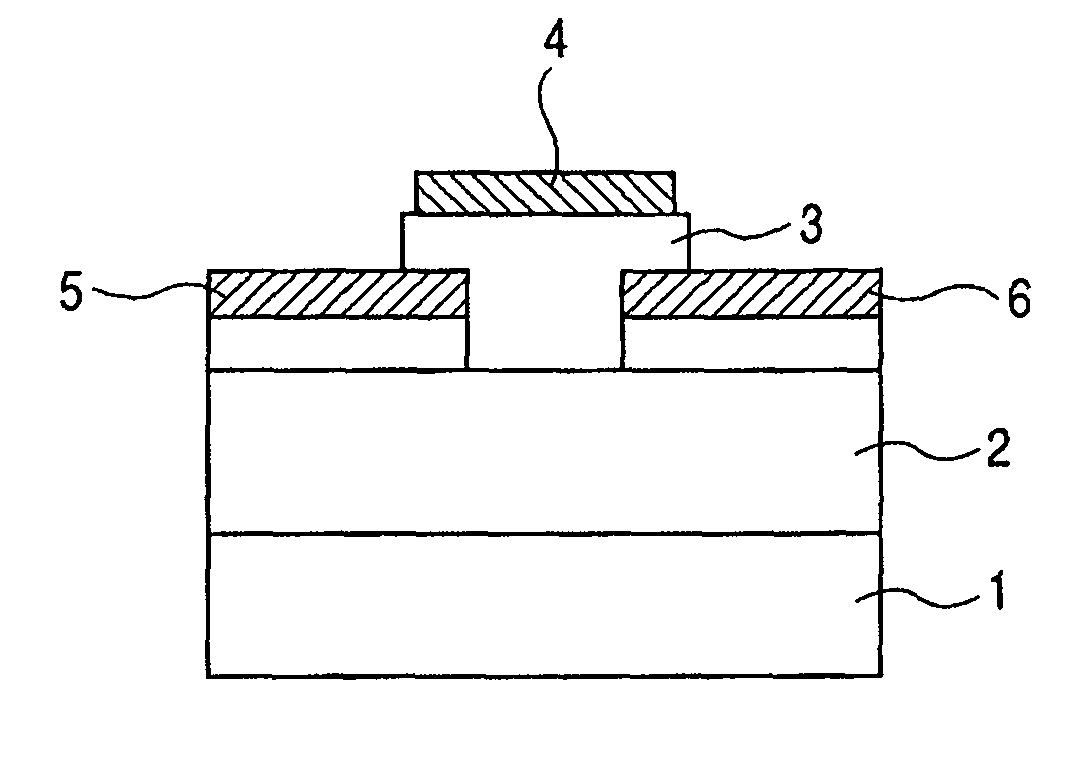

Thin film field effect transistor

ActiveUS8203143B2Increased durabilityImprove stabilitySemiconductor devicesInterface layerField-effect transistor

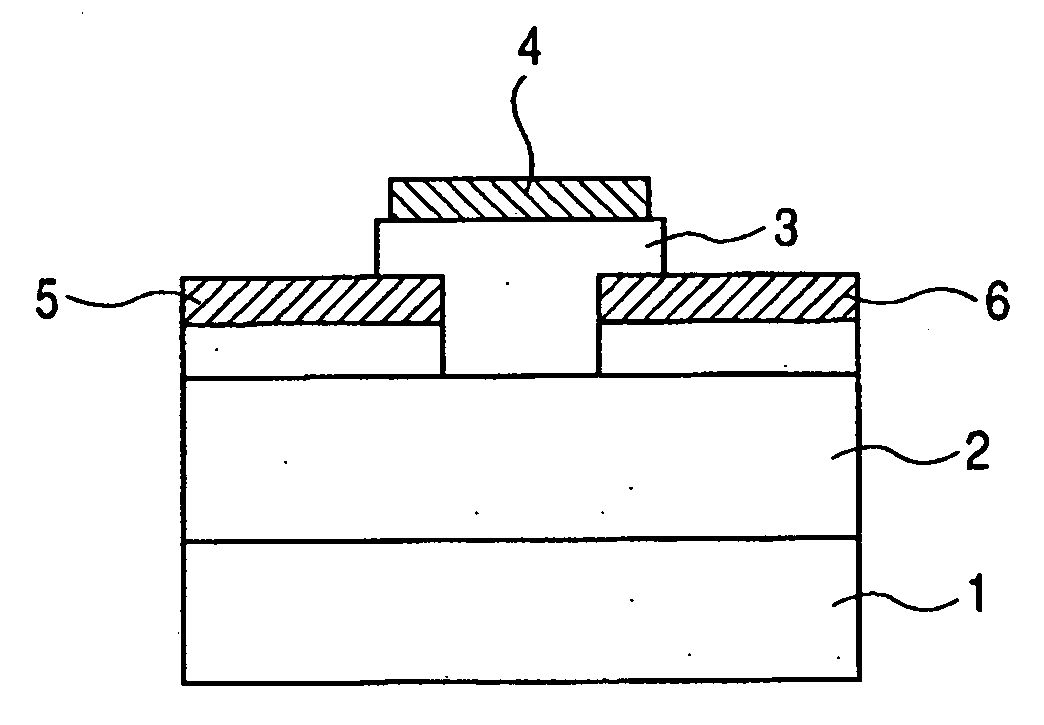

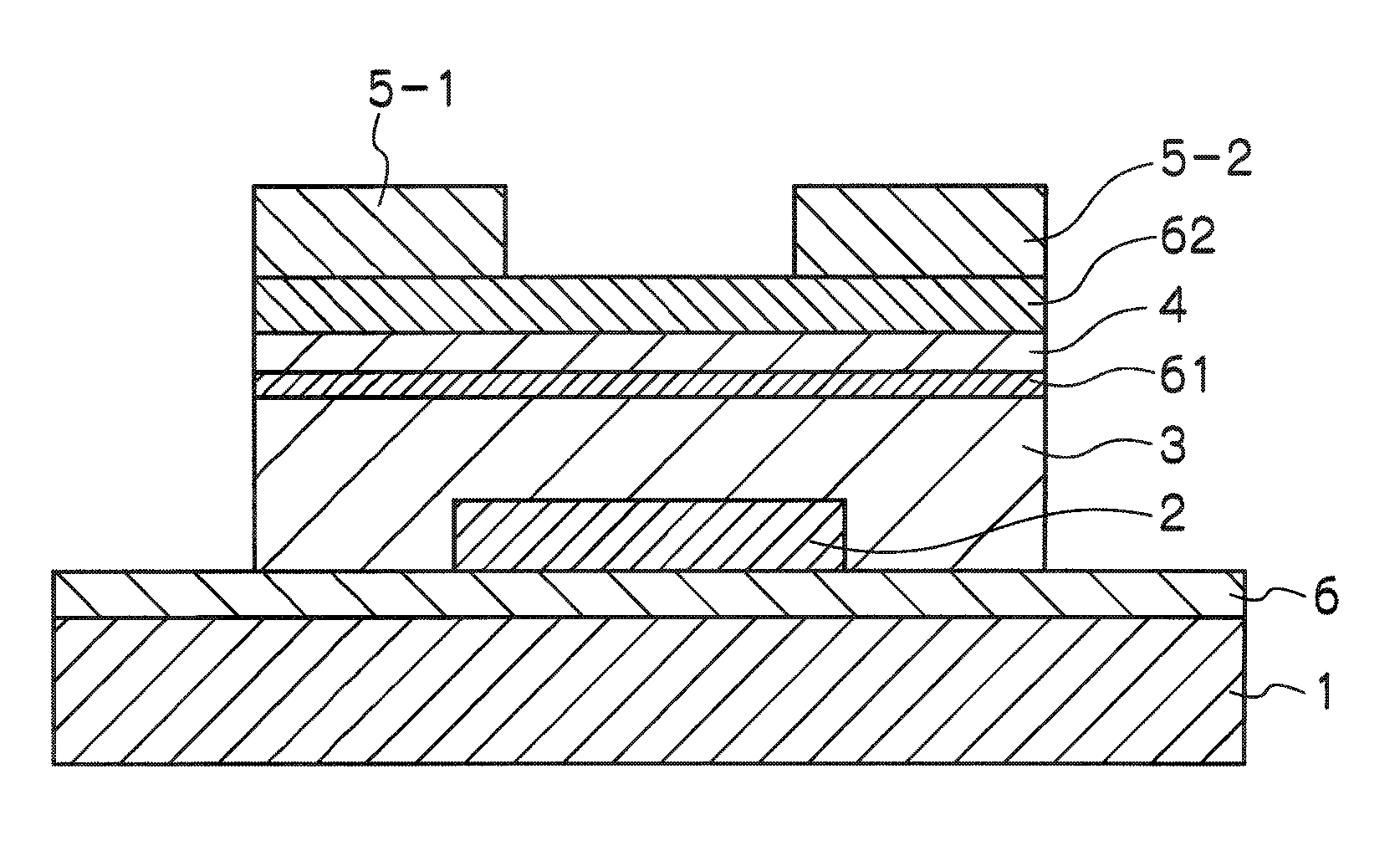

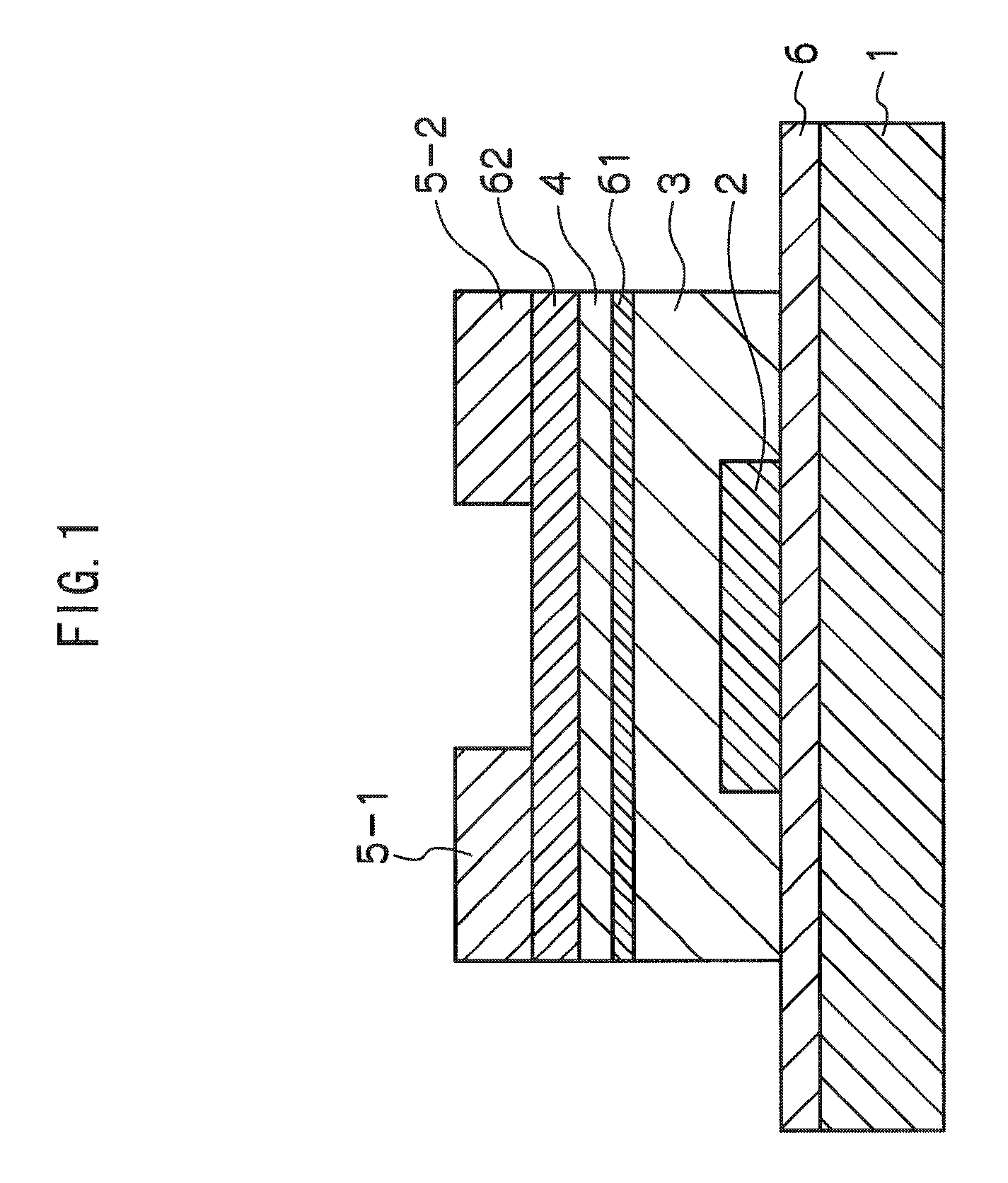

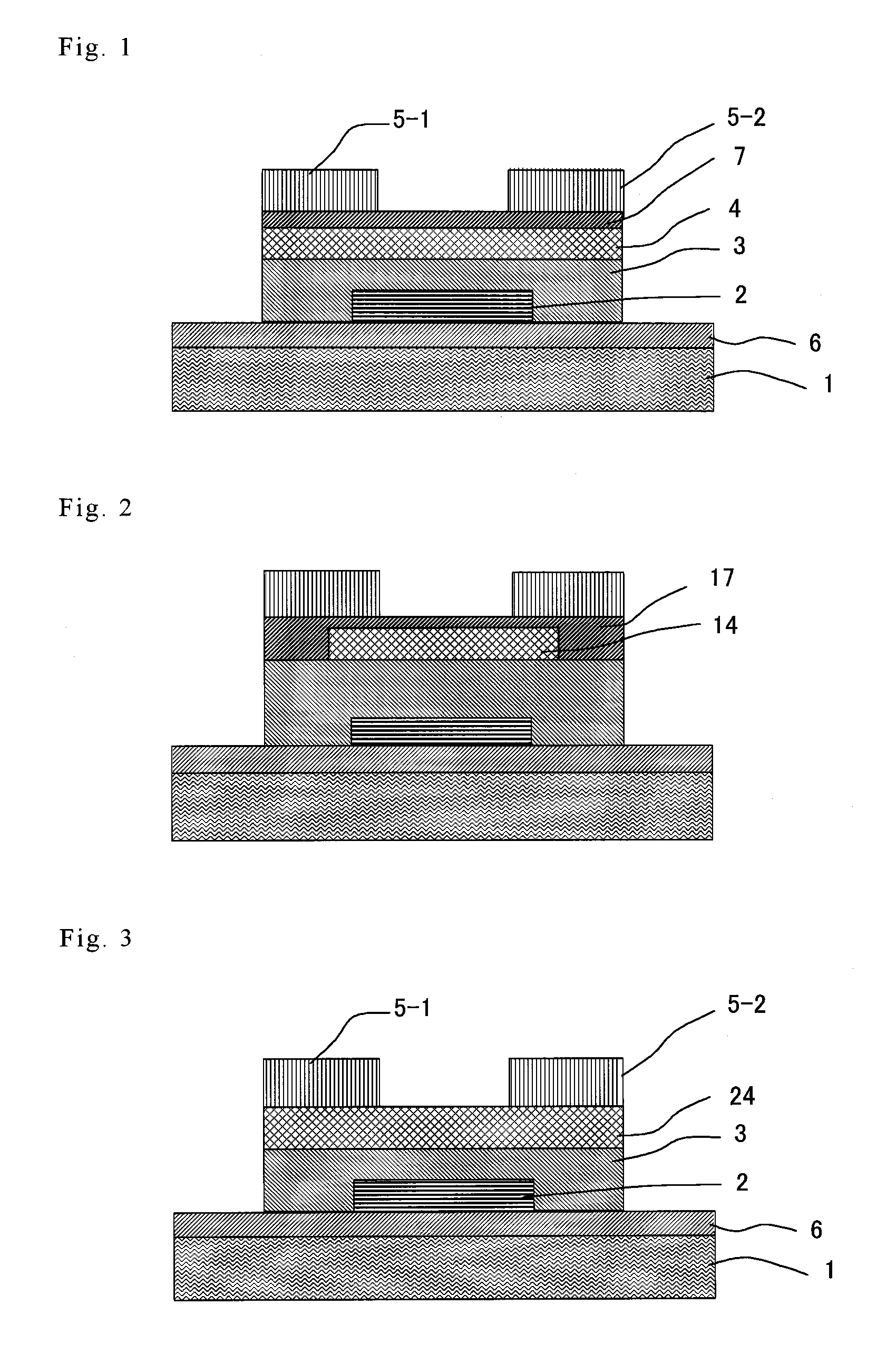

A thin film field effect transistor has at least a gate electrode 2, a gate insulating layer 3, an active layer 4, a source electrode 5-1 and a drain electrode 5-2 on a substrate 1. The active layer includes an amorphous oxide semiconductor including at least In and Zn, a first interface layer 61 is disposed between the gate insulating layer and the active layer such that it is adjacent to at least the active layer, and a second interface layer is disposed on the opposite side of the active layer with respect to the first interface layer such that it is adjacent to the active layer. A content of Ga or Al in the amorphous oxide semiconductor of each of the first interface layer and the second interface layer is higher than a content of Ga or Al in the amorphous oxide semiconductor of the active layer.

Owner:SAMSUNG DISPLAY CO LTD

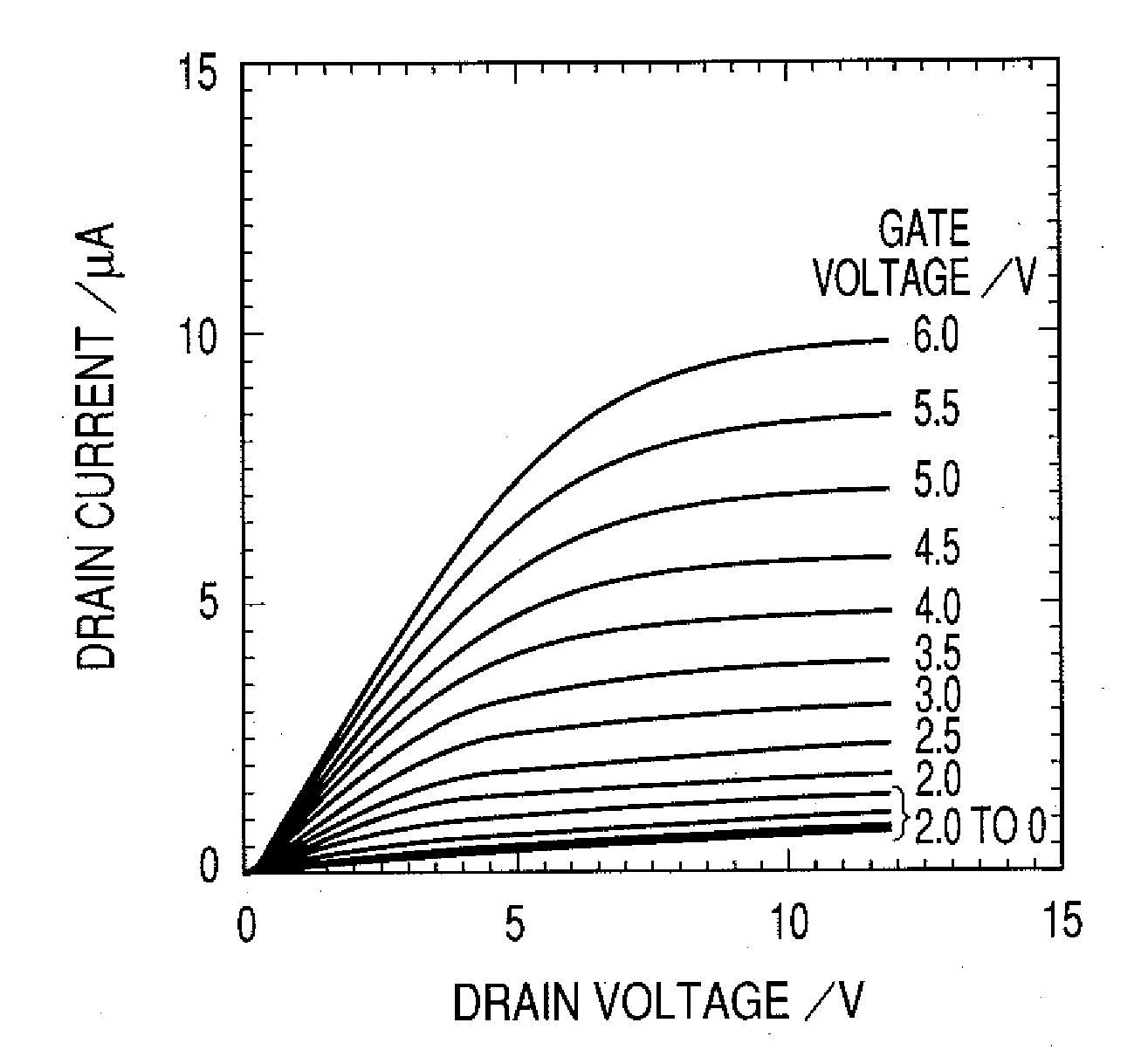

Thin film field effect transistor and display

ActiveUS8188480B2High concentrationElectroluminescent light sourcesSolid-state devicesDisplay deviceField-effect transistor

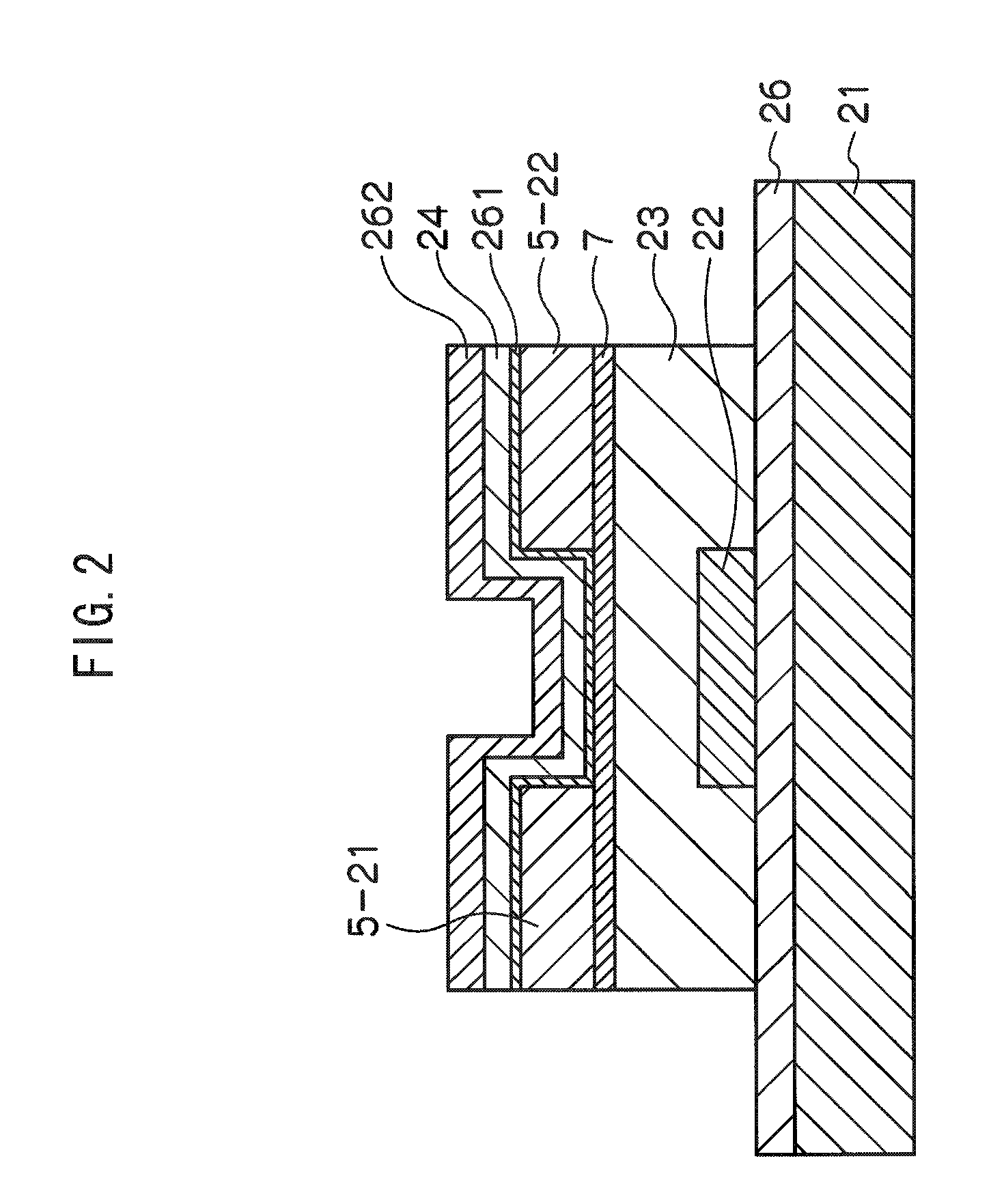

A TFT is provided which includes, on a substrate, at least a gate electrode, a gate insulating layer, an active layer containing an amorphous oxide semiconductor, a source electrode and a drain electrode, wherein a resistance layer containing an amorphous oxide and having a thickness of more than 3 nm is disposed between the active layer and at least one of the source electrode or the drain electrode, and a band gap of the active layer is smaller than a band gap of the resistance layer. Also, a display using the TFT is provided.

Owner:SAMSUNG DISPLAY CO LTD

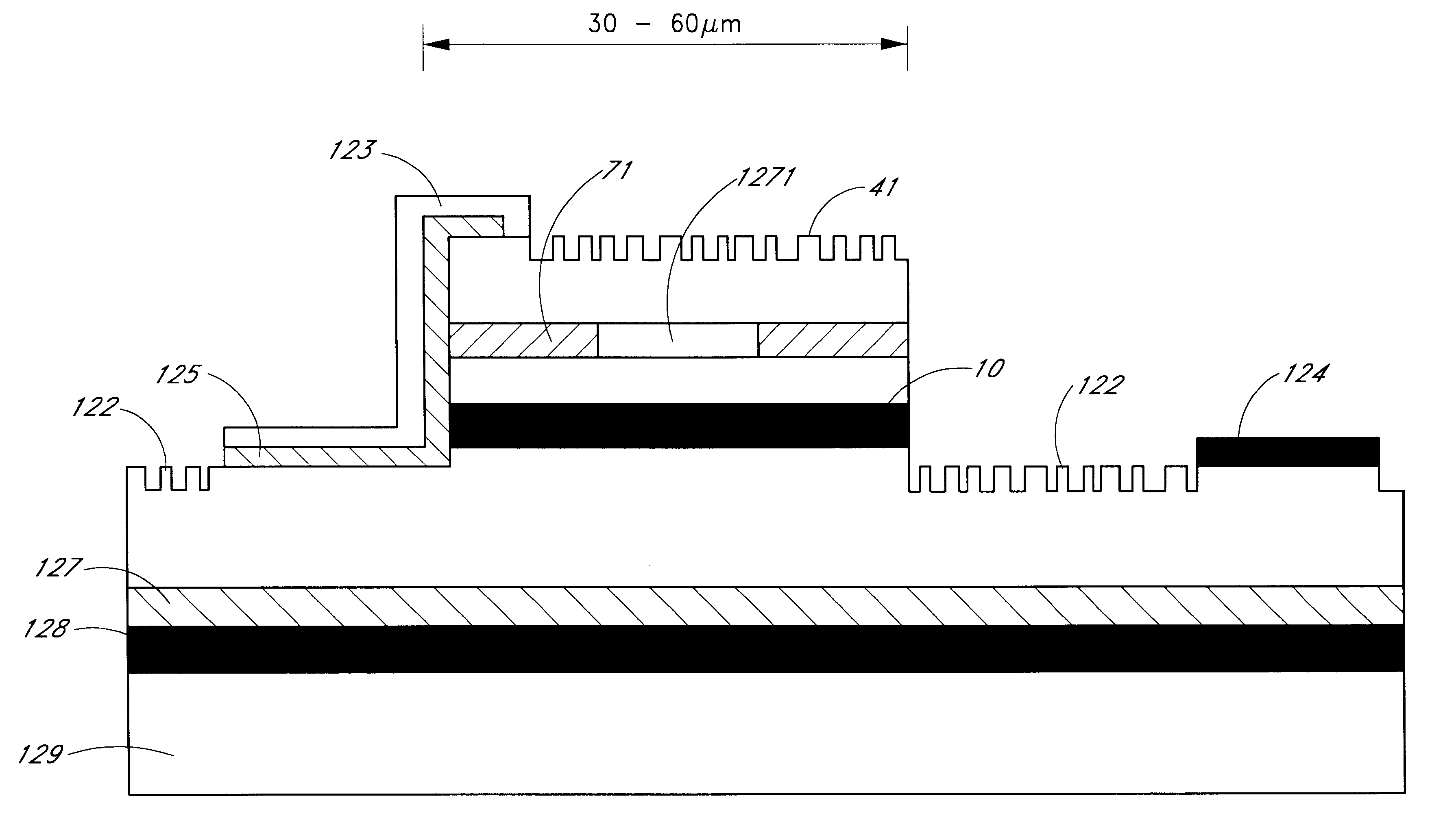

Method of manufacturing surface textured high-efficiency radiating devices and devices obtained therefrom

InactiveUS6504180B1Reduce charge effectReduce surface recombinationSolid-state devicesCoupling light guidesGratingCharge carrier

A device for emitting radiation at a predetermined wavelength is presented. This device has a cavity with an active layer in which said radiation is generated by charge carrier recombination. The edges of the device define the region or space for radiation and / or charge carrier confinement. At least one of the edges of this cavity has a substantially random grating structure. The edge of the device has substantially random grating structure and can extend as at least one edge of a waveguide forming part of this radiation emitting device. The radiation emitting device of the present invention can have a cavity comprising a radiation confinement space that includes confinement features for the charge carriers confining the charge carriers to a subspace being smaller than the radiation confinement space within the cavity. The emitting device can comprise at least two edges forming, in cross-section, a substantially triangular shape. The angle between these two edges is smaller than 45°. At least one of the two edges has a transparent portion. the devices according to the present invention can be arranged in arrays.

Owner:SIGNIFY HLDG BV

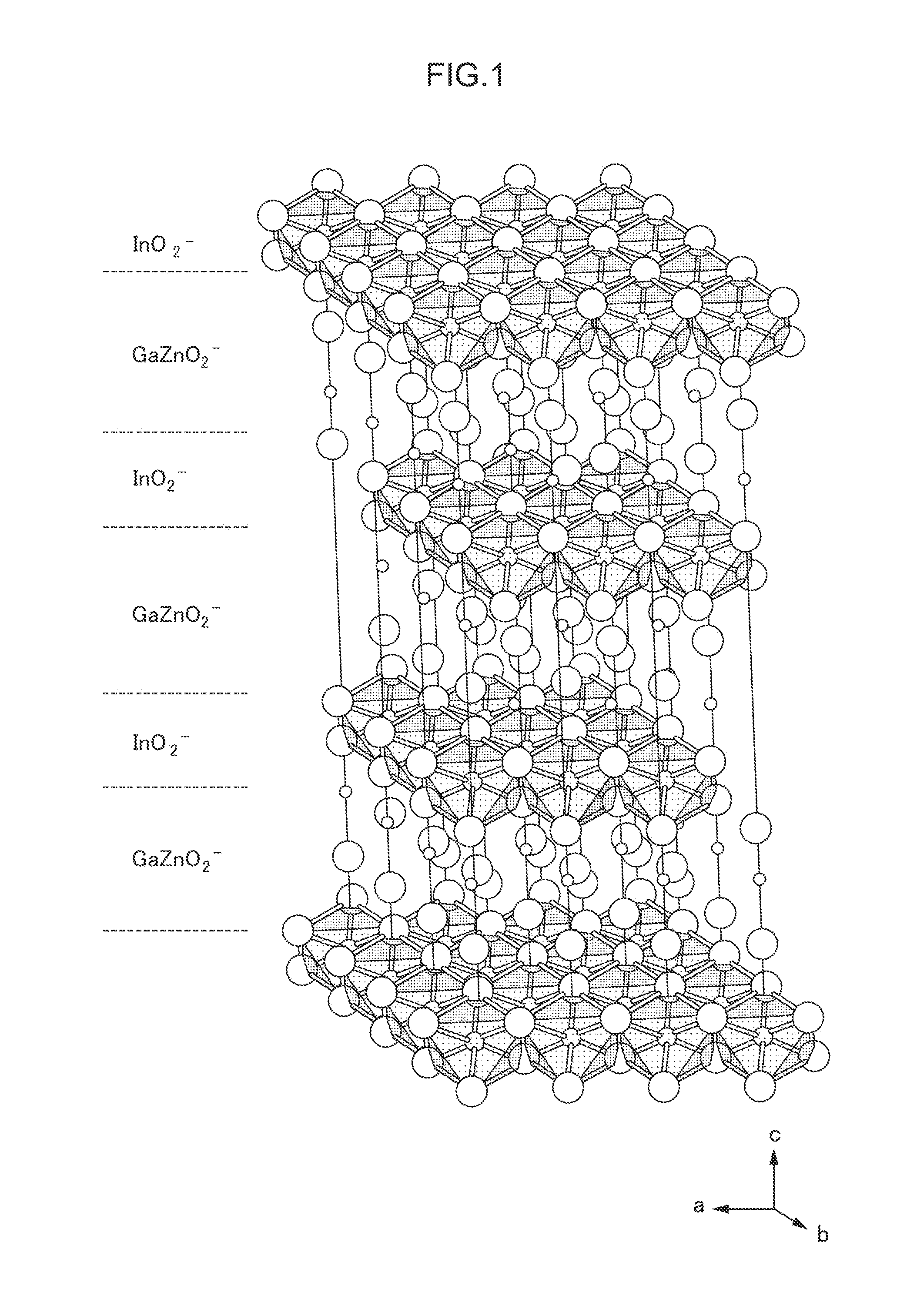

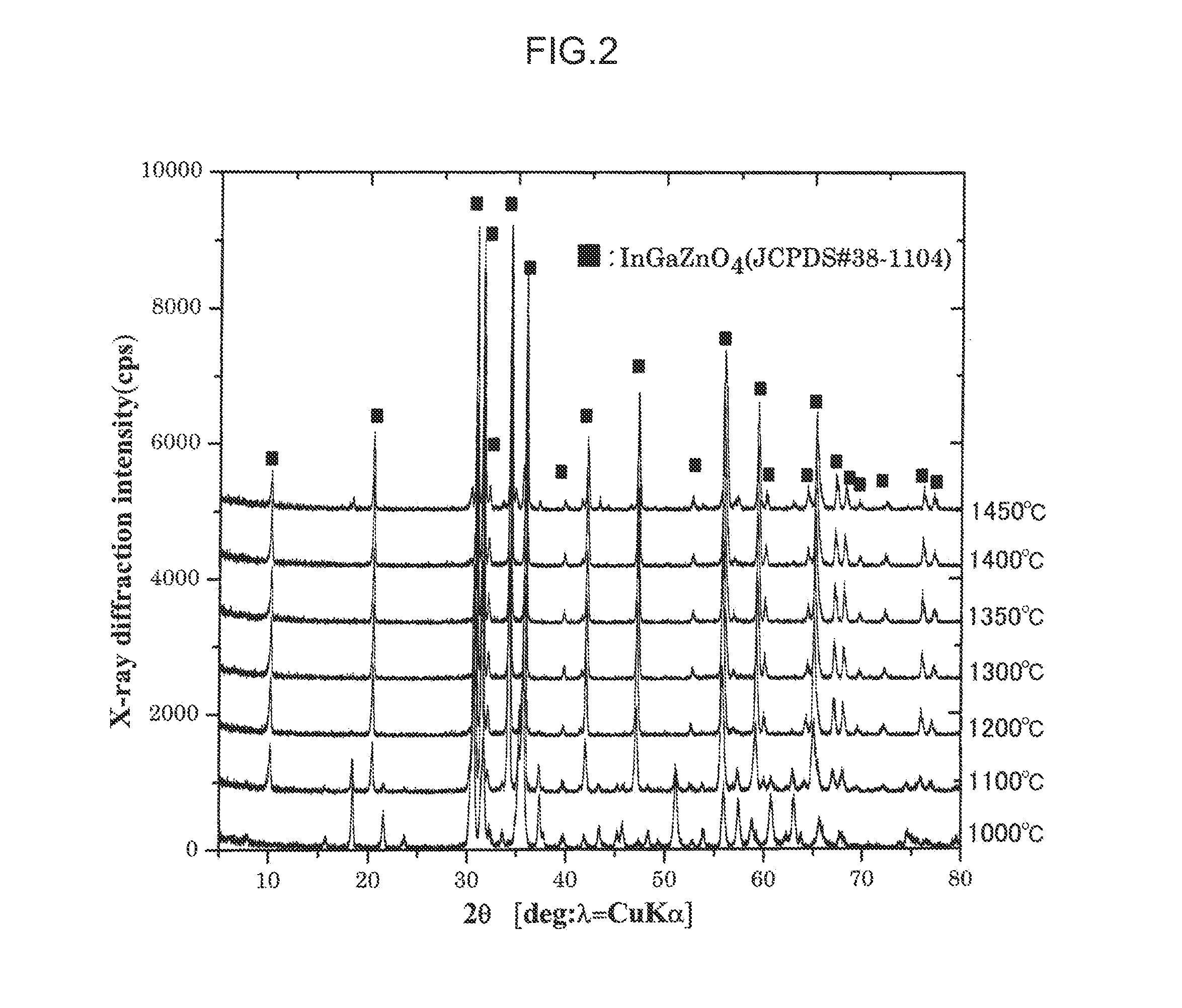

Thin film transistor and method of producing thin film transistor

ActiveUS20100320459A1TransistorSemiconductor/solid-state device manufacturingThin membraneCrystal structure

The invention provides a thin film transistor comprising an active layer, the active layer comprising an IGZO-based oxide material, the IGZO-based oxide material being represented by a composition formula of In2-xGaxZnO4-δ, where 0.75<x<1.10 and 0<δ≦1.29161×exp(−x / 0.11802)+0.00153 and being formed from a single phase of IGZO having a crystal structure of YbFe2O4, and a method of producing the thin film transistor.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor light-emitting device and semiconductor light-emitting device

InactiveUS7087932B2Well formedSolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeCrystallinity

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride semiconductor light emitting device and fabrication method thereof

ActiveUS8129711B2Good effectReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight emitting device

The present invention relates to a GaN based nitride based light emitting device improved in Electrostatic Discharge (ESD) tolerance (withstanding property) and a method for fabricating the same including a substrate and a V-shaped distortion structure made of an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer on the substrate and formed with reference to the n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor light emitting device

ActiveUS8008683B2High luminous efficiencySolid-state devicesSemiconductor devicesElectrical conductorActive layer

The present invention provides a semiconductor light emitting device including a conductive substrate, a first electrode layer, an insulating layer, a second electrode layer, a second semiconductor layer, an active layer, and a first semiconductor layer which are sequentially stacked, wherein an area where the first electrode layer and the first semiconductor layer are in contact with each other is 3 to 13% of an area of the semiconductor light emitting device.

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride based semiconductor device

ActiveUS7084420B2Improve efficiencyEliminate the effects ofNanoopticsSemiconductor lasersDevice materialQuantum well

The present invention provides a nitride based semiconductor device comprising an active layer having a quantum well layer and a quantum barrier layer, wherein the device includes an electron emitting layer formed of at least two repeats of a first nitride semiconductor layer and a second nitride semiconductor layer having different compositions between a n-type nitride semiconductor layer and the active layer, the first nitride semiconductor layer has an energy band gap greater than that of the quantum well layer, smaller than that of the quantum barrier layer, and decreasing closer to the active layer, and the second nitride semiconductor layer has an energy band gap at least higher than that of the adjacent first nitride semiconductor layer(s) and has a thickness capable of tunneling electrons.

Owner:SAMSUNG ELECTRONICS CO LTD

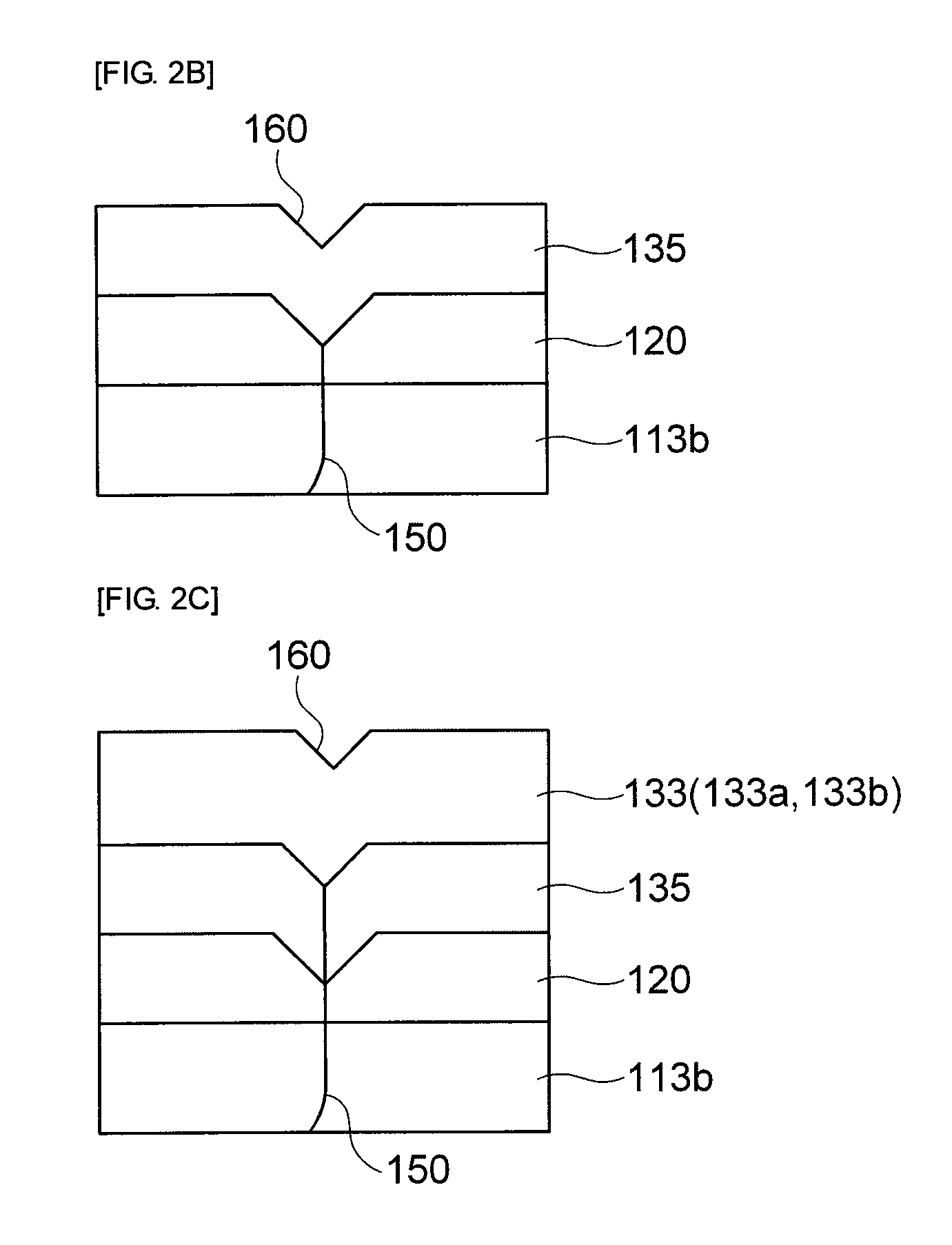

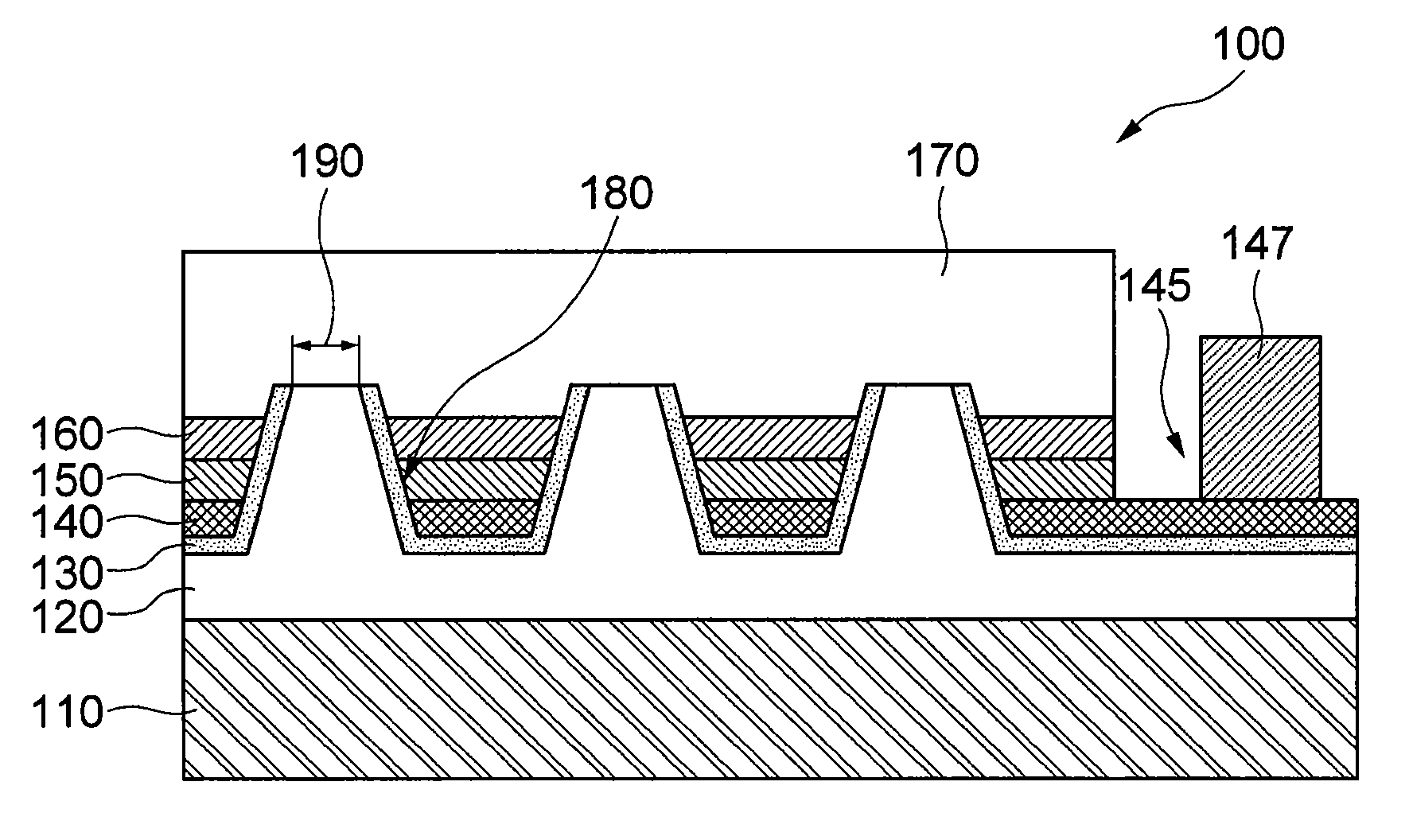

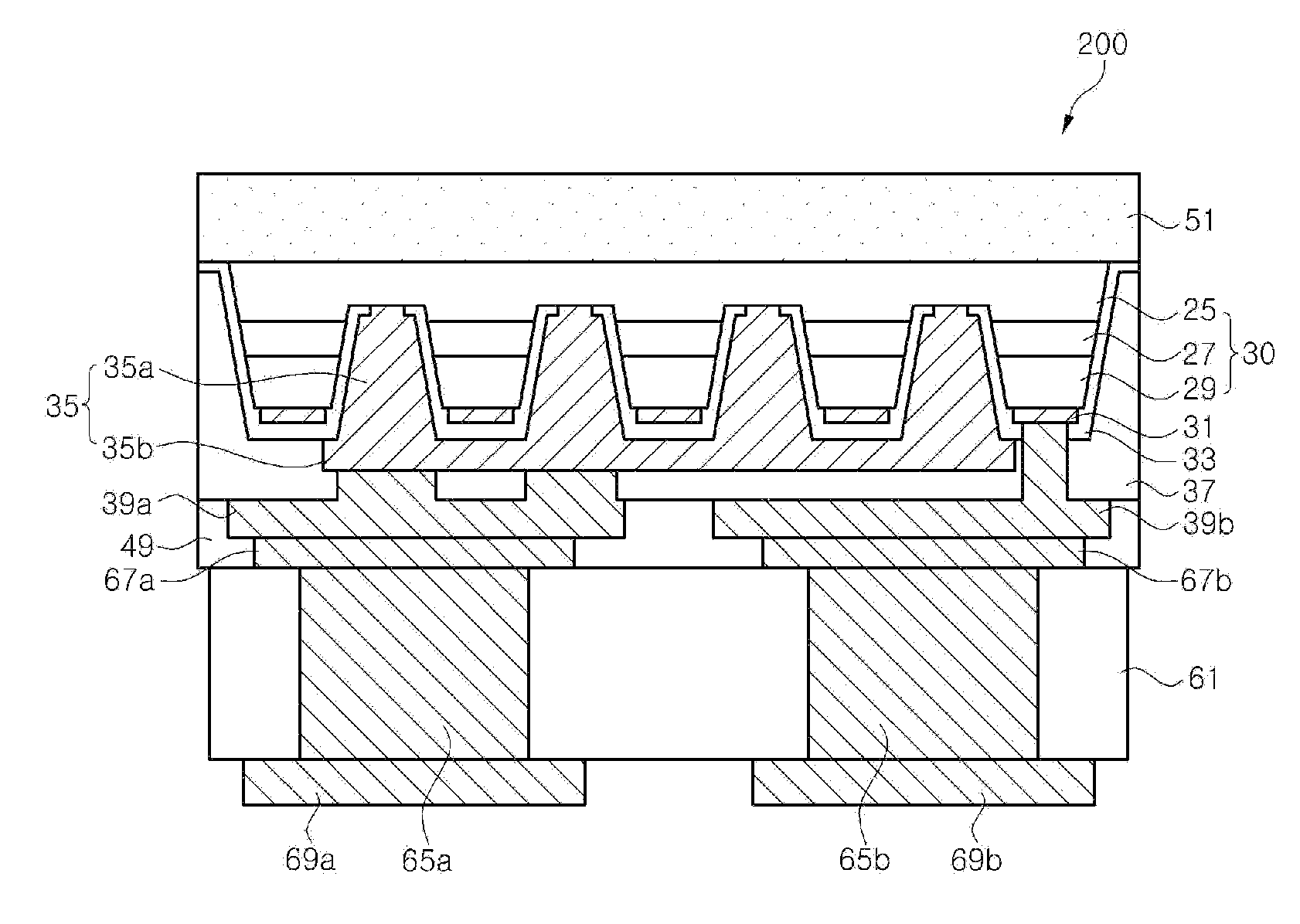

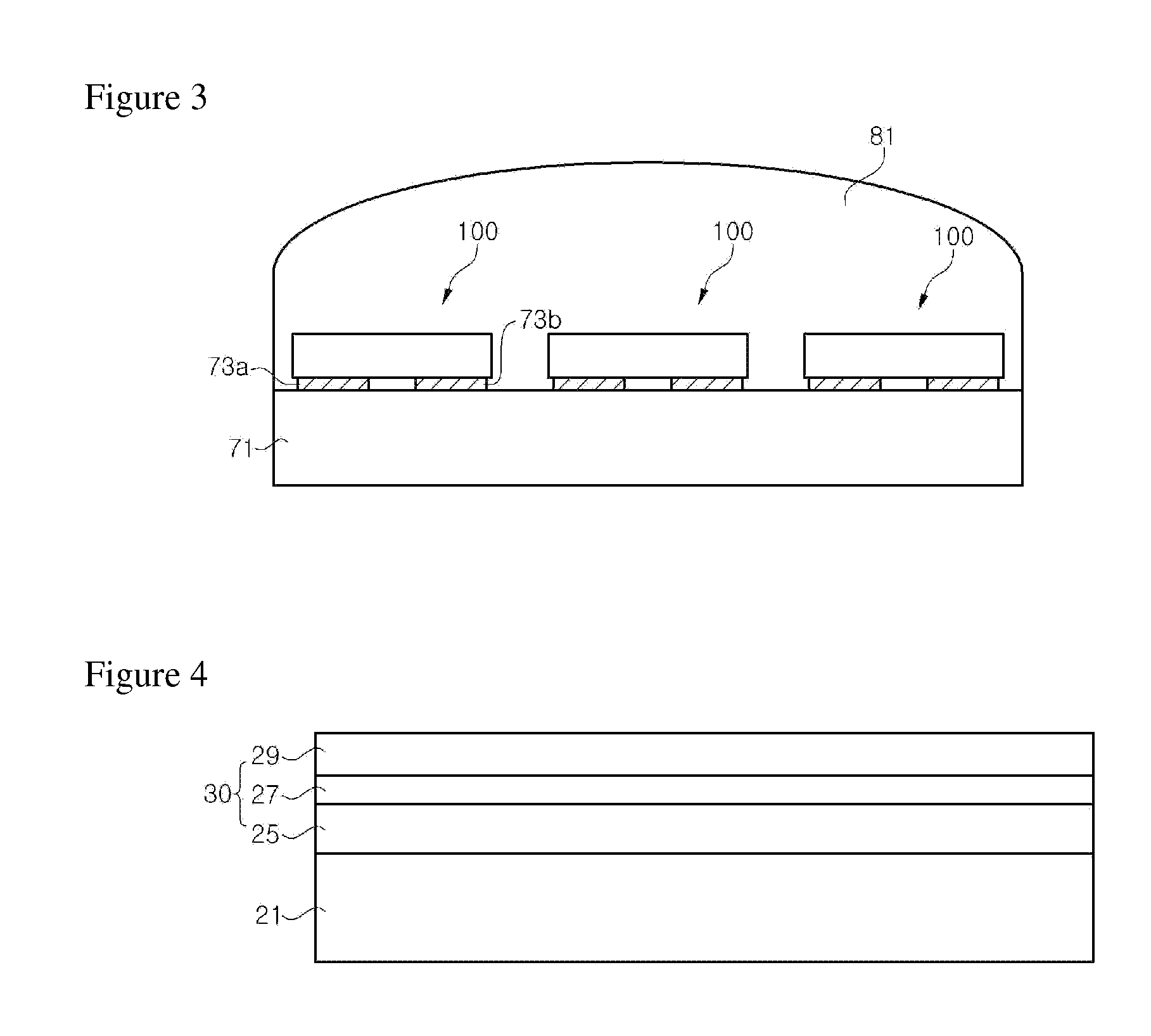

Wafer-level light emitting diode package and method of fabricating the same

ActiveUS20120074441A1Improve efficiencyImprove cooling effectSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

Exemplary embodiments of the present invention provide a wafer-level light emitting diode (LED) package and a method of fabricating the same. The LED package includes a semiconductor stack including a first conductive type semiconductor layer, an active layer, and a second conductive type semiconductor layer; a plurality of contact holes arranged in the second conductive type semiconductor layer and the active layer, the contact holes exposing the first conductive type semiconductor layer; a first bump arranged on a first side of the semiconductor stack, the first bump being electrically connected to the first conductive type semiconductor layer via the plurality of contact holes; a second bump arranged on the first side of the semiconductor stack, the second bump being electrically connected to the second conductive type semiconductor layer; and a protective insulation layer covering a sidewall of the semiconductor stack.

Owner:SEOUL SEMICONDUCTOR

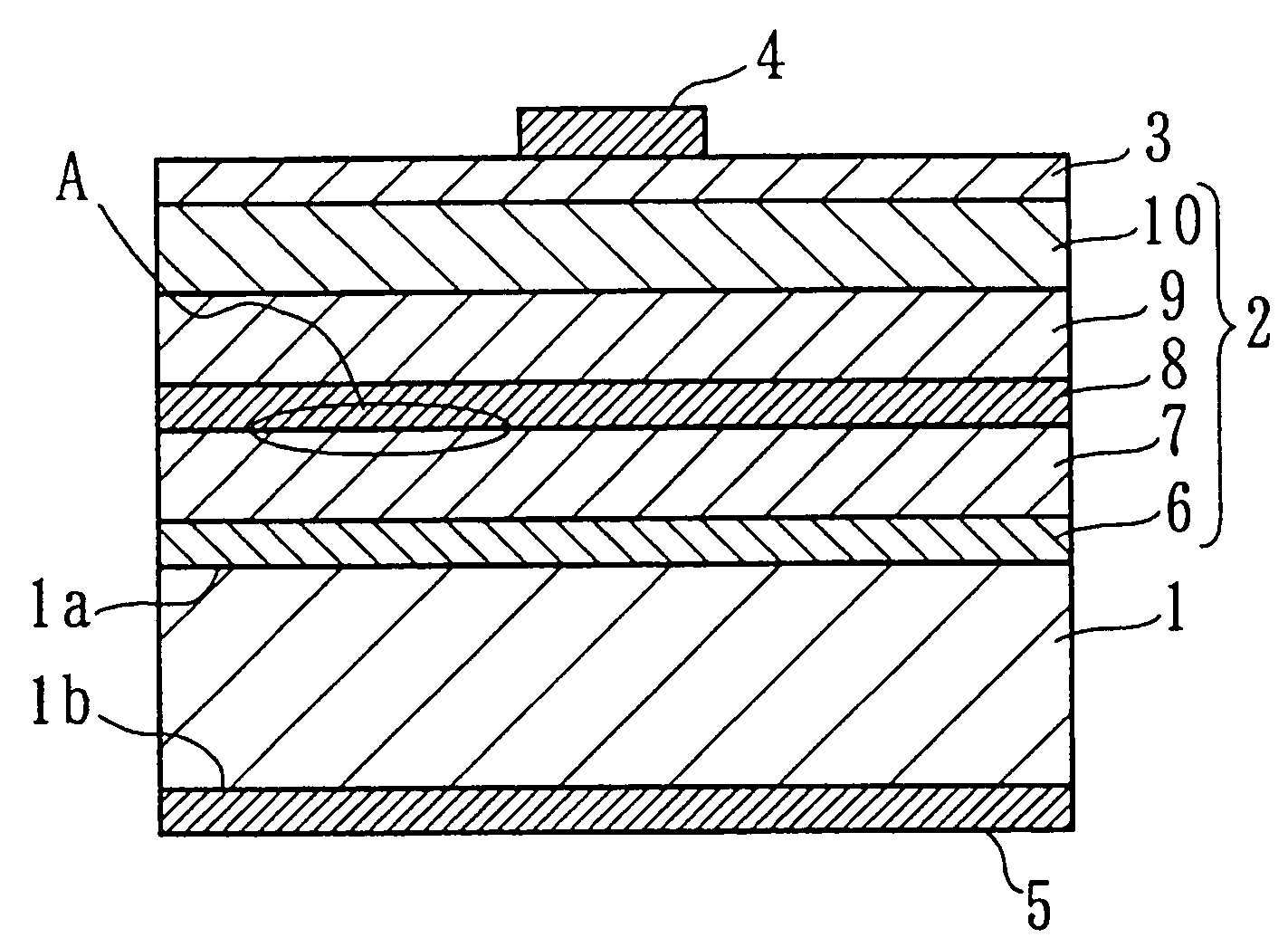

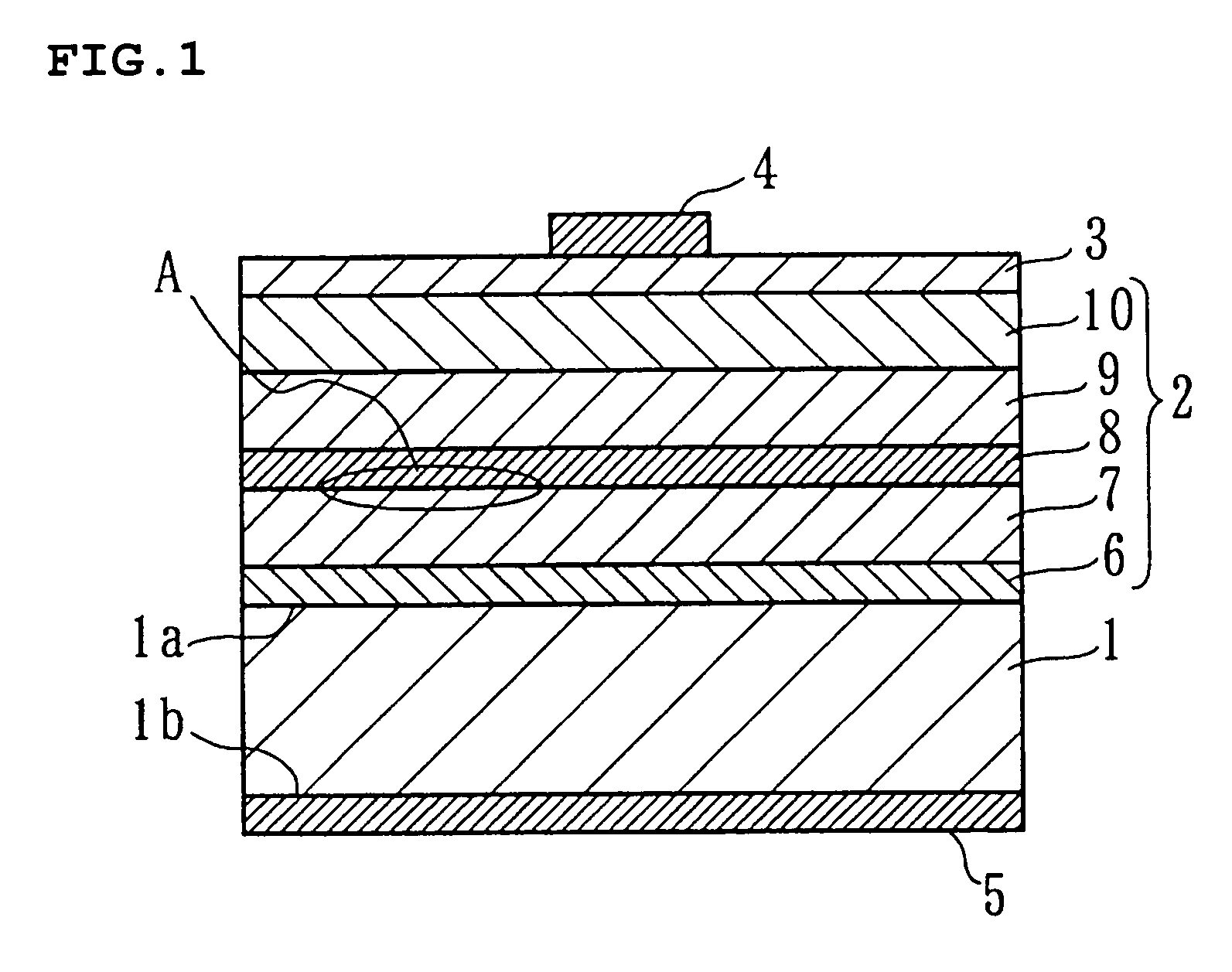

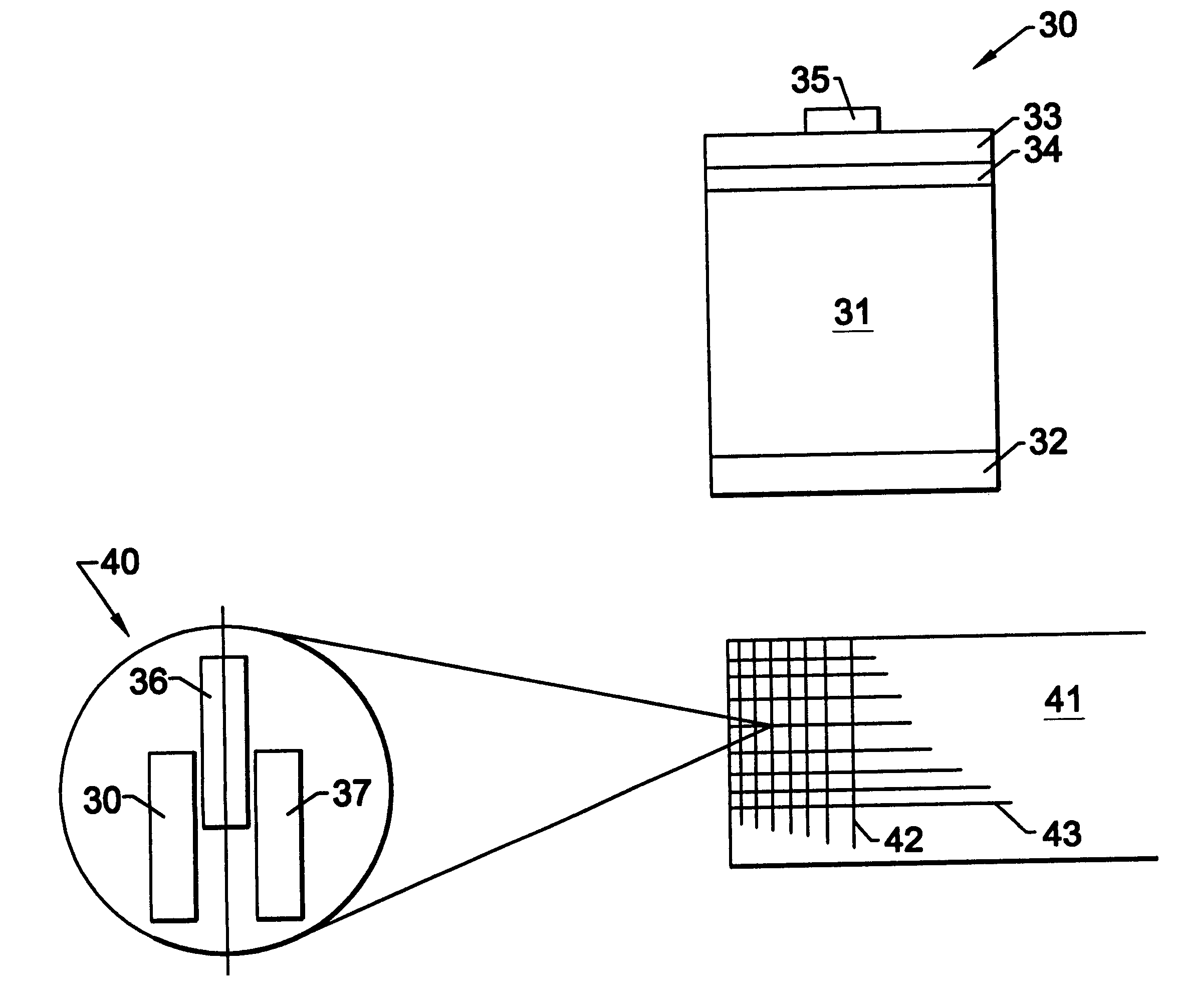

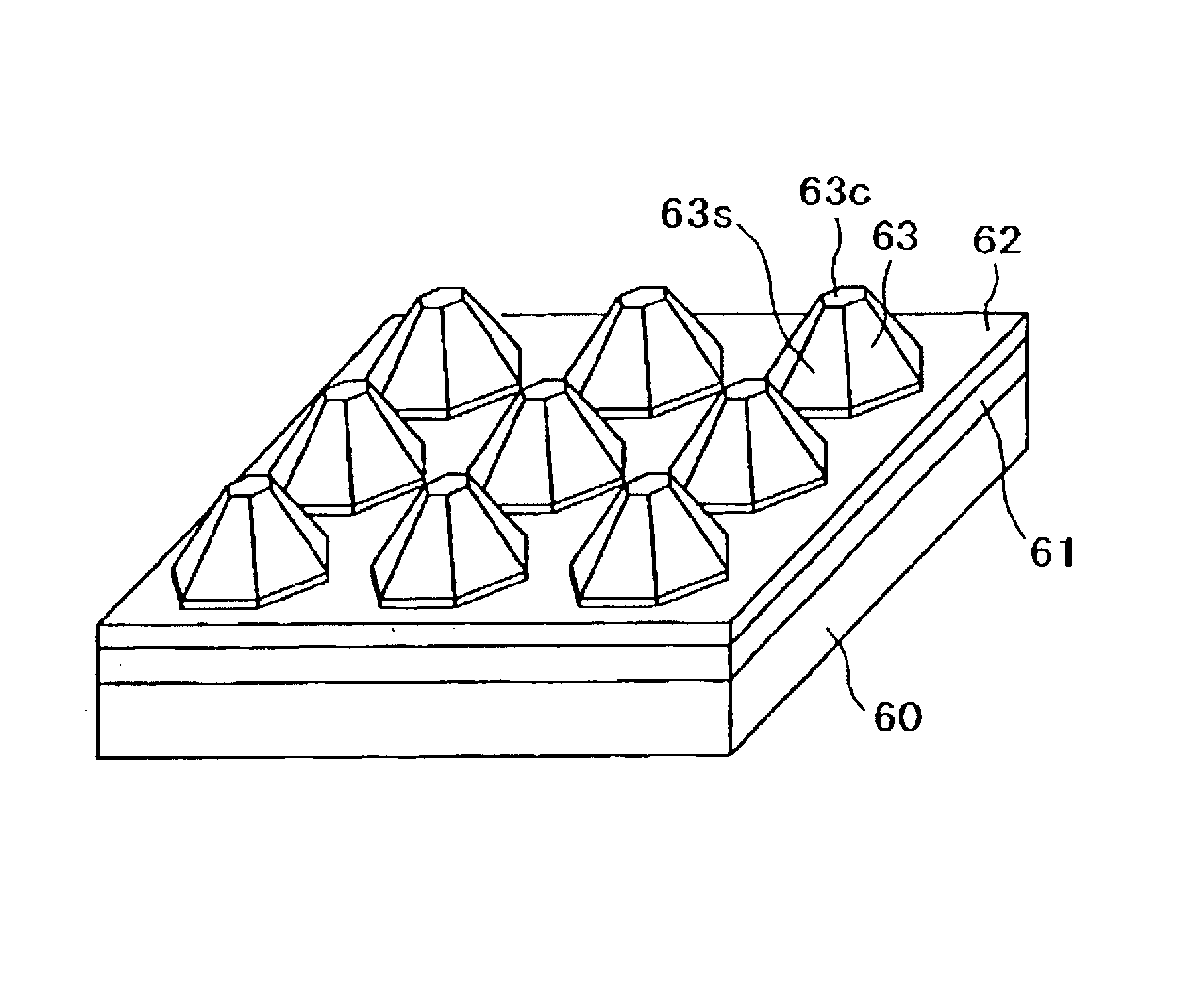

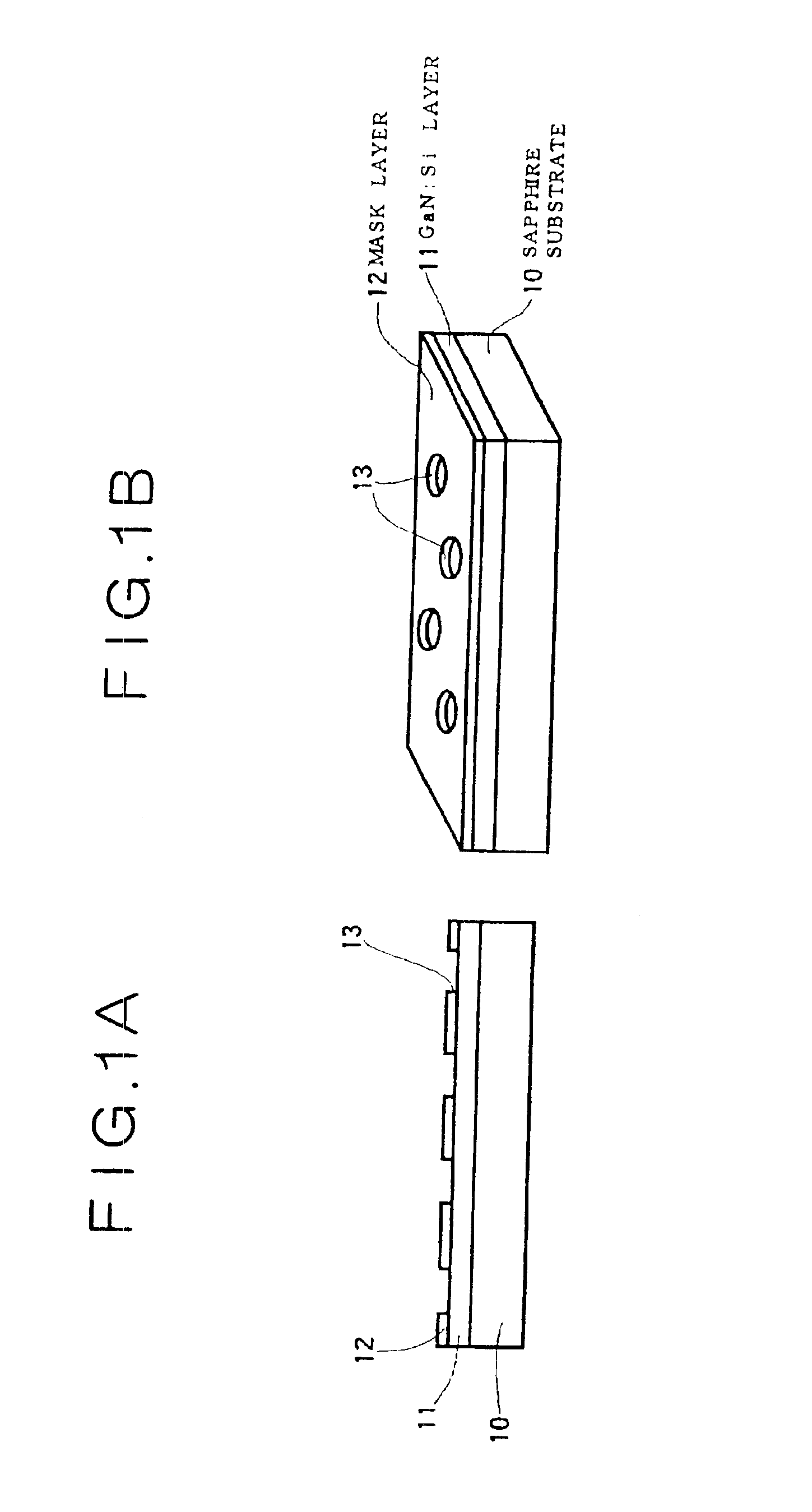

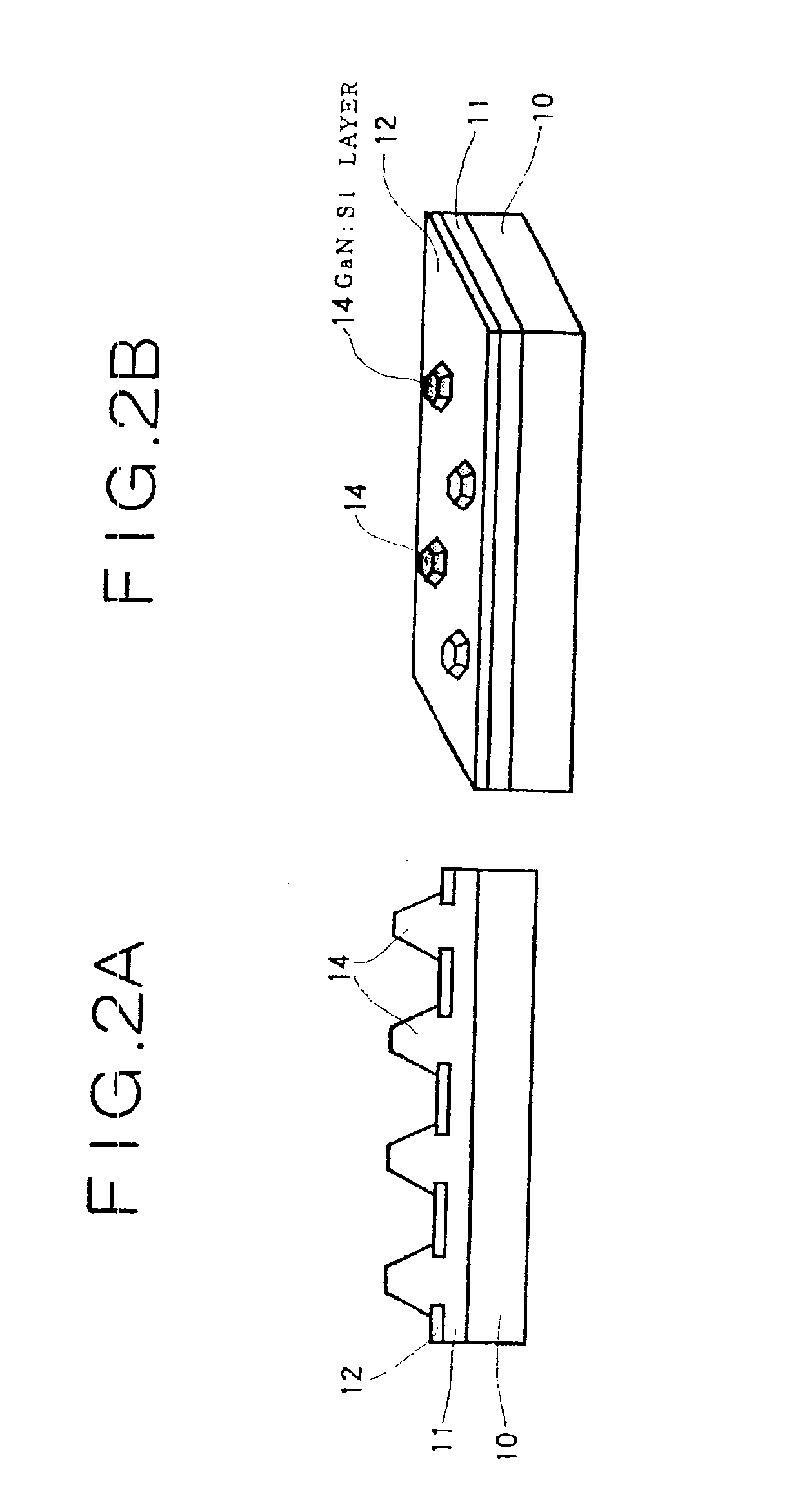

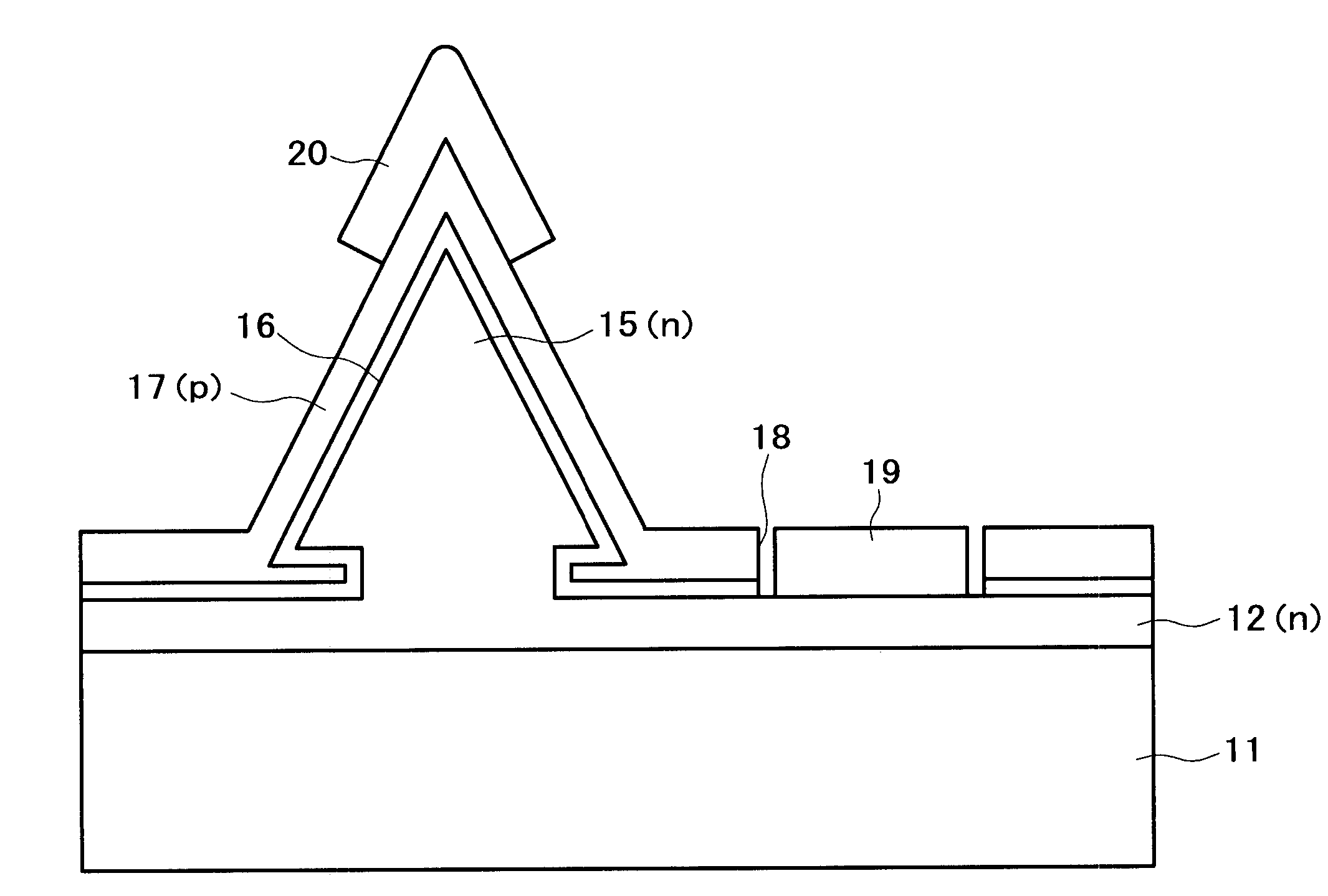

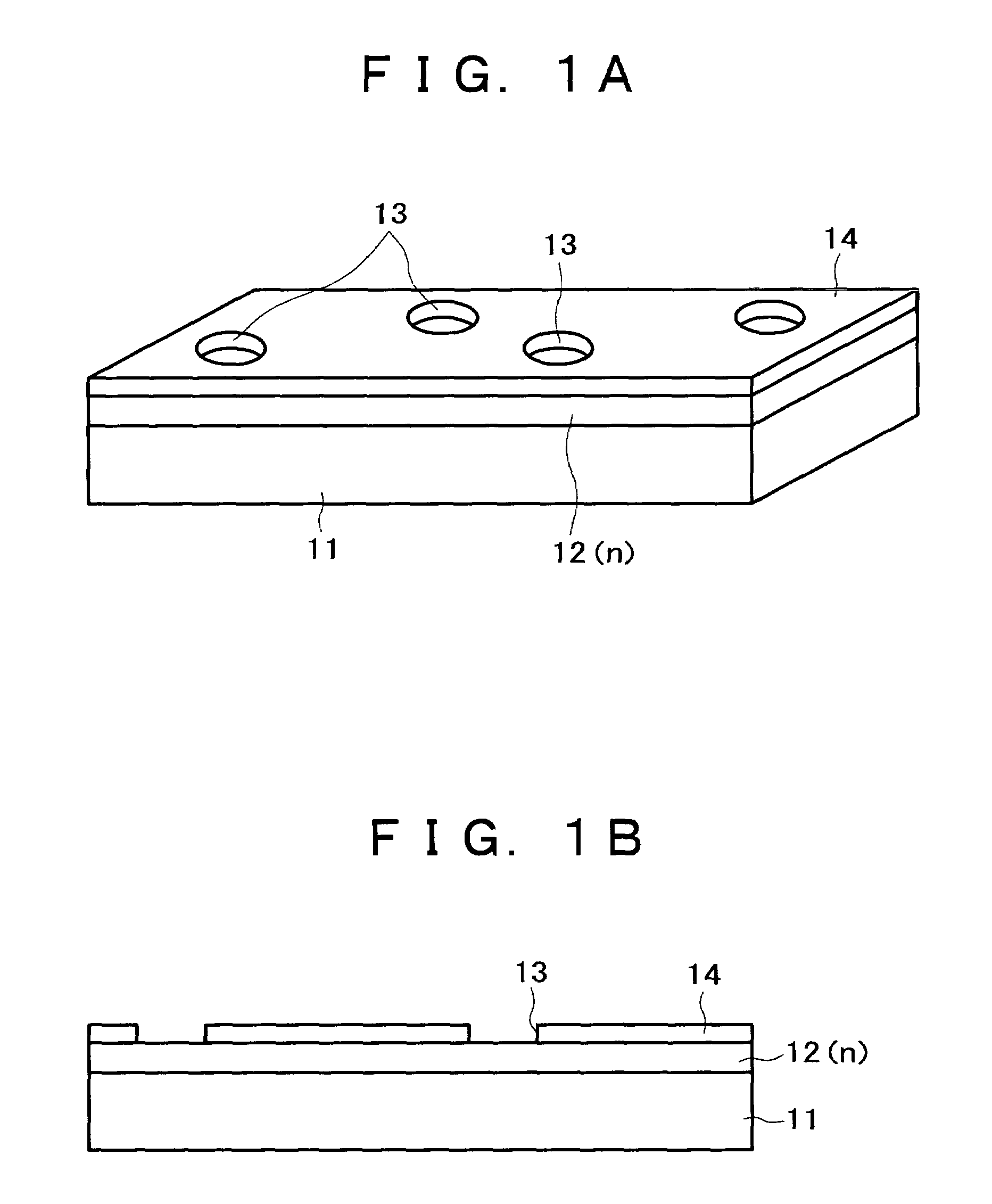

Semiconductor light emitting device integral type semiconductor light emitting unit image display unit and illuminating unit

ActiveUS7002182B2Easily light emittingImprove luminous efficiencySolid-state devicesSemiconductor devicesActive layerLight emitting device

A semiconductor light emitting device with improved luminous efficiency is provided. An underlying n-type GaN layer is grown on a sapphire substrate, and a growth mask made from SiO2 film or the like is formed on the underlying n-type GaN layer. An n-type GaN layer having a hexagonal pyramid shape is selectively grown on a portion, exposed from an opening of the growth mask, of the underlying n-type GaN layer. The growth mask is removed by etching, and then an active layer and a p-type GaN layer are sequentially grown on the entire substrate so as to cover the hexagonal pyramid shaped n-type GaN layer, to form a light emitting device. An n-side electrode and a p-side electrode are then formed.

Owner:SAMSUNG ELECTRONICS CO LTD

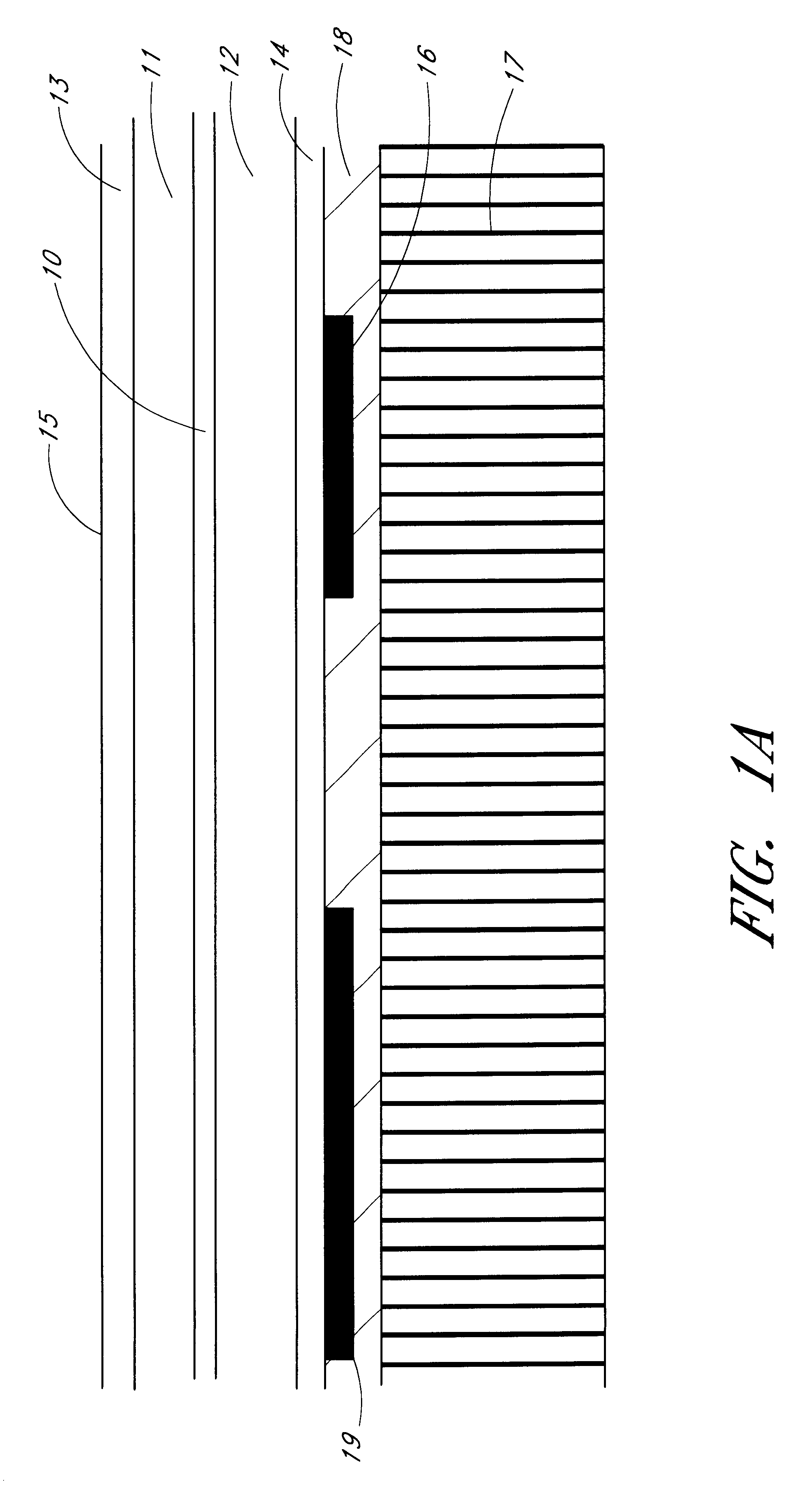

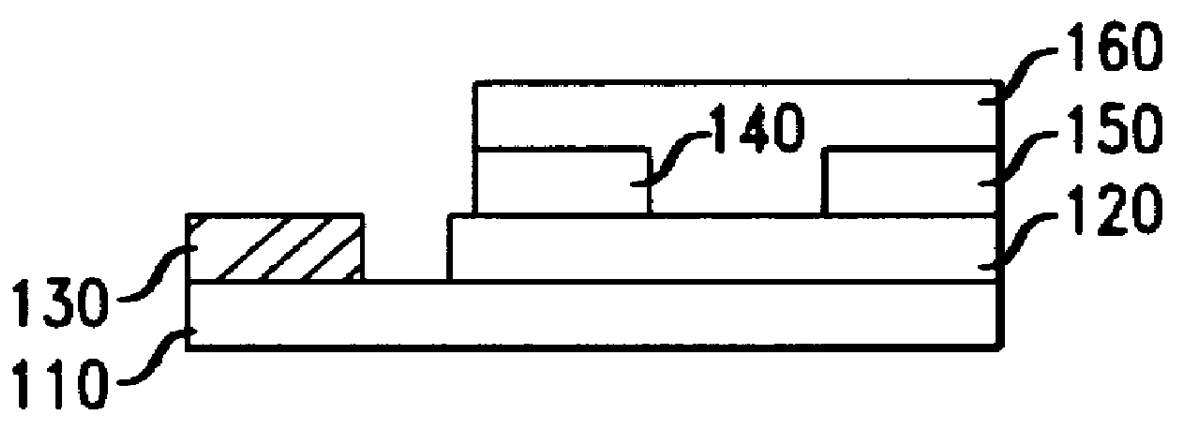

Method of making an organic thin film transistor

A process for fabricating thin film transistors in which the active layer is an organic semiconducting material with a carrier mobility greater than 10-3 cm2 / Vs and a conductivity less than about 10-6 S / cm at 20 DEG C. is disclosed. The organic semiconducting material is a regioregular (3-alkylthiophene) polymer. The organic semiconducting films are formed by applying a solution of the regioregular polymer and a solvent over the substrate. The poly (3-alkylthiophene) films have a preferred orientation in which the thiophene chains has a planar stacking so the polymer backbone is generally parallel to the substrate surface.

Owner:BELL SEMICON LLC +2

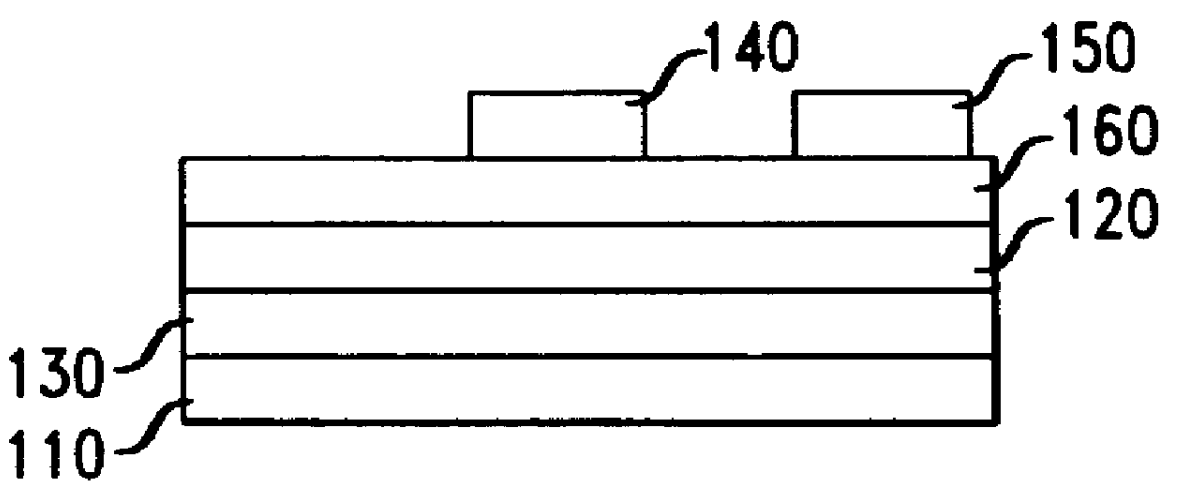

Semiconductor light emitting device and fabrication method thereof

InactiveUS6967353B2Improve luminous efficiencyIncrease brightnessSolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeActive layer

A semiconductor light emitting device includes a crystal layer formed on a substrate, the crystal layer having a tilt crystal plane tilted from the principal plane of the substrate, and a first conductive type layer, an active layer, and a second conductive type layer, which are formed on the crystal layer in such a manner as to extend within planes parallel to the tilt crystal plane, wherein the device has a shape formed by removing the apex and its vicinity of the stacked layer structure formed on the substrate. Such a semiconductor light emitting device is excellent in luminous efficiency even if the device has a three-dimensional device structure. The present invention also provides a method of fabricating the above semiconductor light emitting device.

Owner:SAMSUNG ELECTRONICS CO LTD

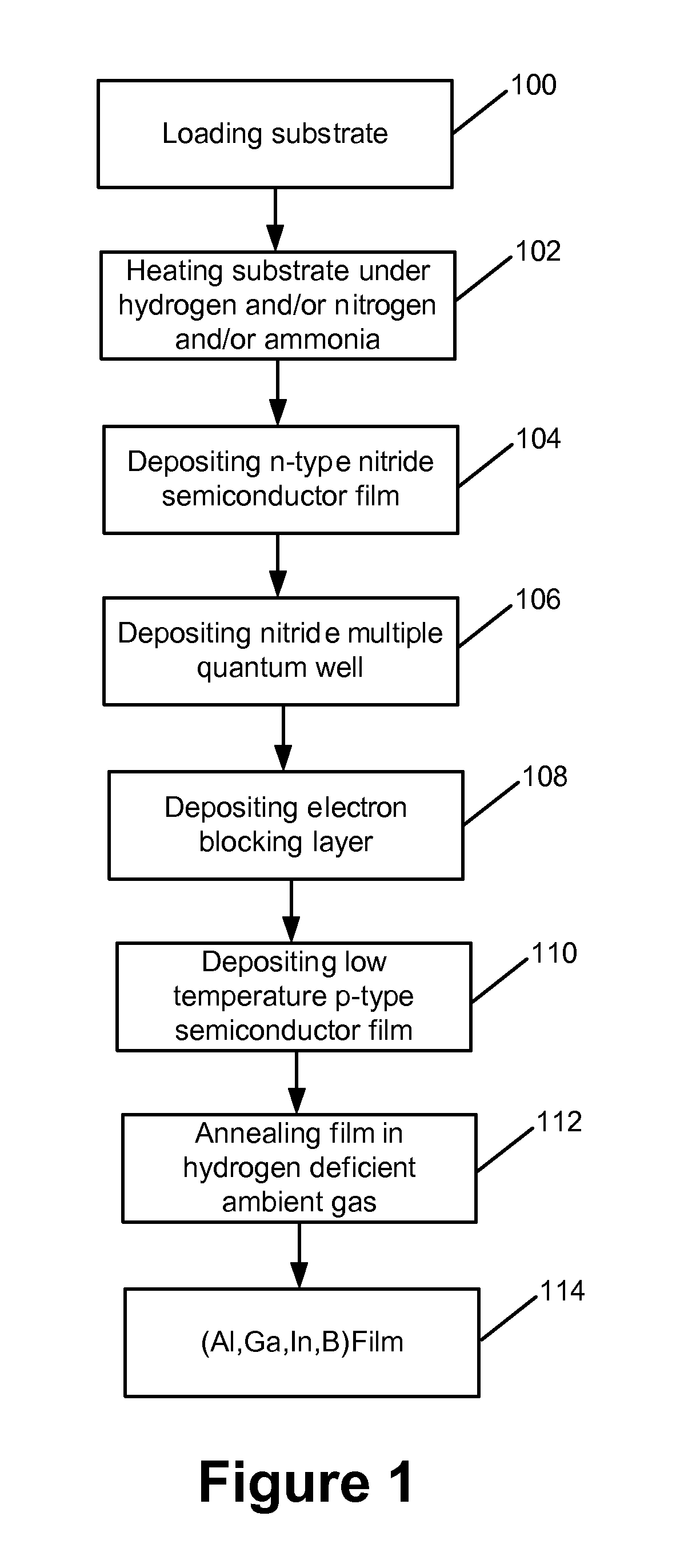

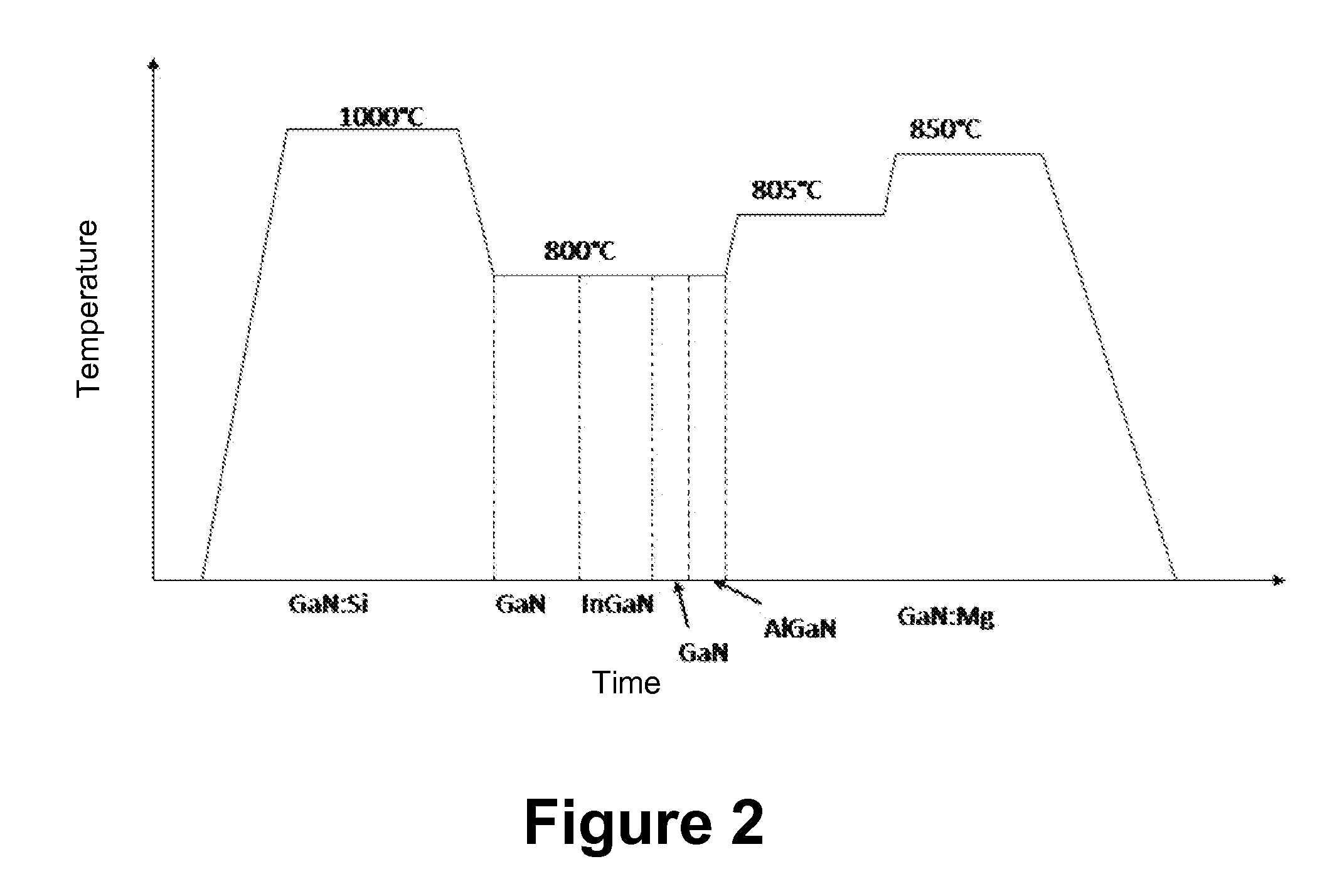

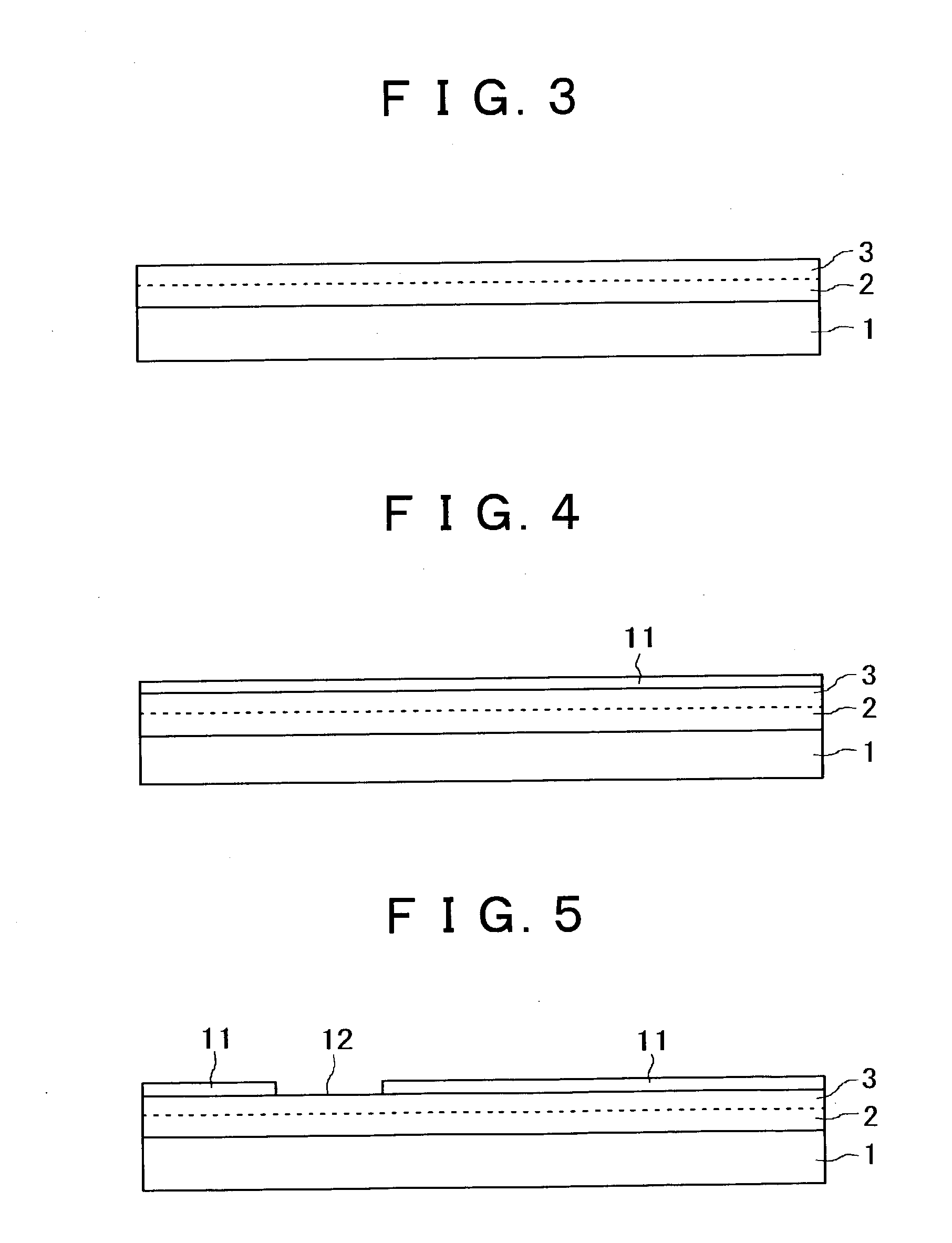

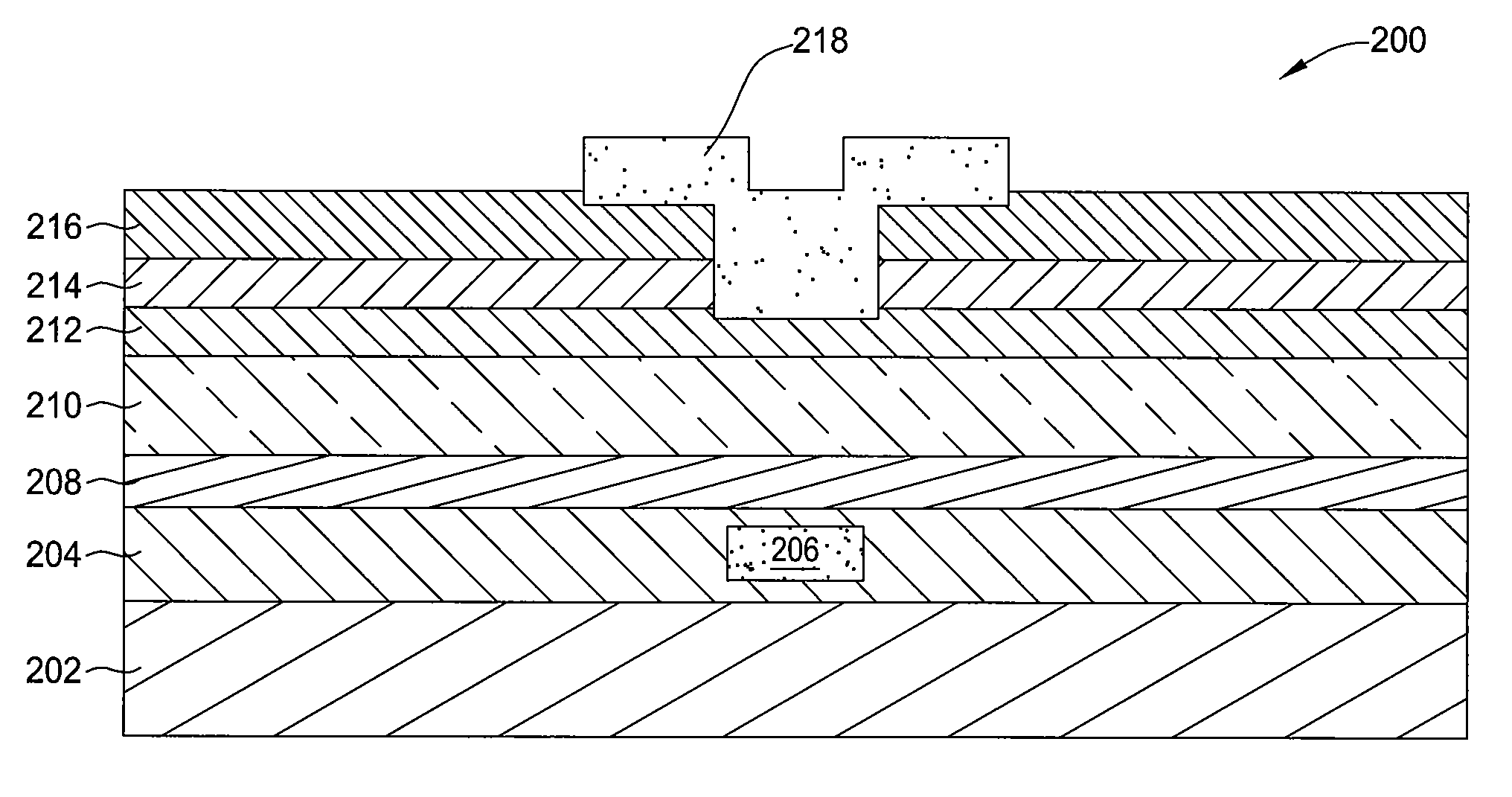

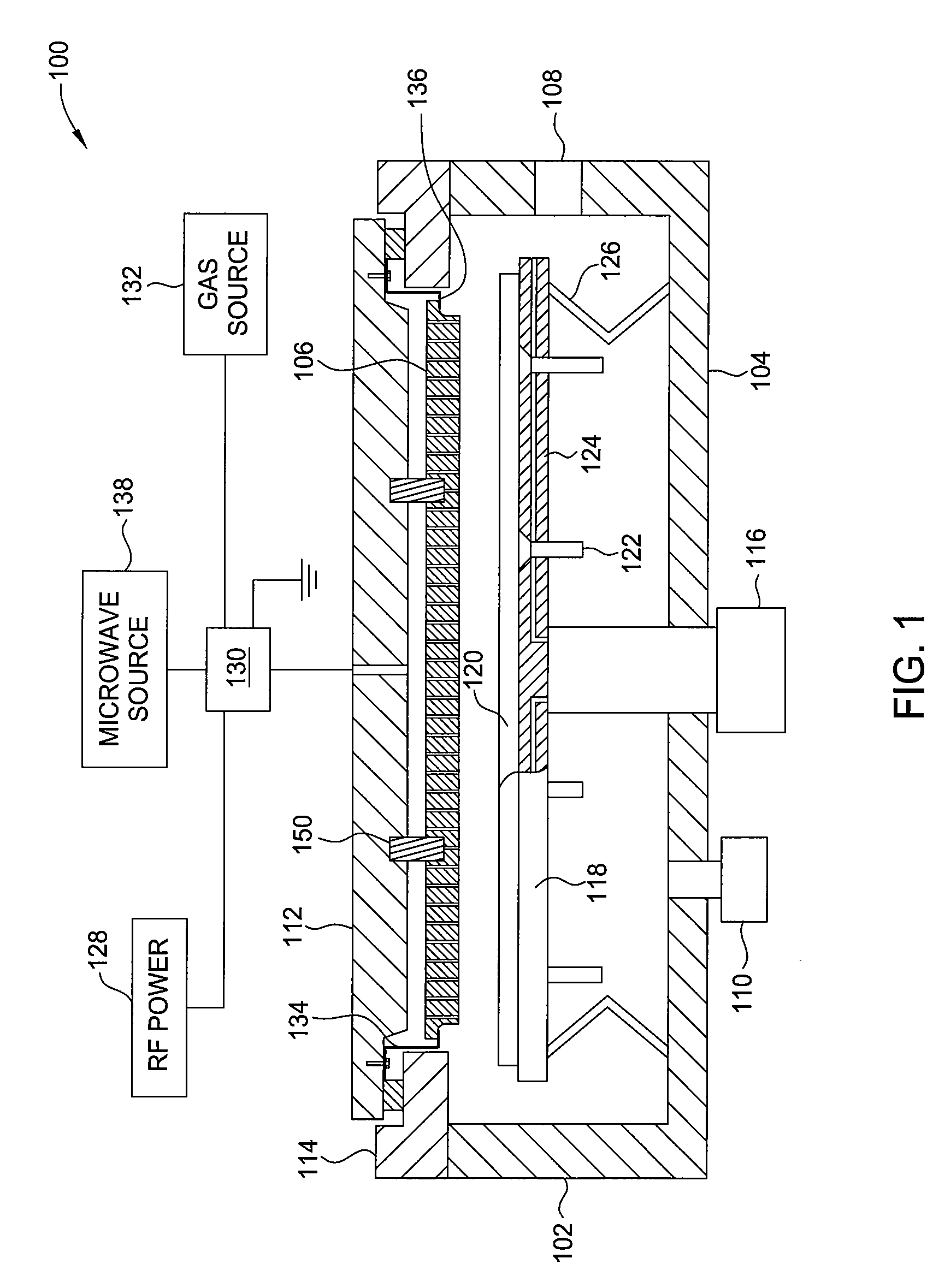

Low temperature thin film transistor process, device property, and device stability improvement

InactiveUS20090261331A1Low deposition rateIncrease deposition rateTransistorSemiconductor/solid-state device manufacturingDevice PropertiesHigh rate

A method and apparatus for forming a thin film transistor is provided. A gate dielectric layer is formed, which may be a bilayer, the first layer deposited at a low rate and the second deposited at a high rate. In some embodiments, the first dielectric layer is a silicon rich silicon nitride layer. An active layer is formed, which may also be a bilayer, the first active layer deposited at a low rate and the second at a high rate. The thin film transistors described herein have superior mobility and stability under stress.

Owner:APPLIED MATERIALS INC

Field effect transistor with amorphous oxide layer containing microcrystals

InactiveUS20090179199A1Reduced electron mobilityLow conductivitySolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorActive layer

A novel amorphous oxide applicable, for example, to an active layer of a TFT is provided. The amorphous oxide comprises microcrystals.

Owner:CANON KK +1

Lithium anodes for electrochemical cells

InactiveUS7247408B2Light weightFinal product manufactureElectrode carriers/collectorsLithium metalReactive gas

Provided is an anode for use in electrochemical cells, wherein the anode active layer has a first layer comprising lithium metal and a multi-layer structure comprising single ion conducting layers and polymer layers in contact with the first layer comprising lithium metal or in contact with an intermediate protective layer, such as a temporary protective metal layer, on the surface of the lithium-containing first layer. Another aspect of the invention provides an anode active layer formed by the in-situ deposition of lithium vapor and a reactive gas. The anodes of the current invention are particularly useful in electrochemical cells comprising sulfur-containing cathode active materials, such as elemental sulfur.

Owner:SION POWER CORP

Power IC having SOI structure

The present invention relates in general to power ICs, etc. having the SOI structure, and more specifically to the structure in which an SOI substrate comprises a base substrate, an SOI oxide film formed on the base substrate, and active layers formed on the SOI oxide film, and also integrates on itself power devices and the corresponding control elements monolithically. Between this base substrate and this SOI oxide film is formed heavily-doped semiconductor regions having a conductivity type opposite to that of this base substrate. Hence, the junction capacitance between the base substrate and the heavily-doped semiconductor regions decreases an actual capacitance between the base substrate and the active layer so that to inhibit or prevent inversion layers from being formed at the bottom of the active layers.

Owner:KK TOSHIBA