Patents

Literature

4386 results about "Charge carrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In physics, a charge carrier is a particle or quasiparticle that is free to move, carrying an electric charge, especially the particles that carry electric charges in electrical conductors. Examples are electrons, ions and holes. In a conducting medium, an electric field can exert force on these free particles, causing a net motion of the particles through the medium; this is what constitutes an electric current. In conducting media, particles serve to carry charge...

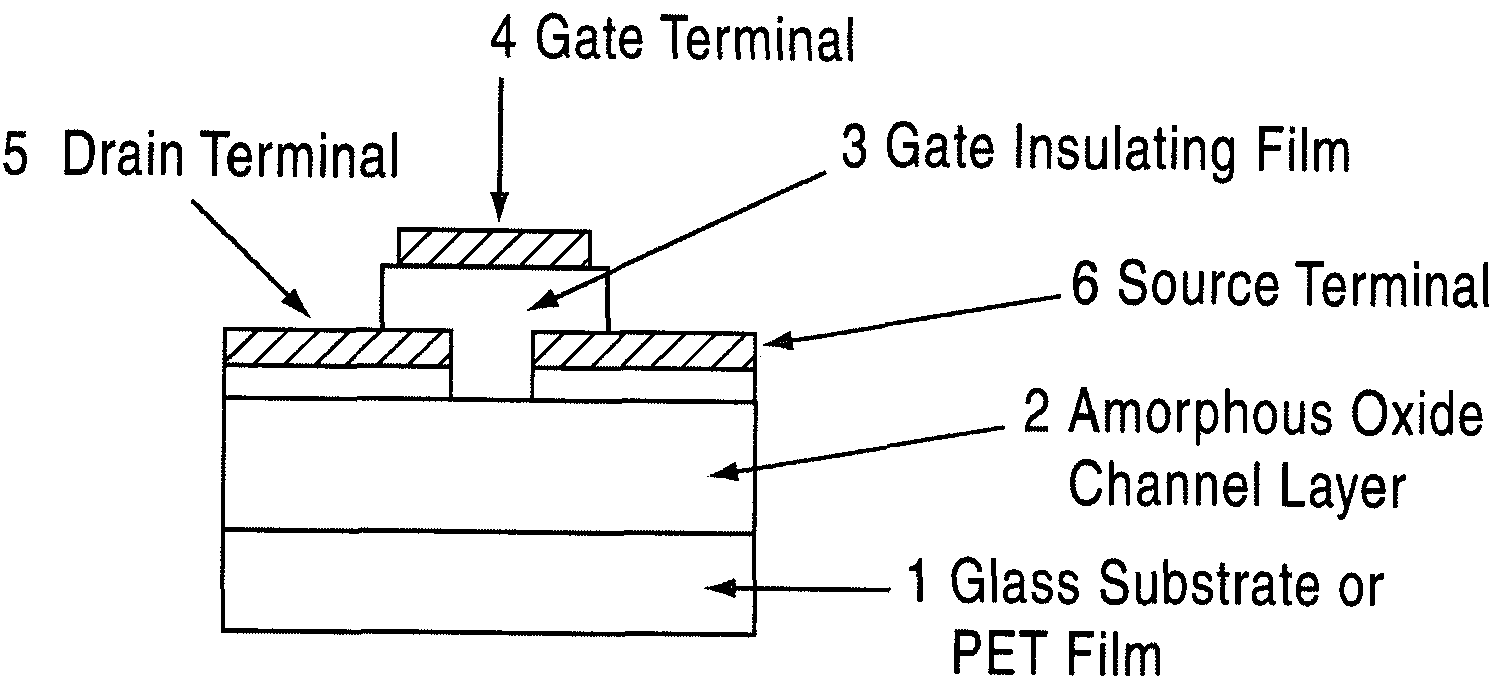

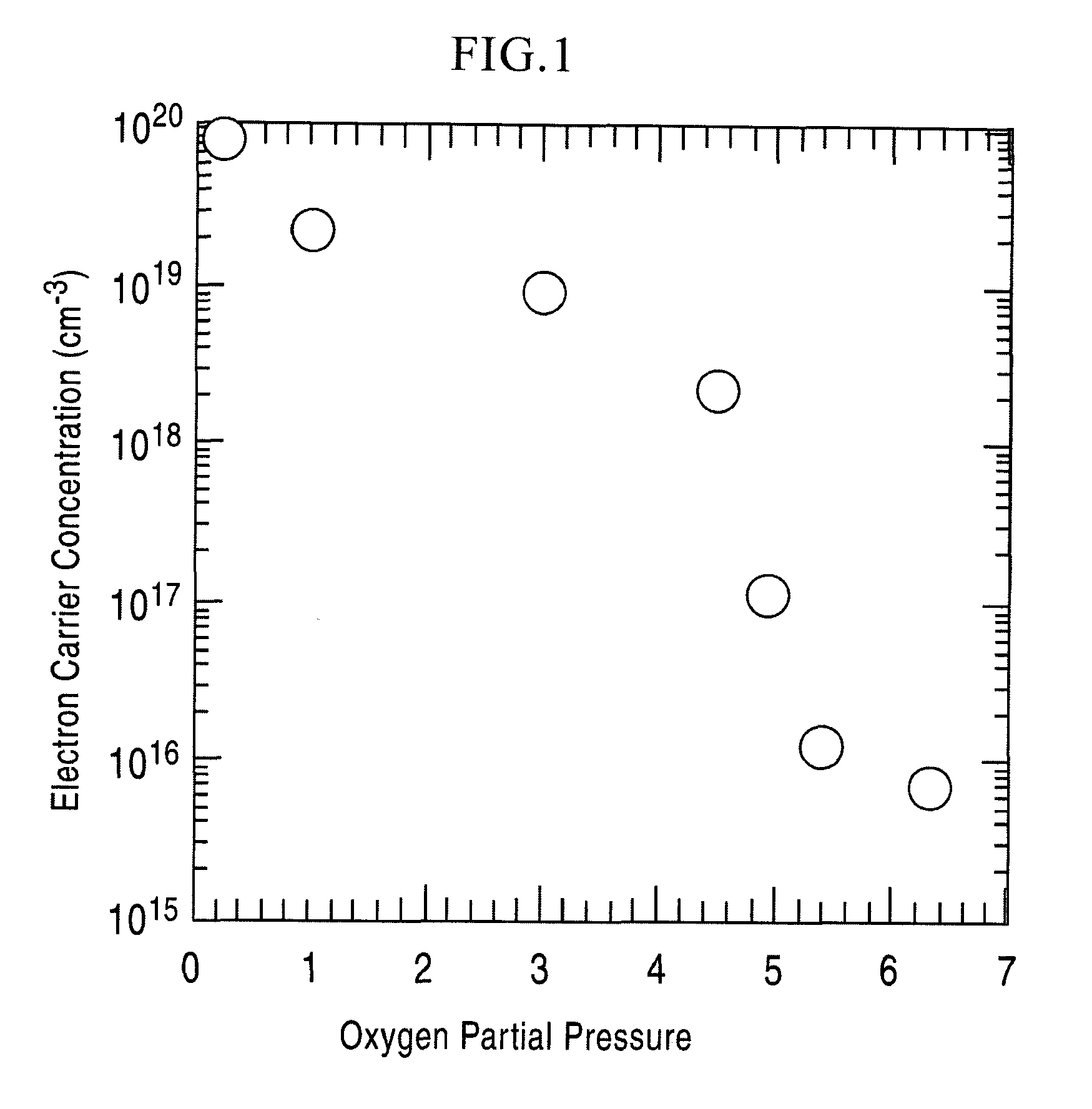

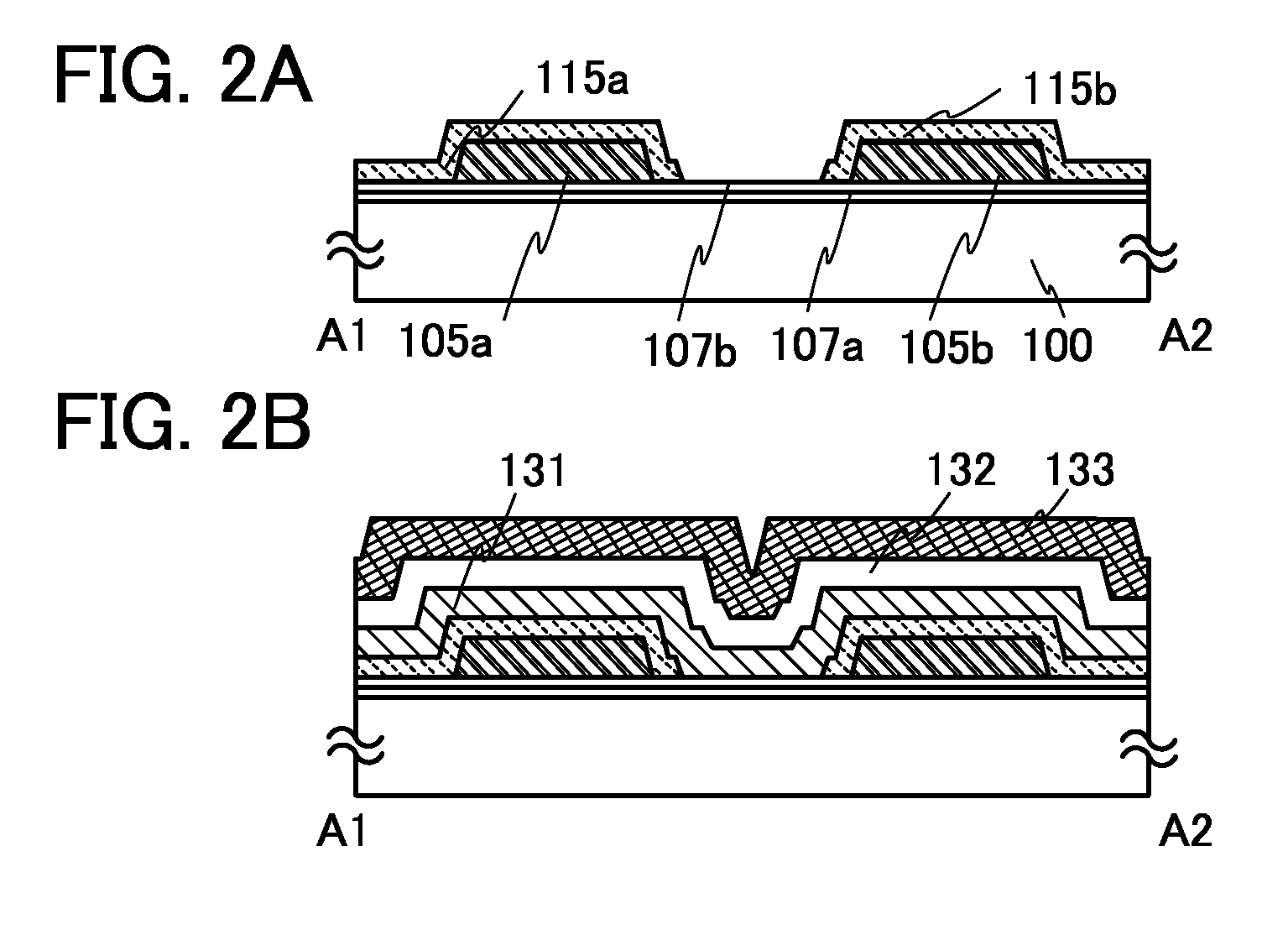

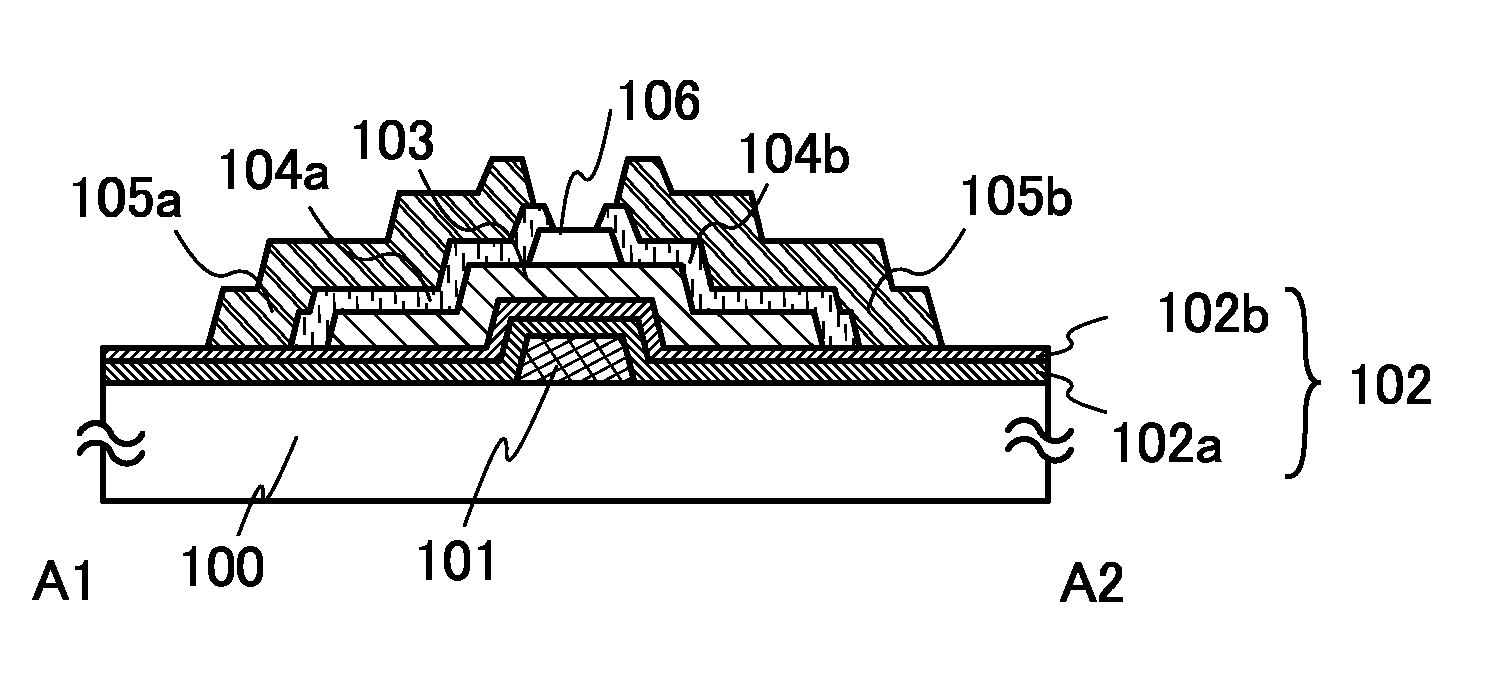

Amorphous Oxide And Thin Film Transistor

InactiveUS20070194379A1High ionicityGeneration of oxygen defects is less frequentTransistorVacuum evaporation coatingCharge carrierElectron

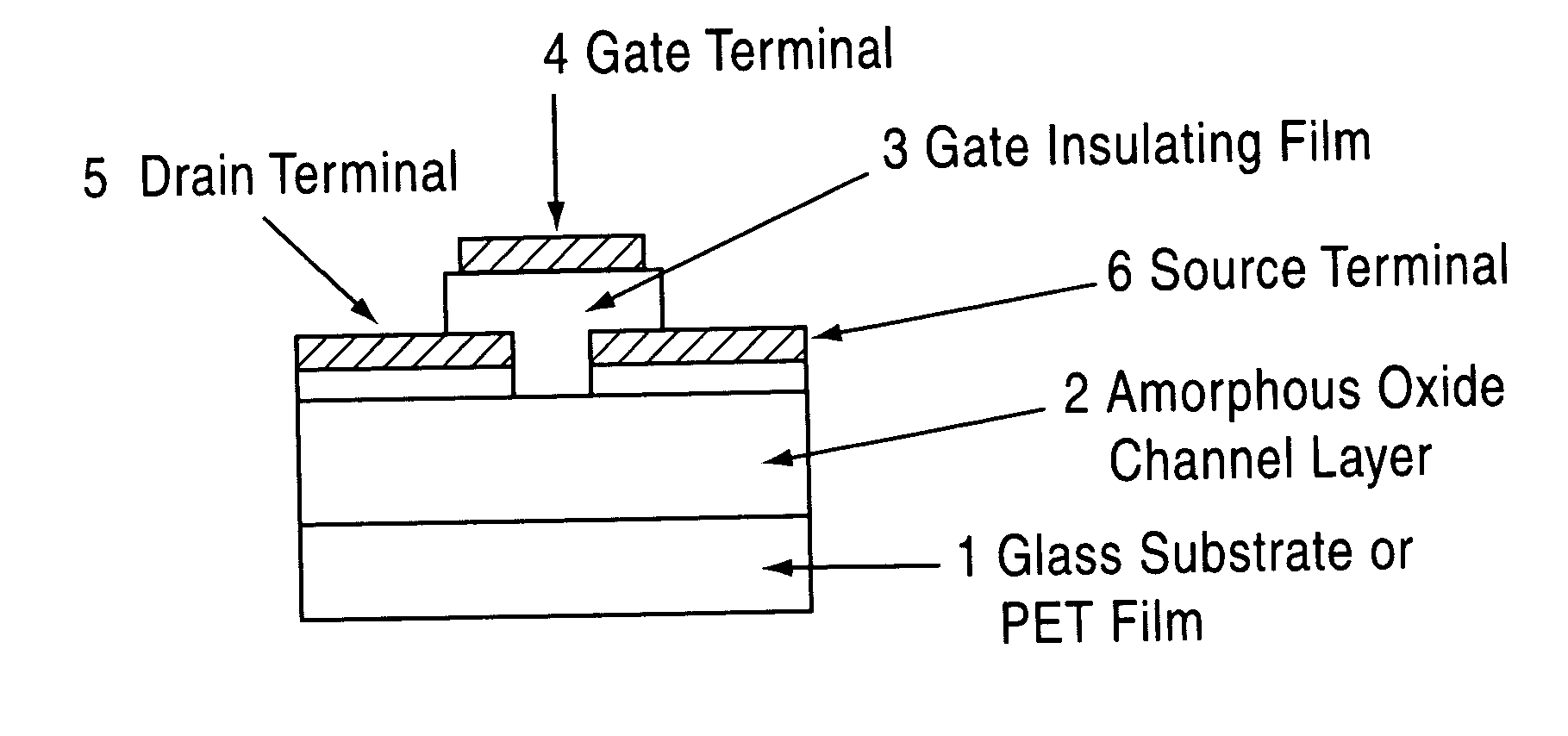

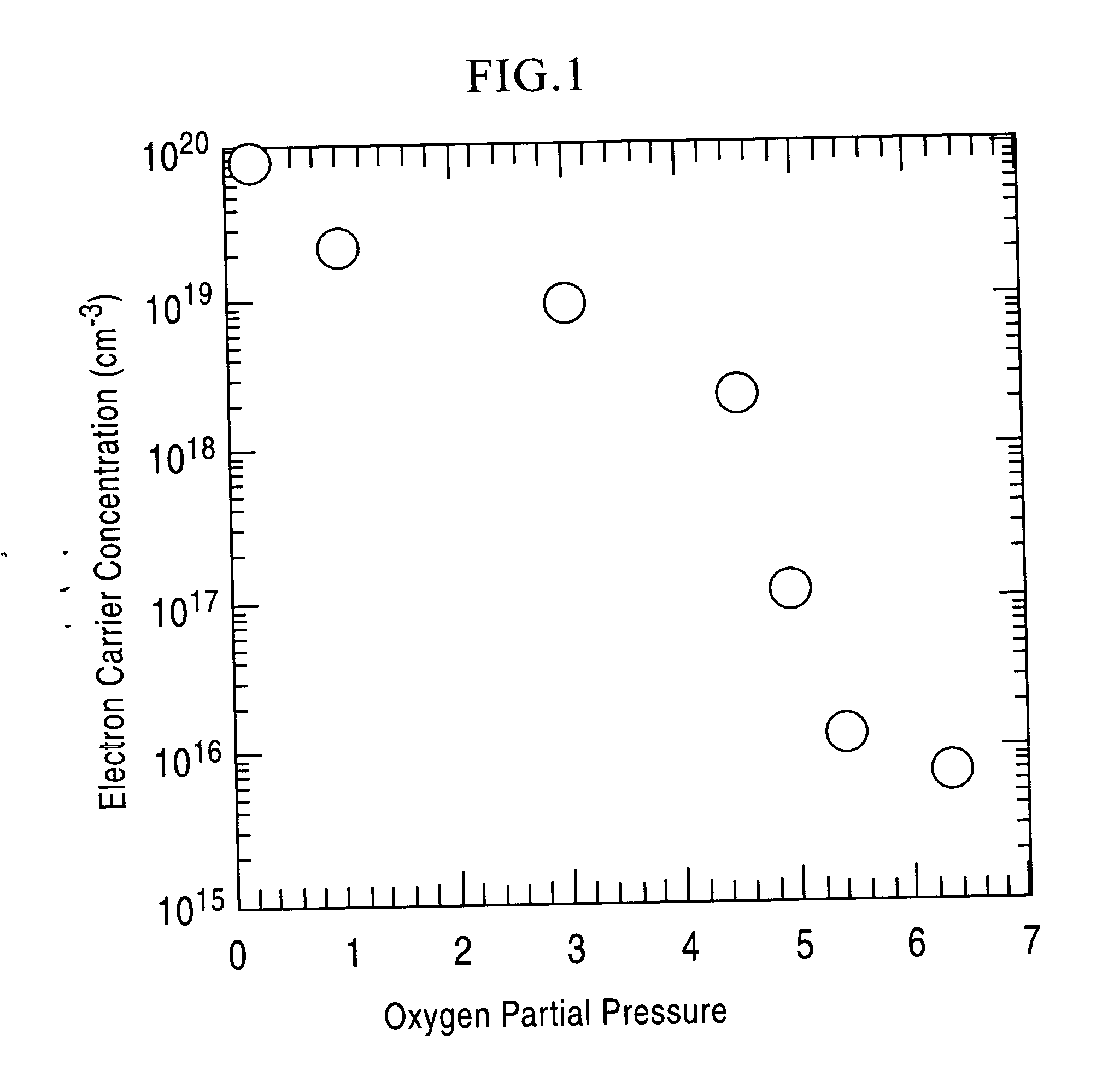

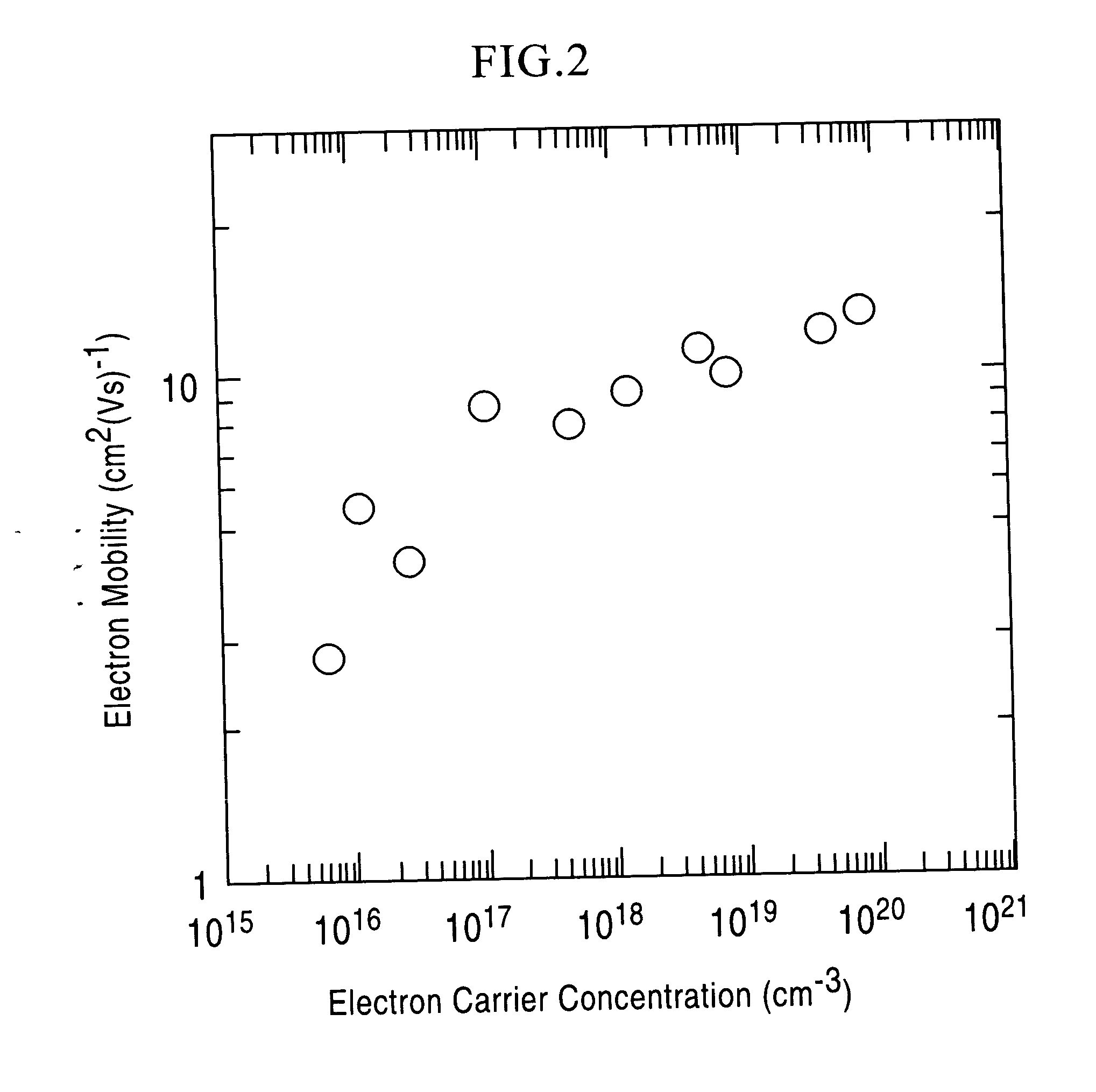

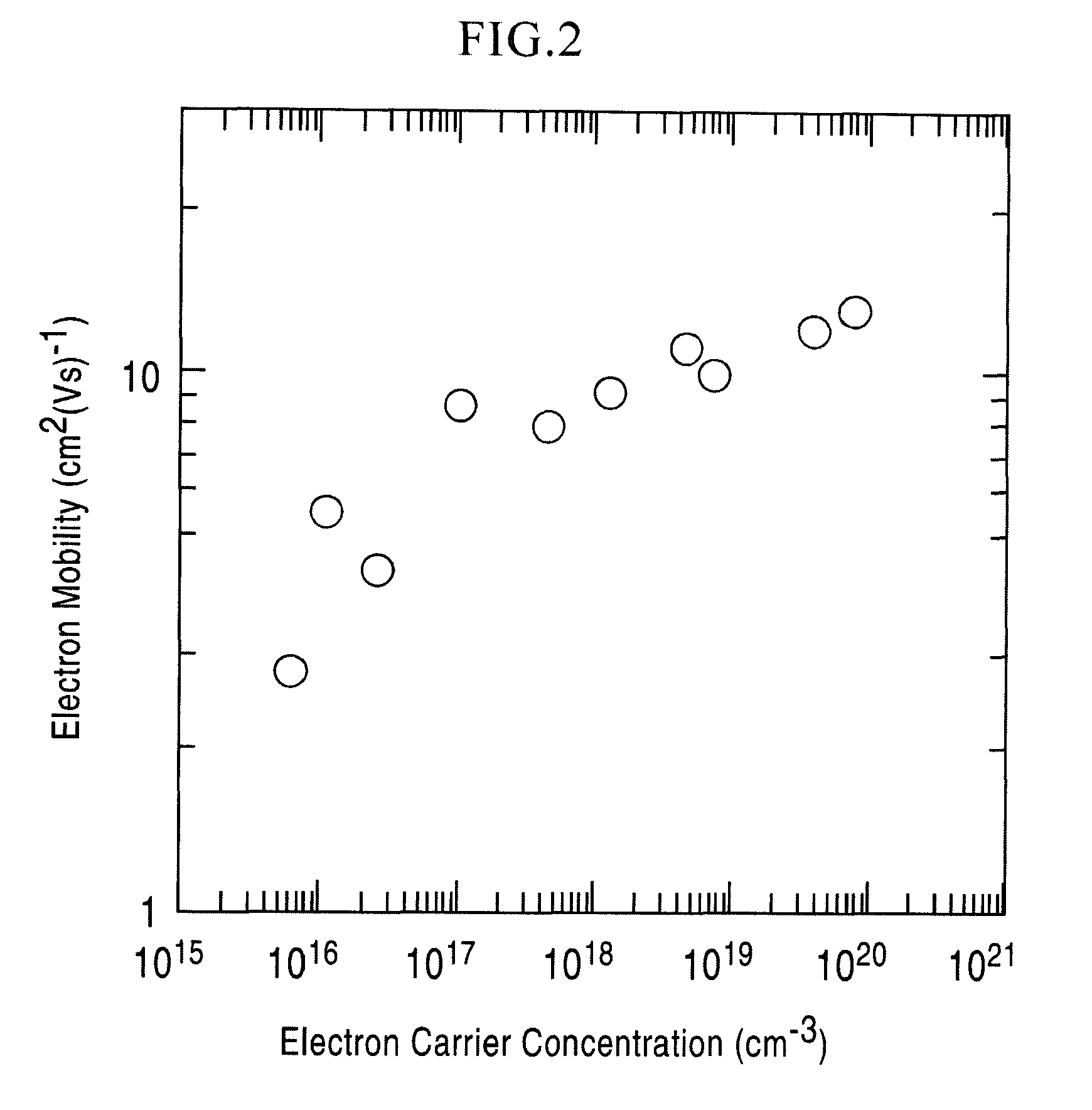

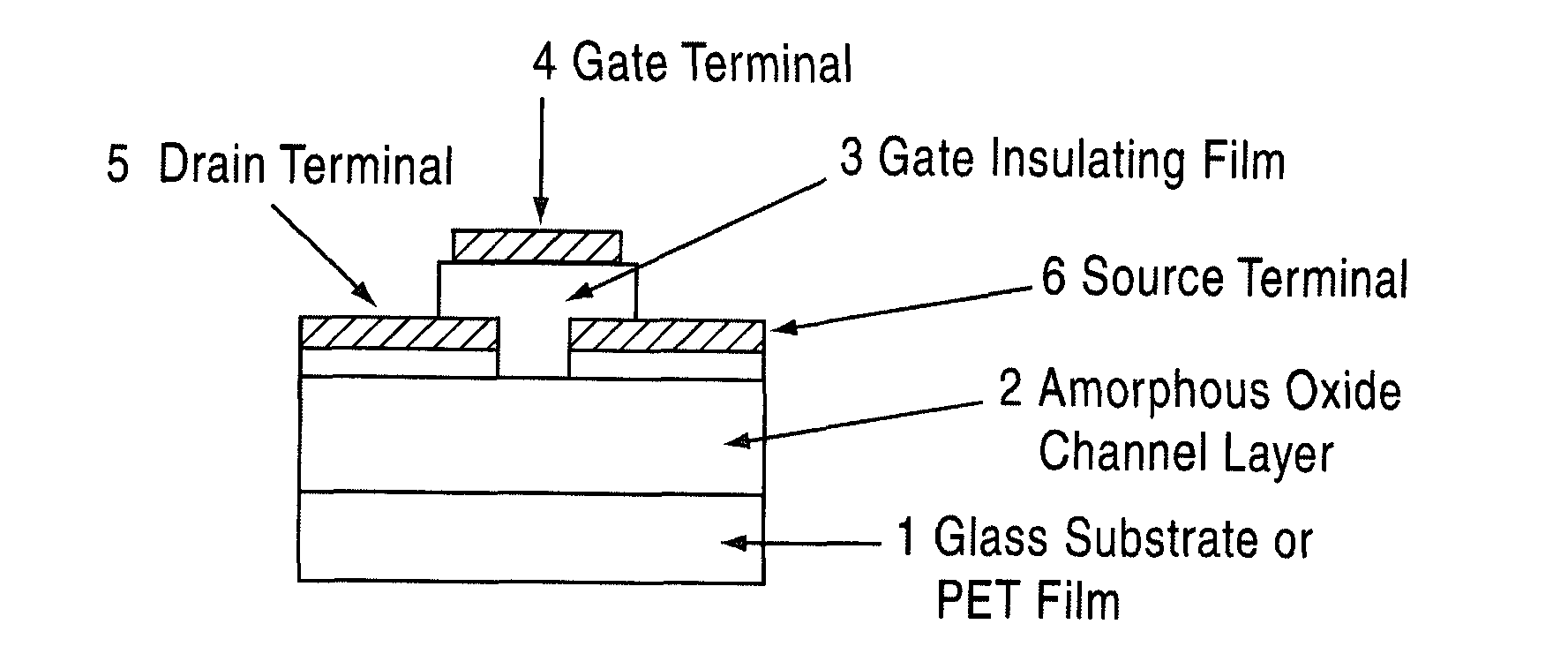

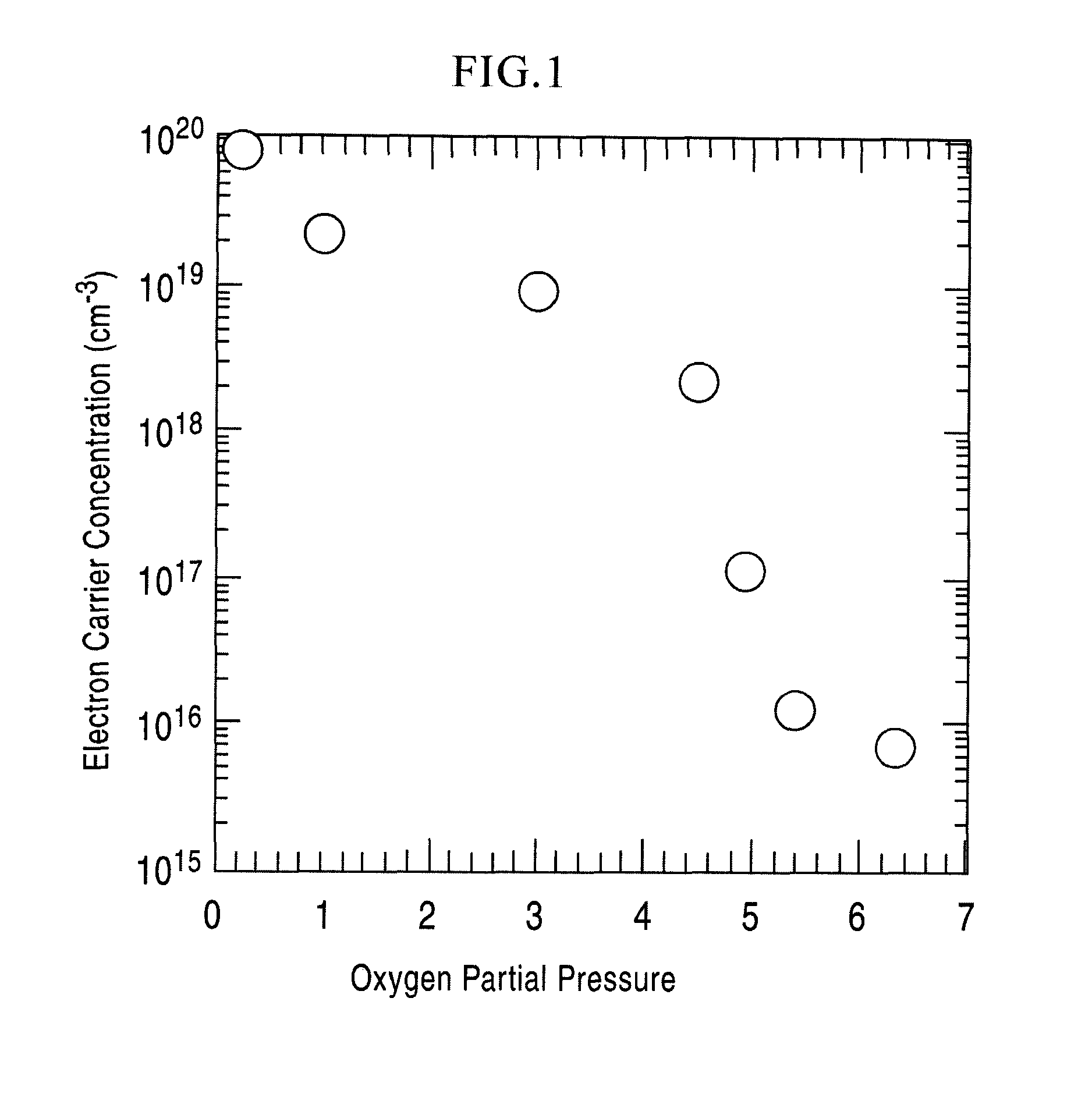

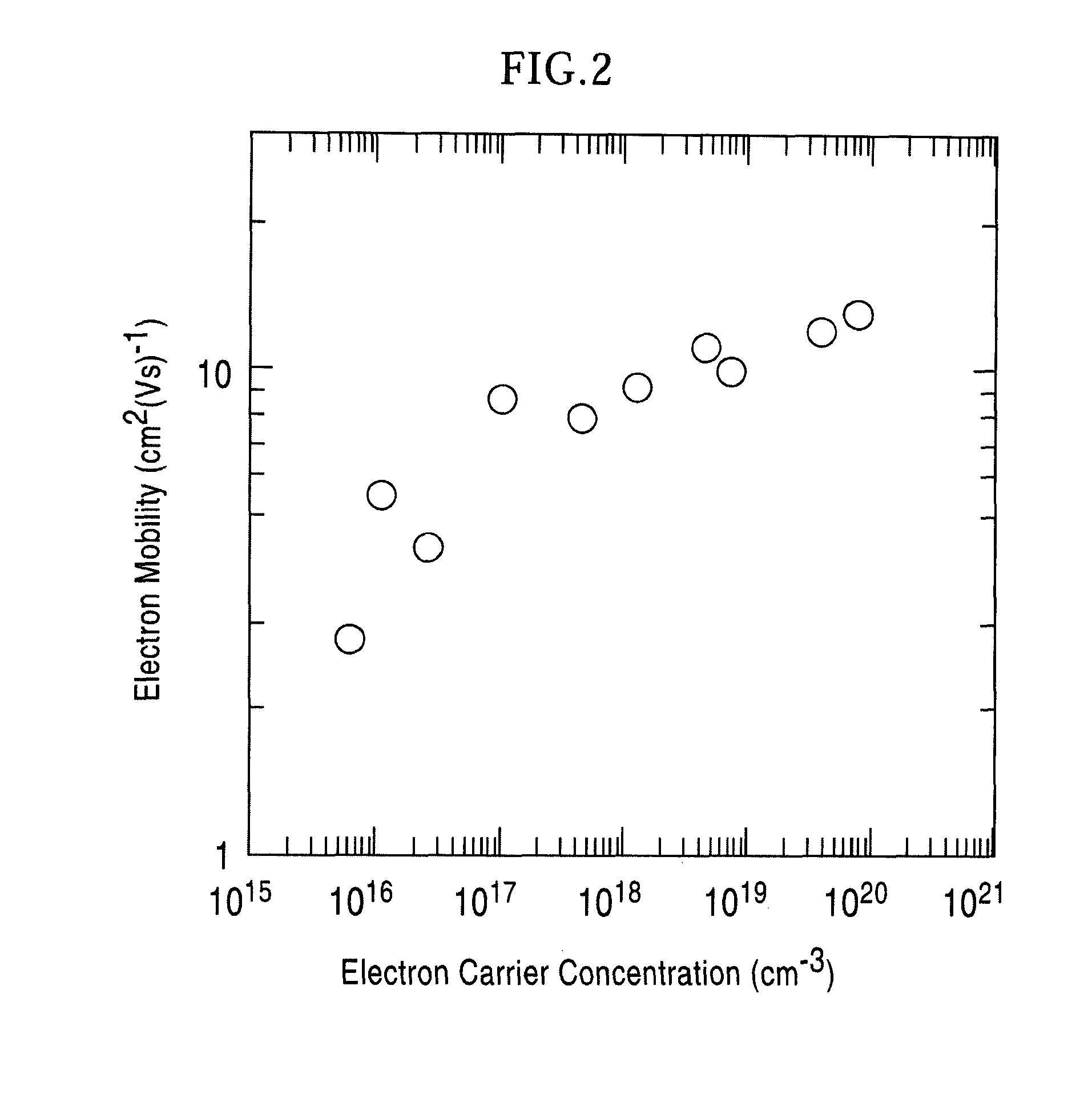

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

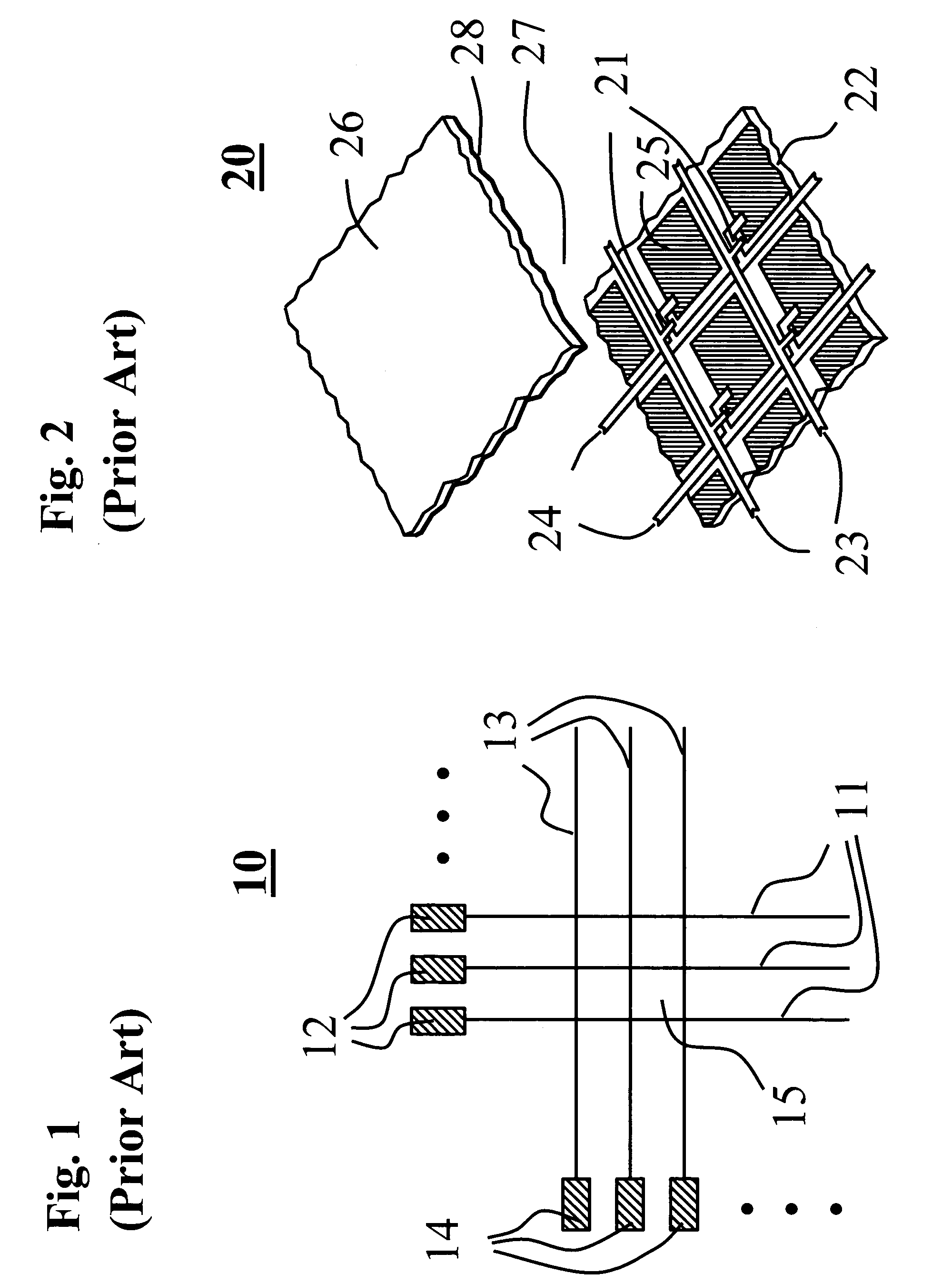

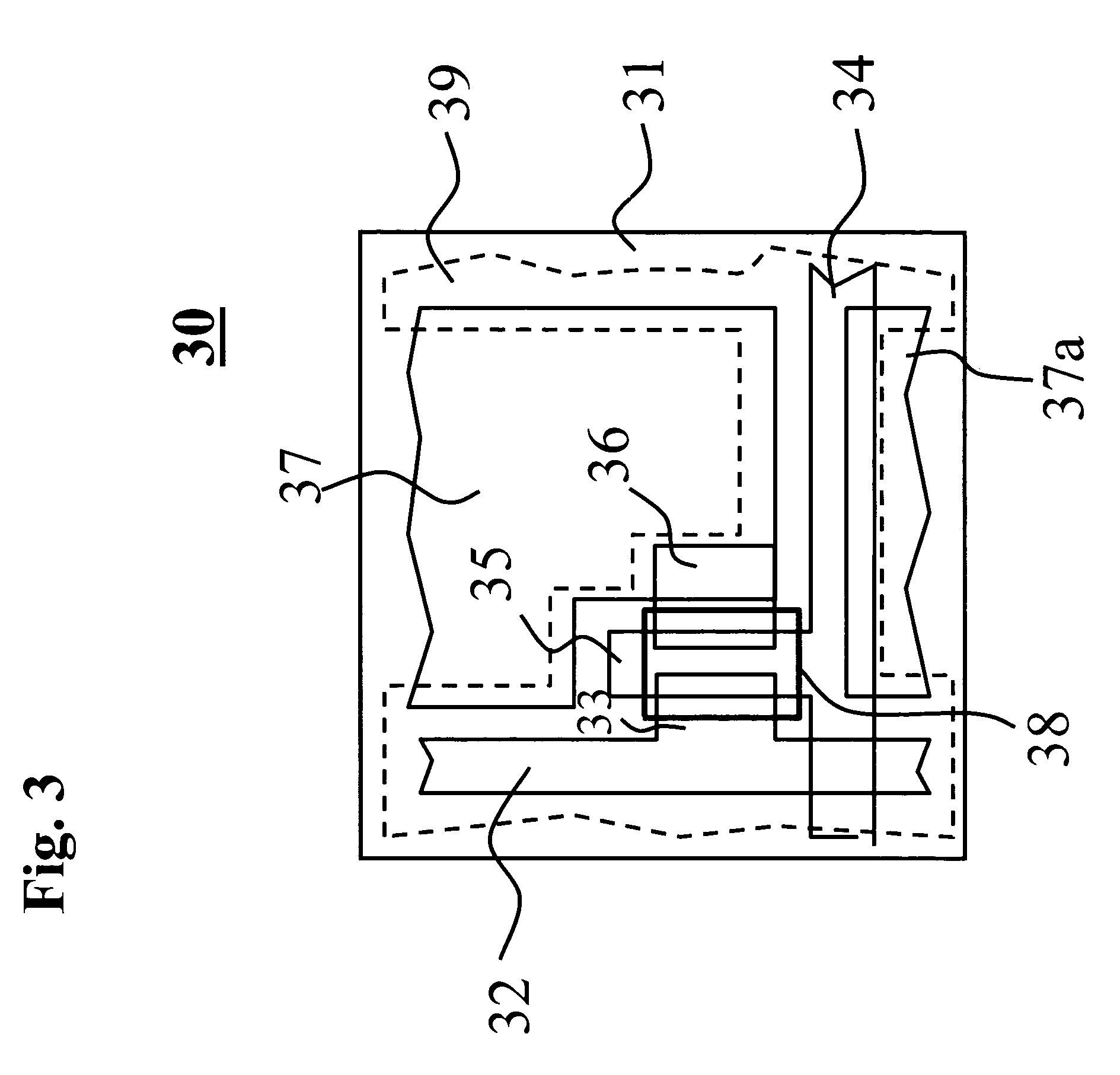

Indium oxide-based thin film transistors and circuits

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

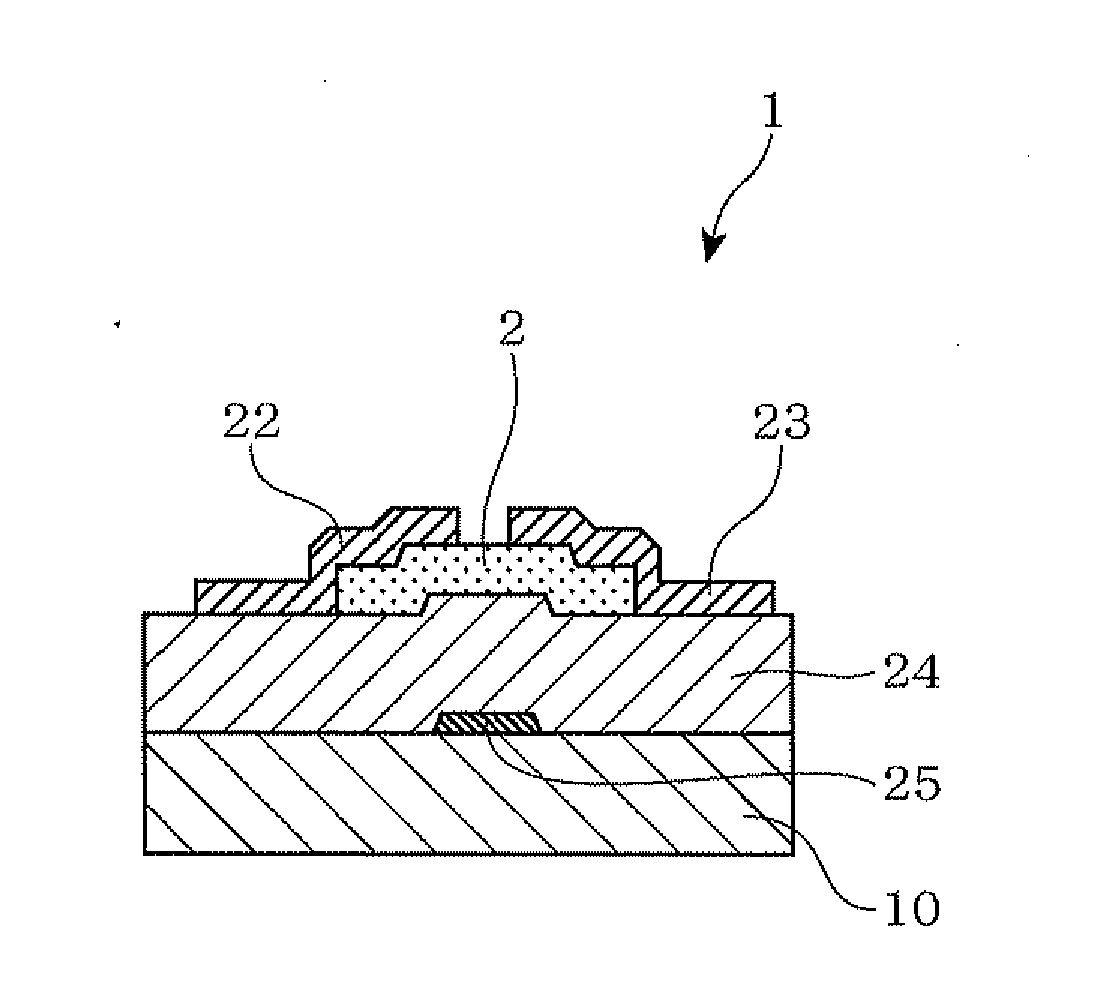

Amorphous oxide and thin film transistor

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

Amorphous oxide and thin film transistor

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP +2

Phosphorescent compound, a phosphorescent composition and an organic light-emitting device

InactiveUS7250226B2Improve efficiencyDischarge tube luminescnet screensLamp detailsOrganic light emitting deviceCharge carrier

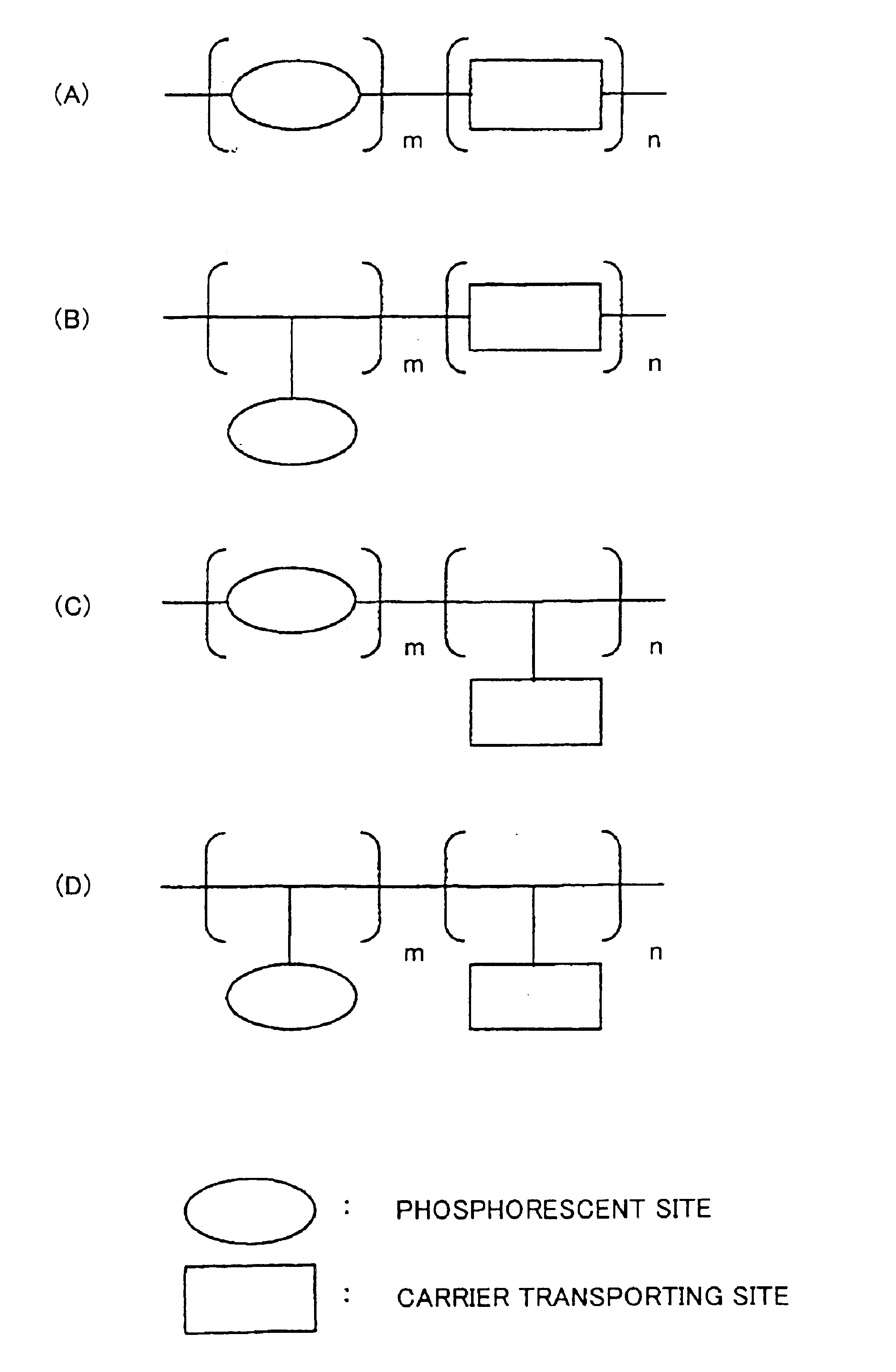

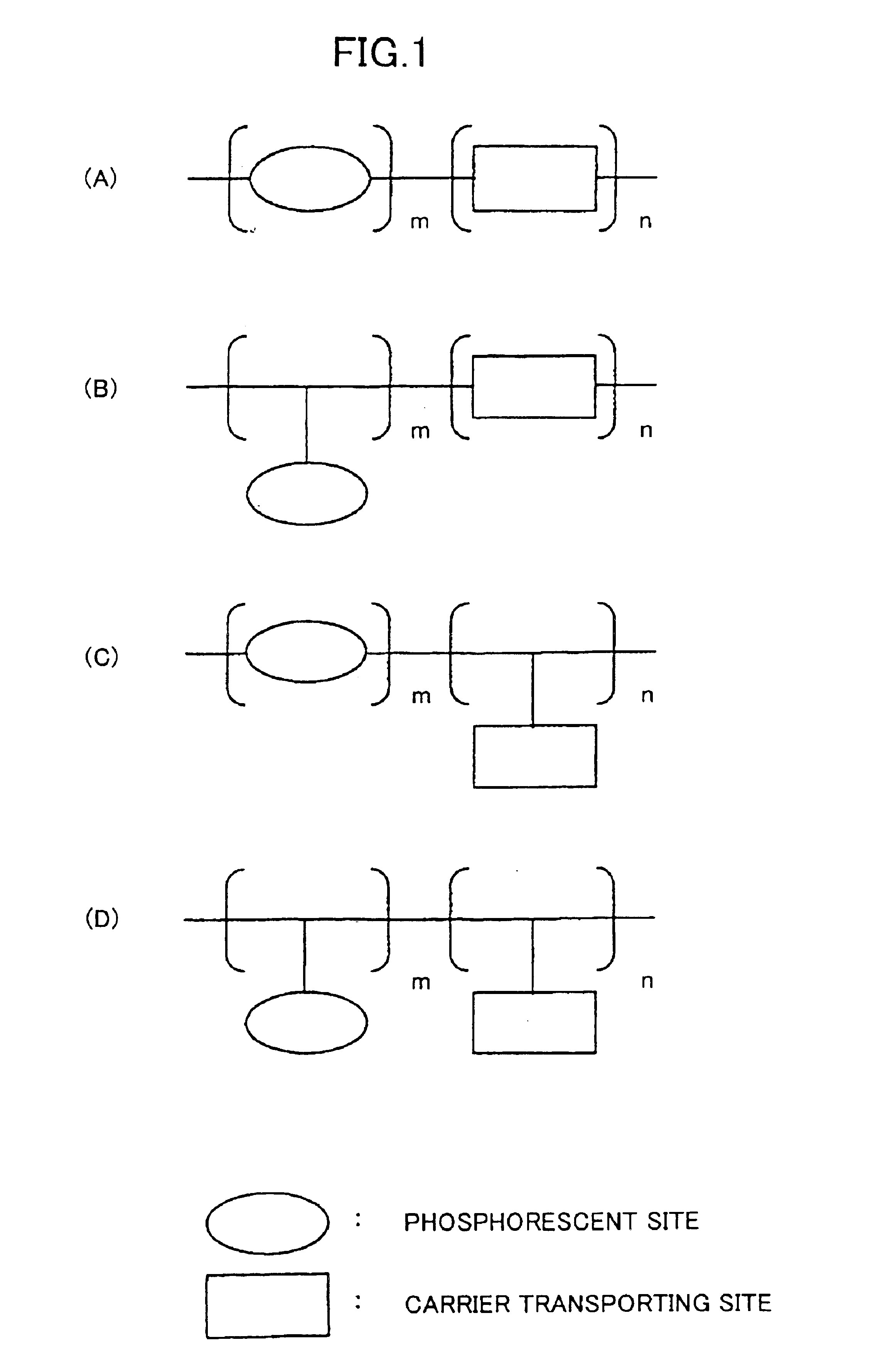

An organic polymeric phosphorescent compound and an organic light-emitting device employing the organic polymeric phosphorescent compound. The phosphorescent compound is a neutral organic polymeric phosphorescent compound emitting phosphorescence and used in an organic light-emitting device, and includes a phosphorescent unit and a carrier transporting unit.

Owner:NIPPON HOSO KYOKAI +1

Indium oxide-based thin film transistors and circuits

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

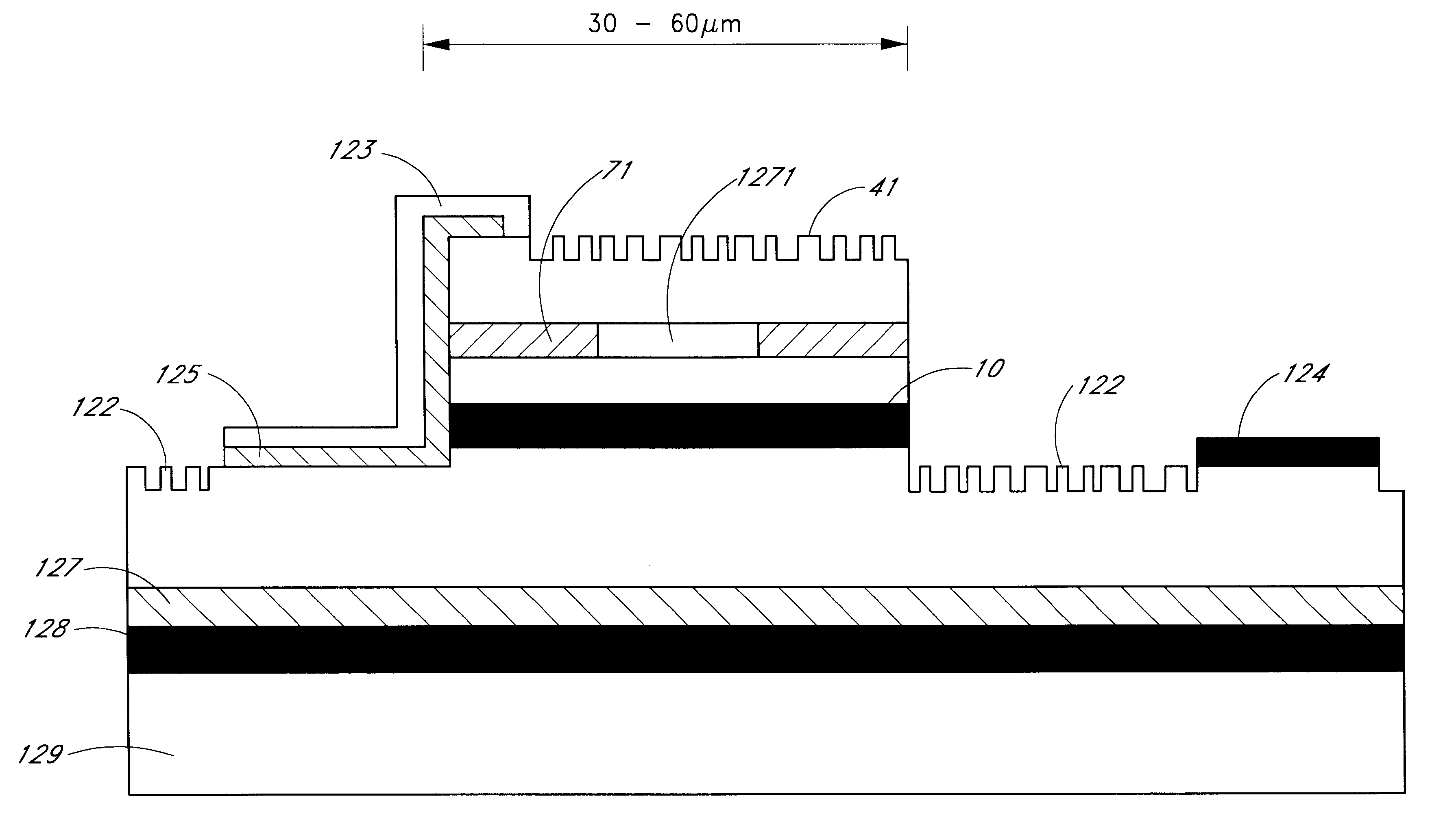

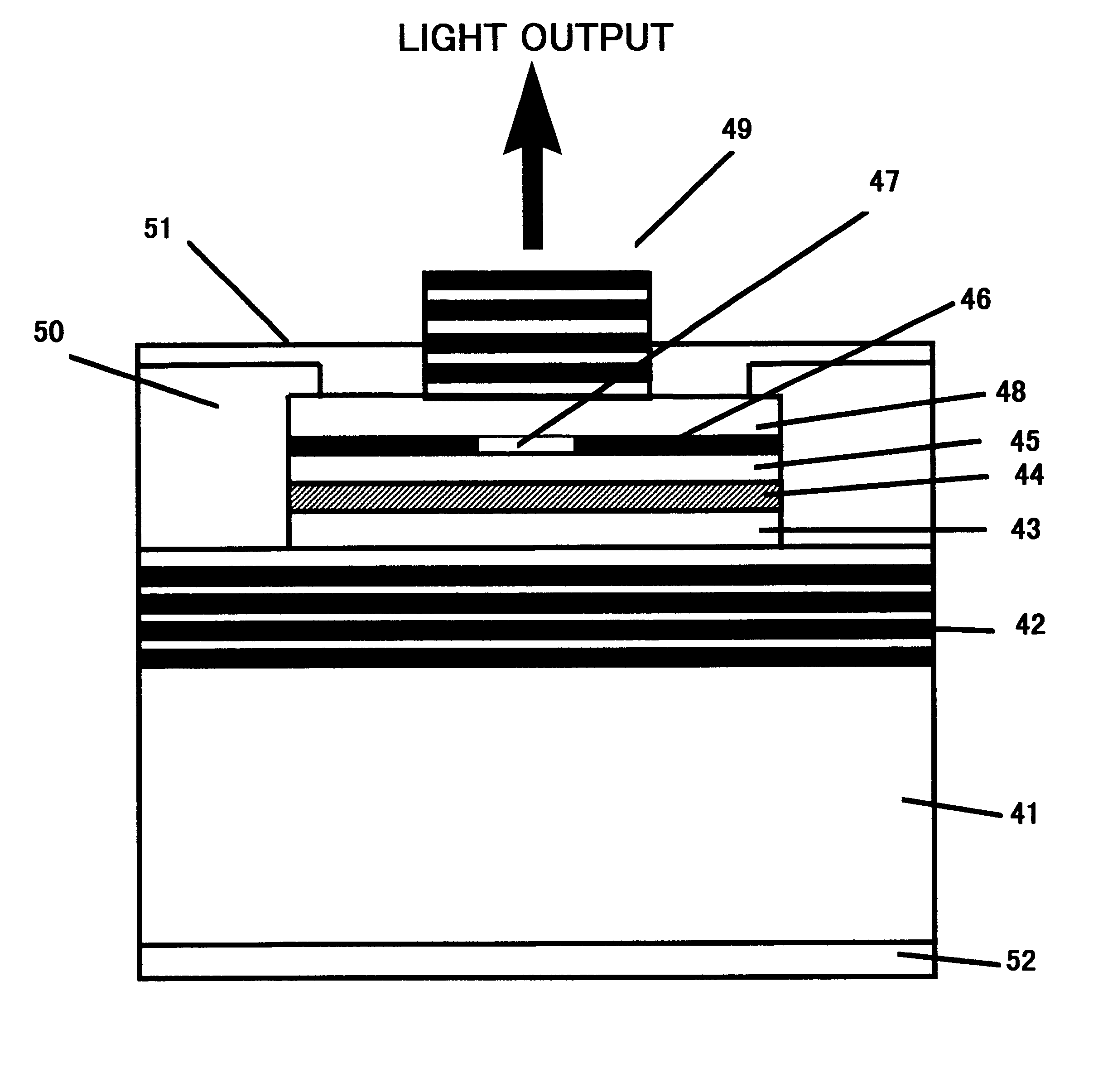

Method of manufacturing surface textured high-efficiency radiating devices and devices obtained therefrom

InactiveUS6504180B1Reduce charge effectReduce surface recombinationSolid-state devicesCoupling light guidesGratingCharge carrier

A device for emitting radiation at a predetermined wavelength is presented. This device has a cavity with an active layer in which said radiation is generated by charge carrier recombination. The edges of the device define the region or space for radiation and / or charge carrier confinement. At least one of the edges of this cavity has a substantially random grating structure. The edge of the device has substantially random grating structure and can extend as at least one edge of a waveguide forming part of this radiation emitting device. The radiation emitting device of the present invention can have a cavity comprising a radiation confinement space that includes confinement features for the charge carriers confining the charge carriers to a subspace being smaller than the radiation confinement space within the cavity. The emitting device can comprise at least two edges forming, in cross-section, a substantially triangular shape. The angle between these two edges is smaller than 45°. At least one of the two edges has a transparent portion. the devices according to the present invention can be arranged in arrays.

Owner:SIGNIFY HLDG BV

Semiconductor device and manufacturing method thereof

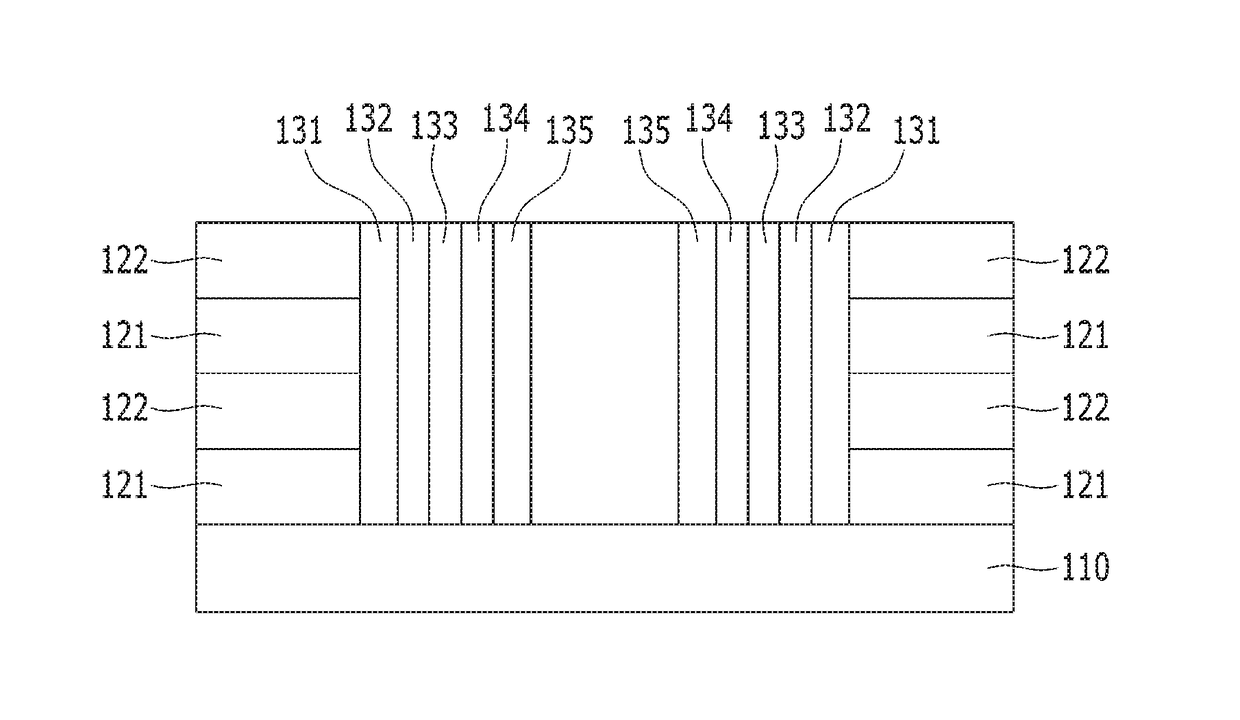

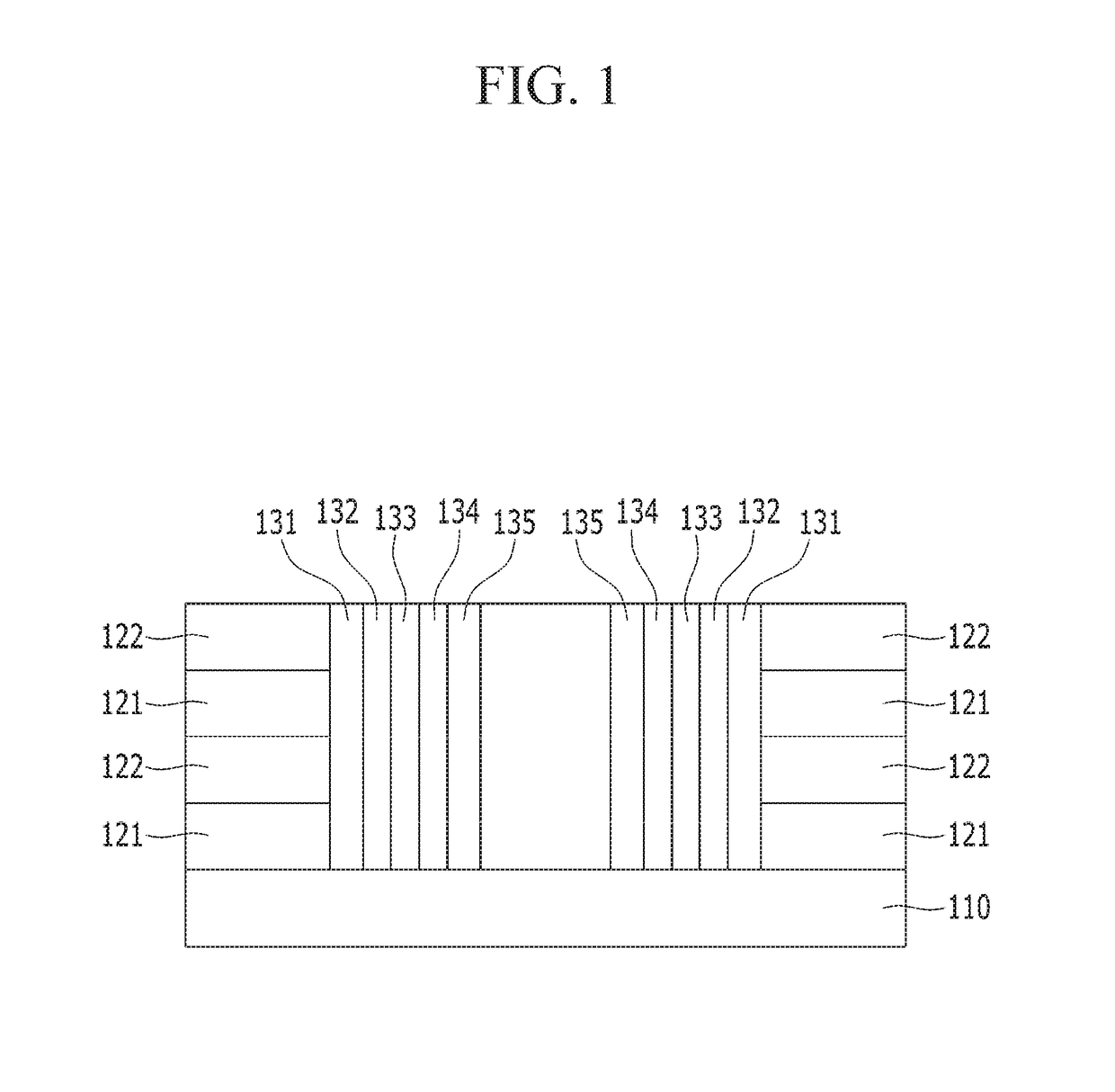

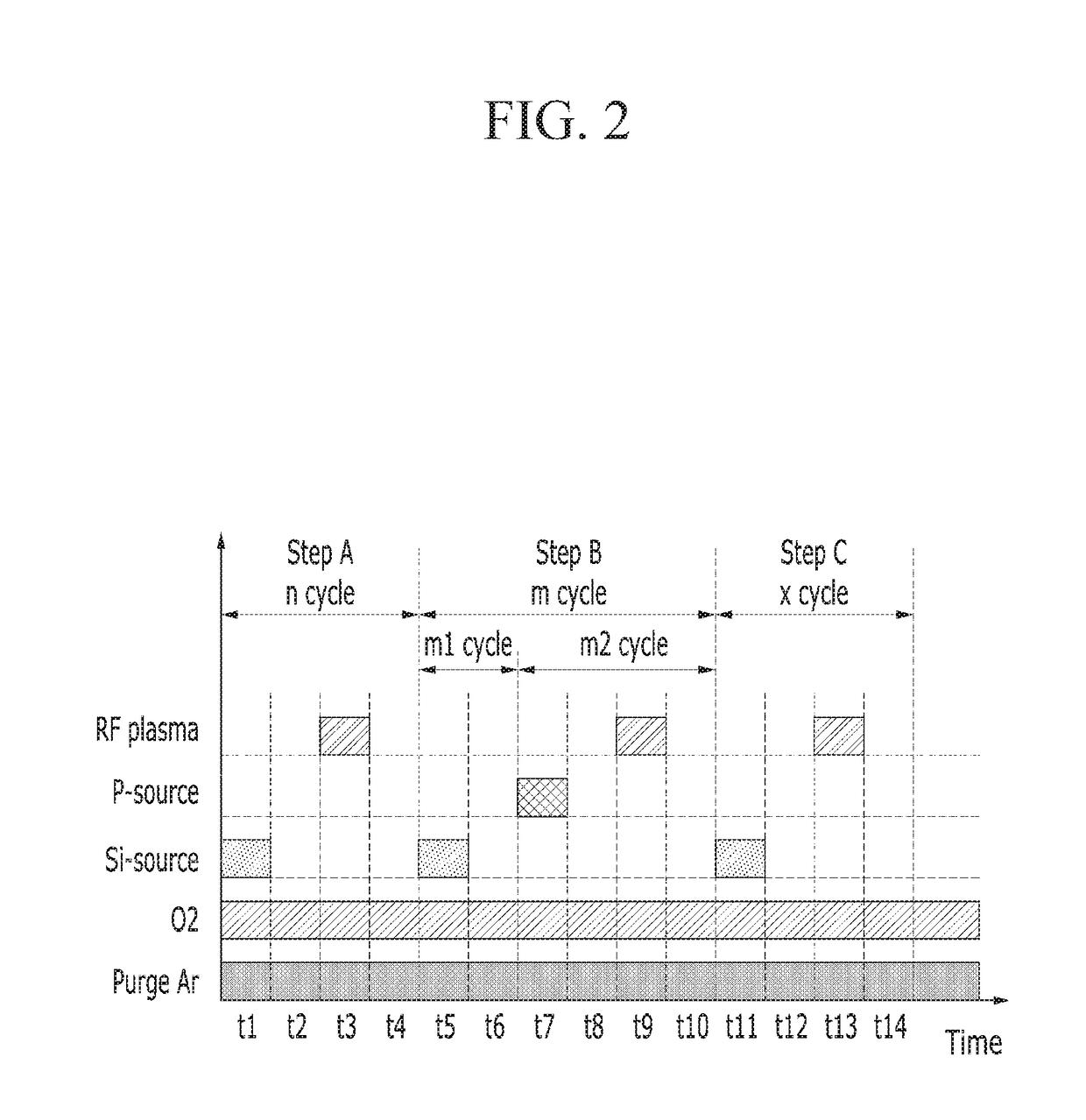

ActiveUS20180047749A1Reduce chargeAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingDopantCharge carrier

Disclosed are a semiconductor device and a manufacturing method thereof. According to the semiconductor device and the manufacturing method thereof according to exemplary embodiments of the present invention, after the dopant source layer is uniformly deposited on a channel layer of the device with the 3-demensional vertical structure by the plasma-enhanced atomic layer deposition (PEALD) method, the deposited dopant source layer is heat-treated so that the dopants are diffused into the channel layer to function as charge carriers, thereby preventing the charges in the channel layer from being reduced. According to the exemplary embodiments of the present invention, the diffusion speed and concentration of the dopant may be controlled by forming the barrier layer between the channel layer and the dopant source layer.

Owner:ASM IP HLDG BV

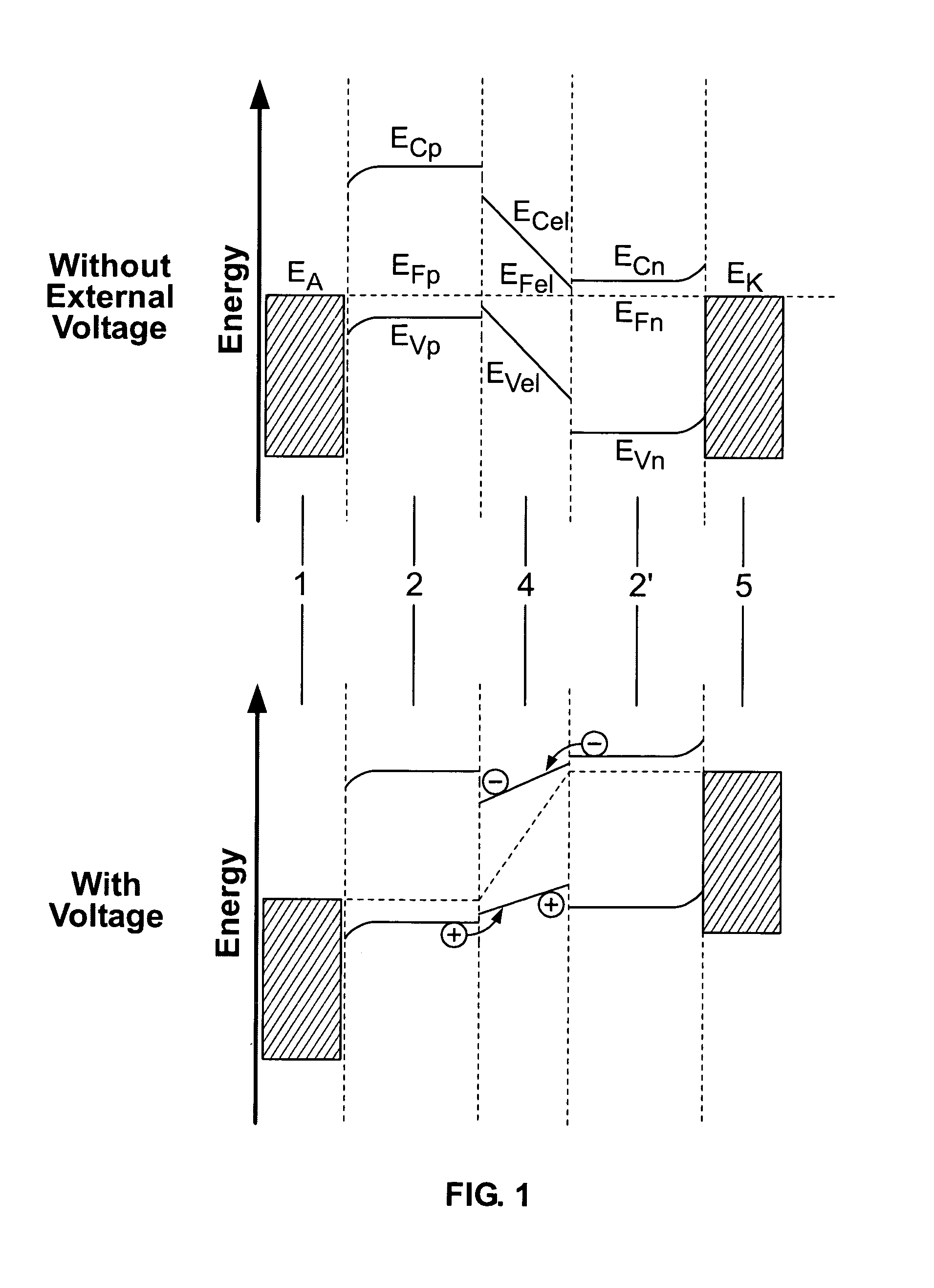

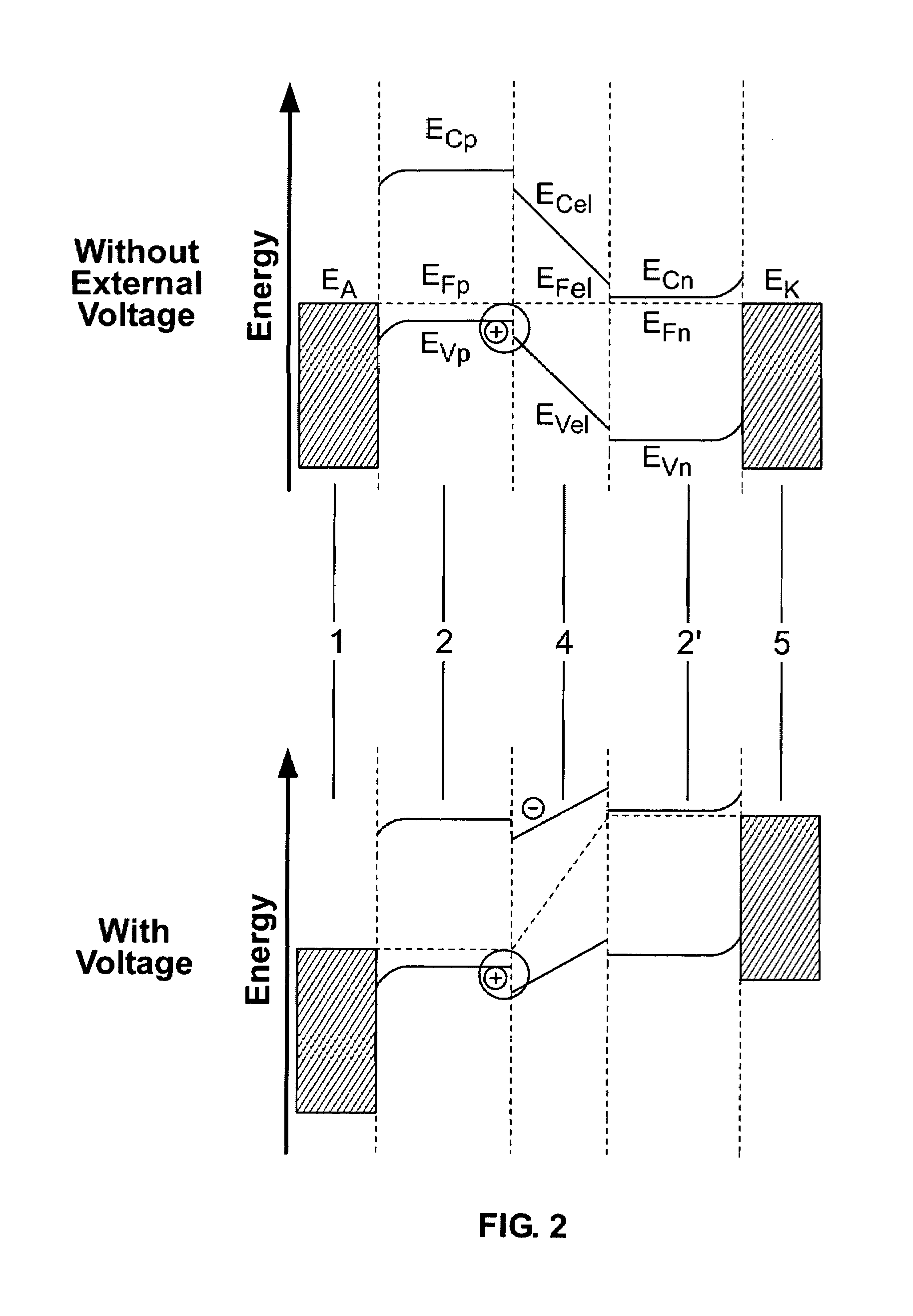

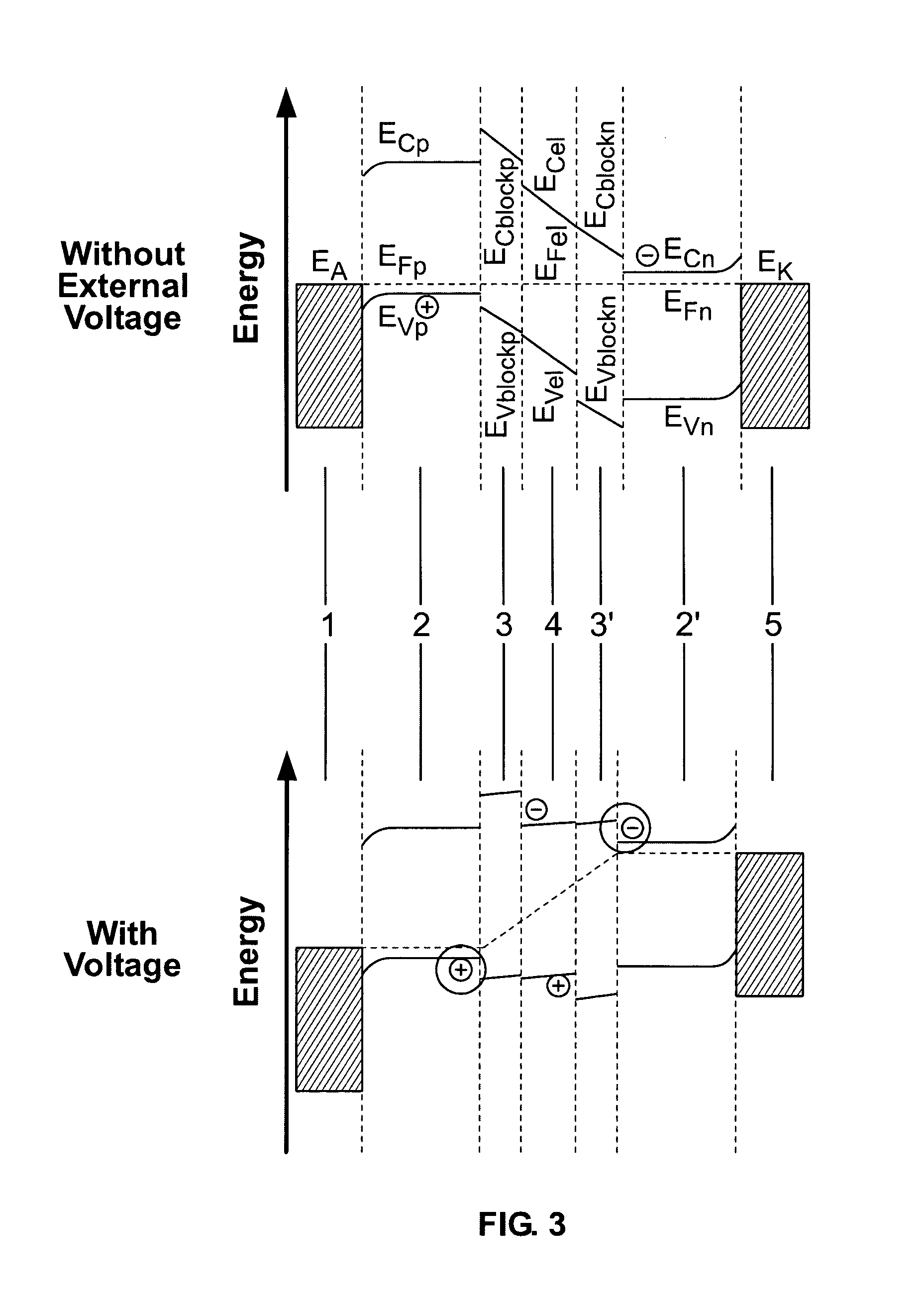

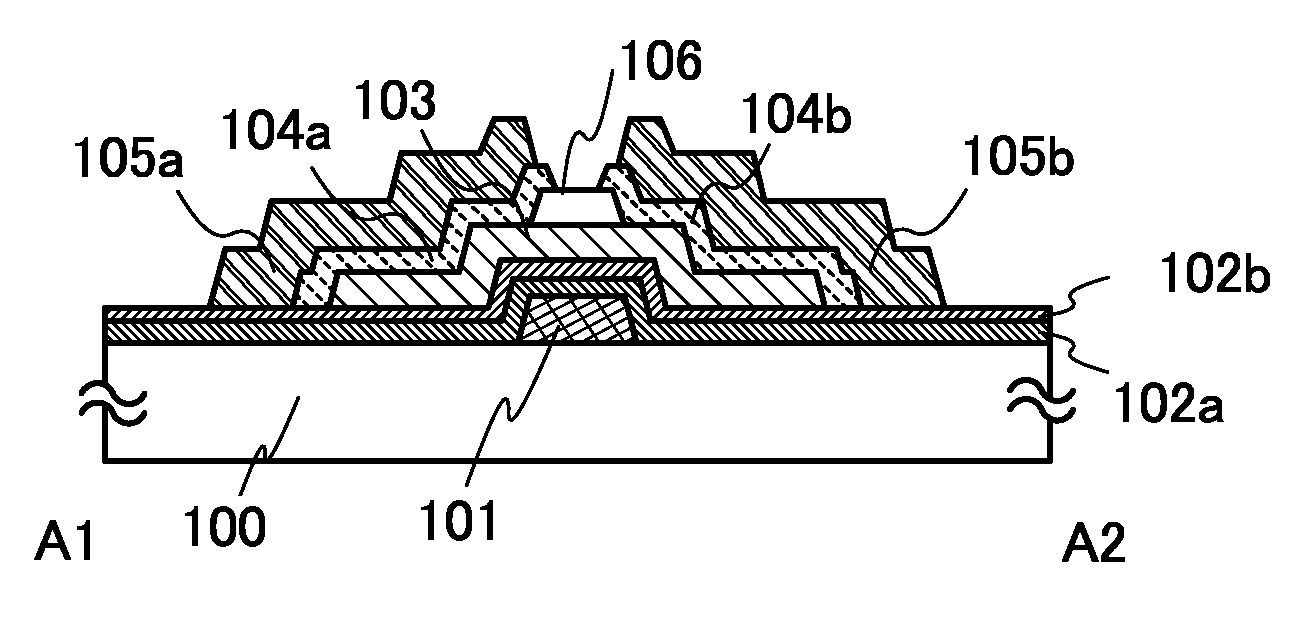

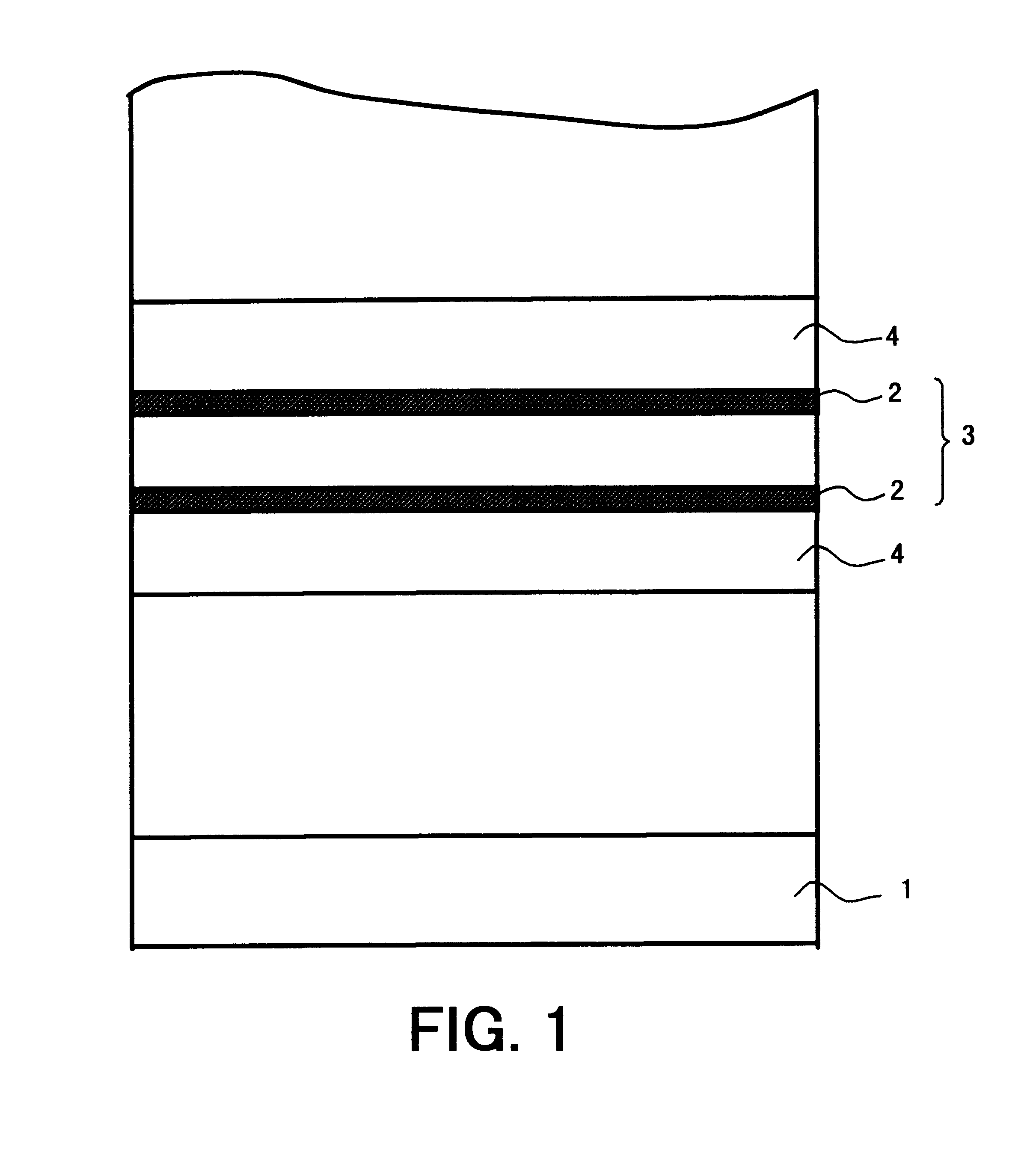

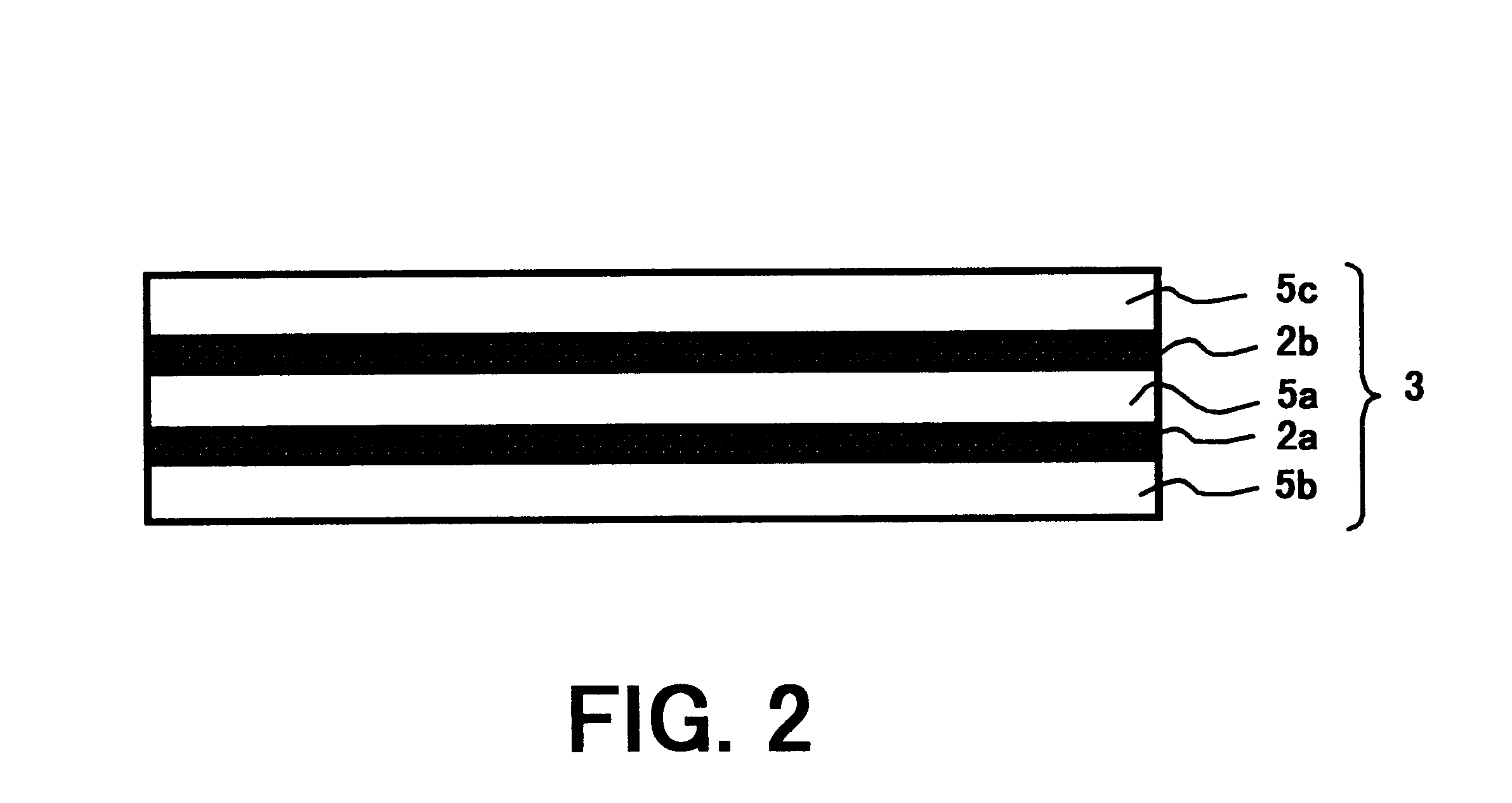

Light emitting component comprising organic layers

InactiveUS7074500B2Inhibit injectionDischarge tube luminescnet screensElectroluminescent light sourcesTransport layerCharge carrier

The invention relates to a light-emmiting component having organic layers, in particular to an organic light-emmiting diode. The component has at least one doped charge carrier transport layer (2), a light-emmiting layer (4) and contact layers (1, 5) and also has a blocking layer (3; 3′) wherein an organic material is provided between the charge carrier transport layer (2, 2′) and the light-emmiting layer (4). The energy levels of the charge carried transport layer are chosen in such a way that efficient doping is possible and the blocking layer nevertheless ensures that non-radiating recombination processes on the interface with the emitting layer are prevented.

Owner:NOVALED GMBH

Semiconductor device and manufacturing method thereof

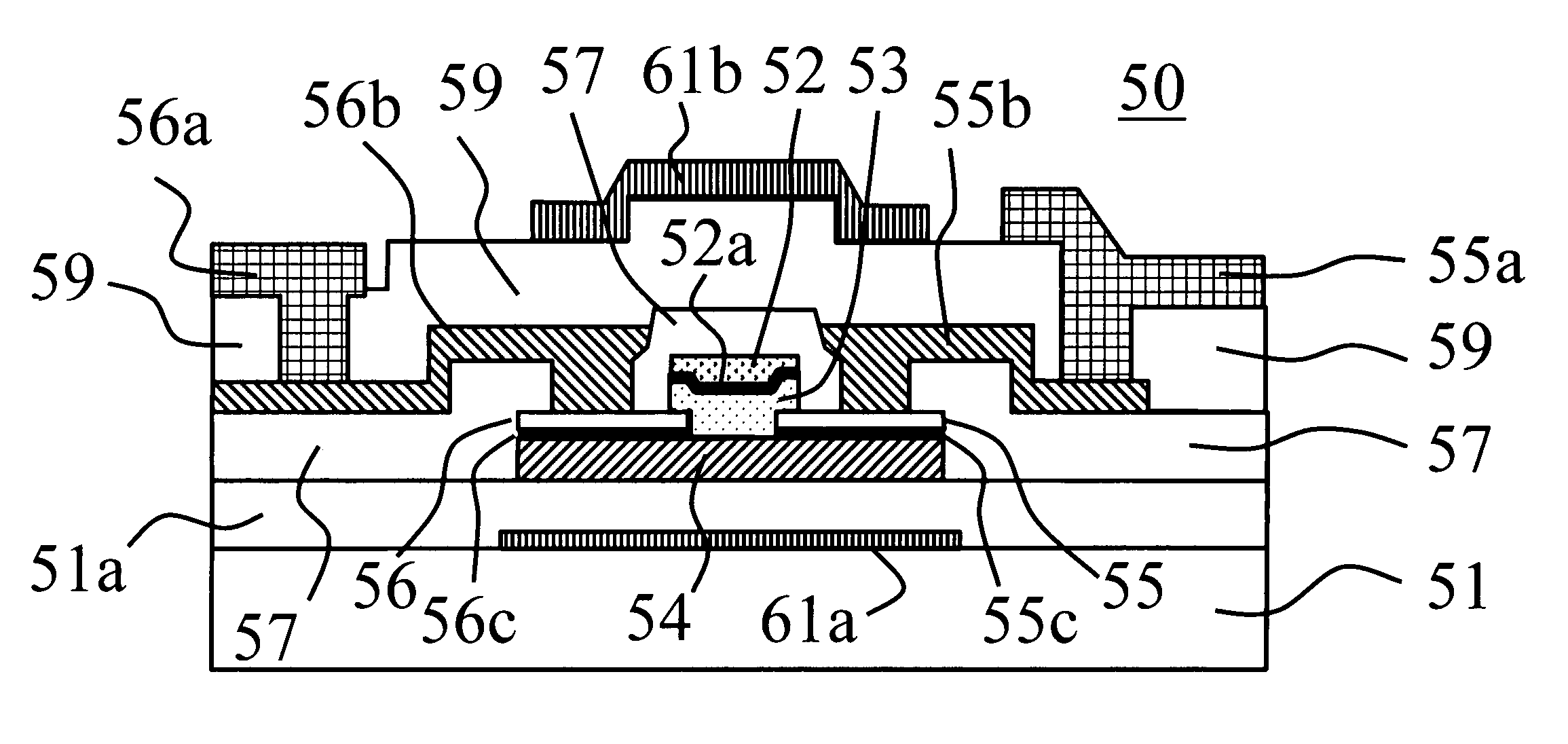

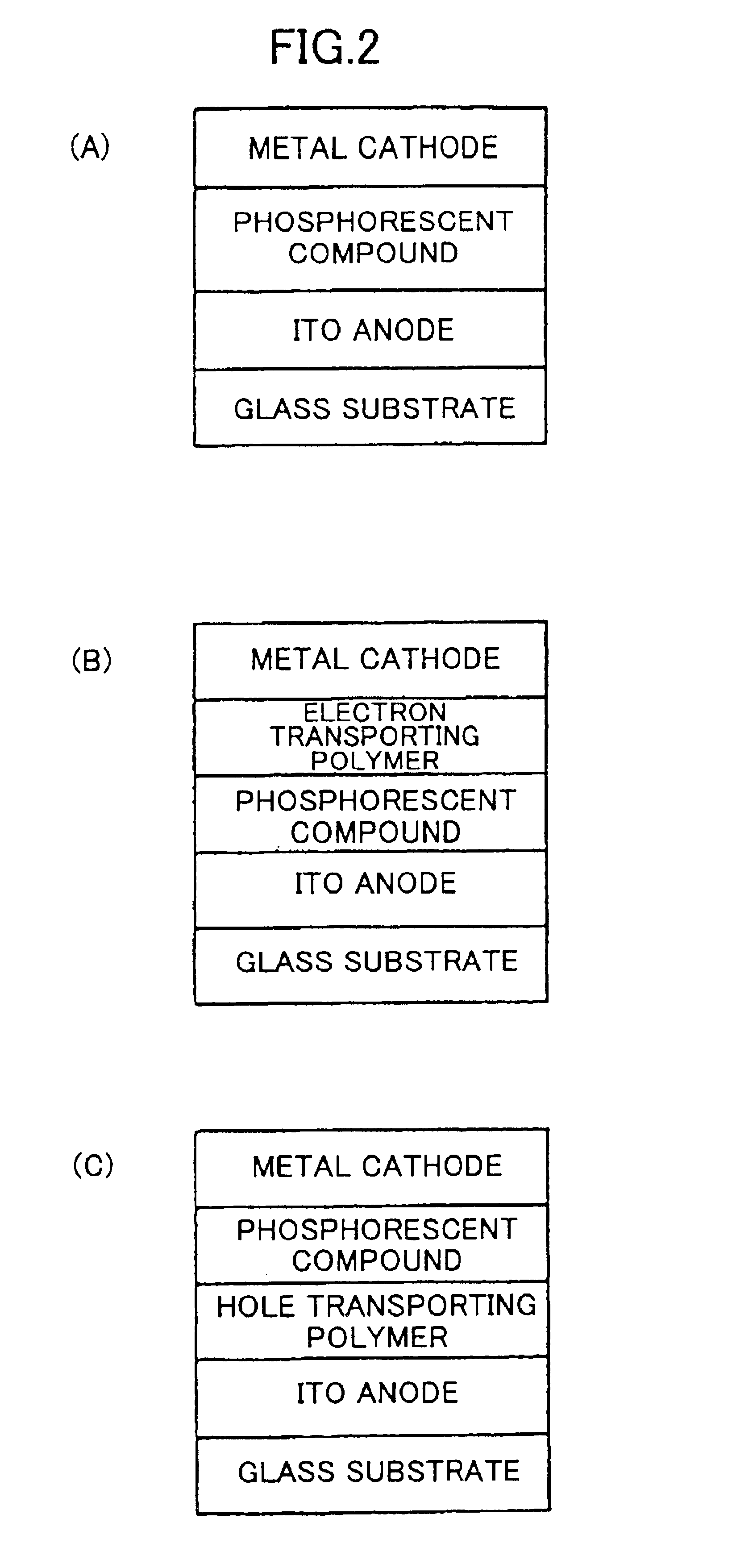

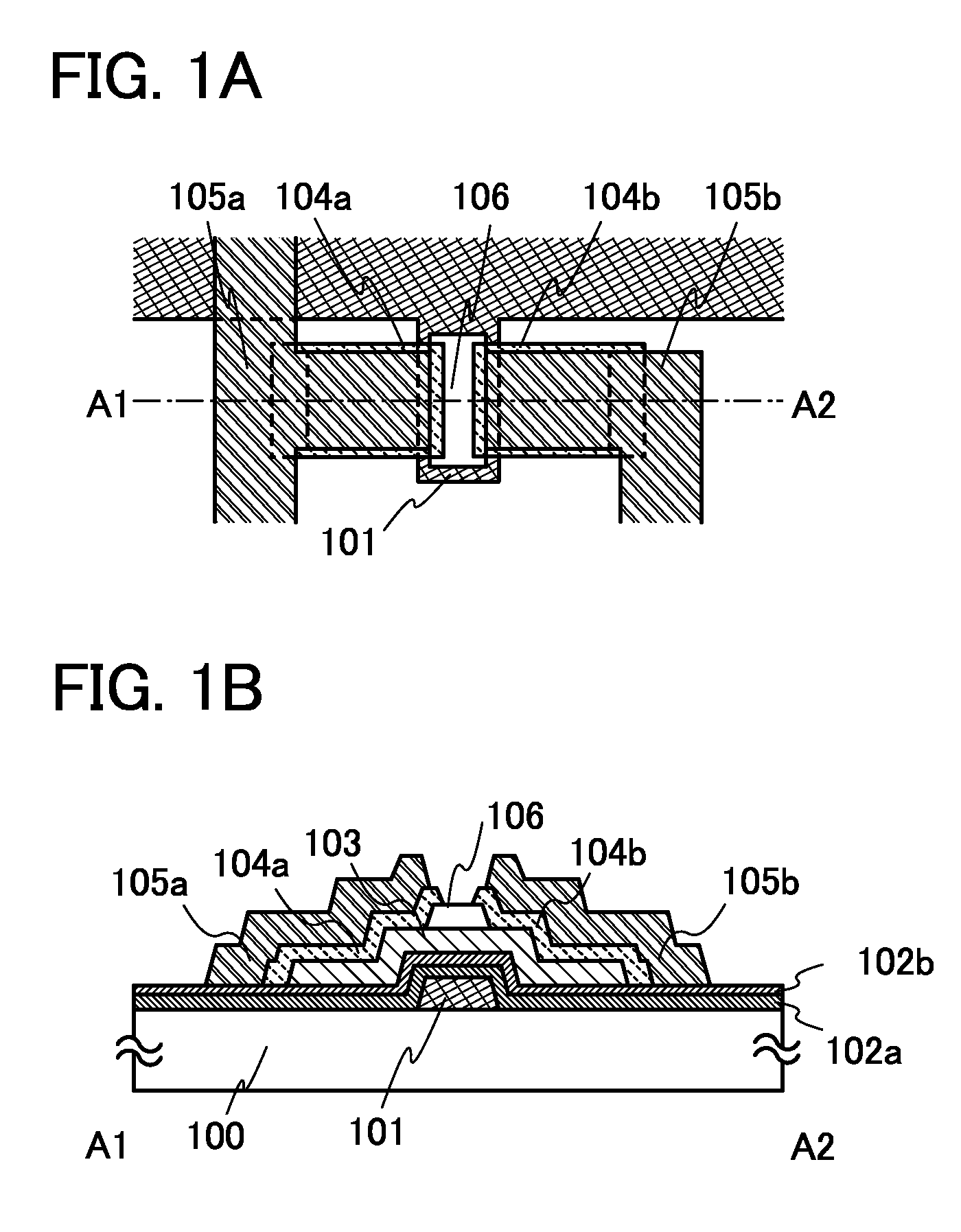

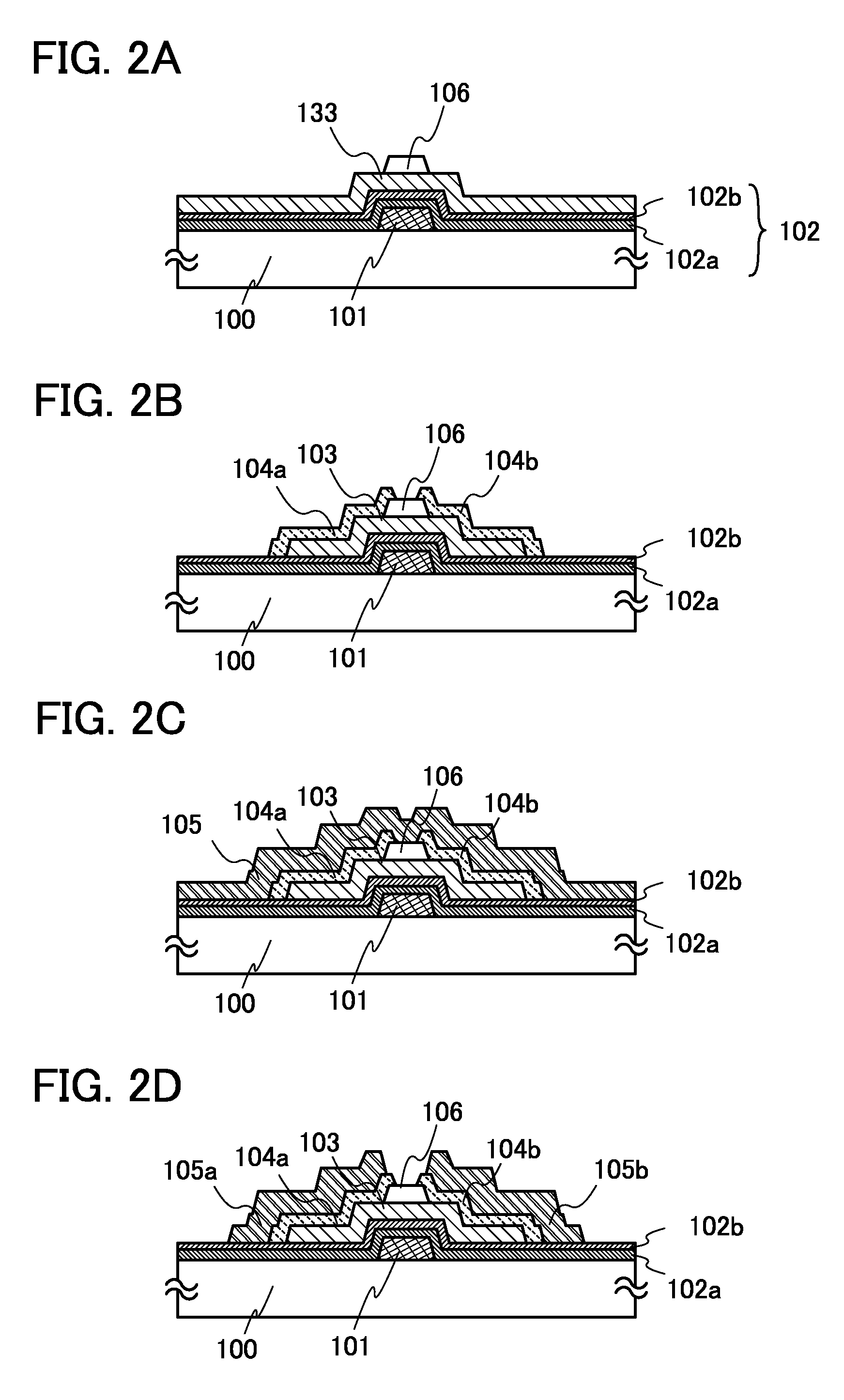

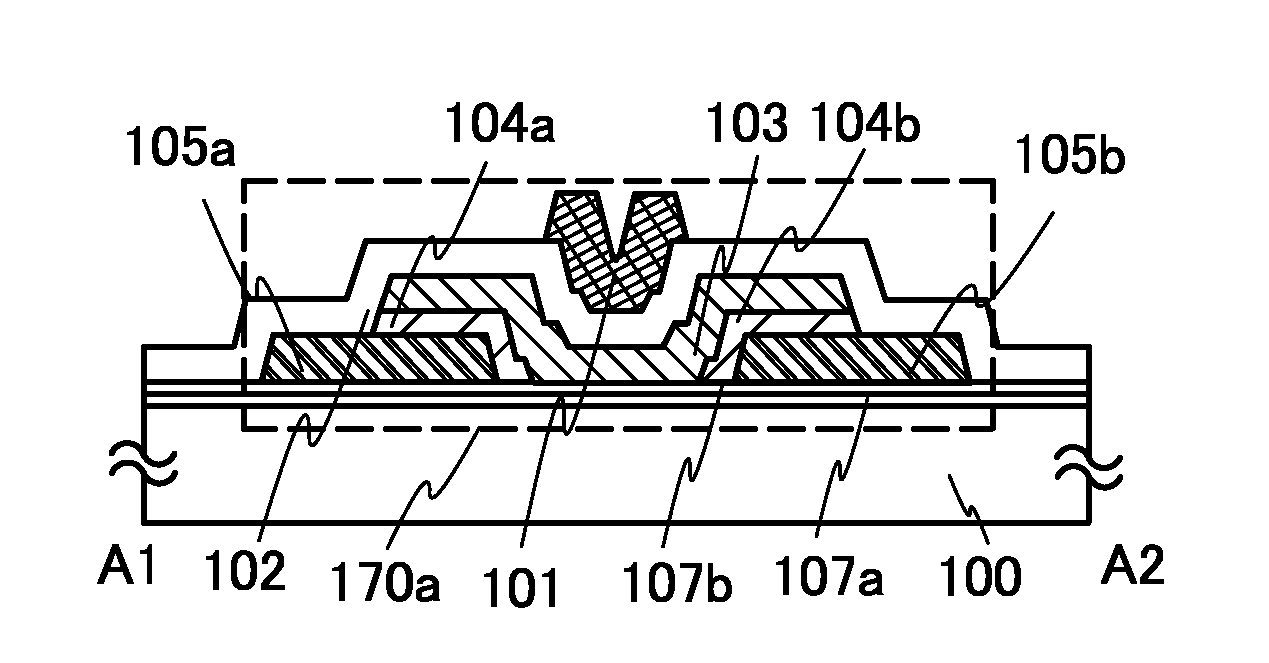

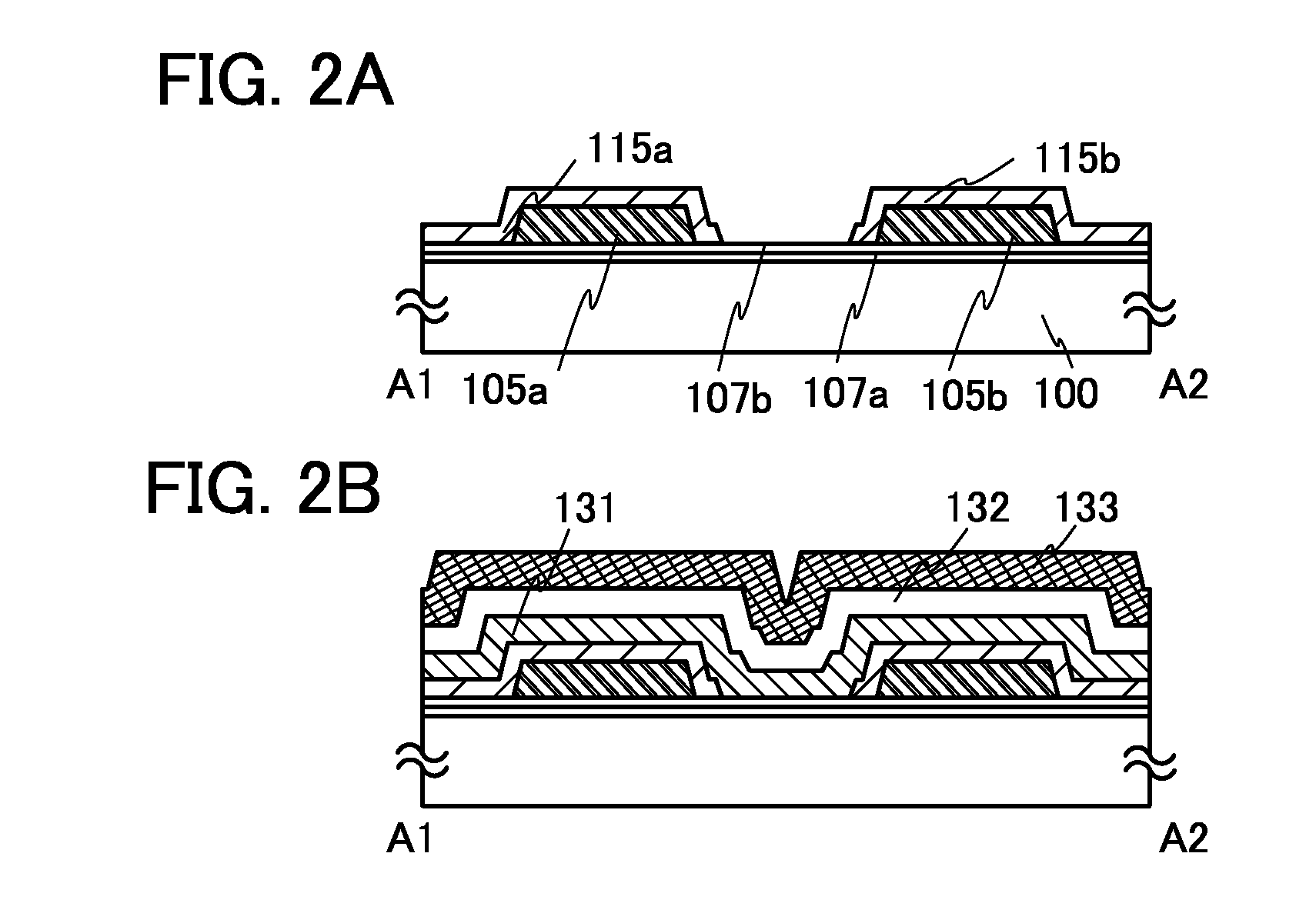

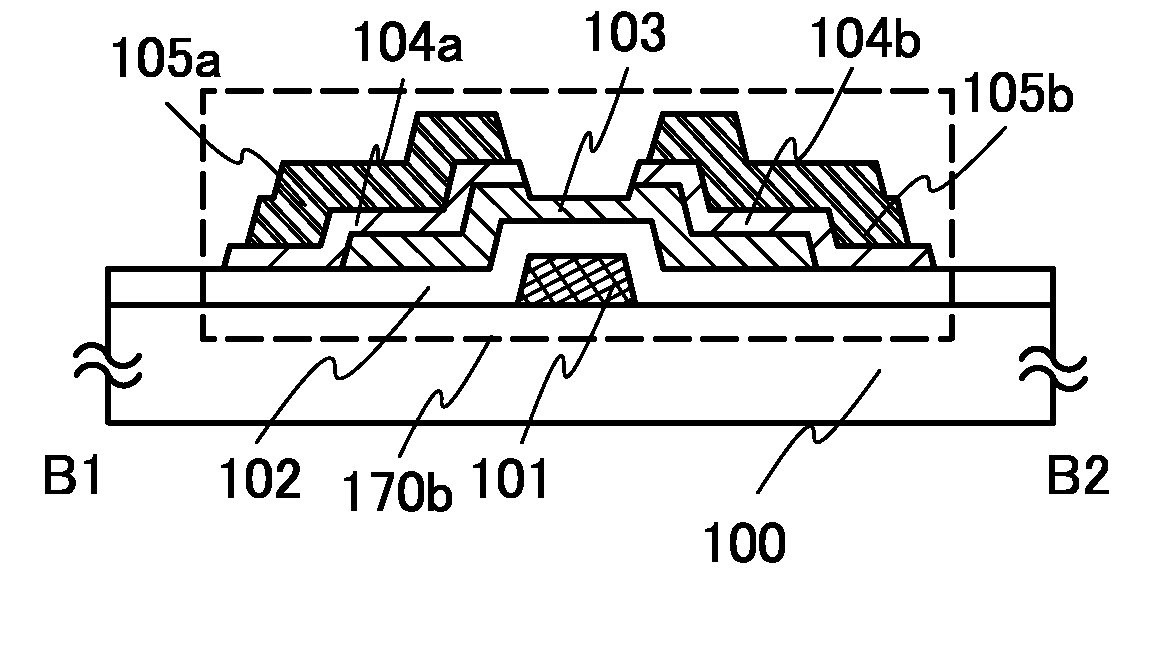

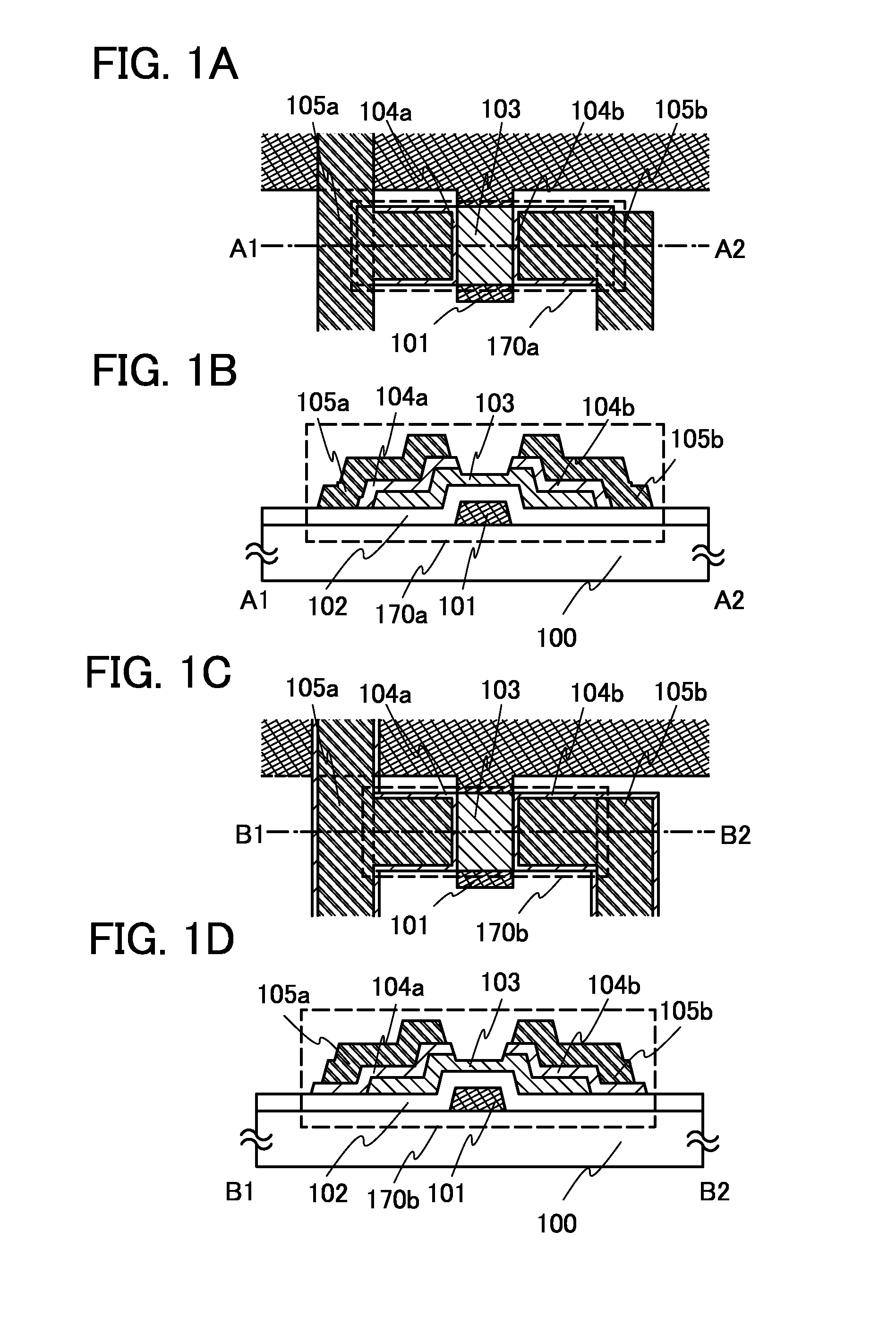

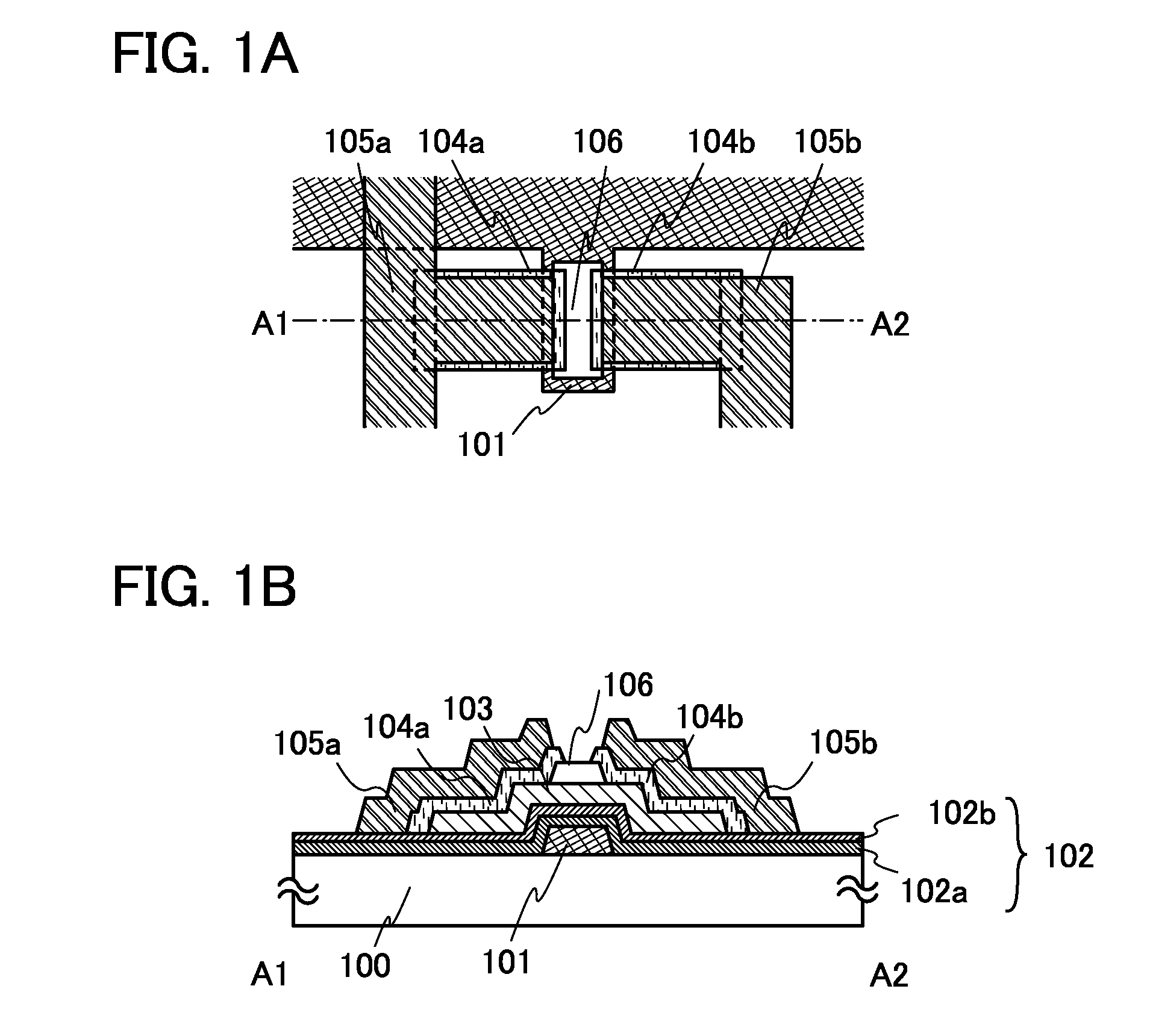

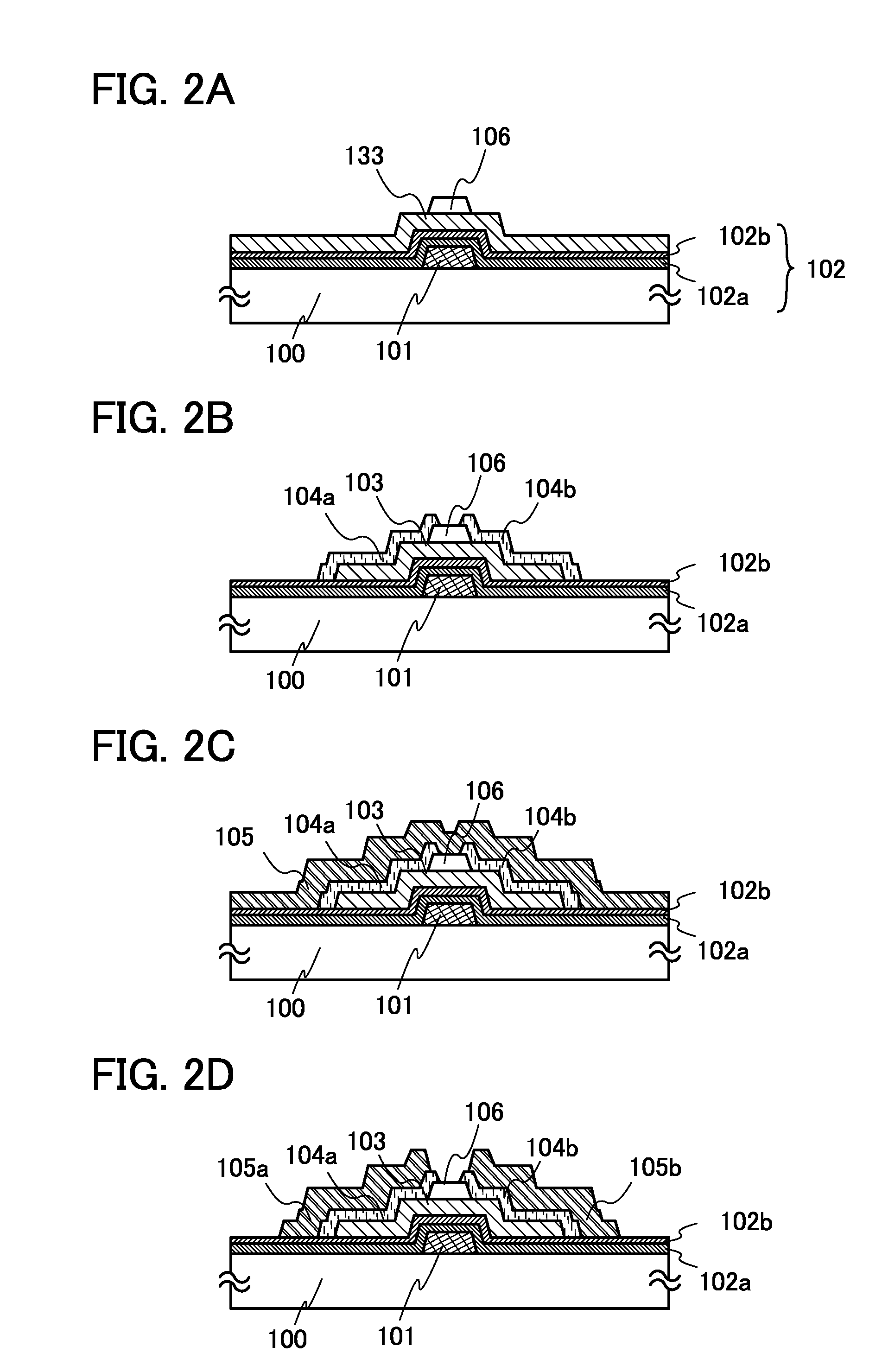

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

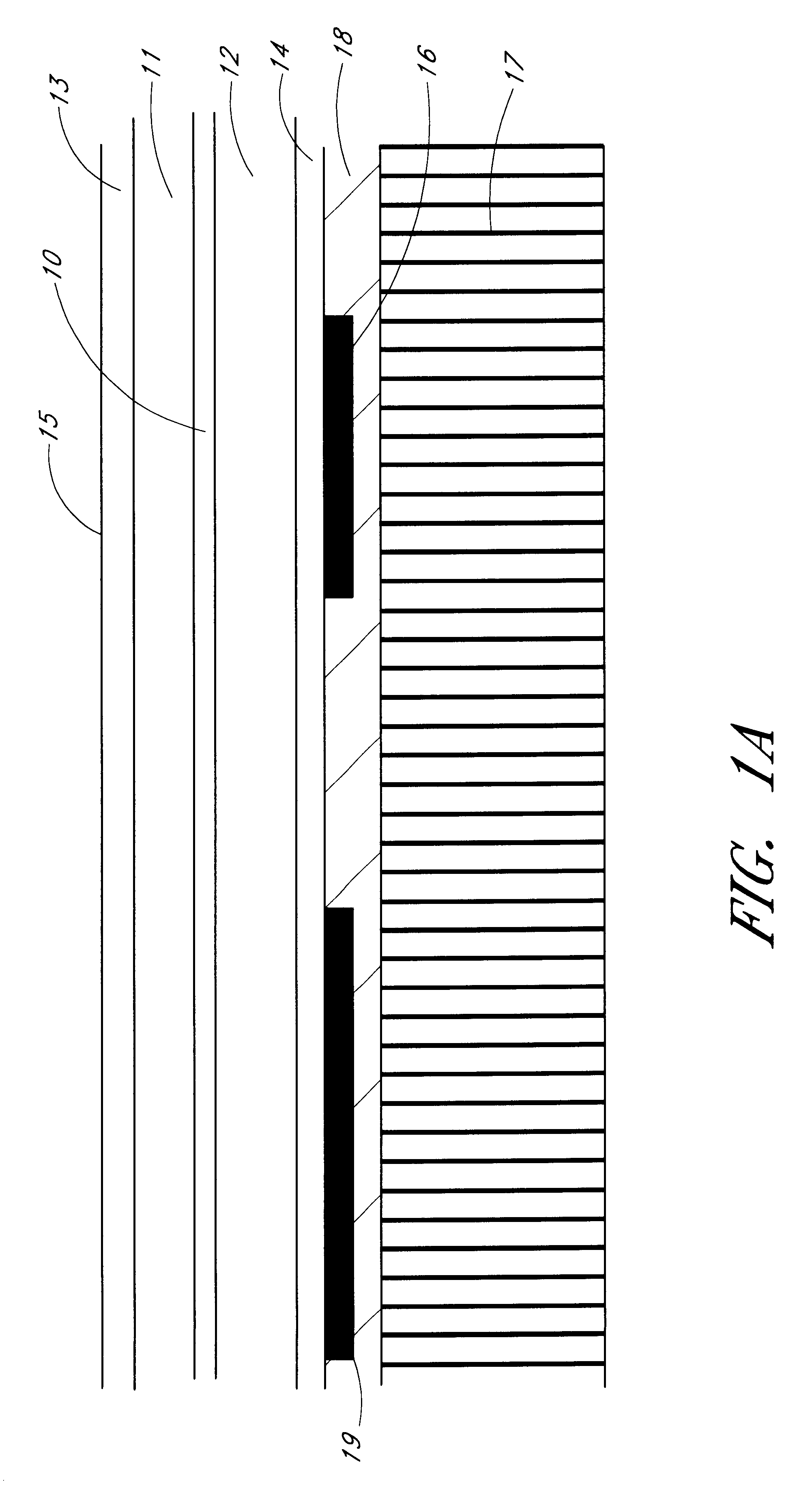

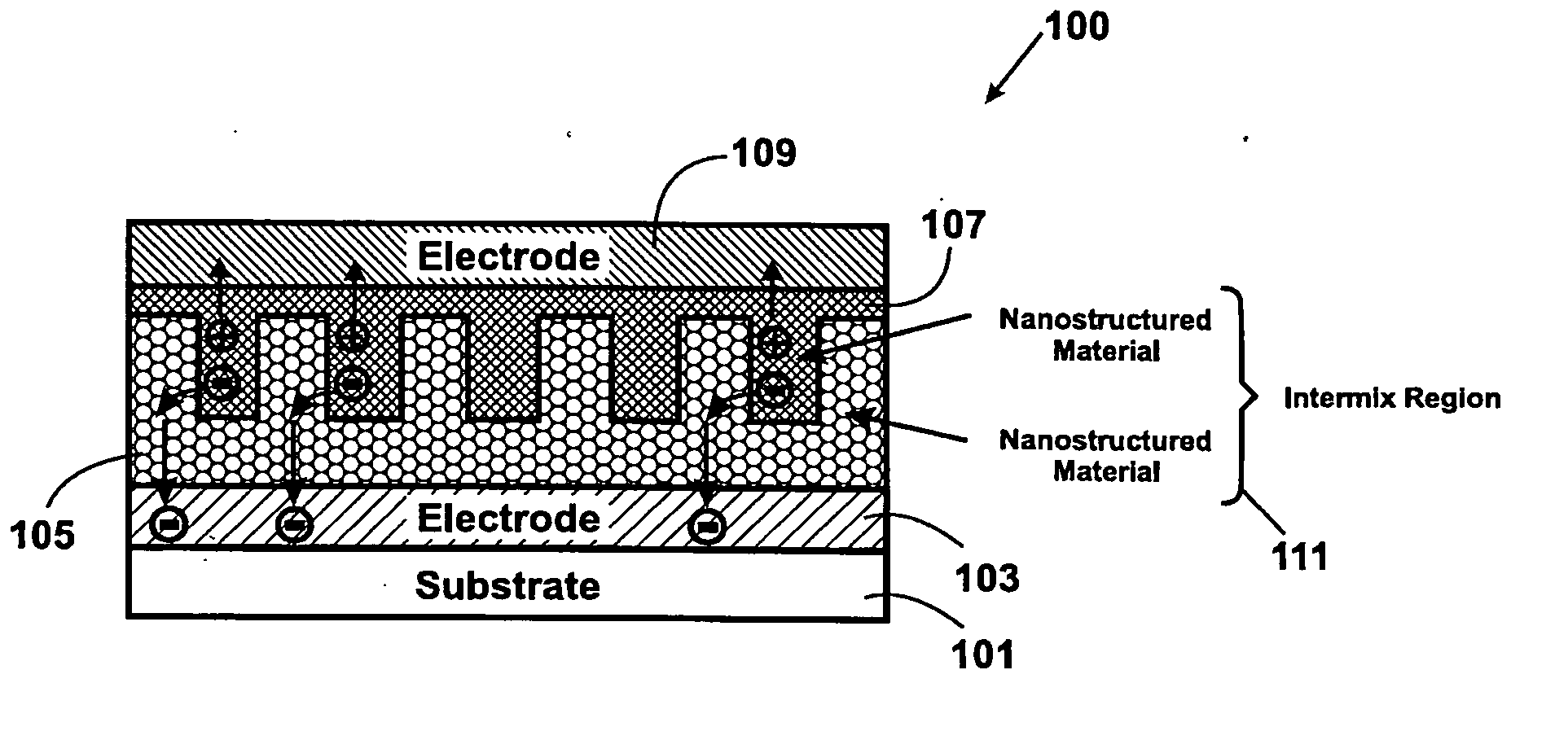

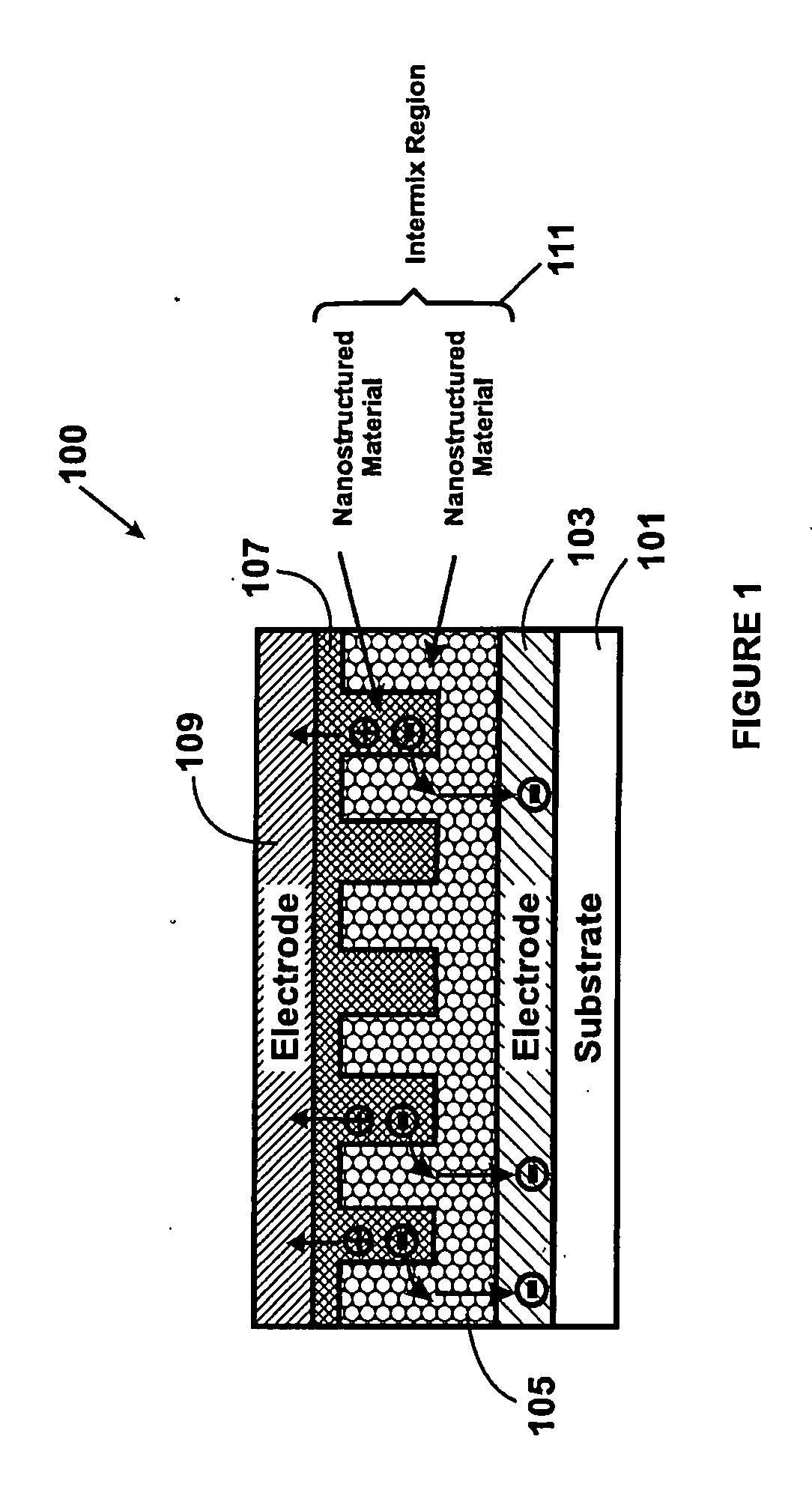

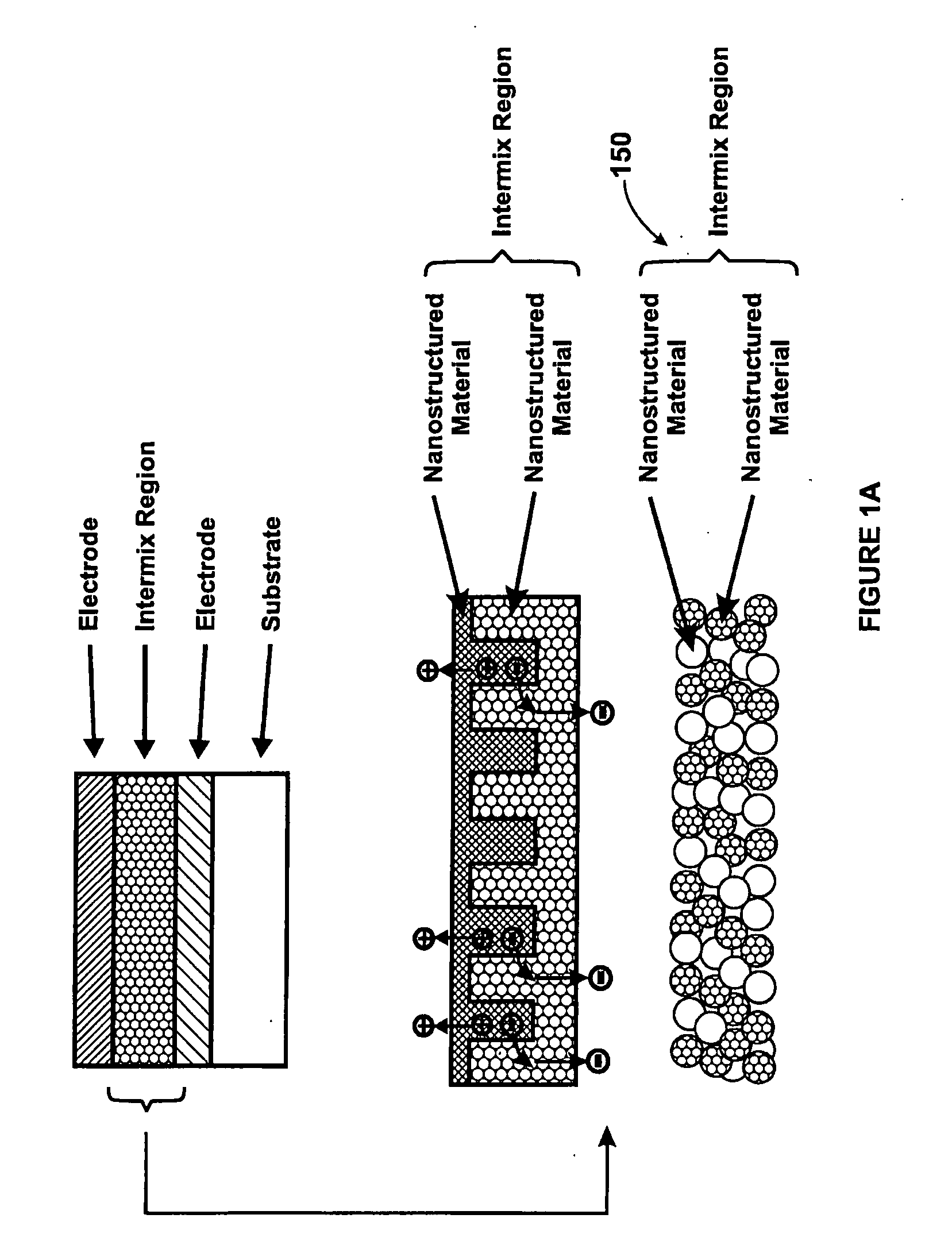

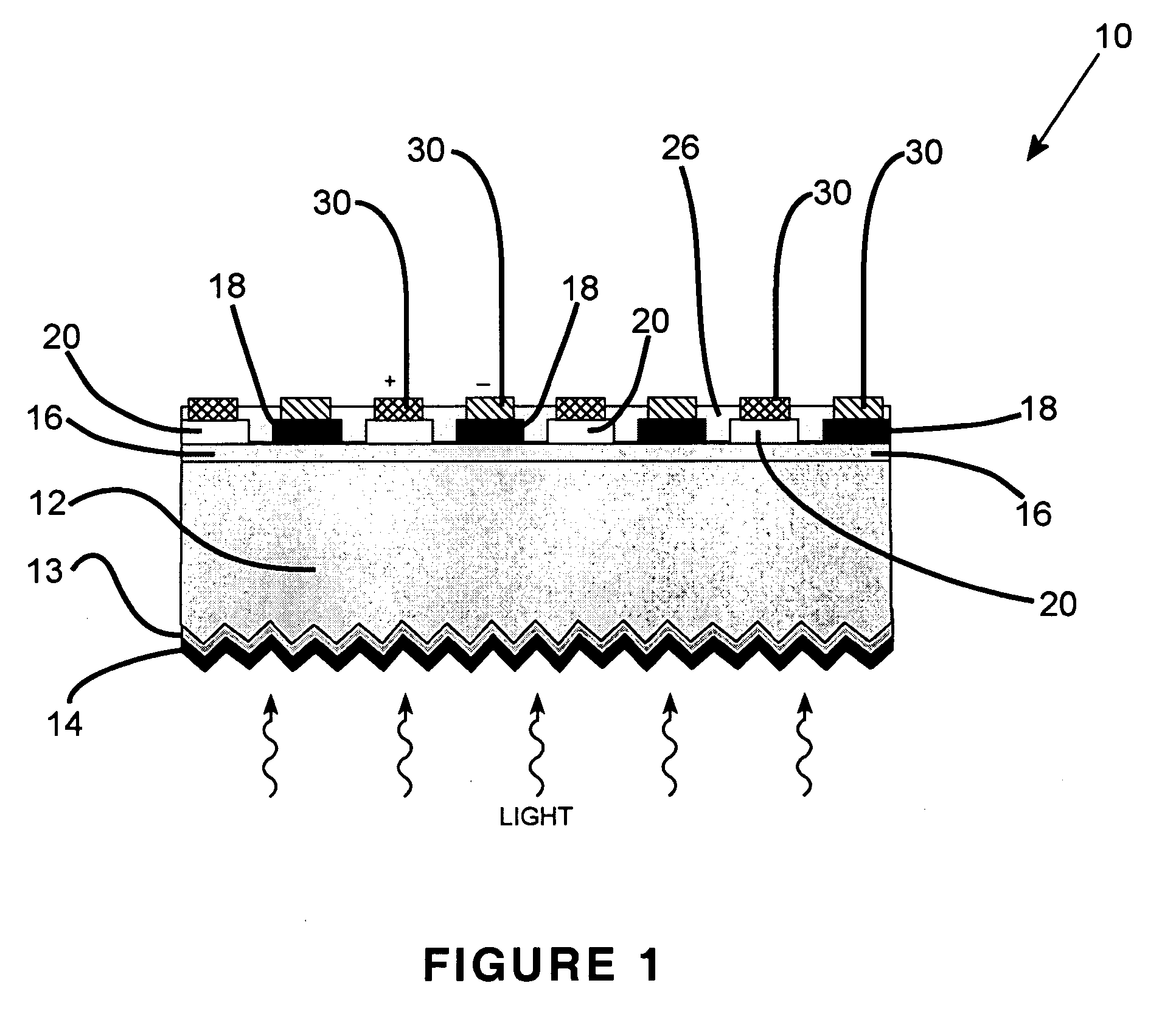

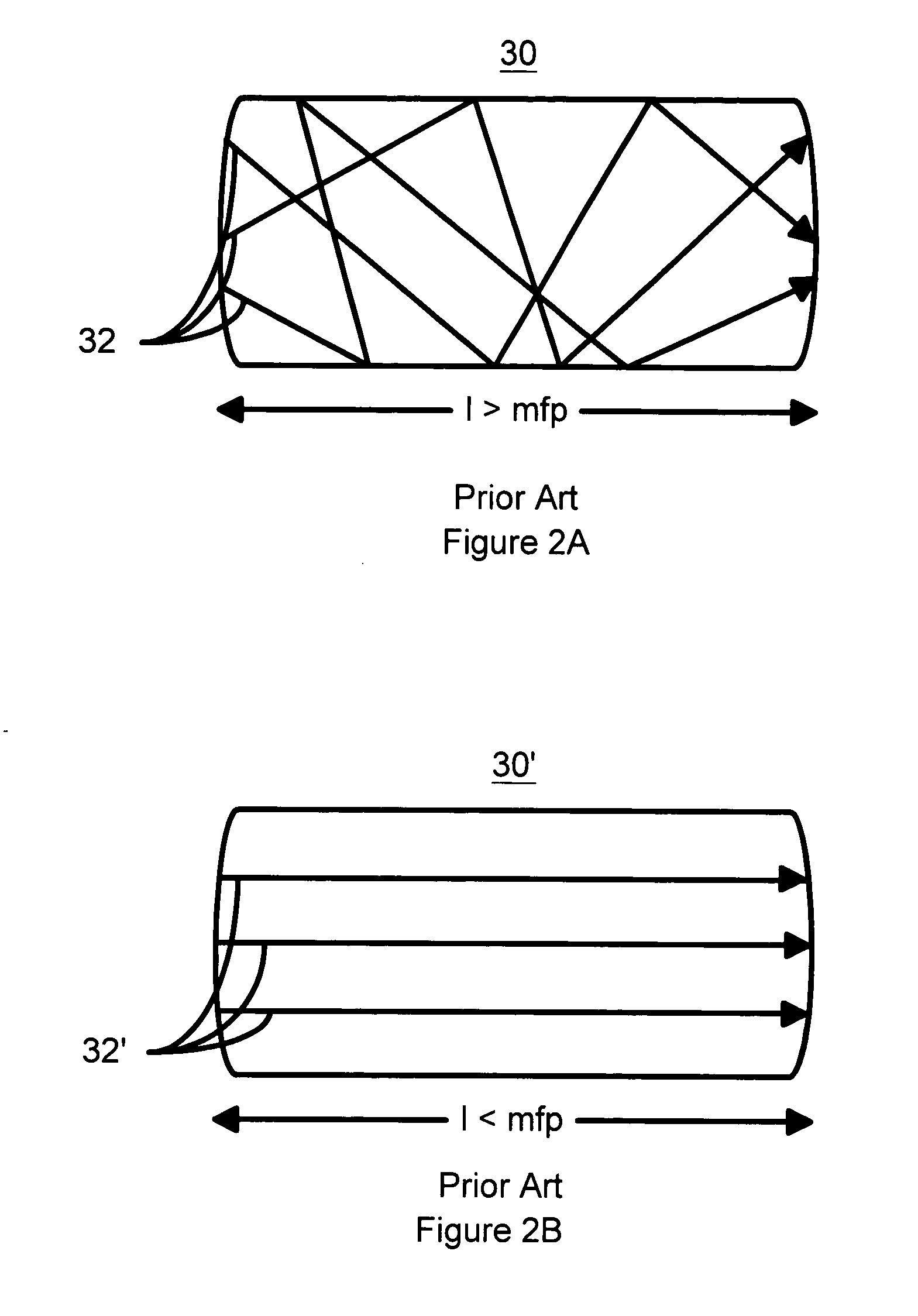

Method and structure for thin film photovoltaic materials using bulk semiconductor materials

ActiveUS20080092953A1Easy to useImprove conversion efficiencyNanoinformaticsPhotovoltaic energy generationSemiconductor materialsCharge carrier

A photovoltaic device and related methods. The device has a structured material positioned between an electron collecting electrode and a hole collecting electrode. An electron transporting / hole blocking material is positioned between the electron collecting electrode and the structured material. In a specific embodiment, negatively charged carriers generated by optical absorption by the structured material are preferentially separated into the electron transporting / hole blocking material. In a specific embodiment, the structured material has an optical absorption coefficient of at least 103 cm−1 for light comprised of wavelengths within the range of about 400 nm to about 700 nm.

Owner:CM MFG

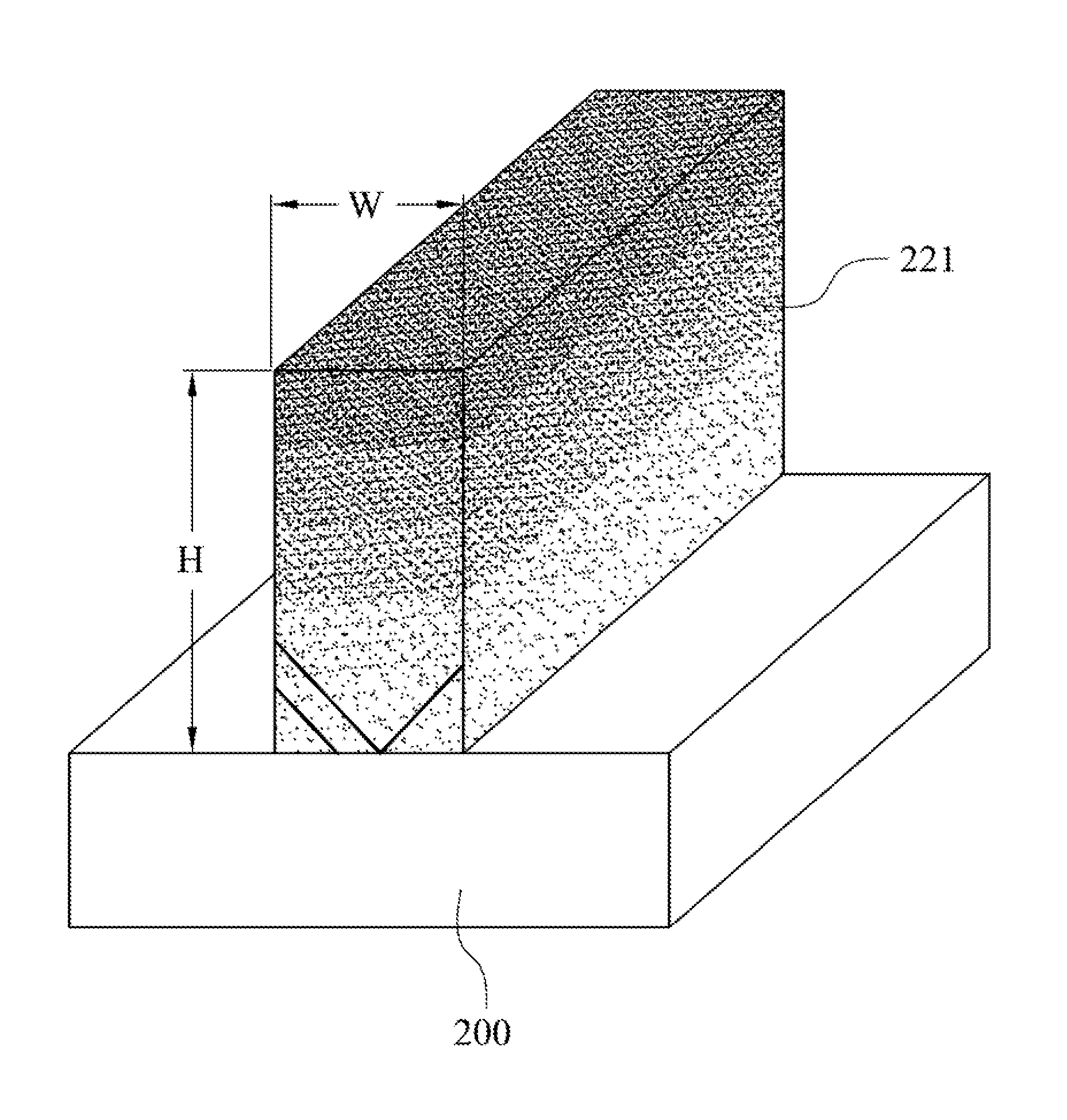

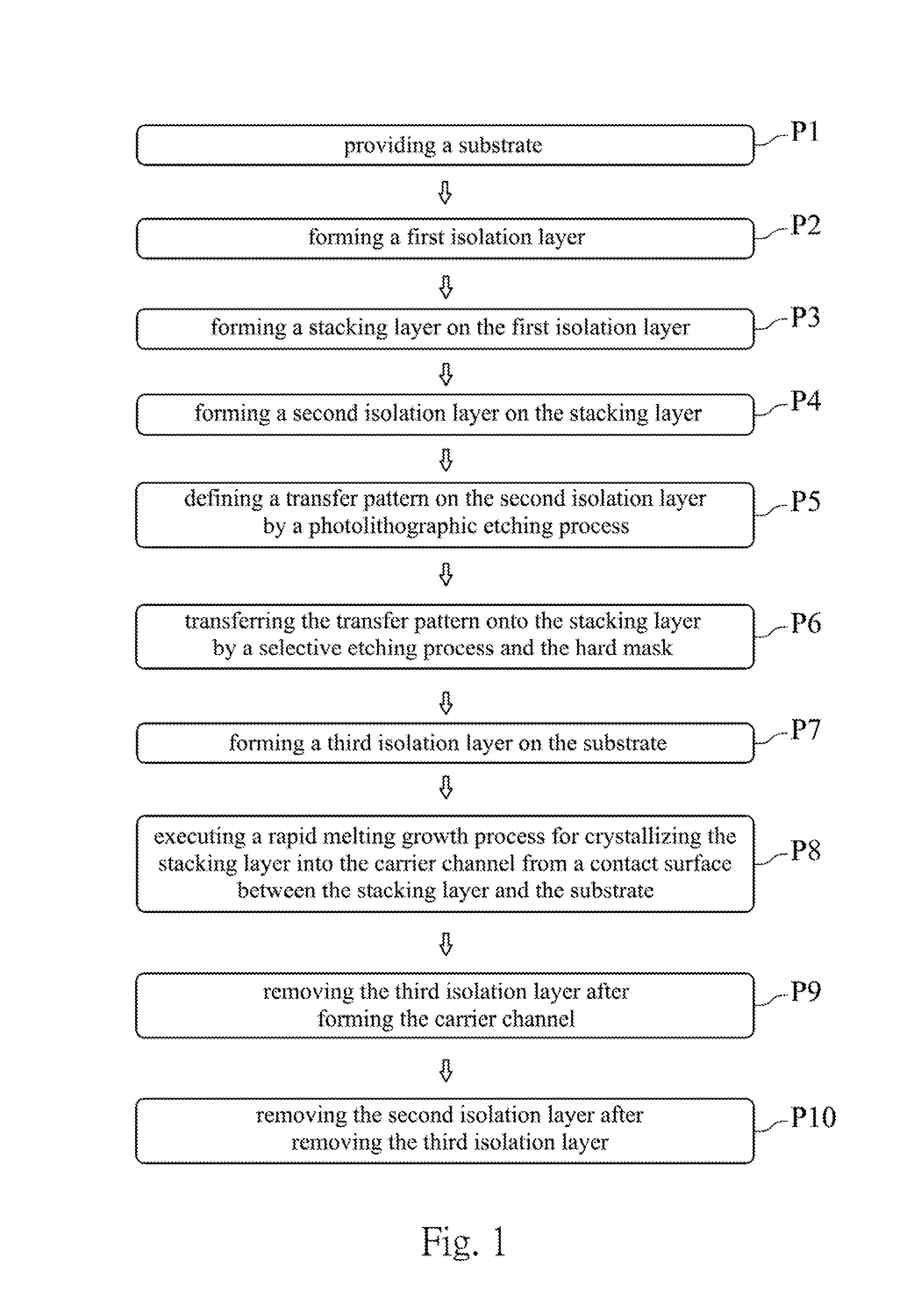

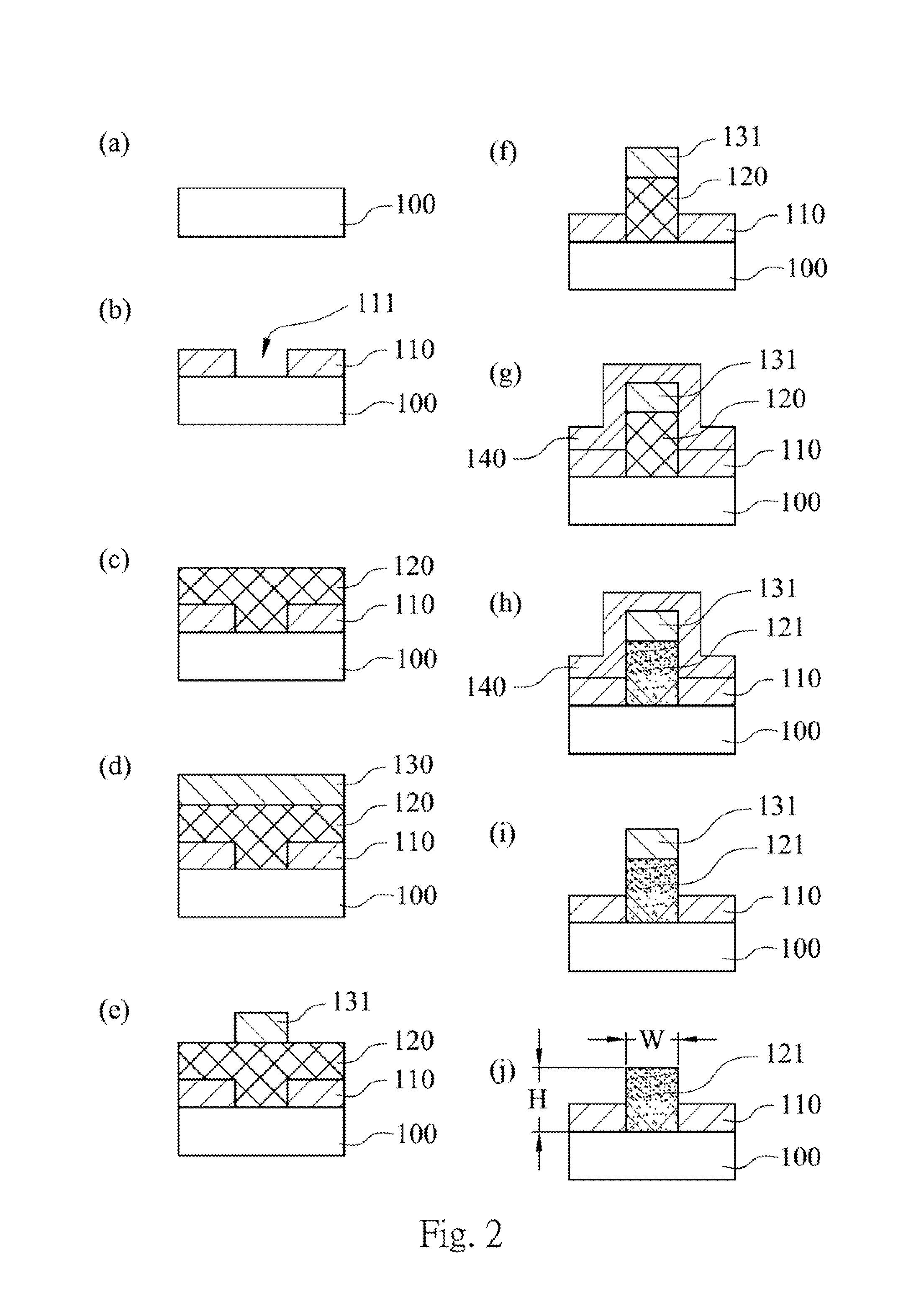

Carrier channel with element concentration gradient distribution and fabrication method thereof

ActiveUS20150332921A1Reduce thermal budgetLow production costTransistorSemiconductor/solid-state device manufacturingCharge carrierConcentration gradient

The present disclosure provides a carrier channel with an element concentration gradient distribution. The carrier channel includes a substrate and a carrier channel structure. The carrier channel structure is stacked on the substrate, wherein a ratio of a height and a width of the carrier channel is greater than 1, and the carrier channel is crystallized from the contact surface by a rapid melting growth process, thus the carrier channel structure has the element concentration gradient distribution.

Owner:NATIONAL TSING HUA UNIVERSITY

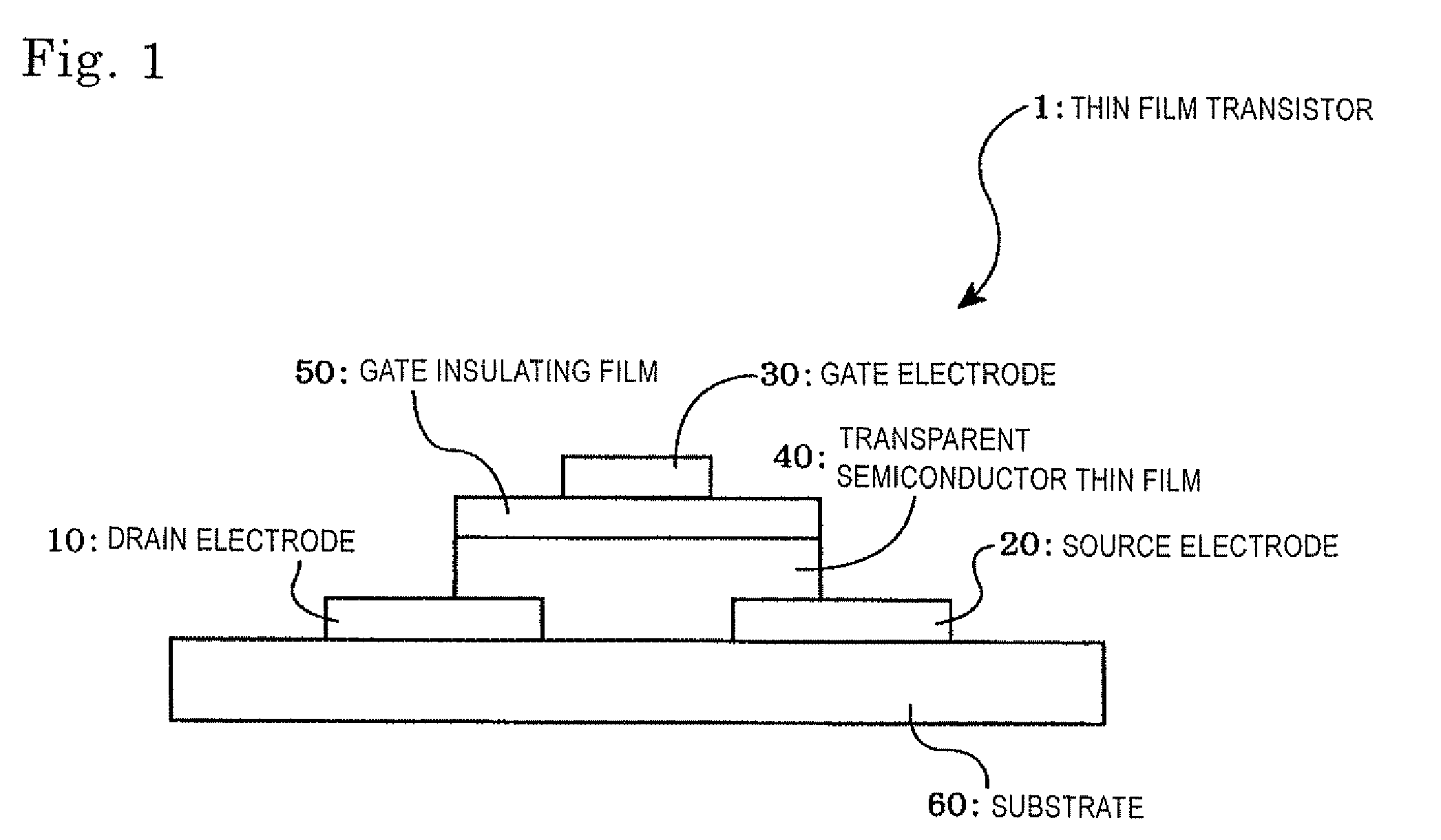

Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel

ActiveUS7998372B2Hardly erroneously operatesSmall currentNanotechConductive materialIndiumActive matrix

Disclosed is a semiconductor thin film which can be formed at a relatively low temperature even on a flexible resin substrate. Since the semiconductor thin film is stable to visible light and has high device characteristics such as transistor characteristics, in the case where the semiconductor thin film is used as a switching device for driving a display, even when overlapped with a pixel part, the luminance of a display panel does not deteriorate. Specifically, a transparent semiconductor thin film 40 is produced by forming an amorphous film containing zinc oxide and indium oxide and then oxidizing the film so that the resulting film has a carrier density of 10+17 cm−3 or less, a Hall mobility of 2 cm2 / V·sec or higher, and an energy band gap of 2.4 EV or more.

Owner:IDEMITSU KOSAN CO LTD

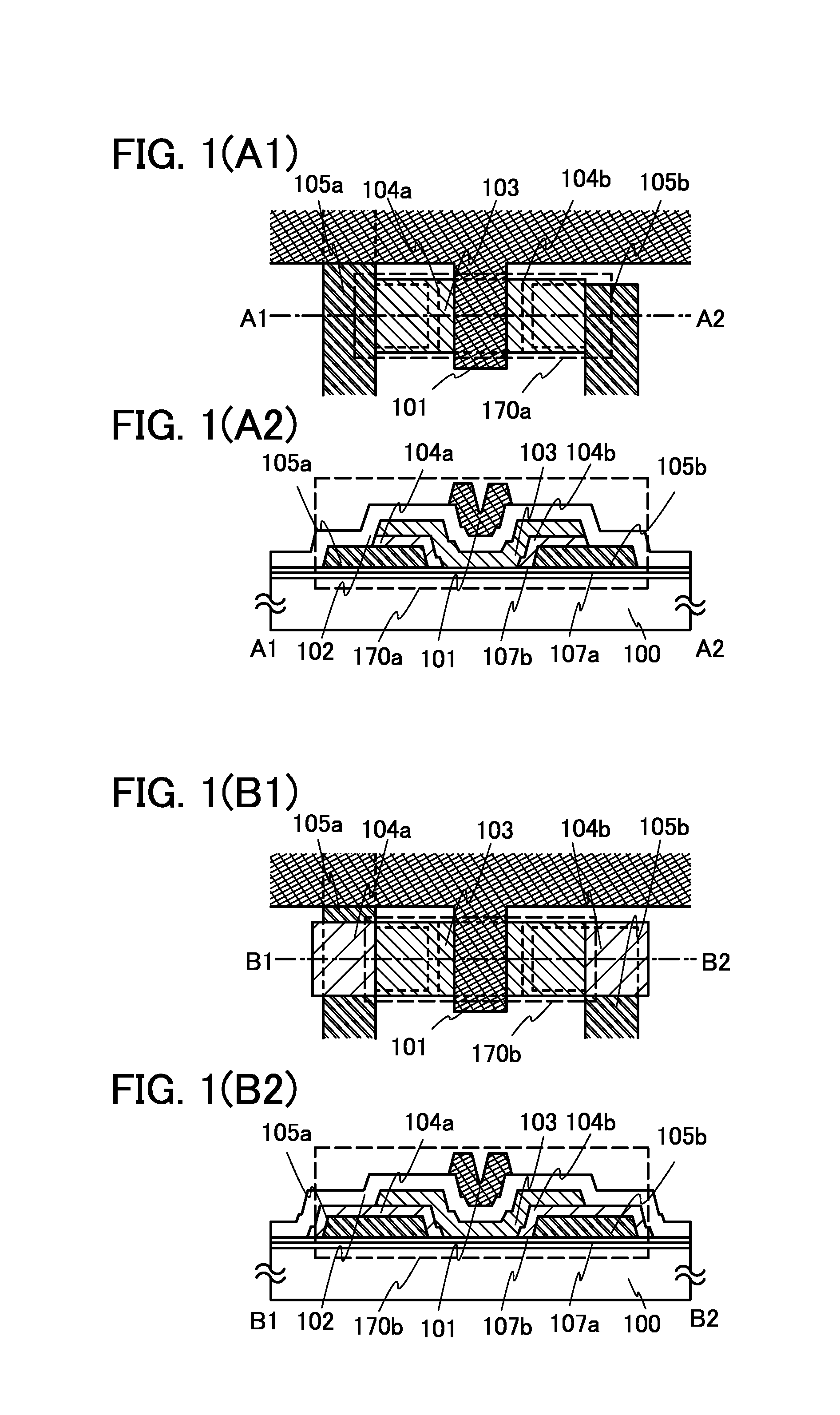

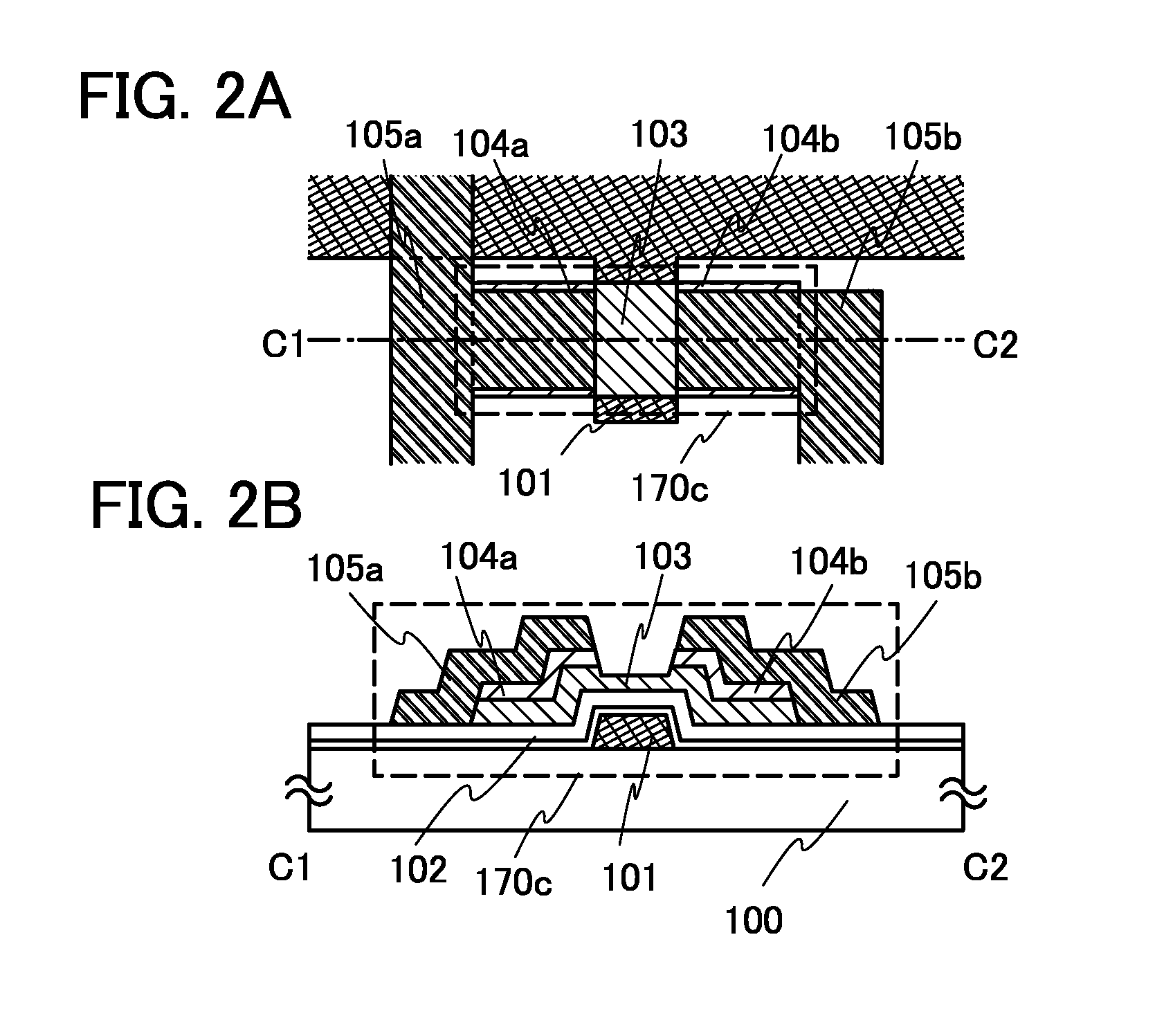

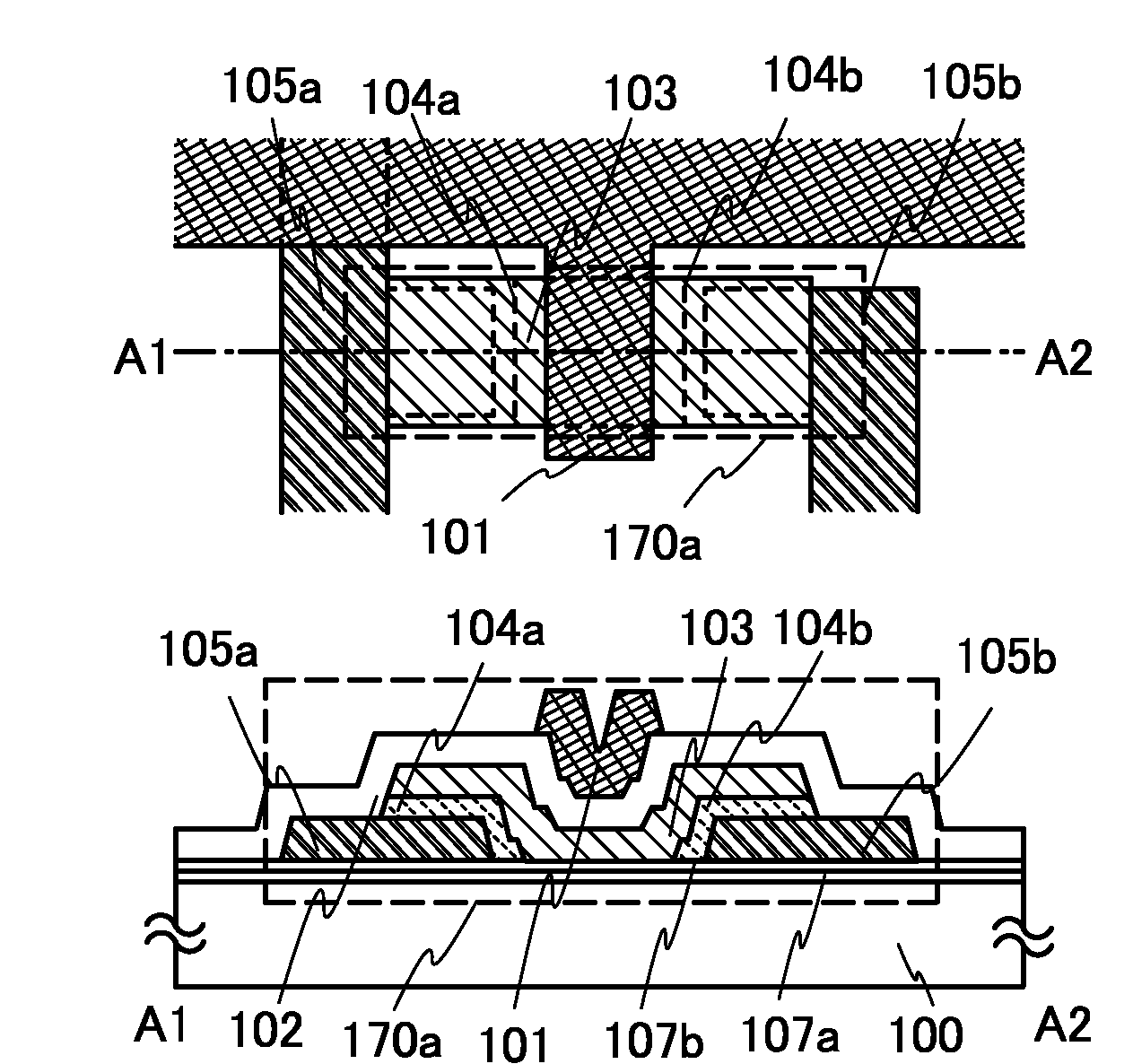

Semiconductor device and method for manufacturing the same

ActiveUS20100032665A1Easy to makeGuaranteed high speed operationTransistorElectroluminescent light sourcesOhmic contactCharge carrier

An embodiment is to include a staggered (top gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

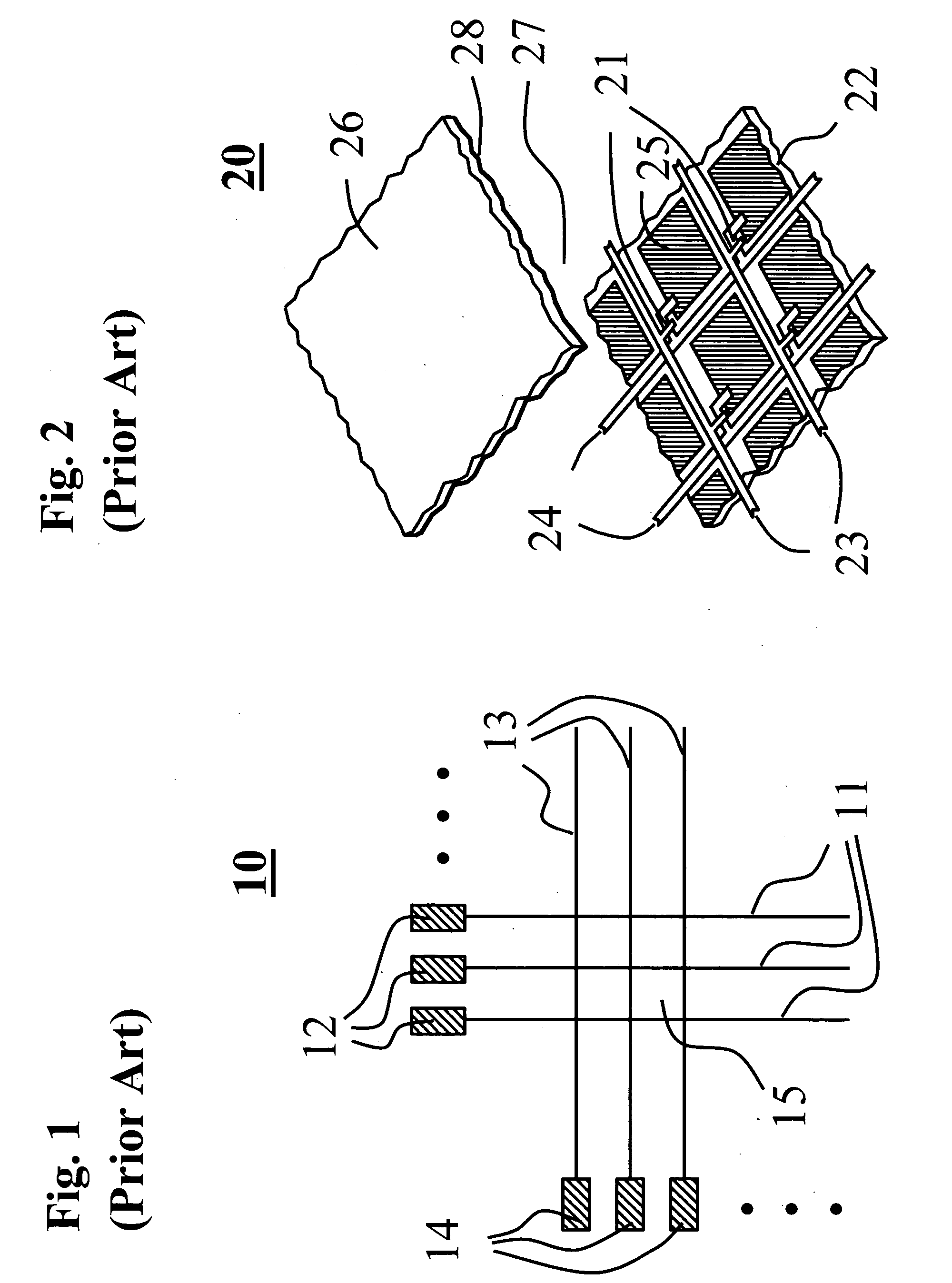

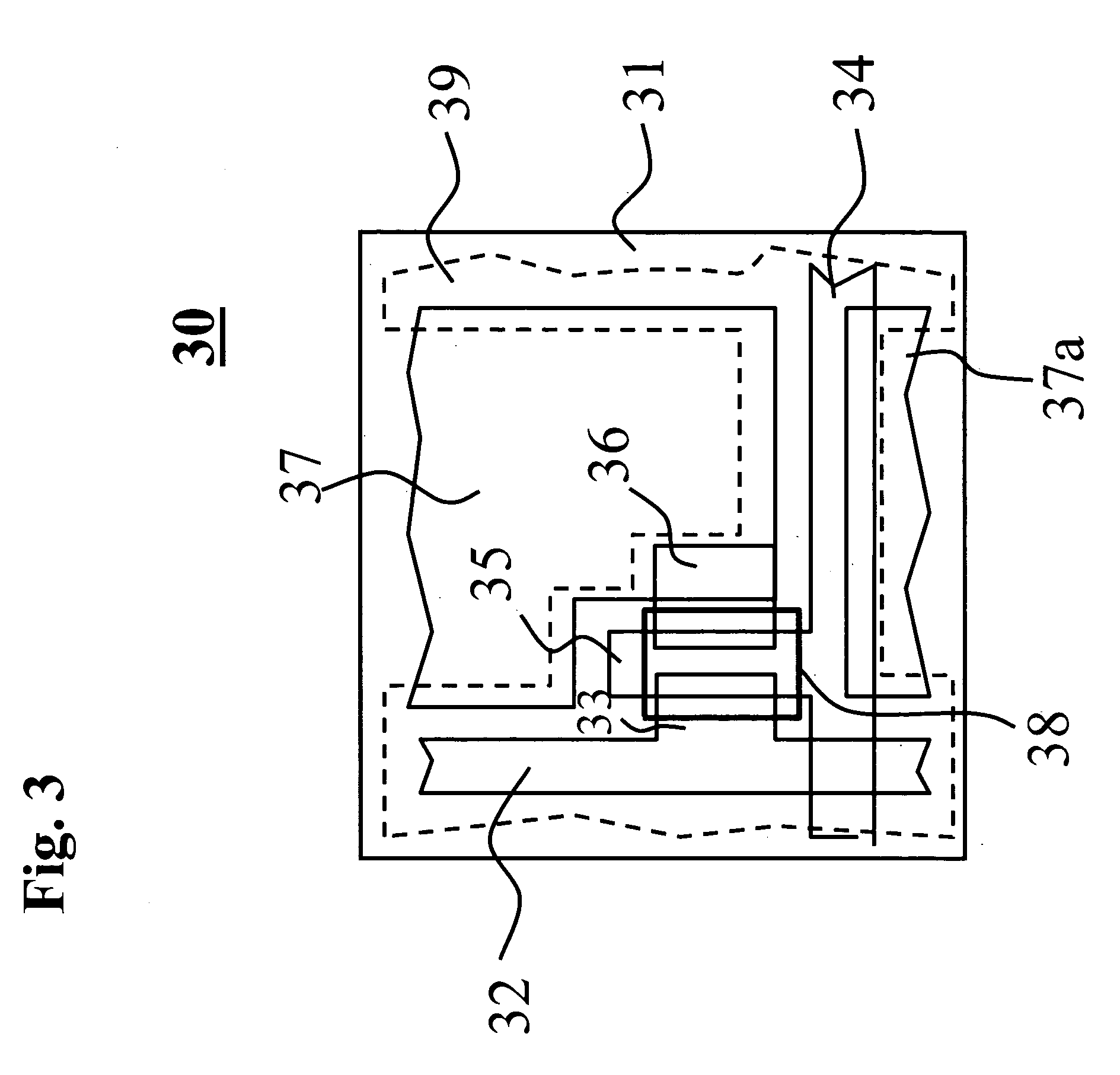

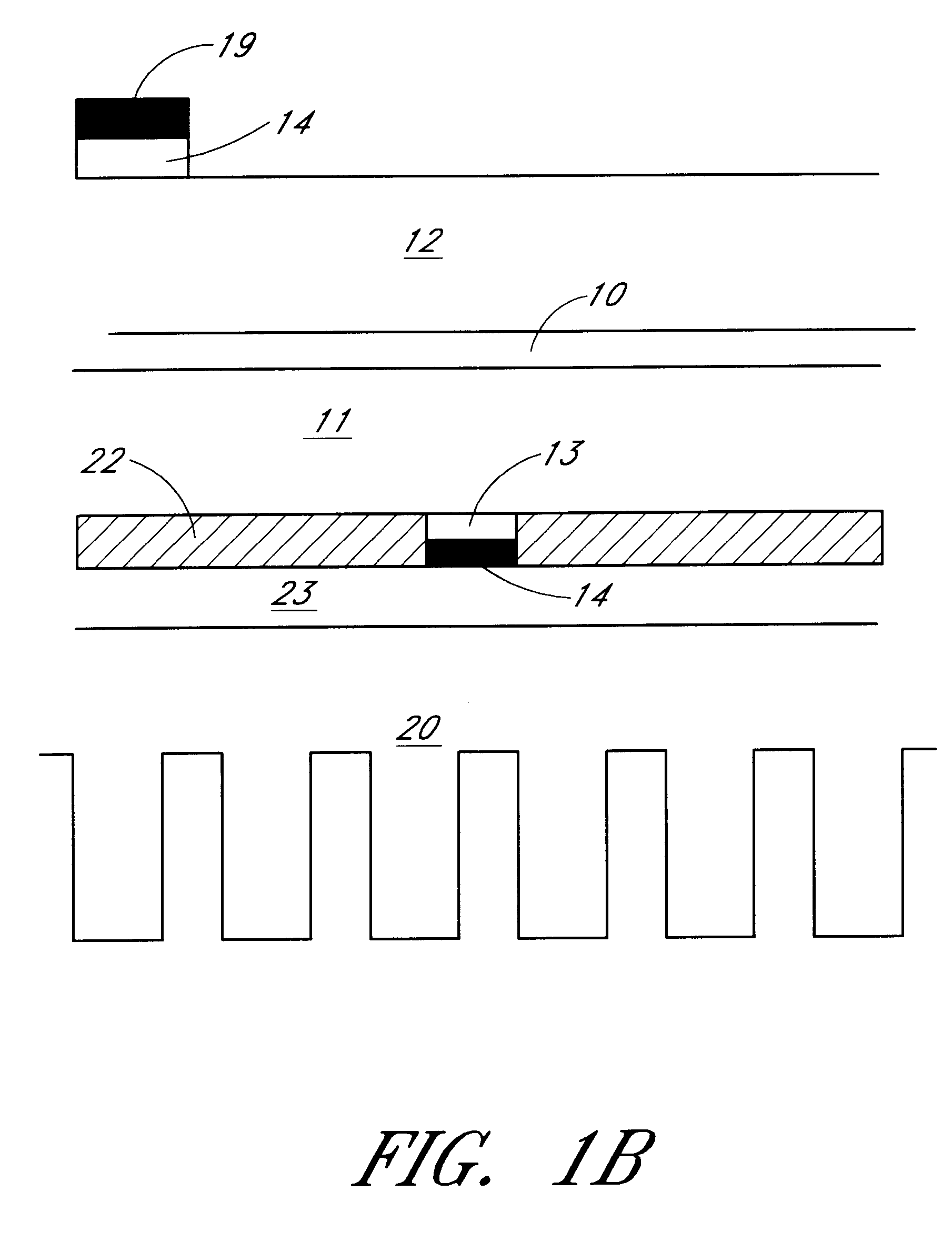

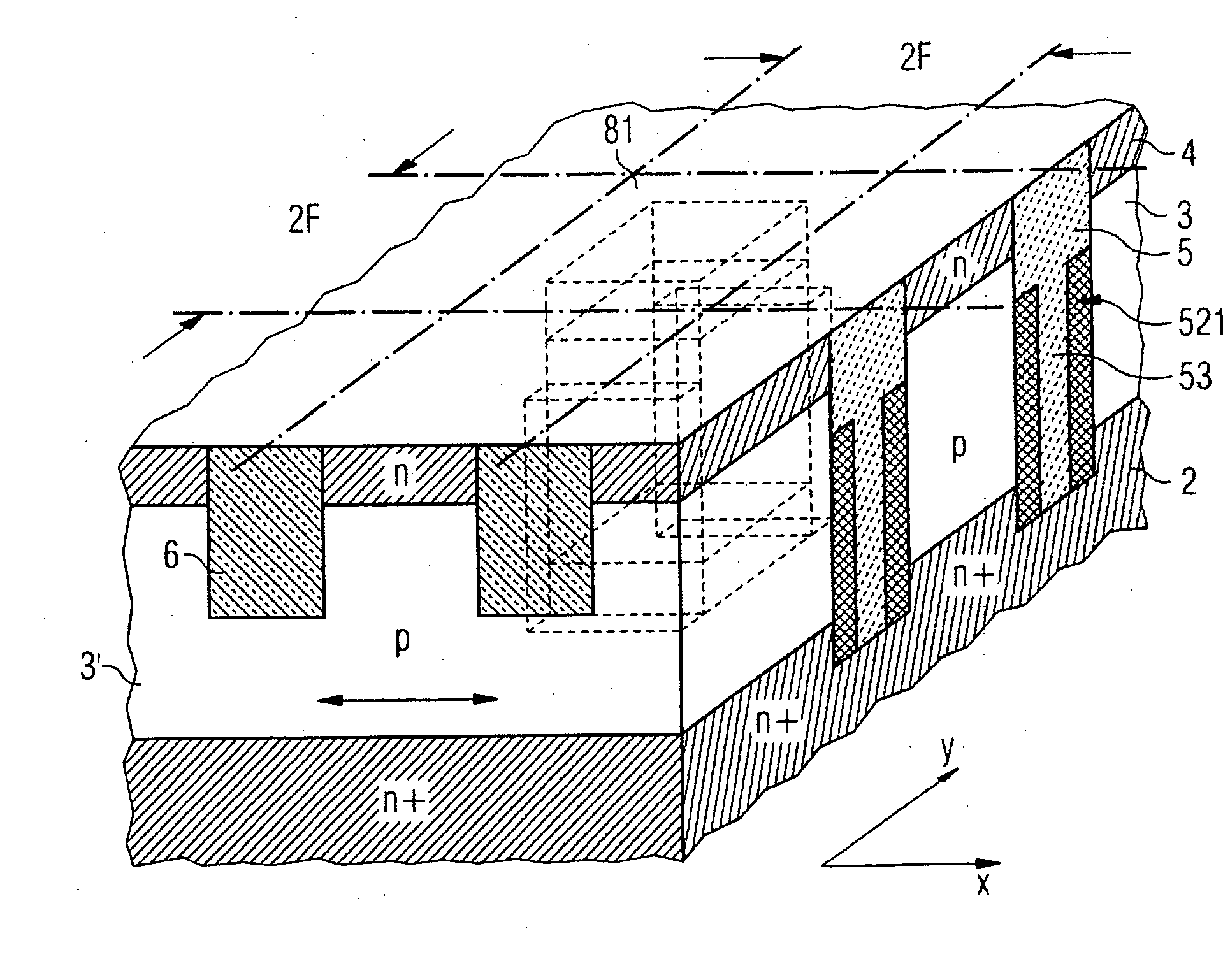

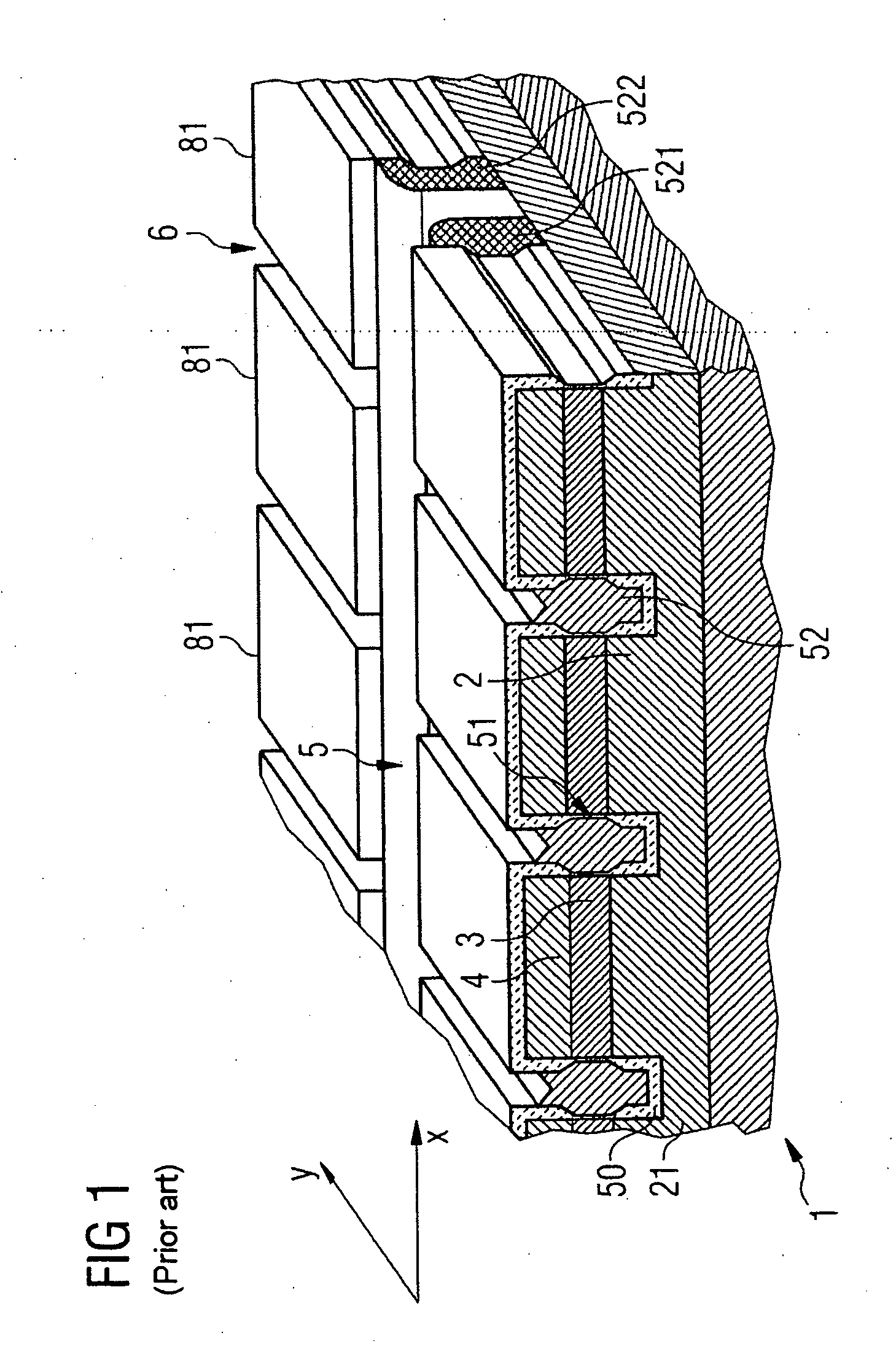

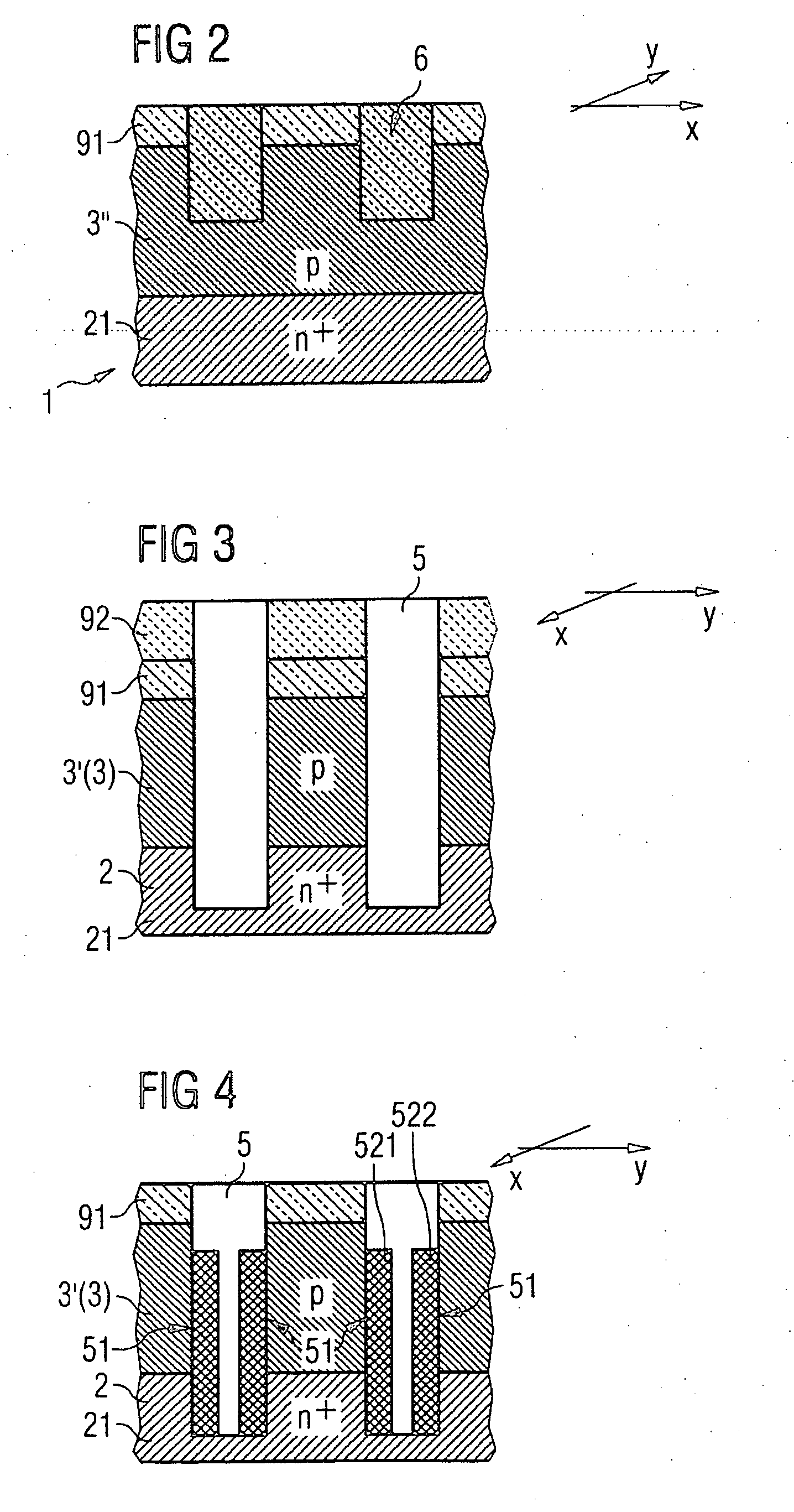

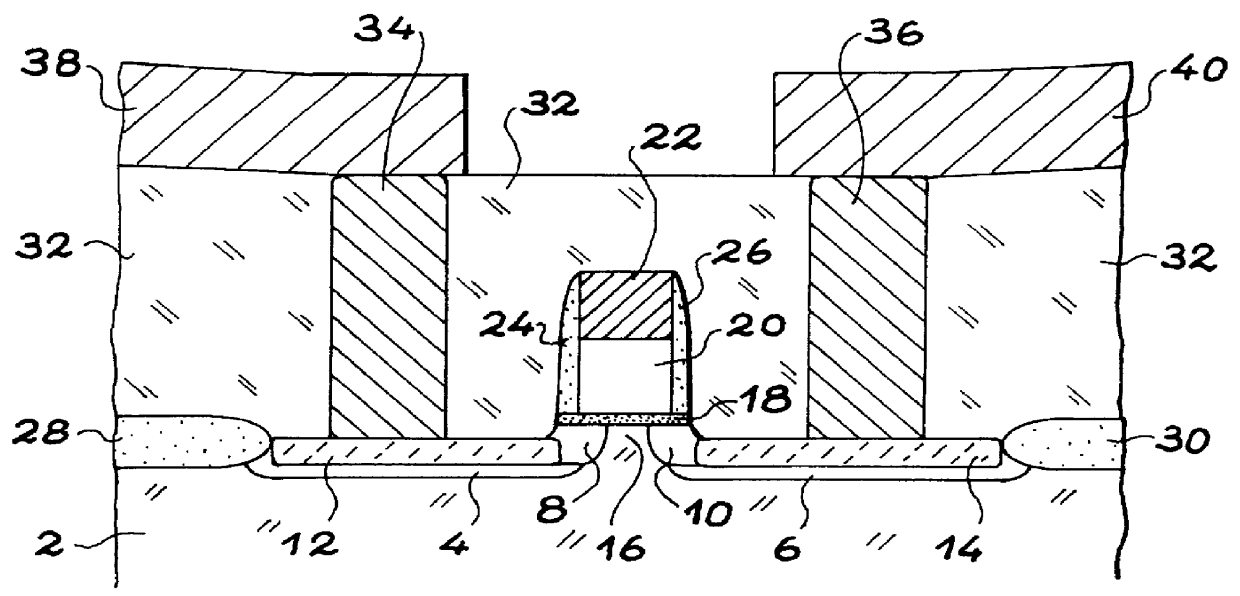

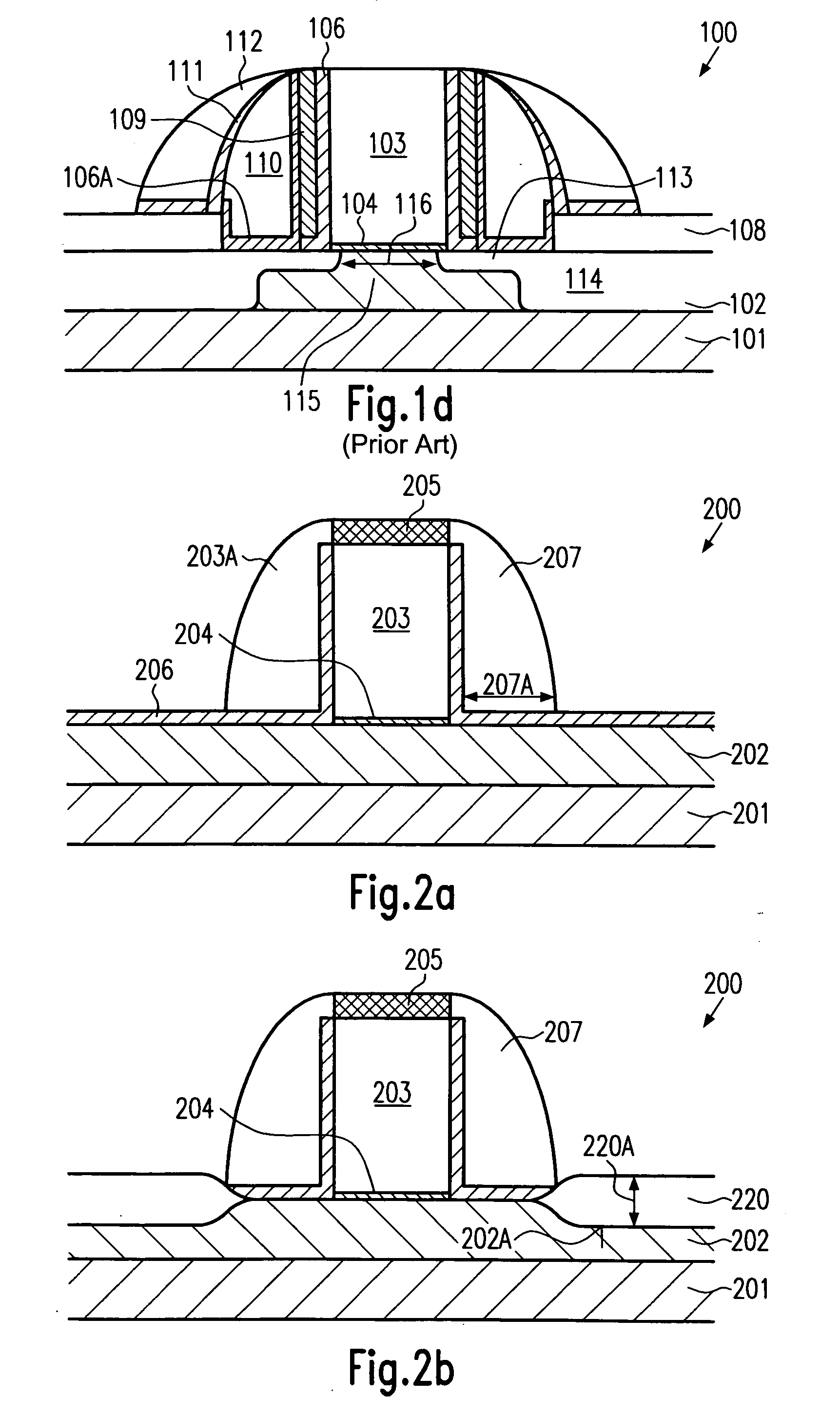

Method of fabricating and architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS20050001257A1Increased area requirementLimited functionTransistorSolid-state devicesFloating body effectDram memory

In a substrate vertical transistor cells are formed and are arranged, in a transistor cell array, row by row in an x direction and column by column in a y direction. Lower source / drain regions of the transistor cells are connected to a common connection plate. Upper source / drain regions of the transistor cells impart a contact connection for instance to a storage capacitor of a DRAM memory cell. Active trenches running between the transistor cells with word lines are formed along the x direction. The word lines form gate electrodes in sections. A potential at the gate electrode controls a conductive channel in an active region arranged in each case between the upper and the lower source / drain connection region. According to the invention, the active regions of adjacent transistor cells are sections of a contiguous layer body and are connected to one another. An accumulation of charge carriers in the active region and floating body effects are avoided without increasing the area requirement of a transistor cell.

Owner:POLARIS INNOVATIONS LTD

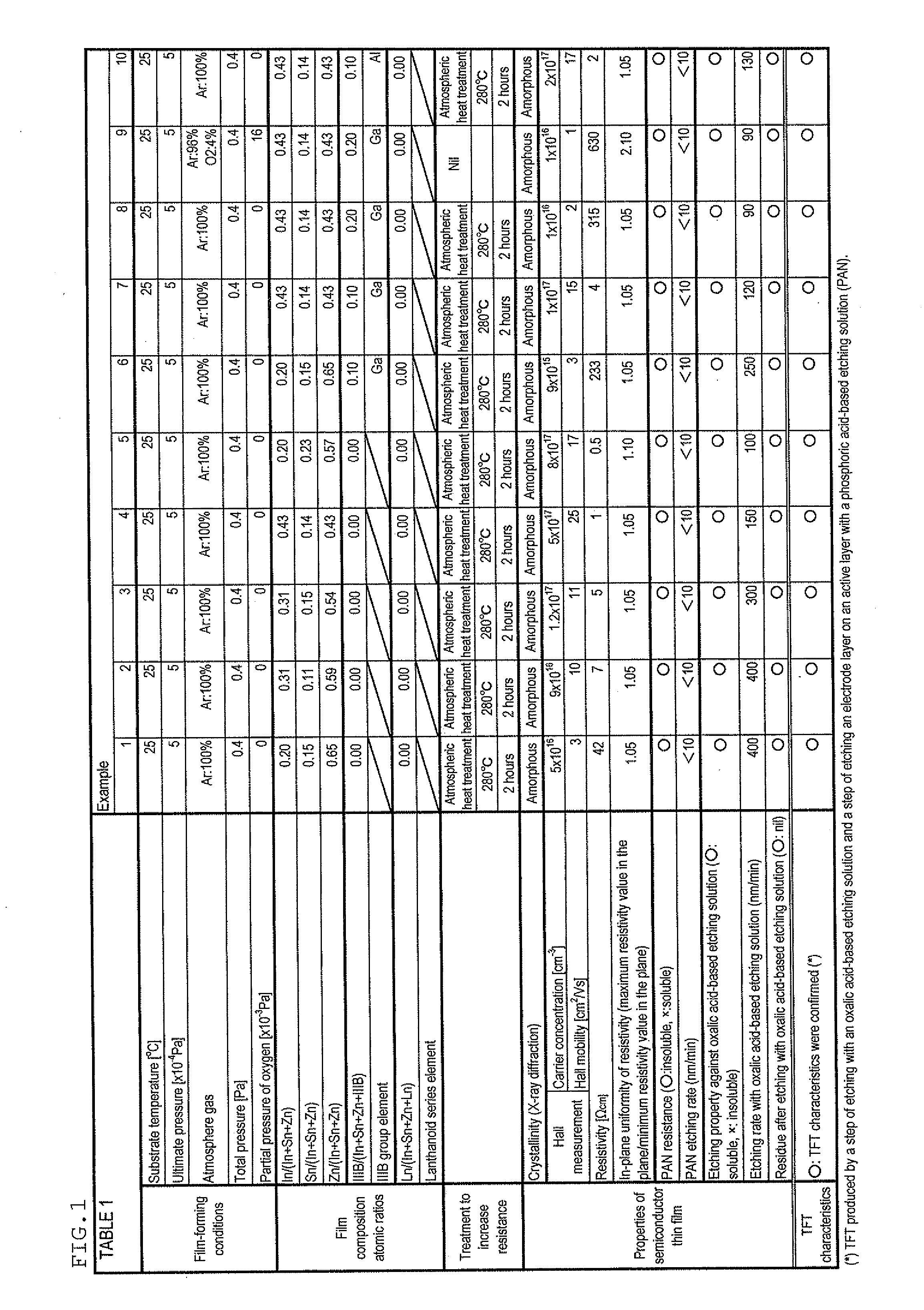

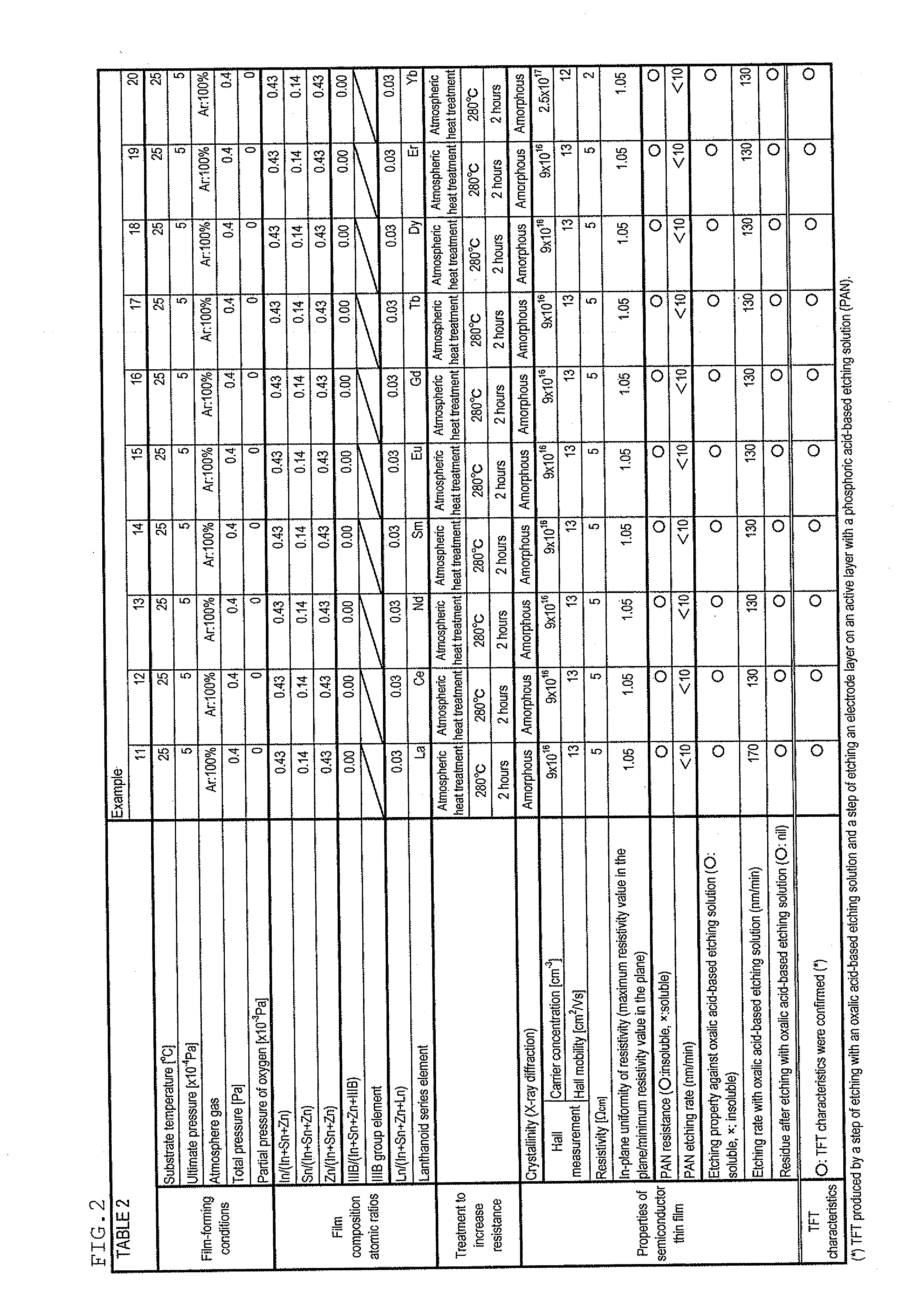

Noncrystalline oxide semiconductor thin film, process for producing the noncrystalline oxide semiconductor thin film, process for producing thin-film transistor, field-effect-transistor, light emitting device, display device, and sputtering target

ActiveUS20100155717A1Improve the immunityEasy to uniformlyCellsVacuum evaporation coatingIndiumPhosphoric acid

This invention provides an amorphous oxide semiconductor thin film, which is insoluble in a phosphoric acid-based etching solution and is soluble in an oxalic acid-based etching solution by optimizing the amounts of indium, tin, and zinc, a method of producing the amorphous oxide semiconductor thin film, etc. An image display device (1) comprises a glass substrate (10), a liquid crystal (40) as a light control element, a bottom gate-type thin film transistor (1) for driving the liquid crystal (40), a pixel electrode (30), and an opposing electrode (50). The amorphous oxide semiconductor thin film (2) in the bottom gate-type thin film transistor (1) has a carrier density of less than 10+18 cm−3, is insoluble in a phosphoric acid-based etching liquid, and is soluble in an oxalic acid-based etching liquid.

Owner:IDEMITSU KOSAN CO LTD

Light emitting devices with layered III-V semiconductor structures

InactiveUS6207973B1Improve crystal qualityFacilitates layerLaser detailsLaser active region structureCharge carrierSemiconductor structure

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

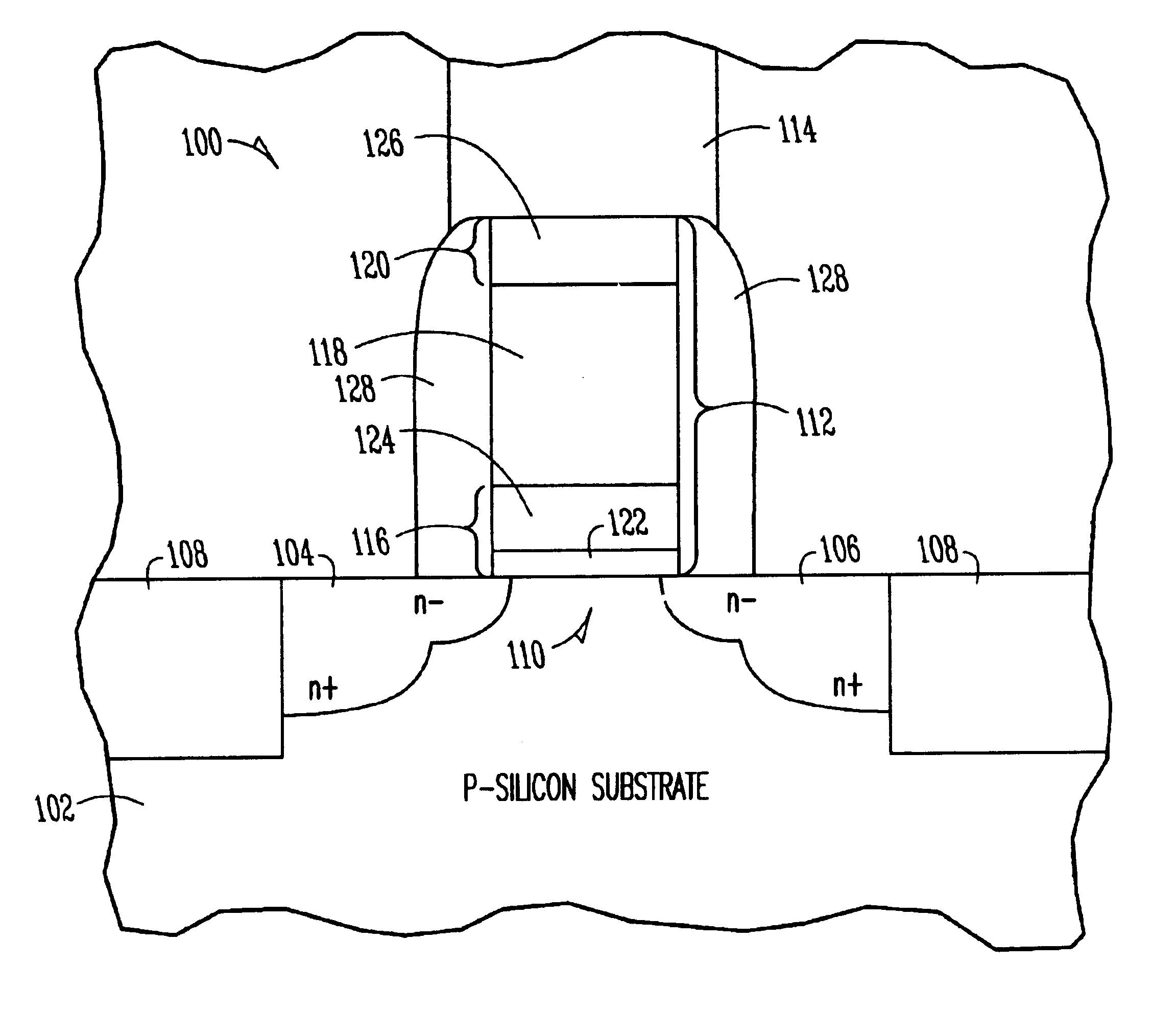

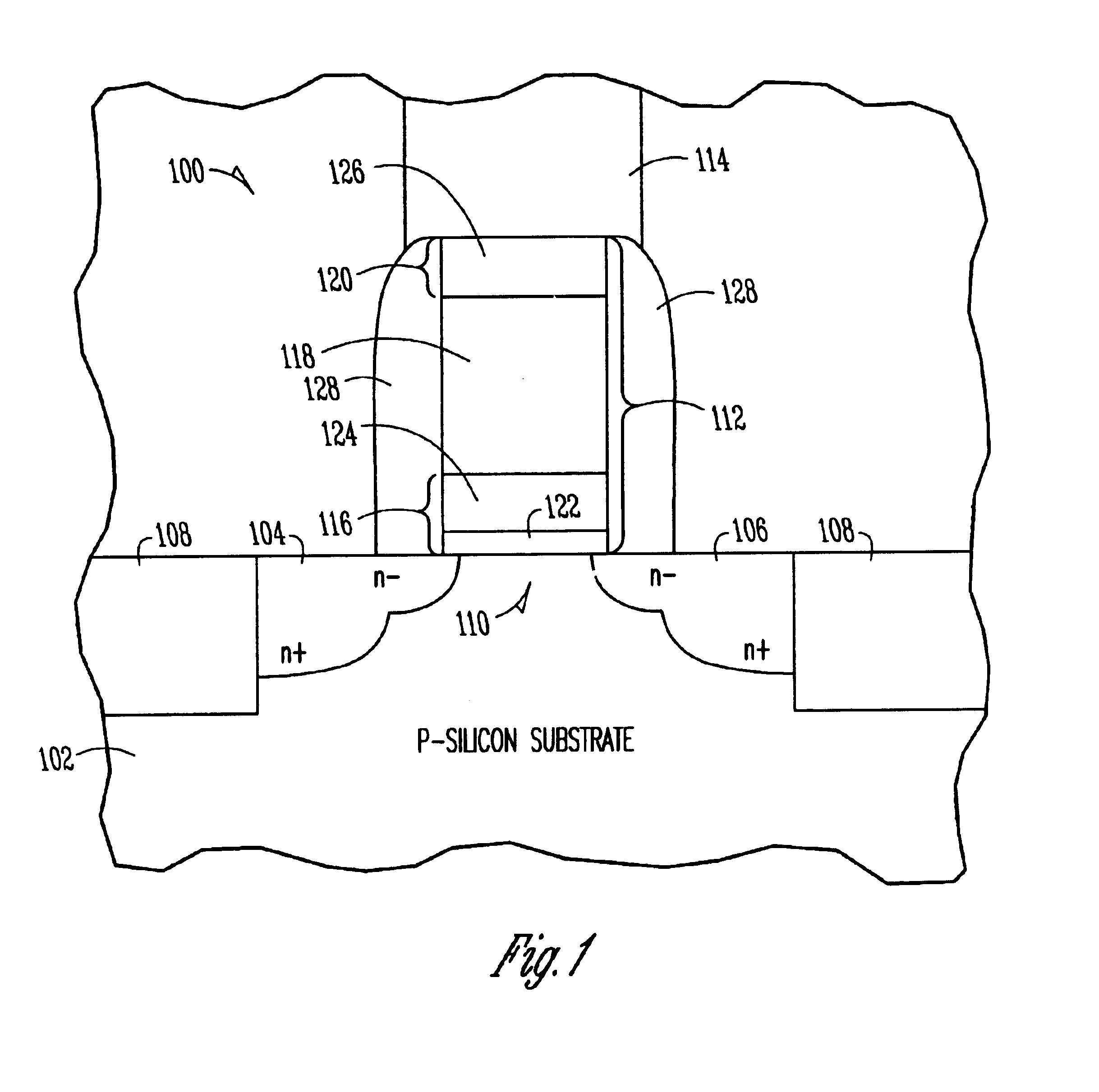

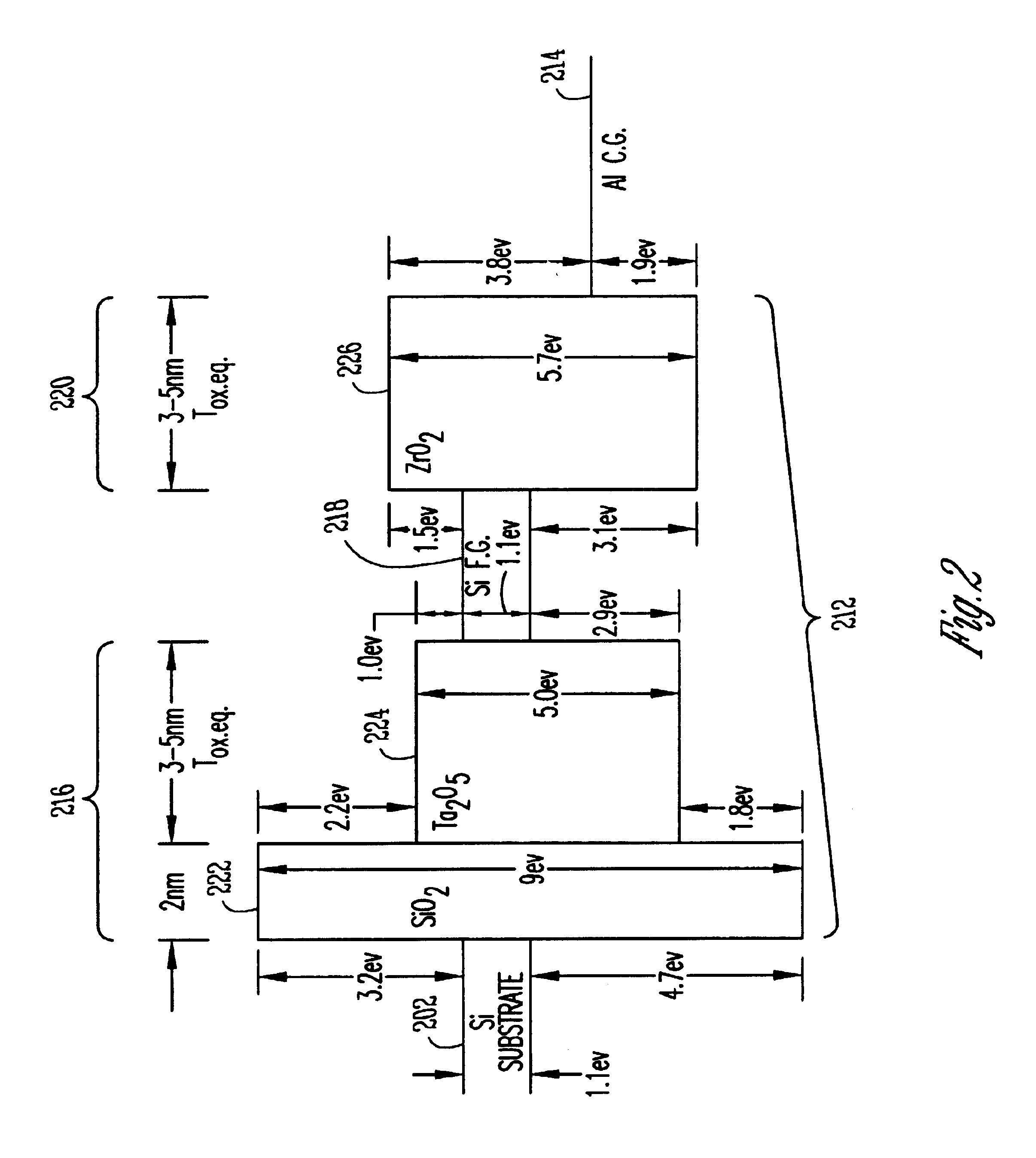

Asymmetric band-gap engineered nonvolatile memory device

Owner:MICRON TECH INC

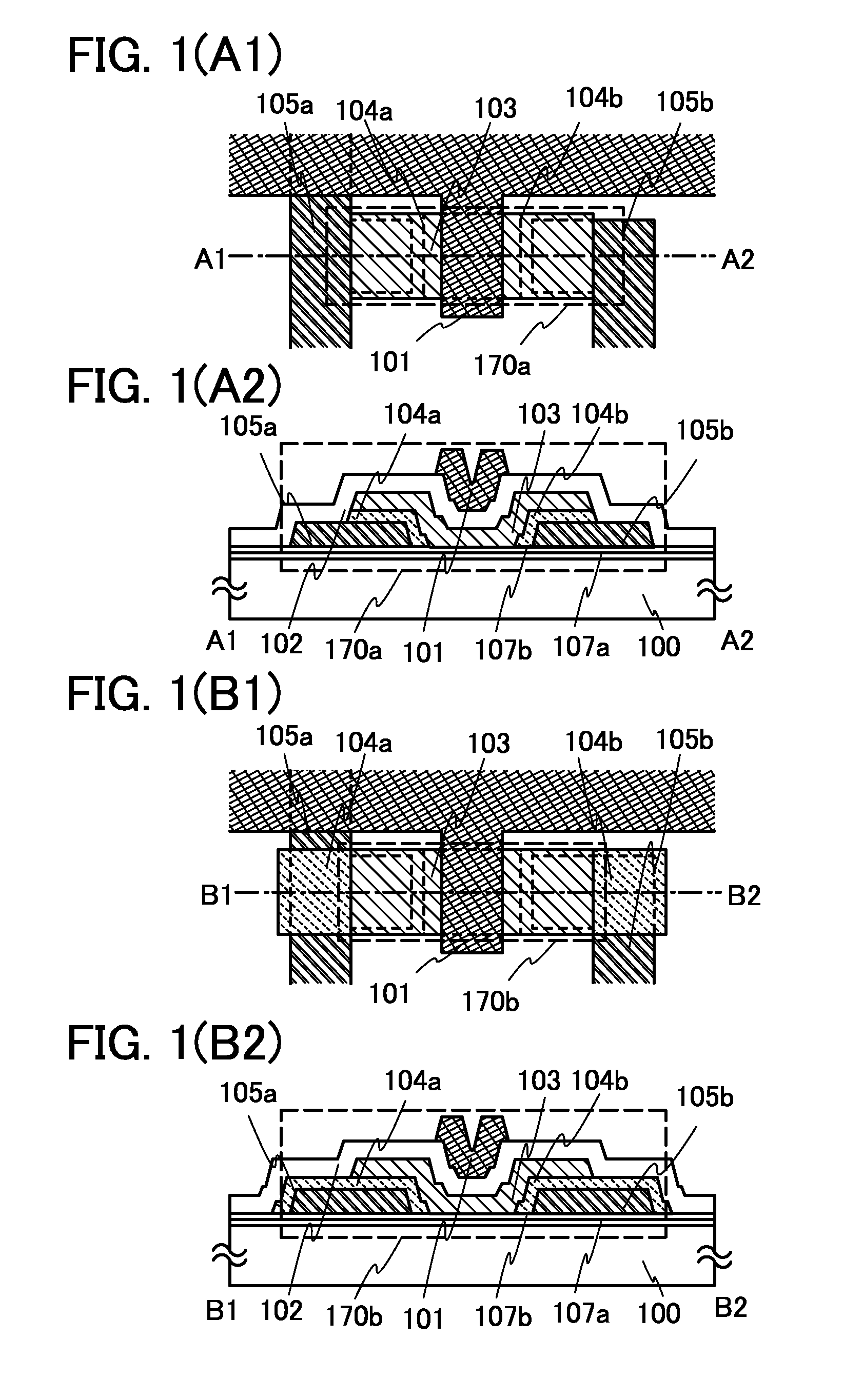

Semiconductor device and method for manufacturing the same

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

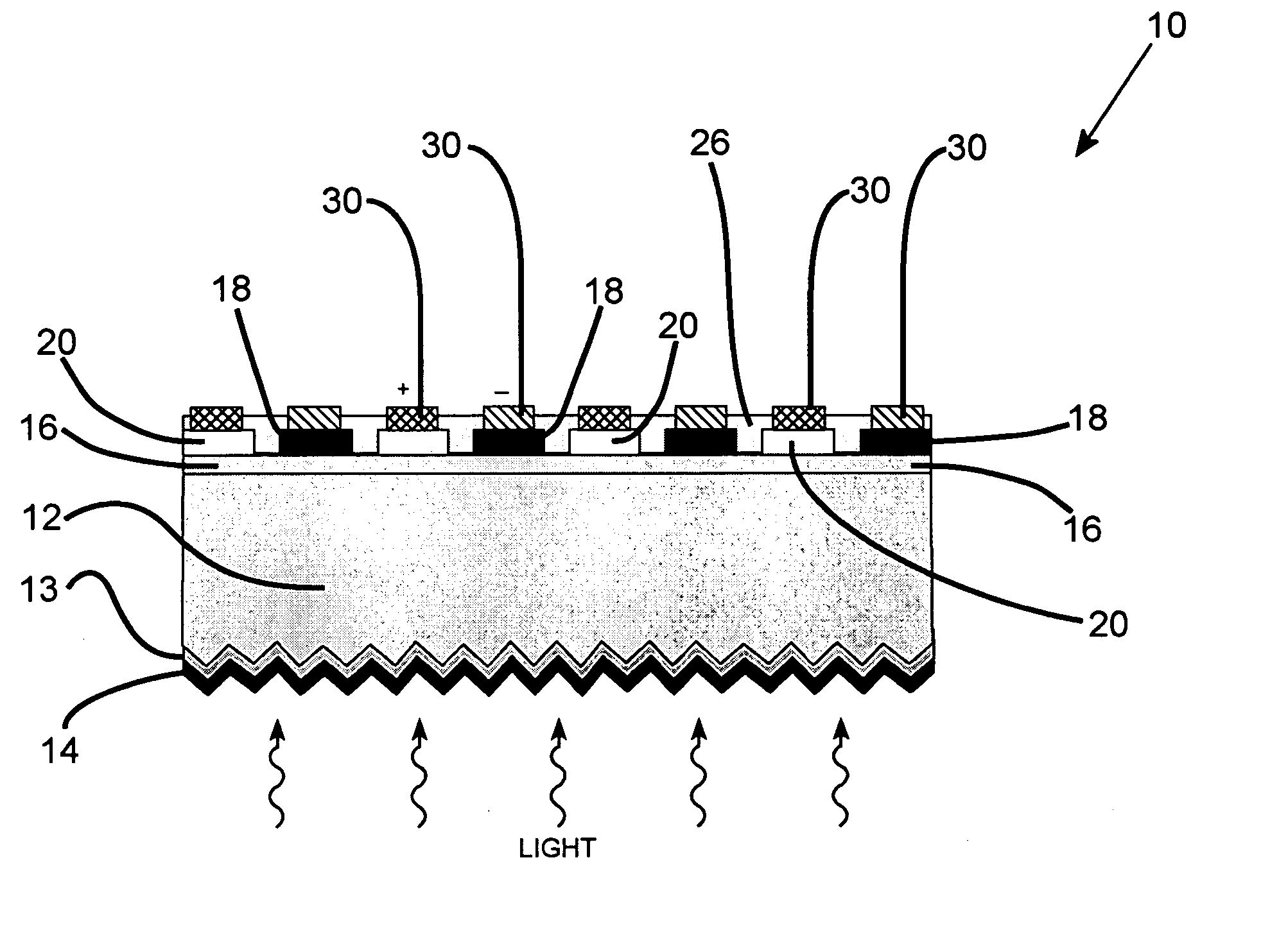

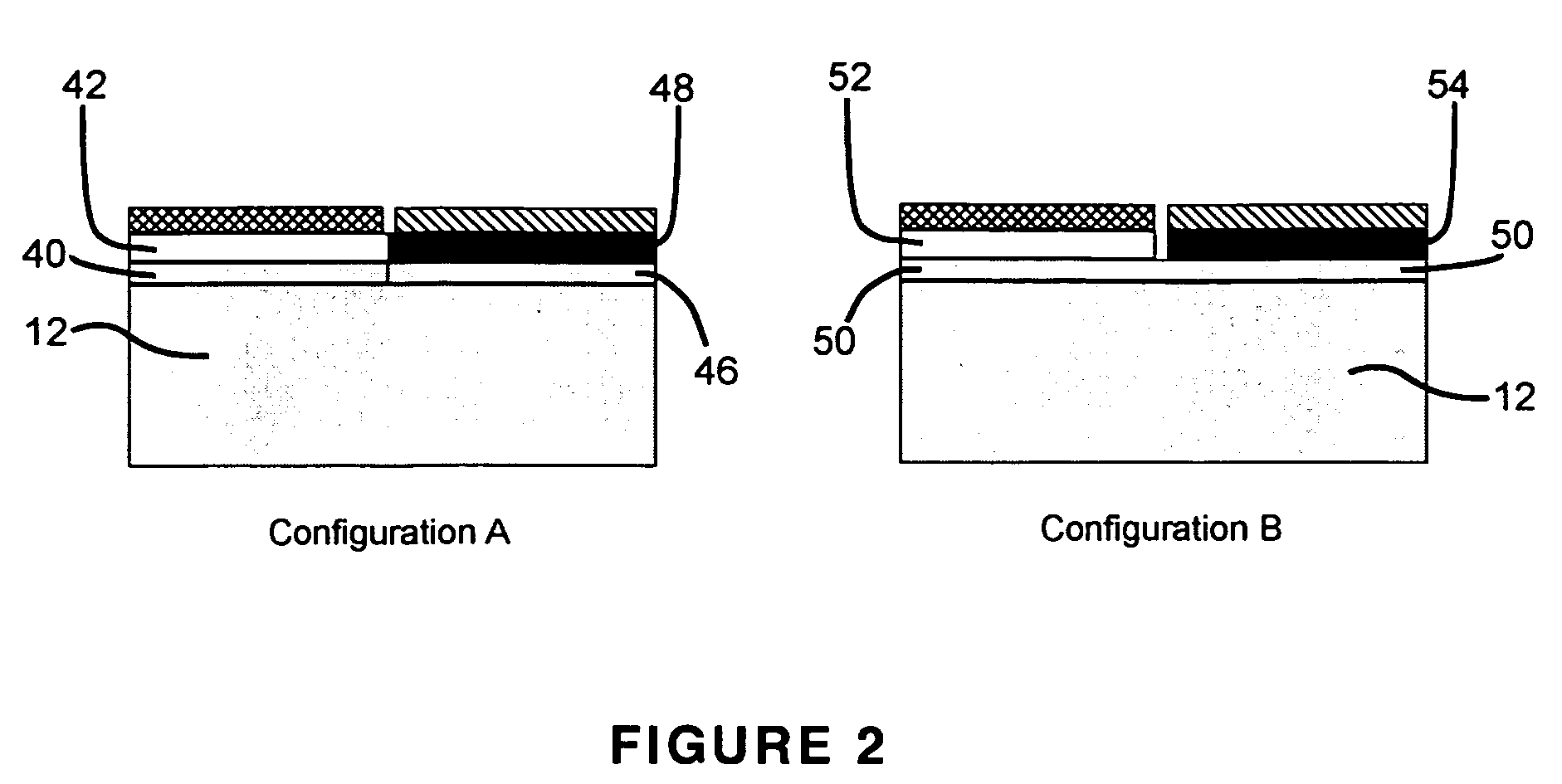

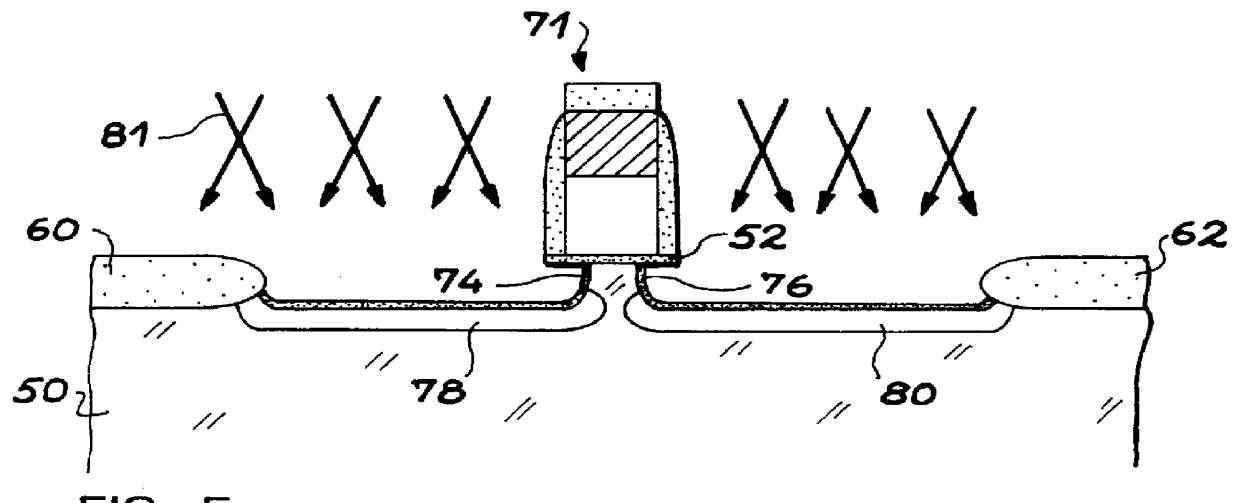

Solar cell

InactiveUS20070169808A1Low costEasy to usePhotovoltaic energy generationSemiconductor devicesHeterojunctionManufacturing technology

The present invention provides a thin film amorphous silicon-crystalline silicon back heterojunction and back surface field device configuration for a heterojunction solar cell. The configuration is attained by the formation of heterojunctions on the back surface of crystalline silicon at low temperatures. Low temperature fabrication allows for the application of low resolution lithography and / or shadow masking processes to produce the structures. The heterojunctions and interface passivation can be formed through a variety of material compositions and deposition processes, including appropriate surface restructing techniques. The configuration achieves separation of optimization requirements for light absorption and carrier generation at the front surface on which the light is incident, and in the bulk, and charge carrier collection at the back of the device. The shadowing losses are eliminated by positioning the electrical contacts at the back thereby removing them from the path of the incident light. Back contacts need optimization only for maximum charge carrier collection without bothering about shading losses. A range of elements / alloys may be used to effect band-bending. All of the above features result in a very high efficiency solar cell. The open circuit voltage of the back heterojunction device is higher than that of an all-crystalline device. The solar cell configurations are equally amenable to crystalline silicon wafer absorber as well as thin silicon layers formed by using a variety of fabrication processes. The configurations can be used for radiovoltaic and electron-voltaic energy conversion devices.

Owner:KHERANI NAZIR P +1

Semiconductor device and method for manufacturing the same

ActiveUS20100032668A1Easy to makeGuaranteed high speed operationTransistorSemiconductor/solid-state device manufacturingCharge carrierOhmic contact

An embodiment is to include a staggered (top gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. A metal oxide layer having higher carrier concentration than the semiconductor layer is provided intentionally as the buffer layer between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

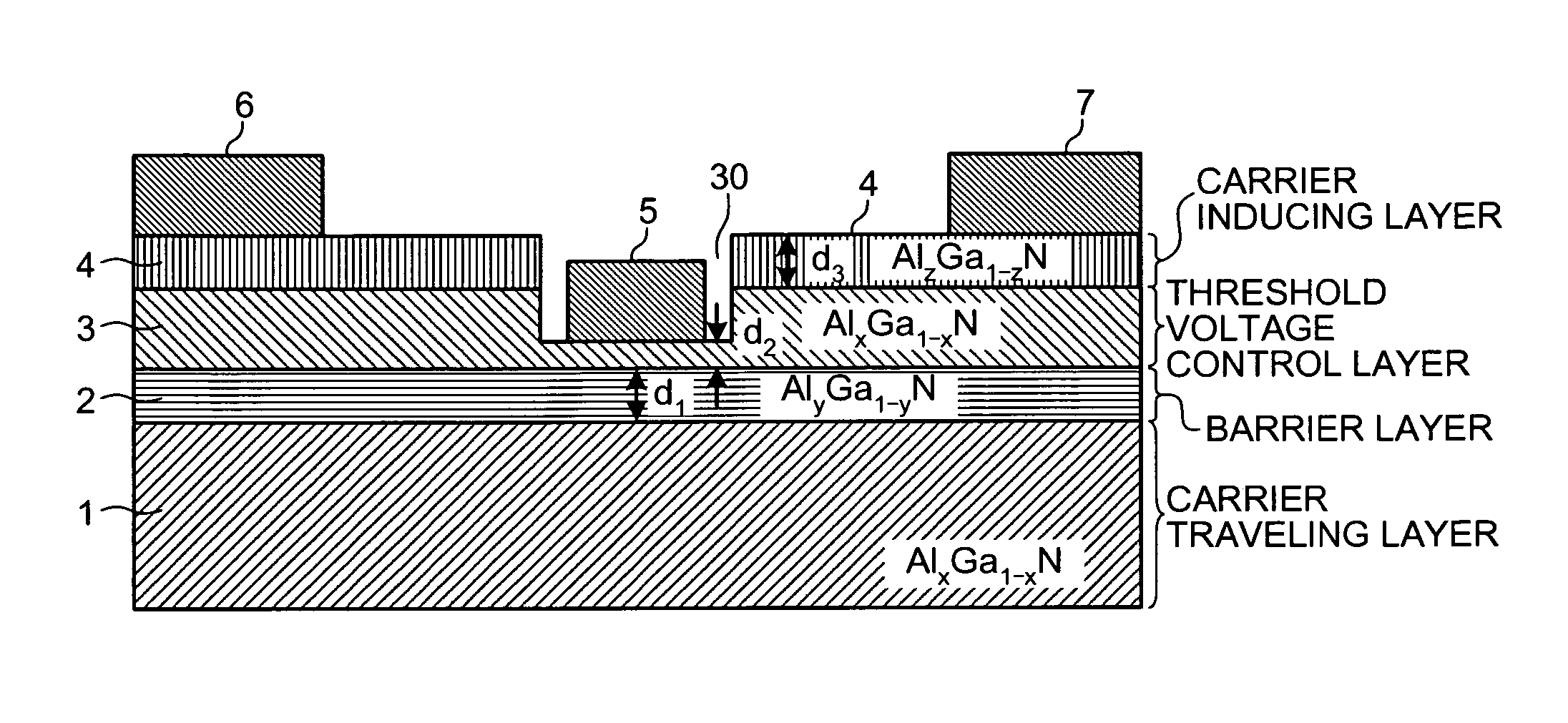

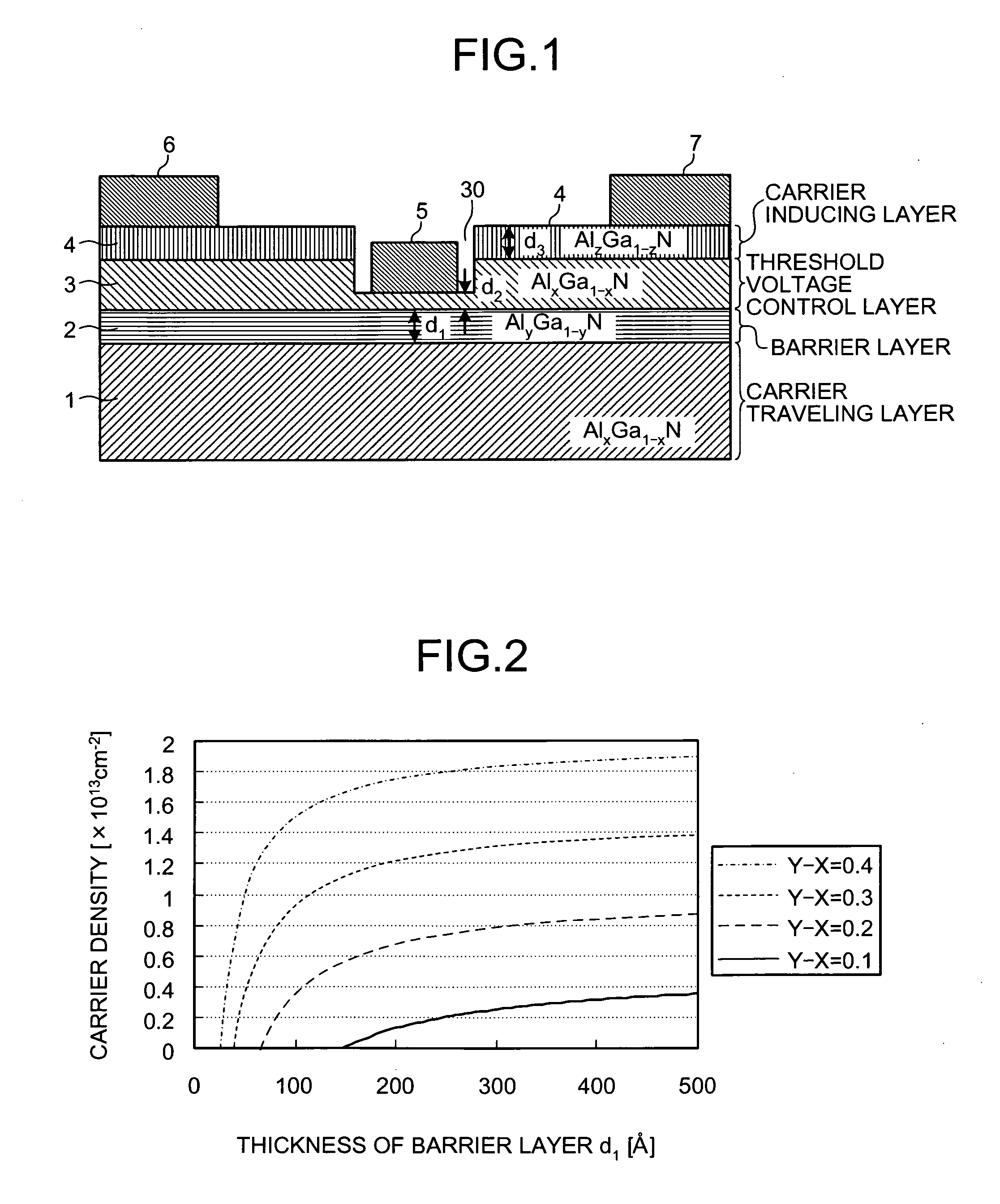

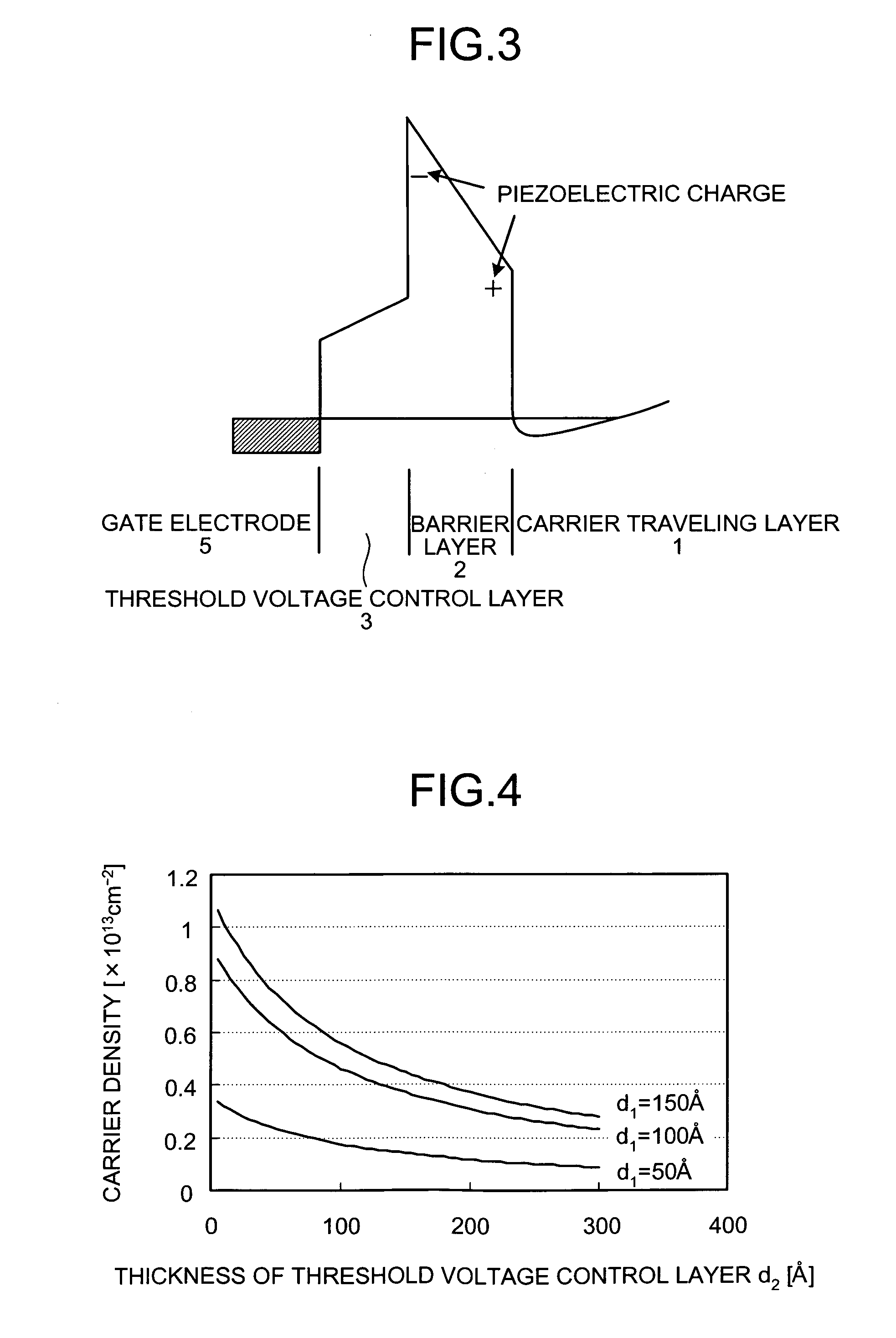

Nitride-based semiconductor device and method of manufacturing the same

The nitride-based semiconductor device includes a carrier traveling layer 1 composed of non-doped AlxGa1-xN (0≦X<1); a barrier layer 2 formed on the carrier traveling layer 1 and composed of non-doped or n-type AlYGa1-YN (0<Y≦1, X<Y) having a lattice constant smaller than that of the carrier traveling layer 1; a threshold voltage control layer 3 formed on the barrier layer 2 and composed of a non-doped semiconductor having a lattice constant equal to that of the carrier traveling layer 1; and a carrier inducing layer 4 formed on the threshold voltage control layer 3 and composed of a non-doped or n-type semiconductor having a lattice constant smaller than that of the carrier traveling layer 1. The nitride-based semiconductor device further includes a gate electrode 5 formed in a recess structure, a source electrode 6 and a drain electrode 7.

Owner:KK TOSHIBA

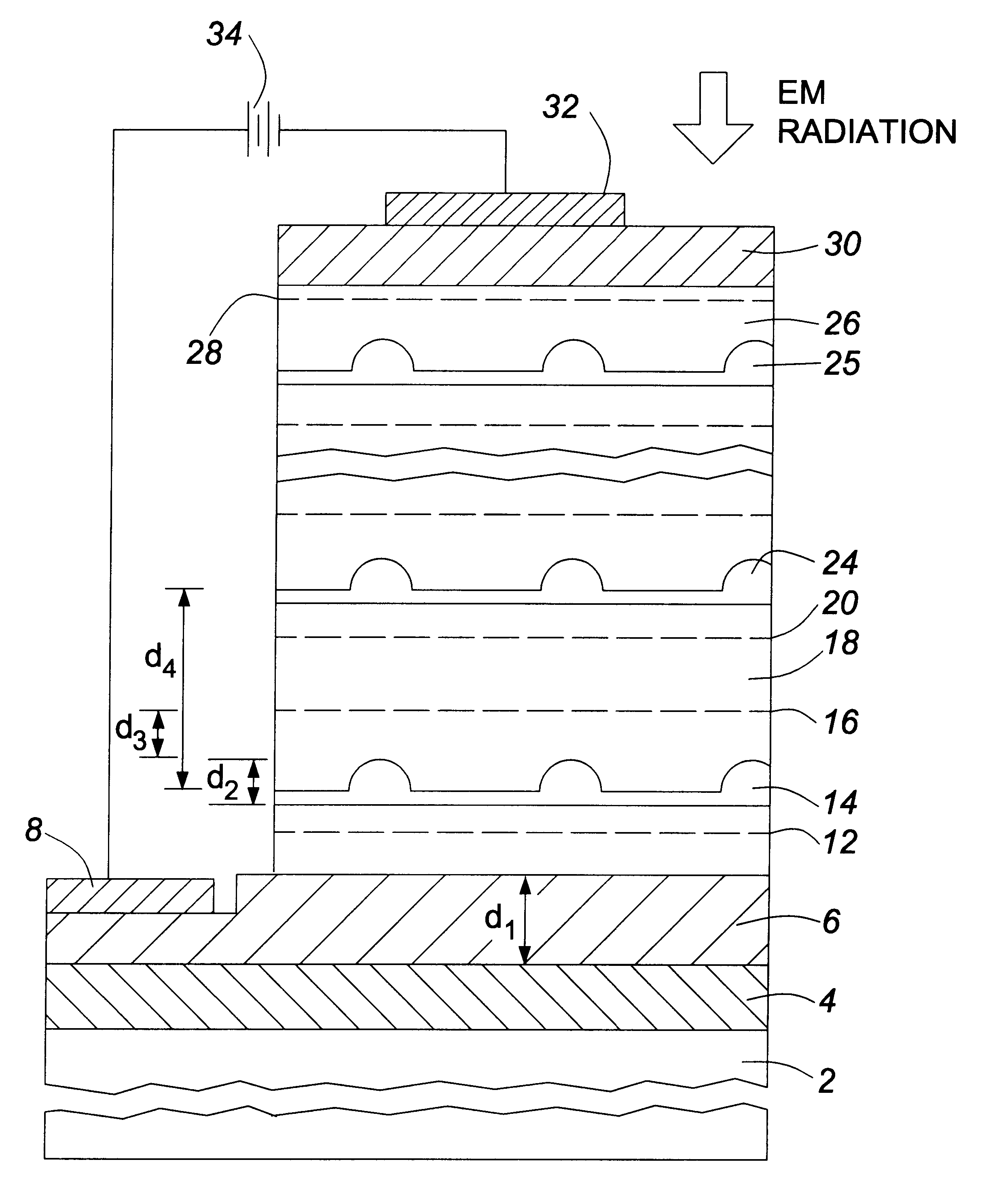

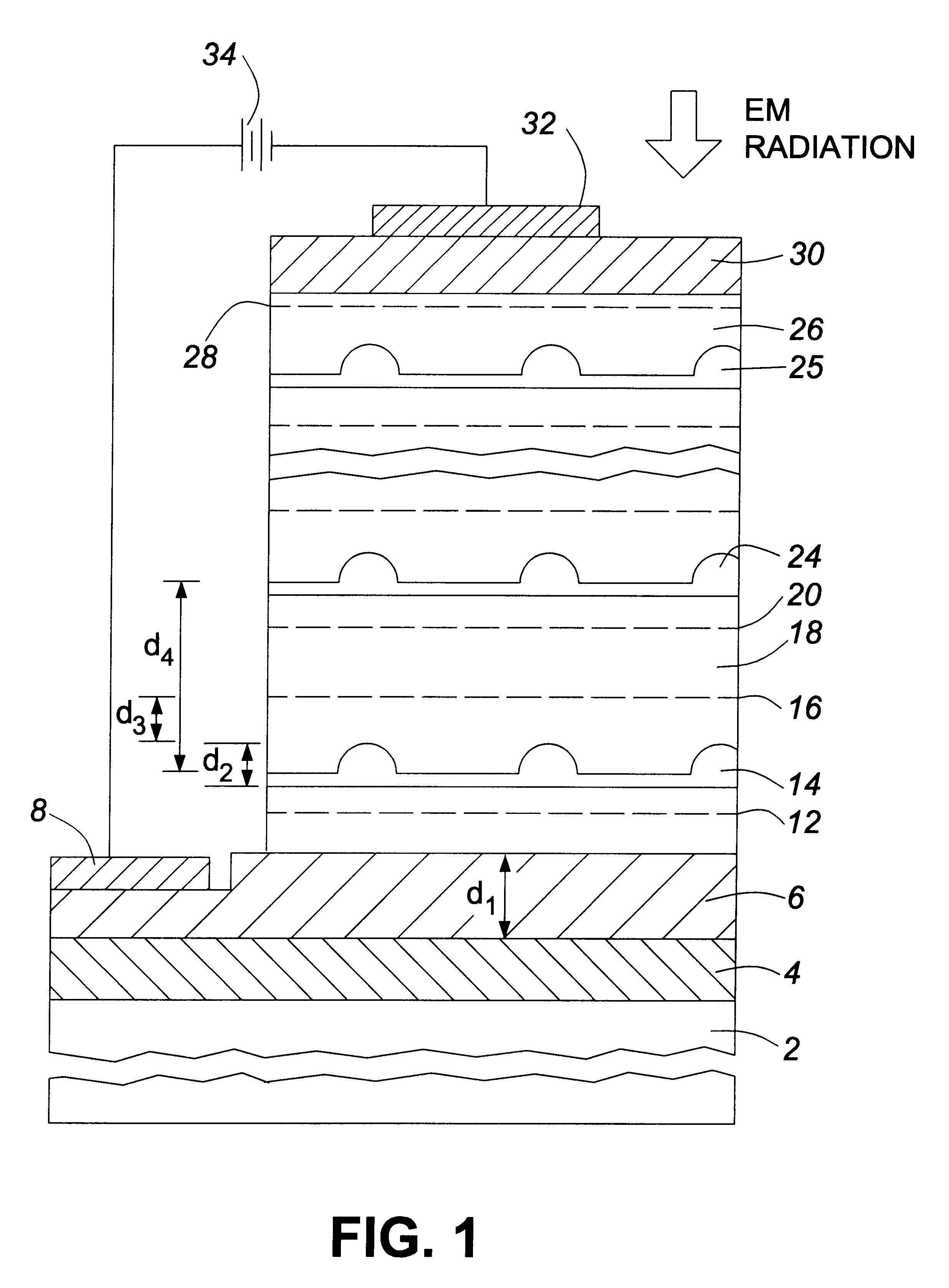

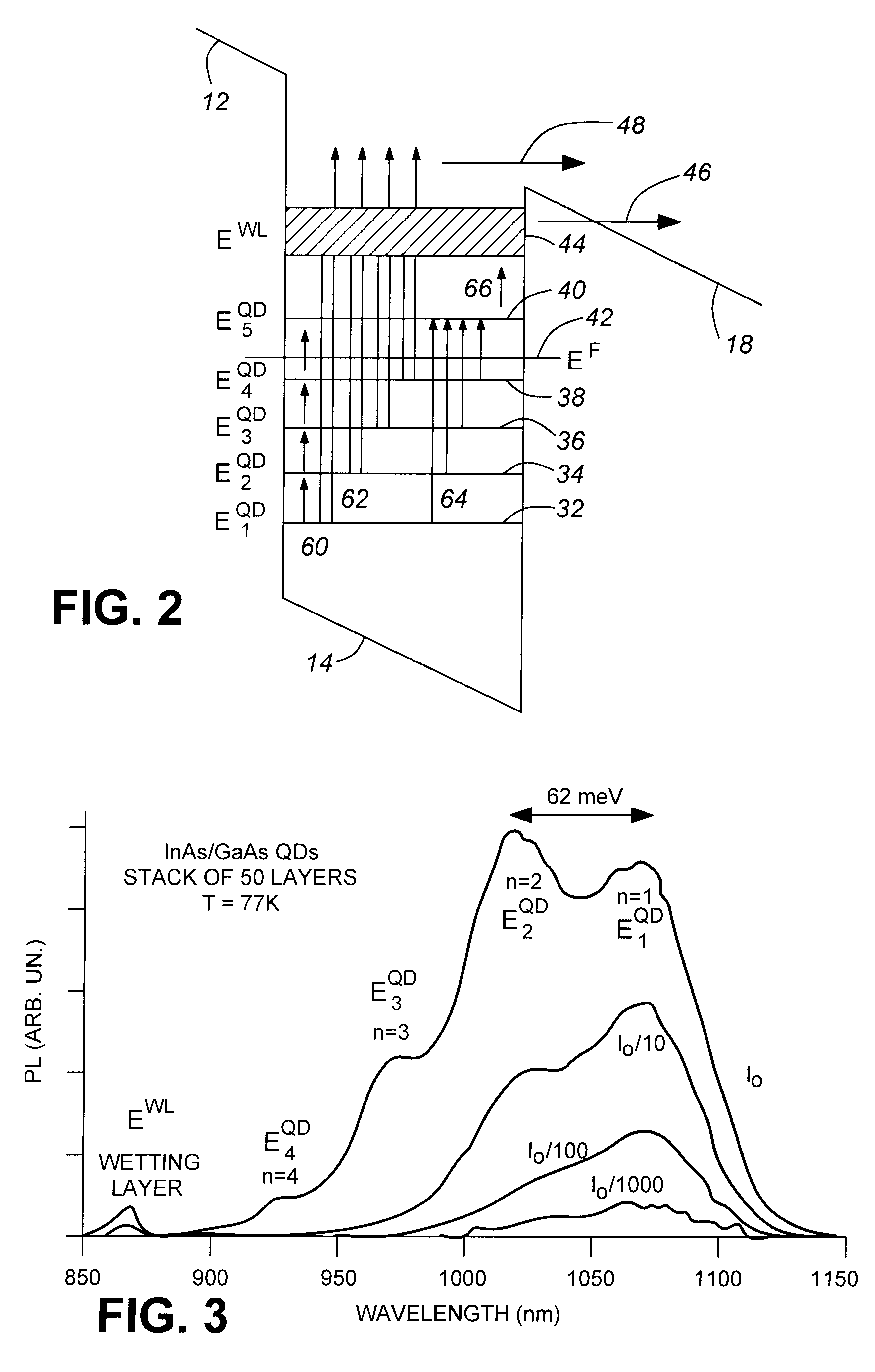

Quantum dot infrared photodetectors (QDIP)

InactiveUS6239449B1Quality improvementNanoinformaticsSemiconductor/solid-state device manufacturingQuantum dot infrared photodetectorsPhotodetector

A photodetector capable of normal incidence detection over a broad range of long wavelength light signals to efficiently convert infrared light into electrical signals. It is capable of converting long wavelength light signals into electrical signals with direct normal incidence sensitivity without the assistance of light coupling devices or schemes. In the apparatus, stored charged carriers are ejected by photons from quantum dots, then flow over the other barrier and quantum dot layers with the help of an electric field produced with a voltage applied to the device, producing a detectable photovoltage and photocurrent. The photodetector has multiple layers of materials including at least one quantum dot layer between an emitter layer and a collector layer, with a barrier layer between the quantum dot layer and the emitter layer, and another barrier layer between the quantum dot layer and the collector.

Owner:NAT RES COUNCIL OF CANADA

Semiconductor device and manufacturing method thereof

ActiveUS20100025676A1Small amount of photocurrentReduce parasitic capacitanceTransistorSolid-state devicesCharge carrierOhmic contact

To offer a semiconductor device including a thin film transistor having excellent characteristics and high reliability and a method for manufacturing the semiconductor device without variation. The summary is to include an inverted-staggered (bottom-gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used for a semiconductor layer and a buffer layer is provided between the semiconductor layer and source and drain electrode layers. An ohmic contact is formed by intentionally providing a buffer layer containing In, Ga, and Zn and having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

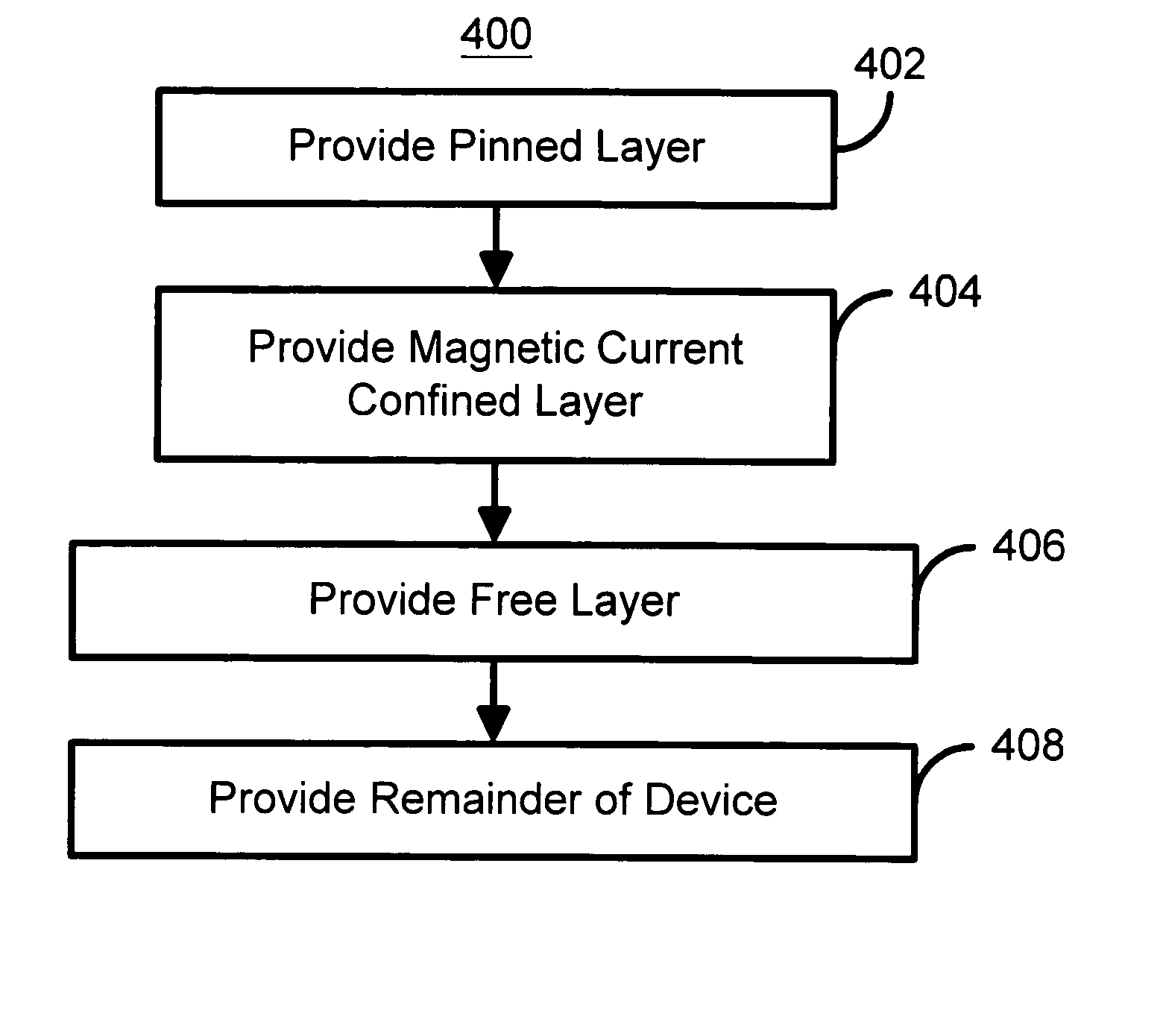

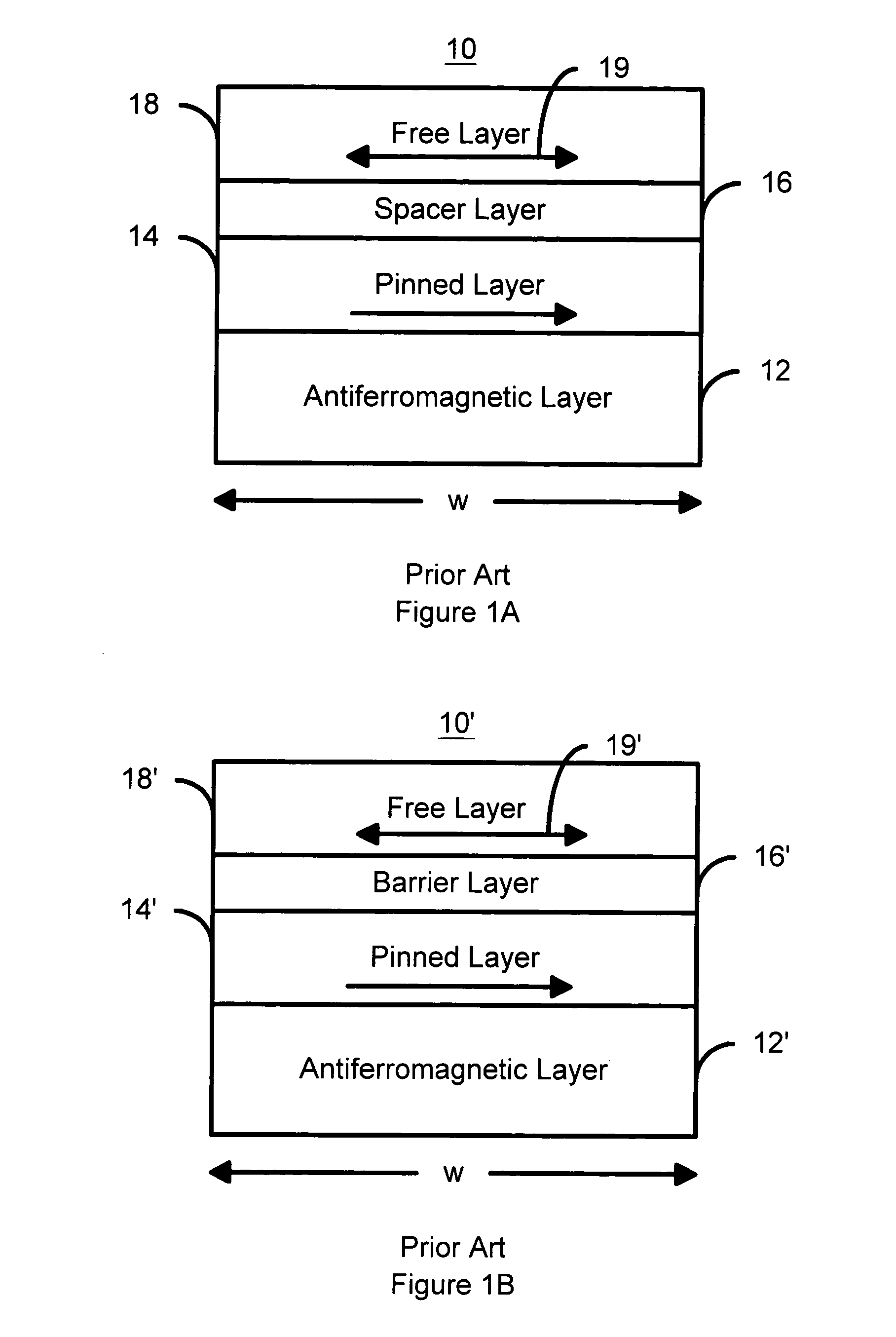

Magnetic elements with ballistic magnetoresistance utilizing spin-transfer and an MRAM device using such magnetic elements

InactiveUS20050136600A1Improve signal outputTransistorNanostructure applicationMagnetic currentCharge carrier

A method and system for providing a magnetic element is disclosed. The method and system include providing a pinned layer, a magnetic current confined layer, and a free layer. The pinned layer is ferromagnetic and has a first pinned layer magnetization. The magnetic current confined layer has at least one channel in an insulating matrix and resides between the pinned layer and the free layer. The channel(s) are ferromagnetic, conductive, and extend through the insulating matrix between the free layer and the pinned layer. The size(s) of the channel(s) are sufficiently small that charge carriers can give rise to ballistic magnetoresistance in the magnetic current confined layer. The free layer is ferromagnetic and has a free layer magnetization. Preferably, the method and system also include providing a second pinned layer and a nonmagnetic spacer layer between the second pinned layer and the free layer. In this aspect, the magnetic element is configured to allow the free layer magnetization to be switched using spin transfer.

Owner:GRANDIS

Process for preparing nanostructured materials of controlled surface chemistry

InactiveUS6669823B1Good dispersionReduce hydrolysis rateMaterial nanotechnologyMolten spray coatingCharge carrierNanostructured materials

A process to prepare stoichiometric-nanostructured materials comprising generating a plasma, forming an "active volume" through introduction of an oxidizing gas into the plasma, before the plasma is expanded into a field-free zone, either (1) in a region in close proximity to a zone of charge carrier generation, or (2) in a region of current conduction between field generating elements, including the surface of the field generation elements, and transferring energy from the plasma to a precursor material to form in the "active volume" at least one stoichiometric-nanostructured material and a vapor that may be condensed to form a stoichiometric-nanostructured material. The surface chemistry of the resulting nanostructured materials is substantially enhanced to yield dispersion stable materials with large zeta-potentials.

Owner:NANOPHASE TECH CORP

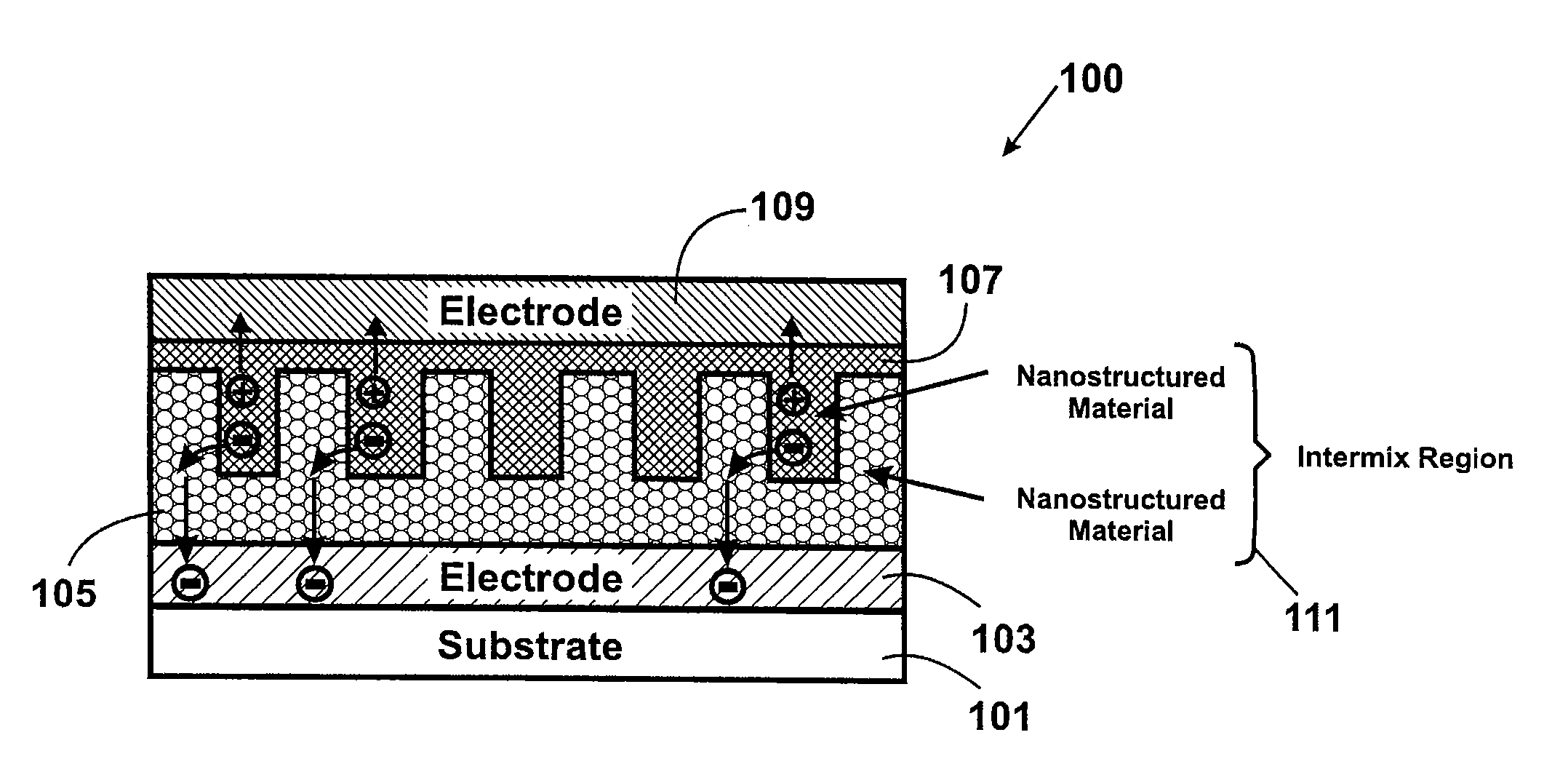

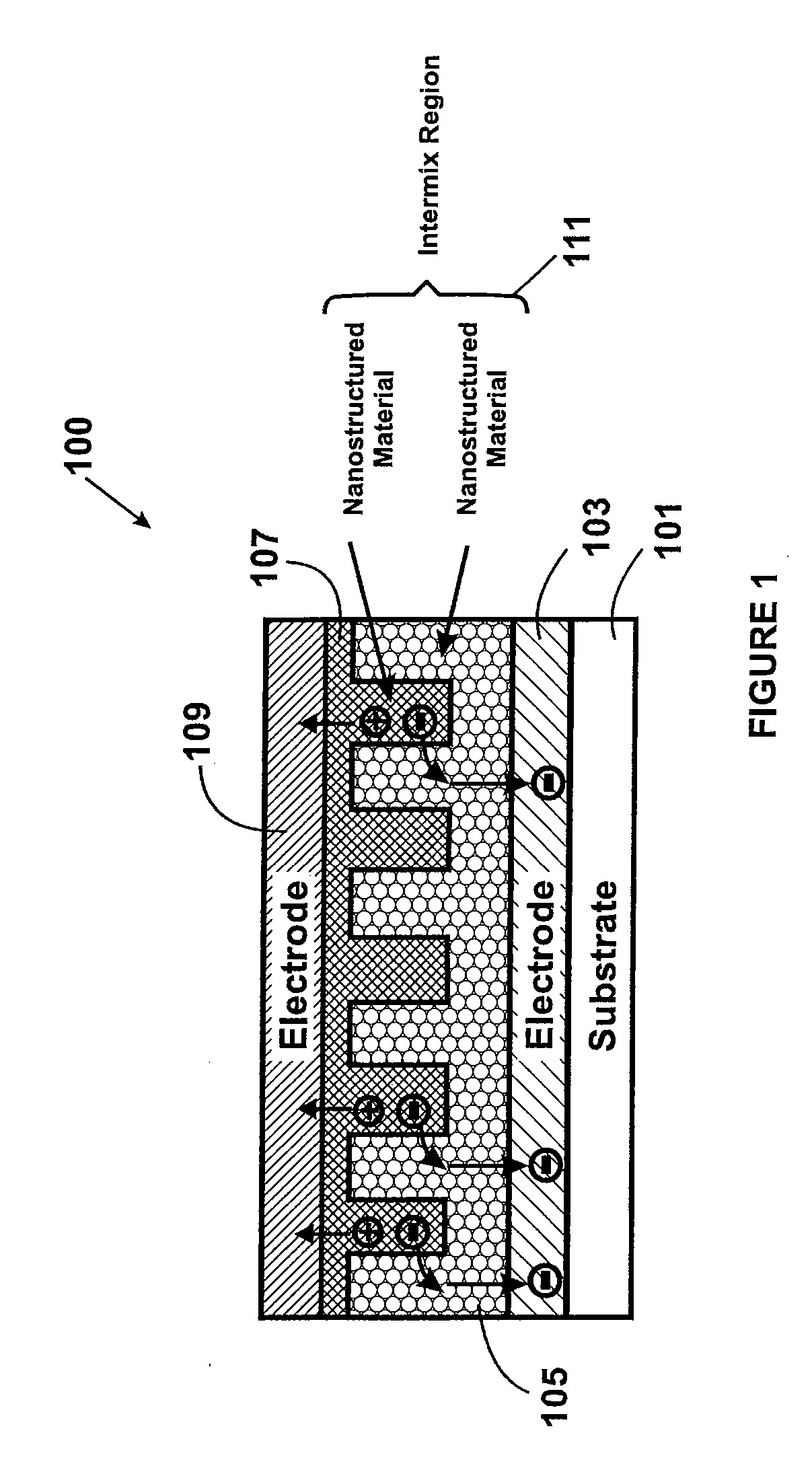

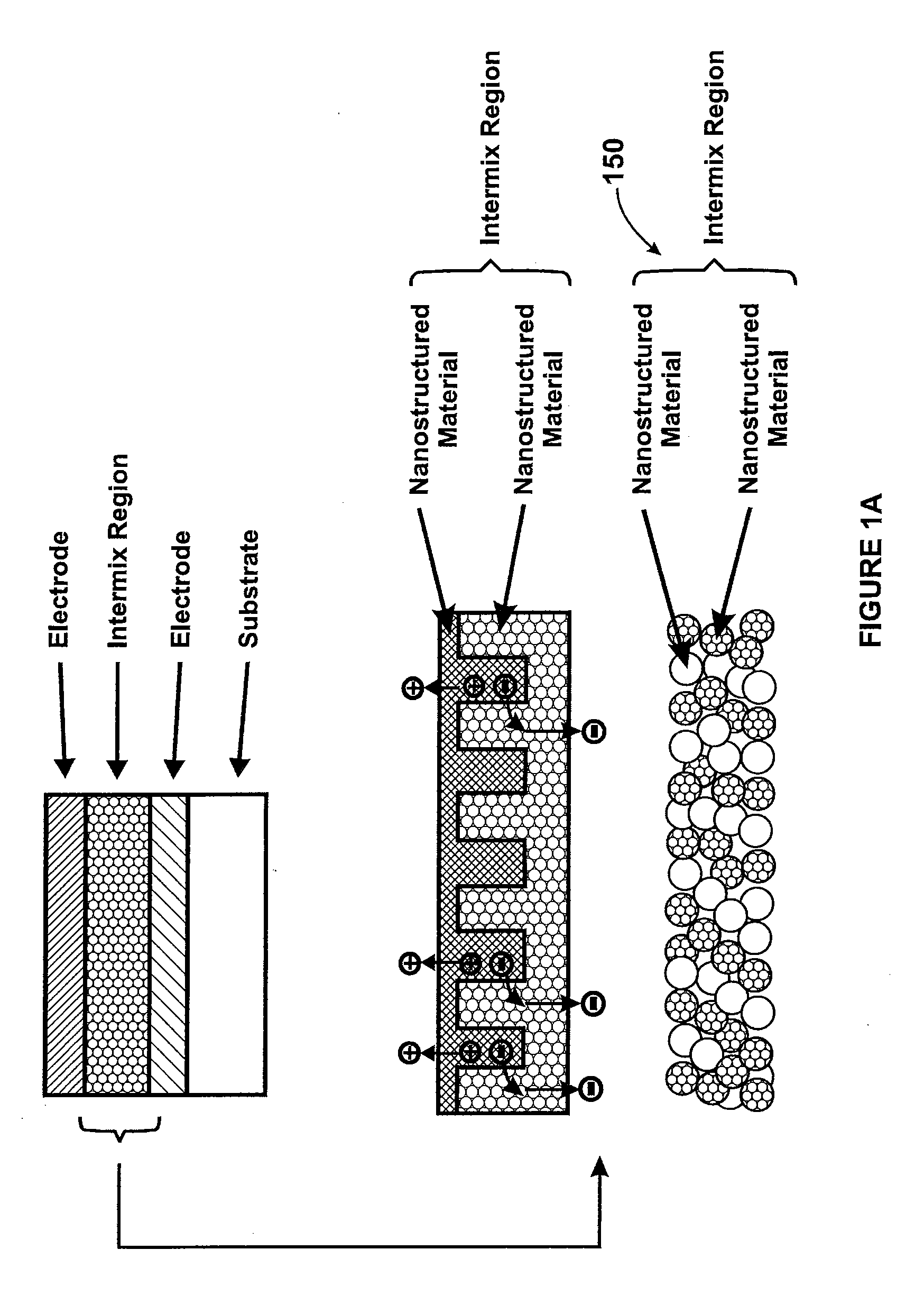

Method and structure for thin film photovoltaic materials using semiconductor materials

ActiveUS20070264488A1Easy to useImprove conversion efficiencyLayered productsConductive materialSemiconductor materialsCharge carrier

A photovoltaic device and related methods. The device has a nanostructured material positioned between an electron collecting electrode and a hole collecting electrode. An electron transporting / hole blocking material is positioned between the electron collecting electrode and the nanostructured material. In a specific embodiment, negatively charged carriers generated by optical absorption by the nanostructured material are preferentially separated into the electron transporting / hole blocking material. In a specific embodiment, the nanostructured material has an optical absorption coefficient of at least 103 cm−1 for light comprised of wavelengths within the range of about 400 nm to about 700 nm.

Owner:CM MFG

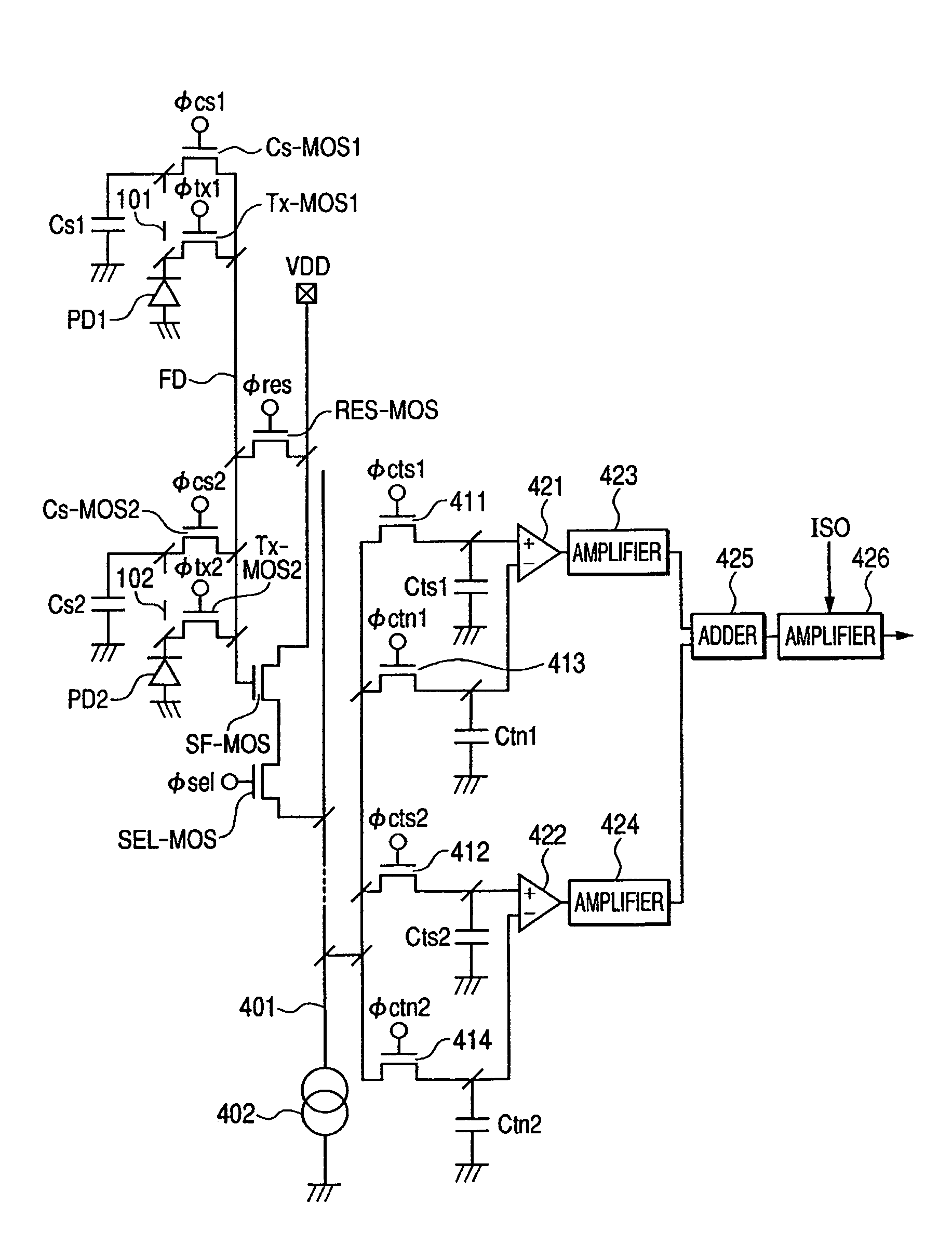

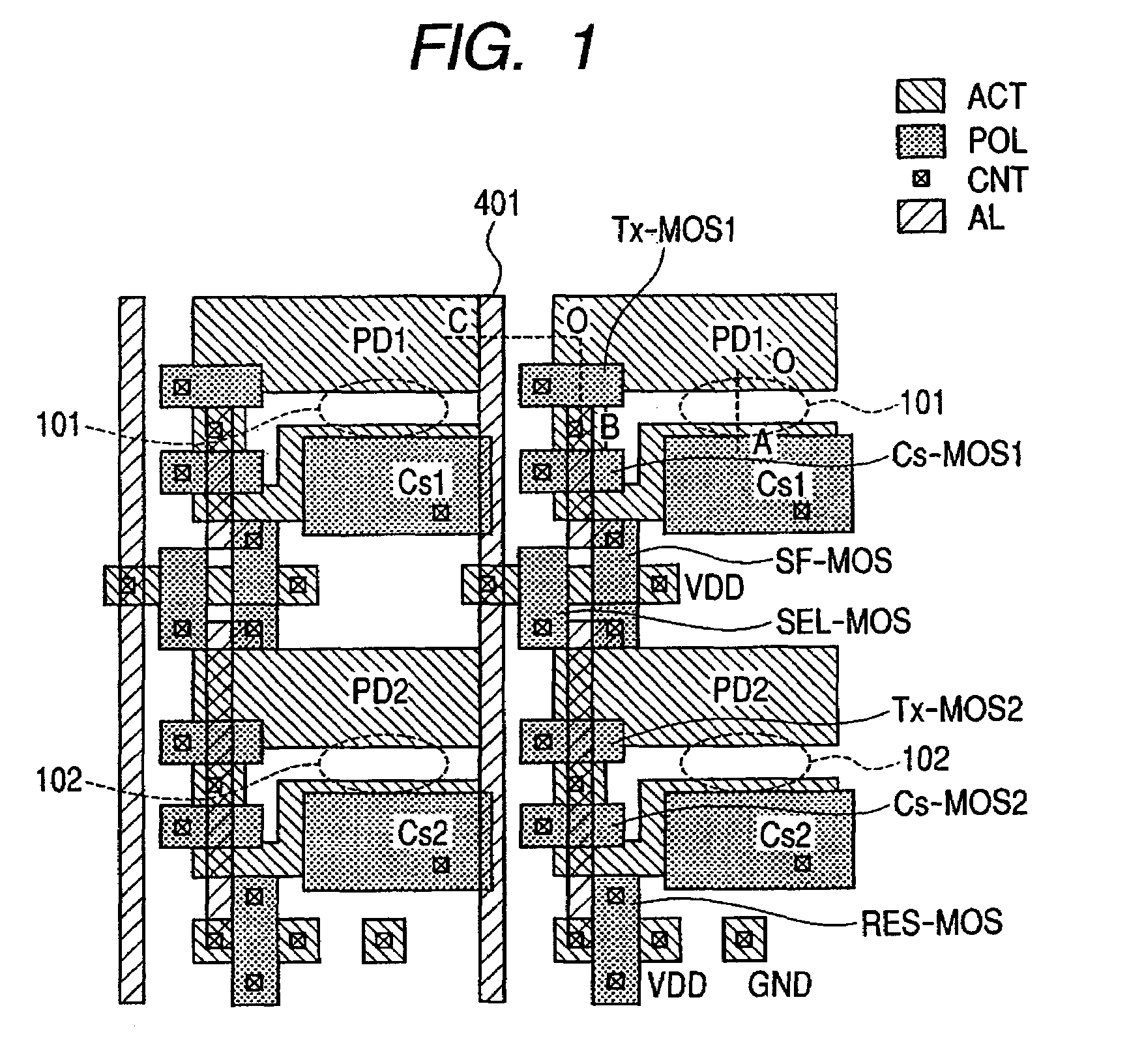

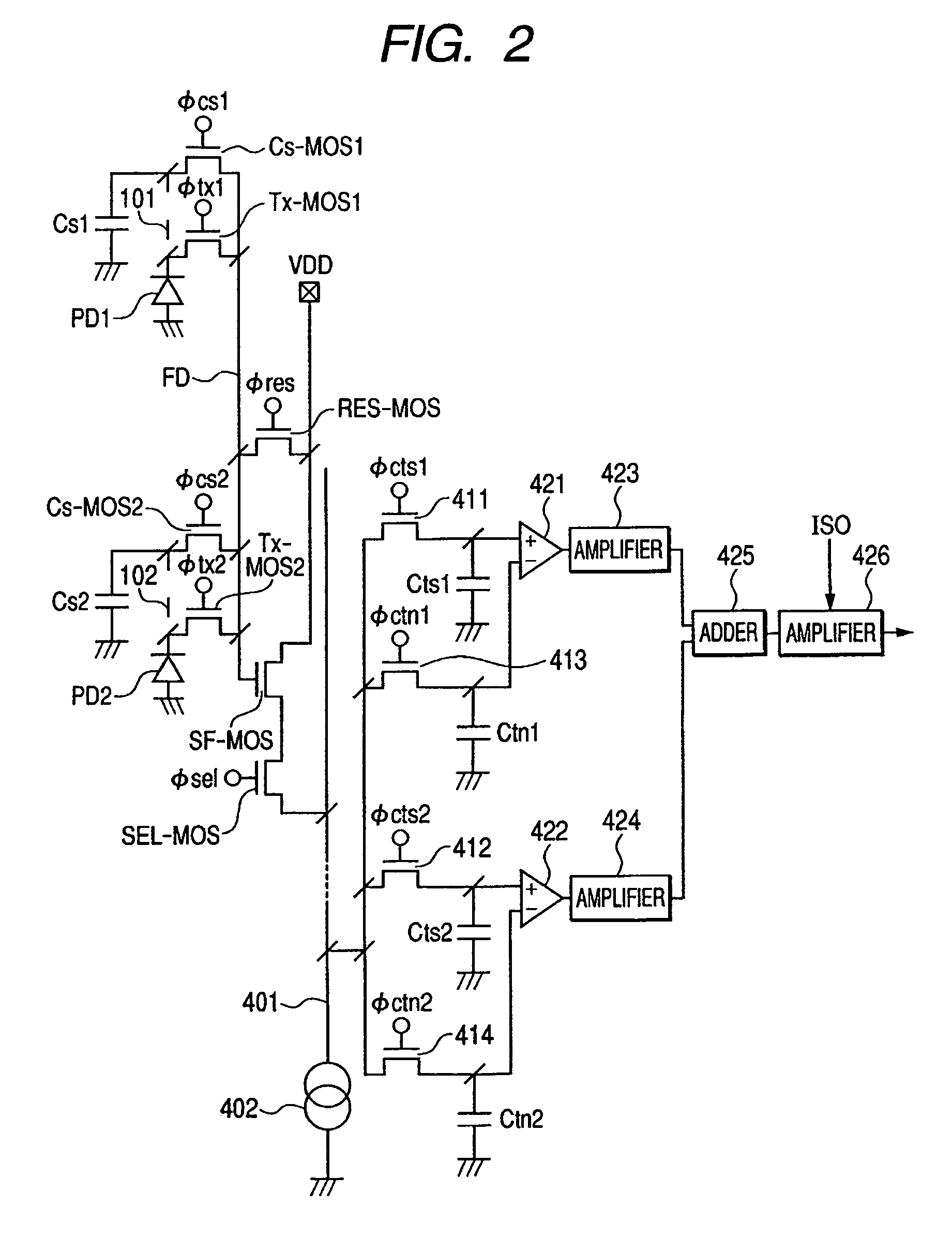

Solid state image pickup device and camera

InactiveUS7321110B2Television system detailsTelevision system scanning detailsCharge carrierPhotoelectric conversion

An solid state image pickup device including a plurality of photoelectric conversion regions (PD1, PD2) for generating carriers by photoelectric conversions to accumulate the generated carriers, an amplifying unit for amplifying the carriers, being commonly provided to at least two photoelectric conversion regions, a first and a second transfer units (Tx-MOS1, Tx-MOS2) for transferring the carriers accumulated in the first and the second photoelectric conversion regions, respectively, a first and a second carrier accumulating units (Cs1, Cs2) for accumulating the carriers flowing out from the first and the second photoelectric conversion regions through a first and a second fixed potential barriers, respectively, and a third and a fourth transfer units (Cs-MOS1, Cs-MOS2) for transferring the carriers accumulated in the first and the second carrier accumulating units to the amplifying unit, respectively.

Owner:CANON KK

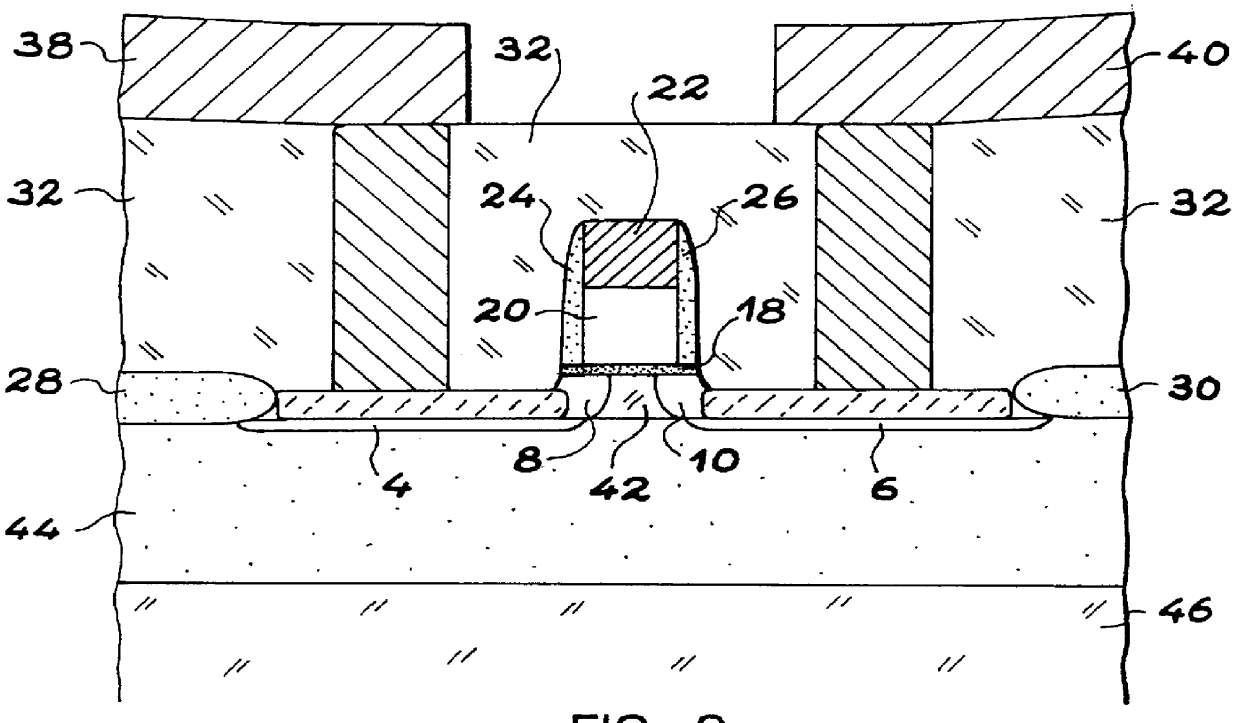

Quantum WELL MOS transistor and methods for making same

PCT No. PCT / FR97 / 01075 Sec. 371 Date Feb. 12, 1998 Sec. 102(e) Date Feb. 12, 1998 PCT Filed Jun. 13, 1997 PCT Pub. No. WO97 / 48135 PCT Pub. Date Dec. 18, 1997A new quantum well MOS transistor is described along with a processes for manufacturing it. In this transistor, the source and drain areas are separated from the channel by sufficiently thin insulating layers to enable the passage of charge carriers by the tunnel effect. Each of the source and drain areas is separated from the substrate by an electrically insulating layer that is sufficiently thick to prevent charge carriers from passing through this insulating layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

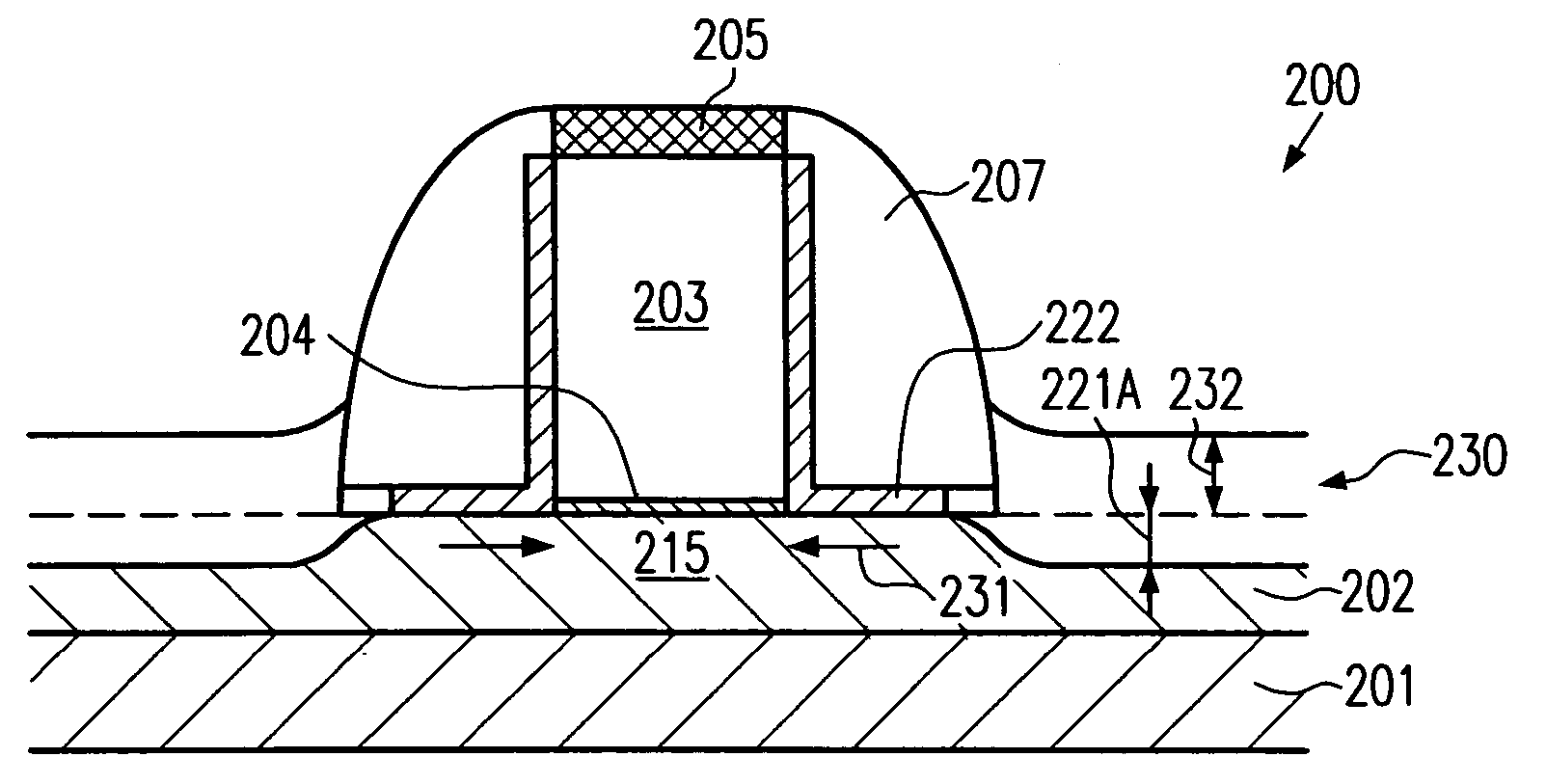

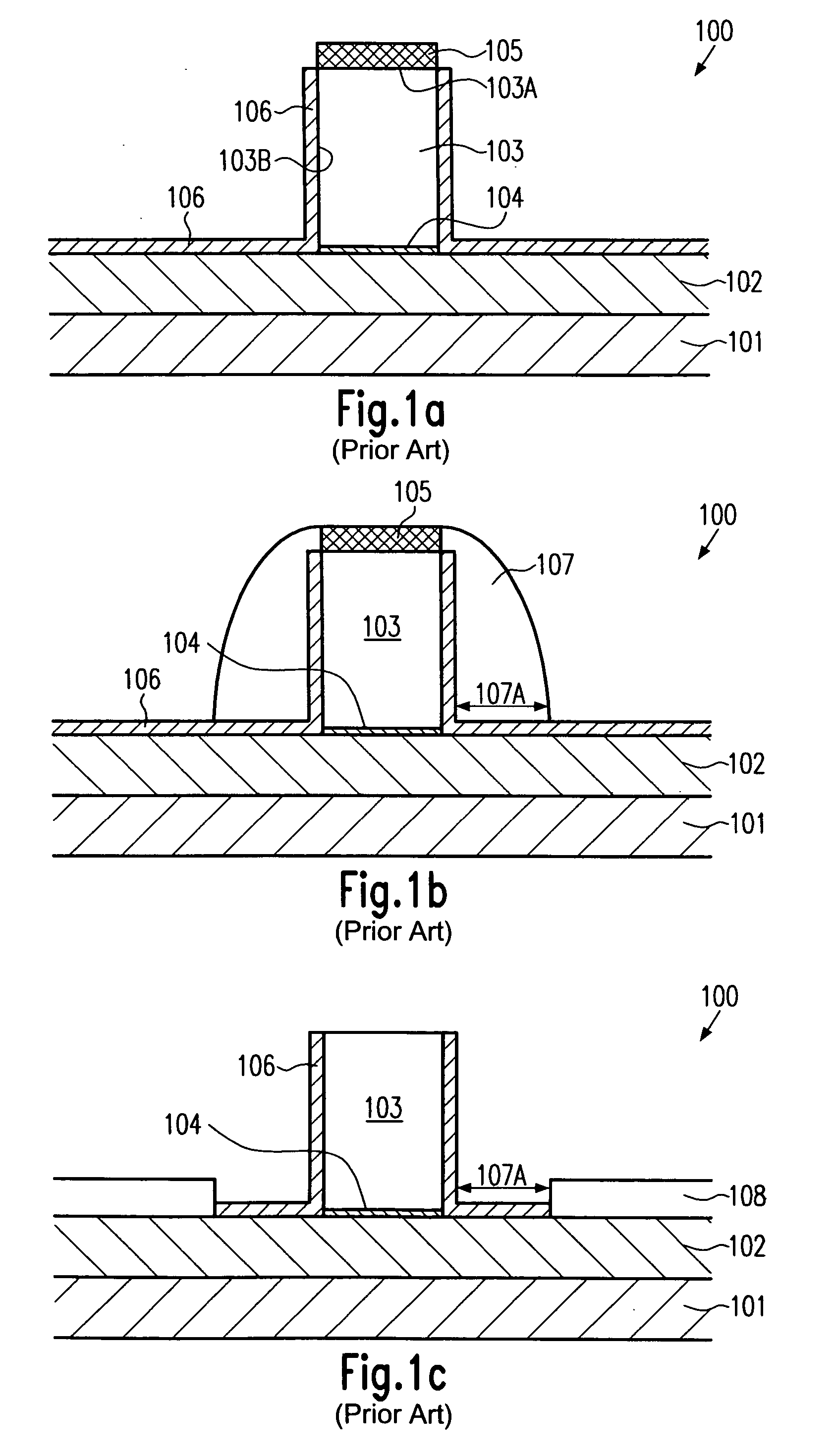

Advanced technique for forming a transistor having raised drain and source regions

InactiveUS20050093075A1Create stressImprove featuresTransistorSemiconductor/solid-state device manufacturingDopantStress induced

By recessing a semiconductor layer, preferably by locally oxidizing the semiconductor layer, a stress-inducing material and / or a dopant species may be introduced into the thinned semiconductor layer in the vicinity of a gate electrode structure by means of a subsequent epitaxial growth process. In particular, the stress-inducing material formed adjacent to the gate electrode structure exerts compressive or tensile stress, depending on the type of material deposited, thereby also enhancing the mobility of the charge carriers in a channel region of the transistor element.

Owner:GLOBALFOUNDRIES INC