Patents

Literature

1574results about How to "High carrier mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

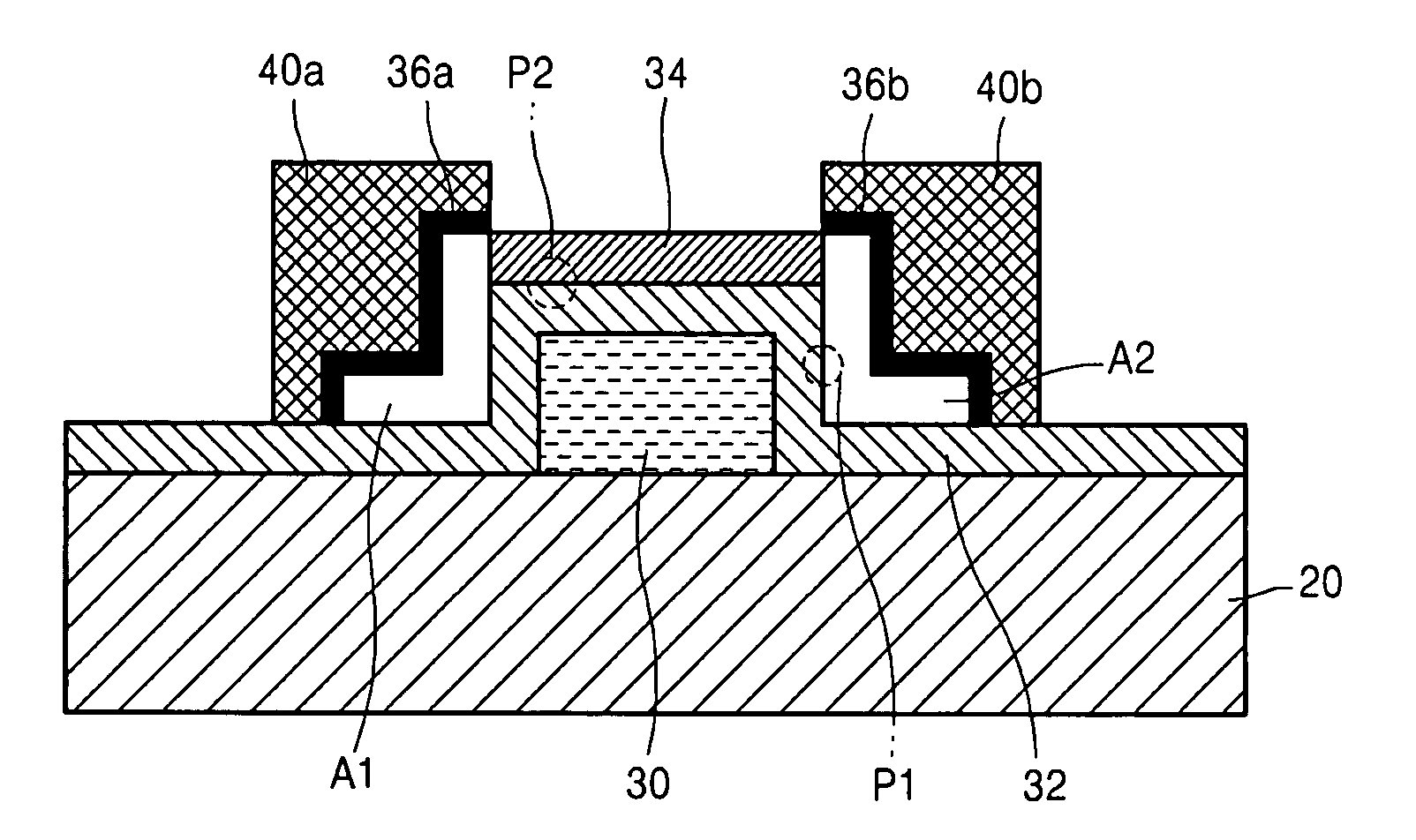

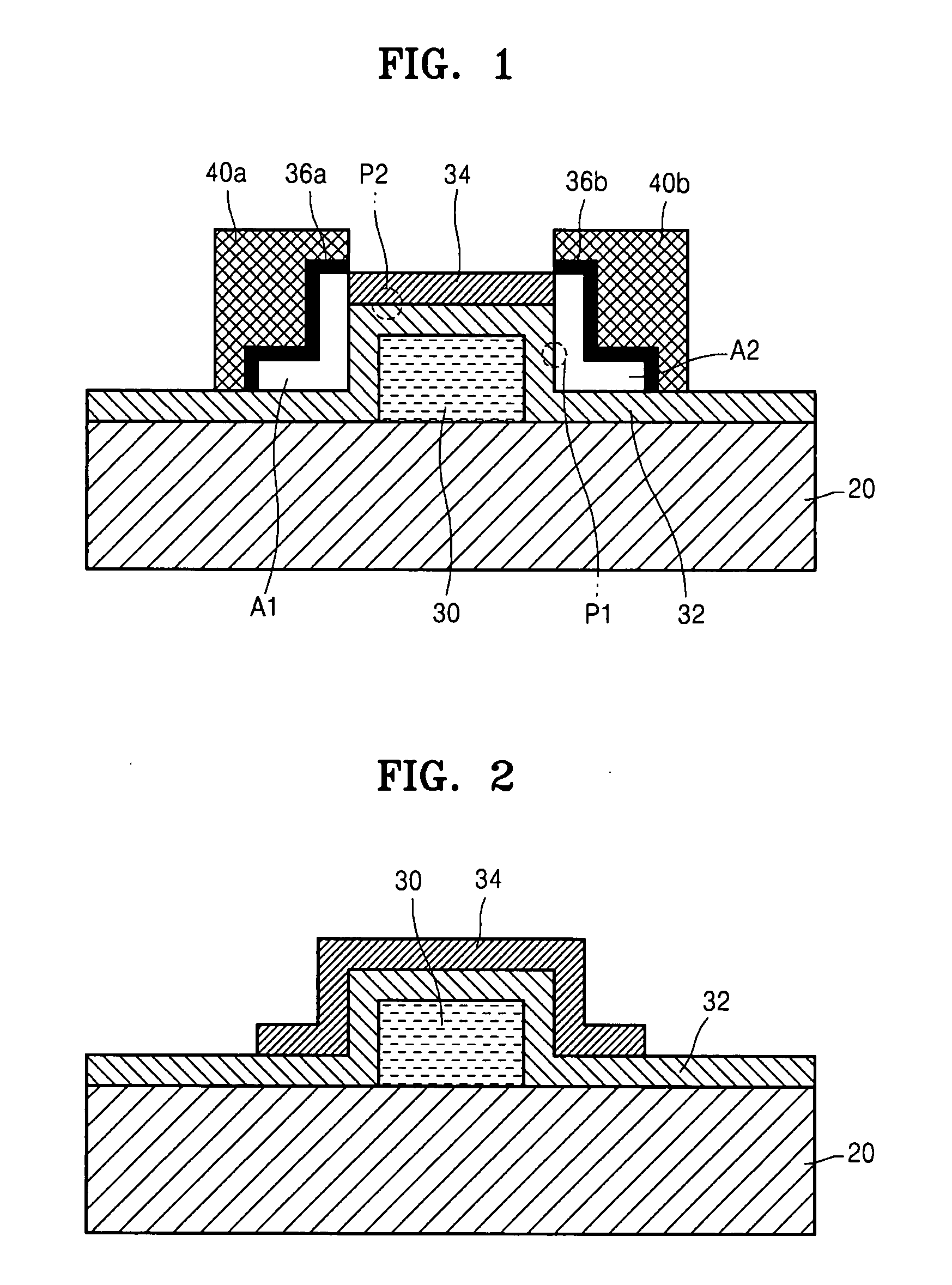

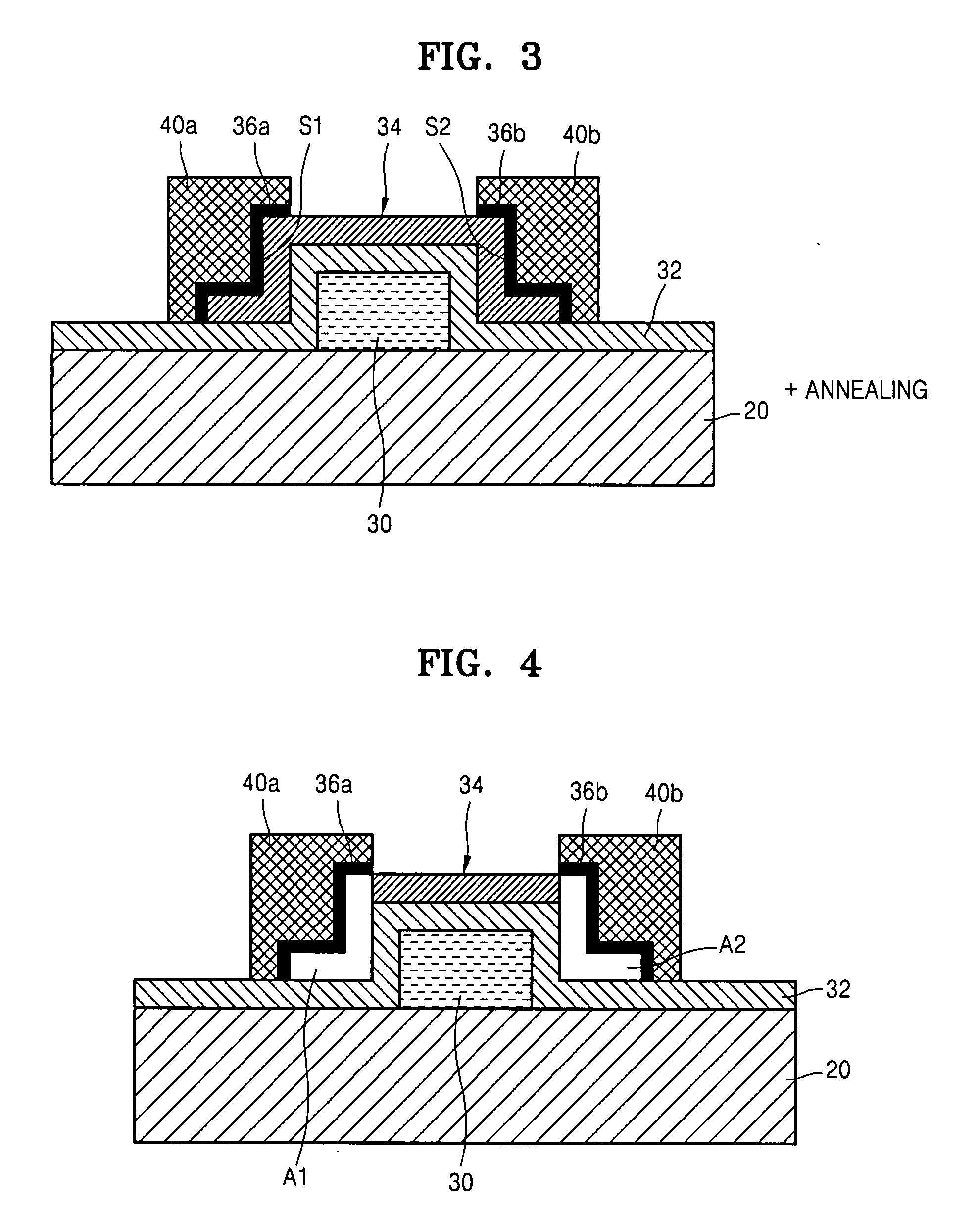

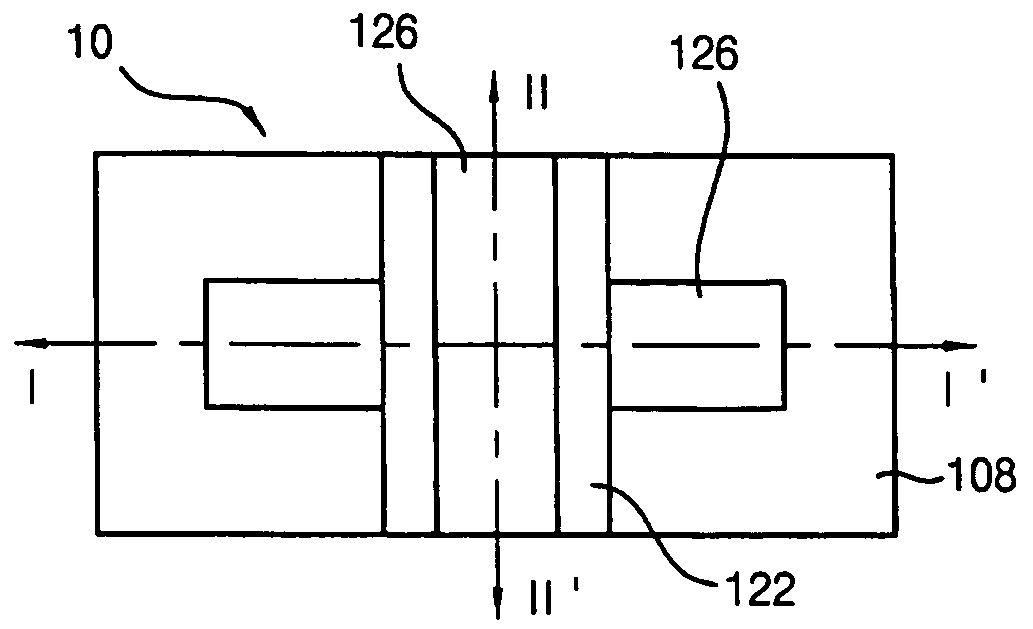

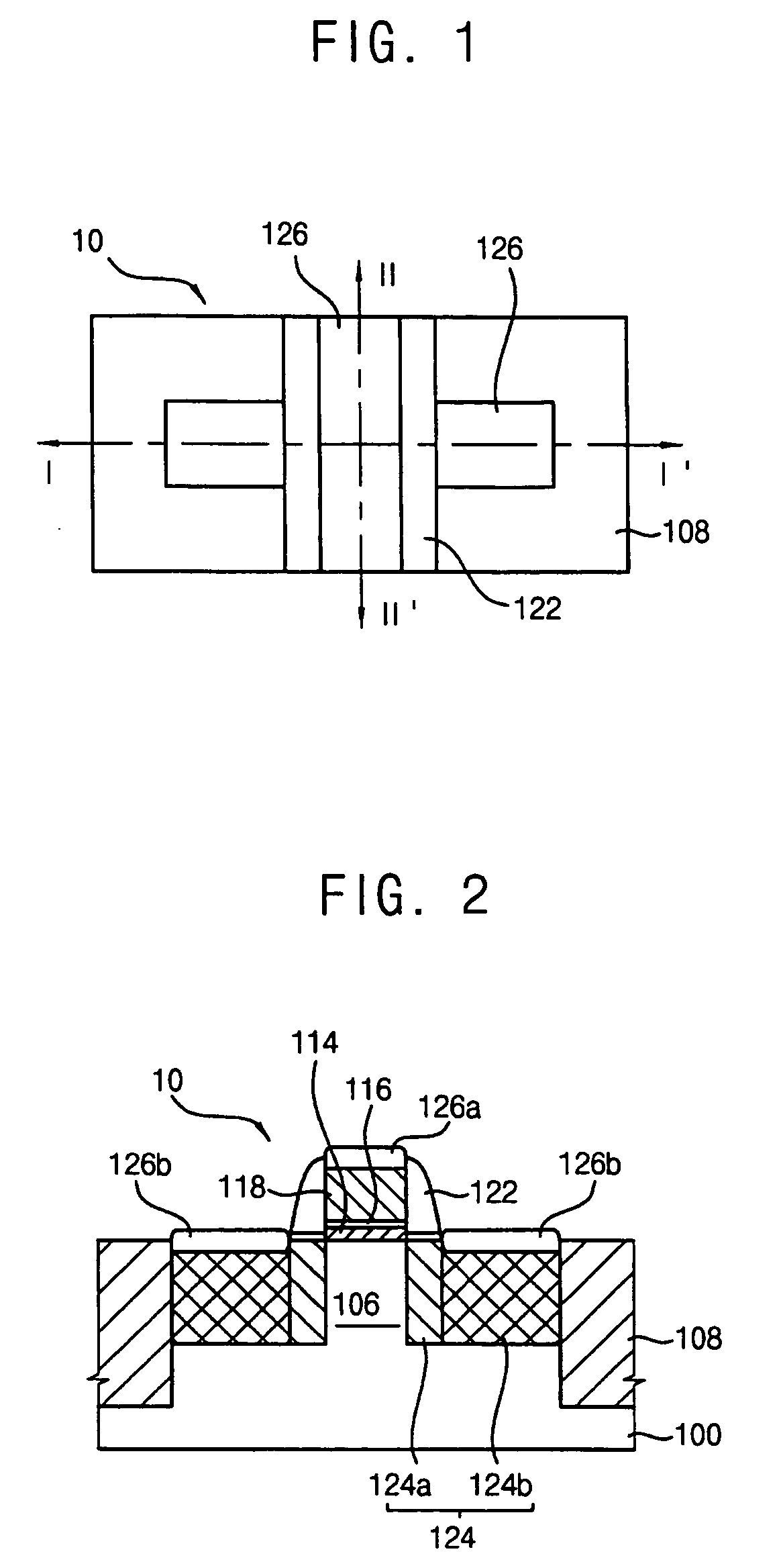

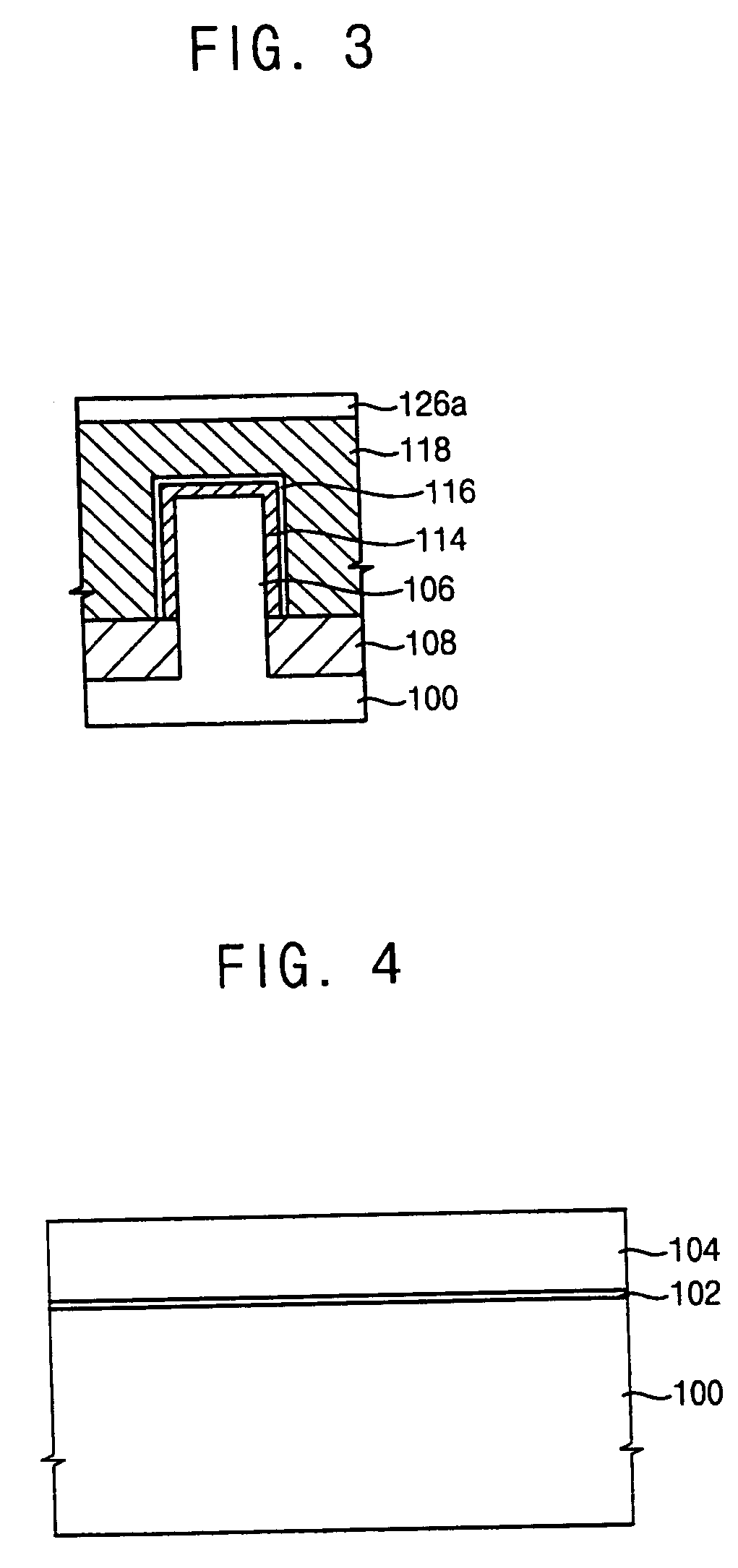

Thin film transistor including selectively crystallized channel layer and method of manufacturing the thin film transistor

ActiveUS20080258140A1Stable contact characteristicHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringIon implantation

Provided are a thin film transistor (TFT) including a selectively crystallized channel layer, and a method of manufacturing the TFT. The TFT includes a gate, the channel layer, a source, and a drain. The channel layer is formed of an oxide semiconductor, and at least a portion of the channel layer contacting the source and the drain is crystallized. In the method of manufacturing the TFT, the channel layer is formed of an oxide semiconductor, and a metal component is injected into the channel layer so as to crystallize at least a portion of the channel layer contacting the source and the drain. The metal component can be injected into the channel layer by depositing and heat-treating a metal layer or by ion-implantation.

Owner:SAMSUNG ELECTRONICS CO LTD

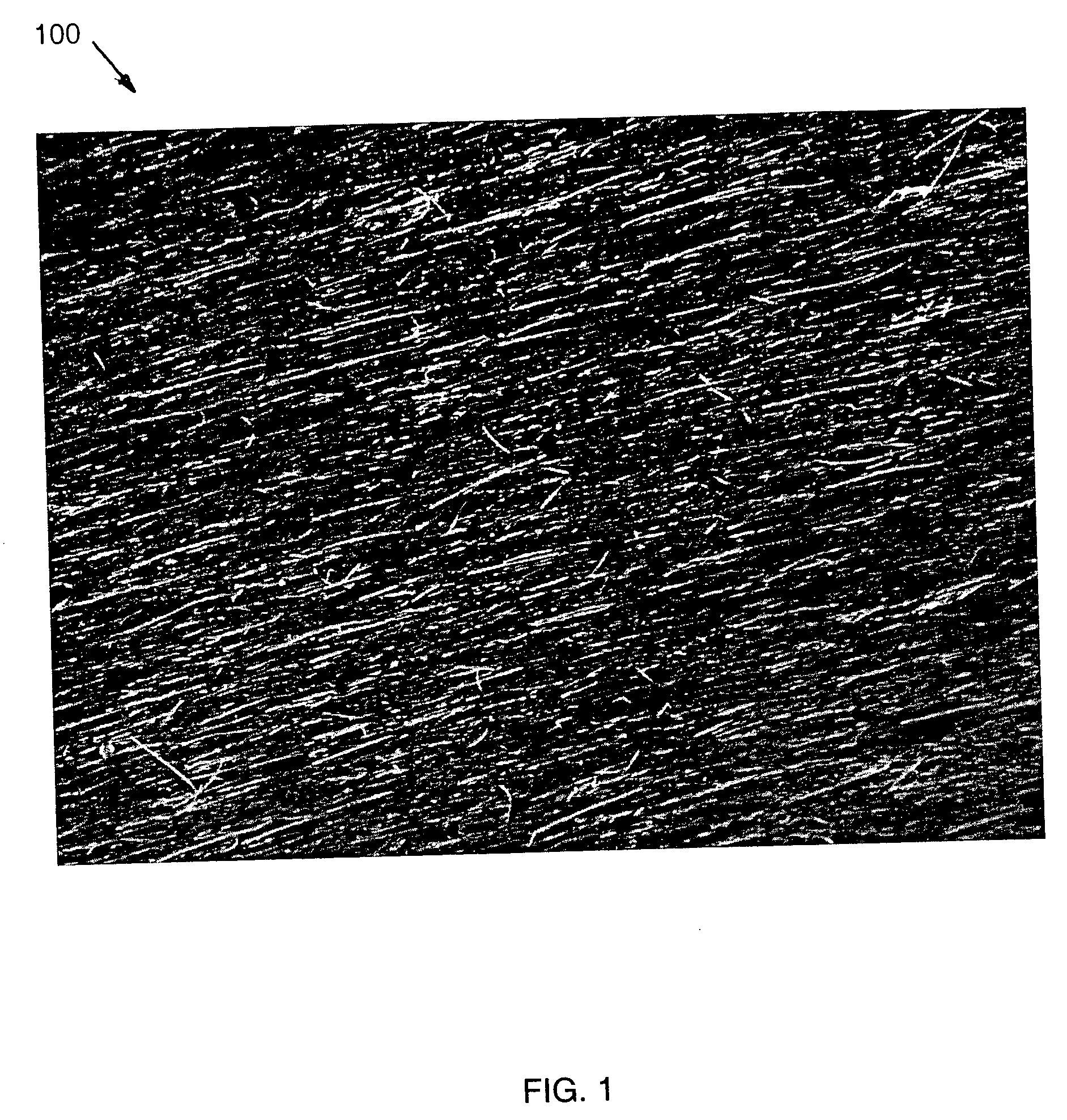

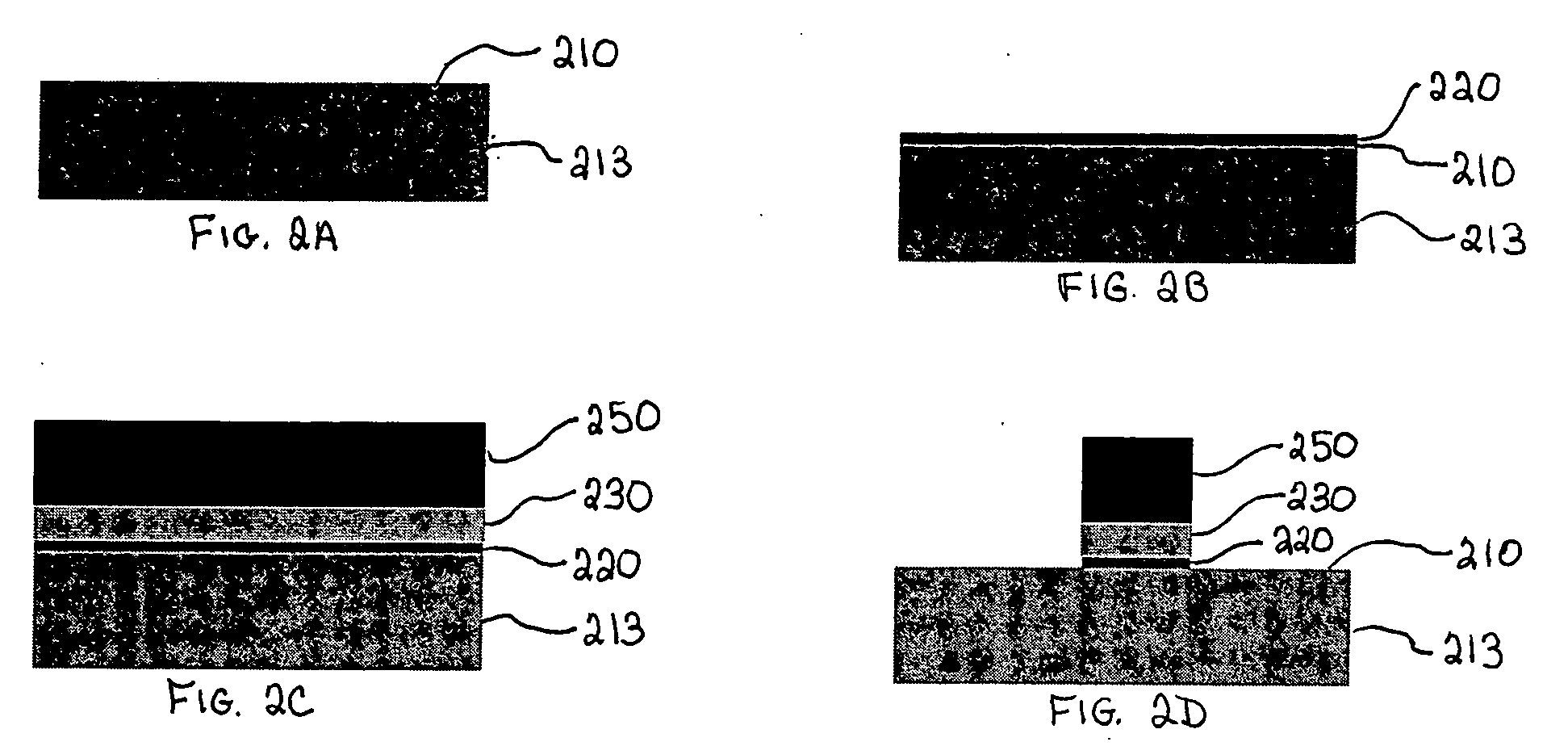

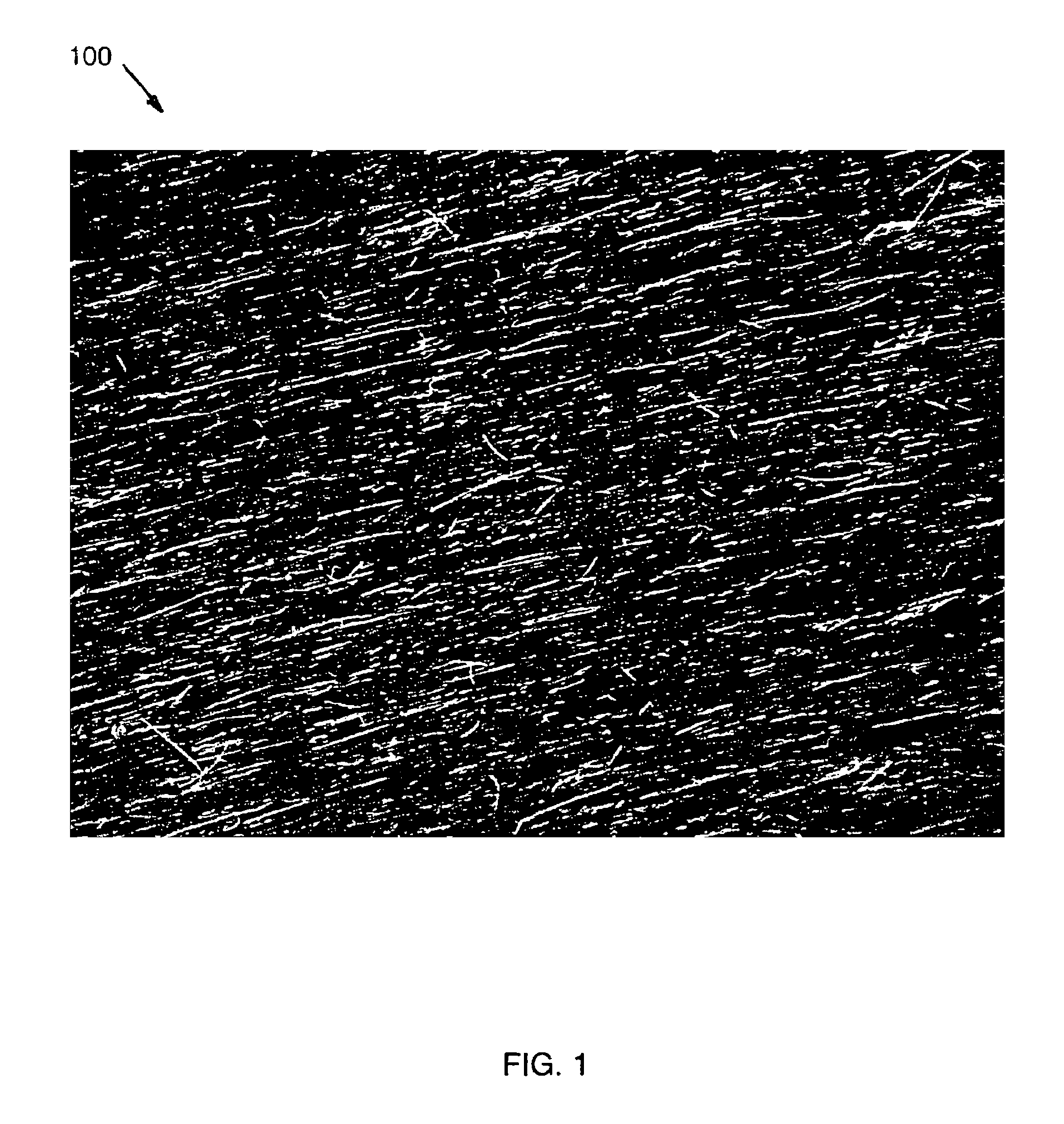

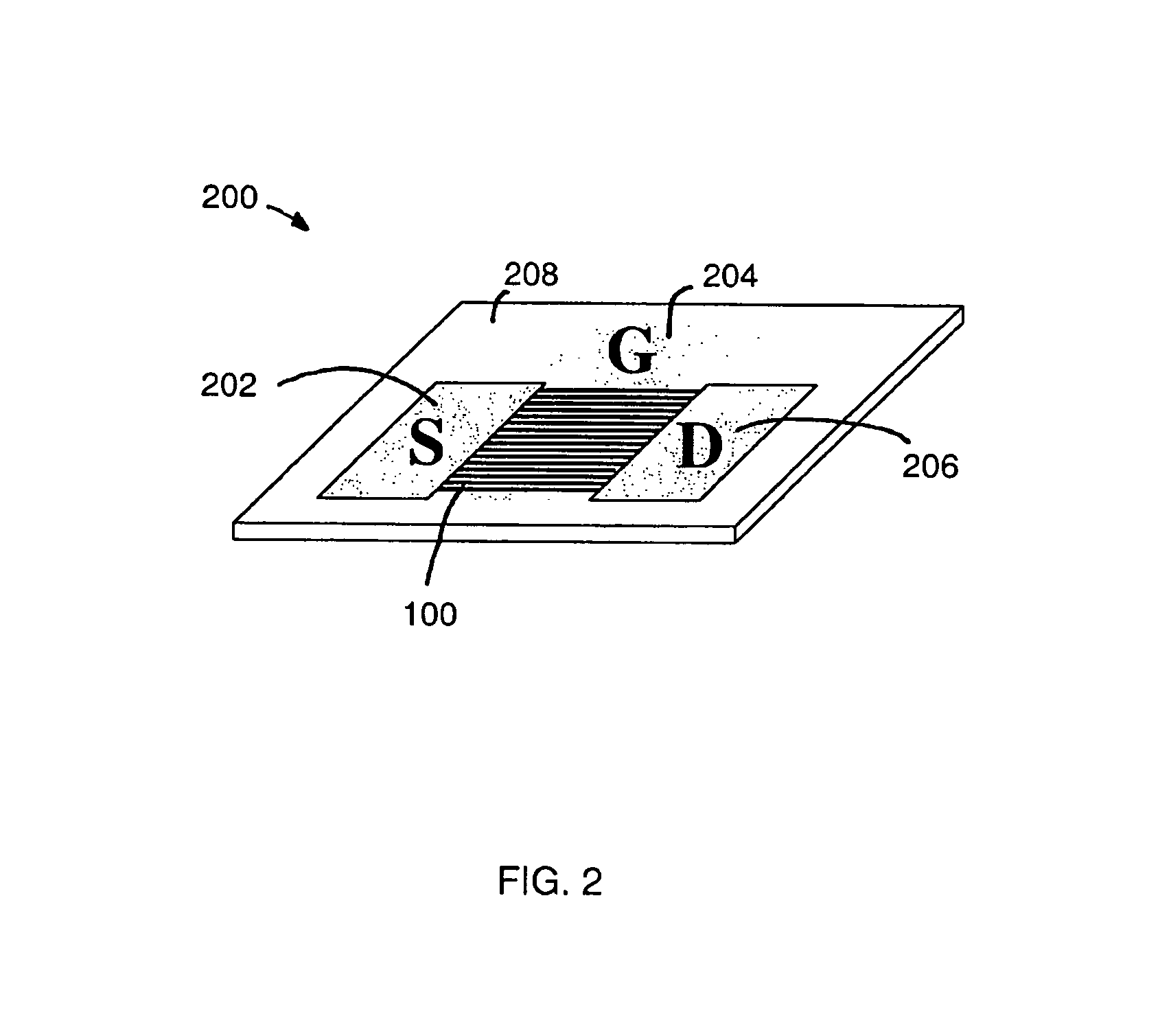

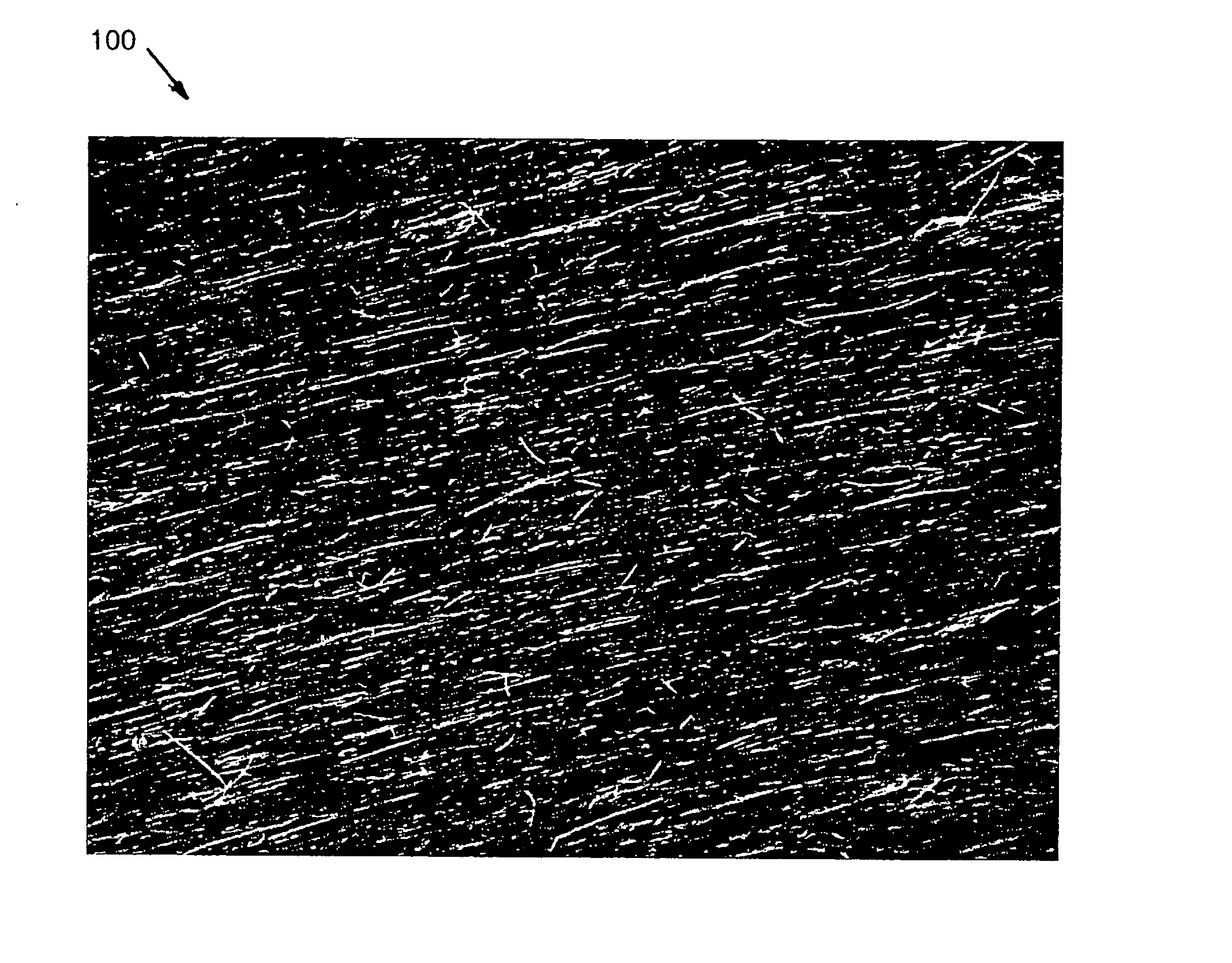

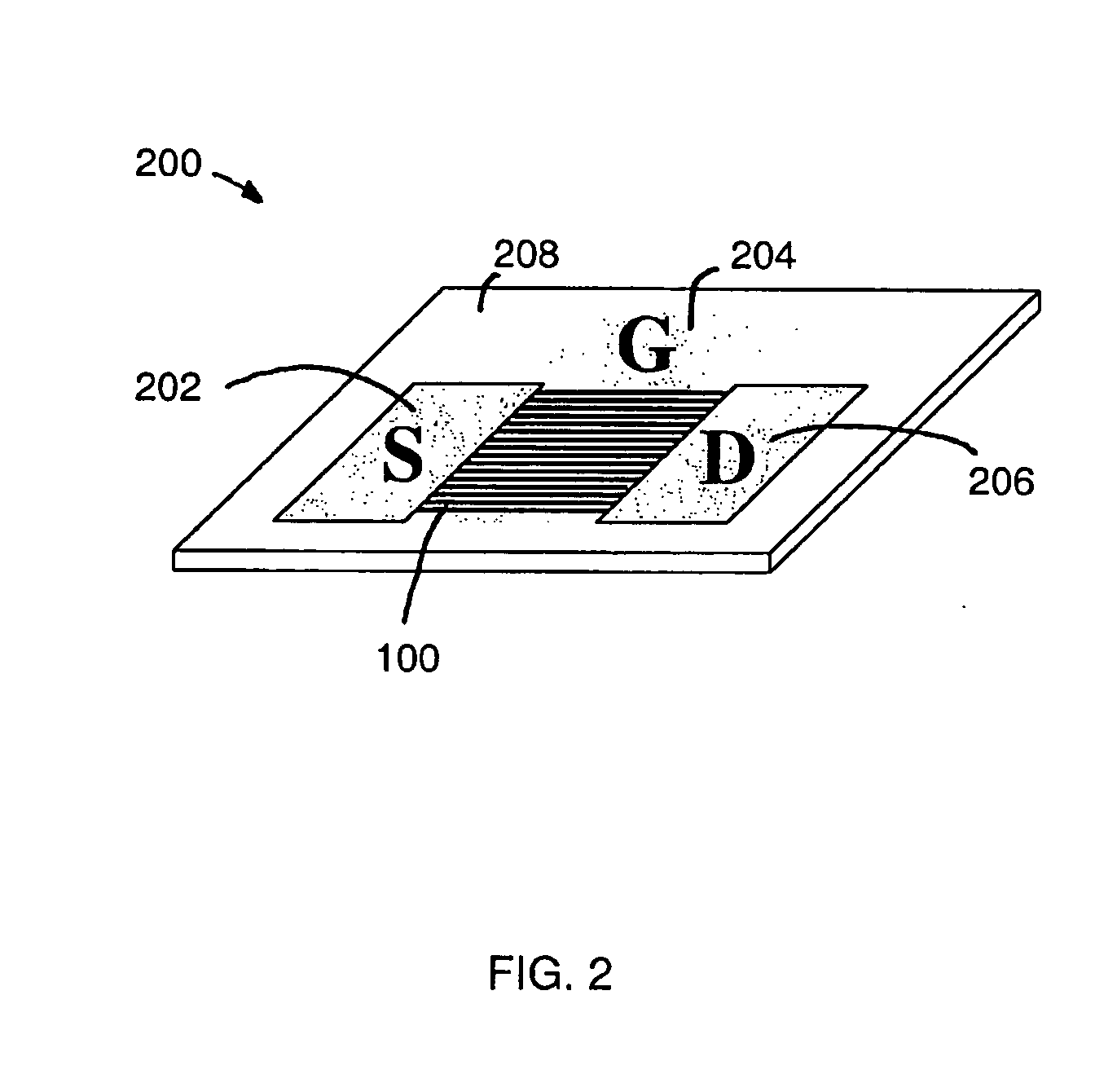

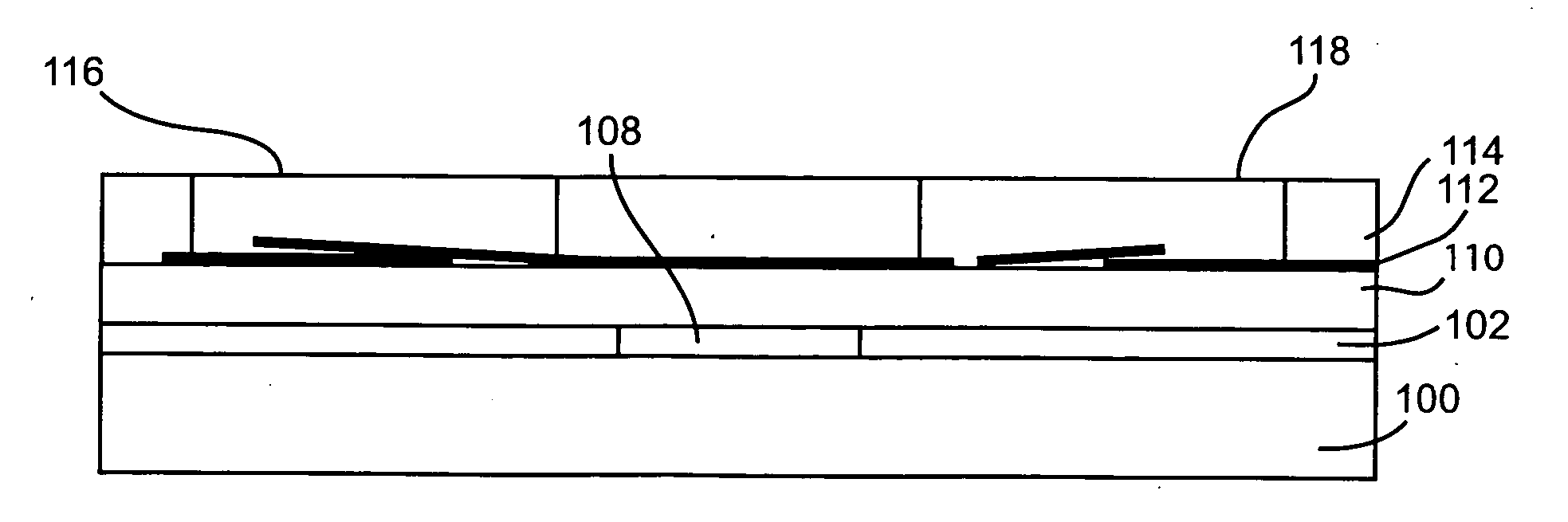

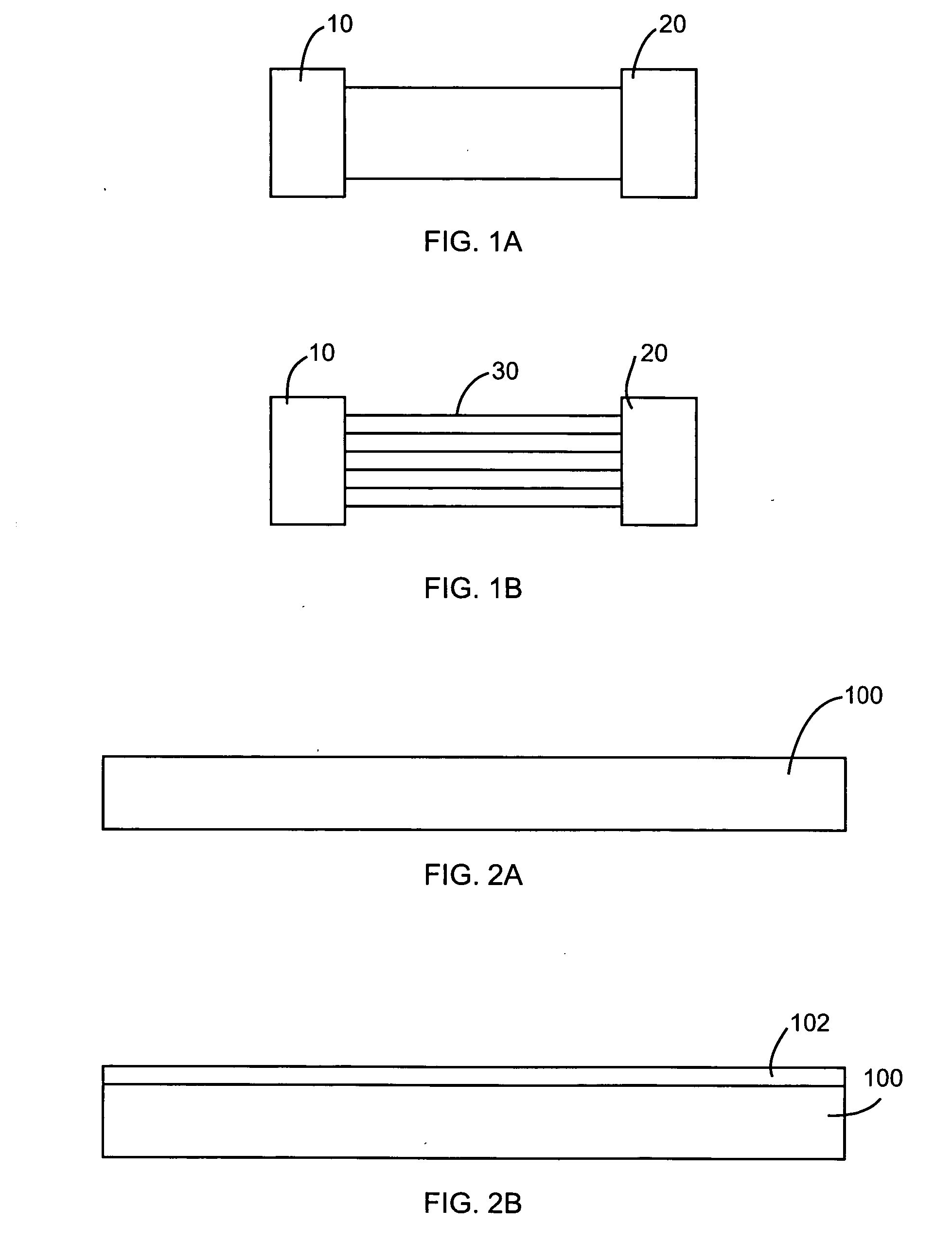

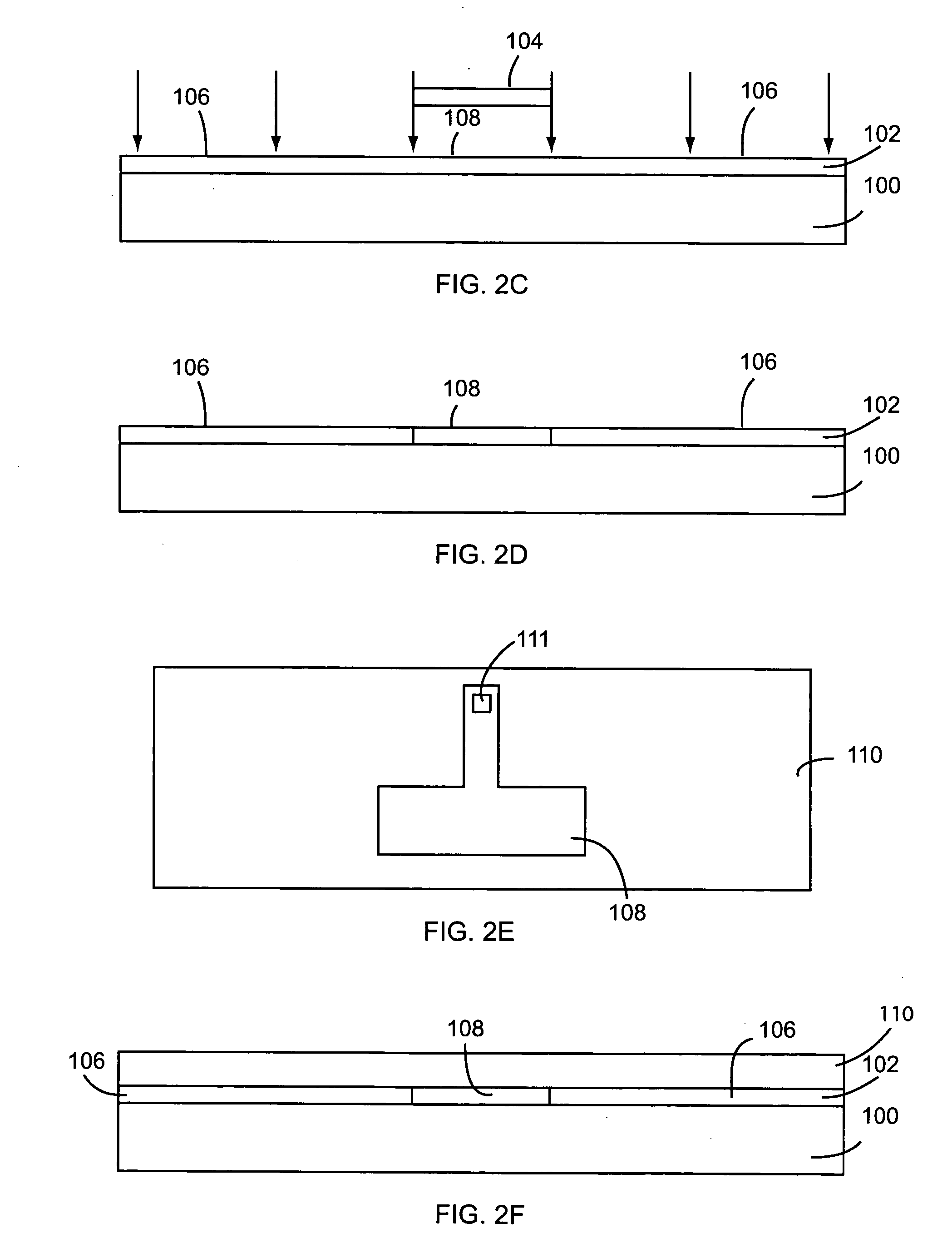

Large-area nanoenabled macroelectronic substrates and uses therefor

ActiveUS20050079659A1Reduce and entirely eliminate scatteringHigh carrier mobilityTransistorNanoinformaticsNanowireDevice material

A method and apparatus for an electronic substrate having a plurality of semiconductor devices is described. A thin film of nanowires is formed on a substrate. The thin film of nanowires is formed to have a sufficient density of nanowires to achieve an operational current level. A plurality of semiconductor regions are defined in the thin film of nanowires. Contacts are formed at the semiconductor device regions to thereby provide electrical connectivity to the plurality of semiconductor devices. Furthermore, various materials for fabricating nanowires, thin films including p-doped nanowires and n-doped nanowires, nanowire heterostructures, light emitting nanowire heterostructures, flow masks for positioning nanowires on substrates, nanowire spraying techniques for depositing nanowires, techniques for reducing or eliminating phonon scattering of electrons in nanowires, and techniques for reducing surface states in nanowires are described.

Owner:ONED MATERIAL INC

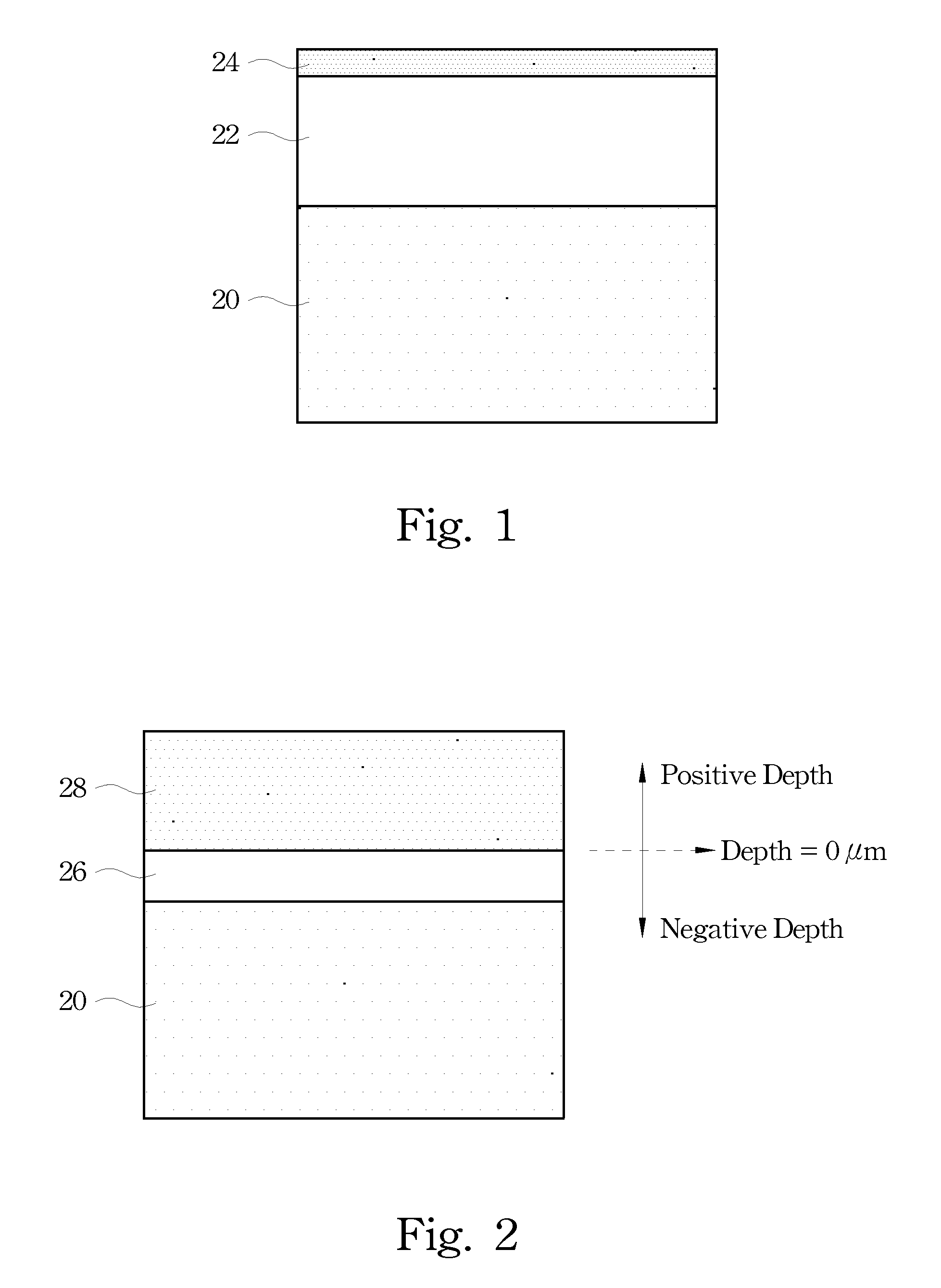

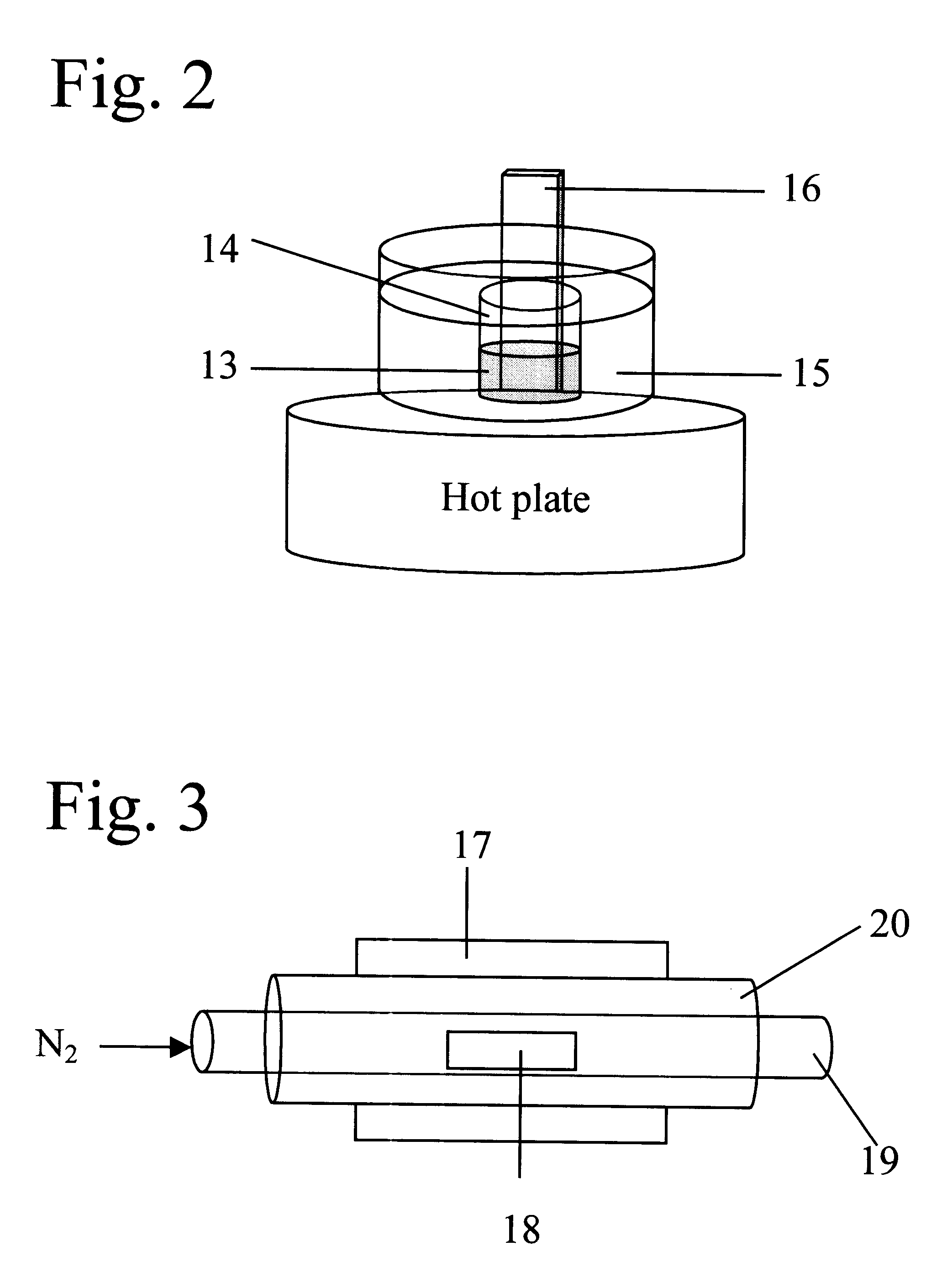

Method for forming an interface between germanium and other materials

InactiveUS20060099782A1Improved carrier mobilityHinder germanium oxide formationSemiconductor/solid-state device manufacturingSemiconductor devicesIntegrated circuitSemiconductor structure

Interfaces that are portions of semiconductor structures used in integrated circuits and optoelectronic devices are described. In one instance, the semiconductor structure has an interface including a semiconductor surface, an interfacial layer including sulfur, and an electrically active layer (e.g., a dielectric or a metal). Such an interface can inhibit oxidation and improve the carrier mobility of the semiconductor structures in which such an interface is incorporated. The interfacial layer can be created by exposure of the semiconductor surface to sulfur donating compounds (e.g., H2S or SF6) and, optionally, heating.

Owner:MASSACHUSETTS INST OF TECH

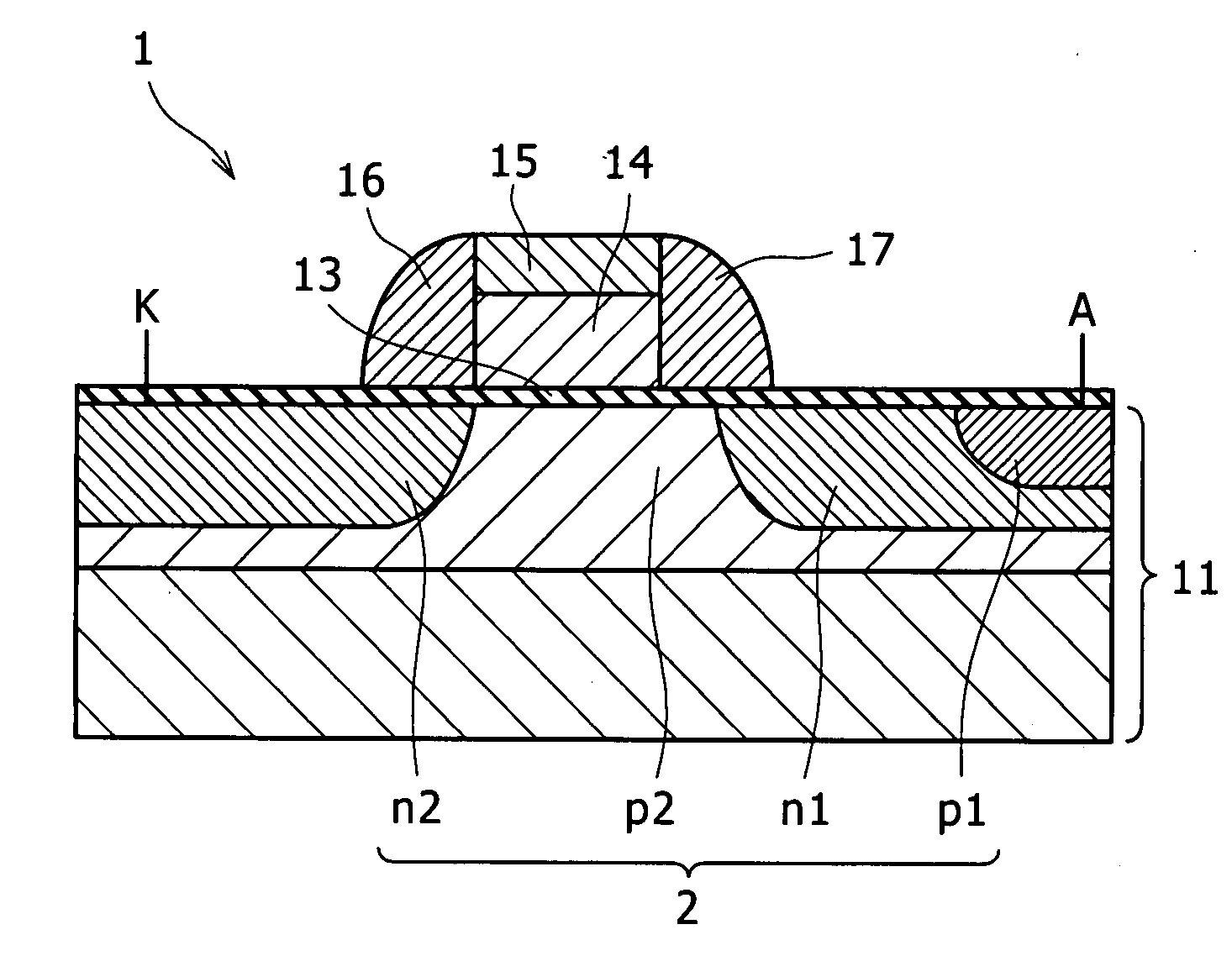

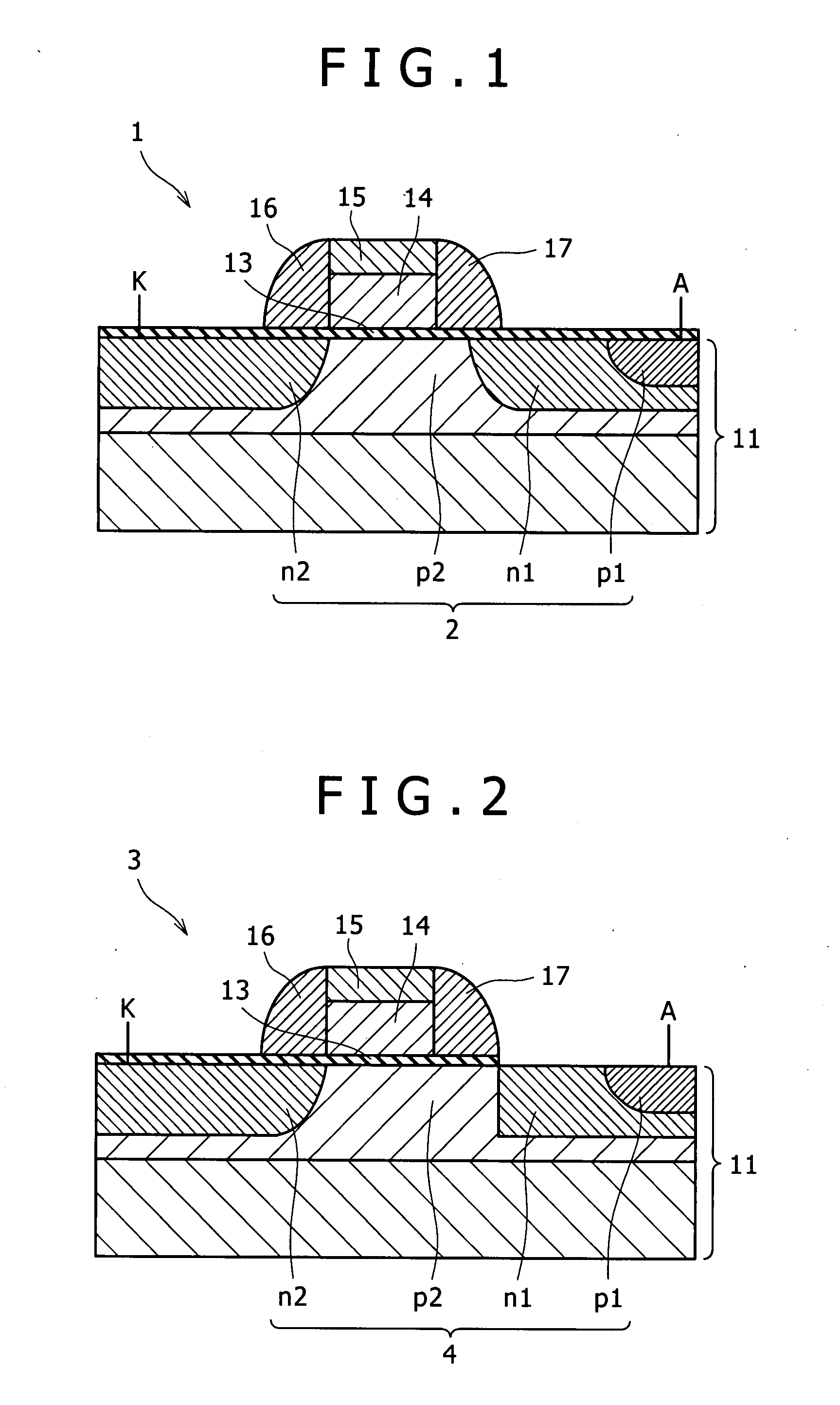

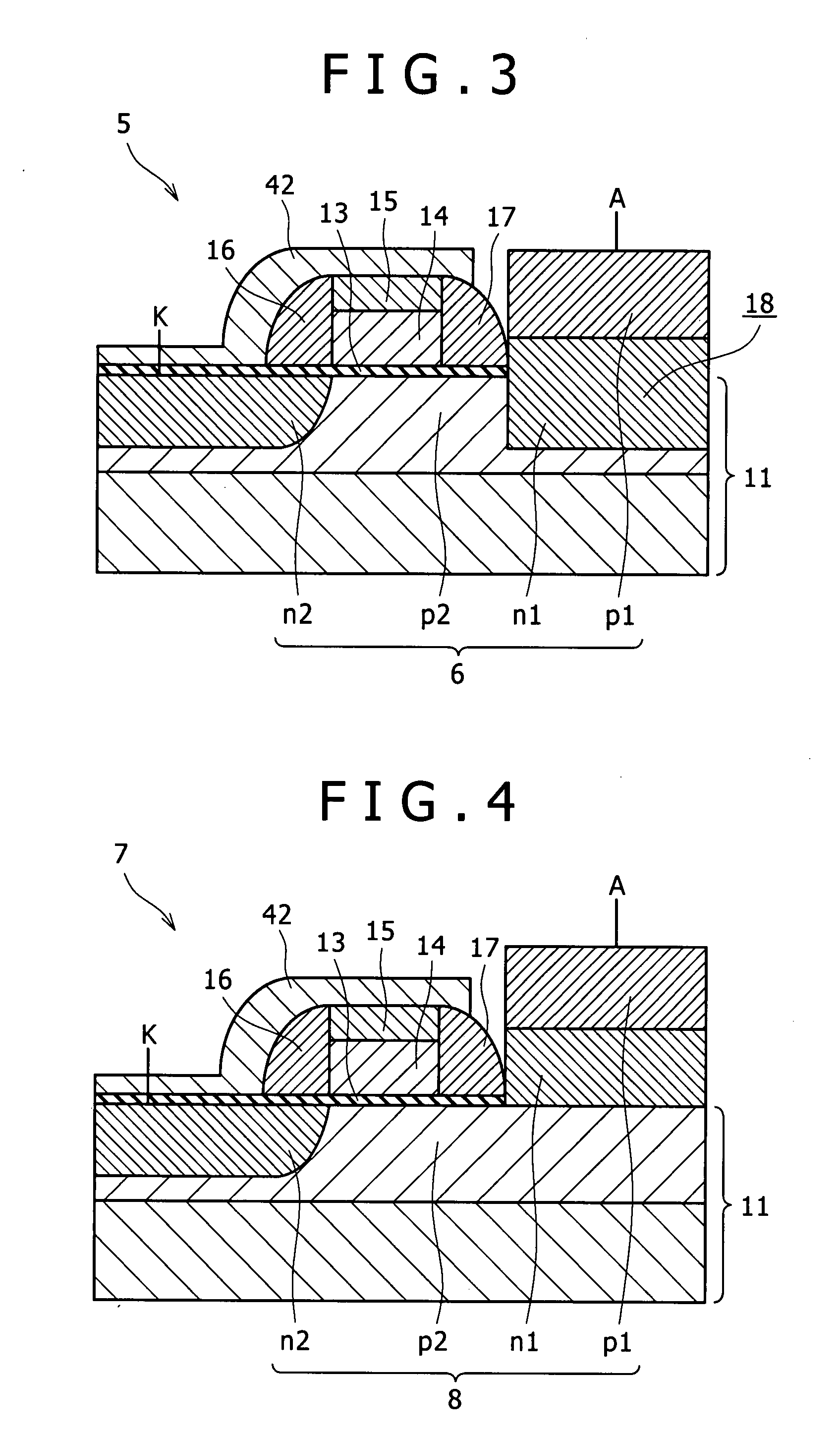

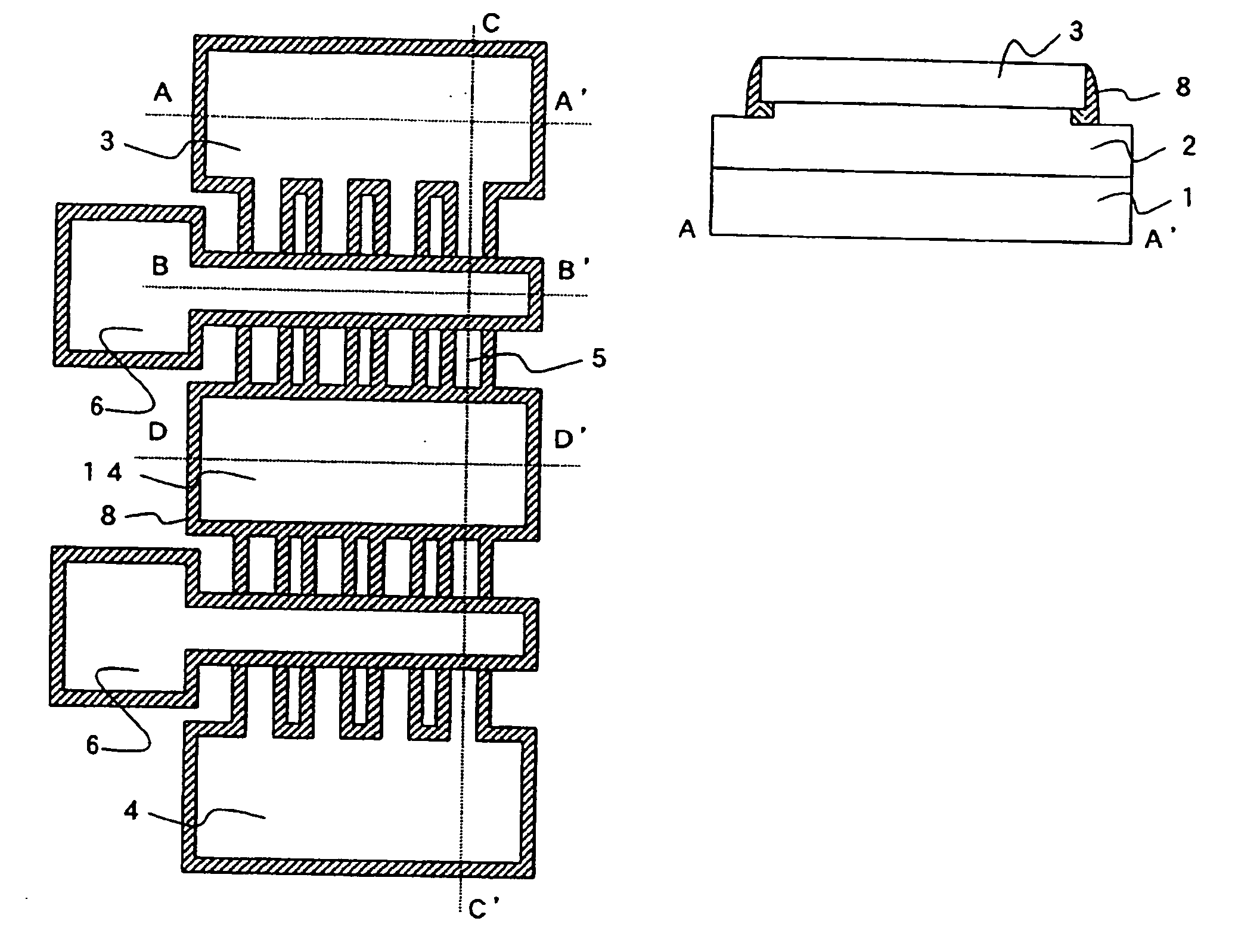

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20080042165A1Increase speedImprove mobilityThyristorSemiconductor/solid-state device manufacturingThyratronSemiconductor

A semiconductor device includes a thyristor configured to be formed through sequential joining of a first region of a first conductivity type, a second region of a second conductivity type opposite to the first conductivity type, a third region of the first conductivity type, and a fourth region of the second conductivity type, and have a gate formed over the third region. The first to fourth regions are formed in a silicon germanium region or germanium region.

Owner:SONY CORP

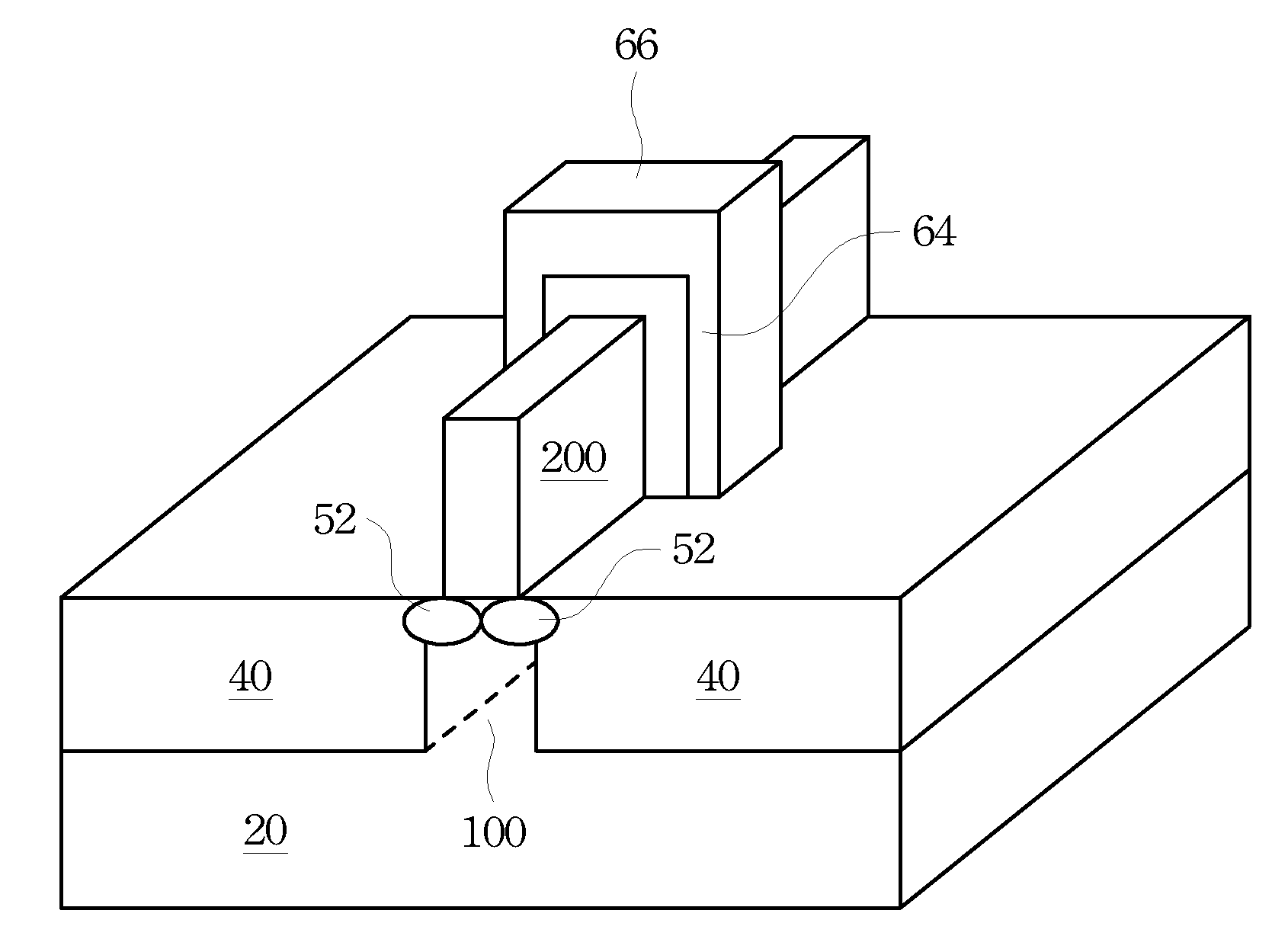

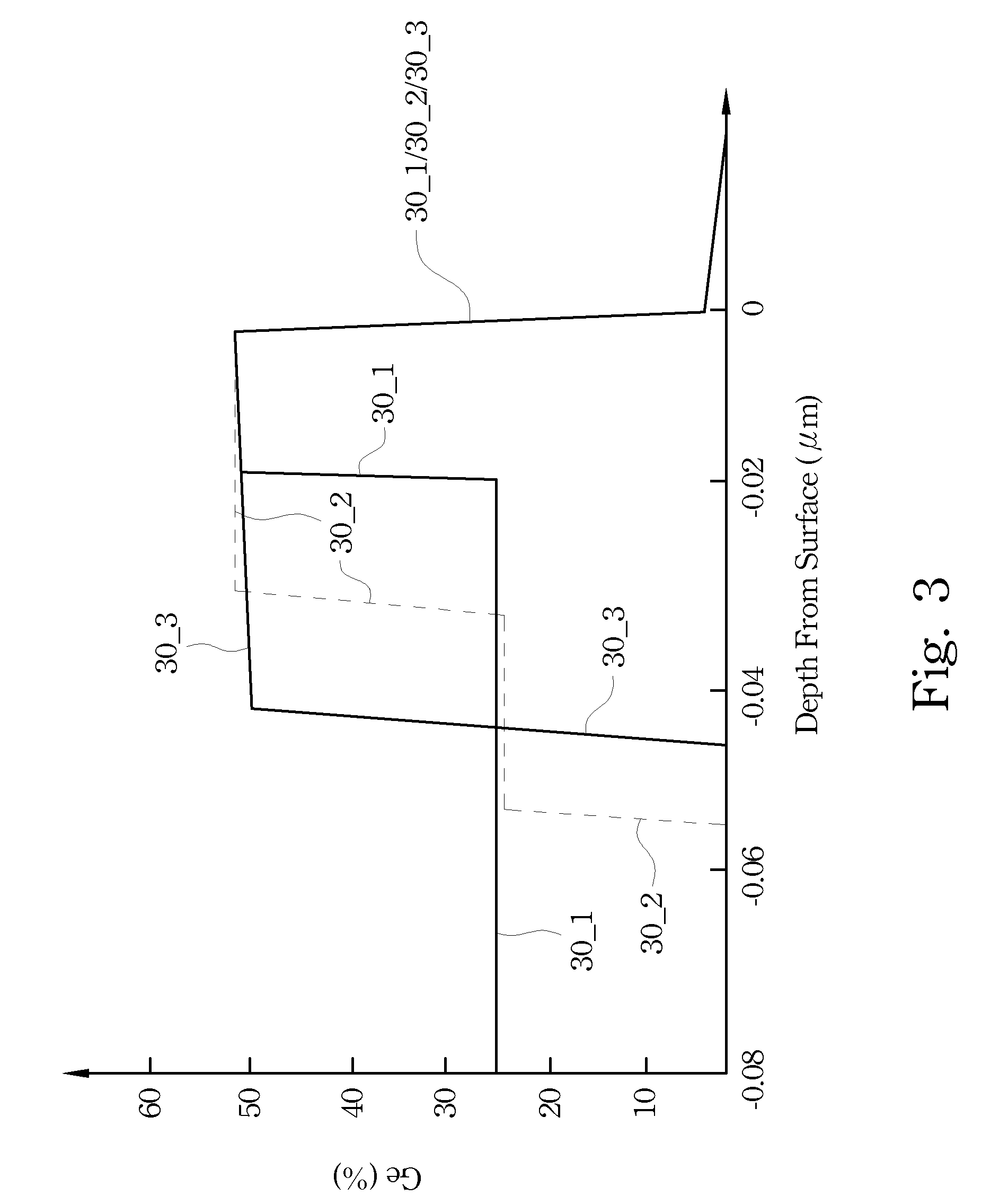

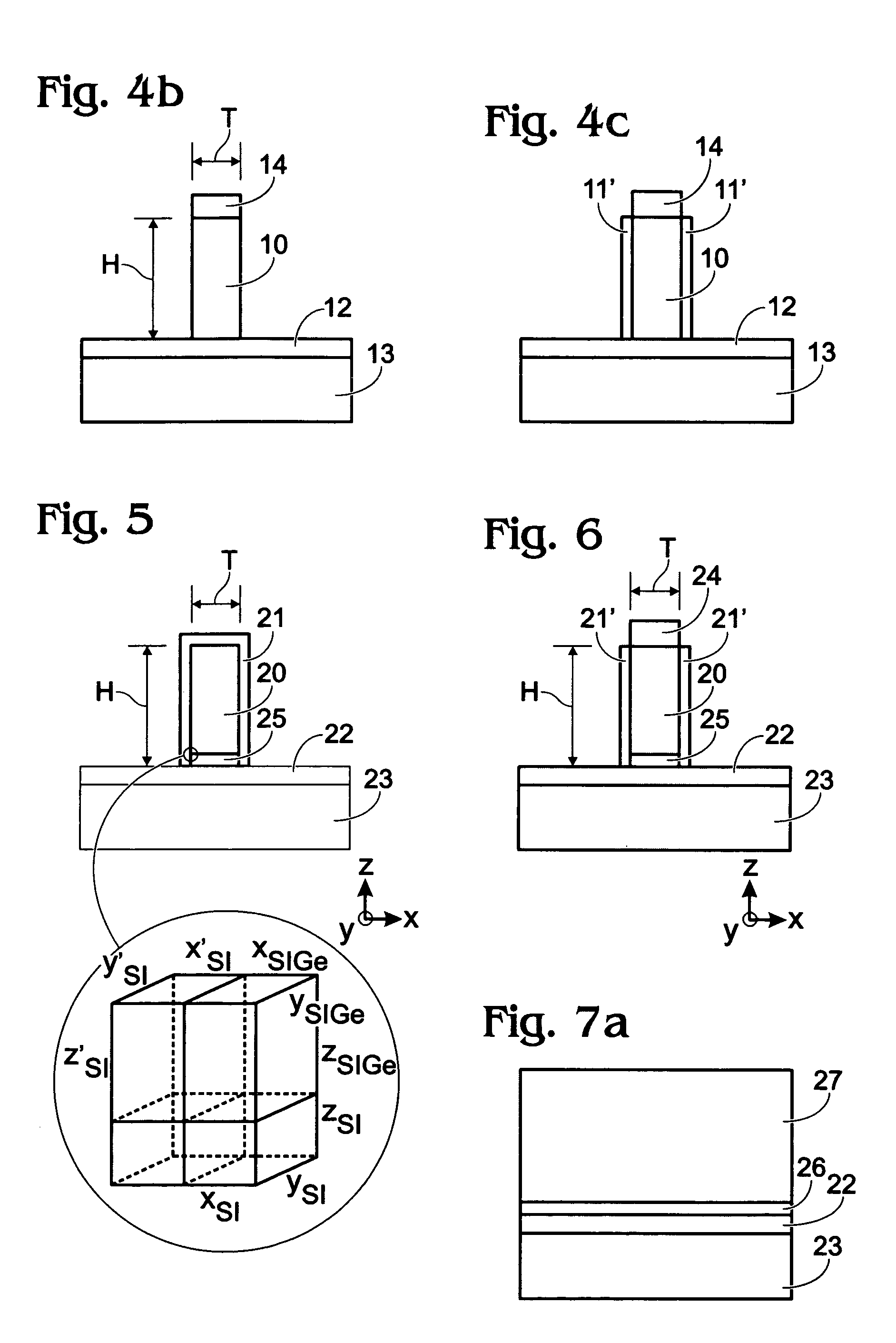

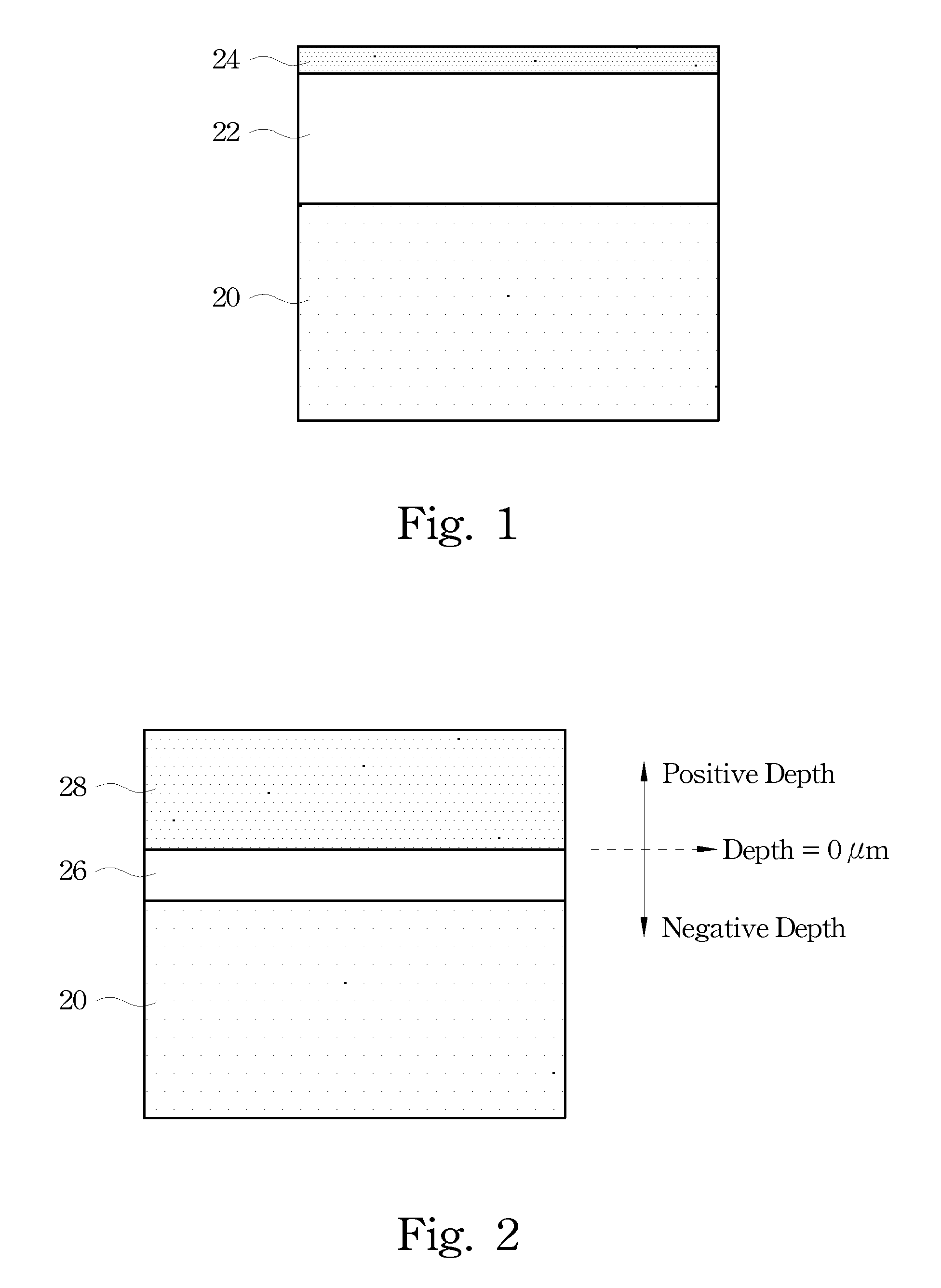

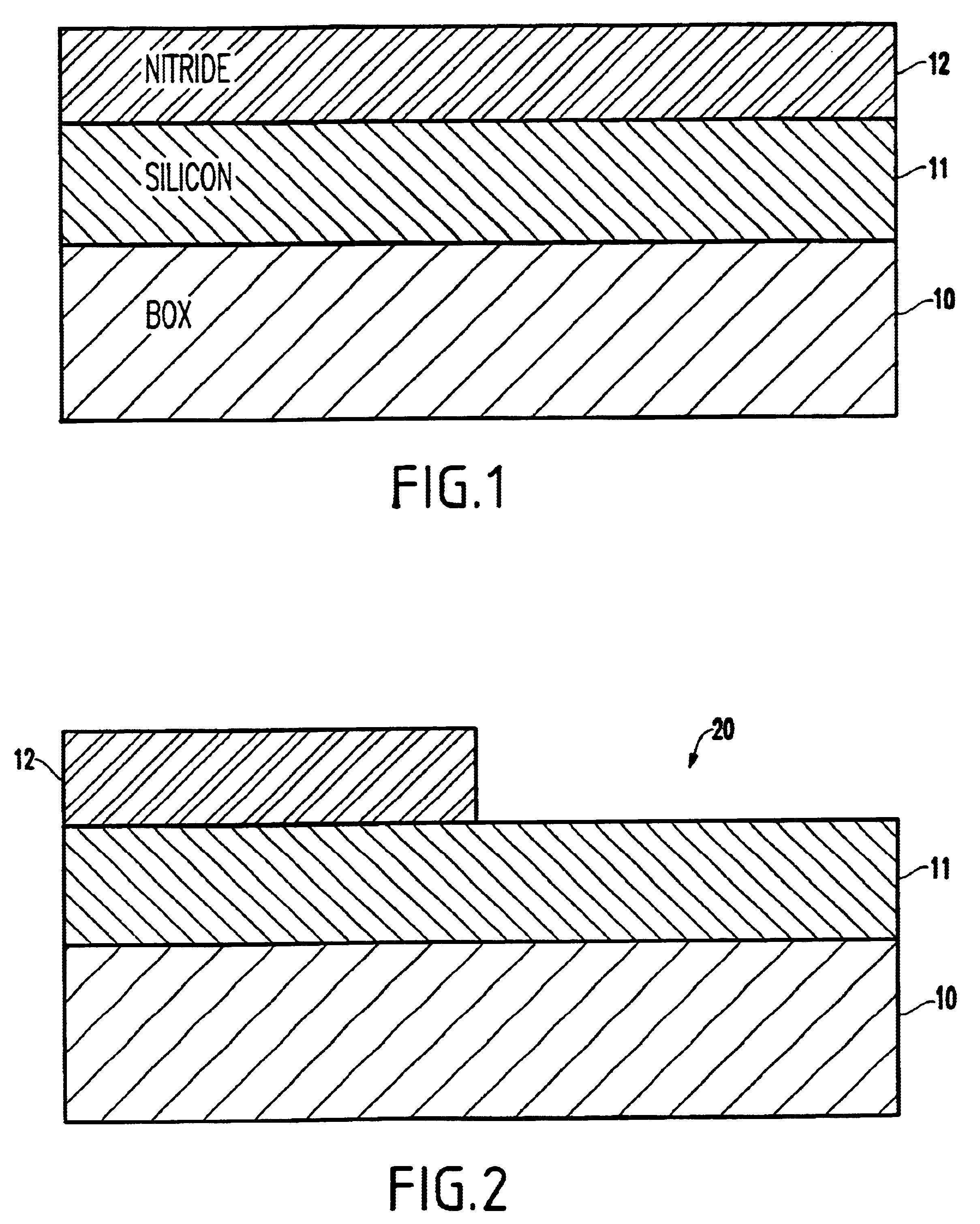

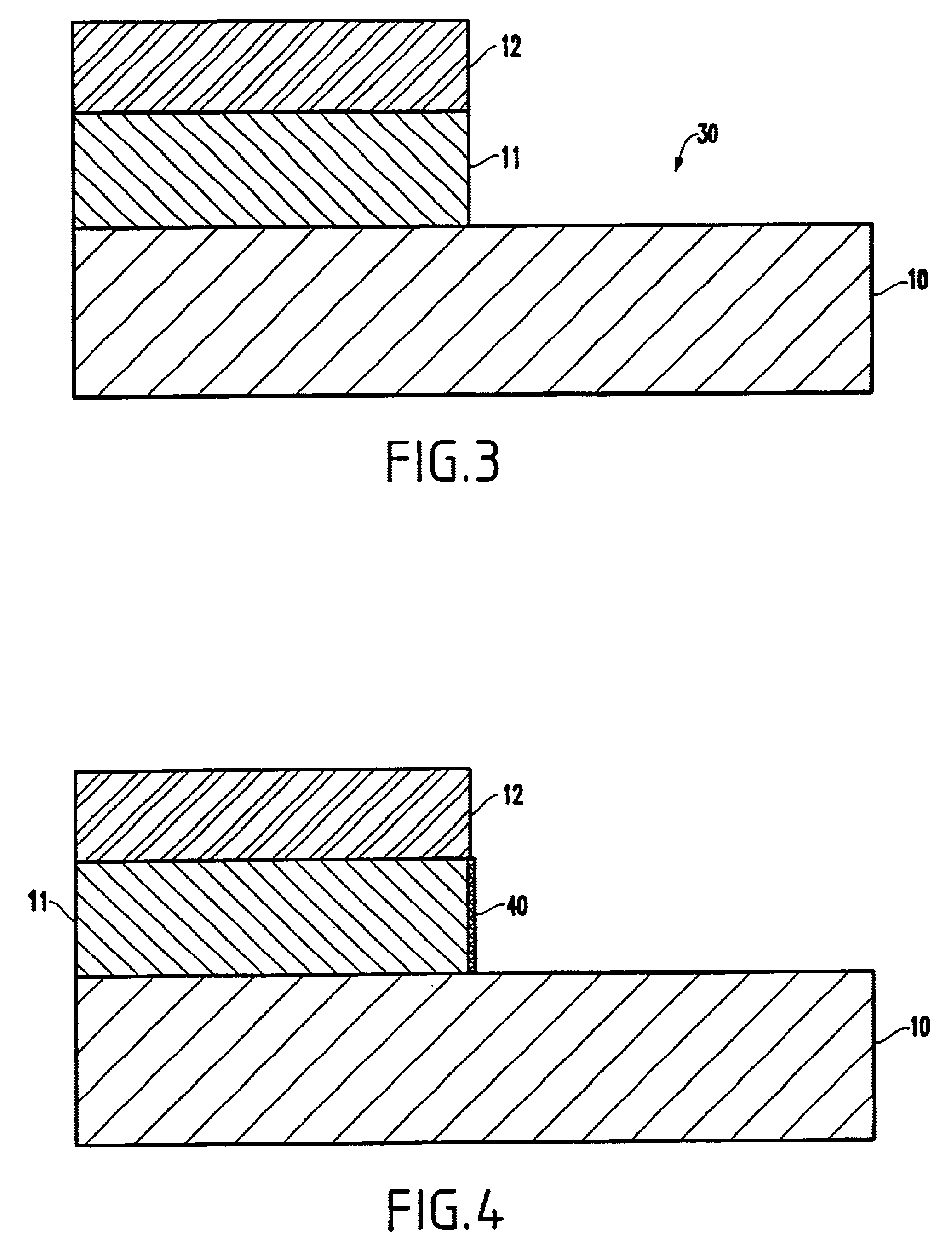

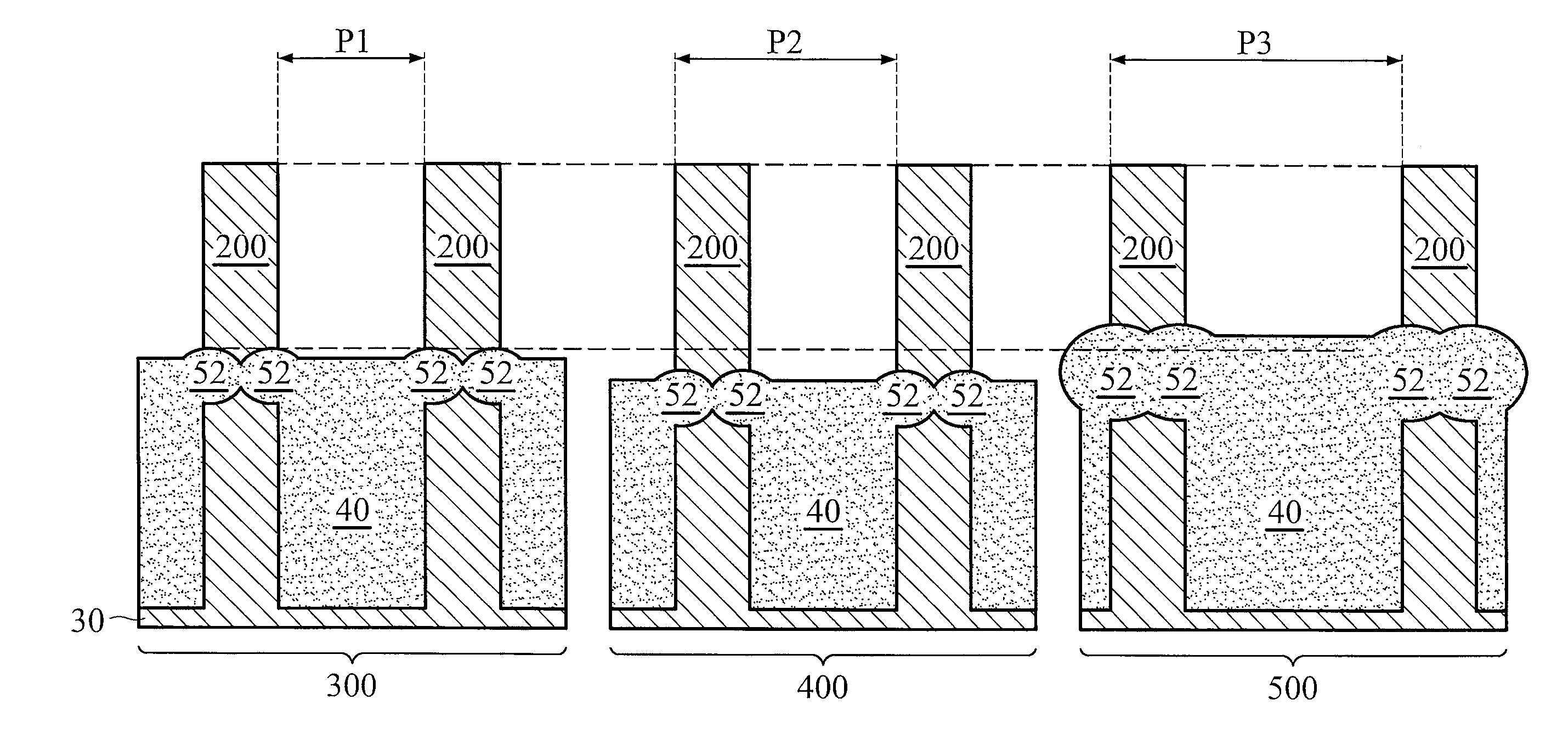

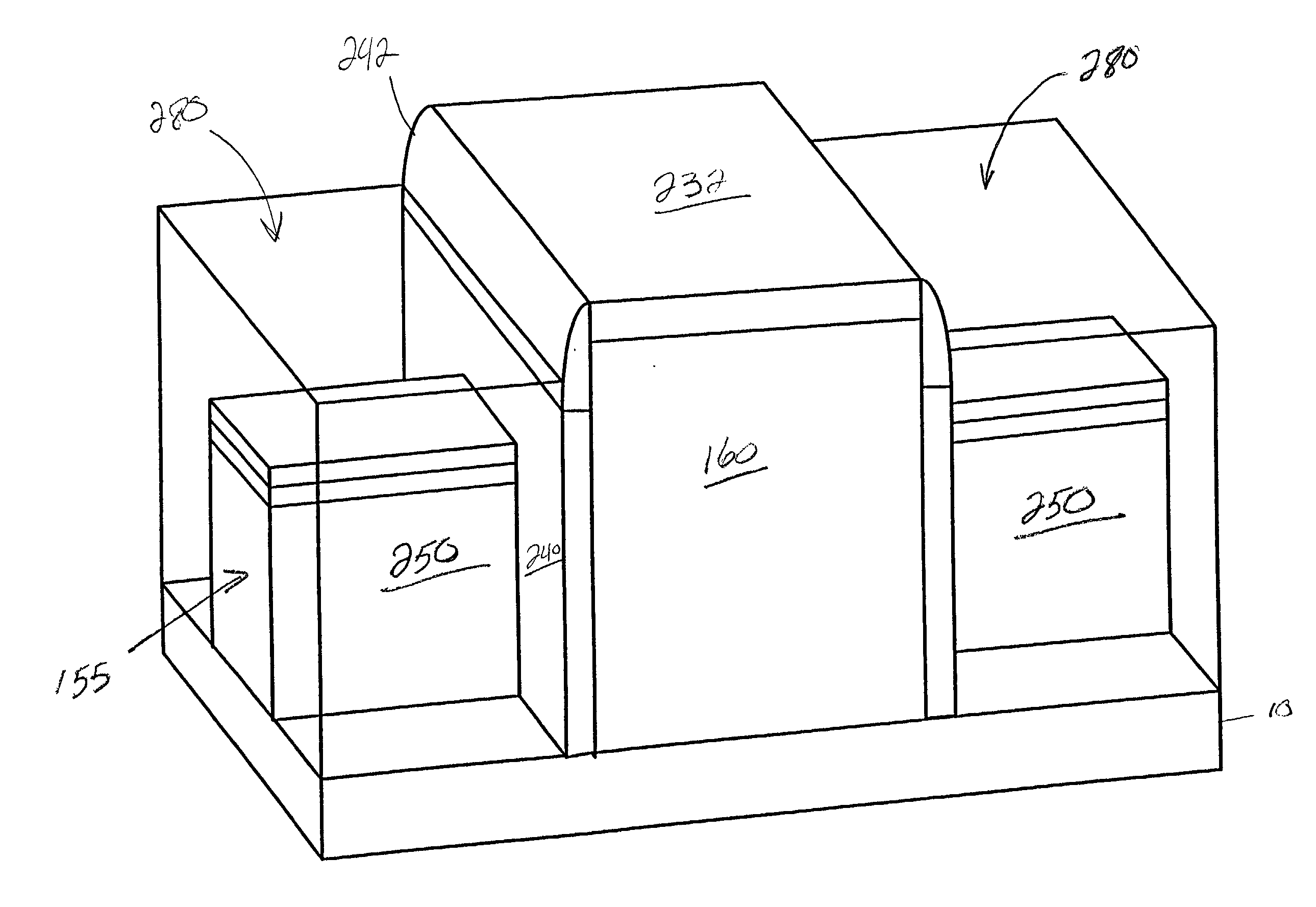

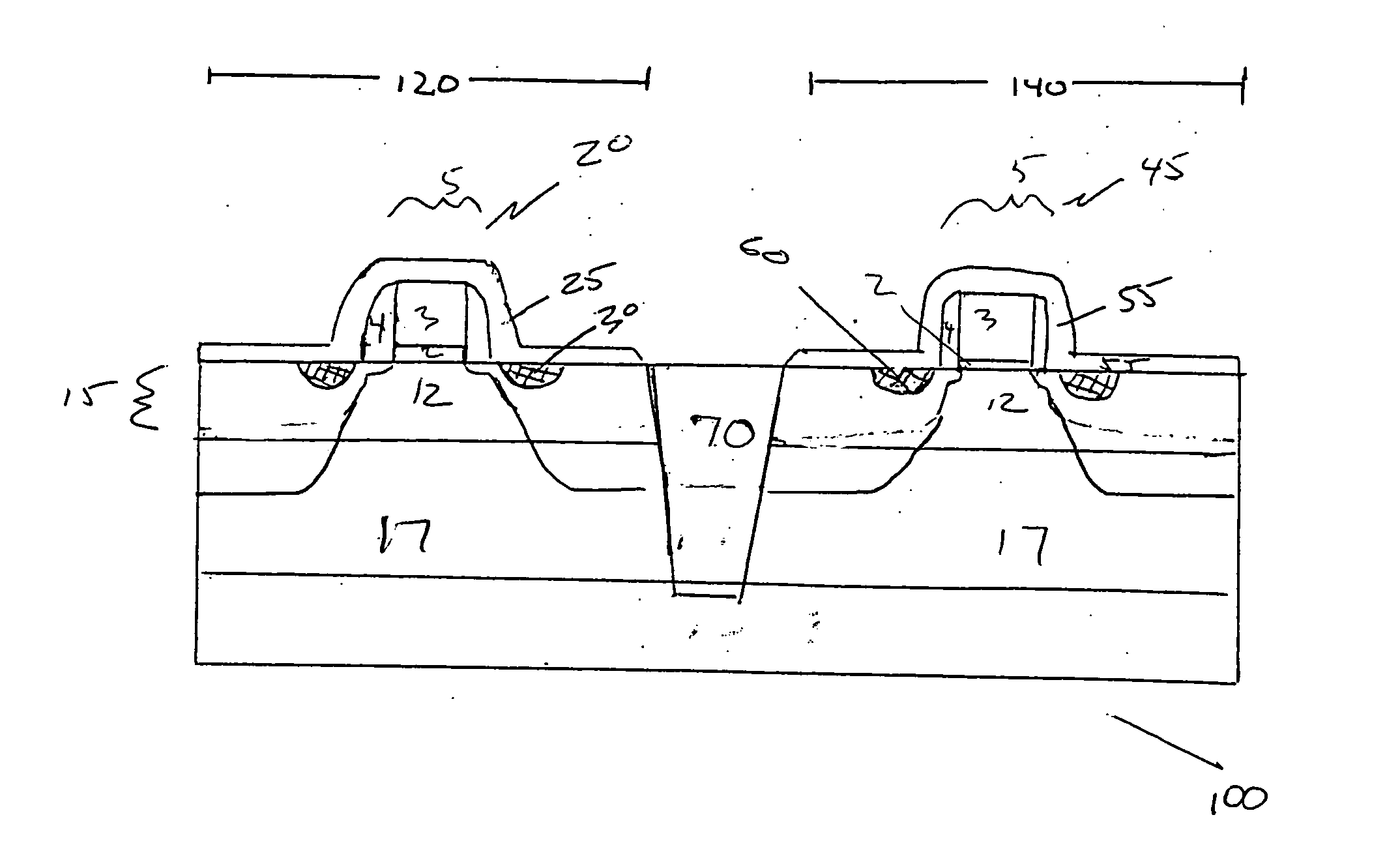

Germanium FinFETs Having Dielectric Punch-Through Stoppers

ActiveUS20100144121A1Total current dropHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesComposite substrateSemiconductor structure

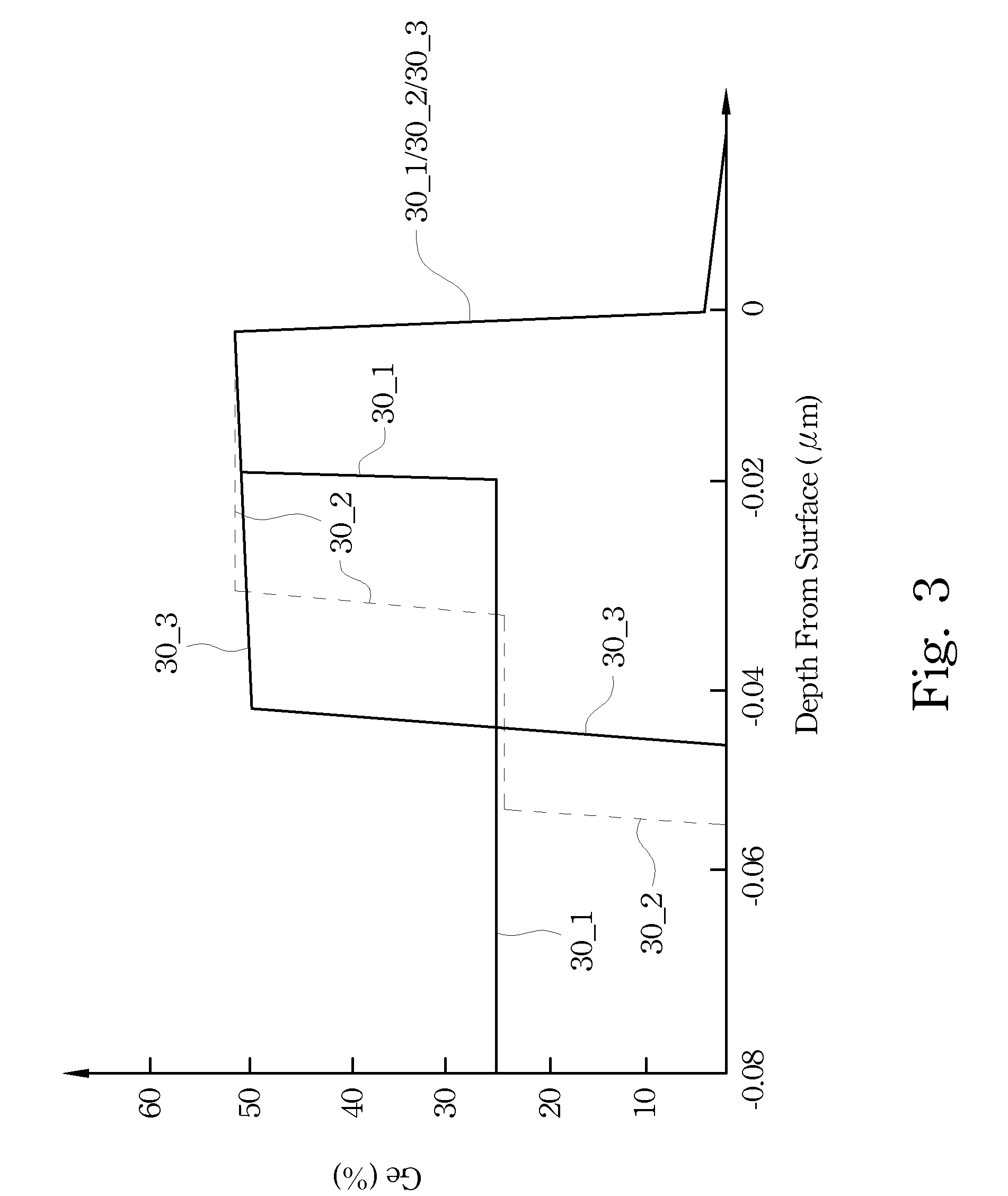

A method of forming a semiconductor structure includes providing a composite substrate, which includes a bulk silicon substrate and a silicon germanium (SiGe) layer over and adjoining the bulk silicon substrate. A first condensation is performed to the SiGe layer to form a condensed SiGe layer, so that the condensed SiGe layer has a substantially uniform germanium concentration. The condensed SiGe layer and a top portion of the bulk silicon substrate are etched to form a composite fin including a silicon fin and a condensed SiGe fin over the silicon fine. The method further includes oxidizing a portion of the silicon fin; and performing a second condensation to the condensed SiGe fin.

Owner:TAIWAN SEMICON MFG CO LTD

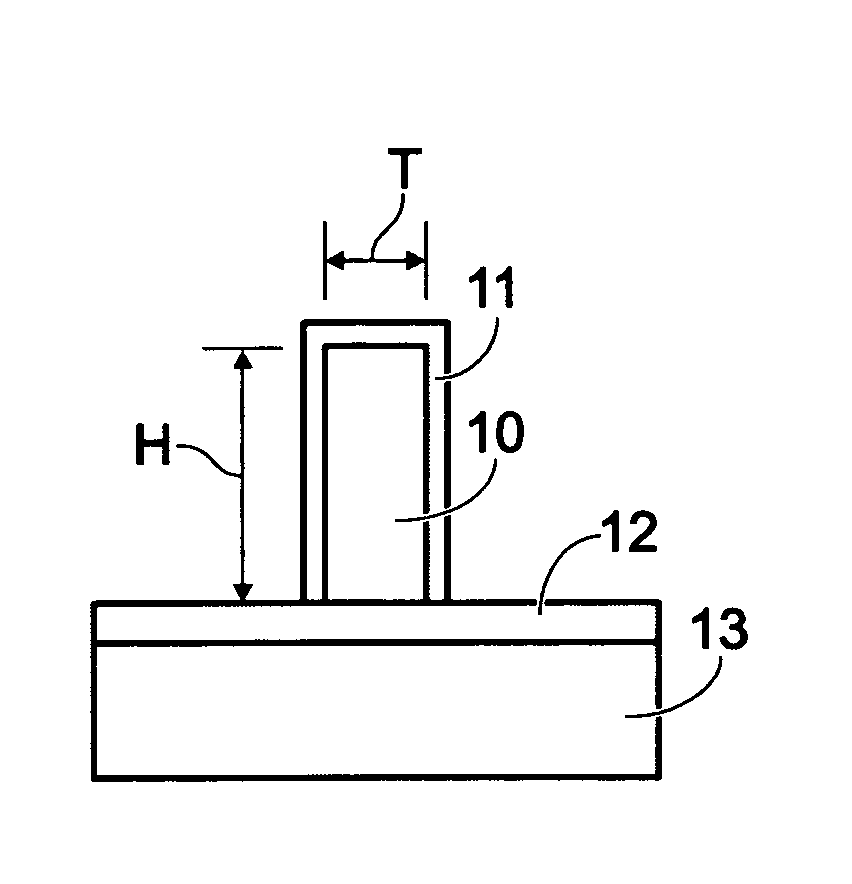

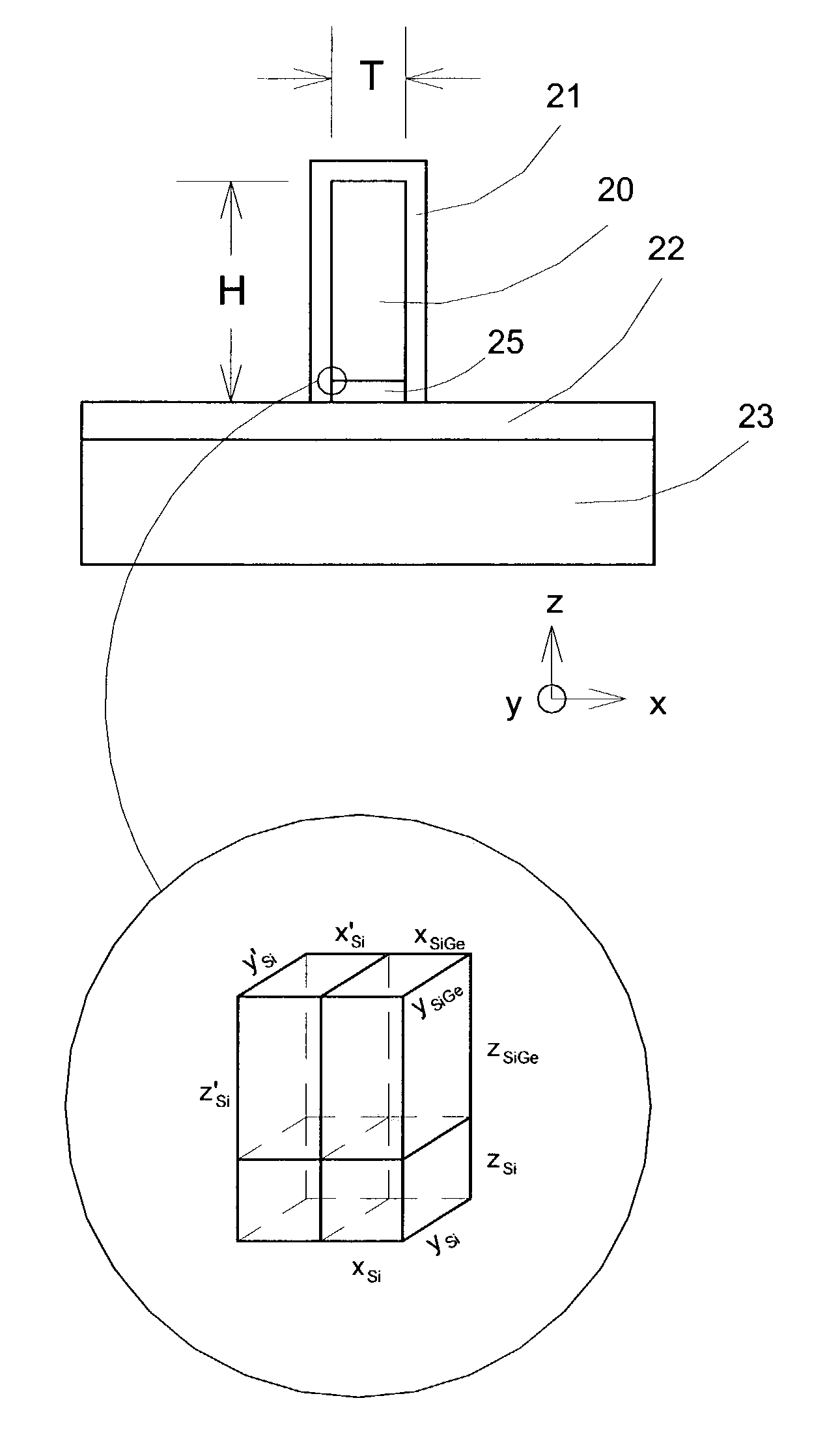

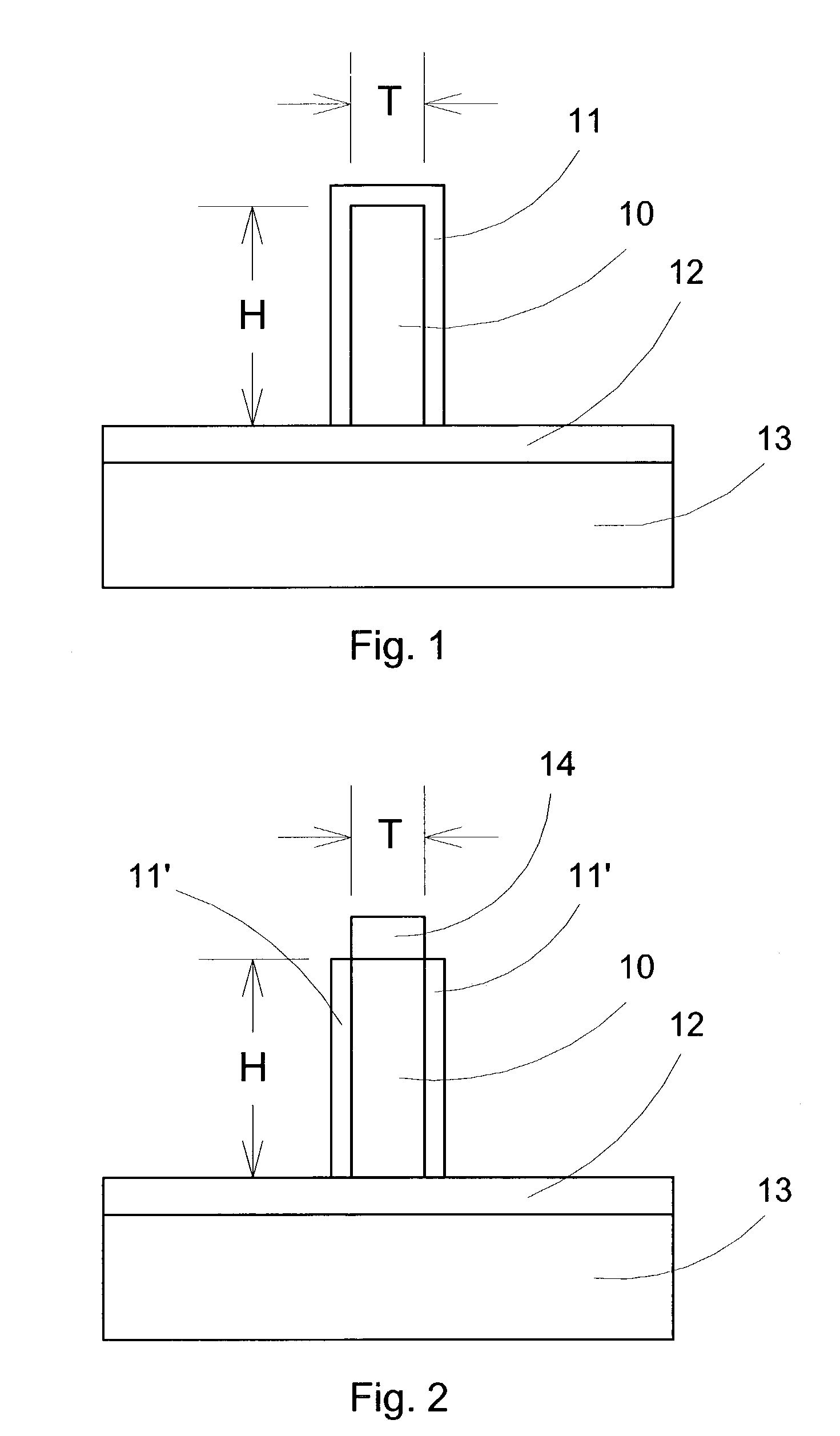

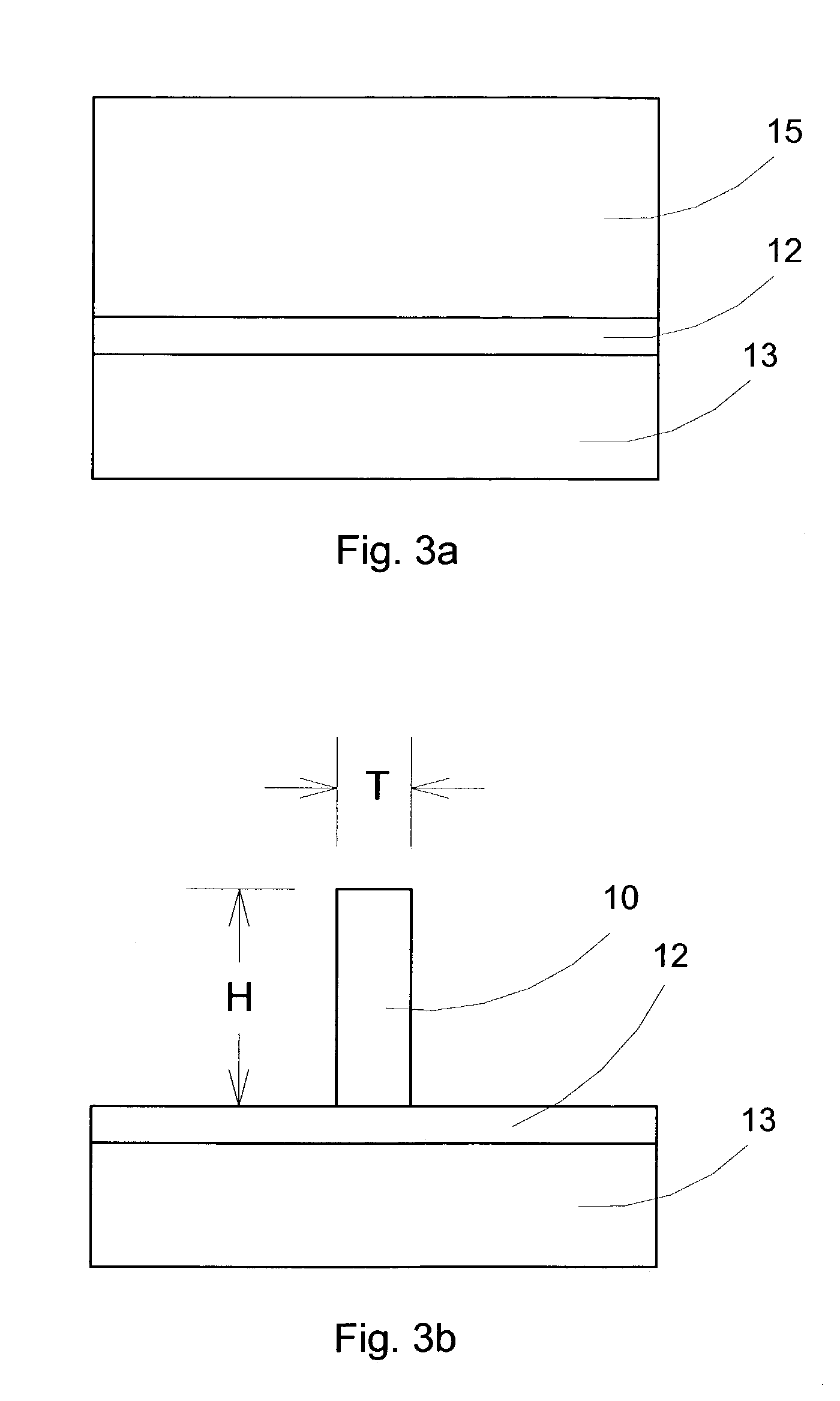

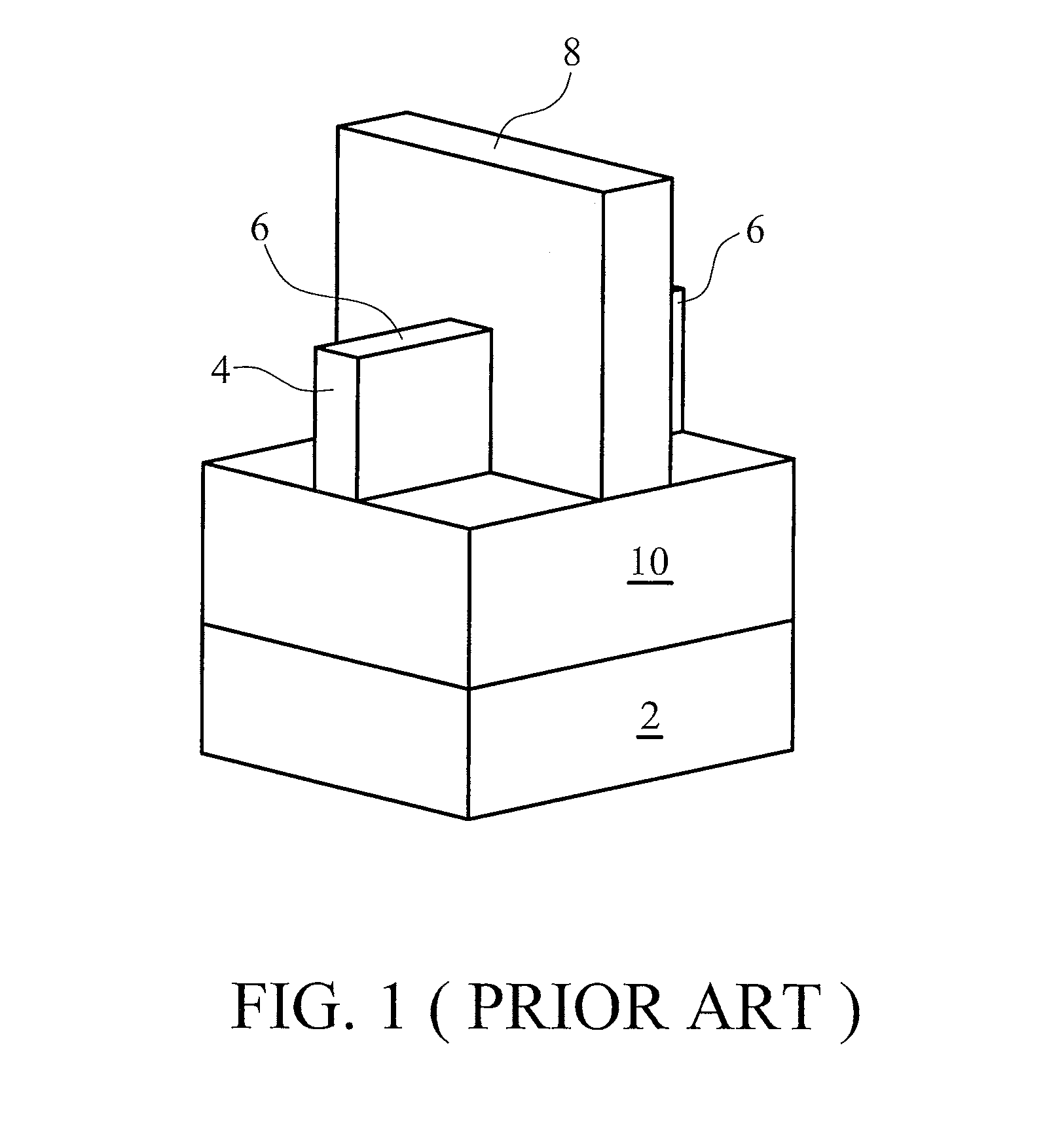

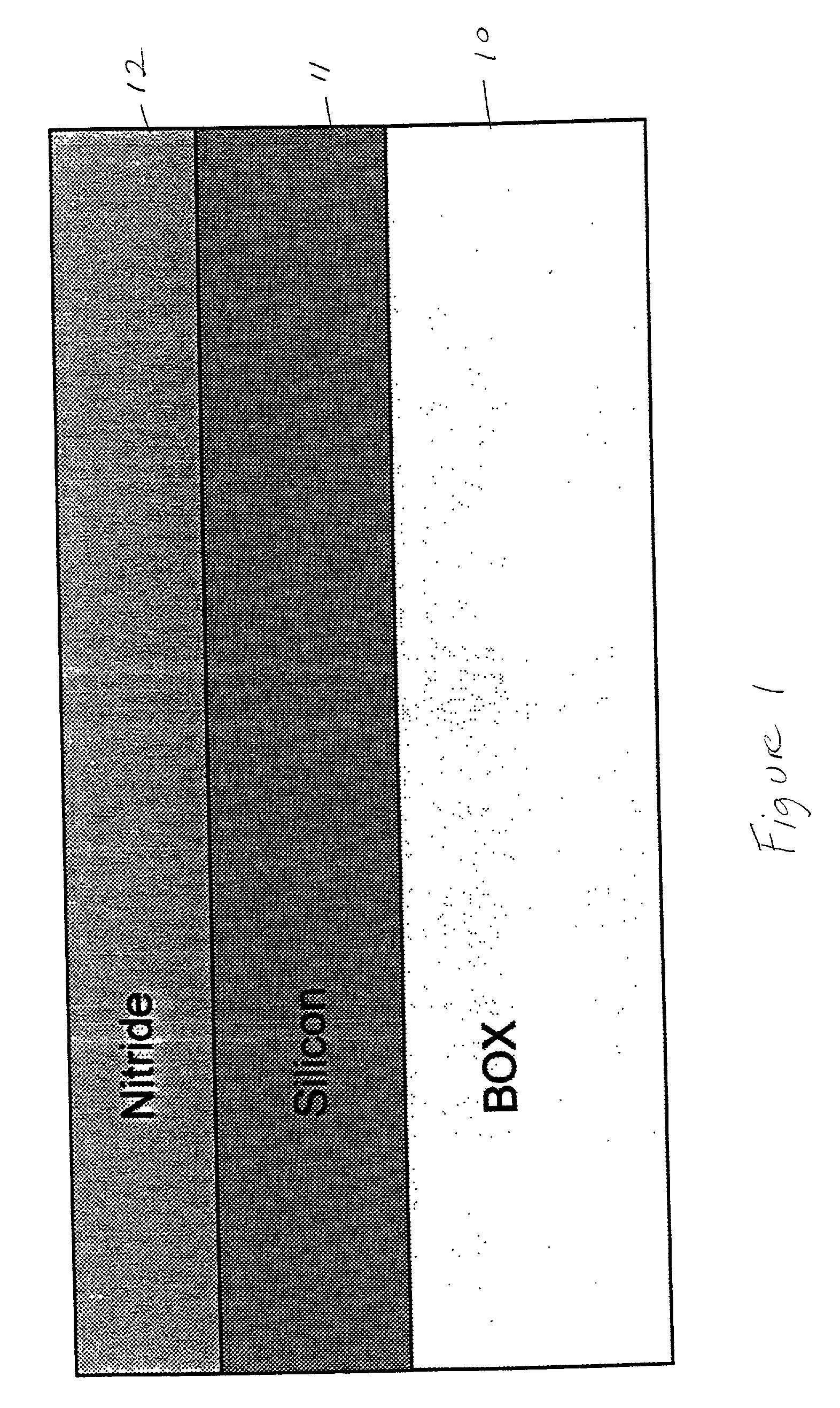

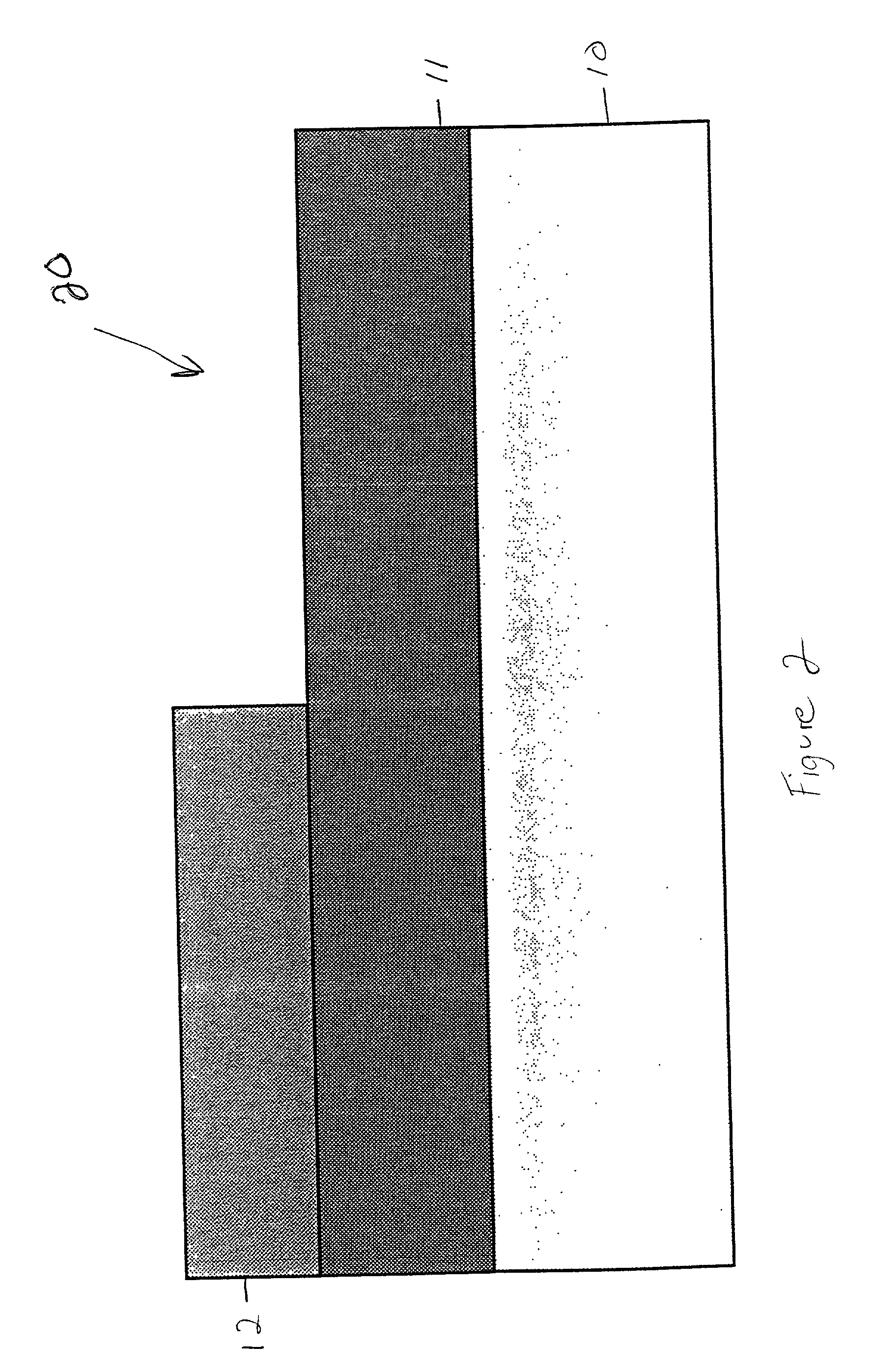

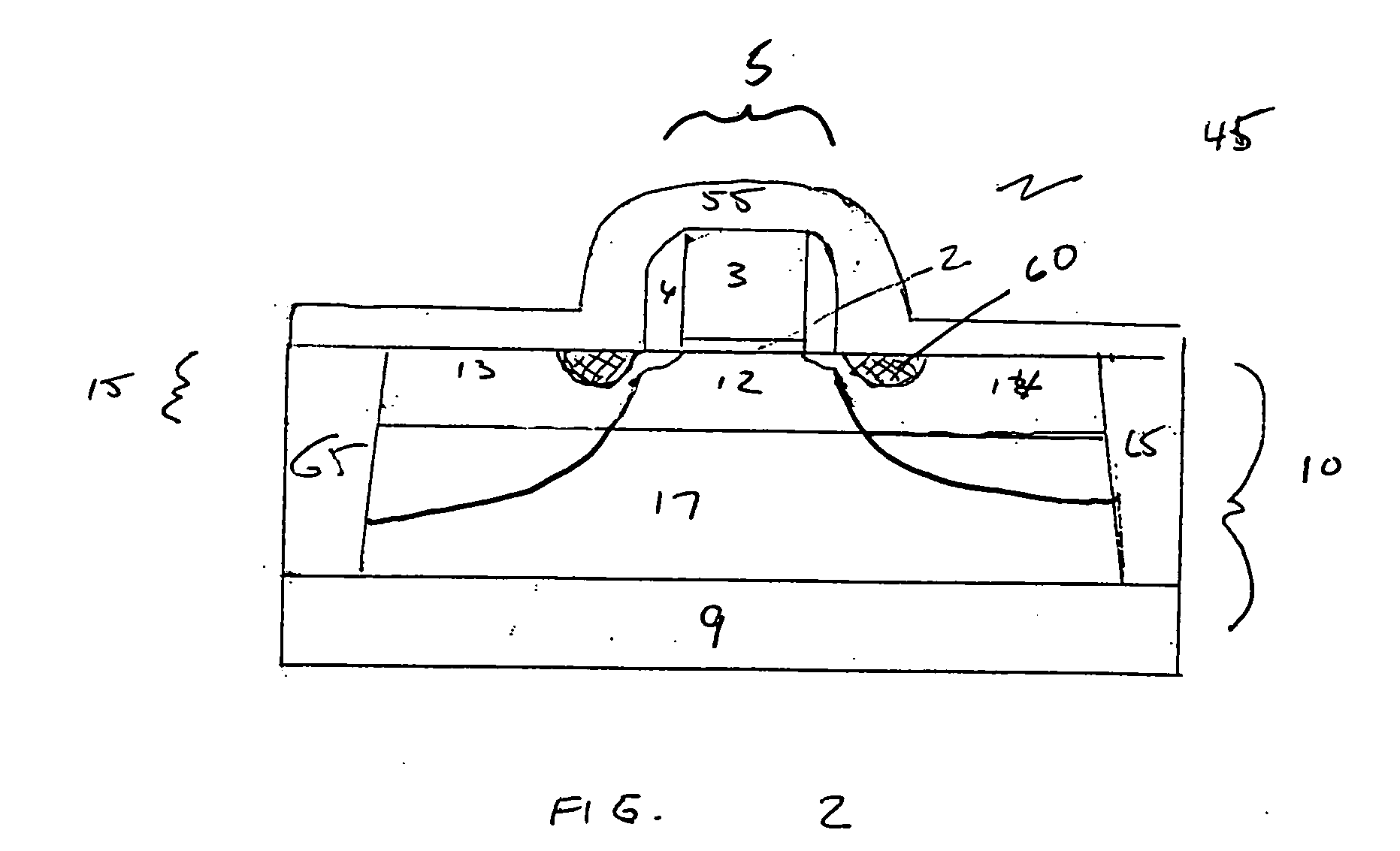

Strained silicon fin structure

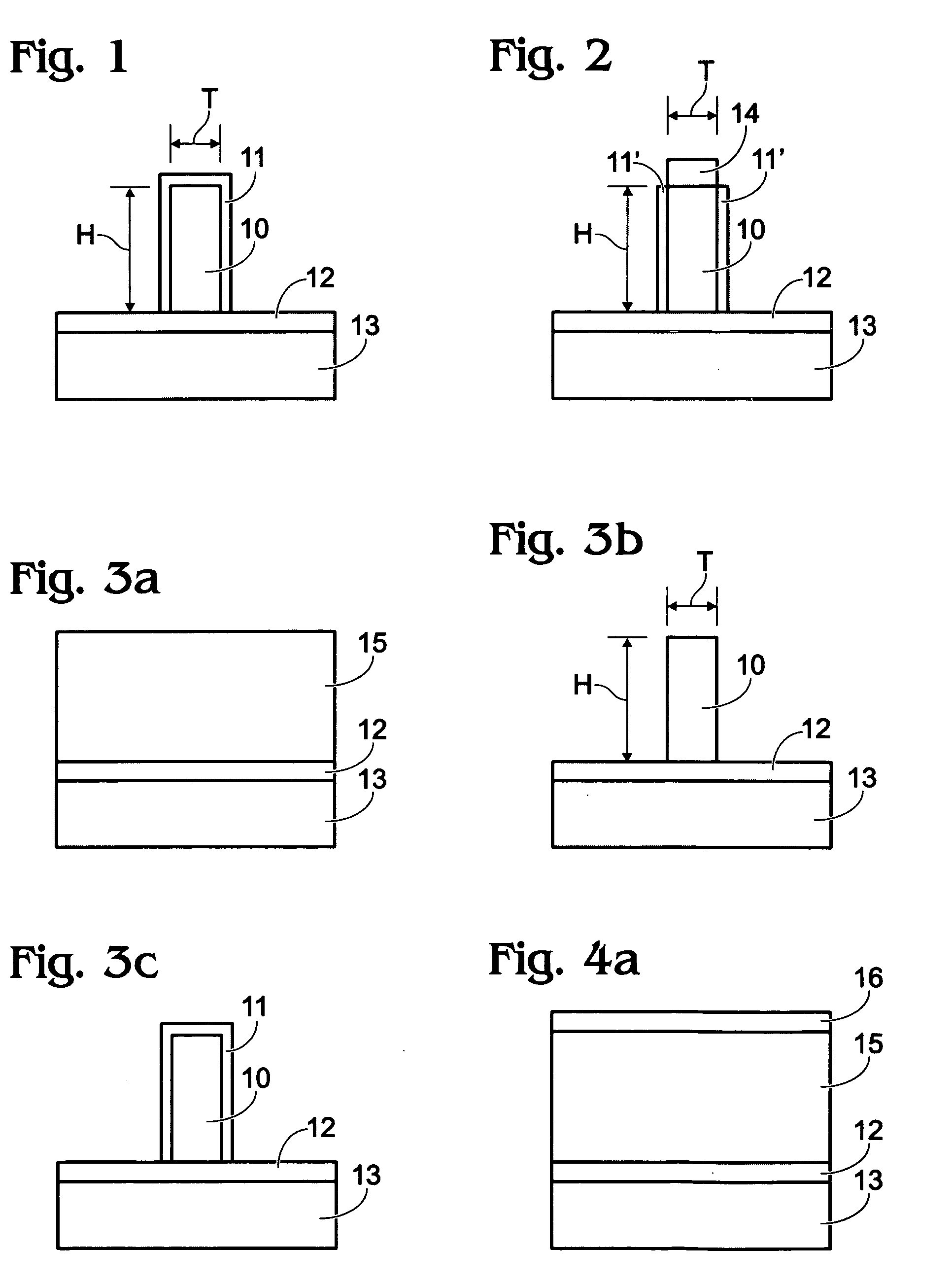

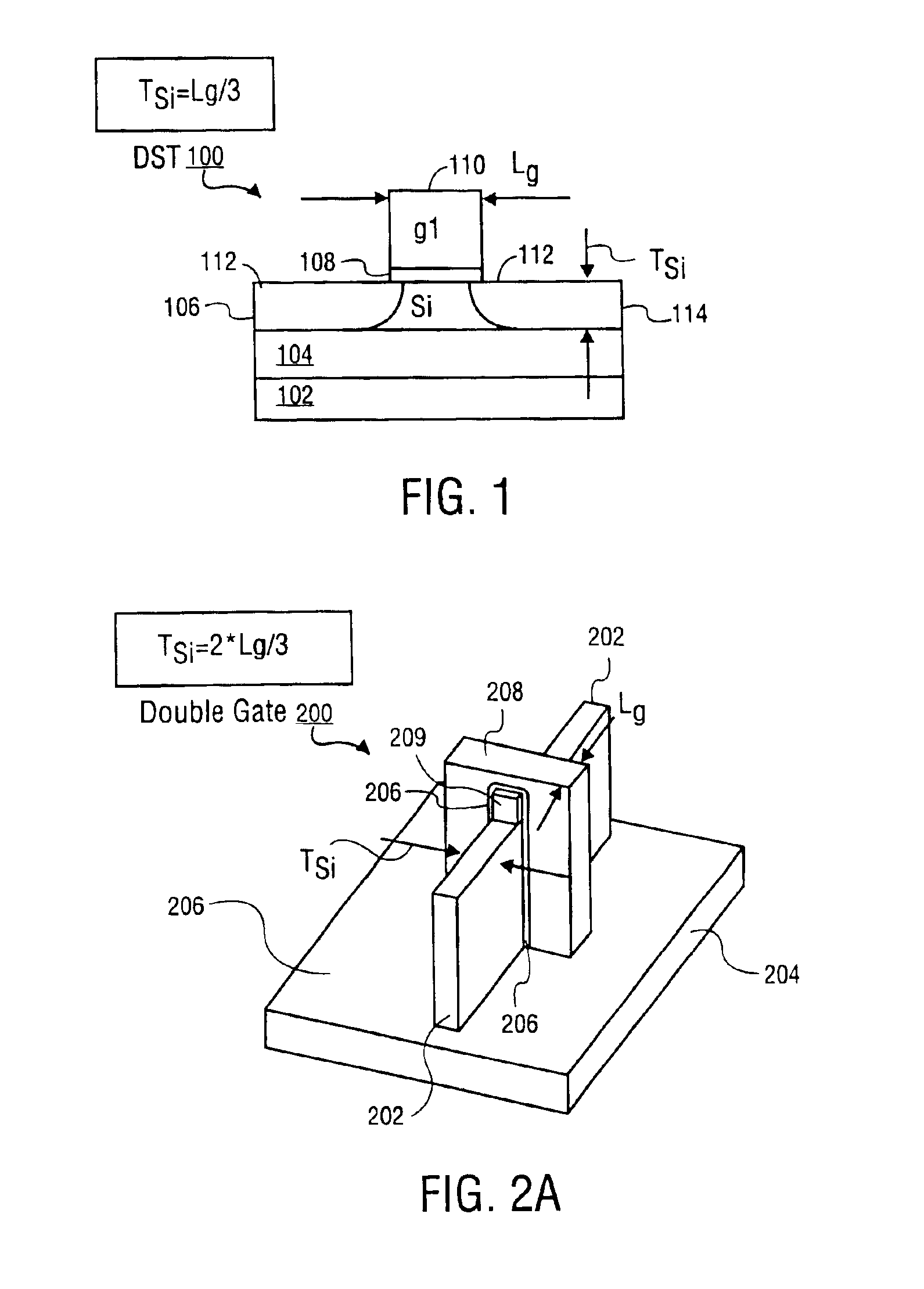

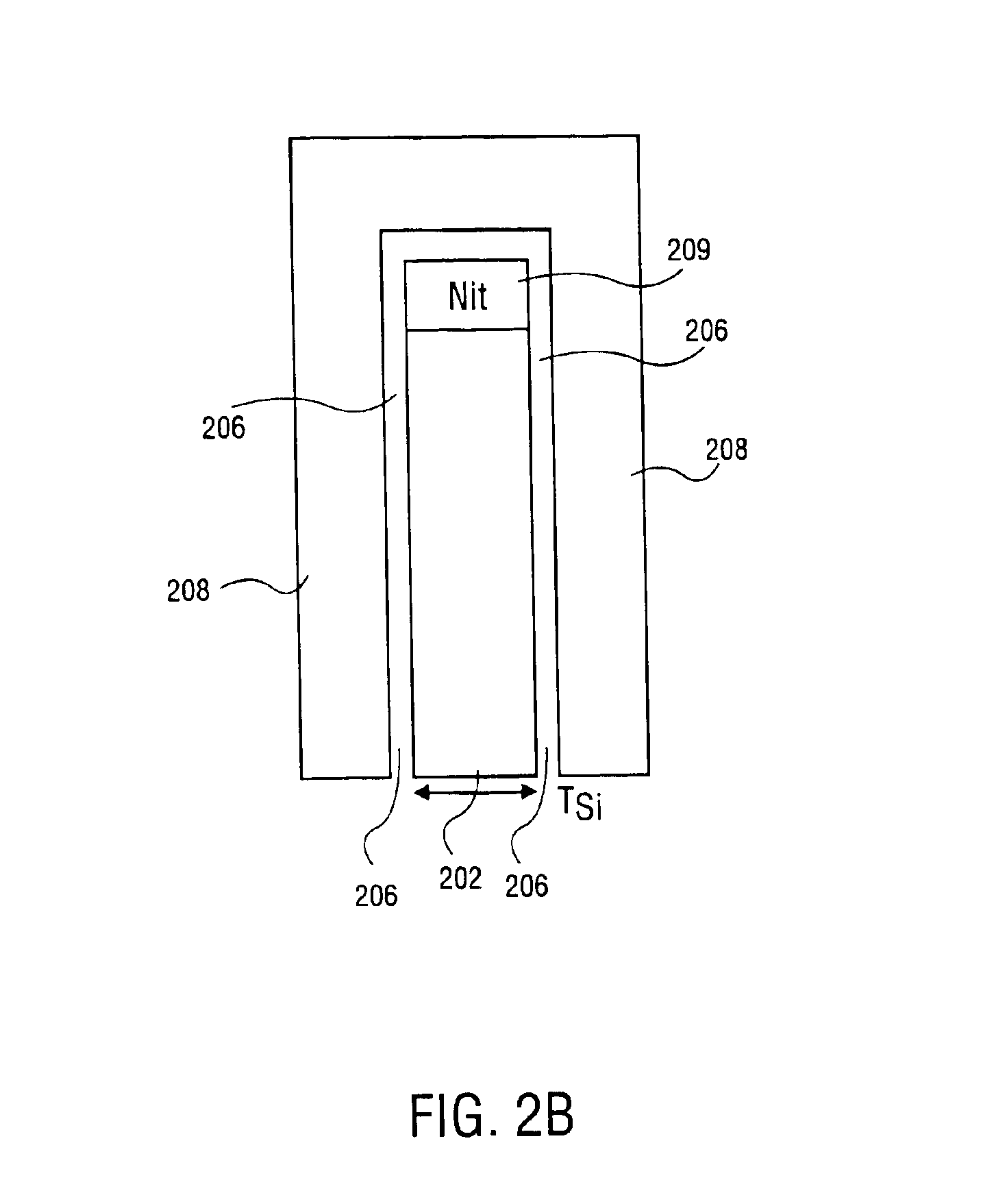

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

Germanium FinFETs having dielectric punch-through stoppers

InactiveUS8048723B2High carrier mobilityTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureComposite substrate

A method of forming a semiconductor structure includes providing a composite substrate, which includes a bulk silicon substrate and a silicon germanium (SiGe) layer over and adjoining the bulk silicon substrate. A first condensation is performed to the SiGe layer to form a condensed SiGe layer, so that the condensed SiGe layer has a substantially uniform germanium concentration. The condensed SiGe layer and a top portion of the bulk silicon substrate are etched to form a composite fin including a silicon fin and a condensed SiGe fin over the silicon fine. The method further includes oxidizing a portion of the silicon fin; and performing a second condensation to the condensed SiGe fin.

Owner:TAIWAN SEMICON MFG CO LTD

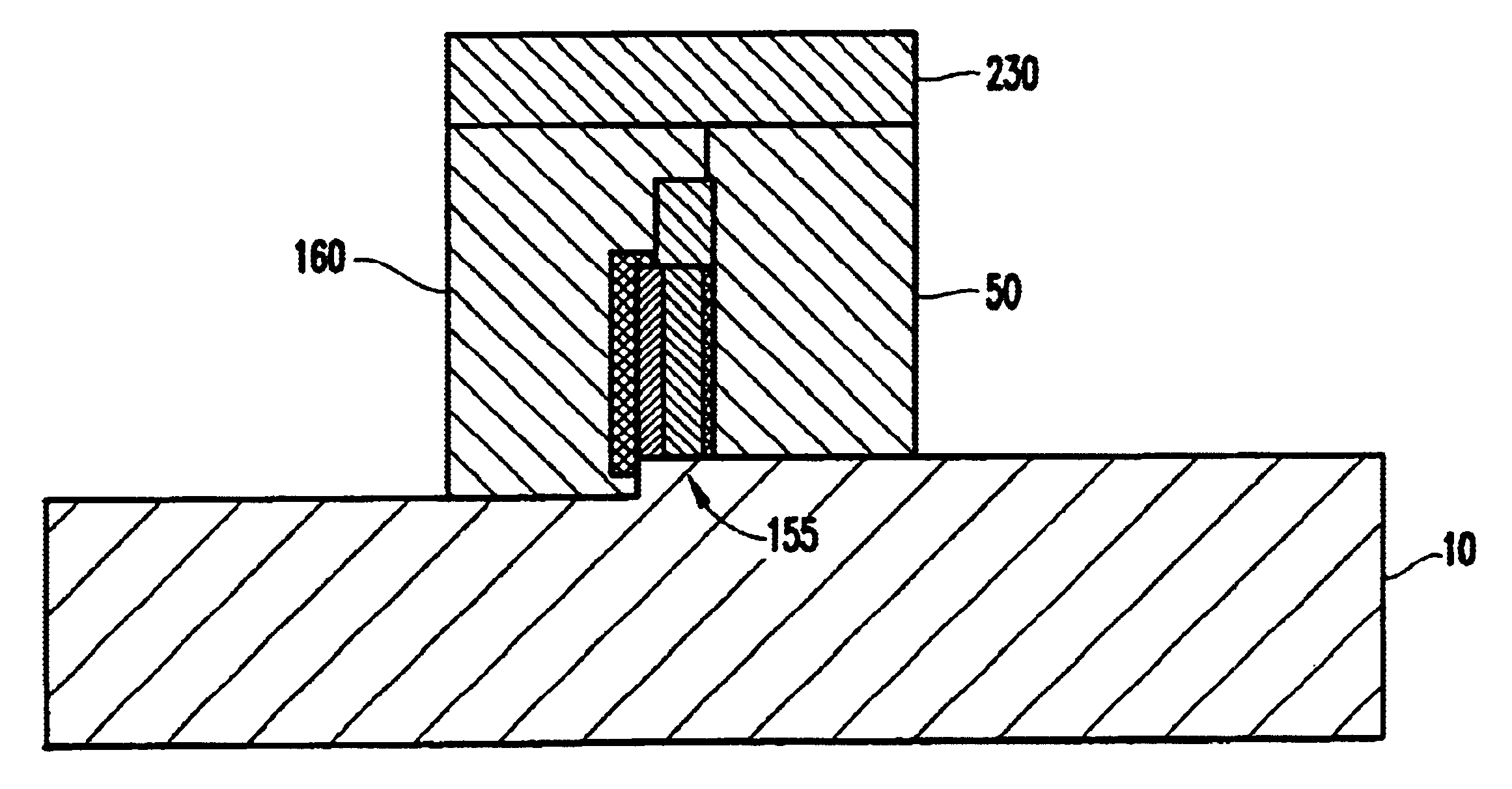

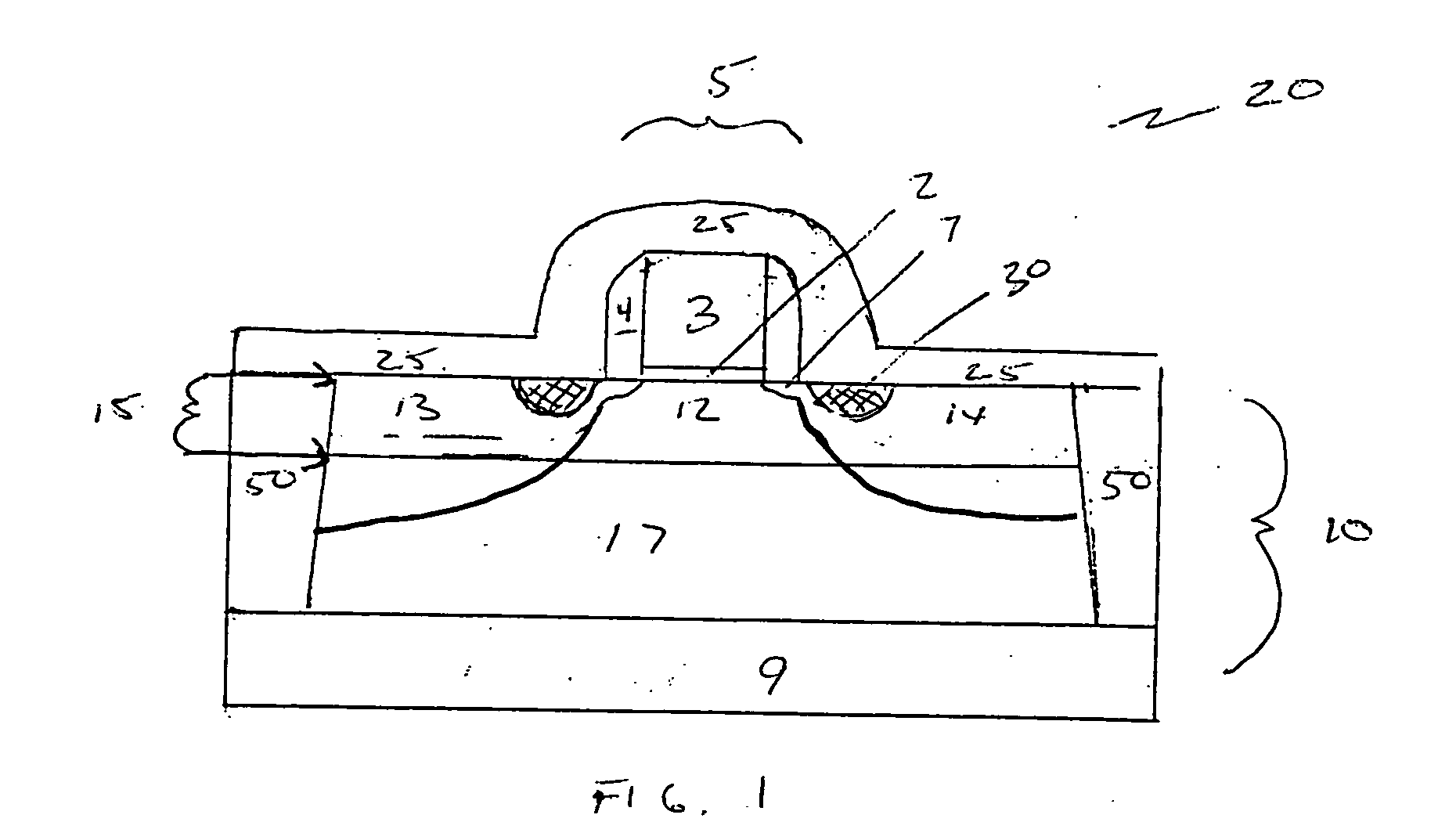

Nonplanar device with stress incorporation layer and method of fabrication

InactiveUS6909151B2Improve performanceHigh carrier mobilityTransistorSolid-state devicesGate dielectricSemiconductor

A semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls is formed on an insulating substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and is formed adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body. A thin film is then formed adjacent to the semiconductor body wherein the thin film produces a stress in the semiconductor body.

Owner:INTEL CORP

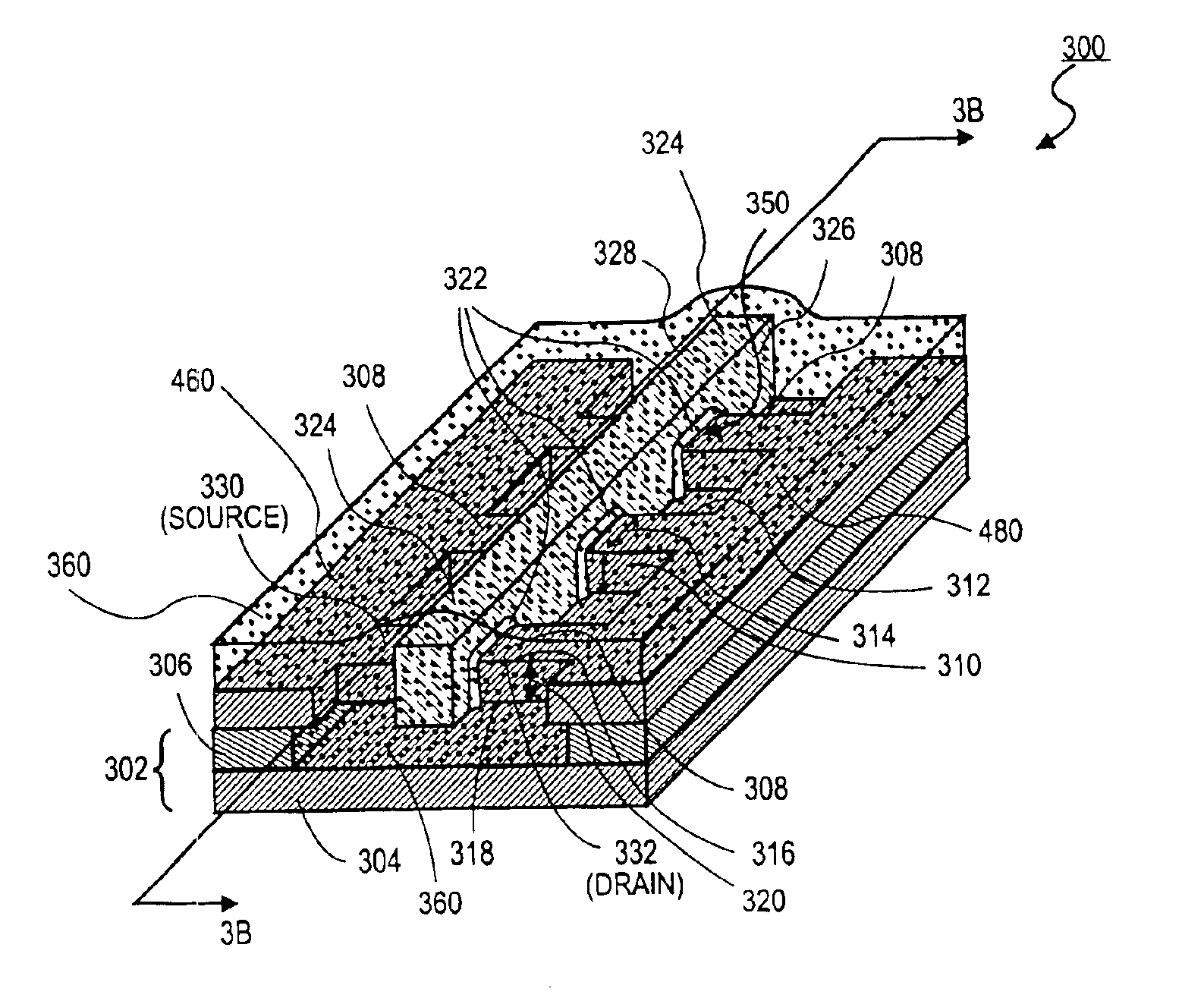

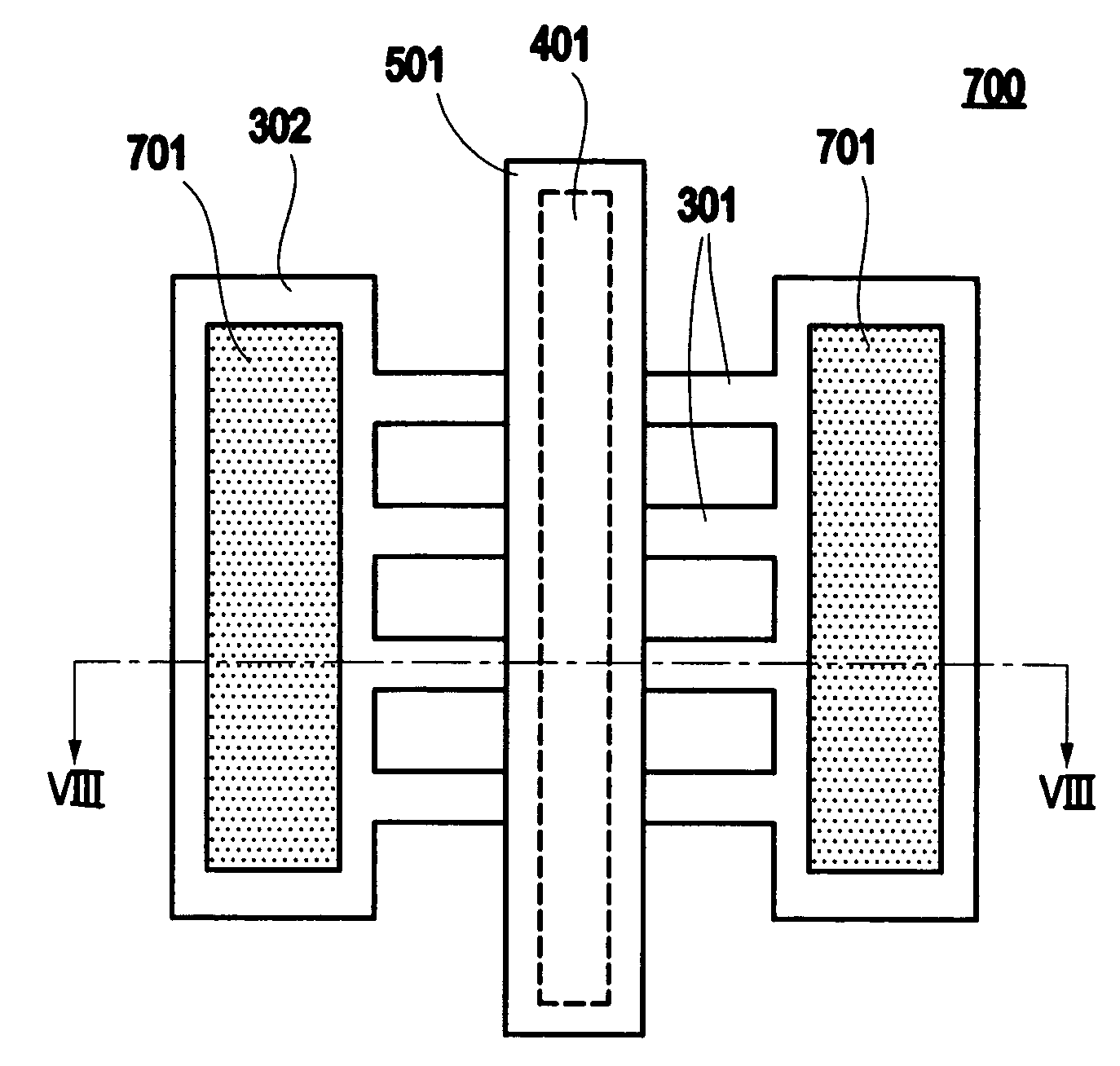

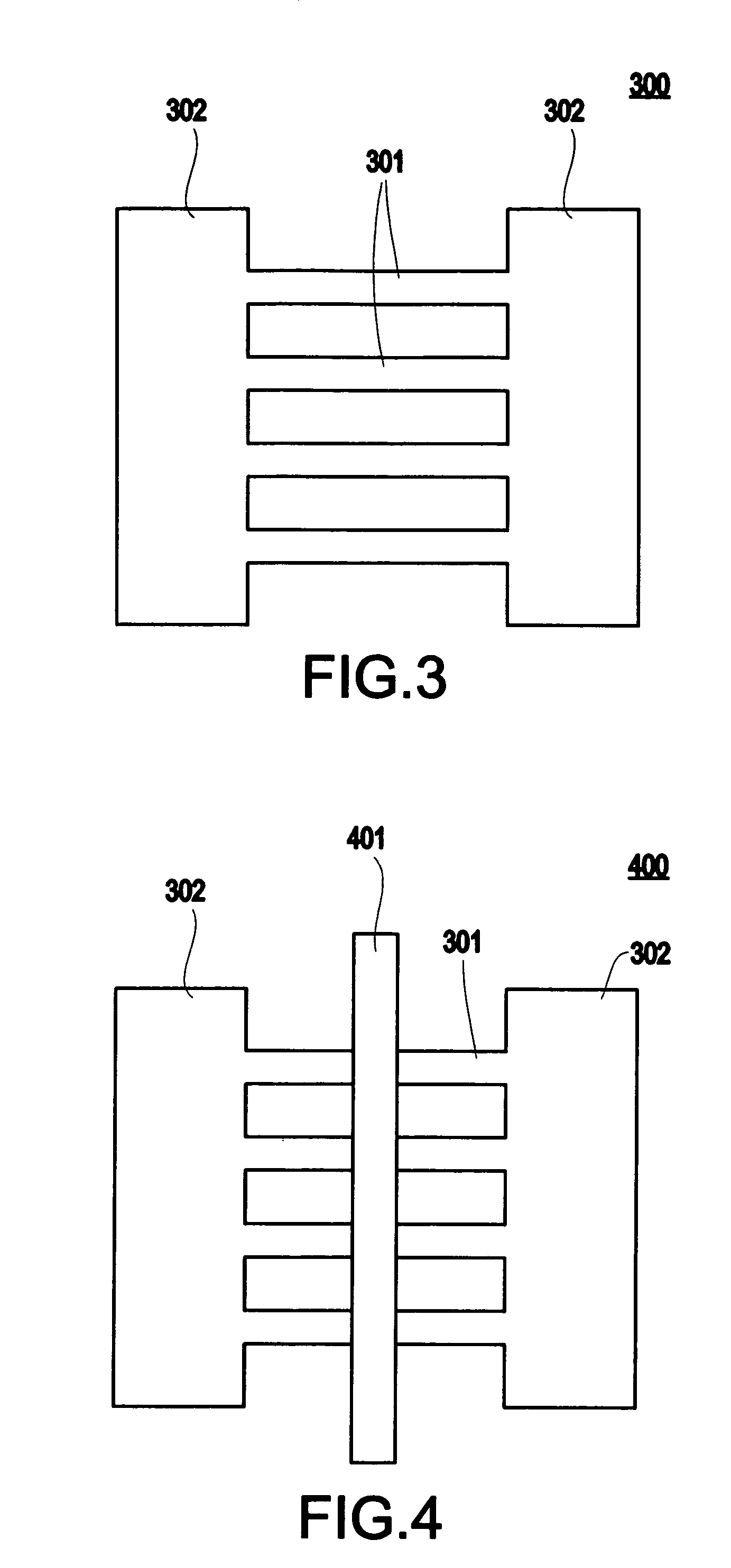

Strained fin FETs structure and method

InactiveUS6635909B2Physical strain on the channel materialHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingSiliconTransistor

A method and structure for a transistor that includes an insulator and a silicon structure on the insulator. The silicon structure includes a central portion and Fins extending from ends of the central portion. A first gate is positioned on a first side of the central portion of the silicon structure. A strain-producing layer could be between the first gate and the first side of the central portion of the silicon structure and a second gate is on a second side of the central portion of the silicon structure.

Owner:MICROSOFT TECH LICENSING LLC

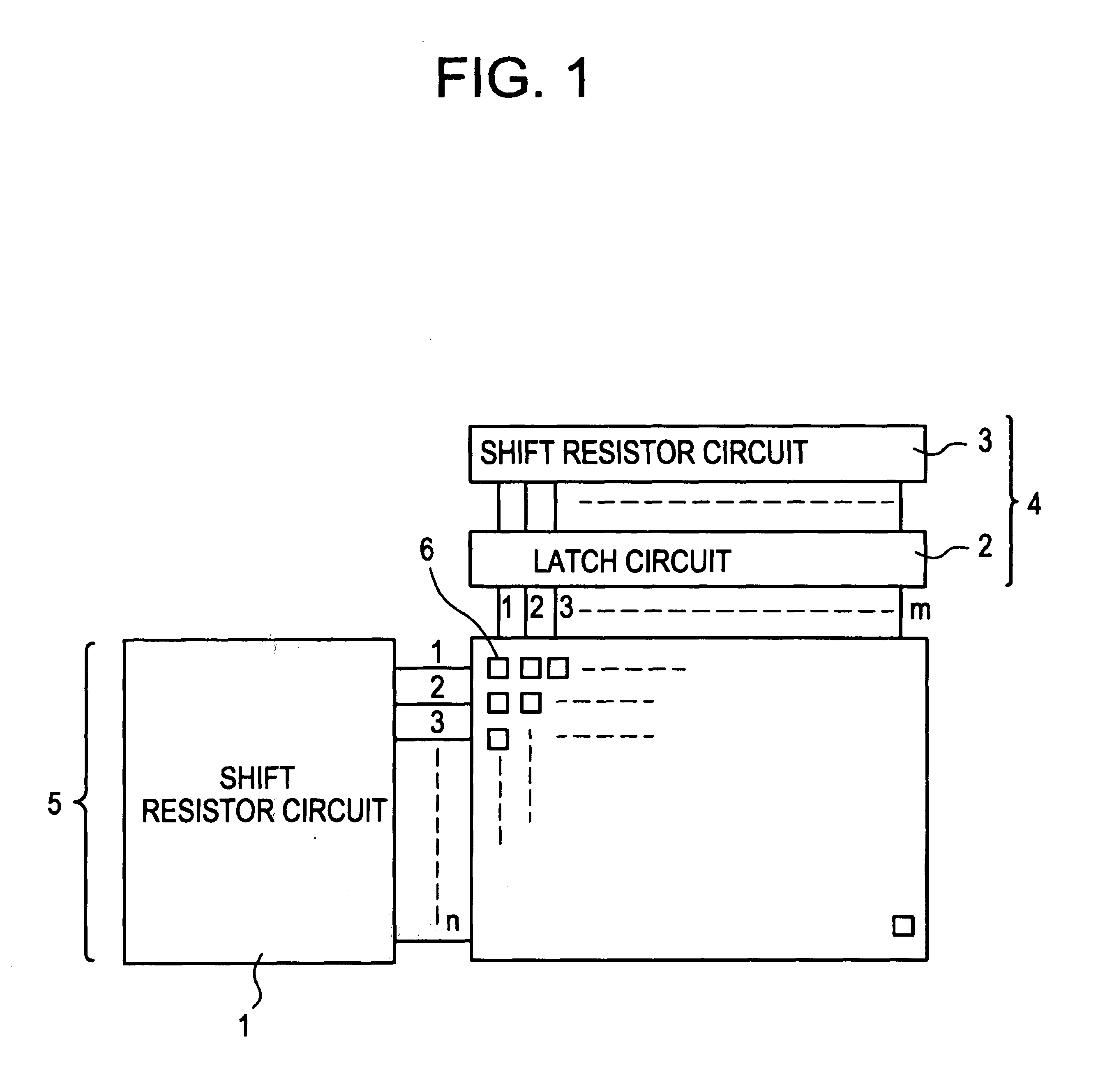

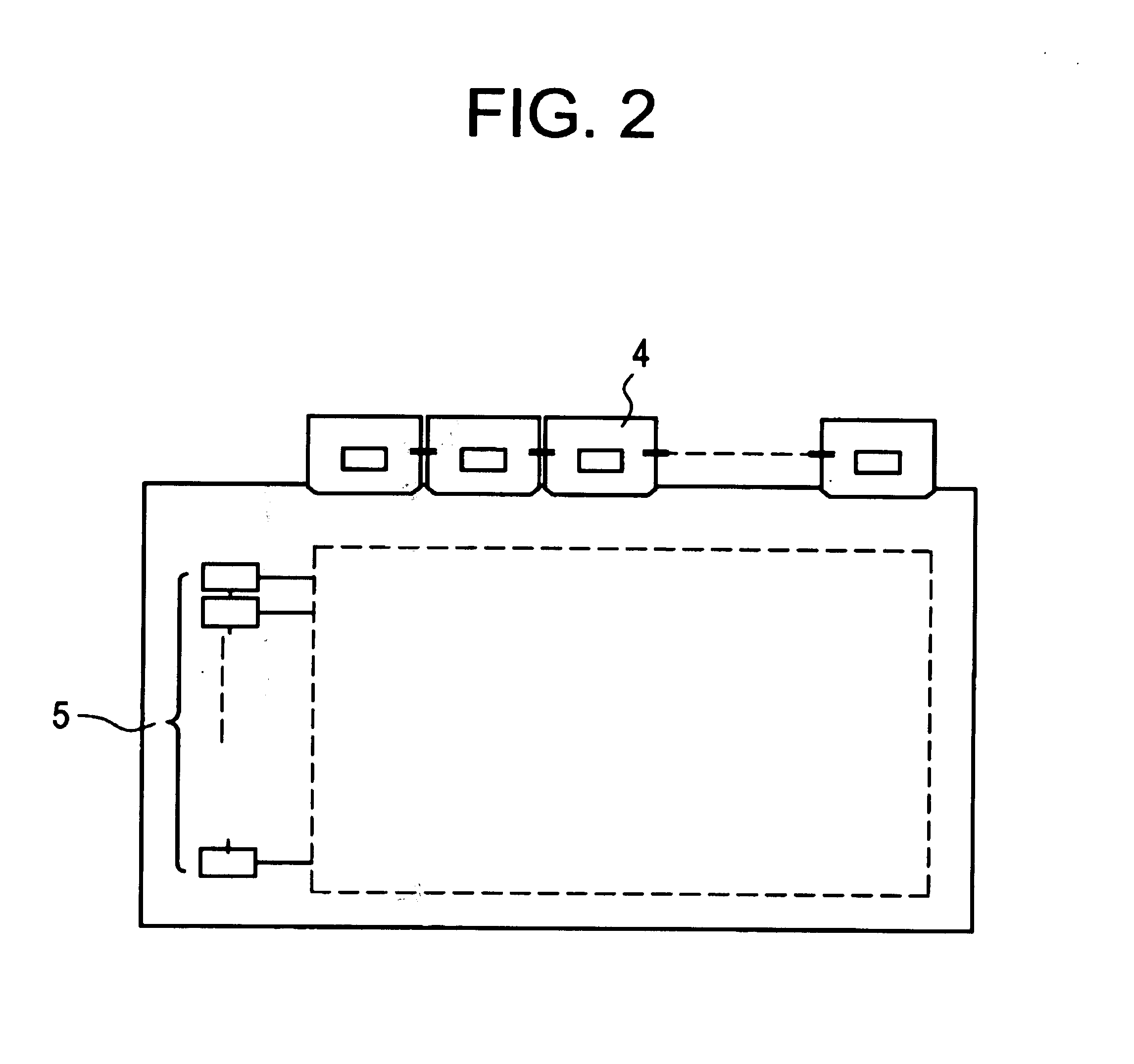

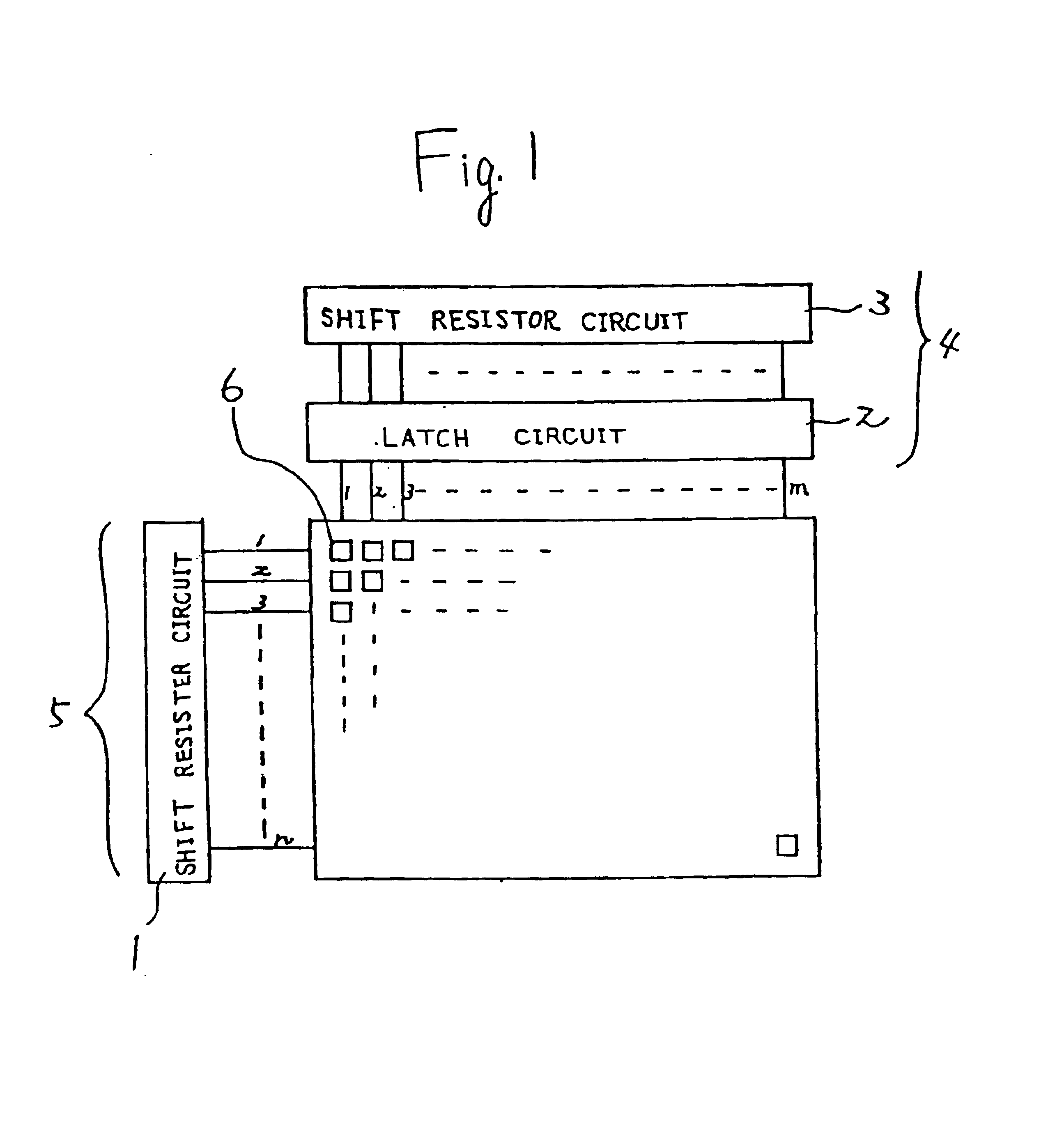

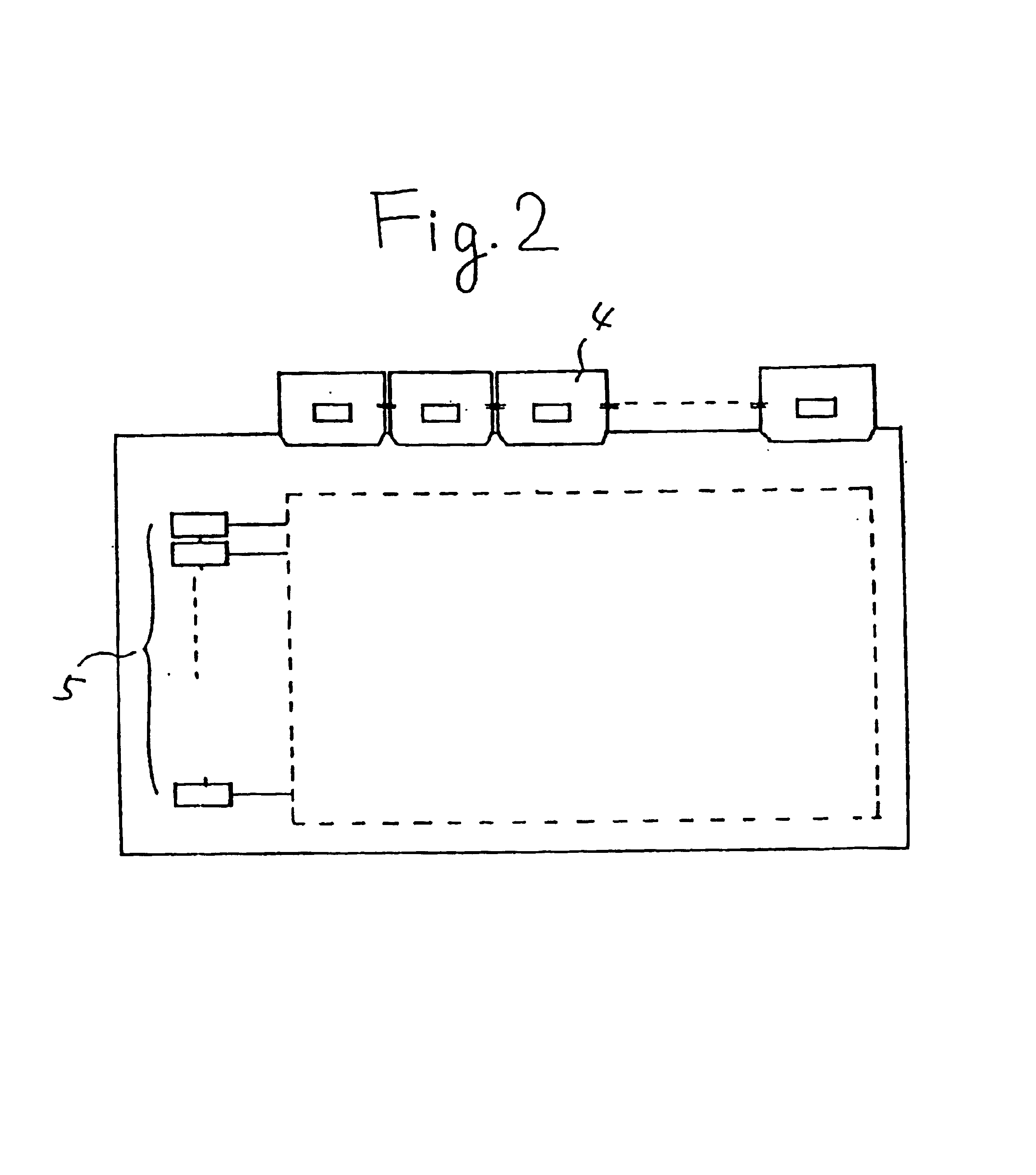

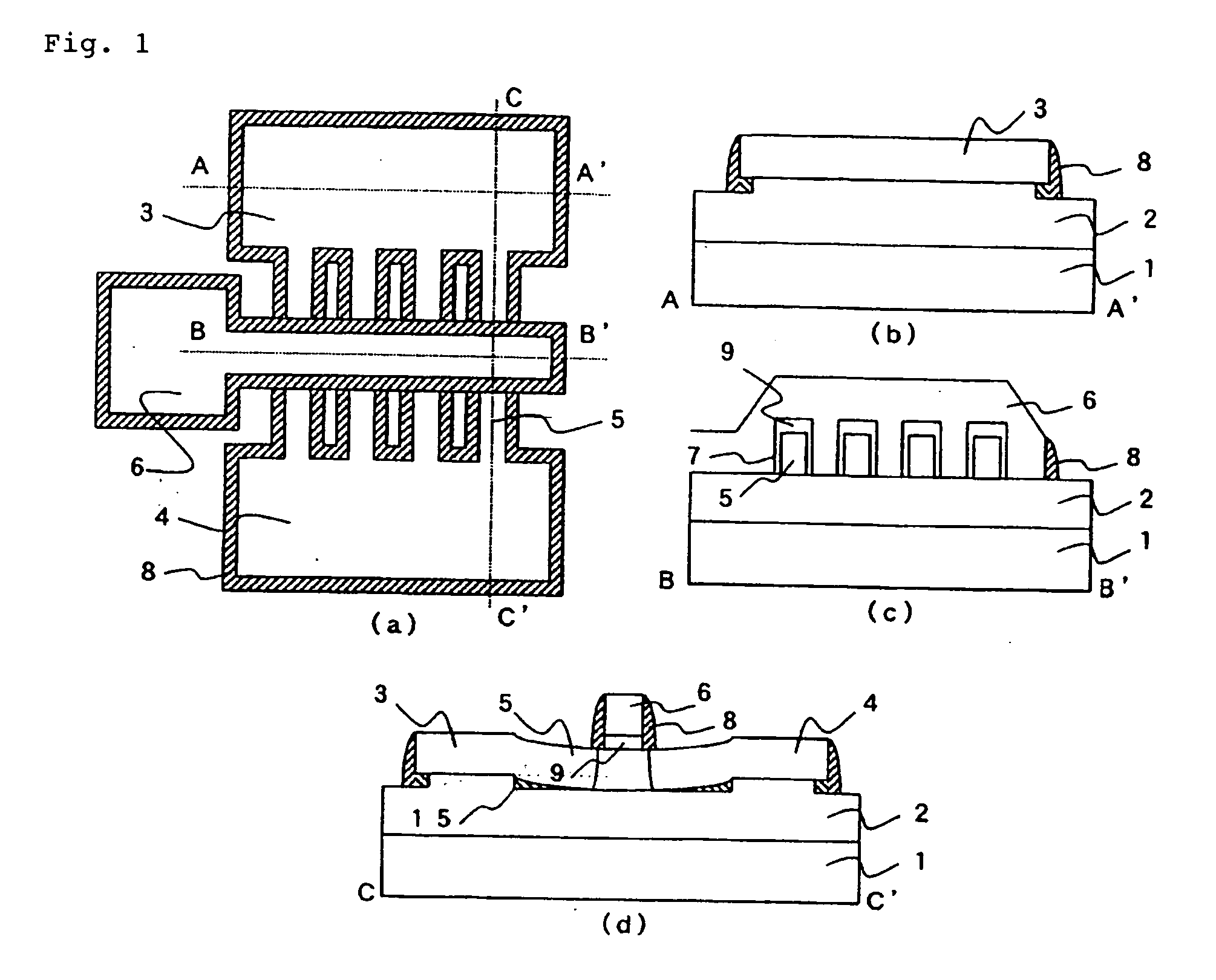

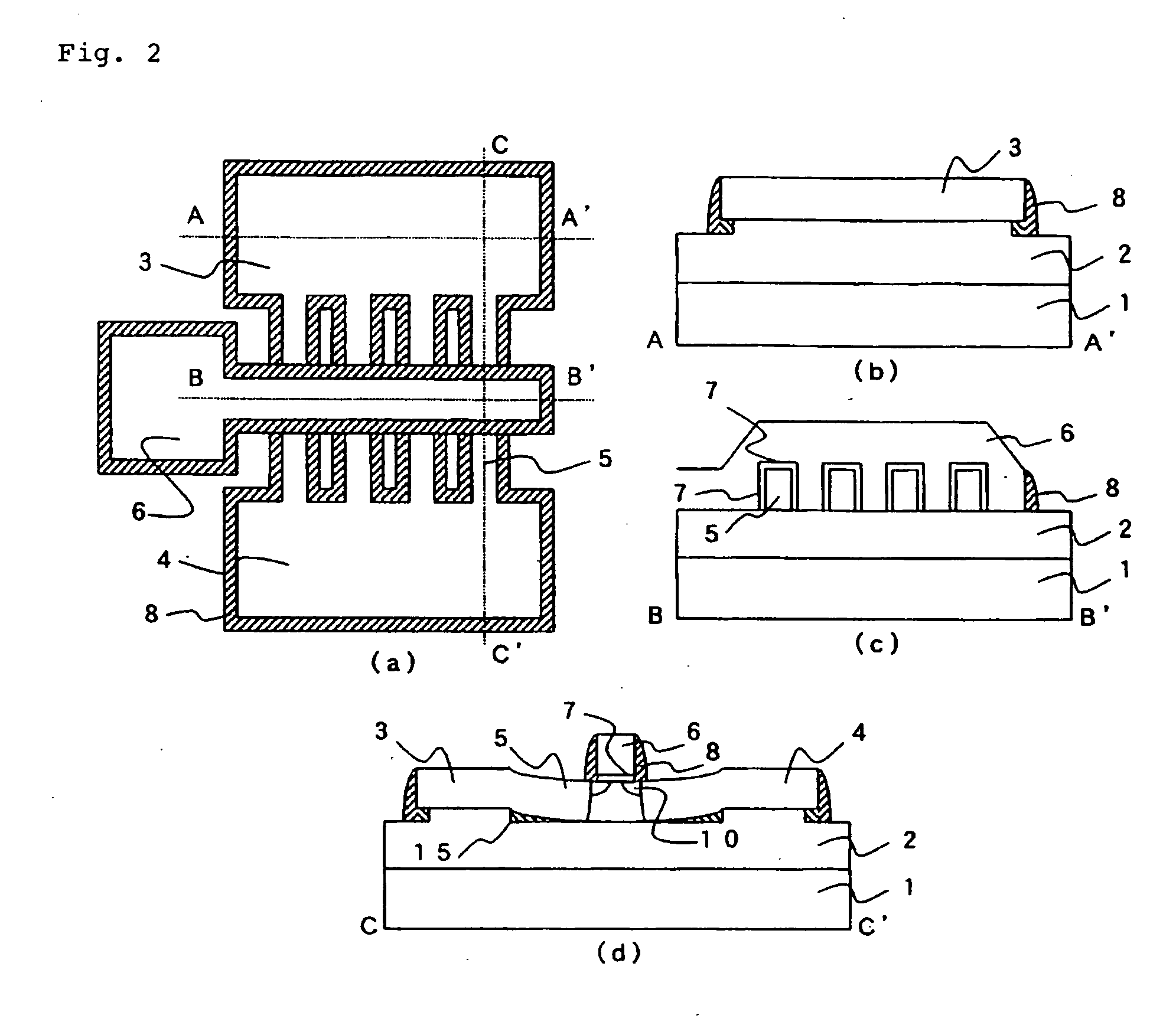

Electro-optical device and method for manufacturing the same

InactiveUS7115902B1High carrier mobilityDegree of improvementSolid-state devicesSemiconductor devicesLiquid-crystal displaySemiconductor chip

An electro-optical device and a method for manufacturing the same are disclosed. The device comprises a pair of substrates and an electro-optical modulating layer (e.g. a liquid crystal layer having sandwiched therebetween, said pair of substrates consisting of a first substrate having provided thereon a plurality of gate wires, a plurality of source (drain) wires, and a pixel matrix comprising thin film transistors, and a second substrate facing the first substrate, wherein, among the peripheral circuits having established on the first substrate and being connected to the matrix wirings for the X direction and the Y direction, only a part of said peripheral circuits is constructed from thin film semiconductor devices fabricated by the same process utilized for an active device, and the rest of the peripheral circuits is constructed from semiconductor chips. The liquid crystal display device according to the present invention is characterized by that the peripheral circuits are not wholly fabricated into thin film transistors, but only those portions having a simple device structure, or those composed of a small number of devices, or those comprising an IC not easily available commercially, or those comprising an expensive integrated circuit, are fabricated by thin film transistors. According to the present invention, an electro-optical device is provided at an increased production yield with a reduced production cost.

Owner:SEMICON ENERGY LAB CO LTD

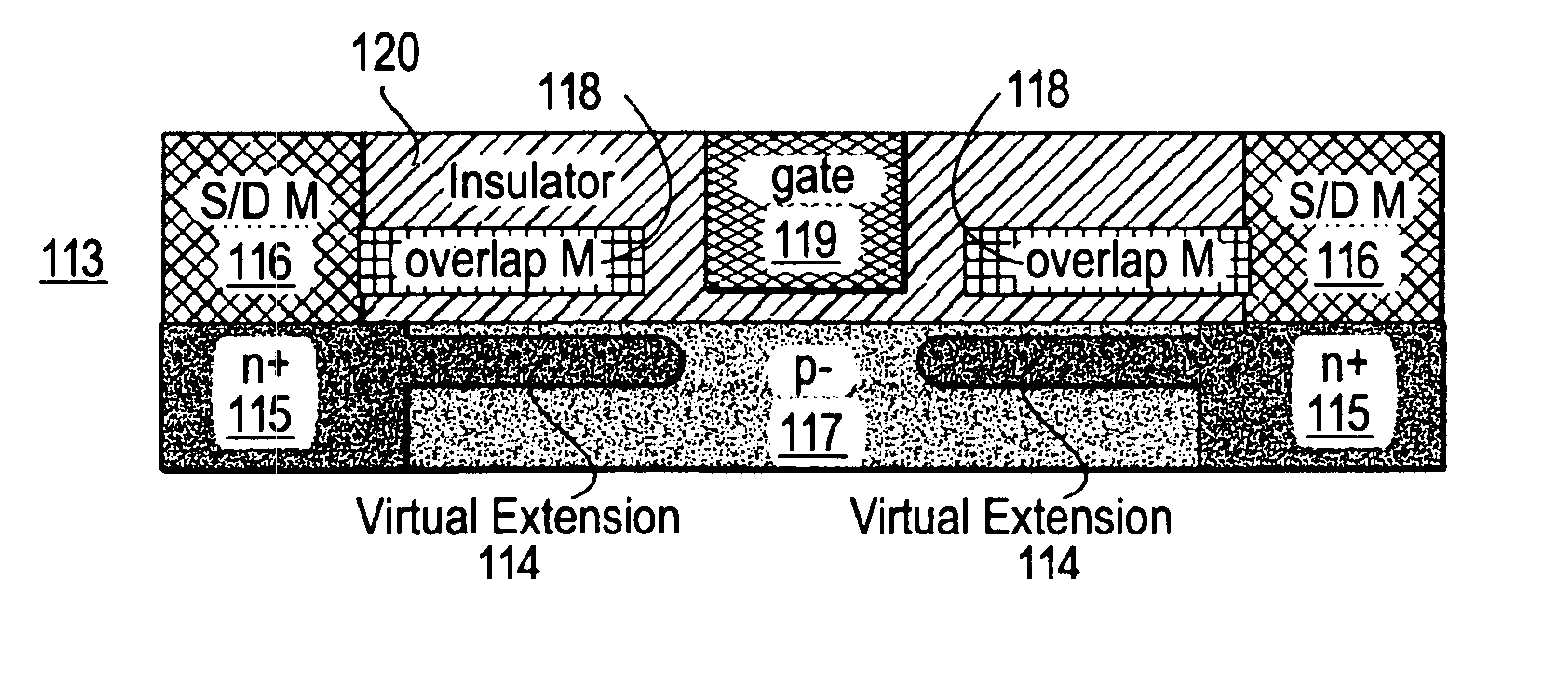

Transistor with workfunction-induced charge layer

ActiveUS6891234B1ConductivityImprove conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorCharge layer

An electrical switching device includes a semiconductor having a channel therein which is proximate to at least on channel tap in an extension region and also to a gate. A conductor (e.g., a metal) is disposed proximate to the extension region but is electrically isolated from both the extension region and the gate (e.g., through the use of one or more insulators). The conductor has a workfunction outside of the bandgap of a semiconductor in the extension region and therefore includes a layer of charge in the extension region. The magnitude and polarity of this layer of charge is controlled through selection of the metal, the semiconductor, and the insulator.

Owner:ACORN SEMI LLC

Strained silicon finFET device

ActiveUS7045401B2Short effectEnhance carrier mobilityTransistorSemiconductor/solid-state device manufacturingCarbon dopedElectron mobility

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

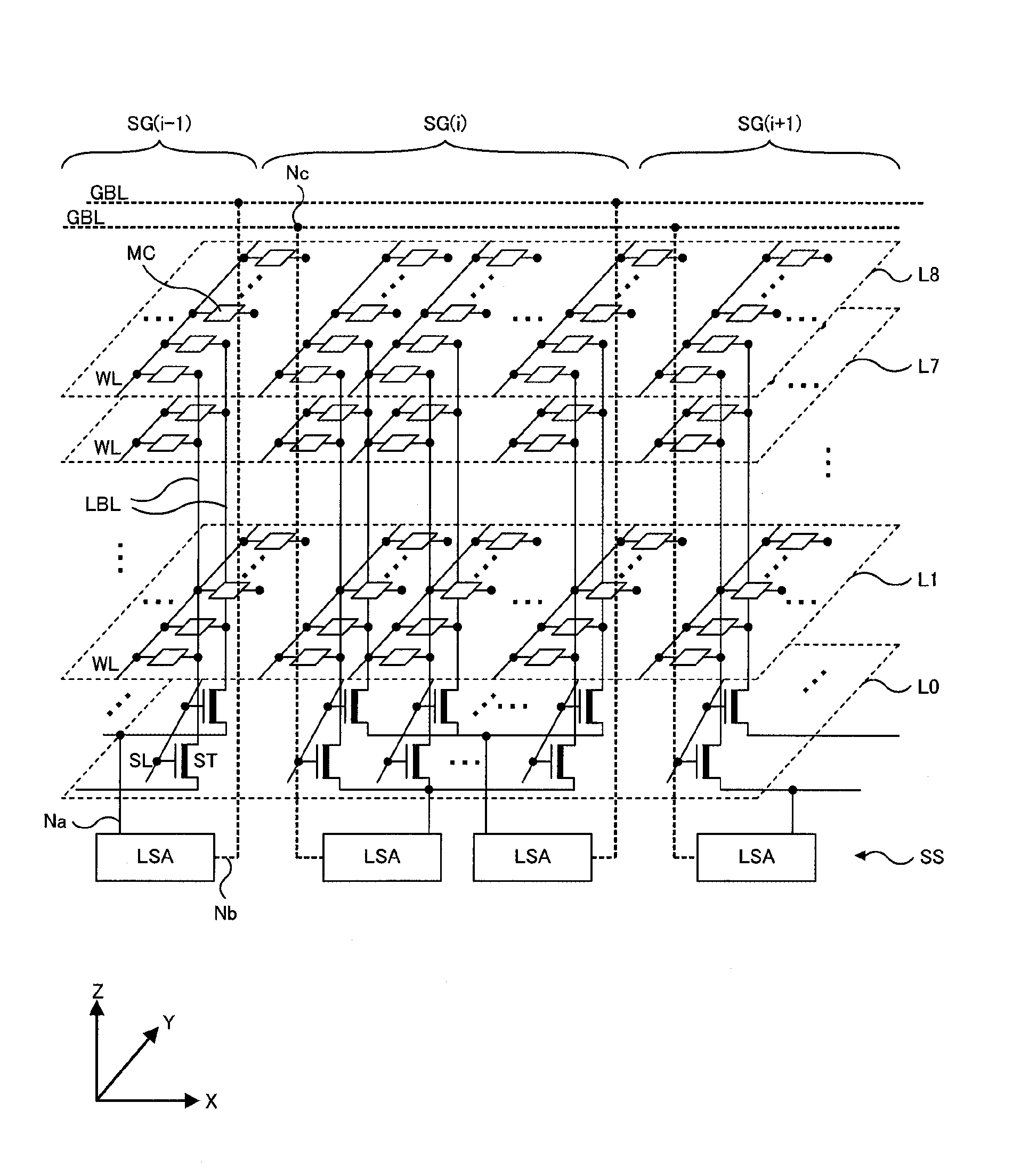

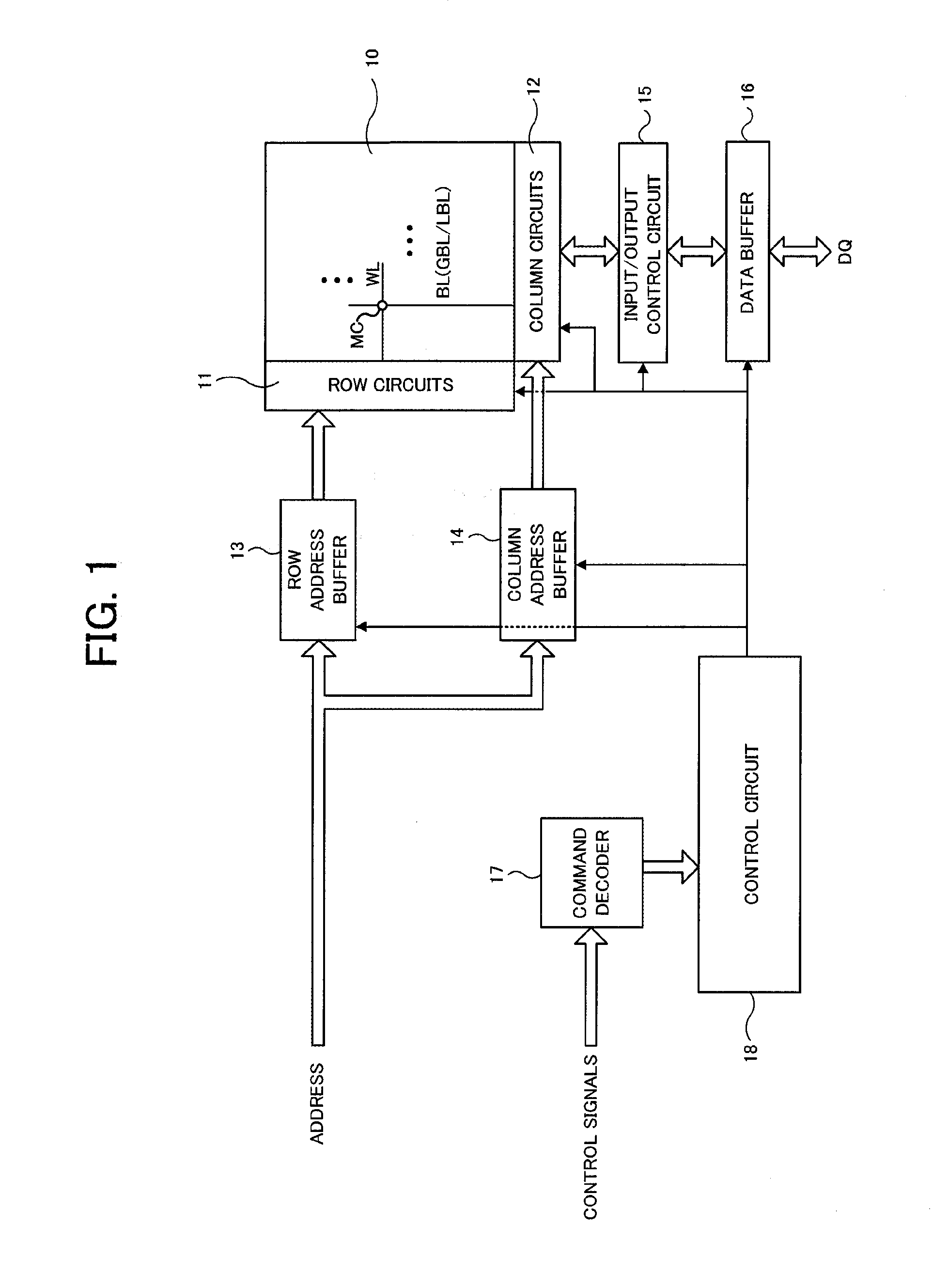

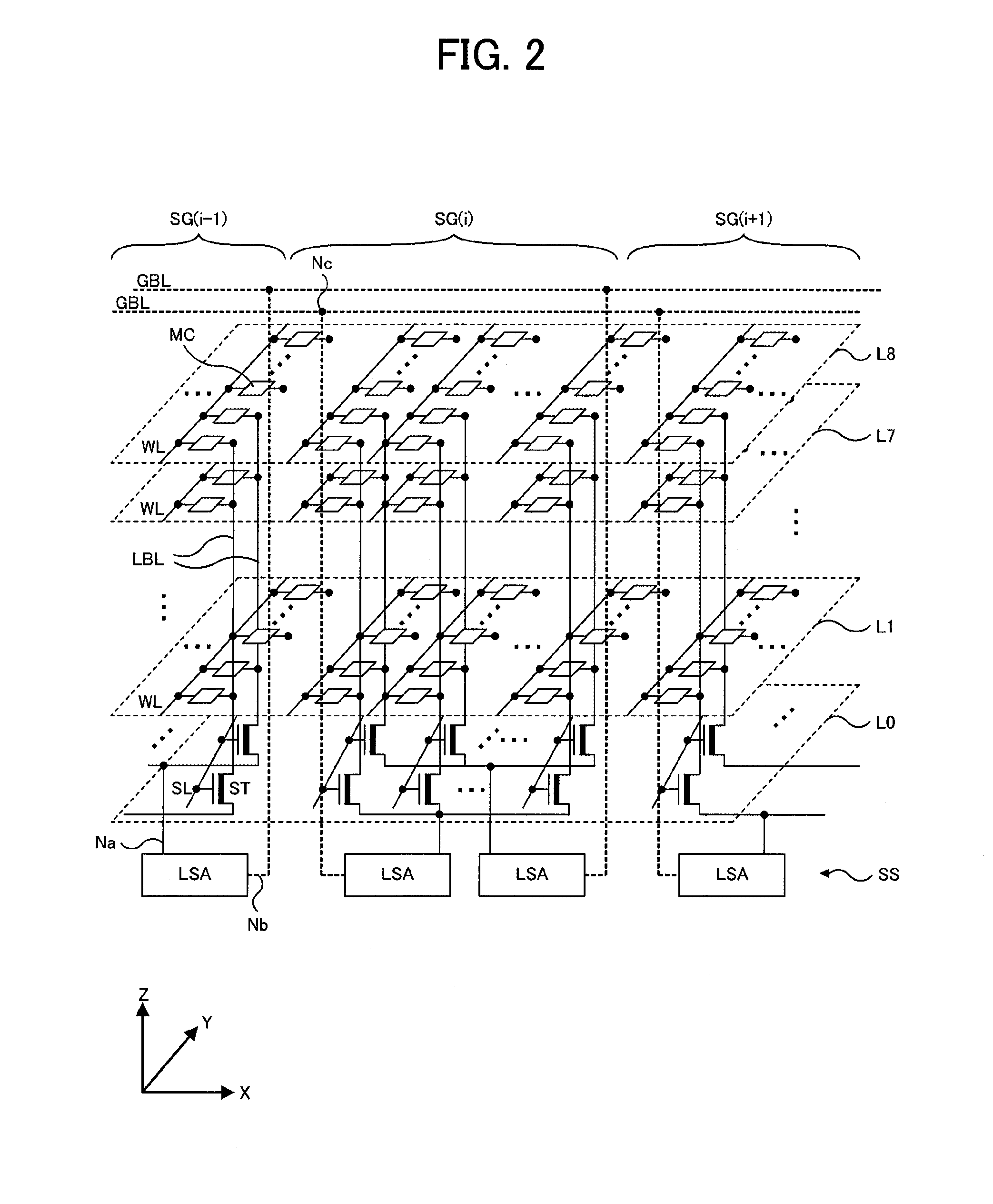

Semiconductor device having stacked layers

InactiveUS20130070506A1High carrier mobilityLow carrier mobilityDigital storageSense amplifierEngineering

A semiconductor device is disclosed in which there are provided a first substrate including memory cells and at least one bit line electrically coupled to the memory cells, and a second substrate including a sense amplifier. Each of the memory cells includes a first transistor, and the sense amplifier includes a second transistor. The second substrate is stacked with the first substrate such that the sense amplifier amplifies data transferred through the bit line from a selected one of the memory cells. The first transistor is lower in carrier mobility than the second transistor.

Owner:LONGITUDE LICENSING LTD

Electro-optical device and method for manufacturing the same

InactiveUS7098479B1High carrier mobilityDegree of improvementTransistorSolid-state devicesIntegrated circuitLiquid-crystal display

An electro-optical device and a method for manufacturing the same are disclosed. The device comprises a pair of substrates and an electro-optical modulating layer (e.g. a liquid crystal layer having sandwiched therebetween, said pair of substrates consisting of a first substrate having provided thereon a plurality of gate wires, a plurality of source (drain) wires, and a pixel matrix comprising thin film transistors, and a second substrate facing the first substrate, wherein, among the peripheral circuits having established on the first substrate and being connected to the matrix wirings for the X direction and the Y direction, only a part of said peripheral circuits is constructed from thin film semiconductor devices fabricated by the same process utilized for an active device, and the rest of the peripheral circuits is constructed from semiconductor chips. The liquid crystal display device according to the present invention is characterized by that the peripheral circuits are not wholly fabricated into thin film transistors, but only those portions having a simple device structure, or those composed of a small number of devices, or those comprising an IC not easily available commercially, or those comprising an expensive integrated circuit, are fabricated by thin film transistors. According to the present invention, an electro-optical device is provided at an increased production yield with a reduced production cost.

Owner:SEMICON ENERGY LAB CO LTD

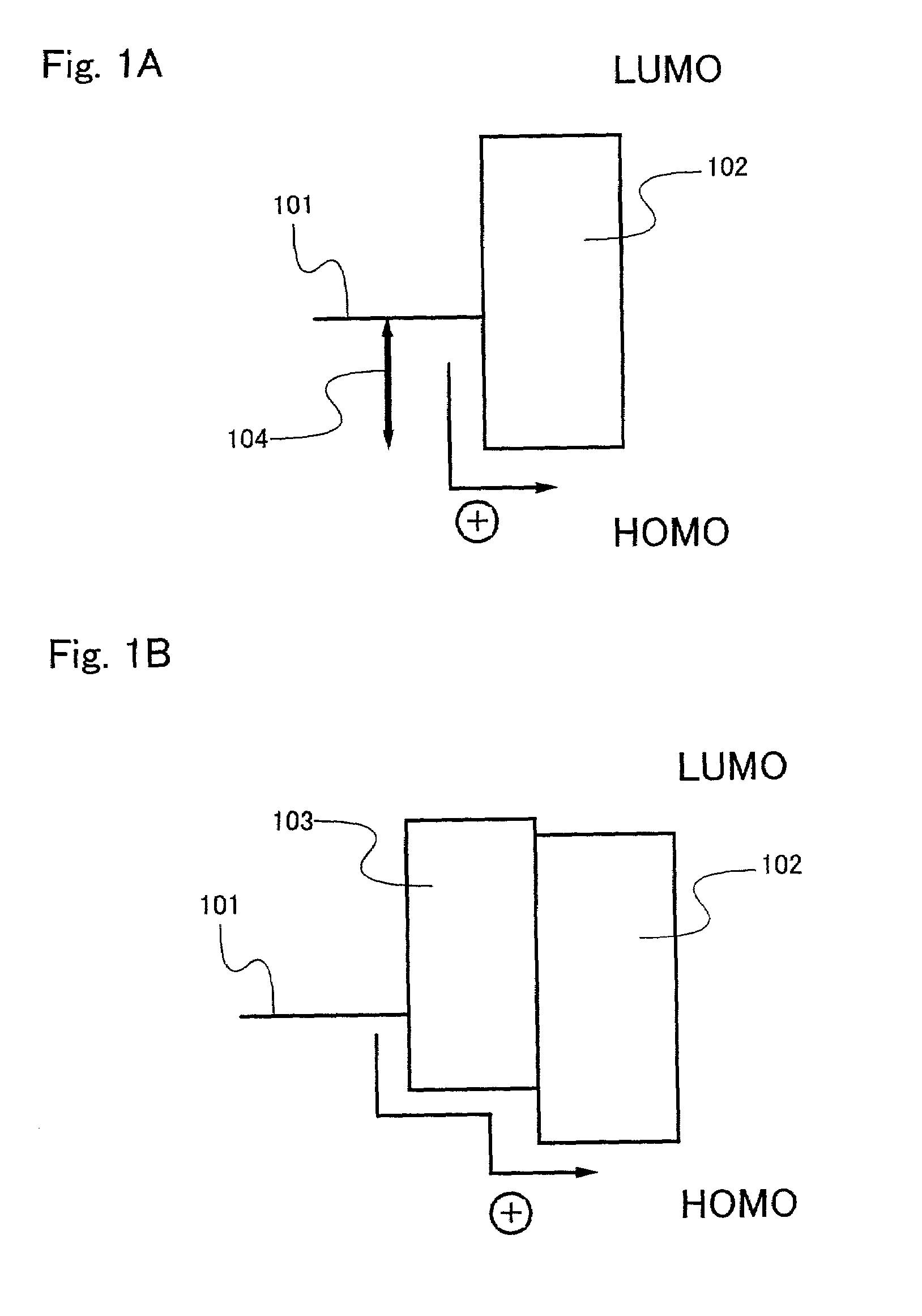

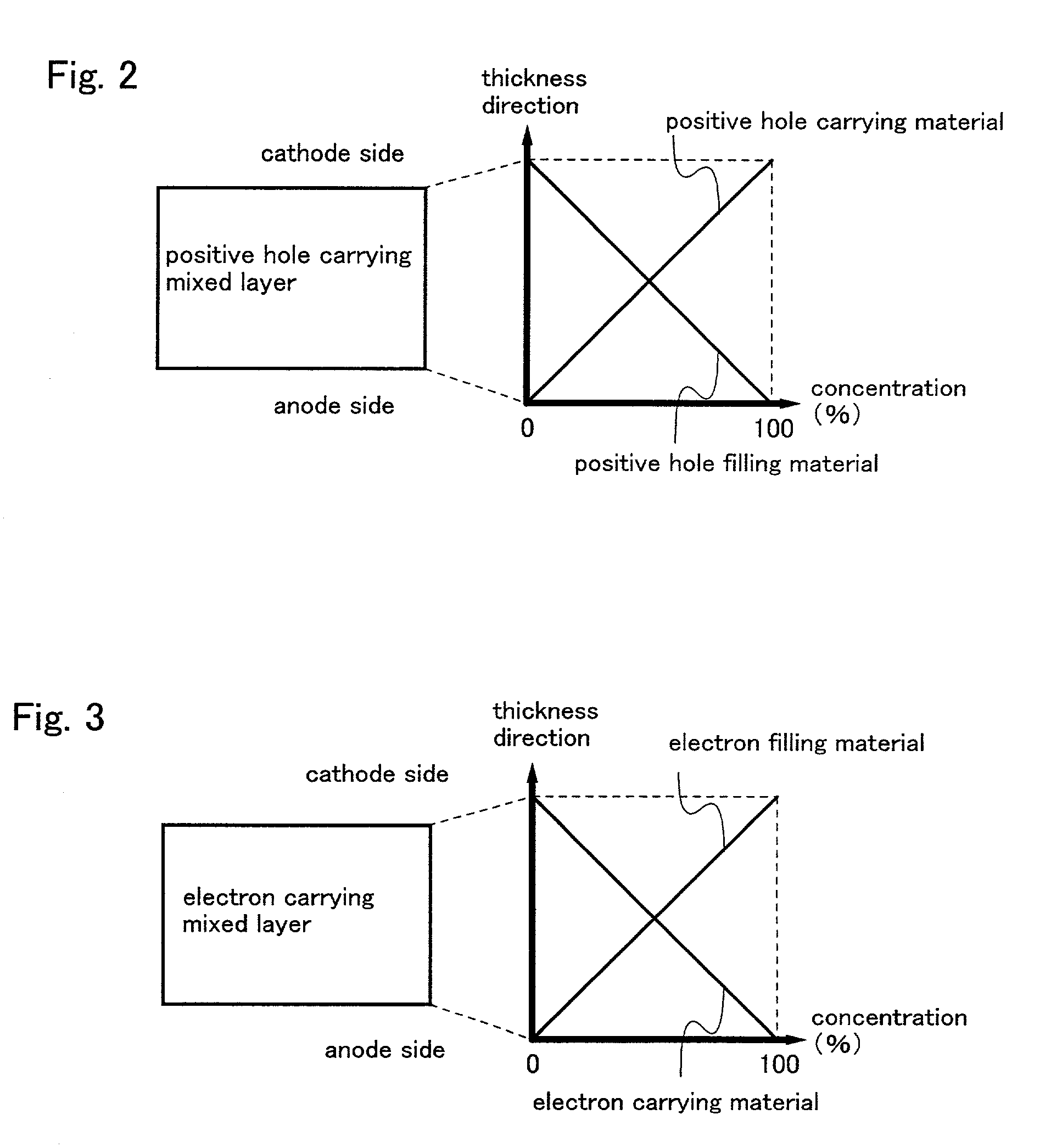

Luminescent device

InactiveUS7572522B2High carrier mobilityEasy to useDischarge tube luminescnet screensCathode ray tubes/electron beam tubesDopantLight emitting device

Owner:SEMICON ENERGY LAB CO LTD

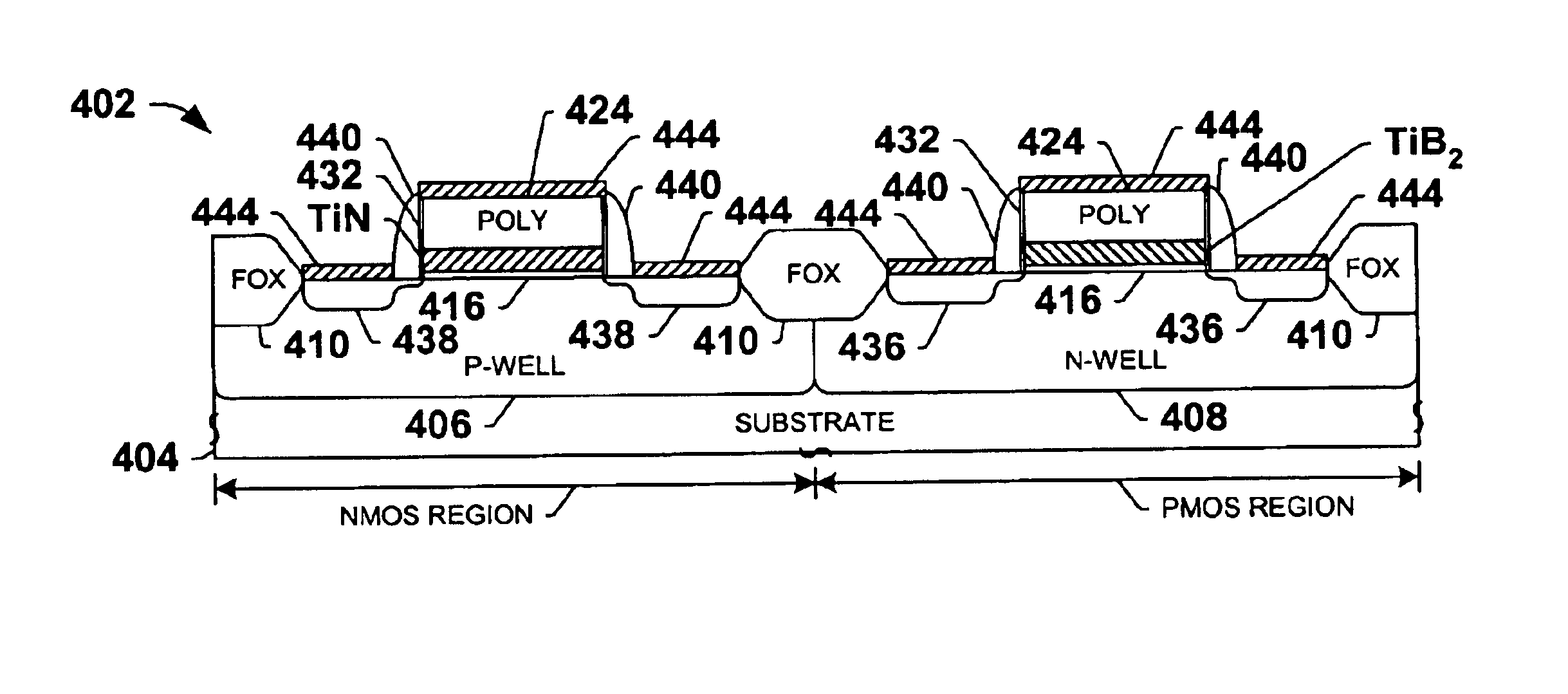

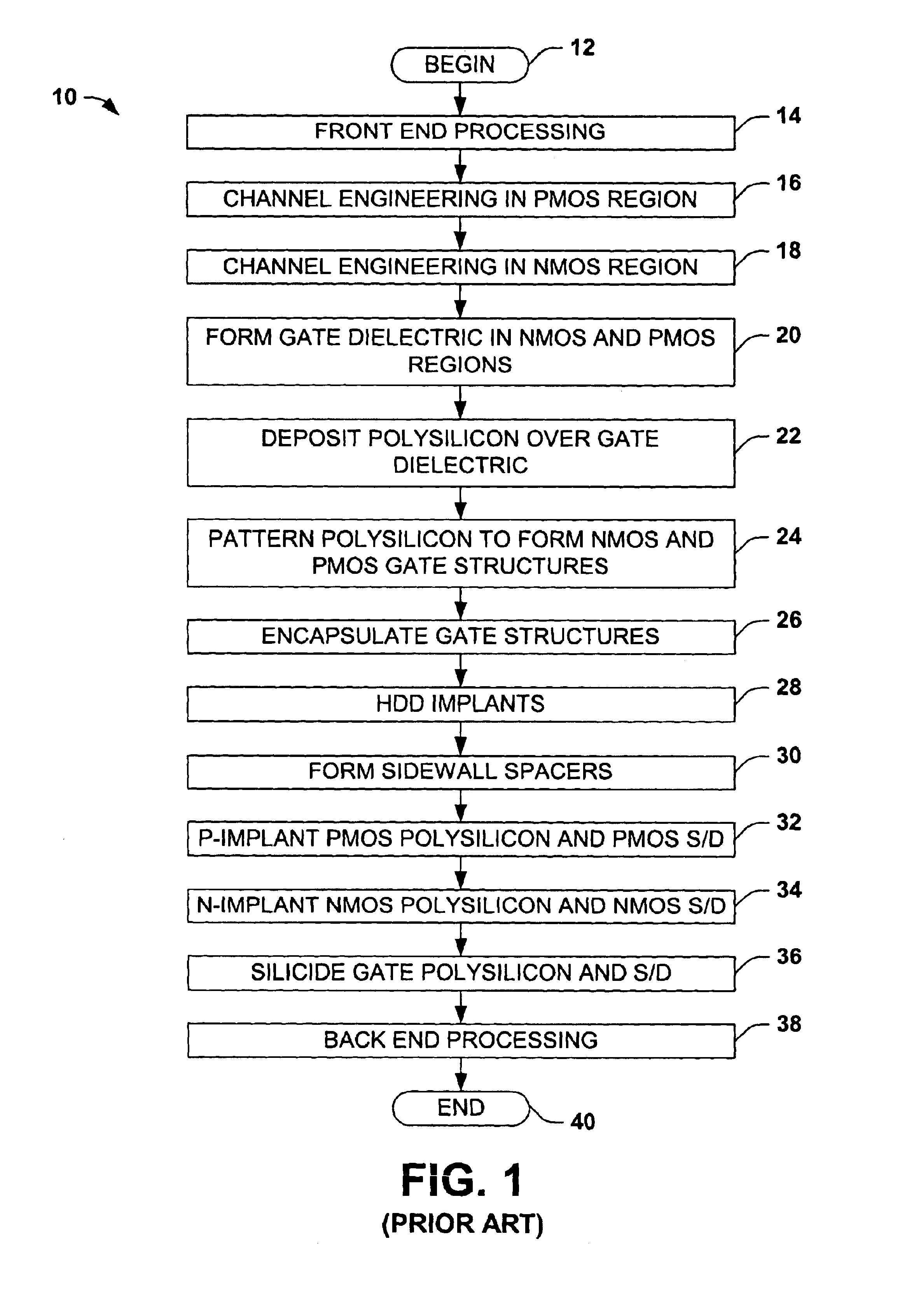

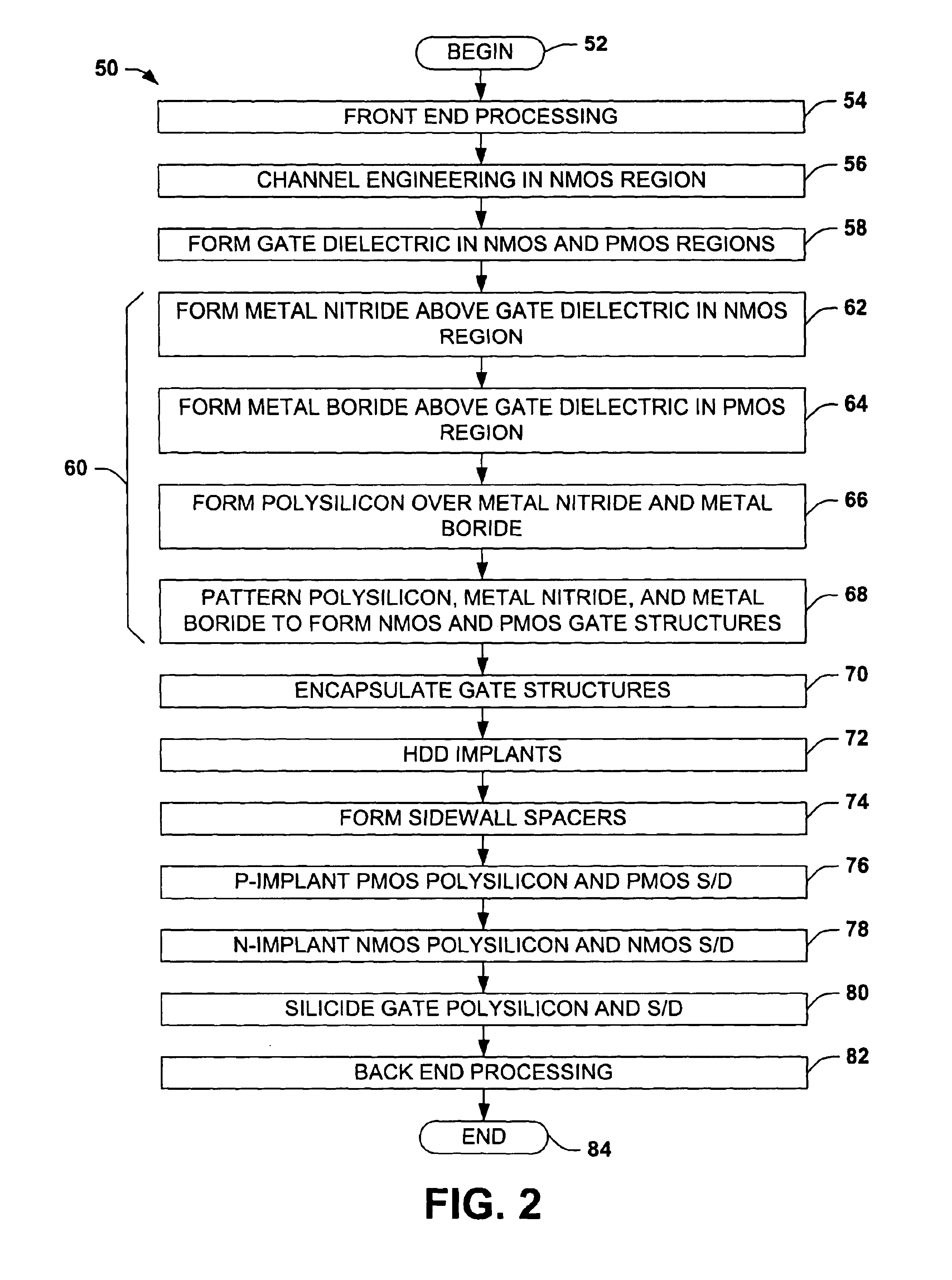

Metal gate MOS transistors and methods for making the same

InactiveUS6936508B2Less dopantsReduce complexitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

Semiconductor devices and fabrication methods are provided, in which metal transistor gates are provided for MOS transistors. Metal boride is formed above a gate dielectric to create PMOS gate structures and metal nitride is formed over a gate dielectric to provide NMOS gate structures. The metal portions of the gate structures are formed from an initial starting material that is either a metal boride or a metal nitride, after which the starting material is provided with boron or nitrogen in one of the PMOS and NMOS regions through implantation, diffusion, or other techniques, either before or after formation of the conductive upper material, and before or after gate patterning. The change in the boron or nitrogen content of the starting material provides adjustment of the material work function, thereby tuning the threshold voltage of the resulting PMOS or NMOS transistors.

Owner:TEXAS INSTR INC

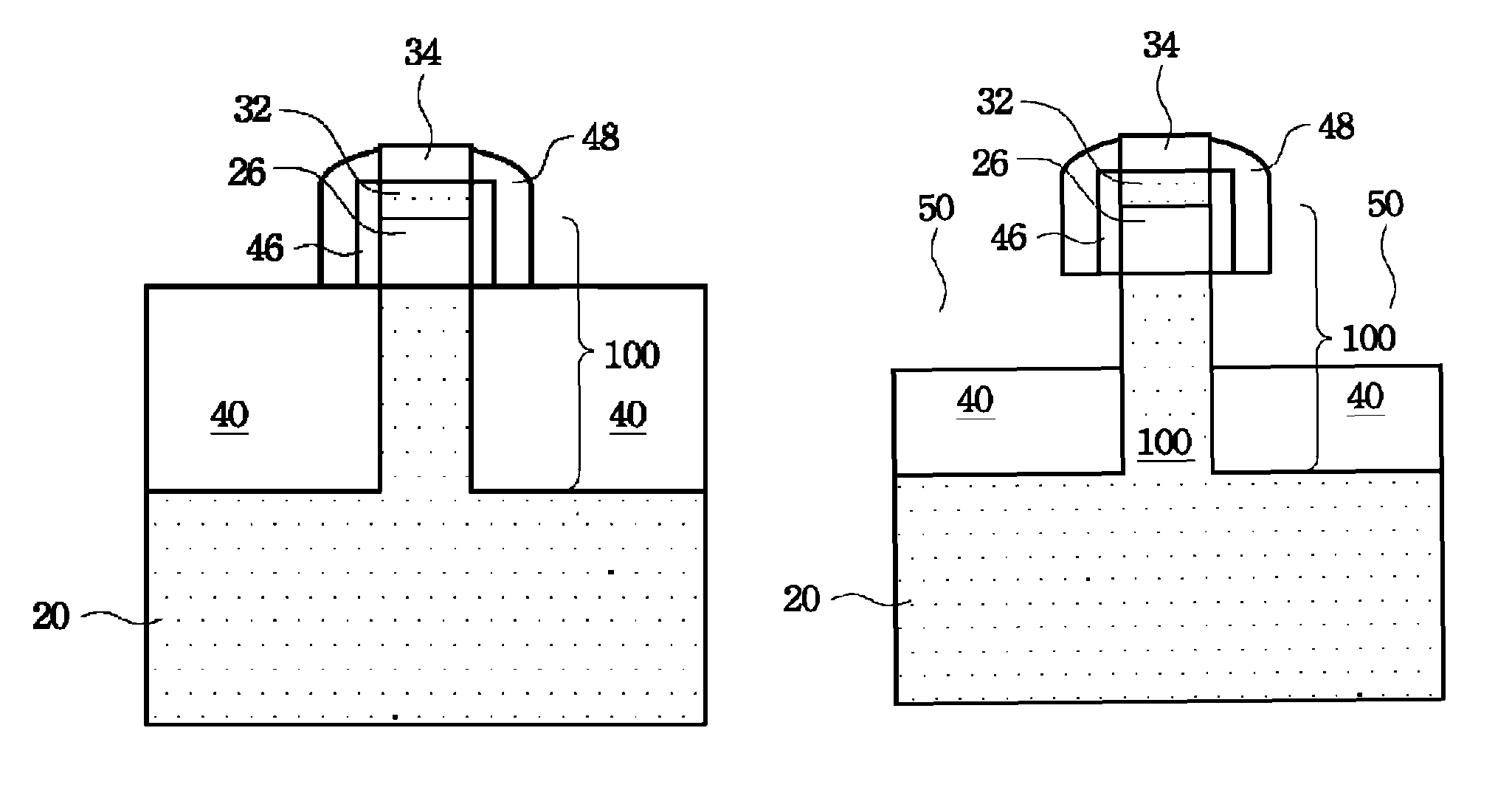

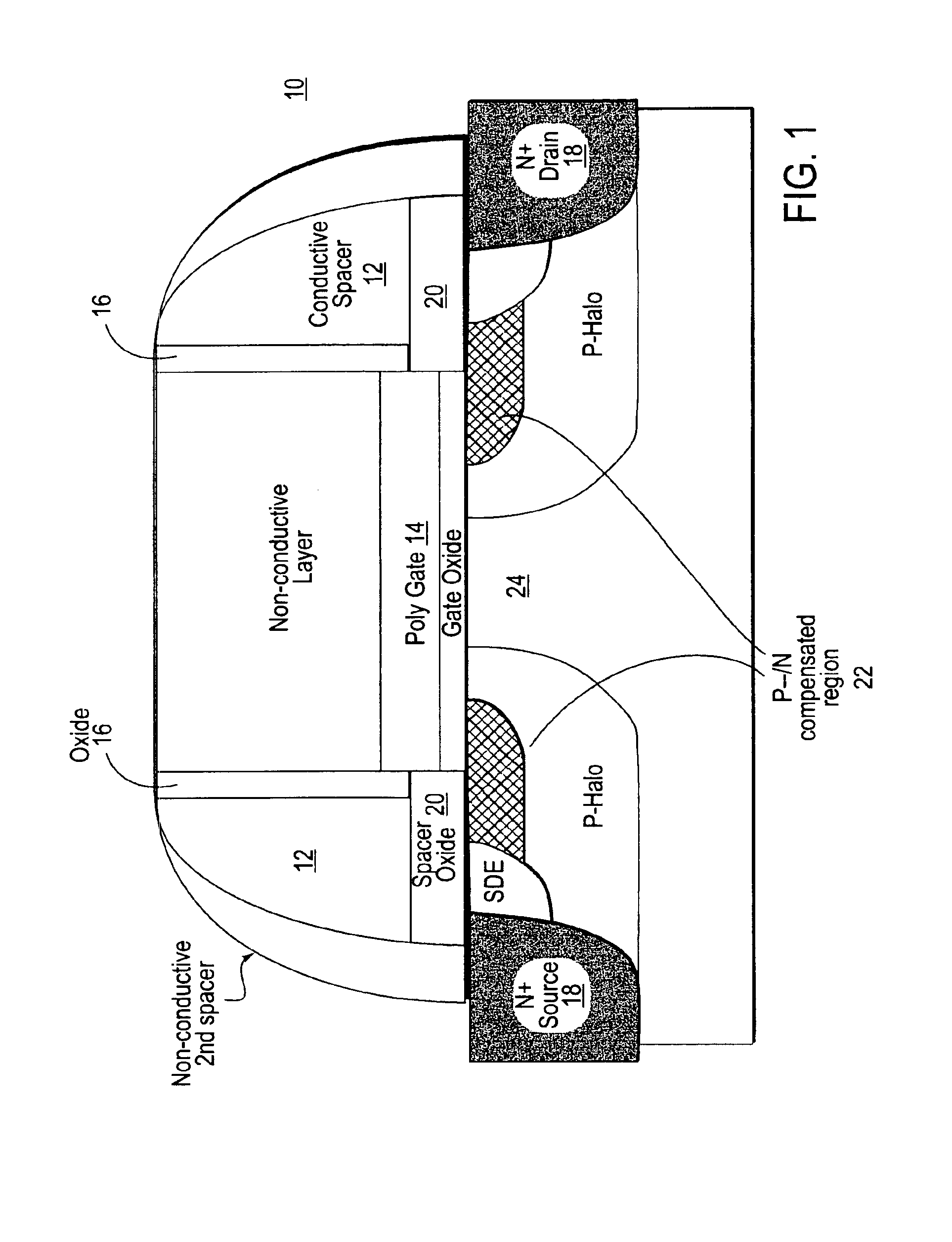

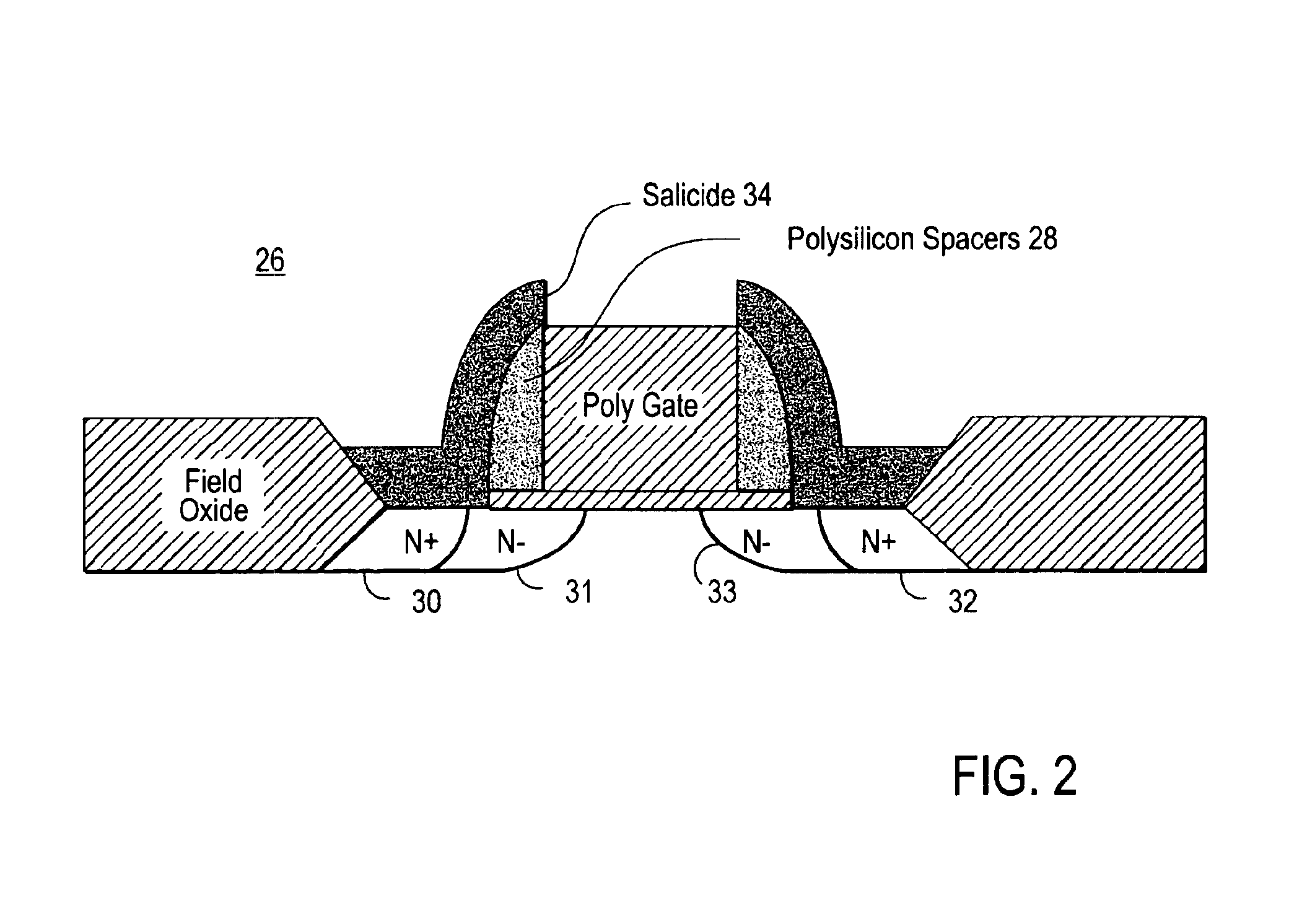

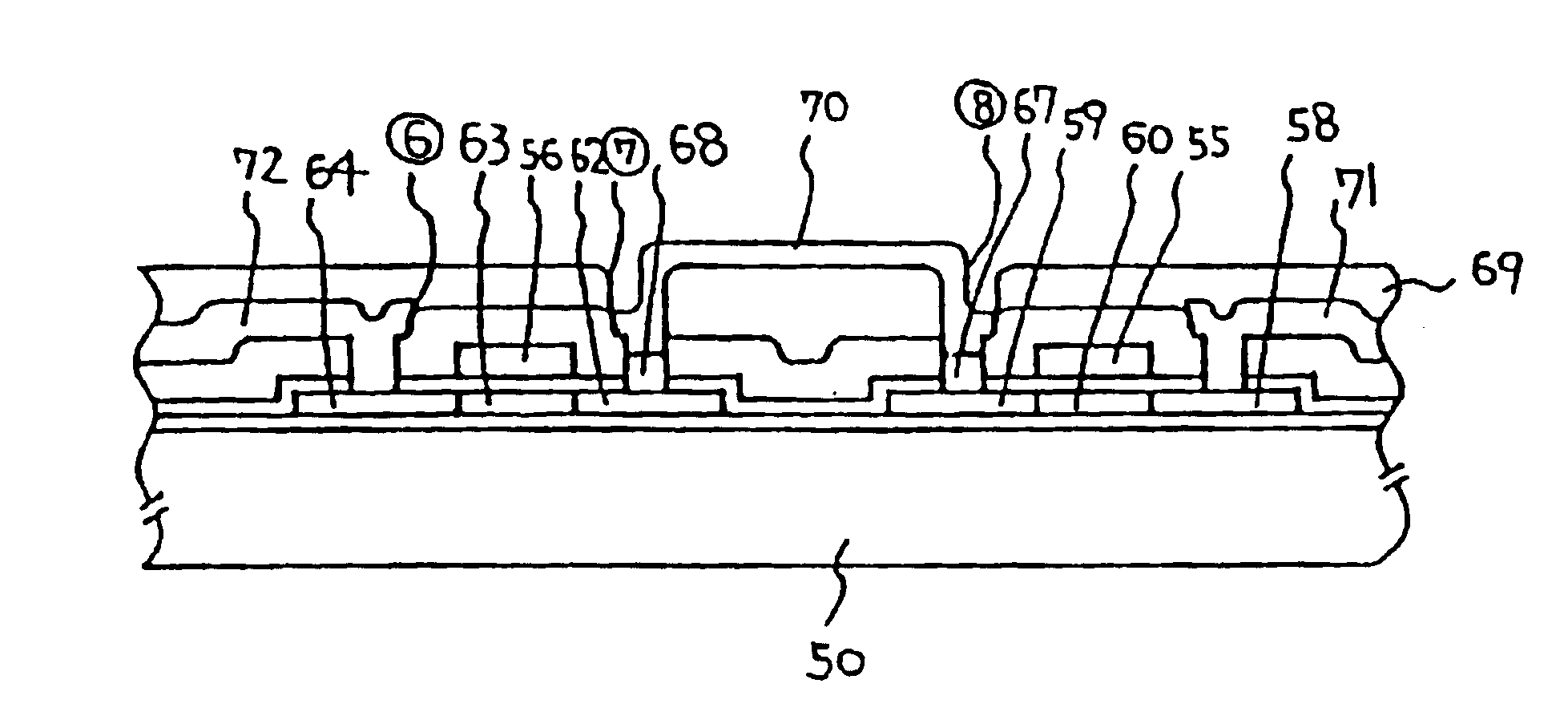

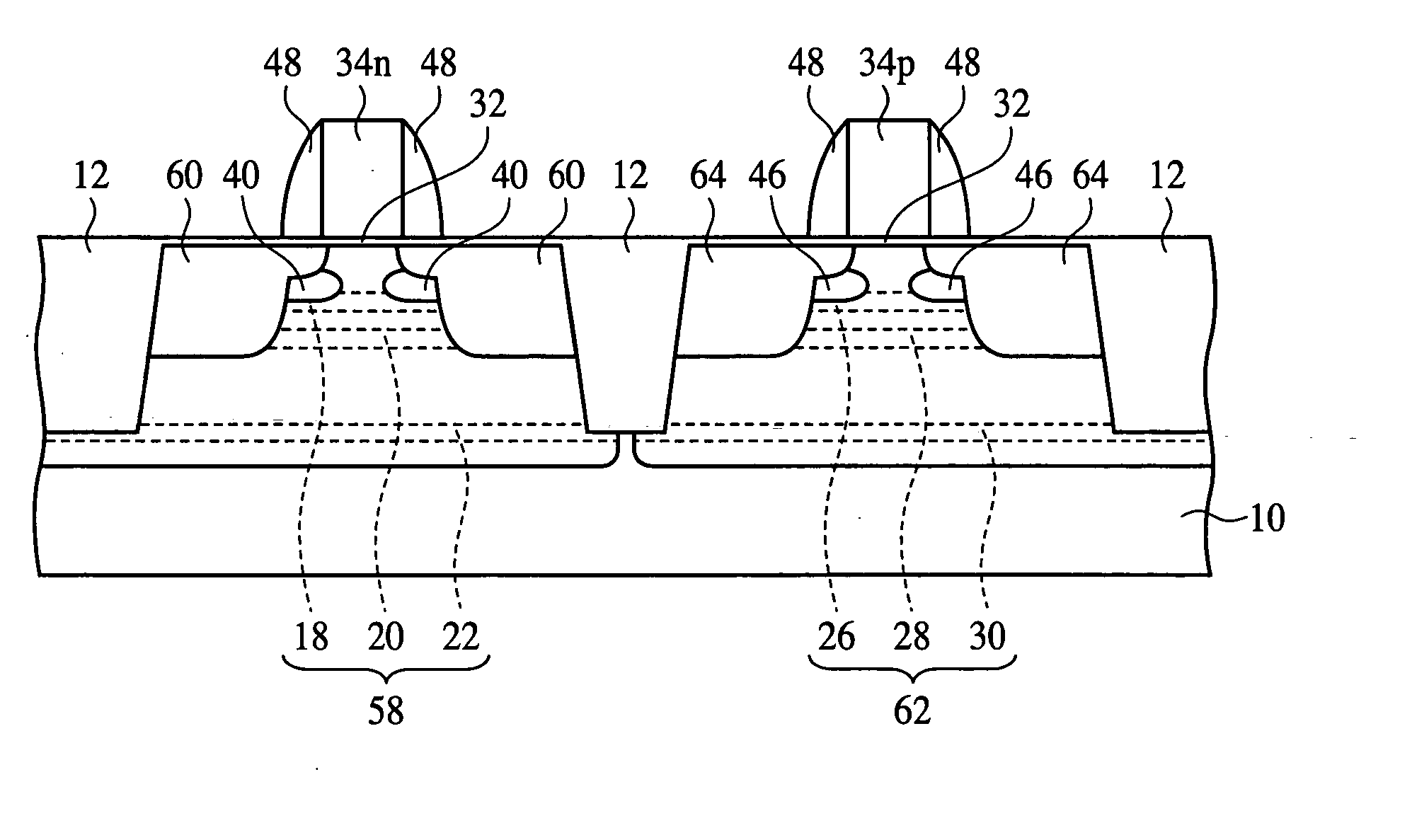

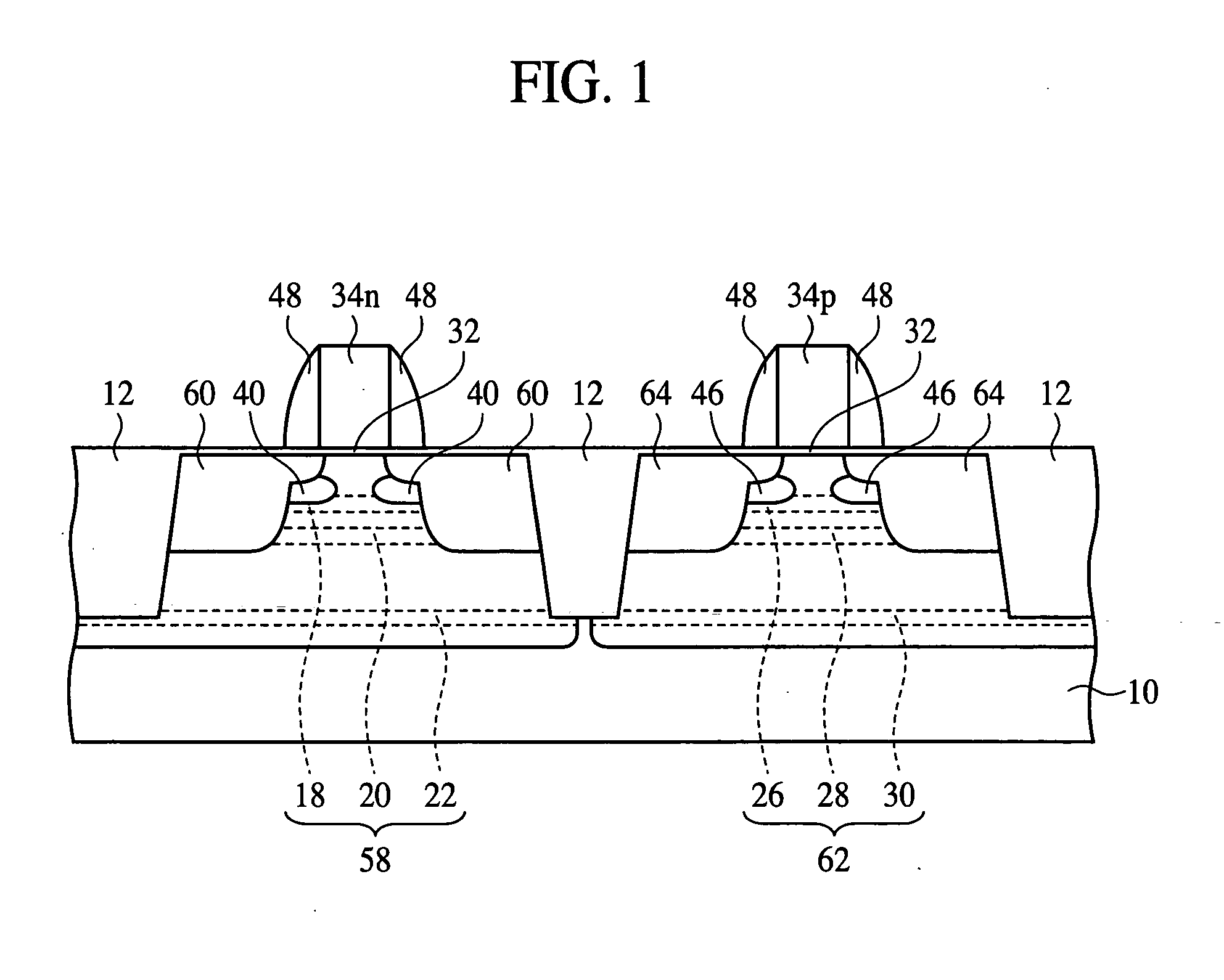

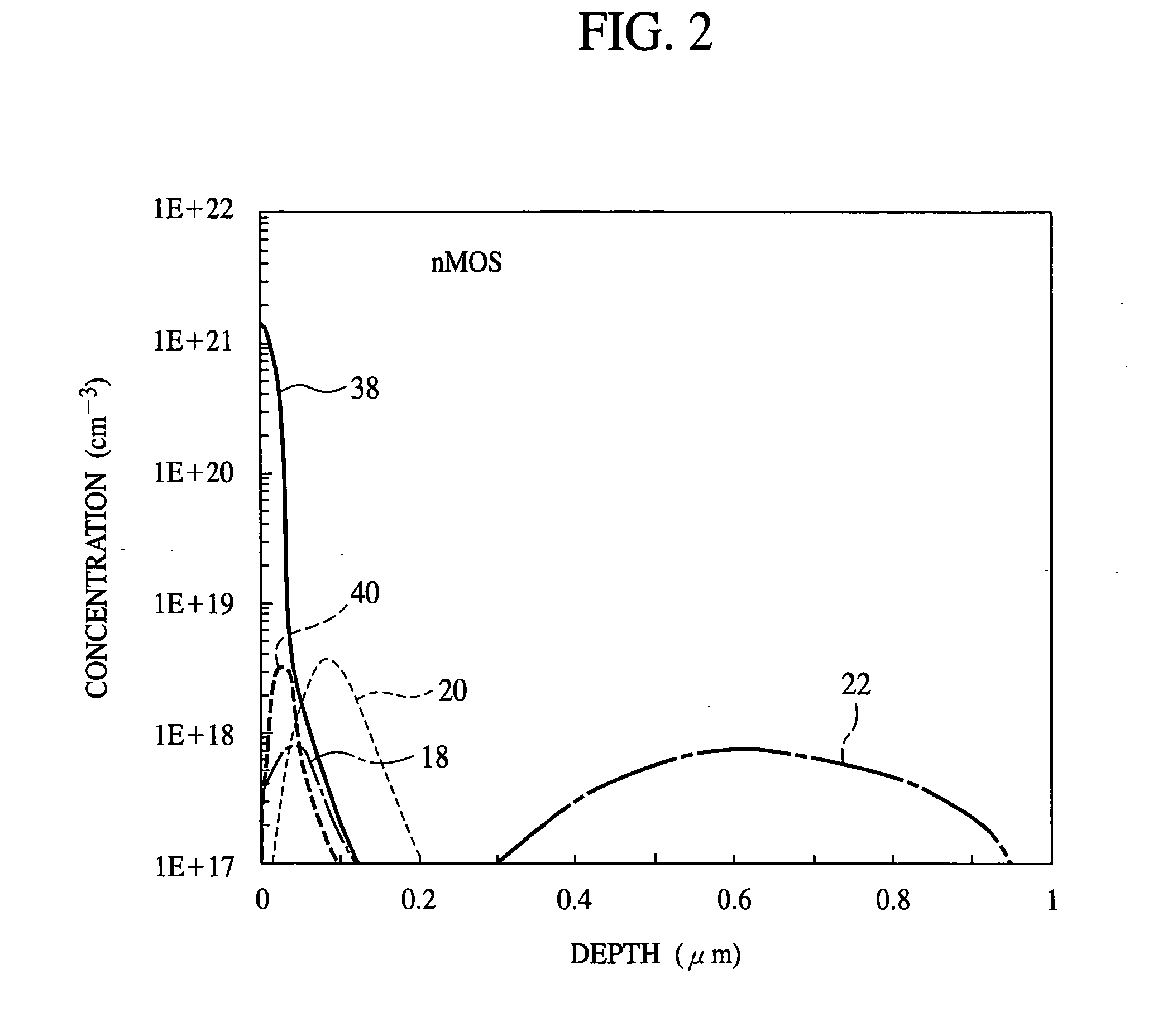

Semiconductor device and method for fabricating the same

InactiveUS20060071278A1High carrier mobilityReduce impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

The semiconductor device comprises a well 58 formed in a semiconductor substrate 10 and having a channel region; a gate electrode 34n formed over the channel region with an insulating film 32 interposed therebetween; source / drain regions 60 formed in the well 58 on both sides of the gate electrode 34n, sandwiching the channel region; and a pocket region 40 formed between the source / drain region and the channel region. The well 58 has a first peak of an impurity concentration at a depth deeper than the pocket region 40 and shallower than the bottom of the source / drain regions 60, and a second peak of the impurity concentration at a depth near the bottom of the source / drain regions 60.

Owner:SOCIONEXT INC

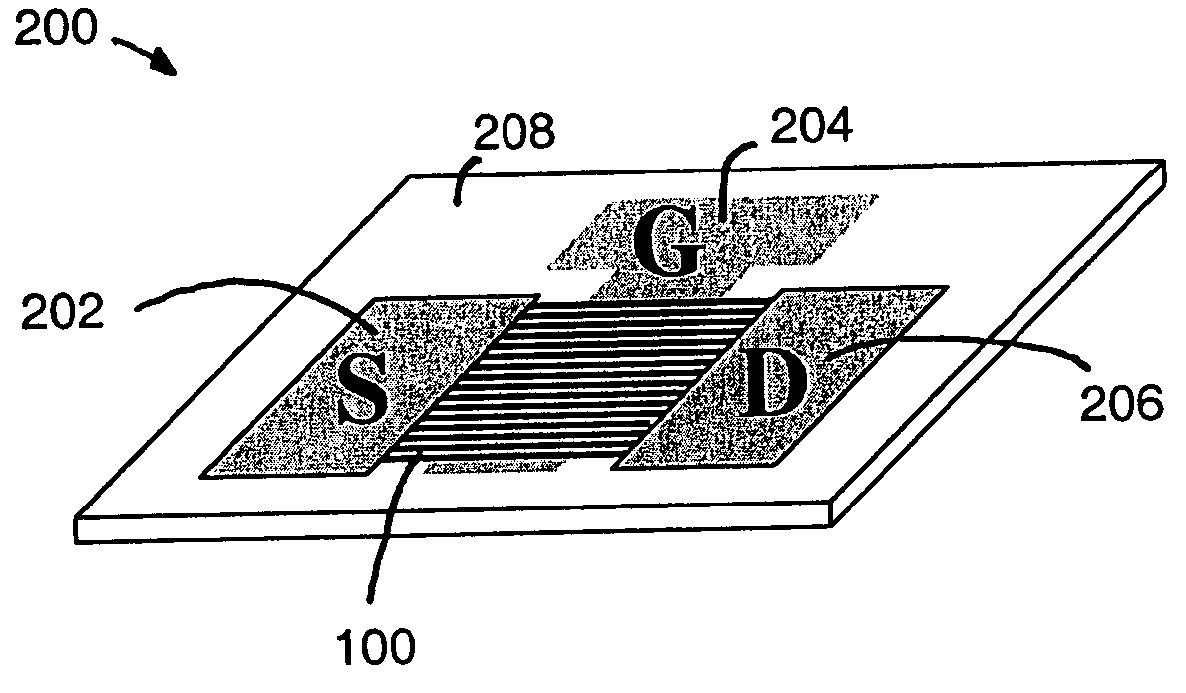

Large-area nanoenabled macroelectronic substrates and uses therefor

InactiveUS7135728B2Reduce and entirely eliminate scatteringHigh carrier mobilityTransistorSemiconductor/solid-state device detailsNanowireElectron scattering

A method and apparatus for an electronic substrate having a plurality of semiconductor devices is described. A thin film of nanowires is formed on a substrate. The thin film of nanowires is formed to have a sufficient density of nanowires to achieve an operational current level. A plurality of semiconductor regions are defined in the thin film of nanowires. Contacts are formed at the semiconductor device regions to thereby provide electrical connectivity to the plurality of semiconductor devices. Furthermore, various materials for fabricating nanowires, thin films including p-doped nanowires and n-doped nanowires, nanowire heterostructures, light emitting nanowire heterostructures, flow masks for positioning nanowires on substrates, nanowire spraying techniques for depositing nanowires, techniques for reducing or eliminating phonon scattering of electrons in nanowires, and techniques for reducing surface states in nanowires are described.

Owner:ONED MATERIAL INC

Large-area nanoenabled macroelectronic substrates and uses therefor

InactiveUS20050110064A1Reduce and entirely eliminate scatteringHigh carrier mobilityTransistorNanoinformaticsNanowirePhonon scattering

A method and apparatus for an electronic substrate having a plurality of semiconductor devices is described. A thin film of nanowires is formed on a substrate. The thin film of nanowires is formed to have a sufficient density of nanowires to achieve an operational current level. A plurality of semiconductor regions are defined in the thin film of nanowires. Contacts are formed at the semiconductor device regions to thereby provide electrical connectivity to the plurality of semiconductor devices. Furthermore, various materials for fabricating nanowires, thin films including p-doped nanowires and n-doped nanowires, nanowire heterostructures, light emitting nanowire heterostructures, flow masks for positioning nanowires on substrates, nanowire spraying techniques for depositing nanowires, techniques for reducing or eliminating phonon scattering of electrons in nanowires, and techniques for reducing surface states in nanowires are described.

Owner:ONED MATERIAL INC

FinFETs having dielectric punch-through stoppers

ActiveUS20090278196A1Total current dropHigh carrier mobilityTransistorSolid-state devicesEngineeringSemiconductor structure

A semiconductor structure includes a semiconductor substrate; a planar transistor on a first portion of the semiconductor substrate, wherein the first portion of the semiconductor substrate has a first top surface; and a multiple-gate transistor on a second portion of the semiconductor substrate. The second portion of the semiconductor substrate is recessed from the first top surface to form a fin of the multiple-gate transistor. The fin is electrically isolated from the semiconductor substrate by an insulator.

Owner:TAIWAN SEMICON MFG CO LTD

Large-area nanoenabled macroelectronic substrates and uses therefor

InactiveUS7064372B2Reduce and entirely eliminate scatteringHigh carrier mobilityTransistorSemiconductor/solid-state device detailsNanowirePhonon scattering

A method and apparatus for an electronic substrate having a plurality of semiconductor devices is described. A thin film of nanowires is formed on a substrate. The thin film of nanowires is formed to have a sufficient density of nanowires to achieve an operational current level. A plurality of semiconductor regions are defined in the thin film of nanowires. Contacts are formed at the semiconductor device regions to thereby provide electrical connectivity to the plurality of semiconductor devices. Furthermore, various materials for fabricating nanowires, thin films including p-doped nanowires and n-doped nanowires, nanowire heterostructures, light emitting nanowire heterostructures, flow masks for positioning nanowires on substrates, nanowire spraying techniques for depositing nanowires, techniques for reducing or eliminating phonon scattering of electrons in nanowires, and techniques for reducing surface states in nanowires are described.

Owner:ONED MATERIAL INC

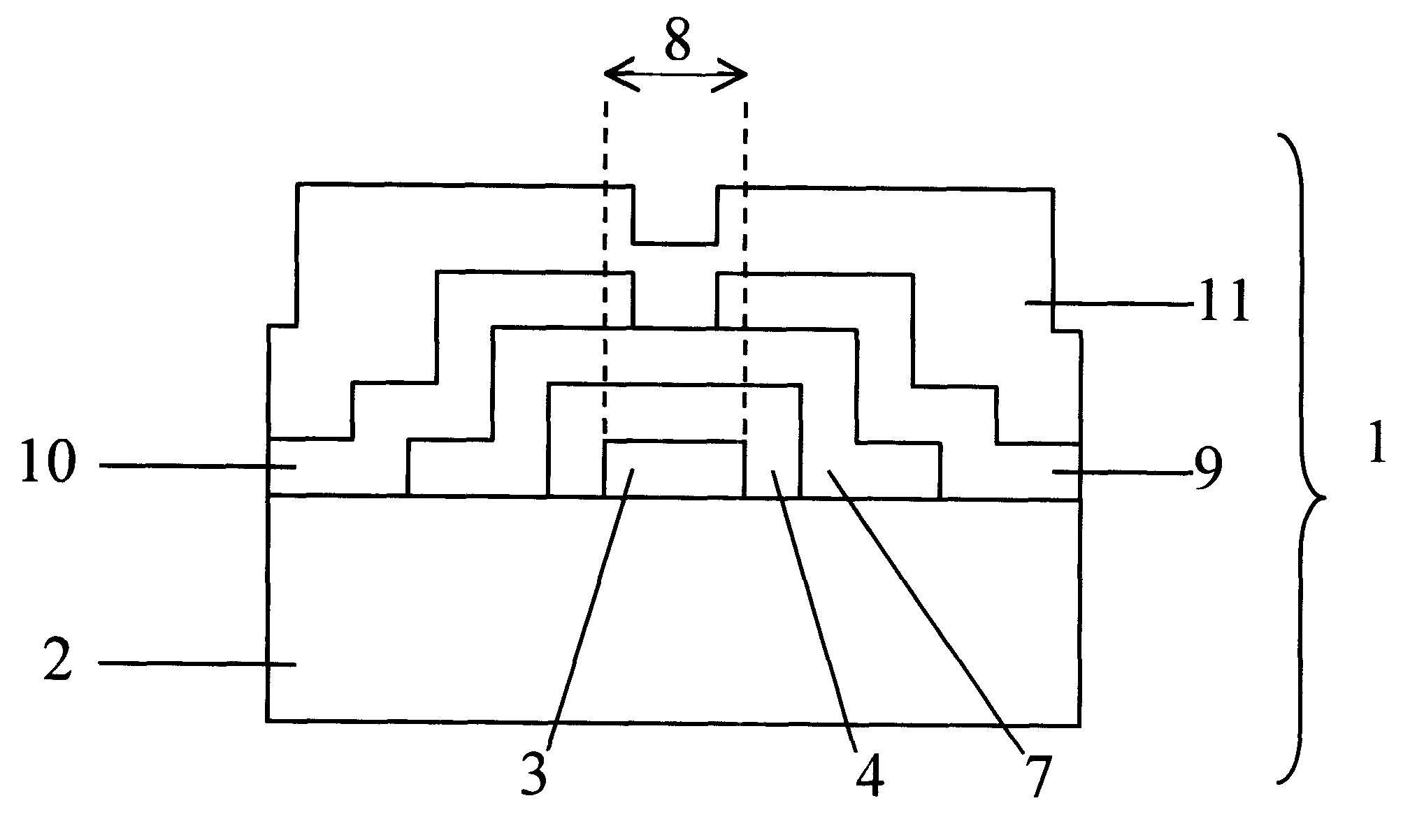

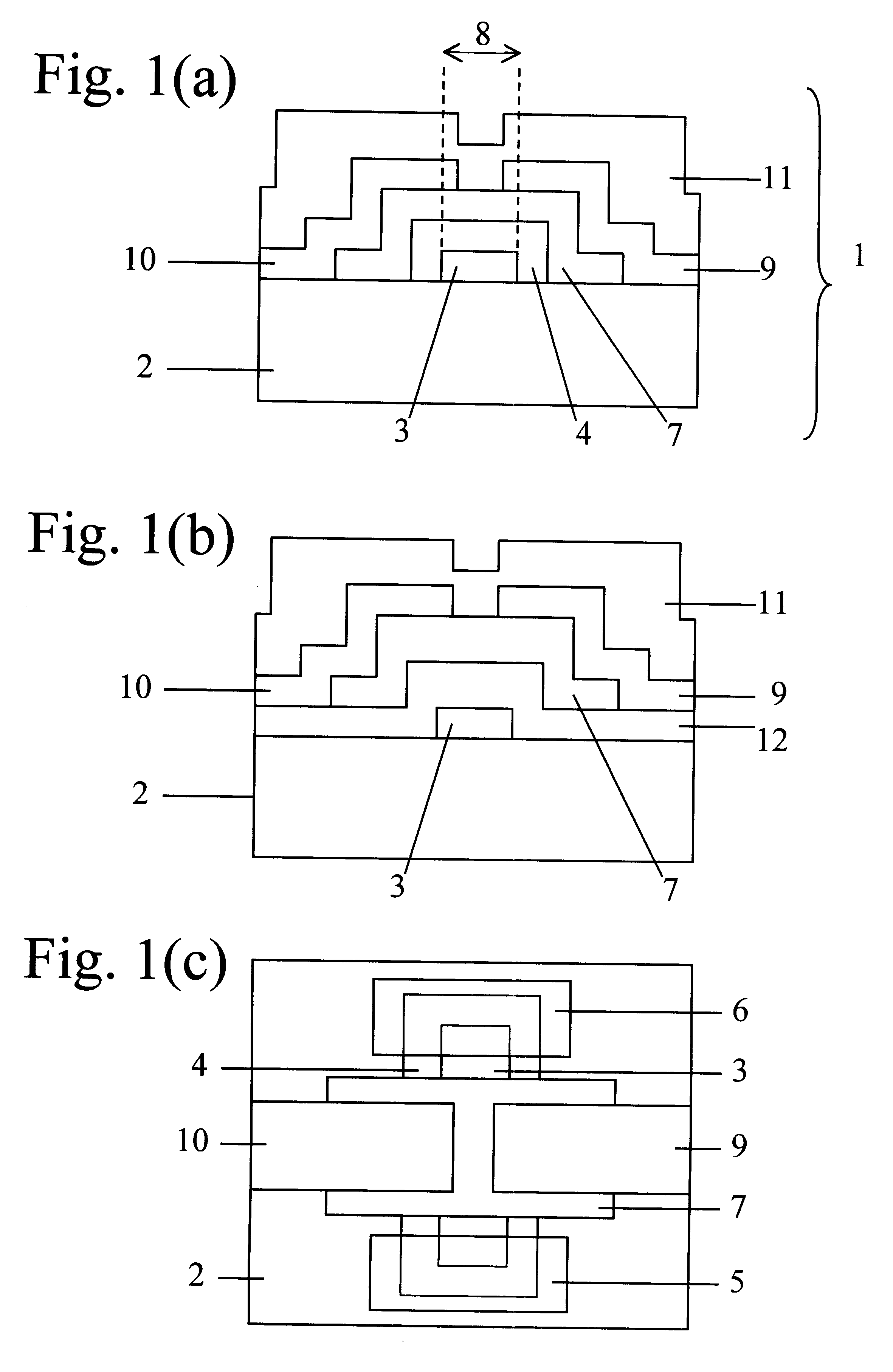

Strained fin fets structure and method

InactiveUS20030178677A1Physical strain on the channel materialHigh carrier mobilityTransistorSolid-state devicesEngineeringSilicon

A method and structure for a transistor that includes an insulator and a silicon structure on the insulator. The silicon structure includes a central portion and Fins extending from ends of the central portion. A first gate is positioned on a first side of the central portion of the silicon structure. A strain-producing layer could be between the first gate and the first side of the central portion of the silicon structure and a second gate is on a second side of the central portion of the silicon structure.

Owner:MICROSOFT TECH LICENSING LLC

Semiconductor Device and Manufacturing Process Therefor

ActiveUS20070241414A1Less dislocation and defectControlled amount of strainTransistorSolid-state devicesManufacturing technologyDevice material

This invention relates to a semiconductor device having a beam made of a semiconductor to which strain is introduced by deflection, and a current is permitted to flow in the beam.

Owner:GK BRIDGE 1

Method and structure for strained finfet devices

ActiveUS20060014338A1High carrier mobilityImprove mobilityTransistorSemiconductor/solid-state device manufacturingEngineeringStressor

A method (and structure) of forming an electronic device includes forming at least one localized stressor region within the device.

Owner:GLOBALFOUNDRIES US INC

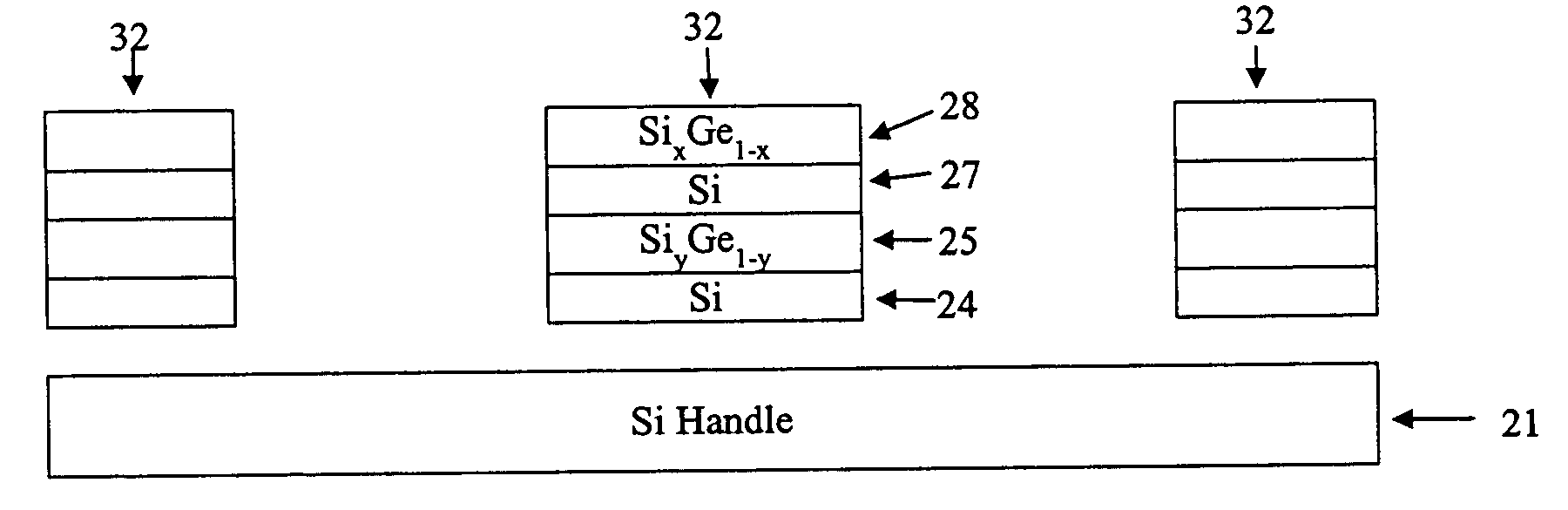

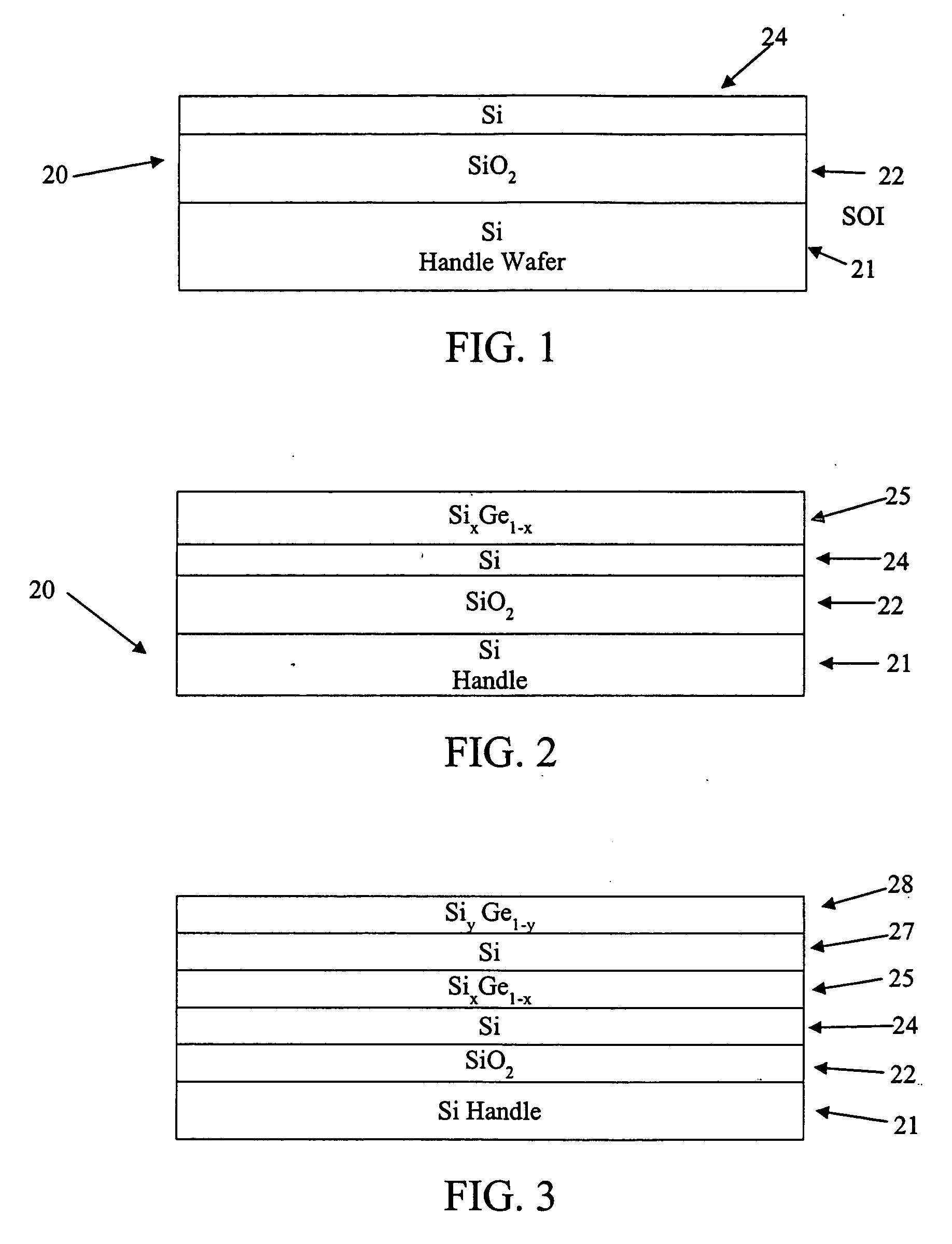

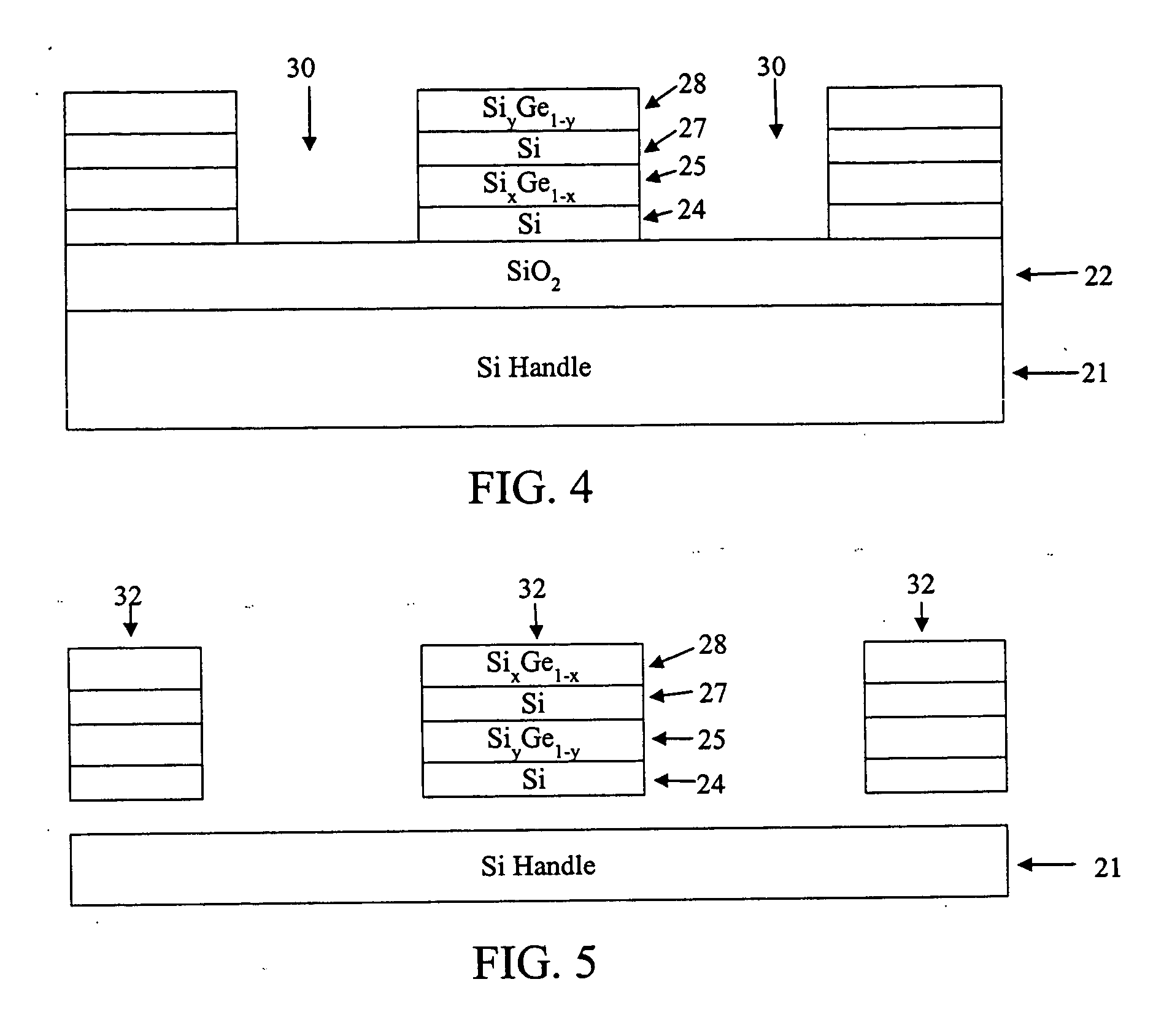

Fabrication of strained heterojunction structures

ActiveUS20060134893A1Improve featuresHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionLayer interface

Growth of multilayer films is carried out in a manner which allows close control of the strain in the grown layers and complete release of the grown films to allow mounting of the released multilayer structures on selected substrates. A layer of material, such as silicon-germanium, is grown onto a template layer, such as silicon, of a substrate having a sacrificial layer on which the template layer is formed. The grown layer has a lattice mismatch with the template layer so that it is strained as deposited. A top layer of crystalline material, such as silicon, is grown on the alloy layer to form a multilayer structure with the grown layer and the template layer. The sacrificial layer is preferentially etched away to release the multilayer structure from the sacrificial layer, relaxing the grown layer and straining the crystalline layers interfaced with it.

Owner:WISCONSIN ALUMNI RES FOUND

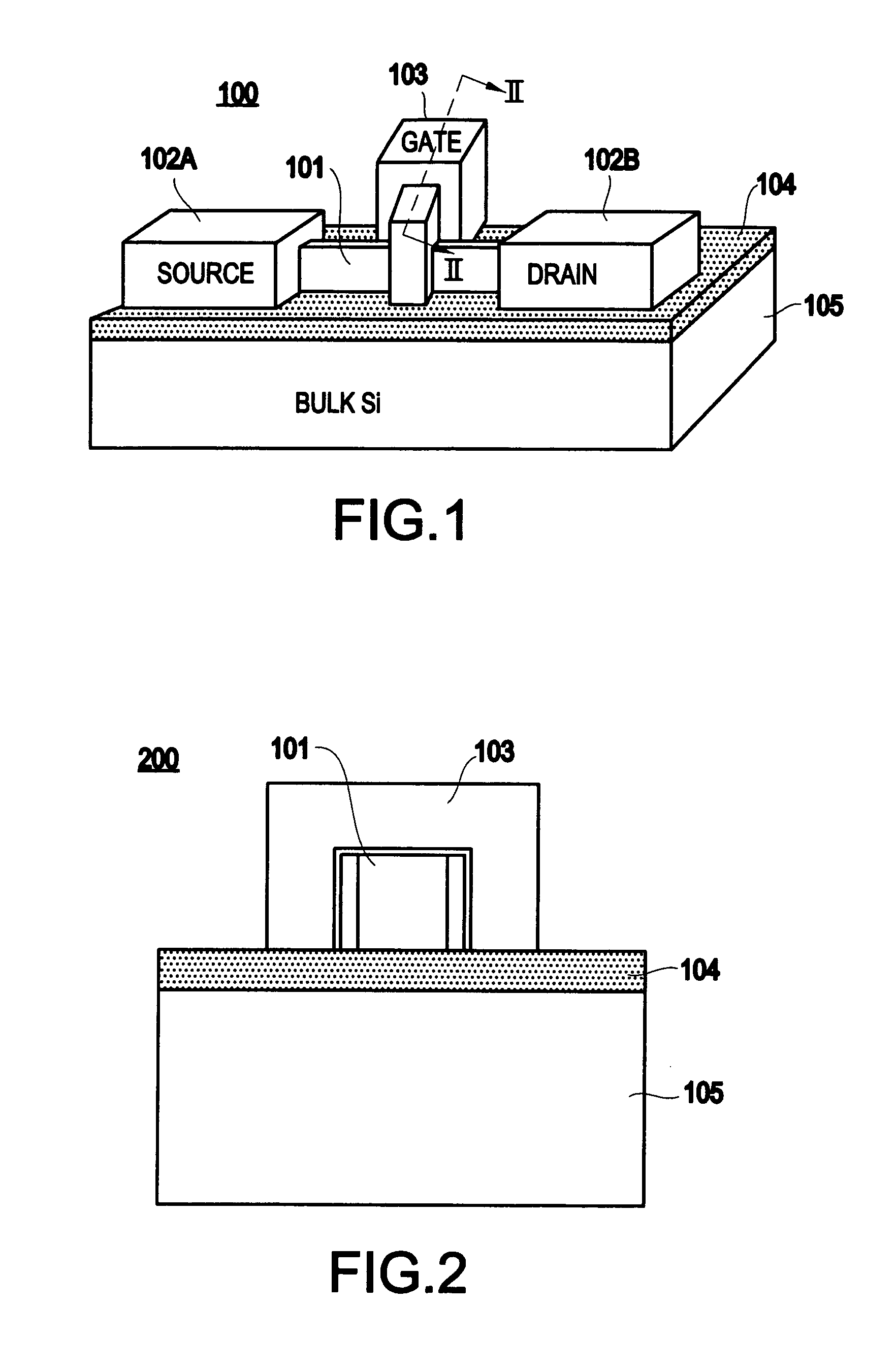

Semiconductor device having a channel layer and method of manufacturing the same

InactiveUS20050263795A1High carrier mobilityImprove channel mobilityTransistorPaper-money handling devicesDriving currentInsulation layer

In a method of forming a semiconductor device having an improved channel layer, the channel layer is formed on a surface of a semiconductor substrate and comprises a material of high carrier mobility such as silicon germanium (SiGe), germanium (Ge) and silicon carbide (SiC) using a selective epitaxial growth process. A gate insulation layer and a gate electrode are formed on the channel layer. Accordingly, a driving current of the semiconductor device increases to thereby improve operation characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

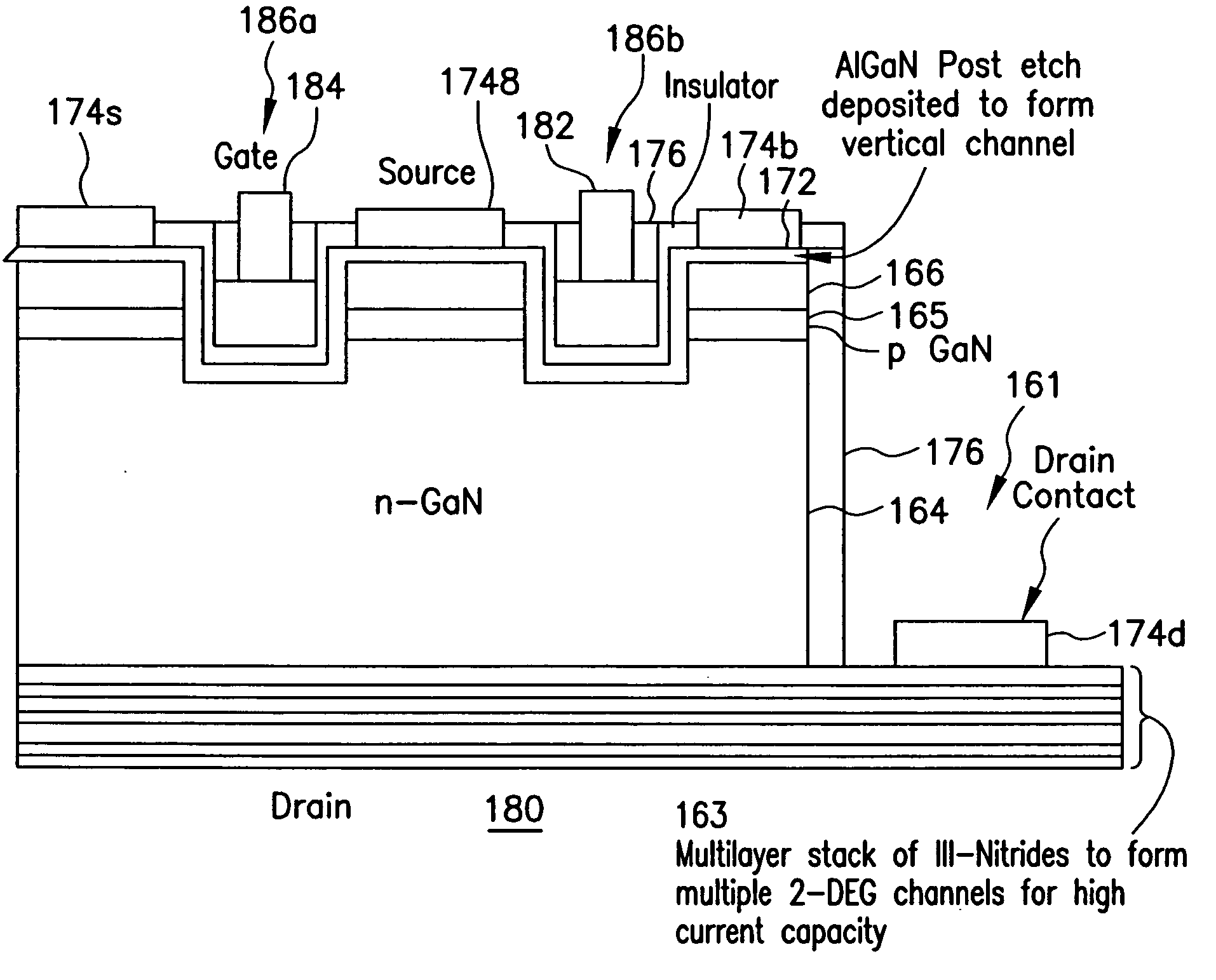

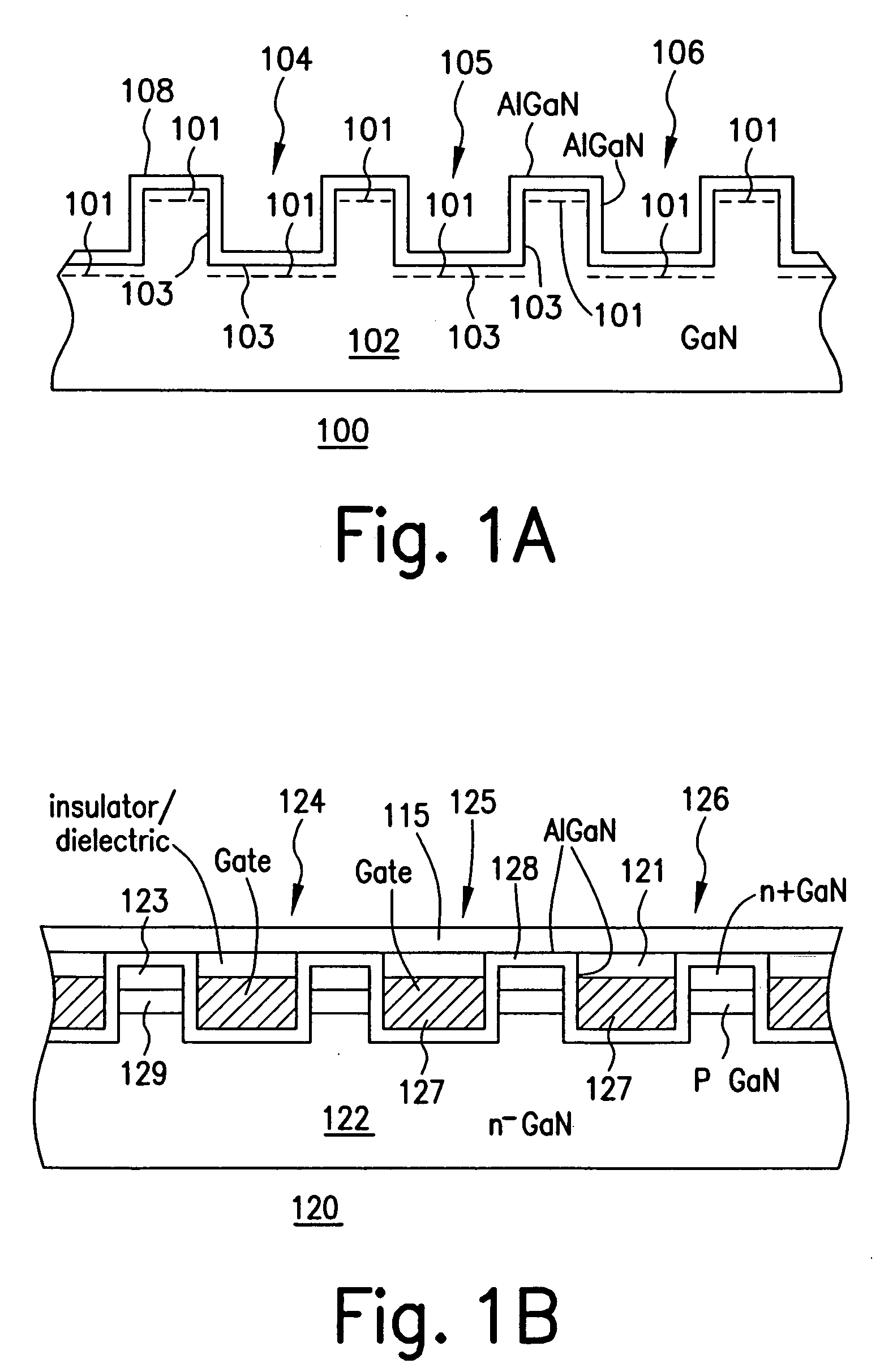

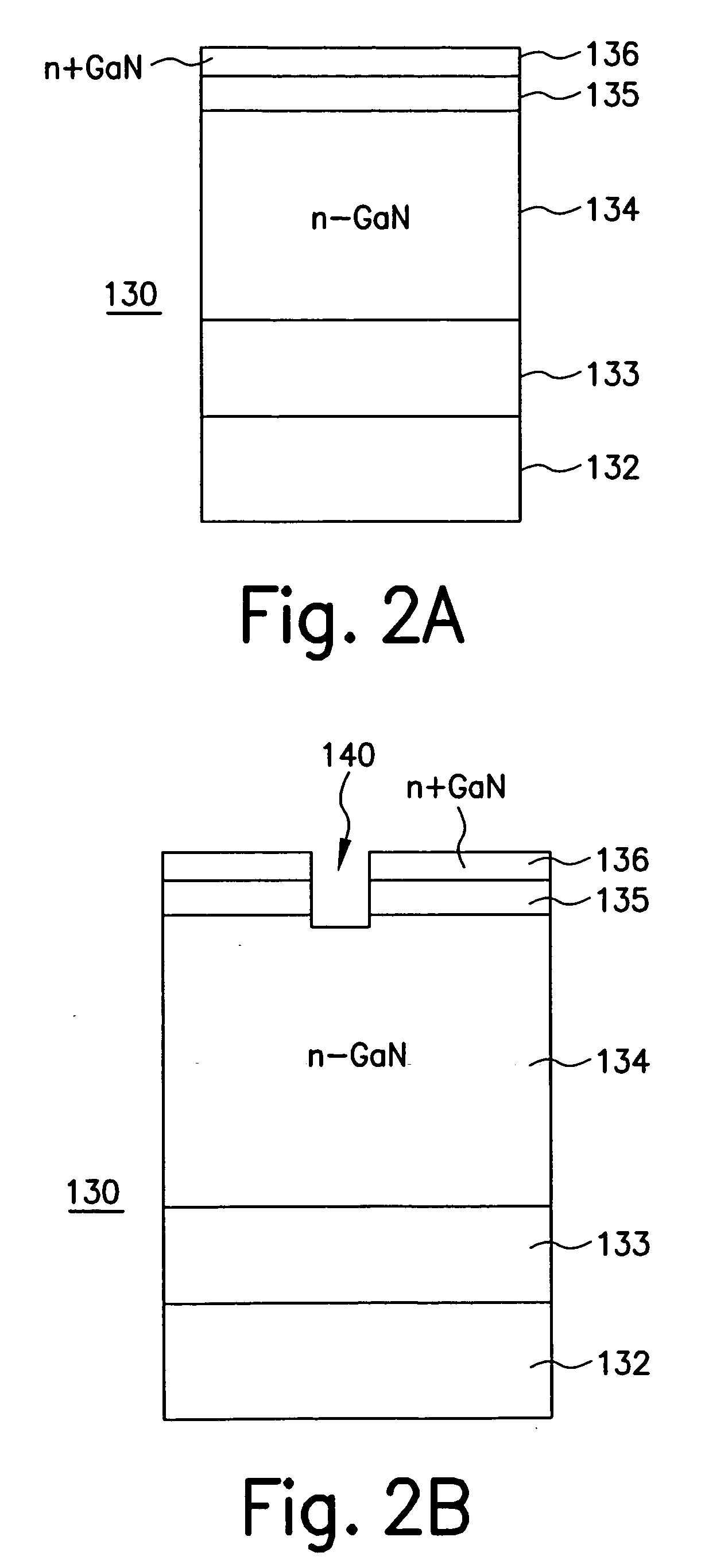

III-nitride semiconductor device with trench structure

ActiveUS20050145883A1Large current throughputHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingElectric fieldDielectric

A III-nitride trench device has a vertical conduction region with an interrupted conduction channel when the device is not on, providing an enhancement mode device. The trench structure may be used in a vertical conduction or horizontal conduction device. A gate dielectric provides improved performance for the device by being capable of withstanding higher electric field or manipulating the charge in the conduction channel. A passivation of the III-nitride material decouples the dielectric from the device to permit lower dielectric constant materials to be used in high power applications.

Owner:INFINEON TECH AMERICAS

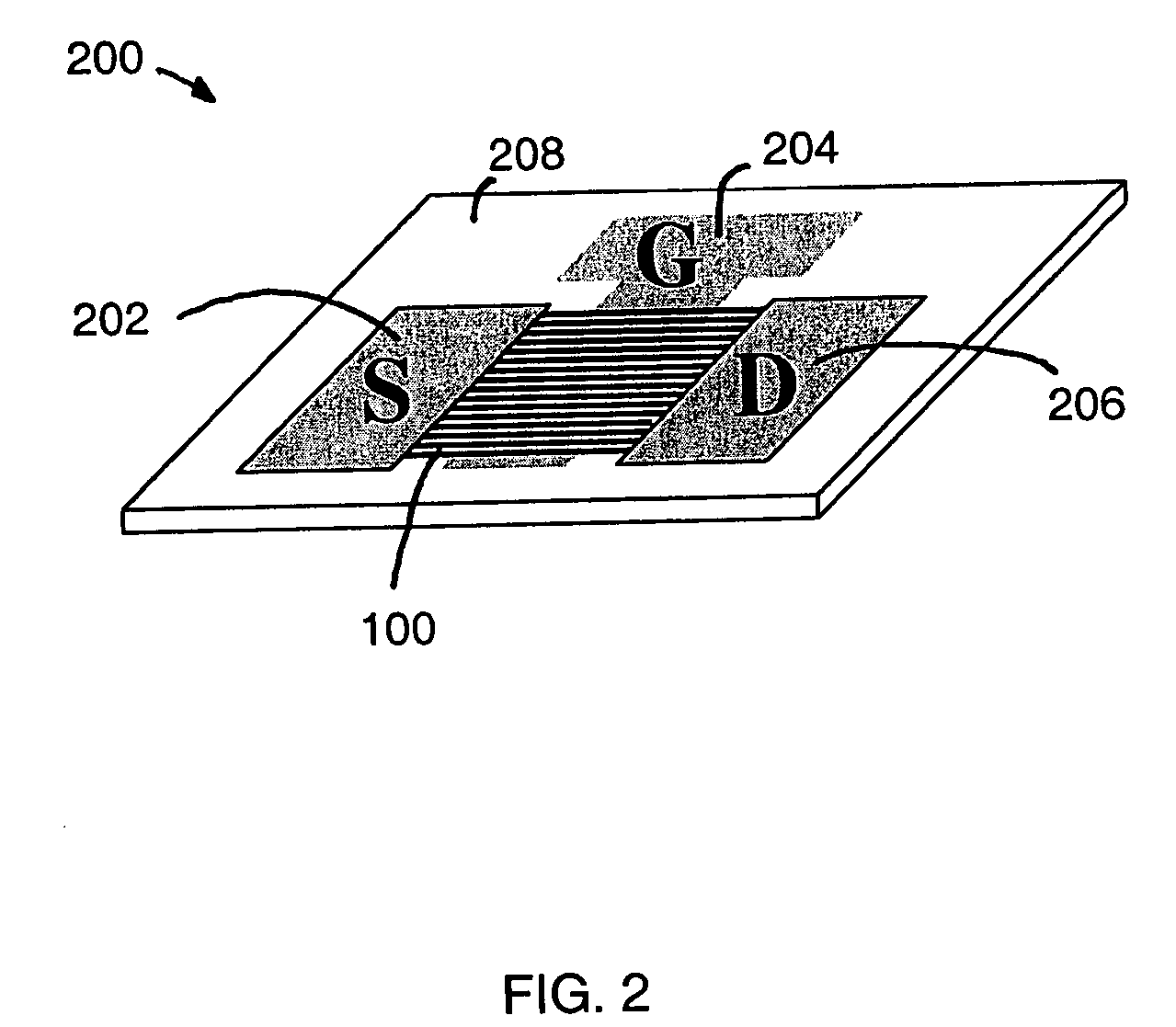

Methods to fabricate thin film transistors and circuits

InactiveUS6225149B1Low costLow thermal budgetTransistorLight-sensitive devicesOptoelectronicsField-effect transistor

A method for fabricating a thin film field effect transistor is described in this invention. The active layer of the thin film transistor (TFT) is formed by a low cost chemical bath deposition method. The fabrication procedure includes deposition of a metal layer on an insulating substrate, patterning of the metal layer to form a metal gate, formation of the di-electric layer, deposition of the active layer and formation of source and drain contacts.

Owner:MCGILL UNIV OFFICE OF TECH TRANSFER

Strained-silicon CMOS device and method

ActiveUS20050285187A1High carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice material

The present invention provides a semiconductor device and a method of forming thereof, in which a uniaxial strain is produced in the device channel of the semiconductor device. The uniaxial strain may be in tension or in compression and is in a direction parallel to the device channel. The uniaxial strain can be produced in a biaxially strained substrate surface by strain inducing liners, strain inducing wells or a combination thereof. The uniaxial strain may be produced in a relaxed substrate by the combination of strain inducing wells and a strain inducing liner. The present invention also provides a means for increasing biaxial strain with strain inducing isolation regions. The present invention further provides CMOS devices in which the device regions of the CMOS substrate may be independently processed to provide uniaxially strained semiconducting surfaces in compression or tension.

Owner:GLOBALFOUNDRIES US INC

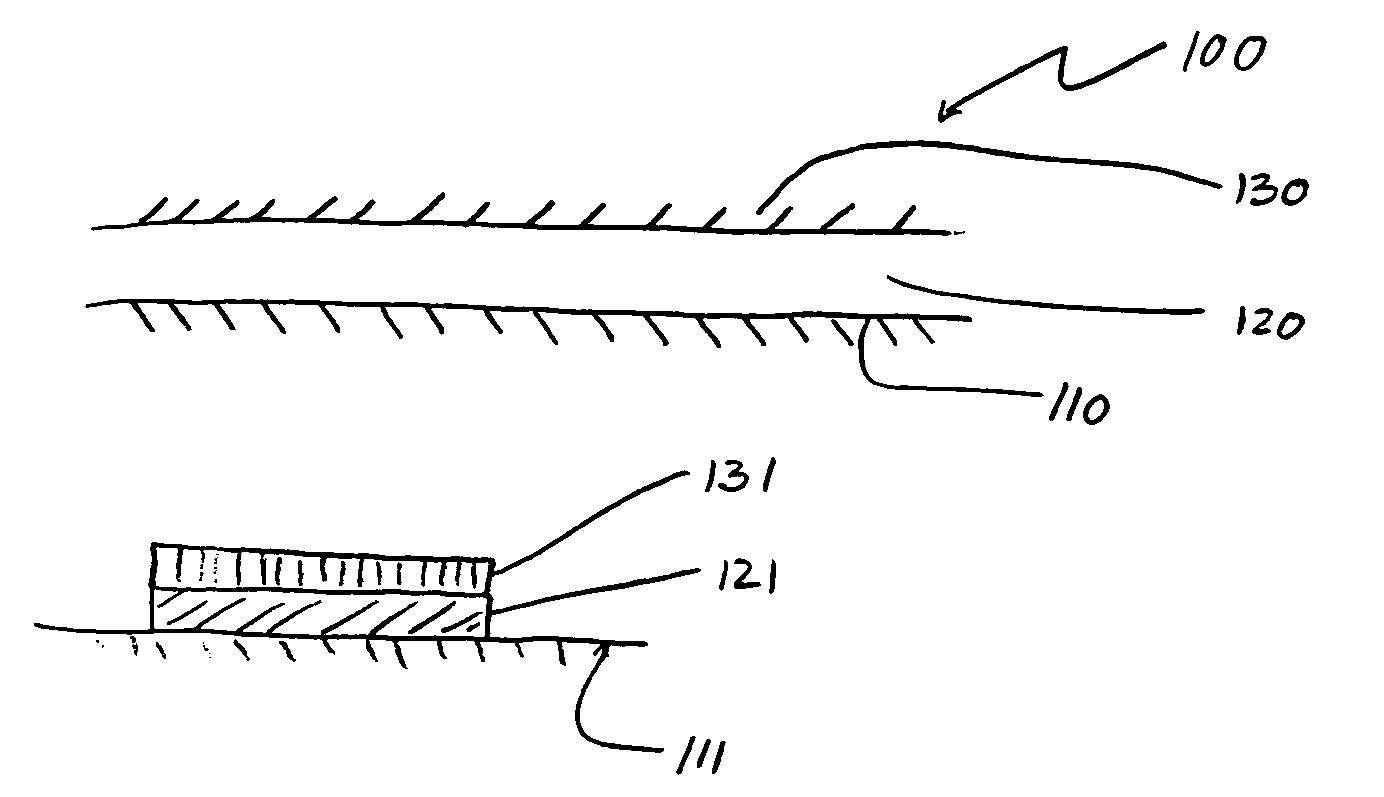

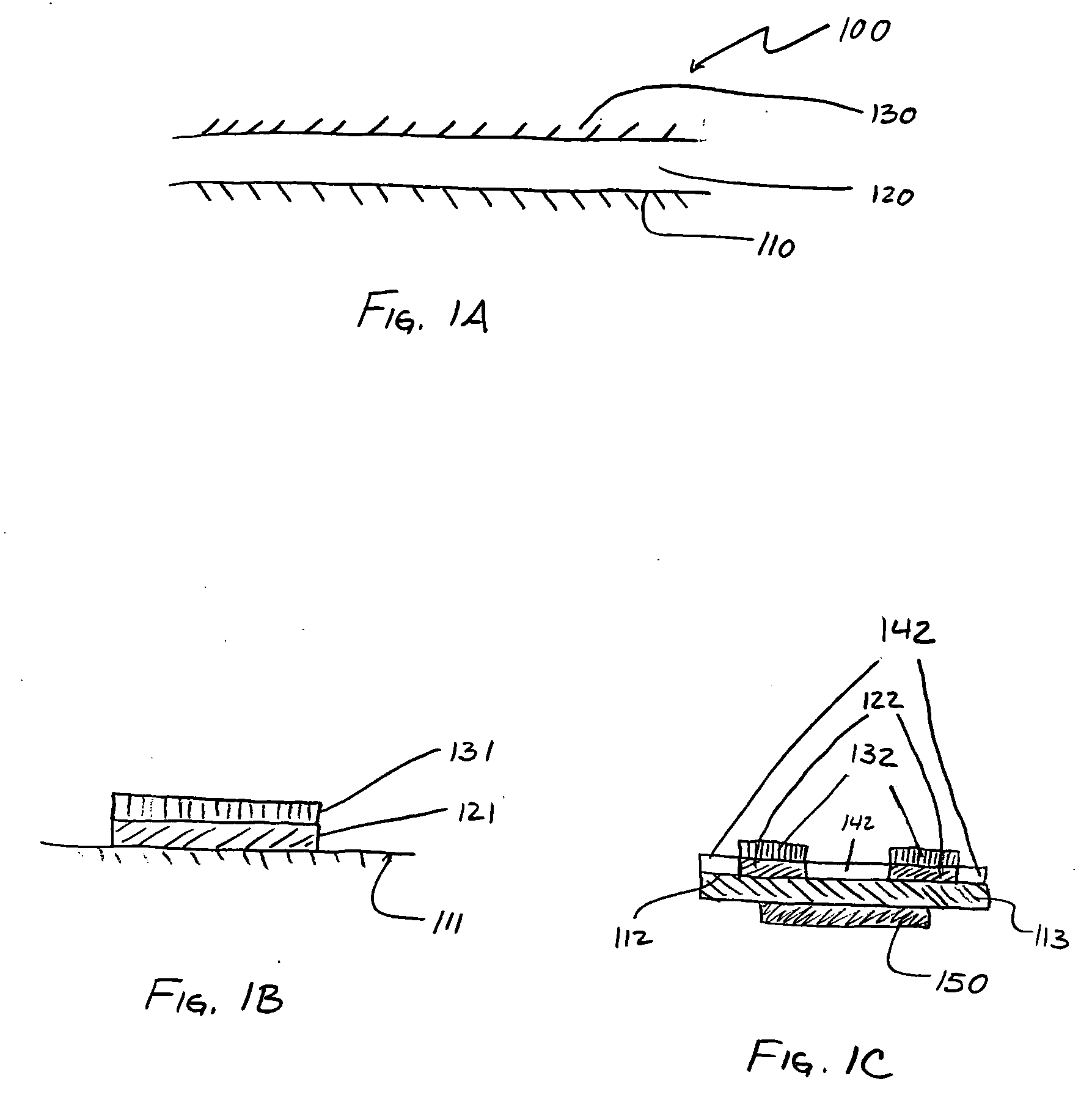

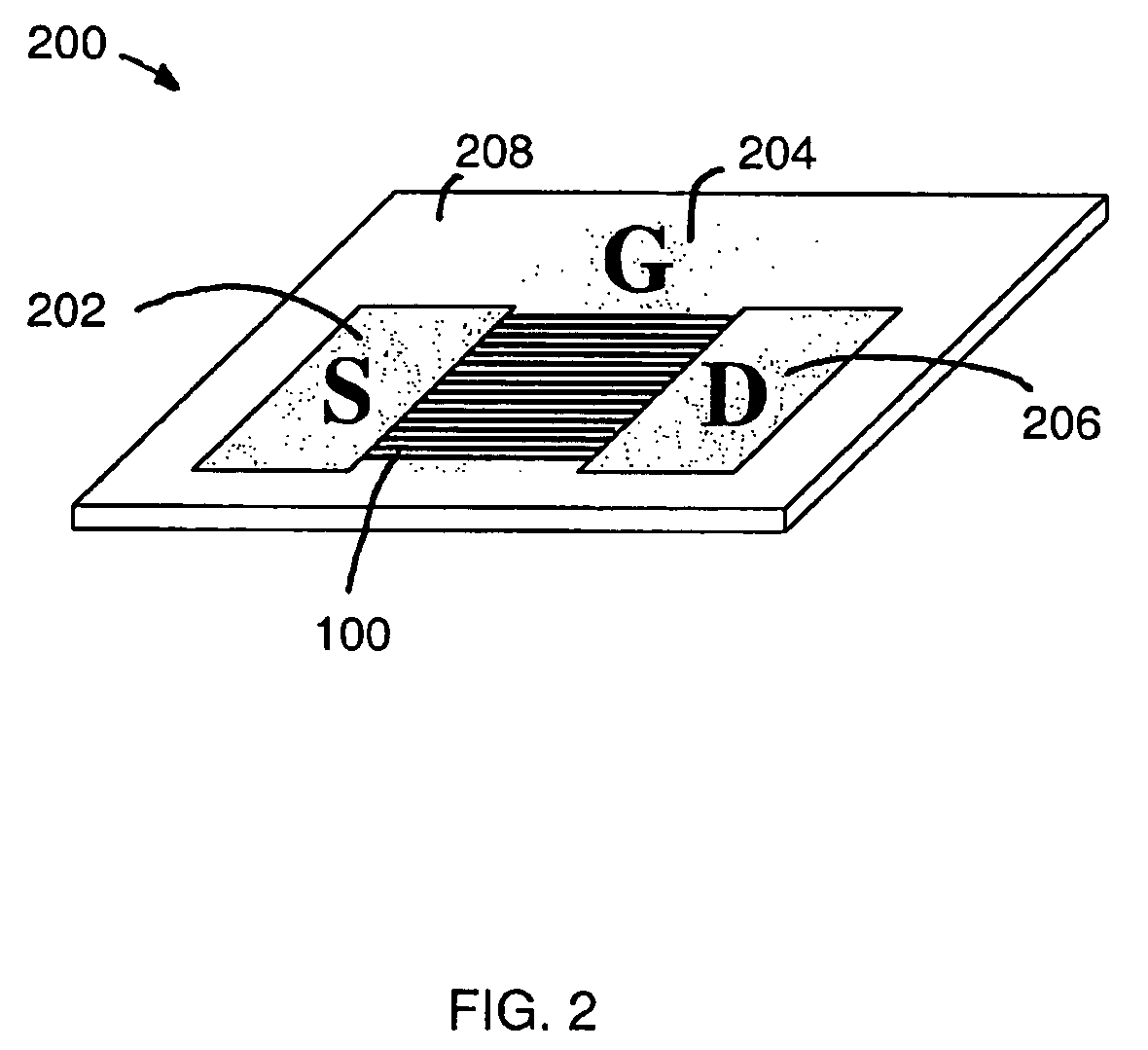

Fully integrated organic layered processes for making plastic electronics based on conductive polymers and semiconductor nanowires

InactiveUS20060214156A1High carrier mobilityLow costFinal product manufactureNanoinformaticsSemiconductorPlastic electronics

The present invention is directed to thin film transistors using nanowires (or other nanostructures such as nanoribbons, nanotubes and the like) incorporated in and / or disposed proximal to conductive polymer layer(s), and production scalable methods to produce such transistors. In particular, a composite material comprising a conductive polymeric material such as polyaniline (PANI) or polypyrrole (PPY) and one or more nanowires incorporated therein is disclosed. Several nanowire-TFT fabrication methods are also provided which in one exemplary embodiment includes providing a device substrate; depositing a first conductive polymer material layer on the device substrate; defining one or more gate contact regions in the conductive polymer layer; depositing a plurality of nanowires over the conductive polymer layer at a sufficient density of nanowires to achieve an operational current level; depositing a second conductive polymer material layer on the plurality of nanowires; and forming source and drain contact regions in the second conductive polymer material layer to thereby provide electrical connectivity to the plurality of nanowires, whereby the nanowires form a channel having a length between respective ones of the source and drain regions.

Owner:NANOSYS INC