Patents

Literature

1460results about How to "High electron mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

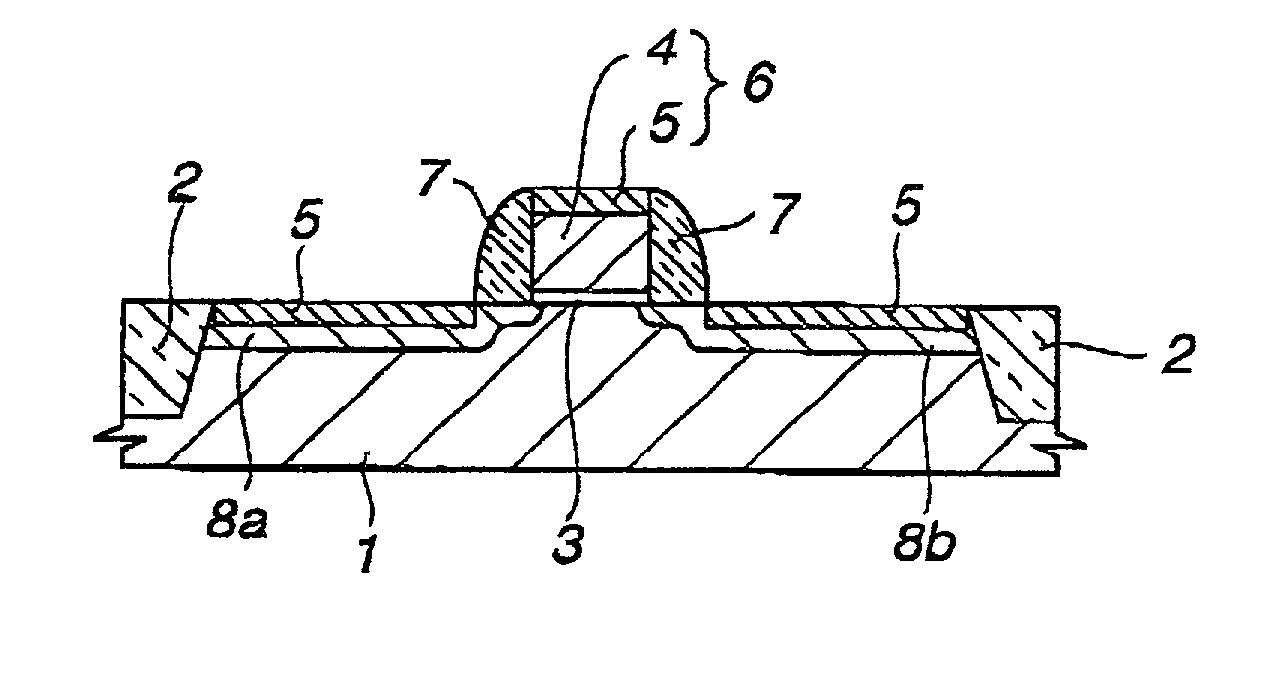

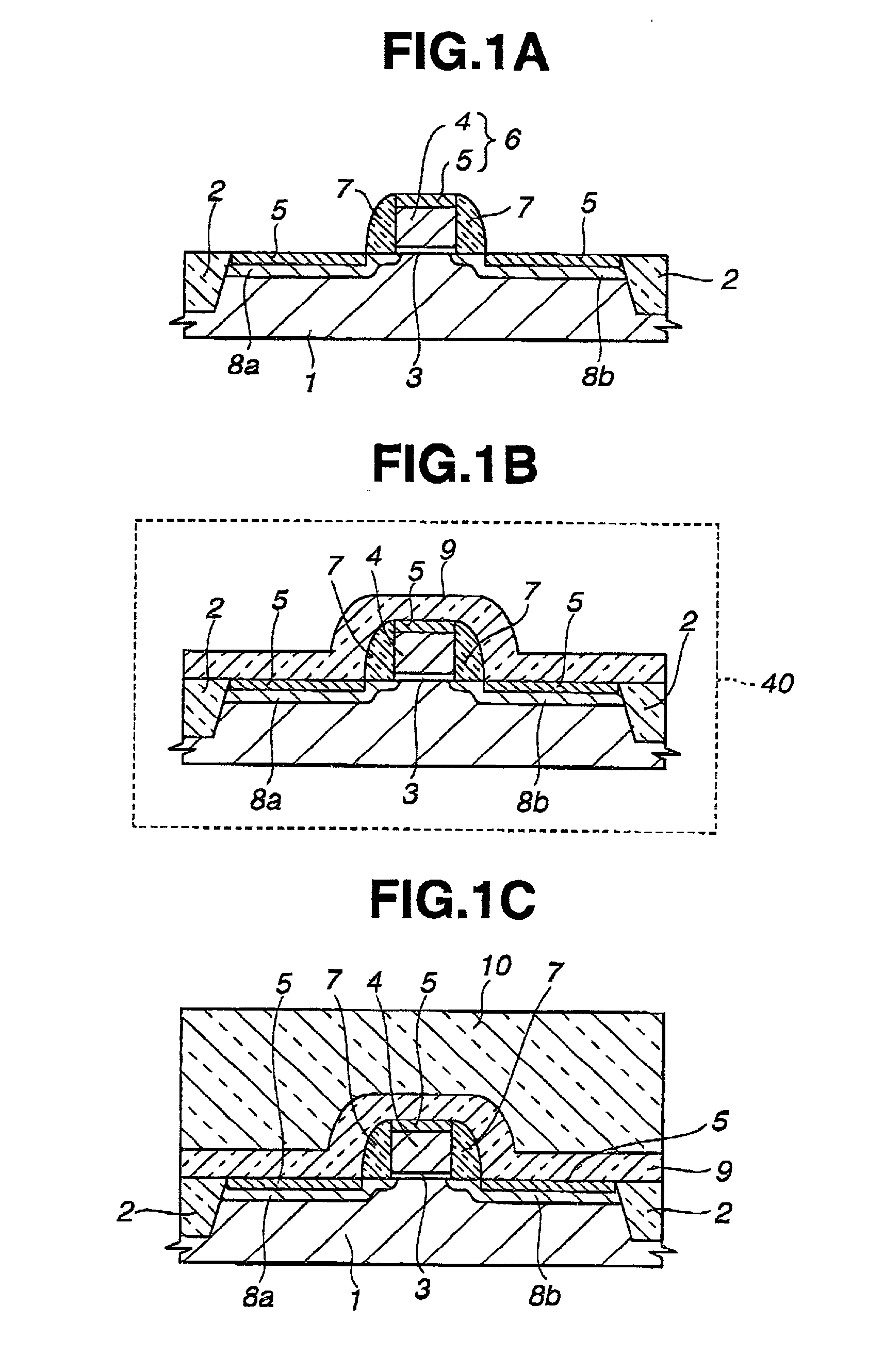

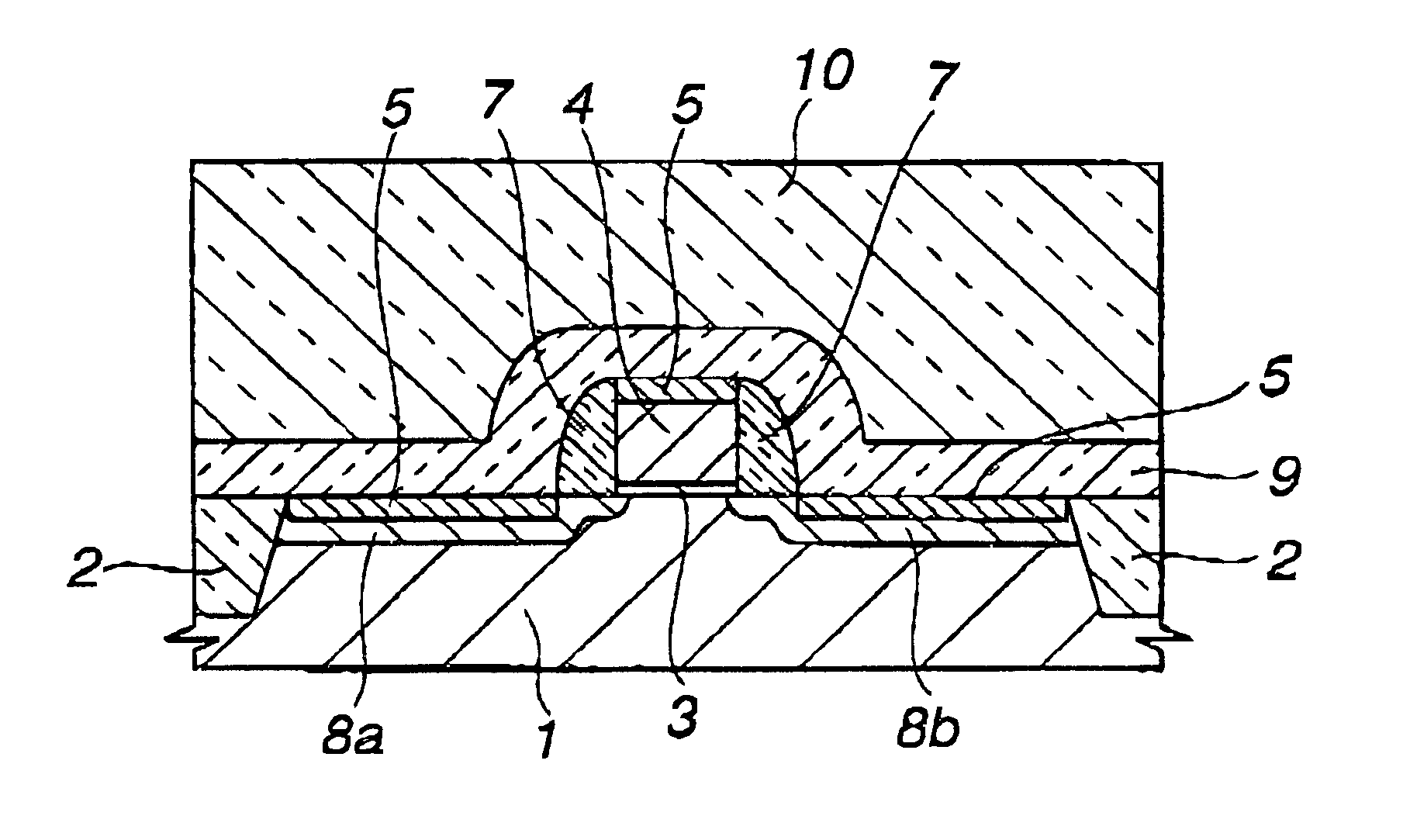

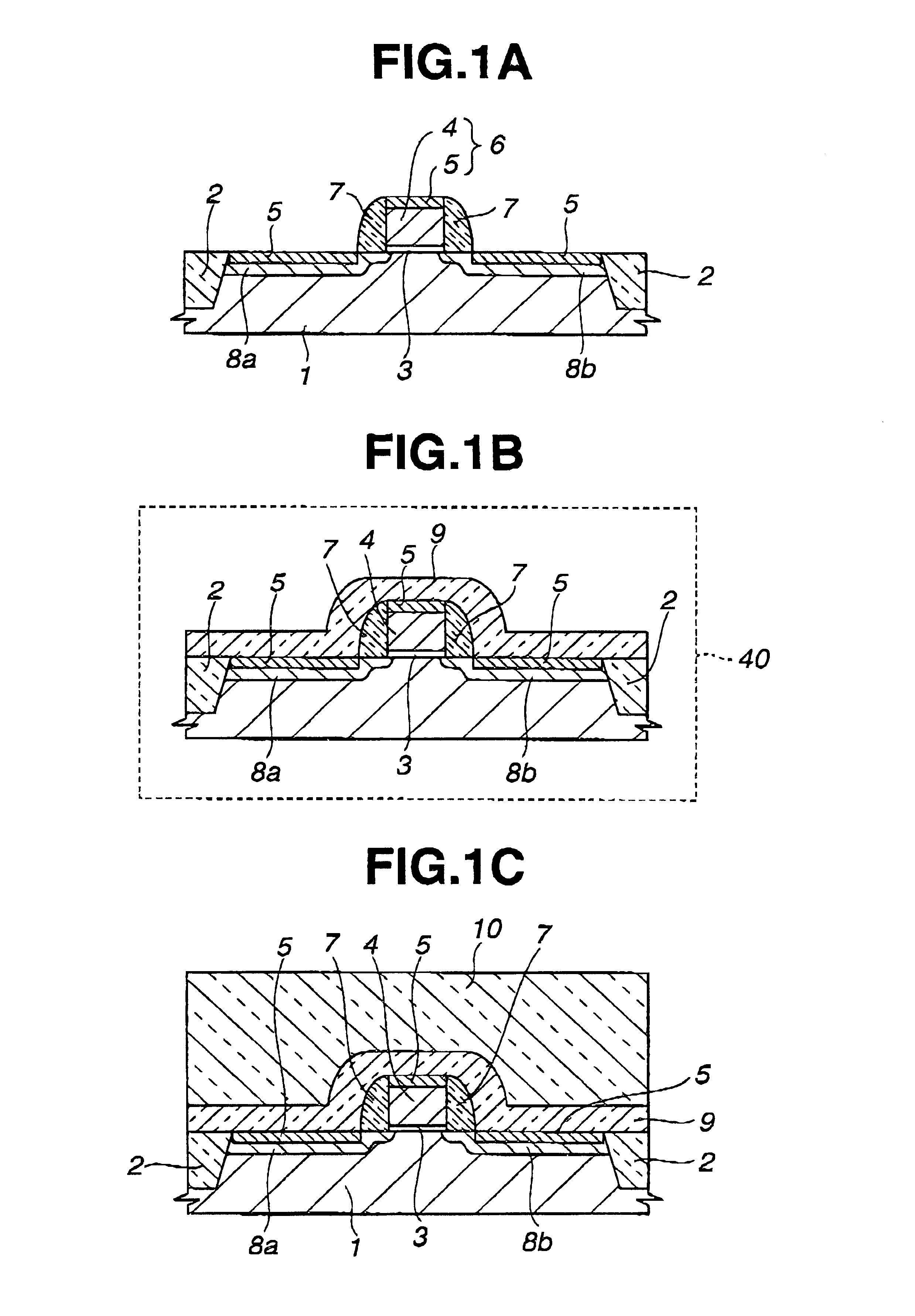

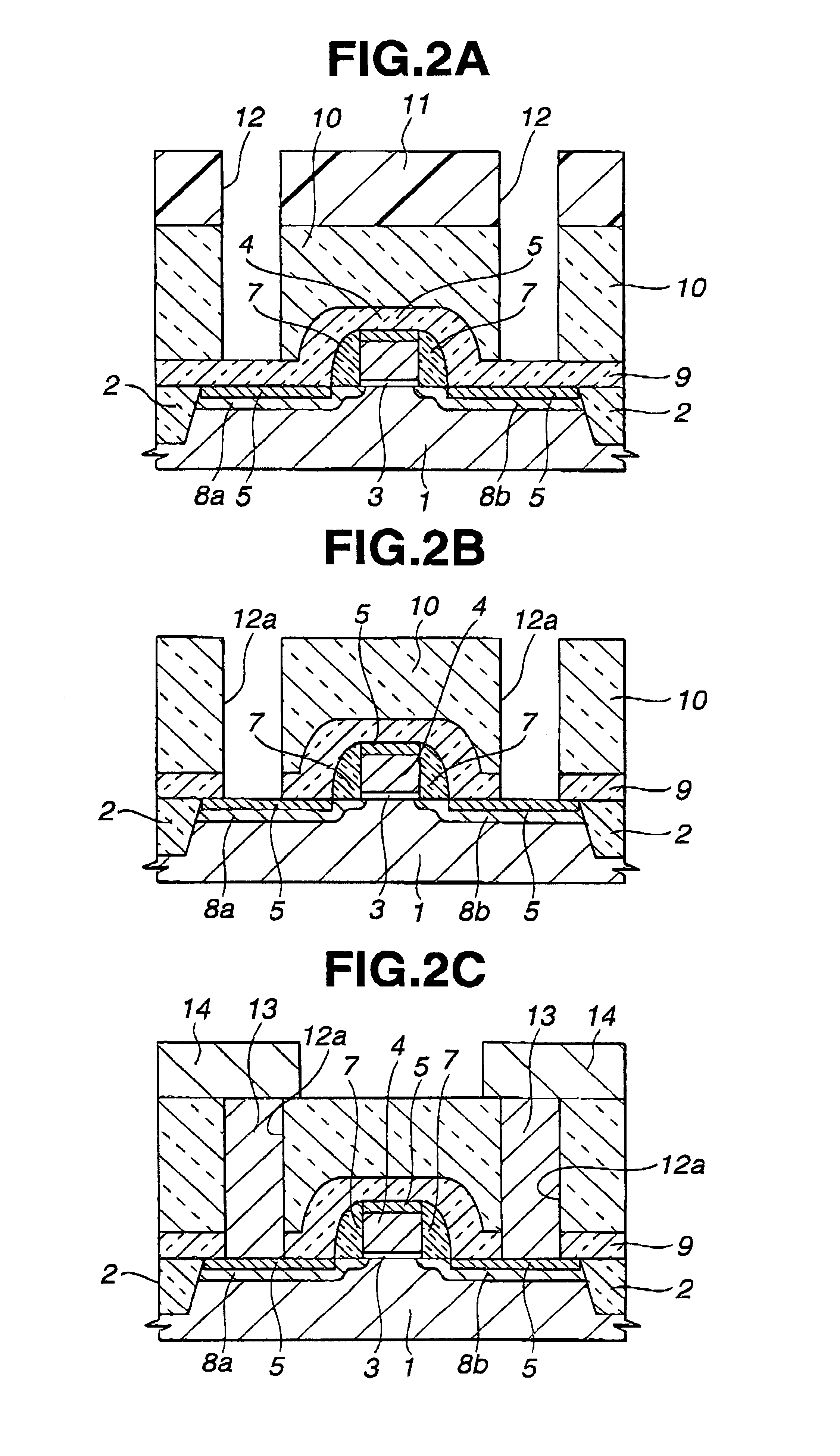

Amorphous Oxide And Thin Film Transistor

InactiveUS20070194379A1High ionicityGeneration of oxygen defects is less frequentTransistorVacuum evaporation coatingCharge carrierElectron

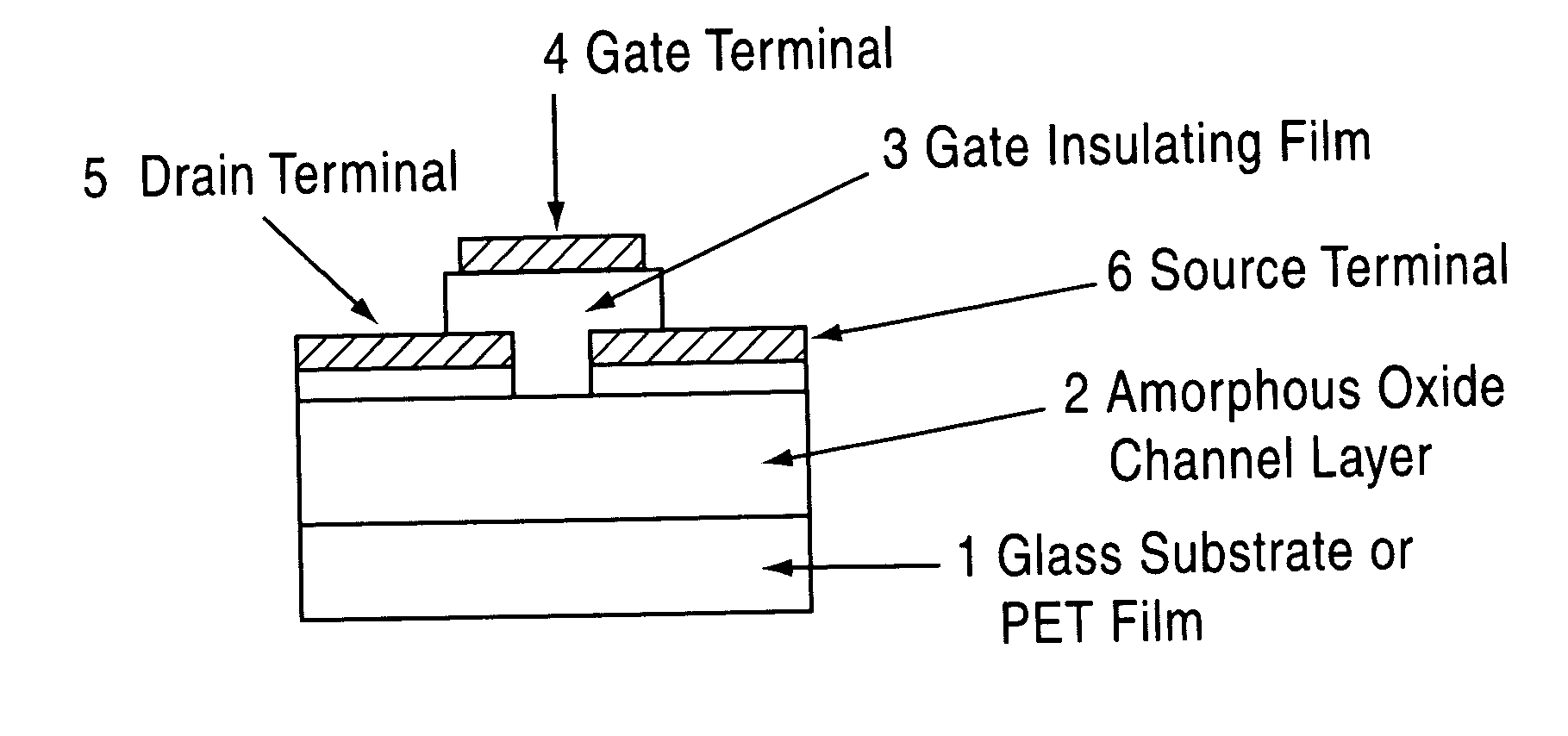

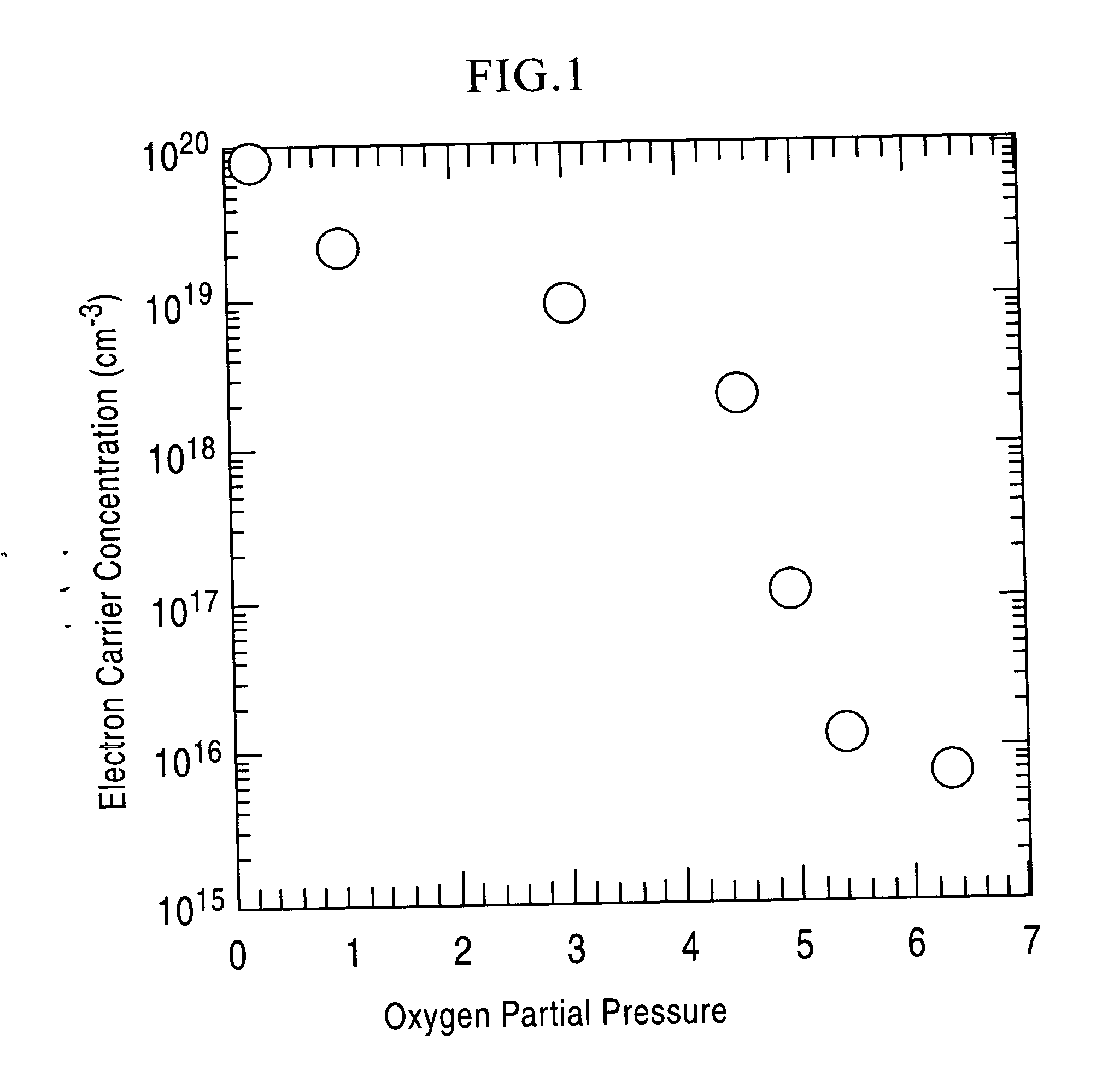

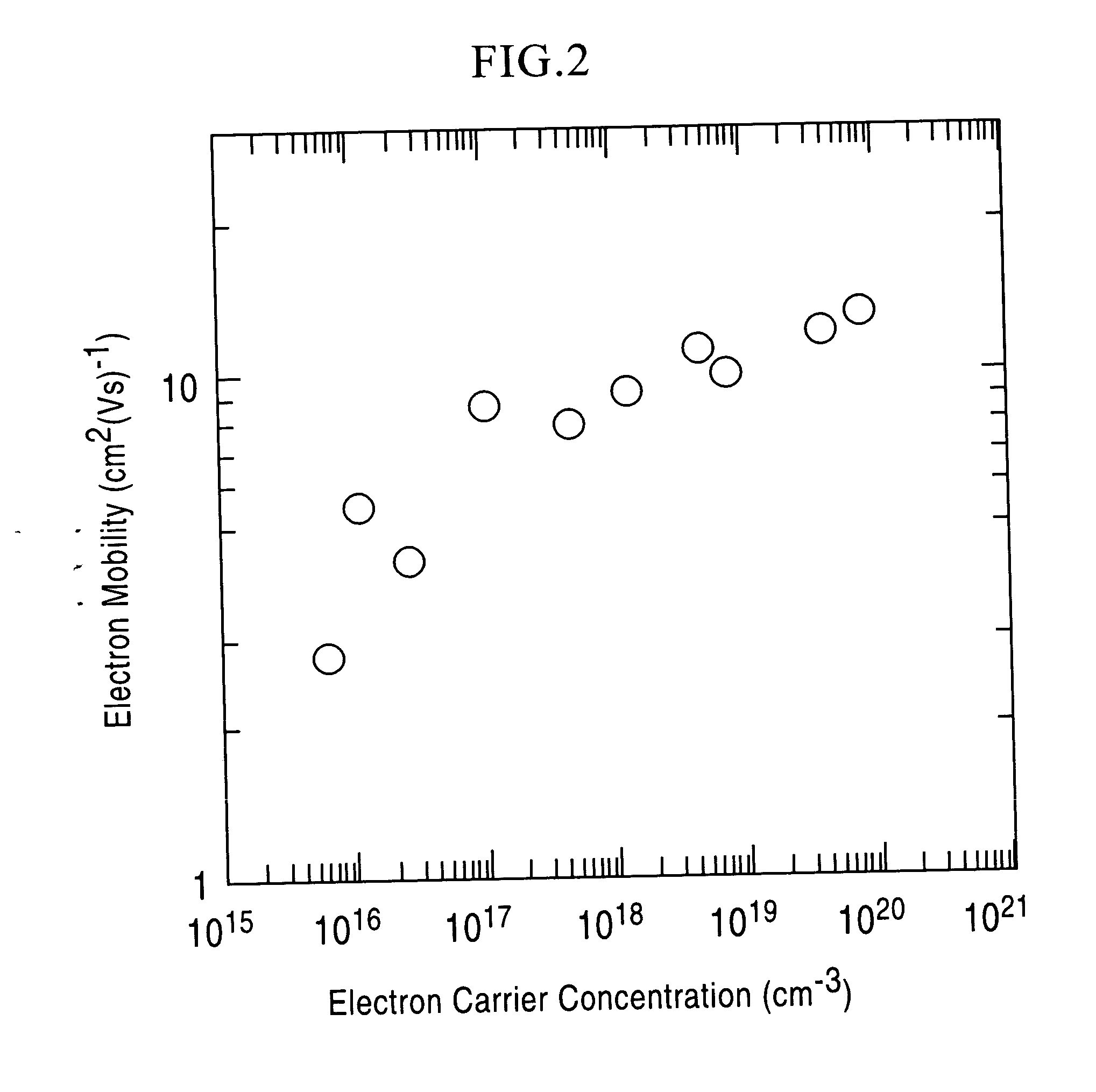

The present invention relates to an amorphous oxide and a thin film transistor using the amorphous oxide. In particular, the present invention provides an amorphous oxide having an electron carrier concentration less than 1018 / cm3, and a thin film transistor using such an amorphous oxide. In a thin film transistor having a source electrode 6, a drain electrode 5, a gate electrode 4, a gate insulating film 3, and a channel layer 2, an amorphous oxide having an electron carrier concentration less than 1018 / cm3 is used in the channel layer 2.

Owner:JAPAN SCI & TECH CORP

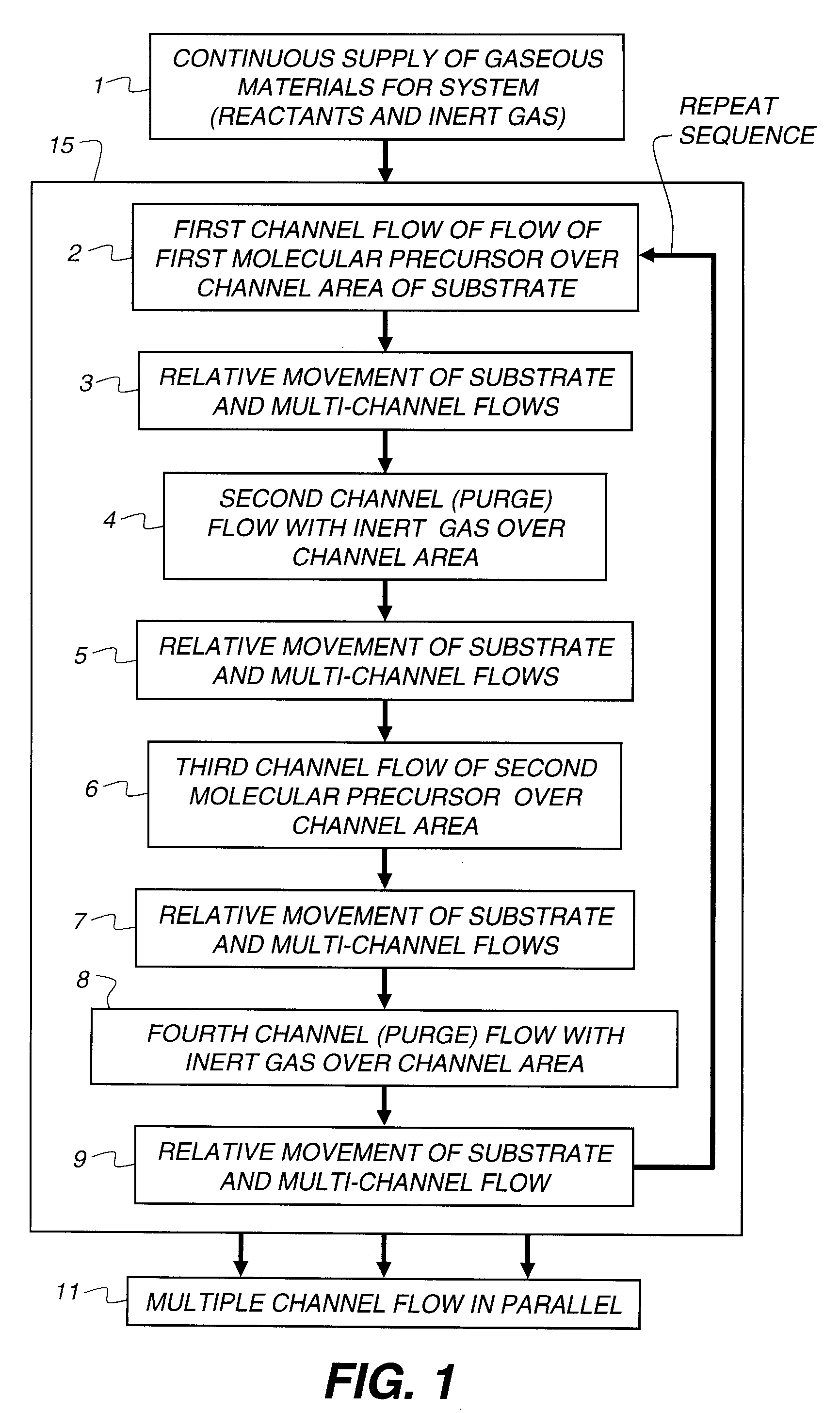

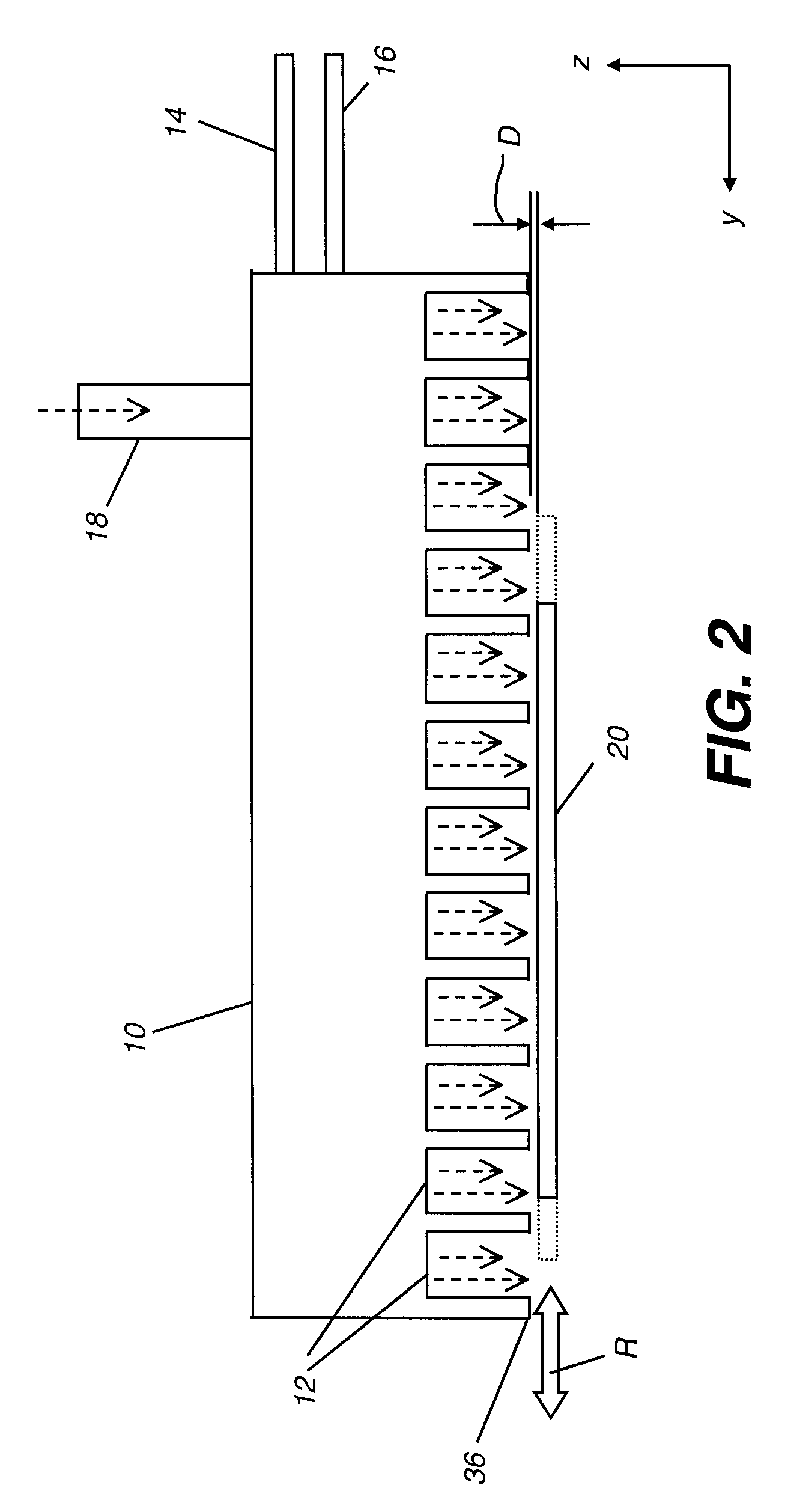

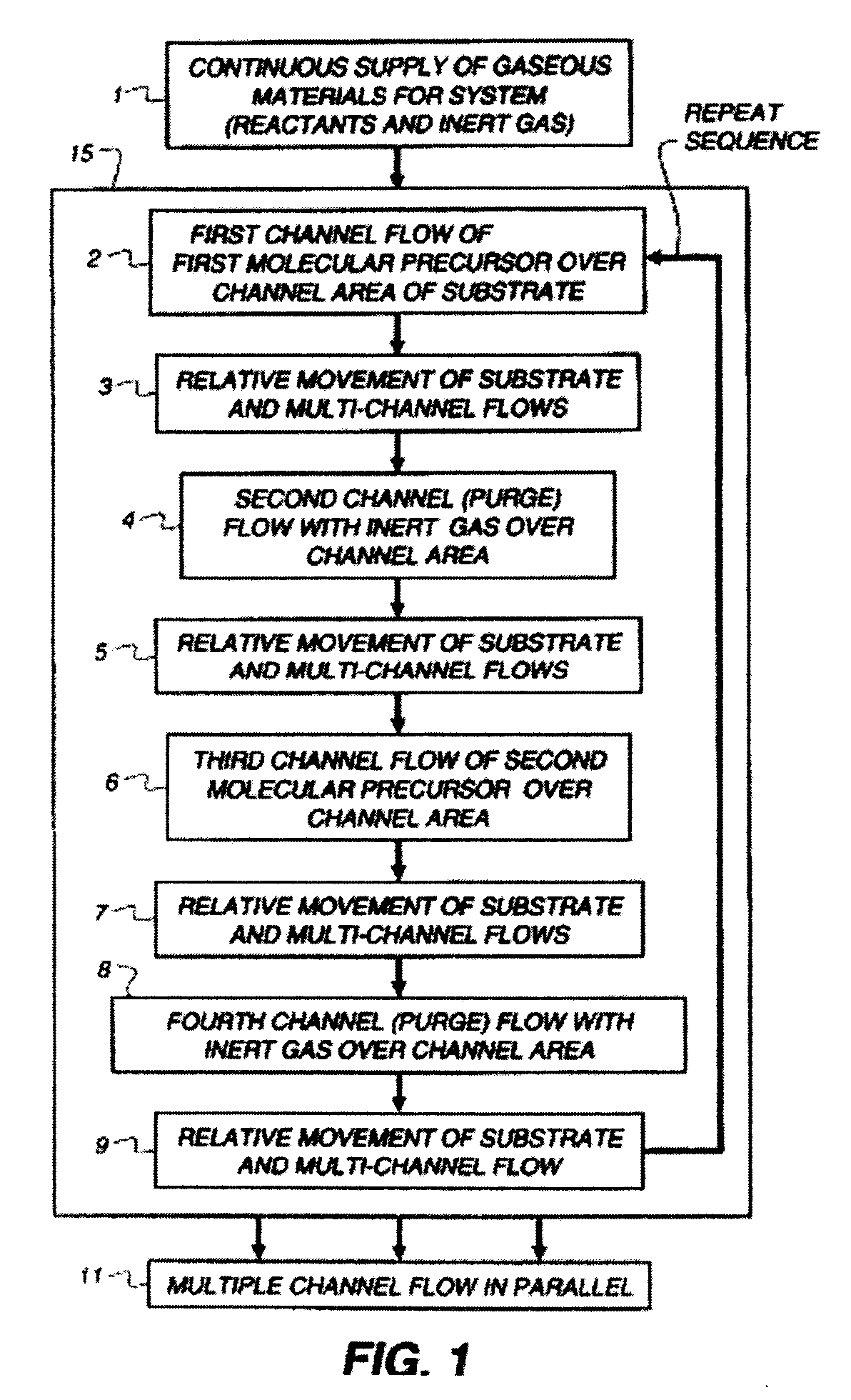

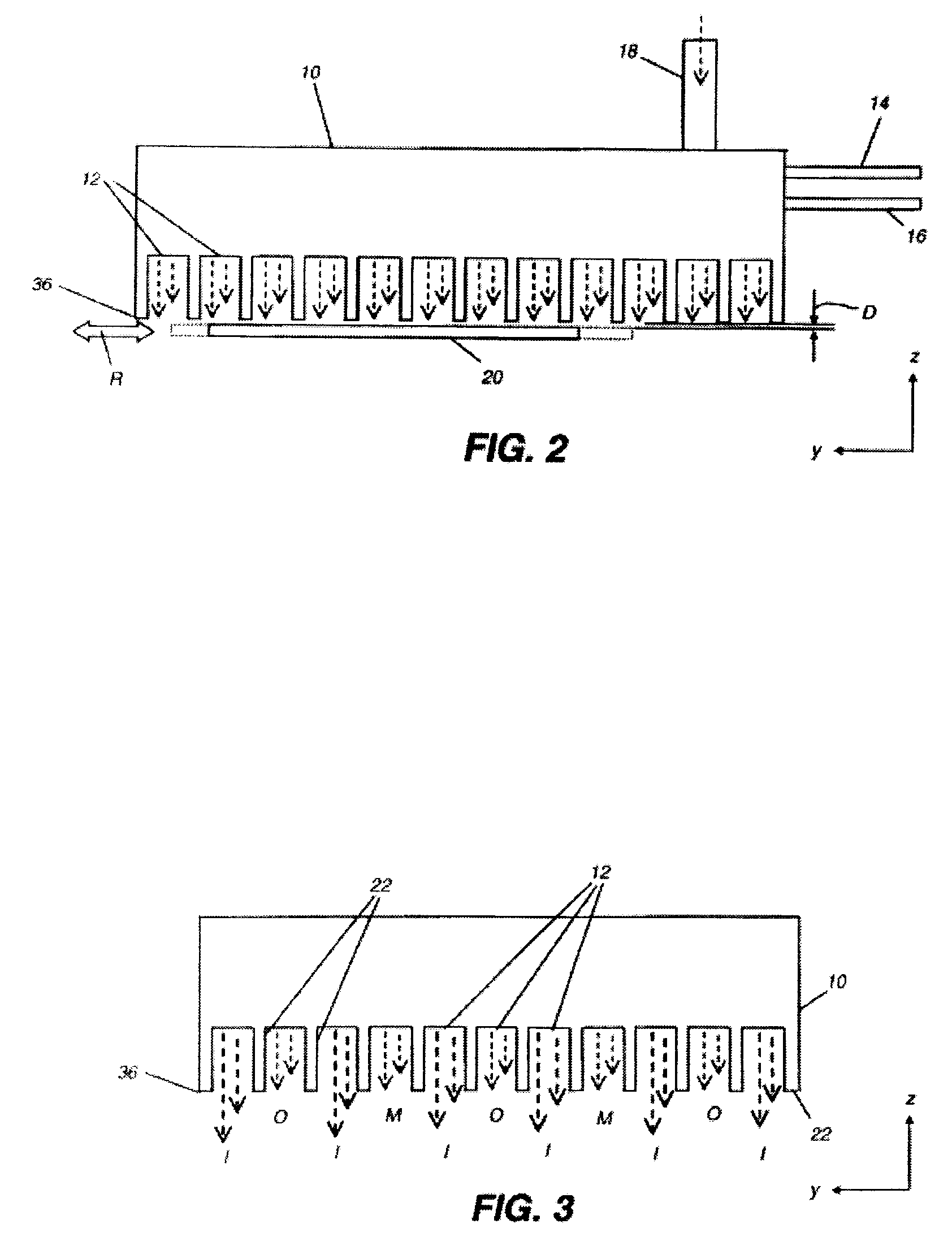

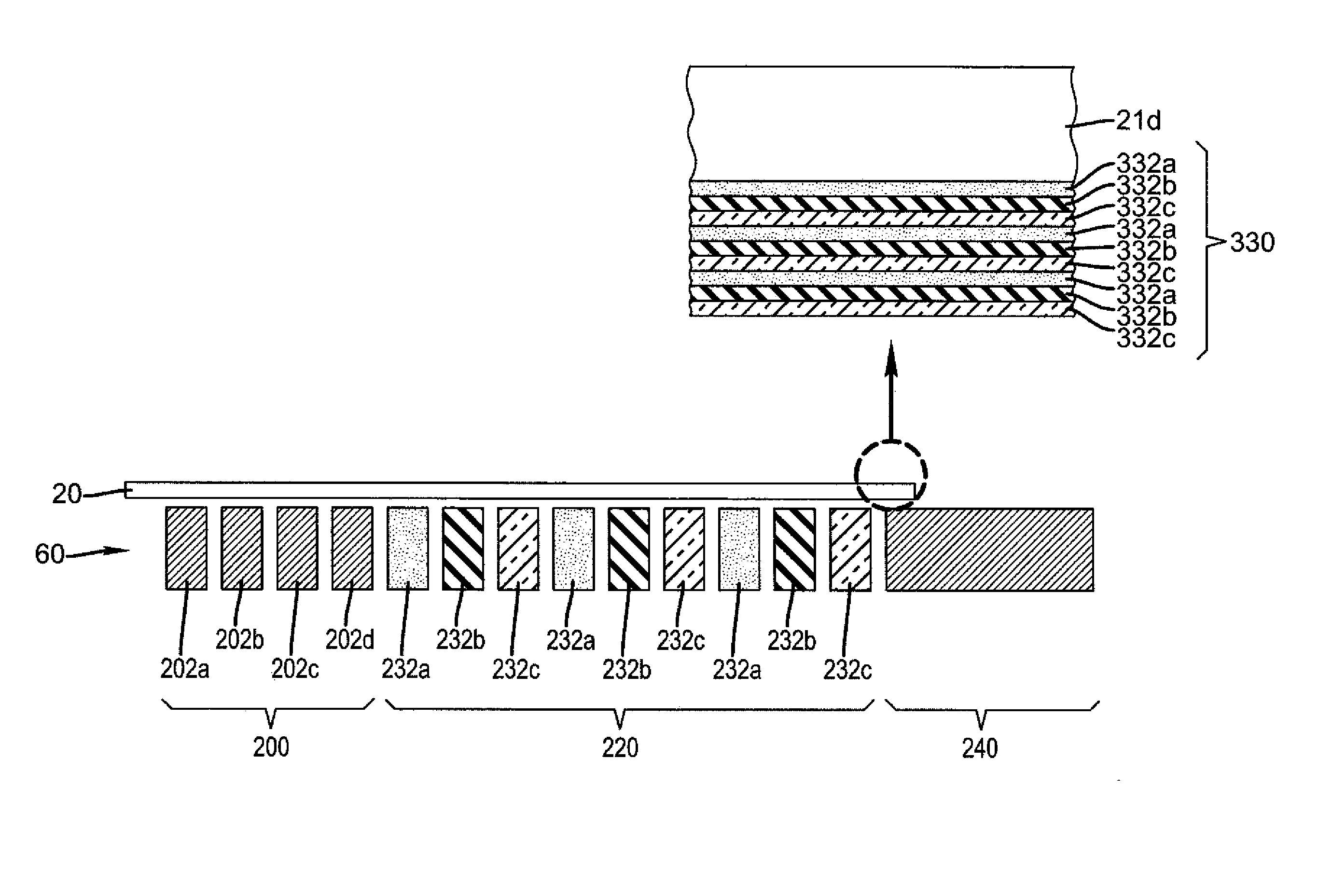

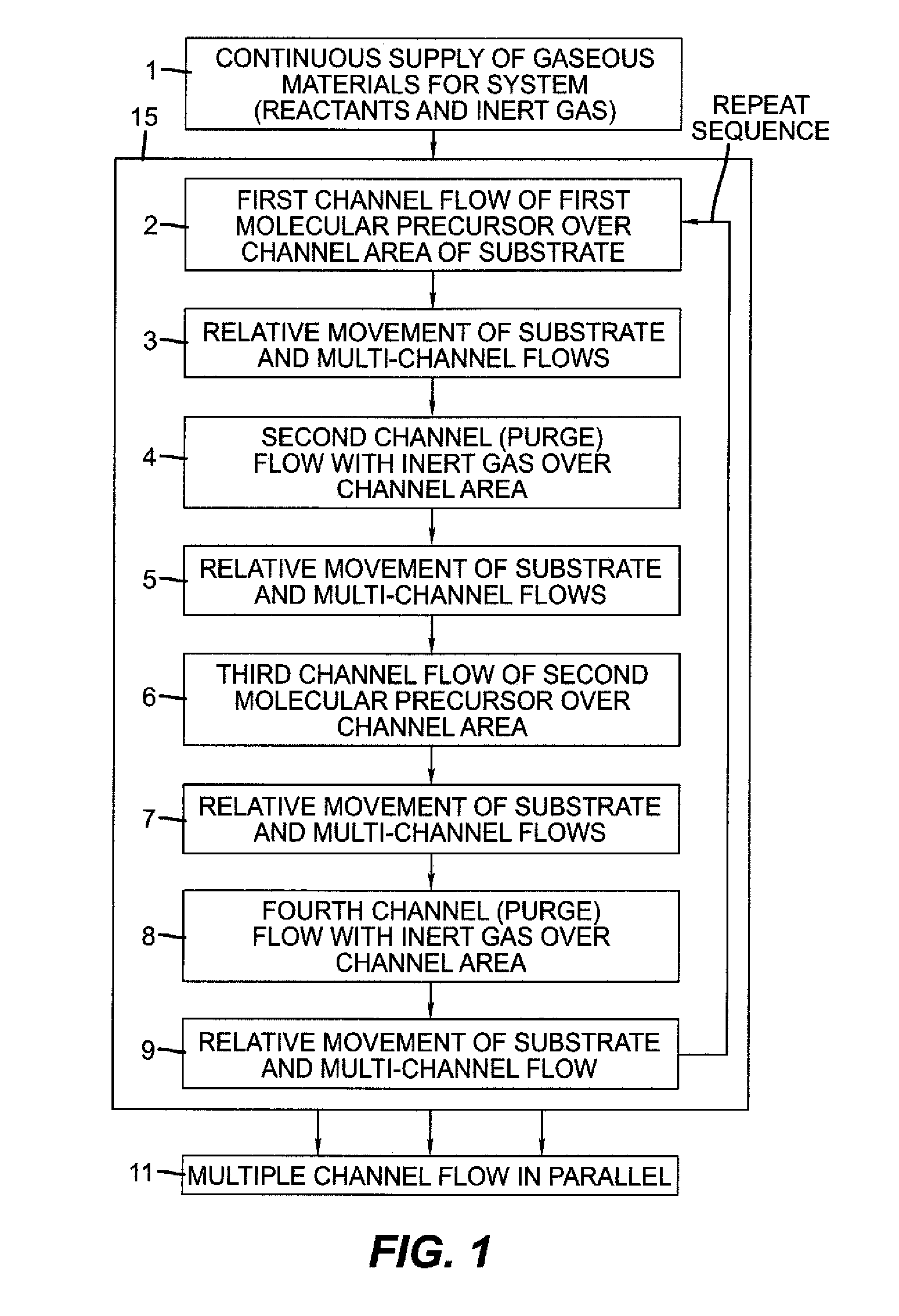

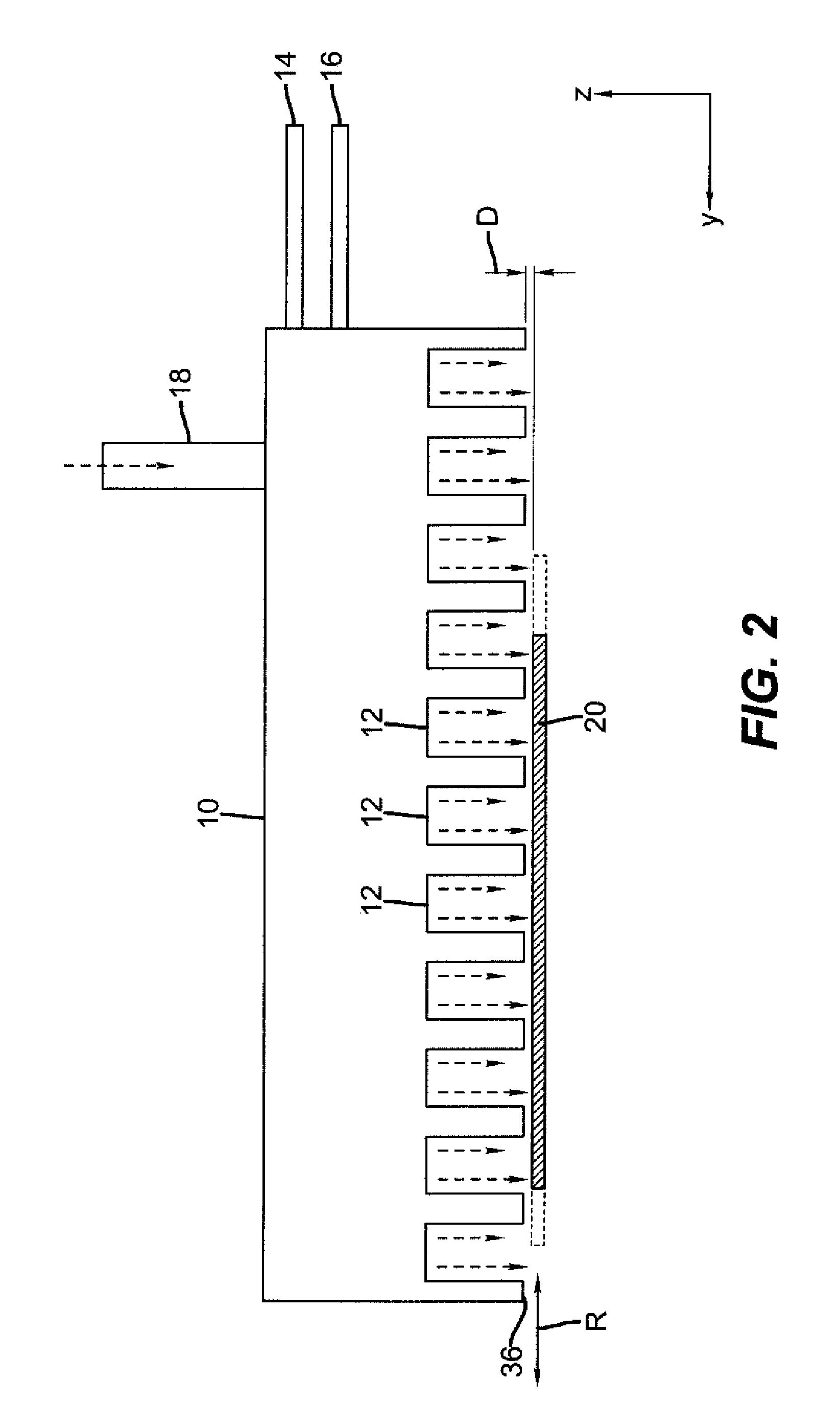

Process for atomic layer deposition

ActiveUS20080182358A1Suitable for processingAllowed to operateAdditive manufacturing apparatusSemiconductor/solid-state device manufacturingZincAtomic layer deposition

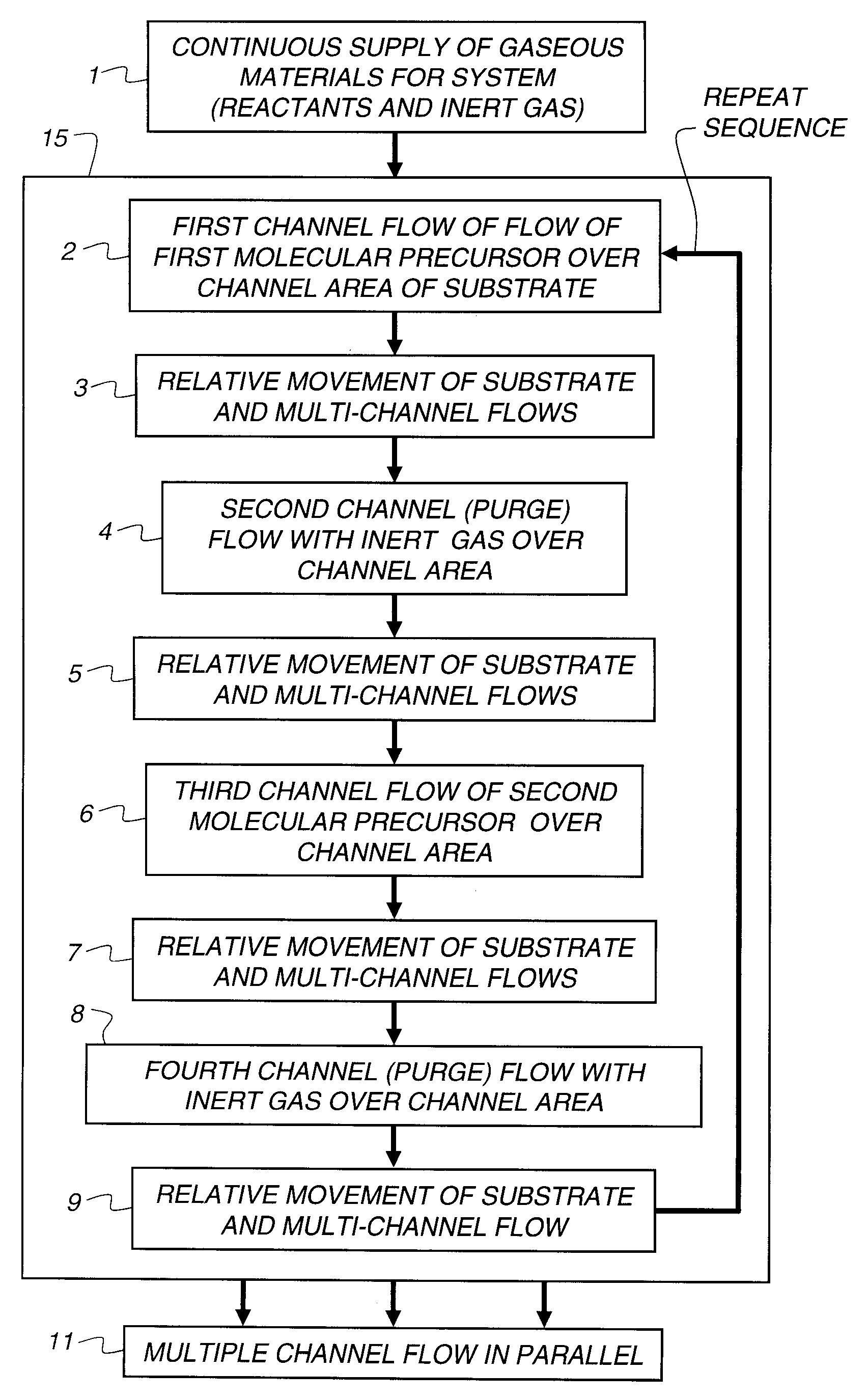

The present invention relates to a process of making a zinc-oxide-based thin film semiconductor, for use in a transistor, comprising thin film deposition onto a substrate comprising providing a plurality of gaseous materials comprising at least first, second, and third gaseous materials, wherein the first gaseous material is a zinc-containing volatile material and the second gaseous material is reactive therewith such that when one of the first or second gaseous materials are on the surface of the substrate the other of the first or second gaseous materials will react to deposit a layer of material on the substrate and wherein the third gaseous material is inert with respect to reacting with the first or second gaseous materials.

Owner:EASTMAN KODAK CO

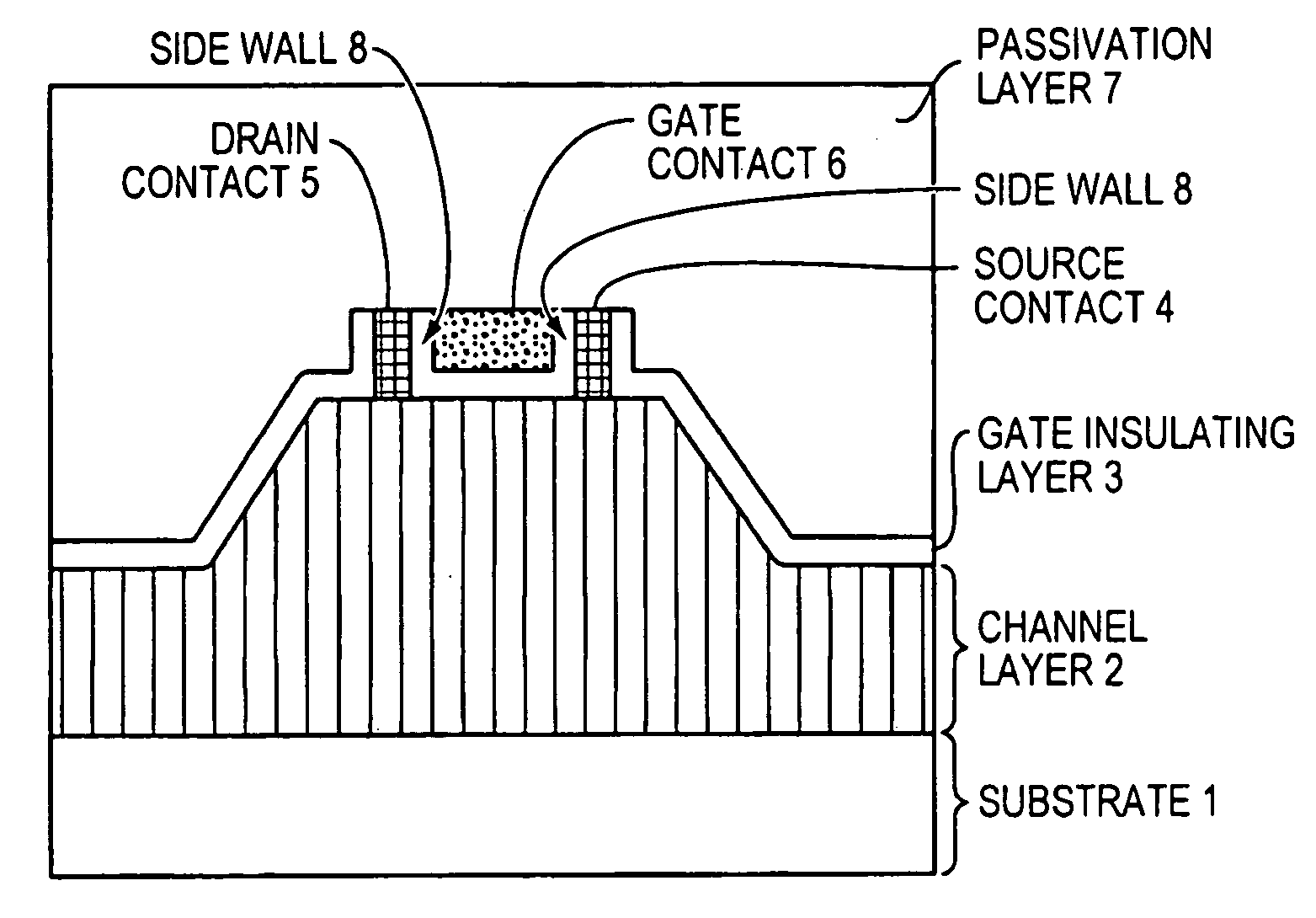

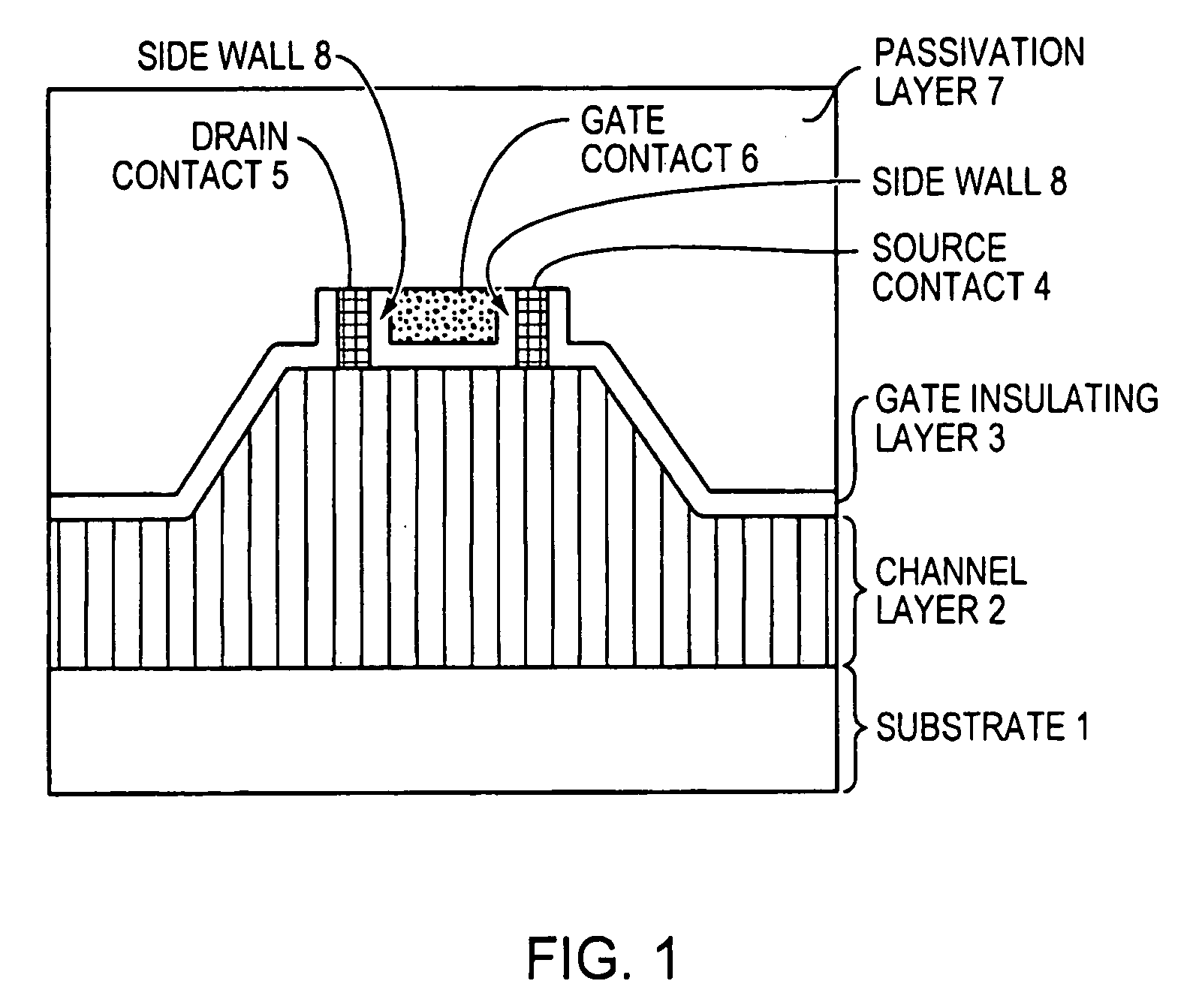

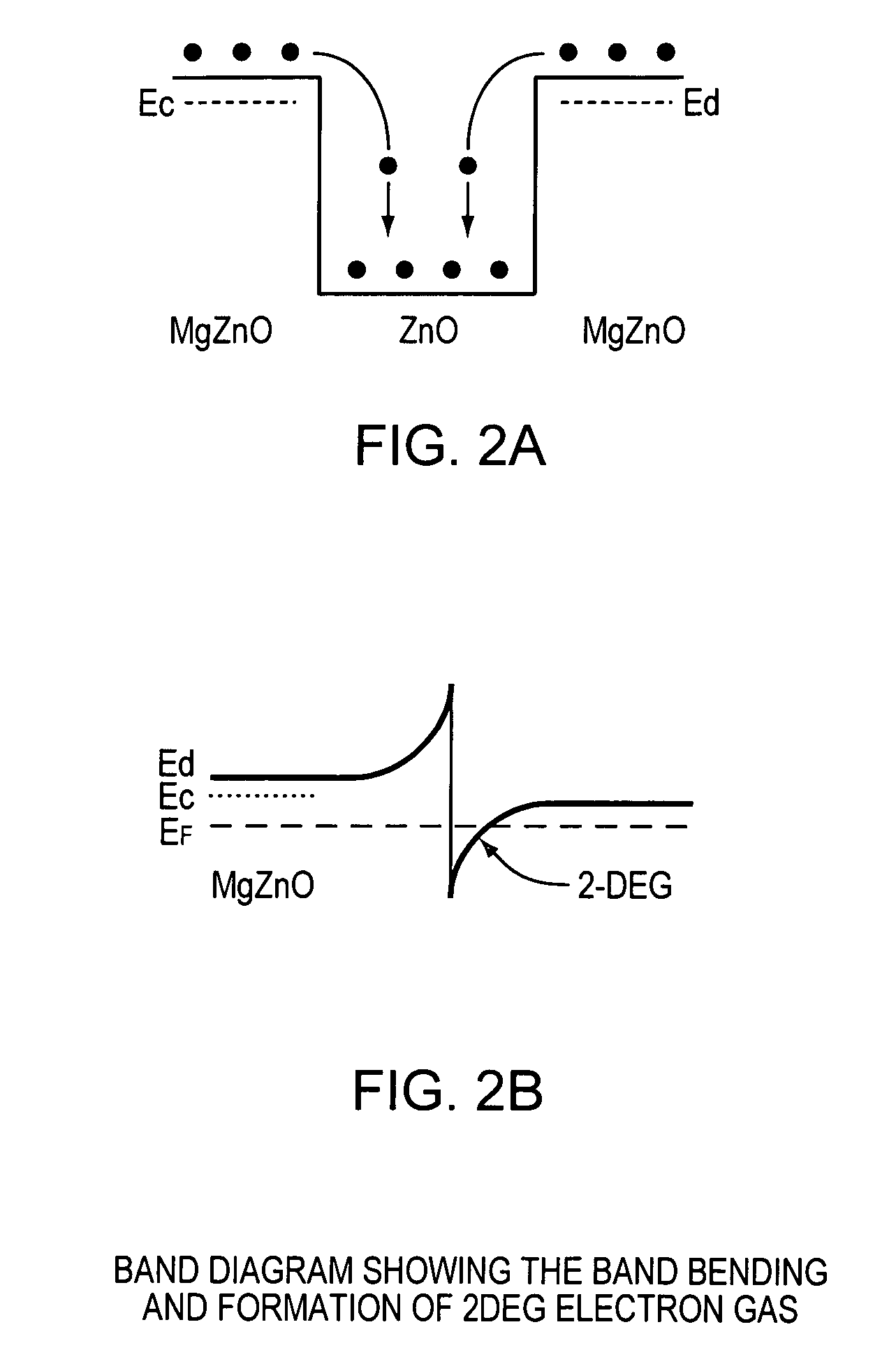

High-electron mobility transistor with zinc oxide

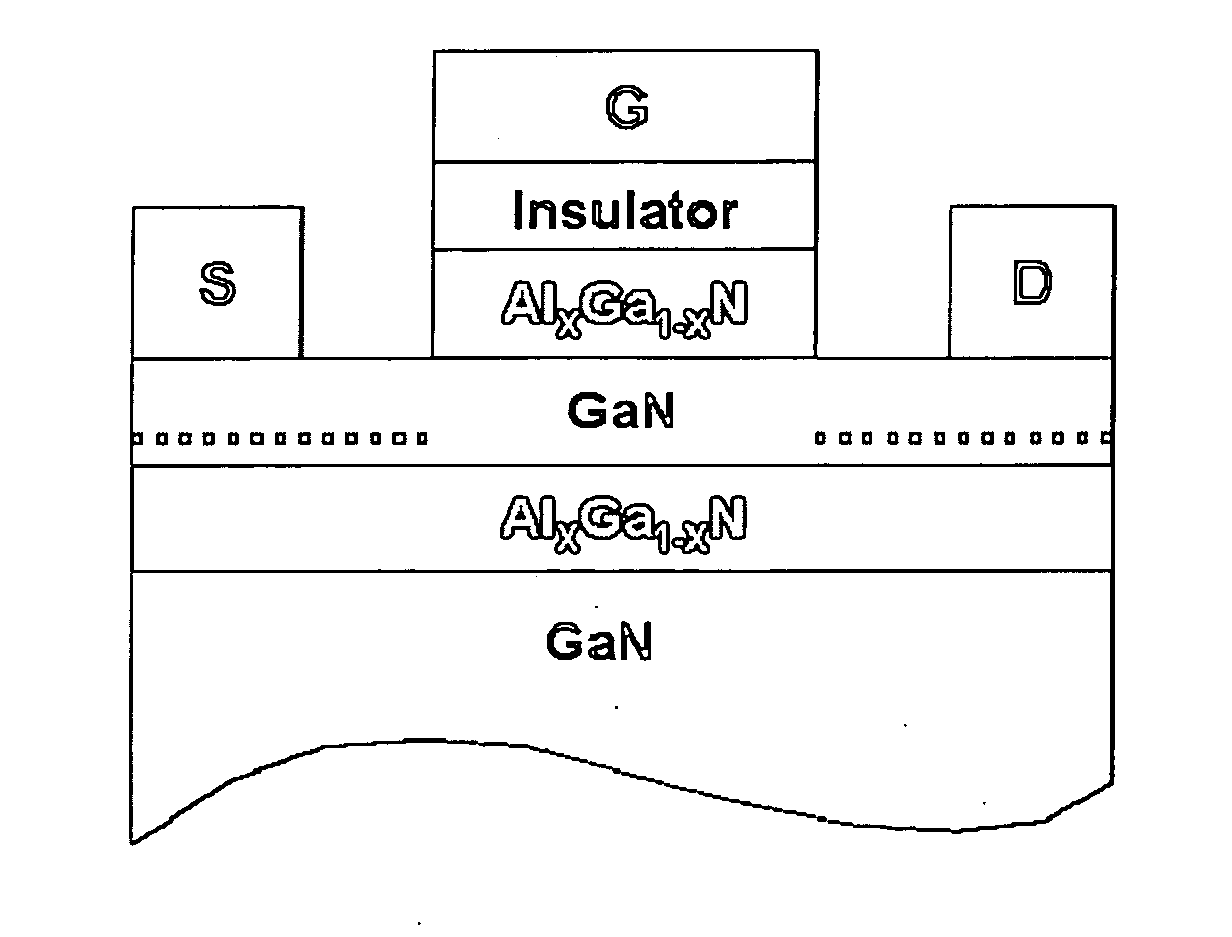

InactiveUS7105868B2Increase heightHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierField-effect transistor

A zinc oxide (ZnO) field effect transistor exhibits large input amplitude by using a gate insulating layer. A channel layer and the gate insulating layer are sequentially laminated on a substrate. A gate electrode is formed on the gate insulating layer. A source contact and a drain contact are disposed at the both sides of the gate contact and are electrically connected to the channel layer via openings. The channel layer is formed from n-type ZnO. The gate insulating layer is made from aluminum nitride / aluminum gallium nitride (AlN / AlGaN) or magnesium zinc oxide (MgZnO), which exhibits excellent insulation characteristics, thus increasing the Schottky barrier and achieving large input amplitude. If the FET is operated in the enhancement mode, it is operable in a manner similar to a silicon metal oxide semiconductor field effect transistor (Si-MOS-type FET), resulting in the formation of an inversion layer.

Owner:NAUSE CATHERINE D

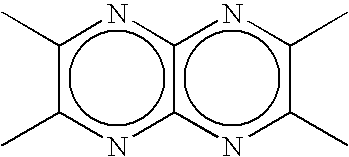

Organic electroluminescent device and material for organic electroluminescent device

ActiveUS20090167167A1Improve performanceHigh electron-accepting propertyOrganic chemistryDischarge tube luminescnet screensOrganic electroluminescenceMolecular physics

Disclosed is a novel compound useful as a constituent of an organic EL device. Also disclosed is a practical organic EL device using this compound. This organic EL device has low driving voltage, long life, and reduced leakage current. Specifically disclosed is a compound characterized by having at least one structure (1) shown below in a molecule. Structure (1)

Owner:IDEMITSU KOSAN CO LTD +1

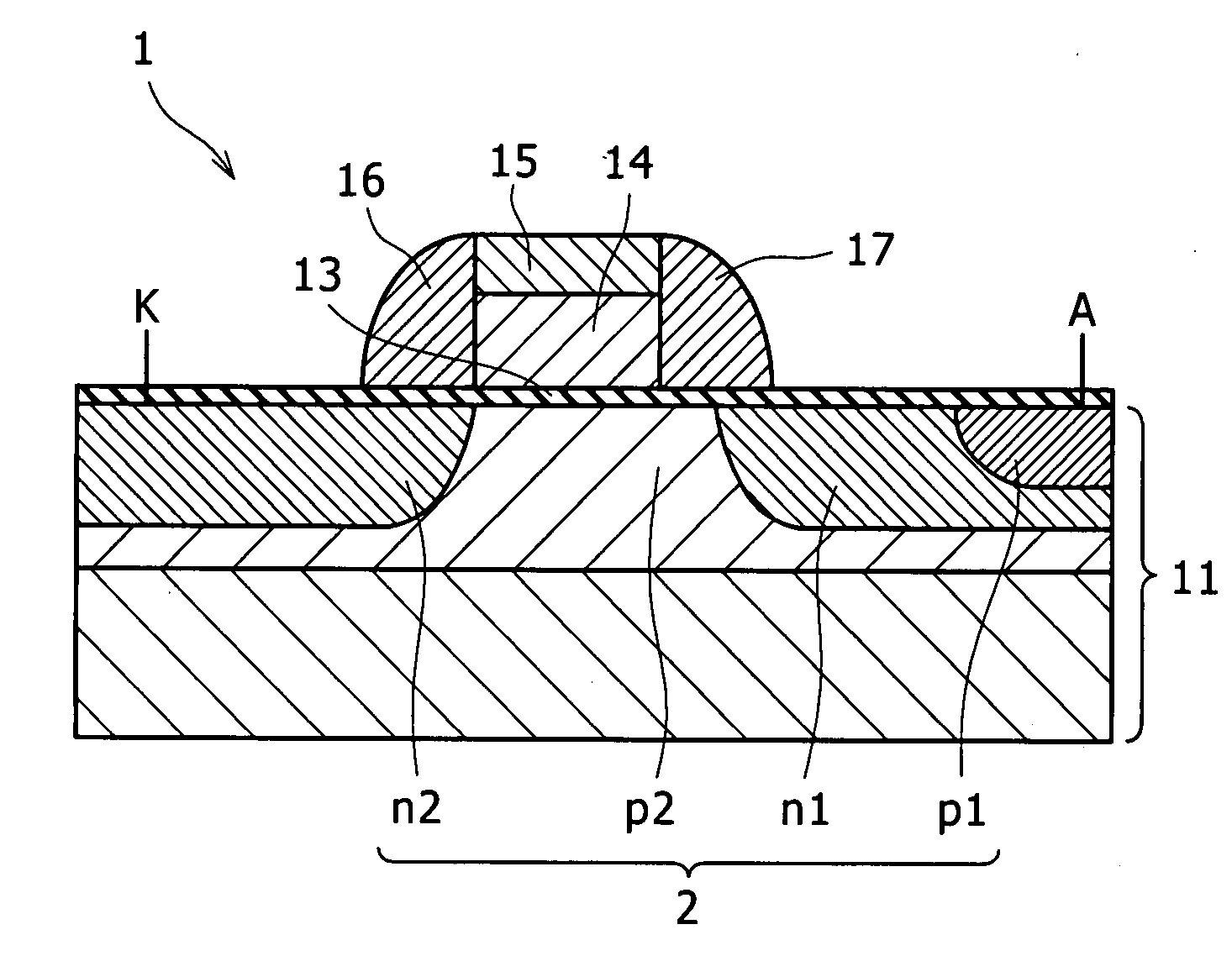

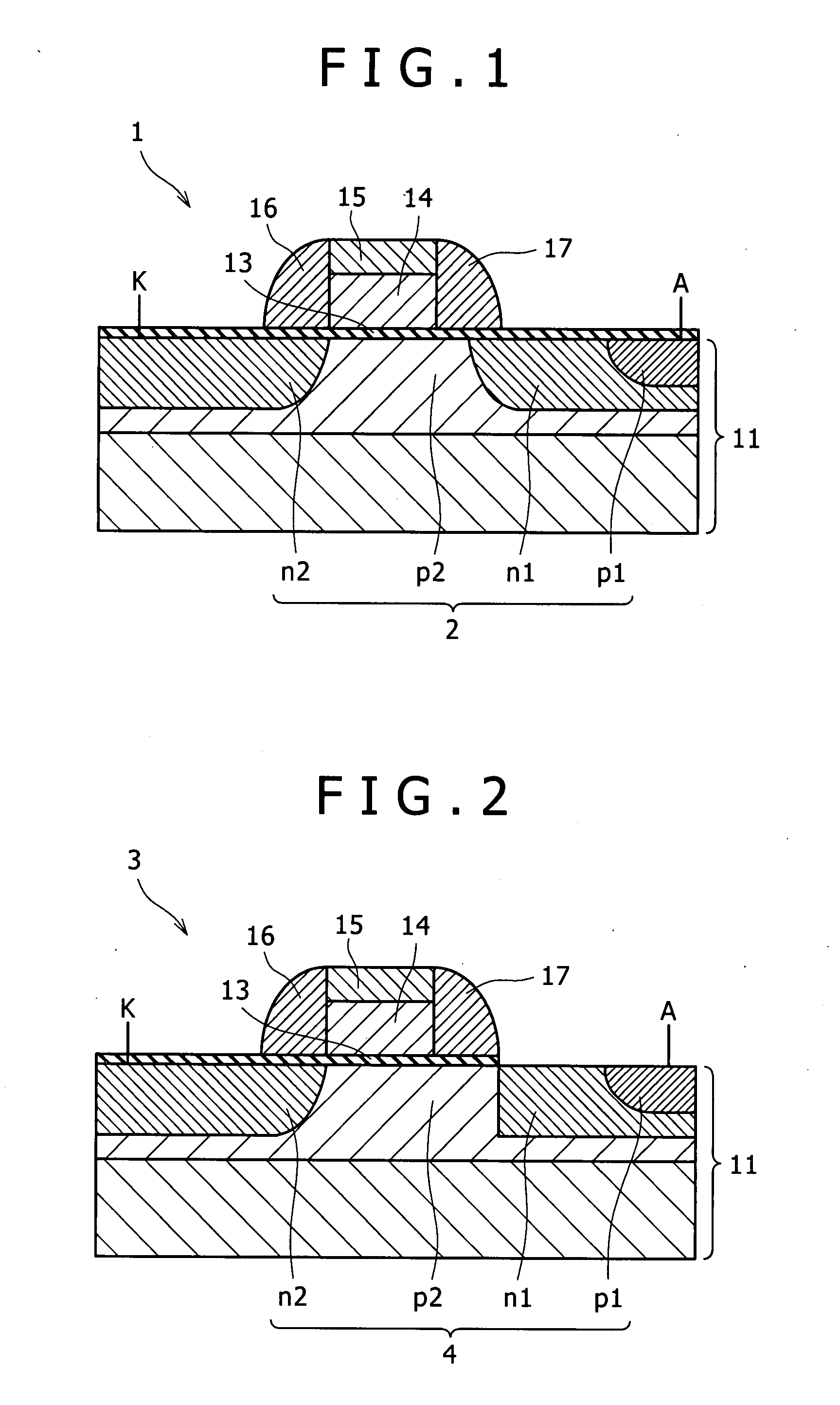

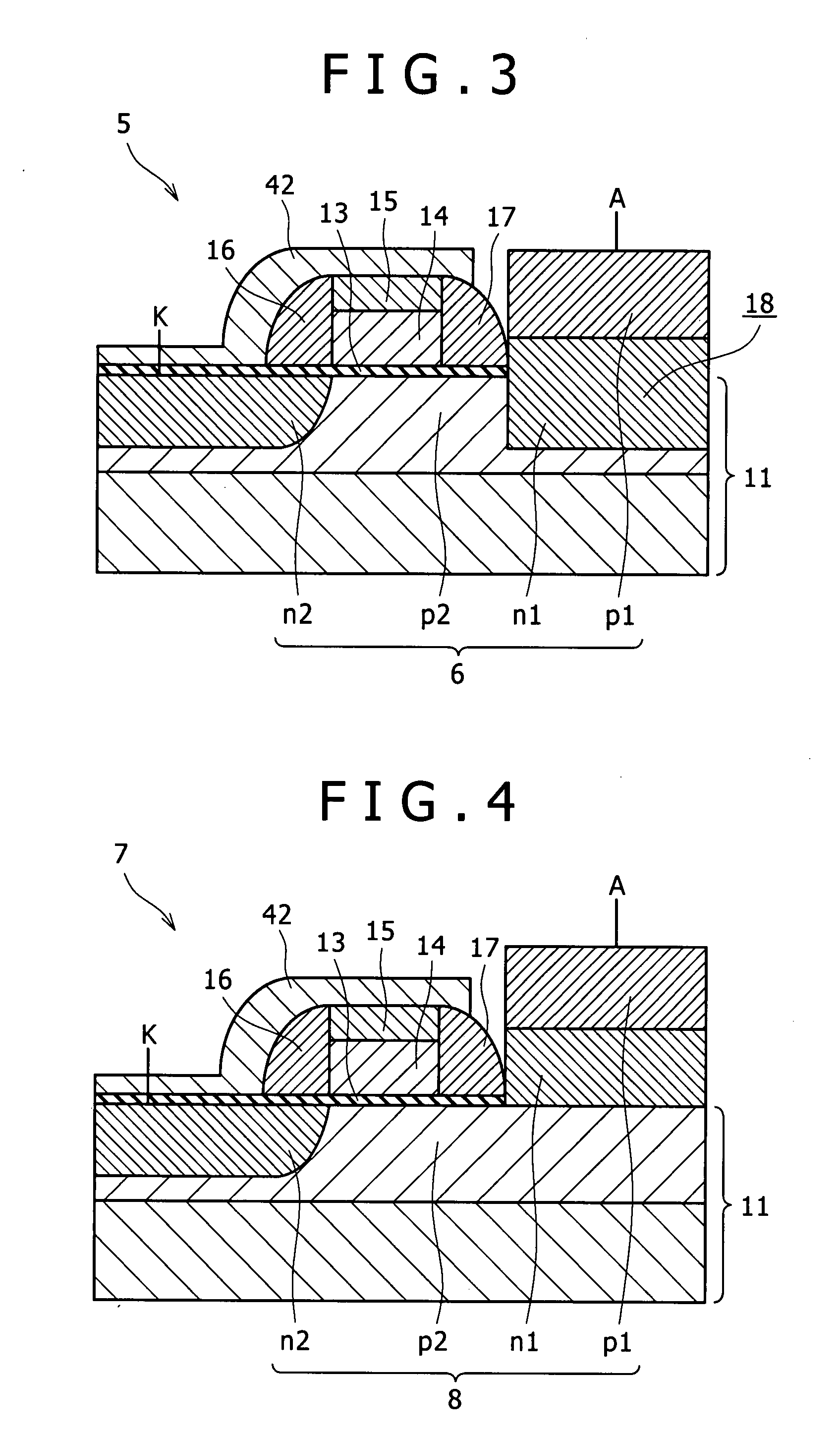

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20080042165A1Increase speedImprove mobilityThyristorSemiconductor/solid-state device manufacturingThyratronSemiconductor

A semiconductor device includes a thyristor configured to be formed through sequential joining of a first region of a first conductivity type, a second region of a second conductivity type opposite to the first conductivity type, a third region of the first conductivity type, and a fourth region of the second conductivity type, and have a gate formed over the third region. The first to fourth regions are formed in a silicon germanium region or germanium region.

Owner:SONY CORP

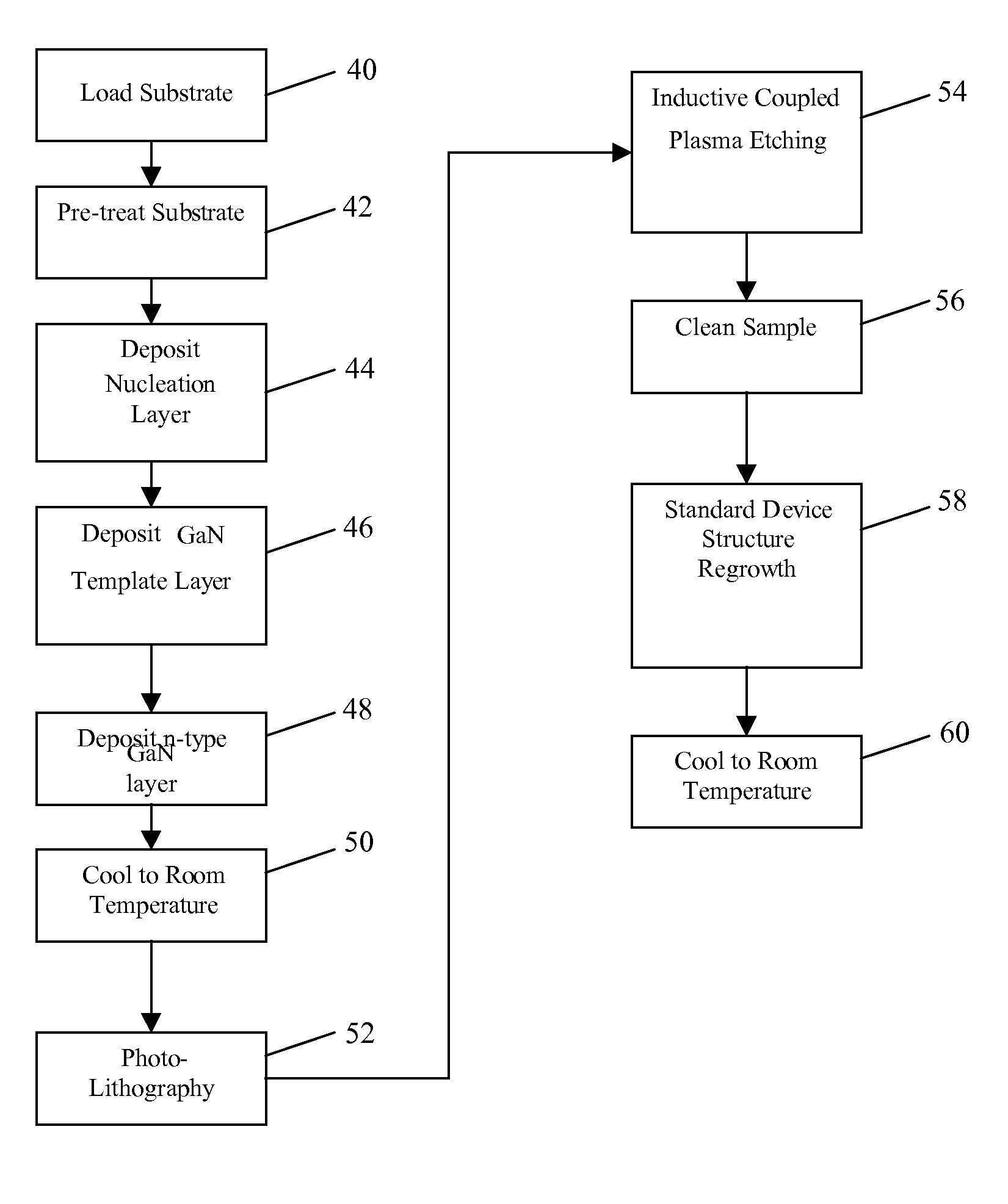

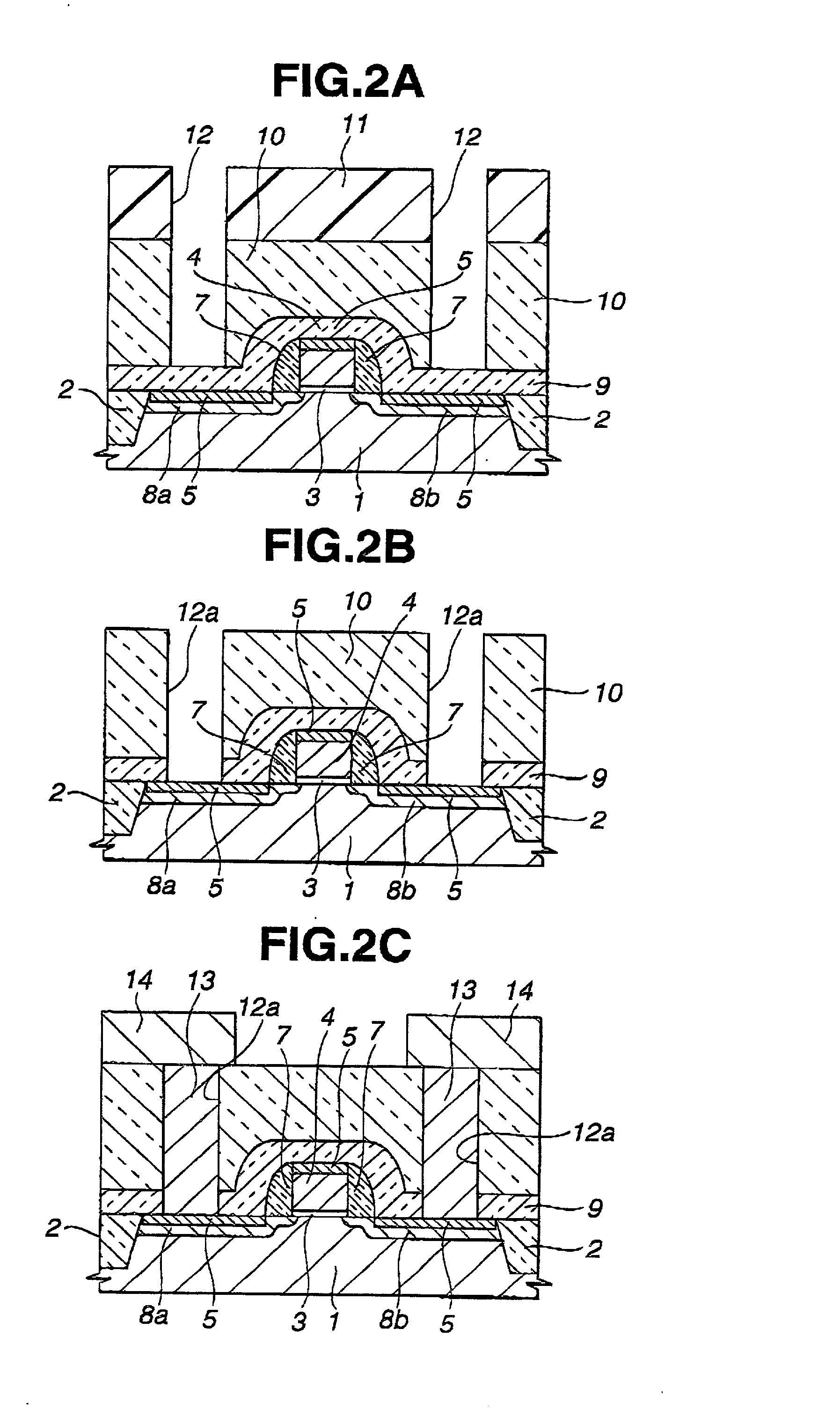

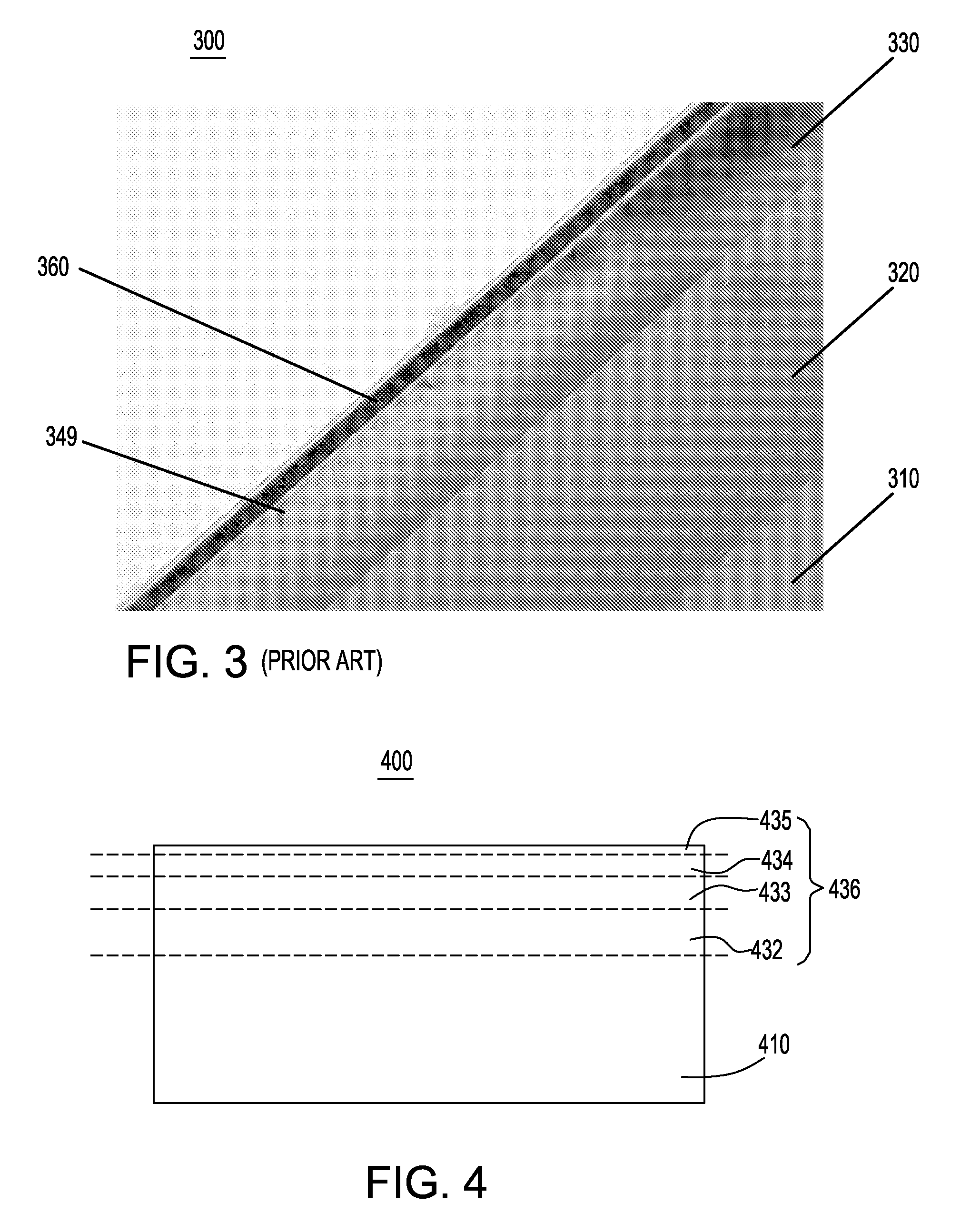

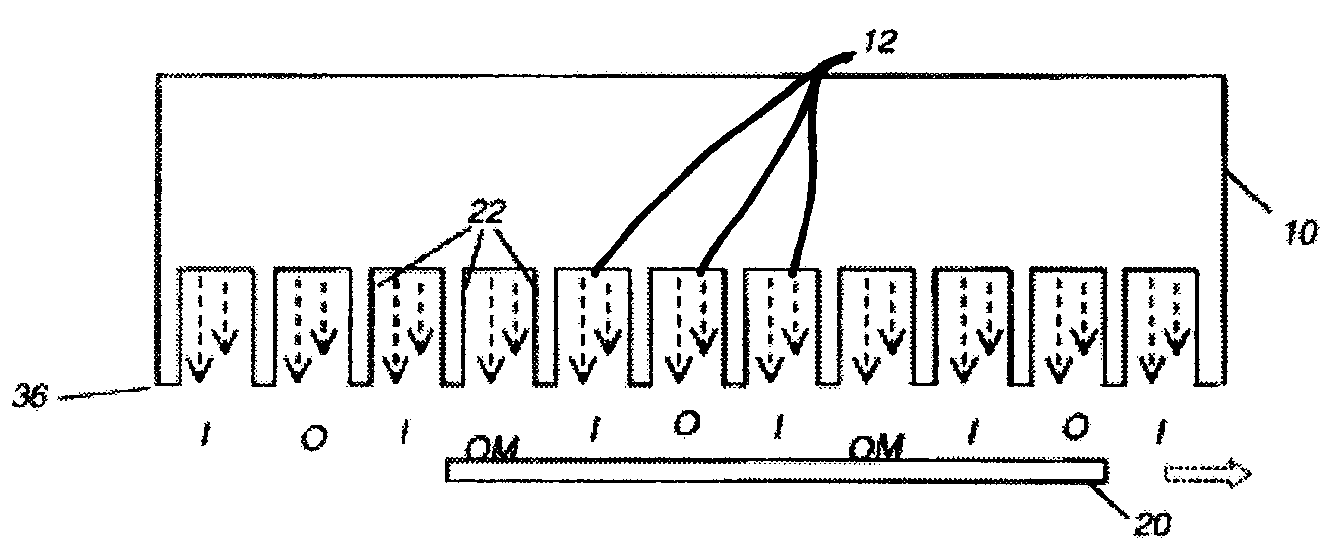

METHOD FOR GROWTH OF SEMIPOLAR (Al,In,Ga,B)N OPTOELECTRONIC DEVICES

ActiveUS20070252164A1Increase mobility of holeHigh electron mobilityPolycrystalline material growthSolid-state devicesLateral overgrowthCrystal orientation

A method of fabricating an optoelectronic device, comprising growing an active layer of the device on an oblique surface of a suitable material, wherein the oblique surface comprises a facetted surface. The present invention also discloses a method of fabricating the facetted surfaces. One fabrication process comprises growing an epitaxial layer on a suitable material, etching the epitaxial layer through a mask to form the facets having a specific crystal orientation, and depositing one or more active layers on the facets. Another method comprises growing a layer of material using a lateral overgrowth technique to produce a facetted surface, and depositing one or more active layers on the facetted surfaces. The facetted surfaces are typically semipolar planes.

Owner:RGT UNIV OF CALIFORNIA

Enhanced deposition control in fabricating devices in a semiconductor wafer

InactiveUS20020081794A1Easy to controlHigh electron mobilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductorSilicon nitride

A method for an enhanced deposition control, comprises forming at least one device within a substrate of a semiconductor wafer, and depositing a silicon nitride layer over the wafer in a reactor at a pressure of at least approximately 104 Pa.

Owner:NEC ELECTRONICS CORP

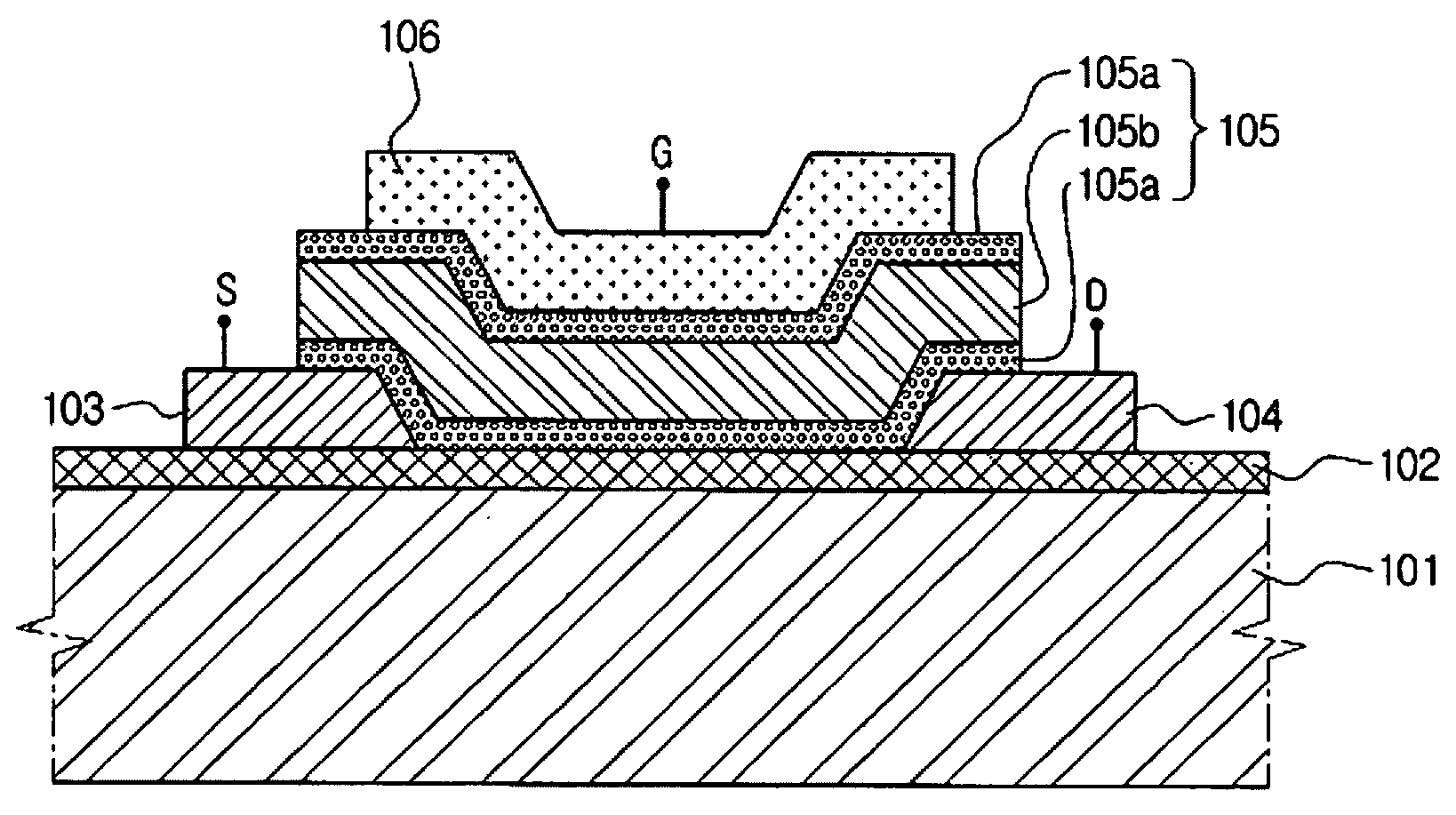

Thin Film Transistor

InactiveUS20090278120A1High electron mobilityMinimize occurrenceTransistorHysteresisElectron mobility

There is provided a thin film transistor (TFT) capable of improving electron mobility and minimizing the occurrence of hysteresis due to traps. The TFT includes a channel layer and a gate insulating layer, wherein the channel layer is made of an oxide semiconductor. In the TFT, the gate insulating layer includes one or more first dielectric layer and a second dielectric layer, and the first dielectric layer has a dielectric constant different from that of the second dielectric layer.

Owner:KOREA INST OF SCI & TECH

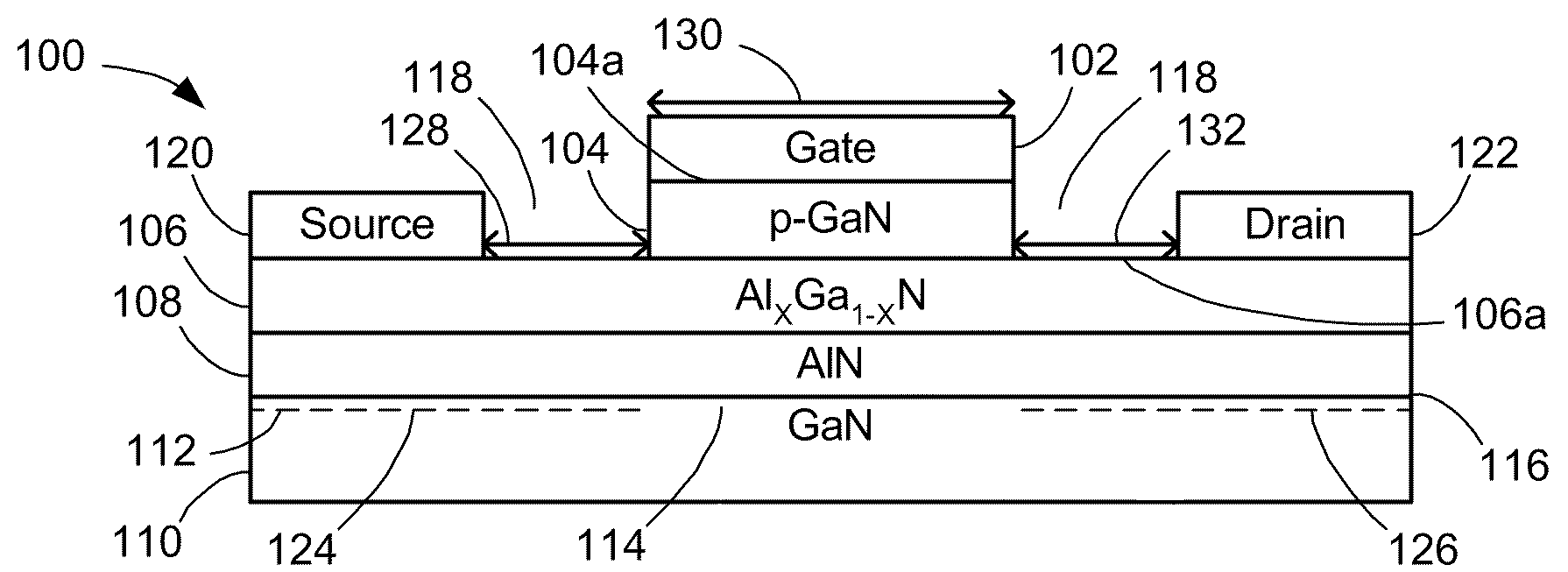

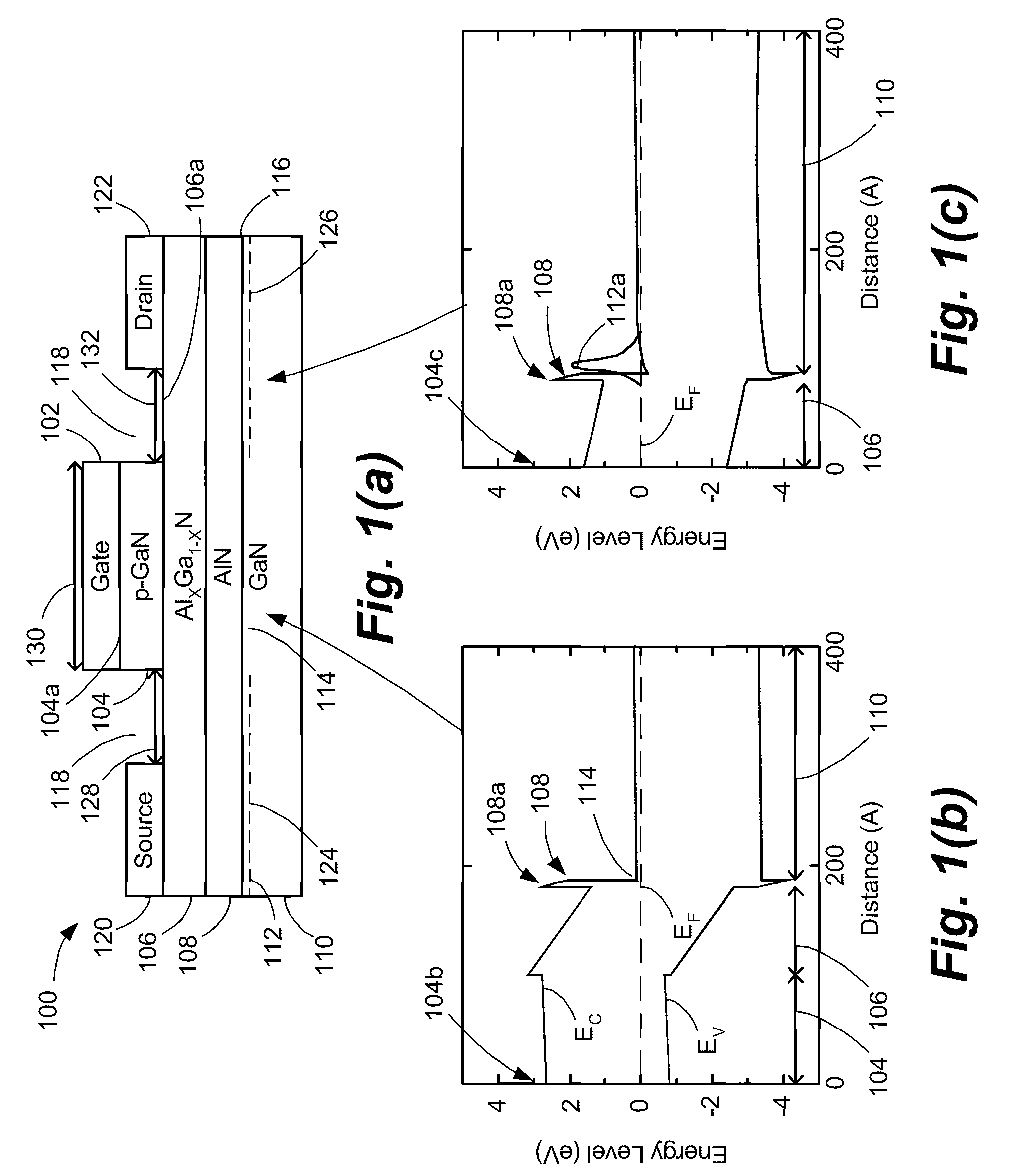

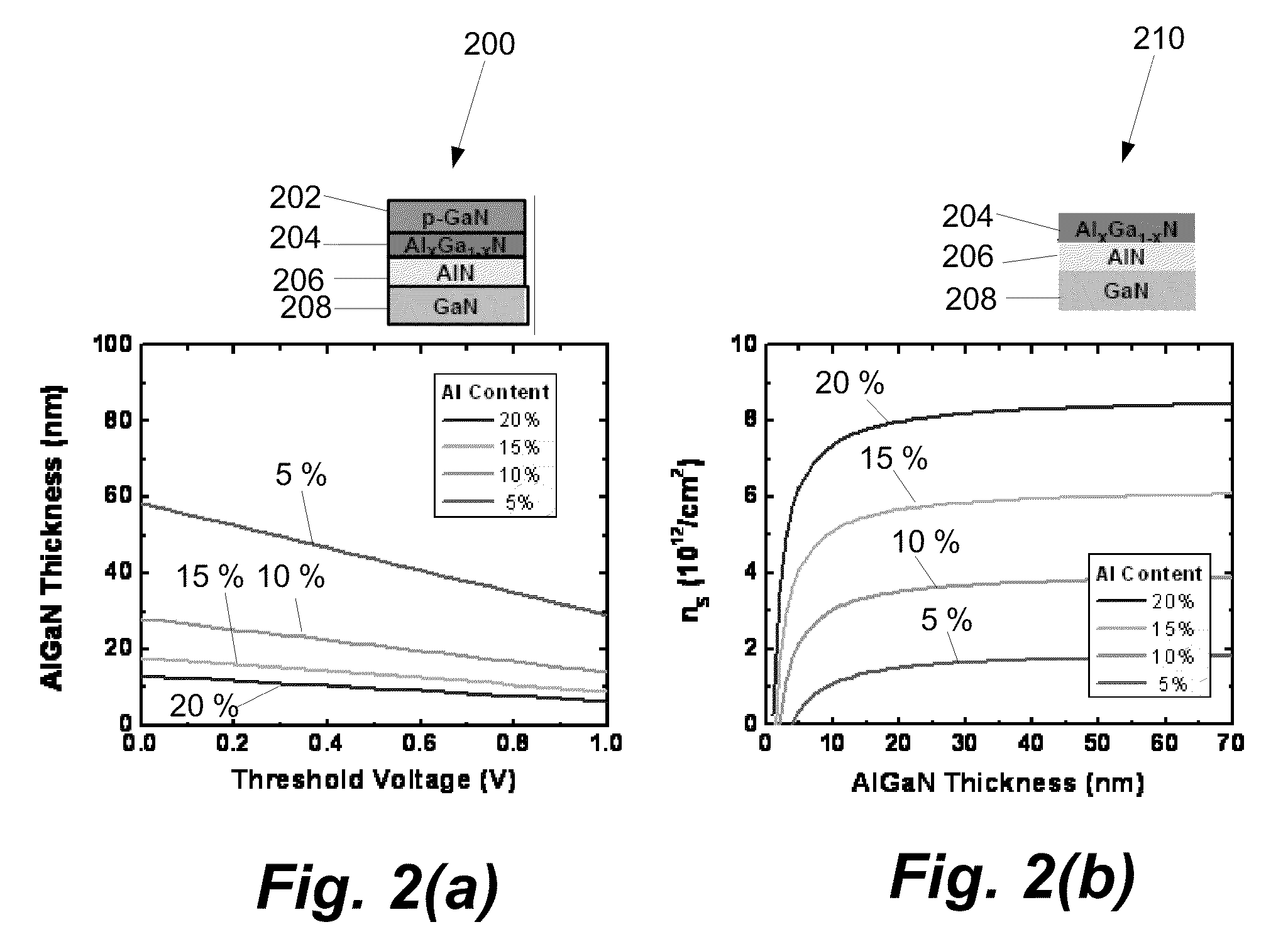

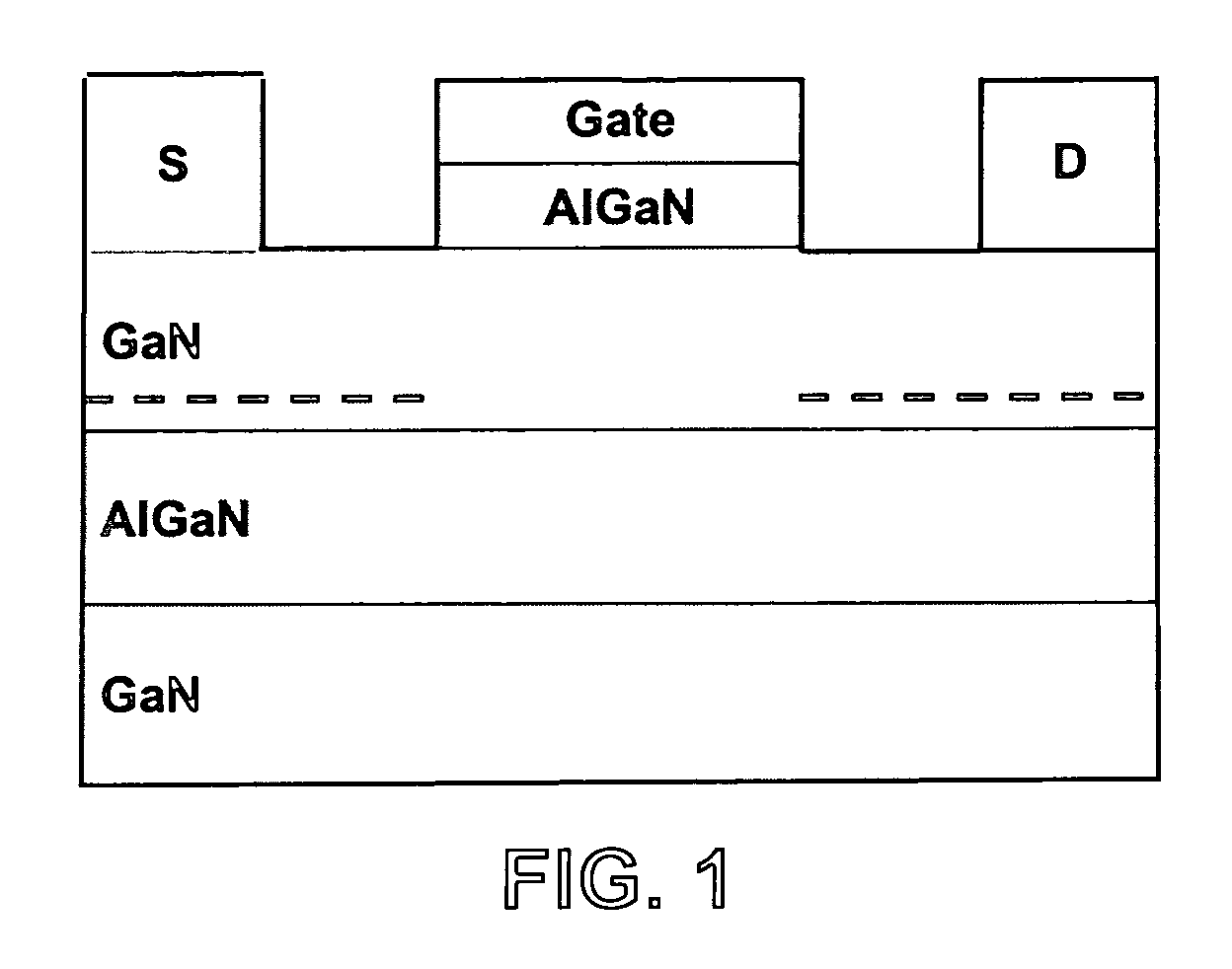

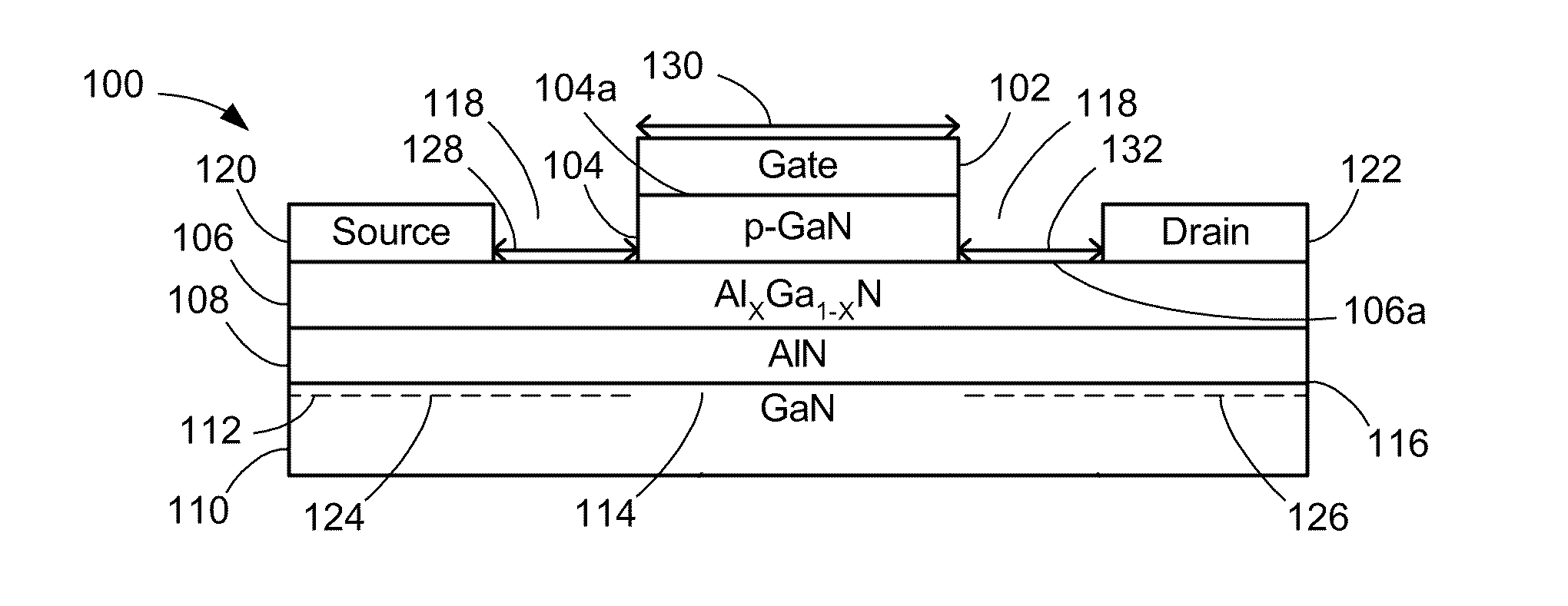

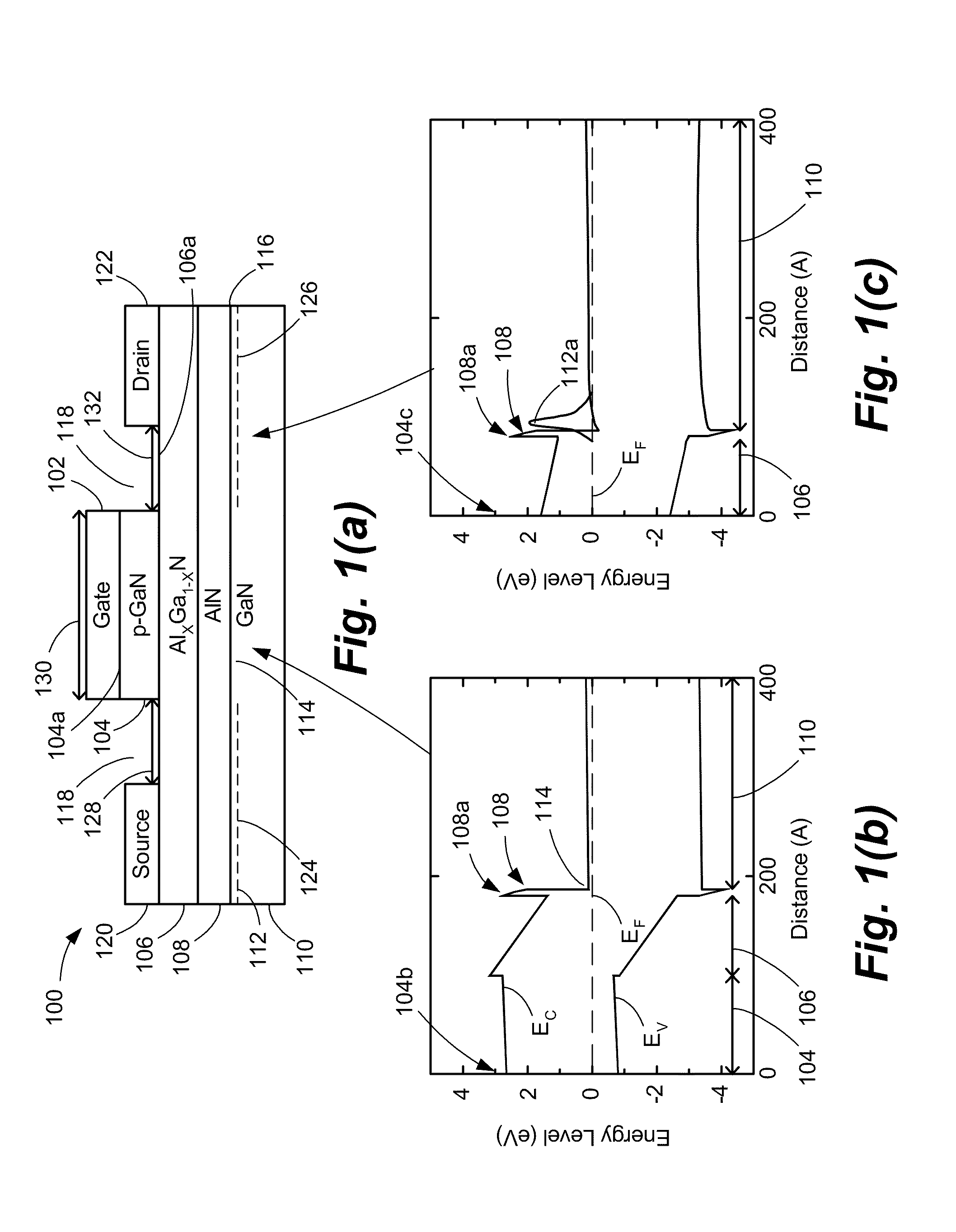

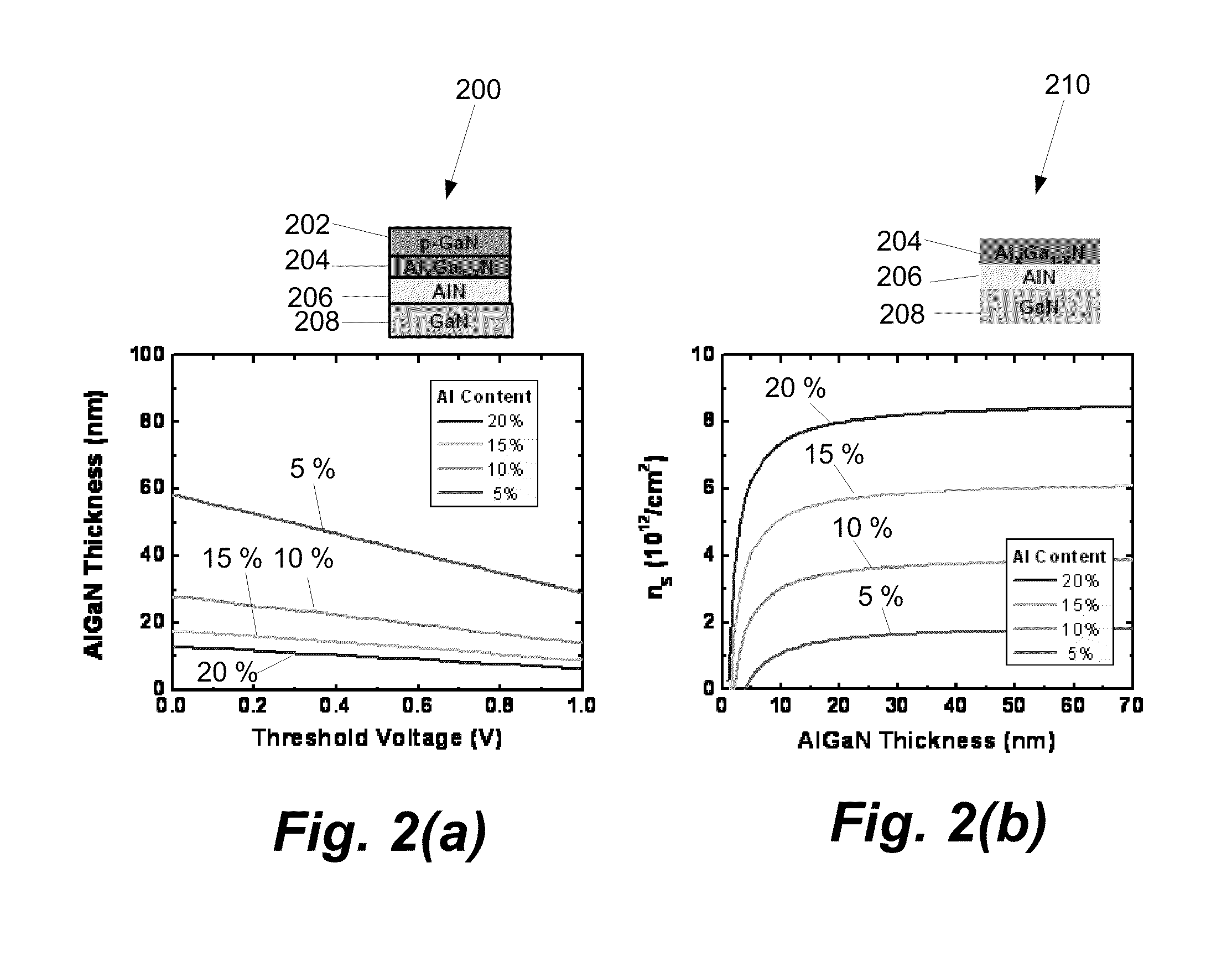

P-GaN/AlGaN/AlN/GaN ENHANCEMENT-MODE FIELD EFFECT TRANSISTOR

ActiveUS20080296618A1Lower on-resistanceHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorField-effect transistor

An enhancement mode High Electron Mobility Transistor (HEMT) comprising a p-type nitride layer between the gate and a channel of the HEMT, for reducing an electron population under the gate. The HEMT may also comprise an Aluminum Nitride (AlN) layer between an AlGaN layer and buffer layer of the HEMT to reduce an on resistance of a channel.

Owner:RGT UNIV OF CALIFORNIA

Complex oxides for use in semiconductor devices and related methods

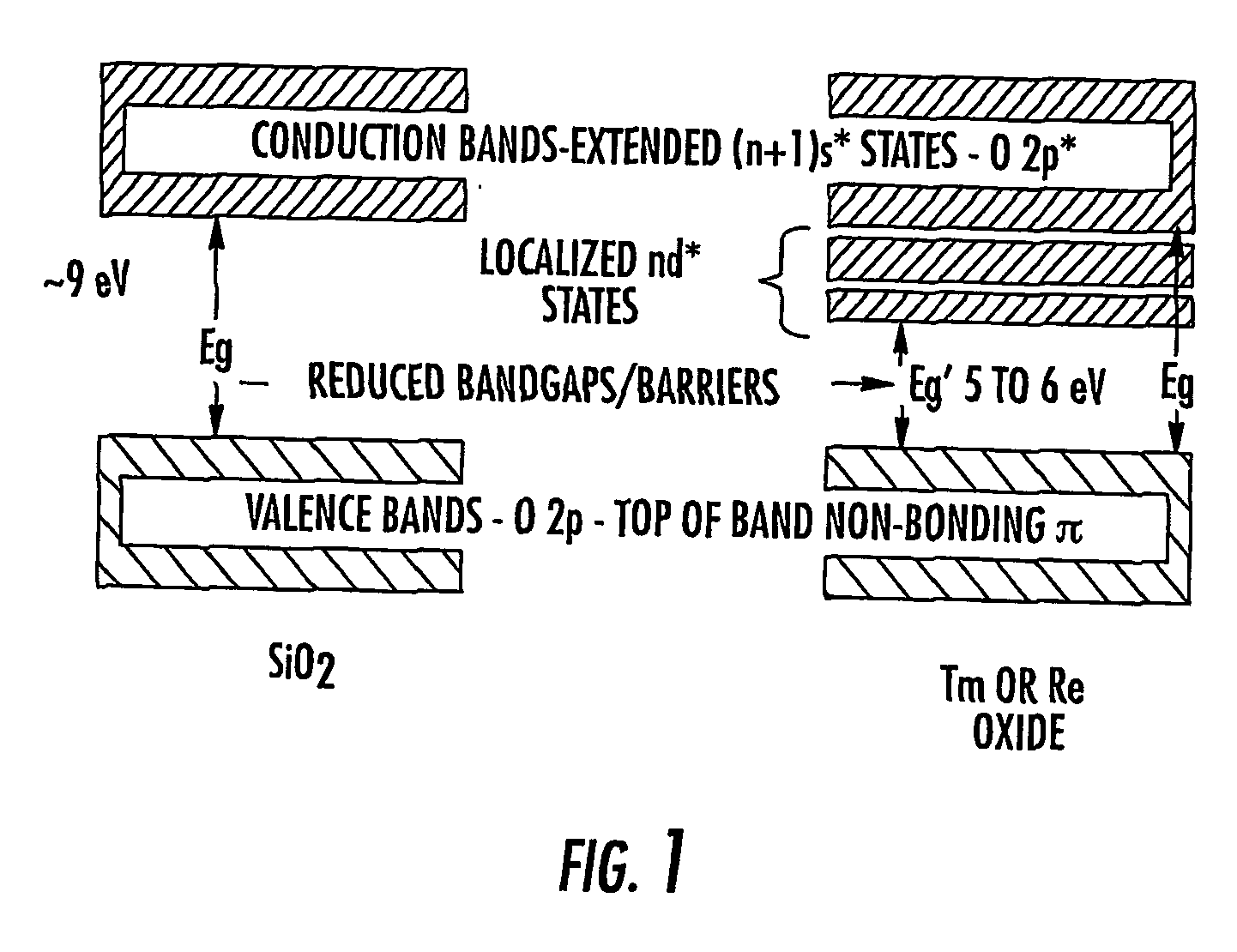

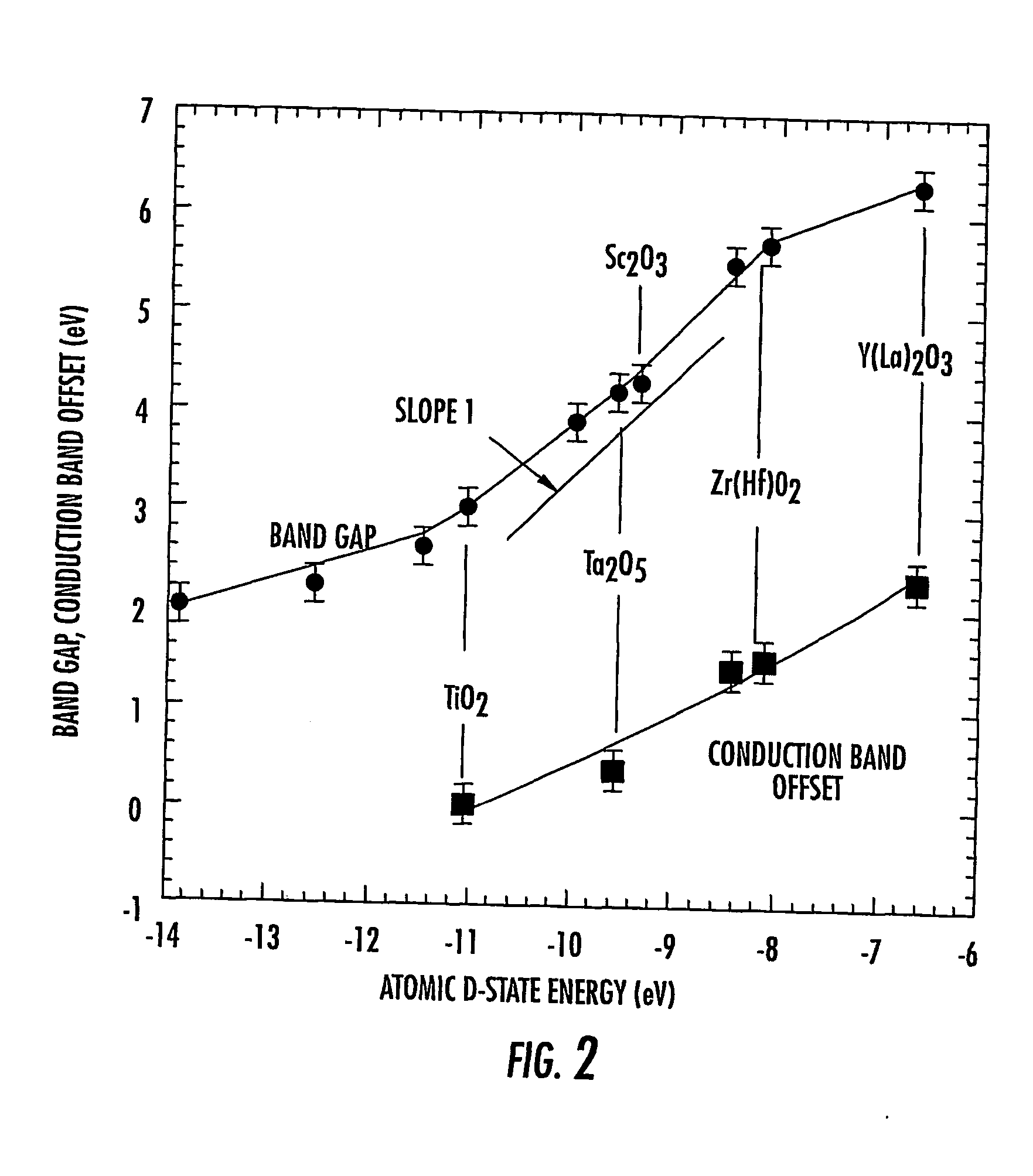

InactiveUS20060157733A1High electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesRare-earth elementPhysics

A semiconductor device includes a semiconductor substrate, a first oxide layer on the semiconductor substrate including an element from the semiconductor substrate, and a second oxide layer on the first oxide layer opposite the semiconductor substrate. The second oxide layer includes a stoichiometric, single-phase complex oxide represented by the formula: AhBjOk, or equivalently (AmOn)a(BqOr)b in which the elemental oxide components, (AmOn) and (BqOr) are combined so that h=j or, equivalently, ma=bq, and a, b, h, j, k, m, n, q and r are non-zero integers; and wherein: A is an element of the lanthanide rare earth elements of the periodic table or the trivalent elements from cerium to lutetium; and B is an element of the transition metal elements of groups IIIB, IVB or VB of the periodic table.

Owner:PENN STATE RES FOUND +1

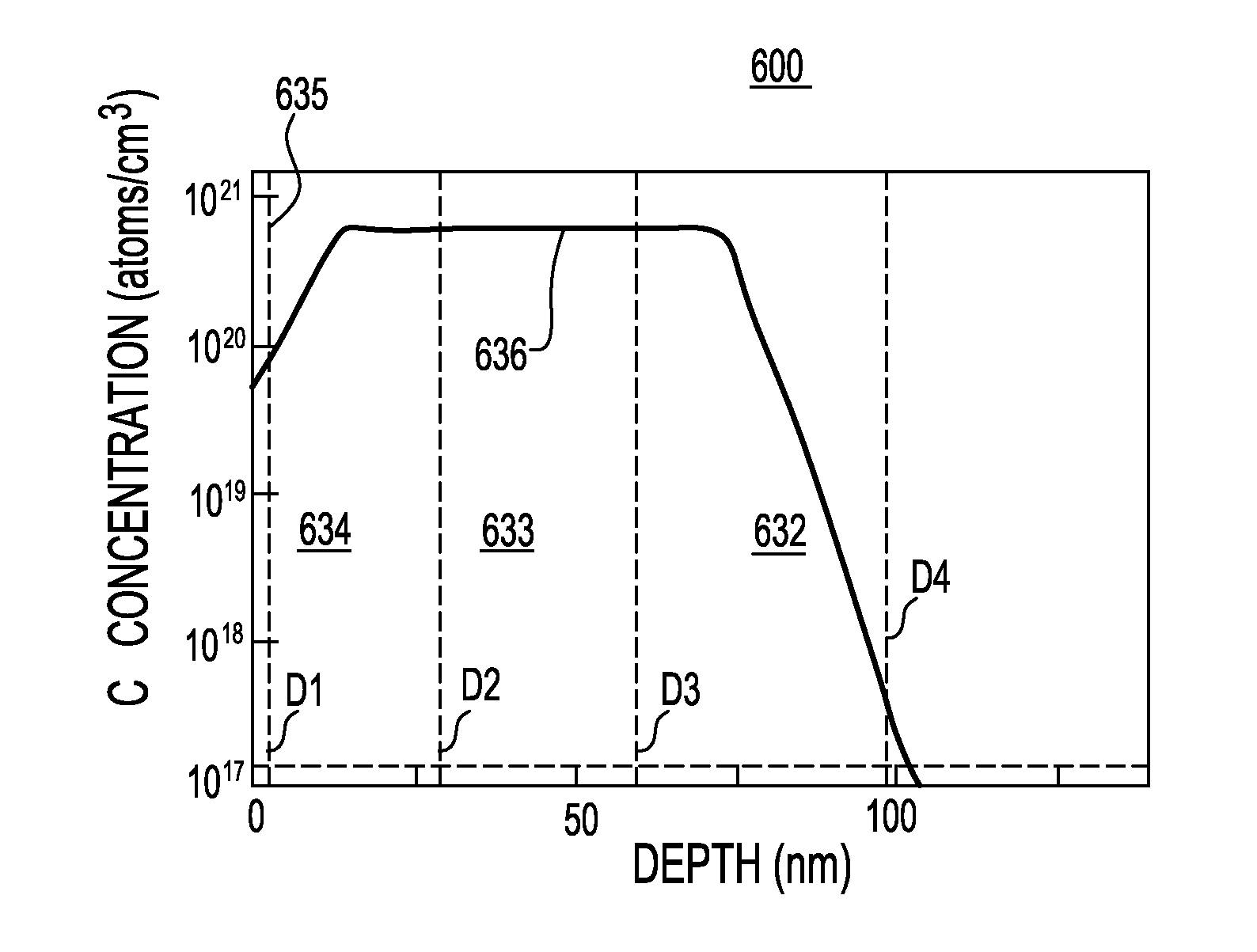

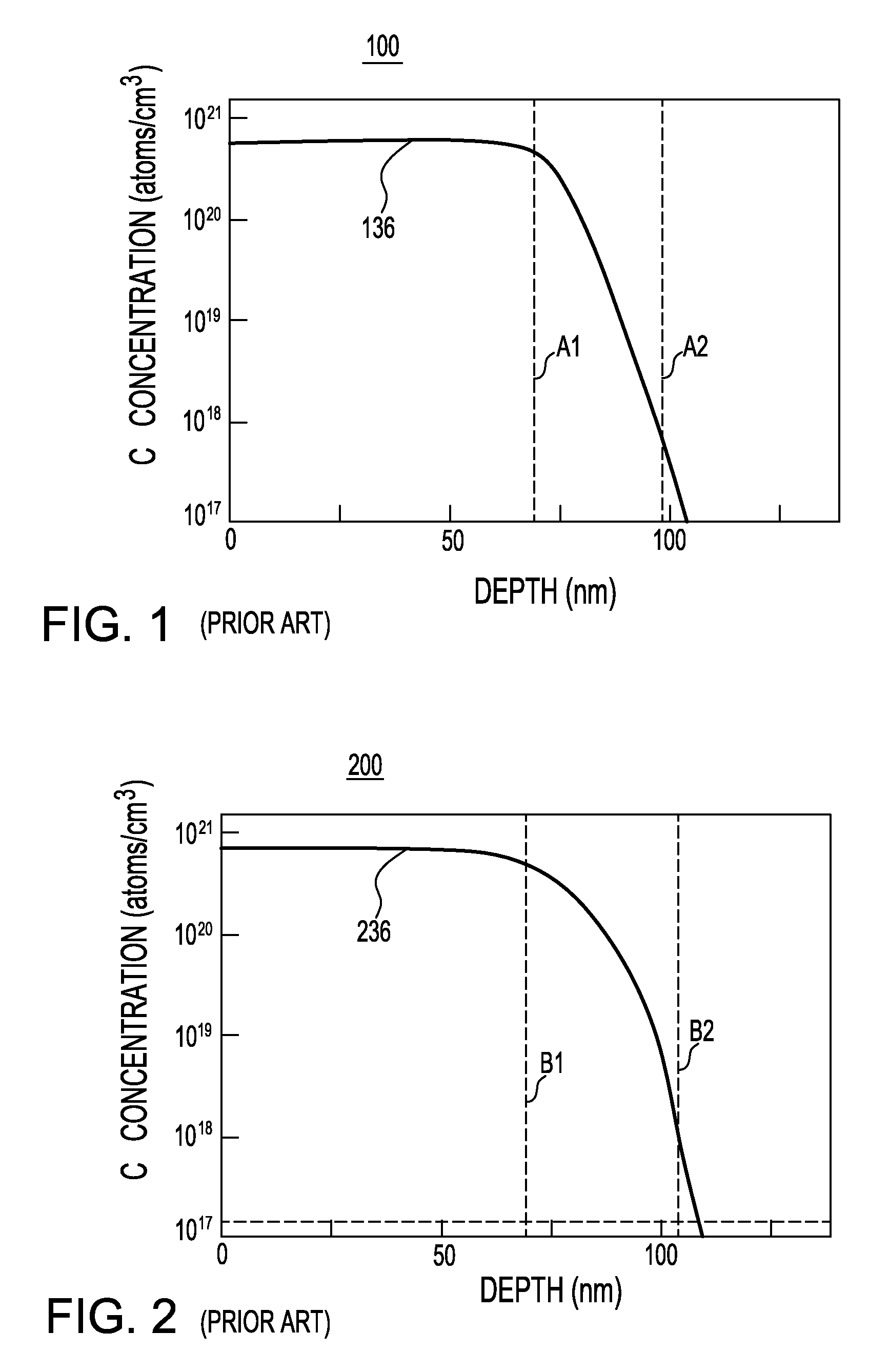

Low defect Si:C layer with retrograde carbon profile

ActiveUS7696000B2High bulk carbon concentrationReduce defect densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationSemiconductor structure

Formation of carbon-substituted single crystal silicon layer is prone to generation of large number of defects especially at high carbon concentration. The present invention provides structures and methods for providing low defect carbon-substituted single crystal silicon layer even for high concentration of carbon in the silicon. According to the present invention, the active retrograde profile in the carbon implantation reduces the defect density in the carbon-substituted single crystal silicon layer obtained after a solid phase epitaxy. This enables the formation of semiconductor structures with compressive stress and low defect density. When applied to semiconductor transistors, the present invention enables N-type field effect transistors with enhanced electron mobility through the tensile stress that is present into the channel.

Owner:GLOBALFOUNDRIES U S INC

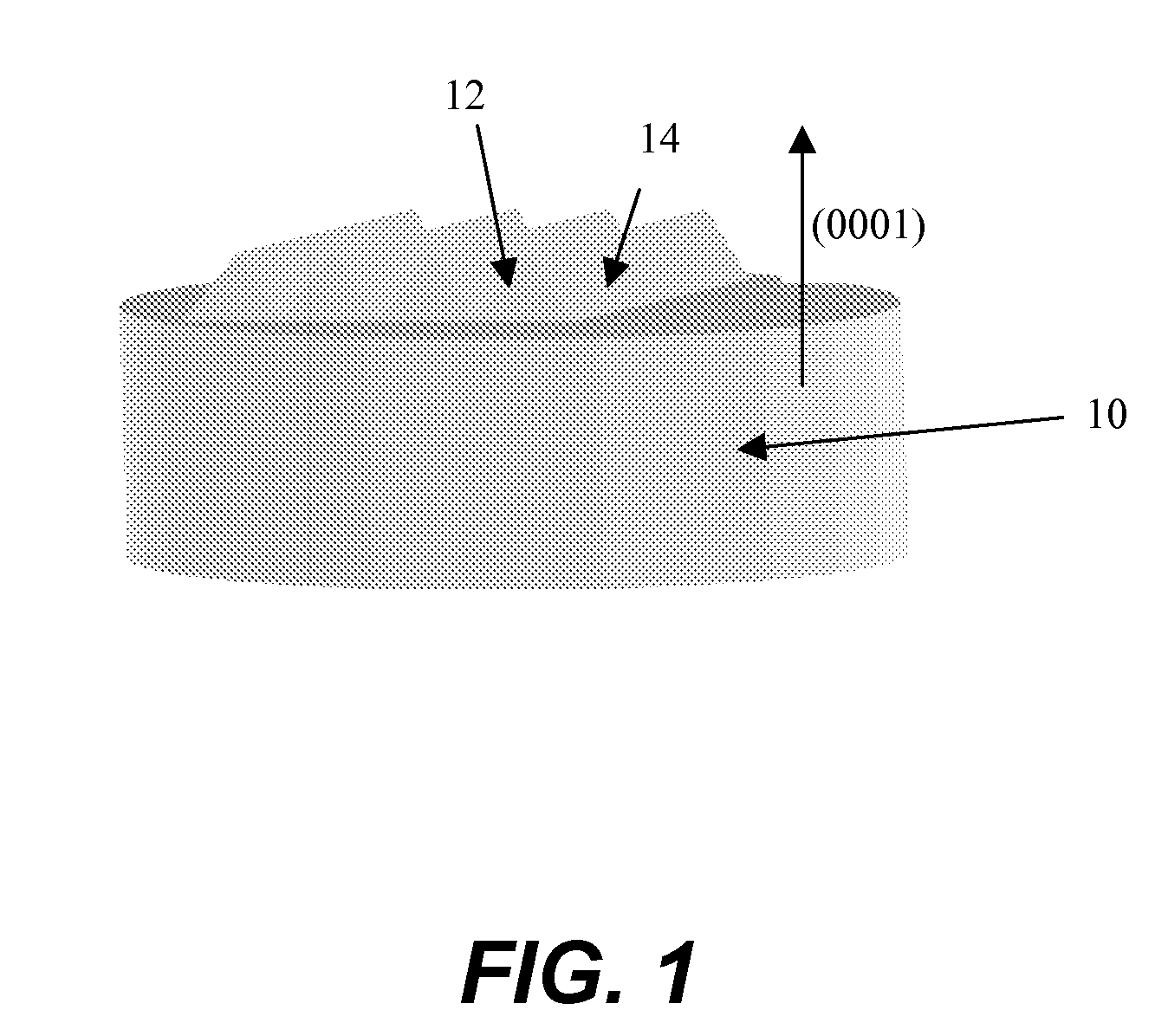

III-V Nitride homoepitaxial material of improved MOVPE epitaxial quality (surface texture and defect density) formed on free-standing (Al,In,Ga)N substrates, and opto-electronic and electronic devices comprising same

InactiveUS20030213964A1Improve material qualityReduce dislocation densityPolycrystalline material growthAfter-treatment detailsCelsius DegreeSource material

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer of improved epitaxial quality deposited on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 10<5>, nitrogen source material partial pressure in a range of from about 1 to about 10<3 >torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 10<2 >microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

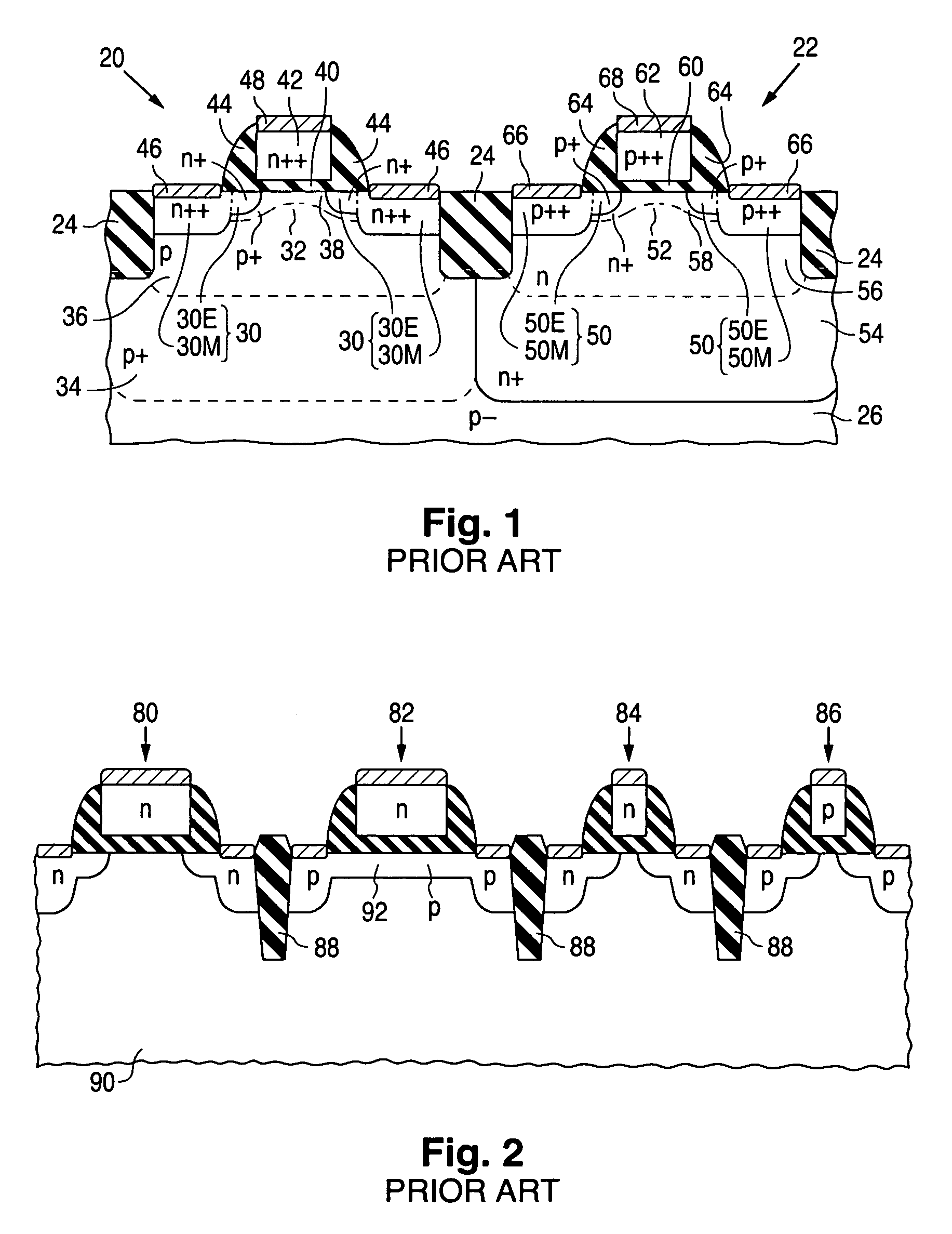

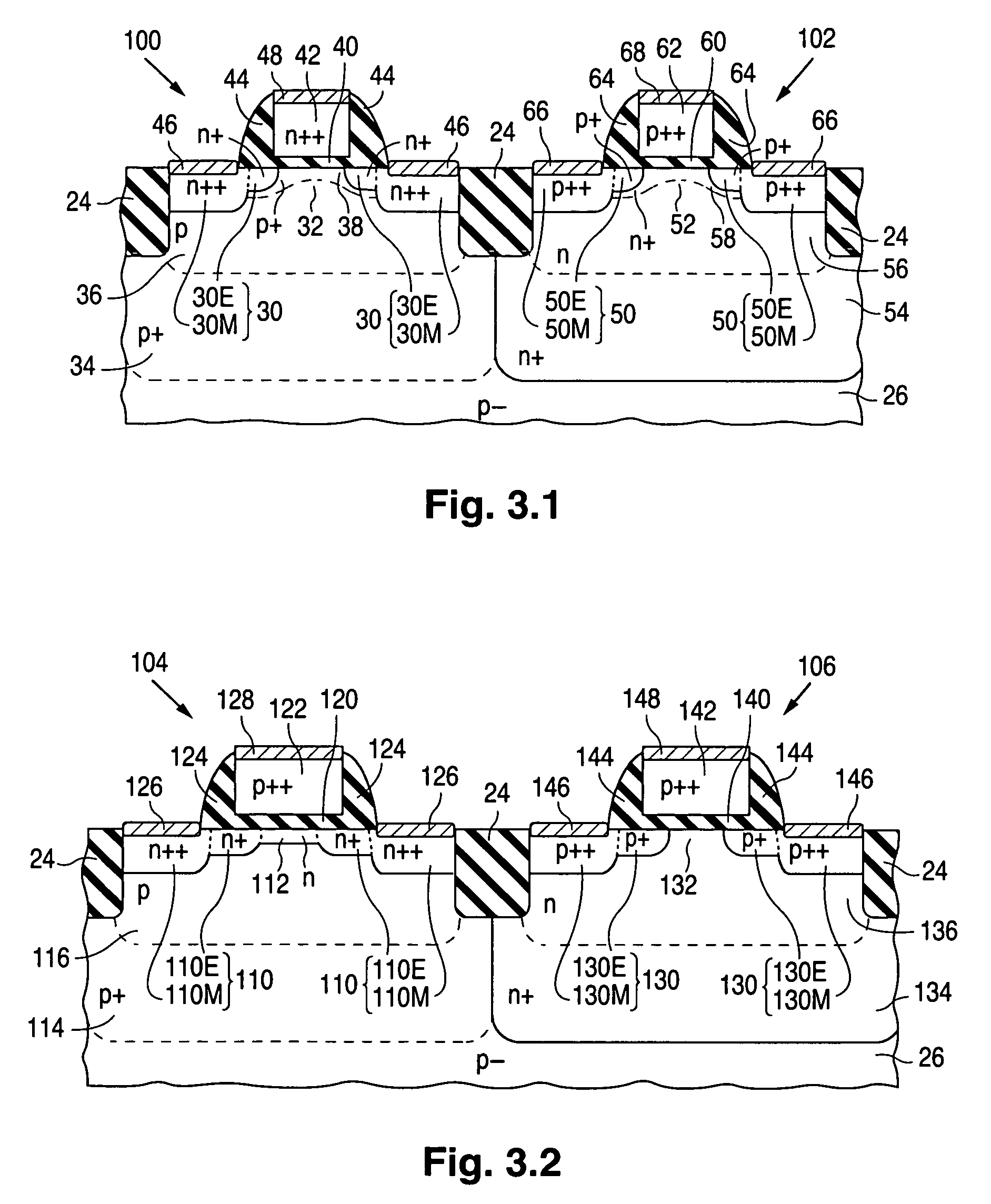

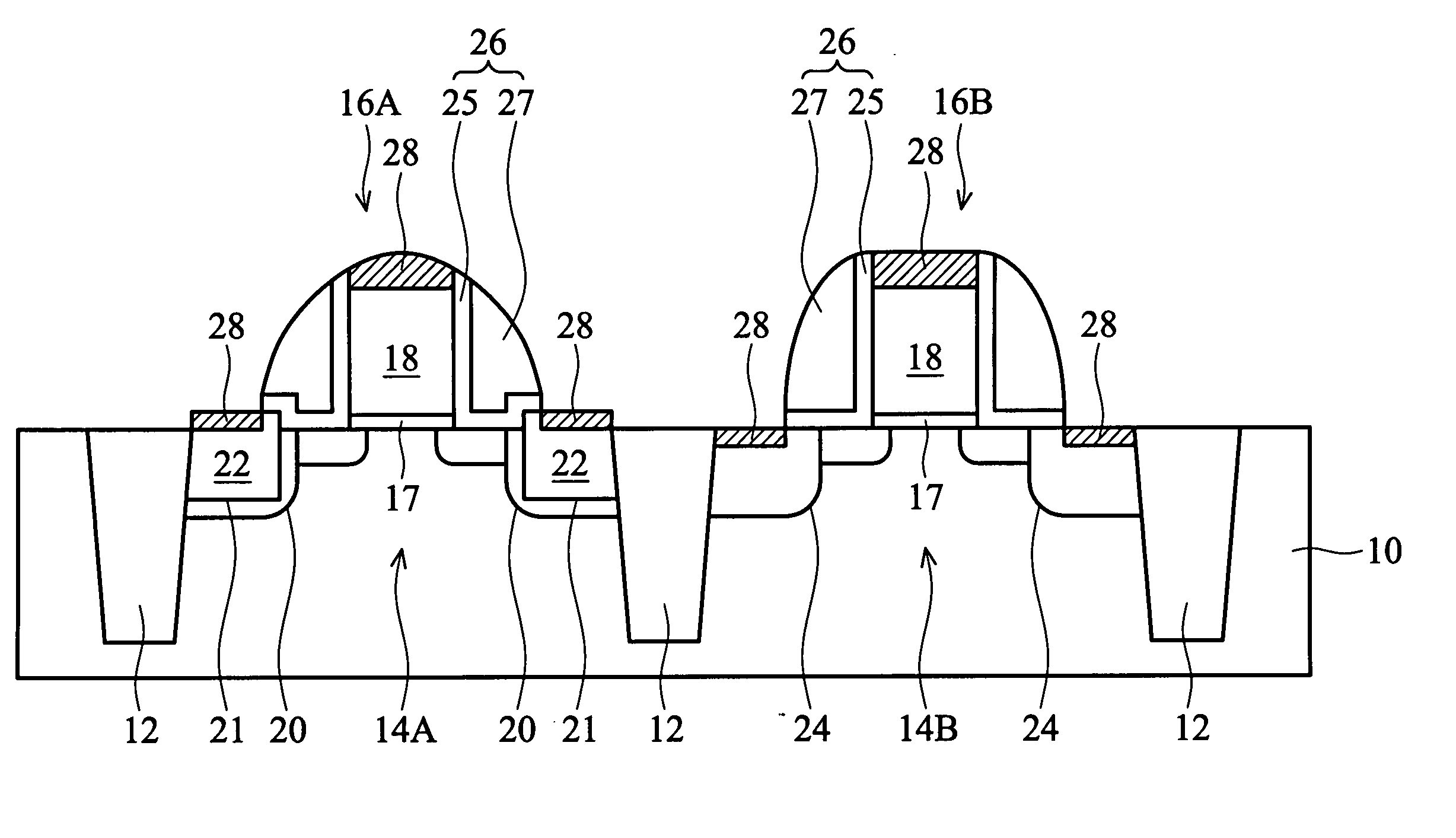

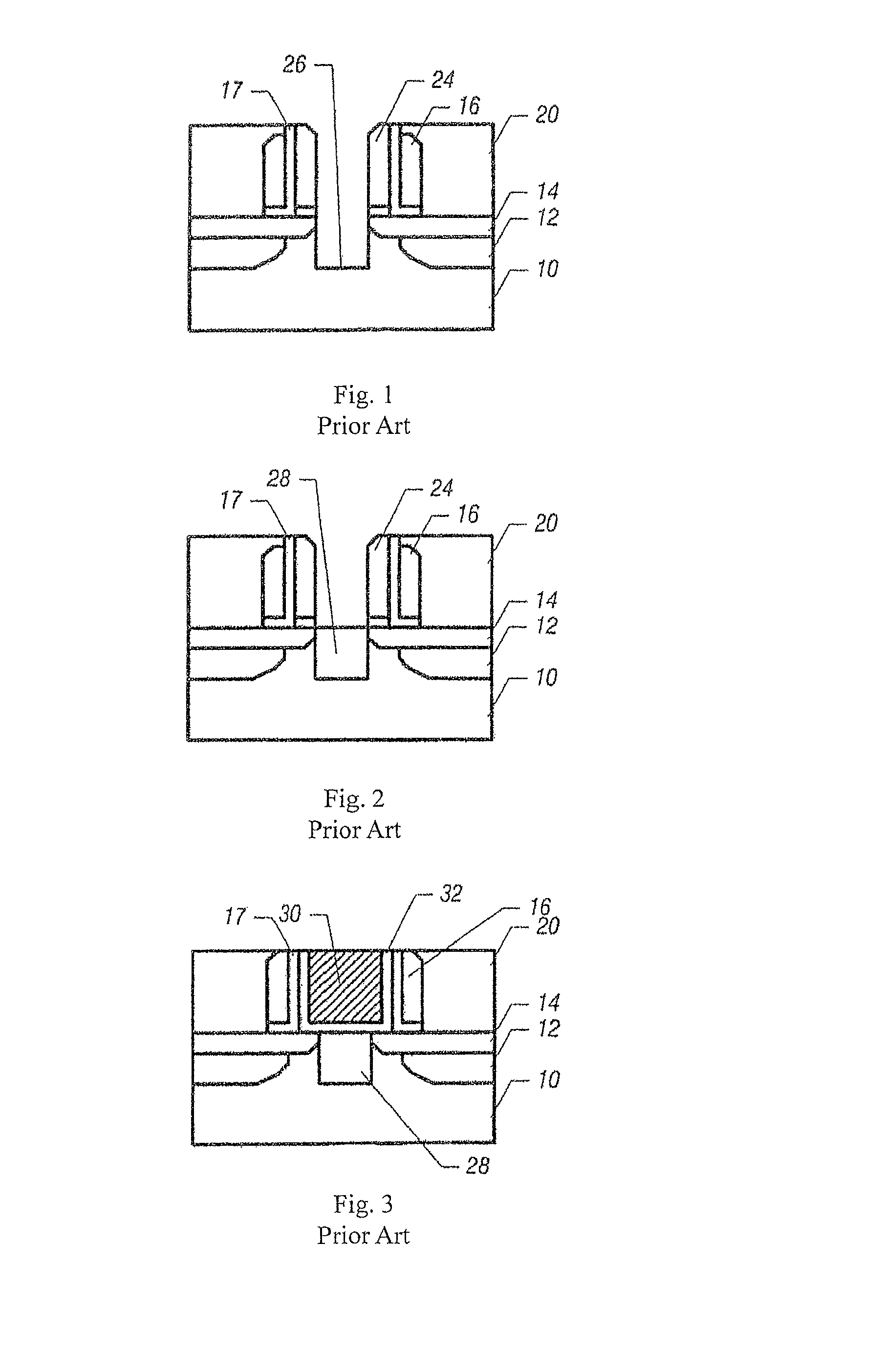

Fabrication of semiconductor structure having N-channel channel-junction field-effect transistor

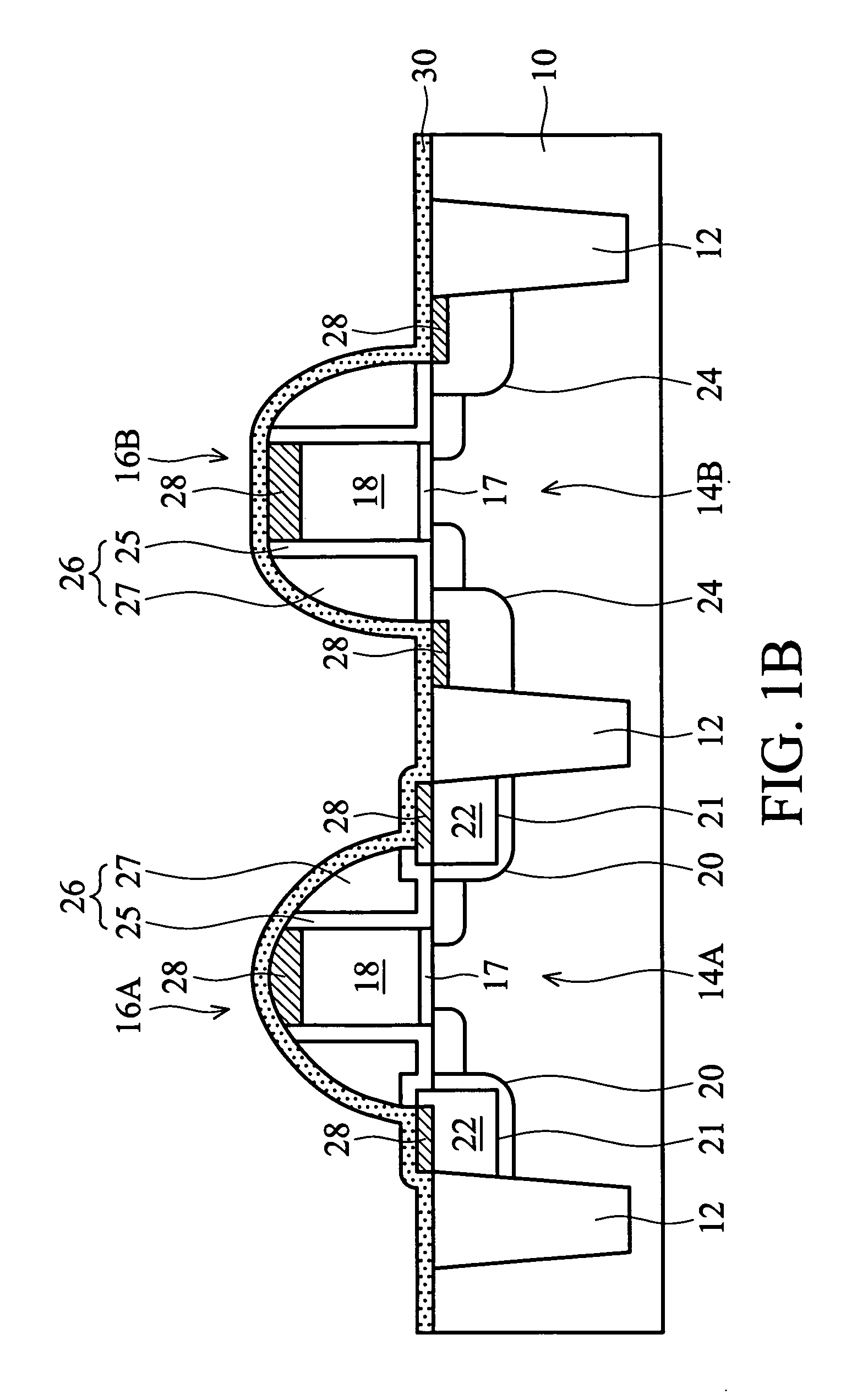

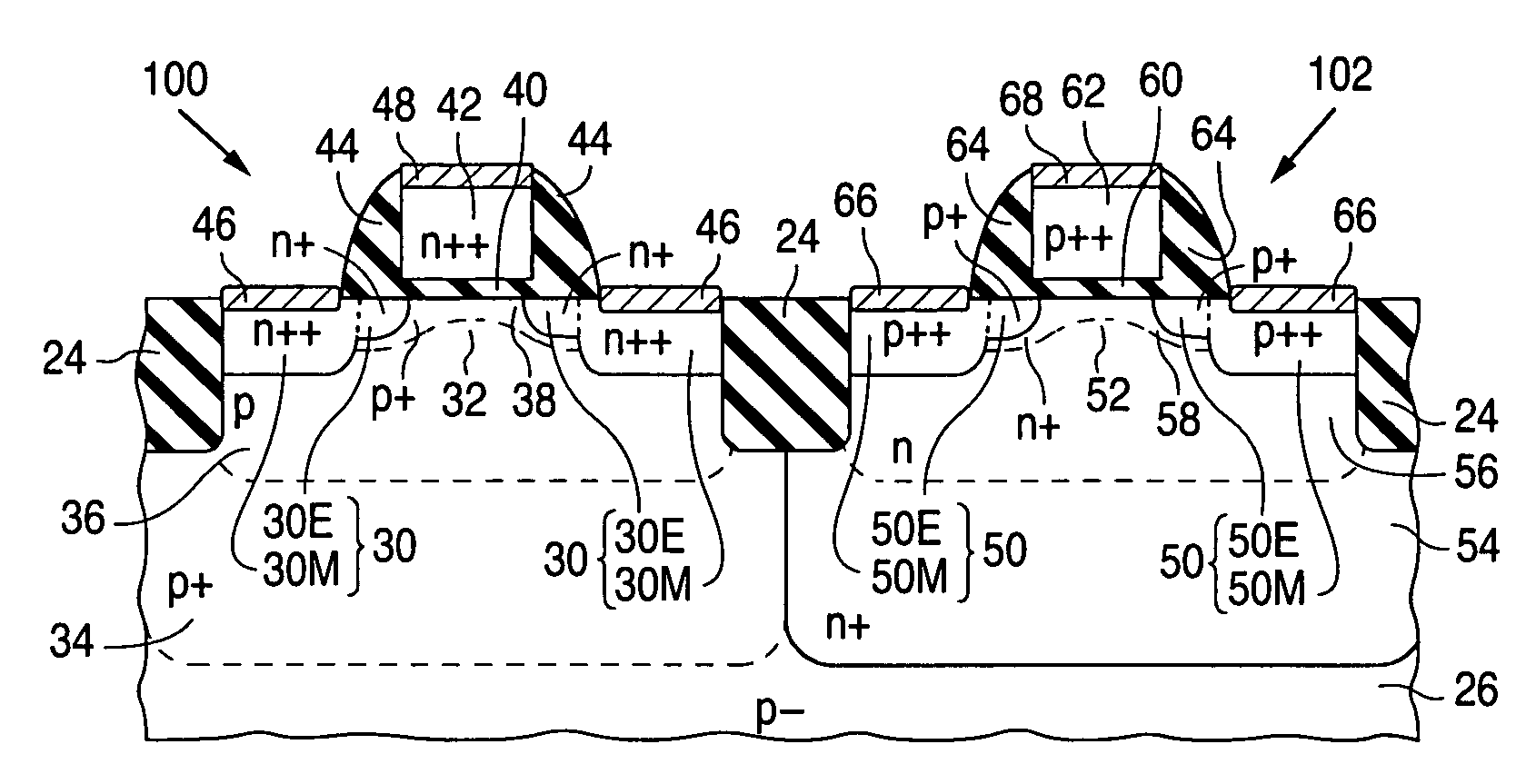

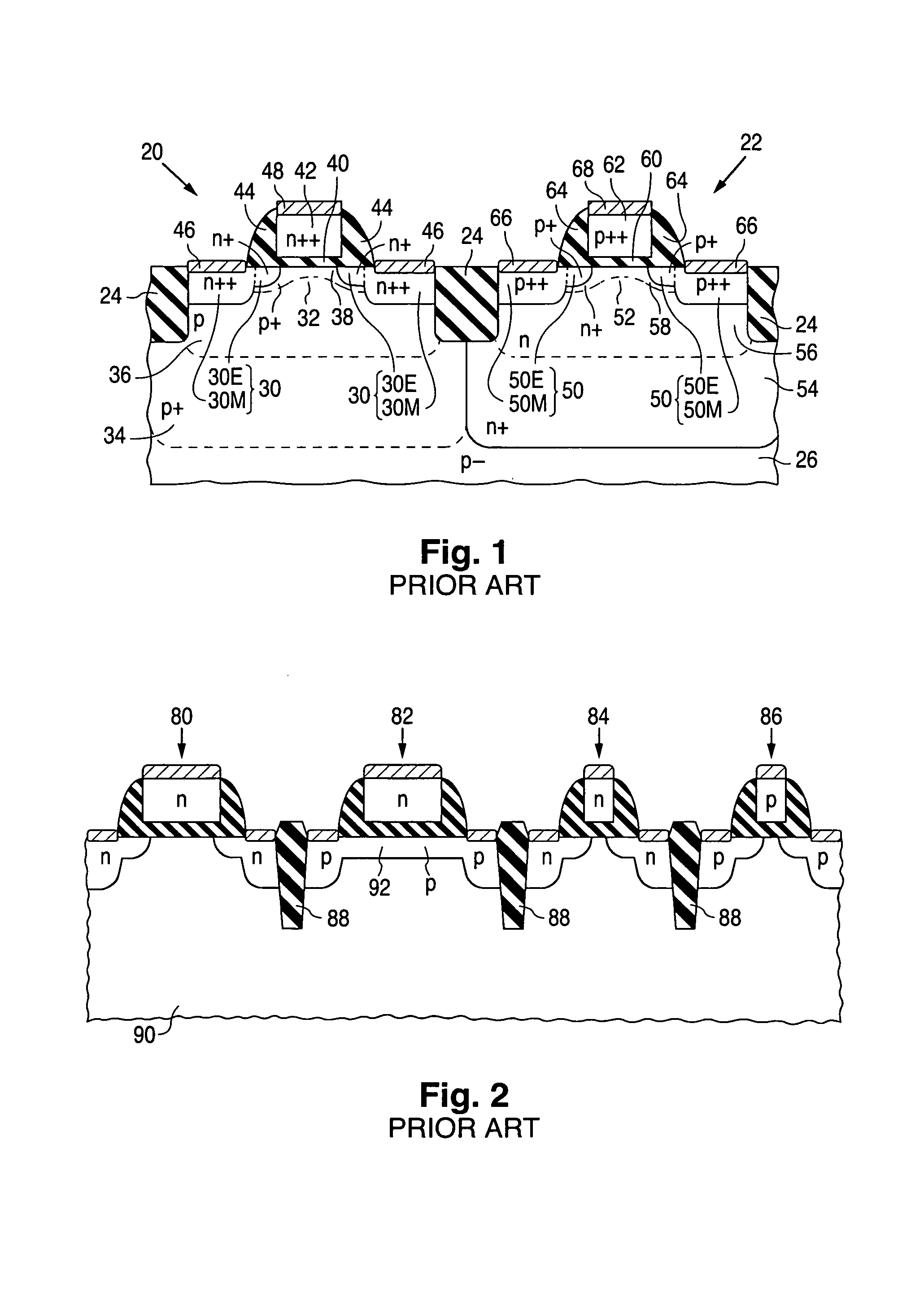

ActiveUS7595243B1Performance characteristicHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally fabricated to be of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. A p-channel surface-channel IGFET (102 or 162), which is typically fabricated to be of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically fabricated to be of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

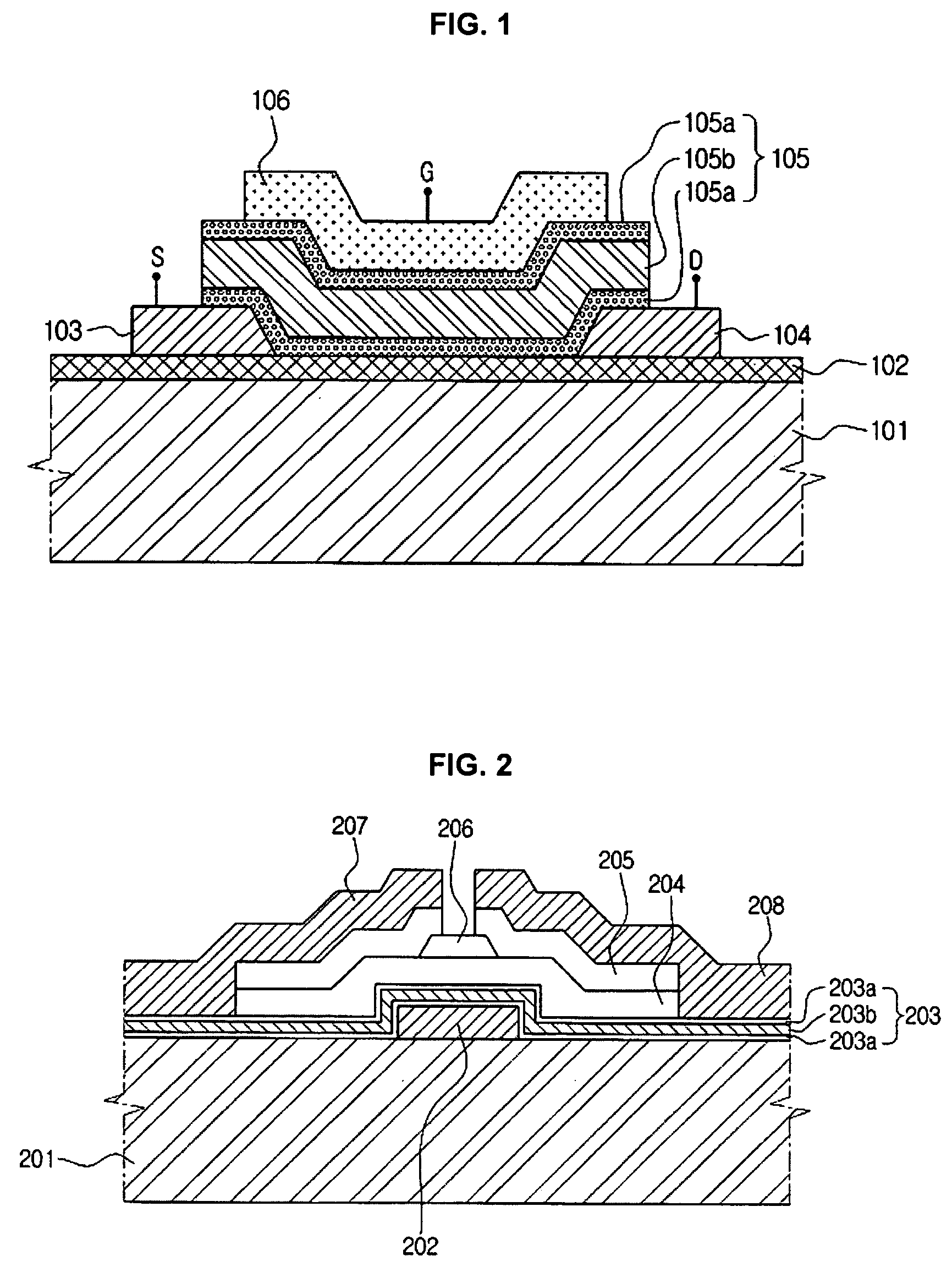

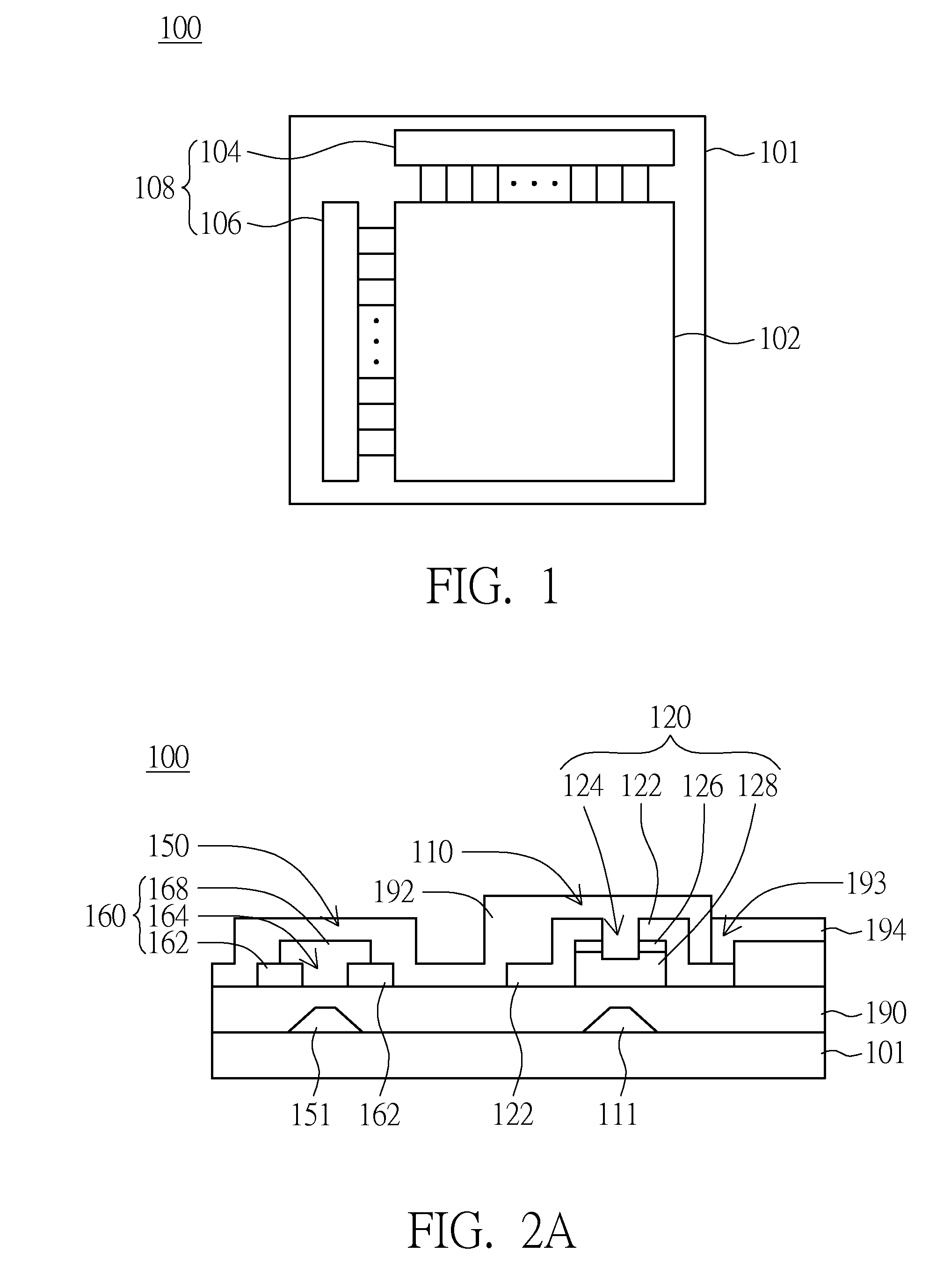

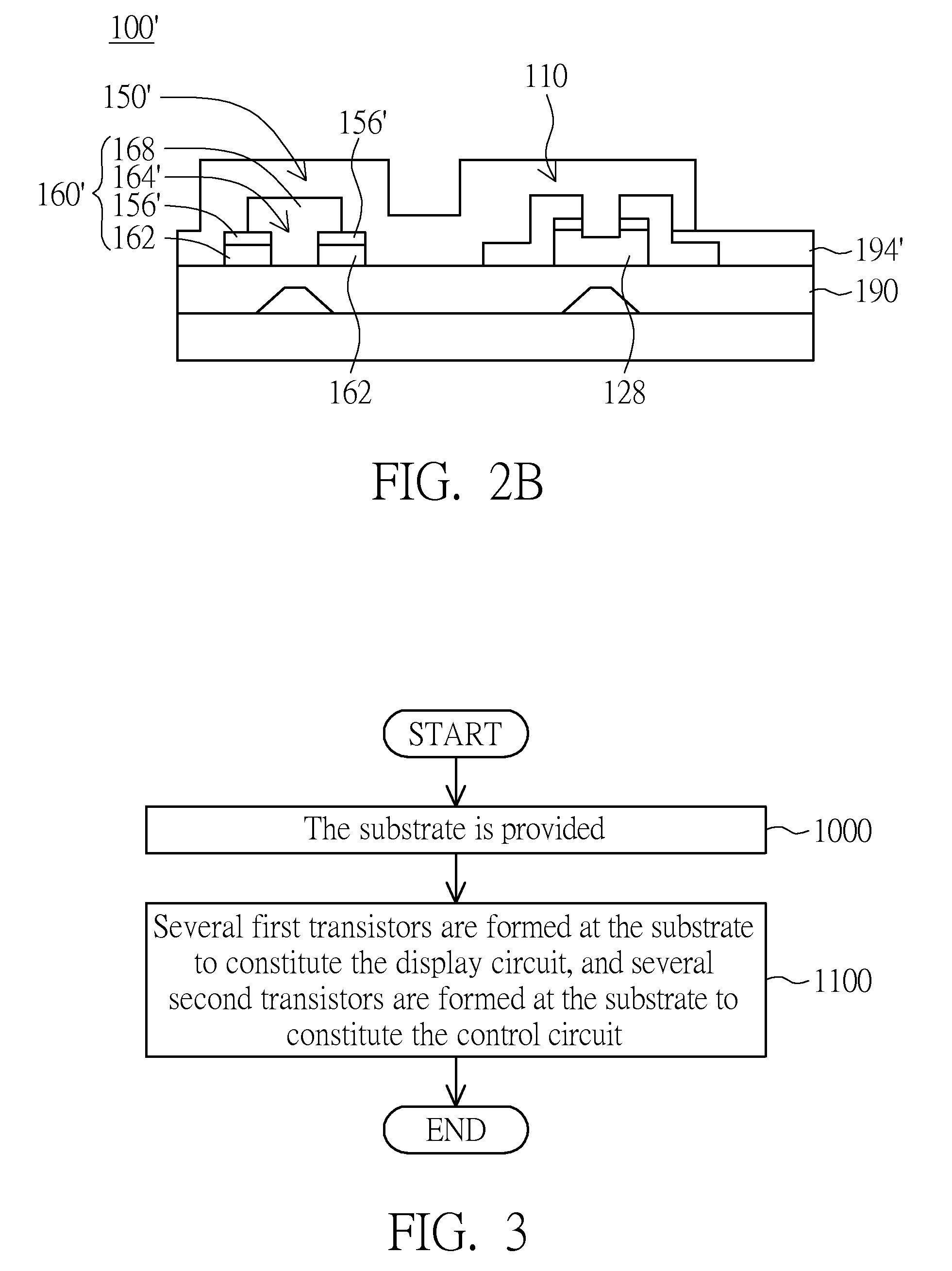

Panel structure and manufacturing method thereof

InactiveUS20090114918A1High electron mobilityManufacturing process compatibleTransistorSolid-state devicesDisplay deviceEngineering

A panel structure and a manufacturing method thereof are provided. The panel structure is disposed in a display device. The panel structure includes a substrate, several first transistors and second transistors. The substrate has a display circuit and a control circuit. The first transistors are disposed at the display circuit of the substrate. Each of the first transistors has a first active layer. The second transistors are disposed at the control circuit of the substrate. Each of the second transistors has a second active layer. The materials of at least one of the first active layer and the second active layer include ZnO.

Owner:WINTEK CORP

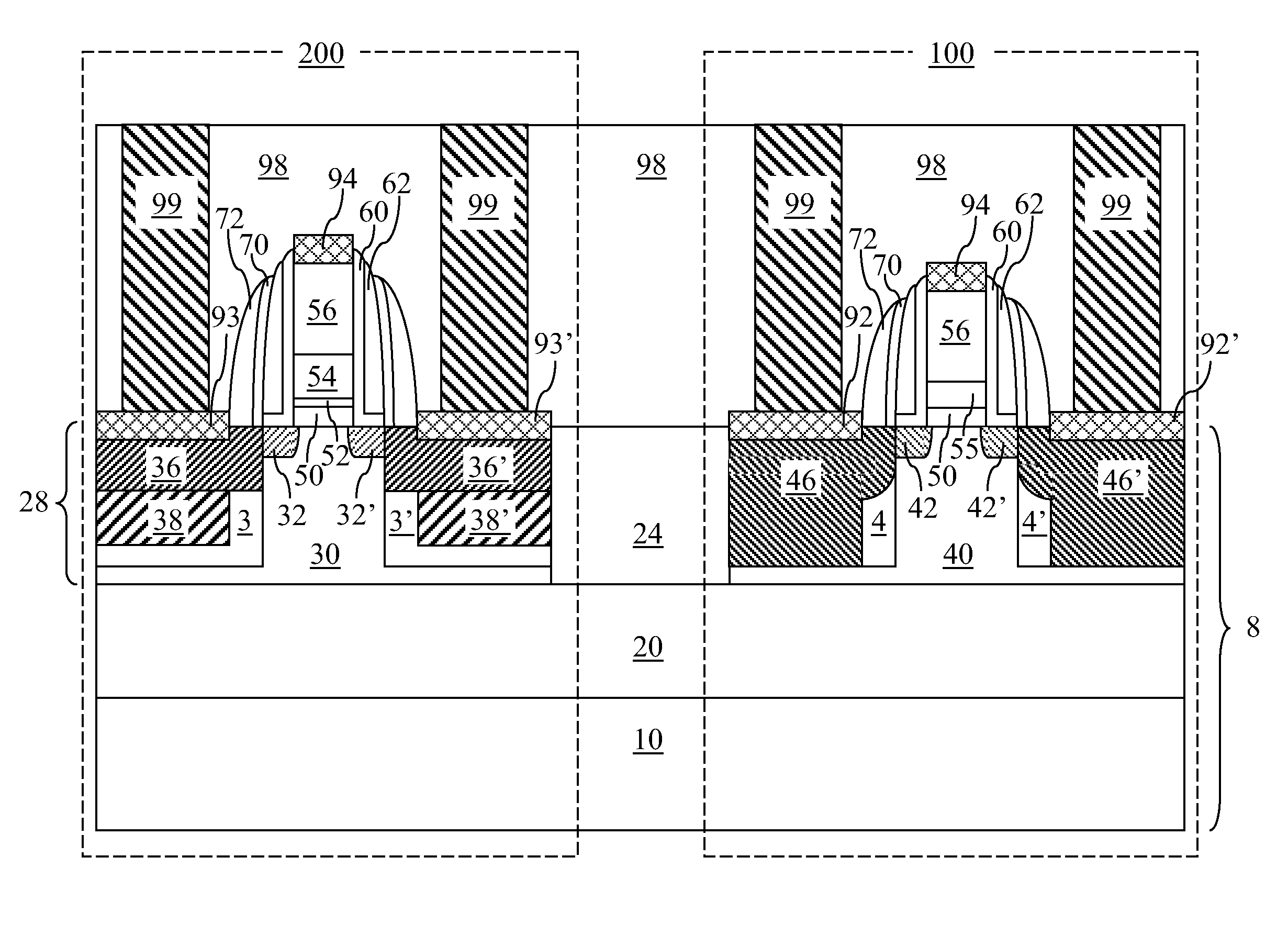

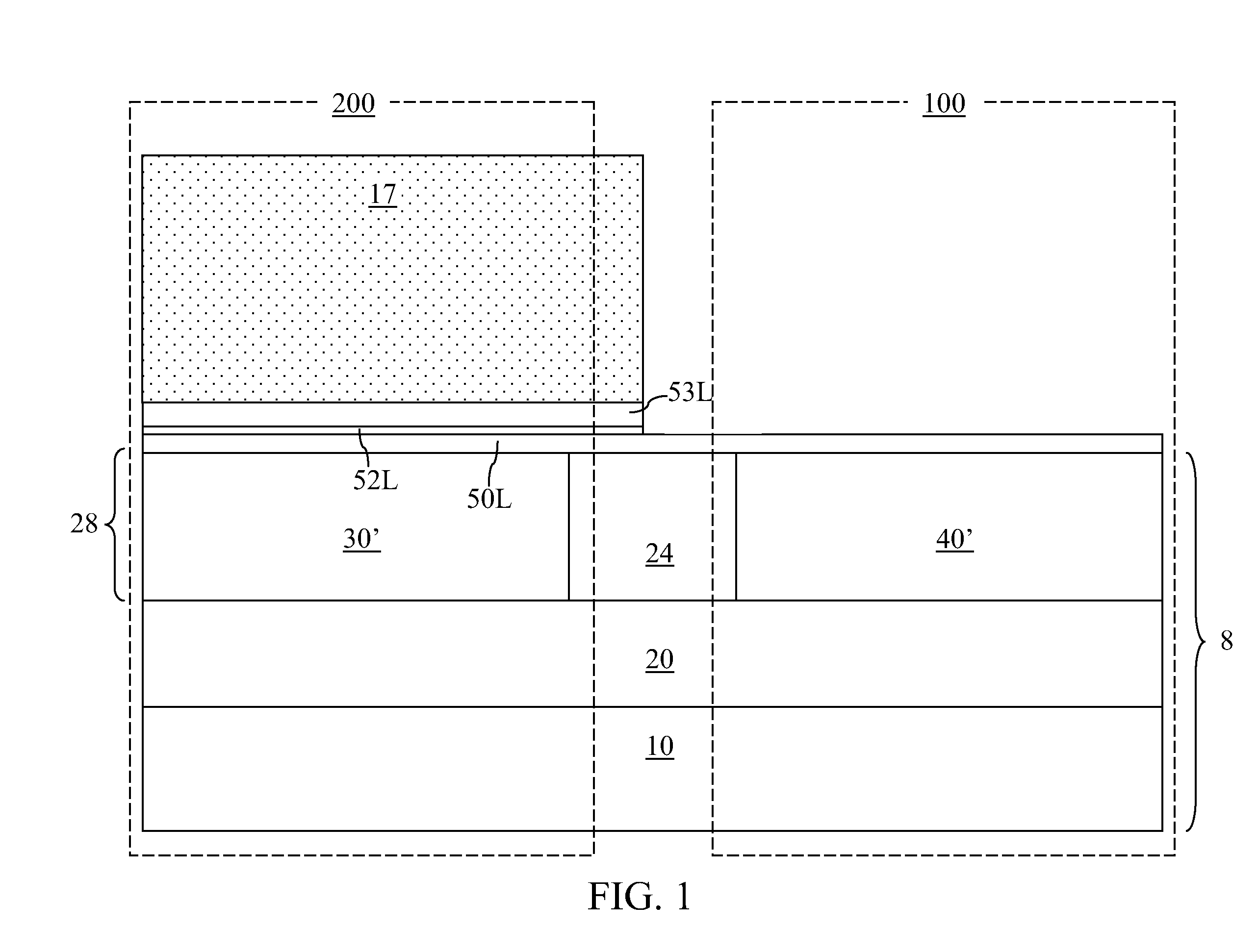

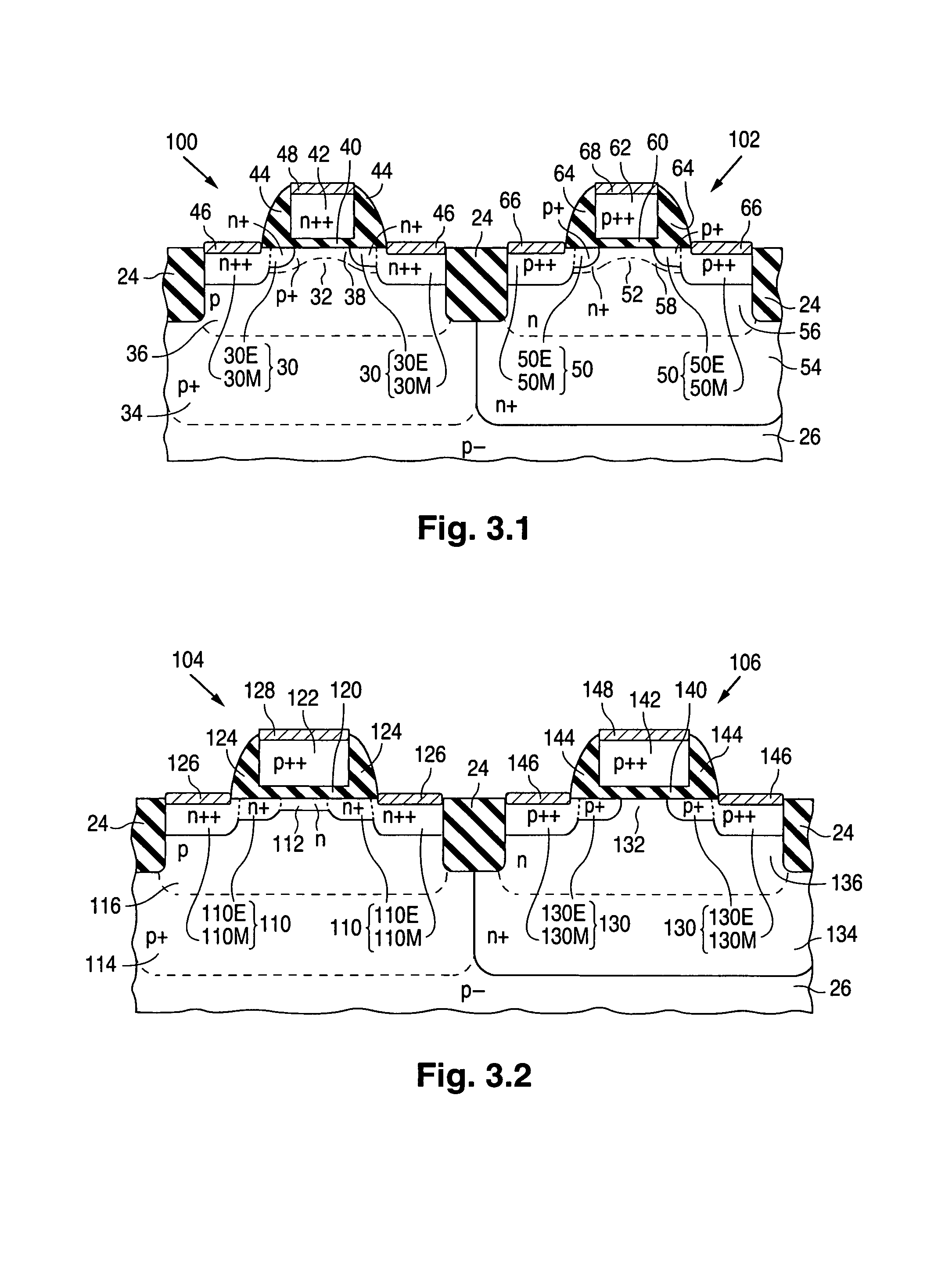

CMOS Transistors With Silicon Germanium Channel and Dual Embedded Stressors

ActiveUS20100224938A1High hole mobilityHigh electron mobilityTransistorSolid-state devicesHigh concentrationMOSFET

A p-type MOSFET of a CMOS structure has a silicon-germanium alloy channel to which a longitudinal compressive stress is applied by embedded epitaxial silicon-germanium alloy source and drain regions comprising a silicon-germanium alloy having a higher concentration of germanium than the channel of the p-type MOSFET. An n-type MOSFET of the CMOS structure has a silicon-germanium alloy channel to which a longitudinal tensile stress is applied by embedded epitaxial silicon source and drain regions comprising silicon. The silicon-germanium alloy channel in the p-type MOSFET provides enhanced hole mobility, while the silicon-germanium alloy channel in the n-type MOSFET provides enhanced electron mobility, thereby providing performance improvement to both the p-type MOSFET and the n-type MOSFET.

Owner:GLOBALFOUNDRIES US INC

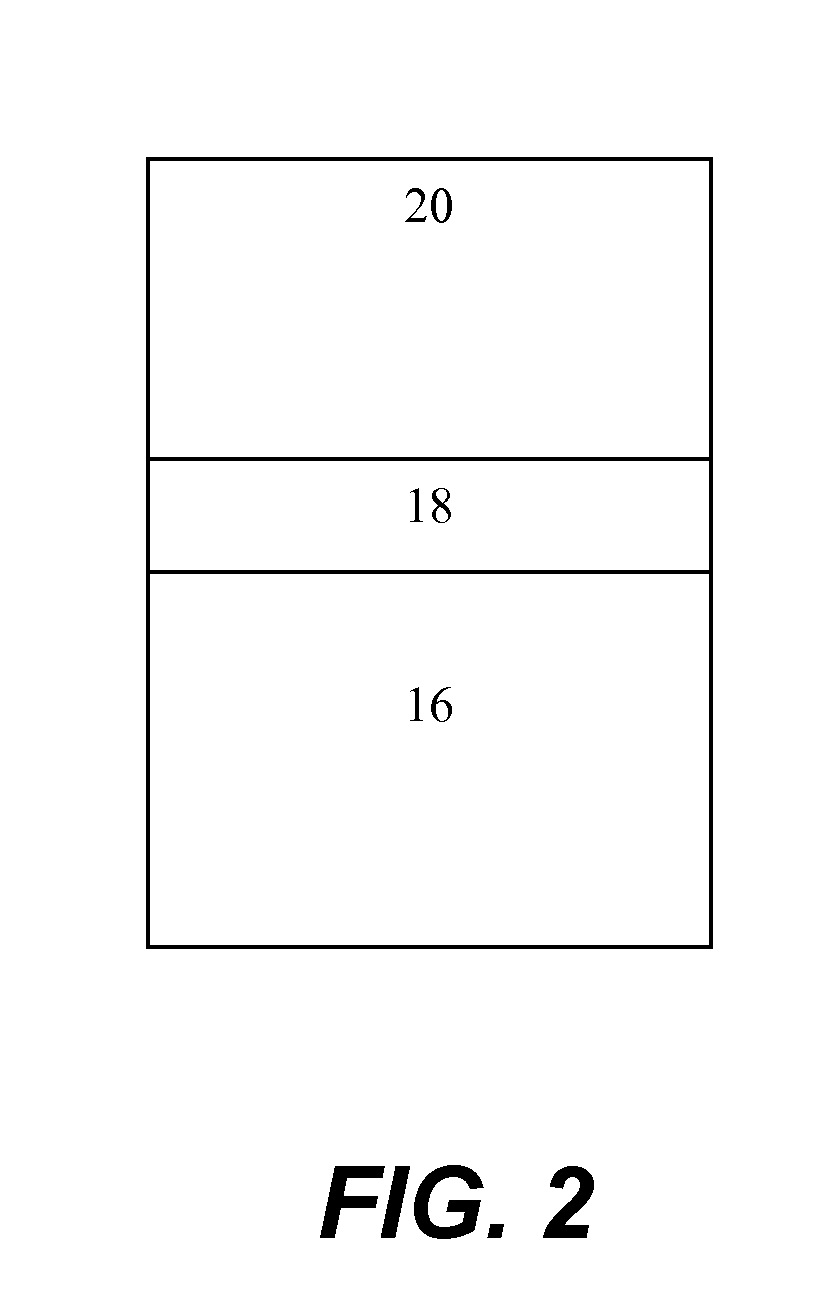

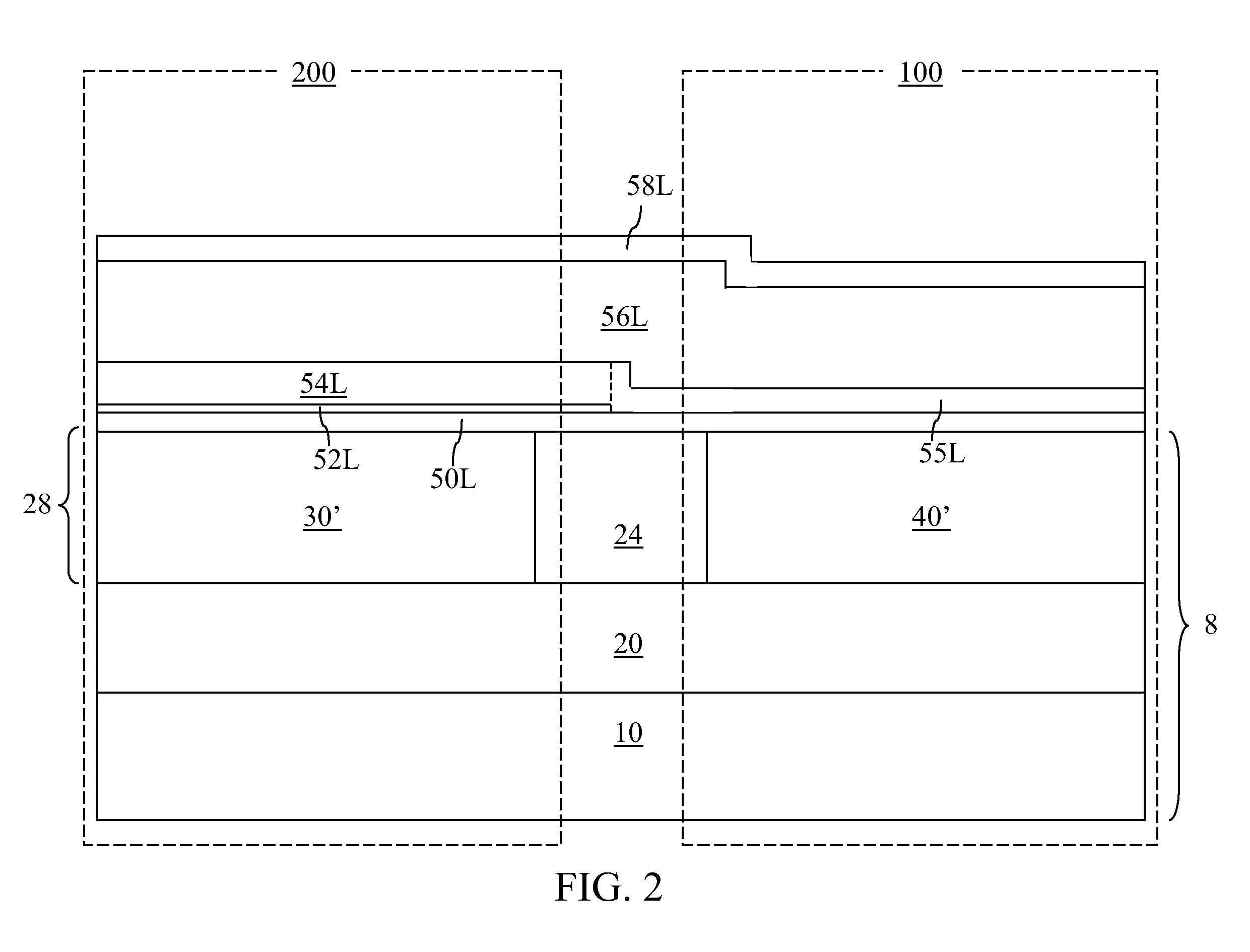

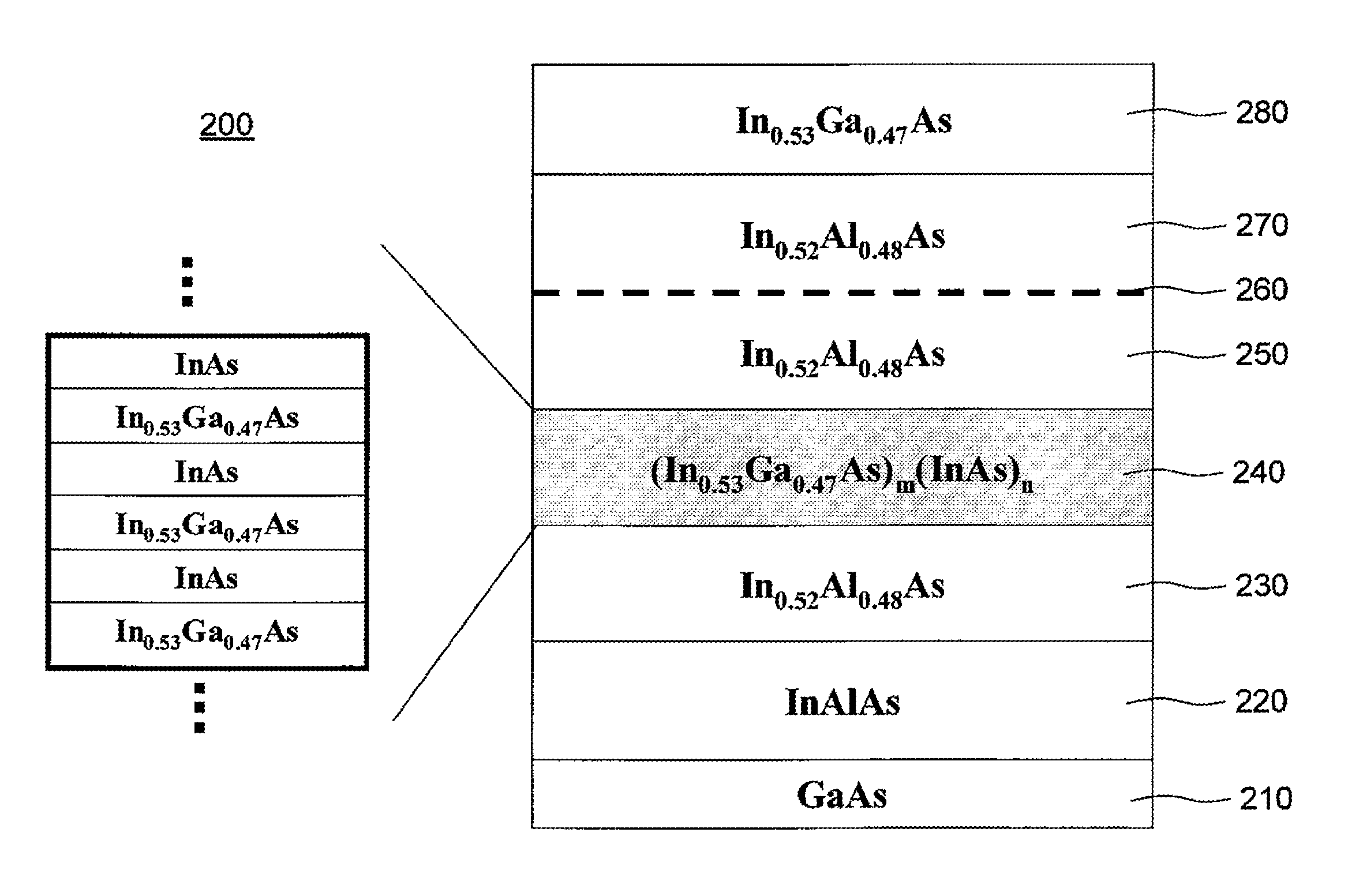

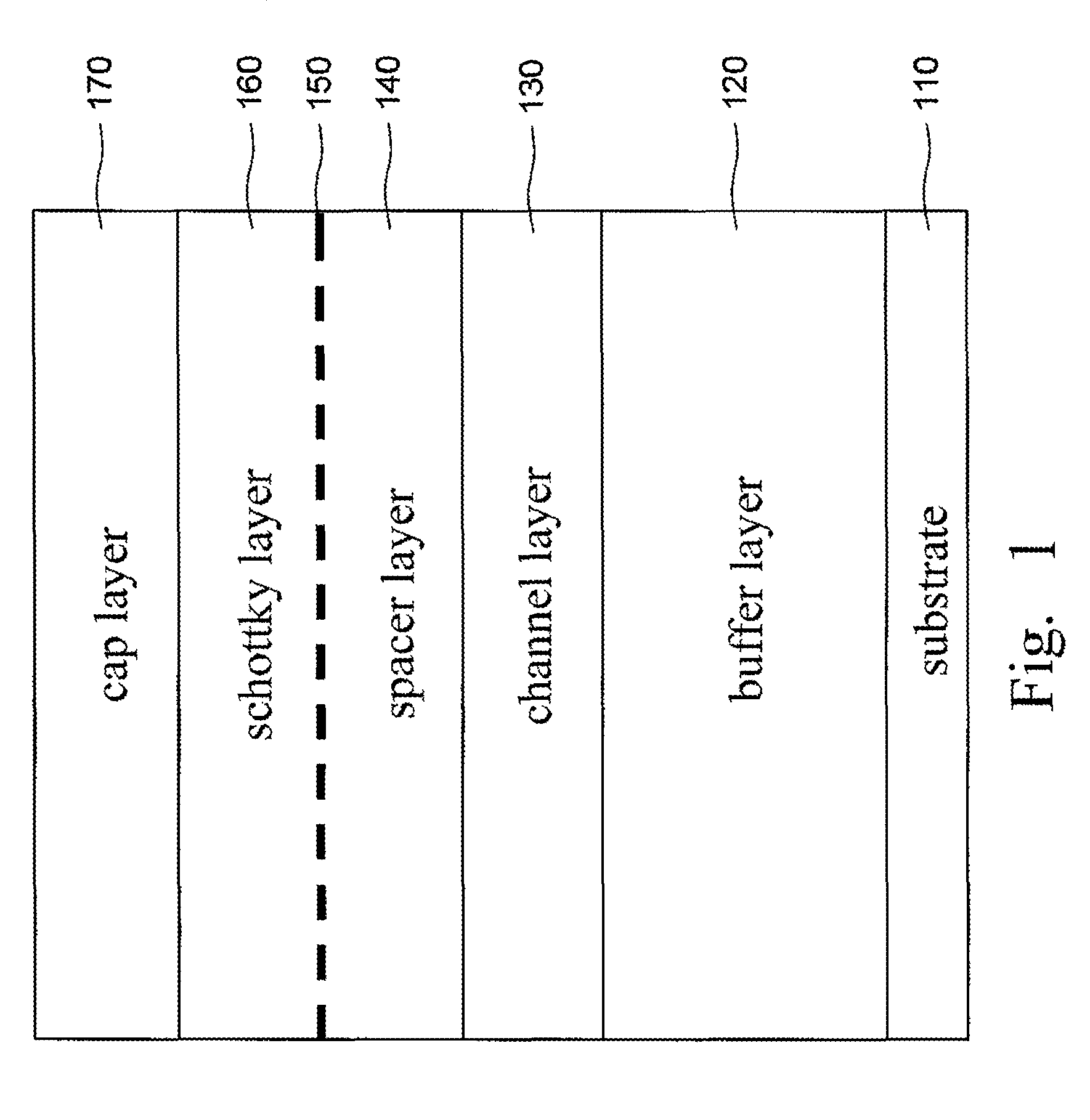

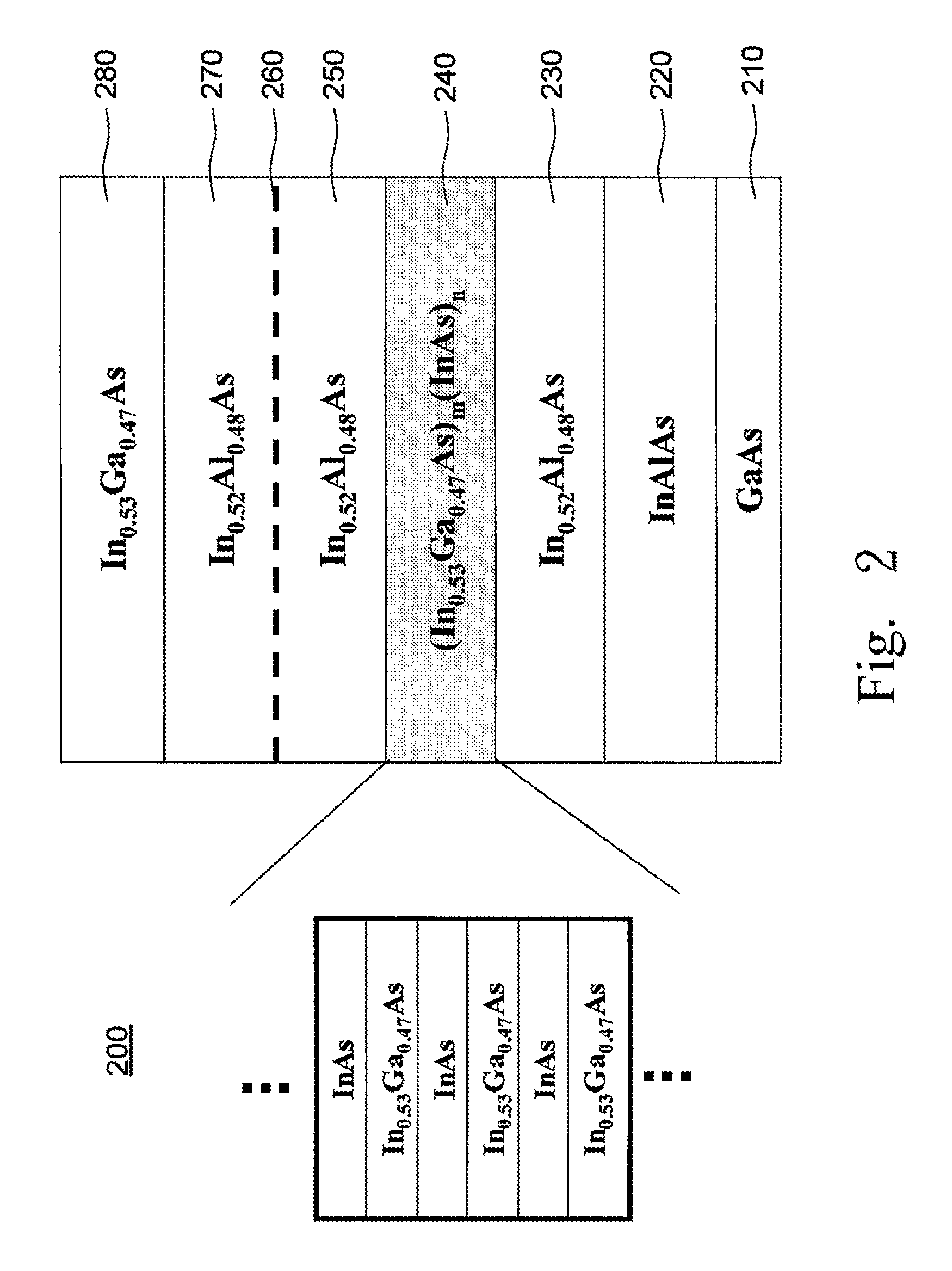

High electron mobility transistor and method for fabricating the same

ActiveUS8169002B2Improve high-frequency characteristicHigh electron mobilityTransistorNanoinformaticsIndium arsenideIndium gallium arsenide

A high electron mobility transistor includes a substrate, a buffer layer, a channel layer, a spacer layer, a schottky layer and a cap layer. The buffer layer is formed on the substrate. The channel layer is formed on the buffer layer, in which the channel layer comprises a superlattice structure formed with a plurality of indium gallium arsenide thin films alternately stacked with a plurality of indium arsenide thin films. The spacer layer is formed on the channel layer. The schottky layer is formed on the spacer layer. The cap layer is formed on the schottky layer.

Owner:YLTLINK TECH CORP

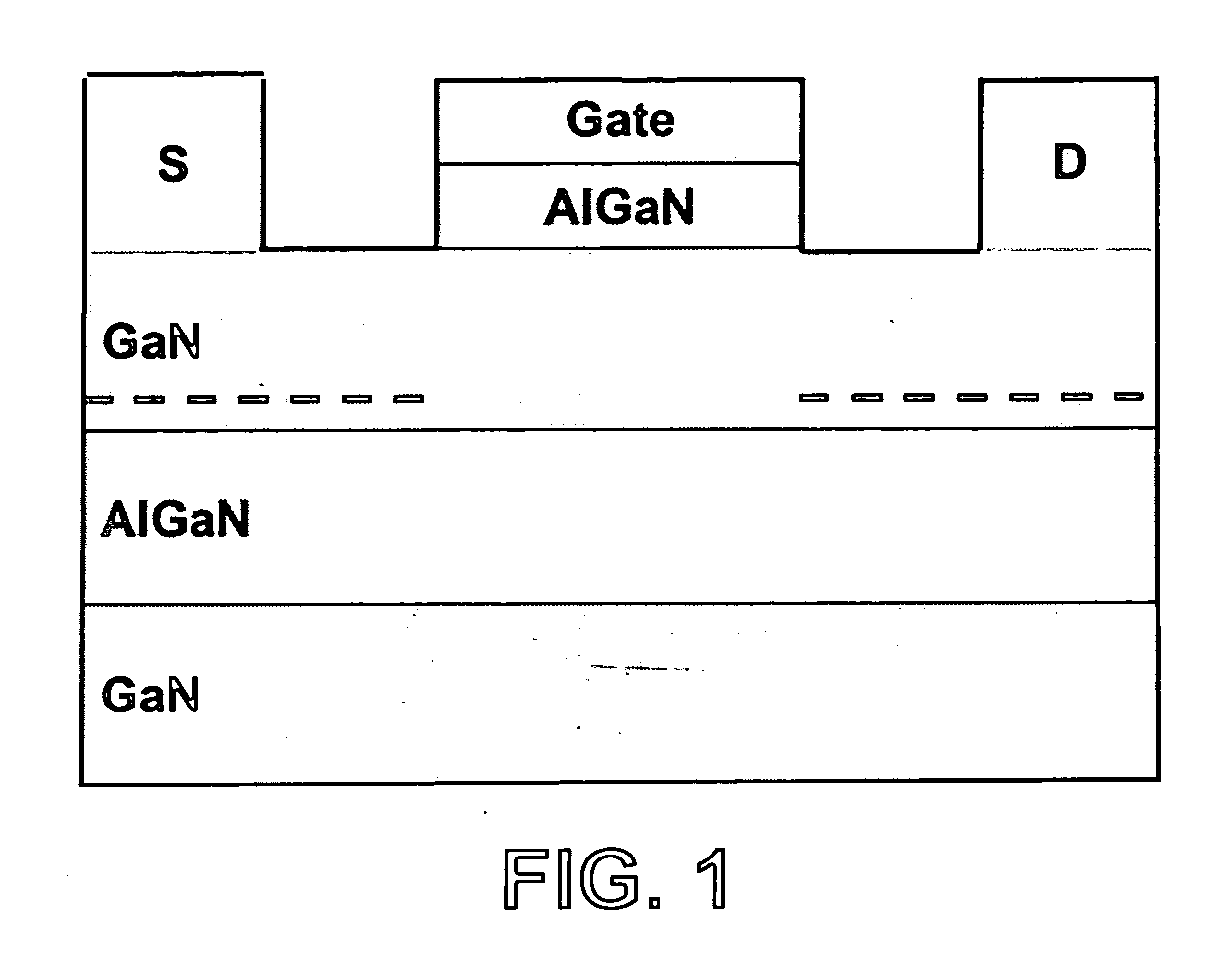

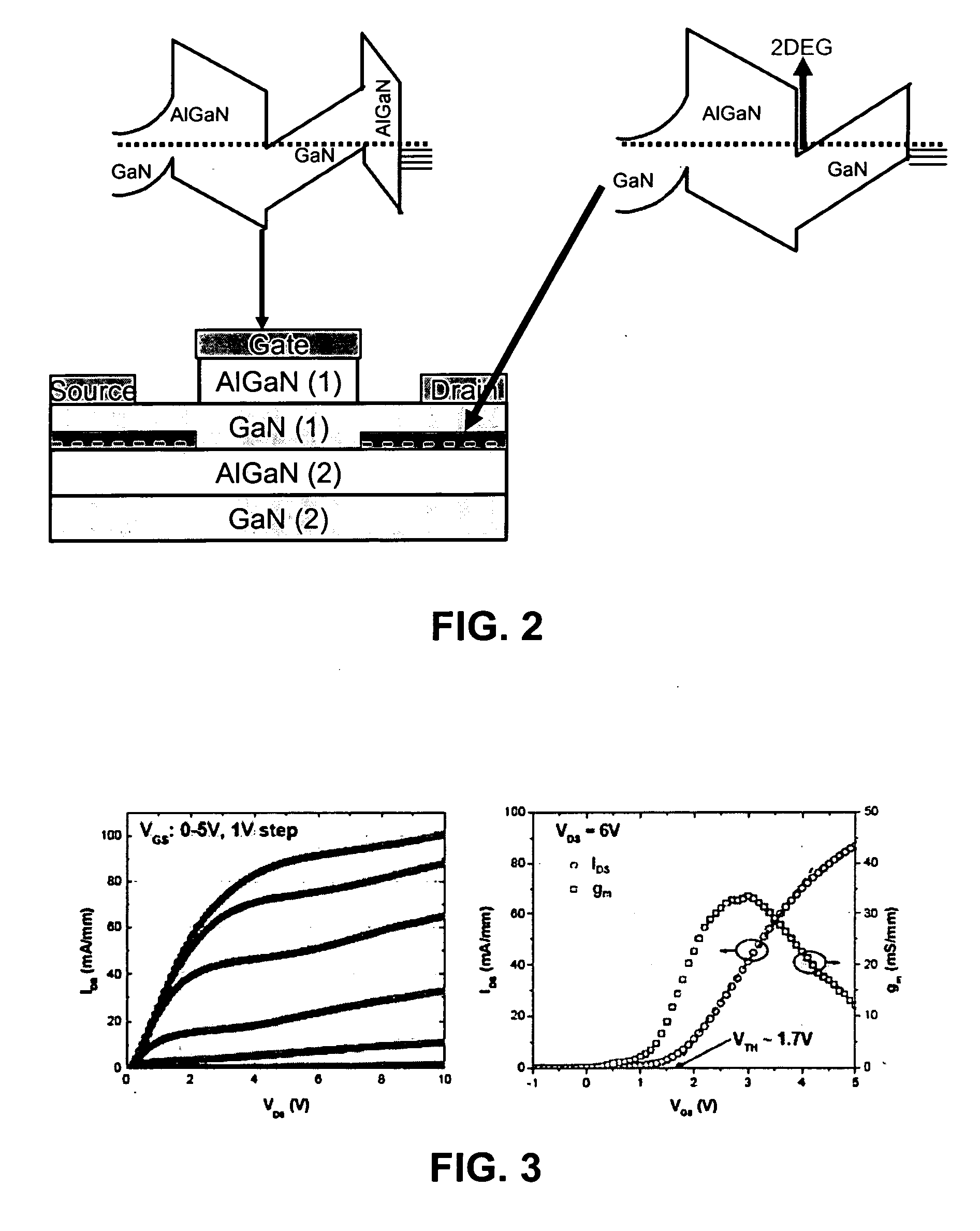

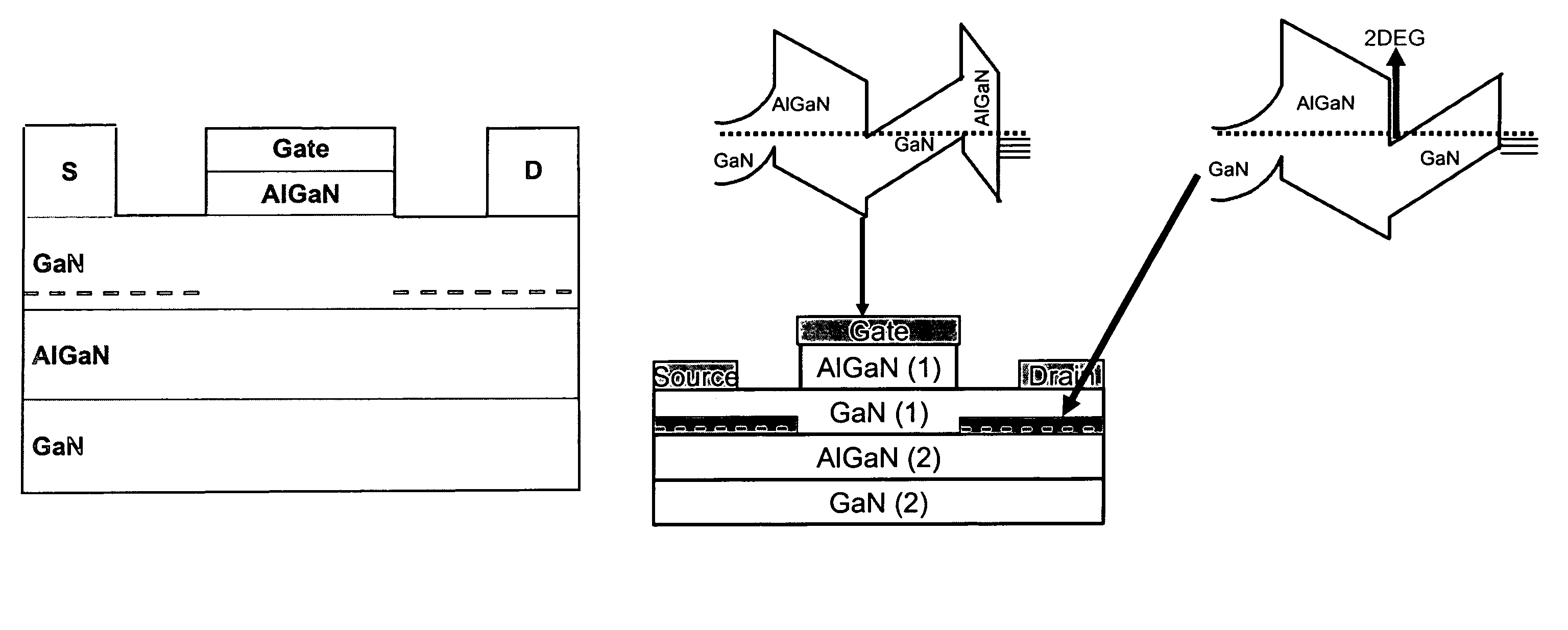

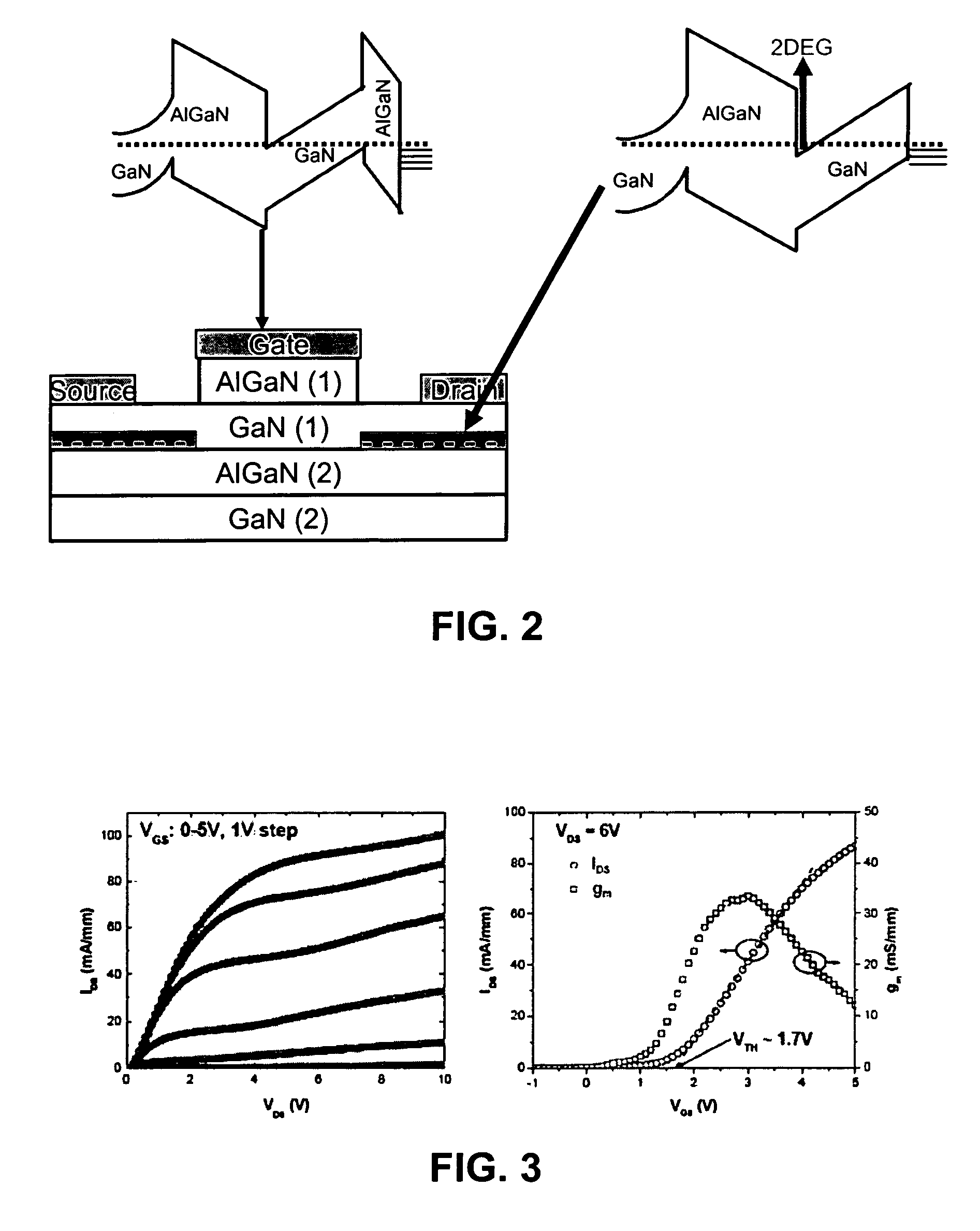

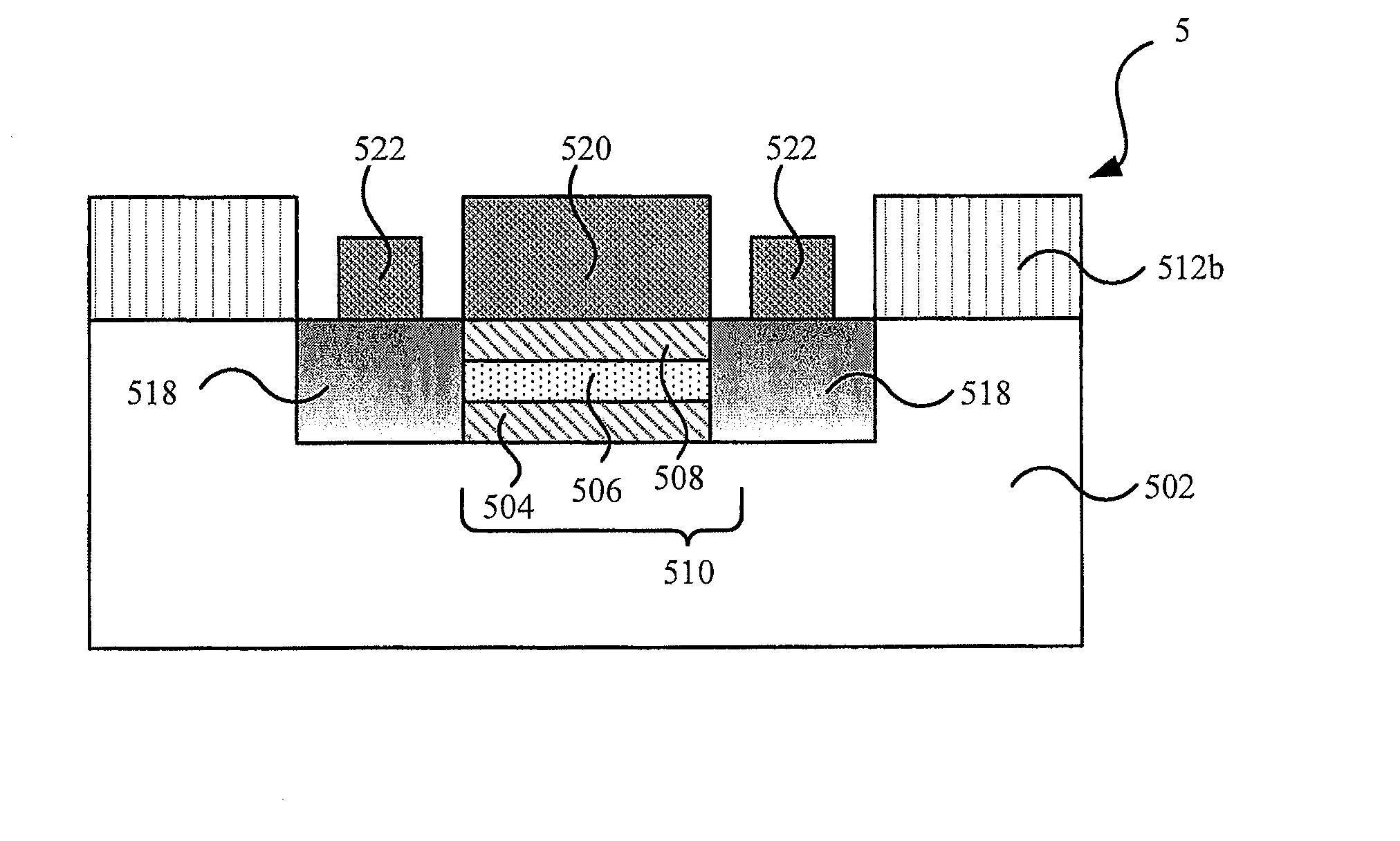

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS20100264461A1High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical polarityField effect

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

Strain enhanced CMOS architecture with amorphous carbon film and fabrication method of forming the same

InactiveUS20070200179A1High carrier mobilityImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSComposite material

A strain enhanced CMOS device using amorphous carbon films and fabrication methods of forming the same. The amorphous carbon (a-C) film, such as fluorinated amorphous carbon (a-C:F), is formed of a tensile film or a compressive film to act a stress capping film on the pMOS device region or the nMOS device region. The amorphous carbon film also acts a contact etching stop layer during a contact hole etching process.

Owner:TAIWAN SEMICON MFG CO LTD

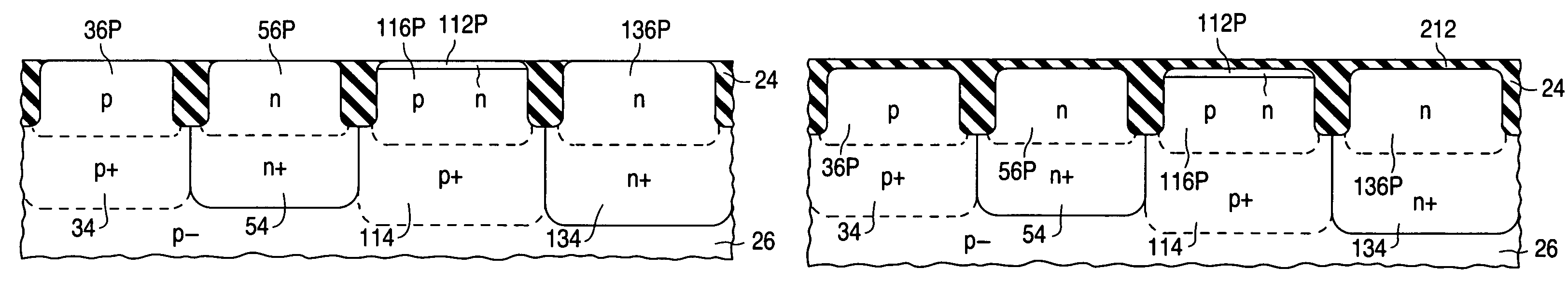

Semiconductor structure having n-channel channel-junction field-effect transistor

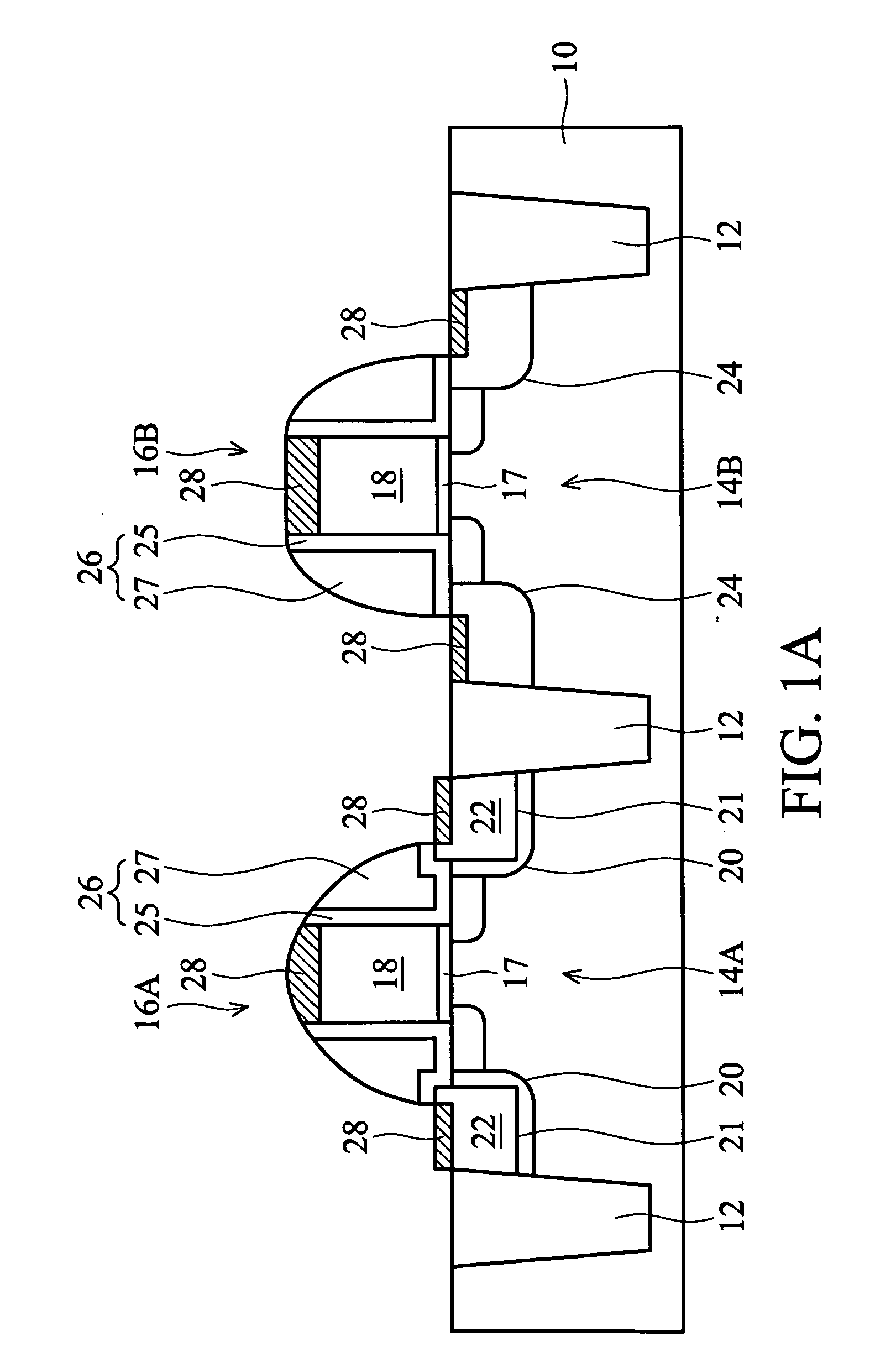

ActiveUS7176530B1Large noise reductionEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. Alternatively or additionally, the channel-junction IGFET may conduct current through a field-induced surface channel. A p-channel surface-channel IGFET (102 or 162), which is typically of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

Enhanced deposition control in fabricating devices in a semiconductor wafer

InactiveUS6656853B2Easy to controlHigh electron mobilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductorTransistor

A method for an enhanced deposition control includes forming a transistor on a substrate of a semiconductor wafer, and depositing a silicon nitride layer on the transistor and the substrate in a reactor at a pressure of at least approximately 10<4 >Pa.

Owner:NEC ELECTRONICS CORP

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS7948011B2High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesField effectHigh electron

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

Process for making doped zinc oxide

ActiveUS20090081826A1Suitable for processingAllowed to operateAdditive manufacturing apparatusConductive materialIndiumZinc

The present invention relates to a process of making a zinc-oxide-based thin film semiconductor, for use in a transistor, comprising thin film deposition onto a substrate comprising providing a plurality of gaseous materials comprising first, second, and third gaseous materials, wherein the first gaseous material is a zinc-containing volatile material and the second gaseous material is reactive therewith such that when one of the first or second gaseous materials are on the surface of the substrate the other of the first or second gaseous materials will react to deposit a layer of material on the substrate, wherein the third gaseous material is inert and wherein a volatile indium-containing compound is introduced into the first reactive gaseous material or a supplemental gaseous material.

Owner:EASTMAN KODAK CO

P-GaN/AlGaN/AlN/GaN enhancement-mode field effect transistor

ActiveUS7728356B2High electron mobilityLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectron populationField-effect transistor

Owner:RGT UNIV OF CALIFORNIA

Semiconductor device with group III-V channel and group IV source-drain and method for manufacturing the same

InactiveUS7928427B1Effective limitLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

The present invention is related to a semiconductor device with group III-V channel and group IV source-drain and a method for manufacturing the same. Particularly, the energy level density and doping concentration of group III-V materials are increased by the heteroepitaxy of group III-V and group IV materials and the structural design of elements. The method comprises: preparing a substrate; depositing a dummy gate material layer on the substrate and defining a dummy gate from the dummy gate material layer by photolithography; performing doping by self-aligned ion implantation using the dummy gate as a mask and performing activation at high temperature, so as to form source-drain; removing the dummy gate; forming a recess in the substrate between the source-drain pair by etching; forming a channel-containing stacked element in the recess by epitaxy; and forming a gate on the channel-containing stacked element.

Owner:NAT CHIAO TUNG UNIV

Electronic components

InactiveUS20060237719A1Improve electrical performanceImprove performanceTransistorSolid-state devicesDopantNanoparticle

A method of manufacturing an electronic component comprising at least one n- or p-doped portion, comprising the steps of: co-depositing inorganic semi-conducting nanoparticles and dopant on a substrate, the nanoparticles being a group four element such as silicon or germanium; fusing the nanoparticles by heating to form a continuous layer; and subsequently; and, recrystallising the layer.

Owner:HEWLETT PACKARD DEV CO LP

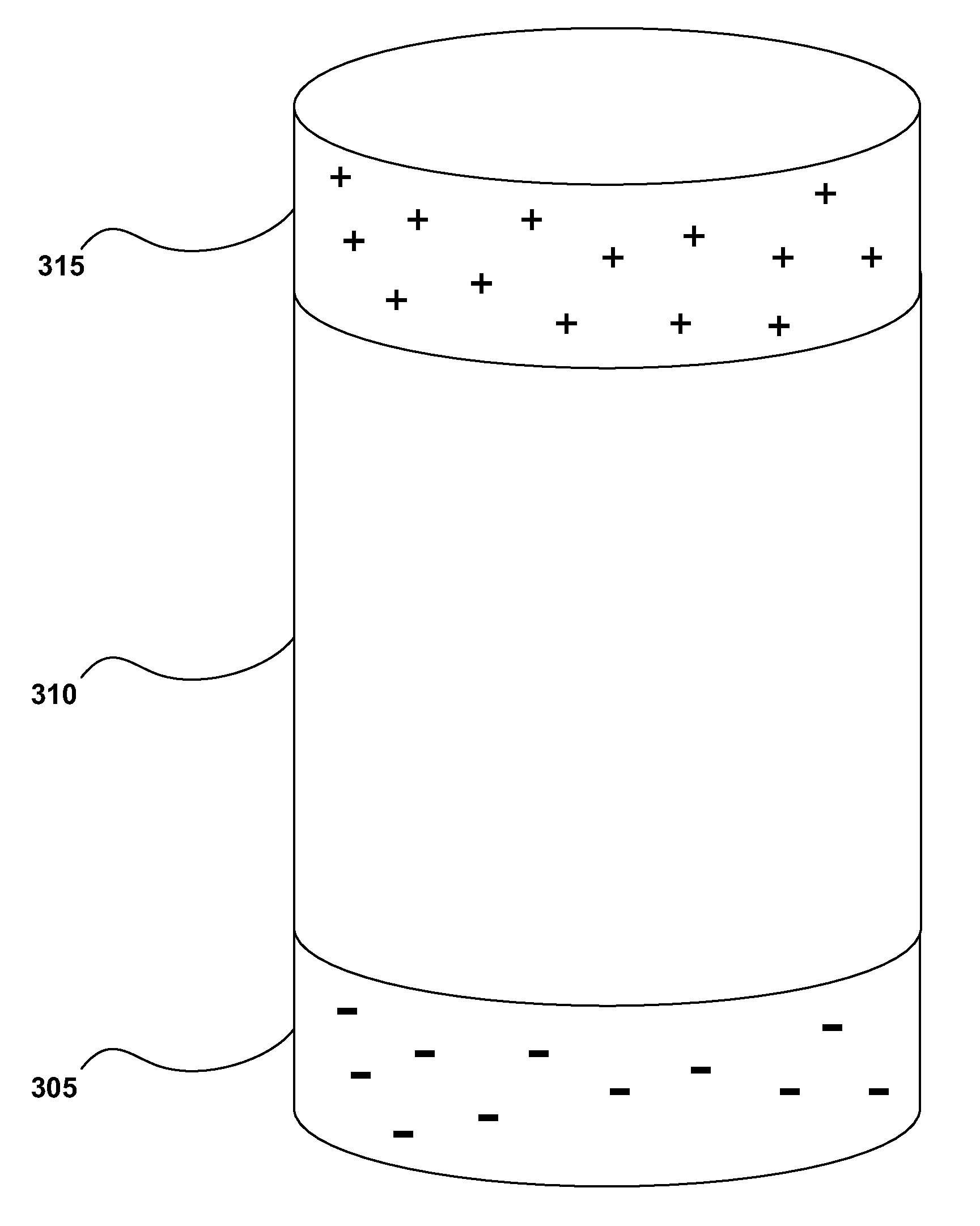

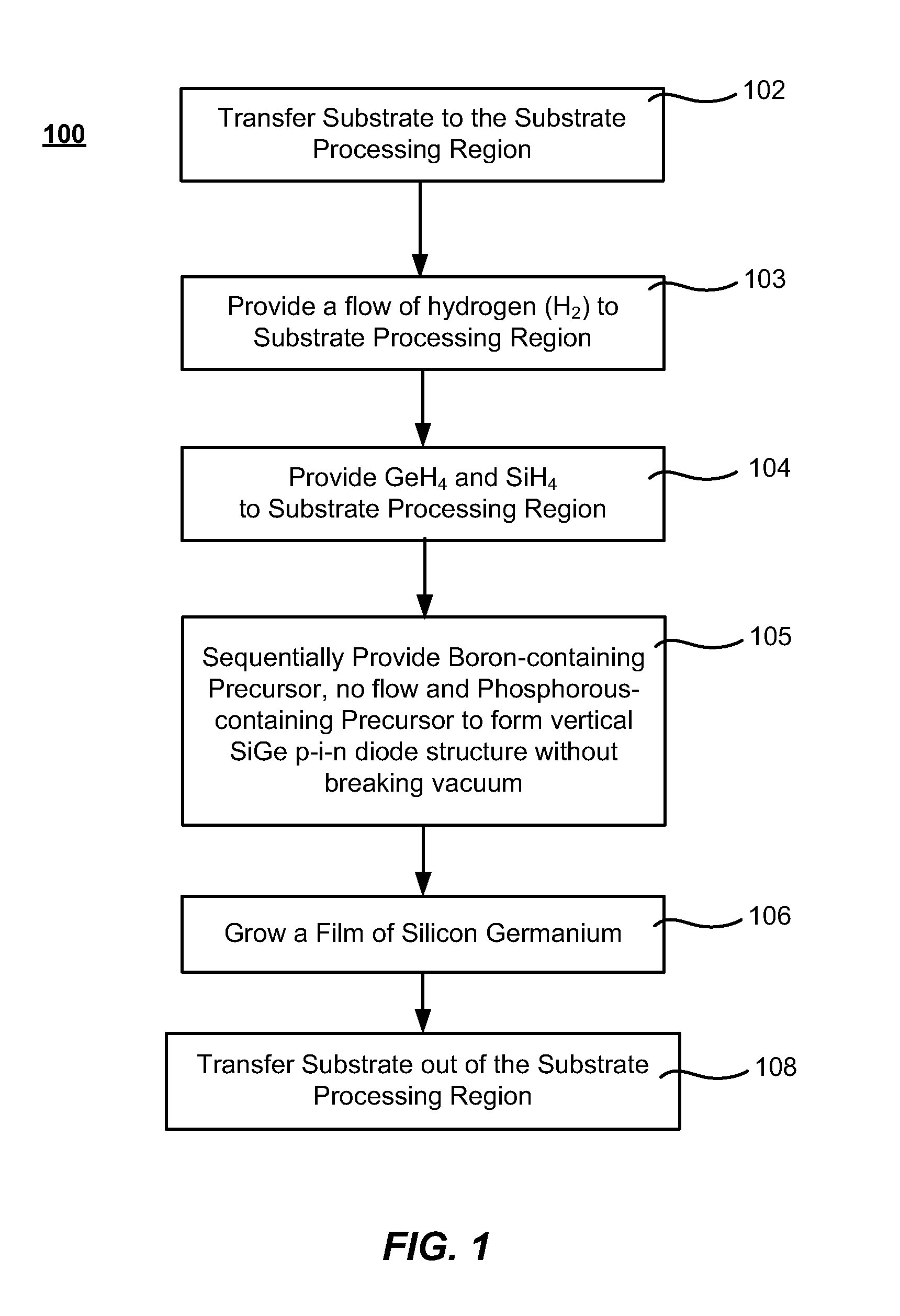

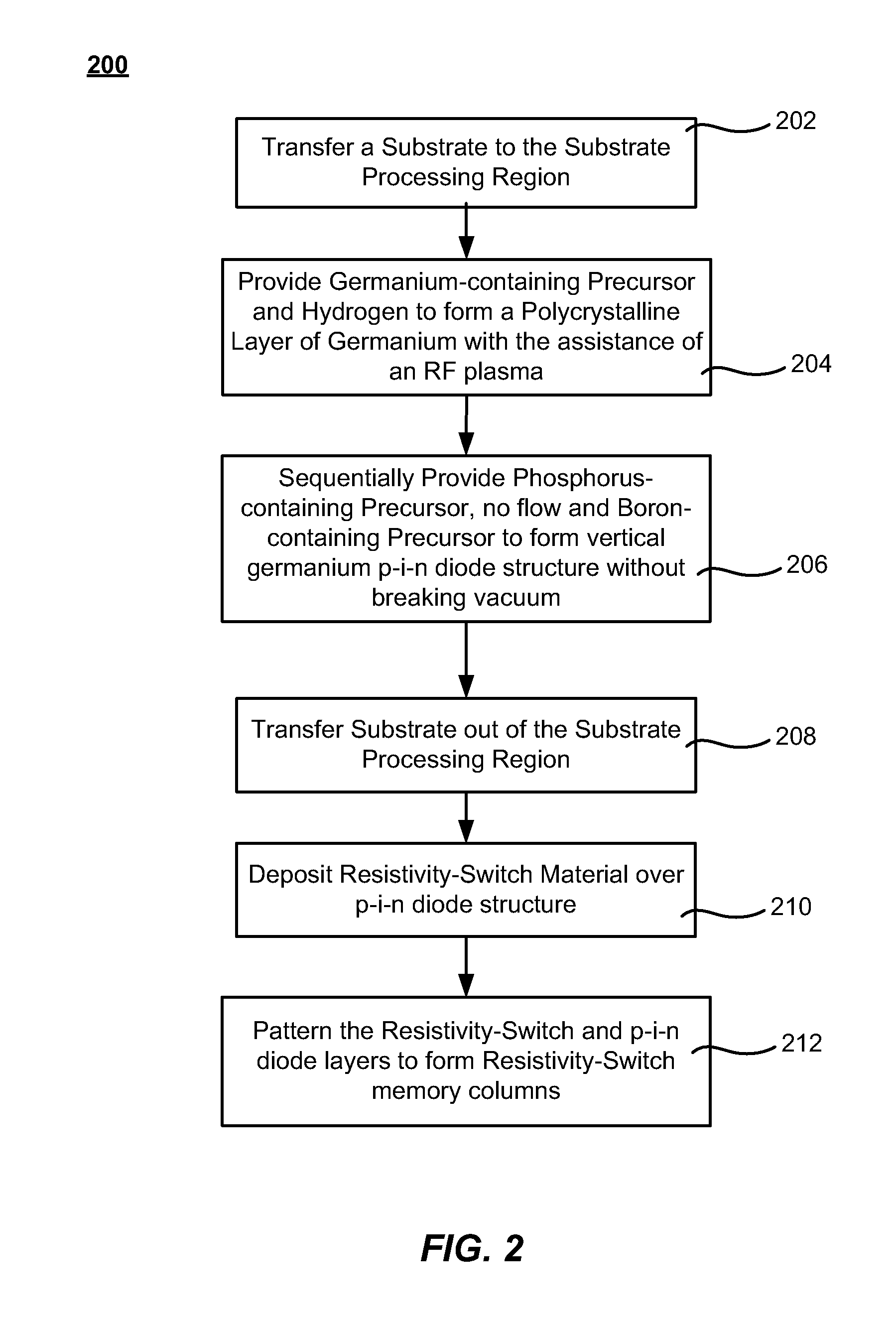

High mobility monolithic p-i-n diodes

InactiveUS20110136327A1Reduce interfaceHigh electron mobilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh current densityDopant

Methods of forming high-current density vertical p-i-n diodes on a substrate are described. The methods include the steps of concurrently combining a group-IV-element-containing precursor with a sequential exposure to an n-type dopant precursor and a p-type dopant precursor in either order. An intrinsic layer is deposited between the n-type and p-type layers by reducing or eliminating the flow of the dopant precursors while flowing the group-IV-element-containing precursor. The substrate may reside in the same processing chamber during the deposition of each of the n-type layer, intrinsic layer and p-type layer and the substrate is not exposed to atmosphere between the depositions of adjacent layers.

Owner:APPLIED MATERIALS INC

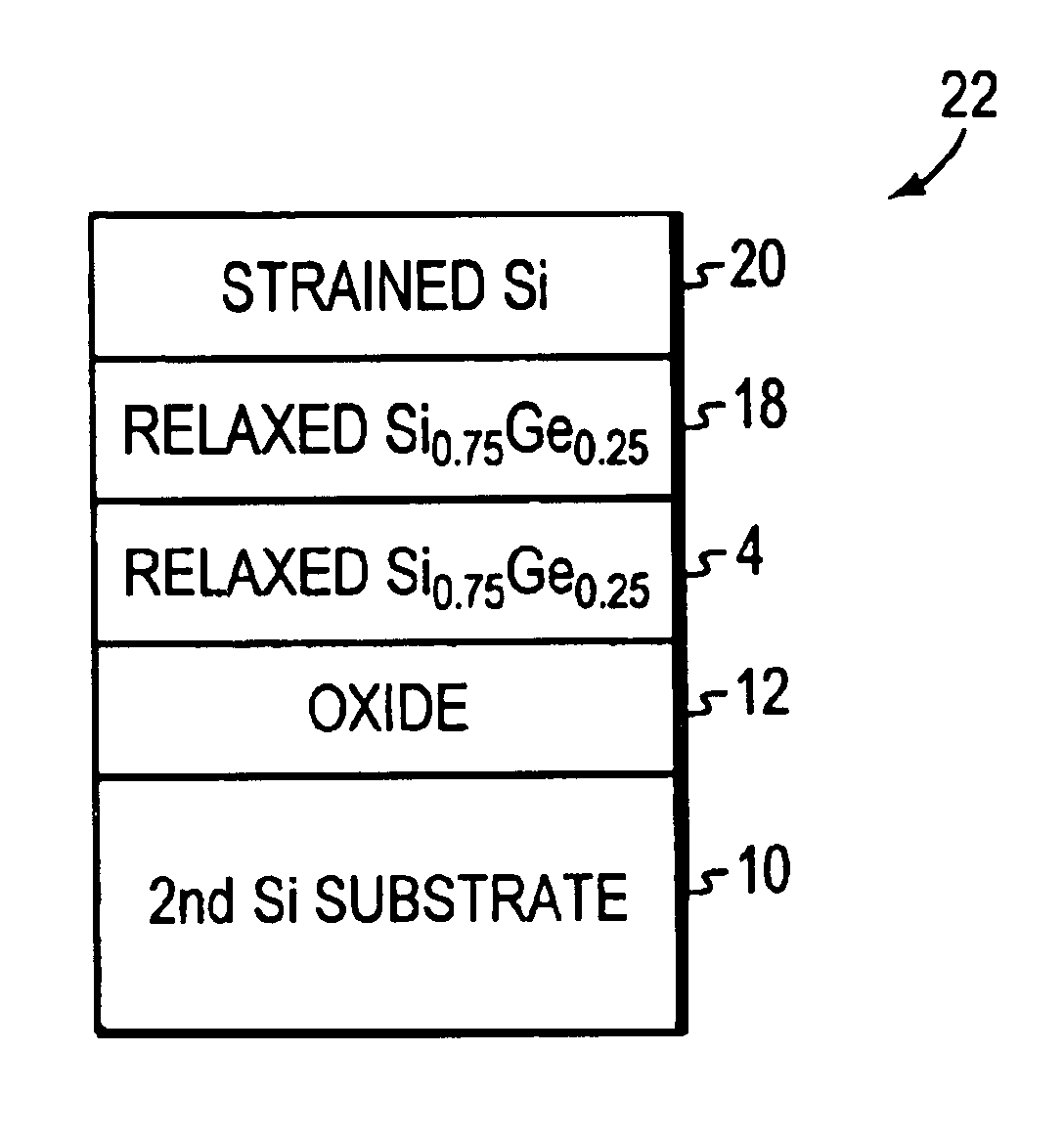

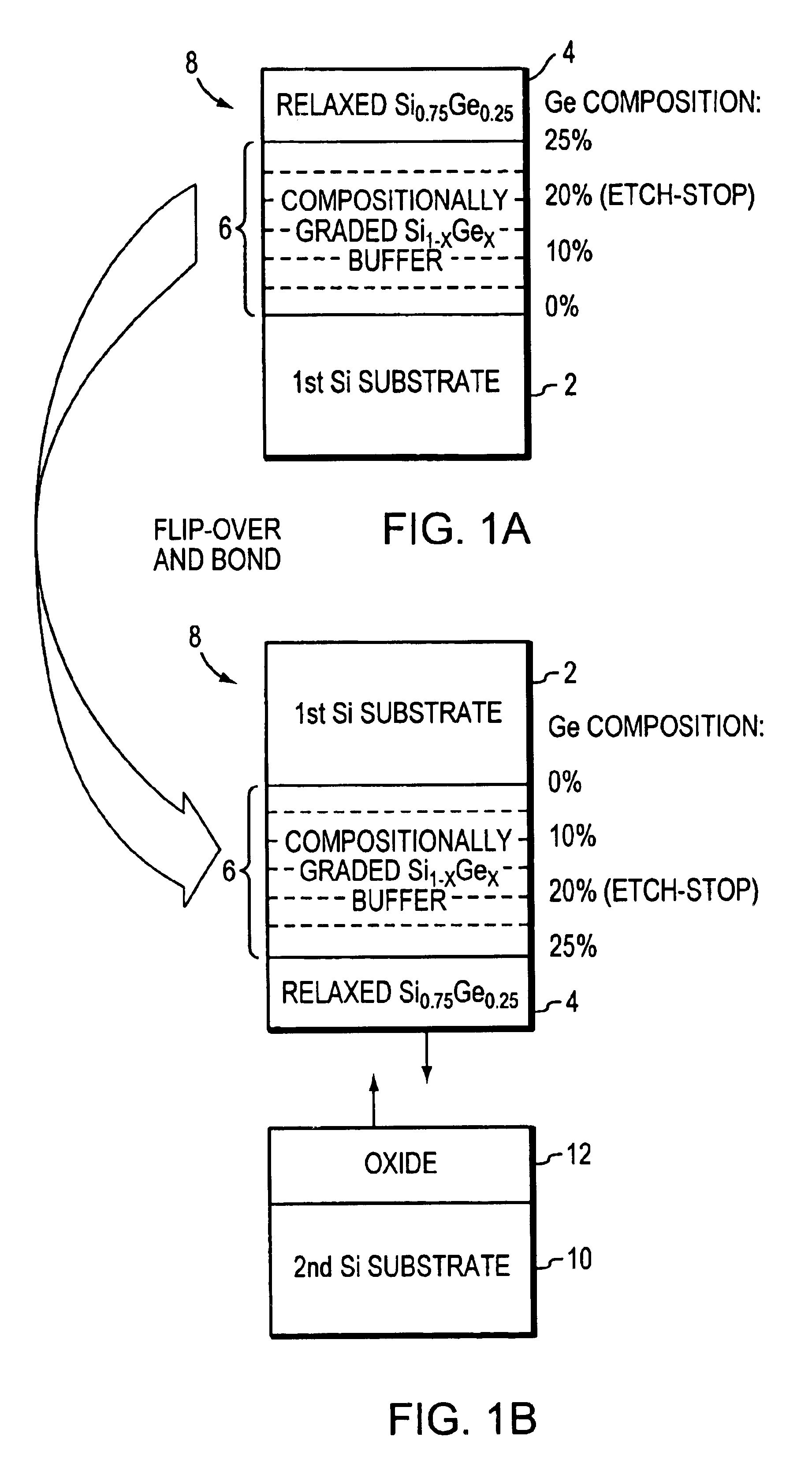

Semiconductor device structure

InactiveUS6940089B2Improvement ingredientsHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureSemiconductor device

Owner:MASSACHUSETTS INST OF TECH

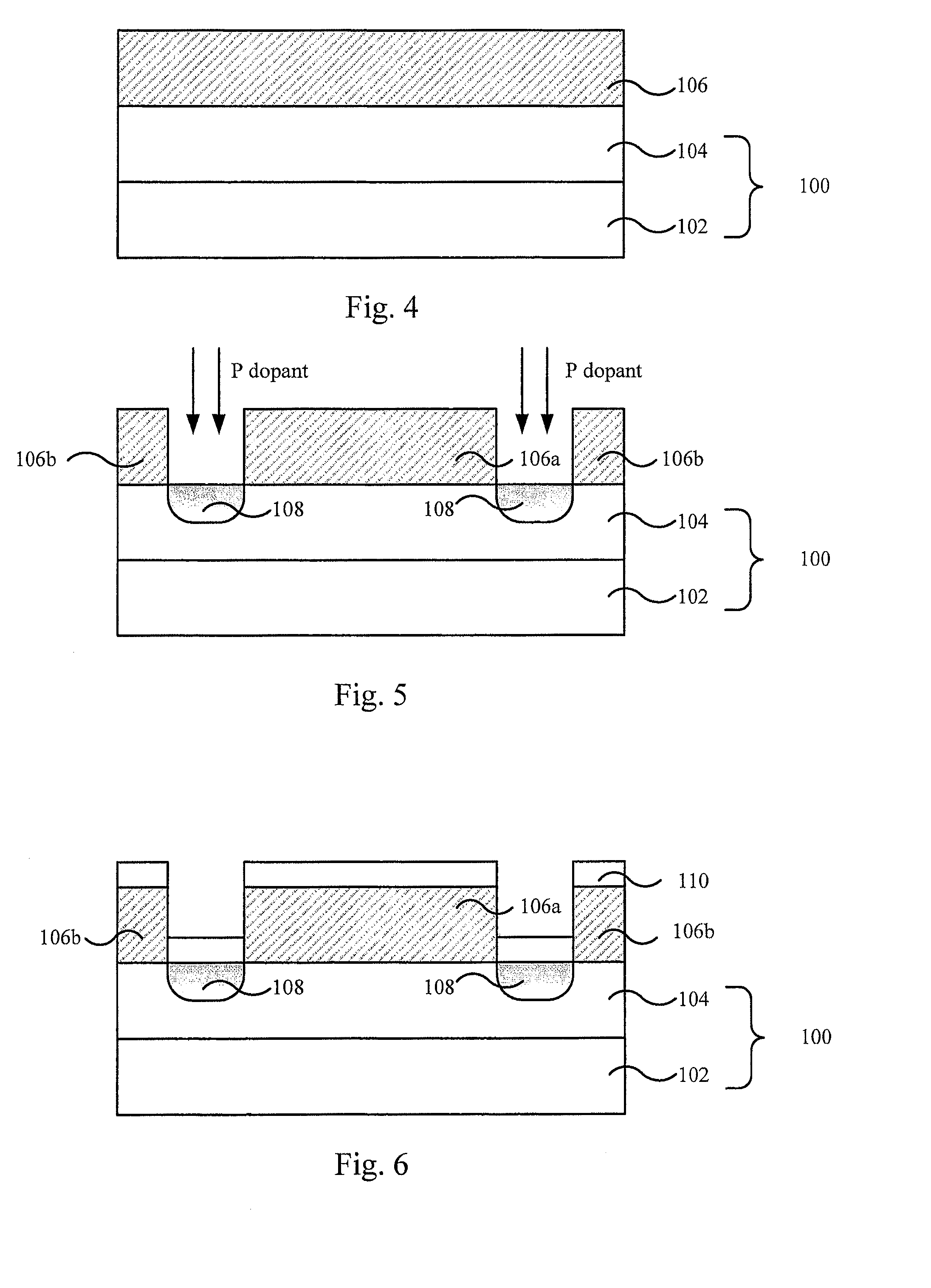

Method for fabricating locally strained channel

InactiveUS6858506B2High electron mobilityImprove device speedTransistorSemiconductor/solid-state device manufacturingDopantGate oxide

A manufacturing method for a semiconductor device is provided, wherein a silicon germanium (Si1-xGex; SiGe) layer and a strained silicon layer are sequentially formed on a semiconductor substrate. A gate oxide layer and a gate structure are further formed on the strained silicon layer. The gate structure and the strained silicon layer are heavily doped with n-type dopants to form a compressed gate and source / drain regions, respectively. A cap layer is further formed over the semiconductor substrate, followed by conducting an annealing process. The cap layer is subsequently removed.

Owner:MACRONIX INT CO LTD

Process for atomic layer deposition

InactiveUS20090081842A1Suitable for processingHigh electron mobilityAdditive manufacturing apparatusSolid-state devicesElectronic componentAtomic layer deposition

The present invention relates to a process of making thin film electronic components and devices, such as thin film transistors, environmental barrier layers, capacitors, insulators and bus lines, where most or all of the layers are made by an atmospheric atomic layer deposition process.

Owner:EASTMAN KODAK CO

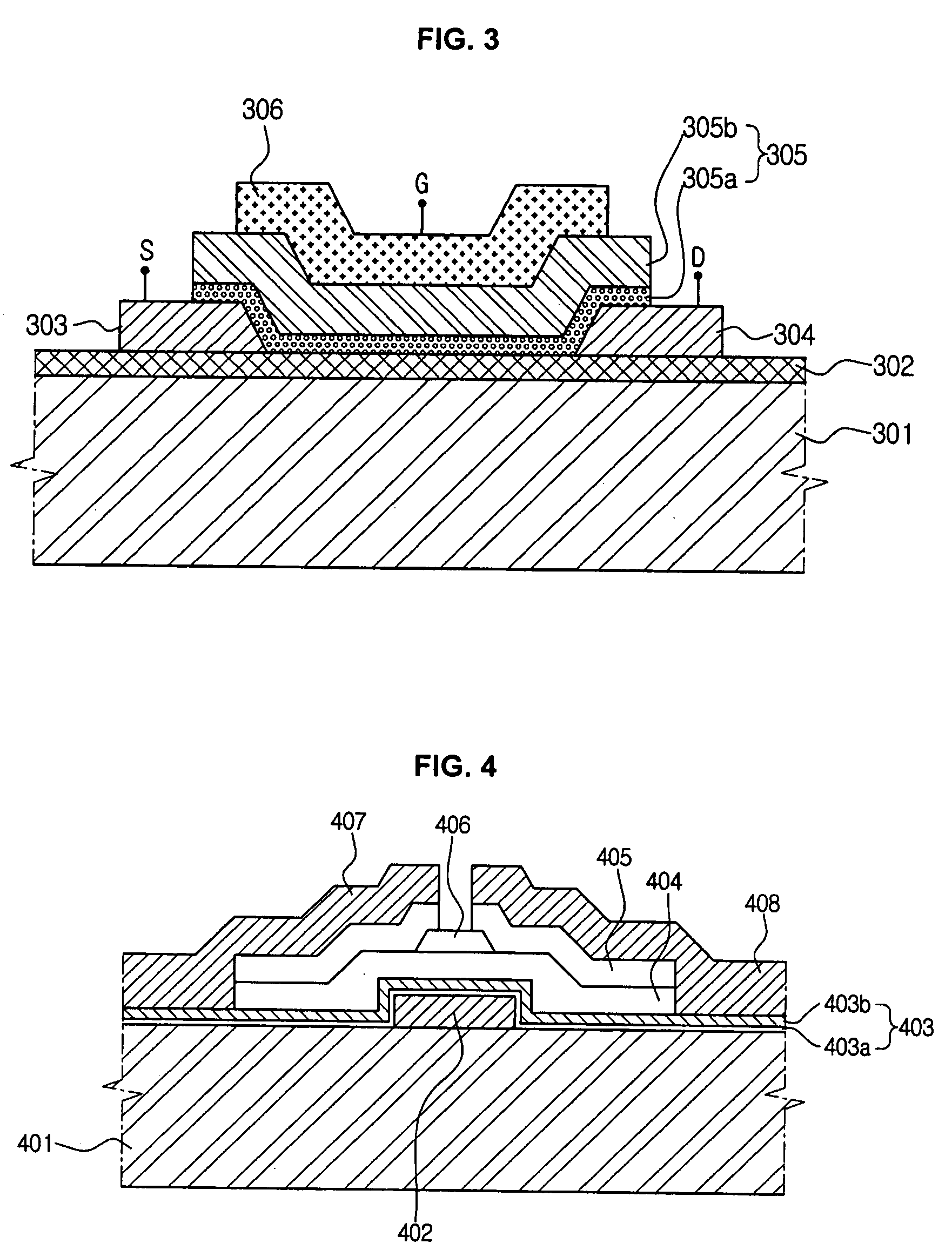

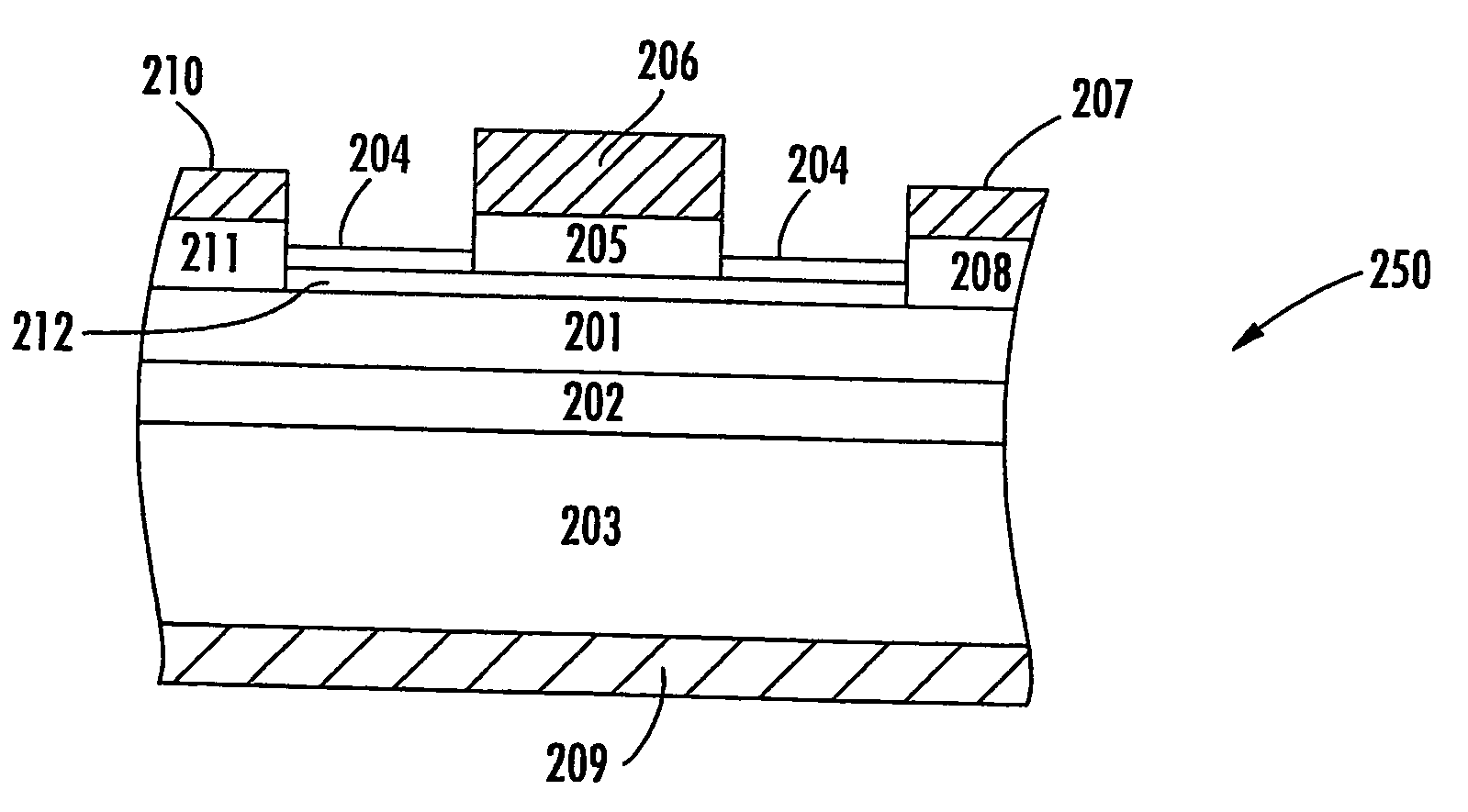

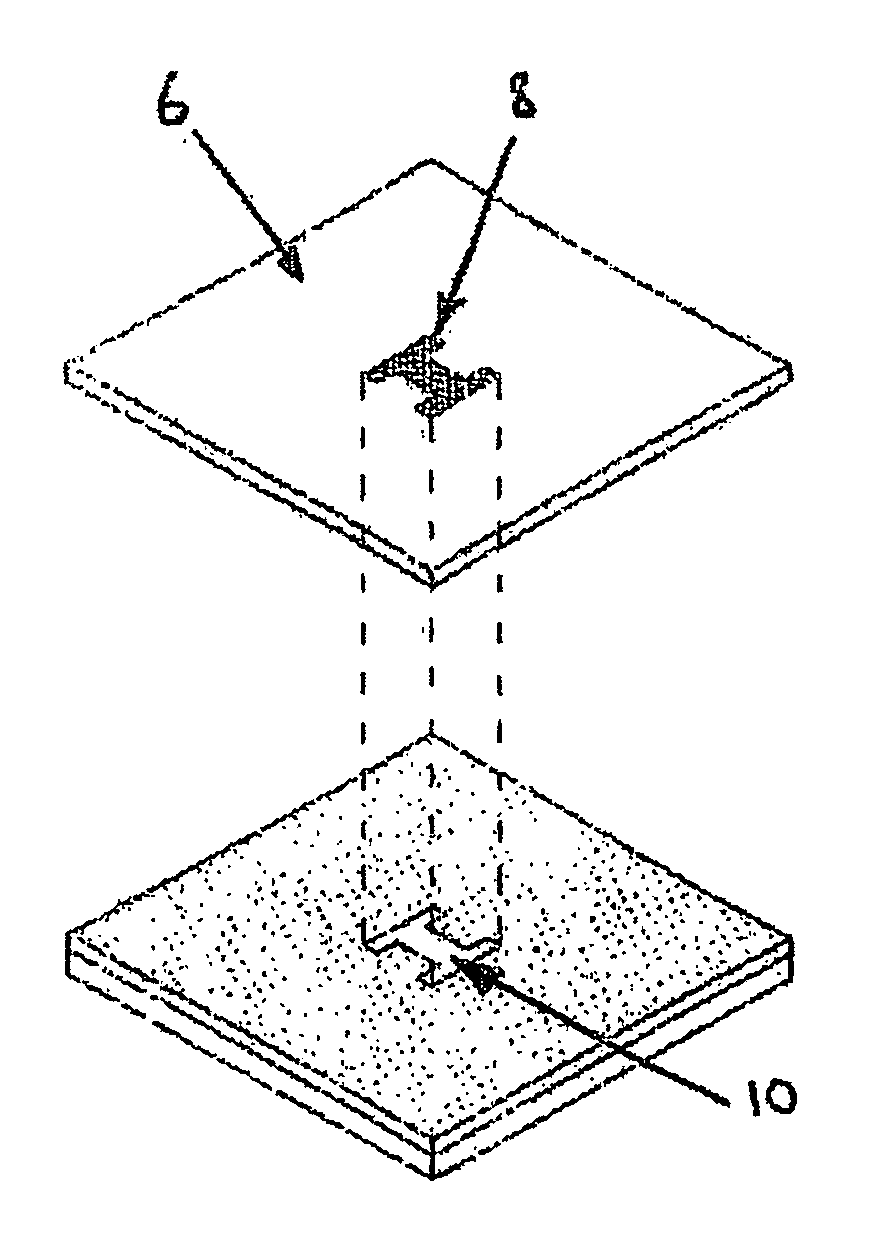

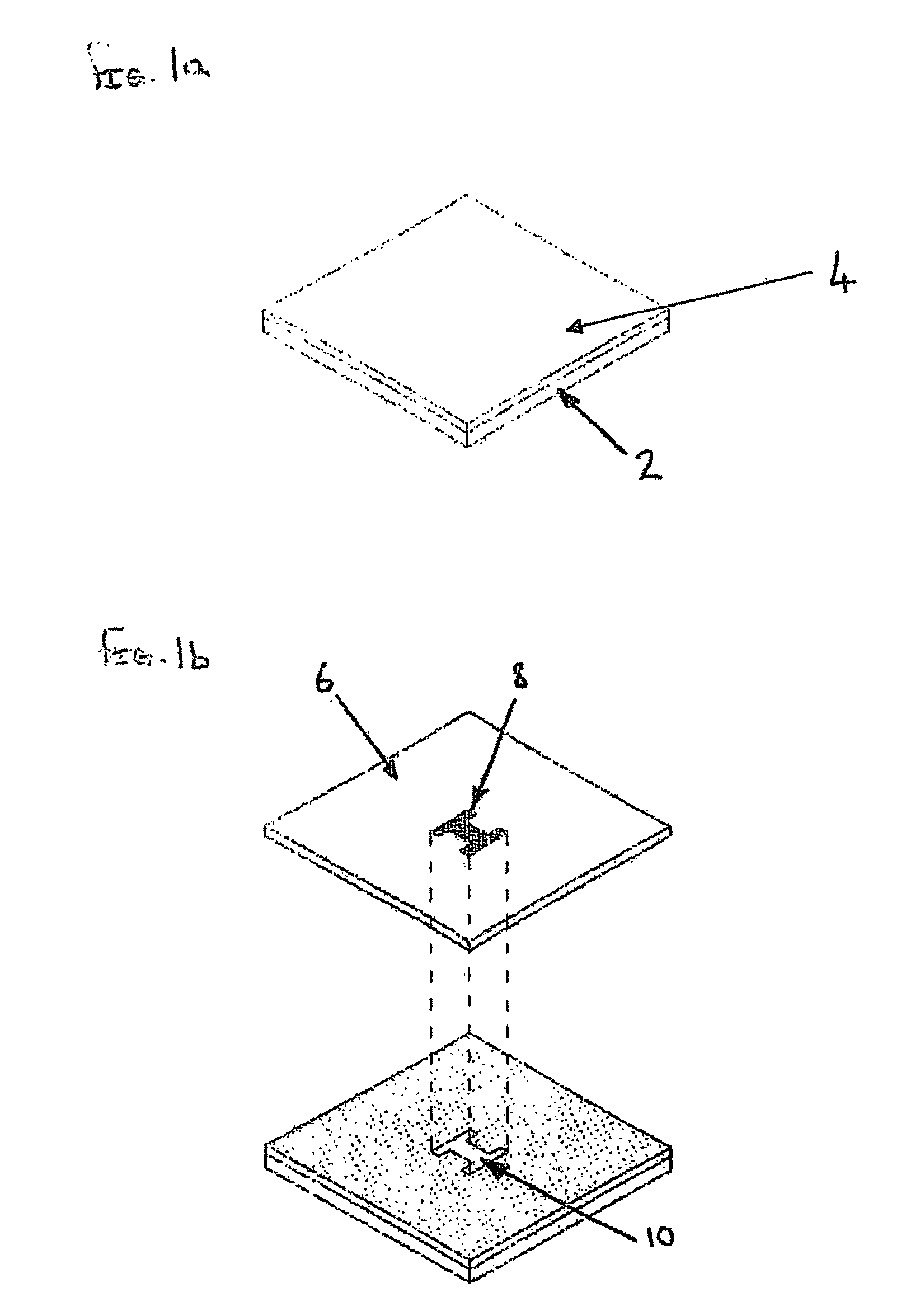

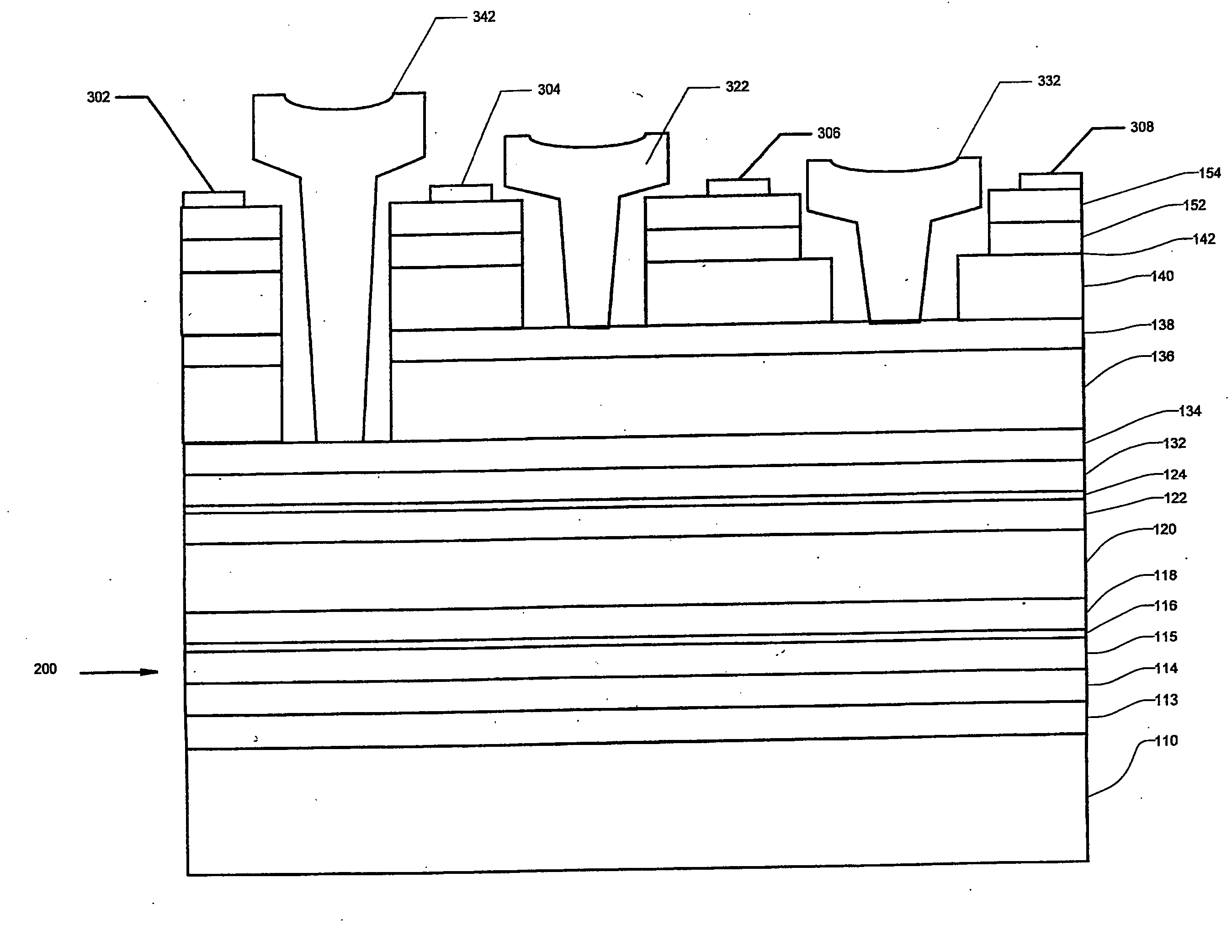

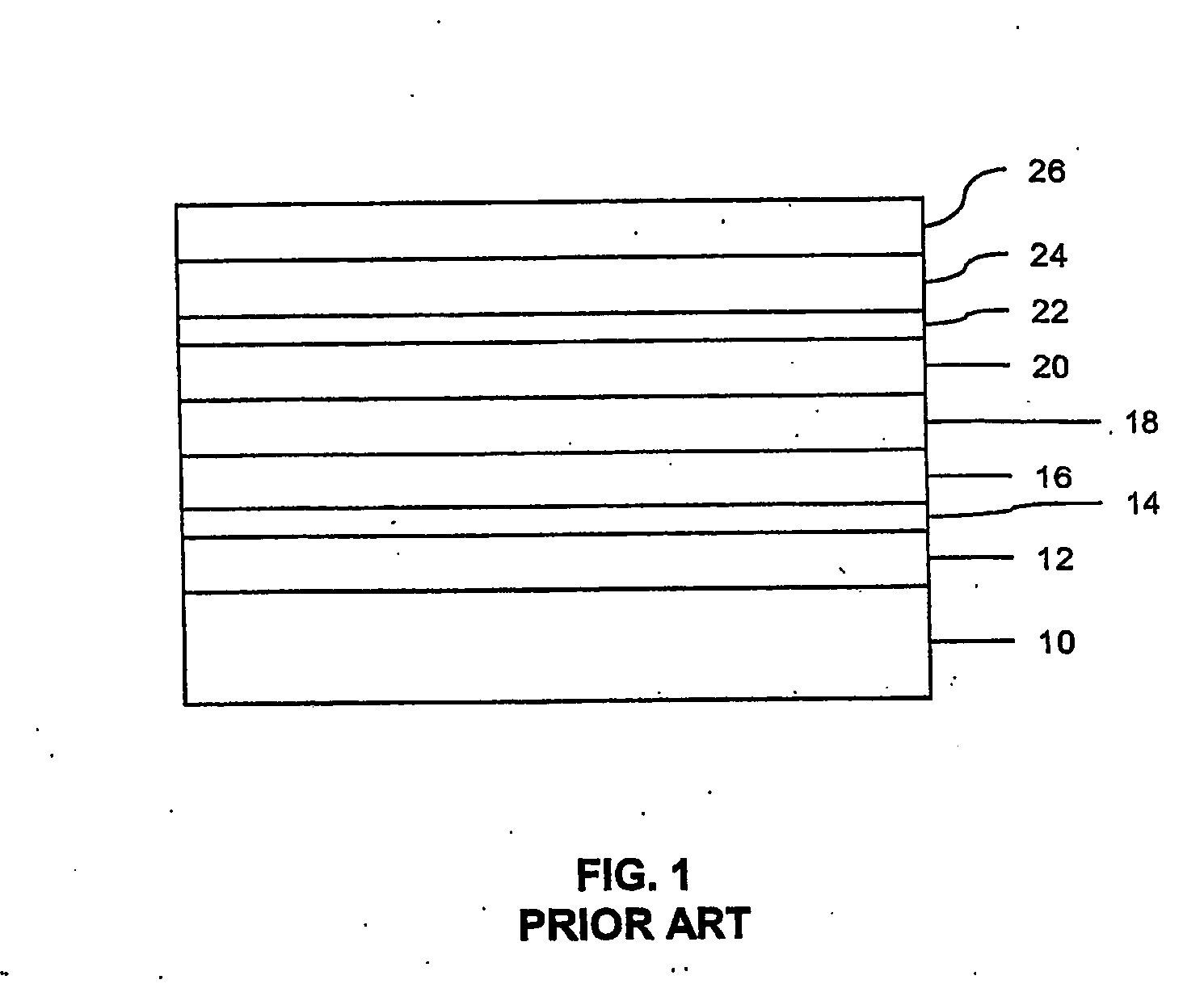

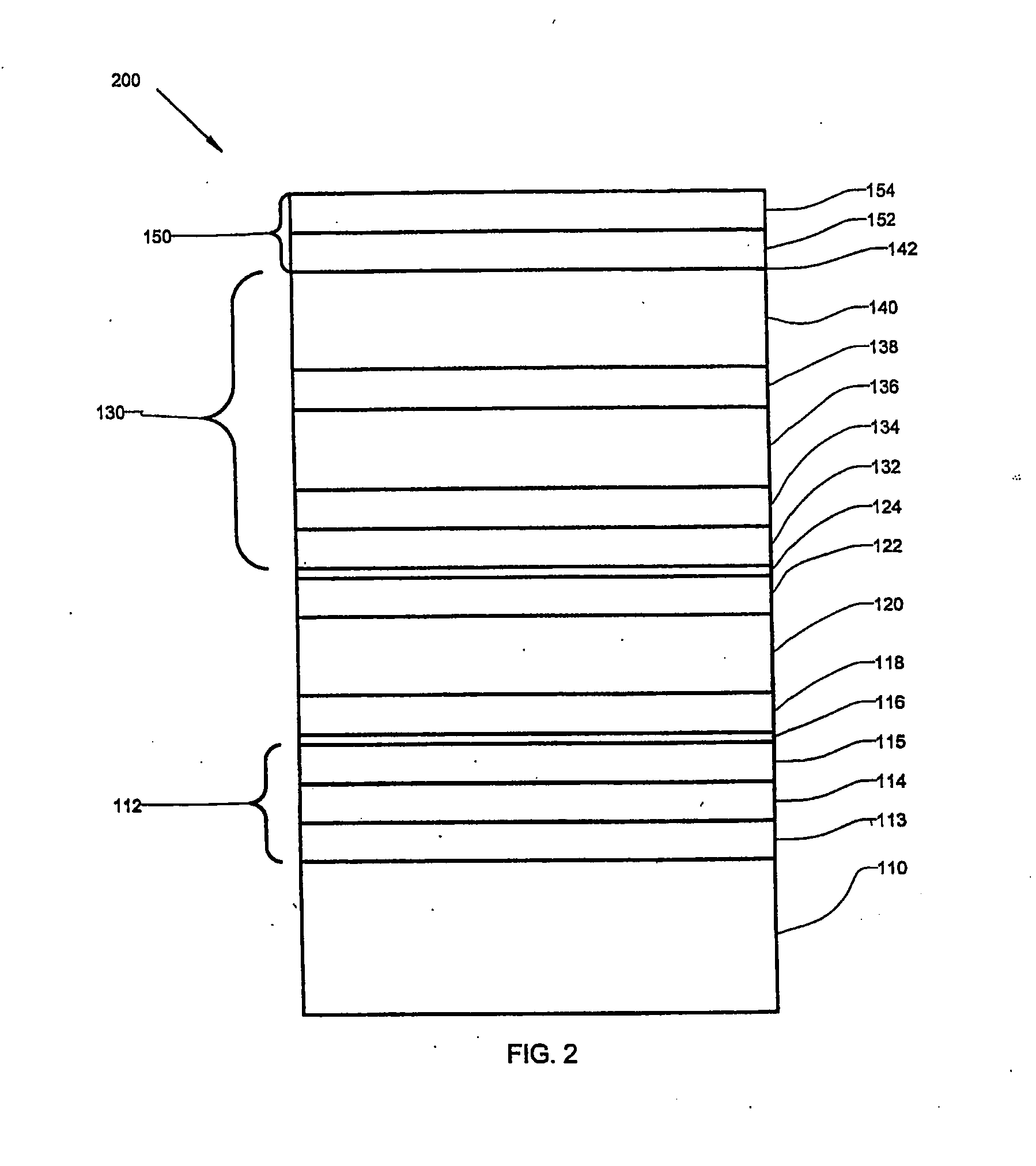

Multi-layer structure for use in the fabrication of integrated circuit devices and methods for fabrication of same

InactiveUS20060208279A1High electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronContact layer

A multi-layer structure for use in the fabrication of integrated circuit devices is adapted for the formation of enhancement mode high electron mobility transistors, depletion mode high electron mobility transistors, and power high electron mobility transistors. The structure has, on a substrate, a channel layer, spacer layer on the channel layer, a first Schottky layer, a second Schottky layer on the first Schottky layer, and a third Schottky layer on the second Schottky layer, and a contact layer on the third Schottky layer. Etch stops are defined intermediate the first and second Schottky layers, intermediate the second and third Schottky layers, and intermediate the third Schottky layer and the contact layer.

Owner:LOCKHEED MARTIN CORP +1