Patents

Literature

1368 results about "Schottky barrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

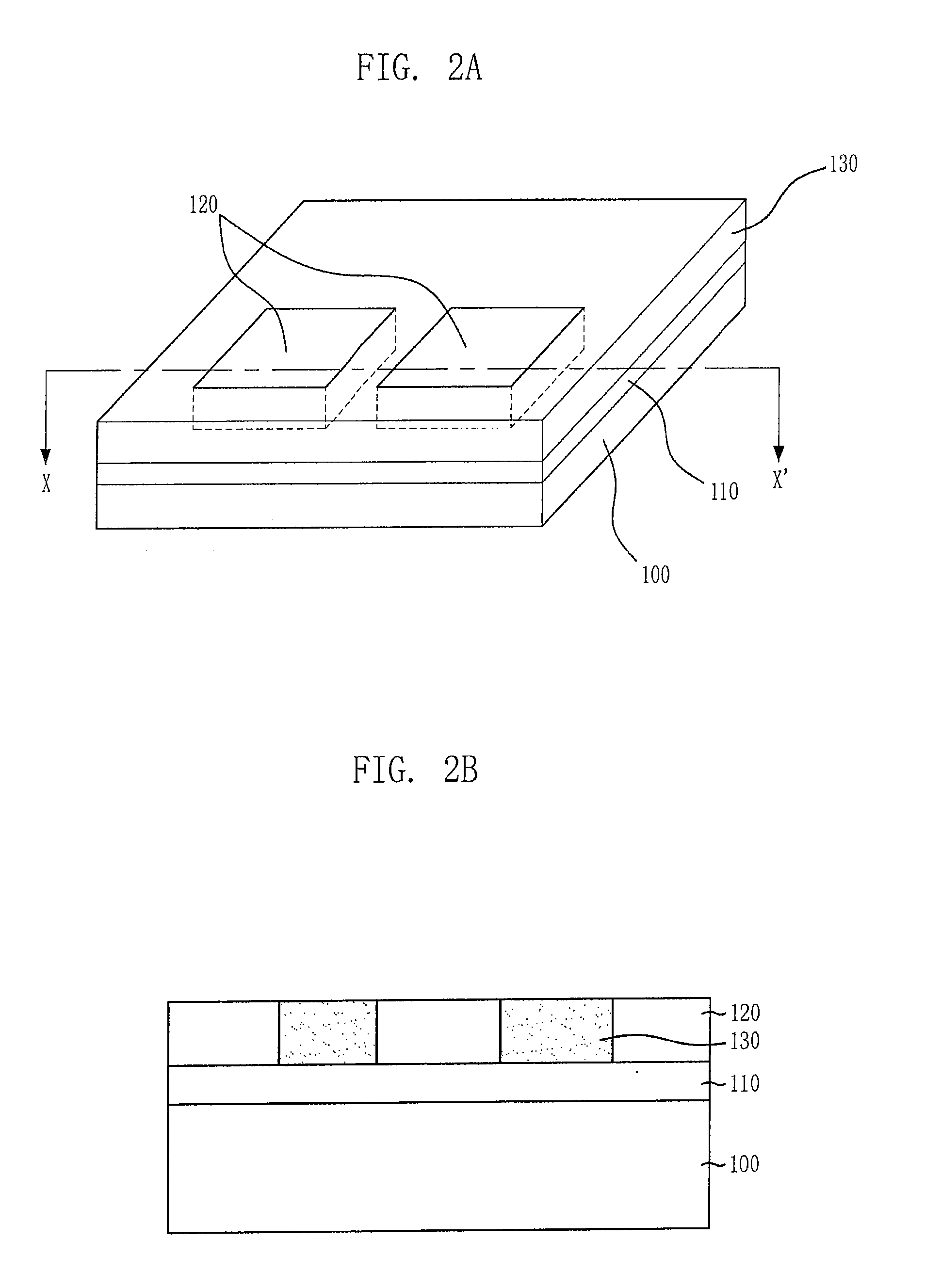

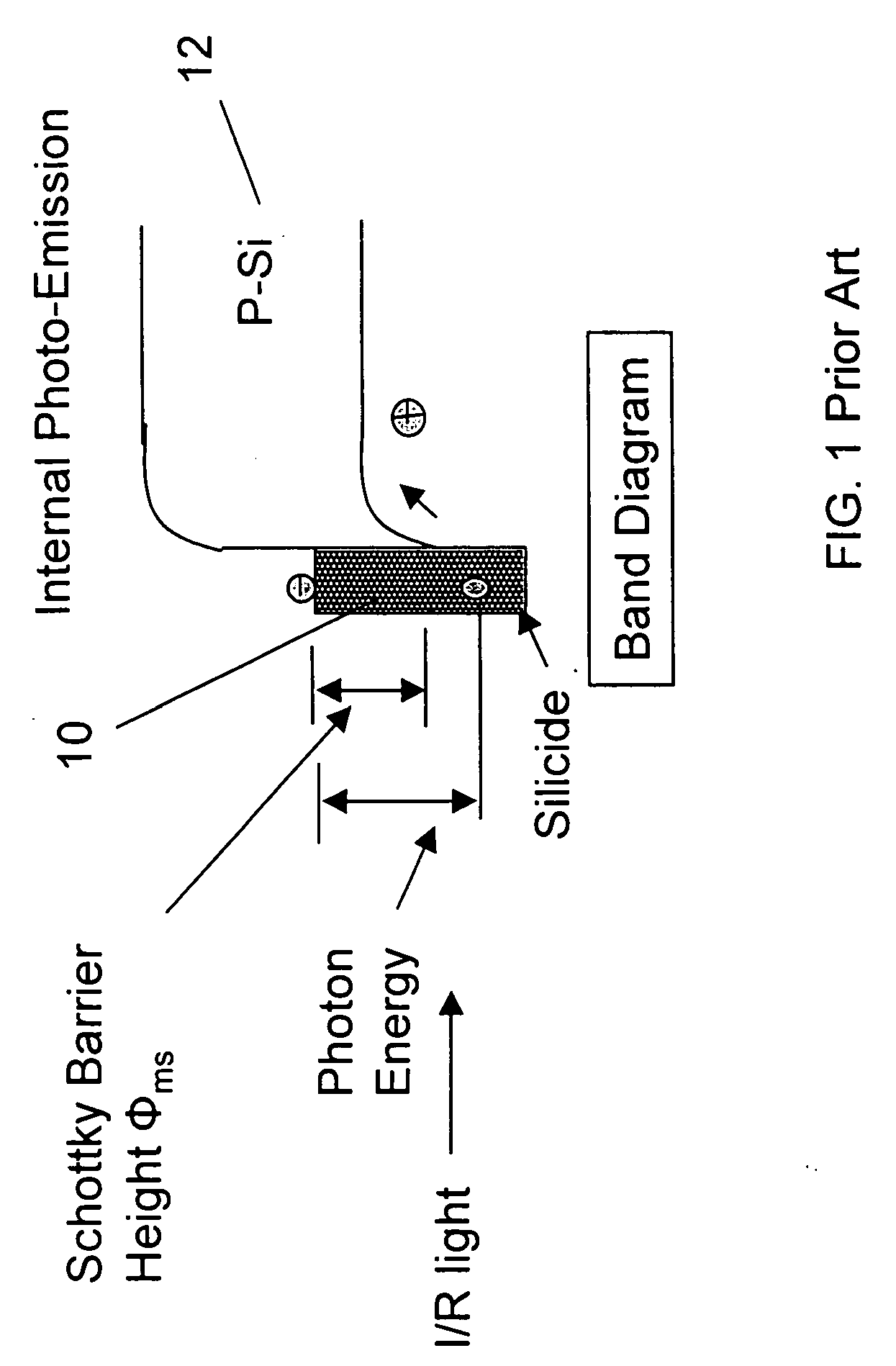

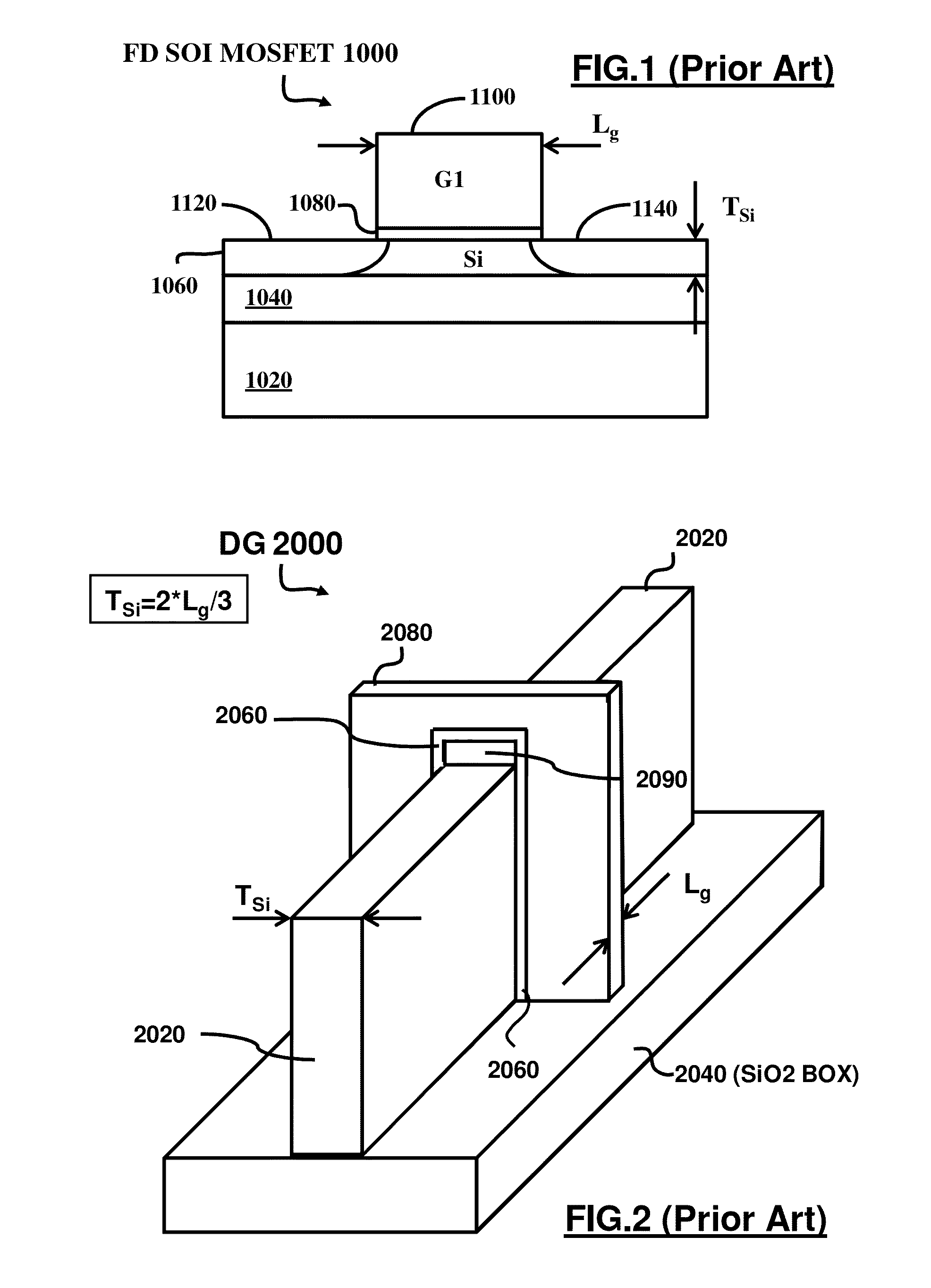

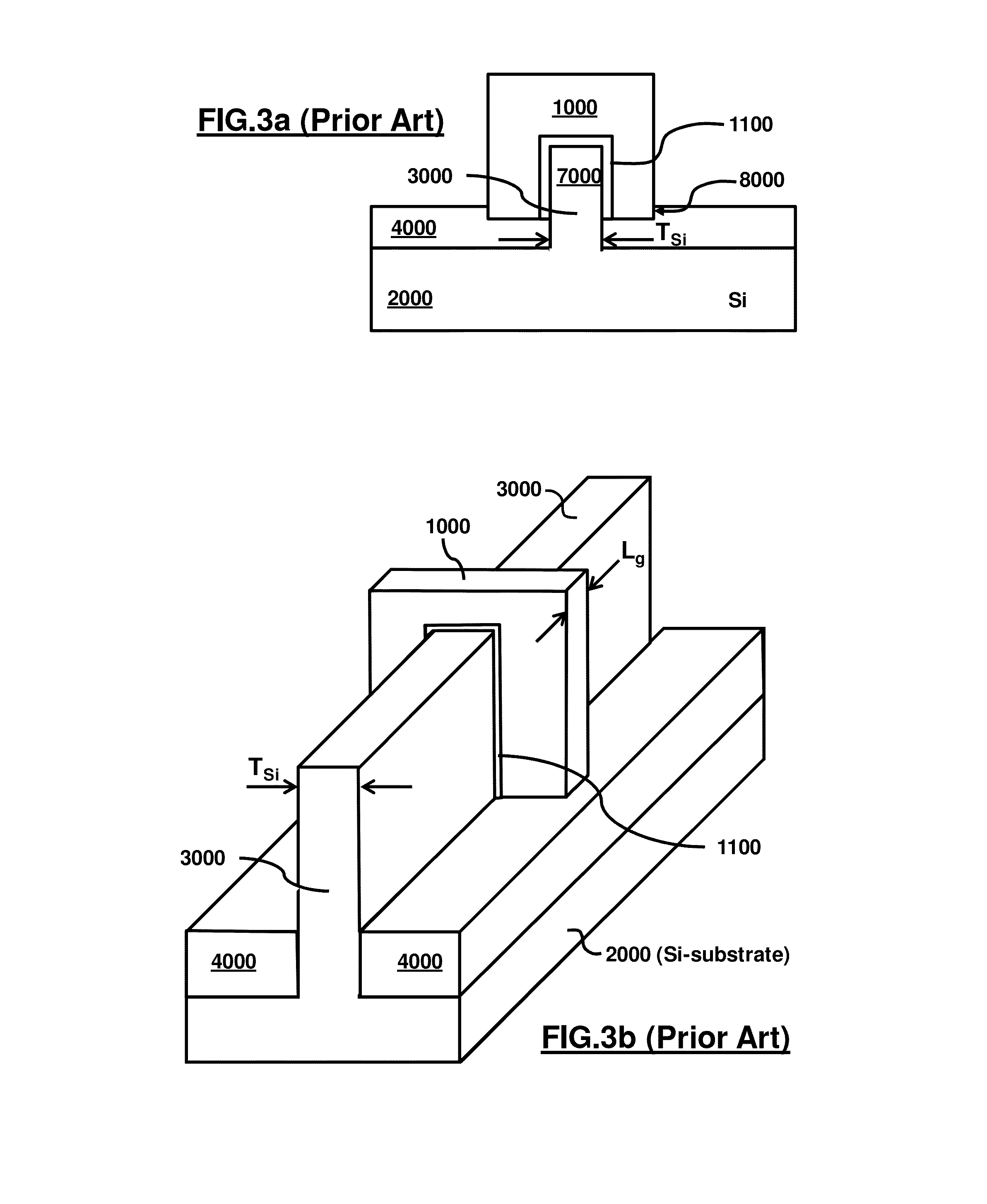

A Schottky barrier, named after Walter H. Schottky, is a potential energy barrier for electrons formed at a metal–semiconductor junction. Schottky barriers have rectifying characteristics, suitable for use as a diode. One of the primary characteristics of a Schottky barrier is the Schottky barrier height, denoted by ΦB (see figure). The value of ΦB depends on the combination of metal and semiconductor.

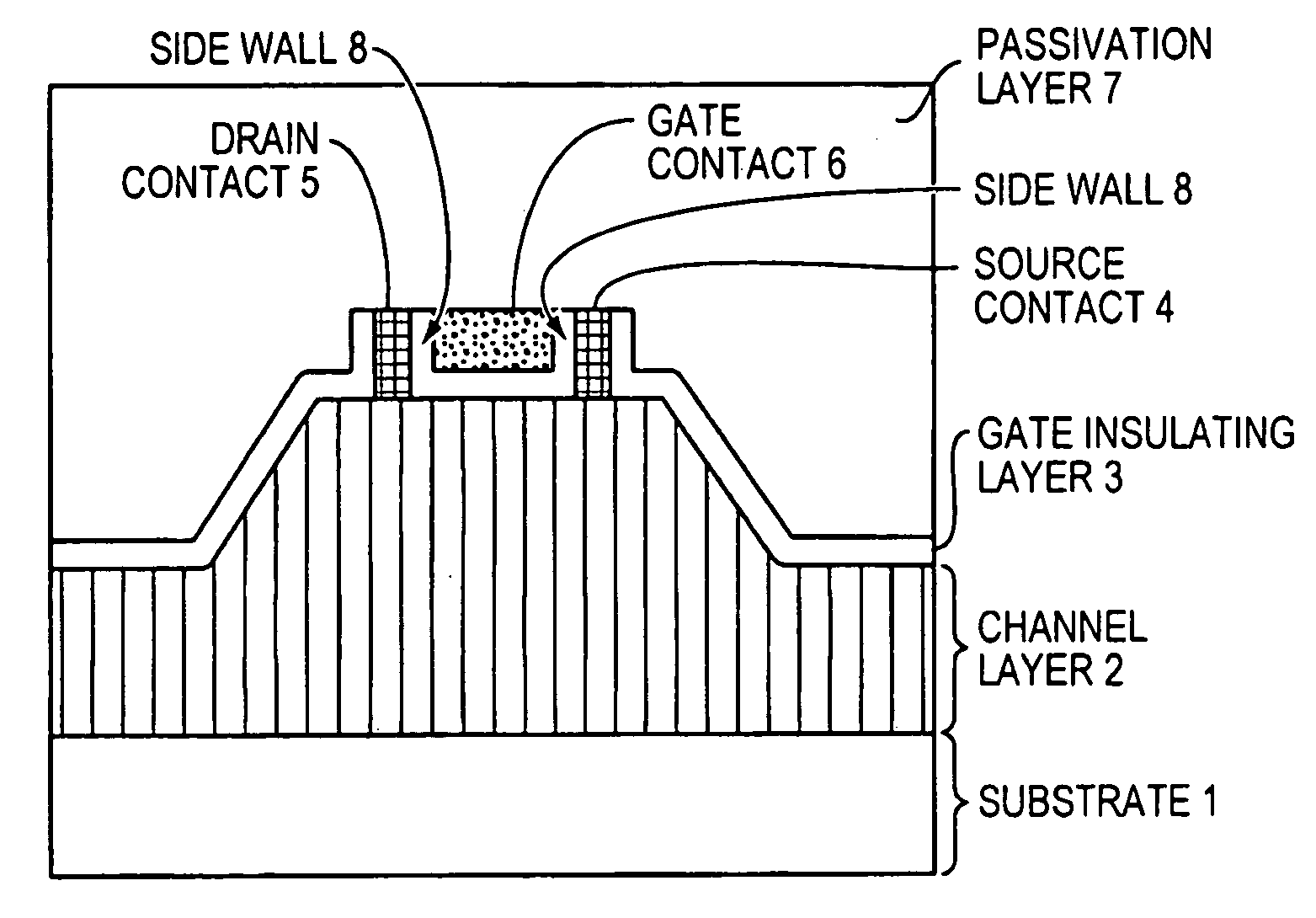

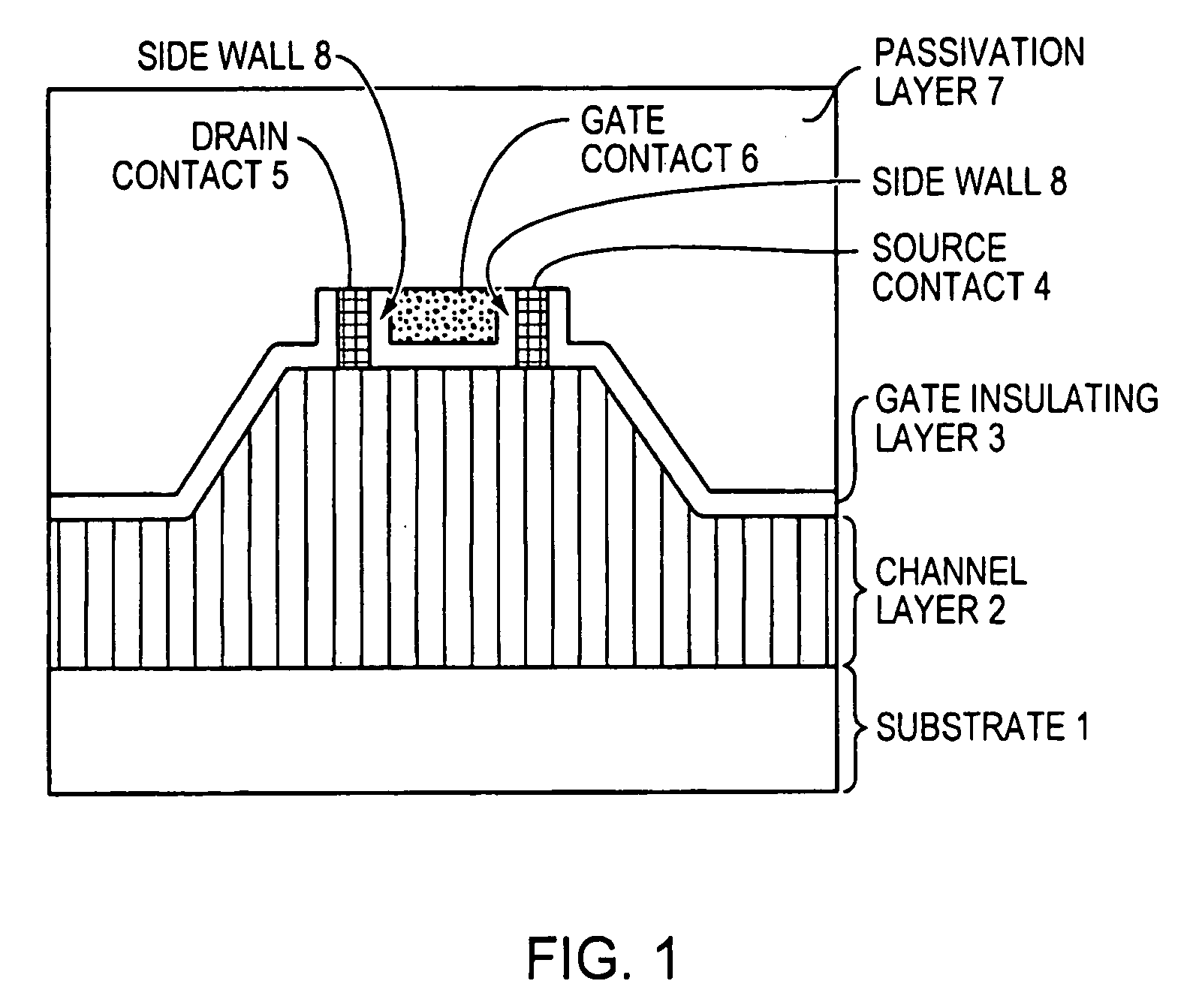

High-electron mobility transistor with zinc oxide

InactiveUS7105868B2Increase heightHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierField-effect transistor

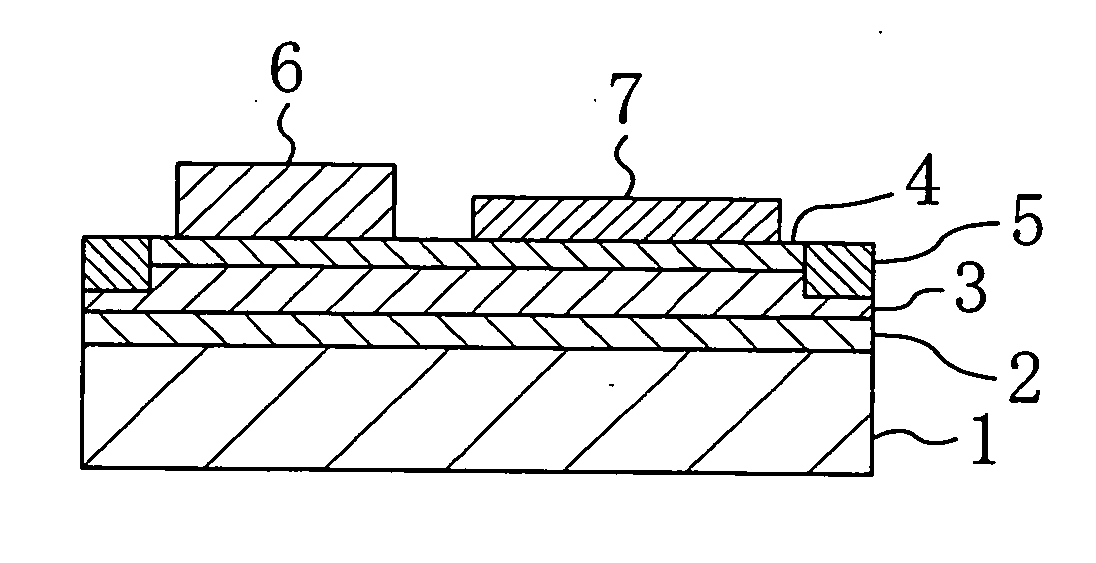

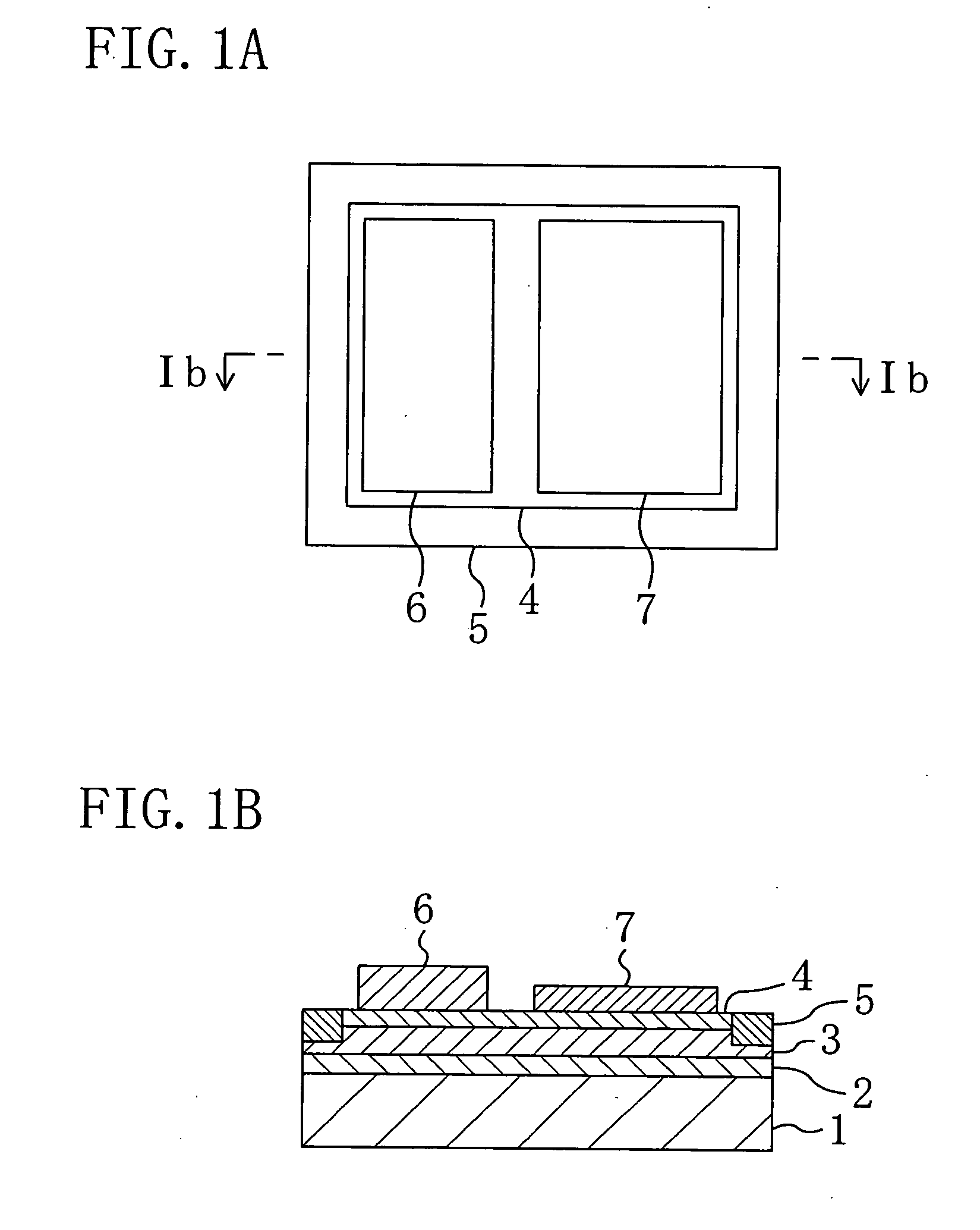

A zinc oxide (ZnO) field effect transistor exhibits large input amplitude by using a gate insulating layer. A channel layer and the gate insulating layer are sequentially laminated on a substrate. A gate electrode is formed on the gate insulating layer. A source contact and a drain contact are disposed at the both sides of the gate contact and are electrically connected to the channel layer via openings. The channel layer is formed from n-type ZnO. The gate insulating layer is made from aluminum nitride / aluminum gallium nitride (AlN / AlGaN) or magnesium zinc oxide (MgZnO), which exhibits excellent insulation characteristics, thus increasing the Schottky barrier and achieving large input amplitude. If the FET is operated in the enhancement mode, it is operable in a manner similar to a silicon metal oxide semiconductor field effect transistor (Si-MOS-type FET), resulting in the formation of an inversion layer.

Owner:NAUSE CATHERINE D

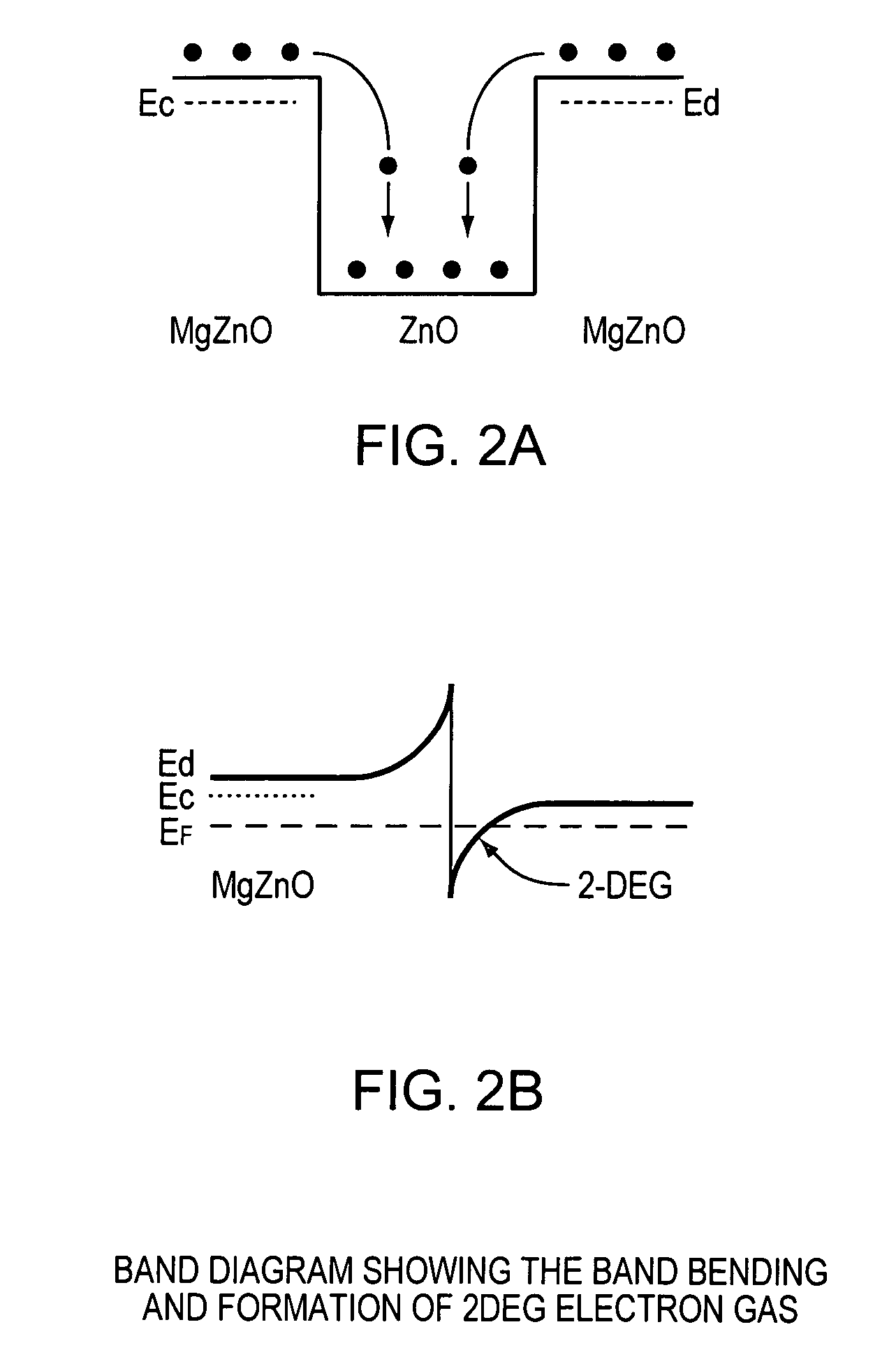

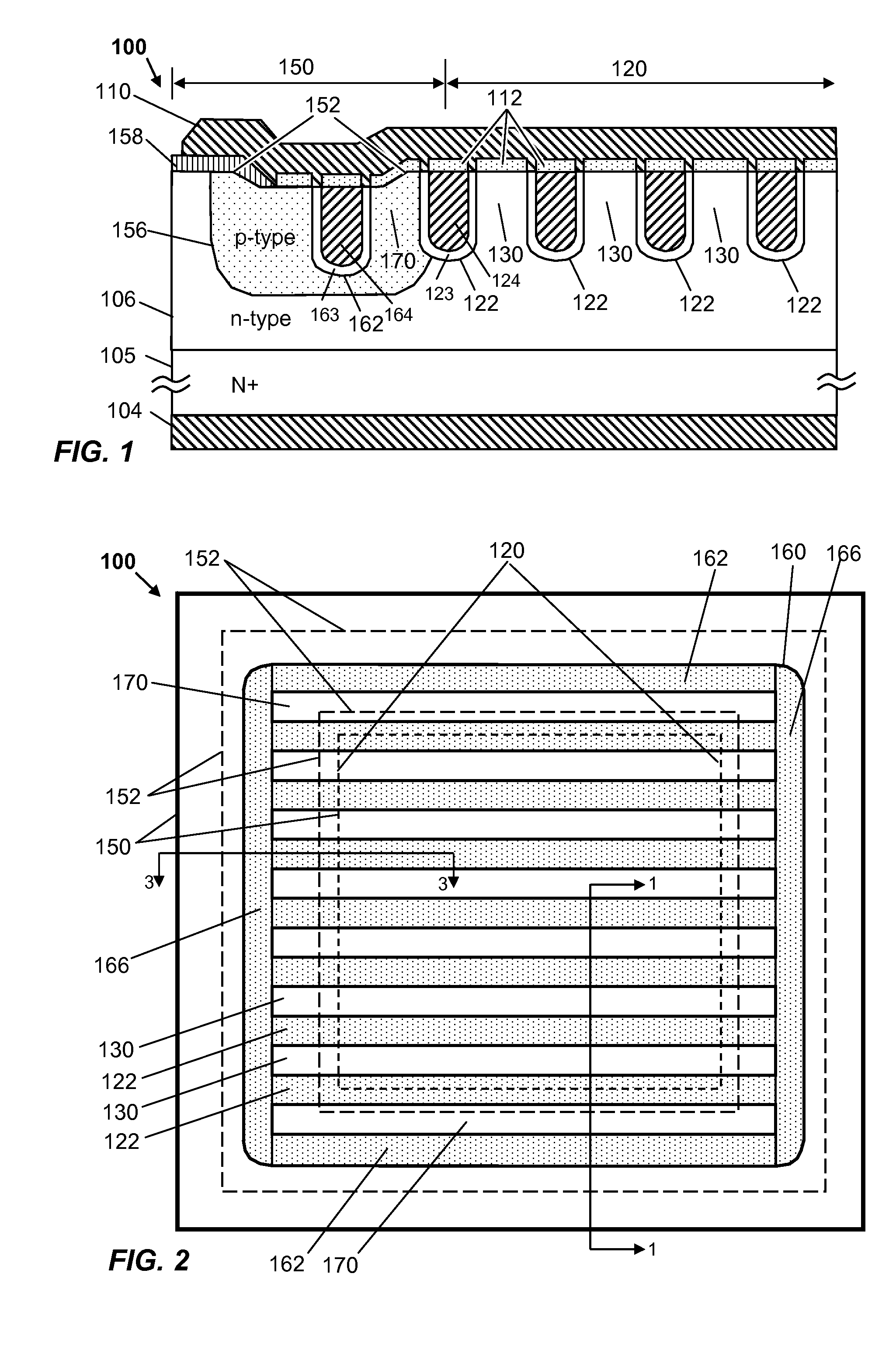

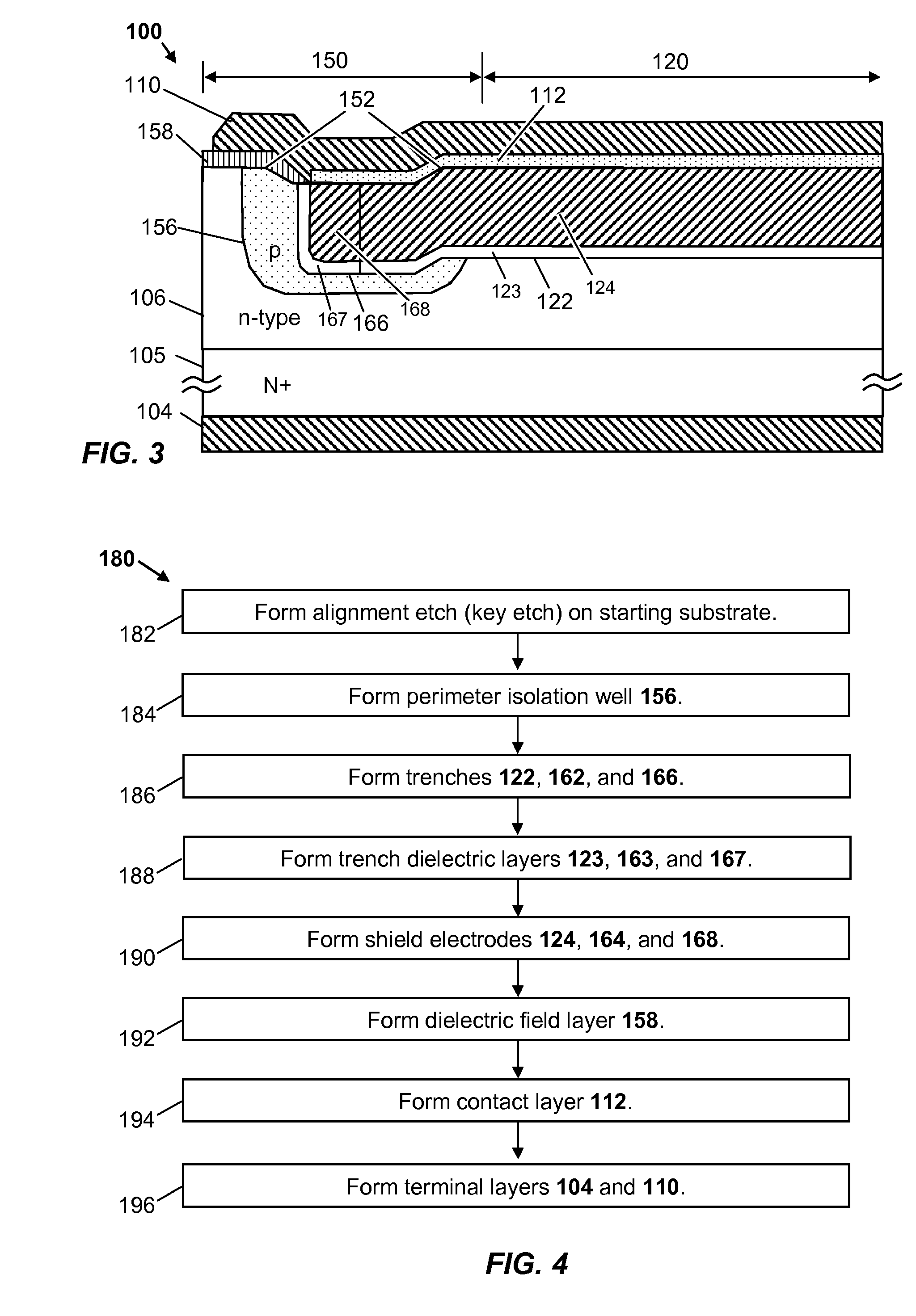

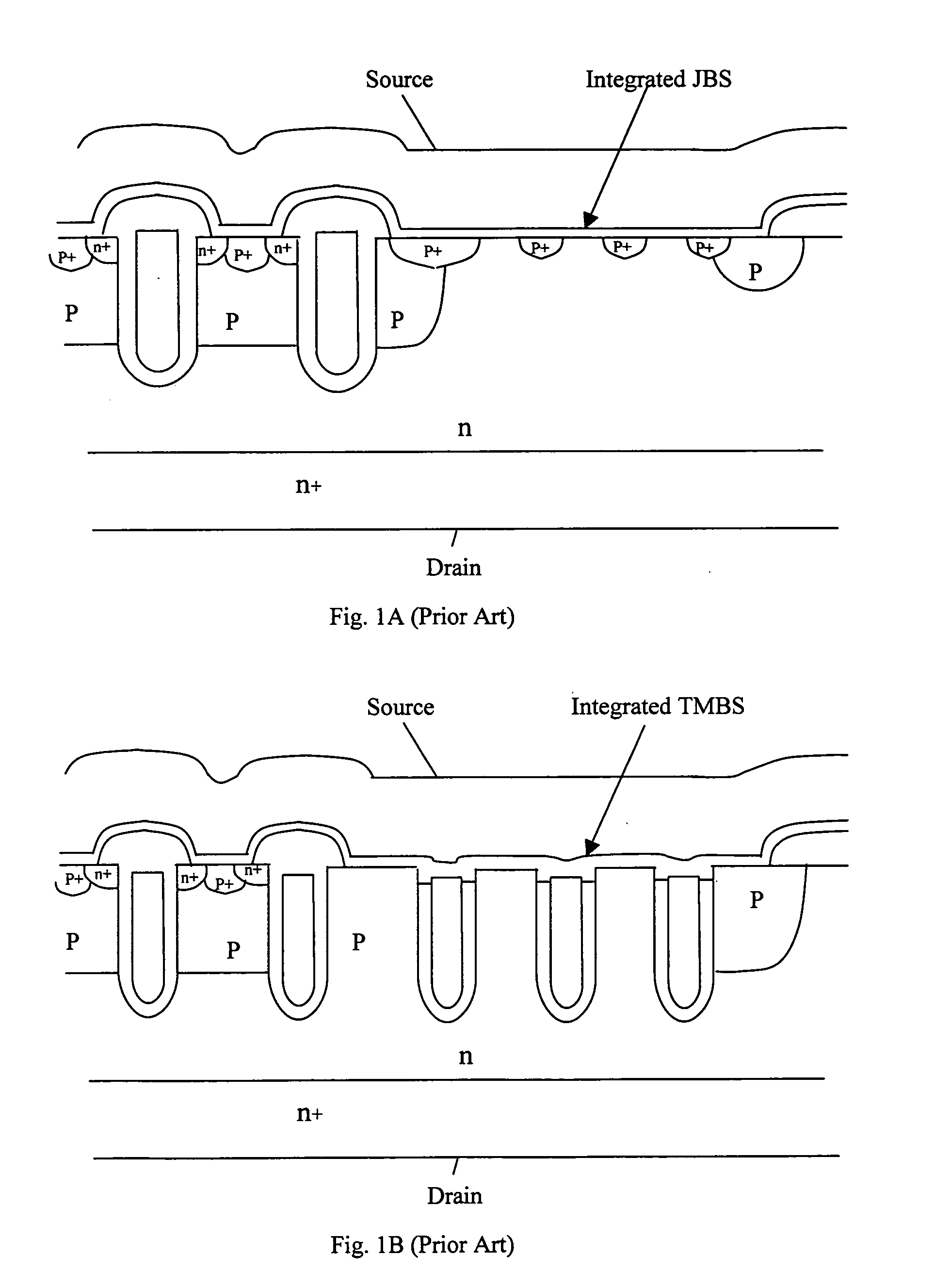

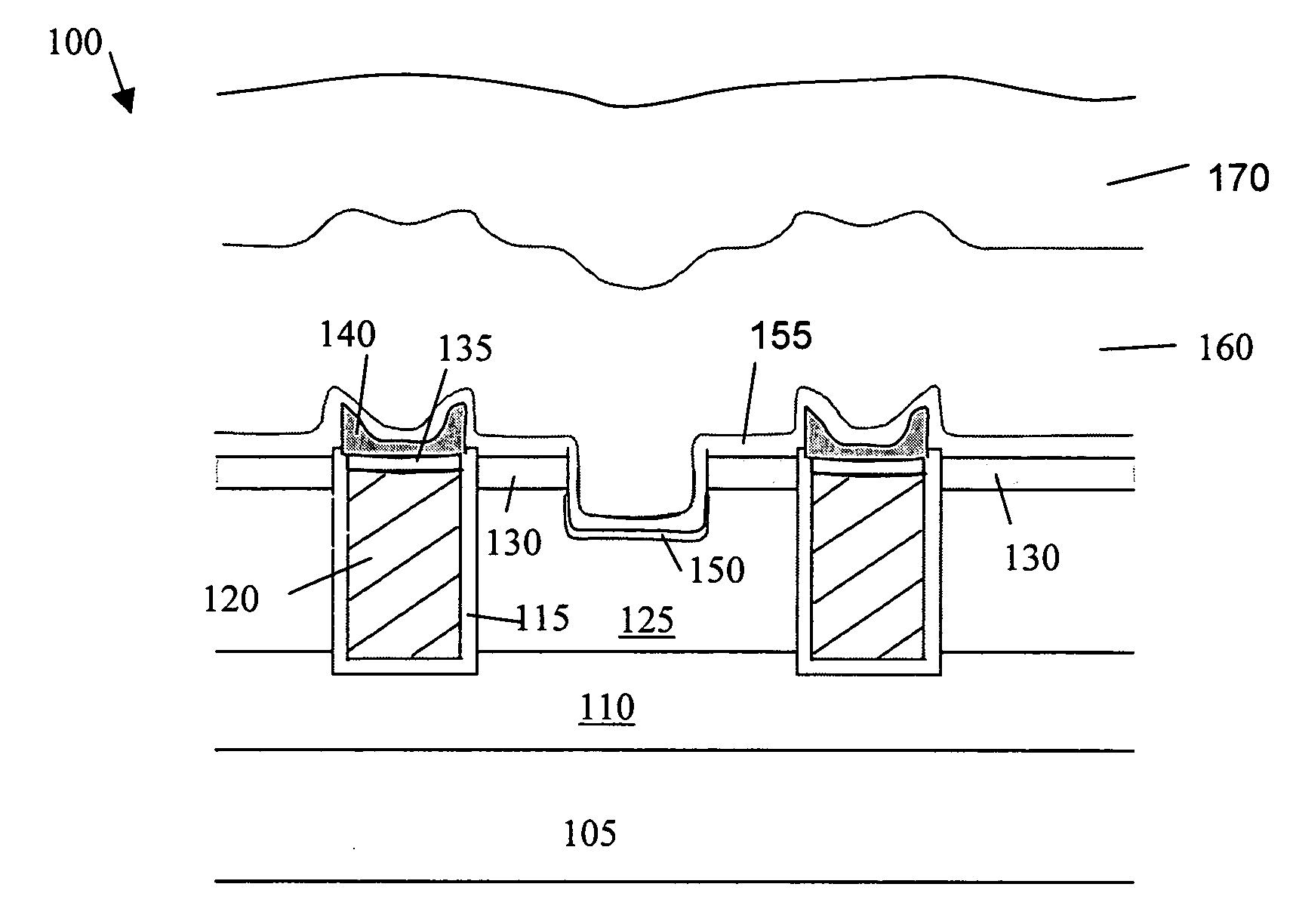

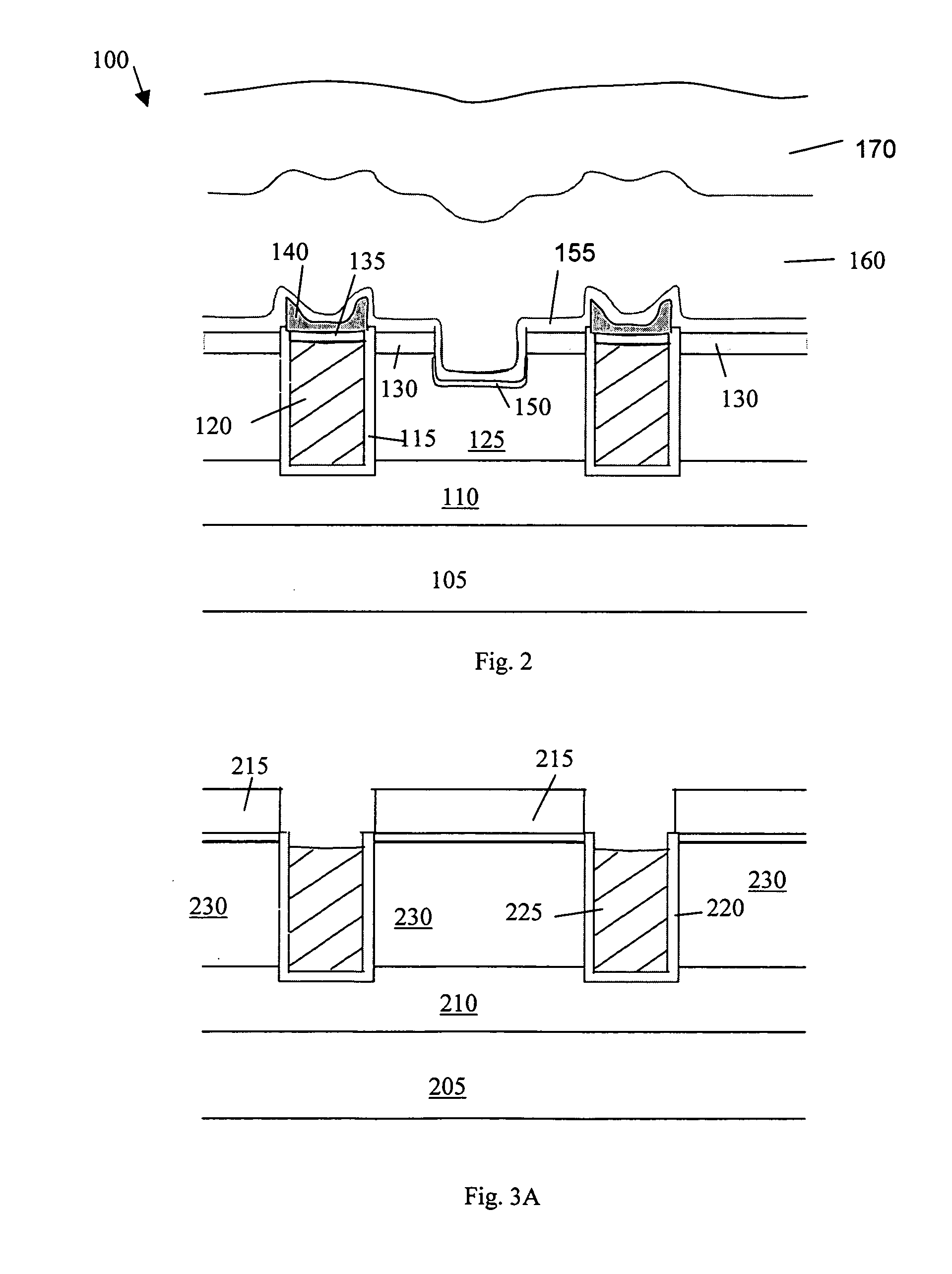

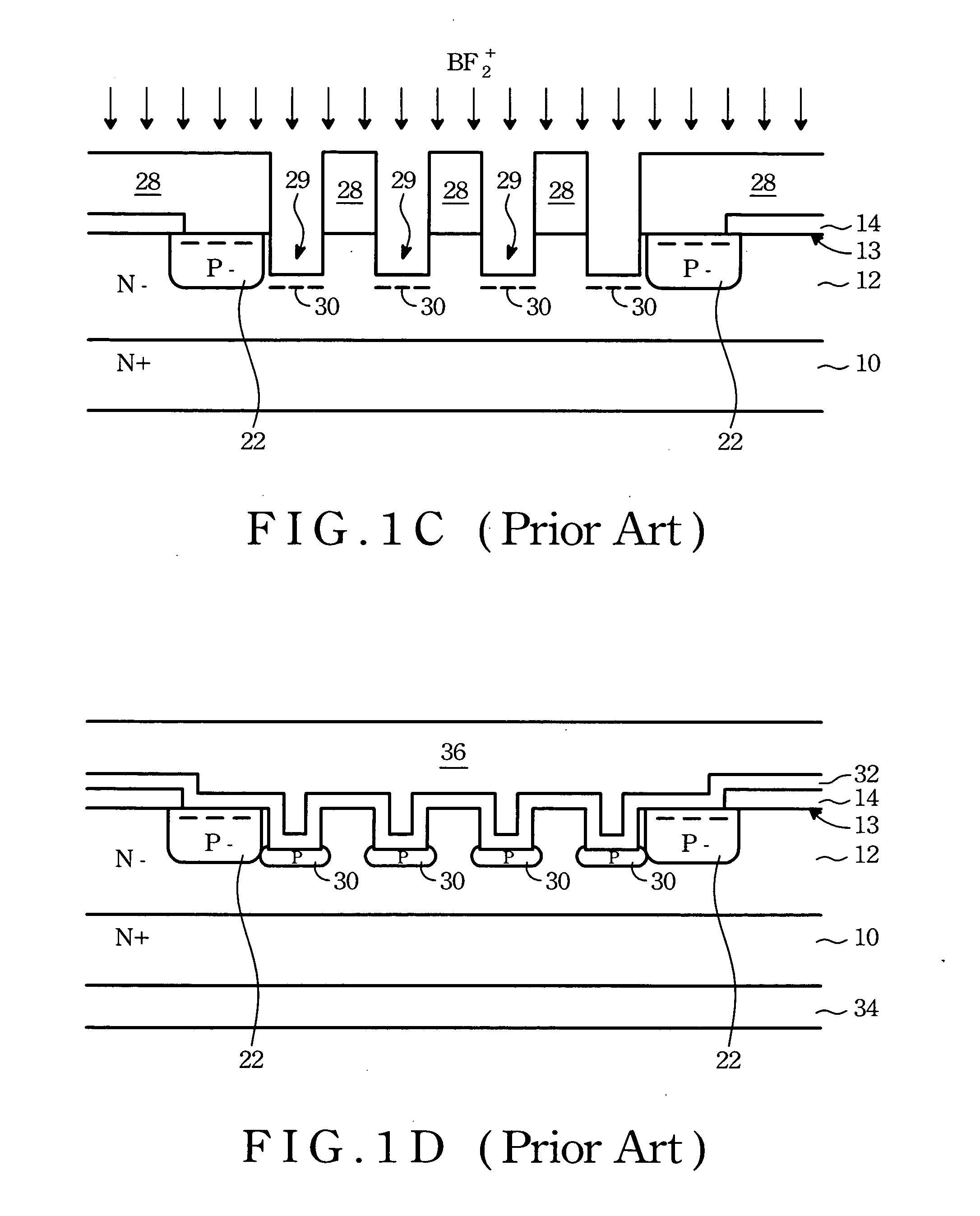

Structures and Methods for Improving Trench-Shielded Semiconductor Devices and Schottky Barrier Rectifier Devices

ActiveUS20100207205A1Improve breakdown voltageBreakdown voltage of deviceTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSchottky barrier

Various structures and methods for improving the performance of trench-shielded power semiconductor devices and the like are described.

Owner:SEMICON COMPONENTS IND LLC

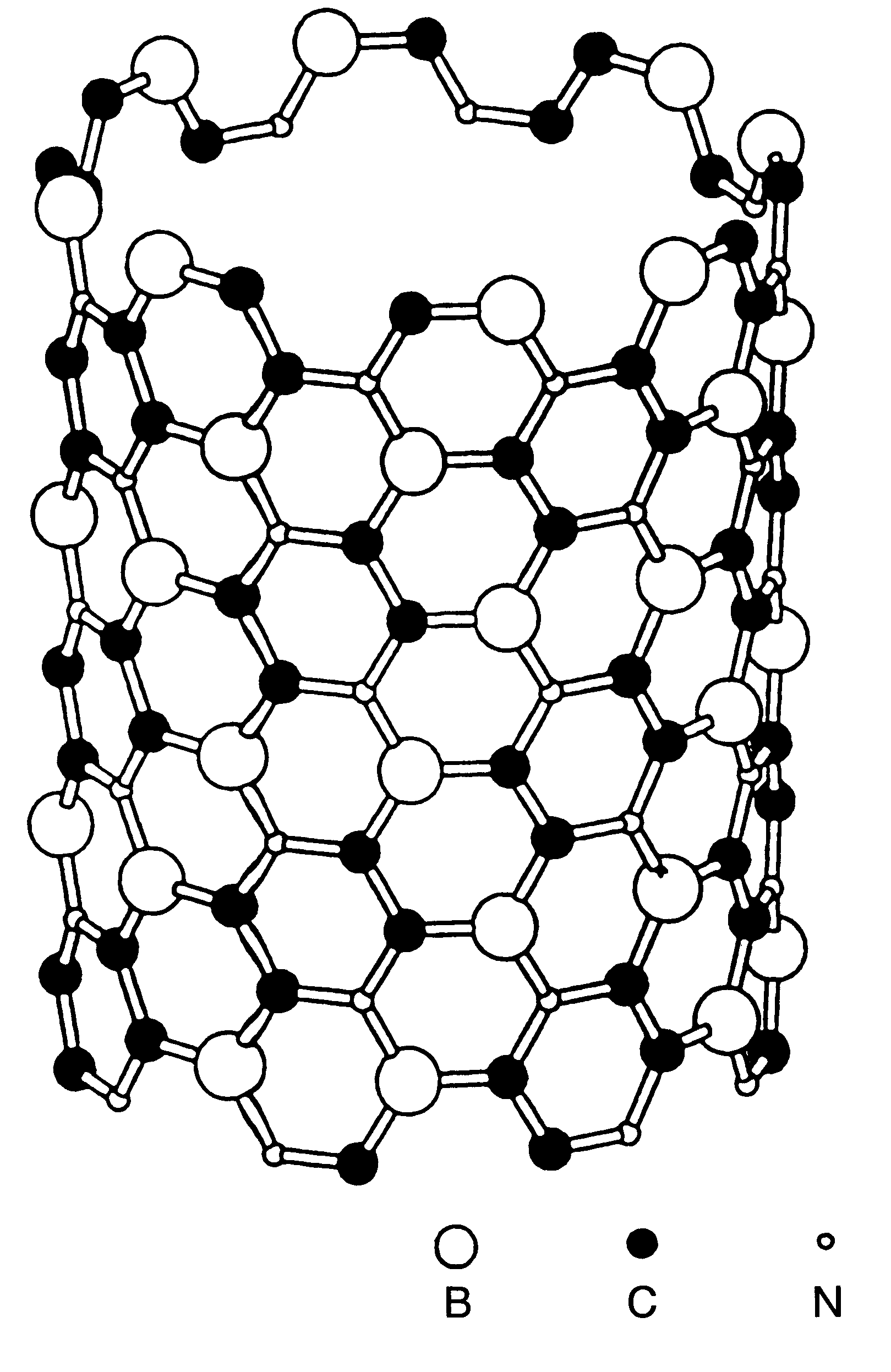

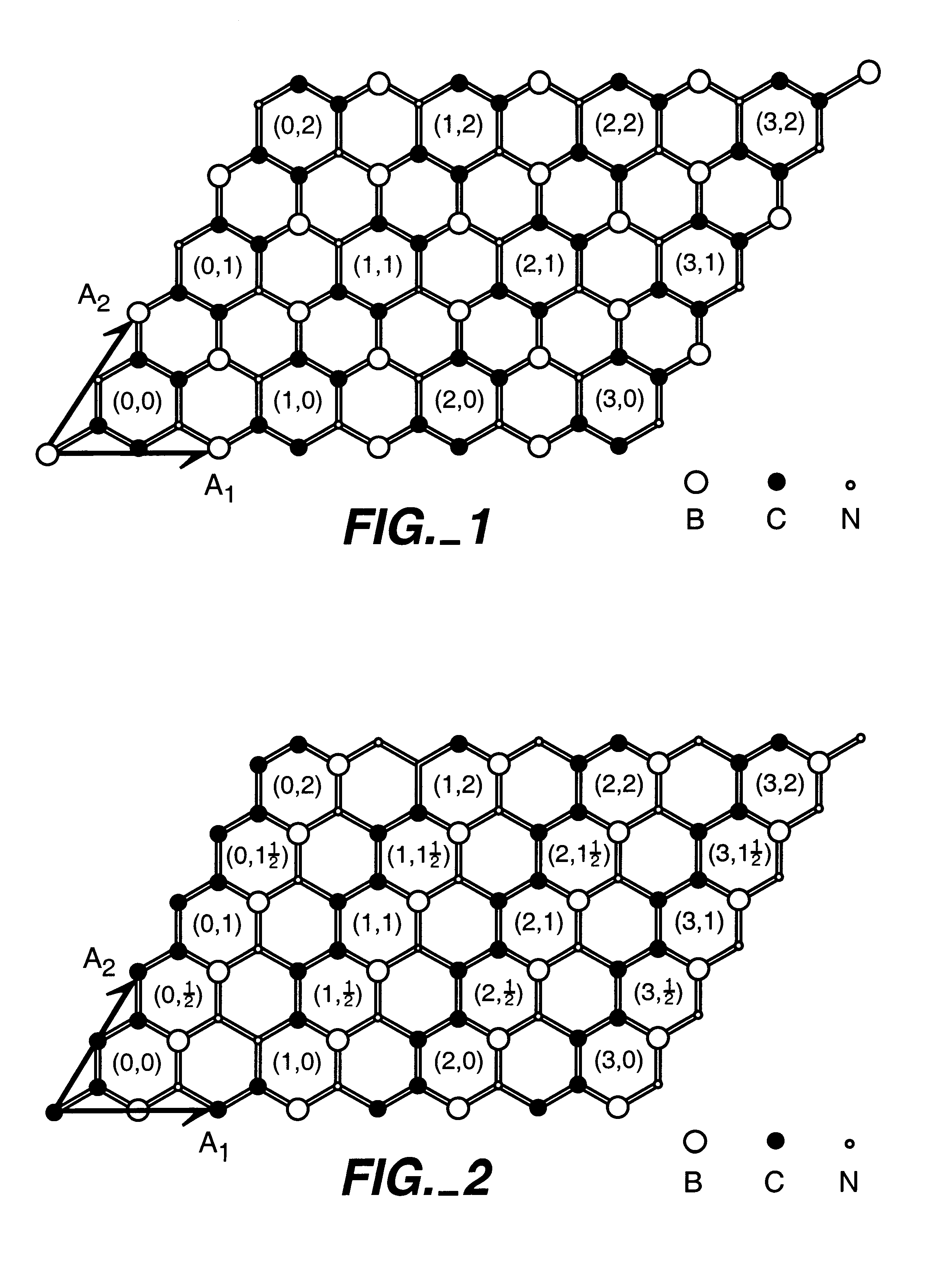

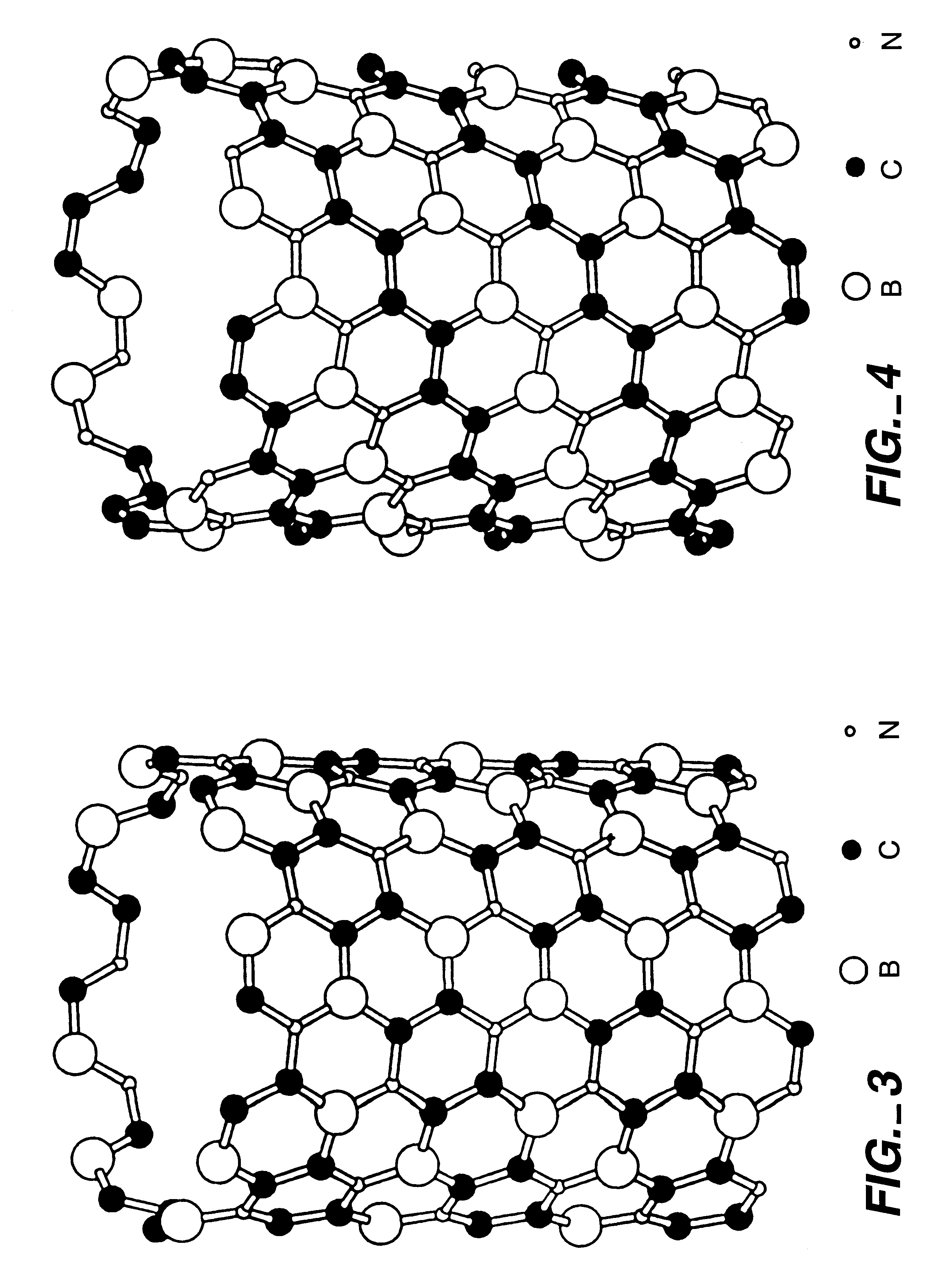

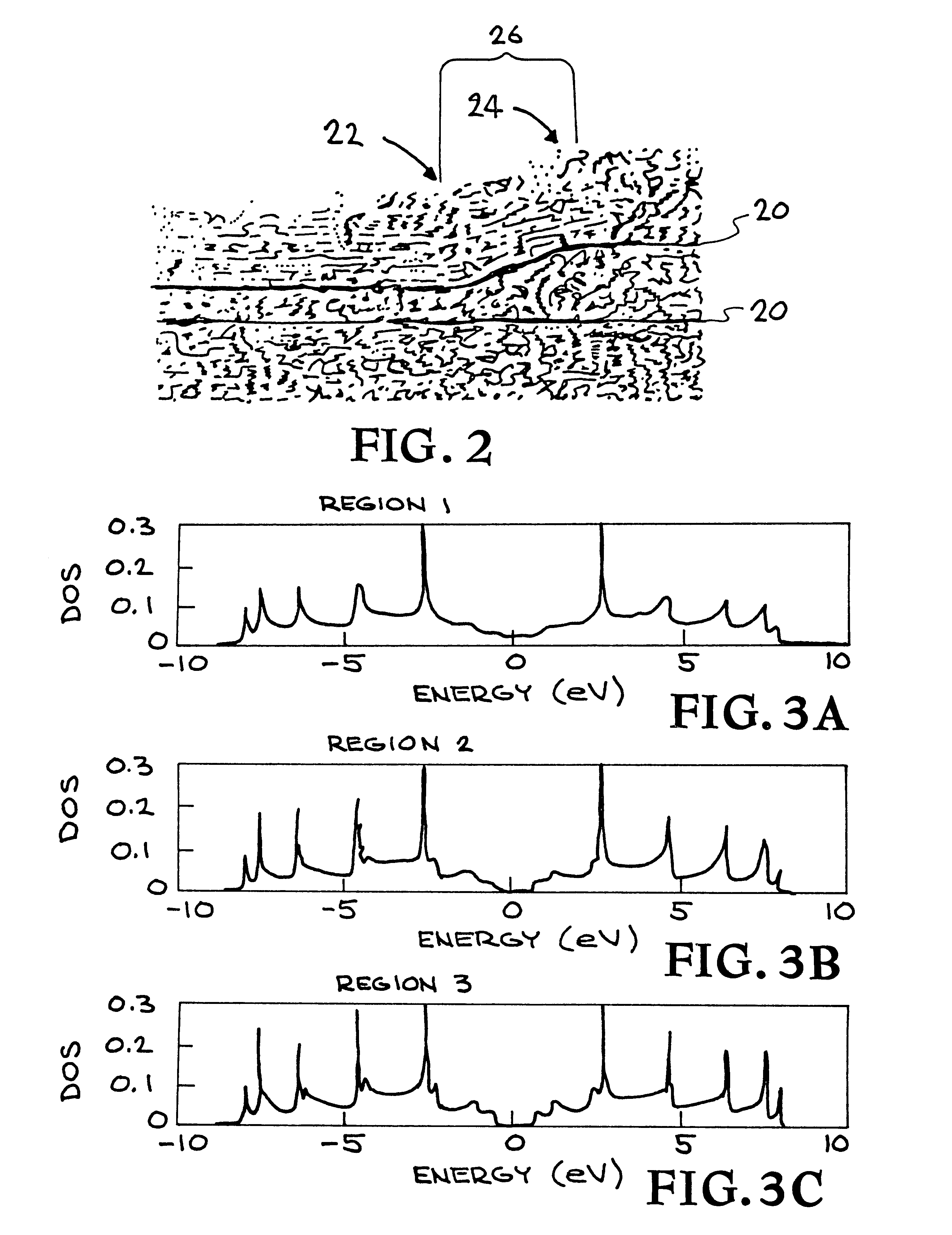

BX CY NZ nanotubes and nanoparticles

Owner:RGT UNIV OF CALIFORNIA

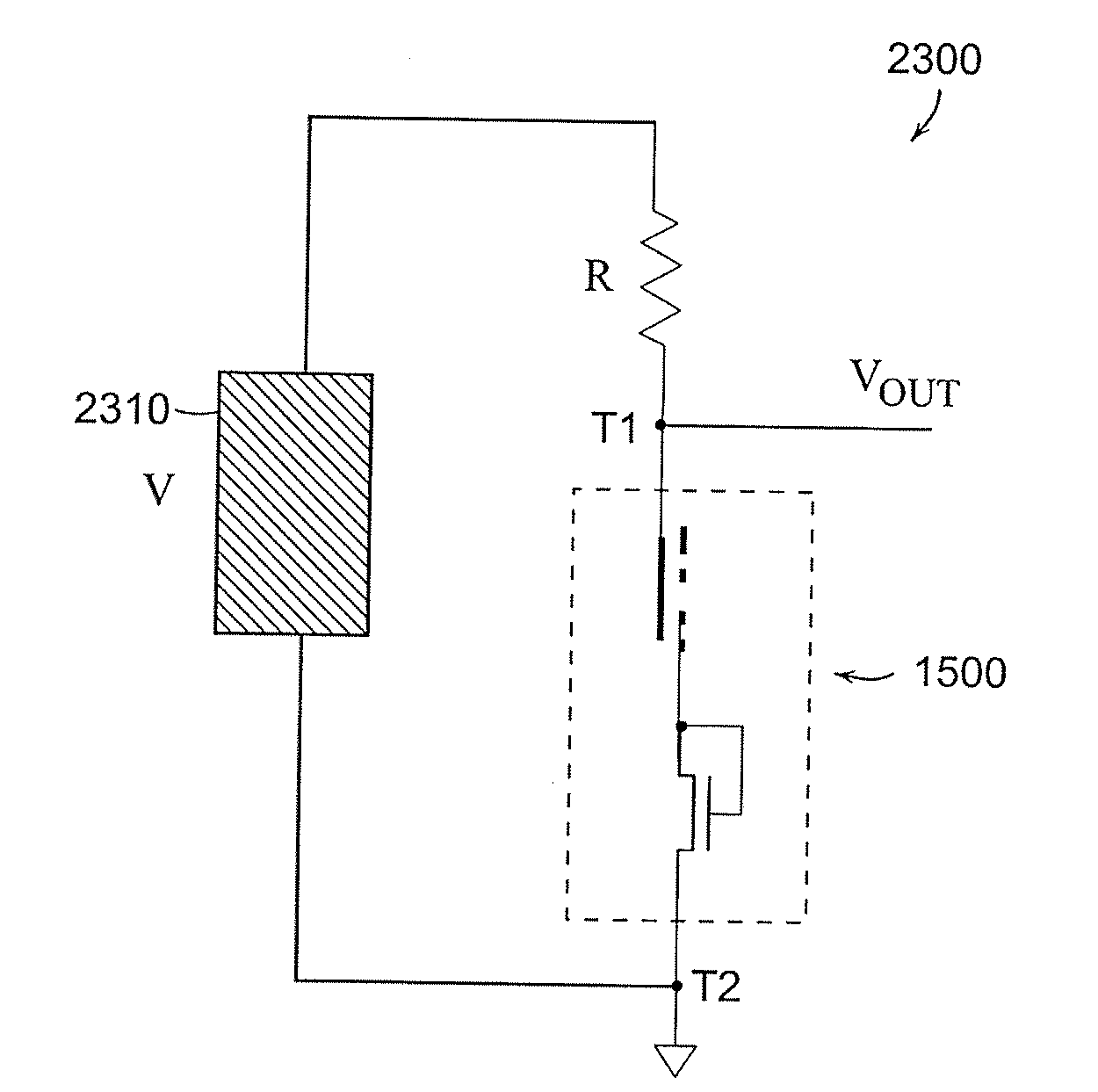

Dynamic schottky barrier MOSFET device and method of manufacture

InactiveUS20050139860A1ThyristorSemiconductor/solid-state device manufacturingMOSFETSchottky barrier

A device for regulating a flow of electric current and its manufacturing method are provided. The device includes metal-insulator-semiconductor source-drain contacts forming Schottky barrier or Schottky-like junctions to the semiconductor substrate. The device includes an interfacial layer between the semiconductor substrate and a metal source and / or drain electrode, thereby dynamically adjusting a Schottky barrier height by applying different bias conditions. The dynamic Schottky barrier modulation provides increased electric current for low drain bias conditions, reducing the sub-linear turn-on characteristic of Schottky barrier MOSFET devices and improving device performance.

Owner:SPINNAKER SEMICON

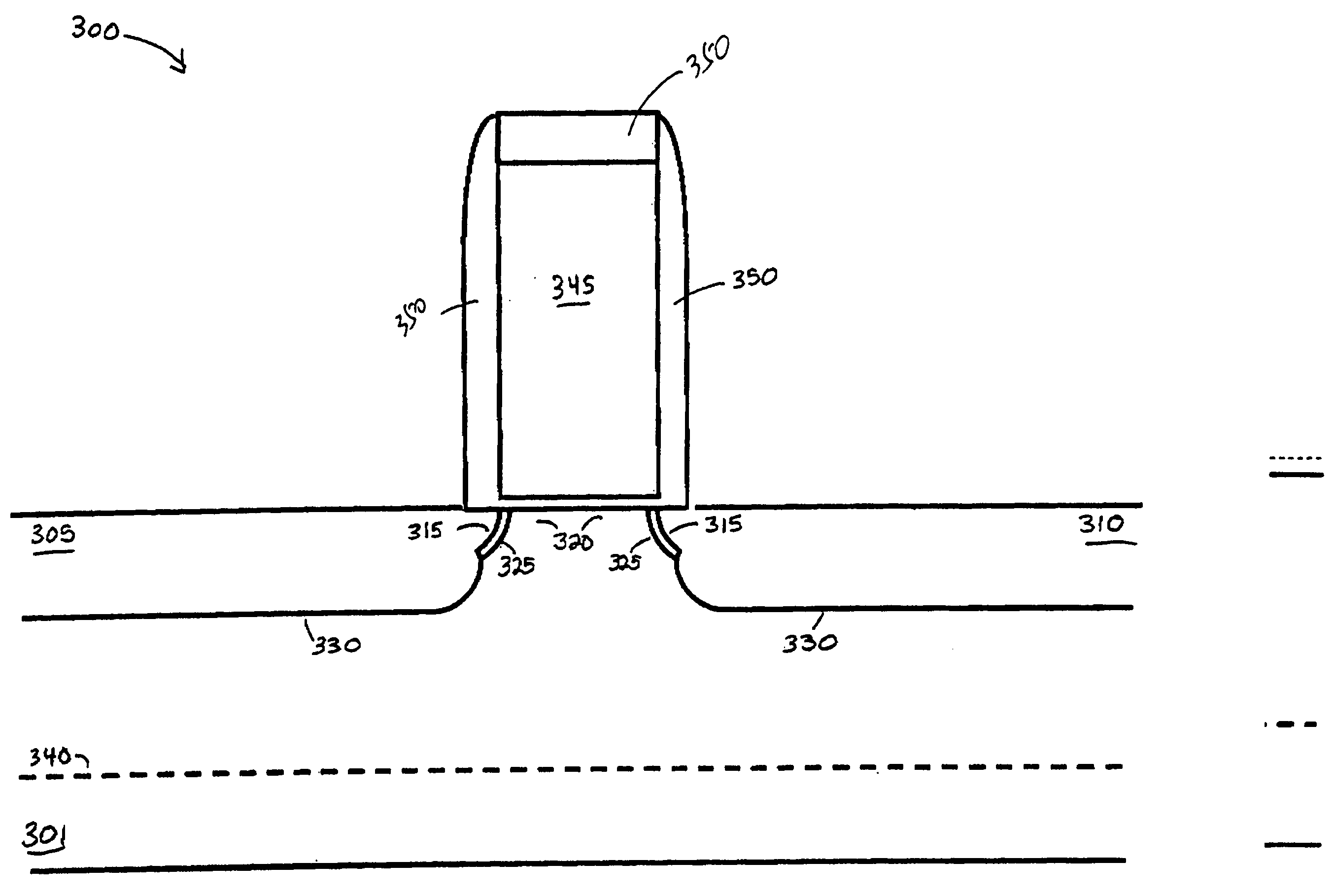

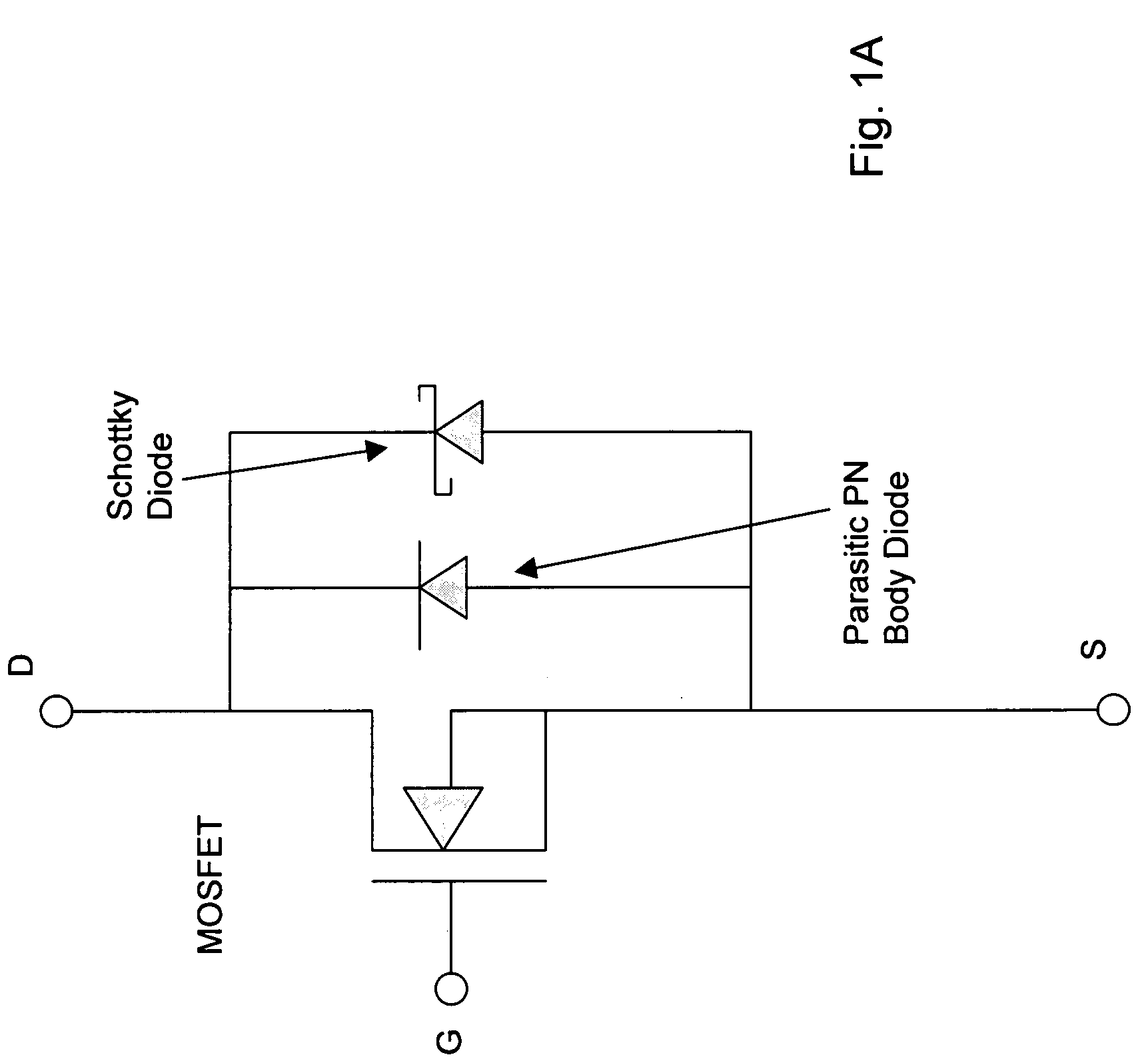

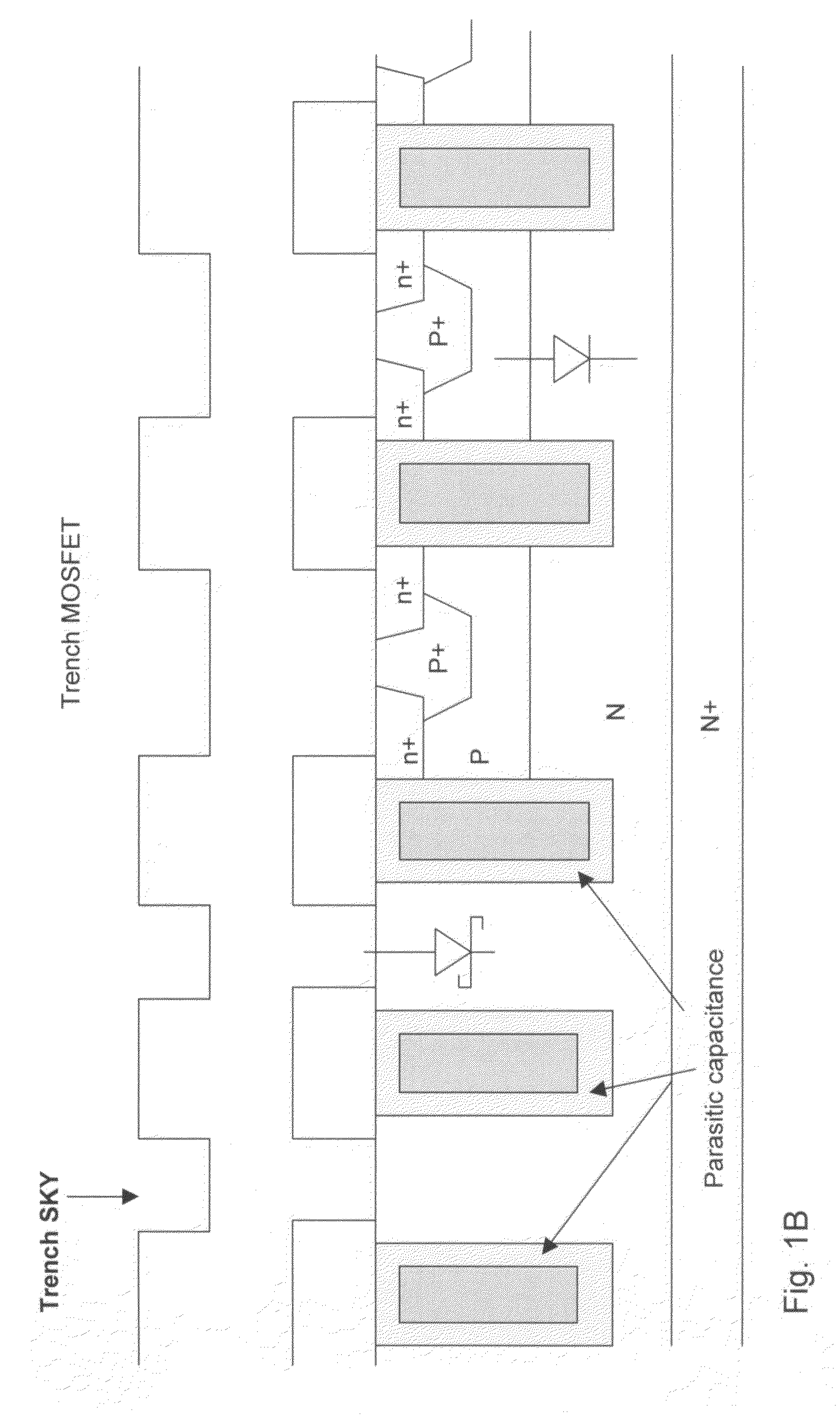

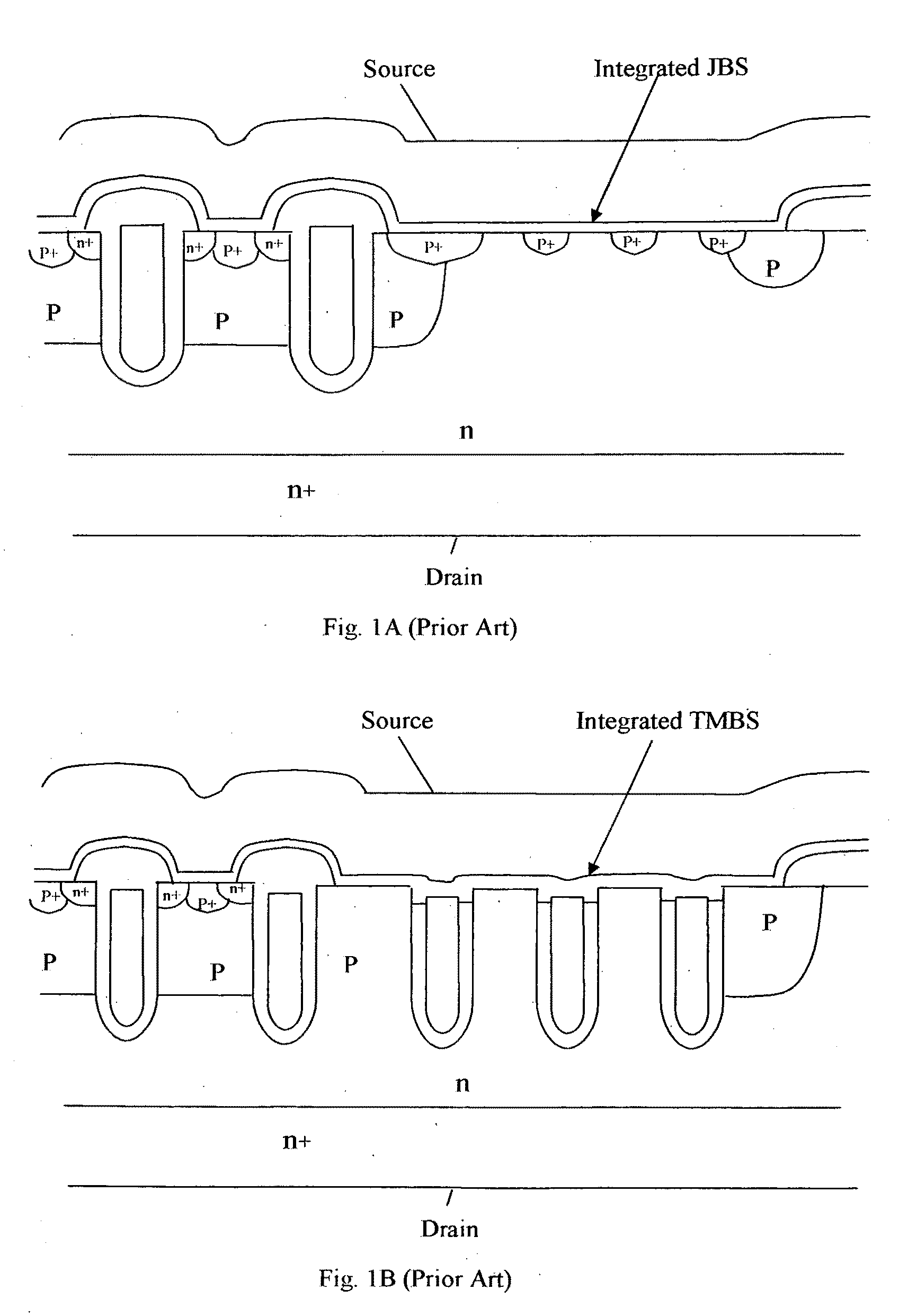

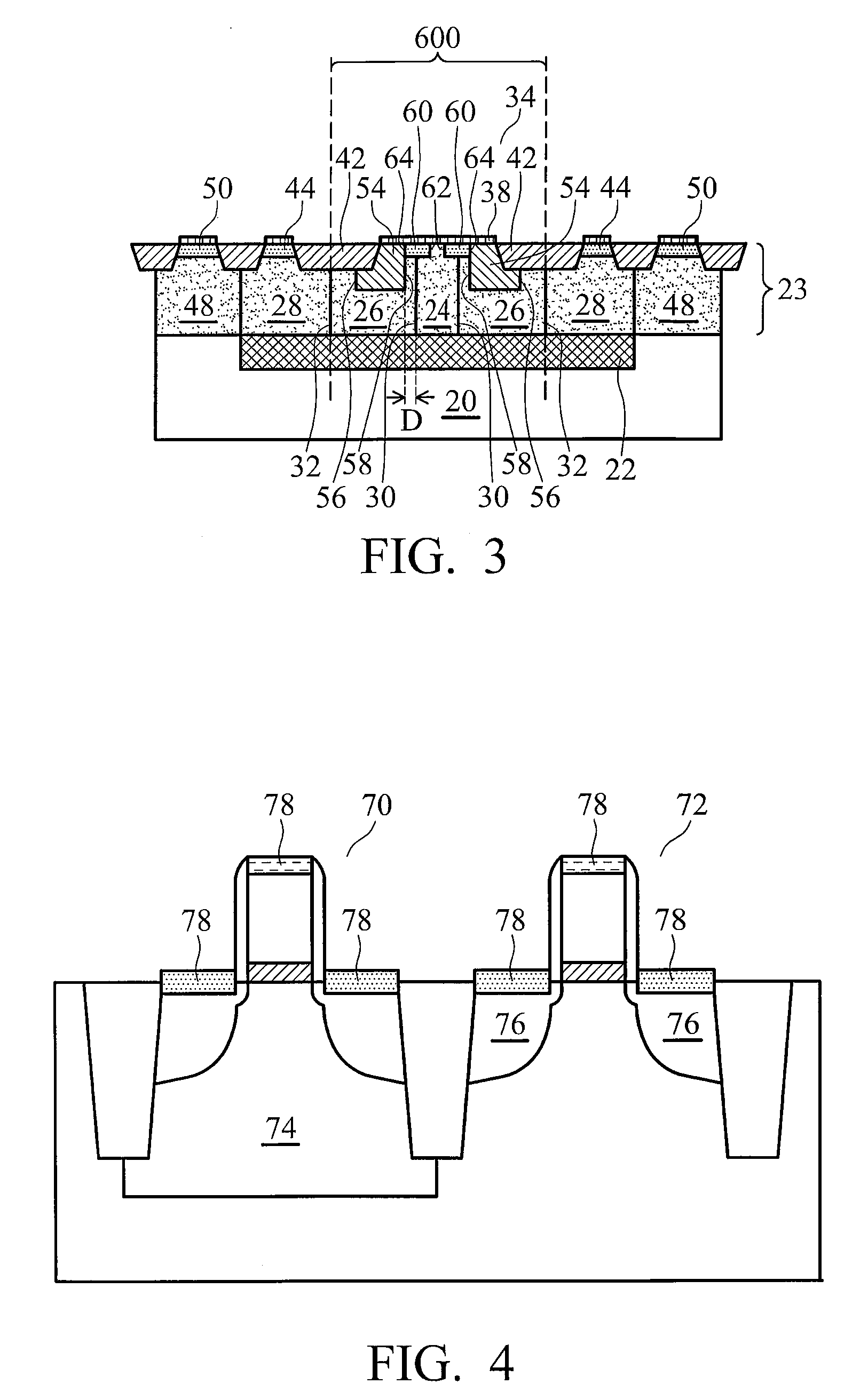

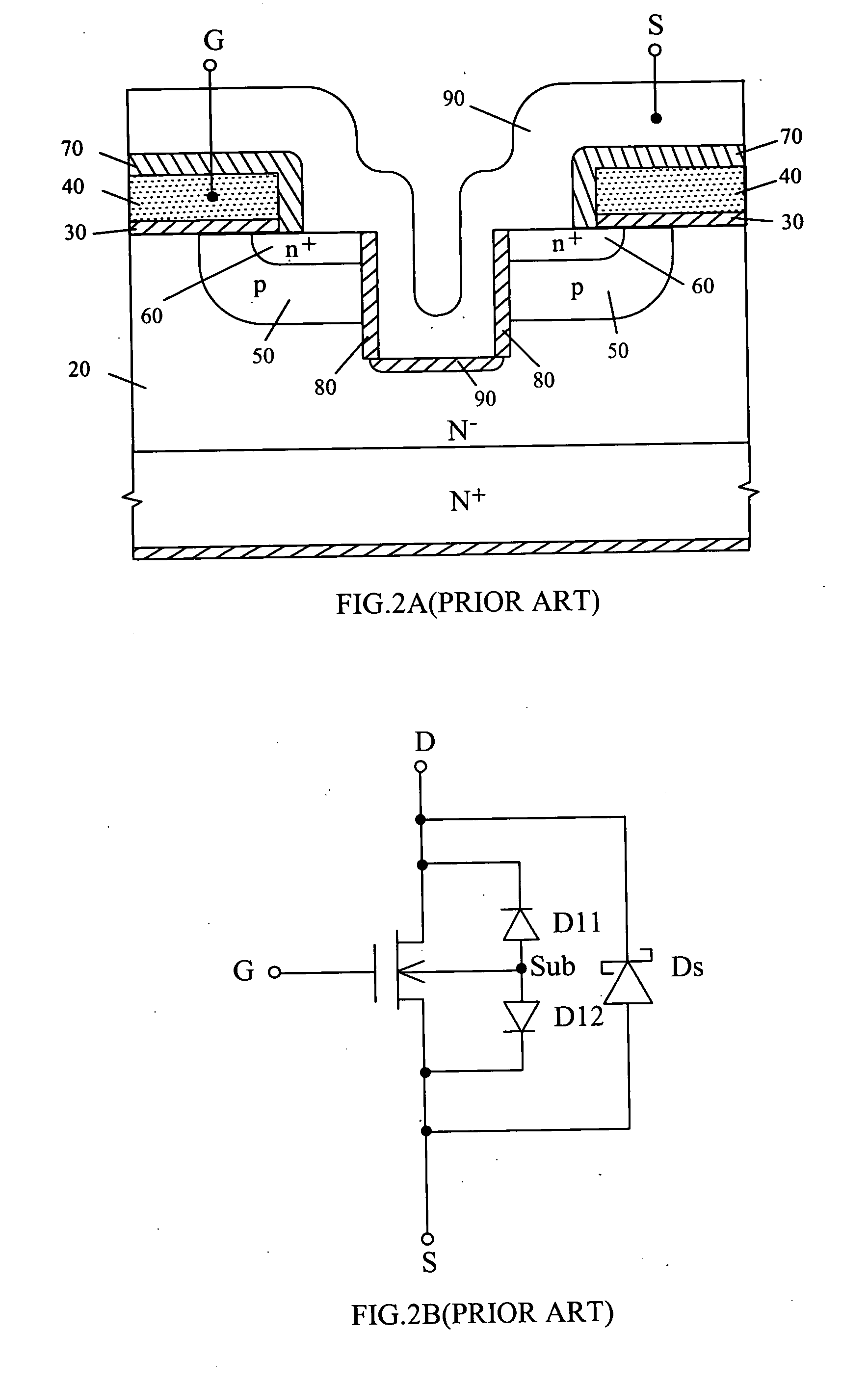

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS20060209887A1Improve device performanceImprove switching performanceTime-division multiplexDiodeMOSFETInsulation layer

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one active cell further includes a trenched source contact opened between the trenches wherein the trenched source contact opened through a source region into a body region for electrically connecting the source region to a source metal disposed on top of an insulation layer wherein a trench bottom surface of the trenched source contact further covered with a conductive material to function as an integrated Schottky barrier diode in said active cell. A shielding structure is disposed at the bottom and insulated from the trenched gate to provide shielding effect for both the trenched gate and the Schottky diode.

Owner:ALPHA & OMEGA SEMICON LTD

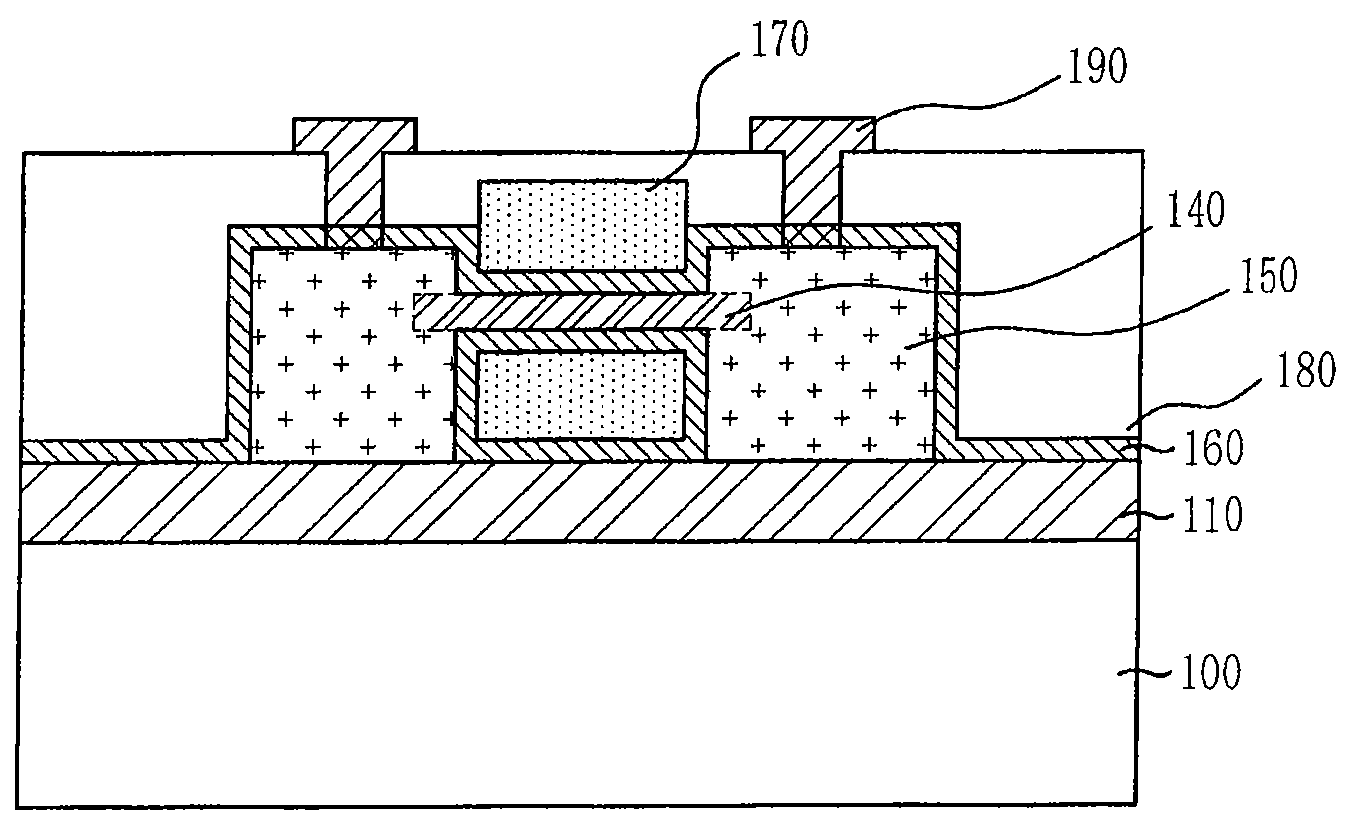

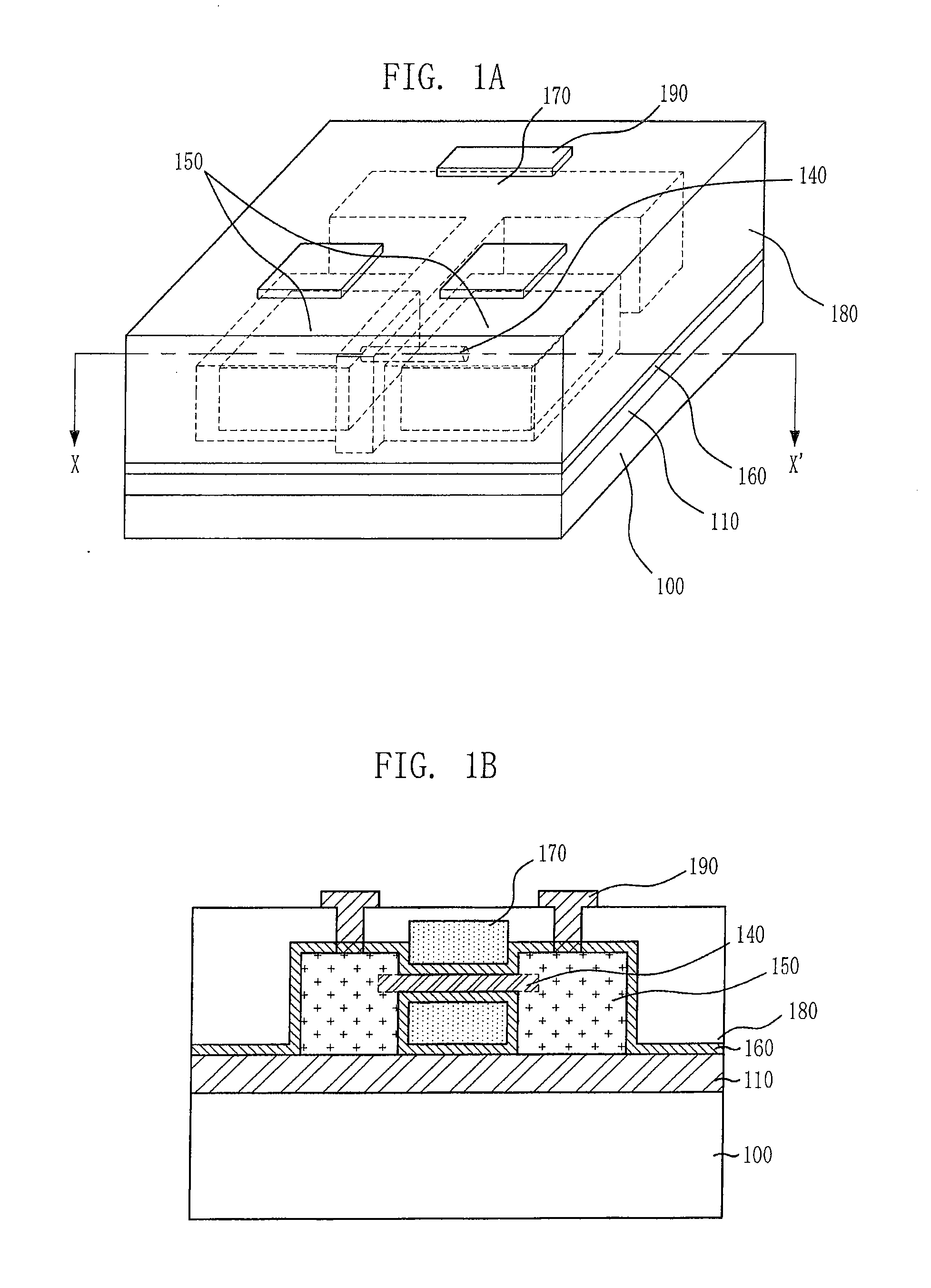

Schottky barrier nanowire field effect transistor and method for fabricating the same

InactiveUS20080128760A1Easy to makeEnsure thermal stabilityNanoinformaticsSolid-state devicesSalicideInsulation layer

Provided is a Schottky barrier nanowire field effect transistor, which has source / drain electrodes formed of metal silicide and a channel formed of a nanowire, and a method for fabricating the same. The Schottky barrier nanowire field effect transistor includes: a channel suspended over a substrate and including a nanowire; metal silicide source / drain electrodes electrically connected to both ends of the channel over the substrate; a gate electrode disposed to surround the channel; and a gate insulation layer disposed between the channel and the gate electrode.

Owner:ELECTRONICS & TELECOMM RES INST

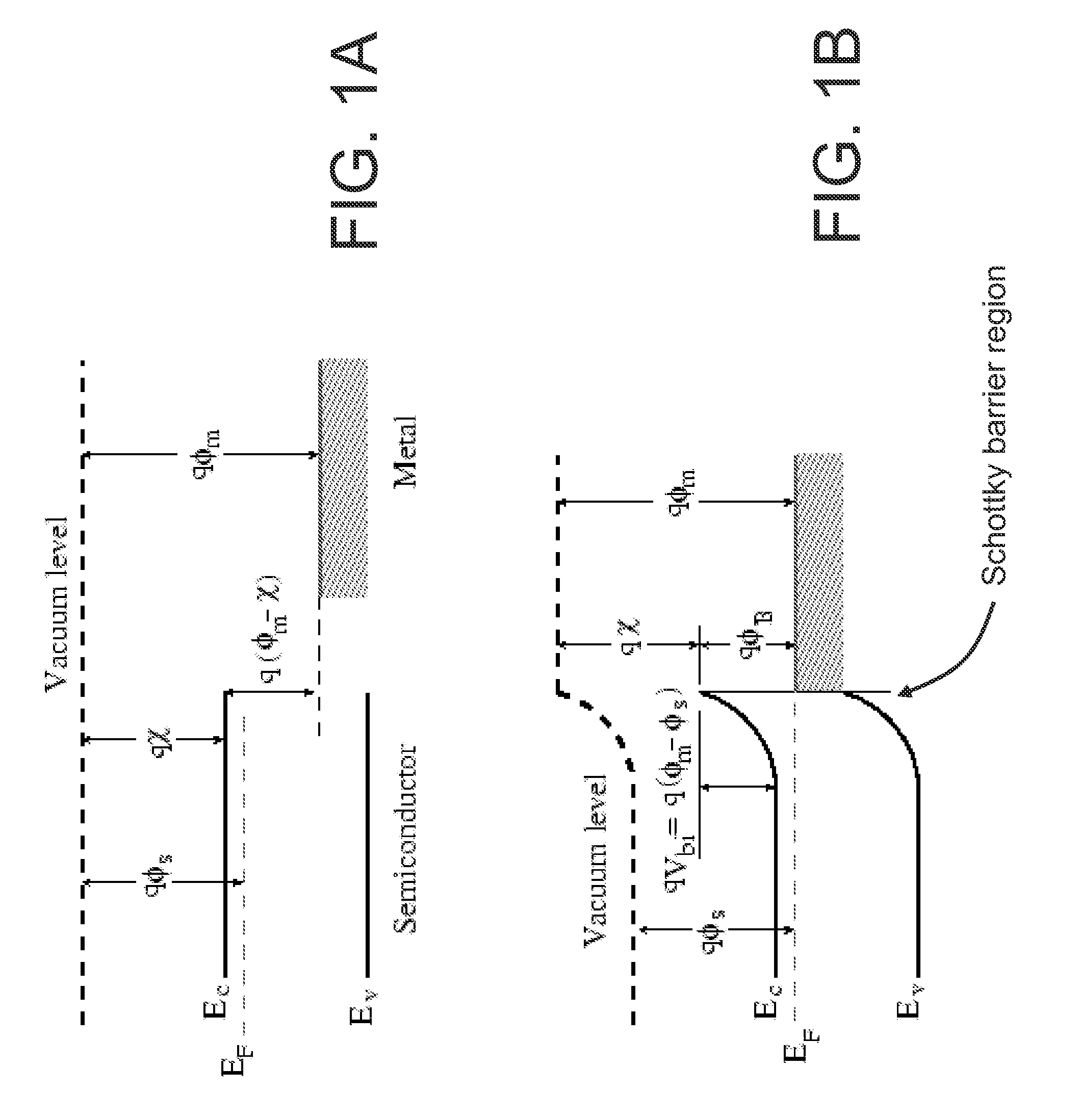

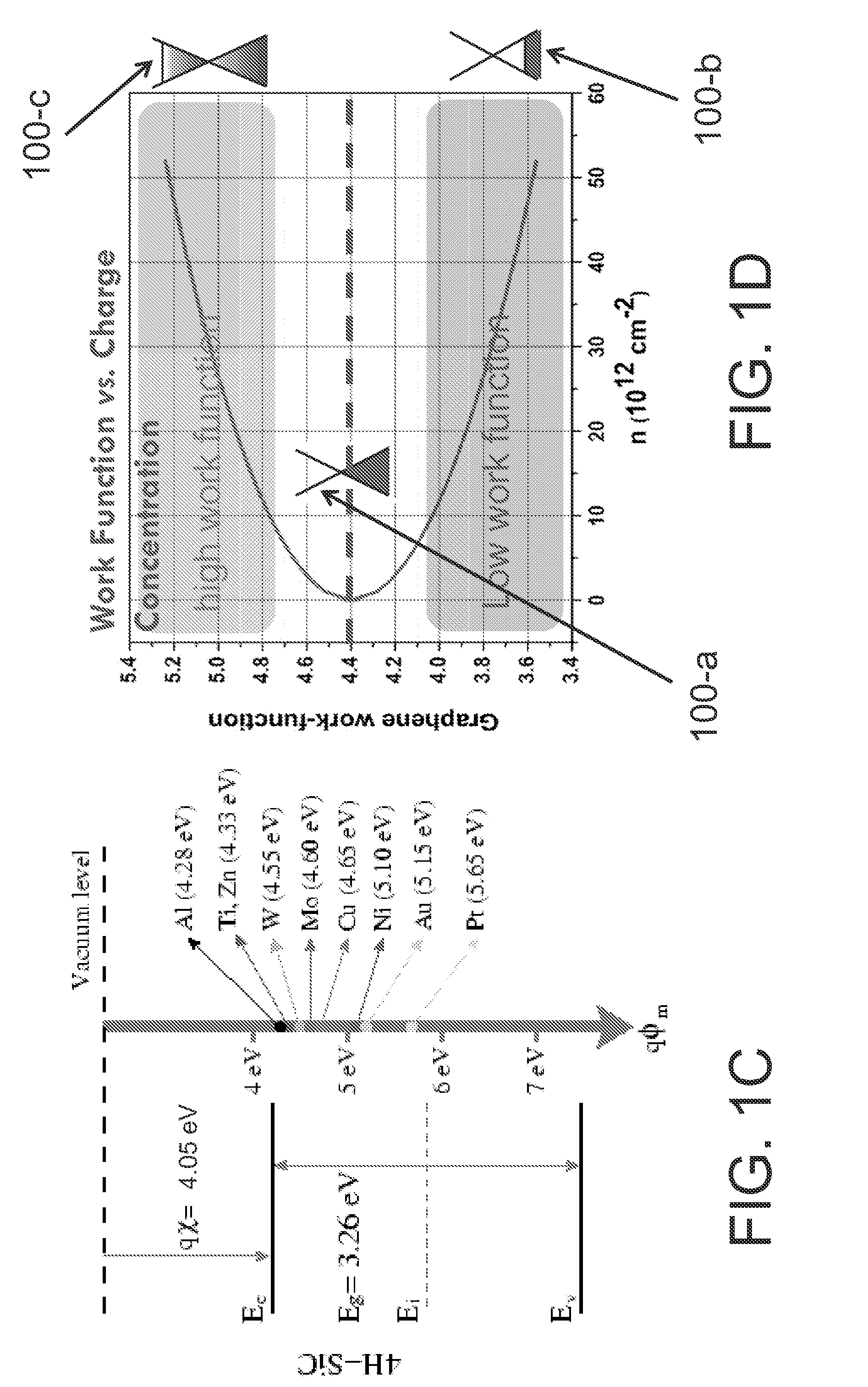

Electronics including graphene-based hybrid structures

InactiveUS20160284811A1High carrier mobilityRobustTransistorSemiconductor/solid-state device manufacturingSchottky barrierSemiconductor materials

Device are described that include a semiconductor material layer and at least one graphene-based electrode disposed over a portion of the semiconductor material layer, such that the at least one graphene-based electrode forms an overlap region with the semiconductor material layer. The device includes a means for providing charge carriers in the at least one graphene-based electrode proximate to the overlap region, to reduce a difference between a work function of the at least one graphene-based electrode and an electron affinity of the semiconductor material layer, to reduce a Schottky barrier height between the semiconductor material layer and the at least one graphene-based electrode.

Owner:MASSACHUSETTS INST OF TECH

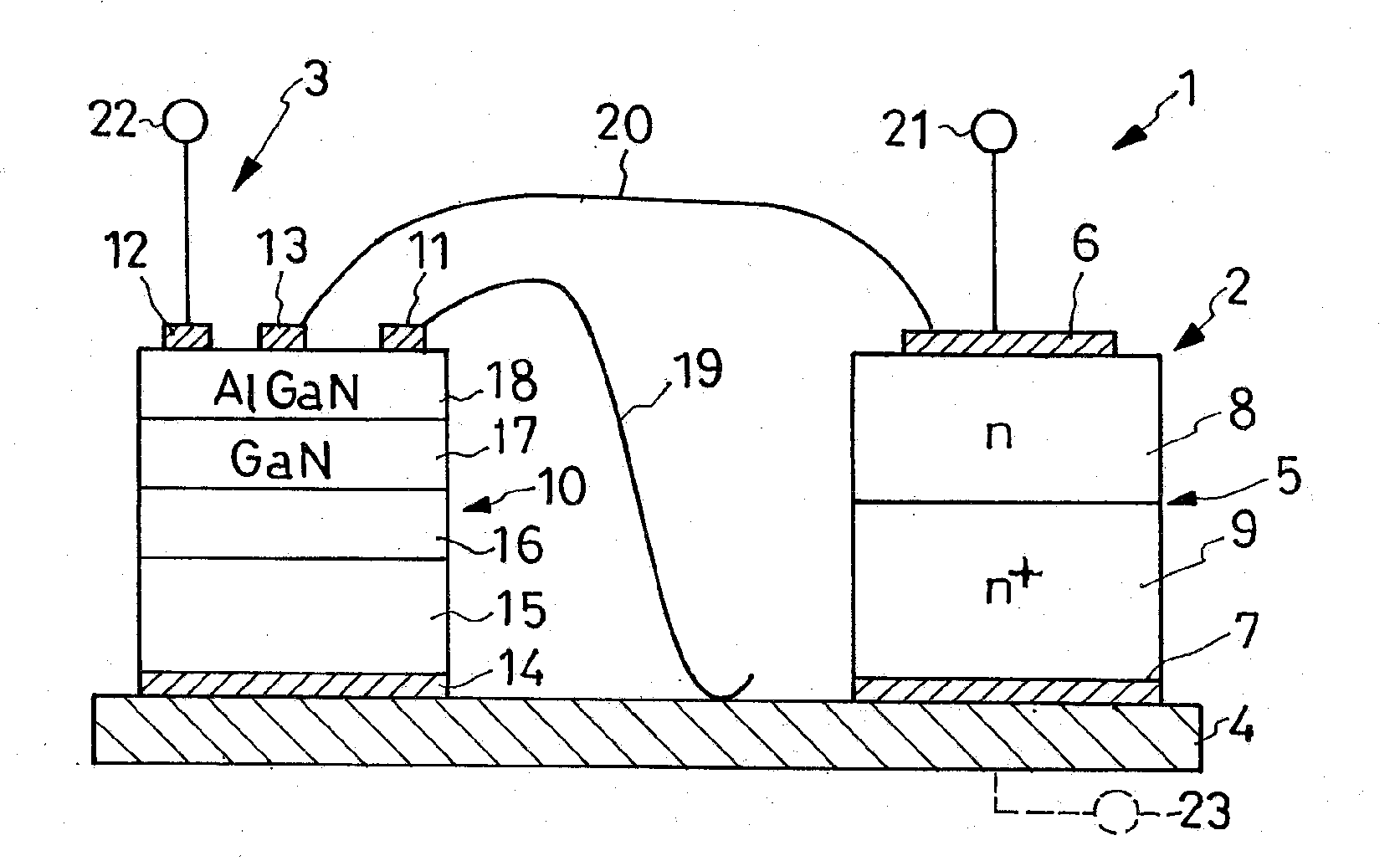

Diode-Like Composite Semiconductor Device

ActiveUS20080191216A1Minimal current capacityPrevent excess flowSolid-state devicesElectronic switchingSchottky barrierCompressive strength

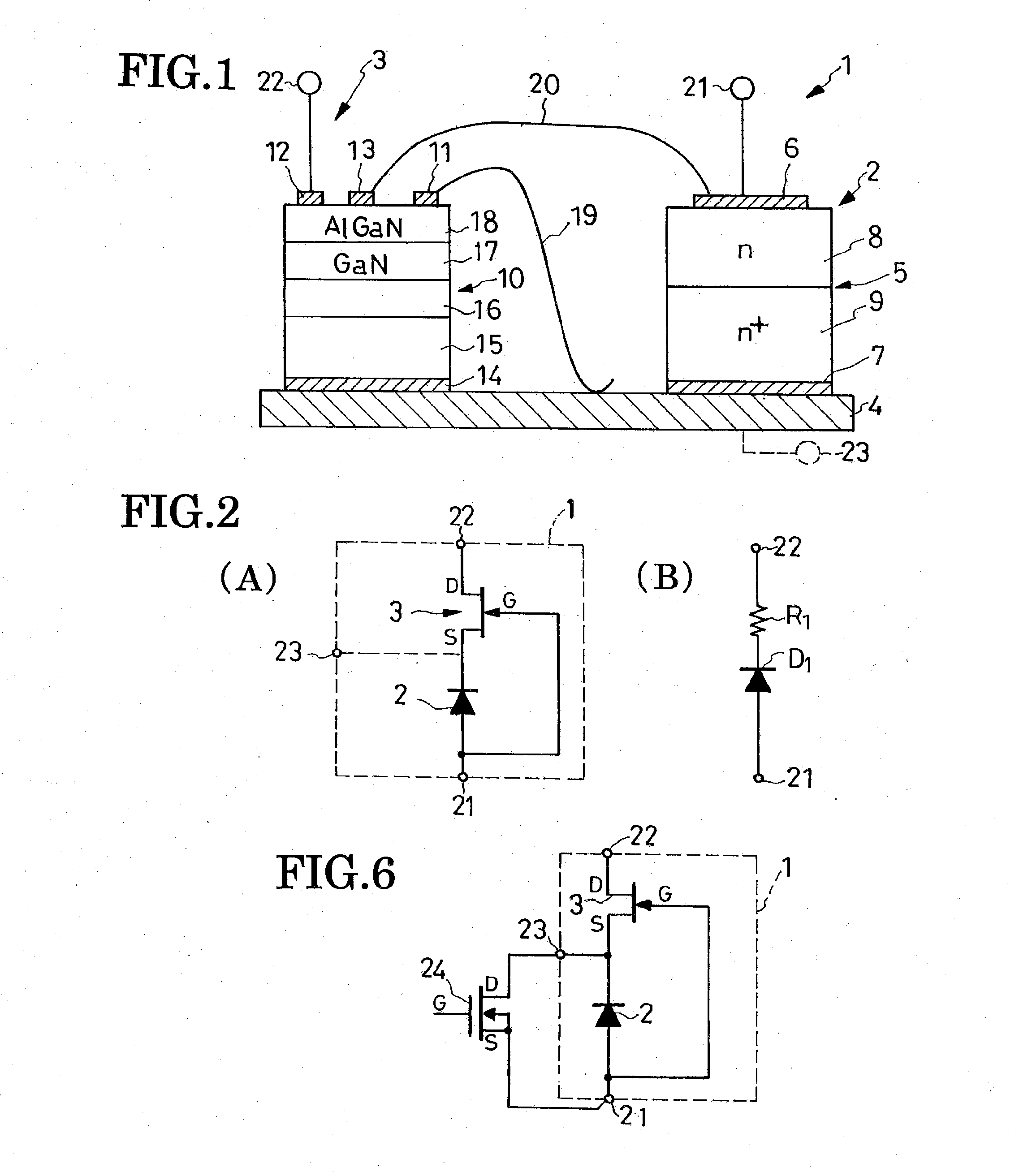

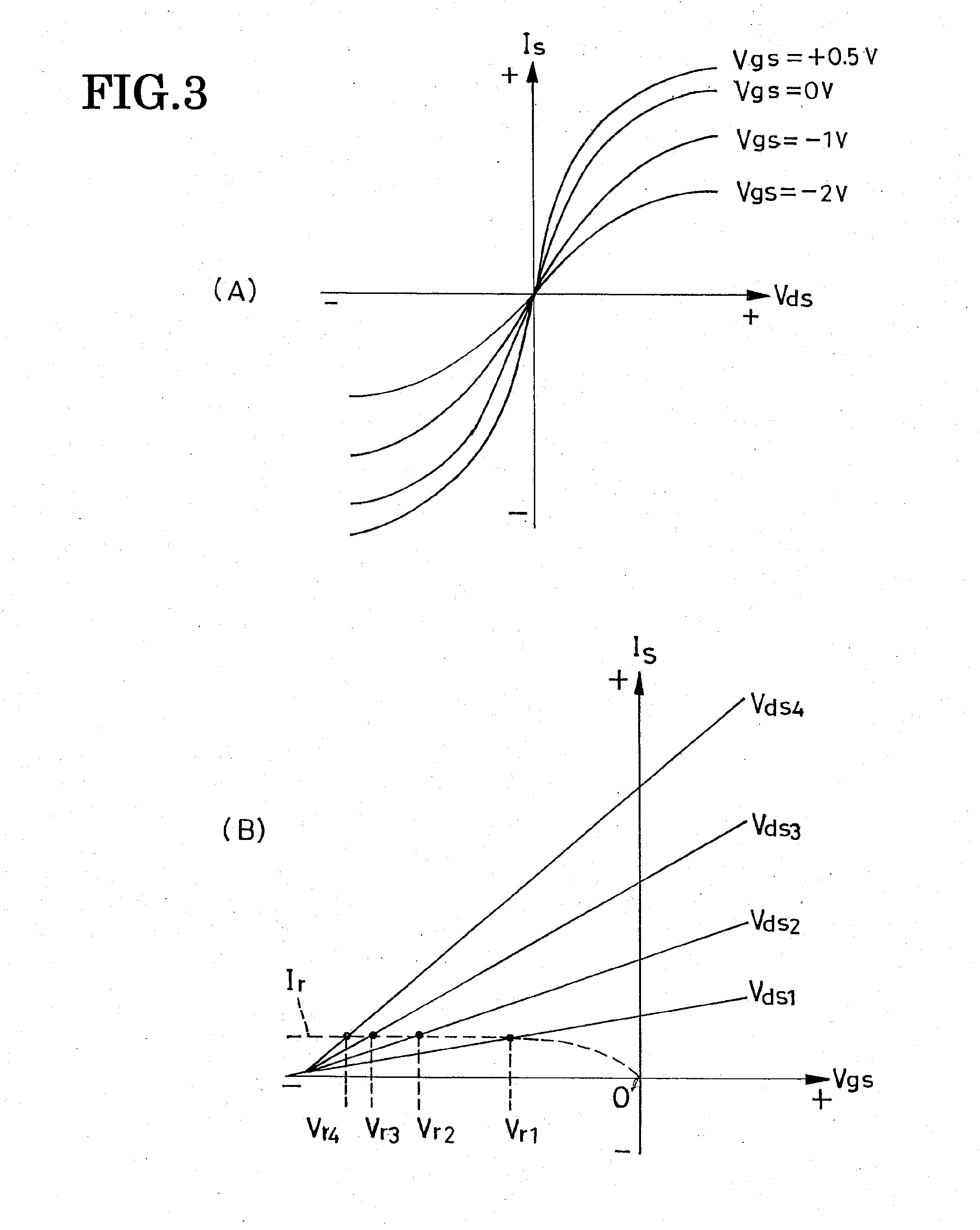

A silicon-made low-forward-voltage Schottky barrier diode is serially combined with a high-antivoltage-strength high-electron-mobility transistor made from a nitride semiconductor that is wider in bandgap than silicon. The Schottky barrier diode has its anode connected to the gate, and its cathode to the source, of the HEMT. This HEMT is normally on. The reverse voltage withstanding capability of the complete device depends upon that between the drain and gate of the HEMT.

Owner:SANKEN ELECTRIC CO LTD

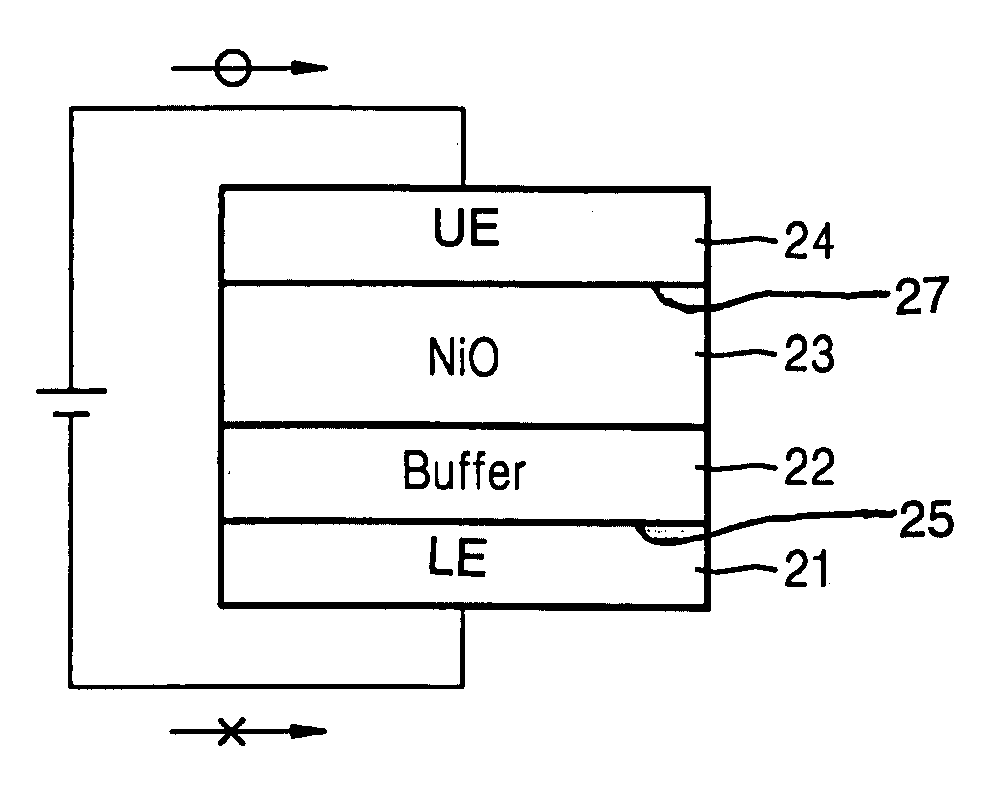

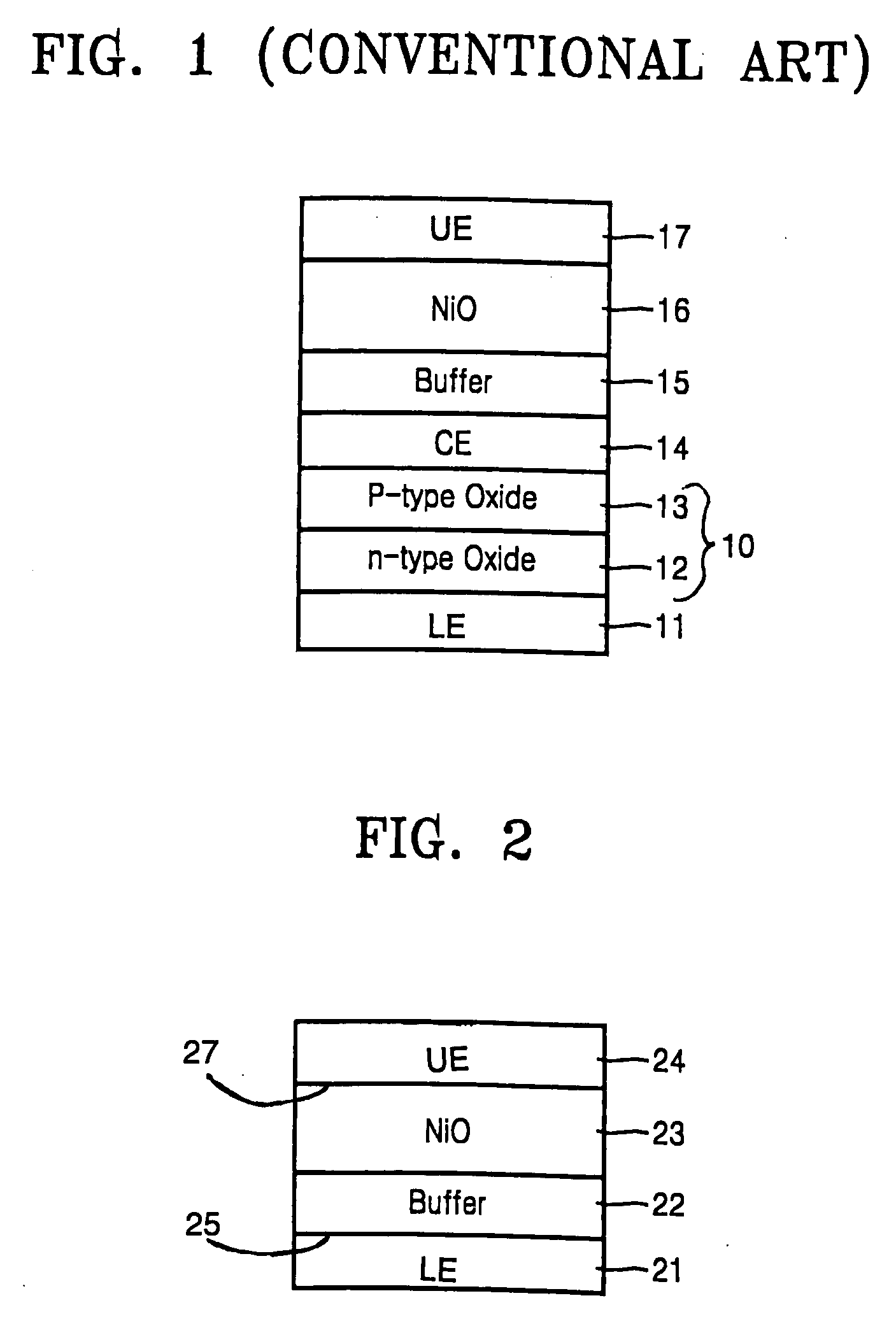

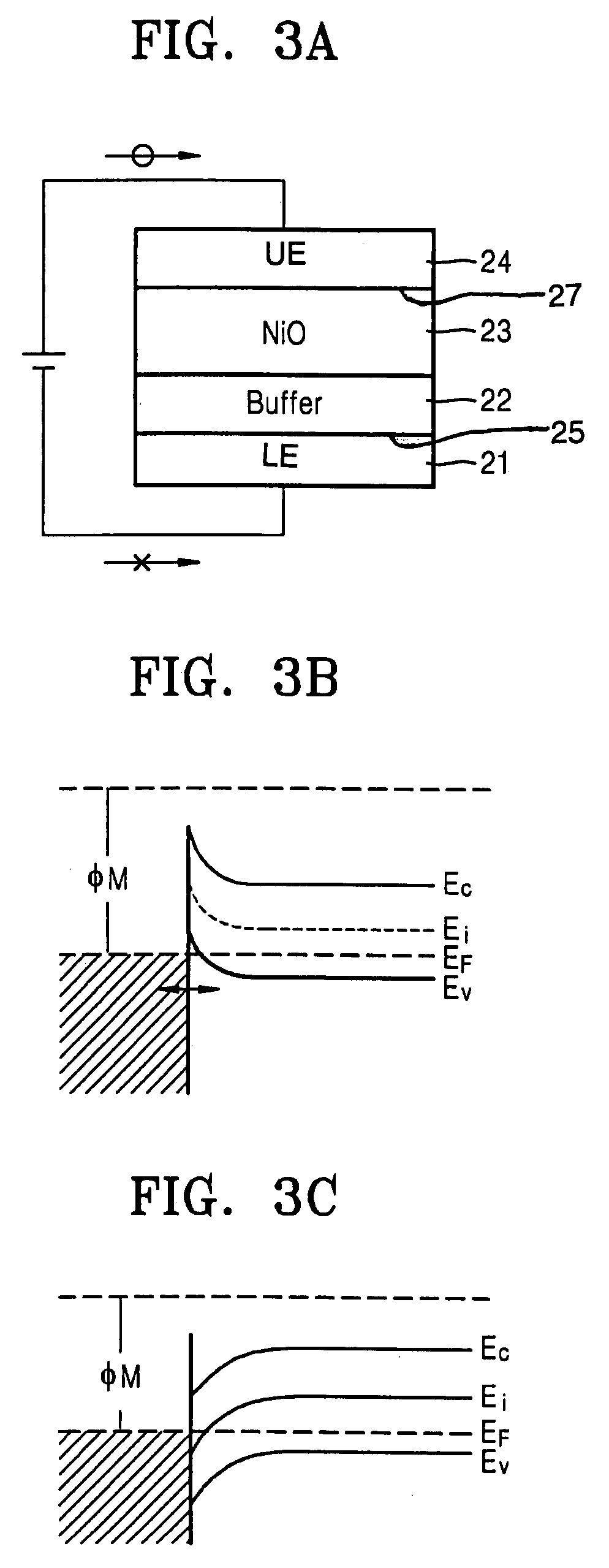

Non-volatile memory device including a variable resistance material

A non-volatile memory device including a variable resistance material is provided. The non-volatile memory device may include a buffer layer, a variable resistance material layer and / or an upper electrode, for example, sequentially formed on a lower electrode. A schottky barrier may be formed on an interface between the buffer layer and the lower electrode. The variable resistance material layer may be formed with a variable resistance property.

Owner:SAMSUNG ELECTRONICS CO LTD

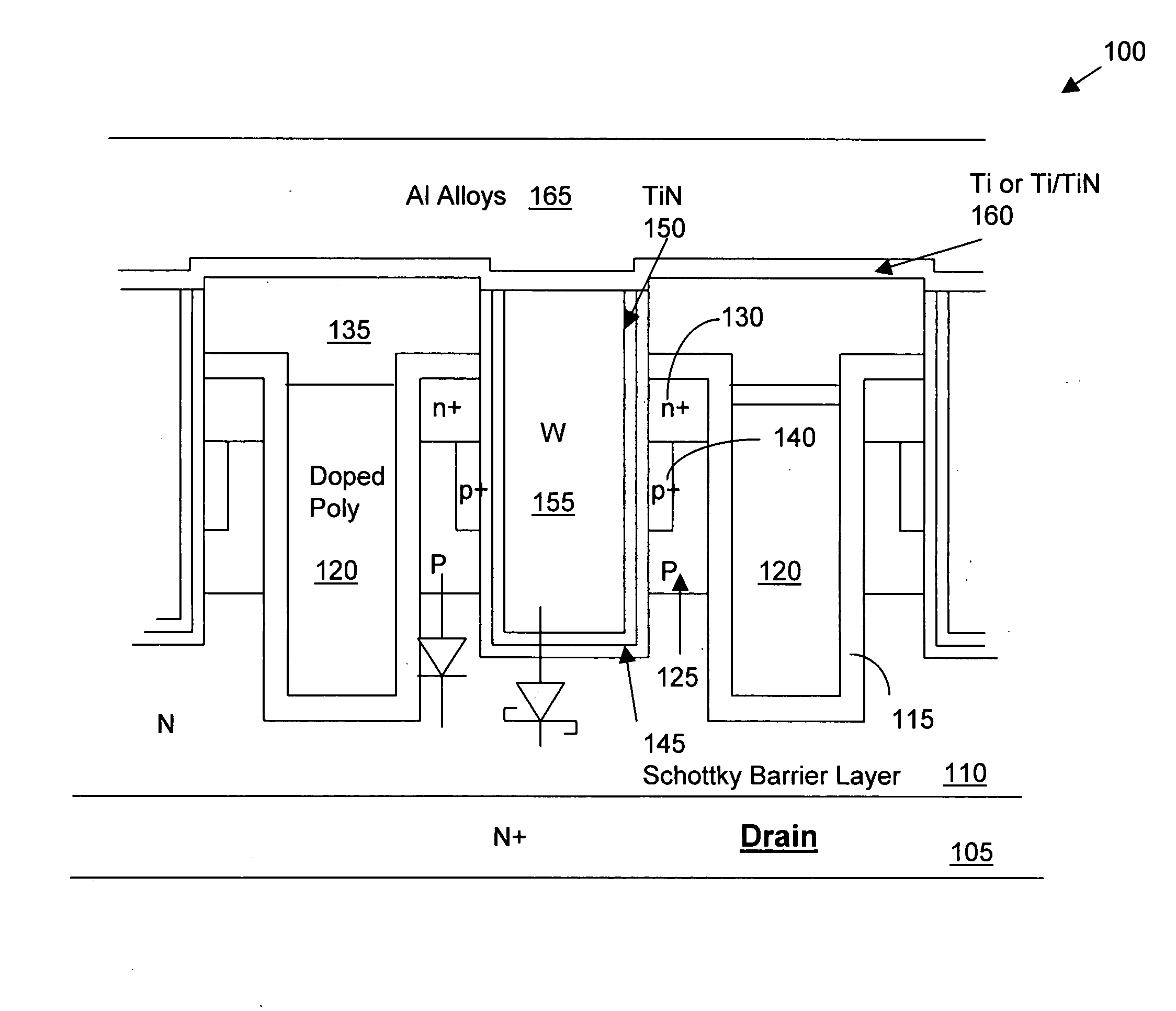

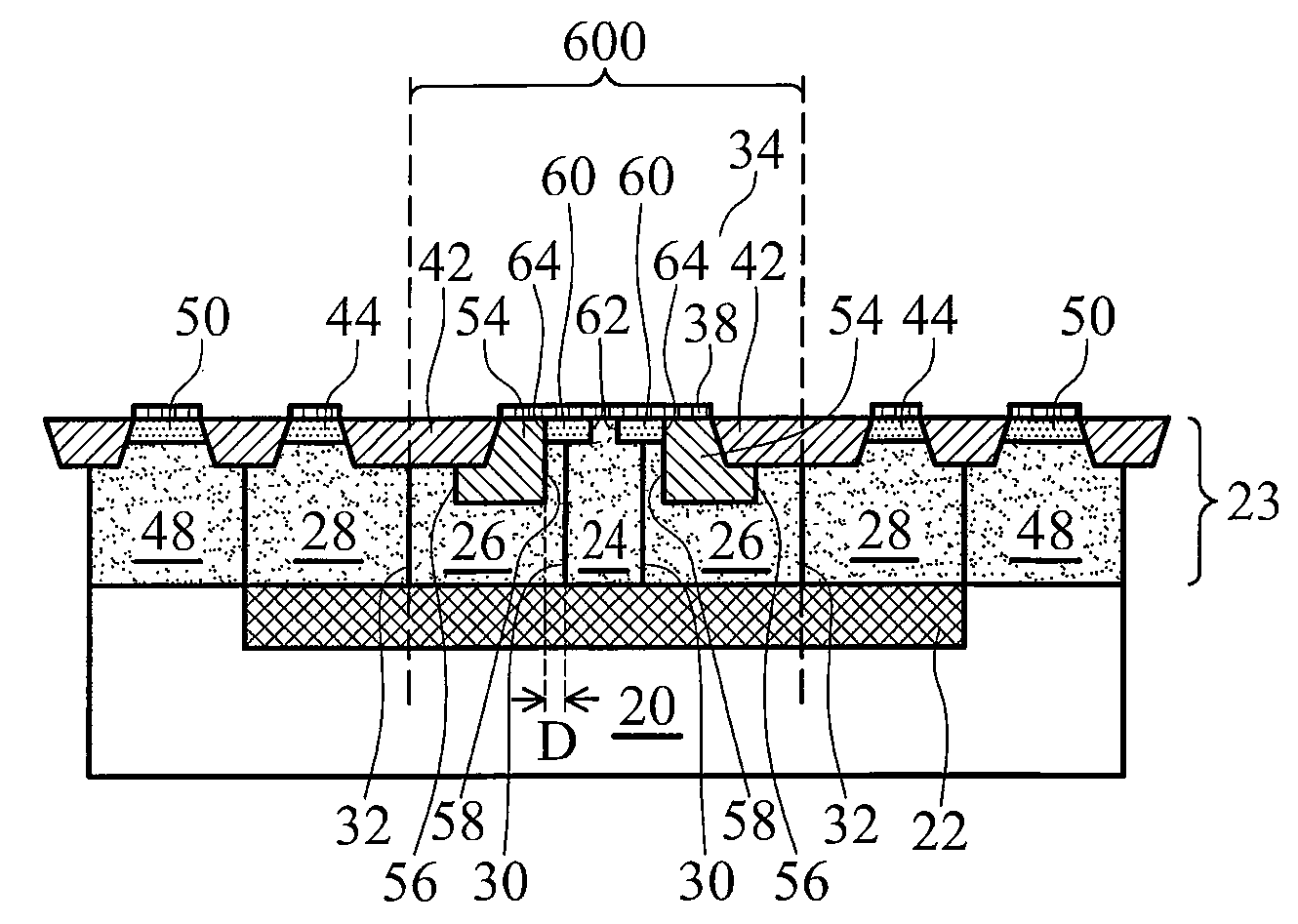

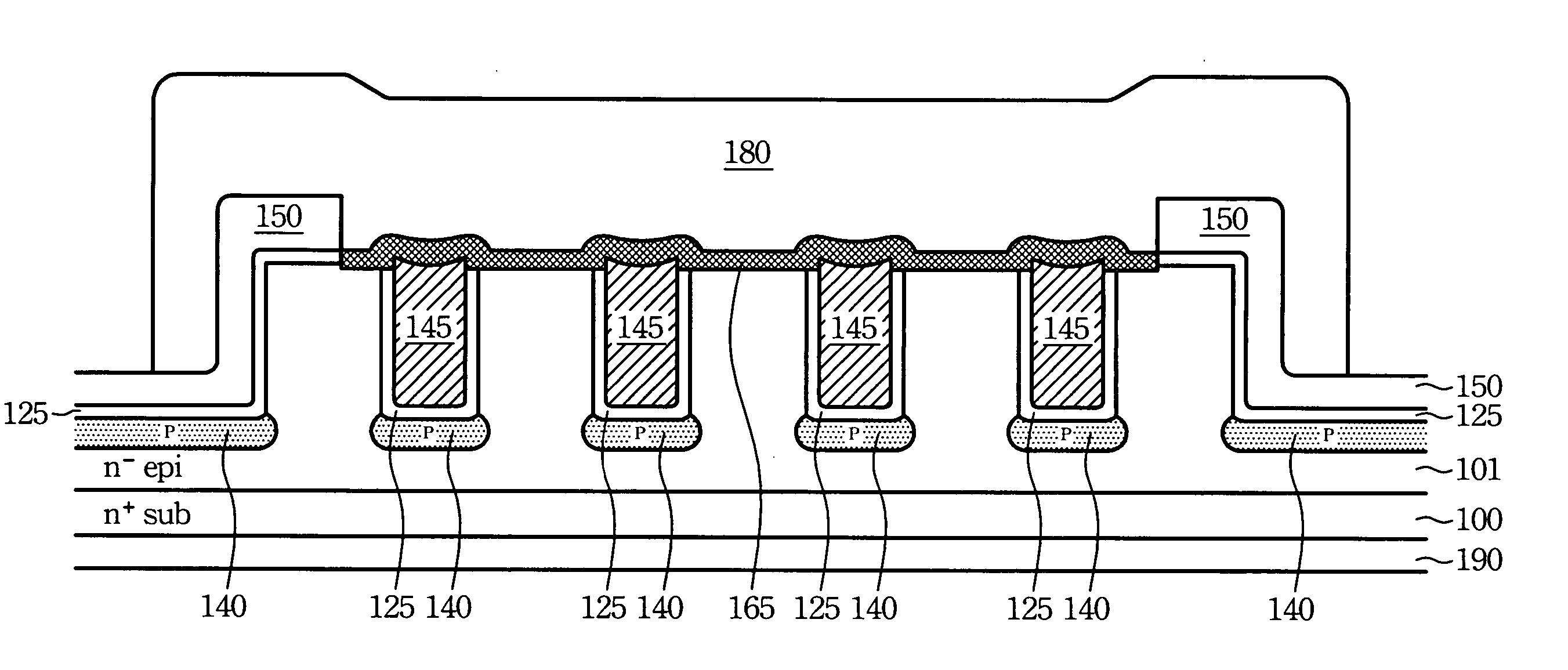

Trenched mosfets with embedded schottky in the same cell

InactiveUS20080246082A1Overcome limitationsReduce parasitic capacitanceSemiconductor/solid-state device manufacturingDiodeMOSFETSchottky barrier

A semiconductor power device includes trenched semiconductor power device comprising a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The semiconductor power device further includes an insulation layer covering the trenched semiconductor power device with a source-body contact trench opened therethrough the source and body regions and extending into an epitaxial layer below the body regions and filled with contact metal plug therein. The semiconductor power device further includes an embedded Schottky diode disposed near a bottom of the source-body contact trench below the contact metal plug wherein the Schottky diode further includes a Schottky barrier layer having a barrier height for reducing a leakage current through the embedded Schottky diode during a reverse bias between the drain and the source.

Owner:FORCE MOS TECH CO LTD

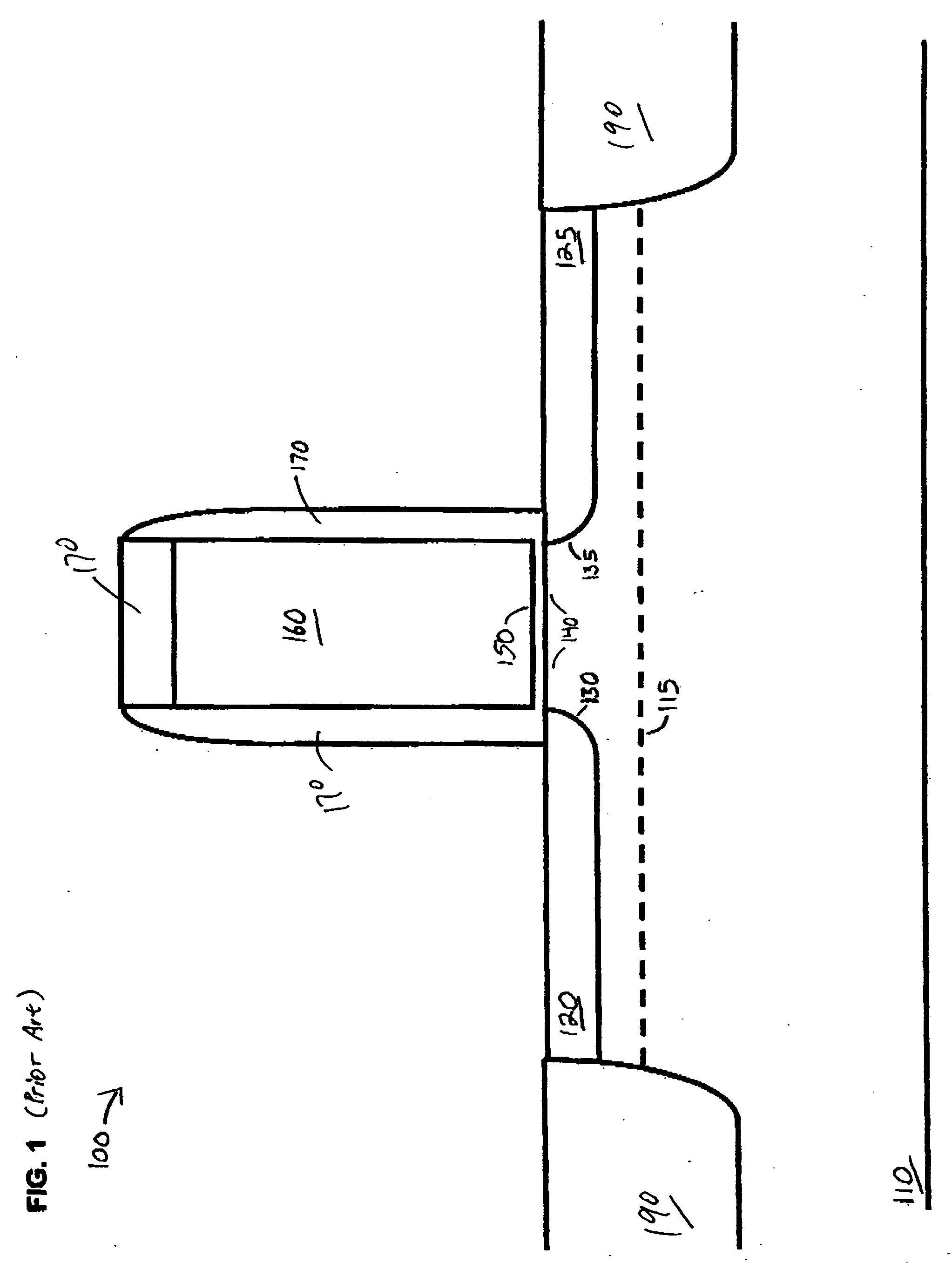

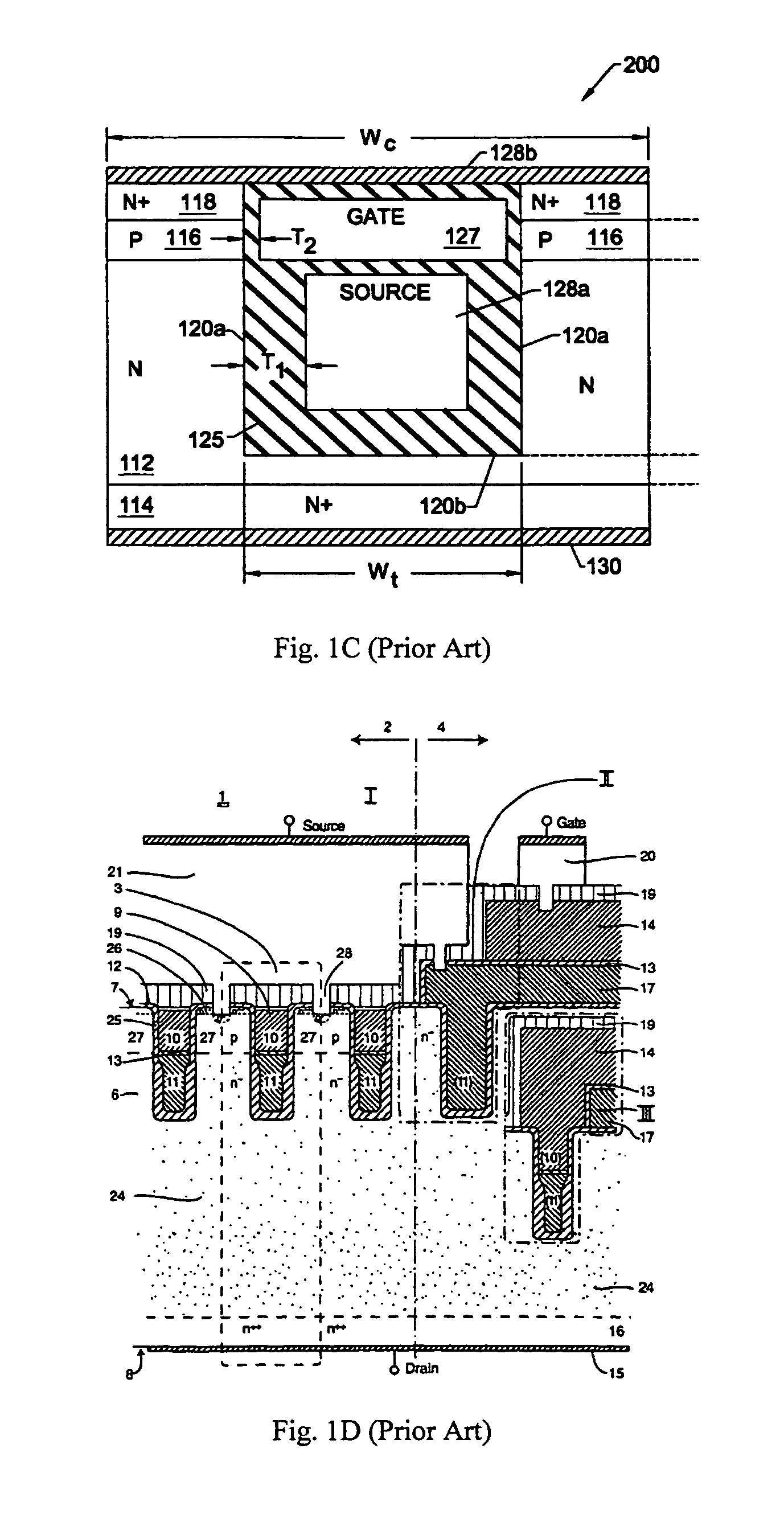

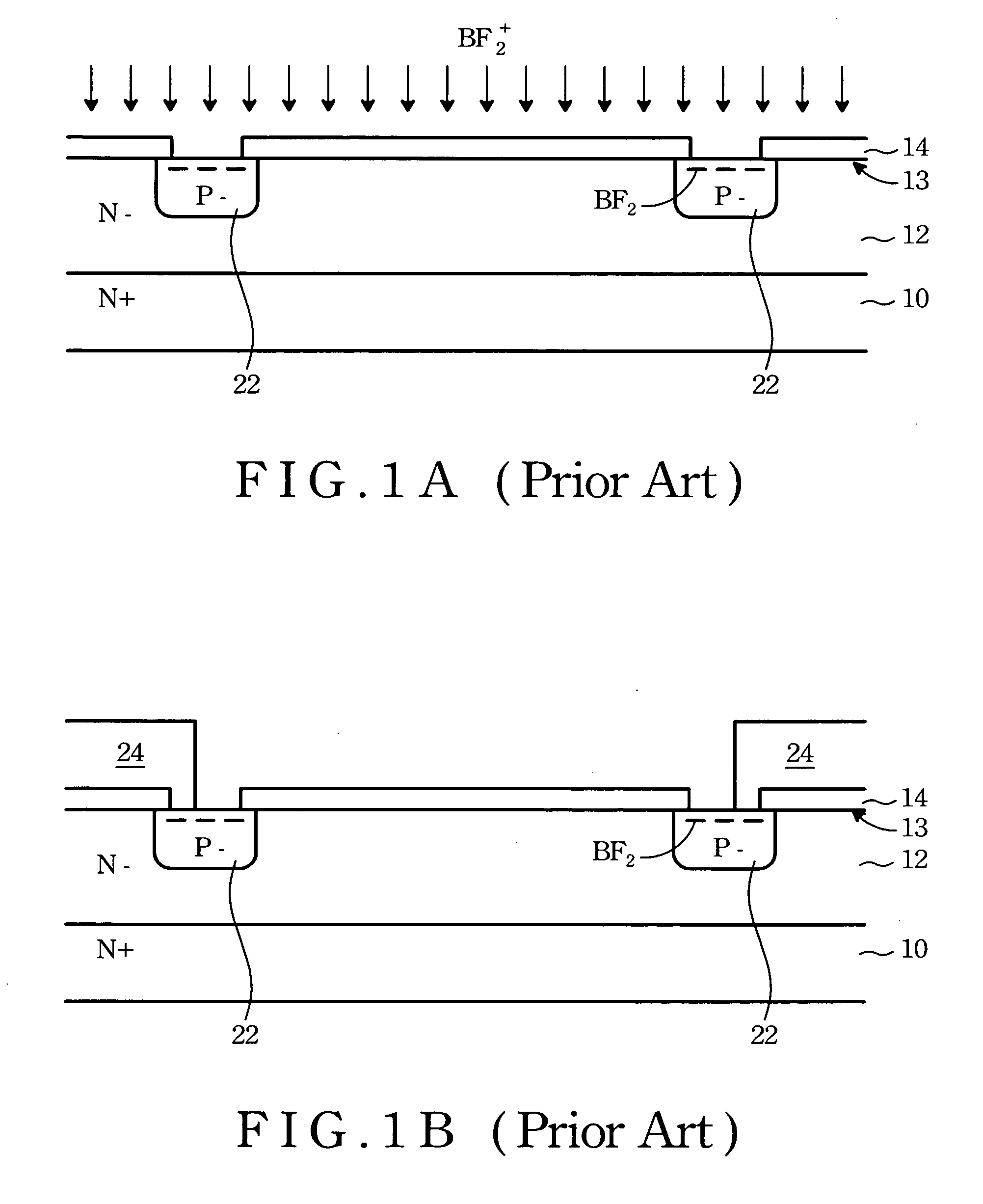

Method of fabrication and device configuration of asymmetrical DMOSFET with Schottky barrier source

ActiveUS20070187751A1Much-reduced contact resistanceTransistorSemiconductor/solid-state device detailsInsulation layerSchottky barrier

A trenched semiconductor power device includes a trenched gate insulated by a gate insulation layer and surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a semiconductor substrate. The source region surrounding the trenched gate includes a metal of low barrier height to function as a Schottky source. The metal of low barrier height further may include a PtSi or ErSi layer. In a preferred embodiment, the metal of low barrier height further includes an ErSi layer. The metal of low barrier height further may be a metal silicide layer having the low barrier height. A top oxide layer is disposed under a silicon nitride spacer on top of the trenched gate for insulating the trenched gate from the source region. A source contact disposed in a trench opened into the body region for contacting a body-contact dopant region and covering with a conductive metal layer such as a Ti / TiN layer. In a preferred embodiment, the semiconductor power device constitutes an asymmetrical double diffusion metal oxide semiconductor field effect transistor (DMOSFET) device.

Owner:ALPHA & OMEGA SEMICON LTD

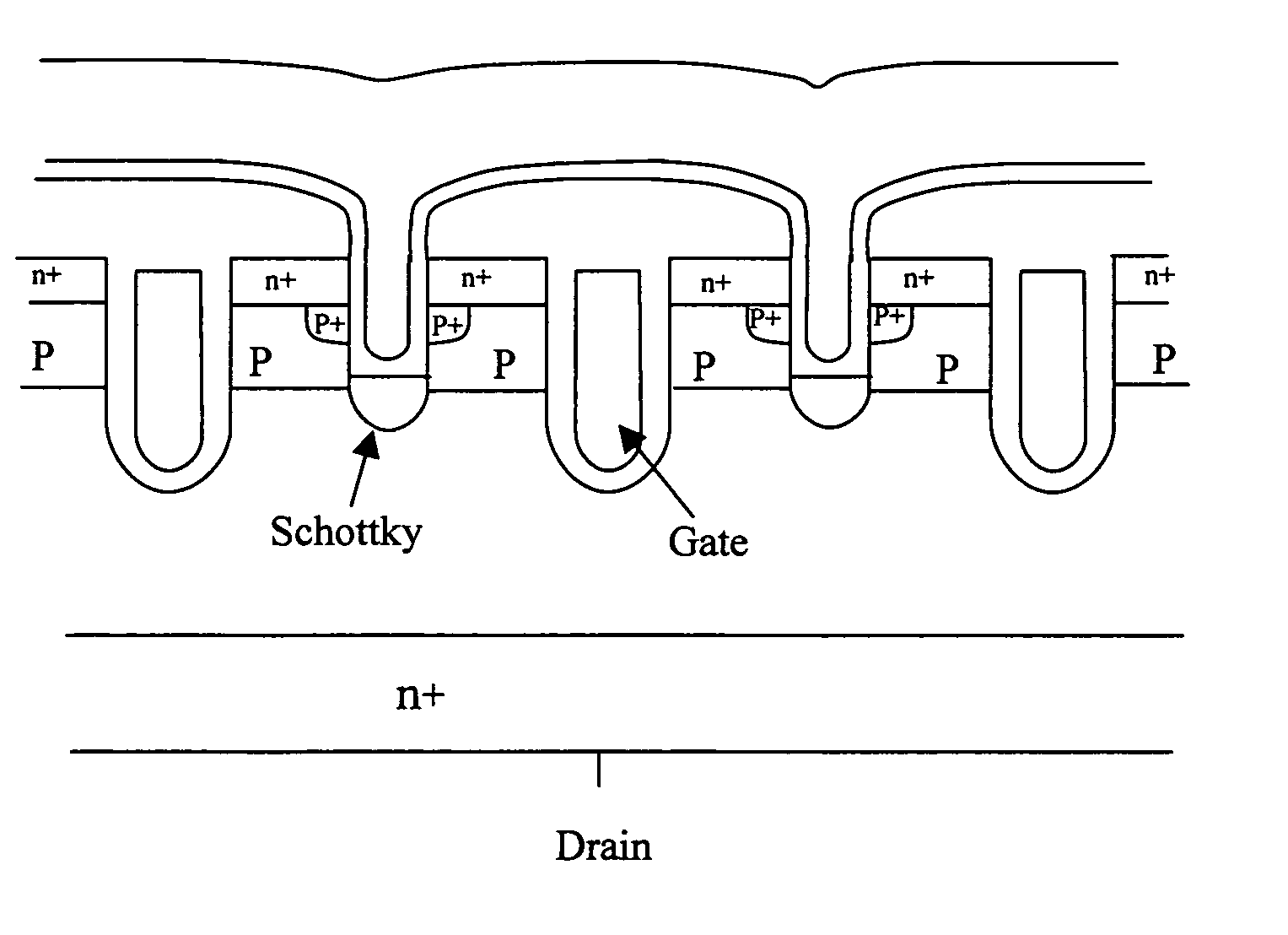

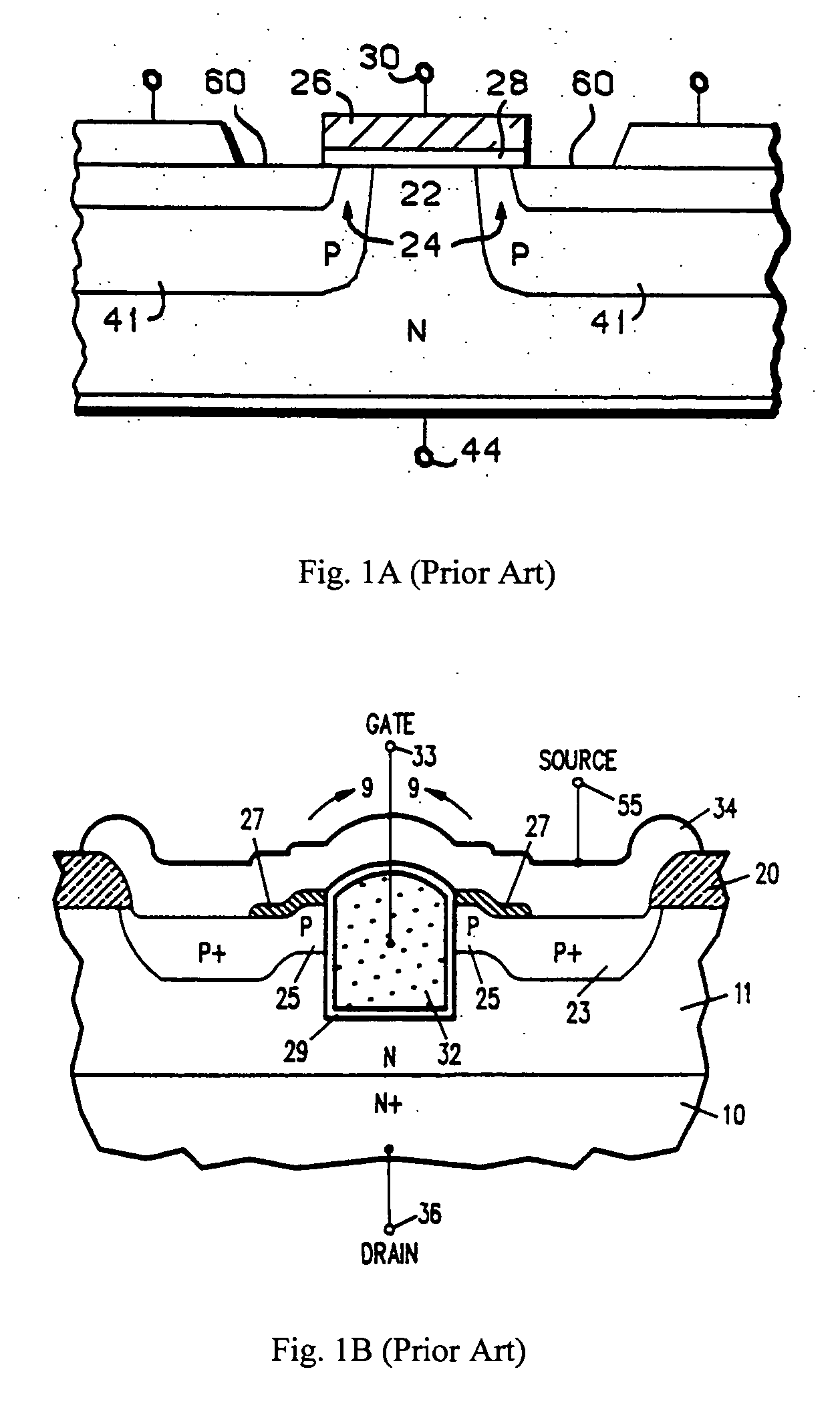

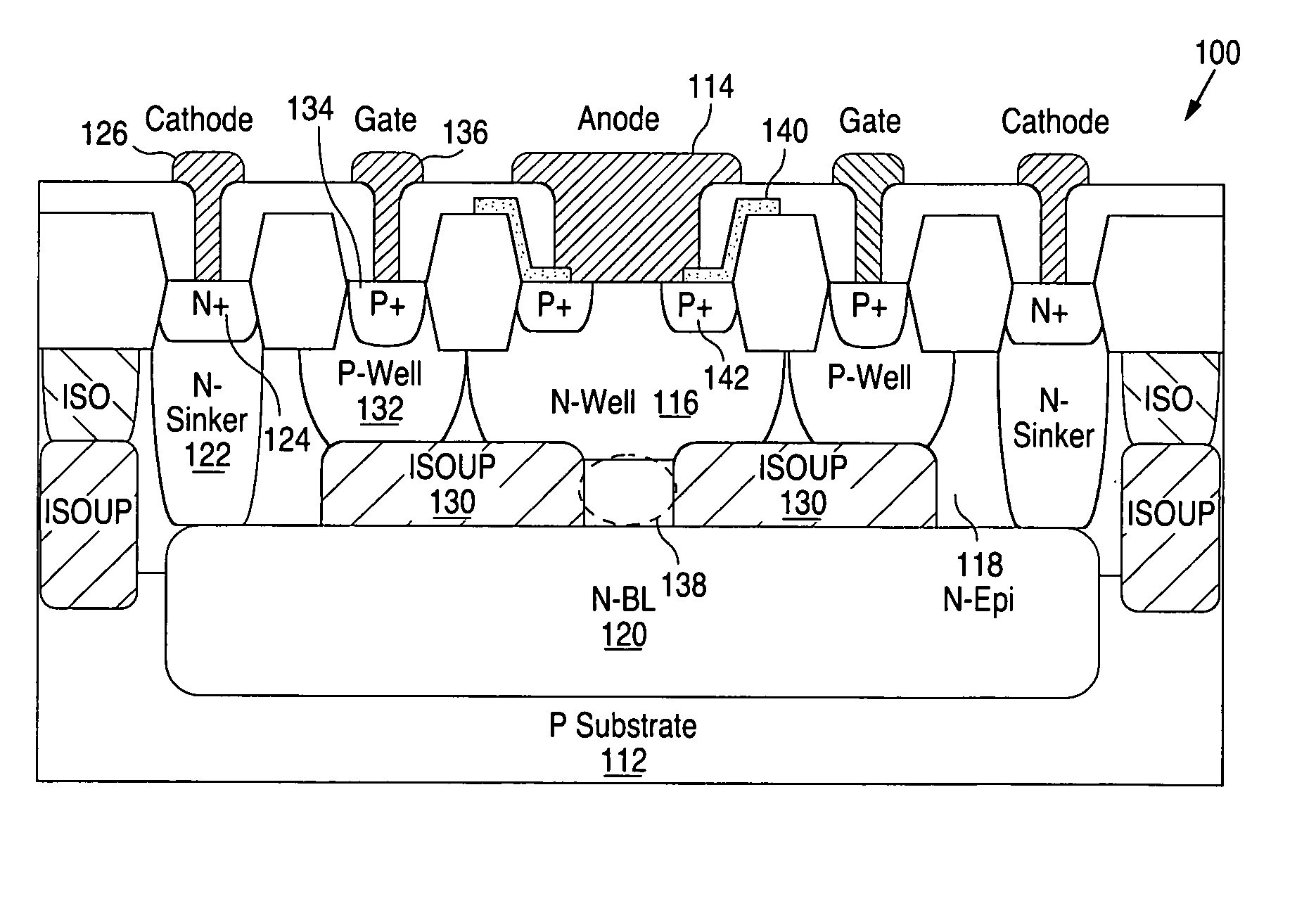

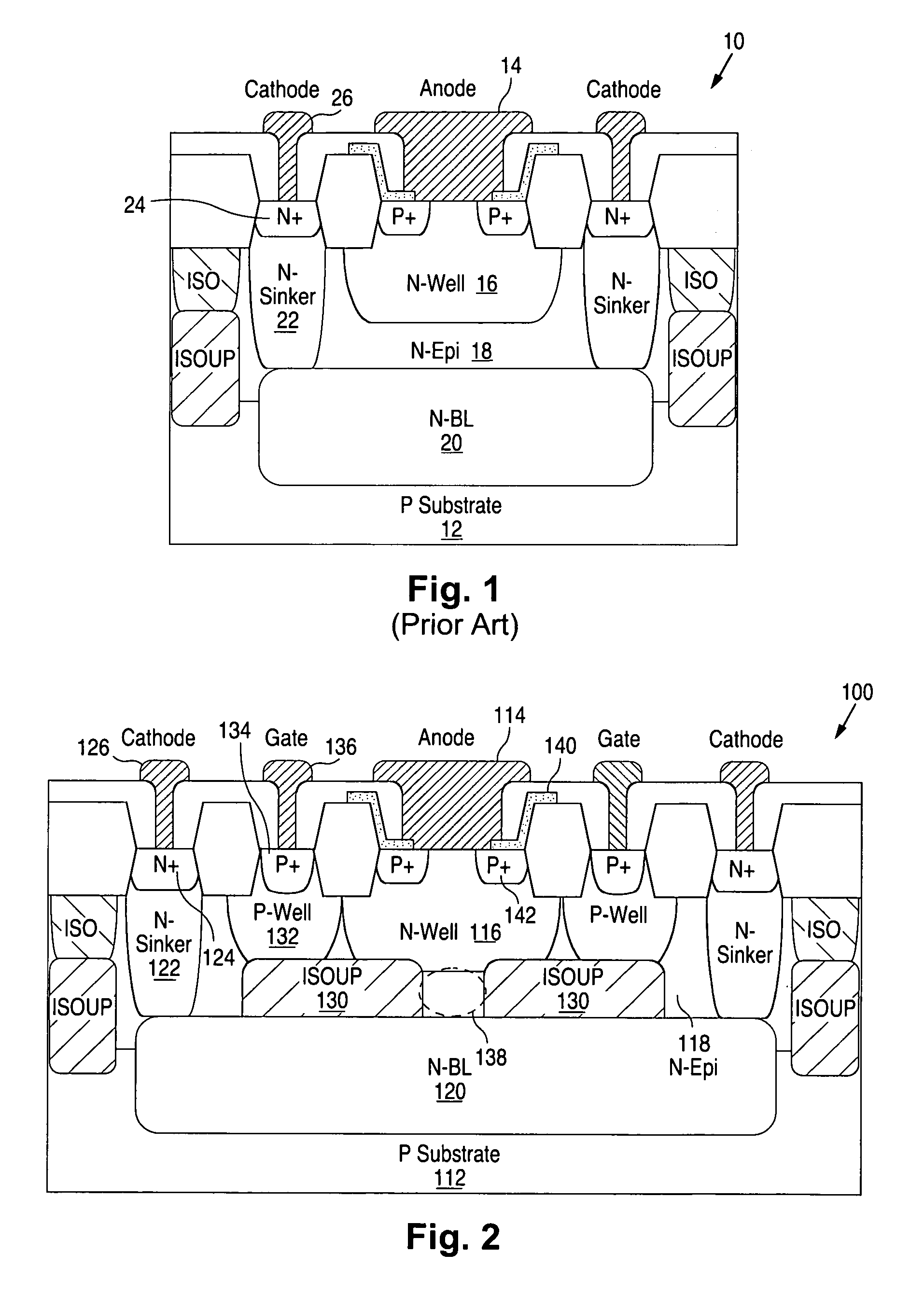

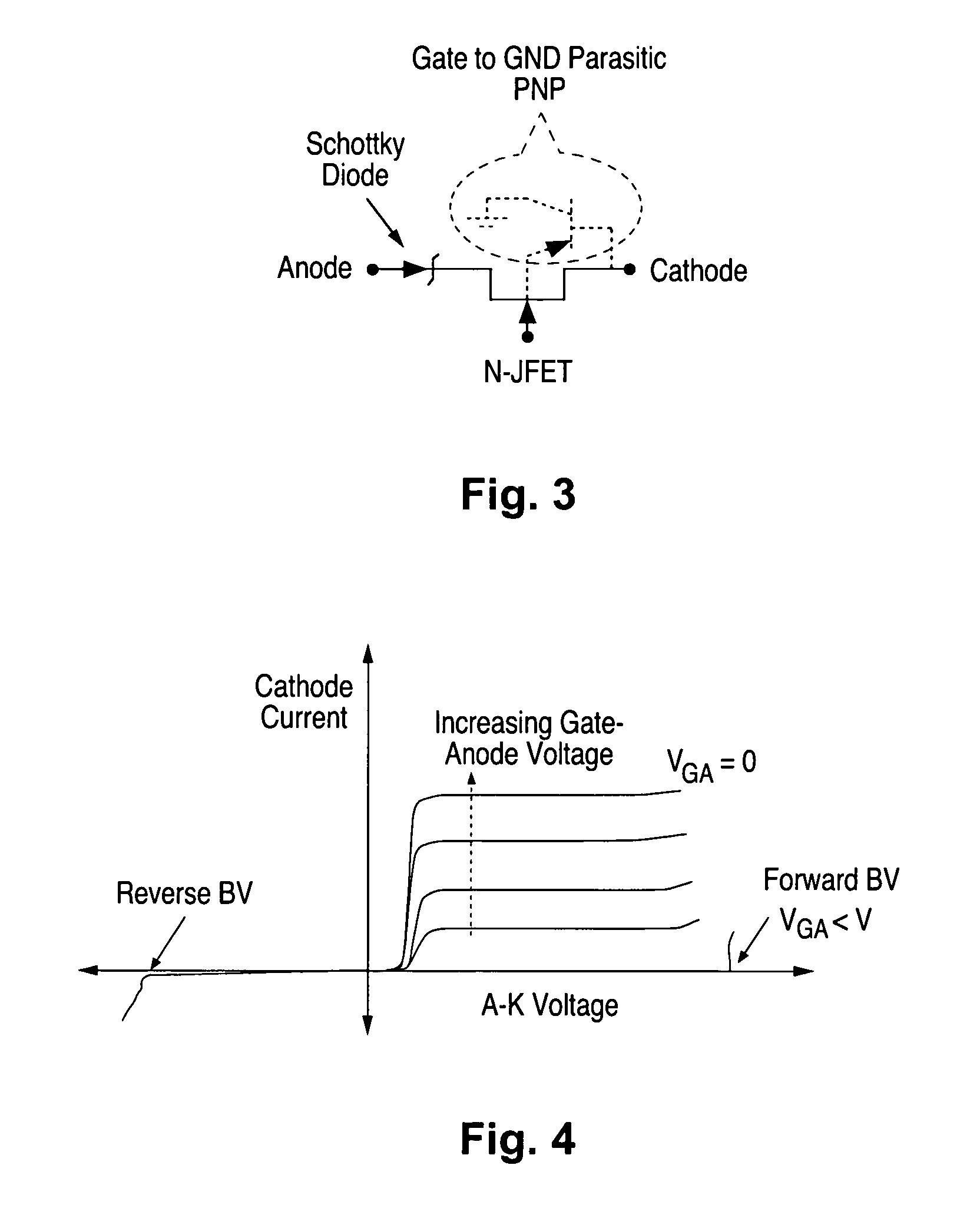

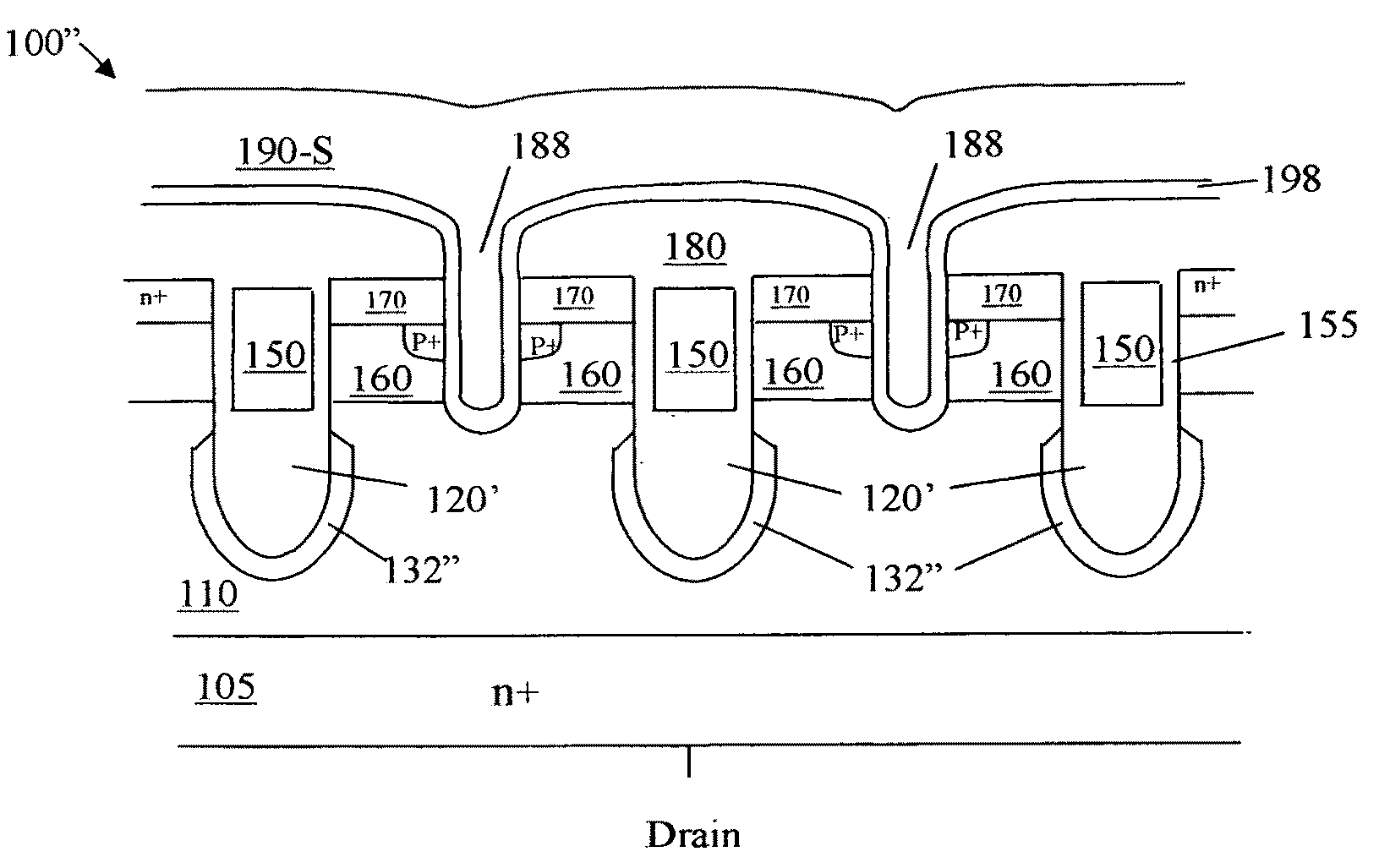

JFET controlled schottky barrier diode

A JFET controlled Schottky barrier diode includes a p-type diffusion region integrated into the cathode of the Schottky diode to form an integrated JFET where the integrated JFET provides on-off control of the Schottky barrier diode. The p-type diffusion region encloses a portion of the forward current path of the Schottky barrier diode where the p-type diffusion region forms the gate of the JFET and the enclosed portion of the forward current path forms the channel region of the JFET. By applying a reverse biased potential to the gate of the JEFT with respect to the anode of the Schottky diode, the forward current of the Schottky diode can be pinched off, thereby providing on-off control over the Schottky diode forward current.

Owner:MICREL

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS20090072301A1Improve switching performanceImprove area efficiencySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETInsulation layer

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one active cell further includes a trenched source contact opened between the trenches wherein the trenched source contact opened through a source region into a body region for electrically connecting the source region to a source metal disposed on top of an insulation layer wherein a trench bottom surface of the trenched source contact further covered with a conductive material to function as an integrated Schottky barrier diode in said active cell. A shielding structure is disposed at the bottom and insulated from the trenched gate to provide shielding effect for both the trenched gate and the Schottky diode.

Owner:ALPHA & OMEGA SEMICON LTD

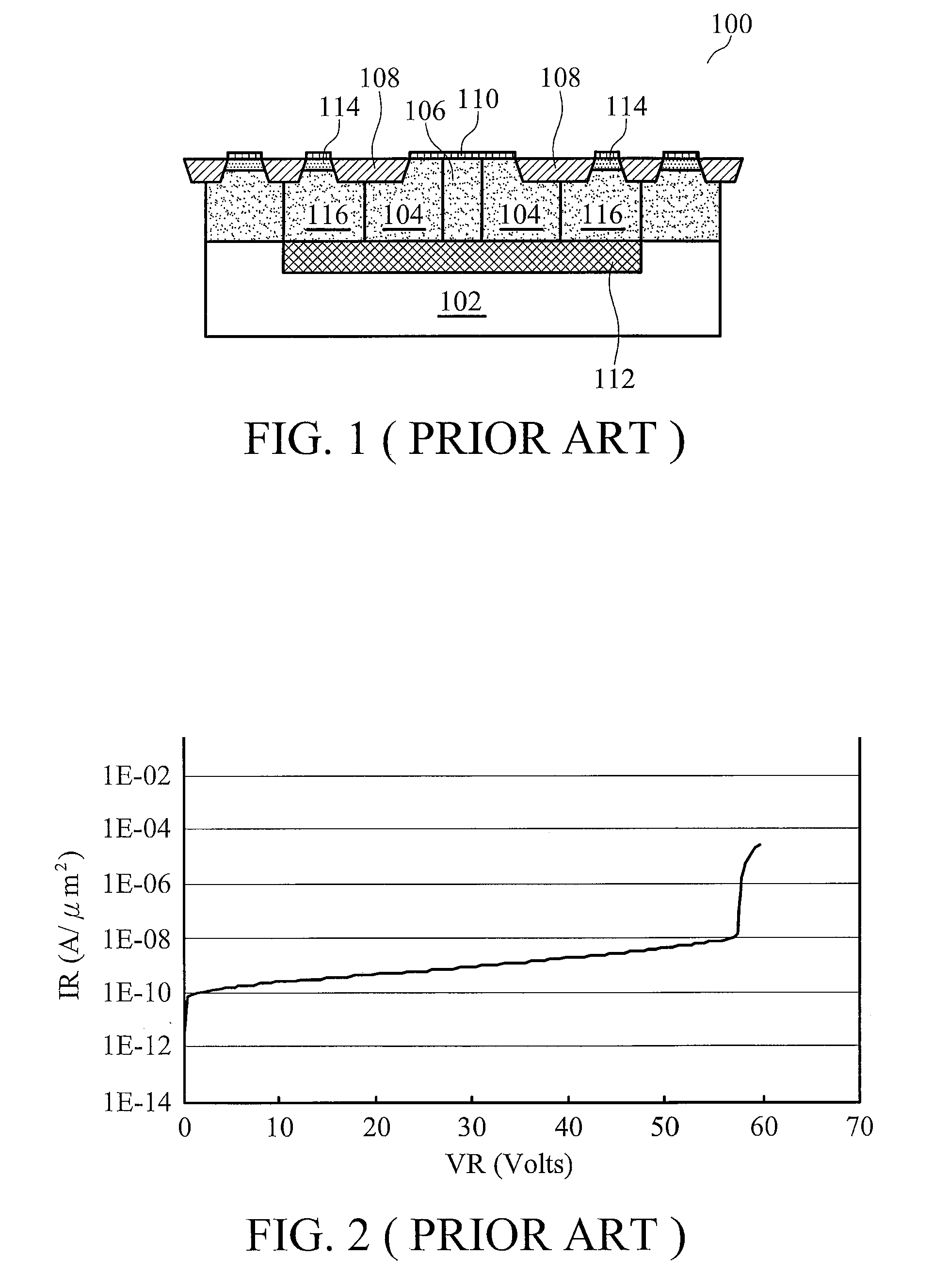

Schottky Diodes Having Low-Voltage and High-Concentration Rings

ActiveUS20090294865A1Improve breakdown voltageReduce leakage currentTransistorSolid-state devicesHigh concentrationSchottky barrier

An integrated circuit structure includes a semiconductor substrate; a first well region of a first conductivity type over the semiconductor substrate; a second well region of a second conductivity type opposite the first conductivity type encircling the first well region; and a metal-containing layer over and adjoining the first well region and extending over at least an inner portion of the second well region. The metal-containing layer and the first well region form a Schottky barrier. The integrated circuit structure further includes an isolation region encircling the metal-containing layer; and a third well region of the second conductivity type encircling at least a central portion of the first well region. The third well region has a higher impurity concentration than the second well region, and includes a top surface adjoining the metal-containing layer, and a bottom surface higher than bottom surfaces of the first and the second well regions.

Owner:TAIWAN SEMICON MFG CO LTD

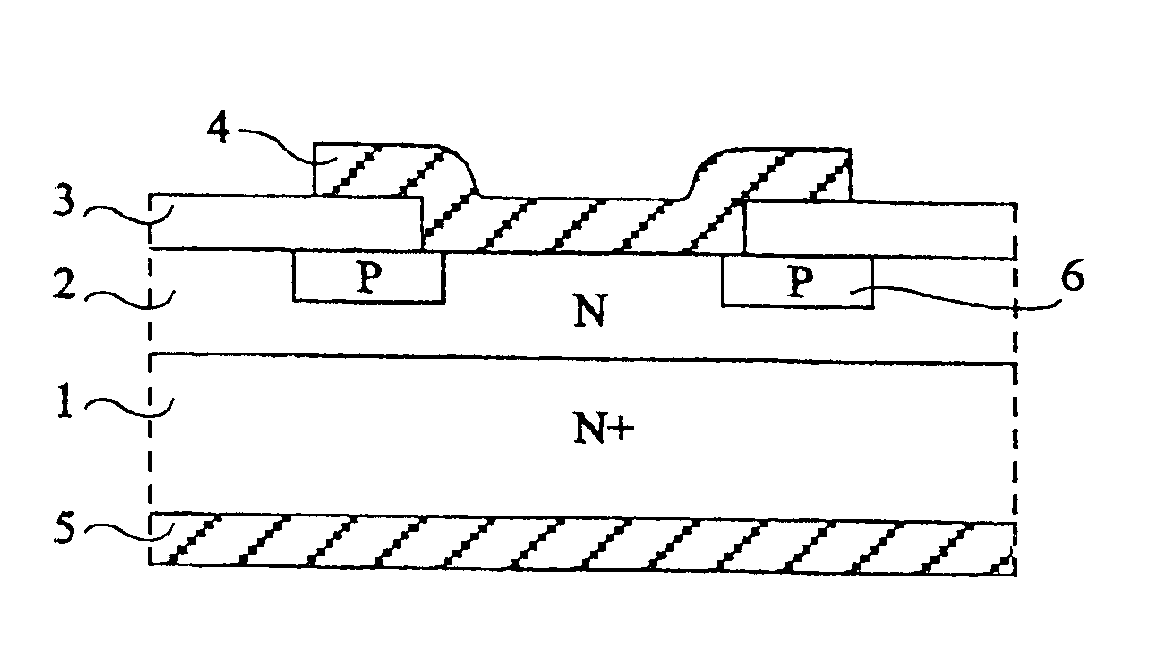

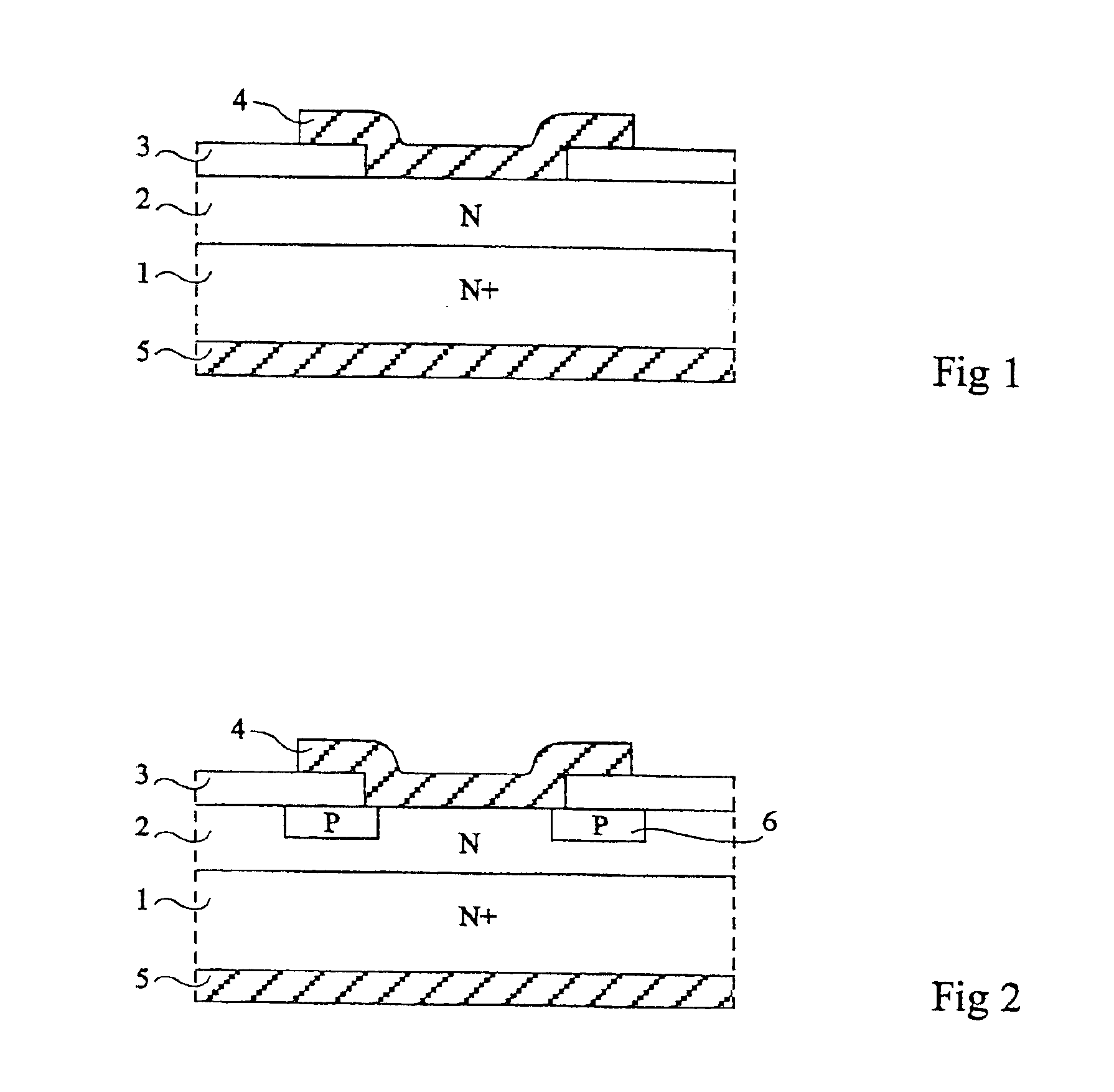

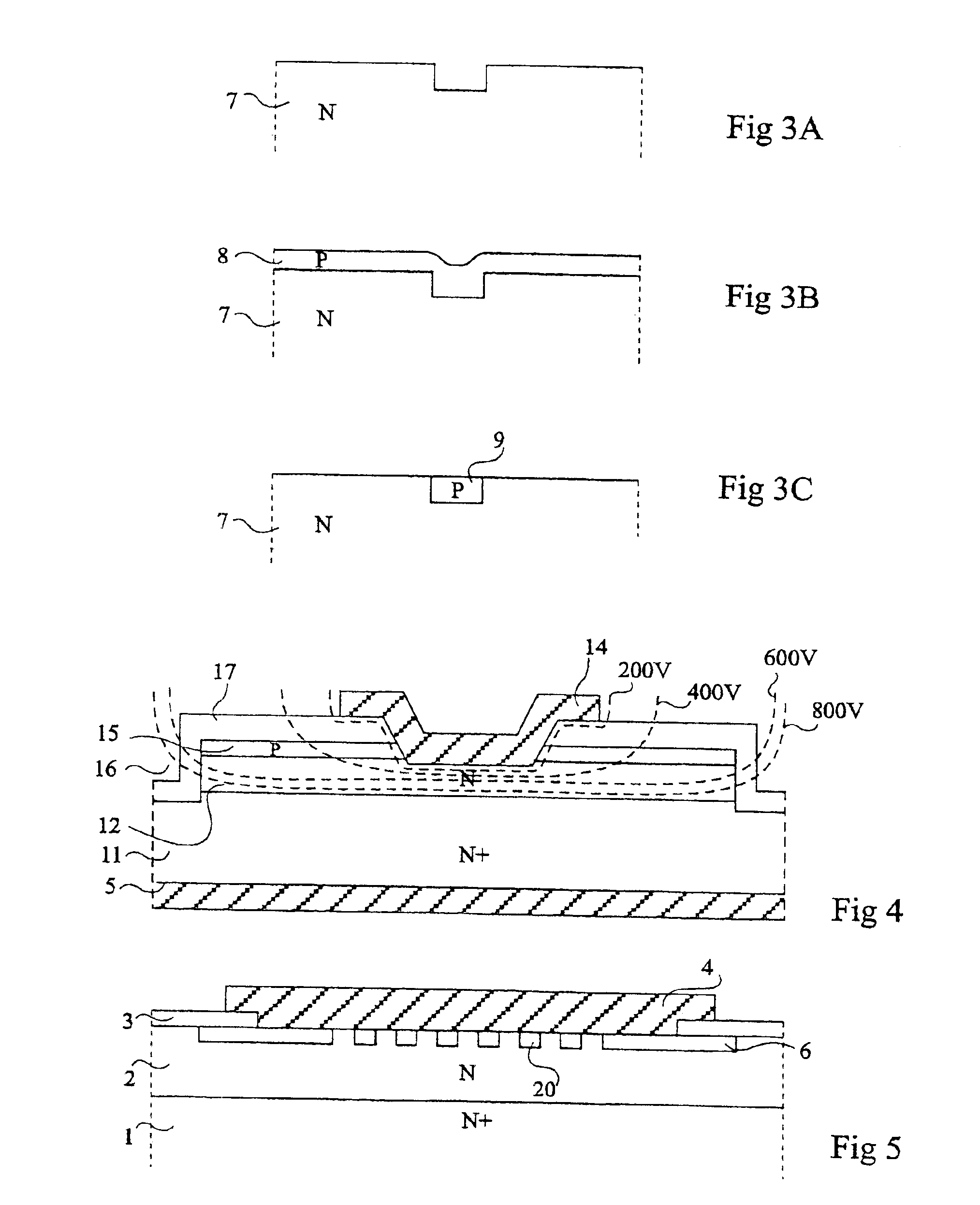

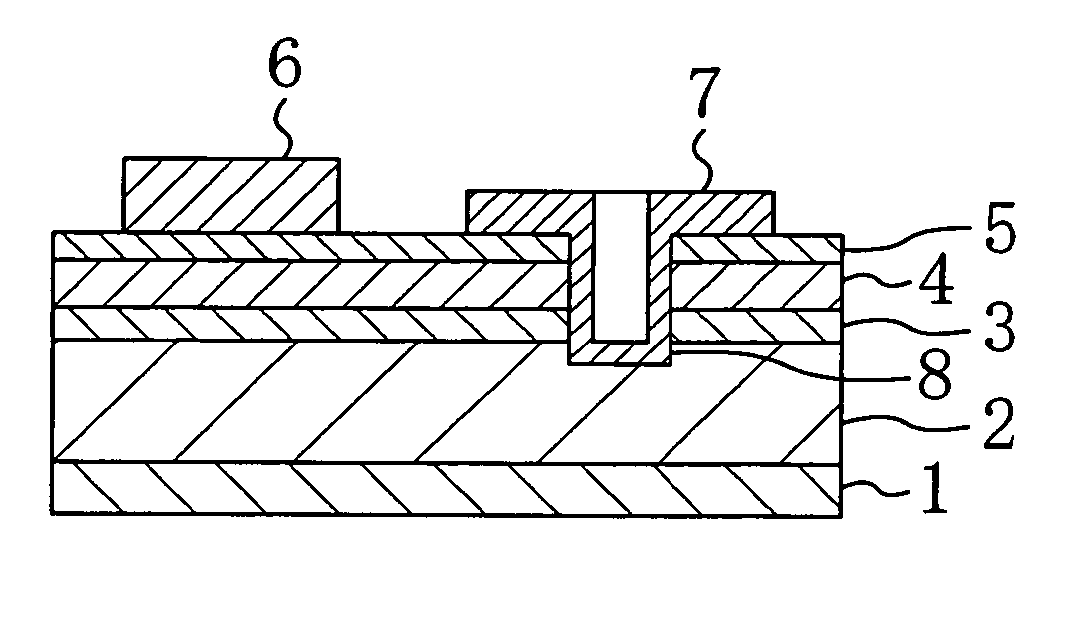

Method for producing a schottky diode in silicon carbide

InactiveUS6897133B2Semiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCarbide

The invention concerns a method for making a vertical Schottky diode on a highly doped N-type silicon carbide substrate (1), comprising steps which consist in forming an N-type lightly doped epitaxial layer (2); etching out a peripheral trench at the active zone of the diode; forming a type P doped epitaxial layer; carrying out a planarization process so that a ring (6) of the P type epitaxial layer remains in the trench; forming an insulating layer (3) on the outer periphery of the component, said insulating layer partly covering said ring; and depositing a metal (4) capable of forming a Schottky barrier with the N type epitaxial layer.

Owner:STMICROELECTRONICS SRL

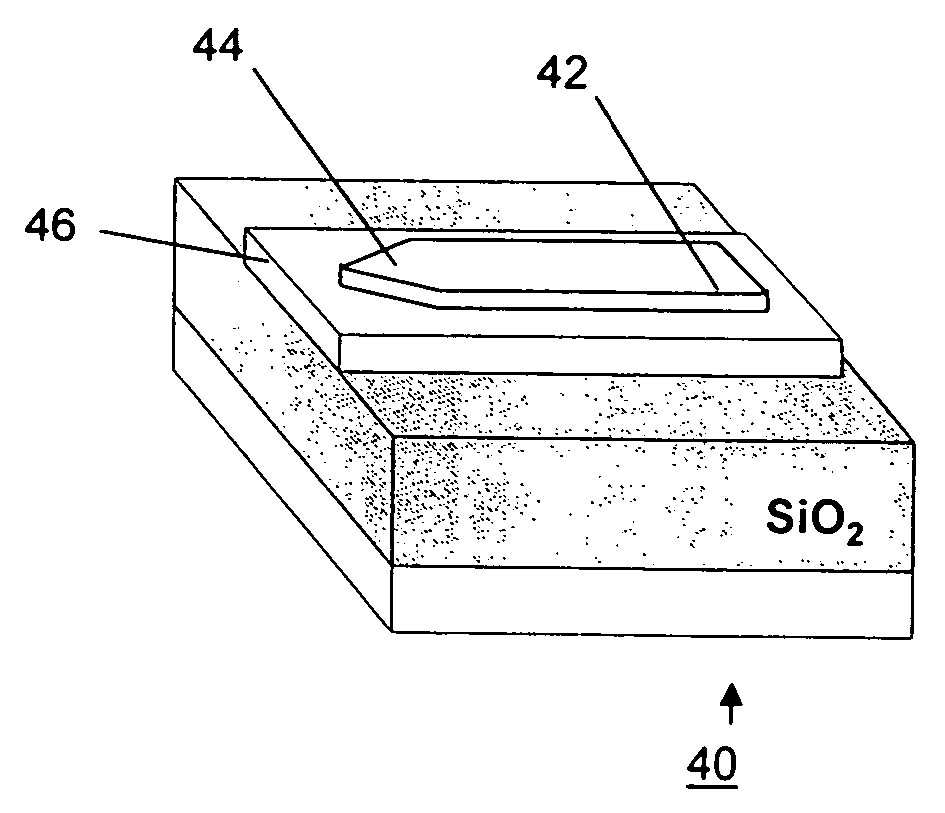

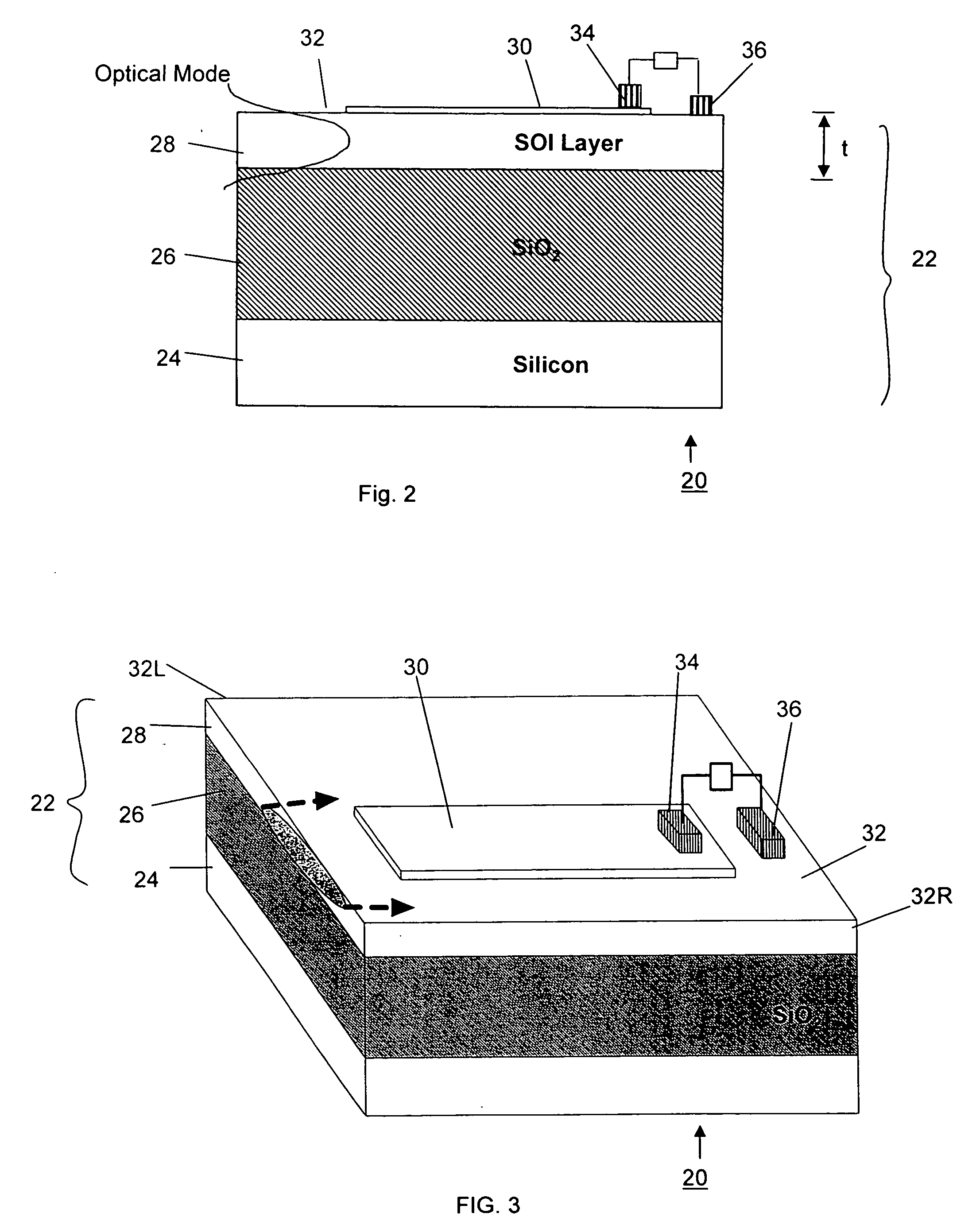

Silicon-based Schottky barrier infrared optical detector

ActiveUS20050110108A1Reduce dark currentEasy to operateOptical waveguide light guidePhotovoltaic energy generationSchottky barrierPhotodetector

A silicon-based IR photodetector is formed within a silicon-on-insulator (SOI) structure by placing a metallic strip (preferably, a silicide) over a portion of an optical waveguide formed within a planar silicon surface layer (i.e., “planar SOI layer”) of the SOI structure, the planar SOI layer comprising a thickness of less than one micron. Room temperature operation of the photodetector is accomplished as a result of the relatively low dark current associated with the SOI-based structure and the ability to use a relatively small surface area silicide strip to collect the photocurrent. The planar SOI layer may be doped, and the geometry of the silicide strip may be modified, as desired, to achieve improved results over prior art silicon-based photodetectors.

Owner:CISCO TECH INC

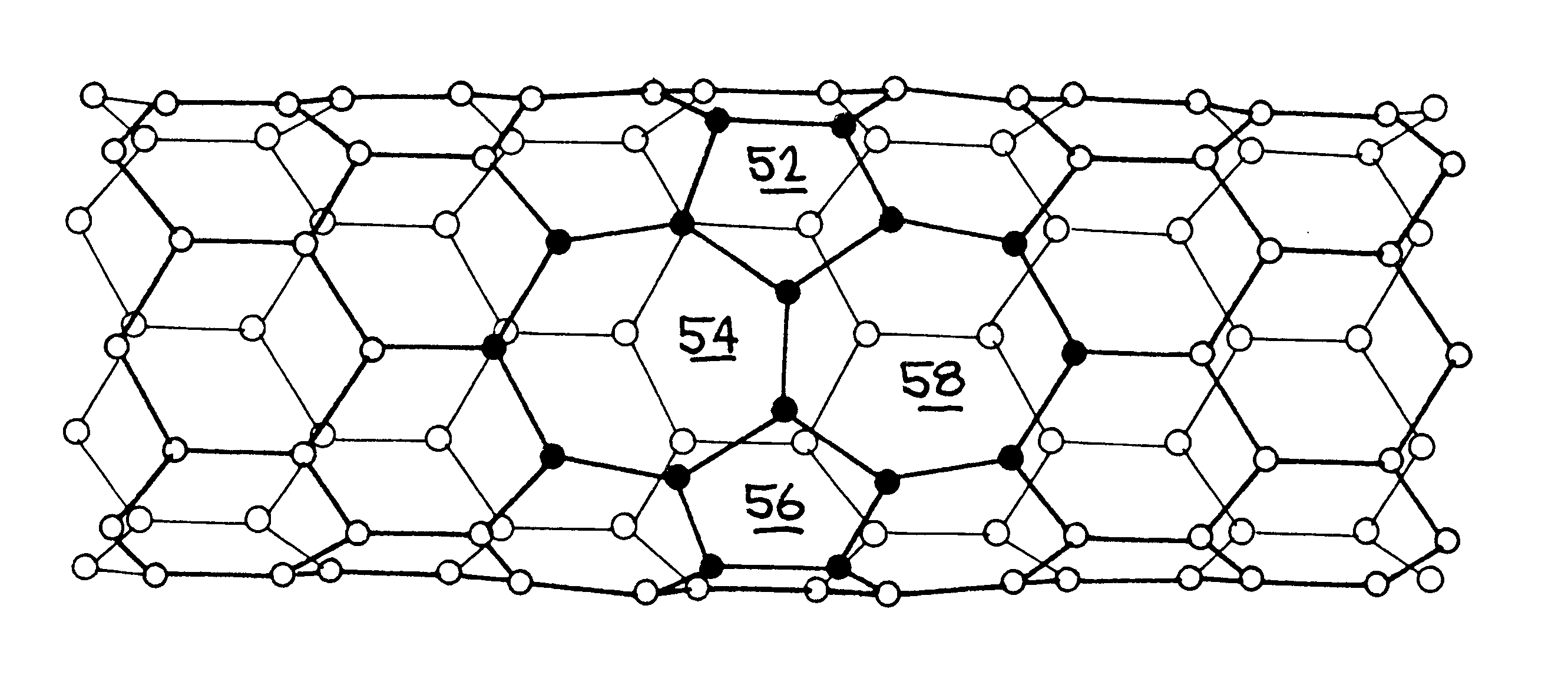

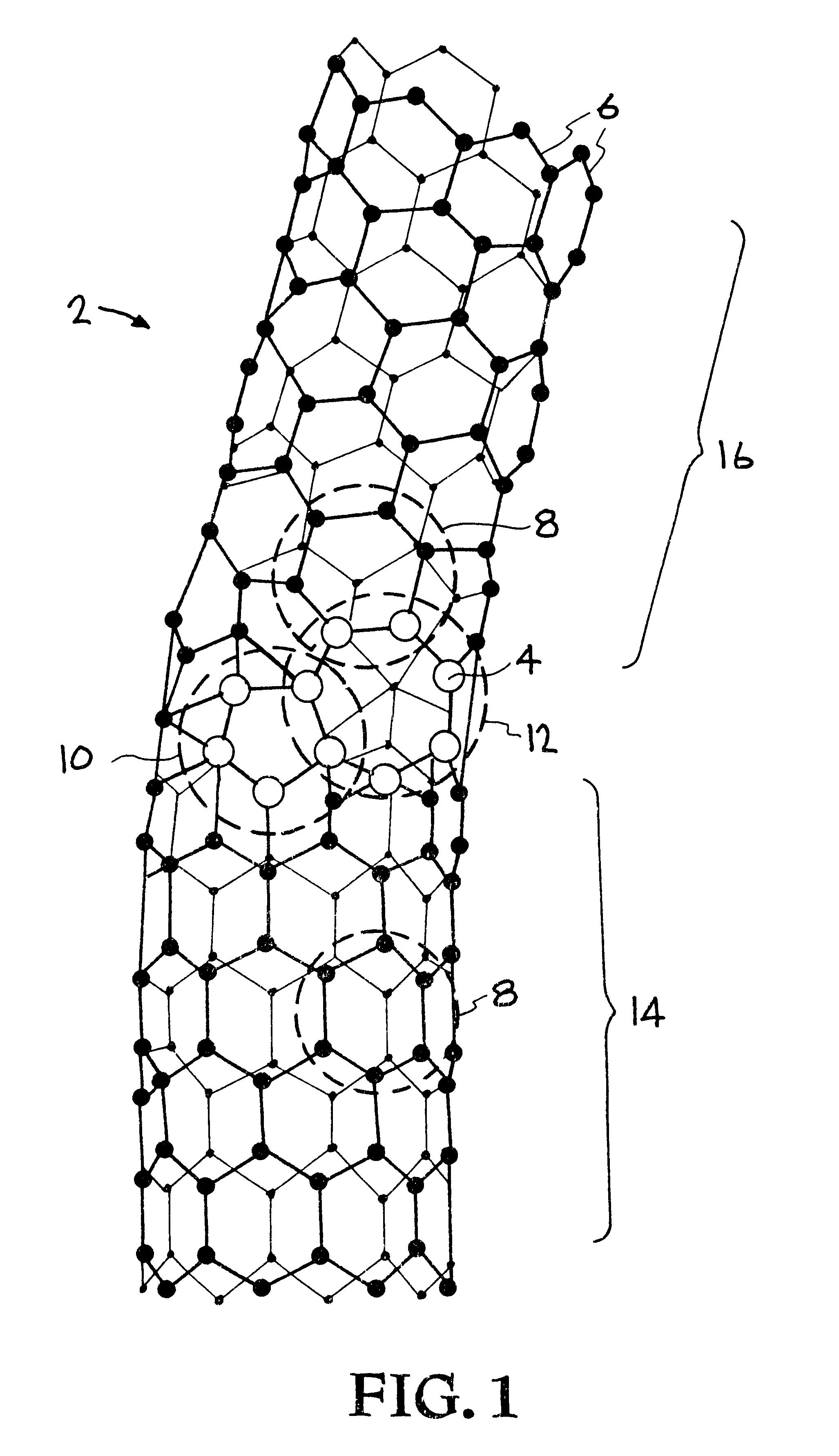

Nanotube junctions

The present invention comprises a new nanoscale metal-semiconductor, semiconductor-semiconductor, or metal-metal junction, designed by introducing topological or chemical defects in the atomic structure of the nanotube. Nanotubes comprising adjacent sections having differing electrical properties are described. These nanotubes can be constructed from combinations of carbon, boron, nitrogen and other elements. The nanotube can be designed having different indices on either side of a junction point in a continuous tube so that the electrical properties on either side of the junction vary in a useful fashion. For example, the inventive nanotube may be electrically conducting on one side of a junction and semiconducting on the other side. An example of a semiconductor-metal junction is a Schottky barrier. Alternatively, the nanotube may exhibit different semiconductor properties on either side of the junction. Nanotubes containing heterojunctions, Schottky barriers, and metal-metal junctions are useful for microcircuitry.

Owner:RGT UNIV OF CALIFORNIA

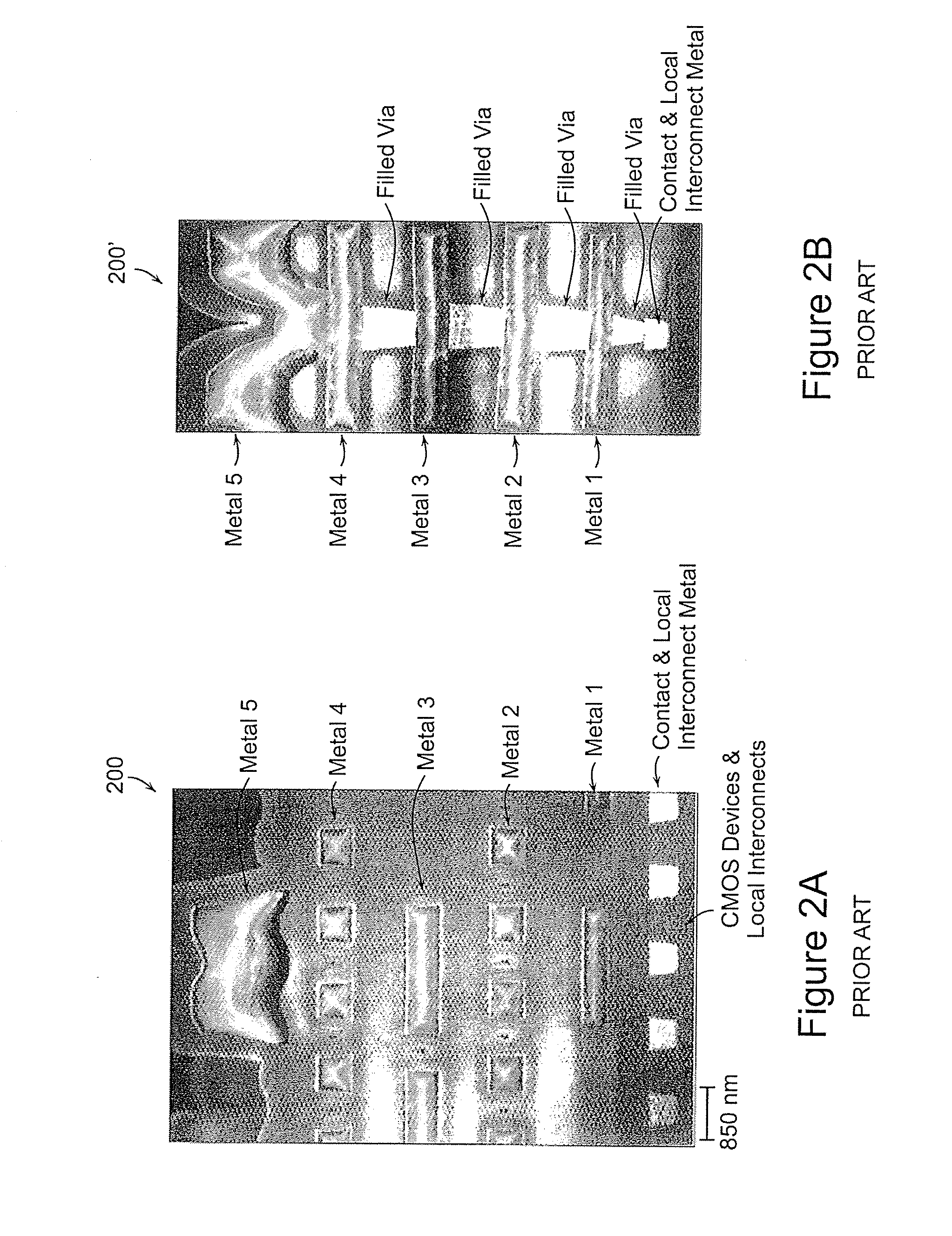

Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same

ActiveUS20080157257A1High resistance stateLow resistance stateSemiconductor/solid-state device detailsNanoinformaticsSchottky barrierSemiconductor materials

Under one aspect, a nanotube diode includes: a cathode formed of a semiconductor material; and an anode formed of nanotubes. The cathode and anode are in fixed and direct physical contact, and are constructed and arranged such that sufficient electrical stimulus applied to the cathode and the anode creates a conductive pathway between the cathode and the anode. In some embodiments, the anode includes a non-woven nanotube fabric having a plurality of unaligned nanotubes. The non-woven nanotube fabric may have a thickness, e.g., of 0.5 to 20 nm. Or, the non-woven nanotube fabric may include a block of nanotubes. The nanotubes may include metallic nanotubes and semiconducting nanotubes, and the cathode may include an n-type semiconductor material. A Schottky barrier can form between the n-type semiconductor material and the metallic nanotubes and / or a PN junction can form between the n-type semiconductor material and the semiconducting nanotubes.

Owner:NANTERO

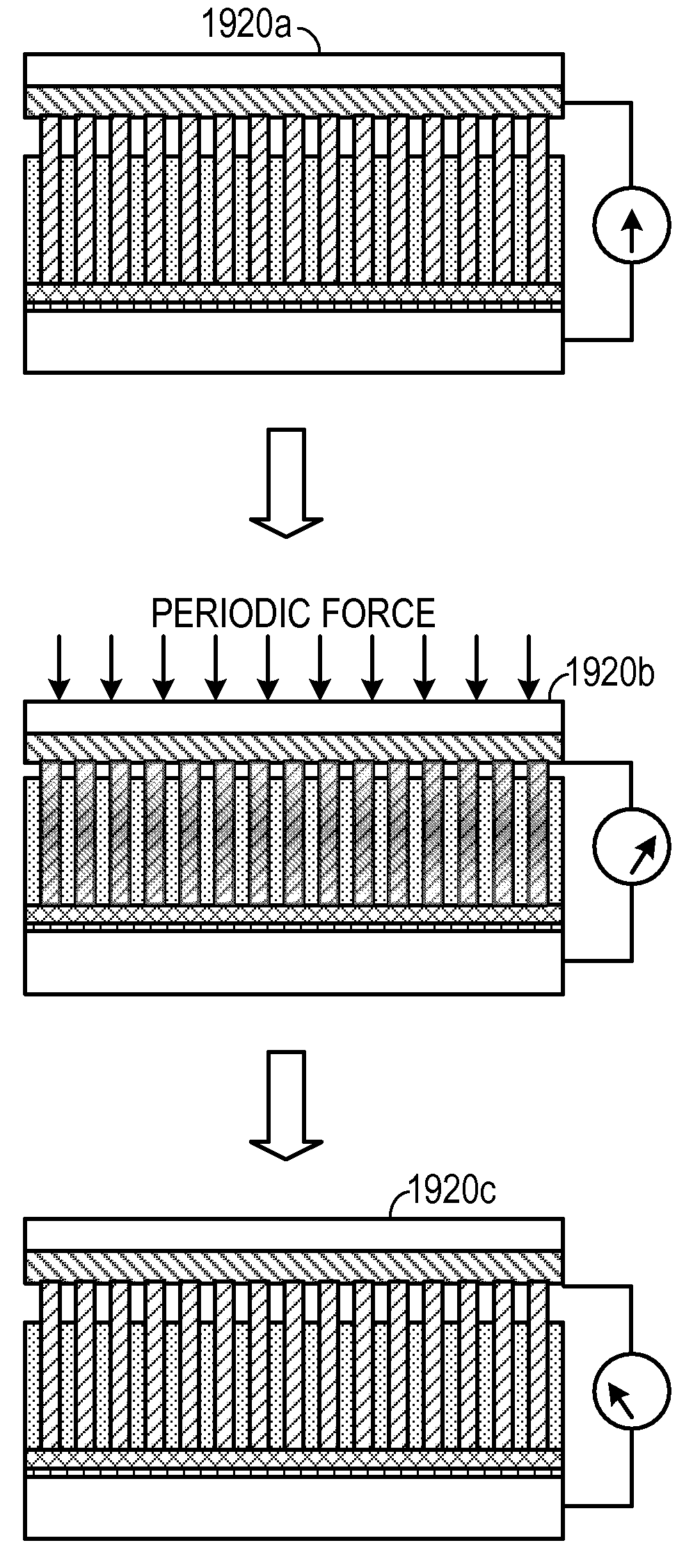

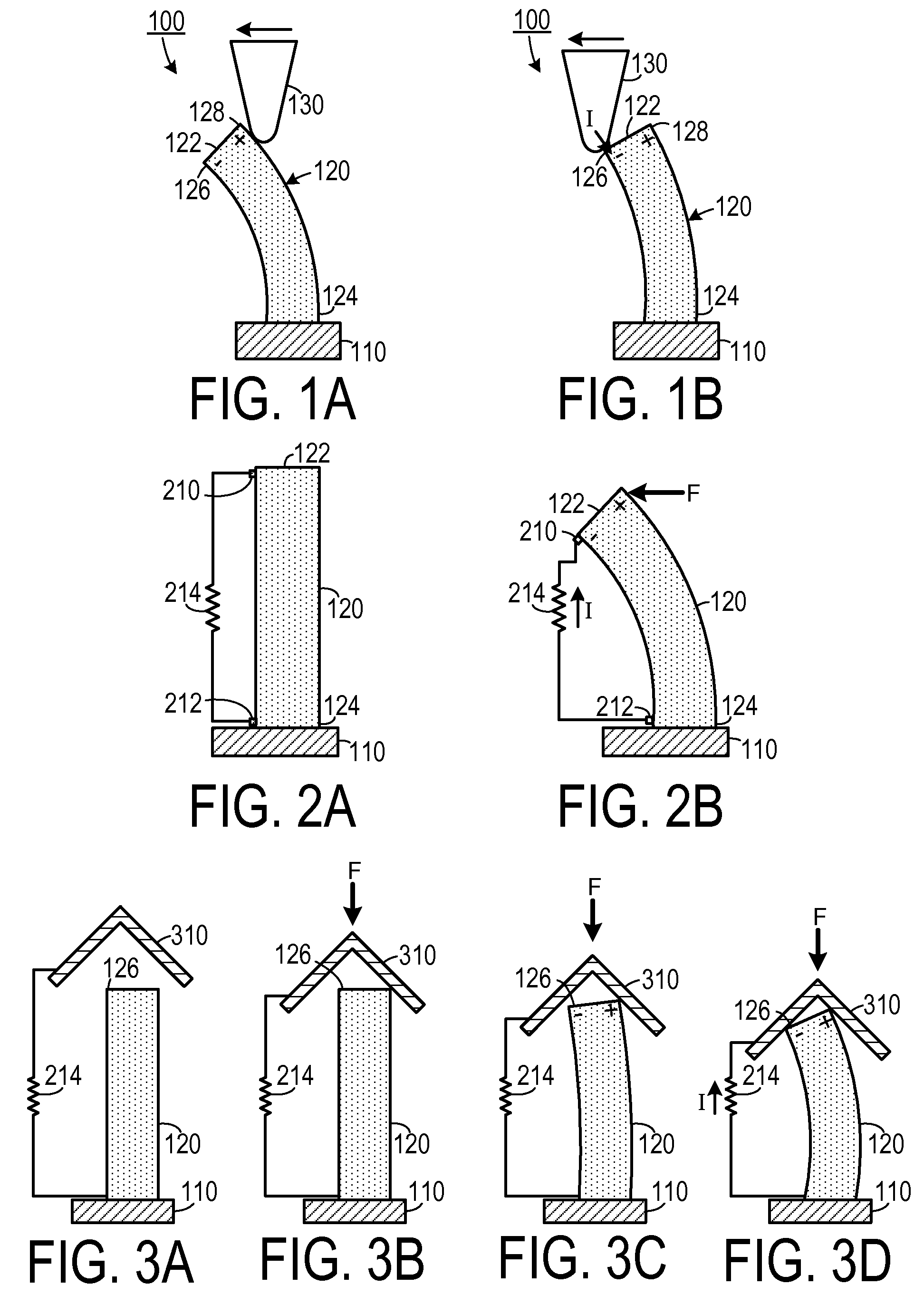

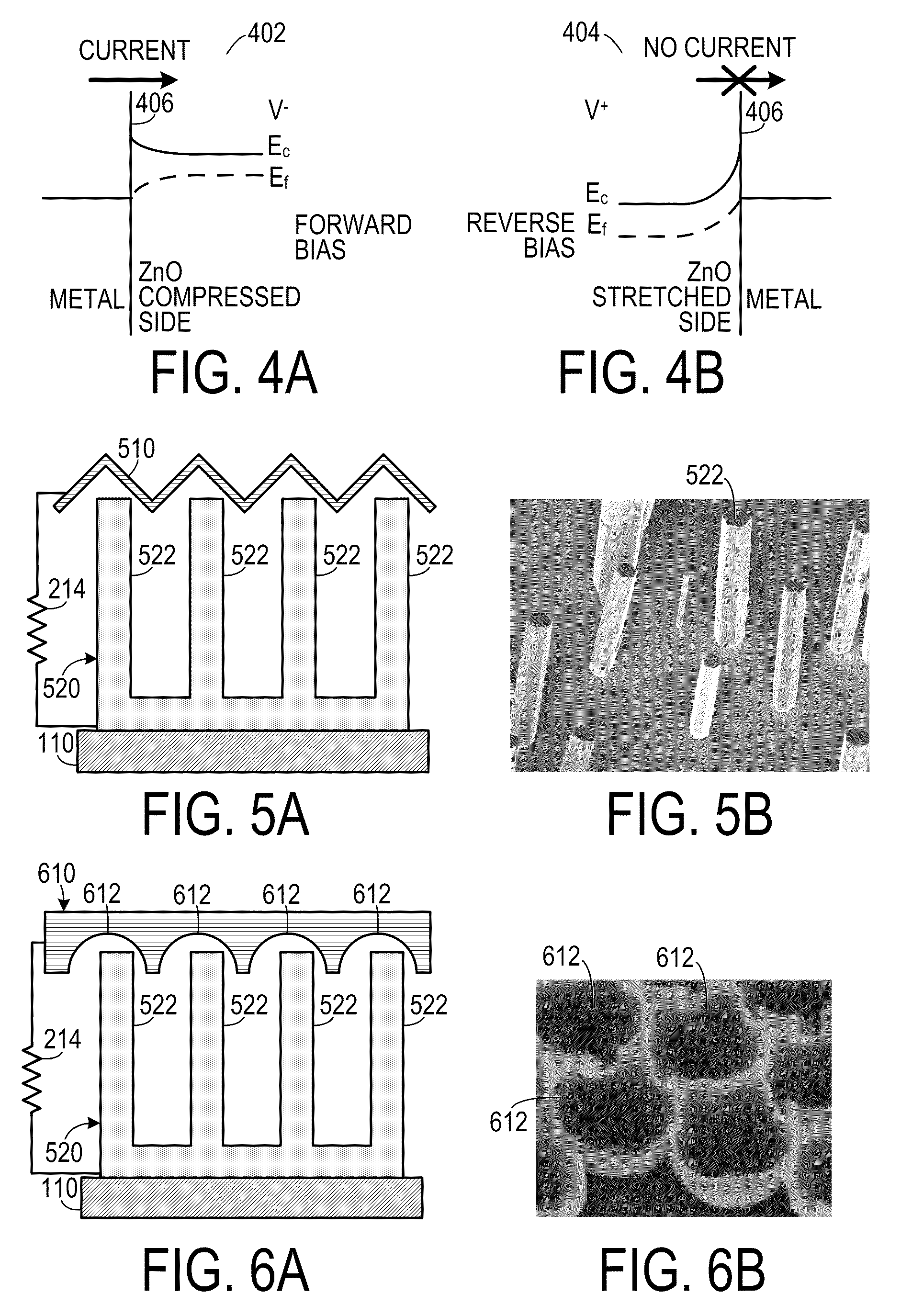

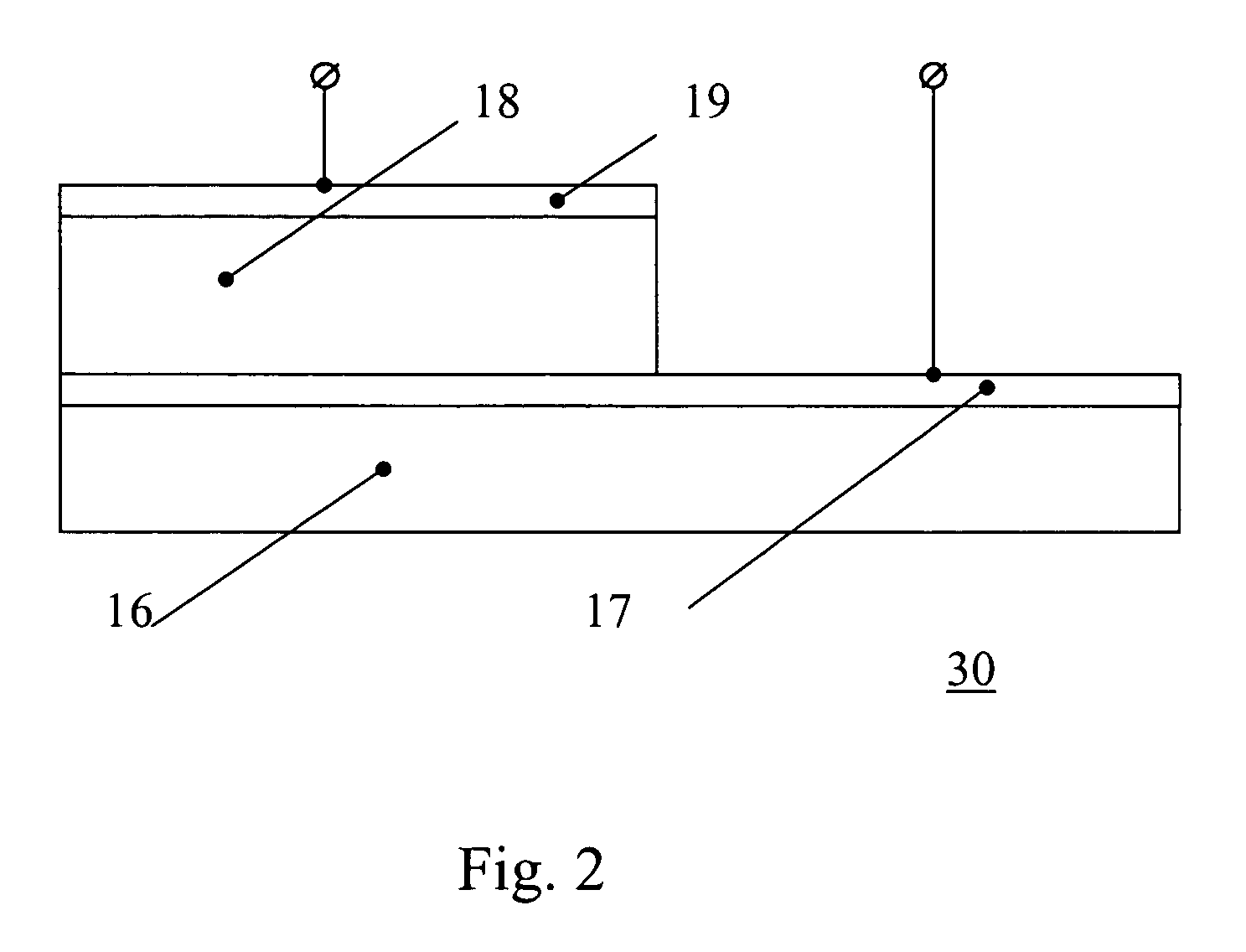

Stacked Mechanical Nanogenerators

ActiveUS20090115293A1Piezoelectric/electrostrictive device manufacture/assemblyNanotechNanogeneratorSchottky barrier

An electric power generator includes a first conductive layer, a plurality of semiconducting piezoelectric nanostructures, a second conductive layer and a plurality of conductive nanostructures. The first conductive layer has a first surface from which the semiconducting piezoelectric nanostructures extend. The second conductive layer has a second surface and is parallel to the first conductive layer so that the second surface faces the first surface of the first conductive layer. The conductive nanostructures depend downwardly therefrom. The second conductive layer is spaced apart from the first conductive layer at a distance so that when a force is applied, the semiconducting piezoelectric nanostructures engage the conductive nanostructures so that the piezoelectric nanostructures bend, thereby generating a potential difference across the at semiconducting piezoelectric nanostructures and also thereby forming a Schottky barrier between the semiconducting piezoelectric nanostructures and the conductive nanostructures.

Owner:GEORGIA TECH RES CORP

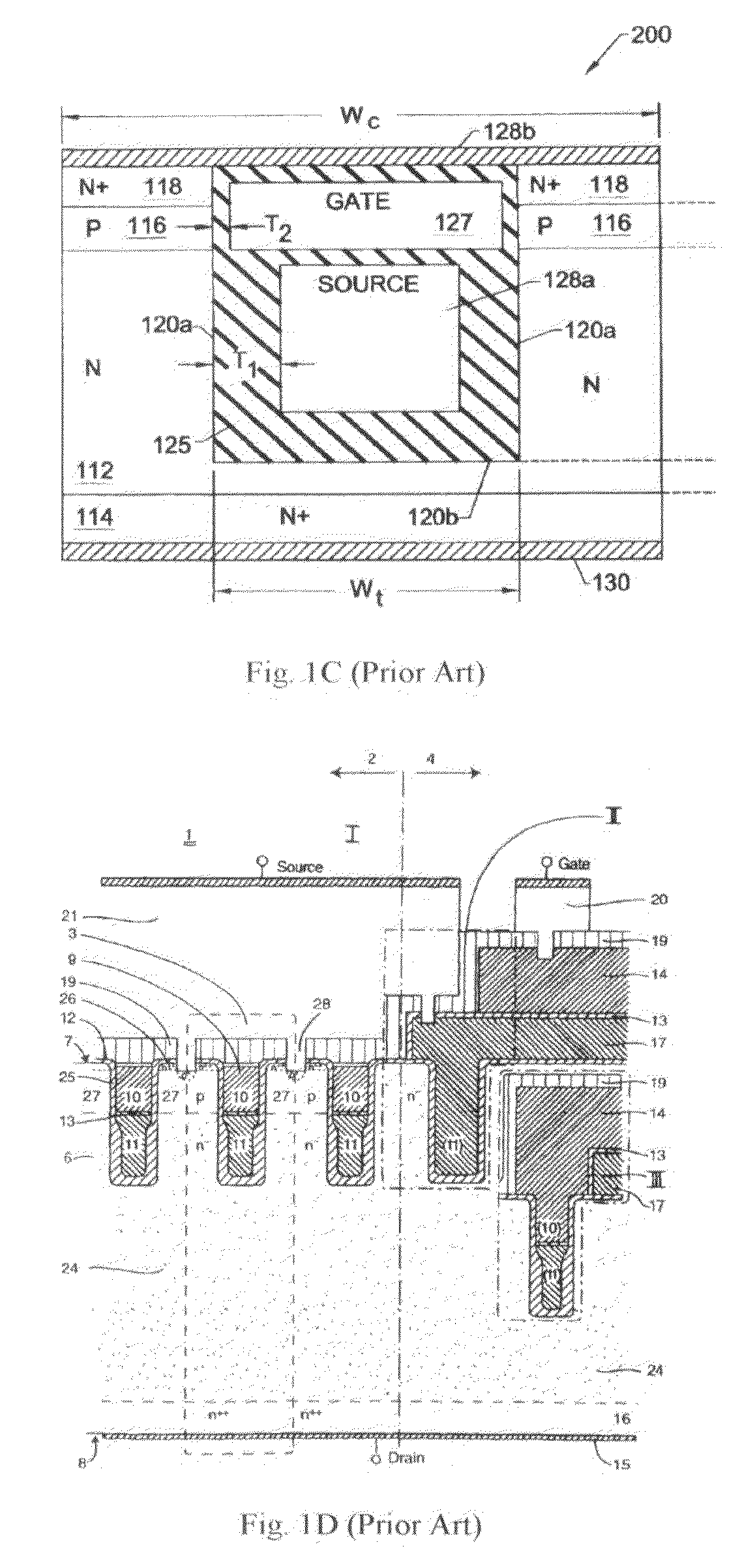

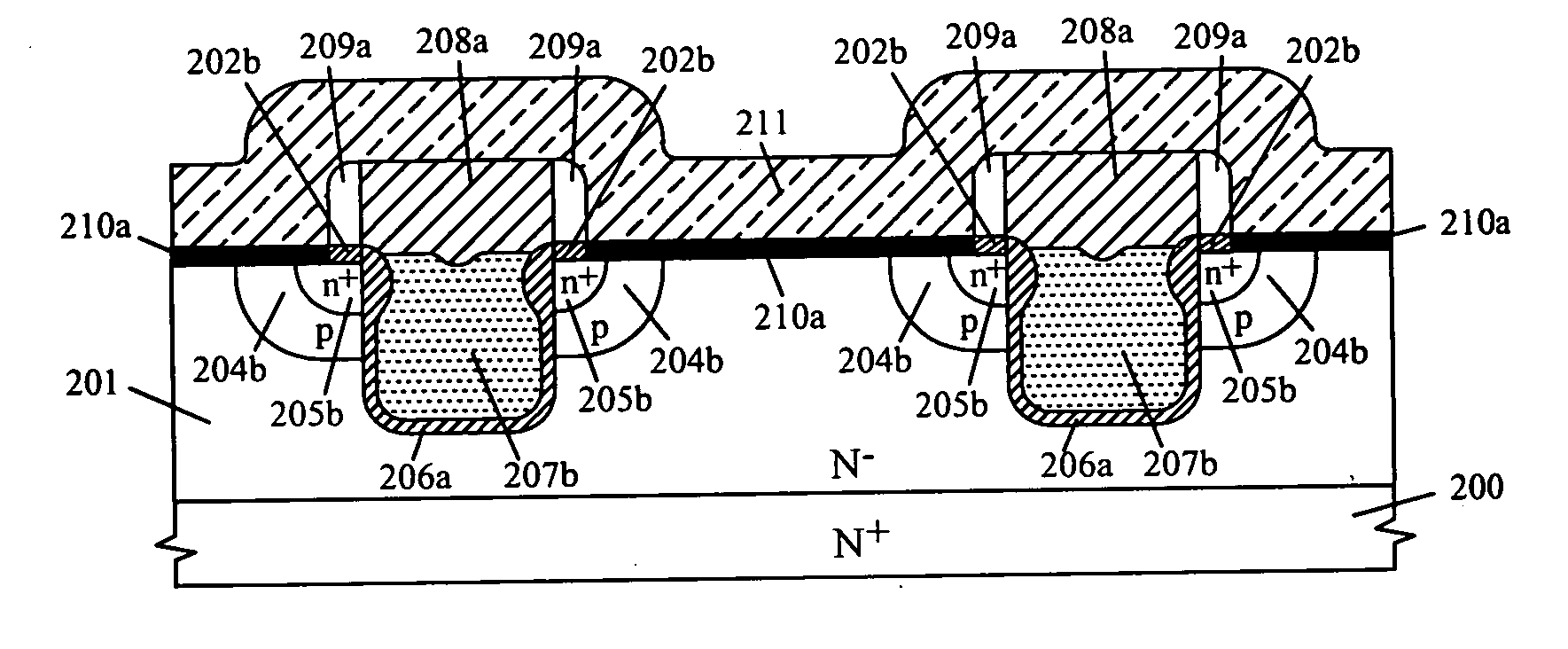

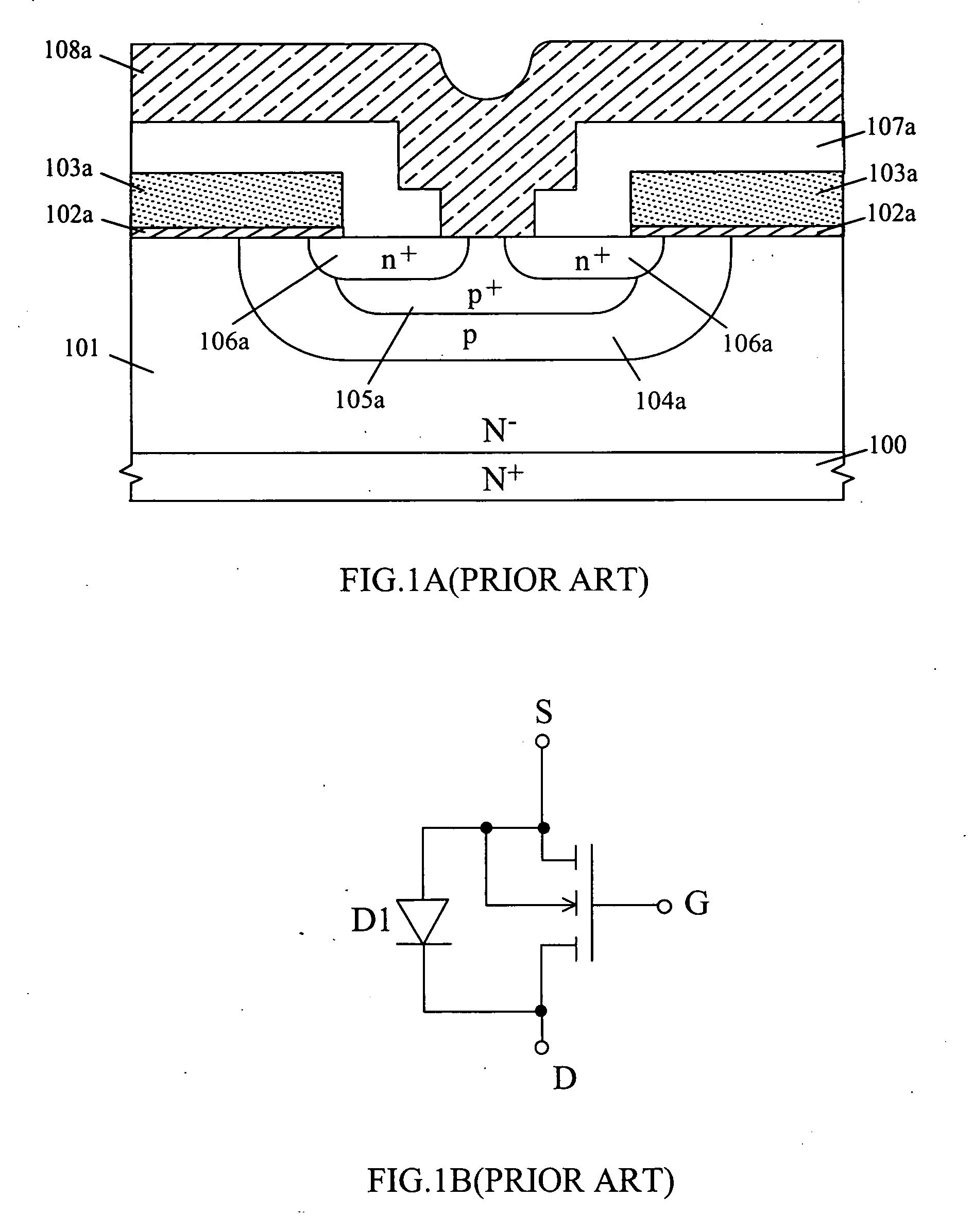

Self-aligned schottky-barrier clamped trench DMOS transistor structure and its manufacturing methods

The self-aligned Schottky-barrier clamped trench DMOS transistor structure of the present invention comprises a Schottky-barrier diode being formed in a middle semiconductor portion of a self-aligned source region. The self-aligned source region comprises a lightly-doped epitaxial semiconductor layer, a moderately-doped base diffusion ring being formed in a surface portion of the lightly-doped epitaxial semiconductor layer surrounded by a trench gate region, a heavily-doped source diffusion ring being formed in a side surface portion of the moderately-doped base diffusion ring, and a self-aligned source contact being formed on a semiconductor surface of the self-aligned source region surrounded by a sidewall dielectric spacer. The trench gate region comprises a self-aligned conductive gate layer being formed over a gate dielectric layer lined over a trenched semiconductor surface in a shallow trench with or without a thicker isolation dielectric layer being formed on a bottom surface of the shallow trench.

Owner:SILICON BASED TECH

Schottky barrier diode and method of making the same

ActiveUS20050230744A1Improve breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSchottky barrierReverse current

A power Schottky rectifier device having a plurality of first trenches filled in with an un-doped polycrystalline silicon layer and each first trenches also has a p-region beneath the bottom of said first trenches to block out reverse current while a reverse biased is applied and to reduce minority carrier while forward biased is applied. Thus, the power Schottky rectifier device can provide first fast switch speed. The power Schottky rectifier device is formed with termination region at an outer portion of the substrate. The manufacture method is also provided.

Owner:WU SHYE LIN +1

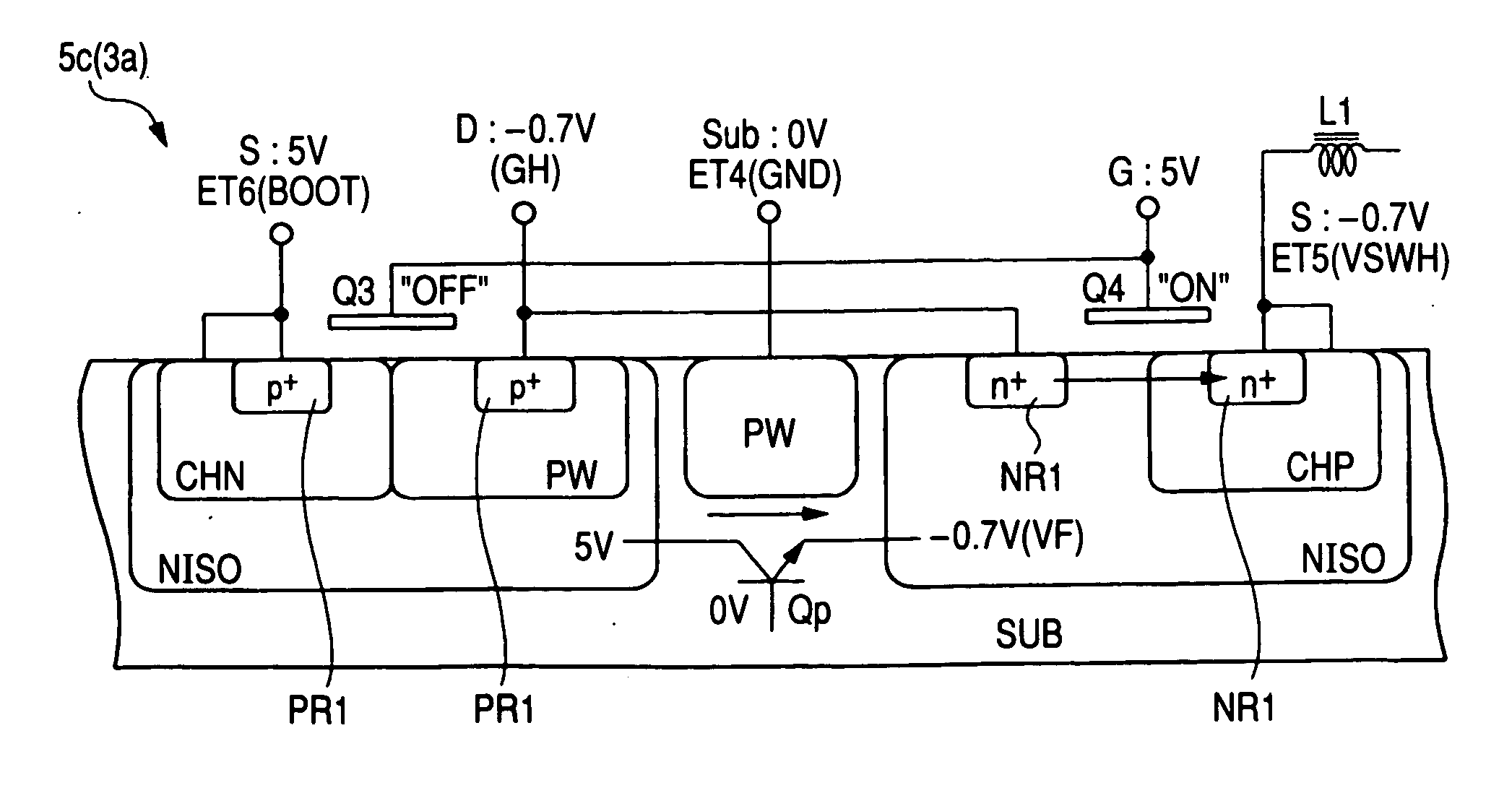

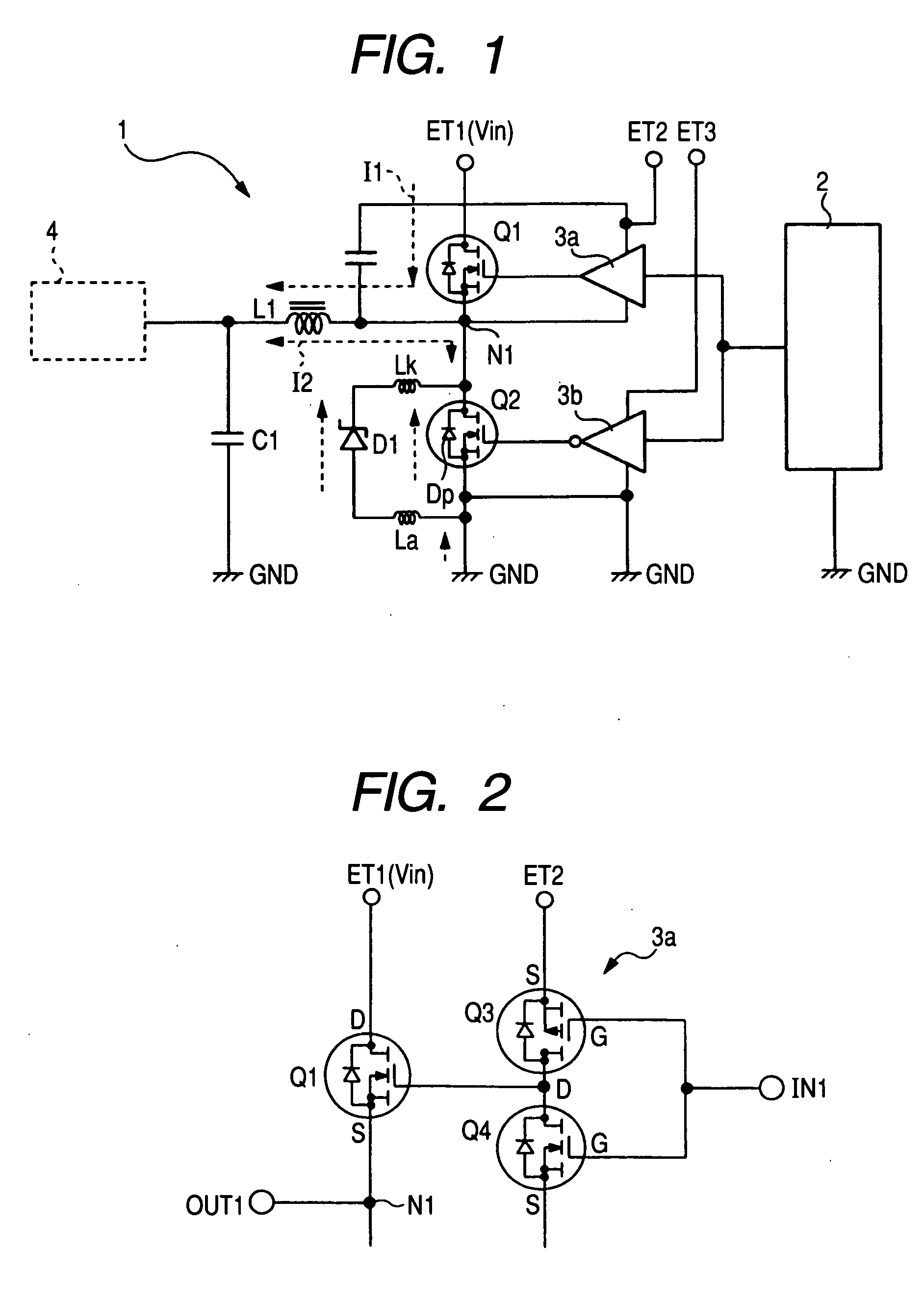

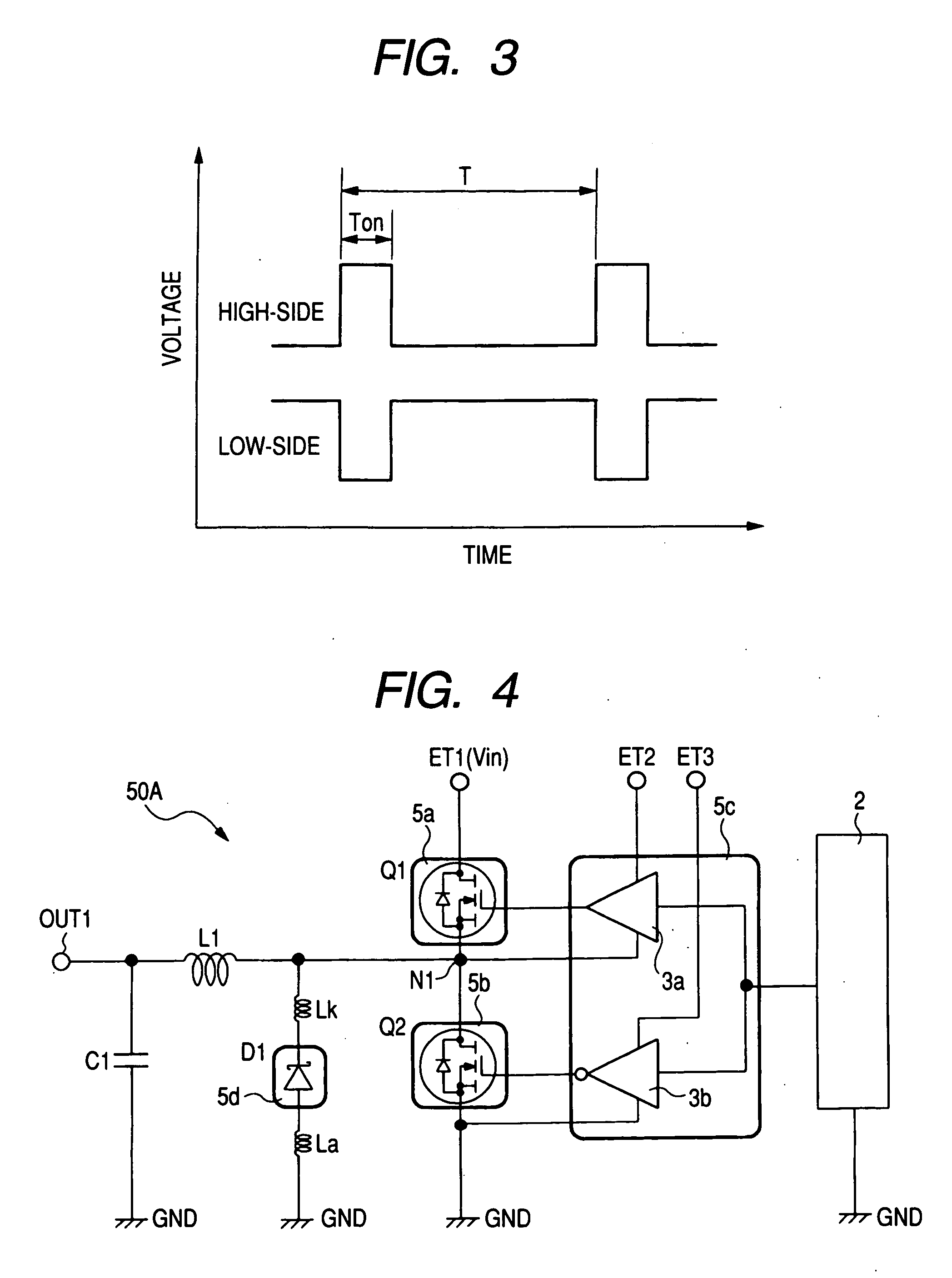

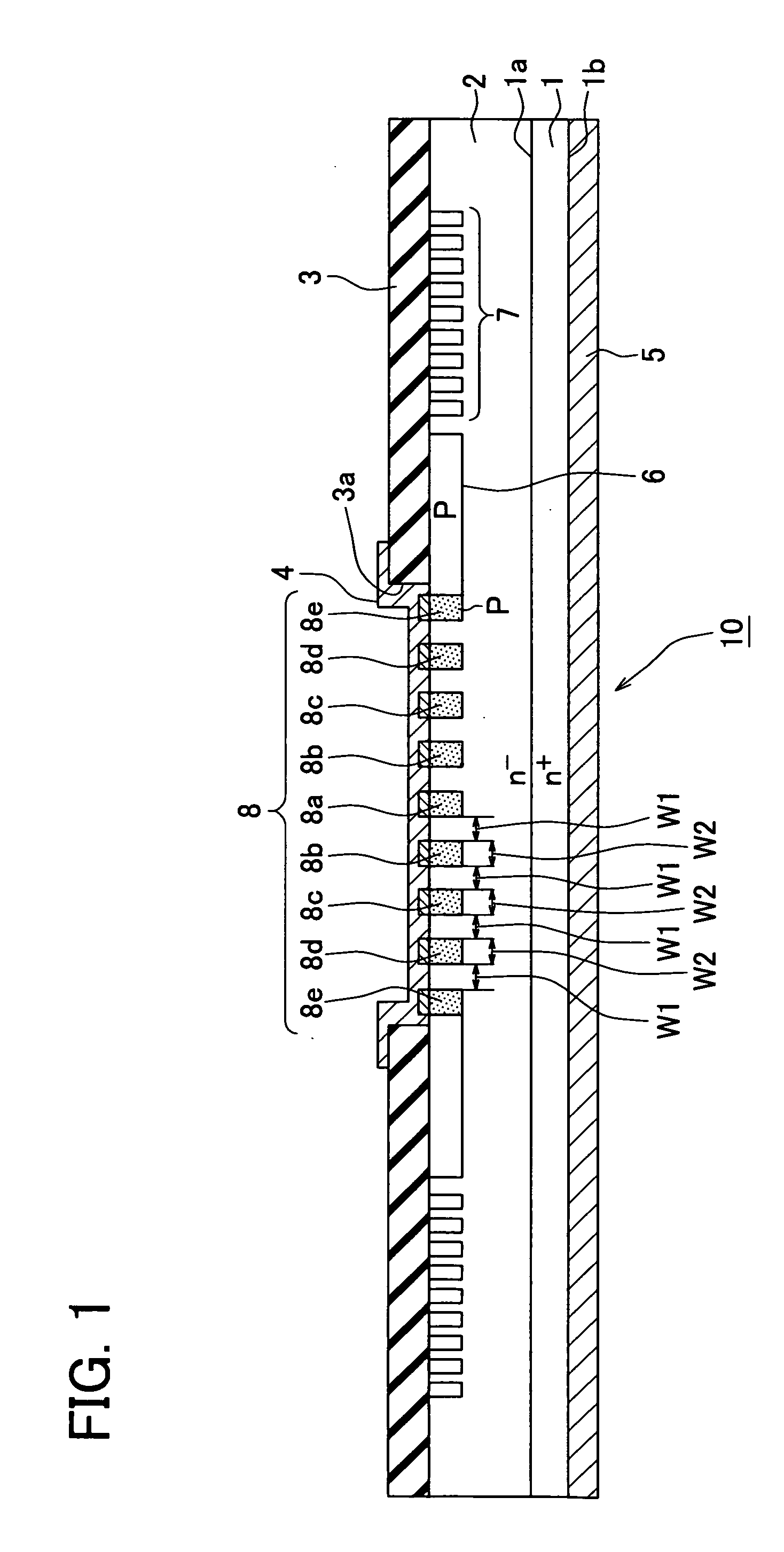

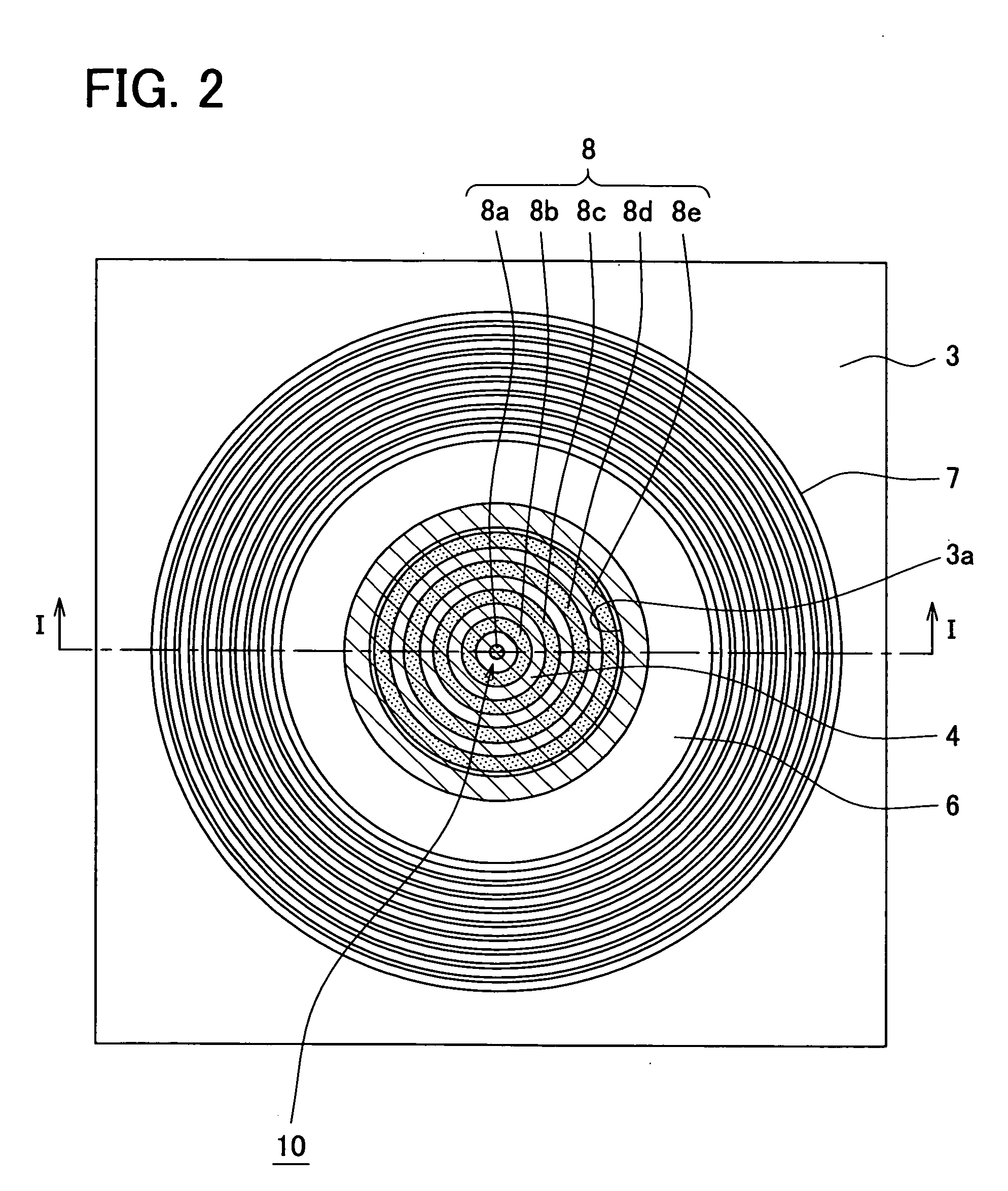

Semiconductor device and a manufacturing method of the same

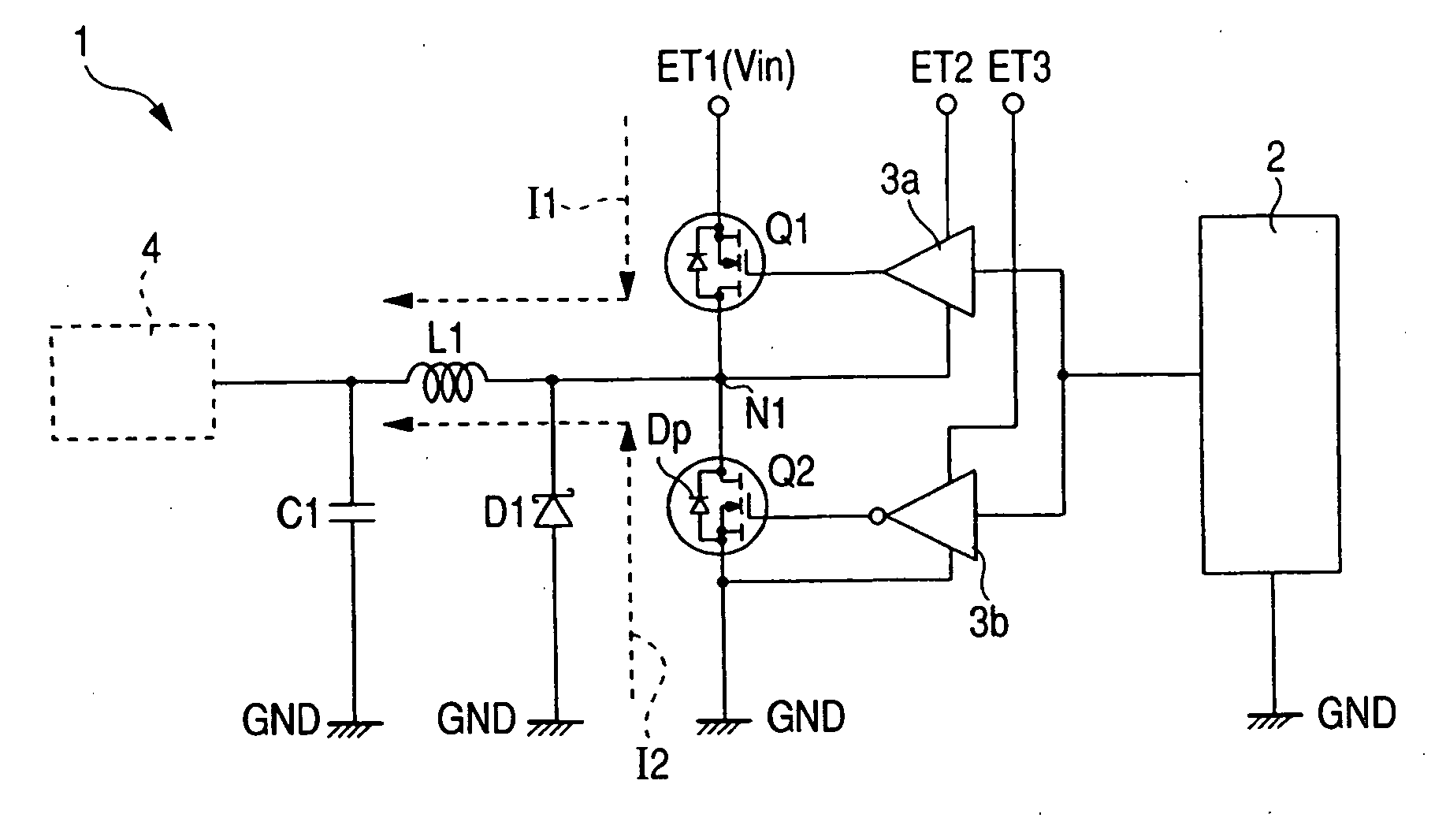

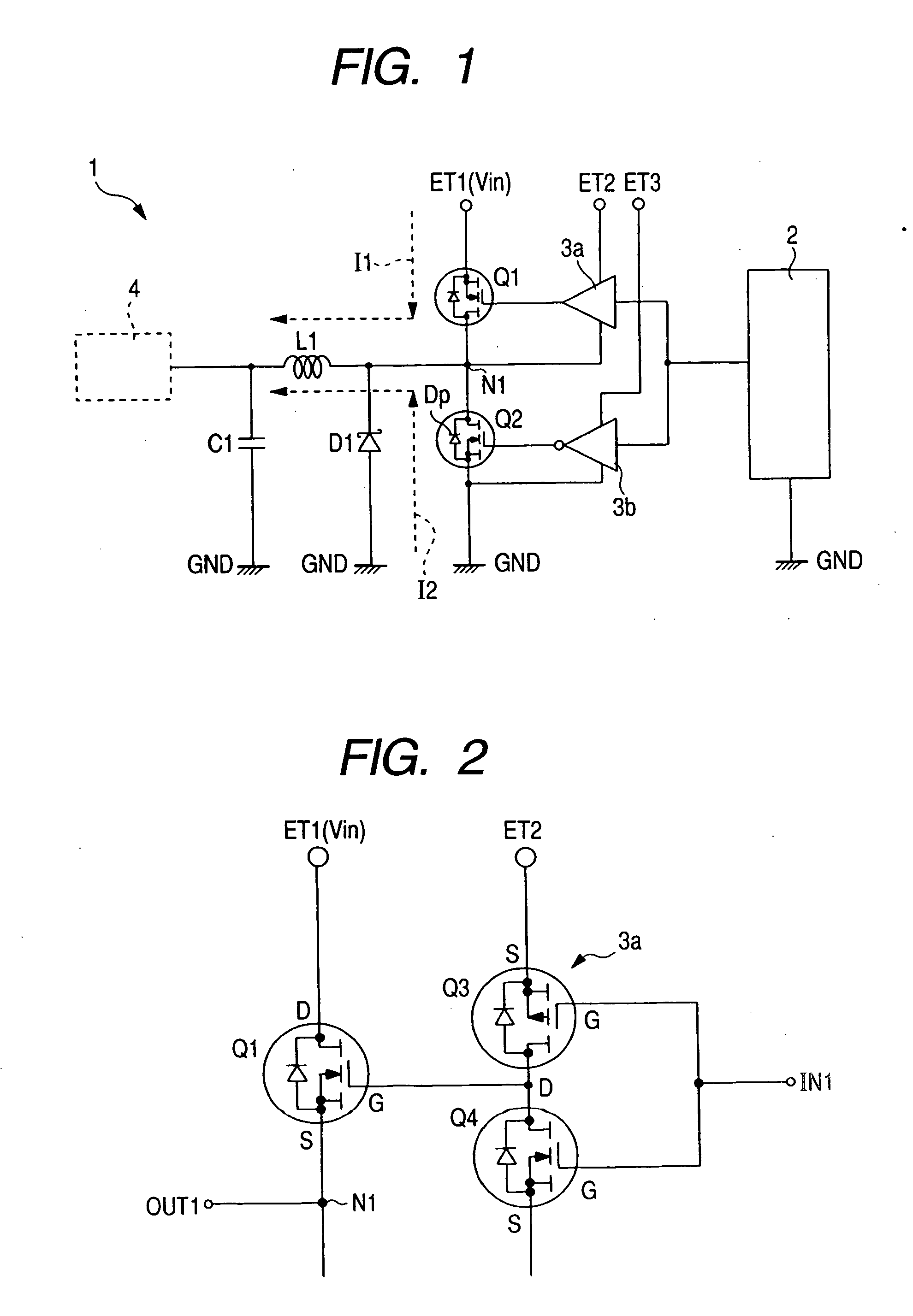

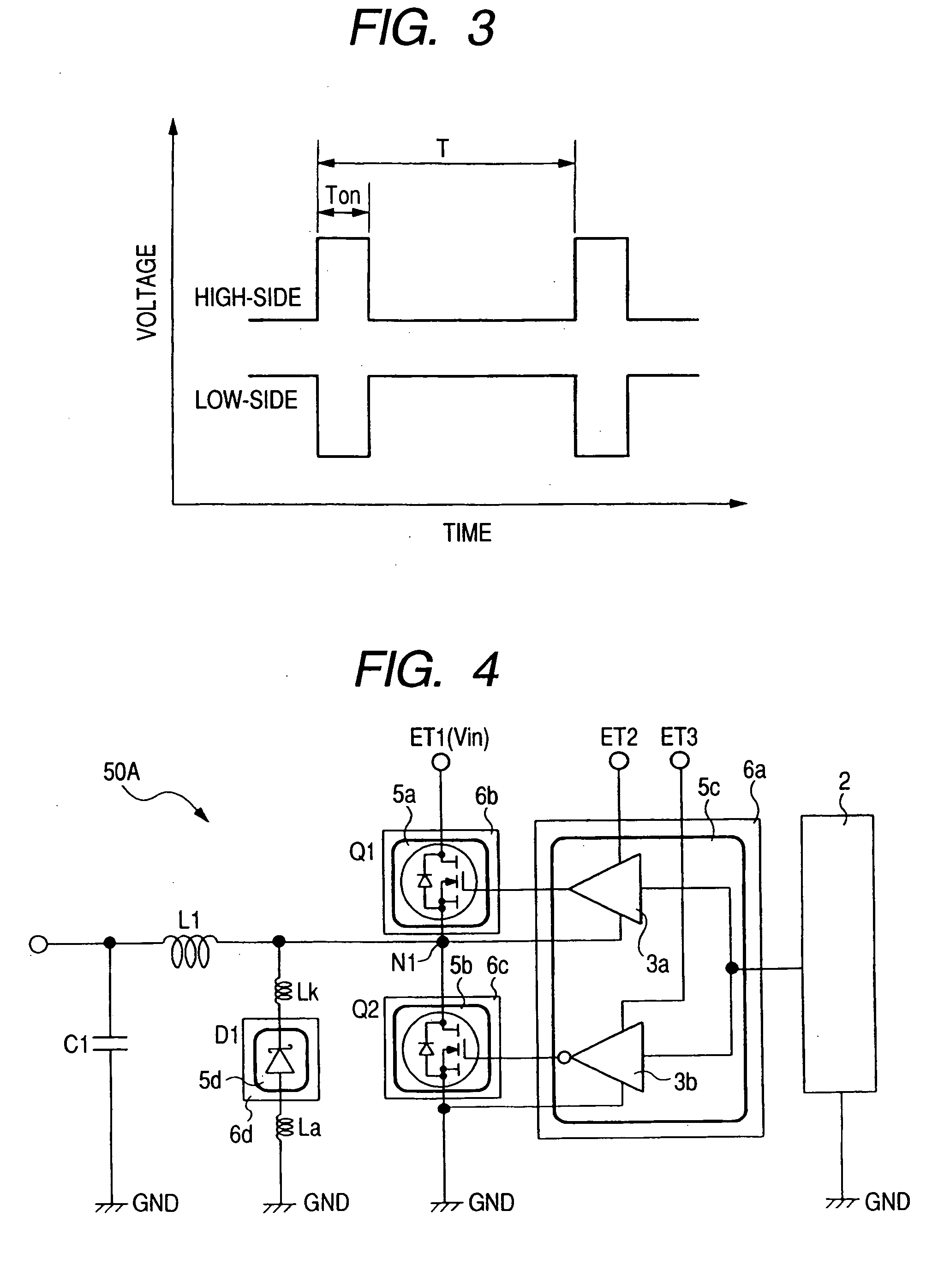

ActiveUS20060022298A1Improve conversion efficiencyReduce inductanceTransistorConversion constructional detailsDc dc converterSchottky barrier

In a non-insulated DC-DC converter having a circuit in which a power MOS•FET high-side switch and a power MOS•FET low-side switch are connected in series, the power MOS•FET low-side switch and a Schottky barrier diode to be connected in parallel with the power MOS•FET GF low-side switch are formed within one semiconductor chip. The formation region SDR of the Schottky barrier diode is disposed in the center in the shorter direction of the semiconductor chips and on both sides thereof, the formation regions of the power MOS•FET low-side switch are disposed. From the gate finger in the vicinity of both long sides on the main surface of the semiconductor chip toward the formation region SDR of the Schottky barrier diode, a plurality of gate fingers are disposed so as to interpose the formation region SDR between them.

Owner:RENESAS ELECTRONICS CORP

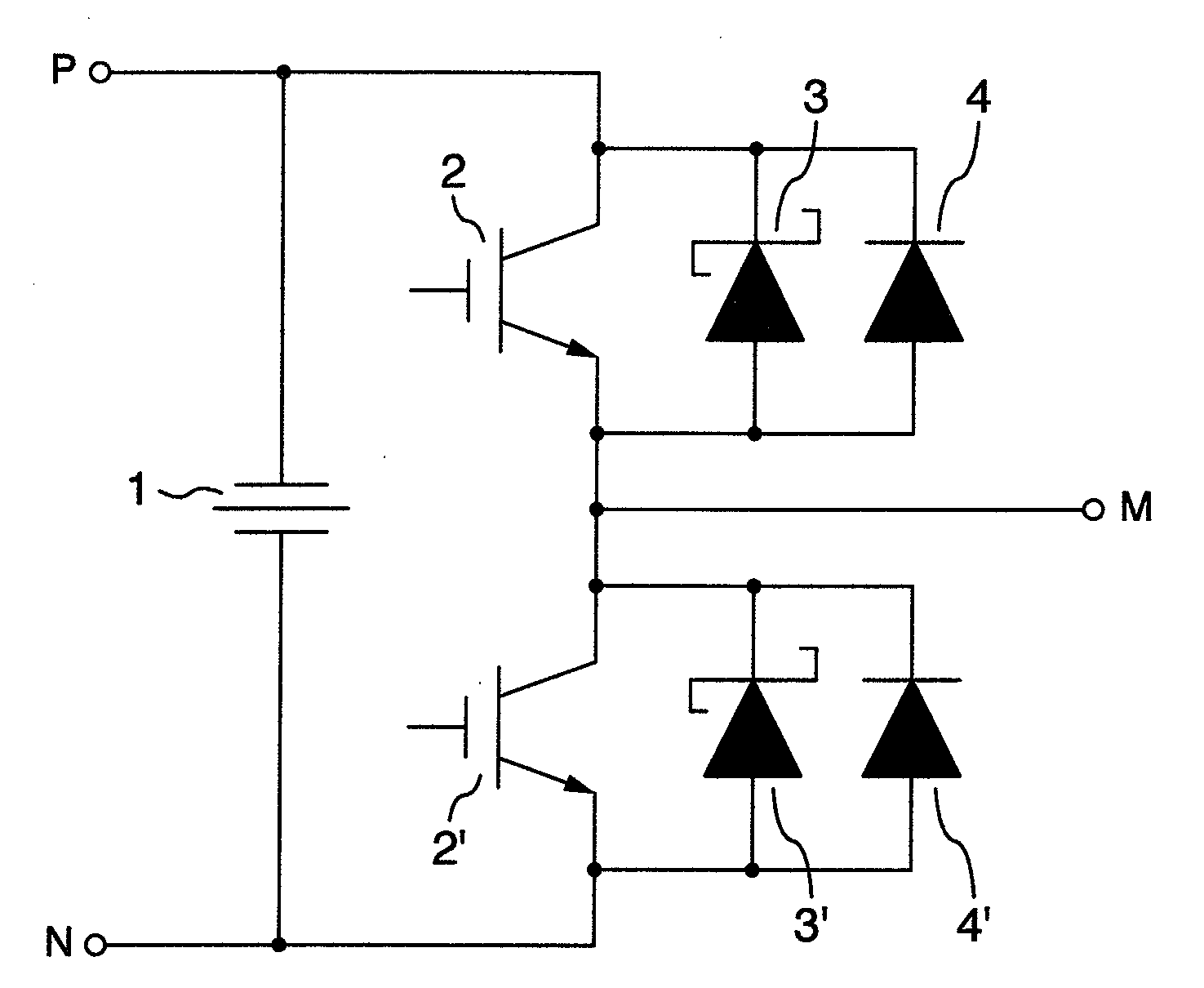

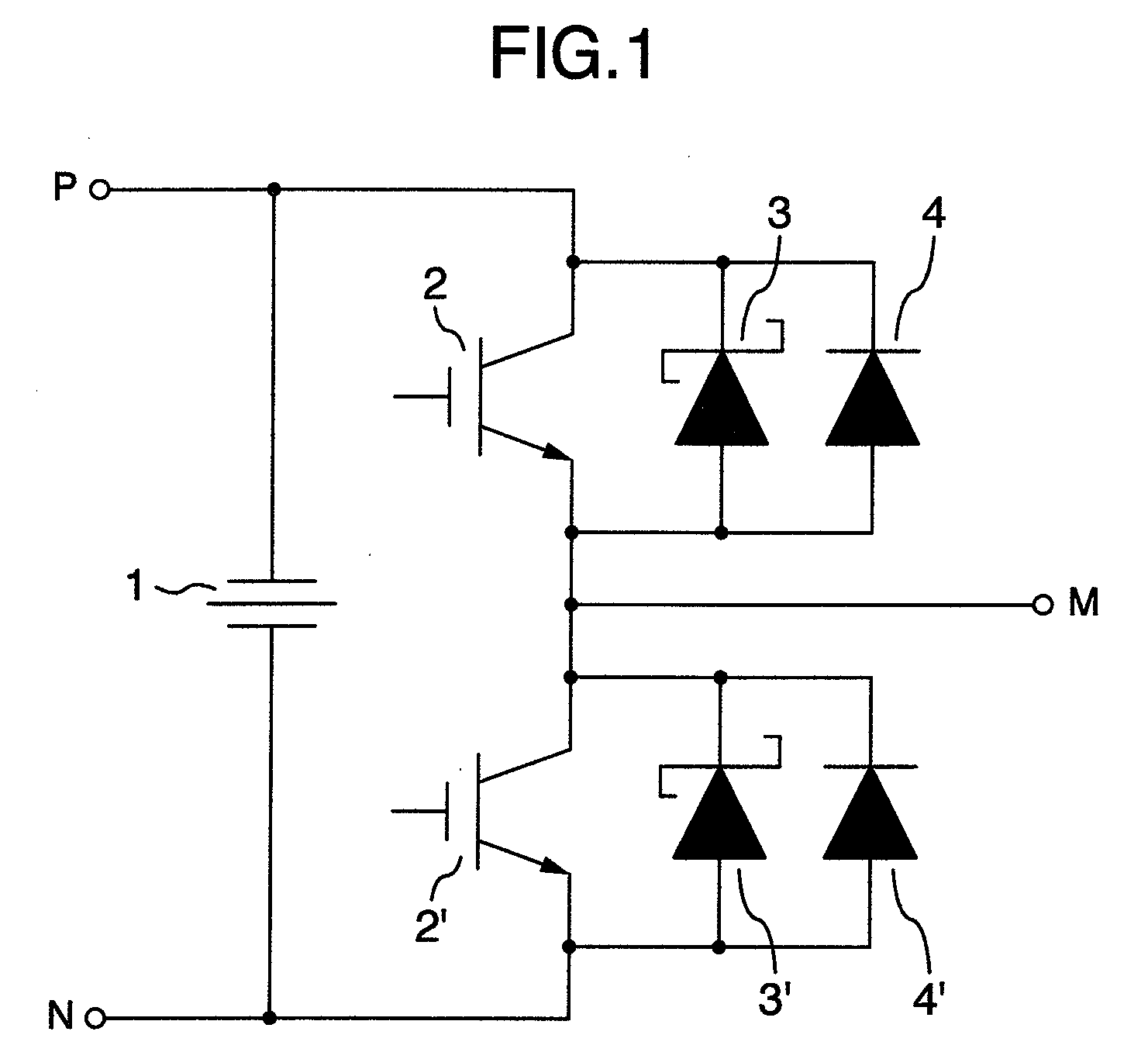

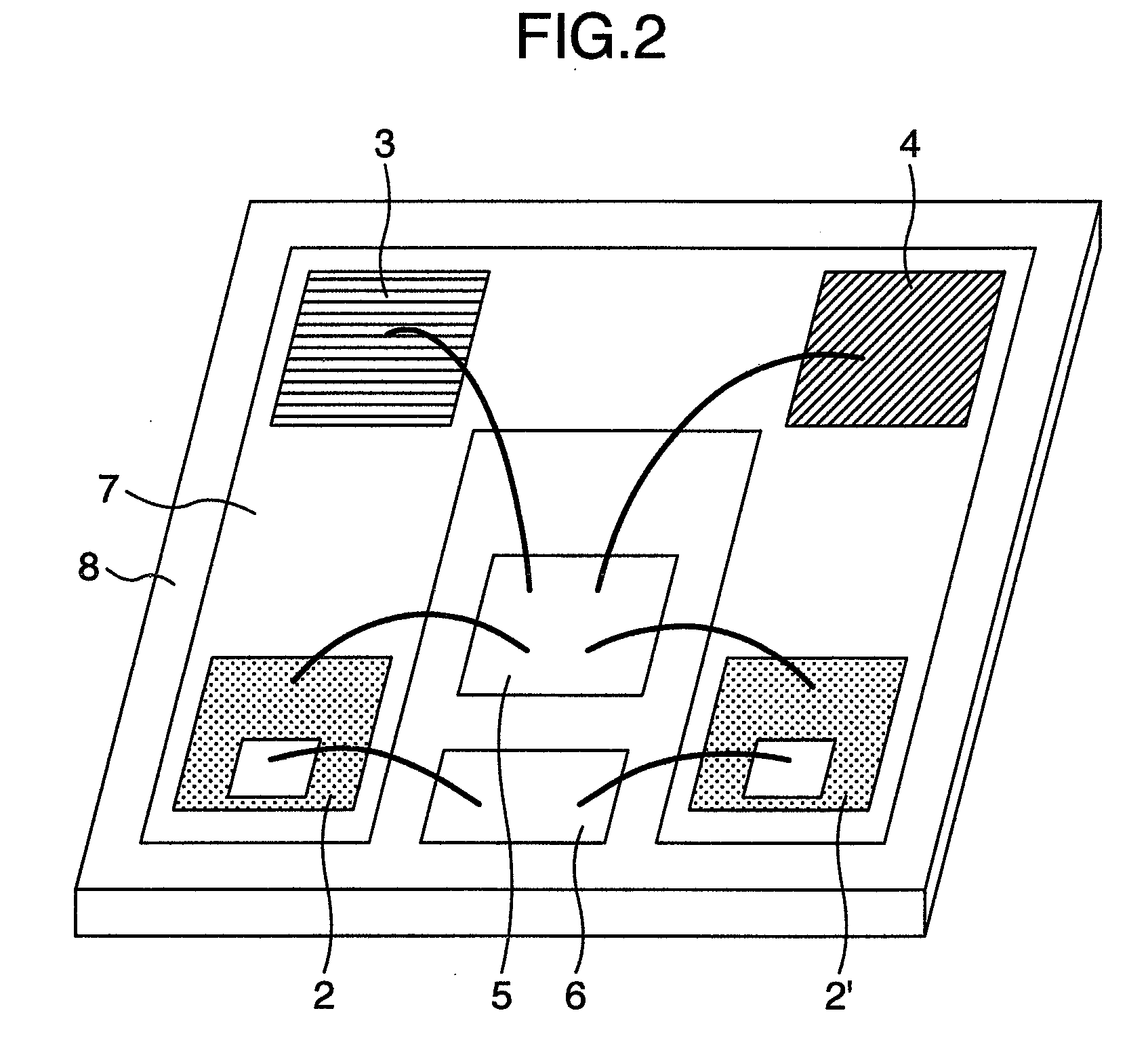

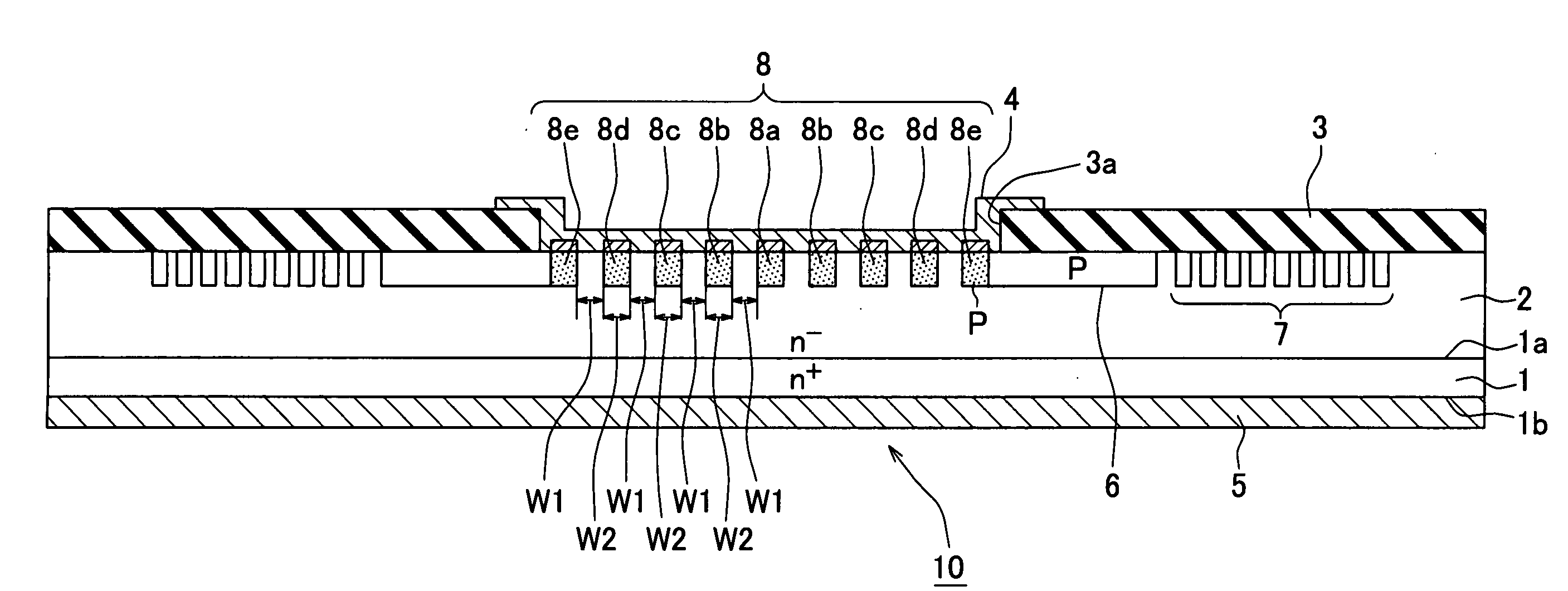

Circuit device having a free wheeling diode, circuit device and power converter using diodes

InactiveUS20090168471A1Emergency protective circuit arrangementsSolid-state devicesCapacitanceSchottky barrier

A circuit device includes at least one switching element and a free wheeling diode connected in parallel to the switching element. The free wheeling diode is made up of a Schottky barrier diode using a semiconductor material having a band gap larger than silicon as its base material and also a silicon PiN diode, which are connected in parallel. The Schottky barrier diode and the silicon PiN diode are provided in the form of separate chips. A circuit system is also provided wherein a diode having a Schottky junction of a compound semiconductor as a rectification element built therein is combined, and a relationship, R2>4L / C, with impedance R (resistance), L (inductance), and C (capacitance) determined by a closed circuit between a power source and a positive or negative terminal when the current of the diode becomes zero during recovery operation, is satisfied.

Owner:HITACHI LTD

SIS semiconductor having junction barrier schottky device

A semiconductor device having a junction barrier Schottky diode includes: a SiC substrate; a drift layer on the substrate; an insulation film on the drift layer having an opening in a cell region; a Schottky barrier diode having a Schottky electrode contacting the drift layer through the opening of the insulation film and an ohmic electrode on the substrate; a terminal structure having a RESURF layer surrounding the cell region; and multiple second conductive type layers on an inner side of the RESURF layer. The second conductive type layers and the drift layer provide a PN diode. The Schottky electrode includes a first Schottky electrode contacting the second conductive type layers with ohmic contact and a second Schottky electrode contacting the drift layer with Schottky contact.

Owner:DENSO CORP

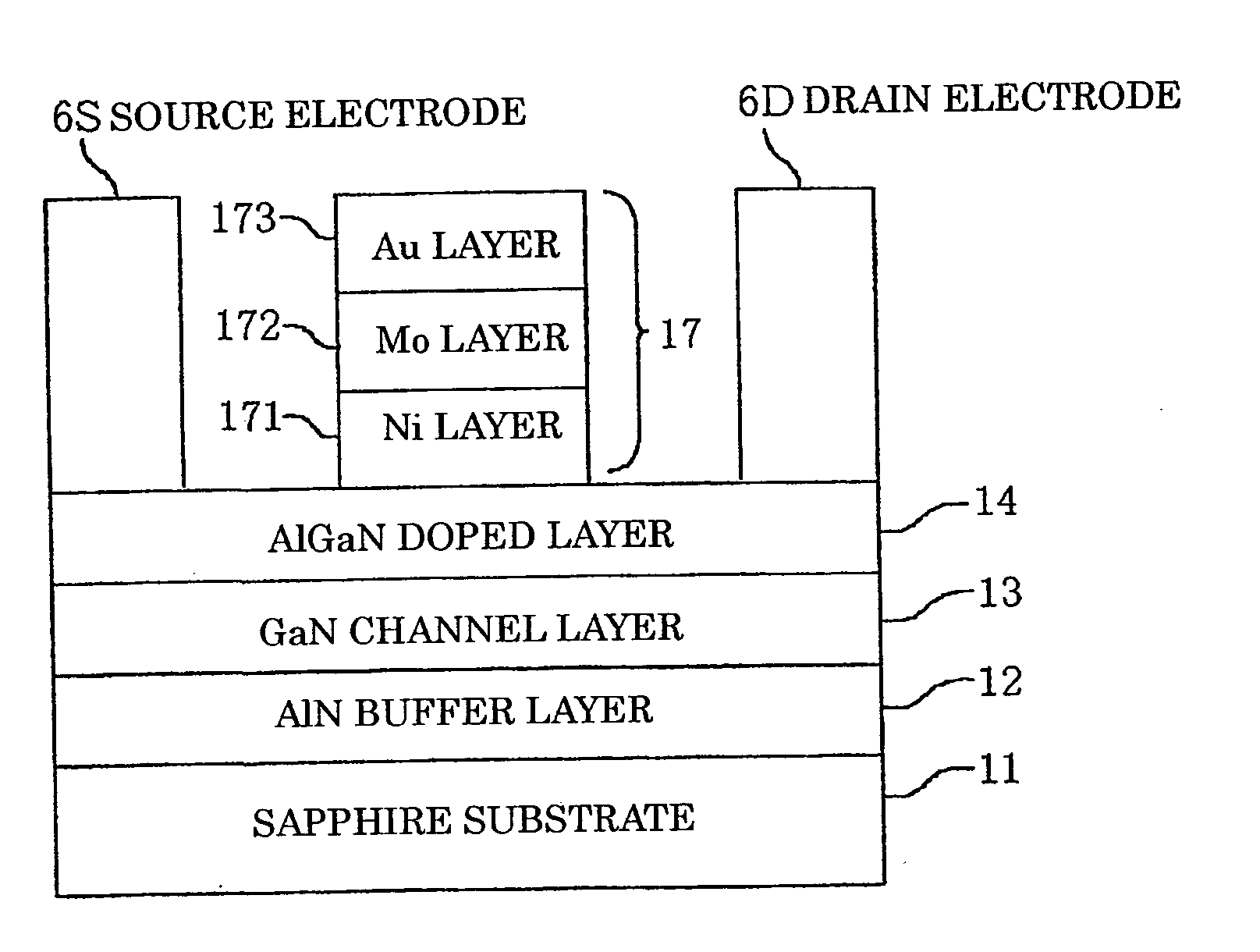

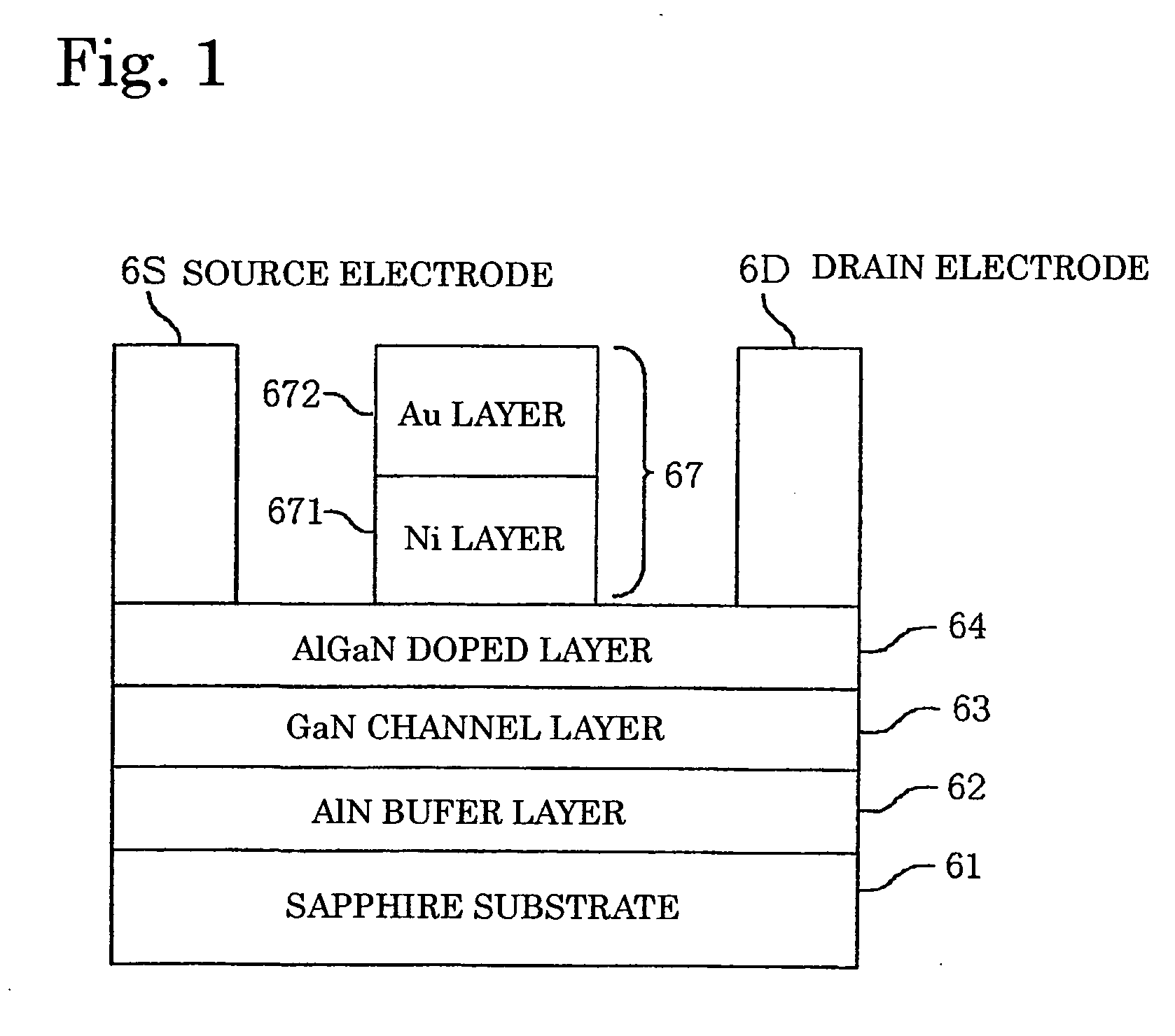

Semiconductor device having schottky junction electrode

InactiveUS20050151255A1Improve heat resistanceImprove power performanceSemiconductor/solid-state device detailsSolid-state devicesSchottky barrierDevice material

A GaN semiconductor device with improved heat resistance of the Schottky junction electrode and excellent power performance and reliability is provided. In this semiconductor device having a Schottky gate electrode 17 which is in contact with an AlGaN electron supplying layer 14, a gate electrode 17 comprises a laminated structure wherein a first metal layer 171 formed of any of Ni, Pt and Pd, a second metal layer 172 formed of any of Mo, Pt, W, Ti, Ta, MoSi, PtSi, WSi, TiSi, TaSi, MoN, WN, TiN and TaN, and a third metal layer formed of any of Au, Cu, Al and Pt. Since the second metal layer comprises a metal material having a high melting point, it works as a barrier to the interdiffusion between the first metal layer and the third metal layer, and the deterioration of the gate characteristics caused by high temperature operation is suppressed. Since the first metal layer contacting the AlGaN electron supplying layer 14 has a high work function, the Schottky barrier is high, and superior Schottky contact is obtained.

Owner:NEC CORP

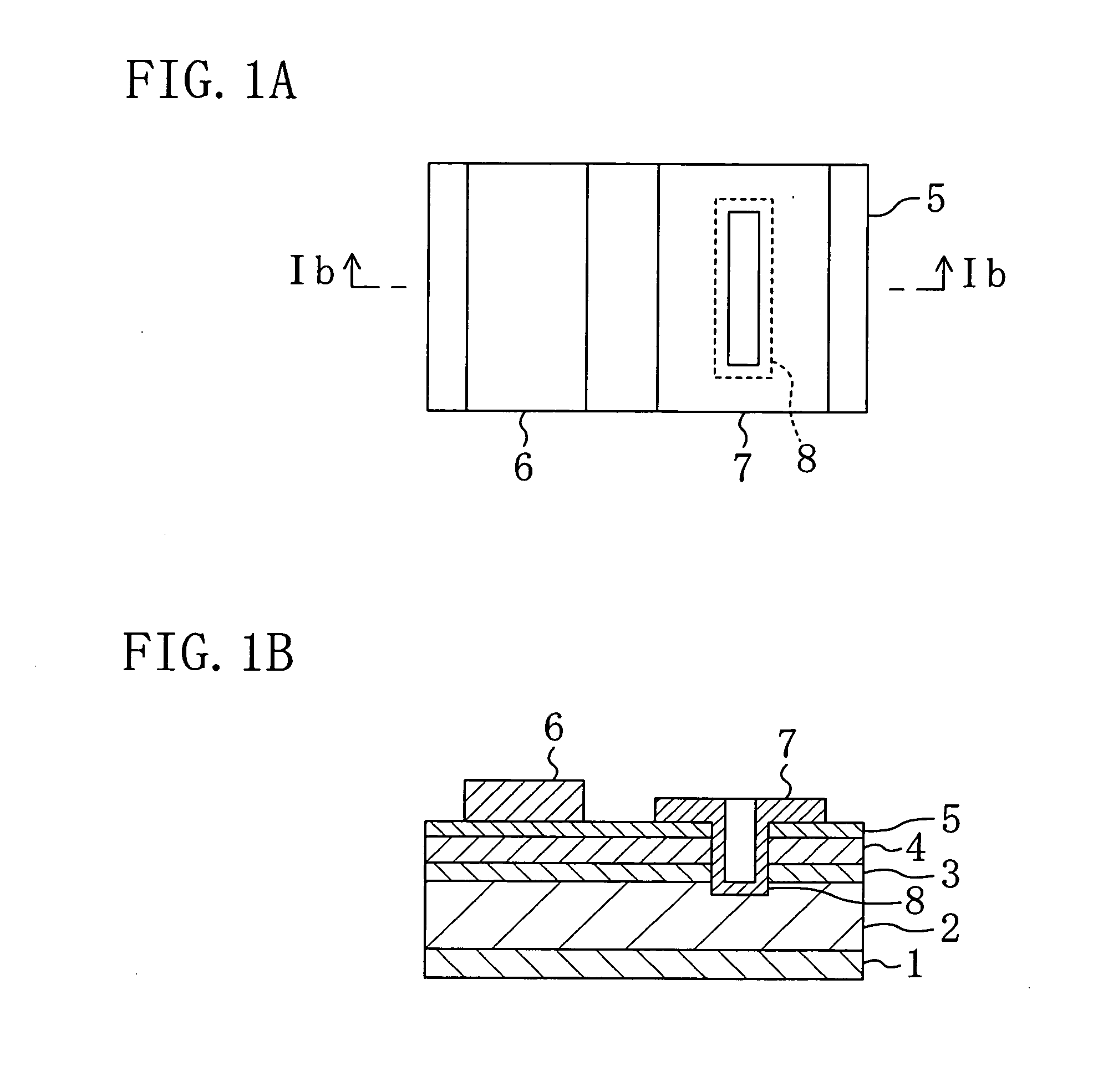

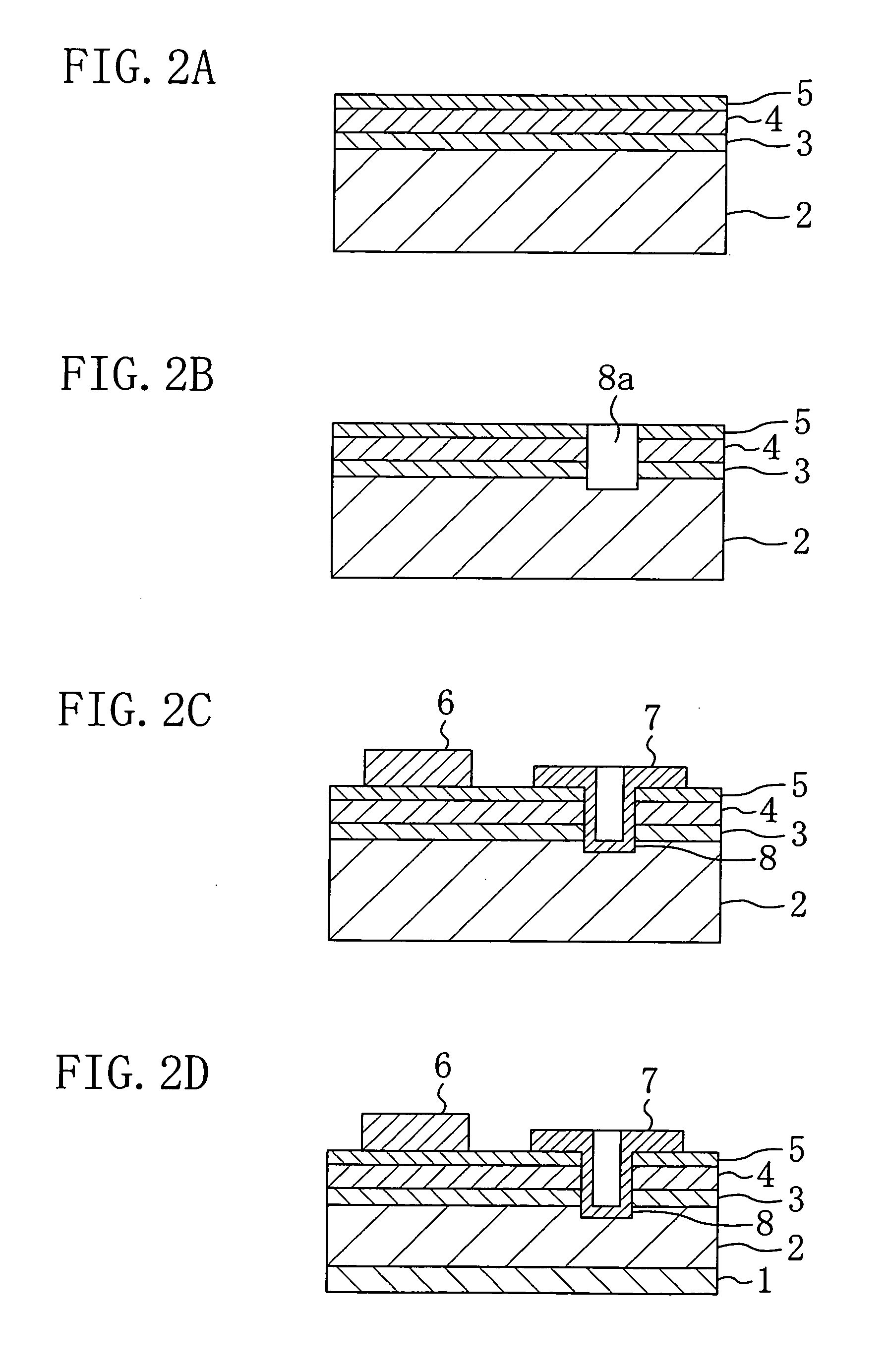

Schottky barrier diode and integrated circuit using the same

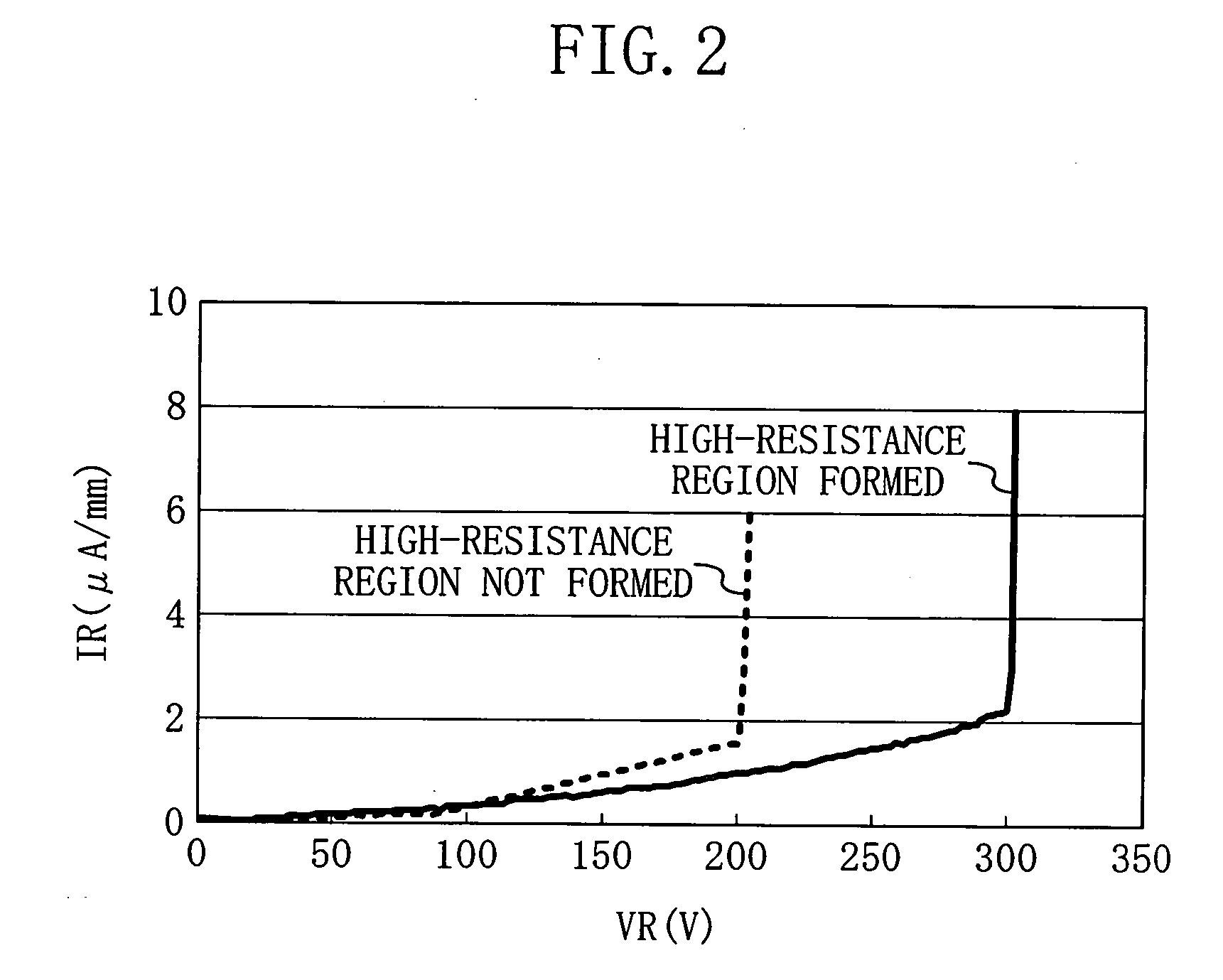

ActiveUS20060108605A1Avoid attenuationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceSchottky barrier

A Schottky barrier diode includes a first semiconductor layer and a second semiconductor layer successively formed above a substrate; and a high-resistance region formed in the first semiconductor layer and the second semiconductor layer and having higher resistance than the first semiconductor layer and the second semiconductor layer. A Schottky electrode and an ohmic electrode spaced from each other are formed on the second semiconductor layer in a portion surrounded with the high-resistance region.

Owner:PANASONIC CORP

Semiconductor device

InactiveUS20050231990A1Shorten the lengthLow sectionTransistorAc-dc conversionPower semiconductor deviceDriver circuit

A non-insulated DC-DC converter a power MOS·FRT for a highside switch and a power MOS·FET for a lowside switch. In the non-insulated DC-DC converter, the power MOS·FET for the highside switch and the power MOS·FET for the lowside switch, driver circuits that control operations of these elements, respectively, and a Schottky barrier diode connected in parallel with the power MOS·FET for the lowside switch are respectively formed in four different semiconductor chips. These four semiconductor chips are housed in one package. The semiconductor chips are mounted over the same die pad. The semiconductor chips are disposed so as to approach each other.

Owner:RENESAS ELECTRONICS CORP

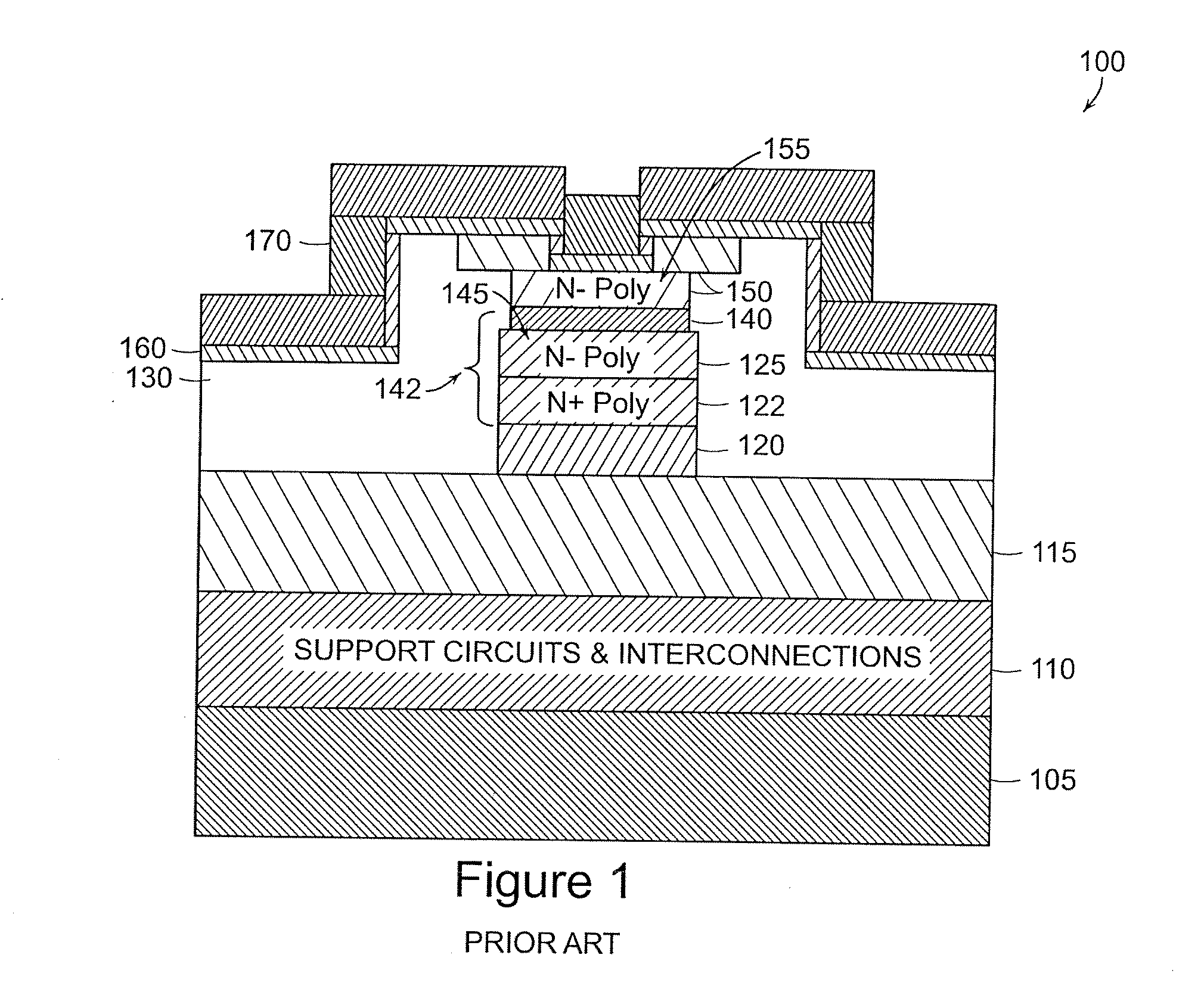

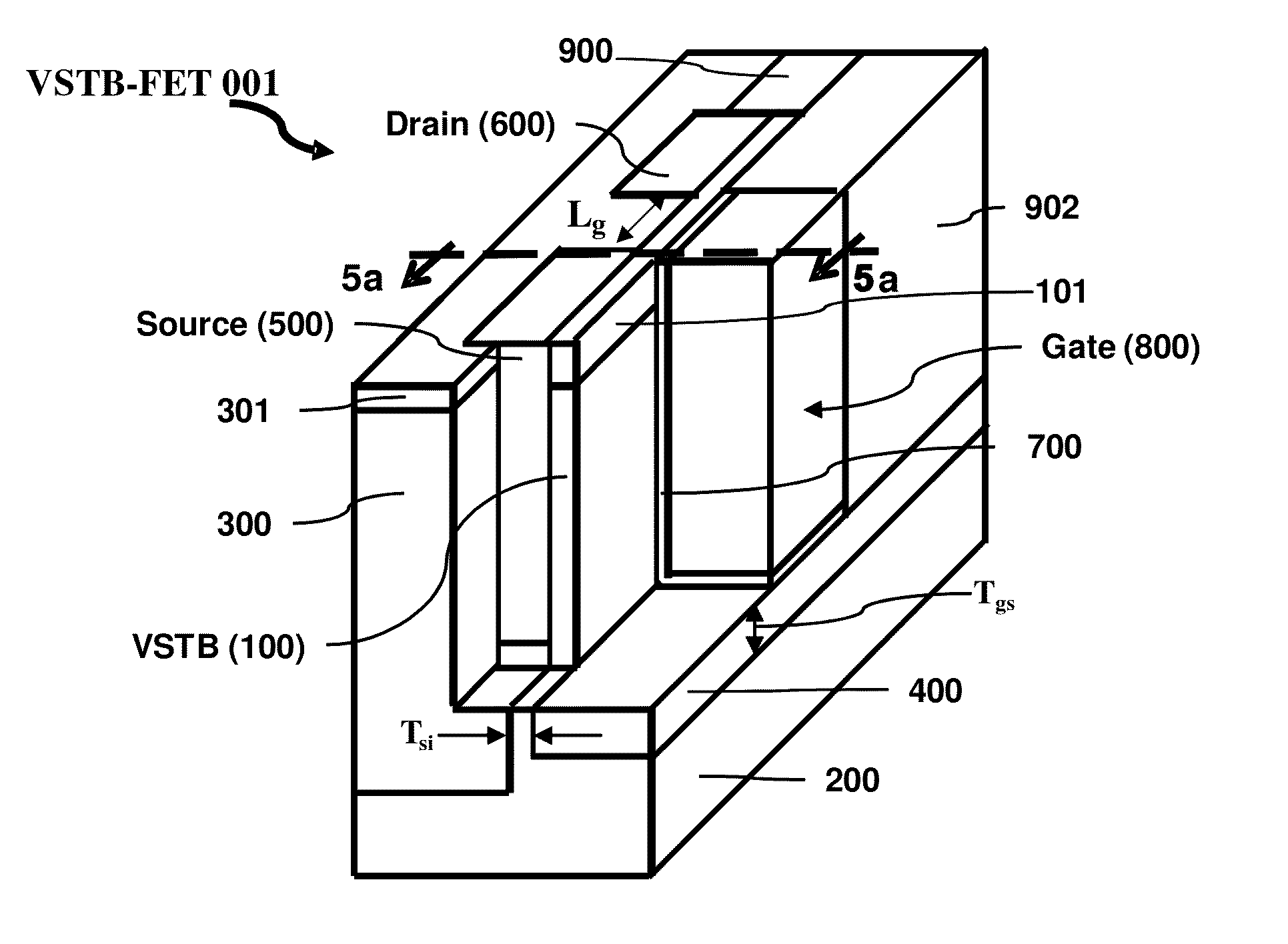

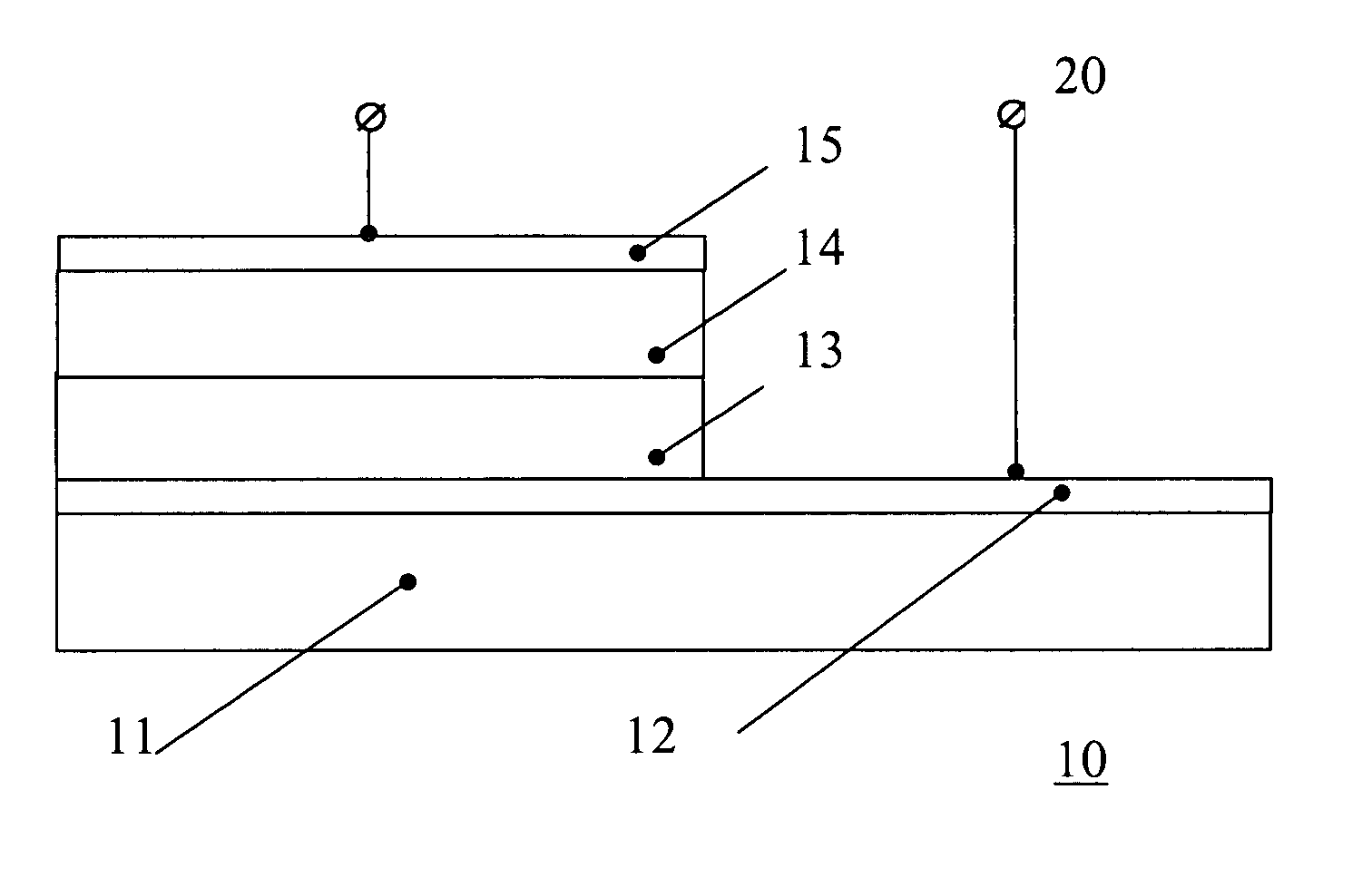

Vertical Super-Thin Body Semiconductor on Dielectric Wall Devices and Methods of Their Fabrication

ActiveUS20140106523A1Strict controlEasy to implementTransistorSemiconductor/solid-state device detailsMOSFETGate dielectric

The present invention is a semiconductor device comprising a semiconducting low doped vertical super-thin body (VSTB) formed on Dielectric Body Wall (such as STI-wall as isolating substrate) having the body connection to bulk semiconductor wafer on the bottom side, isolation on the top side, and the channel, gate dielectric, and gate electrode on opposite to STI side surface. The body is made self-aligned to STI hard mask edge allowing tight control of body thickness. Source and Drain are made by etching holes vertically in STI at STI side of the body and filling with high doped crystalline or poly-Si appropriately doped with any appropriate silicides / metal contacts or with Schottky barrier Source / Drain. Gate first or Gate last approaches can be implemented. Many devices can be fabricated in single active area with body isolation between the devices by iso-plugs combined with gate electrode isolation by iso-trenches. The body can be made as an isolated nano-plate or set nano-wire MOSFET's on the STI wall to form VSTB SOI devices.

Owner:FINSCALE

Organic semiconductor diode

InactiveUS7211824B2Solid-state devicesSemiconductor/solid-state device manufacturingSchottky barrierP–n junction

The present invention relates to organic semiconductor diodes, in particular, to the diodes with nonlinear current-voltage characteristics, which are used for power switching, rectifying variable signals, and frequency mixing. The organic semiconductor diode with the p-n junction comprises an anode, cathode, a hole transport layer in contact with the anode, and an electron transport layer in contact with the cathode, and two transport layers being in contact with each other. Another aspect of the present invention is a Schottky barrier diode comprising anode, cathode, and an organic semiconductor layer, wherein the semiconductor layer is either hole or electron transport layer. At least one of the transport layers is characterized by a globally ordered crystalline structure with intermolecular spacing of 3.4±0.3 Å in the direction of one crystal axis. One more aspect of the present invention is a method for obtaining an organic semiconductor layer with the electron-hole type of conductivity.

Owner:NITTO DENKO CORP

Schottky barrier diode and diode array

ActiveUS20060108659A1Lower resistanceReduce chip areaSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSchottky barrier

A Schottky barrier diode includes a first semiconductor layer and a second semiconductor layer successively formed above a semiconductor substrate with a buffer layer formed between the first and second semiconductor layers and the semiconductor substrate. A Schottky electrode and an ohmic electrode spaced from each other are formed on the second semiconductor layer, and a back face electrode is formed on the back face of the semiconductor substrate. The Schottky electrode or the ohmic electrode is electrically connected to the back face electrode through a via penetrating through at least the buffer layer.

Owner:PANASONIC CORP