Patents

Literature

123 results about "Aluminium gallium nitride" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

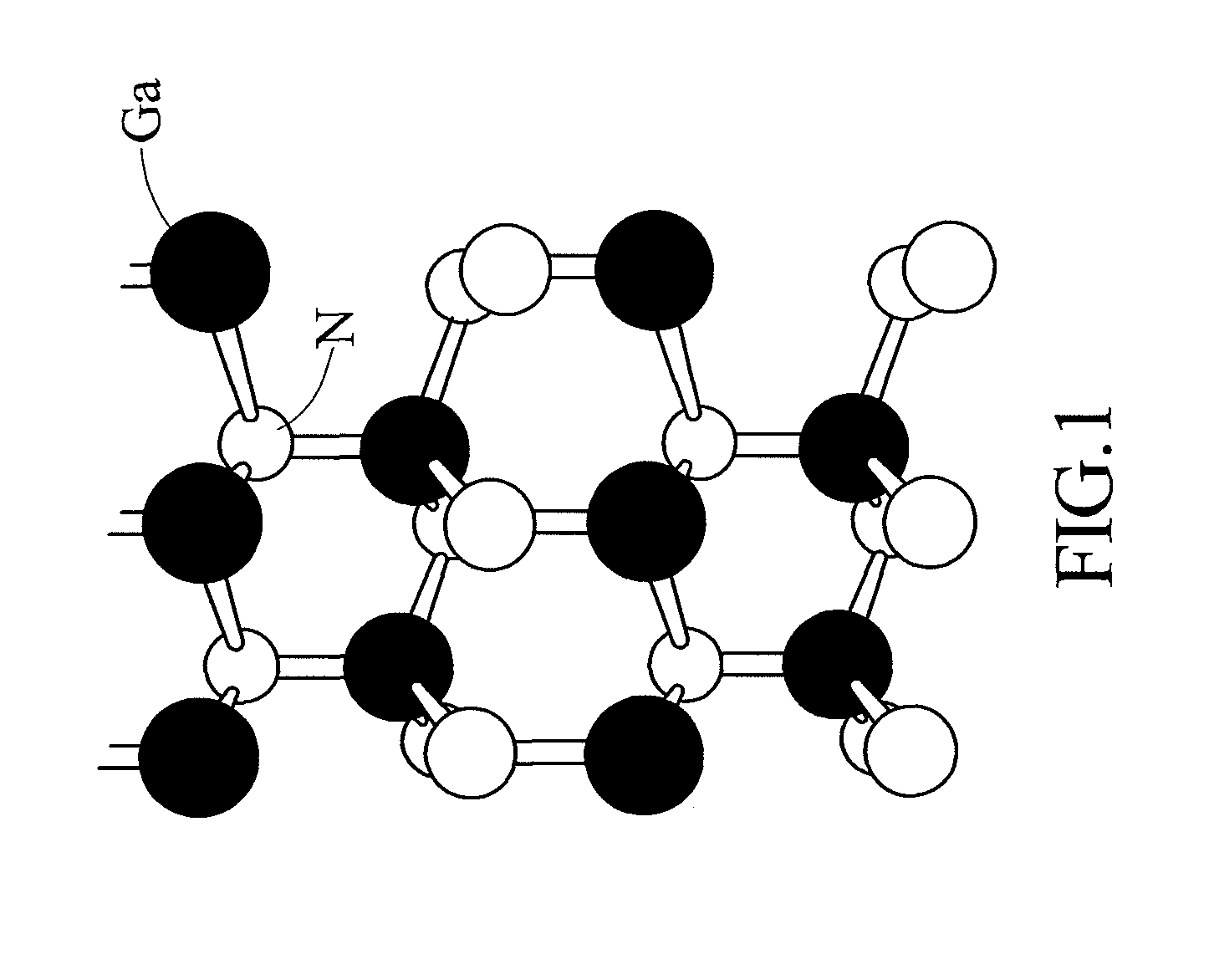

Aluminium gallium nitride (AlGaN) is a semiconductor material. It is any alloy of aluminium nitride and gallium nitride. The bandgap of AlₓGa₁₋ₓN can be tailored from 3.4eV (xAl=0) to 6.2eV (xAl=1). AlGaN is used to manufacture light-emitting diodes operating in blue to ultraviolet region, where wavelengths down to 250 nm (far UV) were achieved. It is also used in blue semiconductor lasers.

High-electron mobility transistor with zinc oxide

InactiveUS7105868B2Increase heightHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierField-effect transistor

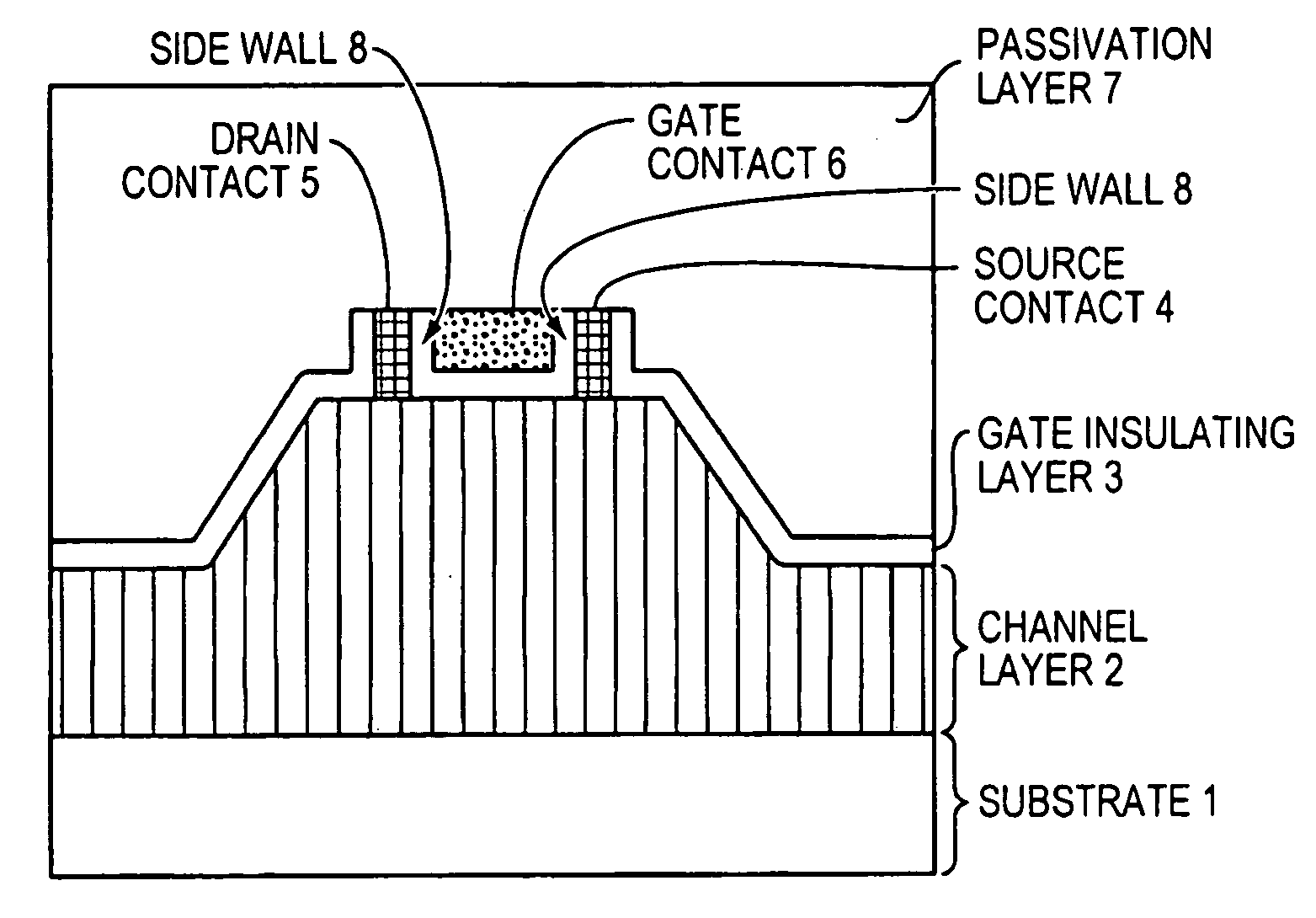

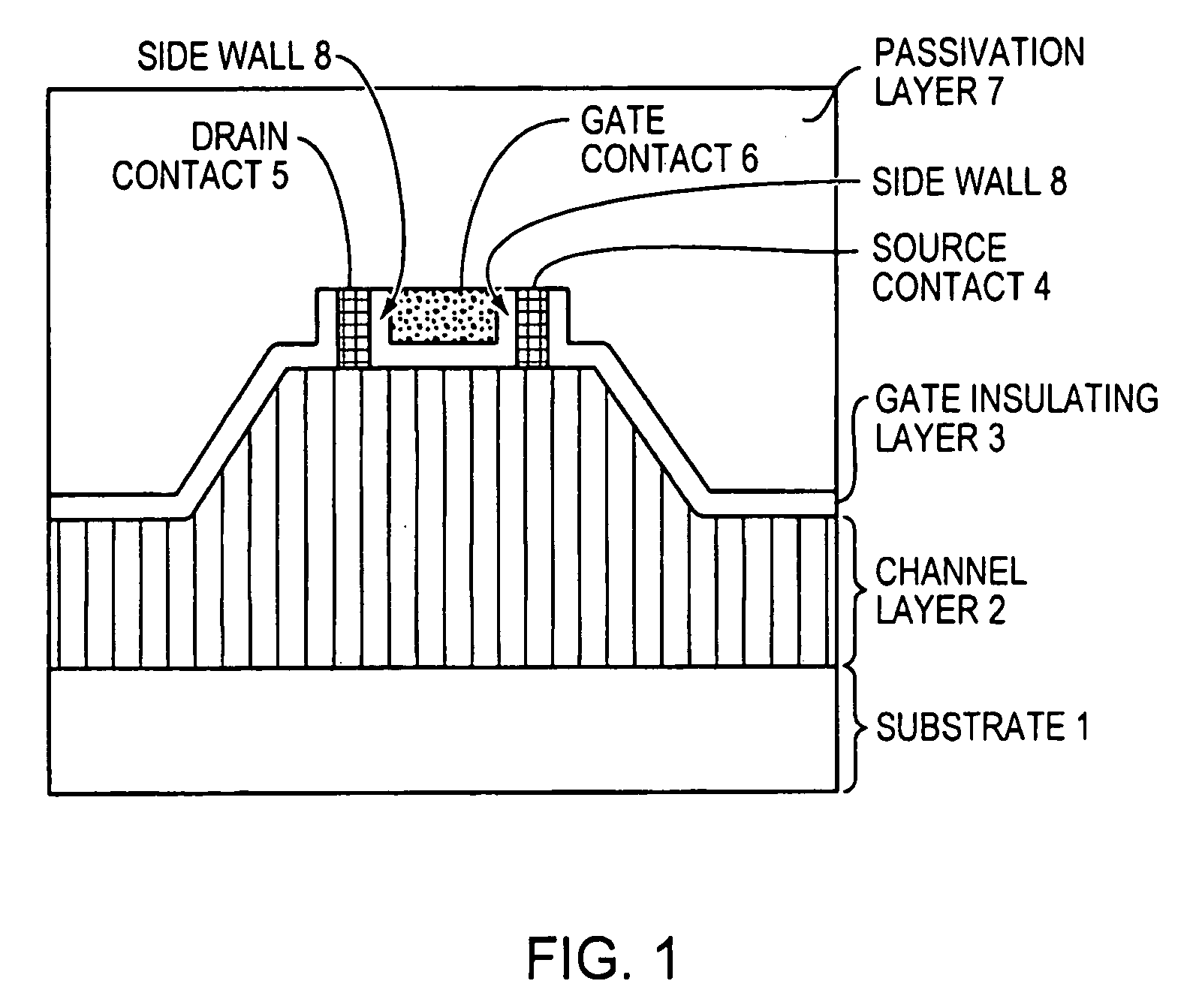

A zinc oxide (ZnO) field effect transistor exhibits large input amplitude by using a gate insulating layer. A channel layer and the gate insulating layer are sequentially laminated on a substrate. A gate electrode is formed on the gate insulating layer. A source contact and a drain contact are disposed at the both sides of the gate contact and are electrically connected to the channel layer via openings. The channel layer is formed from n-type ZnO. The gate insulating layer is made from aluminum nitride / aluminum gallium nitride (AlN / AlGaN) or magnesium zinc oxide (MgZnO), which exhibits excellent insulation characteristics, thus increasing the Schottky barrier and achieving large input amplitude. If the FET is operated in the enhancement mode, it is operable in a manner similar to a silicon metal oxide semiconductor field effect transistor (Si-MOS-type FET), resulting in the formation of an inversion layer.

Owner:NAUSE CATHERINE D

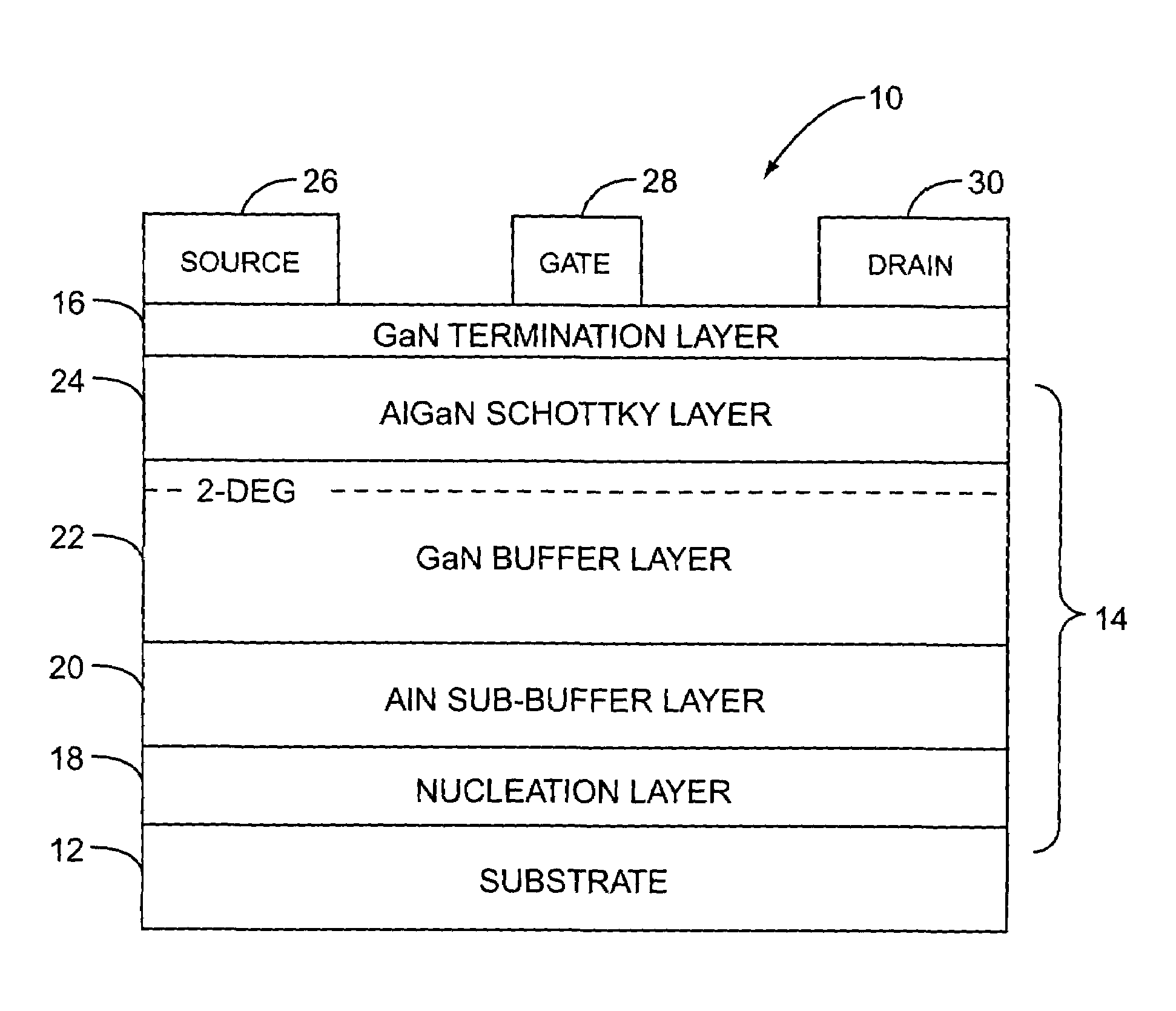

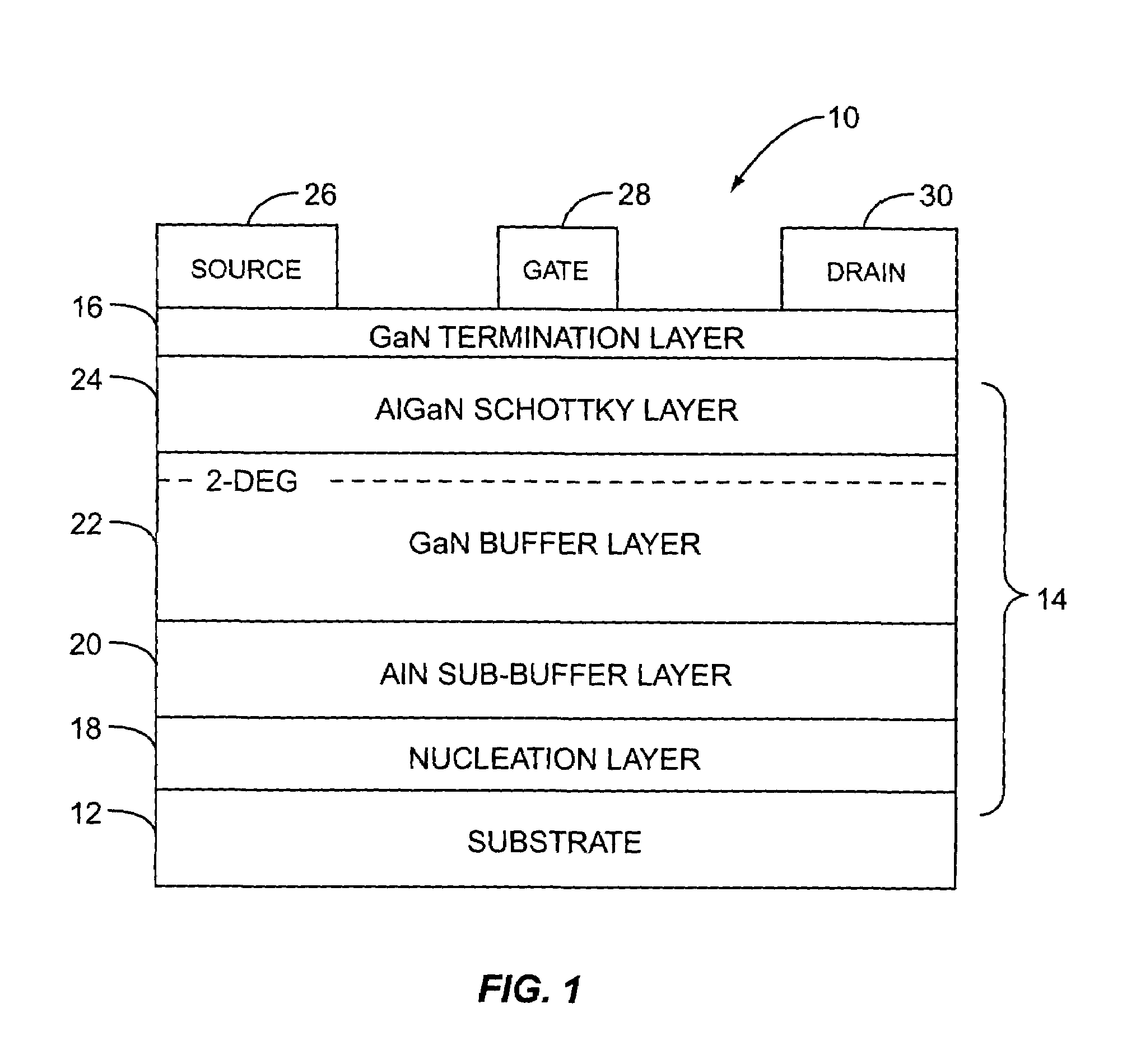

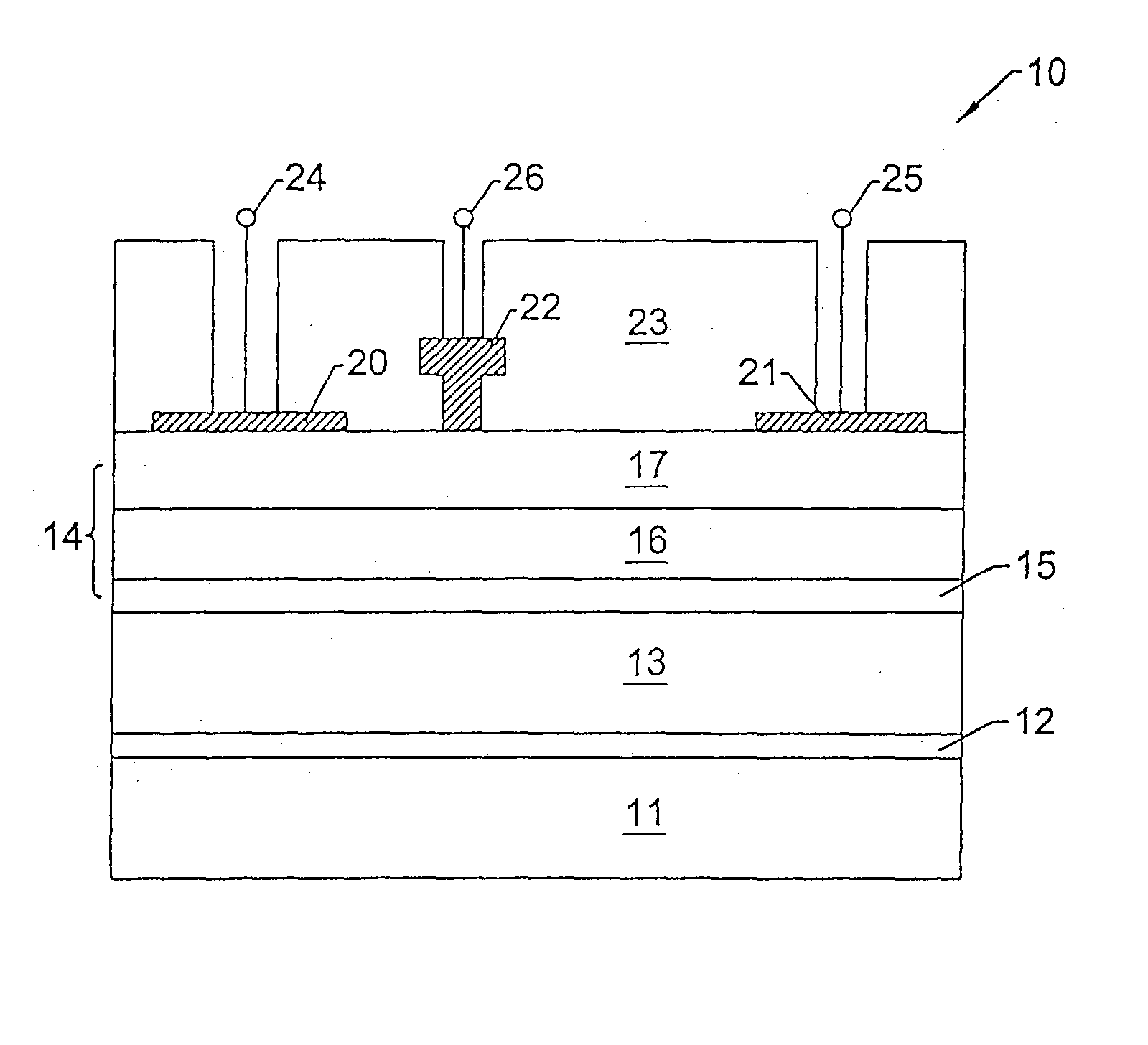

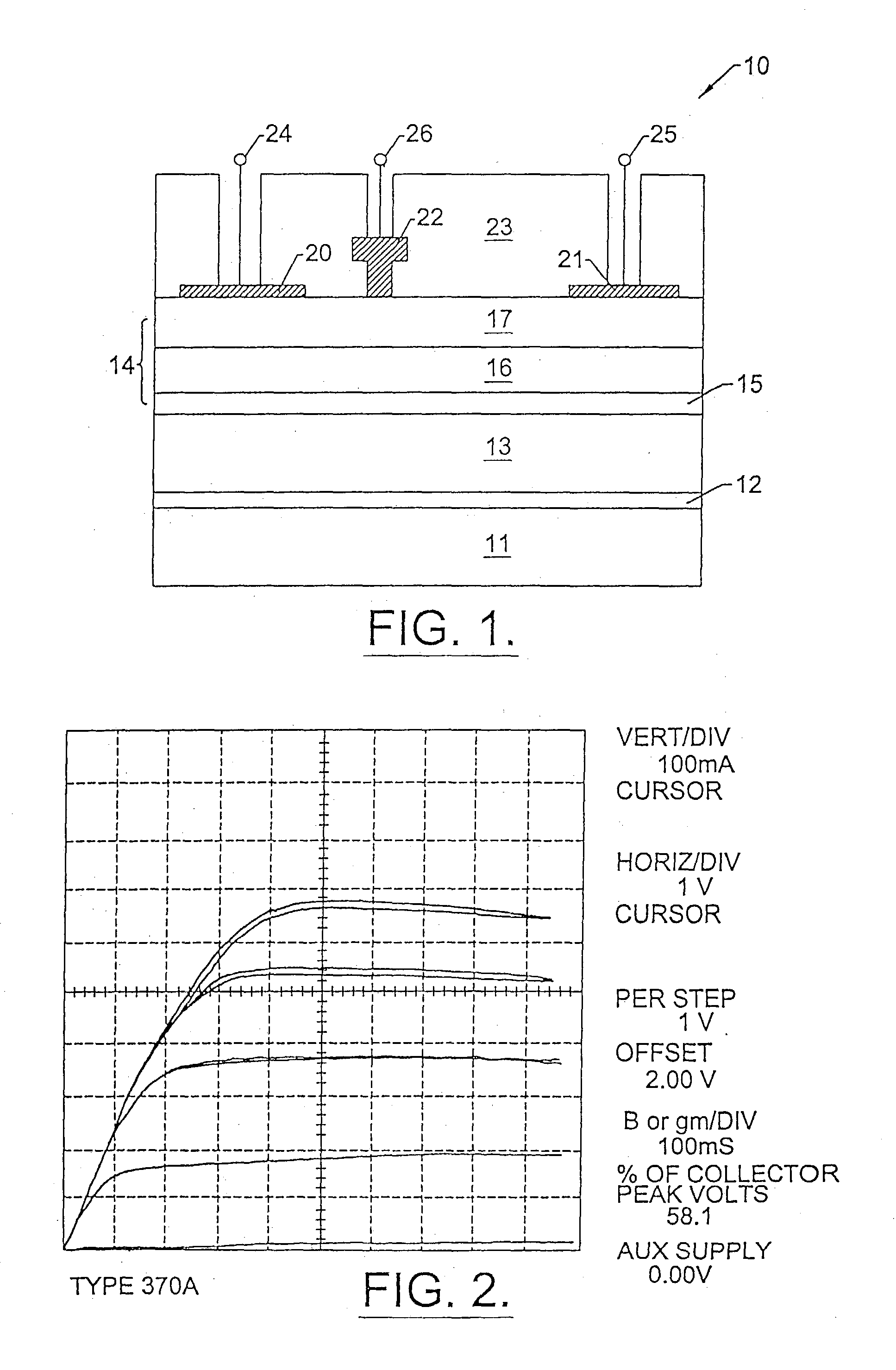

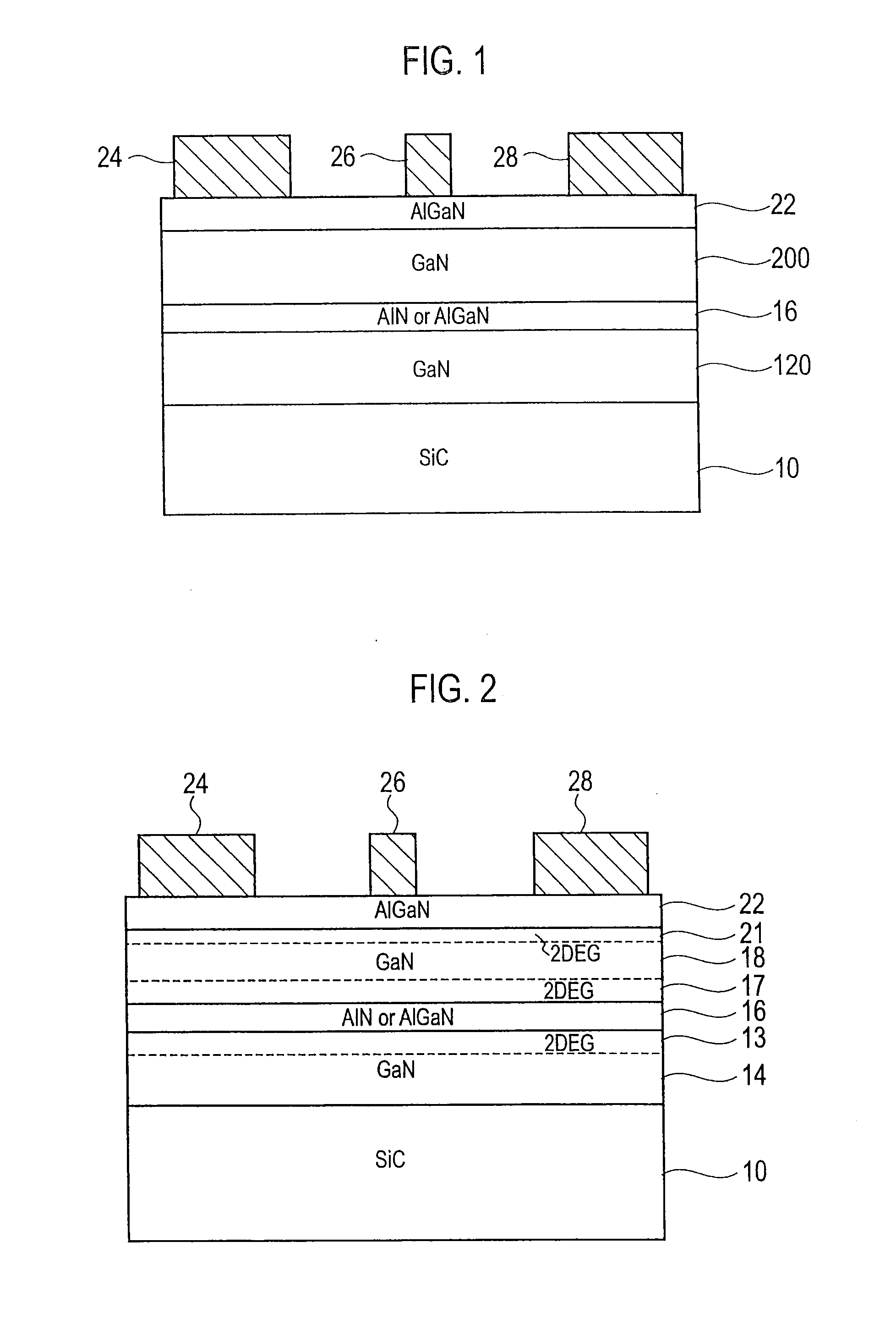

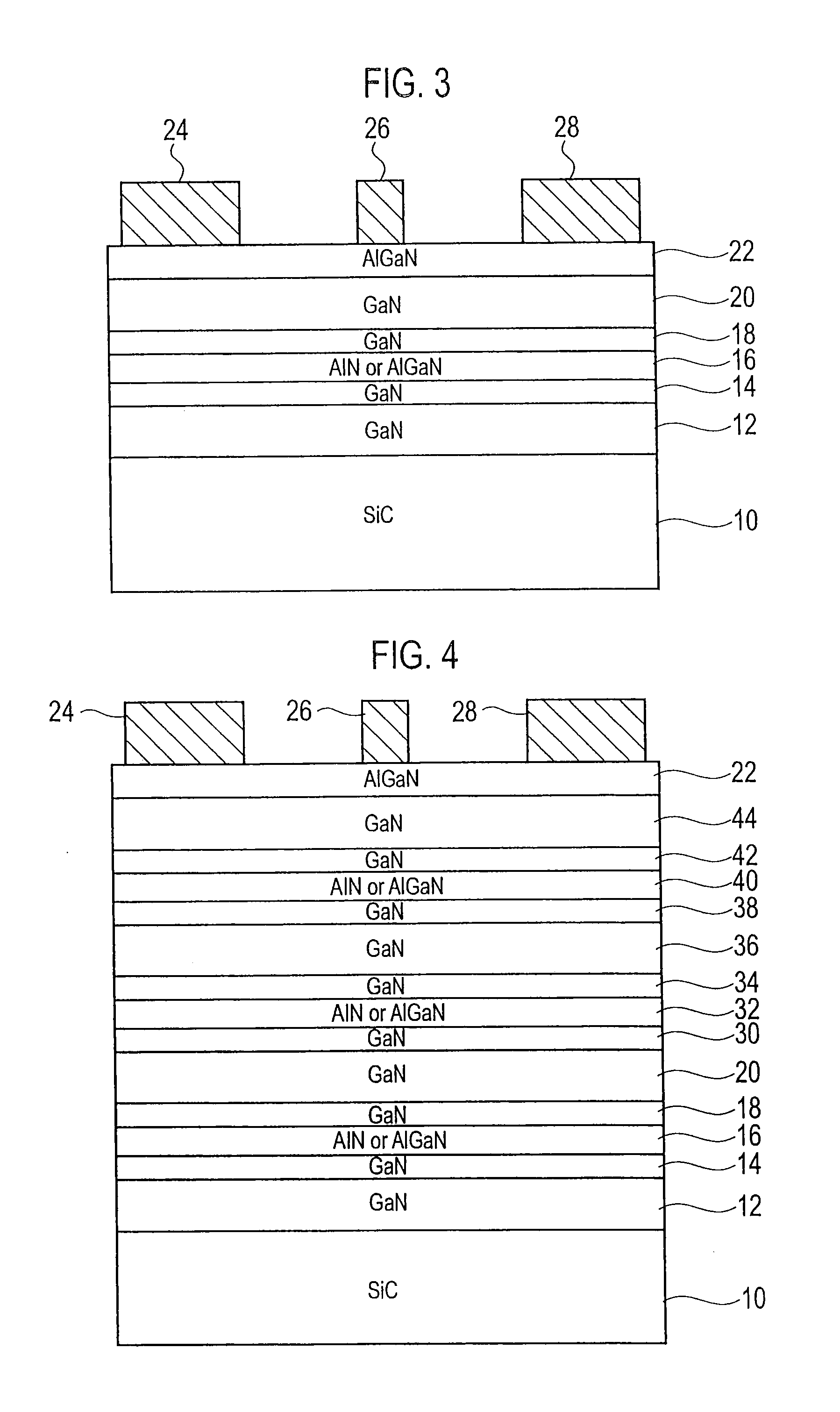

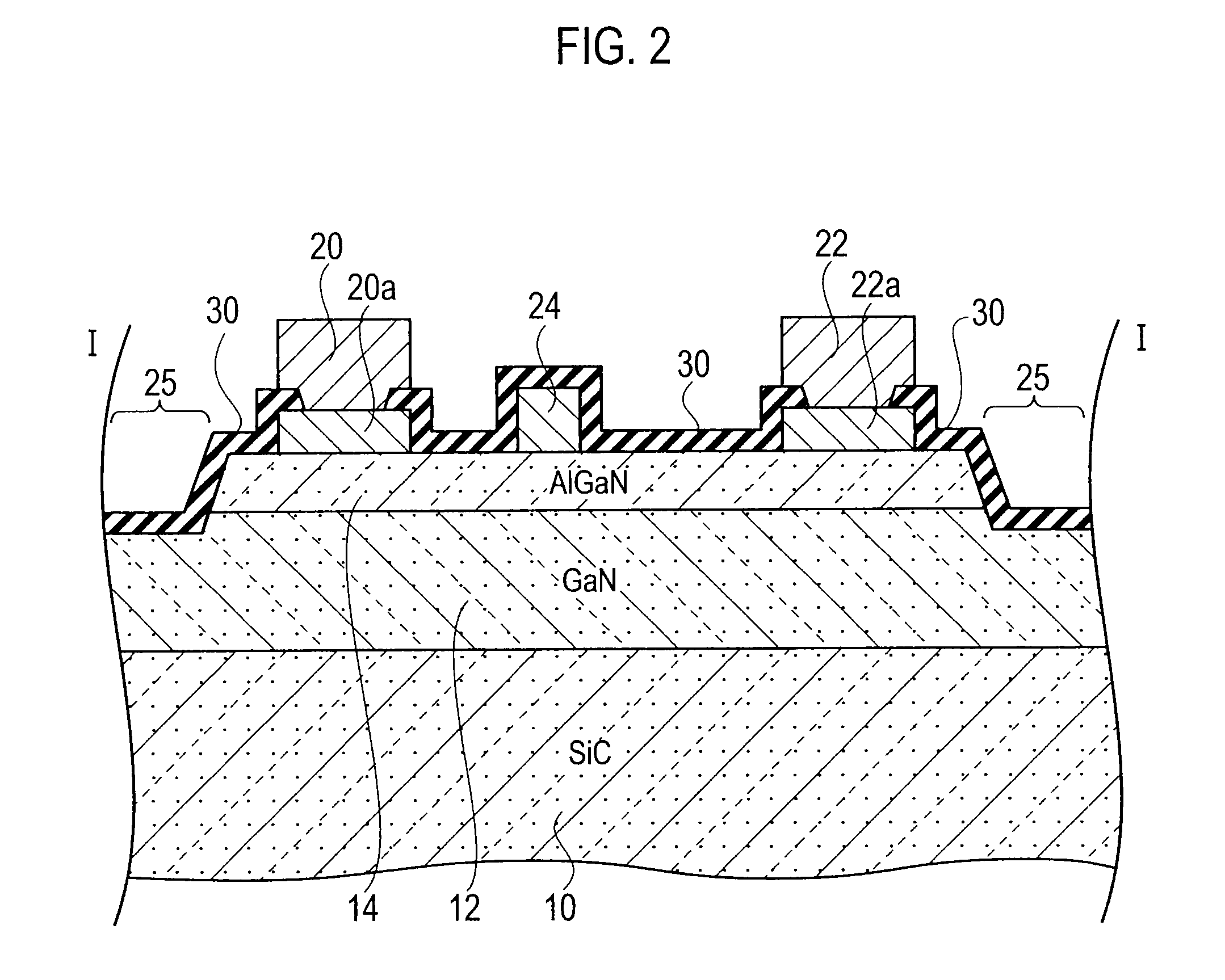

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6316793B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideMaterials science

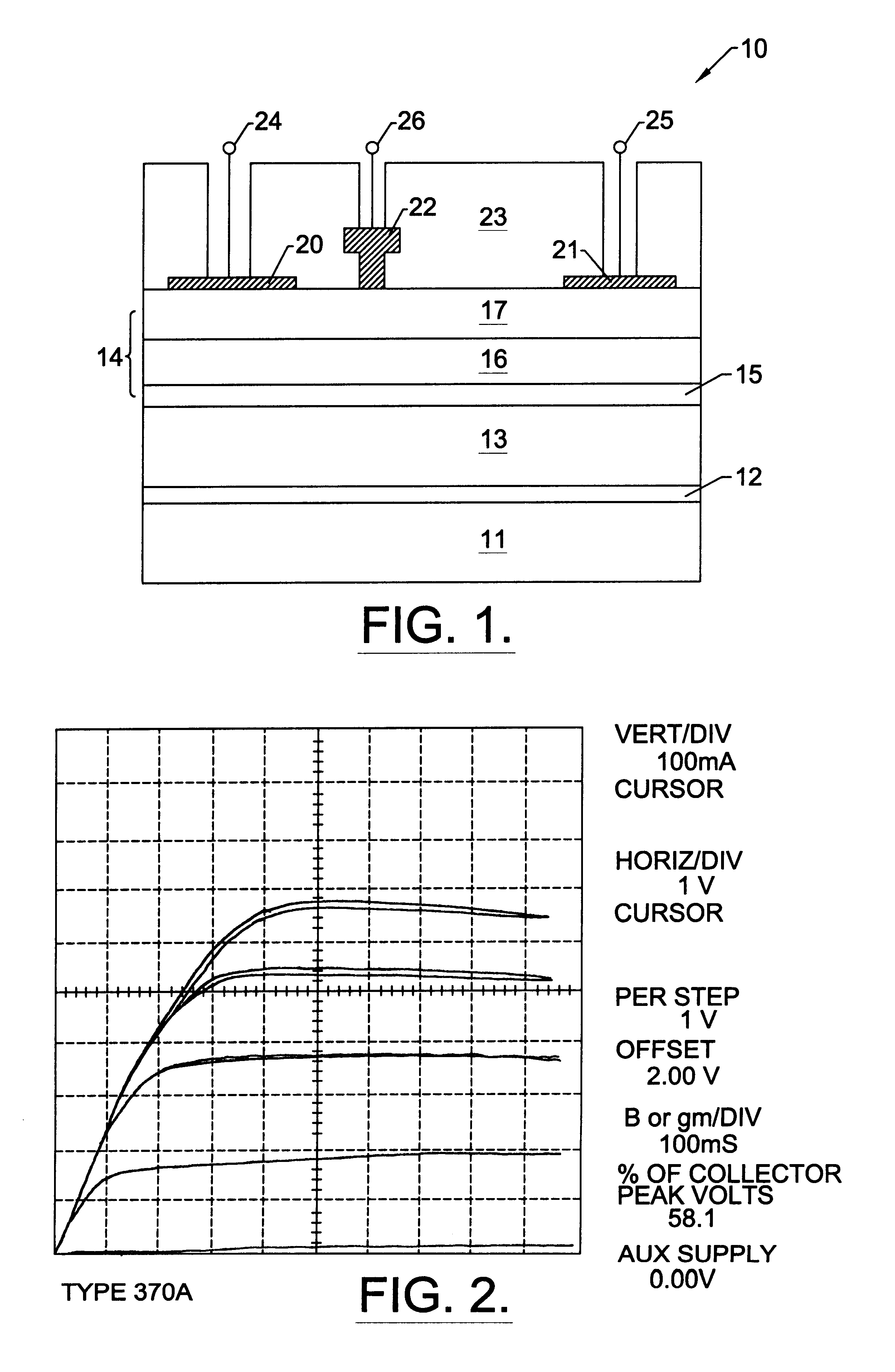

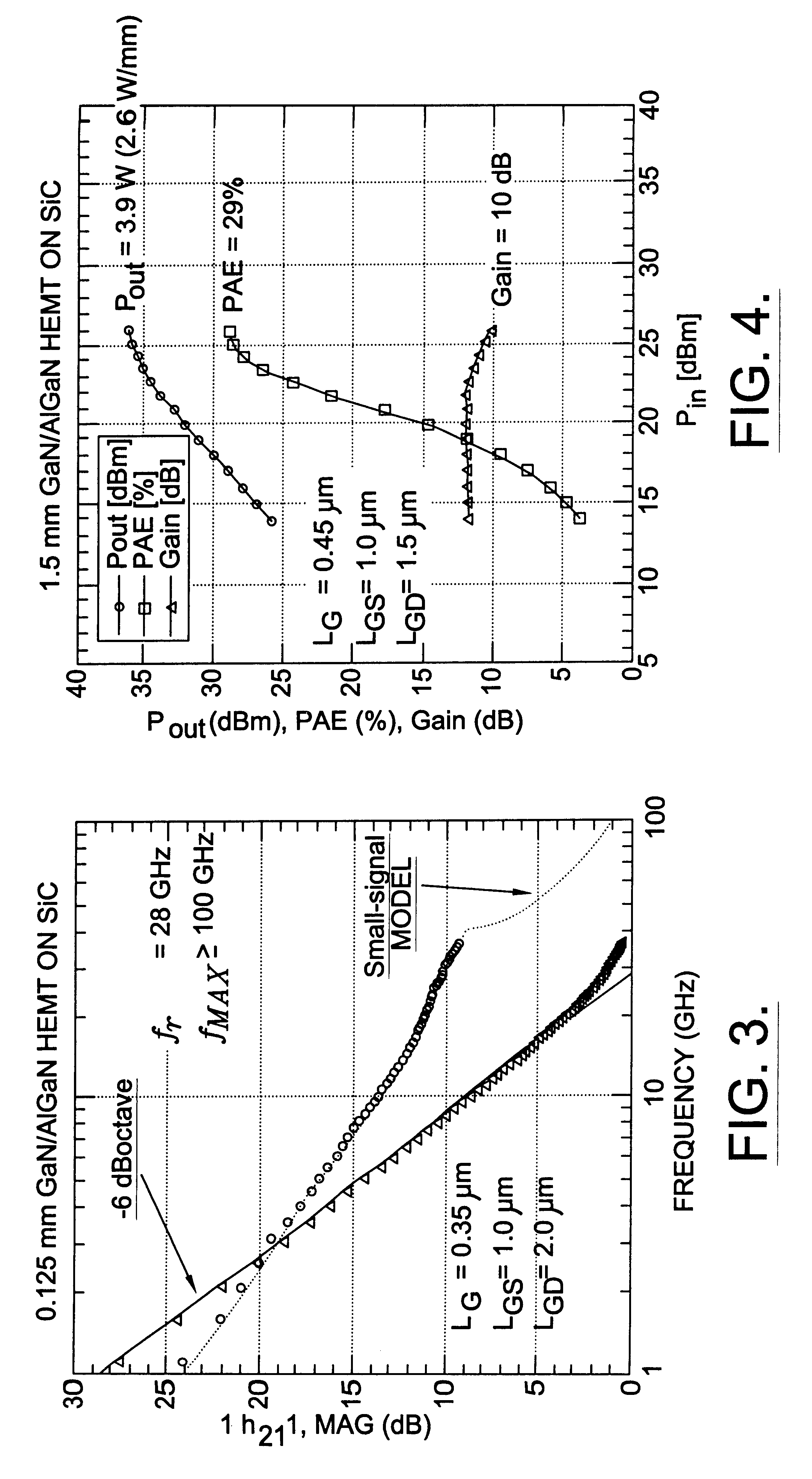

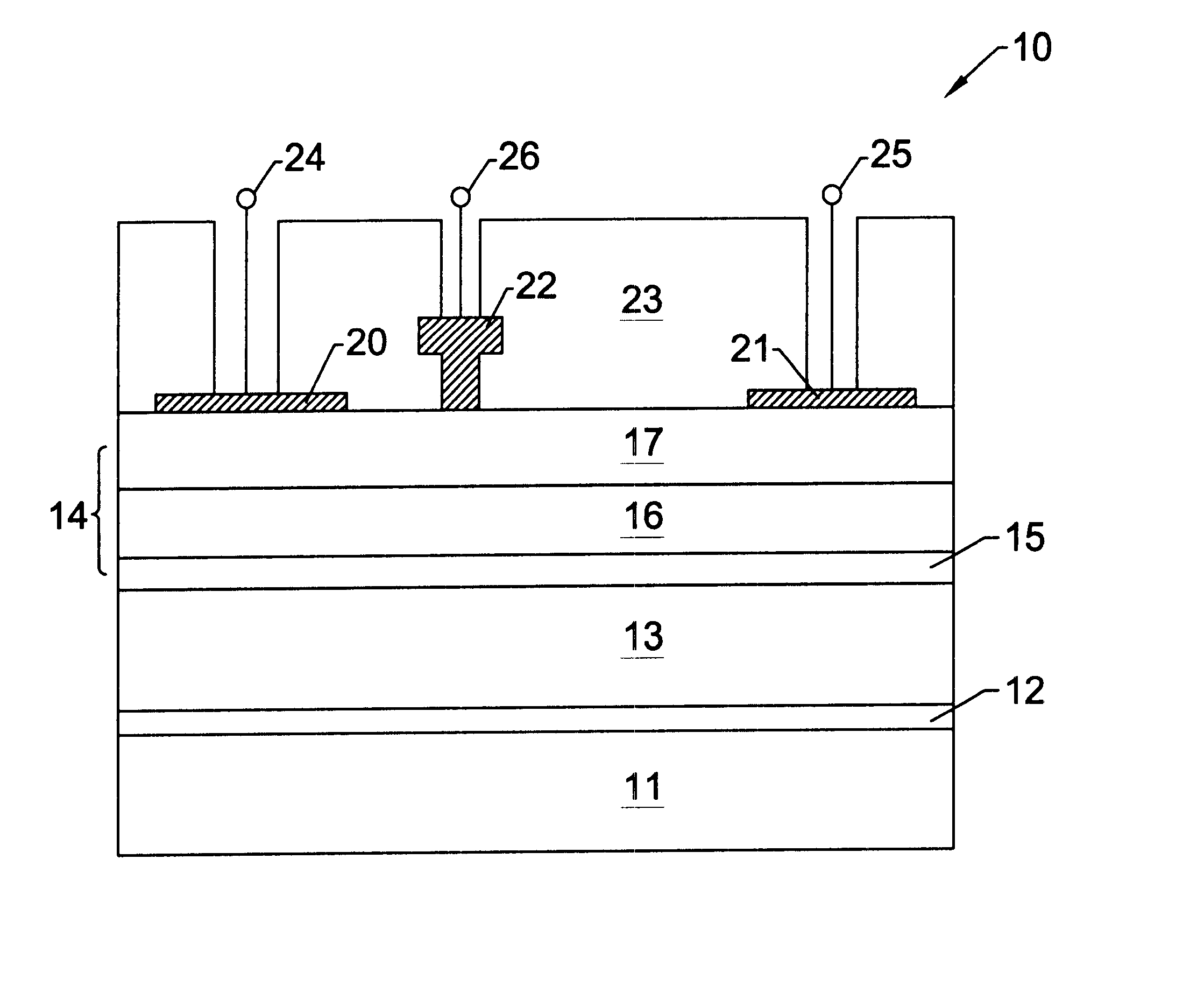

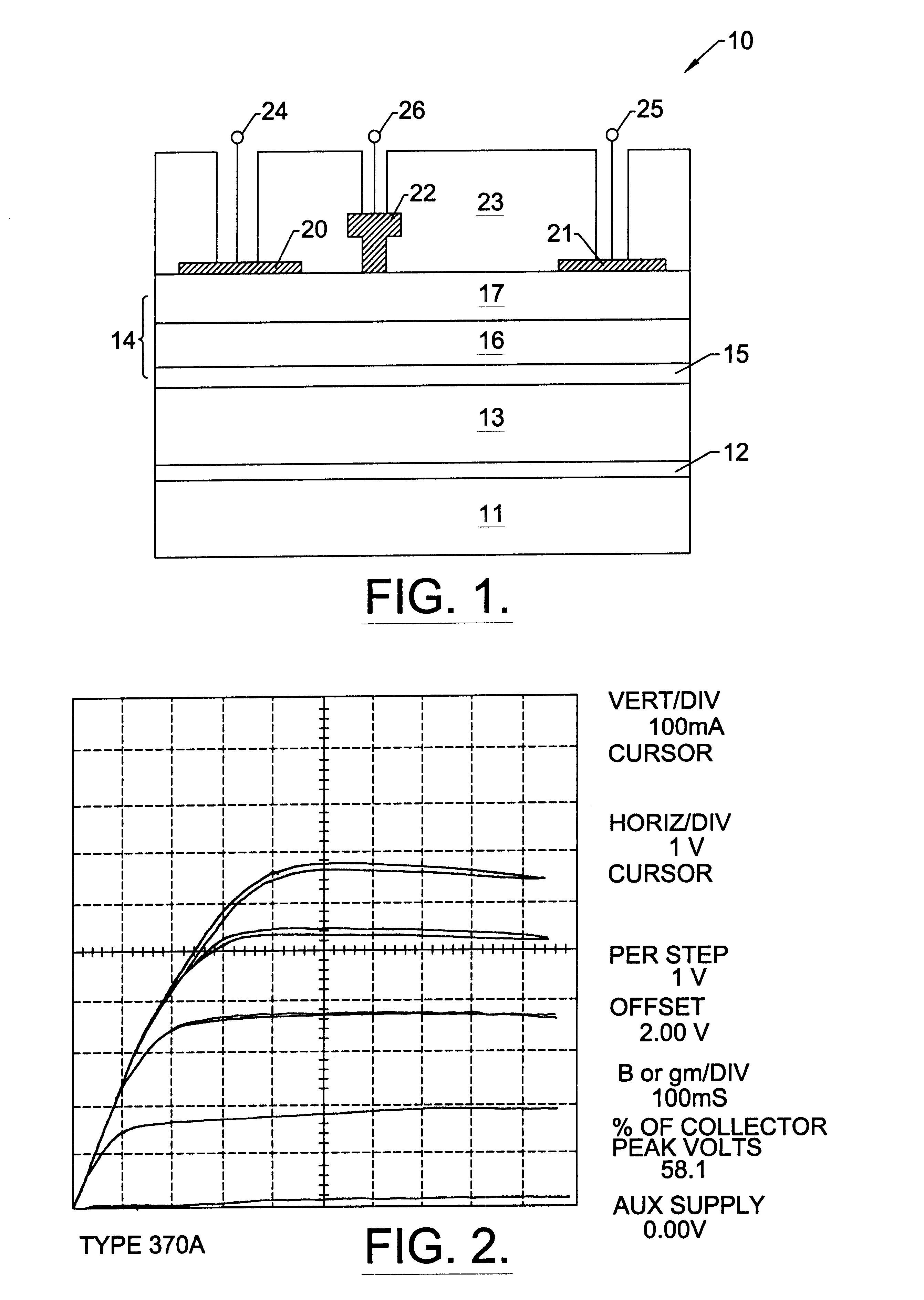

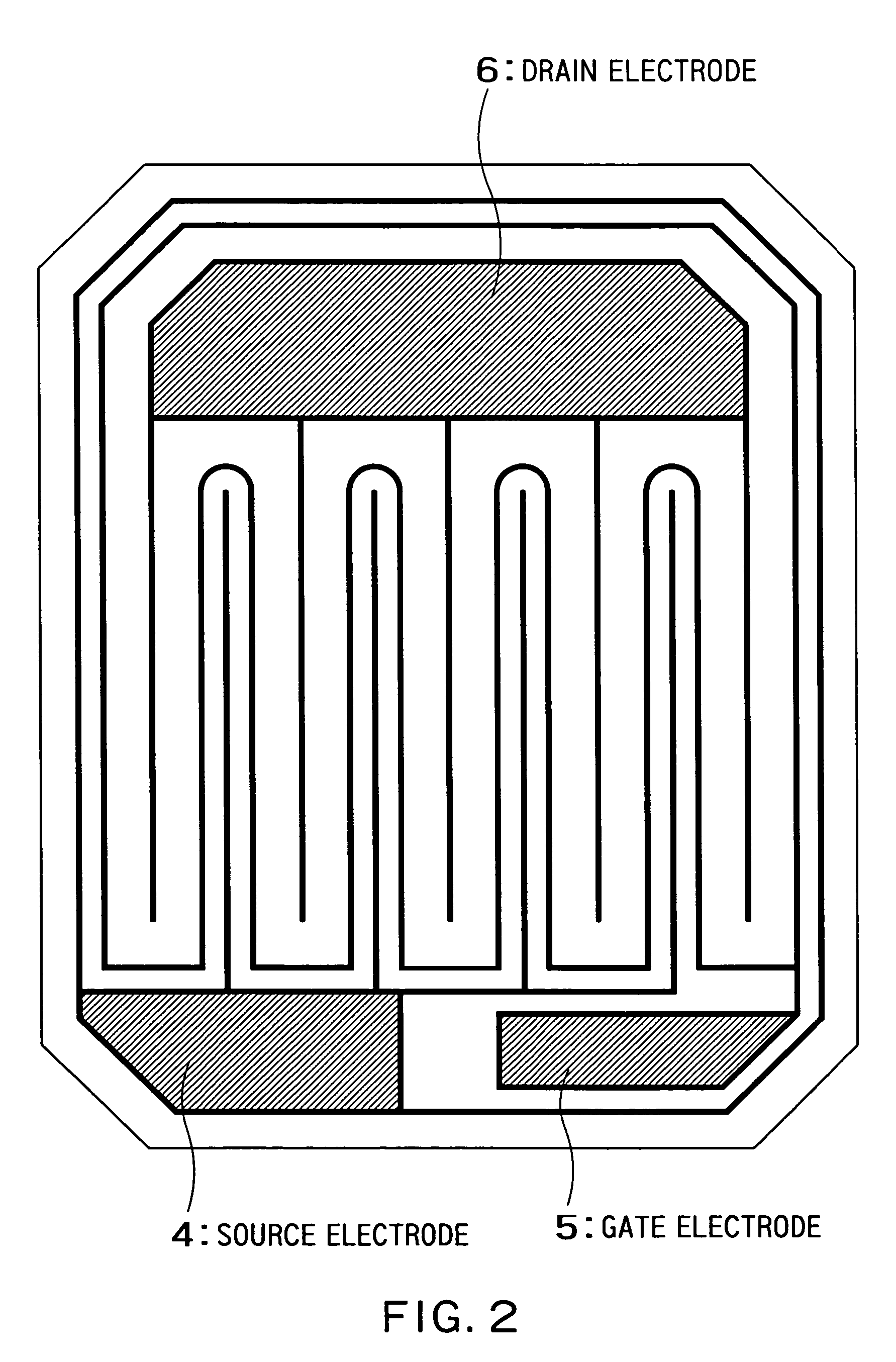

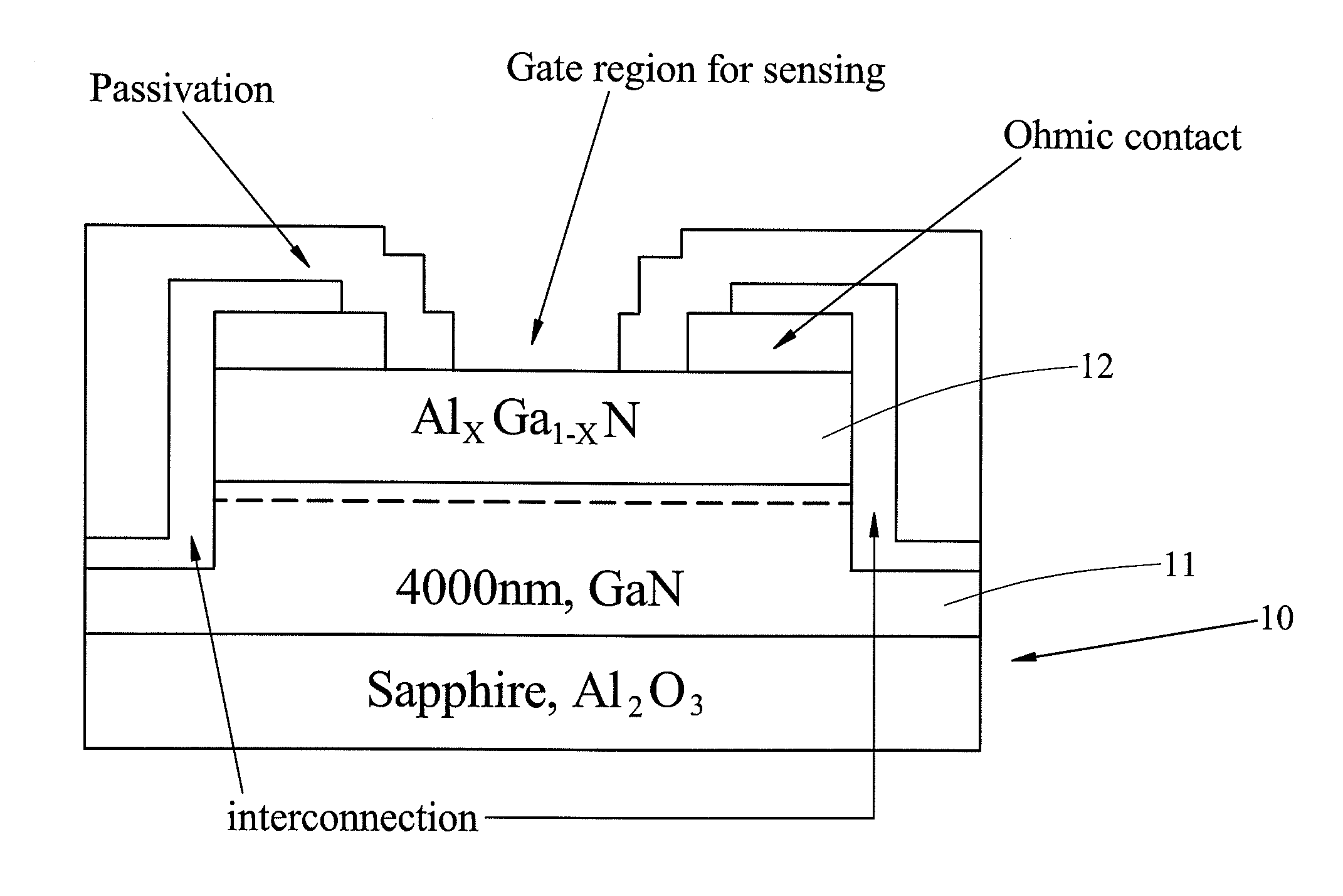

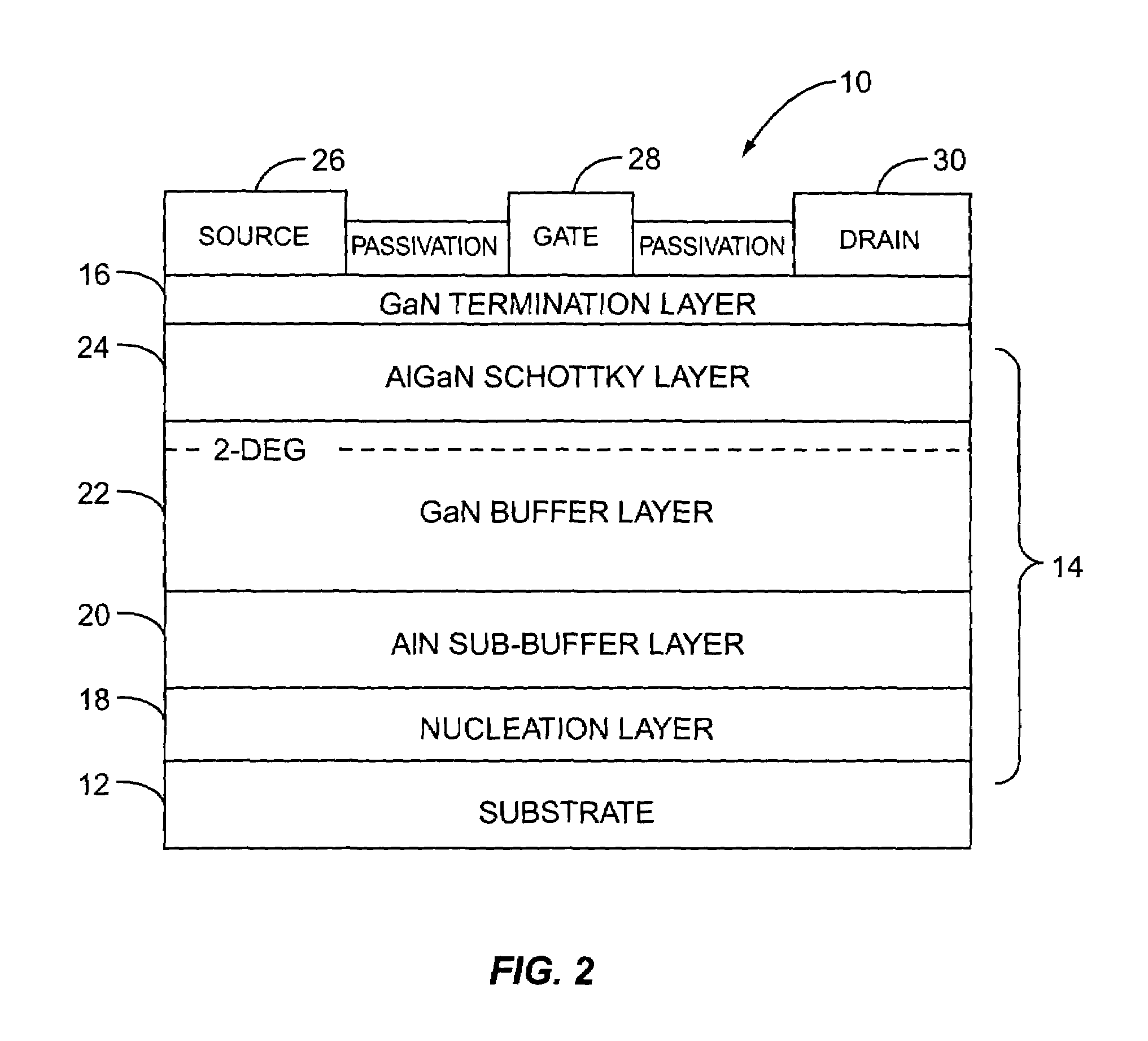

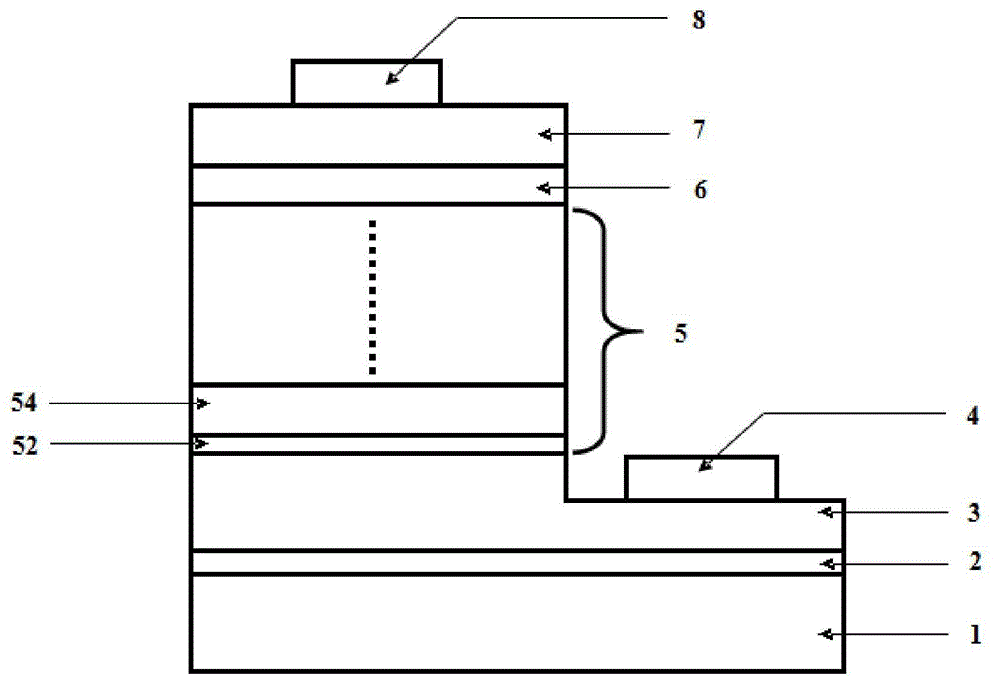

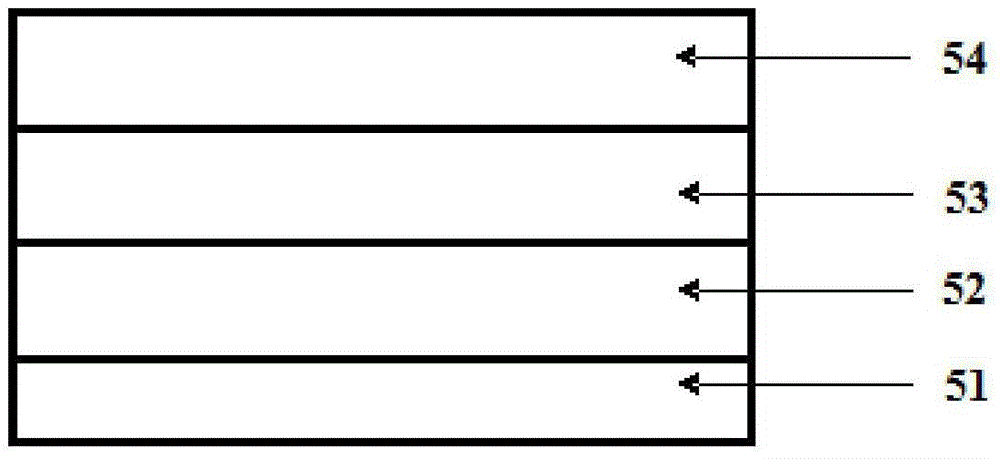

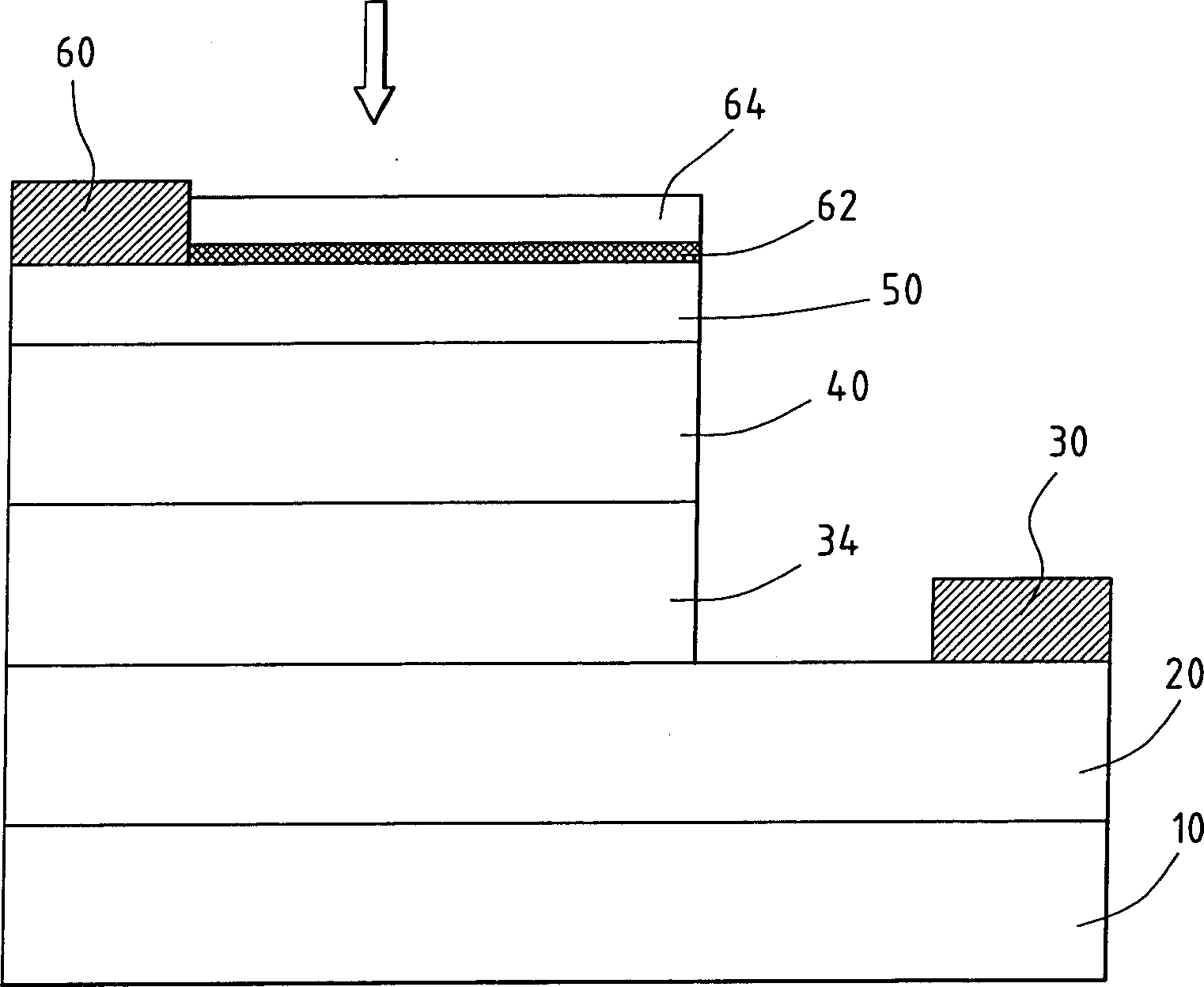

A high electron mobility transistor (HEMT) is disclosed that includes a semi-insulating silicon carbide substrate, an aluminum nitride buffer layer on the substrate, an insulating gallium nitride layer on the buffer layer, an active structure of aluminum gallium nitride on the gallium nitride layer, a passivation layer on the aluminum gallium nitride active structure, and respective source, drain and gate contacts to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6486502B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideNitride

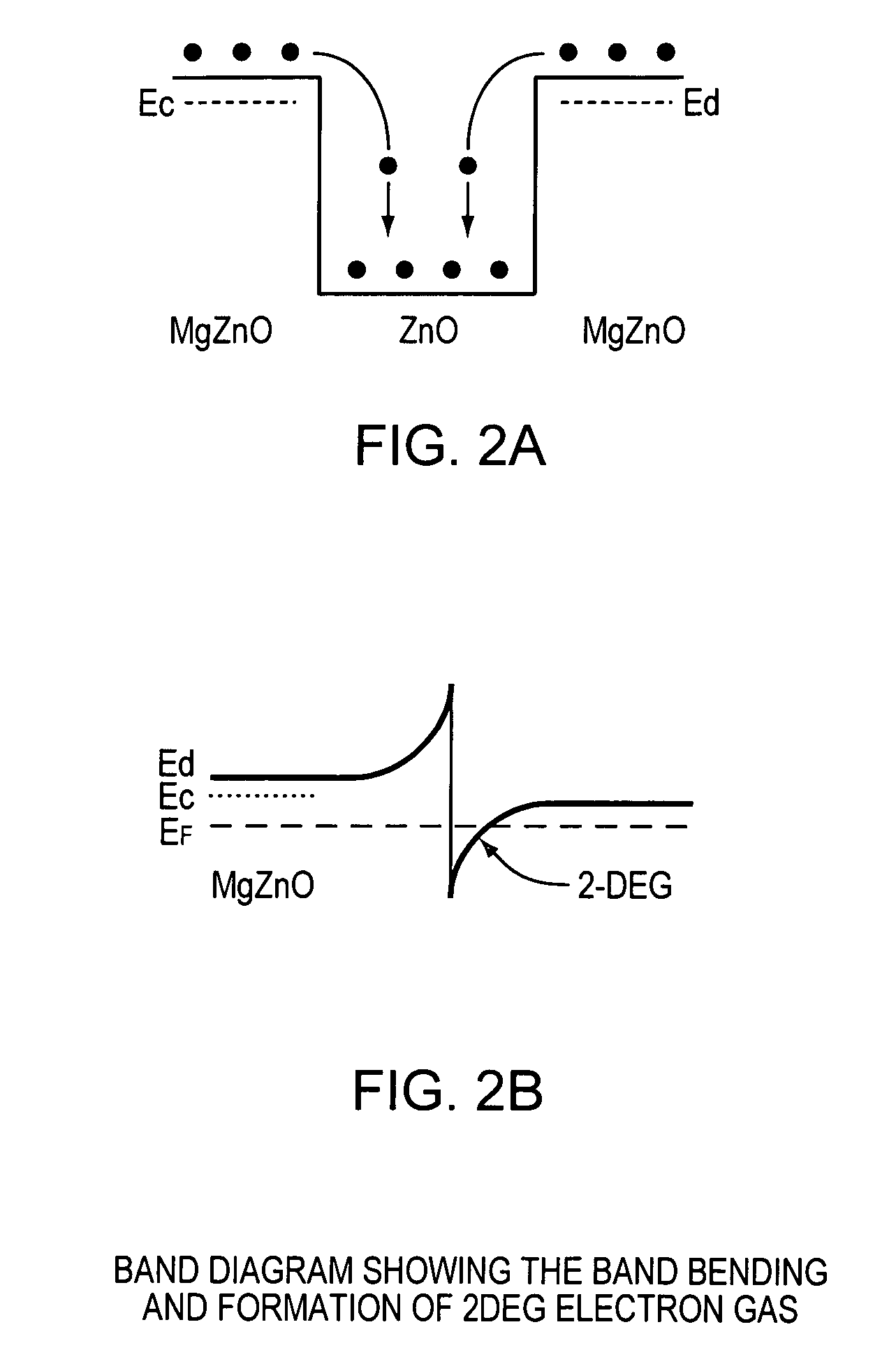

A high electron mobility transistor (HEMT) (10) is disclosed that includes a semi-insulating silicon carbide substrate (11), an aluminum nitride buffer layer (12) on the substrate, an insulating gallium nitride layer (13) on the buffer layer, an active structure of aluminum gallium nitride (14) on the gallium nitride layer, a passivation layer (23) on the aluminum gallium nitride active structure, and respective source, drain and gate contacts (21, 22, 23) to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

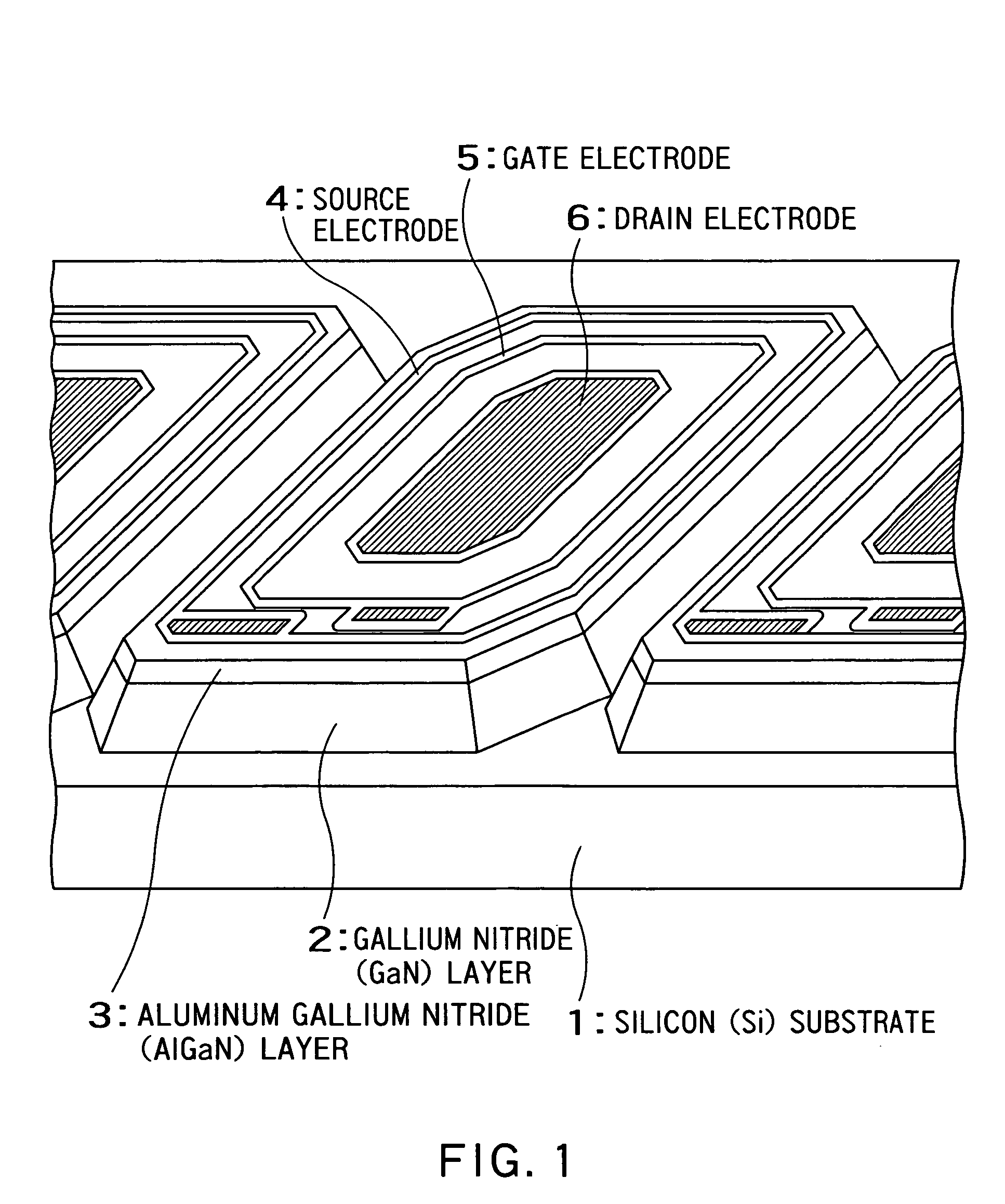

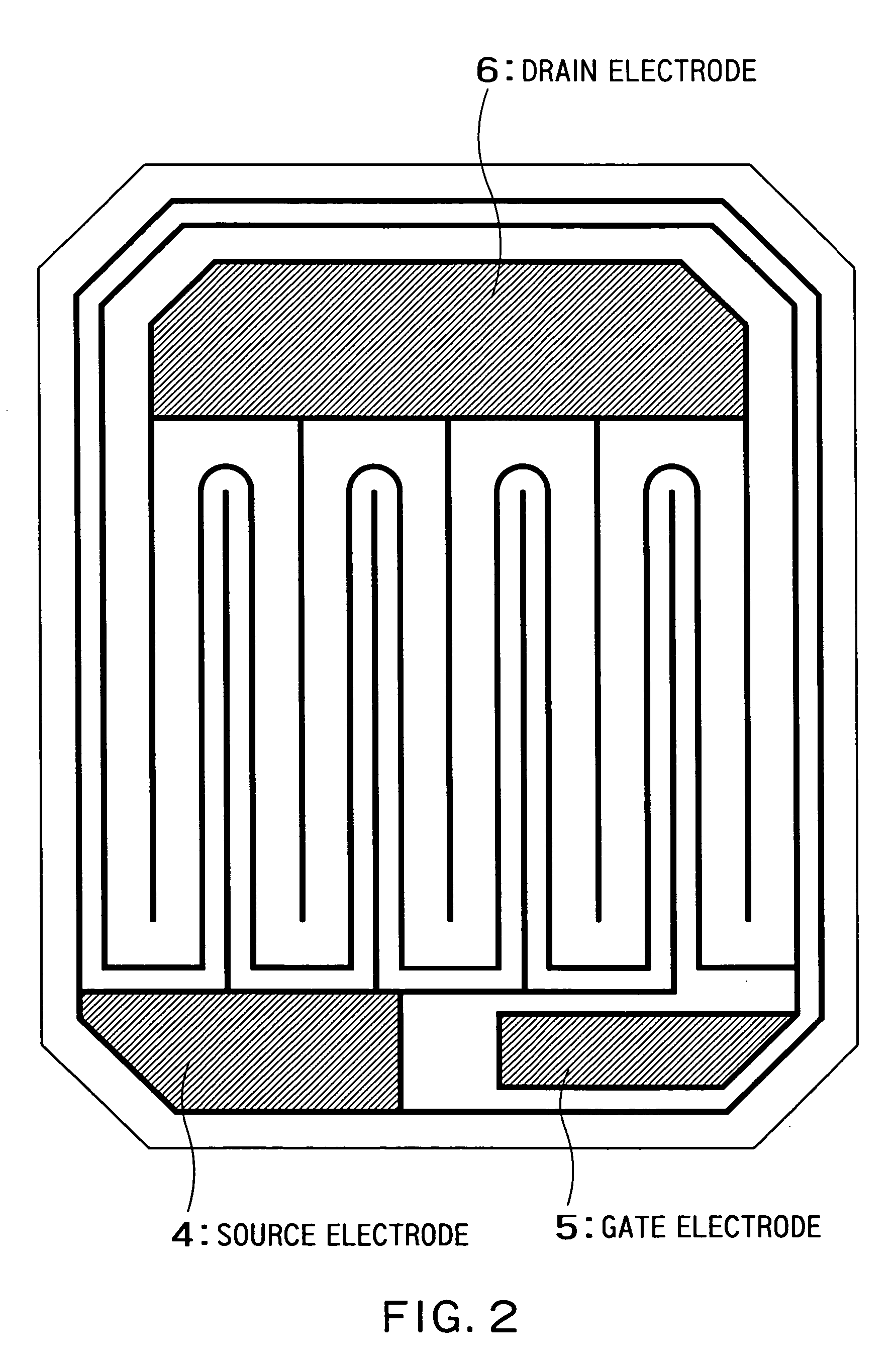

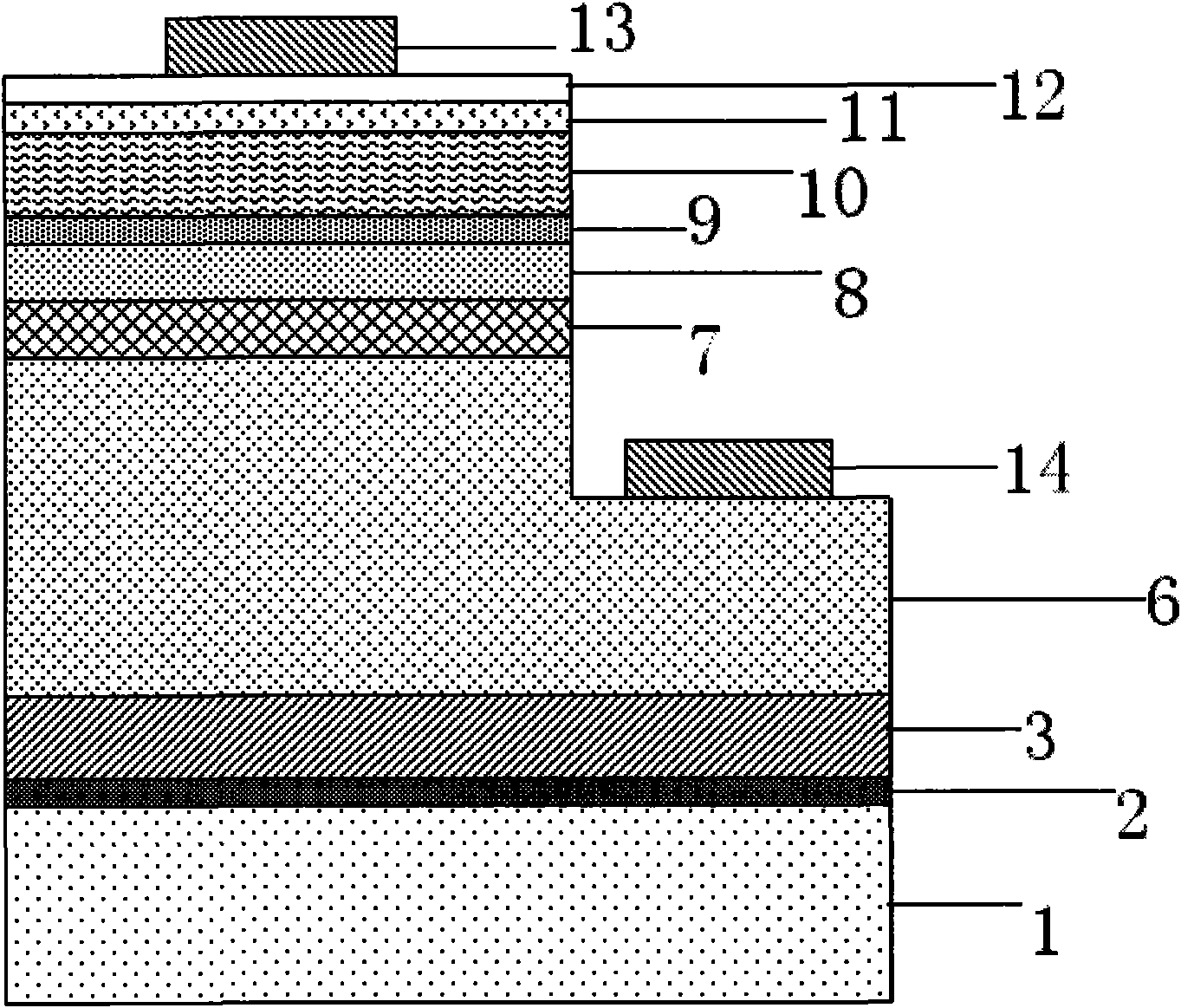

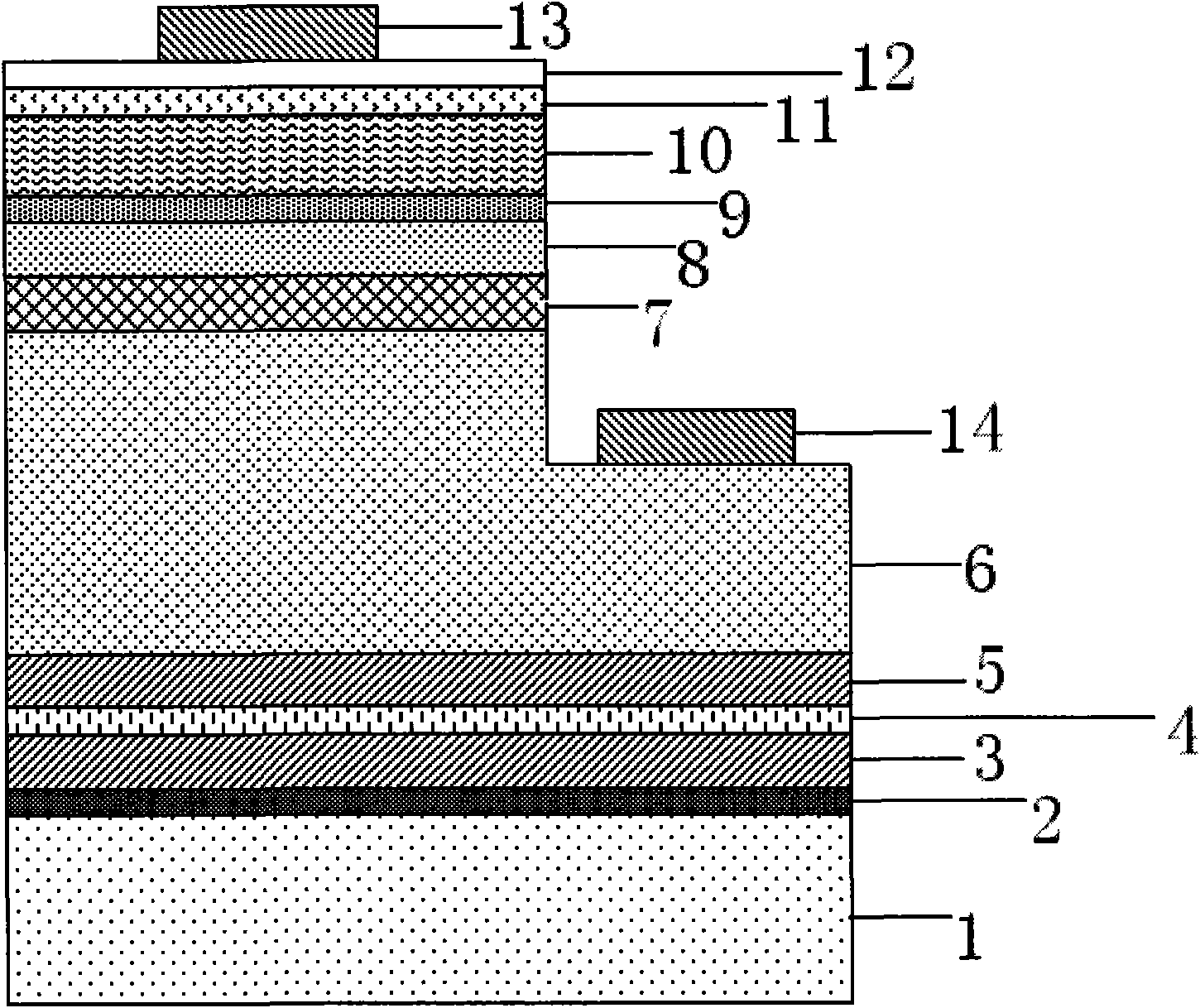

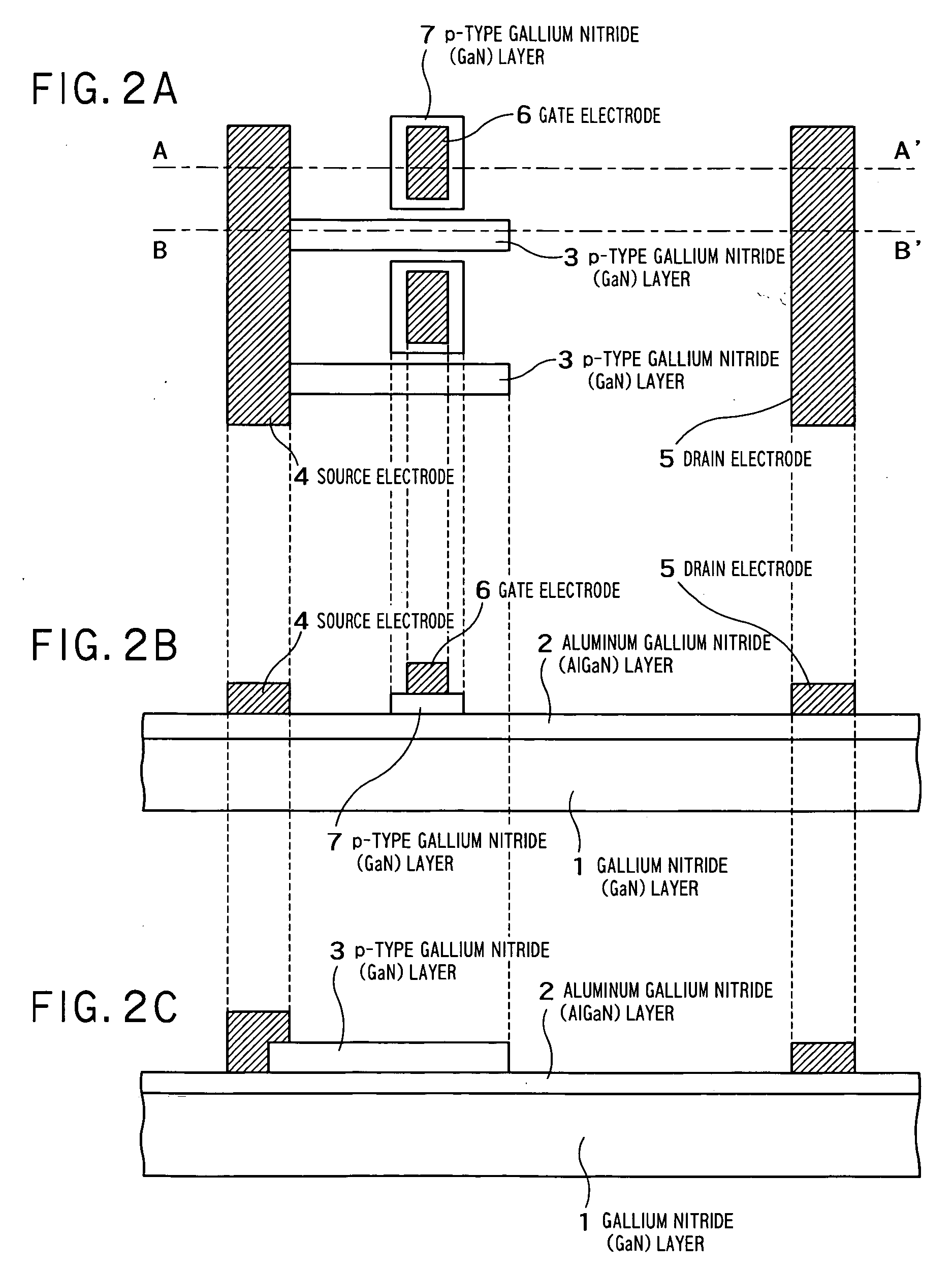

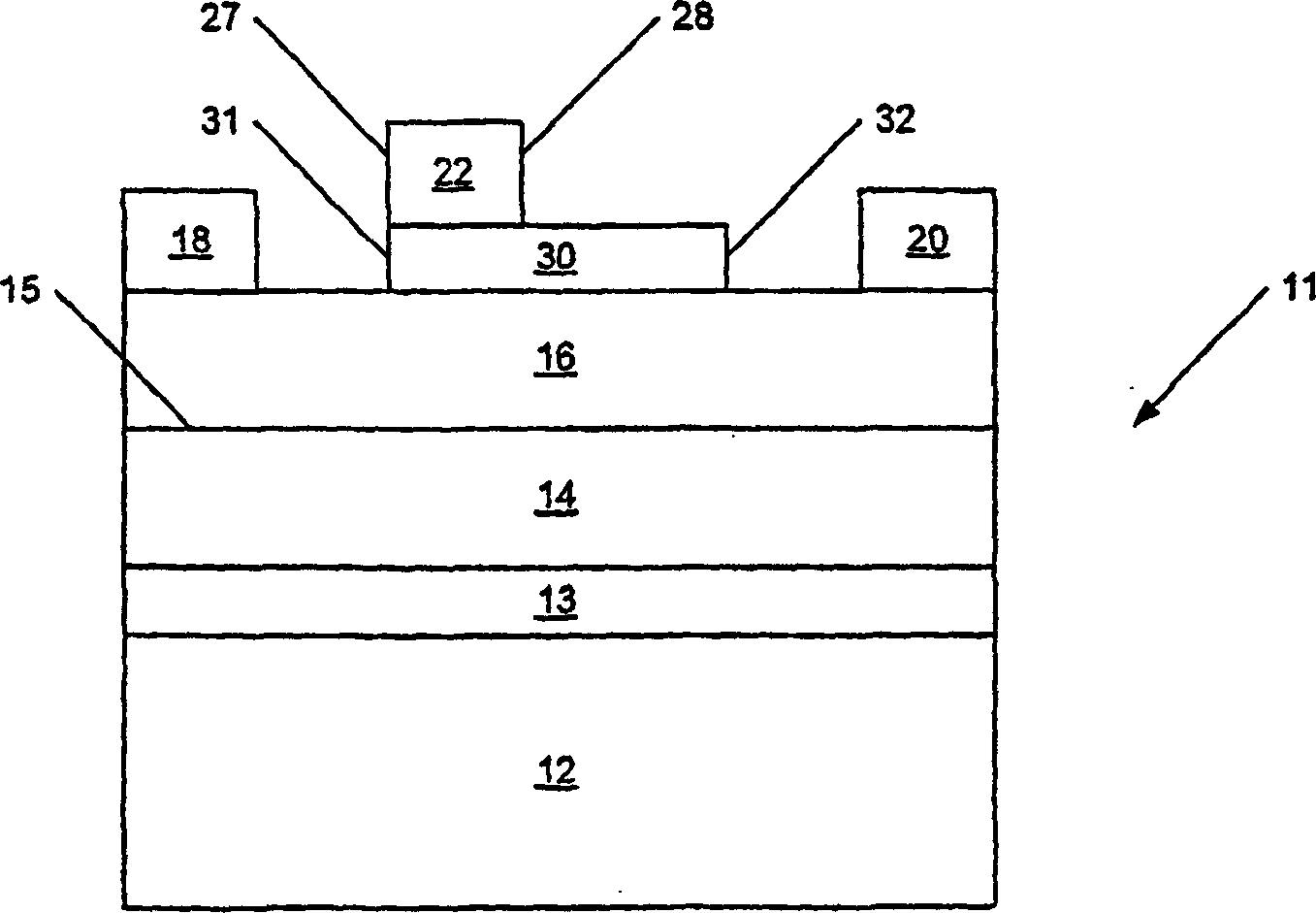

Nitride semiconductor device

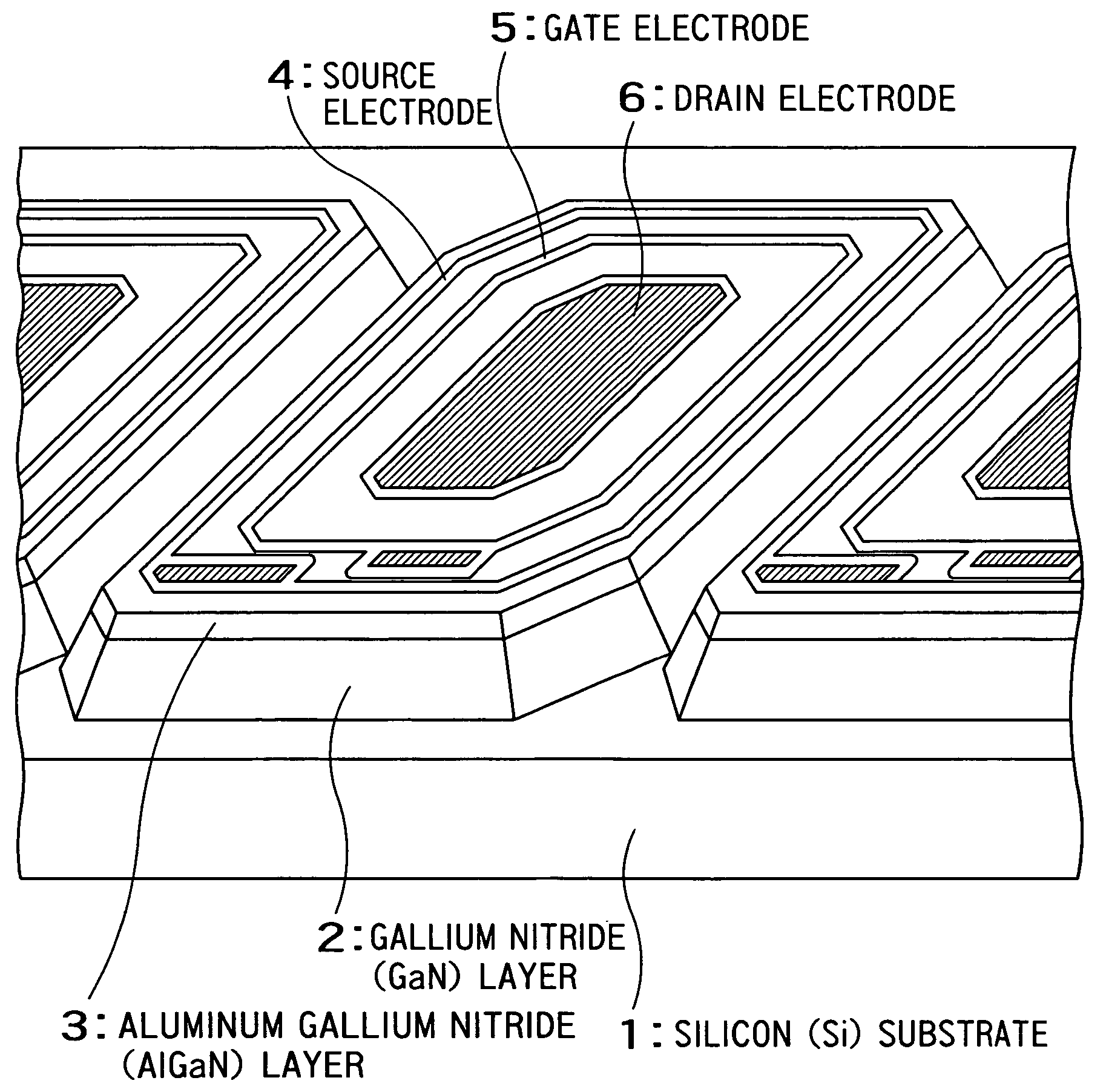

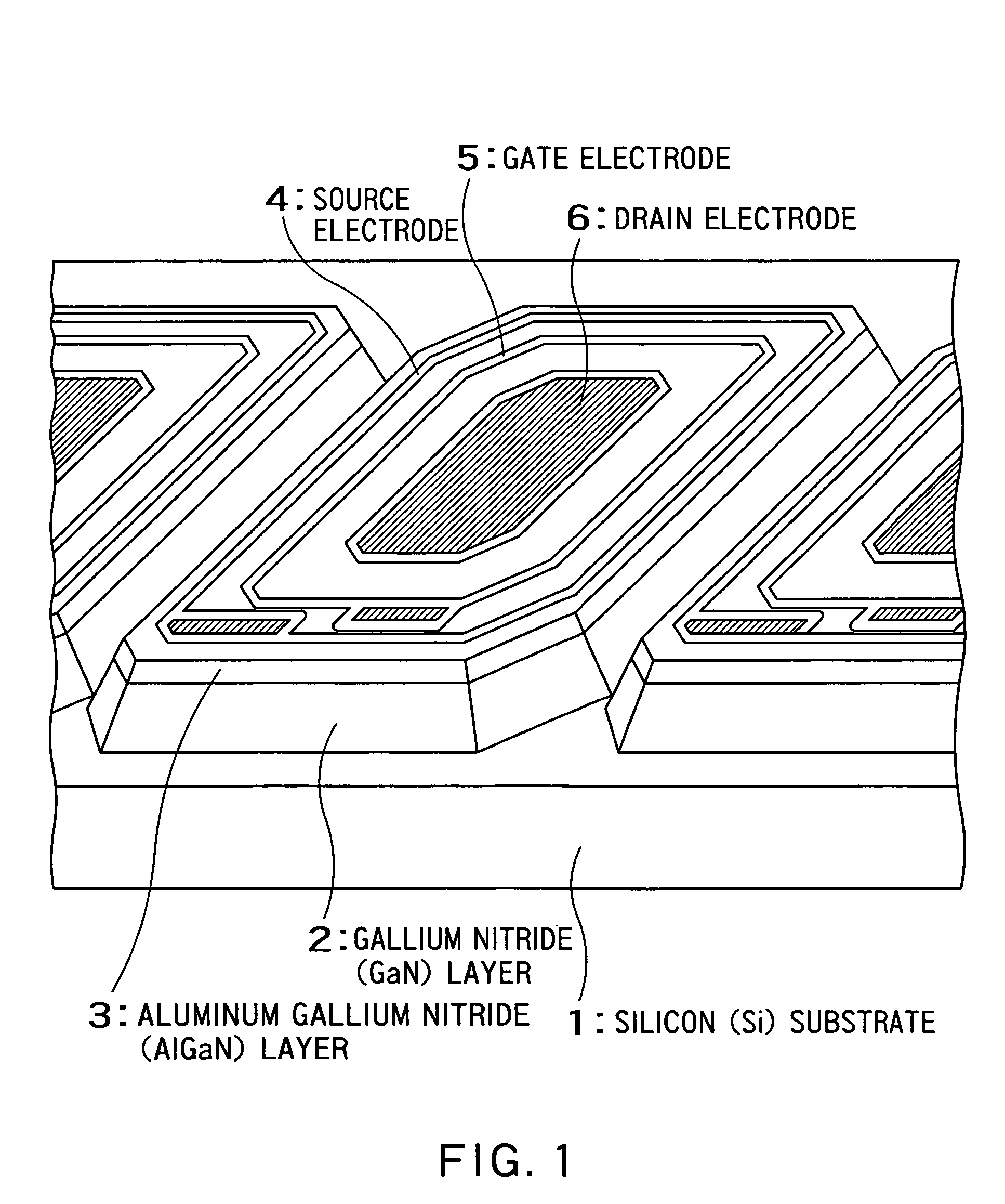

The nitride semiconductor device according to one embodiment of the present invention comprises: a silicon substrate; a first aluminum gallium nitride (AlxGa1-xN (0≦x≦1)) layer formed as a channel layer on the silicon substrate in an island shape; and a second aluminum gallium nitride (AlyGa1-yN (0≦y≦1, x≦y)) layer formed as a barrier layer of a first conductive type or i-type on the first aluminum gallium nitride layer.

Owner:KK TOSHIBA

Nitride semiconductor device such as transverse power FET for high frequency signal amplification or power control

InactiveUS7304331B2Semiconductor/solid-state device manufacturingSemiconductor devicesNon dopedSignal amplification

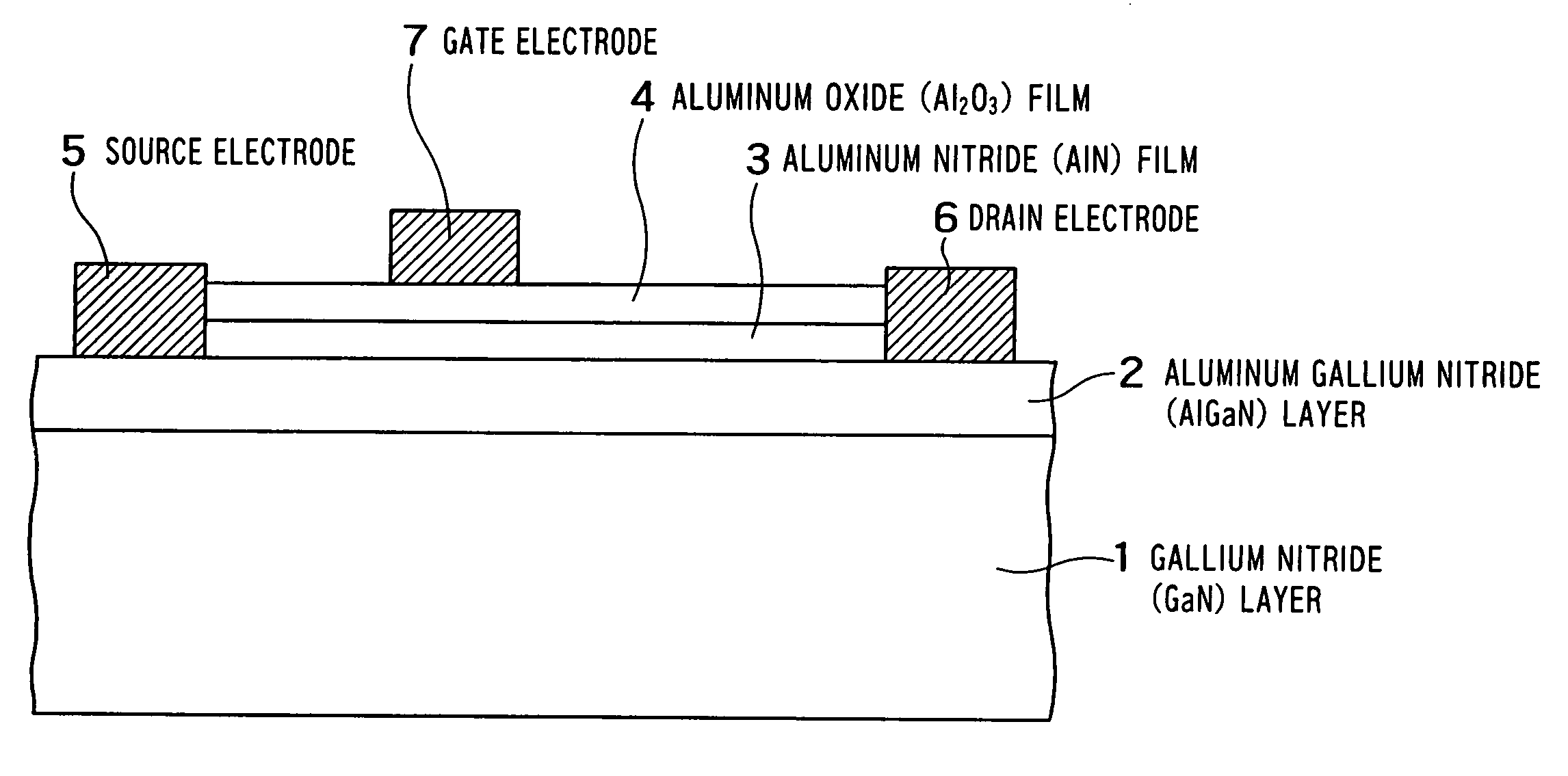

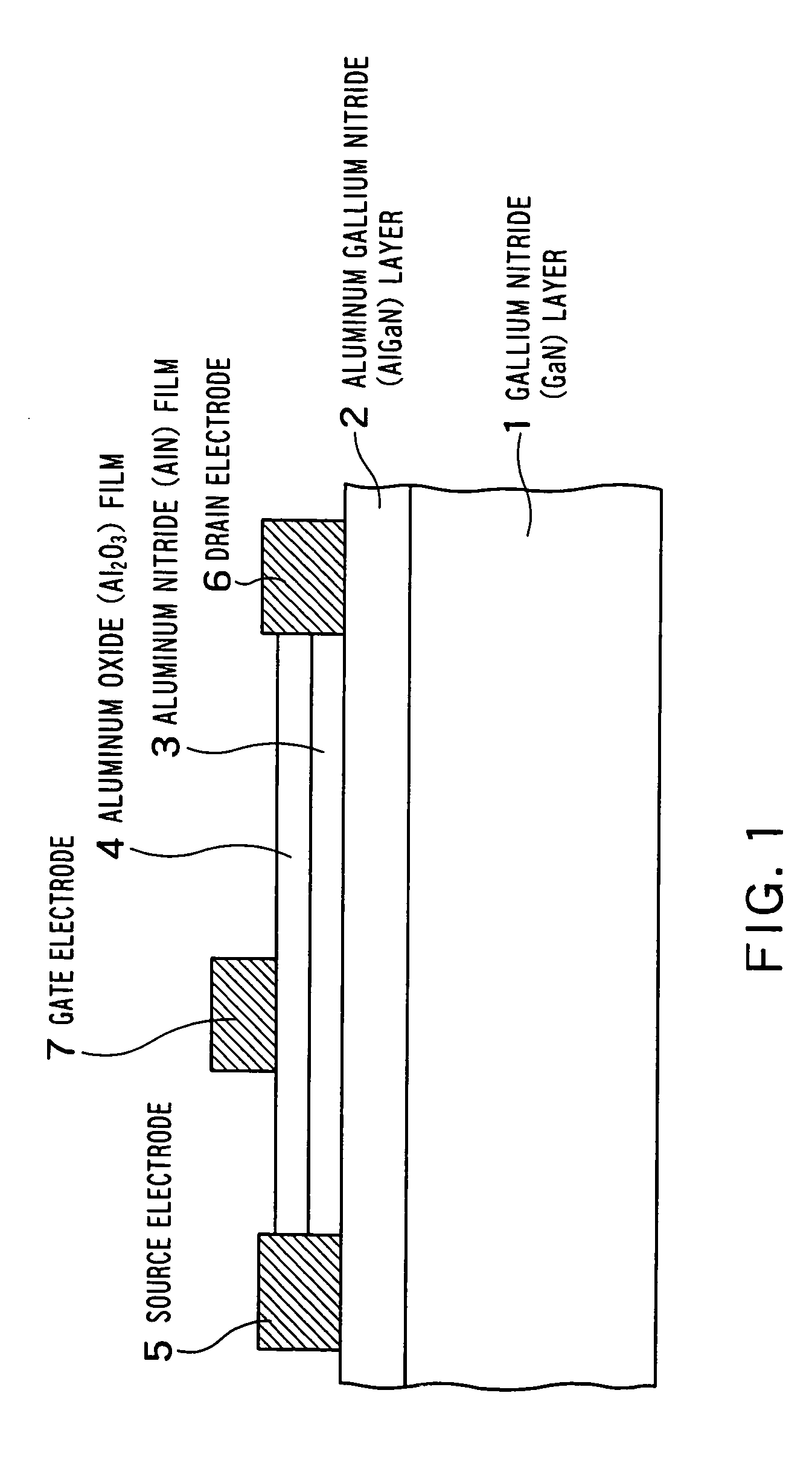

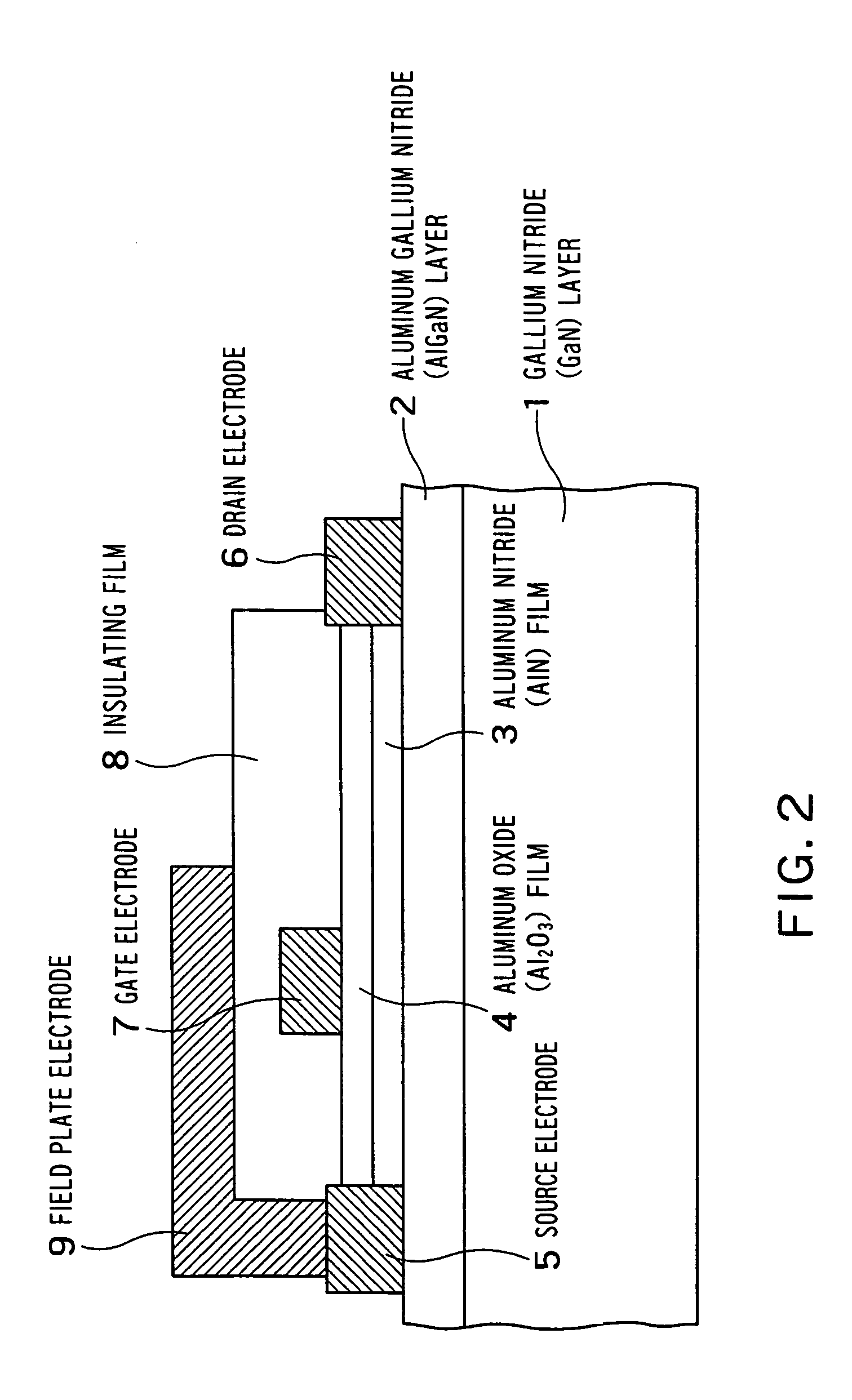

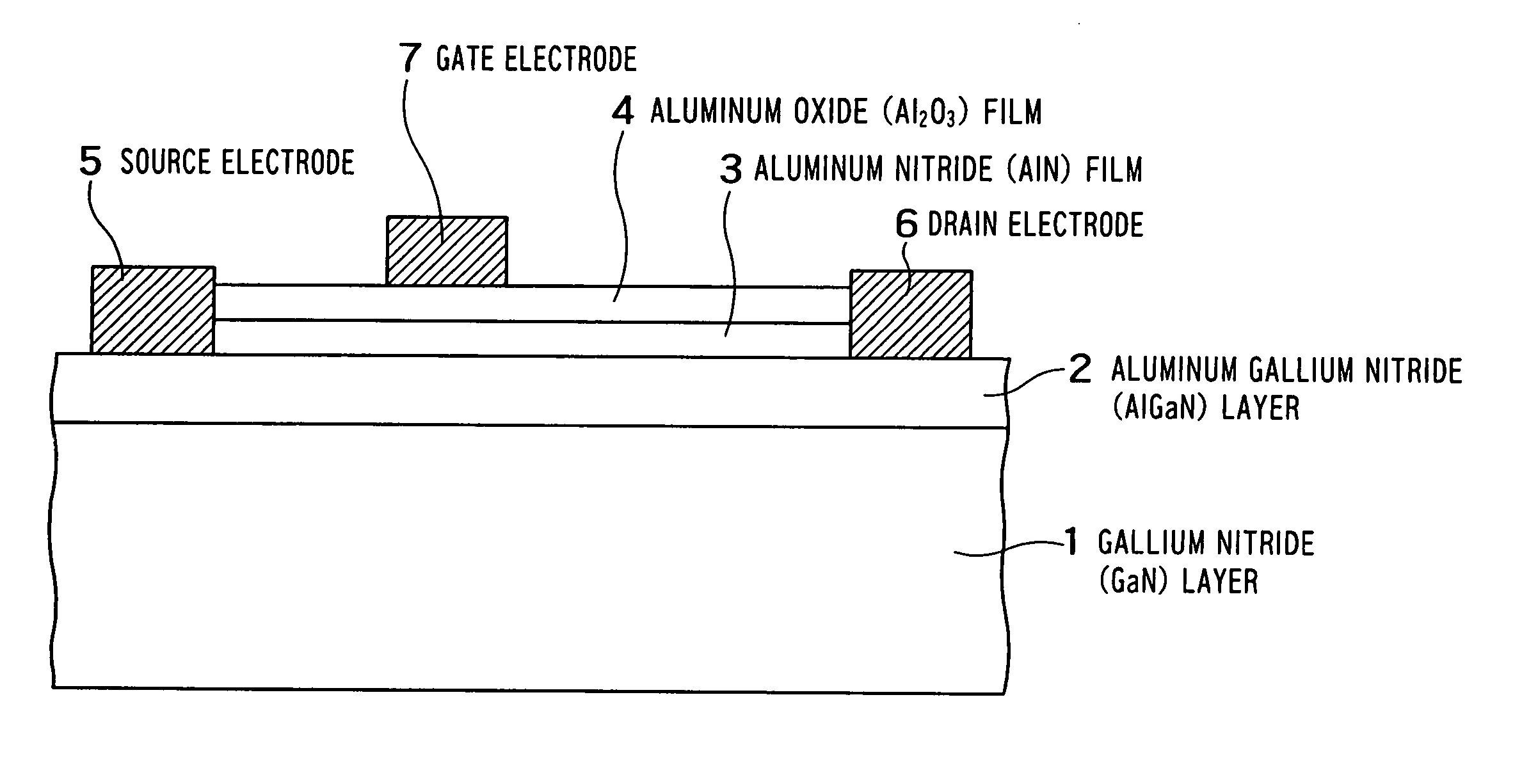

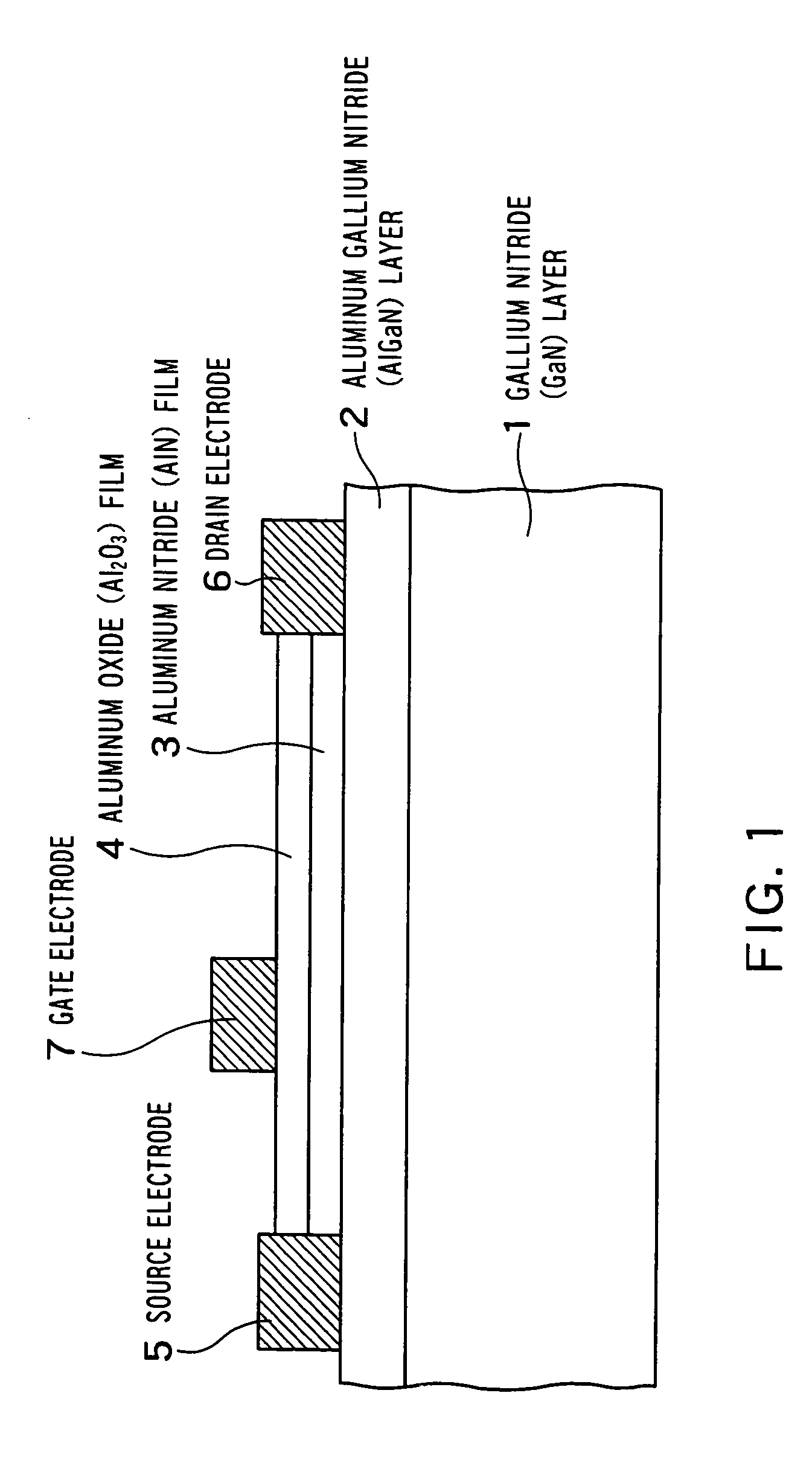

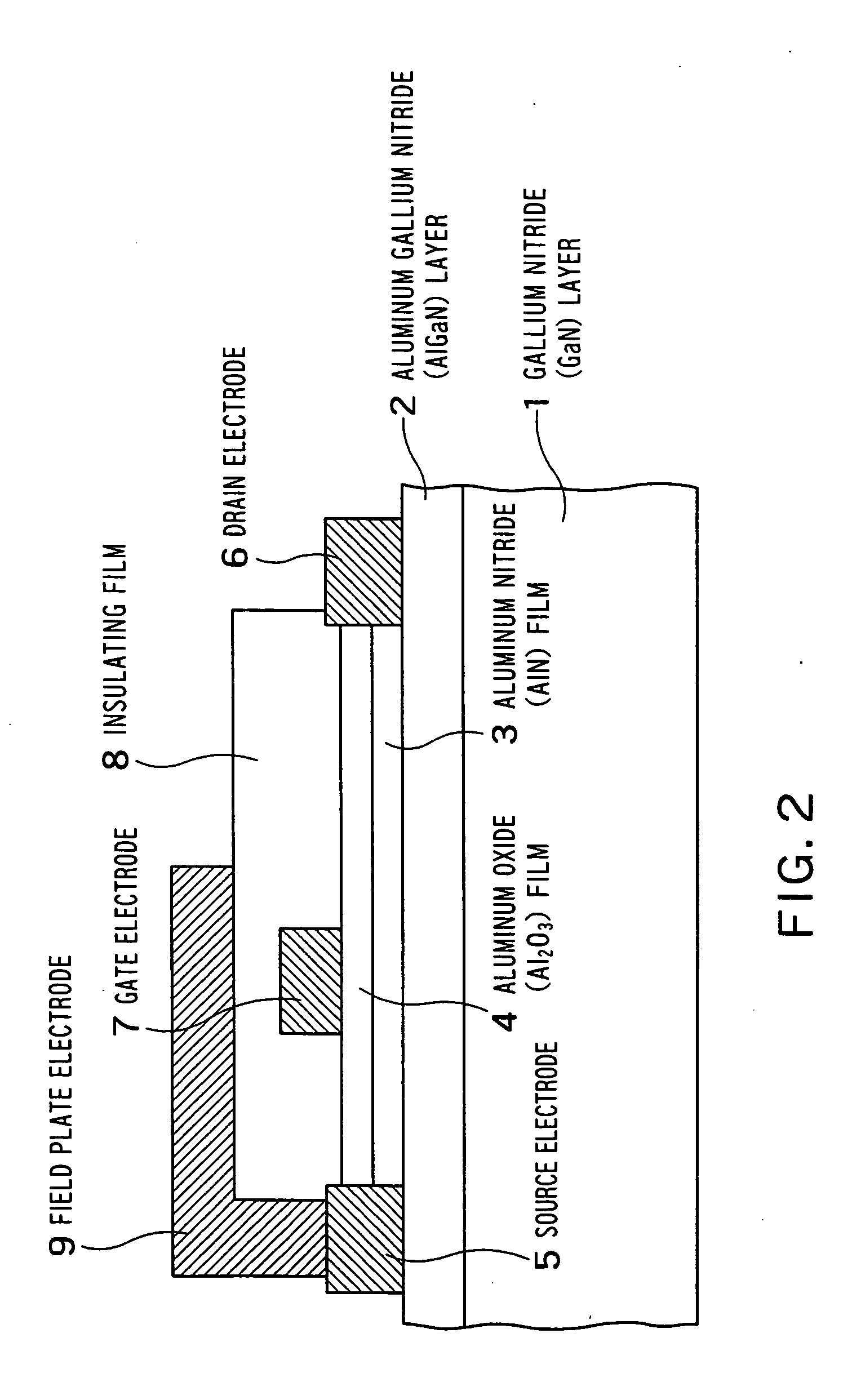

A nitride semiconductor device according to one embodiment of the present invention includes: a non-doped first aluminum gallium nitride (AlxGa1-xN (0≦x≦1)) layer which is formed as a channel layer; a non-doped or n type second aluminum gallium nitride (AlyGa1-yN (0≦y≦1, x <y)) layer which is formed on the first aluminum gallium nitride layer as a barrier layer; an aluminum nitride (AlN) film which is formed on the second aluminum gallium nitride layer as a gate insulating film lower layer; an aluminum oxide (AL2O3) film which is formed on the aluminum nitride film as a gate insulating film upper layer; a source electrode and a drain electrode which are formed as first and second main electrodes to be electrically connected to the second aluminum gallium nitride layer, respectively; and a gate electrode which is formed on the aluminum oxide film as a control electrode.

Owner:KK TOSHIBA

Nitride semiconductor device

InactiveUS20060011915A1Semiconductor/solid-state device manufacturingSemiconductor devicesNon dopedNitride semiconductors

A nitride semiconductor device according to one embodiment of the present invention comprises: a non-doped first aluminum gallium nitride (AlxGa1-xN (0≦x≦1)) layer which is formed as a channel layer; a non-doped or n type second aluminum gallium nitride (AlyGa1-yN (0≦x≦1,x<y)) layer which is formed on the first aluminum gallium nitride layer as a barrier layer; an aluminum nitride (AlN) film which is formed on the second aluminum gallium nitride layer as a gate insulating film lower layer; an aluminum oxide (Al2O3) film which is formed on the aluminum nitride film as a gate insulating film upper layer; a source electrode and a drain electrode which are formed as first and second main electrodes to be electrically connected to the second aluminum gallium nitride layer, respectively; and a gate electrode which is formed on the aluminum oxide film as a control electrode.

Owner:KK TOSHIBA

Nitride semiconductor device

The nitride semiconductor device according to one embodiment of the present invention comprises: a silicon substrate; a first aluminum gallium nitride (AlxGa1−xN (0≦x≦1)) layer formed as a channel layer on the silicon substrate in an island shape; and a second aluminum gallium nitride (AlyGa1−yN (0≦y≦1, x<y)) layer formed as a barrier layer of a first conductive type or i-type on the first aluminum gallium nitride layer.

Owner:KK TOSHIBA

Oxidized low density lipoprotein sensing device for gallium nitride process

InactiveUS7759710B1Detecting the level of protein oxidation in human body quickly, accurately and easilyMaterial analysis by electric/magnetic meansCatheterOxidized low density lipoproteinGallium nitride

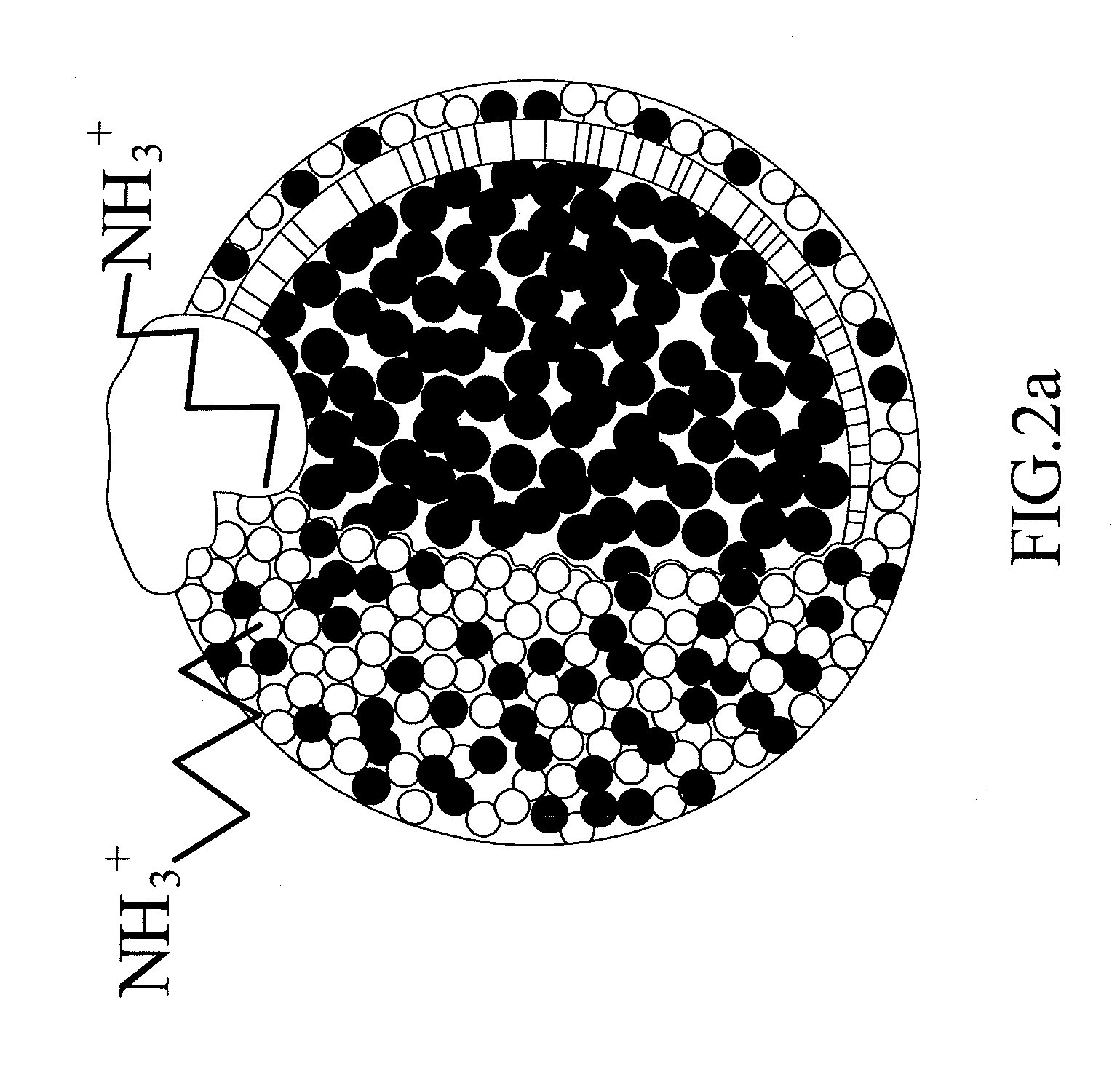

An oxidized low density lipoprotein sensing device for a gallium nitride process is a GaN HEMT device including: a gateless AlGaN / GaN sensing transistor device, a testing window, a source, a drain, two metal connecting wires and a passivation layer. The gateless AlGaN / GaN sensing transistor device has an epitaxial wafer structure including a GaN layer and an aluminum gallium nitride layer. The testing window is disposed on the epitaxial wafer structure. The metal connecting wire is disposed on a source and a drain. The passivation layer is covered onto a surface of the sensing device except the testing window. A built-in piezoelectric field is created by the properties of FET and the polarization effect of AlGaN / GaN to achieve the effect of sensing the level of oxidizing proteins in human body quickly, accurately and easily.

Owner:CHANG GUNG UNIVERSITY

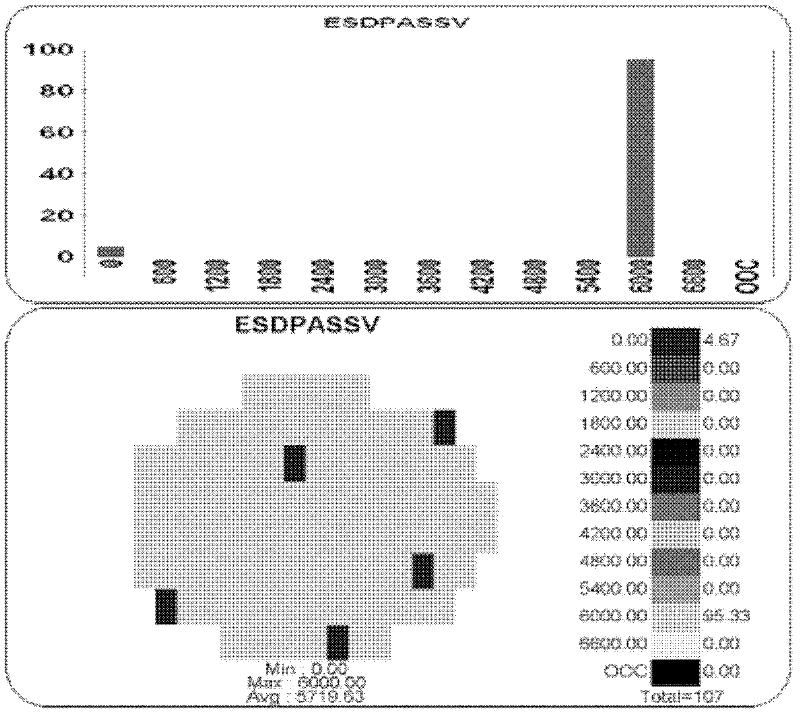

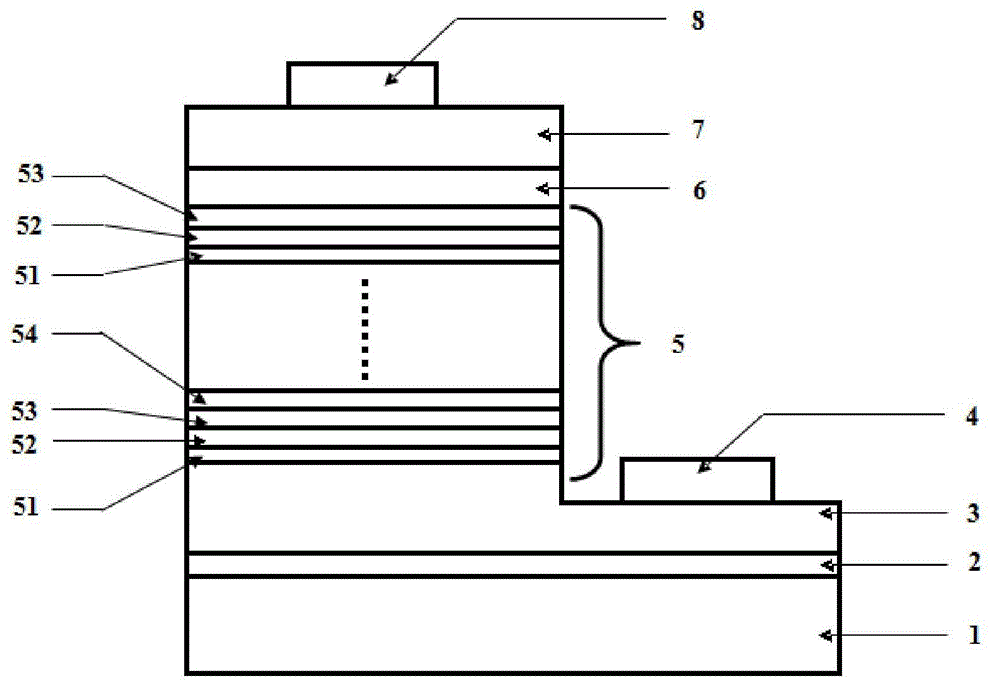

Method for enhancing antistatic ability of GaN-based light-emitting diode

ActiveCN101645480AImprove crystal qualityImprove antistatic performanceSemiconductor devicesGalliumContact layer

The invention discloses a method for enhancing the antistatic ability of GaN-based light-emitting diode. The epitaxial wafer structure of the light-emitting diode sequentially comprises an underlay, alow-temperature buffer layer, an unadulterated GaN high-temperature buffer layer, an aluminum gallium nitride / GaN superlattice structure, the unadulterated GaN high-temperature buffer layer, an N type contact layer, an N type GaN conductive layer, a light-emitting layer multiple quantum well structure MQW, a P type aluminum gallium nitride electric barrier layer, a P type GaN conductive layer and a P type contact layer in a sequence from down to up. In the invention, the aluminum gallium nitride / GaN superlattice periodic structure is inserted in the unalloyed GaN high temperature buffer layer. The insertion of the aluminum gallium nitride / GaN superlattice periodic structure can effectively improve crystal quality of materials, thereby enhancing the antistatic ability of the GaN-based light-emitting diode and improving the reliability and the stability of devices.

Owner:HC SEMITEK CORP

High voltage GaN-based transistor structure

ActiveUS7026665B1Improve performanceImprove passivation effectSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideHigh pressure

The present invention relates to a high voltage and high power gallium nitride (GaN) transistor structure. In general, the GaN transistor structure includes a sub-buffer layer that serves to prevent injection of electrons into a substrate during high voltage operation, thereby improving performance of the GaN transistor structure during high voltage operation. Preferably, the sub-buffer layer is aluminum nitride, and the GaN transistor structure further includes a transitional layer, a GaN buffer layer, and an aluminum gallium nitride Schottky layer.

Owner:QORVO US INC

Group III nitride semiconductor stacked structure and production method thereof

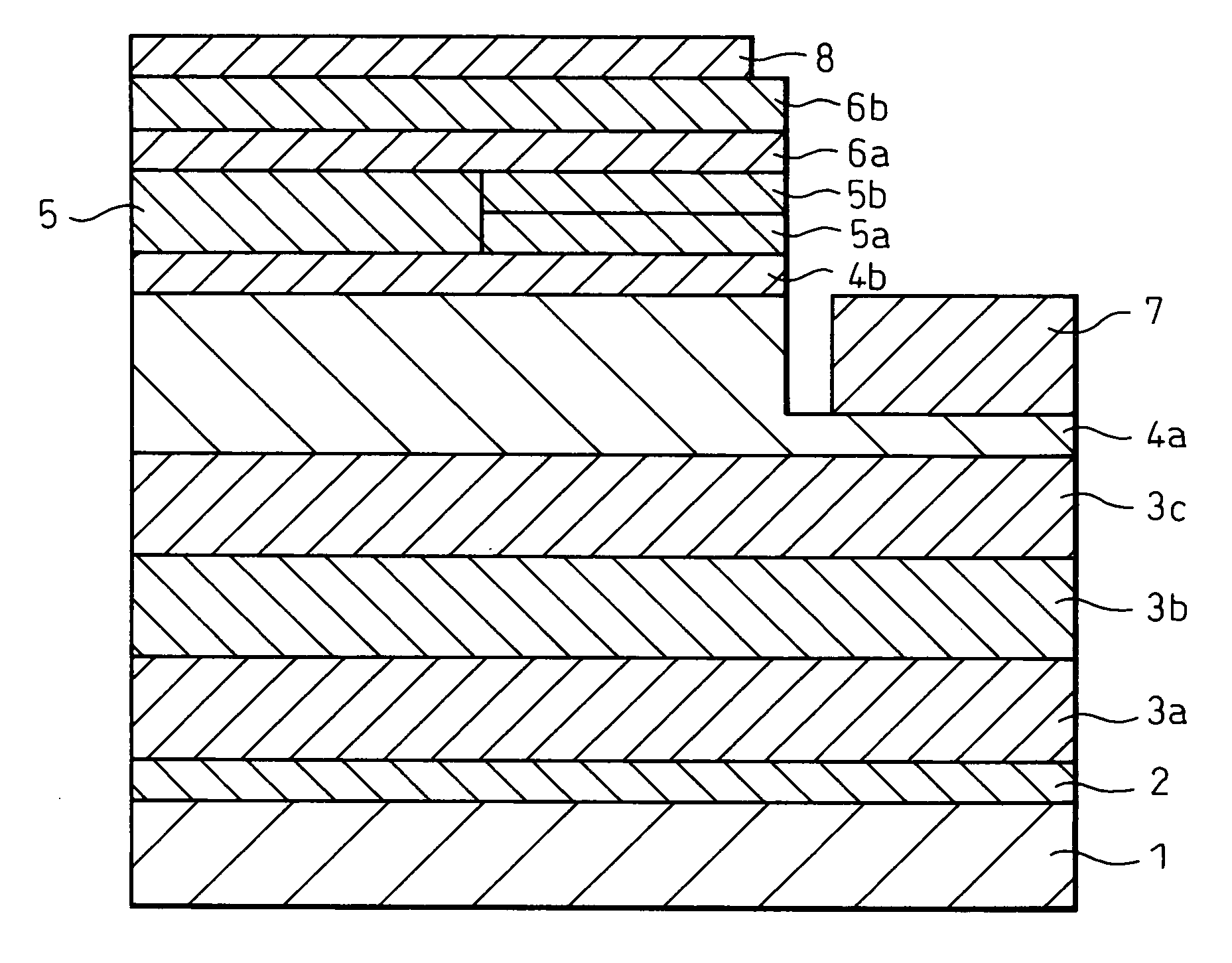

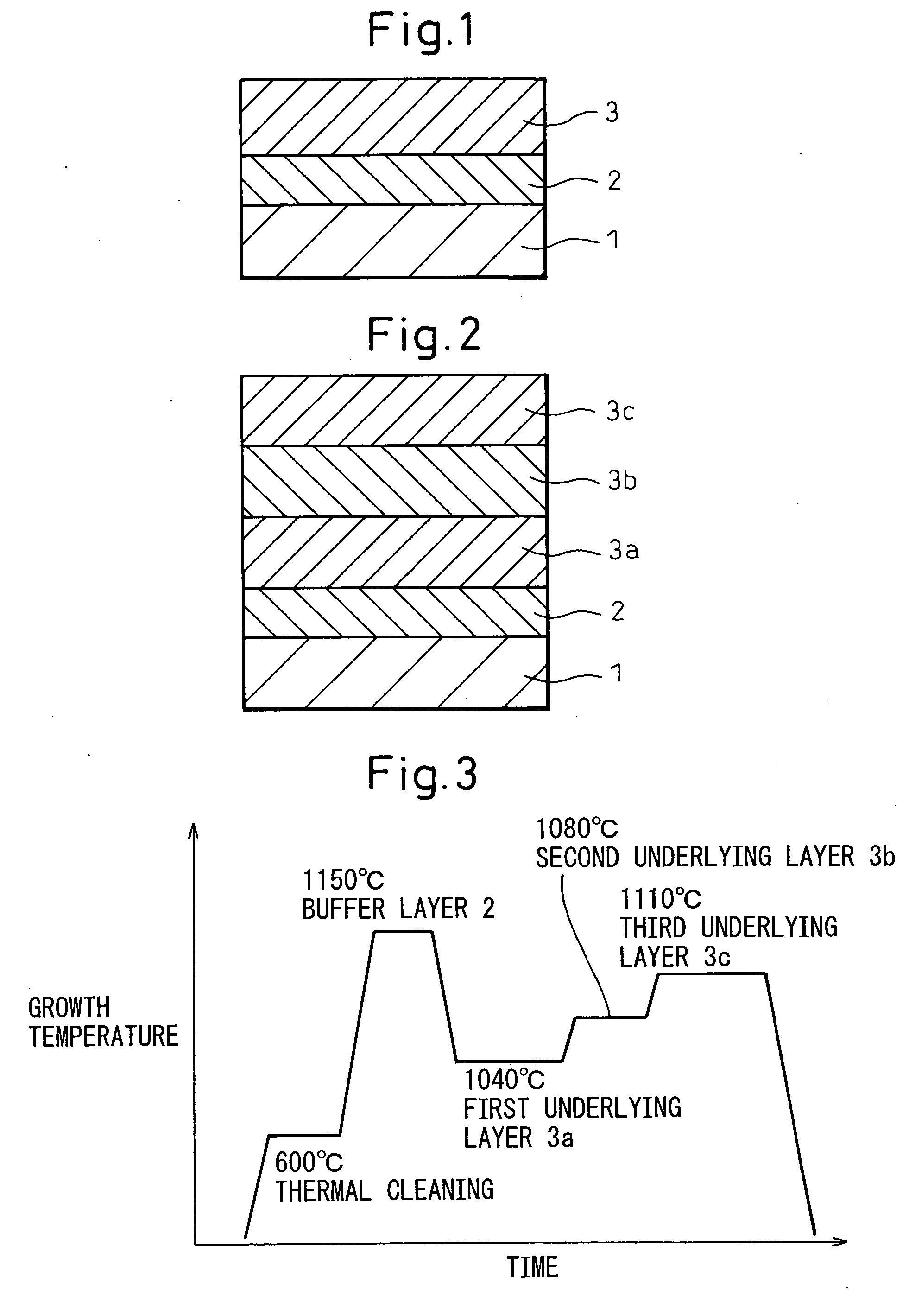

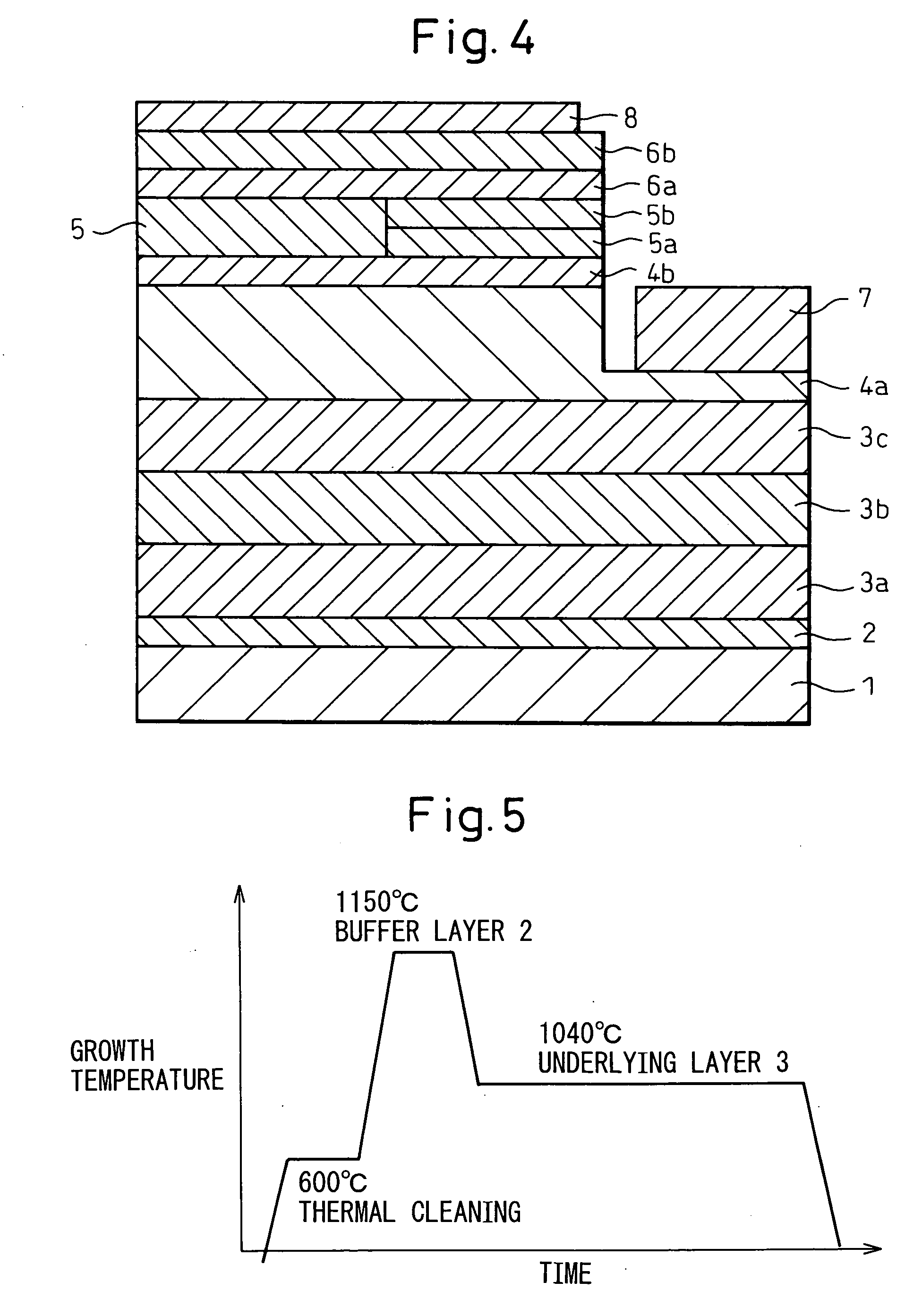

ActiveUS20070080369A1Simple methodInexpensive and highly efficientSolid-state devicesSemiconductor/solid-state device manufacturingNitrogenGallium

An object of the present invention is to provide a group III nitride semiconductor stacked structure having a high-quality A-plane group III nitride semiconductor layer on an R-plane sapphire substrate. The inventive group III nitride semiconductor stacked structure comprises a substrate composed of R-plane sapphire (α-Al2O3), a buffer layer composed of aluminum gallium nitride (AlxGa1−xN: 0≦X≦1) formed on said substrate and an underlying layer composed of an A-plane group III nitride semiconductor (AlxGayInzN1−aMa: 0≦X≦1, 0≦Y≦1, 0≦Z≦1, and X+Y+Z=1; wherein, M represents a group V element other than nitrogen (N), and 0≦a≦1) formed on said buffer layer, wherein the pit density of the surface of said underlying layer is 1×1010 cm−2 or less.

Owner:TOYODA GOSEI CO LTD

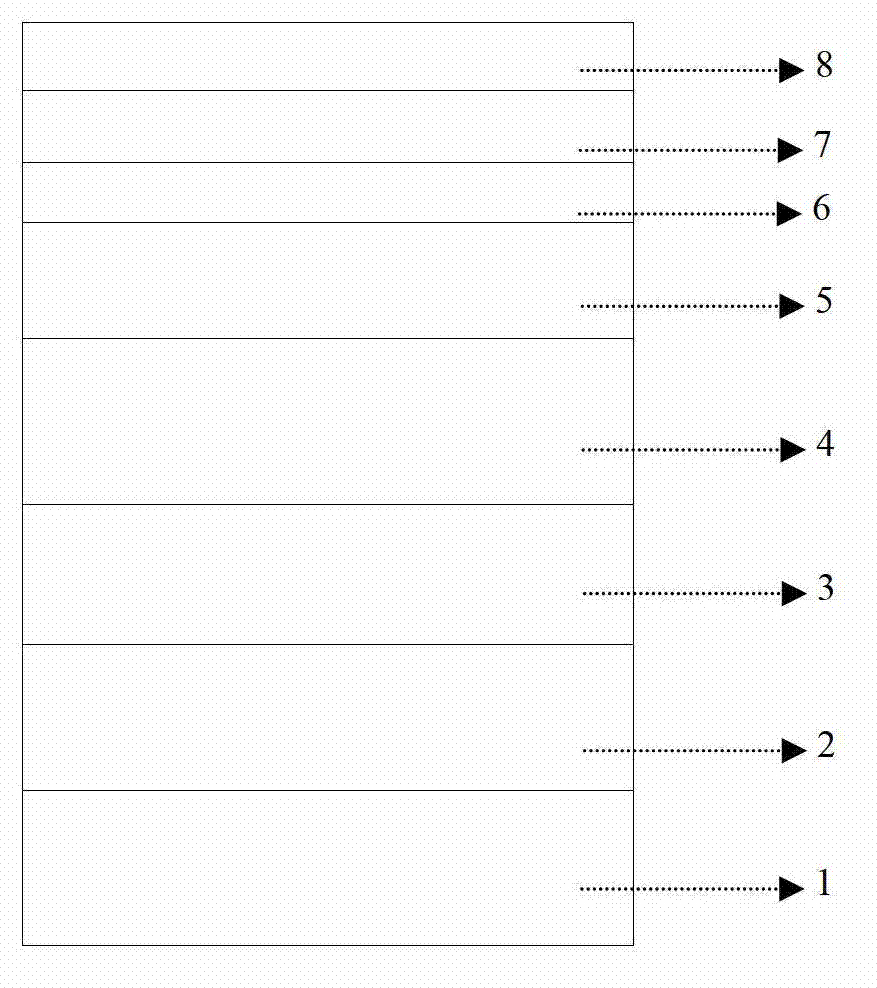

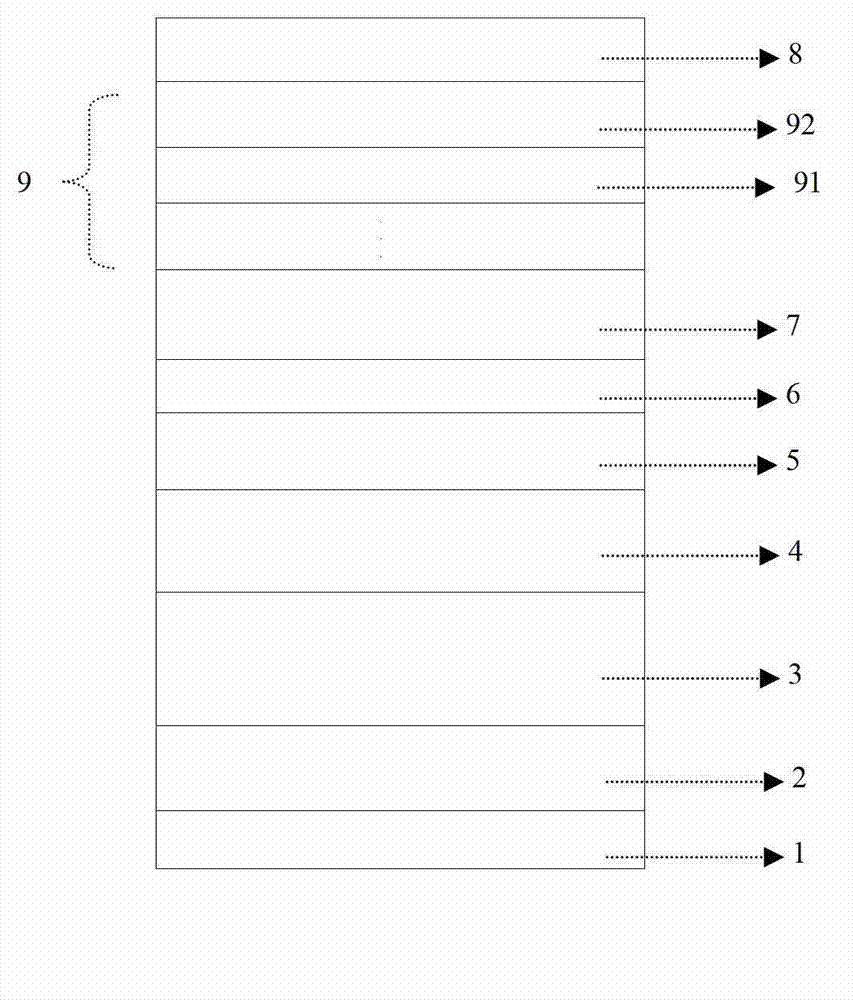

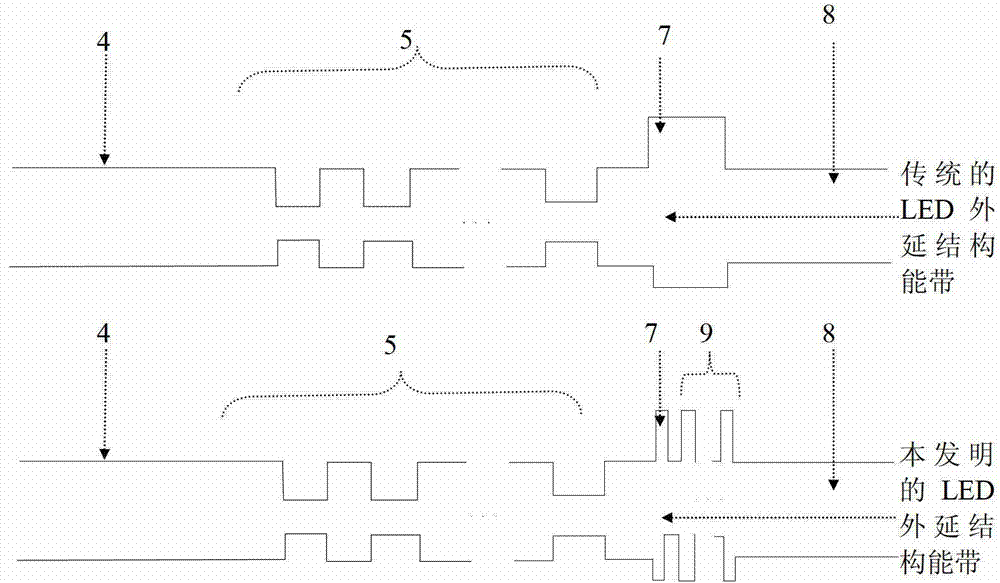

LED (Light Emitting Diode) epitaxial structure with P (Positive) type superlattice and preparation method thereof

ActiveCN103050592AStop SpillFacilitate horizontal expansionSemiconductor devicesPotential wellHigh density

The invention discloses an LED (Light Emitting Diode) epitaxial structure with a P (Positive) type superlattice and a preparation method thereof. The epitaxial structure comprises a substrate, wherein a GaN (Gallium Nitride) buffer layer, an undoped GaN layer, an n (negative) type GaN layer, a multi-quantum well luminous layer, a first P type GaN layer, a P type AlGaN (Aluminium Gallium Nitride) electronic blocking layer and a second P type GaN layer are sequentially arranged on the substrate from bottom to top, and the P type superlattice formed by a PInGaN (P type Indium Gallium Nitride) potential well layer and a PAlGaN potential barrier layer in a periodic interactive overlapping way is arranged between the P type AlGaN electronic blocking layer and the second P type GaN layer. The PInGaN potential well layer in the P type superlattice generates and constrains a great number of holes for the formation of a two-dimensional hole high-density state; the PAlGaN potential barrier layer hinders the escape of the holes; in such a way, the transverse spreading of the holes is improved, the electron overflow can be prevented, the hole injection efficiency is increased and the electron and hole recombination probability is improved; and therefore, the brightness of a chip can be improved by 5-10%.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

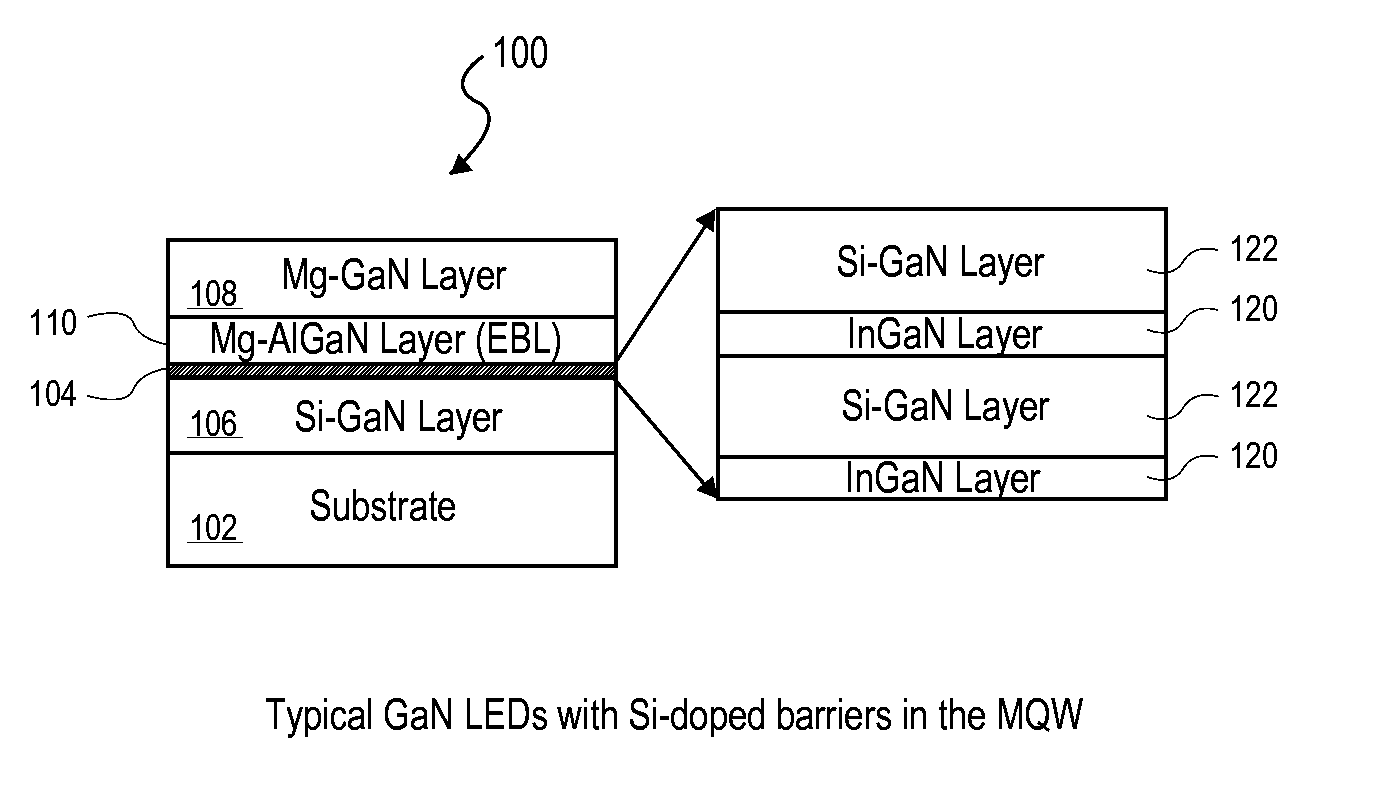

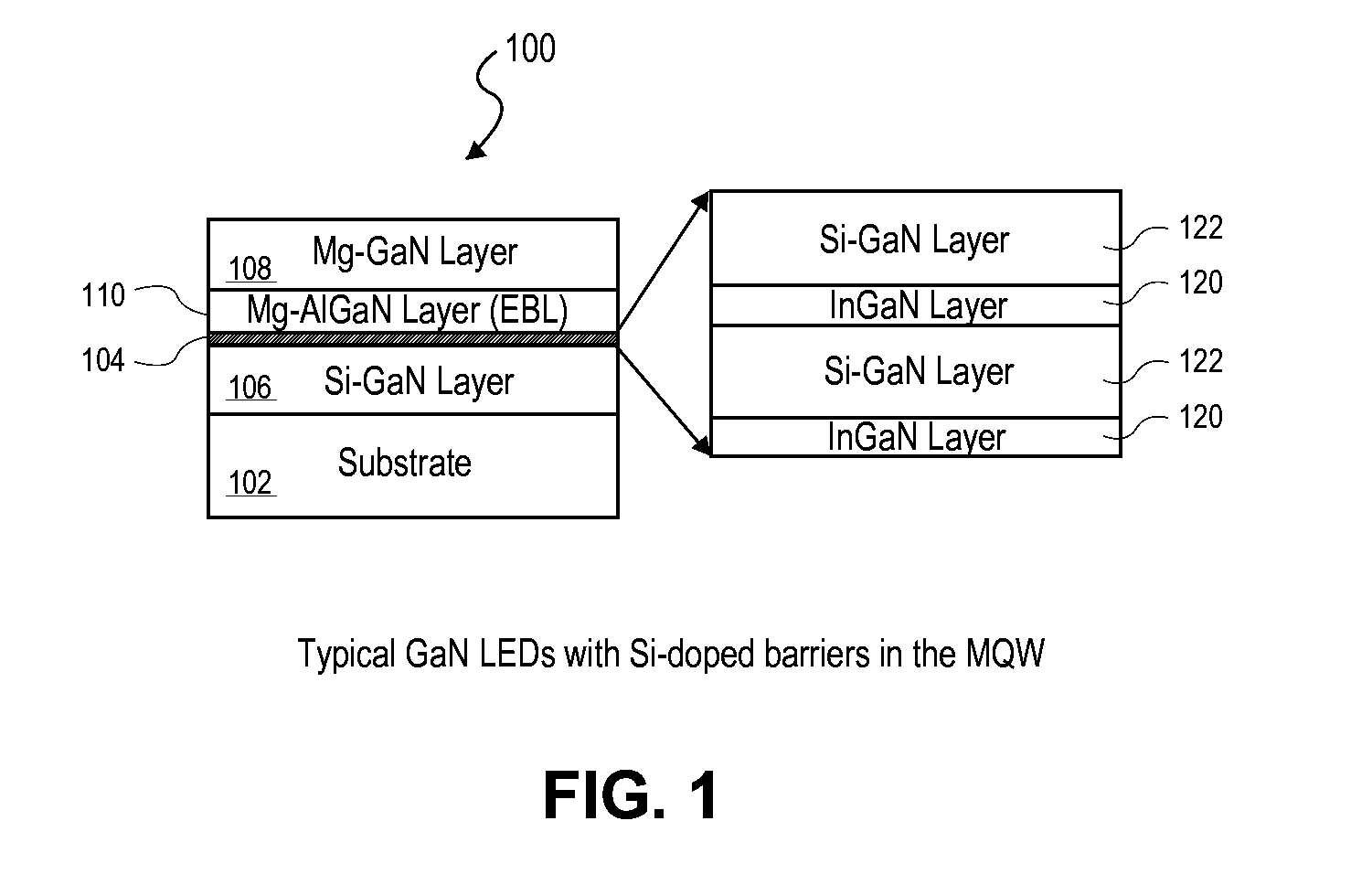

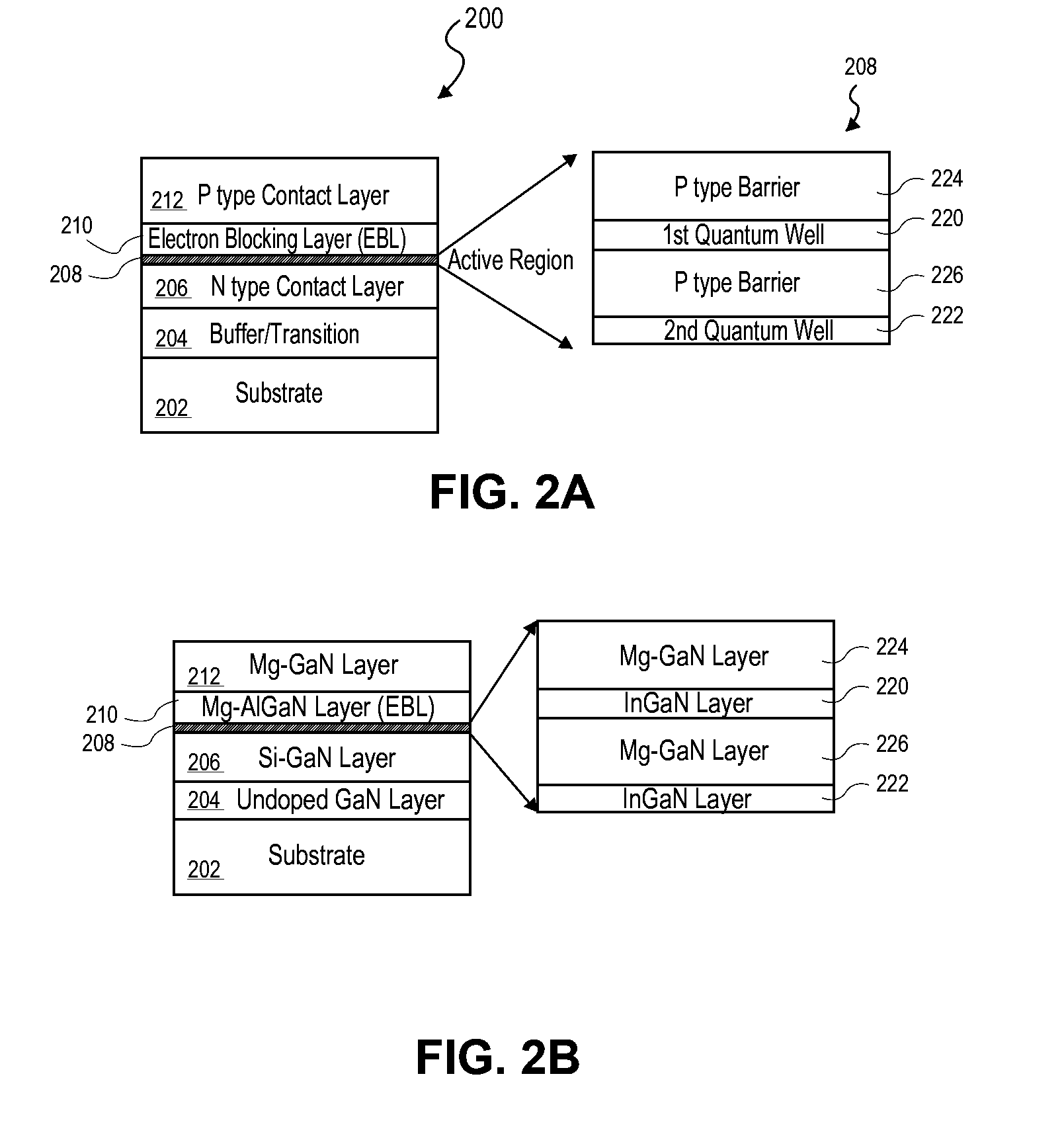

Light emitting diode with enhanced quantum efficiency and method of fabrication

InactiveUS20120235116A1Low costIncrease varietyPolycrystalline material growthConductive materialIndiumAlloy

One embodiment of a quantum well structure comprises an active region including active layers that comprise quantum wells and barrier layers wherein some or all of the active layers are p type doped. P type doping some or all of the active layers improves the quantum efficiency of III-V compound semiconductor light emitting diodes by locating the position of the P-N junction in the active region of the device thereby enabling the dominant radiative recombination to occur within the active region. In one embodiment, the quantum well structure is fabricated in a cluster tool having a hydride vapor phase epitaxial (HVPE) deposition chamber with a eutectic source alloy. In one embodiment, the indium gallium nitride (InGaN) layer and the magnesium doped gallium nitride (Mg—GaN) or magnesium doped aluminum gallium nitride (Mg—AlGaN) layer are grown in separate chambers by a cluster tool to avoid indium and magnesium cross contamination. Doping of group III-nitrides by hydride vapor phase epitaxy using group III-metal eutectics is also described. In one embodiment, a source is provided for HVPE deposition of a p-type or an n-type group III-nitride epitaxial film, the source including a liquid phase mechanical (eutectic) mixture with a group III species. In one embodiment, a method is provided for performing HVPE deposition of a p-type or an n-type group III-nitride epitaxial film, the method including using a liquid phase mechanical (eutectic) mixture with a group III species.

Owner:APPLIED MATERIALS INC

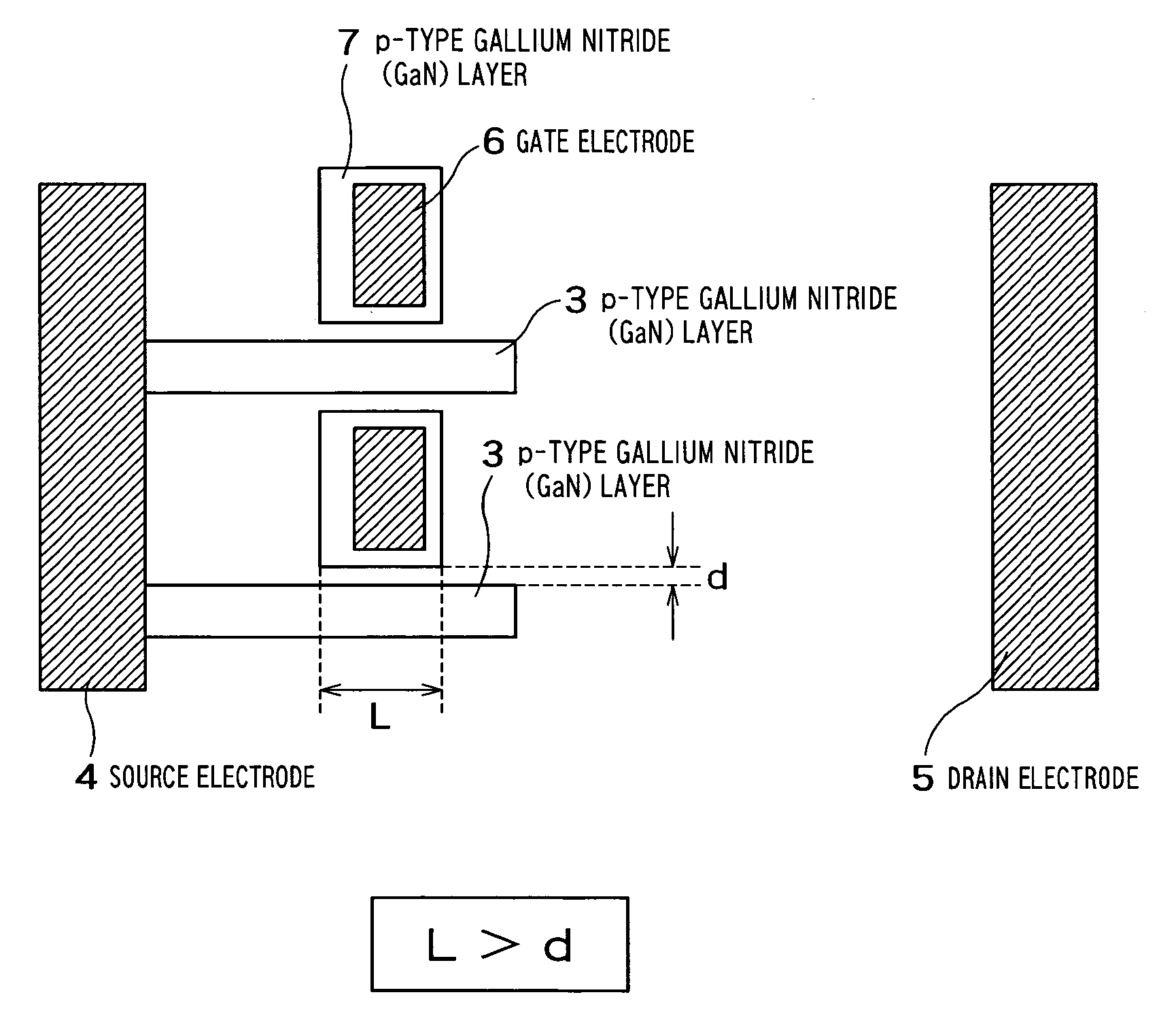

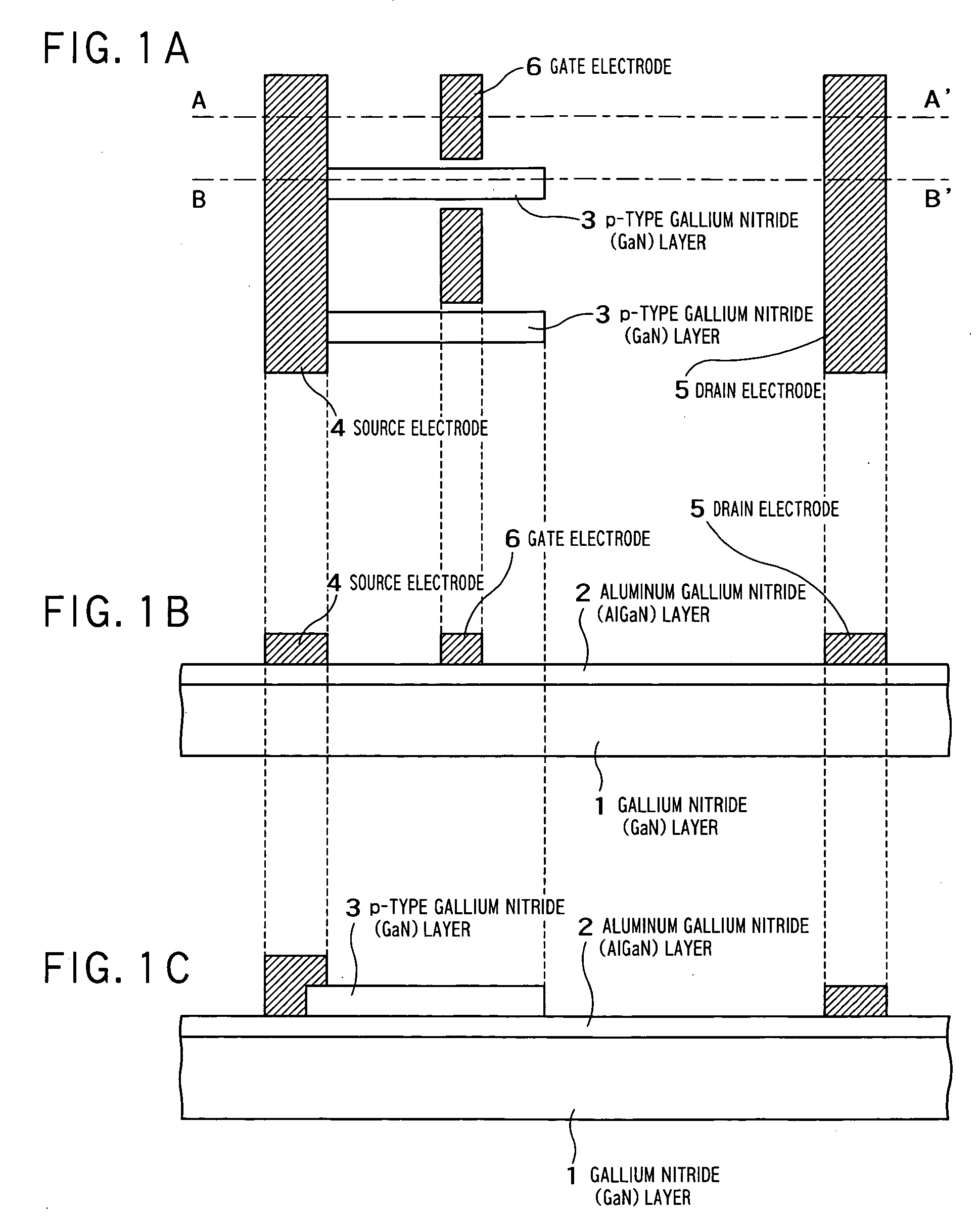

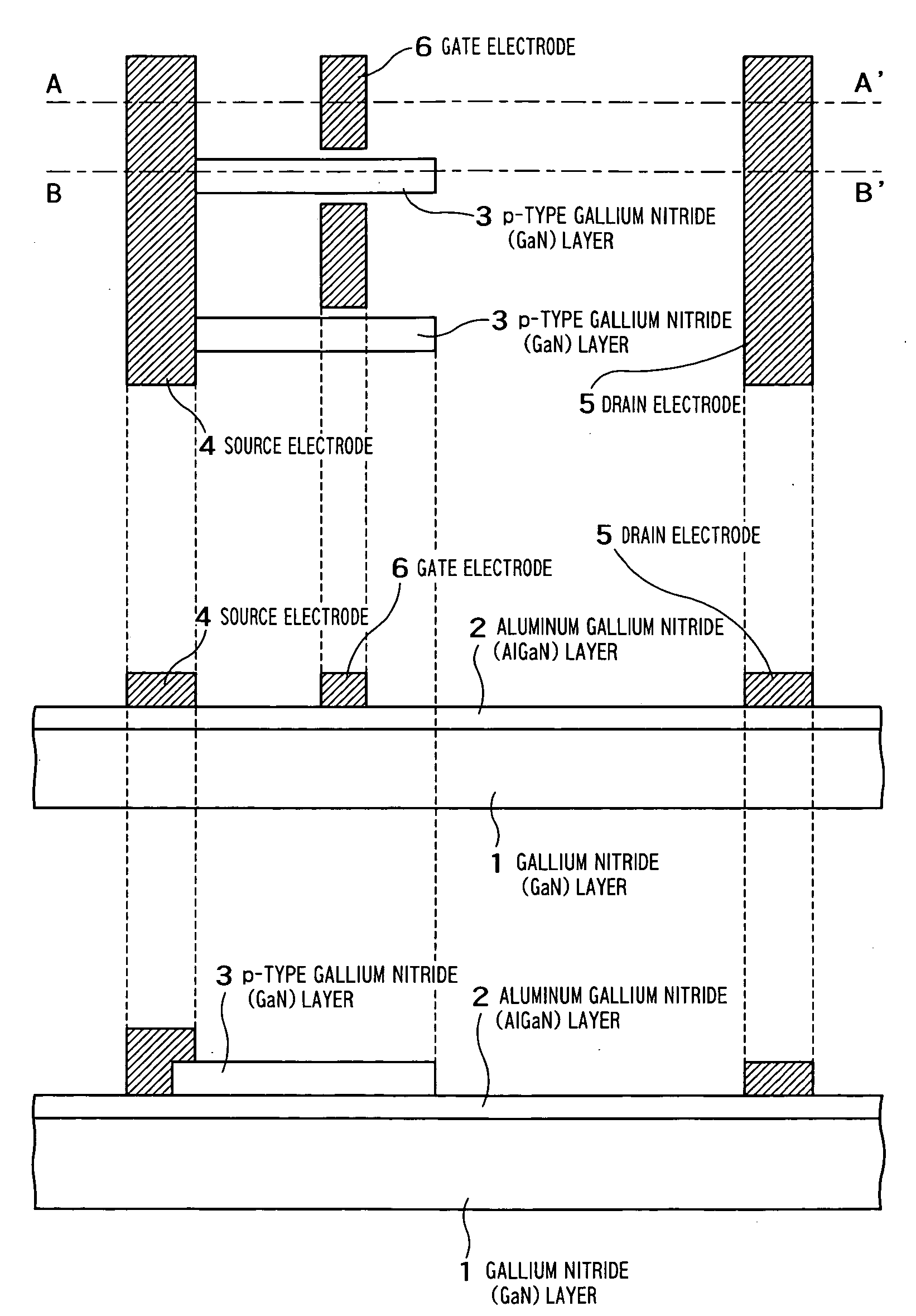

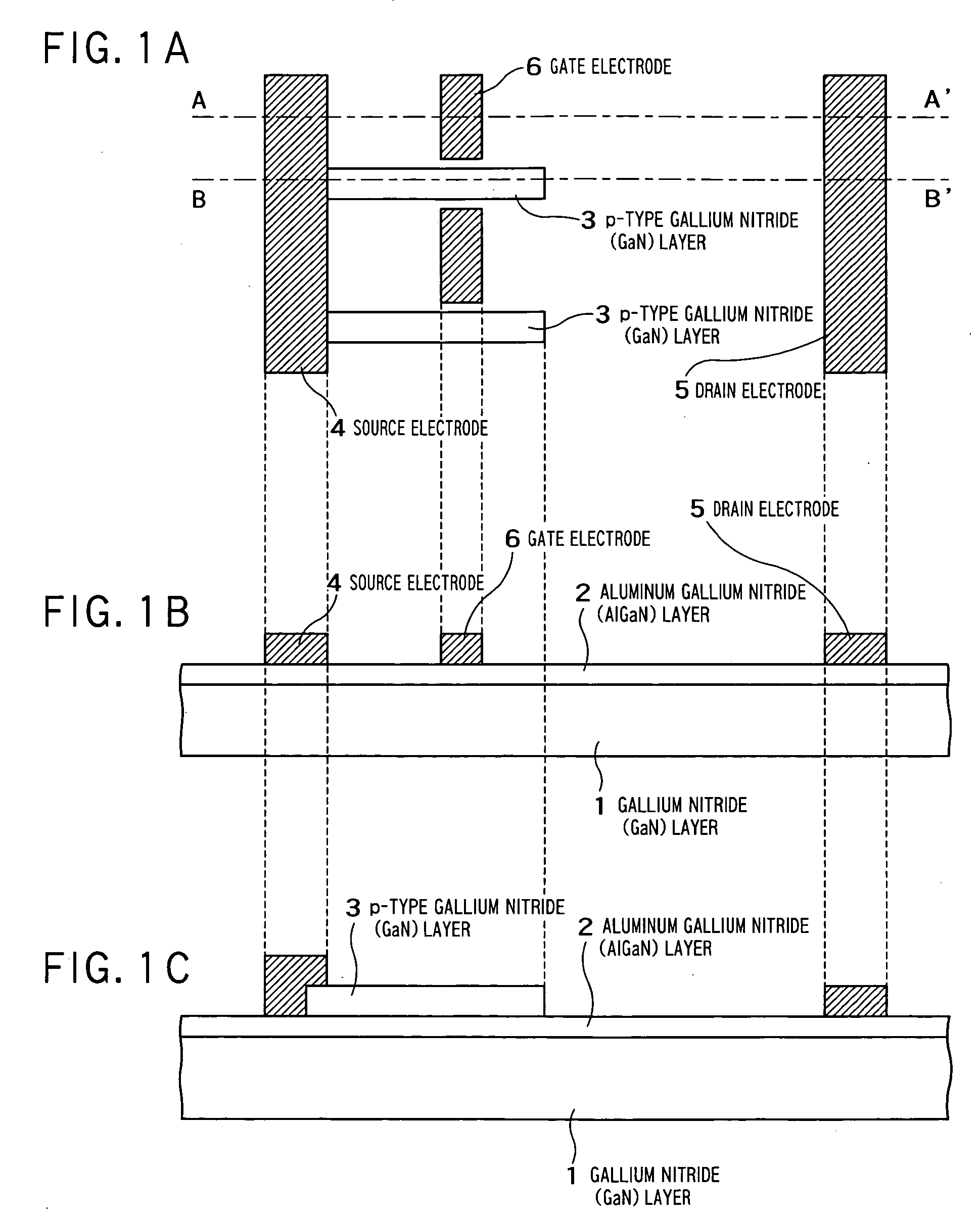

Nitride semiconductor device

In a nitride semiconductor device according to one embodiment of the invention, a p-type gallium nitride (GaN) layer electrically connected to a source electrode and extending and projecting to a drain electrode side with respect to a gate electrode is formed on an undoped or n-type aluminum gallium nitride (AlGaN) layer serving as a barrier layer.

Owner:KK TOSHIBA

High-power gallium nitride based LED with novel structure

InactiveCN101740691AEffective mass is smallIncrease concentrationSemiconductor devicesIndiumGallium nitride

The invention relates to a gallium nitride based light-emitting diode, in particular to a high-power gallium nitride based light-emitting diode structure; the high-power gallium nitride based light-emitting diode comprises a substrate, an N-type gallium nitride layer arranged on the substrate, a AlGaN cavity barrier layer arranged on a high table top of the N-type gallium nitride layer, an asymmetrical multiple quantum well active layer arranged on the cavity barrier layer, a P-type gallium nitride layer arranged on the asymmetrical multiple quantum well active layer, a P+-InGaN conducting layer arranged on the P-type gallium nitride layer, and an indium titanium oxide electrode layer which is arranged on the P+-InGaN conducting layer from bottom to top; a silicon dioxide passivation layer is arranged on the top surface of the whole light-emitting diode and the side surface connected to the high and low table tops, an N electrode is arranged on the lower table top of the N-type gallium nitride layer, and a P-electrode is arranged in the middle of the indium titanium oxide electrode layer. The light-emitting diode structure can improve the injection efficiency of the cavity and improve the photoelectric conversion efficiency.

Owner:SUZHOU NANOJOIN PHOTONICS

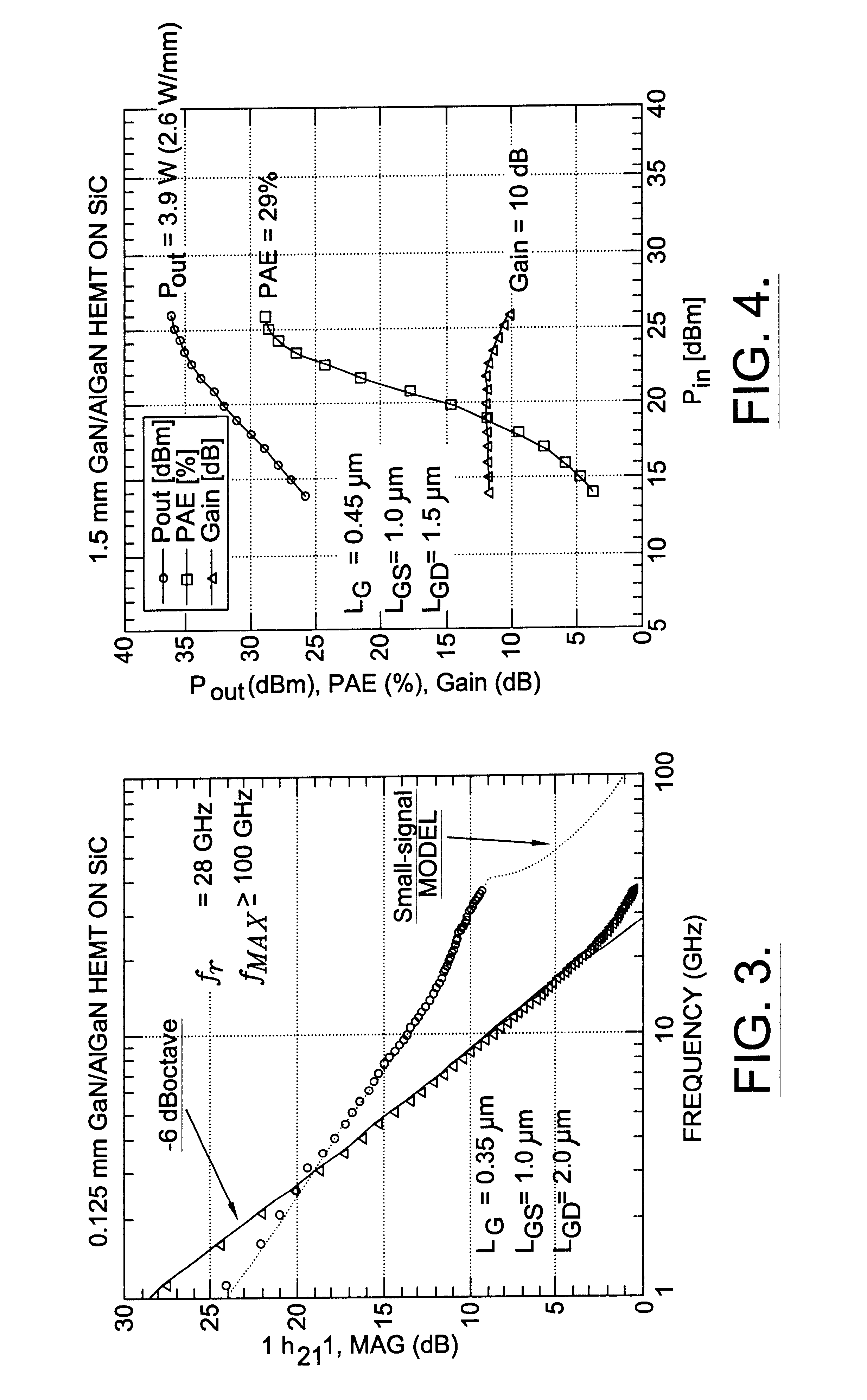

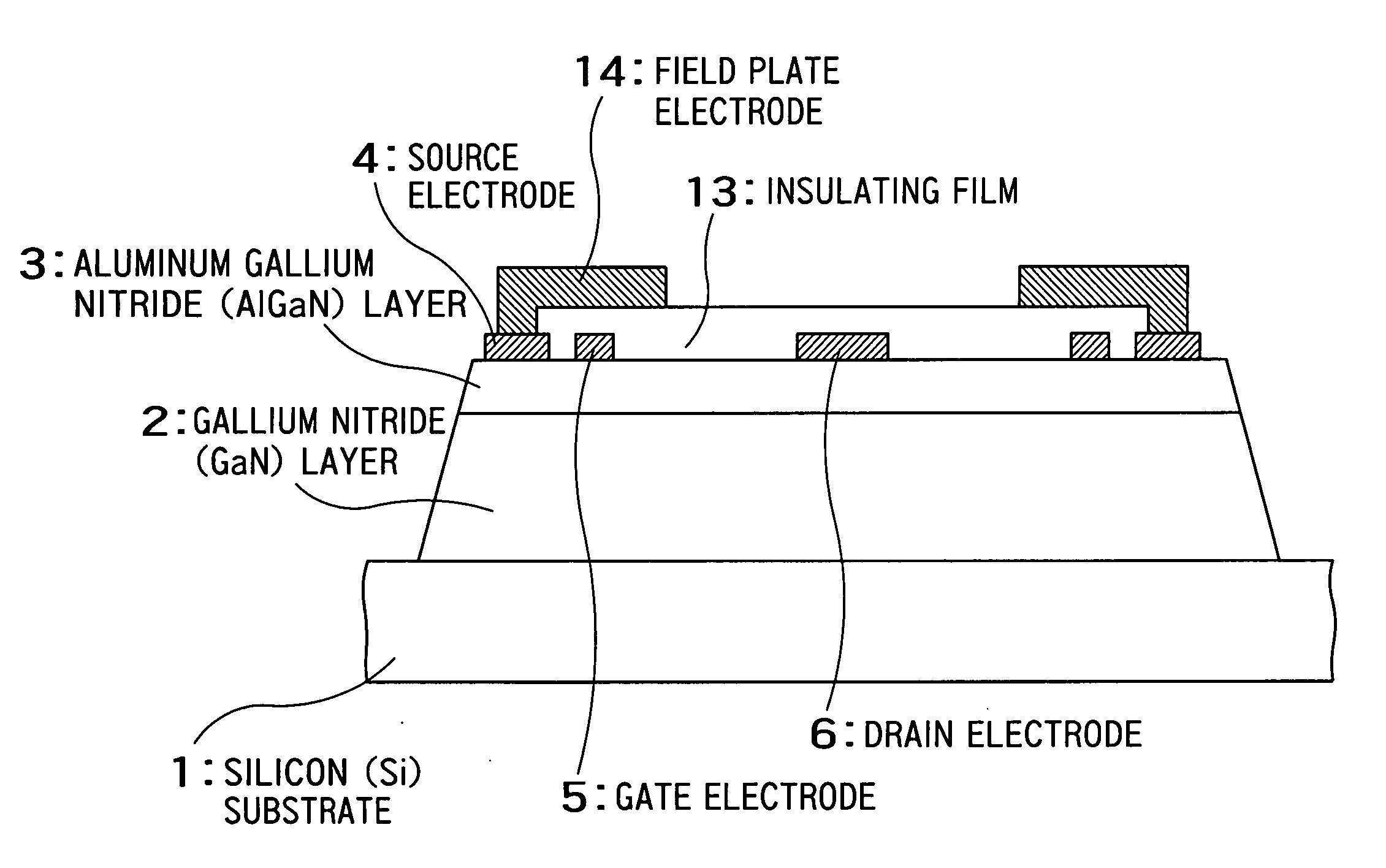

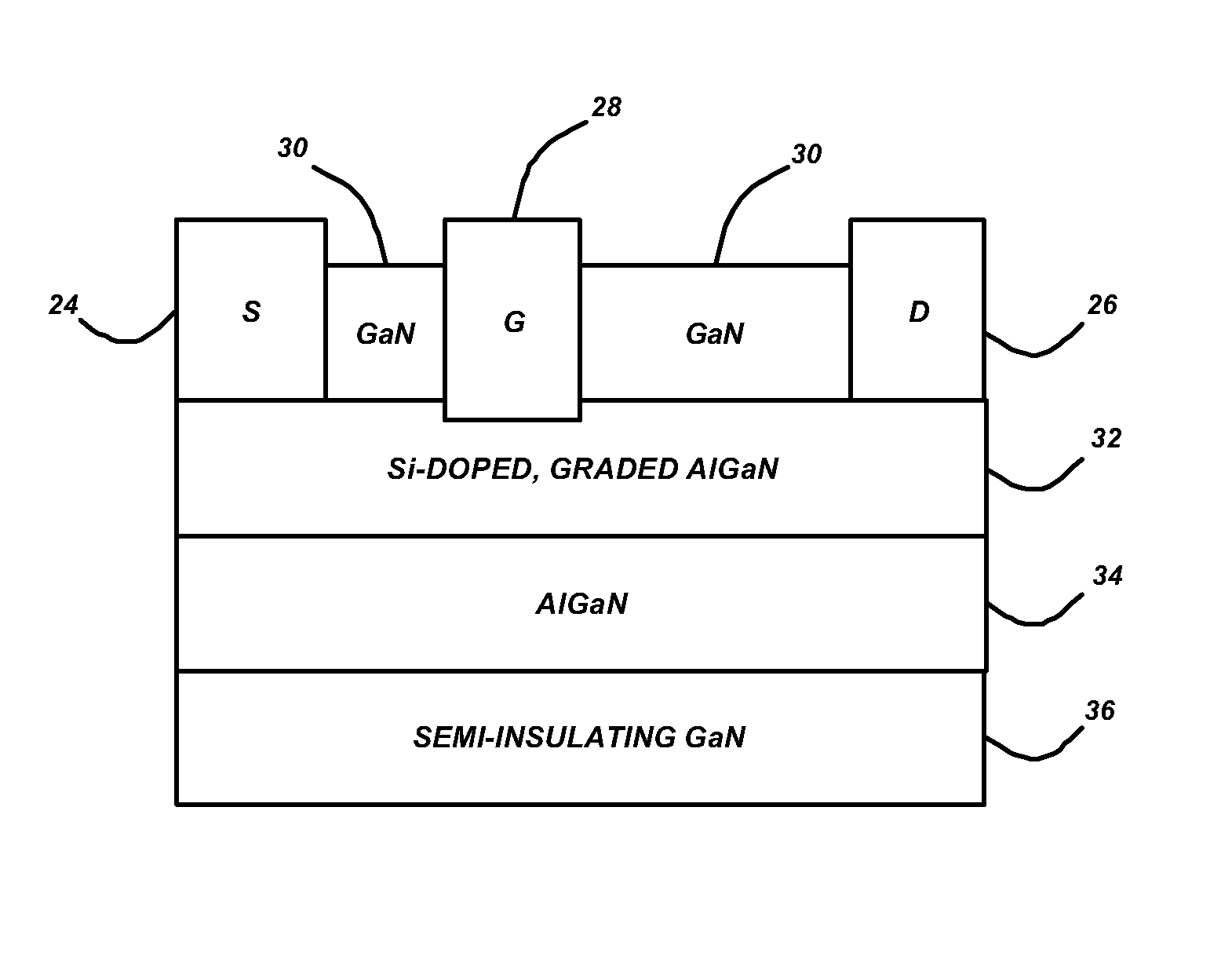

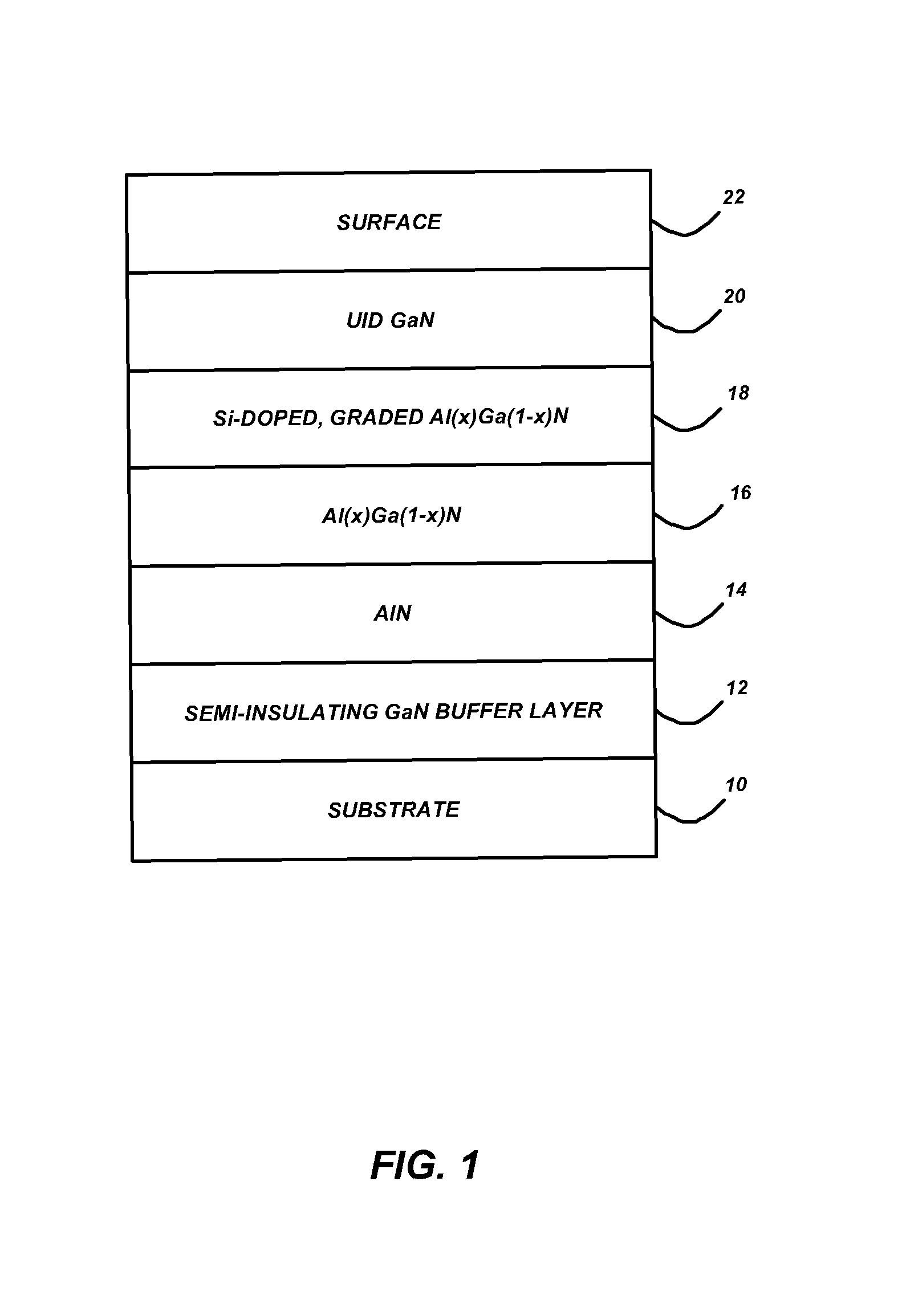

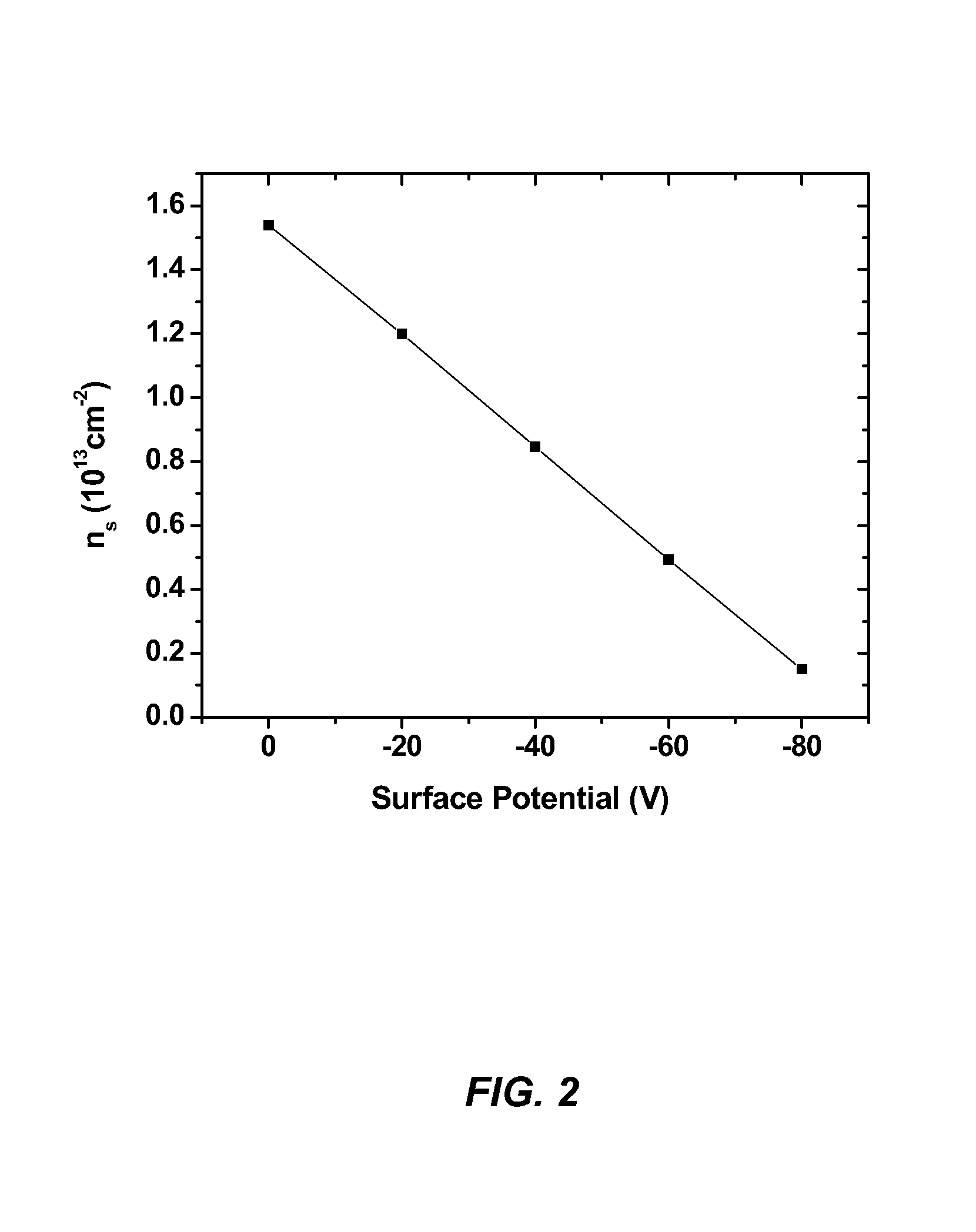

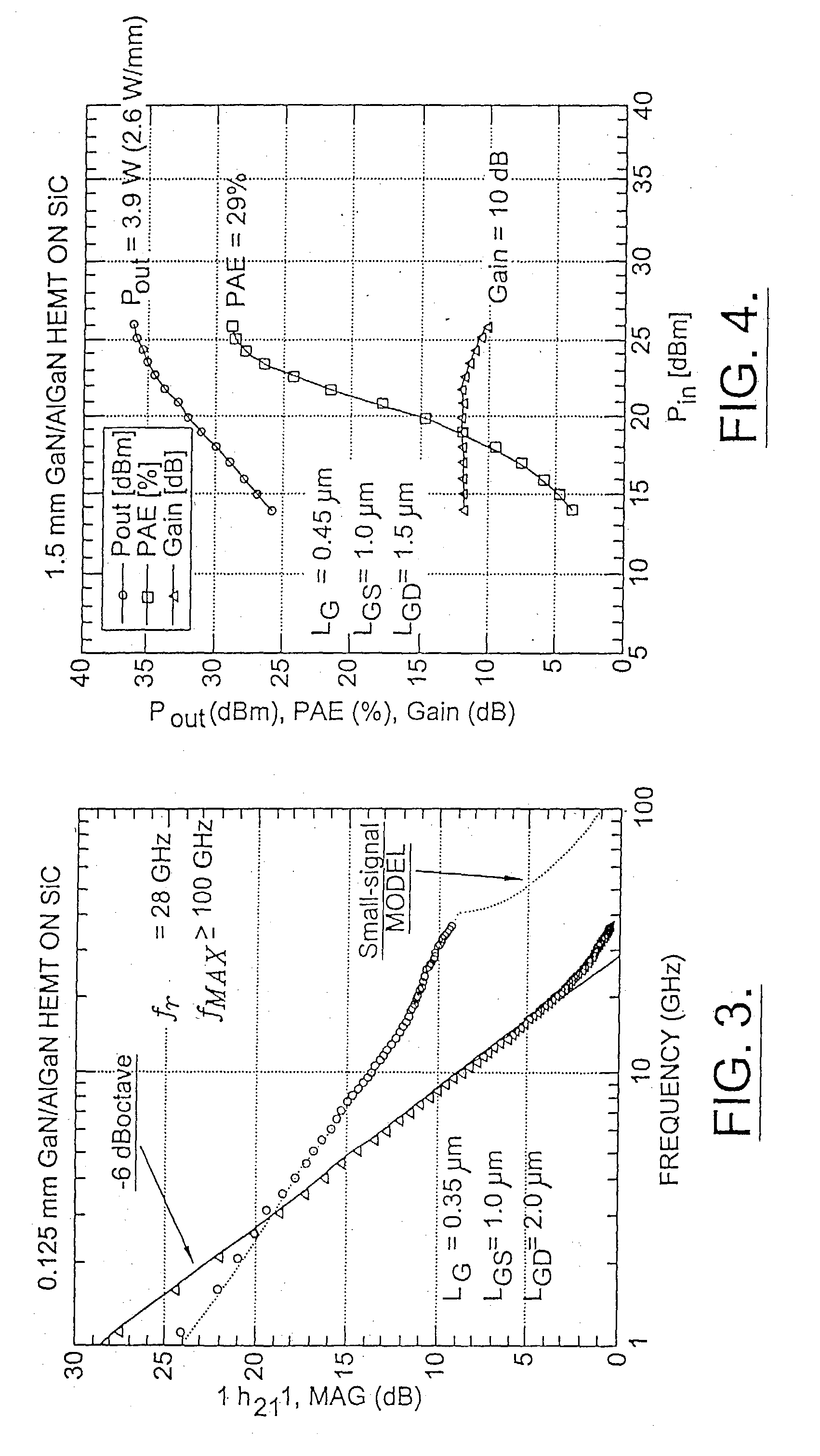

GaN/AlGaN/GaN dispersion-free high electron mobility transistors

InactiveUS7700973B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh electronGallium nitride

A dispersion-free high electron mobility transistor (HEMT), comprised of a substrate; a semi-insulating buffer layer, comprised of gallium nitride (GaN) or aluminum gallium nitride (AlGaN), deposited on the substrate, an AlGaN barrier layer, with an aluminum (Al) mole fraction larger than that of the semi-insulating buffer layer, deposited on the semi-insulating buffer layer, an n-type doped graded AlGaN layer deposited on the AlGaN barrier layer, wherein an Al mole fraction is decreased from a bottom of the n-type doped graded AlGaN layer to a top of the n-type doped graded AlGaN layer, and a cap layer, comprised of GaN or AlGaN with an Al mole fraction smaller than that of the AlGaN barrier layer, deposited on the n-type doped graded AlGaN layer.

Owner:RGT UNIV OF CALIFORNIA

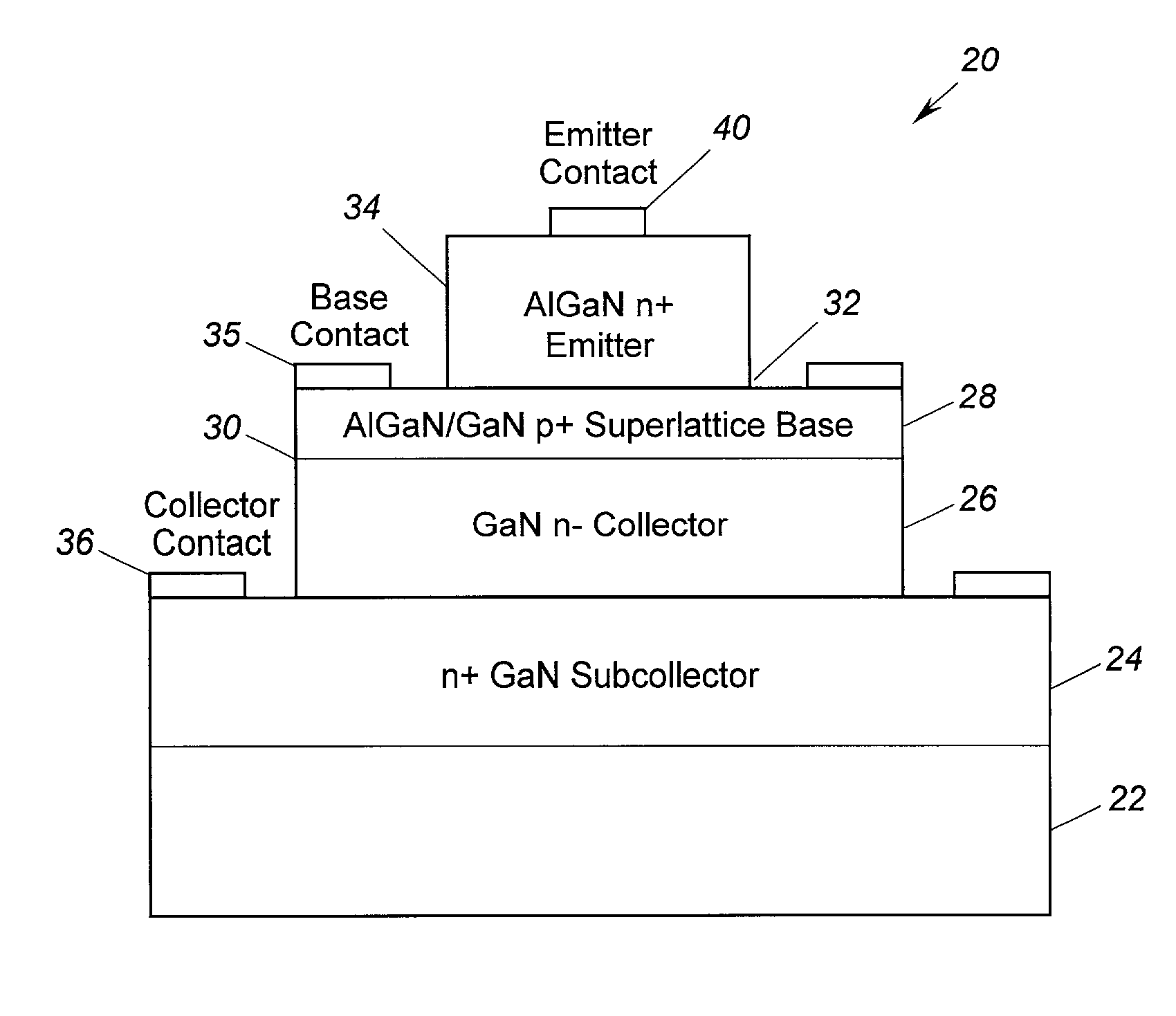

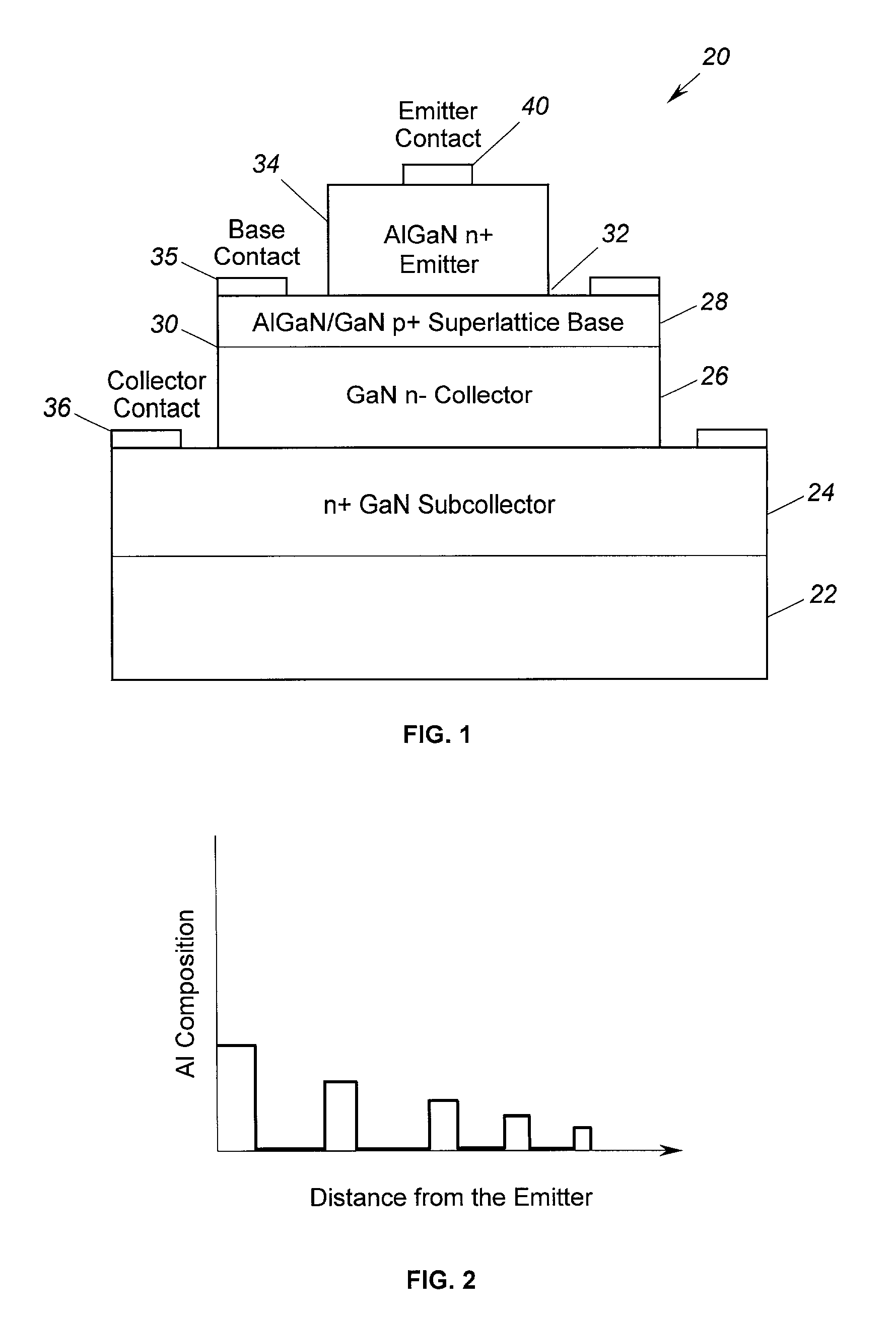

GaN HBT superlattice base structure

InactiveUS20020149033A1Semiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierThin layer

A heterojunction bipolar transistor (HBT) (20) with alternating layers of gallium nitride (GaN) and aluminum gallium nitride (AlGaN) with varying Al composition forming a graded superlattice structure in the base layer (28) includes. The thin layers of AlGaN in the base layer (28) increases the base p-type carrier concentration. Grading of the Al composition in the thin AlGaN layers induces an electrostatic field across the base layer (28) that increases the carrier velocity and reduces the carrier transit time. The structure thus decreases the transit time and at the same time increases the p-type carrier concentration to improve the operating efficiency of the device.

Owner:NORTHROP GRUMAN CORP

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS20030201459A1Increase heightQuality improvementSemiconductor devicesGallium nitrideSemi insulating

A high electron mobility transistor (HEMT) is disclosed that includes a semi-insulating silicon carbide substrate, an aluminum nitride buffer layer on the substrate, an insulating gallium nitride layer on the buffer layer, an active structure of aluminum gallium nitride on the gallium nitride layer, a passivation layer on the aluminum gallium nitride active structure, and respective source, drain and gate contacts to the aluminum gallium nitride active structure.

Owner:SHEPPARD SCOTT THOMAS +2

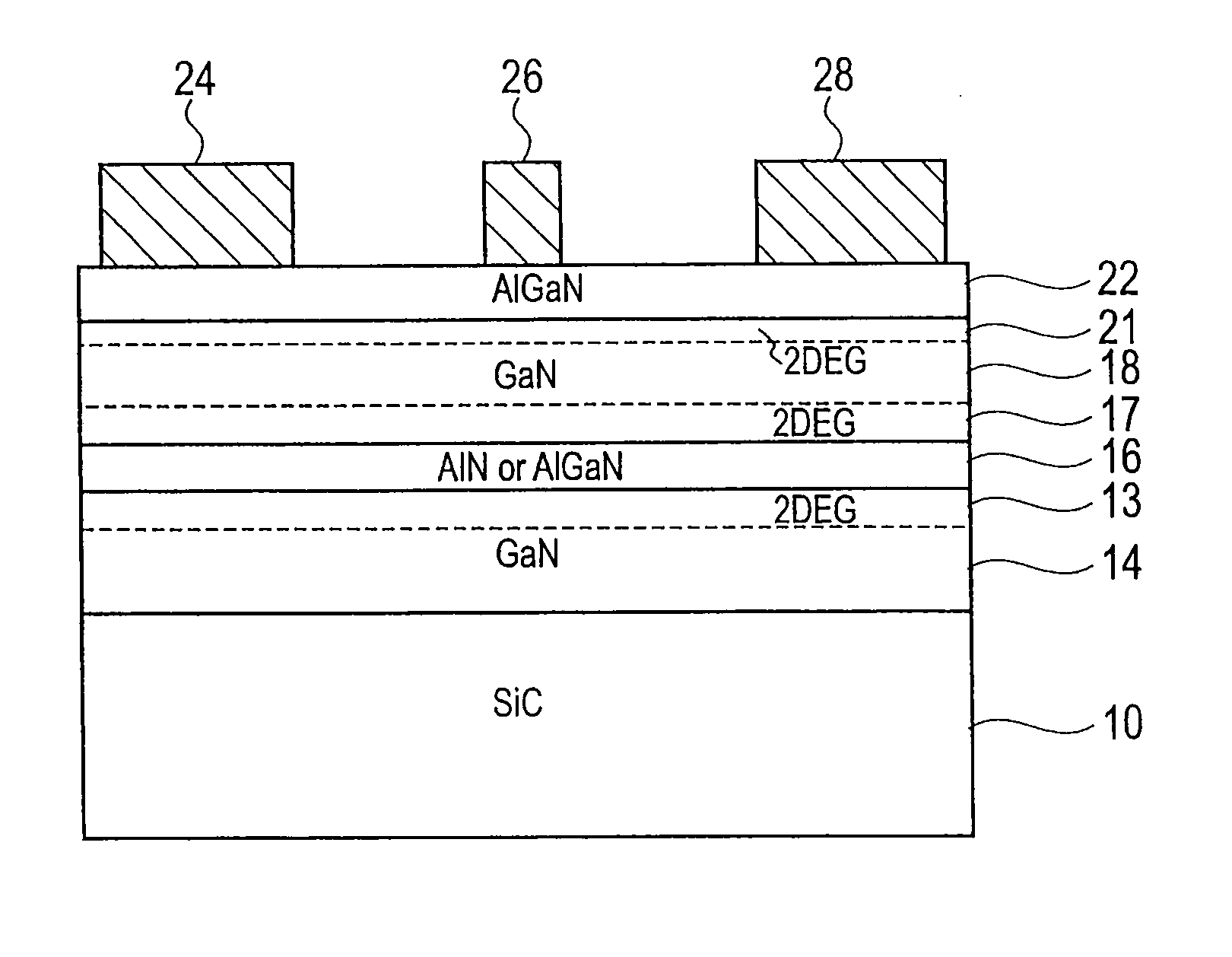

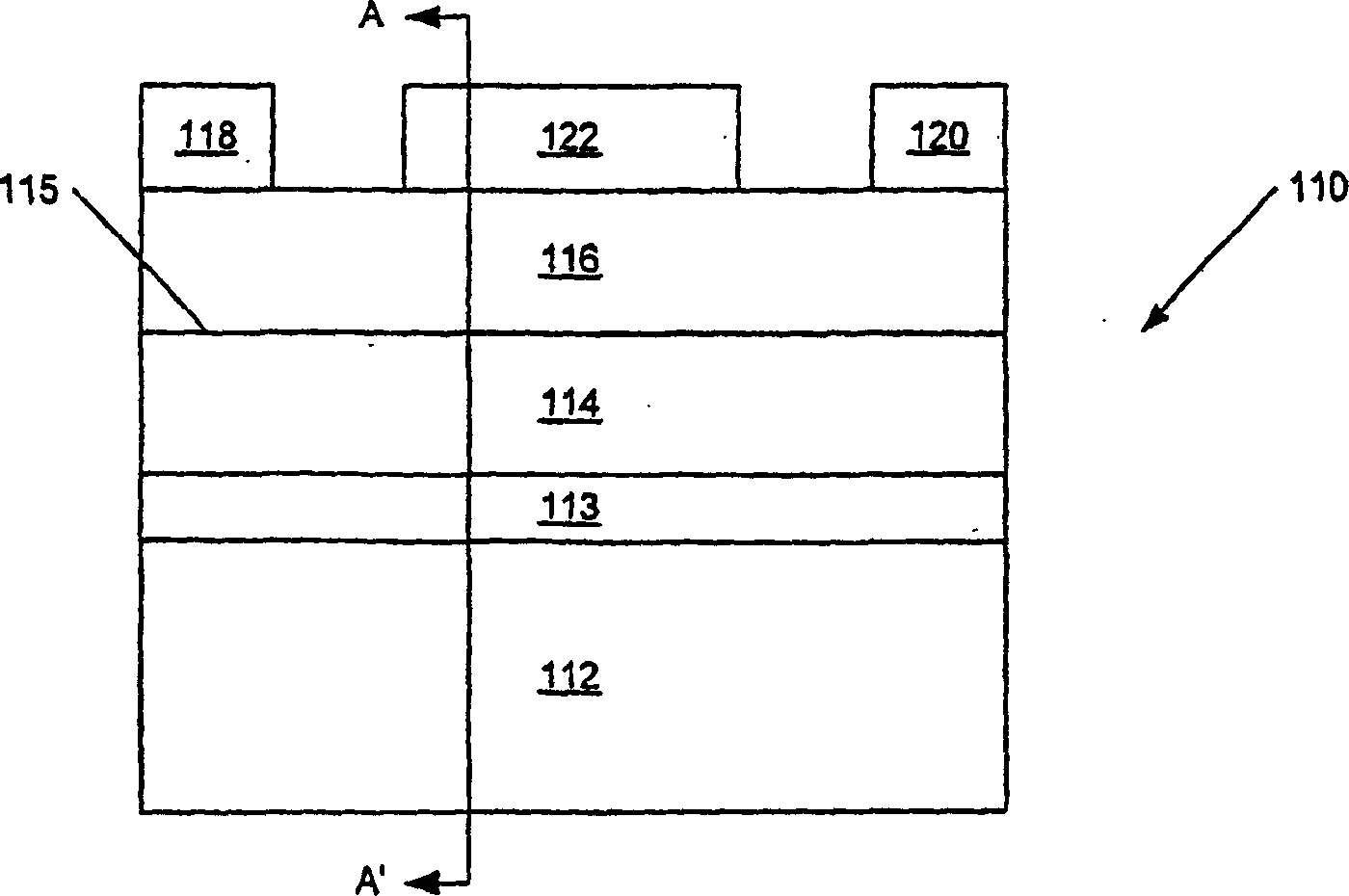

Semiconductor device and fabrication method of the semiconductor device

InactiveUS20090189188A1Improve efficiencyImprove featuresTransistorSemiconductor/solid-state device manufacturingTransition metal atomsHigh resistivity

A semiconductor device and a fabrication method of the semiconductor device, the semiconductor device including: a substrate; a nitride based compound semiconductor layer placed on the substrate and doped with a first transition metal atom; an aluminum gallium nitride layer (AlxGa1-xN) (where 0.1<=x<=1) placed on the nitride based compound semiconductor layer; a nitride based compound semiconductor layer placed on the aluminum gallium nitride layer (AlxGa1-xN) (where 0.1<=x<=1) and doped with a second transition metal atom; an aluminum gallium nitride layer (AlyGa1-yN) (where 0.1<=y<=1) placed on the nitride based compound semiconductor layer doped with the second transition metal atom; and a gate electrode, a source electrode, and a drain electrode which are placed on the aluminum gallium nitride layer (AlyGa1-yN) (where 0.1<=y<=1). Accordingly, piezo charge is inactivated, leakage current and current collapse are reduced, high frequency characteristics can be improved by obtaining a high resistivity semiconductor layer, and stable high frequency performance can be obtained.

Owner:KK TOSHIBA

Semiconductor device and fabrication method for the same

InactiveUS20100052014A1Improve reliabilityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCompound (substance)

A semiconductor device includes a substrate; a nitride based compound semiconductor layer placed on the substrate; an active area which is placed on the nitride based compound semiconductor layer, and is composed of an aluminum gallium nitride layer (AlxGa1-xN) (where 0.1<=x<=1); an isolation region which performs isolation of the active area mutually; a gate electrode, a source electrode, and a drain electrode which have been placed on the active area surrounded by the isolation region; and a trench region formed by etching for a part of the active area under the gate electrode. The semiconductor device is highly reliable, high performance and high power and a fabrication method for the same is also provided.

Owner:KK TOSHIBA

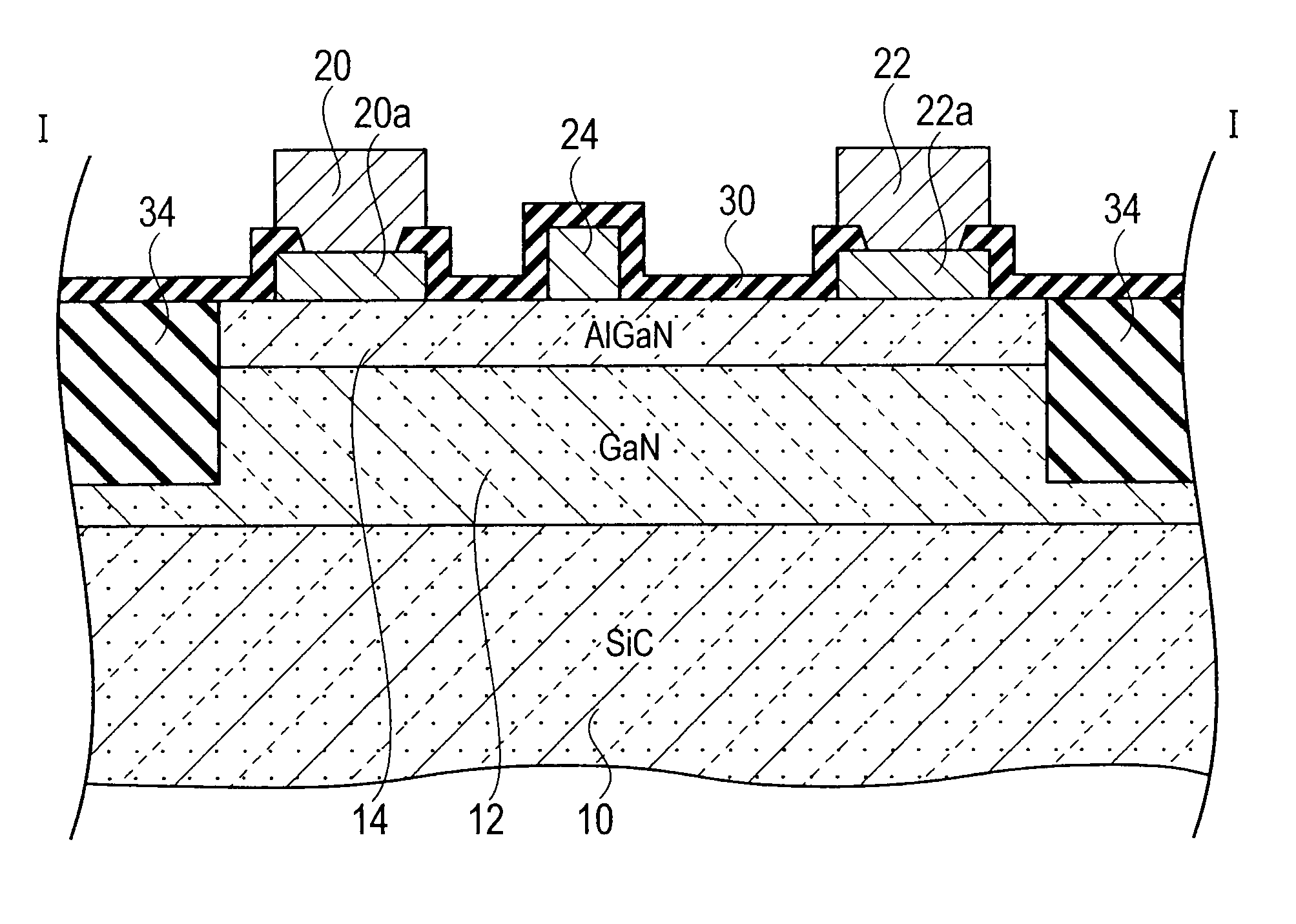

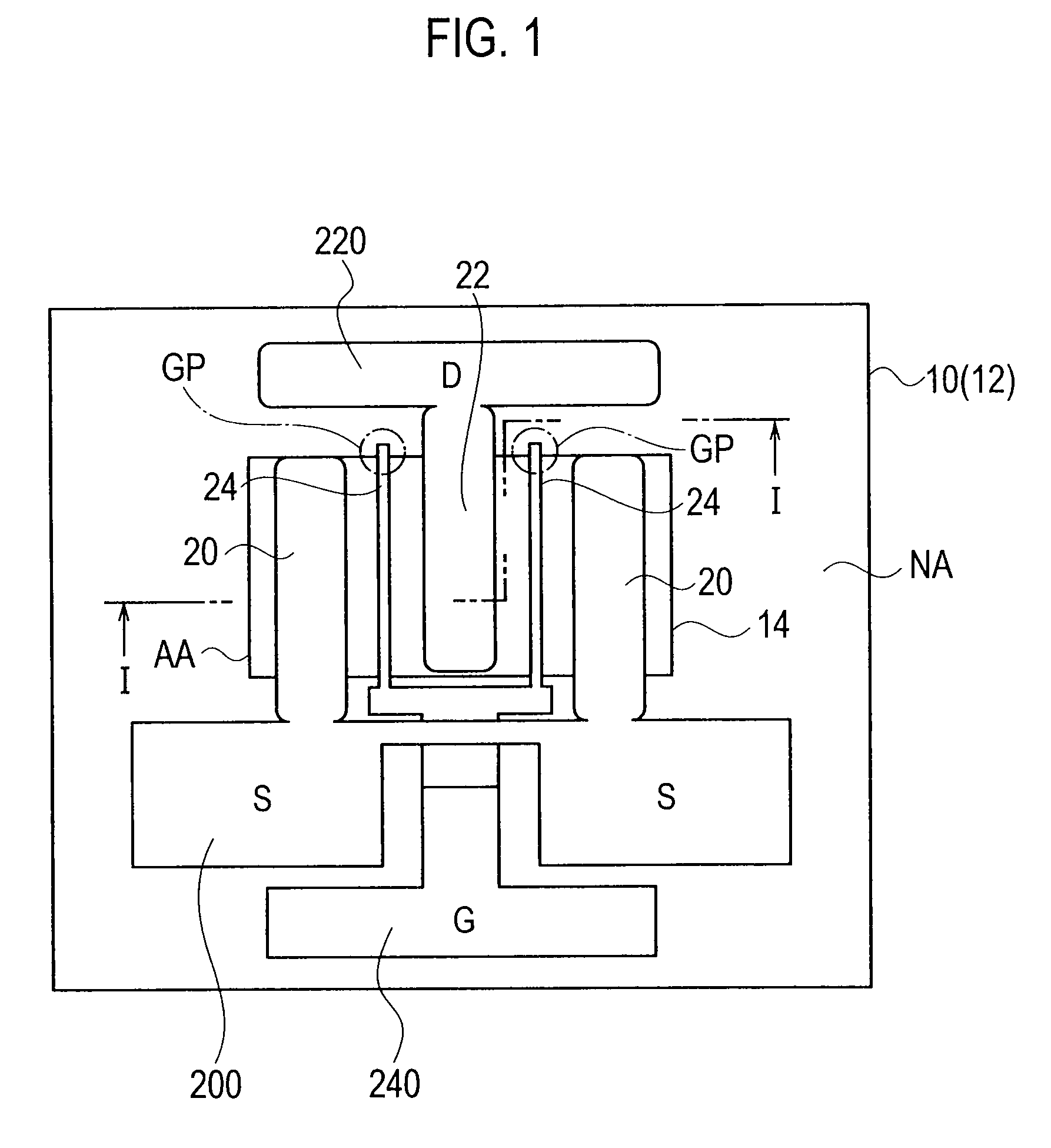

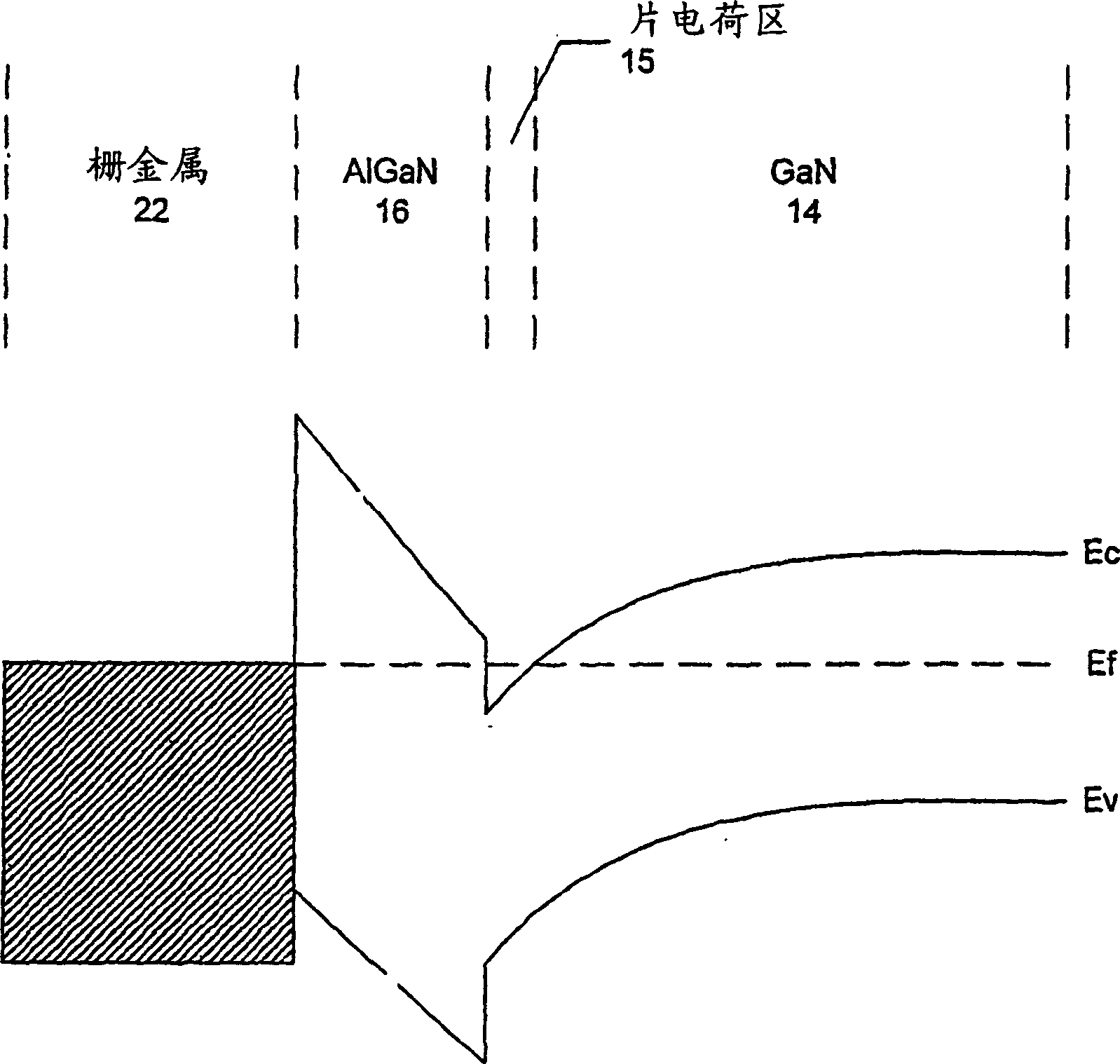

Aluminum gallium nitride/gallium nitride high electron mobility transistors having a gate contact on a gallium nitride based cap segment and methods of fabricating same

InactiveCN1554121ASemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactHigh electron

High electron mobility transistors (HEMTs) and methods of fabricating HEMTs are provided. Devices according to embodiments of the present invention include a gallium nitride (GaN) channel layer and an aluminum gallium nitride (AlGaN) barrier layer on the channel layer. A first ohmic contact is provided on the barrier layer to provide a source electrode and a second ohmic contact is also provided on the barrier layer and is spaced apart from the source electrode to provide a drain electrode. A GaN-based cap segment is provided on the barrier layer between the source electrode and the drain electrode. The GaN-based cap segment has a first sidewall adjacent and spaced apart from the source electrode and may have a second sidewall adjacent and spaced apart from the drain electrode. A non-ohmic contact is provided on the GaN-based cap segment to provide a gate contact. The gate contact has a first sidewall which is substantially aligned with the first sidewall of the GaN-based cap segment. The gate contact extends only a portion of a distance between the first sidewall and the second sidewall of the GaN-based cap segment.

Owner:CREE INC

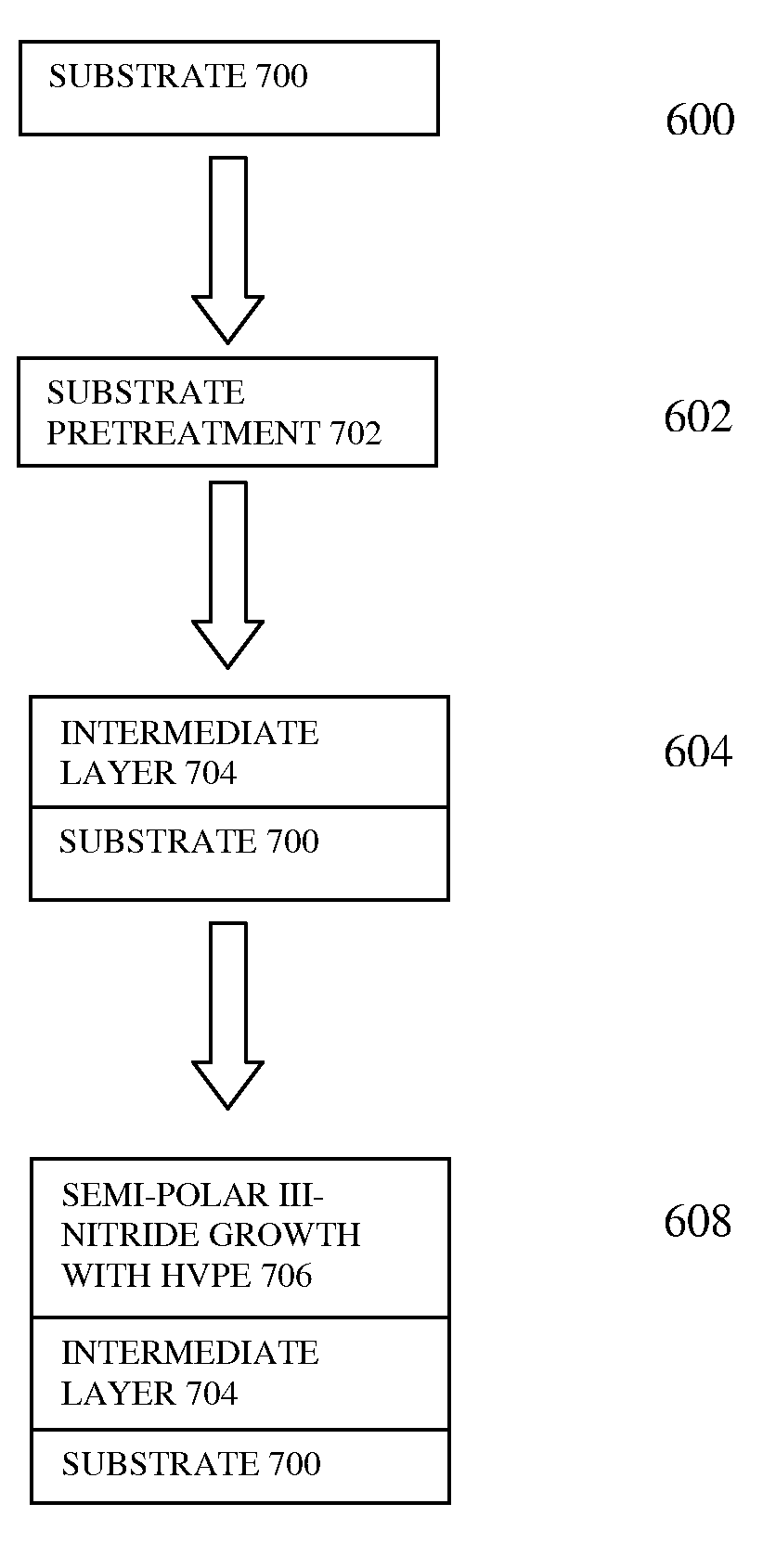

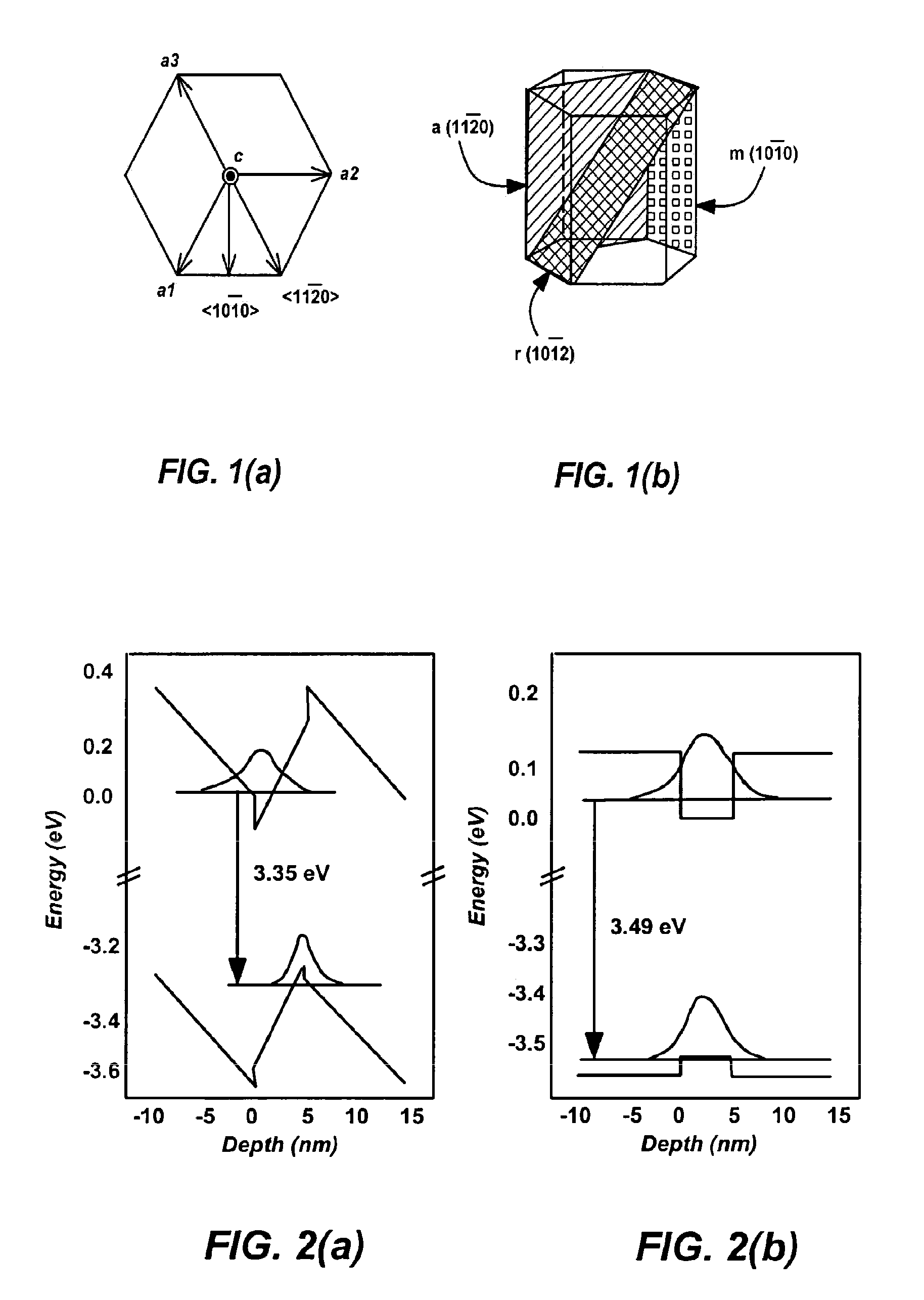

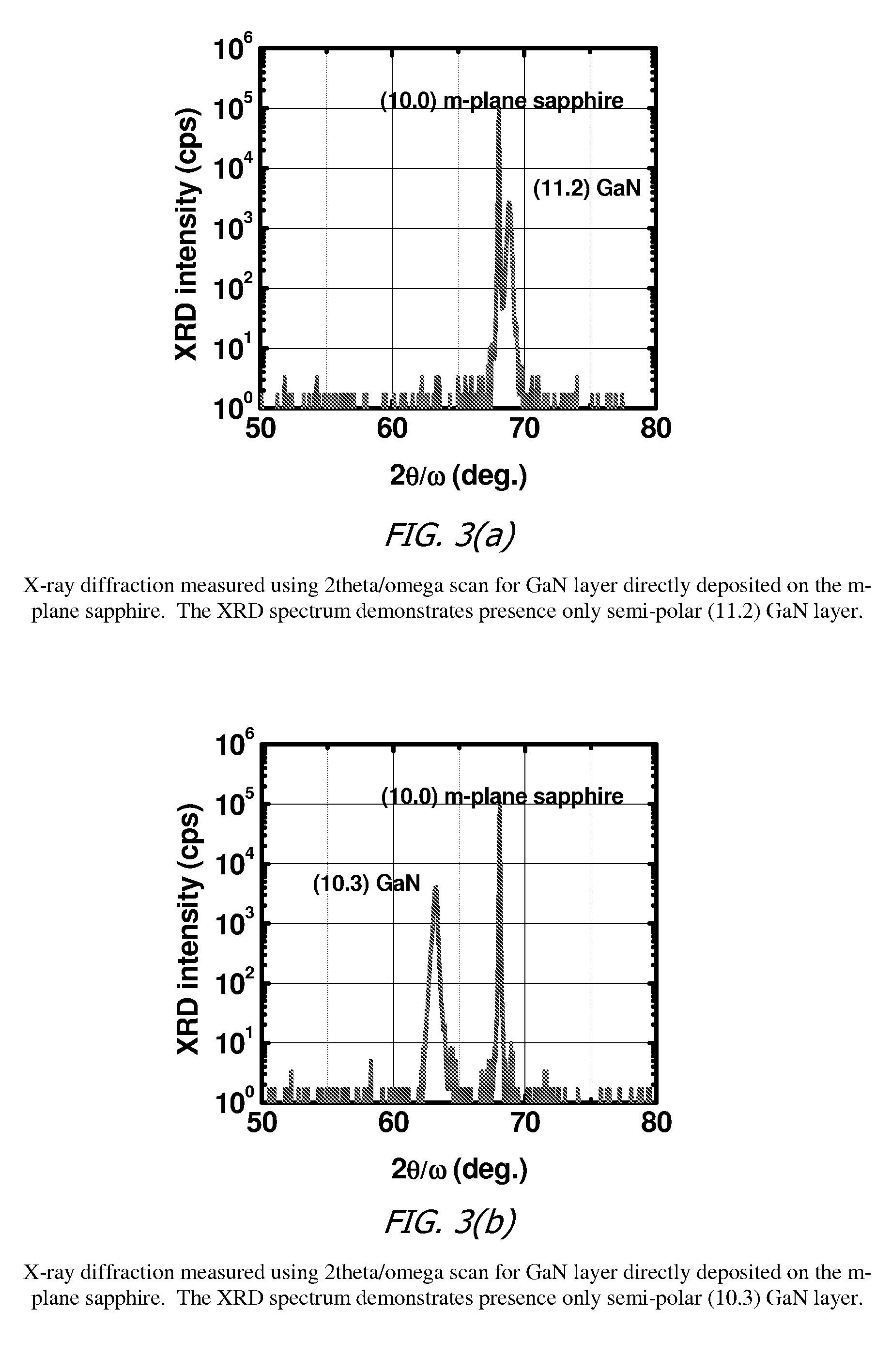

Growth of Planar Non-Polar M-Plane and Semi-Polar Gallium Nitride with Hydride Vapor Phase Epitaxy (HVPE)

ActiveUS20100012948A1Polycrystalline material growthSemiconductor/solid-state device manufacturingGallium nitrideVapor phase

A method of growing planar non-polar m-plane or semi-polar III-Nitride material, such as an m-plane gallium nitride (GaN) epitaxial layer, wherein the III-Nitride material is grown on a suitable substrate, such as an m-plane Sapphire substrate, using hydride vapor phase epitaxy (HVPE). The method includes in-situ pretreatment of the substrate at elevated temperatures in the ambient of ammonia and argon, growing an intermediate layer such as an aluminum nitride (AlN) or aluminum-gallium nitride (AlGaN) on the annealed substrate, and growing the non-polar m-plane III-Nitride epitaxial layer on the intermediate layer using HVPE.

Owner:OSTENDO TECH INC

Nitride semiconductor device

In a nitride semiconductor device according to one embodiment of the invention, a p-type gallium nitride (GaN) layer electrically connected to a source electrode and extending and projecting to a drain electrode side with respect to a gate electrode is formed on an undoped or n-type aluminum gallium nitride (AlGaN) layer serving as a barrier layer.

Owner:KK TOSHIBA

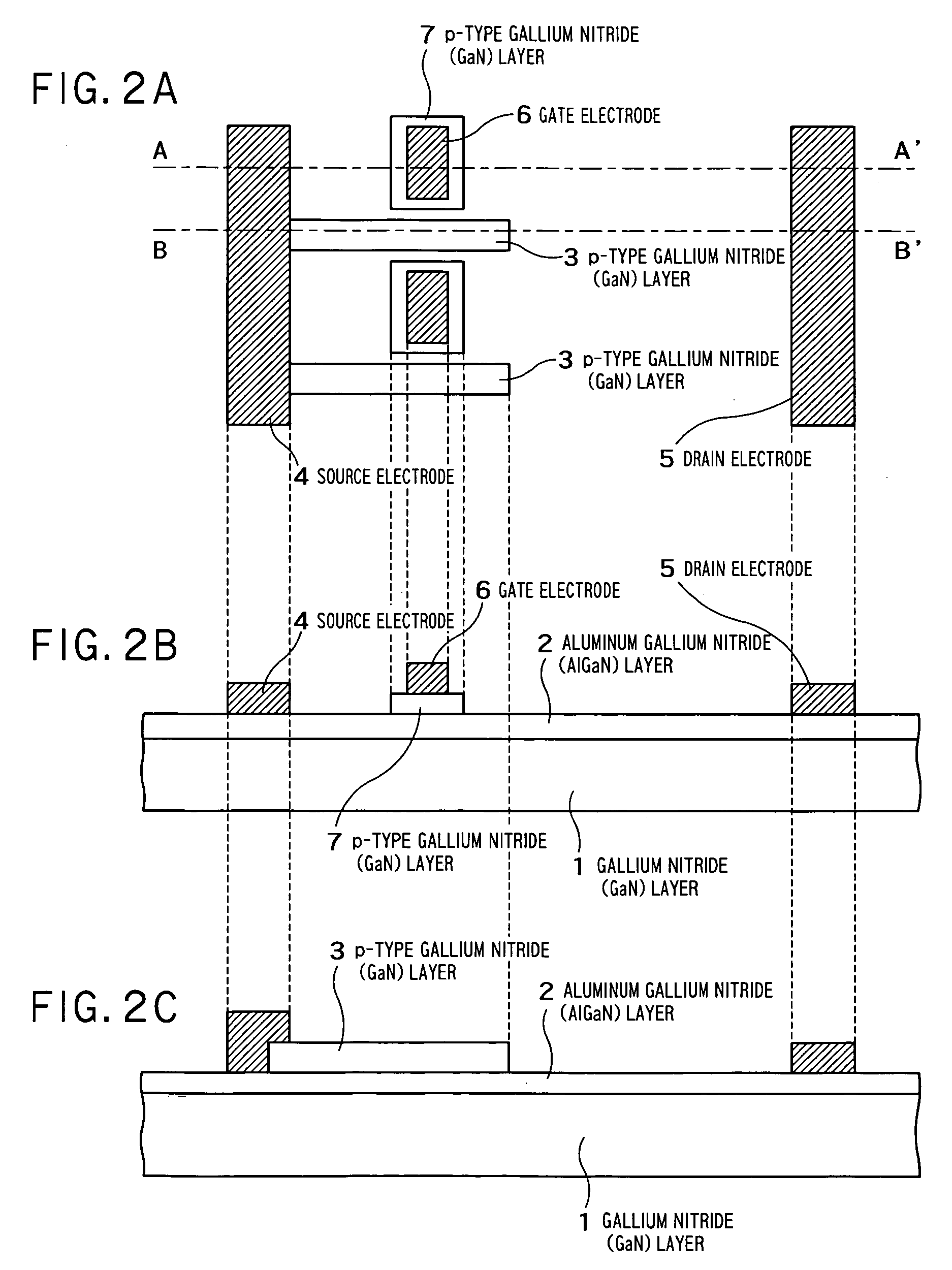

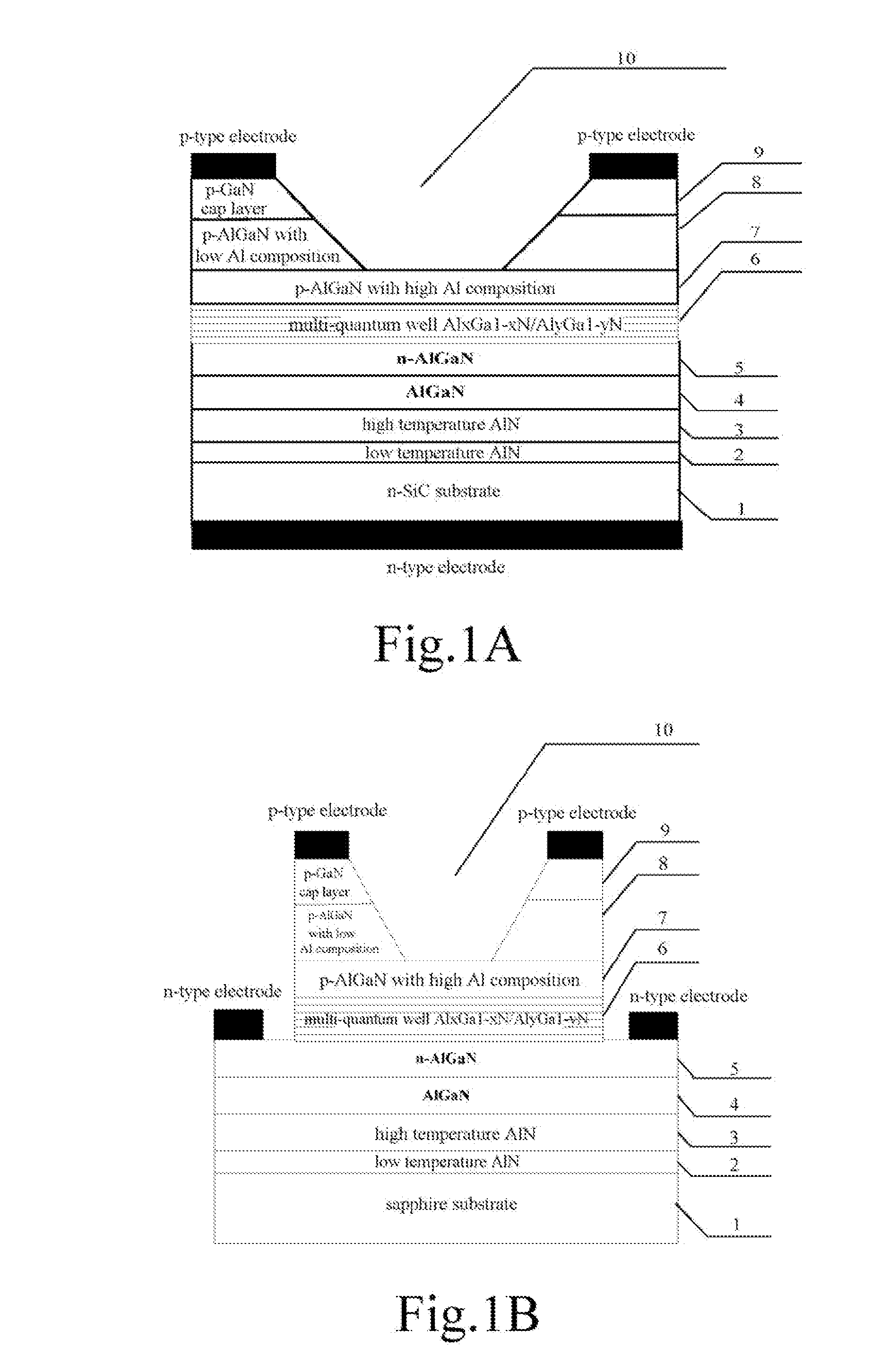

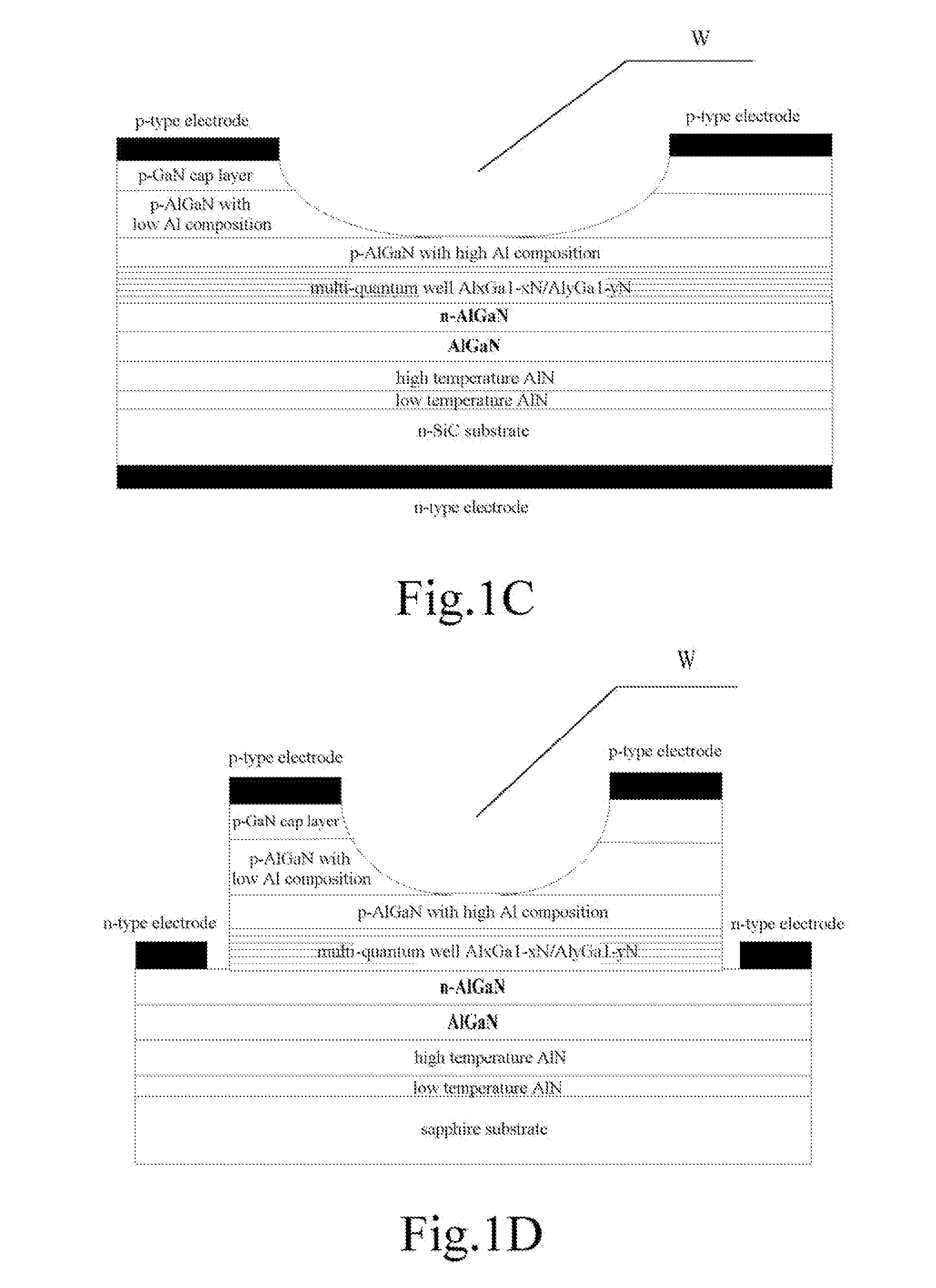

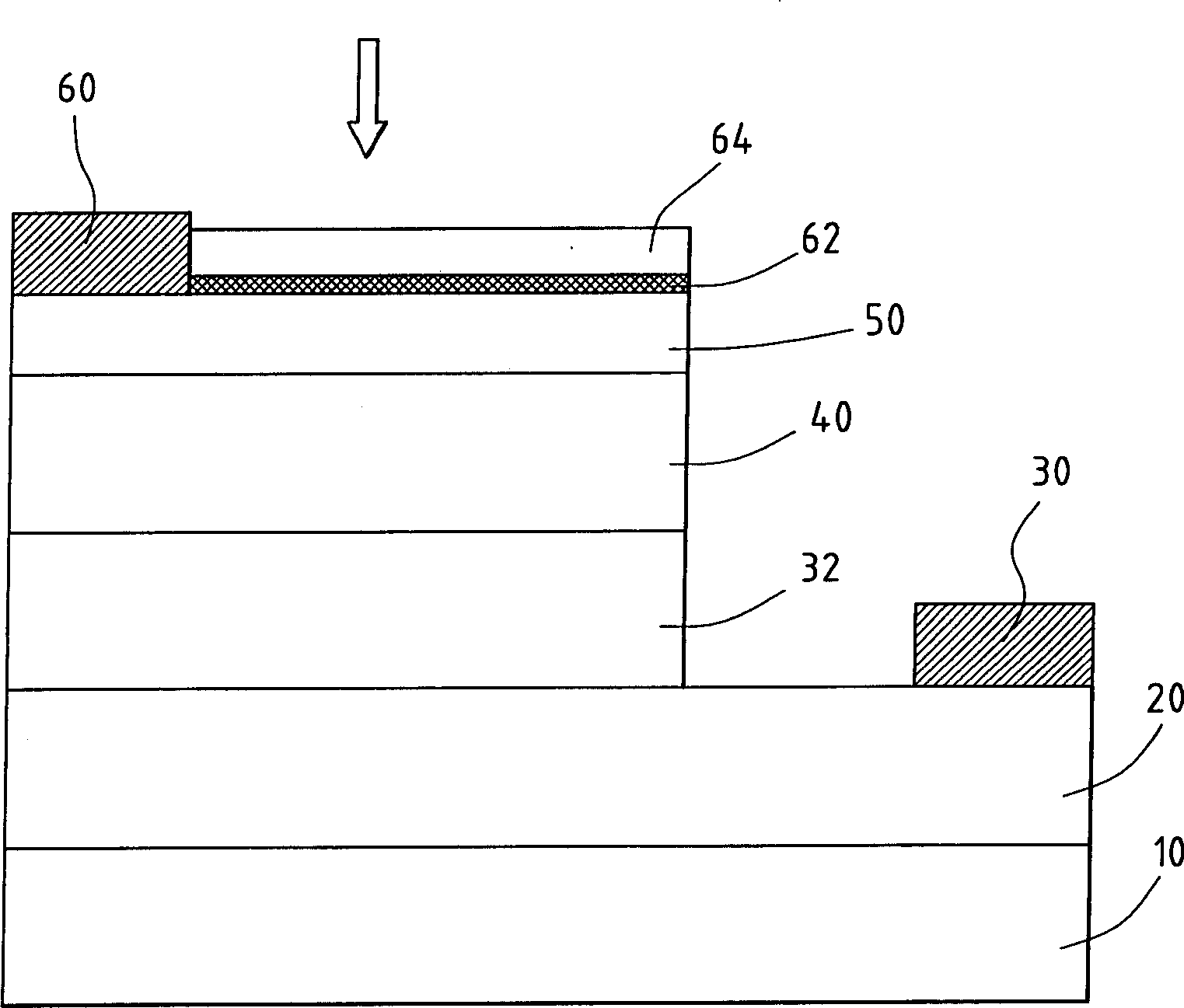

Ultraviolet light emitting diode devices and methods for fabricating the same

InactiveUS20120018753A1Easy to practiceImproved light emissionSemiconductor/solid-state device manufacturingSemiconductor devicesUltraviolet lightsGallium nitride

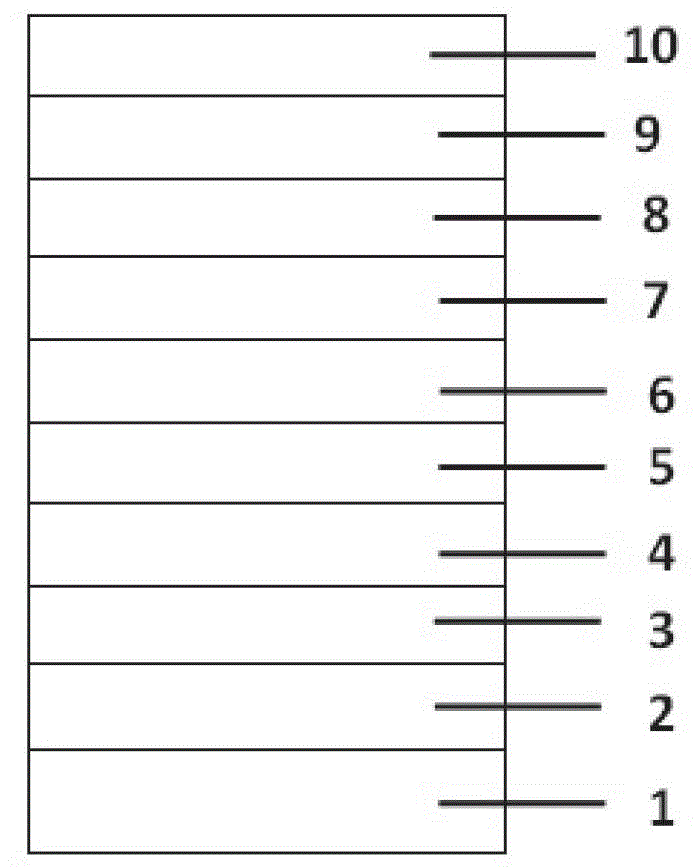

A UV LED device and the method for fabricating the same are provided. The device has aluminum nitride nucleating layers, an intrinsic aluminum gallium nitride epitaxial layer, an n-type aluminum gallium nitride barrier layer, an active region, a first p-type aluminum gallium nitride barrier layer, a second p-type aluminum gallium nitride barrier layer, and a p-type gallium nitride cap layer arranged from bottom to top on a substrate. A window region is etched in the p-type gallium nitride cap layer for emitting the light generated.

Owner:XIDIAN UNIV

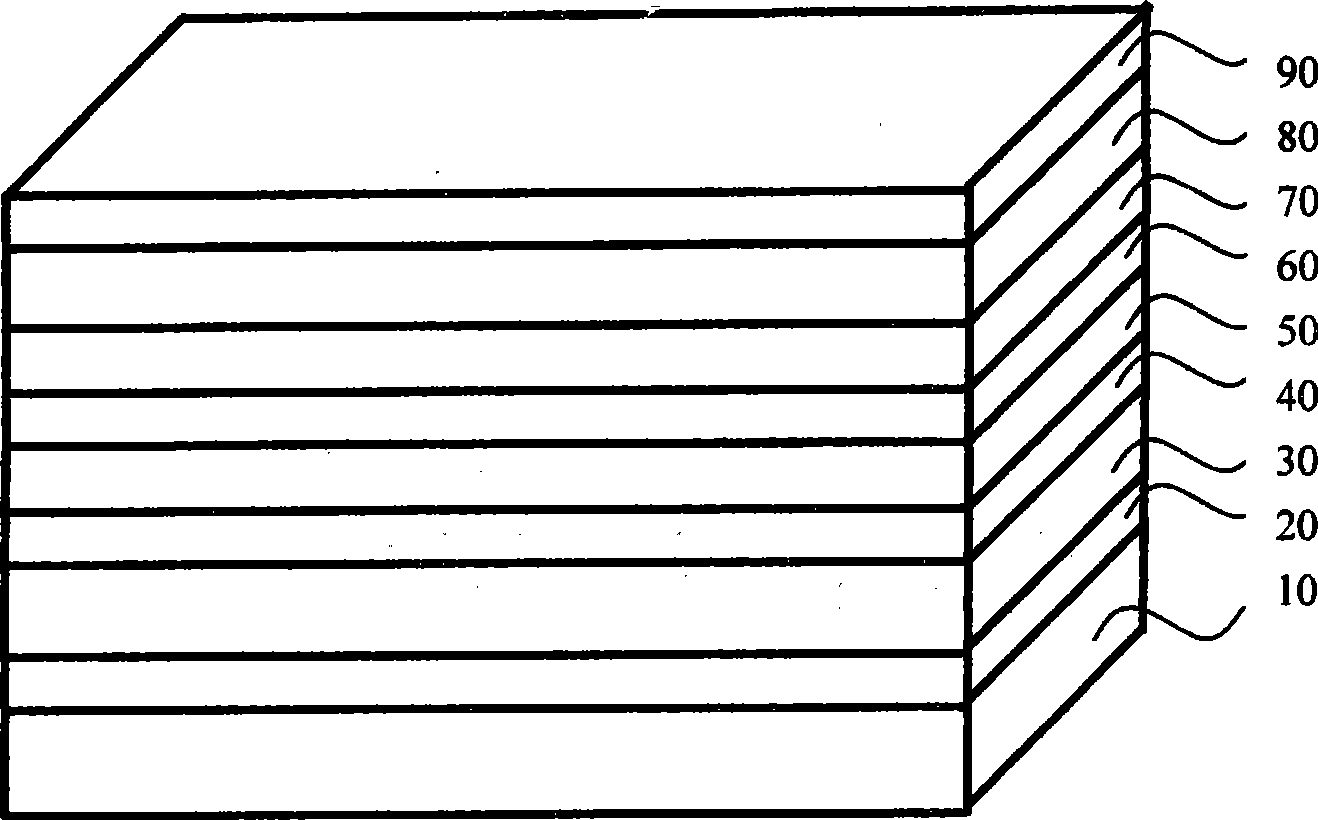

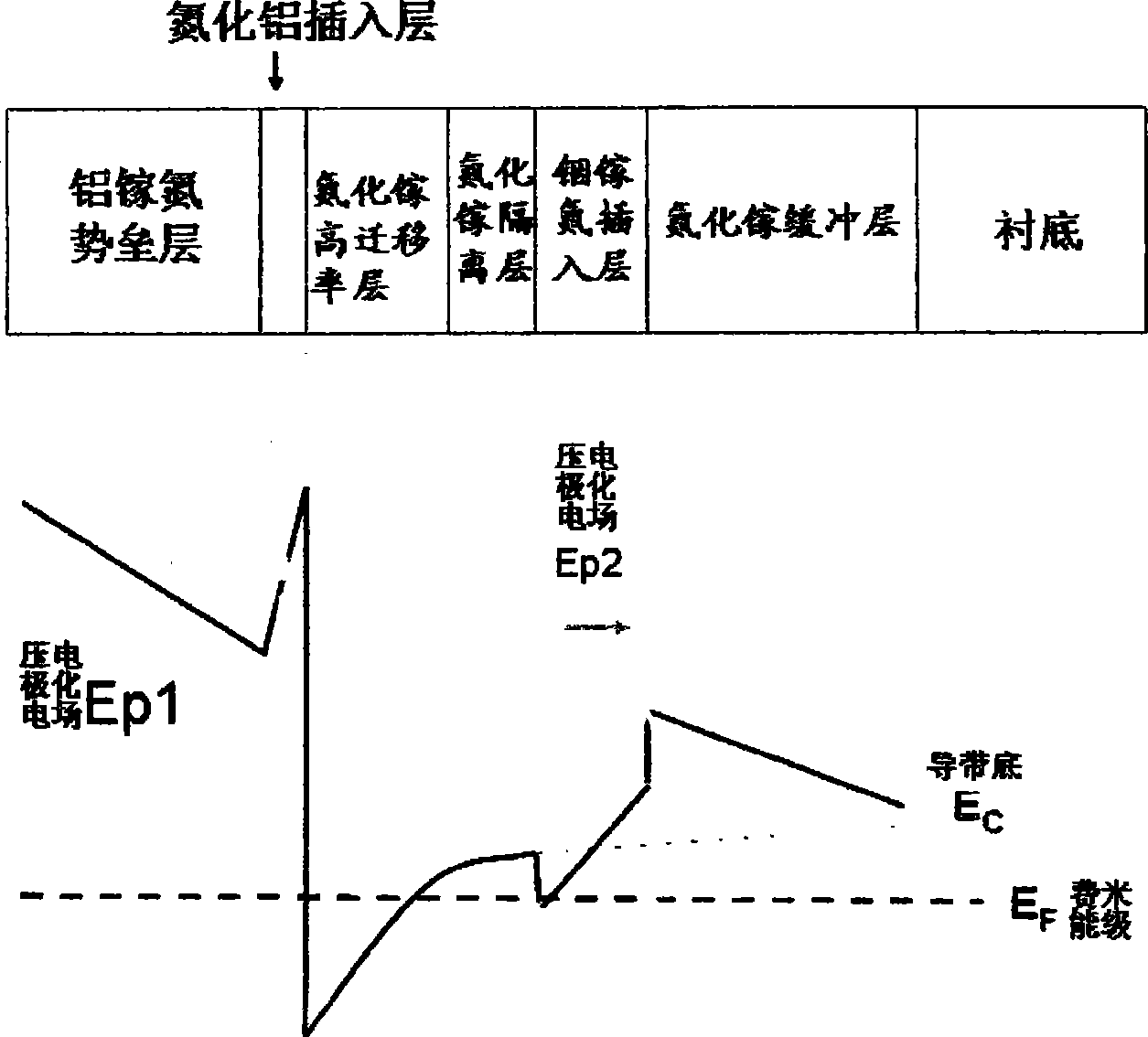

Gallium nitride based transistor structure with high electron mobility

InactiveCN101399284APrevent segregation and spreadHigh conduction band discontinuitySemiconductor devicesIndiumIsolation layer

A gallium nitride-based high electron mobility transistor structure comprises: a substrate; a low temperature nucleating layer is produced on the substrate; a gallium nitride-based high resistivity layer is produced on the low temperature nucleation layer; an indium gallium nitride insertion layer is produced on the gallium nitride-based high resistivity layer; a low temperature gallium nitride isolation layer is produced on the indium gallium nitride insertion layer; a high mobility gallium nitride layer is produced on the low temperature gallium nitride isolation layer; an aluminum nitride insertion layer is produced on the high mobility gallium nitride layer; an aluminium gallium nitride barrier layer is produced on the aluminum nitride insertion layer; a gallium nitride cap layer is produced on the aluminium gallium nitride barrier layer, and the gallium nitride cap layer effectively inhibit the current collapse effect.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method of growing a high quality iii-v compound layer on a silicon substrate

ActiveCN103258844AReduce contentTransistorSemiconductor/solid-state device manufacturingGallium nitrideSemiconductor

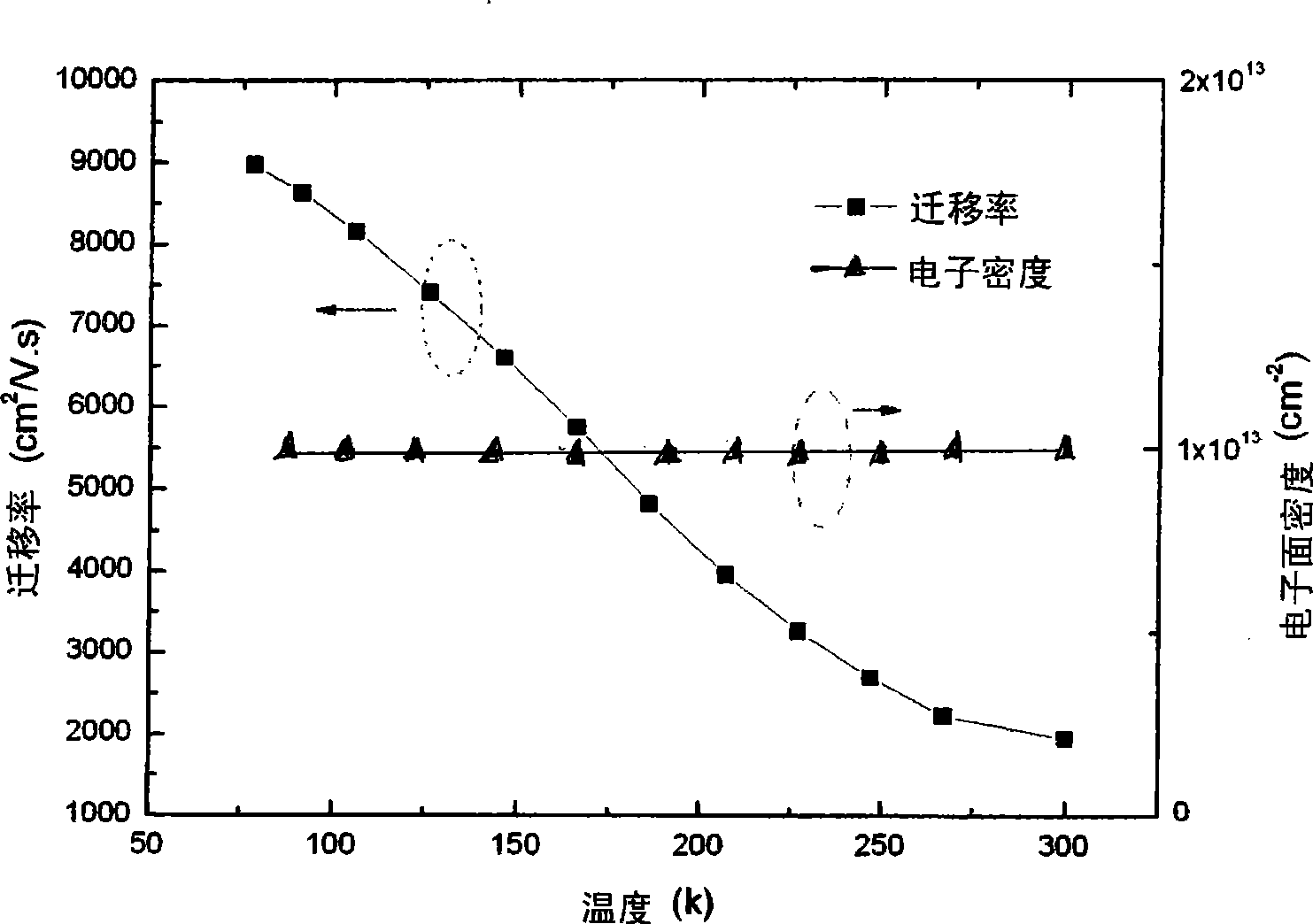

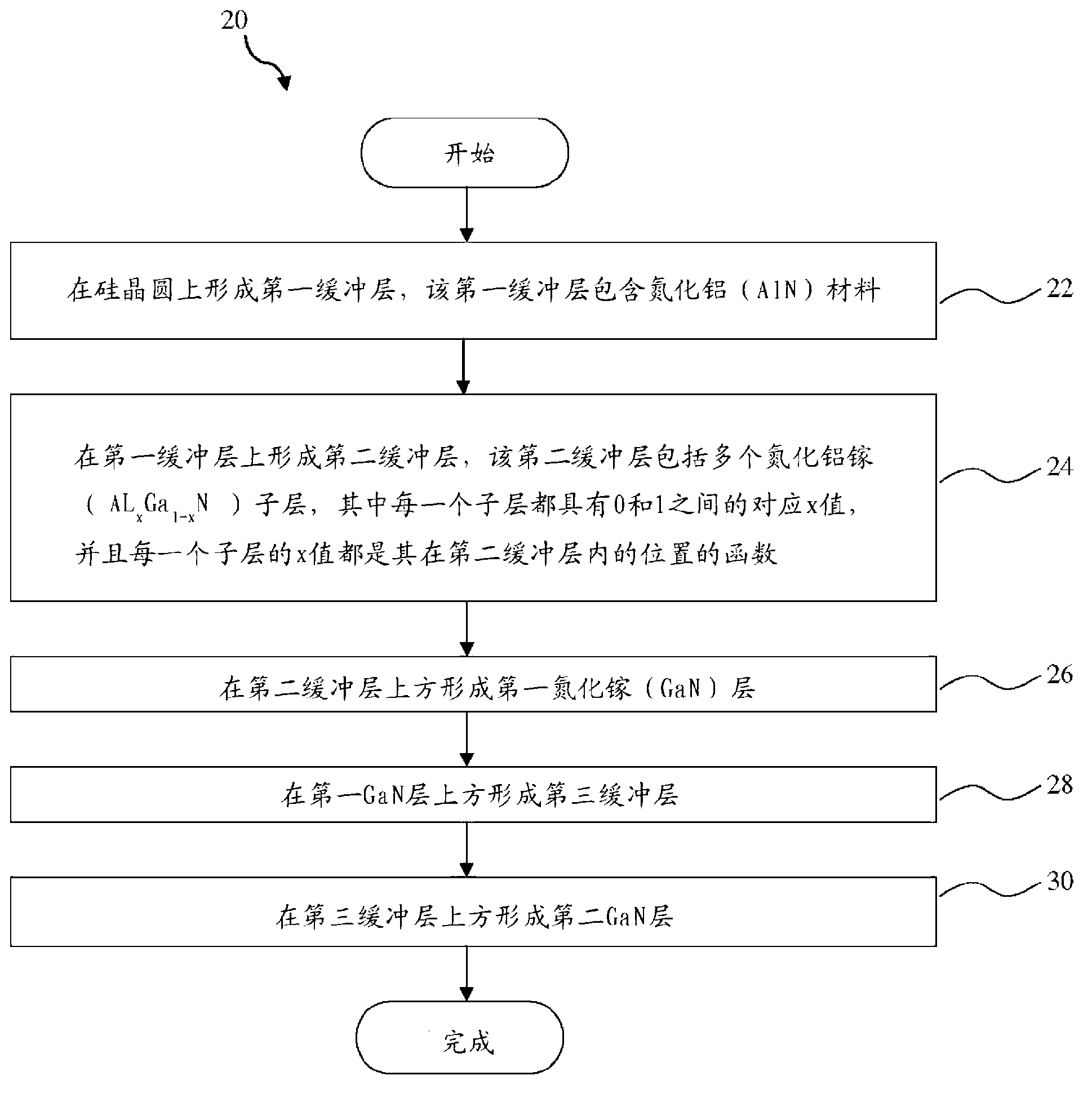

The present disclosure involves a method of fabricating a semiconductor device. A surface of a silicon wafer is cleaned. A first buffer layer is then epitaxially grown on the silicon wafer. The first buffer layer contains an aluminum nitride (AlN) material. A second buffer layer is then epitaxially grown on the first buffer layer. The second buffer layer includes a plurality of aluminum gallium nitride (AlxGa1-xN) sub-layers. Each of the sub-layers has a respective value for x that is between 0 and 1. A value of x for each sub-layer is a function of its position within the second buffer layer. A first gallium nitride (GaN) layer is epitaxially grown over the second buffer layer. A third buffer layer is then epitaxially grown over the first GaN layer. A second GaN layer is then epitaxially grown over the third buffer layer.

Owner:EPISTAR CORP

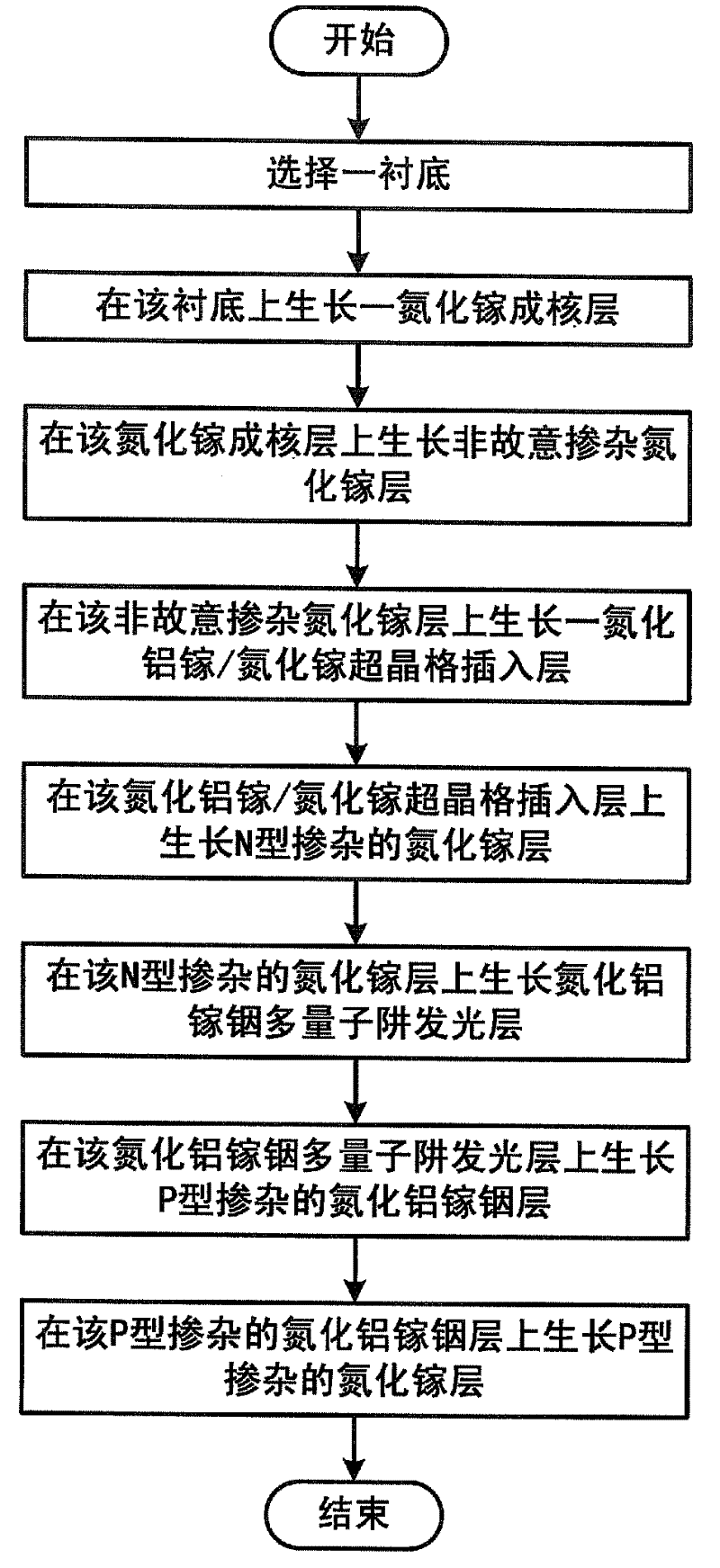

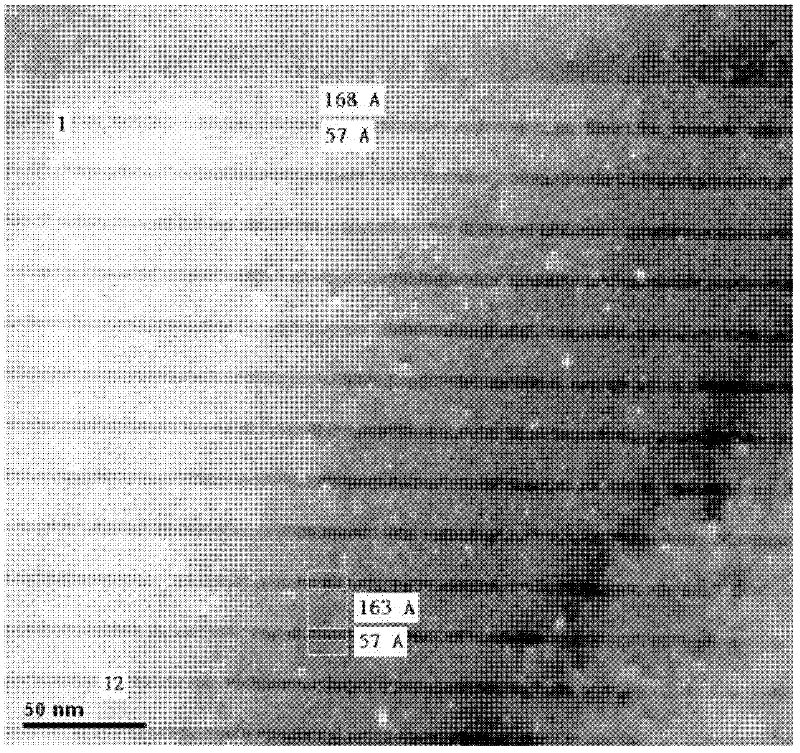

Method for improving antistatic capability of gallium nitride based light emitting diode

InactiveCN102214740AImprove material qualityImprove antistatic performancePolycrystalline material growthSingle crystal growth detailsIndiumLattice mismatch

The invention discloses a method for improving antistatic capability of a gallium nitride based light emitting diode. The method comprises the following steps: selecting a substrate; growing a gallium nitride nucleating layer on the substrate; growing an involuntary doped gallium nitride layer on the gallium nitride nucleating layer; growing an aluminum gallium nitride / gallium nitride superlattice insertion layer on the involuntary doped gallium nitride layer; growing an N-type doped gallium nitride layer on the aluminum gallium nitride / gallium nitride superlattice insertion layer; growing an indium gallium aluminum nitride multiple quantum-well light-emitting layer on the N-type doped gallium nitride layer; growing a P-type doped indium gallium aluminum nitride layer on the indium gallium aluminum nitride multiple quantum-well light-emitting layer; and growing a P-type doped gallium nitride layer on the P-type doped indium gallium aluminum nitride layer. By utilizing the method provided by the invention, the stress caused by lattice mismatch in an epitaxial layer can be modulated, simultaneously the dislocation in the epitaxial layer of the GaN (gallium nitride) can be deflected and combined, thus the density of threading dislocation in the epitaxial layer developed subsequently is reduced, the material quality is improved, and the antistatic capability of the light emitting diode is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Gallium nitride base light-emitting diode with composite potential barrier

ActiveCN103151435AReduce the built-in electric fieldEliminate mismatchSemiconductor devicesPotential wellIndium

The invention discloses a gallium nitride base light-emitting diode with a composite potential barrier. The gallium nitride base light-emitting diode comprises a sapphire substrate, a buffering layer, an n-type gallium nitride epitaxial layer, a multiple quantum well active area, a p-type algan epitaxial layer and a p-type gallium nitride epitaxial layer, wherein the sapphire substrate, the buffering layer, the n-type gallium nitride epitaxial layer, the multiple quantum well active area, the p-type algan epitaxial layer and the p-type gallium nitride epitaxial layer are arranged sequentially from bottom to top. A p-type metal electrode is arranged on the upper surface of the p-type gallium nitride epitaxial layer. An n-type electrode is arranged on a lower platform surface of the n-type gallium nitride epitaxial layer. The multiple quantum well active area comprises 5-20 indium gallium nitride potential well layers which are arranged at intervals from bottom to top. A first kind composite potential barrier layer is arranged between every two indium gallium nitride potential barrier layers. A second kind composite potential well layer is arranged on the upper surface of an indium gallium nitride potential well layer at the top layer. According to the composite potential barrier, at the contact position of an aluminum, gallium and indium nitride layer and an InGaN potential well layer, a built-in electric field which is produced due to a polarization effect can be decreased through adjustment of aluminum (Al) and indium (In). On a contact interface between an AlInGaN layer and a GaN layer, a ratio between the Al and the In is adjusted to be 0.83:0.17, and lattices of the Al and the In are enabled to be matched.

Owner:SOUTHEAST UNIV

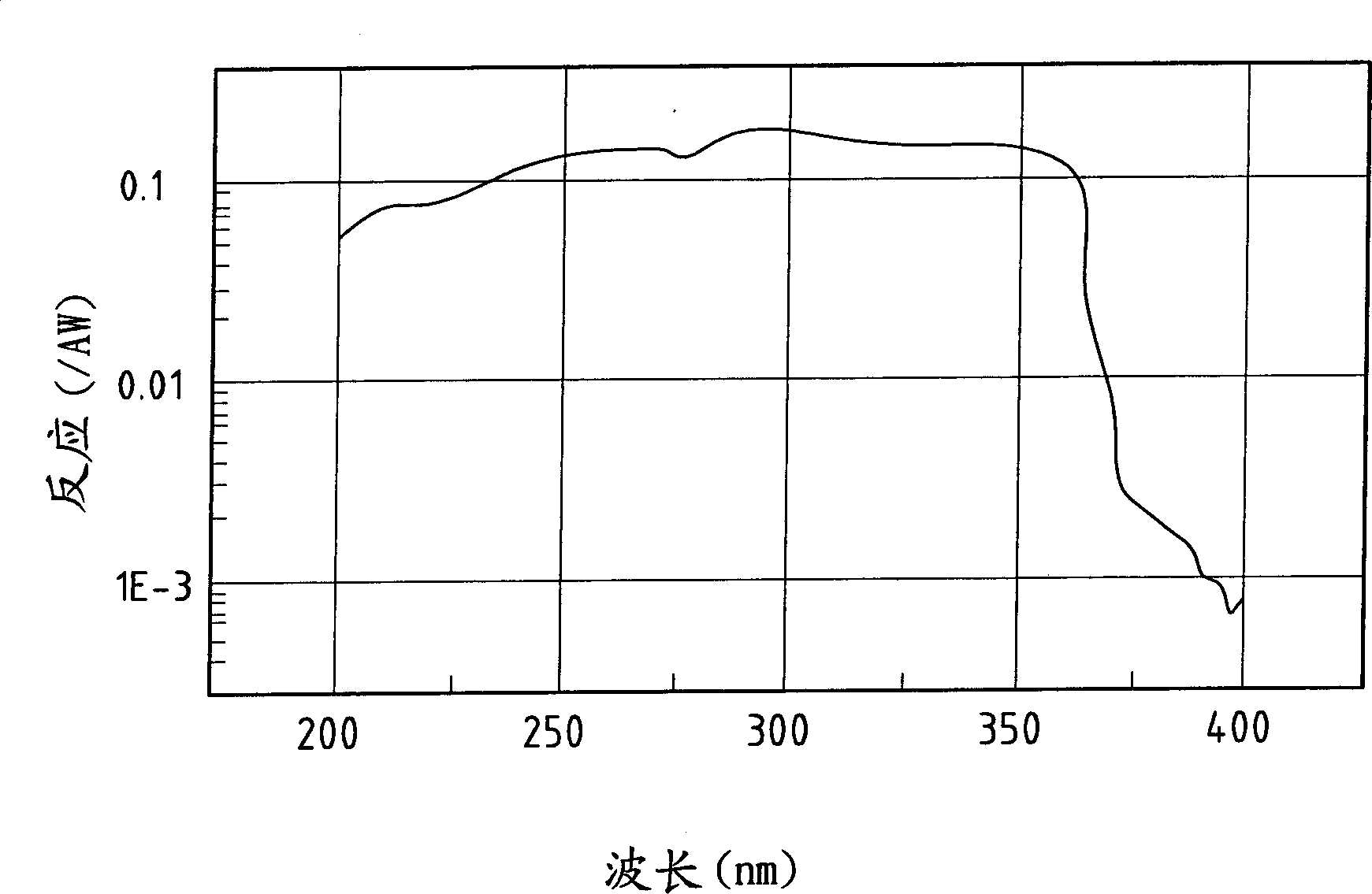

Ultra violet ray photo detector based on gallium nitride semiconductor

The invention provides a GaN semiconductor-based ultraviolet (UV) detector structure, from the substrate up, in sequence comprising n-type contact layer, light absorbing layer, light transmitting layer and p-type contact layer, all made of AlGaInN tetra-compound semiconductor material. By changing Al, Ga and In compositions of the semiconductor material, on one hand, these semiconductor layers can possess the needed energy gap, thus able to be specially sensitive to the optical reaction with respect to specific-wavelength UV; on the other hand, these semiconductor layers can possess matching crystal lattice constants, thus able to avoid the related problem of overlarge stress and simultaneously obtaining a UV detector with higher-quality crystal lattice structure. And the structure further comprises anode on the p-type contact layer, light transmitting Ohm contact layer and anti-reflecting layer as well as cathode on the n-type contact layer.

Owner:FORMOSA EPITAXY INCORPORATION +1

Epitaxial structure for improving luminous efficiency and preparation method thereof

ActiveCN102916096AImprove concentration distributionReduce stressSemiconductor devicesContact layerGallium nitride

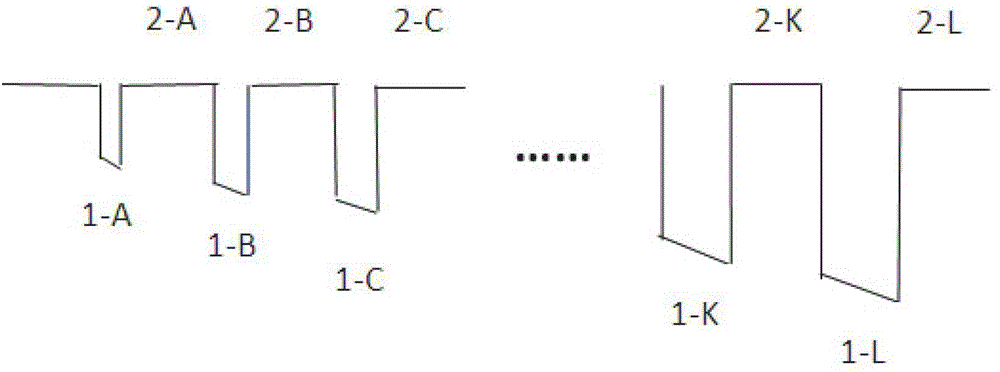

The invention provides an epitaxial structure for improving luminous efficiency. The epitaxial structure for improving the luminous efficiency sequentially comprises a substrate, a first GaN (Gallium Nitride) buffer layer, a second GaN buffer layer, an N-type GaN layer, a multi-quantum well (MQW) structure, a light-emitting layer multi-quantum well structure, a p-type GaN layer, a p-type AlGaN (aluminium gallium nitride) layer, a p-type GaN layer and a p-type contact layer from the bottom up, wherein the multi-quantum well structure consists of n layers of InxGa1-XN / GaN multi-quantum wells; the widths, the depths and the barrier heights of the n layers of the multi-quantum wells increase layer by layer; the barrier widths of the n layers of the multi-quantum wells decrease layer by layer; the well widths increasing layer by layer and the barrier widths decreasing layer by layer form regular correspondence; and n is an integer in a range of 2-12. A preparation method of the epitaxial structure for improving the luminous efficiency can optimize concentration distribution of electrons, reduce stresses generated in growth processes of multi-quantum wells, reduce a quantum confined stark effect (QCSE) and improve the luminous efficiency of the multi-quantum wells.

Owner:宁波安芯美半导体有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com