LED (Light Emitting Diode) epitaxial structure with P (Positive) type superlattice and preparation method thereof

An epitaxial structure and superlattice technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of low hole concentration, low luminous brightness of LED chips, low hole injection efficiency, etc., and achieve simple process steps, Block electron overflow and improve the effect of horizontal expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1 and comparative example 1

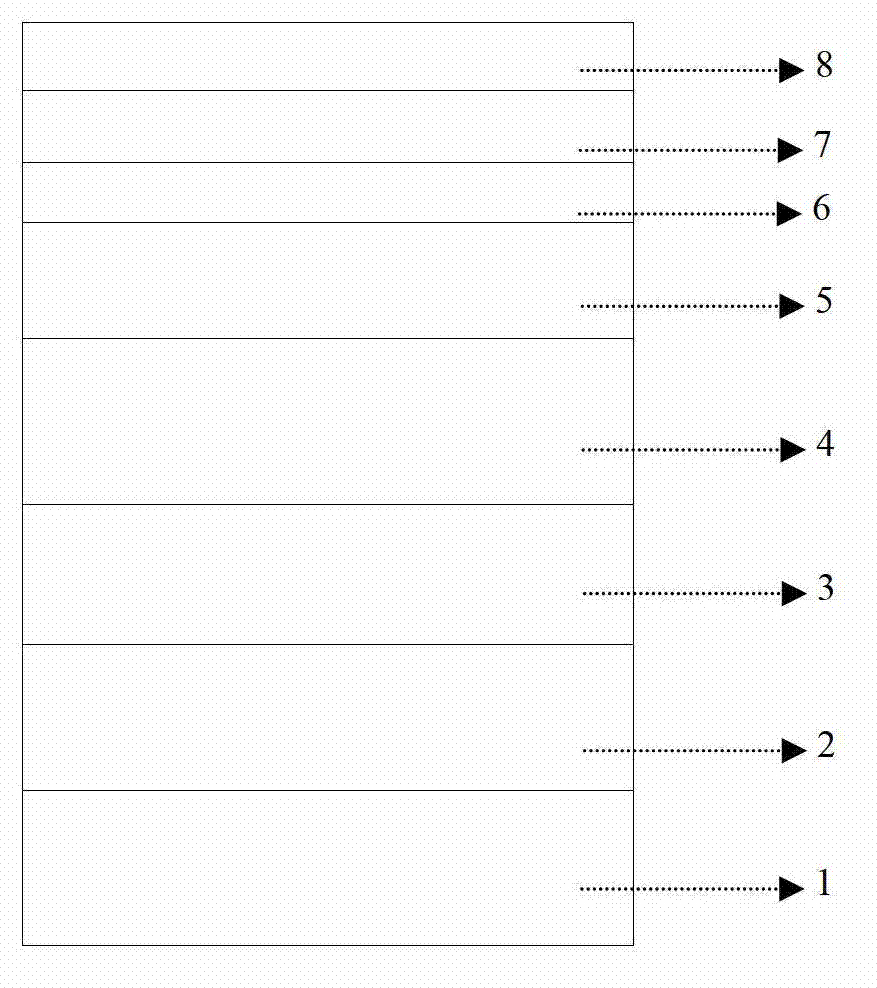

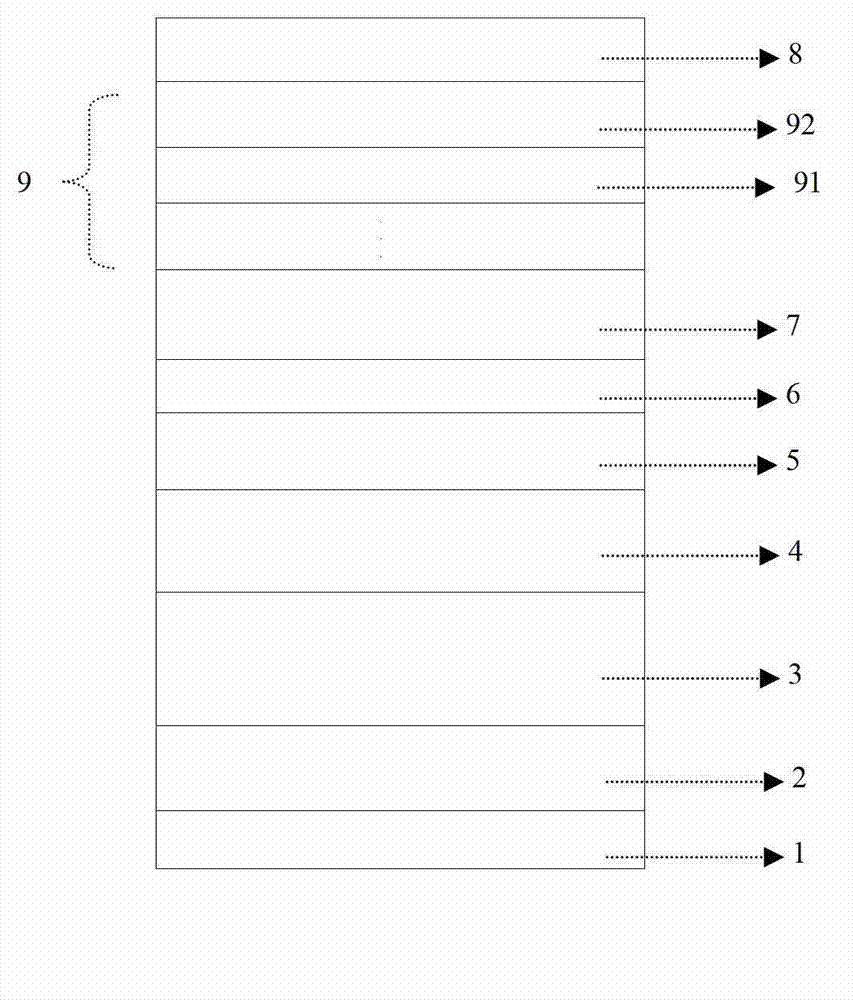

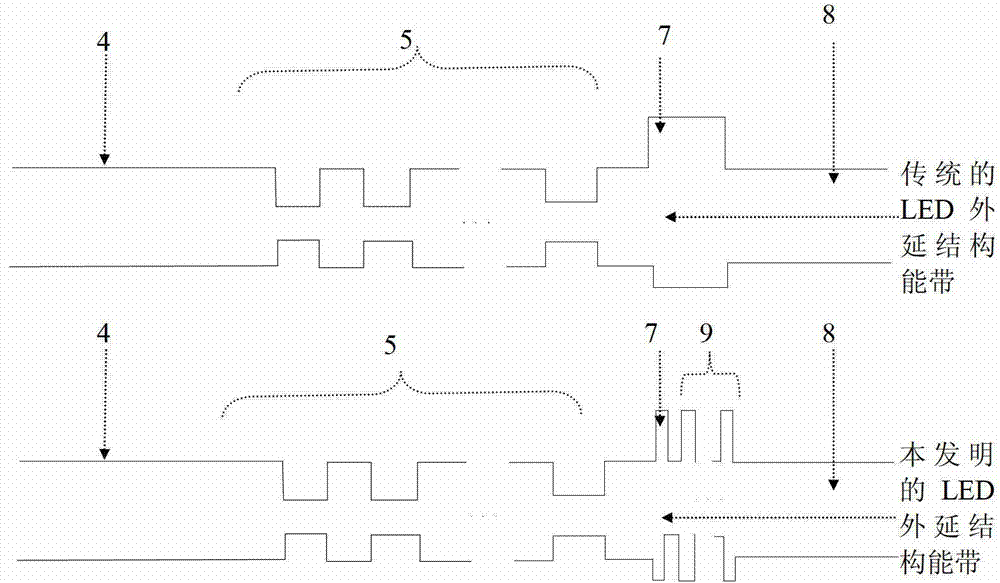

[0097] The process parameters of Step S206 and Step S207 of Example 1, and the process parameters of Step S206 of Comparative Example 1 are shown in Table 1. And the thickness of the PAlGaN (P-type AlGaN electron blocking layer 7) grown in Example 1 is 30nm, and the P-type superlattice 9 consists of two periods of PInGaN potential well layer 91 with a thickness of 5nm and a PAlGaN barrier with a thickness of 5nm The layers 92 are formed by periodically overlapping each other. The thickness of the PAIGaN (P-type AlGaN electron blocking layer 7 ) grown in Comparative Example 1 was 50 nm.

[0098] Step S206 and step S207 of the embodiment 1 of table 1, and the processing parameters of the step S206 of the comparative example 1

[0099]

[0100] In Table 1, each source gas is fed at the same time, and none indicates that no gas is fed during growth.

[0101] The epitaxial wafers obtained in embodiment 1 and comparative example 1 are carried out C-V test respectively, obtain as ...

Embodiment 2 and comparative example 2

[0106] The process parameters of Step S206 and Step S207 of Example 2, and the process parameters of Step S206 of Comparative Example 2 are shown in Table 2. And the thickness of the PAlGaN (P-type AlGaN electron blocking layer 7) grown in Example 2 is 32nm, and the P-type superlattice 9 consists of 3 periods of PInGaN potential well layers 91 with a thickness of 3nm and a PAlGaN barrier with a thickness of 3nm The layers 92 are formed by periodically overlapping each other. The thickness of the PAIGaN (P-type AlGaN electron blocking layer 7 ) grown in Comparative Example 2 was 50 nm.

[0107] Step S206 and step S207 of table 2 embodiment 2, and the process parameter of step S206 of comparative example 2

[0108]

[0109] In Table 2: all source gases are fed at the same time, and none means that they are not fed during growth.

[0110] The epitaxial wafers obtained in Example 2 and Comparative Example 2 were made into chips of 10mil*23mil and 45mil*45mil in the same chip ...

Embodiment 3

[0114] The process parameters of Step S206 and Step S207 of Example 3 are shown in Table 3. And the thickness of the PAlGaN (P-type AlGaN electron blocking layer 7) grown in Example 3 is 36nm, and the P-type superlattice 9 consists of two periods of PInGaN potential well layer 91 with a thickness of 4nm and a PAlGaN barrier with a thickness of 4nm The layers 92 are formed by periodically overlapping each other.

[0115] Step S206 of the embodiment 3 of table 3 and the process parameter of step S207

[0116]

[0117] In Table 3: all source gases are fed at the same time, and none means that they are not fed during growth.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More