Patents

Literature

1476 results about "High resistivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low resistivity is a material intrinsic property which readily allows the movement of electrons. Conversely, a high-resistivity material has a high electrical resistance and impedes the flow of electrons. Elements such as copper and aluminum are known for their low levels of resistivity.

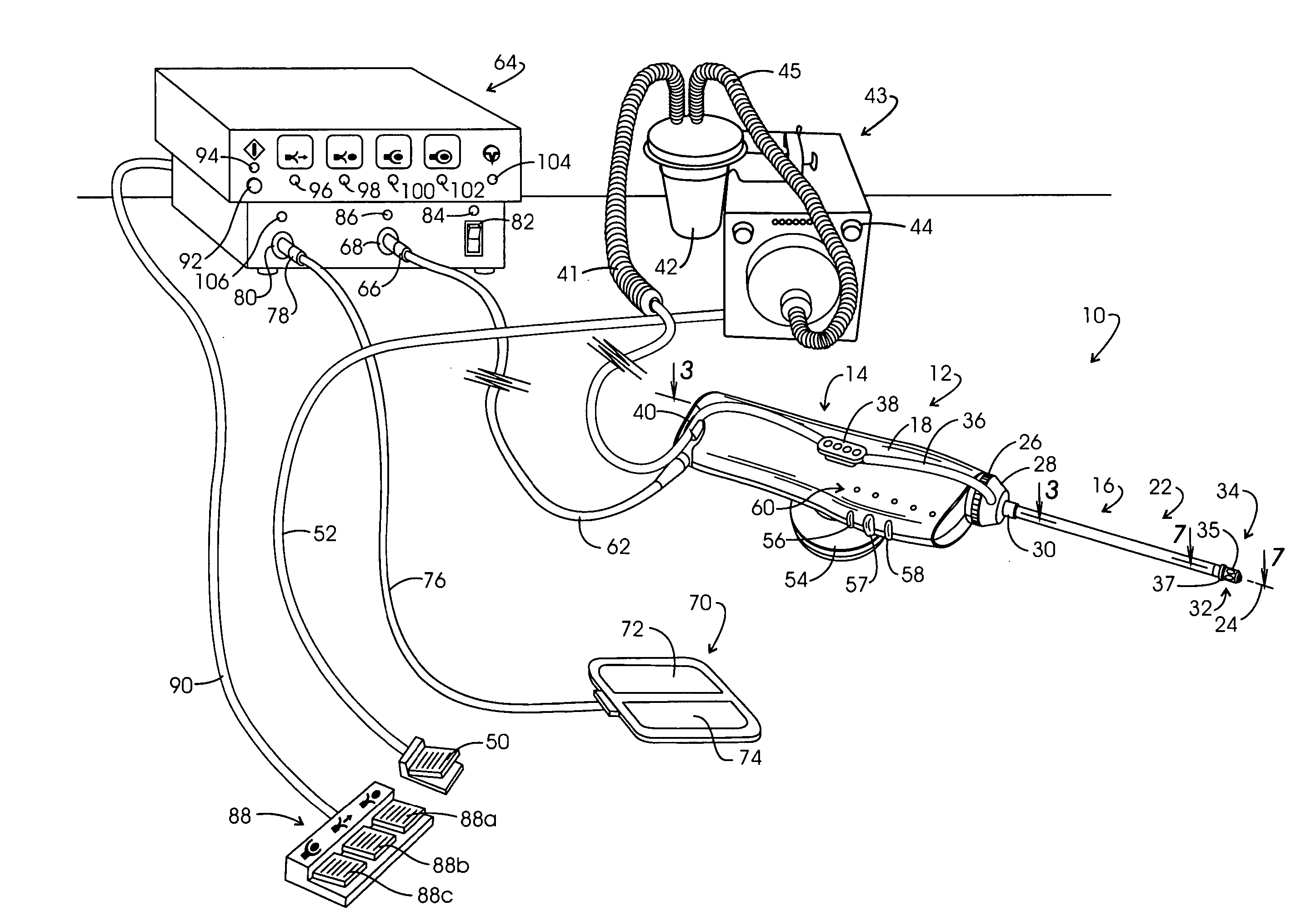

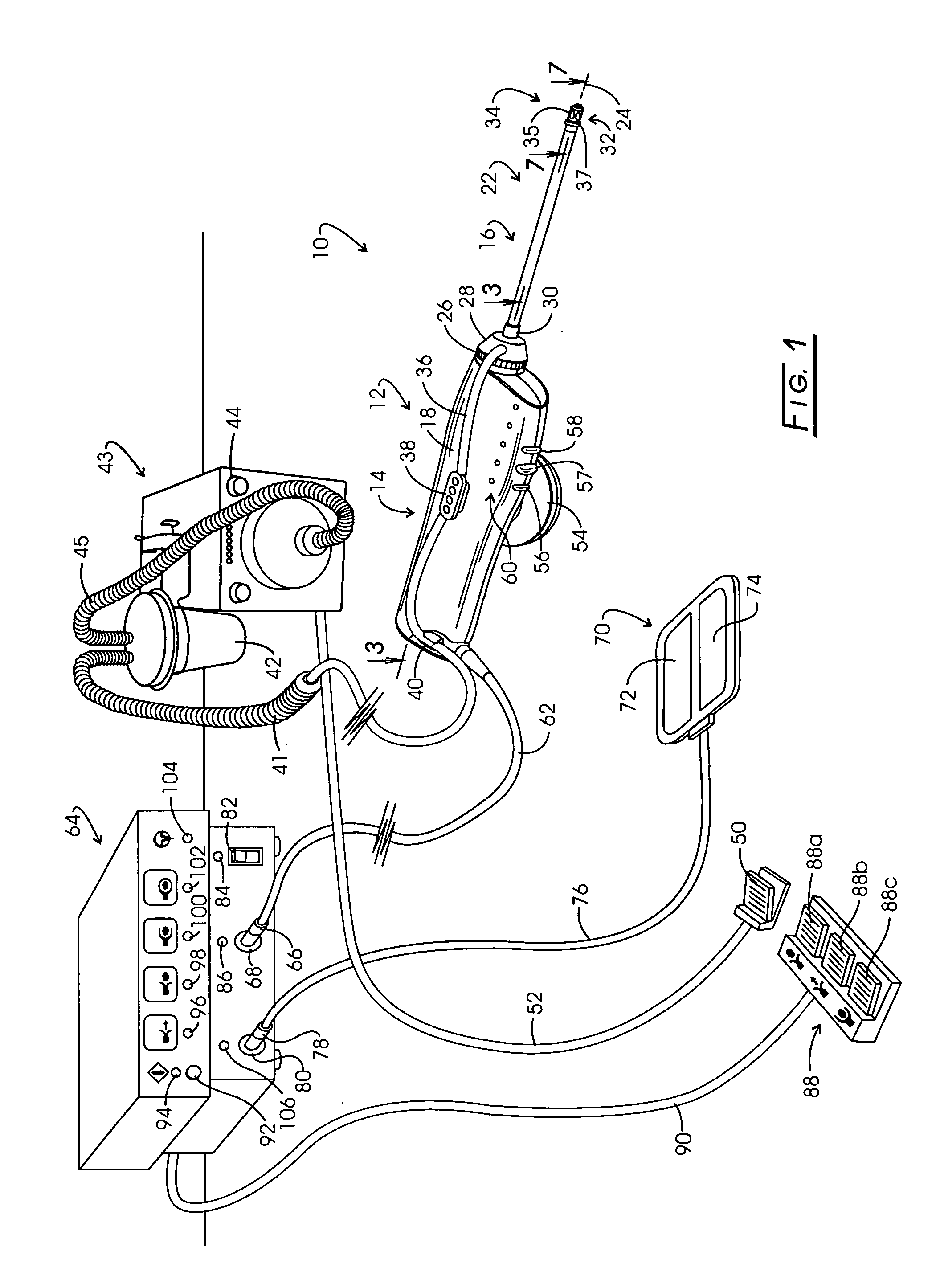

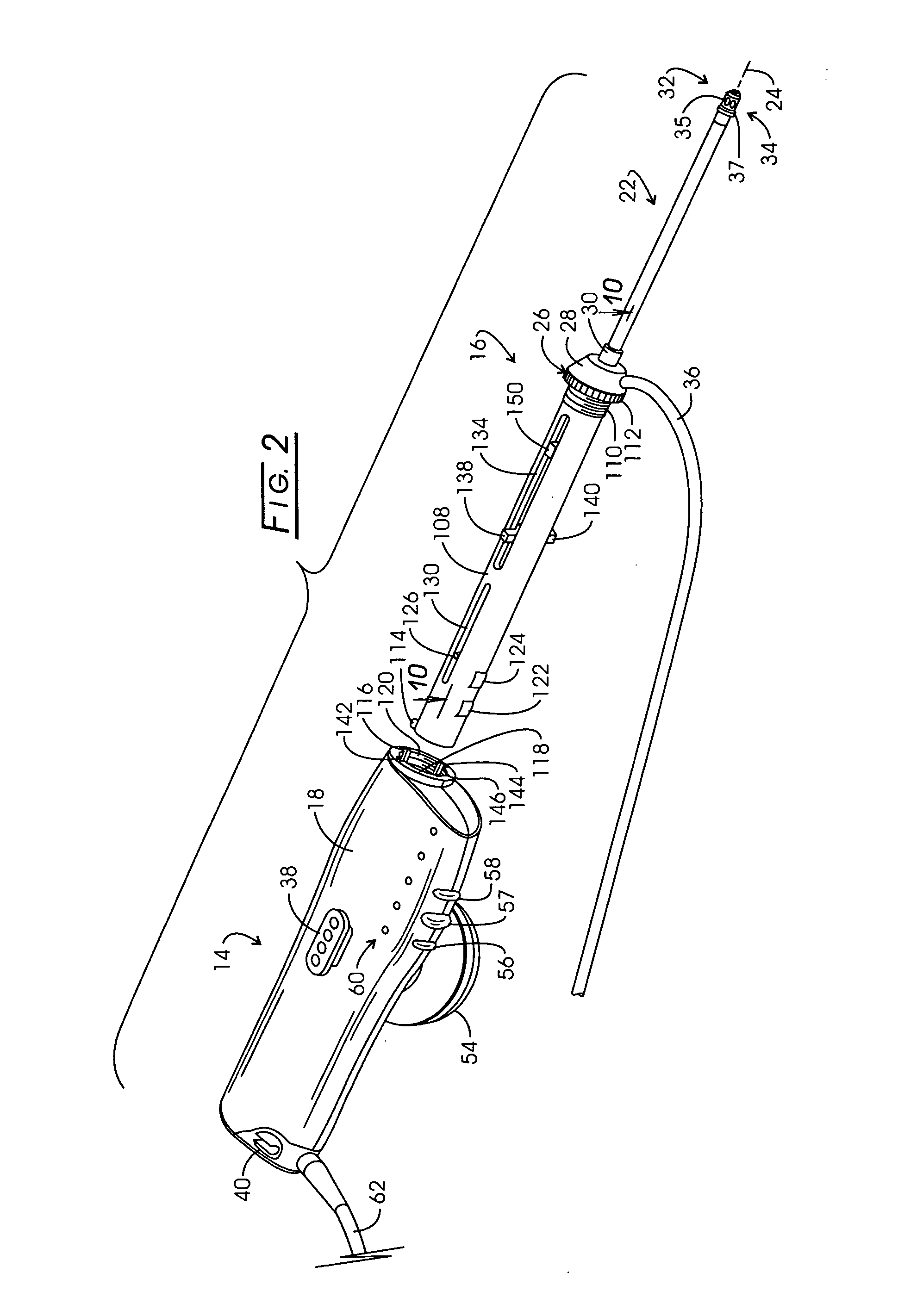

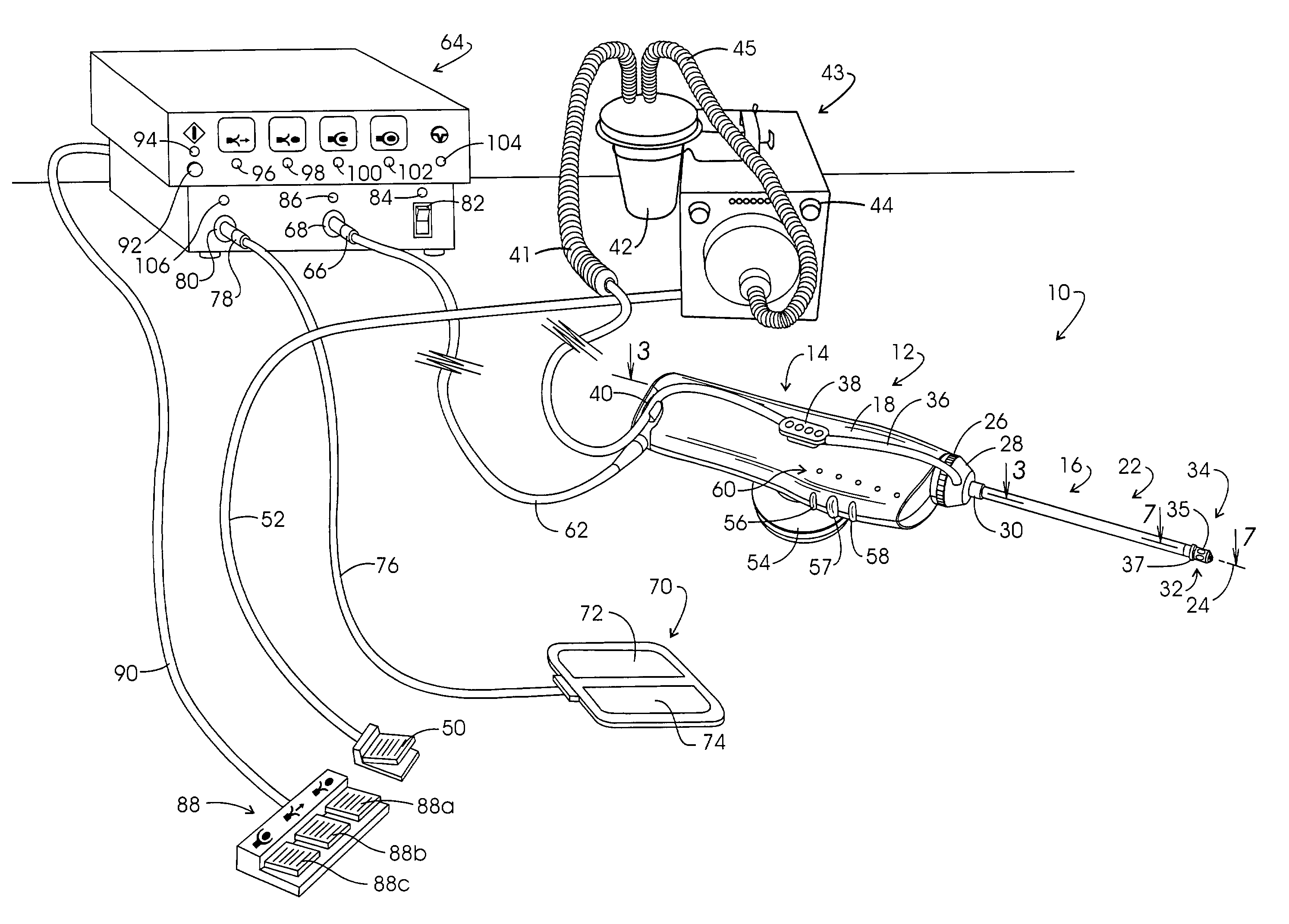

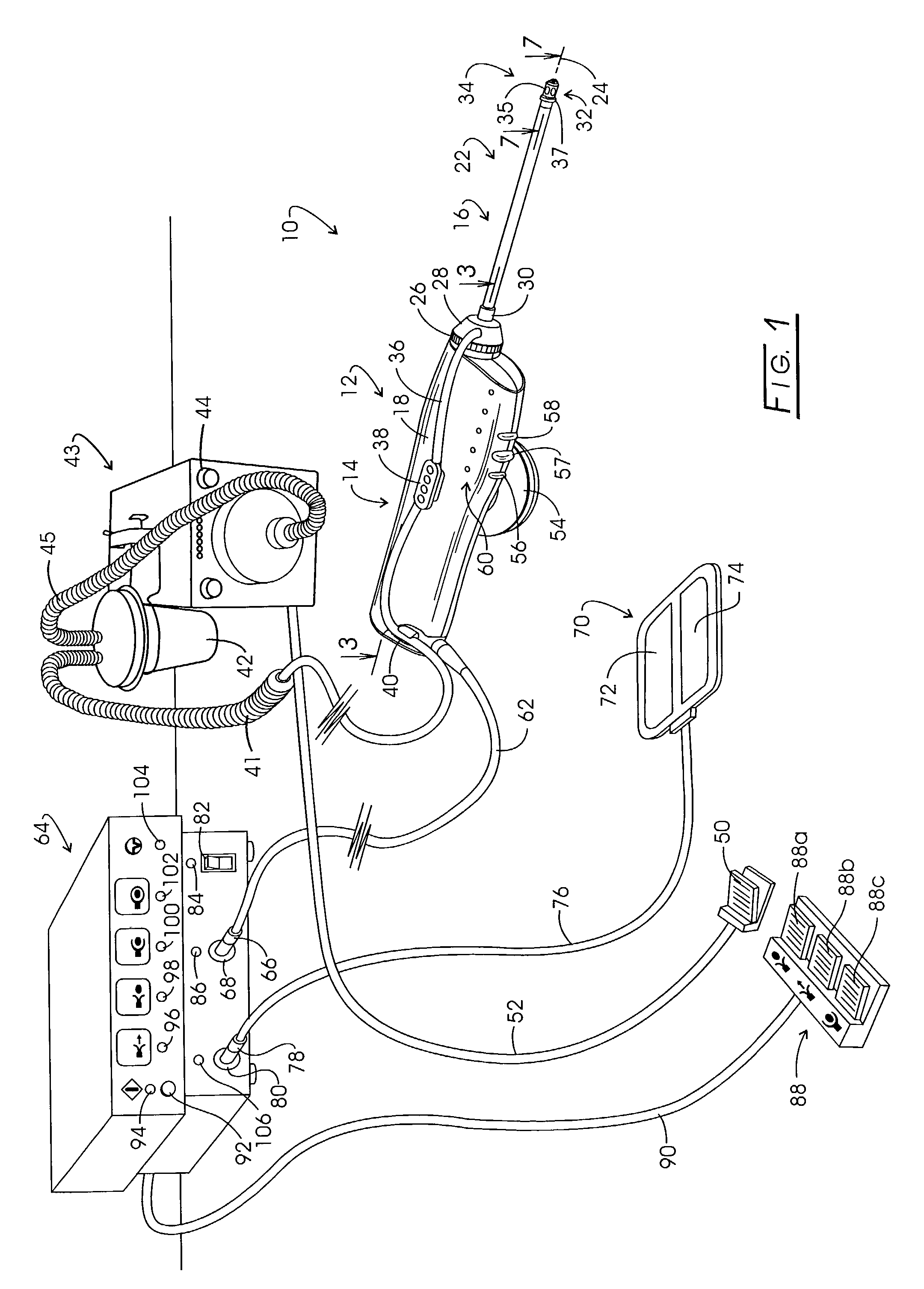

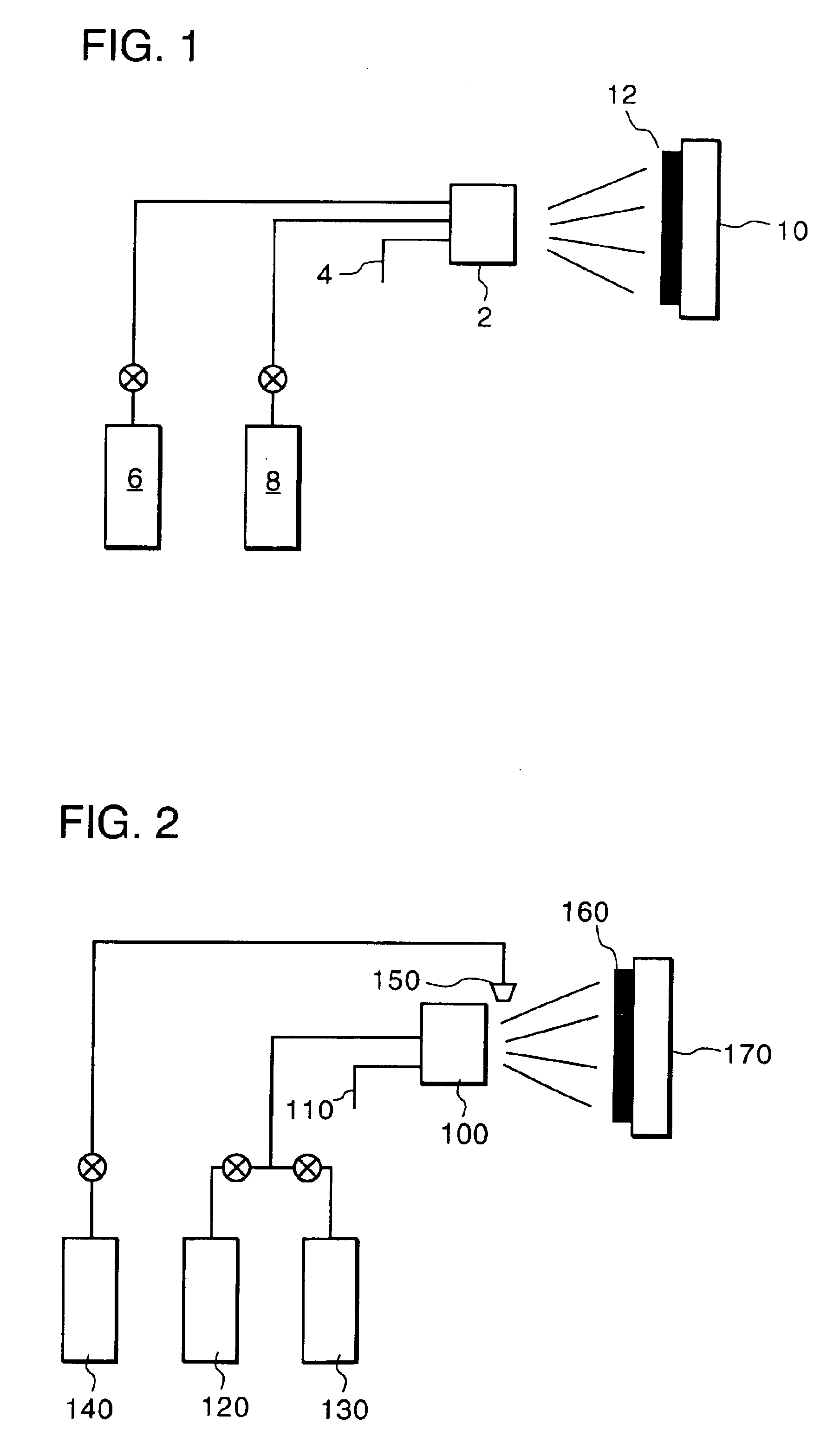

Electrosurgery with infiltration anesthesia

InactiveUS20050267455A1Reliable formationAnaesthesiaSurgical instruments for heatingElectrical resistance and conductanceElectrosurgery

Method for carrying out the recovery of an intact volume of tissue wherein a delivery cannula tip is positioned in confronting adjacency with the volume of tissue to be recovered. The electrosurgical generator employed to form an arc at a capture component extending from the tip is configured having a resistance-power profile which permits recovery of the specimen without excessive thermal artifact while providing sufficient power to sustain a cutting arc. For the recovery procedure, a local anesthetic employing a diluent which exhibits a higher resistivity is utilized and the method for deploying the capture component involves an intermittent formation of a cutting arc with capture component actuation interspersed with pauses of duration effective to evacuate any accumulation or pockets of local anesthetic solution encountered by the cutting electrodes.

Owner:INTACT MEDICAL

Electrosurgery with infiltration anesthesia

InactiveUS7004174B2AnaesthesiaVaccination/ovulation diagnosticsElectrical resistance and conductanceElectrosurgery

Method for carrying out the recovery of an intact volume of tissue wherein a delivery cannula tip is positioned in confronting adjacency with the volume of tissue to be recovered. The electrosurgical generator employed to form an arc at a capture component extending from the tip is configured having a resistance-power profile which permits recovery of the specimen without excessive thermal artifact while providing sufficient power to sustain a cutting arc. For the recovery procedure, a local anesthetic employing a diluent which exhibits a higher resistivity is utilized and the method for deploying the capture component involves an intermittent formation of a cutting arc with capture component actuation interspersed with pauses of duration effective to evacuate any accumulation or pockets of local anesthetic solution encountered by the cutting electrodes.

Owner:COVIDIEN AG

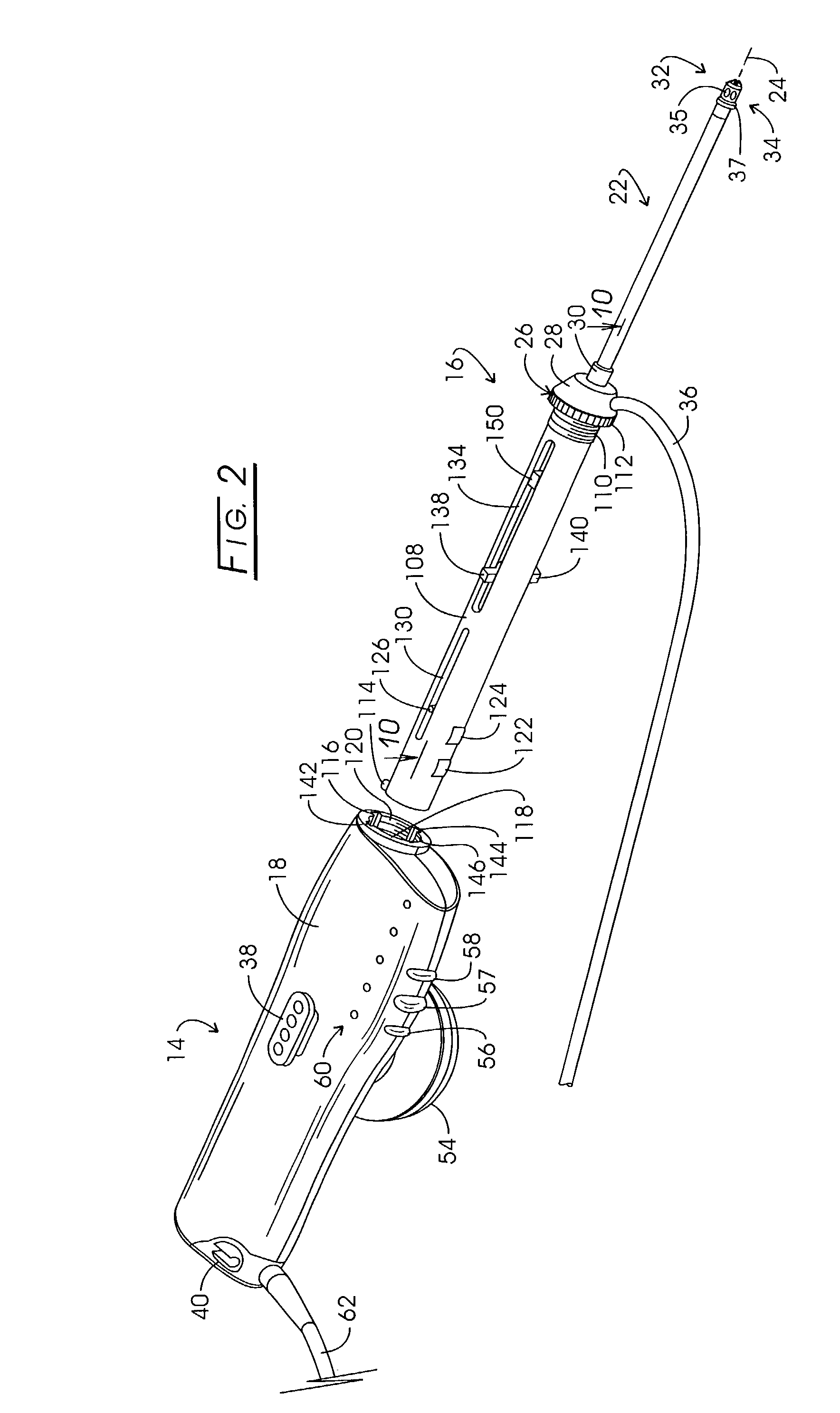

Thin film write head with improved laminated flux carrying structure and method of fabrication

InactiveUS6233116B1High resistivityExcellent soft magnetic propertiesConstruction of head windingsHeads using thin filmsLower poleHigh resistivity

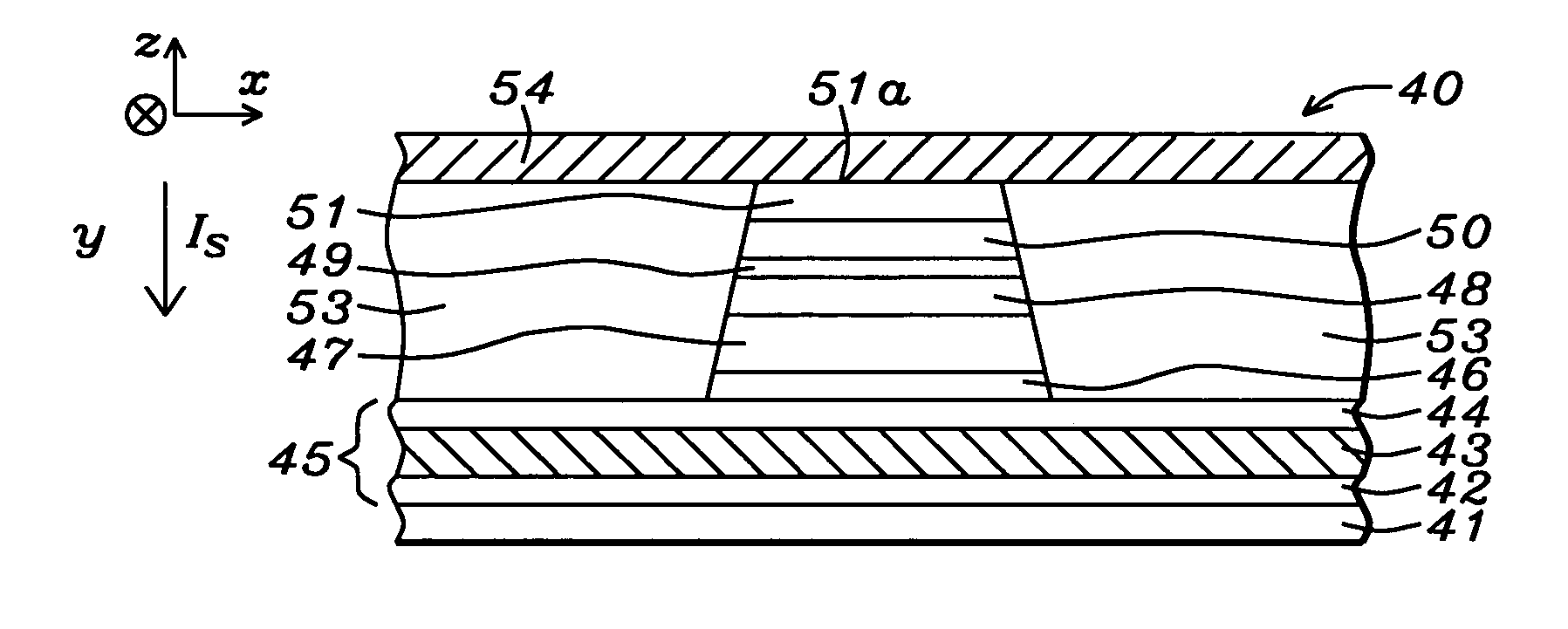

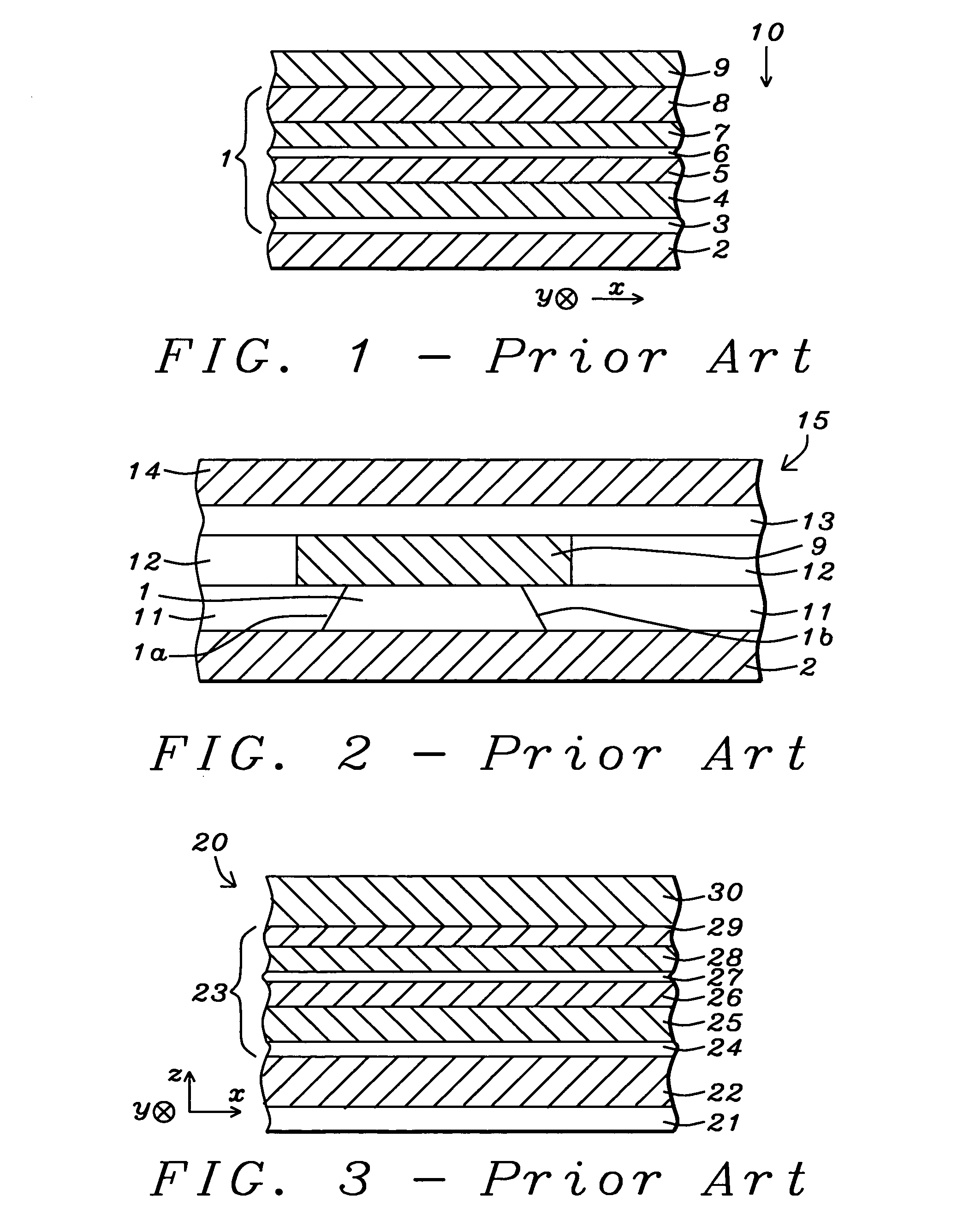

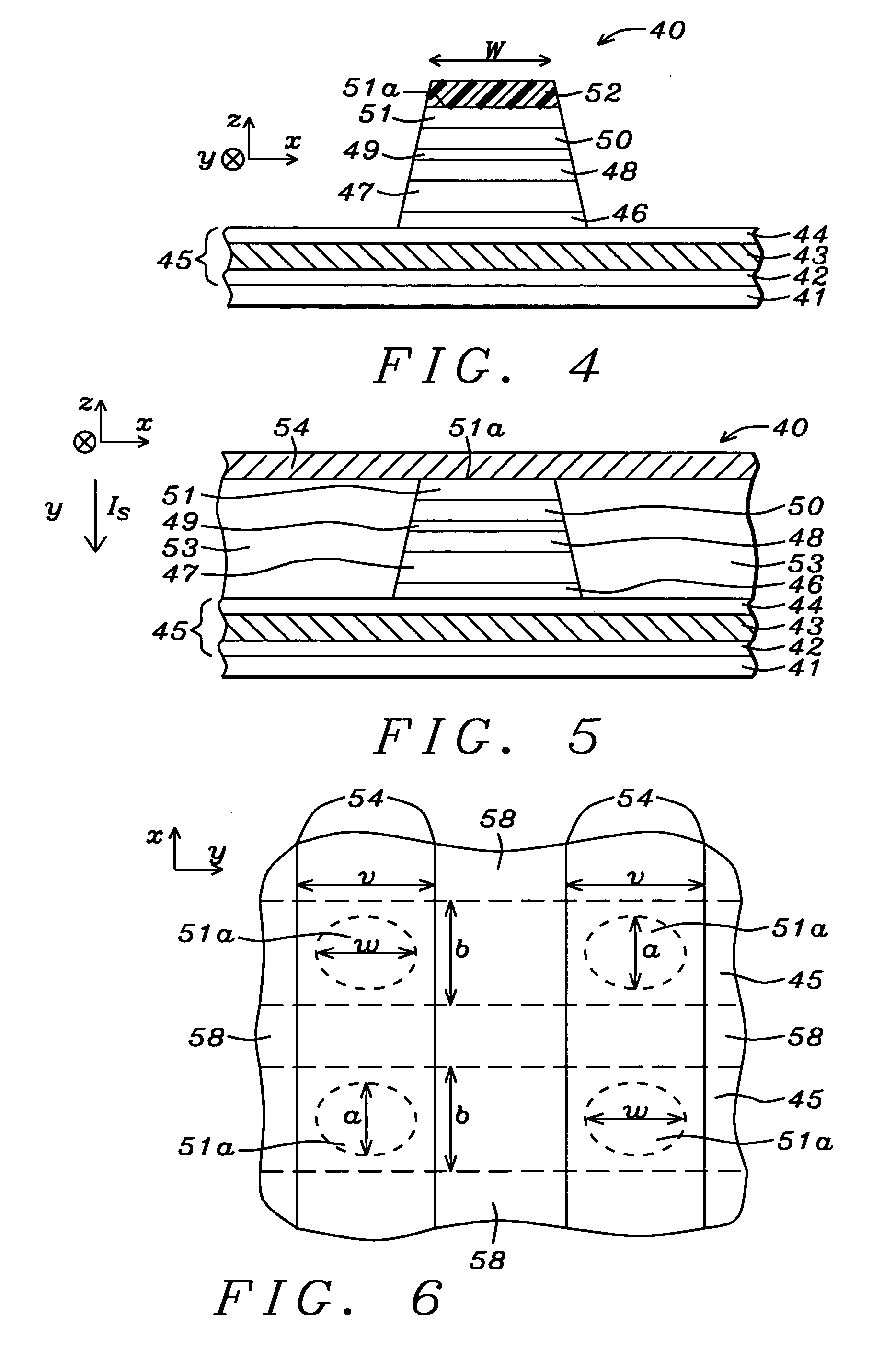

The present invention provides a thin film write head having an improved laminated flux carrying structure and method of fabrication. The preferred embodiment provides laminated layers of: high moment magnetic material, and easily aligned high resistivity magnetic material. In the preferred embodiment, the easily aligned laminating layer induces uniaxial anisotropy, by exchange coupling, to improve uniaxial anisotropy in the high moment material. This allows deposition induced uniaxial anisotropy by DC magnetron sputtering and also provides improved post deposition annealing, if desired. It is preferred to laminate FeXN, such as FeRhN, or other crystalline structure material, with an amorphous alloy material, preferably Co based, such as CoZrCr. In the preferred embodiment, upper and lower pole structures may both be laminated as discussed above. Such laminated structures have higher Bs than structures with insulative laminates, and yokes and pole tips and may be integrally formed, if desired, because flux may travel along or across the laminating layers. The preferred embodiment of the present invention improves soft magnetic properties, reduces eddy currents, improves hard axis alignment while not deleteriously affecting the coercivity, permeability, and magnetostriction of the structure, thus allowing for improved high frequency operation.

Owner:WESTERN DIGITAL TECH INC +1

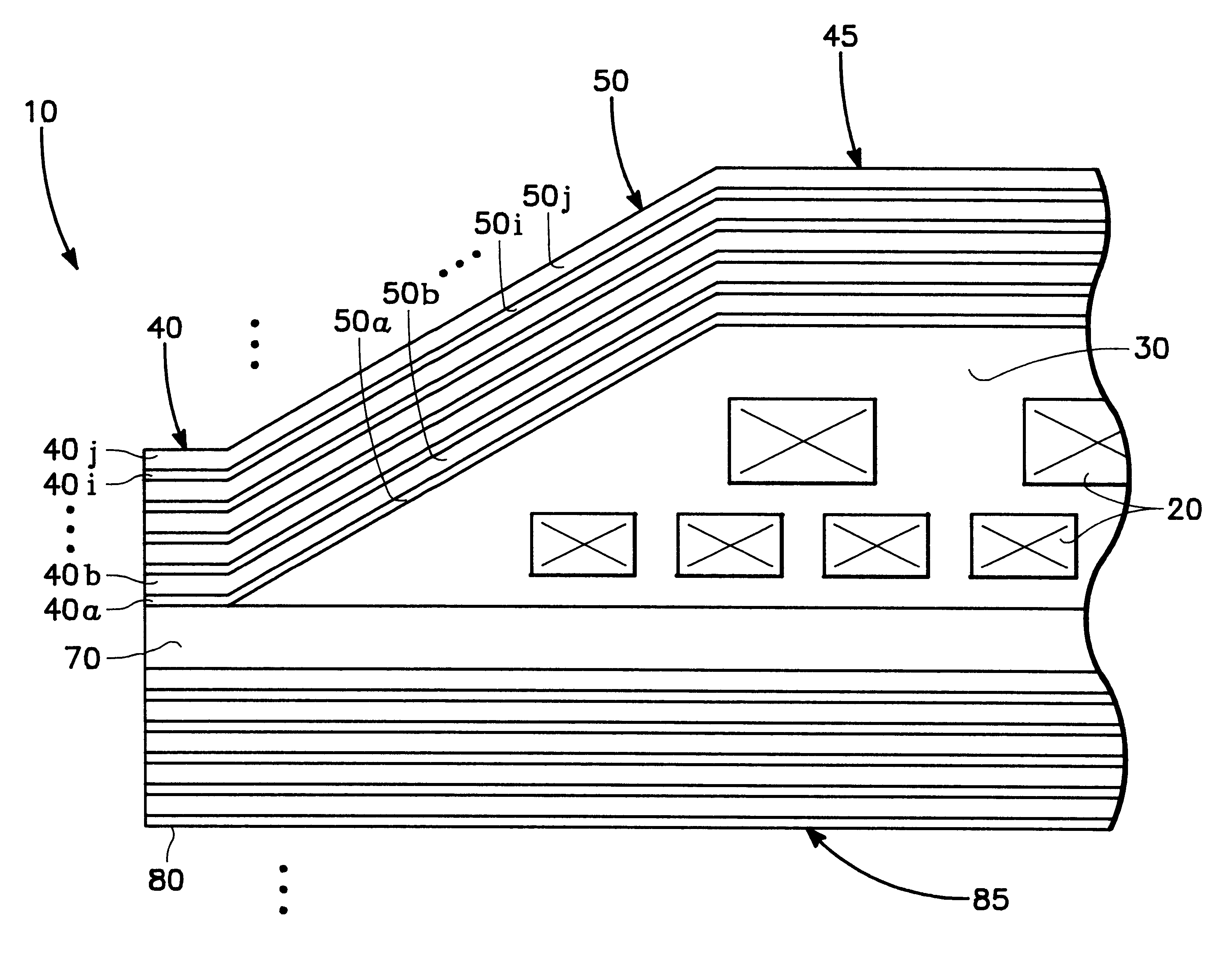

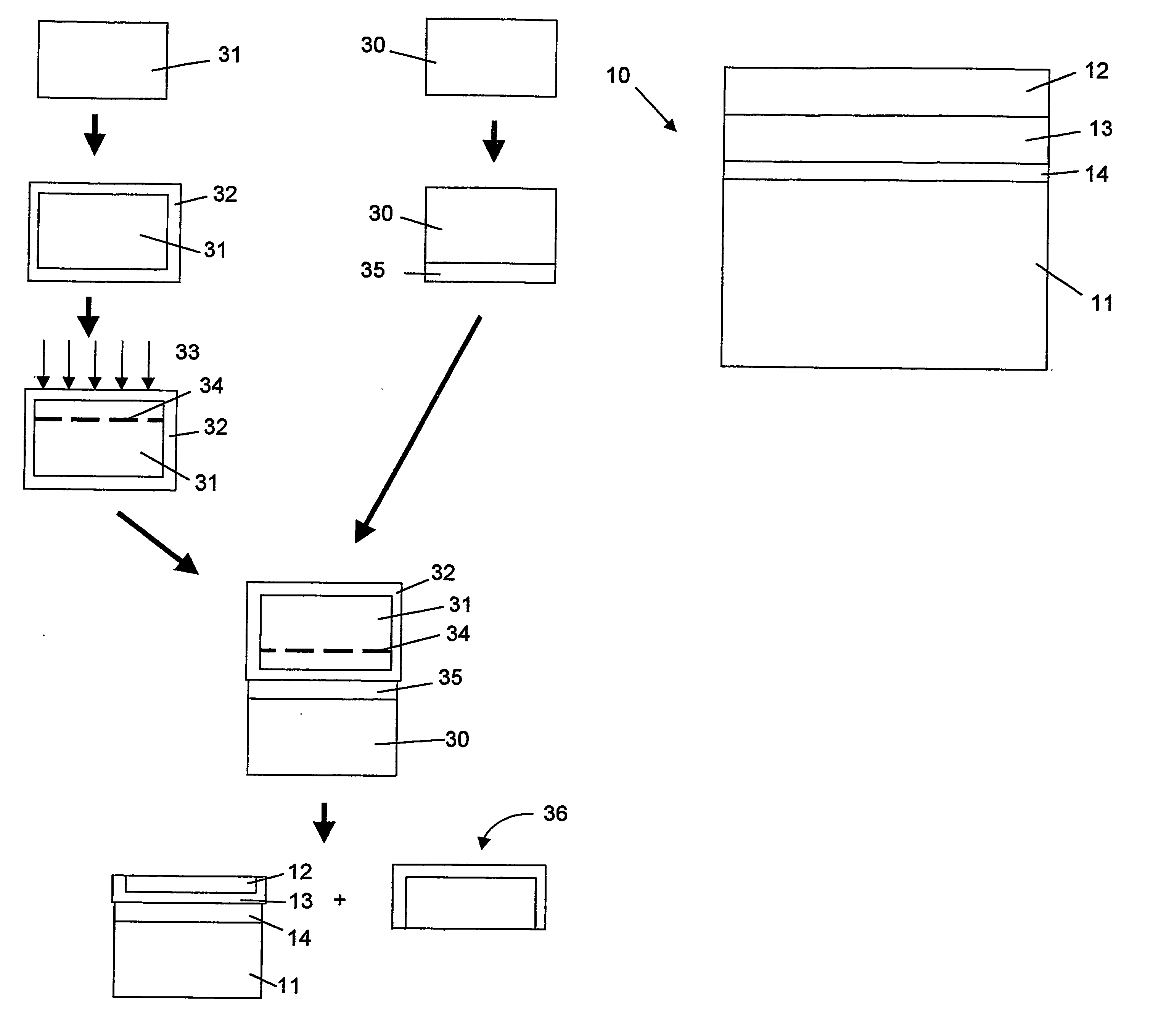

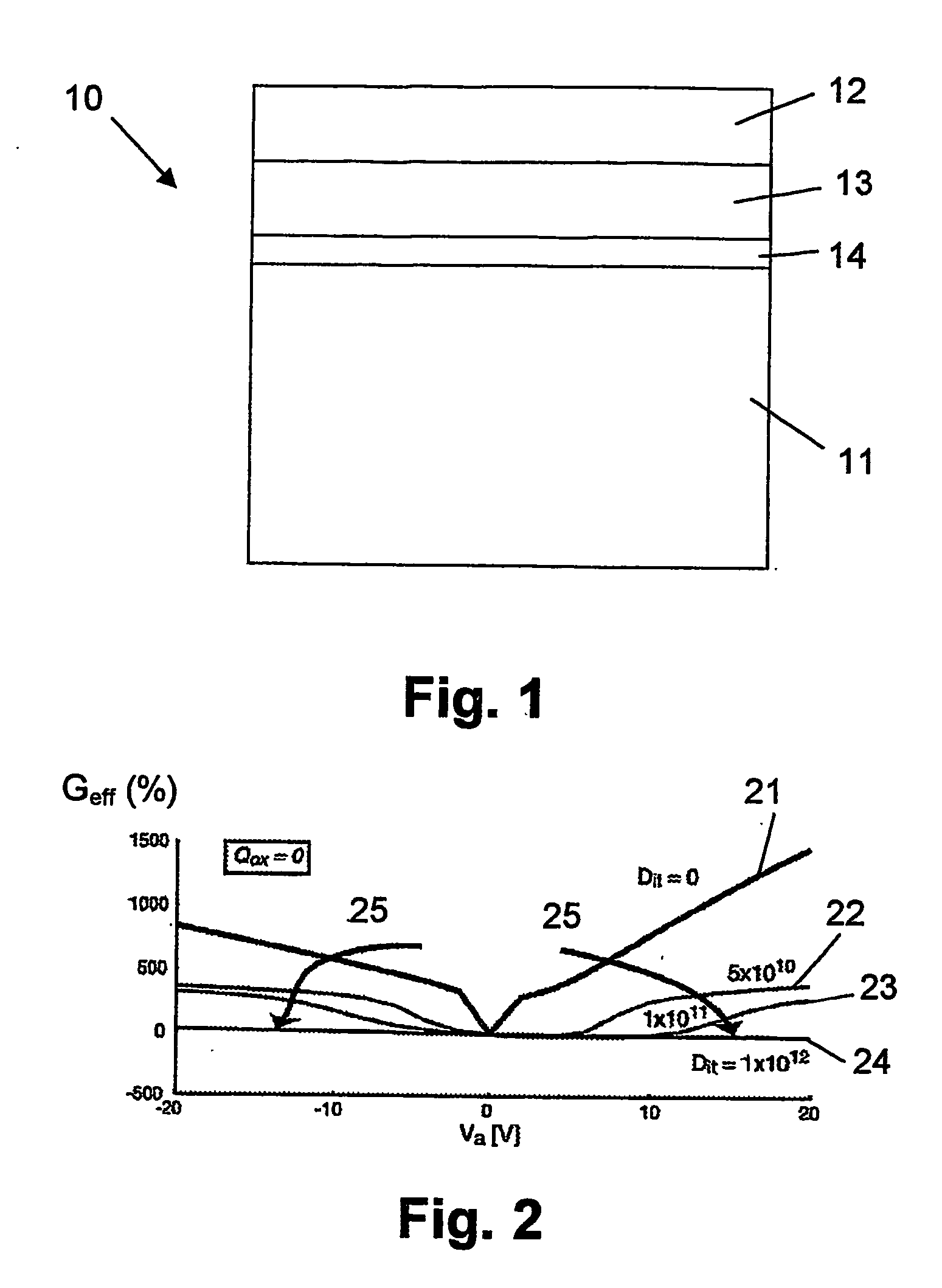

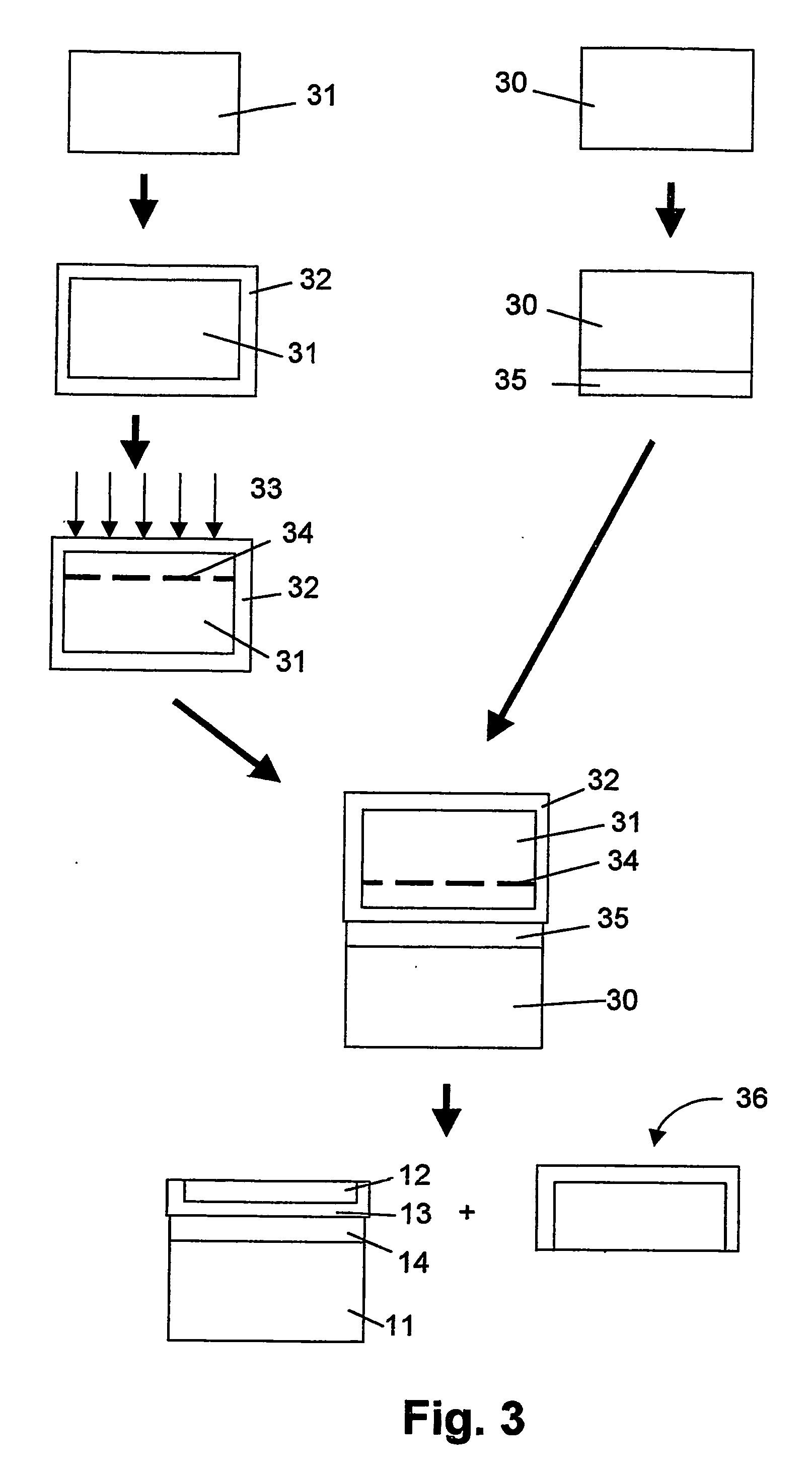

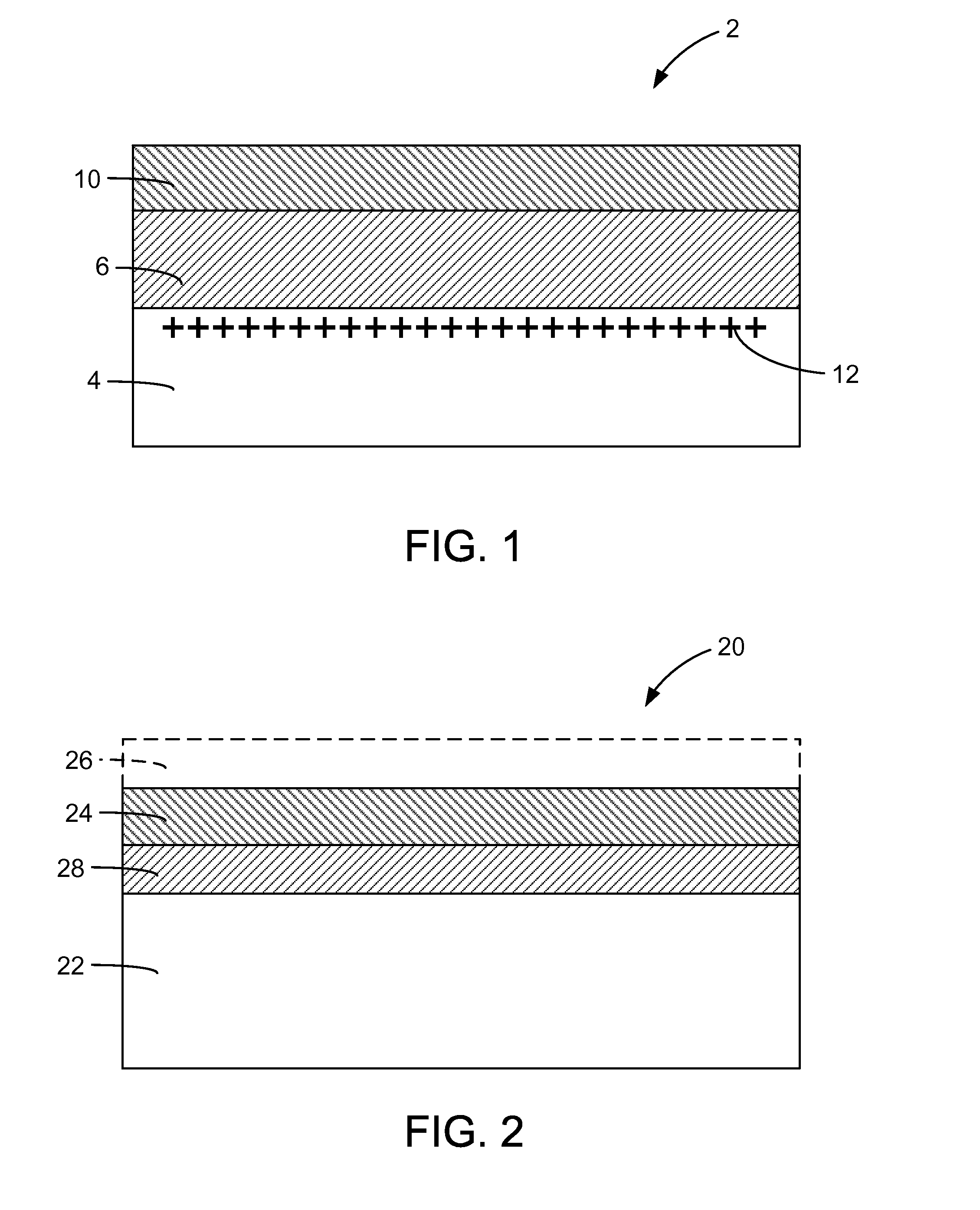

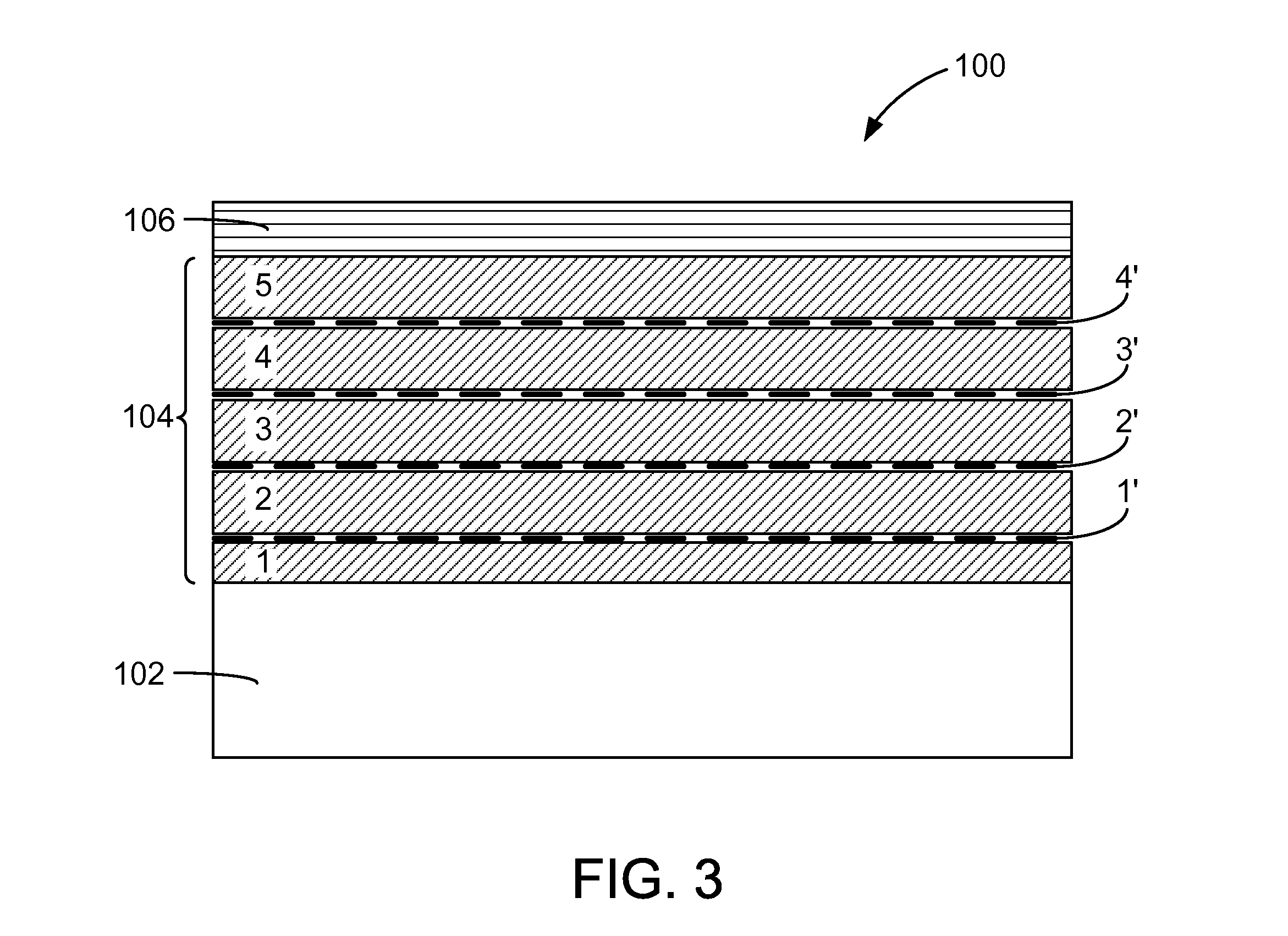

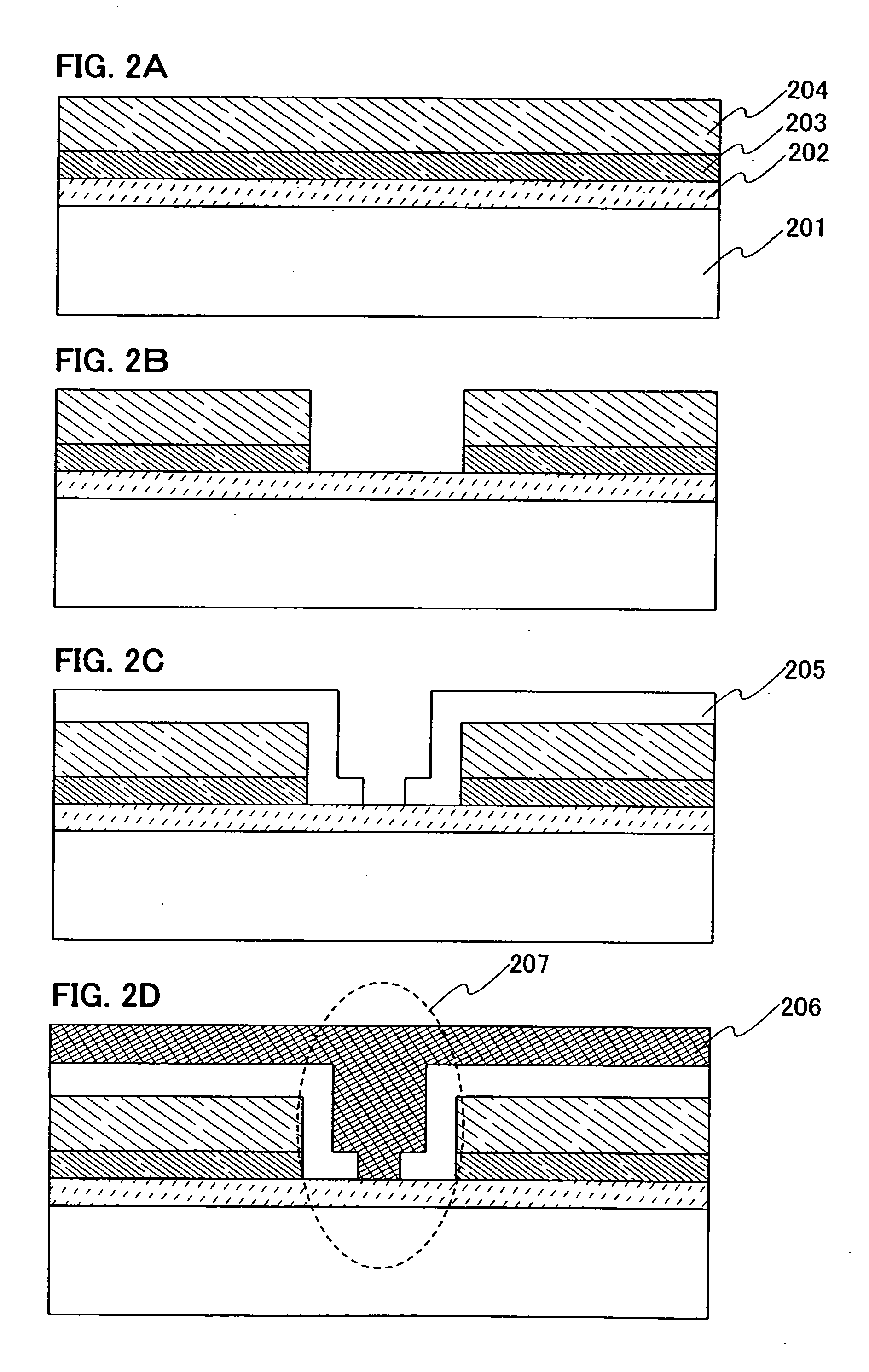

Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

InactiveUS20070032040A1Reduce and minimiseElectrical losses are reducedSolid-state devicesSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

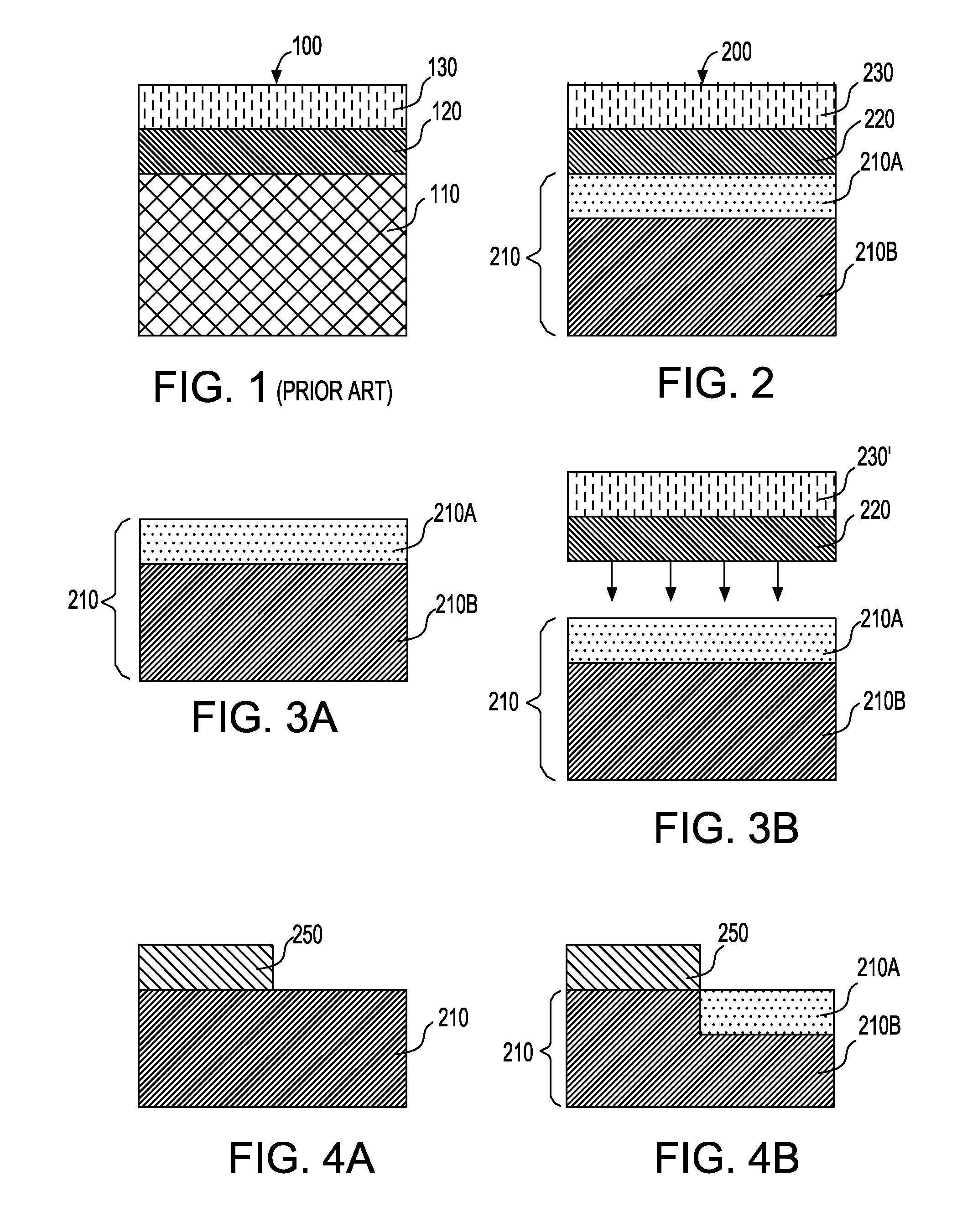

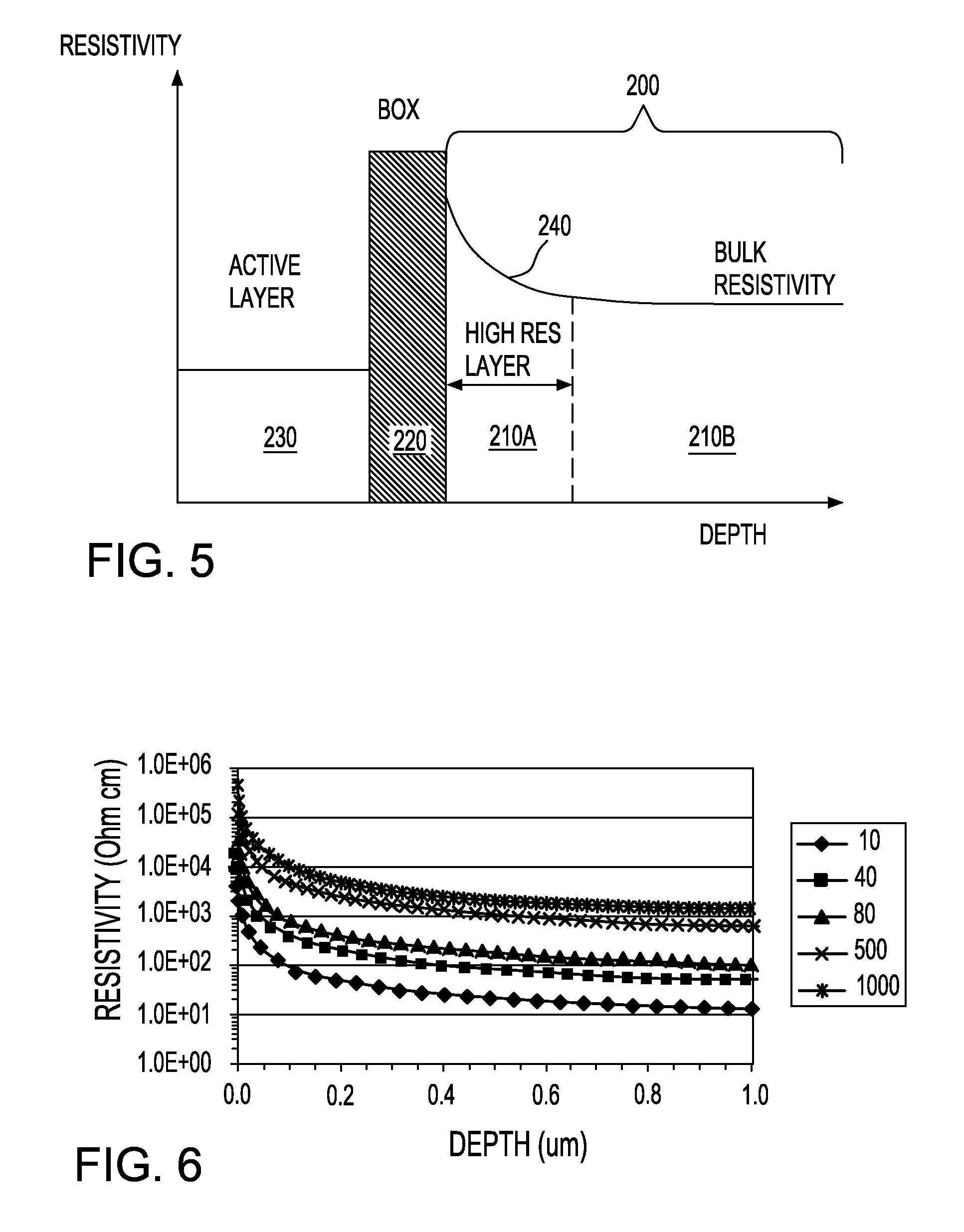

The present invention provides a method of manufacturing a multilayer semiconductor structure featuring reduced ohmic losses with respect to standard multilayer semiconductor structures. The semiconductor structure comprises a high resistivity silicon substrate with resistivity higher than 3 KΩ.cm, an active semiconductor layer and an insulating layer in between the silicon substrate and the active semiconductor layer. The method comprises suppressing ohmic losses inside the high resistivity silicon substrate by increasing, with regard to prior art devices, charge trap density between the insulating layer and the silicon substrate. In particular this may be obtained by applying an intermediate layer in between the silicon substrate and the insulating layer, the intermediate layer comprising grains having a size, wherein the mean size of the grains of the intermediate layer is smaller than 150 nm, preferably smaller than 50 nm.

Owner:UNIV CATHOLIQUE DE LOVAIN

Top spin valve with improved seed layer

InactiveUS6687098B1Improved exchange bias fieldNanostructure applicationNanomagnetismEngineeringHigh resistivity

The present invention provides an improved top spin valve and method of fabrication. In the preferred embodiment of the top spin valve of the present invention, a seed layer is formed of non-magnetic material having the elements Ni and Cr. In the preferred embodiments, the seed layer material has an ion milling rate comparable to that of the free layer material. This allows free layer sidewalls to be formed with shorter tails, improving free layer-to-magnetic bias layer junction, thus improving free layer domain structure and track width. In one embodiment, the seed layer may have NiFeCr, with Cr from about 20% to 50%. In another embodiment, the seed layer may have NiCr, with about 40%. Some embodiments may have the seed layer formed on an optional Ta pre-seed layer. Such embodiments provide an improved fcc (111) texture particularly for NiFe and for NiFe / CoFe free layers grown on a seed layer improving spin valve performance, and especially in embodiments having very thin NiFe free layers, ultra thin NiFe free layers, and free layers without NiFe, such as a free layer of CoFe. Such a seed layer can improve AFM pinning layer texture to improve the exchange bias, thus providing better thermal stability. Such a seed layer also provides high resistivity and can improve the magnetostriction of adjacent NiFe free layer material or improve the soft properties of an adjacent CoFe free layer.

Owner:WESTERN DIGITAL TECH INC

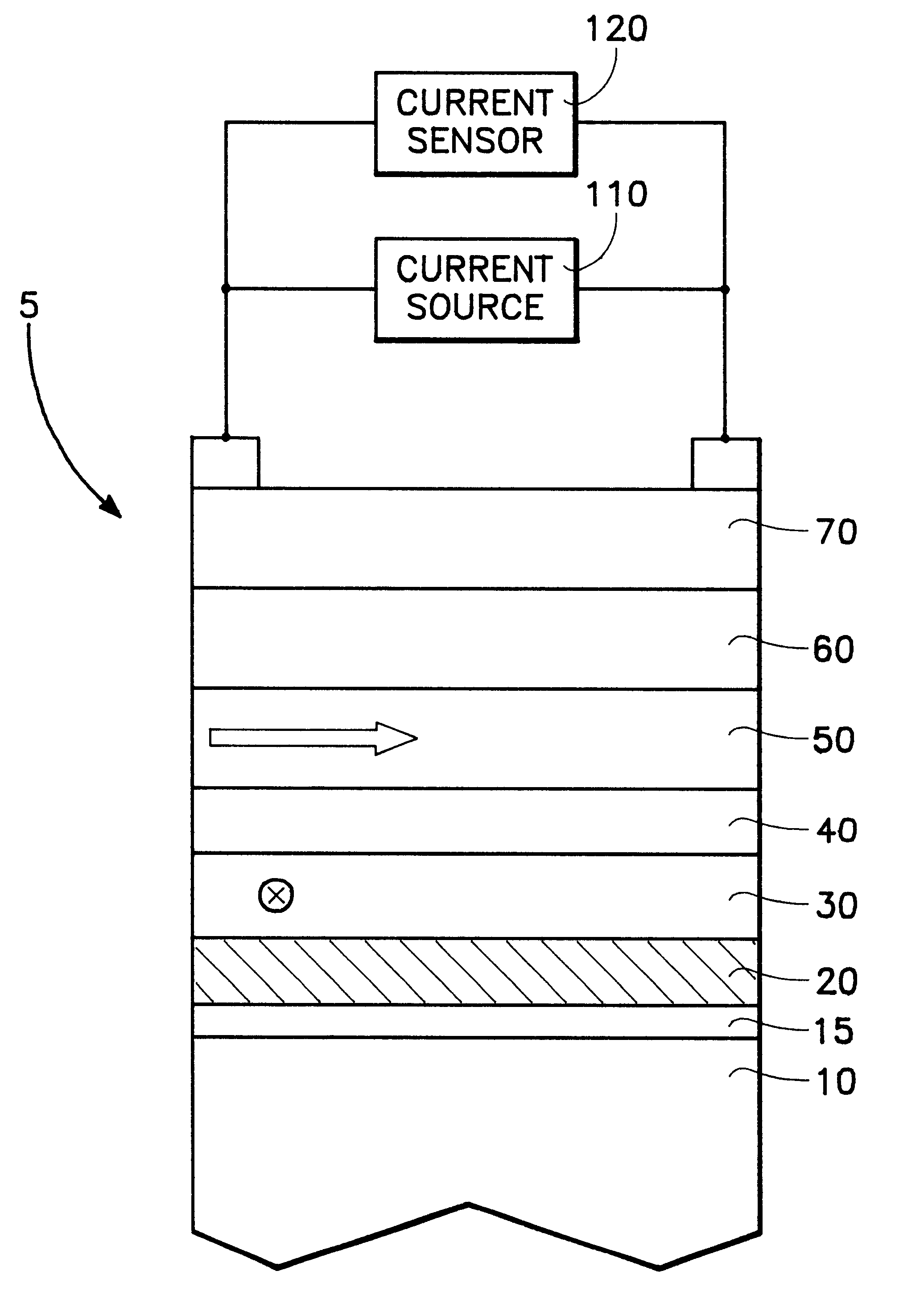

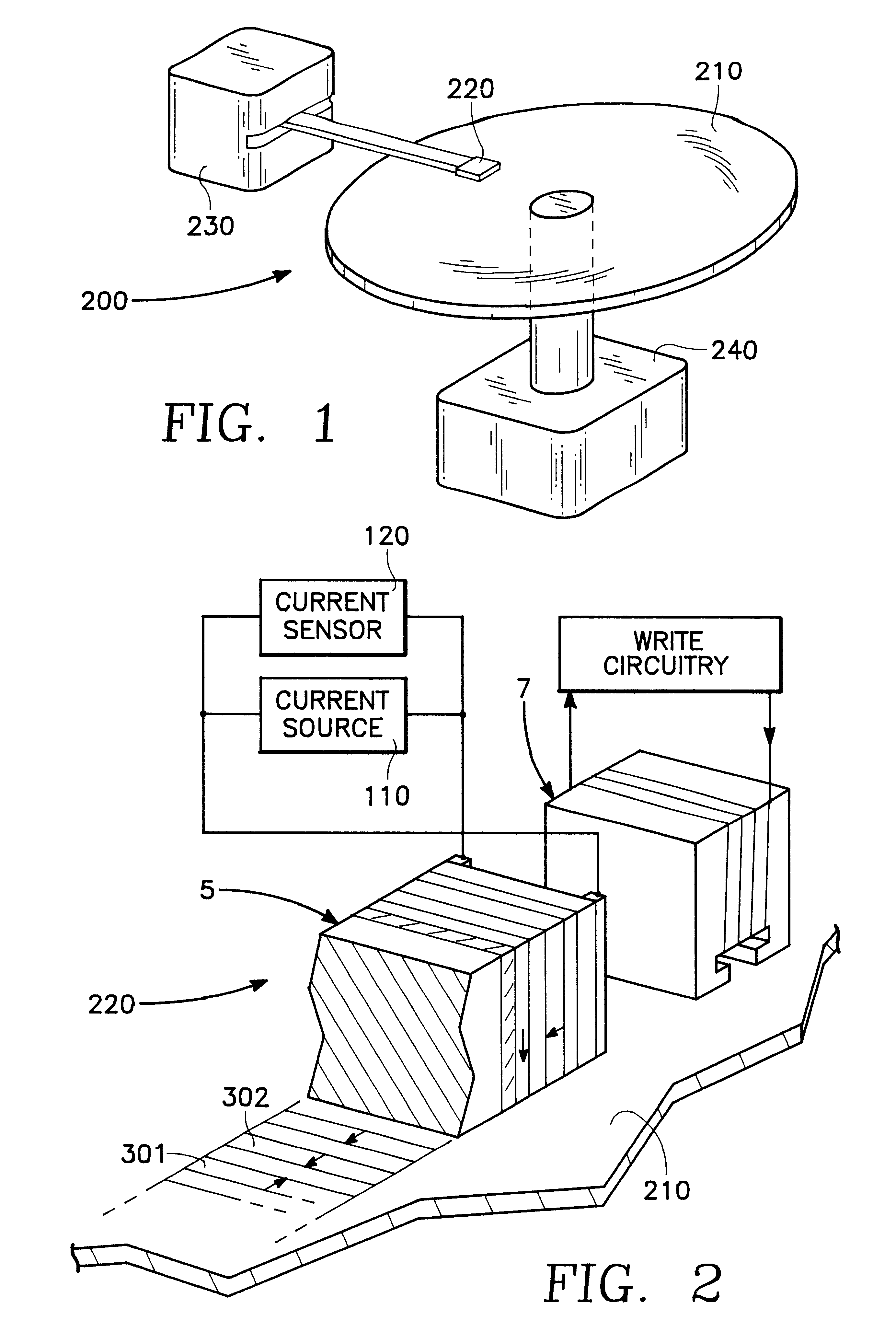

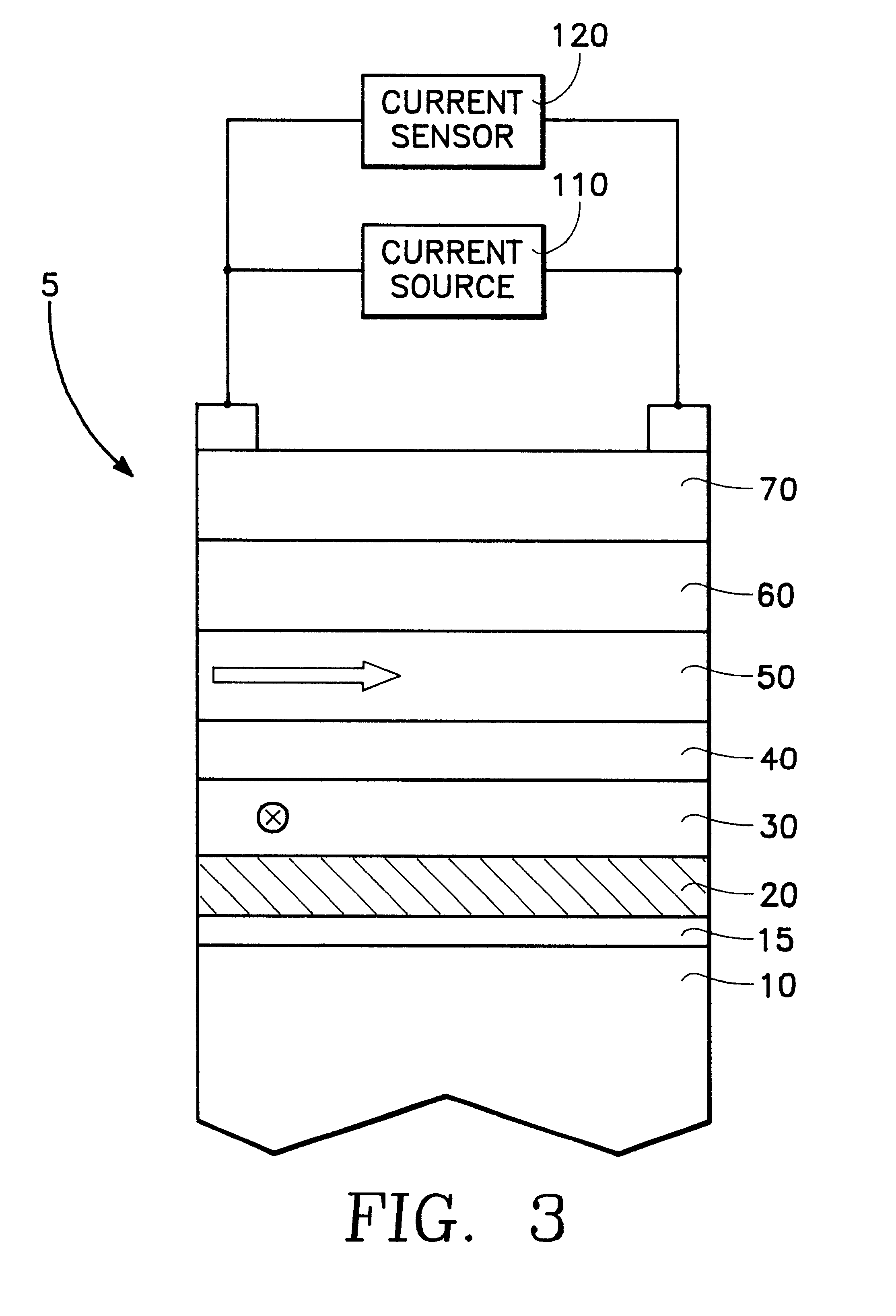

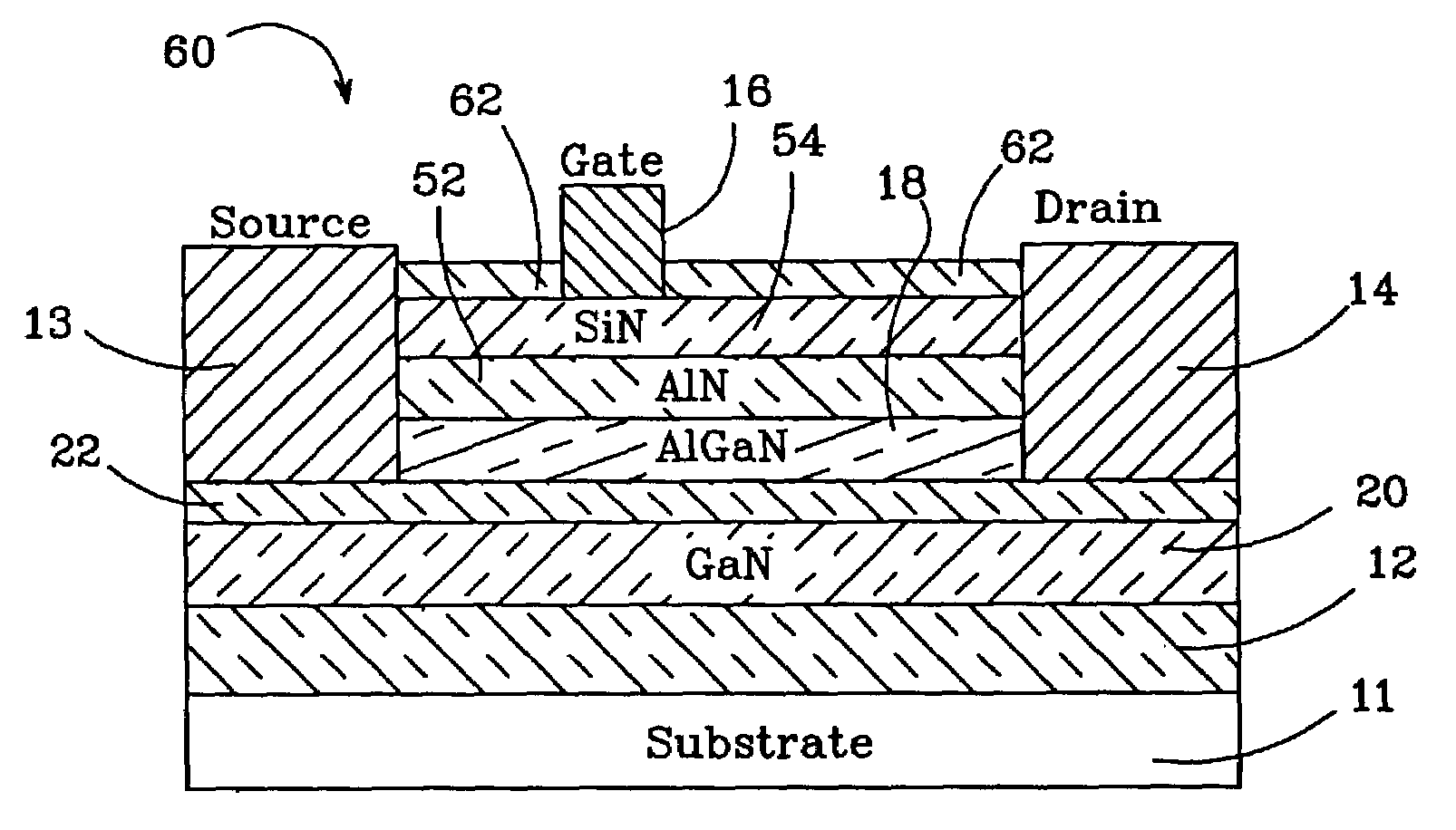

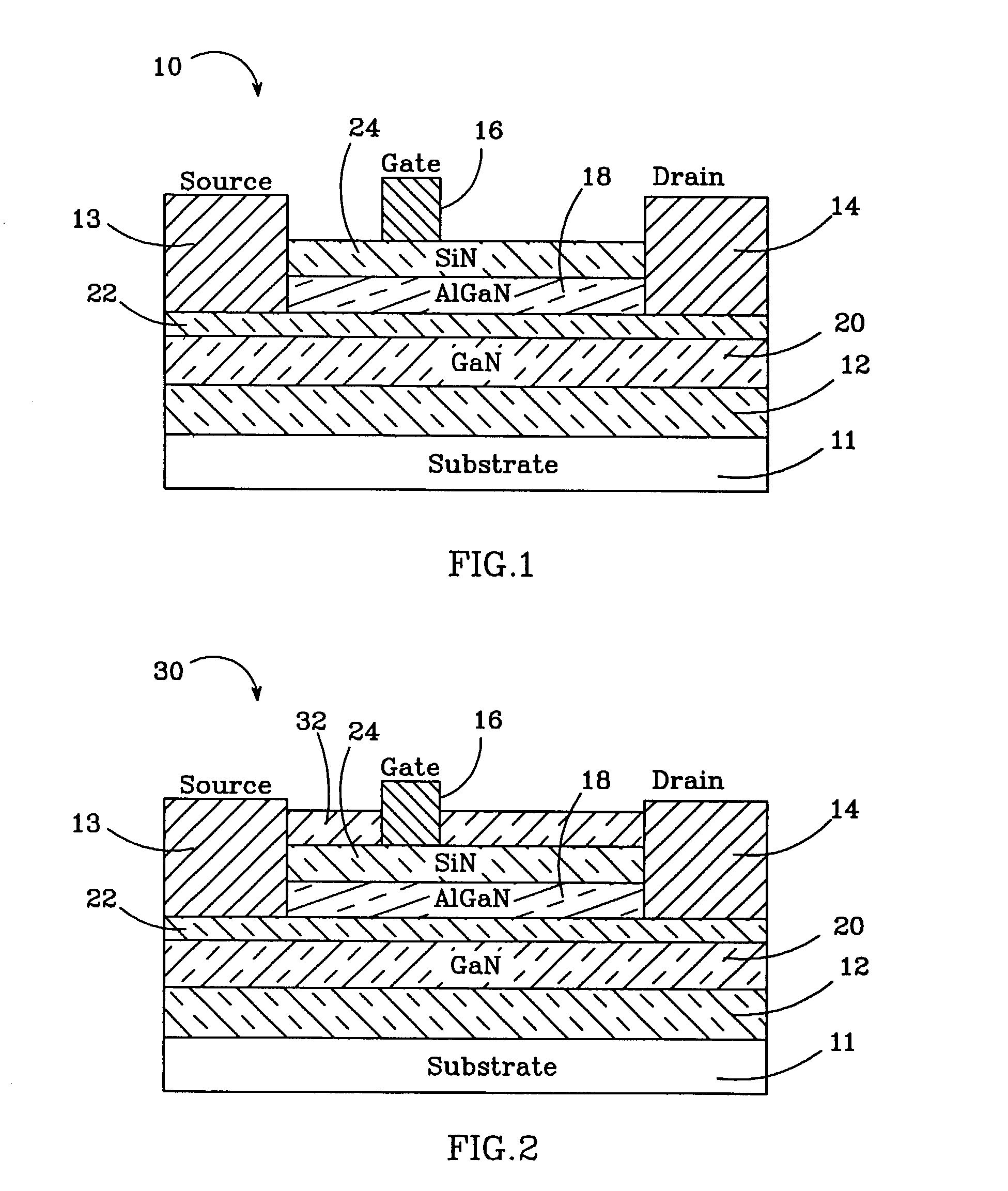

Insulating gate AlGaN/GaN HEMT

InactiveUS7230284B2Reduce trappingReduce gate leakageSemiconductor/solid-state device detailsSolid-state devicesGate leakage currentDriving current

AlGaN / GaN HEMTs are disclosed having a thin AlGaN layer to reduce trapping and also having additional layers to reduce gate leakage and increase the maximum drive current. One HEMT according to the present invention comprises a high resistivity semiconductor layer with a barrier semiconductor layer on it. The barrier layer has a wider bandgap than the high resistivity layer and a 2DEG forms between the layers. Source and drain contacts contact the barrier layer, with part of the surface of the barrier layer uncovered by the contacts. An insulating layer is included on the uncovered surface of the barrier layer and a gate contact is included on the insulating layer. The insulating layer forms a barrier to gate leakage current and also helps to increase the HEMT's maximum current drive. The invention also includes methods for fabricating HEMTs according to the present invention. In one method, the HEMT and its insulating layer are fabricated using metal-organic chemical vapor deposition (MOCVD). In another method the insulating layer is sputtered onto the top surface of the HEMT in a sputtering chamber.

Owner:CREE INC

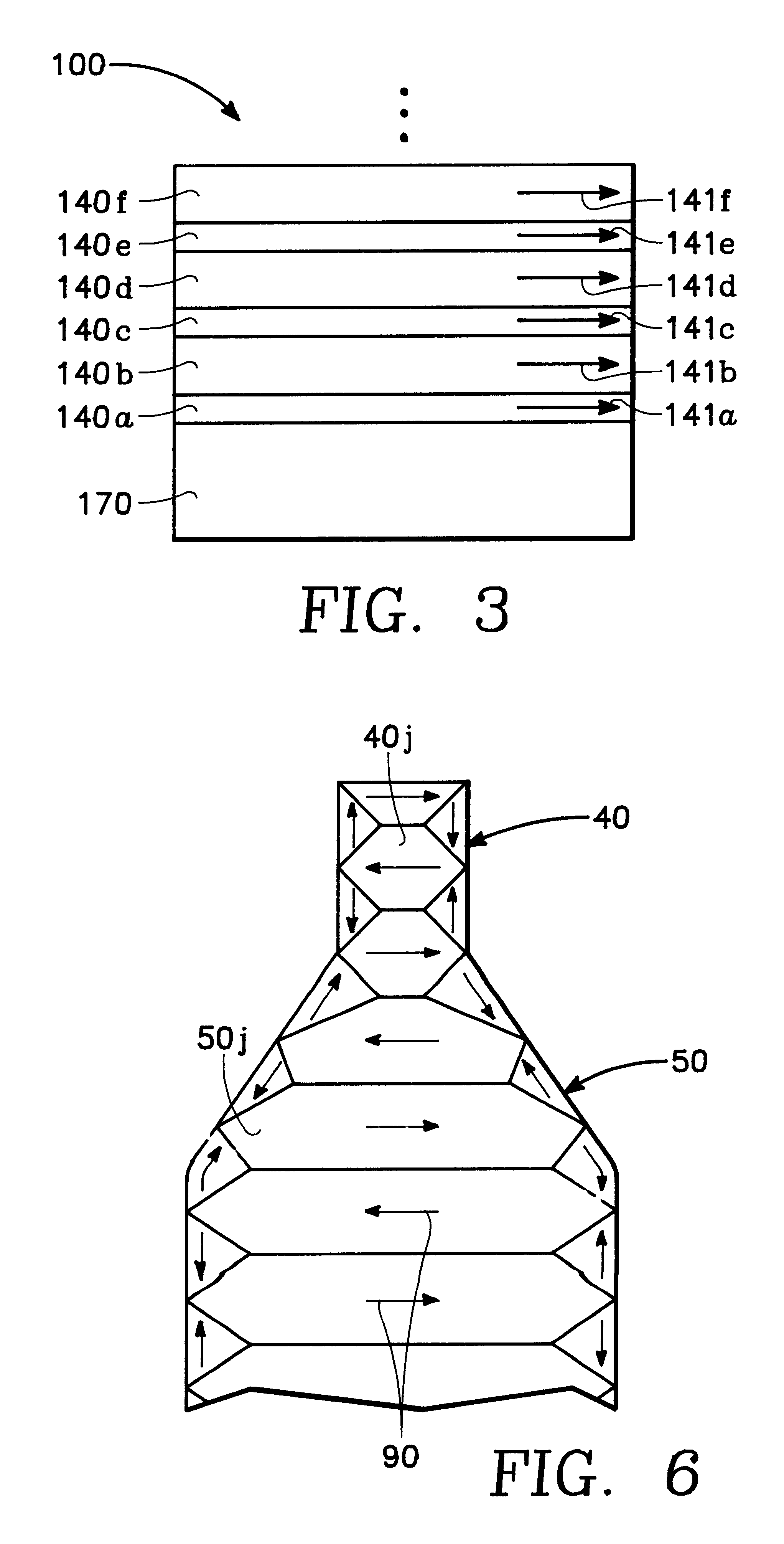

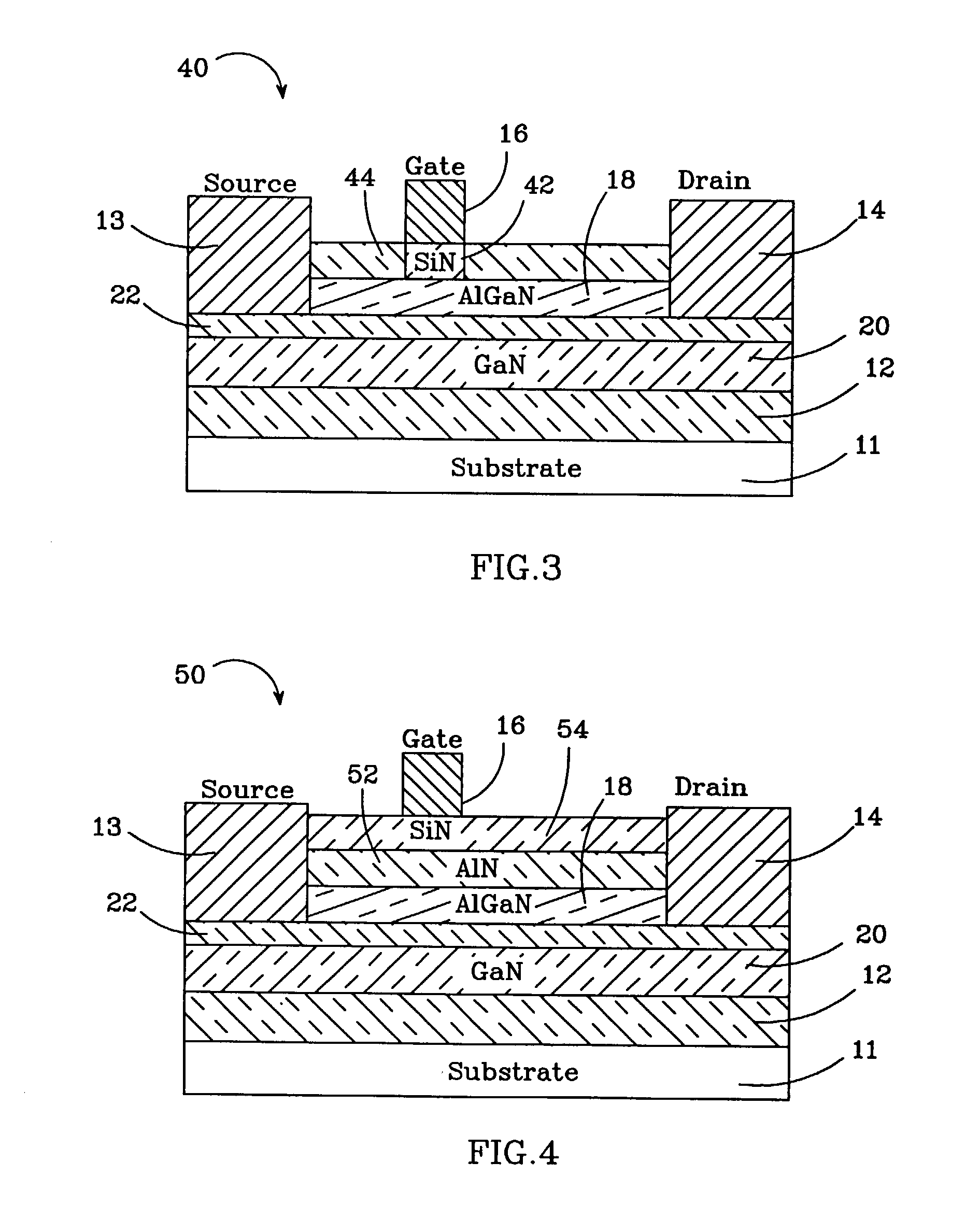

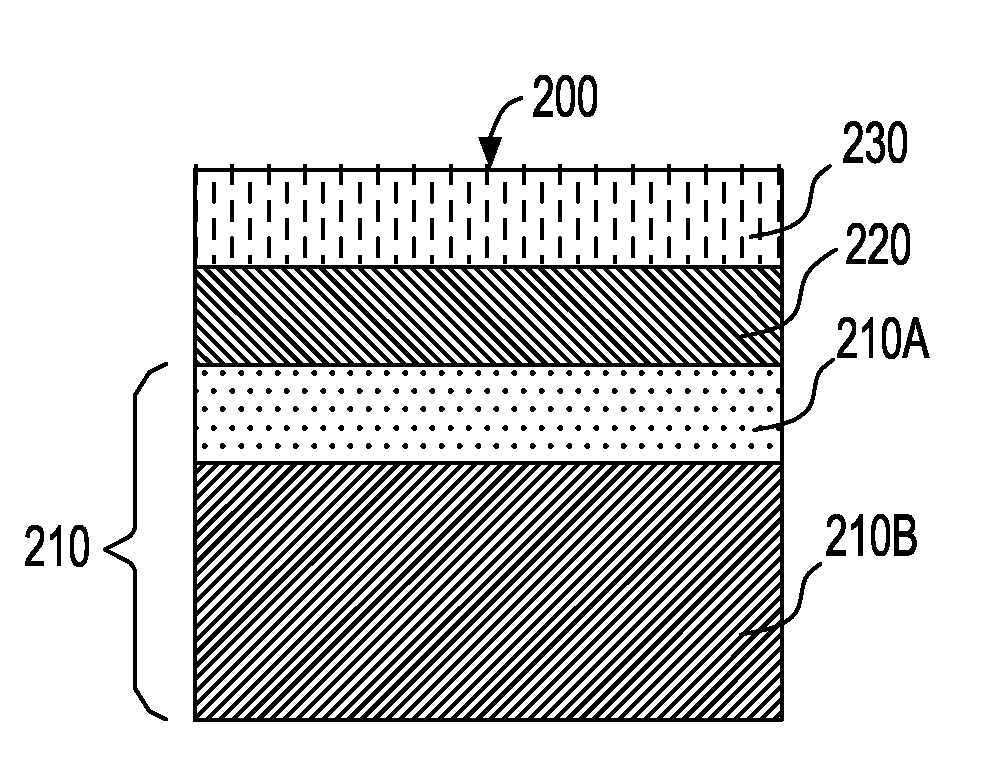

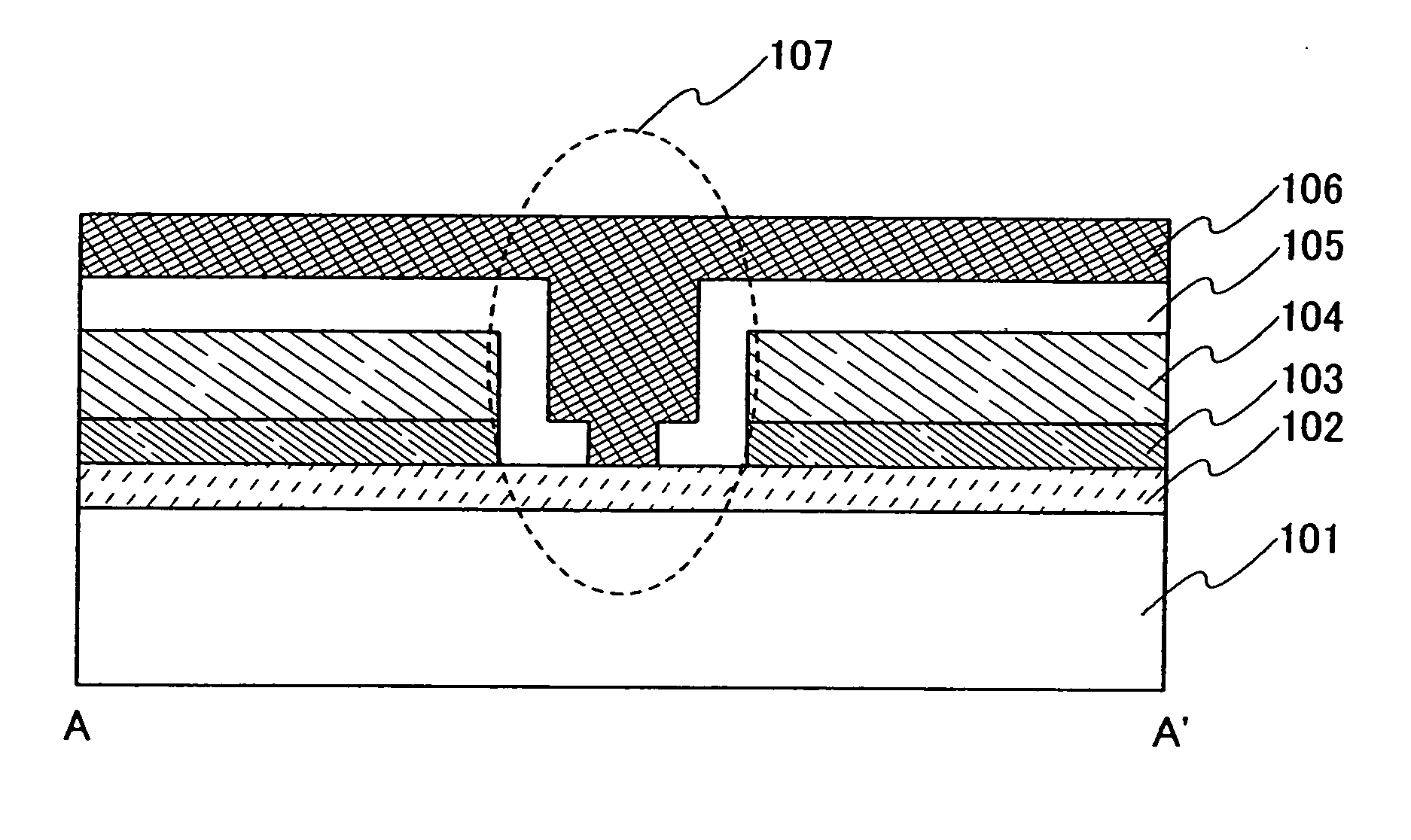

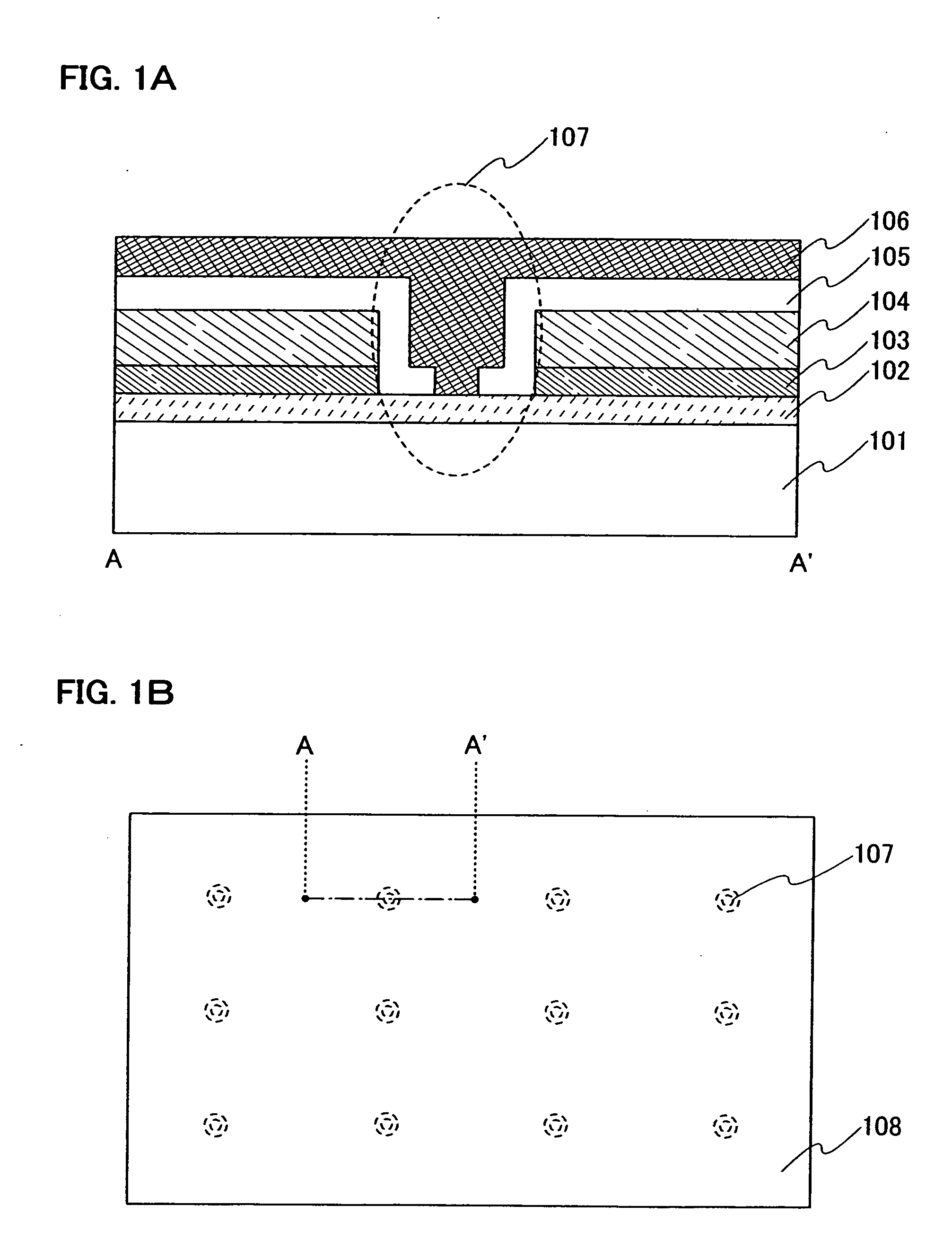

Method of manufacturing high resistivity soi wafers with charge trapping layers based on terminated si deposition

ActiveUS20150115480A1Semiconductor/solid-state device detailsSolid-state devicesWaferingSemiconductor structure

A method of preparing a single crystal semiconductor handle wafer in the manufacture of a silicon-on-insulator device is provided. The method comprises forming a multilayer of passivated semiconductors layers on a dielectric layer of a high resistivity single crystal semiconductor handle wafer. The method additionally comprises forming a semiconductor oxide layer on the multilayer of passivated semiconductor layers. The multilayer of passivated semiconductor layers comprise materials suitable for use as charge trapping layers between a high resistivity substrate and a buried oxide layer in a semiconductor on insulator structure.

Owner:GLOBALWAFERS CO LTD

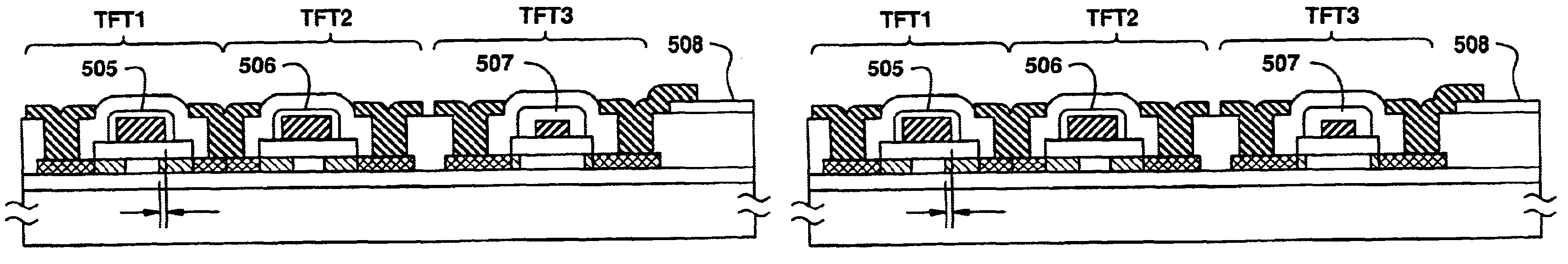

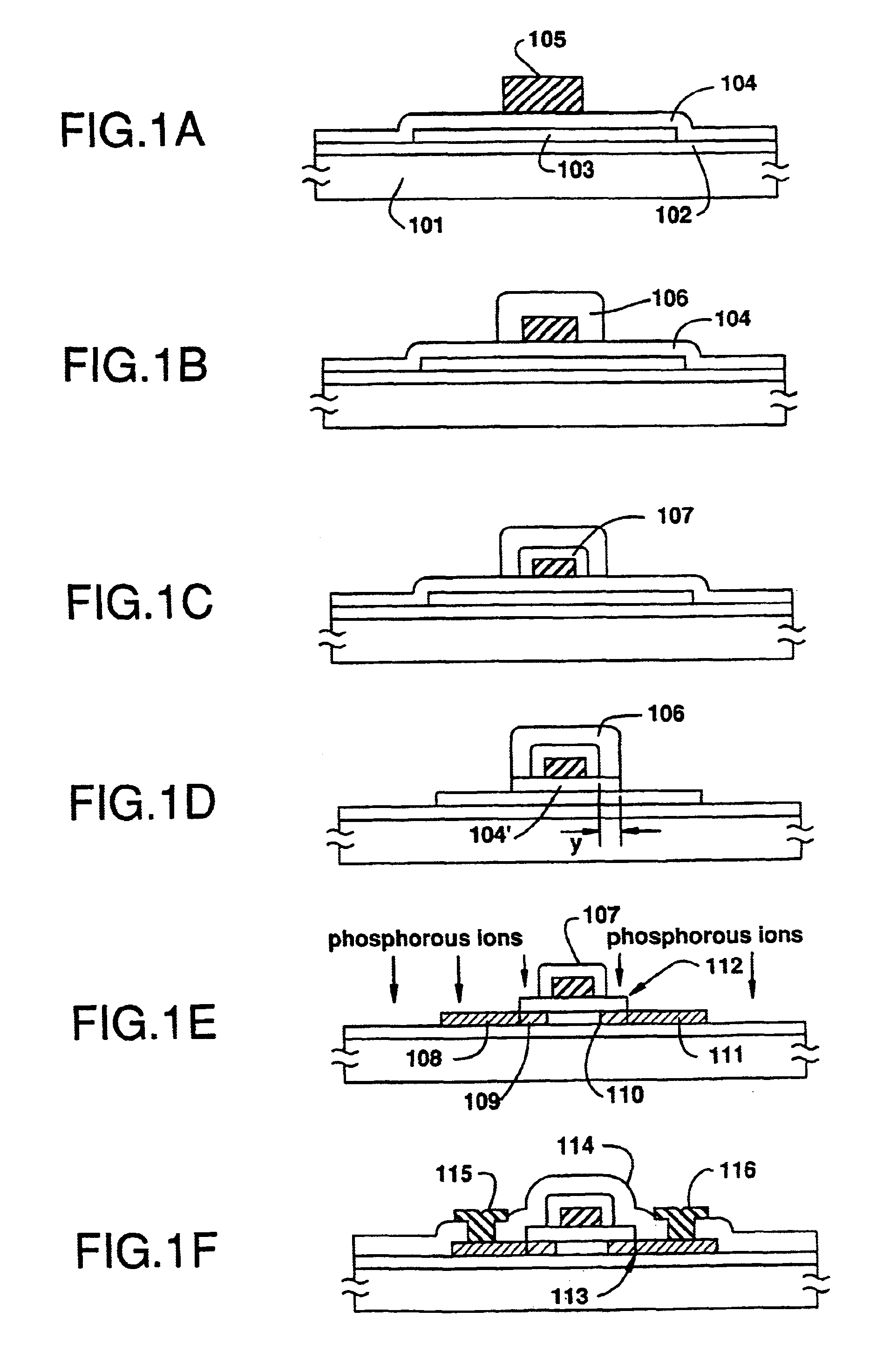

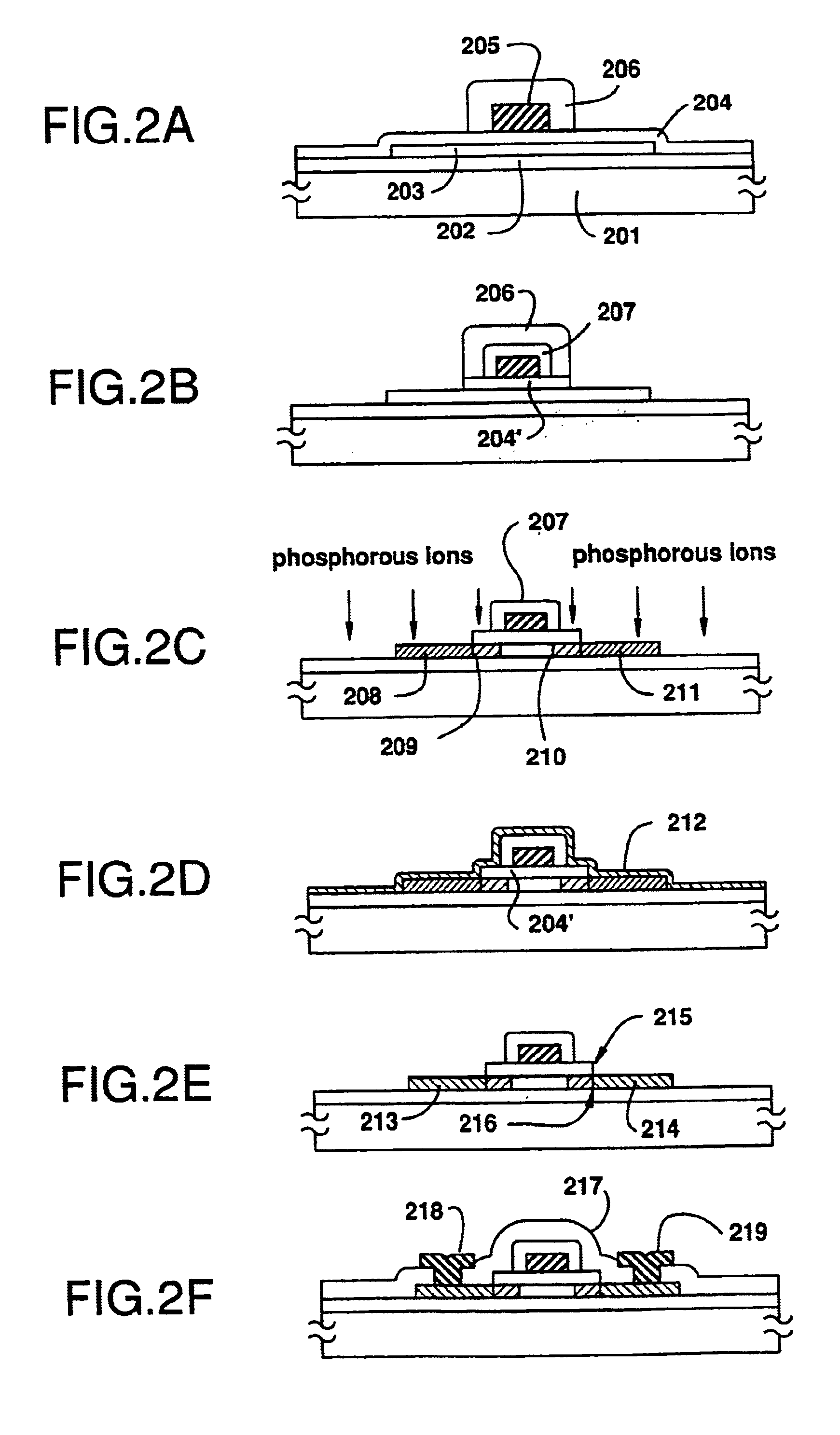

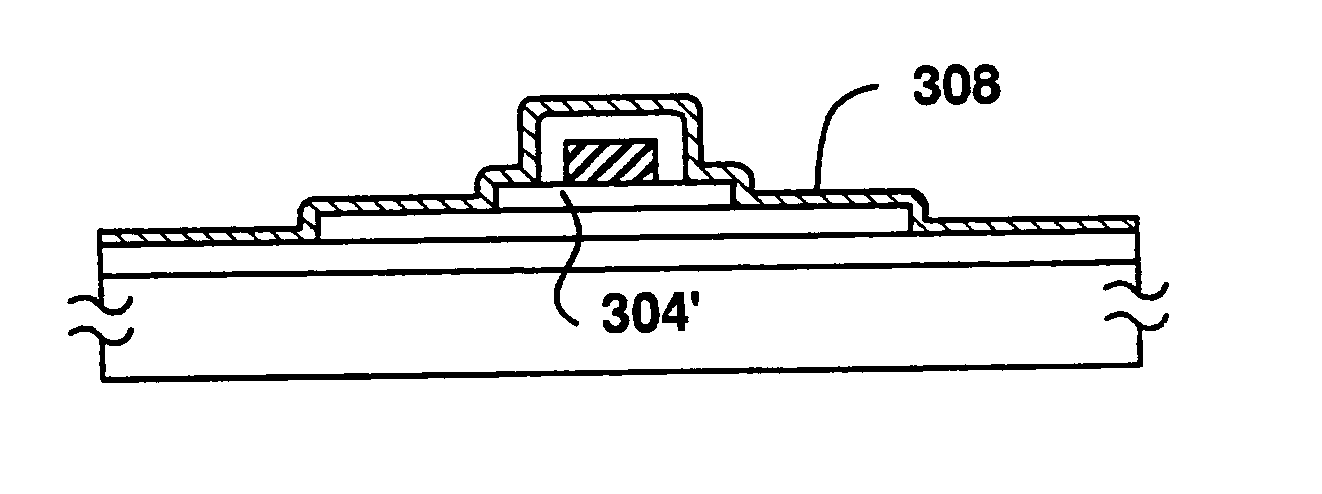

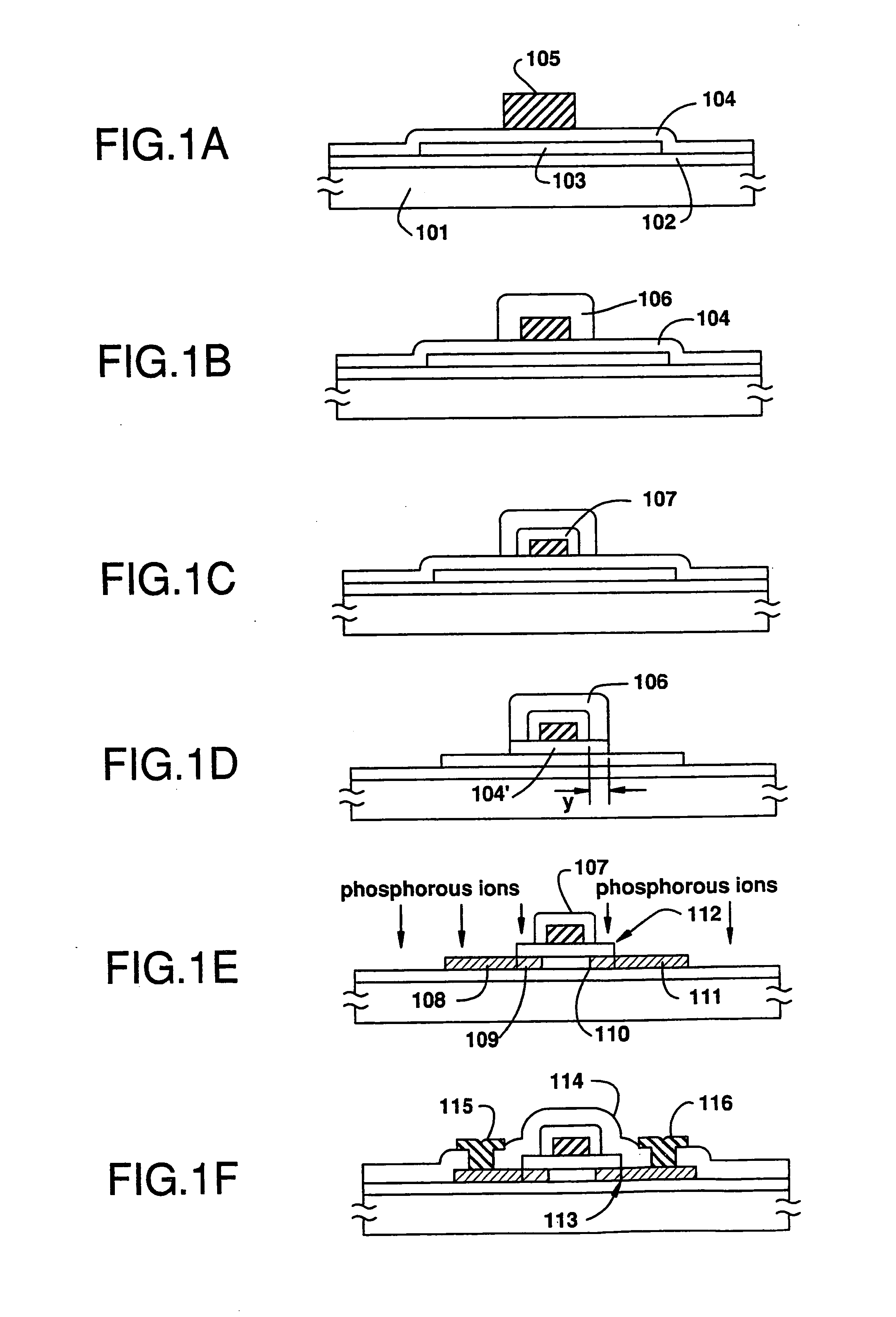

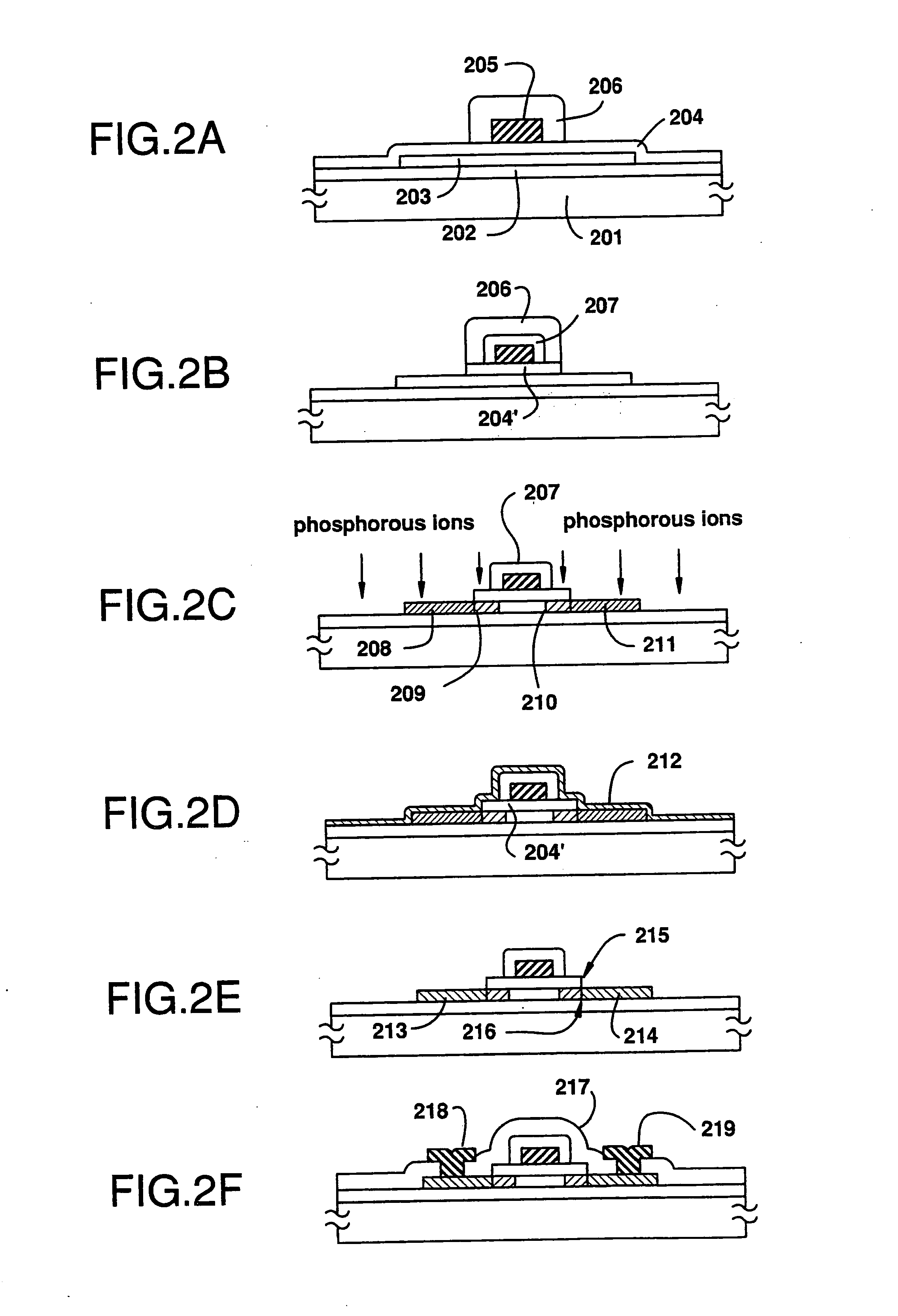

Semiconductor device and method for manufacturing the same

A TFT formed on an insulating substrate source, drain and channel regions, a gate insulating film formed on at least the channel region and a gate electrode formed on the gate insulating film. Between the channel region and the drain region, a region having a higher resistivity is provided in order to reduce an Ioff current. A method for forming this structure comprises the steps of anodizing the gate electrode to form a porous anodic oxide film on the side of the gate electrode; removing a portion of the gate insulating using the porous anodic oxide film as a mask so that the gate insulating film extends beyond the gate electrode but does not completely cover the source and drain regions. Thereafter, an ion doping of one conductivity element is performed. The high resistivity region is defined under the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

Light-emitting diode device and method of manufacturing the same

InactiveUS6255129B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringHigh resistivity

A light-emitting diode device, such as a blue, green, blue-green light-emitting diode, with a one-wire-bonding characteristic and the method of manufacturing the same have been disclosed. The light-emitting diode device has a GaN-based semiconductor laminated structure formed on an insulating substrate. The GaN-based semiconductor laminated structure includes an n-type layer on its bottom side, a p-type layer on its top side, and an active layer, for generating light, sandwiched between the n-type and p-type layers. An annular isolation portion such as a trench or a high resistivity portion formed by ion implantation is formed in the GaN-based semiconductor laminated structure to separate the p-type layer into a central p-type layer and a peripheral p-type layer and to separate the active layer into a central active layer and a peripheral active layer. A p-type electrode is formed on the central p-type layer without electrically connecting to the peripheral p-type layer. A conductive layer is coated to cover the sidewalls and the bottom surface of the insulating substrate and to ohmically contact with the n-type layer. Preferably, an adhesion layer is sandwiched between the sidewalls and the bottom surface of the insulating substrate and the conductive layer to enhance the adhesive property. According to the present invention, the conductive layer may be formed as a mirror-like reflector or a light-transmissive layer.

Owner:EPISTAR CORP

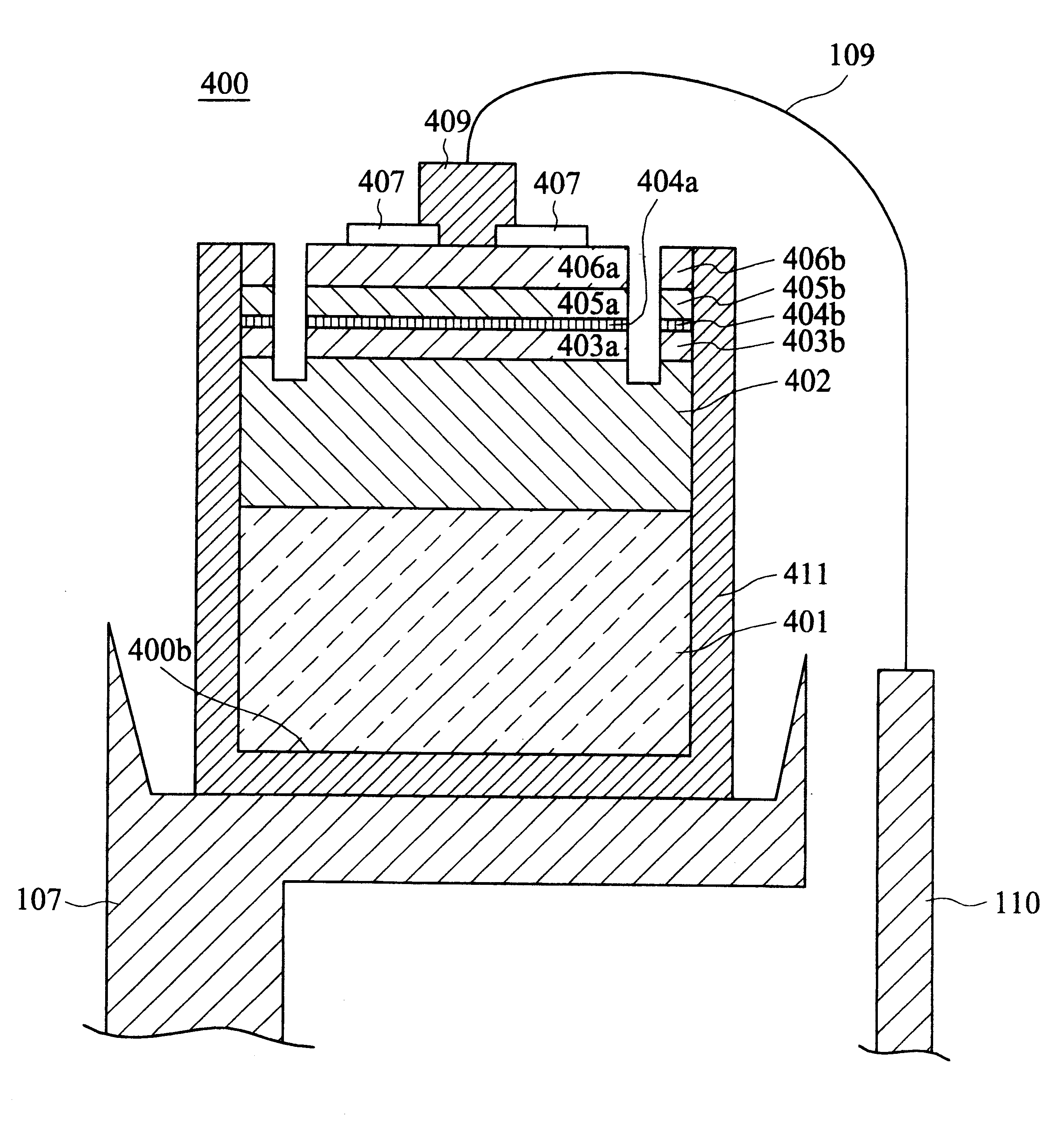

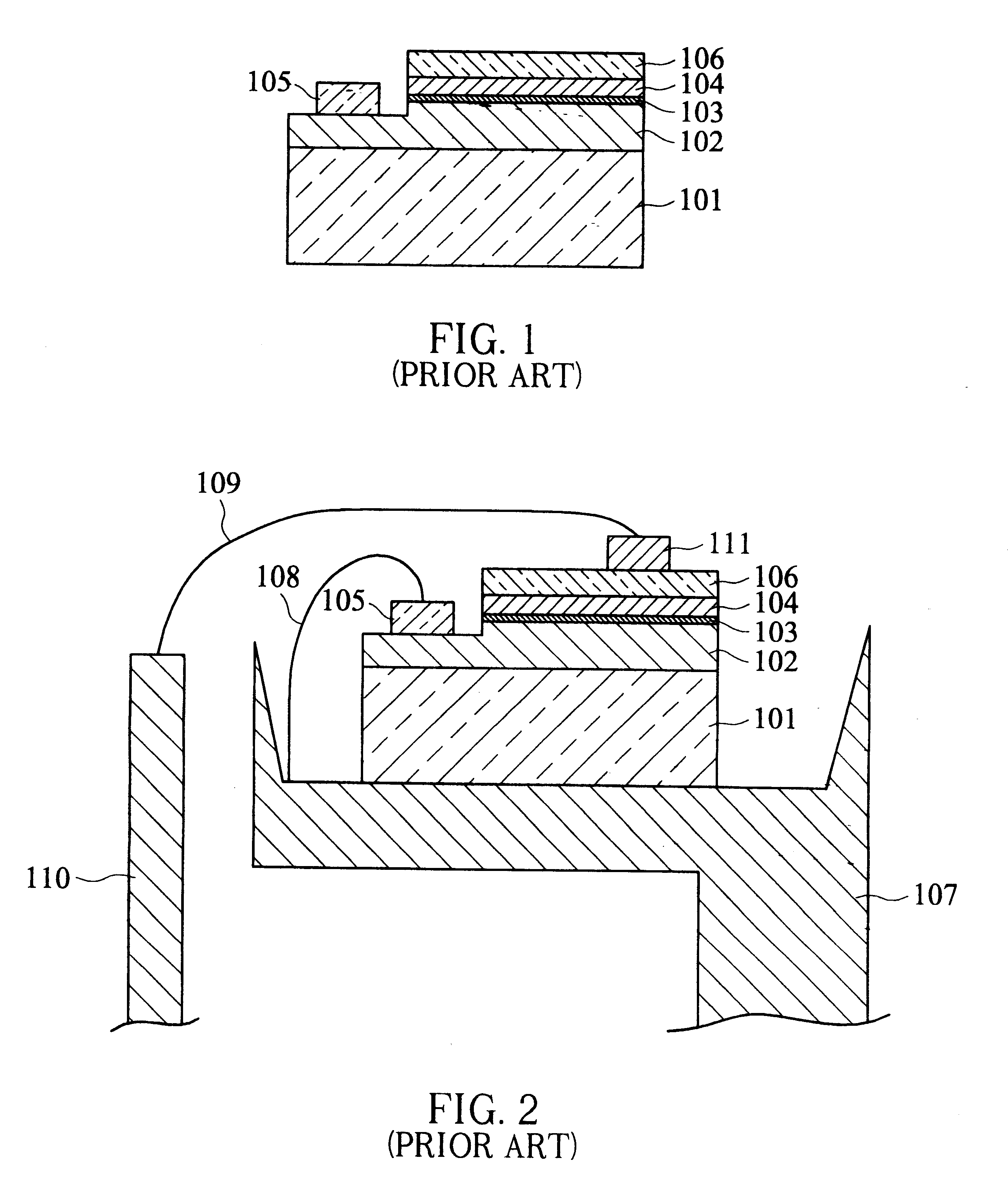

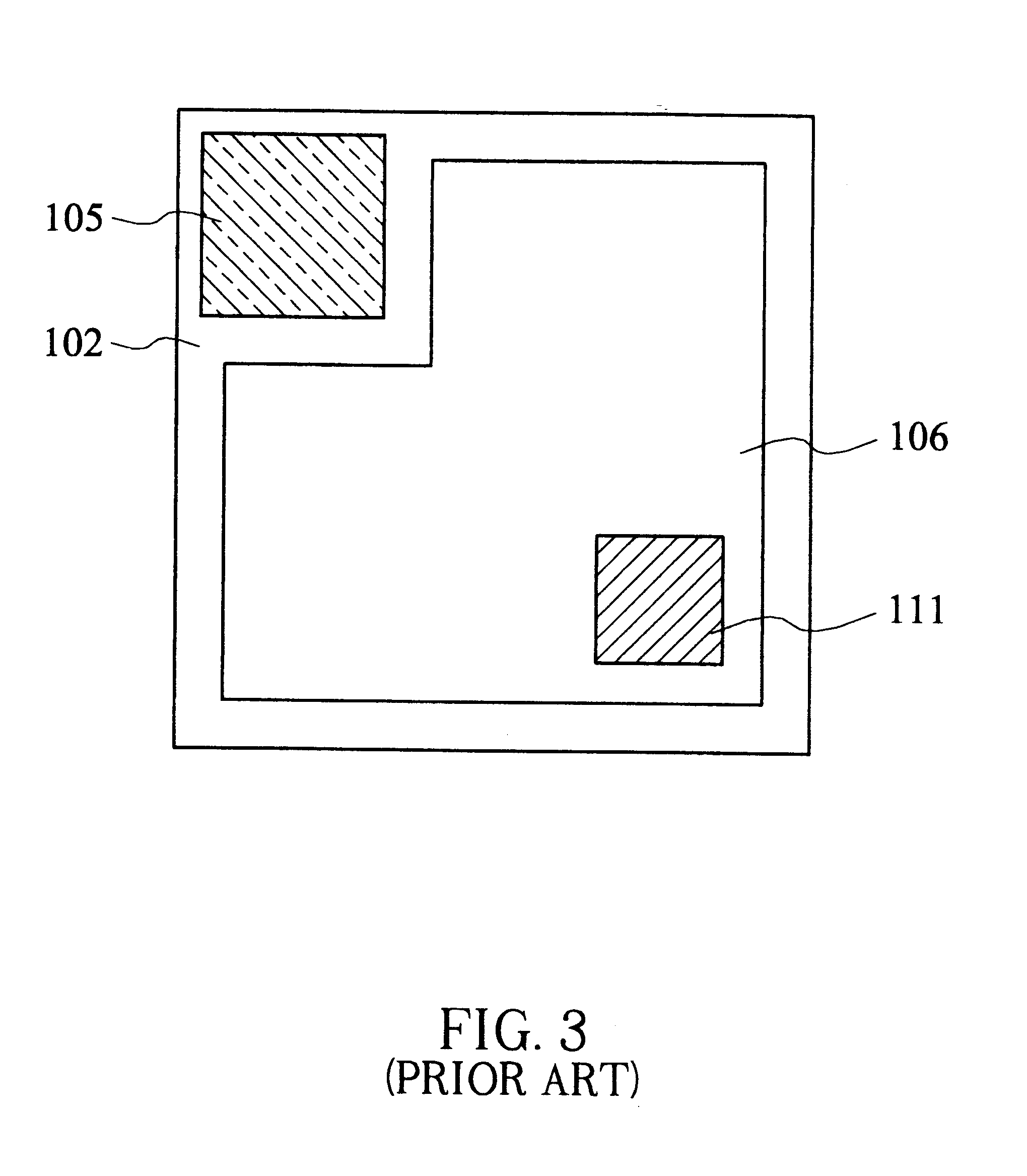

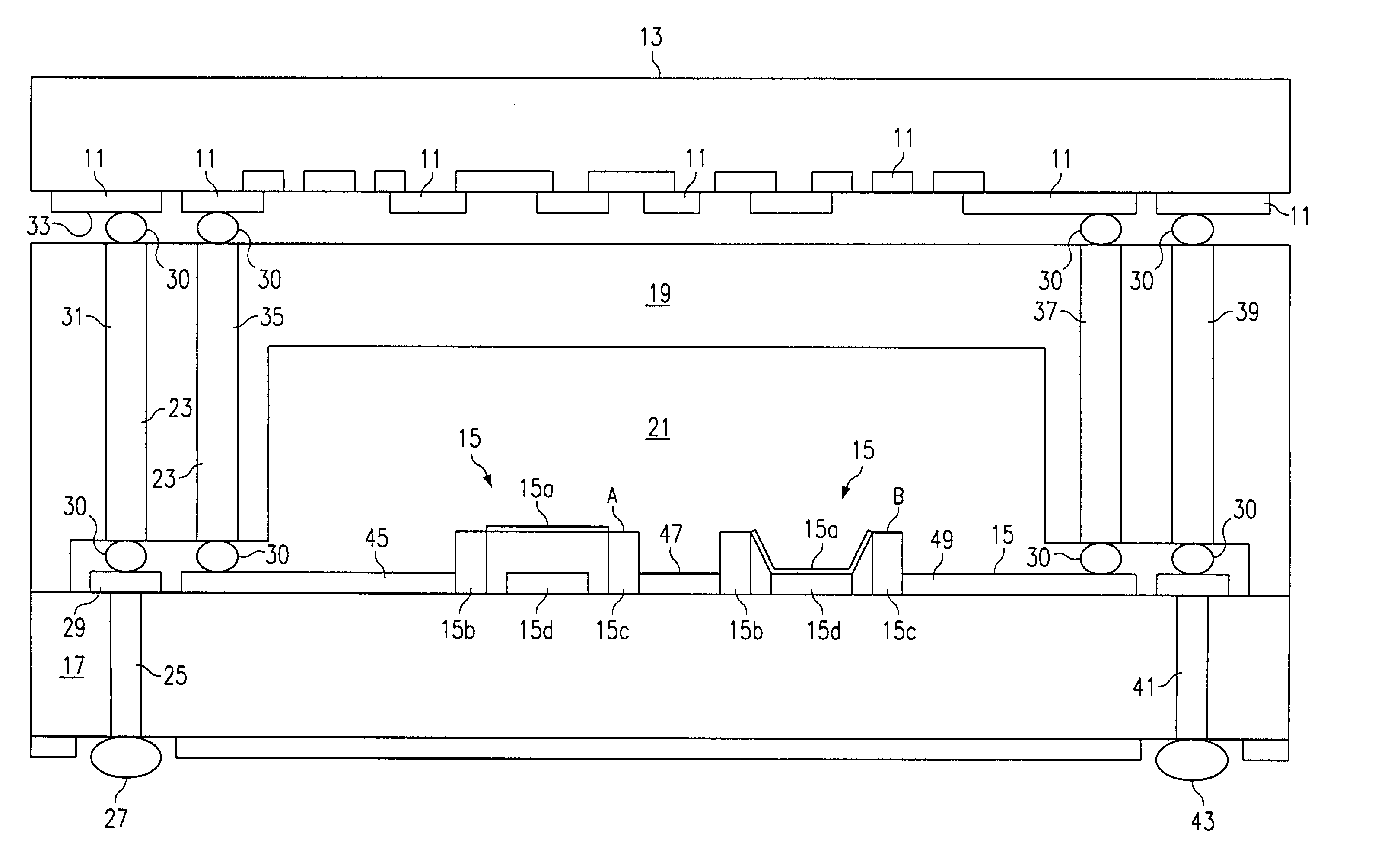

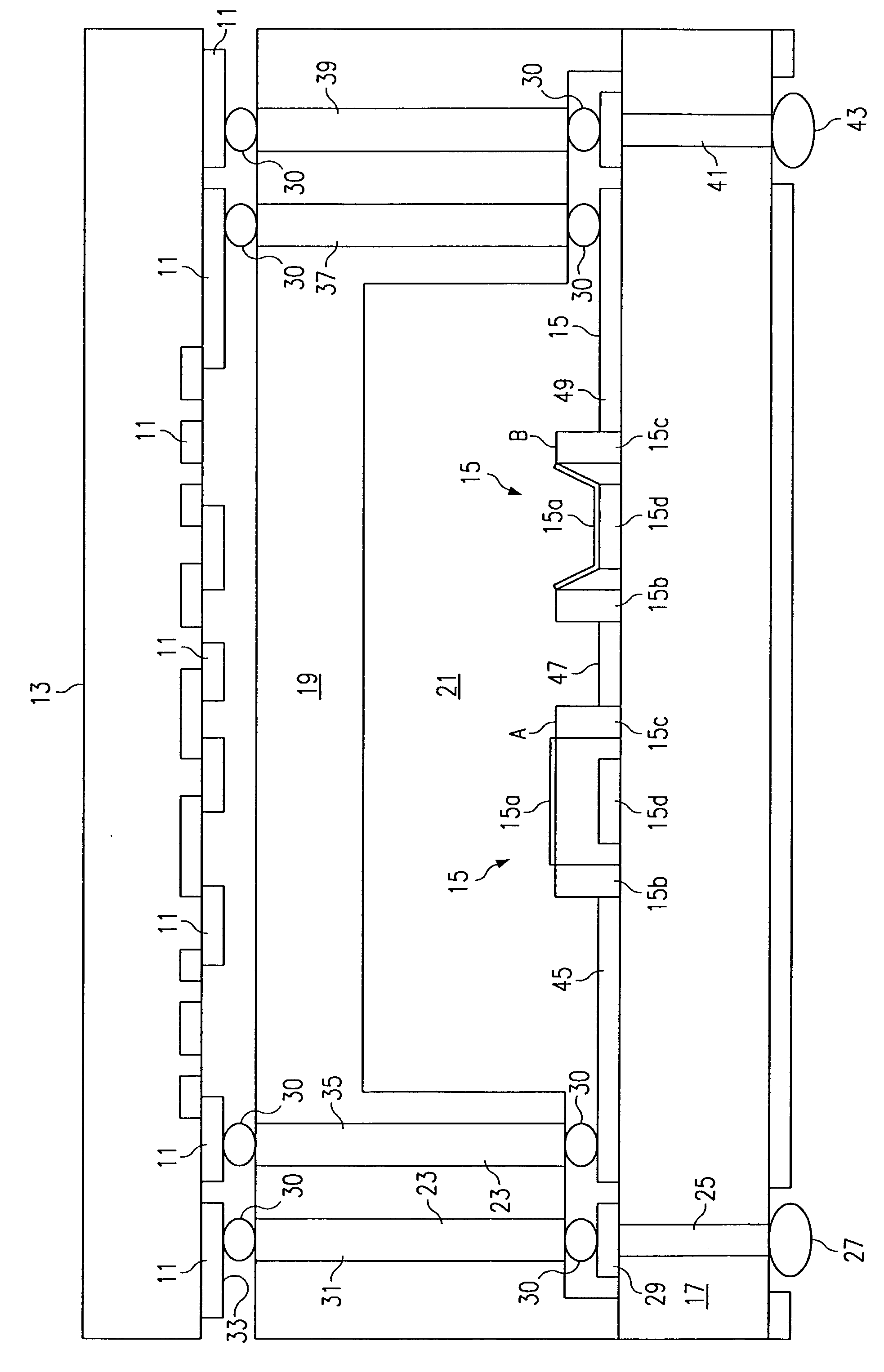

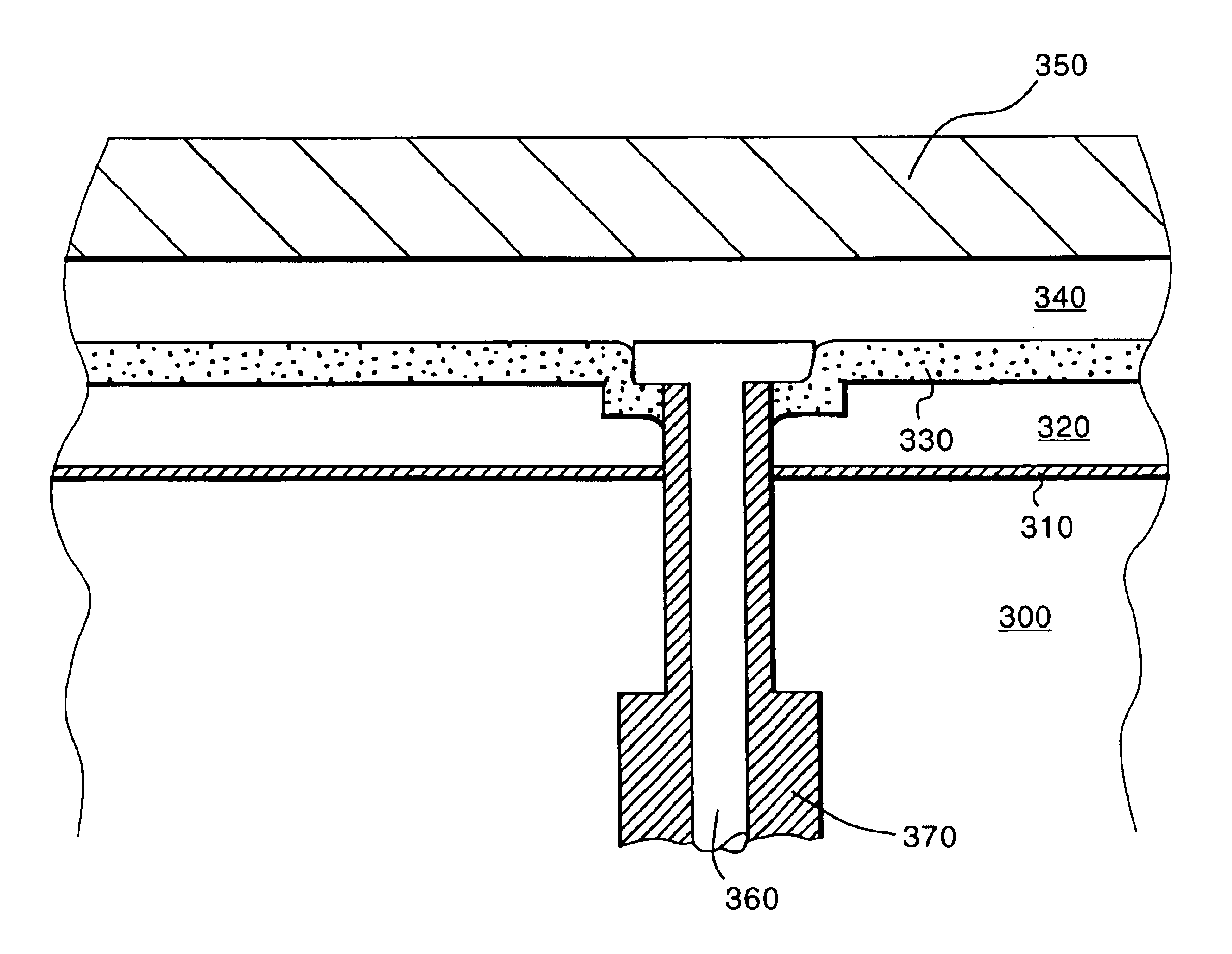

Wafer level interconnection

InactiveUS20030001251A1Television system detailsPiezoelectric/electrostriction/magnetostriction machinesDielectricElectrical conductor

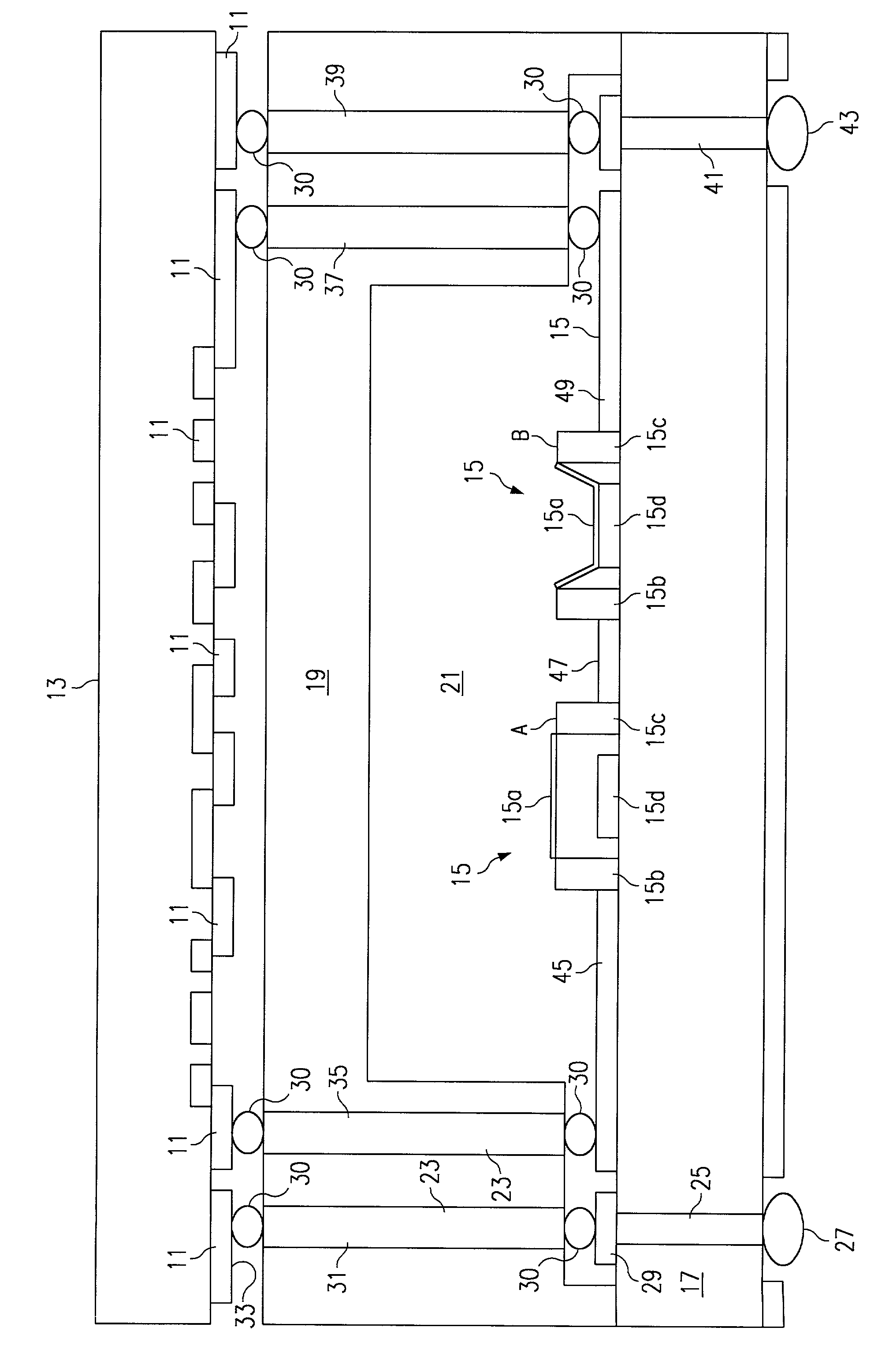

RF MicroElectroMechanical Systems (MEMs) circuitry(15) on a first high resistivity substrate (17)is combined with circuitry (11) onsecond low-resisitivity substrate (13) by overlapping the first high resisitivity substrate (17)and MEMs circuitry (15) with the low resisitivity substrate(13) and circuitry (11) with the MEMs circuitry (15)facing the second circuitry (11). A dielectric lid (19) is placed over the MEMs circuitry (15)and between the first substrate (17)and second substrate (13)with an inert gas in a gap (21)over the MEMs circuitry (15). Interconnecting conductors (25,31,35,37,39,41) extend perpendicular and through the high resistivity substrate (17)and through the dielectric lid (19) to make electrical connection with the low resisitivity substrate (13).

Owner:RAYTHEON CO

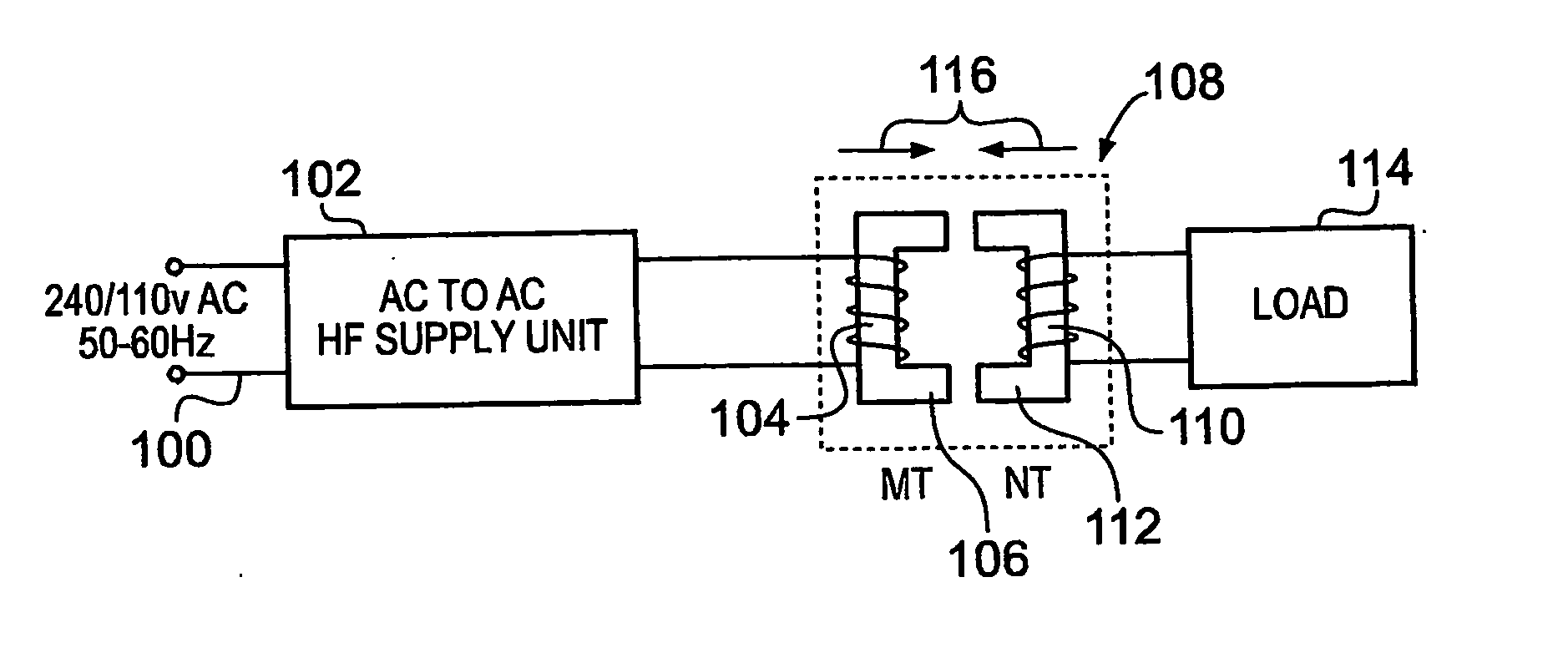

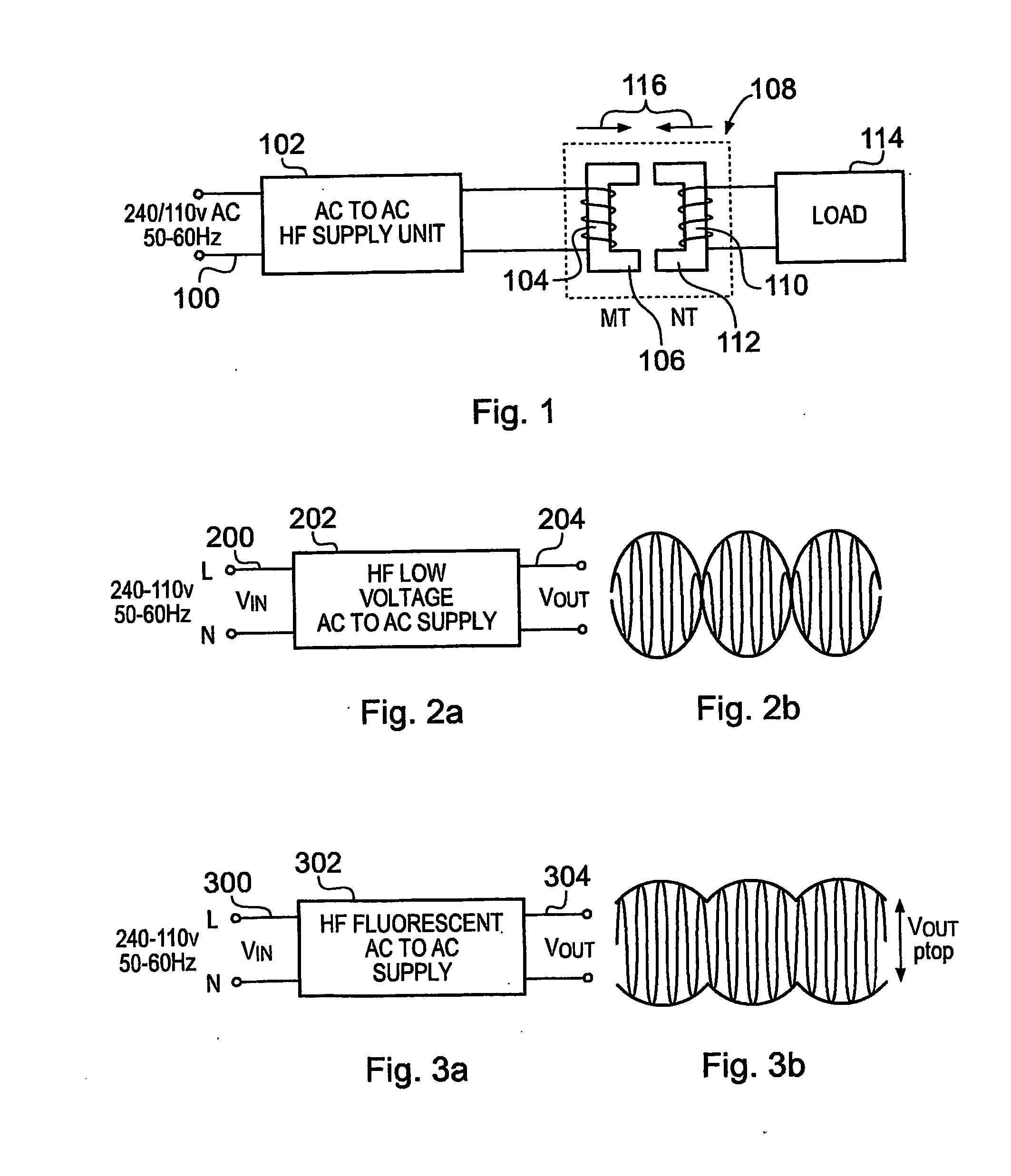

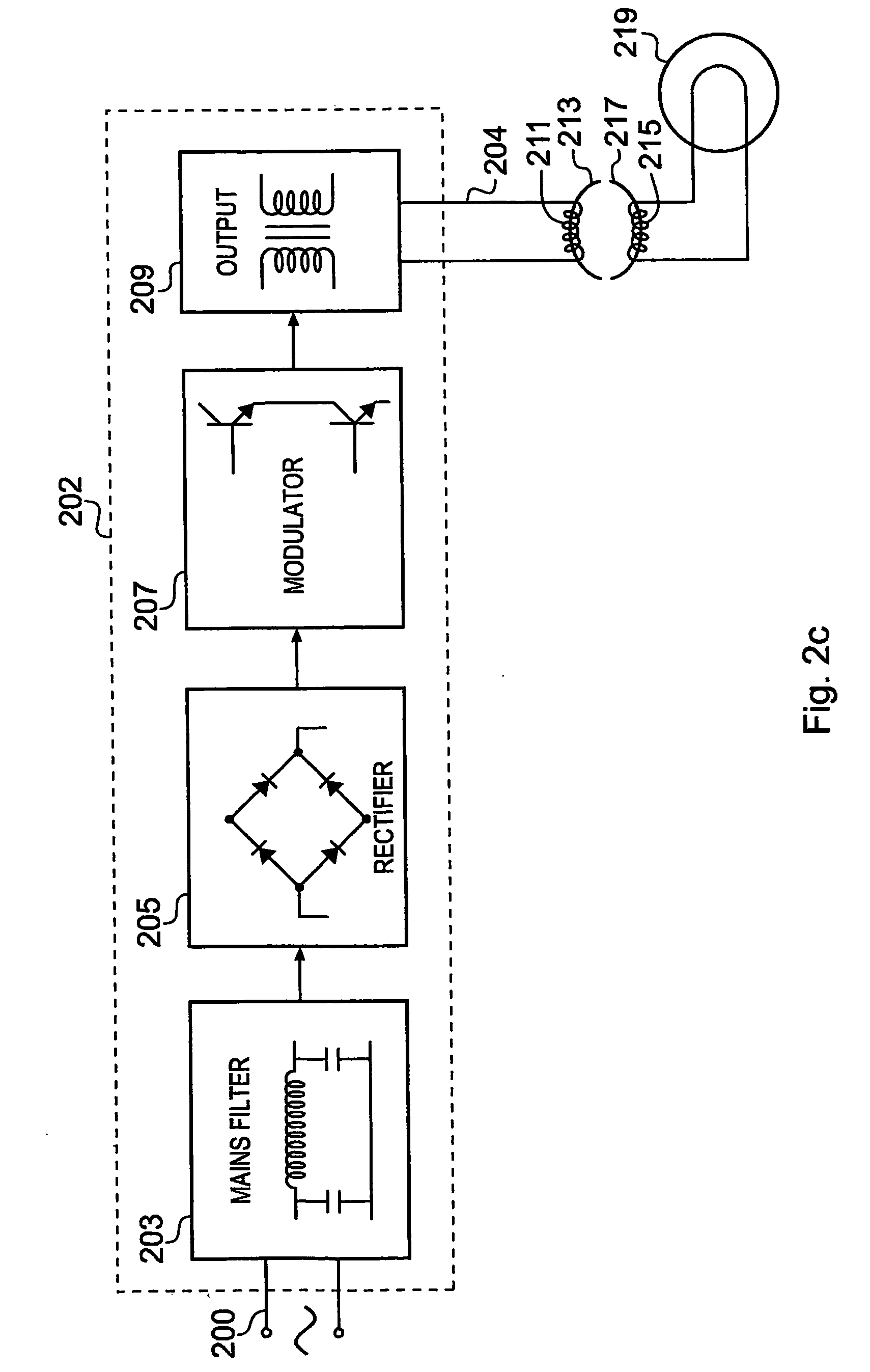

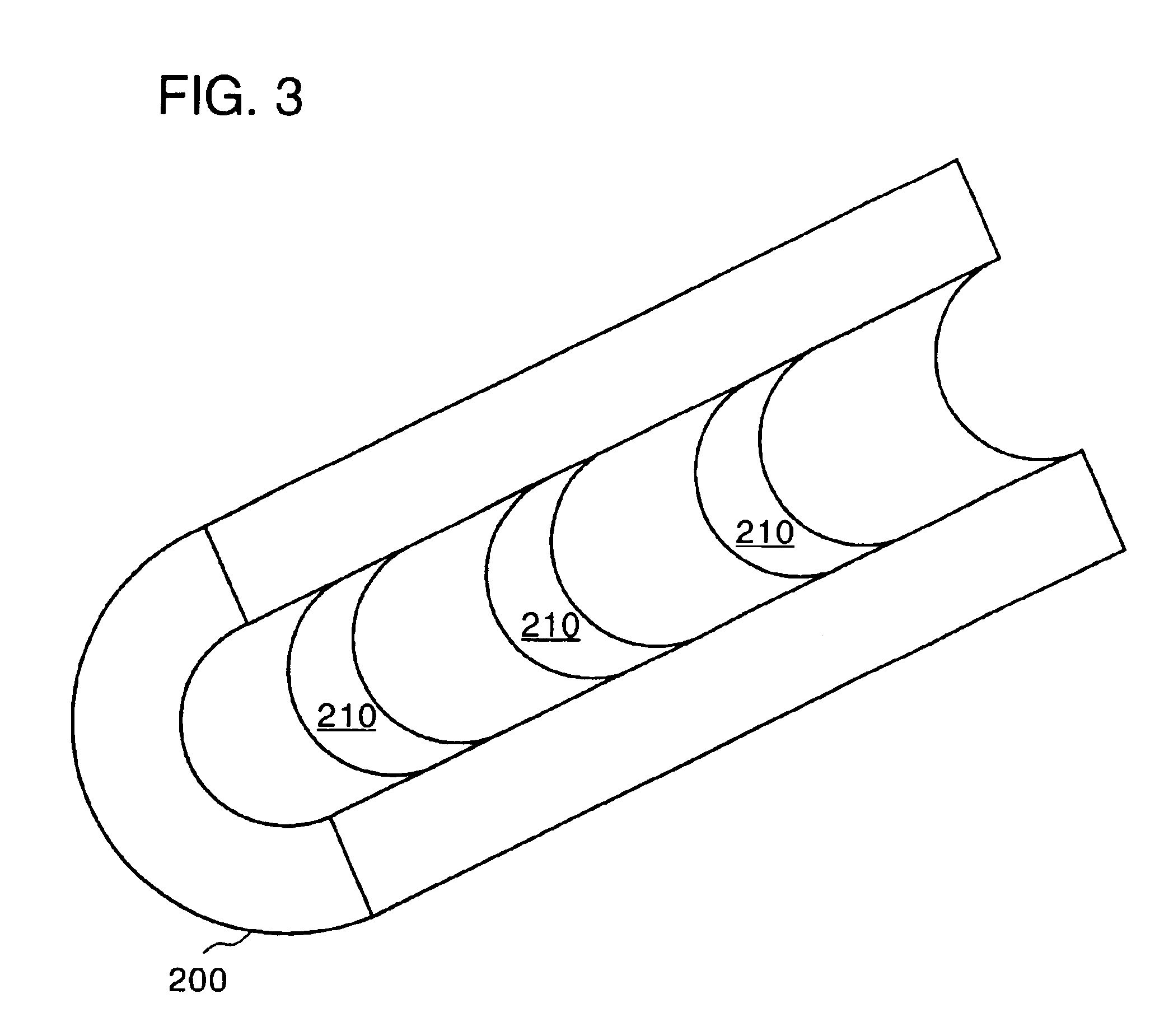

Apparatus for supplying energy to a load and a related system

InactiveUS20070076459A1Avoid eddy currentsImprove system efficiencyPoint-like light sourceConversion with intermediate conversion to dcLow voltageTransformer

Apparatus for supplying energy to a load, comprises a power supply unit (102) e.g. a switched mode electronic transformer or electronic ballast having an input for receiving current at mains frequency and a means for stepping-up said mains frequency to a higher frequency e.g. 30-50 kHz and an output for delivering energy at the higher frequency. A two part connector (108) has a first core portion (106) that has a primary winding (104) connected to the output of the power supply unit and a mating second core portion (112) that has a secondary winding (110) for delivery of energy to a load (114), the core portions being of a high resistivity material, e.g. a ferrite having a resistivity of at least 104 Ωcm. The apparatus may be used to power e.g. low voltage halogen or other incandescent lighting, fluorescent lighting, or an electric motor, a power supply for a computer, radio, television or like electronic device, a heater or the like.

Owner:LIMPKIN GEORGE A +1

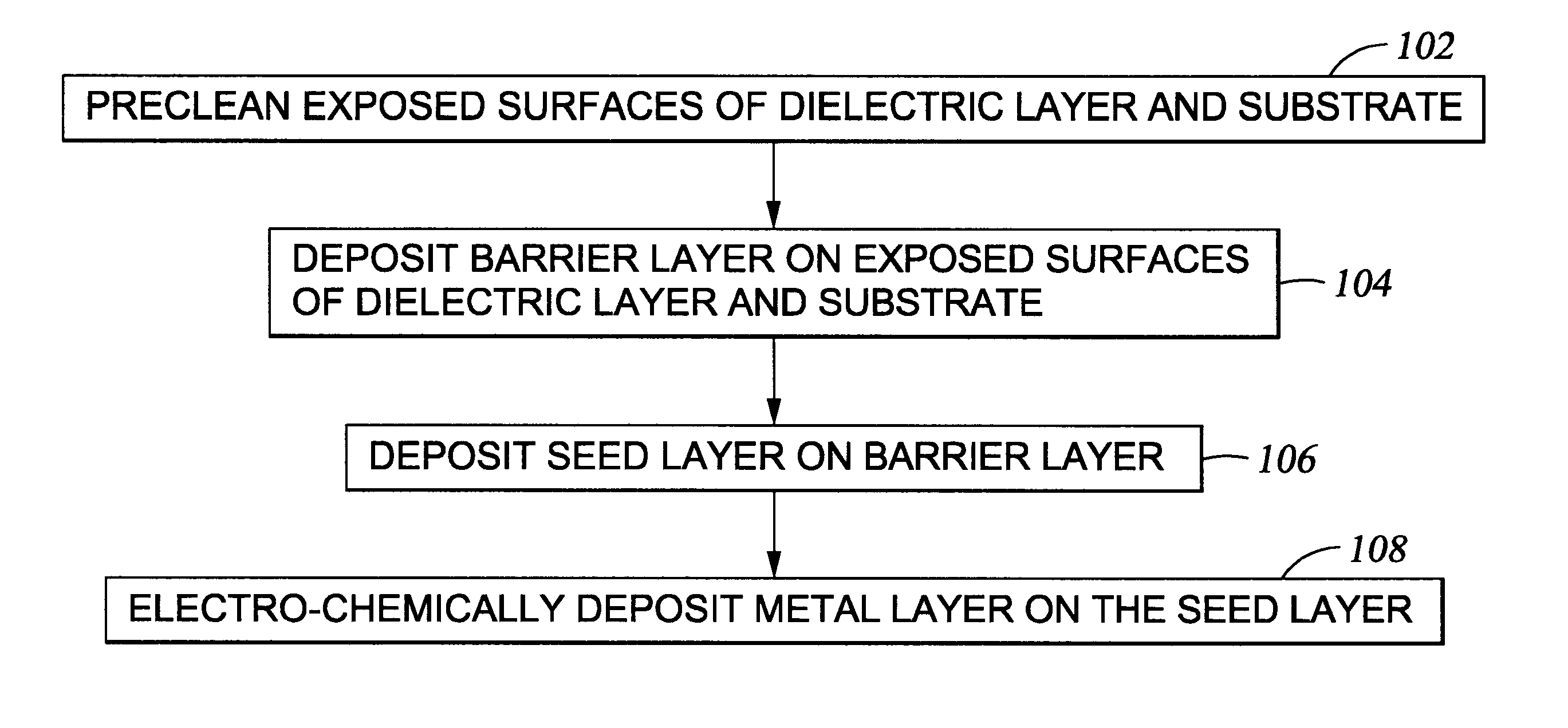

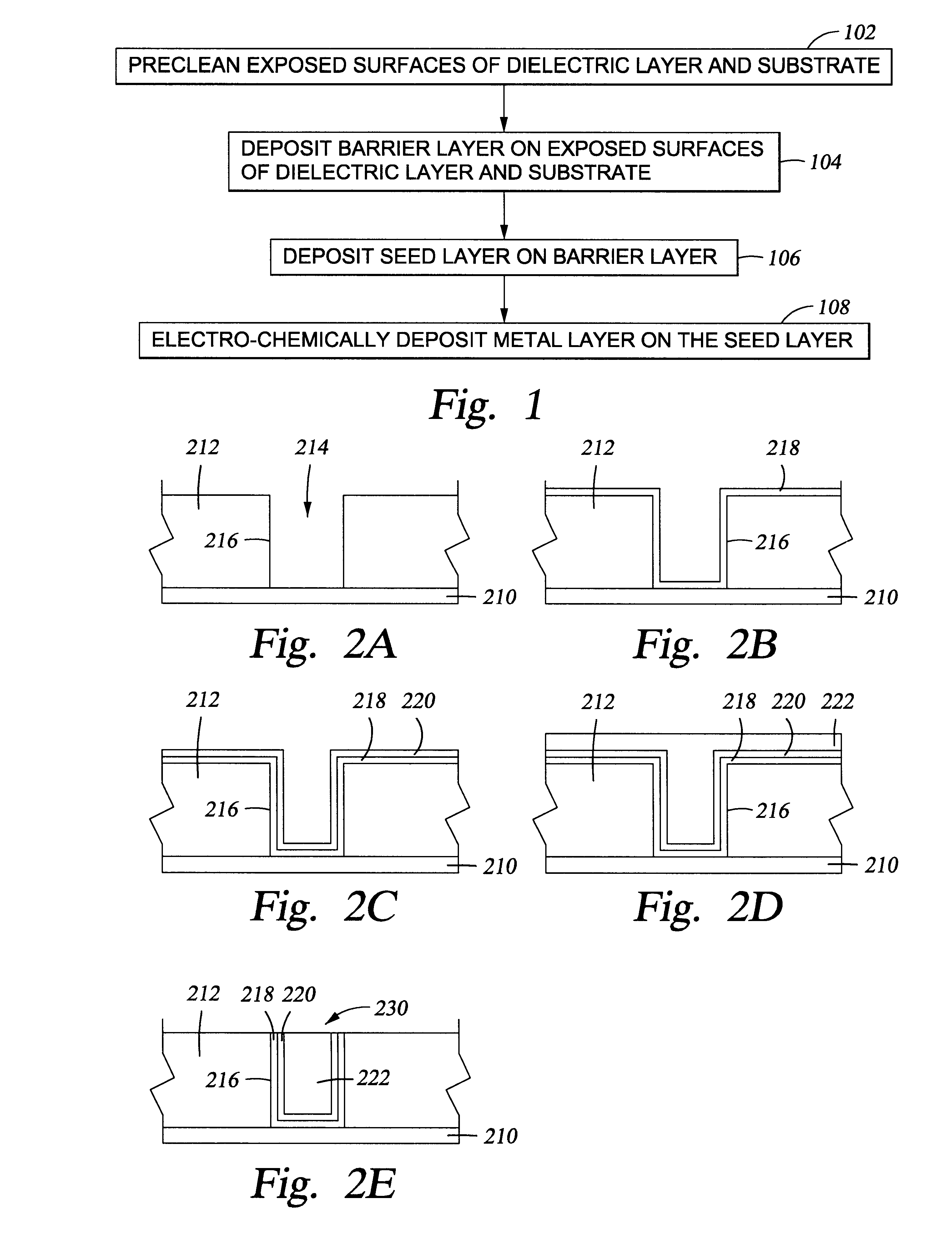

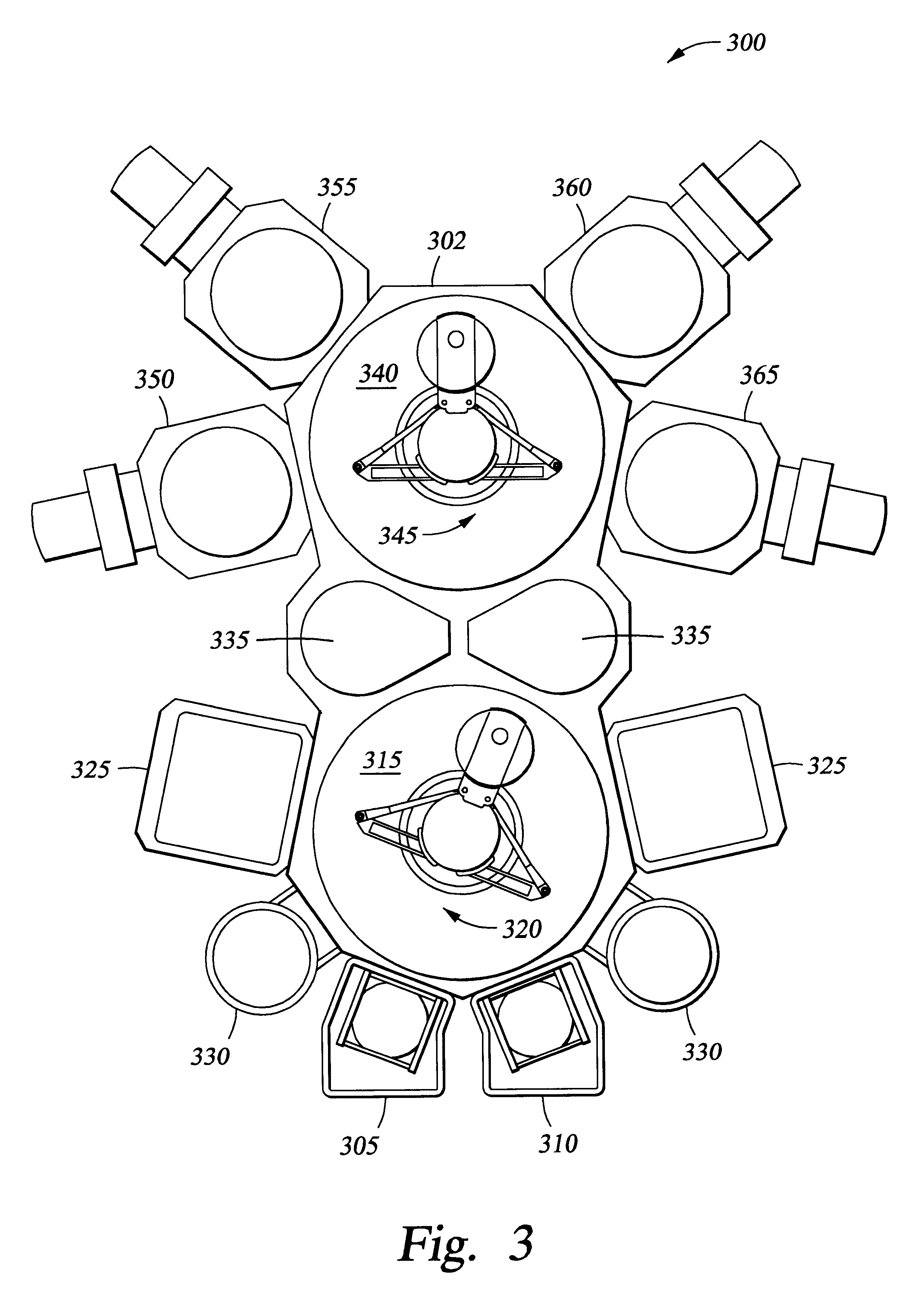

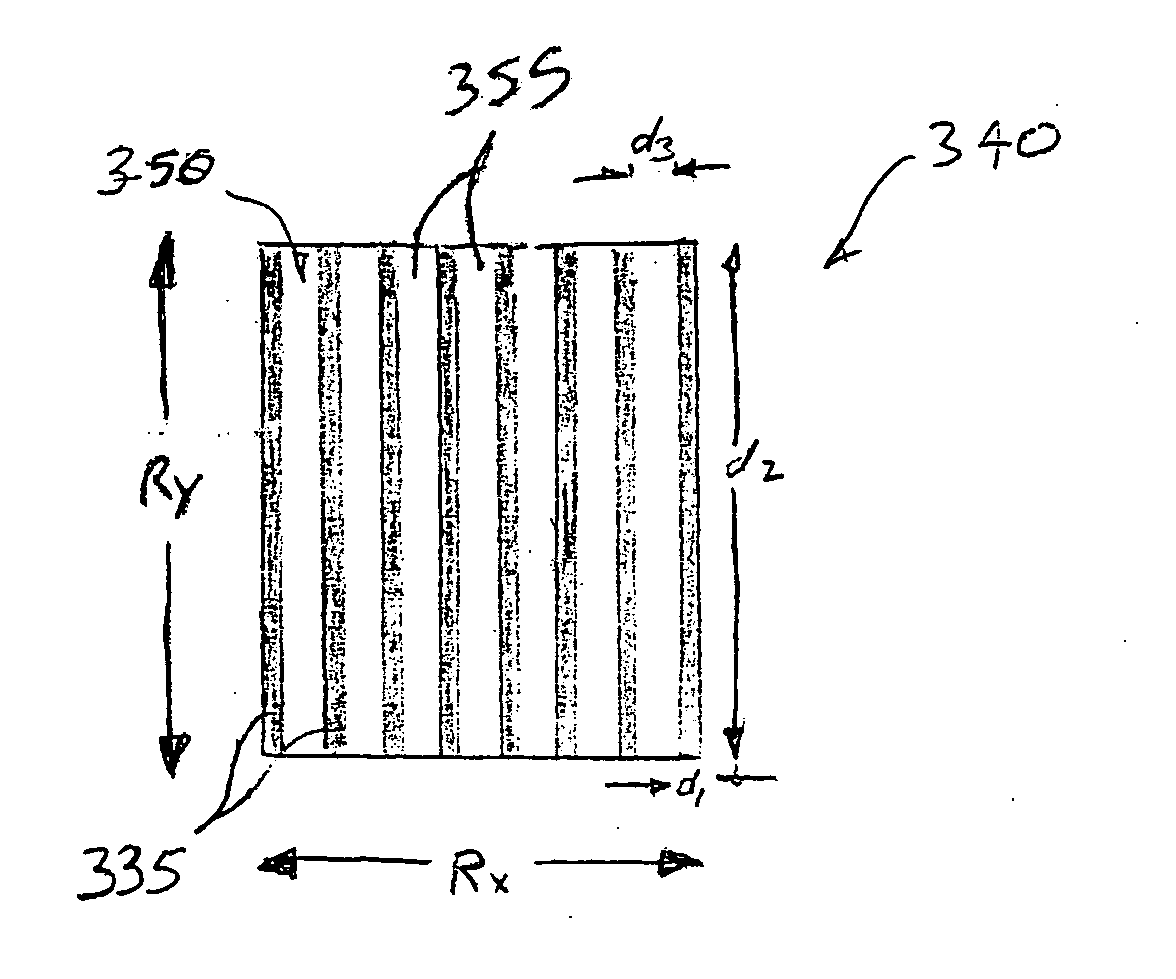

Method for achieving copper fill of high aspect ratio interconnect features

InactiveUS6436267B1AnodisationSemiconductor/solid-state device manufacturingMetal interconnectGas phase

One aspect of the invention provides a consistent metal electroplating technique to form void-less metal interconnects in sub-micron high aspect ratio features on semiconductor substrates. One embodiment of the invention provides a method for filling sub-micron features on a substrate, comprising reactive precleaning the substrate, depositing a barrier layer on the substrate using high density plasma physical vapor deposition; depositing a seed layer over the barrier layer using high density plasma physical vapor deposition; and electro-chemically depositing a metal using a highly resistive electrolyte and applying a first current density during a first deposition period followed by a second current density during a second period.

Owner:APPLIED MATERIALS INC

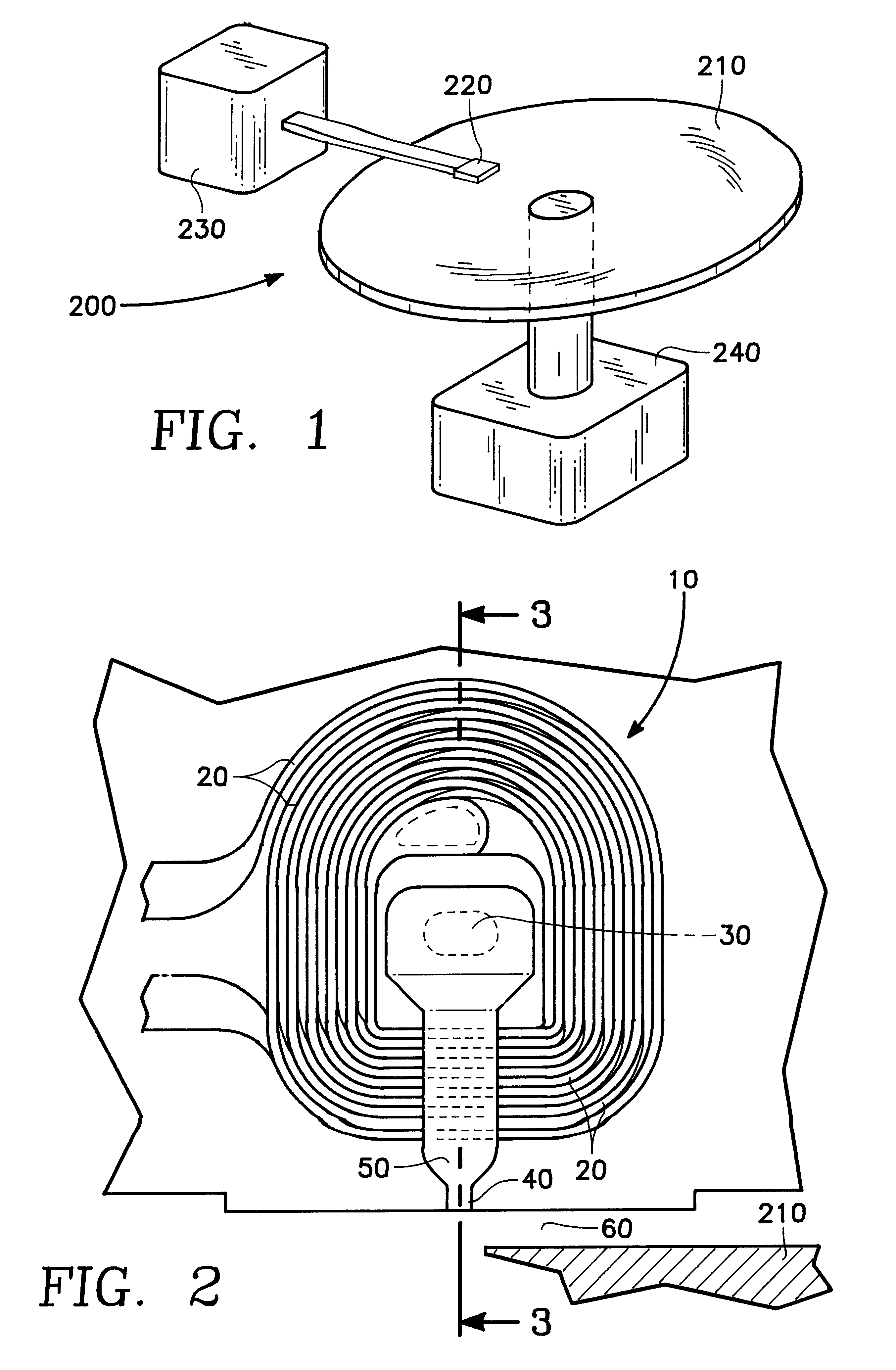

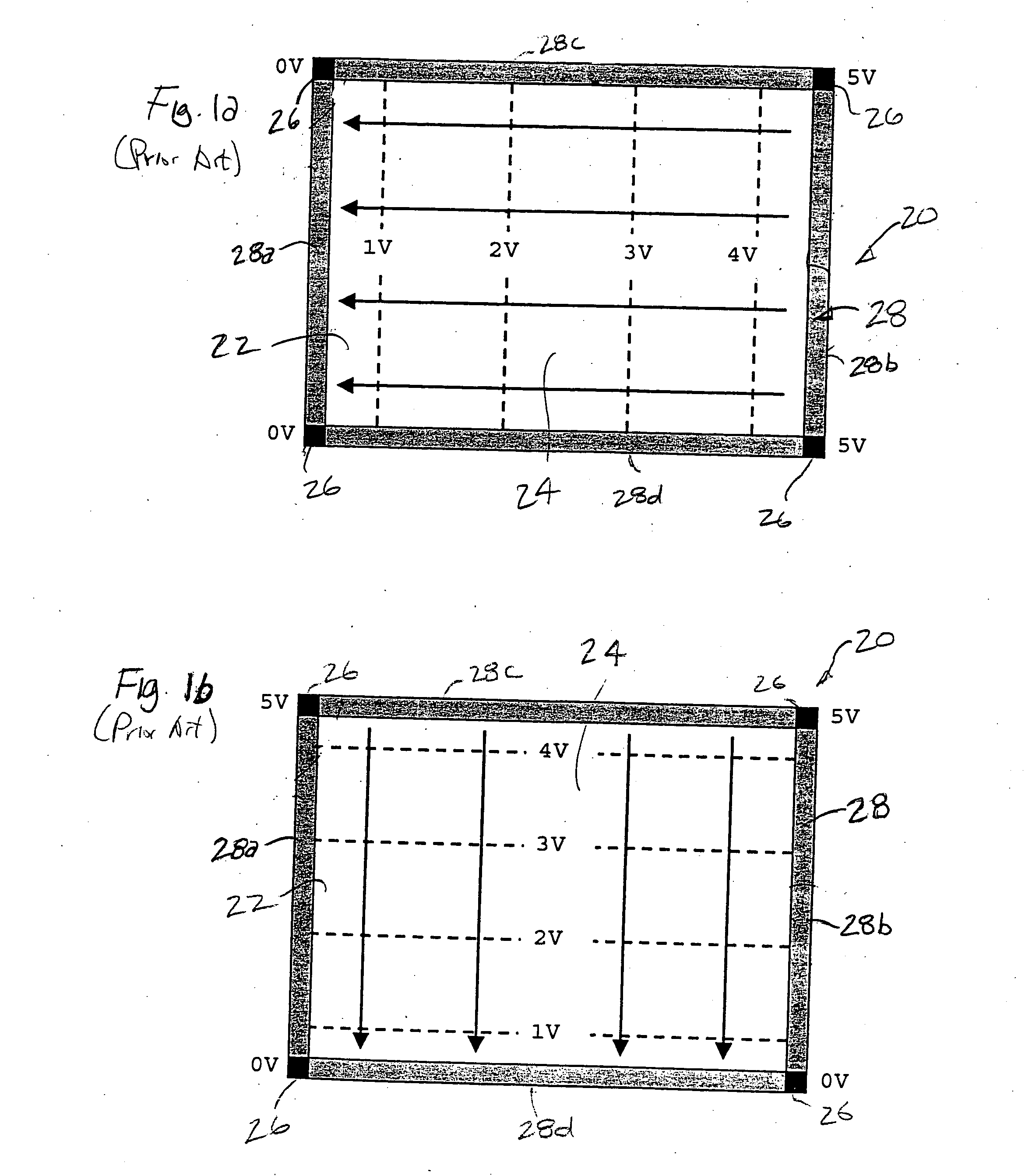

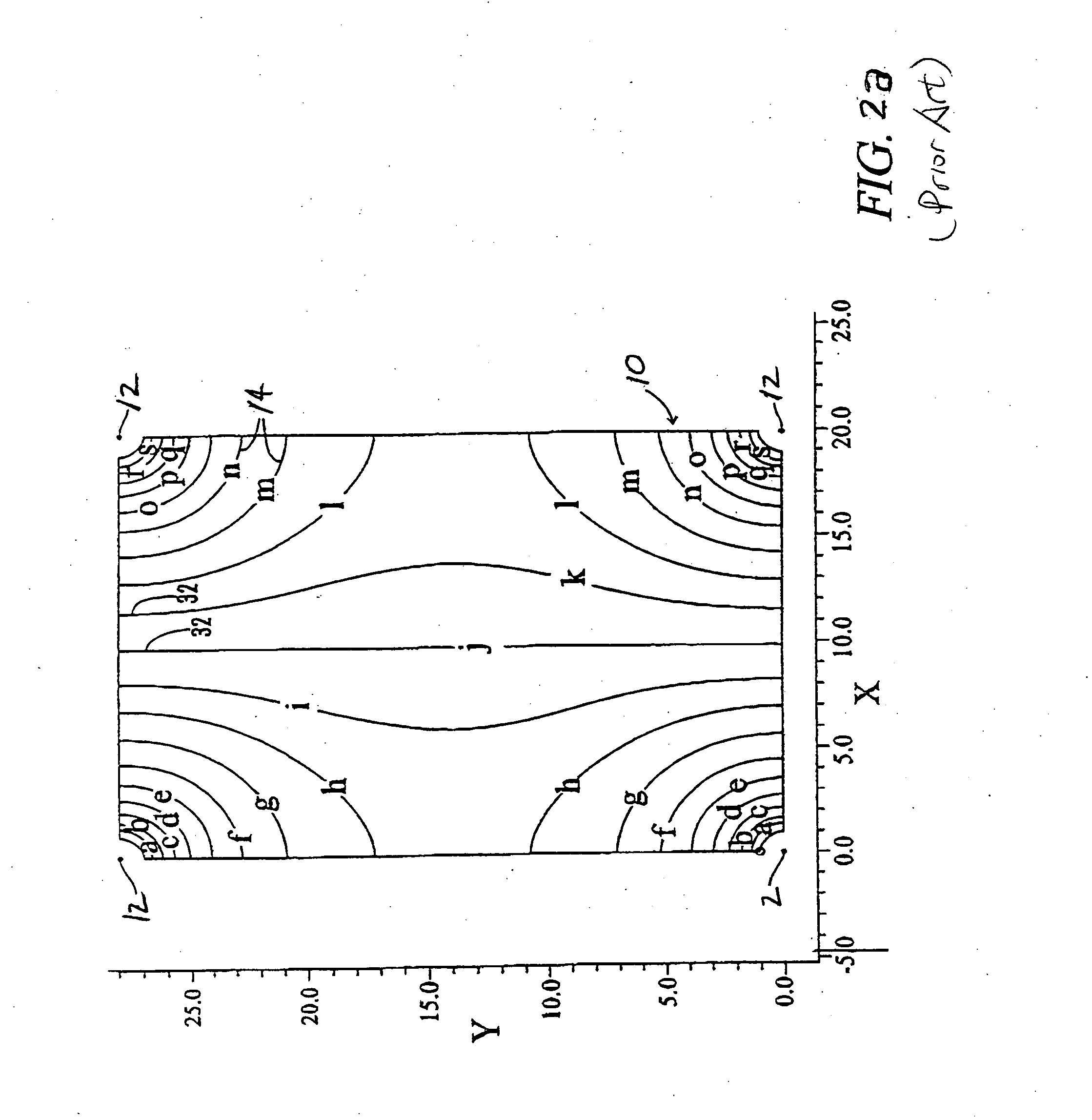

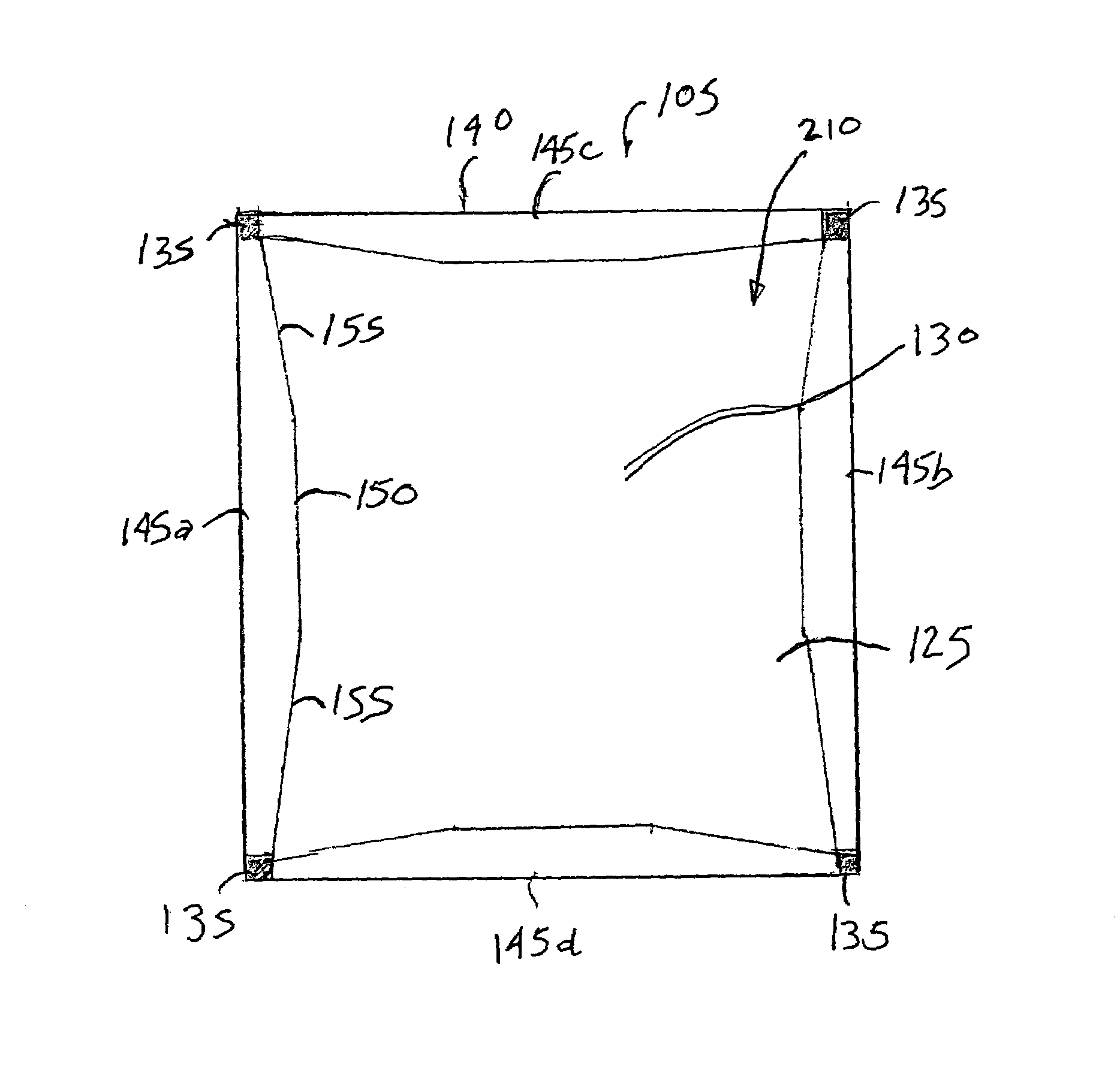

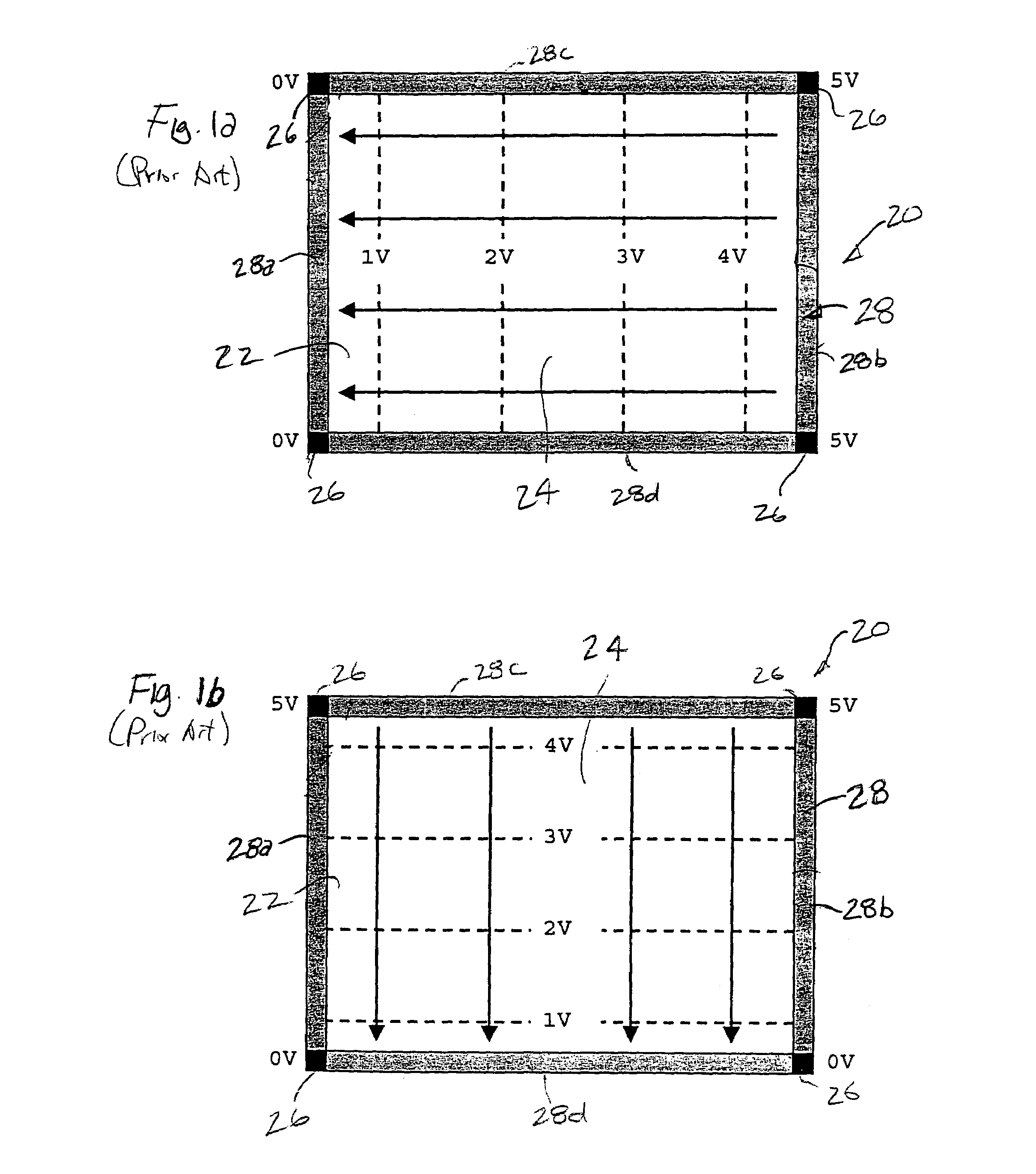

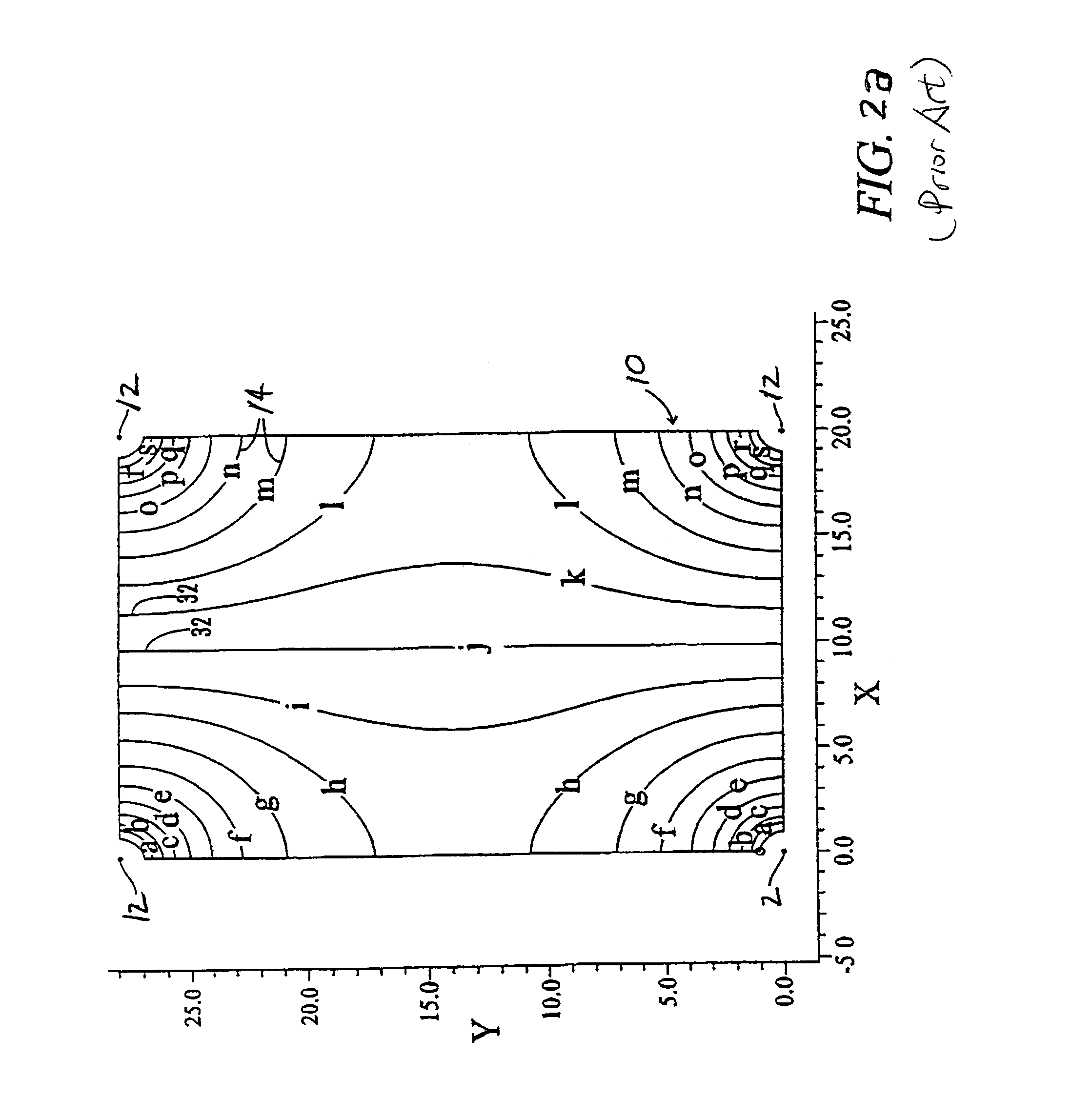

Touch sensor with non-uniform resistive band

InactiveUS20050012644A1Simple manufacturing processIncrease widthElectronic switchingInput/output processes for data processingElectrical resistance and conductanceEngineering

The present inventions are directed to touch sensors with improved topological equivalence between an equipotential space and a Cartesian space to which the equipotential space will be mapped. The touch sensor comprises a substrate with a touch region, and a set of electrodes that are electrically coupled to the touch region. The touch sensor further comprises a plurality of resistive band segments that frames the touch region. The electrodes are located between the resistive band segments. Each resistive band segment has a resistivity that is intermediate between the resistivity of the electrodes and the resistivity of the touch region, thereby providing a transition between the low resistivity electrodes and the high resistivity touch region, and improving the topological equivalence within the corners of the touch region. At least one of the band segments has a non-uniform linear resistance to provide further improvement to the topological equivalence.

Owner:ELO TOUCH SOLUTIONS INC

Wafer level interconnection

InactiveUS20030047799A1Television system detailsPiezoelectric/electrostriction/magnetostriction machinesDielectricElectrical conductor

RF MicroElectroMechanical Systems (MEMS) circuitry (15) on a first high resistivity substrate (17) is combined with circuitry (11) on a second low resistivity substrate (13) by overlapping the first high resistivity substrate (17) and MEMS circuitry (15) with the low resistivity substrate (13) and circuitry (11) with the MEMS circuitry (15) facing the second circuitry (11). A dielectric lid (19) is placed over the MEMS circuitry (15) and between the first substrate (17) and second substrate (13) with an inert gas in a gap (21) over the MEMS circuitry (15). Interconnecting conductors (25, 31, 35, 37, 39, 41) extend perpendicular and through the high resistivity substrate (17) and through the dielectric lid (19) to make electrical connection with the low resistivity substrate (13).

Owner:RAYTHEON CO

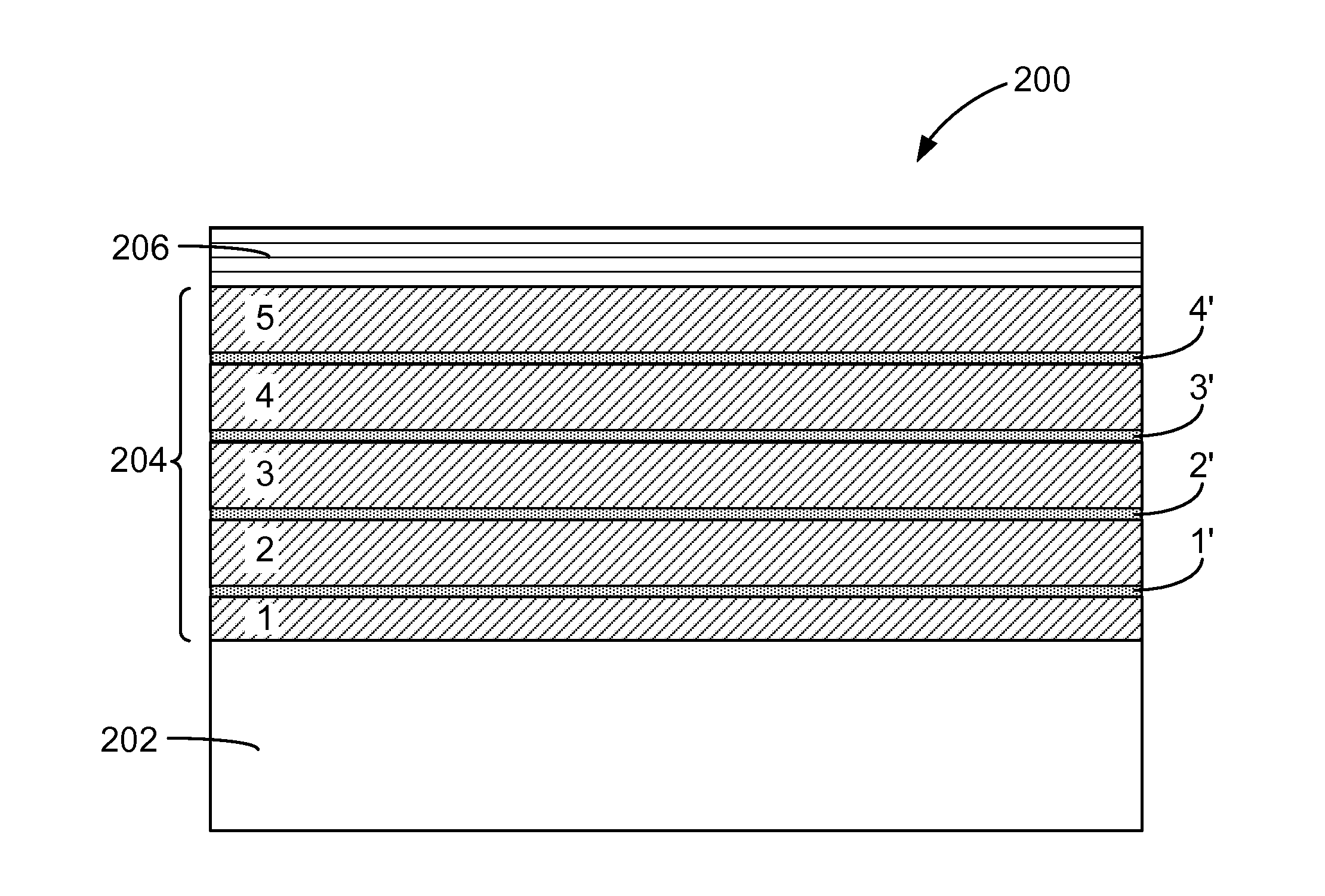

Low-resistivity photon-transparent window attached to photo-sensitive silicon detector

InactiveUS6025585ALow resistivityHigh resistivitySolid-state devicesMaterial analysis by optical meansCMOS sensorX-ray

The invention comprises a combination of a low resistivity, or electrically conducting, silicon layer that is transparent to long or short wavelength photons and is attached to the backside of a photon-sensitive layer of silicon, such as a silicon wafer or chip. The window is applied to photon sensitive silicon devices such as photodiodes, charge-coupled devices, active pixel sensors, low-energy x-ray sensors and other radiation detectors. The silicon window is applied to the back side of a photosensitive silicon wafer or chip so that photons can illuminate the device from the backside without interference from the circuit printed on the frontside. A voltage sufficient to fully deplete the high-resistivity photosensitive silicon volume of charge carriers is applied between the low-resistivity back window and the front, patterned, side of the device. This allows photon-induced charge created at the backside to reach the front side of the device and to be processed by any circuitry attached to the front side. Using the inventive combination, the photon sensitive silicon layer does not need to be thinned beyond standard fabrication methods in order to achieve full charge-depletion in the silicon volume. In one embodiment, the inventive backside window is applied to high resistivity silicon to allow backside illumination while maintaining charge isolation in CCD pixels.

Owner:RGT UNIV OF CALIFORNIA

Novel underlayer for high performance magnetic tunneling junction MRAM

ActiveUS20060002184A1High resistivityConsistent growthNanomagnetismMagnetic measurementsOptoelectronicsHigh resistivity

An MRAM structure is disclosed in which the bottom electrode has an amorphous TaN capping layer to consistently provide smooth and dense growth for AFM, pinned, tunnel barrier, and free layers in an overlying MTJ. Unlike a conventional Ta capping layer, TaN is oxidation resistant and has high resistivity to avoid shunting of a sense current caused by redeposition of the capping layer on the sidewalls of the tunnel barrier layer. Alternatively, the α-TaN layer is the seed layer in the MTJ. Furthermore, the seed layer may be a composite layer comprised of a NiCr, NiFe, or NiFeCr layer on the α-TaN layer. An α-TaN capping layer or seed layer can also be used in a TMR read head. An MTJ formed on an α-TaN capping layer has a high MR ratio, high Vb, and a RA similar to results obtained from MTJs based on an optimized Ta capping layer.

Owner:APPLIED SPINTRONICS +1

Method and apparatus for sensing and characterizing particles

InactiveUS6111398AIndividual particle analysisParticle suspension analysisLiquid mediumHigh resistivity

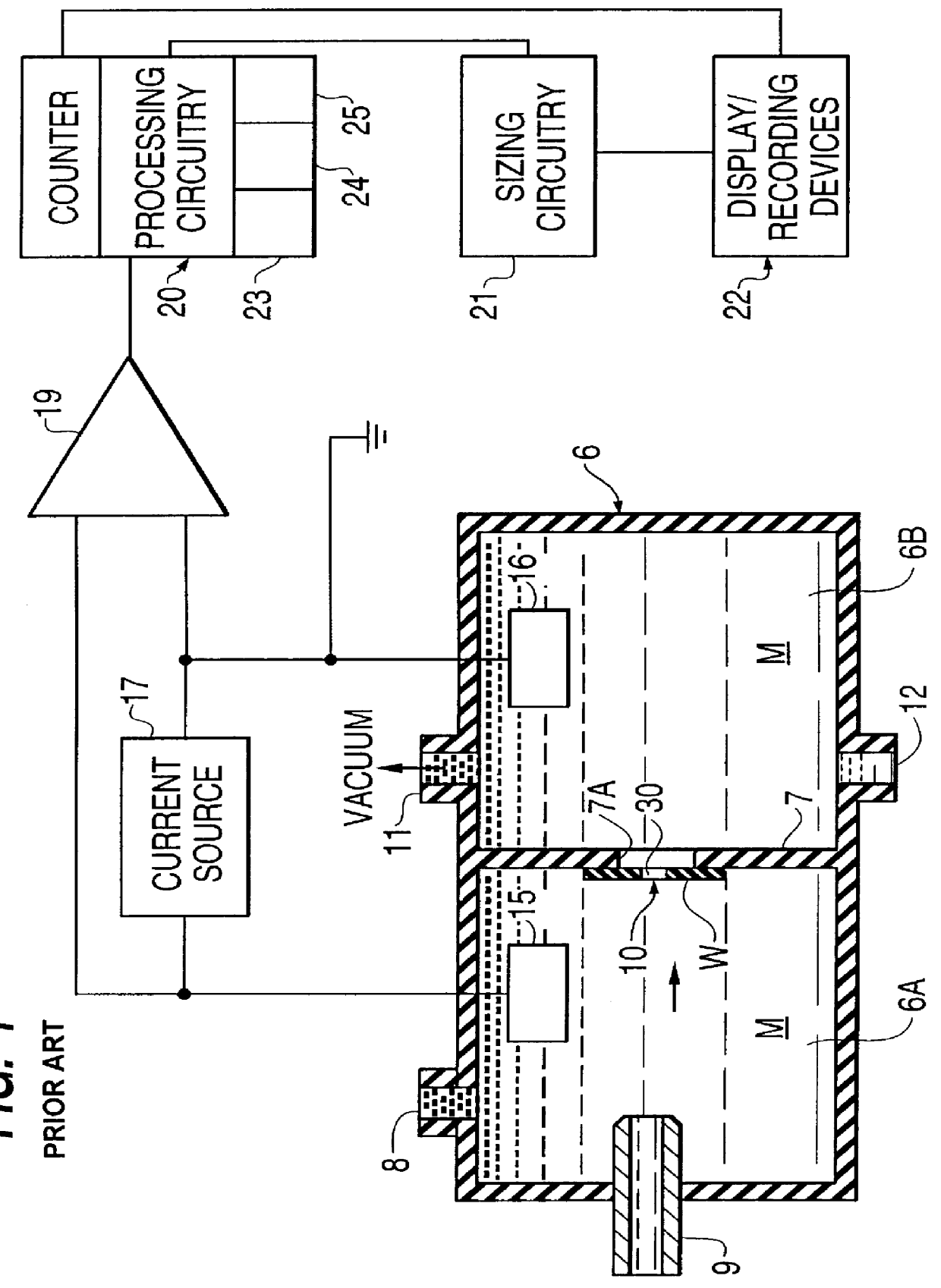

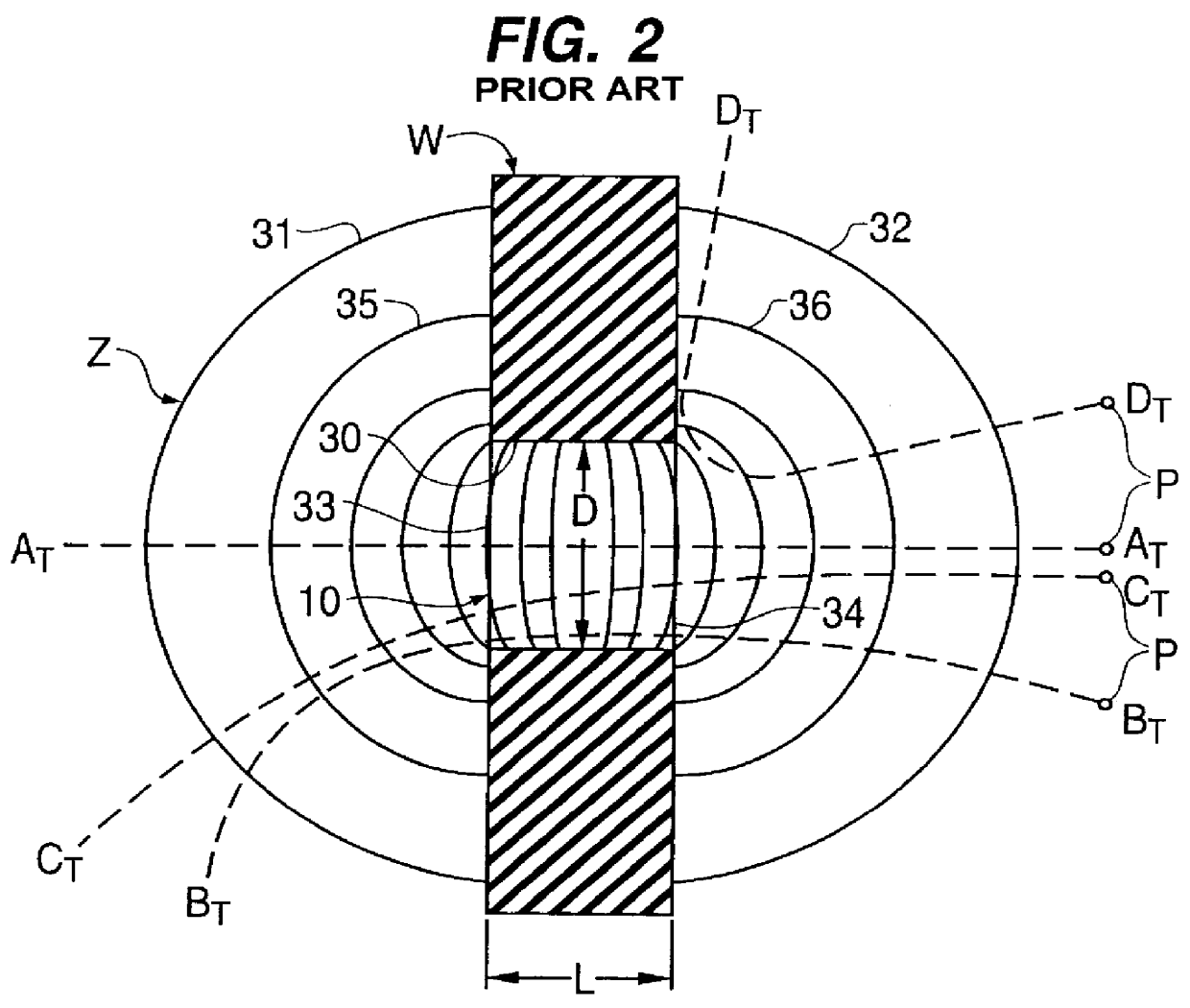

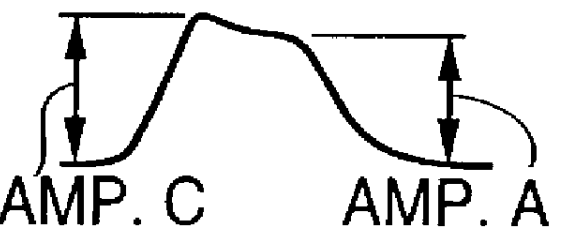

Apparatus for sensing and characterizing particles (e.g., blood cells or ceramic powders) suspended in a liquid medium comprises a conduit through which the particle suspension is caused to pass simultaneously with an electrical current. According to the invention, the interior wall of the conduit effectively varies in resistivity along the length of the conduit to define a delimited central region of high electrical resistivity which is smoothly contiguous on its opposing boundaries to uninsulated distal elements of lesser electrical resistivity. The delimited central region of the conduit functions as a Coulter volumeter conduit. The uninsulated distal elements of the conduit are made to have a dimension along the conduit wall which is at least equal to the axial extent of the effective ambit electric fields of a traditional Coulter volumeter conduit having a cross-sectional geometry identical to that of the delimited central region of high resistivity in the improved volumeter conduit. According to a preferred embodiment of the invention, the delimited central region of the improved volumeter conduit is defined by a traditional Coulter conduit wafer, i.e., a dielectric wafer containing a central circular conduit, and the distal elements of lesser resistivity are defined by uninsulated, electrically conductive, circular collars attached to opposite sides of the conduit wafer. The conduit in the conduit wafer and the openings in the conductive collars collectively form a hydrodynamically smooth volumeter conduit, in which the electric and hydrodynamic fields of the traditional volumeter conduit are advantageously amended in the manner above noted.

Owner:COULTER INTERNATIONAL CORPORATION

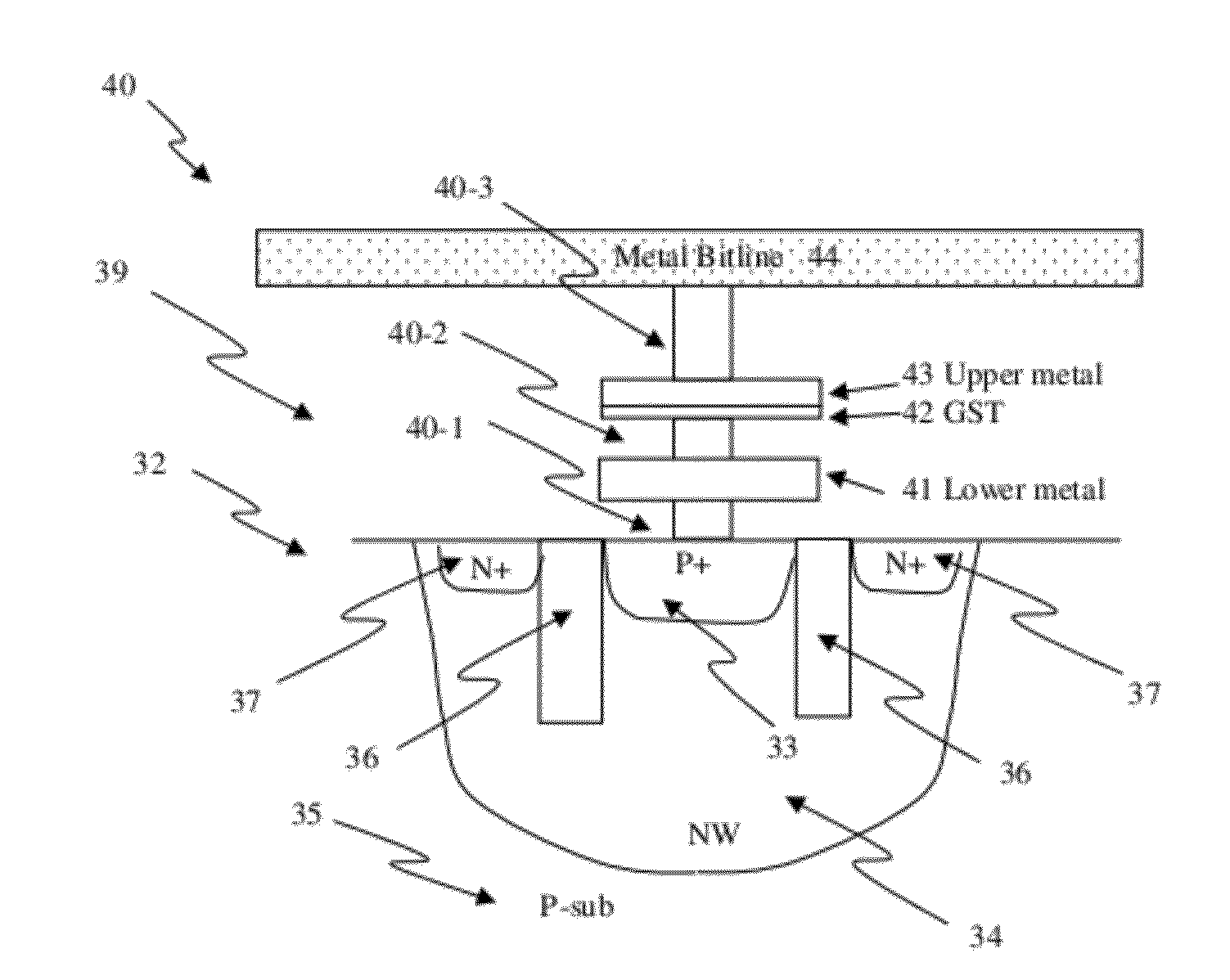

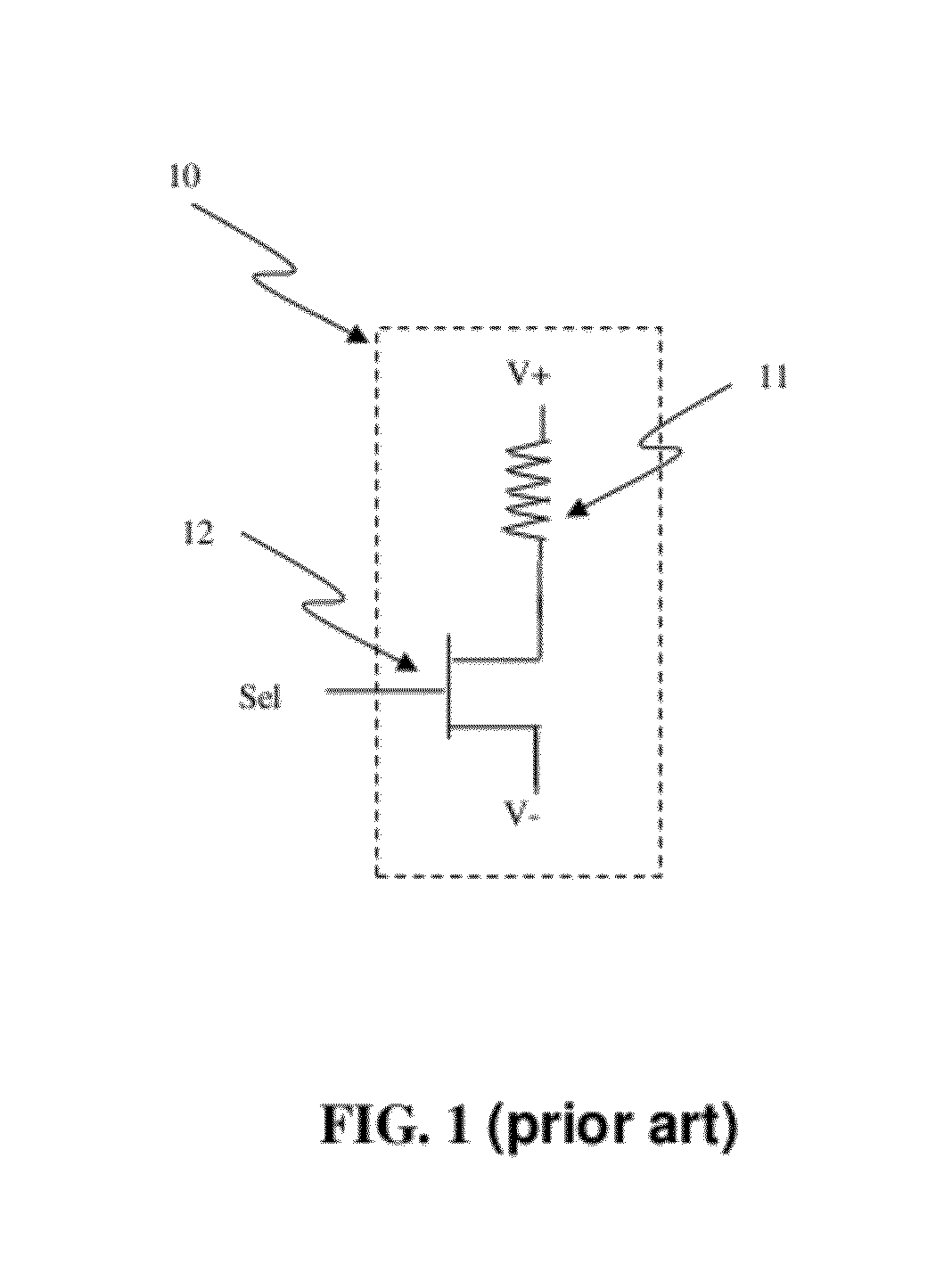

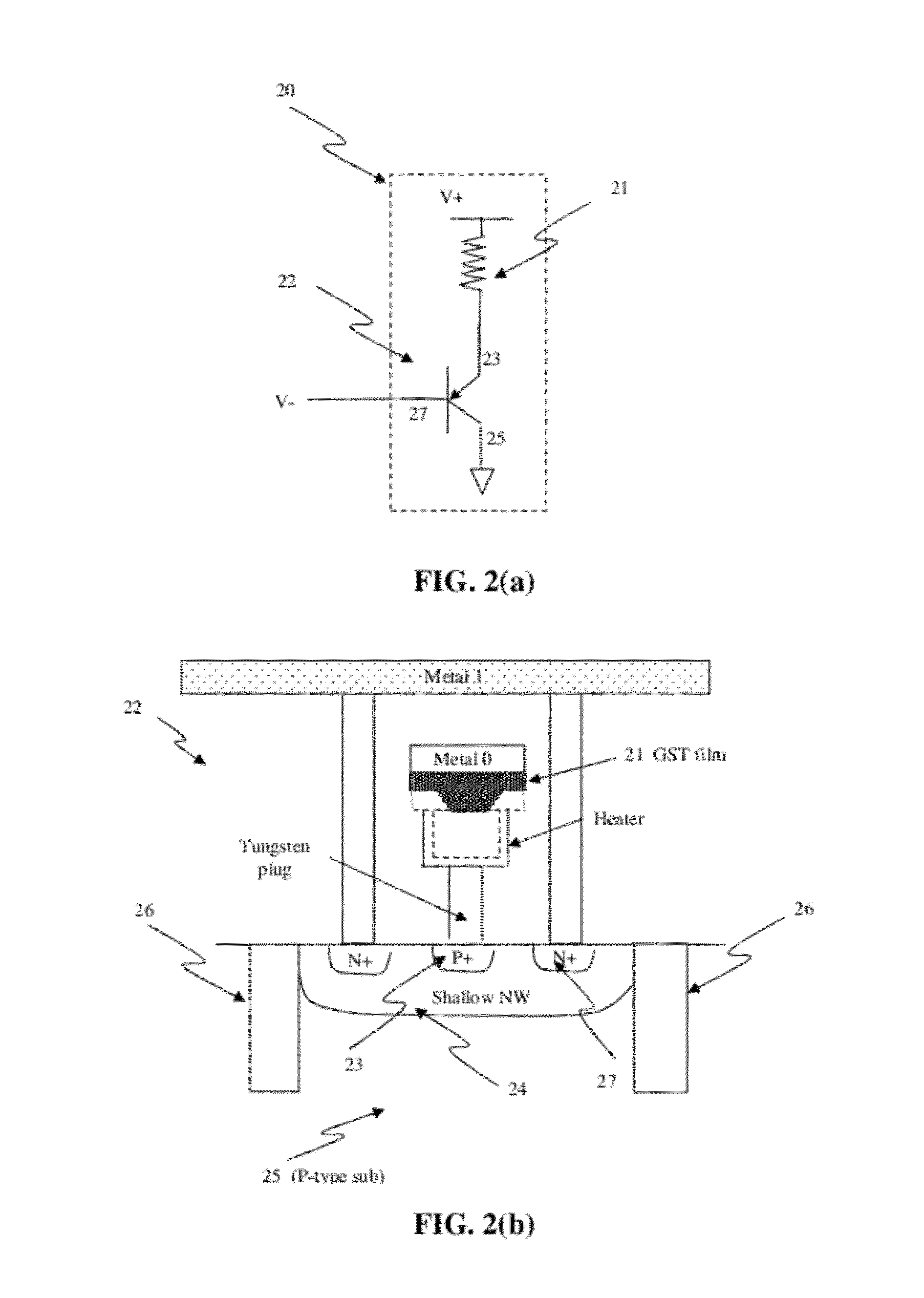

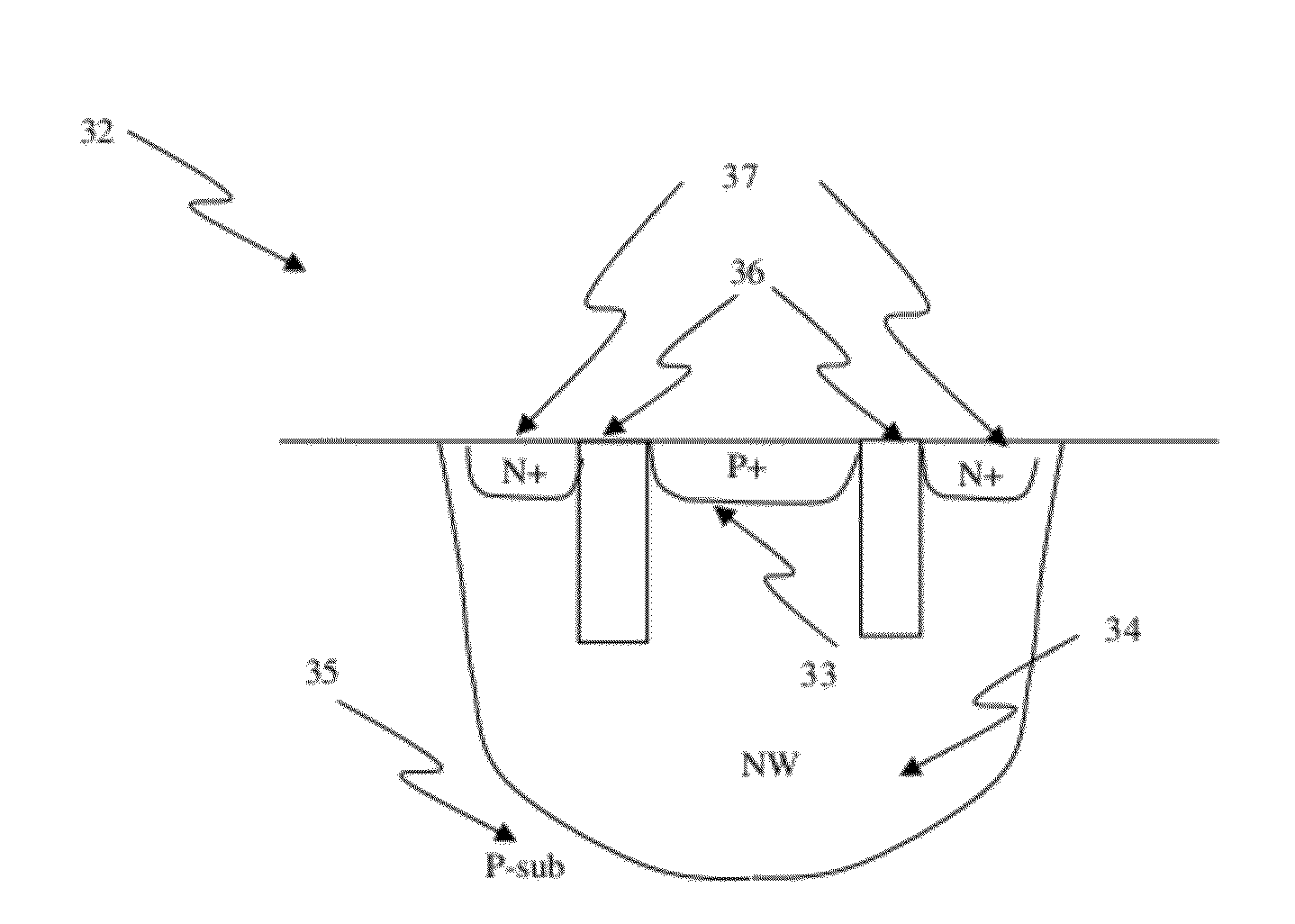

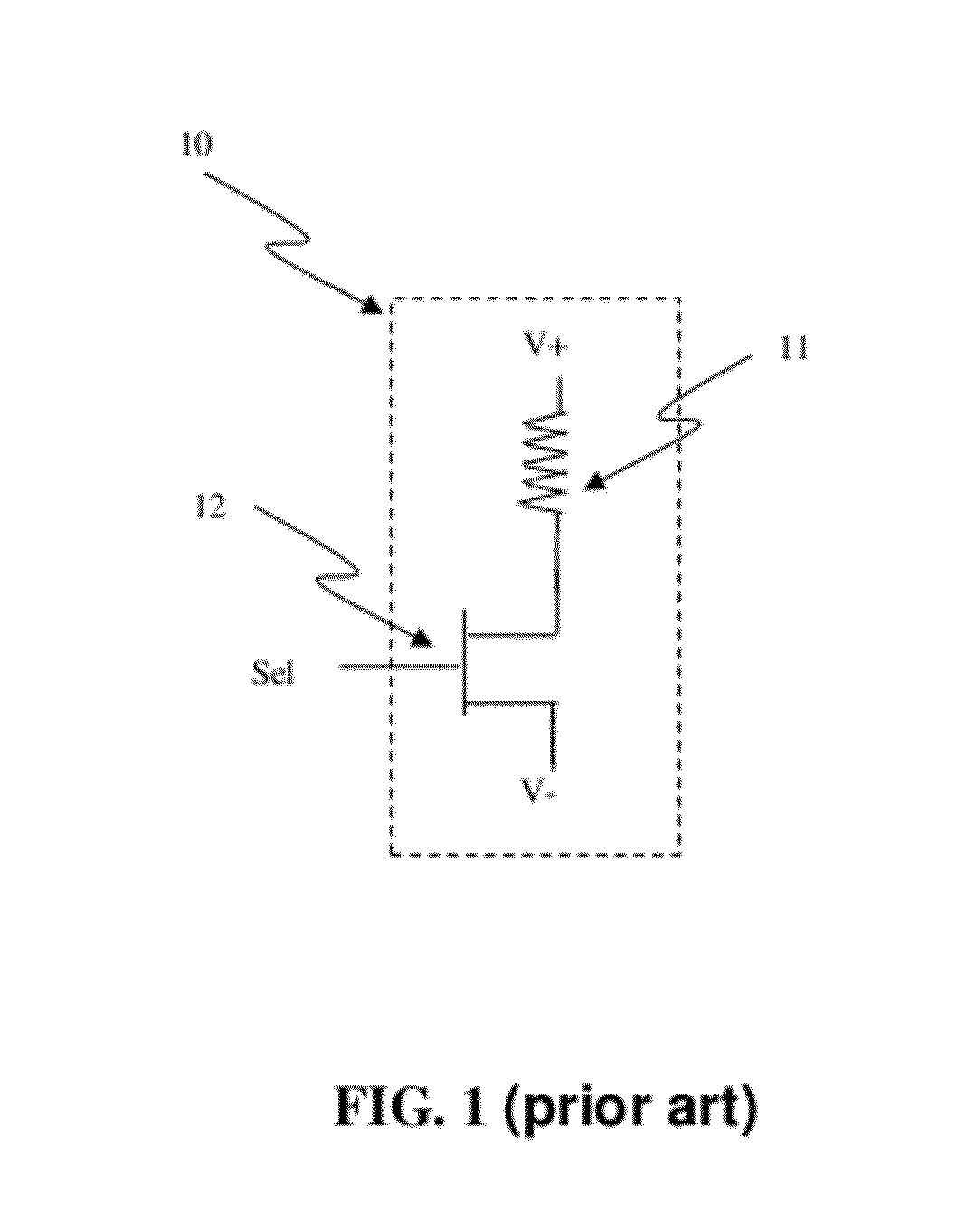

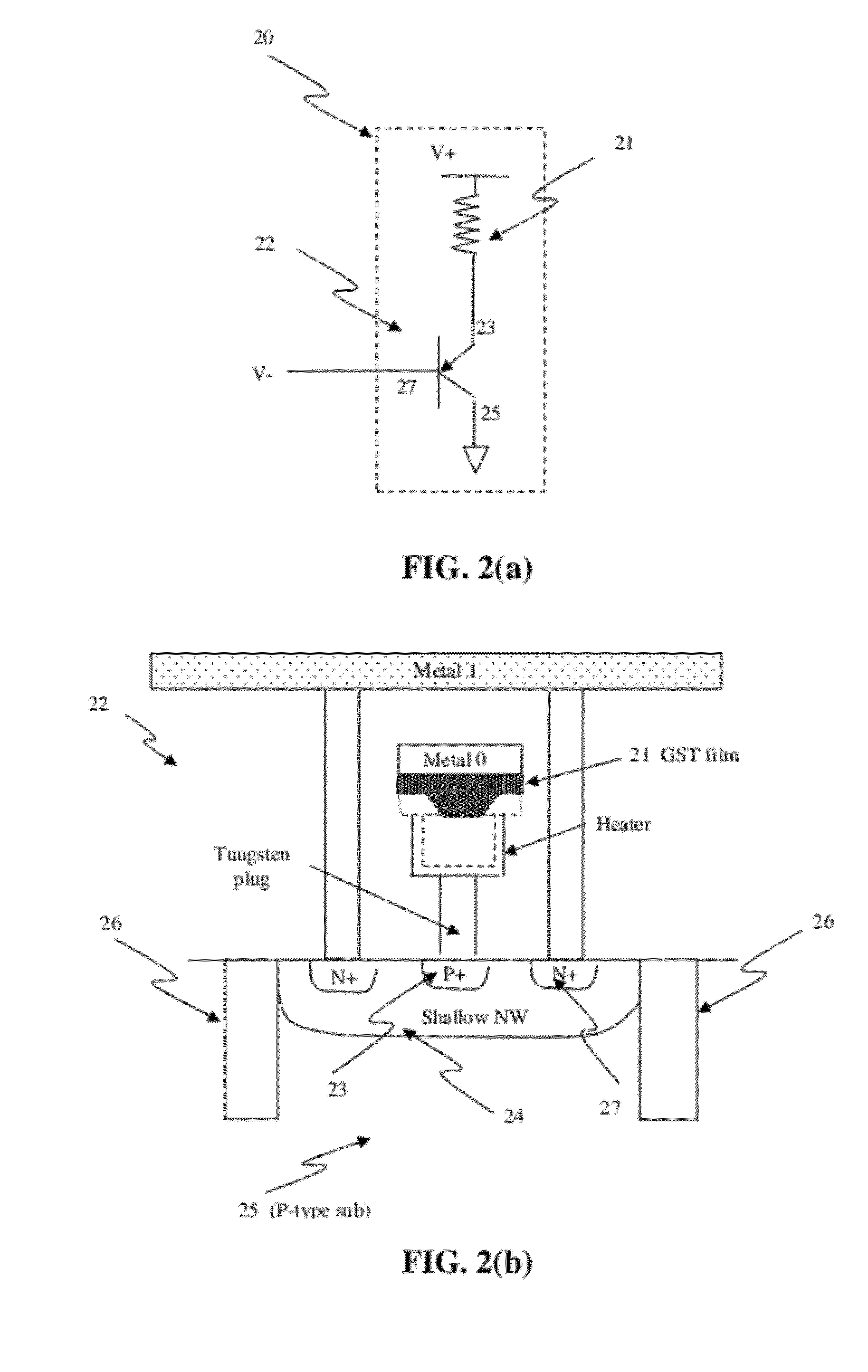

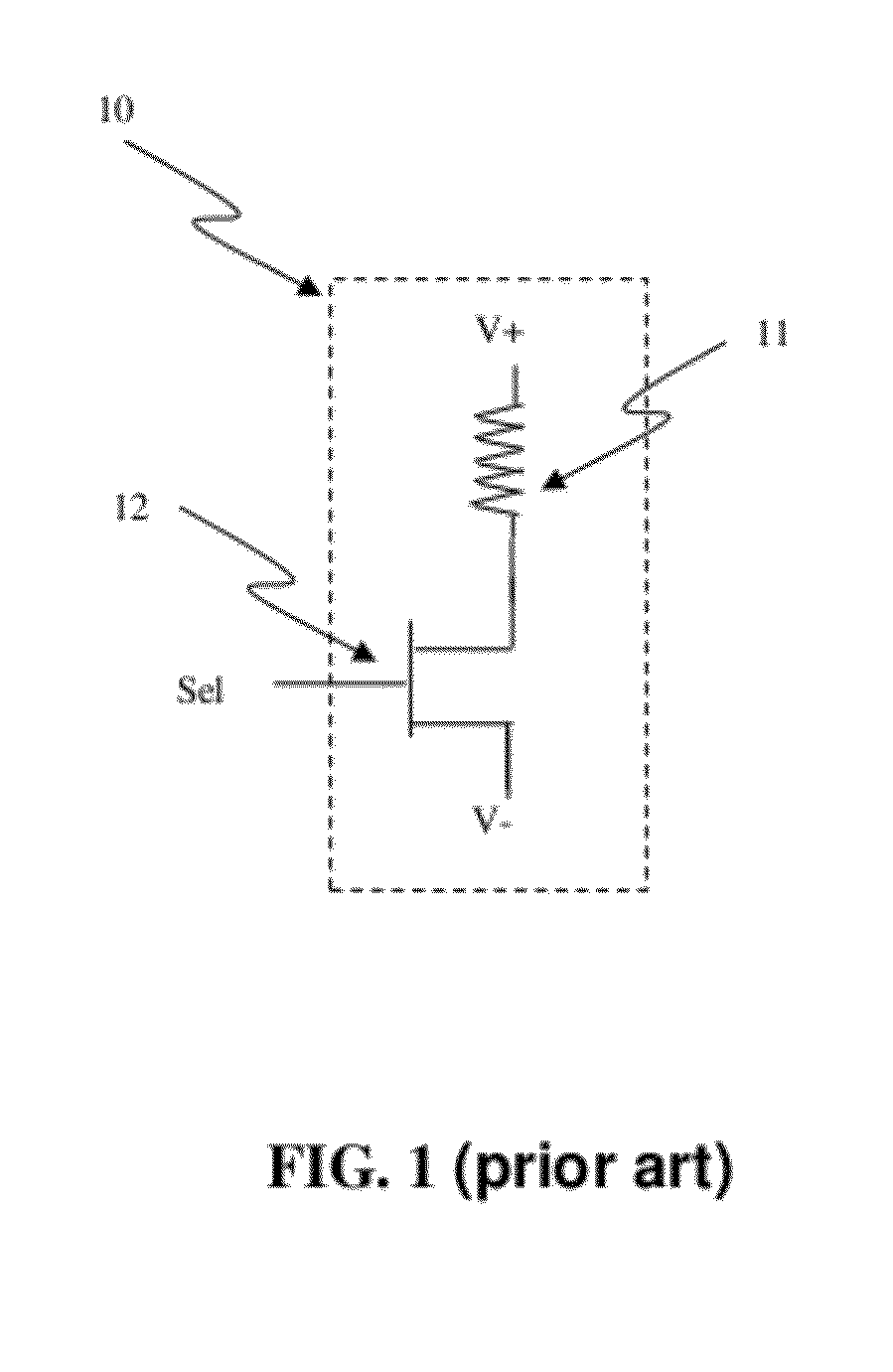

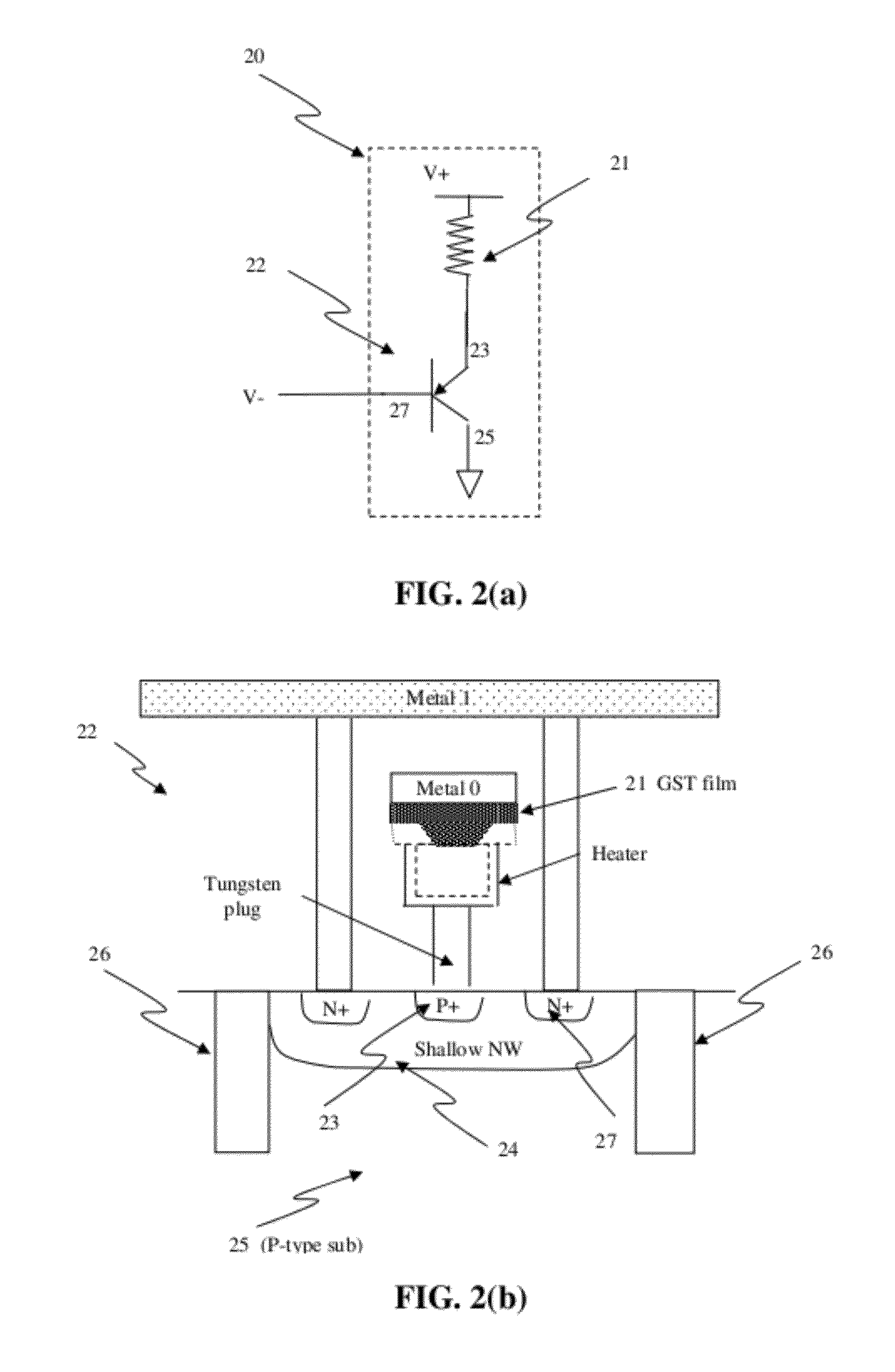

Reversible resistive memory using diodes formed in CMOS processes as program selectors

ActiveUS20120044747A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for reversible resistive memory cells that can be programmed based on magnitude, duration, voltage-limit, or current-limit of a supply voltage or current. These cells are PCM, RRAM, CBRAM, or other memory cells that have a reversible resistive element coupled to a diode. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. The memory cells can be used to construct a two-dimensional memory array with the N terminals of the diodes in a row connected as a wordline and the reversible resistive elements in a column connected as a bitline. By applying a voltage or a current to a selected bitline and to a selected wordline to turn on the diode, a selected cell can be programmed into different states reversibly based on magnitude, duration, voltage-limit, or current-limit. The data in the reversible resistive memory can also be read by turning on a selected wordline to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistive global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

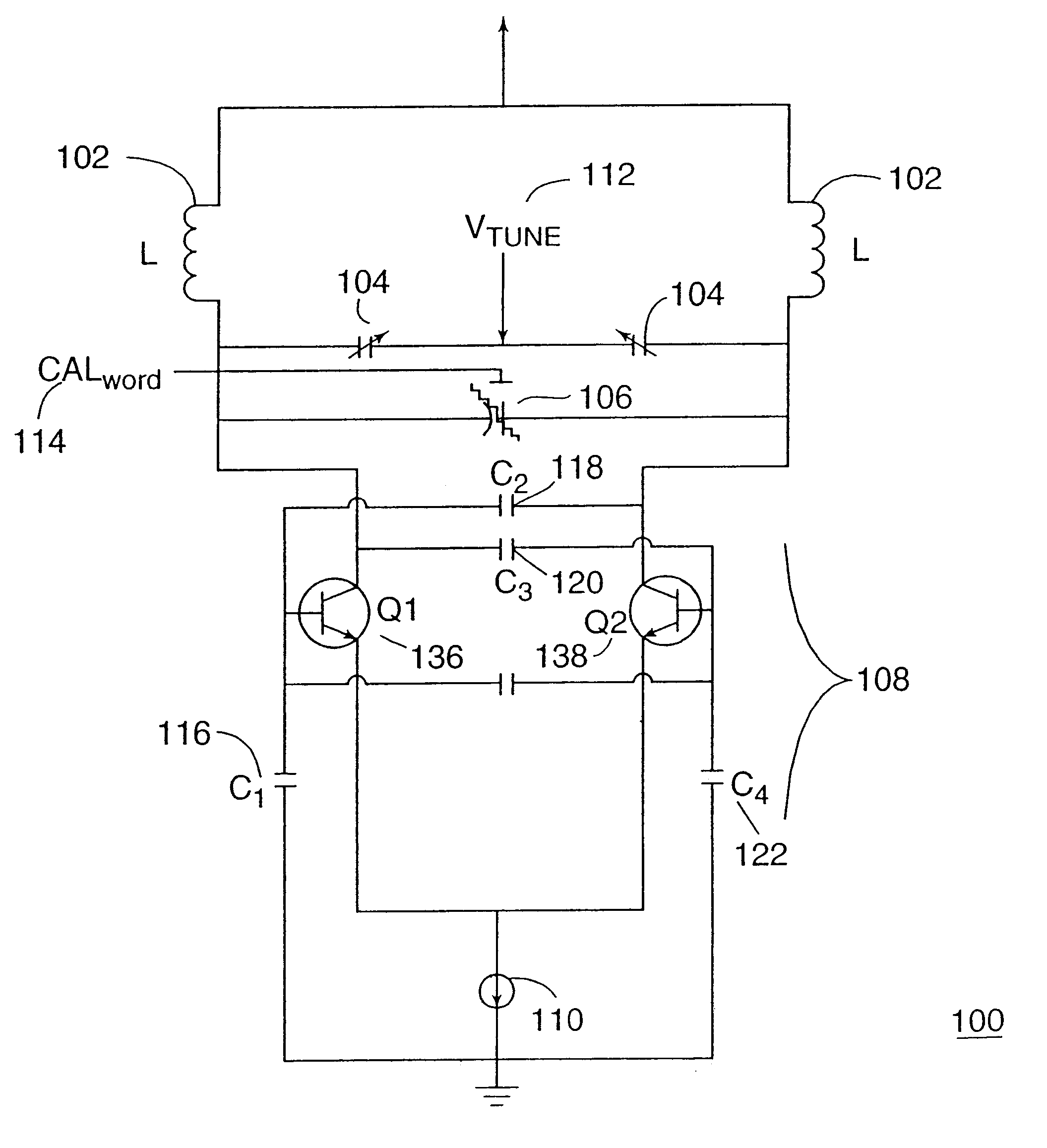

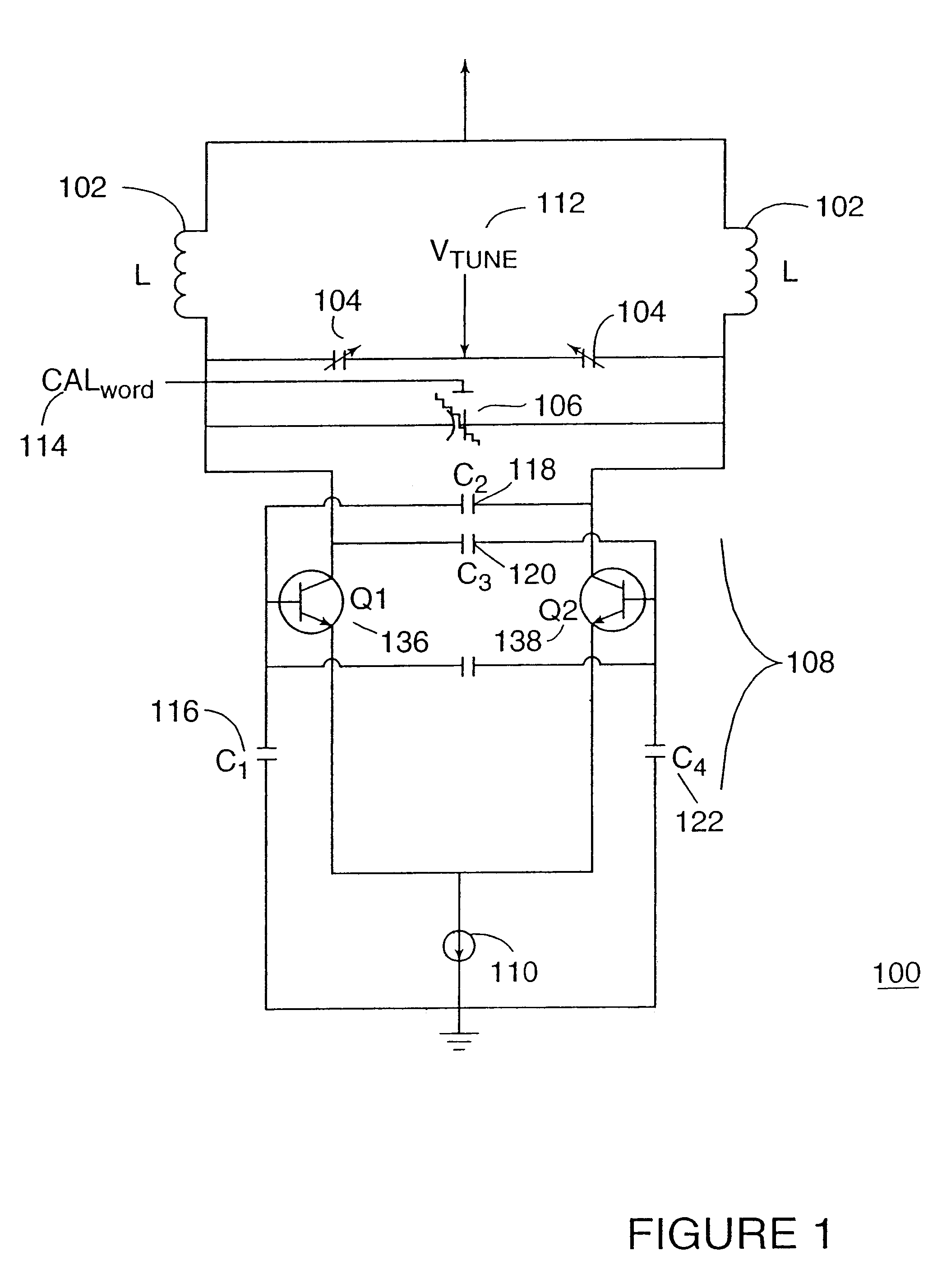

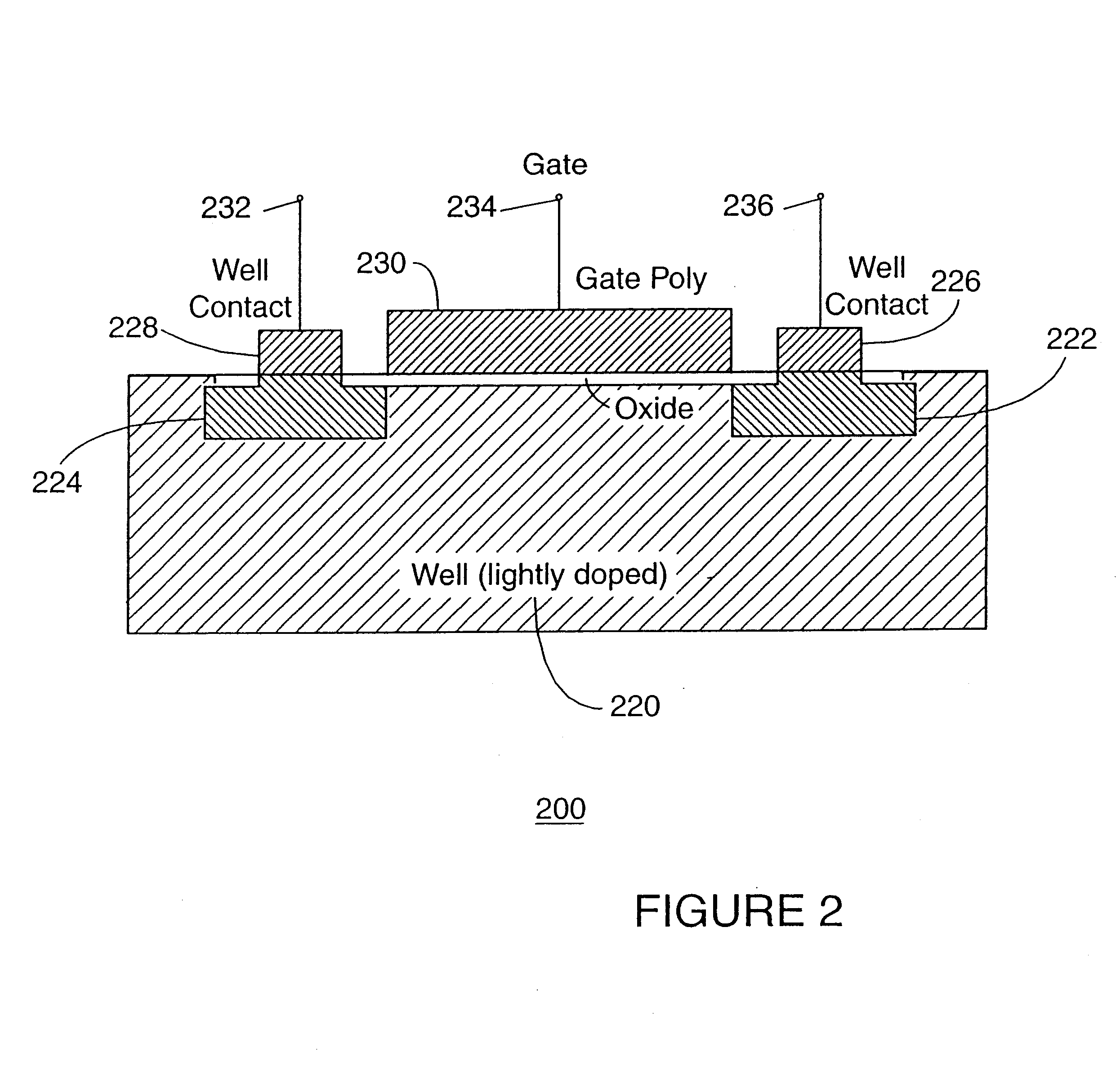

Method and apparatus for fully integrating a voltage controlled oscillator on an integrated circuit

InactiveUS6268778B1Wide tuning capacitance rangeReduce parasitic capacitanceAngle modulation by variable impedencePulse automatic controlLc resonatorSelf resonance

A method and apparatus for fully integrating a Voltage Controlled Oscillator (VCO) on an integrated circuit. The VCO is implemented using a differential-mode circuit design. The differential-mode implementation of the VCO preferably comprises a differential mode LC-resonator circuit, a digital capacitor, a differential pair amplifier, and a current source. The LC-resonator circuit includes at least one tuning varactor and two high Q inductors. The tuning varactor preferably has a wide tuning capacitance range. The tuning varactor is only used to "fine-tune" the center output frequency f0 of the VCO. The center output frequency f0 is coarsely tuned by the digital capacitor. The VCO high Q inductors comprise high gain, high self-resonance, and low loss IC inductors. The IC VCO is fabricated on a high resistivity substrate material using a trench isolated guard ring. The guard ring isolates the fully integrated VCO, and each of its component parts, from RF signals that may be introduced into the IC substrate by other devices. By virtue of the improved performance characteristics provided by the digital capacitor, the analog tuning varactor, the high Q inductor, and the trench isolated guard ring techniques, the inventive VCO is fully integrated despite process variations in IC fabrication.

Owner:CSR TECH INC

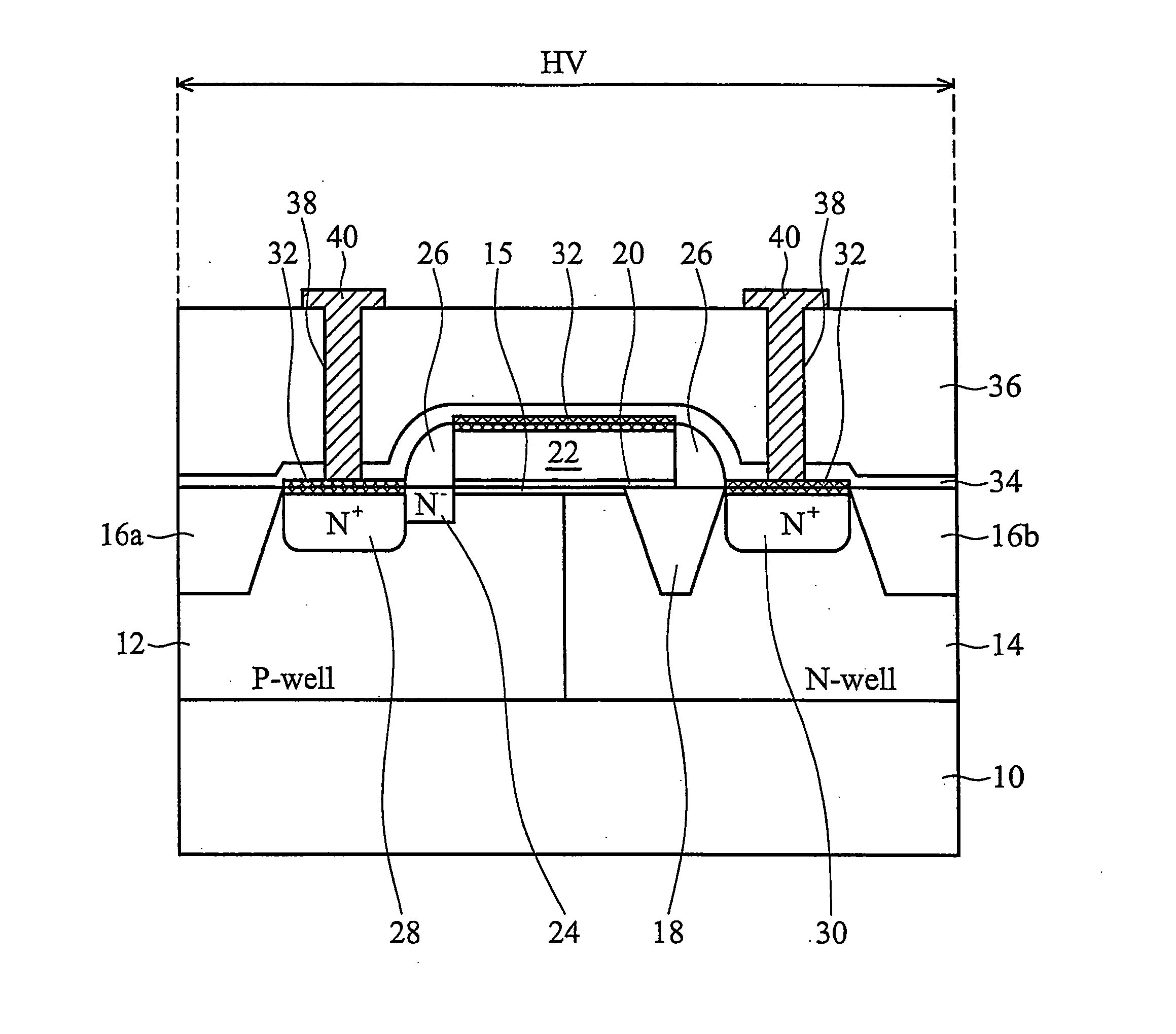

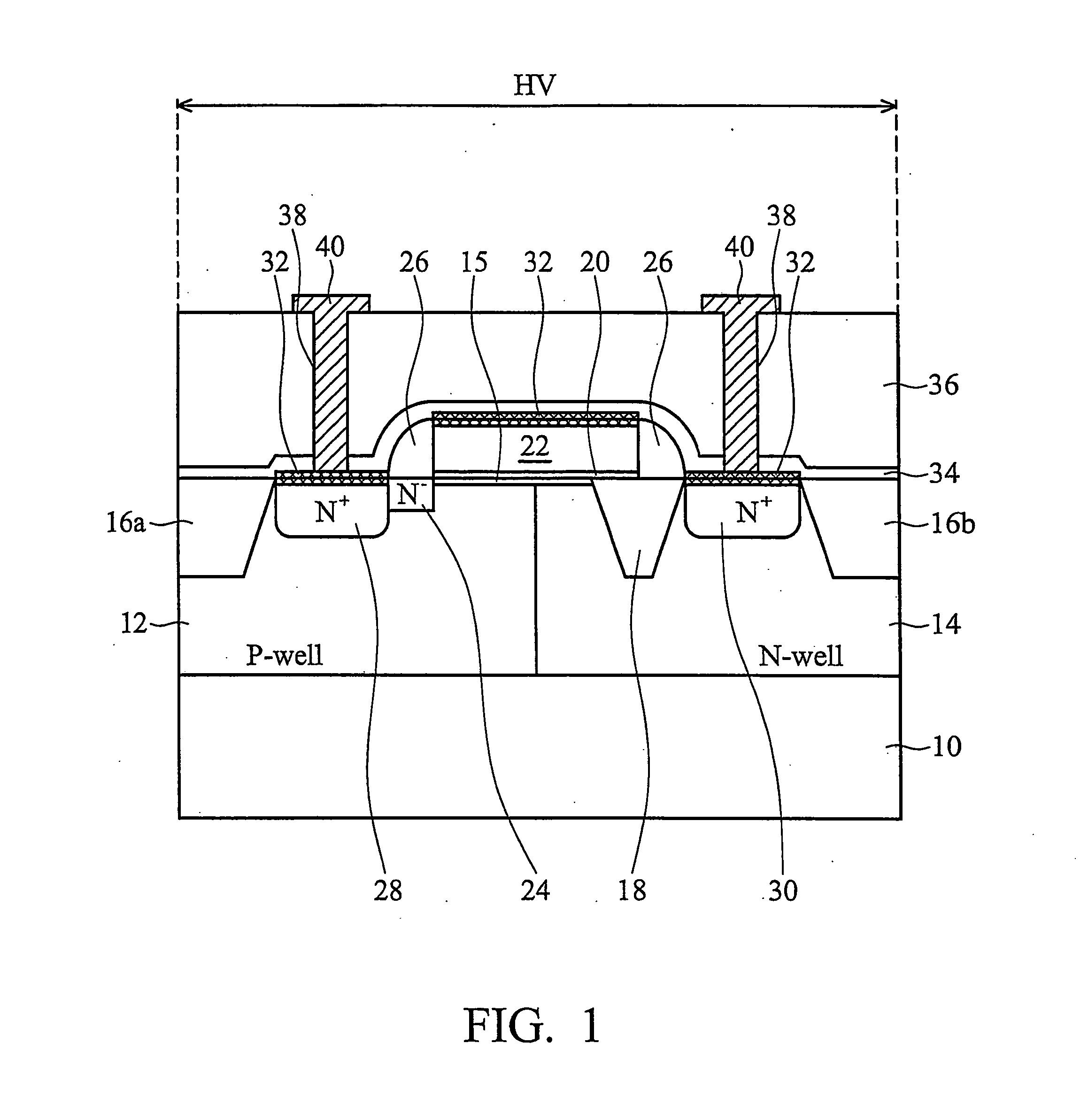

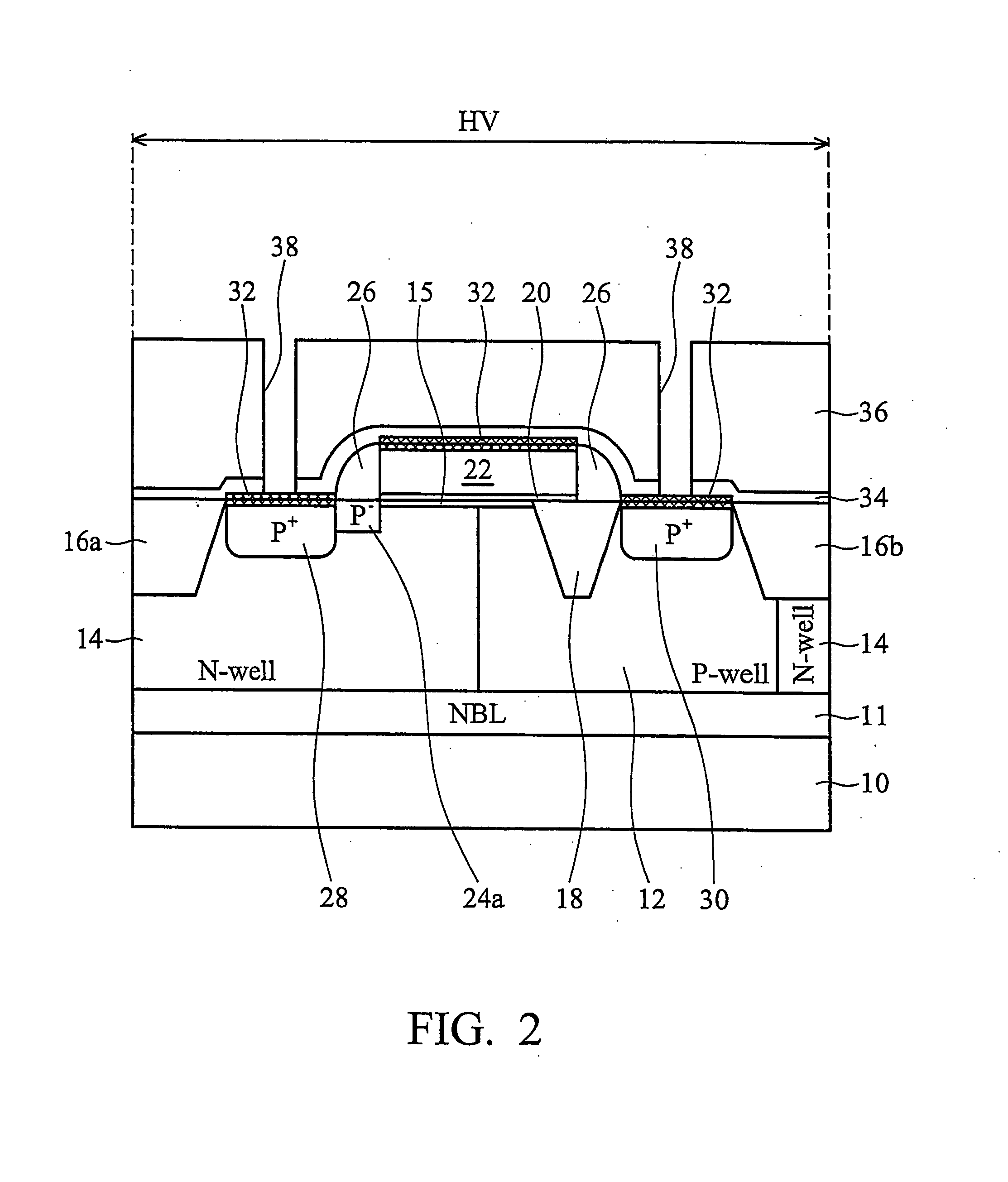

High-voltage transistor device having an interlayer dielectric etch stop layer for preventing leakage and improving breakdown voltage

ActiveUS20060113627A1Prevent leakageImprove breakdown voltageTransistorSolid-state devicesDielectricHigh voltage transistors

A high-voltage transistor device with an interlayer dielectric (ILD) etch stop layer for use in a subsequent contact hole process is provided. The etch stop layer is a high-resistivity film having a resistivity greater than 10 ohm-cm, thus leakage is prevented and breakdown voltage is improved when driving a high voltage greater than 5V at the gate site. A method for fabricating the high-voltage device is compatible with current low-voltage device processes and middle-voltage device processes.

Owner:TAIWAN SEMICON MFG CO LTD

High resistivity soi base wafer using thermally annealed substrate

ActiveUS20090110898A1Reduces interstitial oxygen concentrationSuppresses thermal donor formationSolid-state devicesSemiconductor/solid-state device manufacturingSurface layerHigh resistivity

A method of forming a semiconductor-on-insulator (SOI) substrate using a thermal annealing process to provide a semiconductor base wafer having a thin high resistivity surface layer that is positioned at the interface with the buried insulating layer is provided. Specifically, the inventive method fabricates an a semiconductor-on-insulator (SOI) substrate having an SOI layer and a semiconductor base wafer that are separated, at least in part, by a buried insulating layer, wherein the semiconductor base wafer includes a high resistivity (HR) surface layer located on a lower resistivity semiconductor portion of the semiconductor base wafer, and the HR surface layer forms an interface with the buried insulating layer.

Owner:GLOBALFOUNDRIES US INC

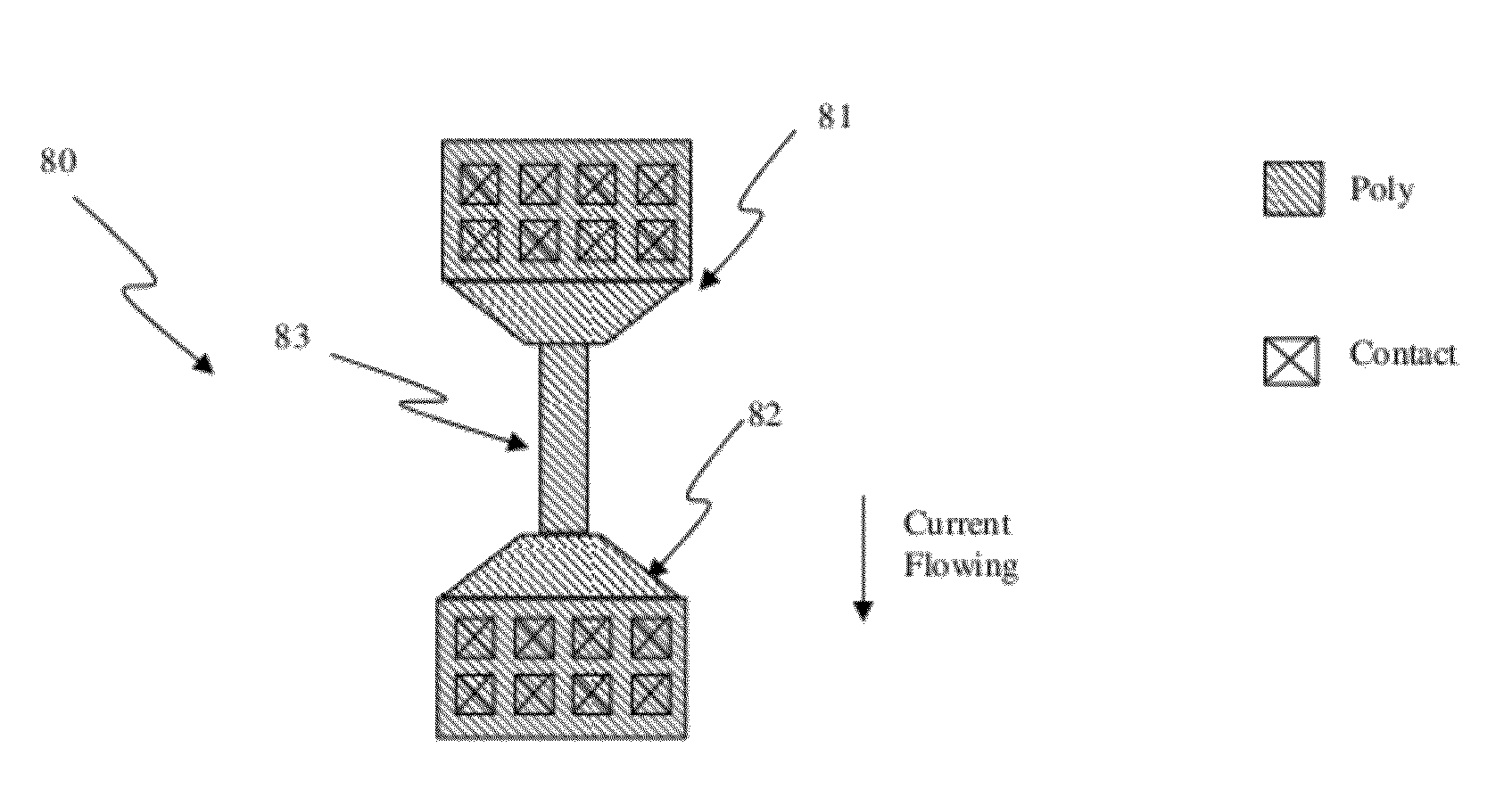

Circuit and system of using at least one junction diode as program selector for memories

ActiveUS20120044758A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

At least one junction diode fabricated in standard CMOS logic processes can be used as program selectors for memory cells that can be programmed based on direction of current flow. These cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to a P terminal of a first diode and to an N terminal of a second diode. The diodes can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diodes. The memory cells can be used to construct a two-dimensional memory array with the N terminals of the first diodes and the P terminals of the second diodes in a row connected as wordline(s) and the resistive elements in a column connected as a bitline. By applying a high voltage to a selected bitline and a low voltage to a selected wordline to turn on the first diode while disabling the second diode, a selected cell can be programmed into one state. Similarly, by applying a low voltage to a selected bitline and a high voltage to a selected wordline to turn on the second diode while disabling the first diode, a selected cell can be programmed into another state. The data in the resistive memory cell can also be read by turning on a selected wordline to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

One-time programmable memories using junction diodes as program selectors

ActiveUS20120044740A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. The OTP device has an OTP element coupled to the diode. The OTP device can be used to construct a two-dimensional OTP memory with the N terminals of the diodes in a row connected as a wordline and the OTP elements in a column connected as a bitline. By applying a high voltage between a selected bitline and a selected wordline to turn on a diode in a selected cell for suitable duration of time, a current flows through an OTP element in series with the program selector may change the resistance state. The cell data in the OTP memory can also be read by turning on a selected wordline and to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

Lighting device

ActiveUS20050258436A1Improve in-plane uniformitySmall and lightPlanar light sourcesMechanical apparatusEffect lightVoltage drop

An object of the invention is to provide a lighting device which can suppress luminance nonuniformity in a light emitting region when the lighting device has large area. A layer including a light emitting material is formed between a first electrode and a second electrode, and a third electrode is formed to connect to the first electrode through an opening formed in the second electrode and the layer including a light emitting material. An effect of voltage drop due to relatively high resistivity of the first electrode can be reduced by electrically connecting the third electrode to the first electrode through the opening.

Owner:SEMICON ENERGY LAB CO LTD

Resistive heaters and uses thereof

InactiveUS6919543B2Thermally matched wellAvoid bendingMolten spray coatingLinings repairBorideCarbide

A metallic resistive heater and a method of production are described. The resistive heater has a metallic component that is electrically conductive (i.e. has low resistivity) and an oxide, nitride, carbide, and or boride derivative of the metallic component that is electrically insulating (i.e., has high resistivity). The resistivity is controlled by controlling the amount of oxide, nitride, carbide, and boride formation during the deposition of the metallic component and the derivative.

Owner:REGAL WARE

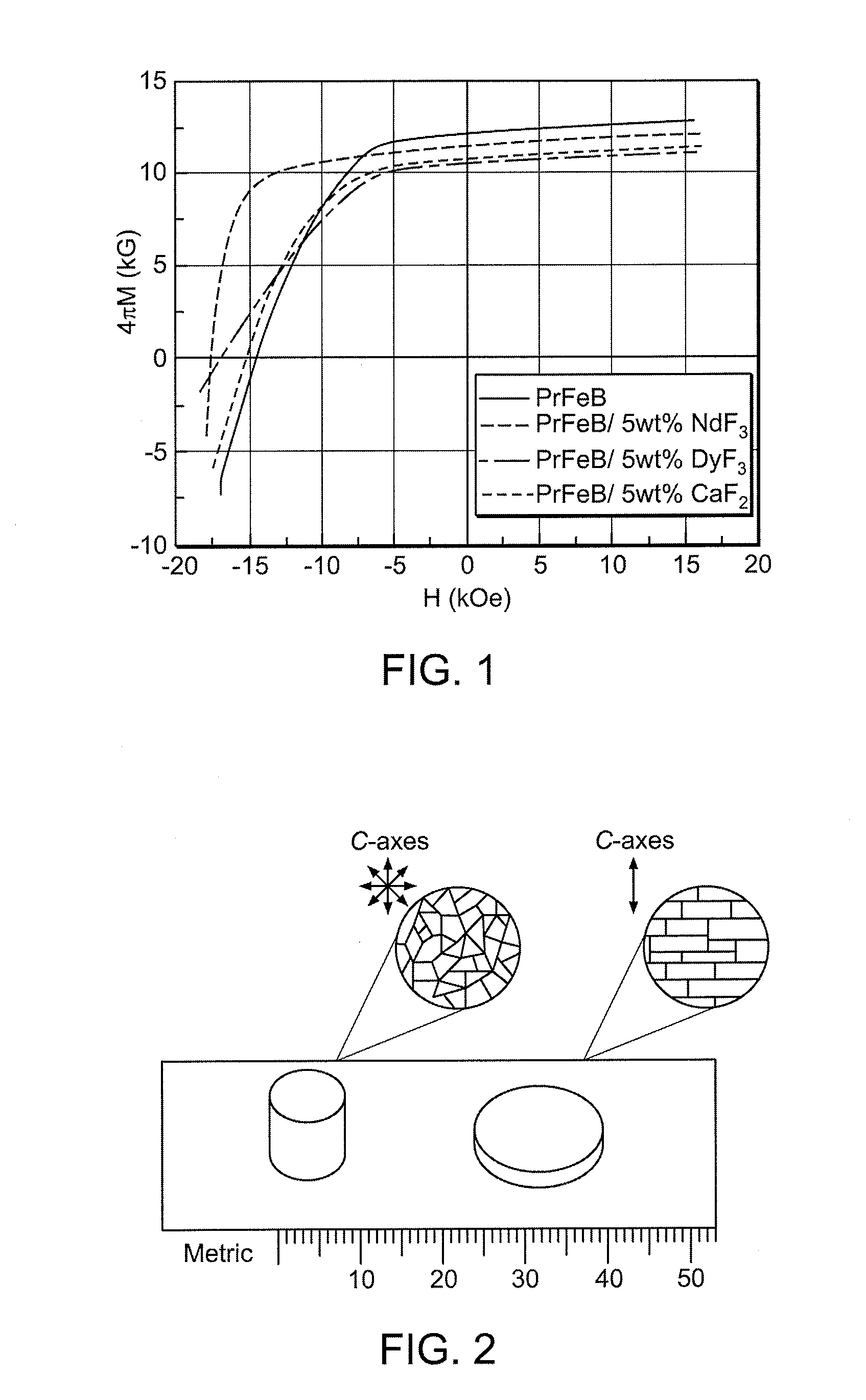

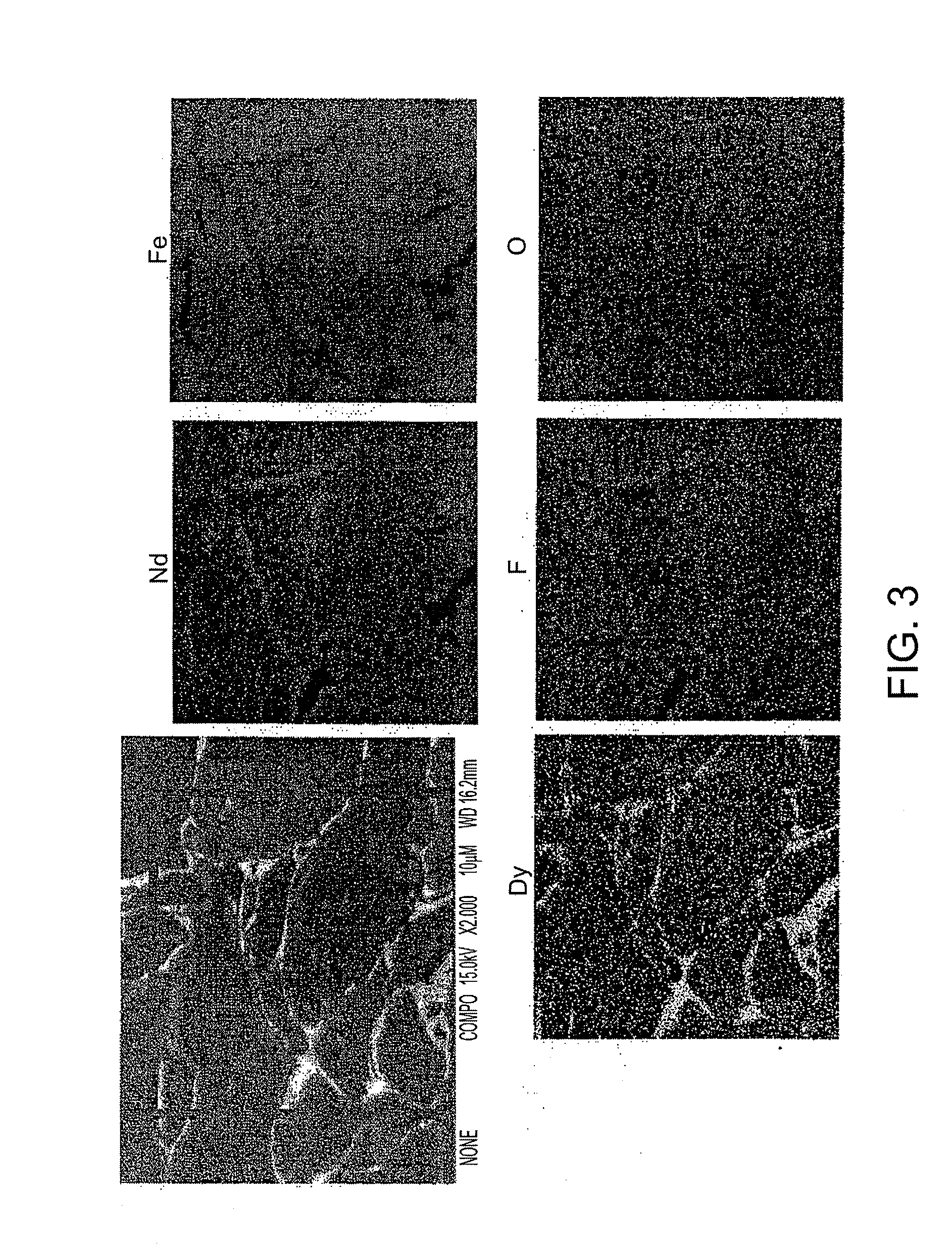

Rare Earth Composite Magnets with Increased Resistivity

InactiveUS20110057756A1Increased electrical resistivityReduce eddy current lossTransportation and packagingMetal-working apparatusDielectricHigh resistivity

Dielectric rare earth fluorides are blended with rare earth magnet powders to produce high-resistivity fluoride composite rare earth magnets.

Owner:ELECTRON ENERGY CORP +1

Touch sensor with non-uniform resistive band

InactiveUS7265686B2Maximizing the effective touch regionReduce errorsElectronic switchingInput/output processes for data processingHigh resistivityLinearity

A touch sensors with improved topological equivalence between an equipotential space and a Cartesian space to which the equipotential space will be mapped. The touch sensor comprises a substrate with a touch region, and a set of electrodes that are electrically coupled to the touch region. The touch sensor further comprises a plurality of resistive band segments that frames the touch region. The electrodes are located between the resistive band segments. Each resistive band segment has a resistivity that is intermediate between the resistivity of the electrodes and the resistivity of the touch region, thereby providing a transition between the low resistivity electrodes and the high resistivity touch region, and improving the topological equivalence within the corners of the touch region. At least one of the band segments has a non-uniform linear resistance to provide further improvement to the topological equivalence.

Owner:ELO TOUCH SOLUTIONS INC

Semiconductor device and method for manufacturing the same

InactiveUS20050142705A1High regionImprove uniformityTransistorSolid-state devicesEngineeringHigh resistivity

Owner:SEMICON ENERGY LAB CO LTD

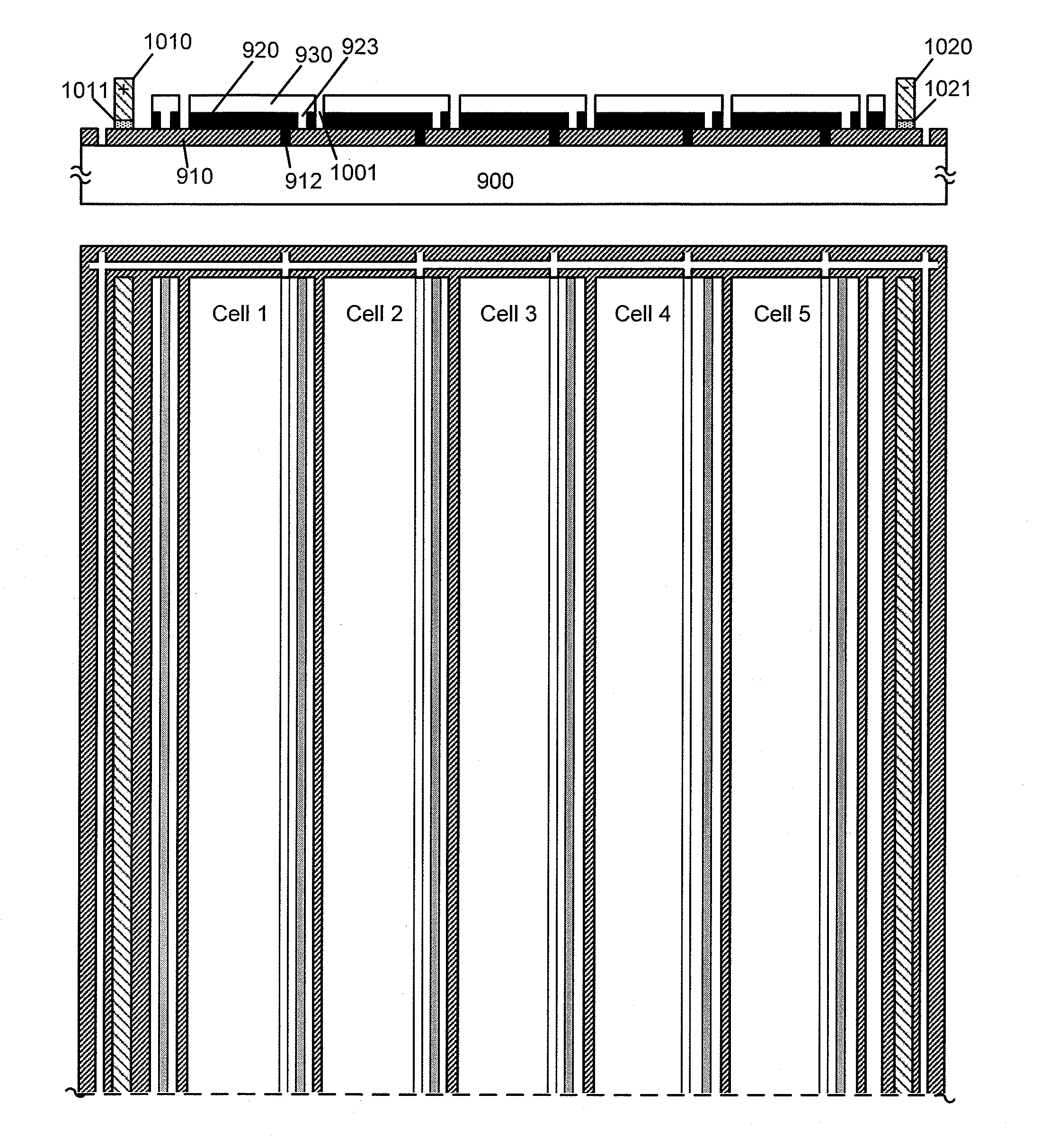

Single Junction CIGS/CIS Solar Module

InactiveUS20110259395A1Low costSimplified thin-film processPV power plantsFinal product manufactureIndiumEngineering

A high efficiency thin-film photovoltaic module is formed on a substrate. The photovoltaic module includes a plurality of stripe shaped photovoltaic cells electrically coupled to each other and physically disposed in parallel to the length one next to another across the width. Each cell includes a barrier material overlying the surface and a first electrode overlying the barrier material. Each cell further includes an absorber formed overlying the first electrode. The absorber includes a copper gallium indium diselenide compound material characterized by an energy band-gap of about 1 eV to 1.1 eV. Each cell additionally includes a buffer material overlying the absorber and a bi-layer zinc oxide material comprising a high resistivity transparent layer overlying the buffer material and a low resistivity transparent layer overlying the high resistivity transparent layer.

Owner:CM MFG

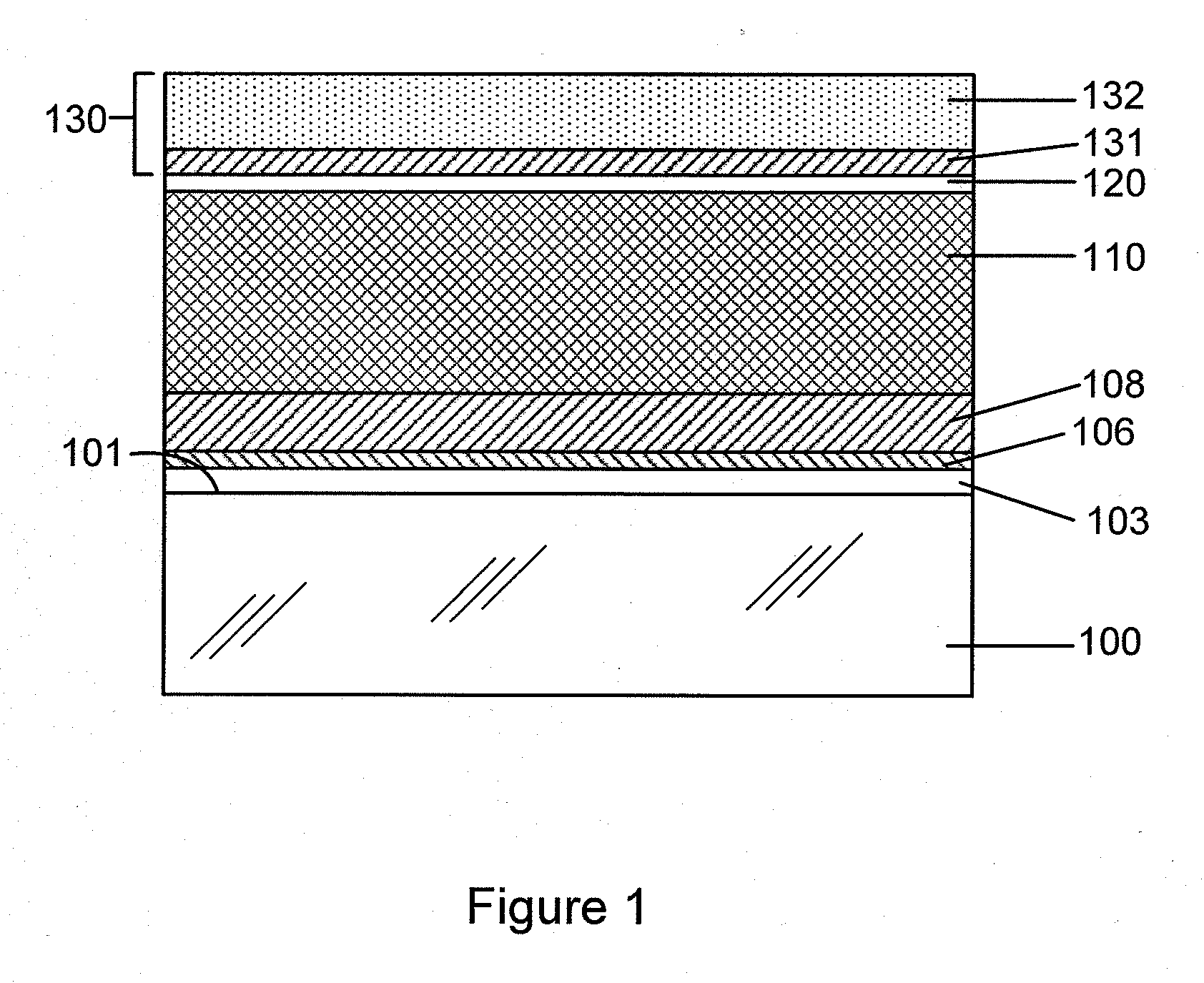

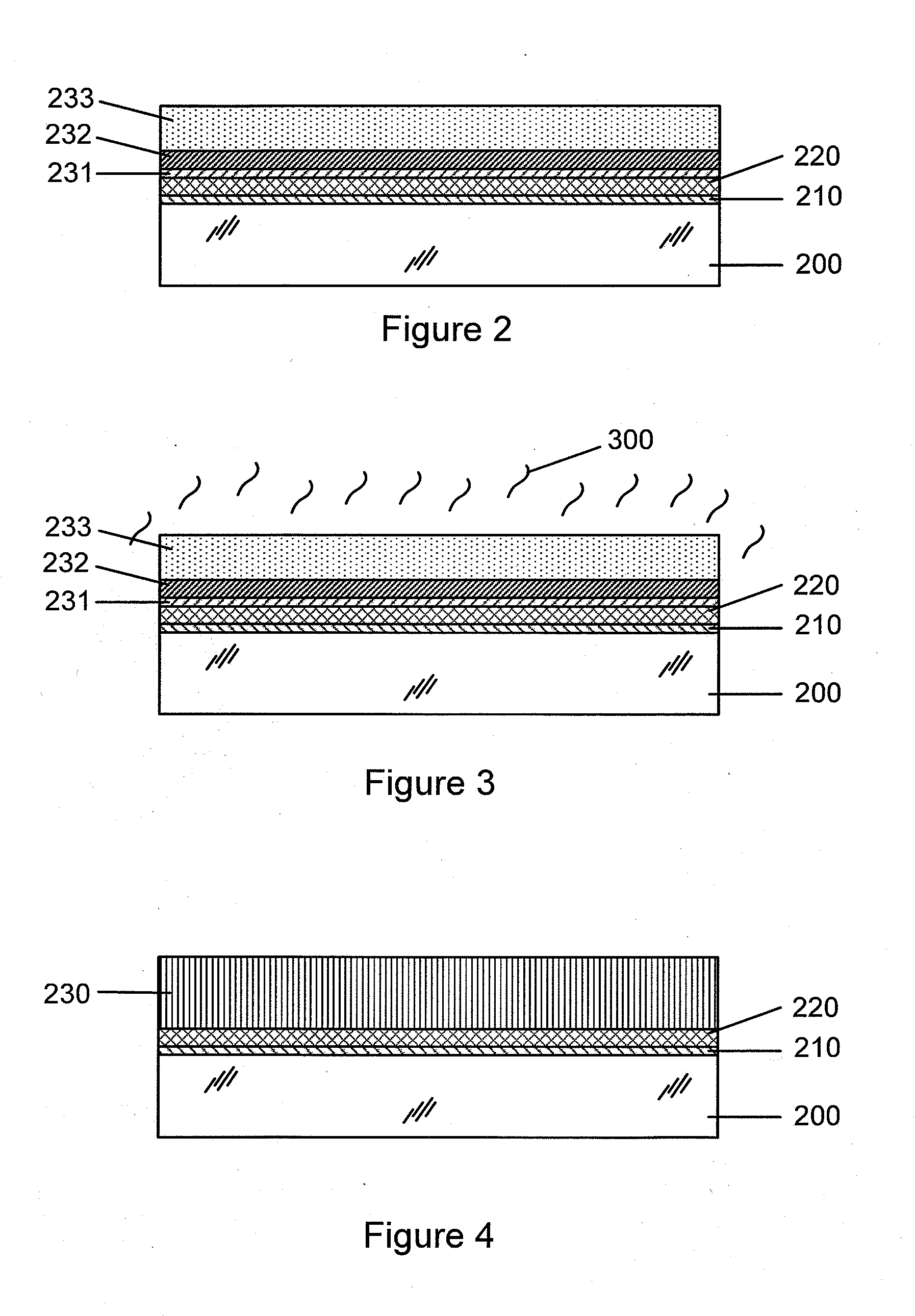

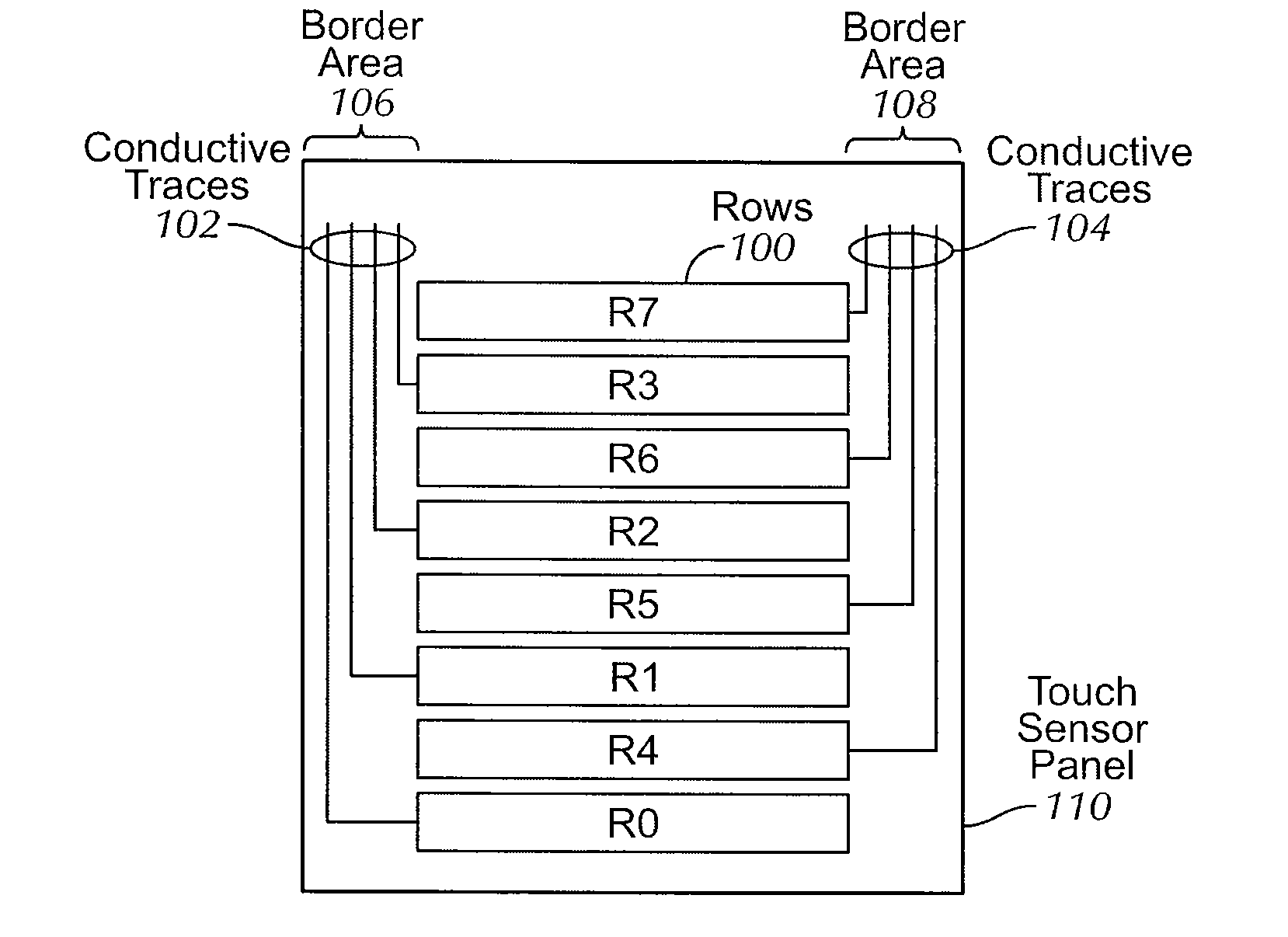

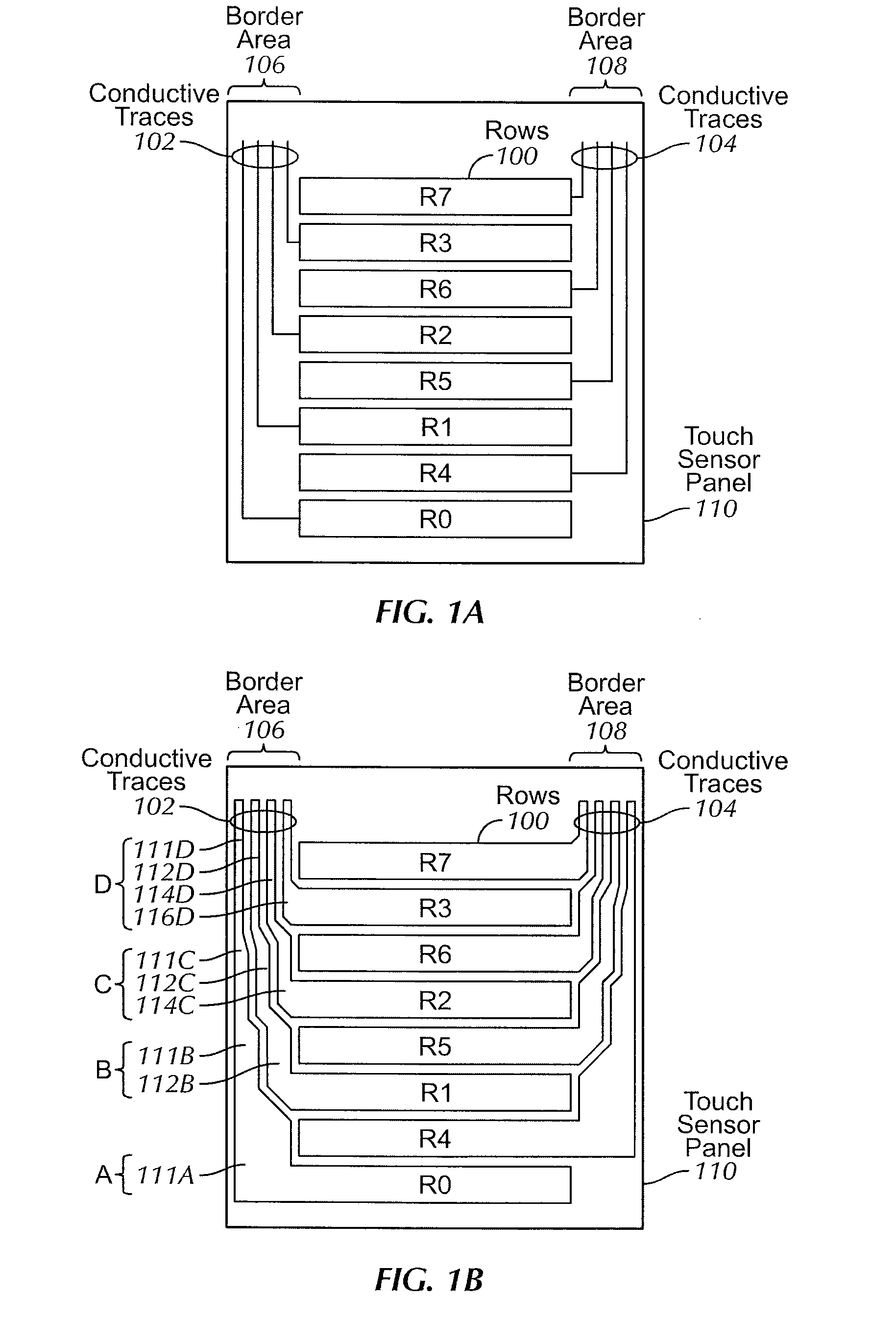

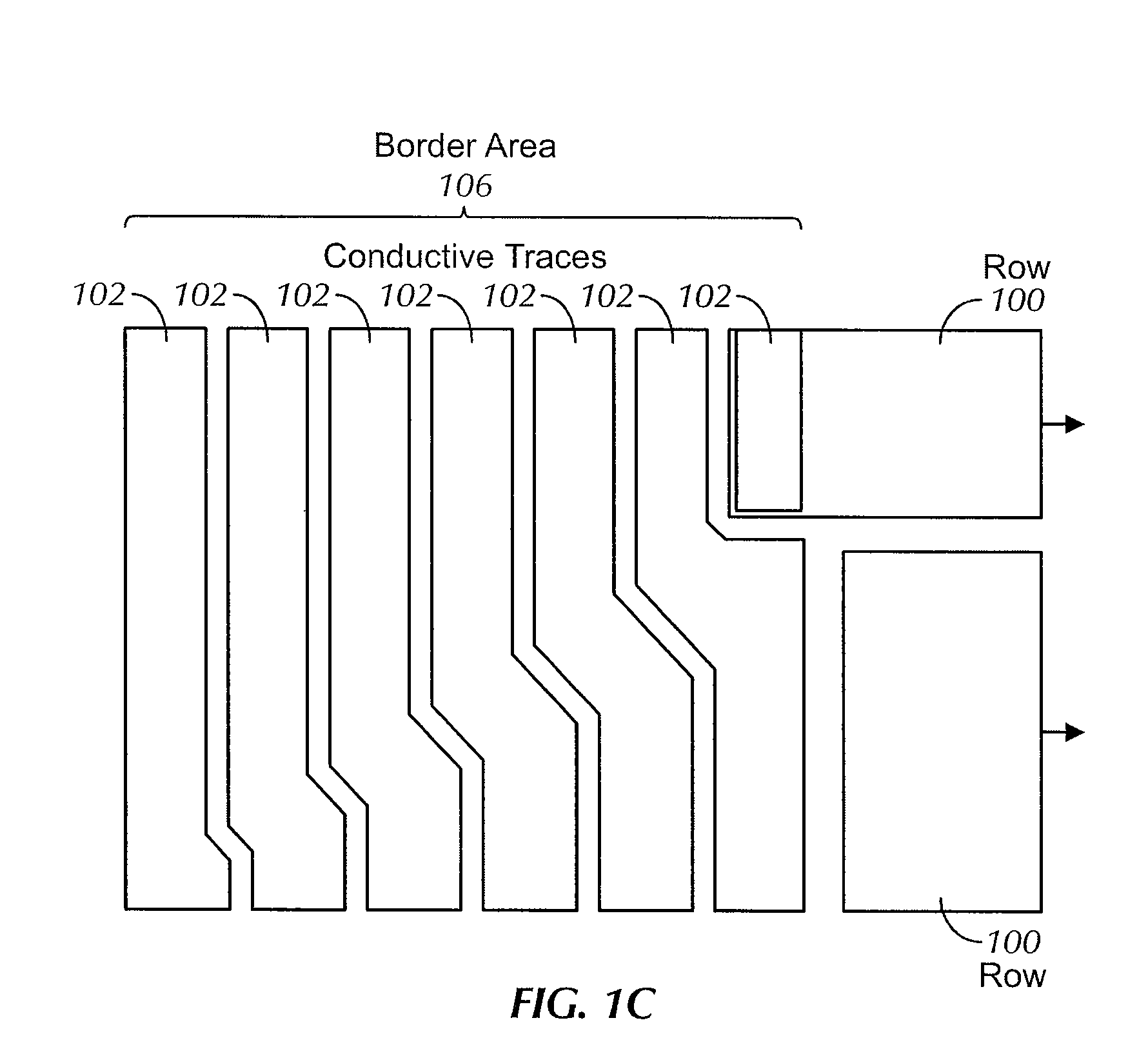

High Resistivity Metal Fan Out

ActiveUS20090303189A1Improve reliabilityGood rejectionTransparent dielectricsConductive pattern reinforcementManufacturing cost reductionHigh resistivity

The formation of metal traces in the border areas of a touch sensor panel to provide improved reliability, better noise rejection, and lower manufacturing costs is disclosed. The metal traces can be coupled to rows on the touch sensor panel in an interleaved manner, so that any two successive rows can be coupled to metal traces in border areas on opposite sides of the touch sensor panel. In addition, by utilizing the full width available in the border areas in some embodiments, the metal traces can be formed from higher resistivity metal, which can reduce manufacturing costs and improve trace reliability. The wider traces can also provide better noise immunity from noise sources such as an LCD by providing a larger fixed-potential surface area and by more effectively coupling the drive lines to the fixed potential.

Owner:APPLE INC