Patents

Literature

1562results about "Conductive pattern reinforcement" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

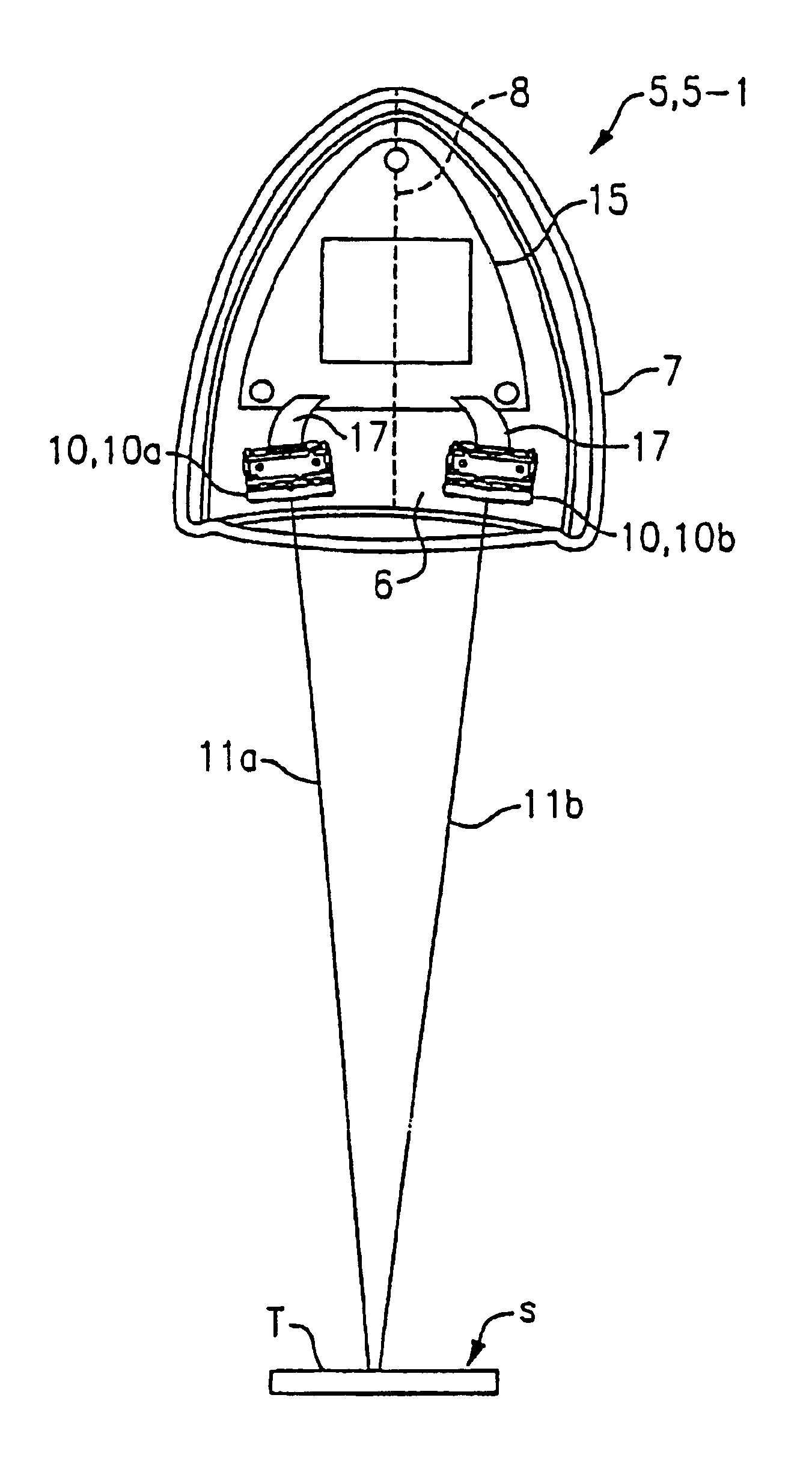

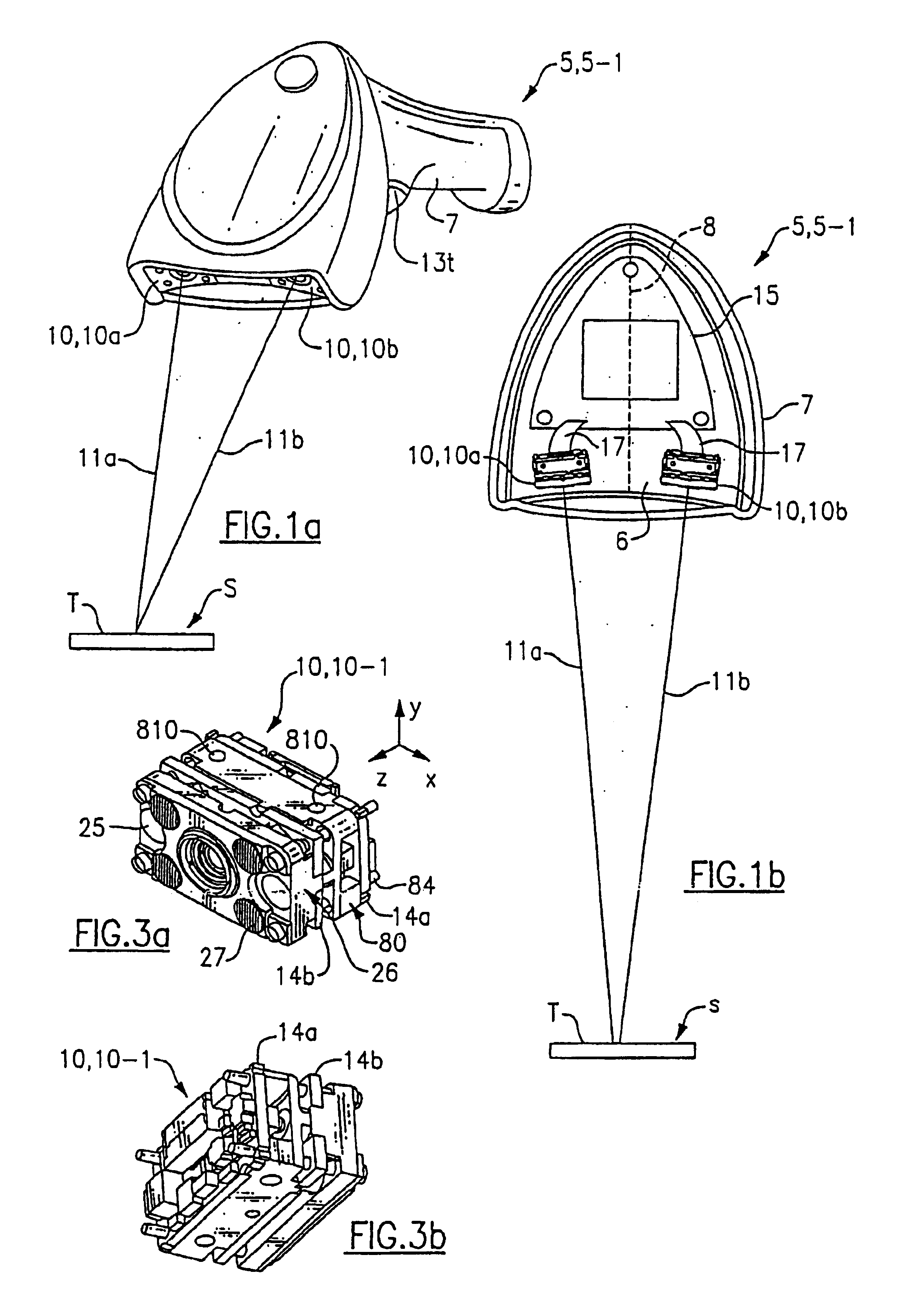

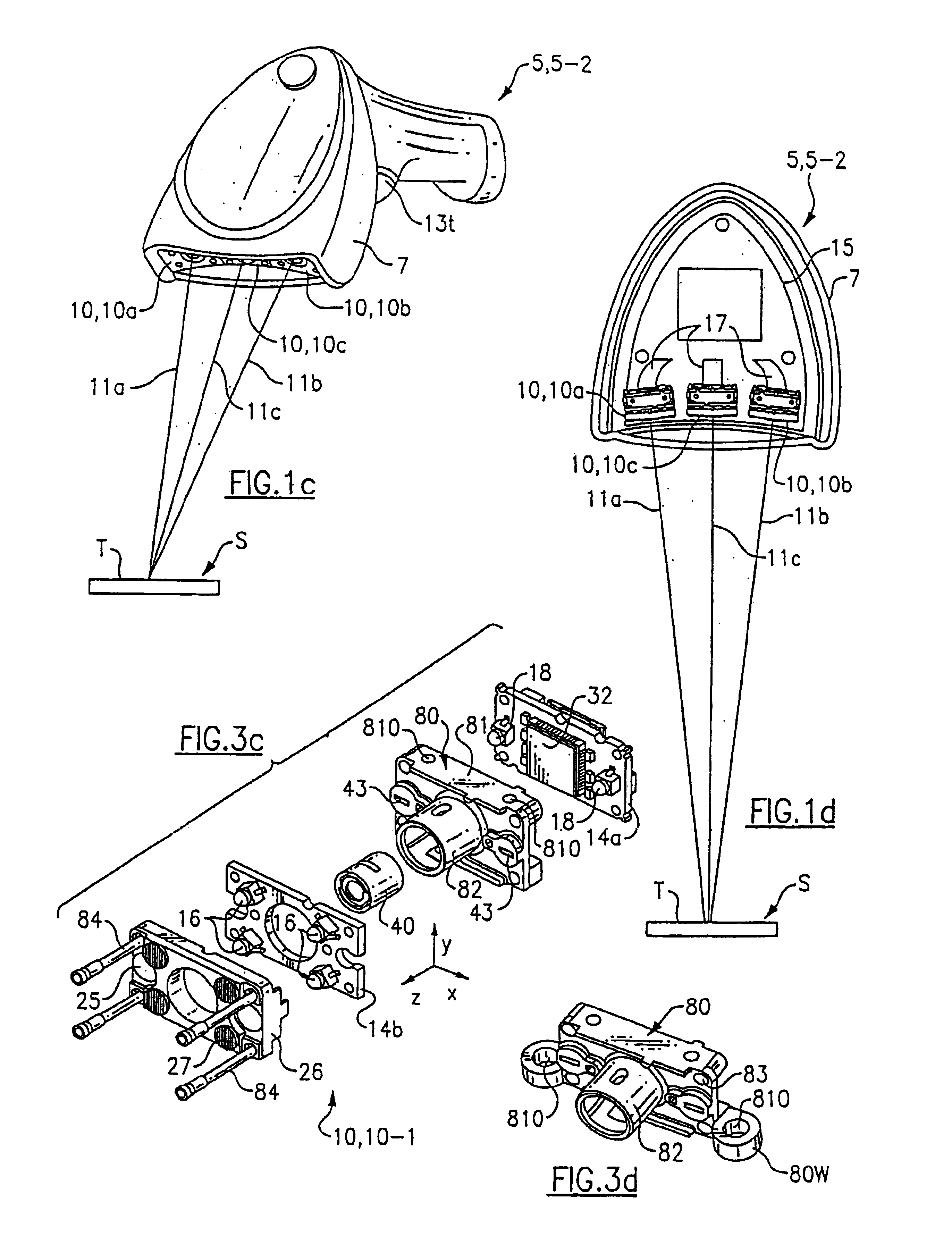

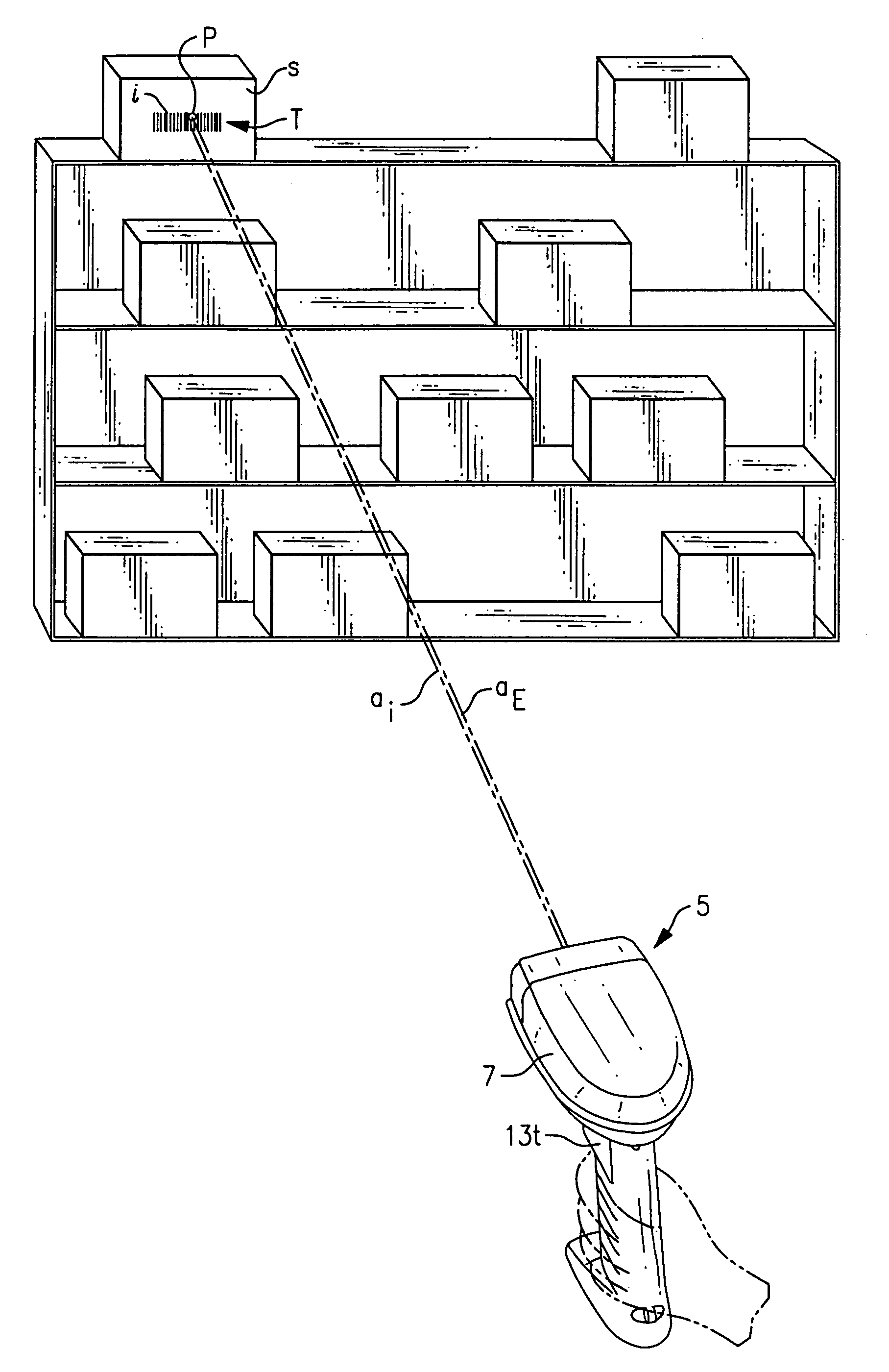

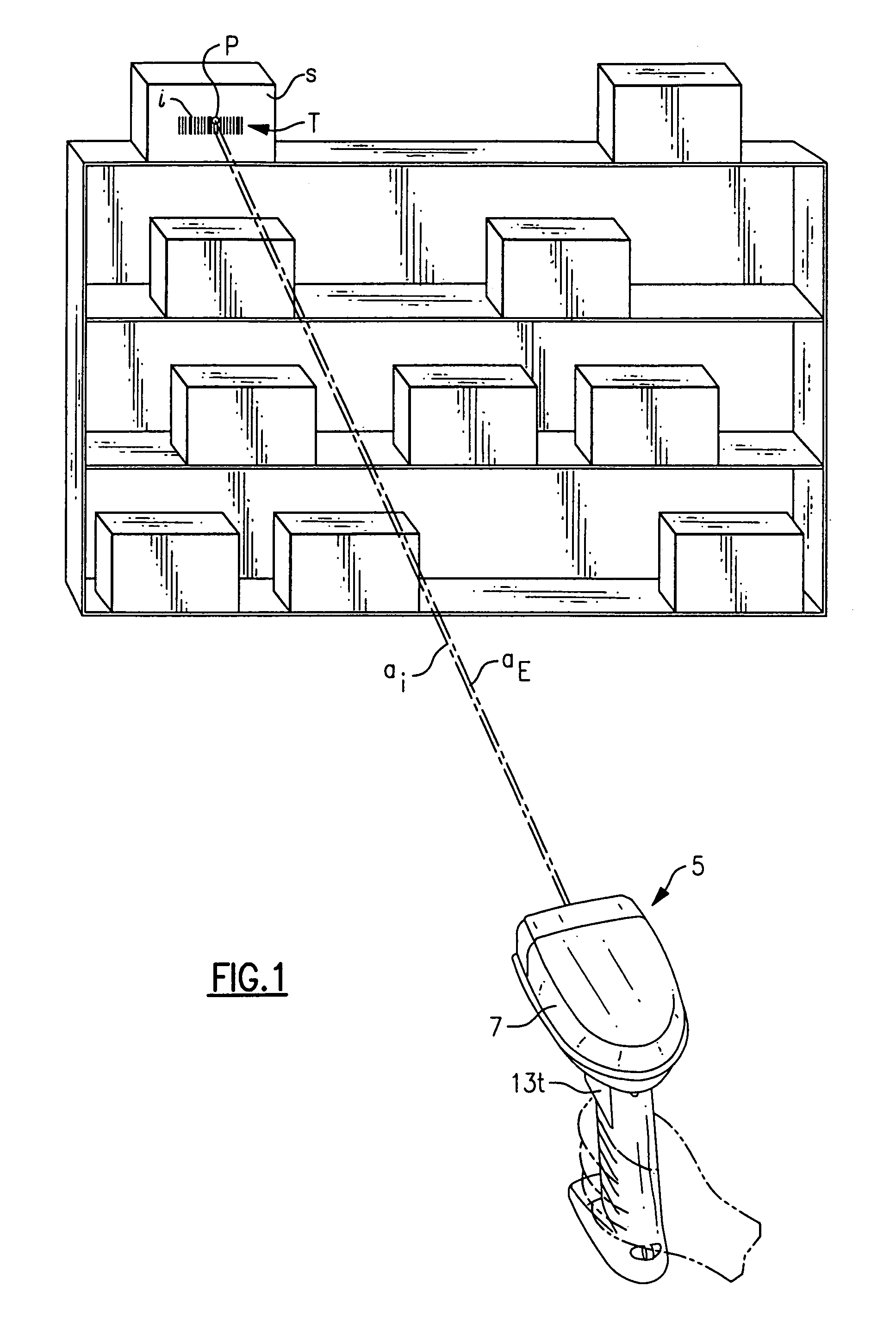

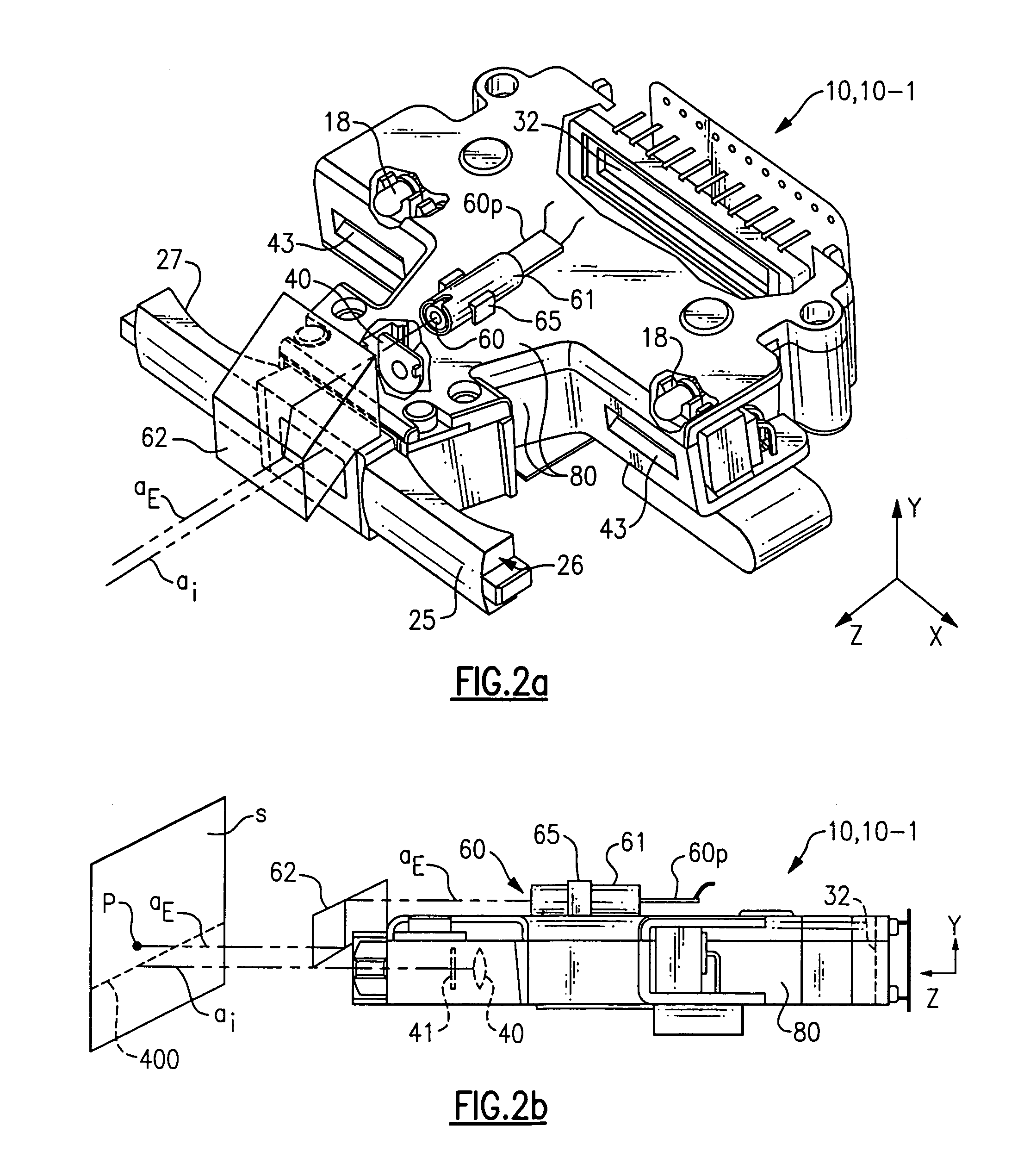

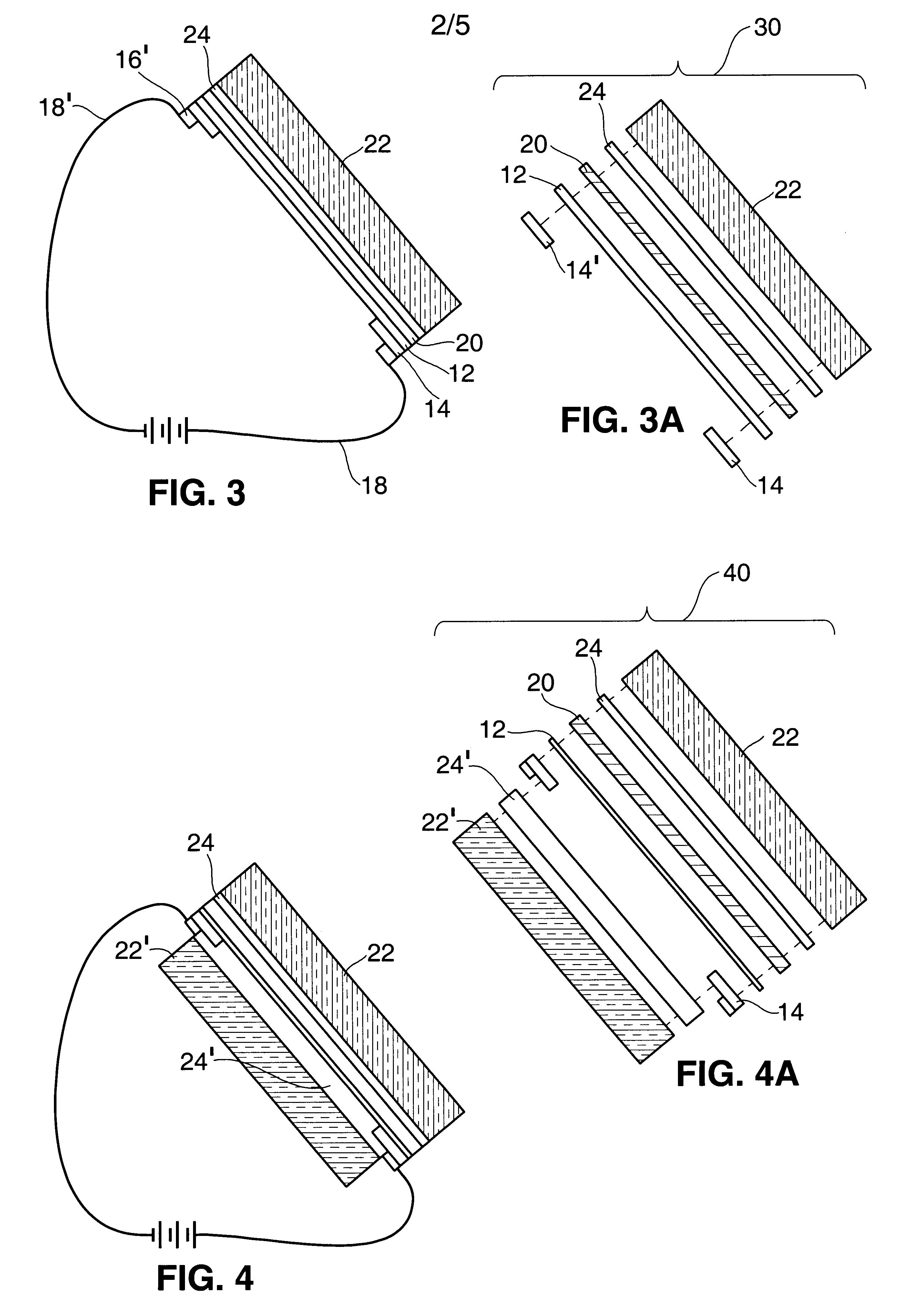

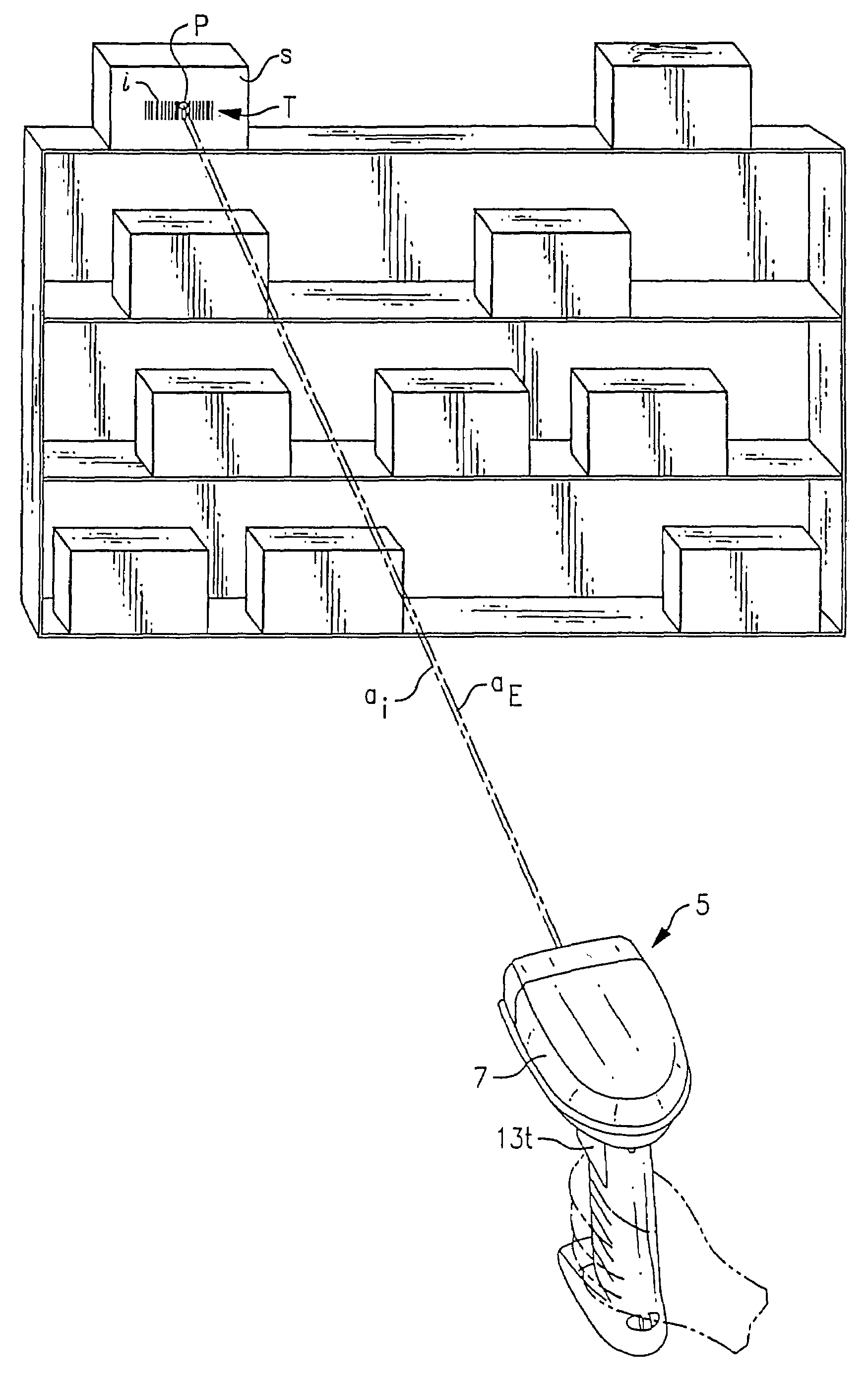

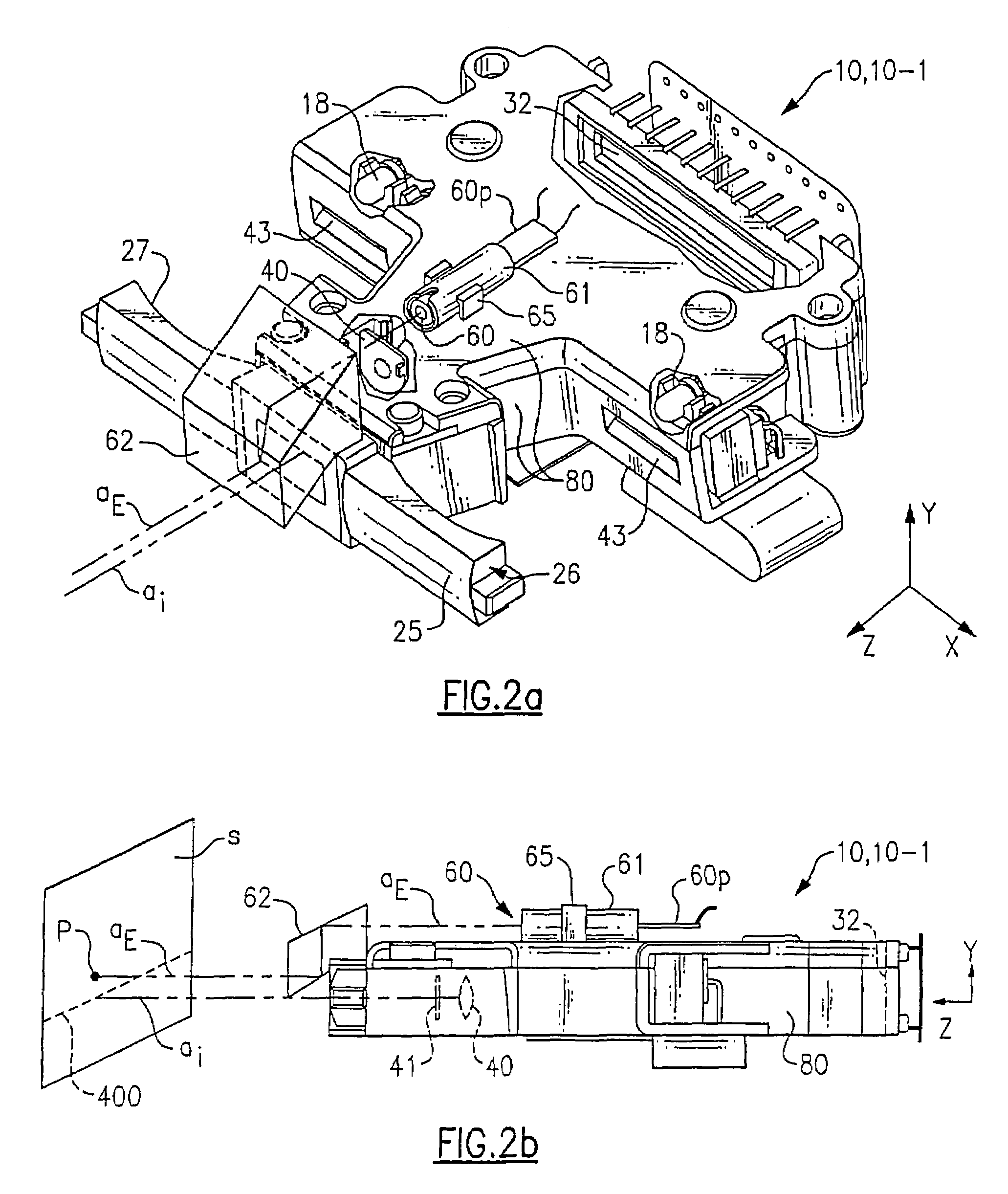

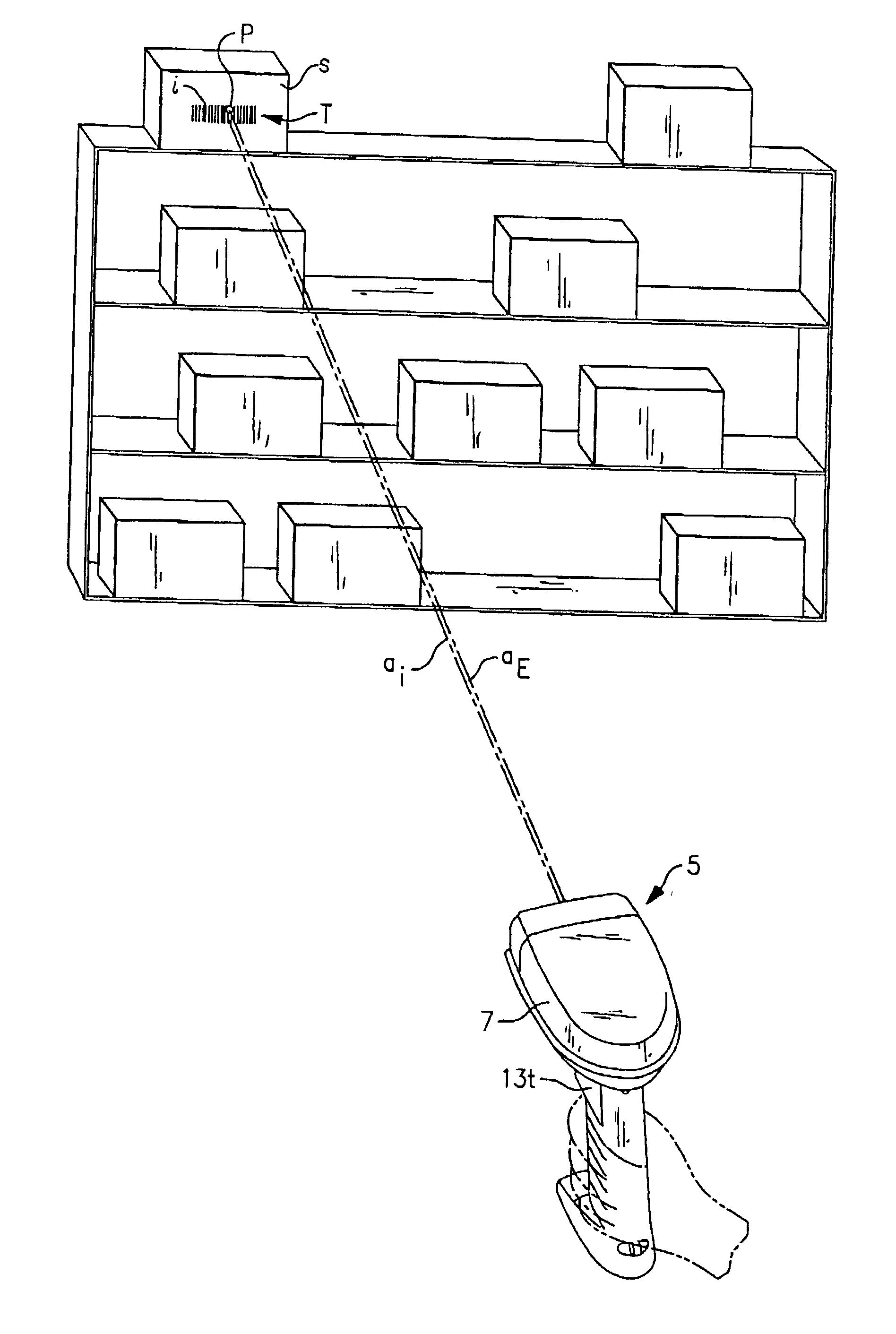

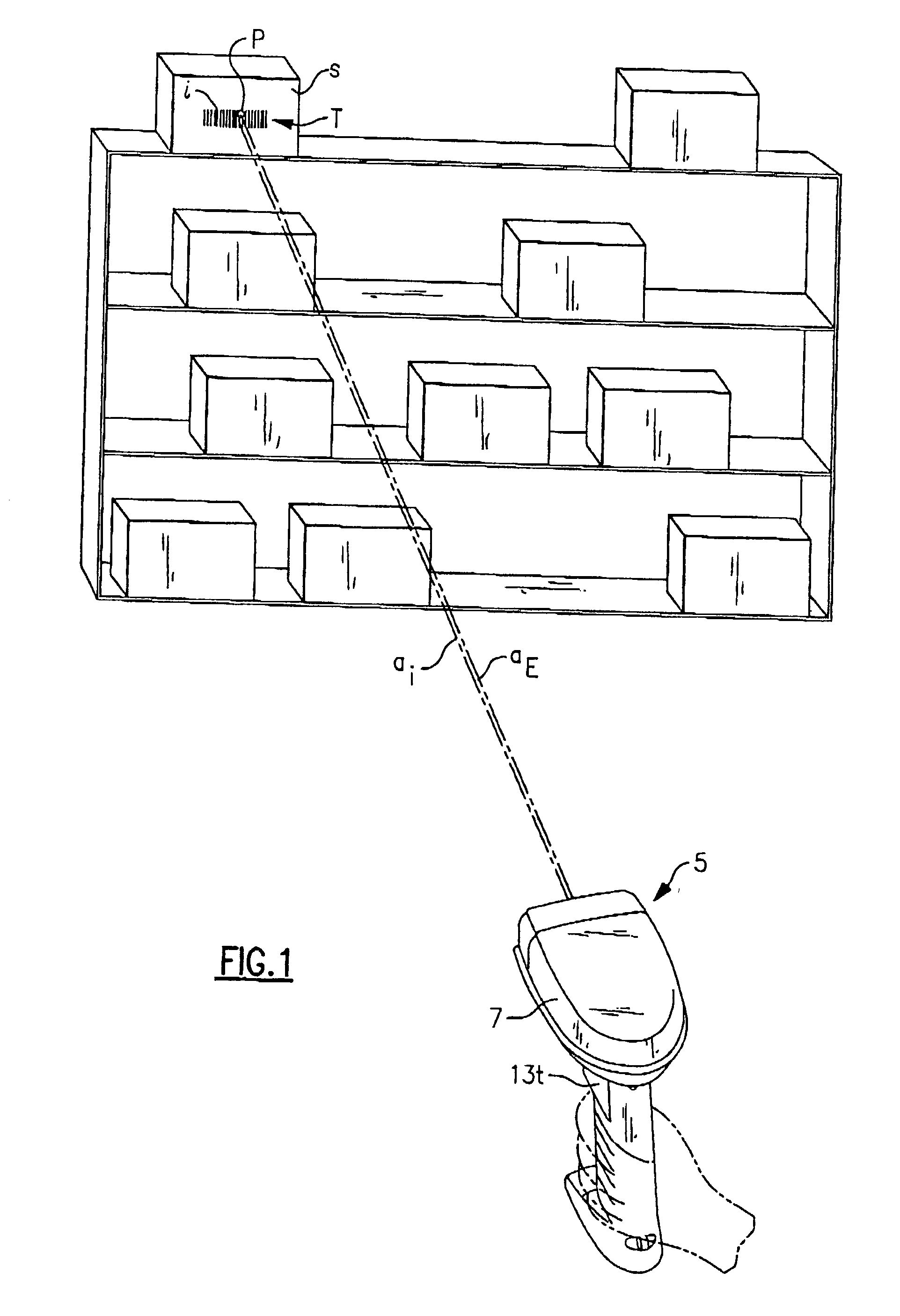

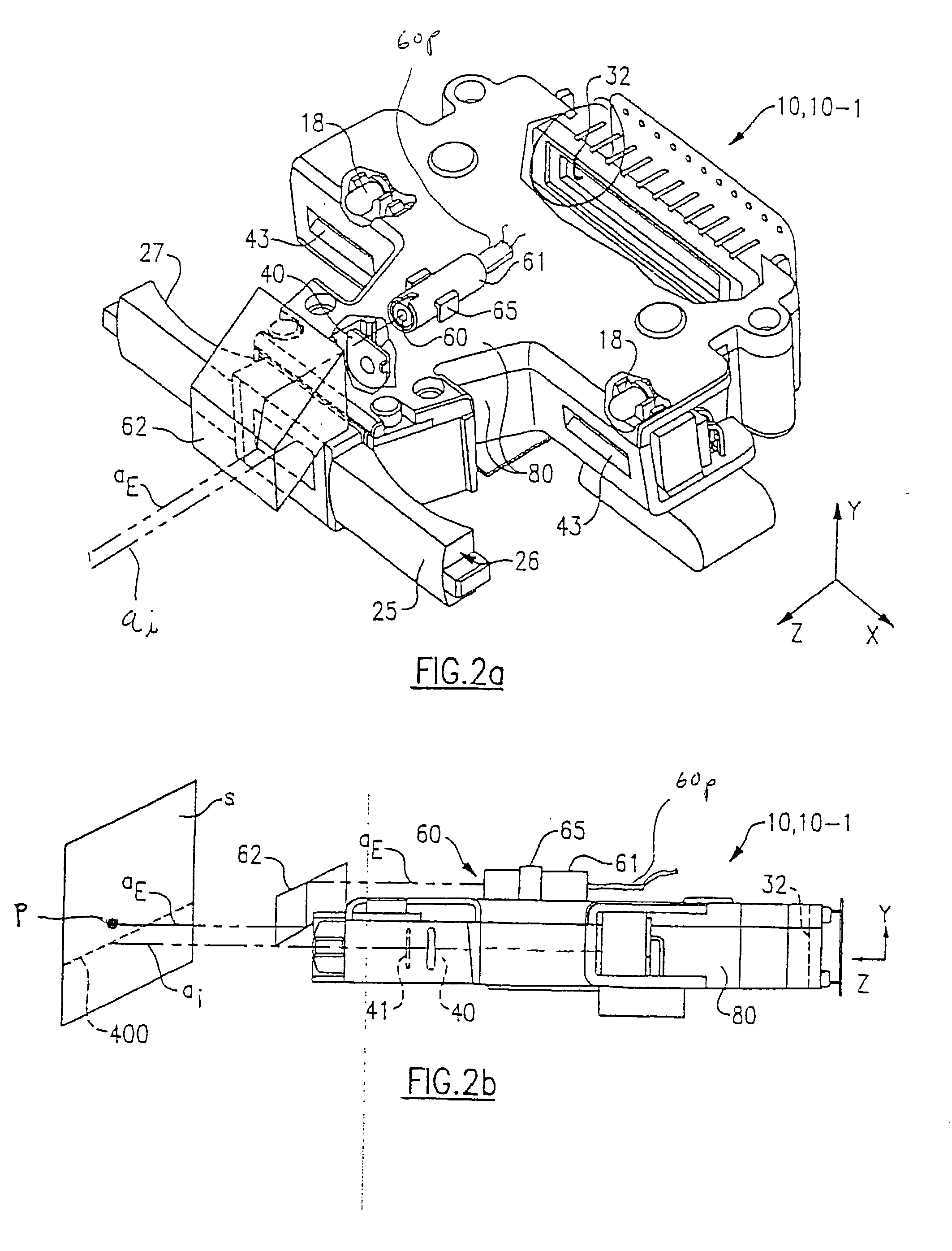

Optical reader having a plurality of imaging modules

InactiveUS7219843B2Easy to combineAdd depthPrinted circuit aspectsVisual representatino by photographic printingFocal positionImaging data

The invention is an optical reader having a plurality of image sensors. Each image sensor of a plural image sensor optical reader can be disposed on an imaging module that can include a light source. In one embodiment, a frame of image data captured via actuation of an image sensor of a first imaging module and actuation of illumination of a second imaging module is subjected to decoding. The various modules of a multiple imaging module reader can be adapted to have different best focus positions so that a field depth of the reader is improved.

Owner:HAND HELD PRODS

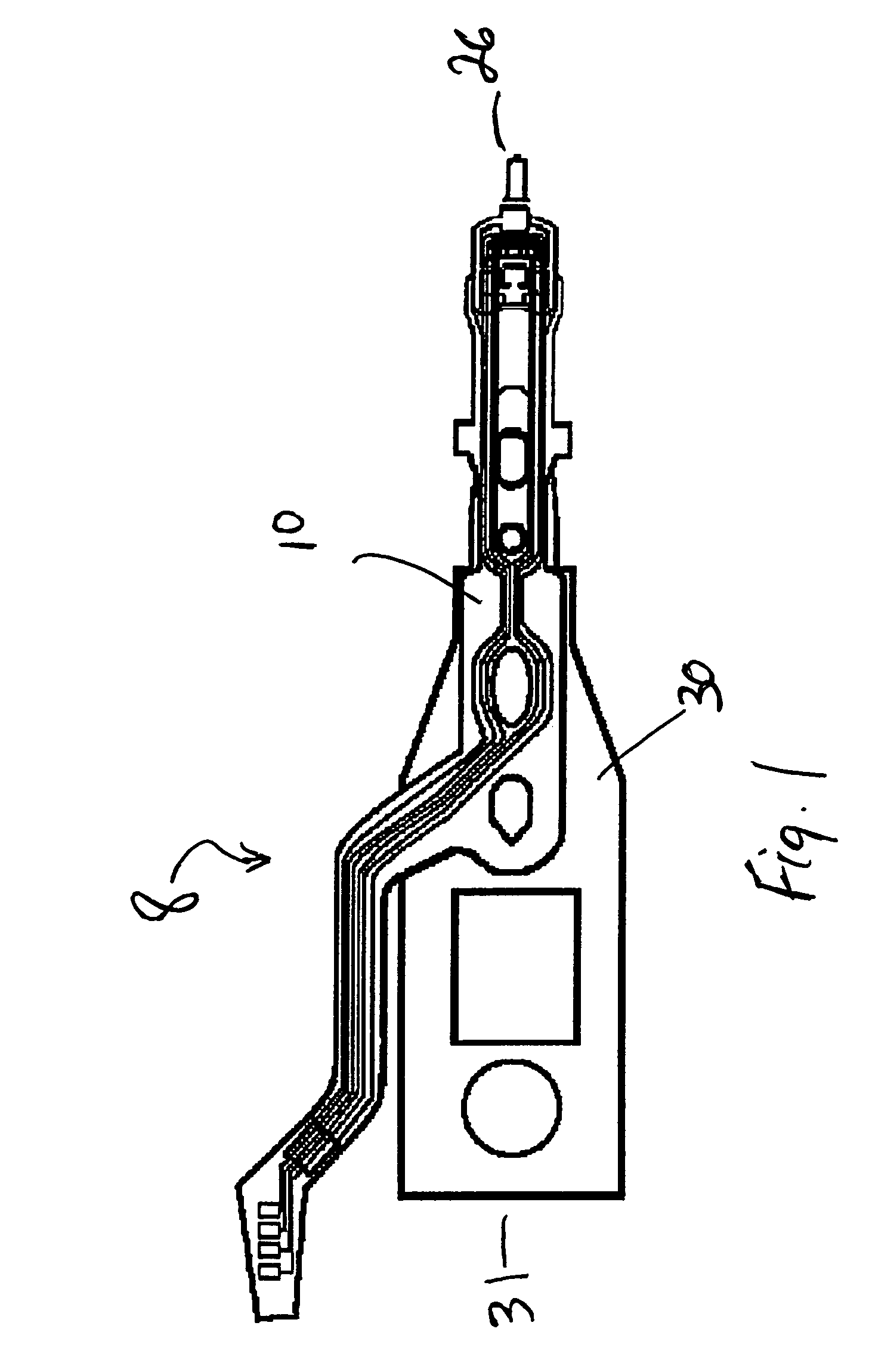

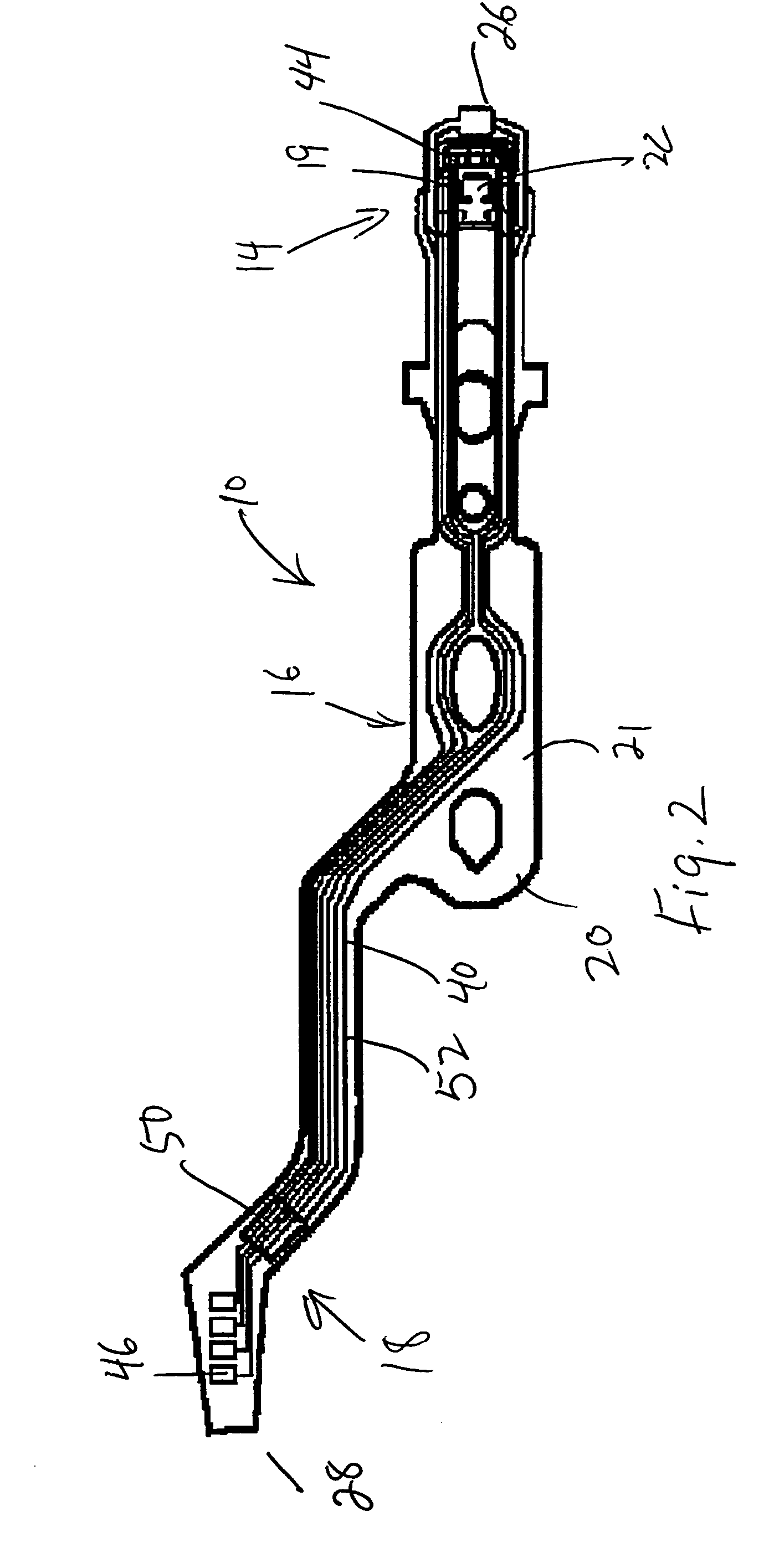

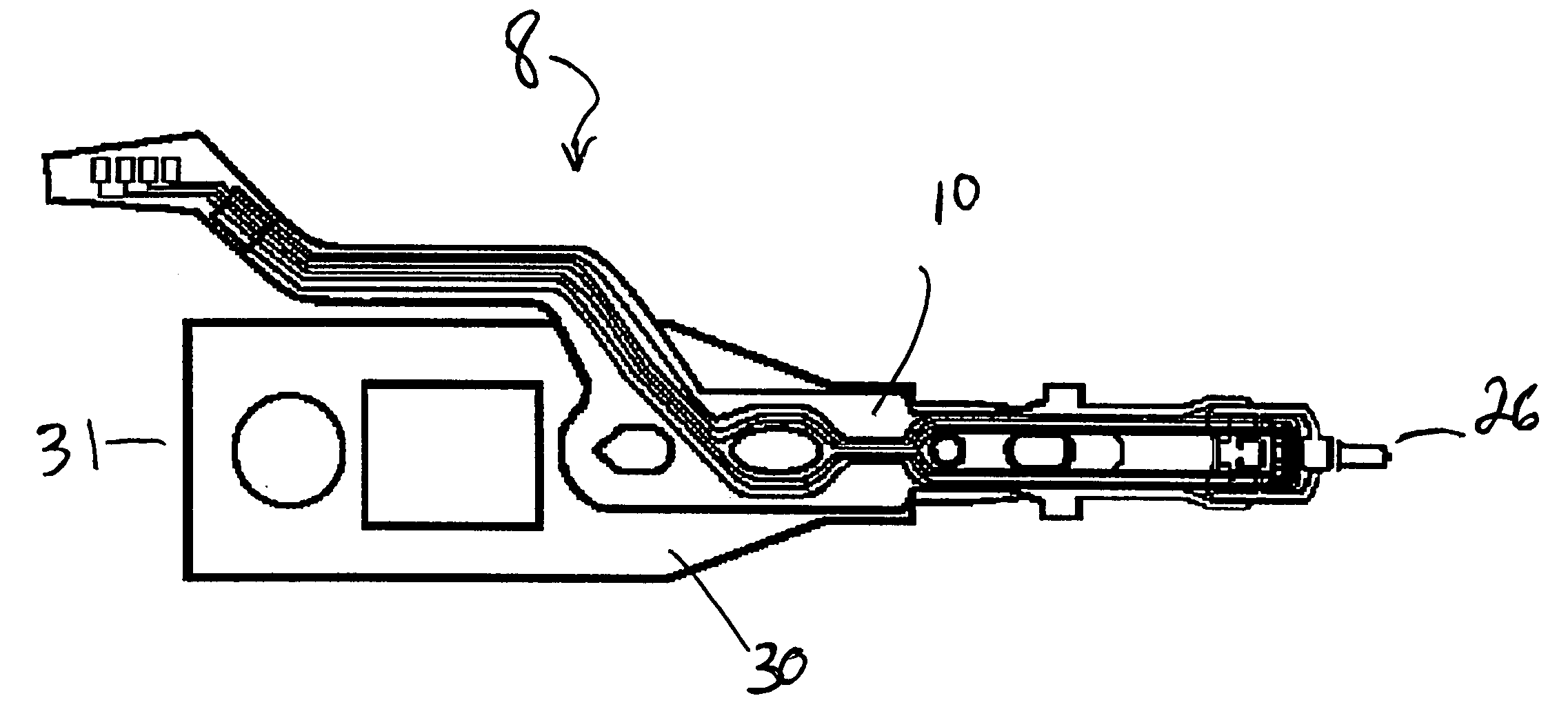

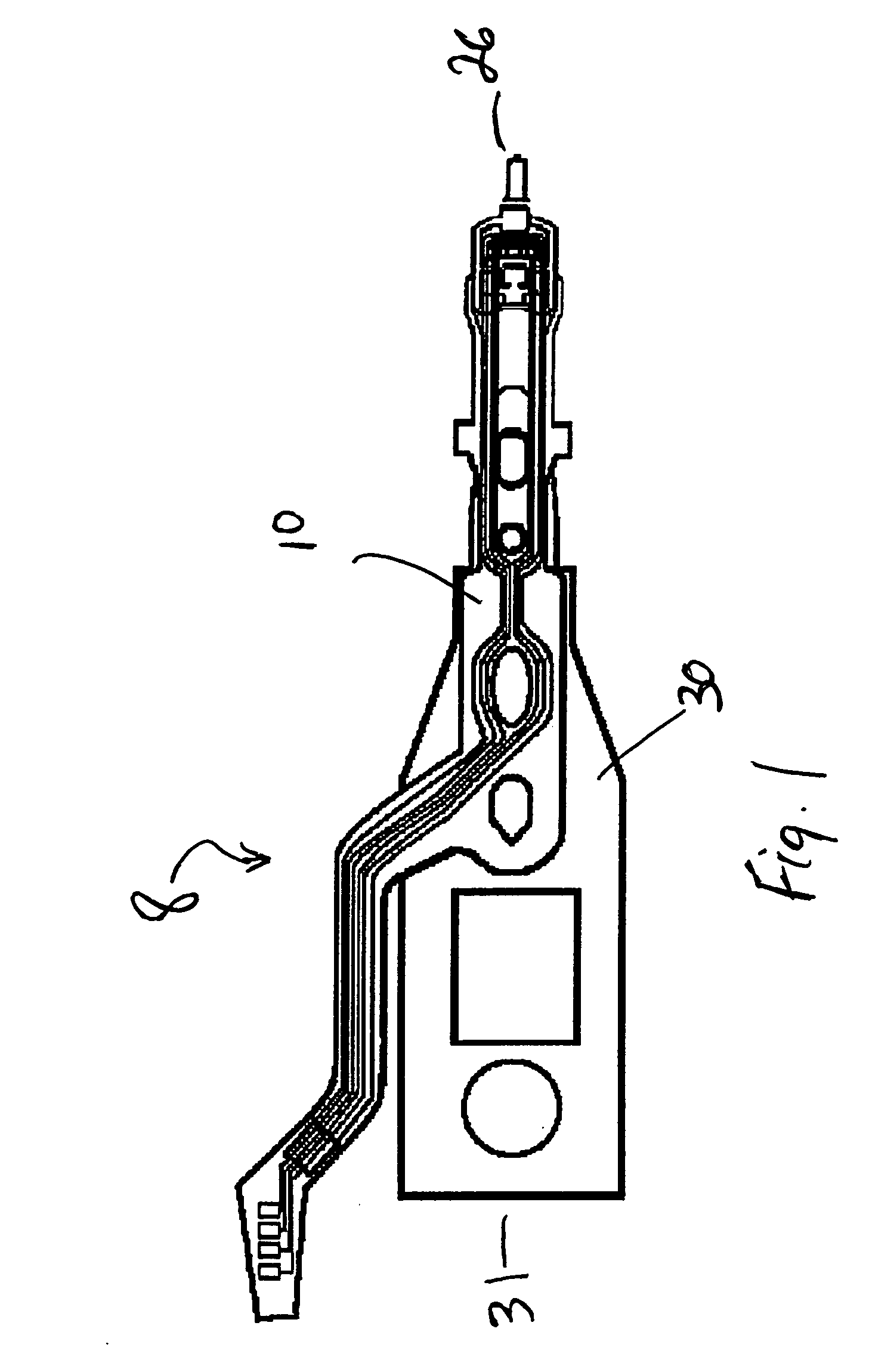

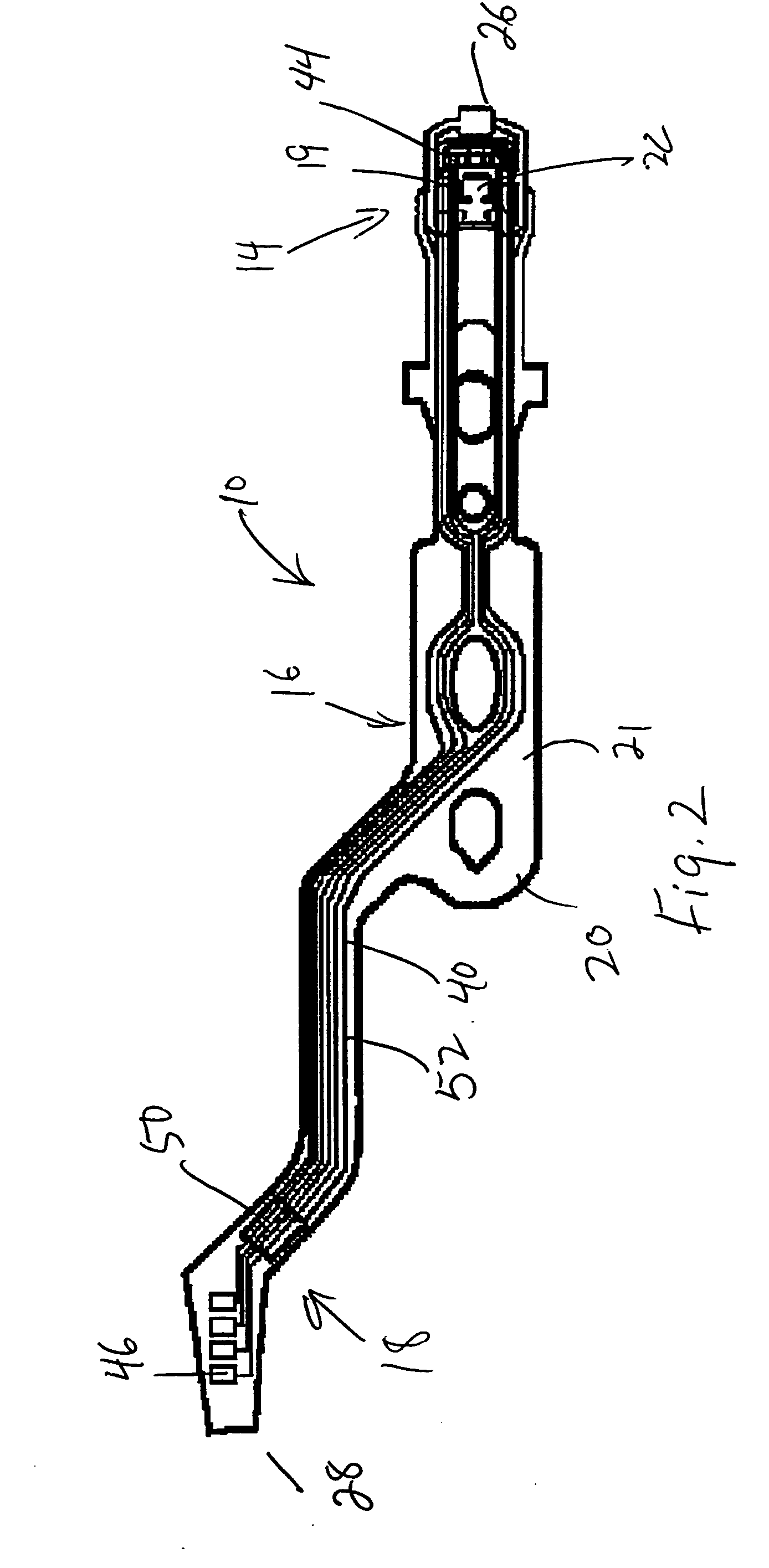

Long range optical reader

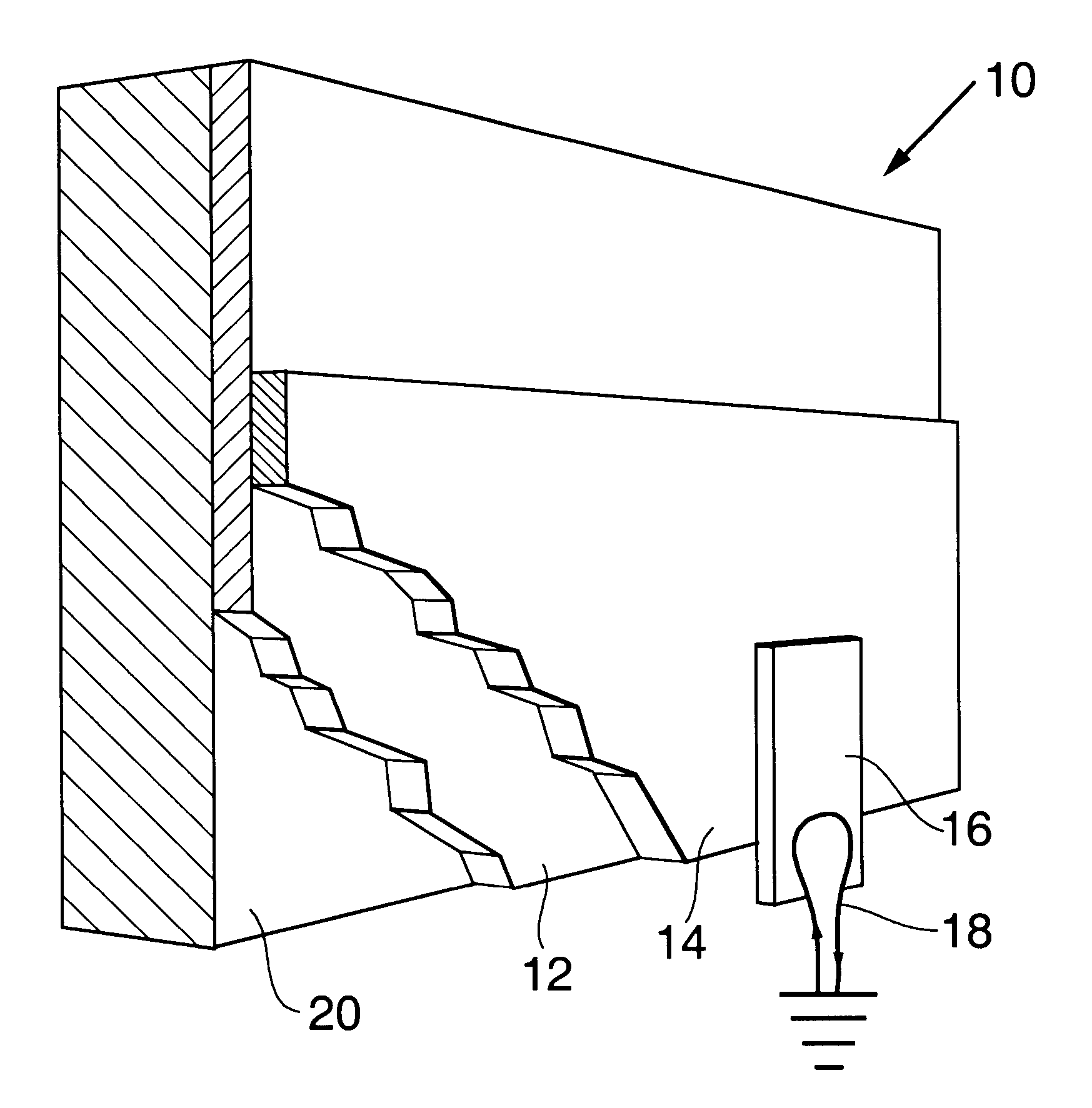

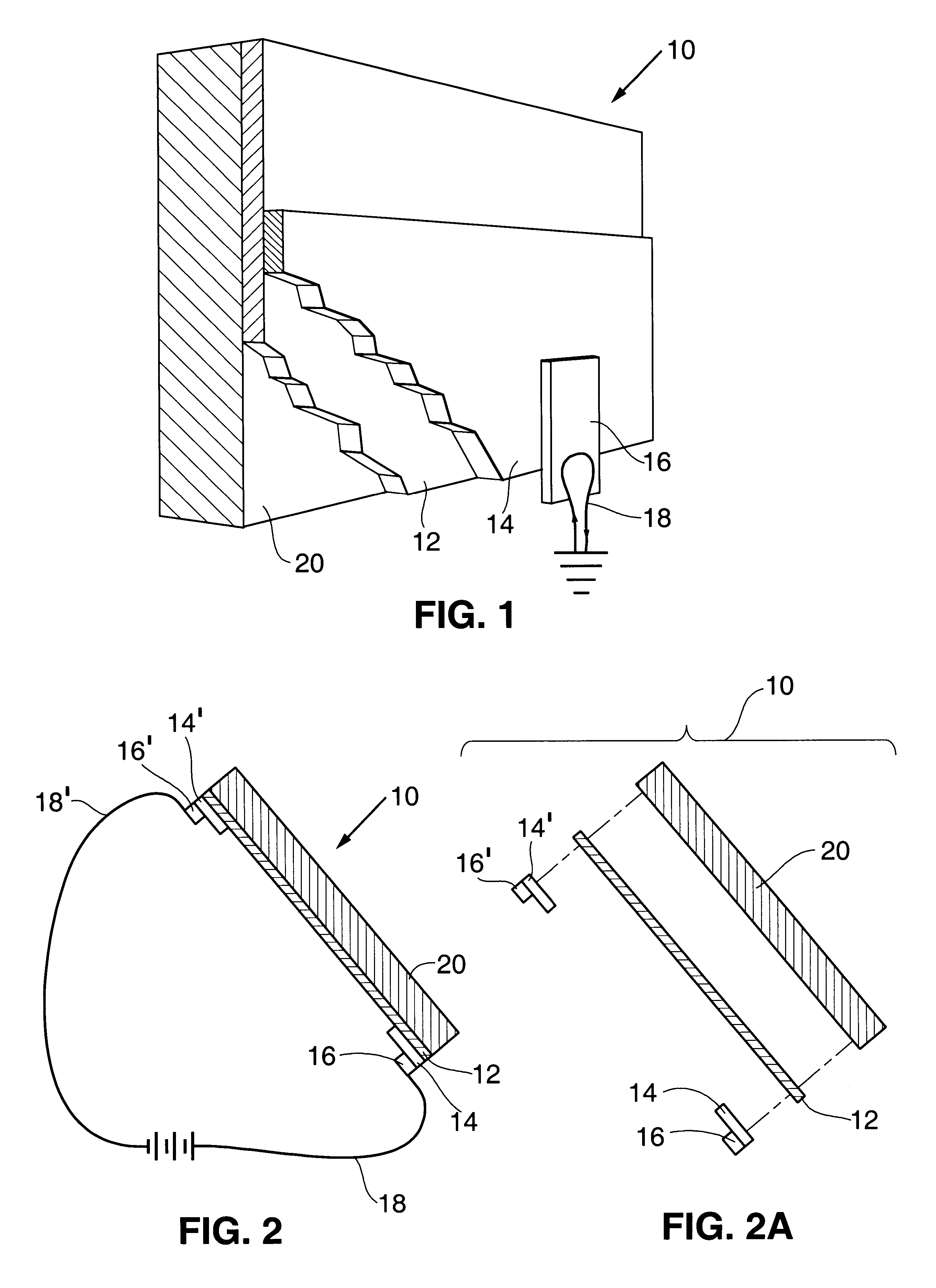

InactiveUS7055747B2Signal strength (signal to noise ratio) of a long range reader can be enhancedIncrease signal strengthPrinted circuit aspectsConductive pattern reinforcementHand heldLaser light

An indicia decoding device can have an image sensor and a laser diode assembly configured to project laser light onto a substrate. When a trigger signal is received by the indicia decoding device, the device can calculate a delay and enable the laser diode assembly if a delay threshold is satisfied. The indicia decoding device, in one embodiment, can include a hand held housing and an imaging module carrying the image sensor.

Owner:HAND HELD PRODS

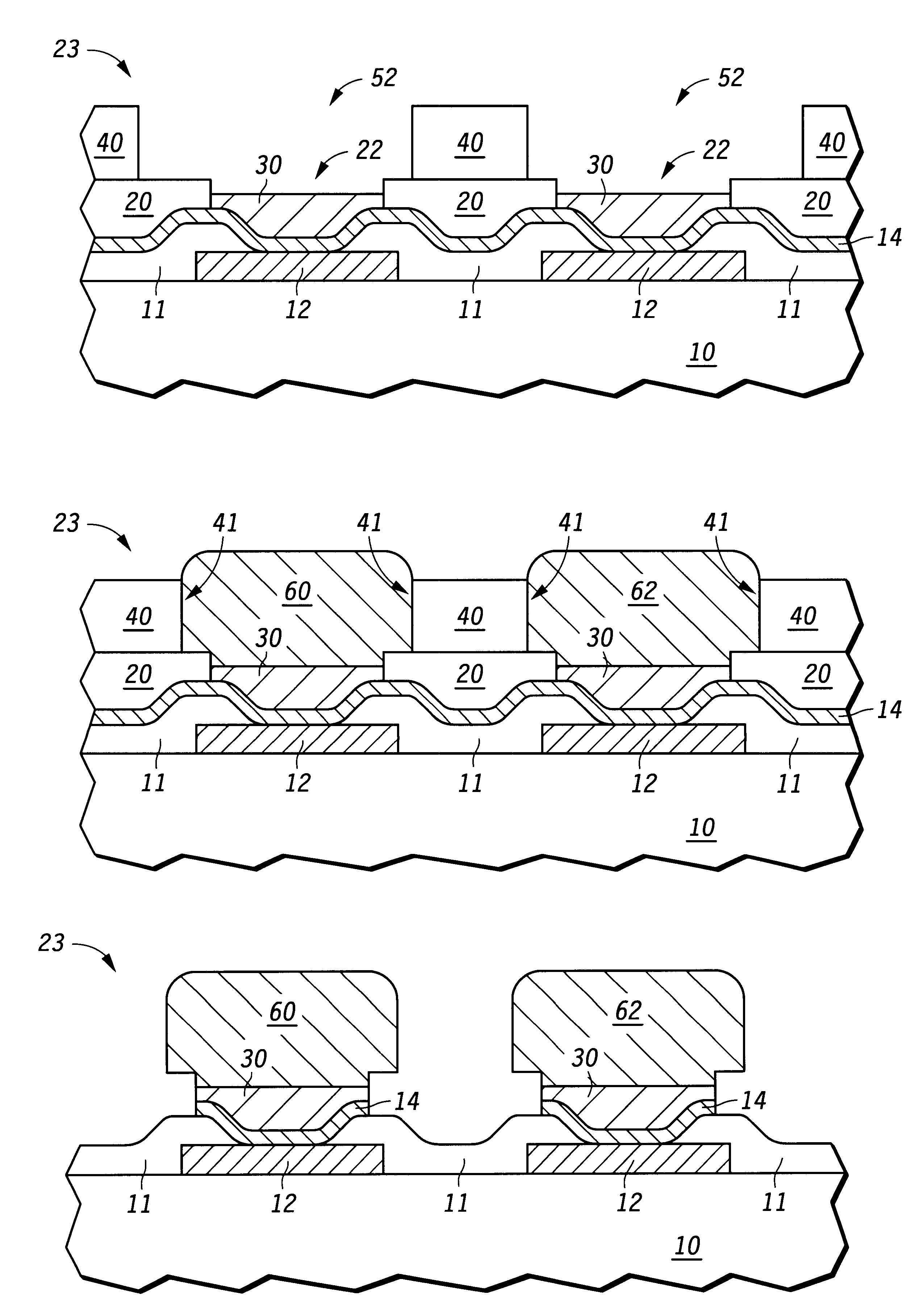

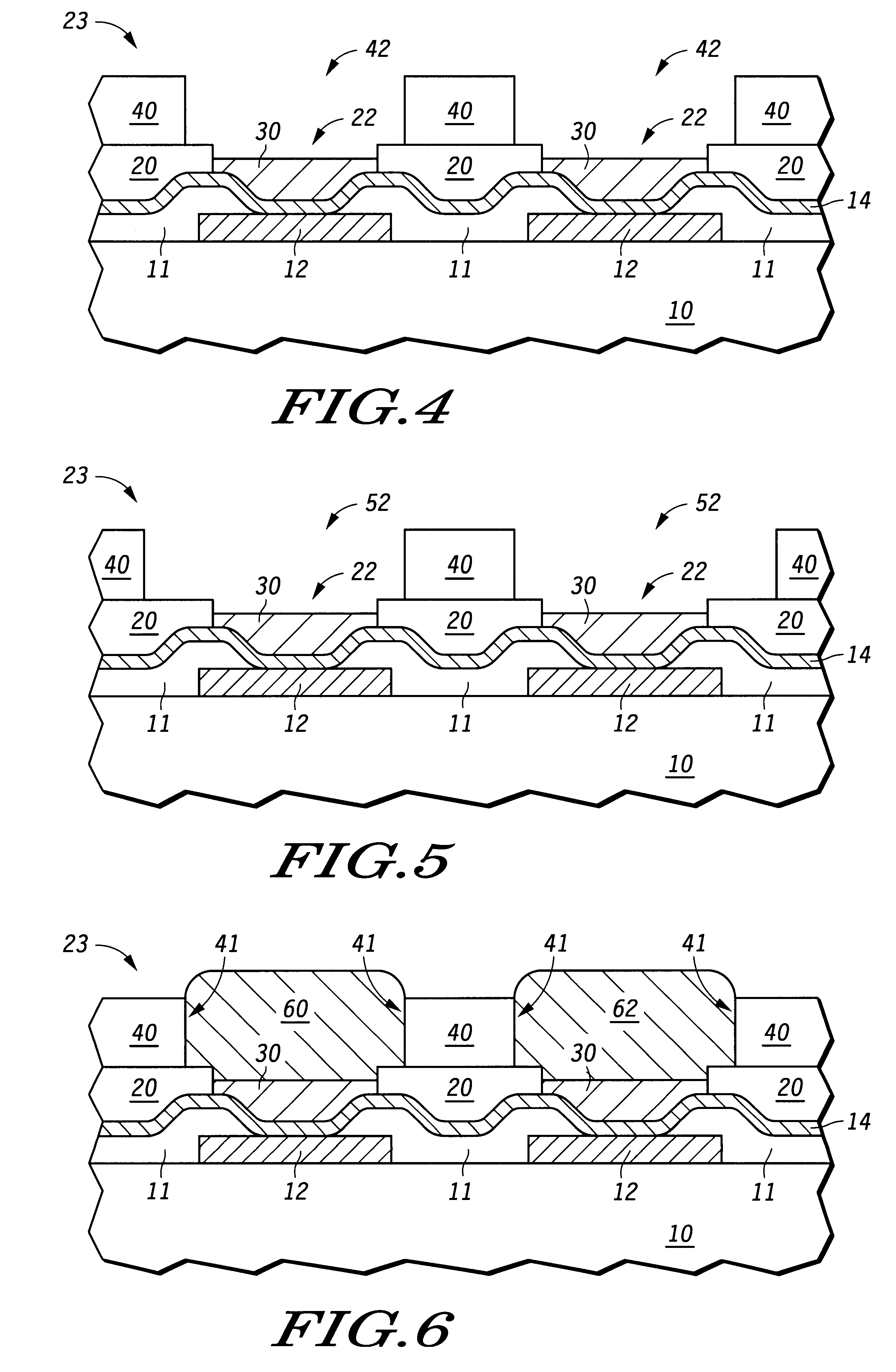

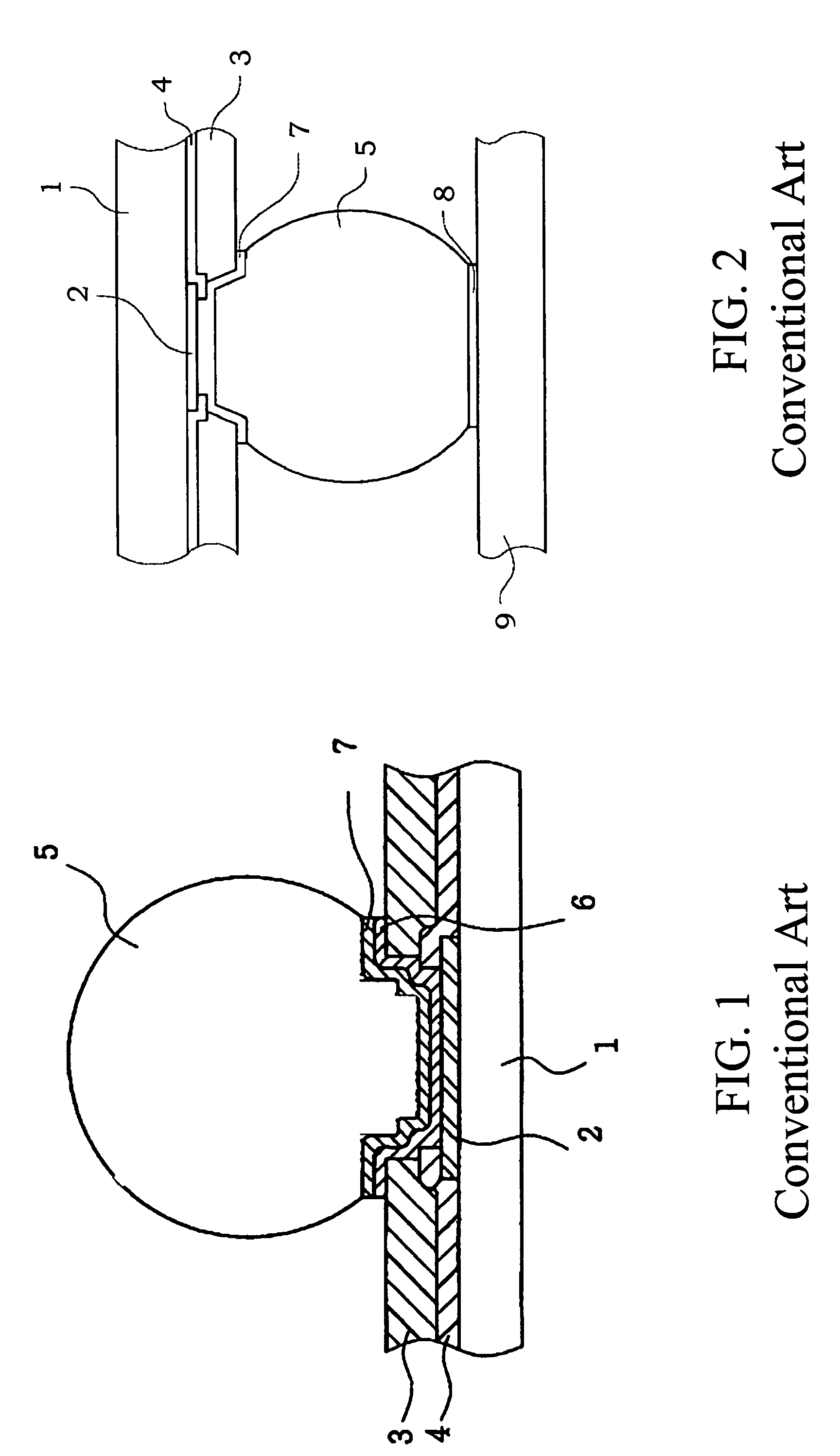

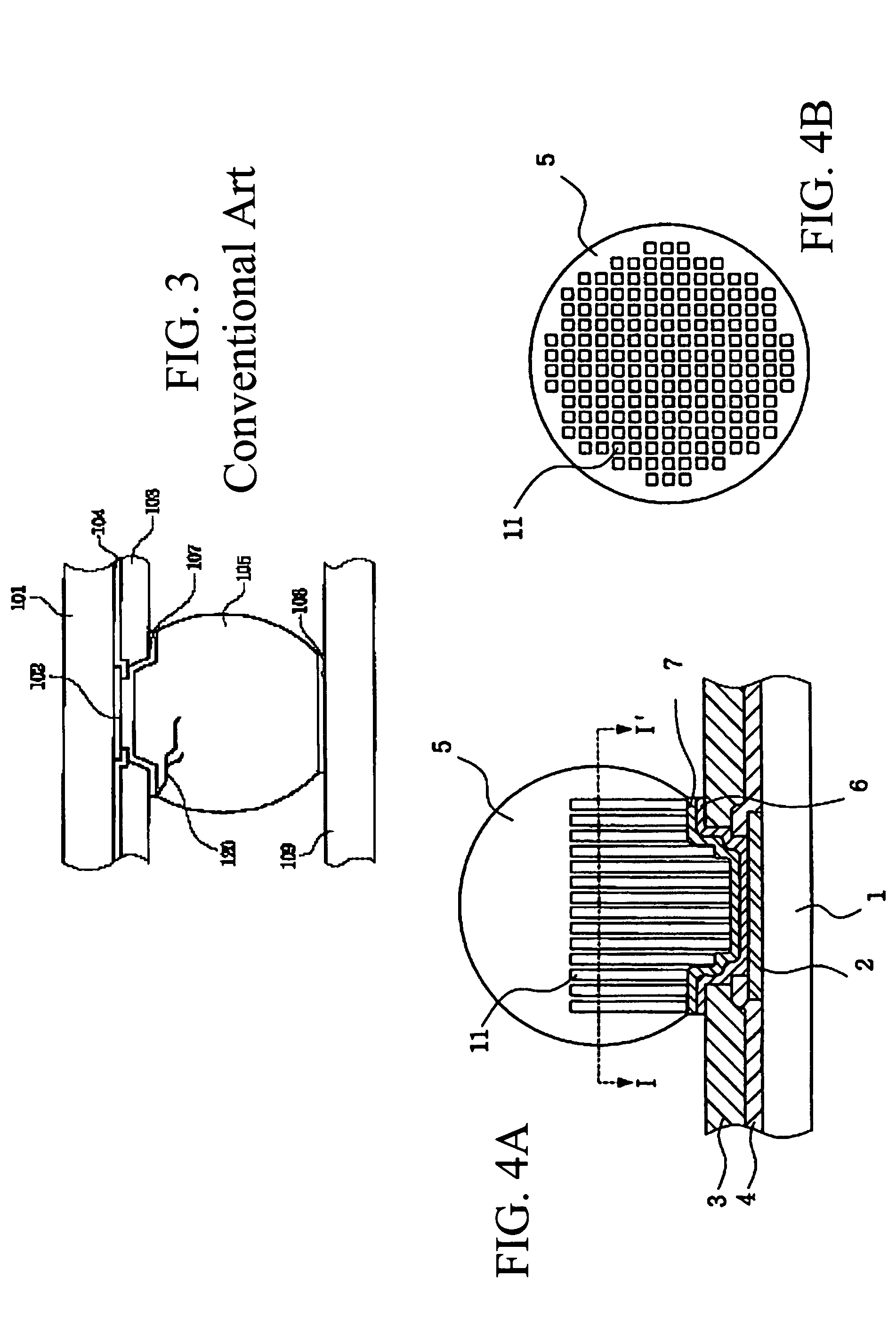

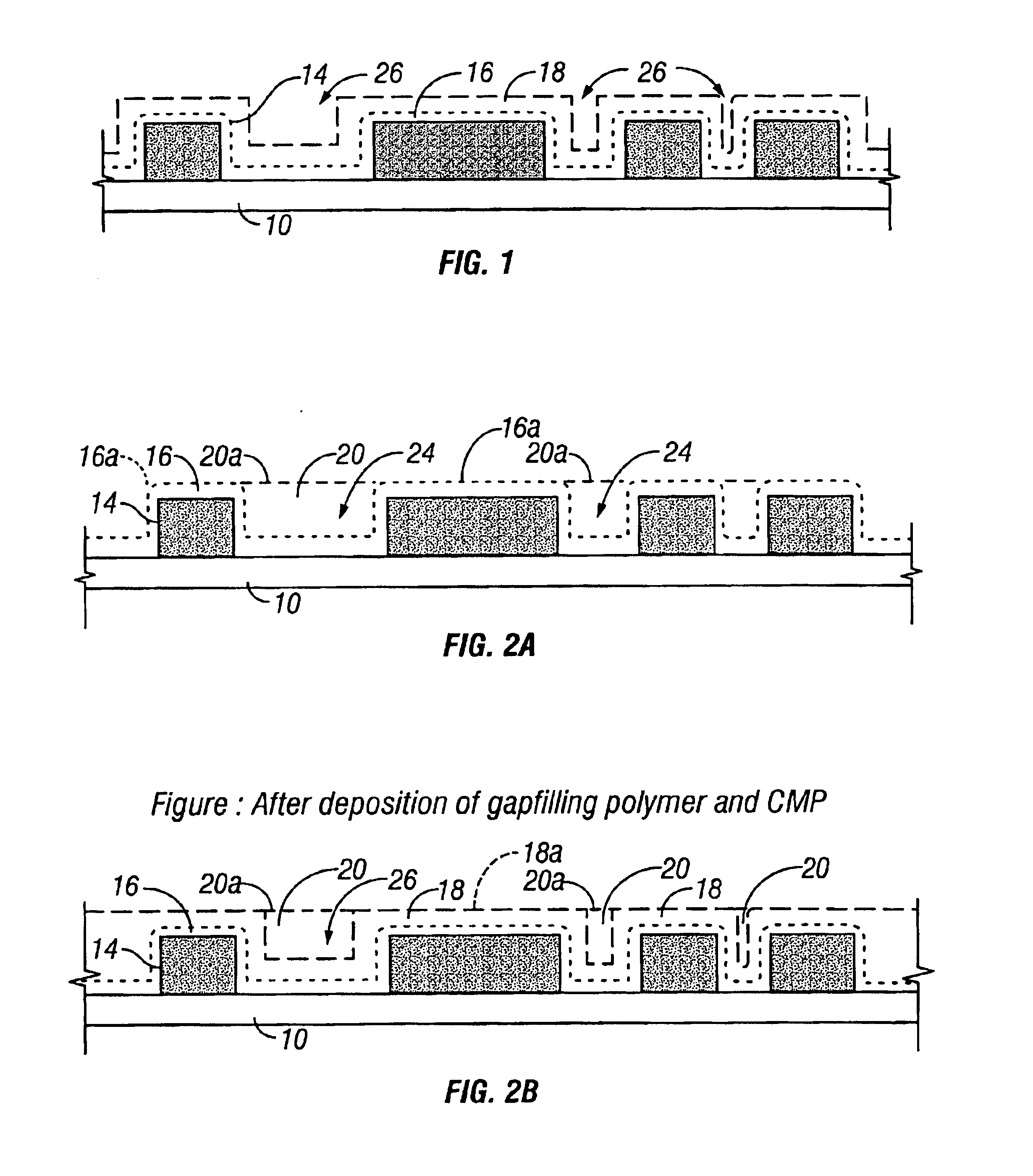

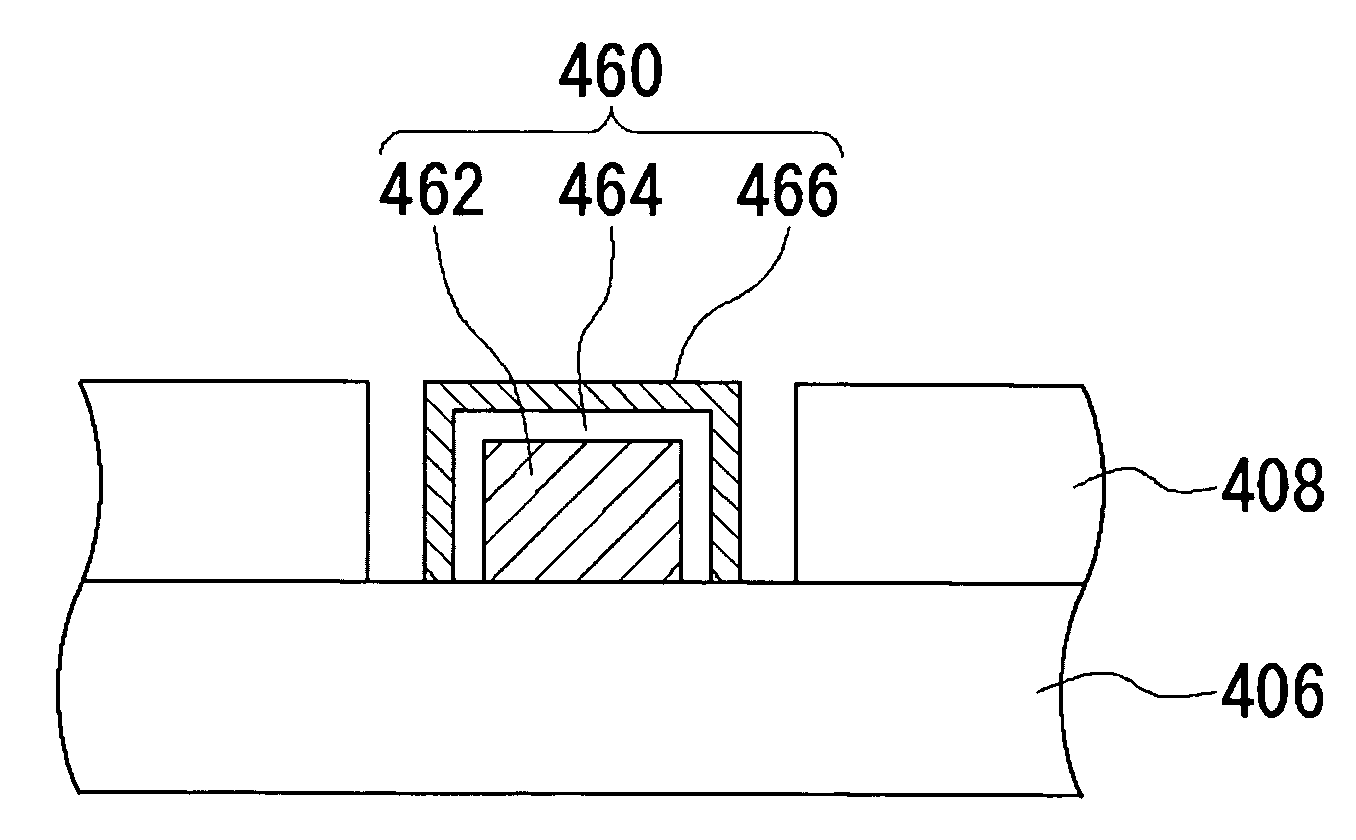

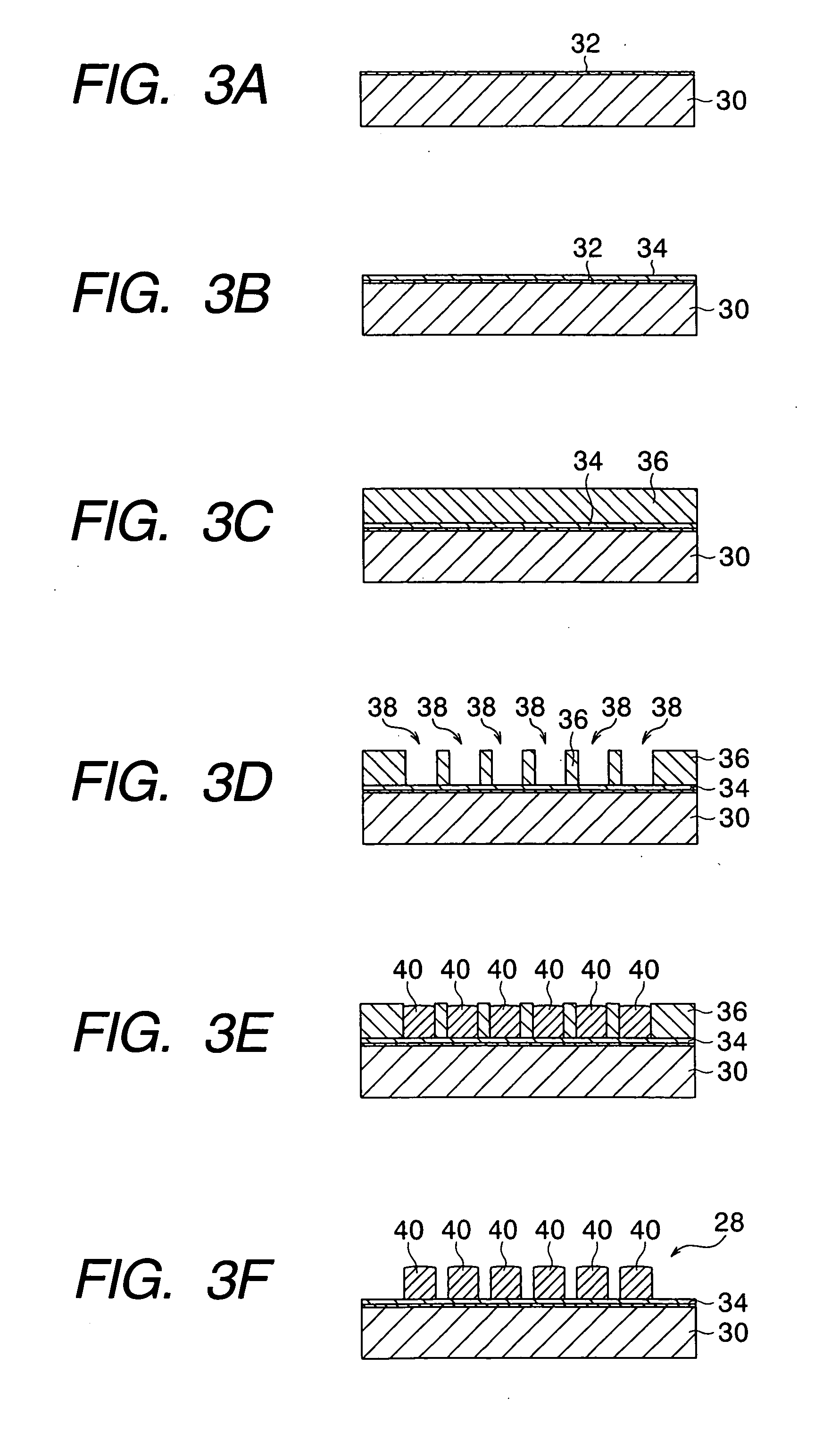

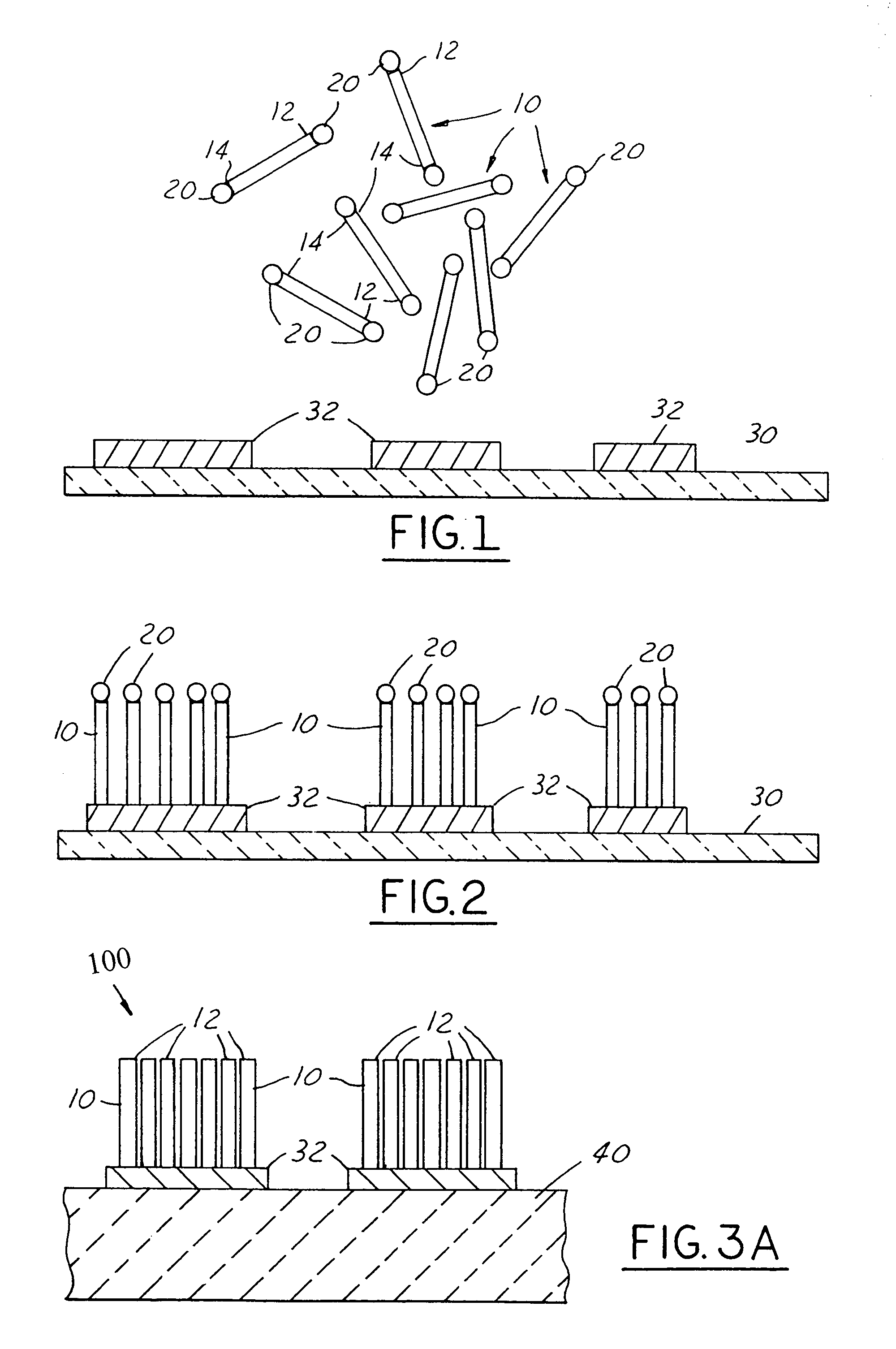

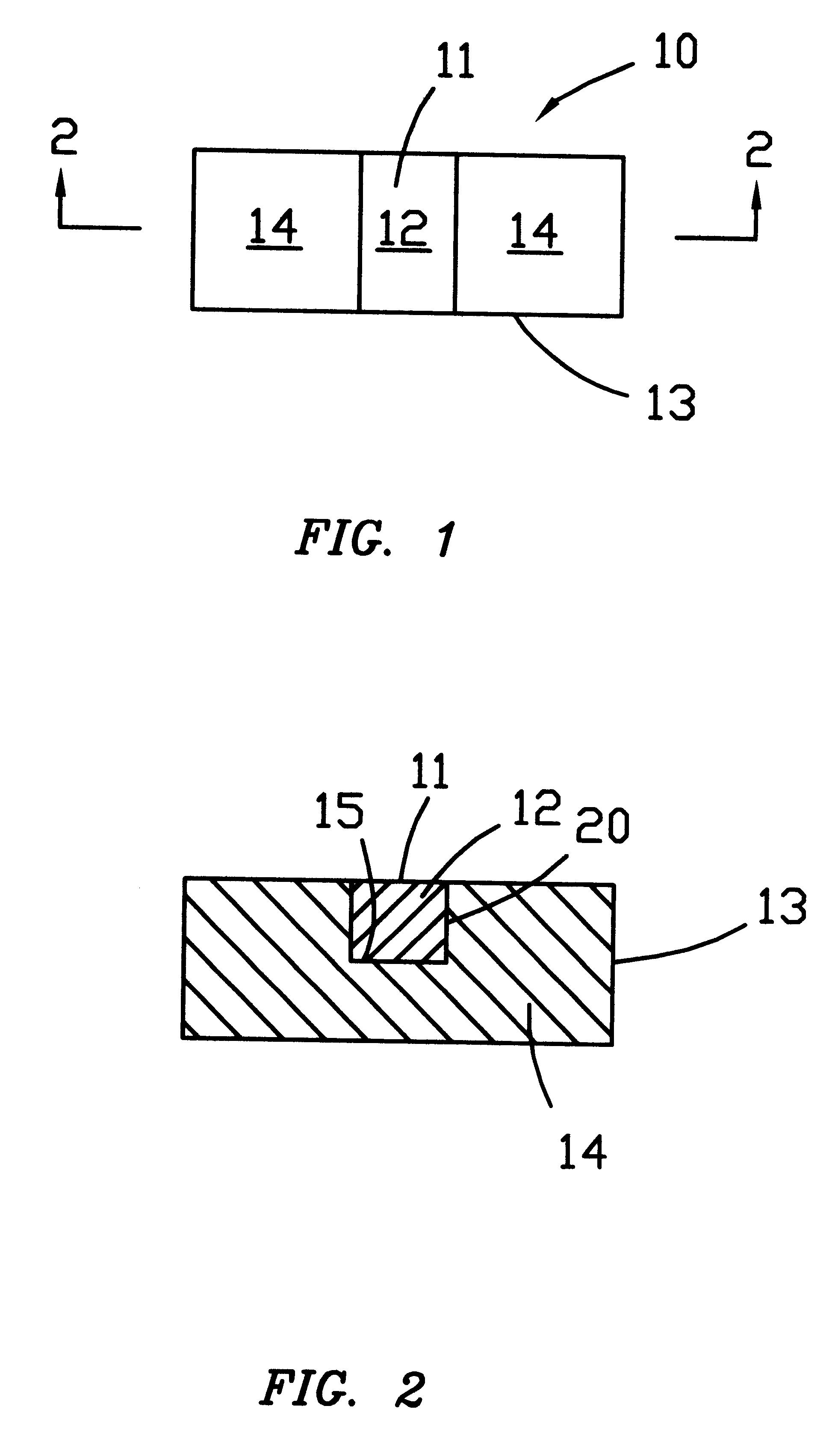

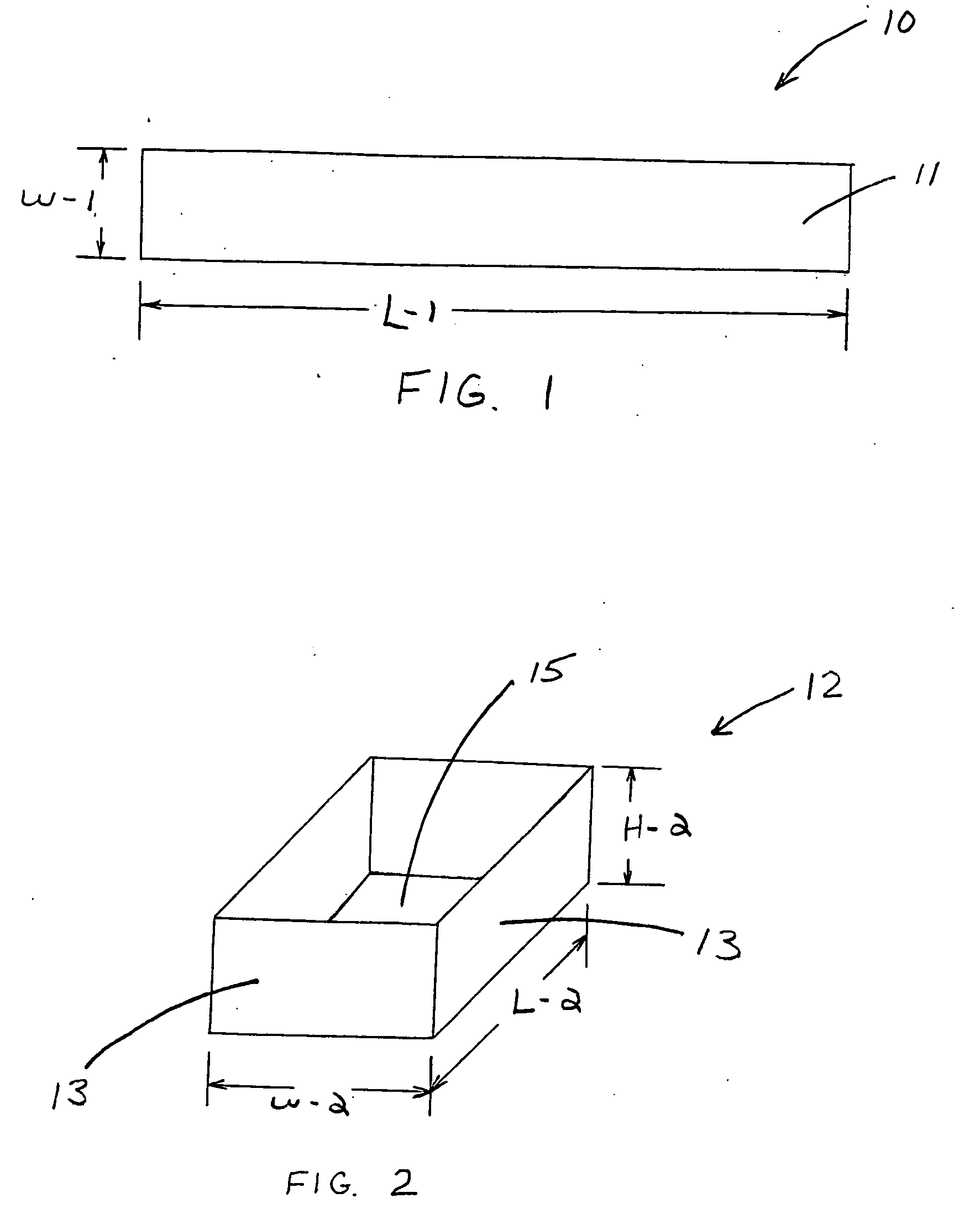

Fine pitch bumping with improved device standoff and bump volume

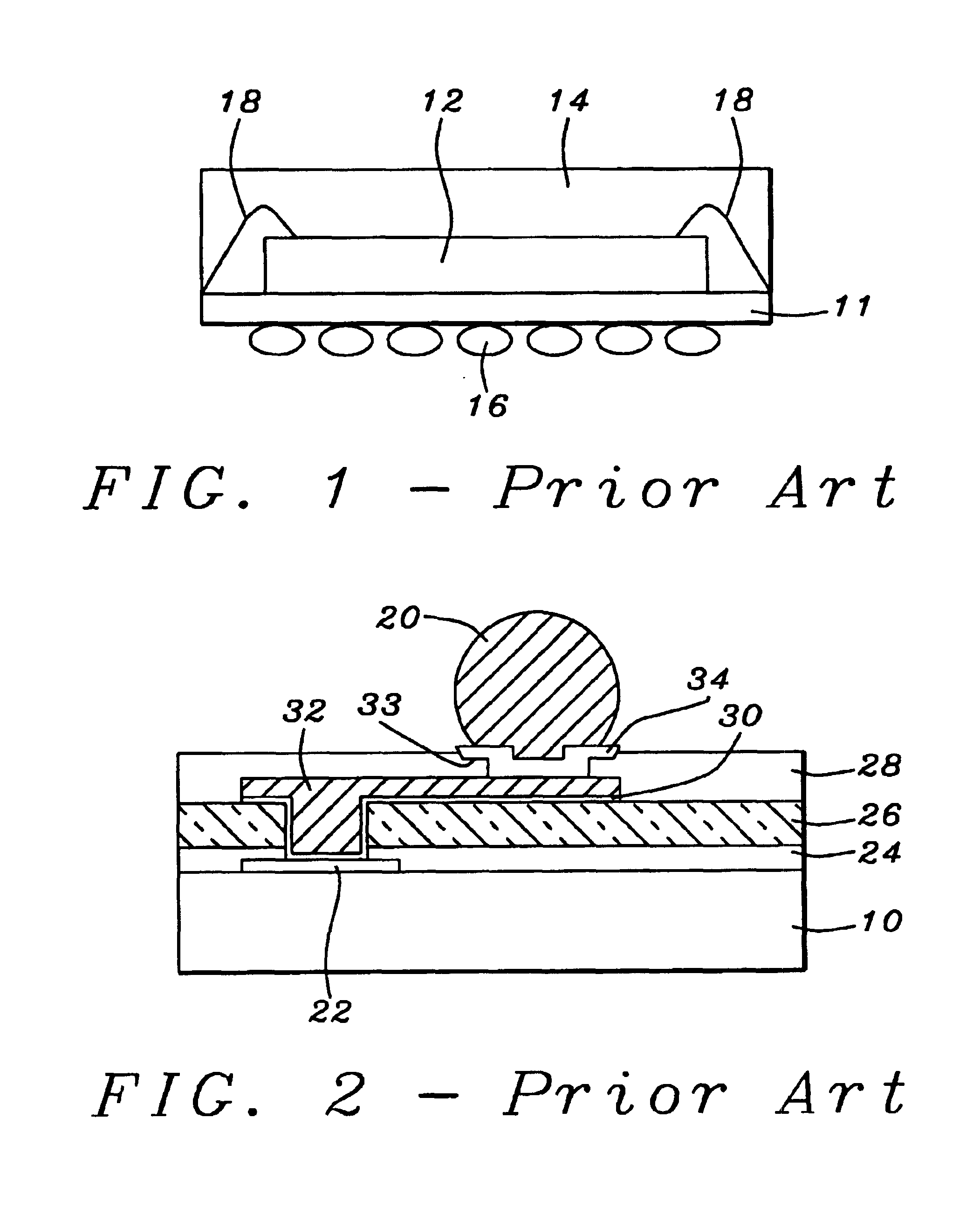

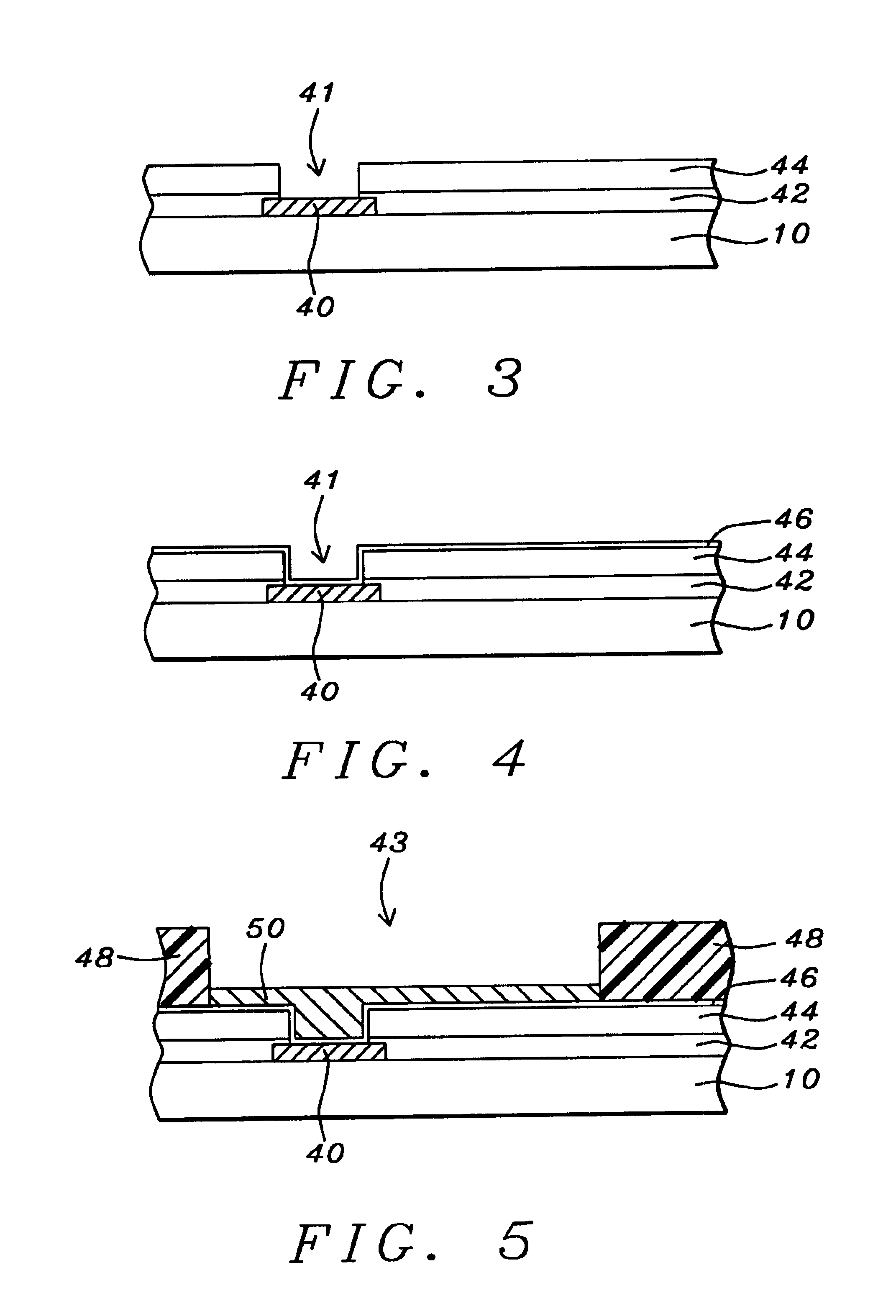

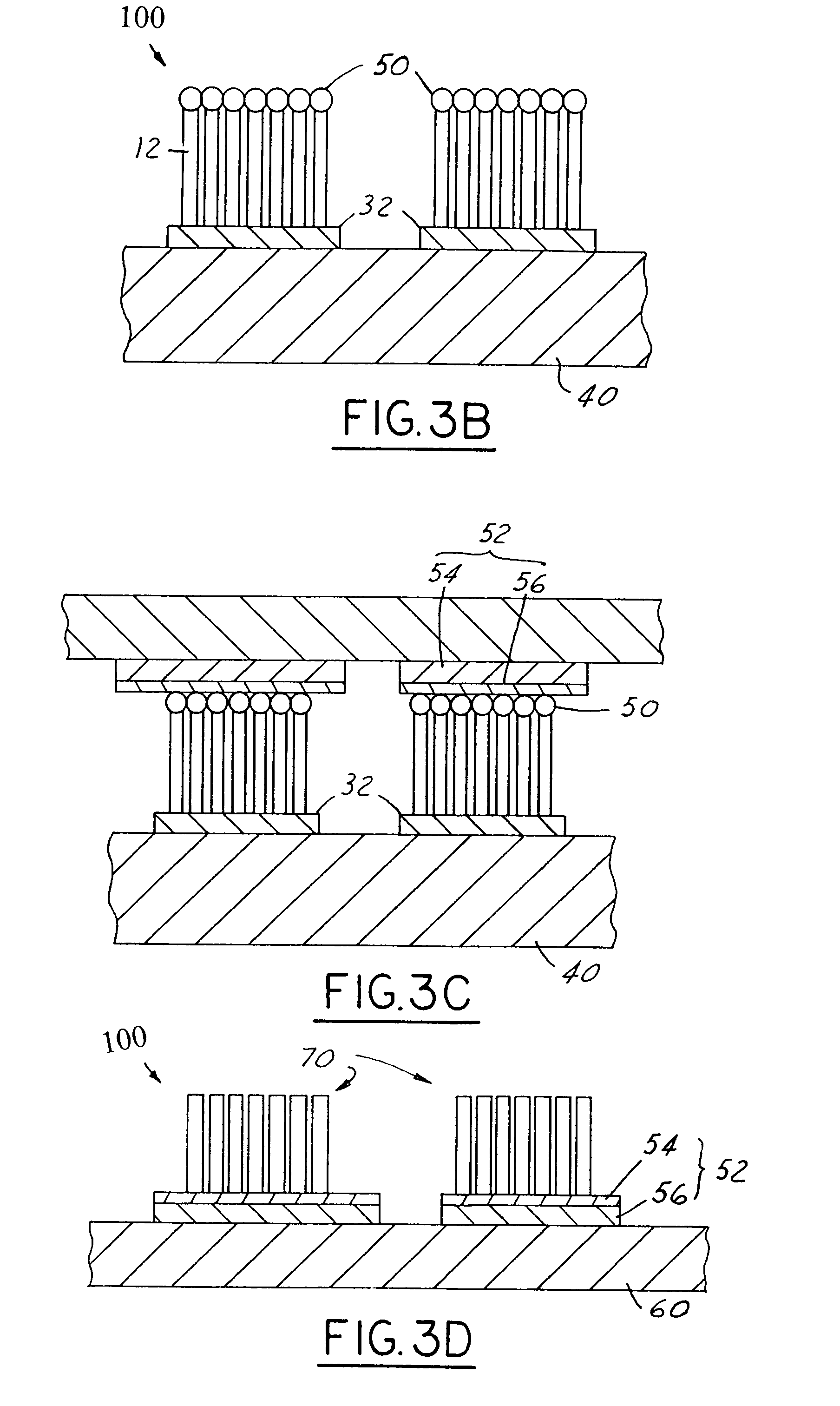

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

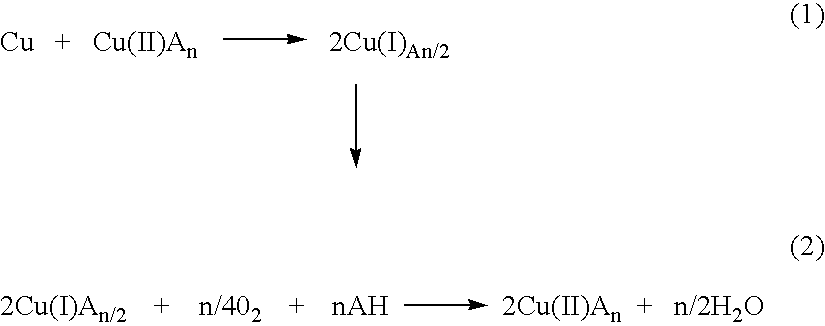

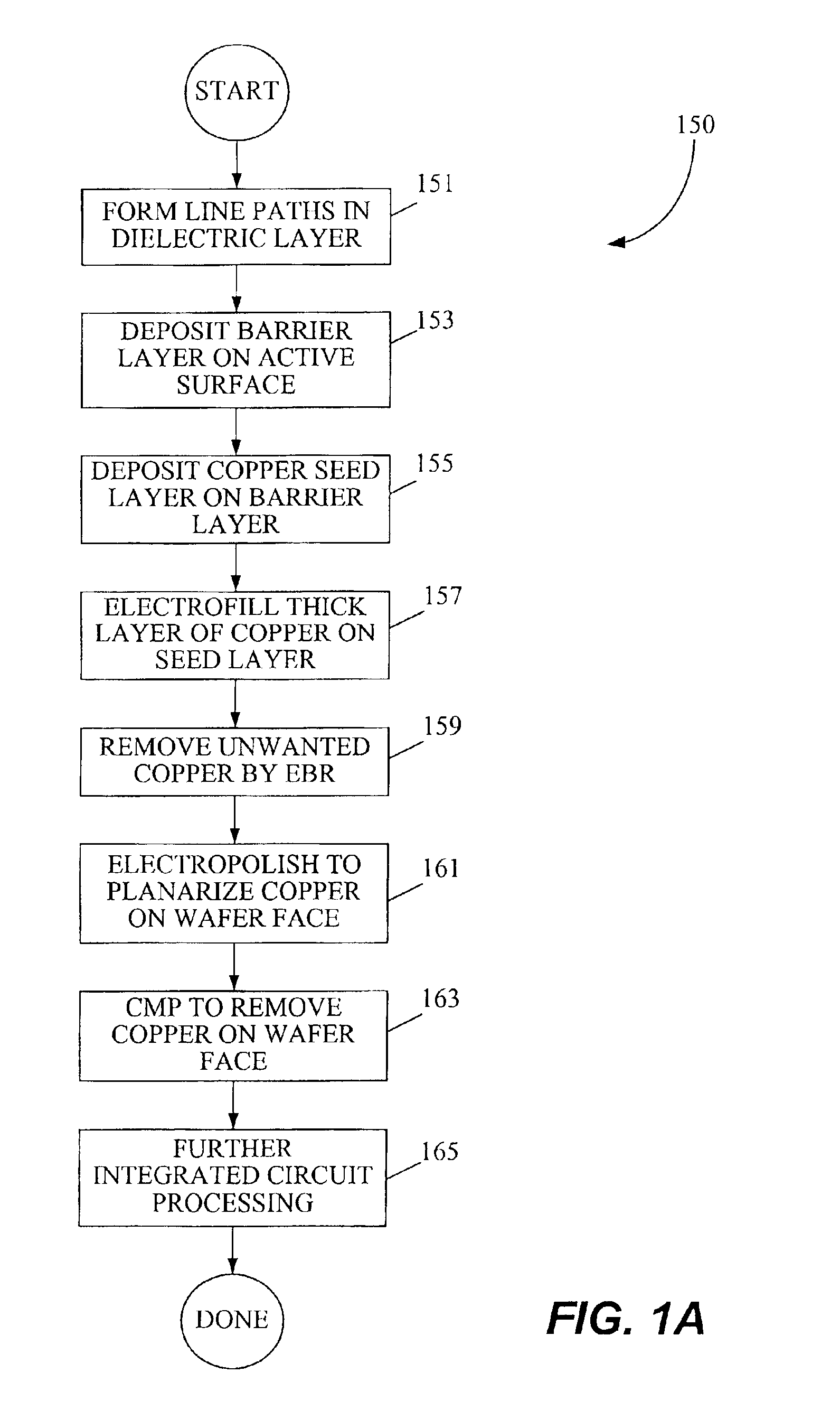

Process for the electrolytic deposition of metal layers

InactiveUS6099711AOptimize allocationImpairing propertyCellsElectrolysisHigh current densityMetal coating

PCT No. PCT / EP96 / 05140 Sec. 371 Date Apr. 23, 1998 Sec. 102(e) Date Apr. 23, 1998 PCT Filed Nov. 21, 1996 PCT Pub. No. WO97 / 19206 PCT Pub. Date May 29, 1997The invention relates to a method for the electrolytic deposition of metal coatings, in particular of copper coatings with certain physical-mechanical and optical properties and uniform coating thickness. According to known methods using soluble anodes and applying direct current, only uneven metal distribution can be attained on complex shaped workpieces. By using a pulse current or pulse voltage method, the problem of the coatings being of varying thickness at various places on the workpiece surfaces can indeed be reduced. However, the further problem of the geometric ratios being changed continuously during the depositing process by dissolving of the anodes is not resolved thus. This can be avoided by using insoluble anodes. In order to guarantee sufficient stability of the anodes and a bright coating even at those points on the workpiece surfaces, onto which the metal is deposited with high current density, it is essential to add compounds of an electrochemically reversible redox system to the depositing solution.

Owner:ATOTECH DEUT GMBH

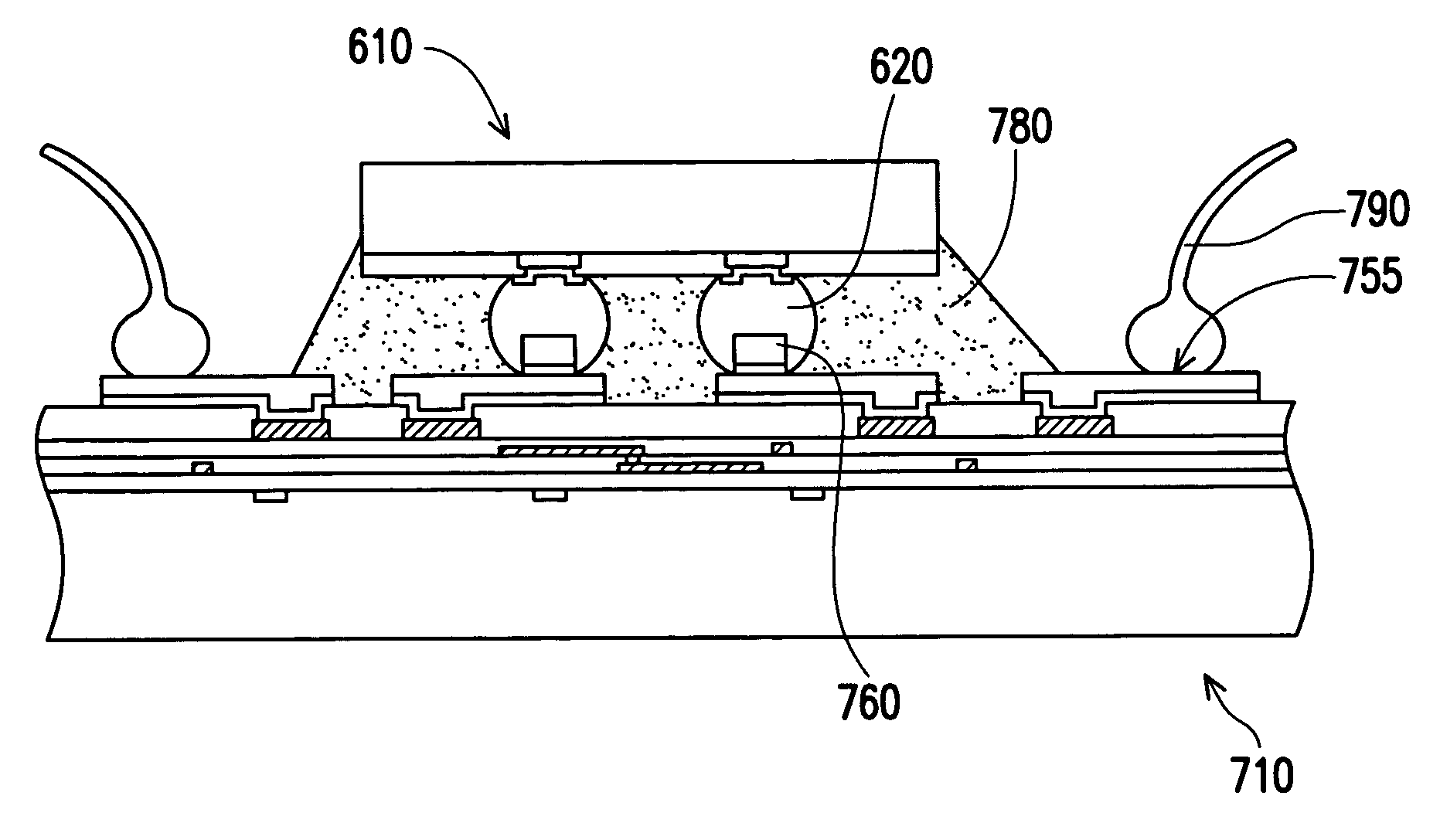

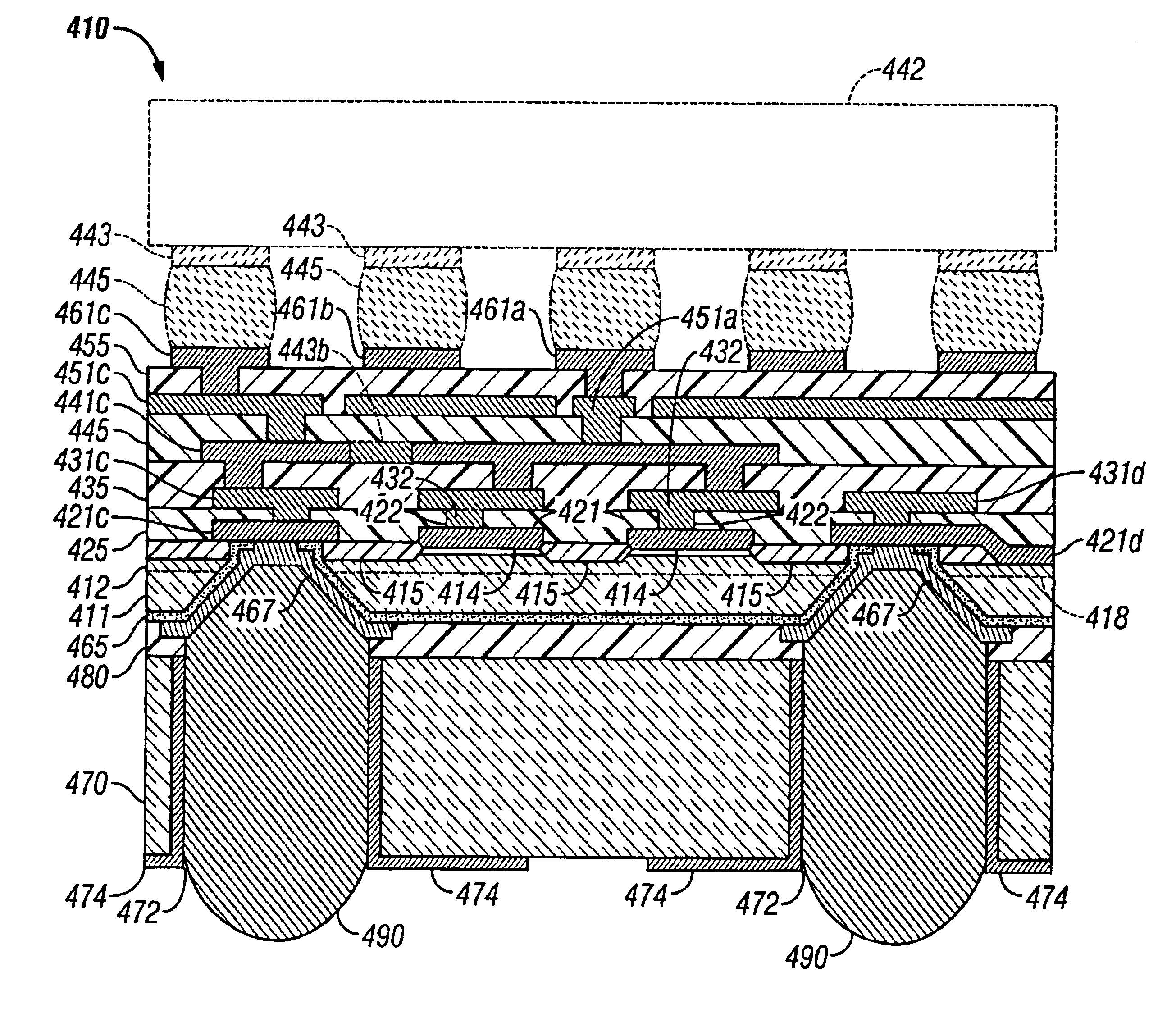

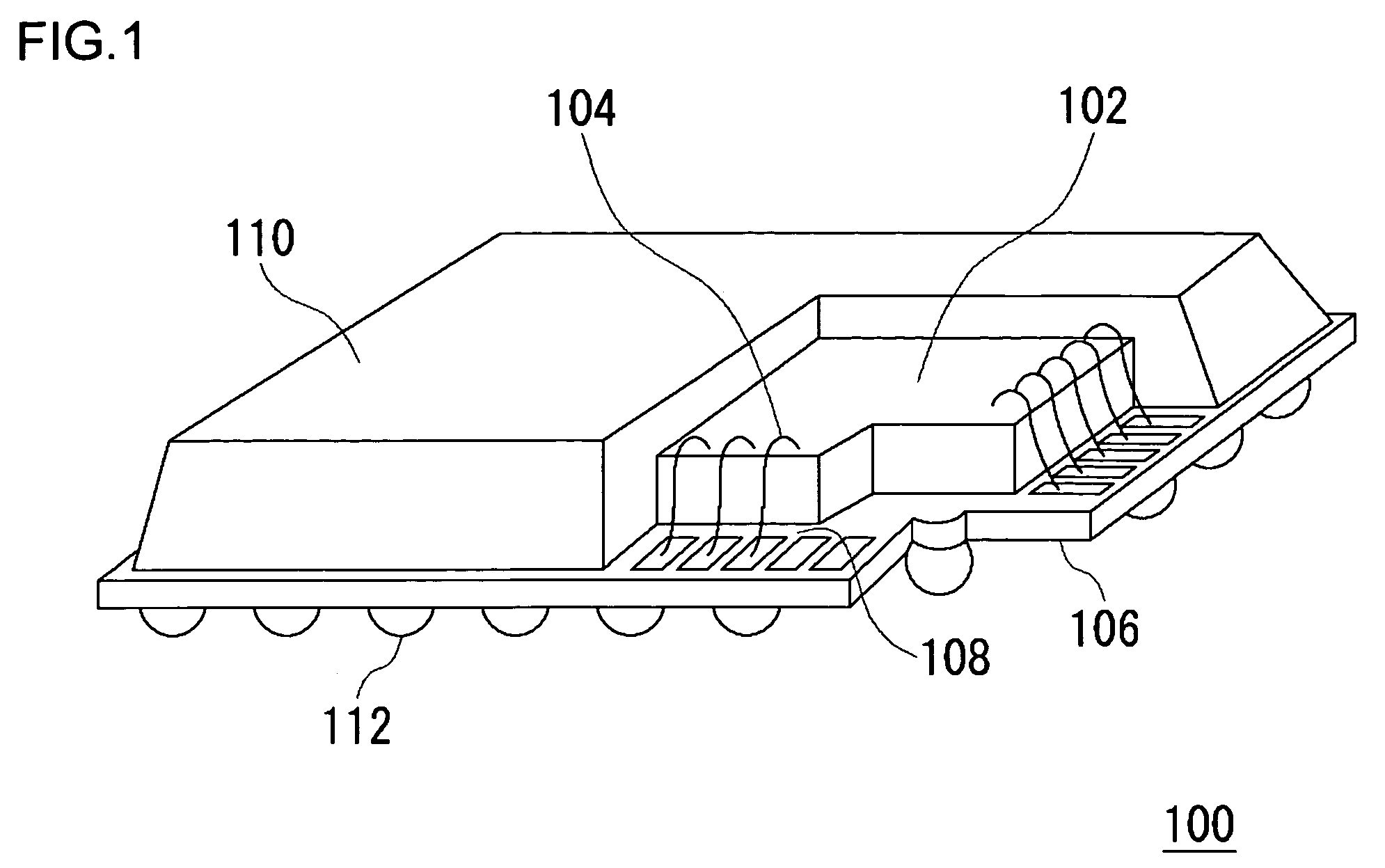

Chip package with multiple chips connected by bumps

InactiveUS7242099B2Improve assembly reliabilityPrecise alignmentPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringChip-scale package

A method of assembling chips. A first chip and a second chip are provided. At least one conductive pillar is formed on the first chip, and a conductive connecting material is formed on the conductive pillar. The second chip also comprises at least one conductive pillar. The first chip is connected to the second chip via the conductive pillars and the conductive connecting material.

Owner:QUALCOMM INC

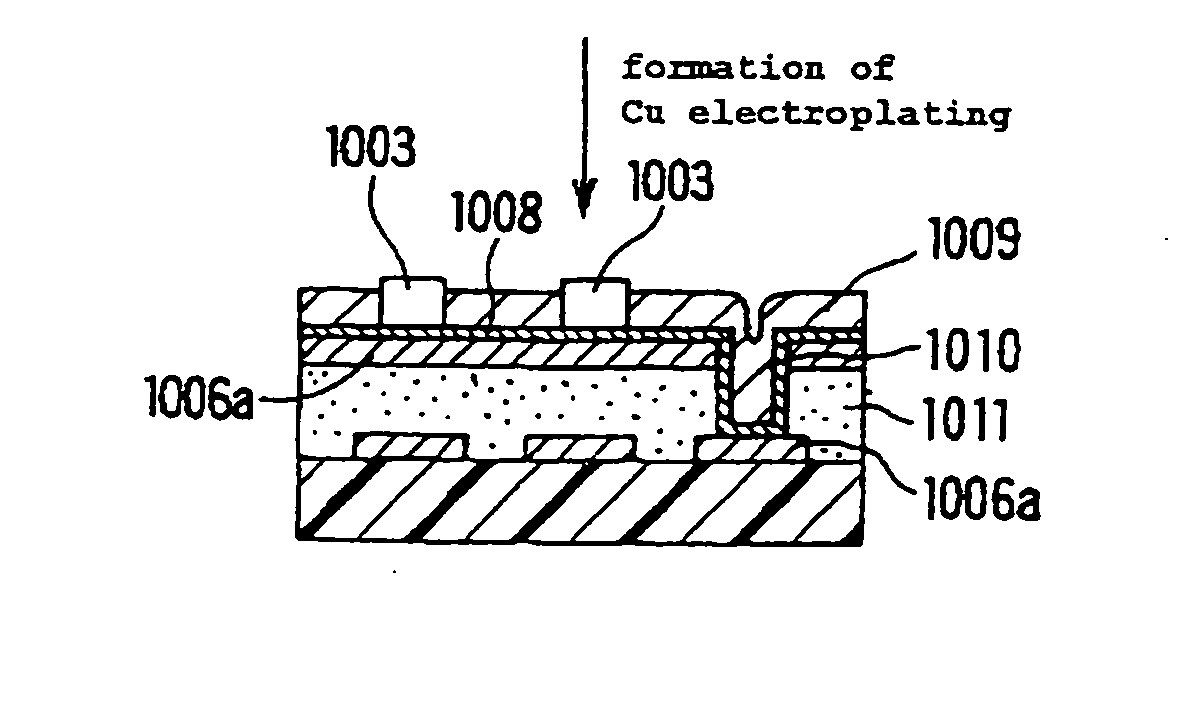

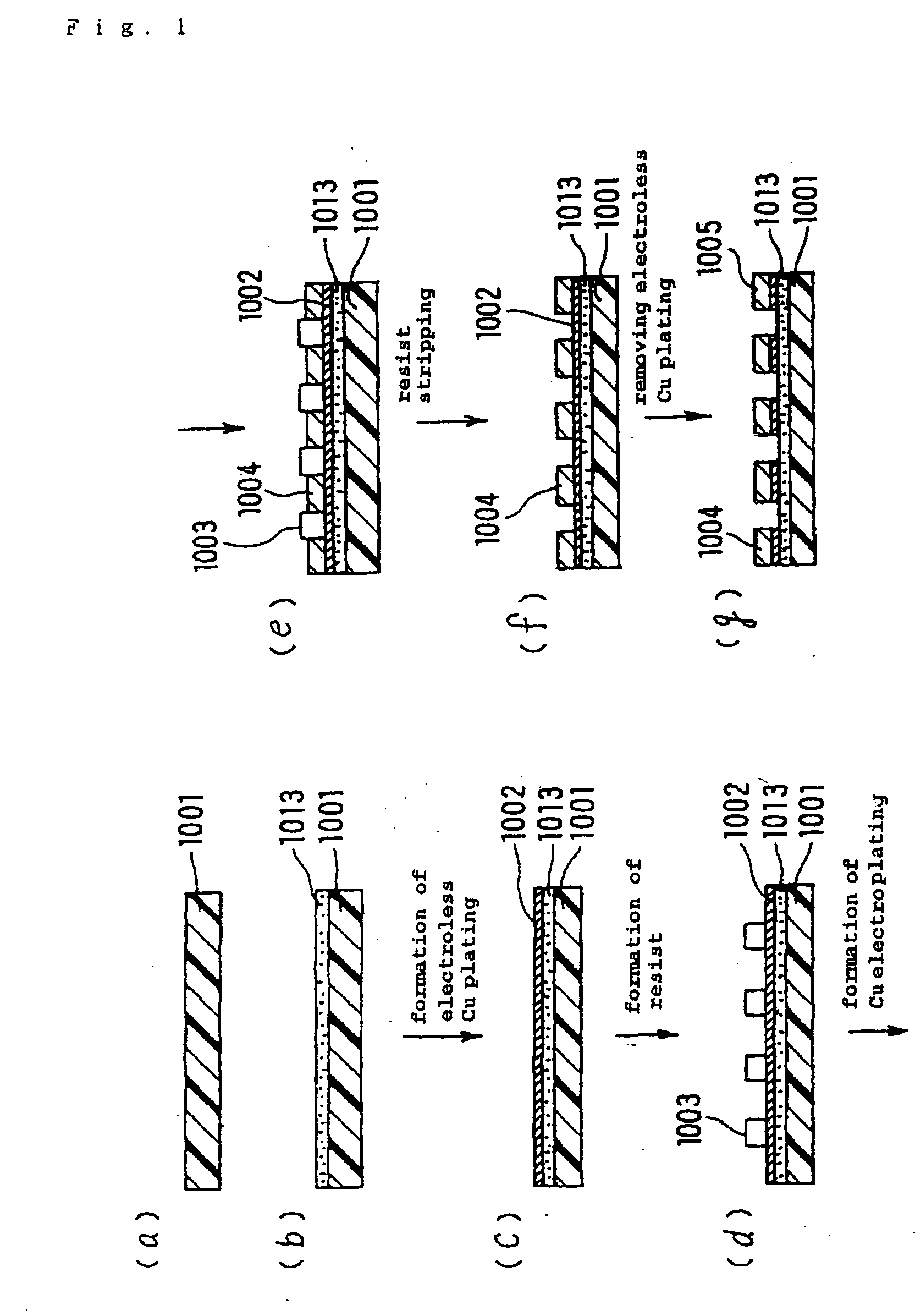

Printed wiring board and its manufacturing method

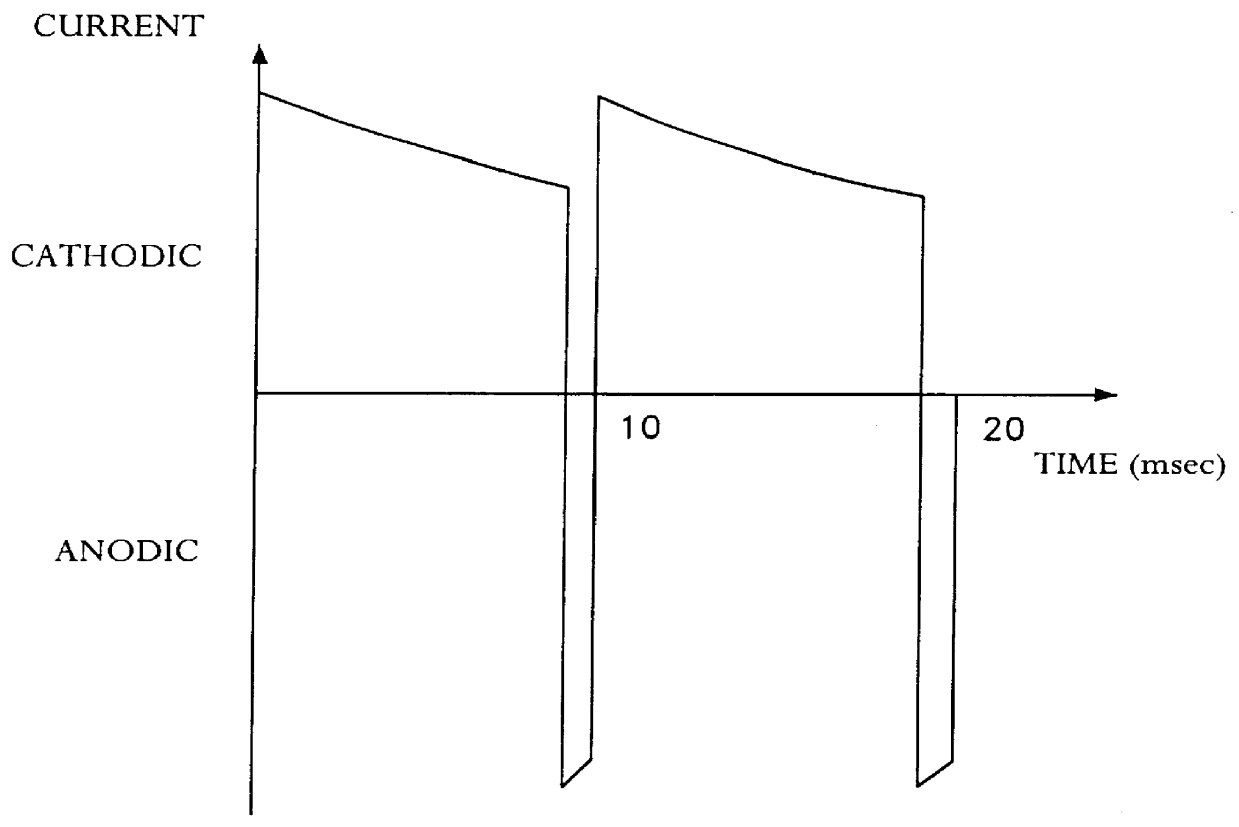

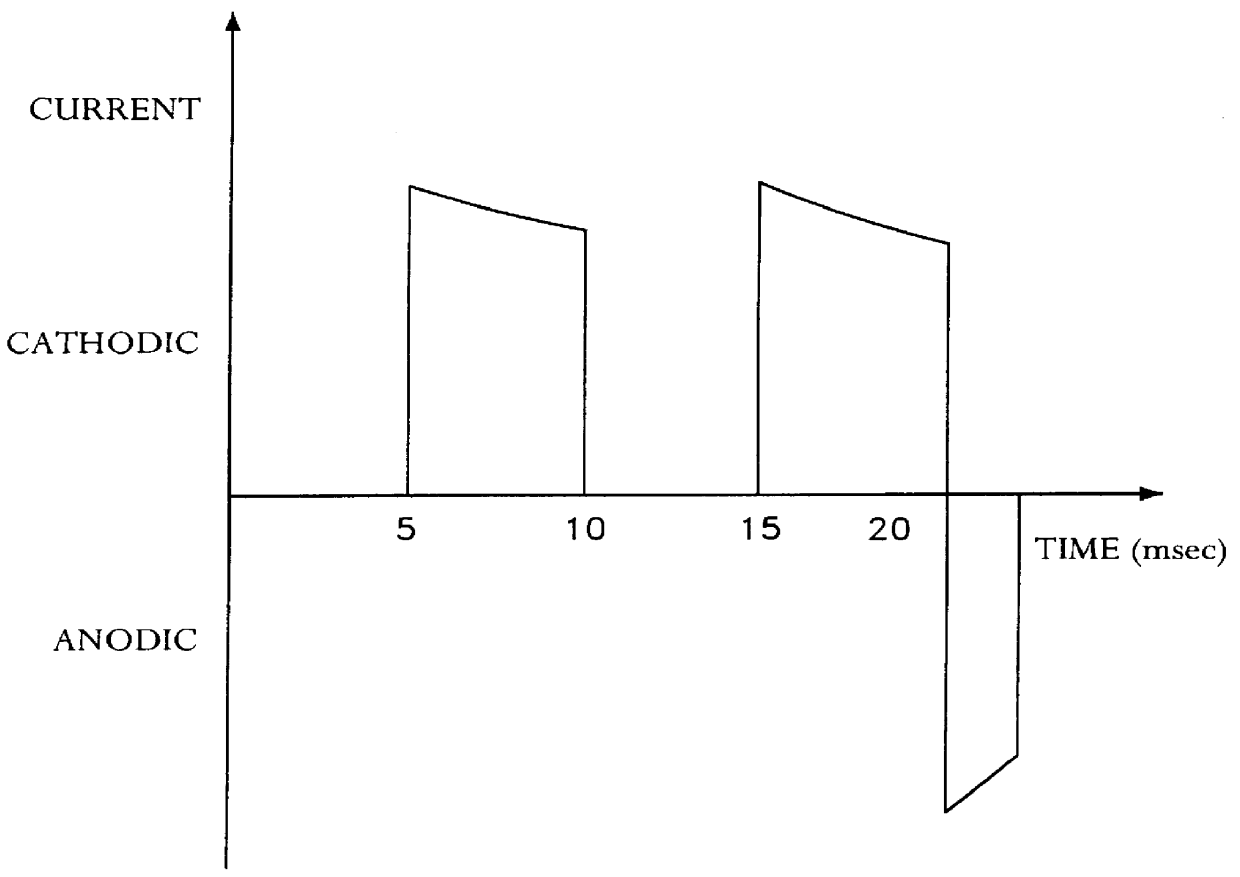

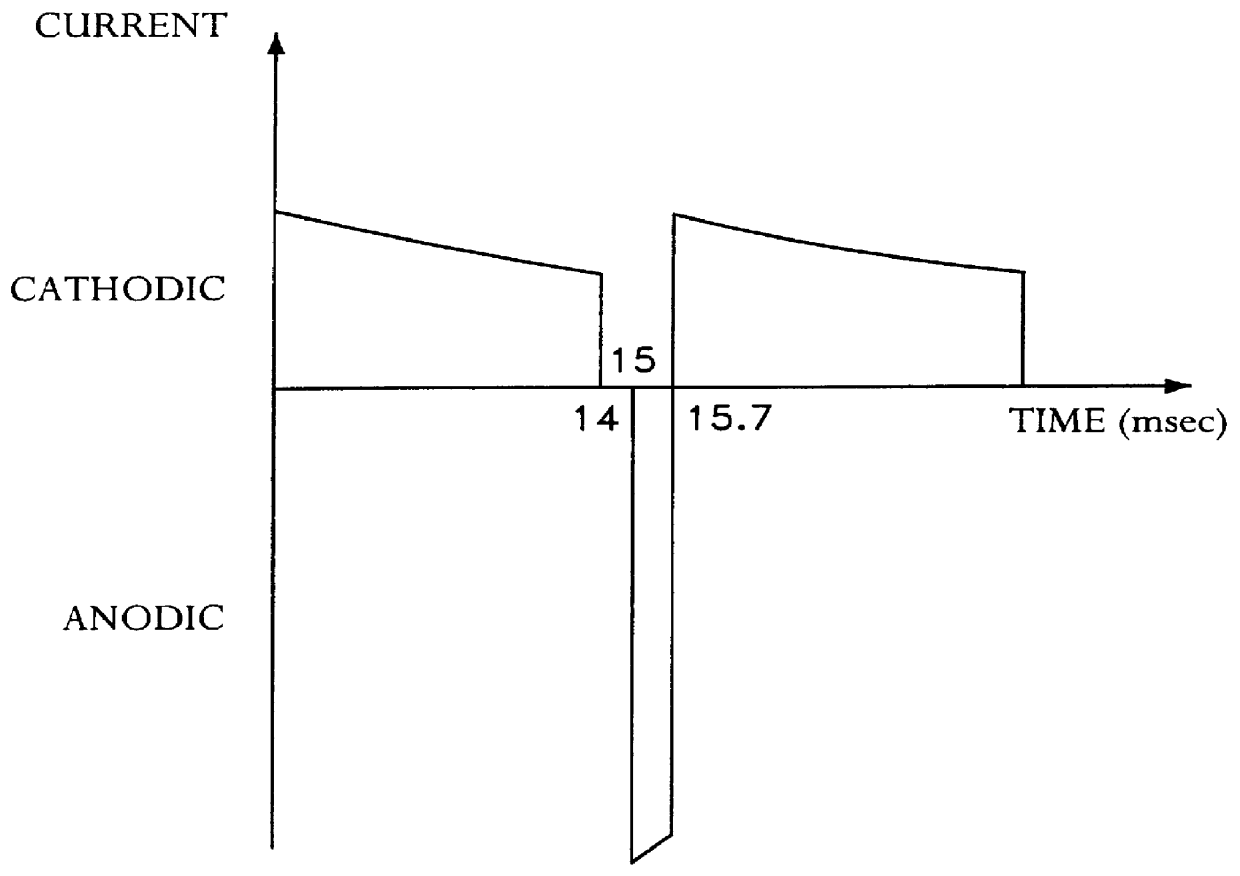

The present invention has for its object to provide a process for manufacturing multilayer printed circuit boards which is capable of simultaneous via hole filling and formation of conductor circuit and via holes of good crystallinity and uniform deposition can be constructed on a substrate and high-density wiring and highly reliable conductor connections can be realized without annealing. The present invention is related to a process for manufacturing multilayer printed circuit boards which comprises disposing an interlayer resin insulating layer on a substrate formed with a conductor circuit, creating openings for formation of via holes in said interlayer resin insulating layer, forming an electroless plated metal layer on said interlayer resin insulating layer, disposing a resist thereon, performing electroplating, stripping the resist off and etching the electroless plated metal layer to provide a conductor circuit and via holes, wherein the electroplating is performed intermittently using said electroless plated metal layer as cathode and a plating metal as anode at a constant voltage between said anode and said cathode.

Owner:IBIDEN CO LTD

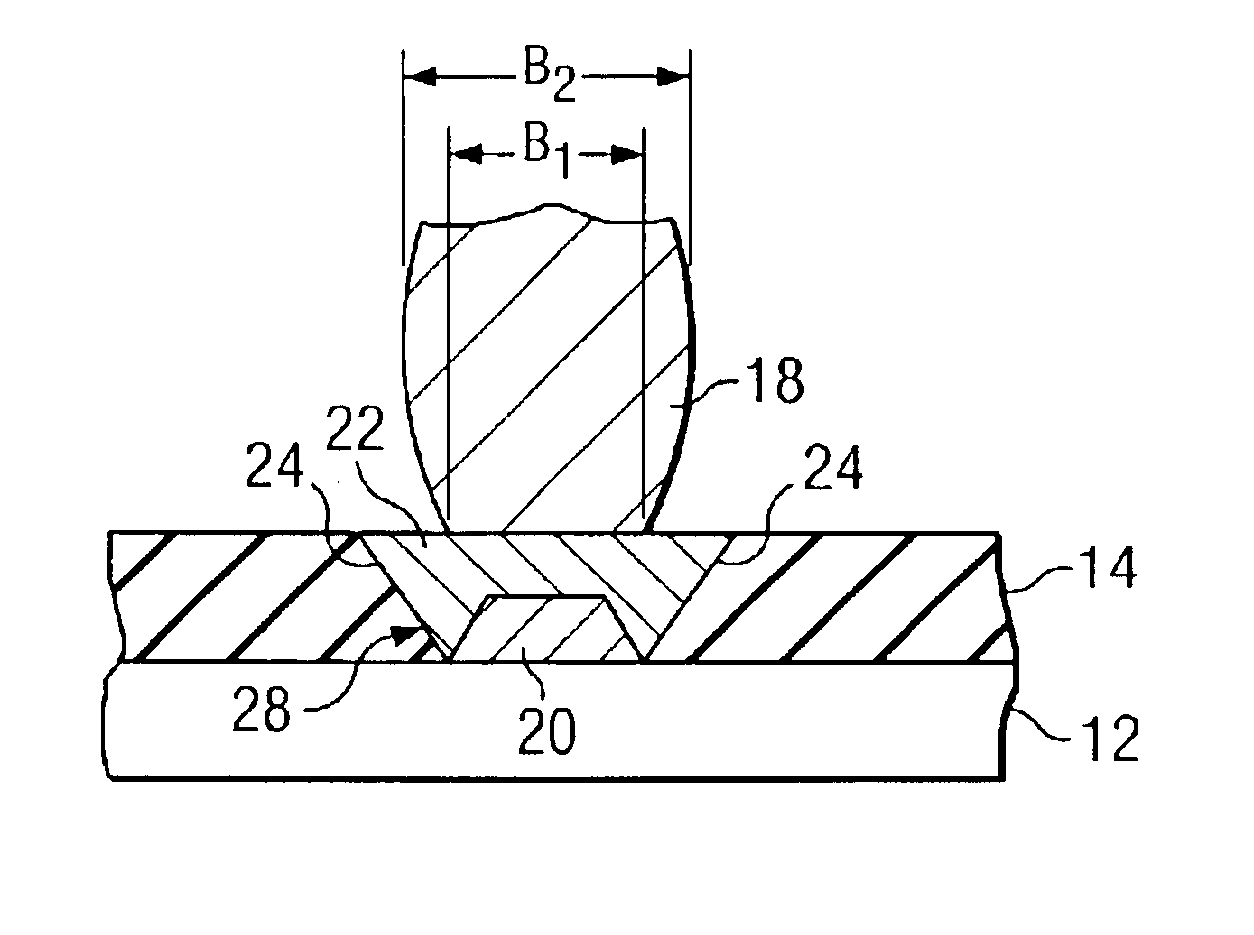

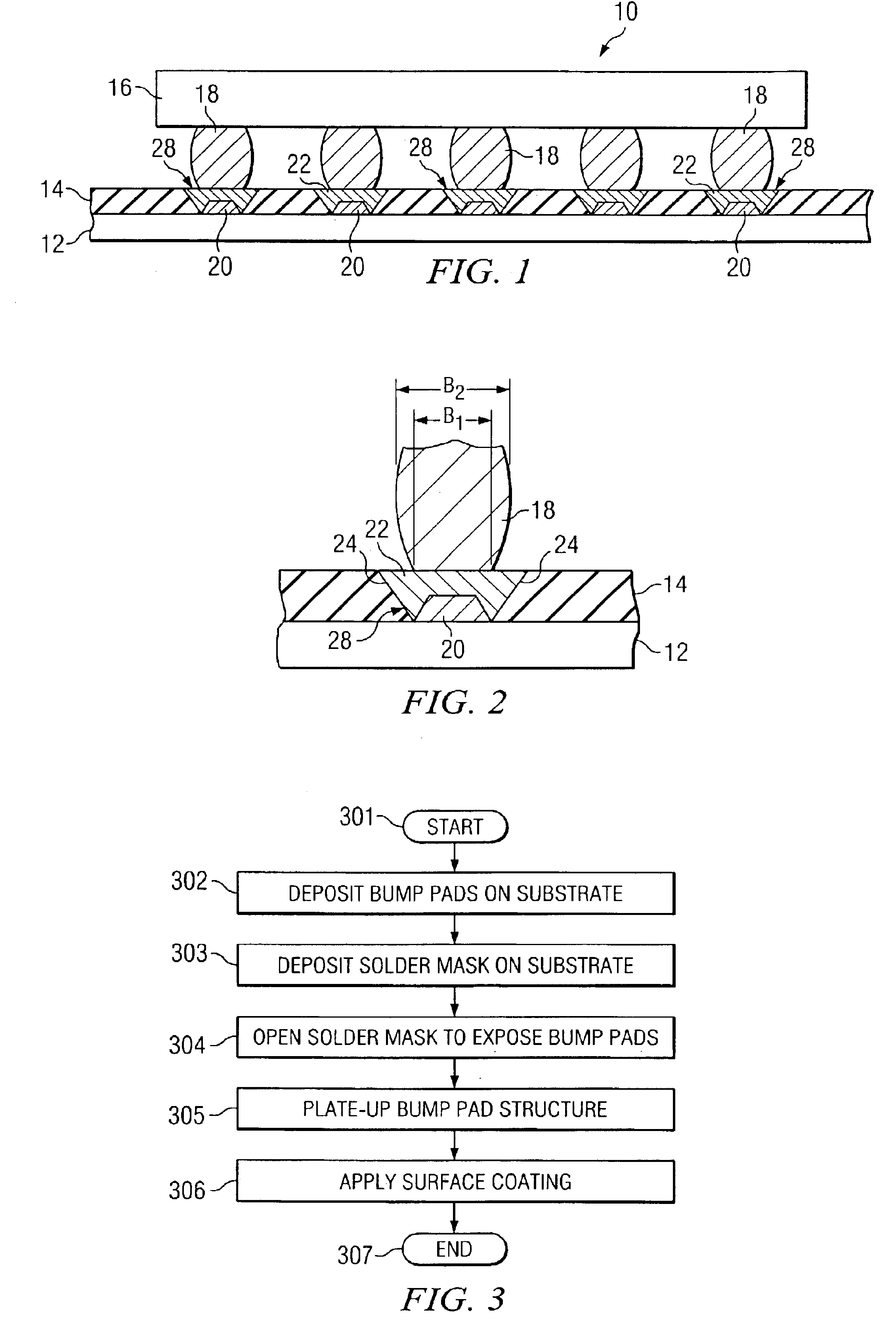

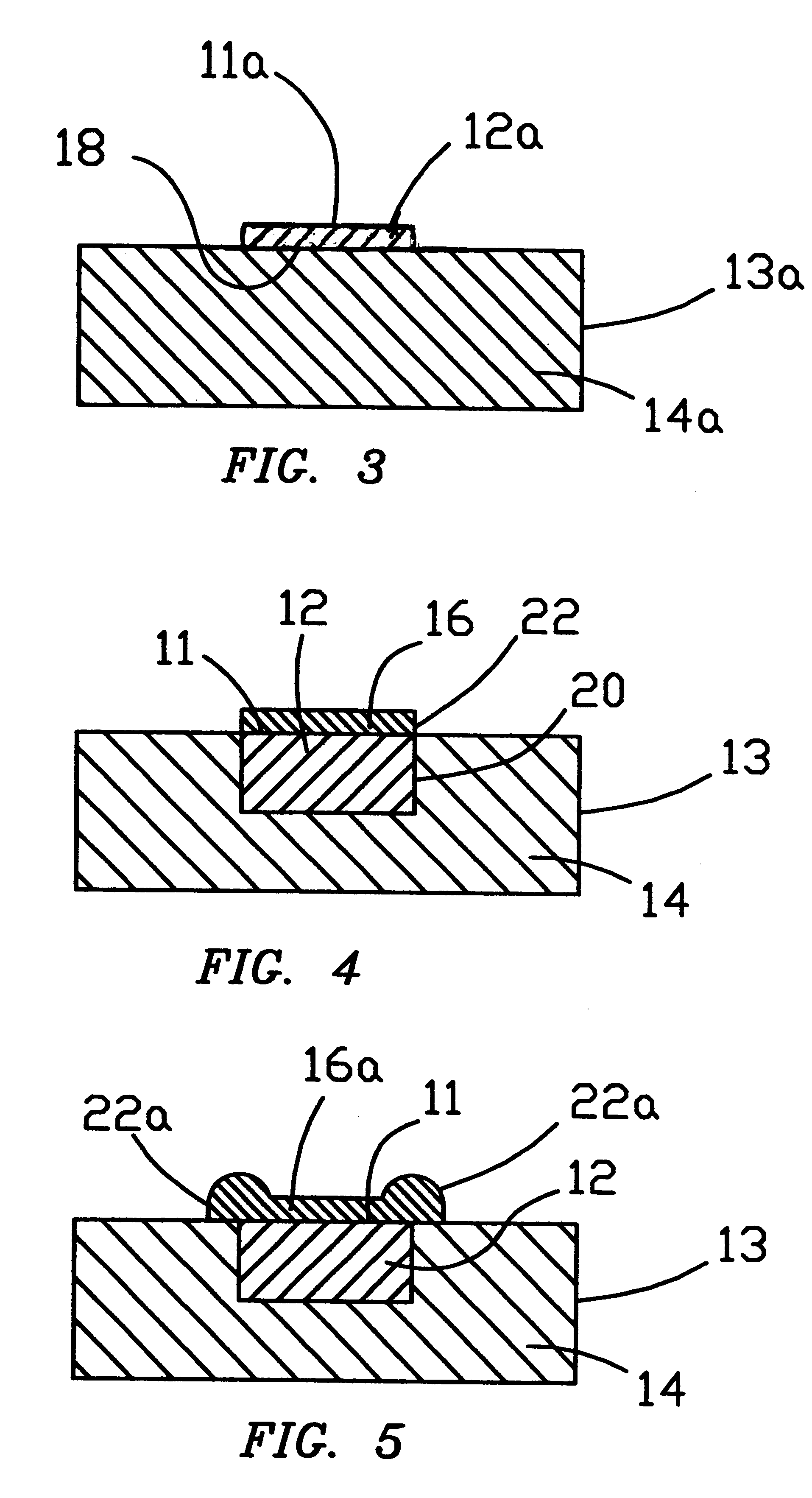

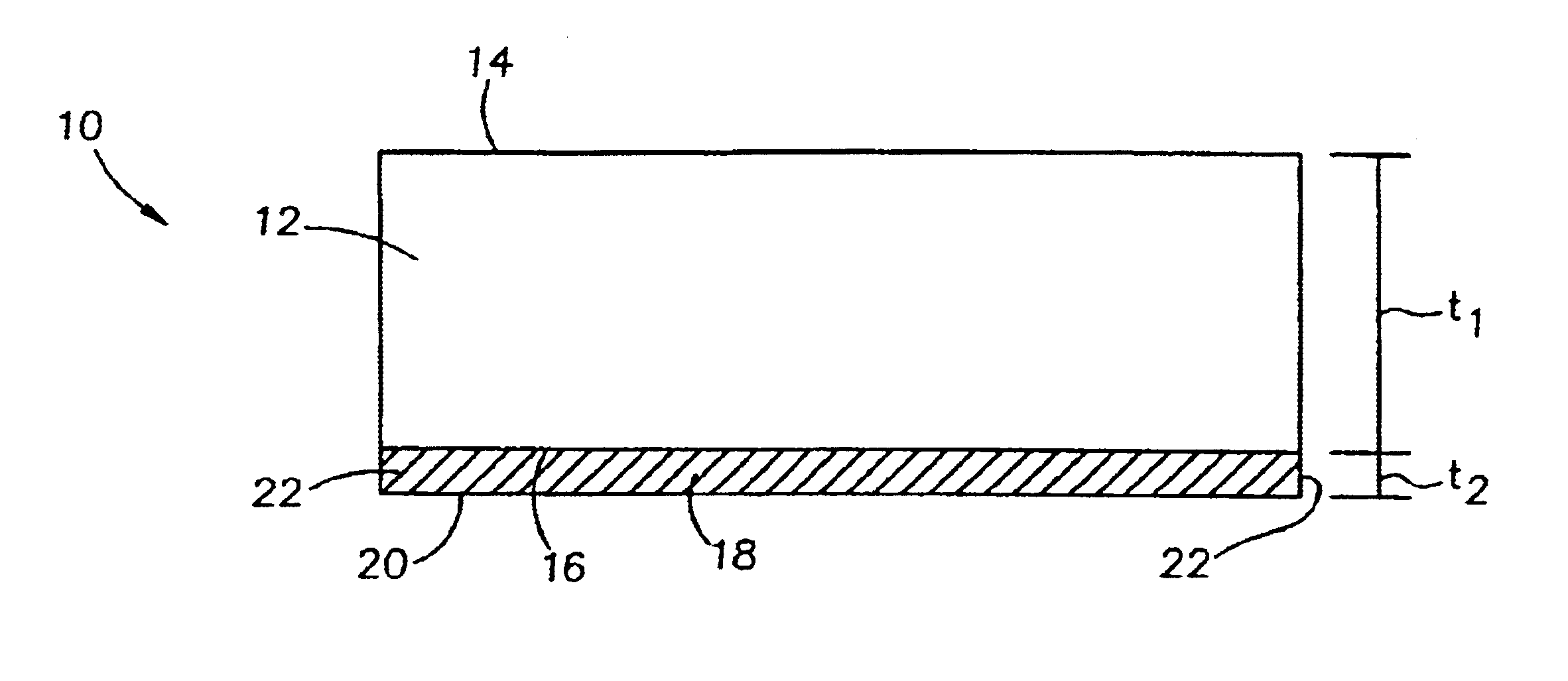

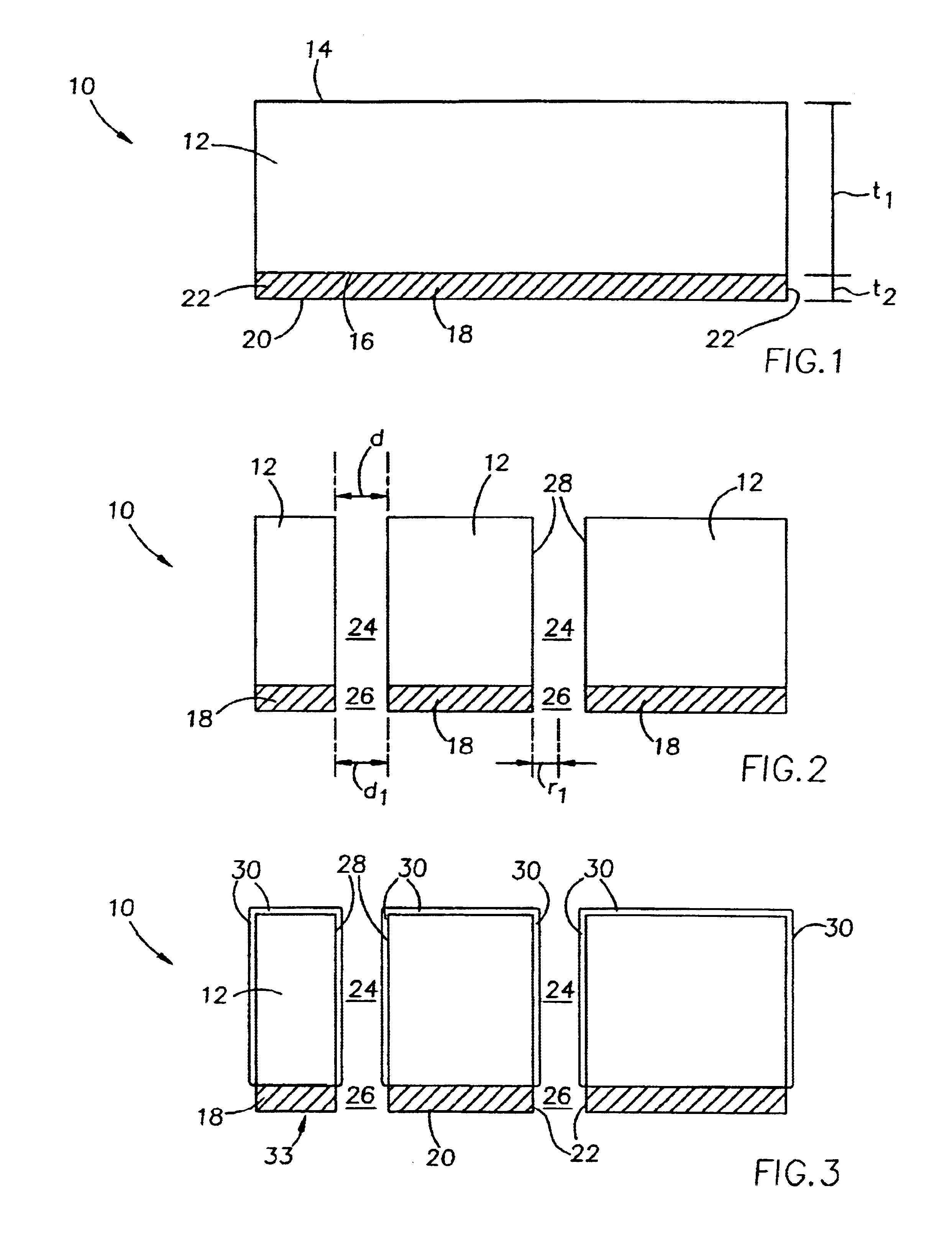

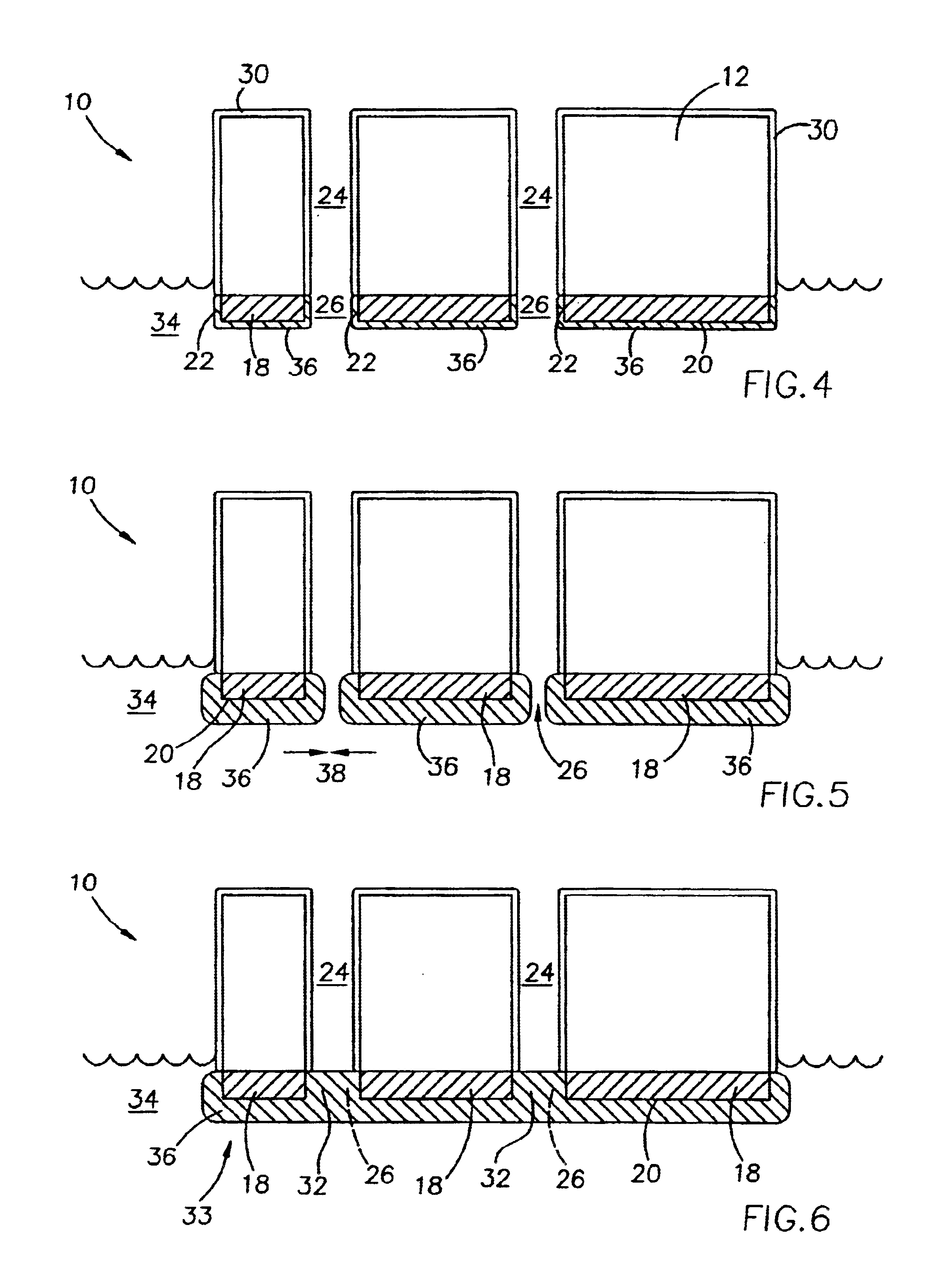

Built-up bump pad structure and method for same

InactiveUS6888255B2Reduce thicknessLess sensitivePrinted circuit assemblingFinal product manufactureSolder maskConductive materials

In accordance with the present invention, a built-up bump pad structure and method for the same are provided. The bump pad structure includes a substrate, a bump pad disposed upon the substrate, a solder mask disposed upon the substrate defining an opening around the bump pad, and a conductive material deposited upon the bump pad such that the conductive material at least partially fills the opening around the bump pad.

Owner:TEXAS INSTR INC

Vacuum deposition of bus bars onto conductive transparent films

InactiveUS6204480B1Suitable for processingWindowsConductive layers on insulating-supportsElectrical resistance and conductanceElectrical connection

Vacuum deposition processes such as sputter-depositing are employed to deposit electrically conductive bus bars onto thin film transparent conductor sheets. These assemblies provide efficient and durable electrical connections to the conductor sheets which can be laminated into glazing structures such as automotive windshields to provide resistance heating for defogging and deicing or the provide an electrical connection for in-window antennas and in window radiation shields.

Owner:SOUTHWALL TECH INC

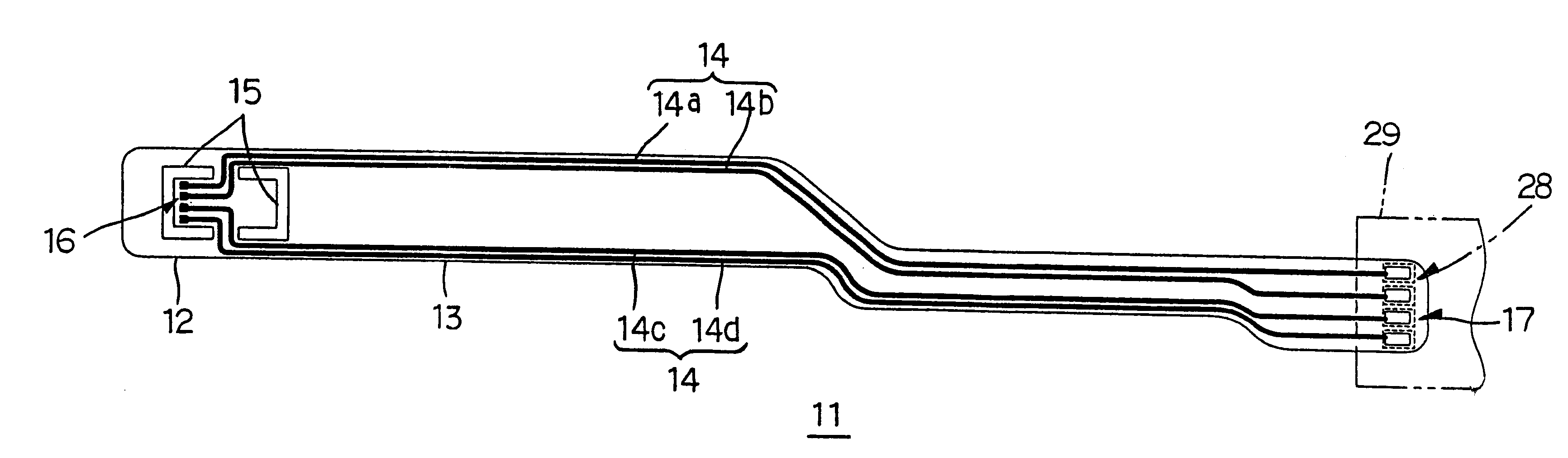

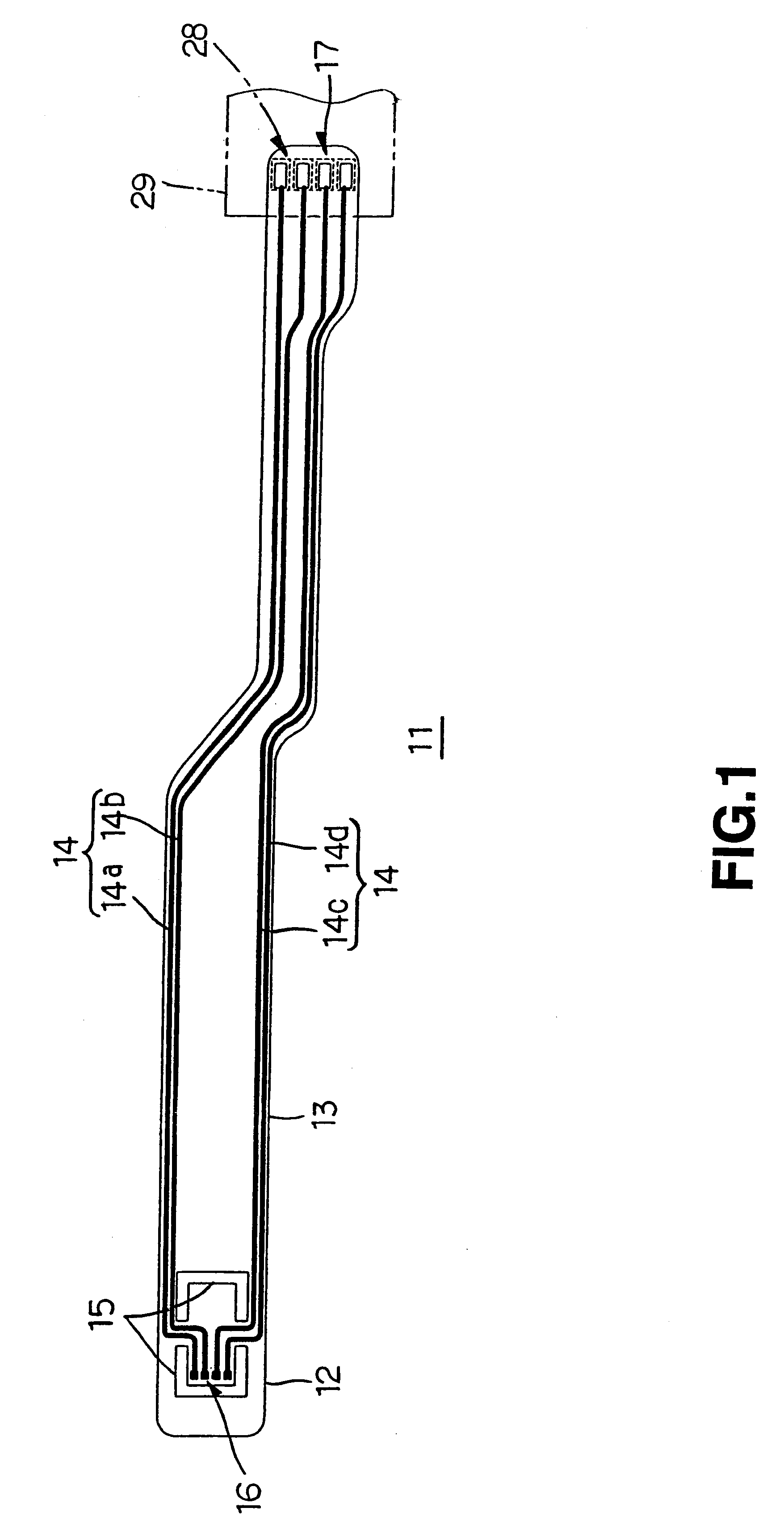

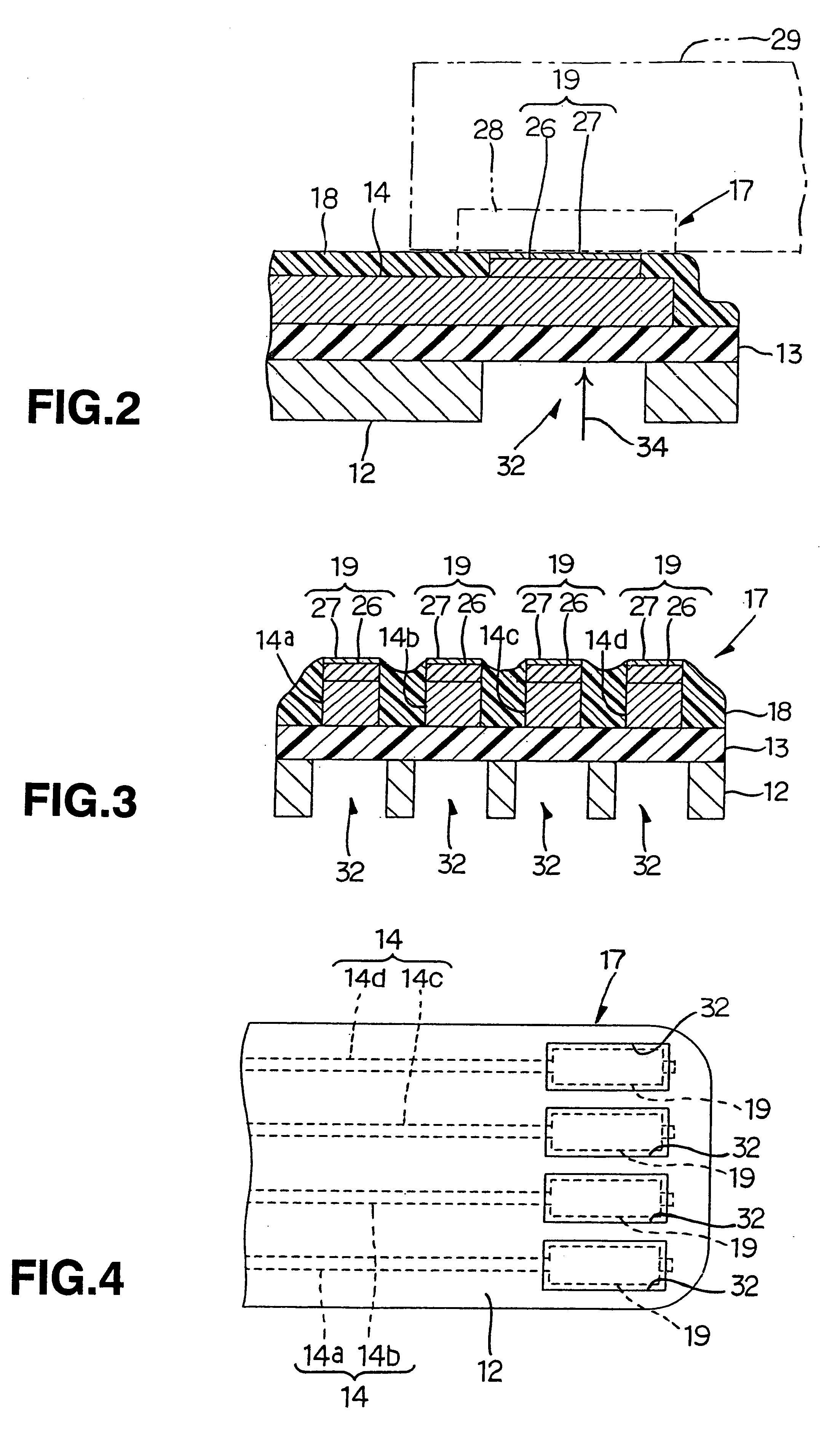

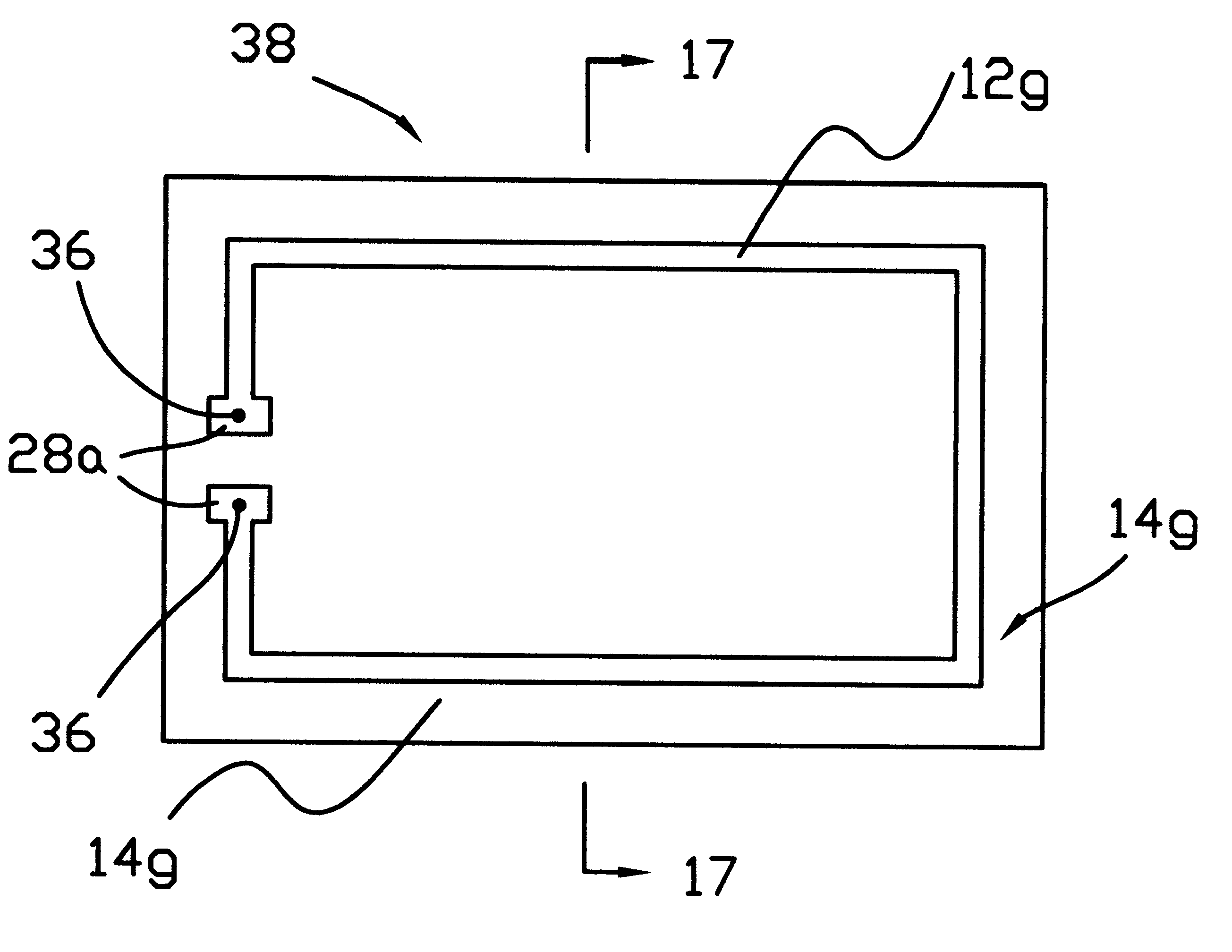

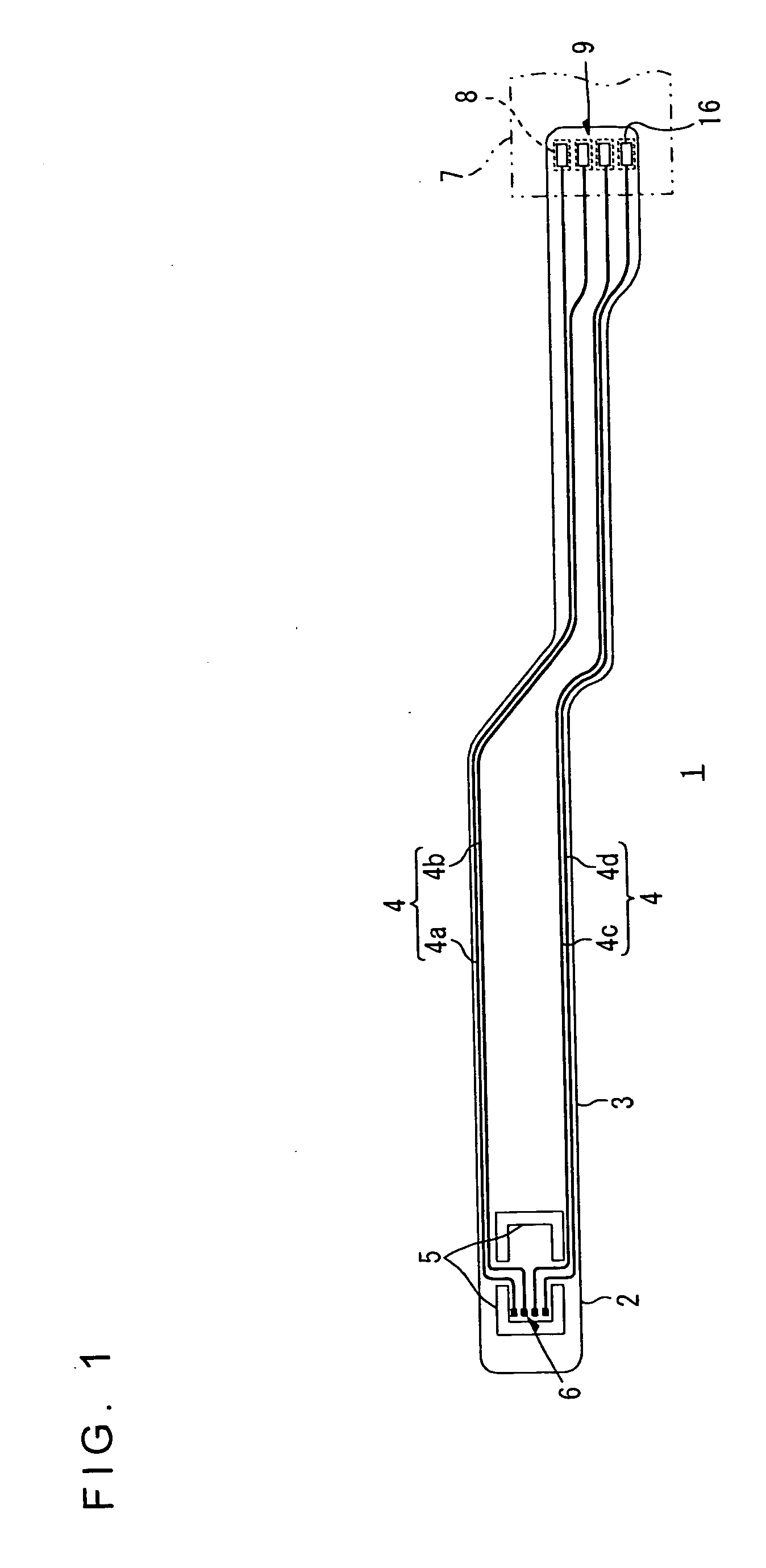

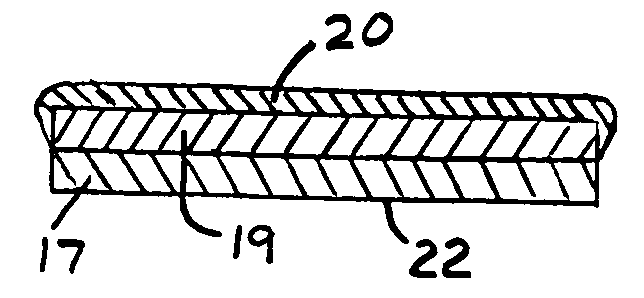

Suspension board with circuit

InactiveUS6399899B1High strengthSimple structureRelieving strain on wire connectionRecord information storageExternal connectionEngineering

To provide a suspension board with circuit that enables its terminals to be bonded to the other terminals with sufficient strength with simple structure, to ensure sufficient bonding reliability, the suspension board with circuit 11 includes a suspension board 12, a base layer 13 formed on the suspension board 12, and a conductive layer 14 formed on the base layer 13 and a cover layer 18 with which the conductive layer 14 is covered, wherein external connection terminals 17 to be bonded to terminals 28 of a read / write board 29 are formed without the suspension board 12 and / or the base layer 13 being formed.

Owner:NITTO DENKO CORP

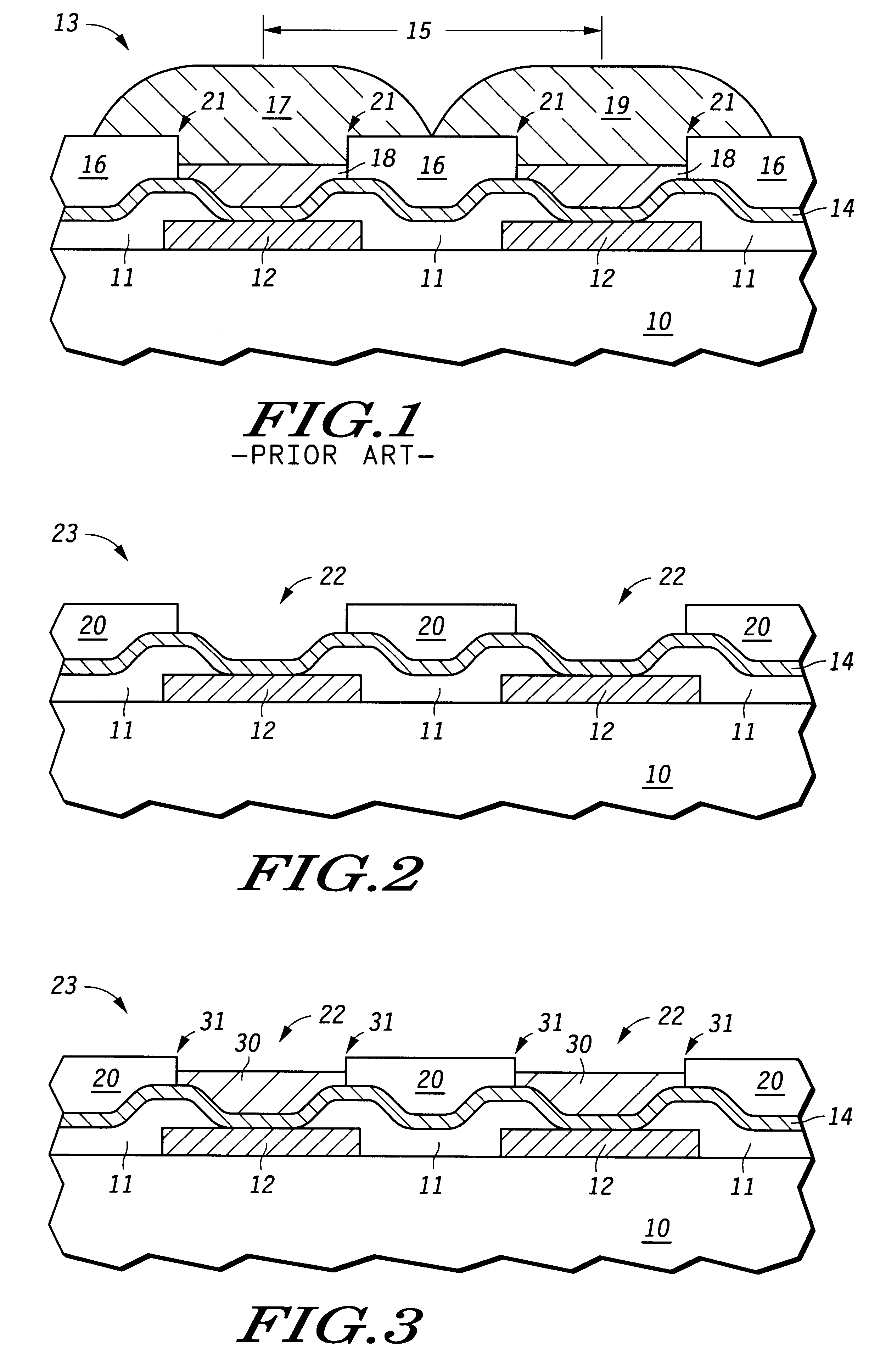

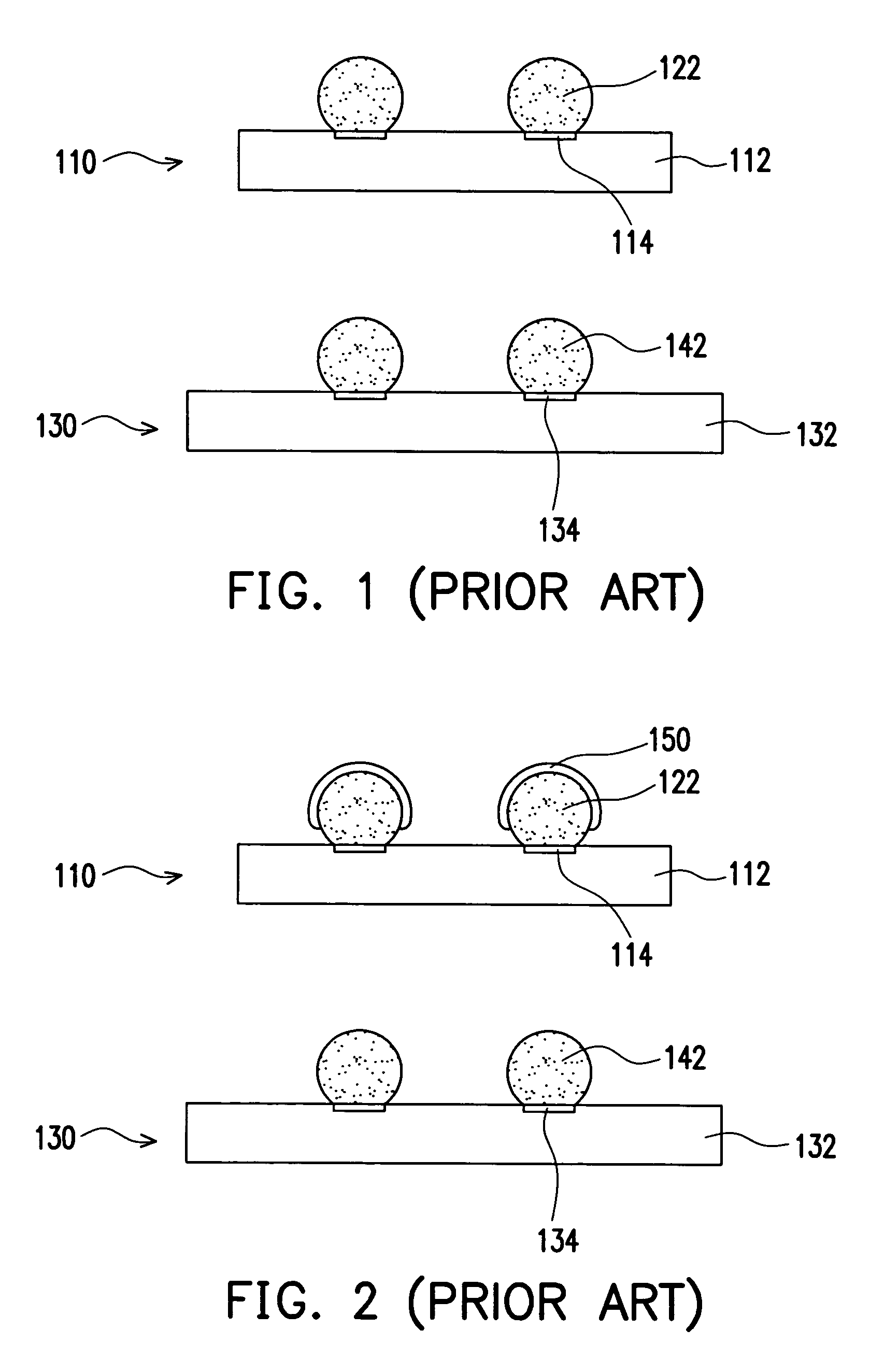

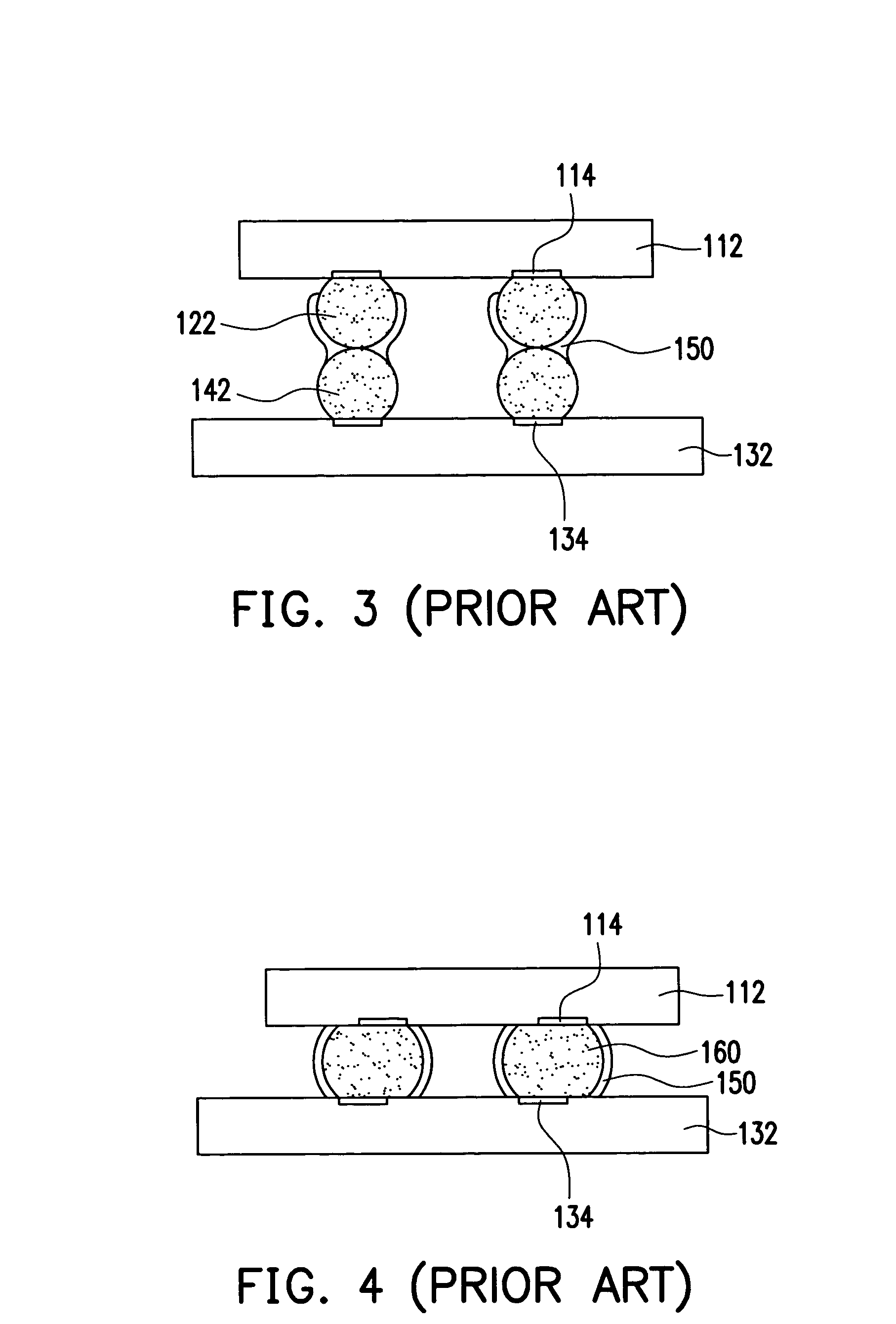

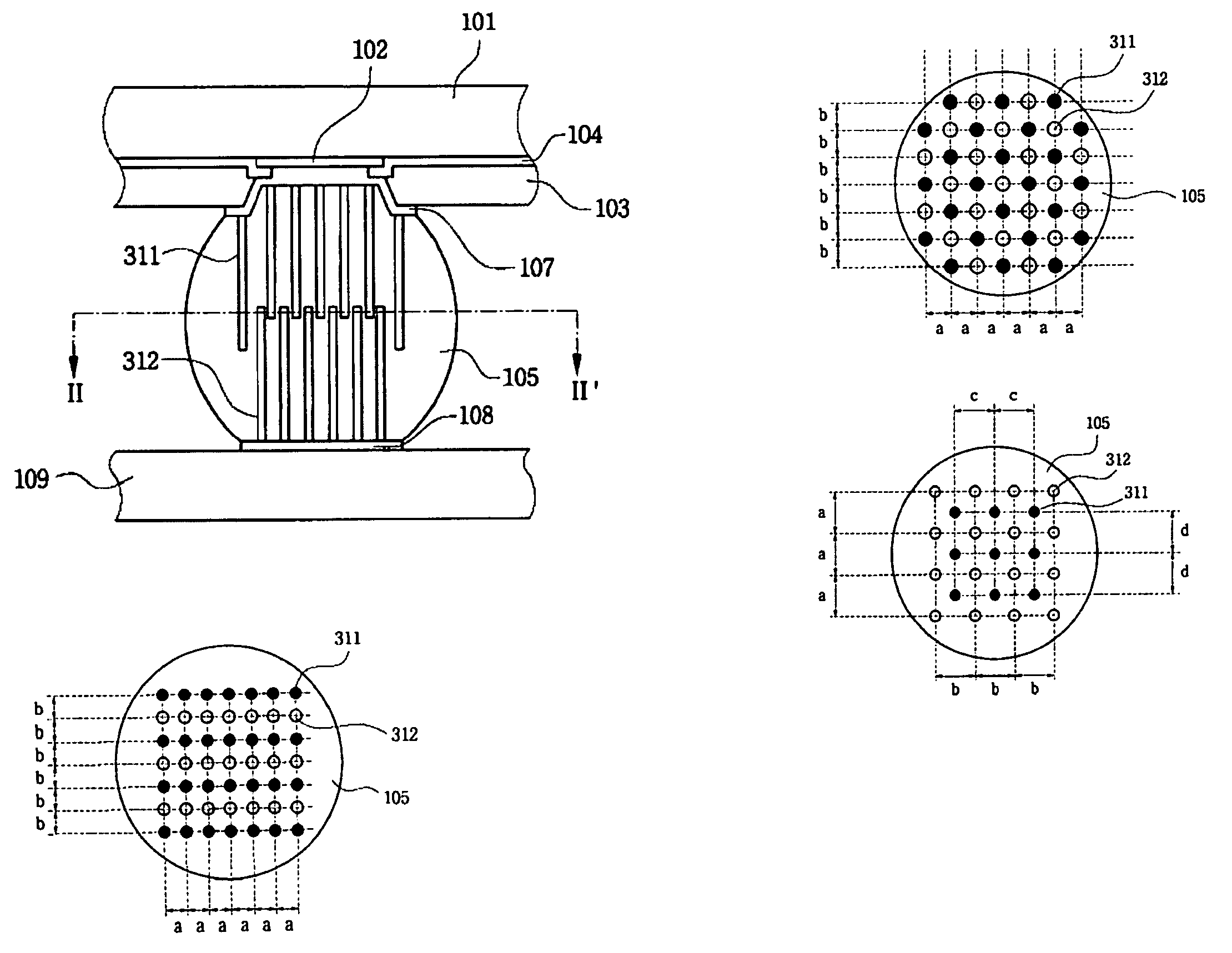

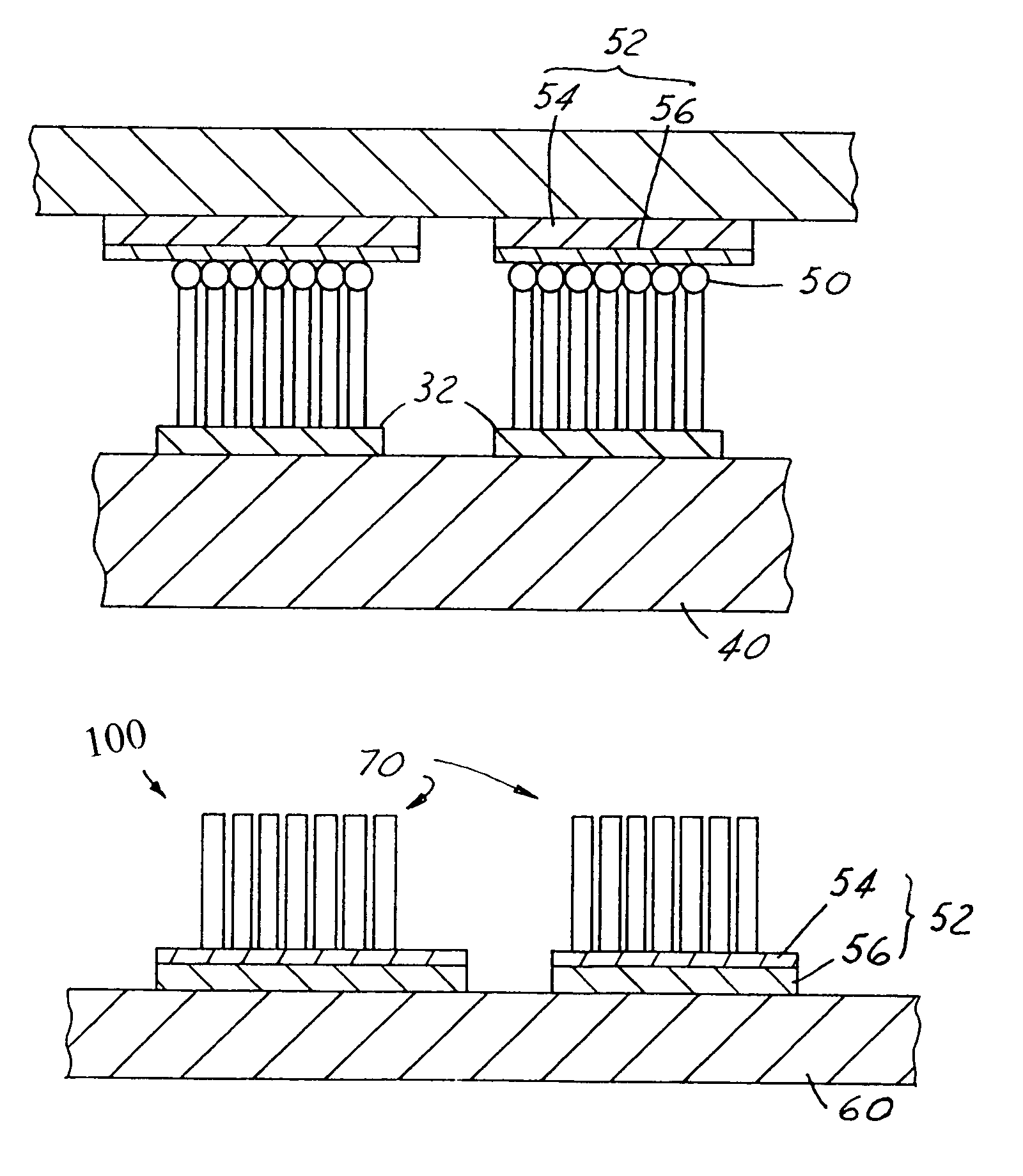

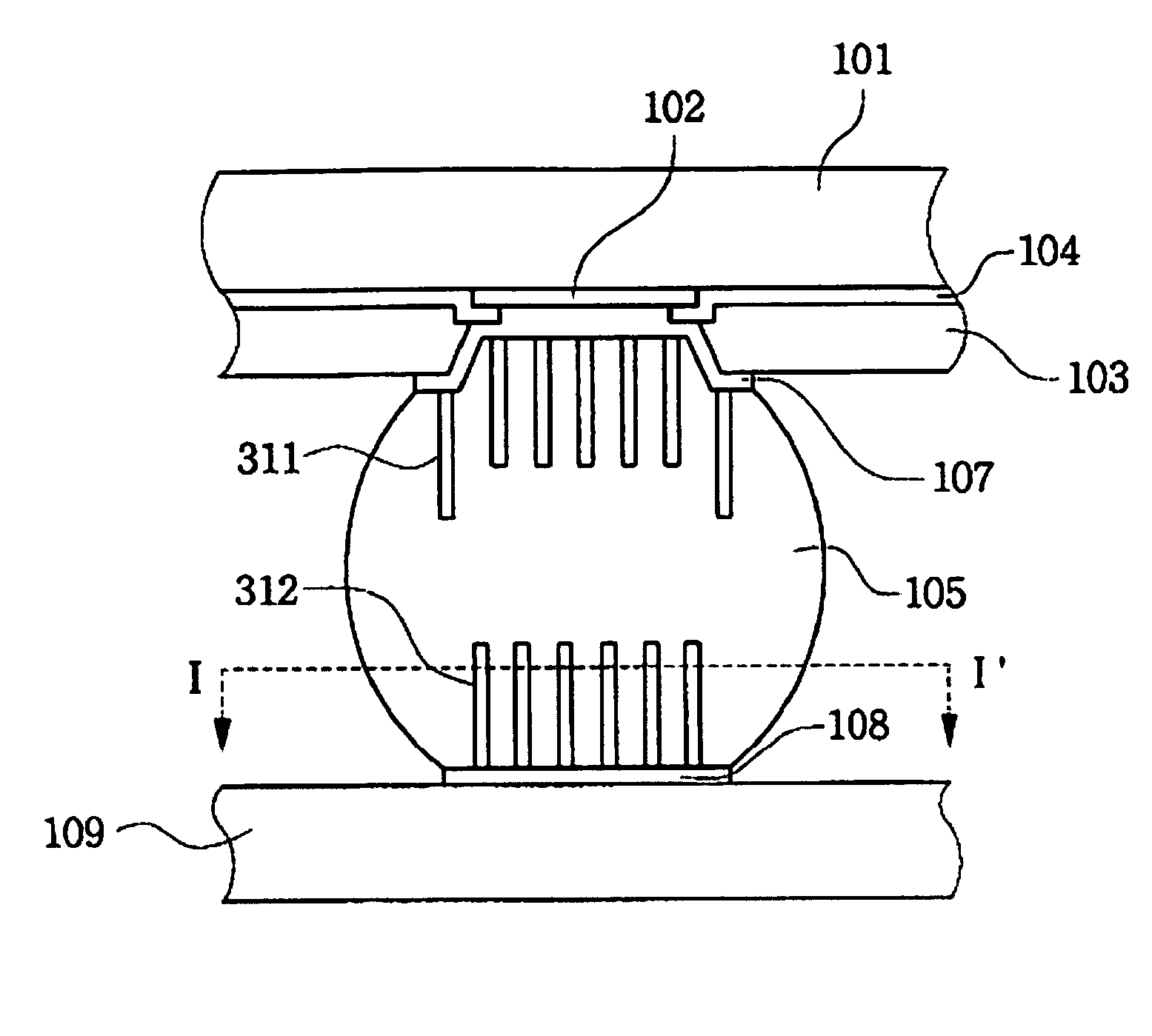

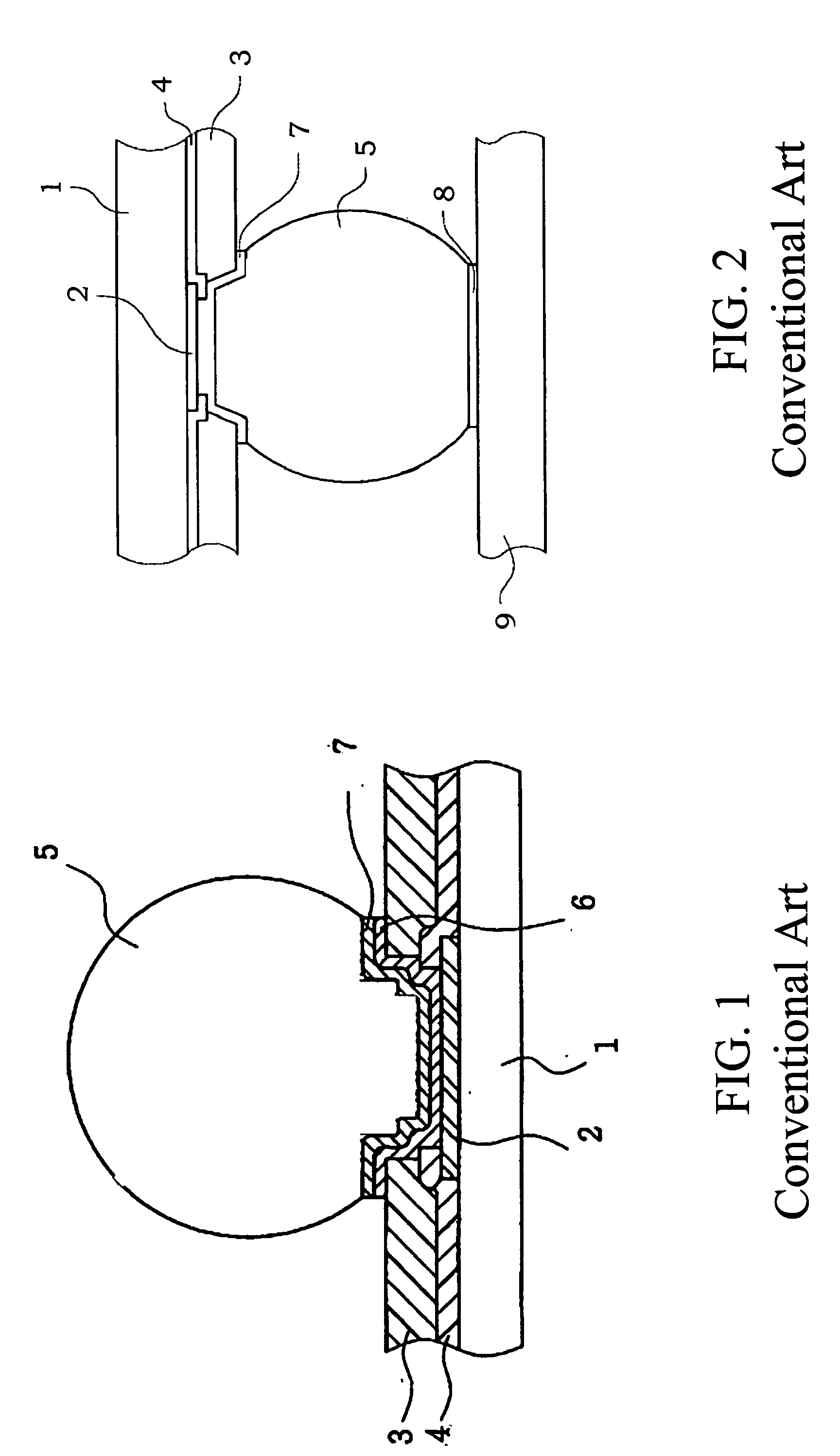

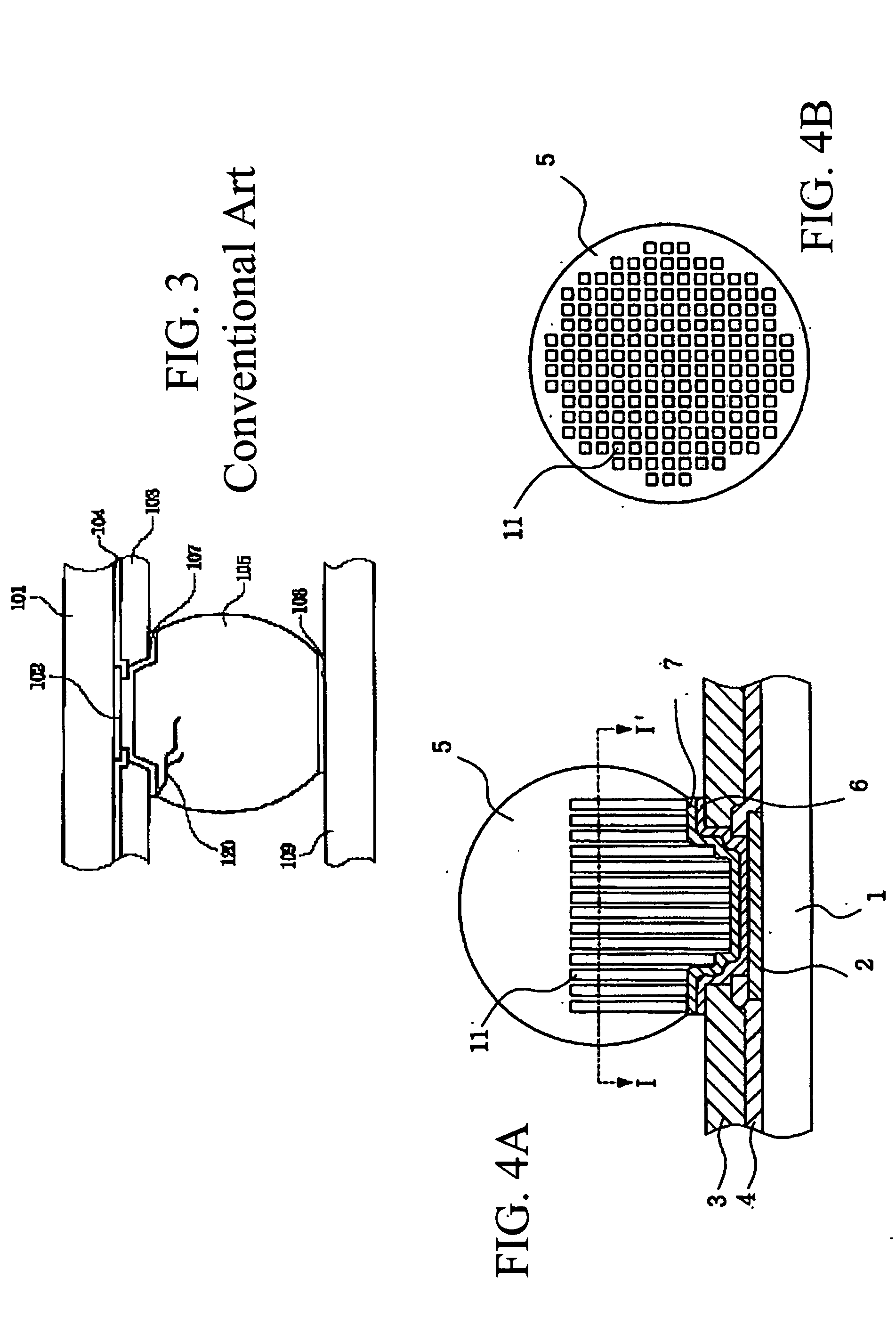

Reinforced solder bump structure and method for forming a reinforced solder bump

A reinforced solder bump connector structure is formed between a contact pad arranged on a semiconductor chip and a ball pad arranged on a mounting substrate. The semiconductor chip includes at least one reinforcing protrusion extending upwardly from a surface of an intermediate layer. The mounting substrate includes at least one reinforcing protrusion extending upwardly from a ball pad, the protrusions from both the chip and the substrate being embedded within the solder bump connector. In some configurations, the reinforcing protrusion from the contact pad and the ball pad are sized and arranged to have overlapping under portions. These overlapping portions may assume a wide variety of configurations that allow the protrusions to overlap without contacting each other including pin arrays and combinations of surrounding and surrounded elements. In each configuration, the reinforcing protrusions will tend to suppress crack formation and / or crack propagation thereby improving reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

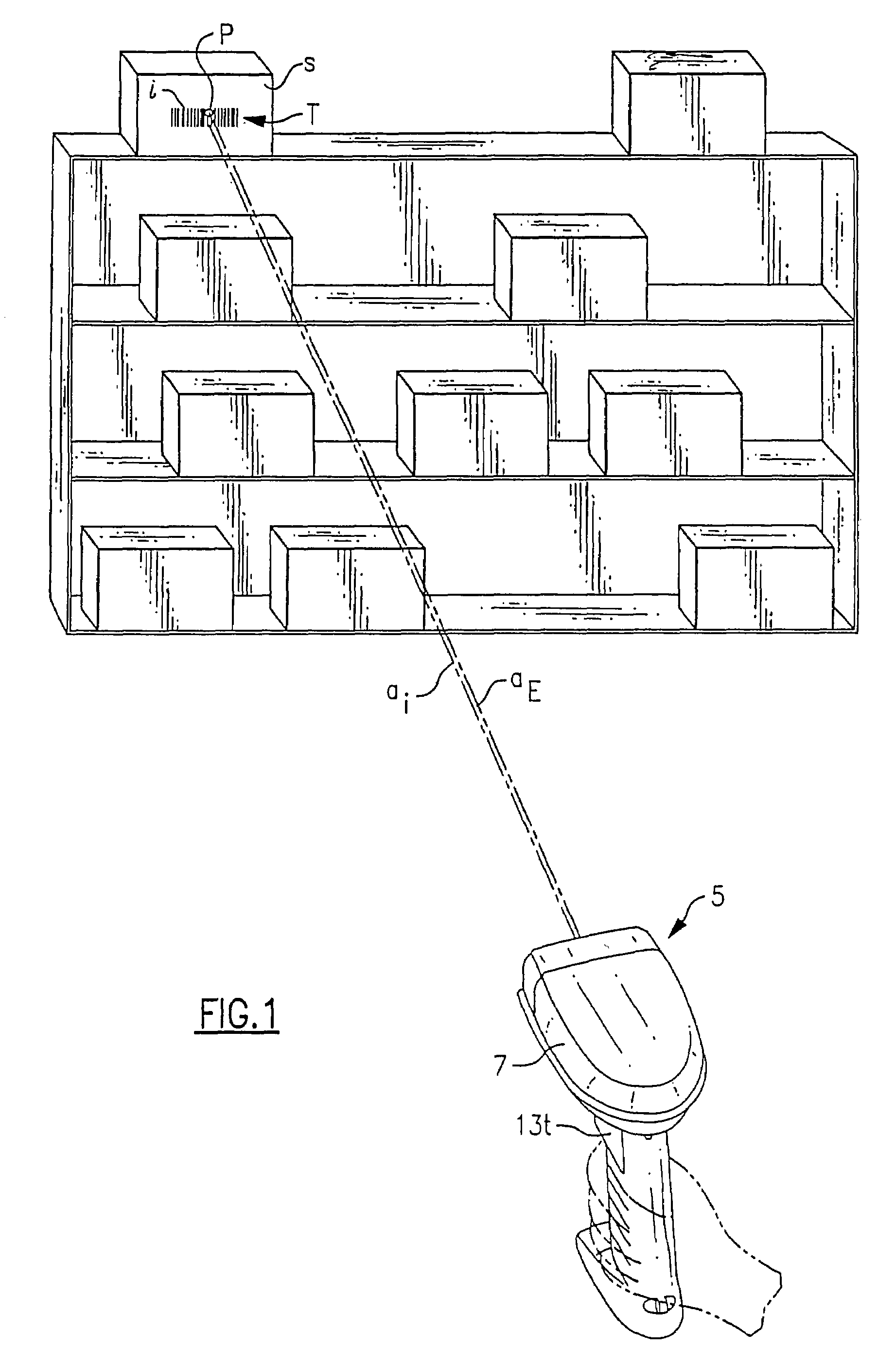

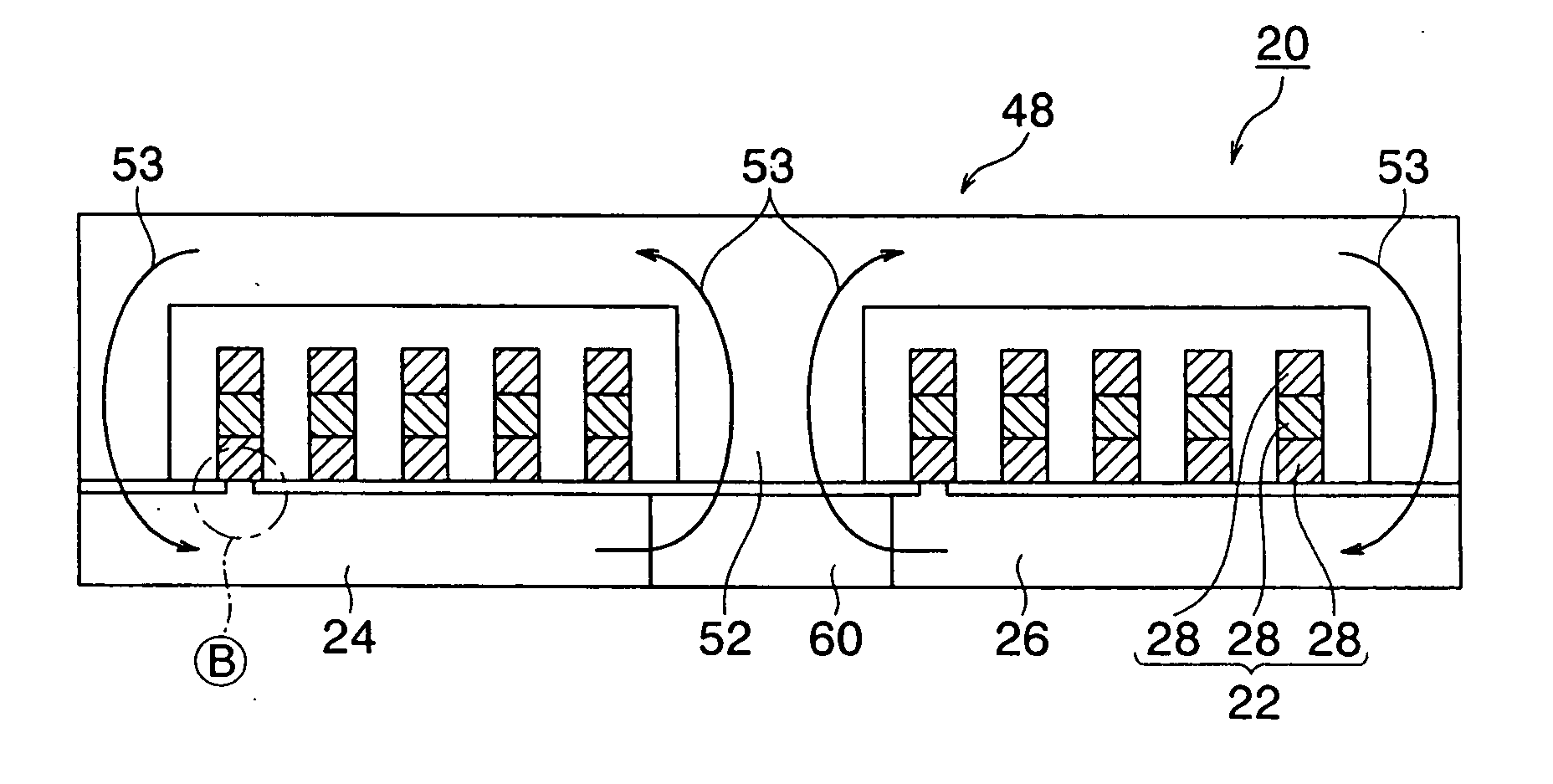

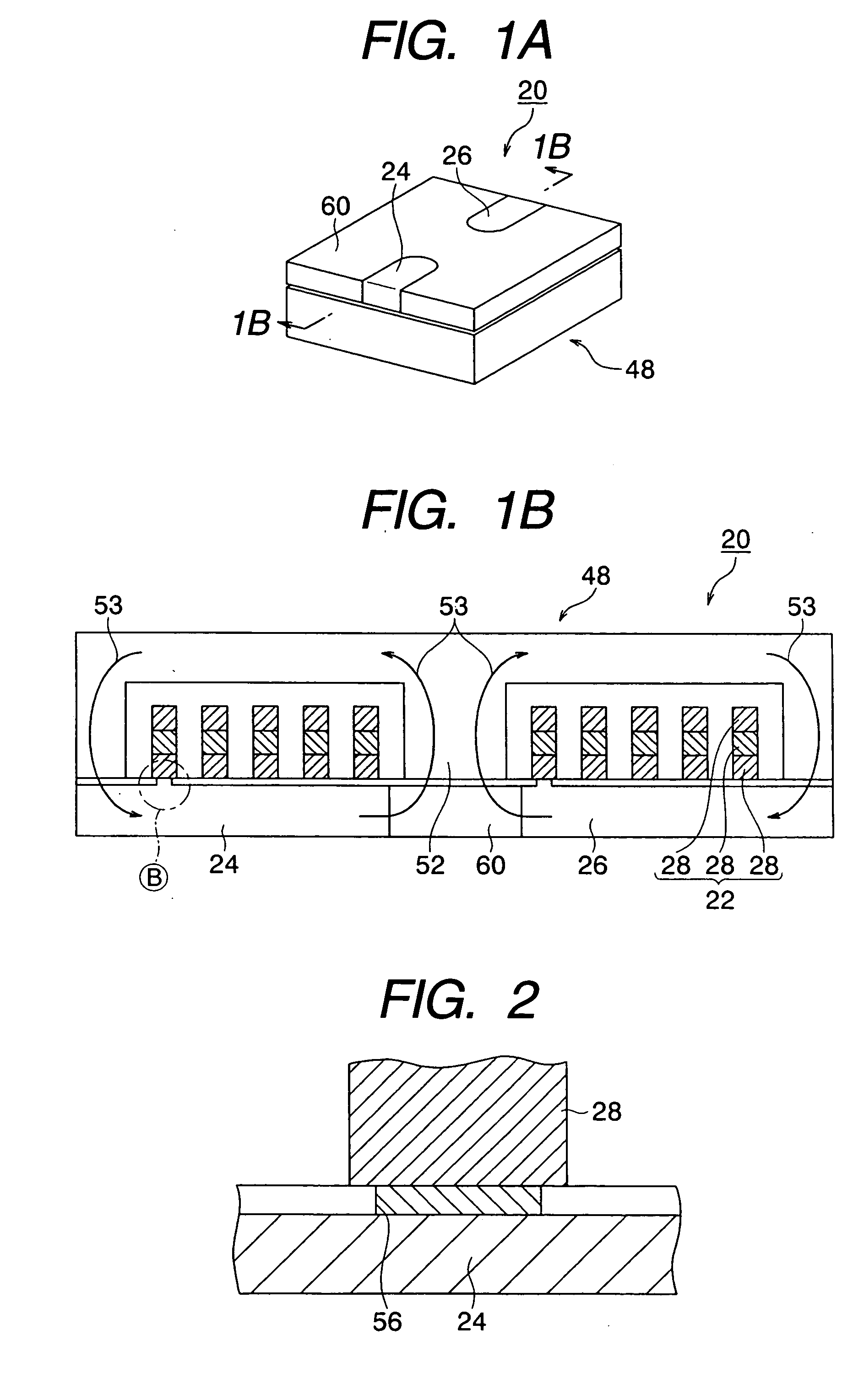

Long range optical reader

InactiveUS7090132B2Increase signal strengthSignal strength (signal to noise ratio) of a long range reader can be enhancedPrinted circuit aspectsElectrical connection printed elementsEngineeringSolder paste

An optical reader in one embodiment can include a substrate defining an opening and solder pads coupled to the substrate proximate the opening. A laser diode including first, second, and third electrical leads can also be coupled to the substrate. First, second and third solder pads can be provided on the substrate and the first, second, and third electrical leads of the laser diode can be coupled to the first, second, and third solder pads. An optical reader in another embodiment can include a substrate having a first surface and a second surface. A laser diode assembly configured to emit a laser beam can be coupled to the first surface and an illumination assembly that can include light emitting diodes can be coupled to the second surface.

Owner:HAND HELD PRODS

Long range optical reader

InactiveUS20030226895A1Signal strength (signal to noise ratio) of a long range reader can be enhancedIncrease signal strengthPrinted circuit aspectsConductive pattern reinforcementOptical readerReading distance

An optical reader including an image sensor, imaging optics, a short range aiming assembly, and a long range aiming assembly. The short range aiming assembly may comprise a plurality of LEDs. The long range aiming assembly may comprise a laser diode assembly which projects an aiming pattern that is readily visible at reading distances of several feet. The optical reader can be configured so that long range aiming assembly is enabled or disabled depending upon a present operating condition.

Owner:HAND HELD PRODS

Copper electroplating method and apparatus

An electroplating apparatus prevents anode-mediated degradation of electrolyte additives by creating a mechanism for maintaining separate anolyte and catholyte and preventing mixing thereof within a plating chamber. The separation is accomplished by interposing a porous chemical transport barrier between the anode and cathode. The transport barrier limits the chemical transport (via diffusion and / or convection) of all species but allows migration of ionic species (and hence passage of current) during application of sufficiently large electric fields within electrolyte.

Owner:NOVELLUS SYSTEMS

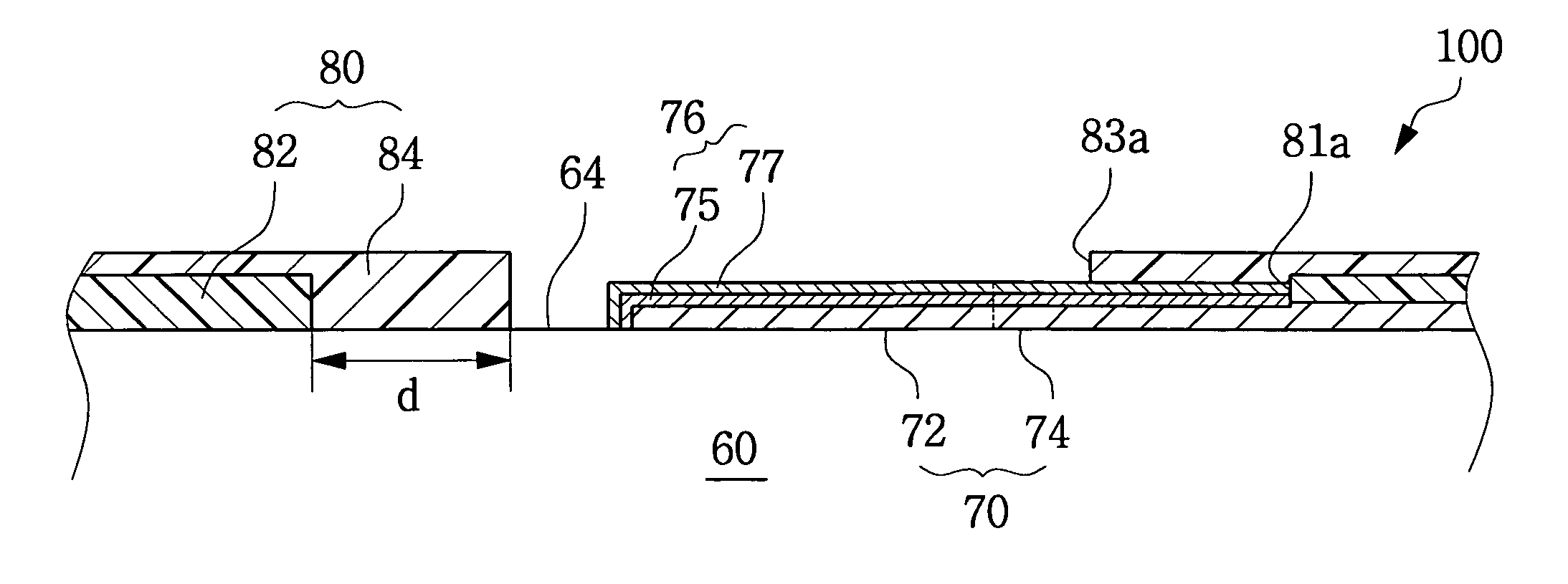

Low fabrication cost, high performance, high reliability chip scale package

InactiveUS6917119B2Minimize damageImprove reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElastomerContact pad

The invention provides a new method and chip scale package is provided. The inventions starts with a substrate over which a contact point is provided, the contact point is exposed through an opening created in the layer of passivation and a layer of polymer or elastomer. A barrier / seed layer is deposited, a first photoresist mask is created exposing the barrier / seed layer where this layer overlies the contact pad and, contiguous therewith, over a surface area that is adjacent to the contact pad and emanating in one direction from the contact pad. The exposed surface of the barrier / seed layer is electroplated for the creation of interconnect traces. The first photoresist mask is removed from the surface of the barrier / seed layer. A second photoresist mask, defining the solder bump, is created exposing the surface area of the barrier / seed layer that is adjacent to the contact pad and emanating in one direction from the contact pad. The solder bump is created in accordance with the second photoresist mask, the second photoresist mask is removed from the surface of the barrier / seed layer, exposing the electroplating and the barrier / seed layer with the metal plating overlying the barrier / seed layer. The exposed barrier / seed layer is etched in accordance with the pattern formed by the electroplating, reflow of the solder bump is optionally performed.

Owner:QUALCOMM INC

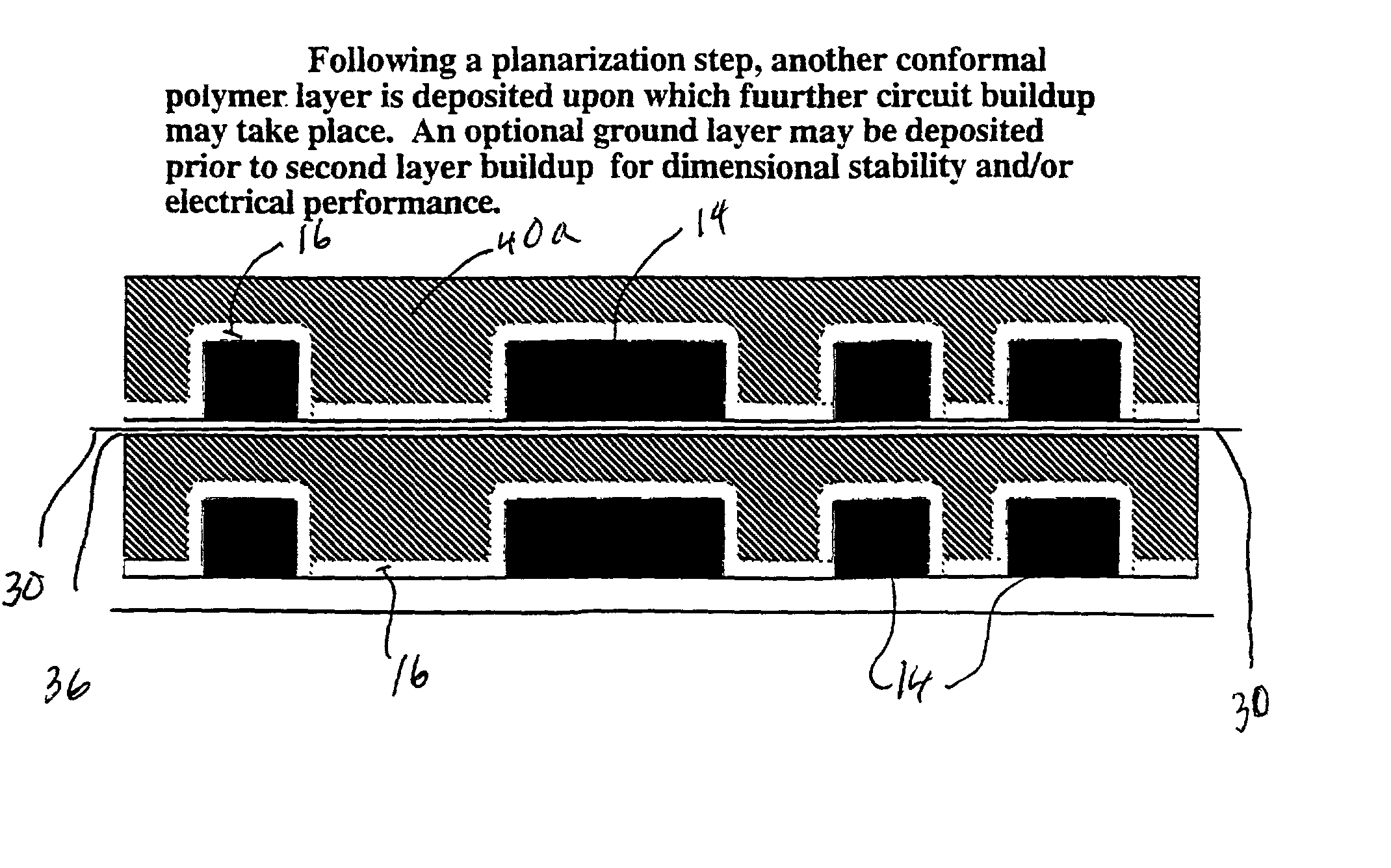

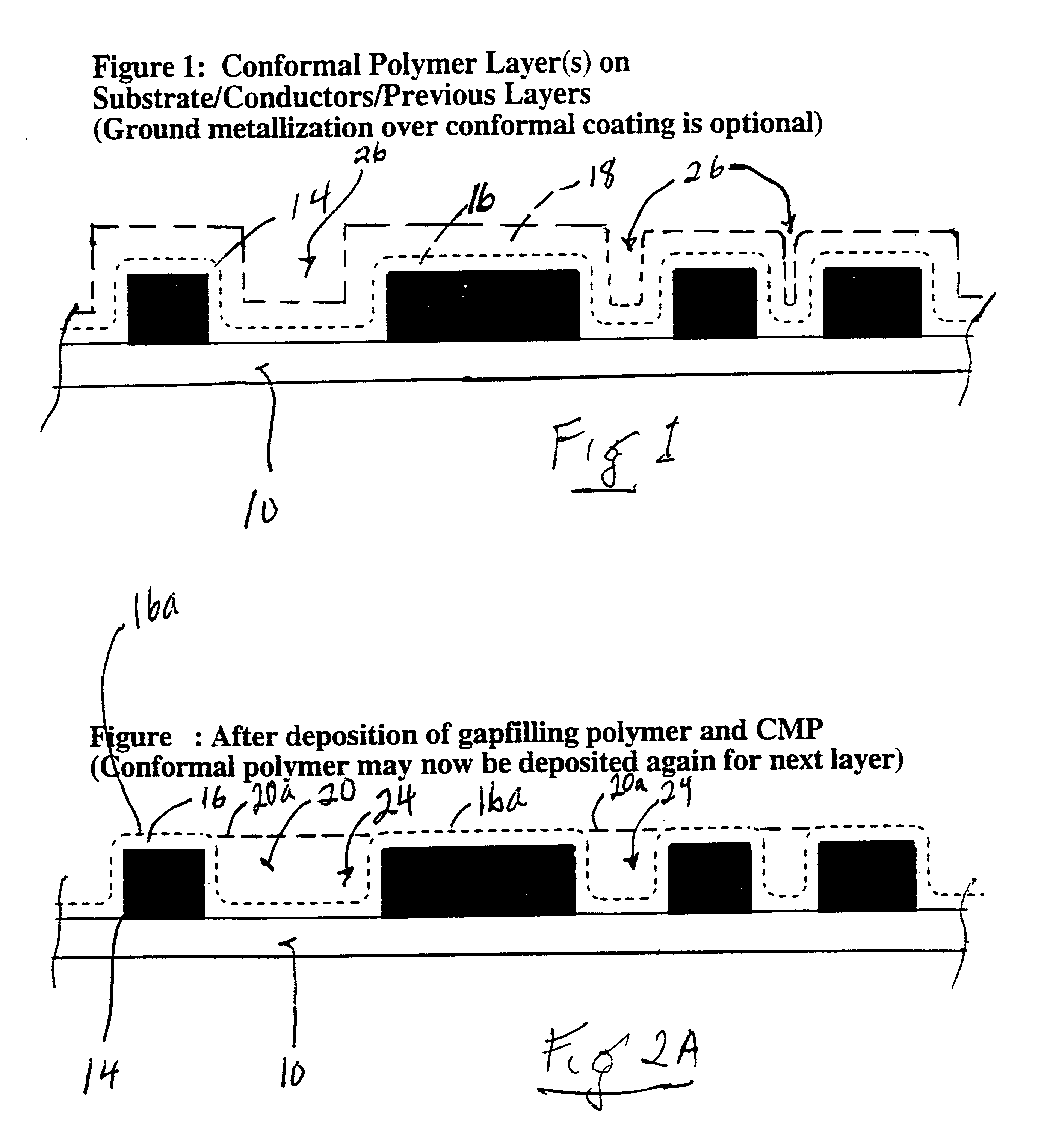

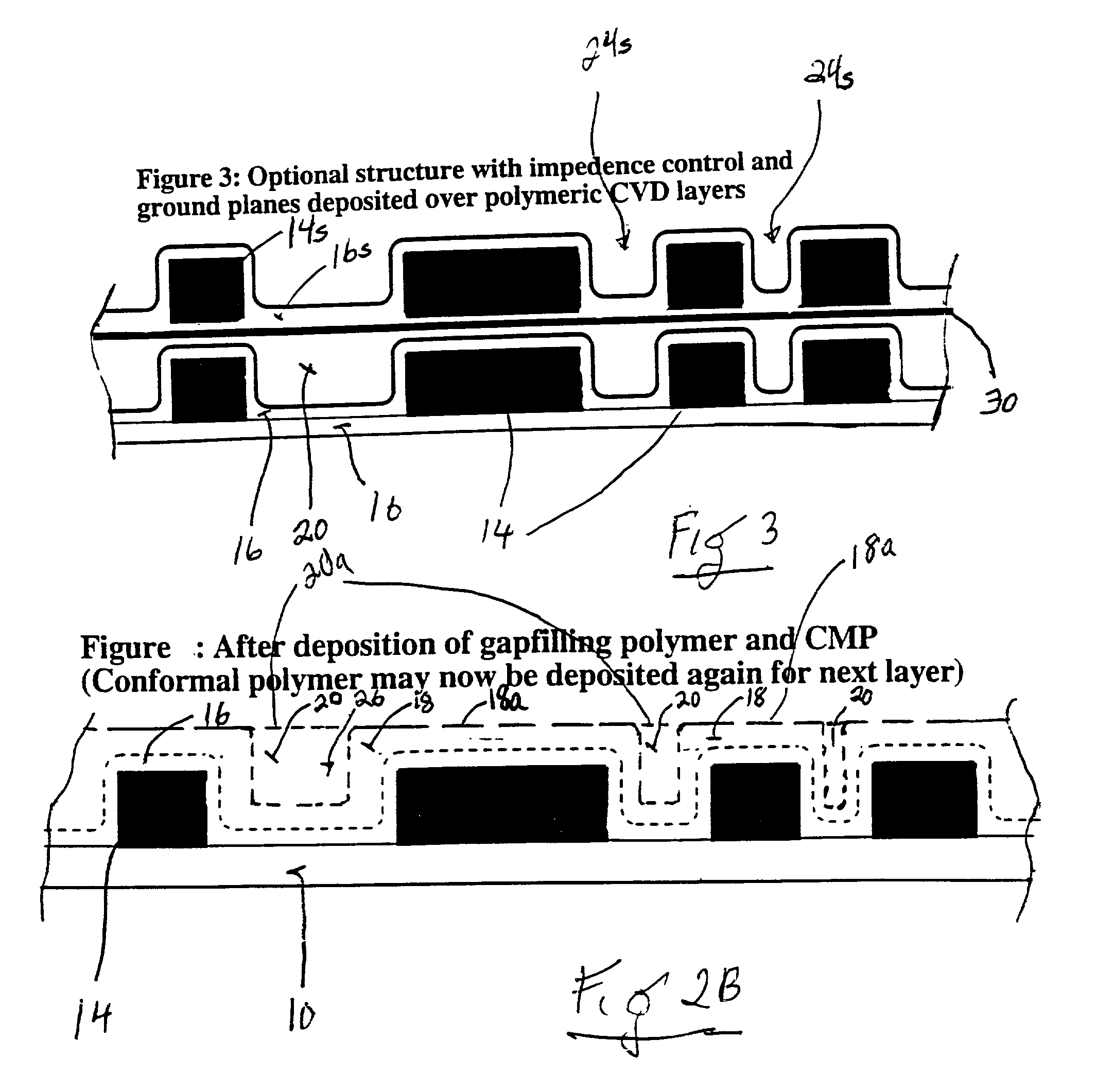

Multi-chip module and method for forming and method for deplating defective capacitors

A method for deplating defective capacitors comprising forming a plurality of capacitors on a semiconductor substrate, forming a plurality of metal contacts on the plurality of capacitors, and depositing a layer of photoresist on the semiconductor substrate. The photoresist layer is patterned so that the plurality of metal contacts are exposed, which are then contacted with an electrically conductive solution. The metal contacts, which are disposed over defective capacitors, are subsequently deplated. A method for forming a multi-chip module comprising forming a thin-film polymeric interconnect structure having a pair of sides, one of which is disposed on a silicon substrate having active or passive devices and the other of which has a computer chip mounted thereon. A multi-chip module formed by the method.

Owner:FUJITSU LTD

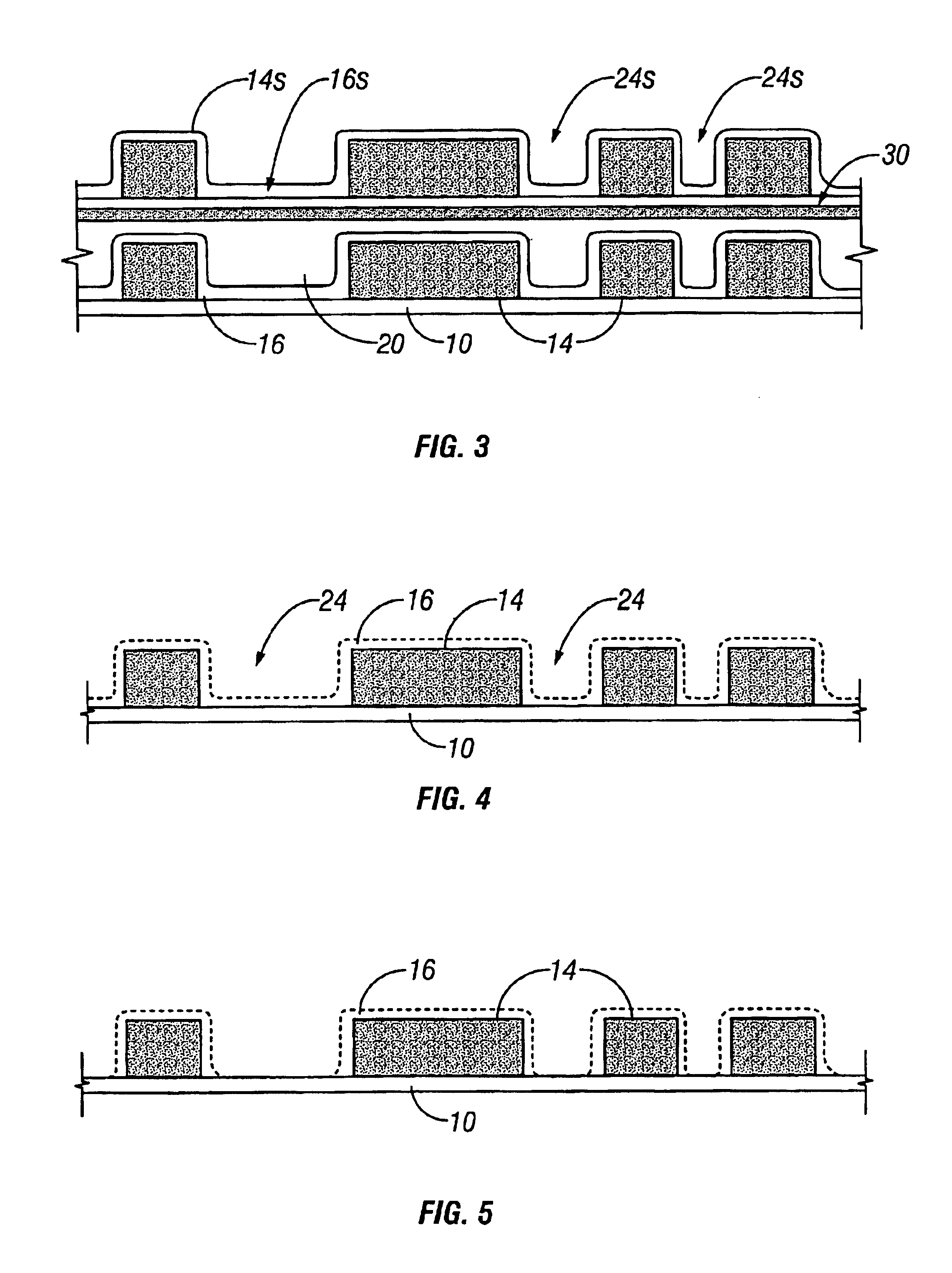

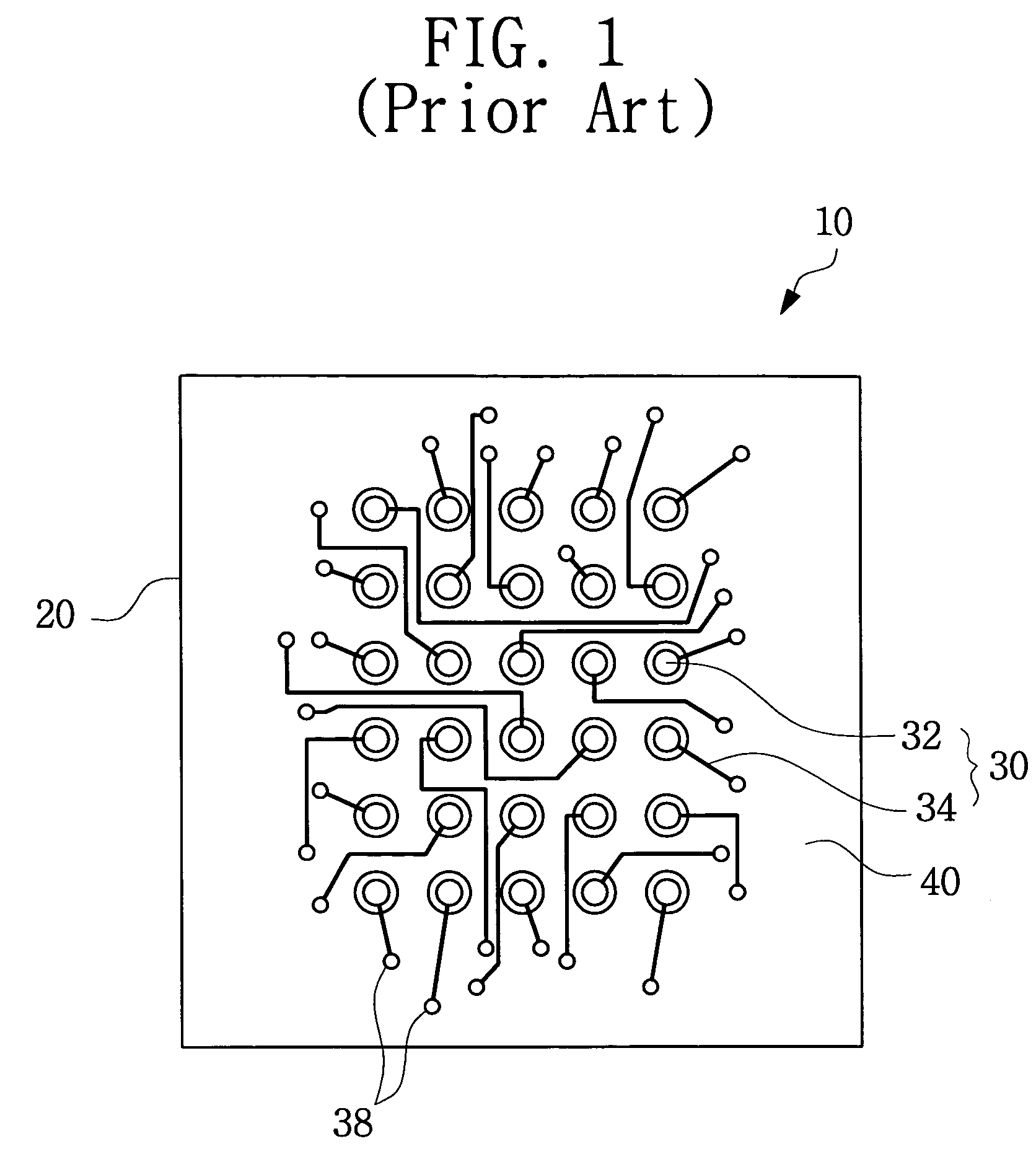

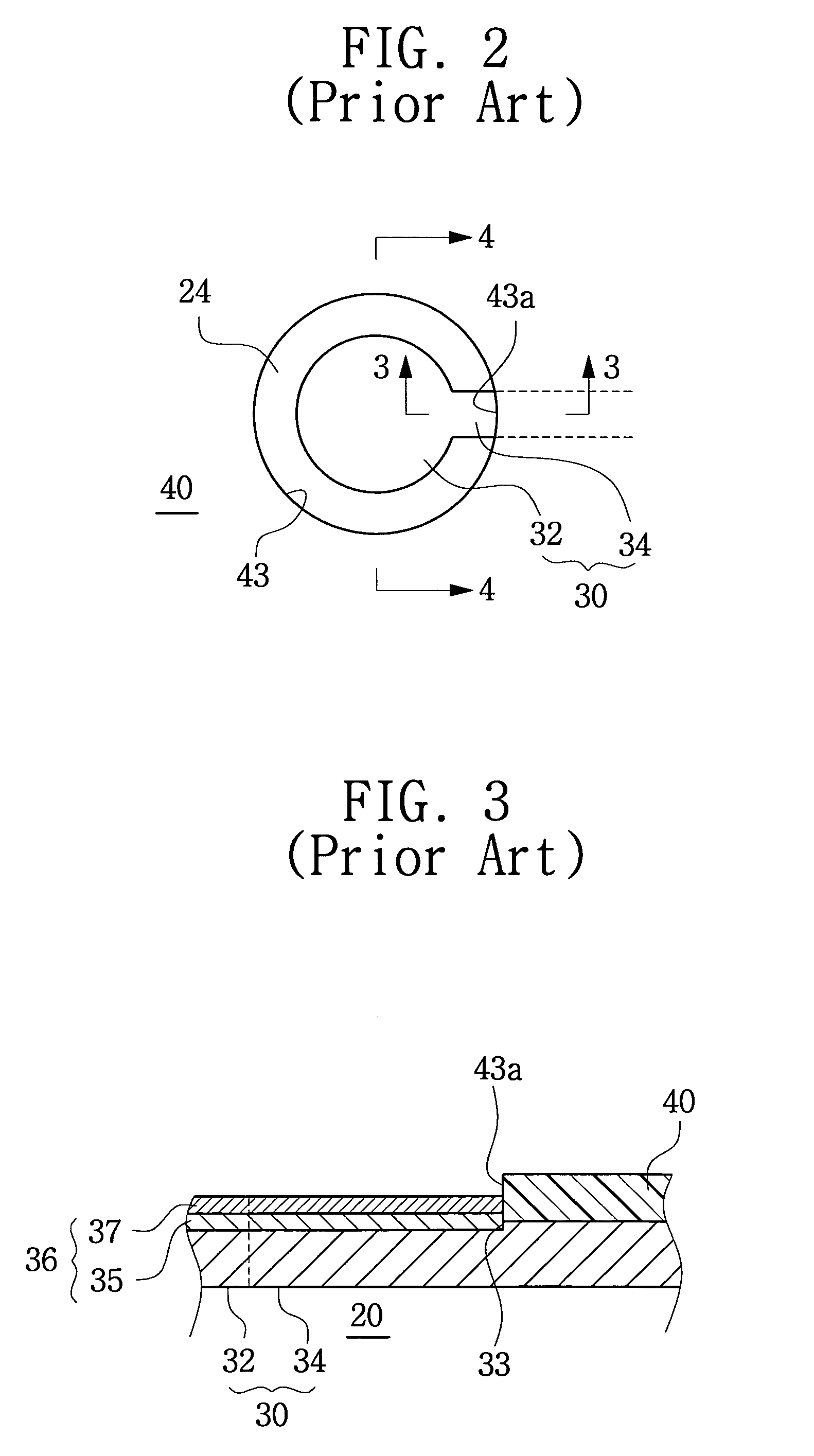

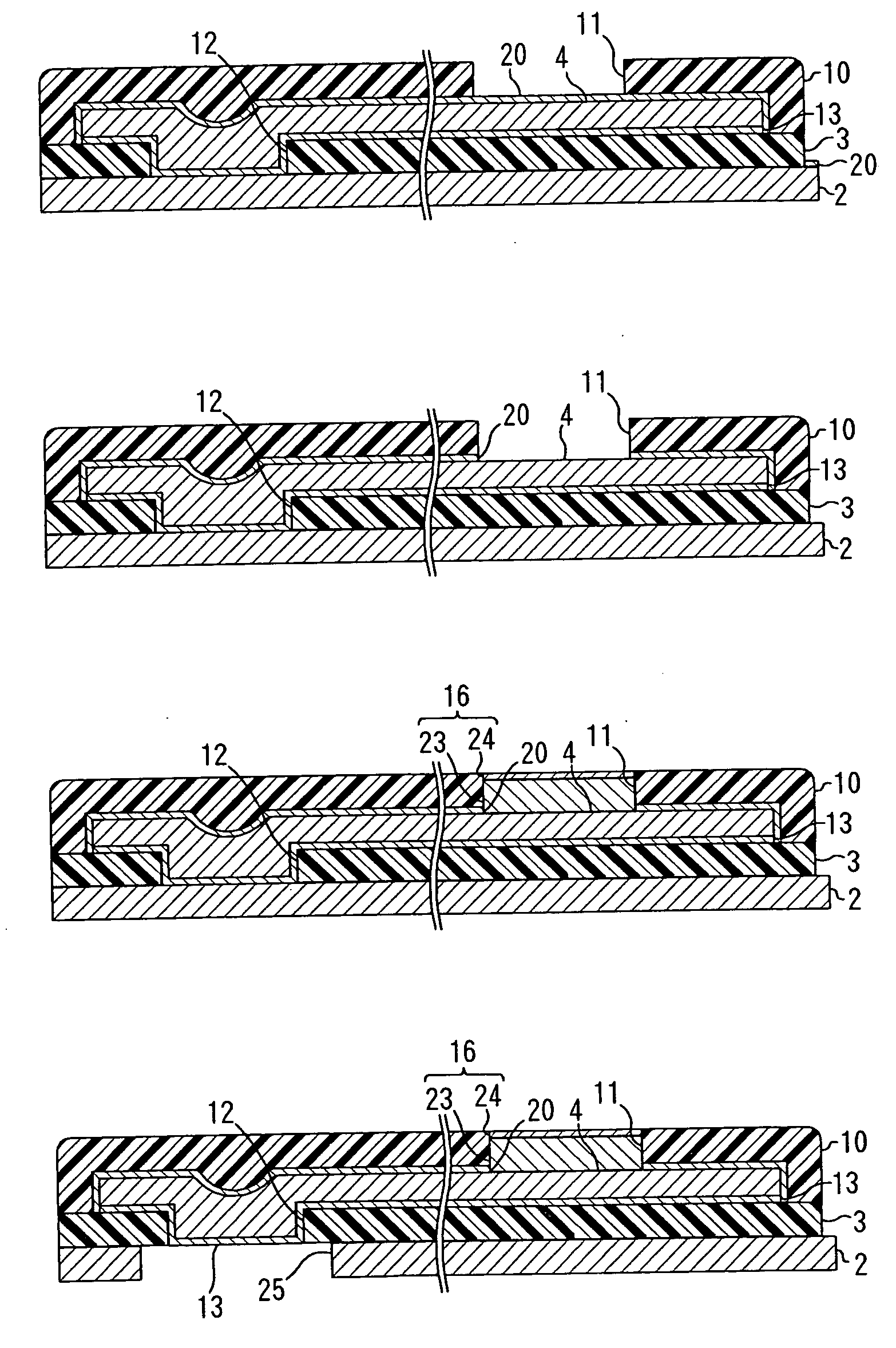

Non-solder mask defined (NSMD) type wiring substrate for ball grid array (BGA) package and method for manufacturing such a wiring substrate

ActiveUS7098407B2Reduce crackingReduce stress concentrationPrinted circuit assemblingSemiconductor/solid-state device detailsStress concentrationSolder mask

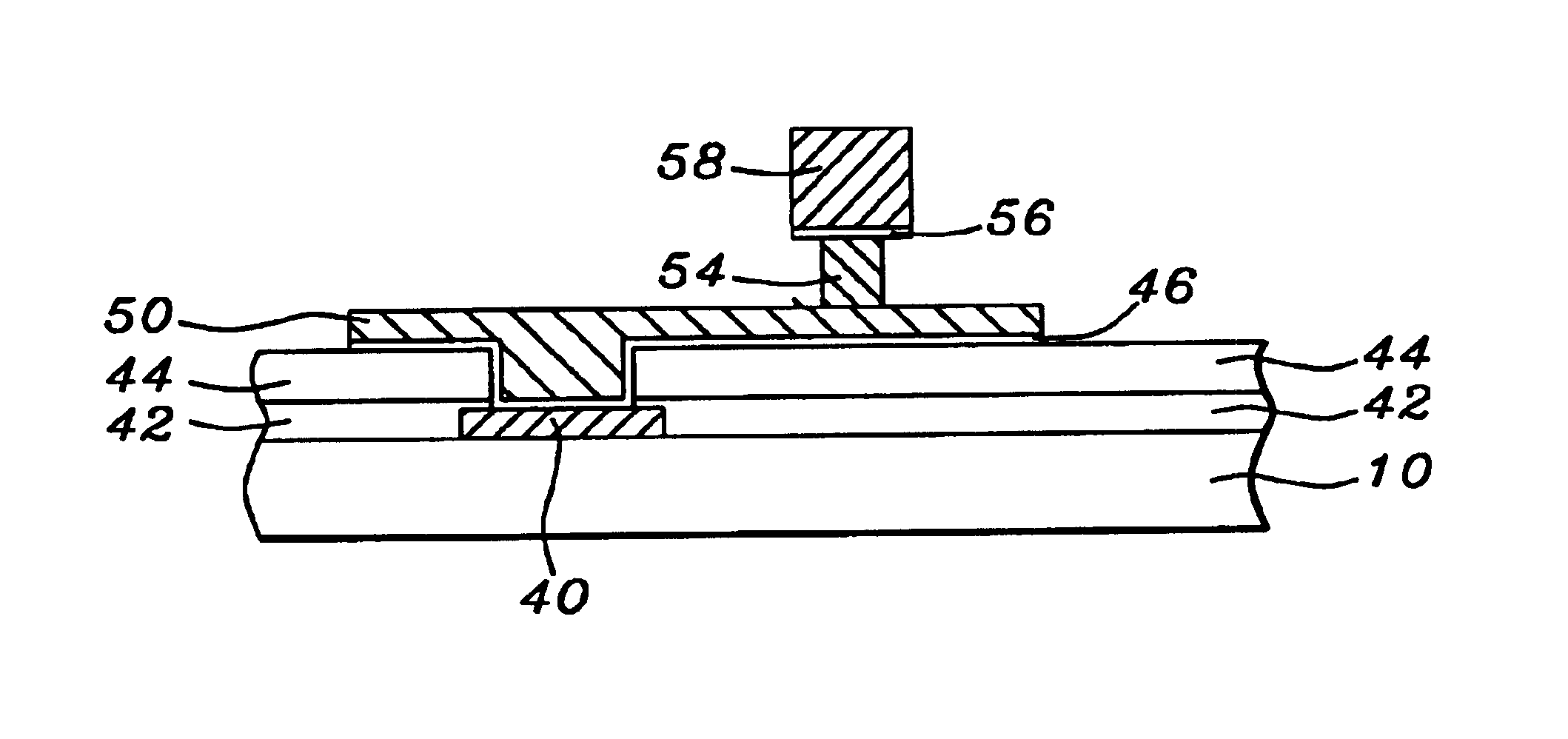

In one embodiment, a pad is formed on a substrate surface. The pad is connected with a connecting pattern. A first mask is formed on the substrate. The first mask has a first opening exposing at least a portion of the pad and a portion of the connecting pattern. A second mask is formed on the first mask. The second mask has a second opening exposing at least a portion of the pad and a portion of the connecting pattern. A boundary surface or sidewall of the first opening is not coplanar with a boundary surface or sidewall of the second opening. Therefore, stresses may be prevented from concentrating on the boundary surface of the first opening, thereby allowing dispersion of the stresses and restraining pattern cracks.

Owner:SAMSUNG ELECTRONICS CO LTD

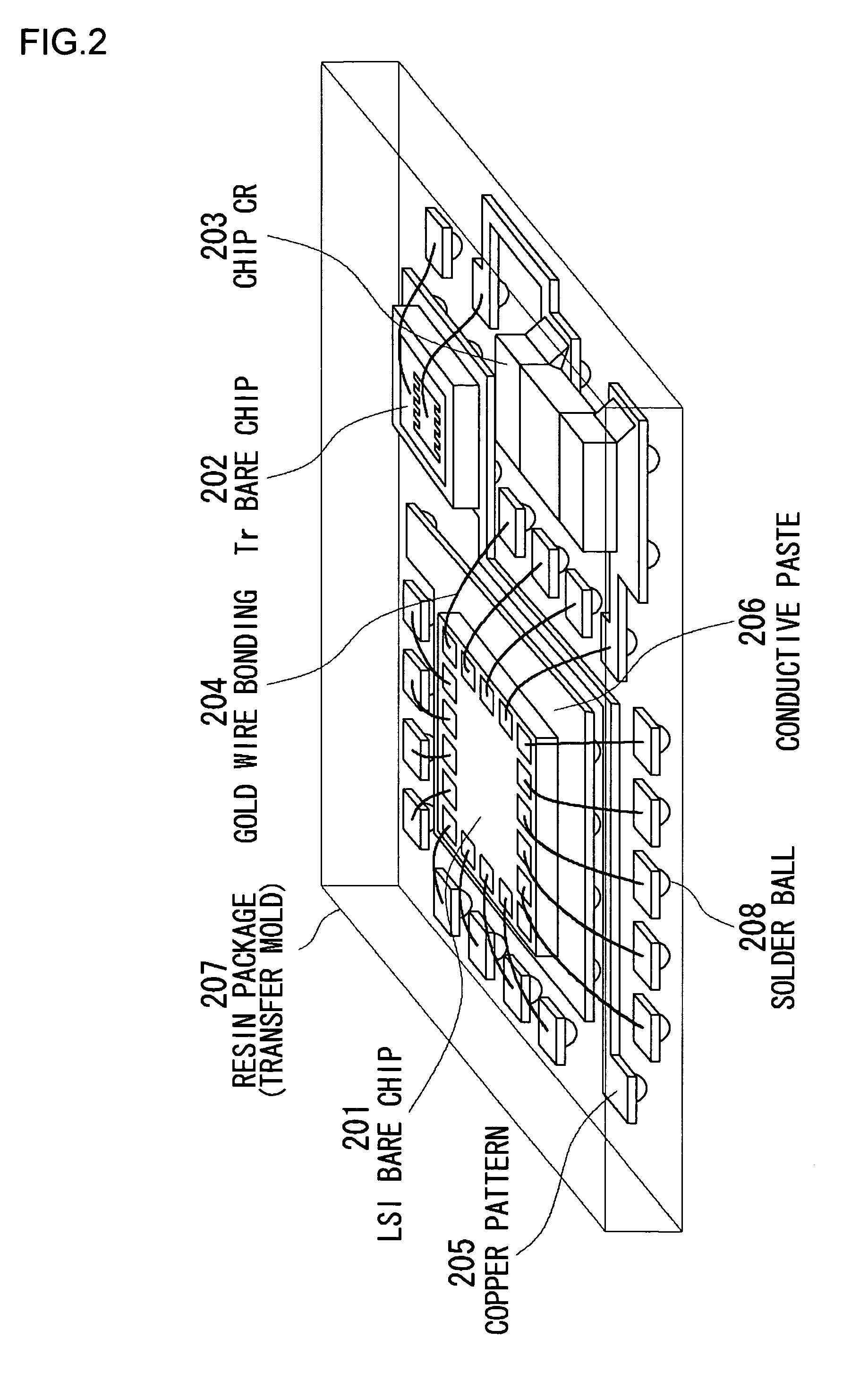

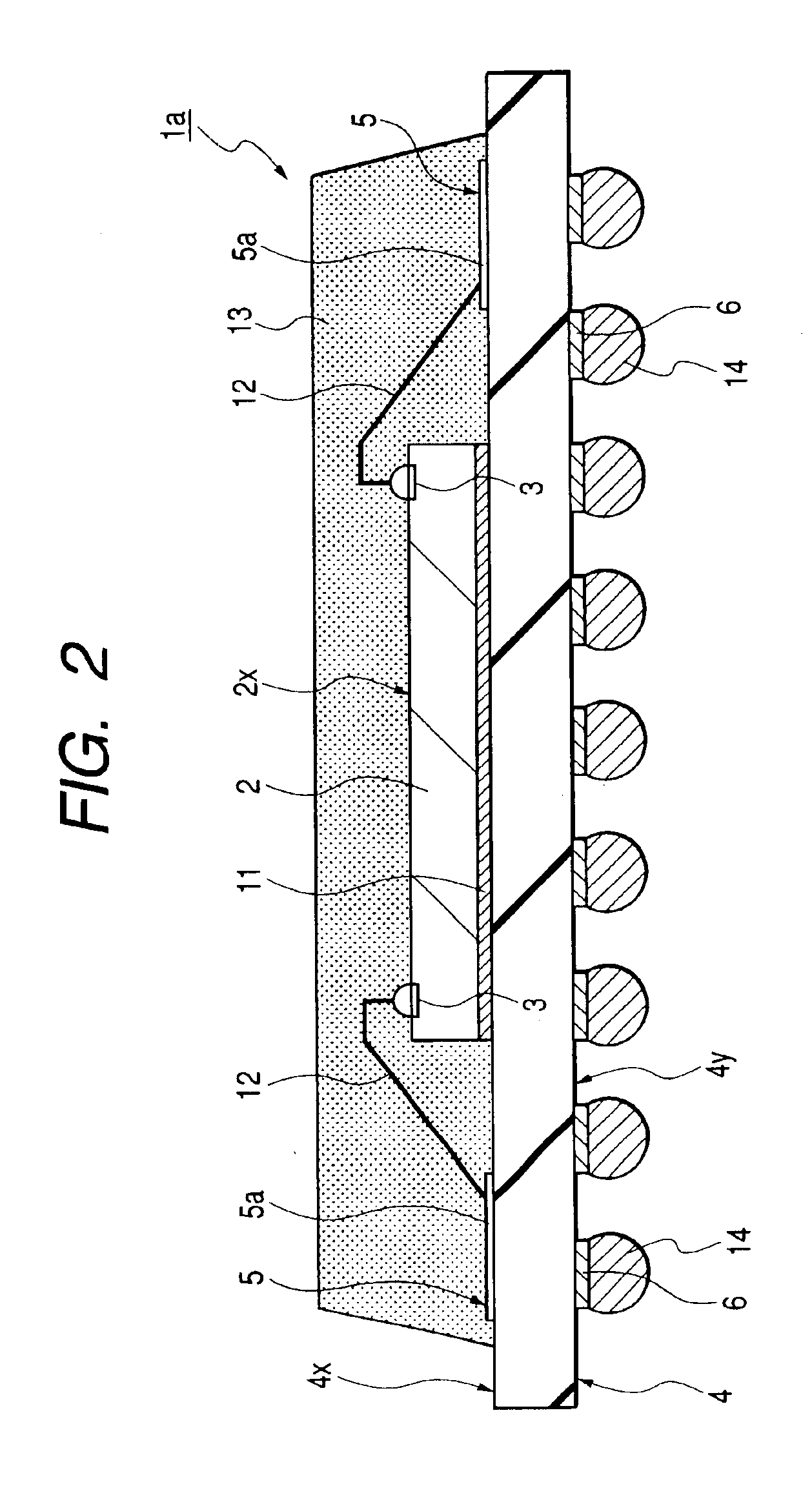

Semiconductor device containing stacked semiconductor chips and manufacturing method thereof

InactiveUS7405484B2Suppress bad connectionElement reliabilityPrinted circuit assemblingInsulating substrate metal adhesion improvementSemiconductor chipAlloy

An adhesive film is formed on an electrode film, and a coating film is formed thereon. Nickel, chrome, molybdenum, tungsten, aluminum or an alloy of them is used as a constituent material of the adhesive film. Gold, silver, platinum or an alloy of them is used as a constituent material of the coating film.

Owner:SANYO ELECTRIC CO LTD

Multi-chip module and method for forming and method for deplating defective capacitors

A method for deplating defective capacitors comprising forming a plurality of capacitors on a semiconductor substrate, forming a plurality of metal contacts on the plurality of capacitors, and depositing a layer of photoresist on the semiconductor substrate. The photoresist layer is patterned so that the plurality of metal contacts are exposed, which are then contacted with an electrically conductive solution. The metal contacts, which are disposed over defective capacitors, are subsequently deplated. A method for forming a multi-chip module comprising forming a thin-film polymeric interconnect structure having a pair of sides, one of which is disposed on a silicon substrate having active or passive devices and the other of which has a computer chip mounted thereon. A multi-chip module formed by the method.

Owner:FUJITSU LTD

High density inductor and method for producing same

InactiveUS20040164835A1Reduce core sizeAccurate shapeTransformers/inductances coils/windings/connectionsSolid-state devicesHigh densityInductor

A method for producing a high density inductor includes the steps of forming a coil having a spiral shape, sealing the coil in the interior of a core member, and forming a terminal electrode for allowing electric conduction to said coil on the outside of said core member. In this method, the coil is formed by repeating a process of forming a wire layer by means of a thin film forming process and a process of forming an additional wire layer on top of the wire layer by means of the thin film forming process to pile up the wire layers. With this production method, it is possible to form a coil with a high aspect ratio. In addition, the inductor is designed in such a way that the core member envelopes only the coil. With that design, it is possible to make the inductor compact.

Owner:TDK CORPARATION

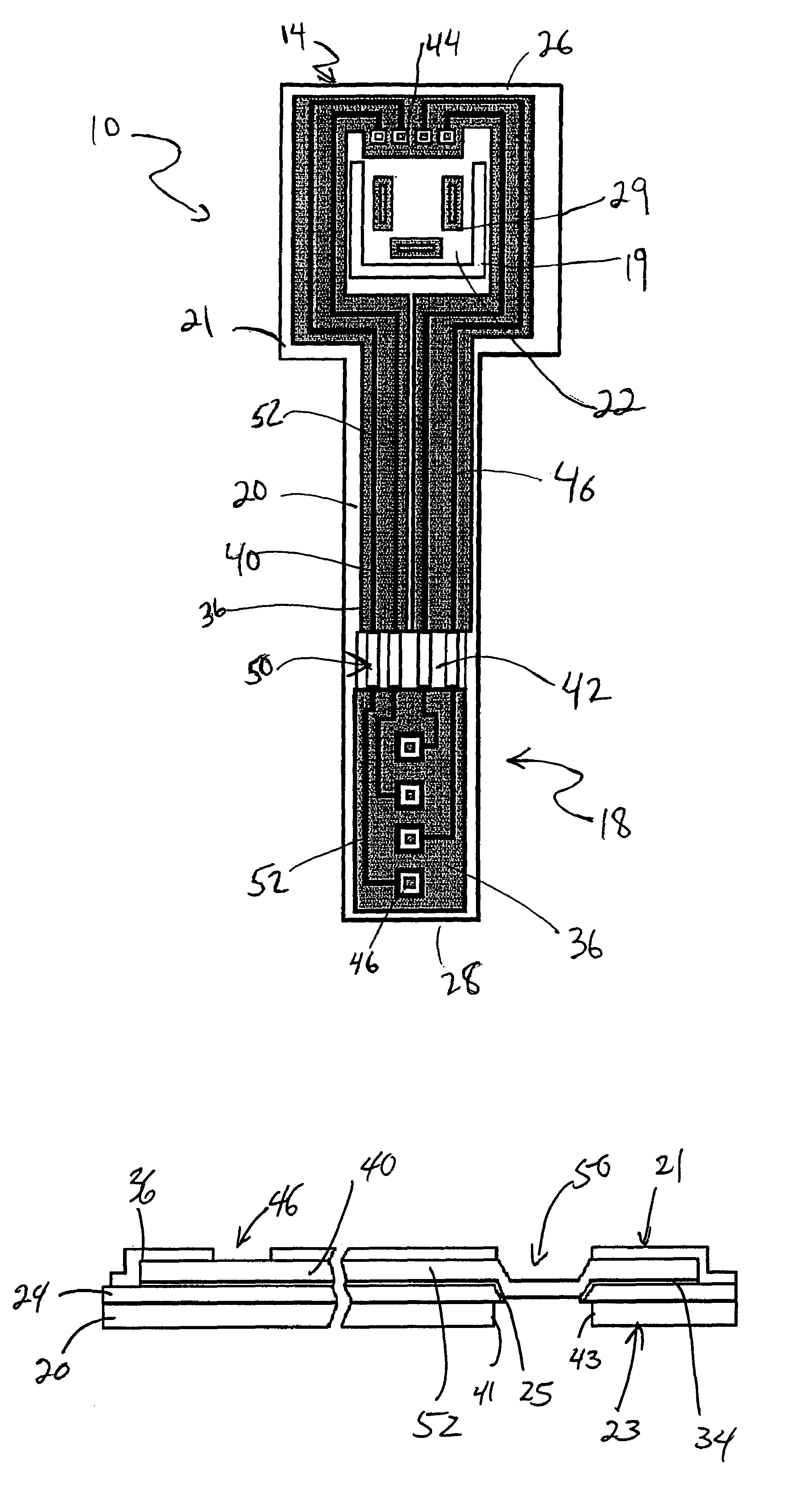

Method for making noble metal conductive leads for suspension assemblies

A method of manufacturing an integrated lead head suspension flexure of the type having conductors on a spring metal layer capable of being etched by a first etching process. The method includes forming a patterned layer having gaps one or more flying lead regions of dielectric material on a major surface of the spring metal layer and forming one or more conductive leads on the flexure, including onto the dielectric material and over exposed spring metal at the gap at each flying lead region. At least the flying lead portion of the conductive lead is formed from conductive material resistant to the first etching process. The method also includes etching a flying lead region of the spring metal layer to remove a portion of the spring metal layer in the flying lead region and expose the flying lead portions of the conductive lead.

Owner:HUTCHINSON TECH

Self-assembled nanometer conductive bumps and method for fabricating

Owner:IND TECH RES INST

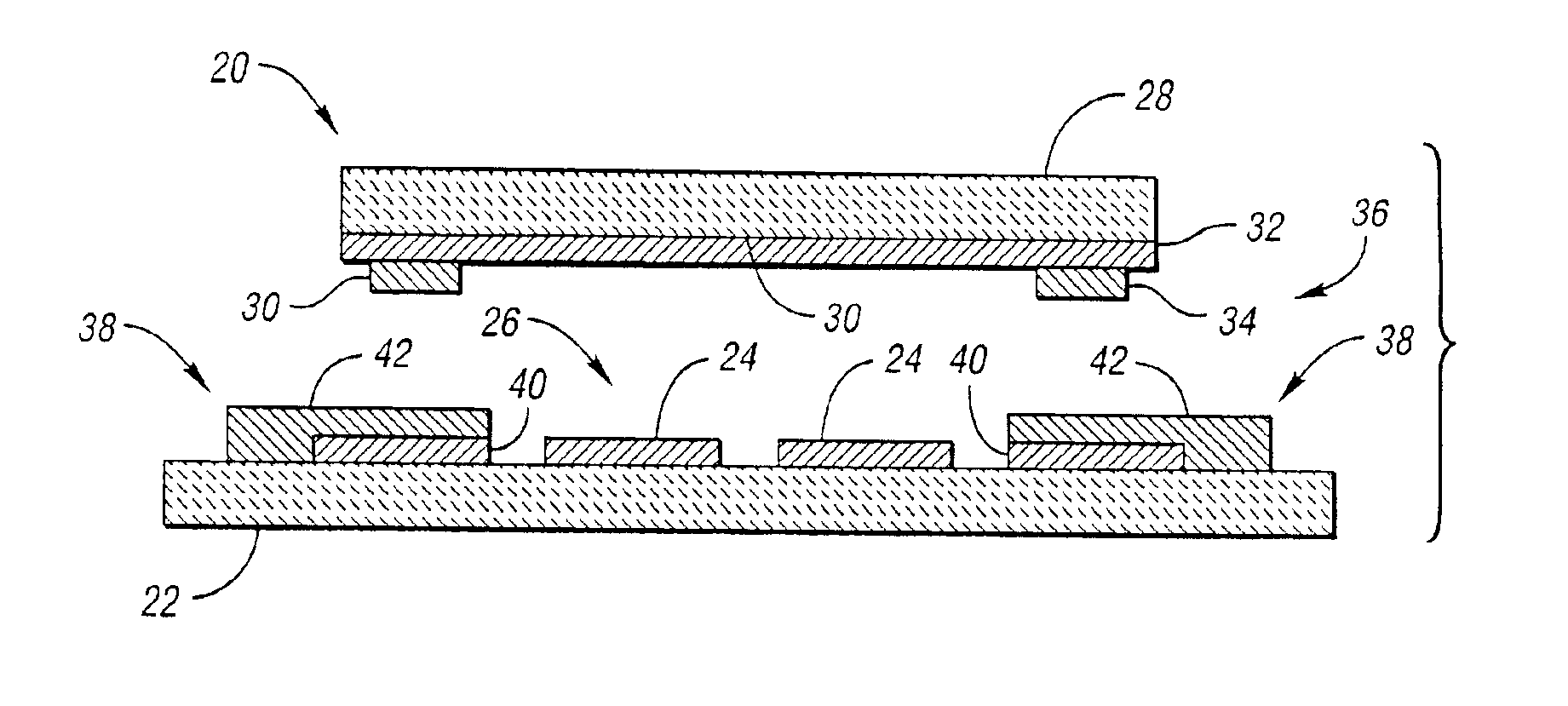

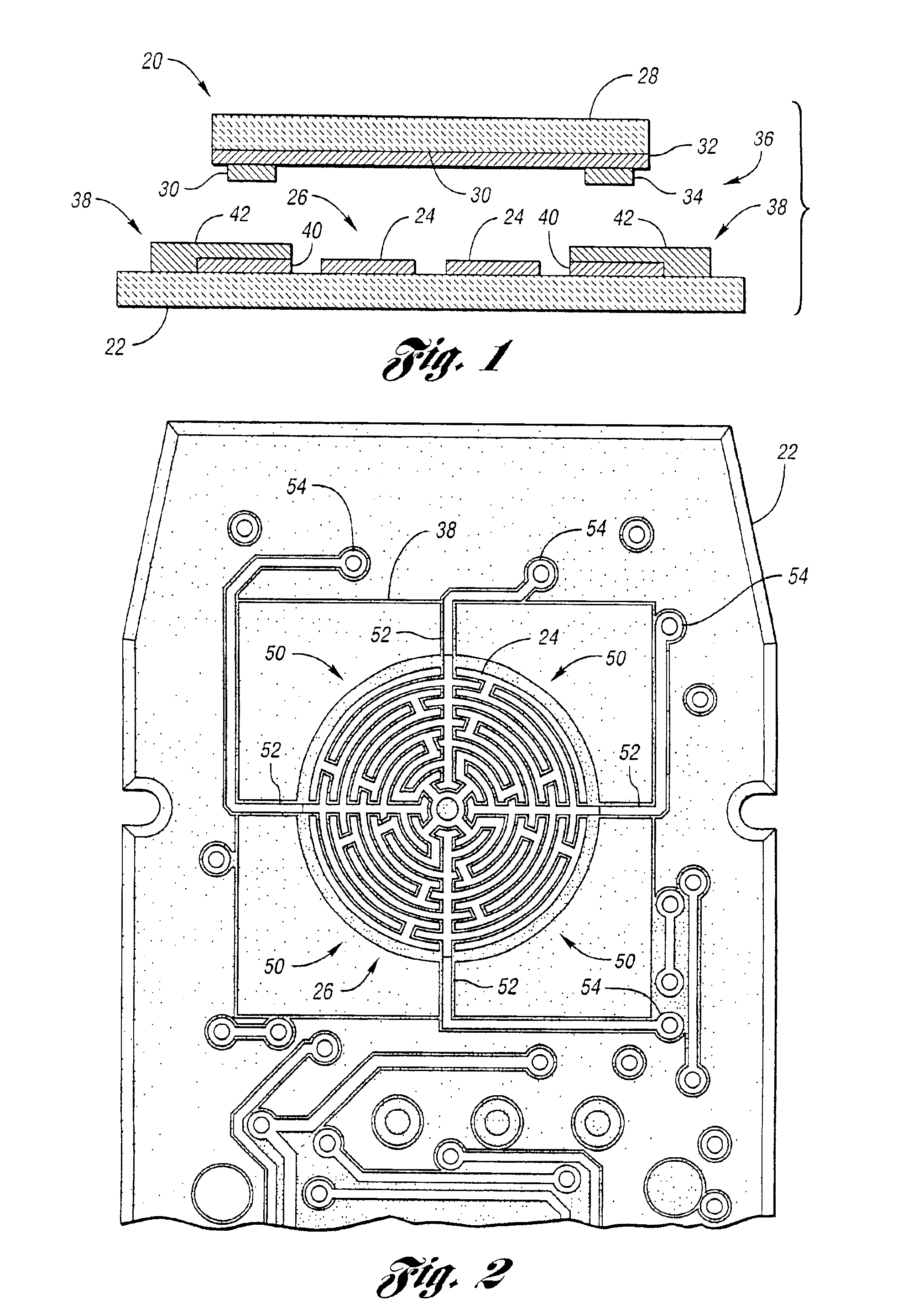

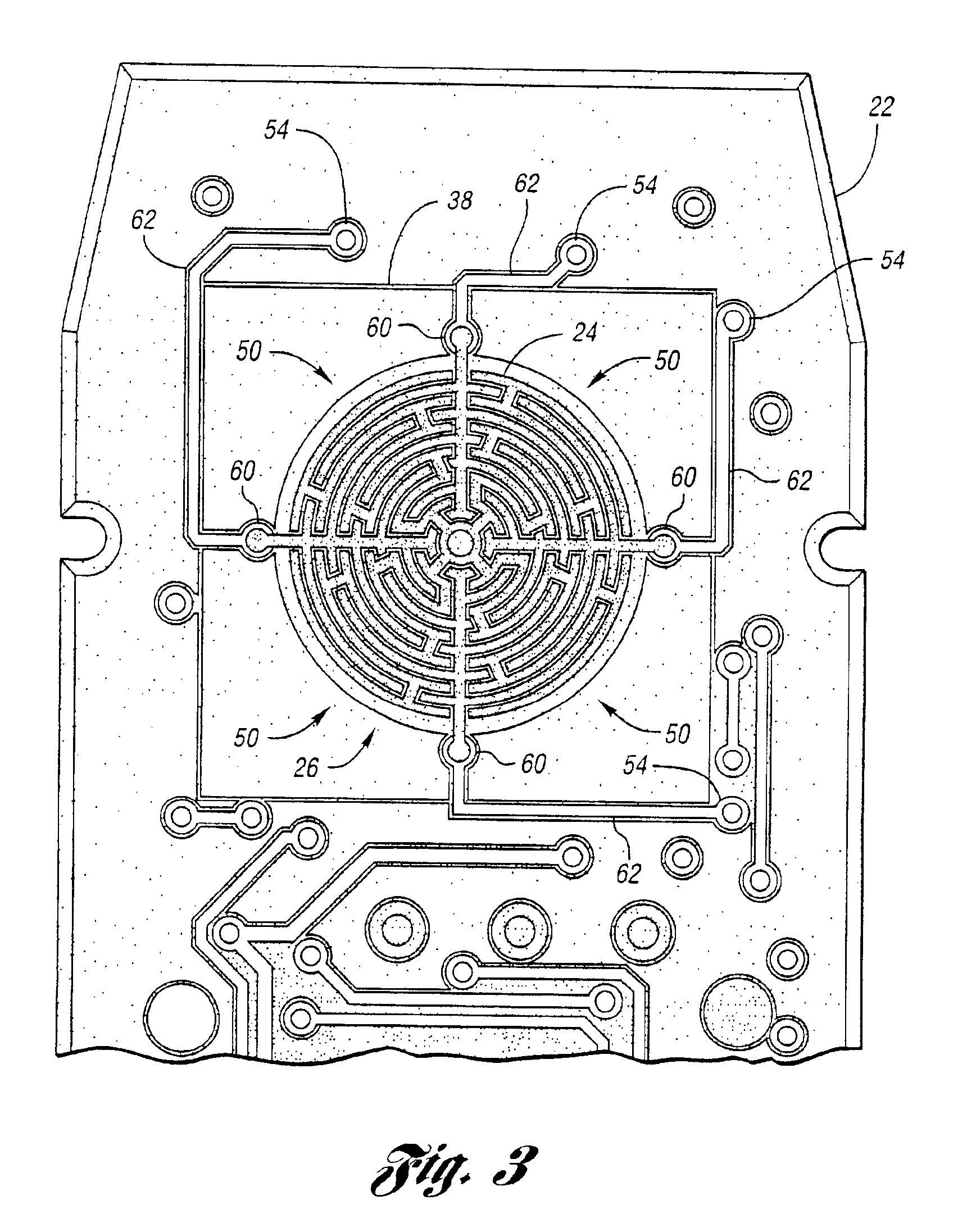

Electronic pressure sensitive transducer apparatus and method for manufacturing same

InactiveUS6909354B2Low costReduce complexityPrinted circuit assemblingPrinted circuit aspectsTransducerEngineering

The cost and complexity of an electronic pressure sensitive transducer are decreased by constructing such a transducer directly on a printed circuit board containing support electronics. Conductive traces are formed on the printed circuit board to define a contact area. A flexible substrate having an inner surface is positioned over the contact area. An adhesive spacer, substantially surrounding the contact area, attaches the flexible substrate to the printed circuit board. At least one resistive layer is deposited on the flexible substrate inner surface. In use, the resistive layer contacts at least two conductive traces in response to pressure applied to the flexible substrate to produce an electrical signal indicative of applied pressure.

Owner:INTERLINK ELECTRONICS

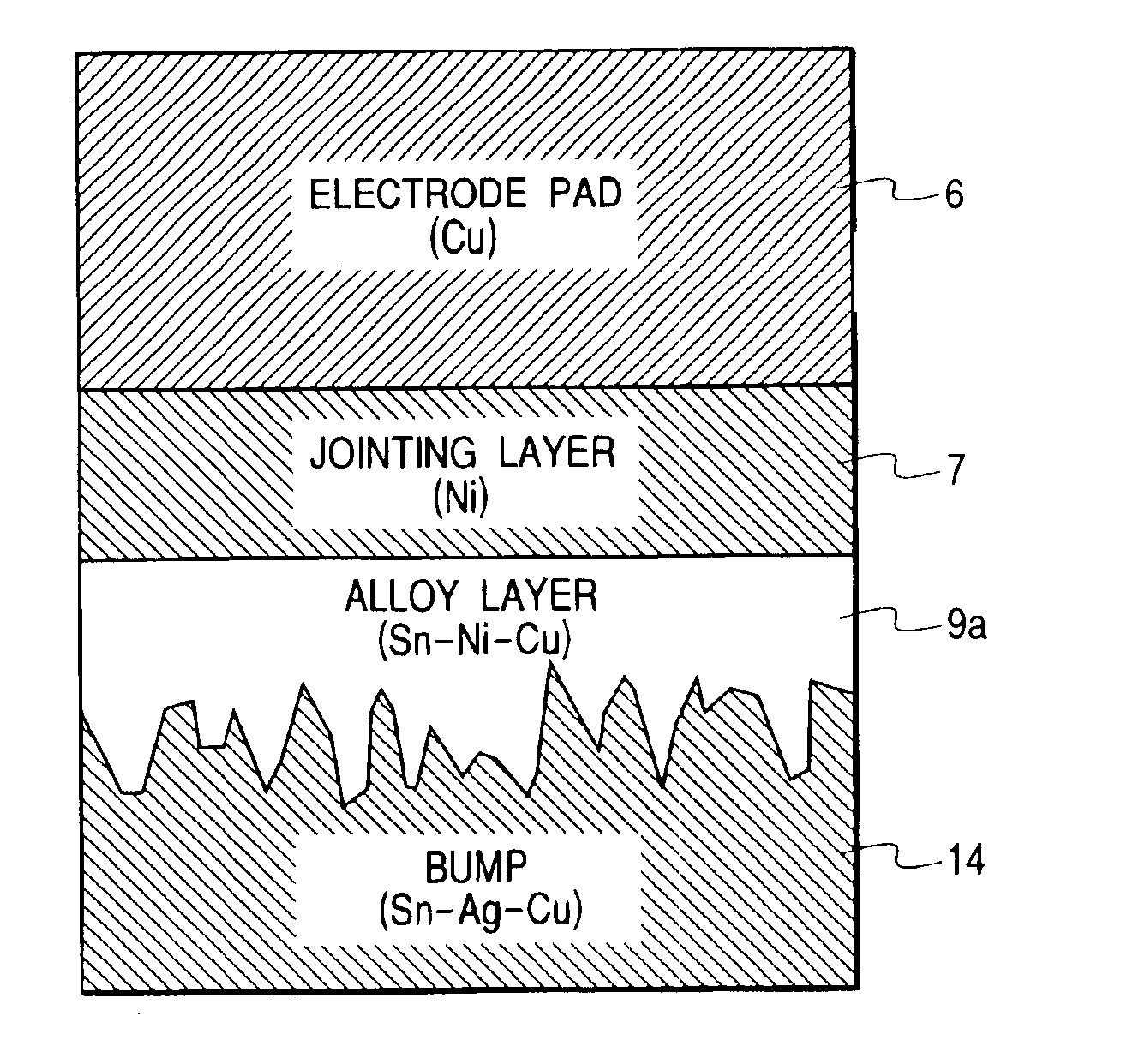

Semiconductor device with joint structure having lead-free solder layer over nickel layer

InactiveUS6879041B2Low melting pointImpact resistancePrinted circuit assemblingSemiconductor/solid-state device detailsDevice materialSulfur

The impact strength resistance of a solder joint portion of a semiconductor device is improved. The semiconductor device has a joint structure wherein a jointing layer which does not contain sulfur substantially is arranged between an underlying conductive layer and a lead-free solder layer and further between the jointing layer and the lead-free solder layer is formed an alloy layer comprising elements of these layers.

Owner:RENESAS ELECTRONICS CORP

Reinforced solder bump structure and method for forming a reinforced solder bump

A reinforced solder bump connector structure is formed between a contact pad arranged on a semiconductor chip and a ball pad arranged on a mounting substrate. The semiconductor chip includes at least one reinforcing protrusion extending upwardly from a surface of an intermediate layer. The mounting substrate includes at least one reinforcing protrusion extending upwardly from a ball pad, the protrusions from both the chip and the substrate being embedded within the solder bump connector. In some configurations, the reinforcing protrusion from the contact pad and the ball pad are sized and arranged to have overlapping under portions. These overlapping portions may assume a wide variety of configurations that allow the protrusions to overlap without contacting each other including pin arrays and combinations of surrounding and surrounded elements. In each configuration, the reinforcing protrusions will tend to suppress crack formation and / or crack propagation thereby improving reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

Electrically conductive patterns, antennas and methods of manufacture

InactiveUS6582887B2Simultaneous aerial operationsAntenna supports/mountingsEngineeringElectrical and Electronics engineering

The invention teaches improved, novel methods and materials for the productions of electrically conductive patterns, antennas and complex circuitry. The invention contemplates the use of directly electroplateable resins for production of these article. The unique suitability of directly electroplateable resins to allow facile manufacture of the electrically conductive patterns desired using a broad range of processing and manufacturing approaches is demonstrated.

Owner:ERTEK

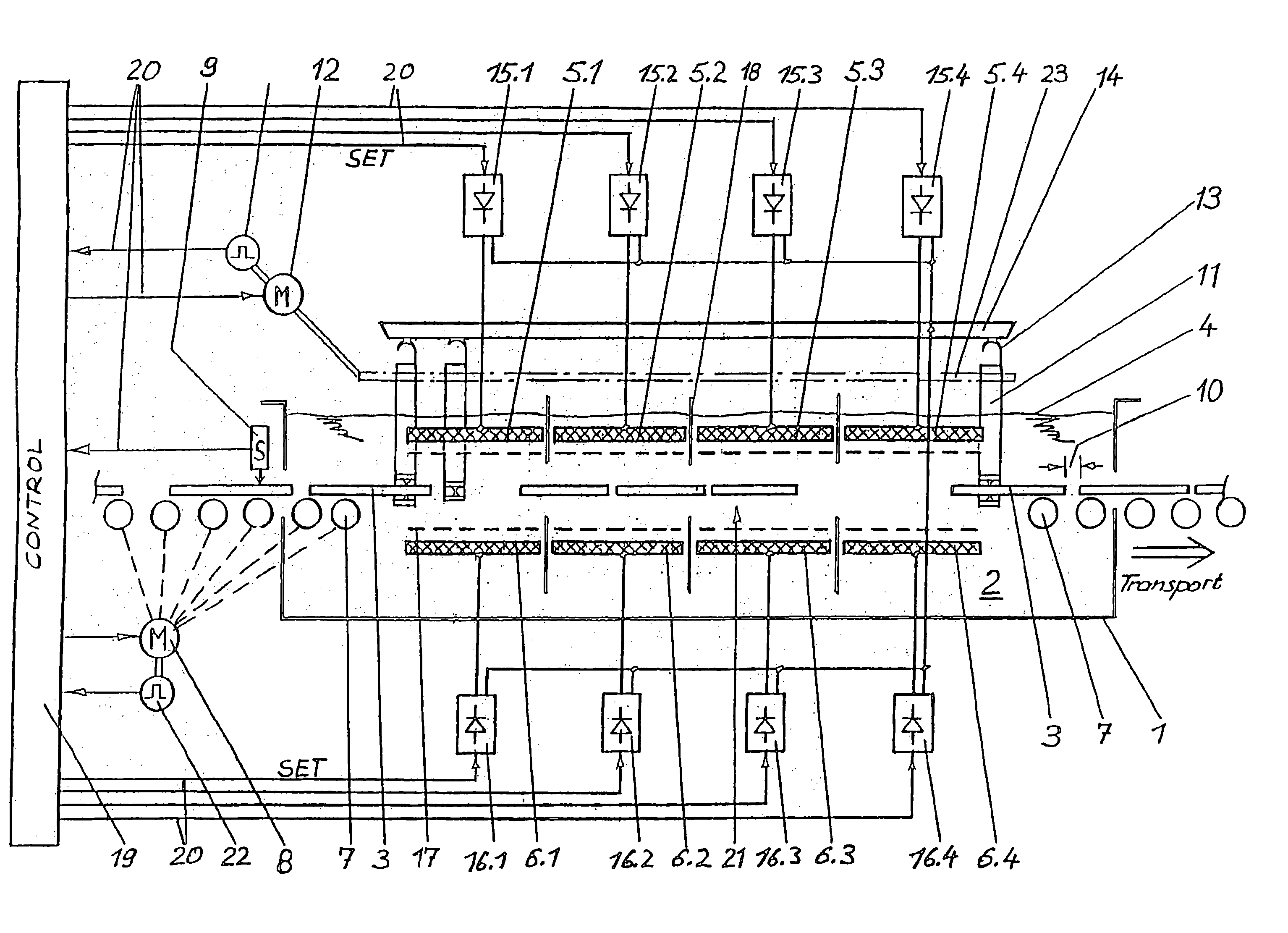

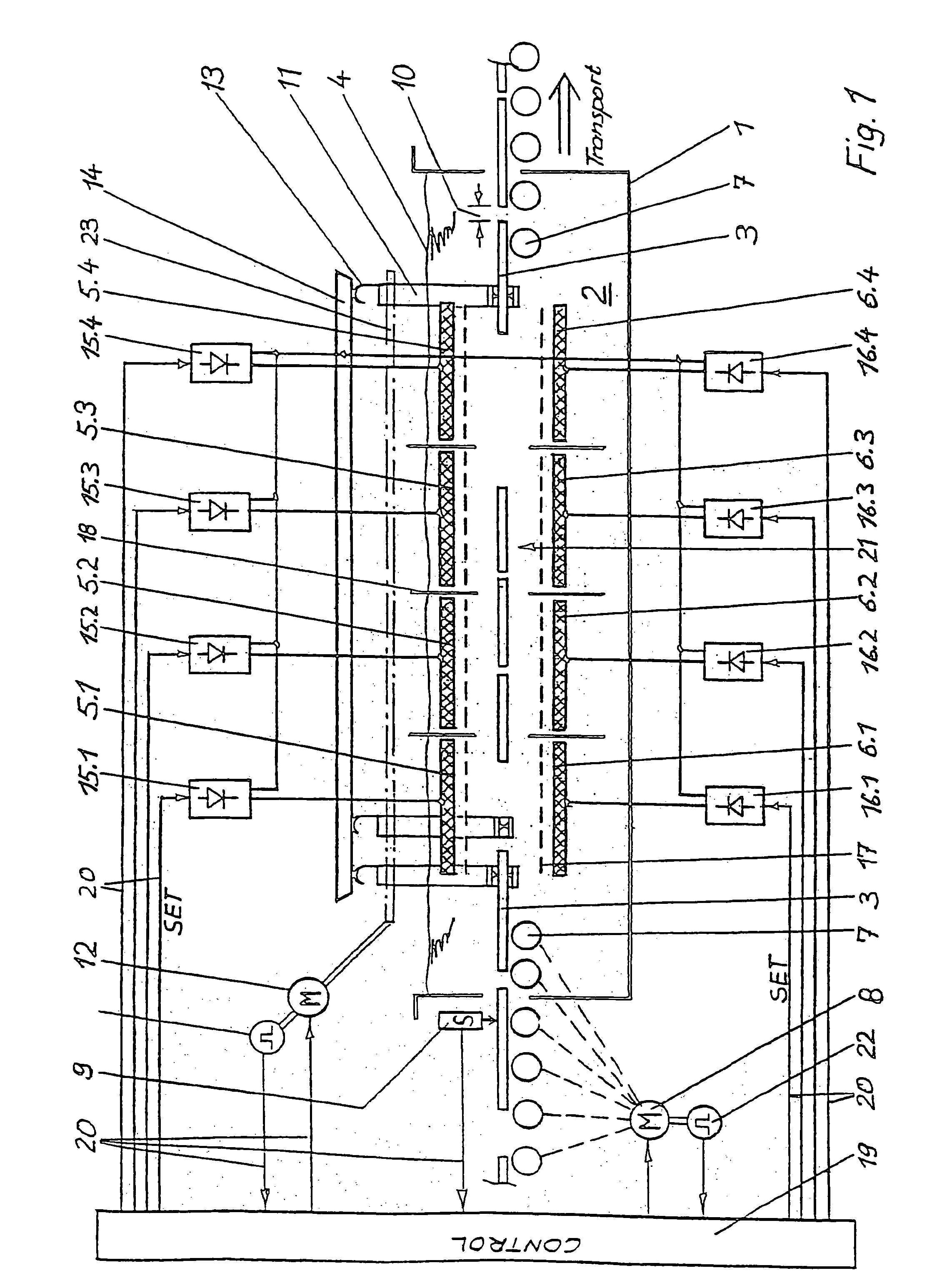

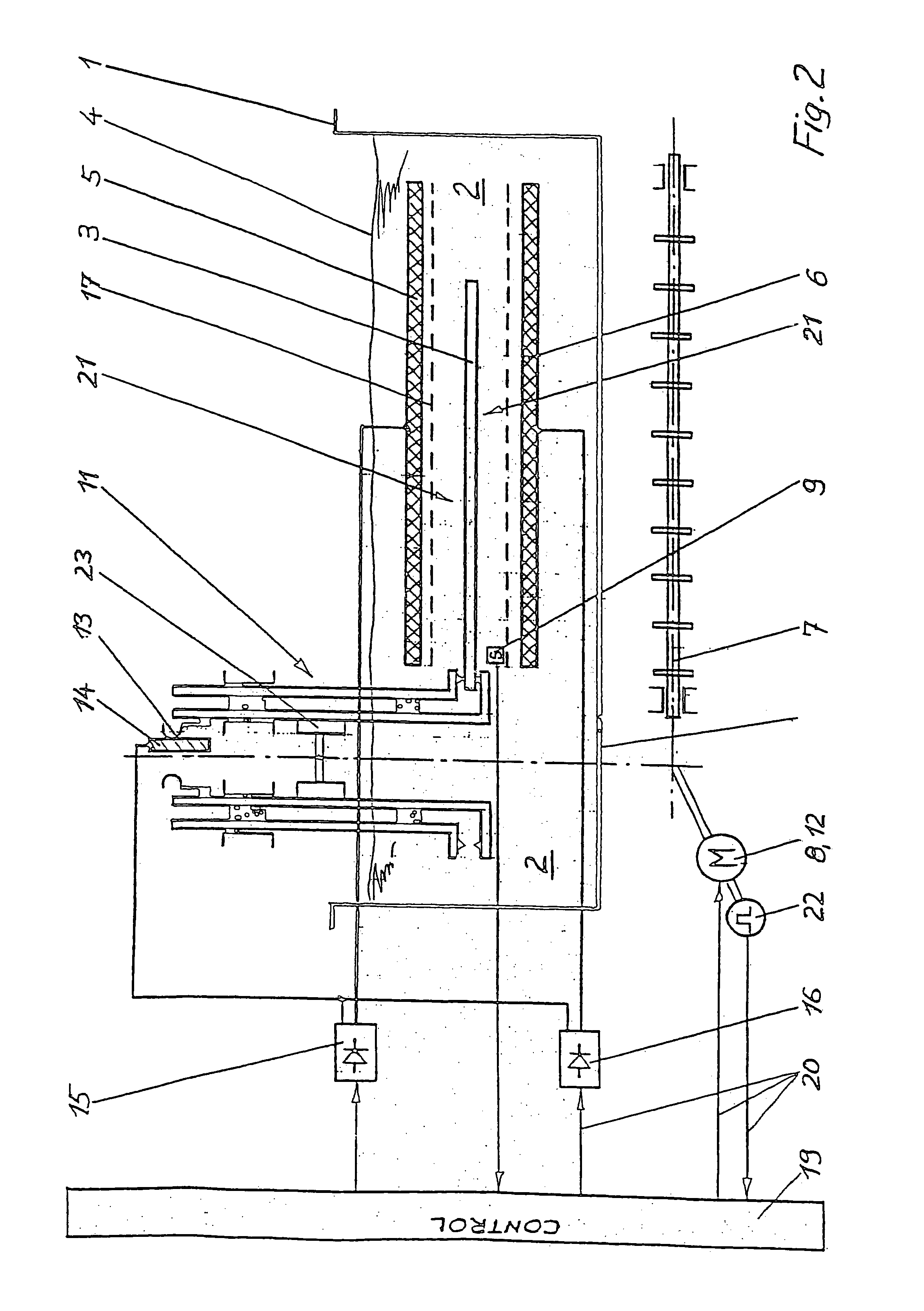

Method and conveyorized system for electrolytically processing work pieces

ActiveUS7563352B2Avoid disadvantagesEasy to adjustCellsConductive pattern reinforcementVolumetric Mass DensityEngineering

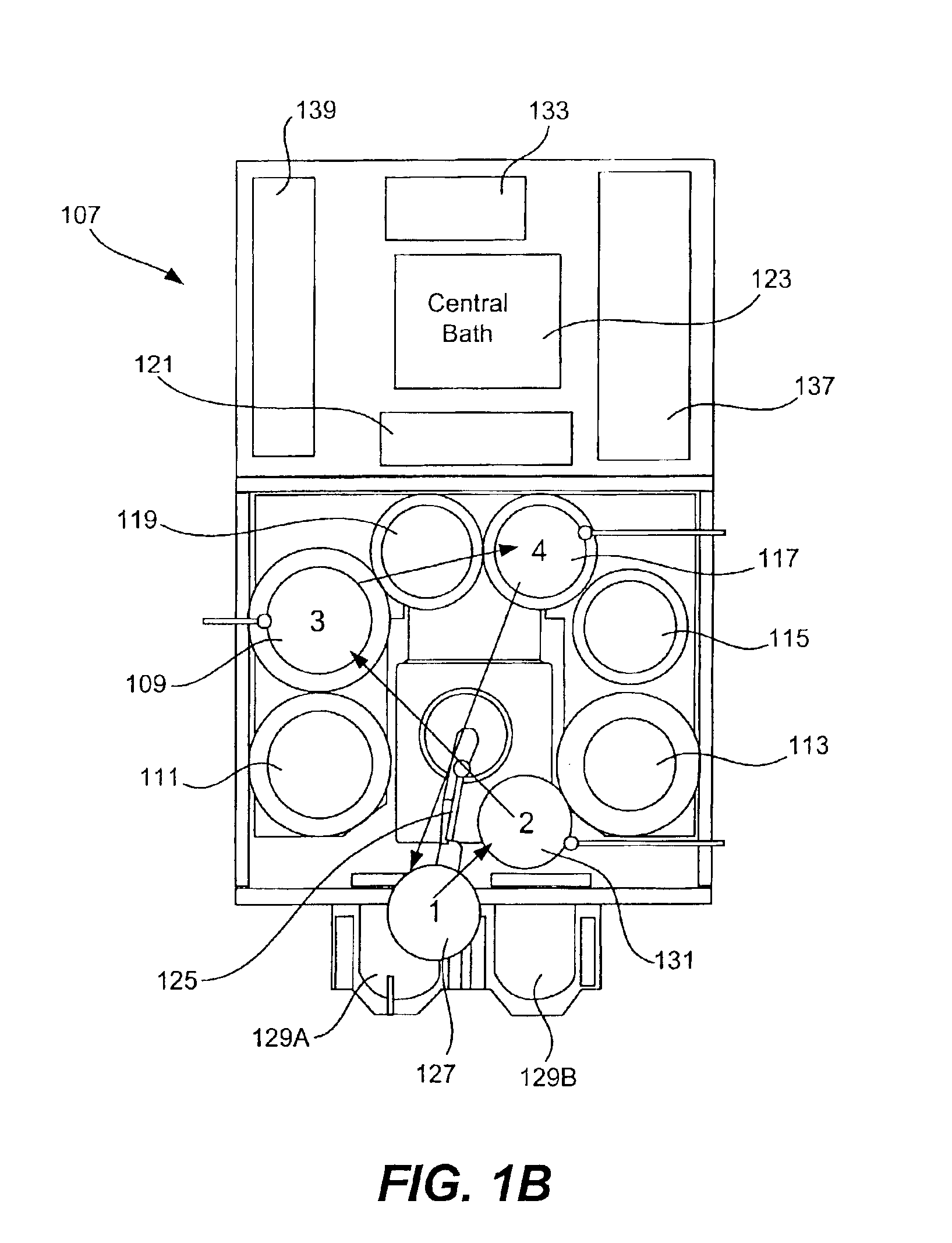

In order to avoid an edge-effect (increased electrical field line density at the edges of electrolytically to be processed work pieces) during the electrolytic processing of work pieces 3.x in a conveyorized system, the electric currents originating from various counter electrodes 5.x in the plant are set to values in function of the electrolytically to be processed surface areas of the work pieces 3.x as far as they are located directly opposite the respective ones of the various counter electrodes 5.x. Moreover, the distance between the work pieces 3.x and the counter electrodes 5.x is chosen to be 50 mm maximum. Means 19 for individually controlling and adjusting every single current supply unit 15.x of the counter electrodes 5.x are provided for this purpose. Said means 19 are configured in such a manner that the respective electric currents originating from the various counter electrodes 5.x are settable to values in function of the electrolytically to be processed surface areas of the work pieces 3.x, as far as they are located directly opposite the respective various counter electrodes 5.x.

Owner:ATOTECH DEUT GMBH

Conductive through wafer vias

InactiveUS6852627B2Low costWell formedSemiconductor/solid-state device detailsVolume/mass flow measurementSemiconductorElectroplating

Methods for fabricating a conductive contact (through-via) through a full thickness of a substrate such as a semiconductor wafer or interposer substrate, and semiconductor devices and systems incorporating the conductive through-via are provided. The conductive contact is fabricated by applying a metal layer onto a backside of a substrate, forming a through-hole through the substrate and the metal layer, sealing the hole in the metal layer by an electroless plating process, and filling the hole by an electroplating or an electroless plating process.

Owner:MICRON TECH INC

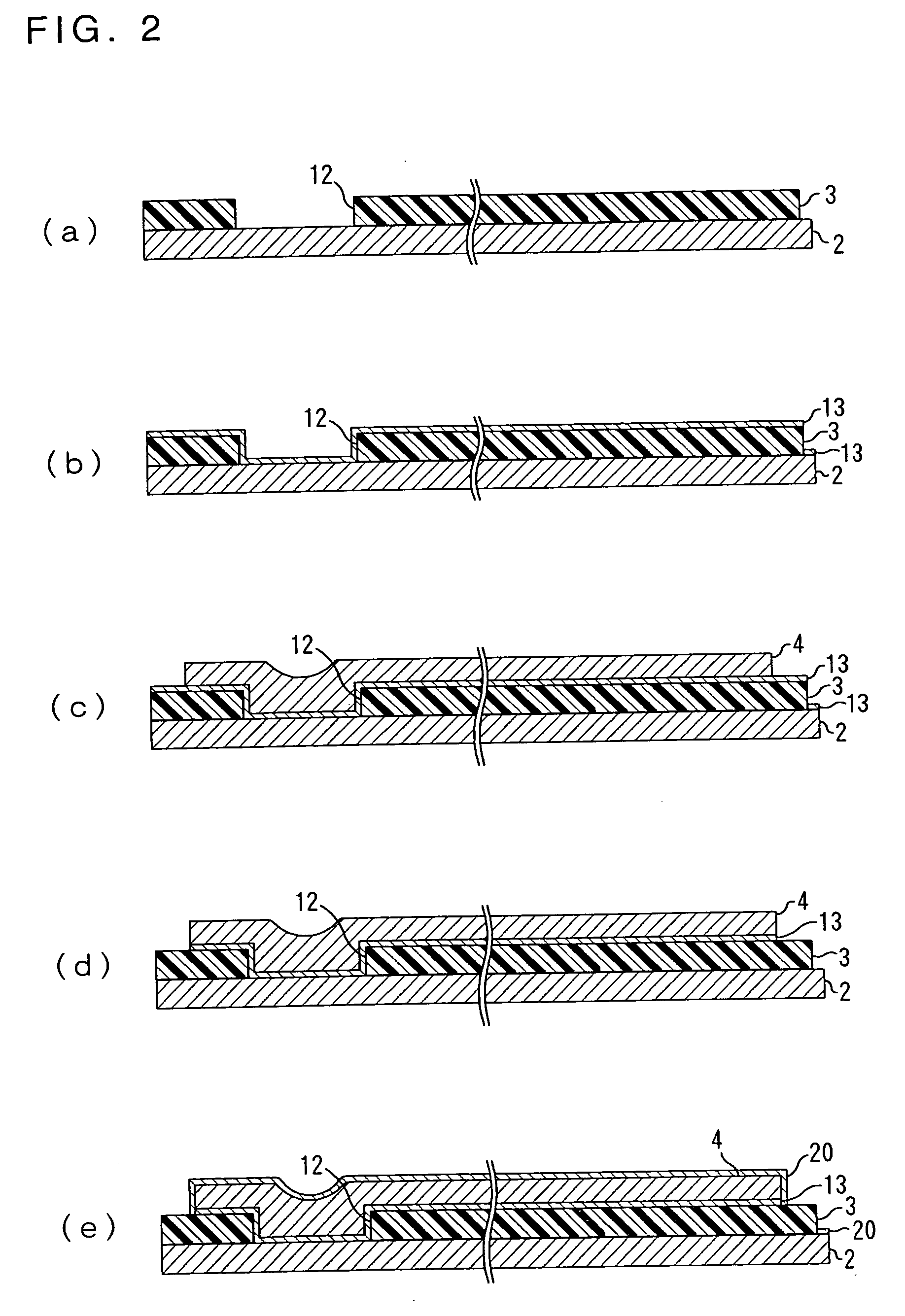

Suspension board with circuit and procuding method thereof

ActiveUS20050061542A1Increase productivityLow costInsulating substrate metal adhesion improvementCircuit arrangements on support structuresThin metalElectrical conductor

A producing method of a suspension board with circuit that can permit a terminal portion to be formed by electrolysis plating without exposing a conductor layer to outside and also can reduce the number of processes, and the suspension board with circuit produced by the same producing method. After an insulating base layer 3 is formed on a suspension board 2 in a specific pattern in which a second opening 12 is formed, a thin metal film 13 is formed on an entire surface of the insulating base layer 3 and on a surface of the suspension board 2 including the second opening 12 exposed from the insulating base layer 3.Then, a conductor layer 4 is formed in the form of a wired circuit pattern on the thin metal film 13. Thereafter, the insulating cover layer 10 is formed in such a manner that a pad opening 11 is formed in the insulating cover layer 10 and then a pad portion 16 is formed in the pad opening 11 using the suspension board 2 as a lead portion of the electrolysis plating. Thereafter, a first opening 25 larger than the second opening 12 is formed in the suspension board 2 at a portion thereof corresponding to the second opening 12.

Owner:NITTO DENKO CORP

Methods and structures for the production of electrically treated items and electrical connections

InactiveUS20050176270A1Printed circuit assemblingPrinted circuit aspectsElectricityConductive polymer

This invention involves unique electroplated items comprising electrically conductive polymers. In addition, continuous production of electrically treated items is facilitated using electrically conductive resins. Many embodiments employ directly electroplateable resins for particular advantage. Unique methods of establishing electroplated electrical connections are taught.

Owner:LUCH DANIEL

Method for making noble metal conductive leads for suspension assemblies

ActiveUS20050254175A1Printed circuit aspectsRecord information storageConductive materialsMetallic Lead

A method of manufacturing an integrated lead head suspension flexure of the type having conductors on a spring metal layer capable of being etched by a first etching process. The method includes forming a patterned layer having gaps one or more flying lead regions of dielectric material on a major surface of the spring metal layer and forming one or more conductive leads on the flexure, including onto the dielectric material and over exposed spring metal at the gap at each flying lead region. At least the flying lead portion of the conductive lead is formed from conductive material resistant to the first etching process. The method also includes etching a flying lead region of the spring metal layer to remove a portion of the spring metal layer in the flying lead region and expose the flying lead portions of the conductive lead.

Owner:HUTCHINSON TECH

Popular searches

Printed circuit non-printed electric components association Sensing by electromagnetic radiation Optical elements Semiconductor/solid-state device manufacturing Welding apparatus Semiconductor devices Pretreated surfaces Electric circuits Multilayer circuit manufacture Printed element electric connection formation