Patents

Literature

10659results about "Multilayer circuit manufacture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

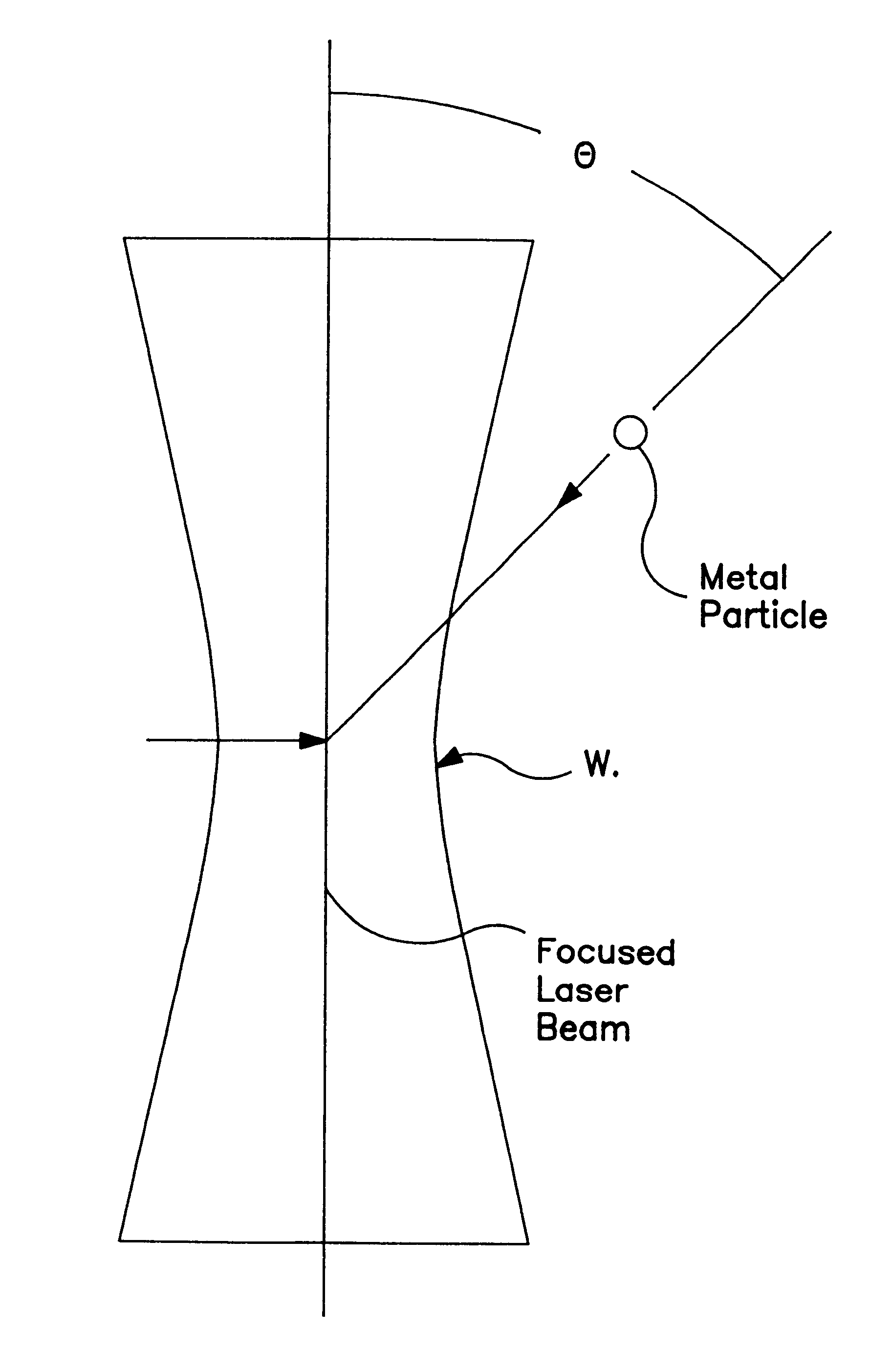

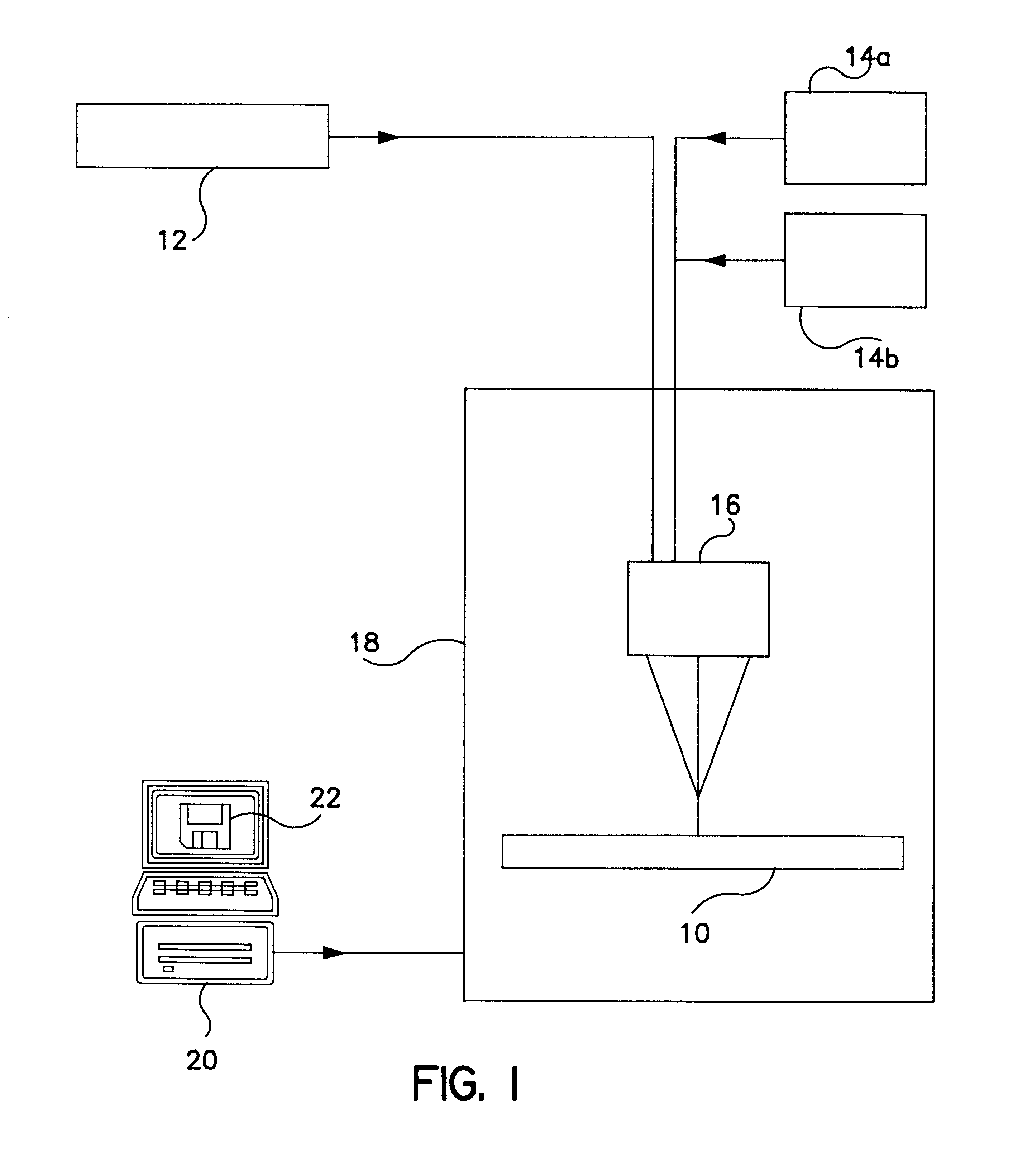

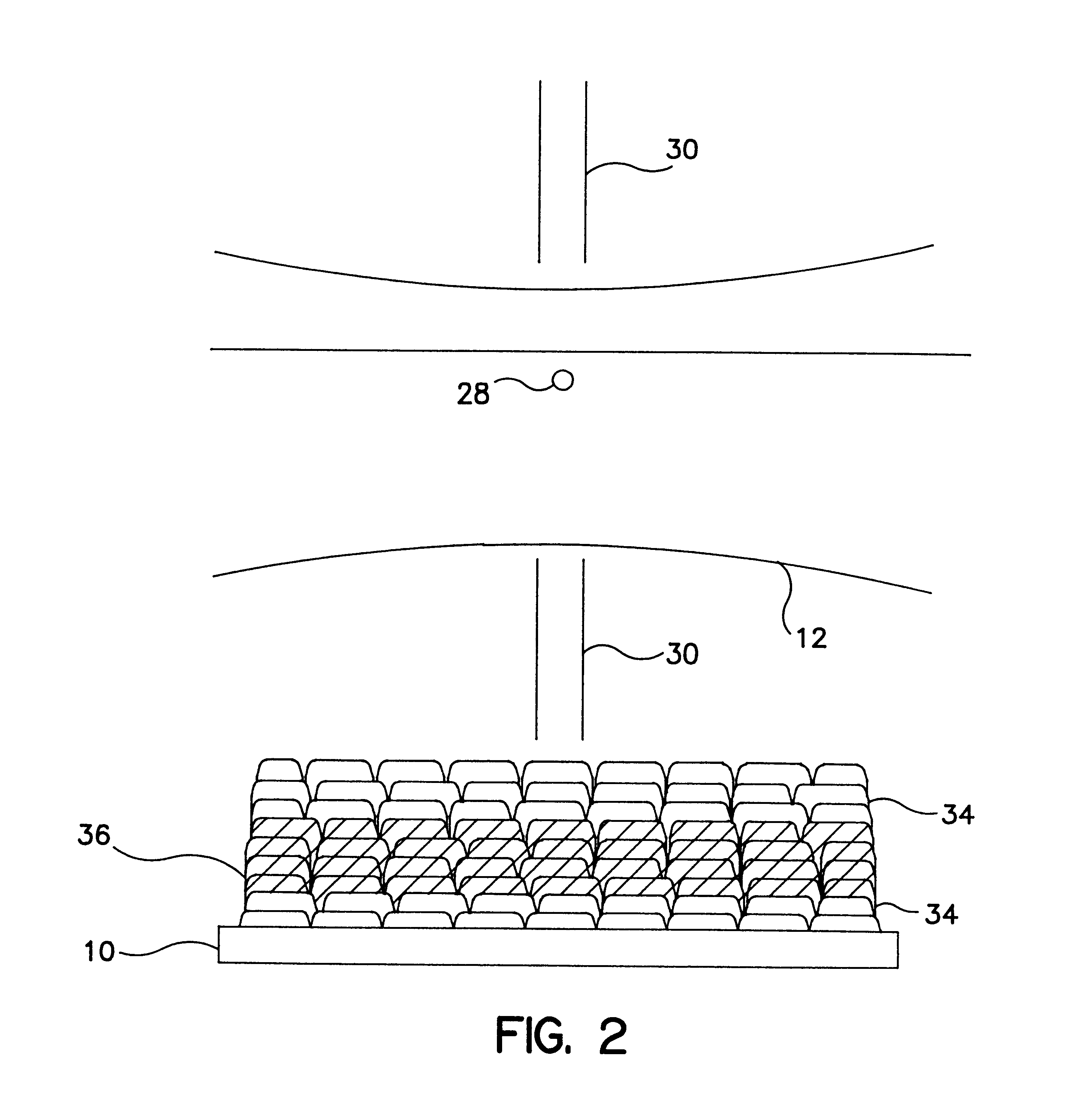

Precision spray processes for direct write electronic components

InactiveUS6251488B1Keep for a long timeIncrease probabilityMolten spray coatingVacuum evaporation coatingElectrical resistance and conductanceElectronic component

This invention combines the precision spray process with in-flight laser treatment in order to produce direct write electronic components. In addition to these components, the process can lay down lines of conductive, inductive, and resistive materials. This development has the potential to change the approach to electronics packaging. This process is revolutionary in that components can be directly produced on small structures, thus removing the need for printed circuit boards.

Owner:OPTOMEC DESIGN CO

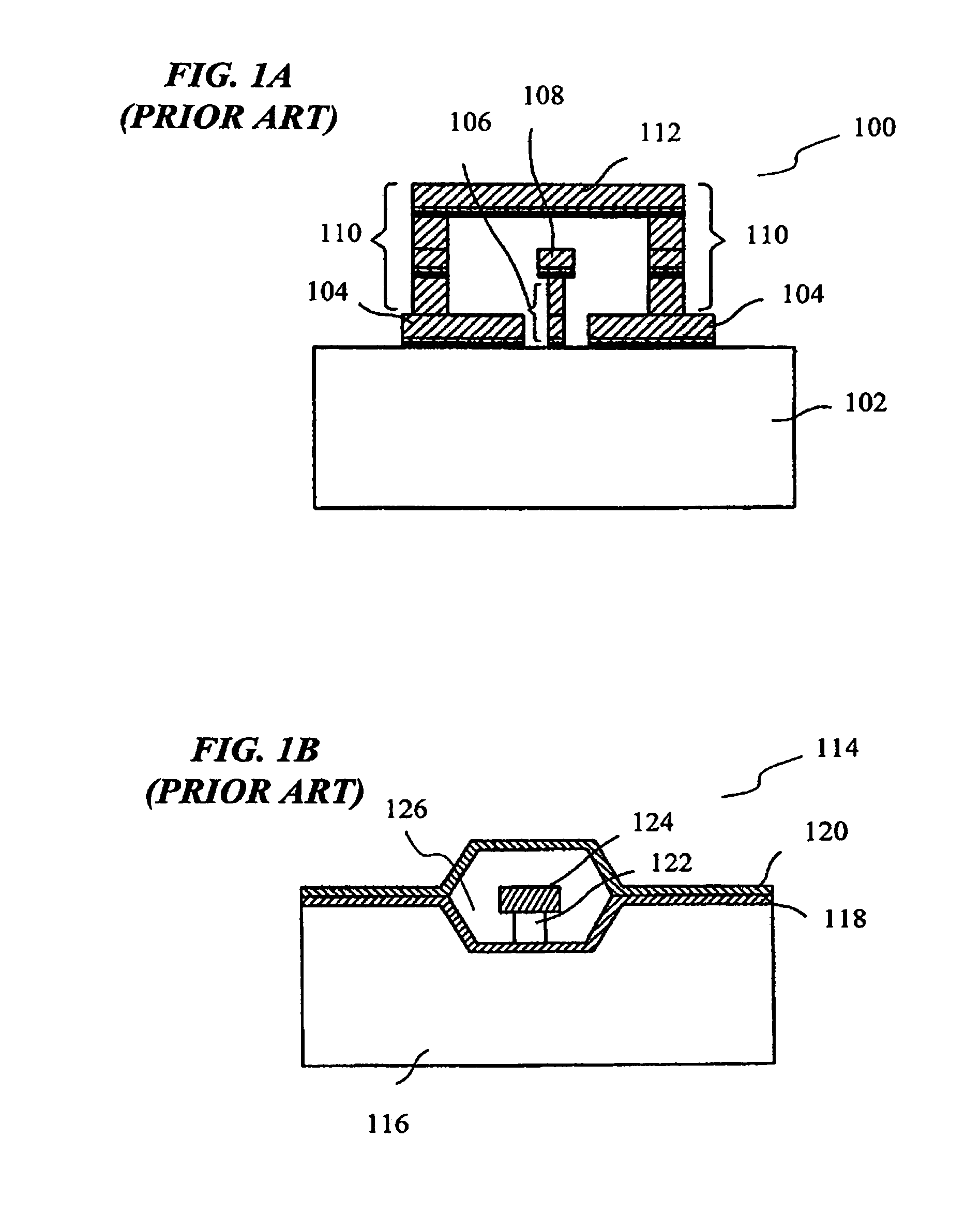

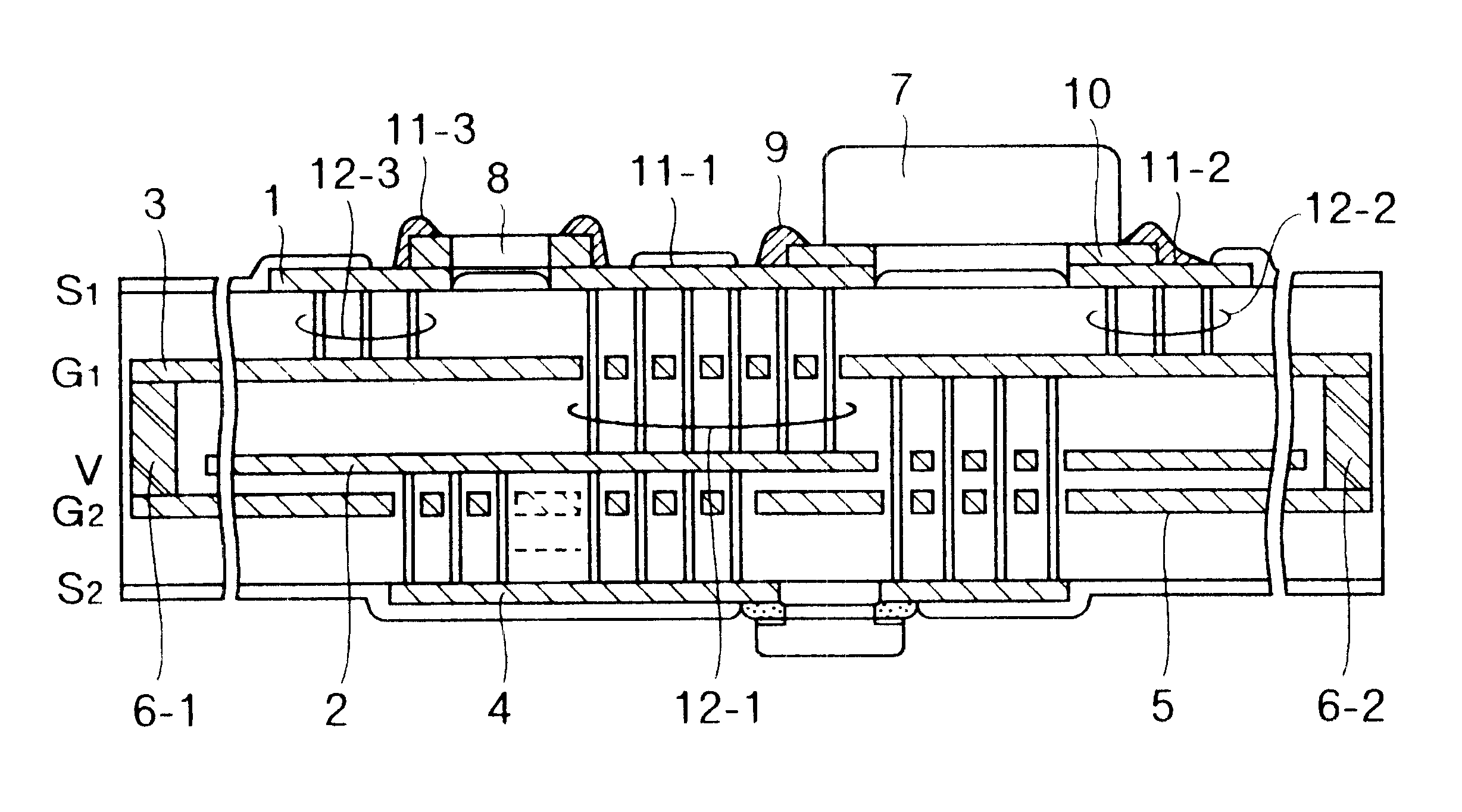

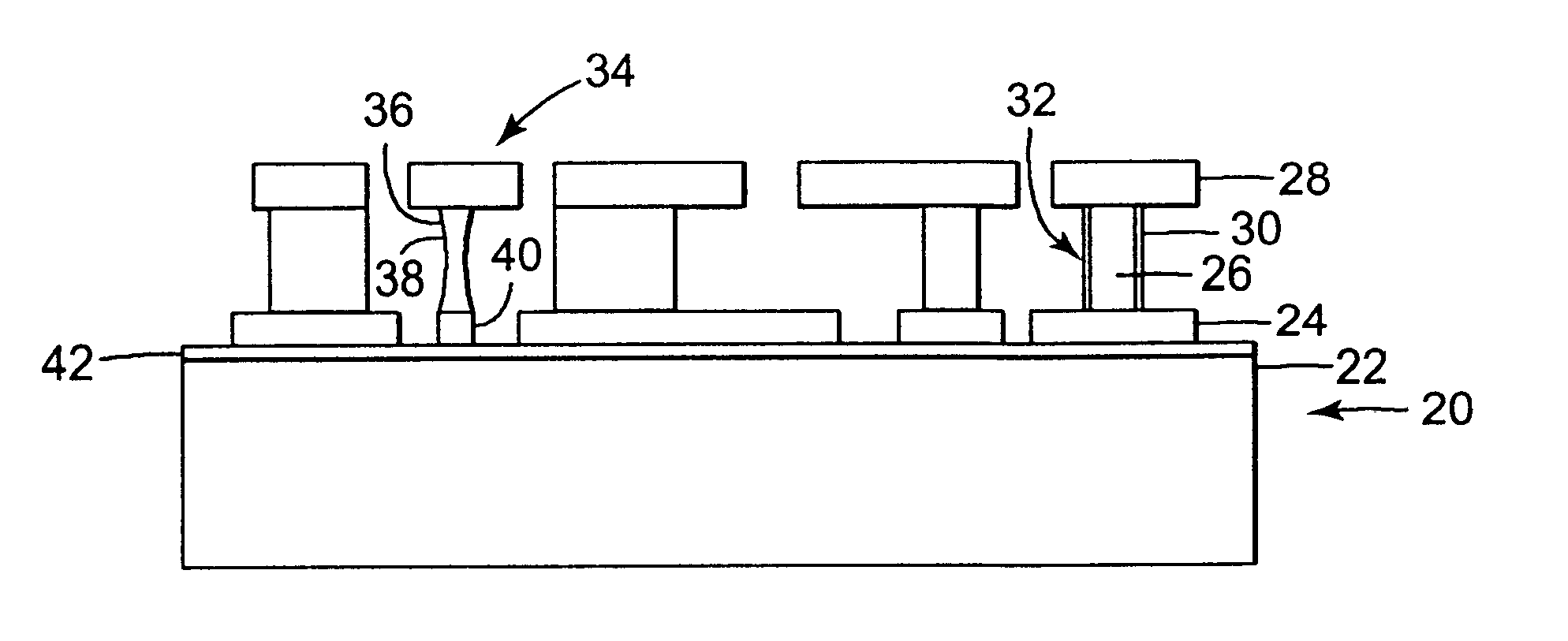

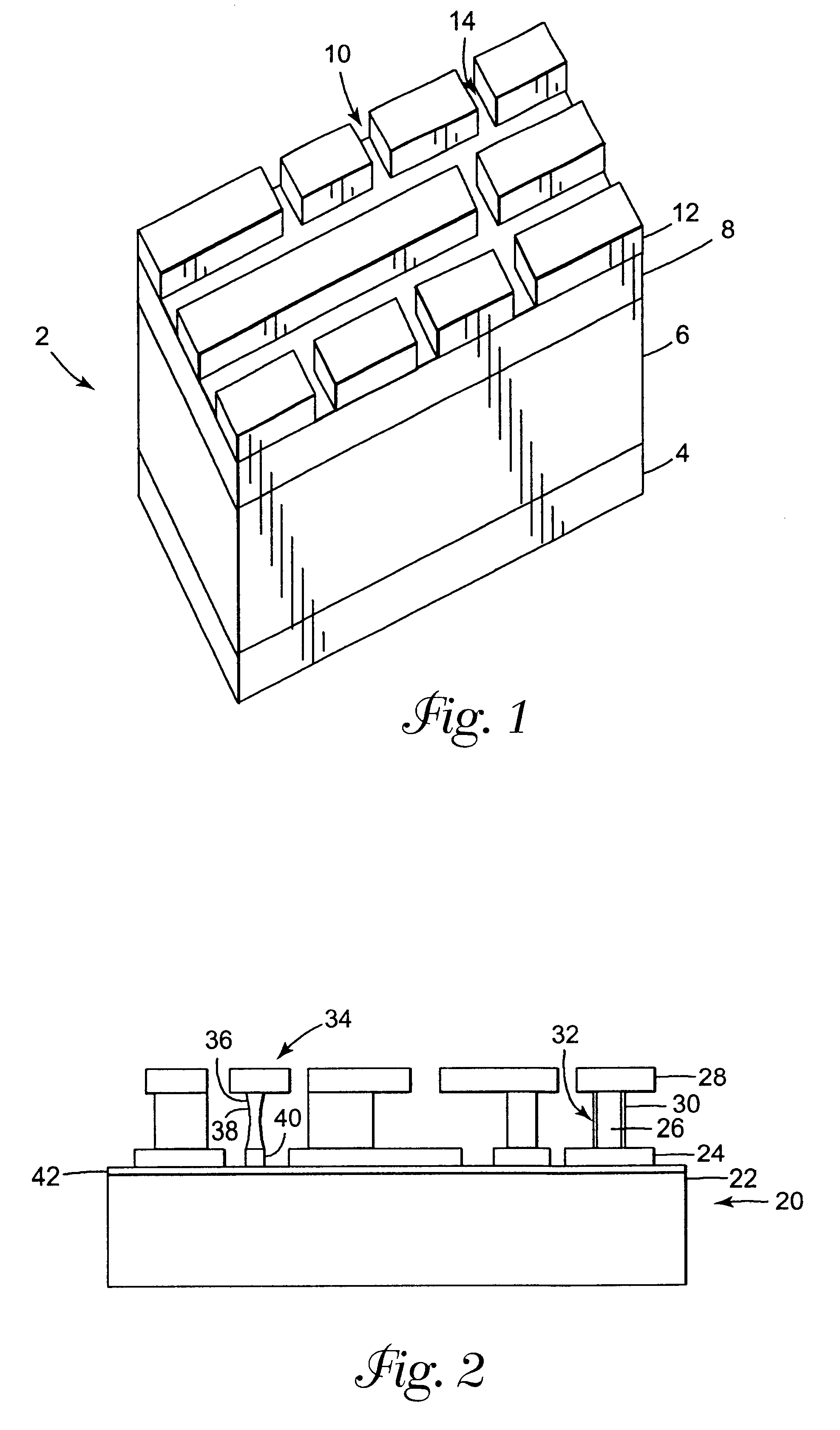

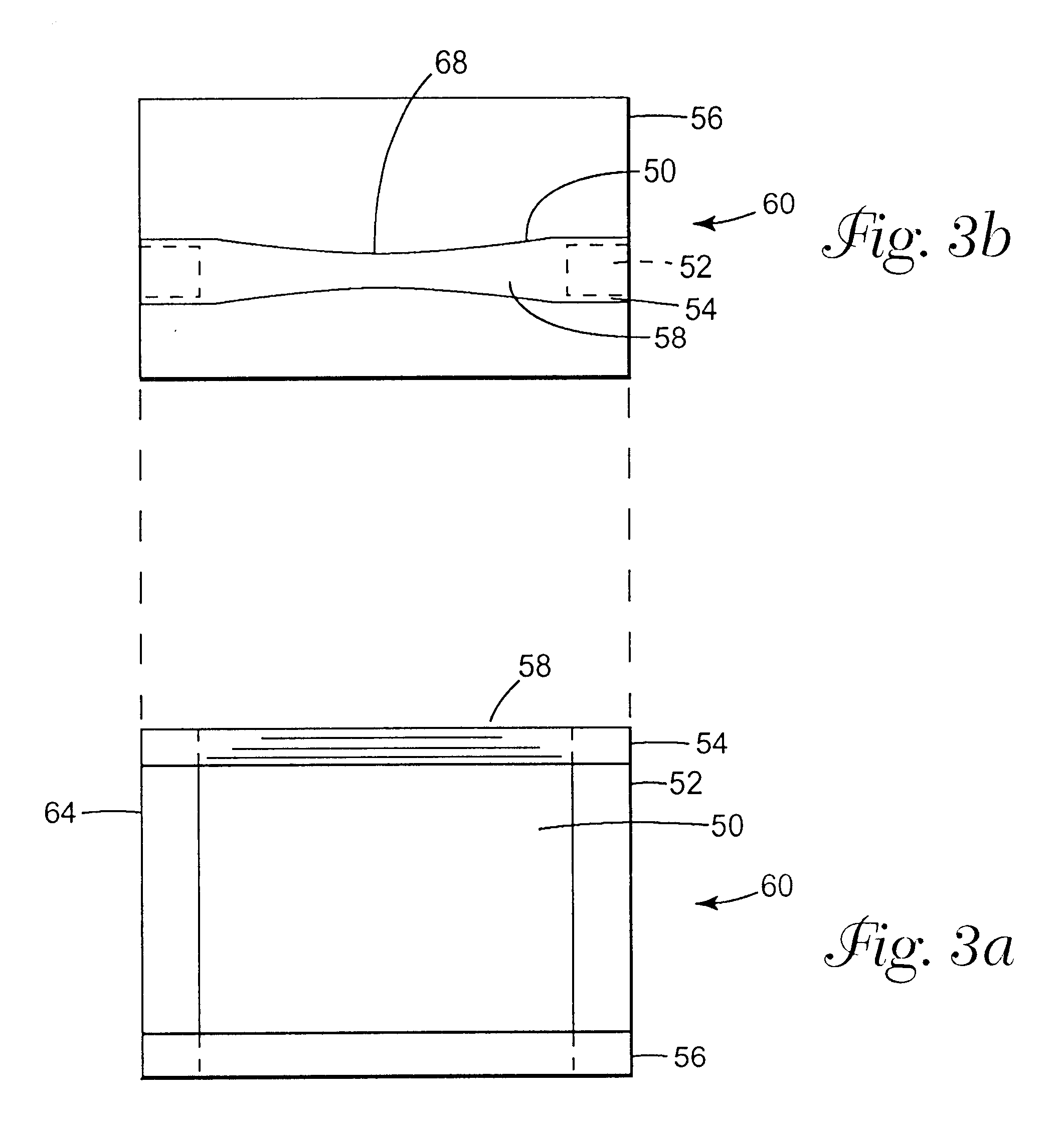

Coaxial waveguide microstructures and methods of formation thereof

ActiveUS7012489B2Printed circuit aspectsCircuit fluid transportElectrical conductorCoaxial waveguides

Provided are coaxial waveguide microstructures. The microstructures include a substrate and a coaxial waveguide disposed above the substrate. The coaxial waveguide includes: a center conductor; an outer conductor including one or more walls, spaced apart from and disposed around the center conductor; one or more dielectric support members for supporting the center conductor in contact with the center conductor and enclosed within the outer conductor; and a core volume between the center conductor and the outer conductor, wherein the core volume is under vacuum or in a gas state. Also provided are methods of forming coaxial waveguide microstructures by a sequential build process and hermetic packages which include a coaxial waveguide microstructure.

Owner:CUBIC CORPORATION

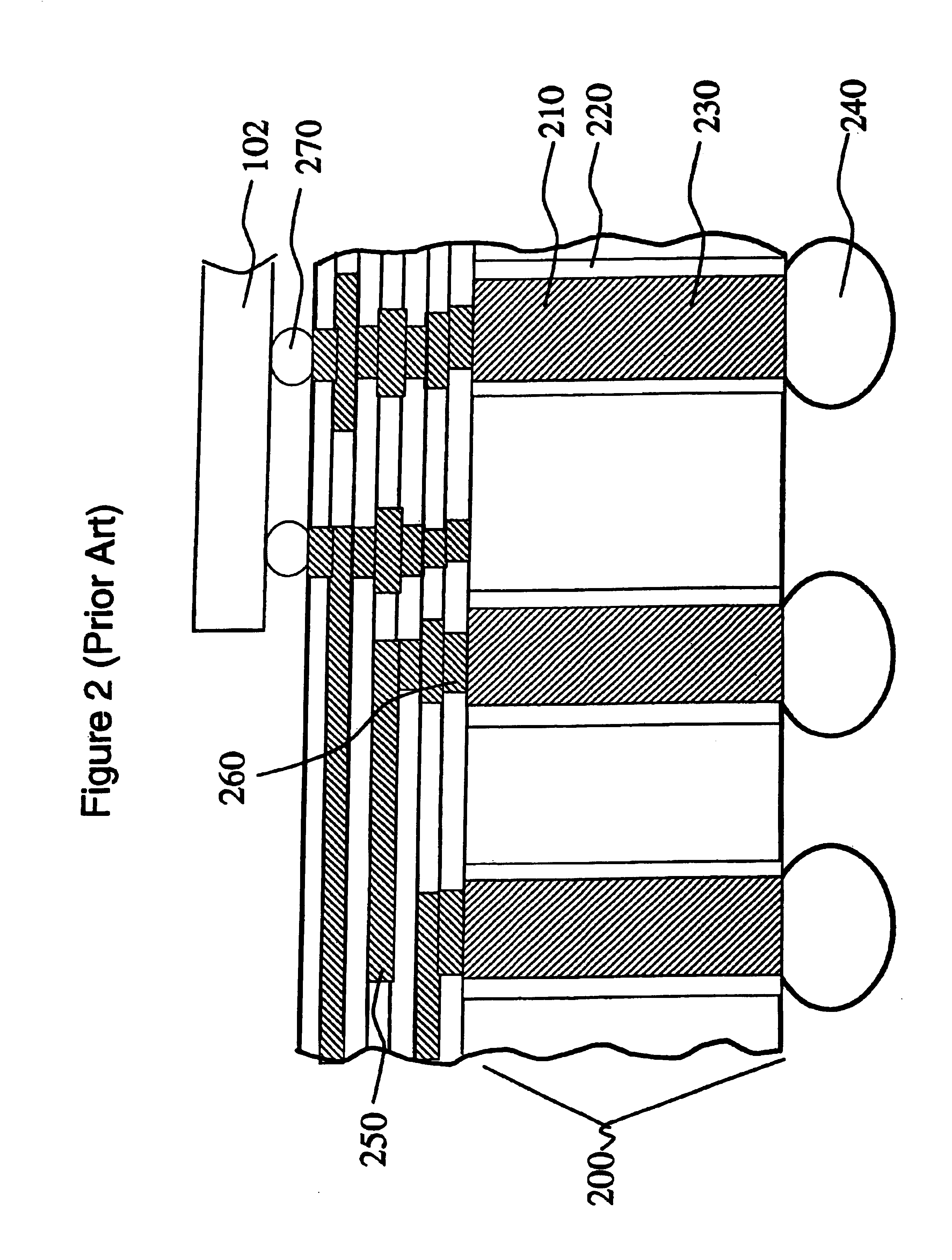

High density chip carrier with integrated passive devices

InactiveUS6962872B2Reduce inductanceEasy accessSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityEngineering

Owner:GLOBALFOUNDRIES U S INC

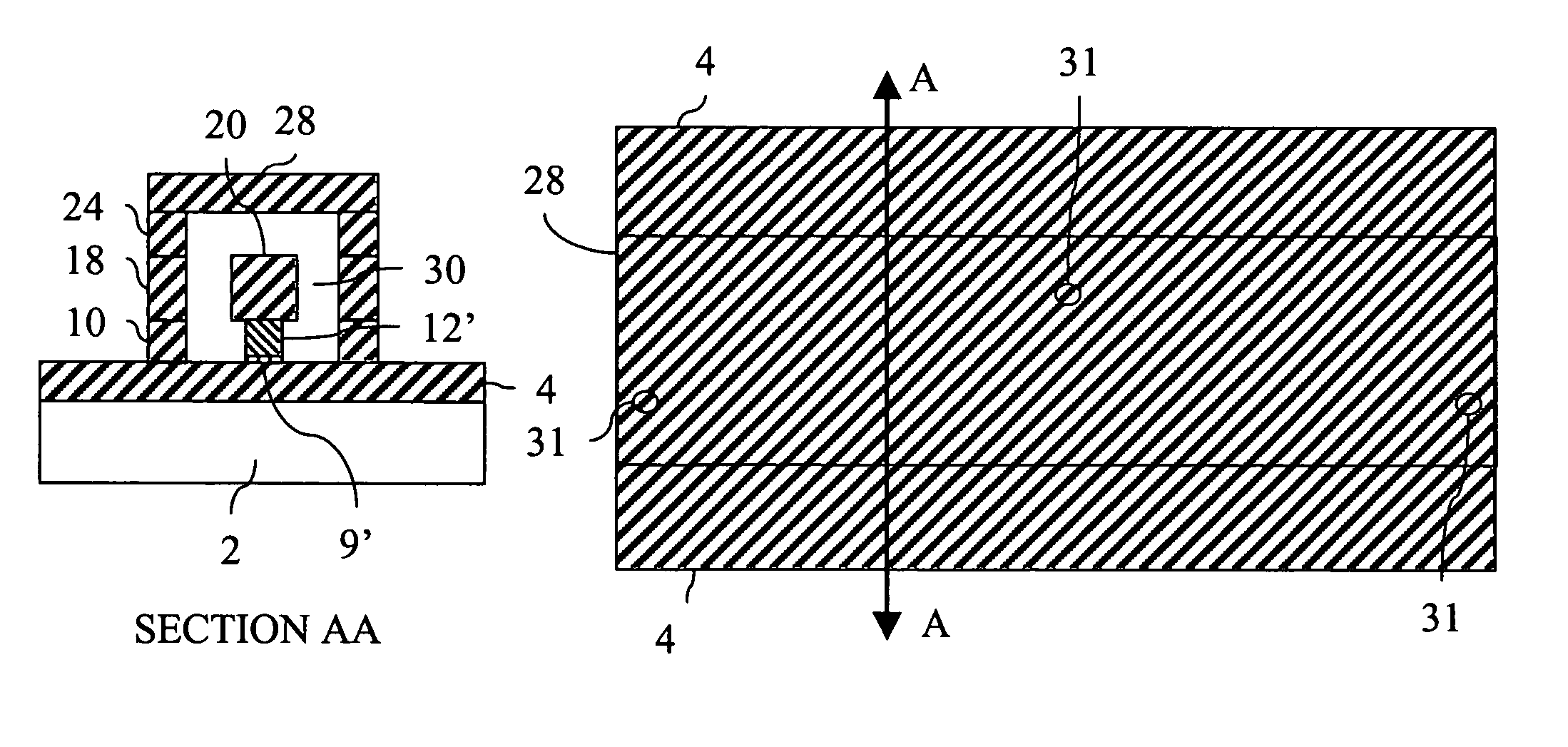

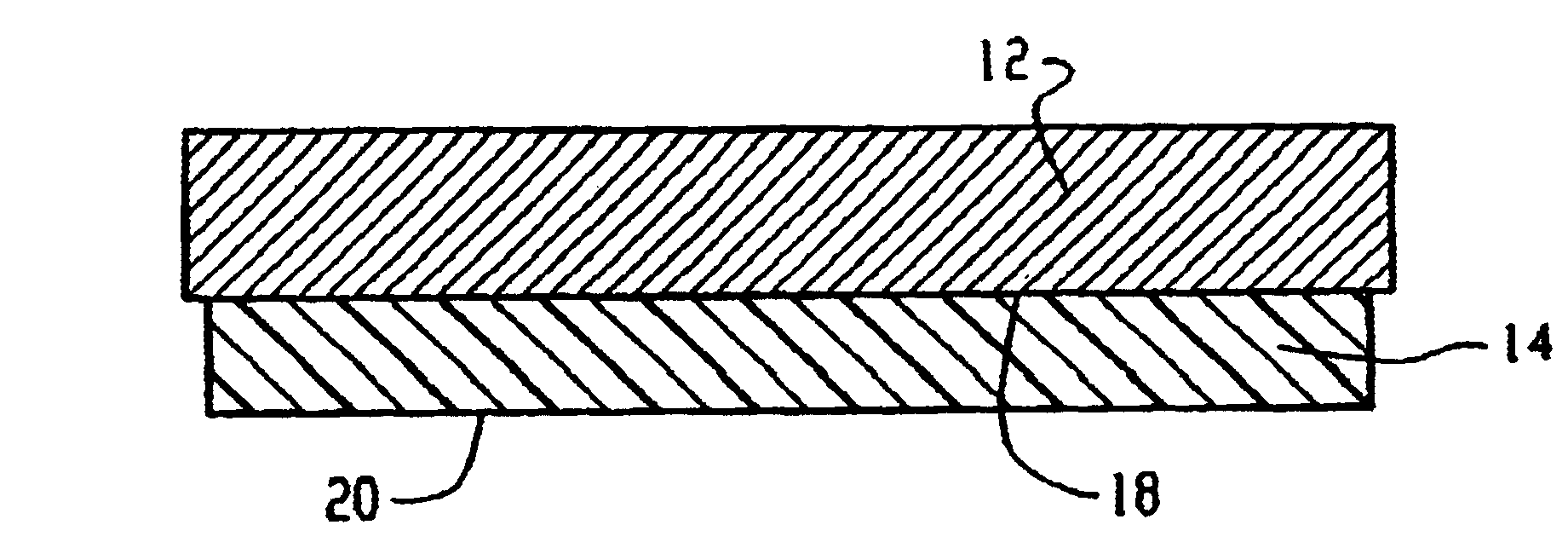

High reliability multlayer circuit substrates and methods for their formation

InactiveUS20040061234A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

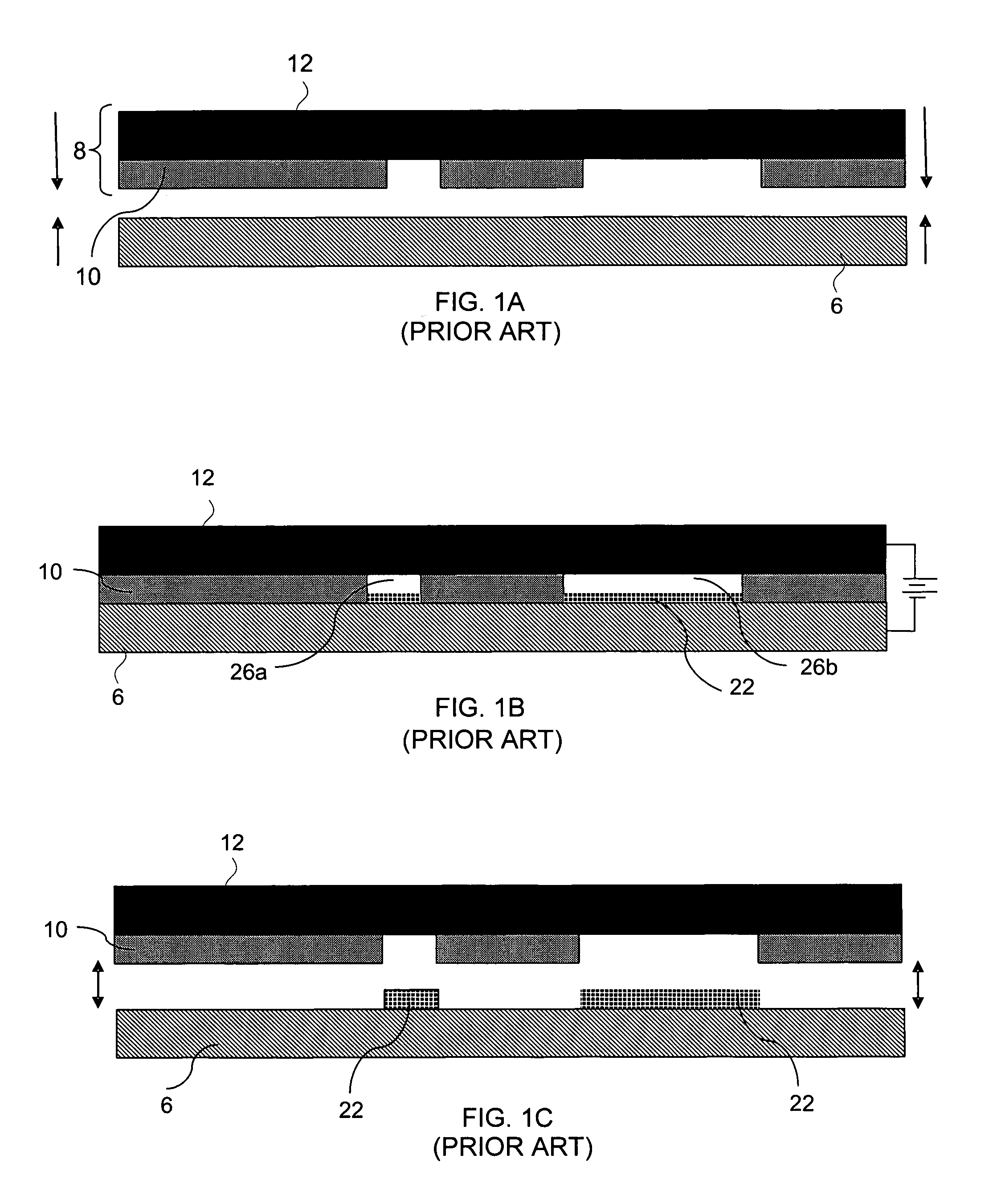

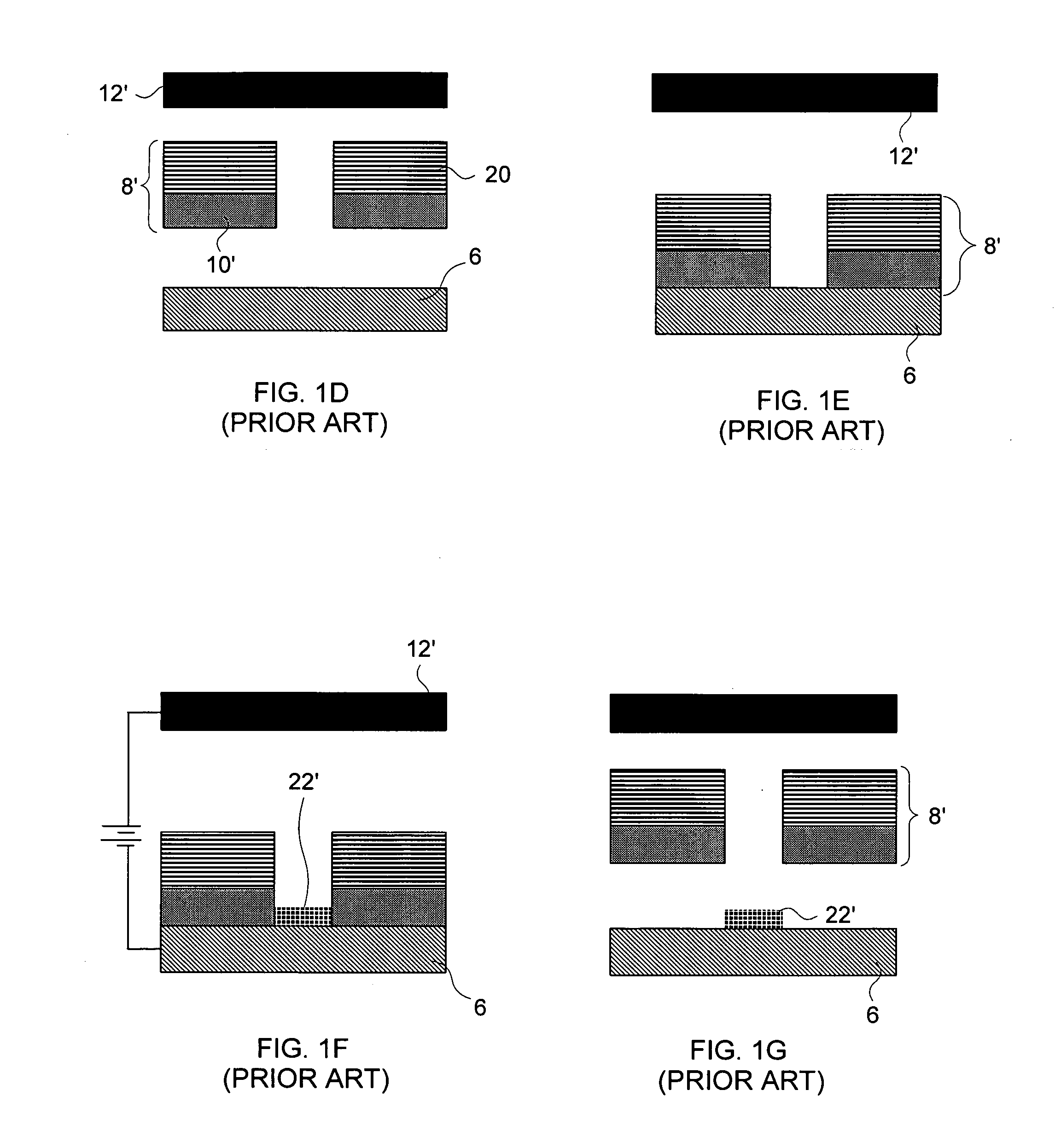

A multilayer circuit substrate for multi-chip modules or hybrid circuits includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by shadow mask techniques. Substrates formed in this manner enable significant increases in interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

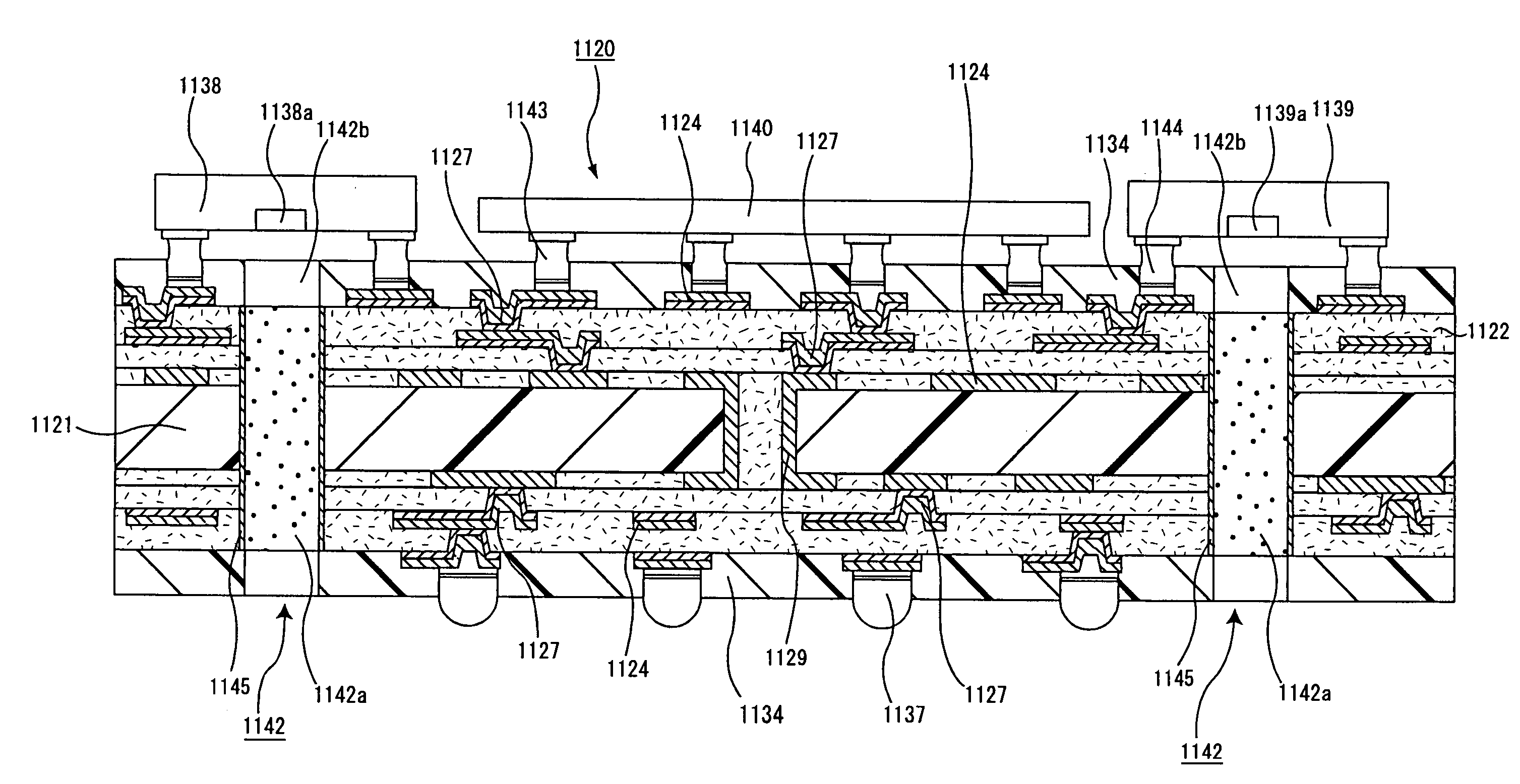

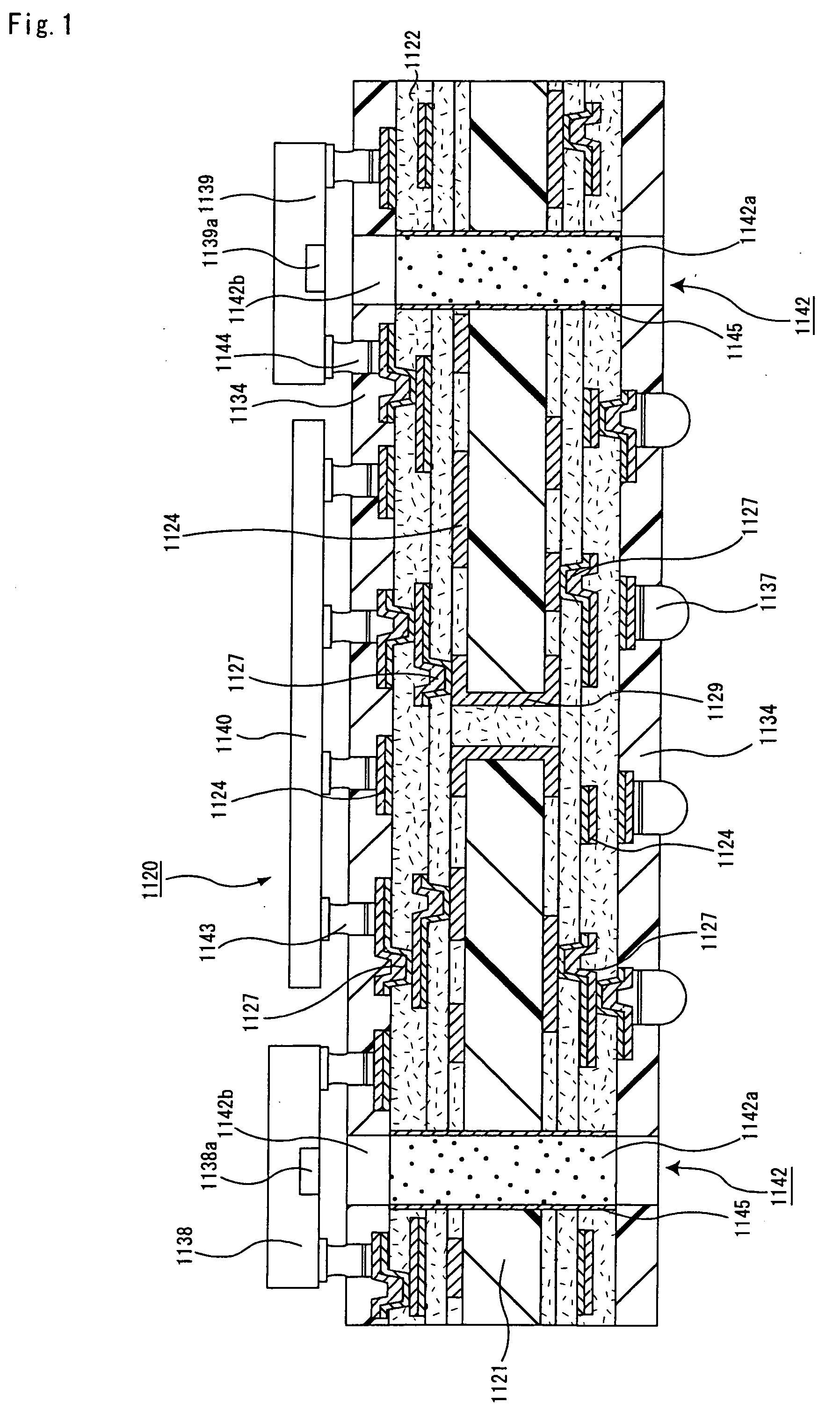

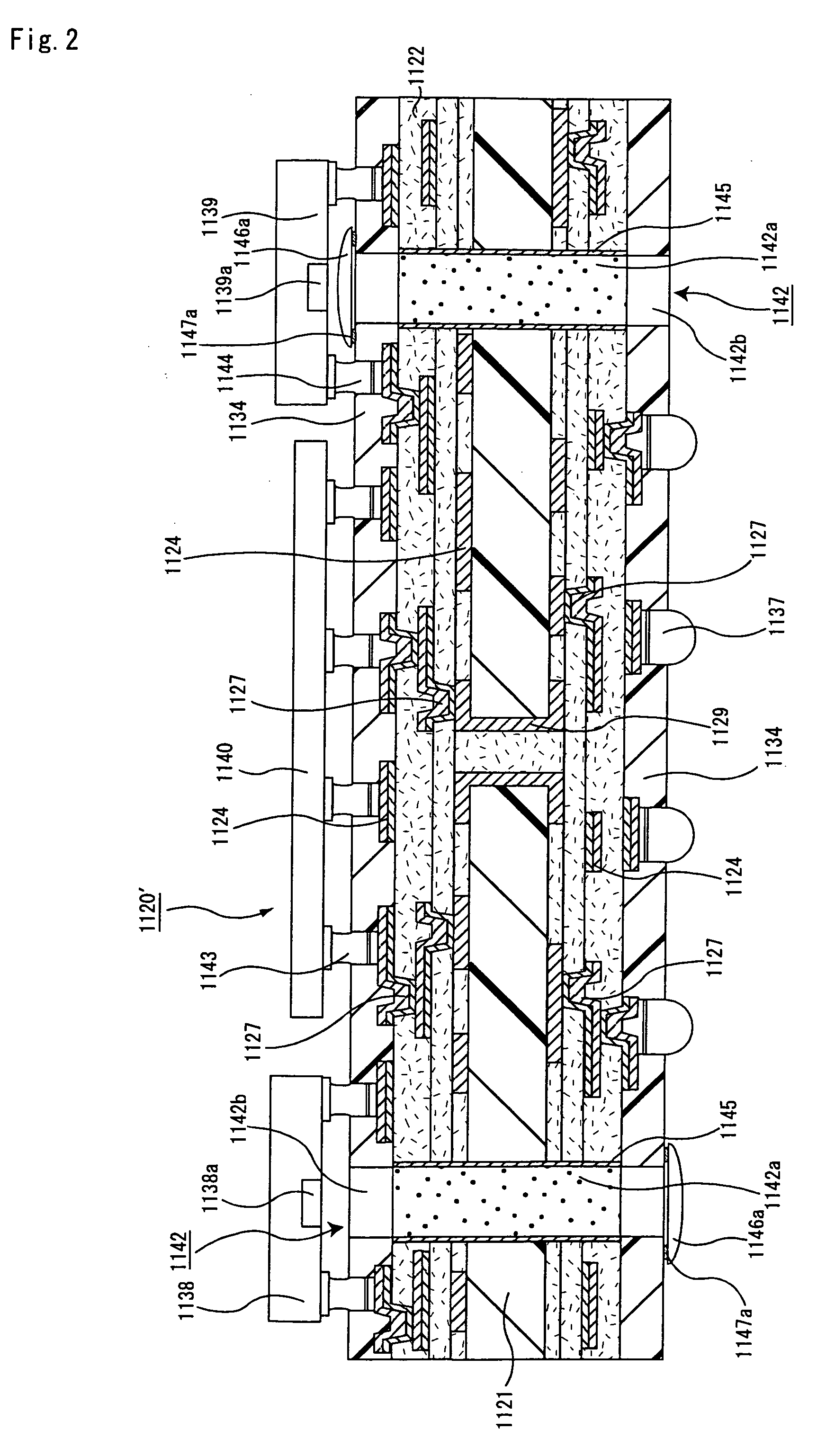

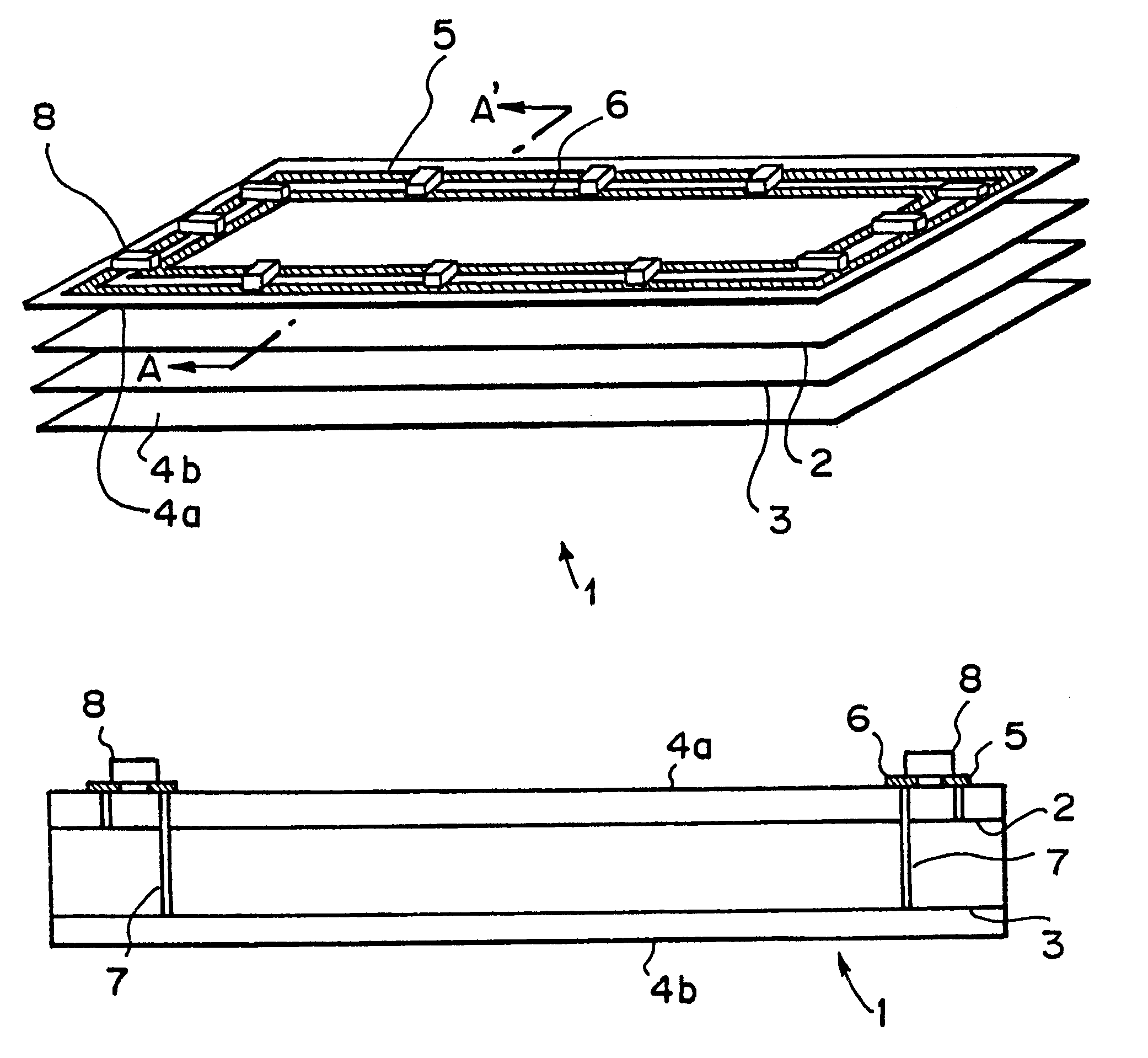

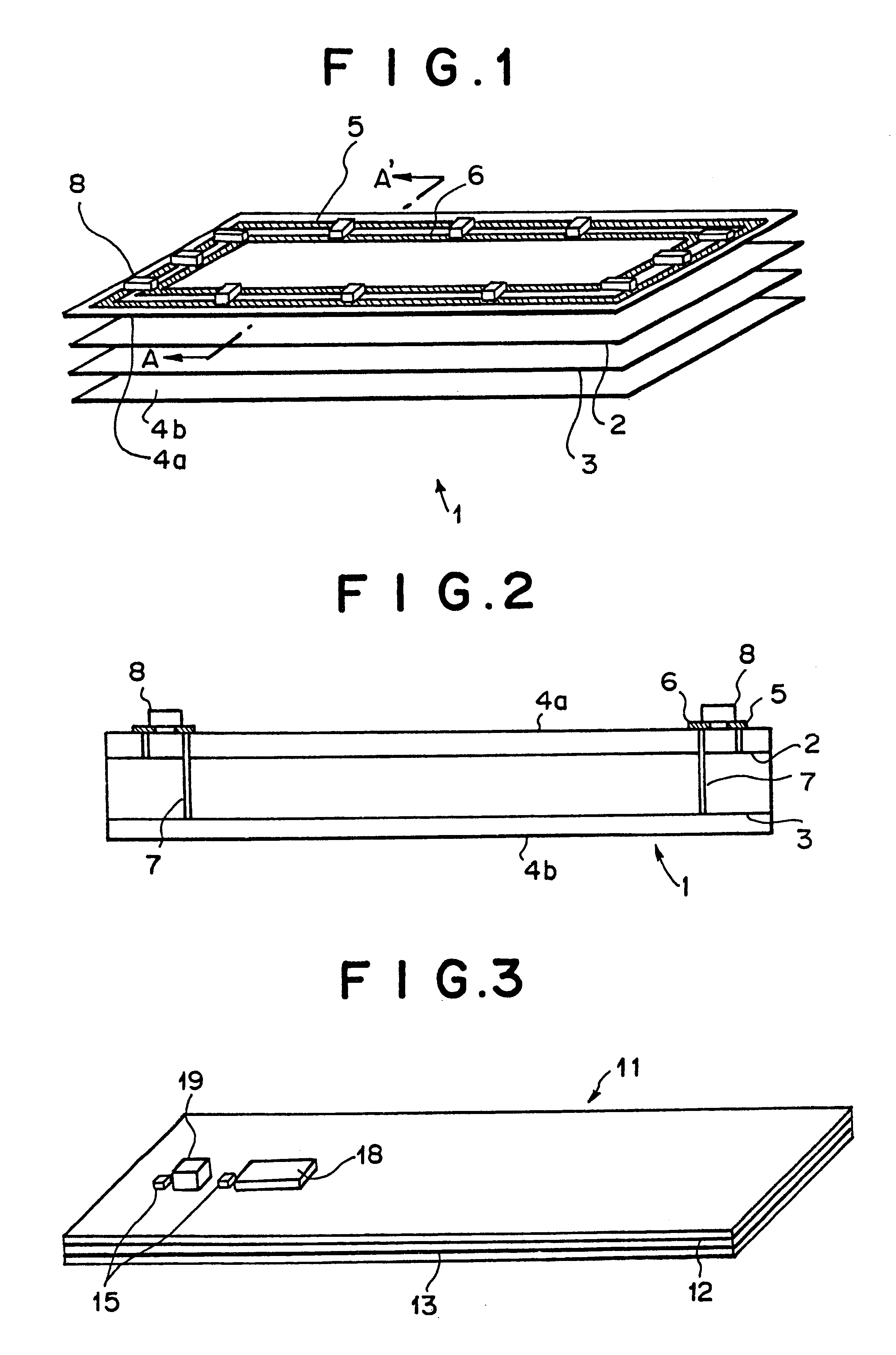

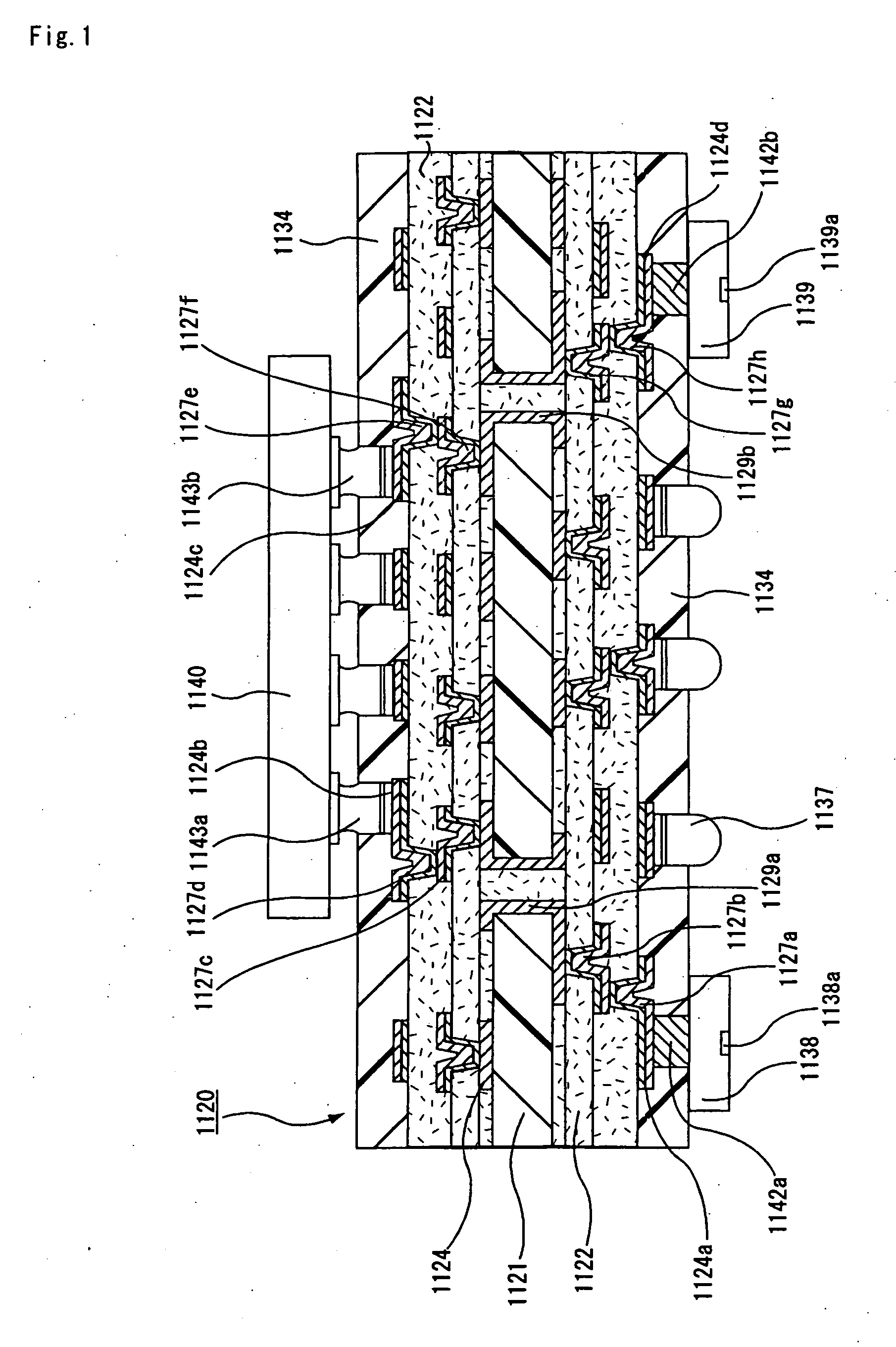

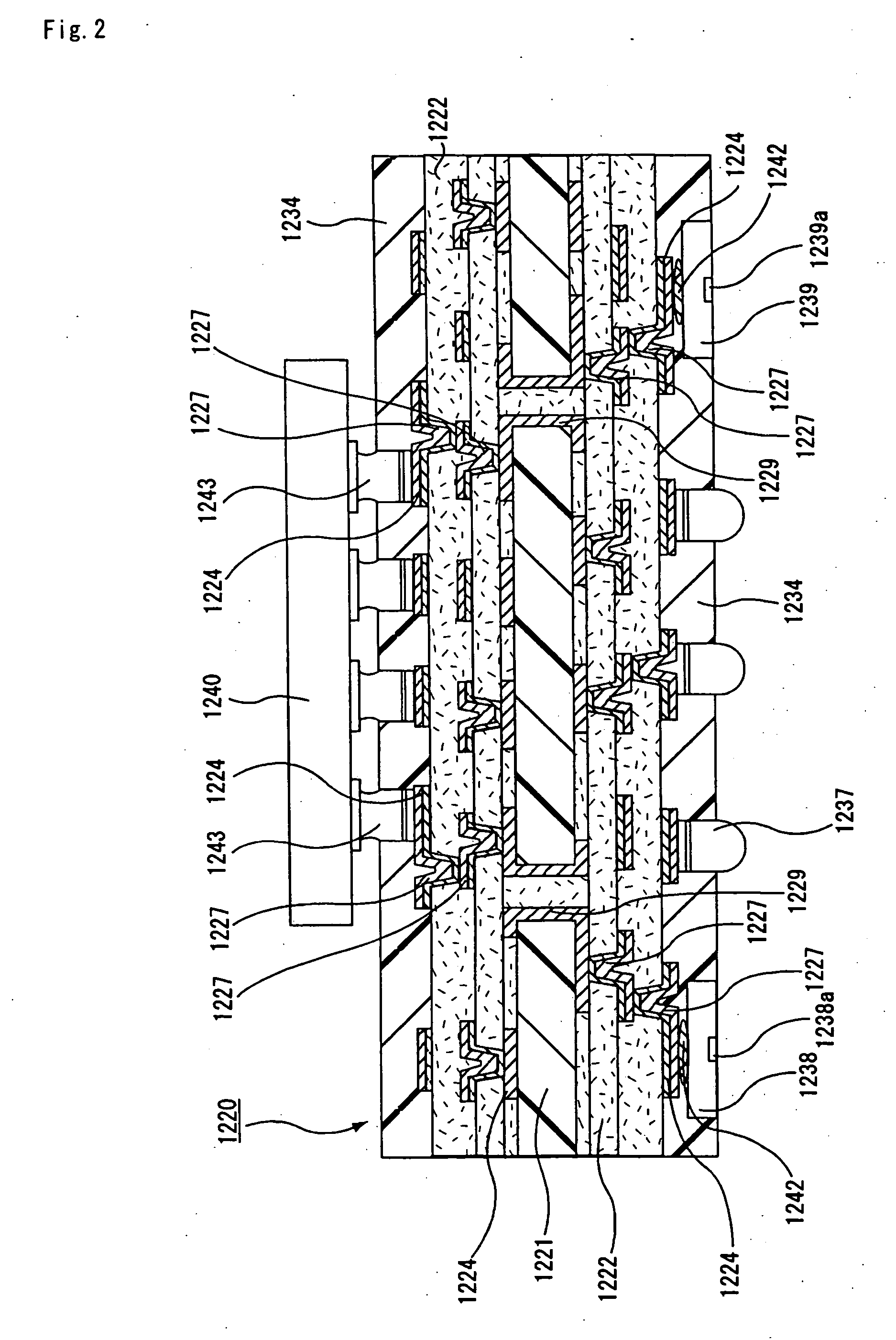

Ic chip mounting substrate, ic chip mounting substrate manufacturing method, optical communication device, and optical communication device manufacturing method

InactiveUS20060012967A1Improve connection reliabilitySmall sizeCircuit optical detailsSolid-state devicesResistElectrical conductor

An object of the present invention is to provide a substrate for mounting an IC chip which is a component for optical communication having an IC chip and an optical component integrally provided thereon, which can ensure a short distance between the IC chip and the optical component, which is excellent in electric signal transmission reliability and which can transmit optical signal through an optical path for transmitting optical signal. The substrate for mounting an IC chip of the present invention is a substrate for mounting an IC chip comprising: a substrate and, as serially built up on both faces thereof, a conductor circuit and an interlaminar insulating layer in an alternate fashion and in repetition; a solder resist layer formed as an outermost layer; and an optical element mounted thereto, wherein an optical path for transmitting optical signal, which penetrates the substrate for mounting an IC chip, is disposed.

Owner:IBIDEN CO LTD

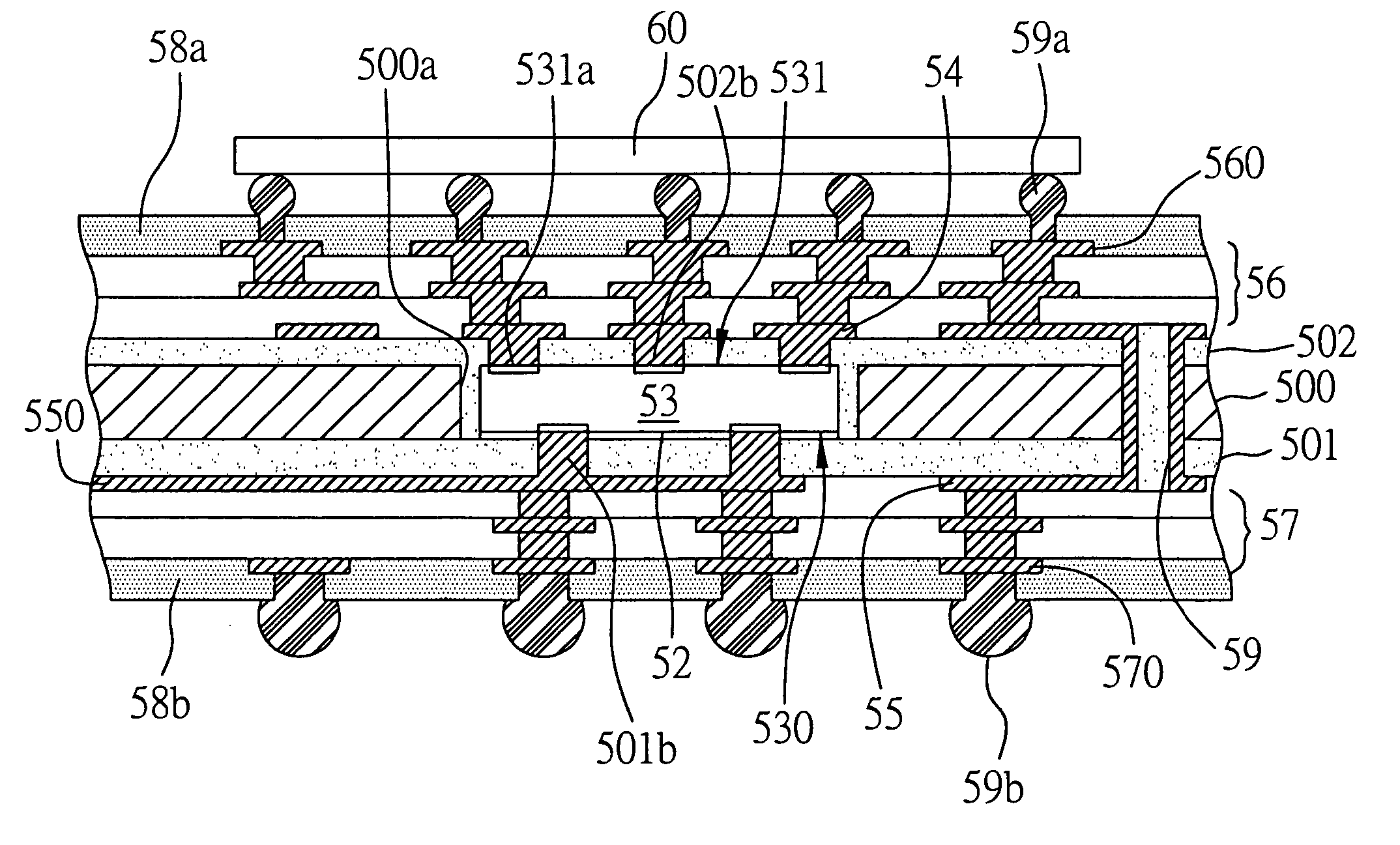

Hybrid wiring board, semiconductor apparatus, flexible substrate, and fabrication method of hybrid wiring board

InactiveUS6329610B1Semiconductor/solid-state device detailsPrinted electric component incorporationInsulation layerEngineering

A first via land of a wiring layer on a first surface of a first insulation layer that is a rigid layer and a second via land of a wiring layer on a second surface of a second insulation layer that is a flexible layer are electrically and mechanically connected with a conductive pillar pierced through a third insulation layer disposed between the first insulation layer and the second insulation layer. In such a structure, a wiring board that can mount a highly integrated semiconductor device, that is small and thin, and that has high reliability can be accomplished.

Owner:KK TOSHIBA

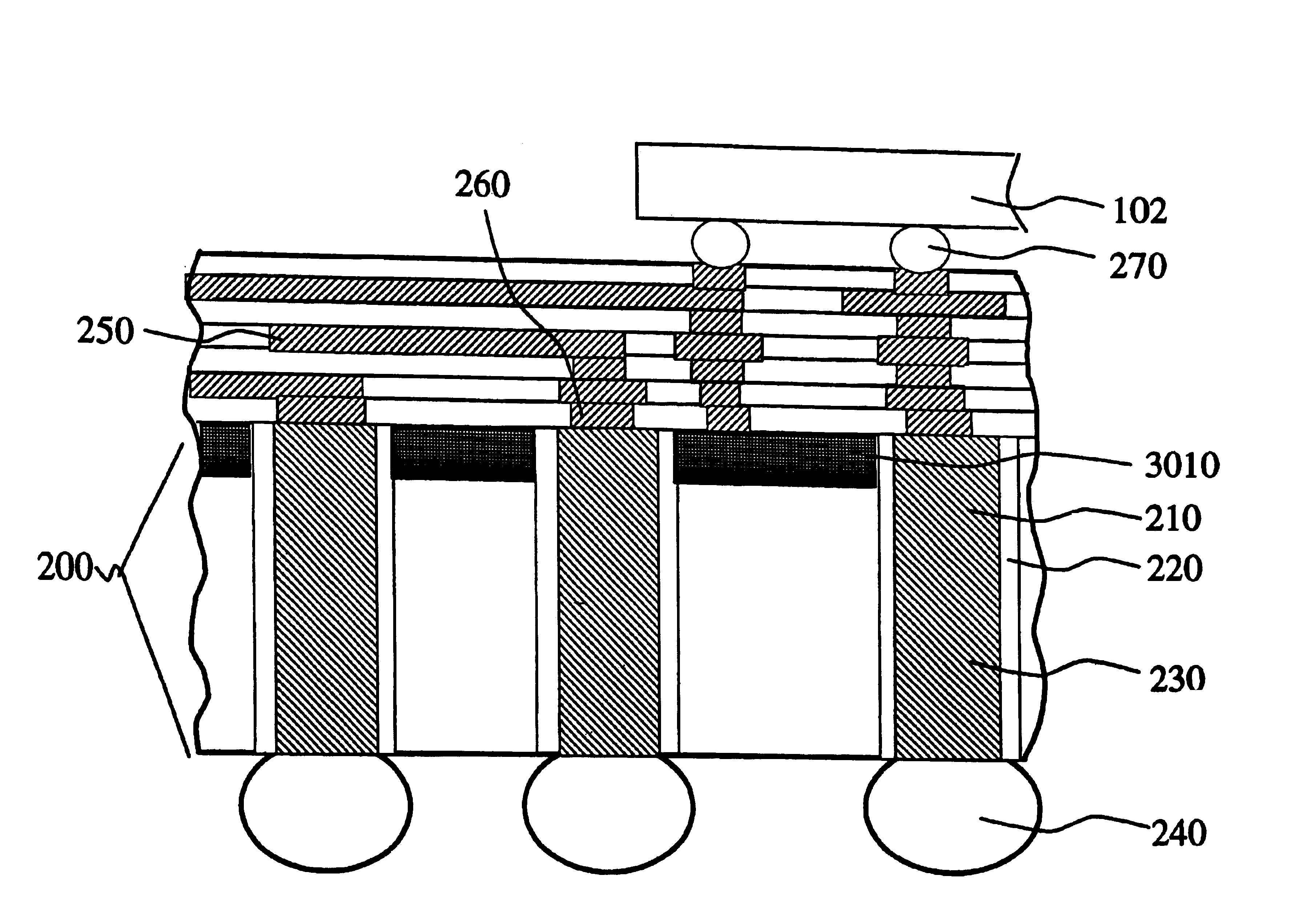

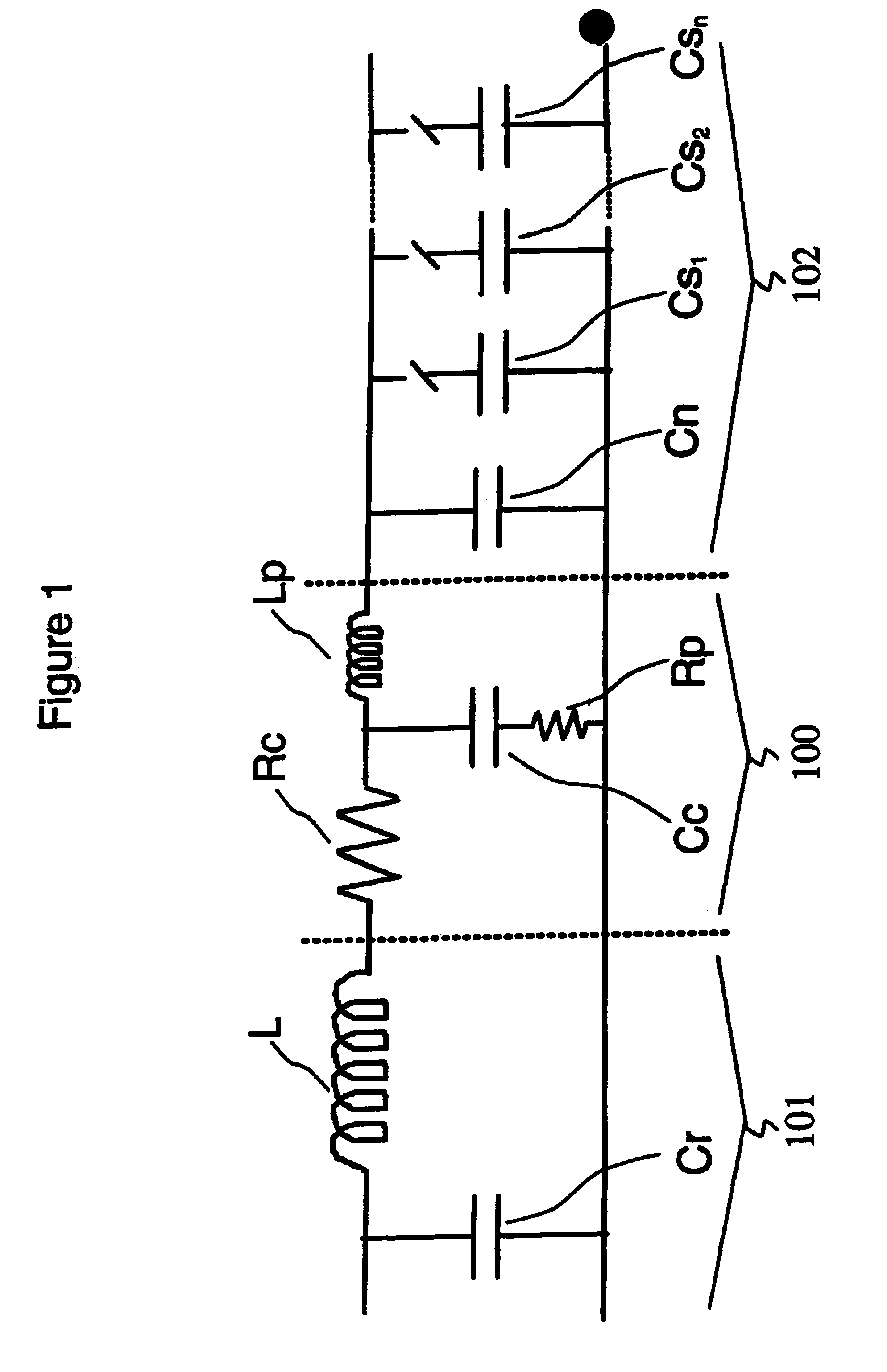

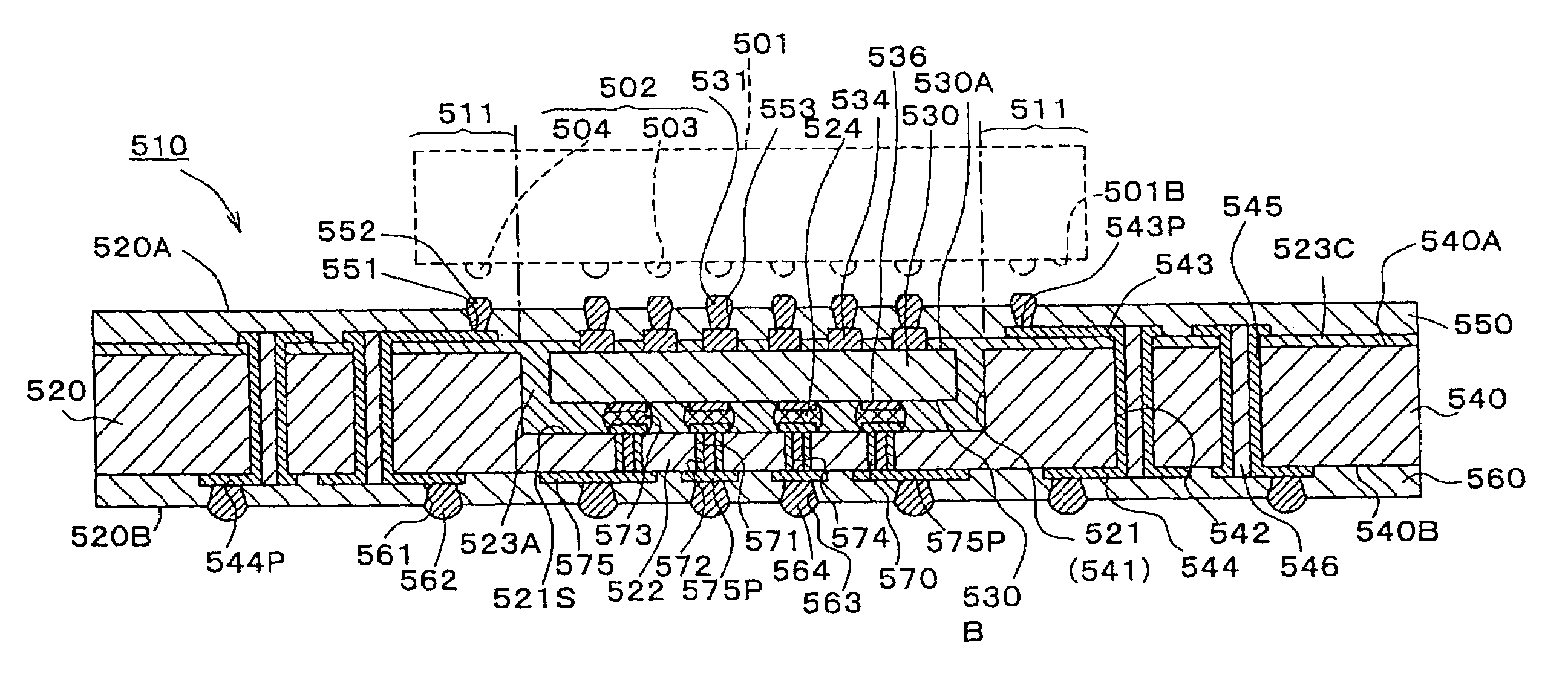

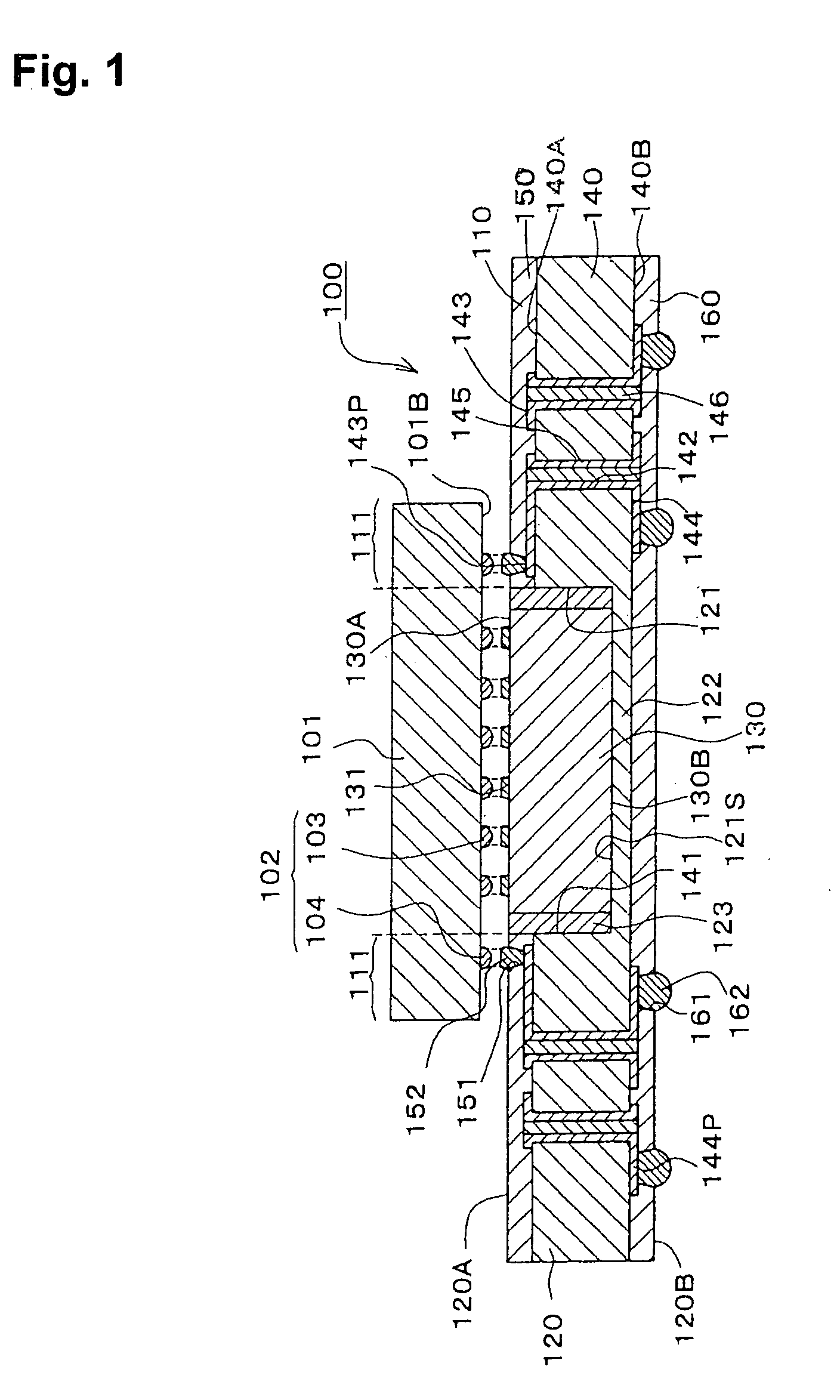

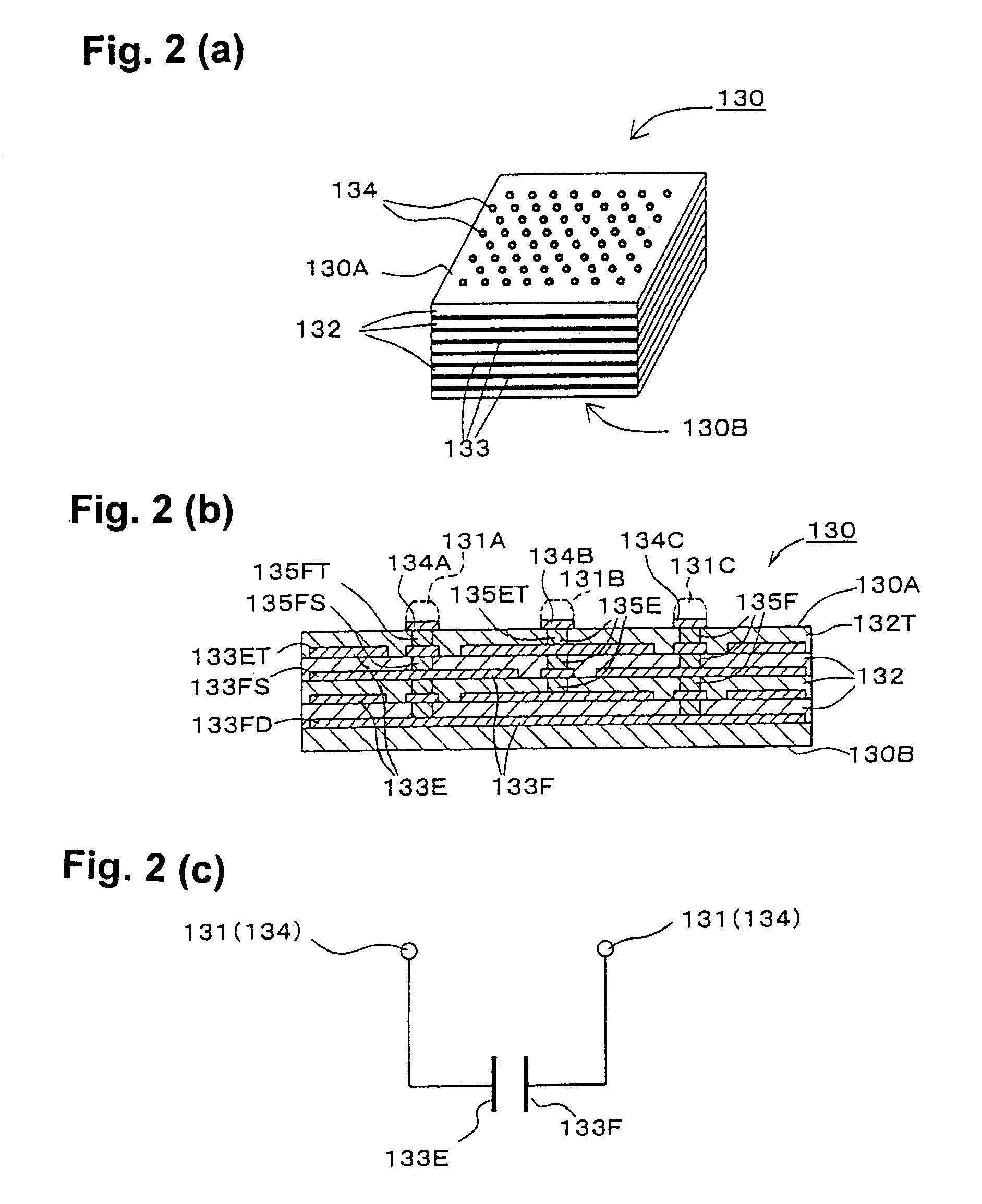

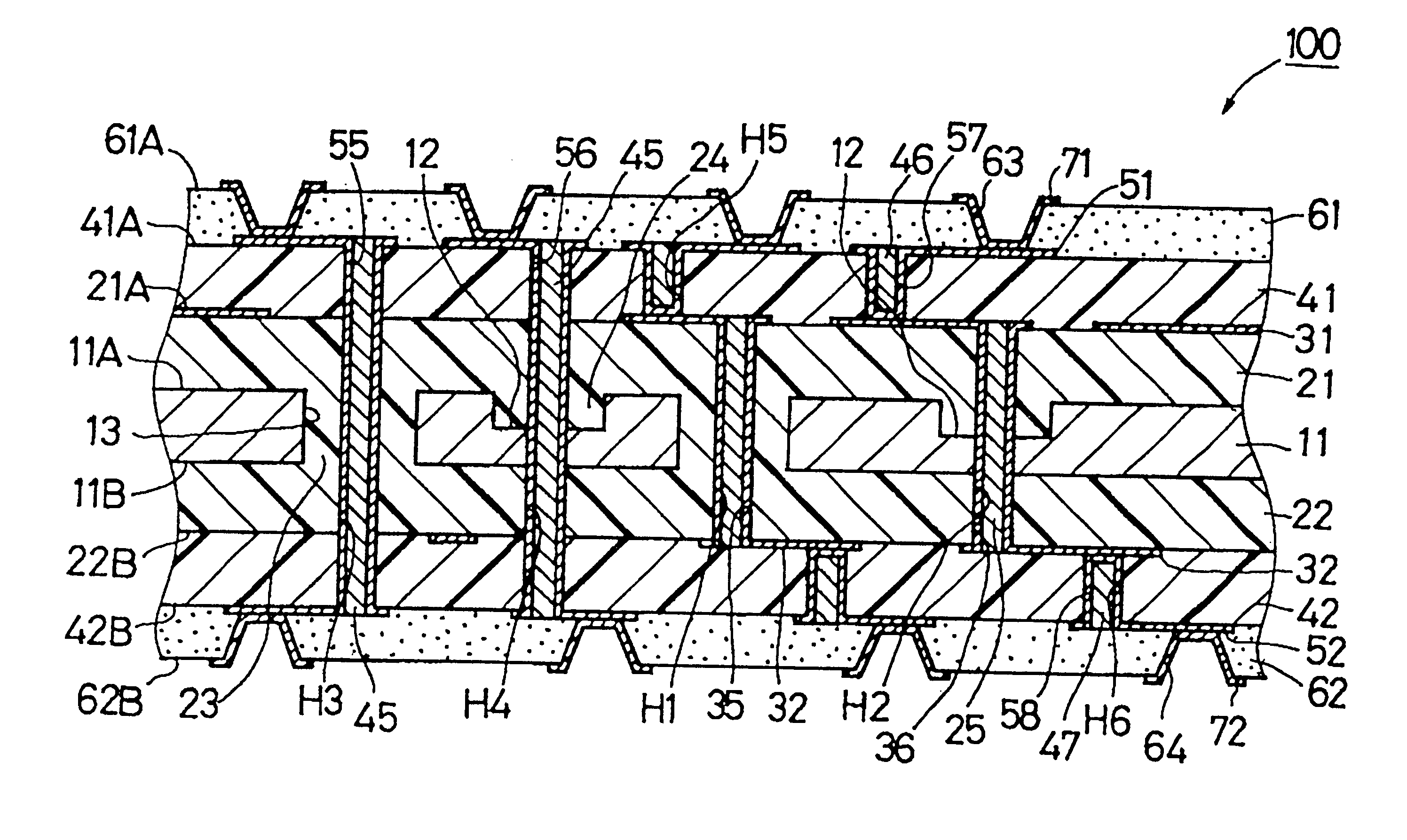

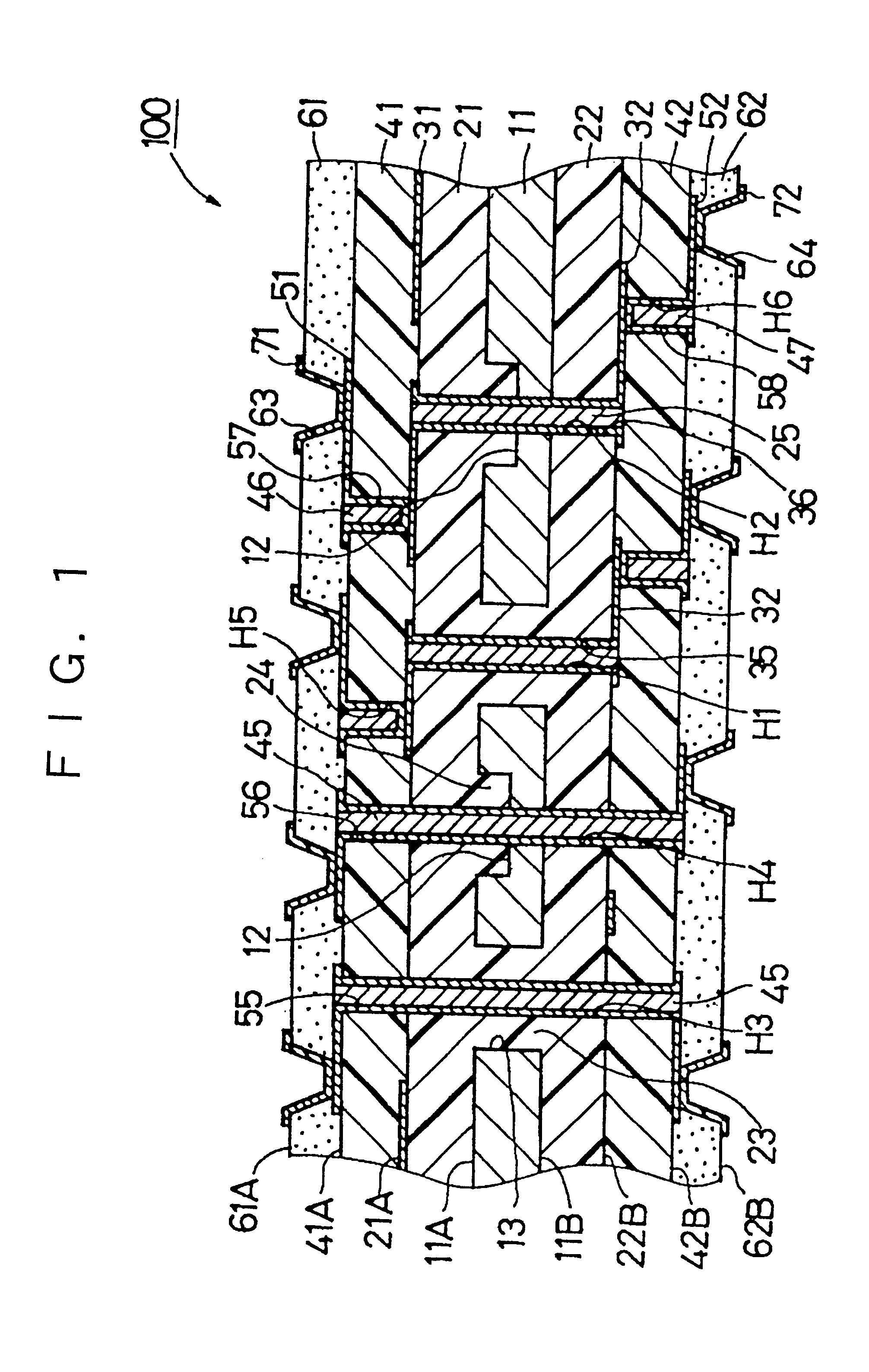

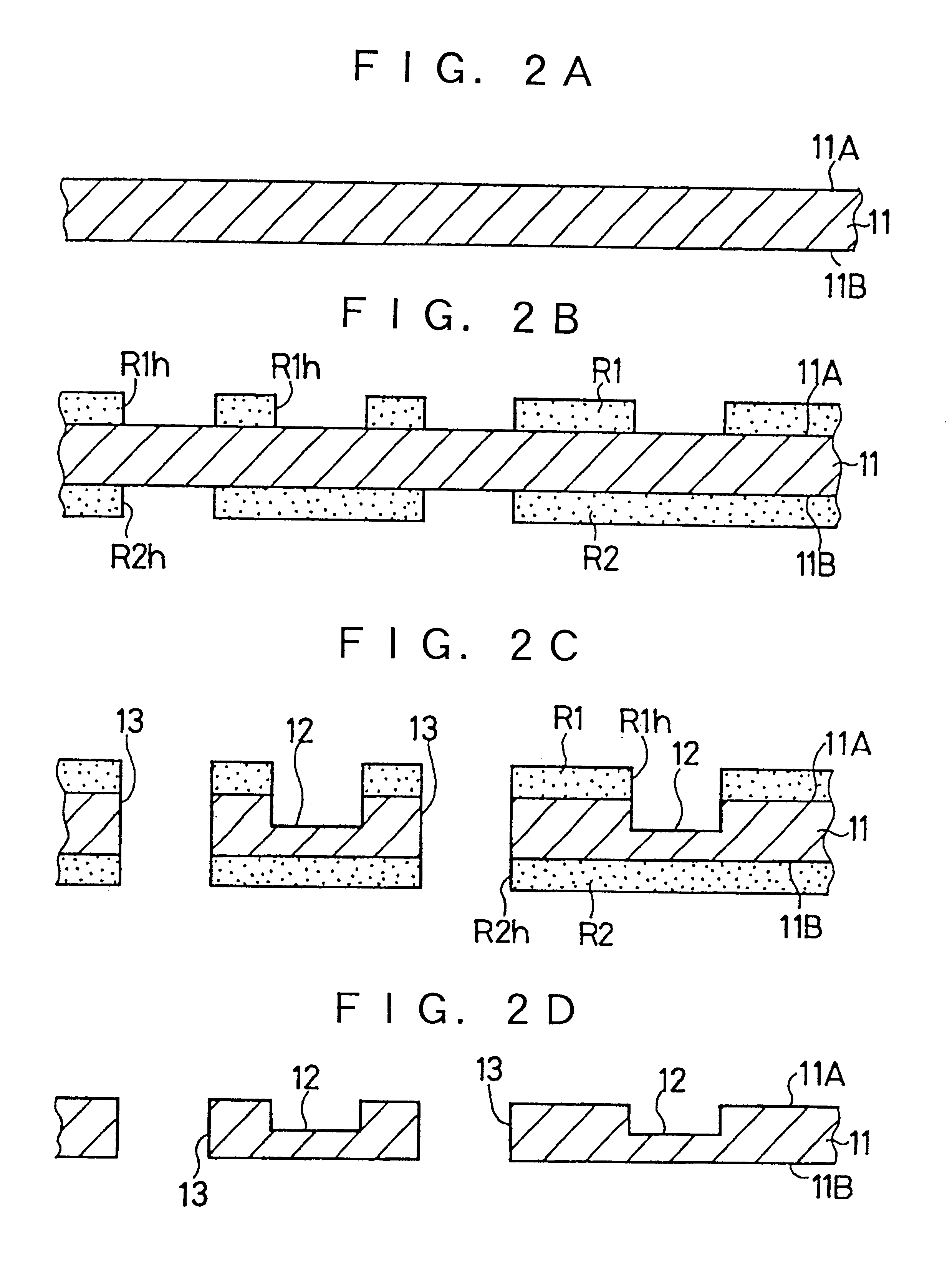

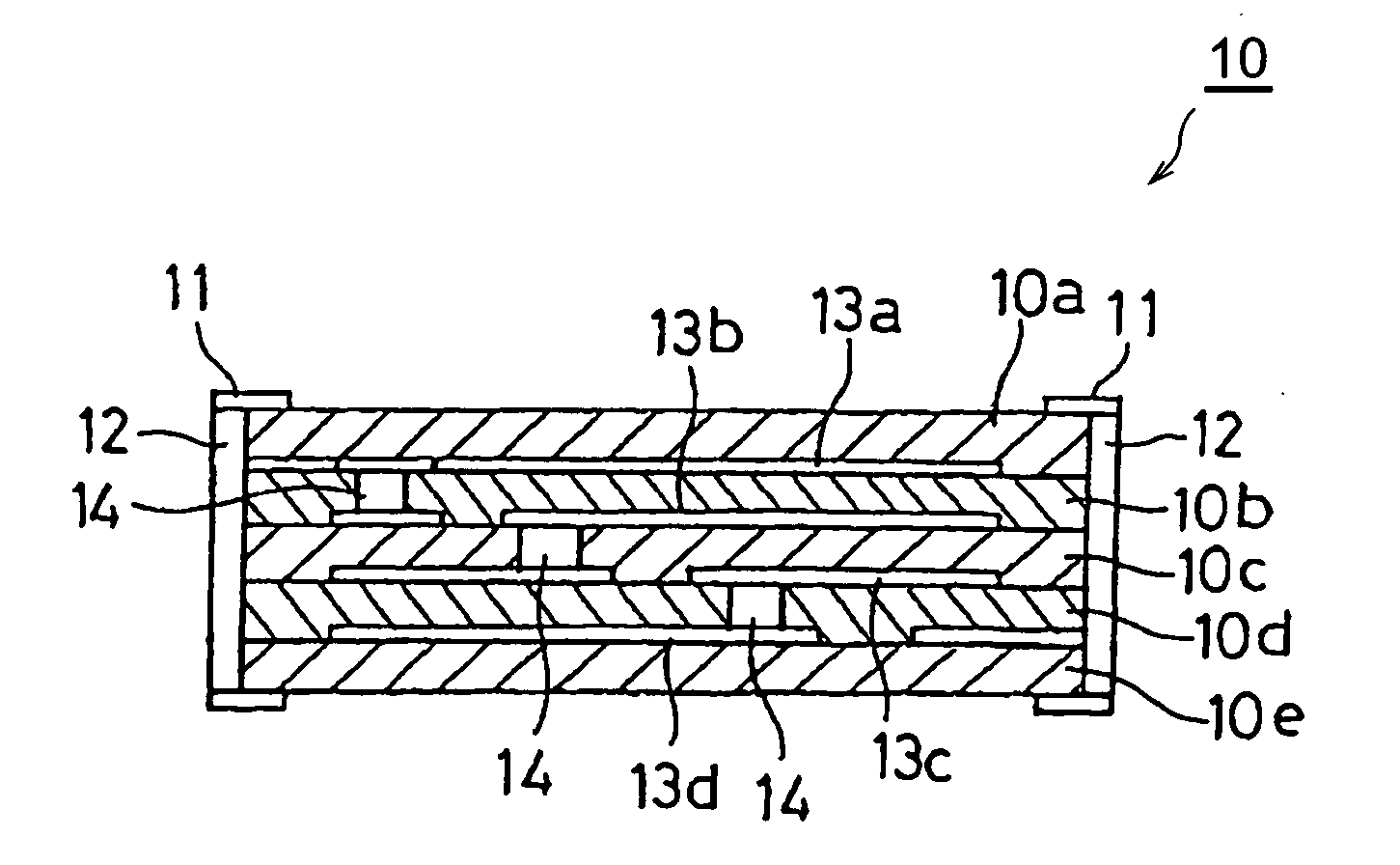

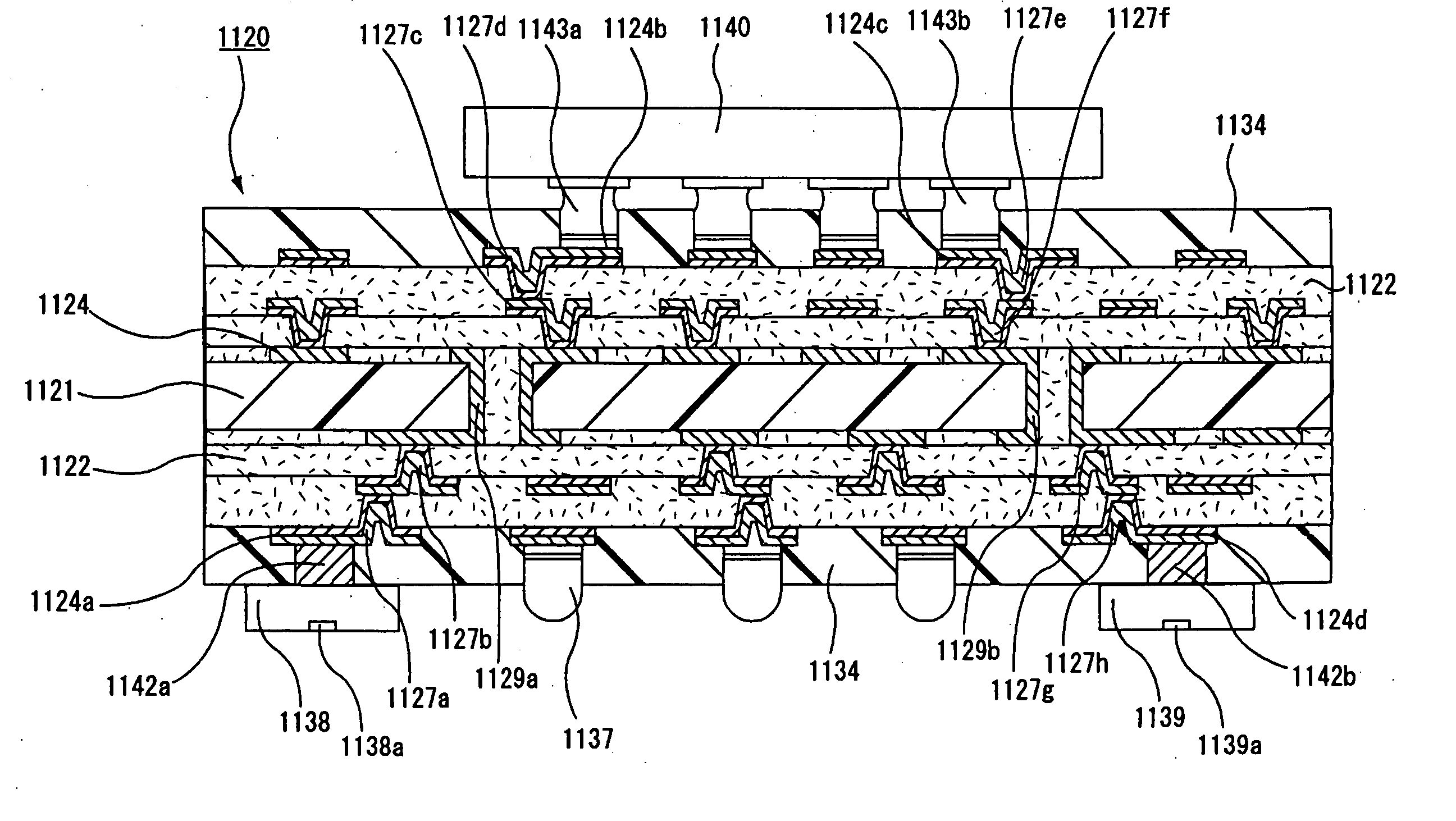

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS6952049B1Firmly connectedReliably eliminate noiseCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceEngineering

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

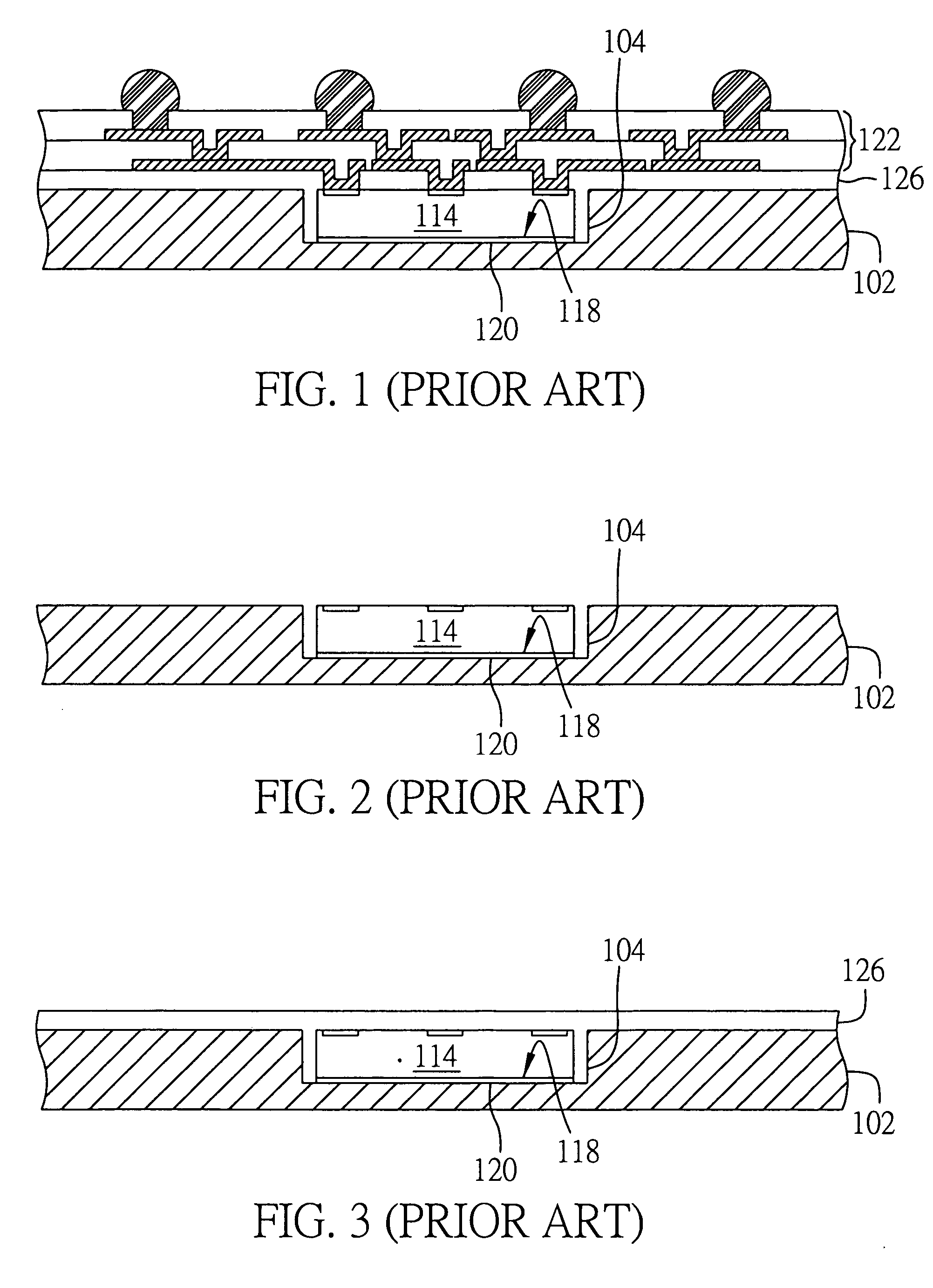

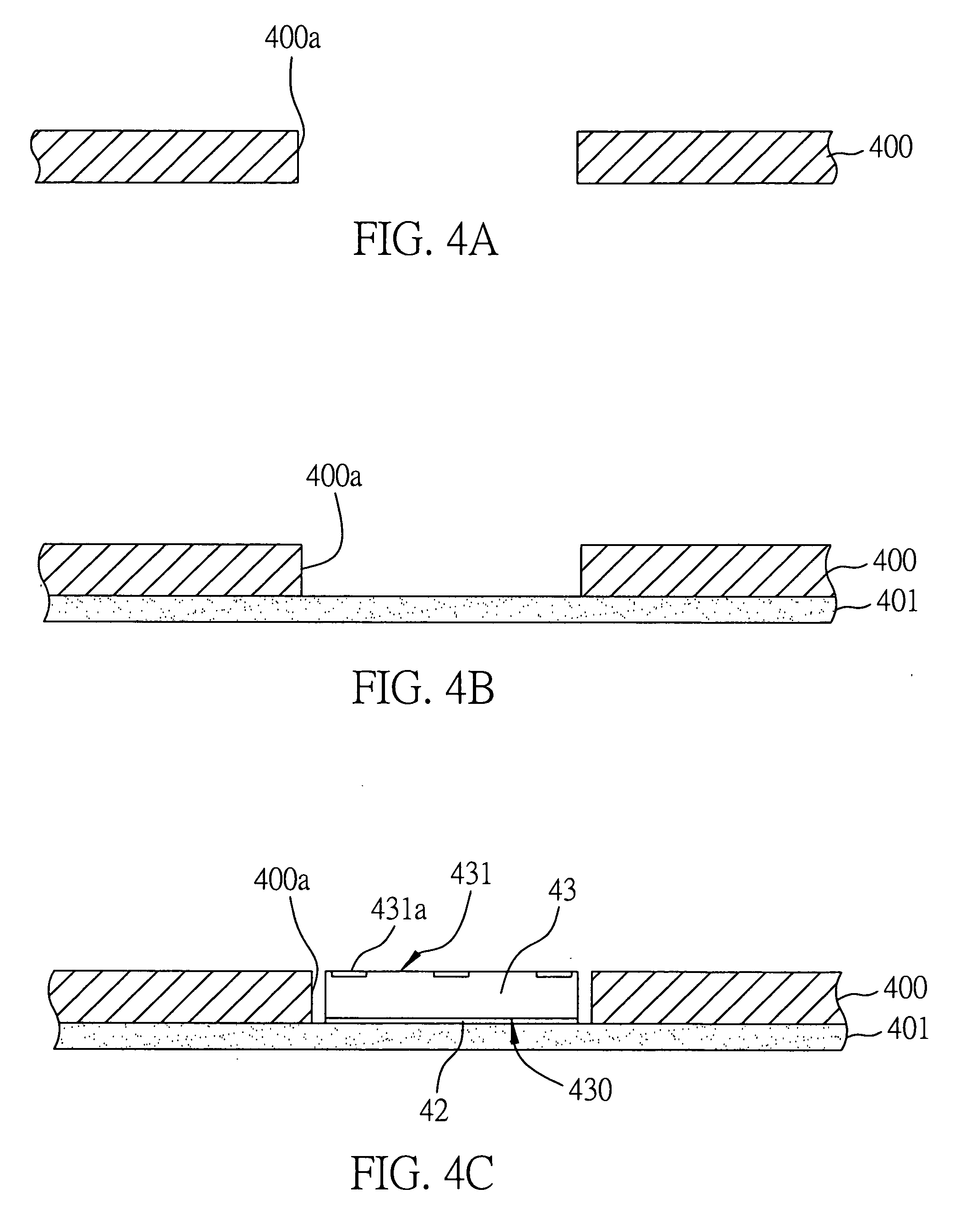

Three dimensional package structure with semiconductor chip embedded in substrate and method for fabricating the same

InactiveUS20060145328A1Avoid disadvantagesImprove cooling effectSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor chipEngineering

A three dimensional package structure with semiconductor chip embedded in substrate and a method for fabricating the same are proposed. A carrier with at least one cavity is mounted on a first insulating layer, and at least one semiconductor chip is mounted on the first insulating layer and received in the cavity of the carrier. A second insulating layer is formed on the carrier and the semiconductor chip. By performing a pressing process on both of the first insulating layer and the second insulating layer, a gap between the carrier and the semiconductor chip is filled. A circuit layer may be formed on the second insulating layer and is electrically connected to the semiconductor chip. Heat dissipating vias are formed in the first insulating layer and are connected to the semiconductor chip and a heat dissipating circuit so as to facilitate dissipation of heat generated from the semiconductor chip.

Owner:PHOENIX PRECISION TECH CORP

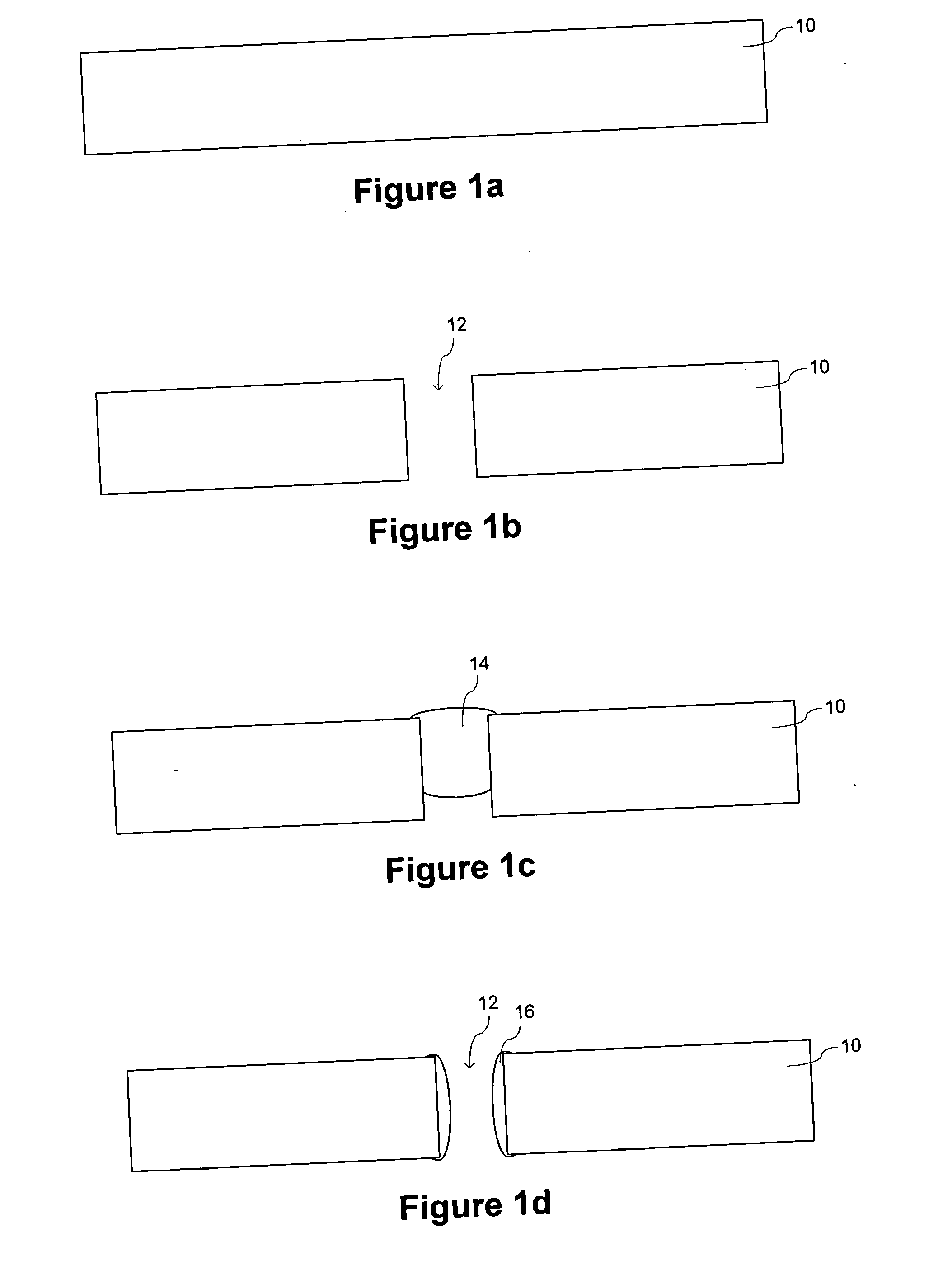

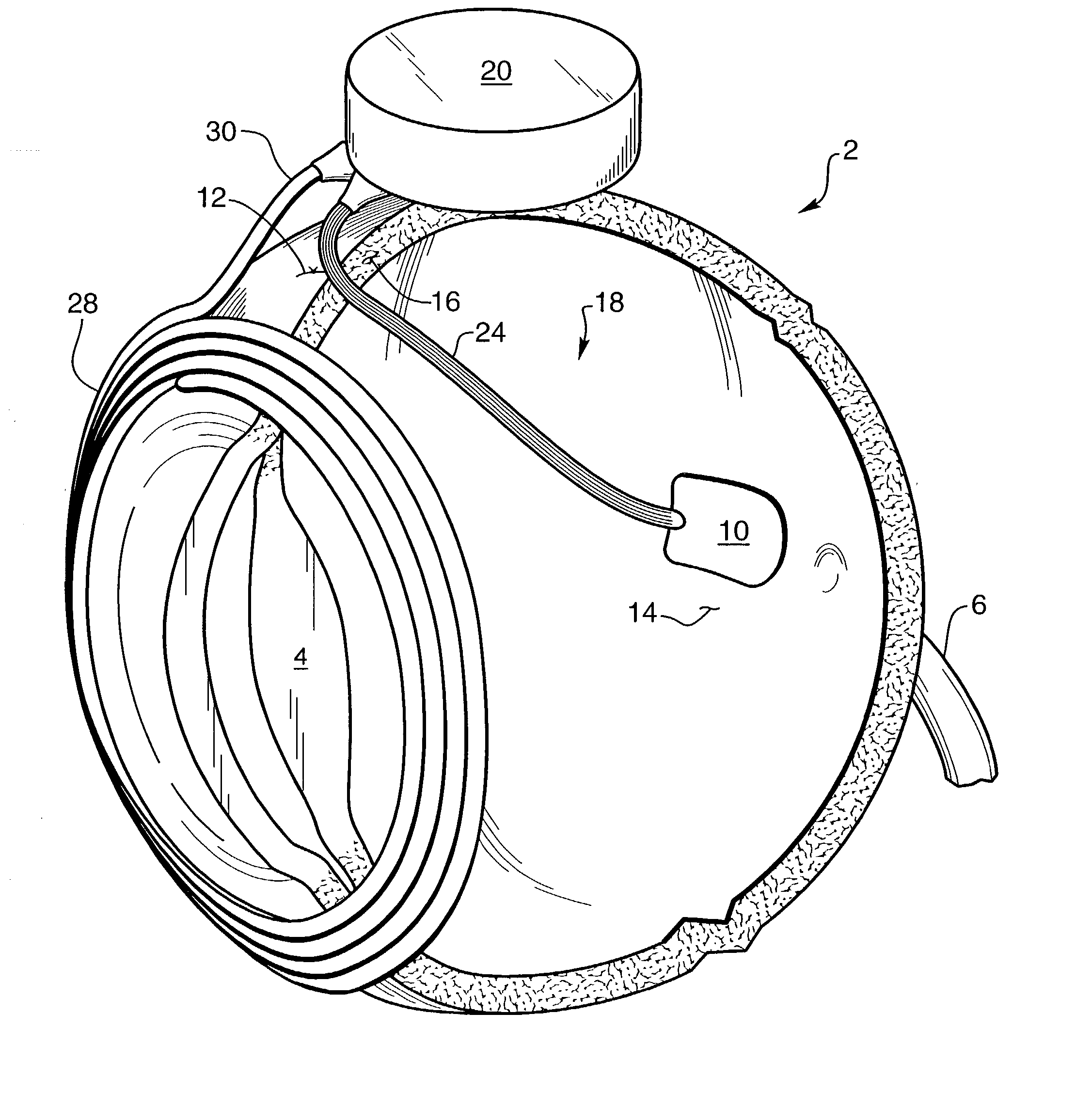

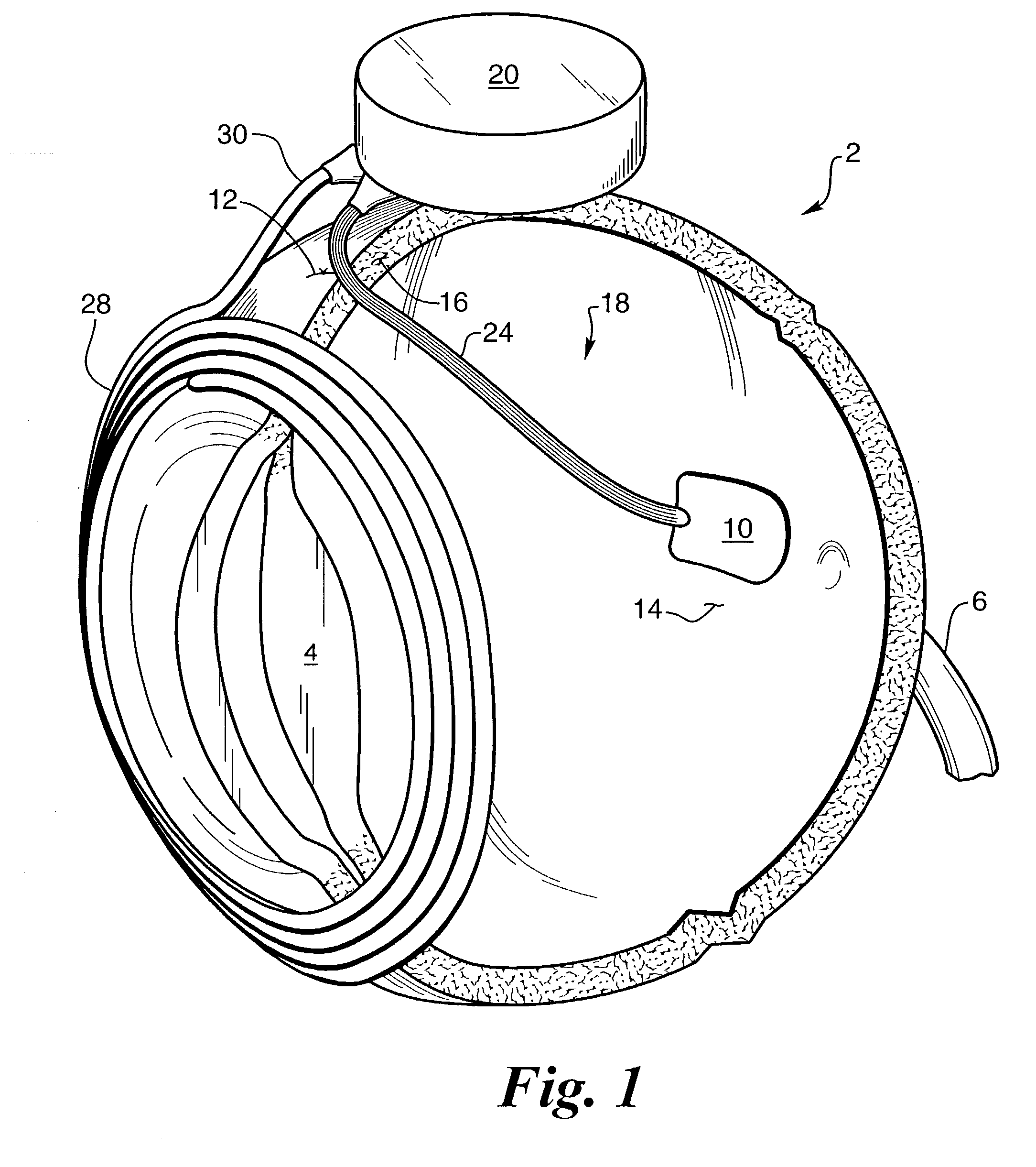

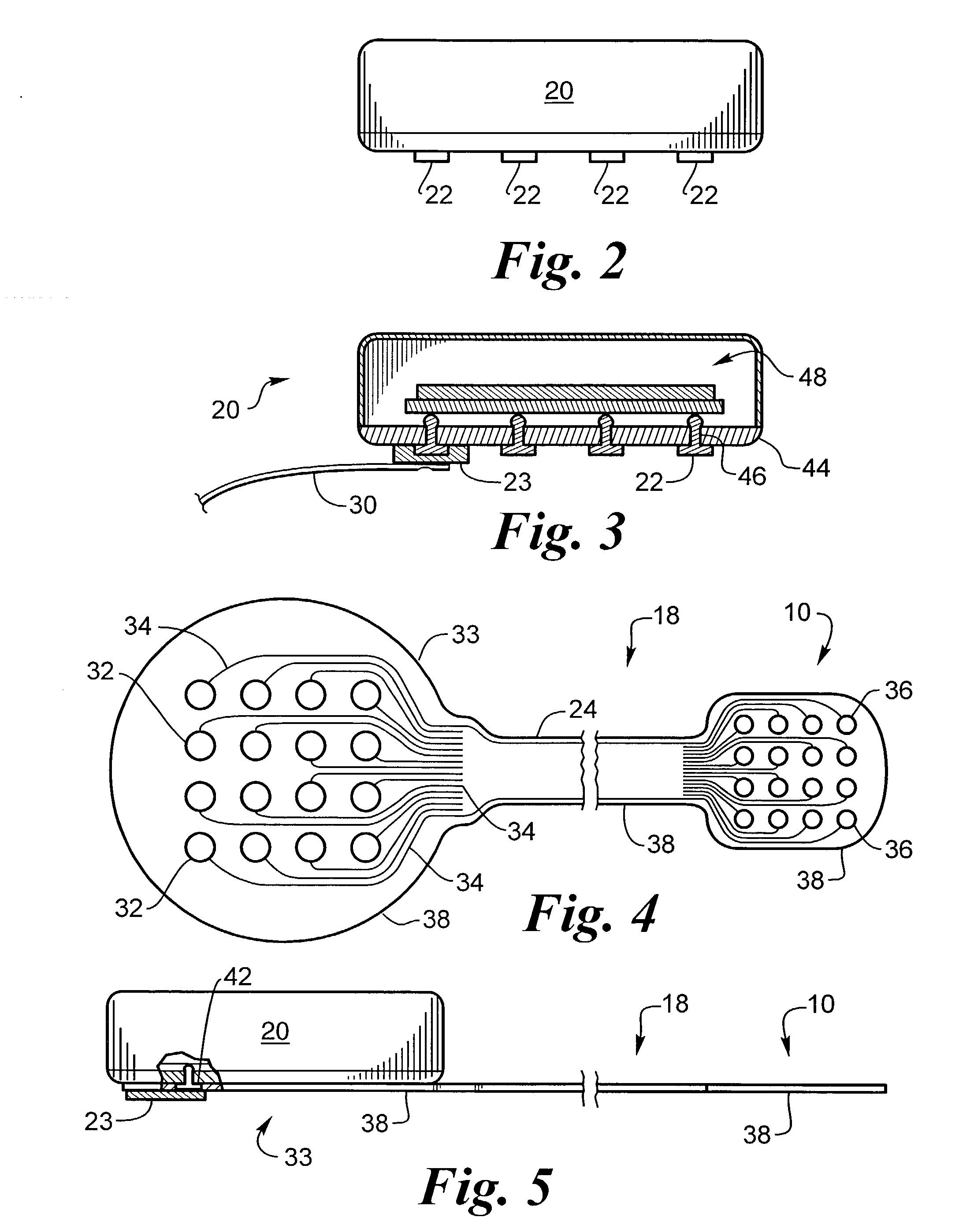

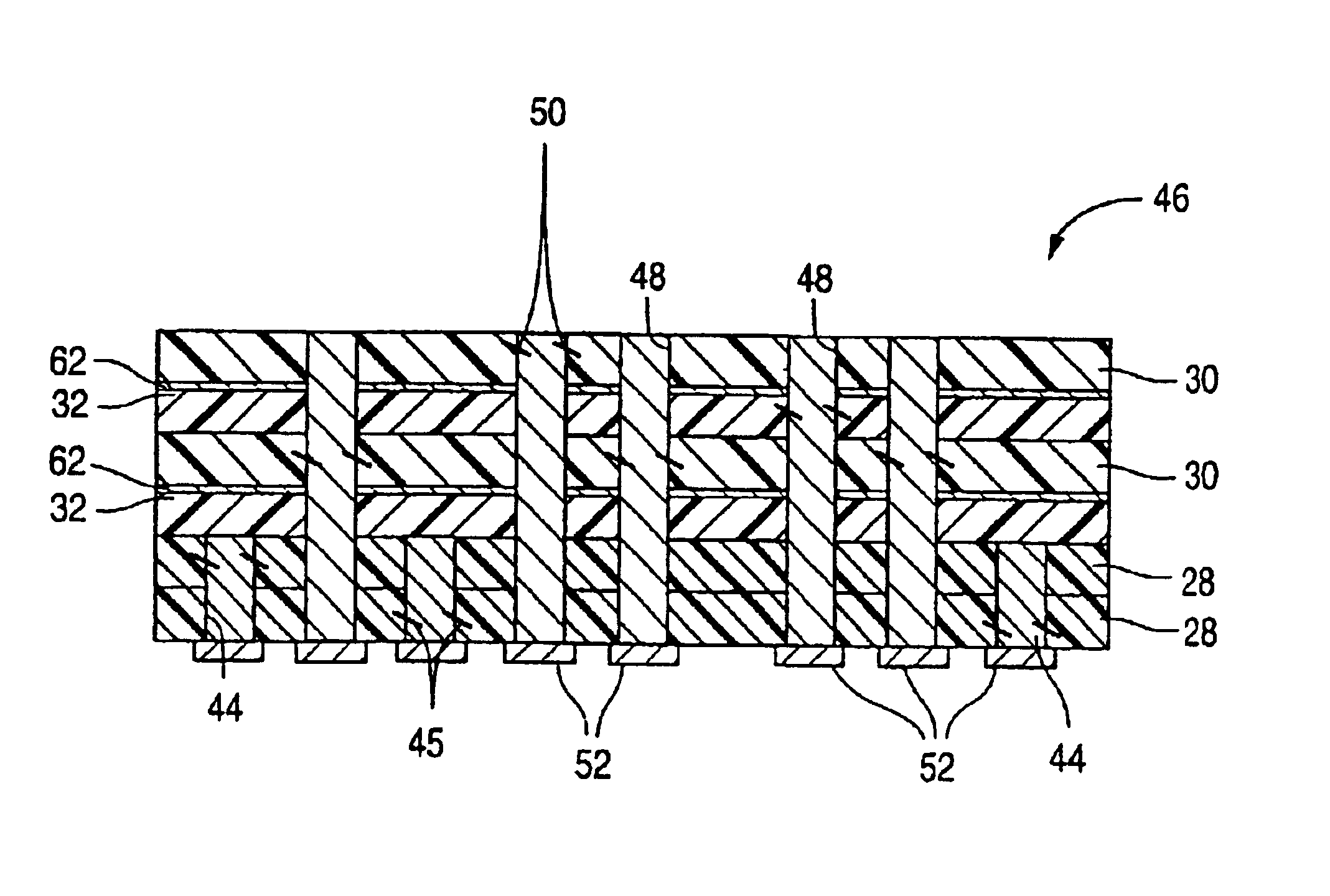

Biocompatible bonding method and electronics package suitable for implantation

ActiveUS20030233134A1Uniform propertySemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsHermetic seal

The invention is directed to a method of bonding a hermetically sealed electronics package to an electrode or a flexible circuit and the resulting electronics package, that is suitable for implantation in living tissue, such as for a retinal or cortical electrode array to enable restoration of sight to certain non-sighted individuals. The hermetically sealed electronics package is directly bonded to the flex circuit or electrode by electroplating a biocompatible material, such as platinum or gold, effectively forming a plated rivet-shaped connection, which bonds the flex circuit to the electronics package. The resulting electronic device is biocompatible and is suitable for long-term implantation in living tissue.

Owner:CORTIGENT INC +1

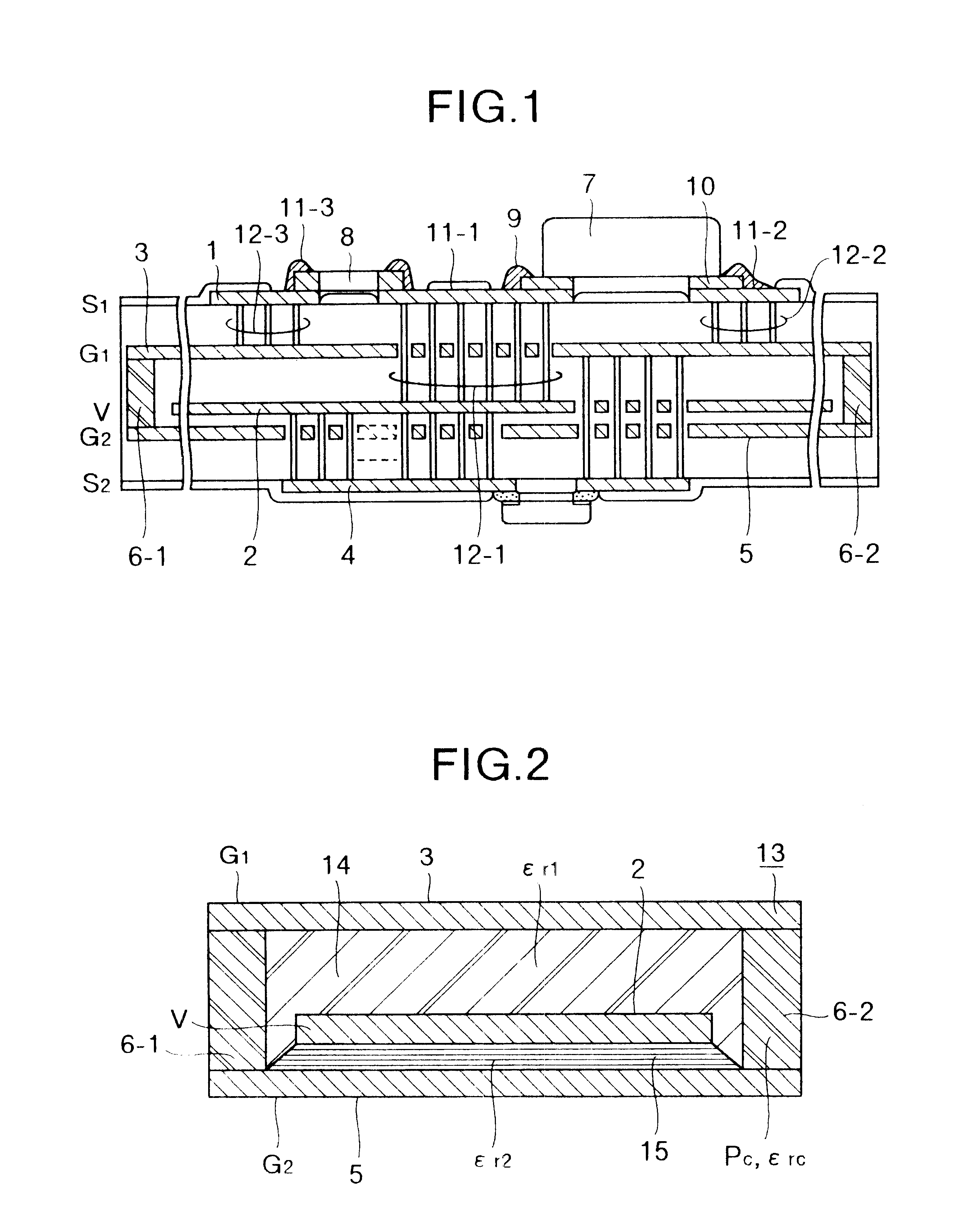

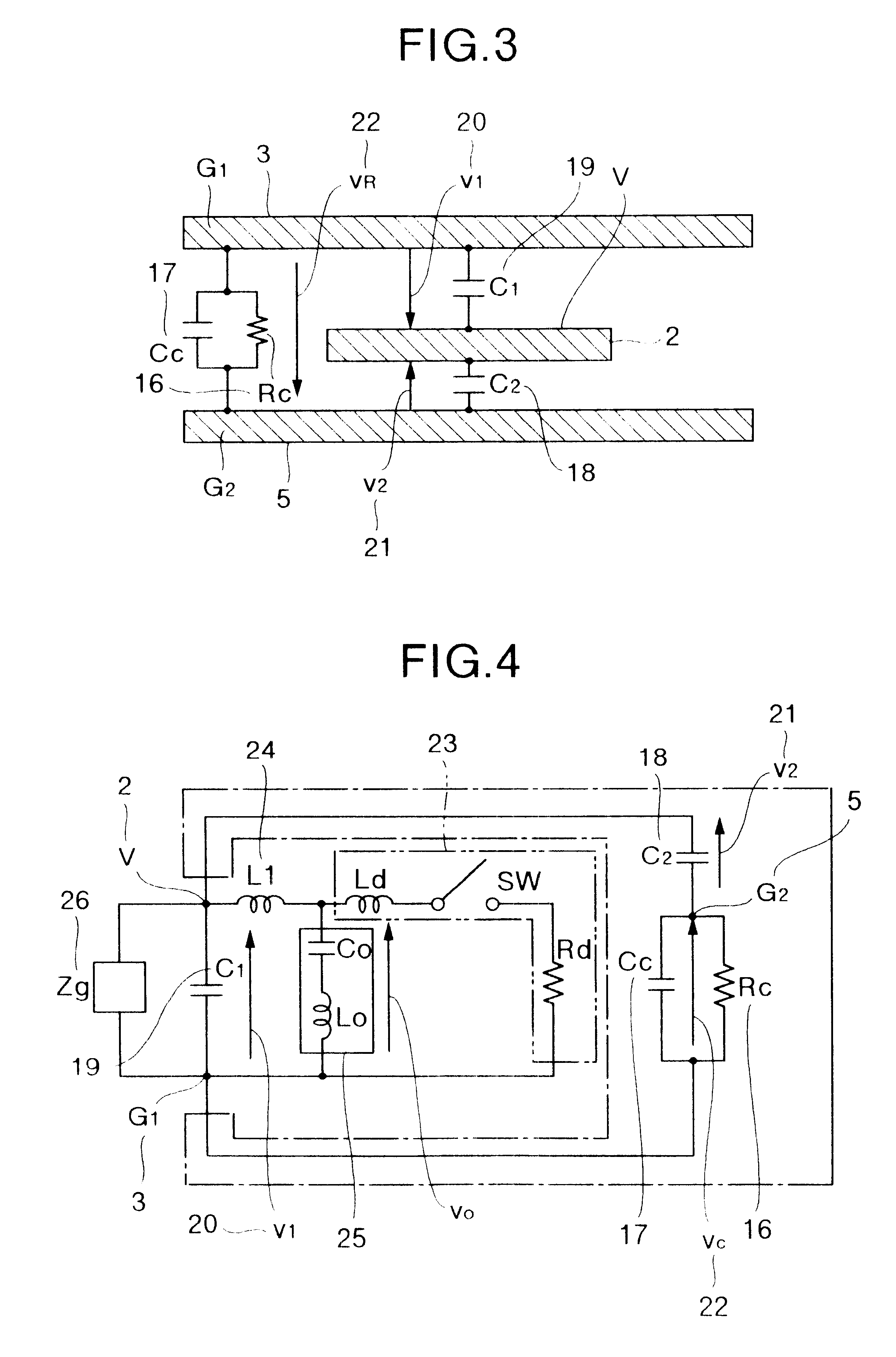

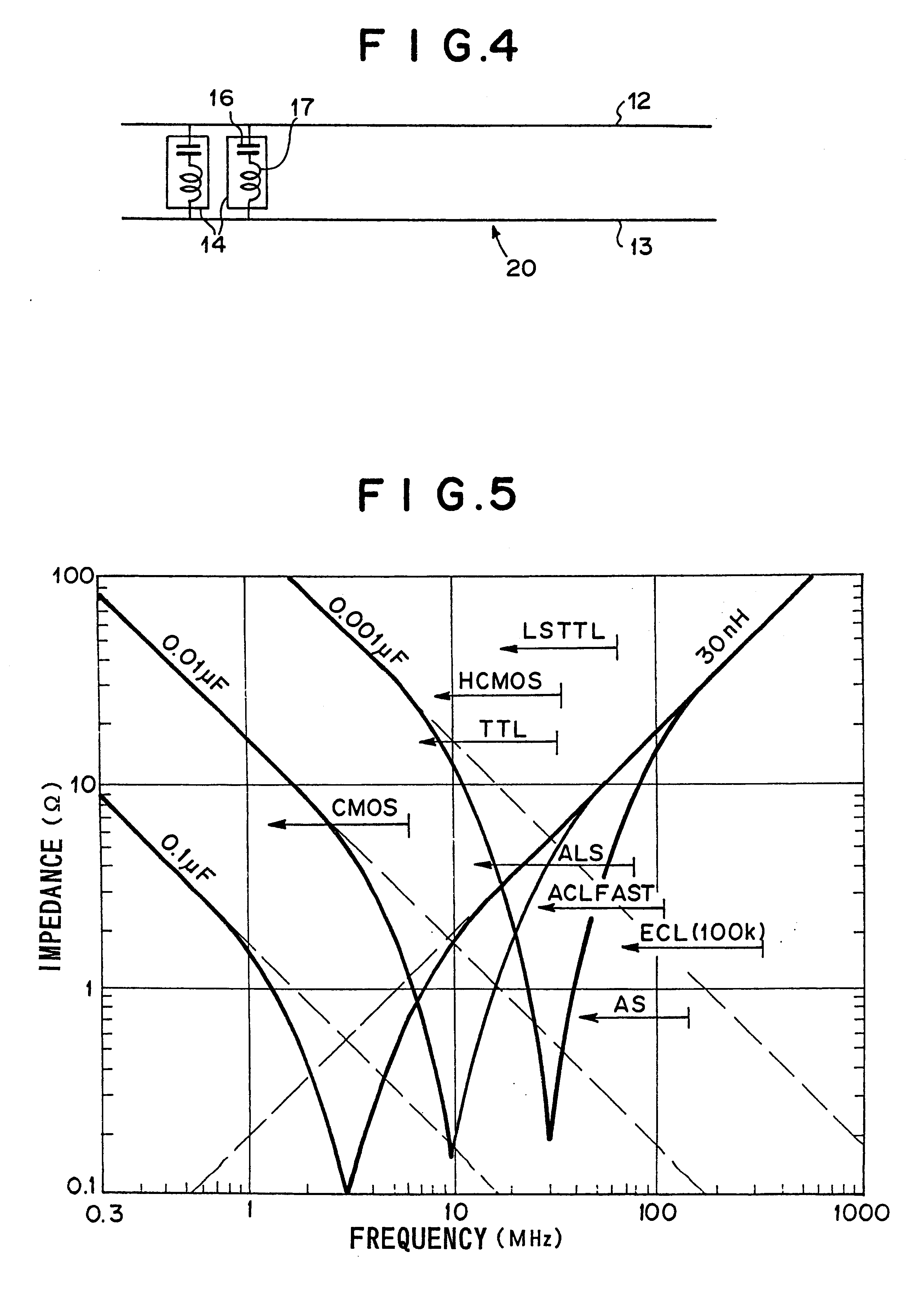

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

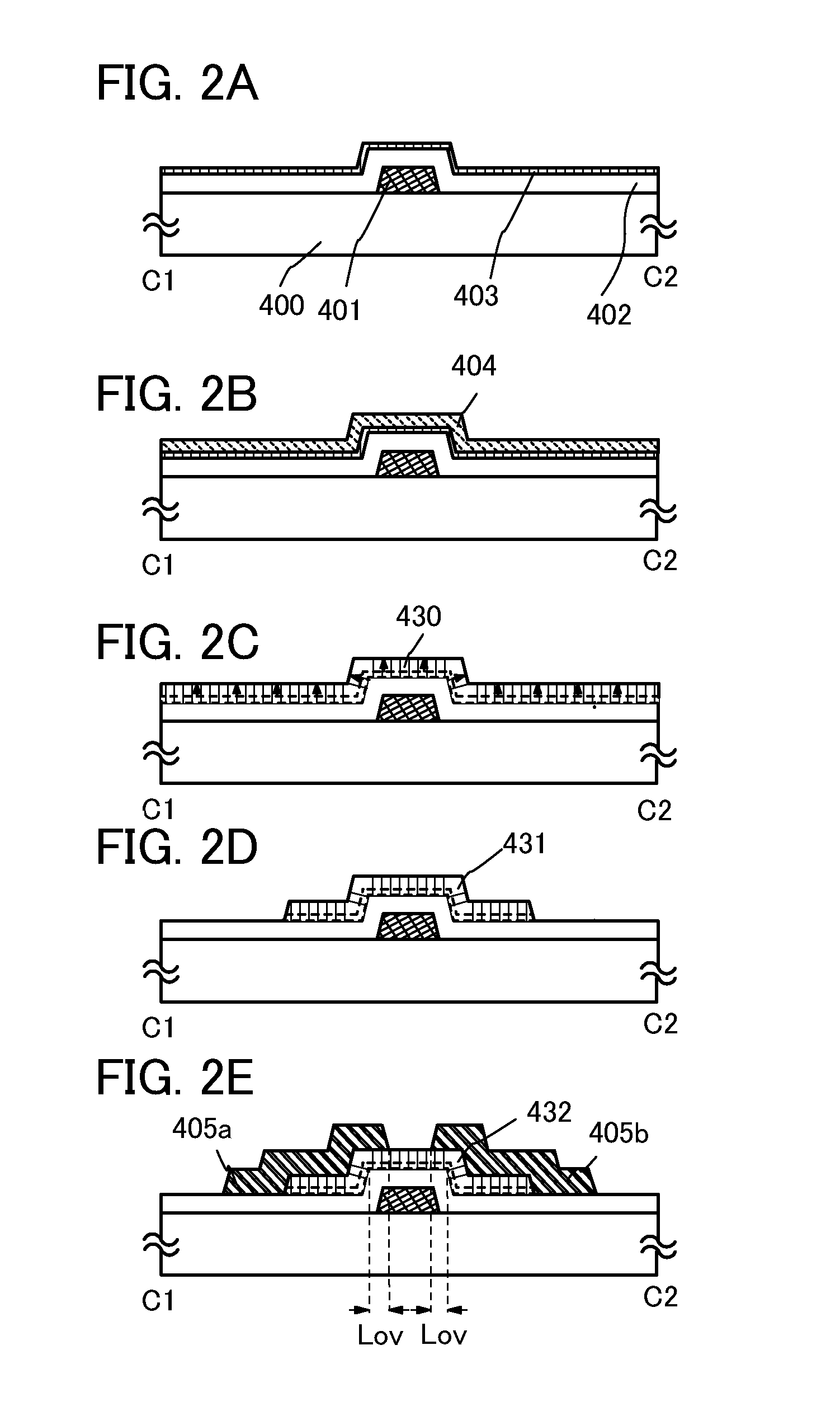

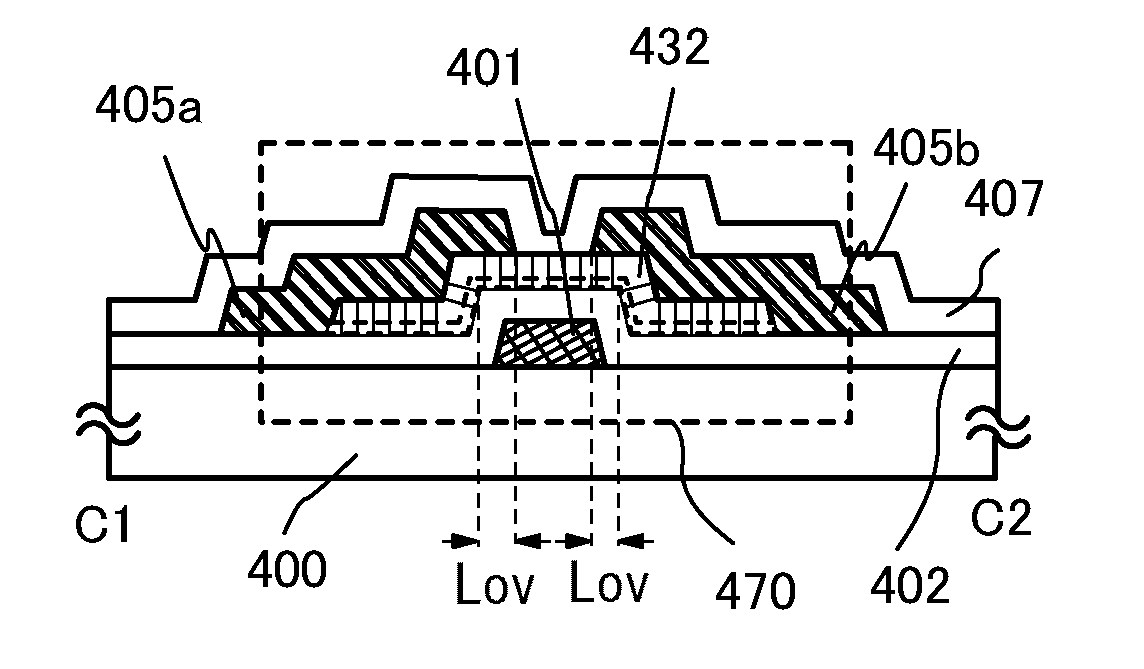

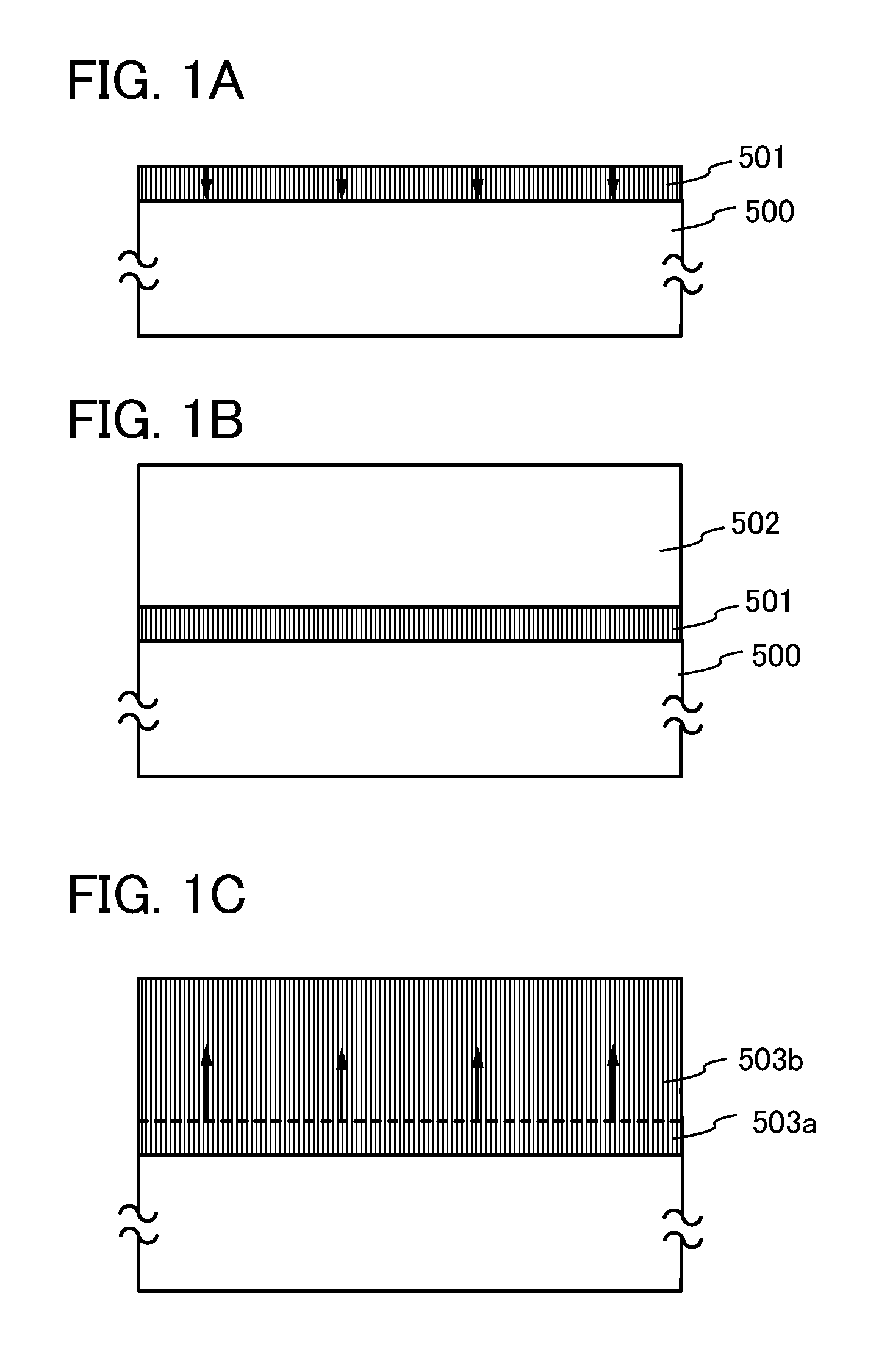

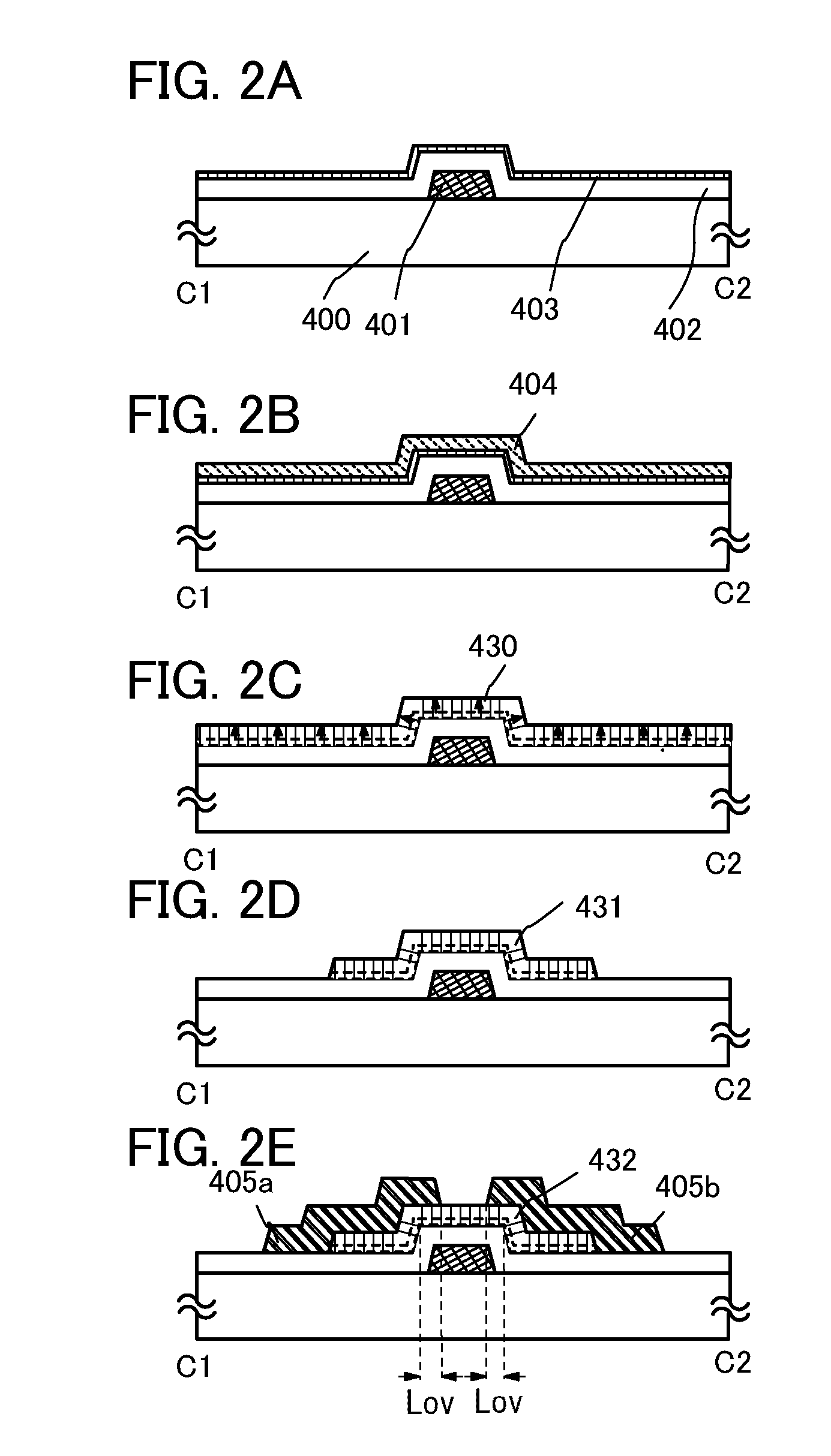

Stacked oxide material, semiconductor device, and method for manufacturing the semiconductor device

ActiveUS20110127521A1Improve mobilityReduced shutdown currentSolid-state devicesVacuum evaporation coatingDevice materialCrystal growth

One embodiment is a method for manufacturing a stacked oxide material, including the steps of forming an oxide component over a base component; forming a first oxide crystal component which grows from a surface toward an inside of the oxide component by heat treatment, and leaving an amorphous component just above a surface of the base component; and stacking a second oxide crystal component over the first oxide crystal component. In particular, the first oxide crystal component and the second oxide crystal component have common c-axes. Same-axis (axial) growth in the case of homo-crystal growth or hetero-crystal growth is caused.

Owner:SEMICON ENERGY LAB CO LTD

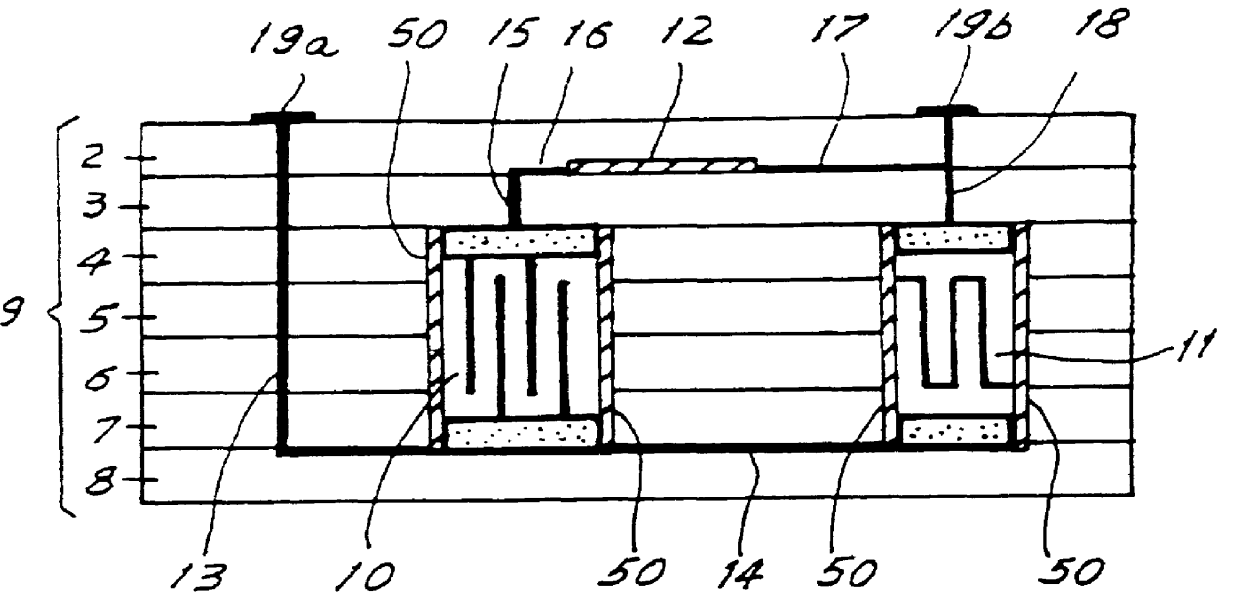

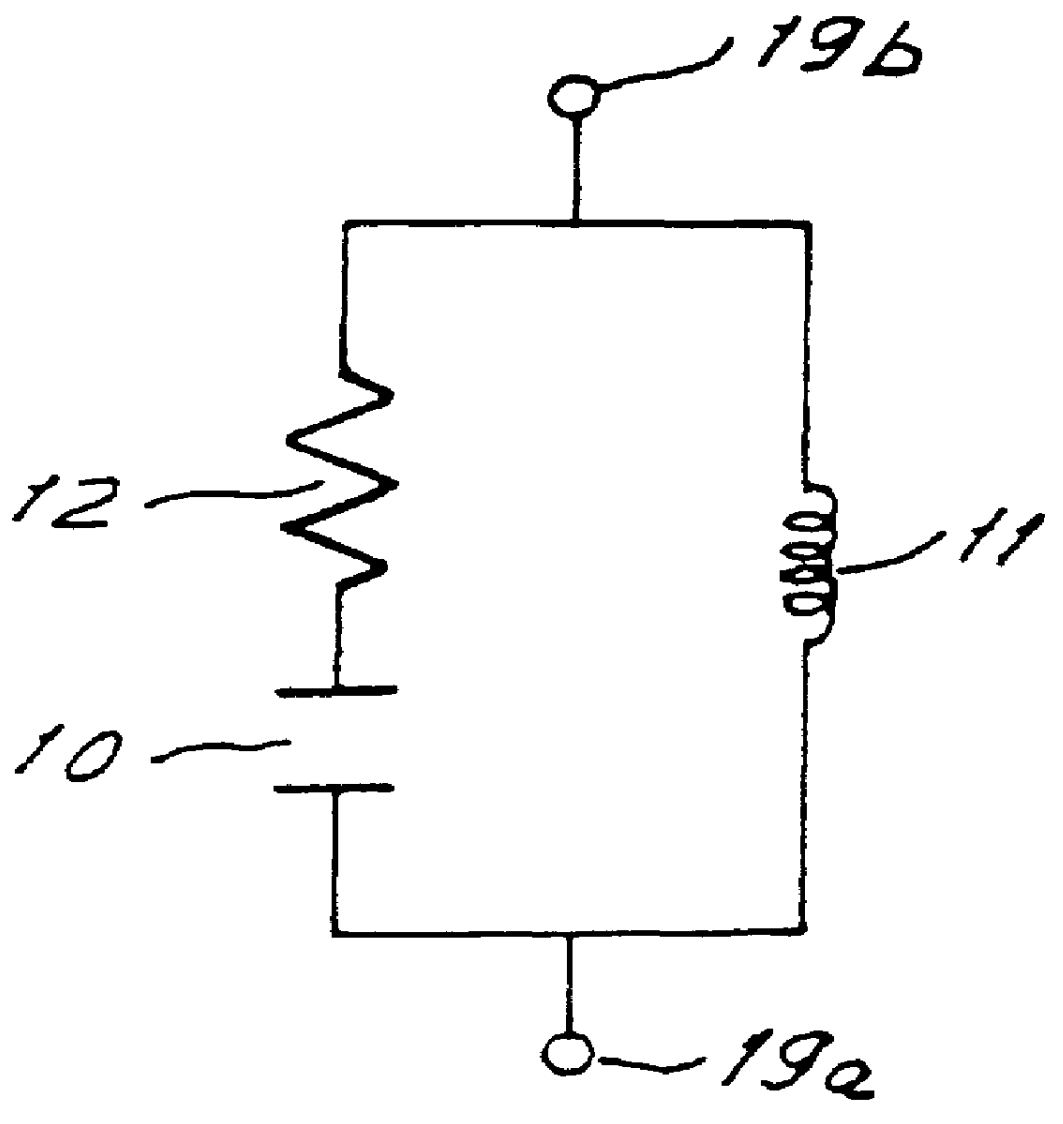

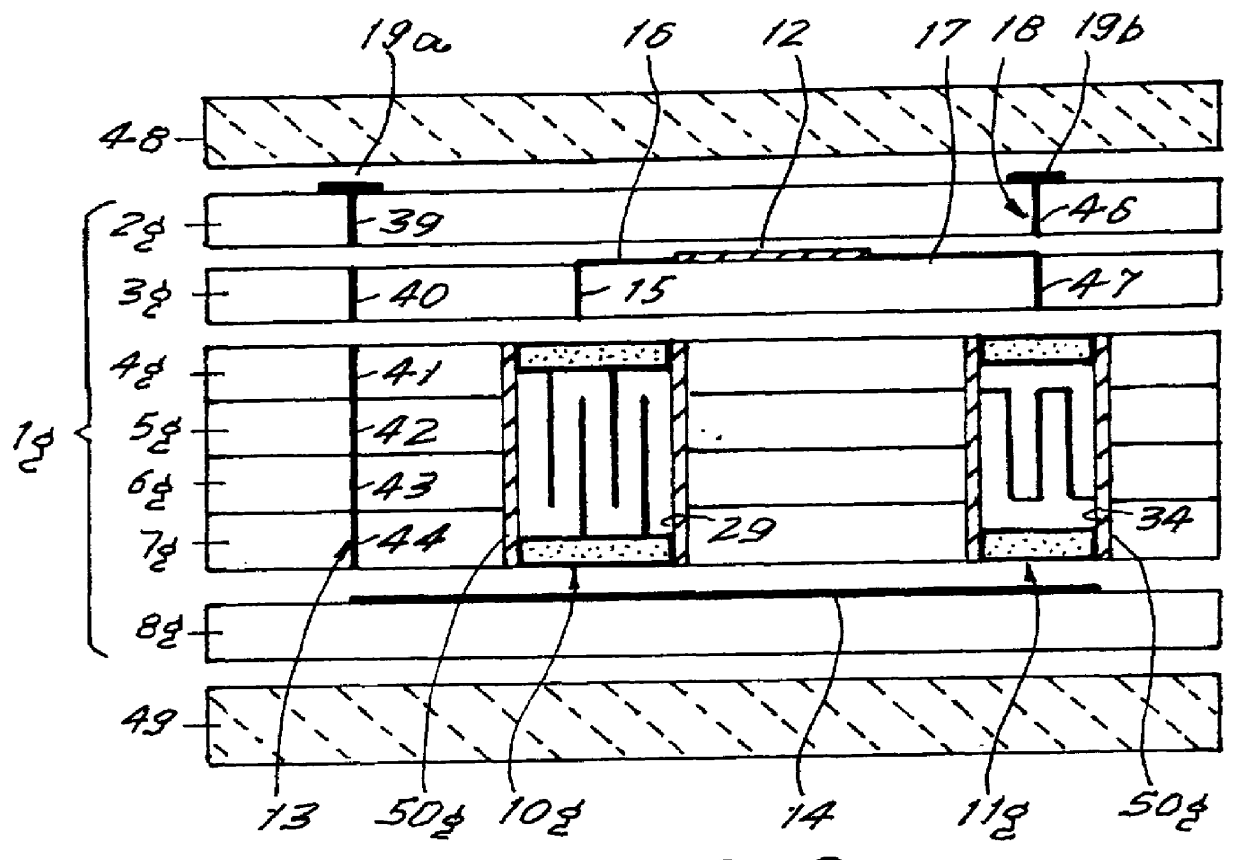

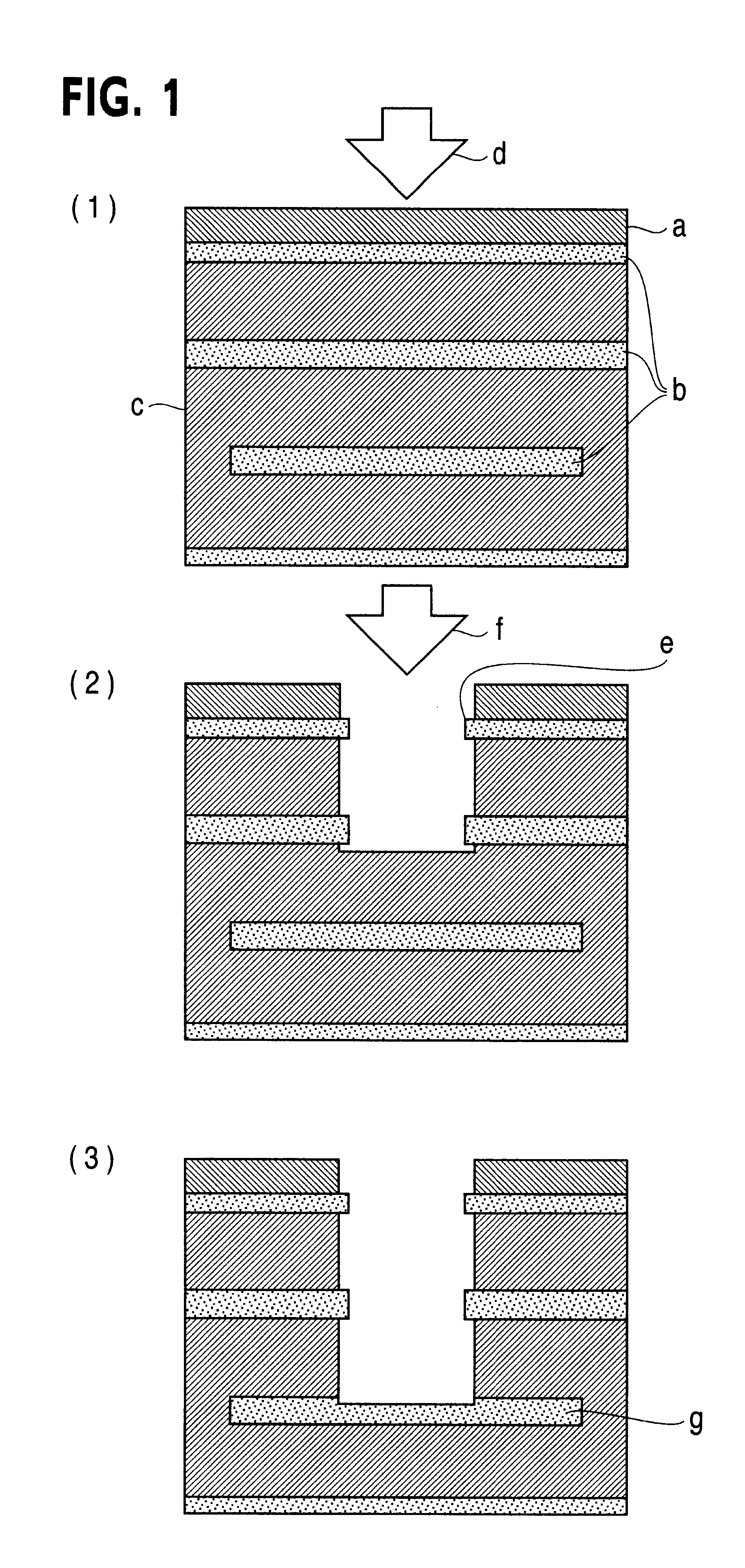

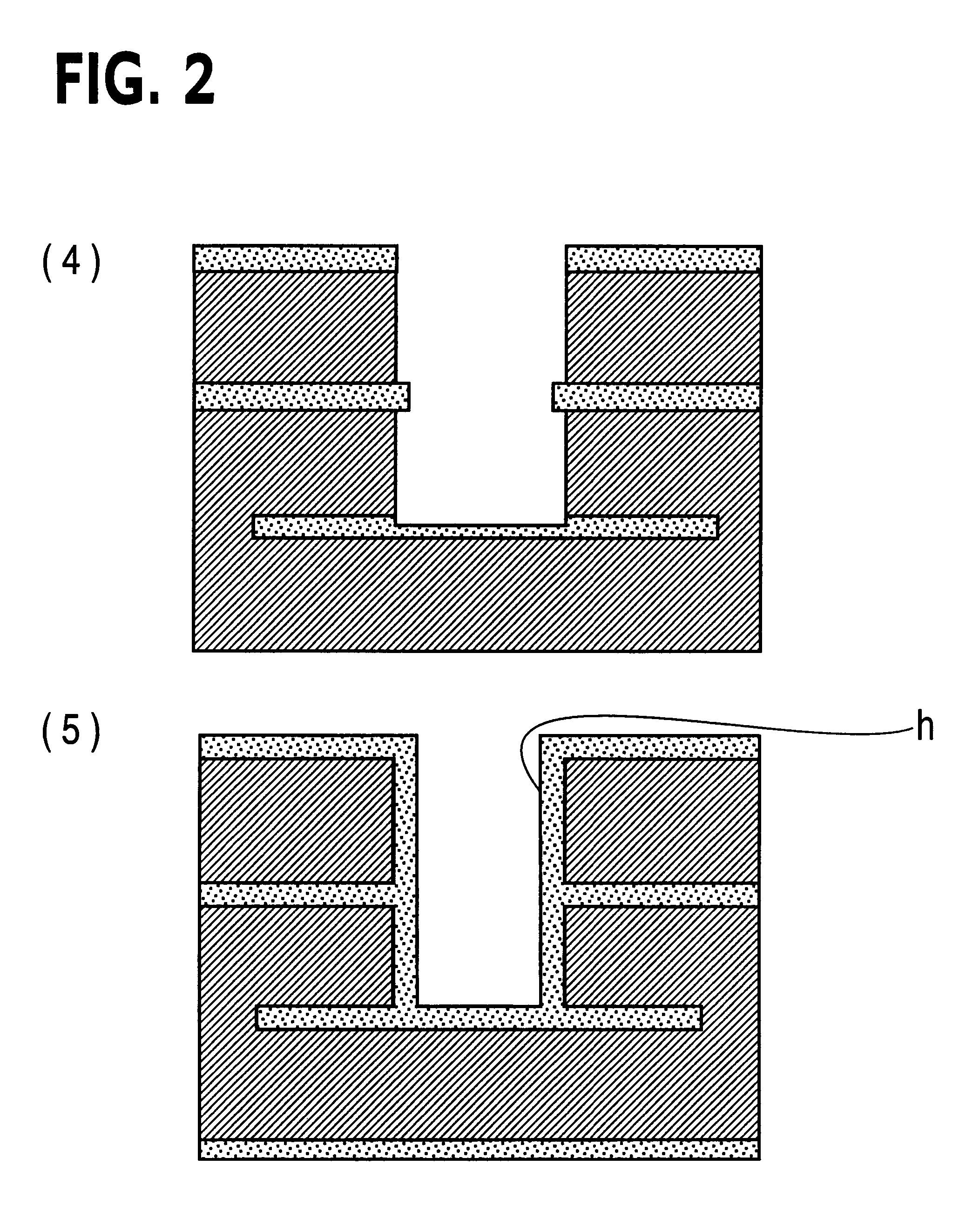

Multi-layer ceramic substrate and method for producing the same

InactiveUS6153290AFinal product manufactureSemiconductor/solid-state device detailsHigh densityInductor

The present invention provides a method for producing a high-density multi-layer ceramic substrate with stable characteristics, the substrate incorporating therein a passive component such as a high-precision capacitor or inductor. The method comprises the steps of providing compact blocks containing a green ceramic functional material to form the passive components; providing a composite green laminate having a plurality of ceramic green sheets comprising a ceramic insulating material and in which the compact blocks are built in pre-disposed spaces and a paste containing a metal inducing, during firing, oxidation reaction accompanied by expansion is provided in space between inside walls of the spaces and the compact blocks; firing the composite green laminate in a state in which the laminate is sandwiched by the sheet-like supports formed of green ceramics that cannot be sintered at the sintering temperature, so as to prevent shrinkage of the laminate; and removing the unsintered sheet-like supports.

Owner:MURATA MFG CO LTD

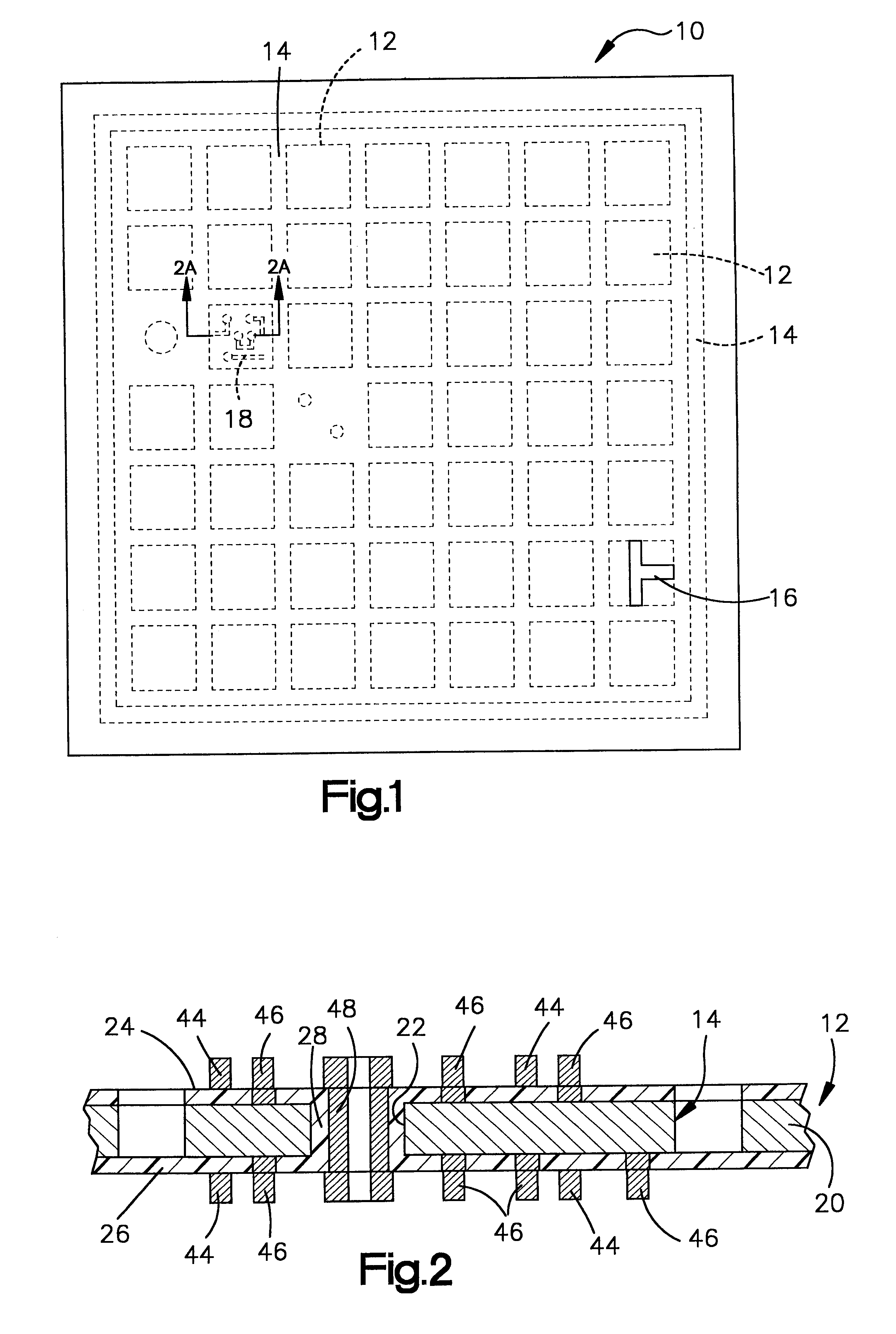

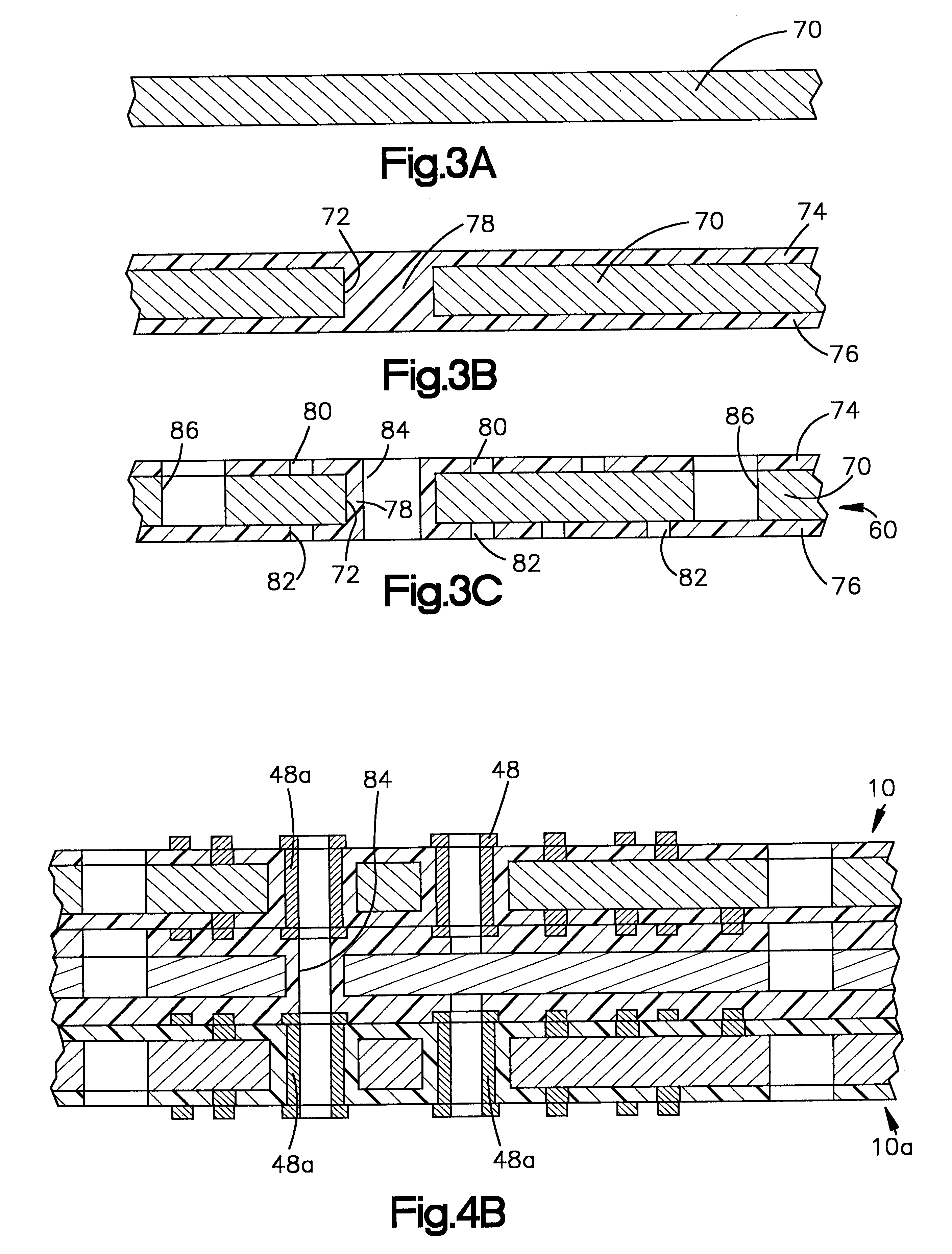

Composite laminate circuit structure and method of forming the same

InactiveUS6175087B1Printed circuit aspectsElectrical connection printed elementsComposite laminatesConductive materials

A method forming a composite laminate structure includes providing first and second circuit board element each having circuitry on at least one face thereof and plated through holes. A voltage plane element is provided having at least one voltage plane having opposite faces with layers of partially cured photodielectric material on each face. At least one hole is photopatterned and etched through the voltage plane element but completely isolated from the voltage plane. Each through hole in the voltage plane element is aligned with a plated through hole in each of the circuit board elements to provide a surface on the voltage plane element communicating with the plated through holes. The voltage plane is laminated between the circuit board elements and the photoimageable material on the voltage plane is fully cured. The surfaces of the voltage plane element communicating with the plated through holes in the circuit board elements are plated with a conducting material to establish a connection between the circuitry on the first and second circuit board elements.

Owner:GLOBALFOUNDRIES INC

Printed circuit board with capacitors connected between ground layer and power layer patterns

InactiveUS6198362B1Magnetic/electric field screeningCurrent interference reductionEngineeringGround pattern

A printed circuit board is disclosed. A top layer power supply pattern and a top layer ground pattern are formed. The top layer power supply pattern and the top layer ground pattern are connected to a power supply layer and a ground layer through a plurality of viaholes, respectively. A plurality of capacitors or a plurality of capacitor resistor series circuits are disposed at predetermined intervals between the top layer power supply pattern and the top layer ground pattern.

Owner:NEC CORP

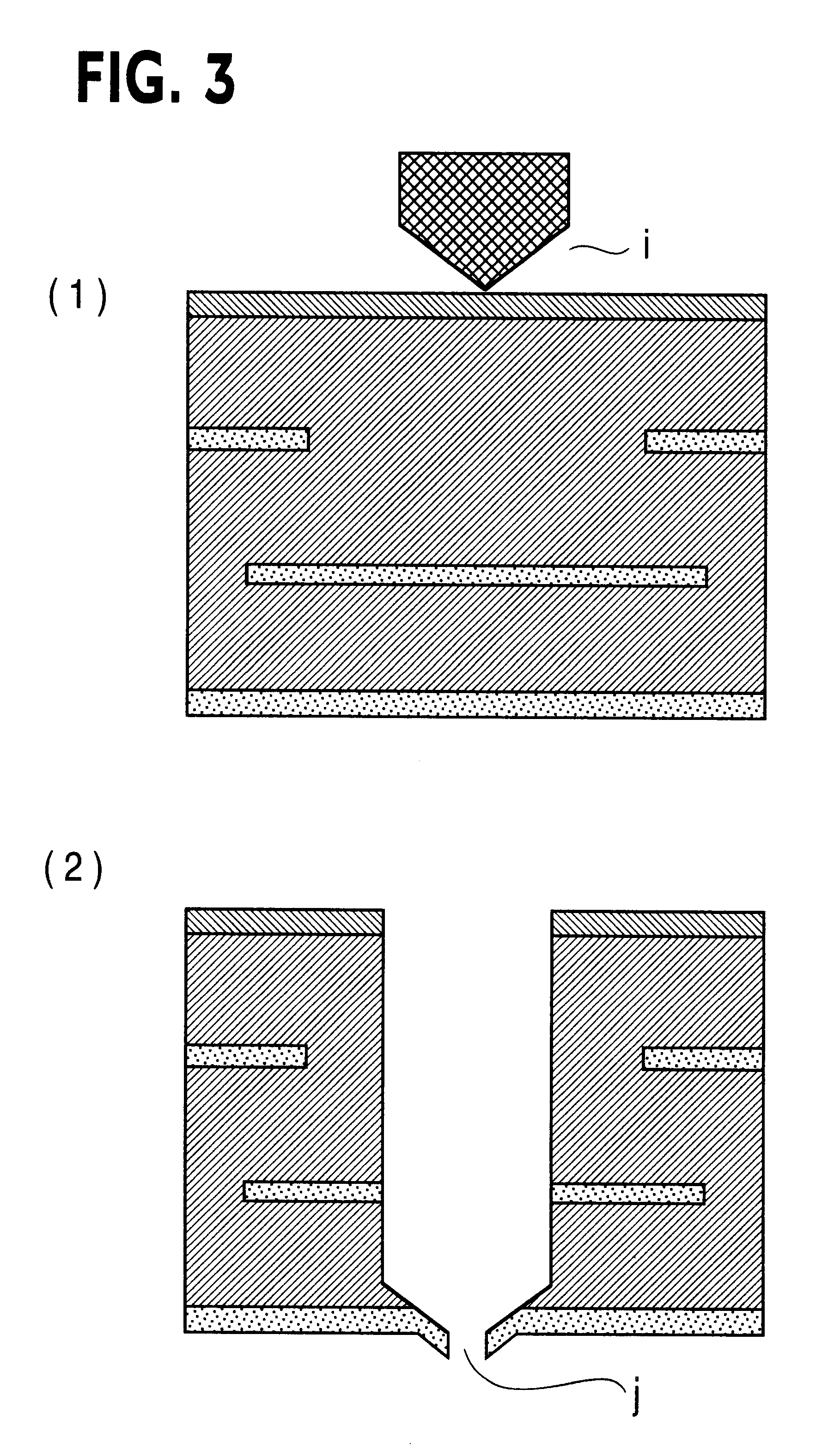

Metal core multilayer resin wiring board with thin portion and method for manufacturing the same

InactiveUS6323439B1Improve rigidityFirmly connectedElectrically conductive connectionsPrinted circuit aspectsEngineeringMachining

A multilayer resin wiring board includes a metal core substrate having a first main surface and a second main surface; a plurality of wiring layers located on the first and second main surfaces of the metal core substrate; a plurality of insulating resin layers, each intervening between the metal core substrate and the wiring layers and between the metal core substrate and the wiring layers and between the wiring layers; and a via formed on the wall of a through hole for connection to the metal core substrate extending through the insulating resin layers and the metal core substrate so as to establish electrical conductivity to the metal core substrate. The metal core substrate has a thin portion which is thinner than the remaining portion of the metal core substrate. The through hole for connection to the metal core substrate is formed through the thin portion by laser machining.

Owner:NGK SPARK PLUG CO LTD

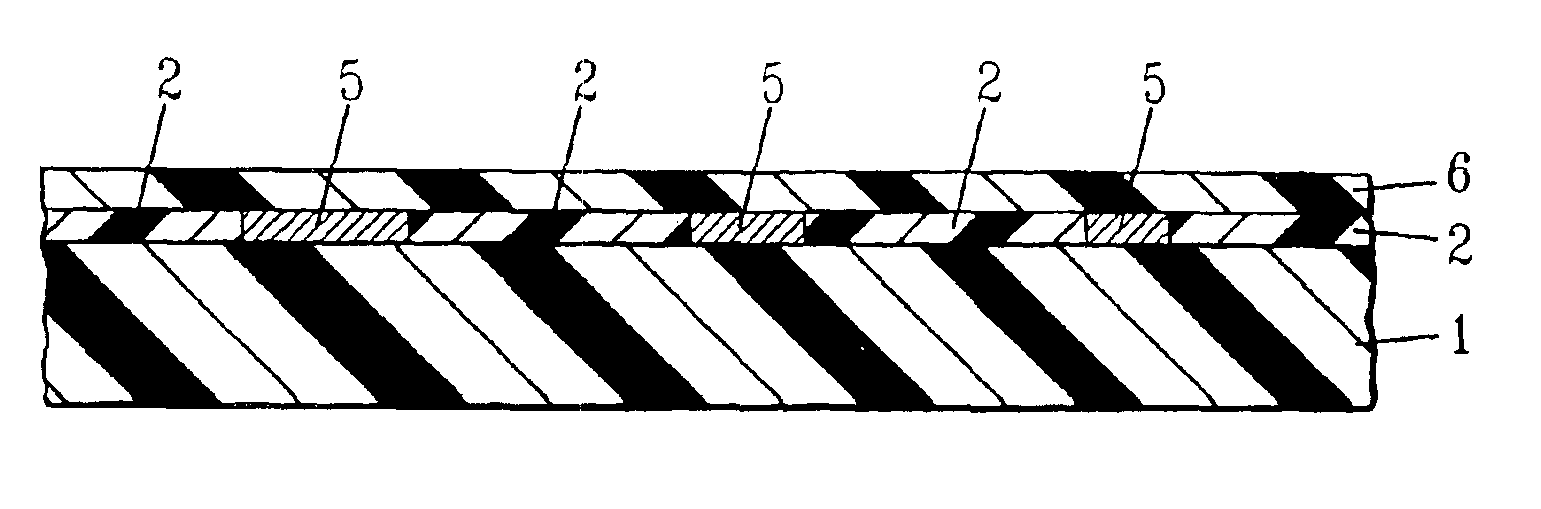

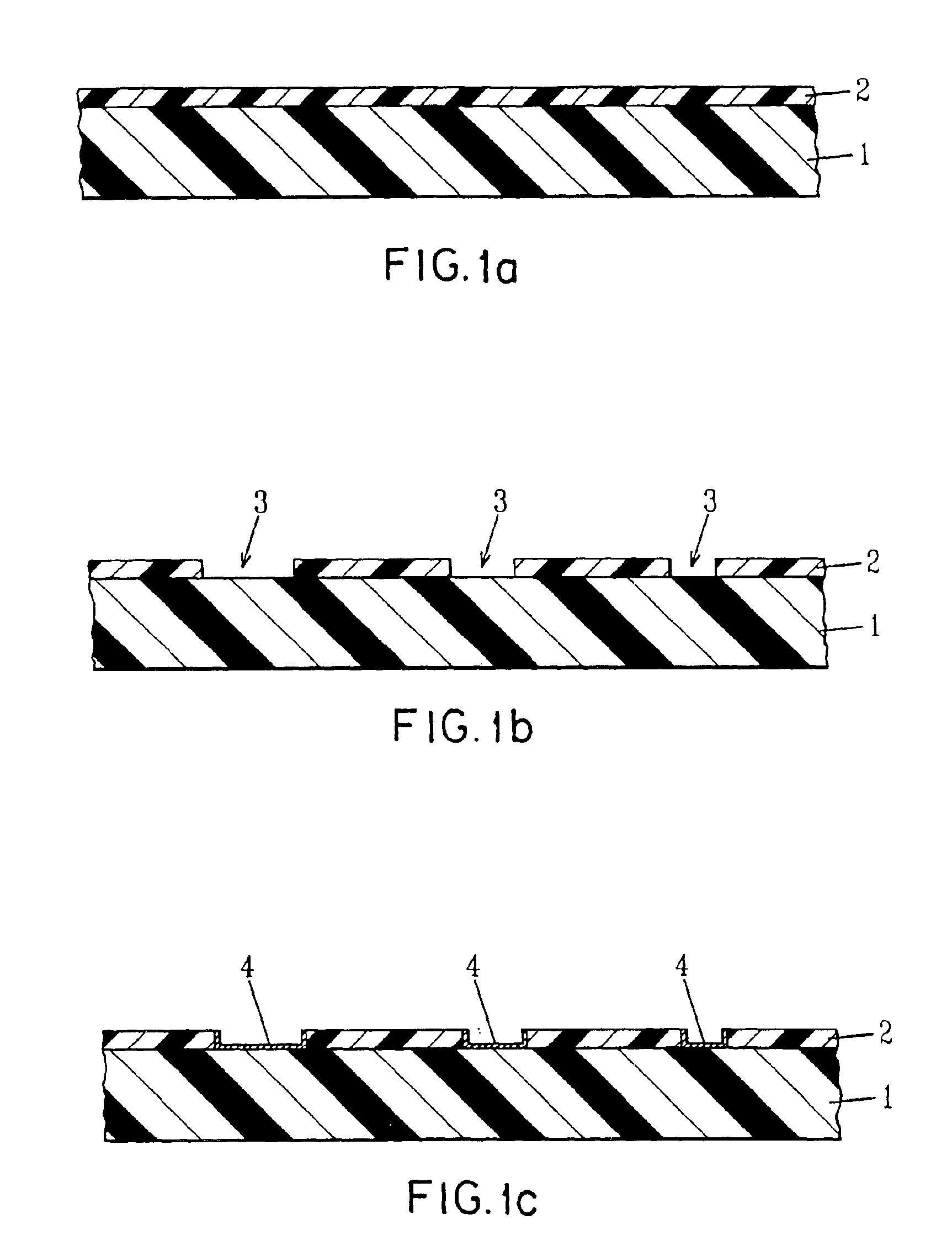

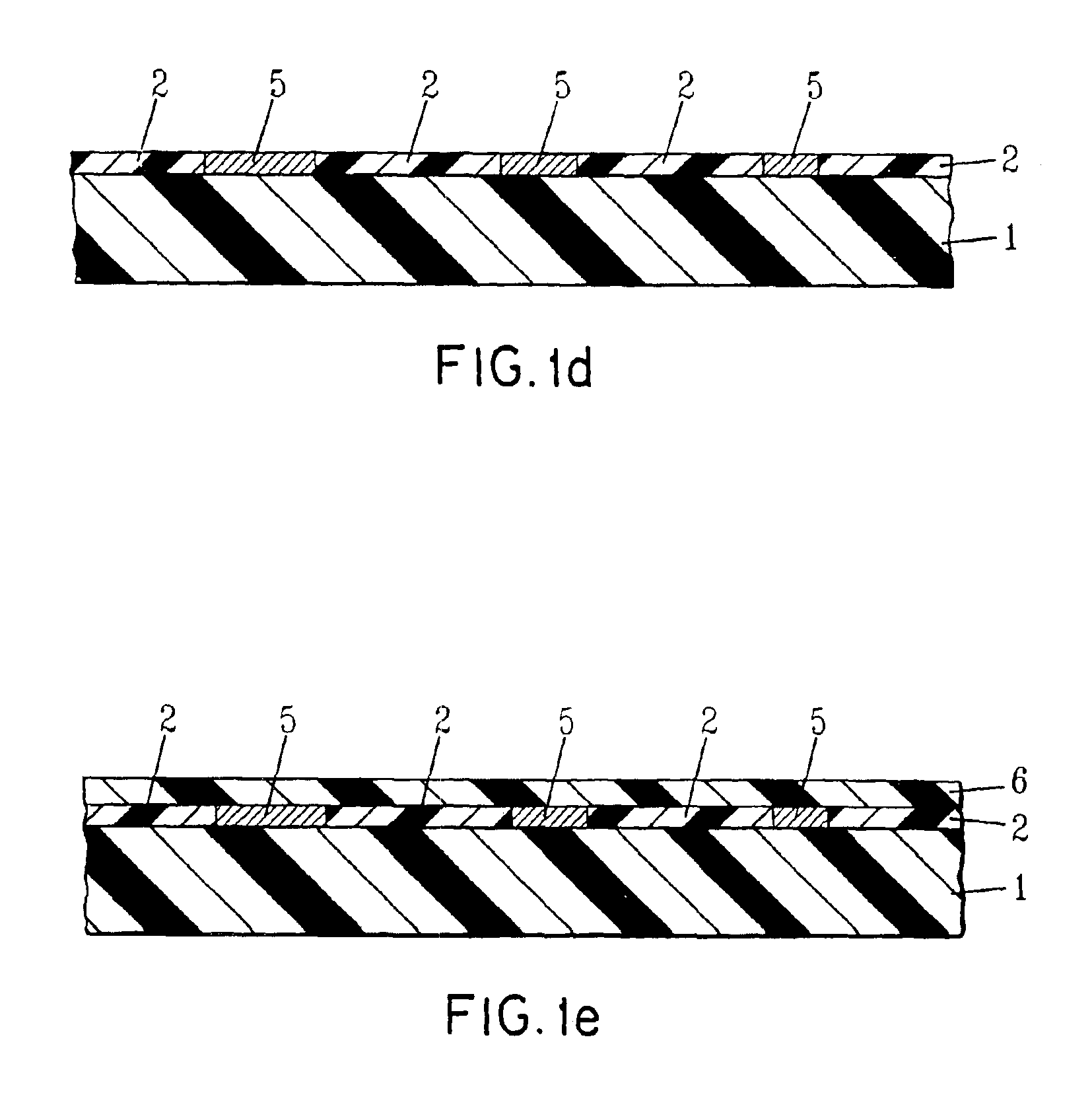

Printed wiring board and its manufacturing method

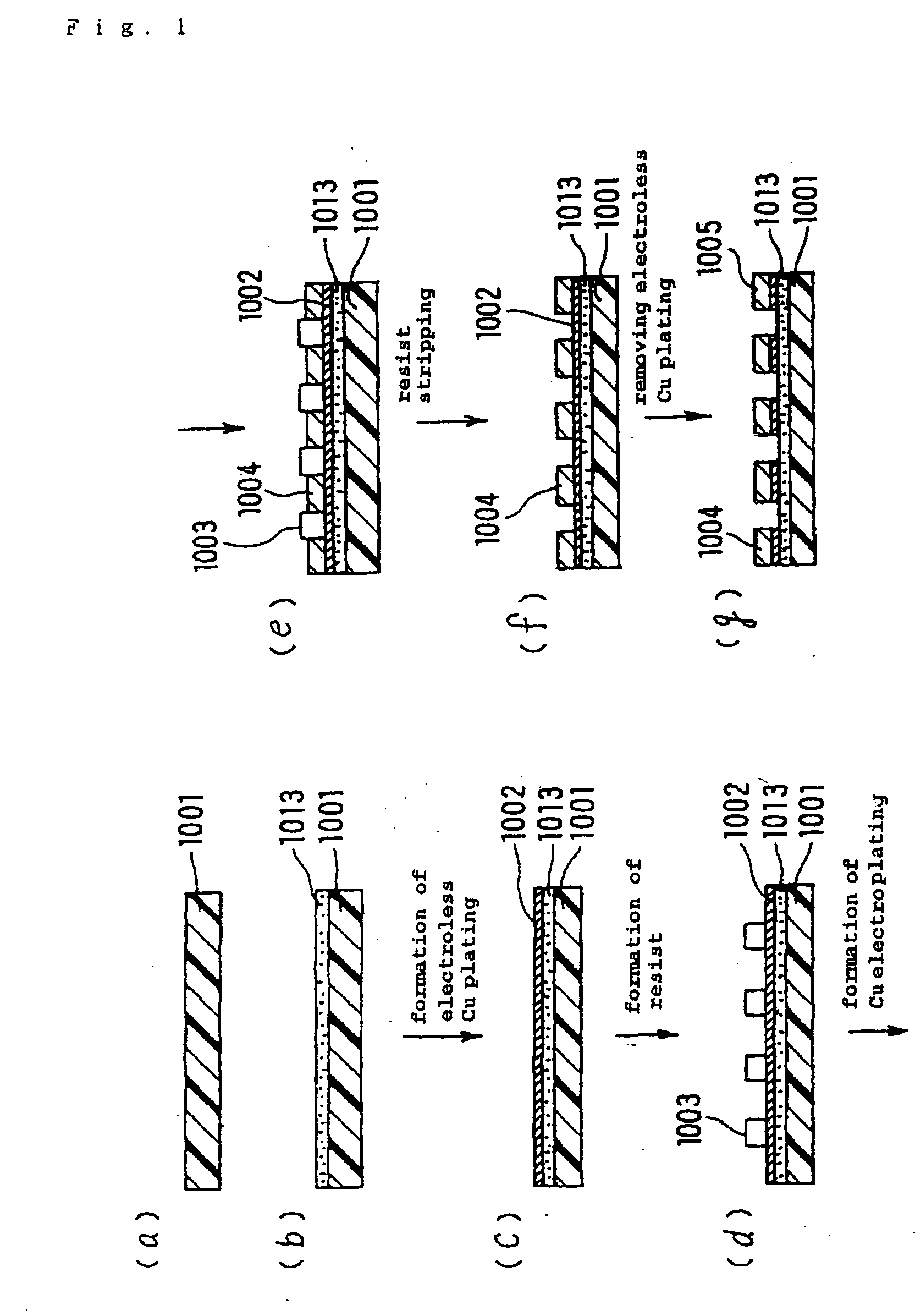

The present invention has for its object to provide a process for manufacturing multilayer printed circuit boards which is capable of simultaneous via hole filling and formation of conductor circuit and via holes of good crystallinity and uniform deposition can be constructed on a substrate and high-density wiring and highly reliable conductor connections can be realized without annealing. The present invention is related to a process for manufacturing multilayer printed circuit boards which comprises disposing an interlayer resin insulating layer on a substrate formed with a conductor circuit, creating openings for formation of via holes in said interlayer resin insulating layer, forming an electroless plated metal layer on said interlayer resin insulating layer, disposing a resist thereon, performing electroplating, stripping the resist off and etching the electroless plated metal layer to provide a conductor circuit and via holes, wherein the electroplating is performed intermittently using said electroless plated metal layer as cathode and a plating metal as anode at a constant voltage between said anode and said cathode.

Owner:IBIDEN CO LTD

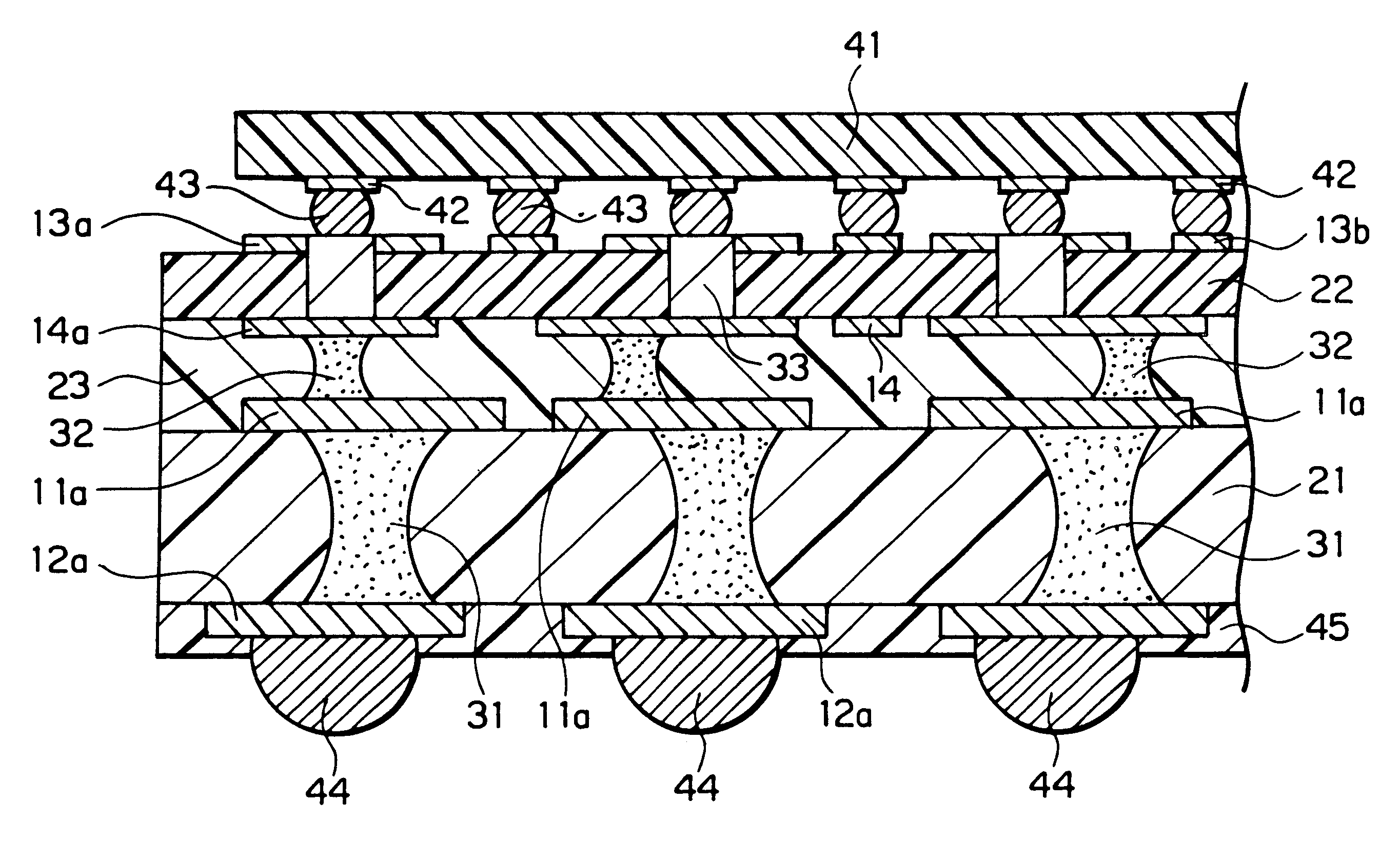

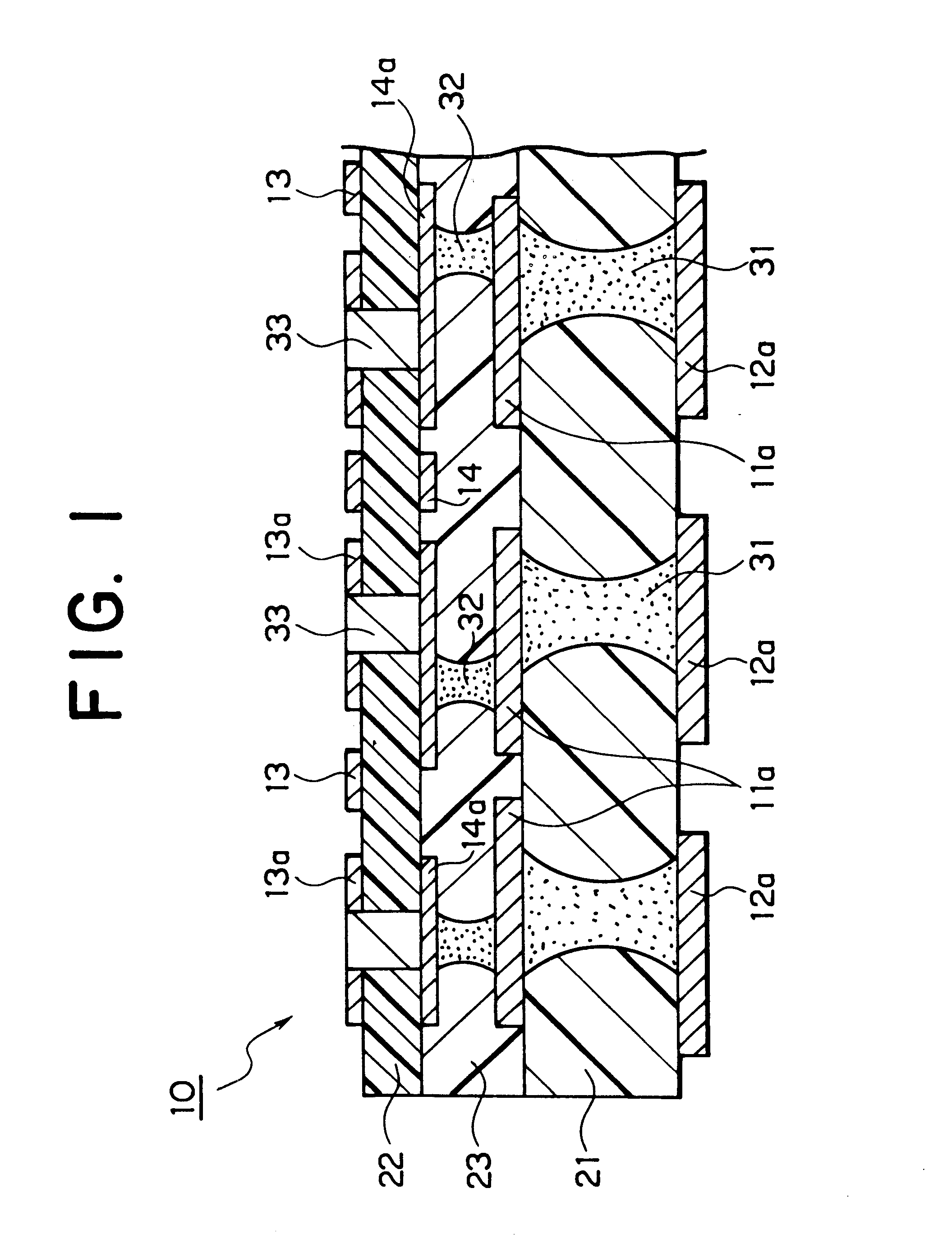

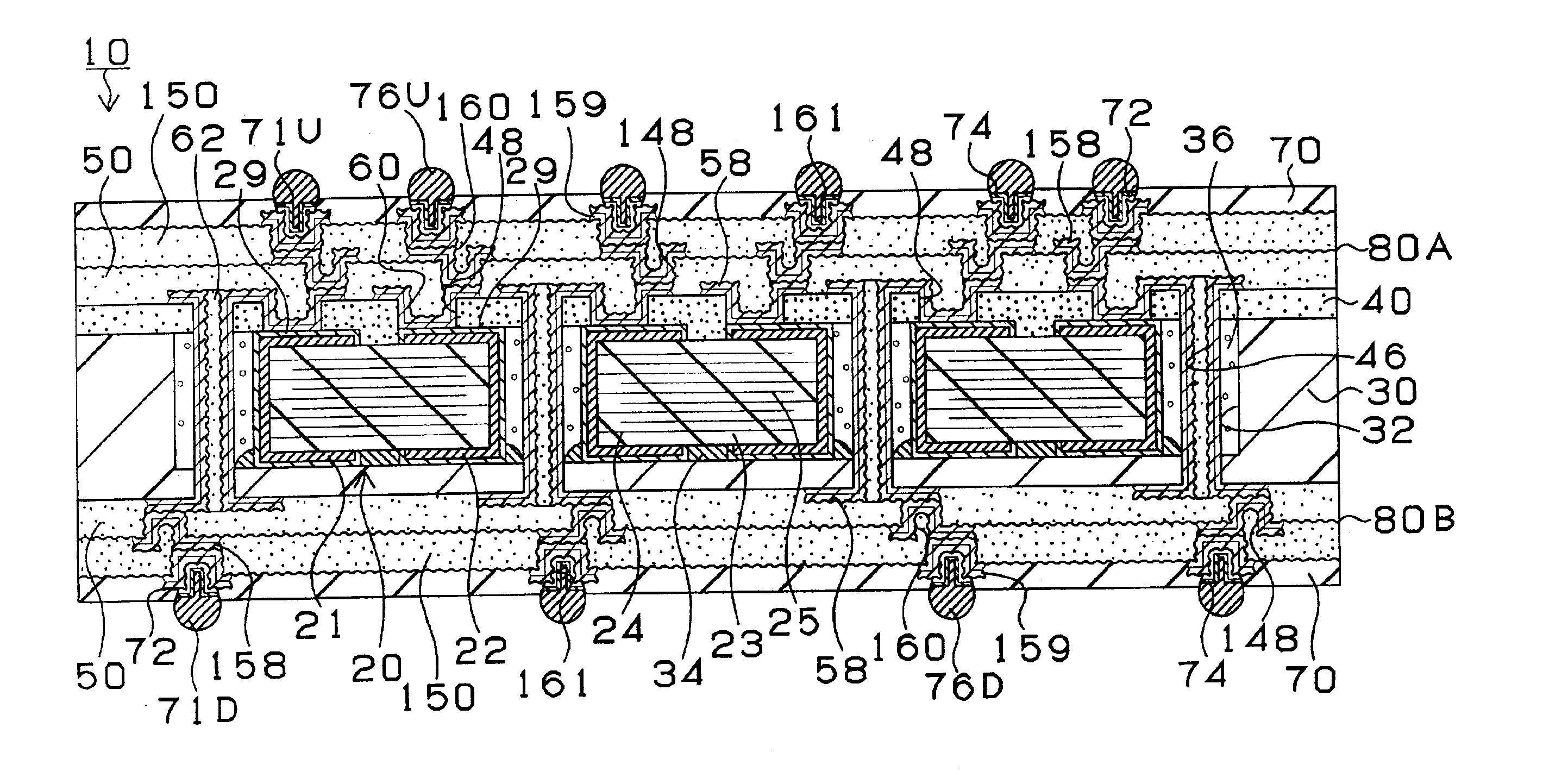

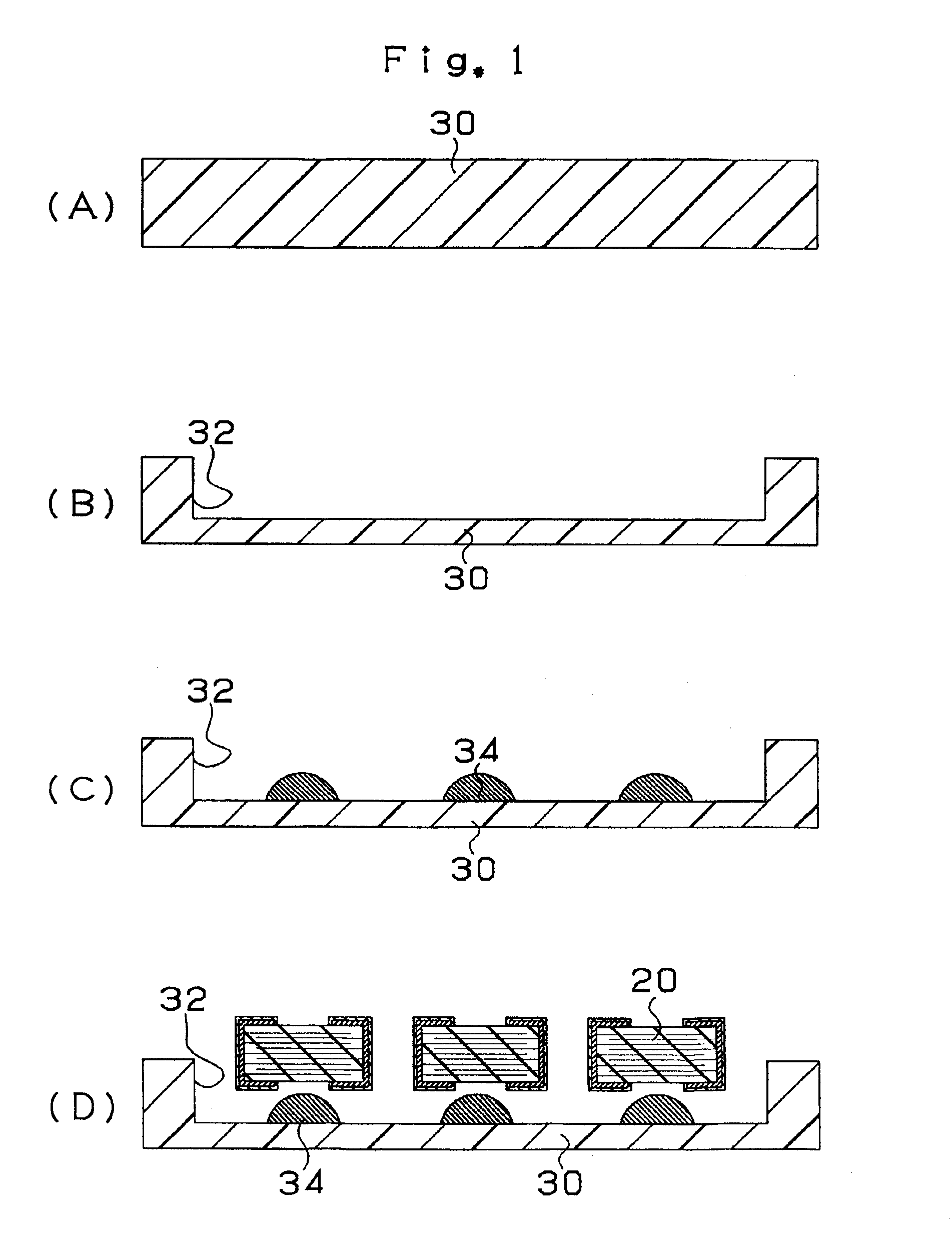

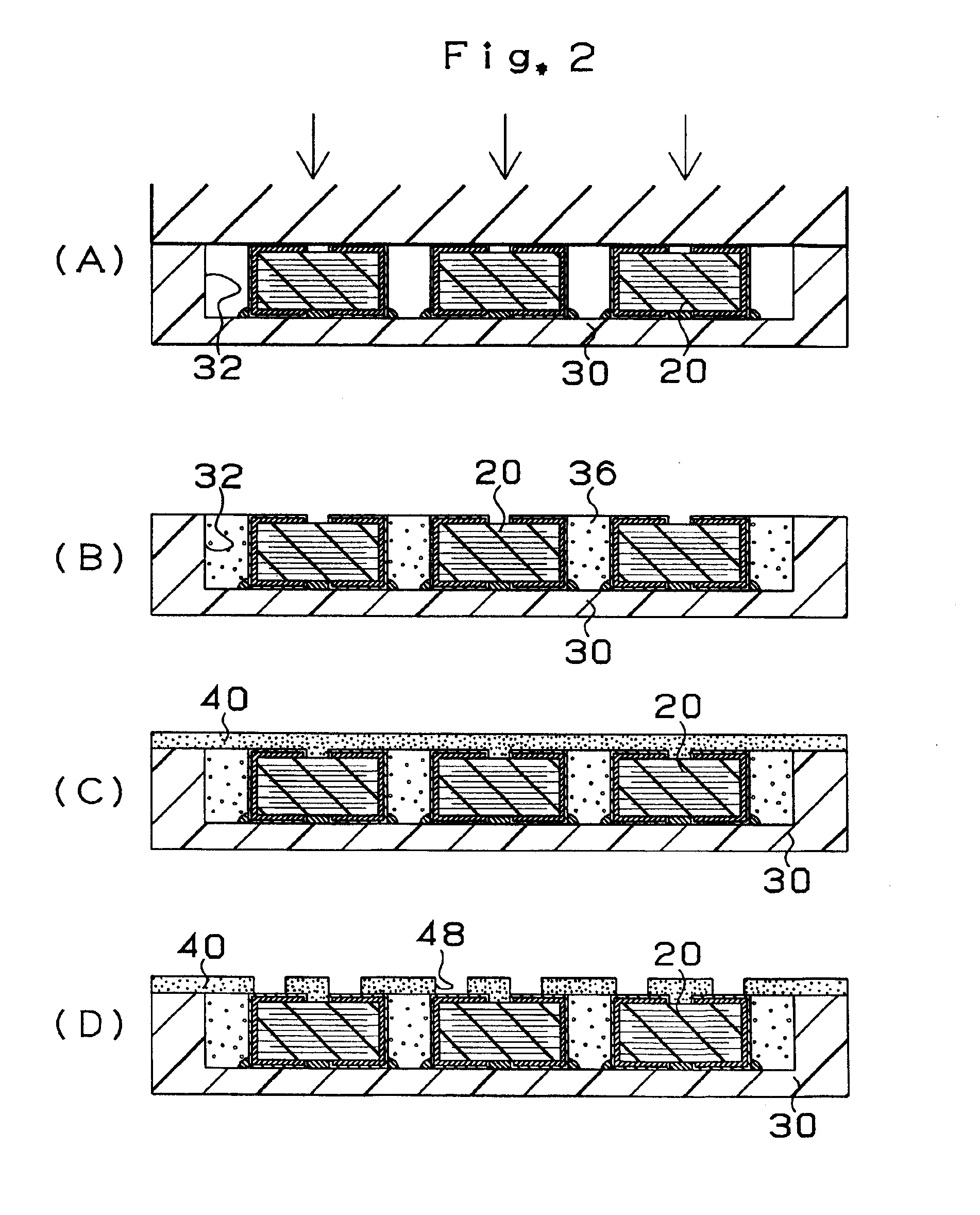

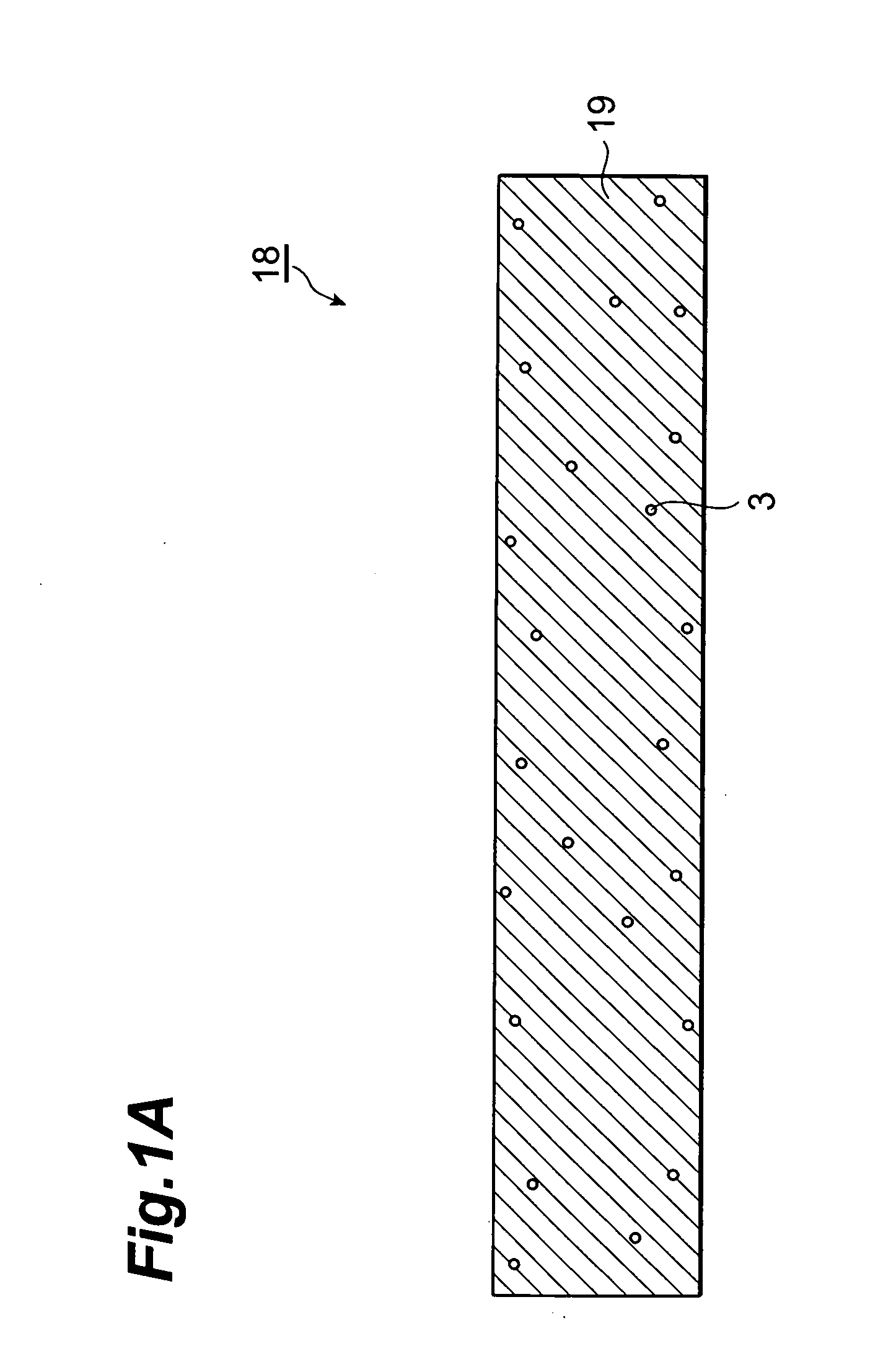

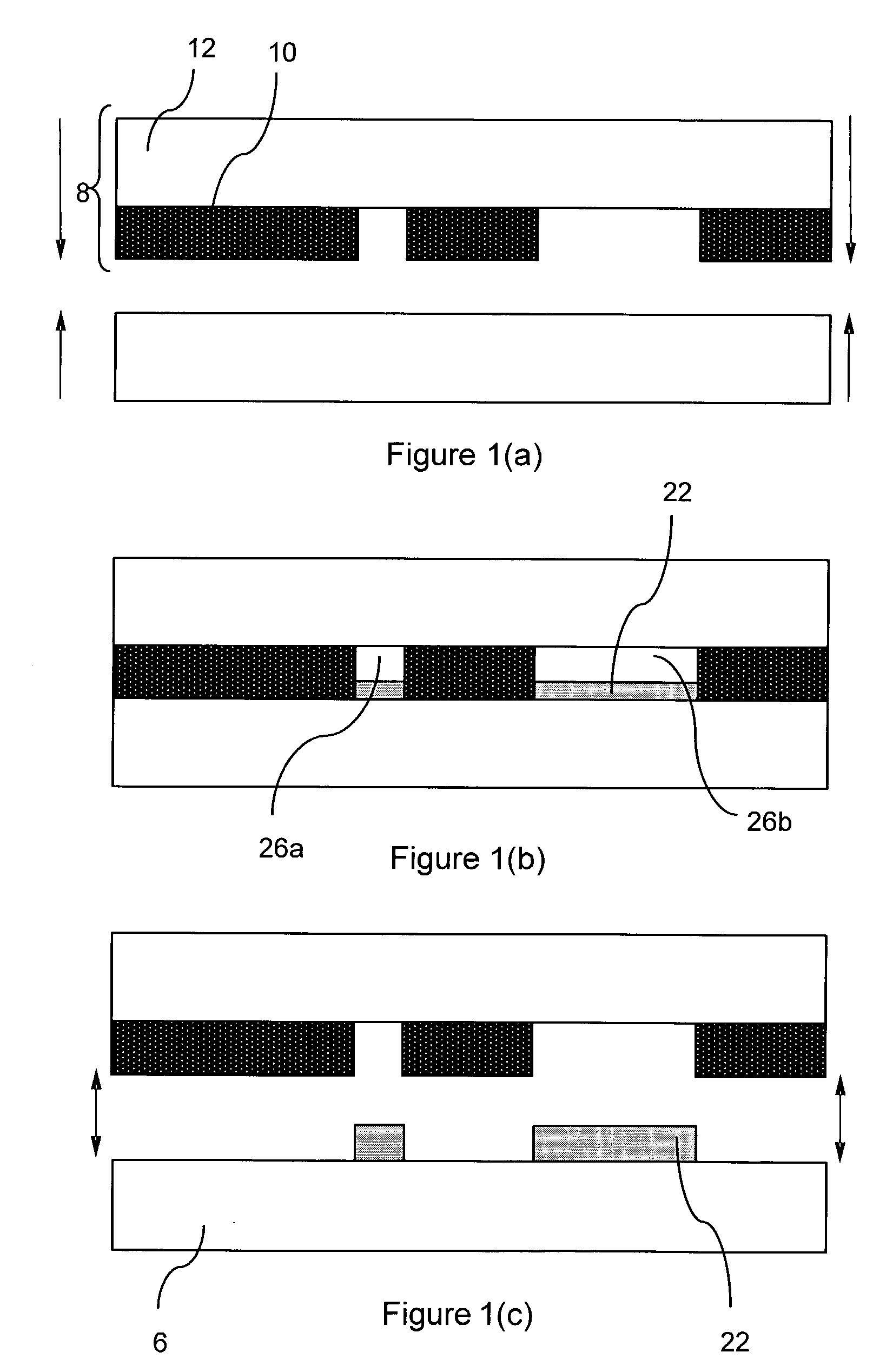

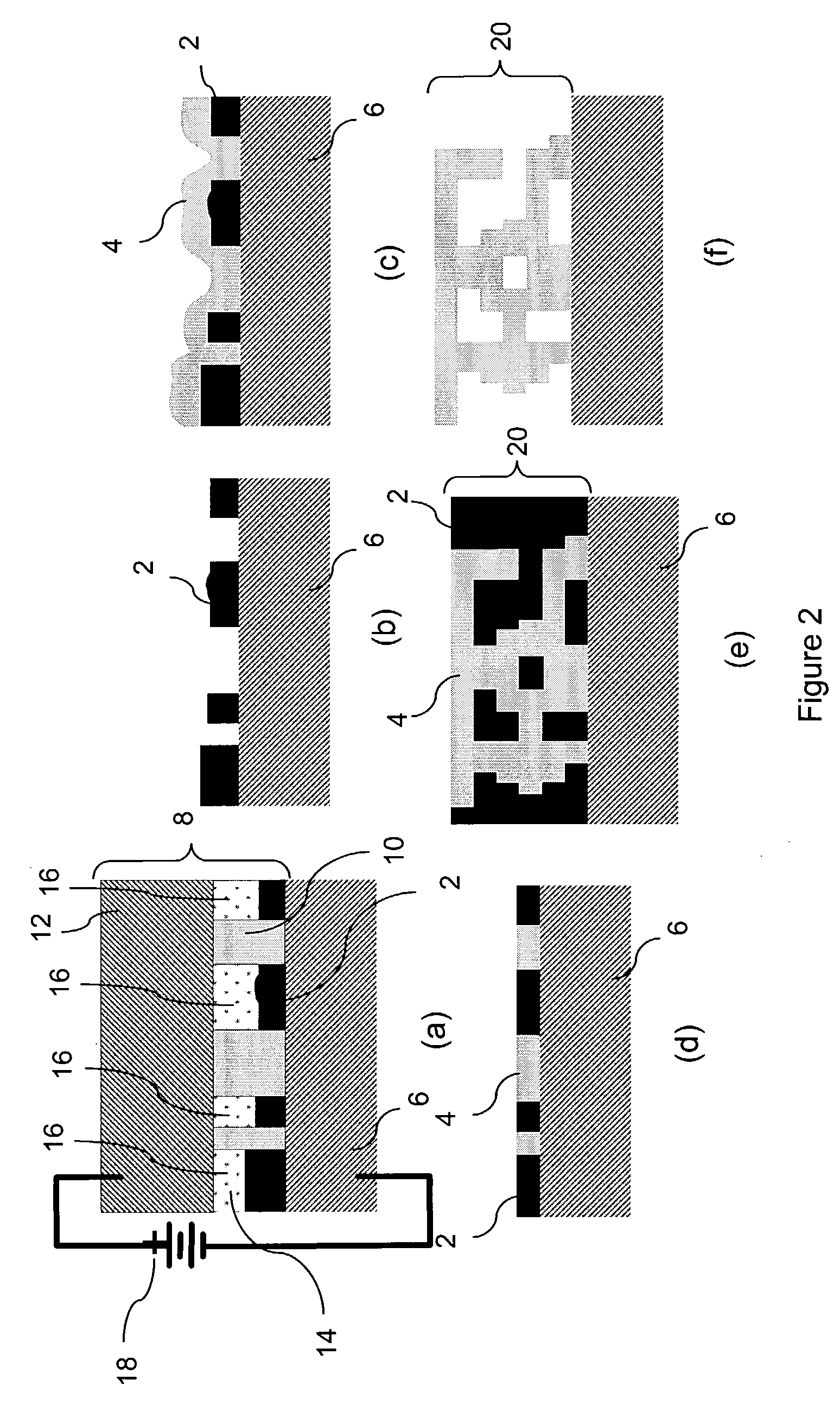

Printing wiring board and method of producing the same and capacitor to be contained in printed wiring board

InactiveUS6876554B1Improve reliabilityFlat surfaceFinal product manufactureSemiconductor/solid-state device detailsEngineeringPrinted circuit board

Chip capacitors 20 are provided in a printed circuit board 10. In this manner, the distance between an IC chip 90 and each chip capacitor 20 is shortened, and the loop inductance is reduced. In addition, the chip capacitors 20 are accommodated in a core substrate 30 having a large thickness. Therefore, the thickness of the printed circuit board does not become large.

Owner:IBIDEN CO LTD

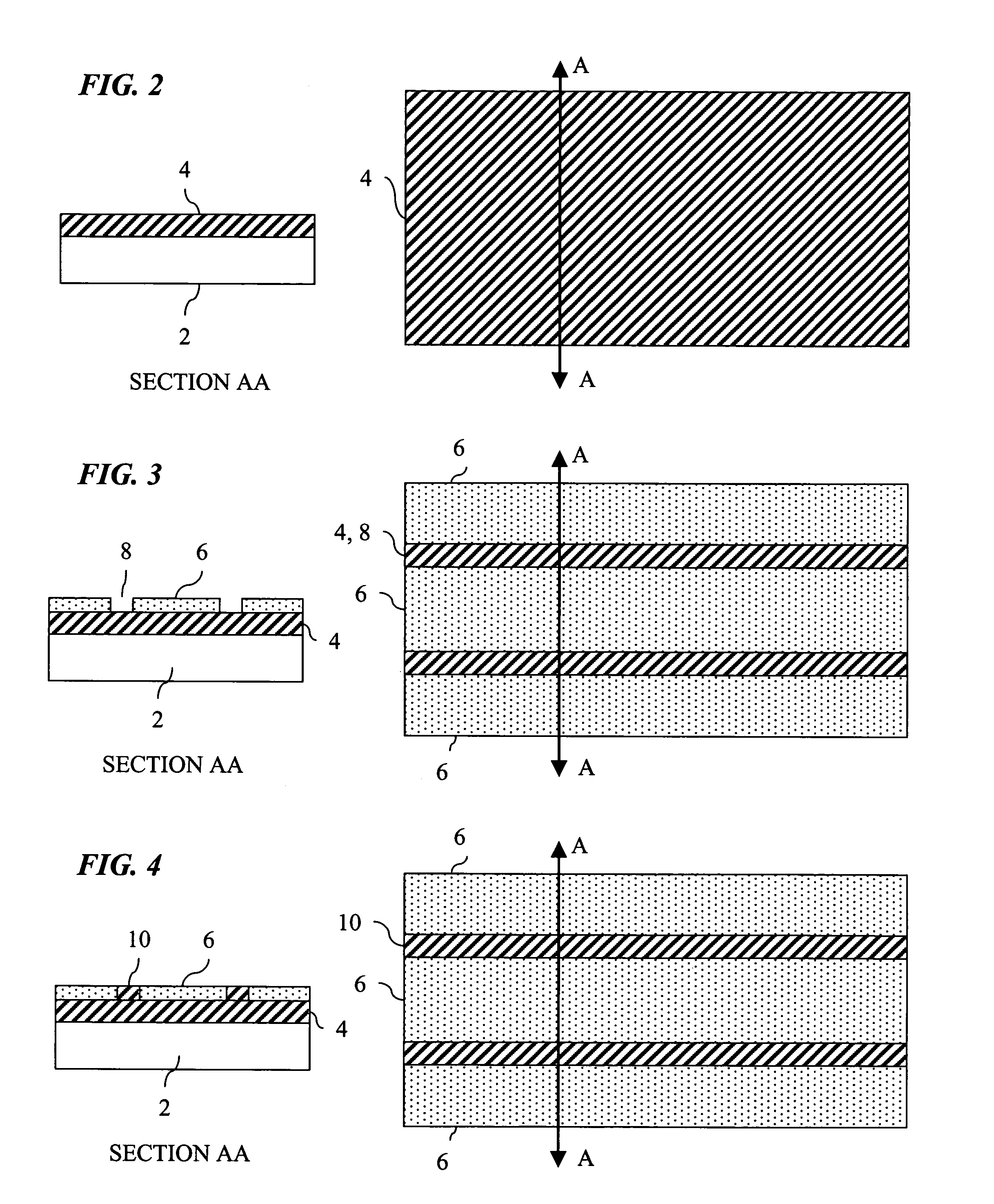

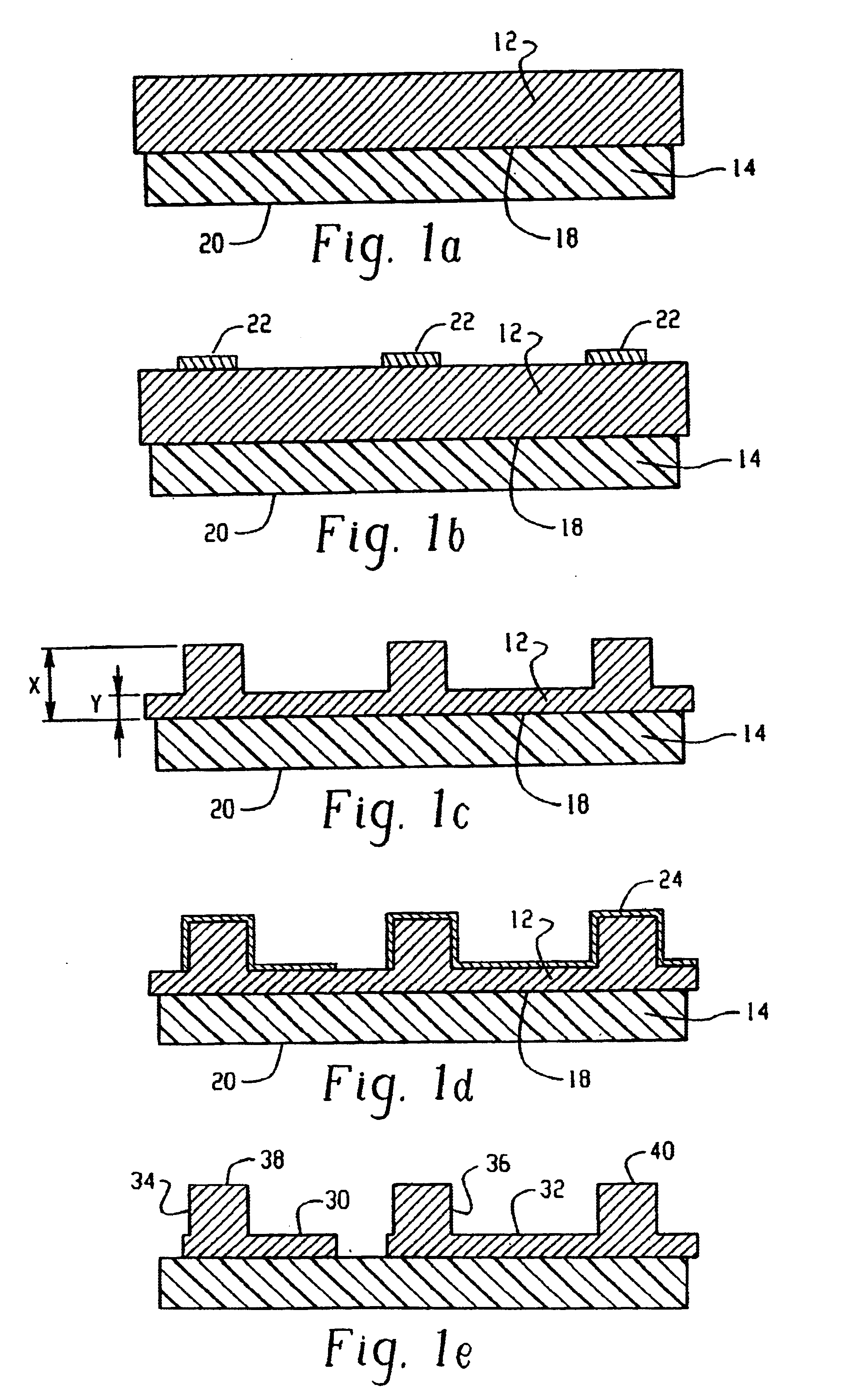

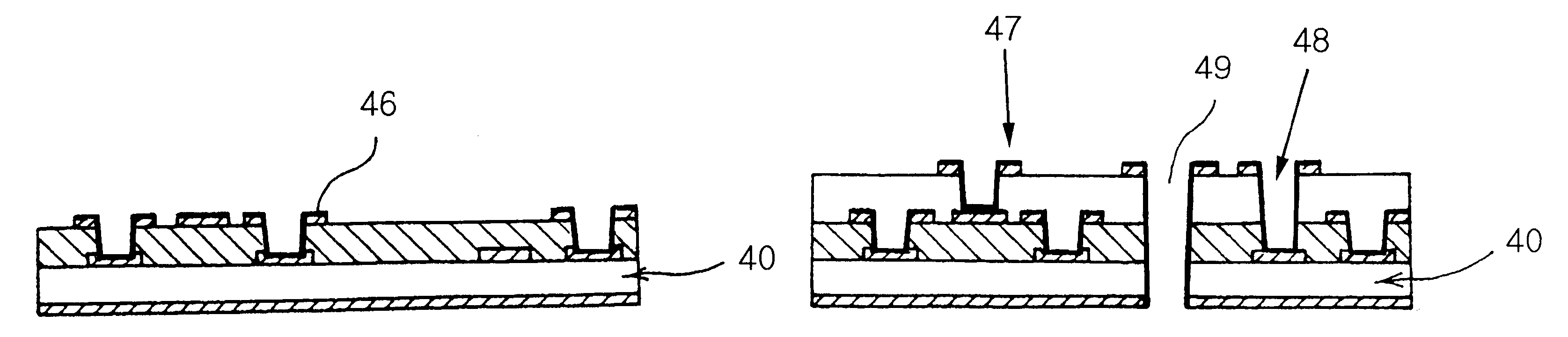

Manufacturing methods for printed circuit boards

InactiveUS6902869B2Improve rigidityEasy to handleLine/current collector detailsWave amplification devicesDielectric substratePhotoresist

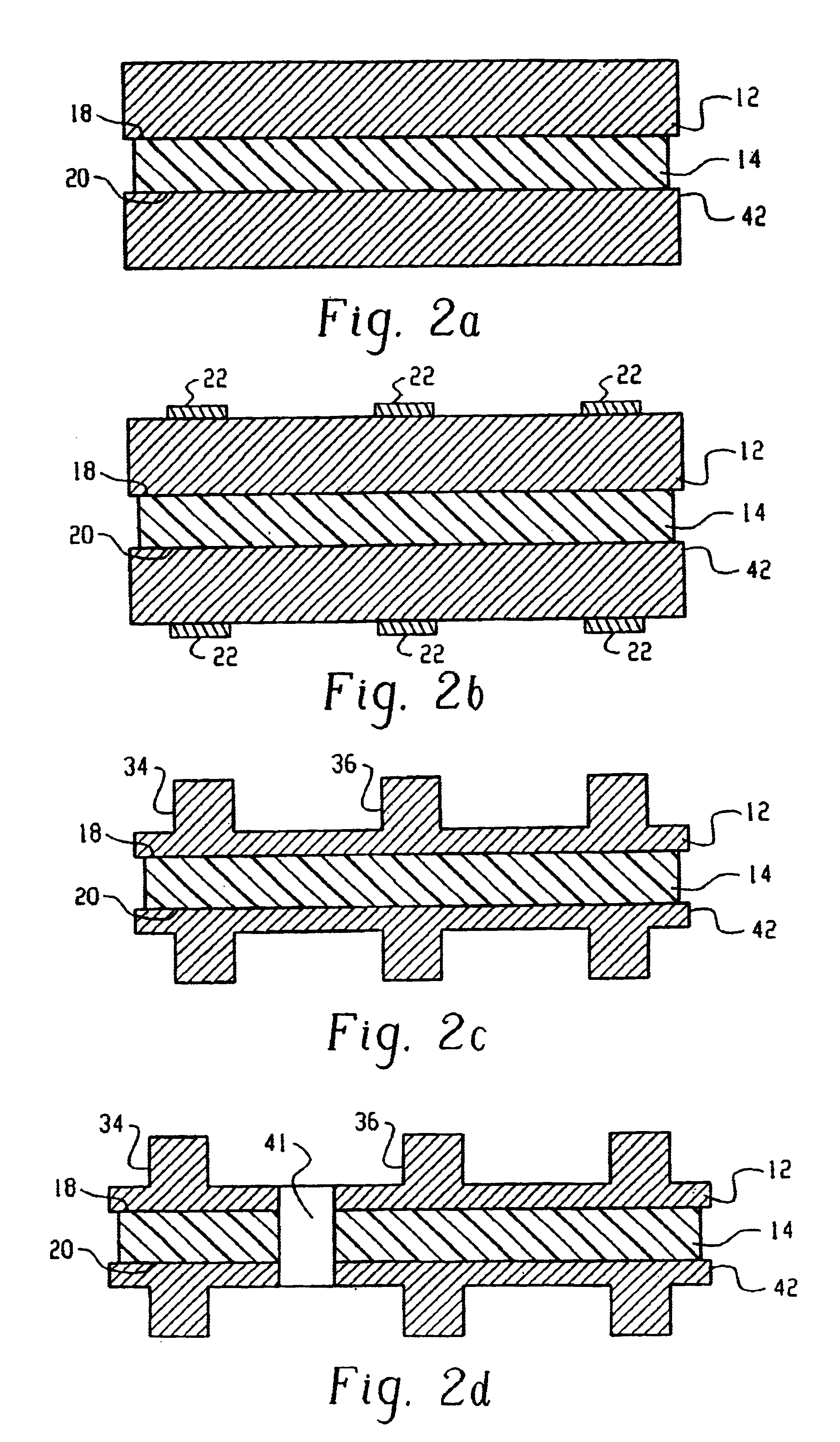

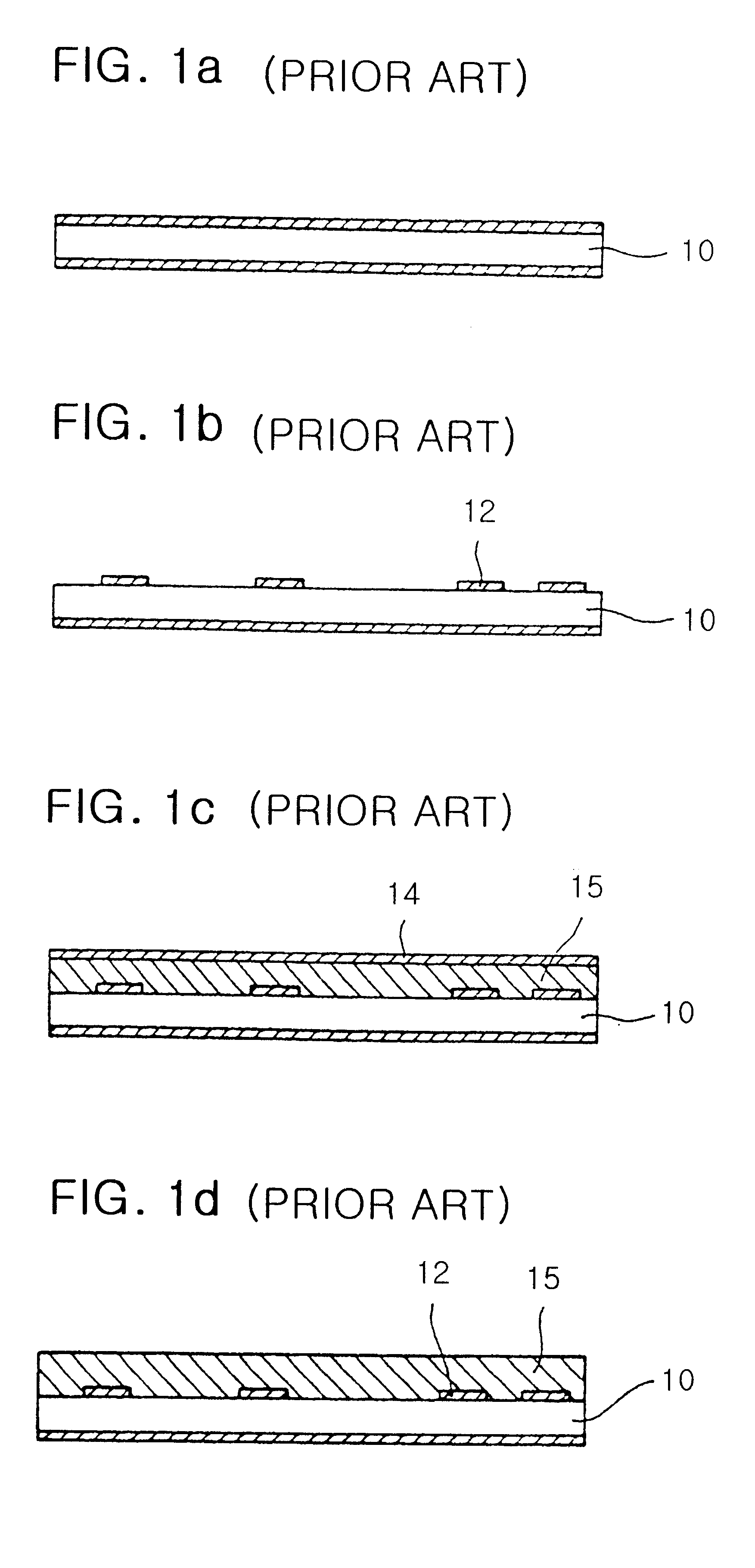

A method of forming a plurality of solid conductive bumps for interconnecting two conductive layers of a circuit board with substantially coplanar upper surfaces. The method comprises the steps of applying a continuous homogenous metal layer onto a dielectric substrate, applying a first photoresist and exposing and developing said first photoresist to define a pattern of conductive bumps; etching the metal layer exposed by said development to form said plurality of conductive bumps; removing said first photoresist; applying a second photoresist onto the metal layer; exposing and developing said second photoresist to define a pattern of conductive bumps and circuit lines; etching the metal layer exposed by said development to form a pattern of circuit lines in said metal layer; and removing said second photoresist. The methods of the present invention also provides for fabricating a multilayer circuit board and a metallic border for providing rigidity to a panel.

Owner:GLOBALFOUNDRIES INC

Structure having laser ablated features and method of fabricating

InactiveUS6919514B2Dense configurationInsulating substrate metal adhesion improvementPrinted circuit secondary treatmentOptoelectronicsMetal

Embedded flush circuitry features are provided by providing a conductive seed layer on the sidewalls and bottom of laser ablated trench features plating a layer of conductive metal onto the seed layer and depositing a layer of dielectric material.

Owner:META PLATFORMS INC

Etching of metallic composite articles

A process for the etching of multiple layers of at least two different metals comprisies:forming a resist pattern over a first layer of metal, said resist pattern having a pattern of openings therein, applying a first etch solution onto said resist pattern so that at least some etch solution contacts exposed areas of the first layer of metal, etching away the majority of the depth of the first metal in exposed areas of metal in the first layer of metal, applying a second etch solution onto the resist pattern the second etch solution having a rate of etch towards the first metal as compared to the first etch solution that is at least 20% less than the millimeter / minute rate of etch of the first etch solution at the same etch solution temperature, removing the second etch solution from said resist pattern after at least the first metal layer has been etched sufficiently to expose areas of a second metal layer underlying the first metal layer by forming an etched first metal layer, and applying a third etch solution to said etched first metal layer, the third etch solution having a faster rate of etch towards the second metal than towards the first metal to etch into said second metal layer without destroying the etched first metal layer.

Owner:BMC INDS

Method for manufacturing build-up multi-layer printed circuit board by using yag laser

A method for manufacturing a build-up multi-layer printed circuit board is disclosed in which a YAG laser is used upon the formation of a via hole in the multi-layer printed circuit board, such that it can have the following advantages: the manufacturing process would become simple; the component packaging density and freedom for the design of the board would be improved; and a high speed of signal process would be ensured. The method for manufacturing a build-up multi-layer printed circuit board includes the steps of: forming a first printed circuit pattern on a copper clad laminate (CCL) by applying a general photo-etching process, the CCL having a copper foil on the one face thereof; stacking a resin-coated (on one face) copper foil (RCC) on the CCL with the first printed circuit pattern formed thereon, and heating and pressing this structure; irradiating a YAG laser to the board with said RCC stacked so as to form a via hole at a predetermined position by removing said RCC; carrying out an electroless and electro copper plating on the board with the via hole formed therein to form a plated layer; and forming a second printed circuit pattern on said plated layer to electrically connect the layers on which the first and second printed circuit patterns are formed.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Multilayered microfluidic DNA analysis system and method

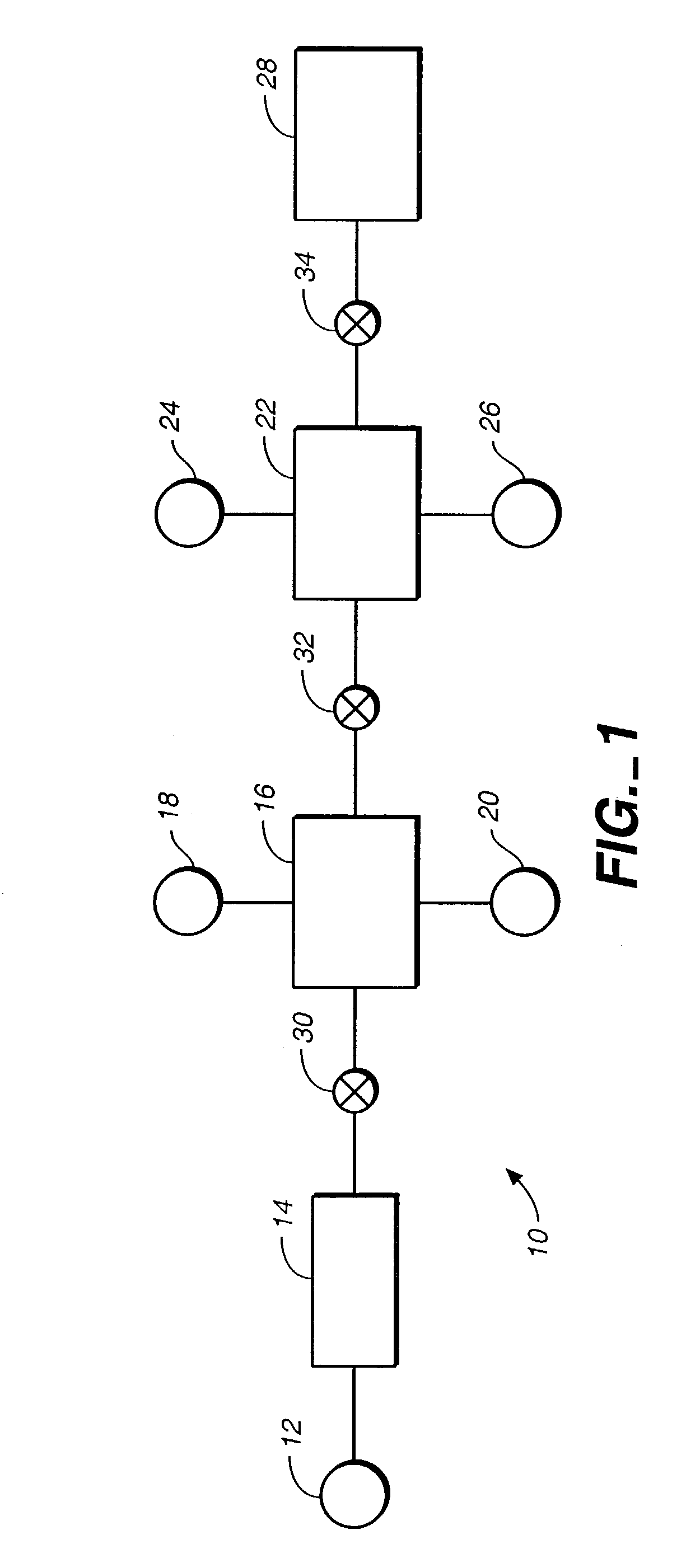

A multilayered microfluidic DNA analysis system includes a cell lysis chamber, a DNA separation chamber, a DNA amplification chamber, and a DNA detection system. The multilayered microfluidic DNA analysis system is provided as a substantially monolithic structure formed from a plurality of green-sheet layers sintered together. The substantially monolithic structure has defined therein a means for heating the DNA amplification chamber and a means for cooling the DNA amplification chamber. The means for heating and means for cooling operate to cycle the temperature of the DNA amplification chamber as required for performing a DNA amplification process, such as PCR.

Owner:GOOGLE TECH HLDG LLC

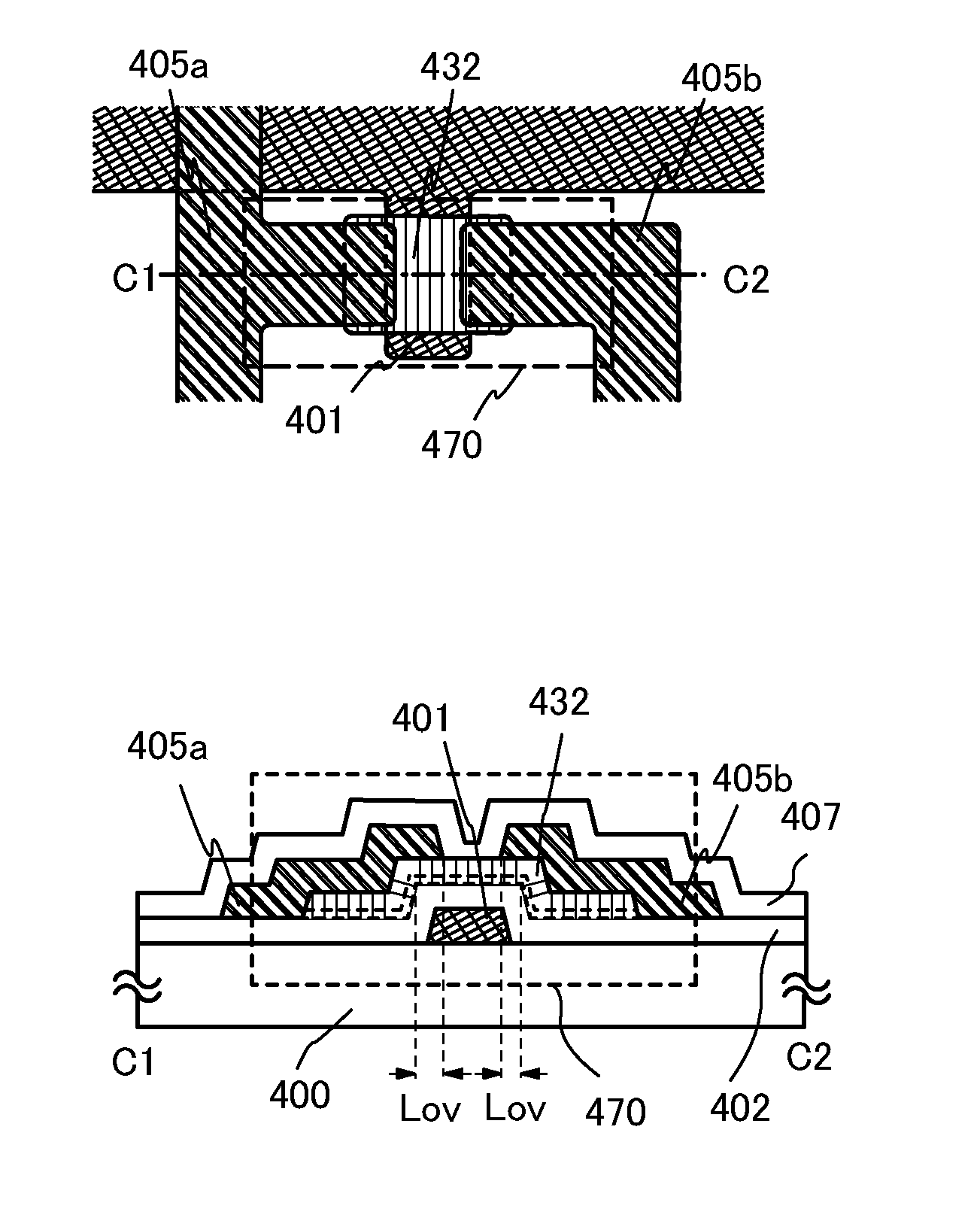

Stacked oxide material, semiconductor device, and method for manufacturing the semiconductor device

ActiveUS20110127579A1Improve mobilityReduced shutdown currentVacuum evaporation coatingSolid-state devicesDevice materialEngineering

One embodiment is a method for manufacturing a stacked oxide material, including the steps of forming a first oxide component over a base component, causing crystal growth which proceeds from a surface toward an inside of the first oxide component by first heat treatment to form a first oxide crystal component at least partly in contact with the base component, forming a second oxide component over the first oxide crystal component; and causing crystal growth by second heat treatment using the first oxide crystal component as a seed to form a second oxide crystal component.

Owner:SEMICON ENERGY LAB CO LTD

Printed wiring board having highly reliably via hole and process for forming via hole

InactiveUS6280641B1Improve reliabilityImprove productivityLight absorption dielectricsDecorative surface effectsBond energyConductive coating

Disclosed are a printed wiring board having micro-via holes highly reliable for conduction and a method of making the micro-via hole by providing a coating or sheet of an organic substance containing 3 to 97% by volume of at least one selected from a metal compound powder, a carbon powder or a metal powder having a melting point of at least 900° C. and a bond energy of at least 300 kJ / mol on a copper foil as an outermost layer of a copper-clad laminate having at least two copper layers, or providing a coating or sheet of the same after oxidizing a copper foil as an outermost layer, irradiating the coating or sheet with a carbon dioxide gas laser at an output of 20 to 60 mJ / pulse, thereby removing a micro-via-hole-forming portion of at least the copper foil as the outermost layer, then irradiating micro-via-hole-forming portions of the remaining layers with a carbon dioxide gas laser at an output of 5 to 35 mJ / pulse to make a micro-via hole which does not penetrate through the copper foil in a bottom of the micro-via hole, and electrically connecting the copper foil as the outermost layer and the copper foil in the bottom of the micro-via hole with a metal plating or an electrically conductive coating composition.

Owner:MITSUBISHI GAS CHEM CO INC

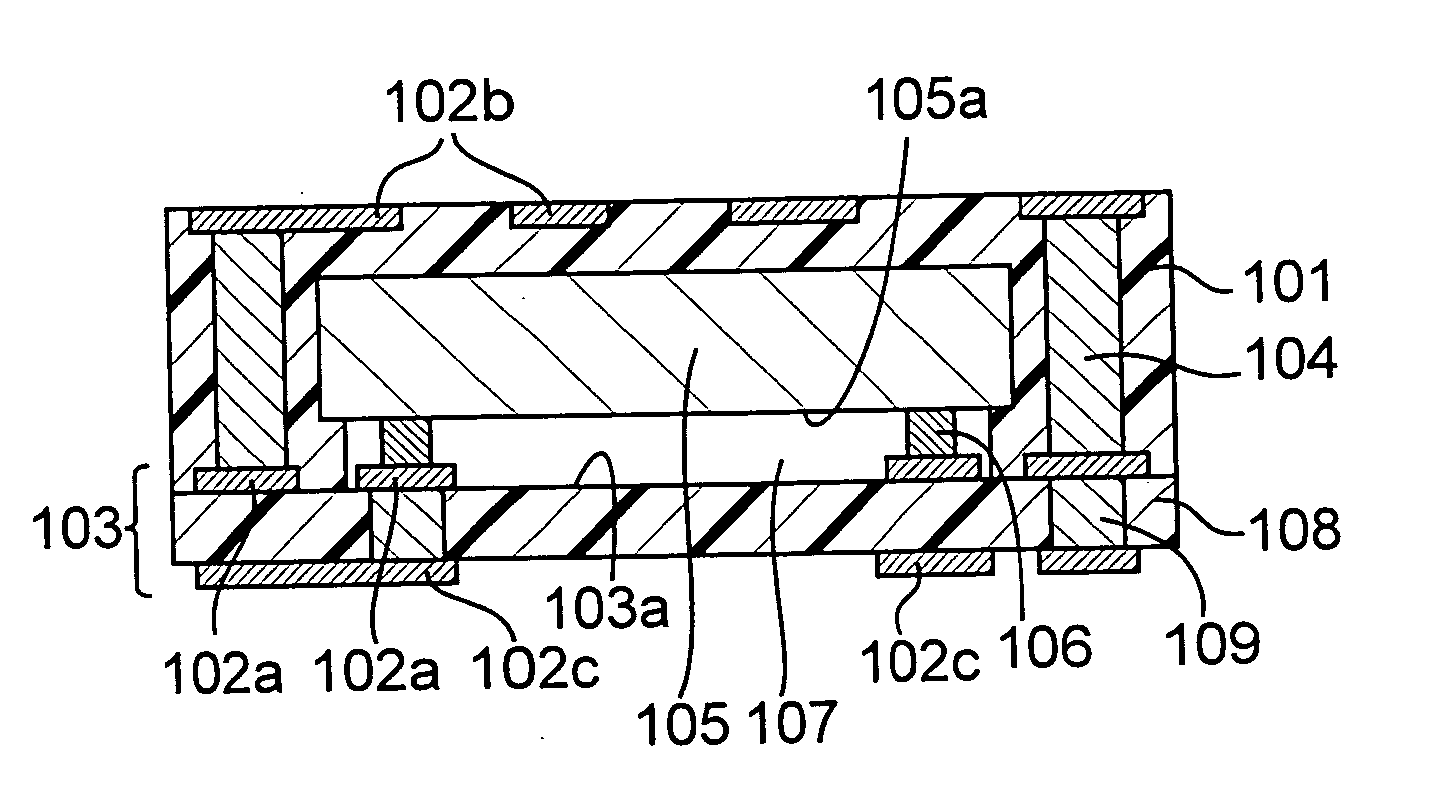

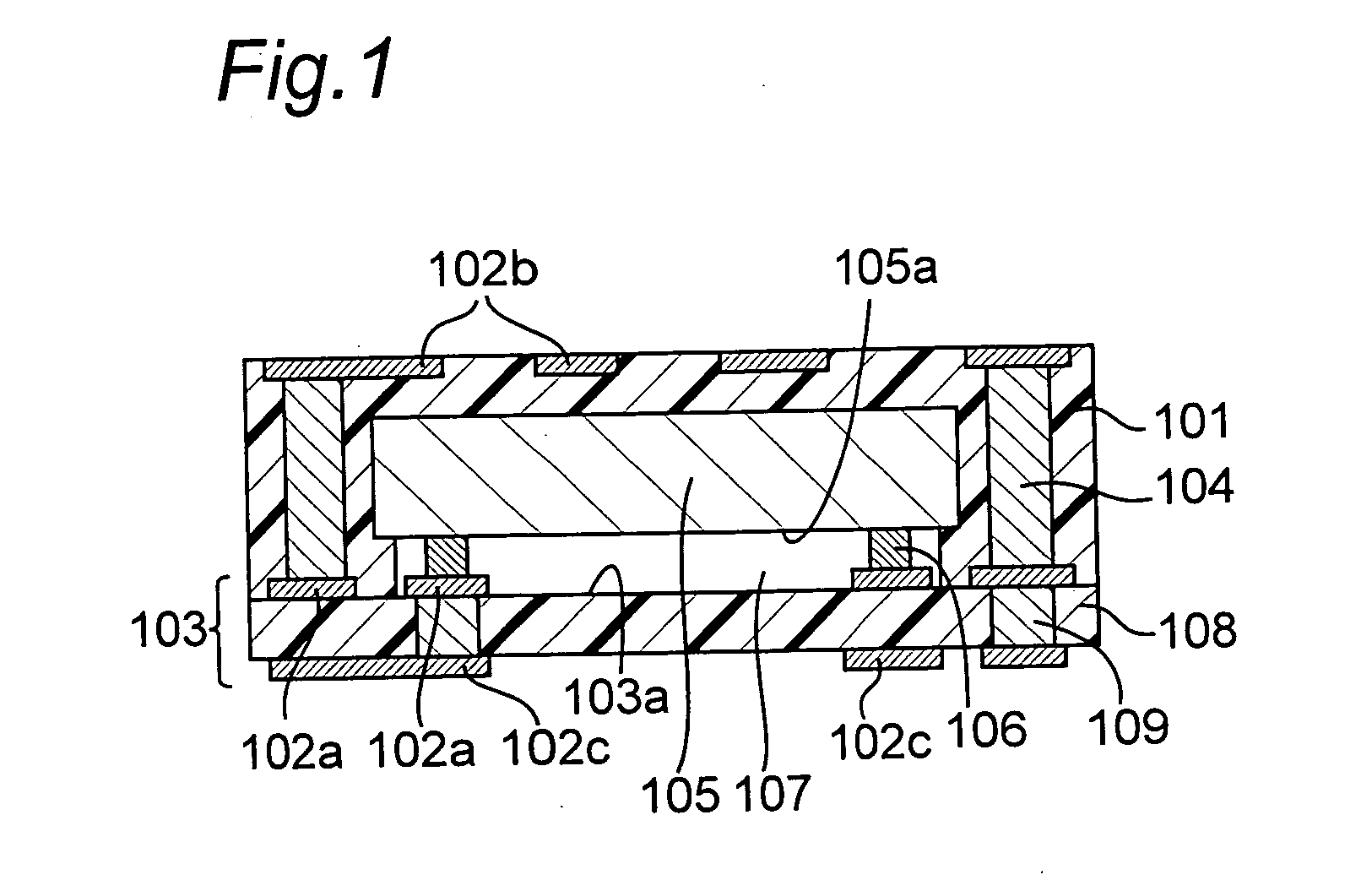

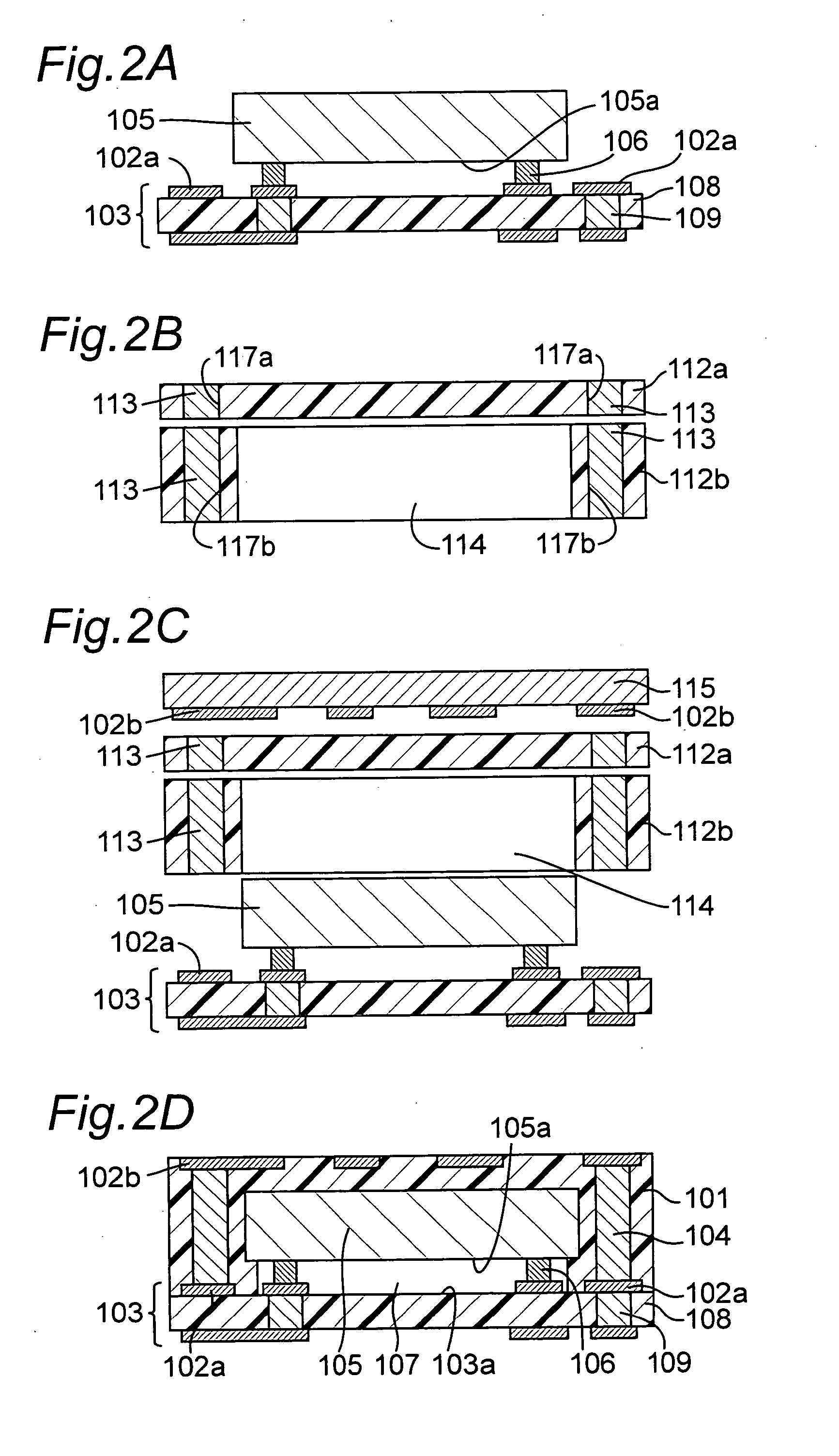

Module with a built-in semiconductor and method for producing the same

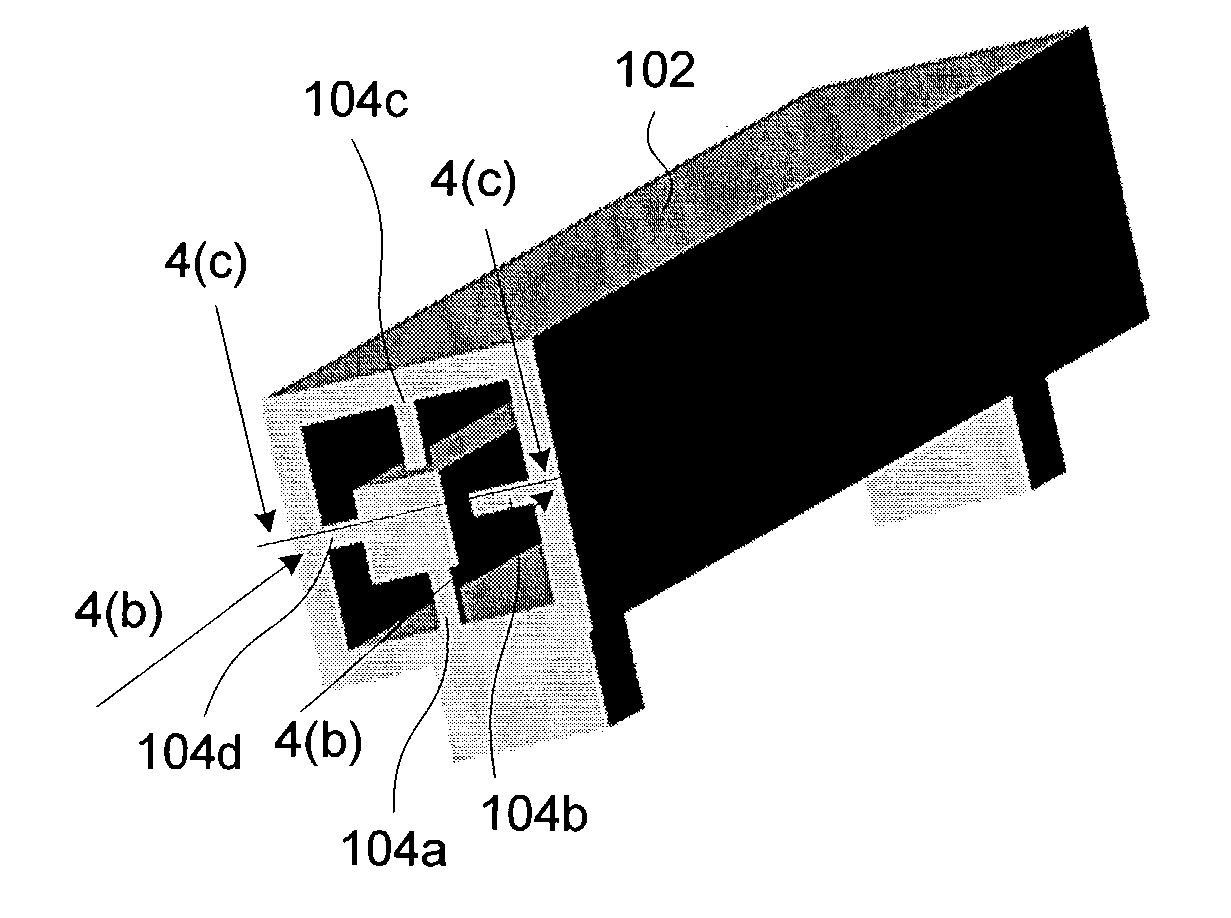

InactiveUS20050001331A1Easy to fillReduce areaTransistorSemiconductor/solid-state device detailsConductive pasteDevice material

In a module with a built-in semiconductor, higher densification is achieved by disposing inner vias close to a semiconductor device. A module which has a space 107 between a first wiring layer 102a and a built-in semiconductor device 105 is obtained by: mounting the semiconductor device 105 on a first wiring layer 102a of a wiring board 103 without using a sealing resin; stacking on the circuit board an electrically insulating substrate having a through bore (inner via) 104 filled with a conductive paste and an opening for receiving the semiconductor device, and a mold release carrier having a second wiring layer 102b in the stated order; and heating and pressurizing so that the semiconductor device 105 is incorporated in a core layer 101 which is formed by curing the electrically insulating substrate.

Owner:PANASONIC CORP

Resin composition, cured resin, sheet-like cured resin, laminated body, prepreg, electronic parts and multilayer boards

InactiveUS20050003199A1Maintain electrical propertiesHigh dielectric constantSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsEpoxyDielectric loss

The invention provides electronic parts which comprise a composite dielectric layer composed of an organic insulating material and a dielectric ceramic powder having a larger relative dielectric constant than the organic insulating material, and which also comprise conductive element sections forming inductor elements, etc., wherein the organic insulating material comprises a cured resin obtained by curing reaction of an epoxy resin with an active ester compound obtained by reaction between a compound with two or more carboxyl groups and a compound with a phenolic hydroxyl group. The dielectric ceramic powders of the described electronic parts have larger relative dielectric constants than the organic insulating materials, and the organic insulating materials have low dielectric loss tangents. It is possible to adequately reduce time-dependent dielectric constant changes in the high-frequency range of 100 MHz and above even with prolonged use at high temperatures of 100° C. and higher, while it is also possible to satisfactorily prevent deformation and other damage to the electronic parts during their handling.

Owner:TDK CORPARATION

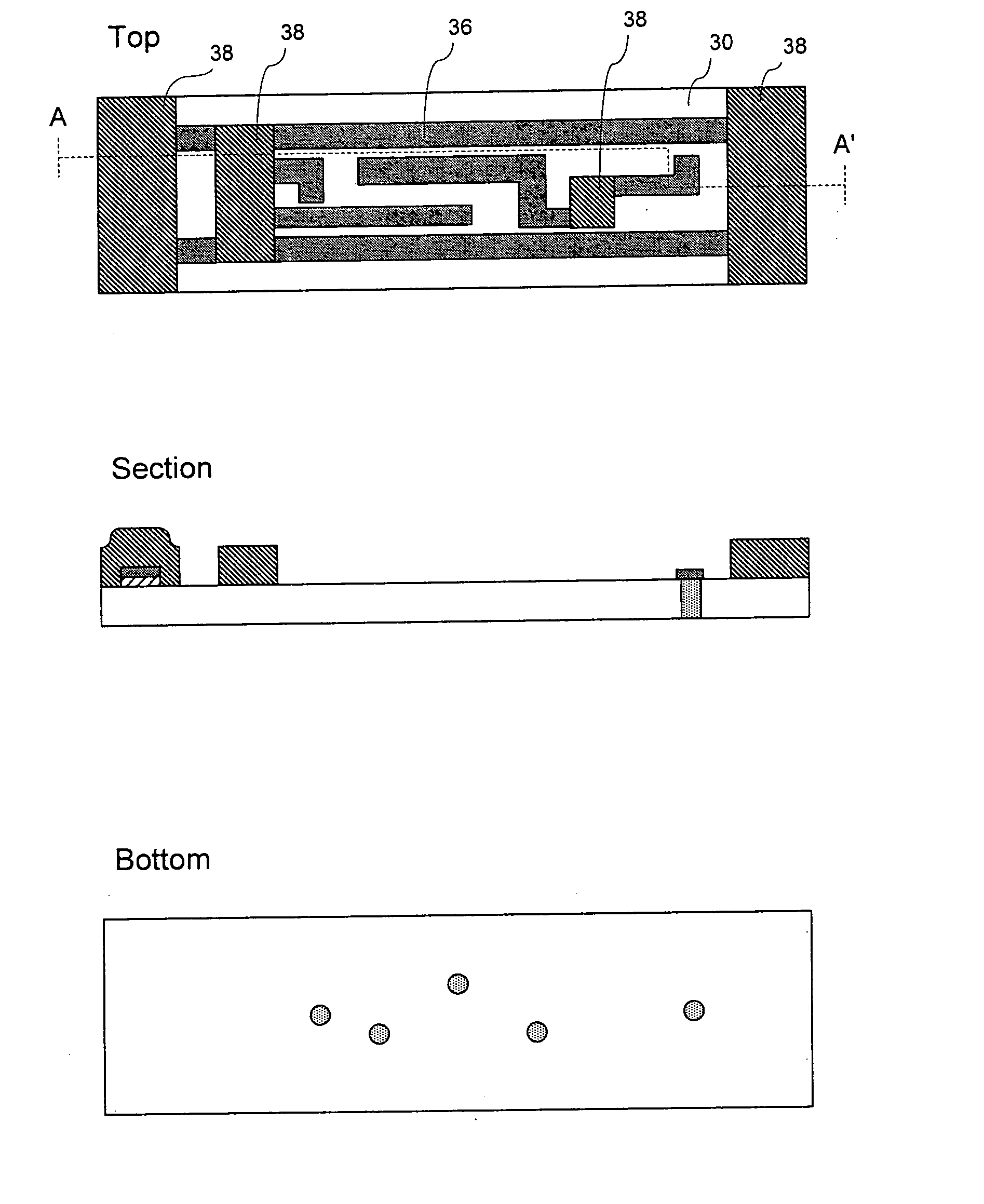

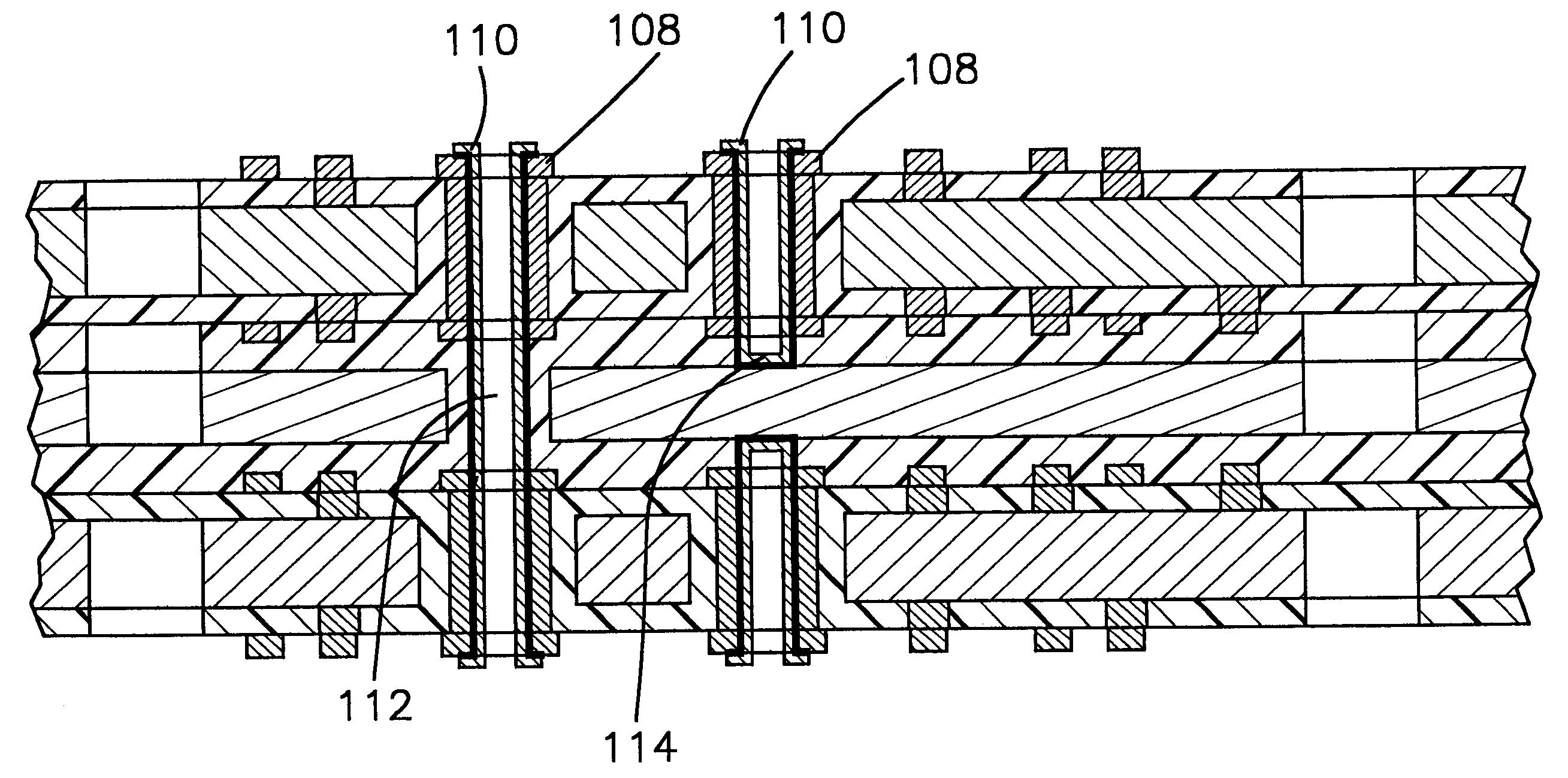

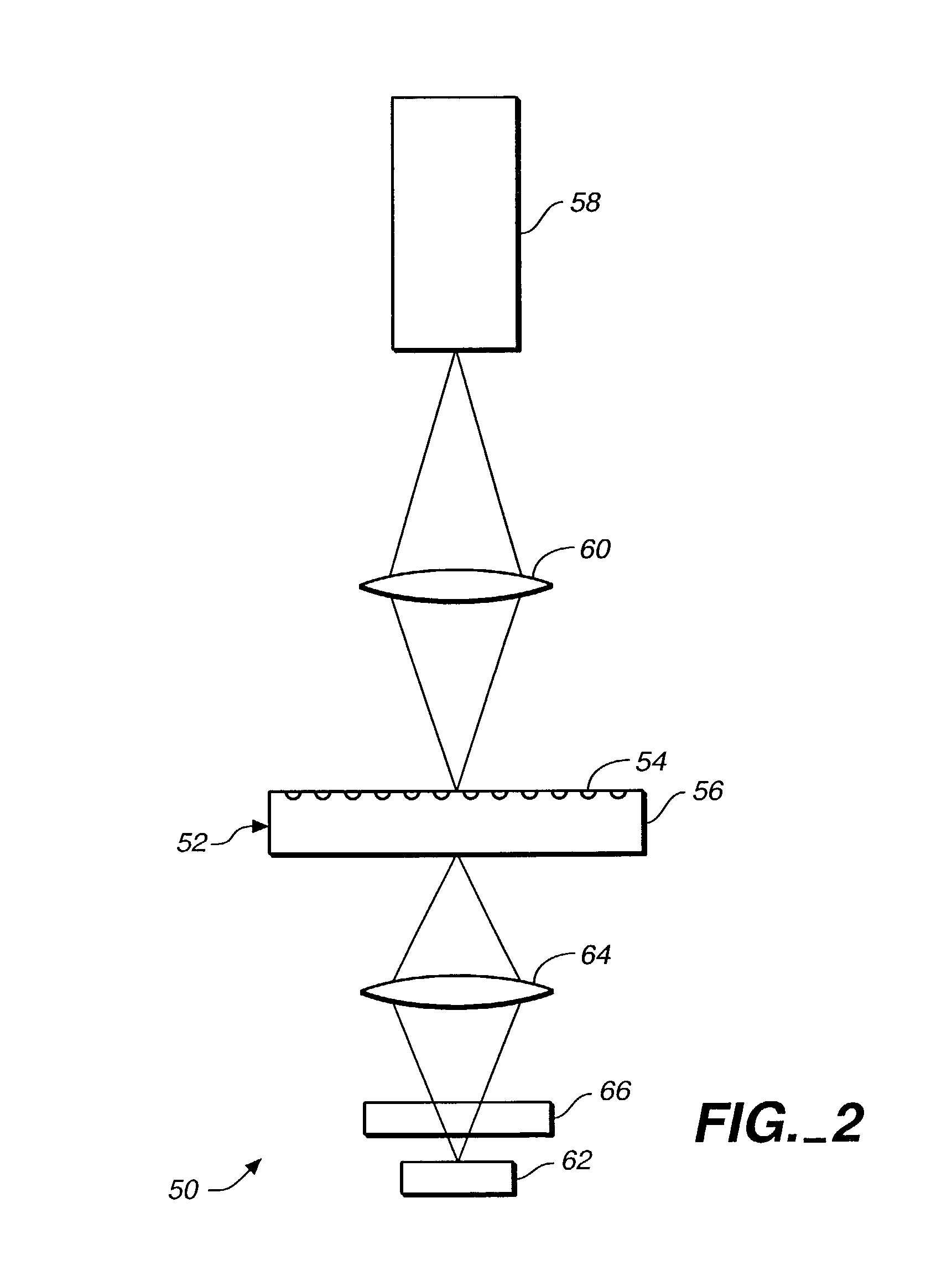

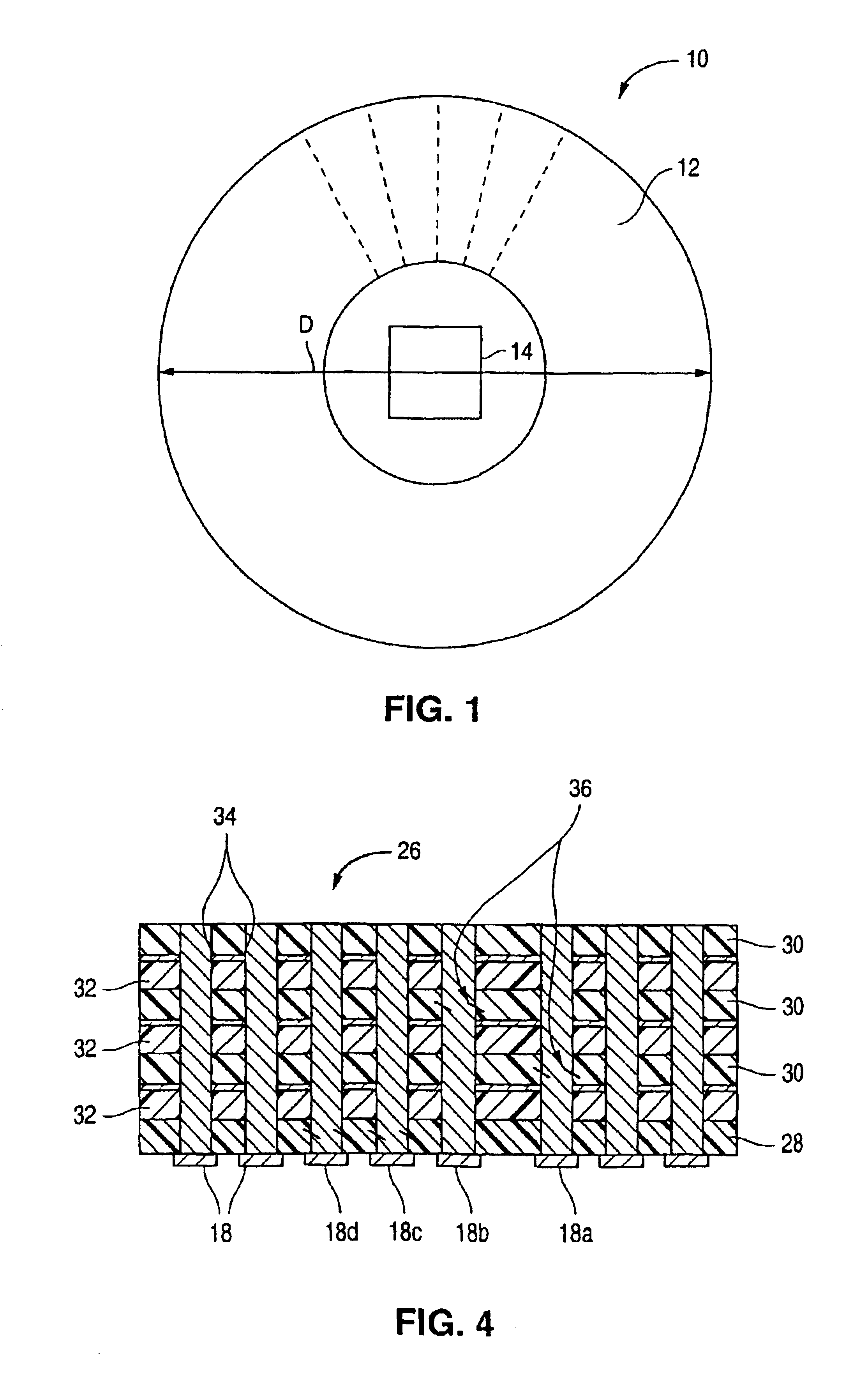

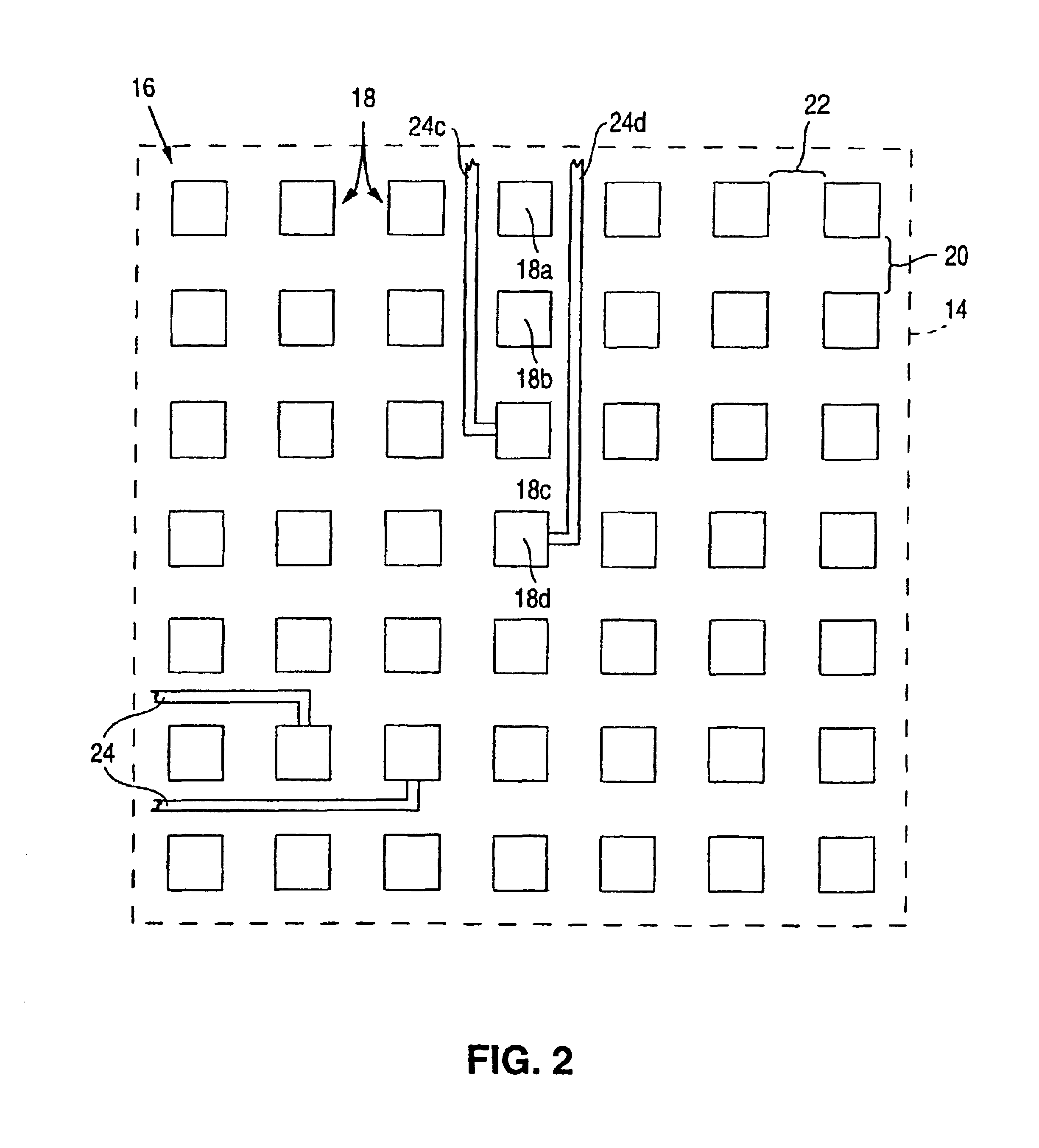

Miniature RF and microwave components and methods for fabricating such components

ActiveUS20030222738A1Add depthAcceleration measurement using interia forcesAdditive manufacturing apparatusElectricityInductor

RF and microwave radiation directing or controlling components are provided that may be monolithic, that may be formed from a plurality of electrodeposition operations and / or from a plurality of deposited layers of material, that may include switches, inductors, antennae, transmission lines, filters, and / or other active or passive components. Components may include non-radiation-entry and non-radiation-exit channels that are useful in separating sacrificial materials from structural materials. Preferred formation processes use electrochemical fabrication techniques (e.g. including selective depositions, bulk depositions, etching operations and planarization operations) and post-deposition processes (e.g. selective etching operations and / or back filling operations).

Owner:MEMGEN

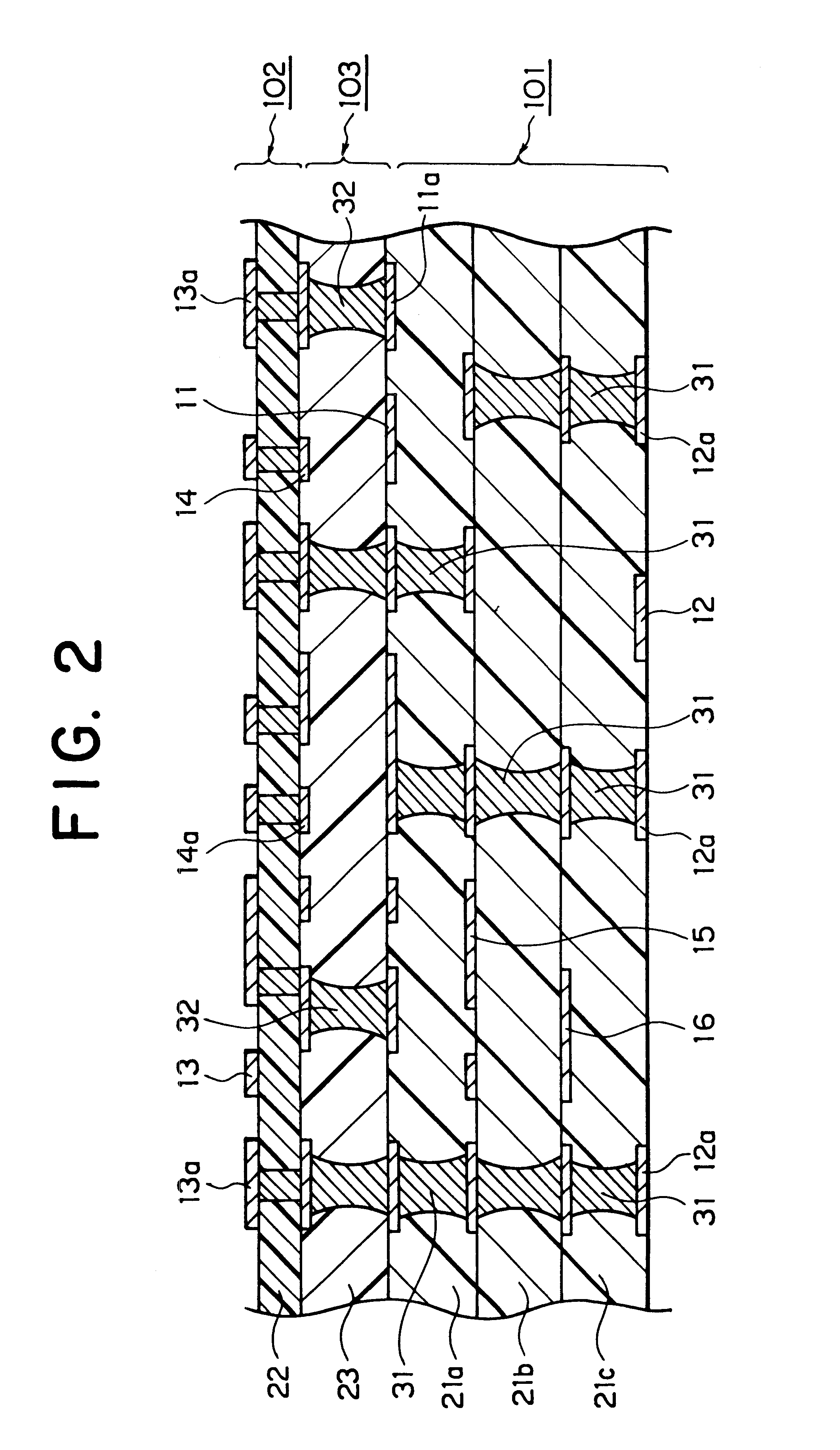

Substrate for mounting IC chip, multilayered printed circuit board, and device for optical communication

InactiveUS20050185880A1Precise positioningHigh positioning accuracyCladded optical fibreCircuit optical detailsElectrical conductorOptical communication

The present invention provides a device for optical communication comprising: a substrate for mounting an IC chip having a light emitting element and a light receiving element mounted at predetermined positions; and a multilayered printed circuit board having an optical waveguide formed at a predetermined position, which is low in connection loss among the mounted optical components and which has excellent connection reliability. The device for optical communication according to the present invention comprises the substrate for mounting an IC chip and the multilayered printed circuit board, wherein the substrate for mounting an IC chip includes conductor circuits, interlaminar insulating layers and via-holes for connecting the conductor circuits, with the interlaminar insulating layers interposed therebetween, to each other, and a light receiving element and a light emitting element are mounted on the substrate for mounting an IC chip.

Owner:IBIDEN CO LTD

Method for manufacturing a multi-layer printed circuit board

InactiveUS6839964B2Easy to routePrinted circuit assemblingPrinted circuit aspectsSignal routingEngineering

A method of manufacturing a multilayer printed circuit board (PCB) is provided, the PCB having blind vias connecting to power layers. A portion of the blind vias in the power layers are grouped together to form a cluster of blind vias. Signal layers, provided separate from the power layers, include signal routing channels, with at least some of the signal routing channels aligned above or below the cluster of blind vias of the power layers.

Owner:FORMFACTOR INC

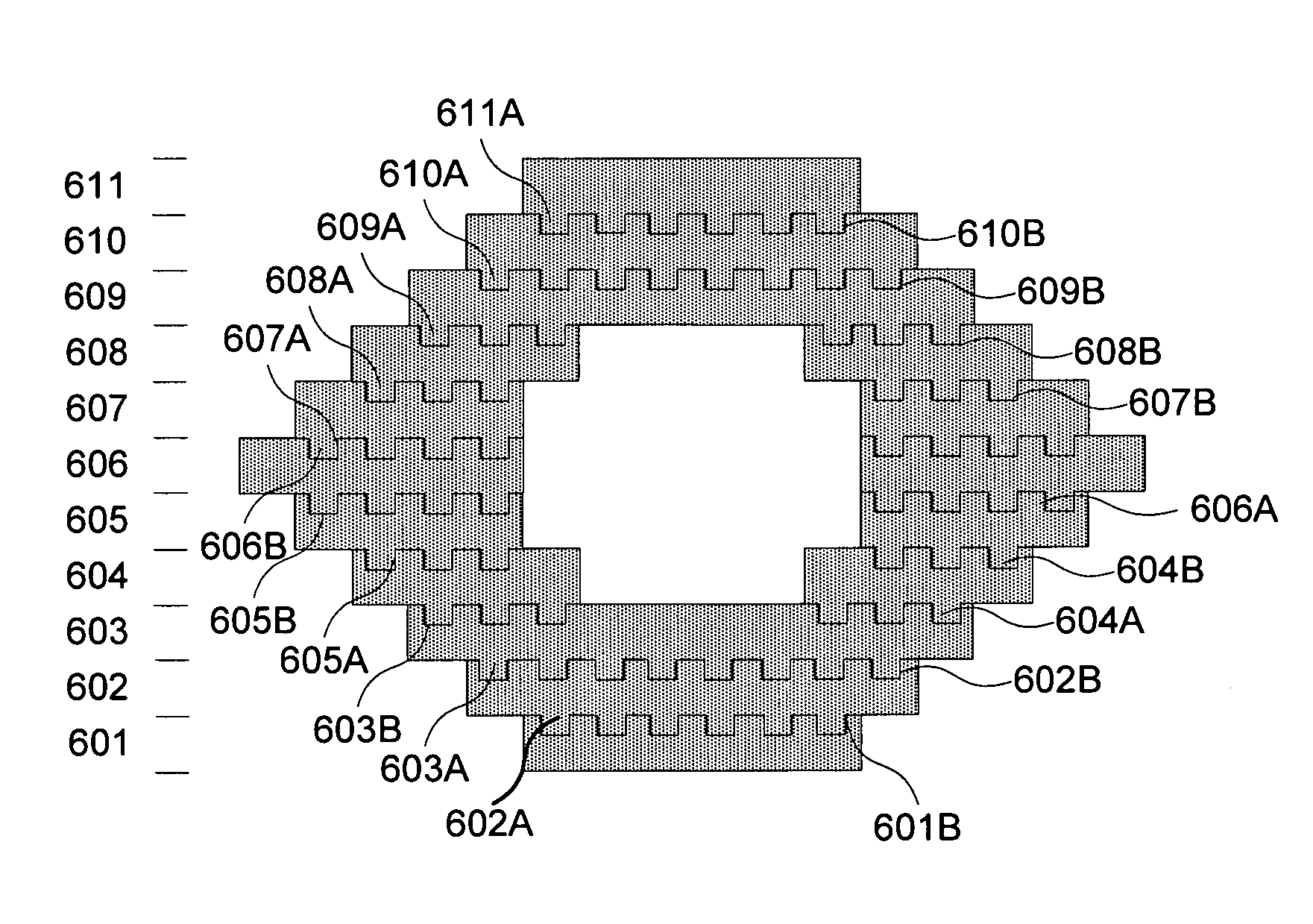

Methods of and apparatus for electrochemically fabricating structures via interlaced layers or via selective etching and filling of voids

ActiveUS7252861B2Advanced manufacturing technologyImprove propertiesAcceleration measurement using interia forcesPretreated surfacesOrder of operationsEngineering

Multi-layer structures are electrochemically fabricated by depositing a first material, selectively etching the first material (e.g. via a mask), depositing a second material to fill in the voids created by the etching, and then planarizing the depositions so as to bound the layer being created and thereafter adding additional layers to previously formed layers. The first and second depositions may be of the blanket or selective type. The repetition of the formation process for forming successive layers may be repeated with or without variations (e.g. variations in: patterns; numbers or existence of or parameters associated with depositions, etchings, and or planarization operations; the order of operations, or the materials deposited). Other embodiments form multi-layer structures using operations that interlace material deposited in association with some layers with material deposited in association with other layers.

Owner:MICROFAB

Popular searches

Sputtering coating Resistor manufacture 3D object support structures Multilayer circuit manufacture Additive manufacturing processes Liquid/solution decomposition chemical coating Railway signalling Conductive pattern formation Solid/suspension decomposition chemical coating Welding/cutting media/materials