Patents

Literature

18561results about "Liquid/solution decomposition chemical coating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

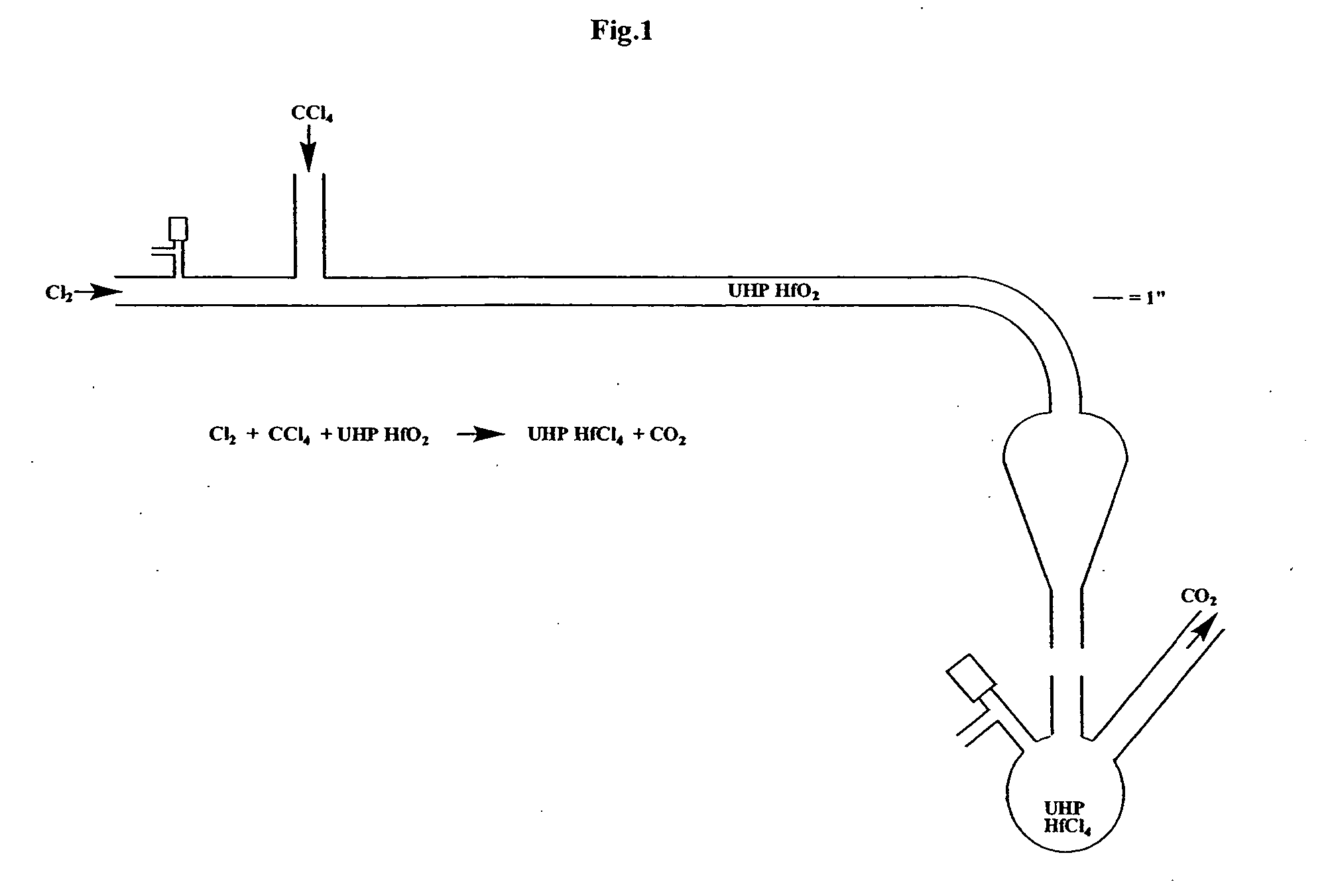

Low zirconium, hafnium-containing compositions, processes for the preparation thereof and methods of use thereof

InactiveUS20060193979A1Improve propertiesDesired morphologyGroup 4/14 organic compounds without C-metal linkagesPretreated surfacesHafniumChemical vapor deposition

This invention relates to hafnium-containing compositions having a zirconium concentration of less than about 500 parts per million, a process for producing the hafnium-containing compositions, organometallic precursor compositions containing a hafnium-containing compound and having a zirconium concentration of less than about 500 parts per million, a process for producing the organometallic precursor compositions, and a method for producing a film or coating from the organometallic precursor compositions. The organometallic precursor compositions are useful in semiconductor applications as chemical vapor deposition (CVD) or atomic layer deposition (ALD) precursors for film depositions.

Owner:PRAXAIR TECH INC

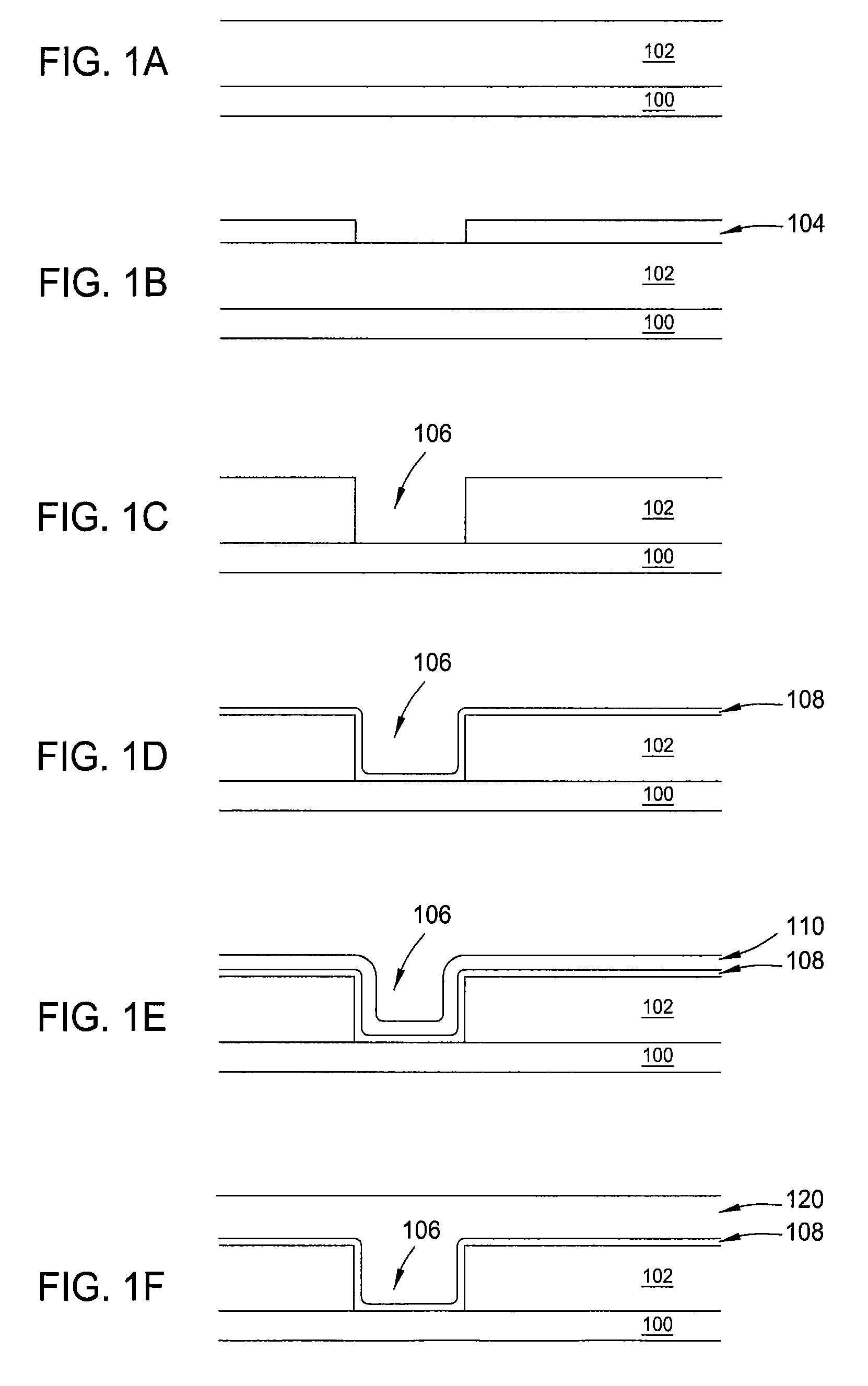

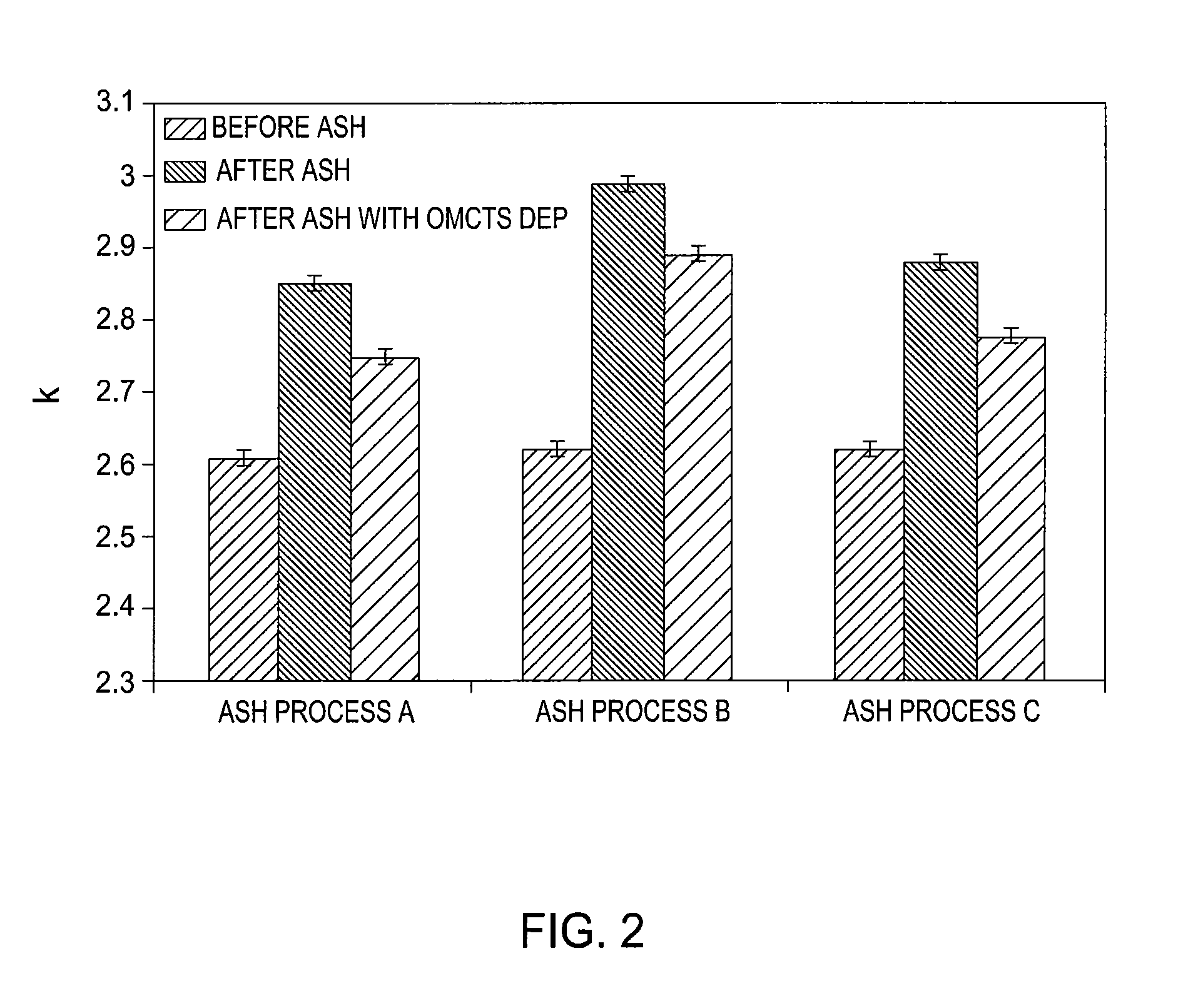

Method to minimize wet etch undercuts and provide pore sealing of extreme low k (k<2.5) dielectrics

ActiveUS8445075B2Constant ratePrevents undercuts and CD lossVacuum evaporation coatingPretreated surfacesNitrogenThin layer

Methods of processing films on substrates are provided. In one aspect, the methods comprise treating a patterned low dielectric constant film after a photoresist is removed from the film by depositing a thin layer comprising silicon, carbon, and optionally oxygen and / or nitrogen on the film. The thin layer provides a carbon-rich, hydrophobic surface for the patterned low dielectric constant film. The thin layer also protects the low dielectric constant film from subsequent wet cleaning processes and penetration by precursors for layers that are subsequently deposited on the low dielectric constant film.

Owner:APPLIED MATERIALS INC

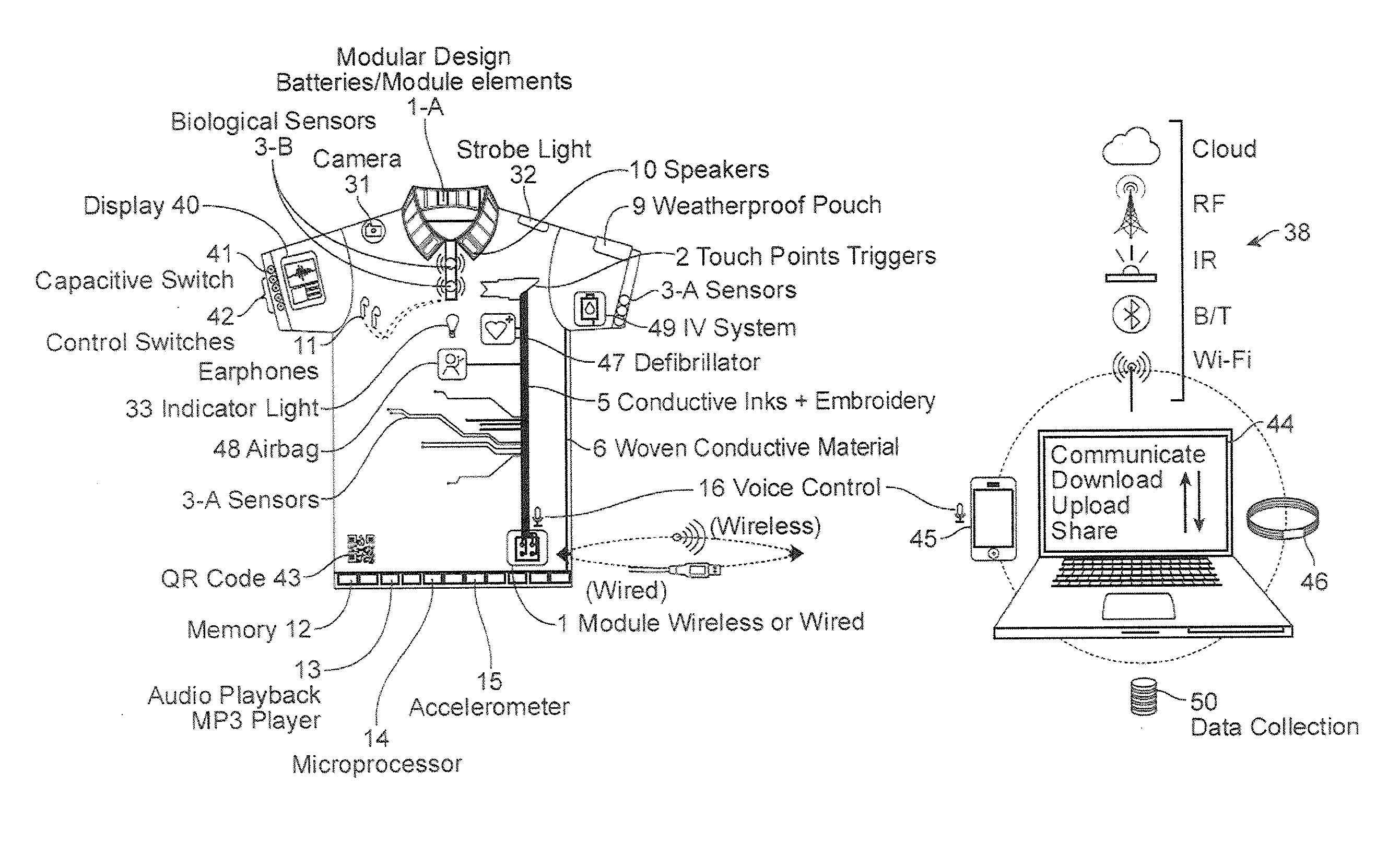

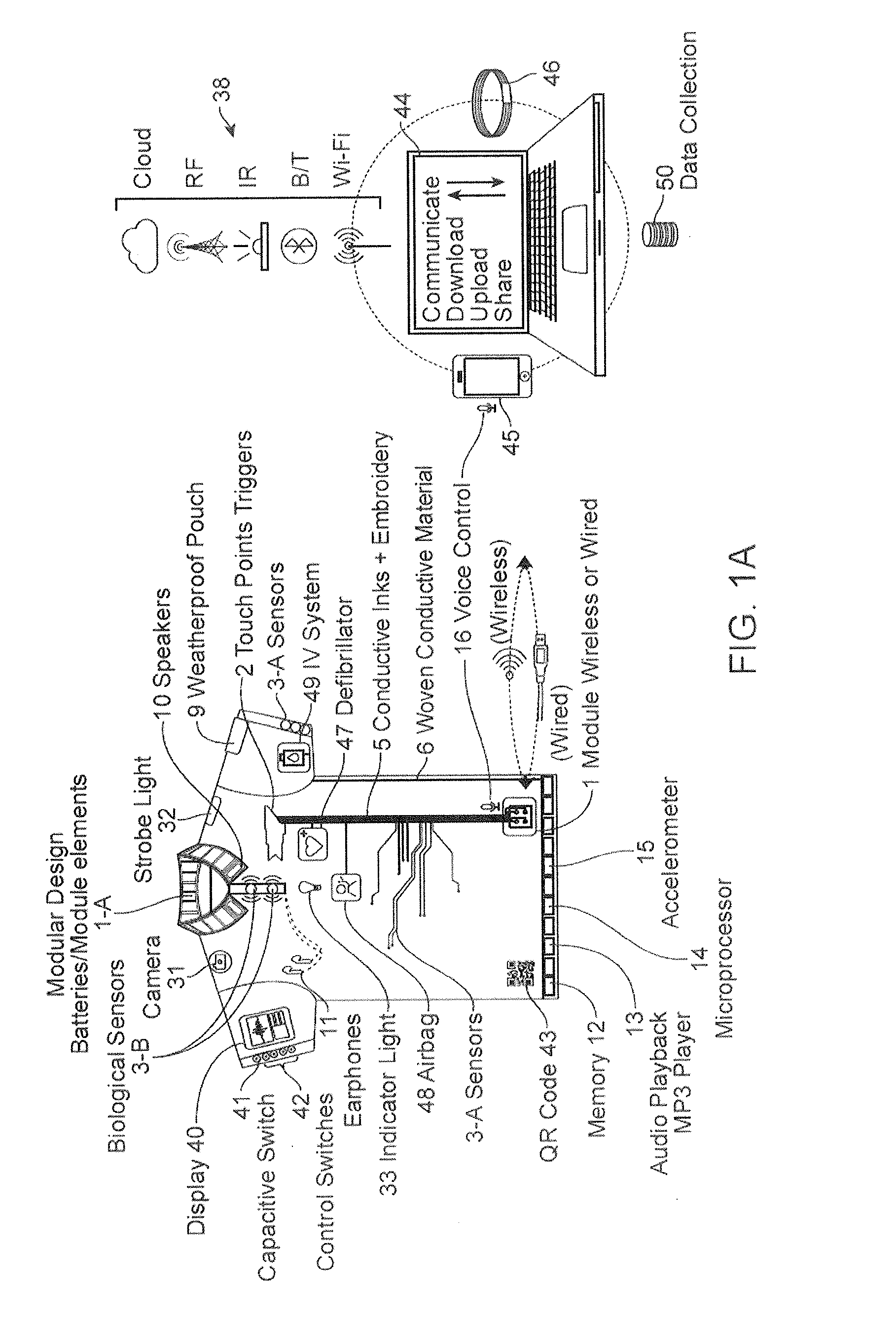

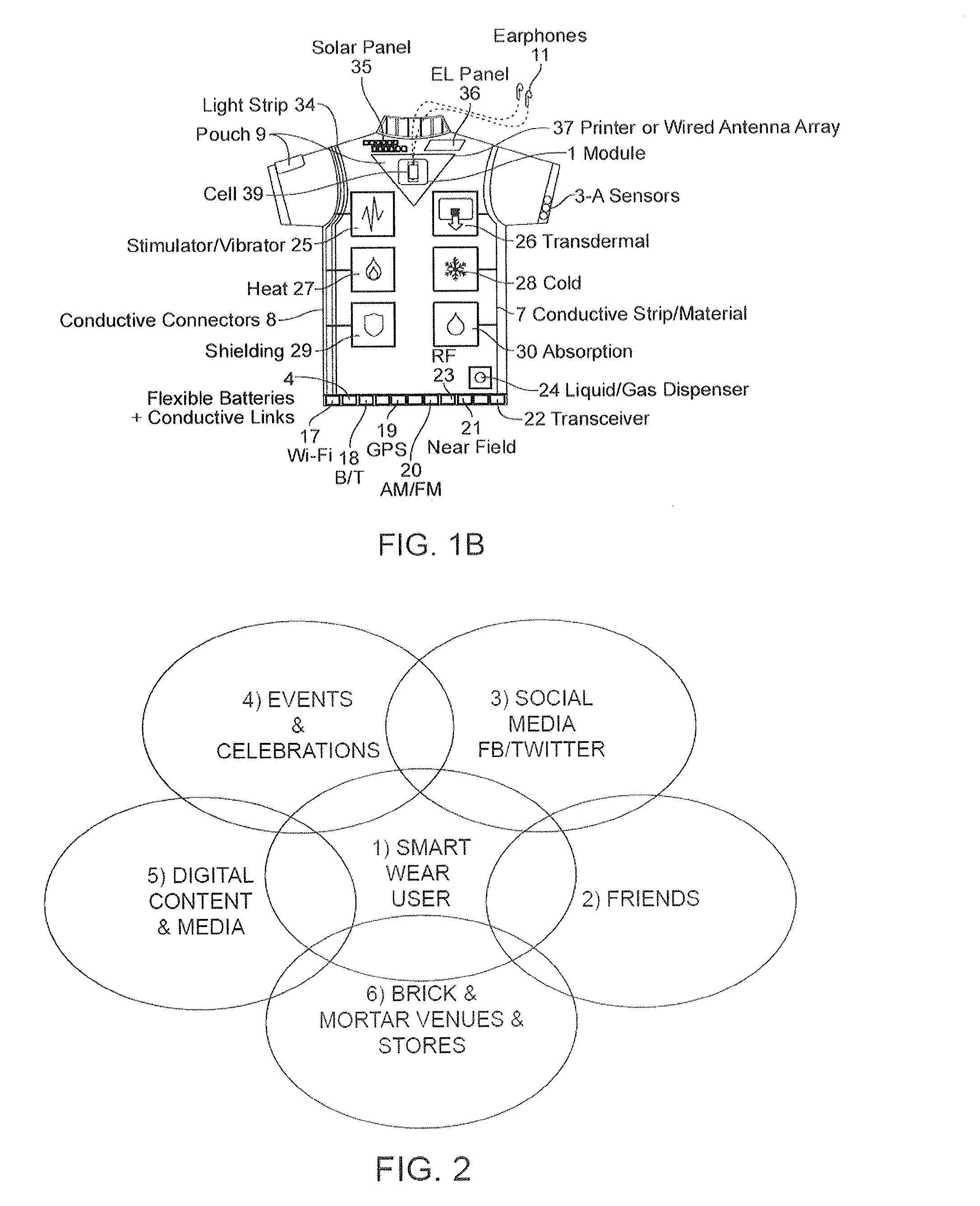

Methods of making garments having stretchable and conductive ink

InactiveUS20140318699A1Stable and continuous positioningRobust detectionPrinted circuit manufactureResistor manufactureAdhesiveSolvent

Methods of forming garments having one or more stretchable conductive ink patterns. Described herein are method of making garments (including compression garments) having one or more highly stretchable conductive ink pattern formed of a composite of an insulative adhesive, a conductive ink, and an intermediate gradient zone between the adhesive and conductive ink. The conductive ink typically includes between about 40-60% conductive particles, between about 30-50% binder; between about 3-7% solvent; and between about 3-7% thickener. The stretchable conductive ink patterns may be stretched more than twice their length without breaking or rupturing.

Owner:L I F E

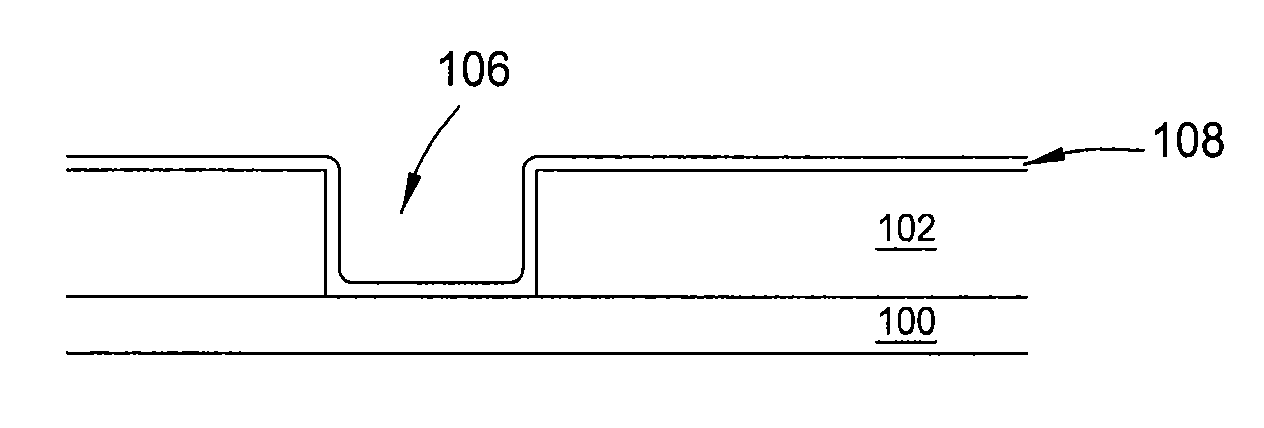

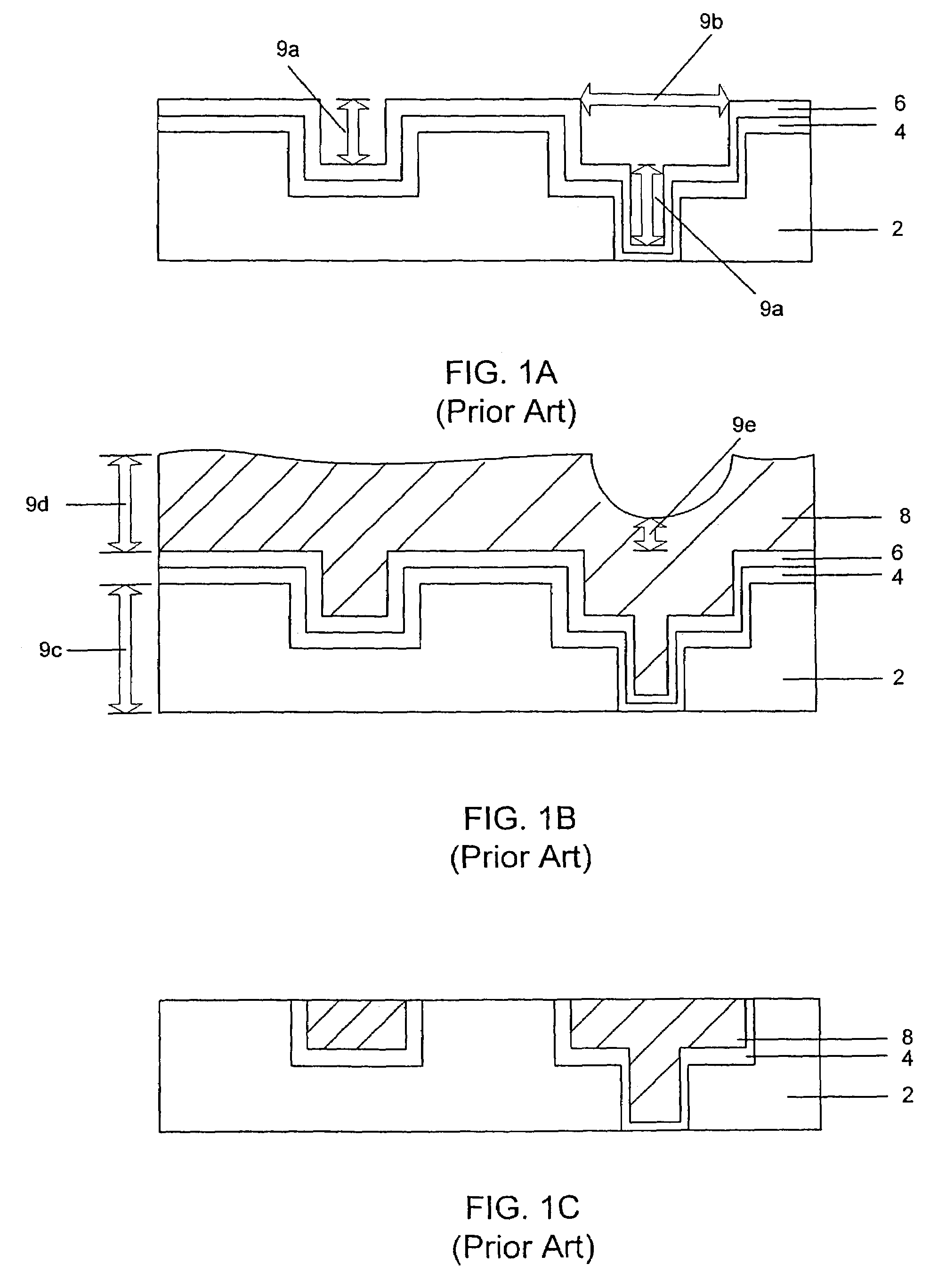

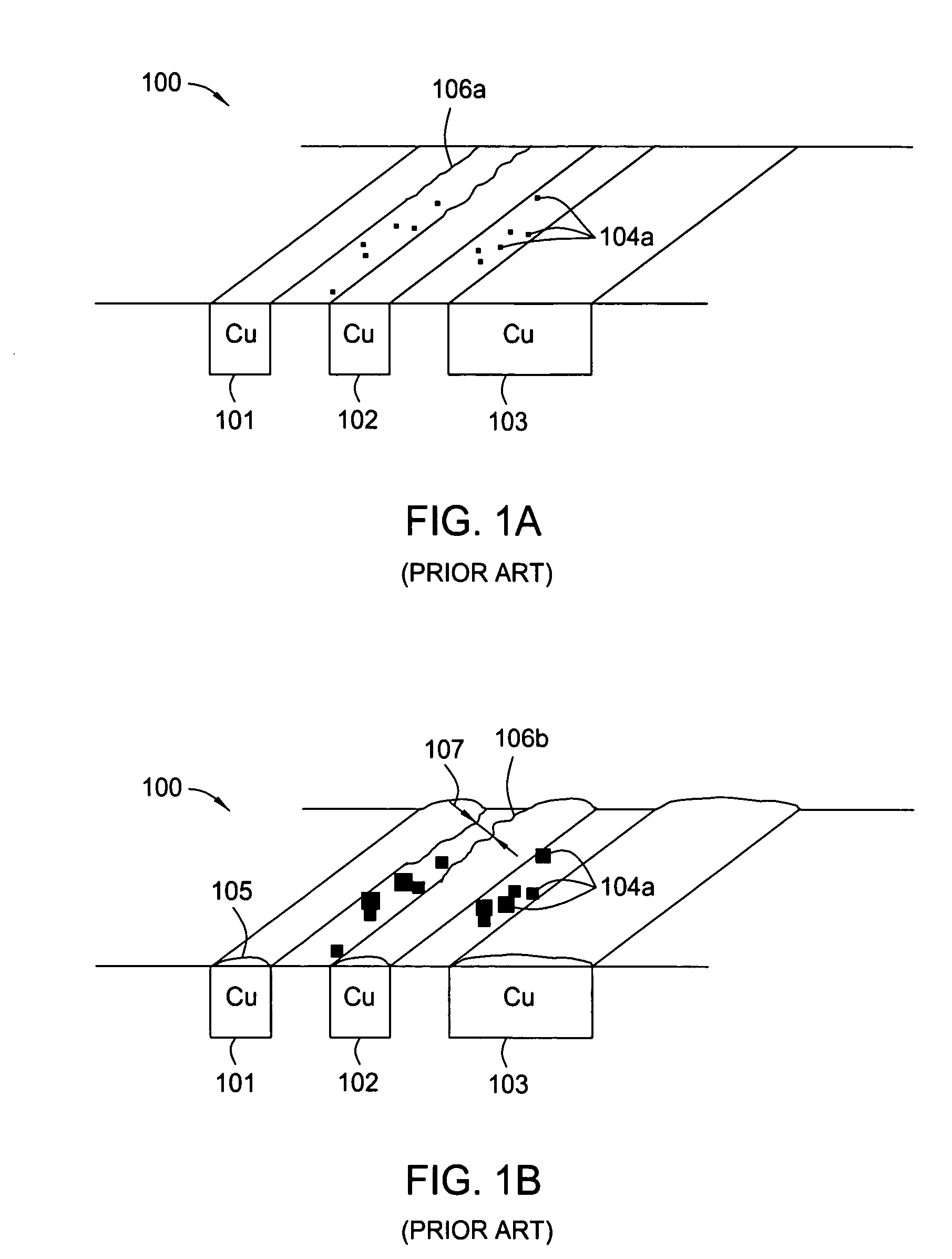

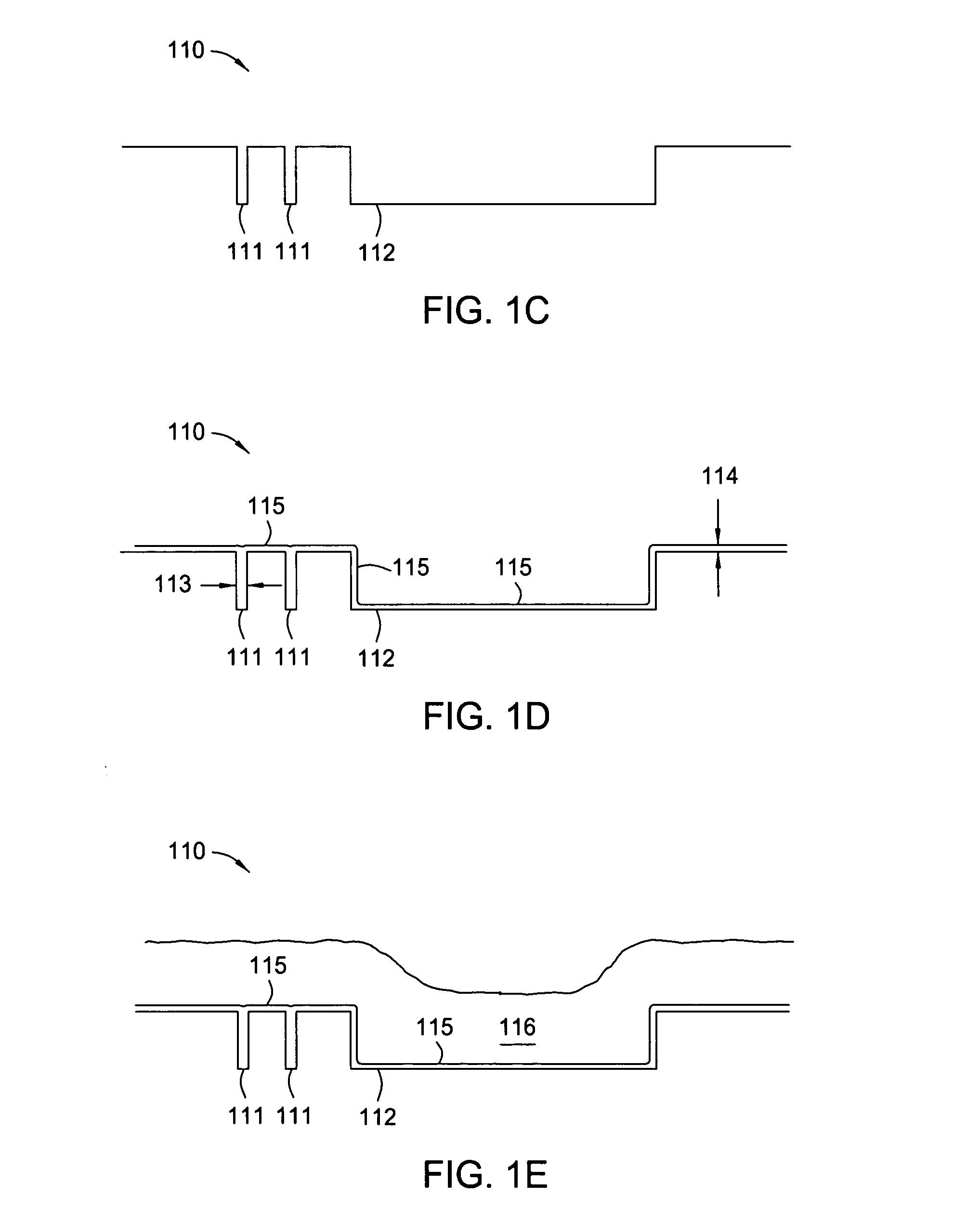

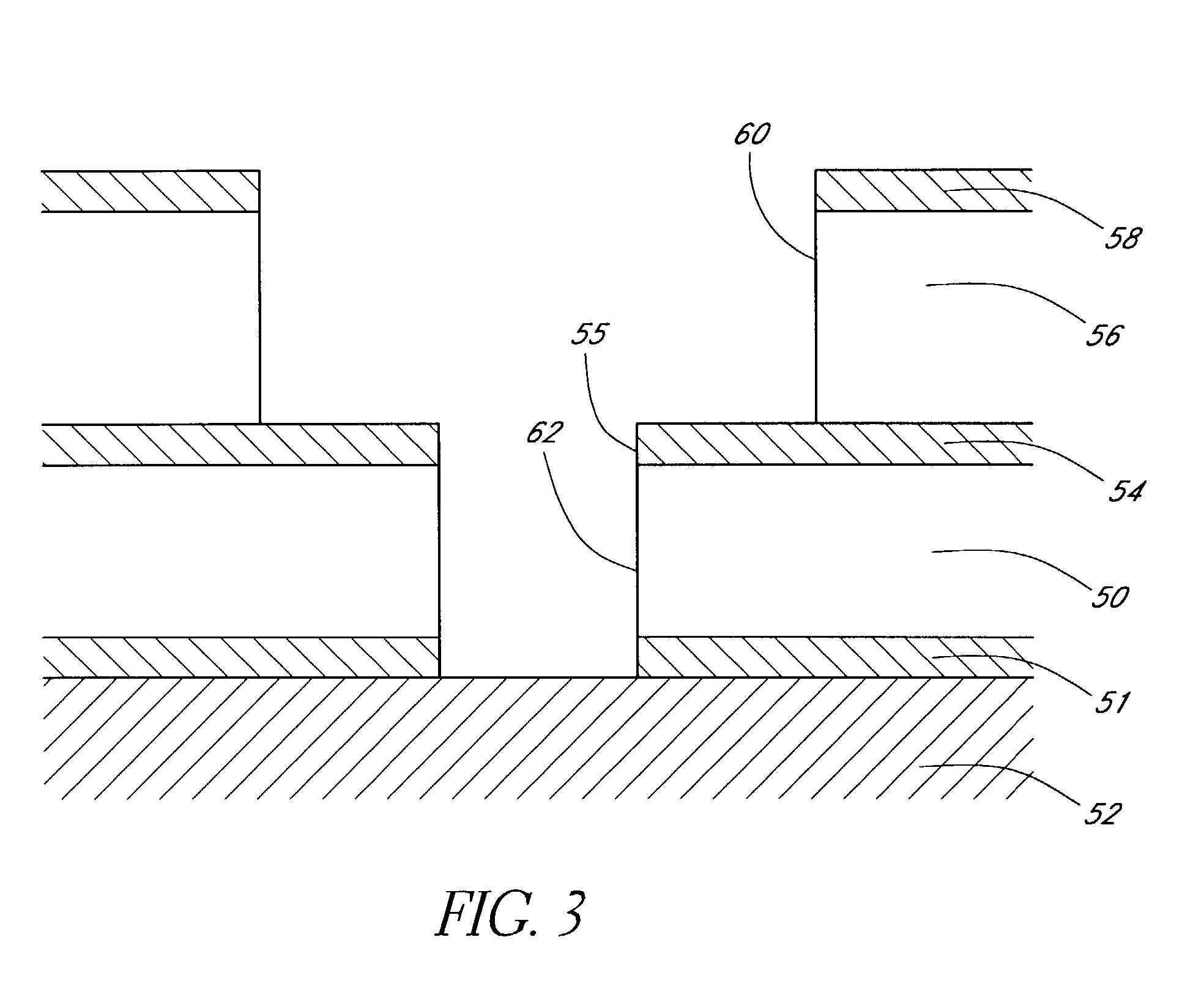

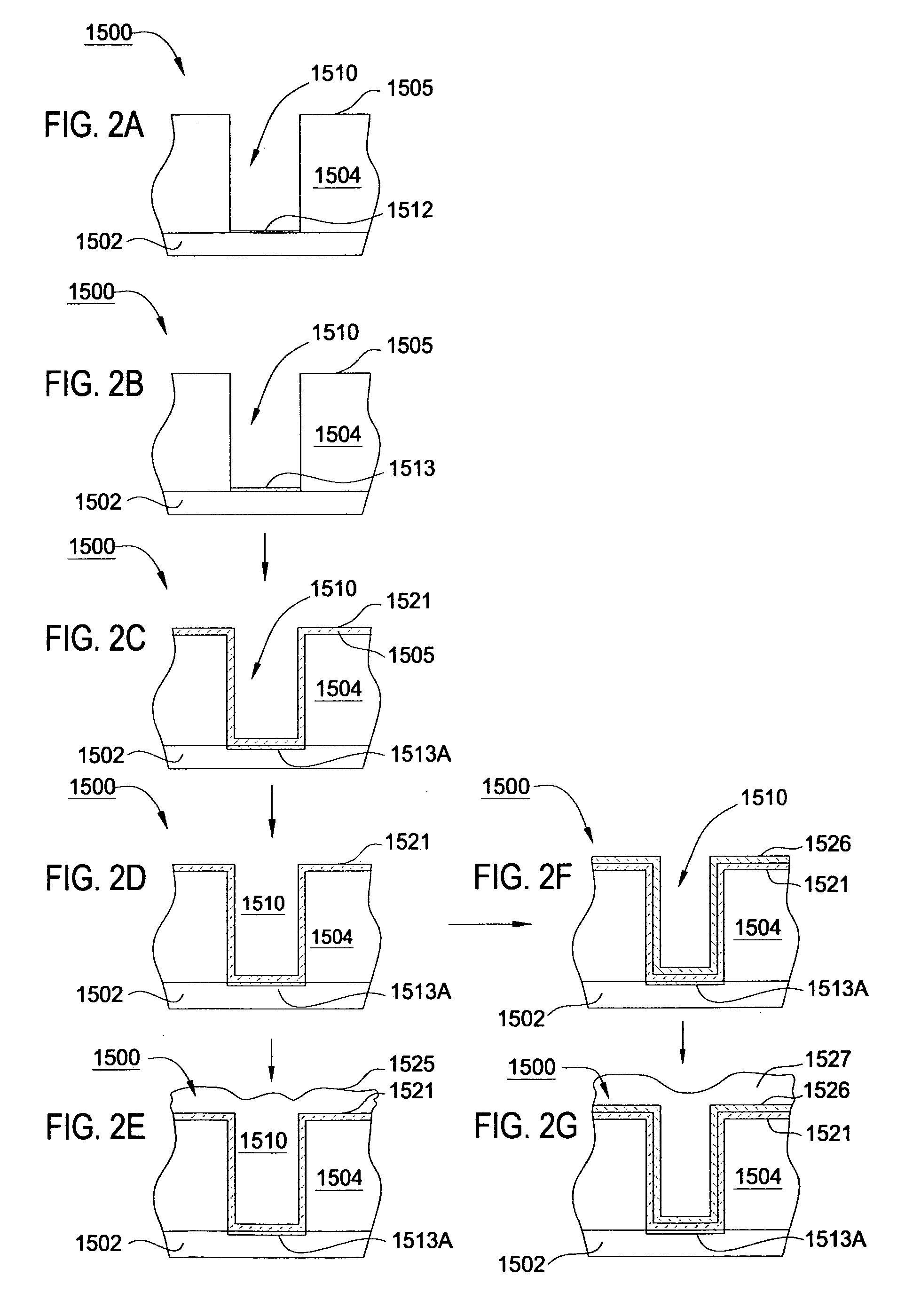

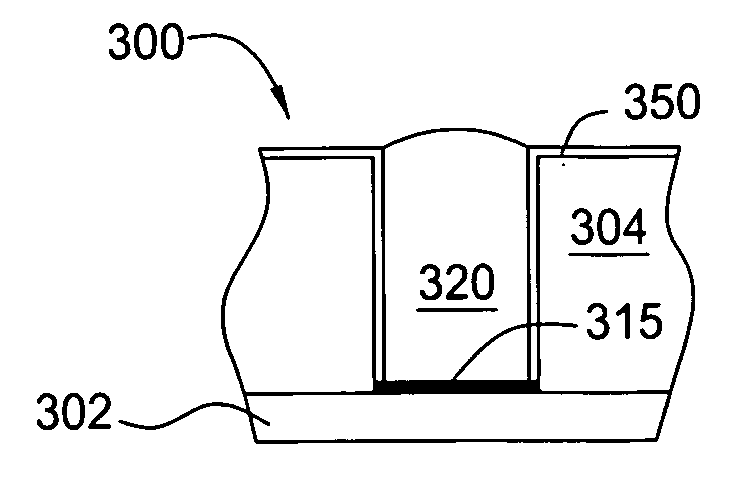

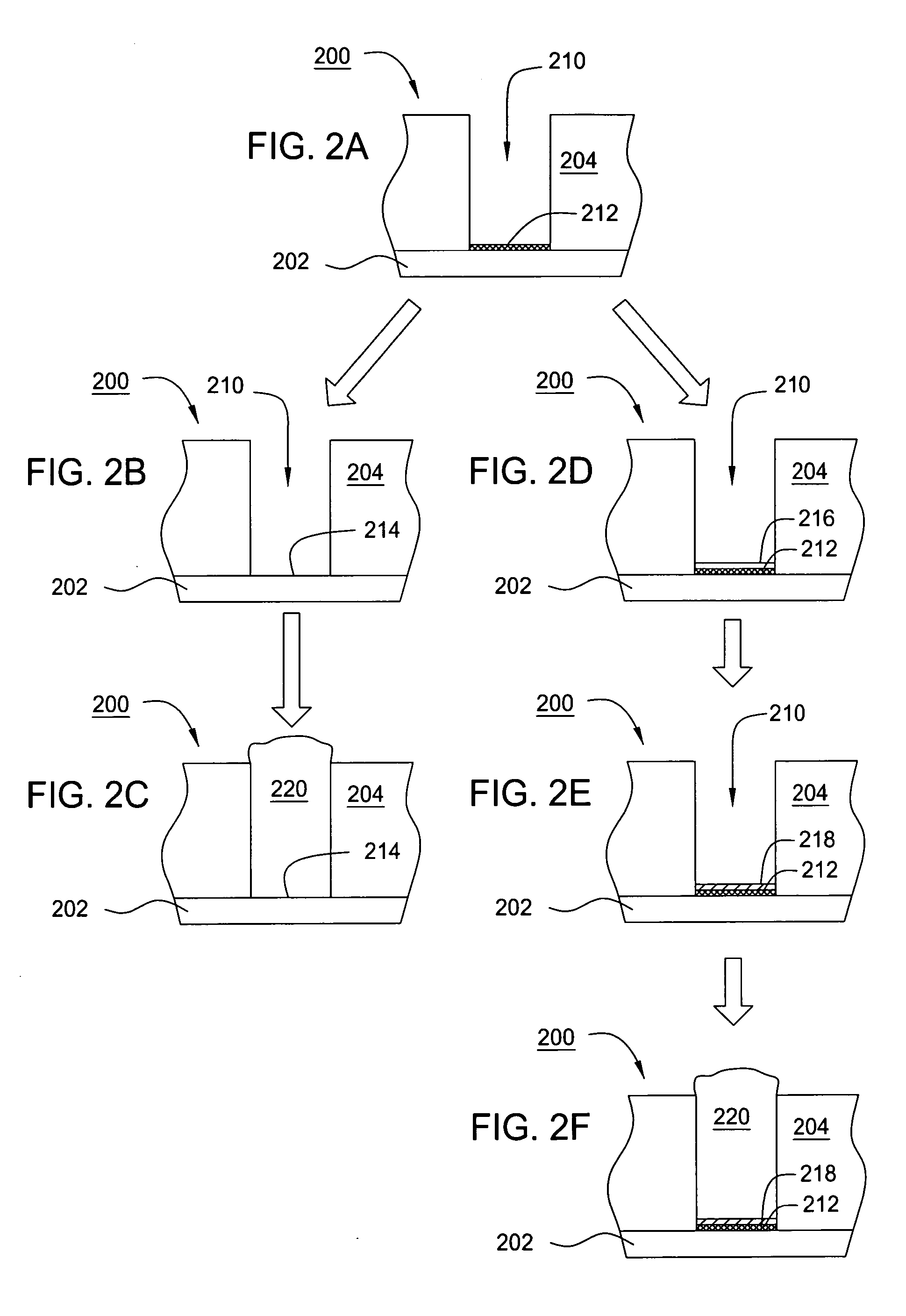

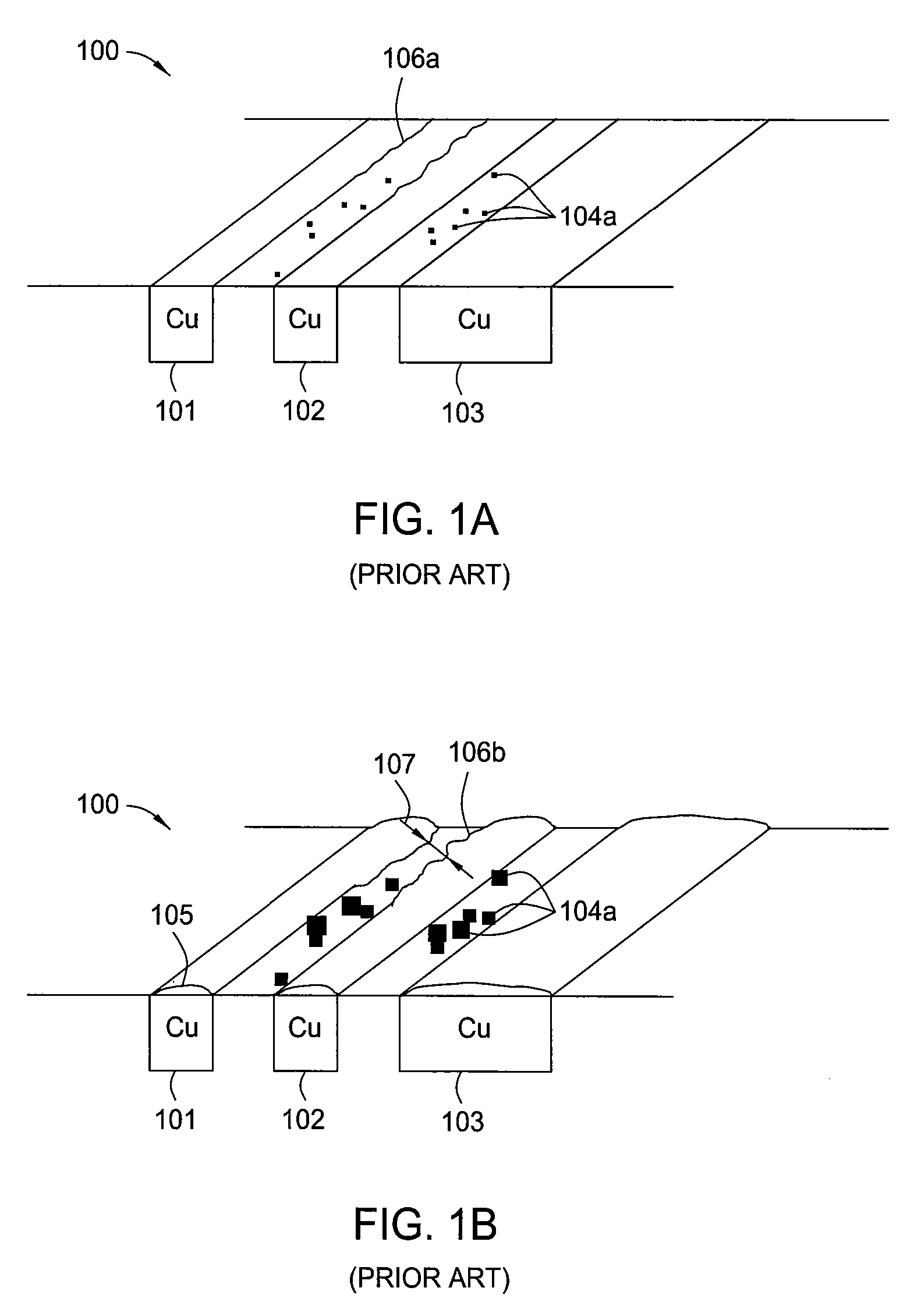

Chip interconnect and packaging deposition methods and structures

InactiveUS7147766B2Prevent removalMinimizing disparitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringConductive materials

The present invention relates to a method for fabricating high performance chip interconnects and packages by providing methods for depositing a conductive material in cavities of a substrate in a more efficient and time saving manner. This is accomplished by selectively removing portions of a seed layer from a top surface of a substrate and then depositing a conductive material in the cavities of the substrate, where portions of the seed layer remains in the cavities. Another method includes forming an oxide layer on the top surface of the substrate such that the conductive material can be deposited in the cavities without the material being formed on the top surface of the substrate. The present invention also discloses methods for forming multi-level interconnects and the corresponding structures.

Owner:NOVELLUS SYSTEMS

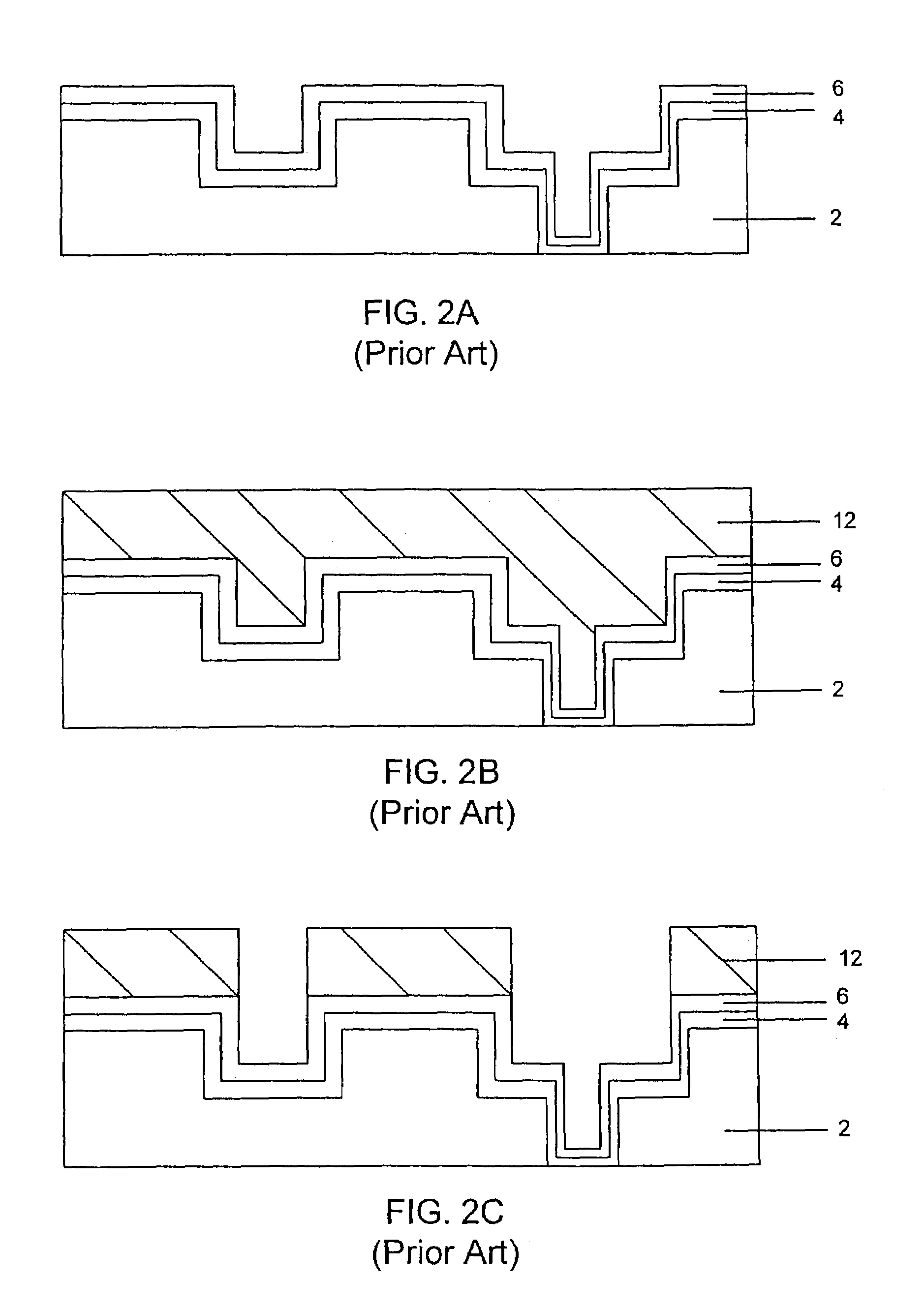

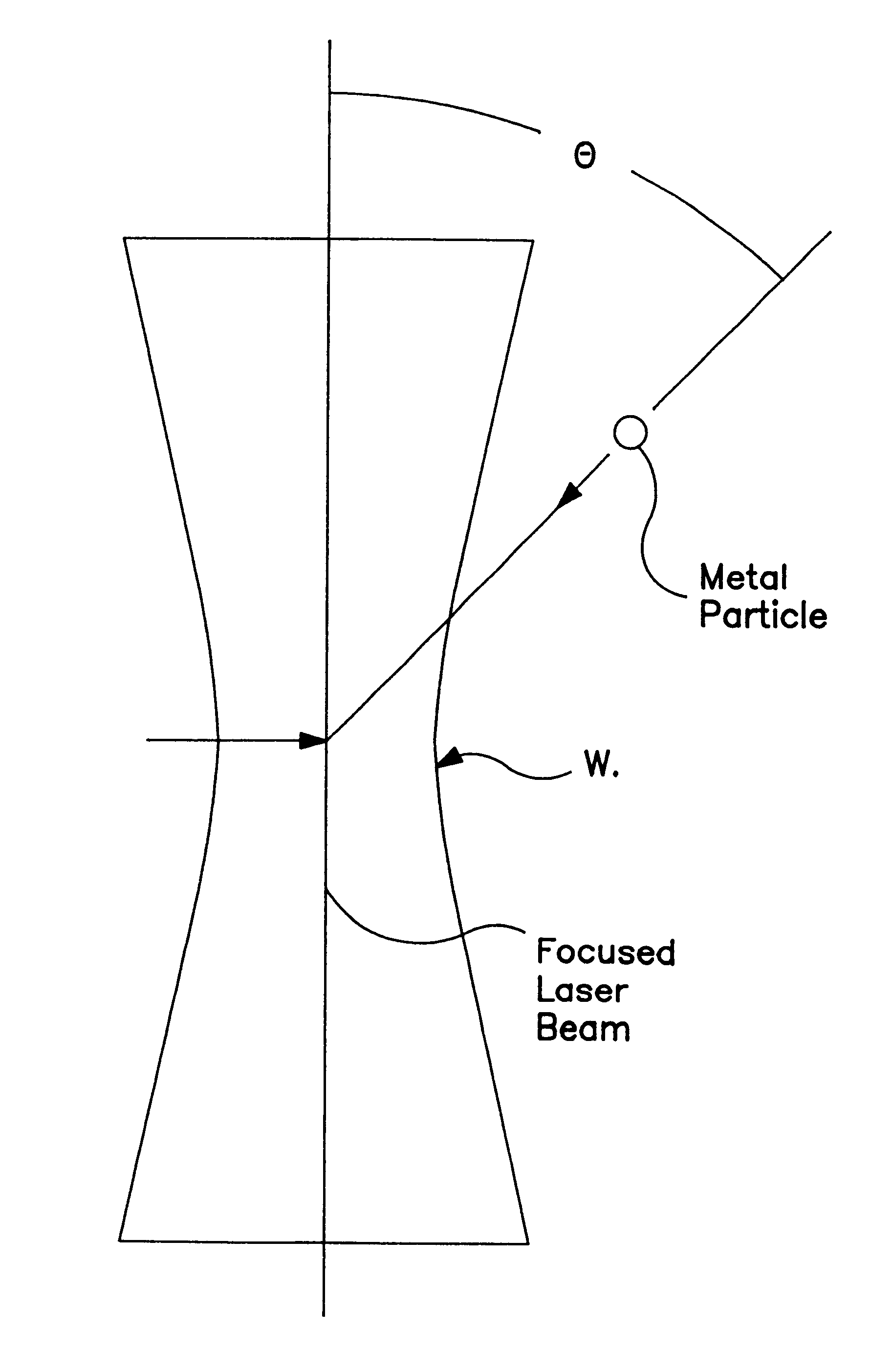

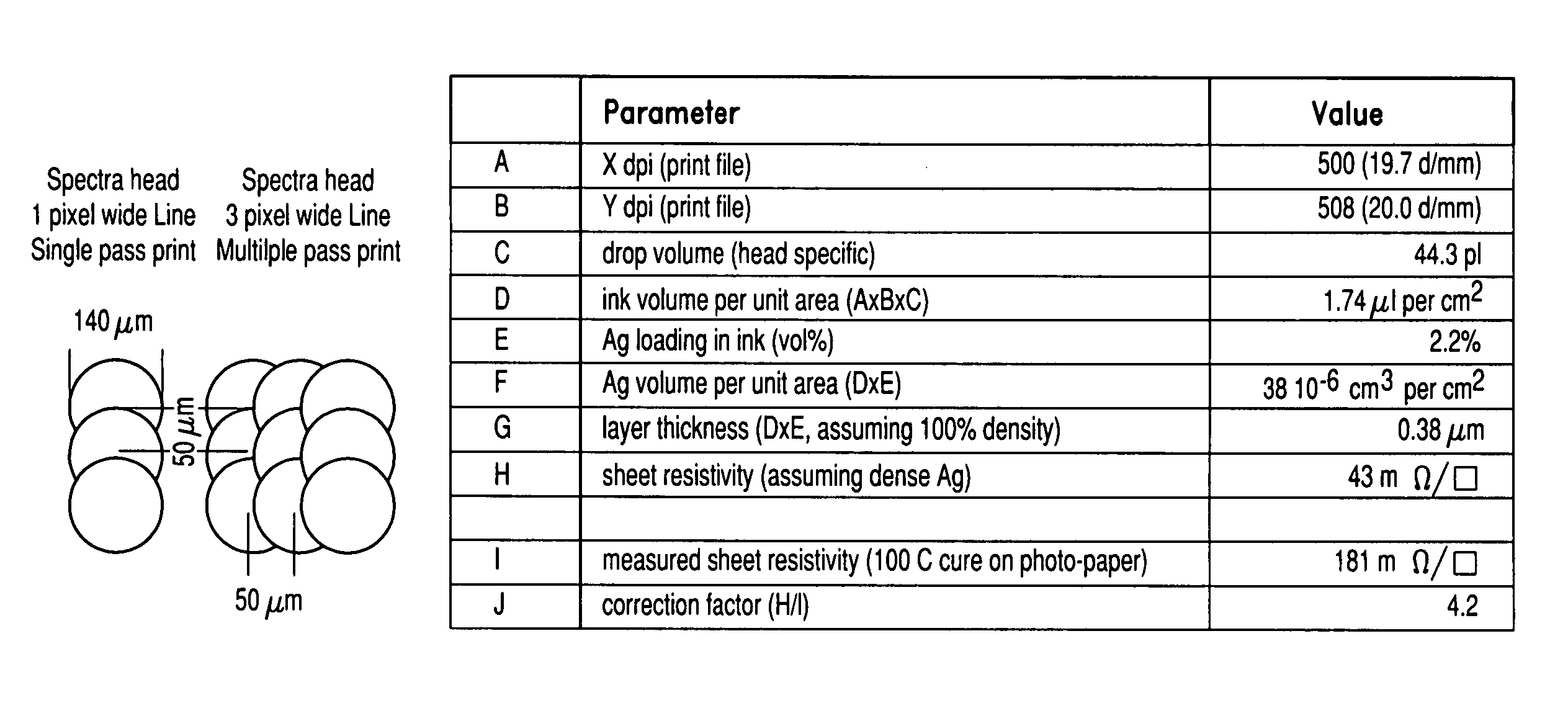

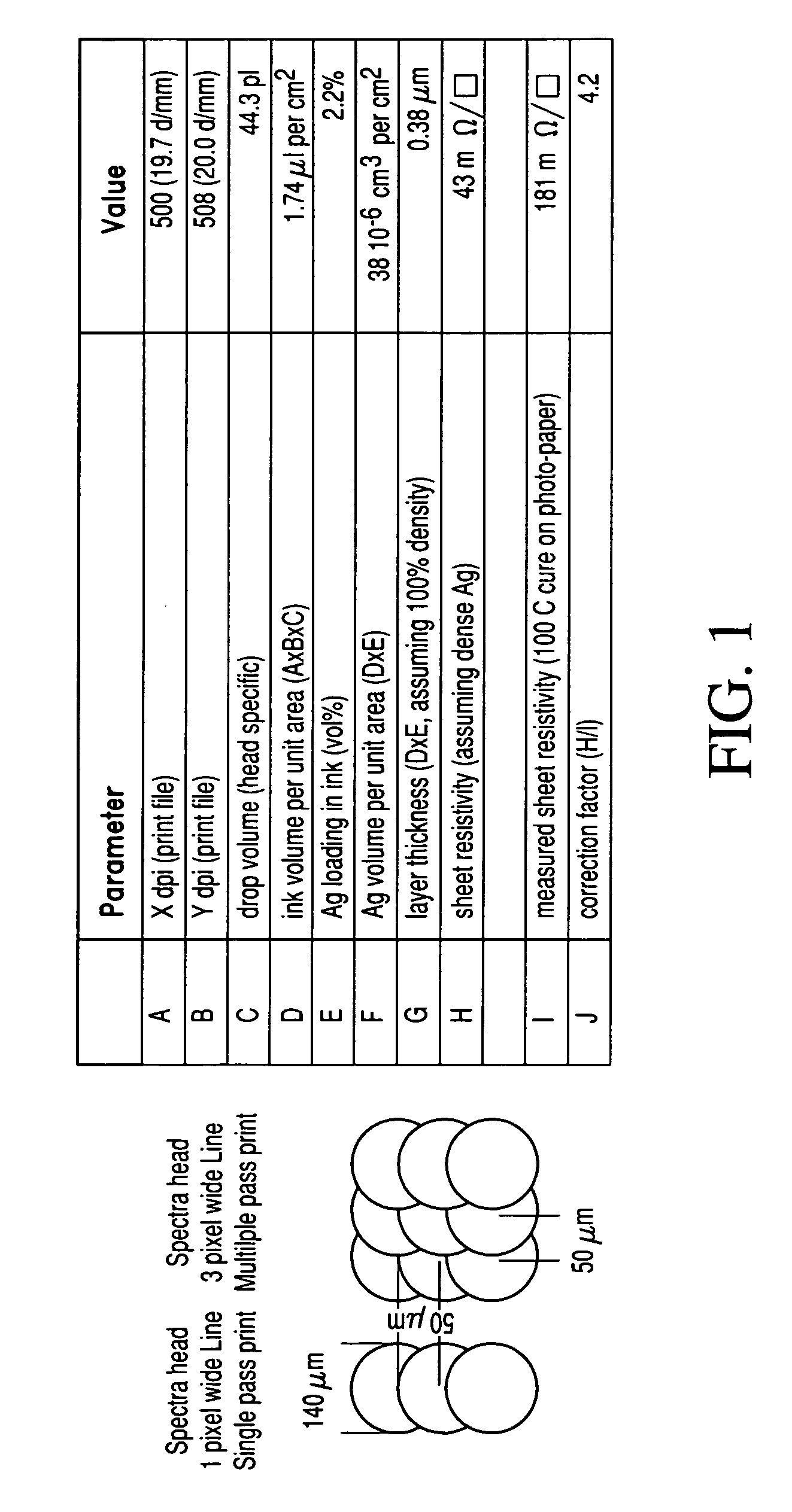

Precision spray processes for direct write electronic components

InactiveUS6251488B1Keep for a long timeIncrease probabilityMolten spray coatingVacuum evaporation coatingElectrical resistance and conductanceElectronic component

This invention combines the precision spray process with in-flight laser treatment in order to produce direct write electronic components. In addition to these components, the process can lay down lines of conductive, inductive, and resistive materials. This development has the potential to change the approach to electronics packaging. This process is revolutionary in that components can be directly produced on small structures, thus removing the need for printed circuit boards.

Owner:OPTOMEC DESIGN CO

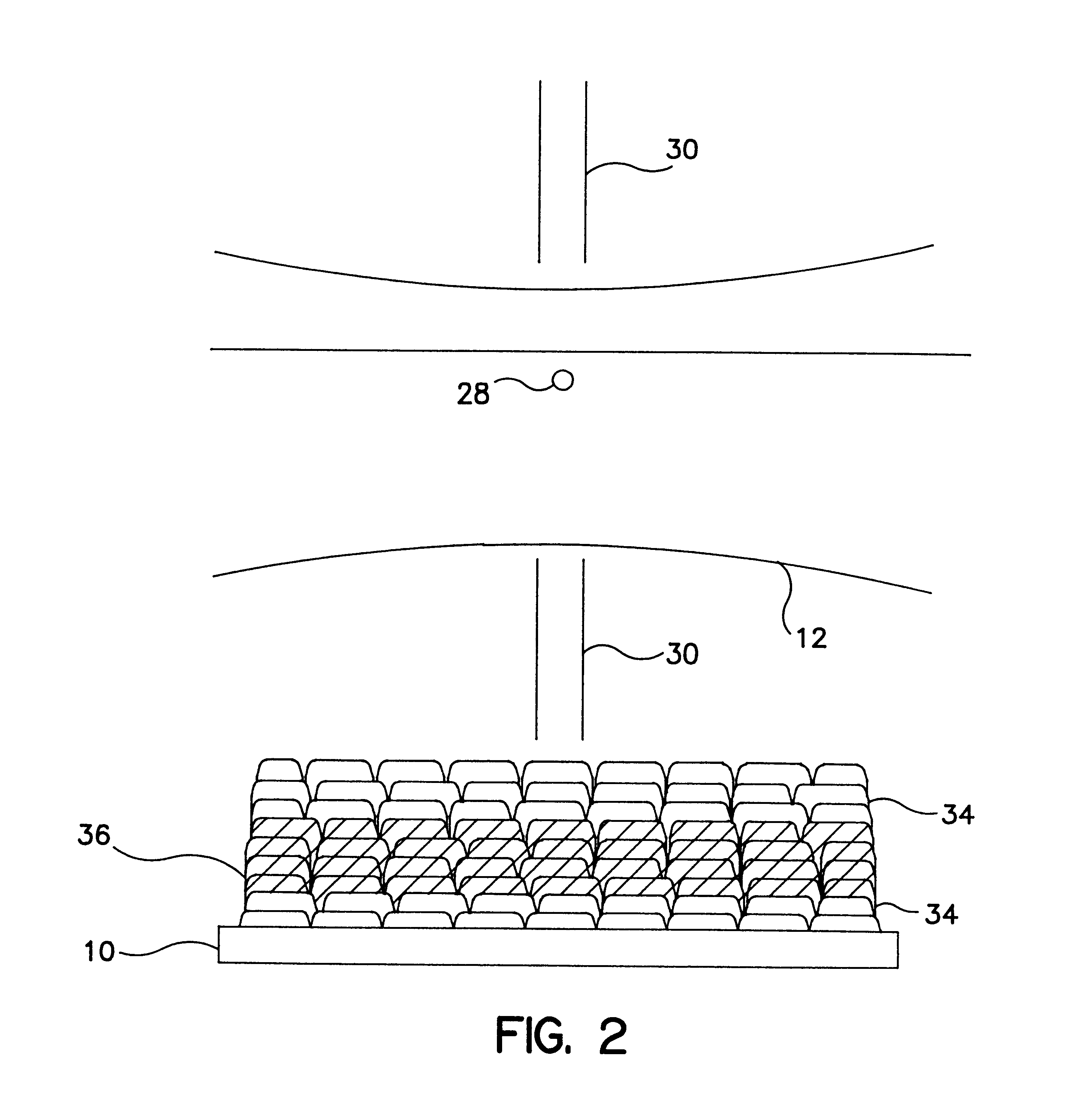

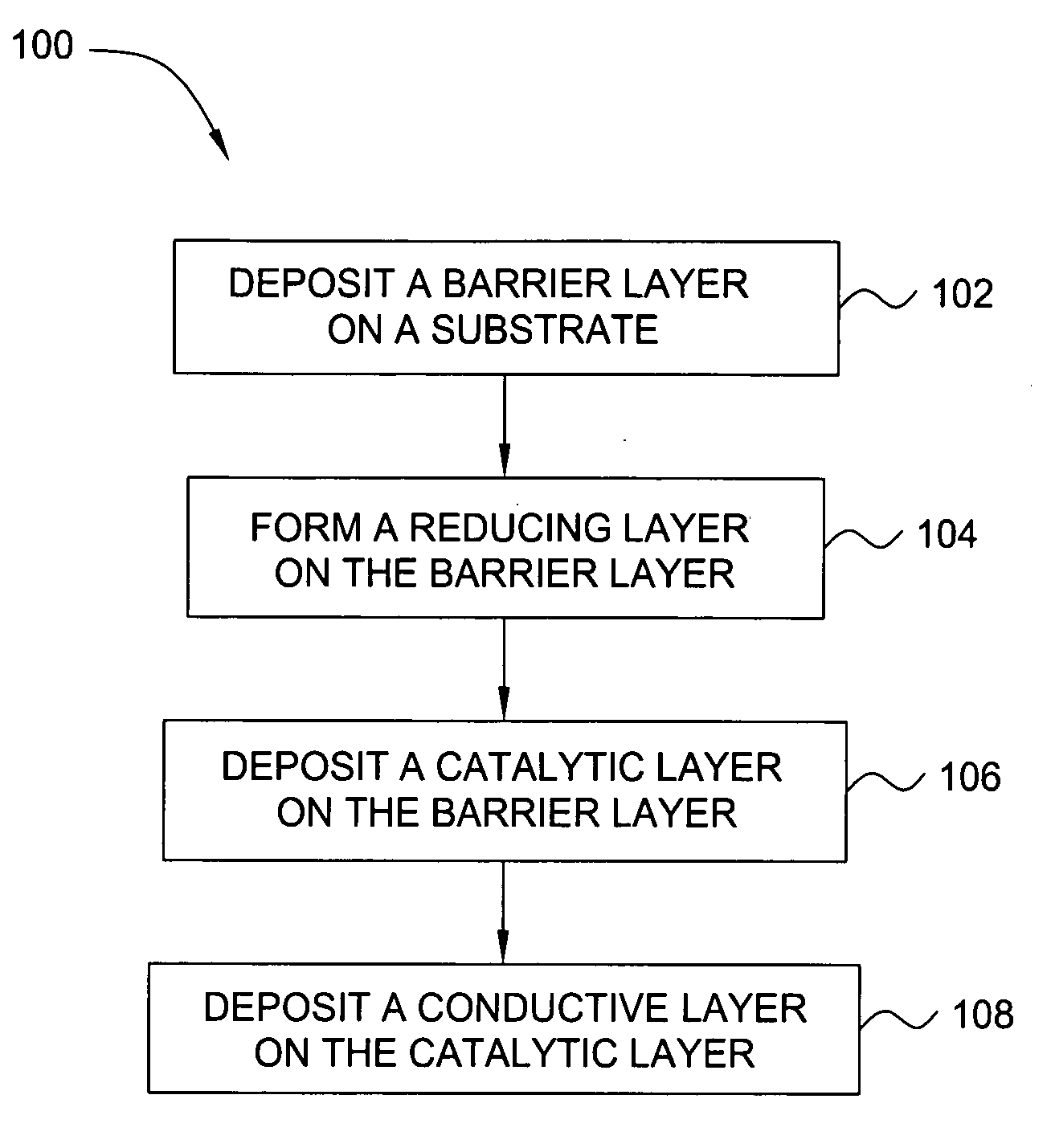

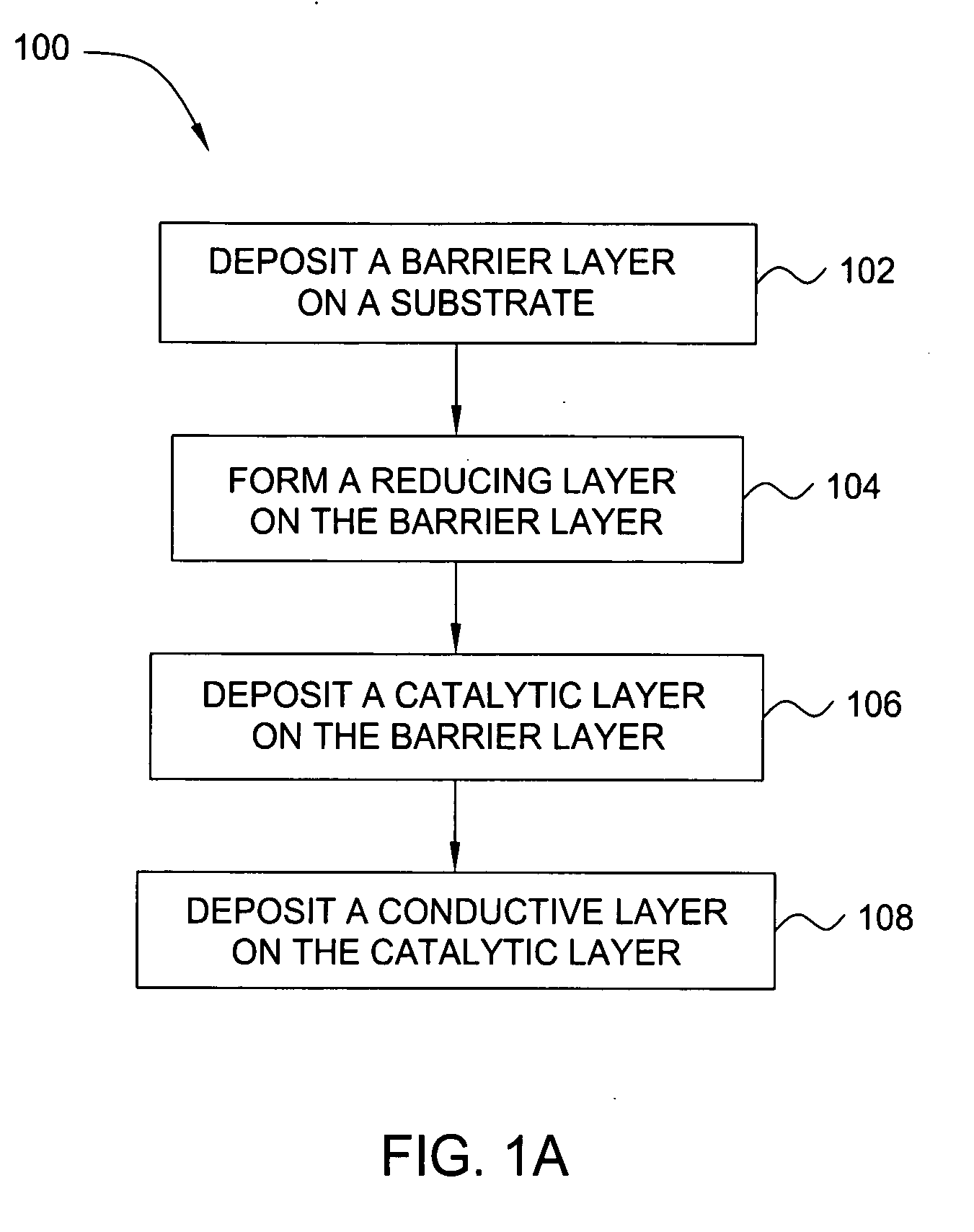

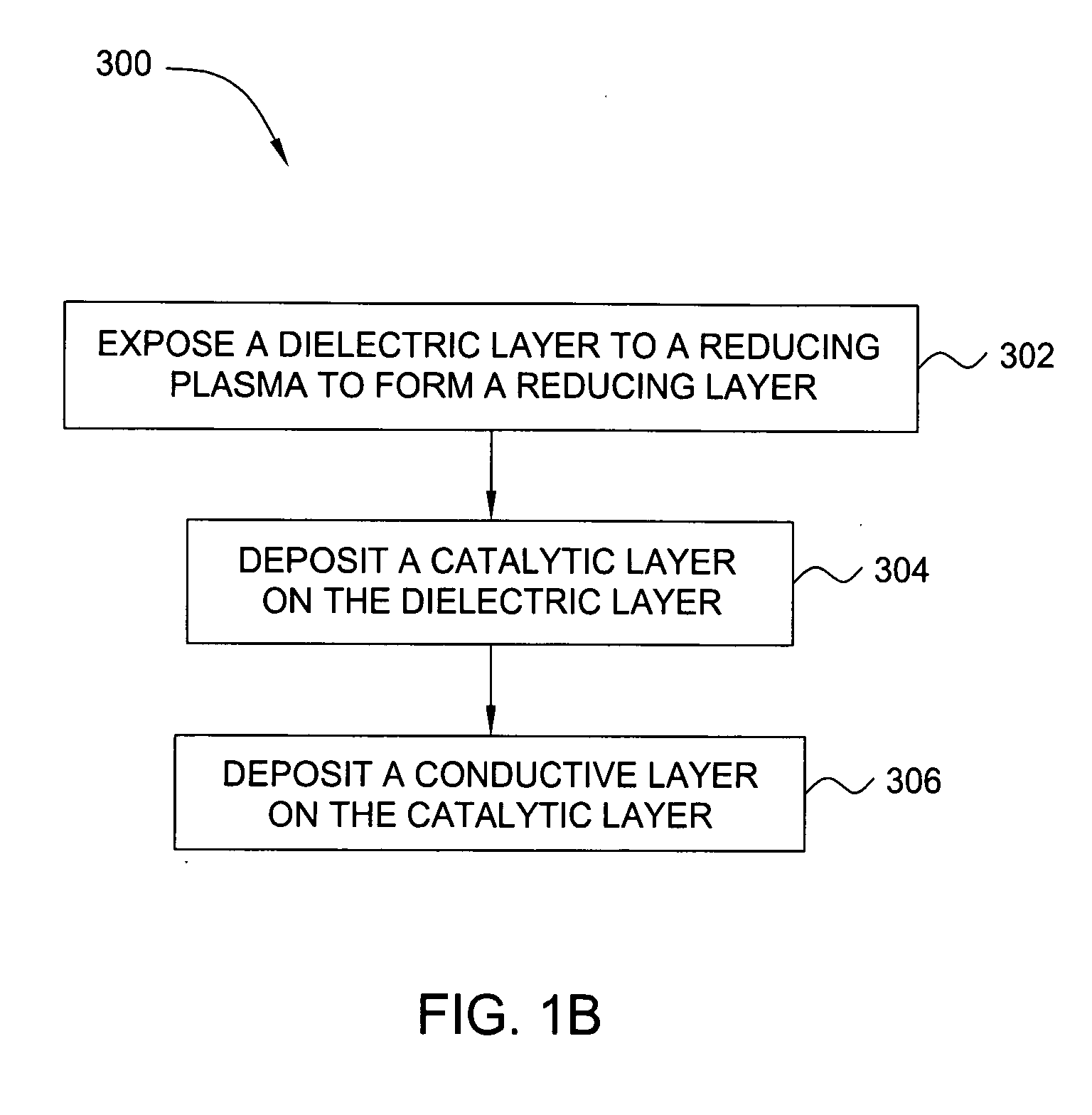

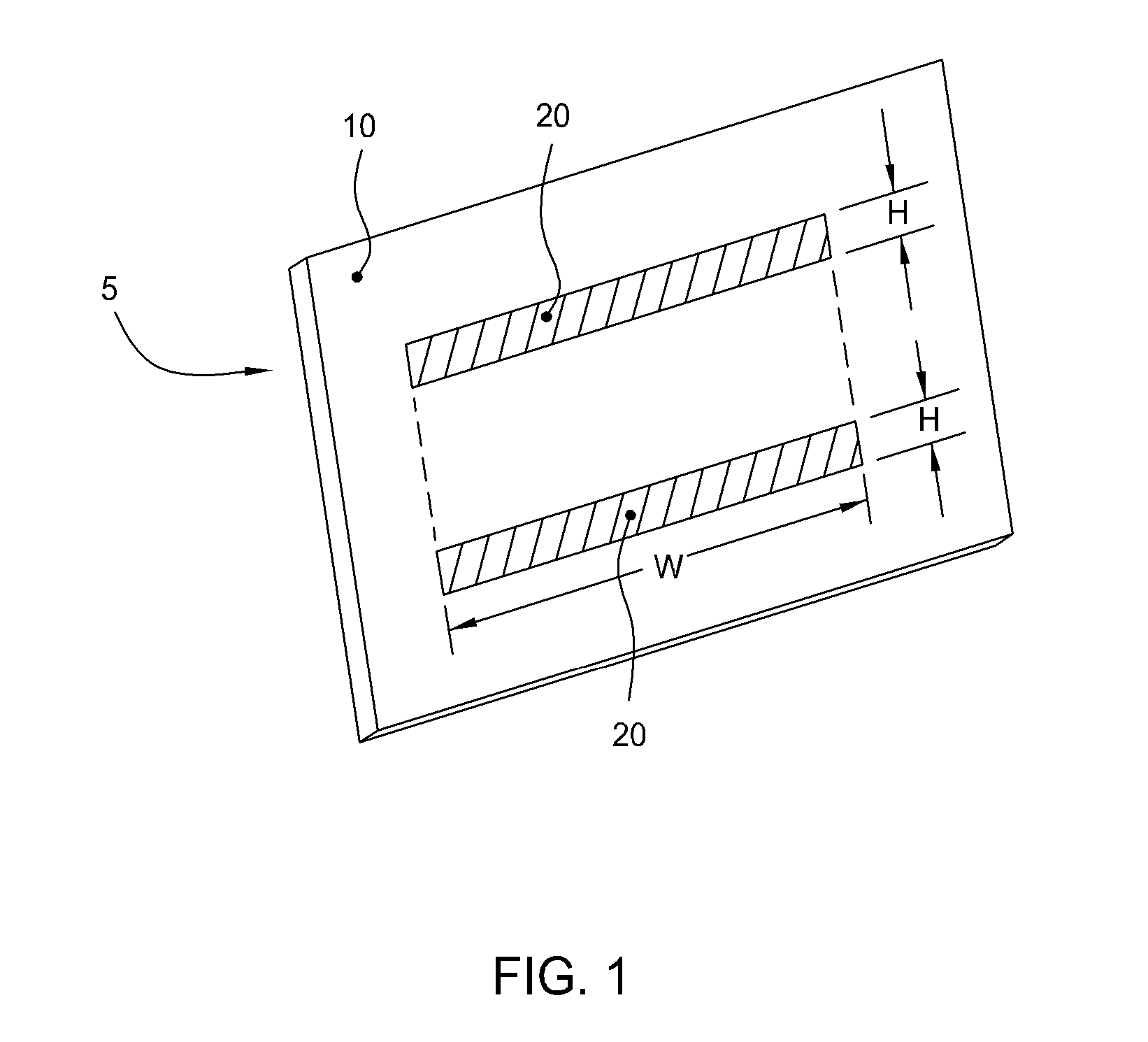

Deposition of an intermediate catalytic layer on a barrier layer for copper metallization

InactiveUS20060240187A1Solid-state devicesSemiconductor/solid-state device manufacturingIridiumSilanes

In one embodiment, a method for depositing a conductive material on a substrate is provided which includes exposing a substrate containing a barrier layer to a volatile reducing precursor to form a reducing layer during a soak process, exposing the reducing layer to a catalytic-metal precursor to deposit a catalytic metal-containing layer on the barrier layer, and depositing a conductive layer (e.g., copper) on the catalytic metal-containing layer. The volatile reducing precursor may include phosphine, diborane, silane, a plasma thereof, or a combination thereof and be exposed to the substrate for a time period within a range from about 1 second to about 30 seconds during the soak process. The catalytic metal-containing layer may contain ruthenium, cobalt, rhodium, iridium, nickel, palladium, platinum, silver, or copper. In one example, the catalytic metal-containing layer is deposited by a vapor deposition process utilizing ruthenium tetroxide formed by an in situ process.

Owner:APPLIED MATERIALS INC

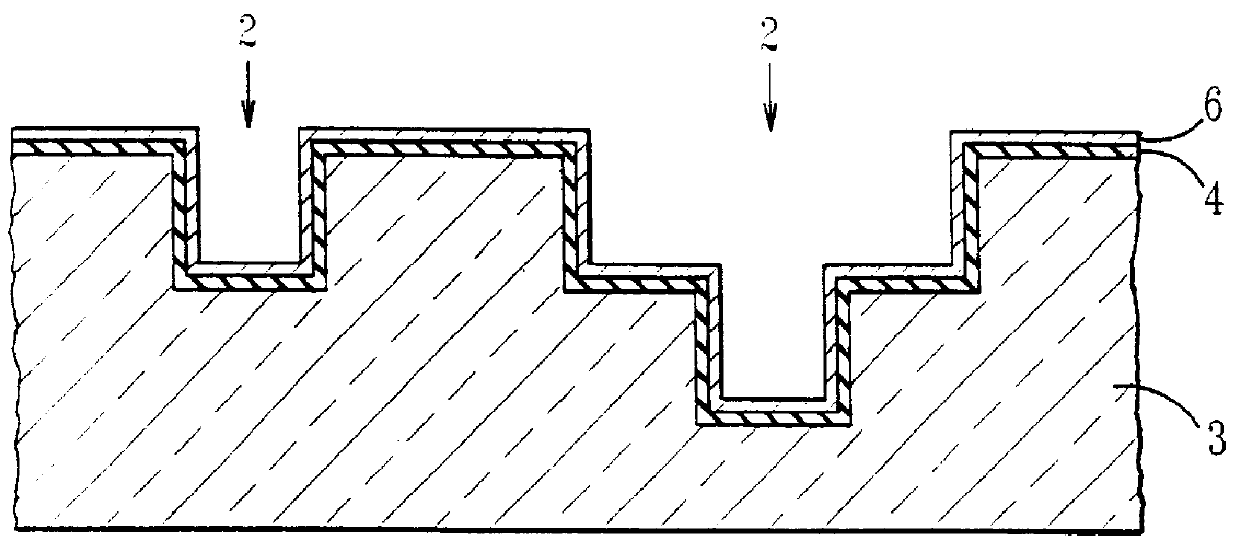

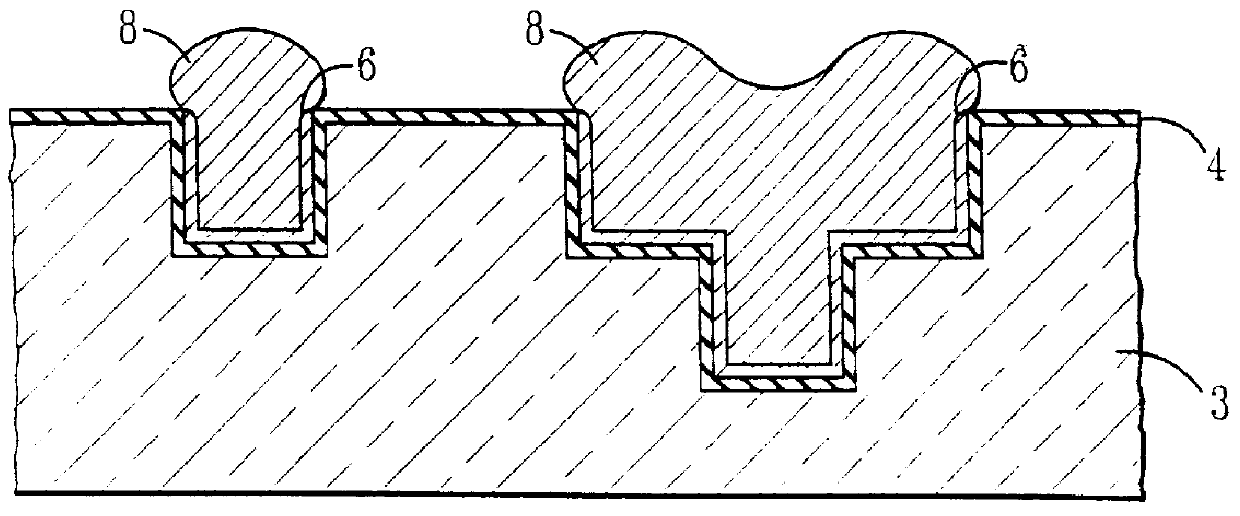

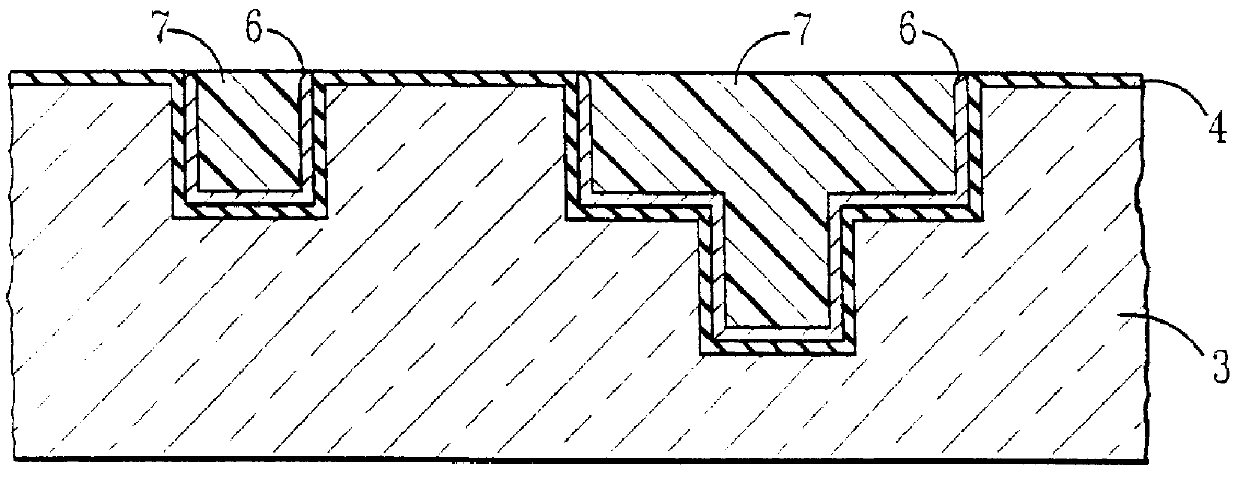

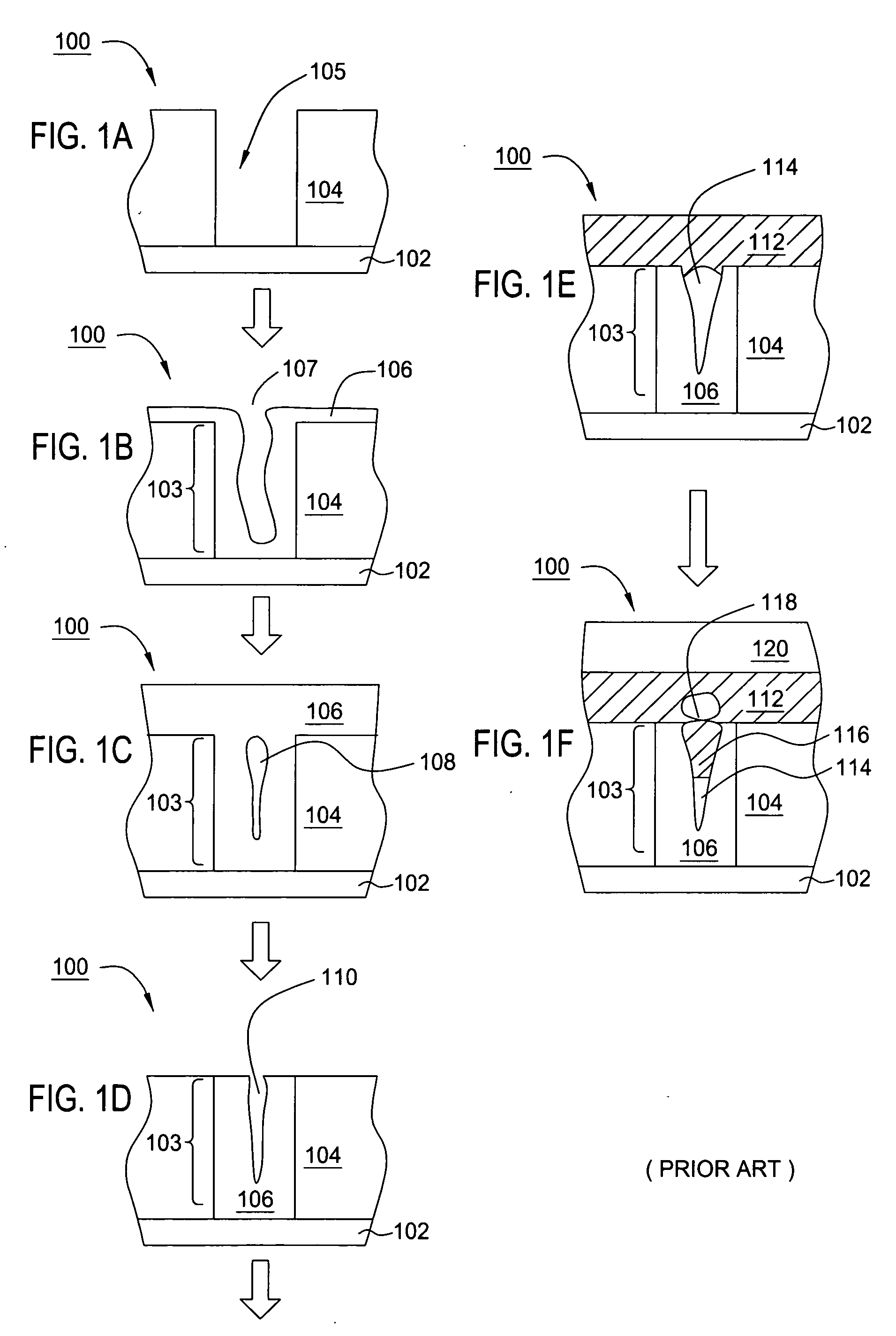

Method to selectively fill recesses with conductive metal

InactiveUS6140234AShorten the timeIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor structure

Recesses in a semiconductor structure are selectively plated by providing electrical insulating layer over the semiconductor substrate and in the recesses followed by forming a conductive barrier over the insulating layer; providing a plating seed layer over the barrier layer; depositing and patterning a photoresist layer over the plating seed layer; planarizing the insulated horizontal portions by removing the horizontal portions of the seed layer between the recesses; removing the photoresist remaining in the recesses; and then electroplating the patterned seed layer with a conductive metal using the barrier layer to carry the current during the electroplating to thereby only plate on the seed layer. In an alternative process, a barrier film is deposited over recesses in an insulator. Then, relatively thick resists are lithographically defined on the field regions, on top of the barrier film over the recesses. A plating base or seedlayer is deposited, so as to be continuous on the horizontal regions of the recesses in the insulator, but discontinuous on their surround wall. The recesses are then plated using the barrier film without seedlayers at the periphery of the substrate wafers for electrical contact. After electroplating, the resist is removed by lift-off process and exposed barrier film is etched by RIE method or by CMP. Also provided is a semiconductor structure obtained by the above processes.

Owner:GLOBALFOUNDRIES INC

Metal nitride carbide deposition by ALD

InactiveUS7410666B2Material nanotechnologySemiconductor/solid-state device detailsHydrogen halideCorrosive chemical

Owner:ASM INTERNATIONAL

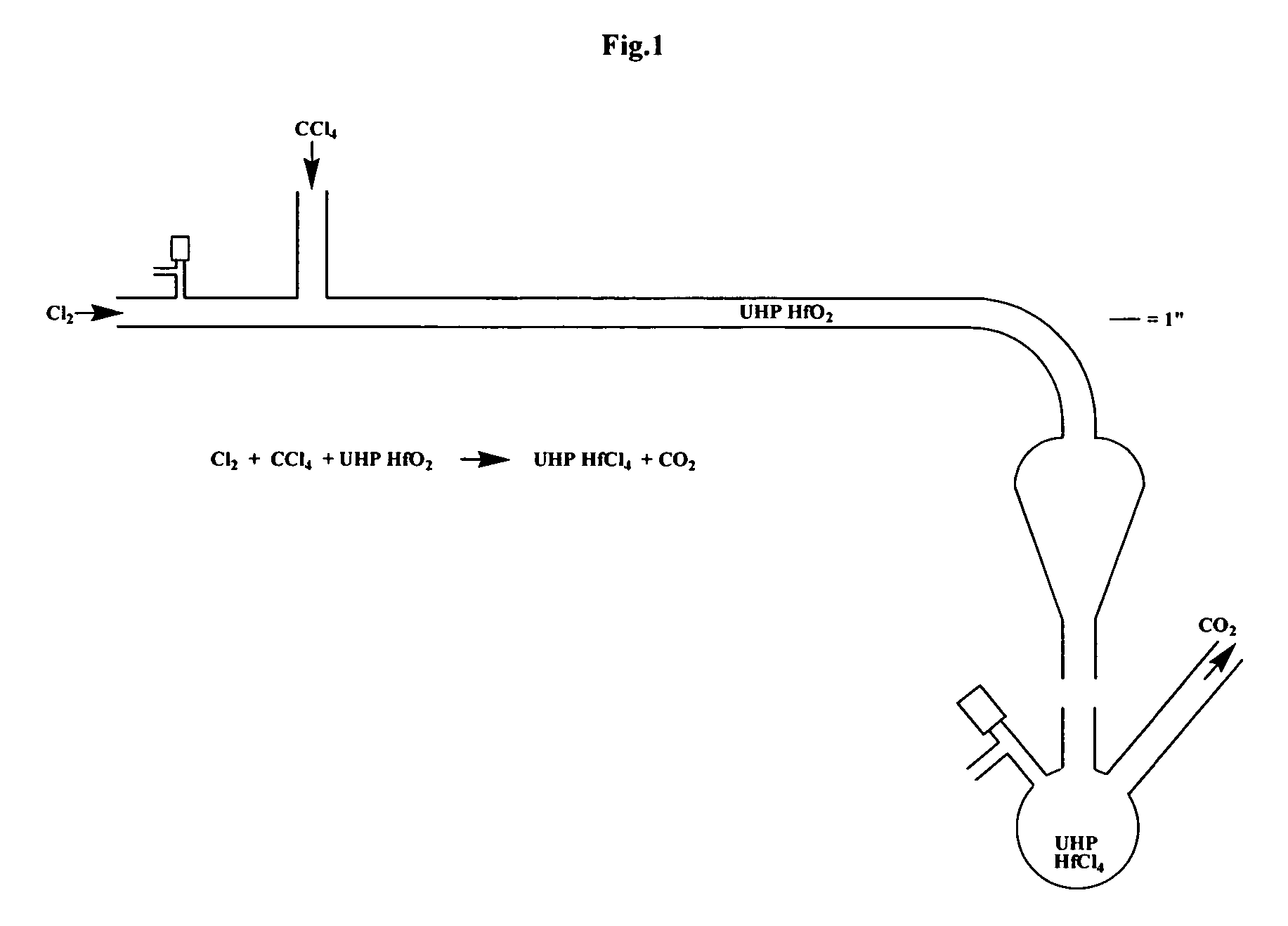

Low zirconium hafnium halide compositions

InactiveUS20050214458A1Improve smoothnessShort incubation timeSemiconductor/solid-state device manufacturingTitanium organic compoundsGas phaseHafnium

This invention relates to hafnium halide compositions having a zirconium concentration of less than about 1000 parts per million, a process for producing the hafnium halide compositions having a zirconium concentration of less than about 1000 parts per million, organometallic compound precursors, a process for producing the organometallic compound precursors, and a method for producing a film or coating from the organometallic compound precursors. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:PRAXAIR INC

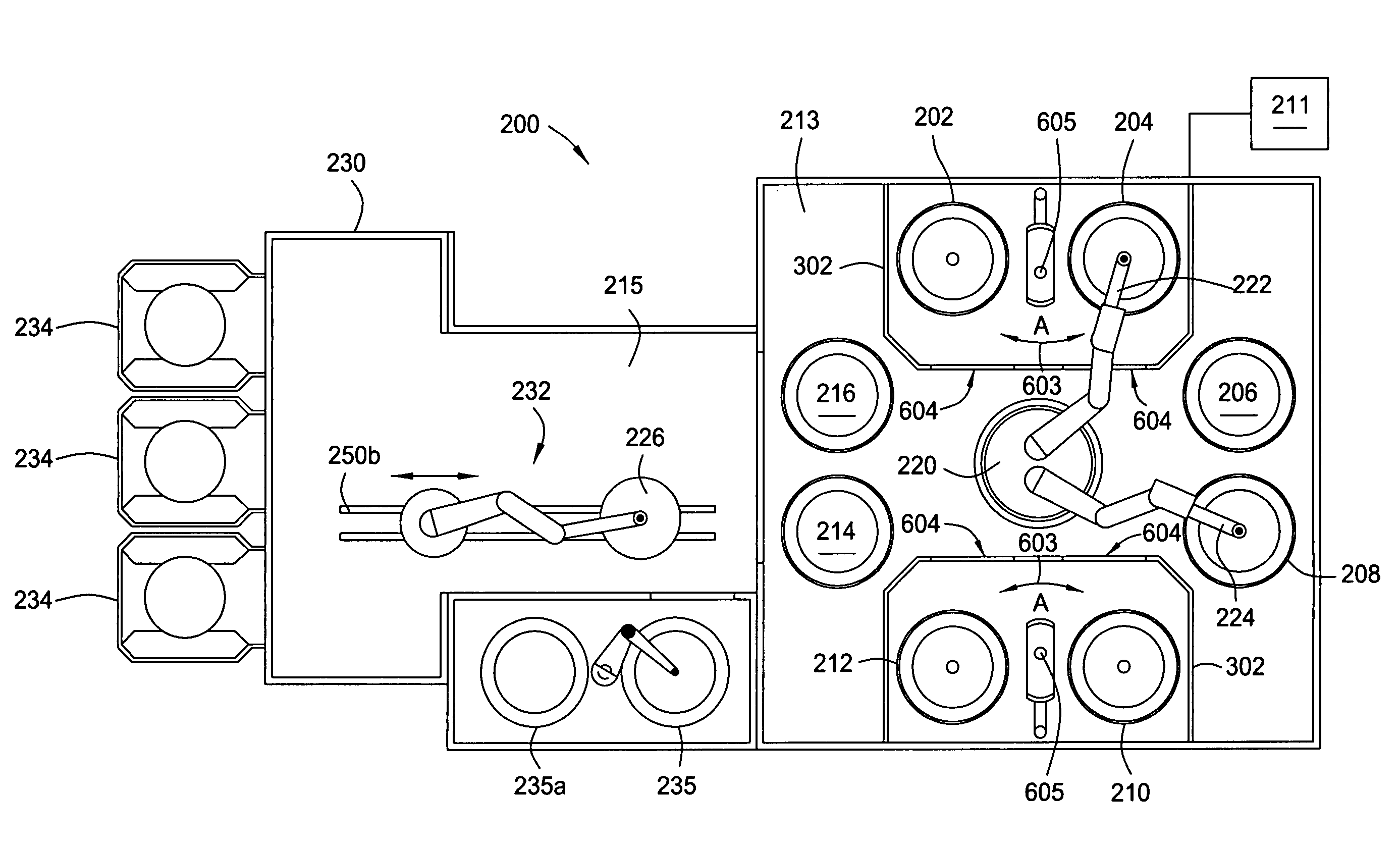

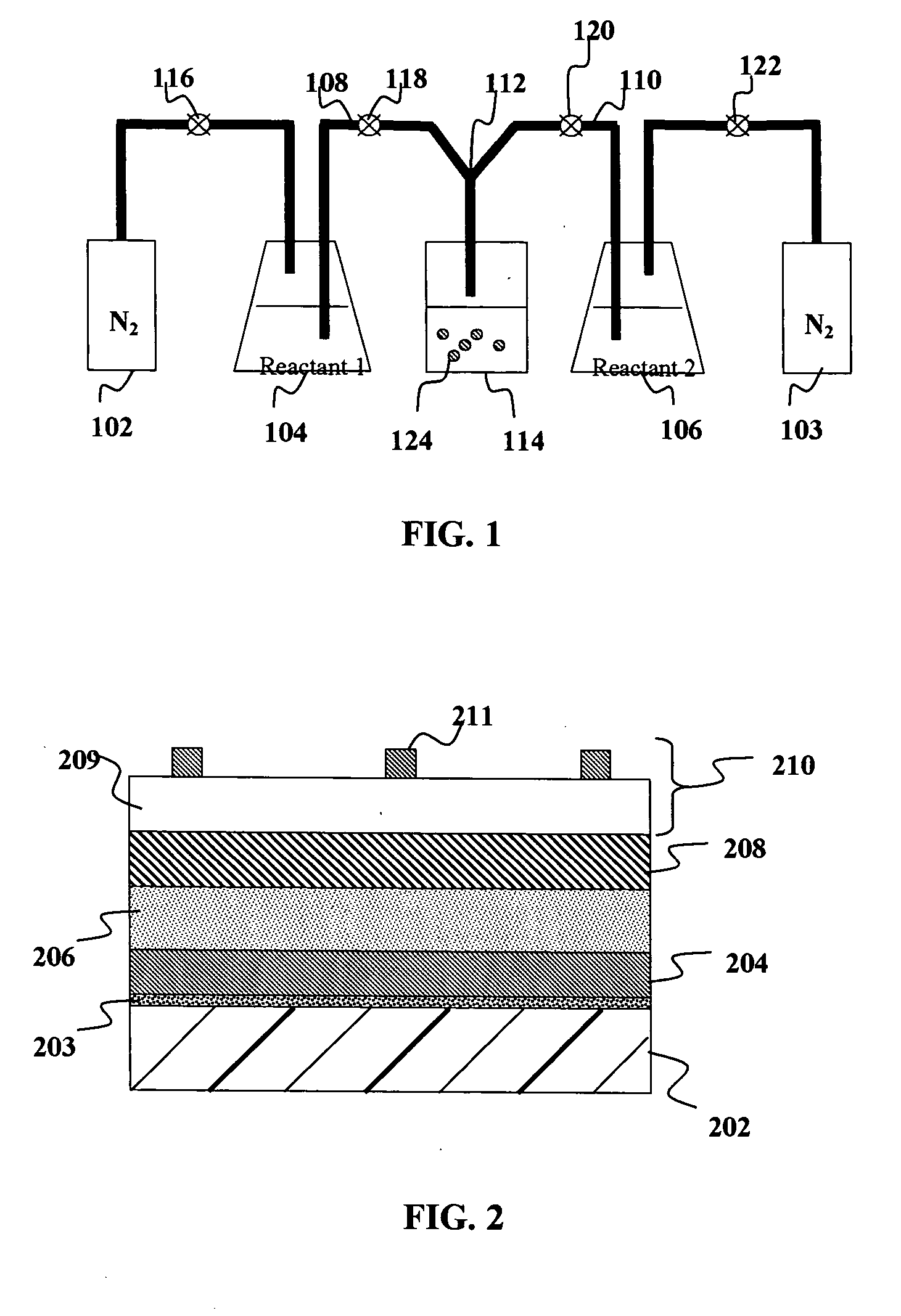

Integrated electroless deposition system

InactiveUS20060033678A1Static indicating devicesSemiconductor/solid-state device manufacturingRutheniumEngineering

Embodiments of the invention provide a cluster tool configured to deposit a material onto a substrate surface by using one or more electroless, electrochemical plating, CVD and / or ALD processing chambers. In one aspect, a ruthenium-containing catalytic layer is formed. Embodiments of the invention provide a hybrid deposition system configured to deposit a seed layer on a substrate with an electroless process and to subsequently fill interconnect features on the substrate with an ECP cell. Other aspects provide an electroless deposition system configured to deposit a seed layer on a substrate, fill interconnect features on a substrate, or sequentially deposit both a seed layer and fill interconnect features on the substrate. One embodiment provides an electroless deposition system configured to form a capping layer over substrate interconnects. The system includes a vapor dryer for pre- and post-deposition cleaning of substrates as well as a brush box chamber for post-deposition cleaning.

Owner:APPLIED MATERIALS INC

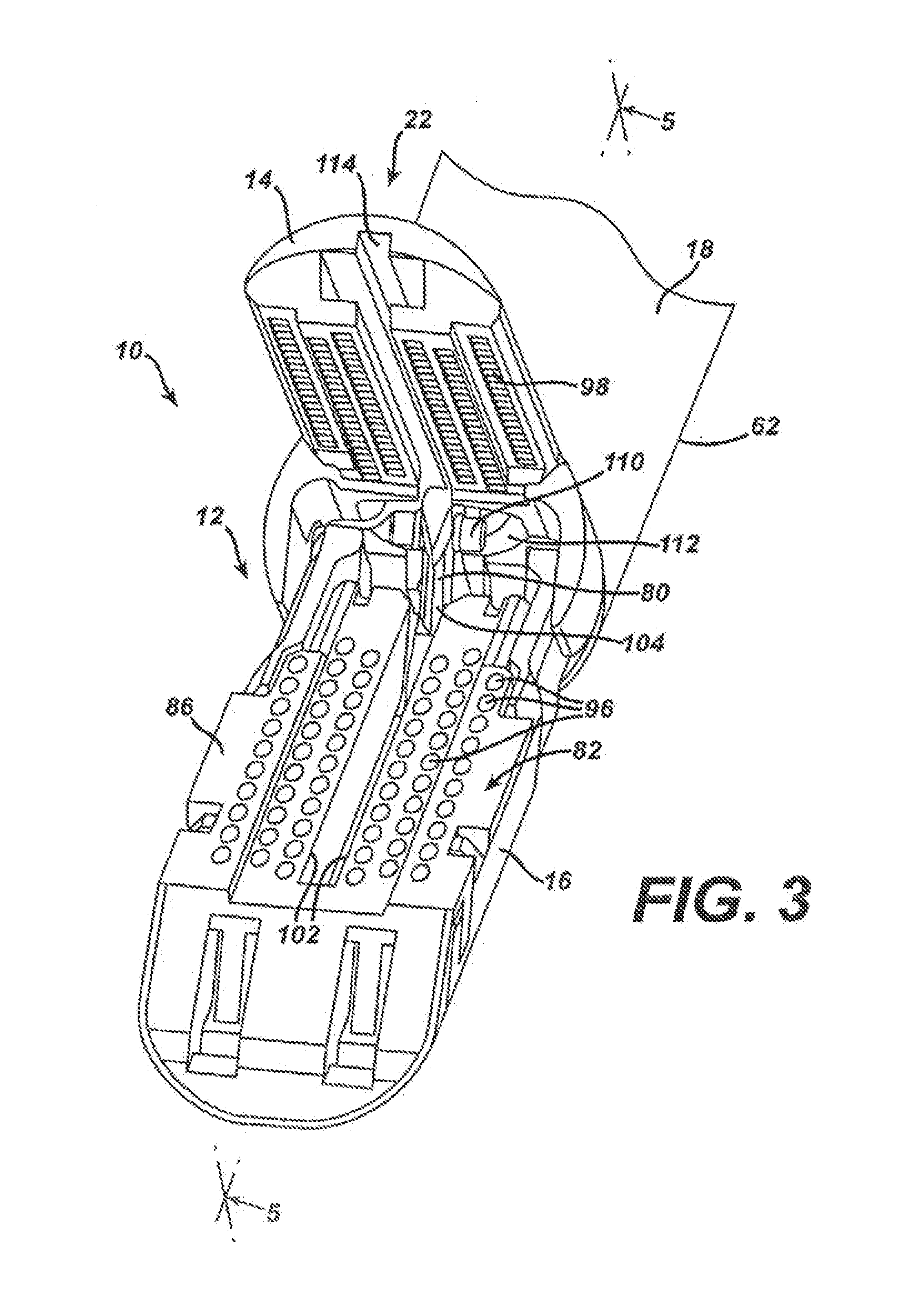

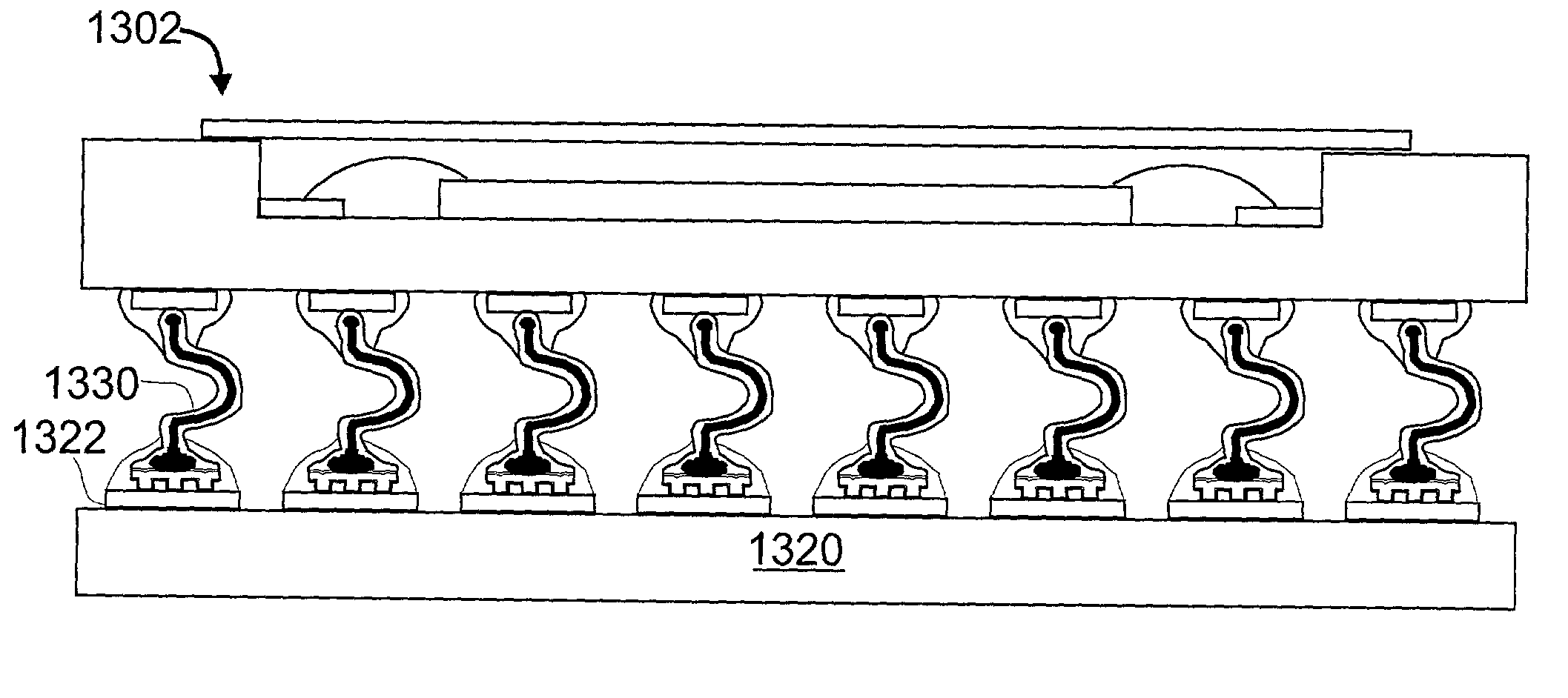

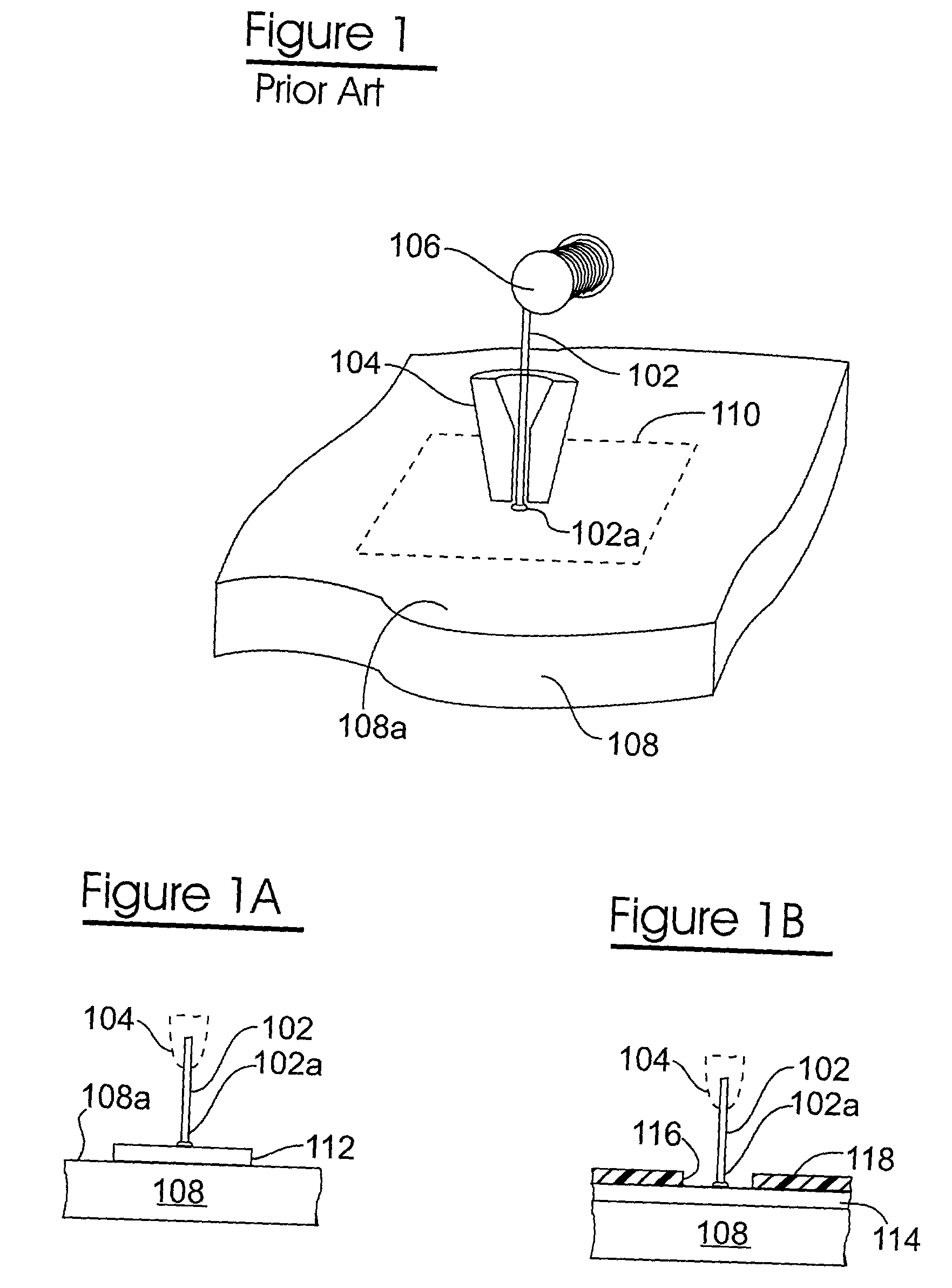

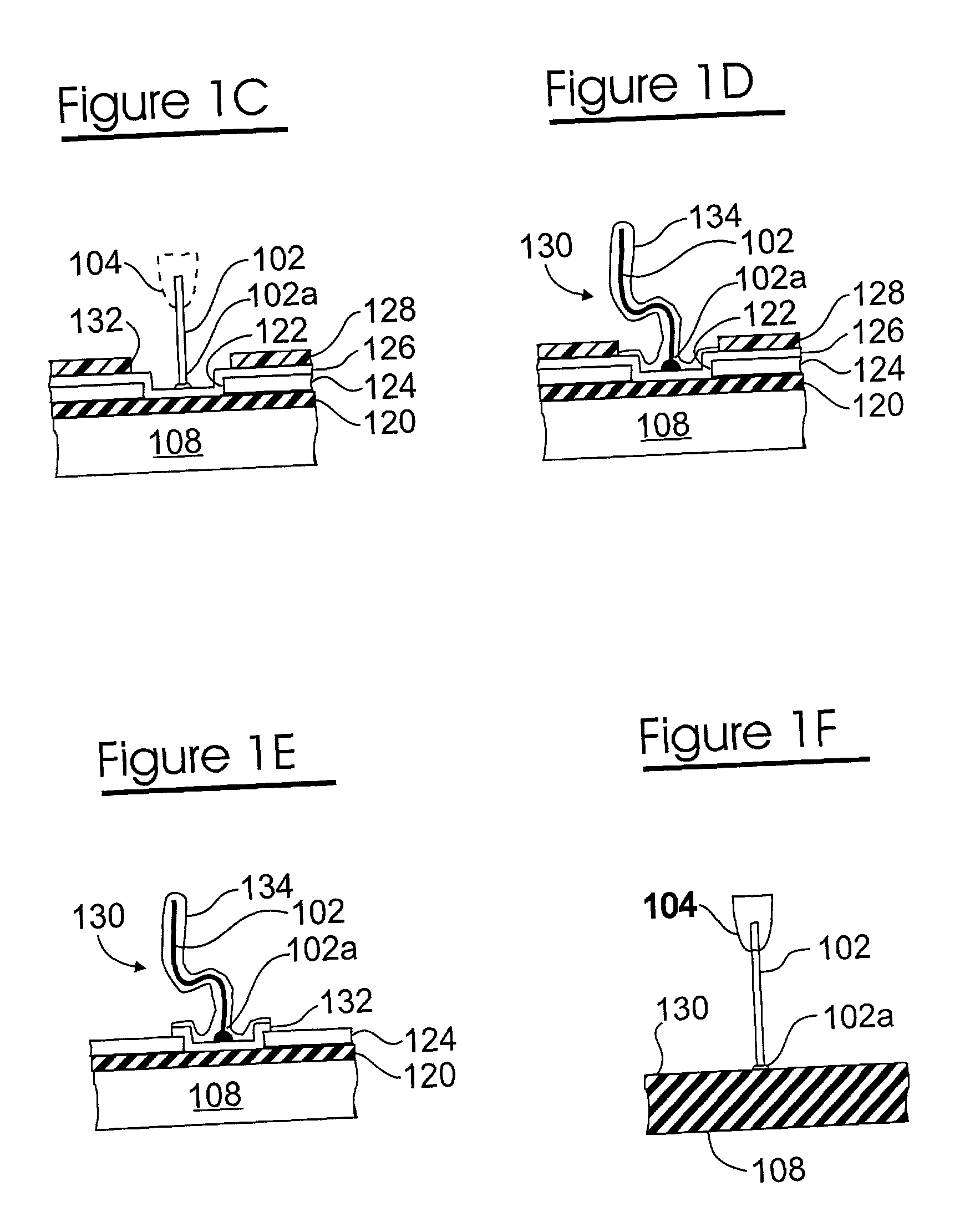

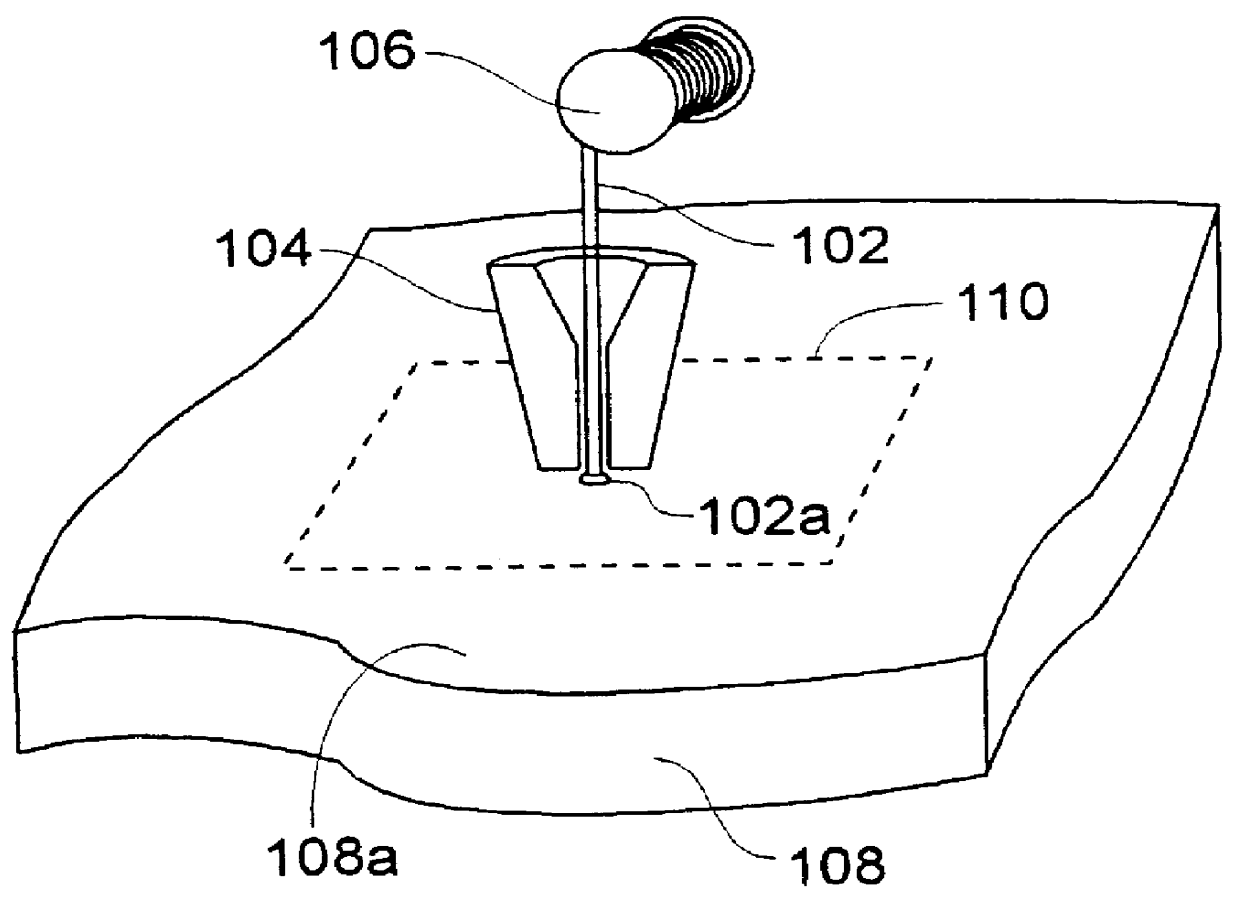

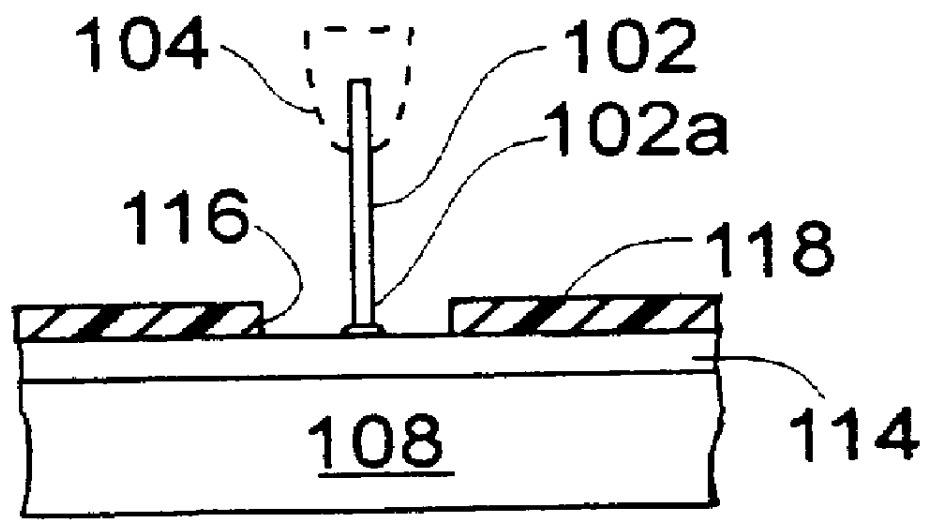

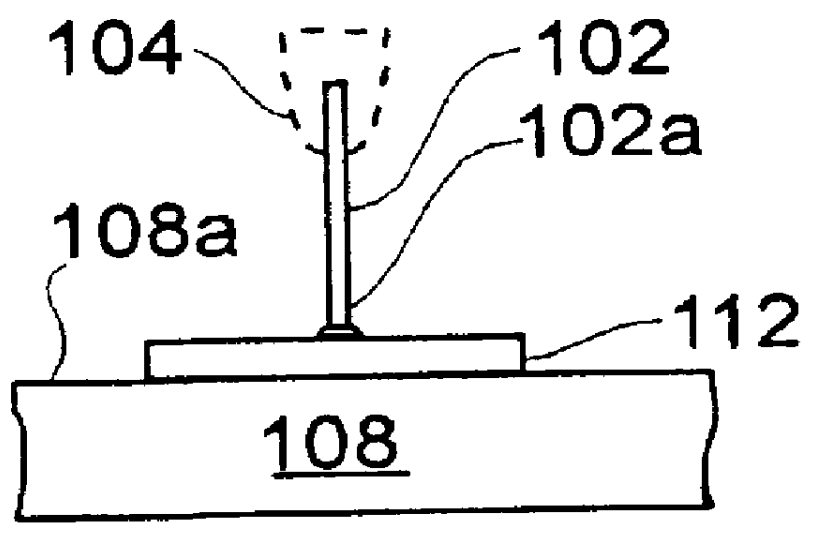

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

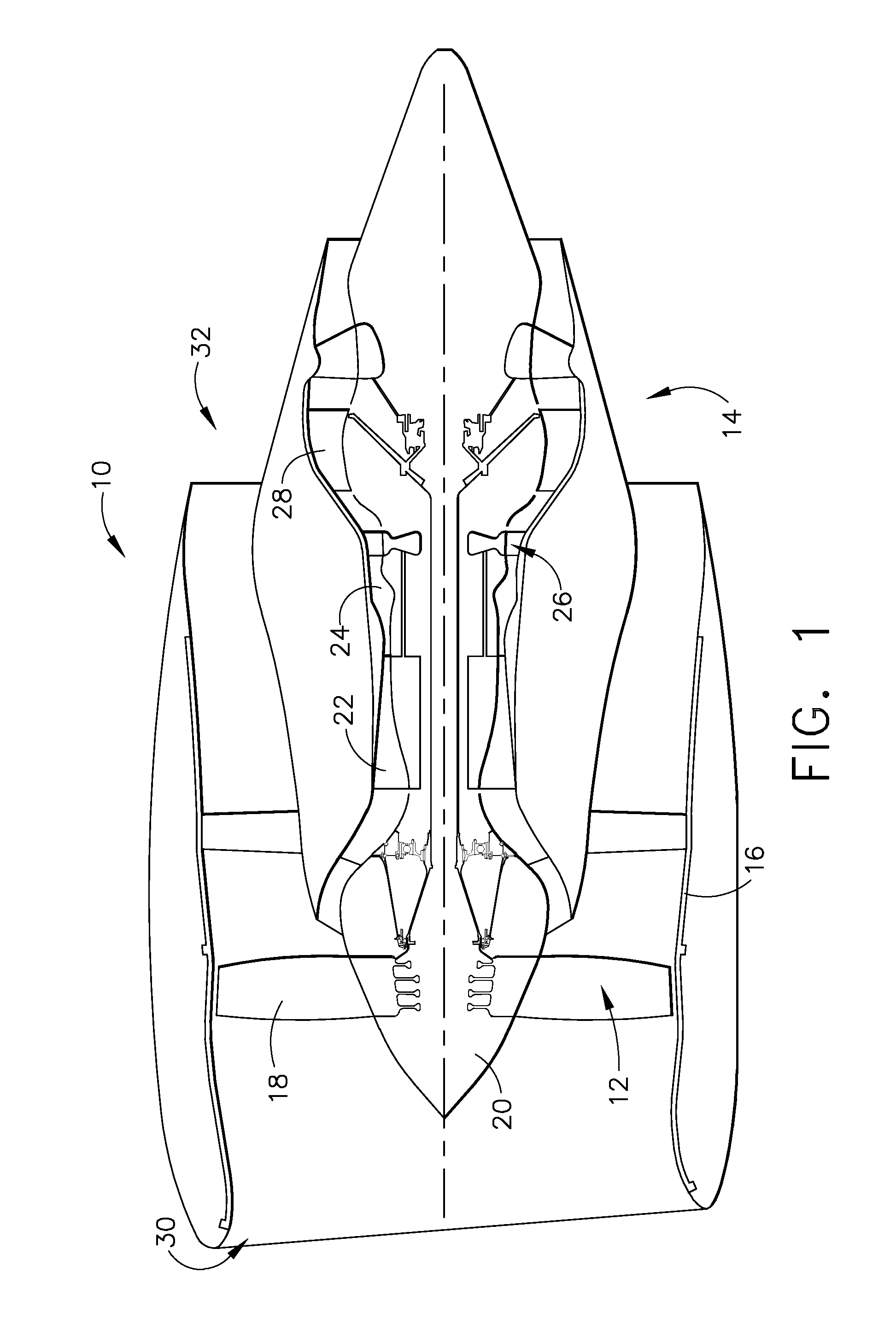

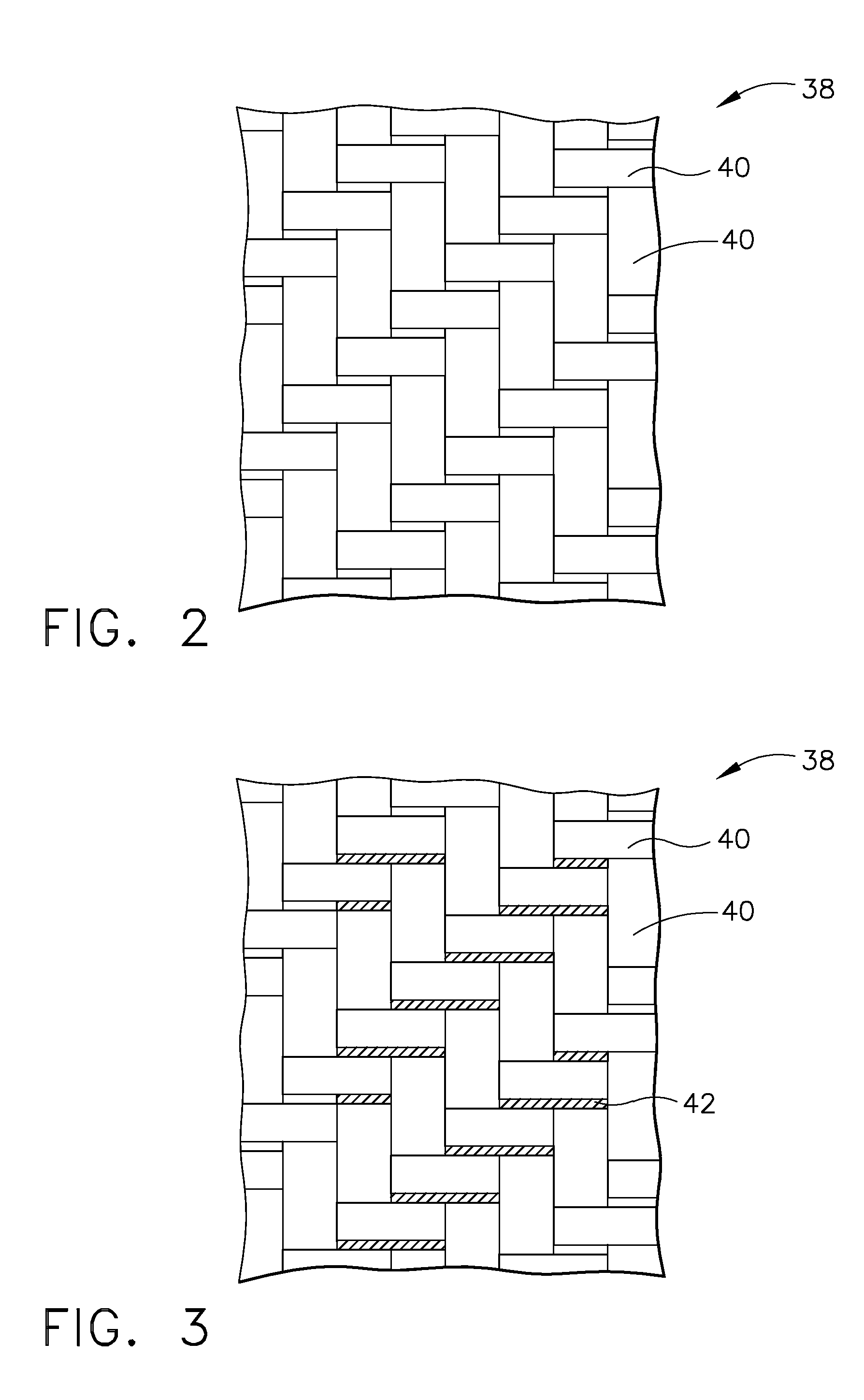

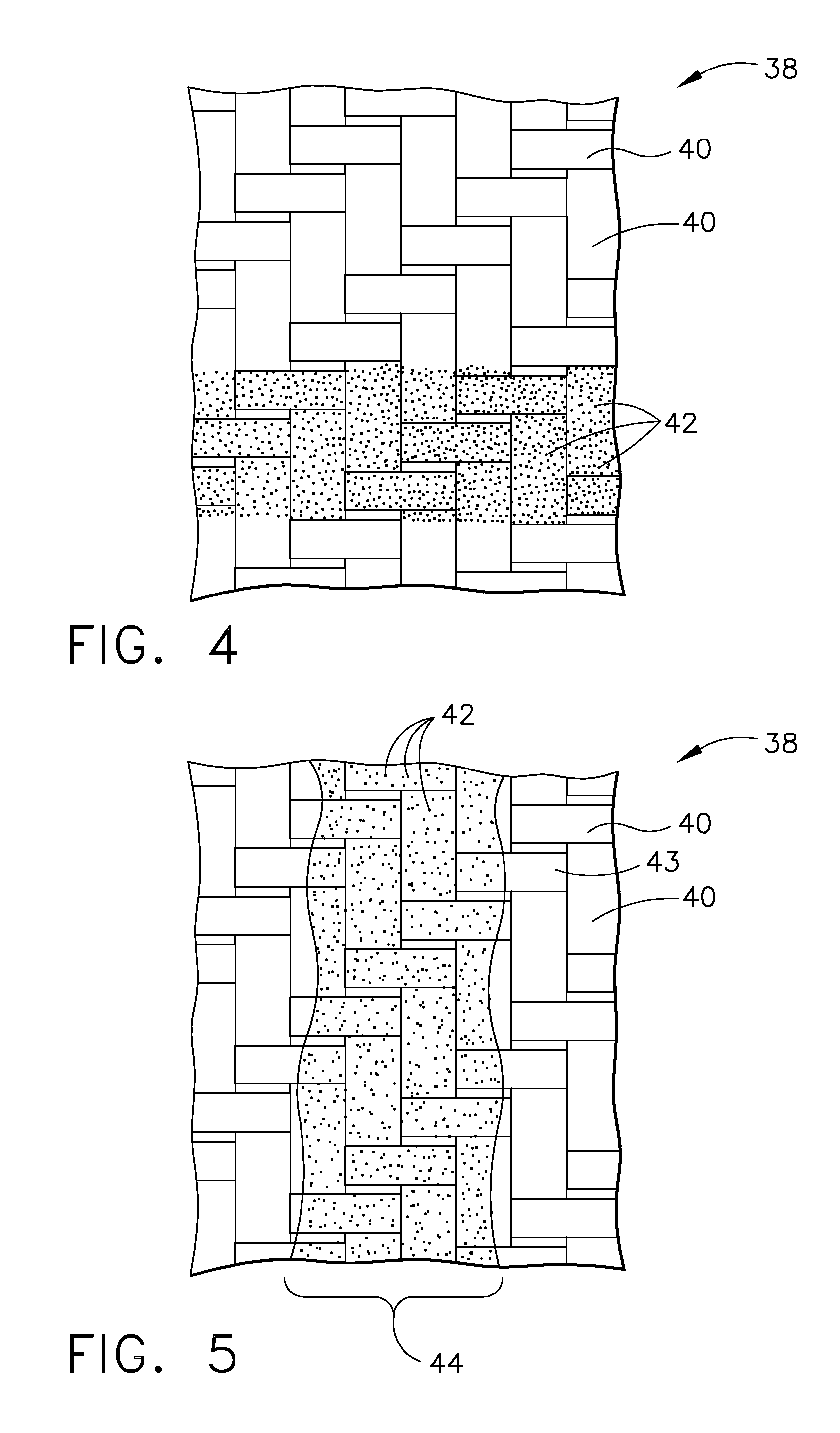

Methods of making articles having toughened and untoughened regions

ActiveUS20100148396A1Weight increaseHigh strengthPretreated surfacesLiquid/solution decomposition chemical coatingProviding materialFracture toughness

Methods of making an article having at least one toughened region and at least one untoughened region involving providing a material, applying a toughening agent to a portion of the material, shaping the material to produce a preform, applying an untoughened resin to the preform, and curing the preform having the applied untoughened resin to produce the at least one toughened region and the at least one untoughened region wherein the toughened region comprises a toughened resin having a fracture toughness of at least about 1.0 MPa-m1 / 2.

Owner:GENERAL ELECTRIC CO

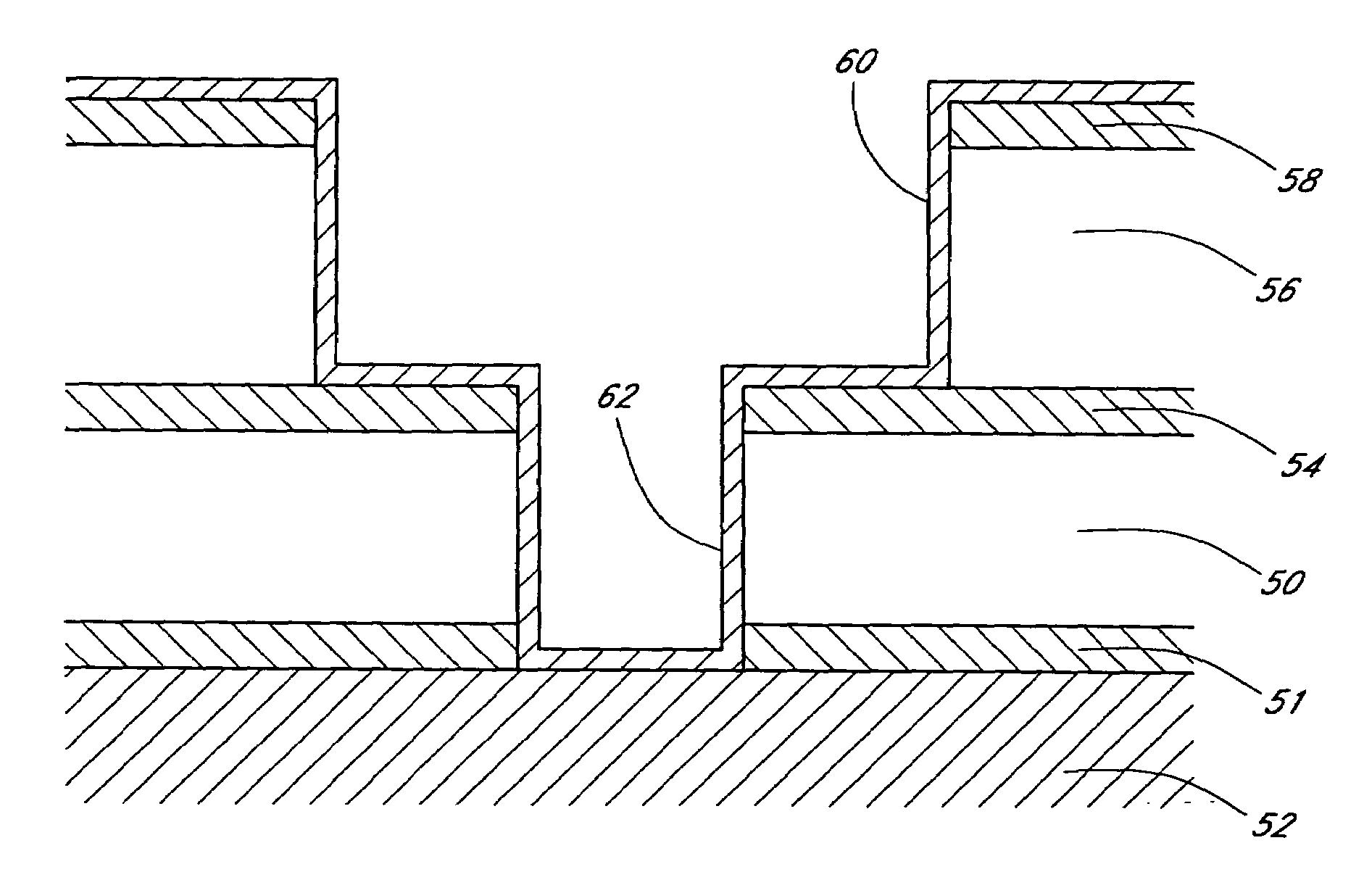

Method of electroless plating copper on nitride barrier

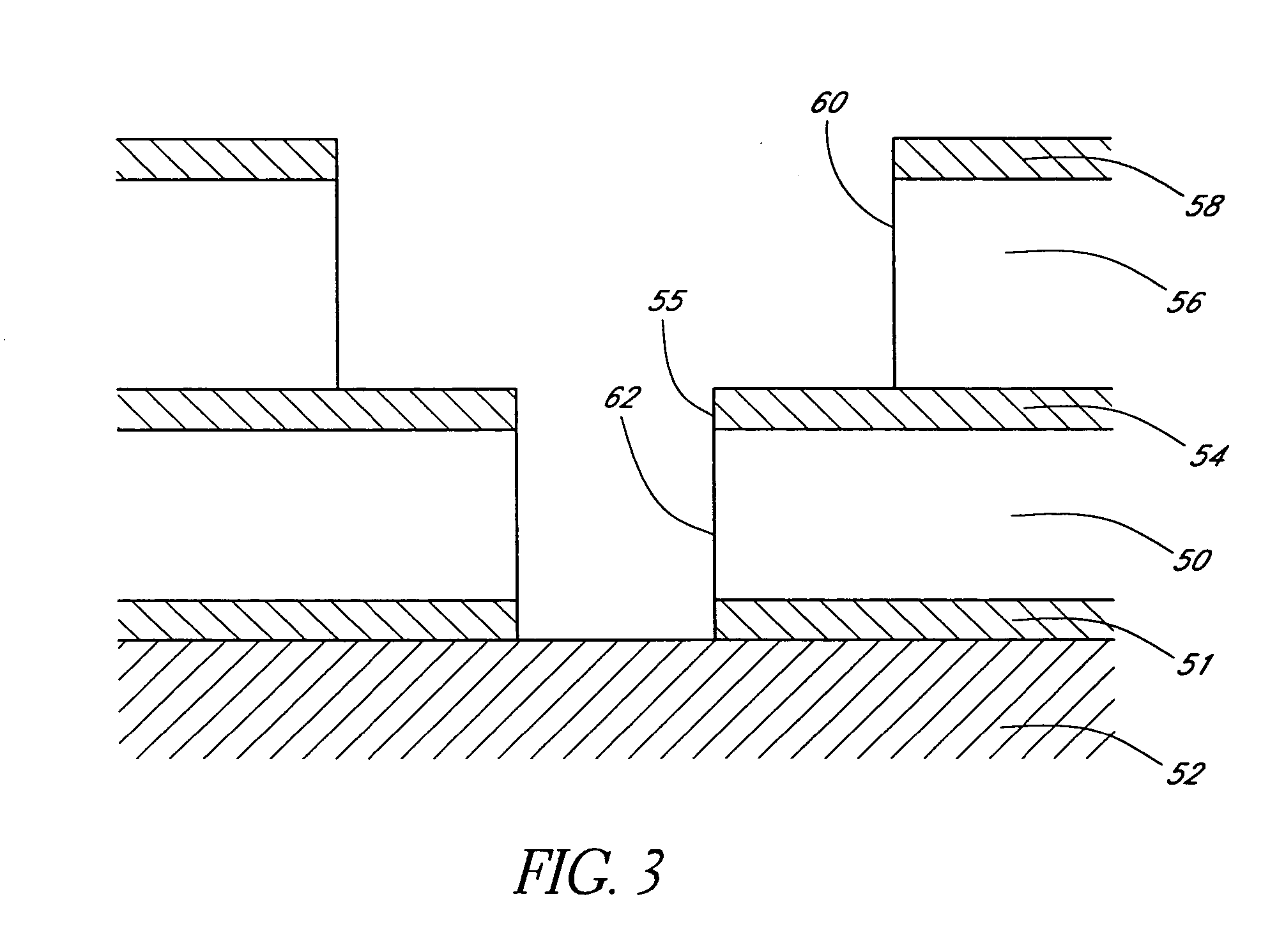

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

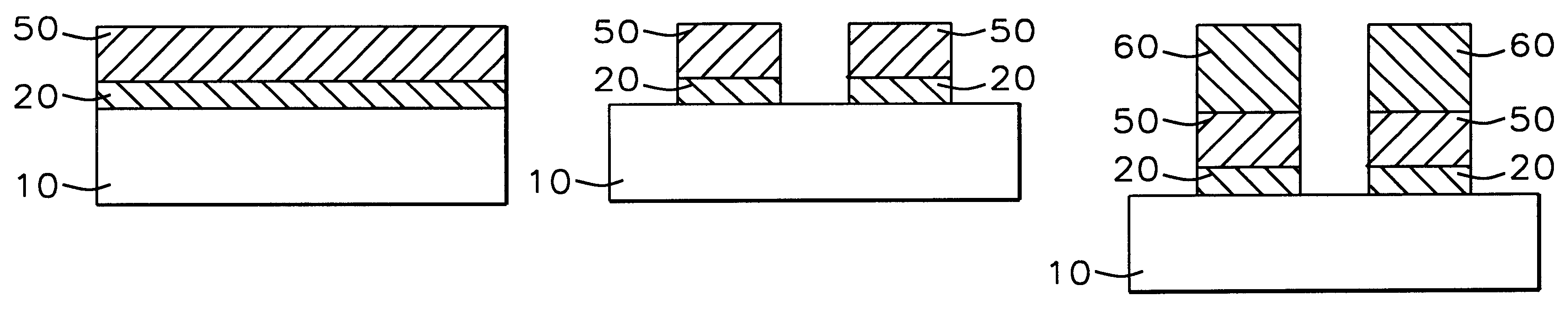

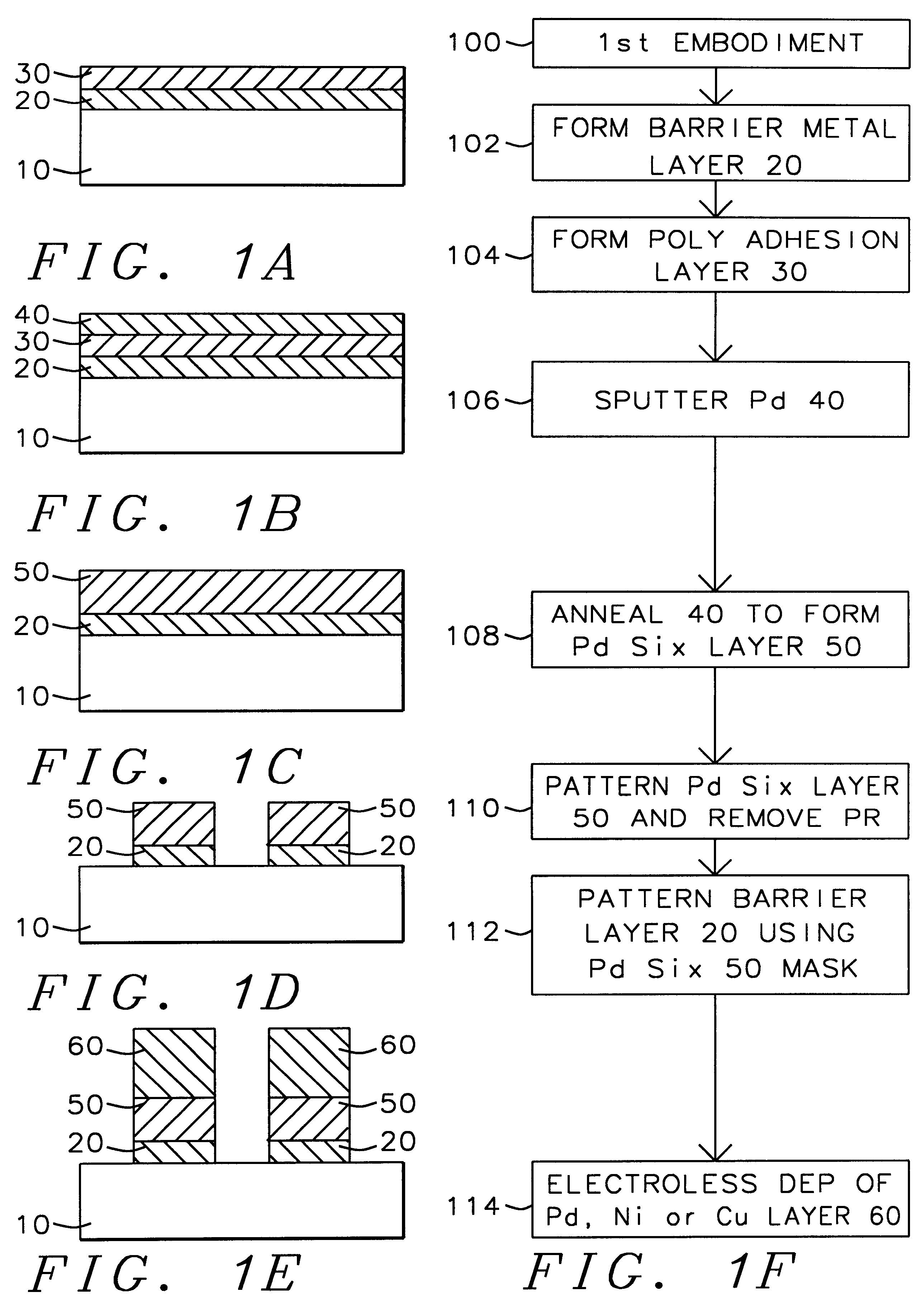

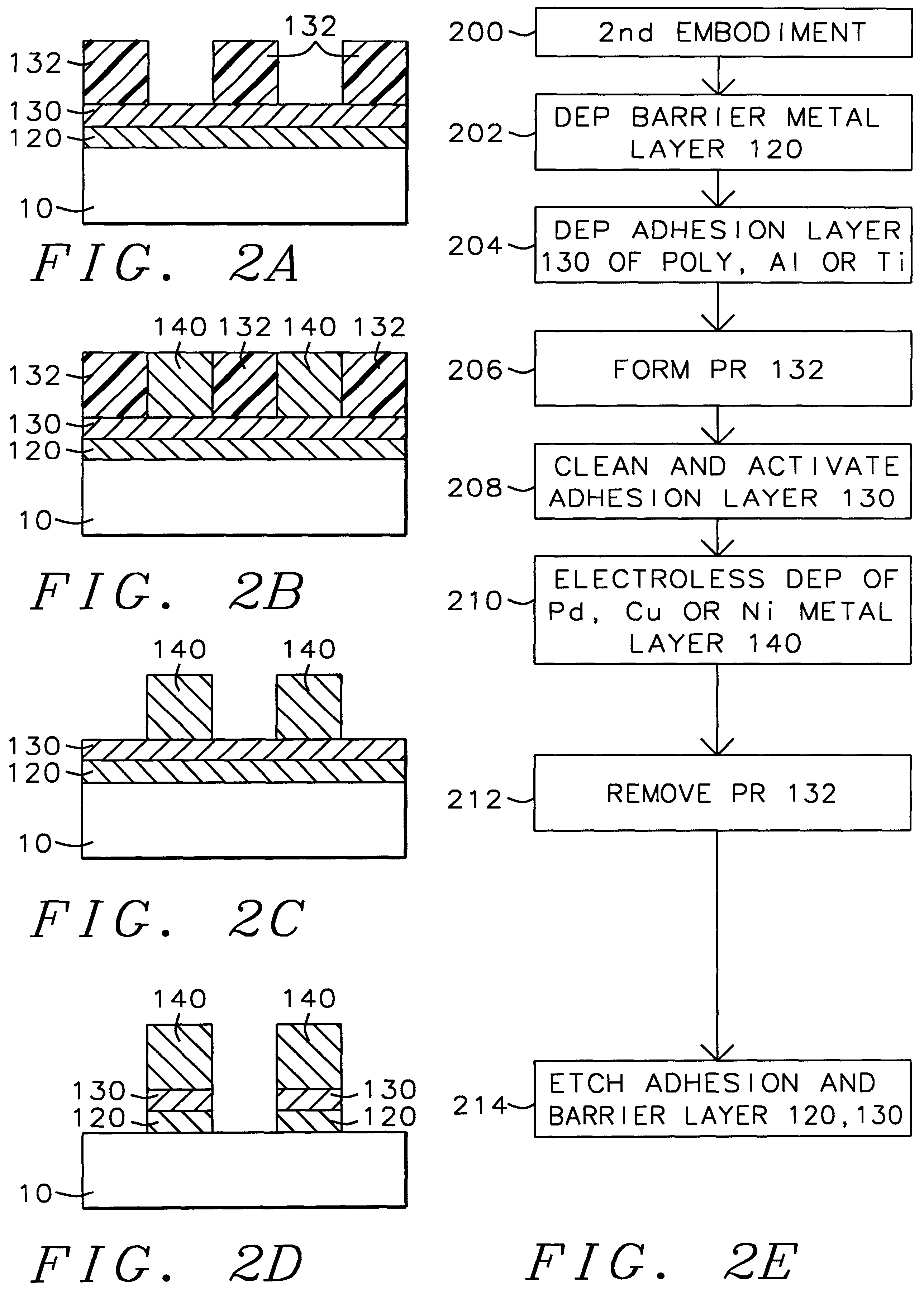

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

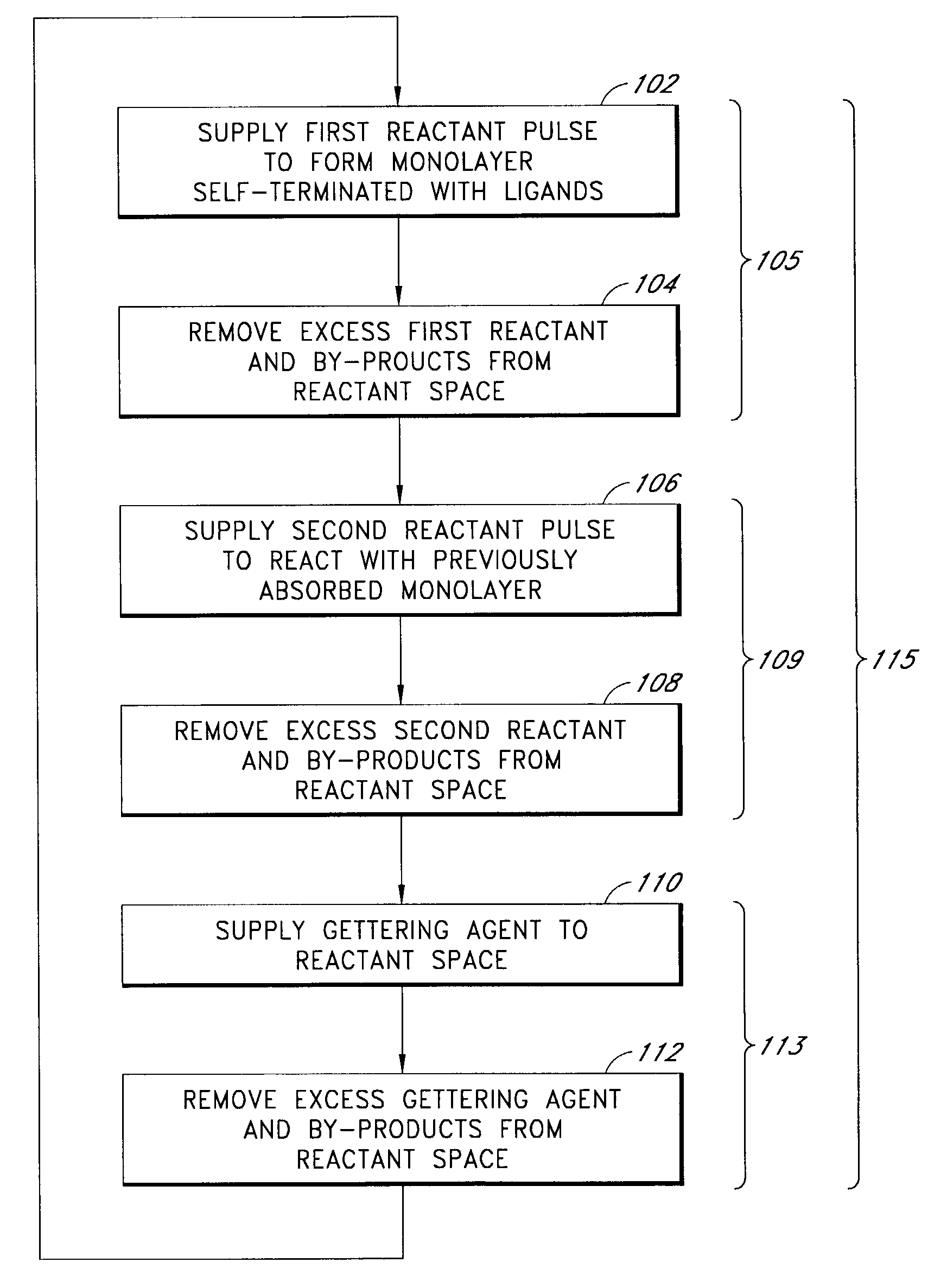

Metal nitride deposition by ALD with reduction pulse

The present methods provide tools for growing conformal metal thin films, including metal nitride, metal carbide and metal nitride carbide thin films. In particular, methods are provided for growing such films from aggressive chemicals. The amount of corrosive chemical compounds, such as hydrogen halides, is reduced during the deposition of transition metal, transition metal carbide, transition metal nitride and transition metal nitride carbide thin films on various surfaces, such as metals and oxides. Getter compounds protect surfaces sensitive to hydrogen halides and ammonium halides, such as aluminum, copper, silicon oxide and the layers being deposited, against corrosion. Nanolaminate structures incorporating metallic thin films, and methods for forming the same, are also disclosed.

Owner:ASM INTERNATIONAL

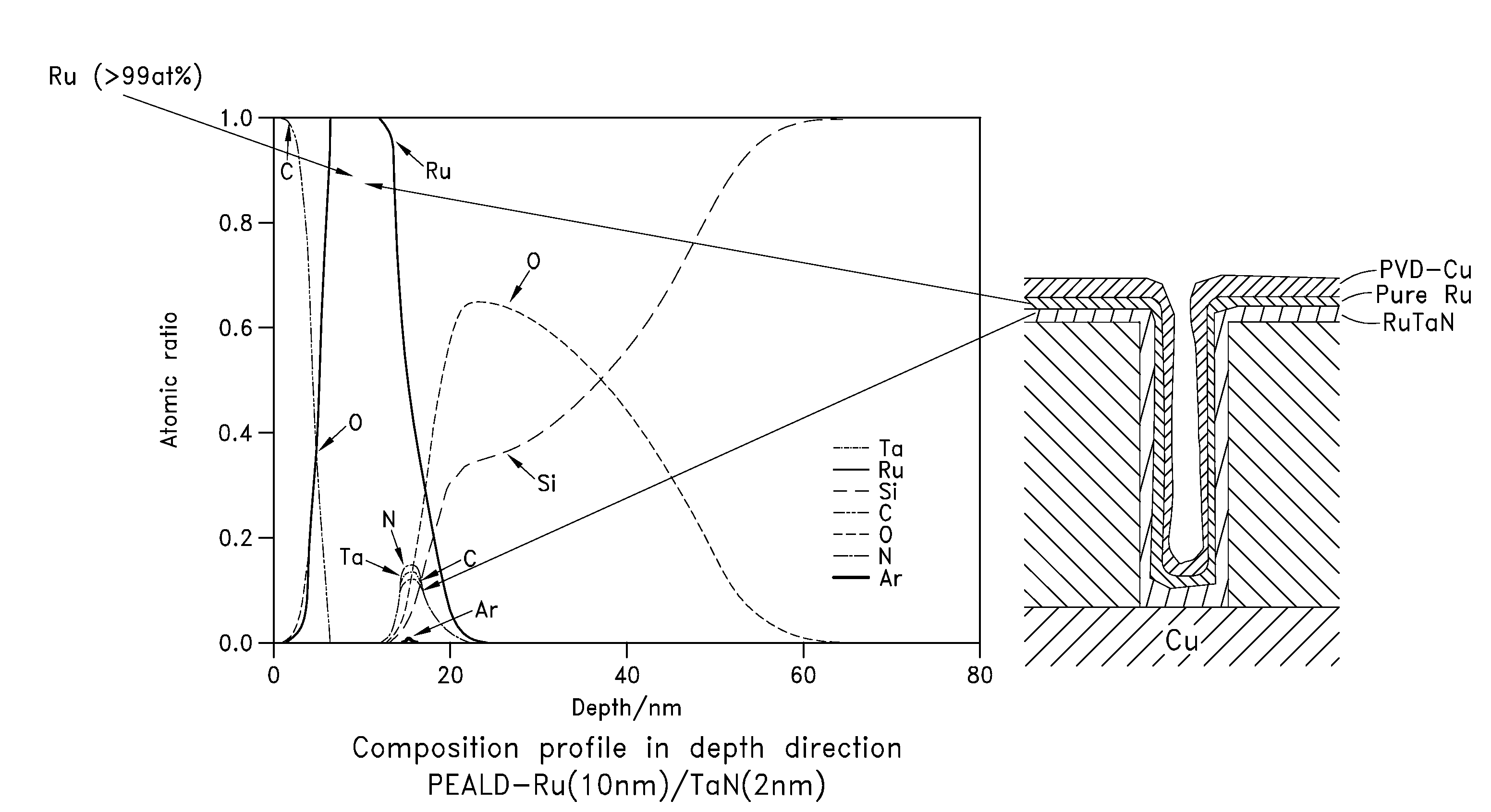

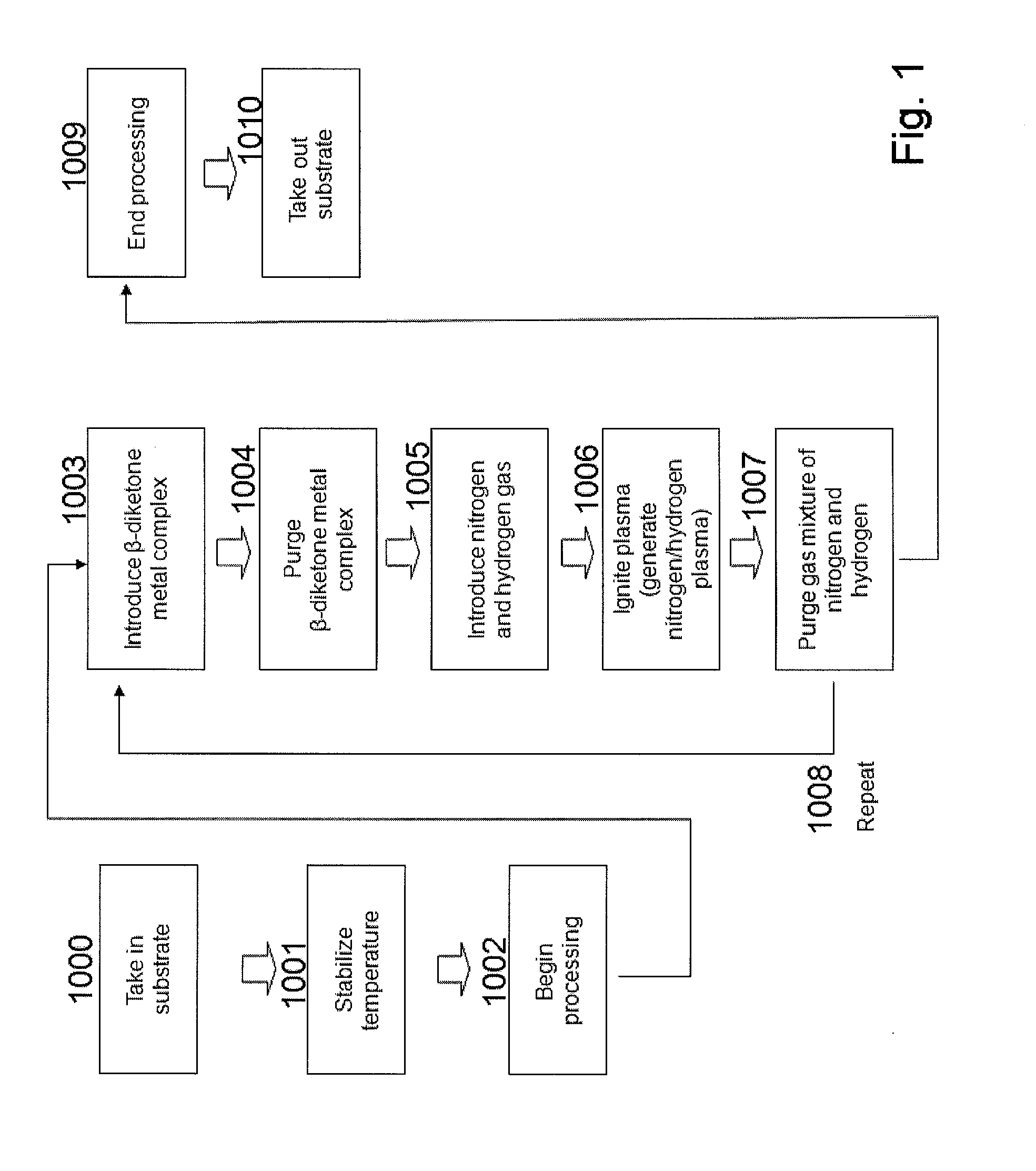

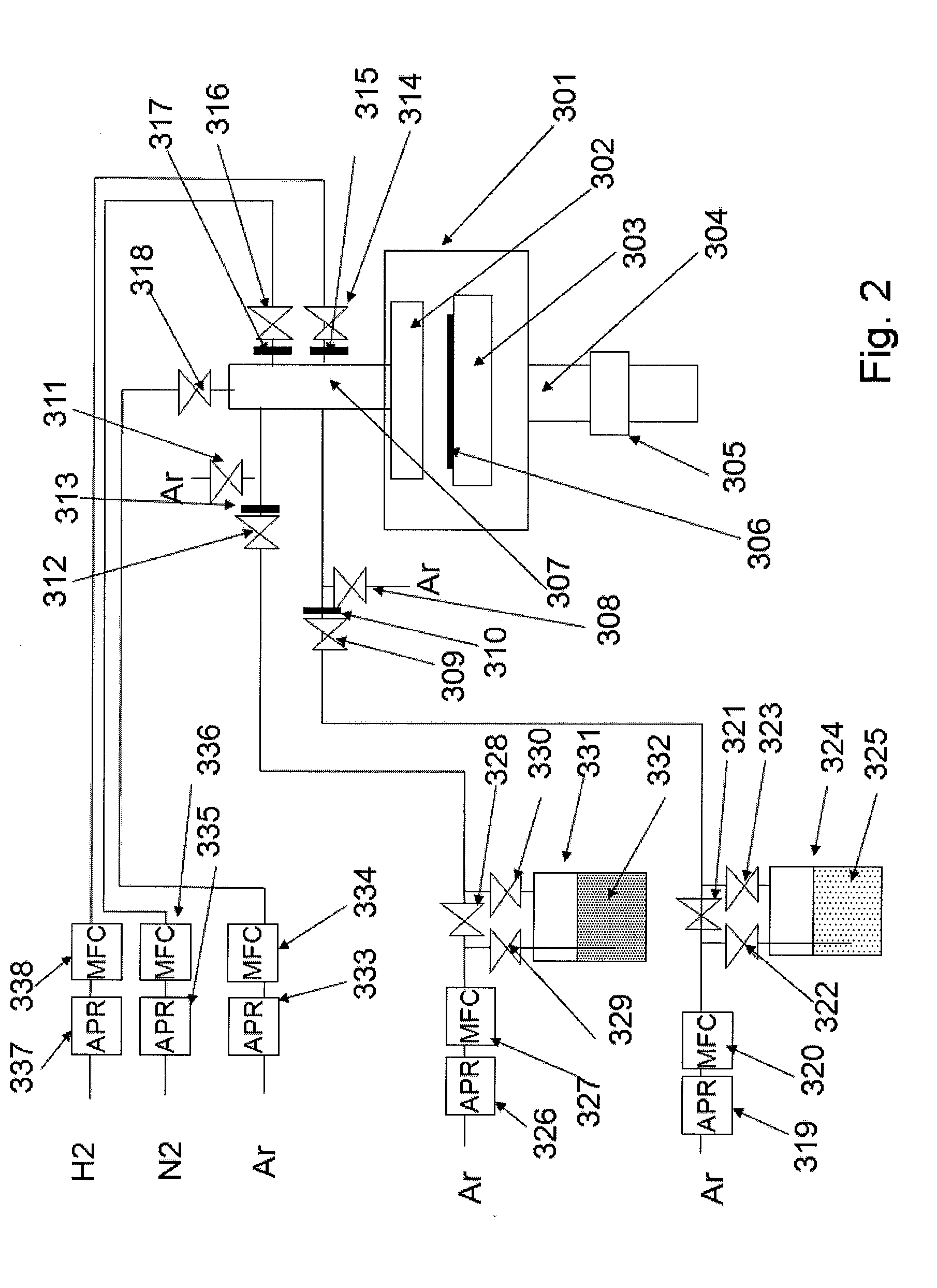

Method for forming metal film by ald using beta-diketone metal complex

ActiveUS20100092696A1Improve shielding effectRapid and reliable mannerVacuum evaporation coatingPretreated surfacesDiketoneHydrogen

A method of forming a single-metal film on a substrate by plasma ALD includes: contacting a surface of a substrate with a β-diketone metal complex in a gas phase; exposing molecule-attached surface to a nitrogen-hydrogen mixed plasma; and repeating the above steps, thereby accumulating atomic layers to form a single-metal film on the substrate.

Owner:ASM JAPAN

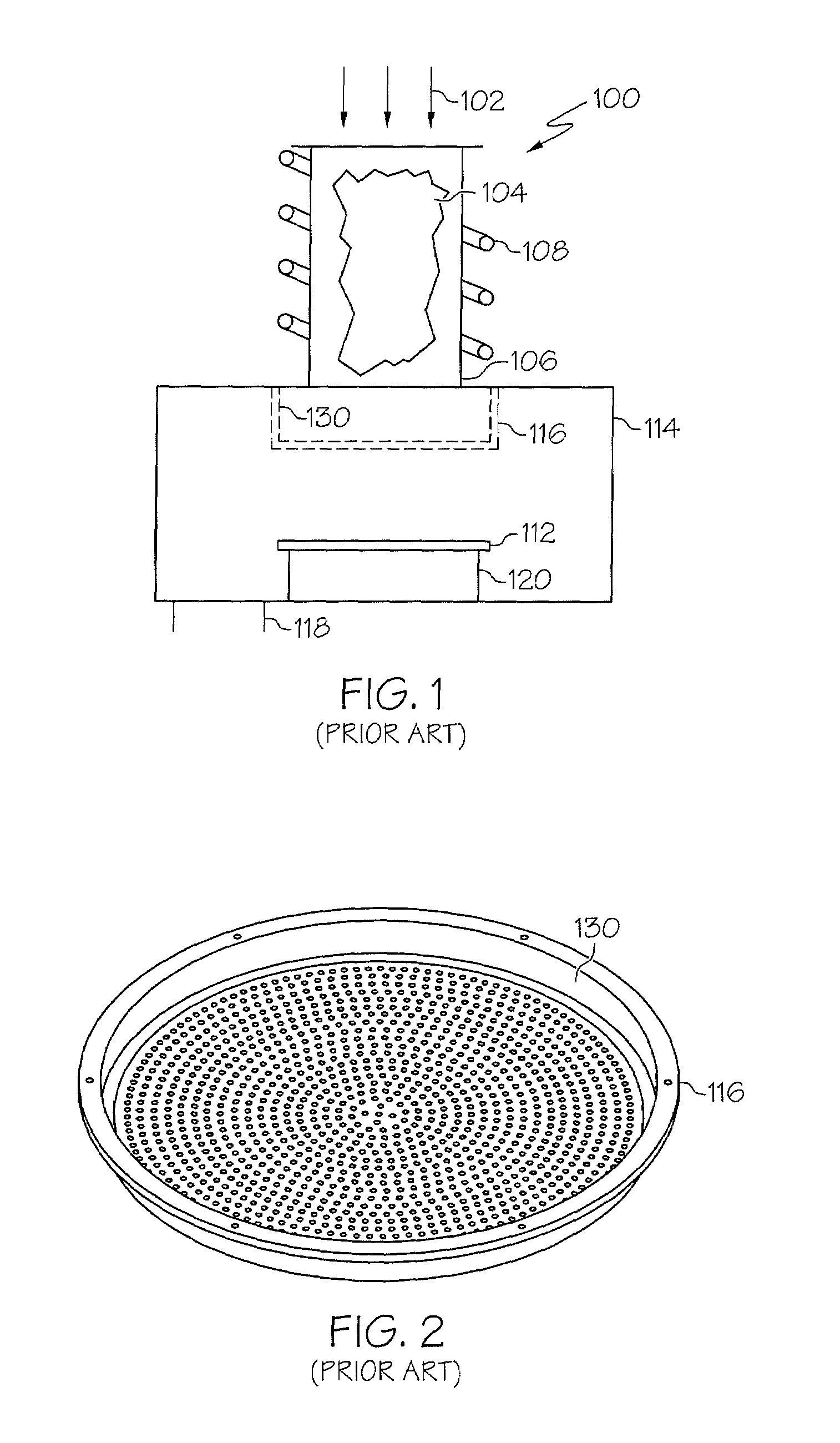

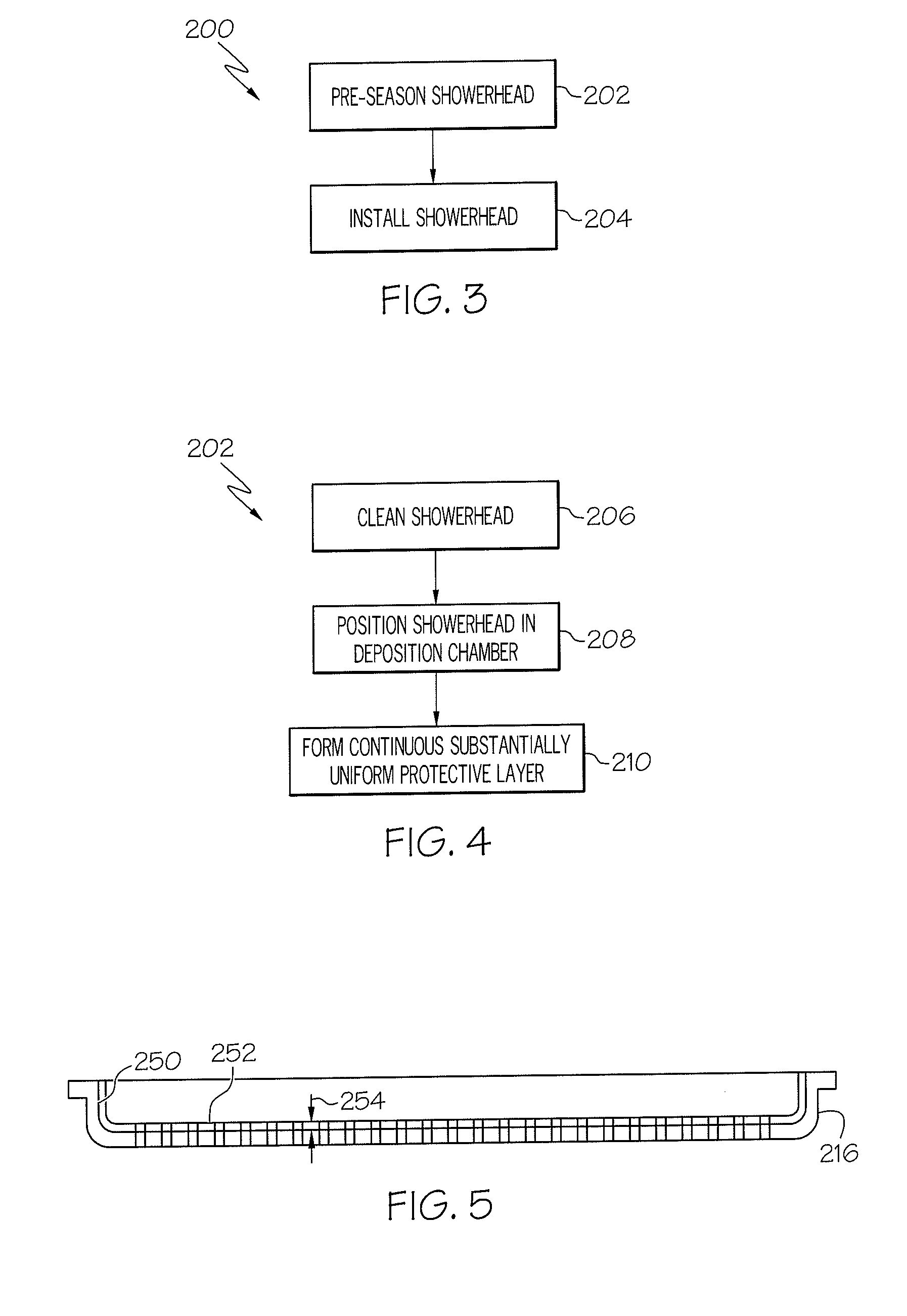

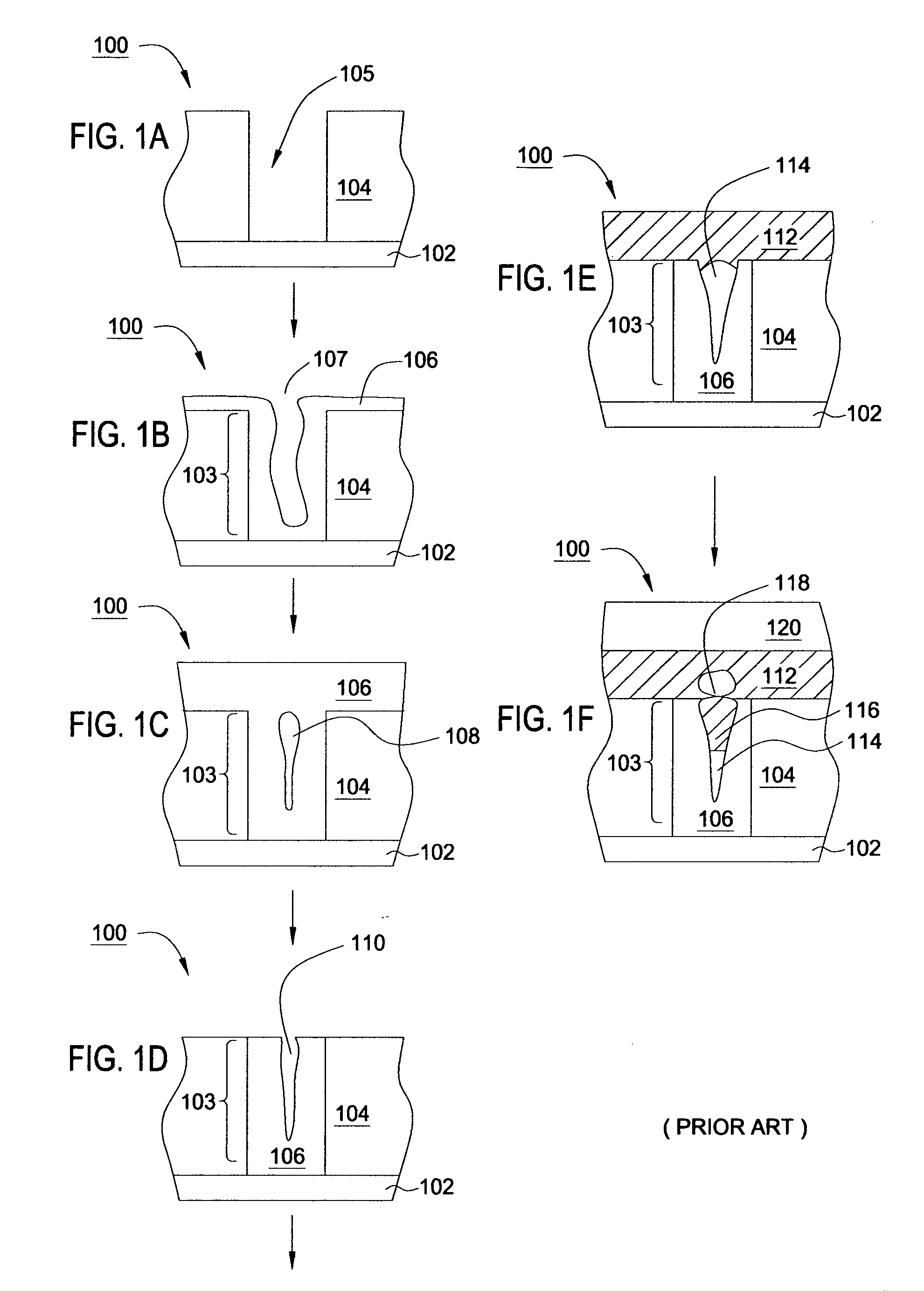

Plasma Reaction Apparatus Having Pre-Seasoned Showerheads and Methods for Manufacturing the Same

InactiveUS20080216958A1Wave amplification devicesElectric discharge tubesPlasma reactionAnalytical chemistry

Plasma reaction apparatus having pre-seasoned showerheads and methods for pre-seasoning a showerhead of a plasma reaction apparatus are provided. In an embodiment, a method for seasoning a showerhead prior to installation in a plasma reaction apparatus comprises cleaning the showerhead, positioning the showerhead in a deposition chamber, and forming a continuous, substantially uniform protective layer on the showerhead.

Owner:NOVELLUS SYSTEMS

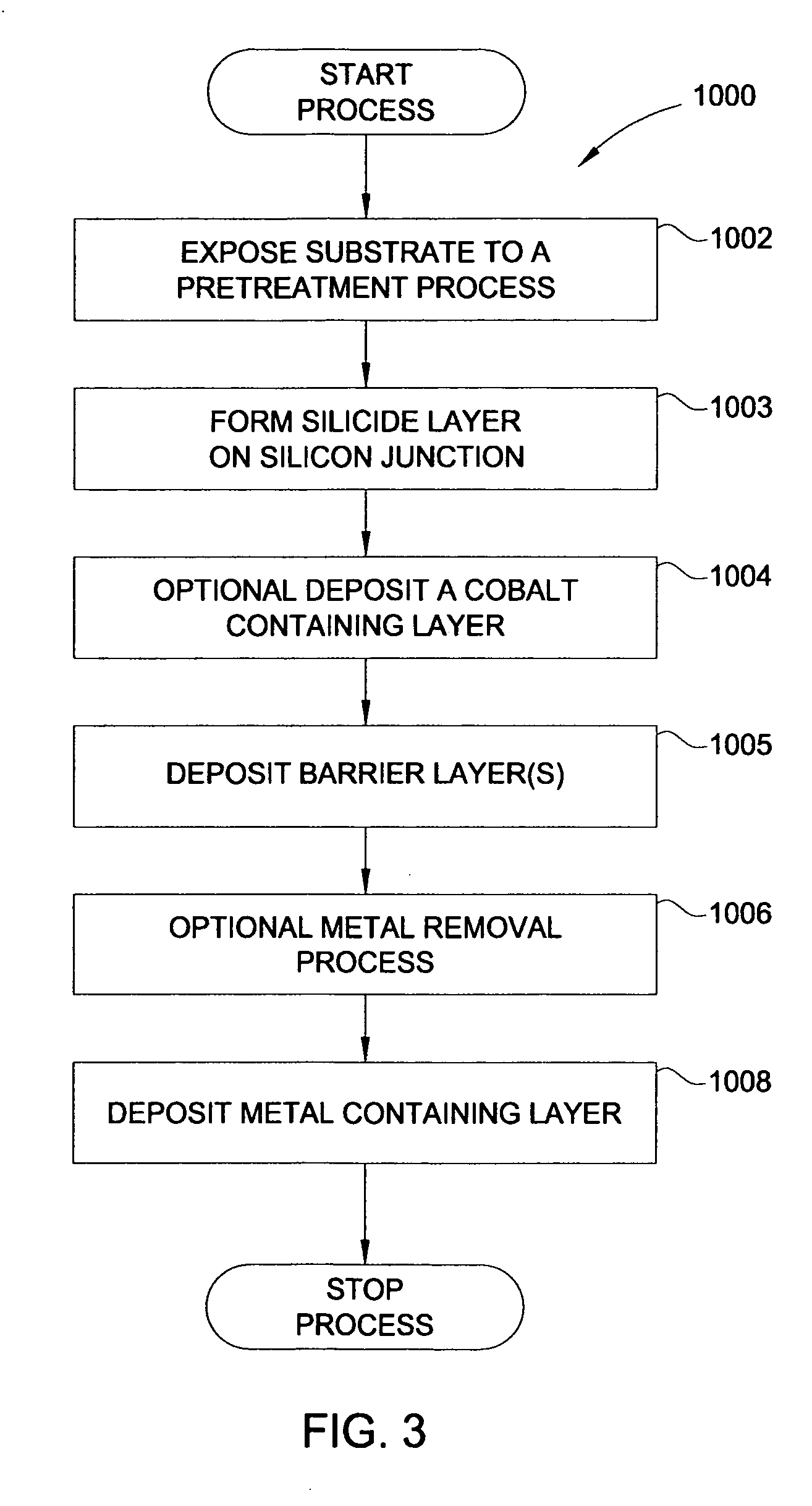

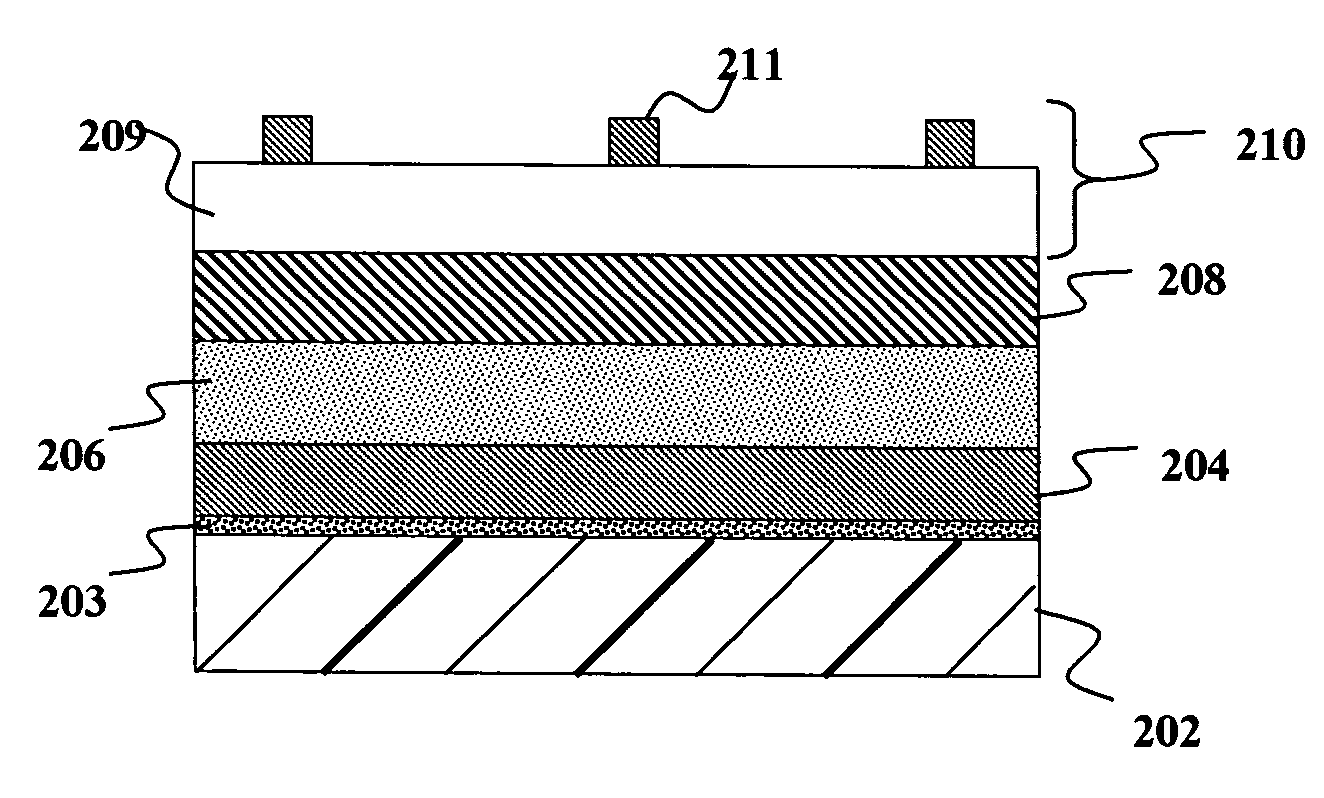

Contact metallization scheme using a barrier layer over a silicide layer

ActiveUS20060251800A1Material nanotechnologySemiconductor/solid-state device detailsDevice materialElectroless deposition

Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and / or electroless deposition processes. In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one aspect, the contact level feature is filled with a copper alloy by use of an electroless deposition process. In another aspect, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an ECP, PVD, CVD, and / or ALD deposition process. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection.

Owner:APPLIED MATERIALS INC

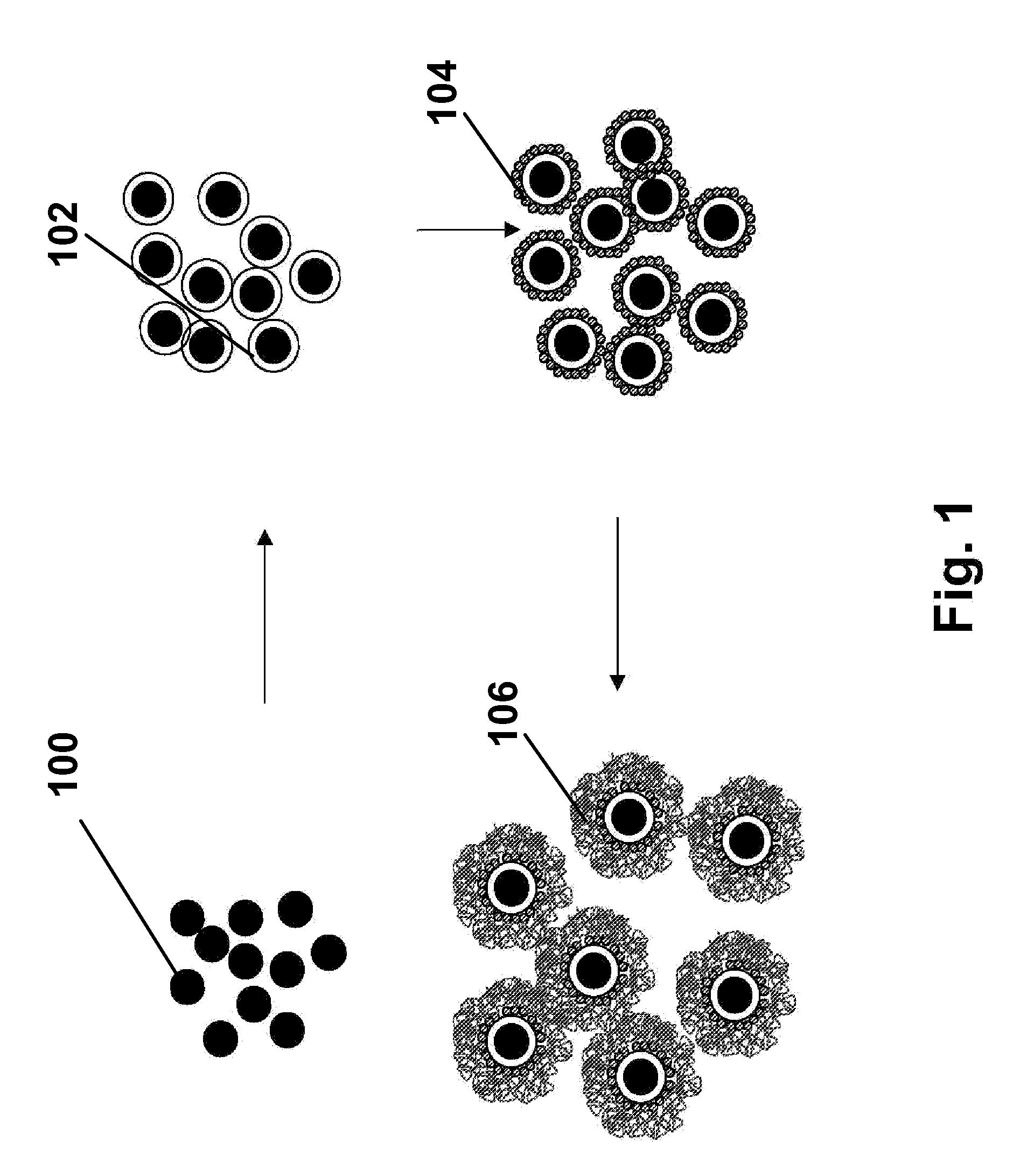

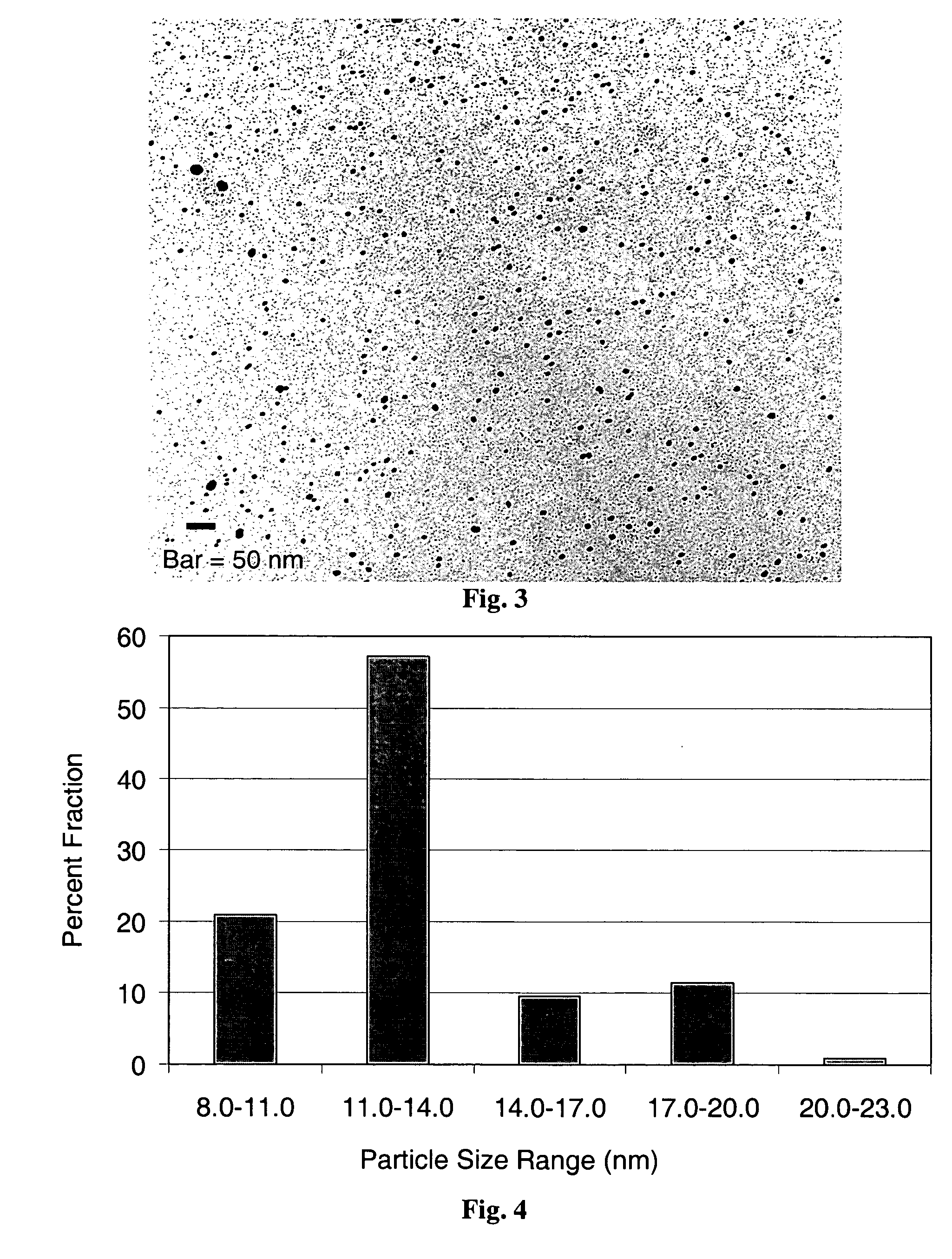

Solution-based fabrication of photovoltaic cell

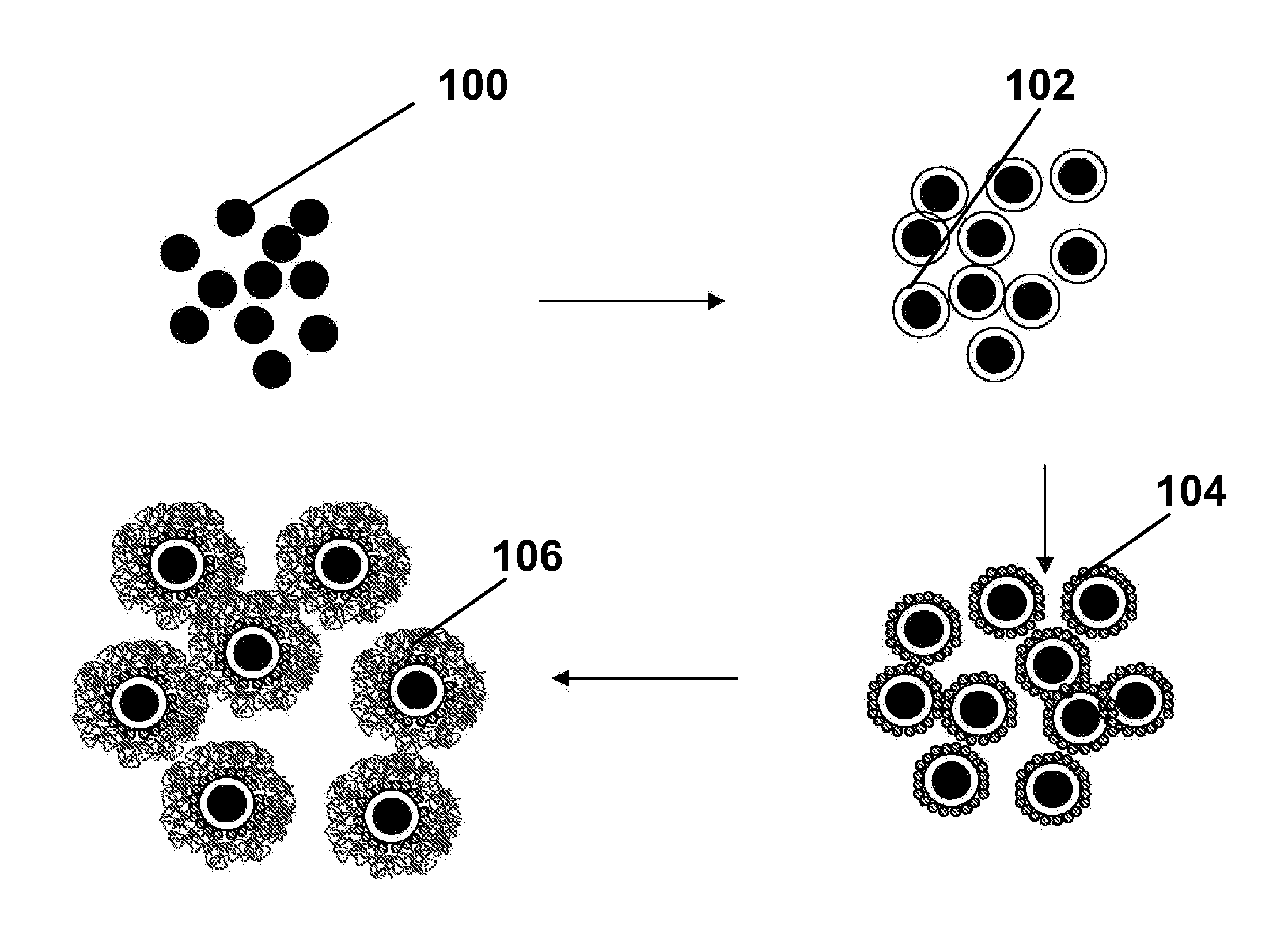

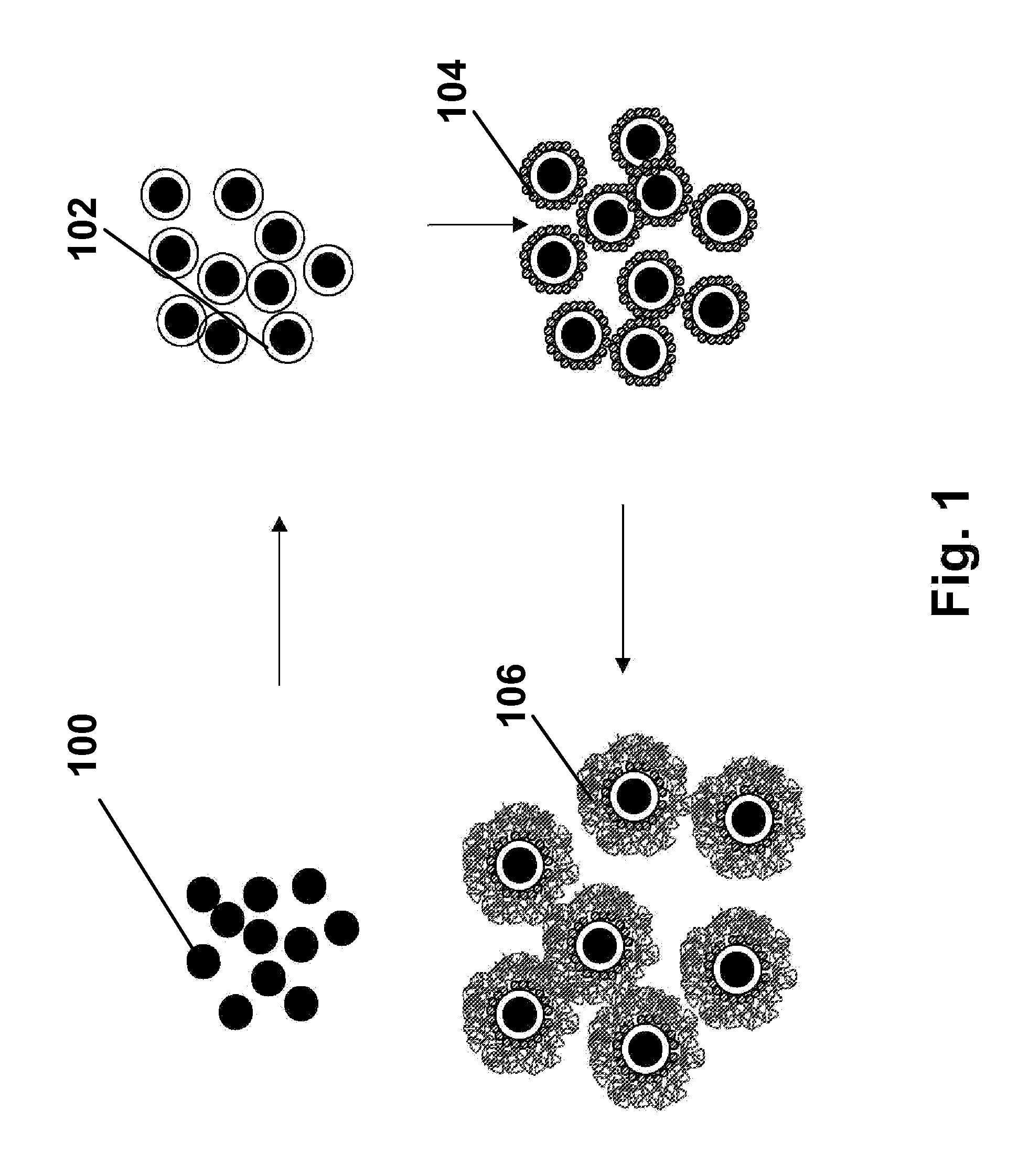

InactiveUS20050183767A1Improve overall utilizationLow costMaterial nanotechnologyNanostructure manufactureNanoparticleSolar cell

An ink for forming CIGS photovoltaic cell active layers is disclosed along with methods for making the ink, methods for making the active layers and a solar cell made with the active layer. The ink contains a mixture of nanoparticles of elements of groups IB, IIIA and (optionally) VIA. The particles are in a desired particle size range of between about 1 nm and about 500 nm in diameter, where a majority of the mass of the particles comprises particles ranging in size from no more than about 40% above or below an average particle size or, if the average particle size is less than about 5 nanometers, from no more than about 2 nanometers above or below the average particle size. The use of such ink avoids the need to expose the material to an H2Se gas during the construction of a photovoltaic cell and allows more uniform melting during film annealing, more uniform intermixing of nanoparticles, and allows higher quality absorber films to be formed.

Owner:AERIS CAPITAL SUSTAINABLE IP

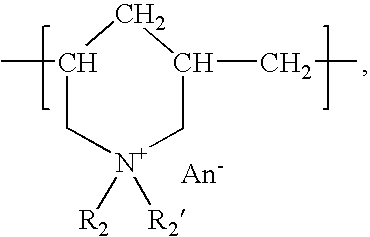

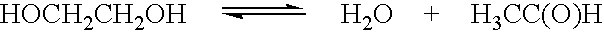

Method for applying an LbL coating onto a medical device

The present invention provides an improved LbL-coating process for modifying the surface of a medical device, preferably an ophthalmic device, more preferably a contact lens. An LbL coating on a contact lens, which is prepared according to the process of the invention, can have increased hydrophilicity characterized by an averaged contact angle of about 80 degree or less, preferably about 50 degrees or less, while maintaining the desired bulk properties such as oxygen permeability and ion permeability of lens material.

Owner:ALCON INC

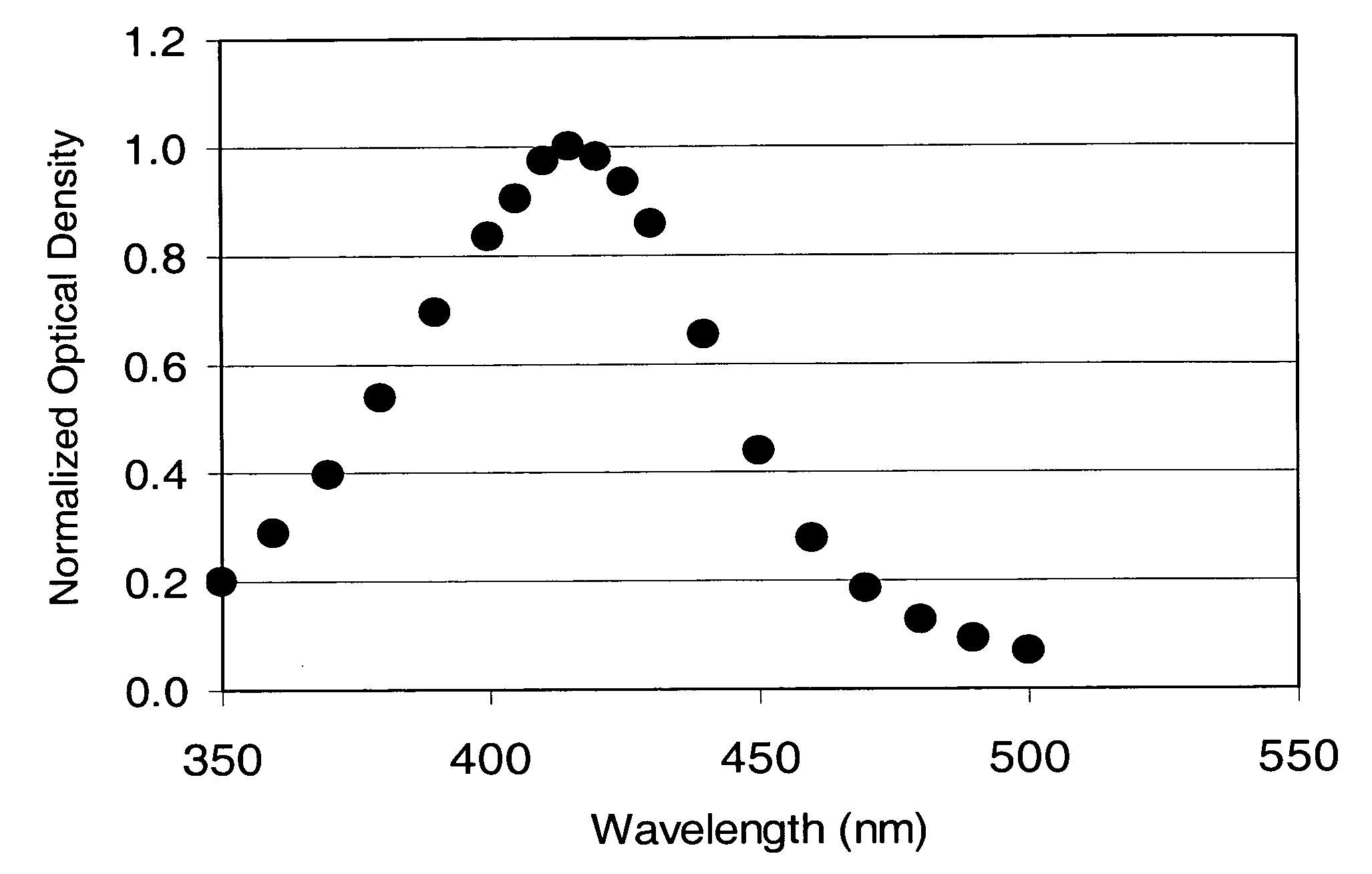

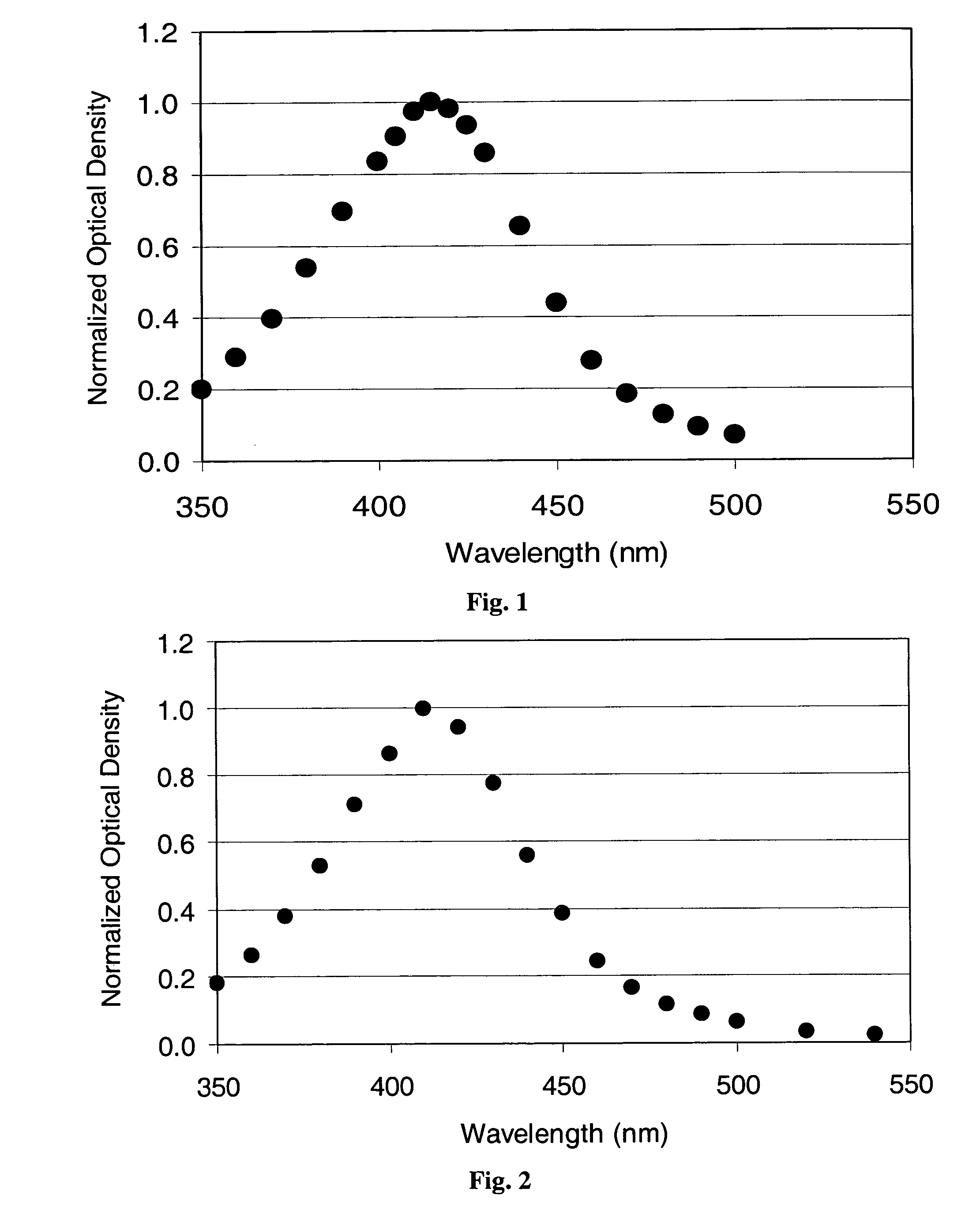

Antimicrobial silver compositions

The present invention comprises methods and compositions for antimicrobial silver compositions comprising silver nanoparticles. The present invention further comprises compositions for preparing silver nanoparticles comprising at least one stabilizing agent, one or more silver compounds, at least one reducing agent and a solvent. In one aspect, the stabilizing agent comprises a surfactant or a polymer. The polymer may comprise polymers such as polyacrylamides, polyurethanes, and polyamides. In one aspect, the silver compound comprises a salt comprising a silver cation and an anion. The anion may comprise saccharinate derivatives, long chain fatty acids, and alkyl dicarboxylates. The methods of the present invention comprise treating devices with the silver nanoparticle compositions, including, but not limited to, such devices as woven wound care materials, catheters, patient care devices, and collagen matrices. The present invention further comprises treatment of humans and animals wacr6ith the antimicrobial devices described herein.

Owner:AVENT INC

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

Electroless deposition process on a silicon contact

ActiveUS20060264043A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideAlloy

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

Metal nanoparticle compositions

InactiveUS20060189113A1Low processing (curing)Improve mechanical propertiesMaterial nanotechnologyTransportation and packagingNanometreViscosity

Owner:CABOT CORP

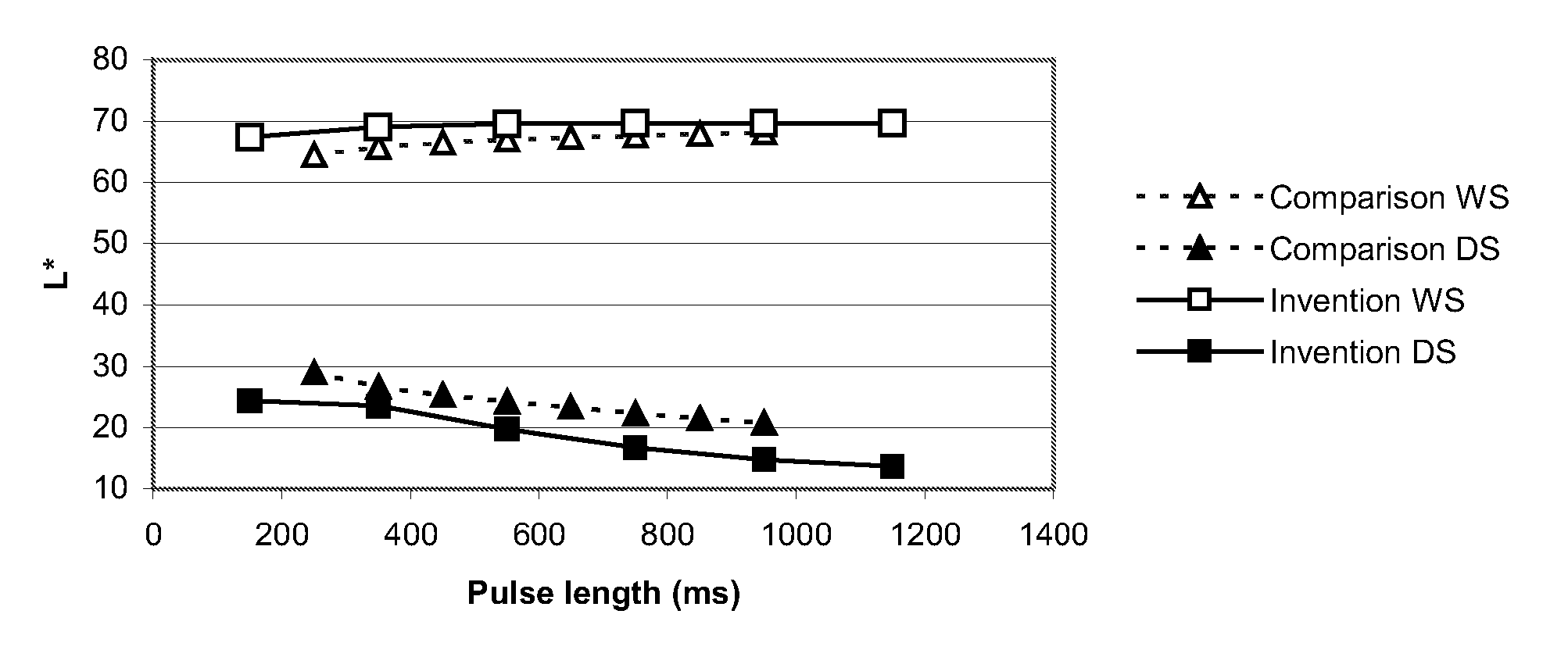

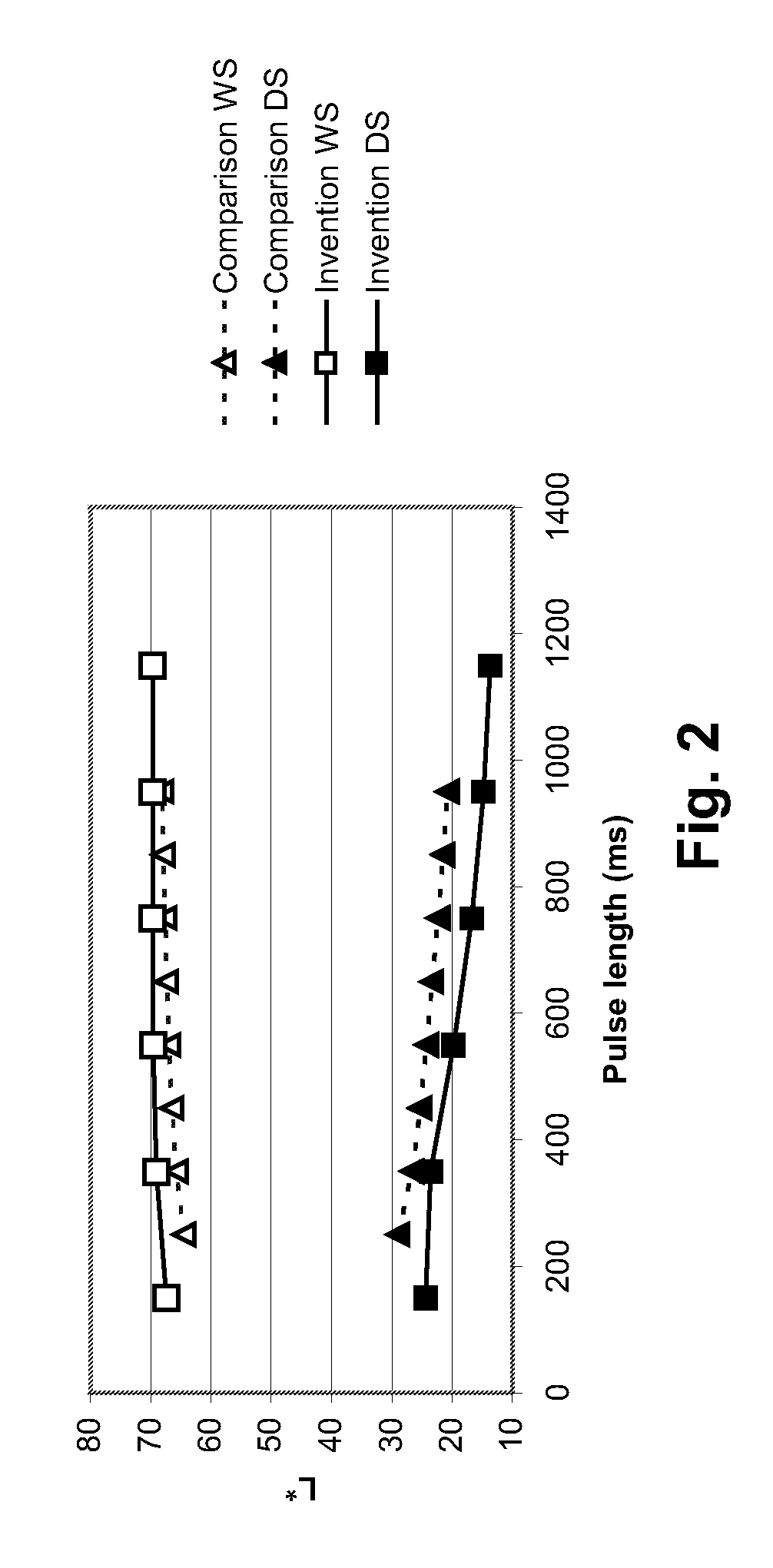

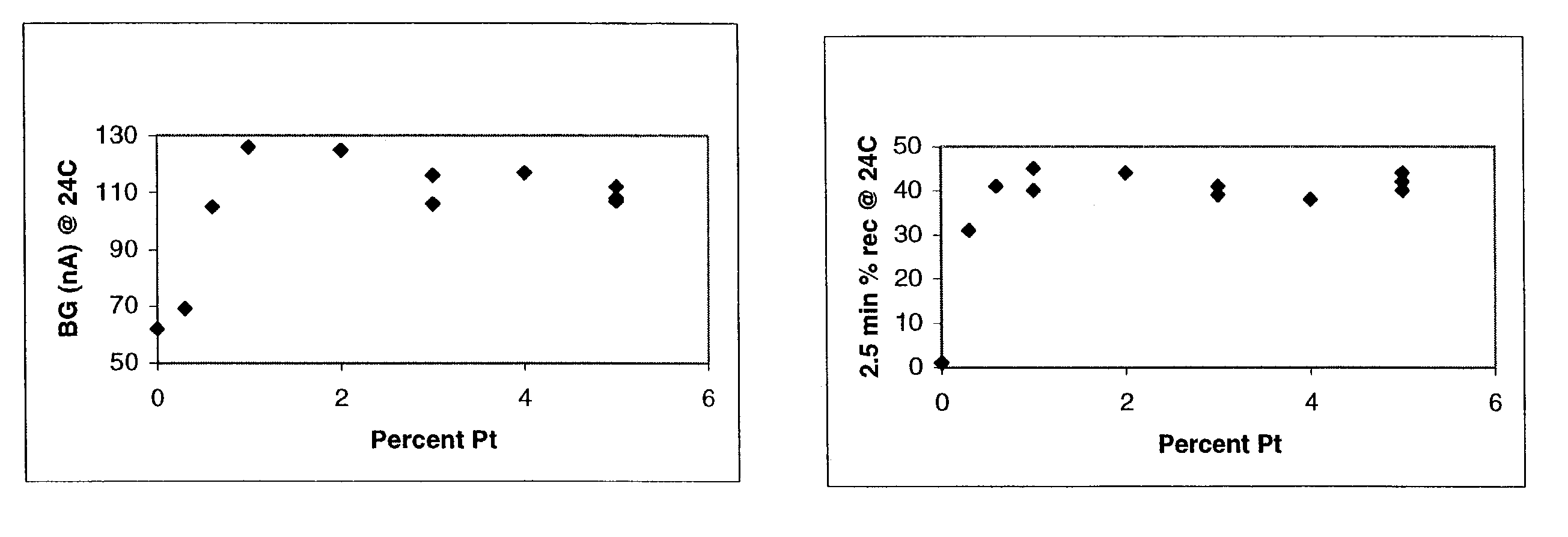

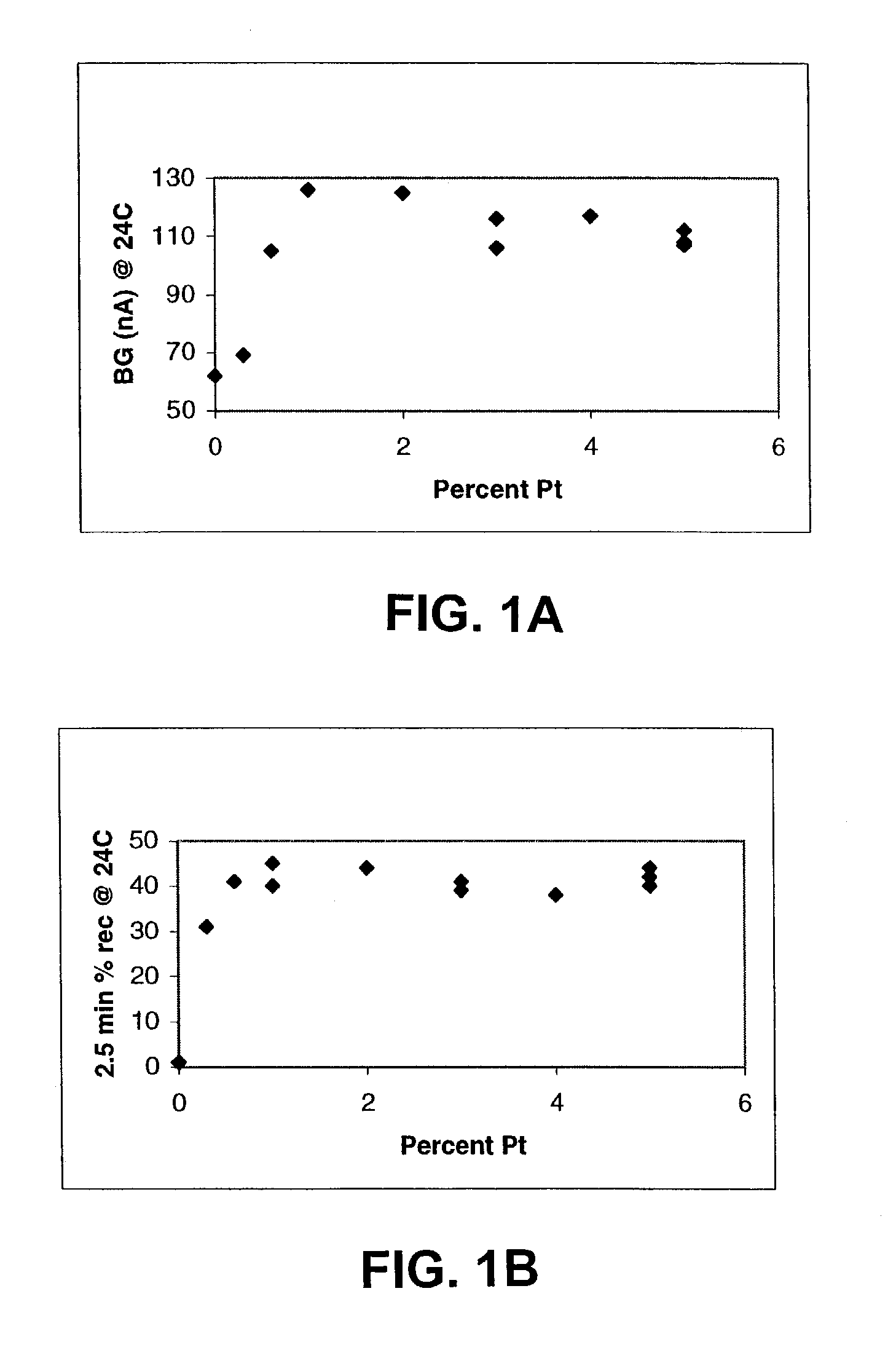

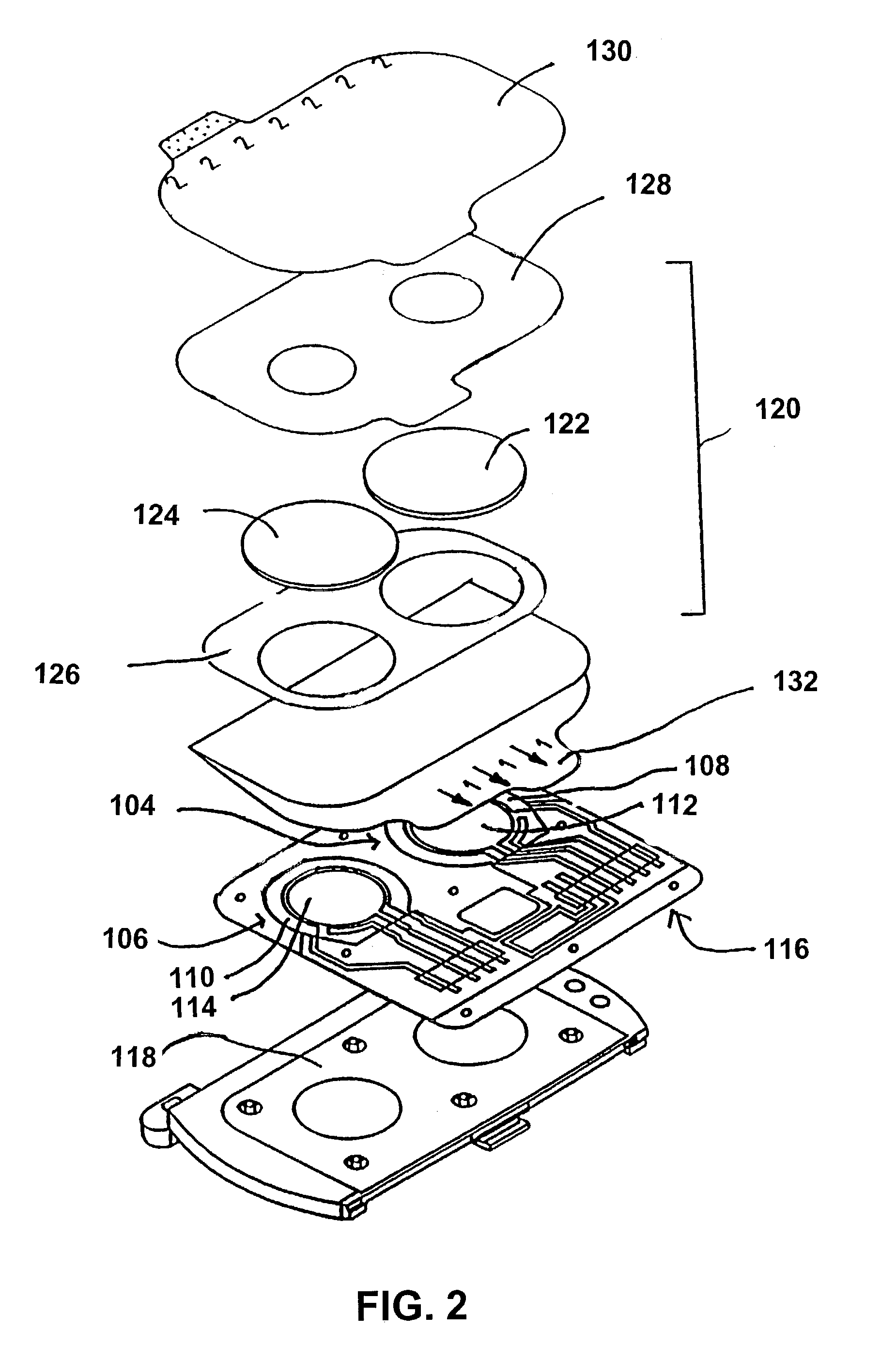

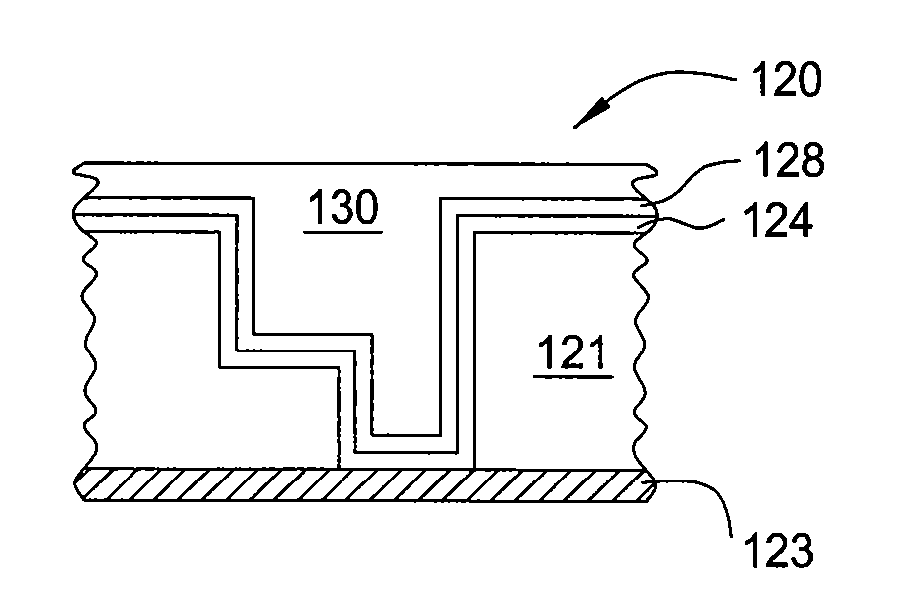

Highly catalytic screen-printing ink

ActiveUS7018568B2Easy to produceConductive layers on insulating-supportsConductive materialConductive polymerPrinting ink

The invention is directed to conductive polymer compositions, catalytic ink compositions (e.g., for use in screen-printing), electrodes produced by deposition of an ink composition, methods of making, and methods of using thereof. An exemplary ink material comprises platinum black and / or platinum-on-carbon as the catalyst, graphite as a conducting material, a polymer binding material, and an organic solvent. The polymer binding material is typically a copolymer of hydrophilic and hydrophobic monomers. The conductive polymer compositions of the present invention can be used, for example, to make electrochemical sensors. Such sensors can be used in a variety of analyte monitoring devices to monitor analyte amount or concentrations in subjects, for example, glucose monitoring devices to monitor glucose levels in subjects with diabetes.

Owner:LIFESCAN IP HLDG LLC +1

Integrated electroless deposition system

InactiveUS20070111519A1Electrolysis componentsSemiconductor/solid-state device manufacturingEngineeringElectroless deposition

Embodiments of the invention provide methods for depositing a material onto a surface of a substrate by using one or more electroless, electrochemical plating, CVD and / or ALD processes. Embodiments of the invention provide a method for depositing a seed layer on a substrate with an electroless process and to subsequently fill interconnect features on the substrate with an ECP process on a single substrate processing platform. Other aspects provide a method for depositing a seed layer on a substrate, fill interconnect features on a substrate, or sequentially deposit both a seed layer and fill interconnect features on the substrate. One embodiment provides a method for forming a capping layer over substrate interconnects. Methods include the use of a vapor dryer for pre- and post-deposition cleaning of substrates as well as a brush box chamber for post-deposition cleaning.

Owner:APPLIED MATERIALS INC

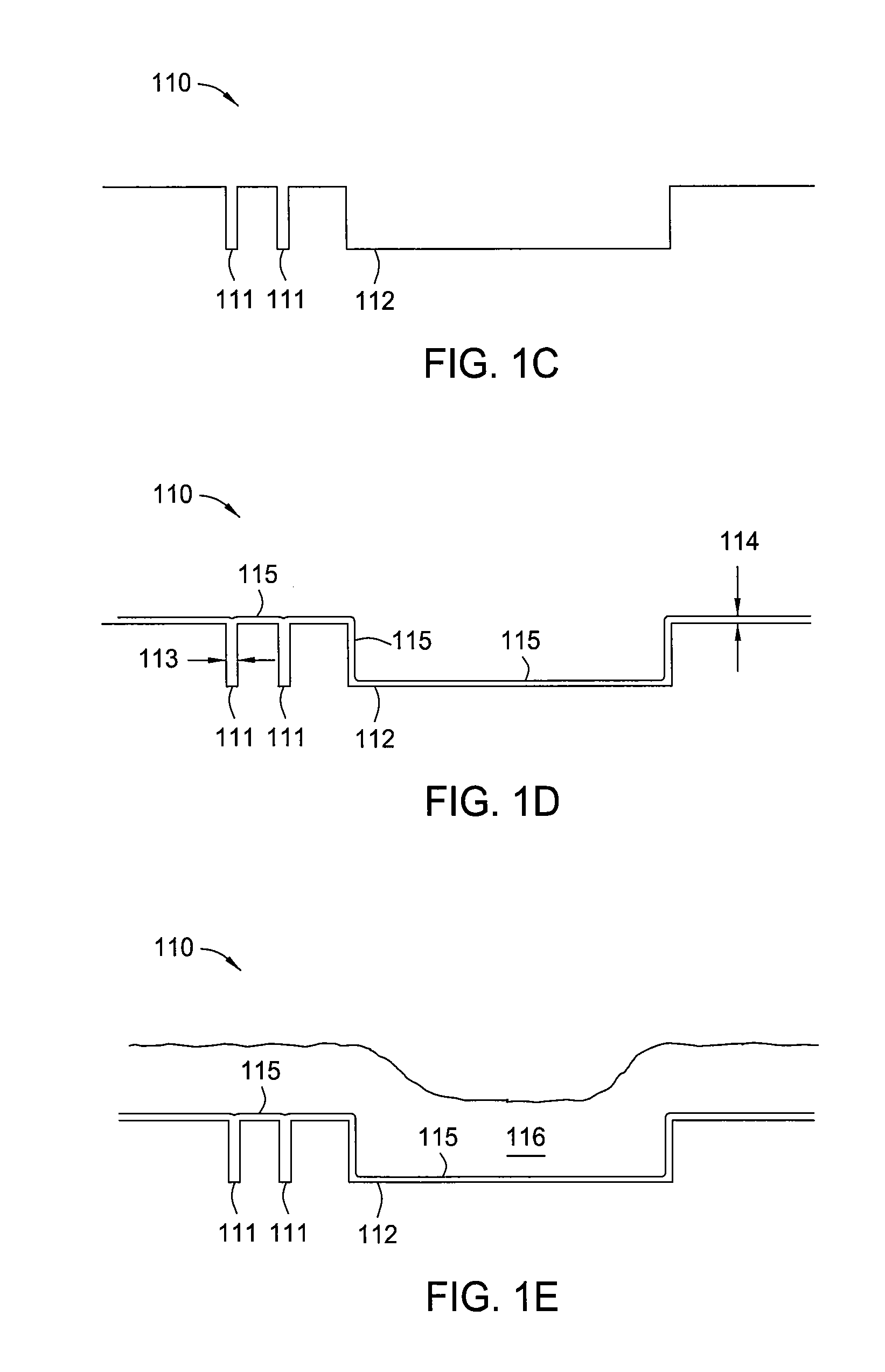

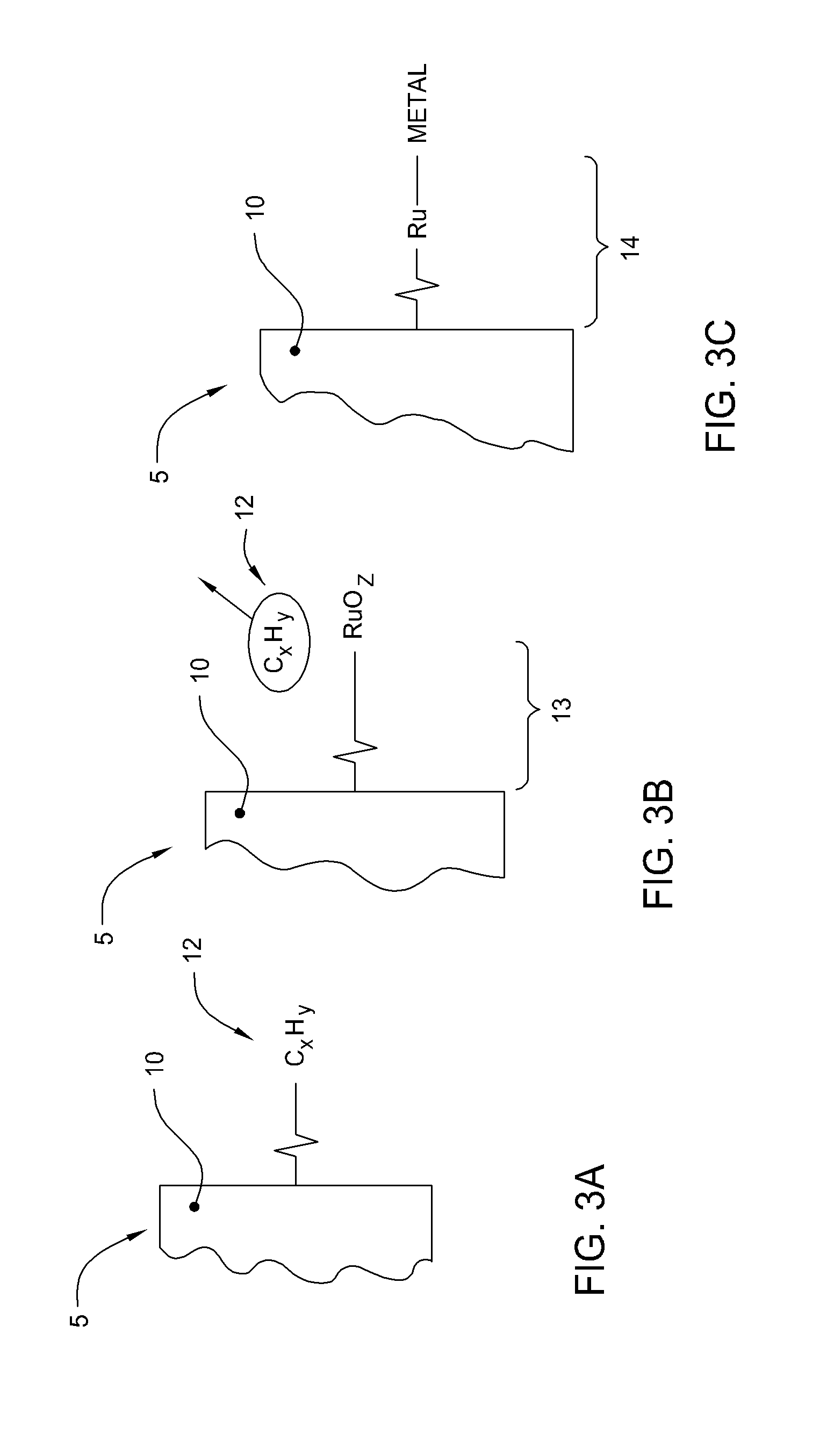

Patterned electroless metallization processes for large area electronics

The present invention generally provides an apparatus and method for selectively forming a metallized feature, such as an electrical interconnect feature, on a electrically insulating surface of a substrate. The present invention also provides a method of forming a mechanically robust, adherent, oxidation resistant conductive layer selectively over either a defined pattern or as a conformal blanket film. Embodiments of the invention also generally provide a new chemistry, process, and apparatus to provide discrete or blanket electrochemically or electrolessly platable ruthenium or ruthenium dioxide containing adhesion and initiation layers. In general, aspects of the present invention can be used for flat panel display processing, semiconductor processing, solar cell device processing, or any other substrate processing, being particularly well suited for the application of stable adherent coating on glass as well as flexible plastic substrates. This invention may be especially useful for the formation of electrical interconnects on the surface of flat panel display or solar cell type substrates where the line sizes are generally larger than semiconductor devices or where the formed feature are not generally as dense.

Owner:APPLIED MATERIALS INC

Popular searches

Time-pieces with integrated devices Pigment treatment with macromolecular organic compounds Pigment treatment with organosilicon compounds Semiconductor devices Electrophoretic coatings Electrographic process Record carriers used with machines Non-linear optics Input/output processes for data processing Base-materials