Patents

Literature

2332 results about "Salicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The term salicide refers to a technology used in the microelectronics industry used to form electrical contacts between the semiconductor device and the supporting interconnect structure. The salicide process involves the reaction of a metal thin film with silicon in the active regions of the device, ultimately forming a metal silicide contact through a series of annealing and/or etch processes. The term "salicide" is a compaction of the phrase self-aligned silicide. The description "self-aligned" suggests that the contact formation does not require photolithography patterning processes, as opposed to a non-aligned technology such as polycide.

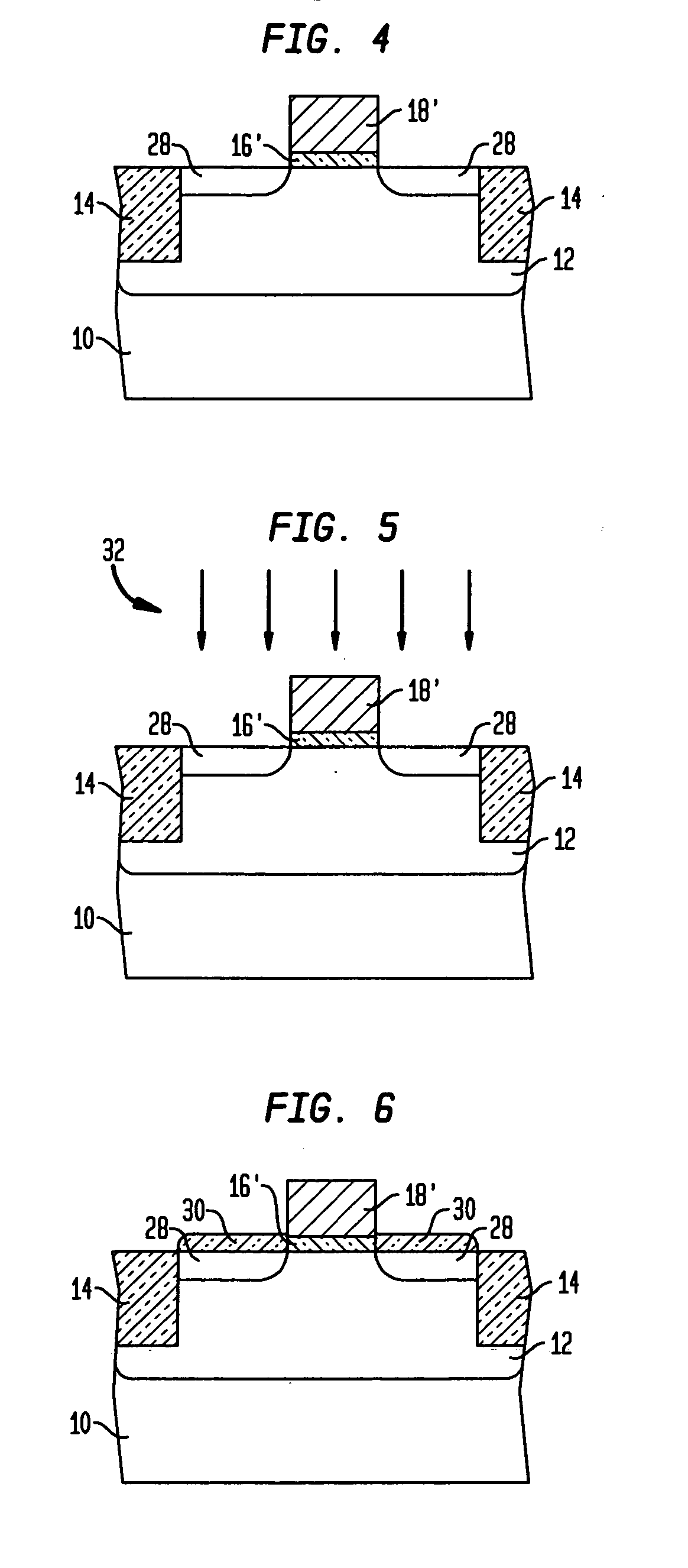

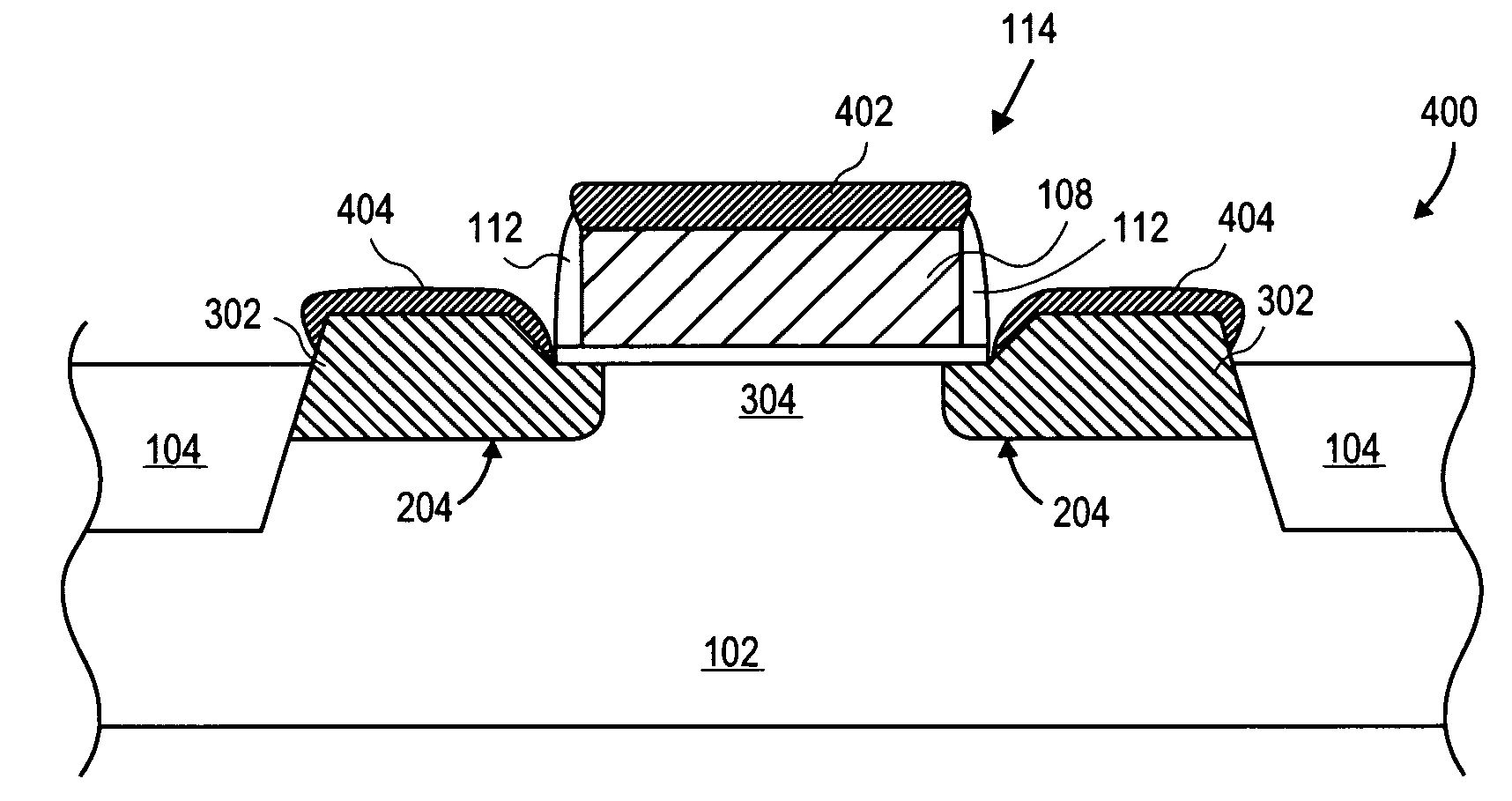

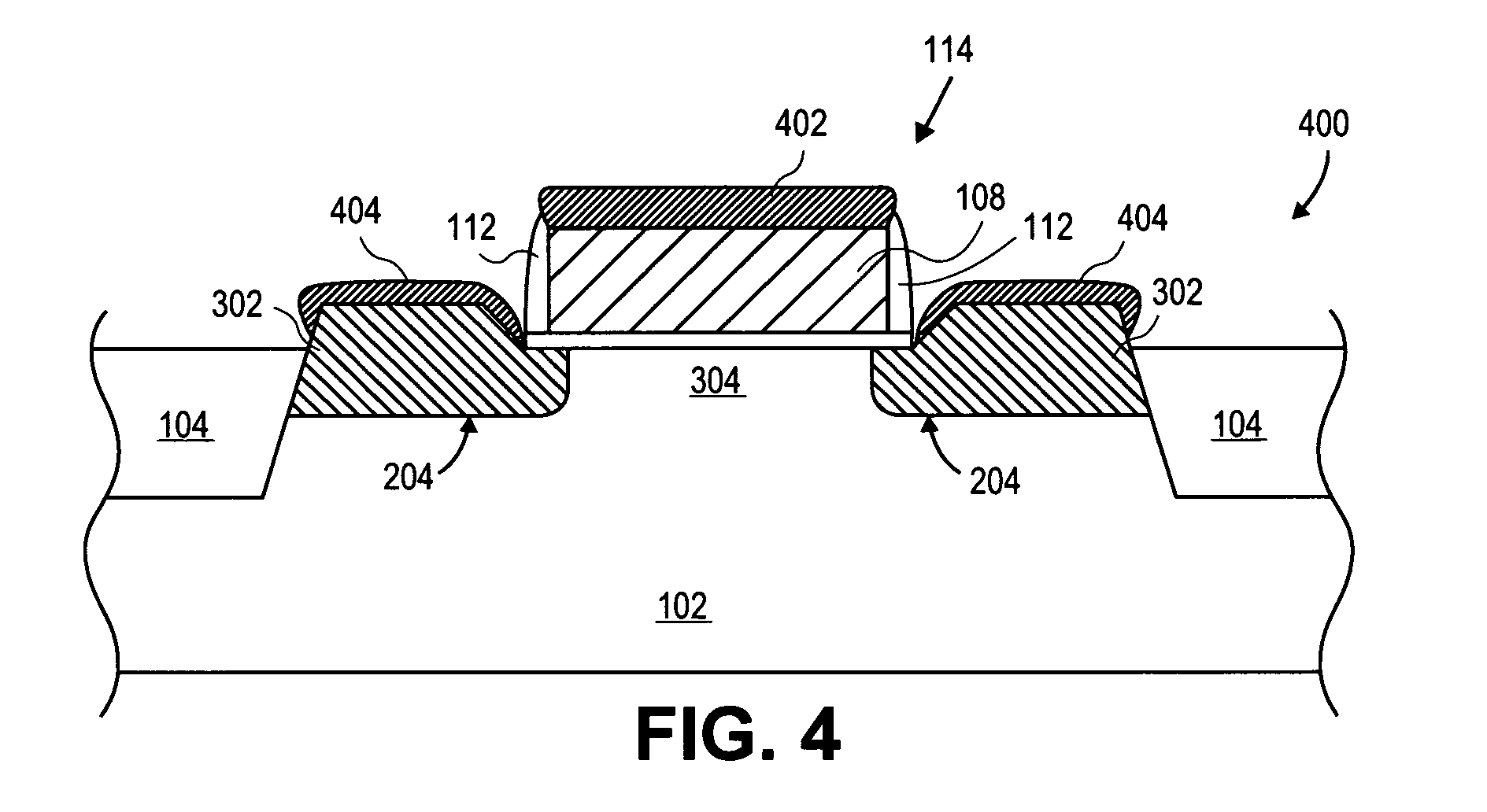

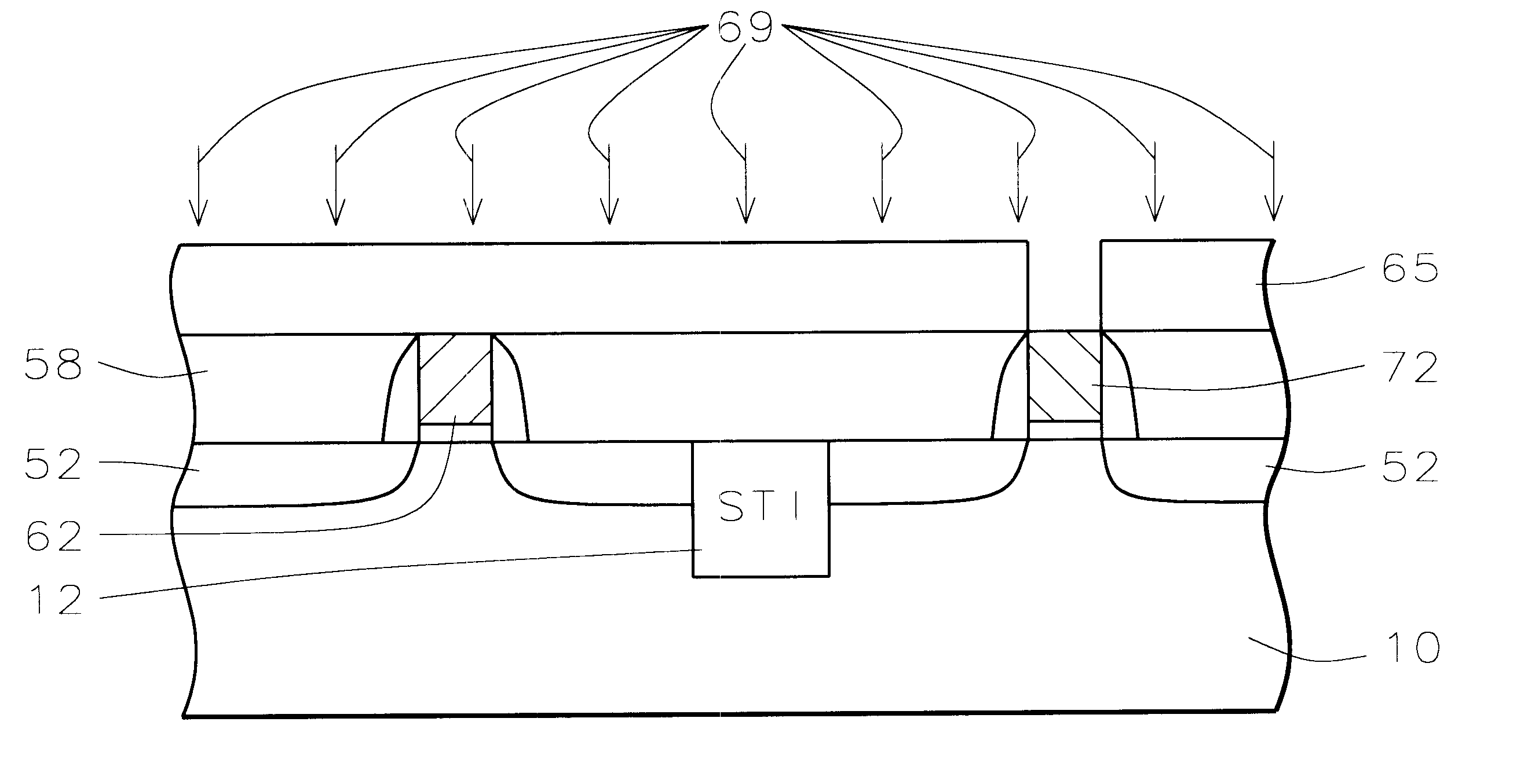

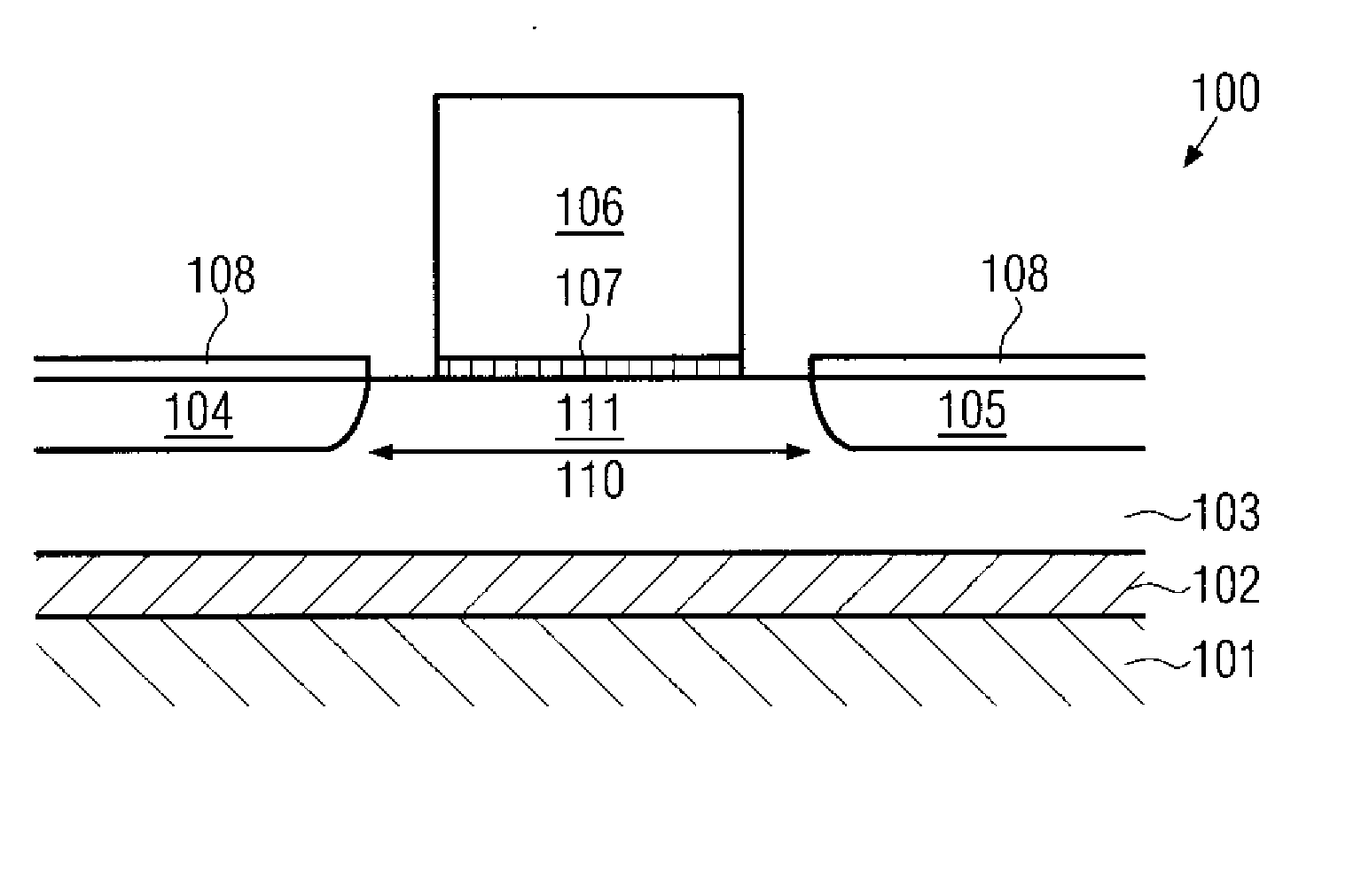

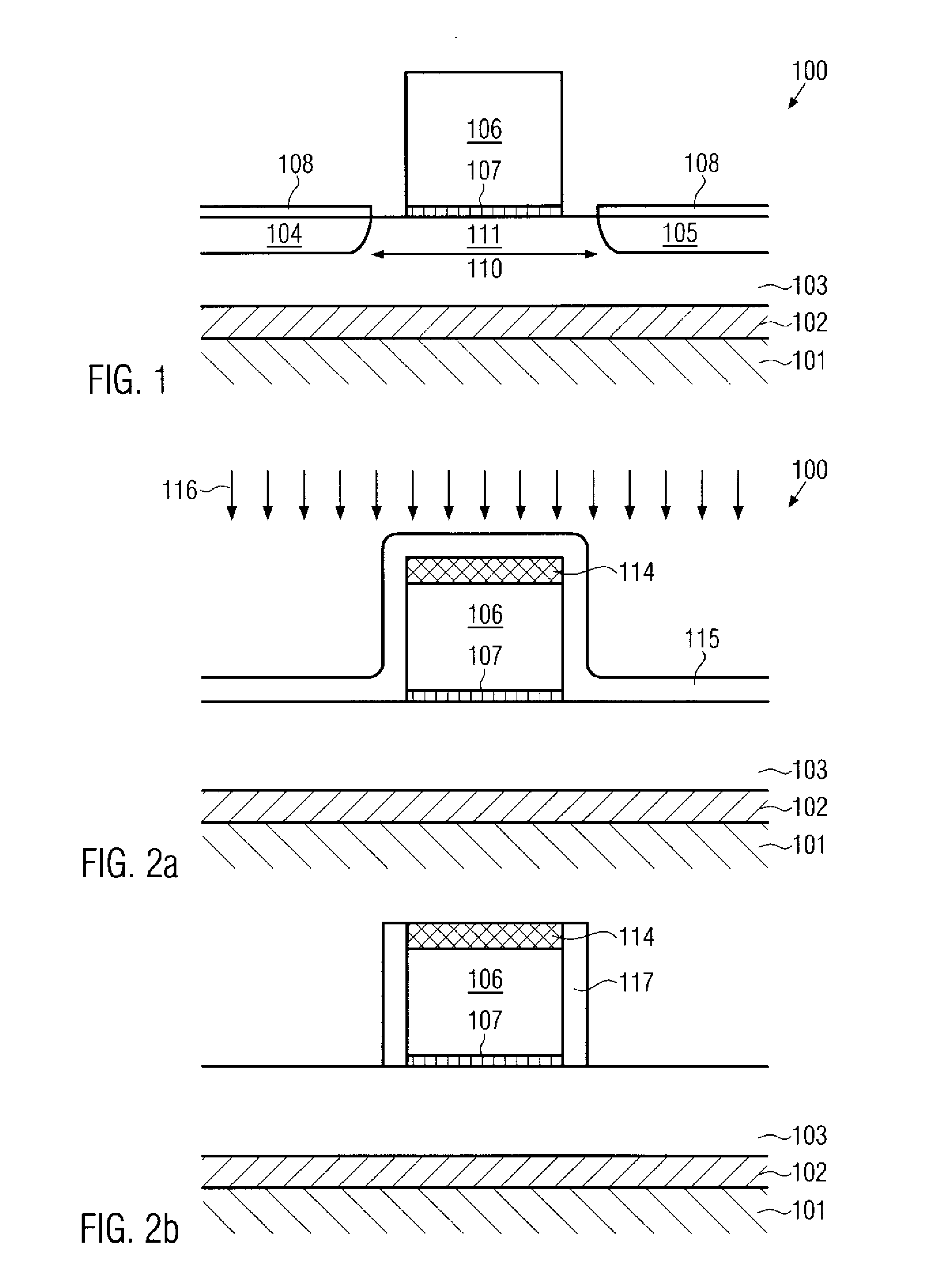

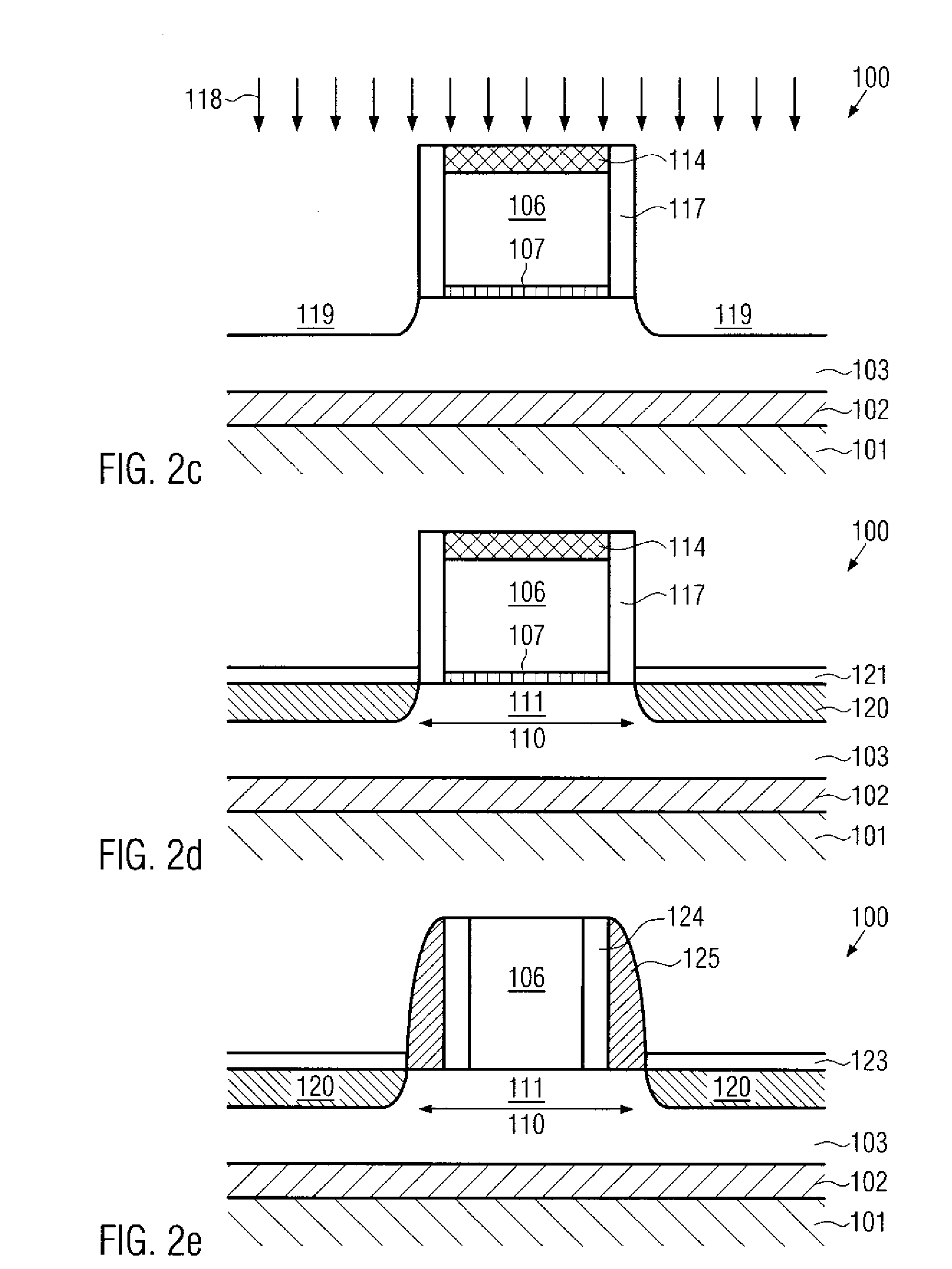

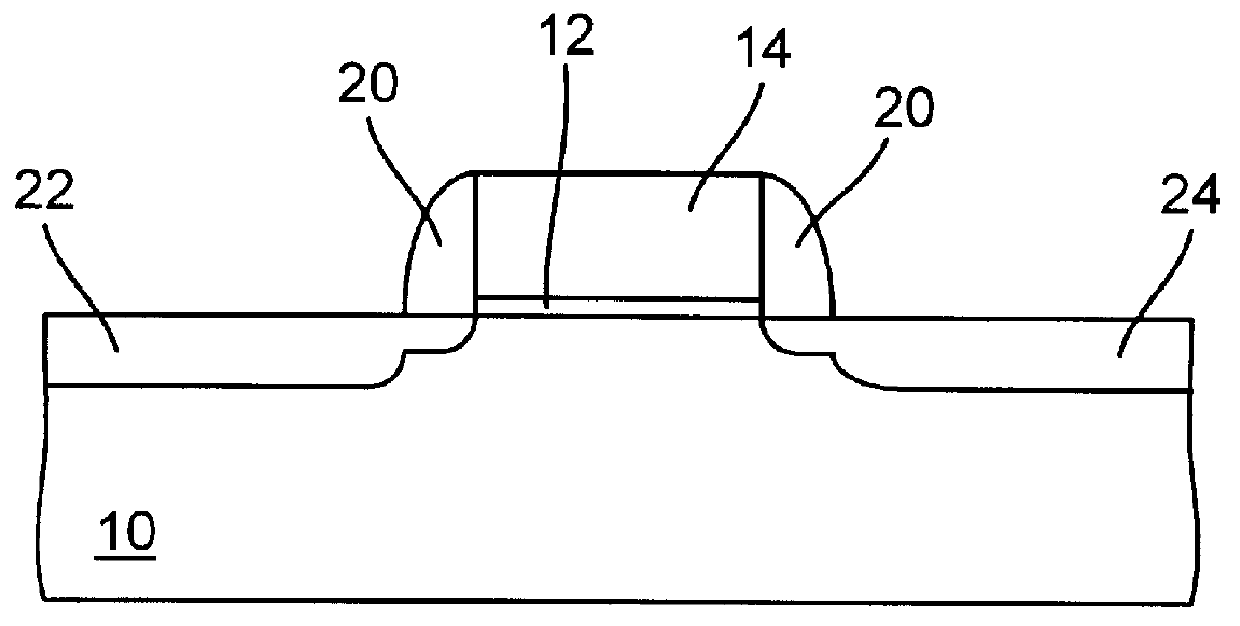

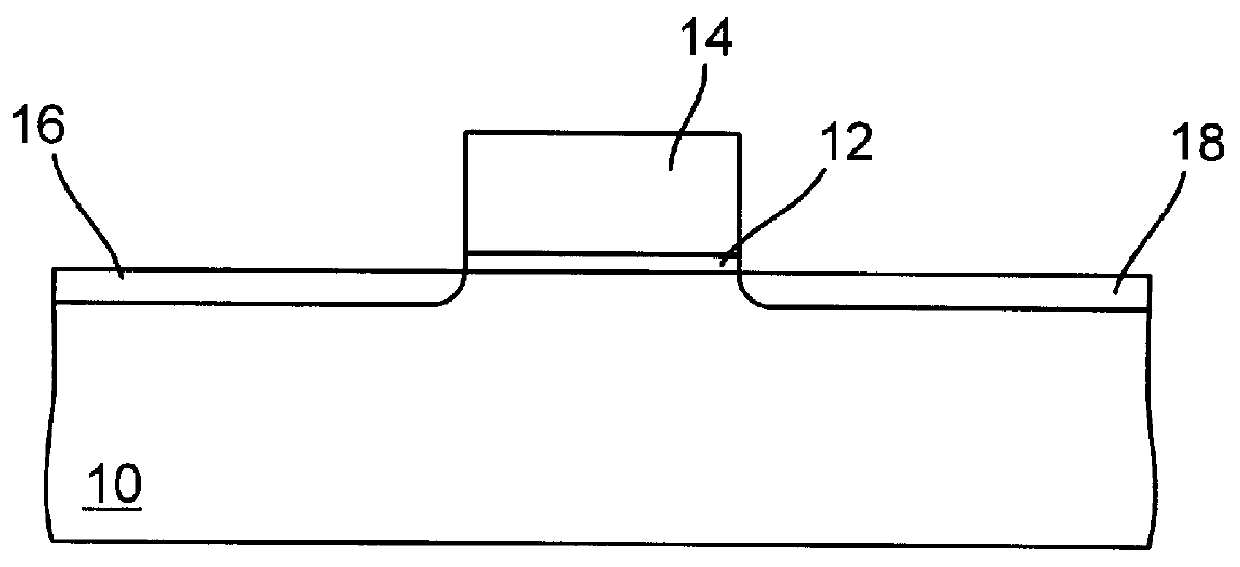

Opto-thermal annealing methods for forming metal gate and fully silicided gate field effect transistors

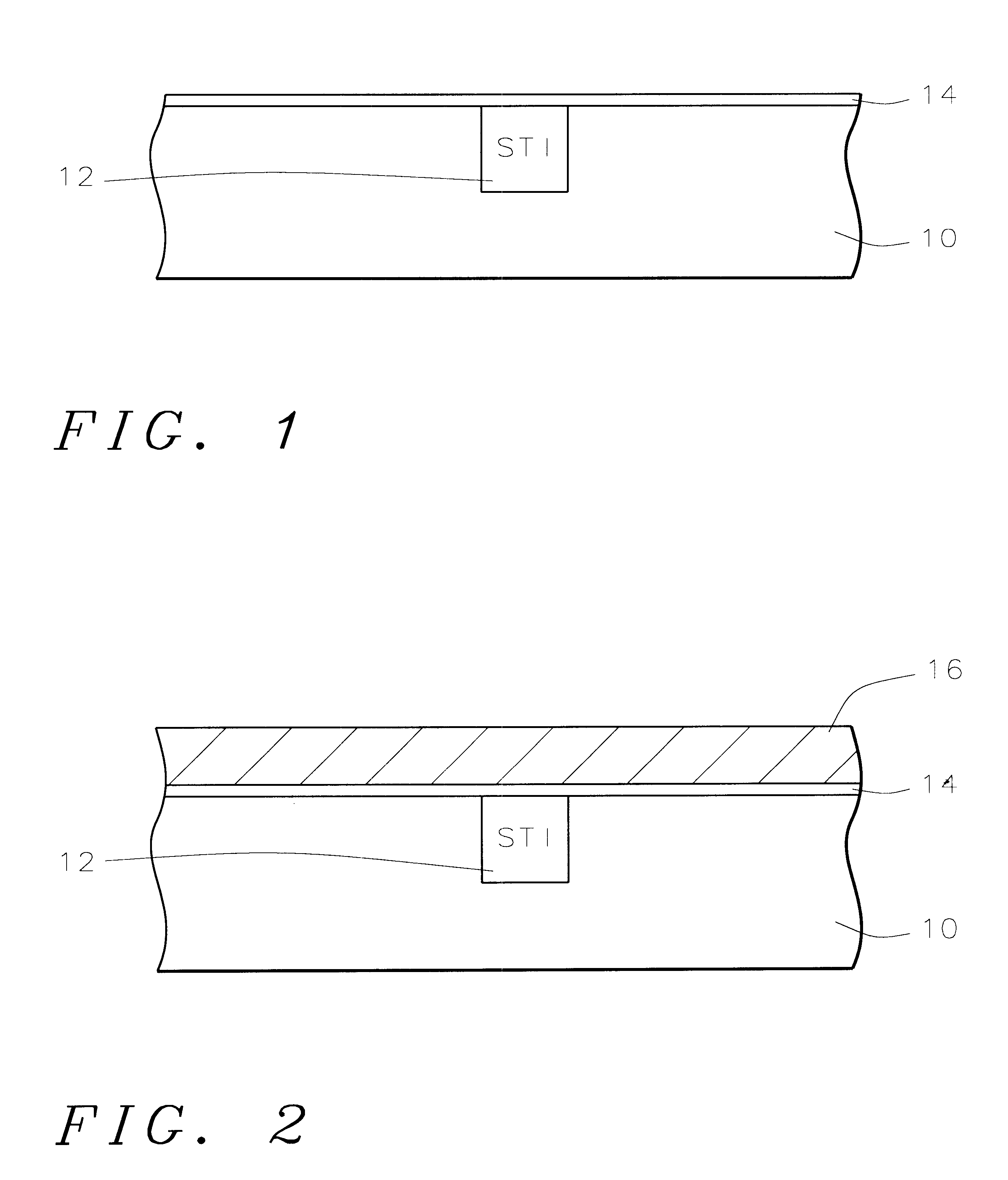

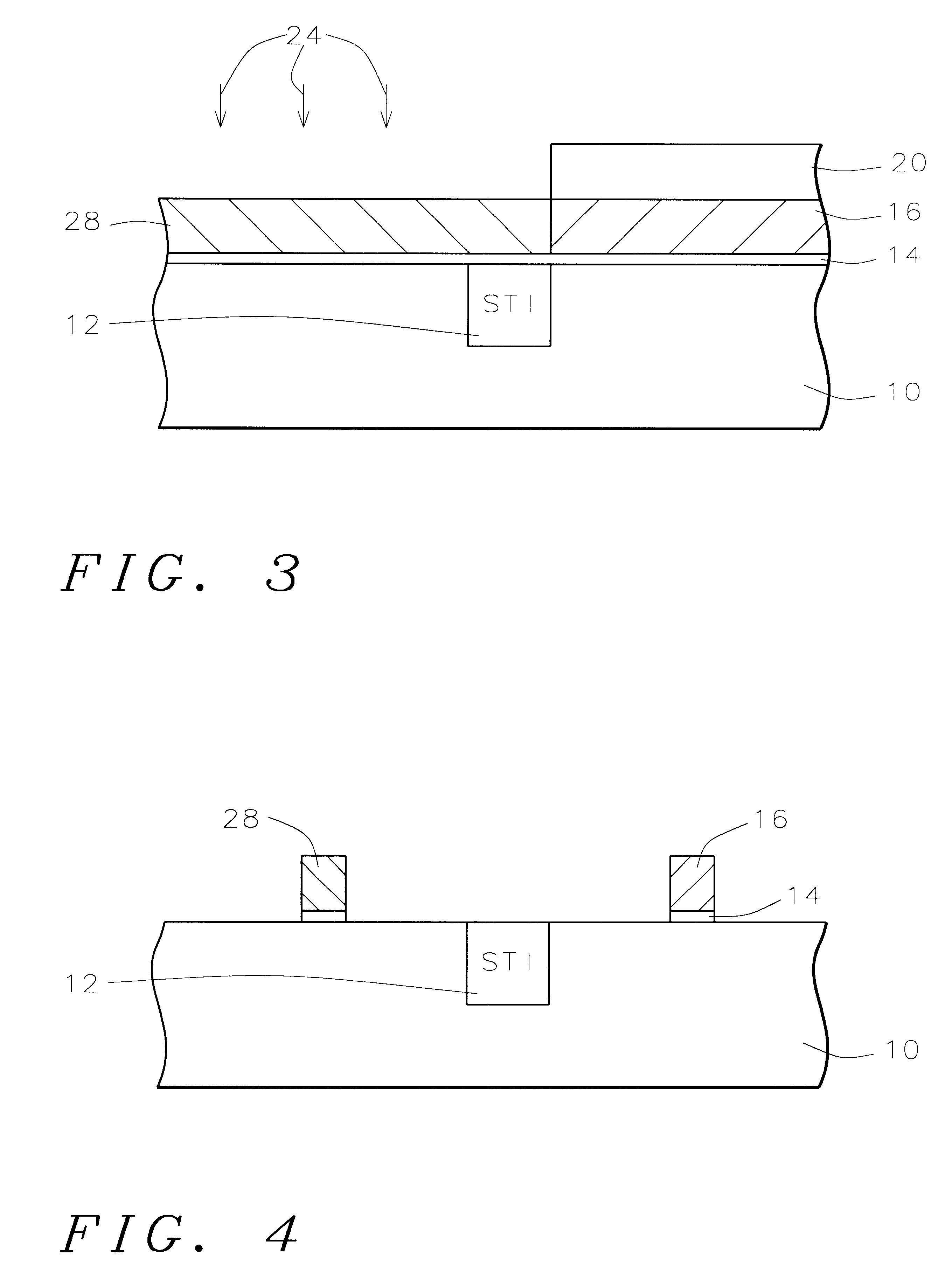

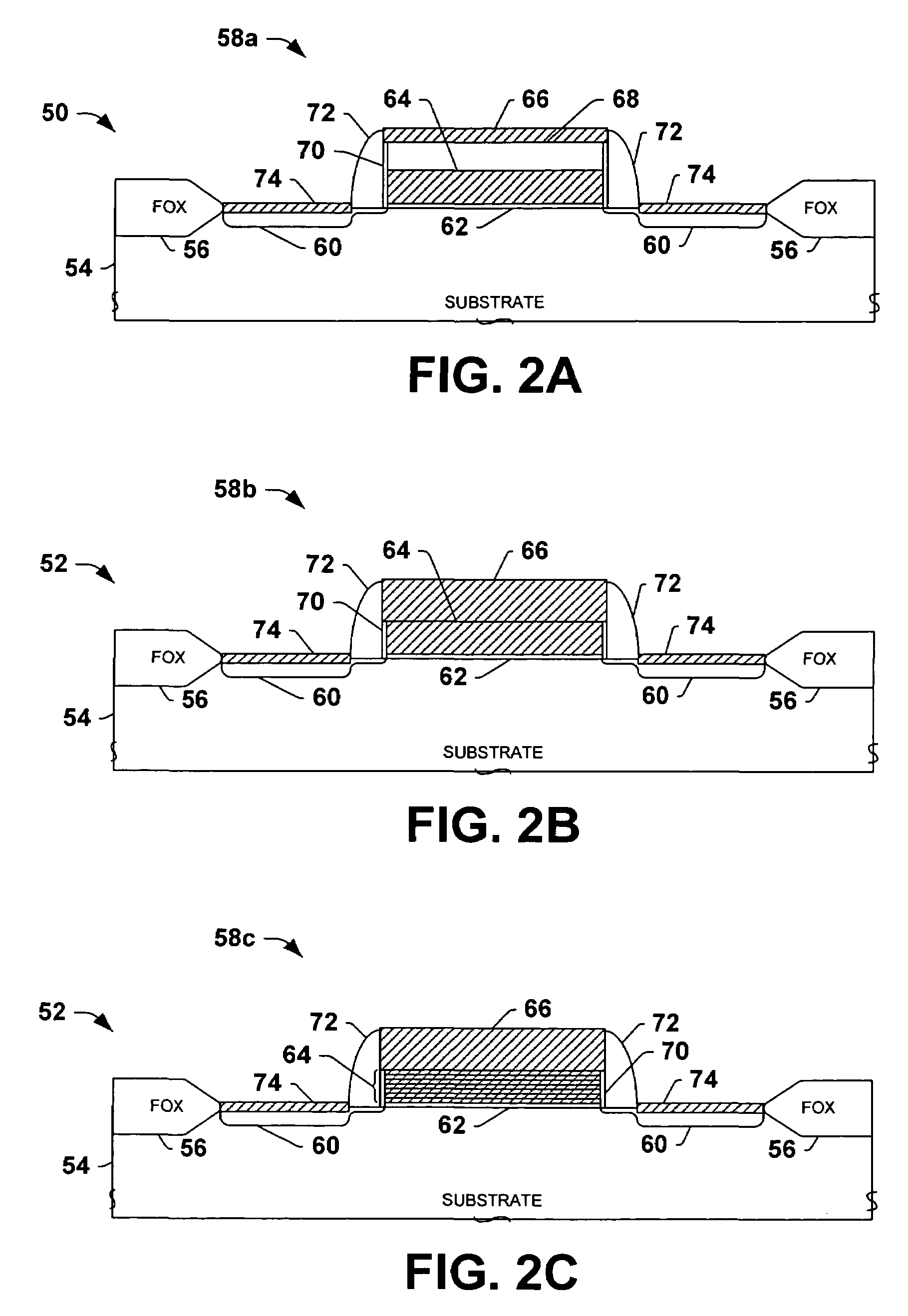

ActiveUS20070249131A1Avoid opto-thermal annealing damageAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideGate dielectric

An opto-thermal annealing method for forming a field effect transistor uses a reflective metal gate so that electrical properties of the metal gate and also interface between the metal gate and a gate dielectric are not compromised when opto-thermal annealing a source / drain region adjacent the metal gate. Another opto-thermal annealing method may be used for simultaneously opto-thermally annealing: (1) a silicon layer and a silicide forming metal layer to form a fully silicided gate; and (2) a source / drain region to form an annealed source / drain region. An additional opto-thermal annealing method may use a thermal insulator layer in conjunction with a thermal absorber layer to selectively opto-thermally anneal a silicon layer and a silicide forming metal layer to form a fully silicide gate.

Owner:TAIWAN SEMICON MFG CO LTD

Methods for depositing nickel films and for making nickel silicide and nickel germanide

ActiveUS20130115768A1Semiconductor/solid-state device manufacturingSemiconductor devicesGas phaseMetal silicide

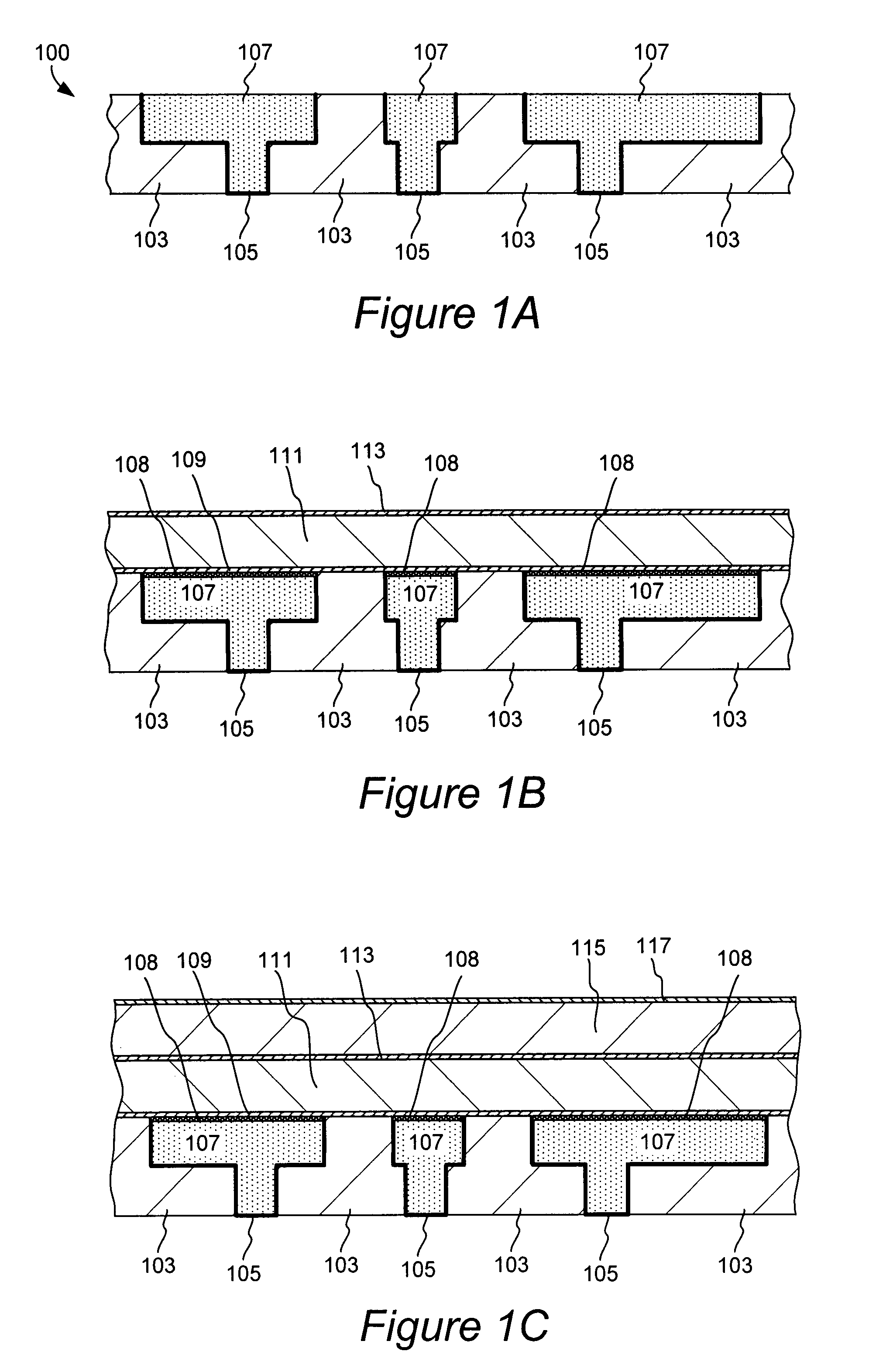

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD. Nickel thin films can be used directly in silicidation and germanidation processes.

Owner:ASM INTERNATIONAL

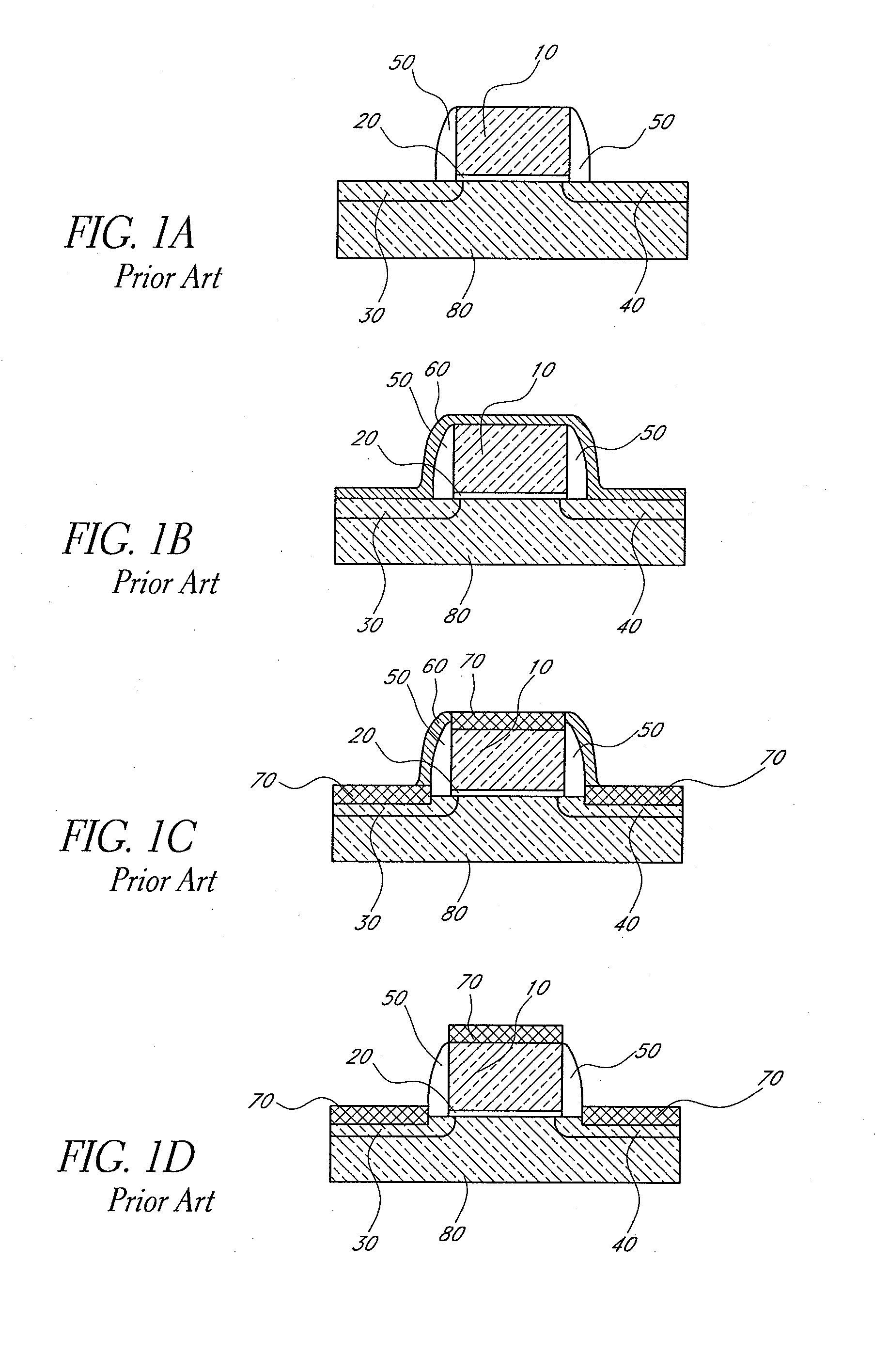

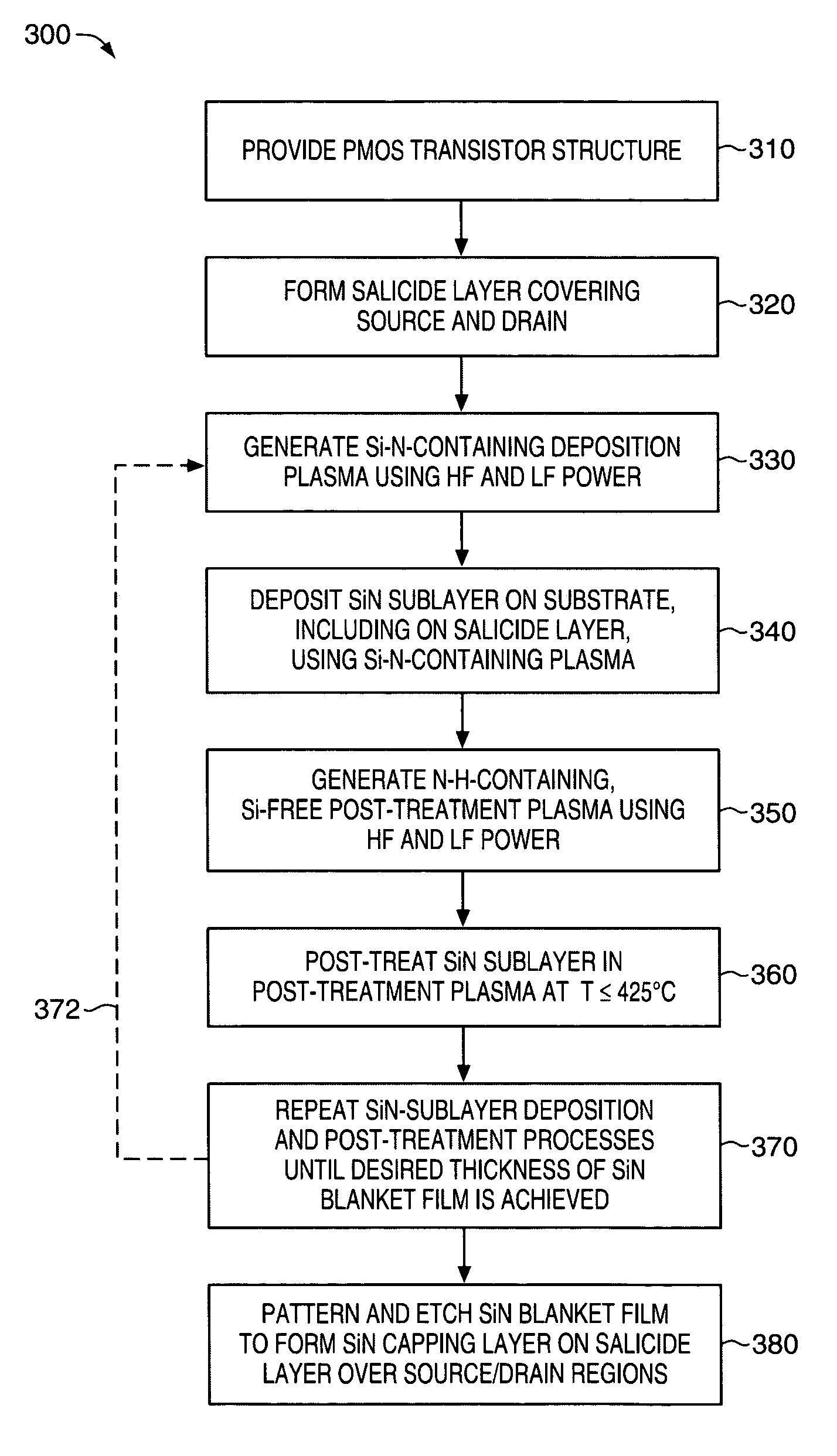

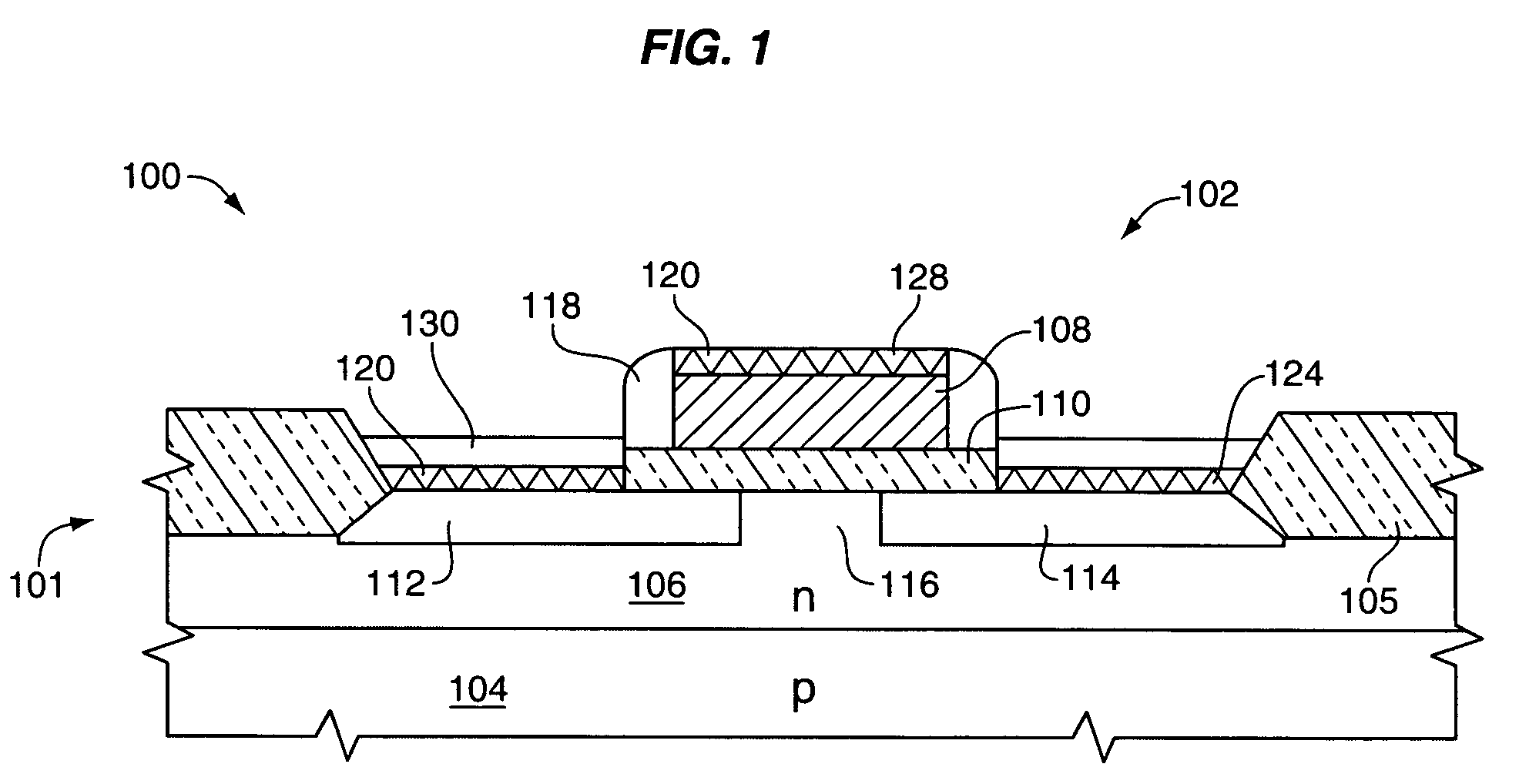

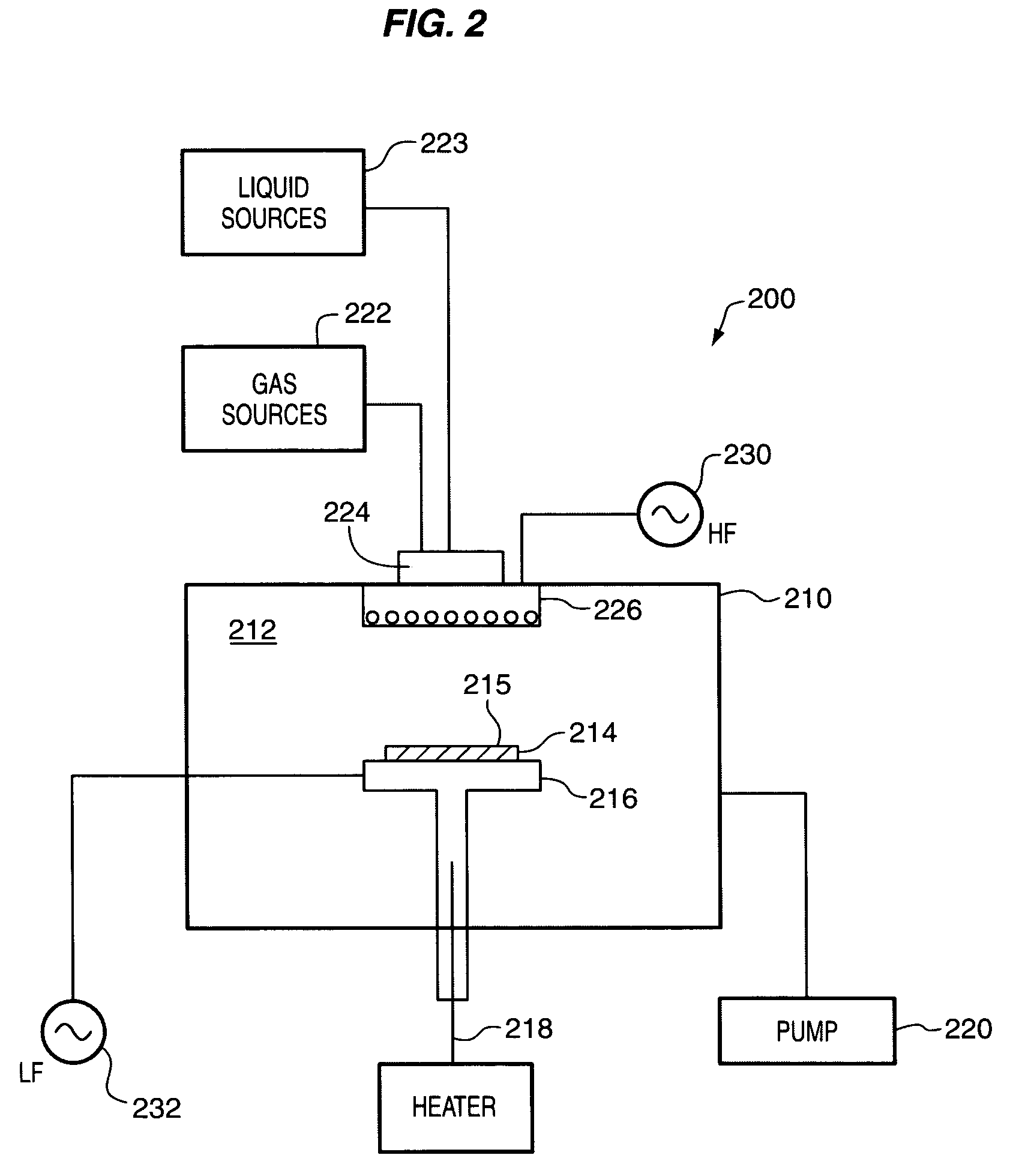

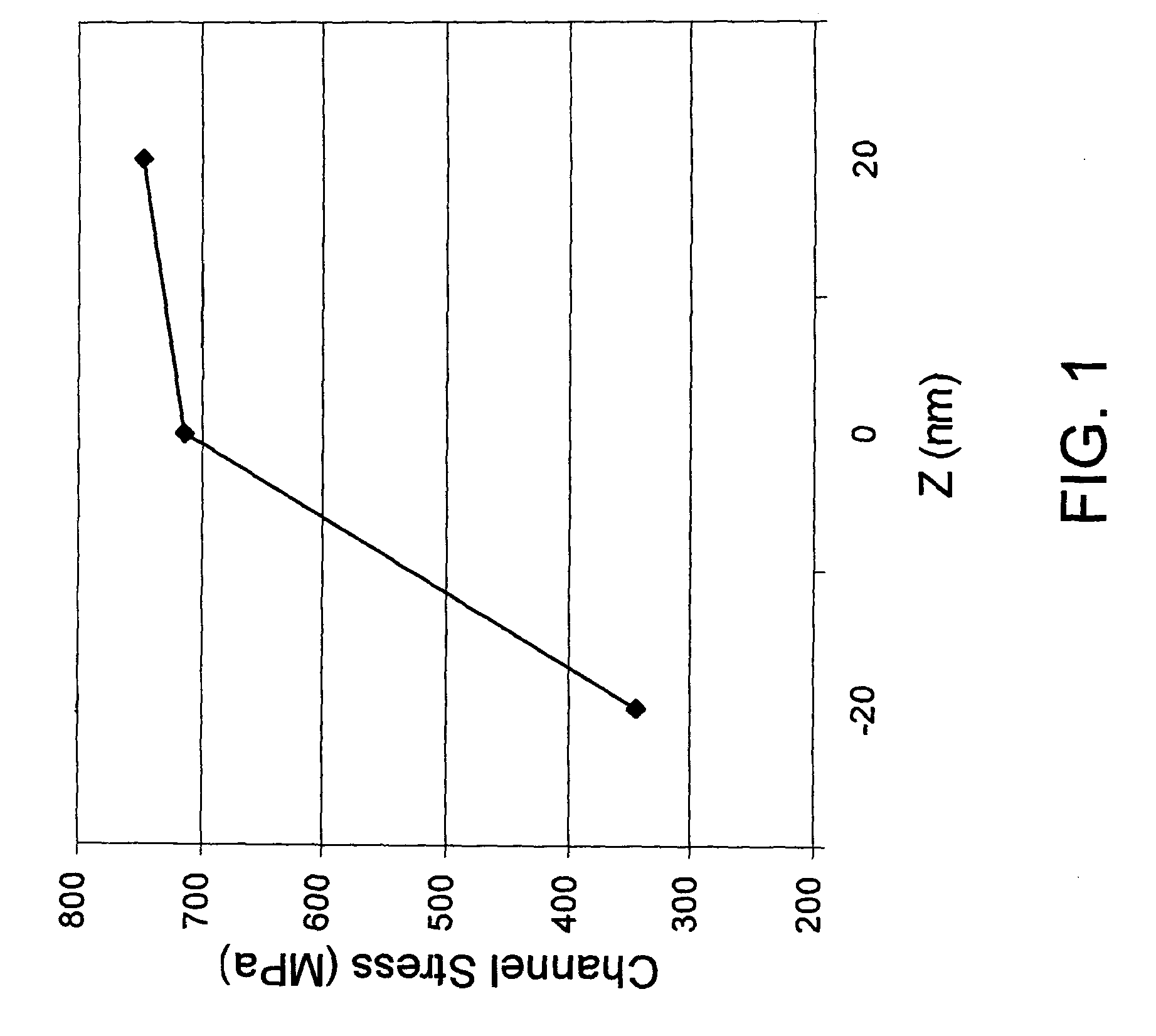

PMOS transistor with compressive dielectric capping layer

ActiveUS7214630B1Preserving material qualityImprove performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSalicideOxidation state

A salicide layer is deposited on the source / drain regions of a PMOS transistor. A dielectric capping layer having residual compressive stress is formed on the salicide layer by depositing a plurality of PECVD dielectric sublayers and plasma-treating each sublayer. Compressive stress from the dielectric capping layer is uniaxially transferred to the PMOS channel through the source-drain regions to create compressive strain in the PMOS channel. To form a compressive dielectric layer, a deposition reactant mixture containing A1 atoms and A2 atoms is provided in a vacuum chamber. Element A2 is more electronegative than element A1, and A1 atoms have a positive oxidation state and A2 atoms have a negative oxidation state when A1 atoms are bonded with A2 atoms. A deposition plasma is generated by applying HF and LF radio-frequency power to the deposition reactant mixture, and a sublayer of compressive dielectric material is deposited. A post-treatment plasma is generated by applying HF and LF radio-frequency power to a post-treatment gas that does not contain at least one of A1 atoms and A2 atoms. Compressive stress in the dielectric sublayer is increased by treating the sublayer in the post-treatment plasma. Processes of depositing a dielectric sublayer and post-treating the sublayer in plasma are repeated until a desired thickness is achieved. The resulting dielectric layer has residual compressive stress.

Owner:NOVELLUS SYSTEMS

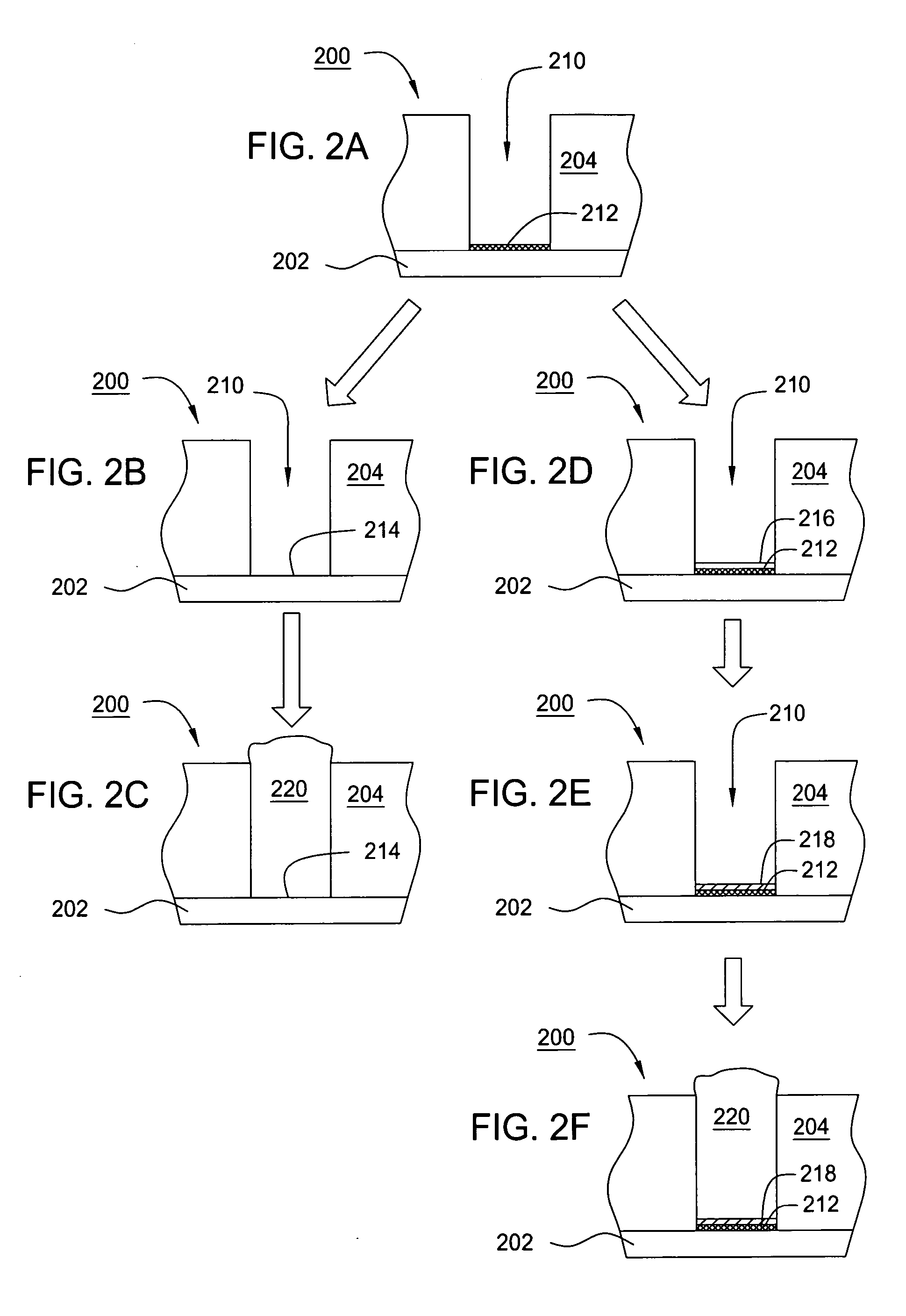

Electroless deposition process on a silicon contact

ActiveUS20060264043A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideAlloy

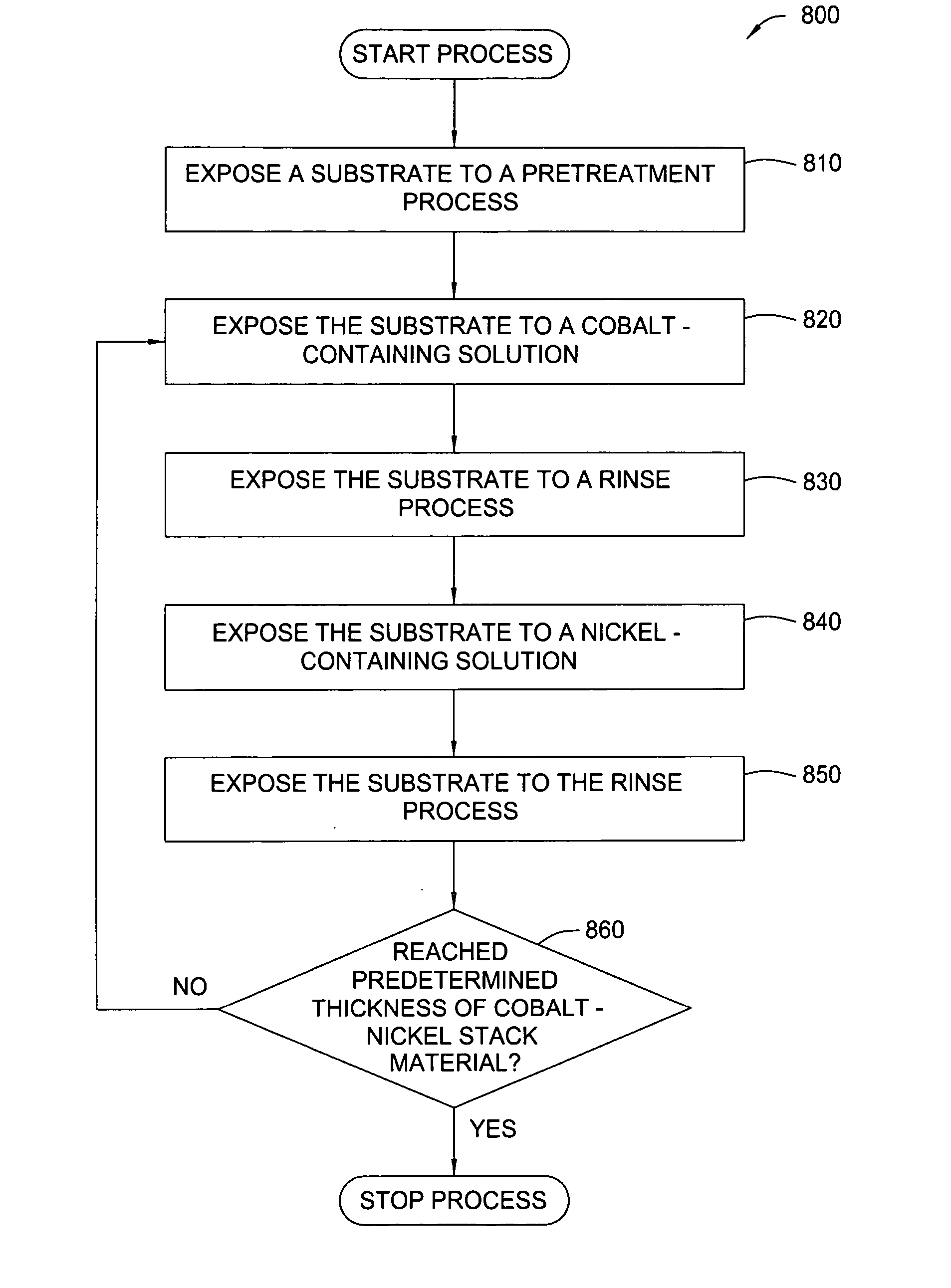

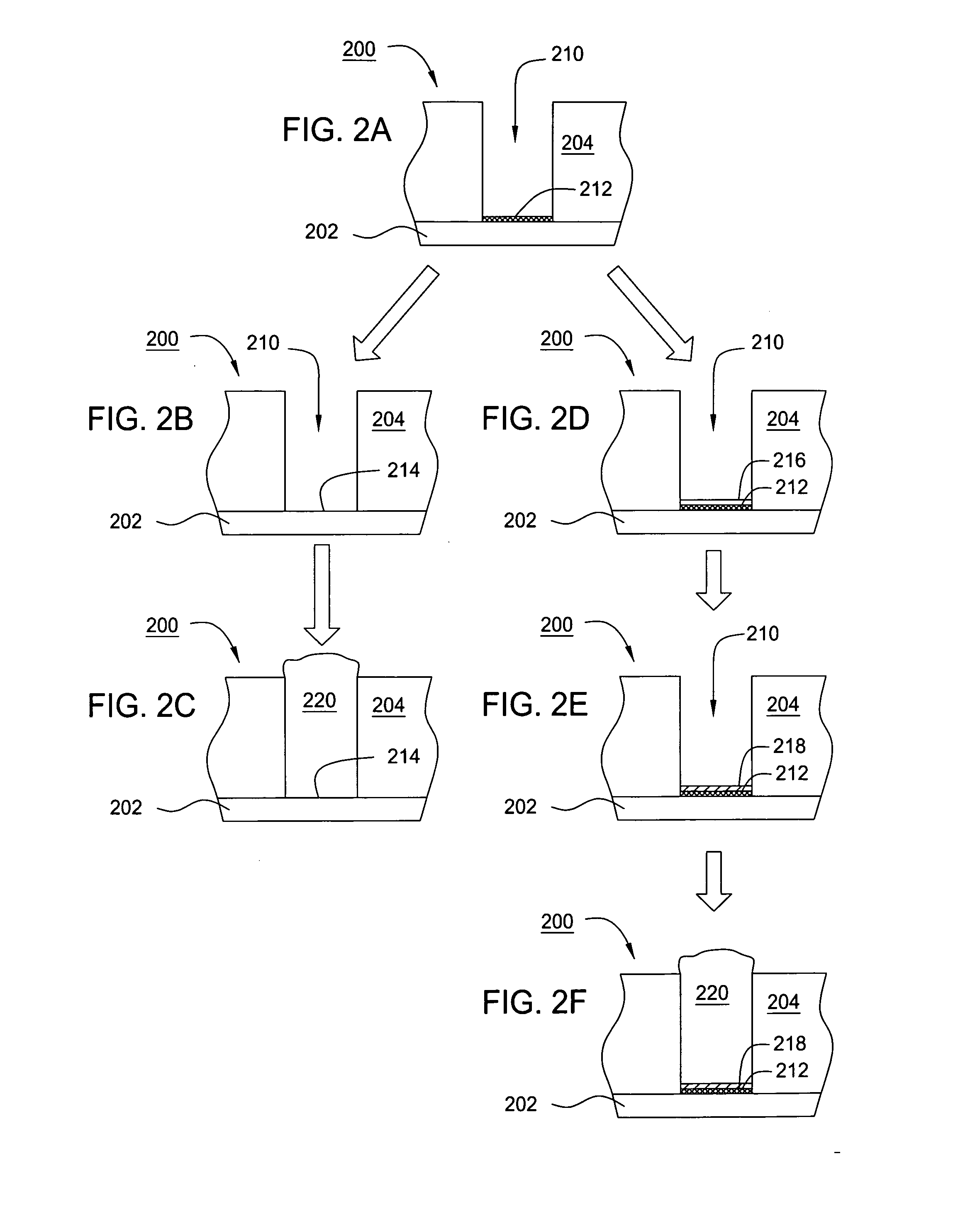

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

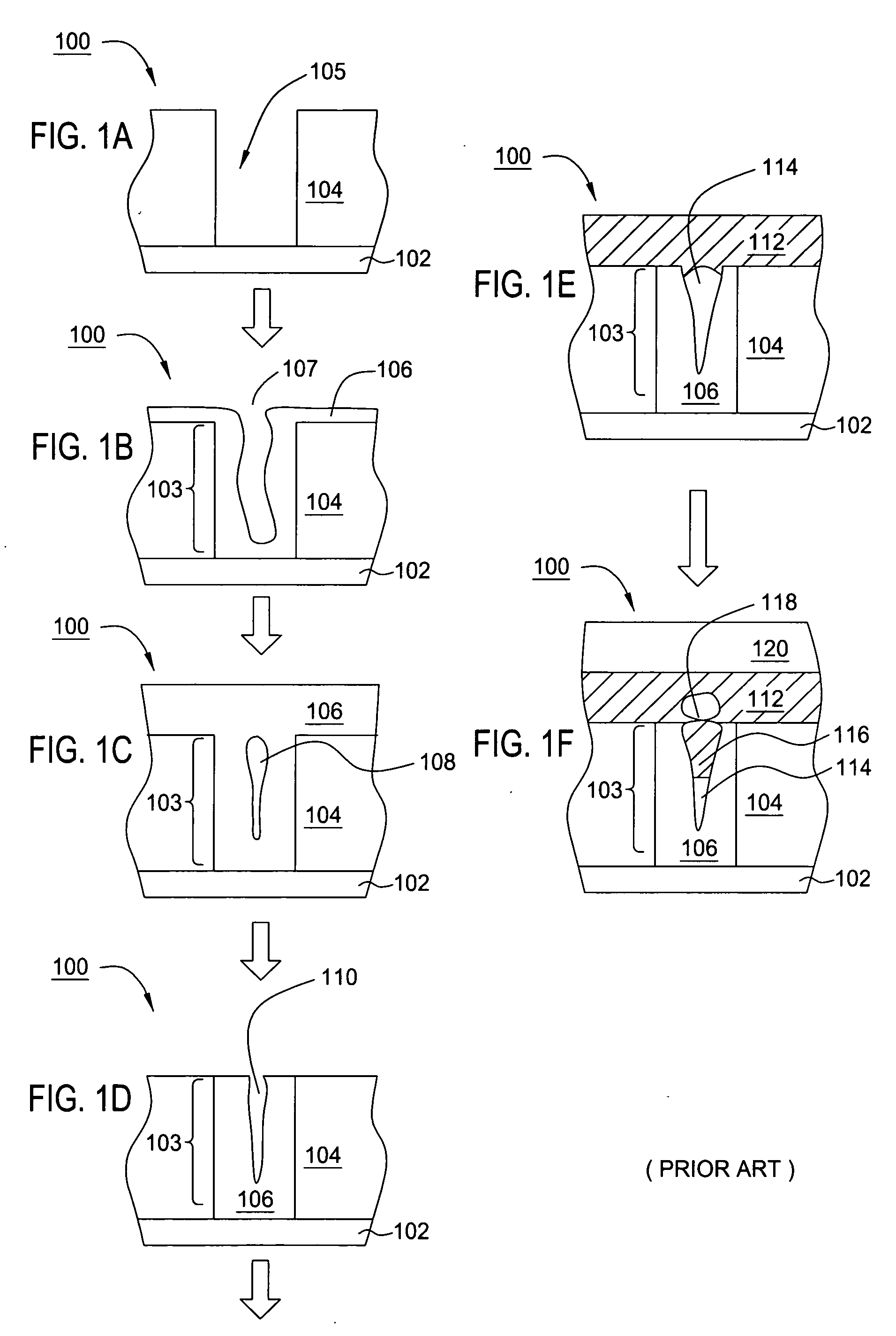

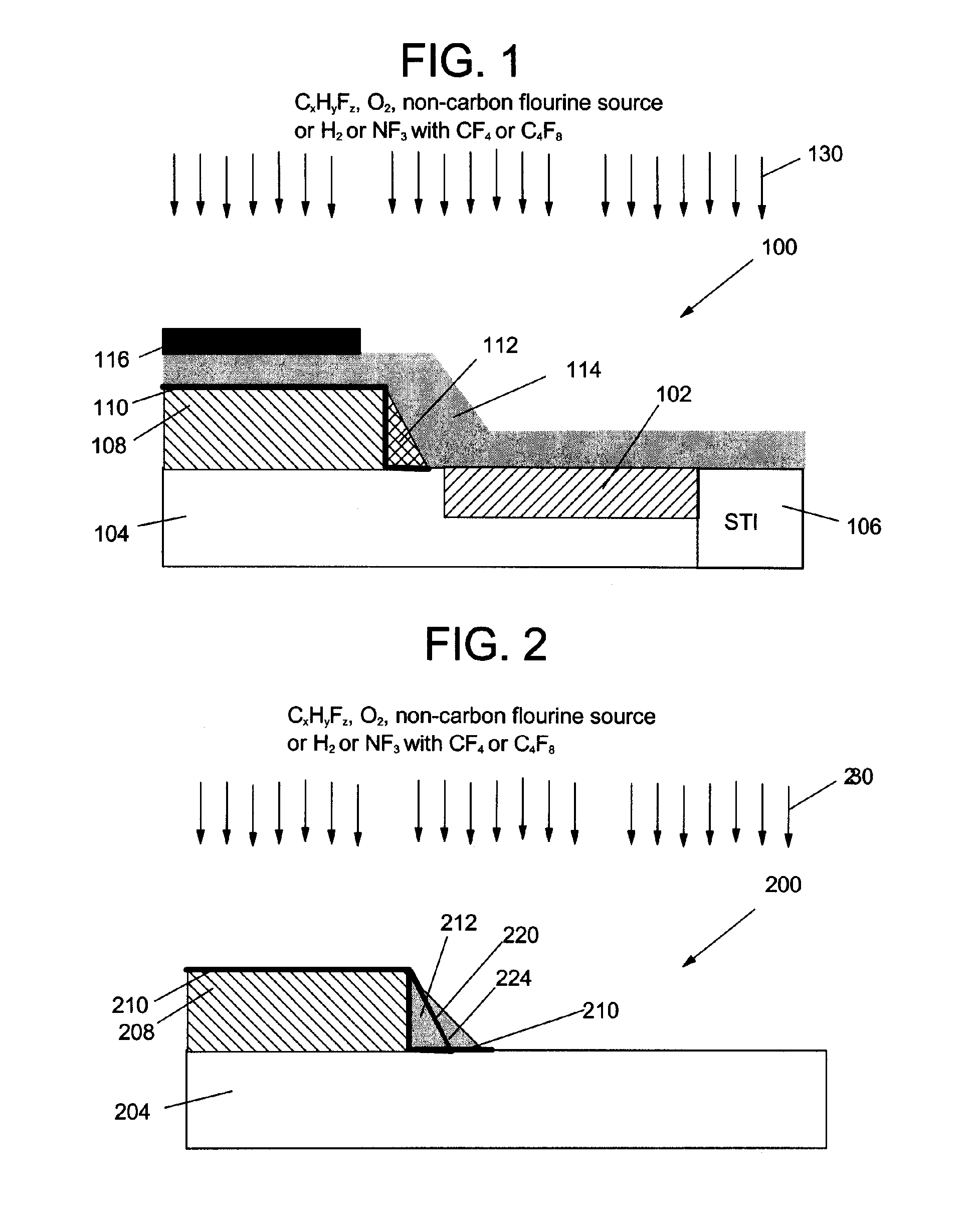

Silicon nitride etching methods

ActiveUS7288482B2Semiconductor/solid-state device manufacturingSulfur hexafluorideOctafluorocyclobutane

Methods of etching silicon nitride material, and more particularly, etching nitride selective to silicon dioxide or silicide, are disclosed. The methods include exposing a substrate having silicon nitride thereon to a plasma including at least one fluorohydrocarbon and a non-carbon containing fluorine source such as sulfur hexafluoride (SF6). The plasma may also include oxygen (O2) and the fluorohydrocarbons may include at least one of: trifluoromethane (CHF3), difluoromethane (CH2F2), and methyl fluoride (CH3F). In an alternative embodiment, the plasma includes one of hydrogen (H2) and nitrogen trifluoride (NF3) and one of tetrafluoromethane (CF4) and octafluorocyclobutane (C4F8). The methods are preferably carried out using a low bias voltage, e.g. <100 V.

Owner:IBM CORP +1

Electroless deposition process on a silicide contact

InactiveUS20060246217A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideElectroless deposition

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

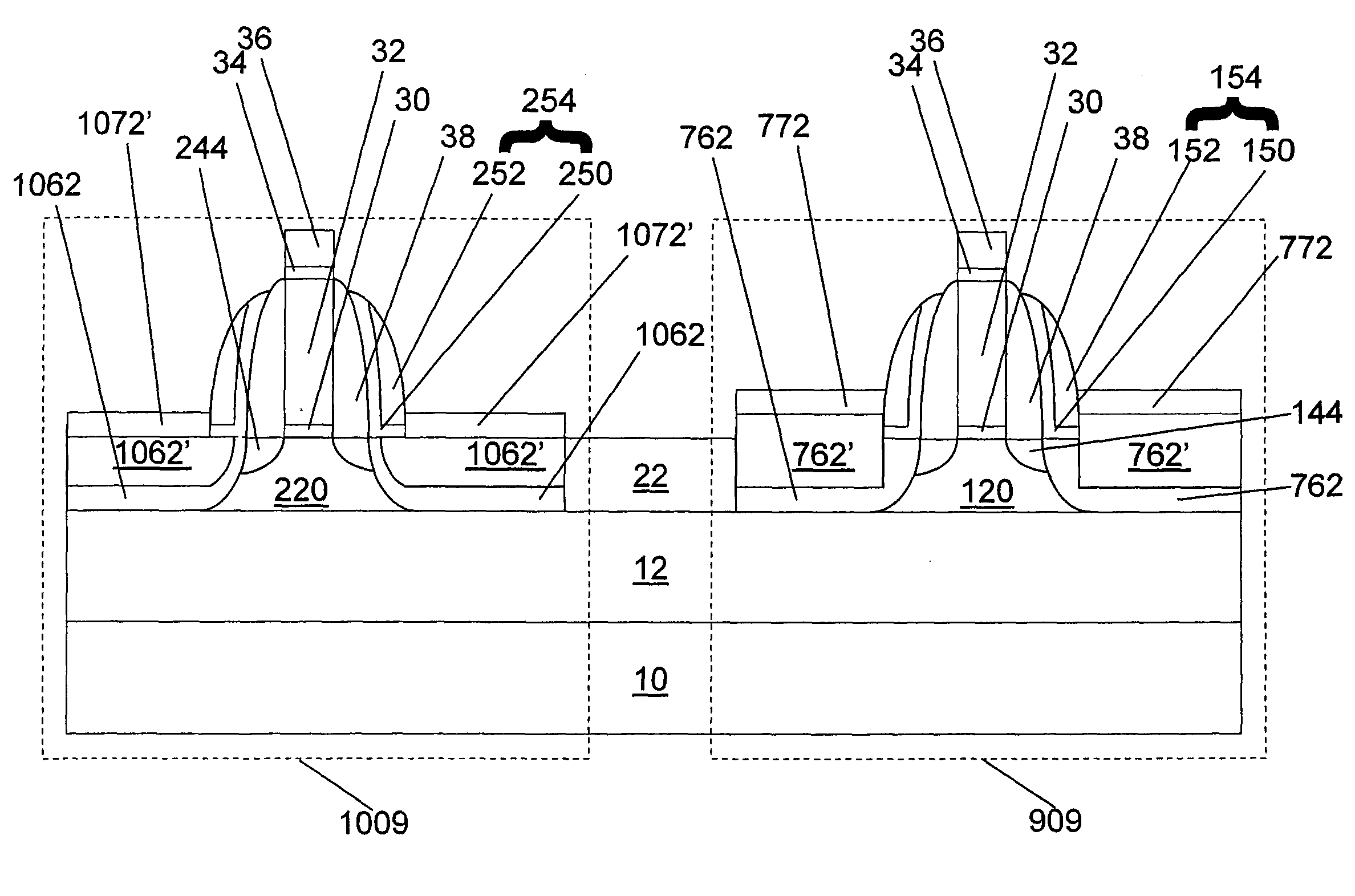

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched semiconductor regions underlying source and drain regions

Owner:SEMICON MFG INT (SHANGHAI) CORP

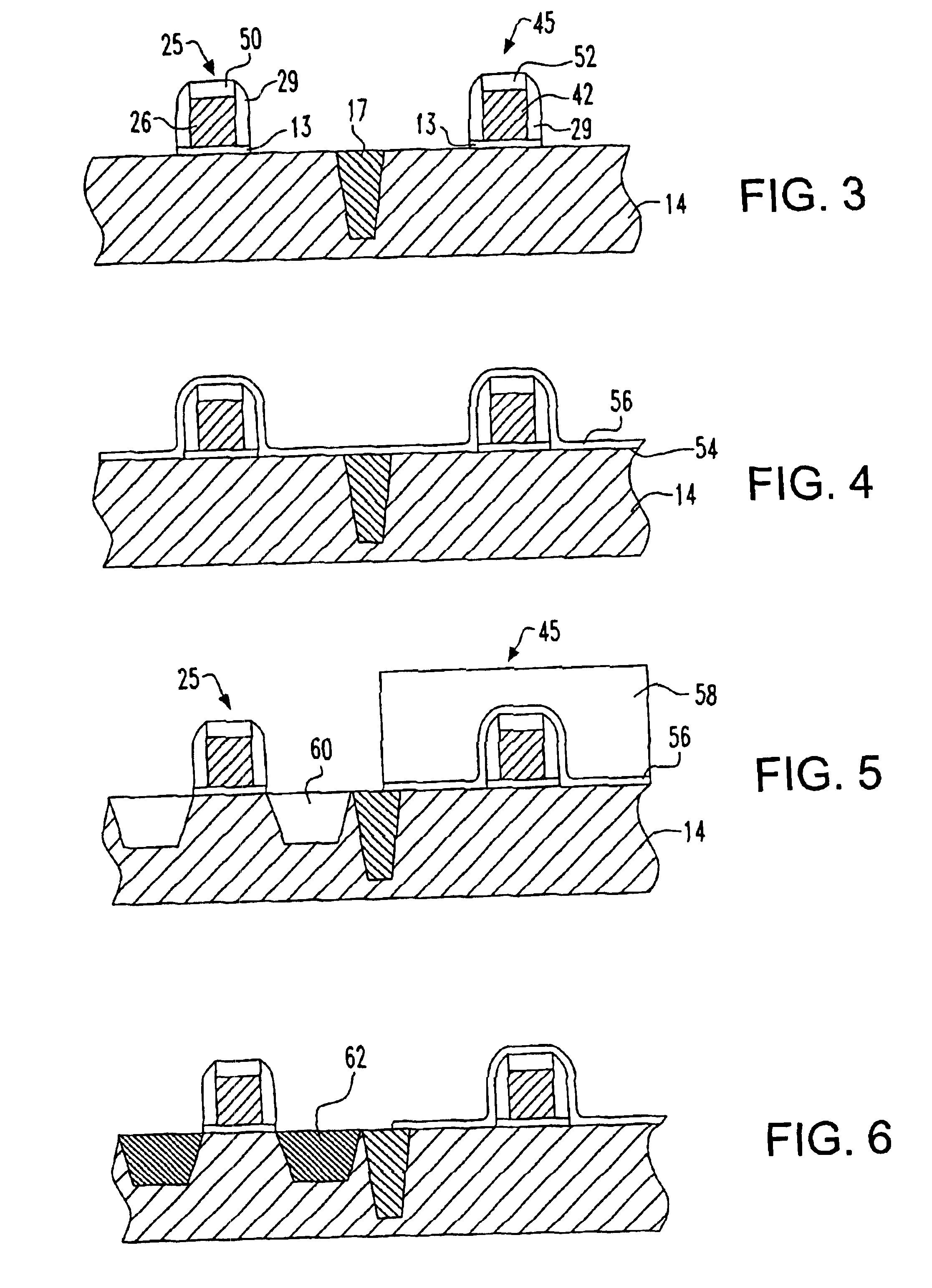

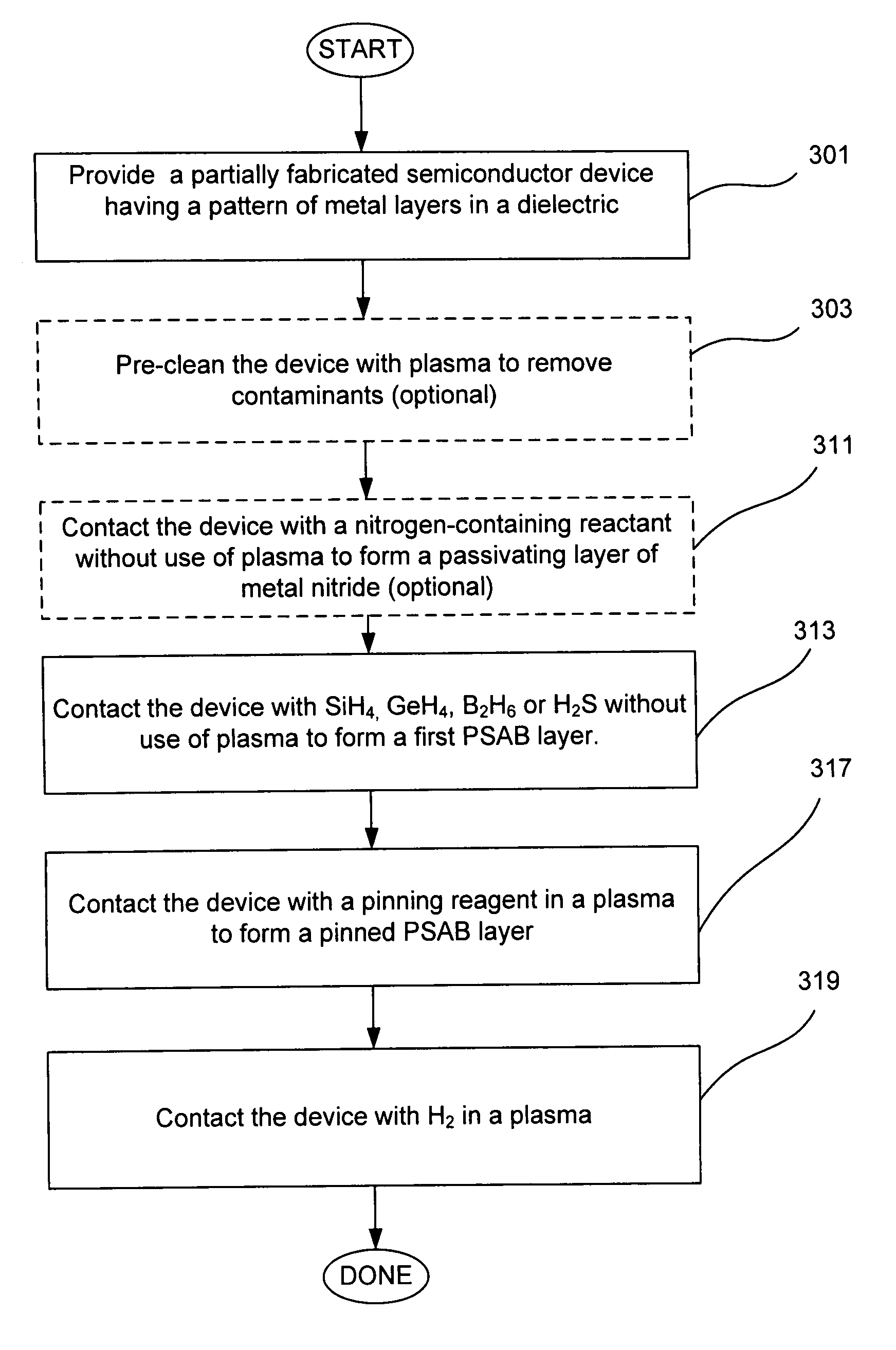

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7727880B1Improving several propertyDecrease in metal electromigrationSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

Protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. In a Damascene interconnect, PSAB layer typically resides at an interface between the metal layer and a dielectric diffusion barrier layer. PSAB layers promote improved adhesion between a metal layer and an adjacent dielectric diffusion barrier layer. Further, PSAB layers can protect metal surfaces from inadvertent oxidation during fabrication process. A PSAB layer may be formed entirely within the top portion of a metal layer, by, for example, chemically converting metal surface to a thin layer of metal silicide. Thickness of PSAB layers, and, consequently resistance of interconnects can be controlled by partially passivating metal surface prior to formation of PSAB layer. Such passivation can be accomplished by controllably treating metal surface with a nitrogen-containing compound to convert metal to metal nitride.

Owner:NOVELLUS SYSTEMS

Silicide protection during contact metallization and resulting semiconductor structures

ActiveUS9111907B2Avoid damageOvercomes shortcomingSemiconductor/solid-state device detailsSolid-state devicesSalicideSemiconductor structure

Owner:GLOBALFOUNDRIES U S INC

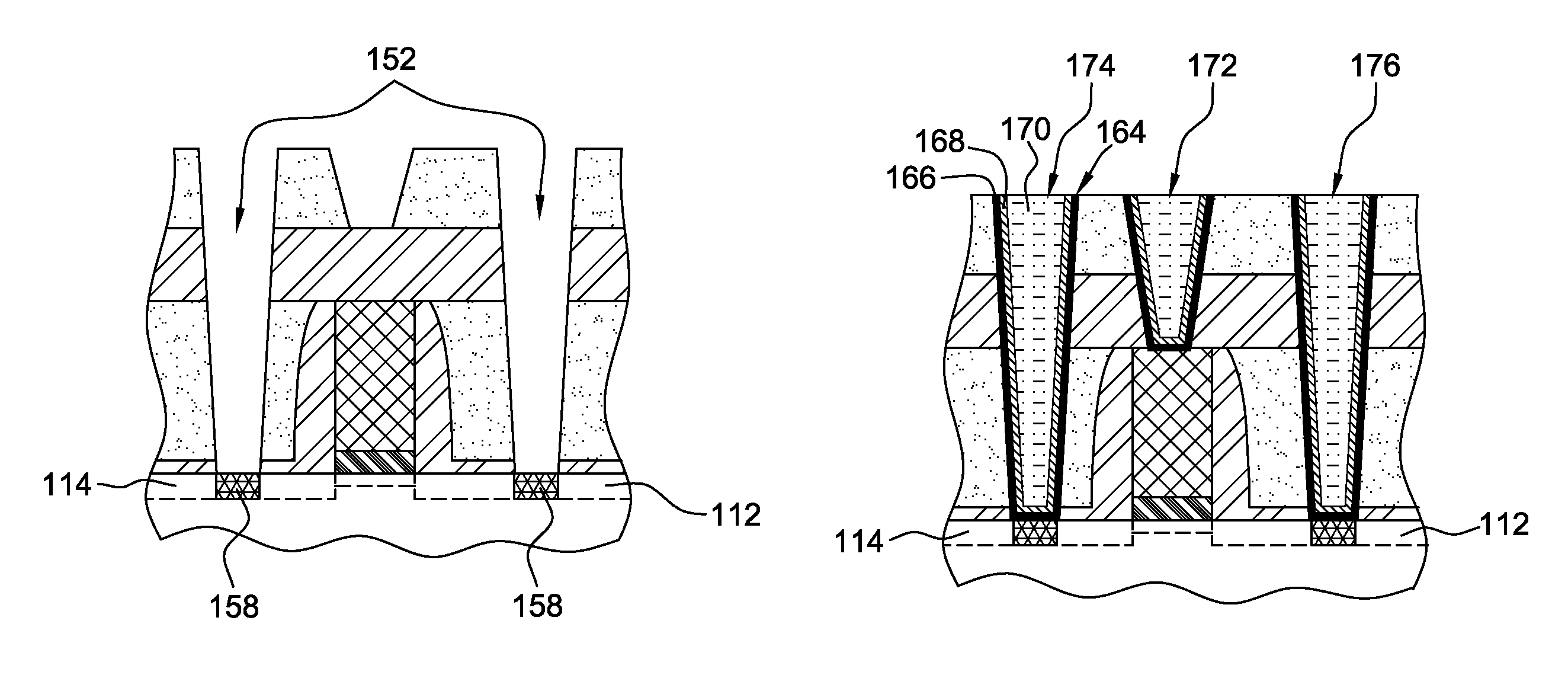

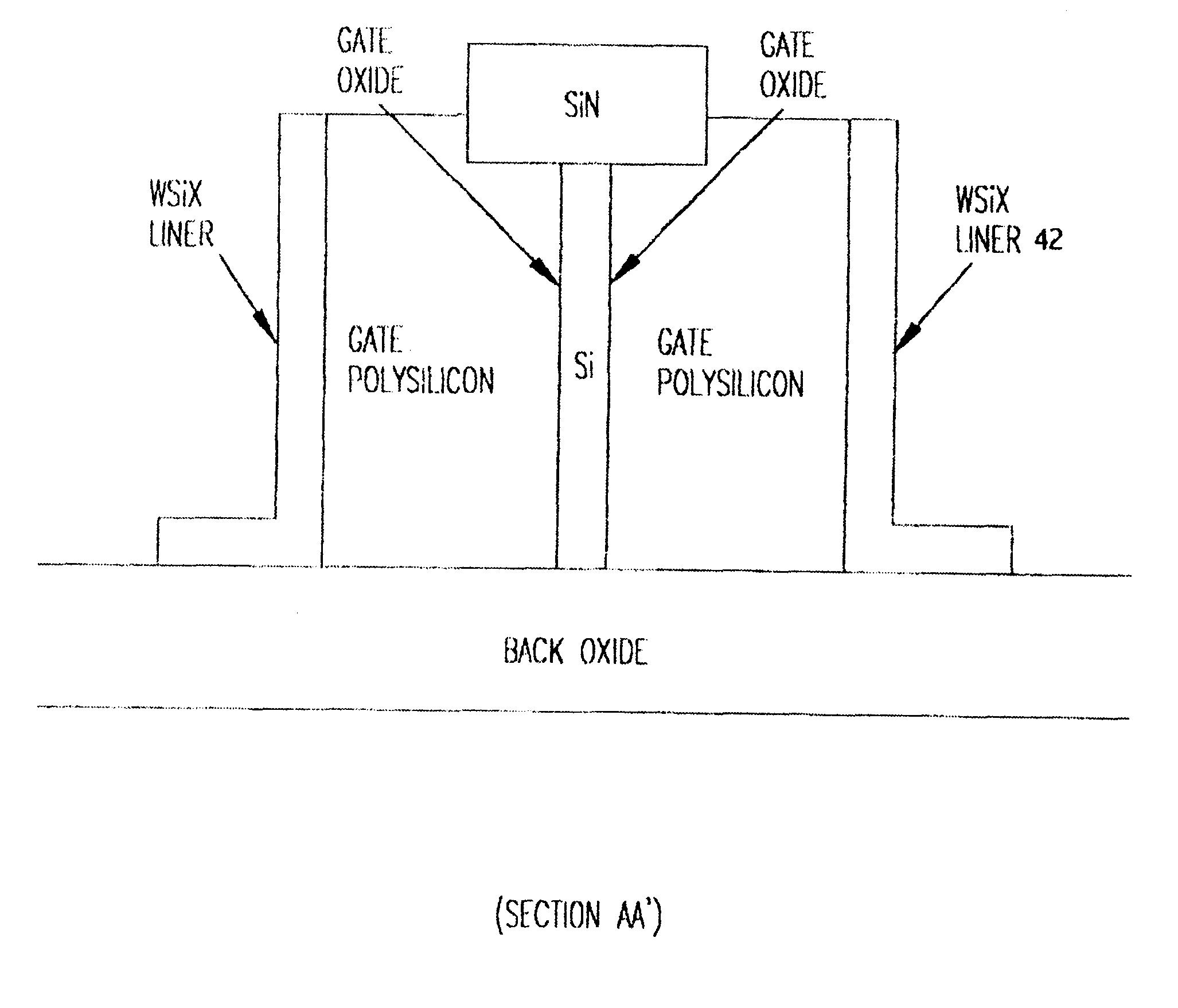

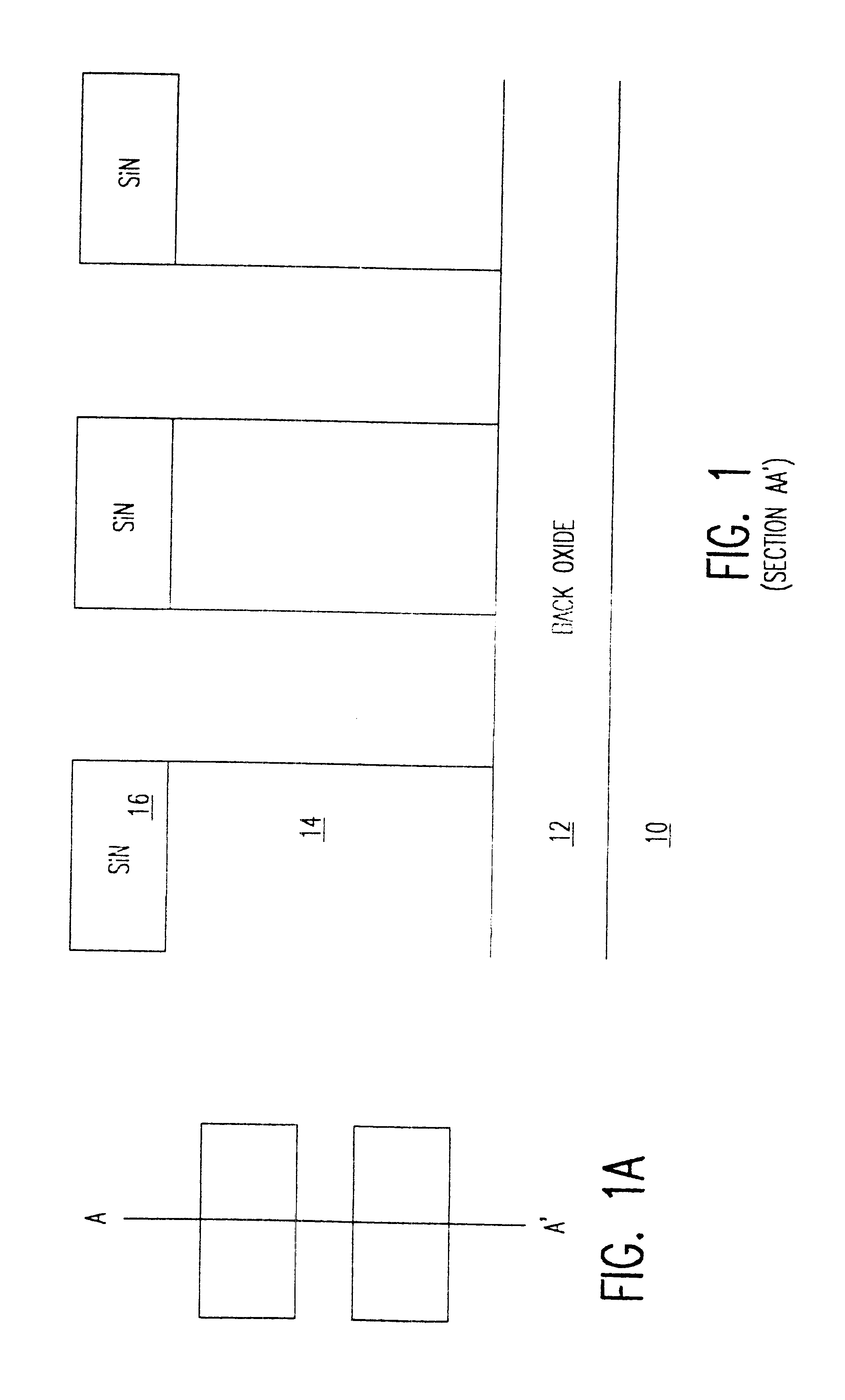

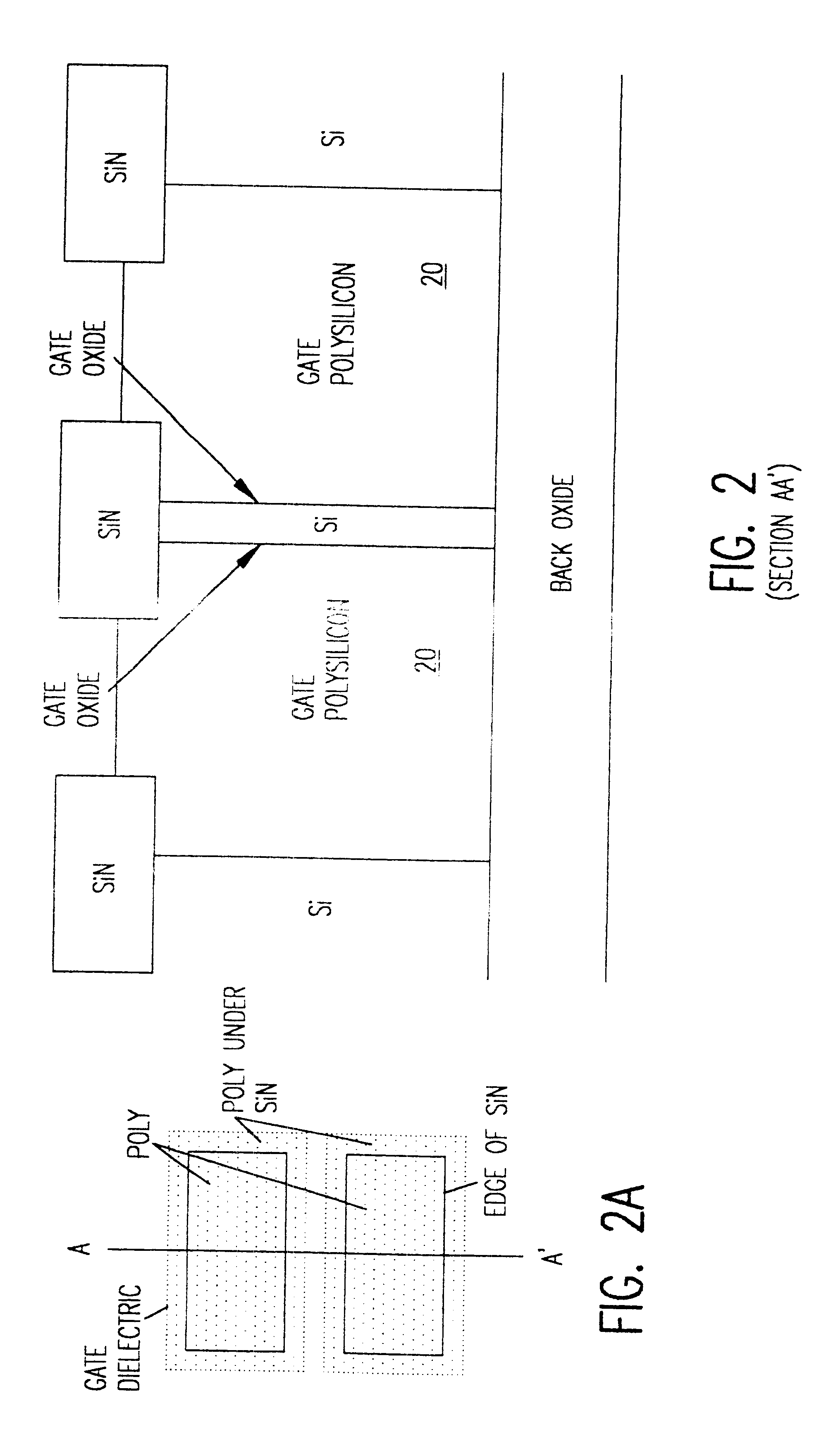

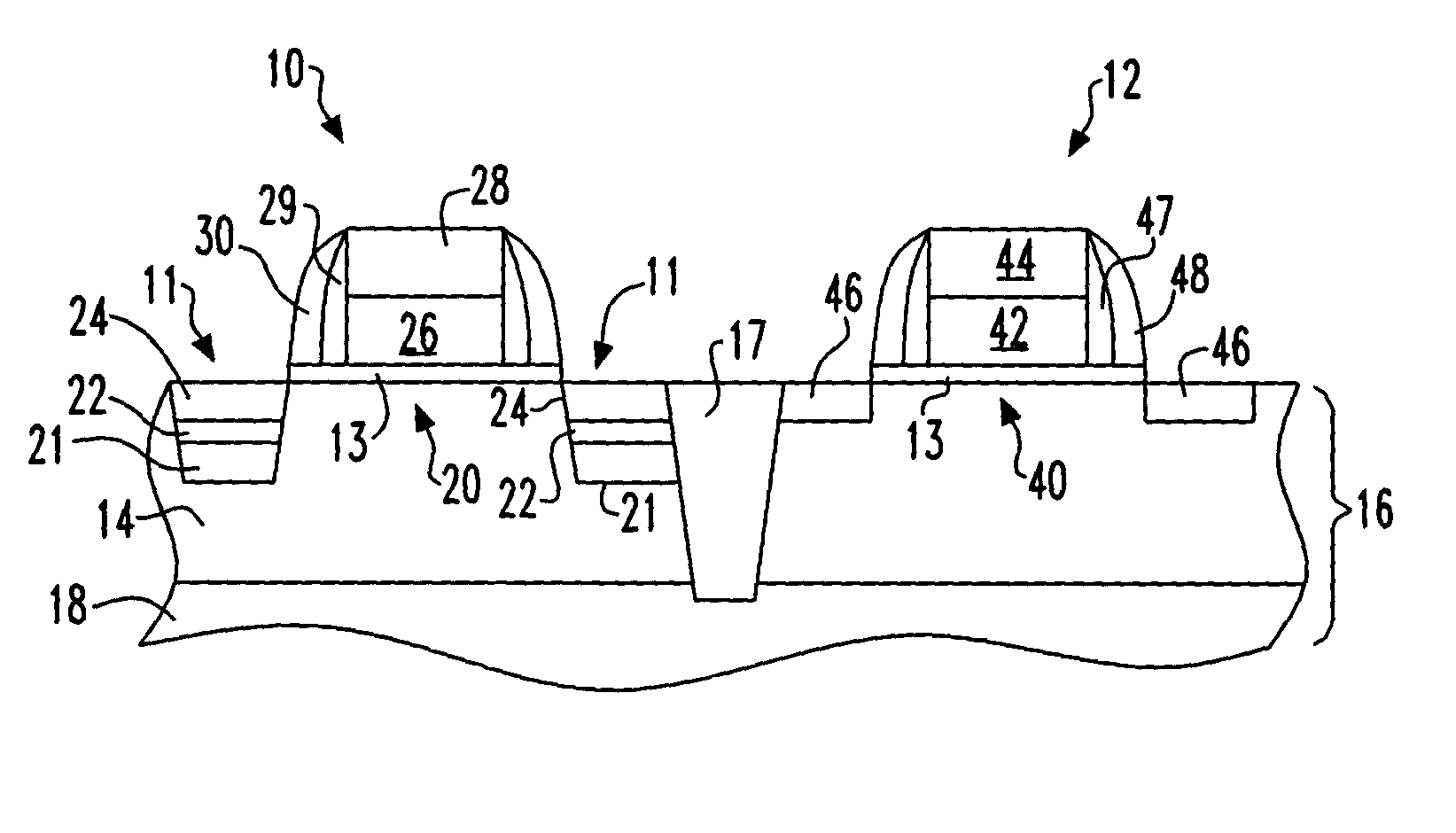

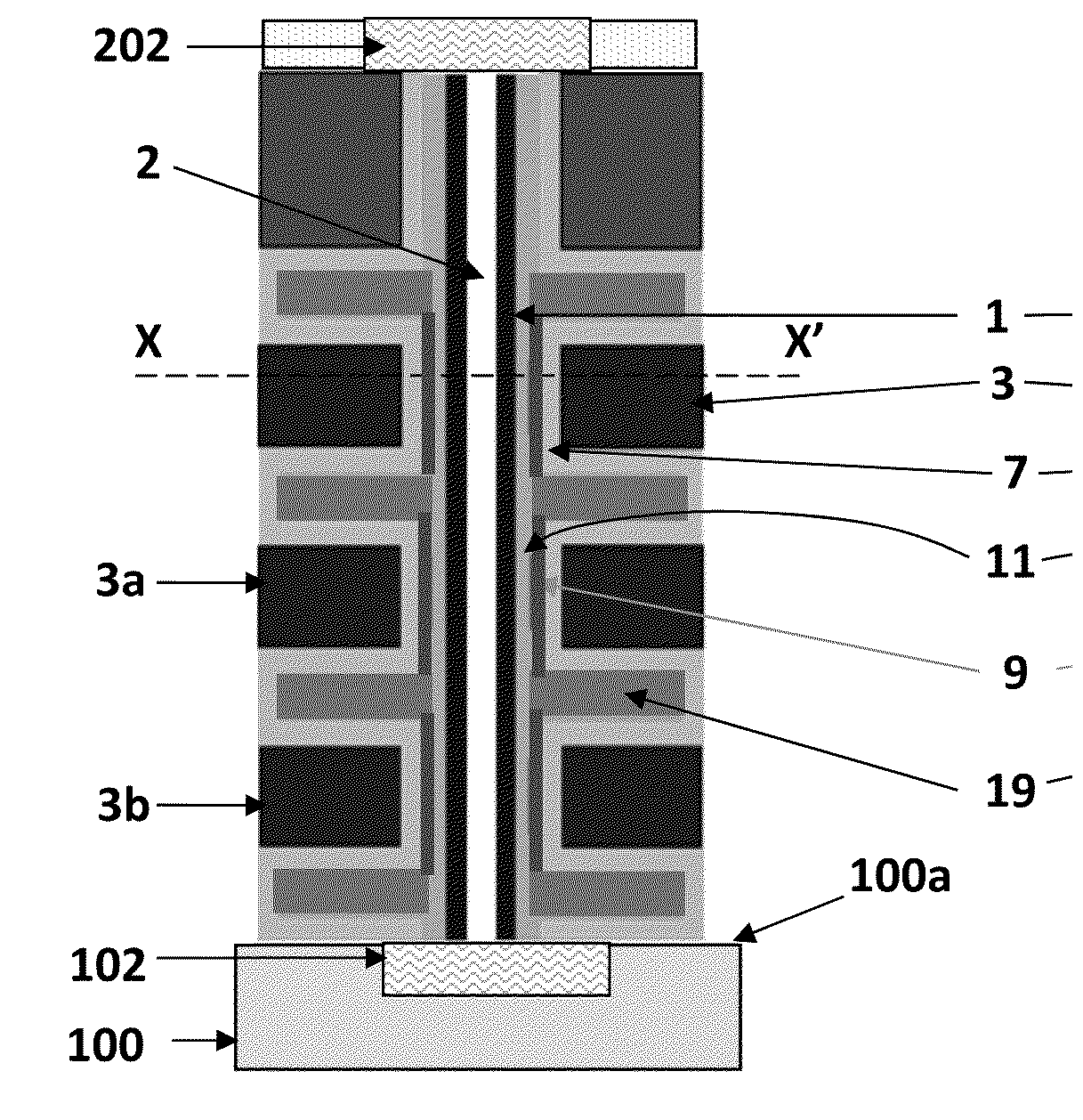

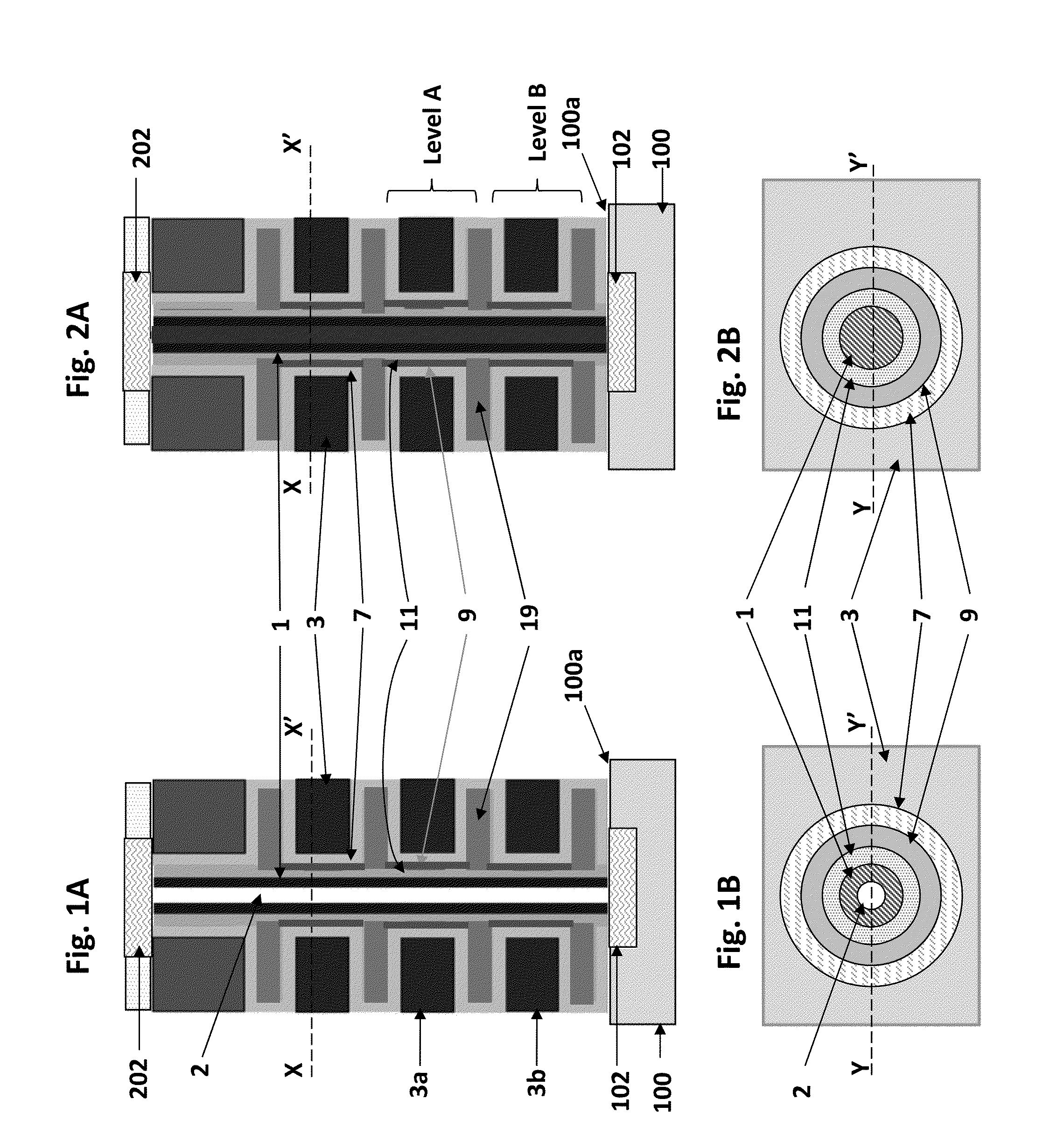

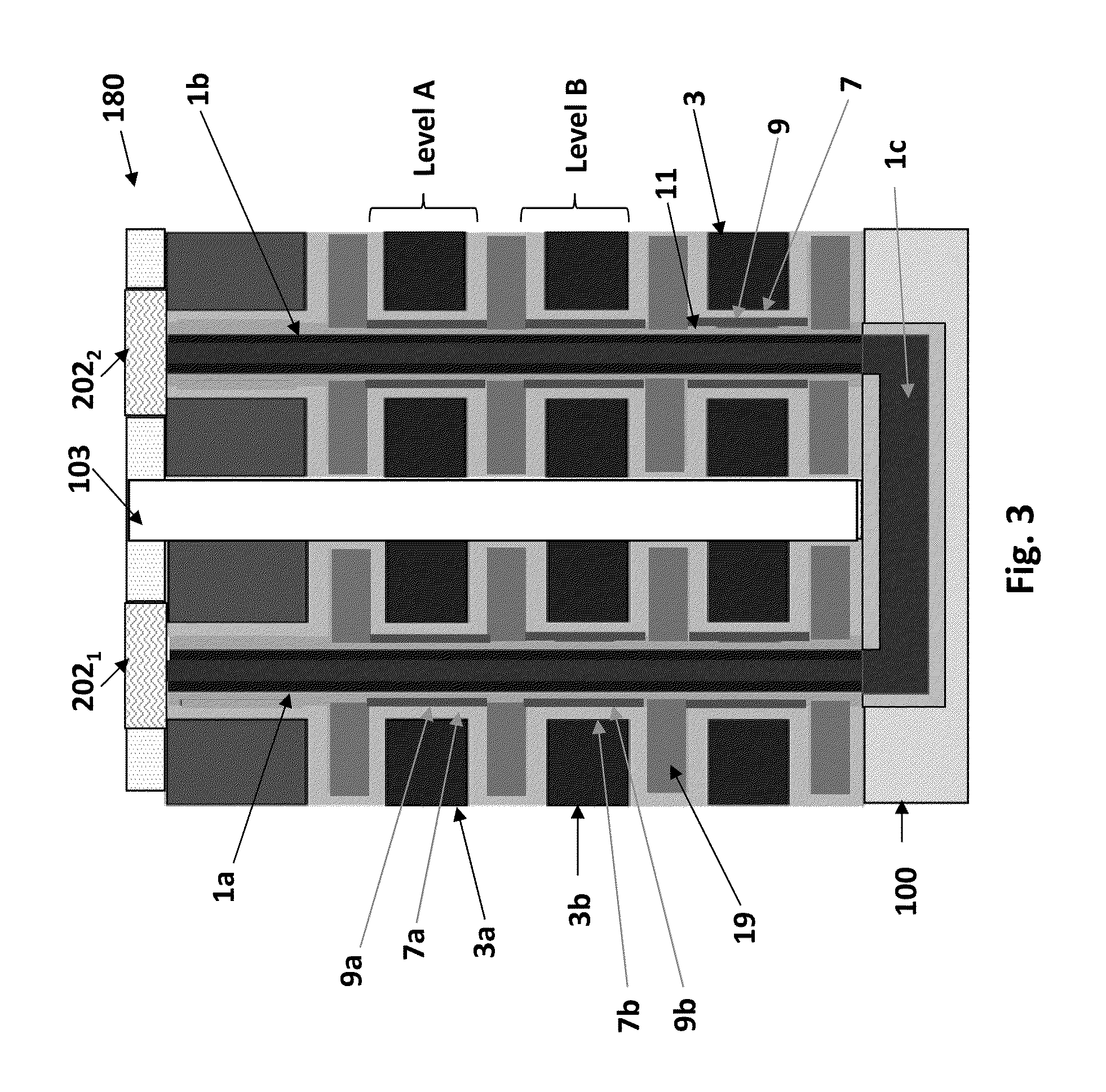

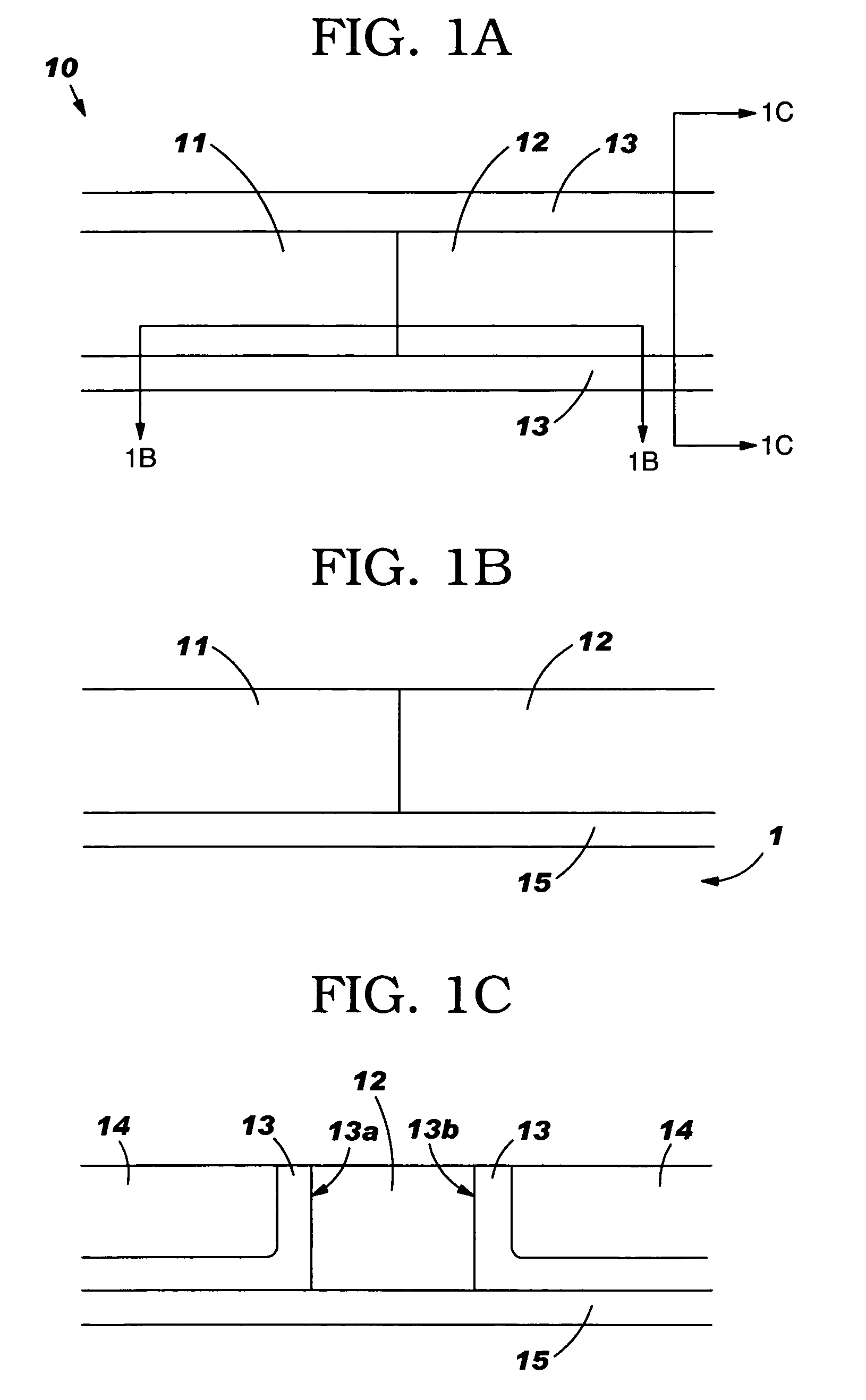

Double gate trench transistor

A field effect transistor is formed with a sub-lithographic conduction channel and a dual gate which is formed by a simple process by starting with a silicon-on-insulator wafer, allowing most etching processes to use the buried oxide as an etch stop. Low resistivity of the gate, source and drain is achieved by silicide sidewalls or liners while low gate to junction capacitance is achieved by recessing the silicide and polysilicon dual gate structure from the source and drain region edges.

Owner:IBM CORP

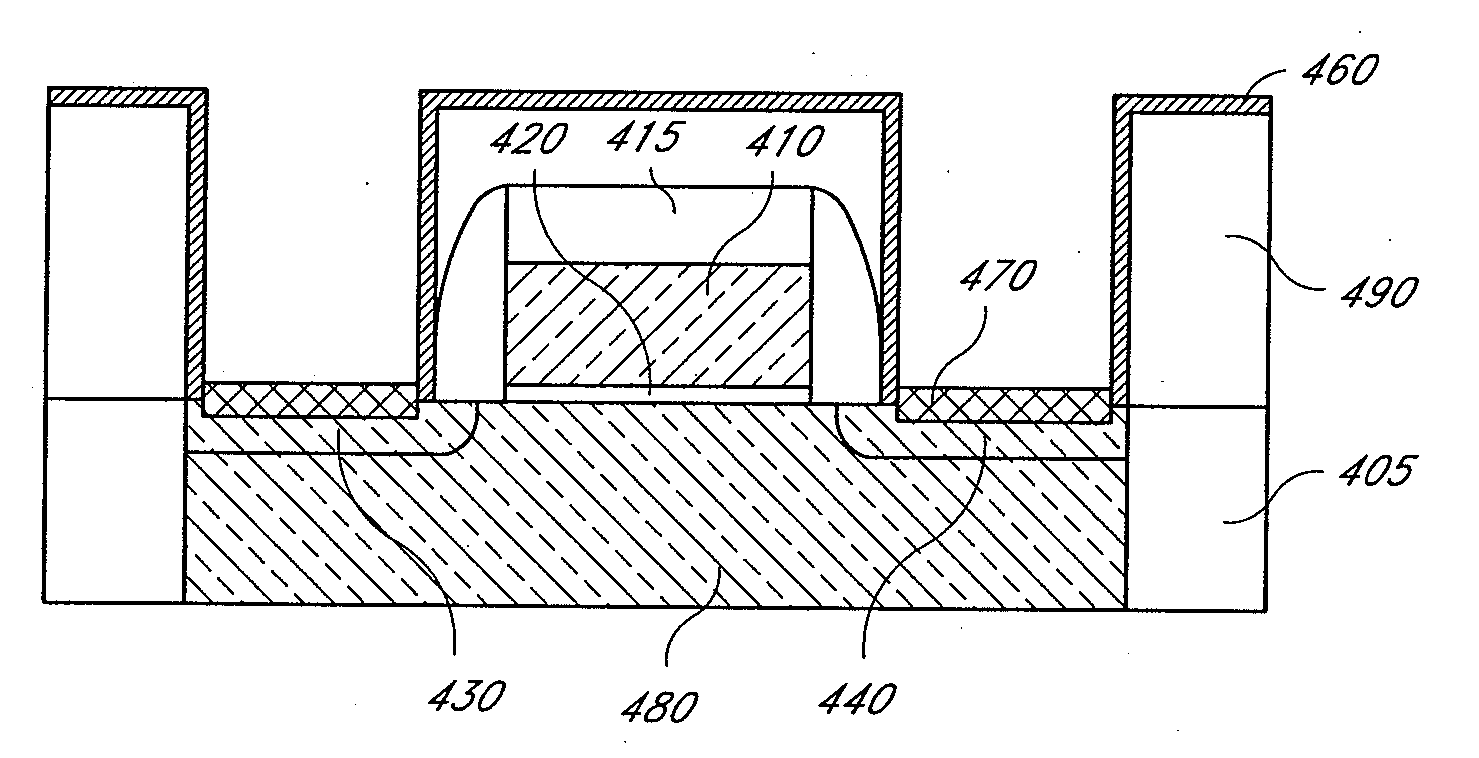

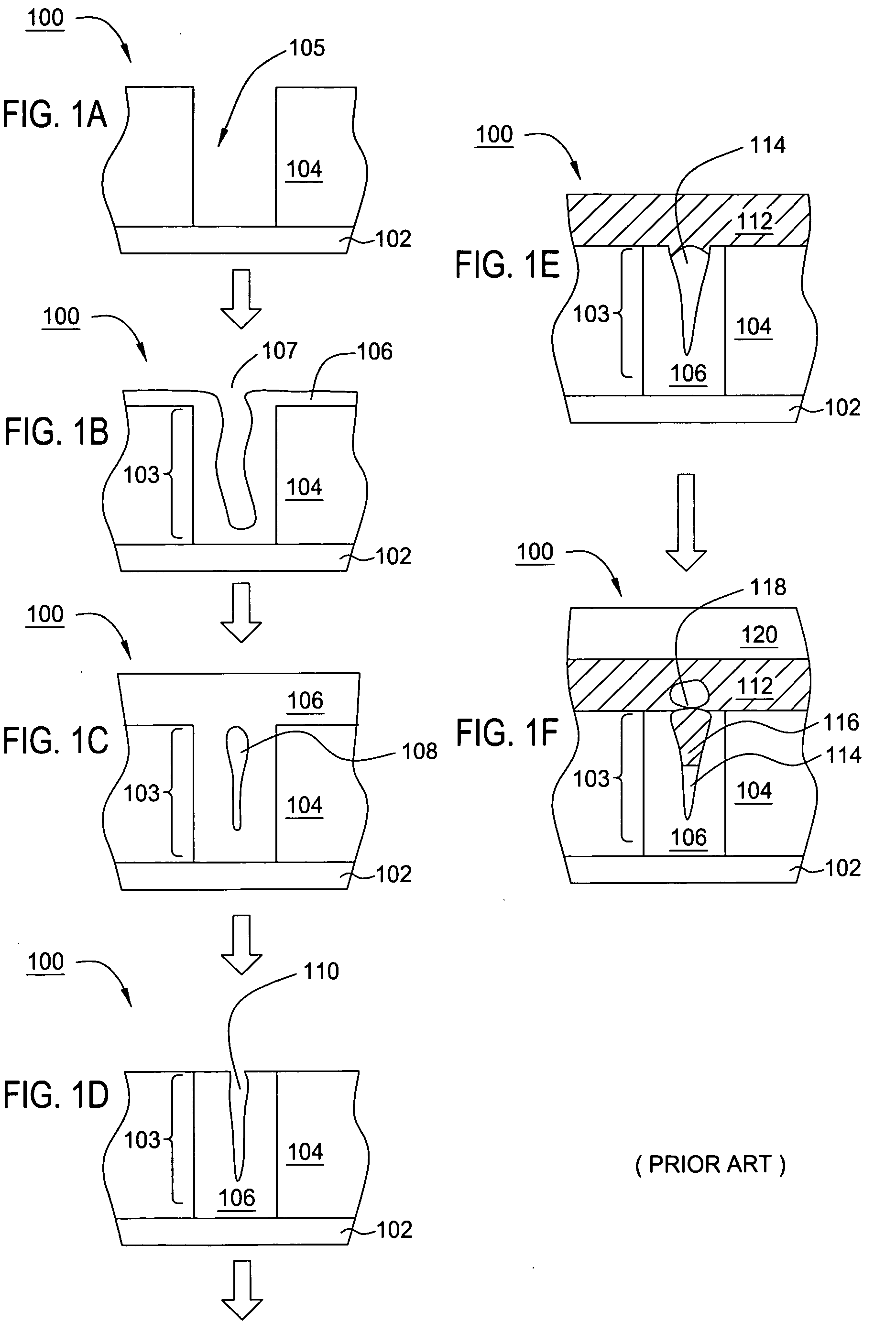

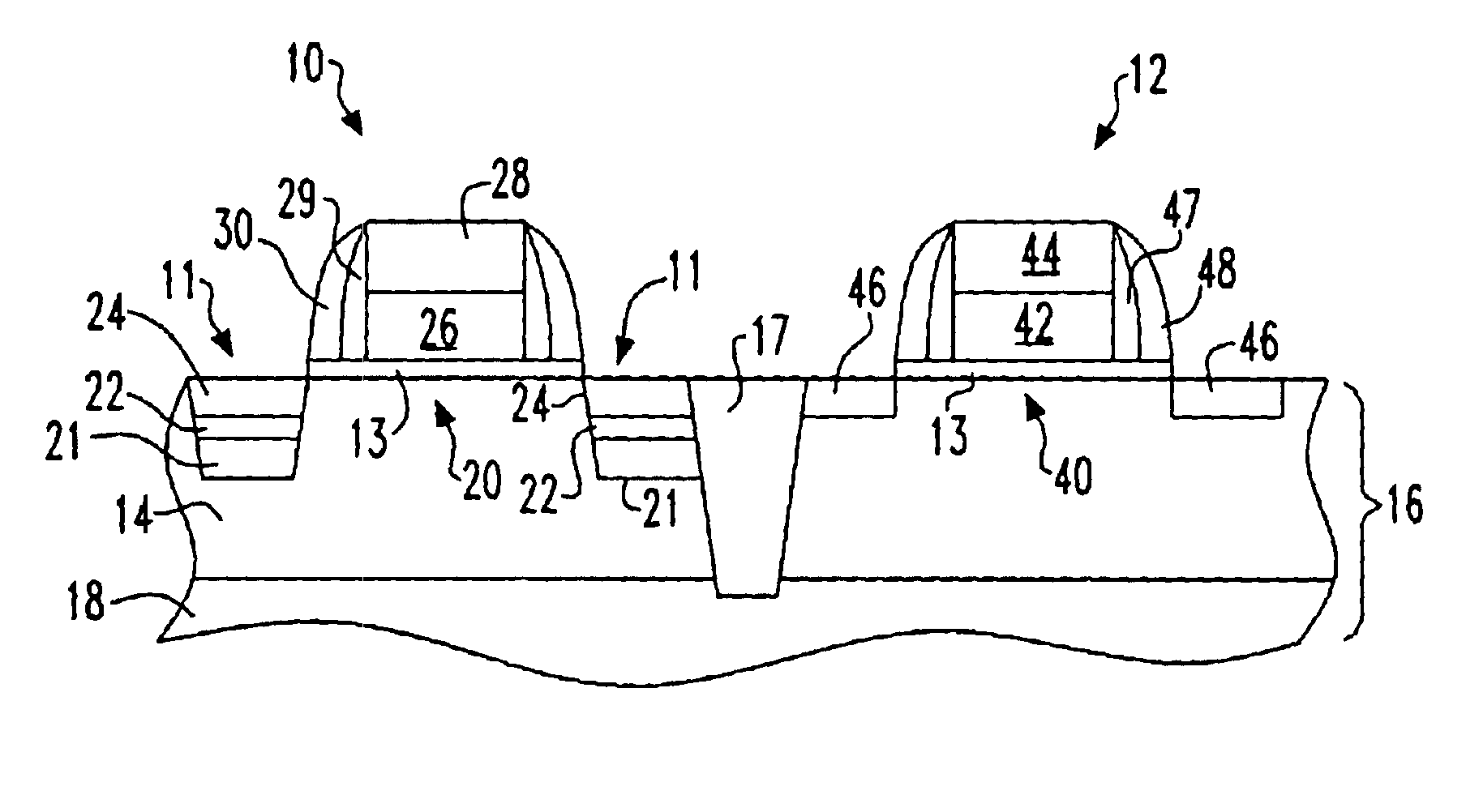

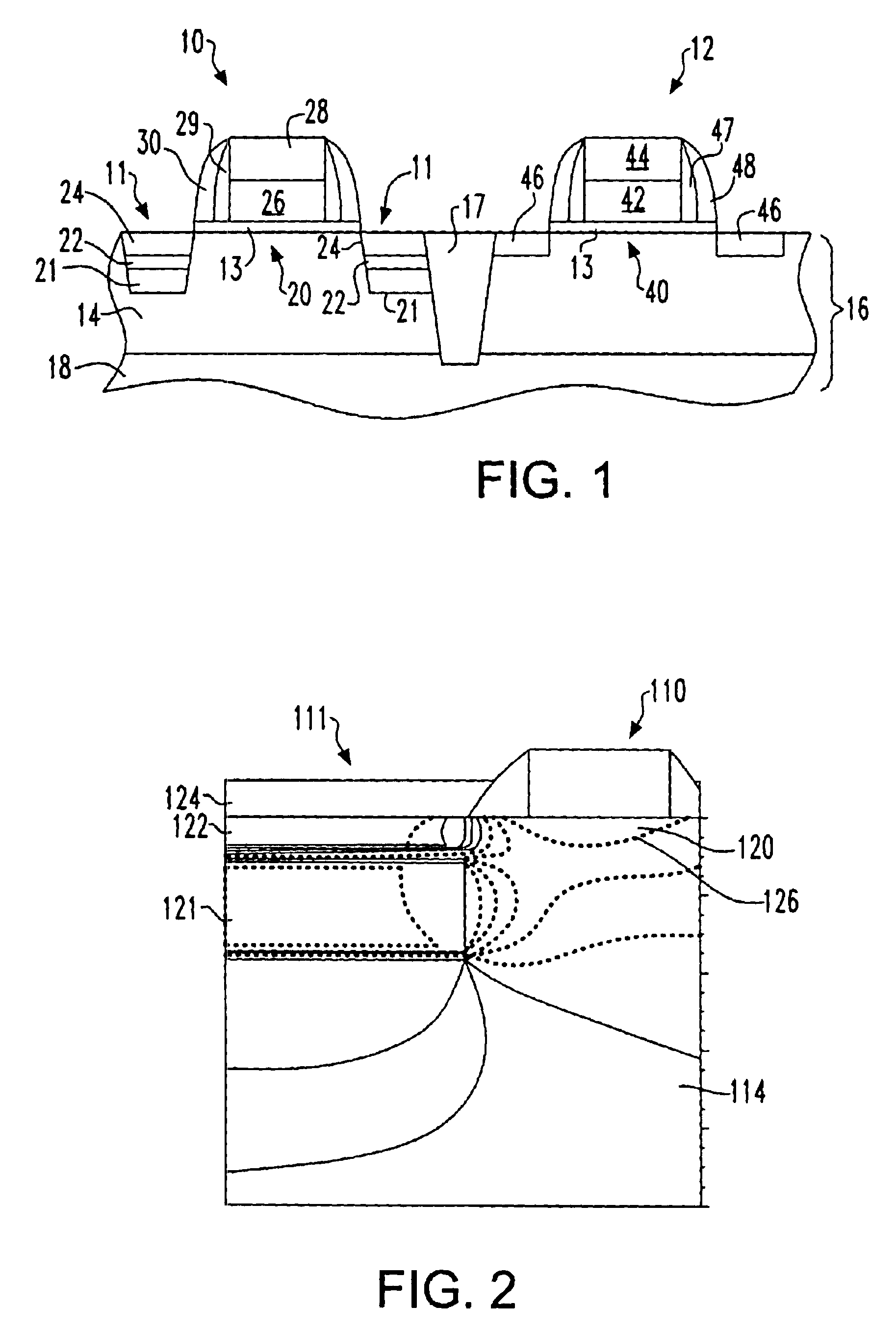

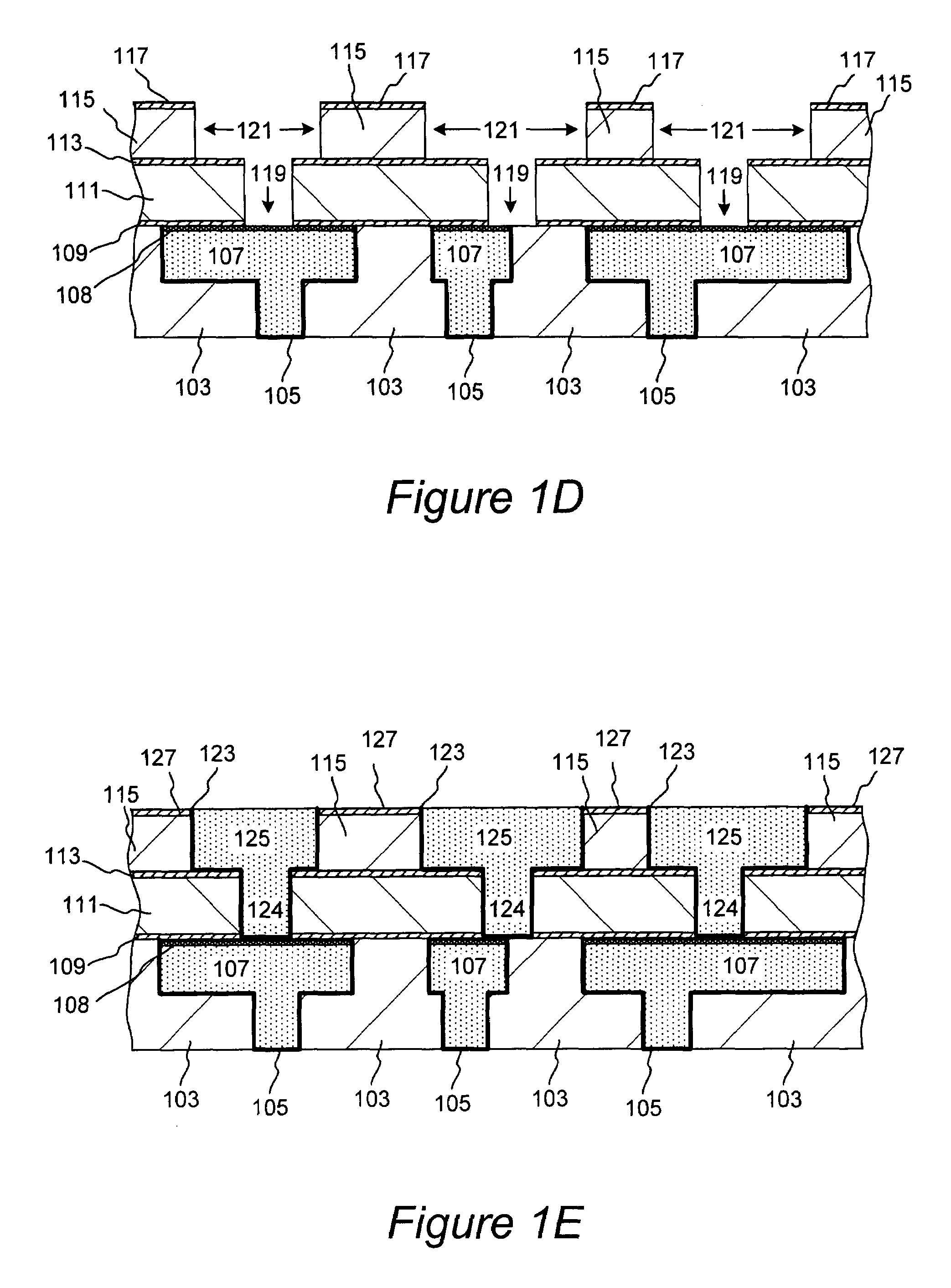

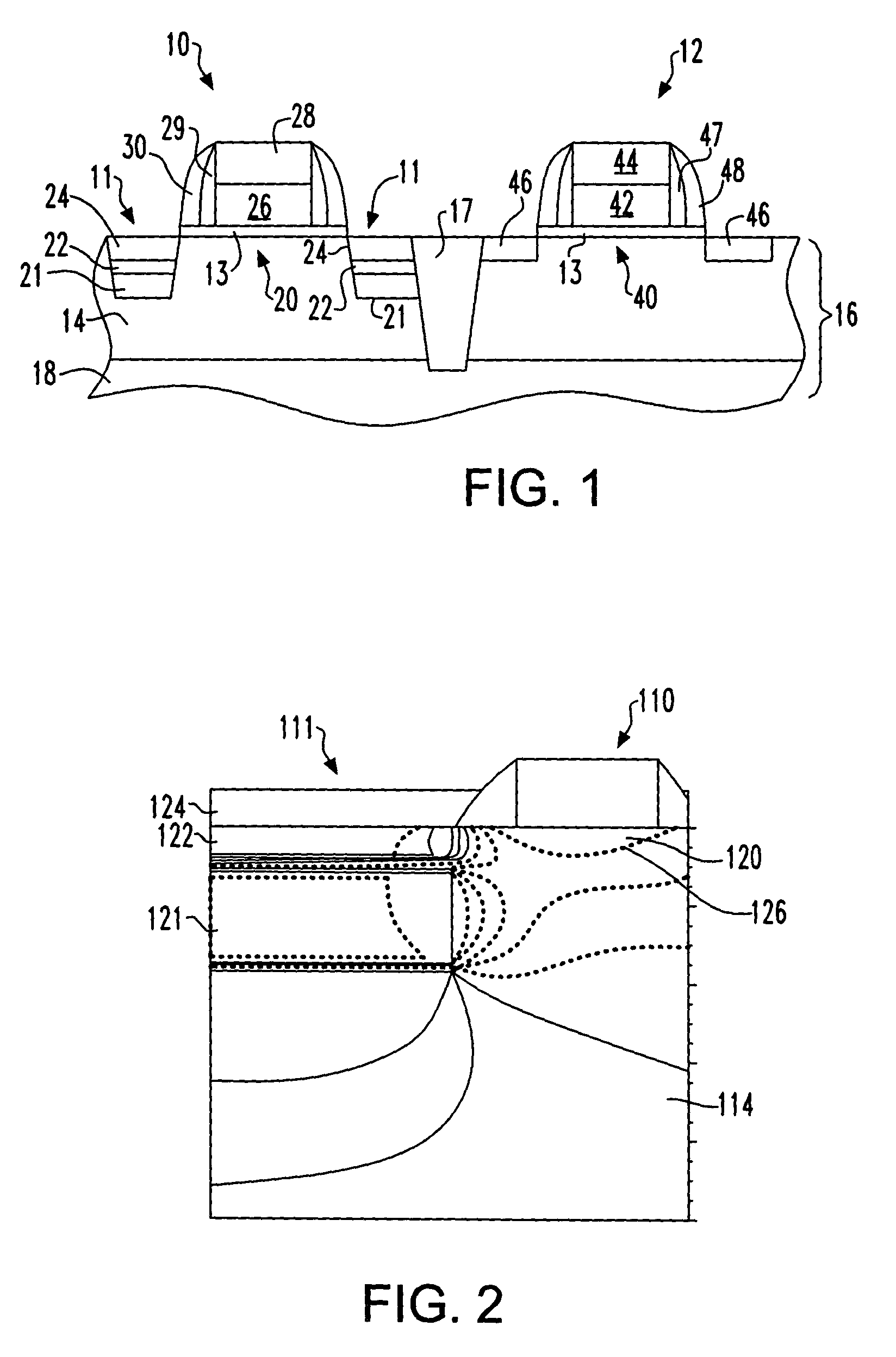

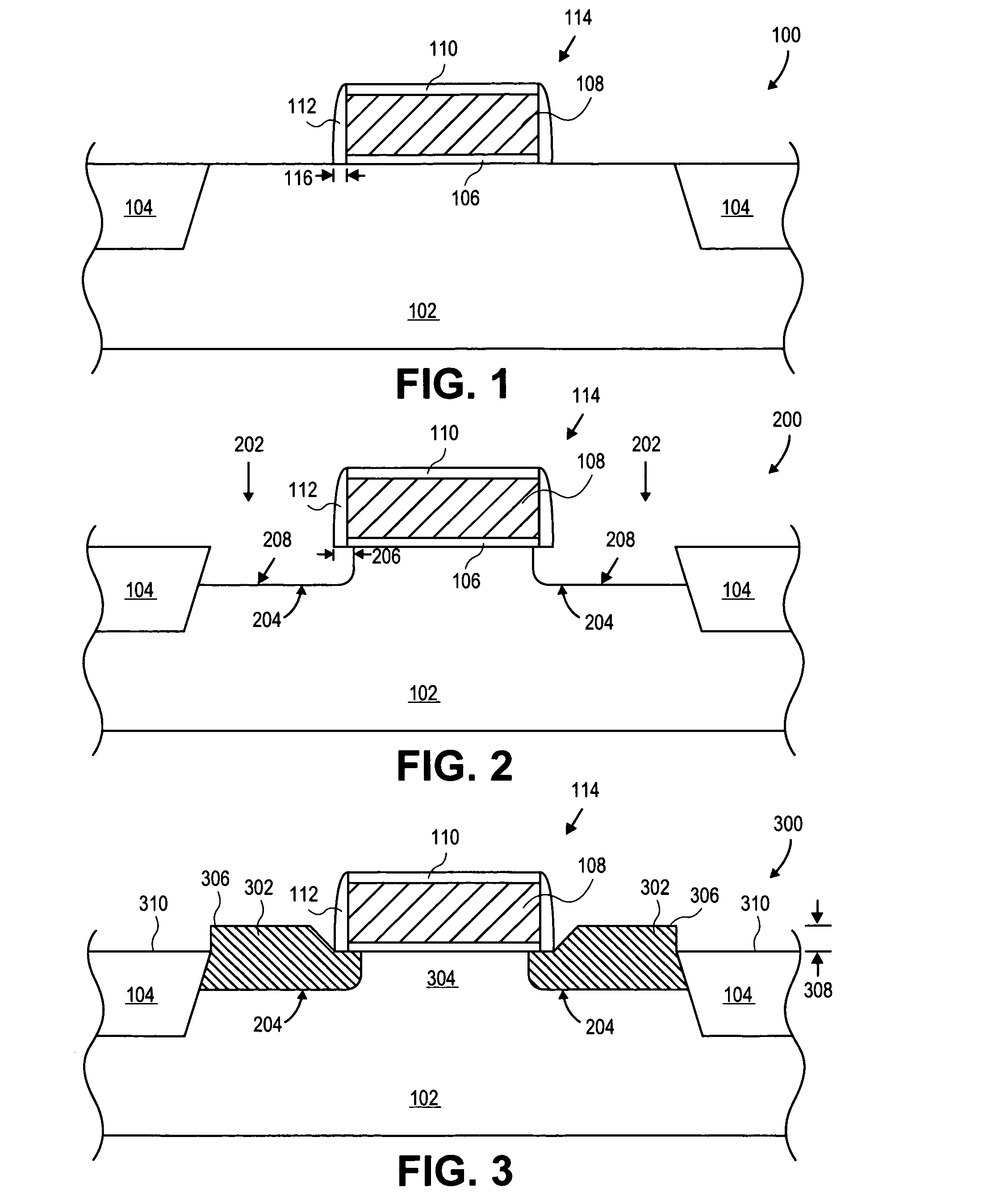

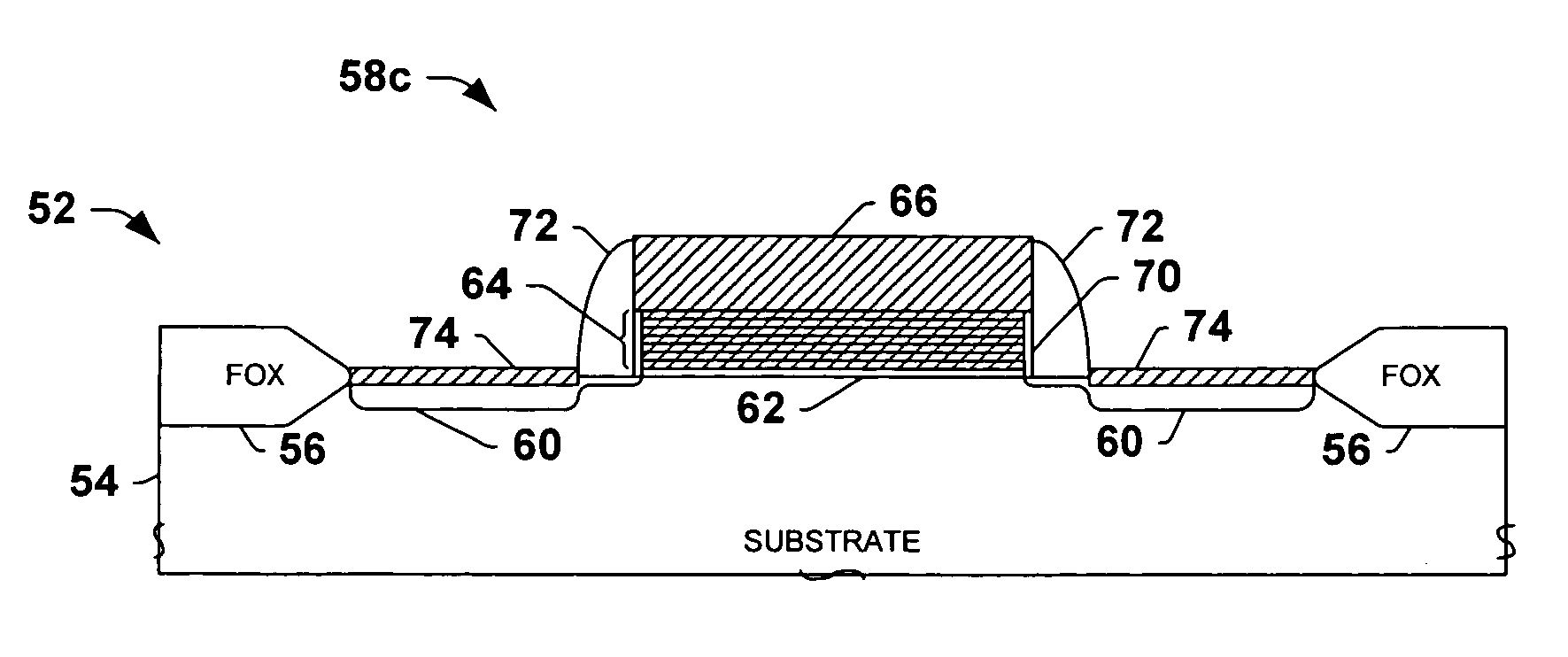

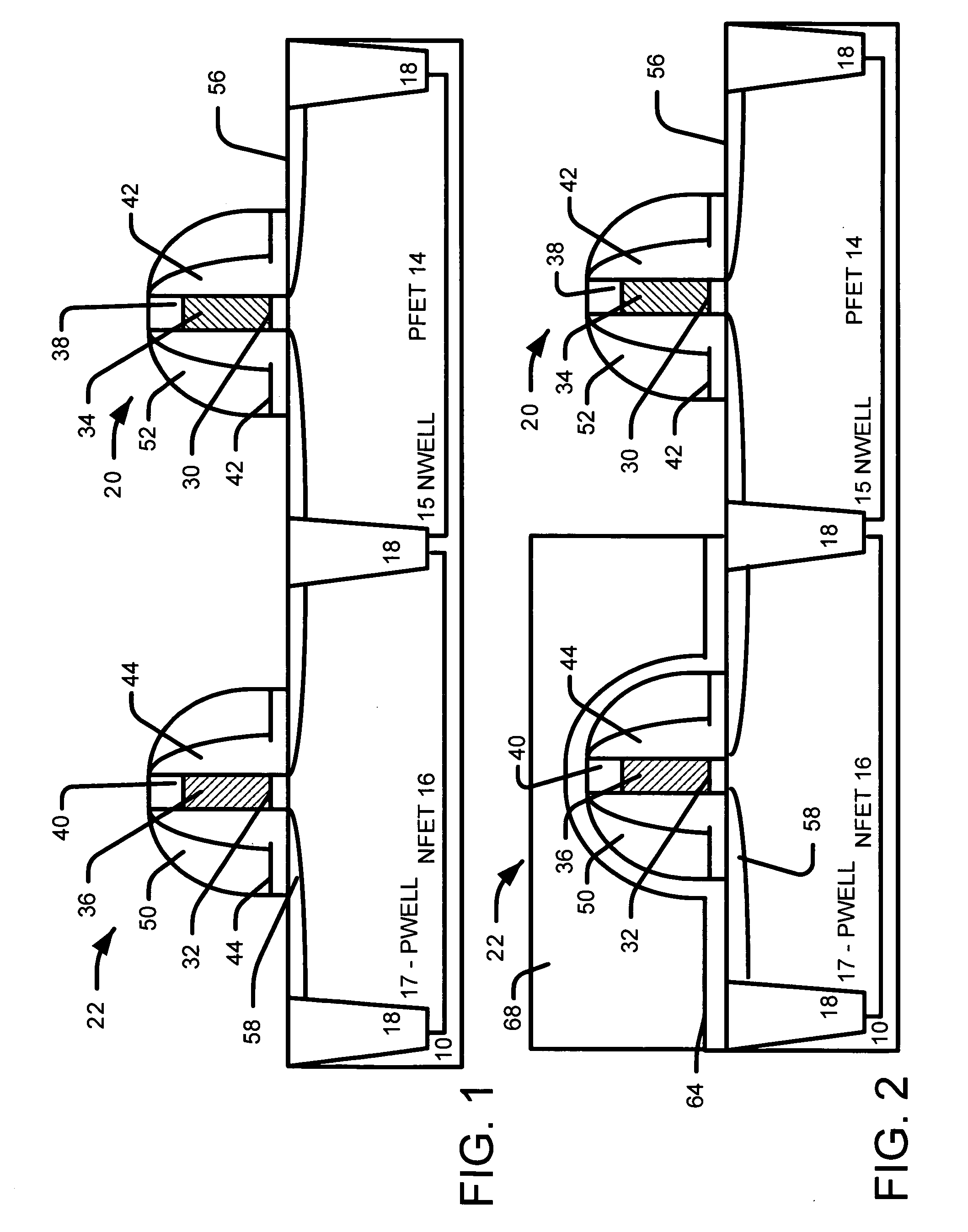

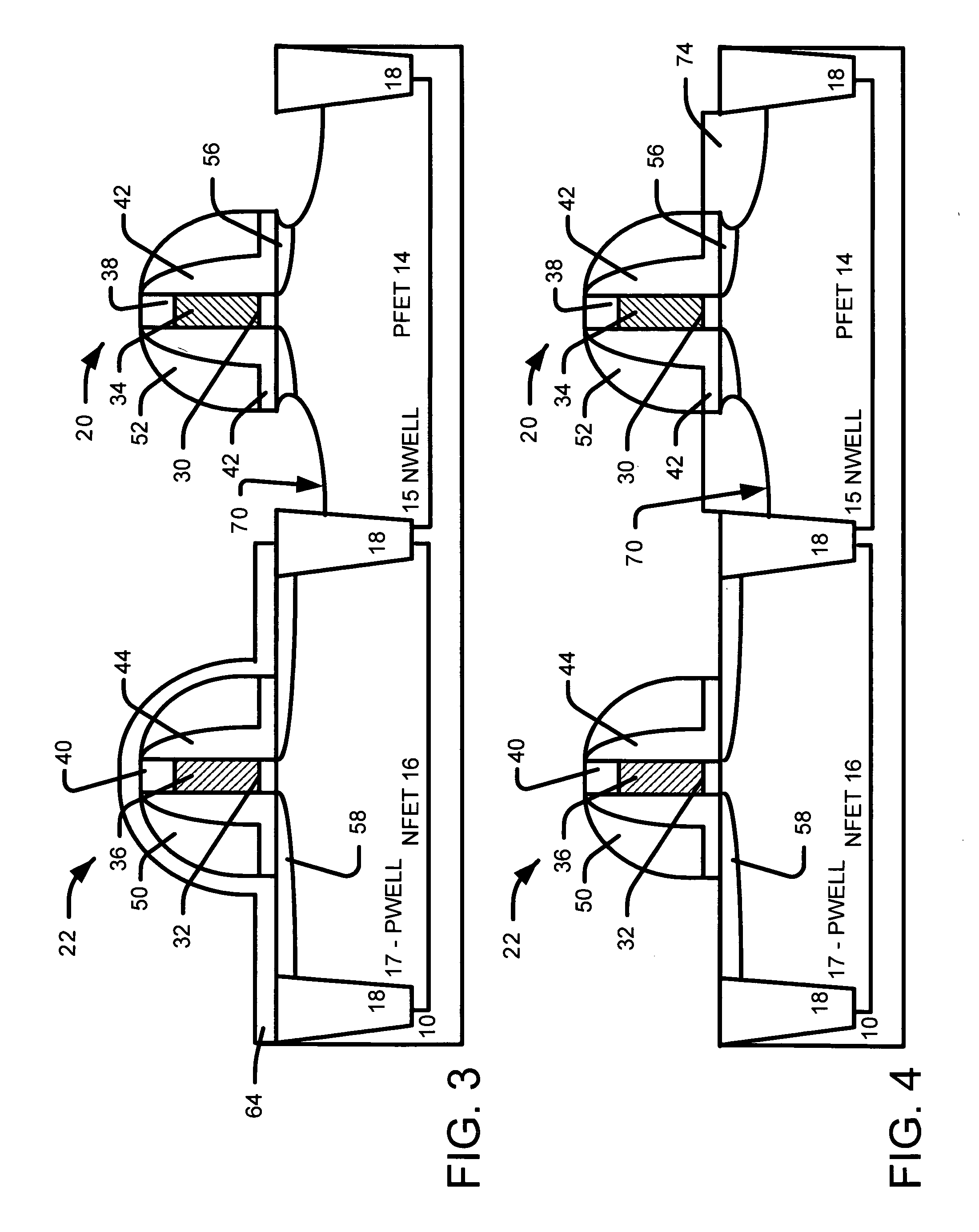

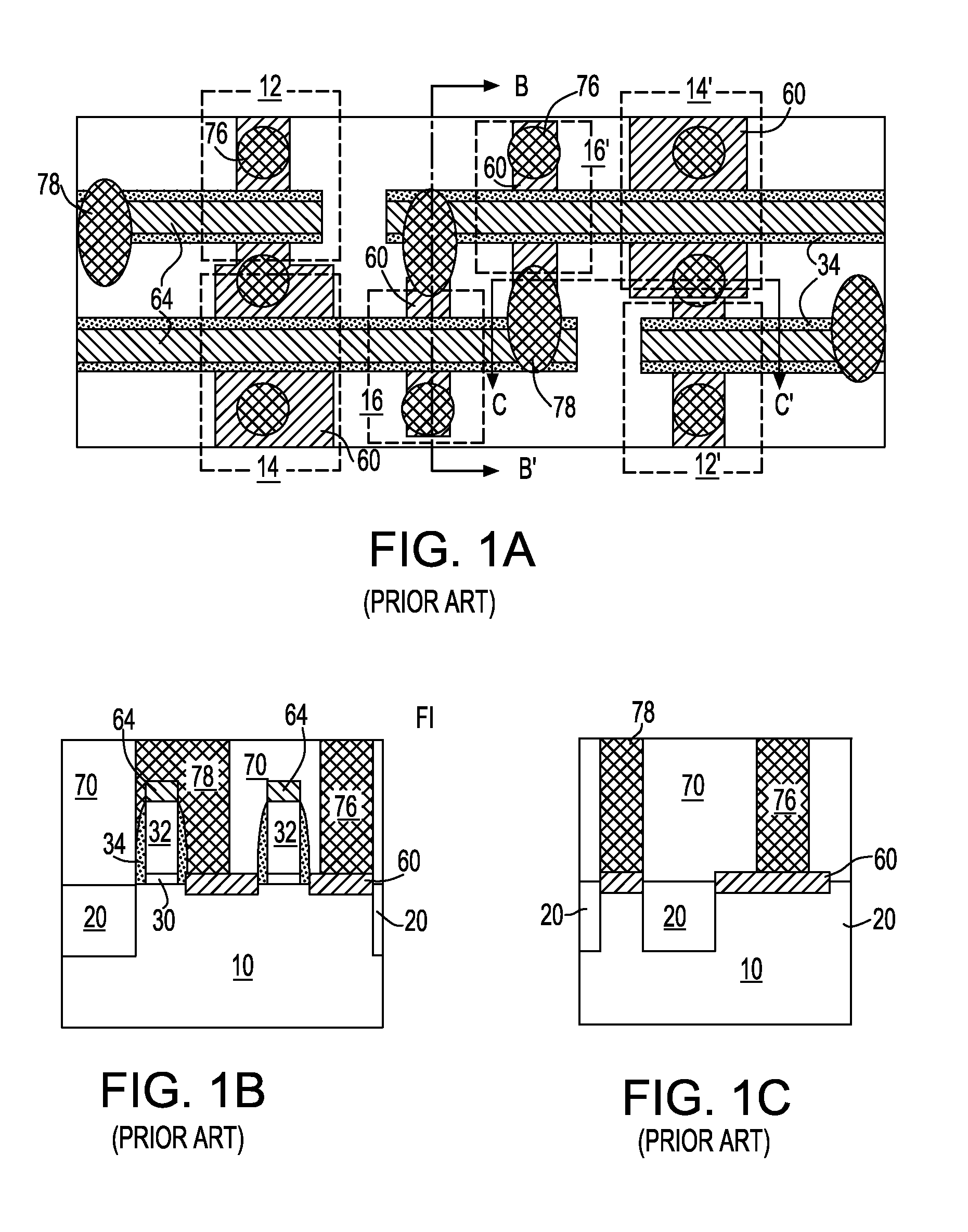

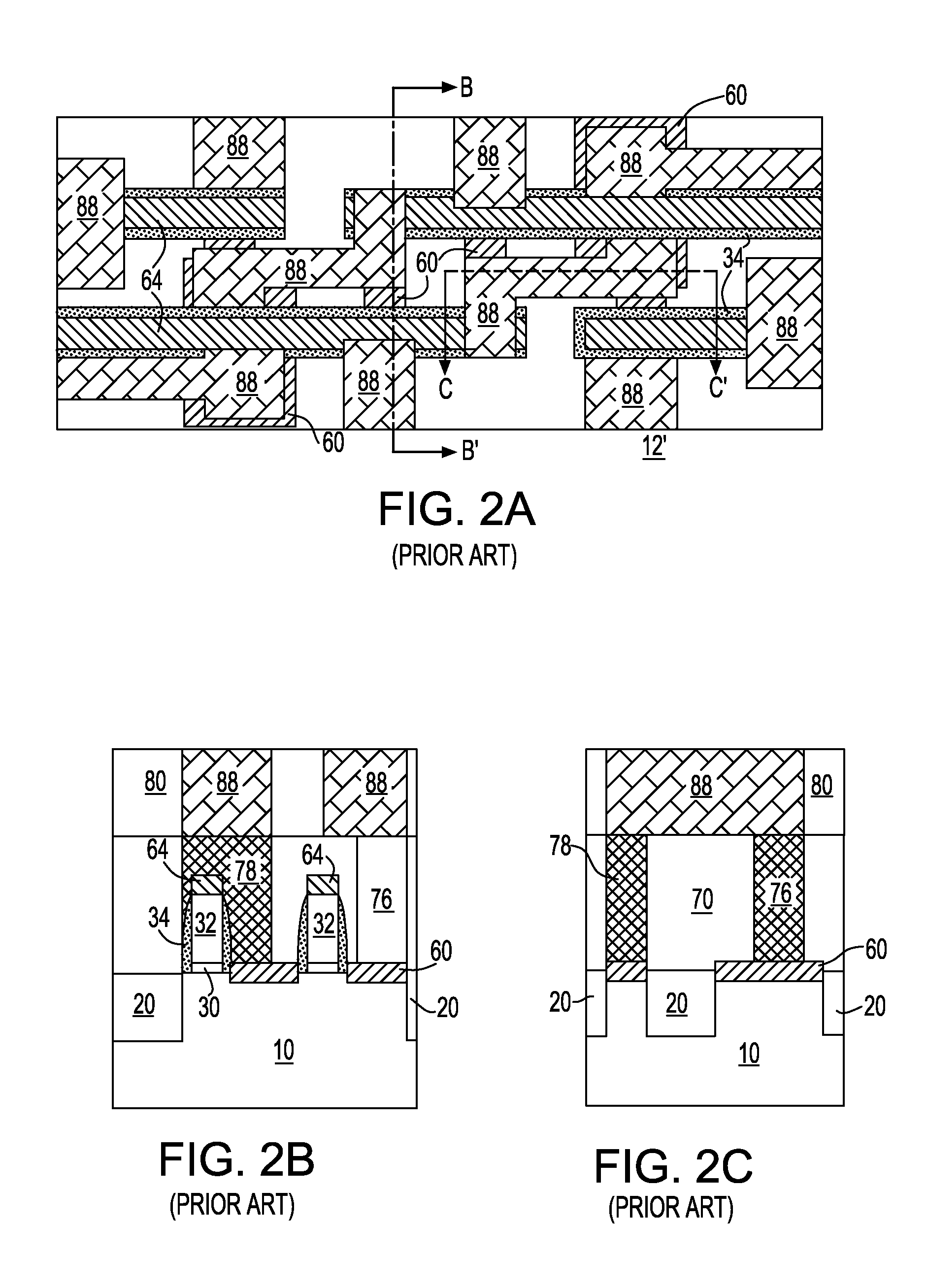

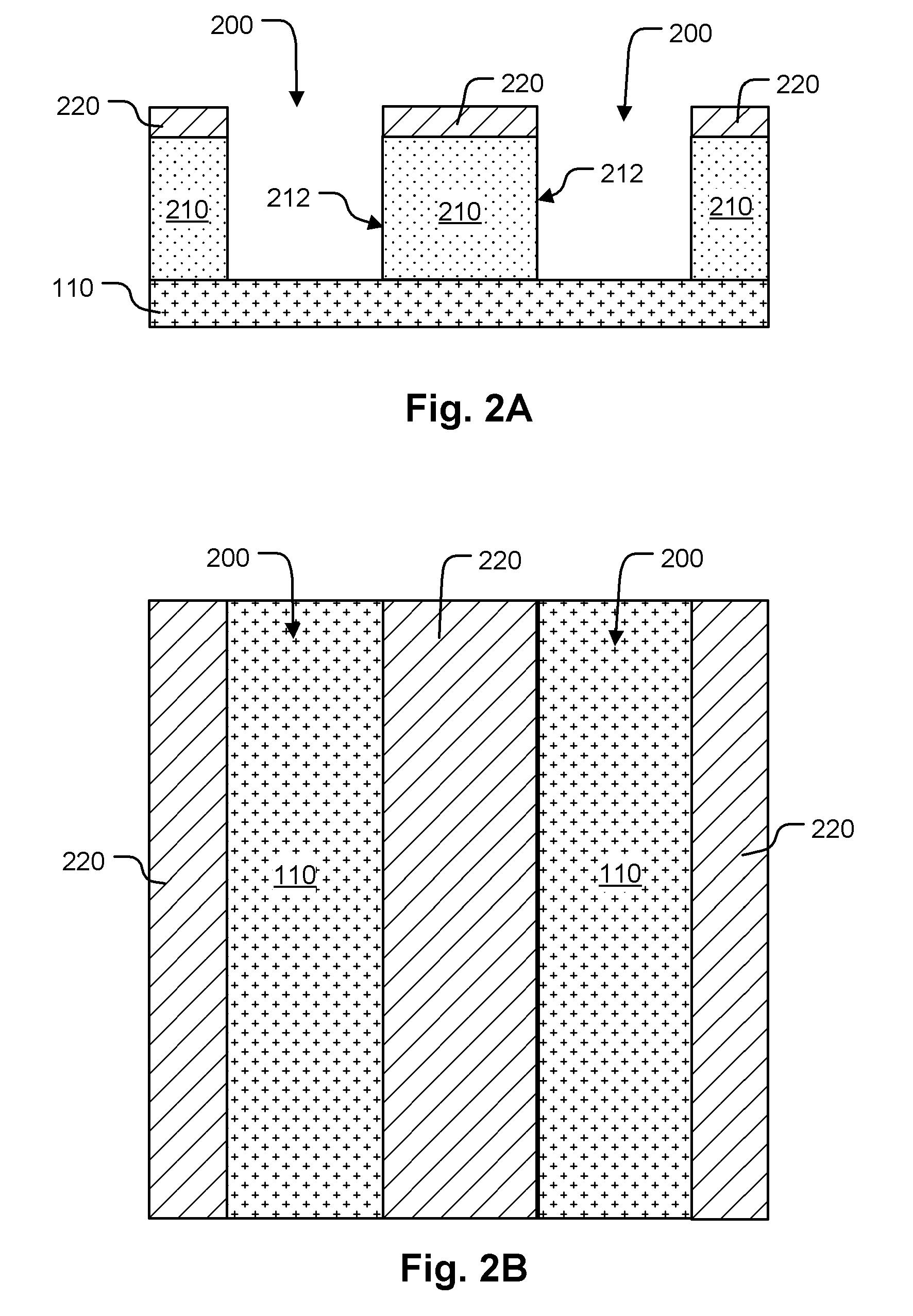

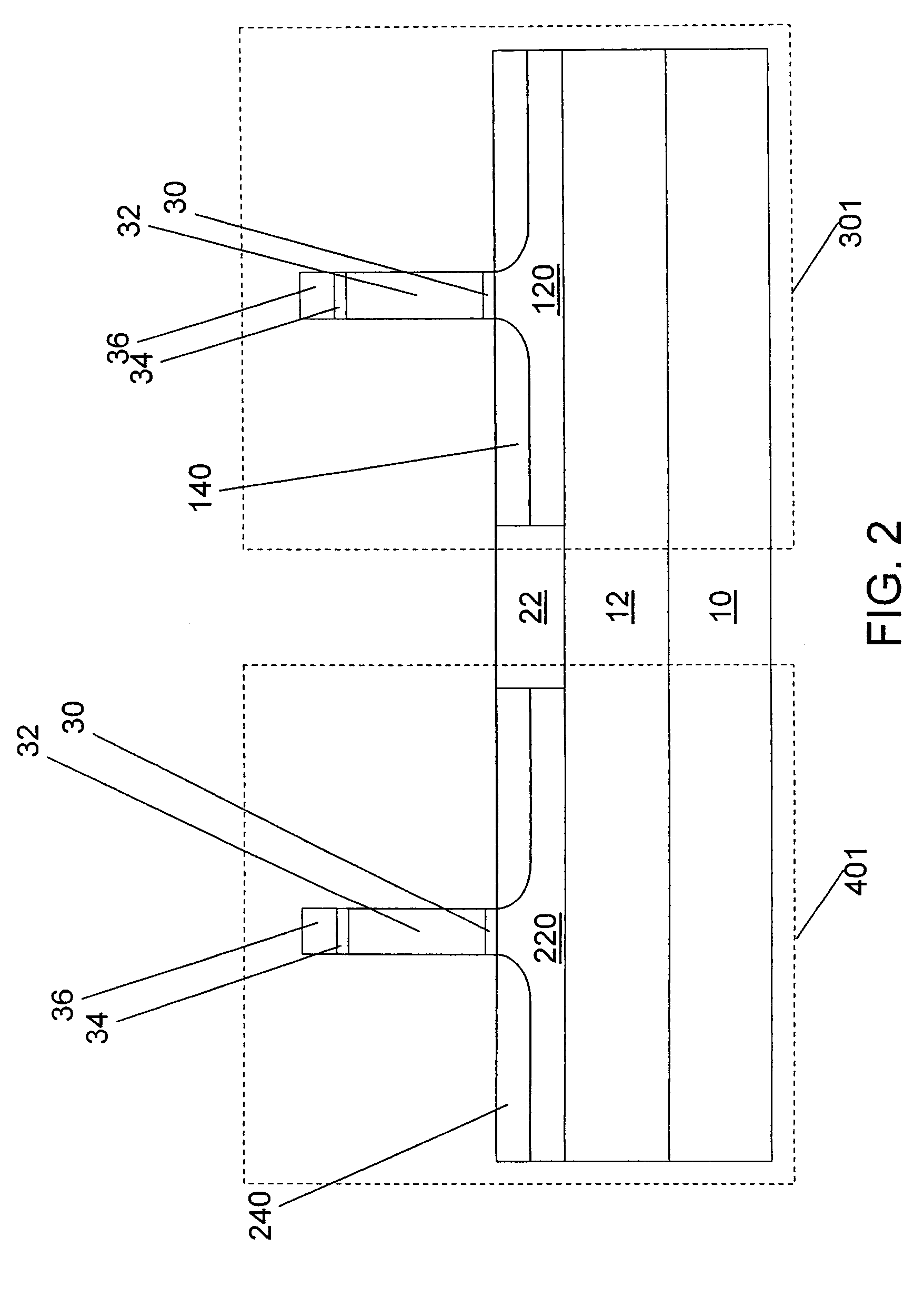

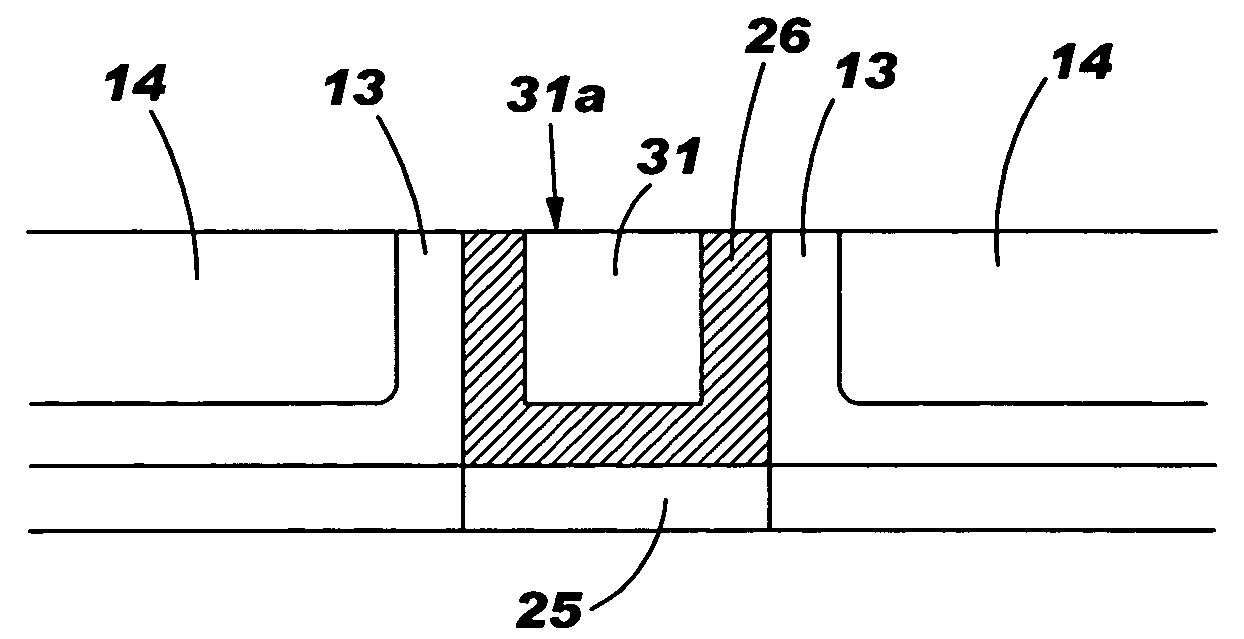

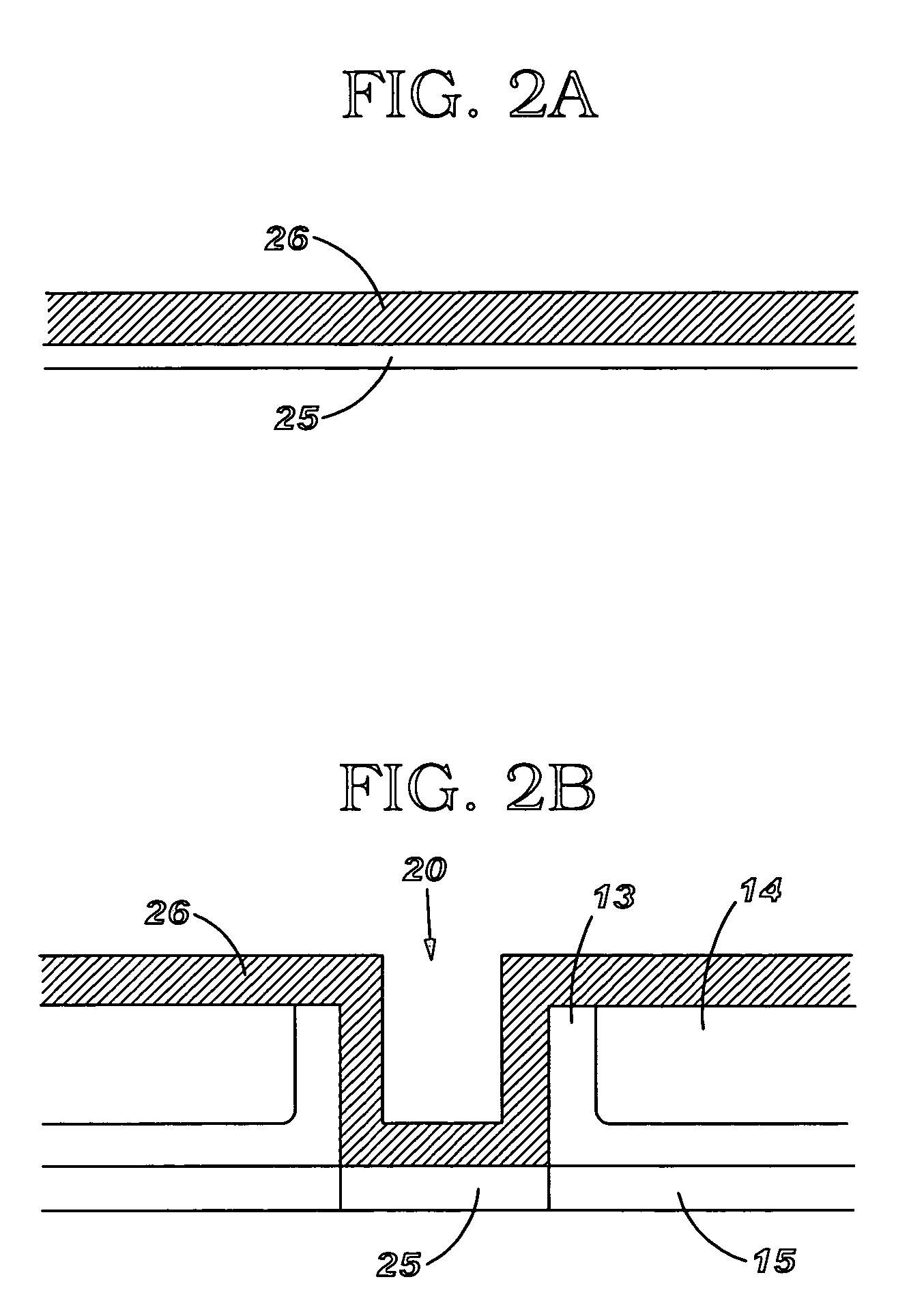

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched source and drain regions

A p-type field effect transistor (PFET) and an n-type field effect transistor (NFET) of an integrated circuit are provided. A first strain is applied to the channel region of the PFET but not the NFET via a lattice-mismatched semiconductor layer such as silicon germanium disposed in source and drain regions of only the PFET and not of the NFET. A process of making the PFET and NFET is provided. Trenches are etched in the areas to become the source and drain regions of the PFET and a lattice-mismatched silicon germanium layer is grown epitaxially therein to apply a strain to the channel region of the PFET adjacent thereto. A layer of silicon can be grown over the silicon germanium layer and a salicide formed from the layer of silicon to provide low-resistance source and drain regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP

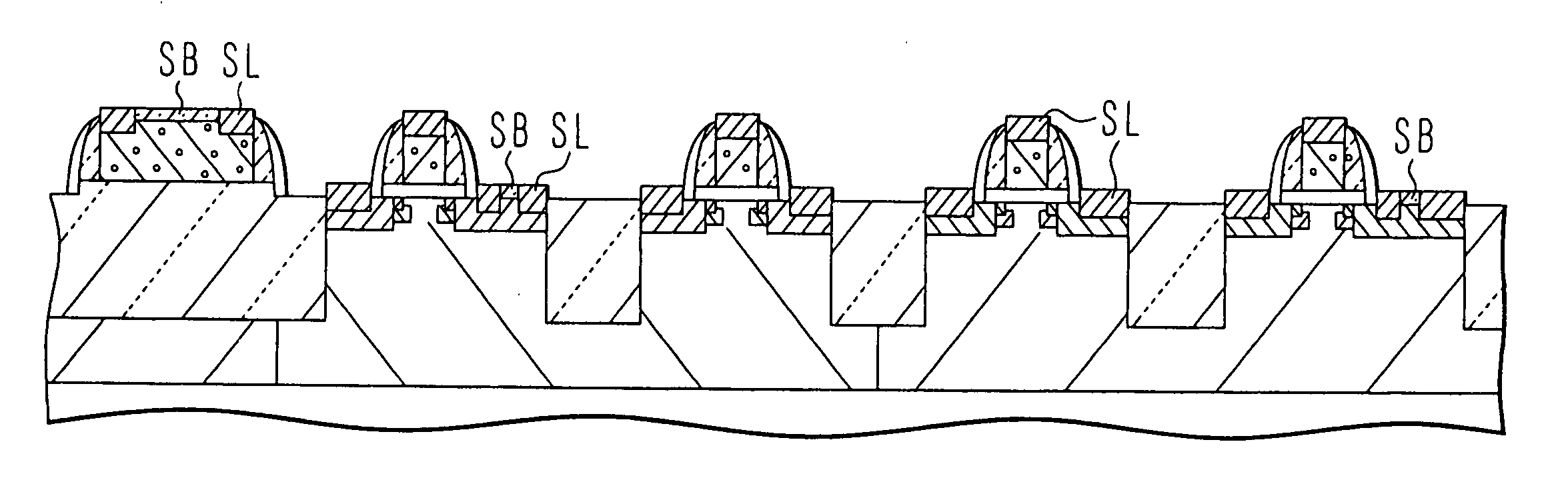

Schottky barrier nanowire field effect transistor and method for fabricating the same

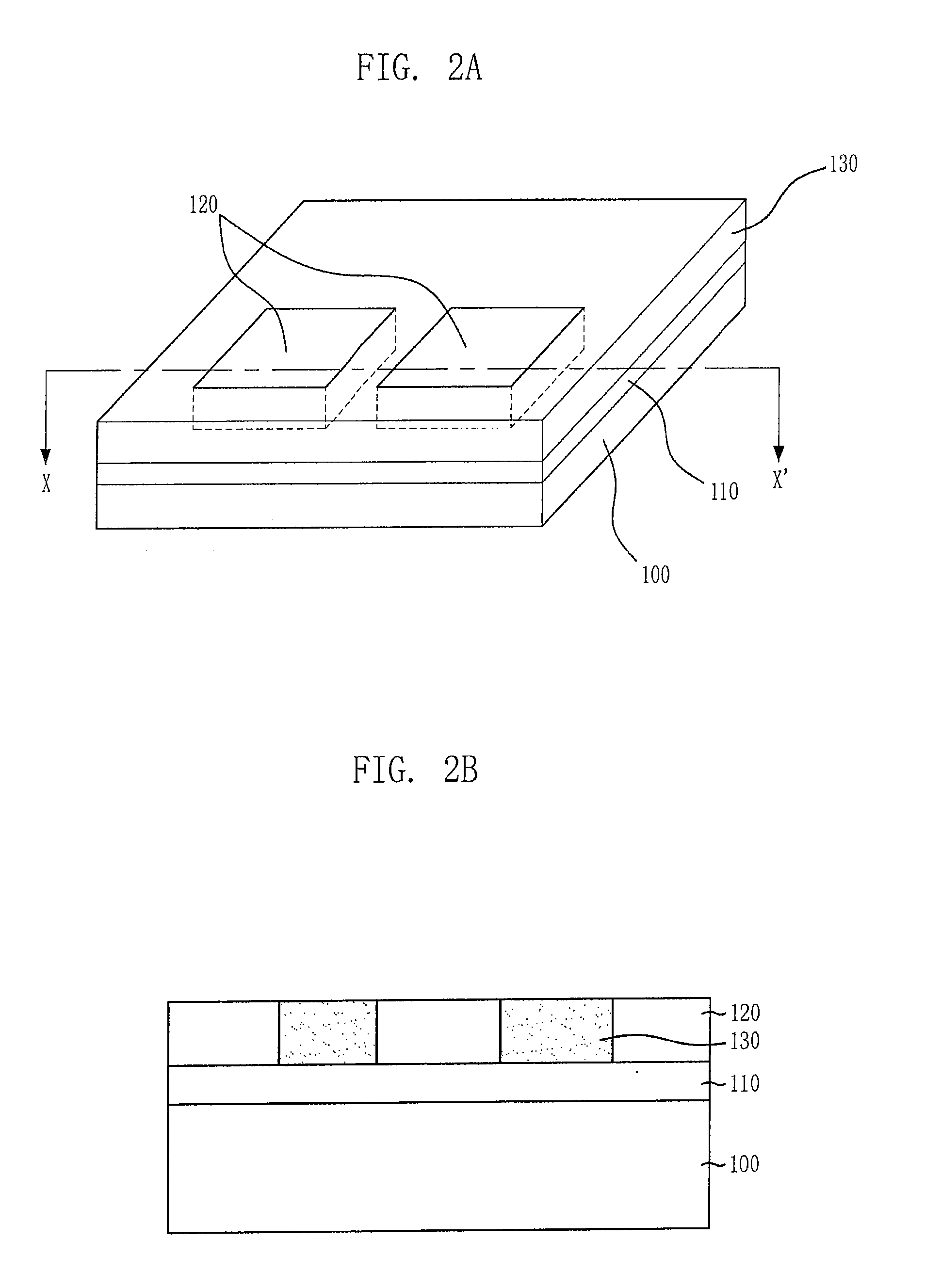

InactiveUS20080128760A1Easy to makeEnsure thermal stabilityNanoinformaticsSolid-state devicesSalicideInsulation layer

Provided is a Schottky barrier nanowire field effect transistor, which has source / drain electrodes formed of metal silicide and a channel formed of a nanowire, and a method for fabricating the same. The Schottky barrier nanowire field effect transistor includes: a channel suspended over a substrate and including a nanowire; metal silicide source / drain electrodes electrically connected to both ends of the channel over the substrate; a gate electrode disposed to surround the channel; and a gate insulation layer disposed between the channel and the gate electrode.

Owner:ELECTRONICS & TELECOMM RES INST

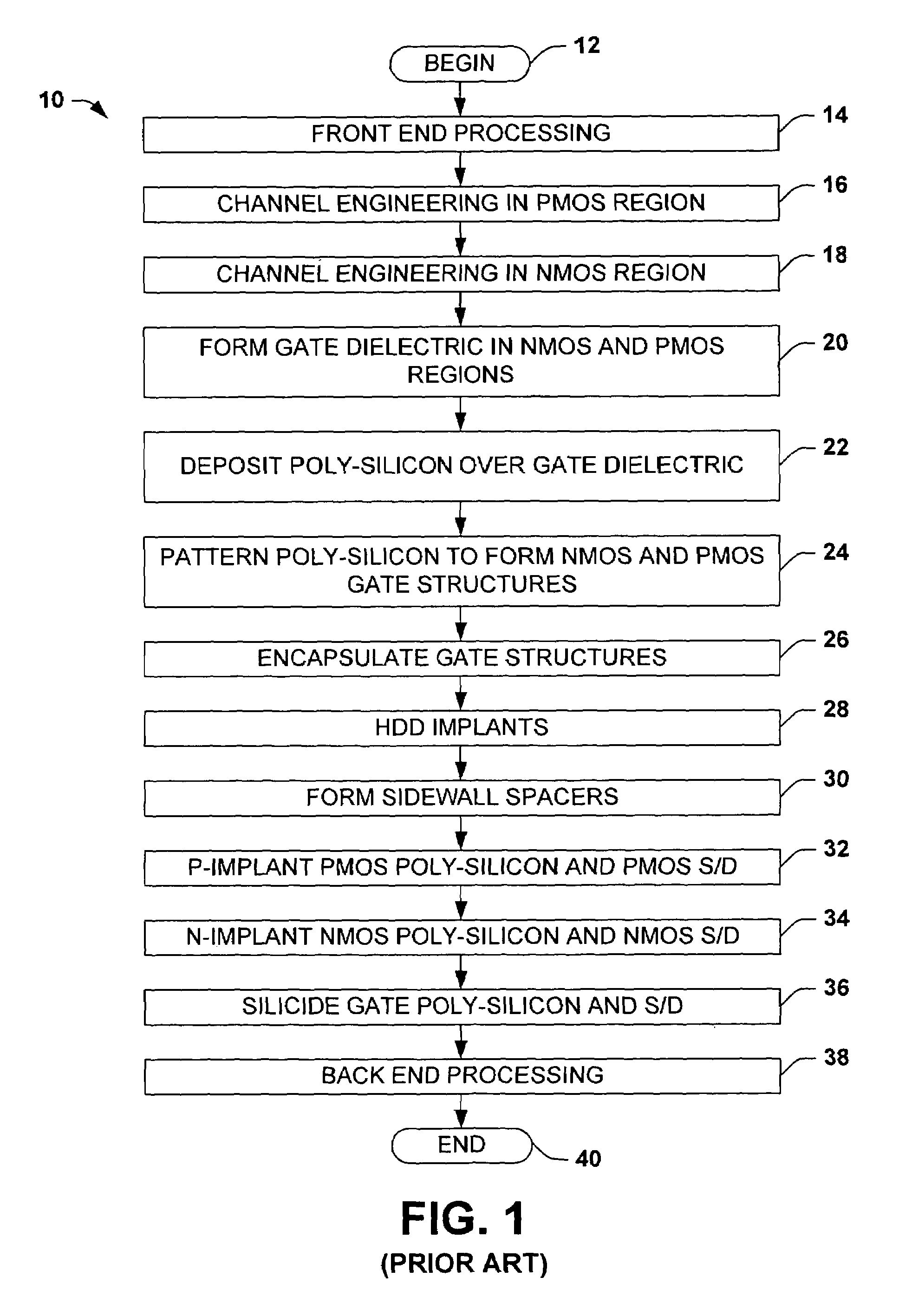

Method for forming an integrated circuit

ActiveUS7402872B2Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

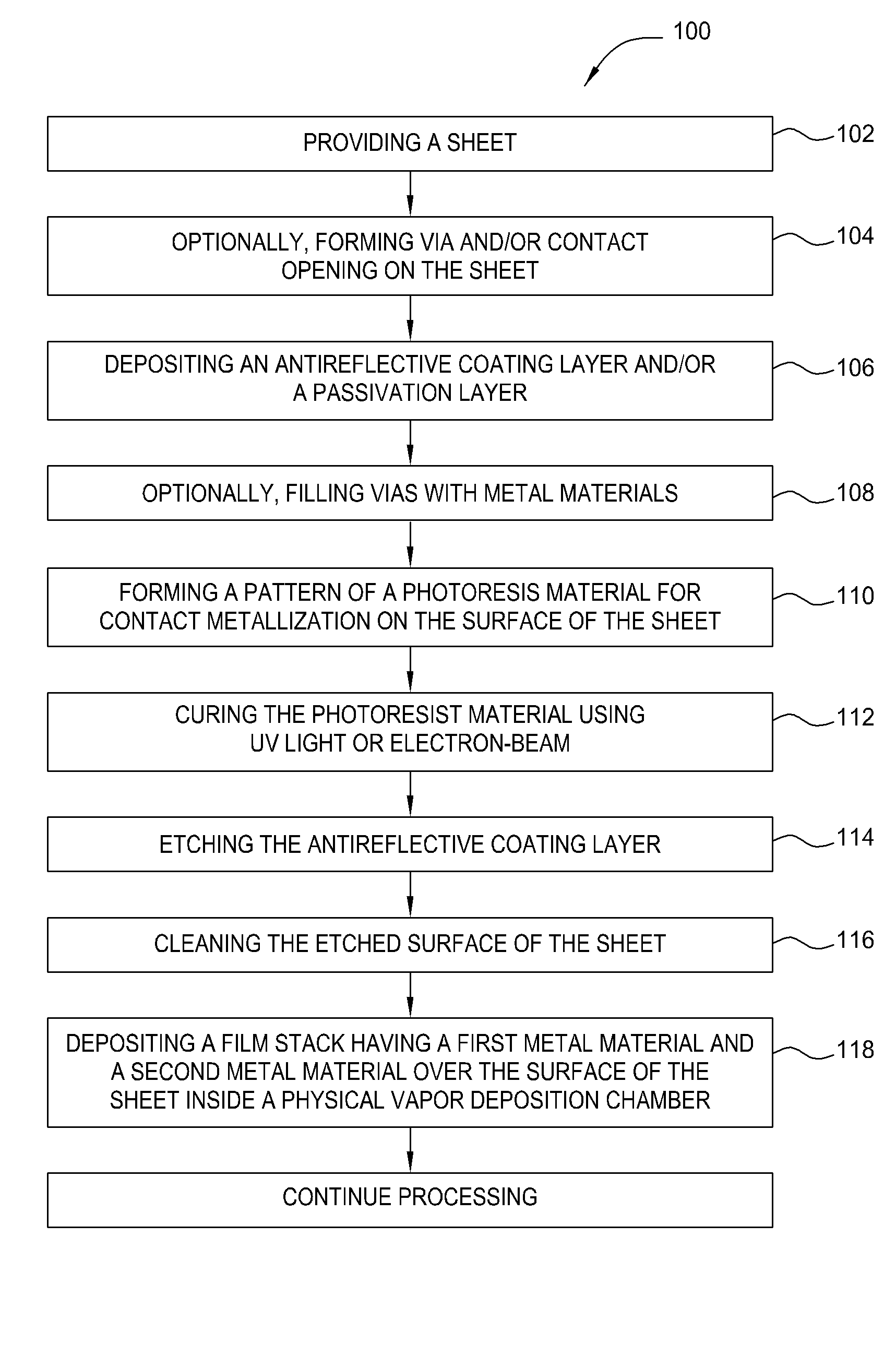

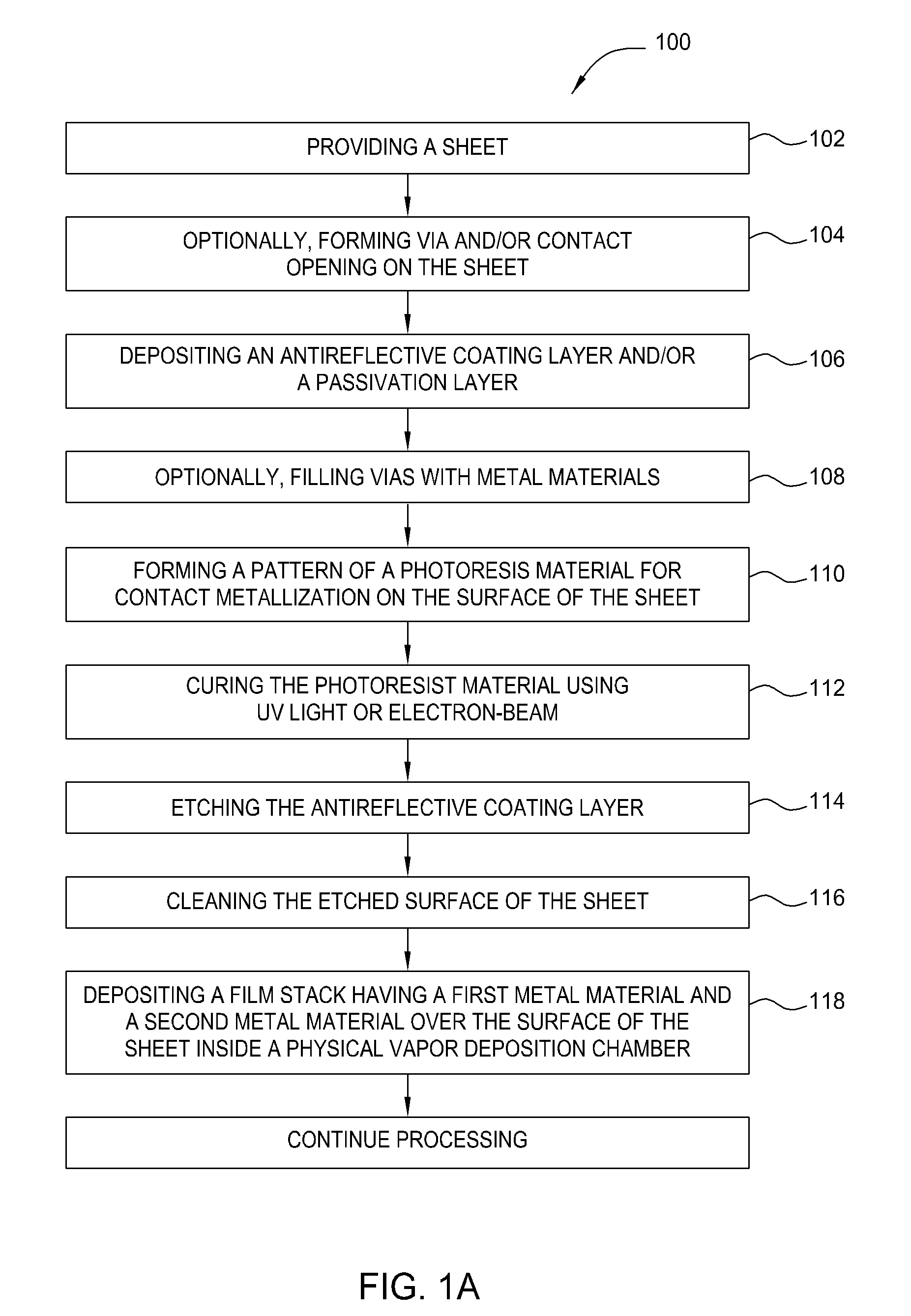

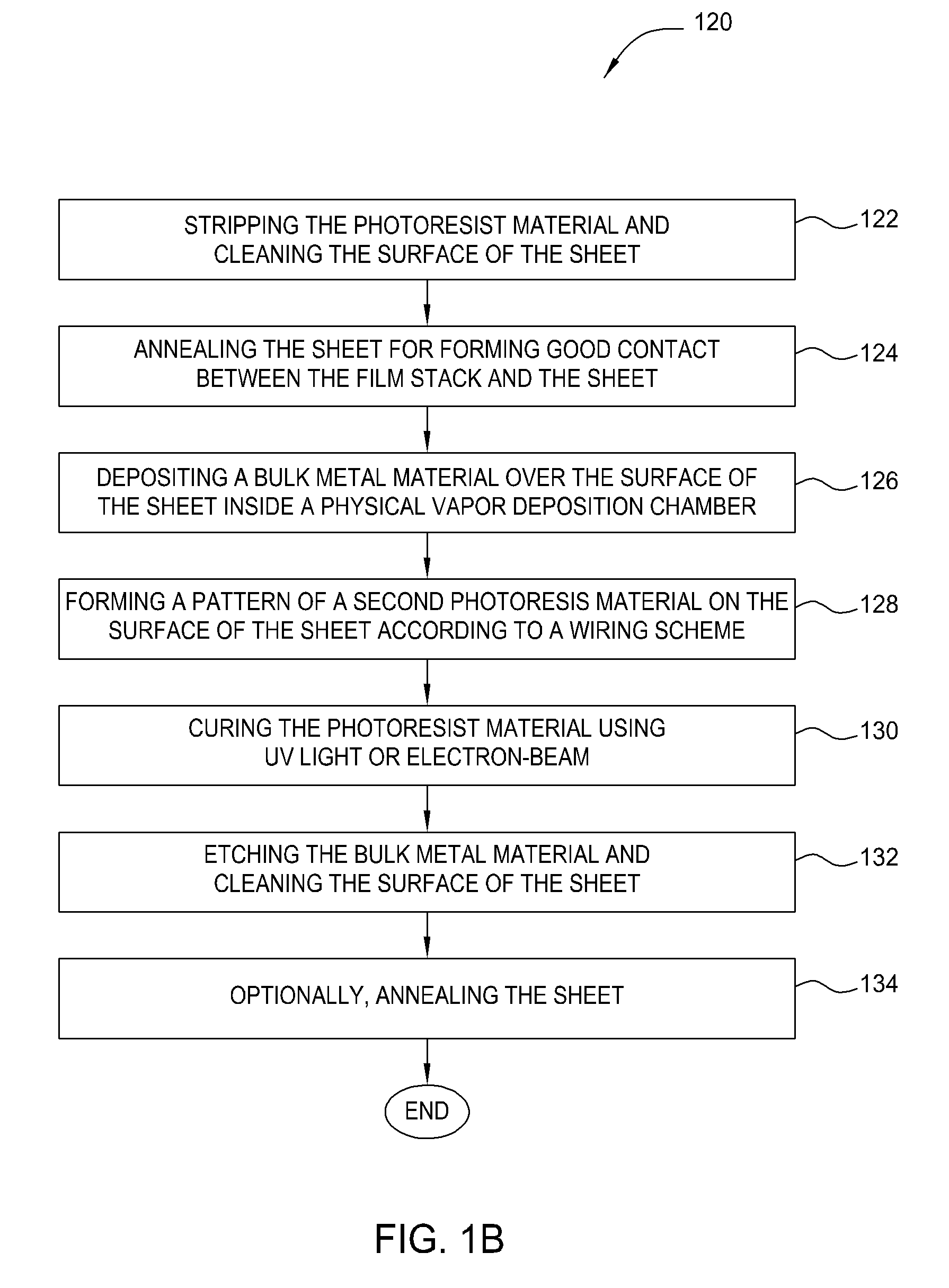

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

Dual metal gate process: metals and their silicides

InactiveUS6475908B1High and work functionImprove work functionOperating chairsSemiconductor/solid-state device manufacturingSalicideCMOS

Methods for forming dual-metal gate CMOS transistors are described. An NMOS and a PMOS active area of a semiconductor substrate are separated by isolation regions. A metal layer is deposited over a gate dielectric layer in each active area. Silicon ions are implanted into the metal layer in one active area to form an implanted metal layer which is silicided to form a metal silicide layer. Thereafter, the metal layer and the metal silicide layer are patterned to form a metal gate in one active area and a metal silicide gate in the other active area wherein the active area having the gate with the higher work function is the PMOS active area. Alternatively, both gates may be metal silicide gates wherein the silicon concentrations of the two gates differ. Alternatively, a dummy gate may be formed in each of the active areas and covered with a dielectric layer. The dielectric layer is planarized thereby exposing the dummy gates. The dummy gates are removed leaving gate openings to the semiconductor substrate. A metal layer is deposited over a gate dielectric layer within the gate openings to form metal gates. One or both of the gates are silicon implanted and silicided. The PMOS gate has the higher work function.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

MOS transistor gates with thin lower metal silicide and methods for making the same

ActiveUS7045456B2Easy to implantEasy to controlTransistorSemiconductor/solid-state device manufacturingSalicideGate dielectric

Methods are presented for fabricating transistor gate structures, wherein upper and lower metal suicides are formed above a gate dielectric. In one example, the lower silicide is formed by depositing a thin first silicon-containing material over the gate dielectric, which is implanted and then reacted with a first metal by annealing to form the lower silicide. A capping layer can be formed over the first metal prior to annealing, to prevent oxidation of the metal prior to silicidation, and a barrier layer can be formed over the lower silicide to prevent reaction with subsequently formed silicon material. In another example, the lower silicide is a multilayer silicide structure including a plurality of metal silicide sublayers.

Owner:TEXAS INSTR INC

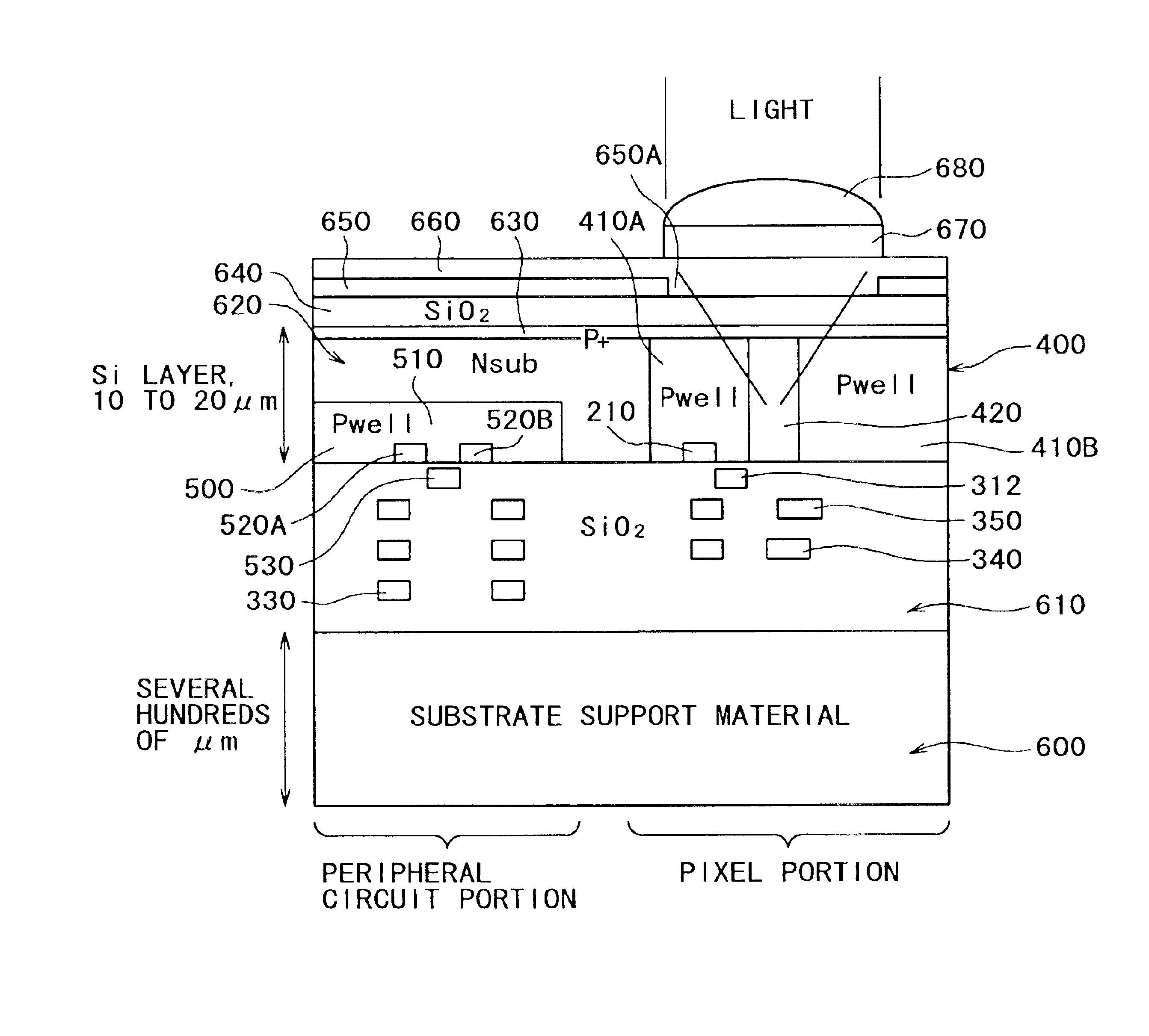

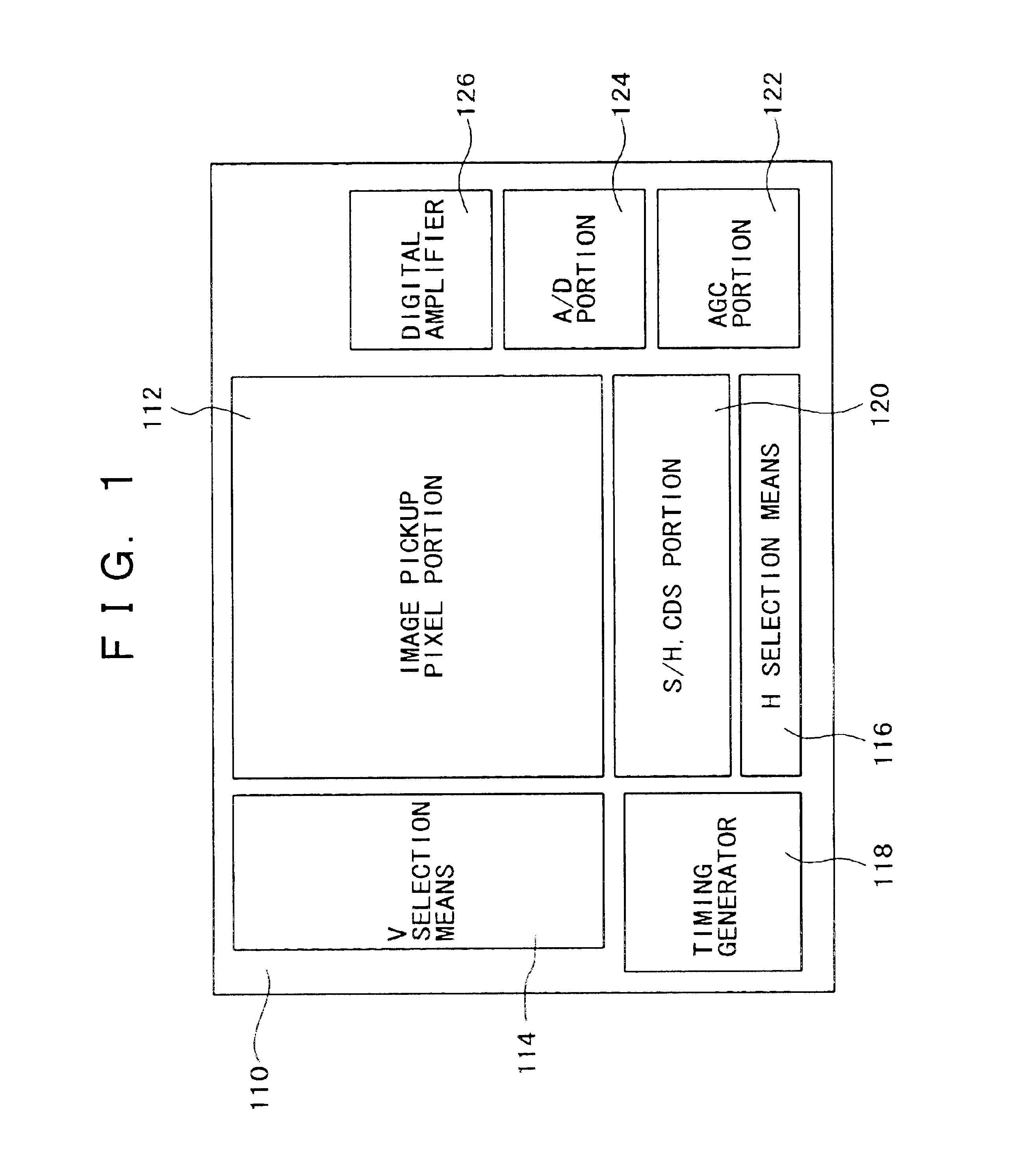

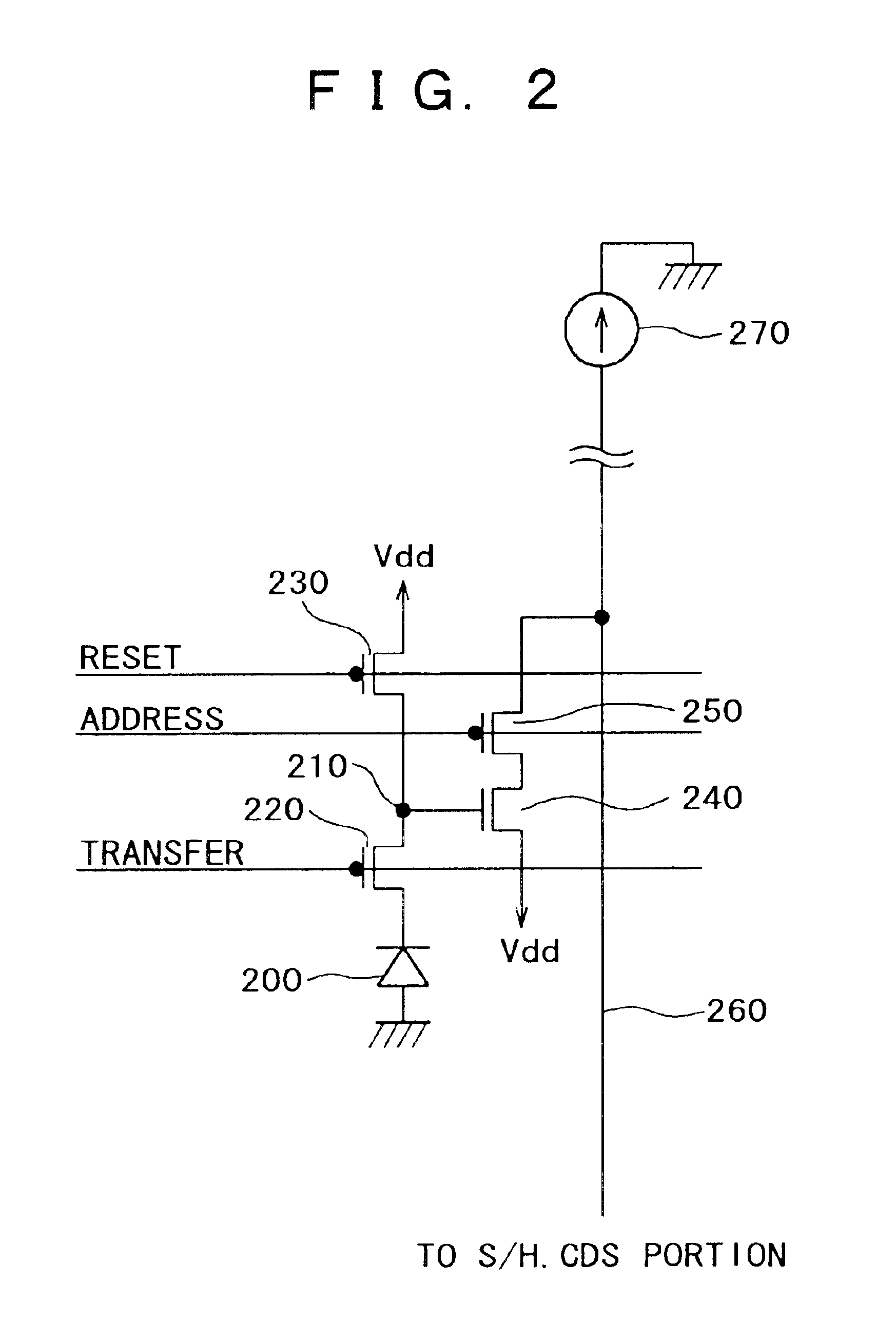

Solid state image pickup device and method of producing solid state image pickup device

Owner:SONY CORP

Three dimensional NAND device with semiconductor, metal or silicide floating gates and method of making thereof

ActiveUS20140225181A1TransistorSemiconductor/solid-state device manufacturingSalicideDielectric layer

A method of making a monolithic three dimensional NAND string includes forming a stack of alternating layers of a first material and a second material, etching the stack to form a front side opening in the stack, selectively forming a plurality of discrete semiconductor, metal or silicide charge storage regions on portions of the second material layers exposed in the front side opening, forming a tunnel dielectric layer and semiconductor channel layer in the front side opening, etching the stack to form a back side opening in the stack, removing at least a portion of the second material layers through the back side opening to form back side recesses between the first material layers, forming a blocking dielectric in the back side recesses through the back side opening, and forming control gates over the blocking dielectric in the back side recesses through the back side opening.

Owner:SANDISK TECH LLC

Semiconductor device and its manufacturing method

InactiveUS20050227440A1Simple processEfficient preparation methodTransistorSolid-state devicesDevice materialMetal silicide

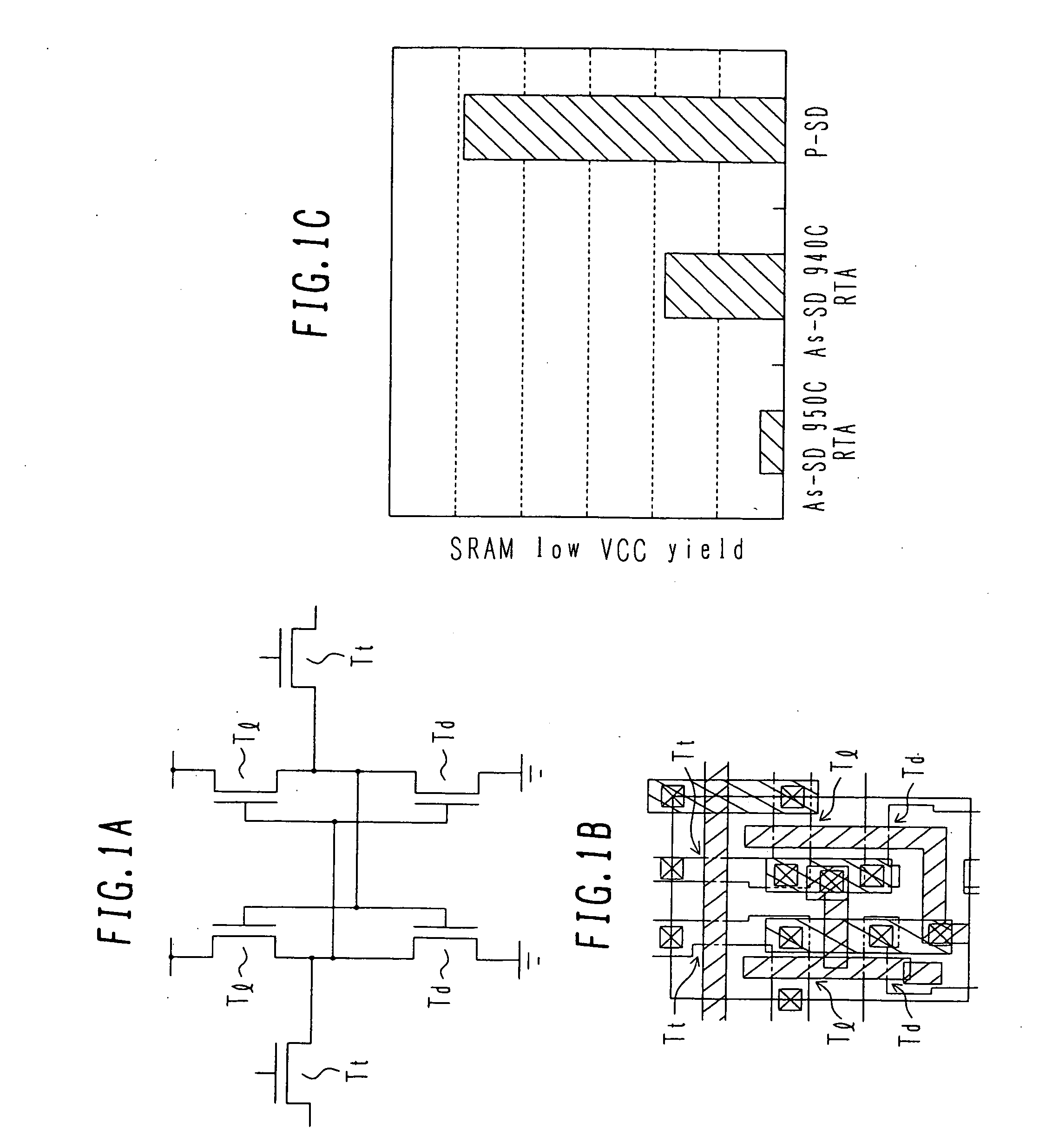

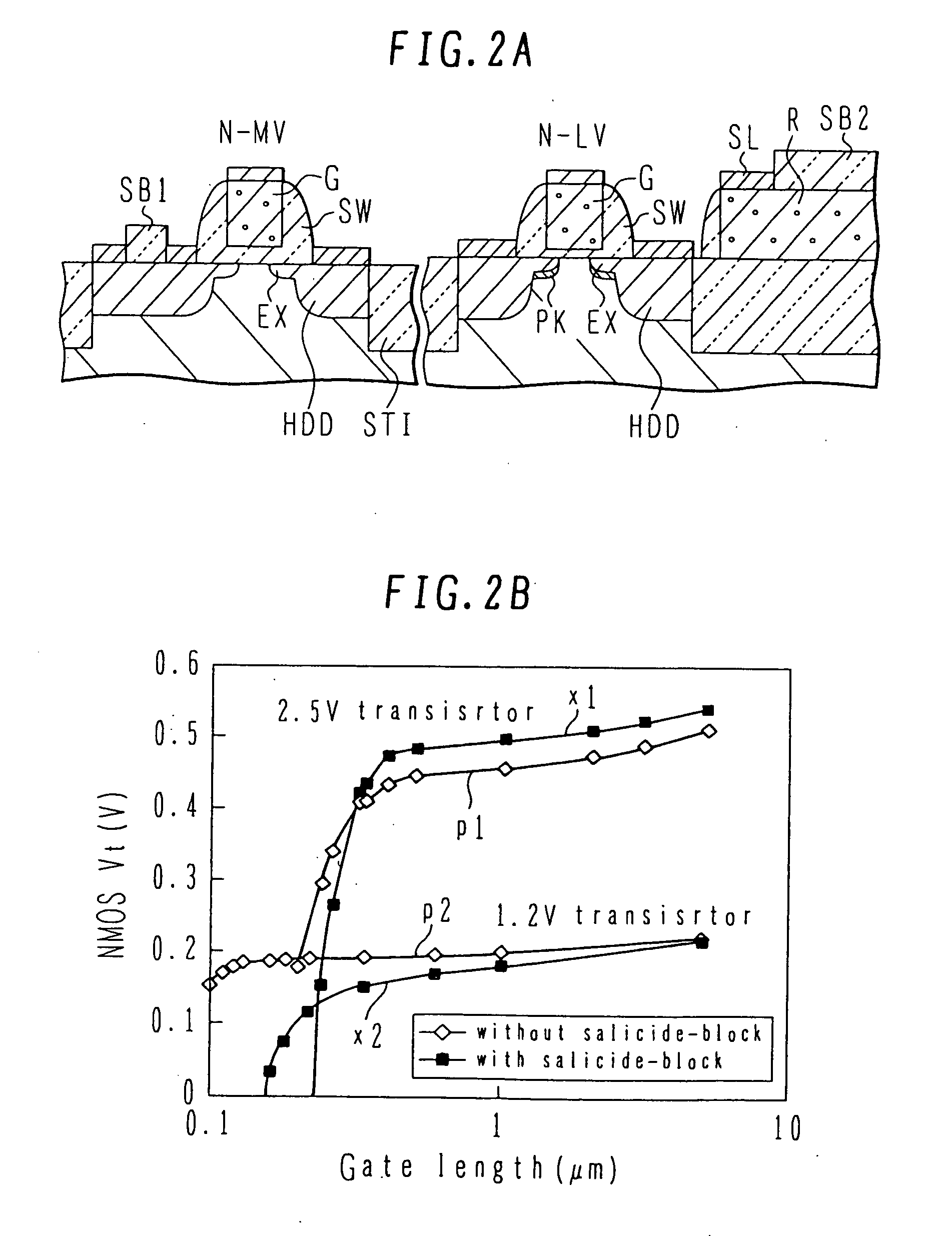

A semiconductor device manufacturing method includes, forming isolation region having an aspect ratio of 1 or more in a semiconductor substrate, forming a gate insulating film, forming a silicon gate electrode and a silicon resistive element, forming side wall spacers on the gate electrode, heavily doping a first active region with phosphorus and a second active region and the resistive element with p-type impurities by ion implantation, forming salicide block at 500° C. or lower, depositing a metal layer covering the salicide block, and selectively forming metal silicide layers. The method may further includes, forming a thick and a thin gate insulating films, and performing implantation of ions of a first conductivity type not penetrating the thick gate insulating film and oblique implantation of ions of the opposite conductivity type penetrating also the thick gate insulating film before the formation of side wall spacers.

Owner:FUJITSU LTD

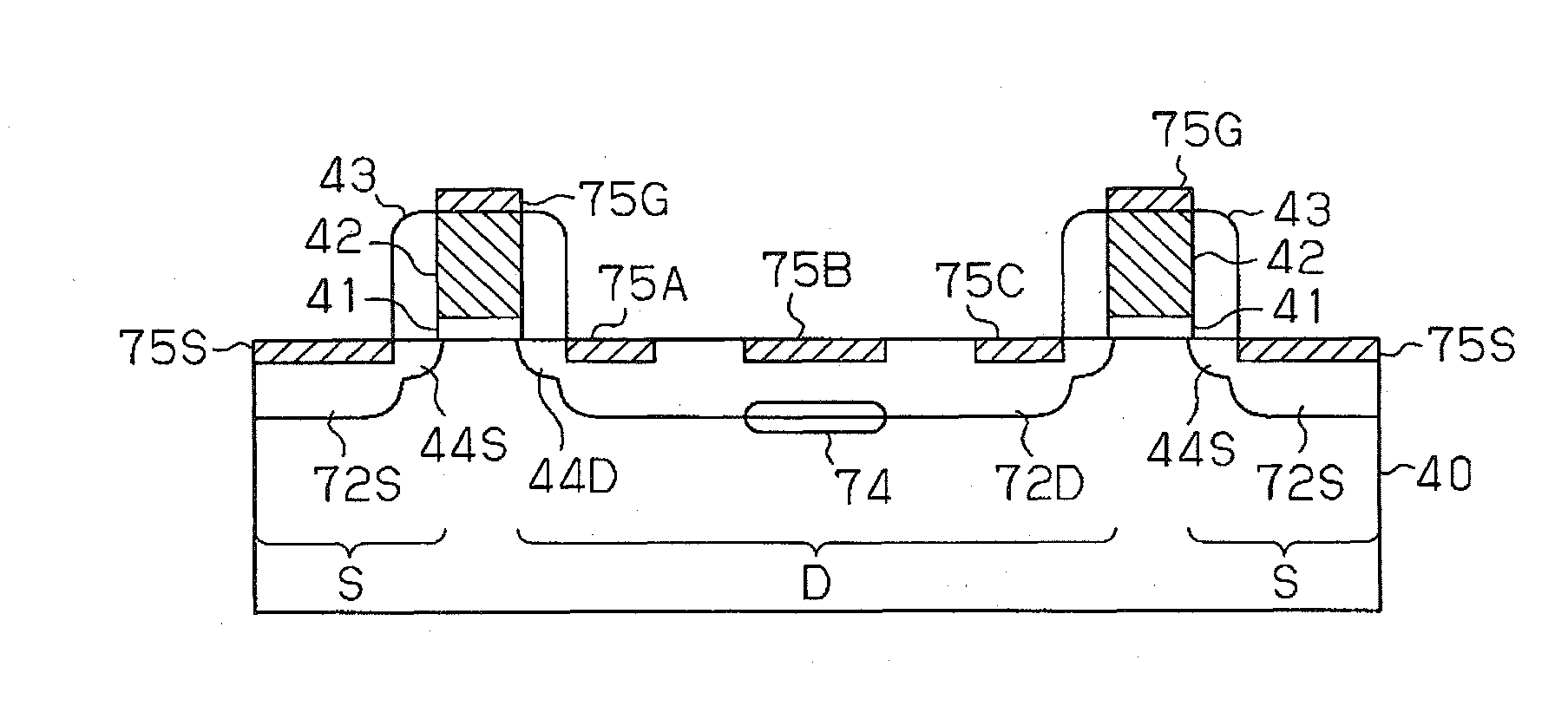

Electro-static discharge protection device, semiconductor device, and method for manufacturing electro-static discharge protection device

An electrostatic discharge protection device including a gate electrode formed on a substrate. First and second diffusion regions of a first conductivity type are formed in the substrate with the gate electrode located in between. A first silicide layer is formed in the first diffusion region. A silicide block region is formed between the gate electrode and the first suicide layer. A third diffusion region is formed below the first silicide layer to partially overlap the first diffusion region. The third diffusion region and first silicide layer have substantially the same shapes and dimensions. The third diffusion region and a portion below the gate electrode located at the same depth as the third diffusion region contain impurities of a second conductivity type. The third diffusion region has an impurity concentration that is higher than that of the portion below the gate electrode.

Owner:SOCIONEXT INC

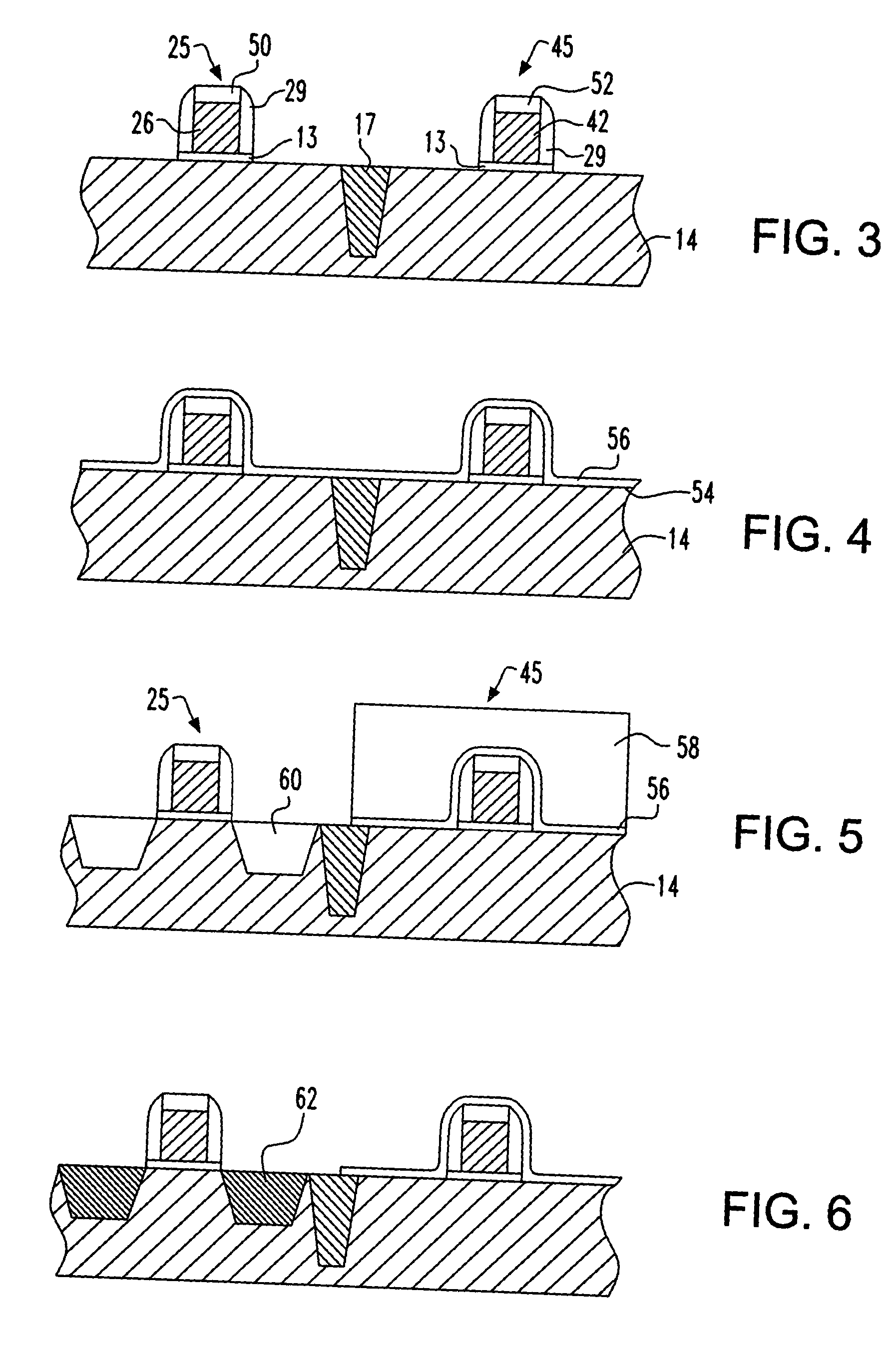

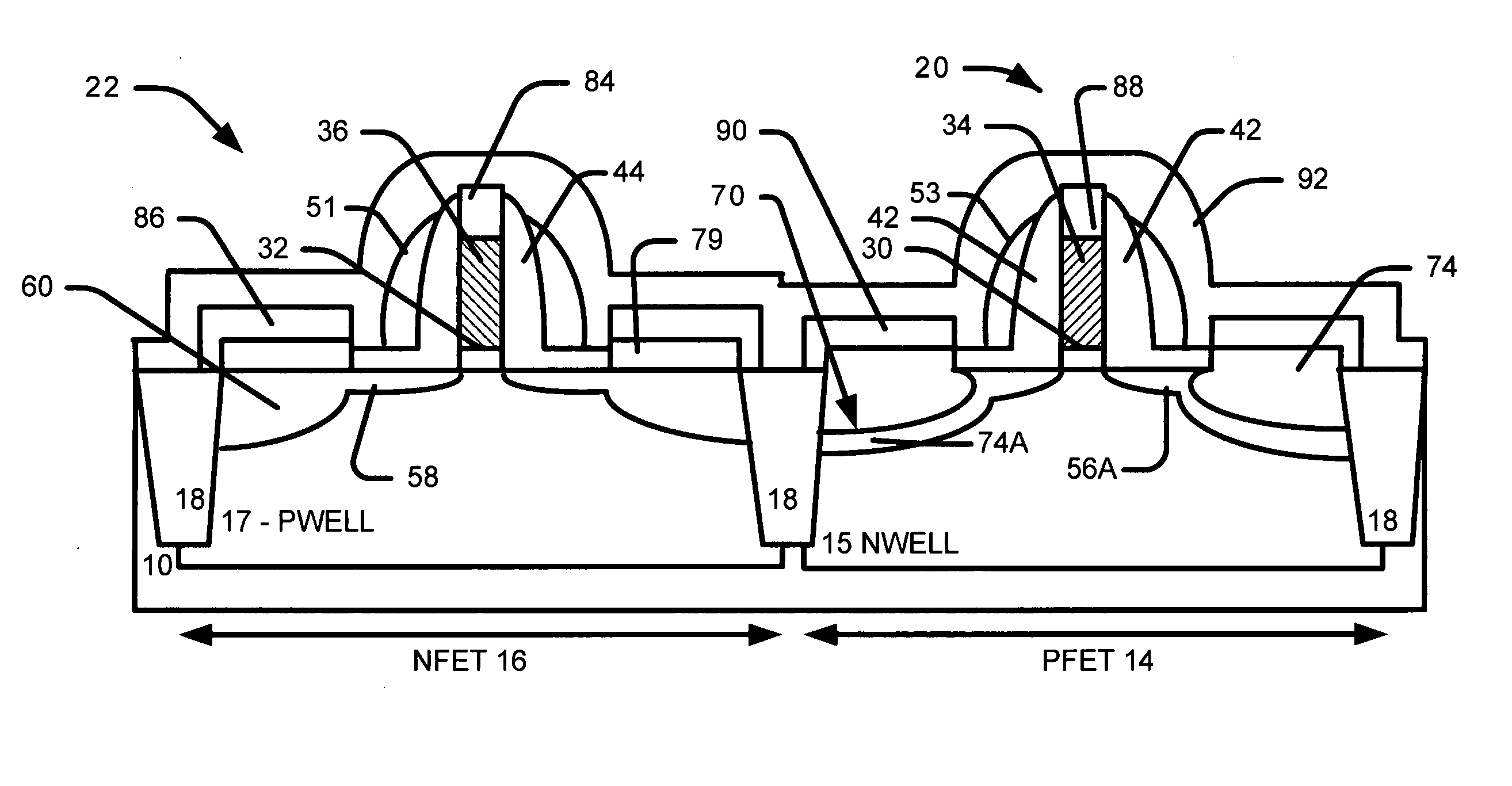

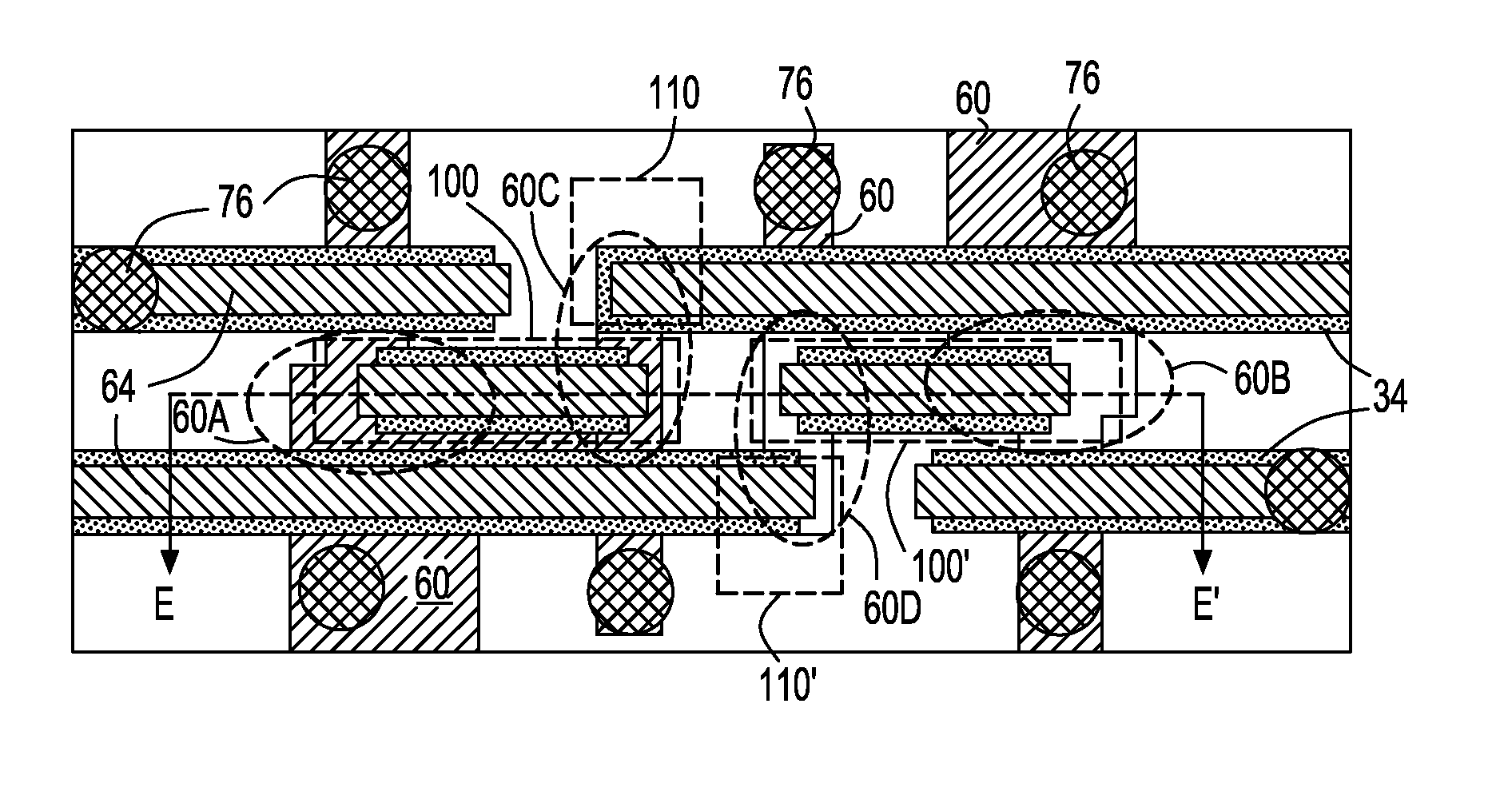

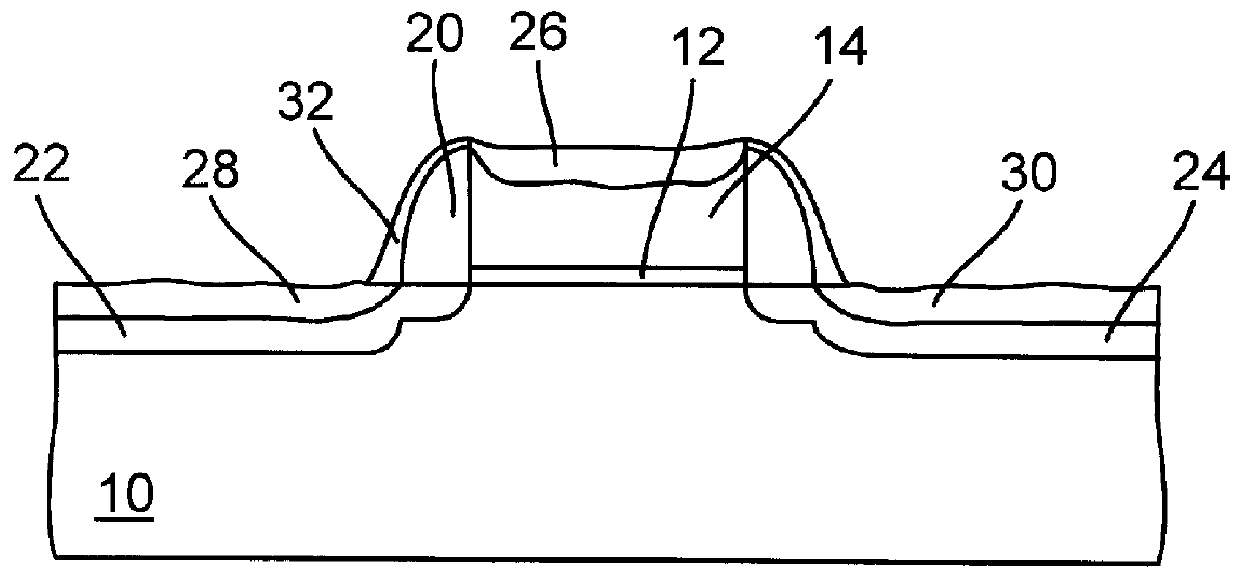

Formation of raised source/drain structures in NFET with embedded SiGe in PFET

A structure and method for forming raised source / drain structures in a NFET device and embedded SiGe source / drains in a PFET device. We provide a NFET gate structure over a NFET region in a substrate and PFET gate structure over a PFET region. We provide NFET SDE regions adjacent to the NFET gate and provide PFET SDE regions adjacent to the PFET gate. We form recesses in the PFET region in the substrate adjacent to the PFET second spacers. We form a PFET embedded source / drain stressor in the recesses. We form a NFET S / D epitaxial Si layer over the NFET SDE regions and a PFET S / D epitaxial Si layer over PFET embedded source / drain stressor. The epitaxial Si layer over PFET embedded source / drain stressor is consumed in a subsequent salicide step to form a stable and low resistivity silicide over the PFET embedded source / drain stressor. We perform a NFET S / D implant by implanting N-type ions into NFET region adjacent to the NFET gate structure and into the NFET S / D stressor Si layer to form the raised NFET source / drains.

Owner:TAIWAN SEMICON MFG CO LTD +1

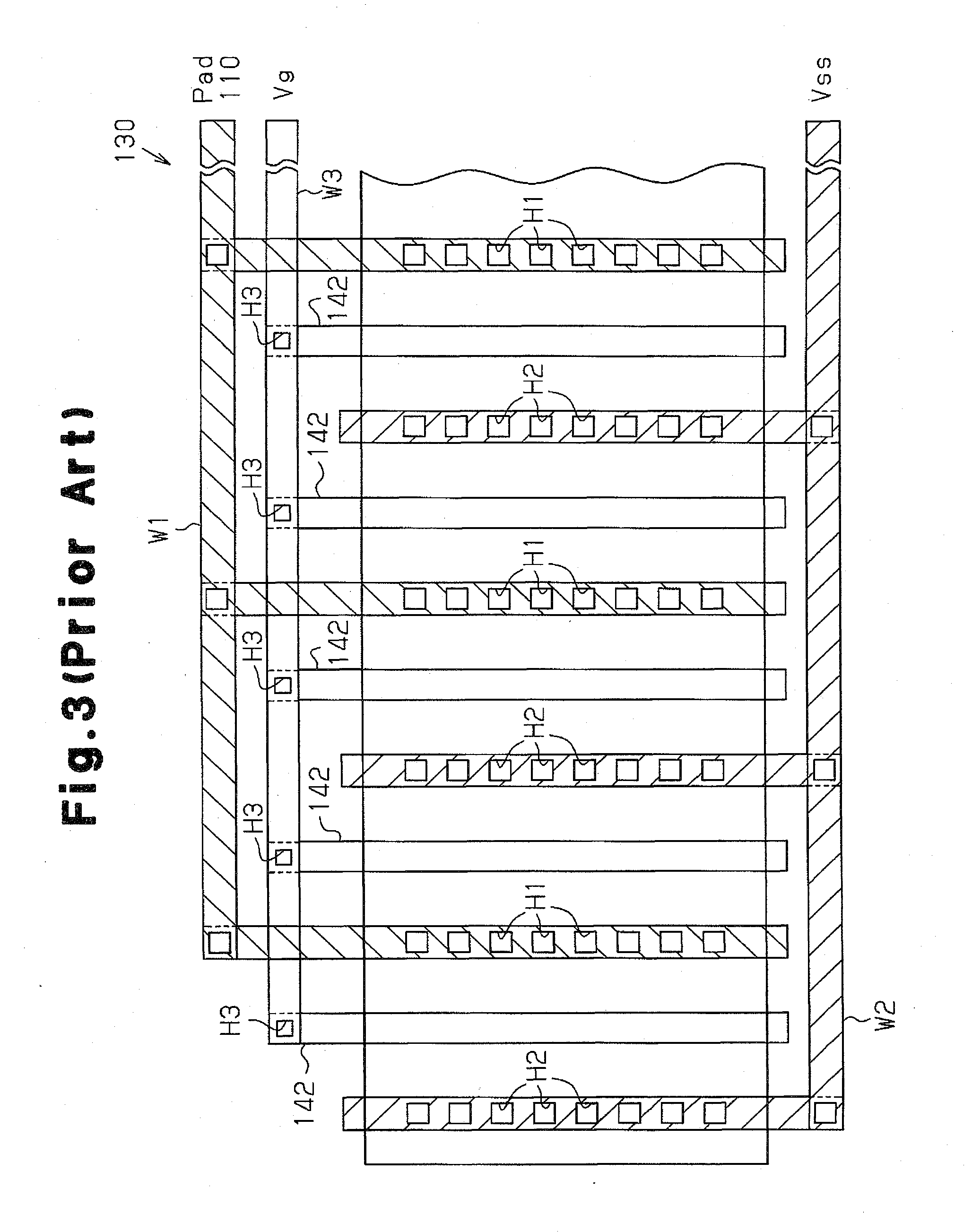

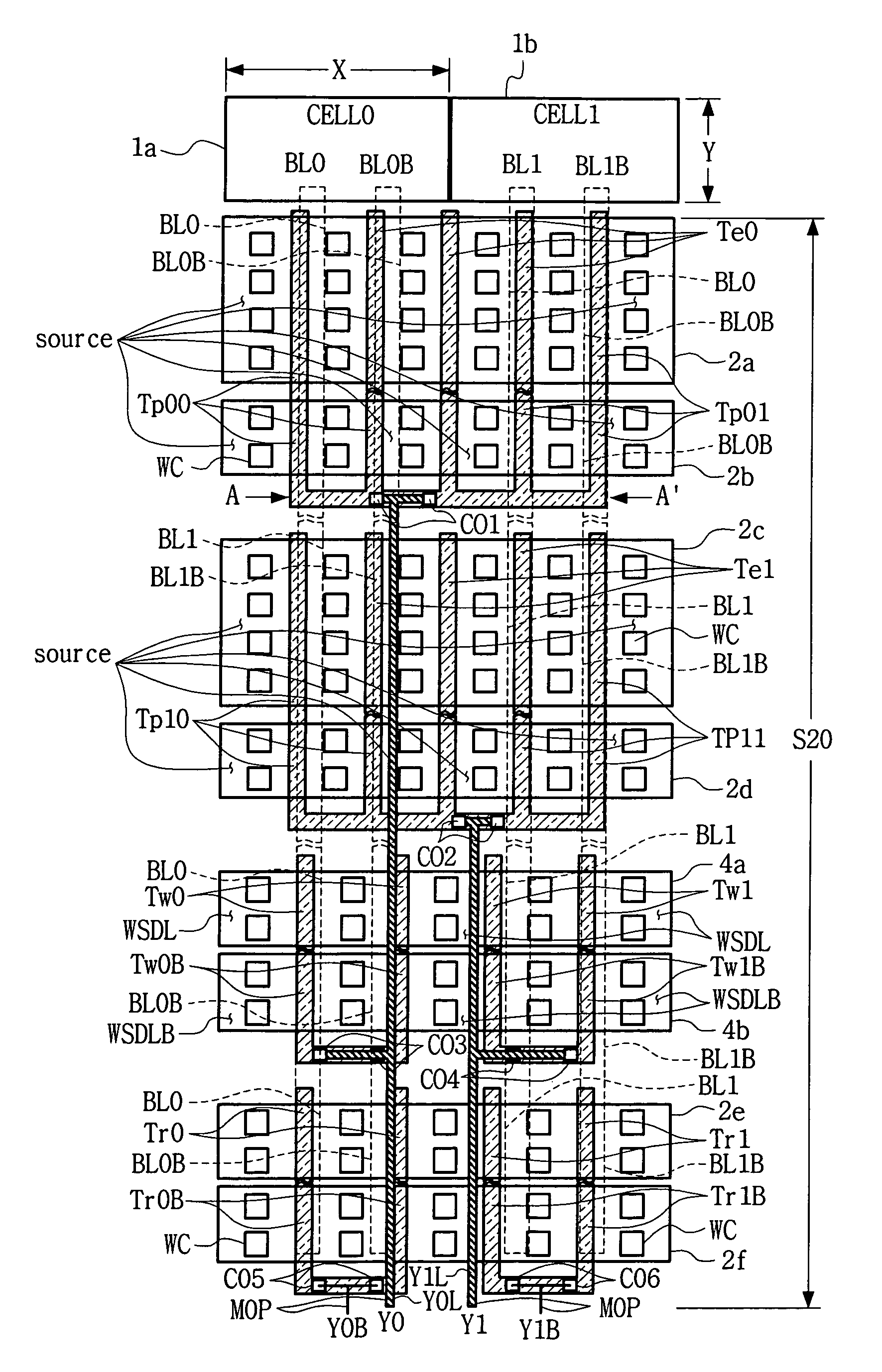

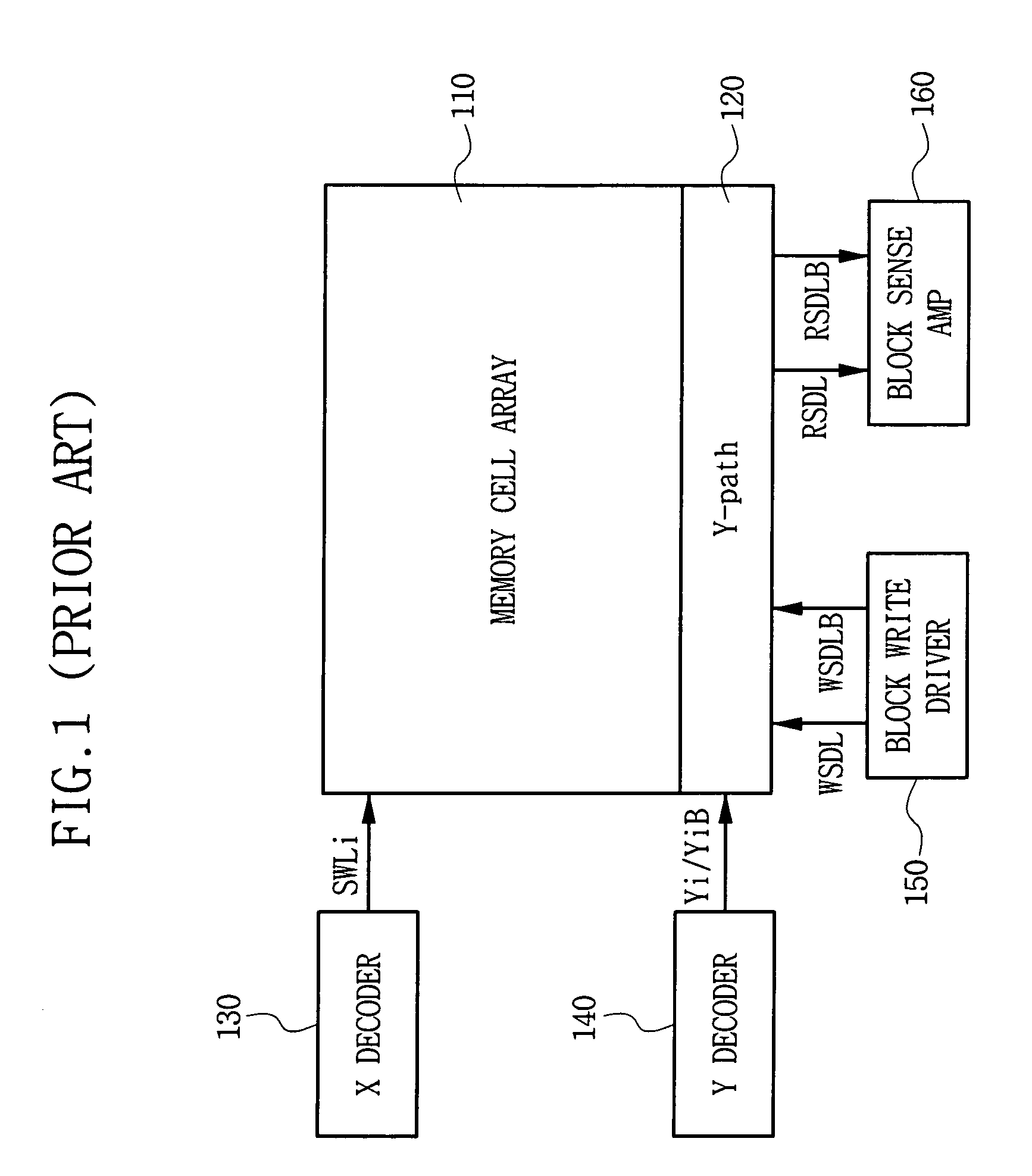

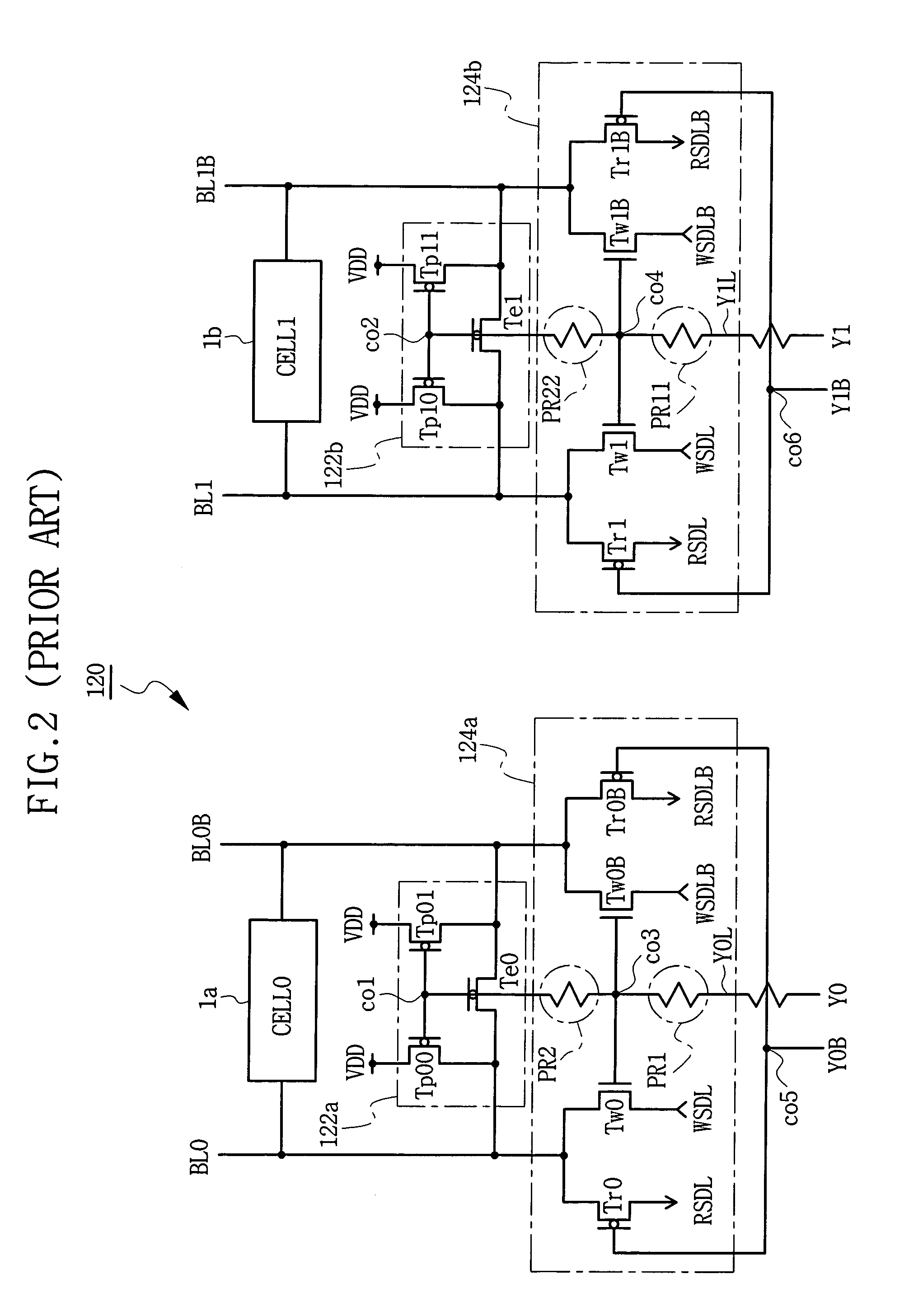

Circuit wiring layout in semiconductor memory device and layout method

InactiveUS7564134B2Reduced footprintSmooth wiringTransistorSemiconductor/solid-state device detailsMOSFETMetal silicide

An improved circuit wiring layout provides smooth circuit wiring in a peripheral circuit region adjacent to a memory cell region of a semiconductor memory device, and eliminates a write-speed limiting factor. Forming a metal (instead of a metal silicided polysilicon) wiring layer to be connected to a gate layer, to transmit an electrical signal to the gates of FET (e.g., MOSFET (Metal Oxide Semiconductor Field Effect Transistor) transistors formed in the peripheral circuit region; the metal wiring layer is formed (e.g., using one metal damascene process), on a layer different from a word line layer formed on the gate layer (e.g., using another metal damascene process), thereby obtaining a layout of a peripheral circuit region having a reduced area and without using a silicide process.

Owner:SAMSUNG ELECTRONICS CO LTD

Formation of silicided surfaces for silicon/carbon source/drain regions

Formation of a silicide layer on the source / drain regions of a field effect transistor with a channel under tensile strain is disclosed. The strain is originated by the silicon / carbon source / drain regions which are grown by CVD deposition. In order to form the silicide layer, a silicon cap layer is deposited in situ by CVD. The silicon cap layer is then employed to form a silicide layer made of a silicon / cobalt compound. This method allows the formation of a silicide cobalt layer in silicon / carbon source / drain regions, which was until the present time not possible.

Owner:GLOBALFOUNDRIES INC

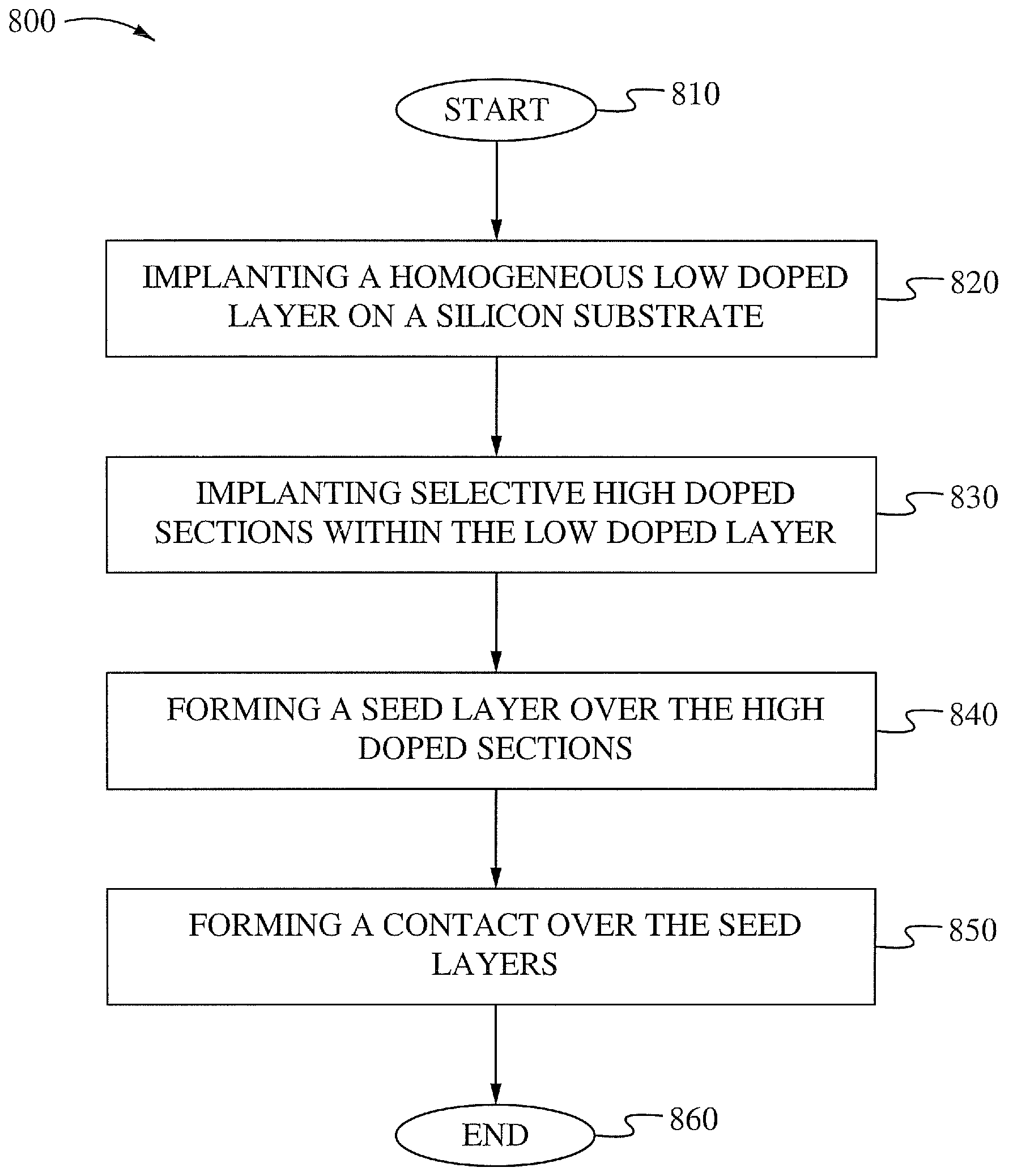

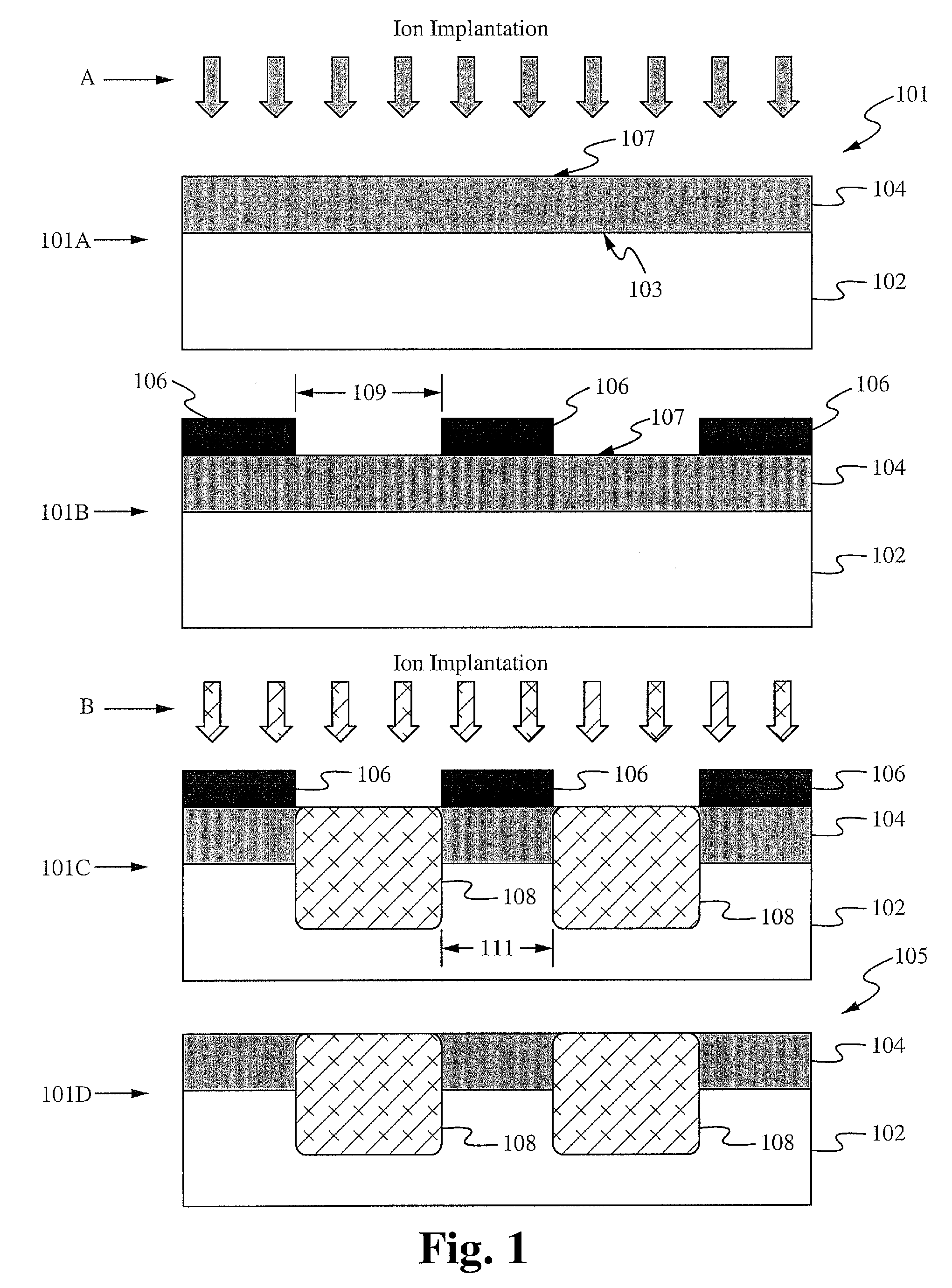

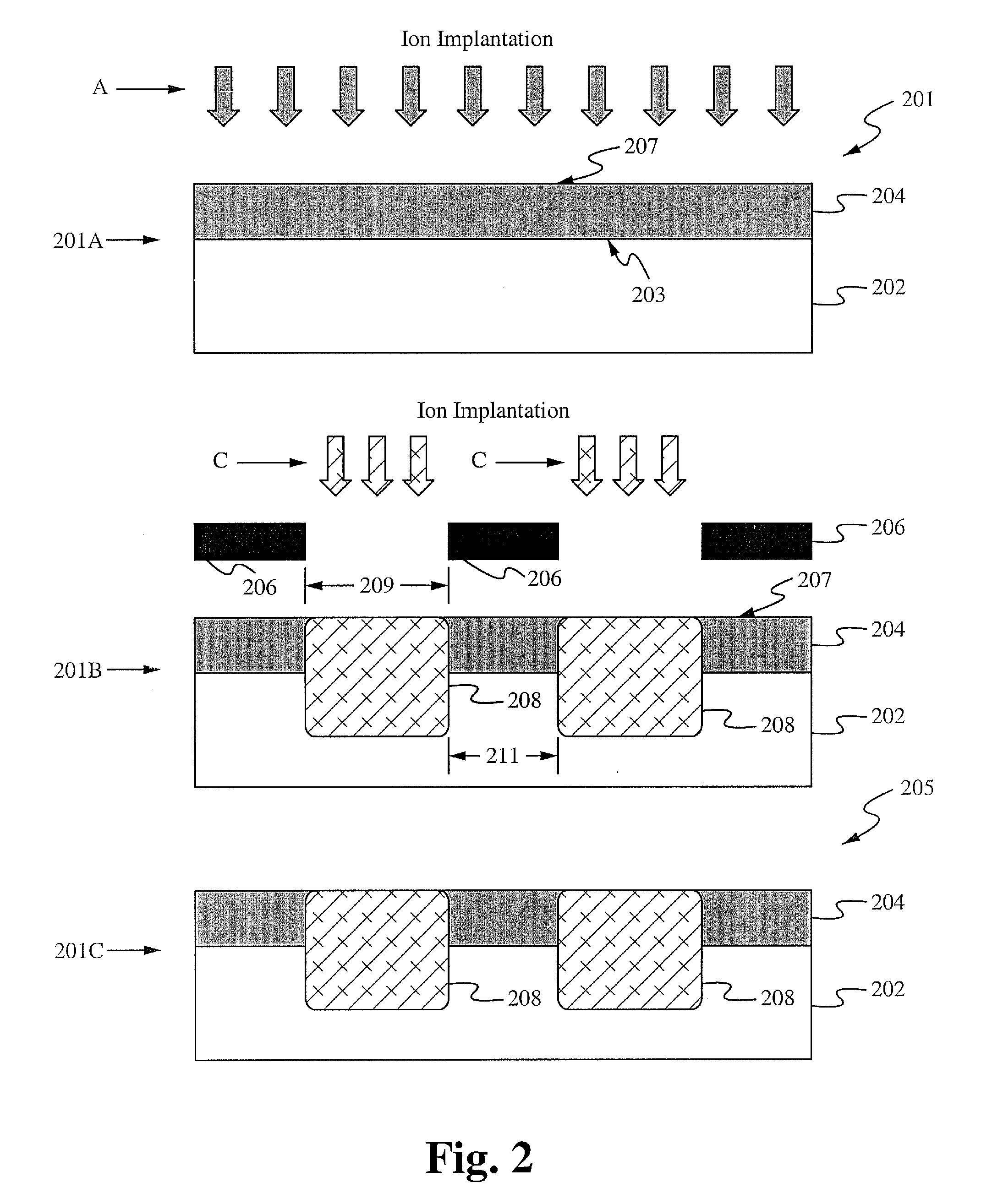

Solar cell fabrication using implantation

InactiveUS20090308439A1Low temperature annealingLower temperature annealingFinal product manufactureSemiconductor/solid-state device manufacturingAnti-reflective coatingDopant

A solar cell device and method of making are provided. The device includes a silicon substrate including a preexisting dopant. A homogeneous lightly doped region is formed on a surface of the silicon substrate to form a junction between the preexisting dopant and the lightly doped region. A heavily doped region is selectively implanted on the surface of the silicon substrate. A seed layer is formed over the heavily doped region. A metal contact is formed over the seed layer. The device can include an anti-reflective coating. In one embodiment, the heavily doped region forms a parabolic shape. The heavily doped regions can each be a width on the silicon substrate a distance in the range 50 to 200 microns. Also, the heavily doped regions can be laterally spaced on the silicon substrate a distance in the range 1 to 3 mm from each other. The seed layer can be a silicide. The silicon substrate can include fiducial markers configured for aligning the placement of the heavily doped regions during an ion implantation process.

Owner:INTEVAC

Metal silicide alloy local interconnect

A local interconnect is formed with a gate conductor line that has an exposed sidewall on an active area of a semiconductor substrate. The exposes sidewall comprises a silicon containing material that may form a silicide alloy upon silicidation. During a silicidation process, a gate conductor sidewall silicide alloy forms on the exposed sidewall of the gate conductor line and an active area silicide is formed on the active area. The two silicides are joined to provide an electrical connection between the active area and the gate conductor line. Multiple sidewalls may be exposed on the gate conductor line to make multiple connections to different active area silicides.

Owner:GLOBALFOUNDRIES INC

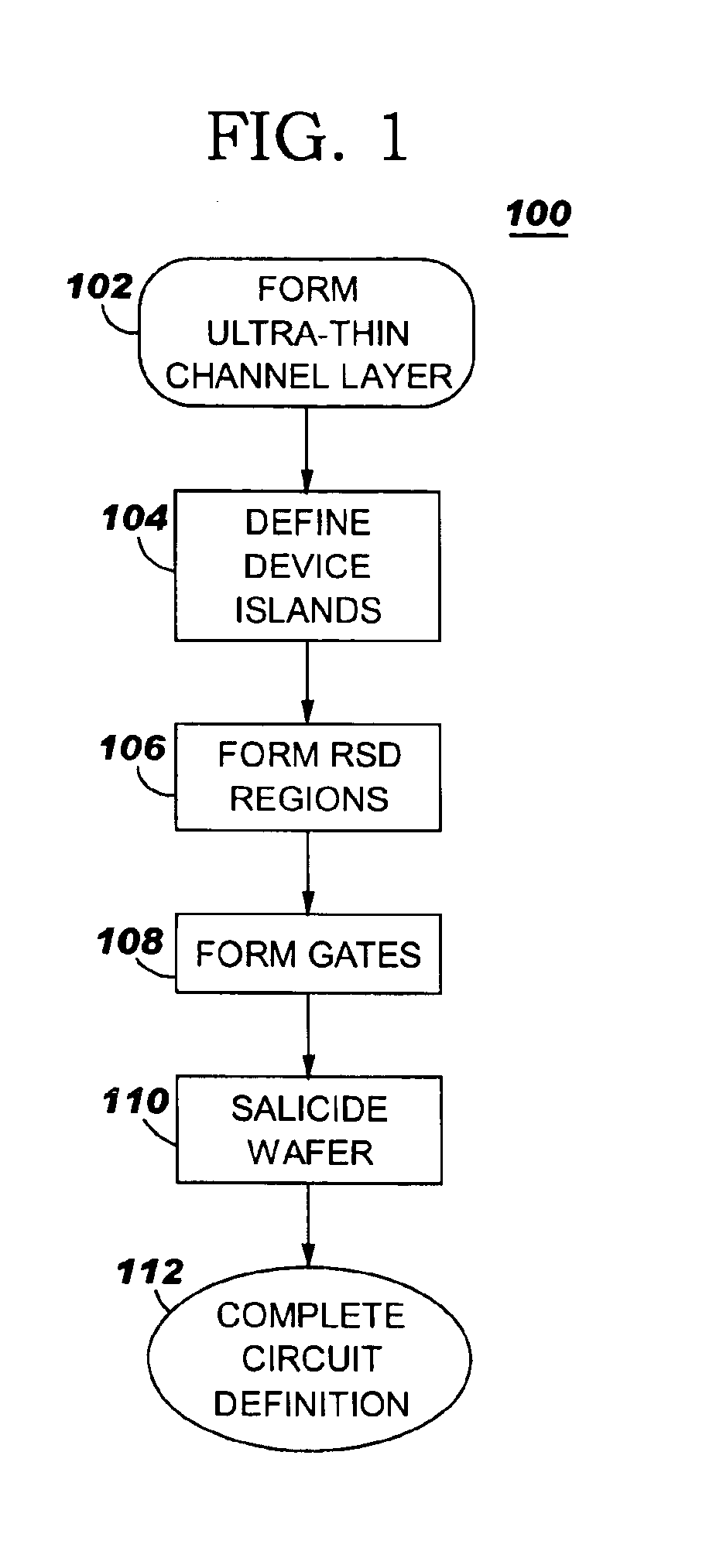

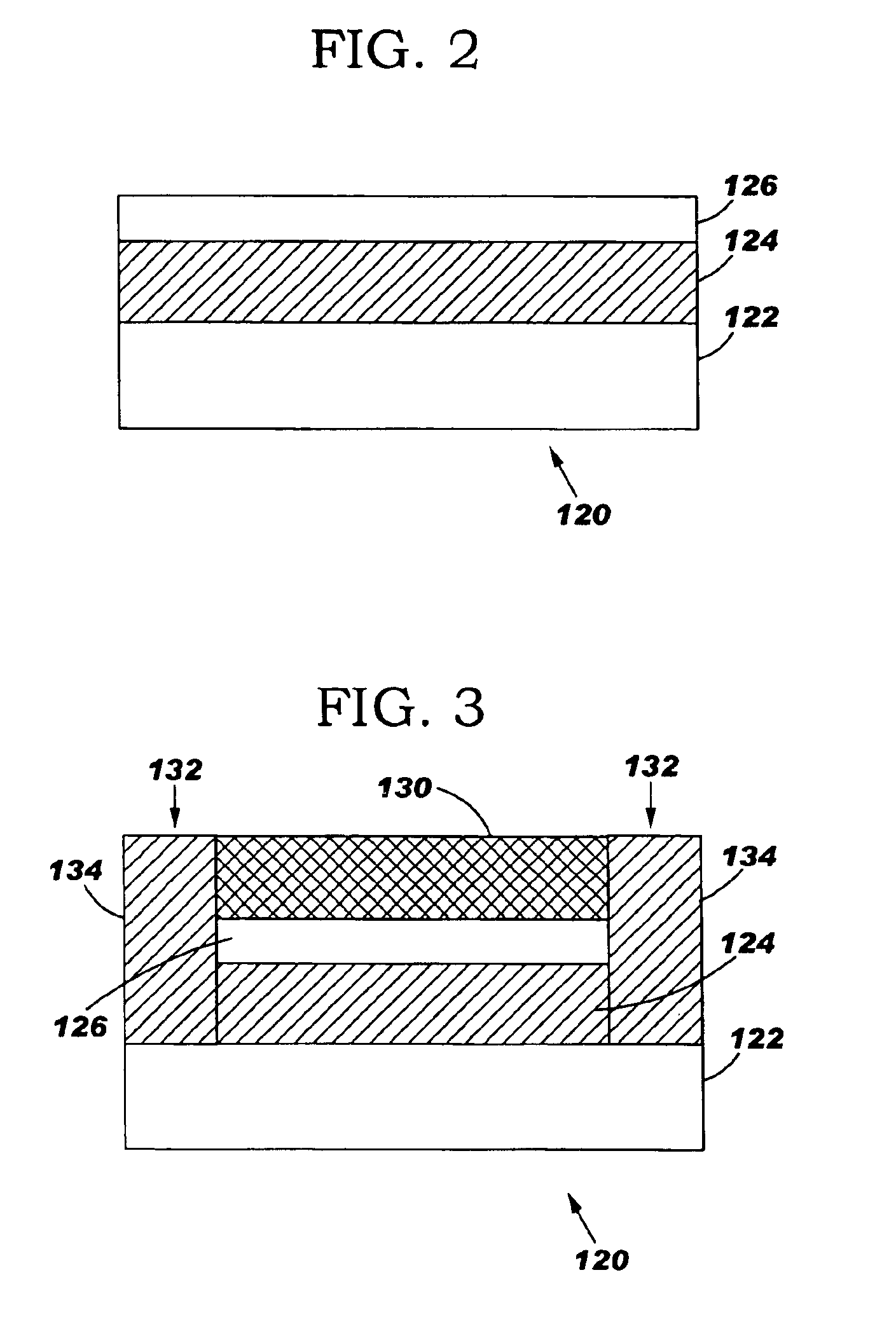

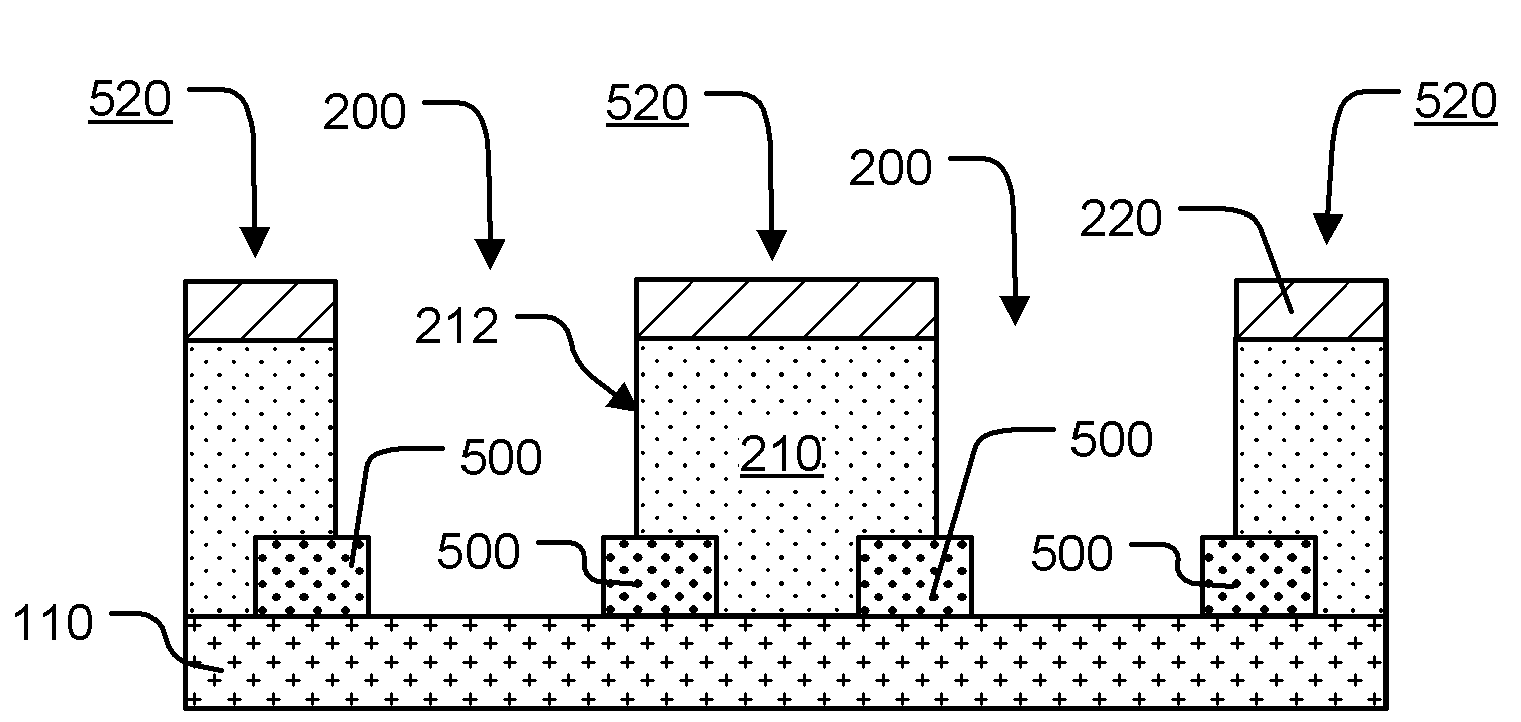

High performance FET with elevated source/drain region

InactiveUS6864540B1Improve field effect transistor (FET) performanceReduce ultra-thin channel FET series resistanceTransistorSolid-state devicesDielectricSalicide

The invention includes a field effect transistor (FET) on an insulator layer, and integrated circuit (IC) on SOI chip including the FETs and a method of forming the IC. The FETs include a thin channel with raised source / drain (RSD) regions at each end on an insulator layer, e.g., on an ultra-thin silicon on insulator (SOI) chip. Isolation trenches at each end of the FETs, i.e., at the end of the RSD regions, isolate and define FET islands. Insulating sidewalls at each RSD region sandwich the FET gate between the RSD regions. The gate dielectric may be a high K dielectric. Salicide on the RSD regions and, optionally, on the gates reduce device resistances.

Owner:IBM CORP

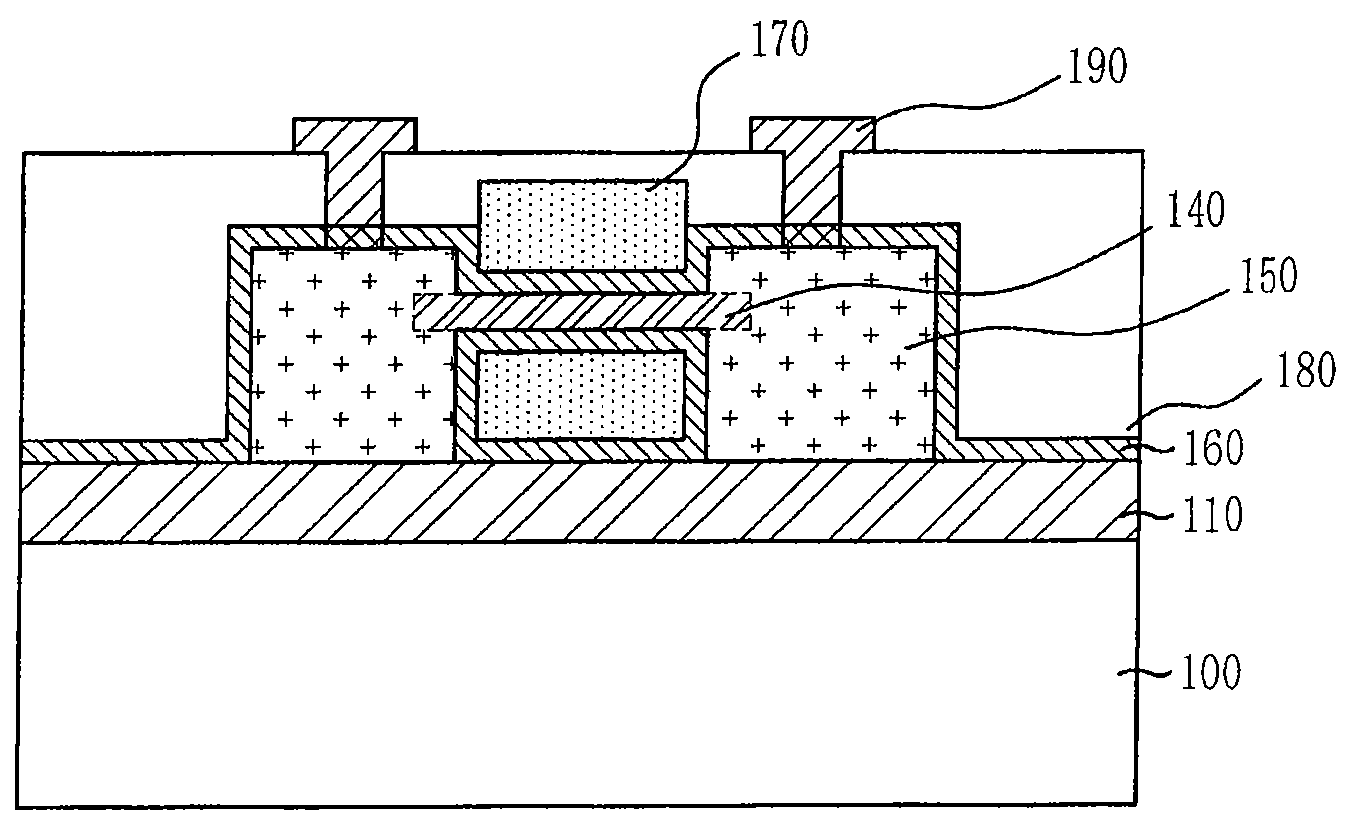

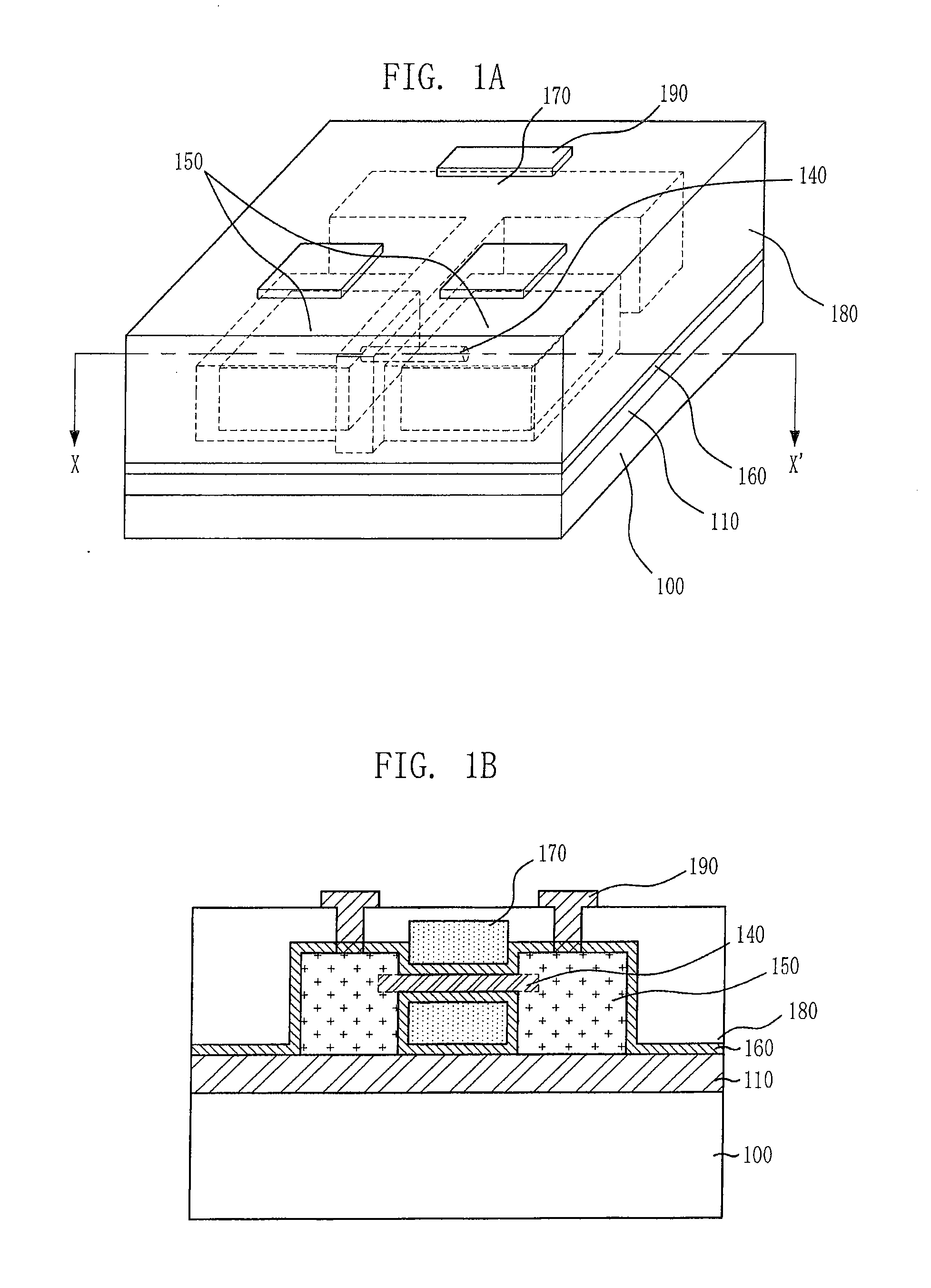

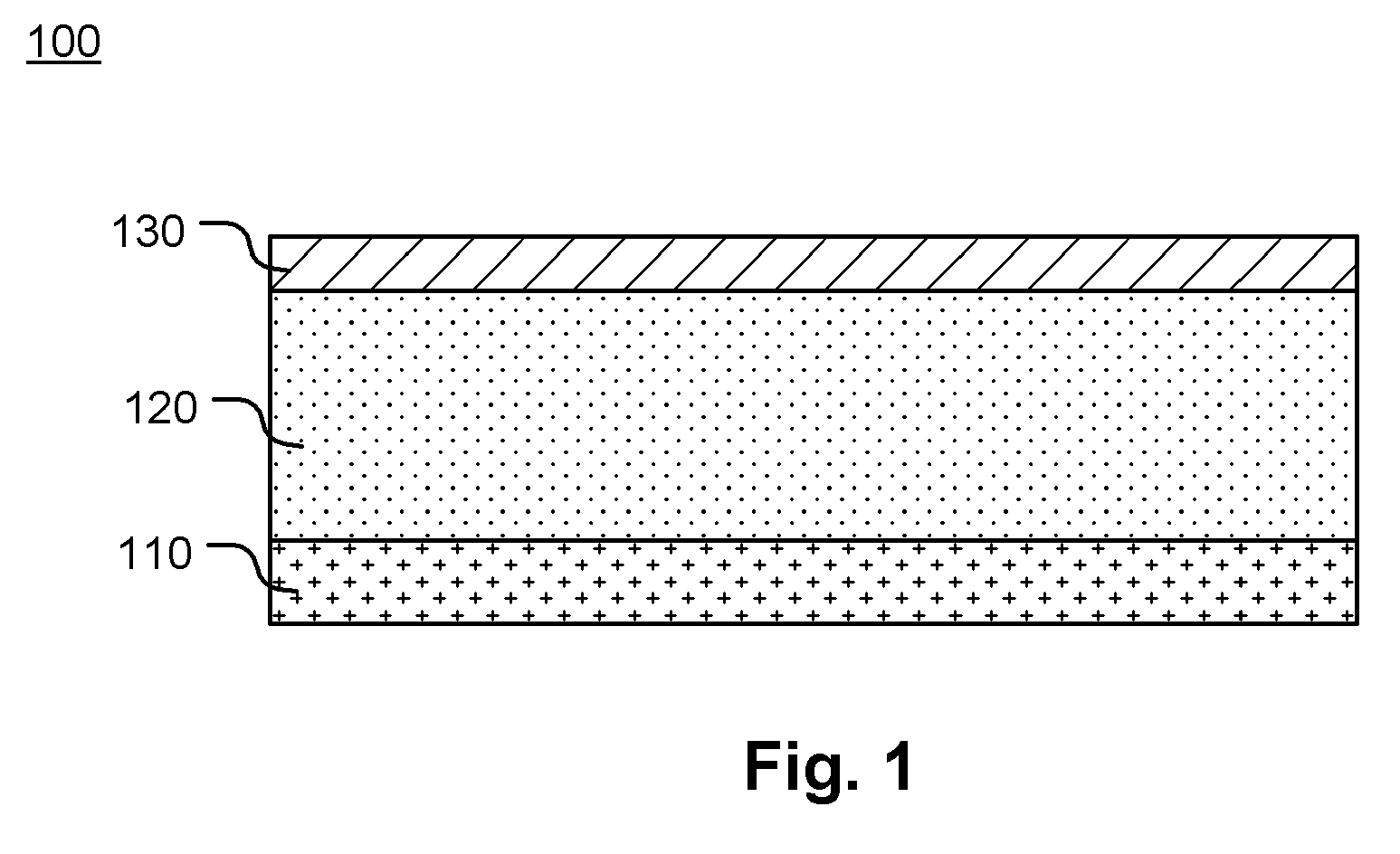

Buried silicide structure and method for making

ActiveUS20100301304A1Easy to manufactureImprove conductivitySolid-state devicesSemiconductor/solid-state device manufacturingSalicideHigh density

Methods for manufacturing buried silicide lines are described herein, along with high density stacked memory structures. A method for manufacturing an integrated circuit as described herein includes forming a semiconductor body comprising silicon. A plurality of trenches are formed in the semiconductor body to define semiconductor lines comprising silicon between adjacent trenches, the semiconductor lines having sidewalls. A silicide precursor is deposited within the trenches to contact the sidewalls of the semiconductor lines, and a portion of the silicide precursor is removed to expose upper portions of the sidewalls and leave remaining strips of silicide precursor along the sidewalls. Silicide conductors are then formed by inducing reaction of the strips of silicide with the silicon of the semiconductor lines.

Owner:MACRONIX INT CO LTD

Structure and method for mobility enhanced MOSFETs with unalloyed silicide

ActiveUS8217423B2Stable and low contact resistanceReduce contact resistanceTransistorSolid-state devicesMOSFETSalicide

While embedded silicon germanium alloy and silicon carbon alloy provide many useful applications, especially for enhancing the mobility of MOSFETs through stress engineering, formation of alloyed silicide on these surfaces degrades device performance. The present invention provides structures and methods for providing unalloyed silicide on such silicon alloy surfaces placed on semiconductor substrates. This enables the formation of low resistance contacts for both mobility enhanced PFETs with embedded SiGe and mobility enhanced NFETs with embedded Si:C on the same semiconductor substrate. Furthermore, this invention provides methods for thick epitaxial silicon alloy, especially thick epitaxial Si:C alloy, above the level of the gate dielectric to increase the stress on the channel on the transistor devices.

Owner:AURIGA INNOVATIONS INC

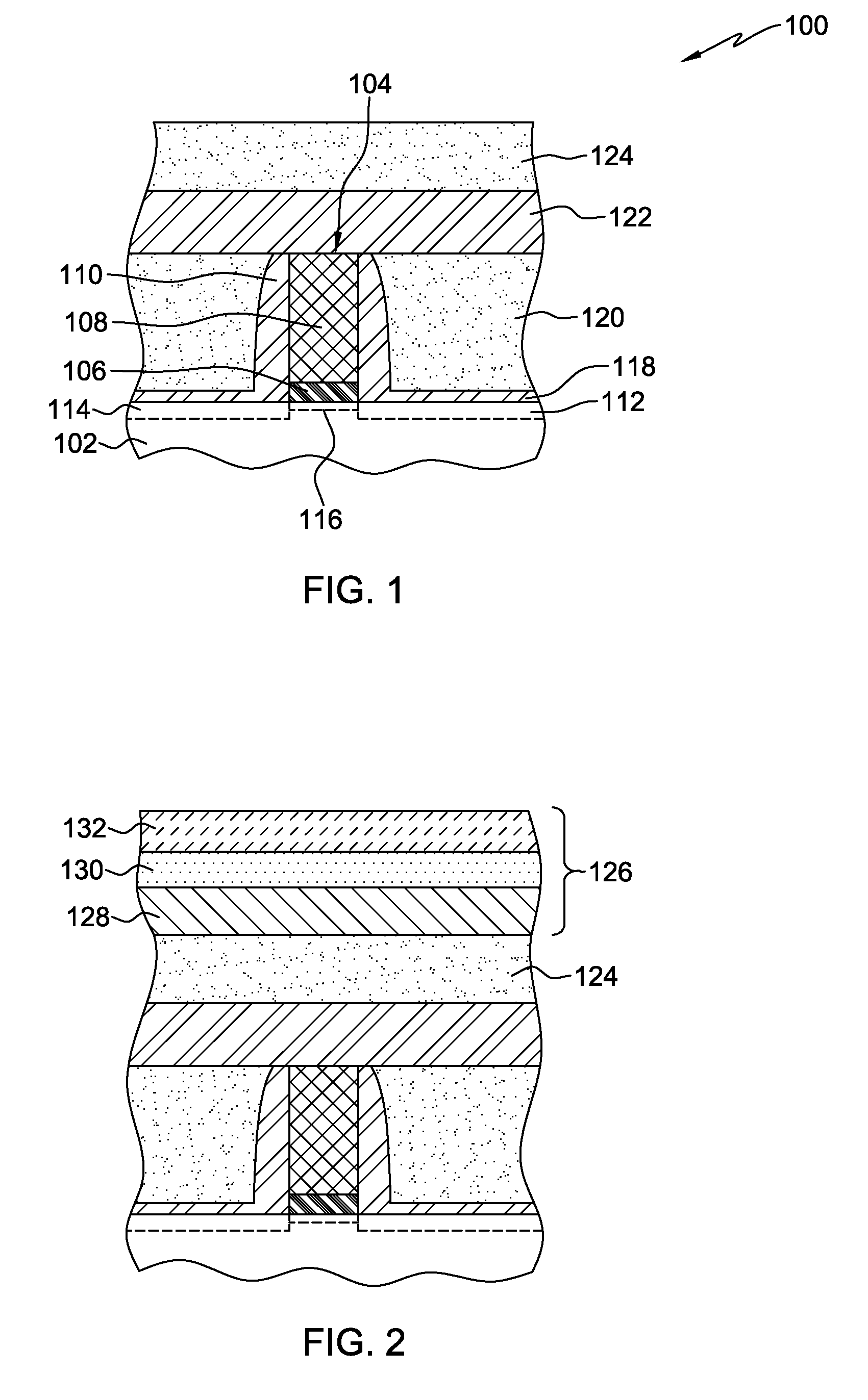

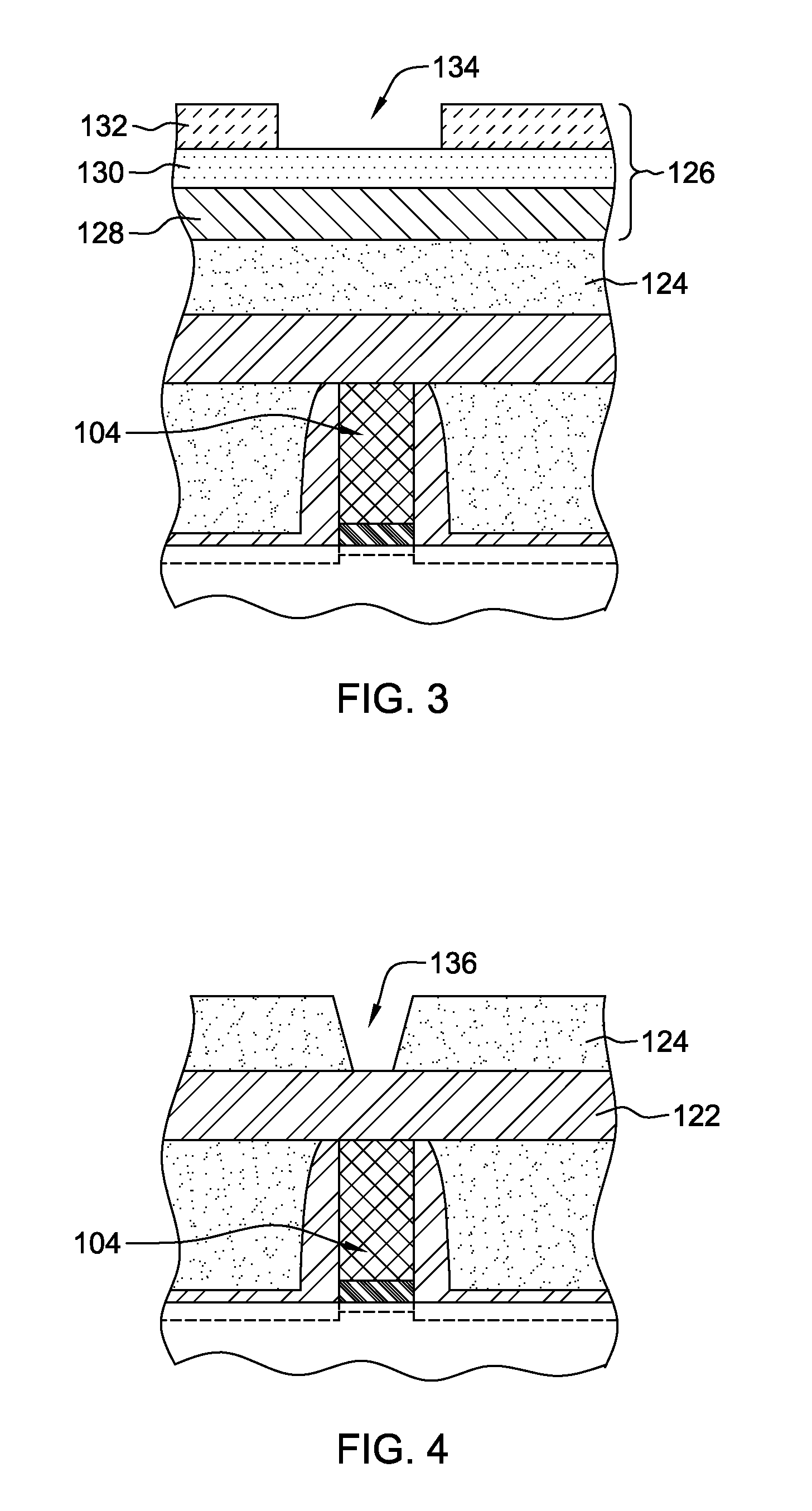

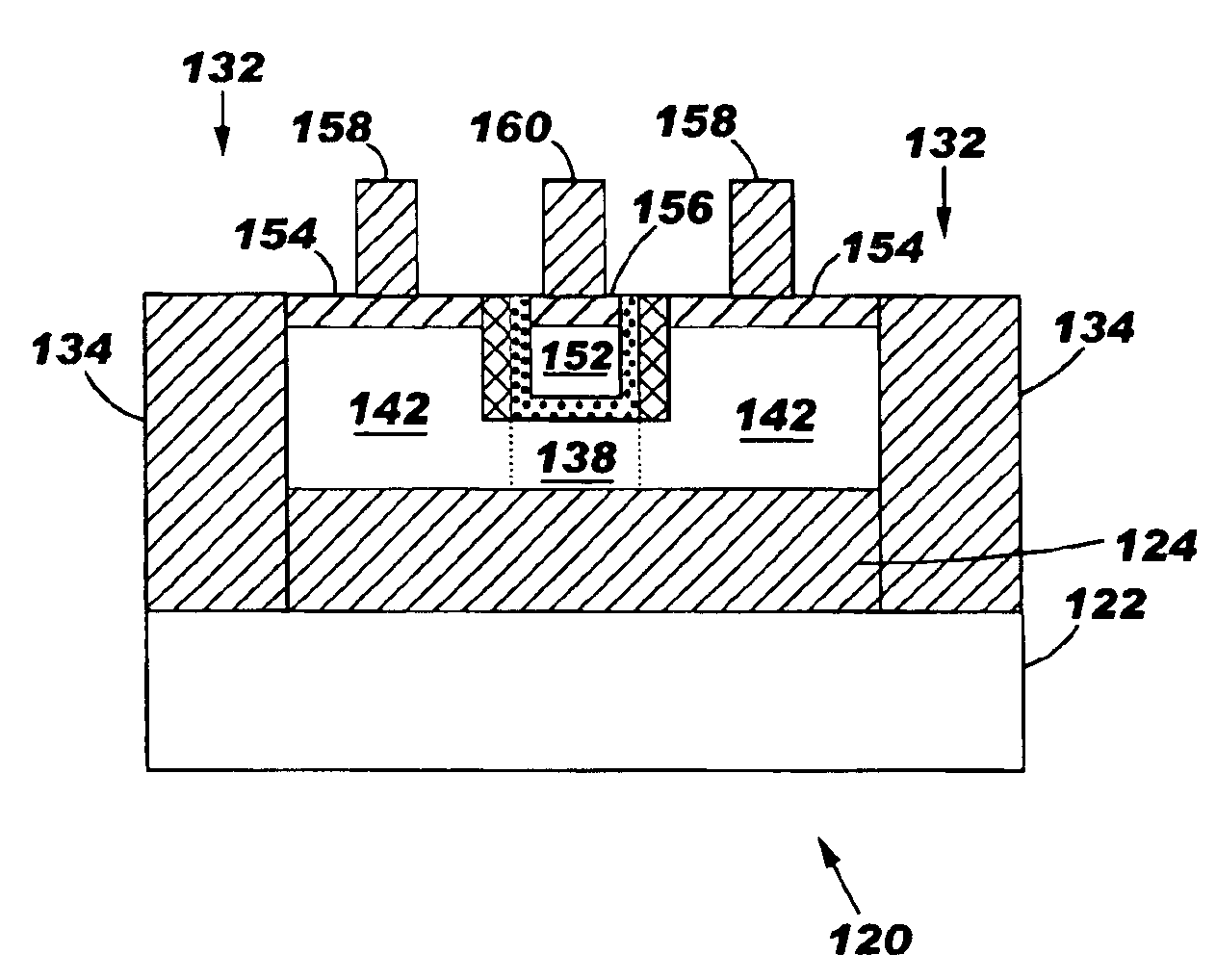

FET gate structure with metal gate electrode and silicide contact

A method is provided for fabricating a single-metal or dual metal replacement gate structure for a semiconductor device; the structure includes a silicide contact to the gate region. A dummy gate structure and sacrificial gate dielectric are removed to expose a portion of the substrate; a gate dielectric is formed thereon. A metal layer is formed overlying the gate dielectric and the dielectric material. This metal layer may conveniently be a blanket metal layer covering a device wafer. A silicon layer is then formed overlying the metal layer; this layer may also be a blanket wafer. A planarization or etchback process is then performed, so that the top surface of the dielectric material is exposed while other portions of the metal layer and the silicon layer remain in the gate region and have surfaces coplanar with the top surface of the dielectric material. A silicide contact is then formed which is in contact with the metal layer in the gate region.

Owner:GLOBALFOUNDRIES U S INC

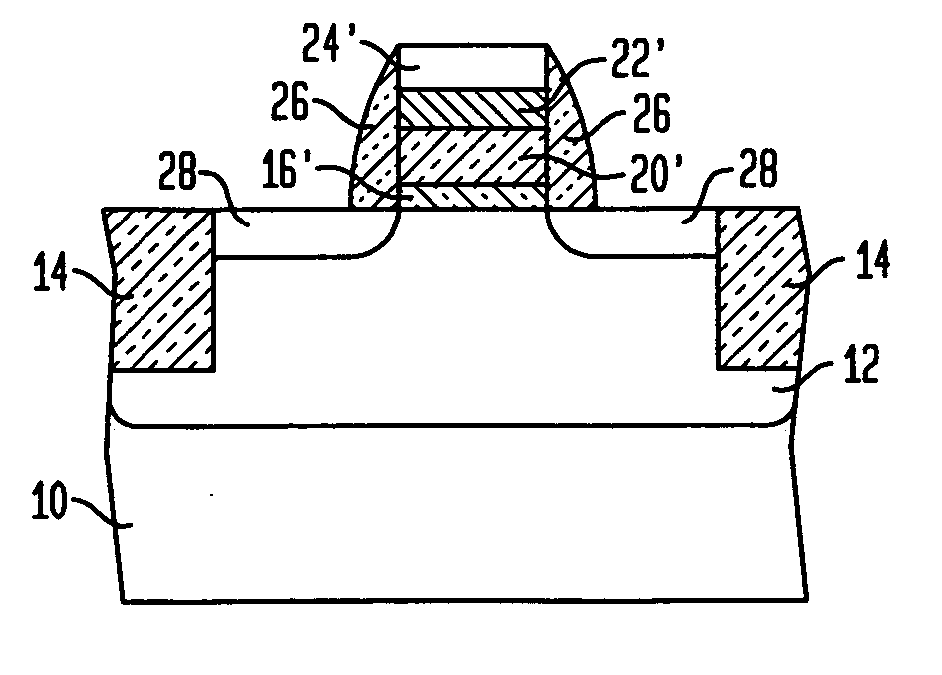

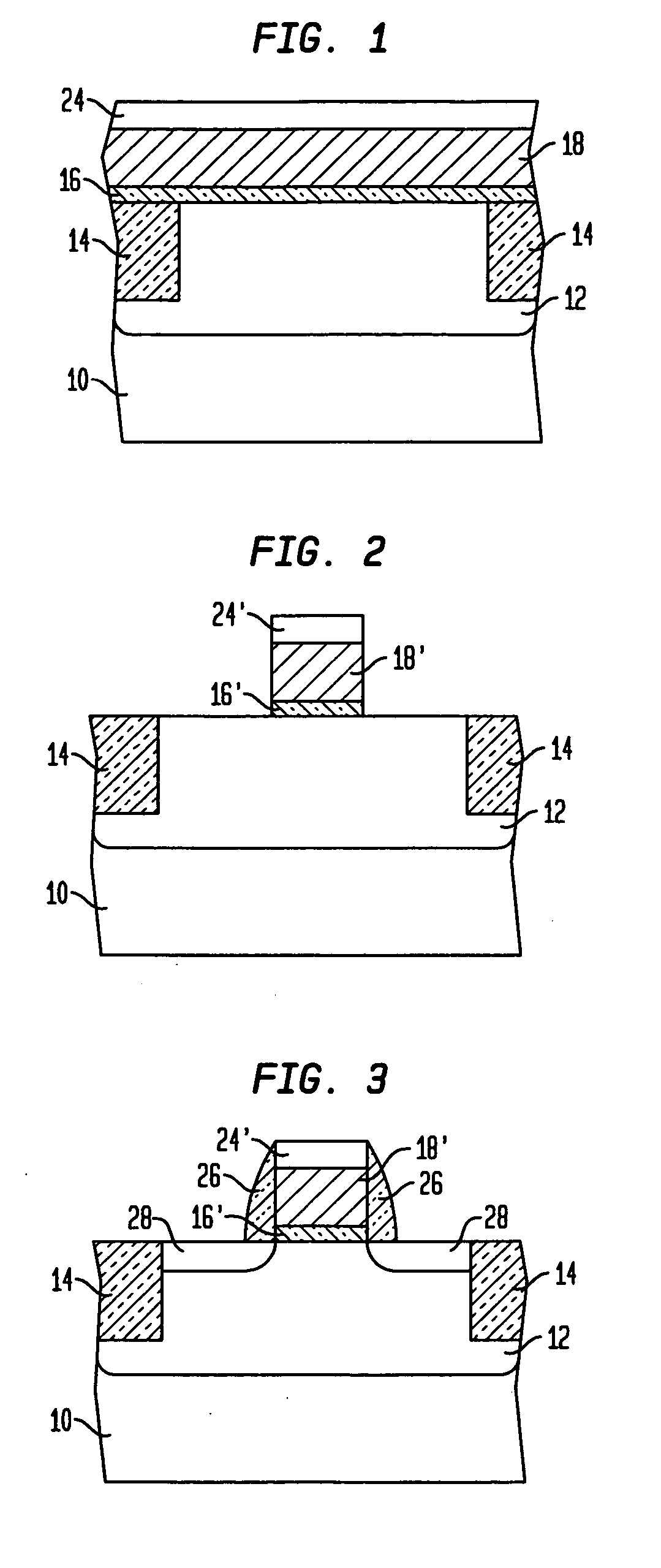

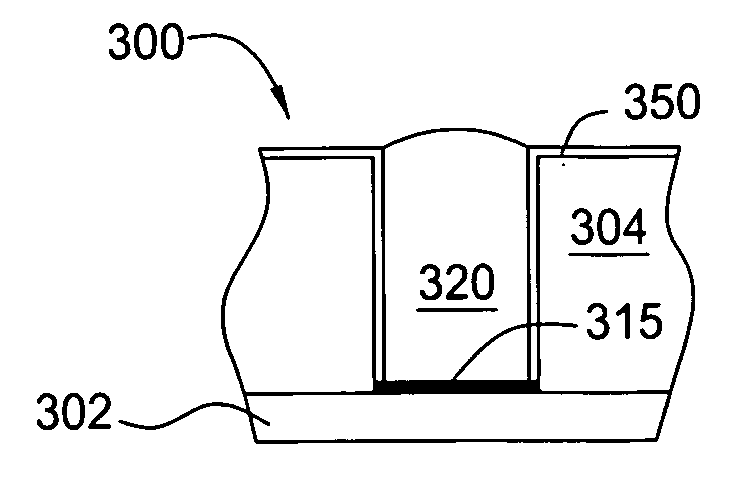

One step salicide process without bridging

Silicidation of a polysilicon line having frcc upper sidewalls is performed so that no stress is applied to the sidewalls of the polysilicon line, resulting in the formation of a reduced stress silicide structure. This is accomplished by forming a polysilicon line having spacers on either side which extend above the upper surface of the polysilicon line but which are spaced from the edge of the polysilicon line. A layer of a metal such as titanium or tungsten is provided in contact with the top surface polysilicon line. The structure is annealed to cause the metal to react with the polysilicon to form a layer of silicide. Since the upper side portions of the polysilicon line are spaced away from the spacers during the silicidation anneal, the growing silicide region has room to expand without being subjected to lateral stresses in the silicidation process. The suicide is formed in a reduced stress condition, as compared to conventional processes, so that the silicide layer produced will be more readily converted to the desired low resistivity phase of silicide.

Owner:UNITED MICROELECTRONICS CORP