Patents

Literature

361 results about "Nickel silicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

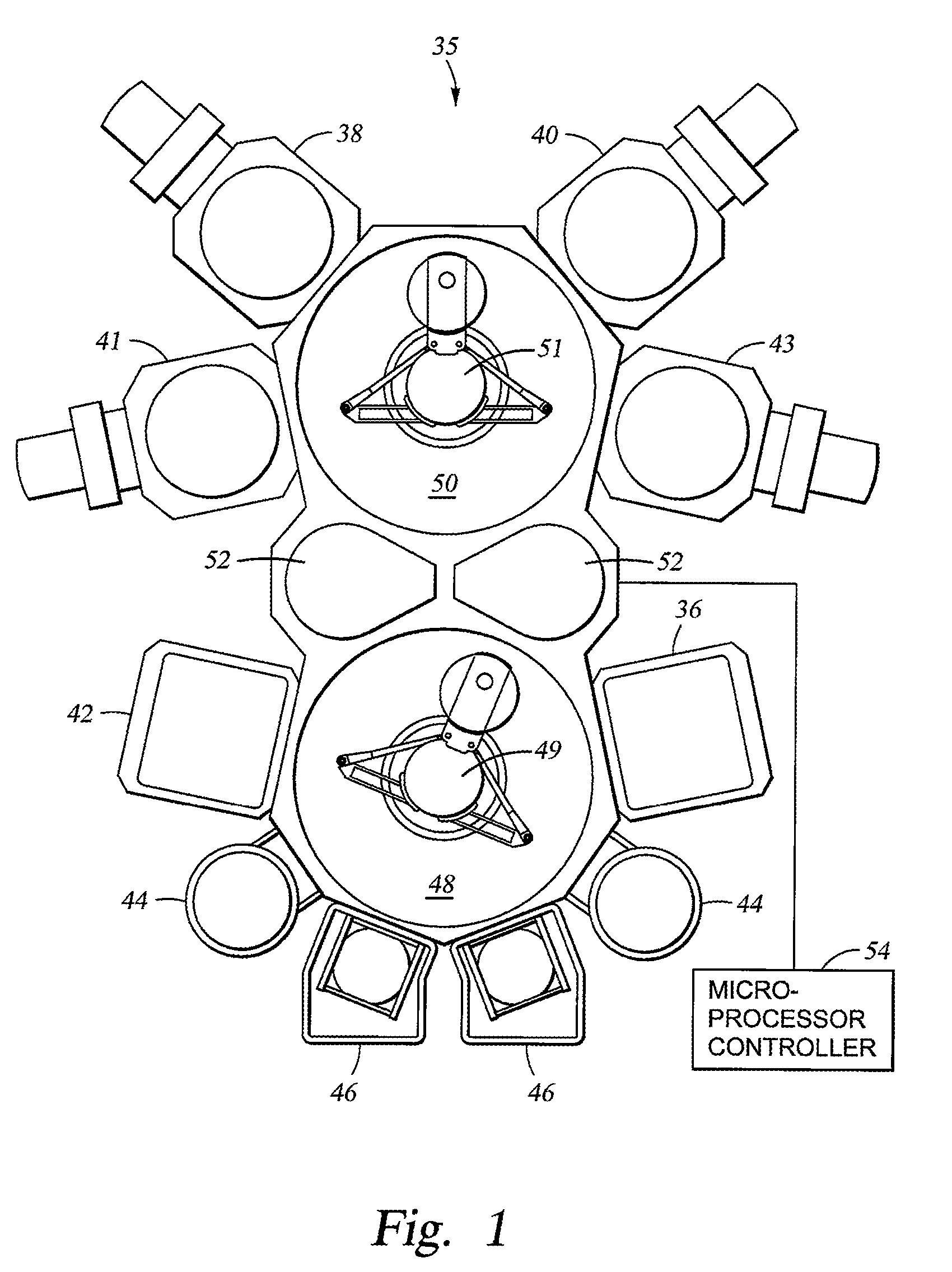

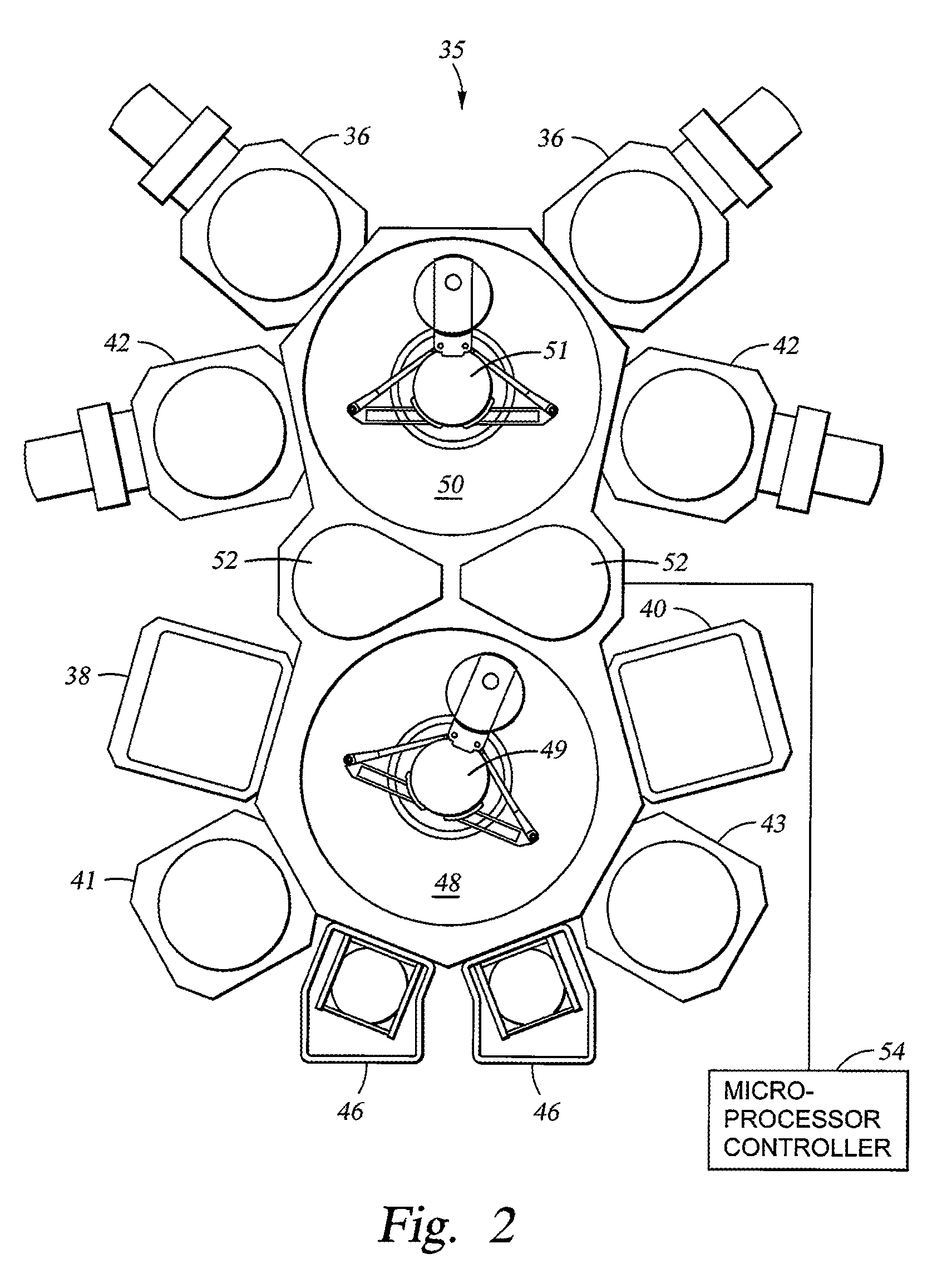

Methods for depositing nickel films and for making nickel silicide and nickel germanide

ActiveUS20130115768A1Semiconductor/solid-state device manufacturingSemiconductor devicesGas phaseMetal silicide

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD. Nickel thin films can be used directly in silicidation and germanidation processes.

Owner:ASM INTERNATIONAL

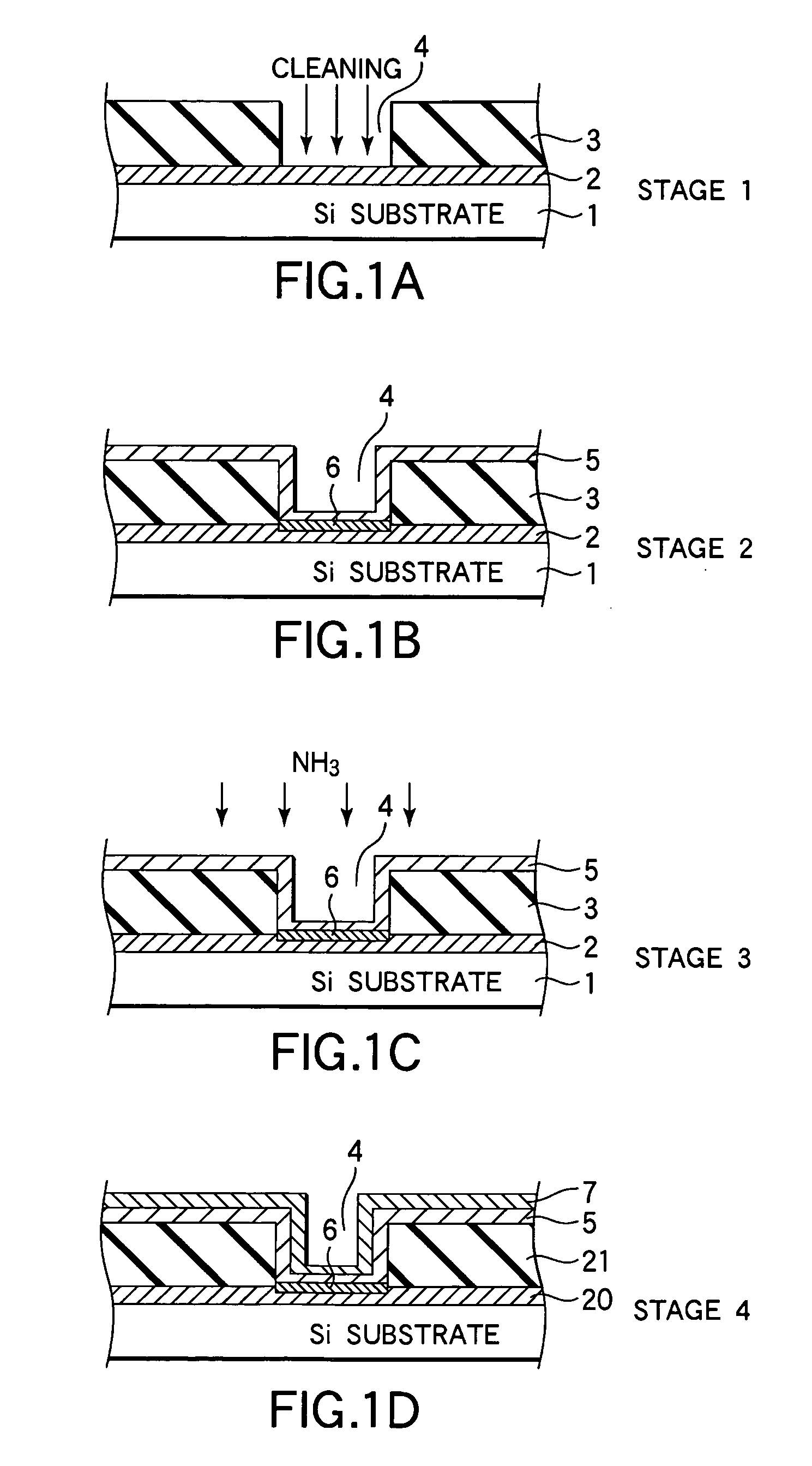

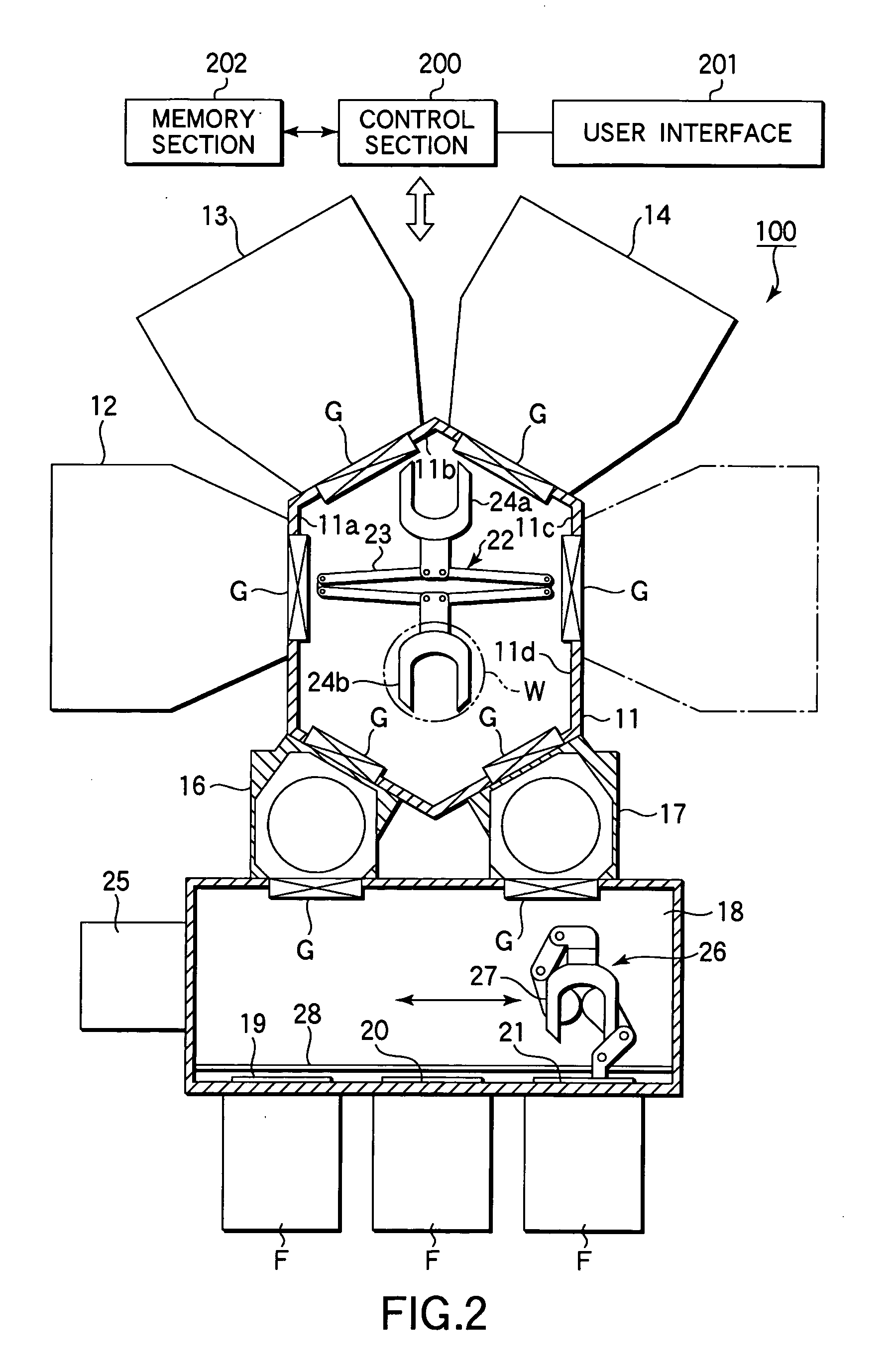

Method of manufacturing semiconductor device

ActiveUS20070238321A1Improve reliabilityVariation in electrical propertyTransistorElectrostatic cleaningEngineeringSemiconductor

Provided is a method of manufacturing a semiconductor device. After a semiconductor wafer is placed over a wafer stage with which a dry cleaning chamber of a film forming apparatus is equipped, dry cleaning treatment is given over the surface of the semiconductor wafer with a reducing gas. Then, the semiconductor wafer is heat treated at a first temperature of from 100 to 150° C. by using a shower head kept at 180° C. The semiconductor wafer is then vacuum-transferred to a heat treatment chamber, wherein the semiconductor wafer is heat treated at a second temperature of from 150 to 400° C. A product remaining over the main surface of the semiconductor wafer is thus removed. The present invention makes it possible to manufacture a semiconductor device having improved reliability and production yield by reducing variations in the electrical properties of a nickel silicide layer.

Owner:RENESAS ELECTRONICS CORP

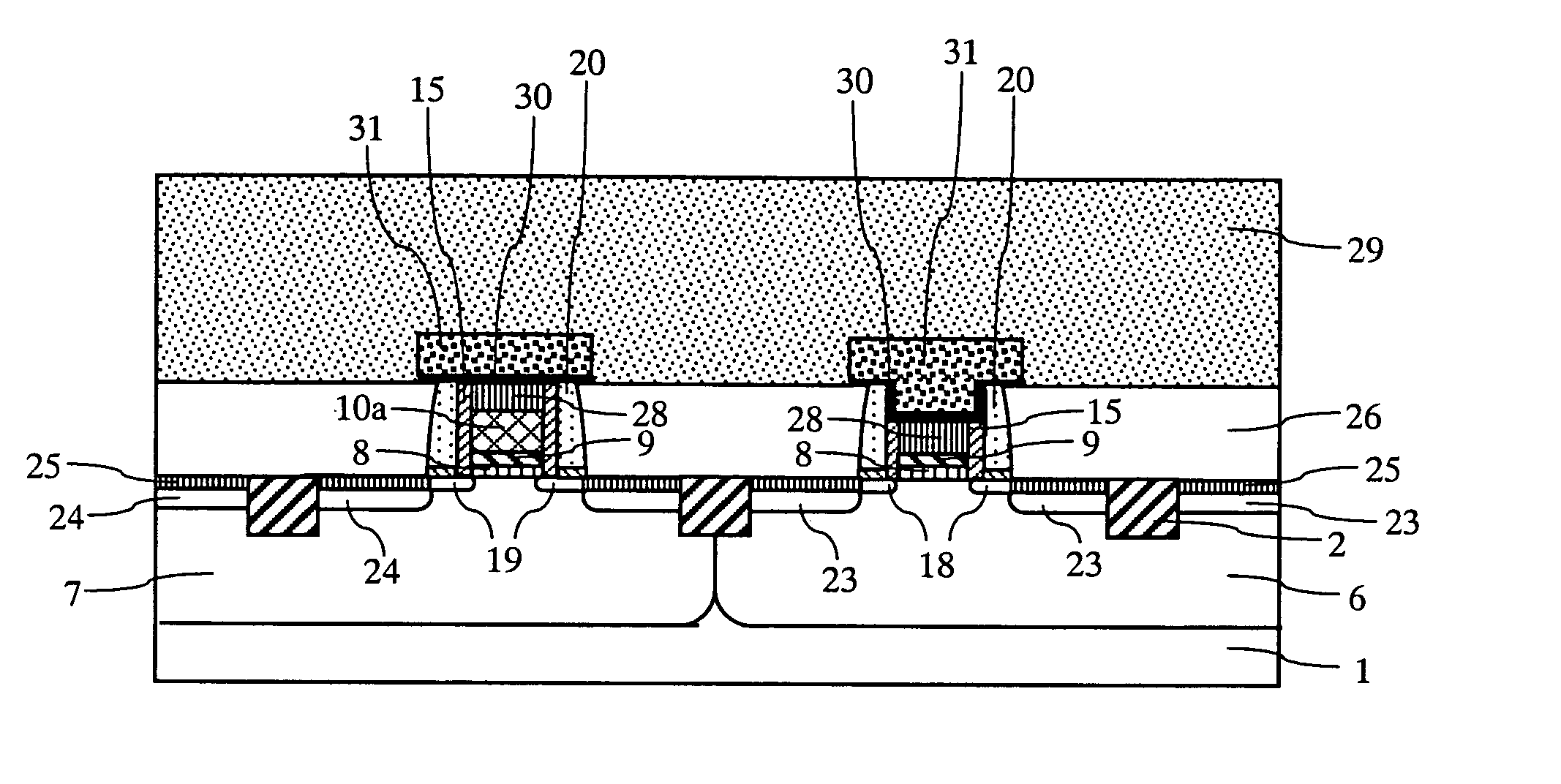

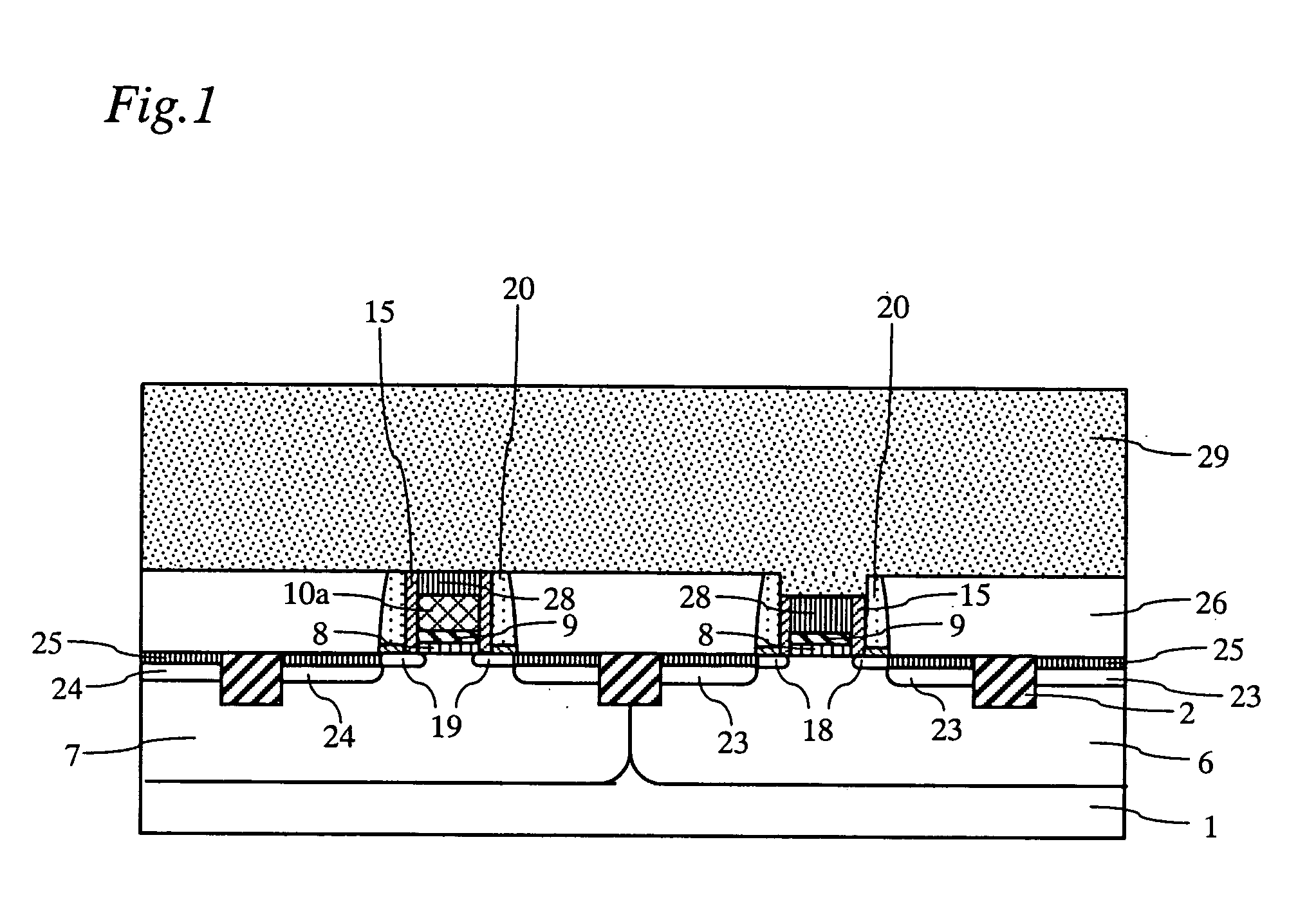

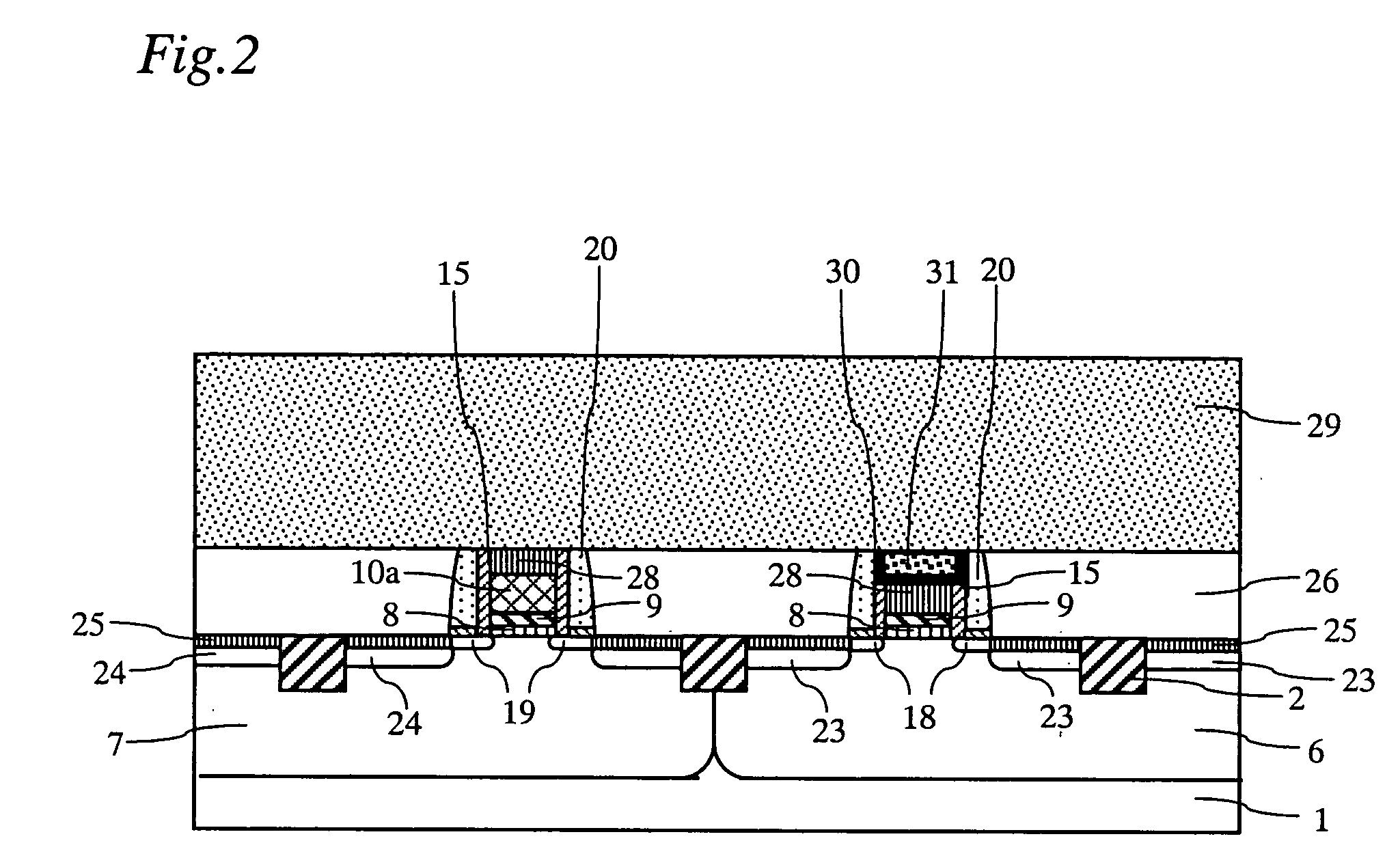

Method for manufacturing a semiconductor integrated circuit device circuit device

ActiveUS20100129974A1Increased integration scaleLower gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideField-effect transistor

When a natural oxide film is left at the interface between a metal silicide layer and a silicon nitride film, in various heating steps (steps involving heating of a semiconductor substrate, such as various insulation film and conductive film deposition steps) after deposition of the silicon nitride film, the metal silicide layer partially abnormally grows due to oxygen of the natural oxide film occurring on the metal silicide layer surface. A substantially non-bias (including low bias) plasma treatment is performed in a gas atmosphere containing an inert gas as a main component on the top surface of a metal silicide film of nickel silicide or the like over source / drain of a field-effect transistor forming an integrated circuit. Then, a silicon nitride film serving as an etching stop film of a contact process is deposited. As a result, without causing undesirable cutting of the metal silicide film, the natural oxide film over the top surface of the metal silicide film can be removed.

Owner:RENESAS ELECTRONICS CORP

Deposition methods for barrier and tungsten materials

Embodiments are provided for a method to deposit barrier and tungsten materials on a substrate. In one embodiment, a method provides forming a barrier layer on a substrate and exposing the substrate to a silane gas to form a thin silicon-containing layer on the barrier layer during a soak process. The method further provides depositing a tungsten nucleation layer over the barrier layer and the thin silicon-containing layer during an atomic layer deposition process and depositing a tungsten bulk layer on the tungsten nucleation layer during a chemical vapor deposition process. In some examples, the barrier layer contains metallic cobalt and cobalt silicide, or metallic nickel and nickel silicide. In other examples, the barrier layer contains metallic titanium and titanium nitride, or metallic tantalum and tantalum nitride.

Owner:APPLIED MATERIALS INC

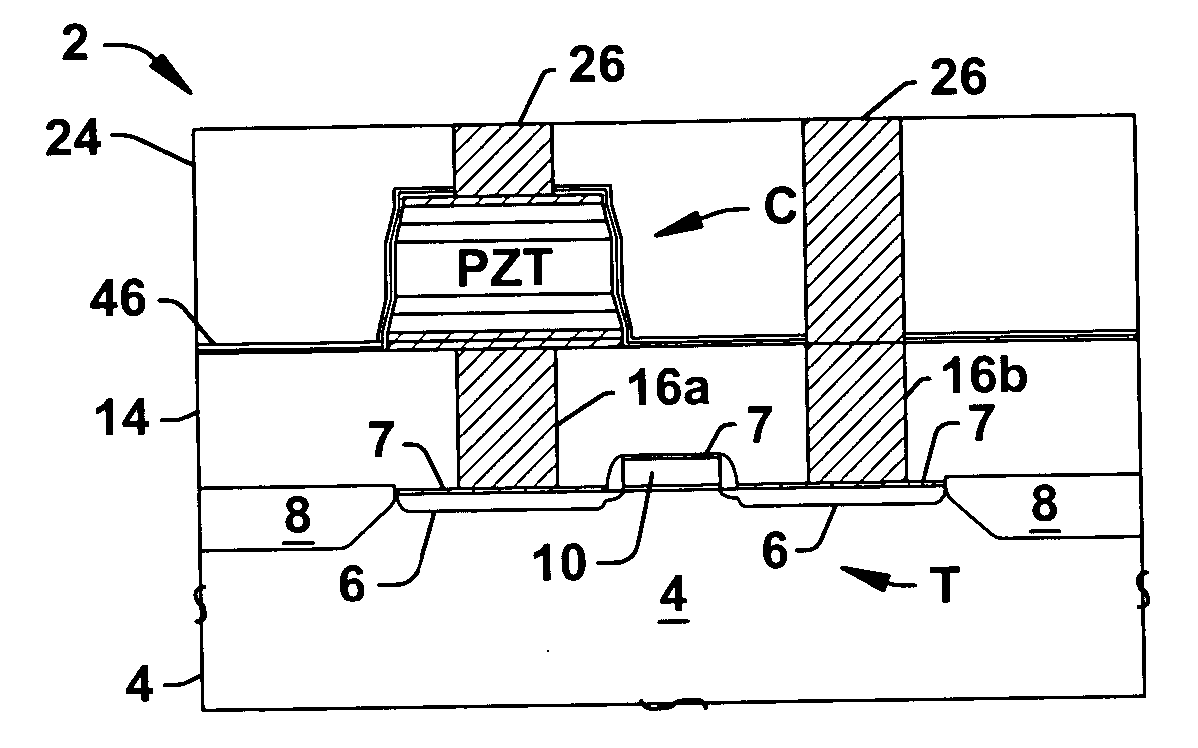

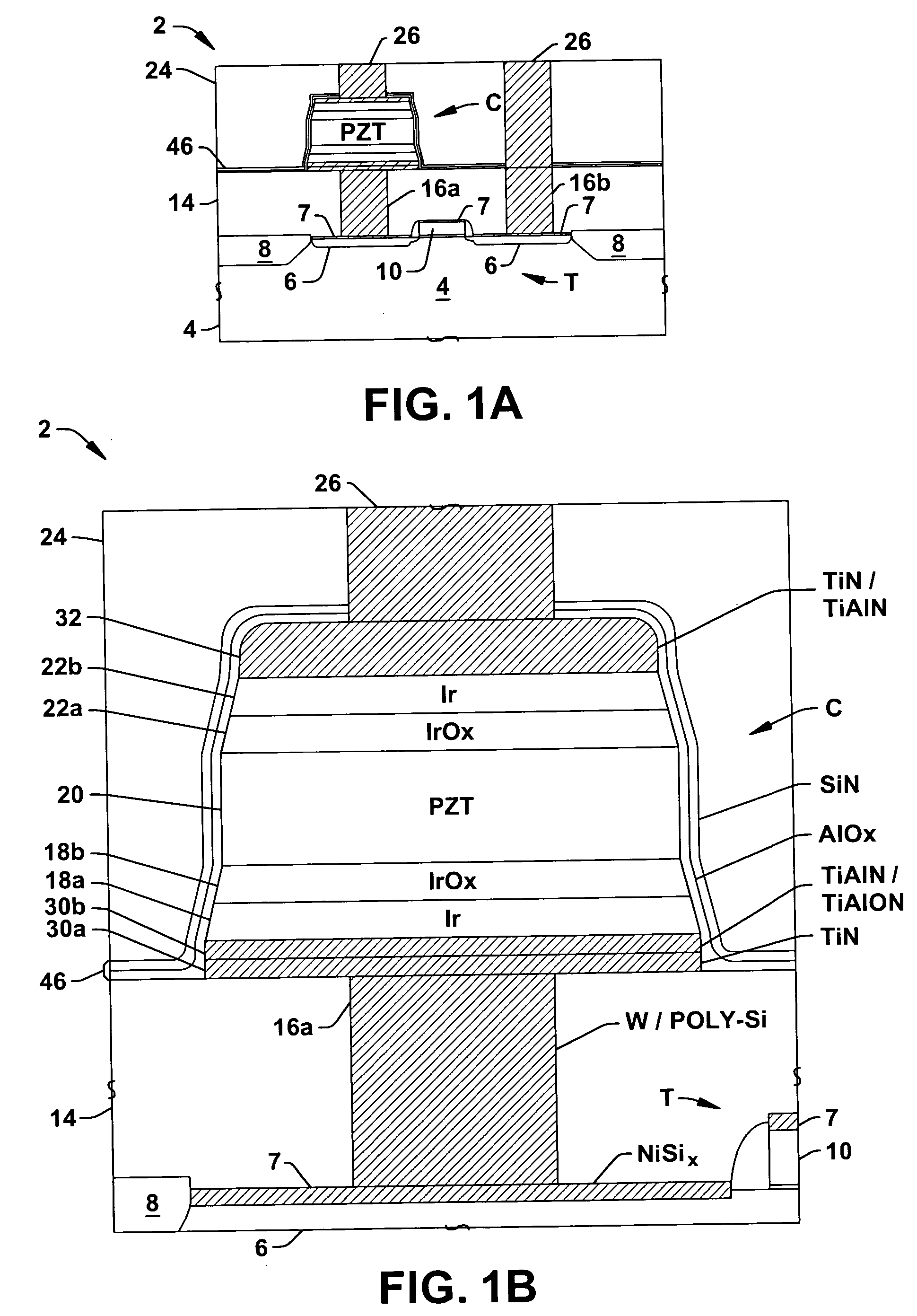

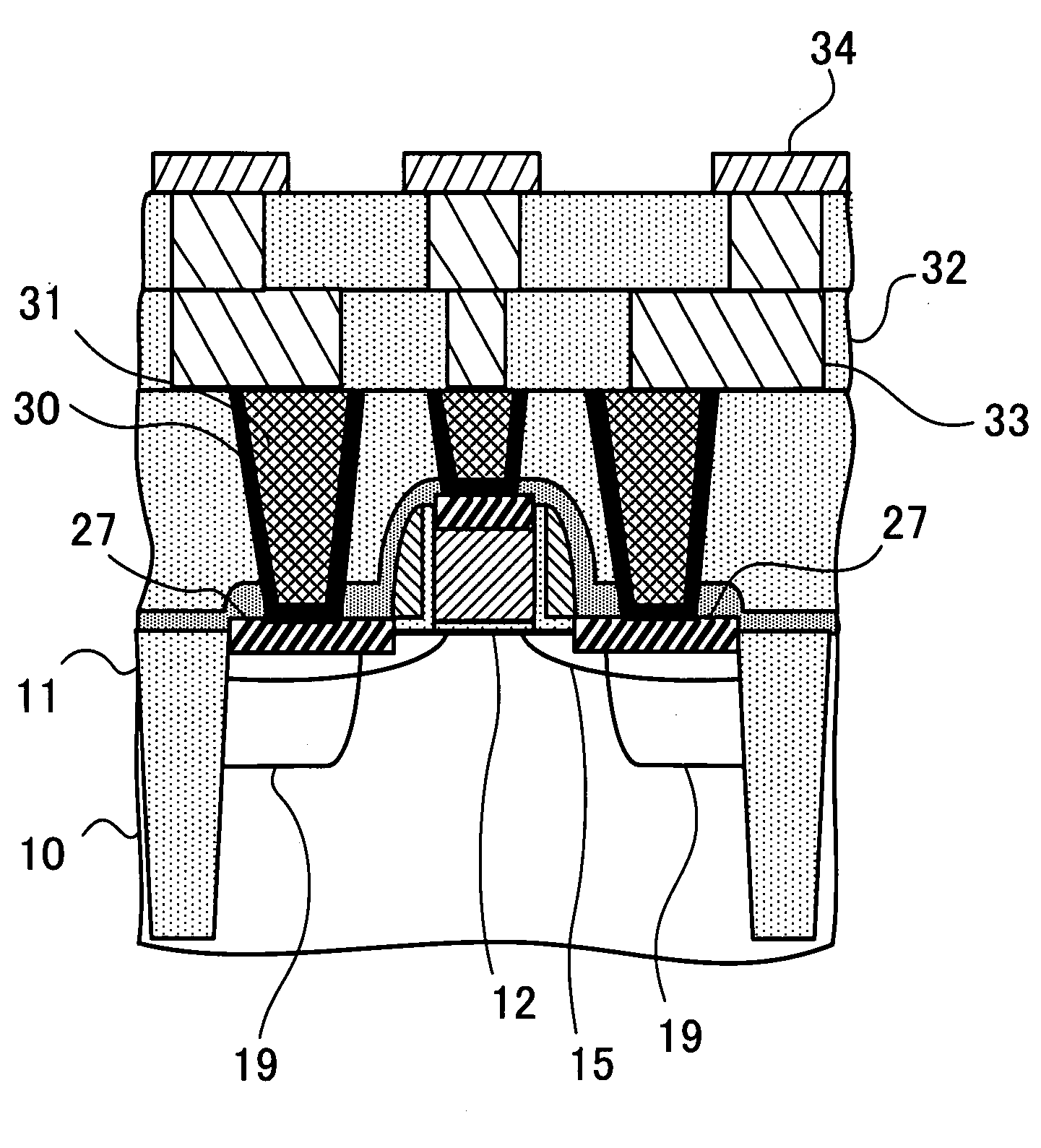

Ferroelectric memory cells and methods for fabricating ferroelectric memory cells and ferroelectric capacitors thereof

InactiveUS20060073613A1High crystallinityReduce pruningSolid-state devicesSemiconductor/solid-state device manufacturingDielectricDevice material

Methods (100) are provided for fabricating a ferroelectric capacitor in a semiconductor device wafer, comprising forming (118) a lower electrode, depositing (126) PZT ferroelectric material on the lower electrode at a temperature below 450 degrees C., and forming (128) an upper electrode on the PZT. Methods are also provided for fabricating a ferroelectric memory cell in a semiconductor device wafer, comprising forming (106) a transistor in the wafer, forming (108) a nickel silicide structure on the gate or a source / drain of the transistor, forming (110) a dielectric over the transistor, forming (112) a conductive contact extending through the dielectric to the silicide structure, forming (114, 116, 118, 120) a lower electrode on at least a portion of the conductive contact, forming (126) PZT ferroelectric material above and in contact with the lower electrode at a temperature below 450 degrees C., forming (128, 132) an upper electrode above and in contact with the PZT, and patterning (134) the upper electrode, the PZT, and the lower electrode to form a patterned ferroelectric capacitor.

Owner:TEXAS INSTR INC

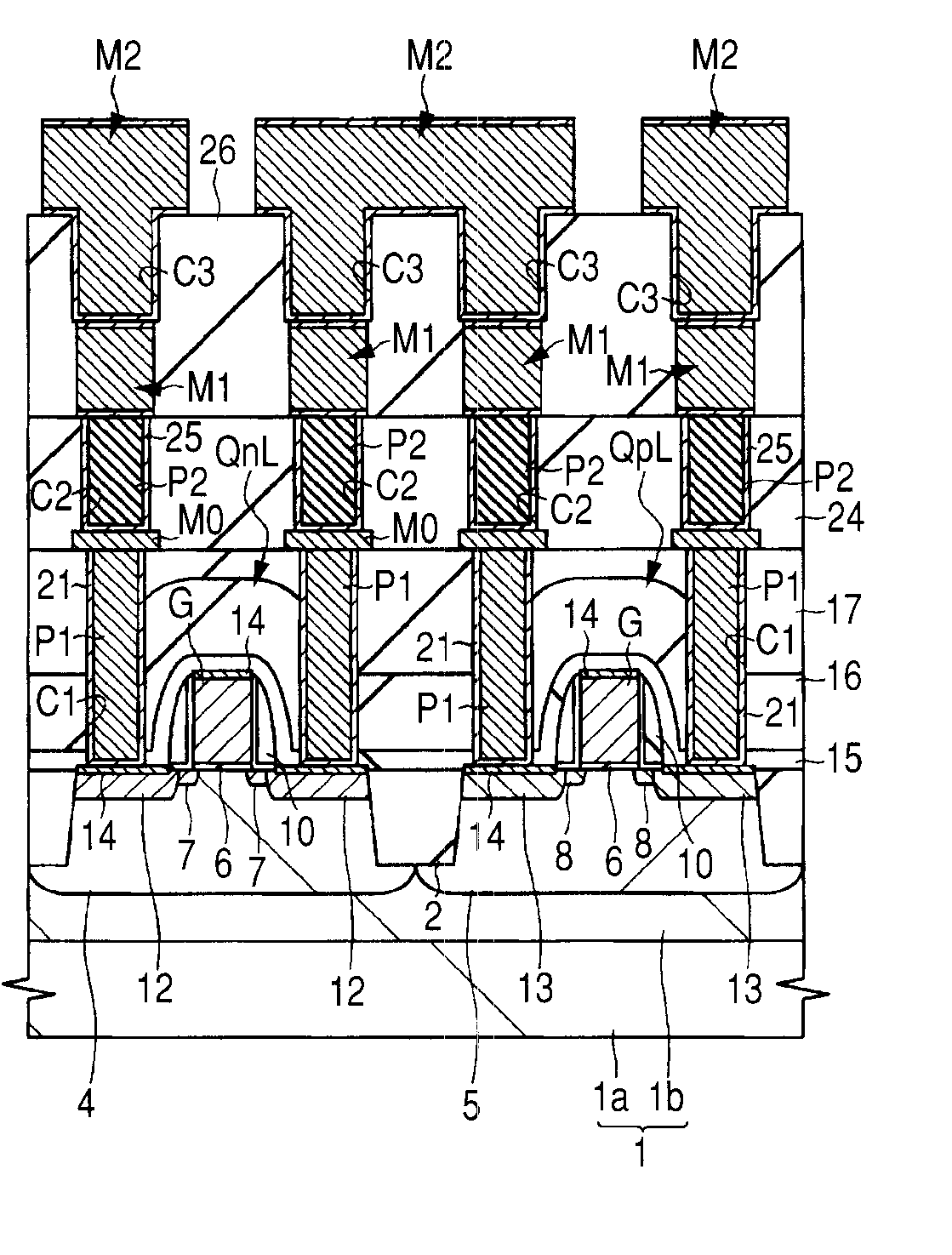

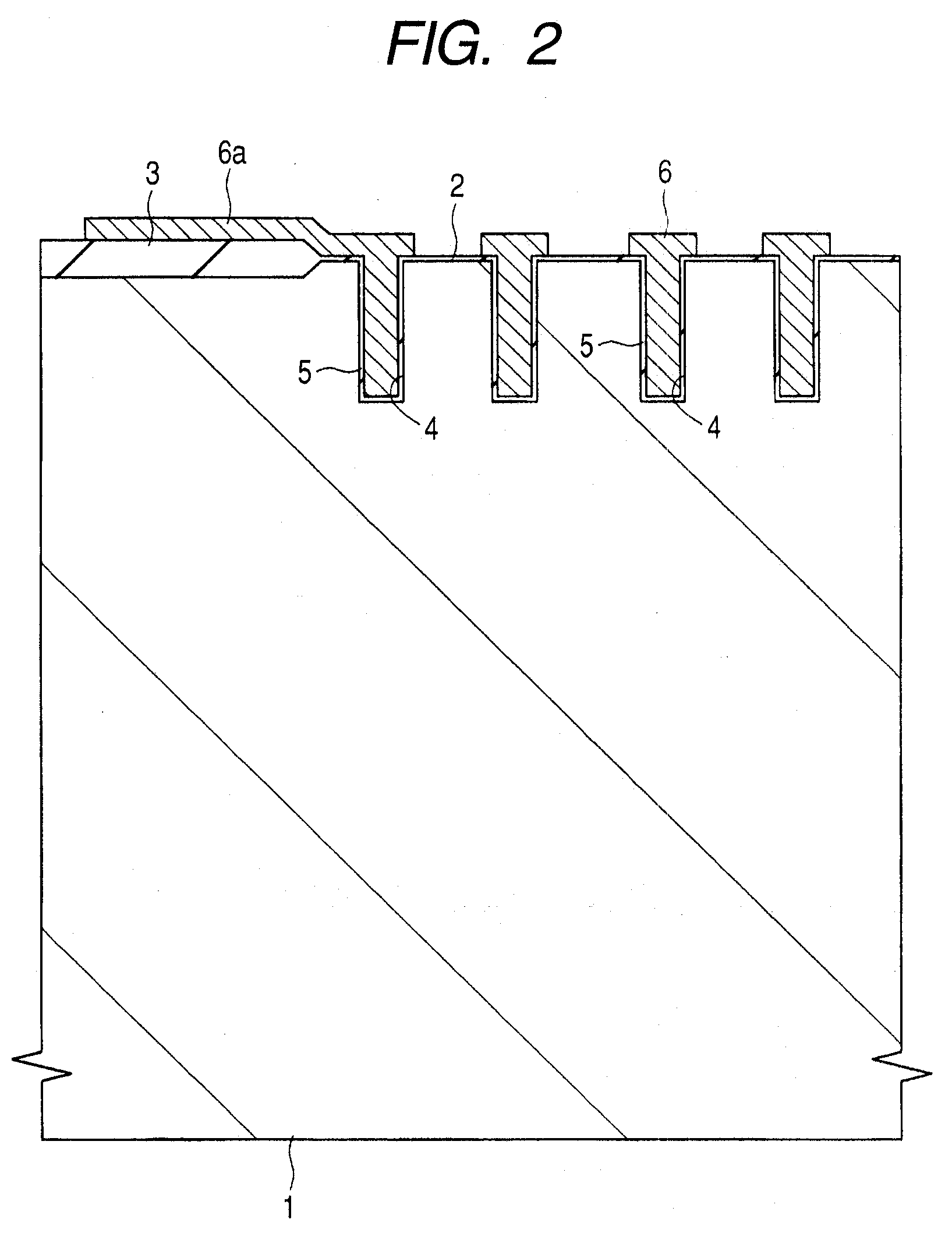

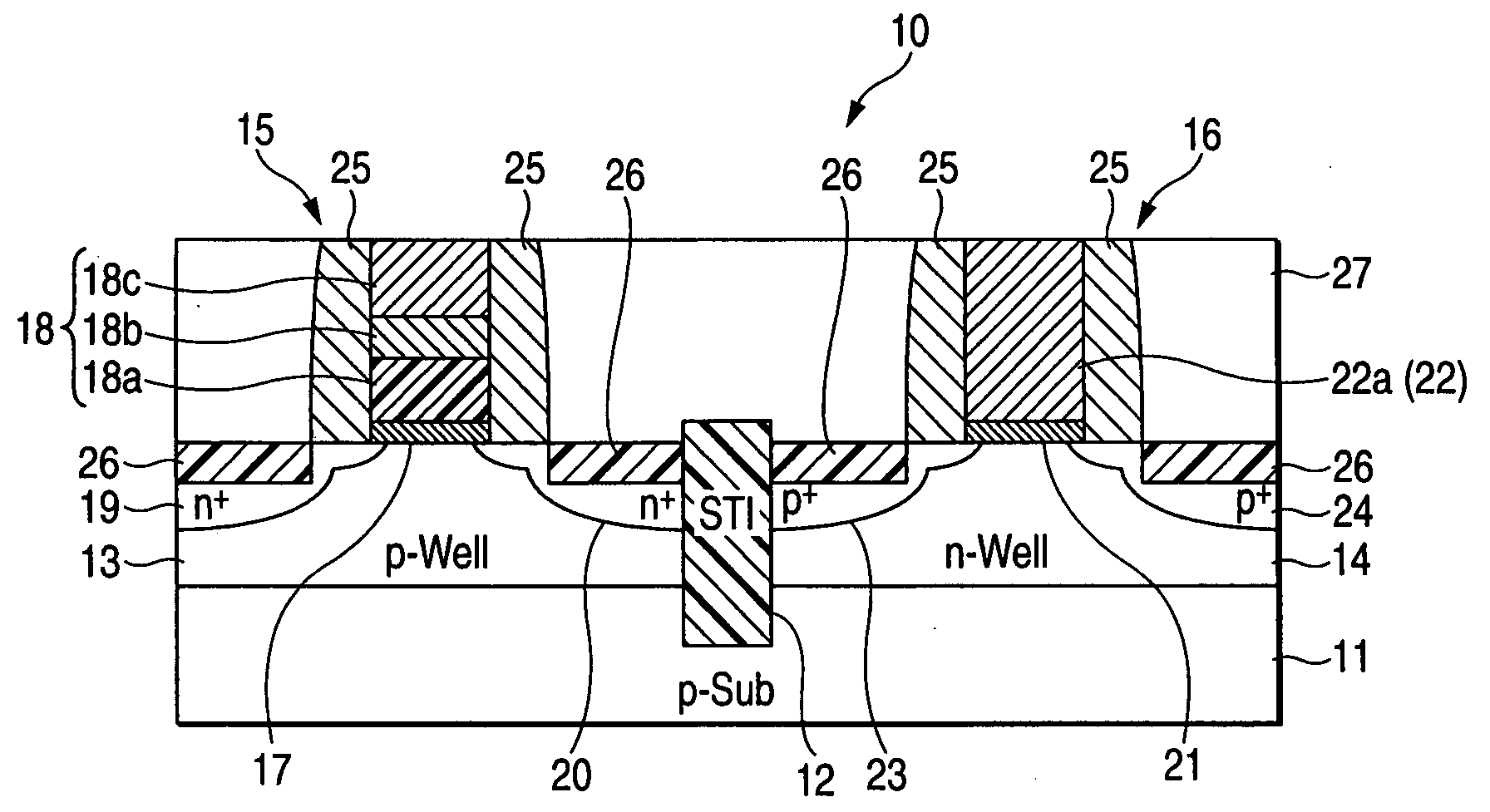

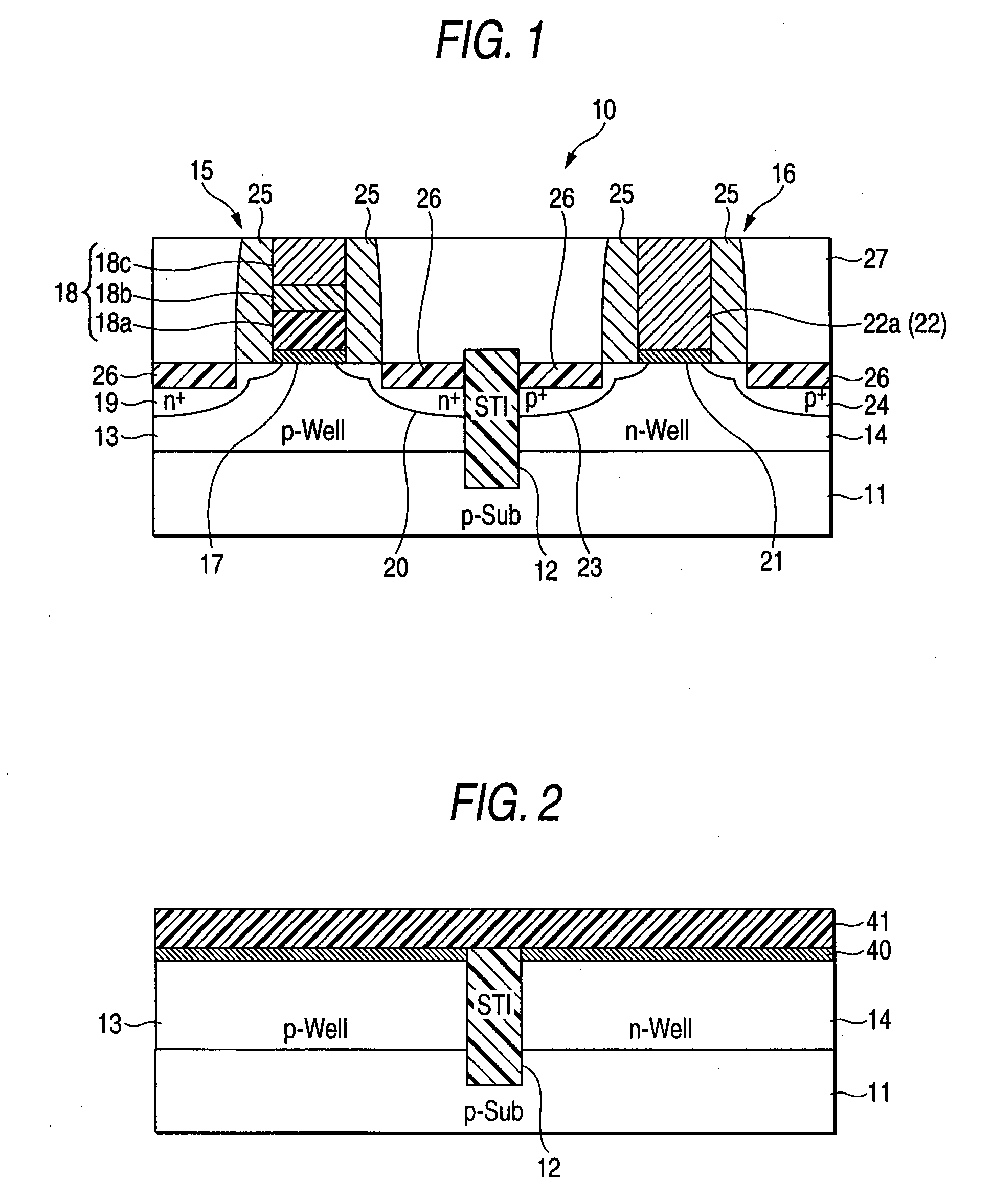

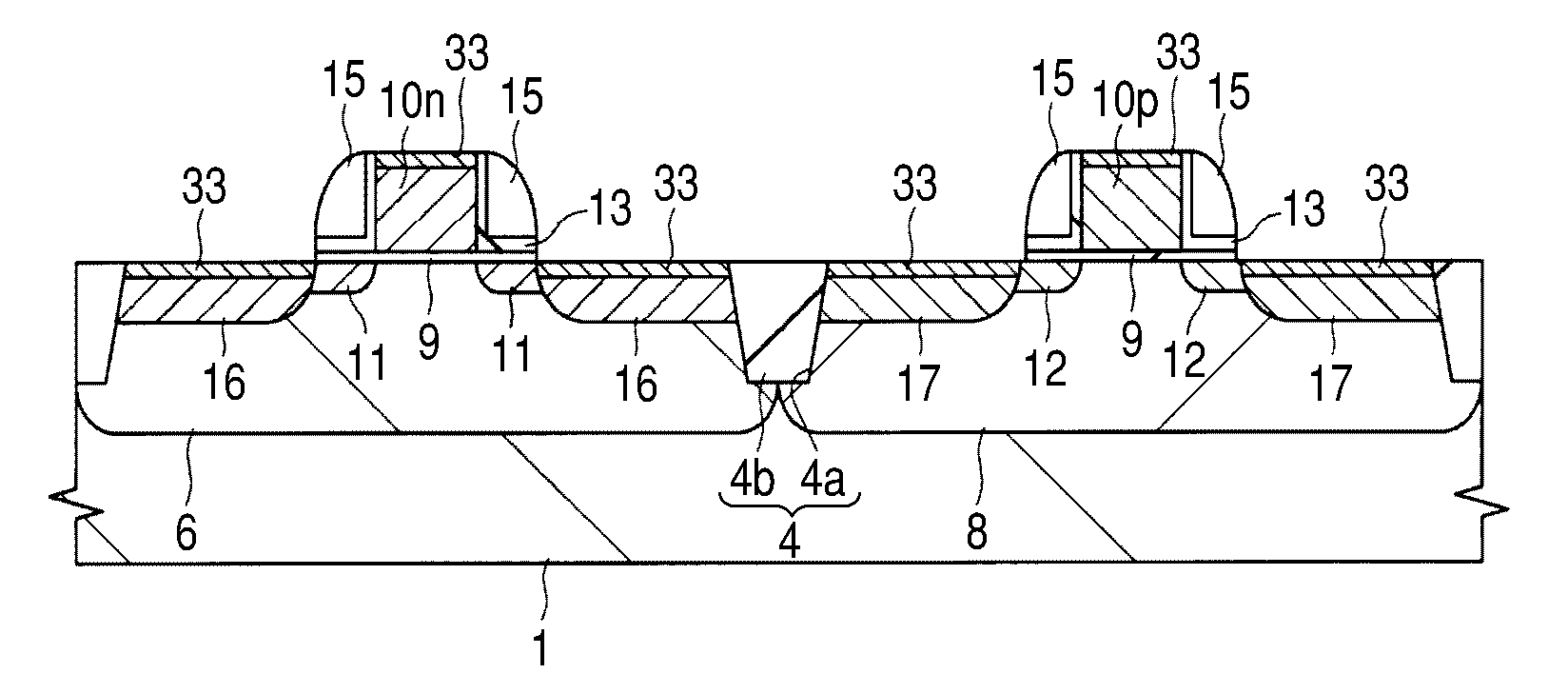

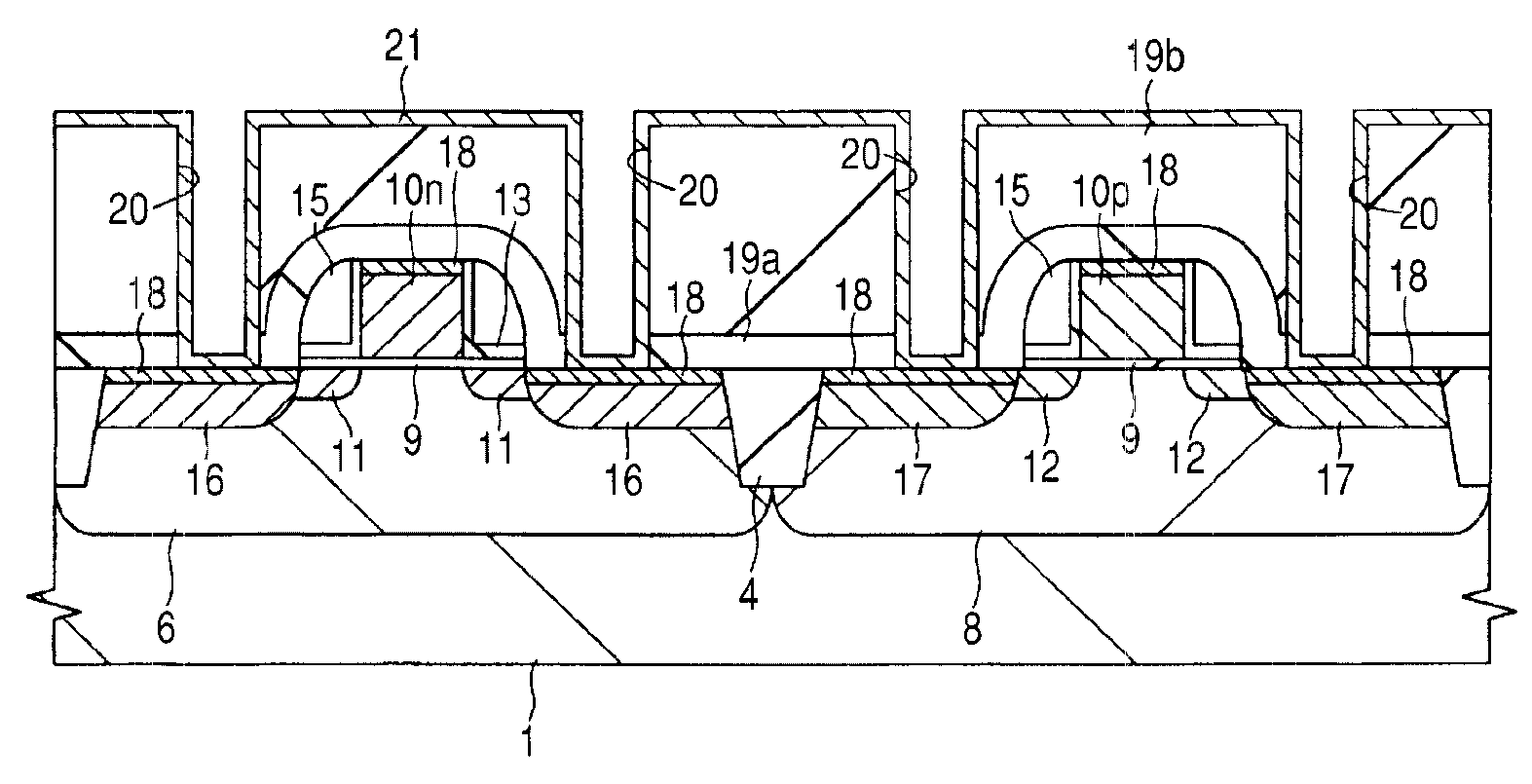

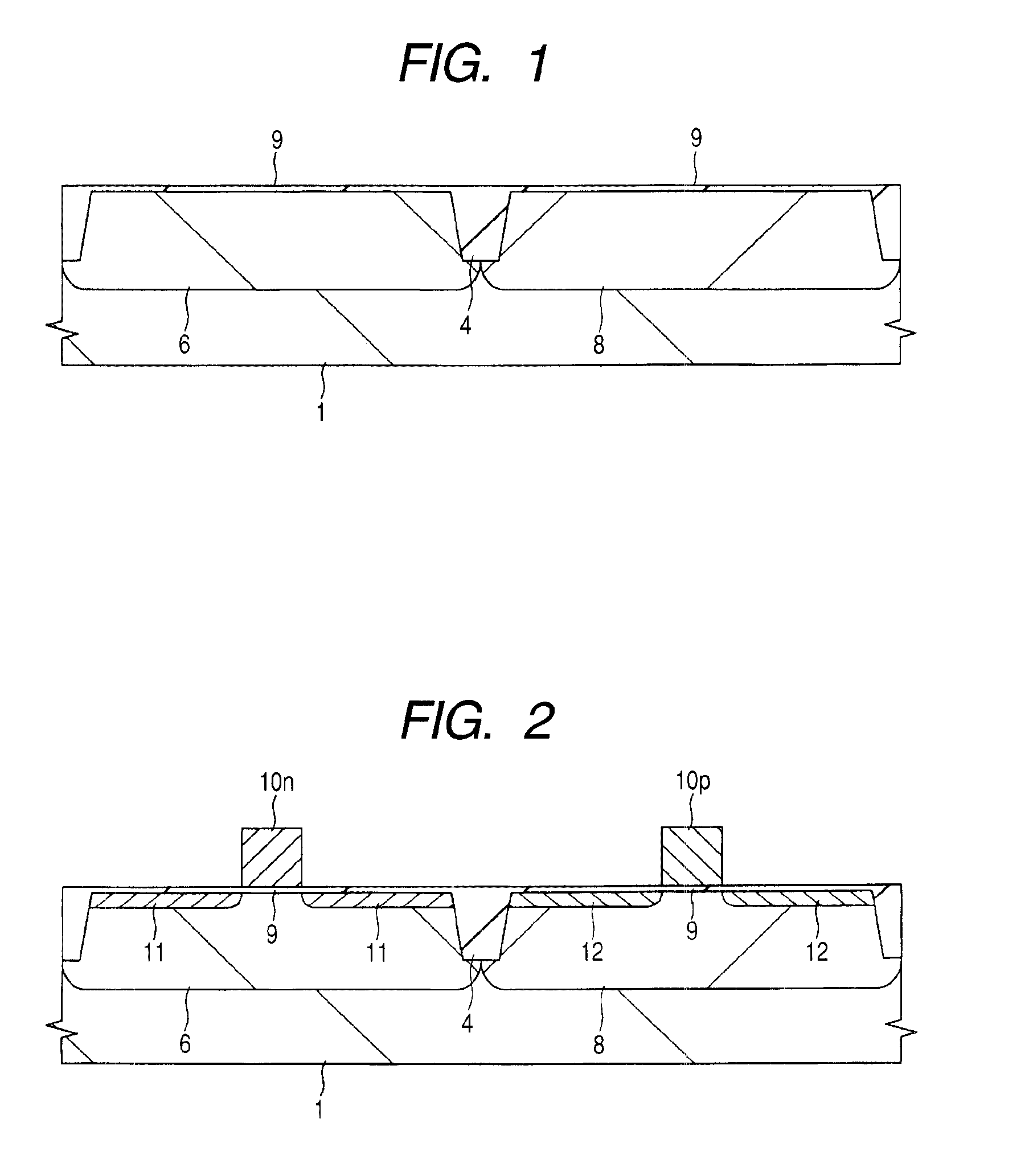

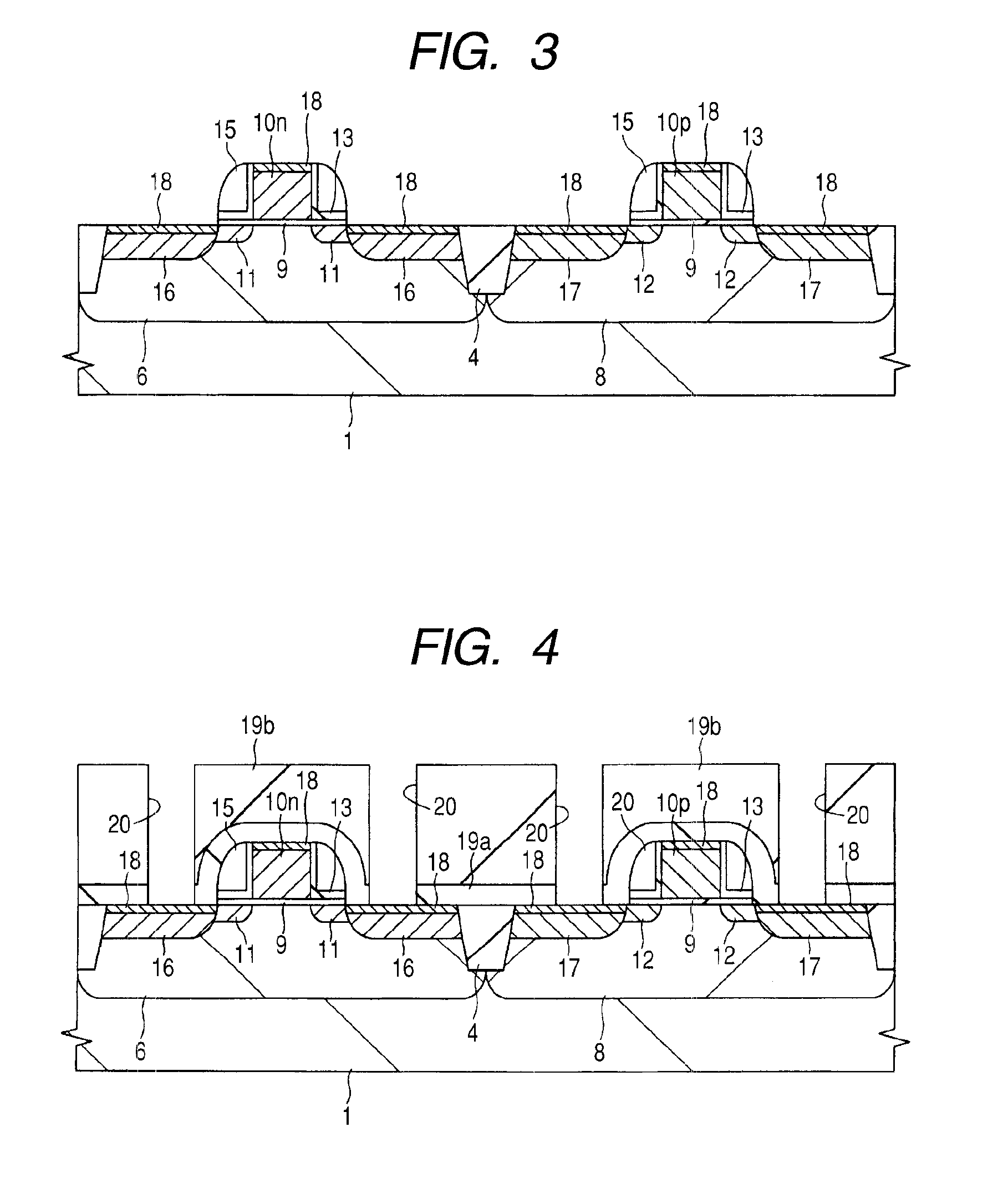

Semiconductor device and manufacturing method therefor

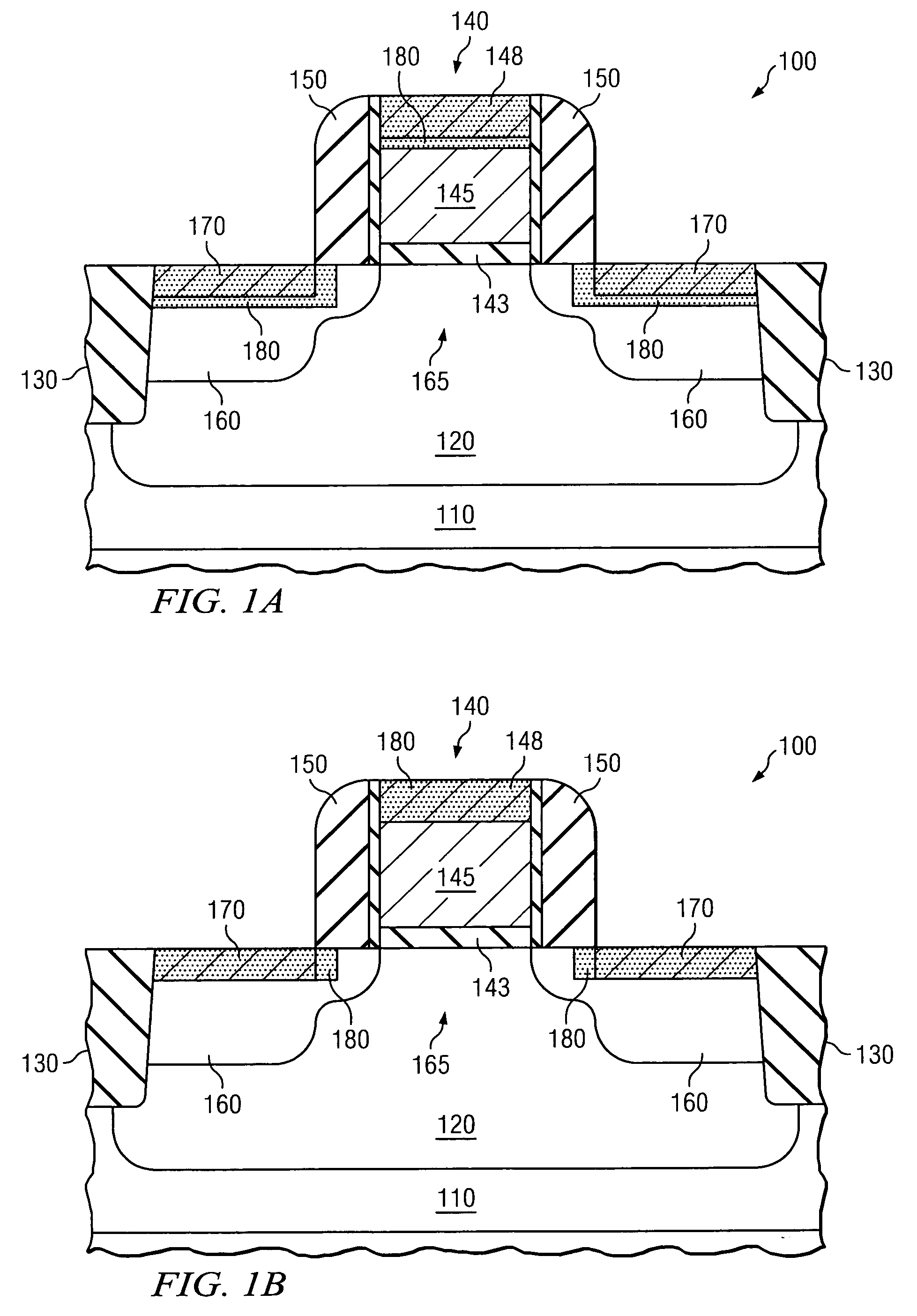

InactiveUS20050199963A1High dielectric constantTransistorSolid-state devicesDielectricGate dielectric

An element isolation dielectric film is formed around device regions in a silicon substrate. The device regions are an n-type diffusion region, a p-type diffusion region, a p-type extension region, an n-type extension region, a p-type source / drain region, an n-type source / drain region, and a nickel silicide film. Each gate dielectric film includes a silicon oxide film and a hafnium silicate nitride film. The n-type gate electrode includes an n-type silicon film and a nickel silicide film, and the p-type gate electrode includes a nickel silicide film. The hafnium silicate nitride films are not on the sidewalls of the gate electrodes.

Owner:KK TOSHIBA

Deposition methods for barrier and tungsten materials

Embodiments are provided for a method to deposit barrier and tungsten materials on a substrate. In one embodiment, a method provides forming a barrier layer on a substrate and exposing the substrate to a silane gas to form a thin silicon-containing layer on the barrier layer during a soak process. The method further provides depositing a tungsten nucleation layer over the barrier layer and the thin silicon-containing layer during an atomic layer deposition process and depositing a tungsten bulk layer on the tungsten nucleation layer during a chemical vapor deposition process. In some examples, the barrier layer contains metallic cobalt and cobalt silicide, or metallic nickel and nickel silicide. In other examples, the barrier layer contains metallic titanium and titanium nitride, or metallic tantalum and tantalum nitride.

Owner:APPLIED MATERIALS INC

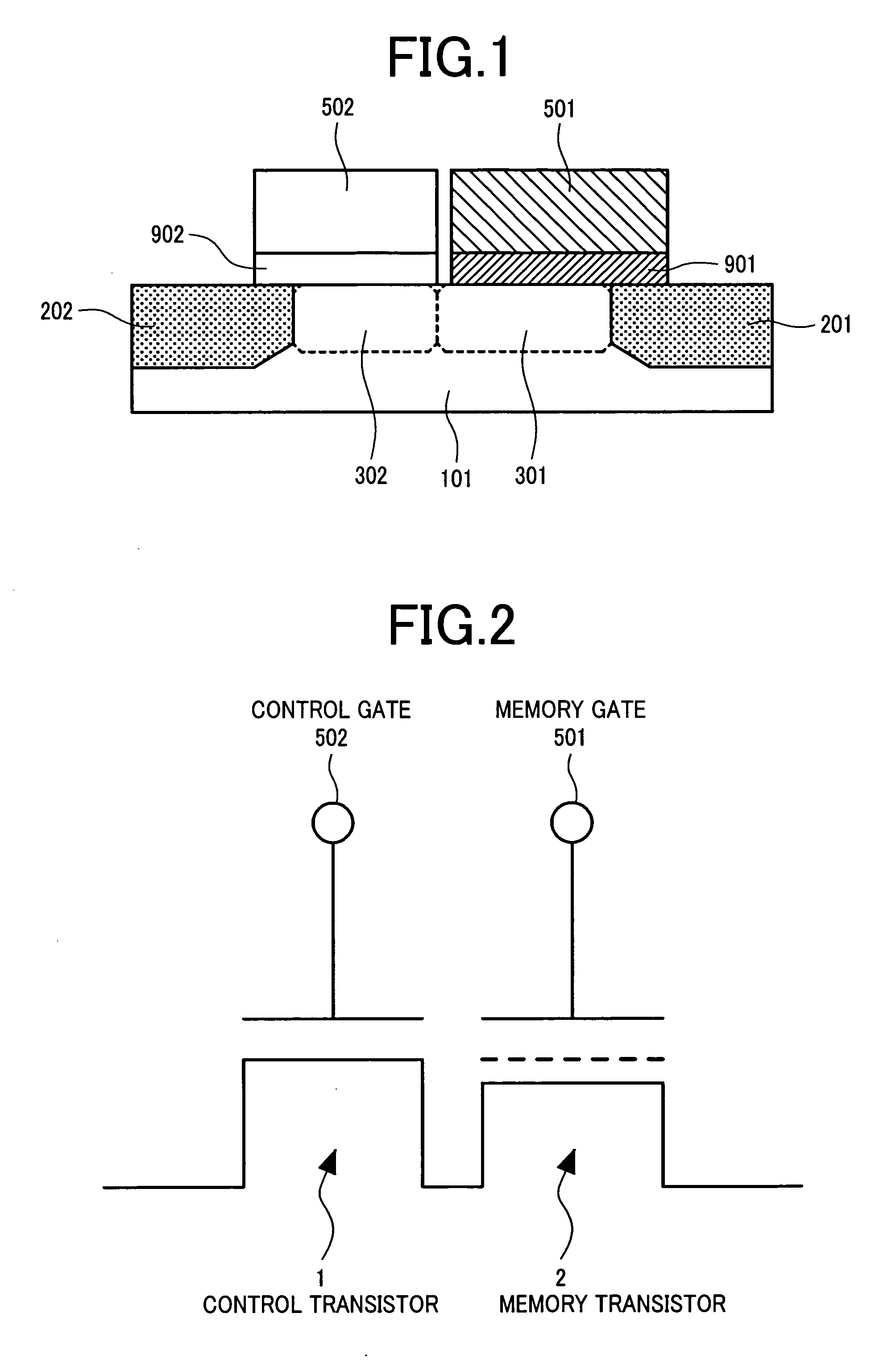

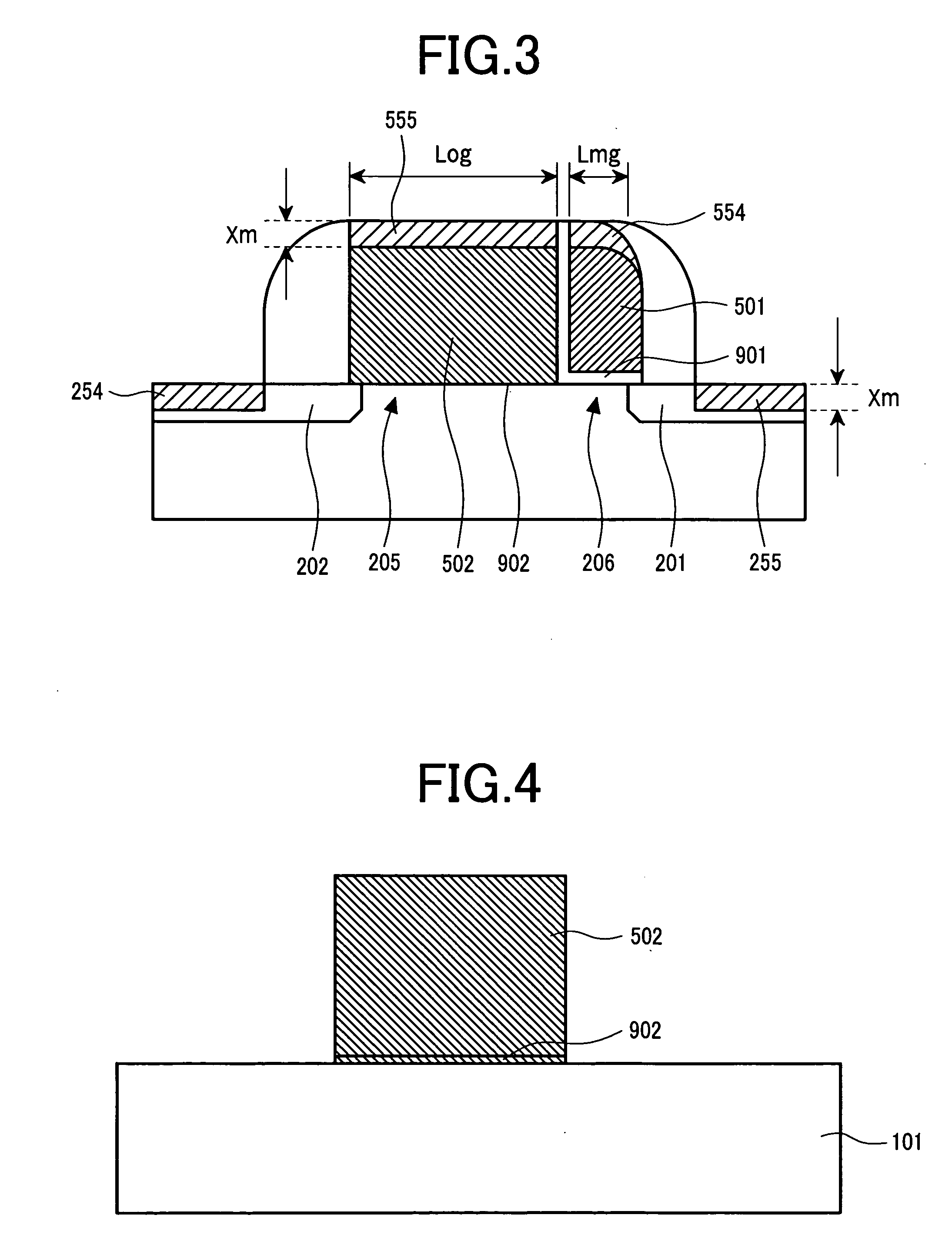

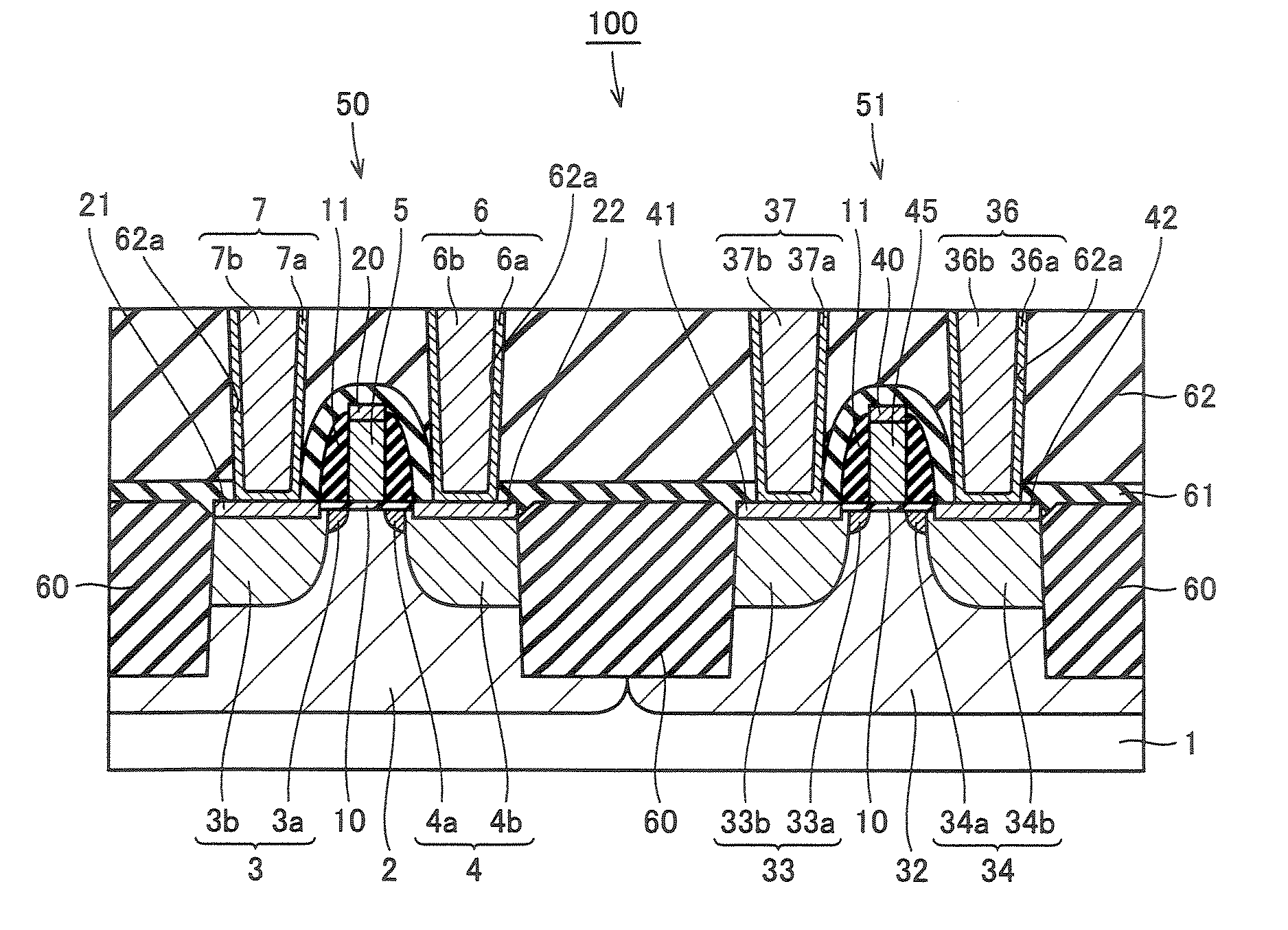

Nonvolatile semiconductor memory and making method thereof

InactiveUS20050176202A1Lower resistanceMaximizing thicknessTransistorSolid-state devicesDiffusion layerLow resistance

A nonvolatile semiconductor memory device of a split gate structure having a gate of low resistance suitable to the arrangement of a memory cell array is provided. When being formed of a side wall spacer, a memory gate is formed of polycrystal silicon and then replaced with nickel silicide. Thus, its resistance can be lowered with no effect on the silicidation to the selection gate or the diffusion layer.

Owner:RENESAS ELECTRONICS CORP

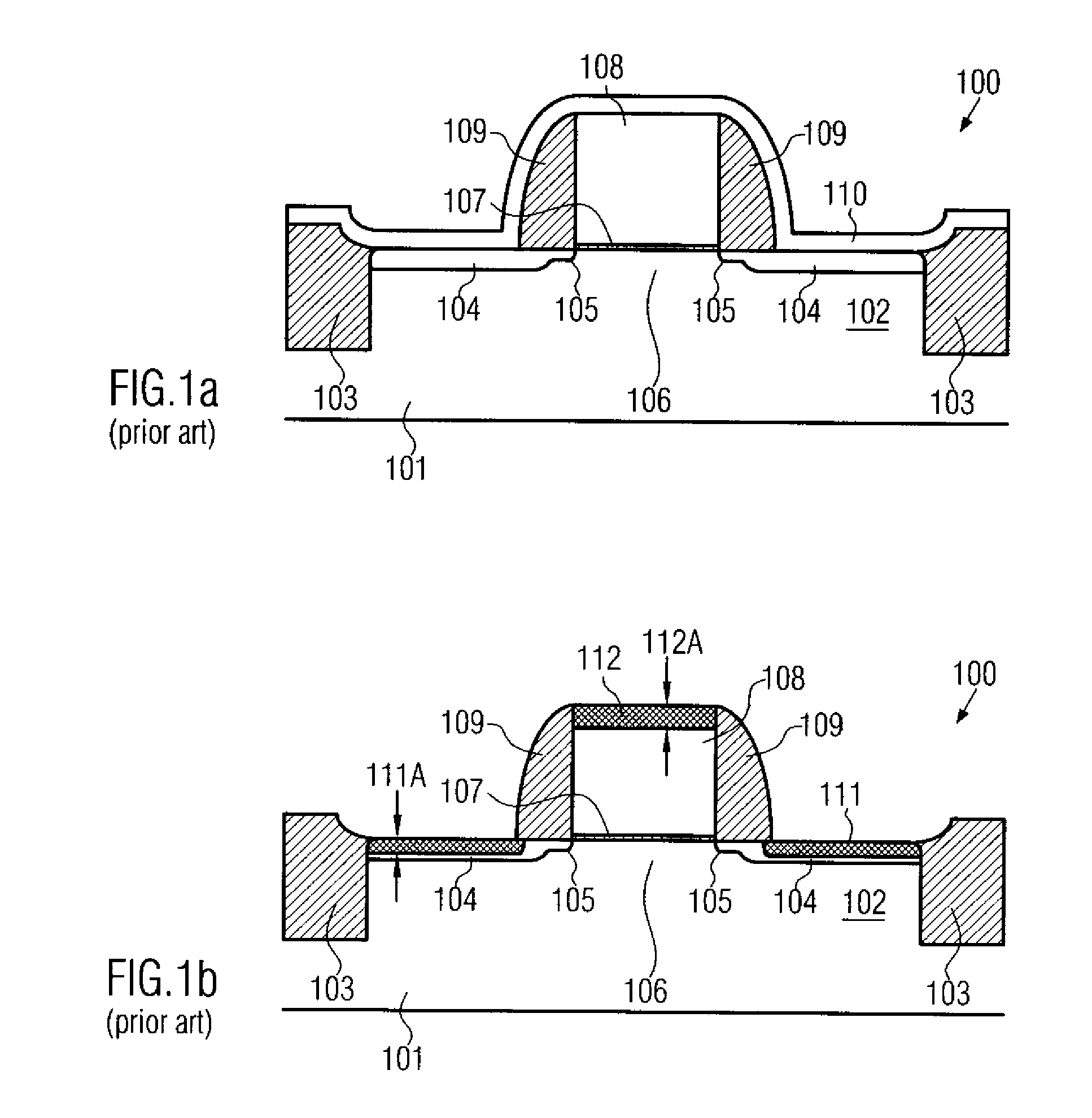

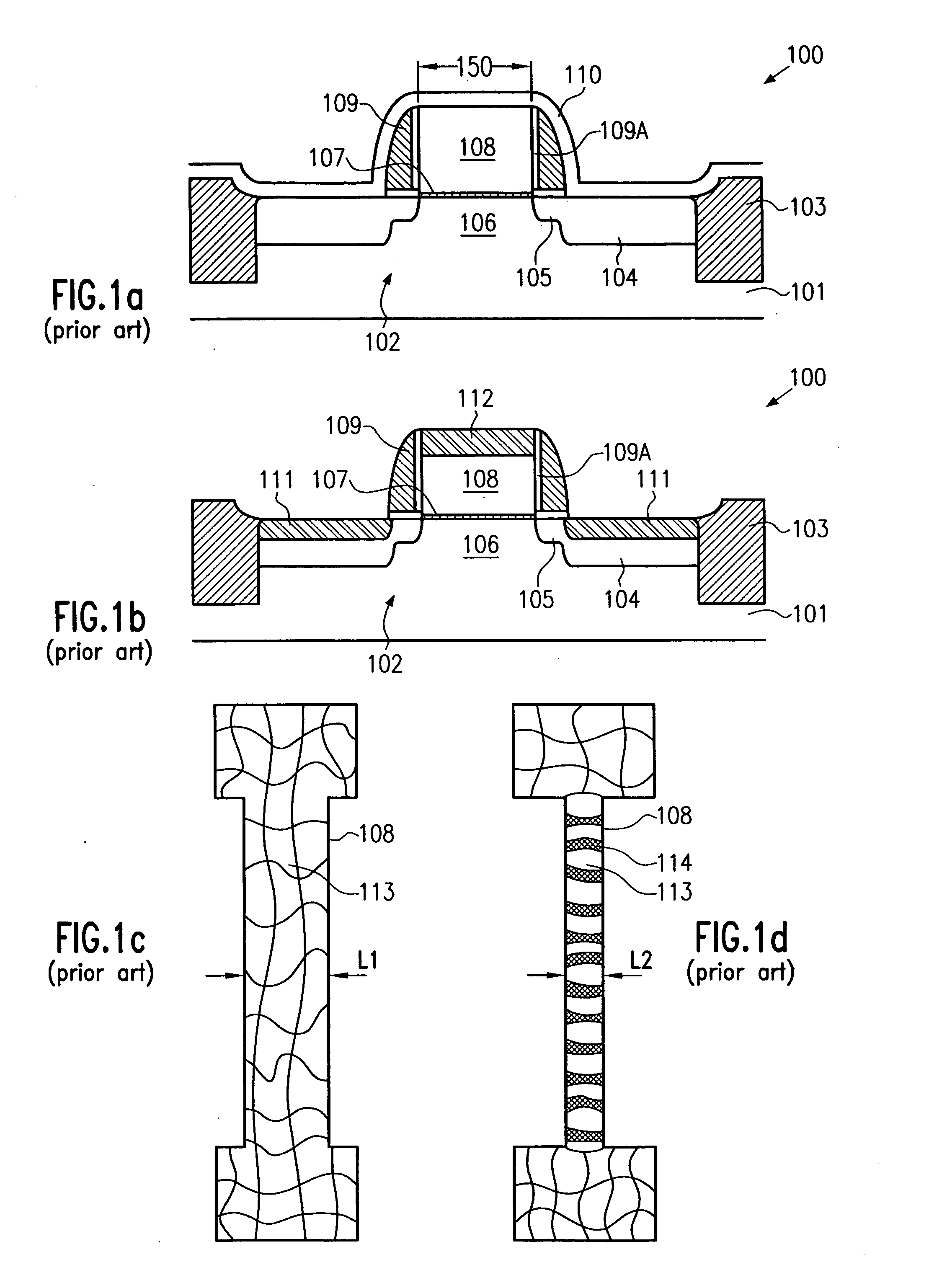

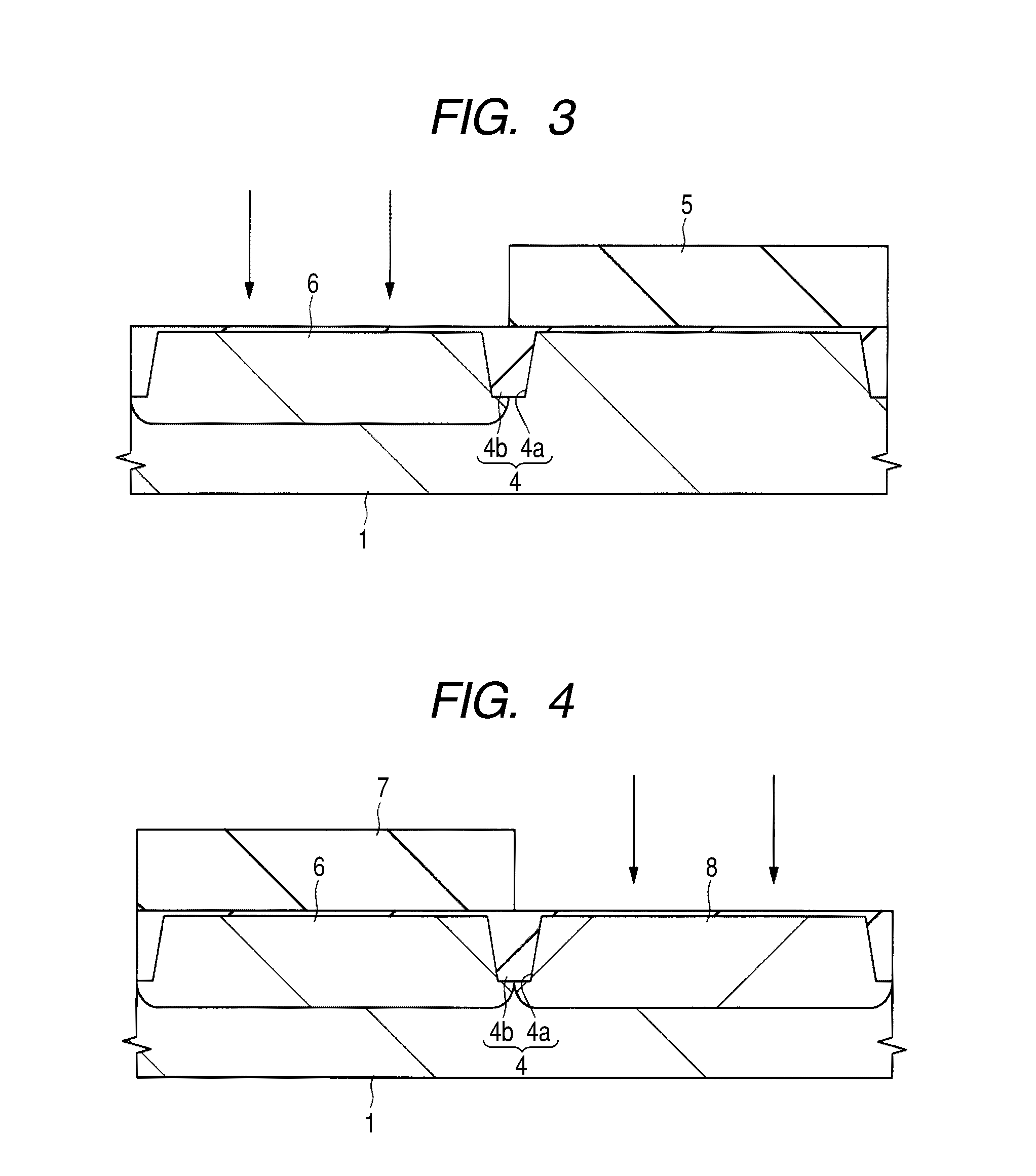

Circuit element having a metal silicide region thermally stabilized by a barrier diffusion material

InactiveUS6838363B2InterdiffusionReduce formationSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

The introduction of a barrier diffusion material, such as nitrogen, into a silicon-containing conductive region, for example the drain and source regions and the gate electrode of a field effect transistor, allows the formation of nickel silicide, which is substantially thermally stable up to temperatures of 500° C. Thus, the device performance may significantly improve as the sheet resistance of nickel silicide is significantly less than that of nickel disilicide.

Owner:GLOBALFOUNDRIES US INC

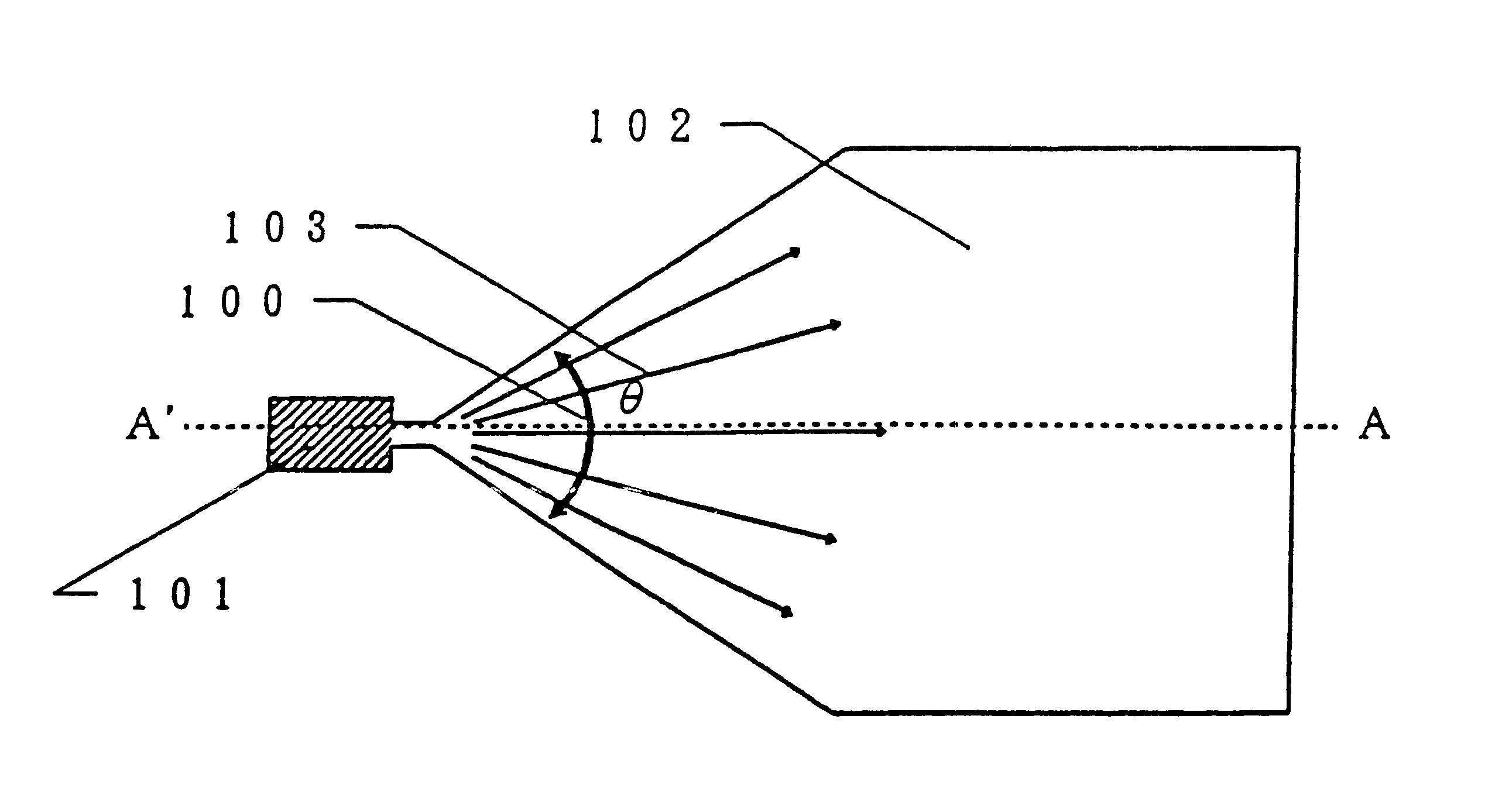

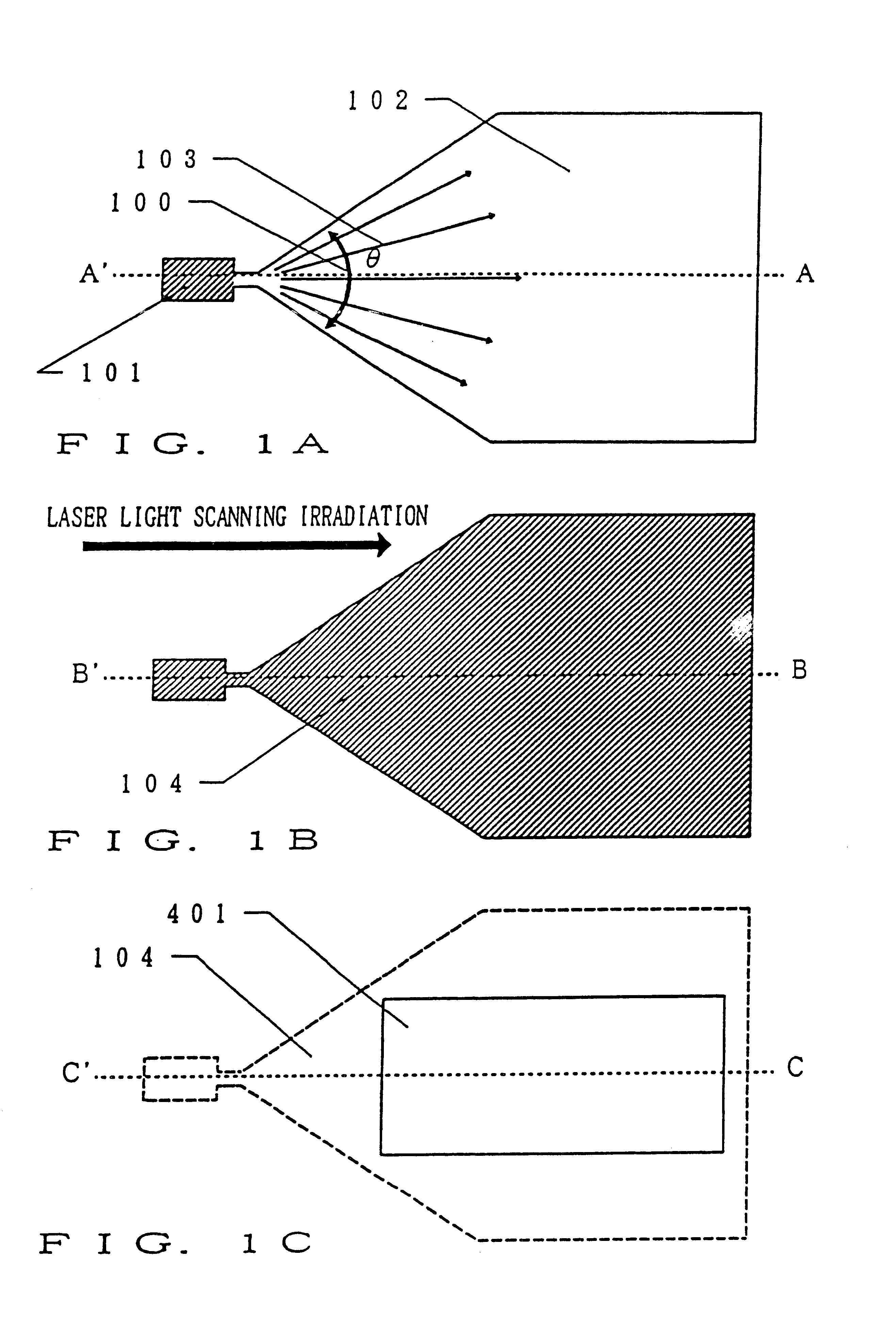

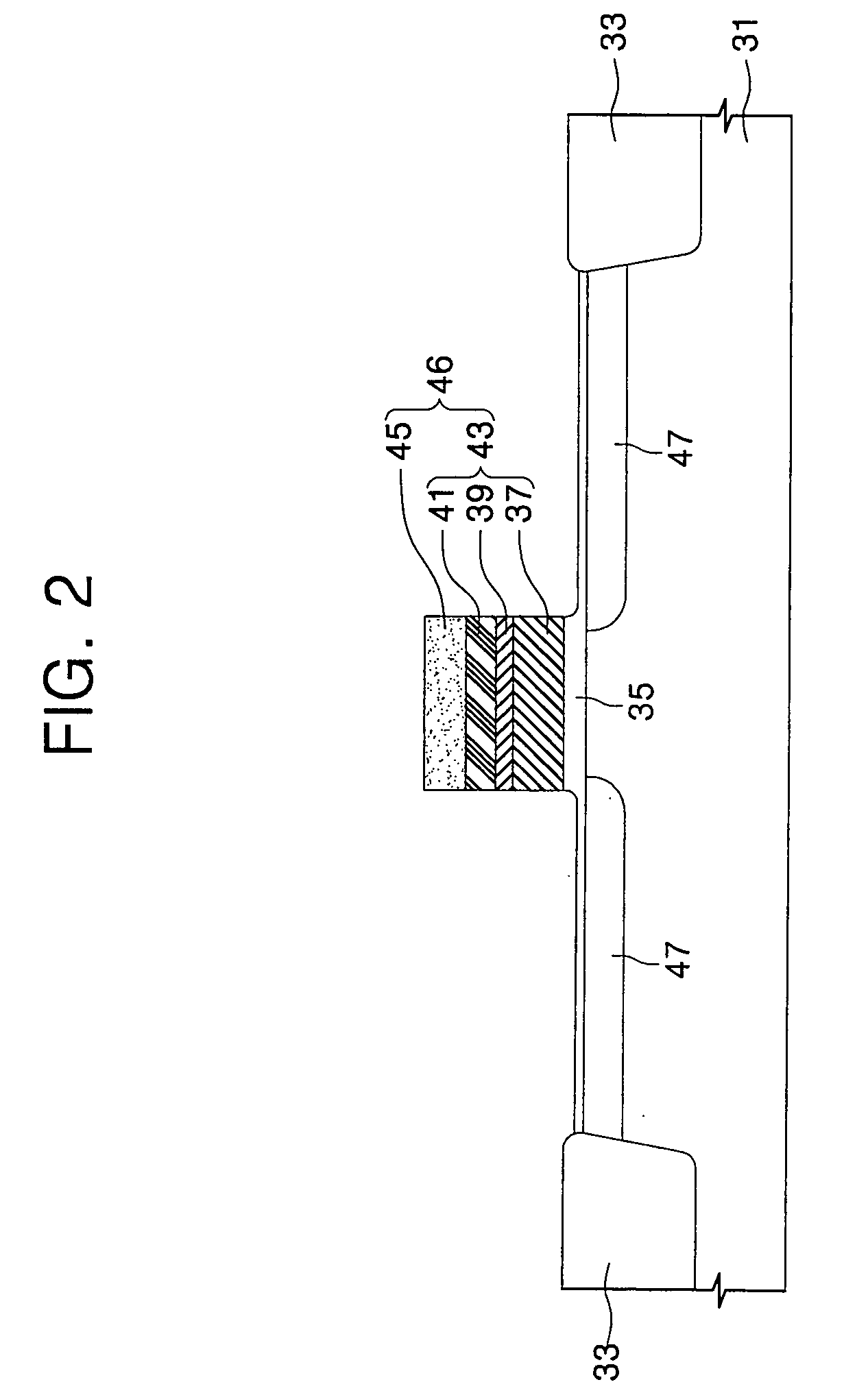

Method for producing semiconductor device

InactiveUS6479329B2Semiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalLaser light

Owner:SEMICON ENERGY LAB CO LTD

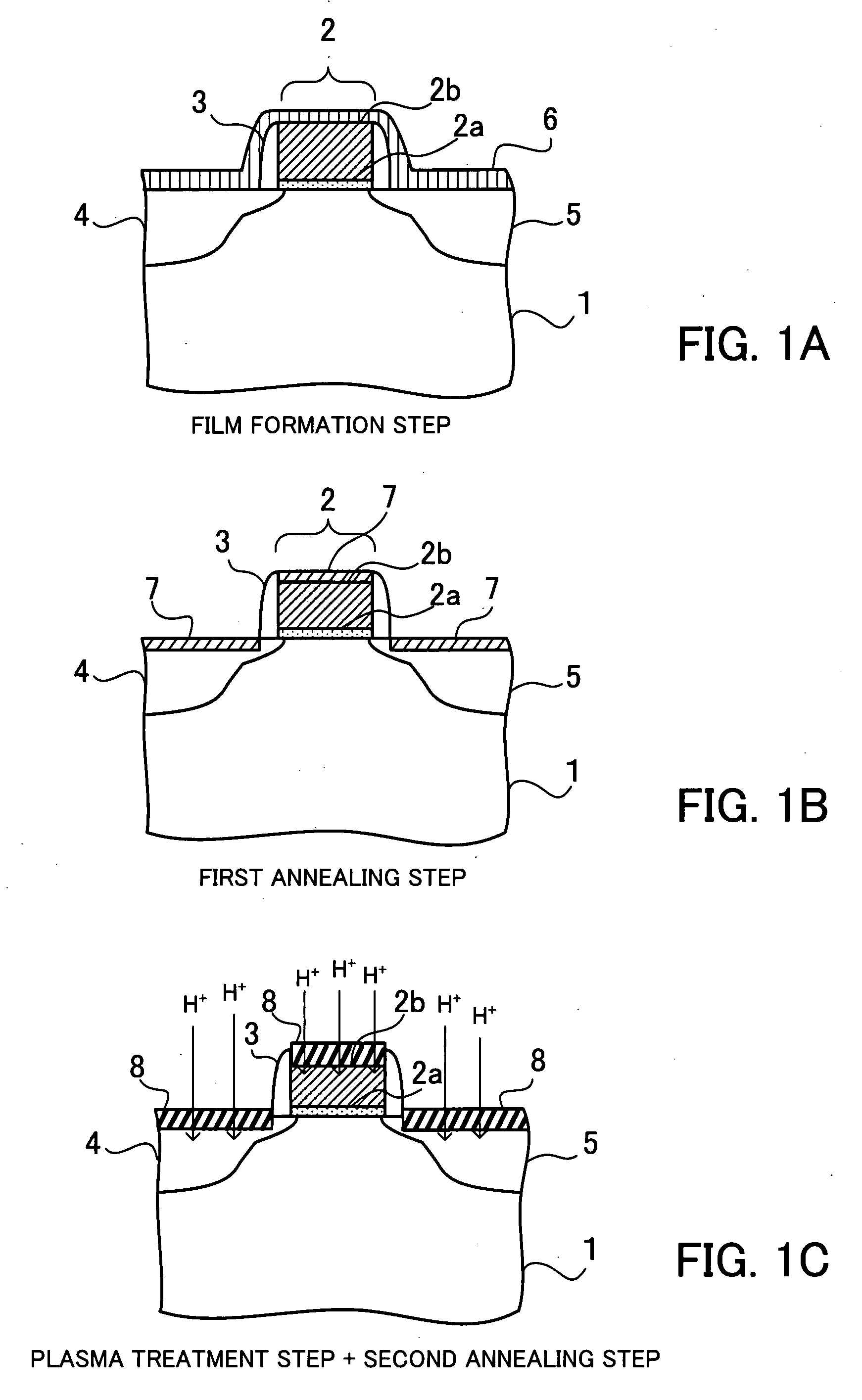

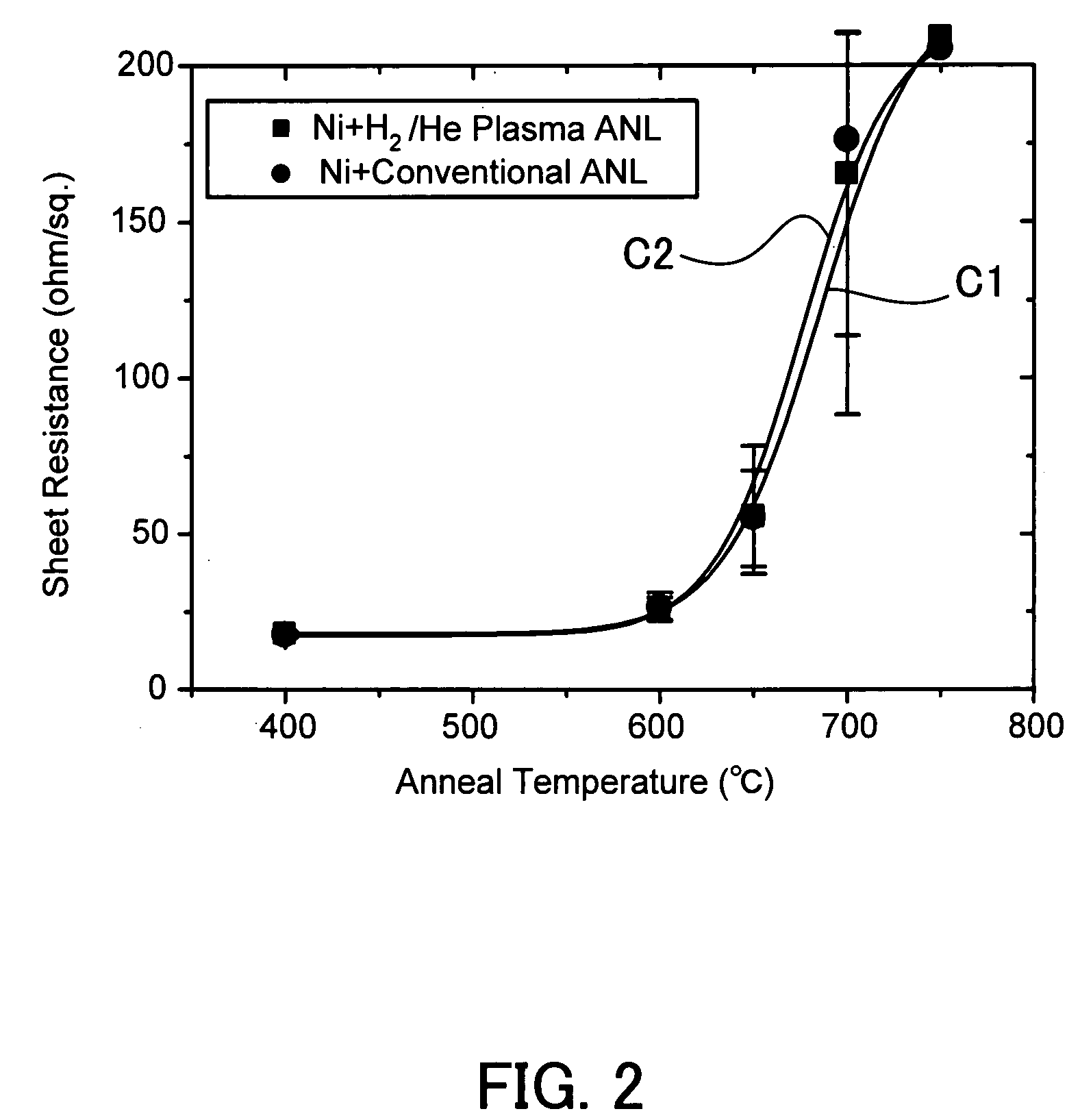

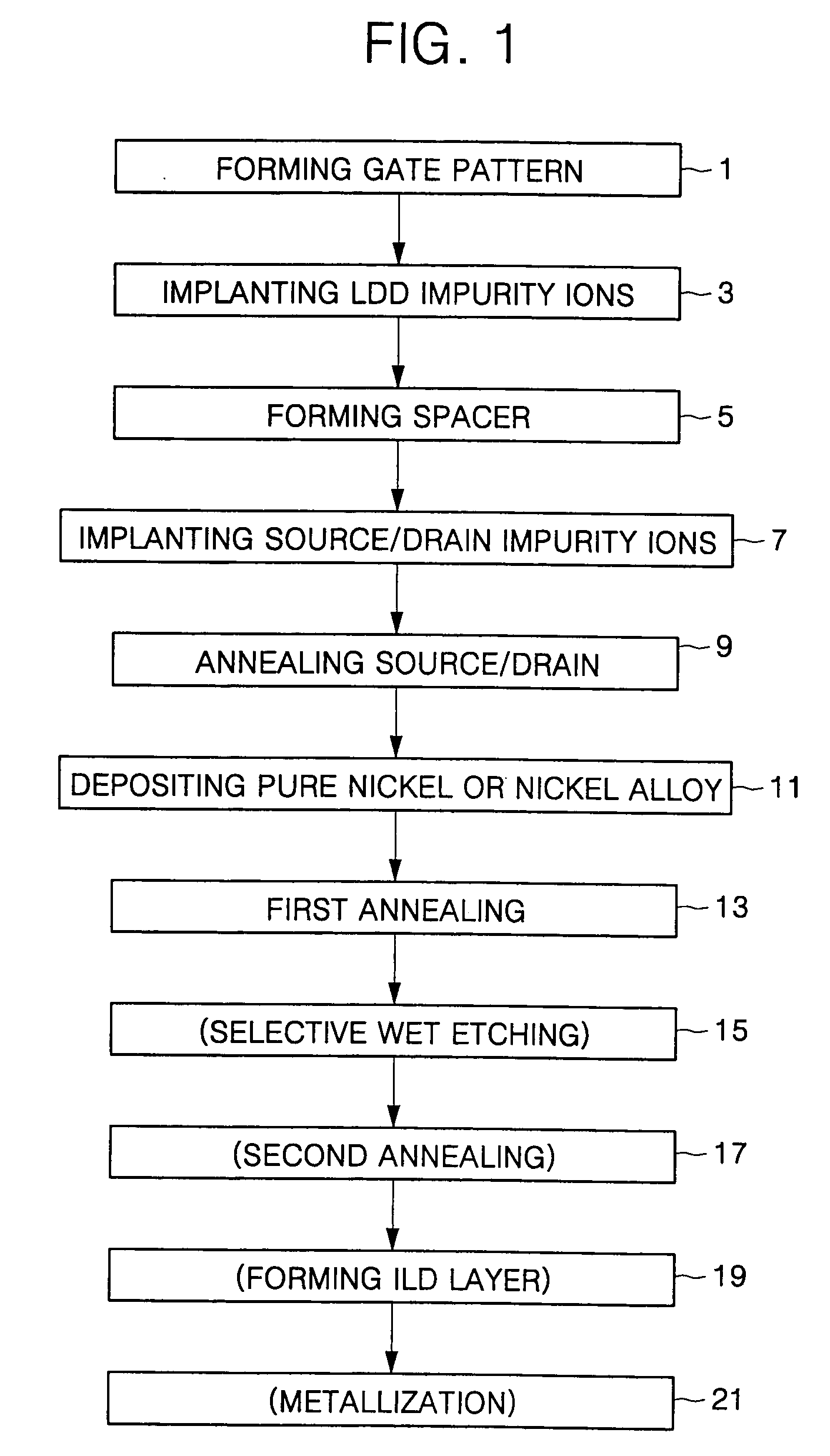

Method for fabricating semiconductor device

InactiveUS20080124922A1Improve thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSalicideHydrogen

A semiconductor device fabrication method by which the thermal stability of nickel silicide can be improved. Nickel (or a nickel alloy) is formed over a semiconductor substrate on which a gate region, a source region, and a drain region are formed. Dinickel silicide is formed by performing a first annealing step, followed by a selective etching step. By performing a plasma treatment step, plasma which contains hydrogen ions is generated and the hydrogen ions are implanted in the dinickel silicide or the gate region, the source region, and the drain region under the dinickel silicide. The dinickel silicide is phase-transformed into nickel silicide by performing a second annealing step.

Owner:FUJITSU SEMICON LTD

Manufacturing method of semiconductor device

ActiveUS20080311718A1Improve operating rateReduce contact resistanceTransistorSolid-state devicesTitanium nitrideNickel silicide

The present invention is to possible to avoid an inconvenience at a coupling portion between a barrier metal film obtained by depositing a titanium nitride film on a titanium film and thus having a film stack structure and a metal film filled, via the barrier metal film, in a connecting hole opened in an insulating film. The manufacturing method of a semiconductor device includes the steps of: forming a contact hole and exposing a nickel silicide layer from the bottom of the contact hole; forming a thermal reaction Ti film by a thermal reaction using a TiCl4 gas, forming a plasma reaction Ti film by a plasma reaction using a TiCl4 gas, carrying out plasma treatment with an H2 gas to decrease the chlorine concentration of the plasma reaction Ti film and at the same time to reduce an oxide film on the surface of the nickel silicide layer; forming a nitrogen-rich TiN film over the surface of the plasma reaction Ti film and at the same time reducing the oxide film on the surface of the nickel silicide layer by thermal nitridation treatment with an NH3 gas and plasma treatment with an NH3 gas.

Owner:RENESAS ELECTRONICS CORP

Nickel salicide processes and methods of fabricating semiconductor devices using the same

InactiveUS20050158996A1Improve thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSalicideDevice material

A nickel salicide process includes preparing a substrate having a silicon region and an insulating region containing silicon. Nickel is deposited on the substrate, and the nickel is annealed at a first temperature of 300° C. to 380° C. to selectively form a mono-nickel mono-silicide layer on the silicon region and to leave an unreacted nickel layer on the insulating region. The unreacted nickel layer is selectively removed to expose the insulating region and to leave the mono-nickel mono-silicide layer on the silicon region. Subsequently, the mono-nickel mono-silicide layer is annealed at a second temperature which is higher than the first temperature to form a thermally stable mono-nickel mono-silicide layer and without a phase transition of the mono-nickel mono-silicide layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and structure for reducing contact resistance between silicide contact and overlying metallization

InactiveUS20070275548A1Lower resistance contactReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMetal silicide

A semiconductor structure in which the contact resistance in the contact opening is reduced as well as a method of forming the same are provided. This is achieved in the present invention by replacing conventional contact metallurgy, such as tungsten, or a metal silicide, such as Ni silicide or Cu silicide, with a metal germanide-containing contact material. The term “metal germanide-containing” is used in the present application to denote a pure metal germanide (i.e., MGe alloy) or a metal germanide that includes Si (i.e., MSiGe alloy).

Owner:GLOBALFOUNDRIES INC

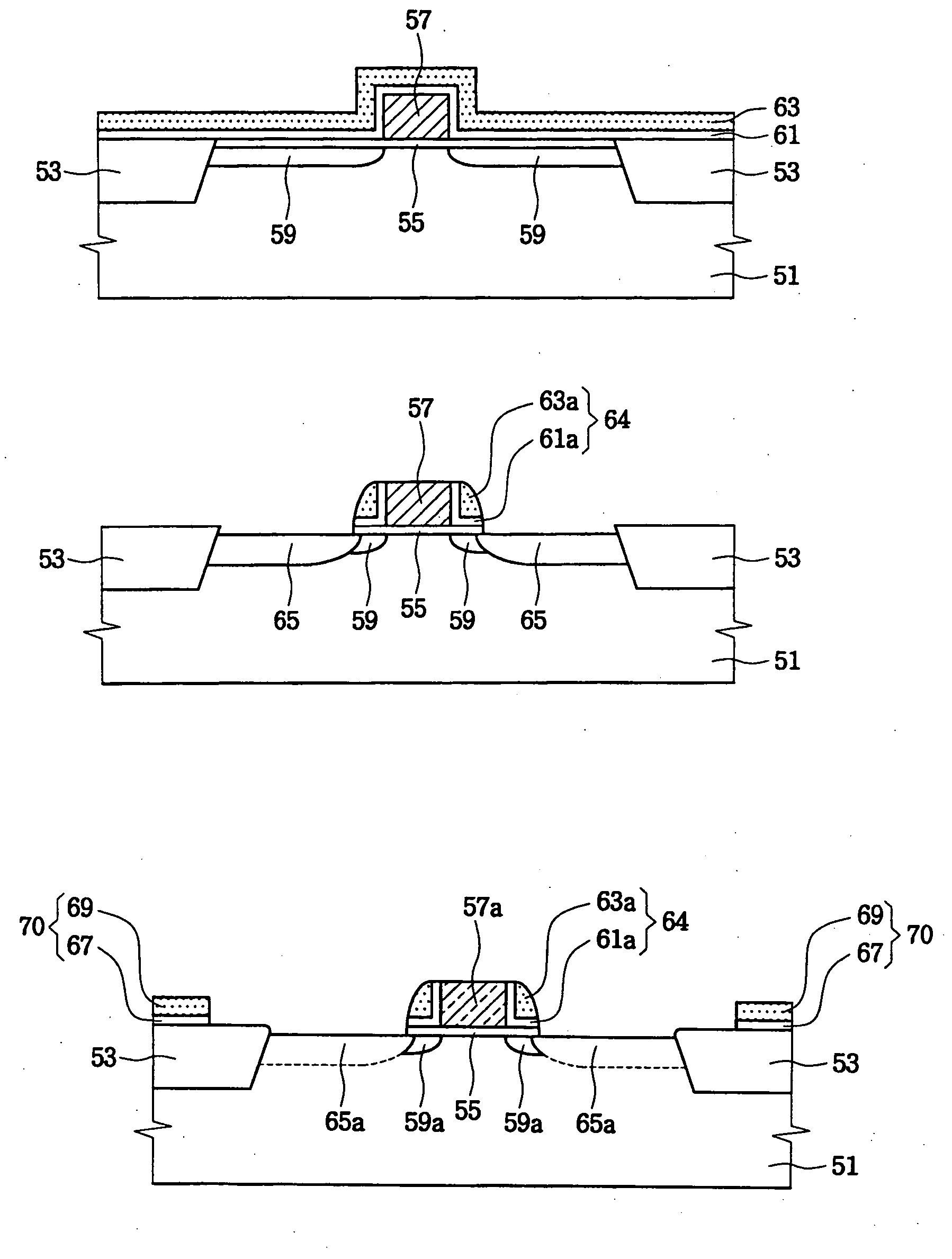

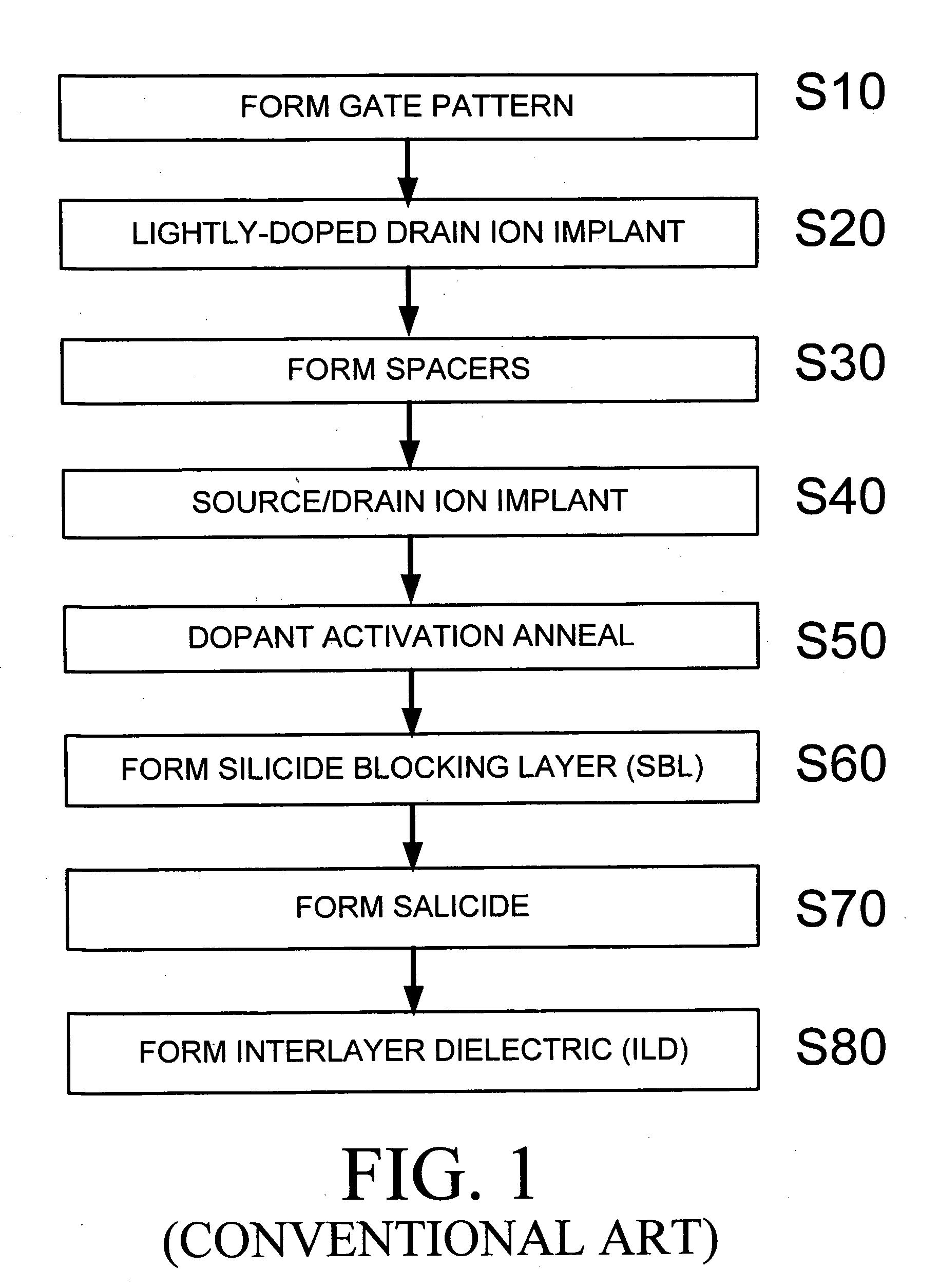

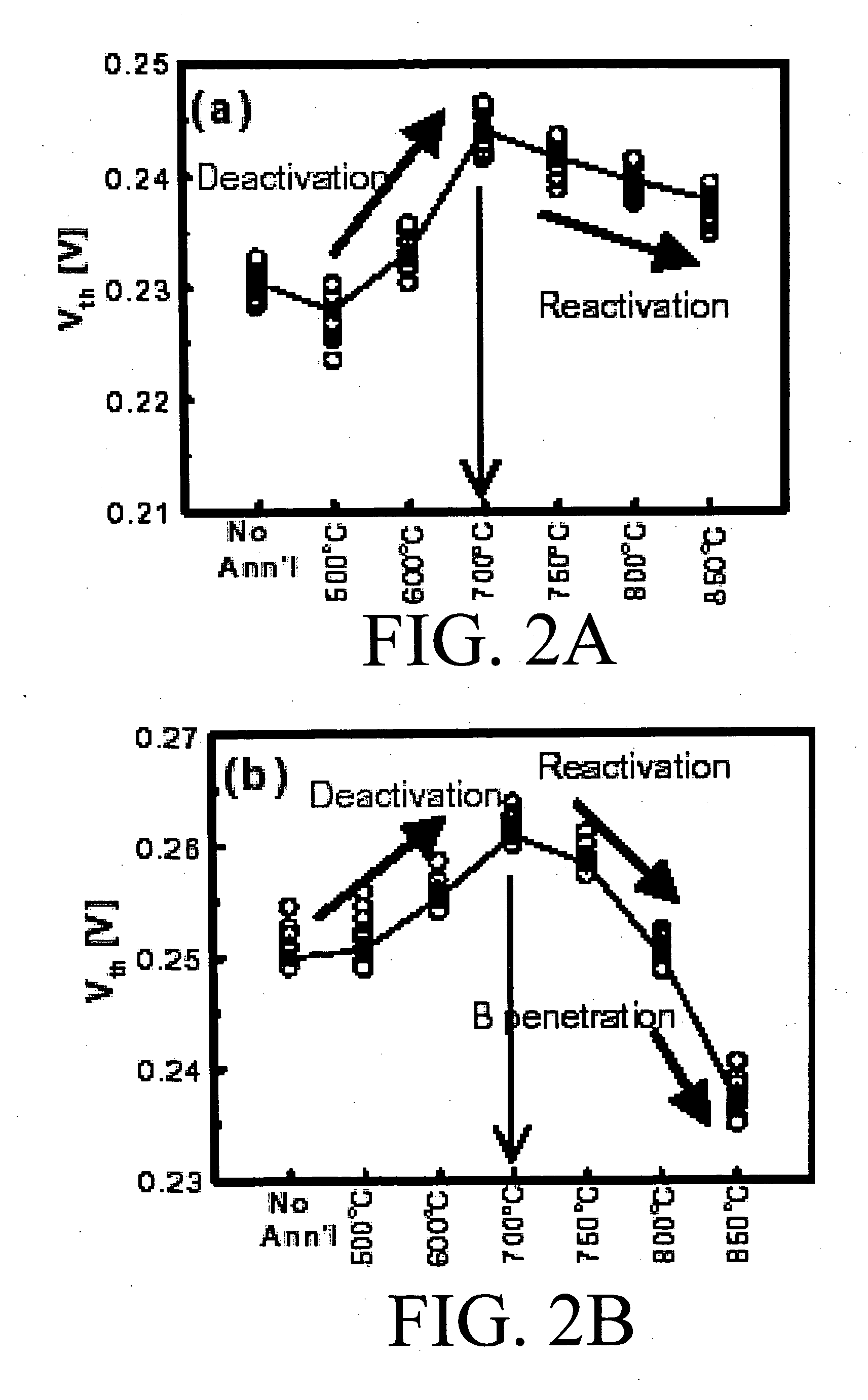

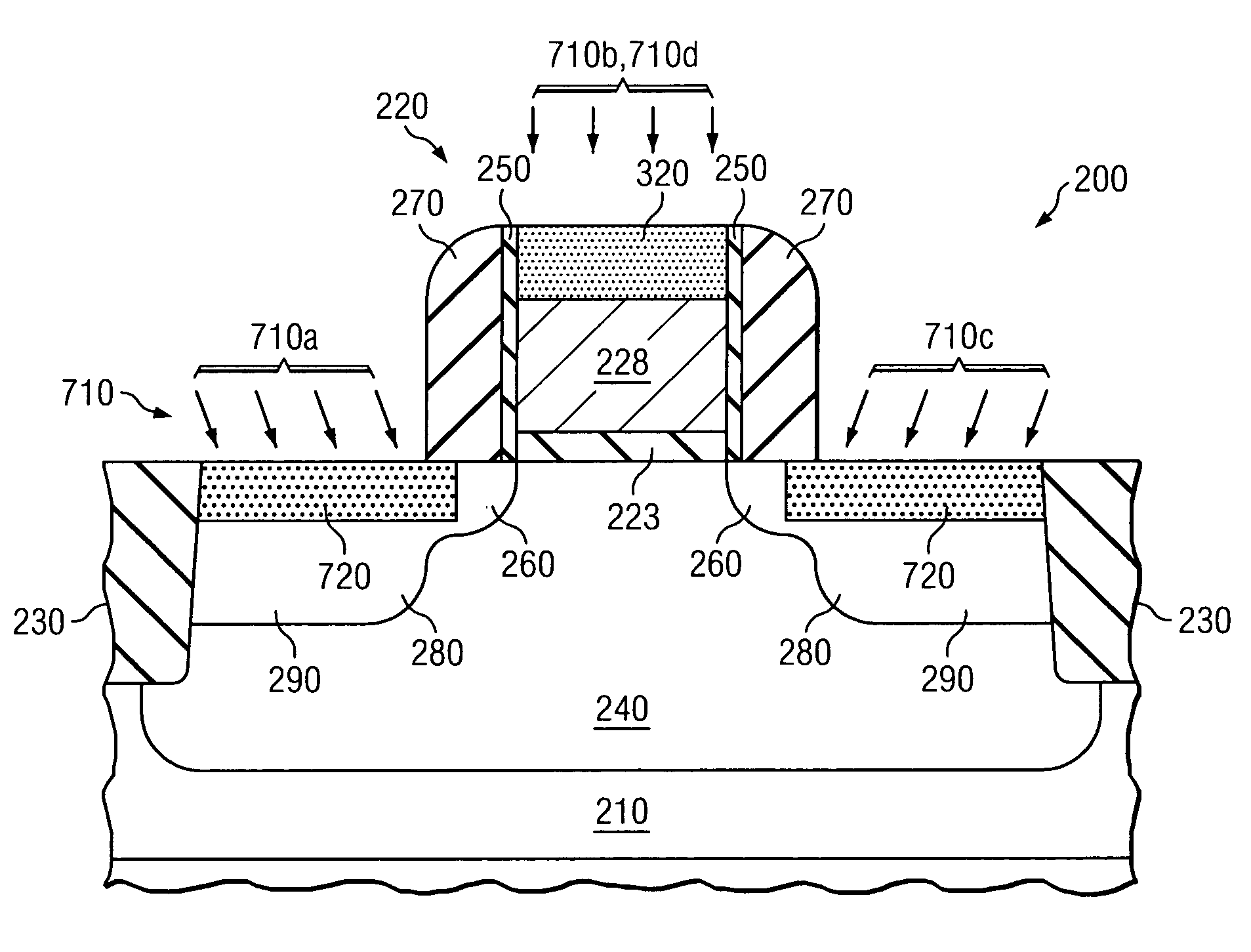

Nickel salicide process with reduced dopant deactivation

Provided are exemplary methods for forming a semiconductor devices incorporating silicide layers formed at temperatures below about 700° C., such as nickel silicides, that are formed after completion of a silicide blocking layer (SBL). The formation of the SBL tends to deactivate dopant species in the gate, lightly-doped drain and / or source / drain regions. The exemplary methods include a post-SBL activation anneal either in place of or in addition to the traditional post-implant activation anneal. The use of the post-SBL anneal produces CMOS transistors having properties that reflect reactivation of sufficient dopant to overcome the SBL process effects, while allowing the use of lower temperature silicides, including nickel silicides and, in particular, nickel silicides incorporating a minor portion of an alloying metal, such as tantalum, the exhibits reduced agglomeration and improved temperature stability.

Owner:SAMSUNG ELECTRONICS CO LTD

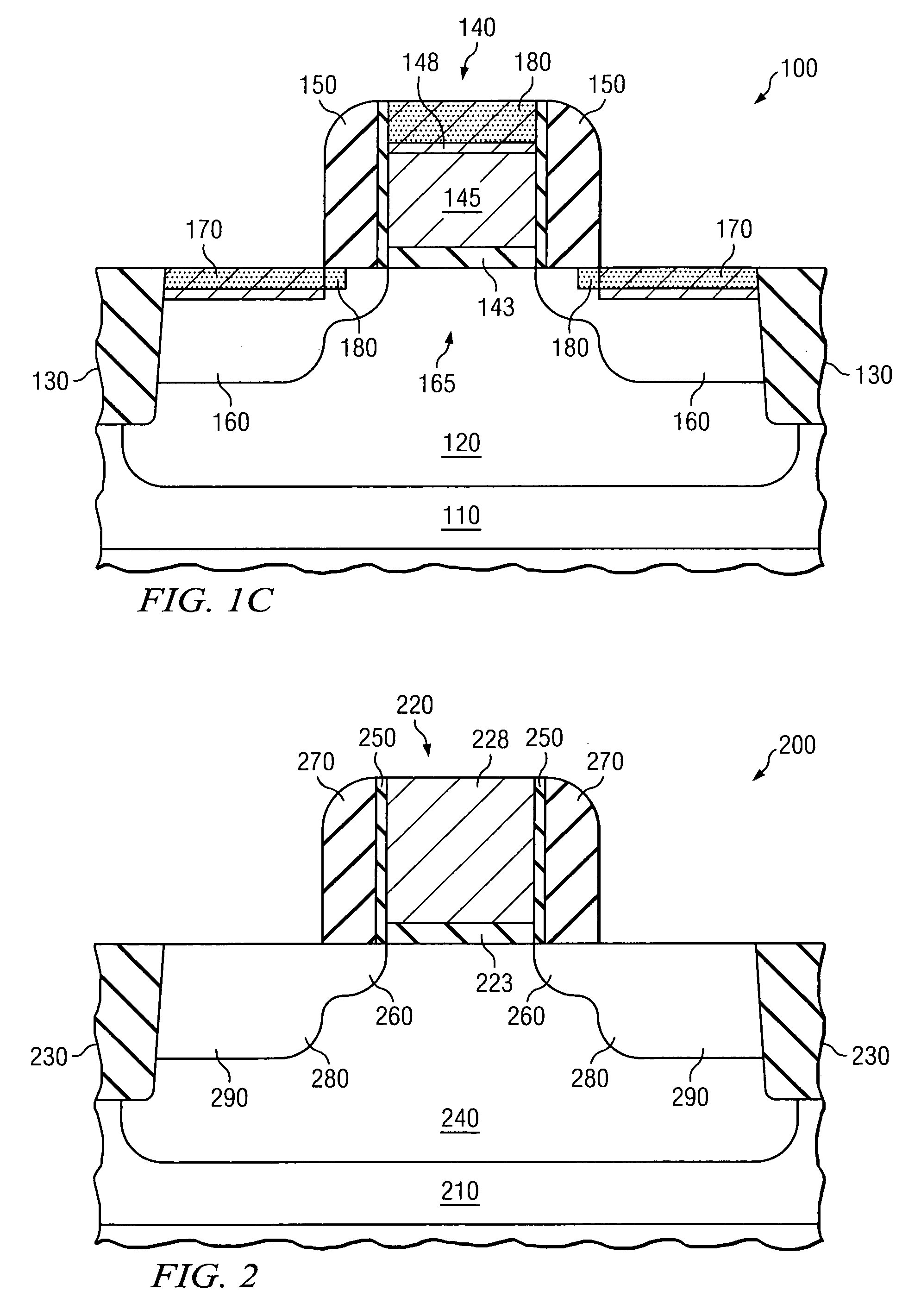

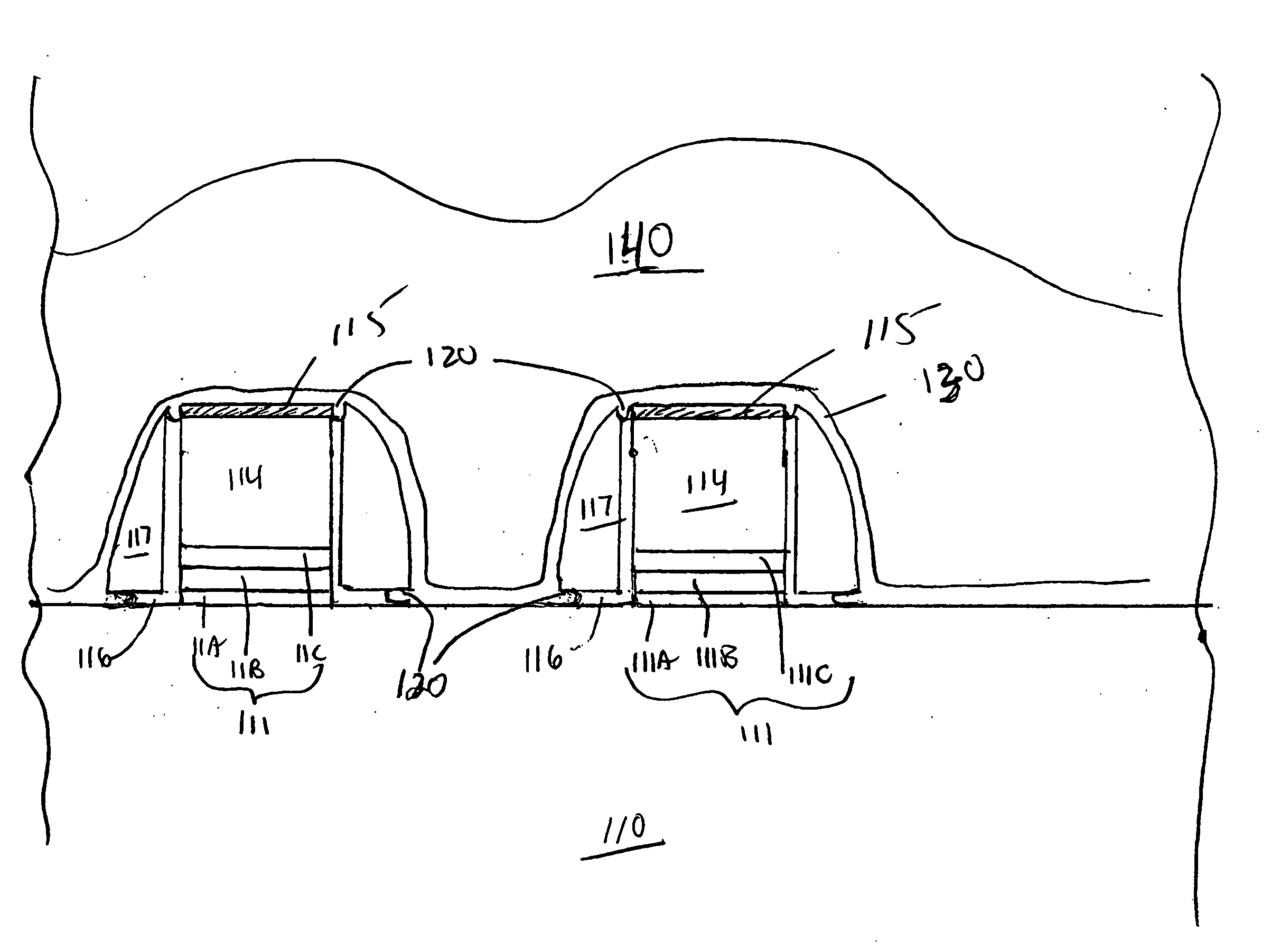

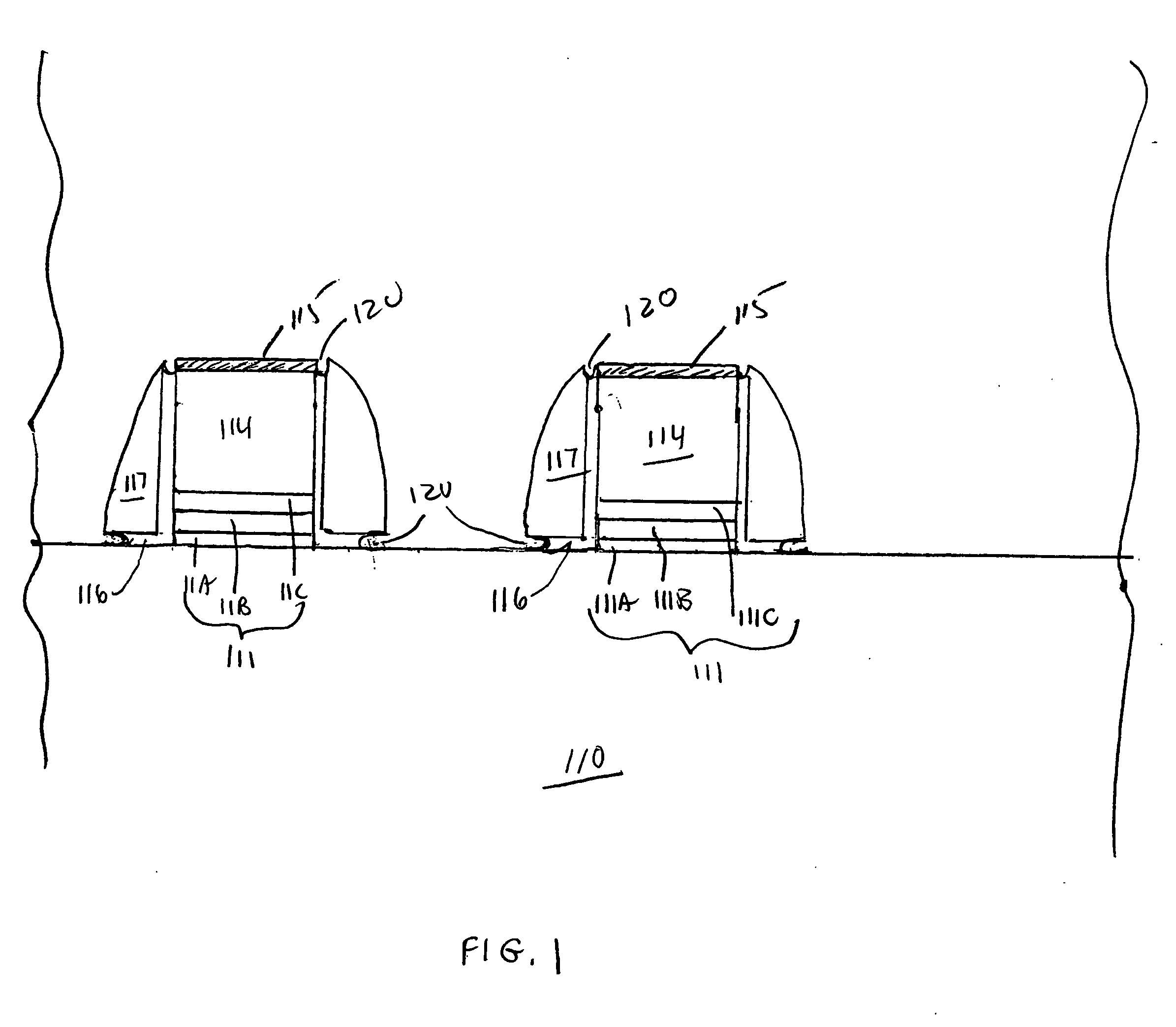

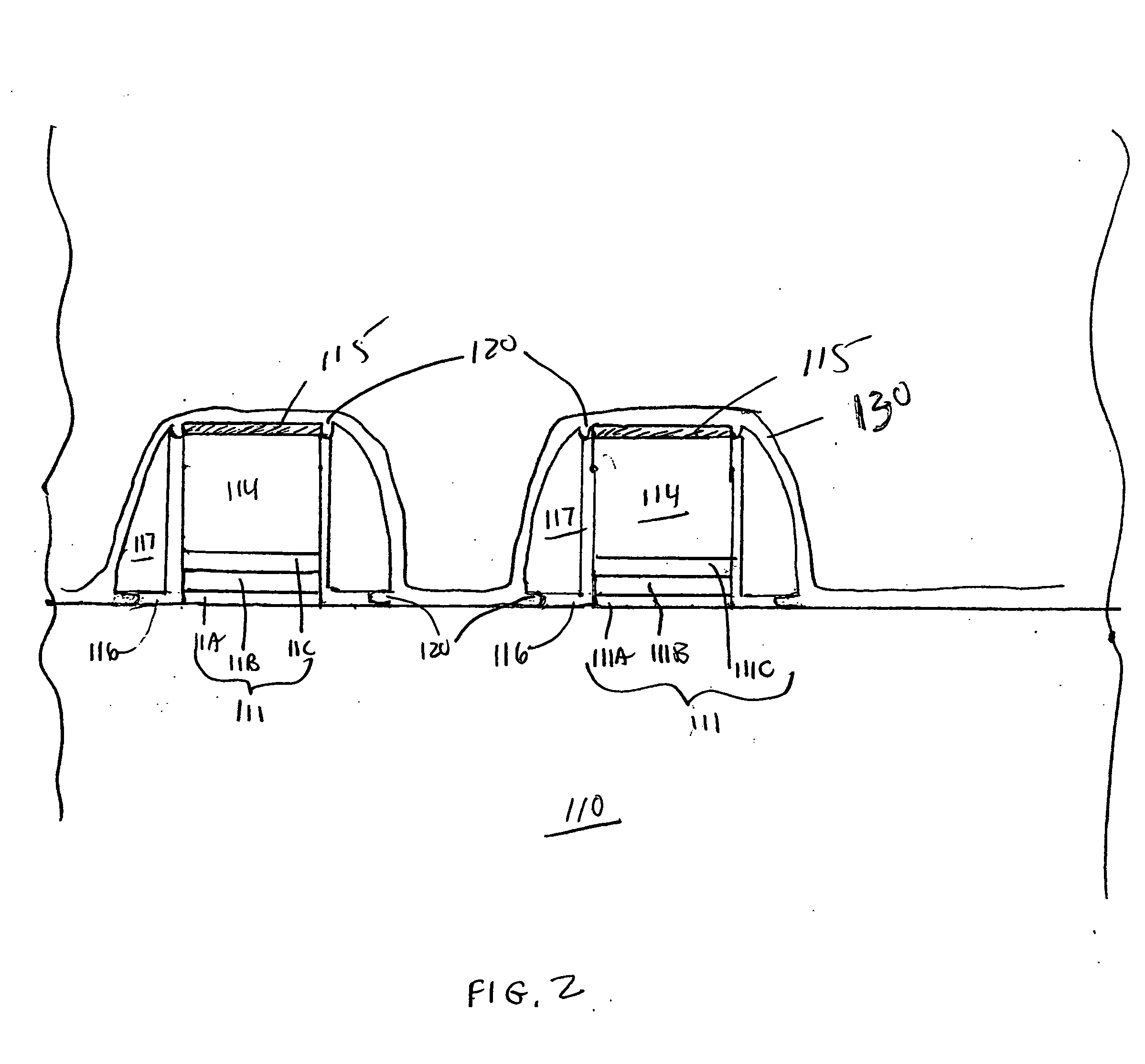

Nickel silicide including indium and a method of manufacture therefor

The present invention provides a semiconductor device, a method of manufacture therefore and a method for manufacturing an integrated circuit including the same. The semiconductor device, among other elements, may include a substrate (110), as well as a nickel silicide region (170) located over the substrate (110), the nickel silicide region (170) having an amount of indium located therein.

Owner:TEXAS INSTR INC

Method for forming self-aligned metal silicide contacts

InactiveUS20070254479A1Minimizes deleterious formation of residual materialReduce riskSemiconductor/solid-state device manufacturingEtchingPlatinum silicide

The present invention relates to a method for forming self-aligned metal silicide contacts over at least two silicon-containing semiconductor regions that are spaced apart from each other by an exposed dielectric region. Preferably, each of the self-aligned metal silicide contacts so formed comprises at least nickel silicide and platinum silicide with a substantially smooth surface, and the exposed dielectric region is essentially free of metal and metal silicide. More preferably, the method comprises the steps of nickel or nickel alloy deposition, low-temperature annealing, nickel etching, high-temperature annealing, and aqua regia etching.

Owner:TAIWAN SEMICON MFG CO LTD

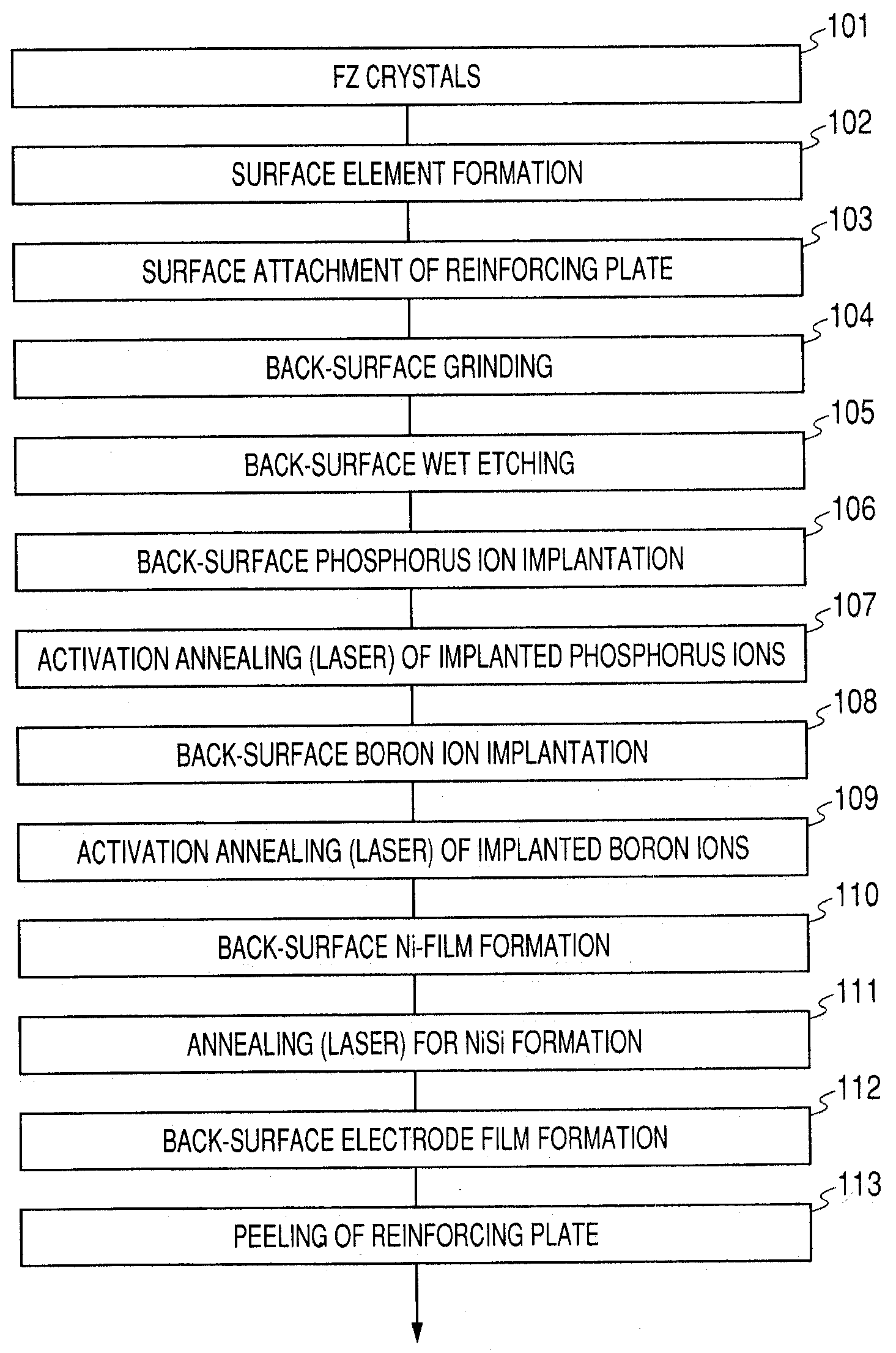

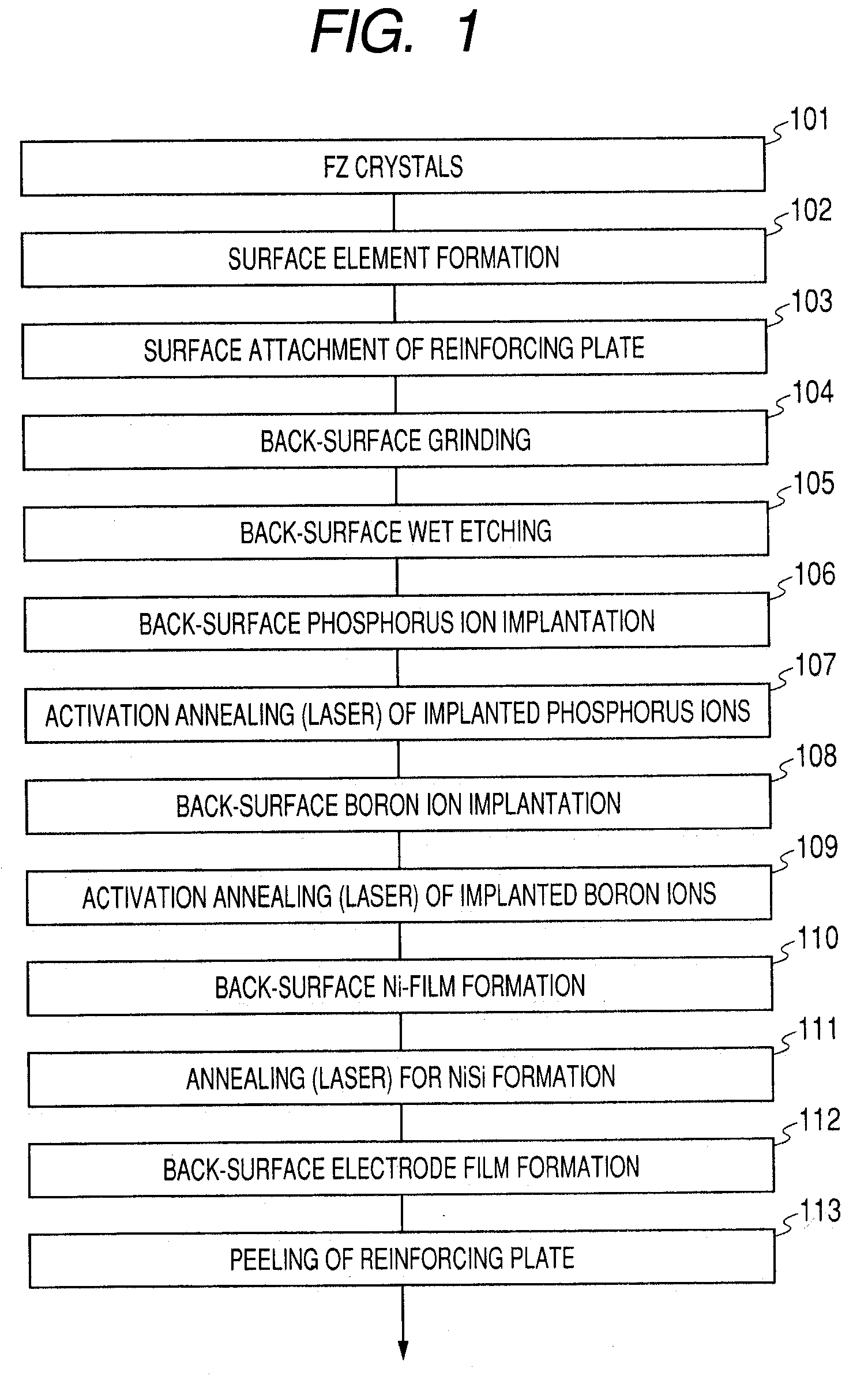

Manufacturing method of a semiconductor device

ActiveUS20080076238A1Improve breakdown voltageImprove switching characteristicsSemiconductor/solid-state device detailsSolid-state devicesOhmic contactGold film

Provided is a technology of carrying out activation annealing of n type impurity ions implanted for the formation of a field stop layer (n+ type semiconductor region) and activation annealing of p type impurity ions implanted for the formation of a collector region (p+ type semiconductor region) in separate steps to adjust an activation ratio of the n type impurity ions in the field stop layer to 60% or greater and an activation ratio of the p type impurity ions in the collector region to from 1 to 15%. This makes it possible to form an IGBT having a high breakdown voltage and high-speed switching characteristics. Moreover, use of a film stack made of nickel silicide, titanium, nickel and gold films for a collector electrode makes it possible to provide an ohmic contact with the collector region.

Owner:RENESAS ELECTRONICS CORP

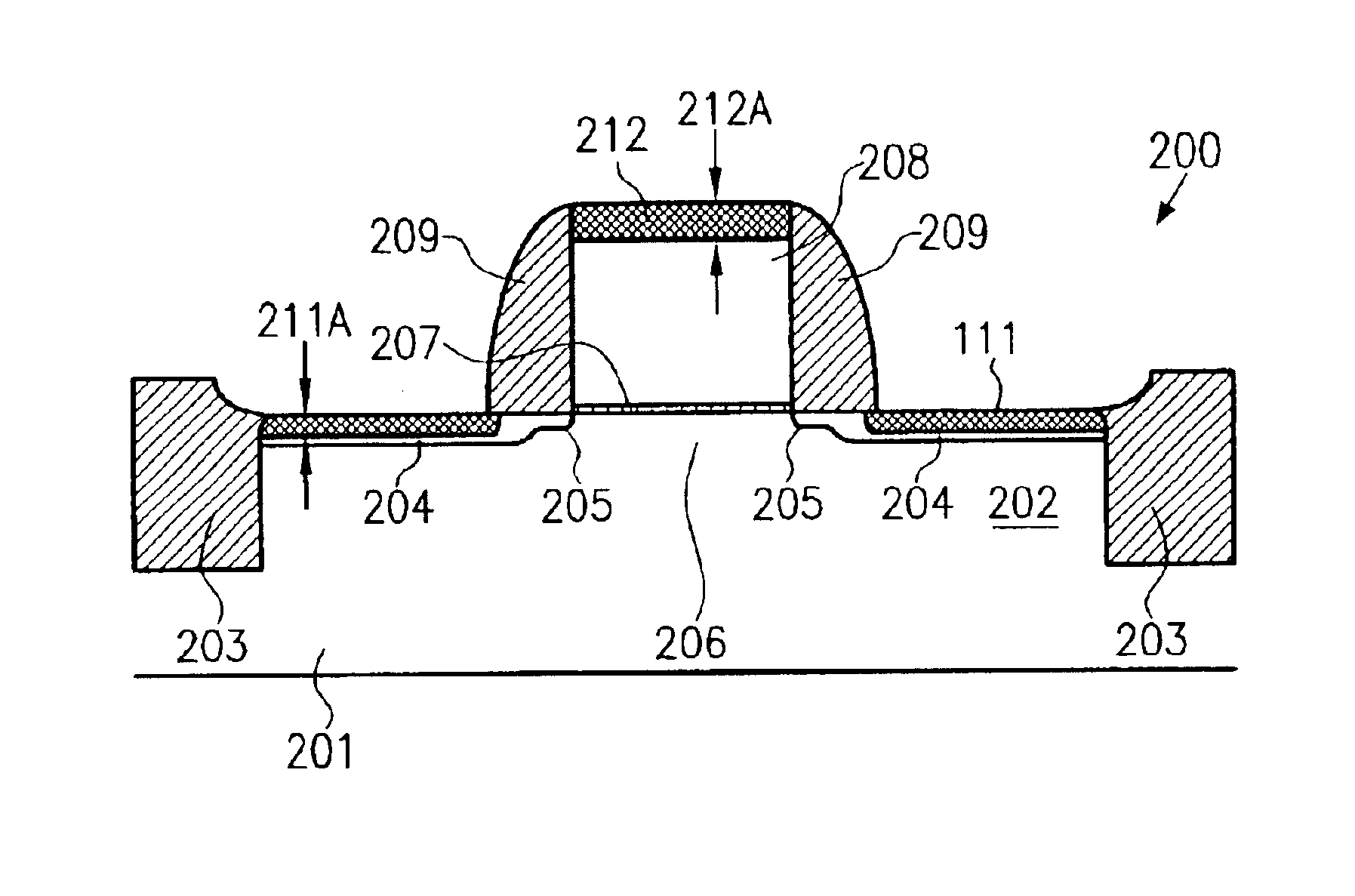

Semiconductor device and manufacturing method thereof

A semiconductor device includes: a P-type semiconductor layer formed in a surface region of a semiconductor substrate; a first gate insulating film formed on the P-type semiconductor layer; a first gate electrode; and a first source region and a first drain region formed in the P-type semiconductor layer to interpose a region under the first gate electrode in a direction of gate length. The first gate electrode includes: a first silicide film formed on the first gate insulating film and containing nickel silicide having a first composition ratio of nickel to silicon as a main component; a conductive film formed on the first silicide film; and a second silicide film formed on the conductive film and containing nickel silicide having a second composition ratio of nickel to silicon as a main component. The second composition ratio is larger than the first composition ratio.

Owner:KK TOSHIBA

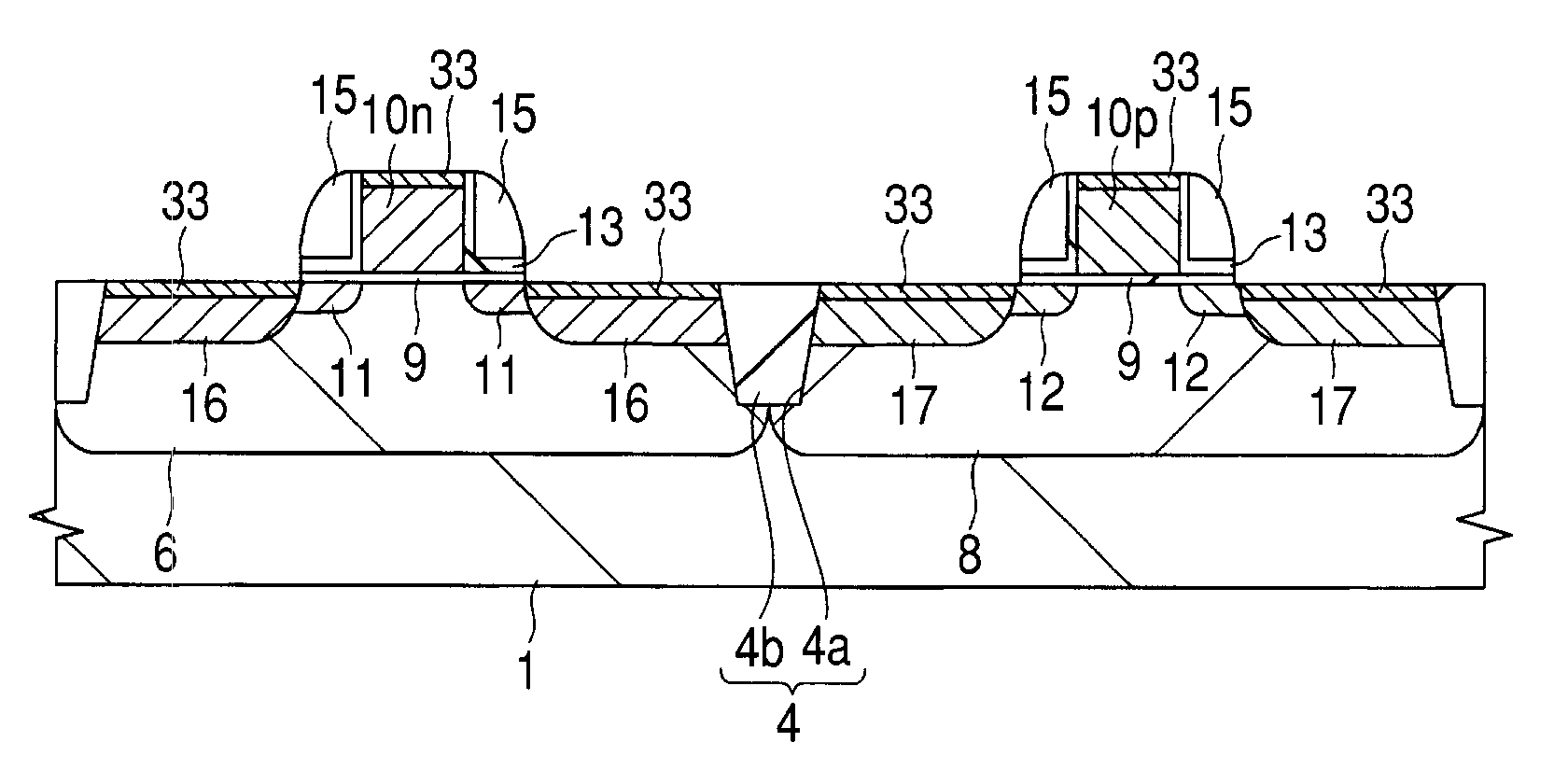

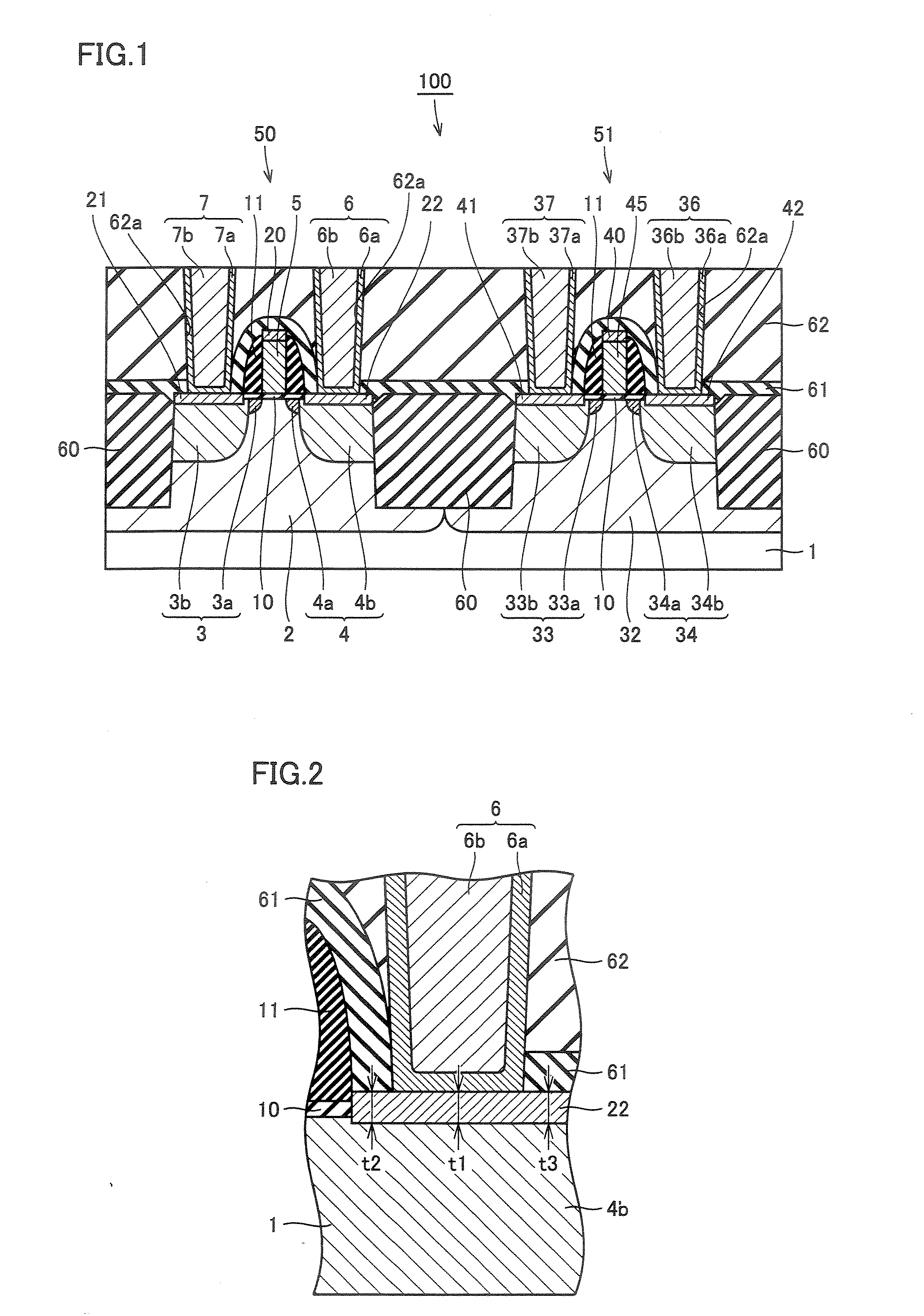

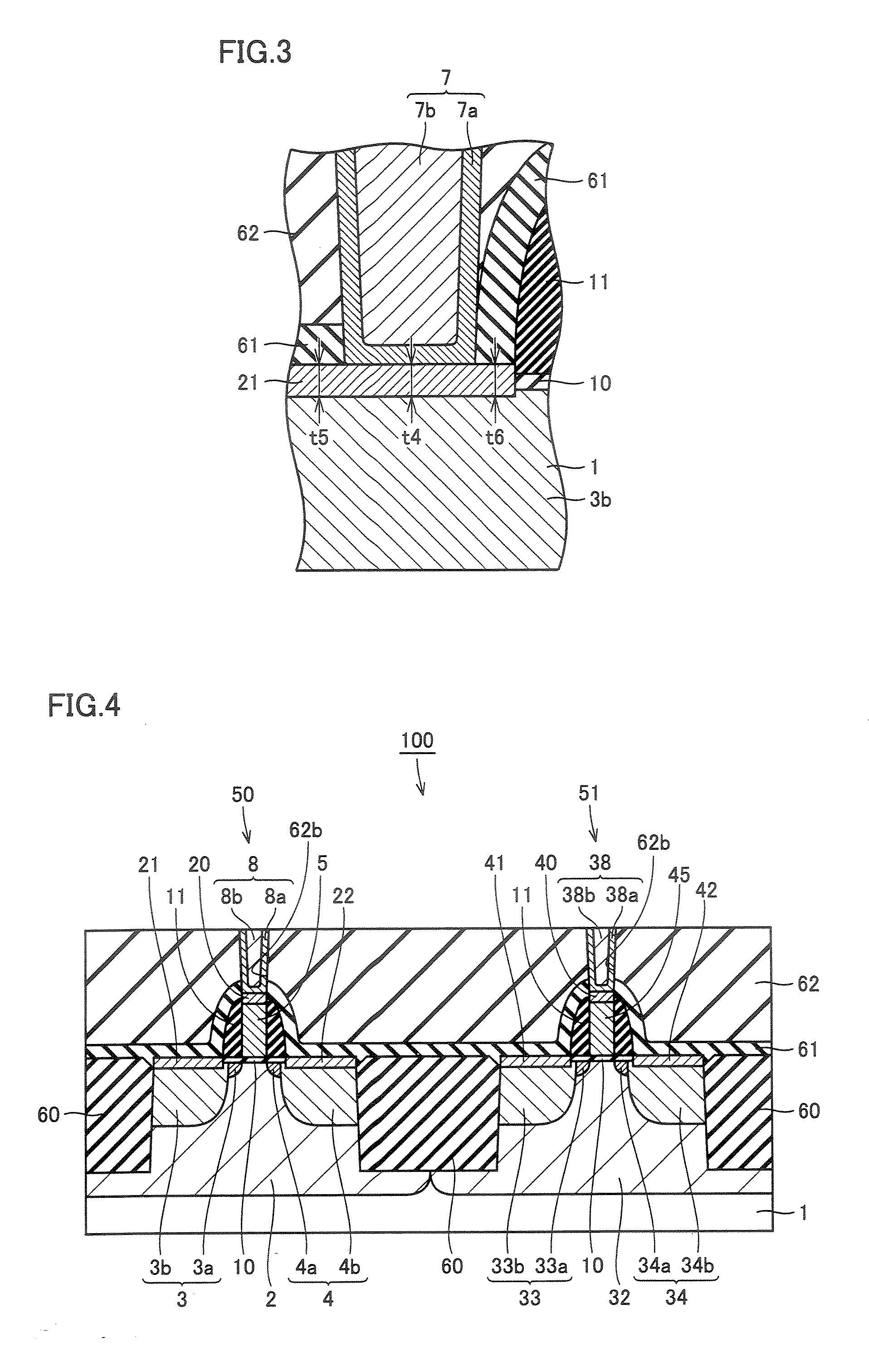

Semiconductor device and method of manufacturing the same

ActiveUS20070161218A1Uniform thicknessTransistorSemiconductor/solid-state device manufacturingSalicideHydrogen

A method of manufacturing a semiconductor device according to the present invention includes the steps of introducing first impurities of a first conductivity type into a main surface of a semiconductor substrate 1 to form a first impurity region, introducing second impurities of a second conductivity type to form a second impurity region, forming a first nickel silicide film on the first impurity region and forming a second nickel silicide film on the second impurity region, removing an oxide film formed on each of the first and second nickel silicide films by using a mixed gas having an NH3 gas and a gas containing a hydrogen element mixed therein, and forming a first conducting film on the first nickel silicide film and forming a second conducting film on the second nickel silicide film, with the oxide film removed.

Owner:RENESAS ELECTRONICS CORP

Method for Forming Ti Film and Tin Film, Contact Structure, Computer Readable Storing Medium and Computer Program

InactiveUS20070257372A1Reduce contact resistanceSuppress film peelingElectric discharge tubesSemiconductor/solid-state device detailsNickel silicideTin

A cleaning process is performed on the surface of a nickel silicide film serving as an underlayer. Then, a Ti film is formed to have a film thickness of not less than 2 nm but less than 10 nm by CVD using a Ti compound gas. Then, the Ti film is nitrided. Then, a TiN film is formed on the Ti film thus nitrided, by CVD using a Ti compound gas and a gas containing N and H.

Owner:TOKYO ELECTRON LTD

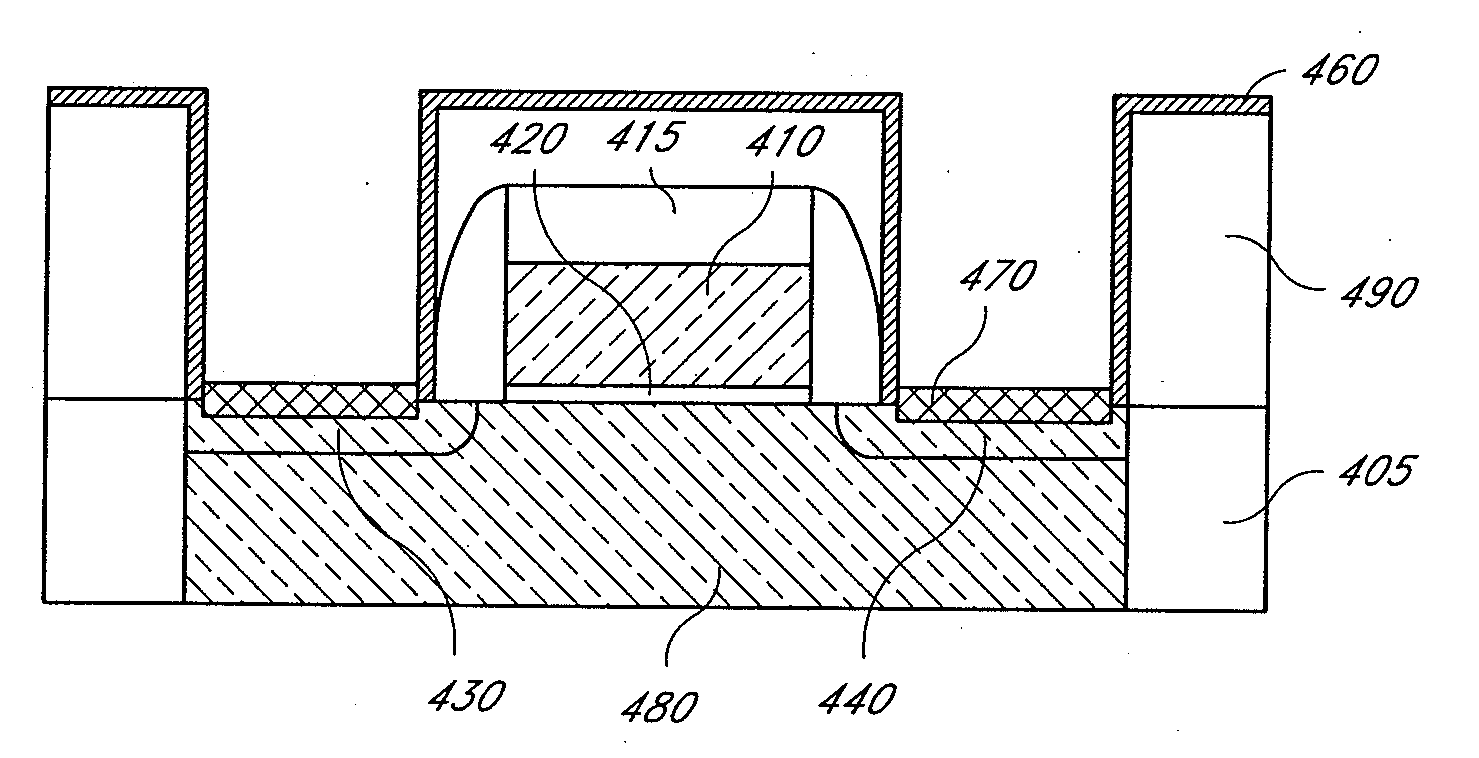

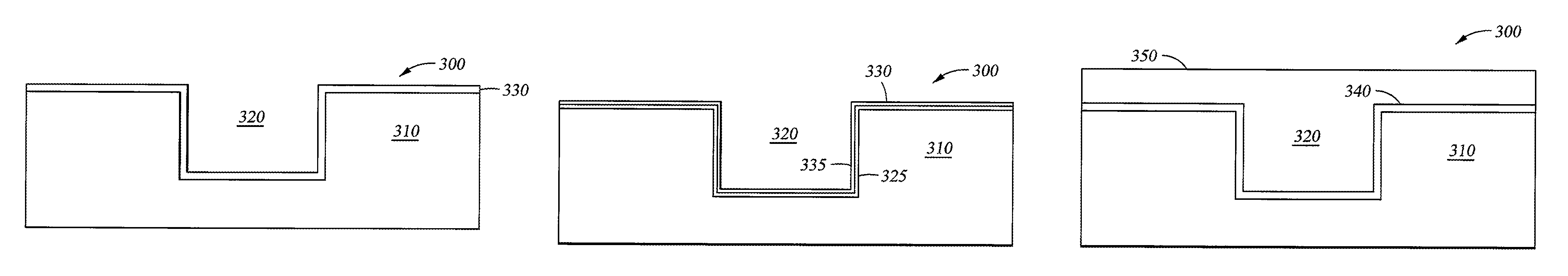

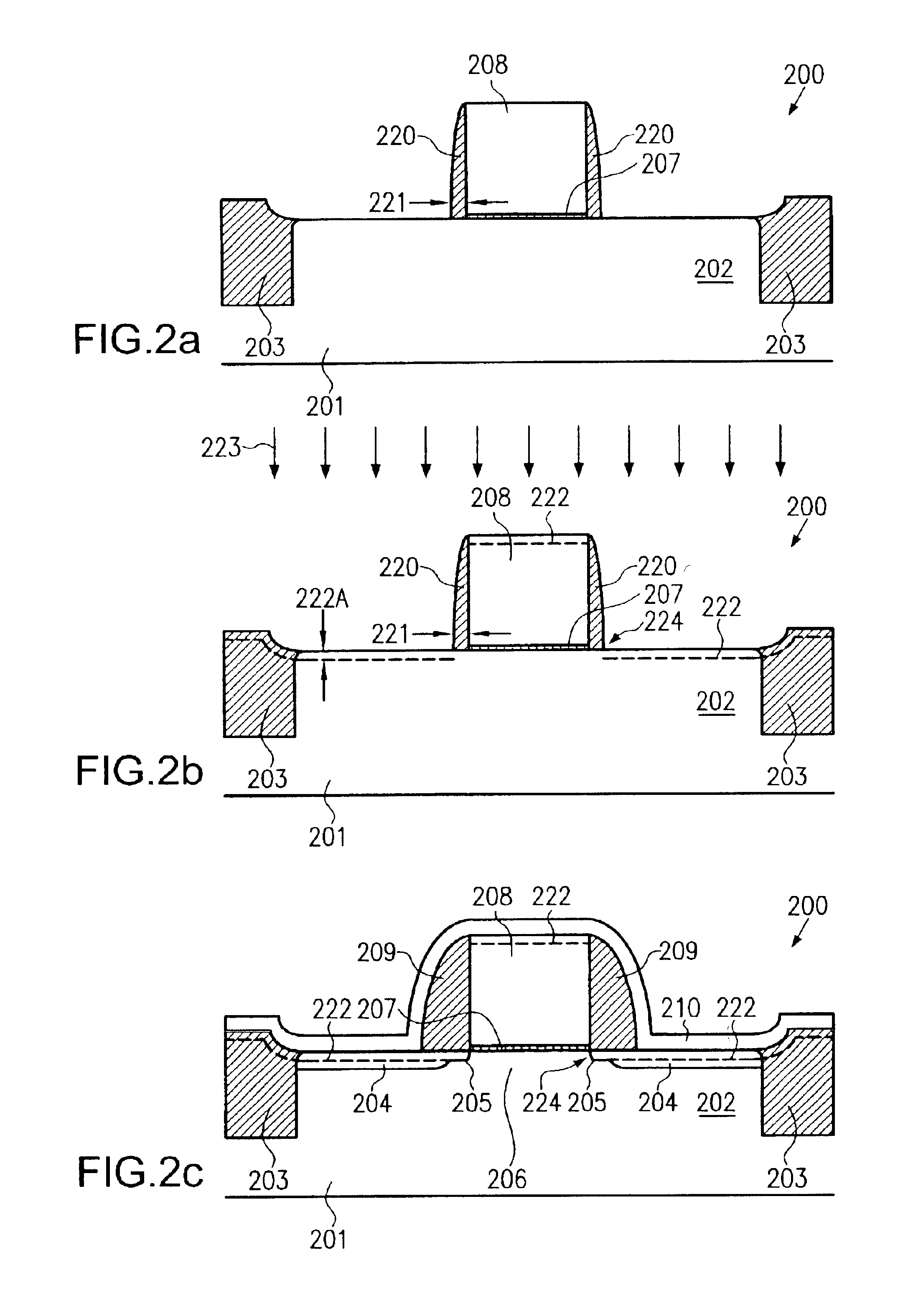

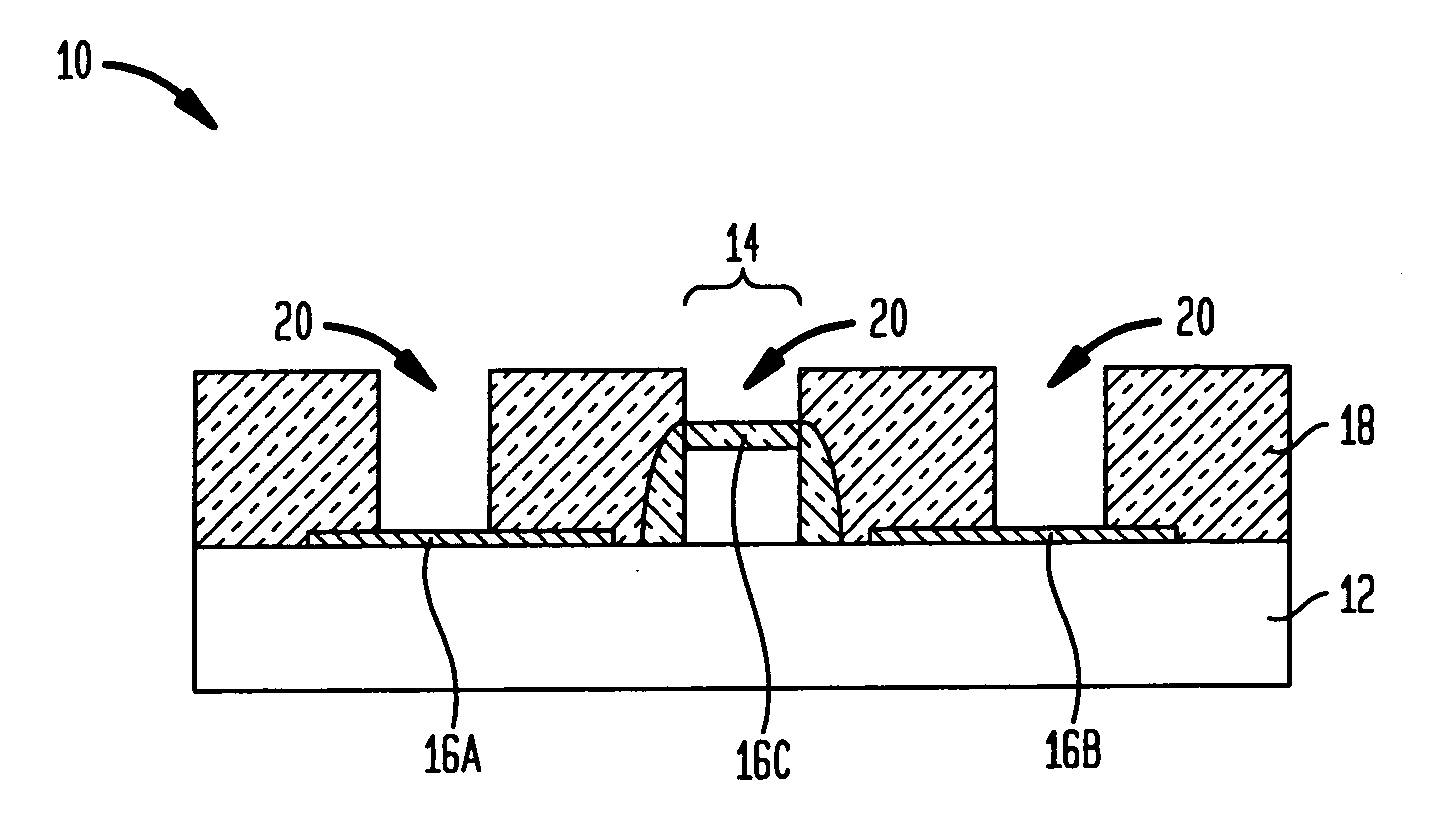

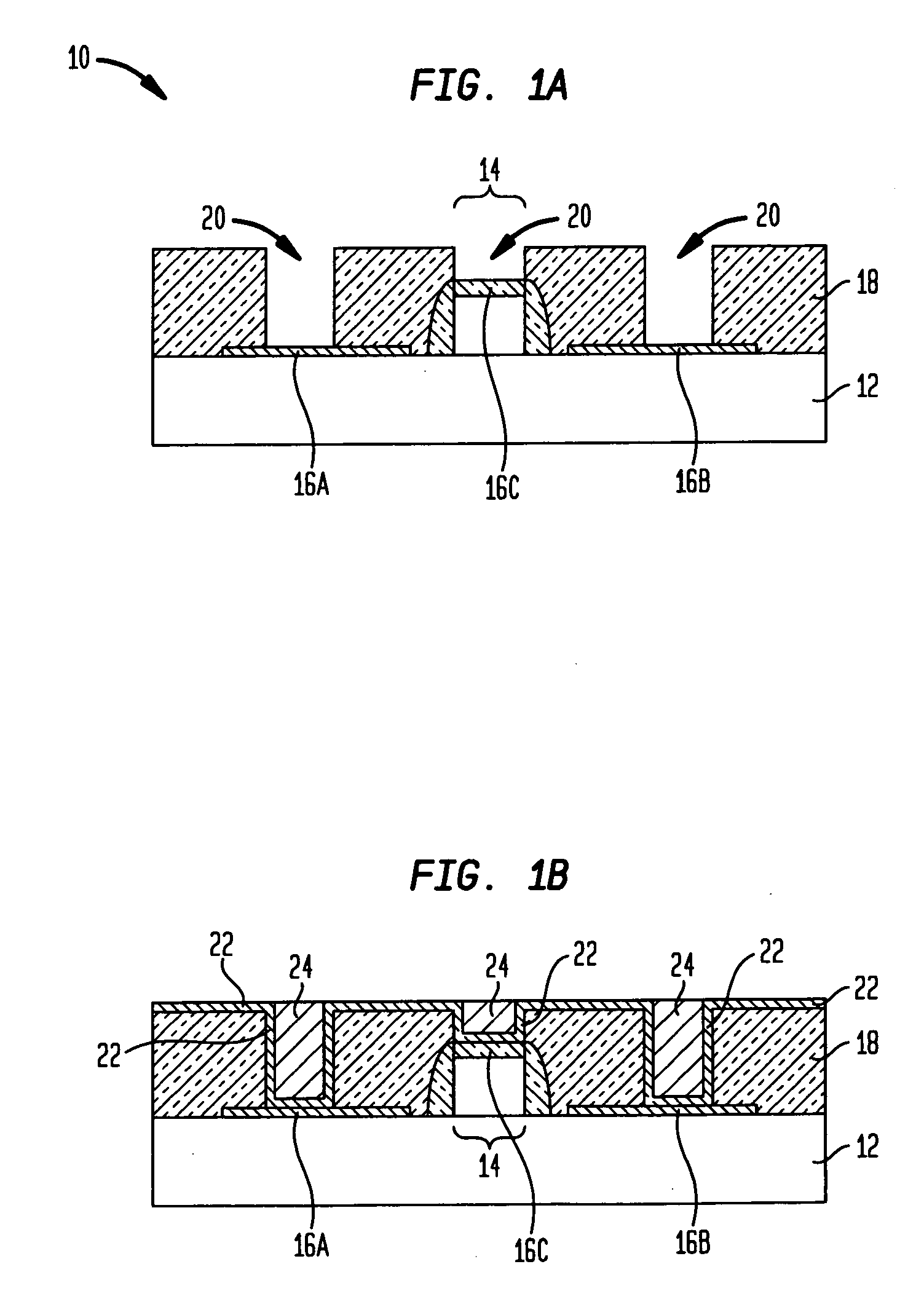

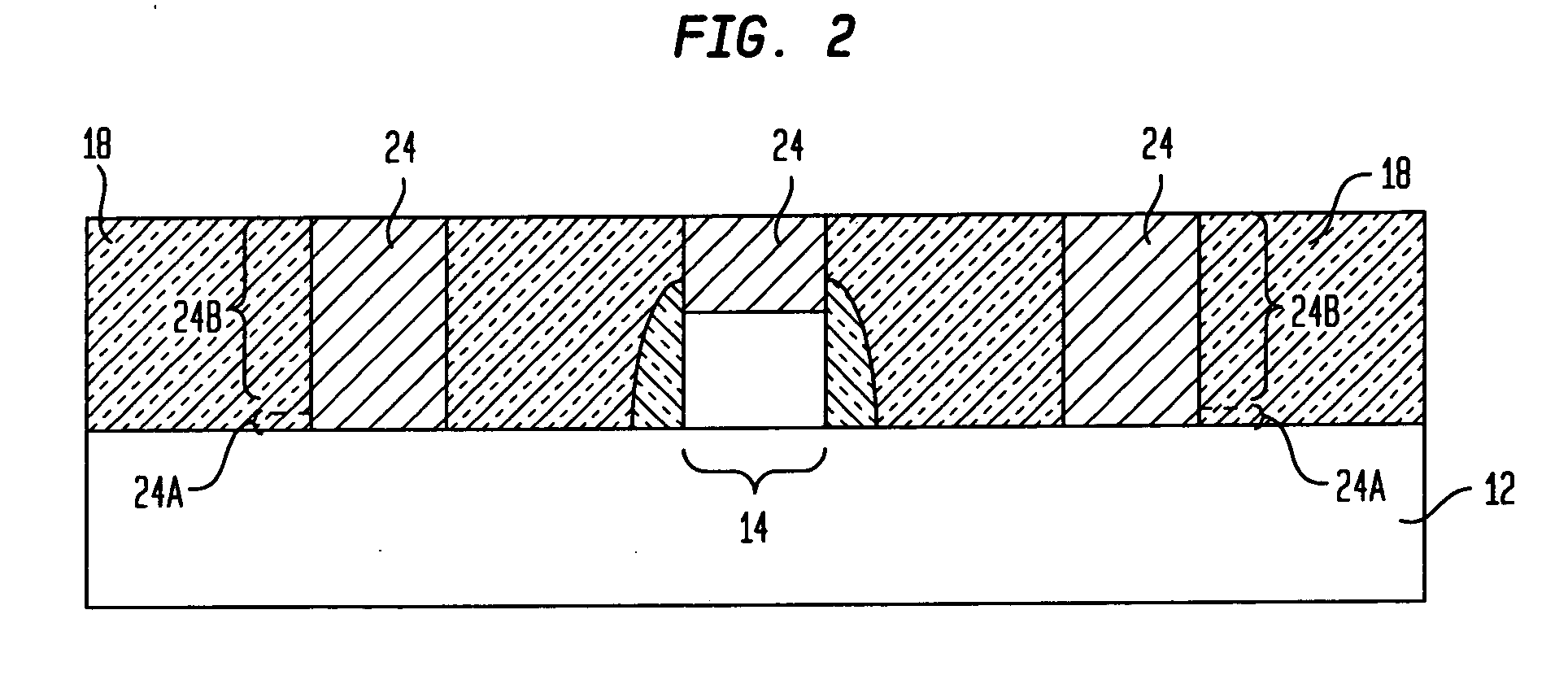

Conformal liner for gap-filling

InactiveUS20080096364A1Improve reliabilityIncrease productionSemiconductor/solid-state device manufacturingSilicon oxideAtomic layer deposition

Gap filling between features which are closely spaced is significantly improved by initially depositing a thin conformal layer followed by depositing a layer of gap filling dielectric material. Embodiments include depositing a thin conformal layer of silicon nitride or silicon oxide, as by atomic layer deposition or pulsed layer deposition, into the gap between adjacent gate electrode structures such that it flows into undercut regions of dielectric spacers on side surfaces of the gate electrode structures, and then depositing a layer of BPSG or P-HDP oxide on the thin conformal layer into the gap. Embodiments further include depositing the layers at a temperature less than 430° C., as by depositing a P-HDP oxide after depositing the conformal liner when the gate electrode structures include a layer of nickel silicide.

Owner:GLOBALFOUNDRIES INC +1

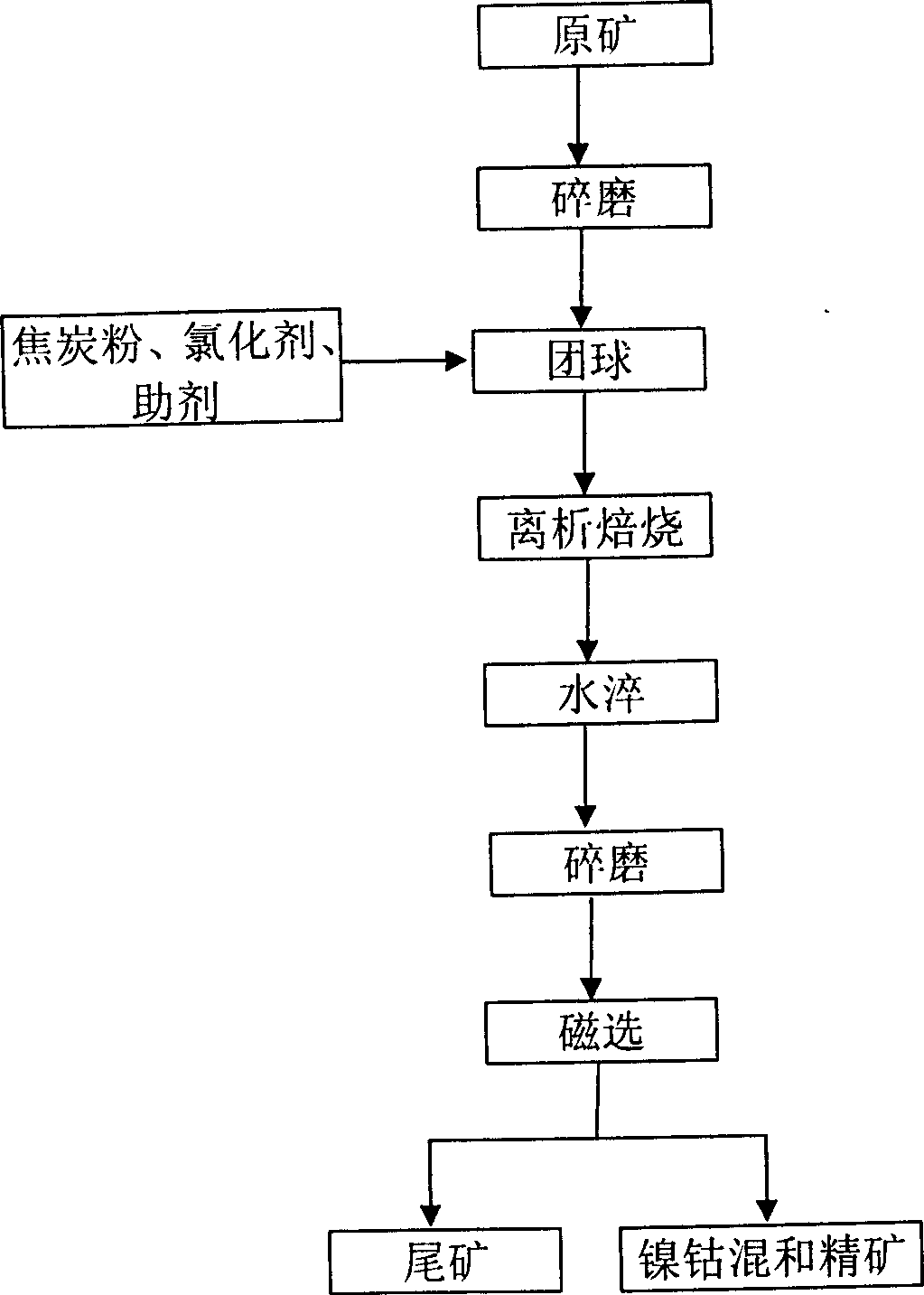

Method for recovering nickel and cobalt from nickel oxide ore and nickel silicide ore

InactiveCN1827799ASimple processShort investment cycleProcess efficiency improvementMagnetic separationSilicic acidCobalt

The invention relates the reclaiming nickel-to-cobalt method from nickel oxide ore and silicic acid nickel ore, comprising the following steps: milling the nickel oxide ore and silicic acid nickel ore to -200 mesh, adding 5-15% coke breeze, 10-30% chloration agent, and 0.1-1.0% adjuvant to make 5-15mm pellet, adopting chloridising separating and roasting, controlling the high temperature of rotary kiln at 1000-1300Deg.C and back kiln at 400-600Deg.C, the rotation rate of rotary kiln being 0.75-2 revolution per minute, time being 1-2 hours, then putting the product into magnet separator whose magnetic density is 1500-3000G, finally getting the cobalt-nickel ore, whose nickel grade is 5-15%, and recovery ratio is 80-85%, and whose cobalt grade is 0.3-1.7%, and recovery ratio is 70-80%.

Owner:KUNMING UNIV OF SCI & TECH +1

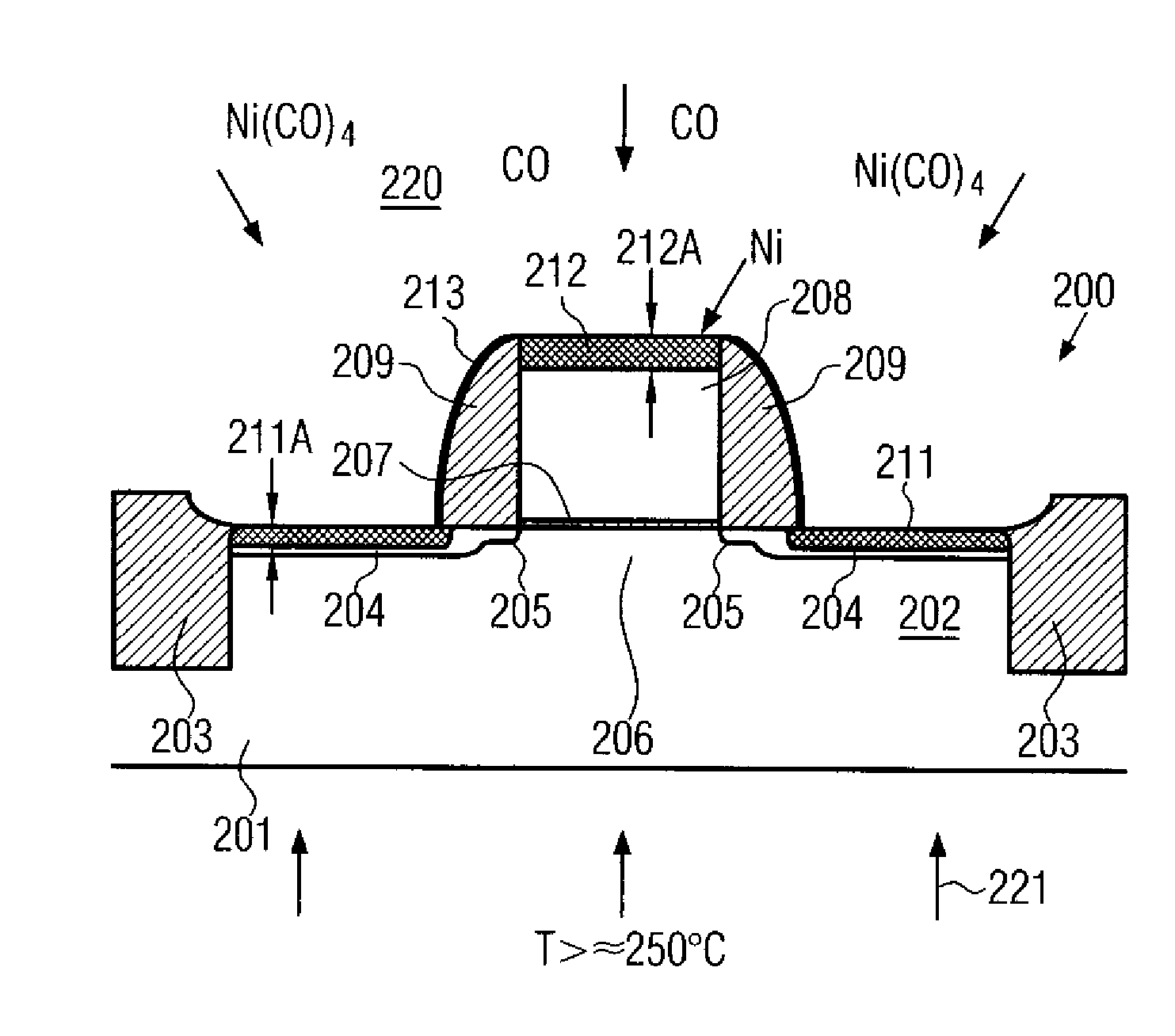

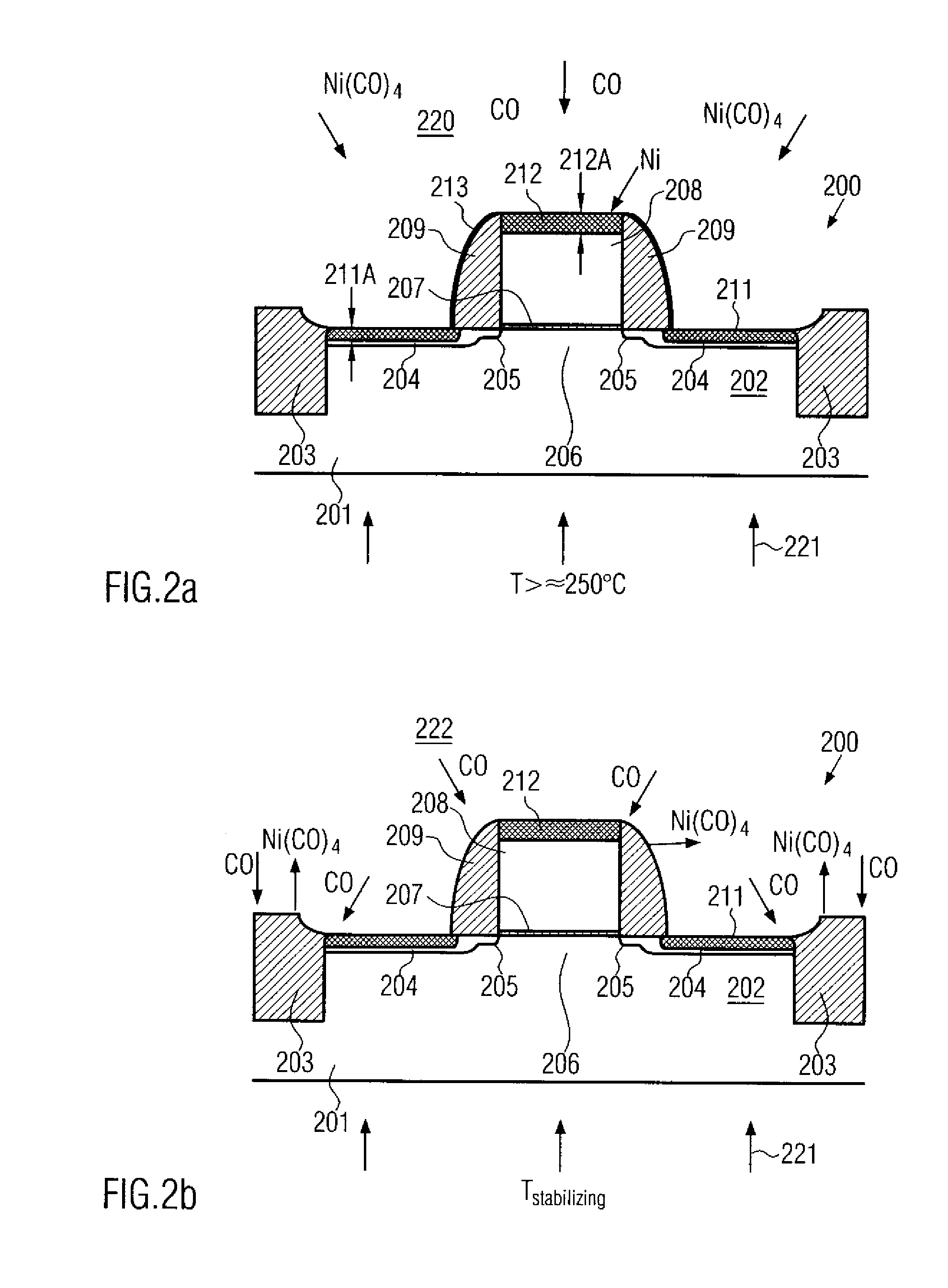

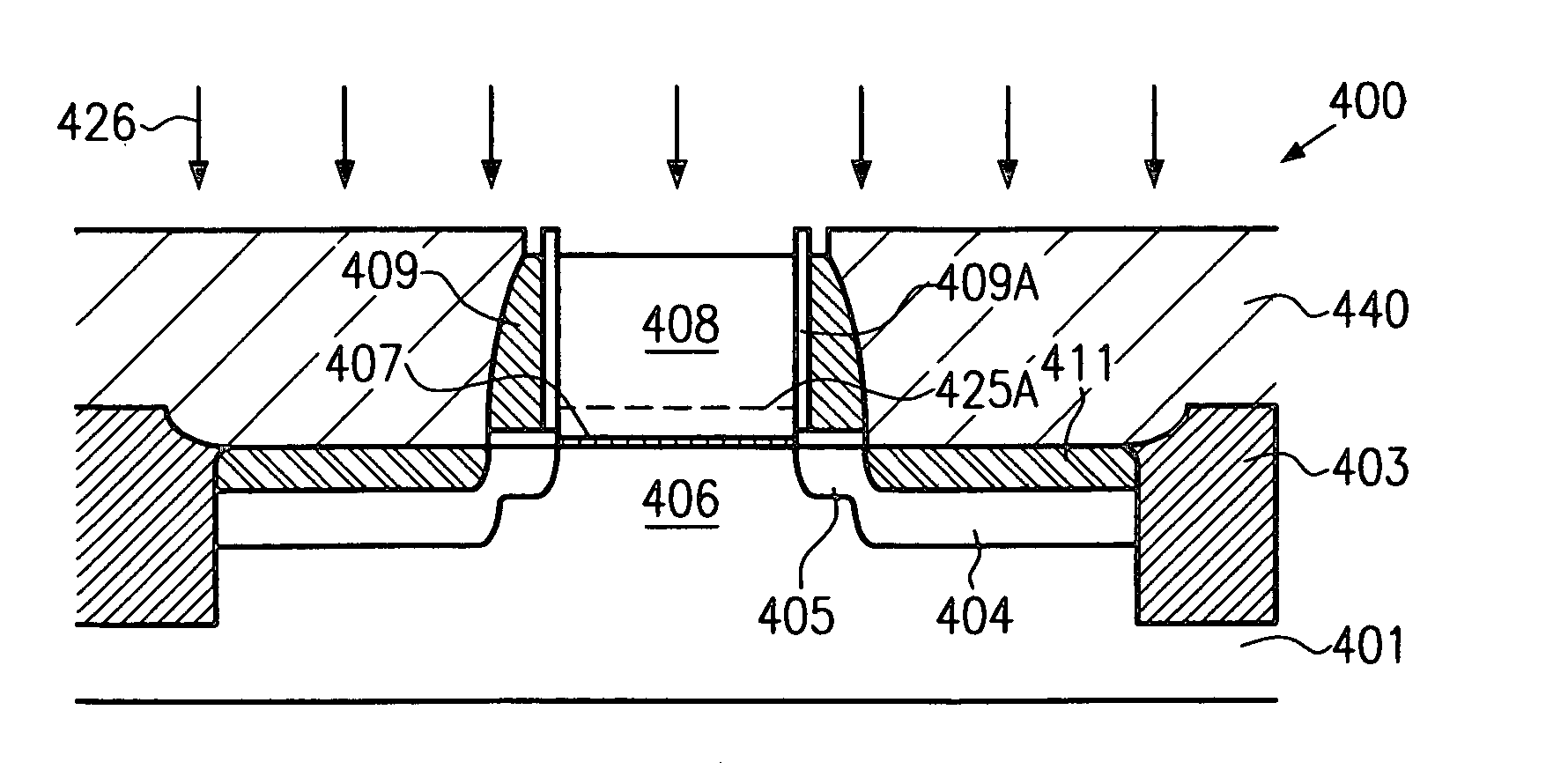

Technique for forming nickel silicide by depositing nickel from a gaseous precursor

Nickel silicide is formed on the basis of a gaseous precursor, such as nickel tetra carbonyl, wherein the equilibrium of the decomposition of this gas may be controlled to obtain a highly selective nickel silicide formation rate. Moreover, any etch step for removing excess nickel may be avoided, since only minute amounts of nickel may form on exposed surfaces, which may then be effectively removed by correspondingly shifting the equilibrium. Consequently, reduced process complexity, enhanced controllability and enhanced tool lifetime may be obtained.

Owner:ADVANCED MICRO DEVICES INC

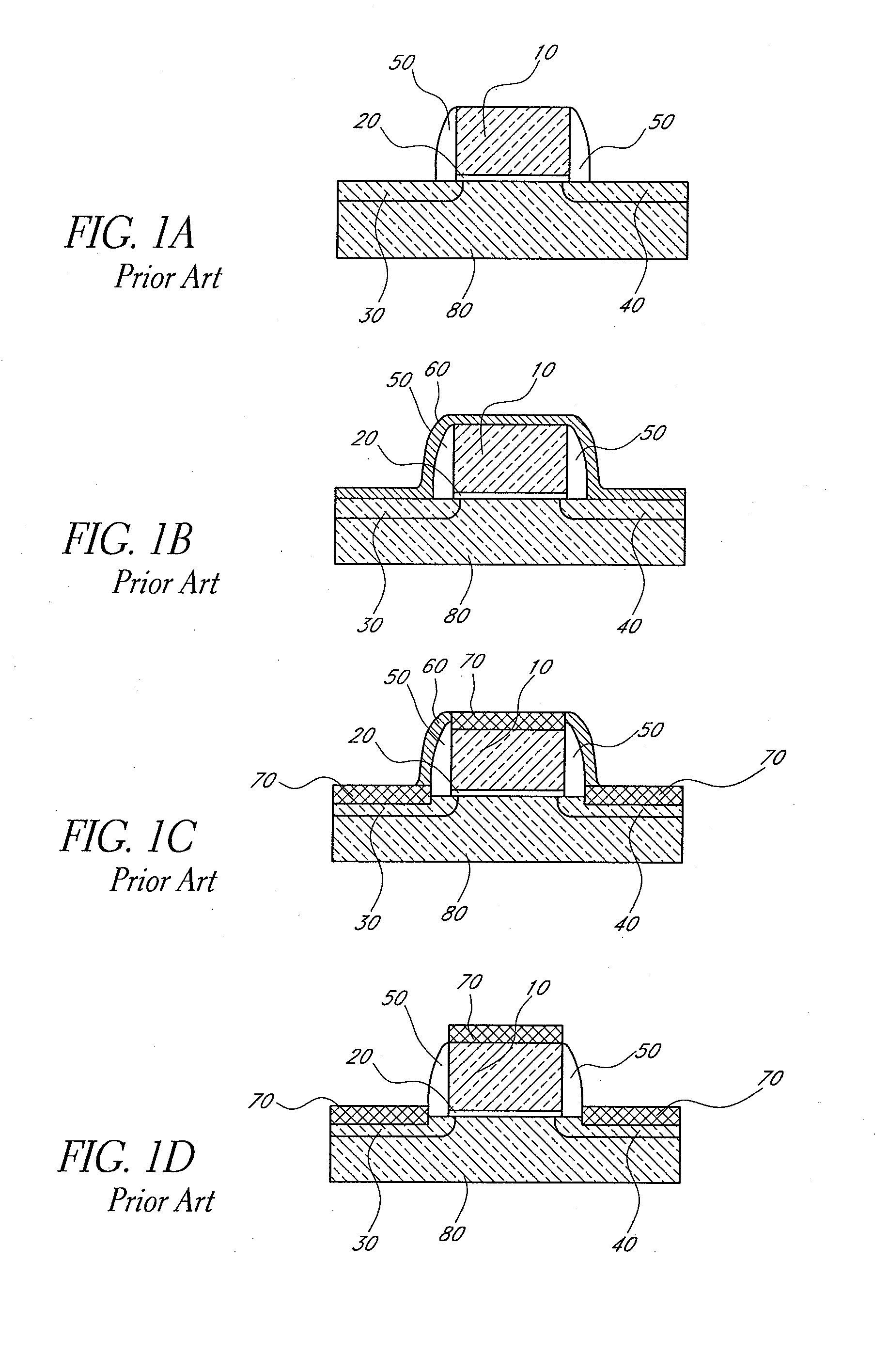

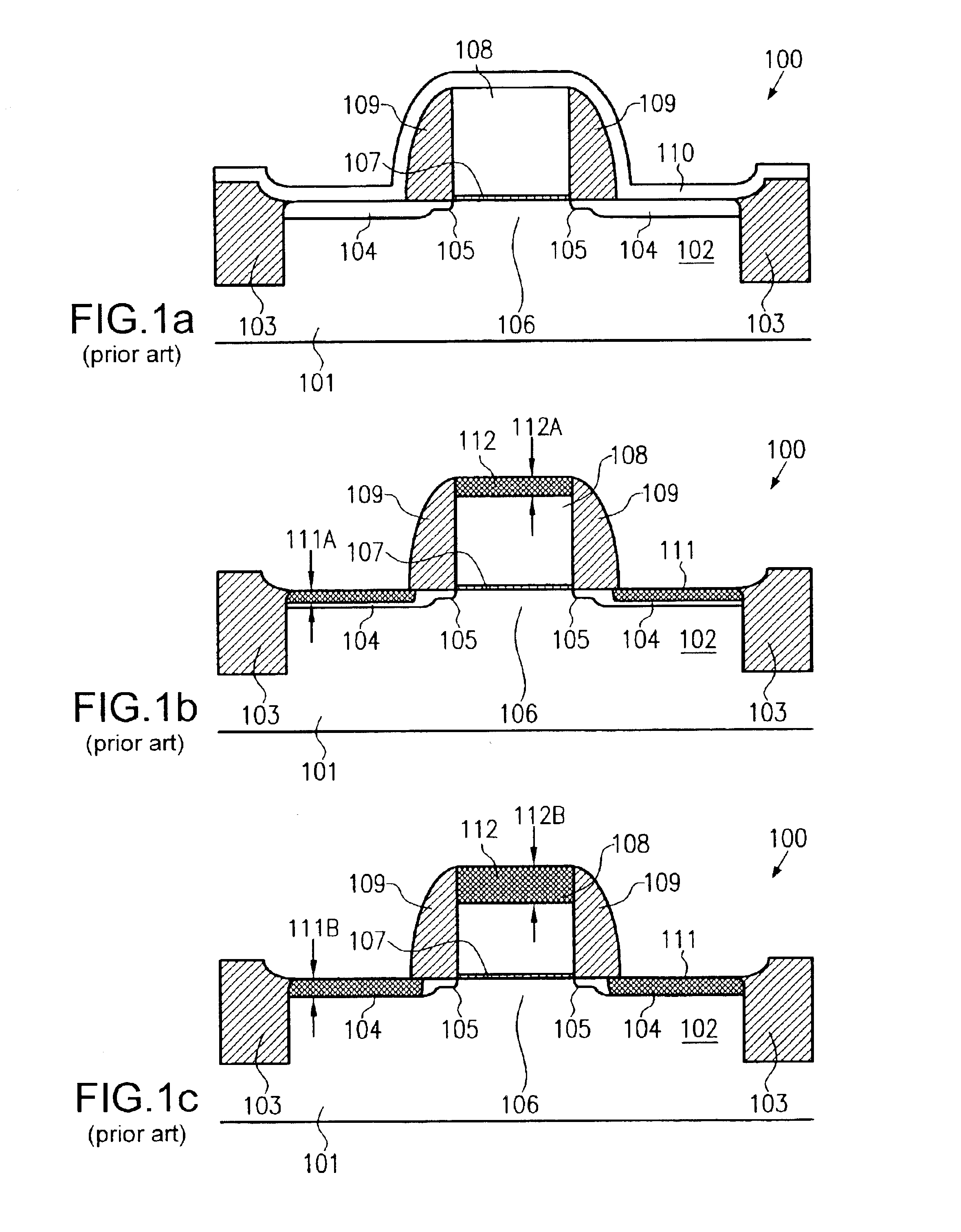

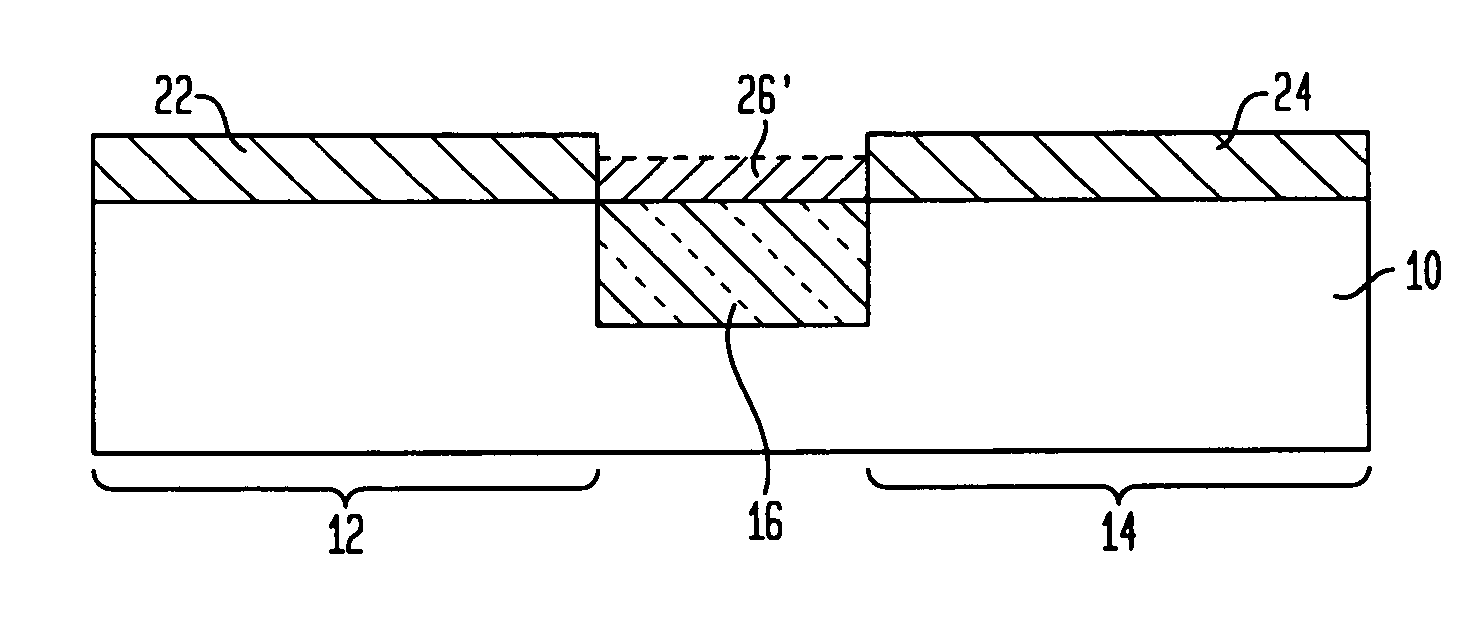

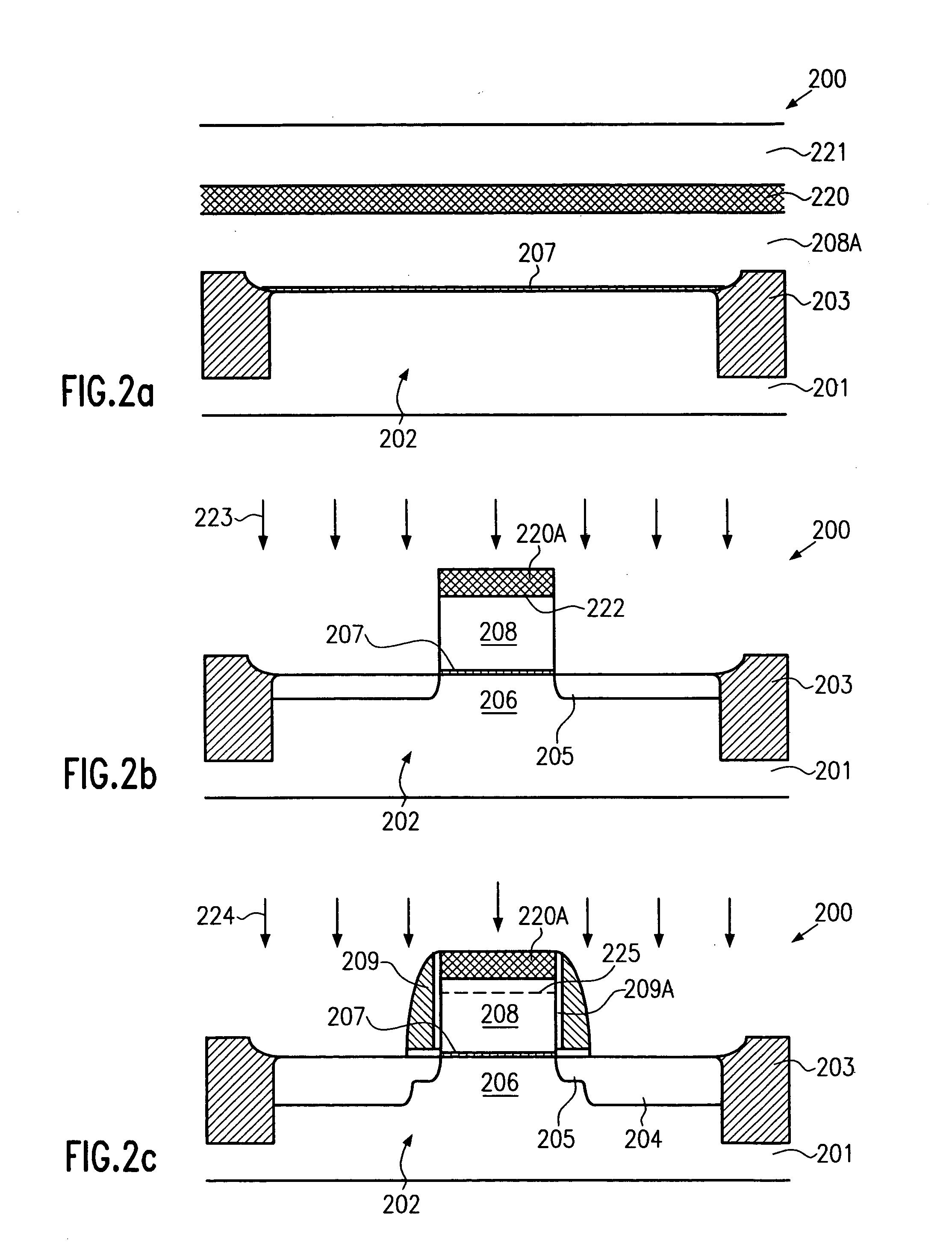

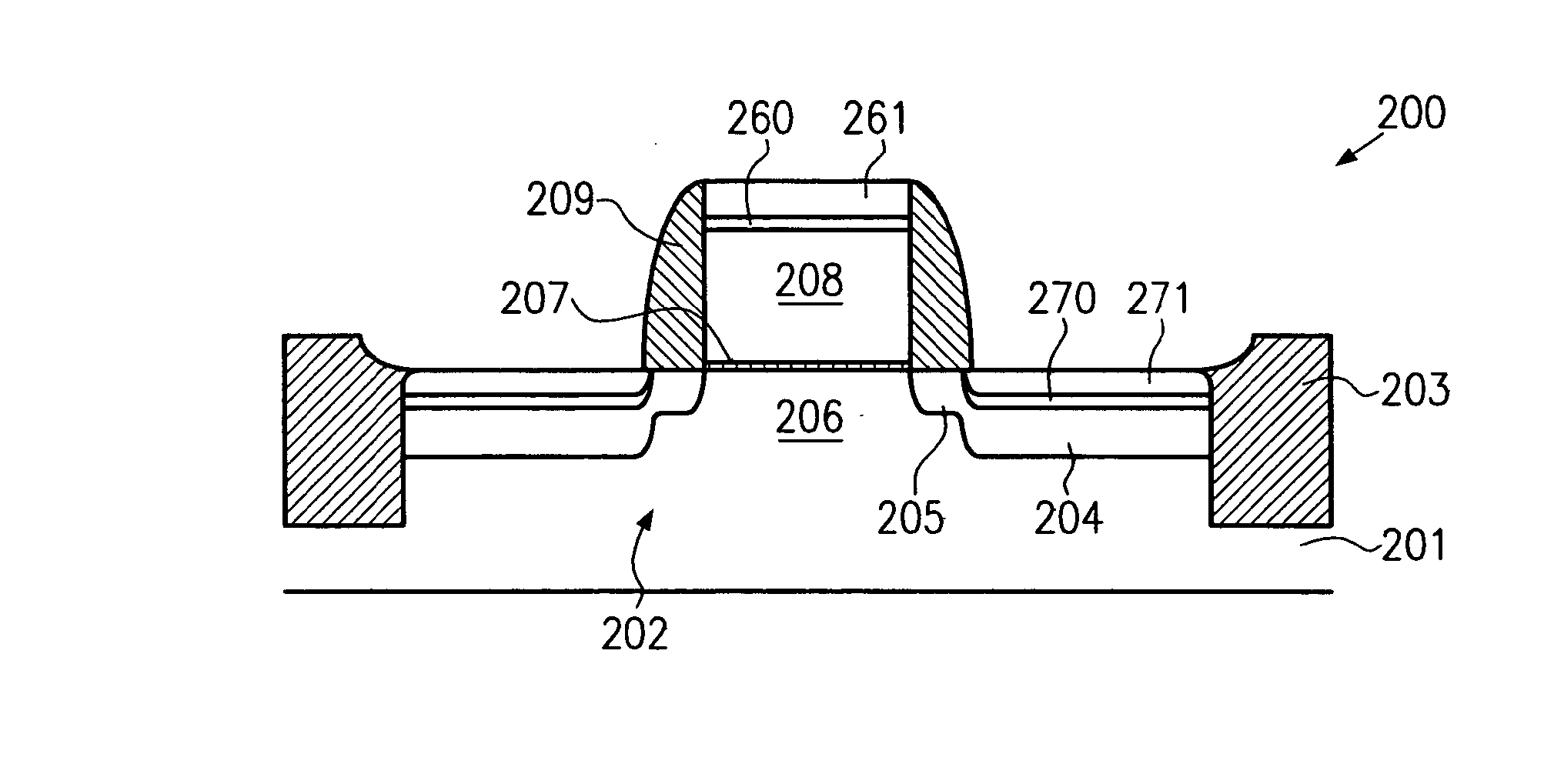

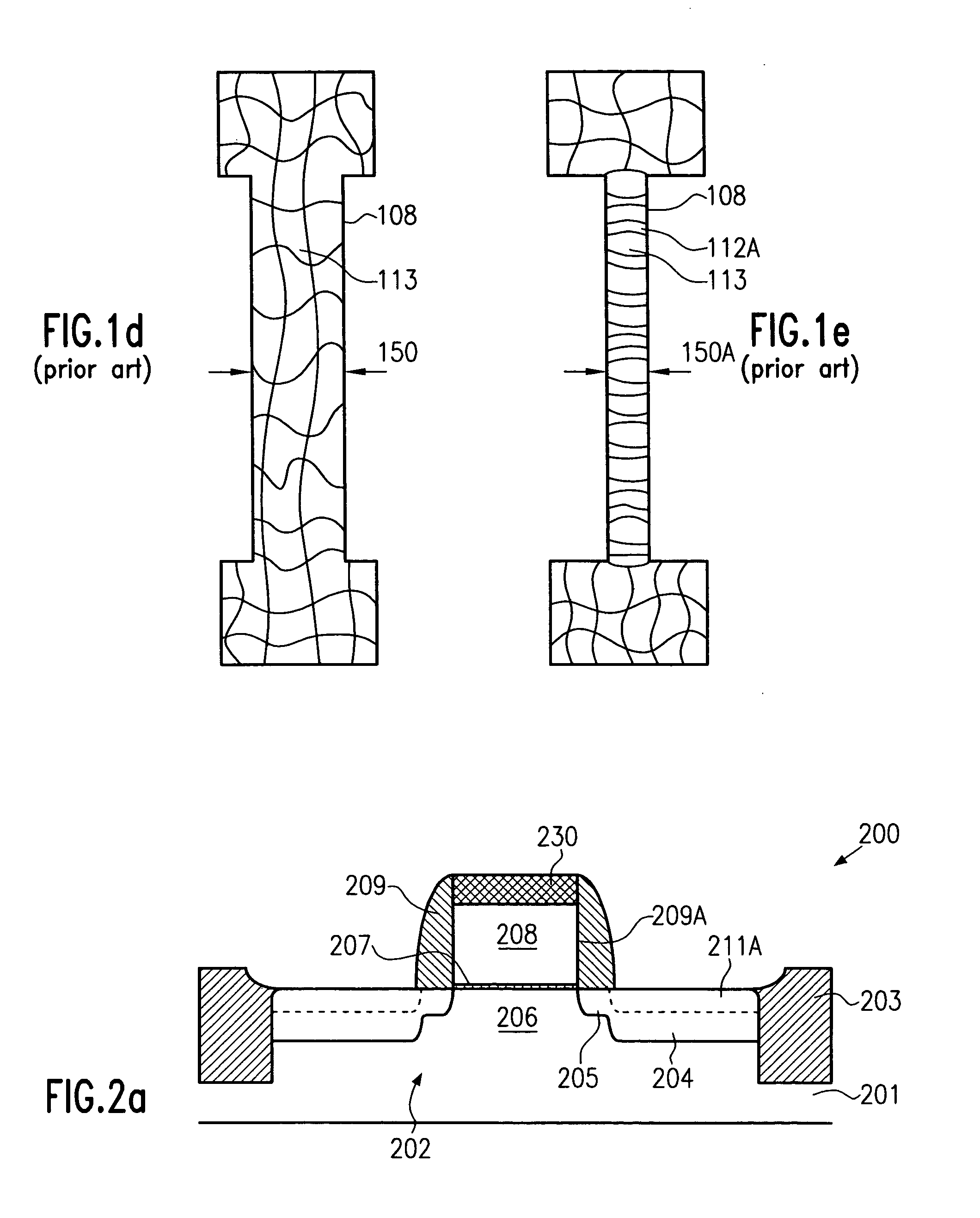

Polysilicon line having a metal silicide region enabling linewidth scaling

ActiveUS20050026379A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantMetal silicide

By maintaining the gate electrode covered during the process flow for forming metal silicide regions in the drain and source of a field effect transistor, an appropriate metal silicide may be formed on the gate electrode which meets the requirement for aggressive gate length scaling. Preferably, a nickel silicide is formed on the gate electrode, whereas the drain and source regions receive the well-established cobalt disilicide. Additionally, the gate electrode dopant profile is effectively decoupled from the drain and source dopant profile.

Owner:ADVANCED MICRO DEVICES INC

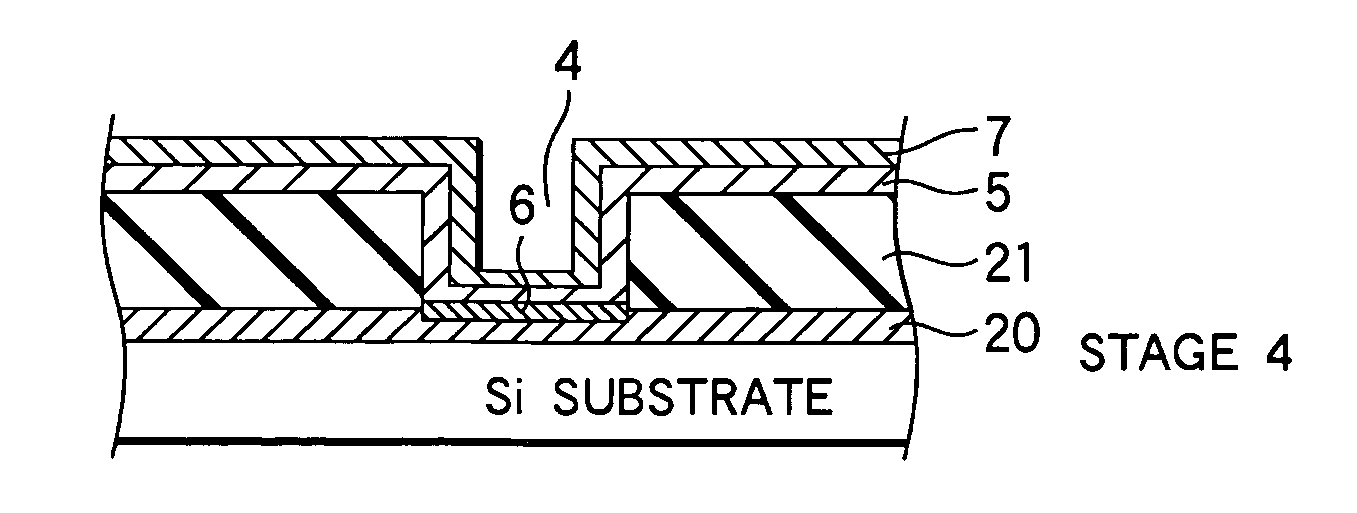

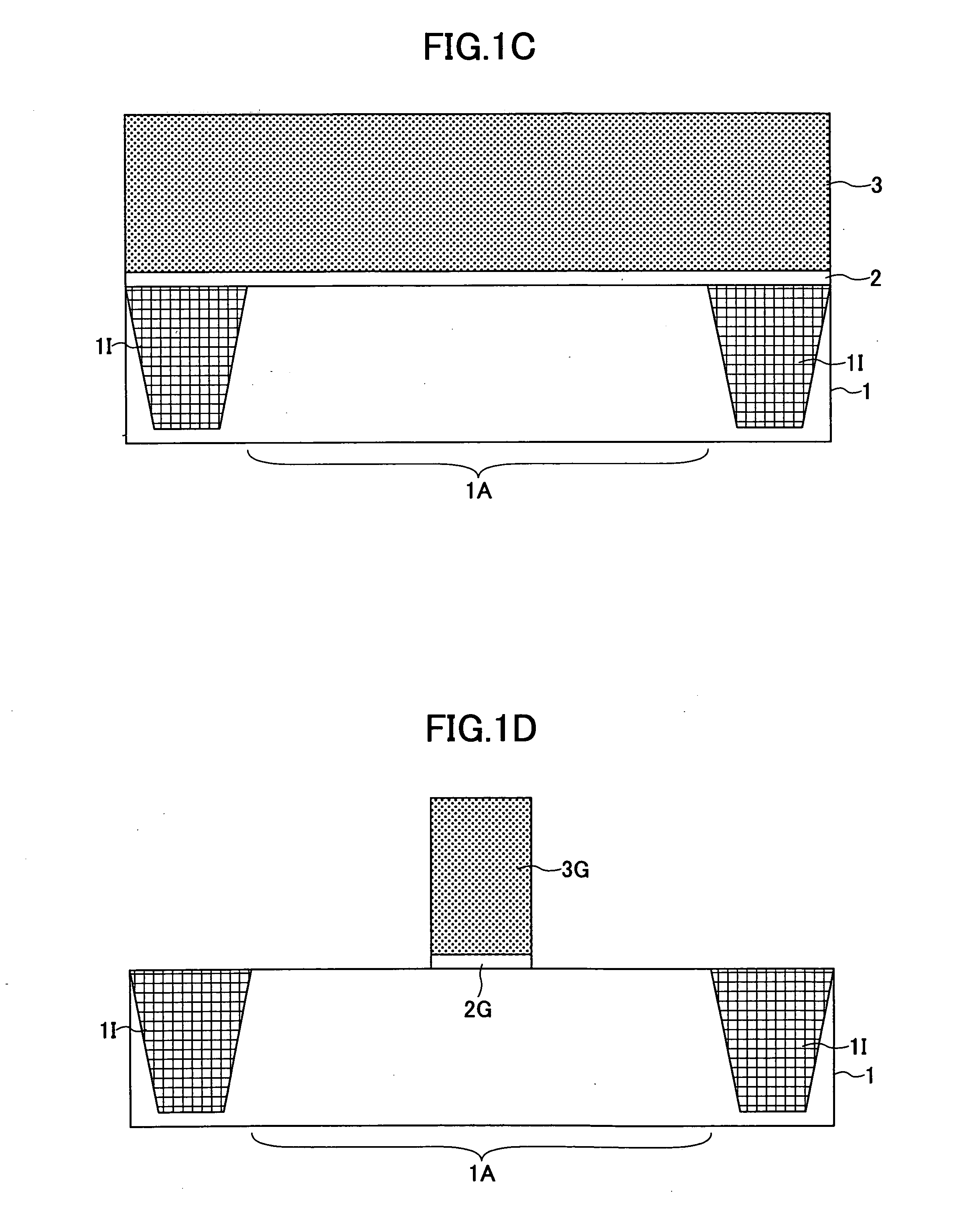

Method of manufacturing a semiconductor device

ActiveUS20090191707A1Lower resistanceImprove production yieldTransistorSemiconductor/solid-state device detailsPlatinumMetal silicide

To provide a technique capable of improving the reliability of a semiconductor element and its product yield by reducing the variations in the electrical characteristic of a metal silicide layer. After forming a nickel-platinum alloy film over a semiconductor substrate 1, by carrying out a first thermal treatment at a thermal treatment temperature of 210 to 310° C. using a heater heating device, the technique causes the nickel-platinum alloy film and silicon to react with each other to form a platinum-added nickel silicide layer in a (PtNi)2Si phase. Subsequently, after removing the unreacted nickel-platinum alloy film, the technique carries out a second thermal treatment having the thermal treatment temperature higher than that of the first thermal treatment to form the platinum-added nickel silicide layer in a PtNiSi phase. The temperature rise rate of the first thermal treatment is set to 10° C. / s or more (for example, 30 to 250° C. / s) and the temperature rise rate of the second thermal treatment is set to 10° C. / s or more (for example, 10 to 250° C. / s).

Owner:RENESAS ELECTRONICS CORP

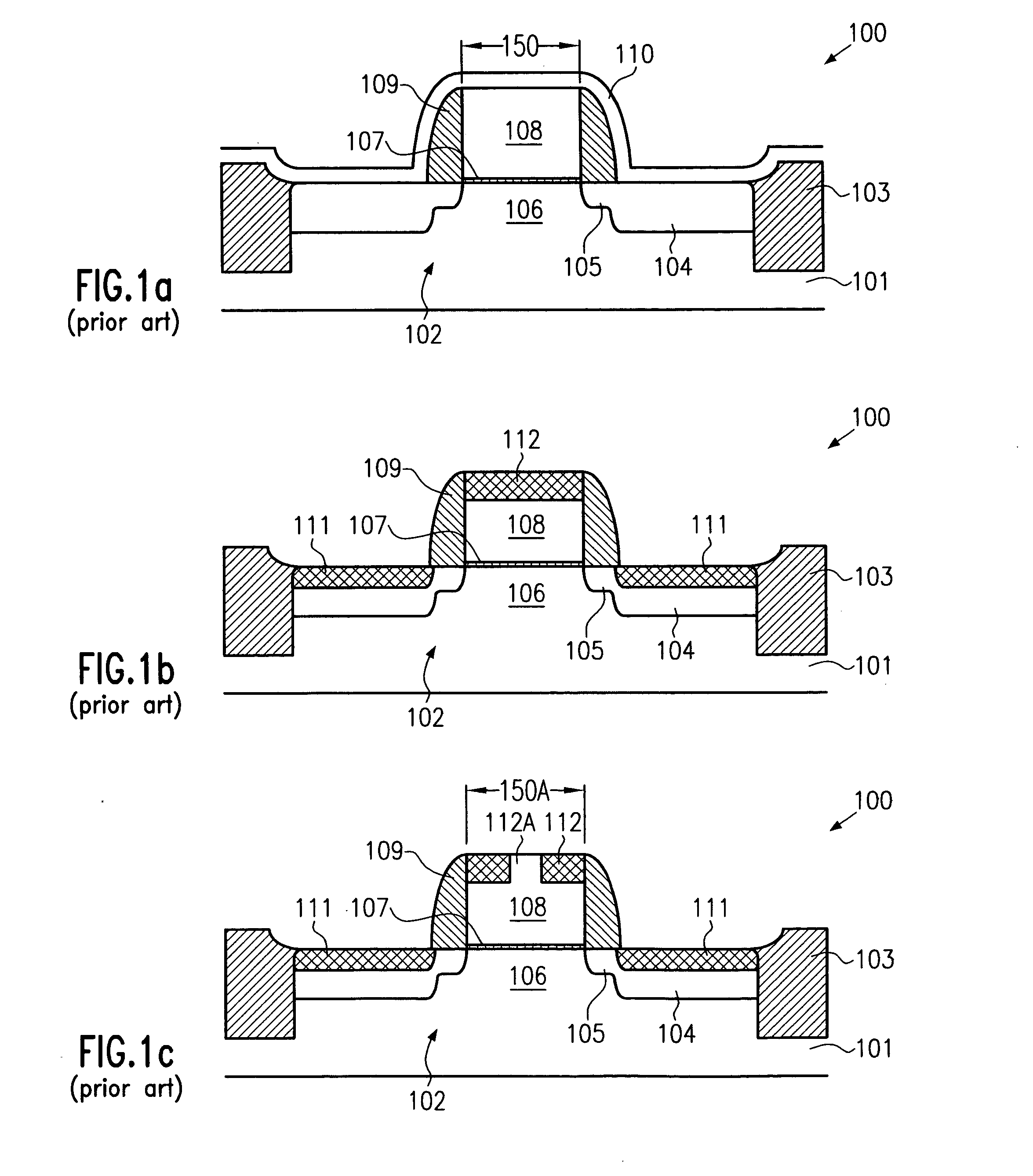

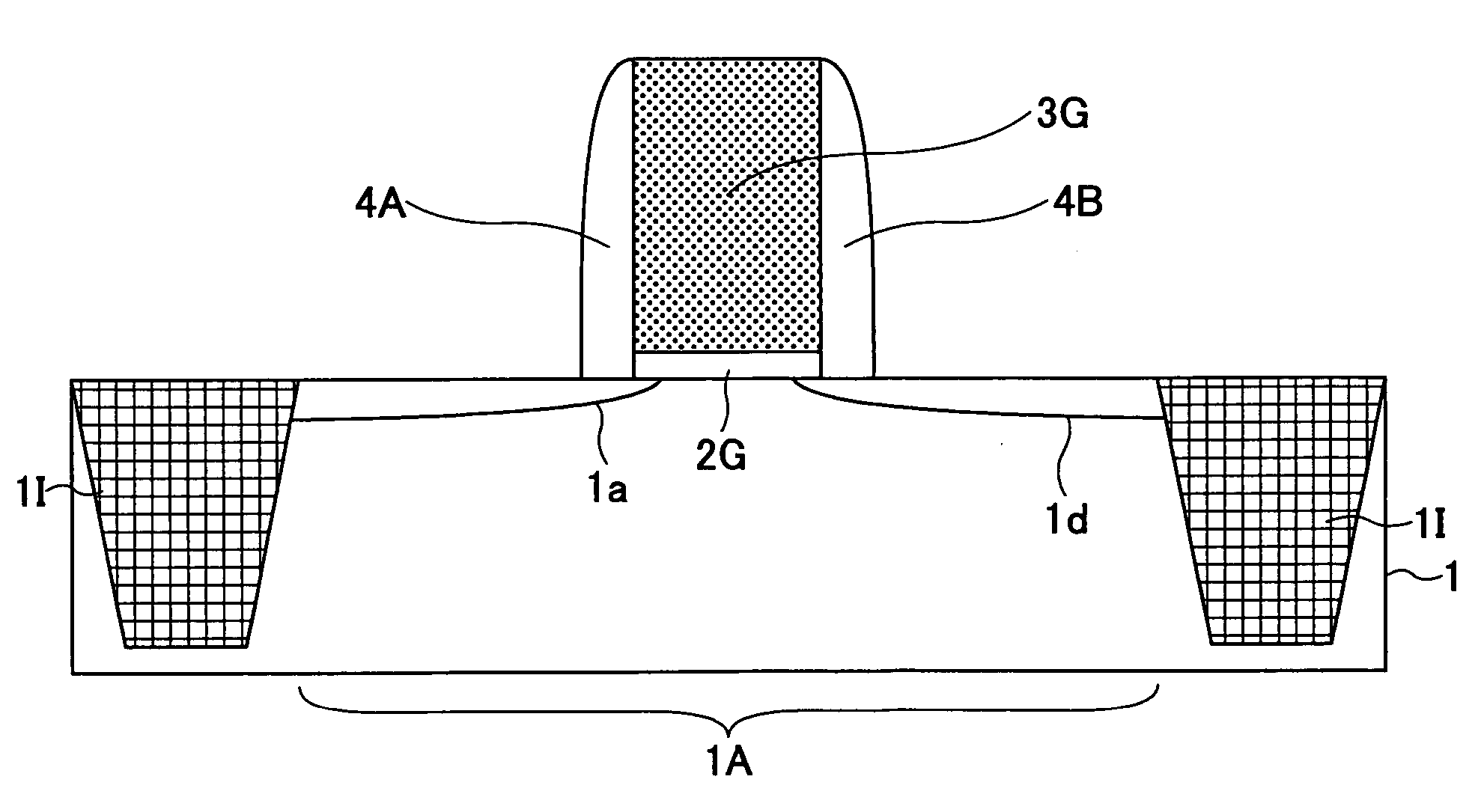

Semiconductor device having a nickel/cobalt silicide region formed in a silicon region

InactiveUS20050070082A1Improve bindingImproved contact characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceDevice material

By forming a buried nickel silicide layer followed by a cobalt silicide layer in silicon-containing regions, such as a gate electrode of a field effect transistor, the superior characteristics of both silicides may be combined so as to provide the potential for further device scaling without unduly compromising the sheet resistance and the contact resistance of scaled silicon circuit features.

Owner:ADVANCED MICRO DEVICES INC

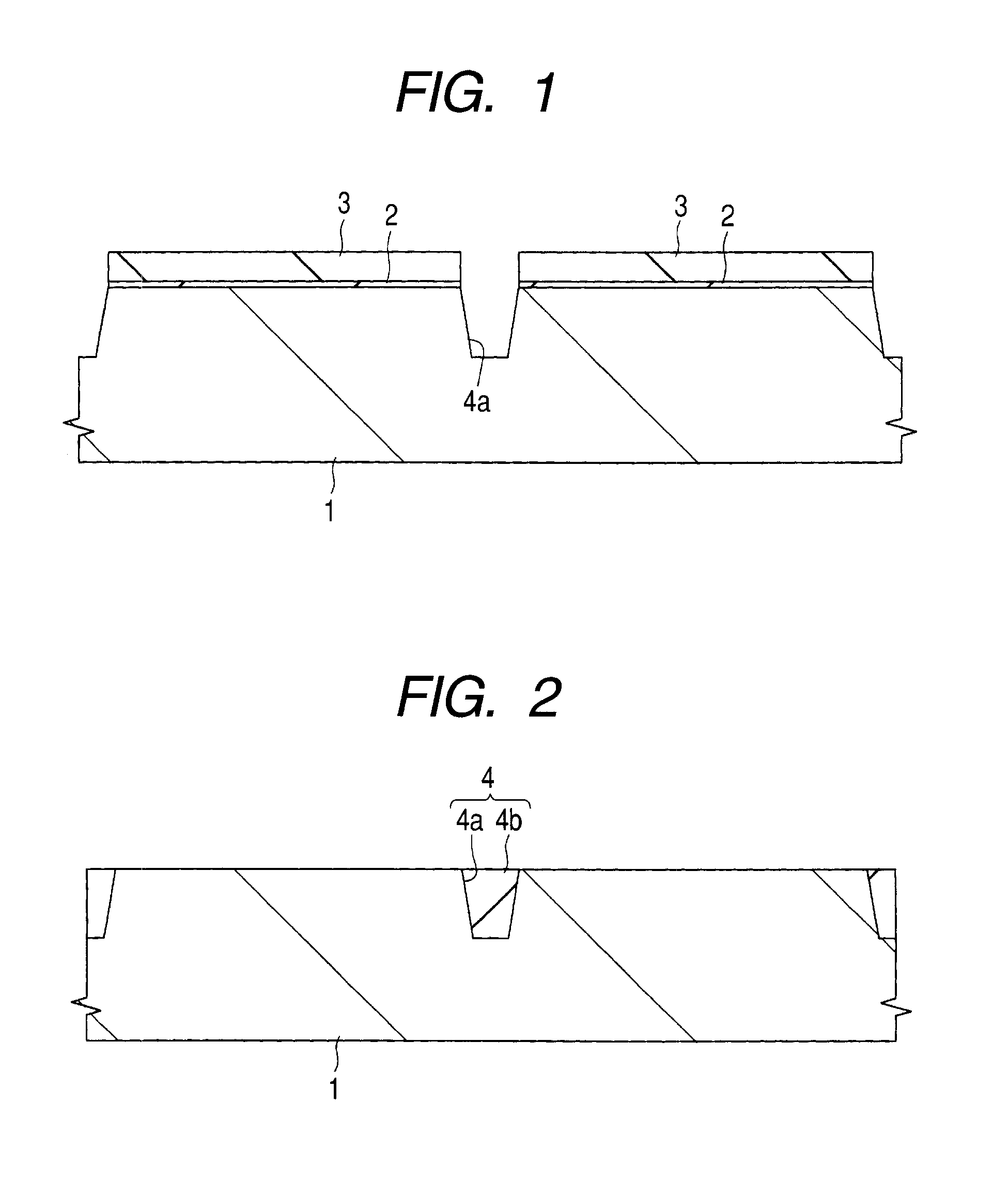

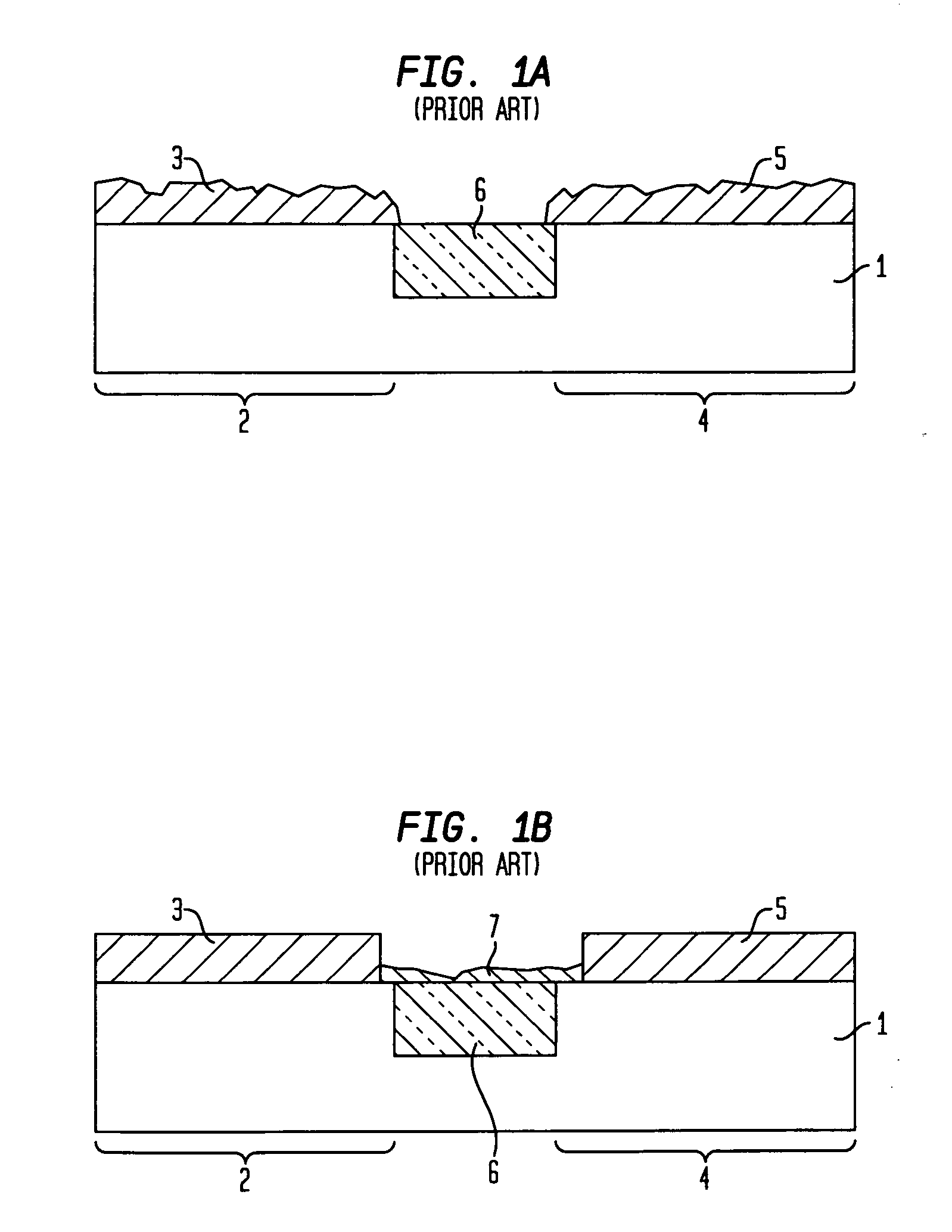

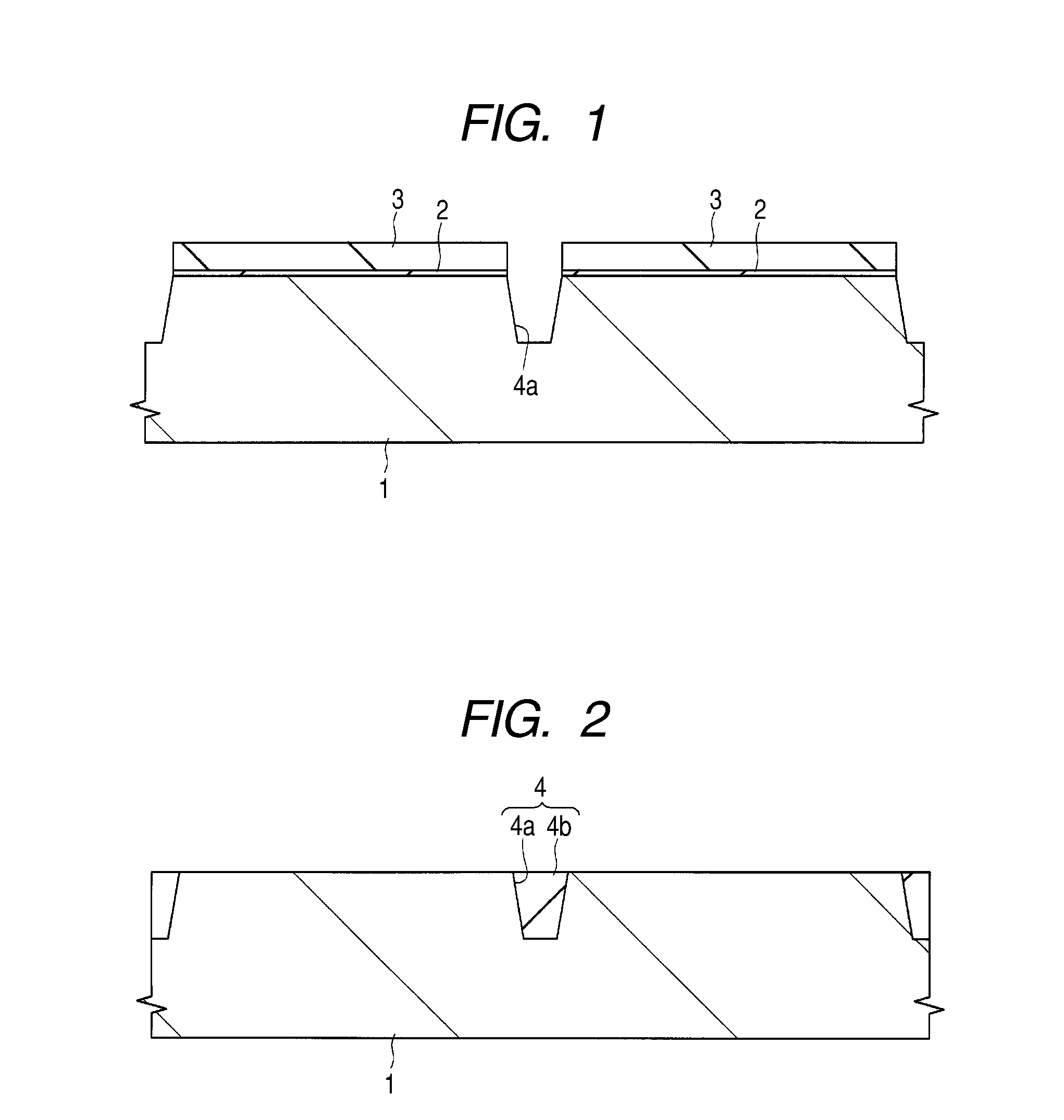

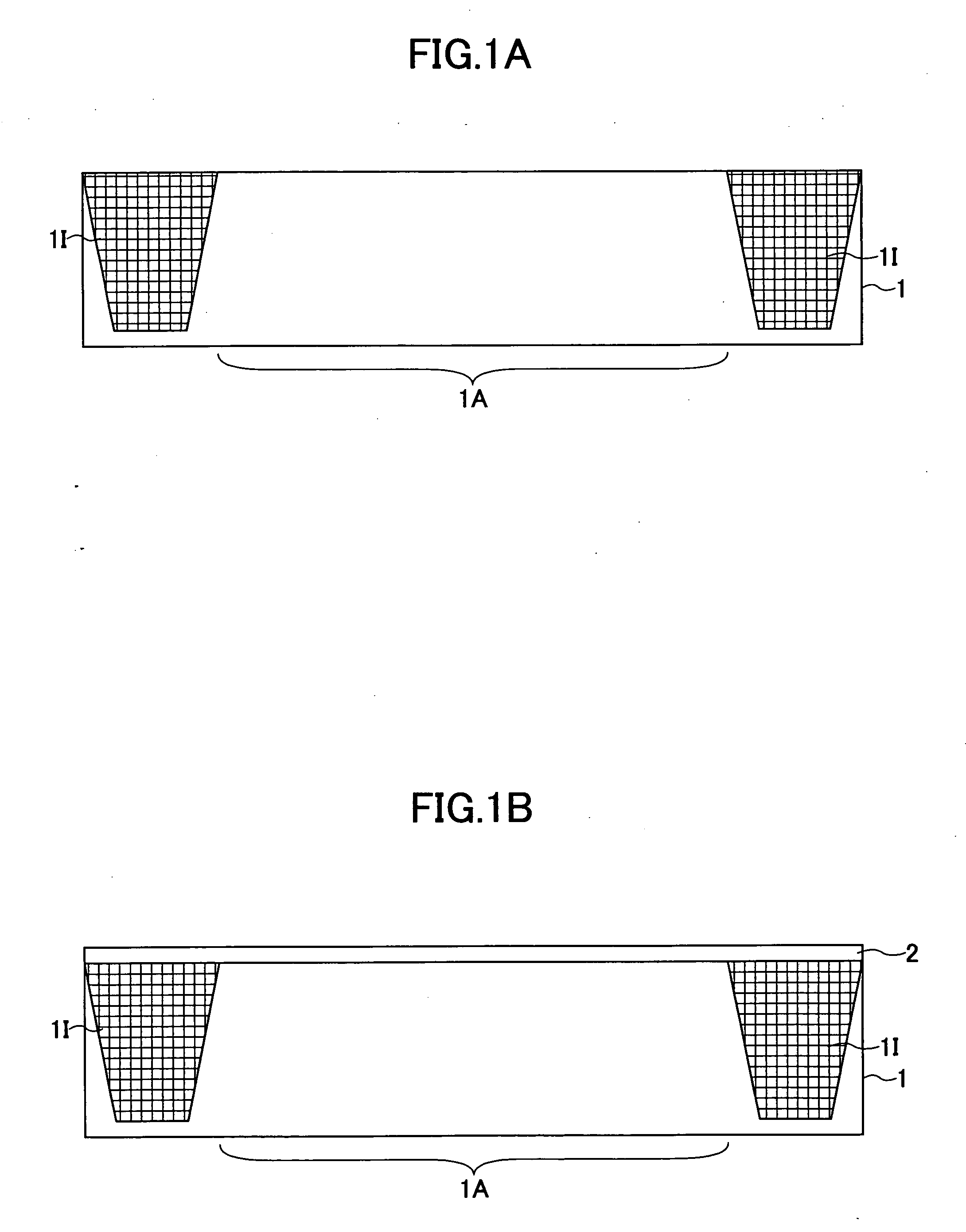

Fabrication process of a semiconductor device

InactiveUS20070166974A1Reduce depthReduce the amount requiredTransistorSemiconductor/solid-state device manufacturingEtchingManufacturing technology

A method of fabricating a semiconductor device comprises the step of forming a nickel monosilicide layer selectively over a silicon region defined by an insulation film by a self-aligned process. The self-aligned process comprises the steps of forming a metallic nickel film on a silicon substrate on which the insulation film and the silicon region are formed, such that the metallic nickel film covers the insulation film and the silicon region, forming a first nickel silicide layer primarily of a Ni2Si phase on a surface of the silicon region of the metallic nickel film by applying an annealing process to the silicon substrate, removing the metallic nickel film, after the step of forming the first nickel silicide layer, by a selective wet etching process, and converting the first nickel silicide layer to a second nickel silicide layer primarily of a NiSi phase by a thermal annealing process conducted in a silane gas.

Owner:FUJITSU SEMICON LTD

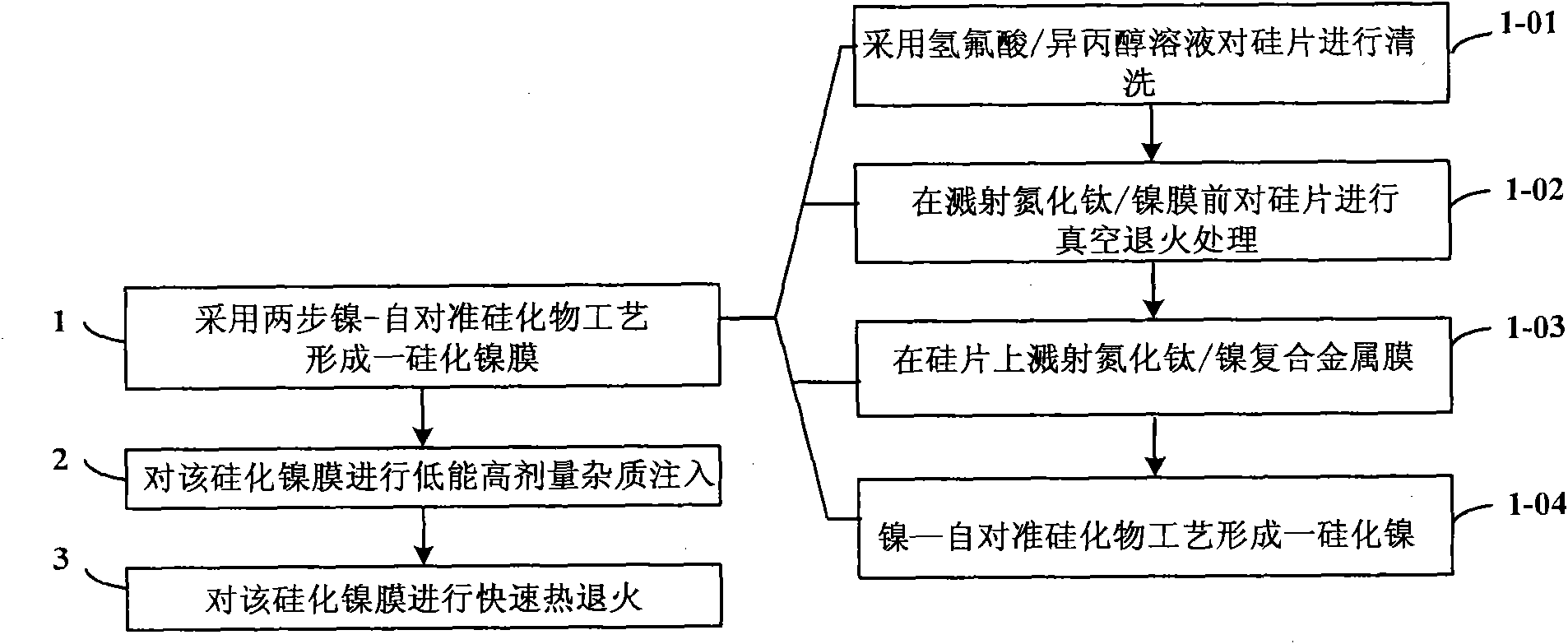

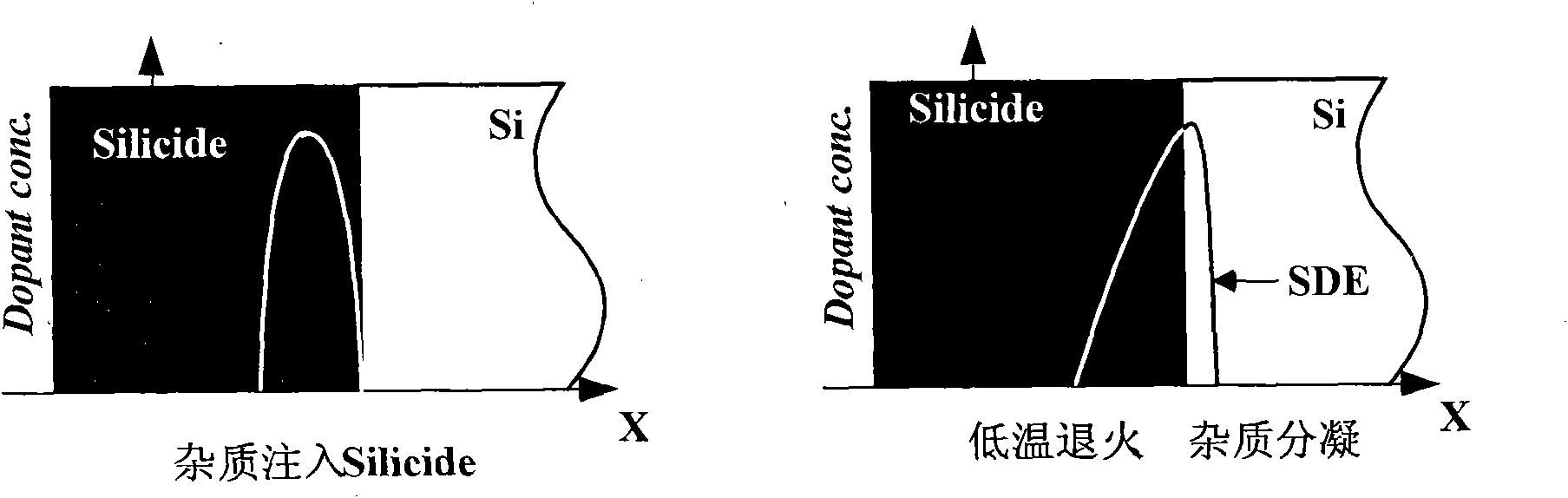

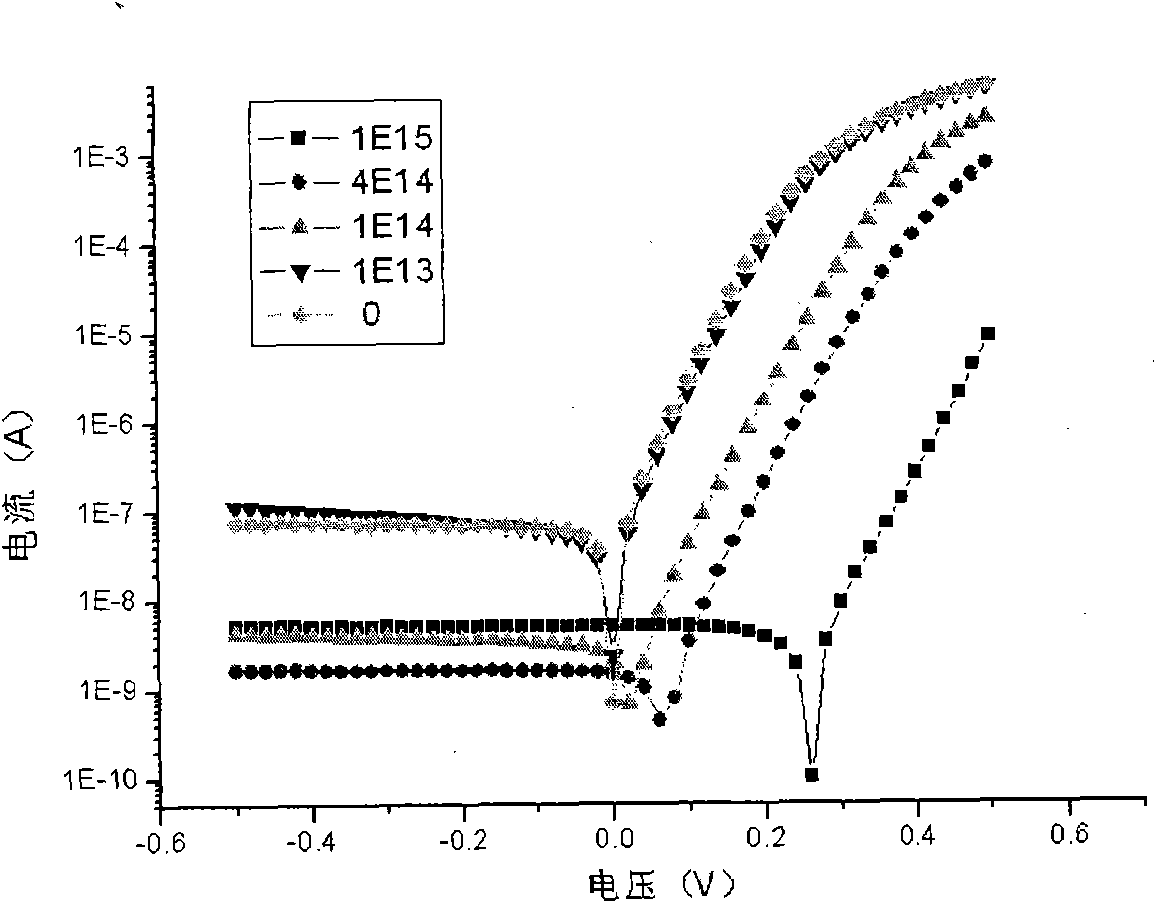

Method for regulating metallic silicides source/drain Schottky barrier height

InactiveCN101807526AEasy to integrateCompatibleSemiconductor/solid-state device manufacturingSalicideSchottky barrier

The invention discloses a method for regulating metallic silicides source / drain Schottky barrier height. The method comprises the steps as follows: step 1: using a two-step nickel-self-alignment silicide process to form a nickel silicide film; step 2: injecting low energy high dosage impurities to the nickel silicide film; and step 3: rapidly thermally annealing the nickel silicide film. The invention has the advantages of capability of using the existing process, simple process, easy operation, low cost and easy integration, thereby achieving good compatibility with CMOS process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method of manufacturing a semiconductor device

InactiveUS20090149020A1Reduce contact resistanceSuppressing and preventing diffusionSemiconductor/solid-state device detailsSolid-state devicesCouplingEngineering

A technology is provided which allows, in a coupling portion obtained by burying a conductive material within a coupling hole bored in an insulating film, the removal of a natural oxide film on the surface of a silicide layer which is present at the bottom portion of the coupling hole. A coupling hole is bored in an interlayer insulating film (first and second insulating films) to expose the surface of a nickel silicide layer at the bottom portion of the coupling hole. Then, reduction gases including a HF gas and a NH3 gas is supplied to the principal surface of a semiconductor wafer to form a product by a reduction reaction, and remove the natural oxide film on the surface of the nickel silicide layer. At this time, the flow rate ratio (HF / NH3 gas flow rate ratio) between the NF gas and the NH3 gas is adjusted to be more than 1 and not more than 5. Preferably, the temperature of the semiconductor wafer is adjusted to be not more than 30° C. Thereafter, a heating process is performed at 400° C. to the semiconductor wafer to remove the product remaining on the principal surface of the semiconductor wafer, and subsequently form a barrier metal film.

Owner:RENESAS ELECTRONICS CORP