Patents

Literature

7185 results about "Contact resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The term contact resistance refers to the contribution to the total resistance of a system which can be attributed to the contacting interfaces of electrical leads and connections as opposed to the intrinsic resistance, which is an inherent property, independent of the measurement method. This effect is often described by the term electrical contact resistance (ECR) and may vary with time, most often decreasing, in a process known as resistance creep. The idea of potential drop on the injection electrode was introduced by William Shockley to explain the difference between the experimental results and the model of gradual channel approximation. In addition to the term ECR, interface resistance, transitional resistance, or just simply correction term are also used. The term parasitic resistance is used as a more general term, of which it is usually assumed that contact resistance is a major component.

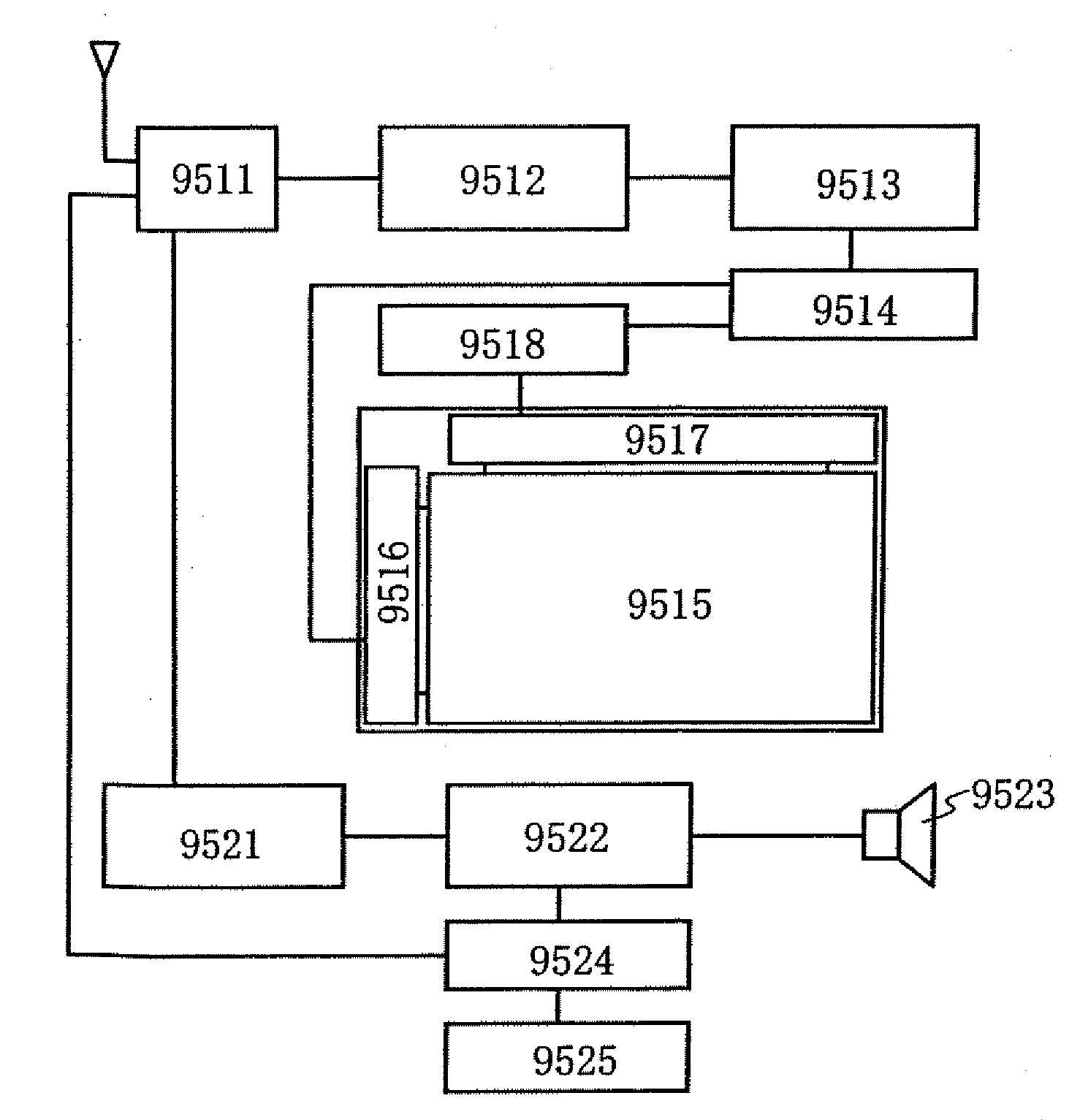

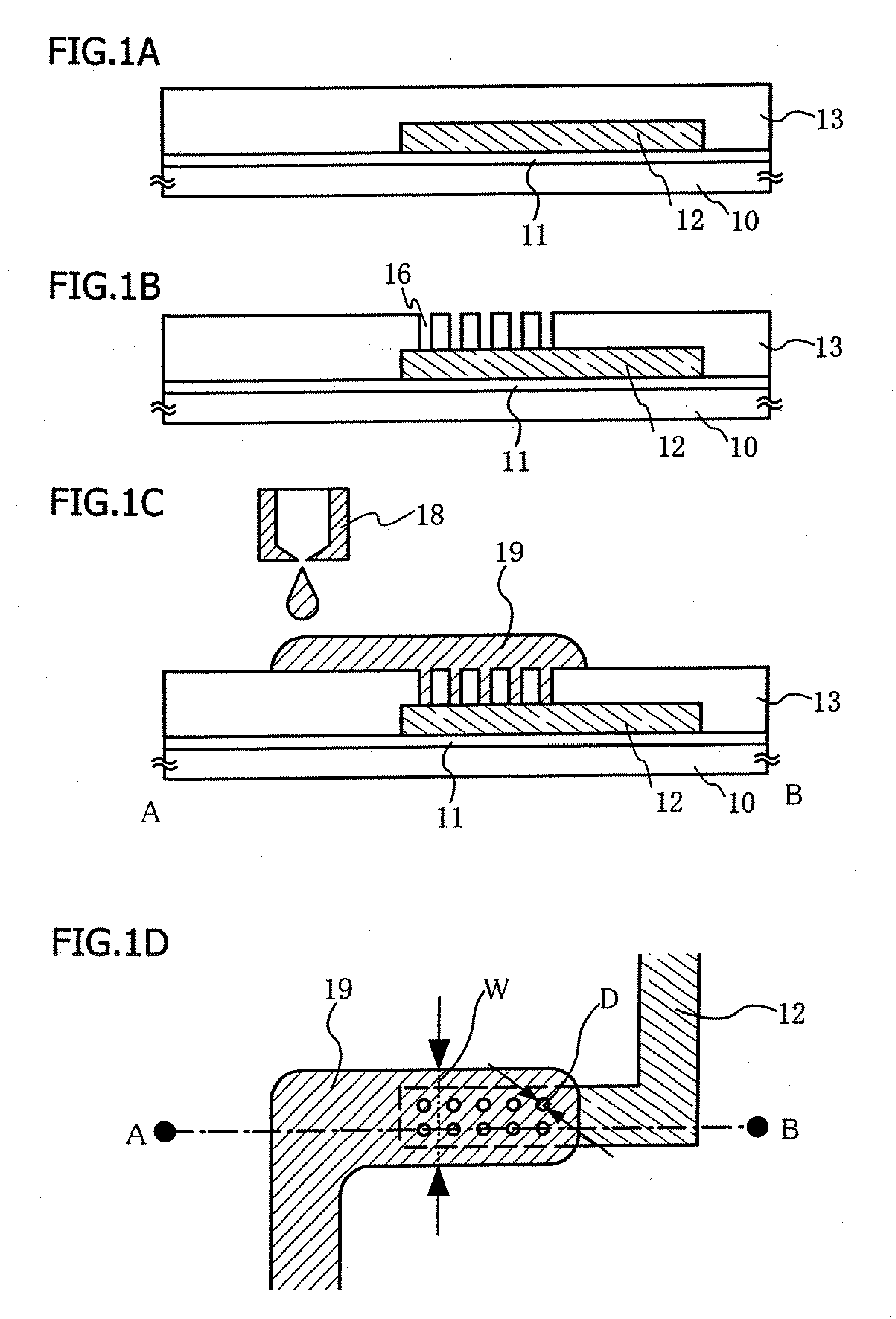

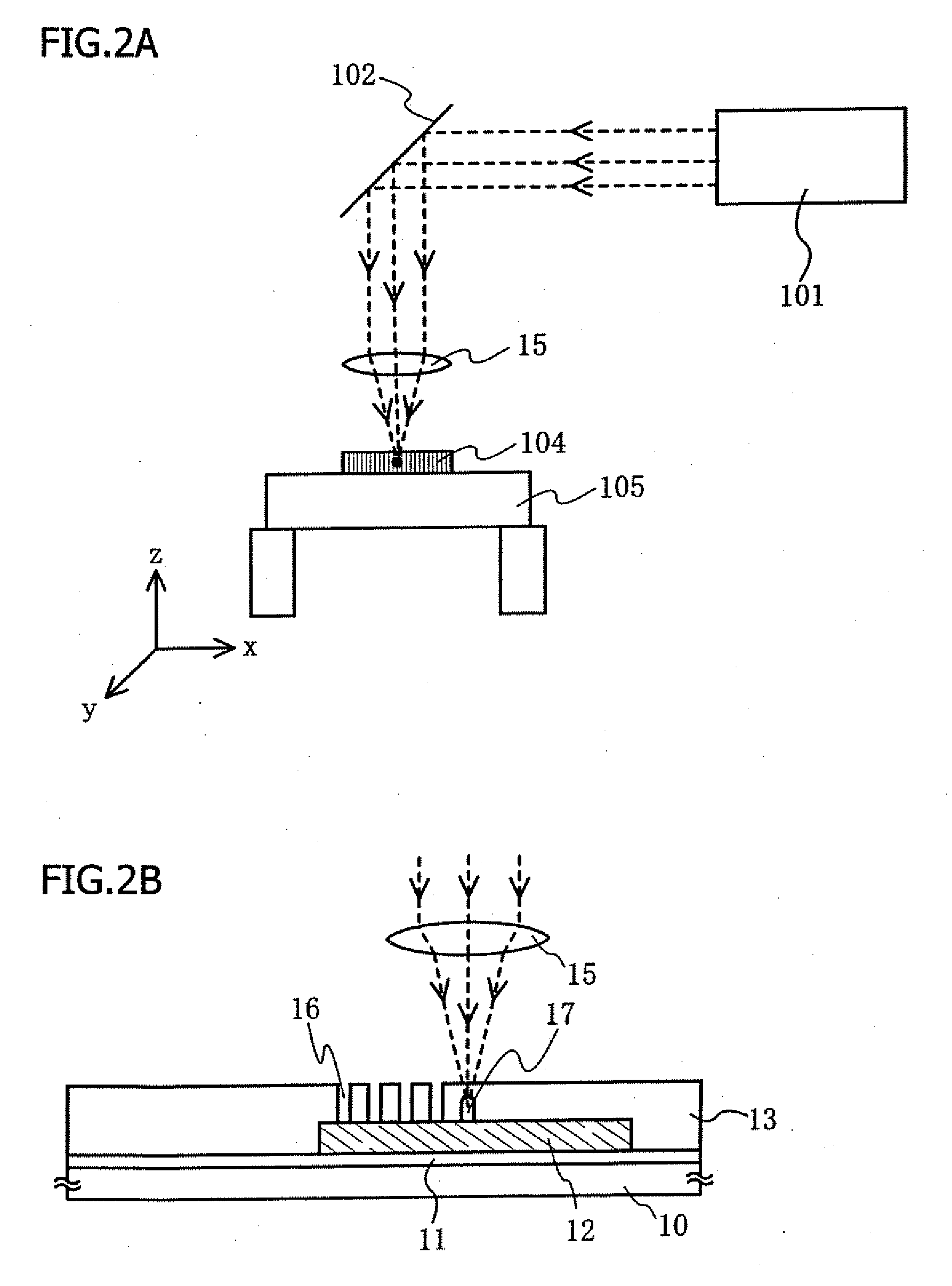

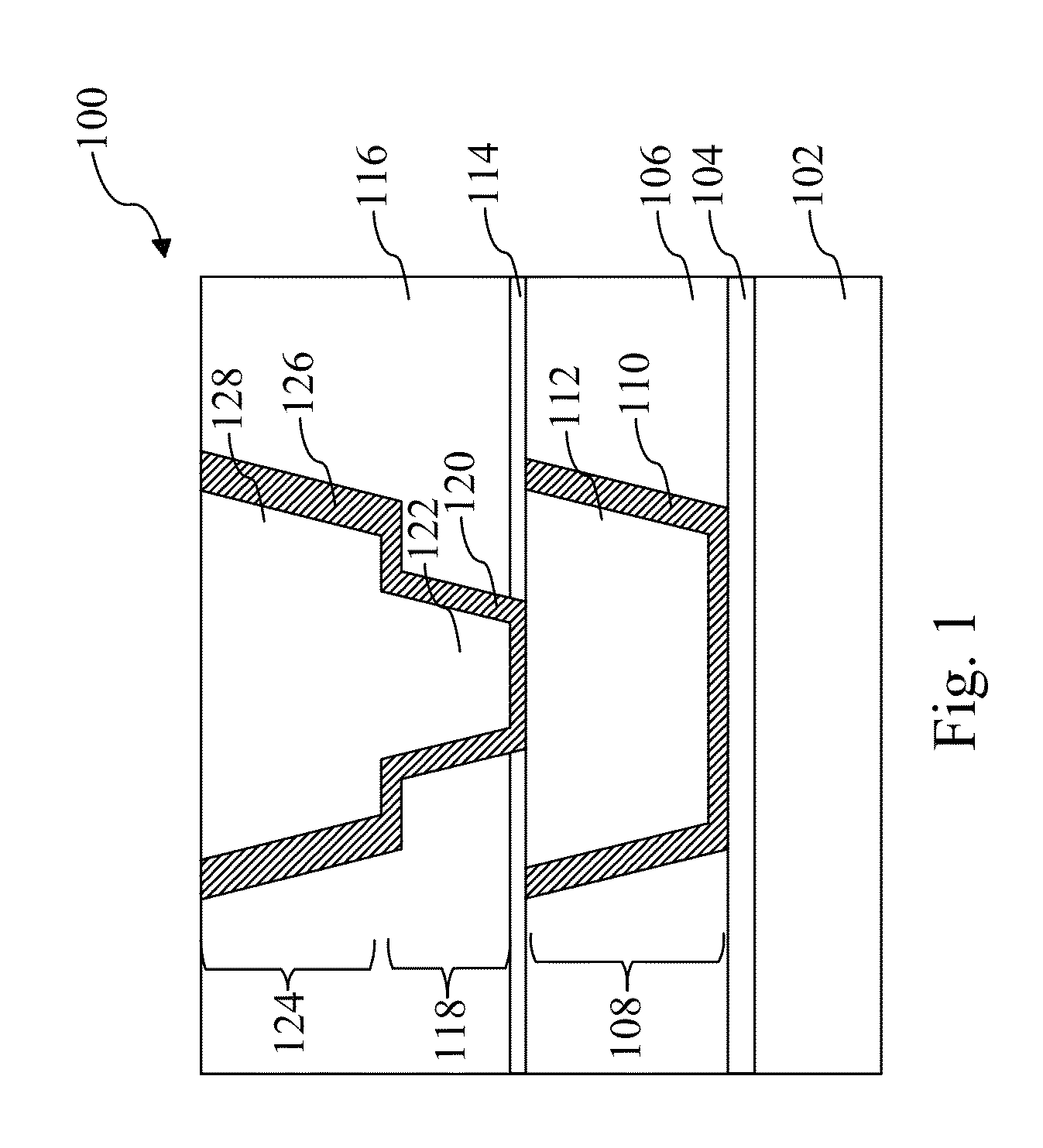

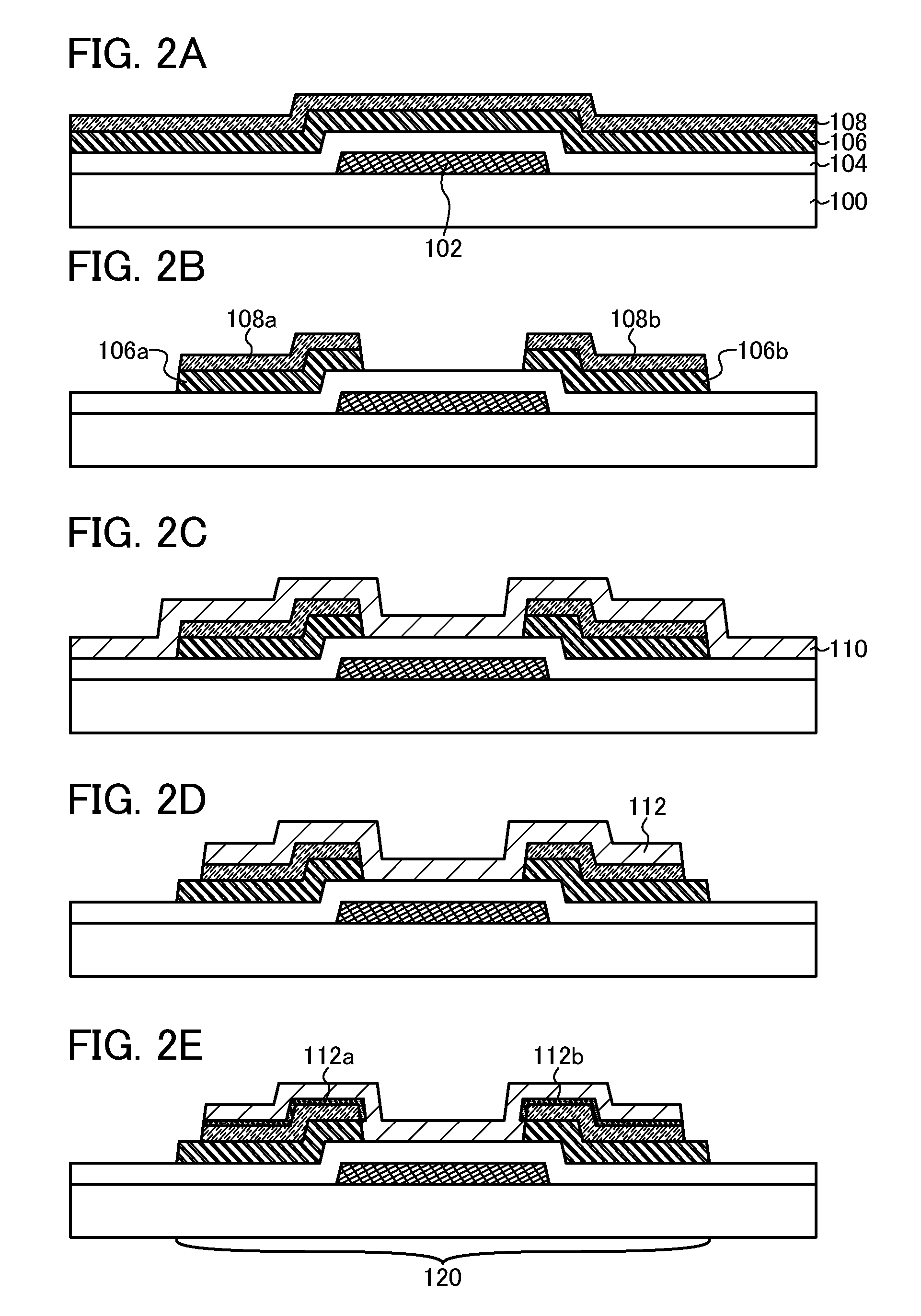

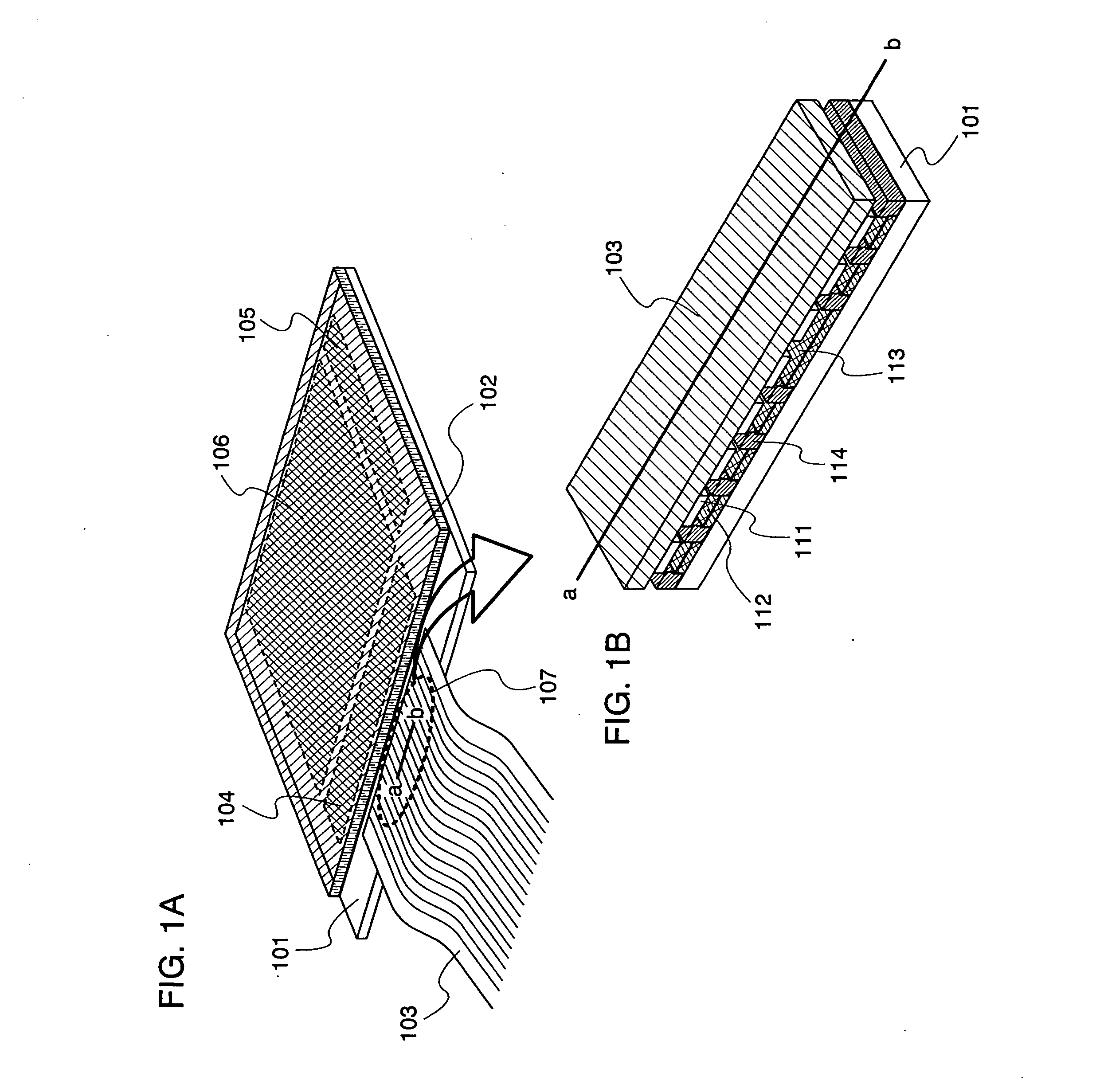

Semiconductor device and method for manufacturing the same, and electric device

InactiveUS20090073325A1Simple stepsHighly integratedTransistorTelevision system detailsElectrical resistance and conductanceLongest Diameter

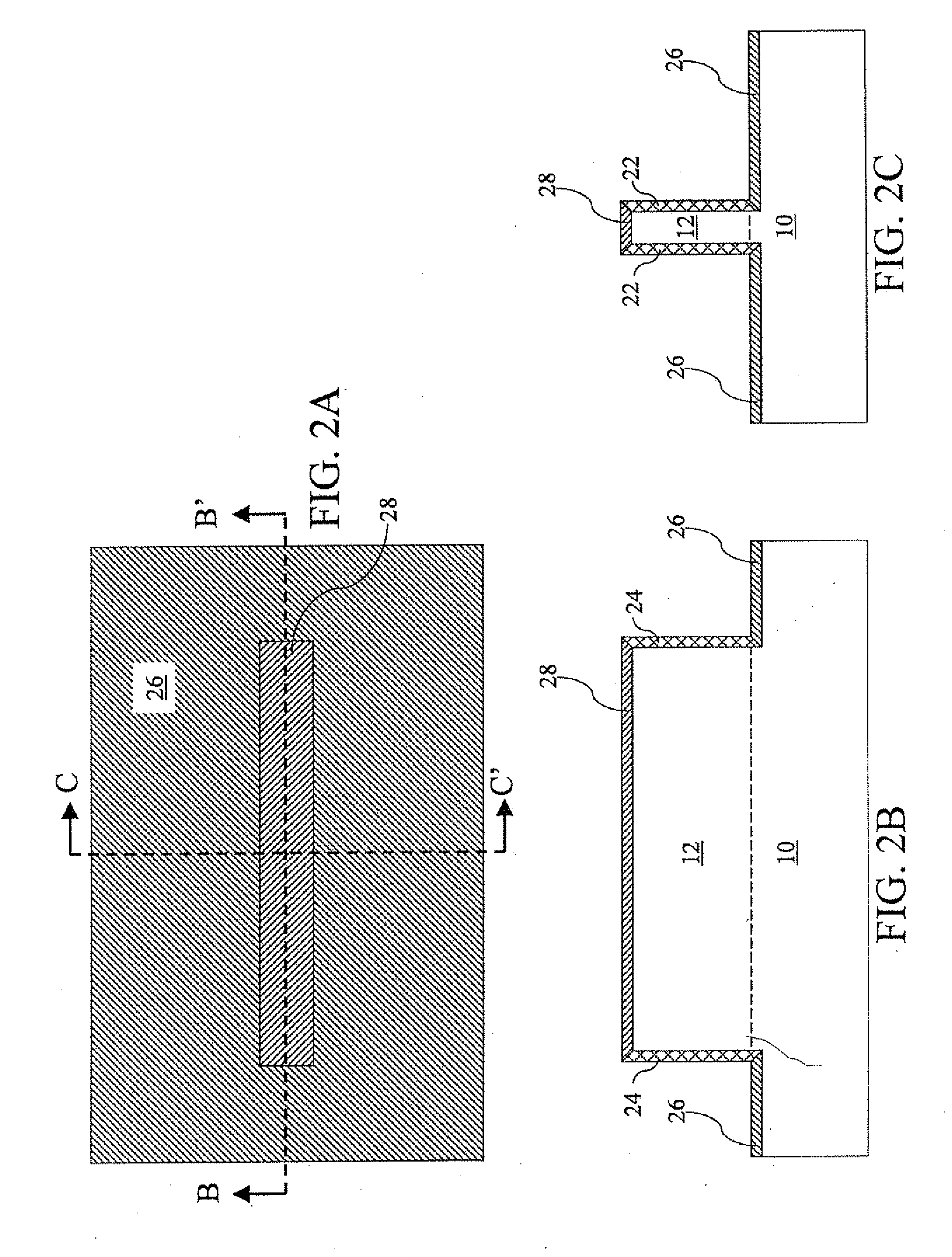

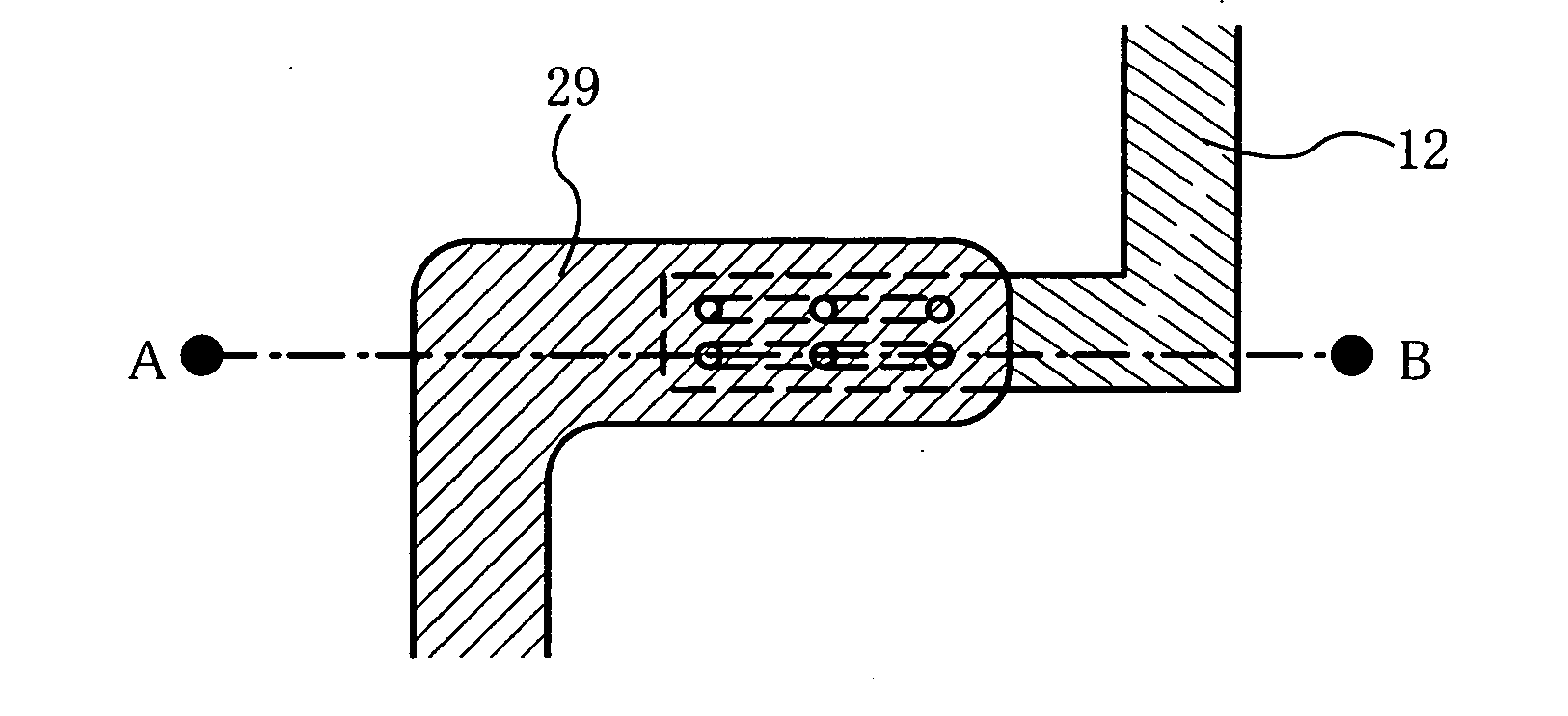

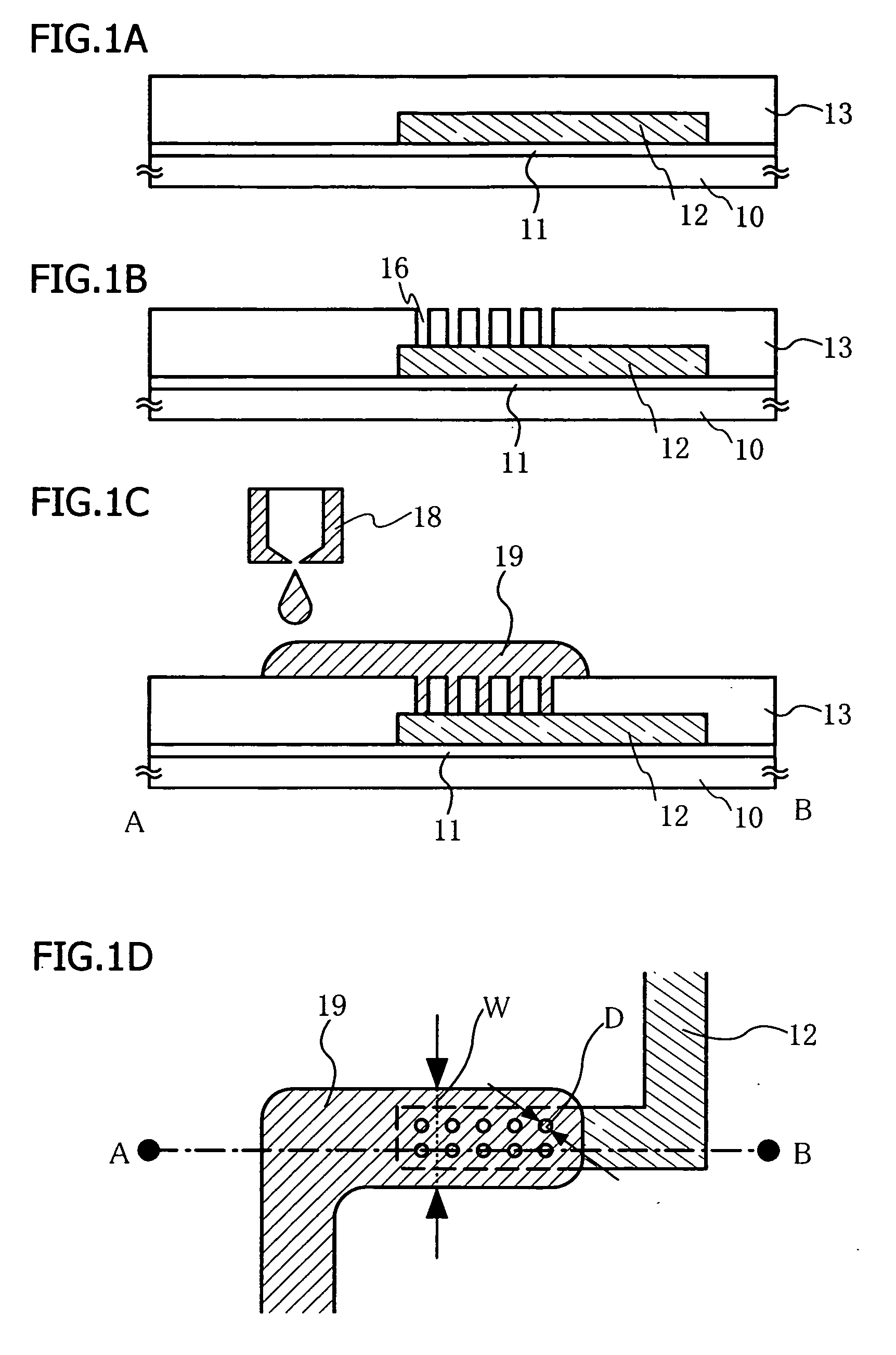

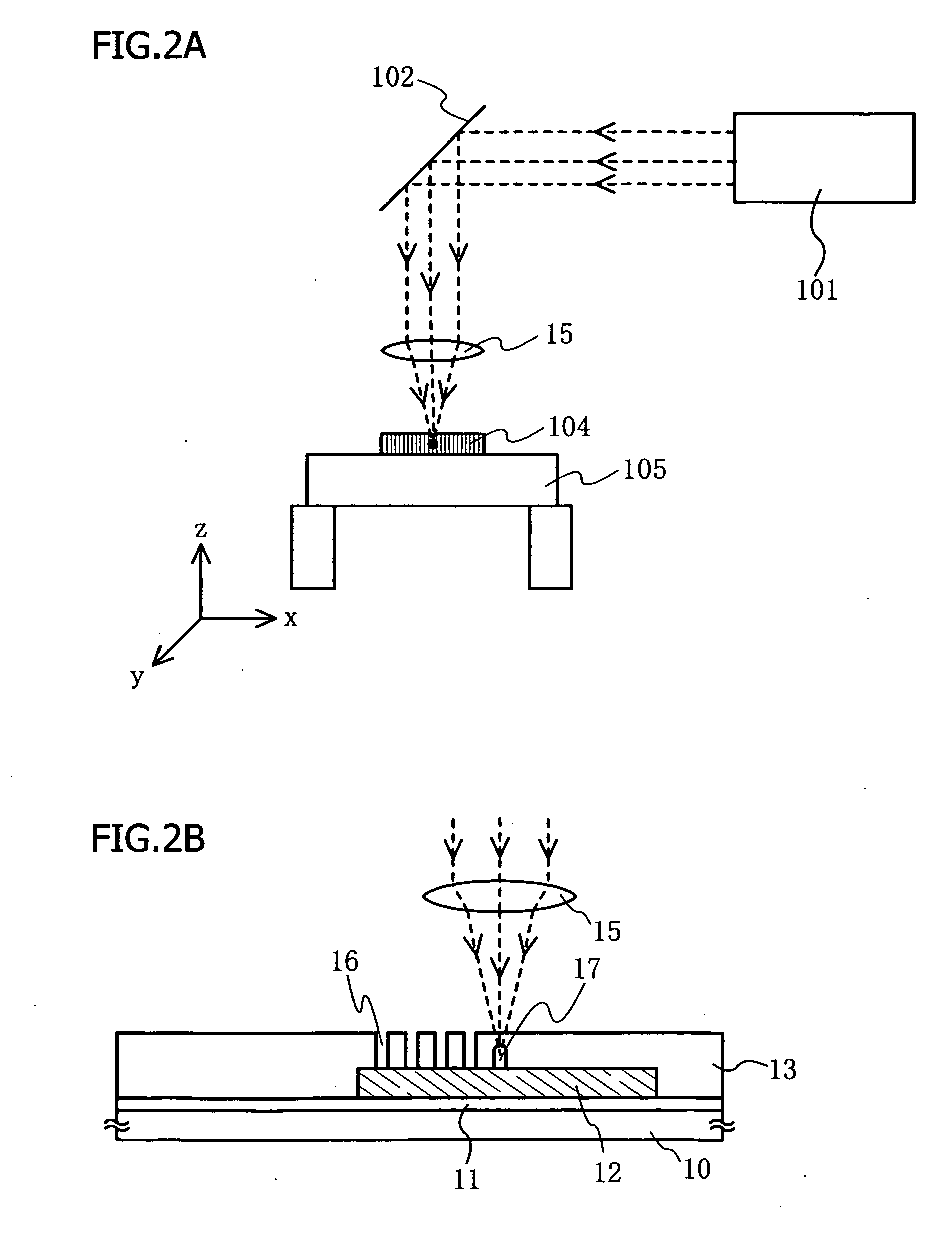

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

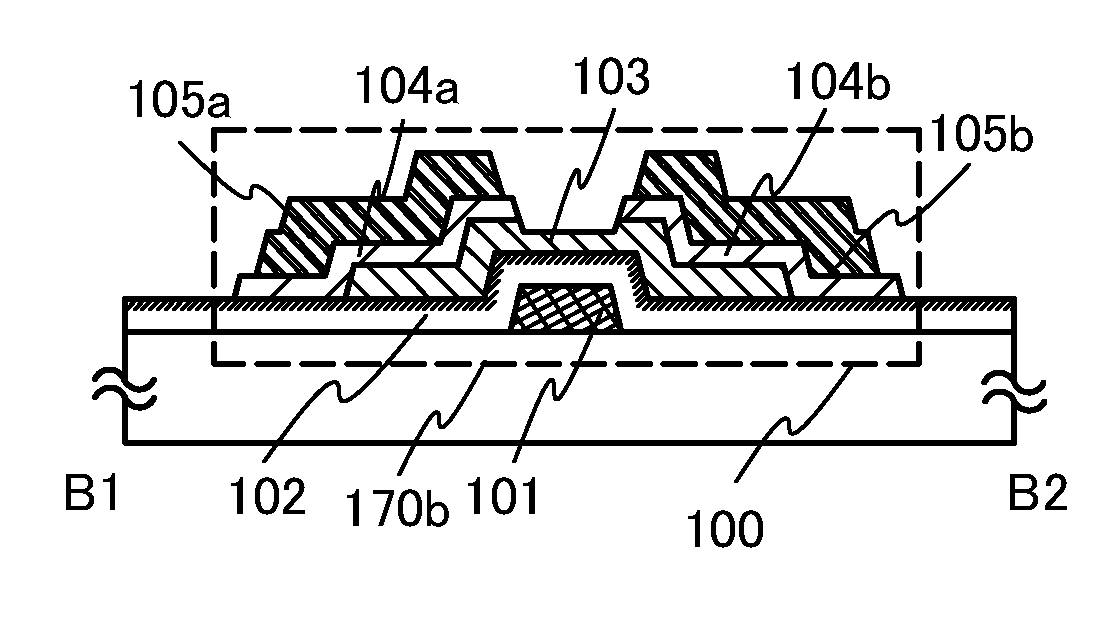

Semiconductor device and method for manufacturing the same

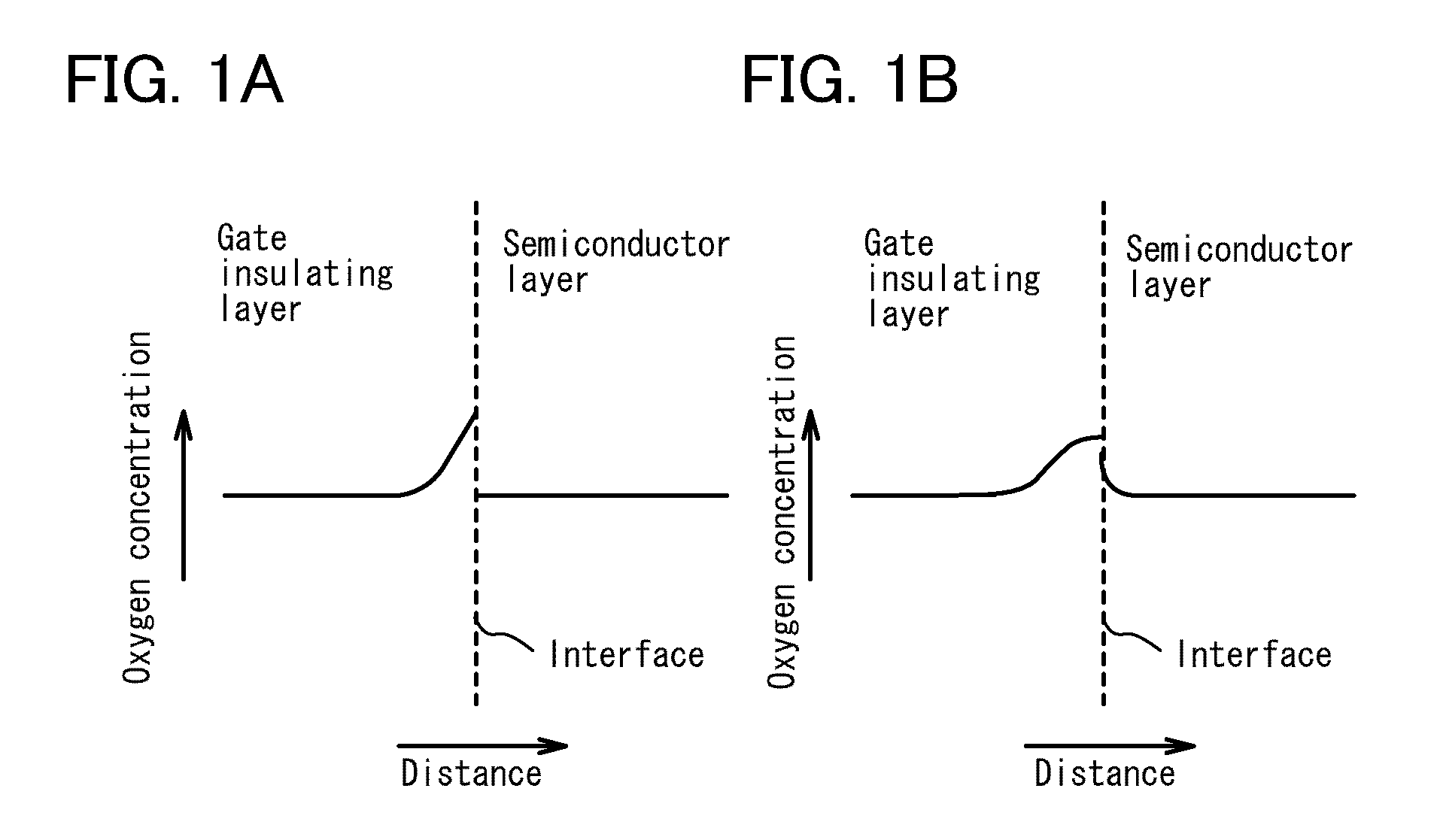

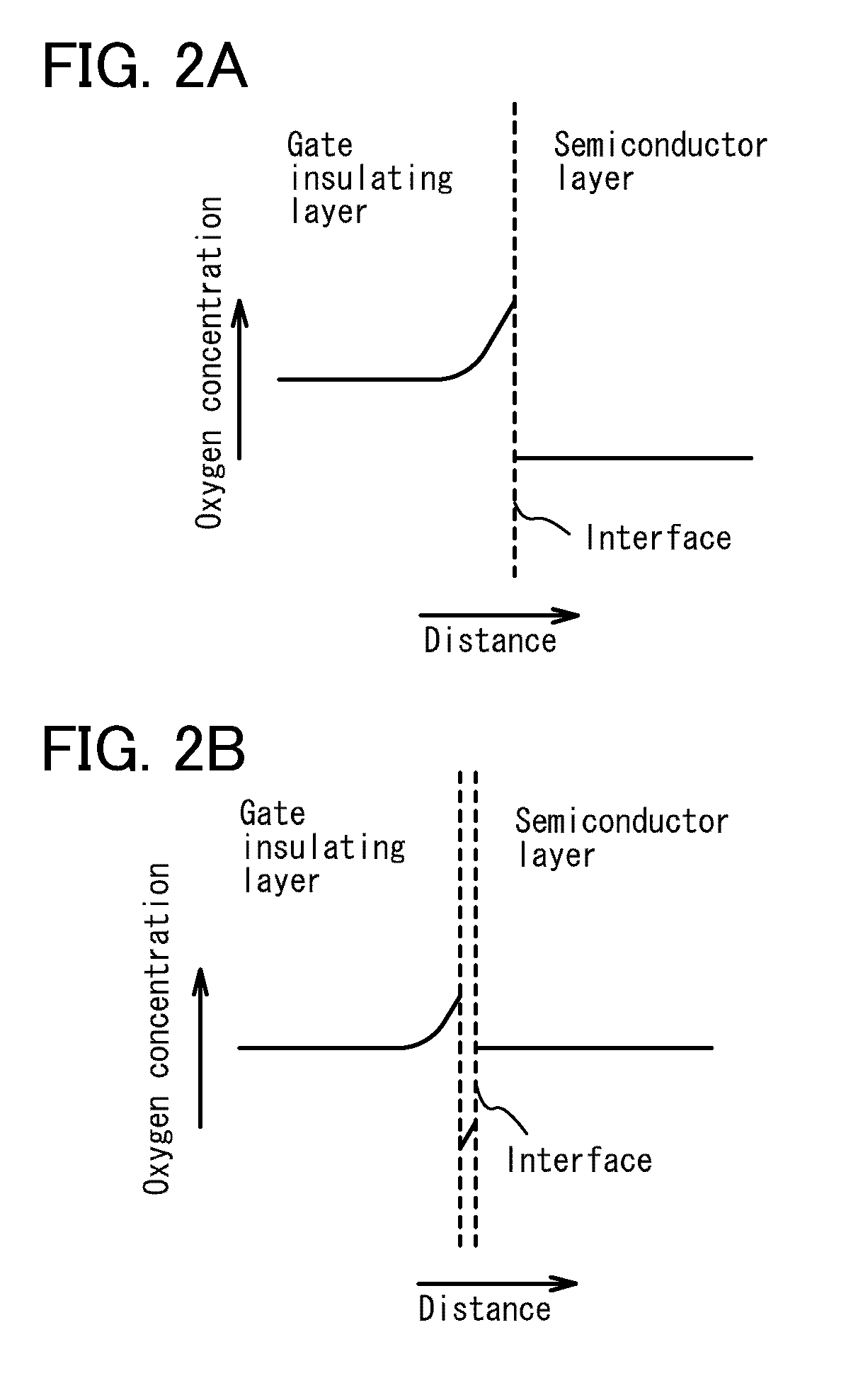

ActiveUS20100051949A1Small currentHigh on-off ratioTransistorStatic indicating devicesMetallic materialsOxygen deficient

A thin film transistor structure in which a source electrode and a drain electrode formed from a metal material are in direct contact with an oxide semiconductor film may lead to high contact resistance. One cause of high contact resistance is that a Schottky junction is formed at a contact plane between the source and drain electrodes and the oxide semiconductor film. An oxygen-deficient oxide semiconductor layer which includes crystal grains with a size of 1 nm to 10 nm and has a higher carrier concentration than the oxide semiconductor film serving as a channel formation region is provided between the oxide semiconductor film and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

Device for reducing contact resistance of a metal

ActiveUS8736056B2Semiconductor/solid-state device detailsSolid-state devicesChemical vapor depositionAtomic layer deposition

A structure for an integrated circuit with reduced contact resistance is disclosed. The structure includes a substrate, a cap layer deposited on the substrate, a dielectric layer deposited on the cap layer, and a trench embedded in the dielectric layer. The trench includes an atomic layer deposition (ALD) TaN or a chemical vapor deposition (CVD) TaN deposited on a side wall of the trench, a physical vapor deposition (PVD) Ta or a combination of the PVD Ta and a PVD TaN deposited on the ALD TaN or CVD TaN, and a Cu deposited on the PVD Ta or the combination of the PVD Ta and the PVD TaN deposited on the ALD TaN or the CVD TaN. The structure further includes a via integrated into the trench at bottom of the filled trench.

Owner:TAIWAN SEMICON MFG CO LTD

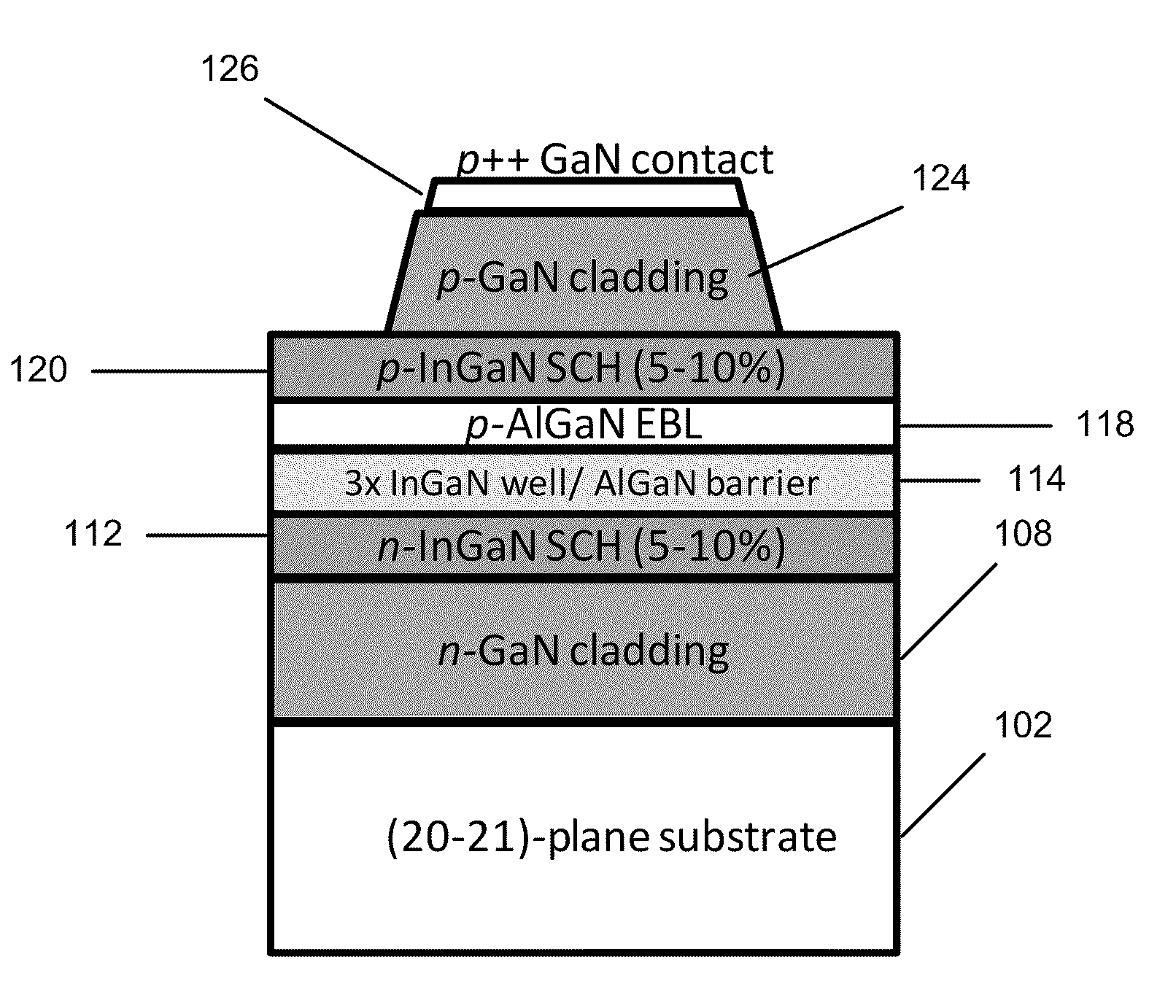

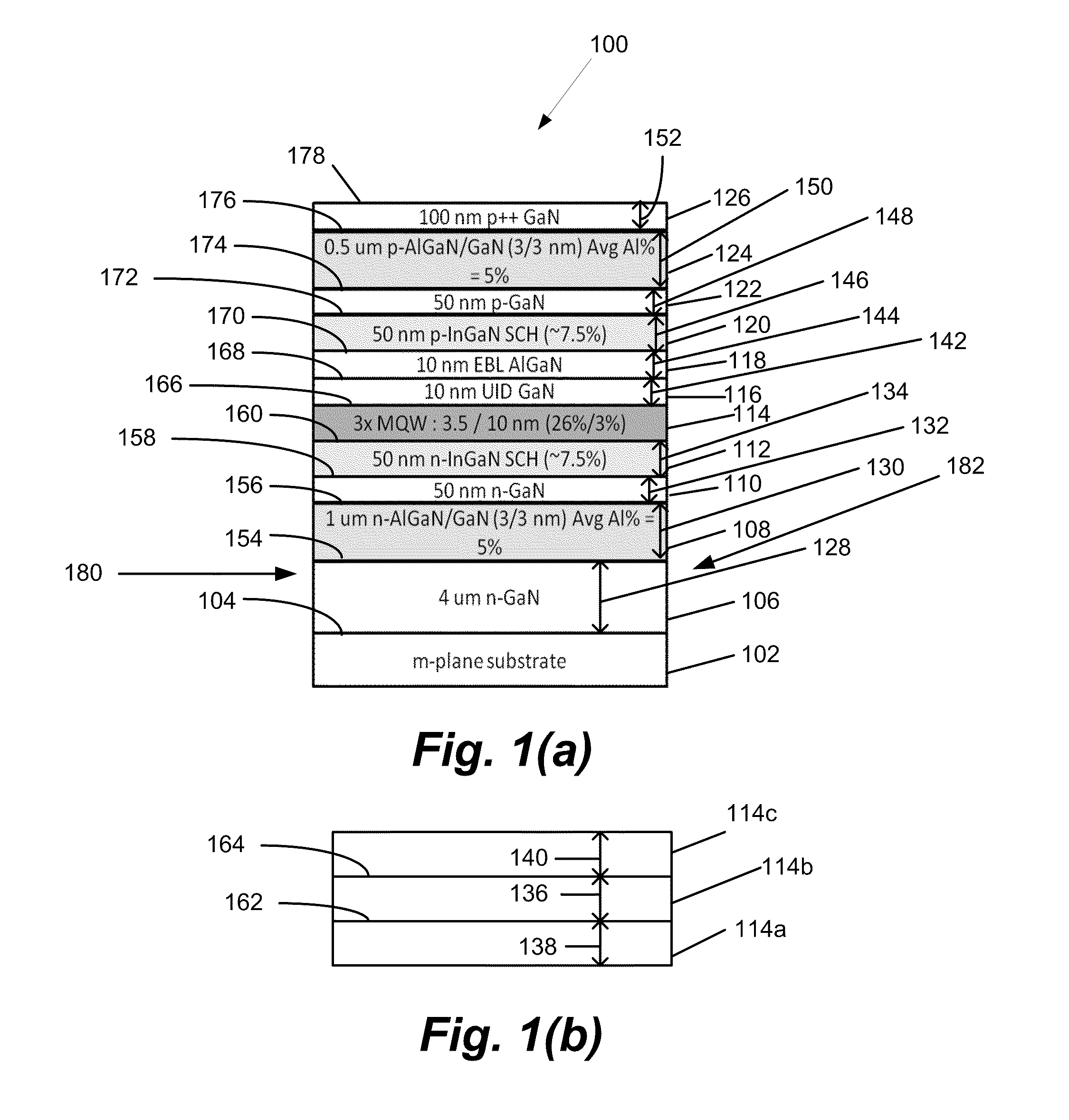

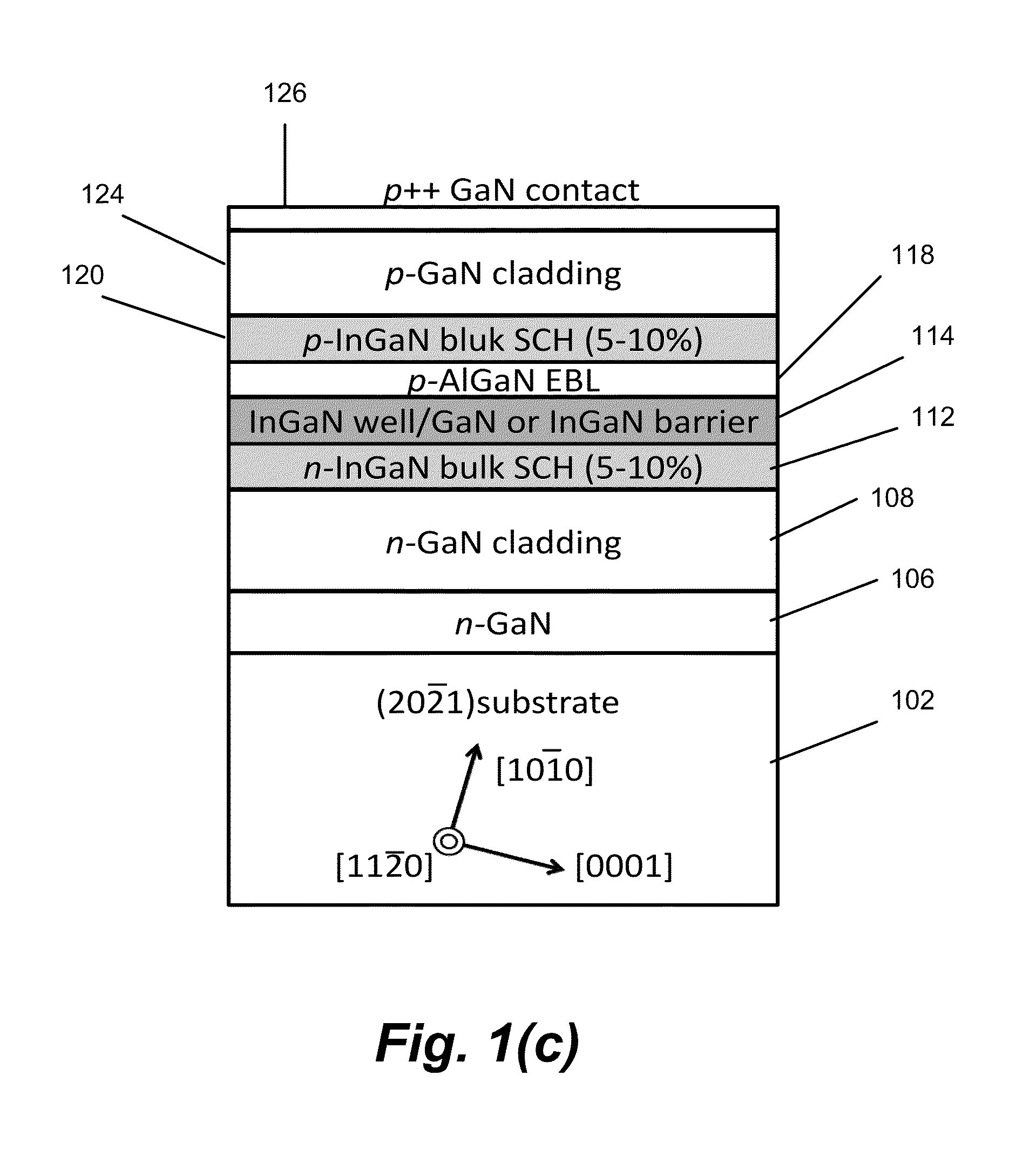

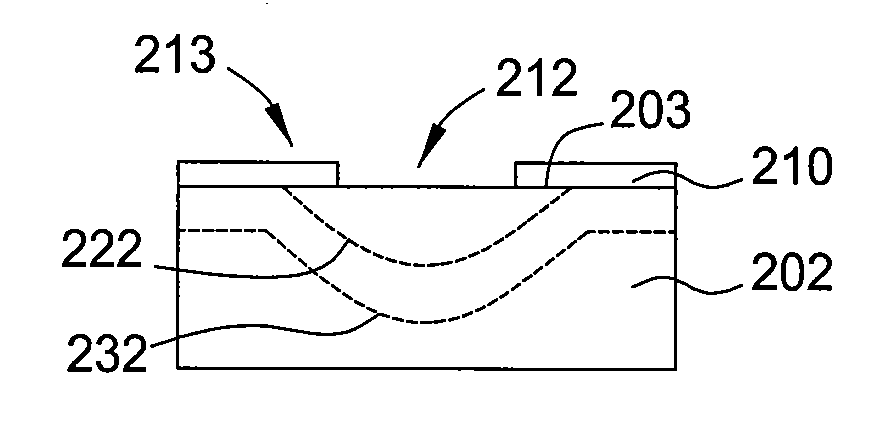

LONG WAVELENGTH NONPOLAR AND SEMIPOLAR (Al,Ga,In)N BASED LASER DIODES

InactiveUS20100309943A1Simple structureImprove electricityOptical wave guidanceLaser detailsContact layerStimulated emission

A laser diode, grown on a miscut nonpolar or semipolar substrate, with lower threshold current density and longer stimulated emission wavelength, compared to conventional laser diode structures, wherein the laser diode's (1) n-type layers are grown in a nitrogen carrier gas, (2) quantum well layers and barrier layers are grown at a slower growth rate as compared to other device layers (enabling growth of the p-type layers at higher temperature), (3) high Al content electron blocking layer enables growth of layers above the active region at a higher temperature, and (4) asymmetric AlGaN SPSLS allowed growth of high Al containing p-AlGaN layers. Various other techniques were used to improve the conductivity of the p-type layers and minimize the contact resistance of the contact layer.

Owner:RGT UNIV OF CALIFORNIA

Programmable Resistive Ram and Manufacturing Method

ActiveUS20070173019A1Large sectionSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceReduced size

Programmable resistive RAM cells have a resistance that depends on the size of the contacts. Manufacturing methods and integrated circuits for lowered contact resistance are disclosed that have contacts of reduced size.

Owner:MACRONIX INT CO LTD

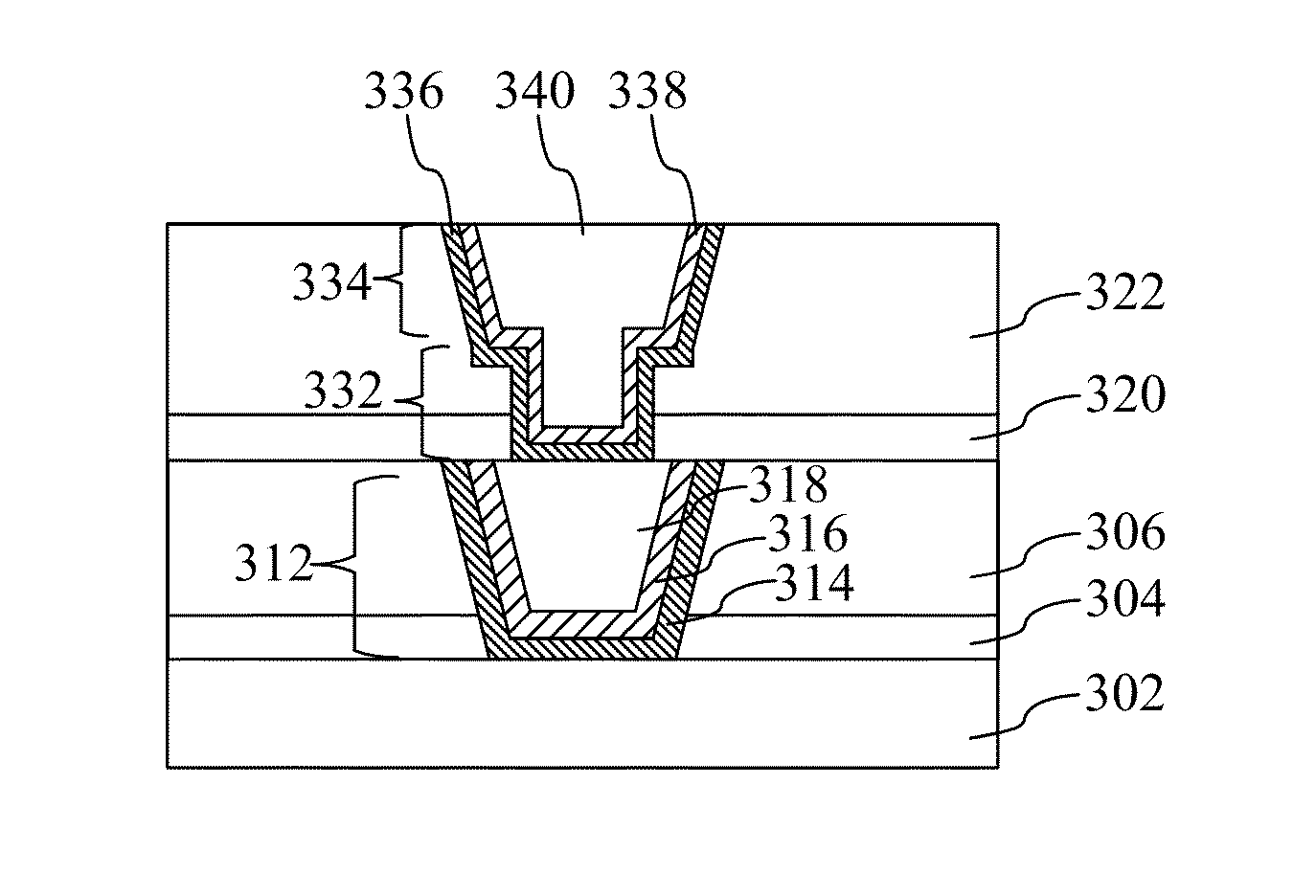

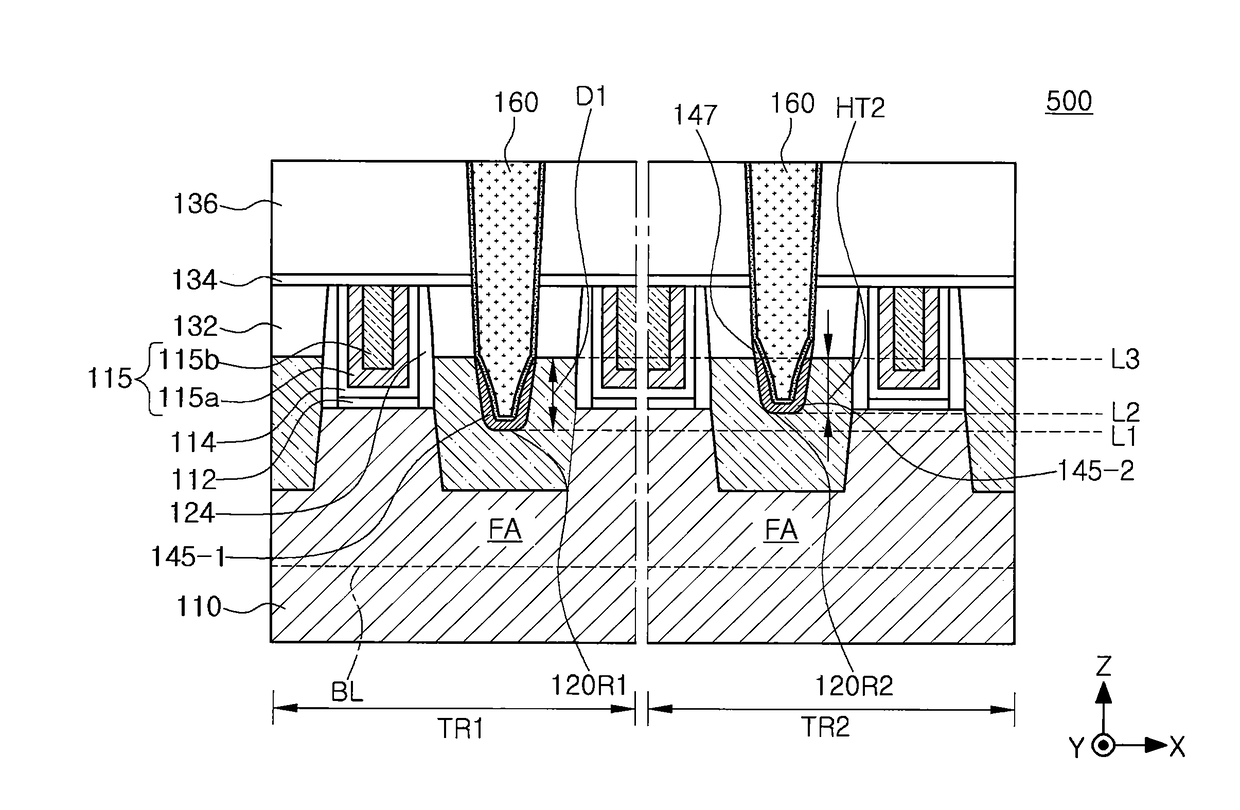

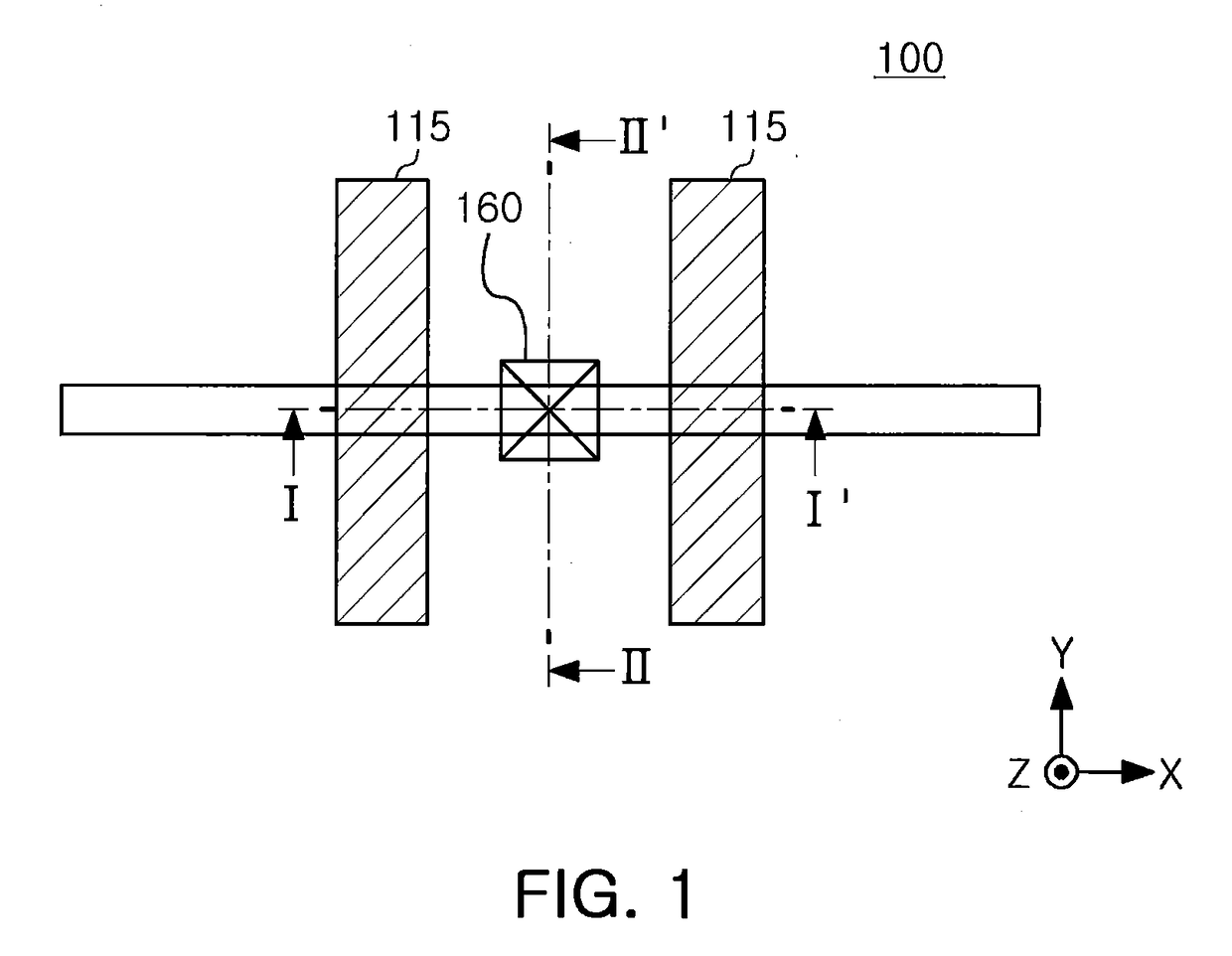

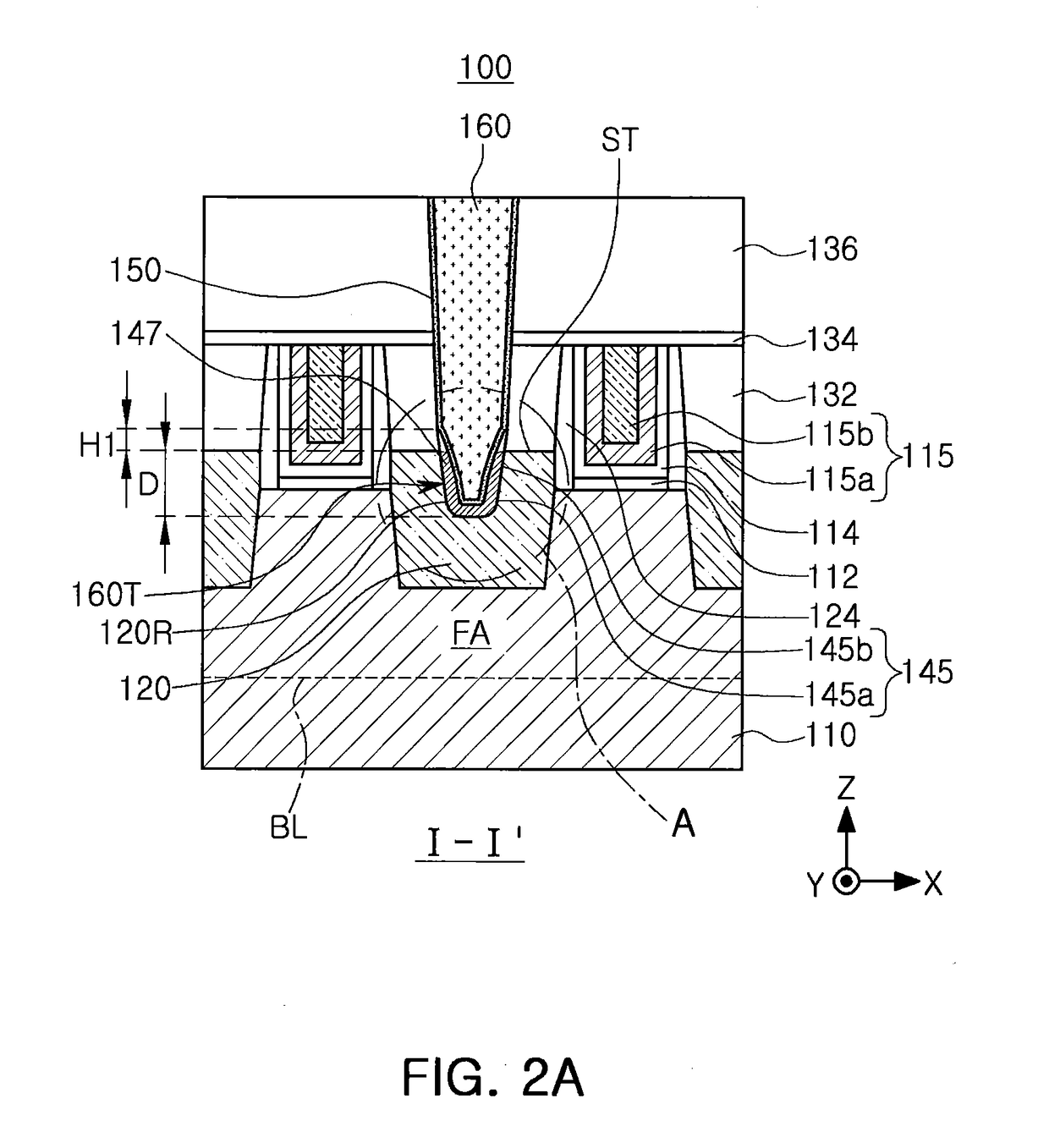

Semiconductor Devices Having Reduced Contact Resistance

ActiveUS20180090583A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialMetal silicide

A semiconductor device includes a substrate including an active region, a gate structure, source / drain regions, ones of the source / drain regions having an upper surface in which a recessed region is formed, a contact plug on the source / drain regions and extending in a direction substantially perpendicular to an upper surface of the substrate from an interior of the recessed region, a metal silicide film on an internal surface of the recessed region and including a first portion between a bottom surface of the recessed region and a lower surface of the contact plug and a second portion between a side wall of the recessed region and a side surface of the contact plug, and a metal layer connected to an upper portion of the metal silicide film and on a side surface of a region of the contact plug.

Owner:SAMSUNG ELECTRONICS CO LTD

Graphene-based transistor

ActiveUS20090020764A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A graphene layer is formed on a surface of a silicon carbide substrate. A dummy gate structure is formed over the fin, in the trench, or on a portion of the planar graphene layer to implant dopants into source and drain regions. The dummy gate structure is thereafter removed to provide an opening over the channel of the transistor. Threshold voltage adjustment implantation may be performed to form a threshold voltage implant region directly beneath the channel, which comprises the graphene layer. A gate dielectric is deposited over a channel portion of the graphene layer. After an optional spacer formation, a gate conductor is formed by deposition and planarization. The resulting graphene-based field effect transistor has a high carrier mobility due to the graphene layer in the channel, low contact resistance to the source and drain region, and optimized threshold voltage and leakage due to the threshold voltage implant region.

Owner:GLOBALFOUNDRIES US INC

Semiconductor integrated circuit device and manufacturing method thereof

InactiveUS20050073051A1Minimize the possibilityEfficient removalTransistorSemiconductor/solid-state device detailsHigh energyUltraviolet lights

A manufacturing process for a semiconductor integrated circuit device which prevents occurrence of reaction between metal wiring and a boron-doped silicon plug over it in heat treatment for a MOS transistor to be formed over them and reduces the possibility of rise in contact resistance. Metal boride is formed on an exposed metal surface in the bottom of an opening made in an interlayer insulating film over the metal wiring. In order to facilitate formation of such metal boride, metal oxide remaining on the metal surface is removed with an aqueous ammonia solution. The meal surface is irradiated with high energy ultraviolet light in order to remove organic matter remaining in the opening and facilitate removal of the metal oxide with the aqueous ammonia solution.

Owner:RENESAS ELECTRONICS CORP

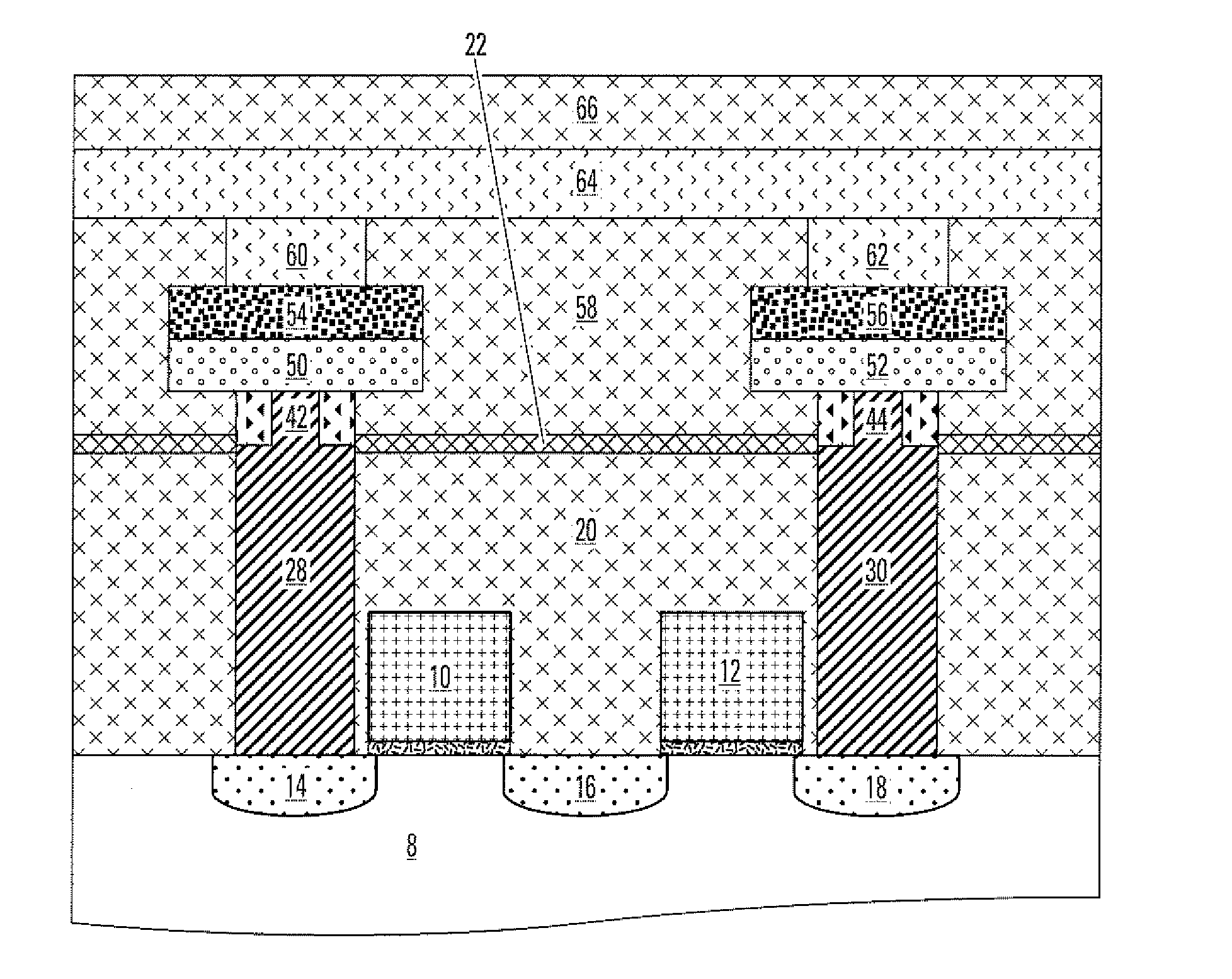

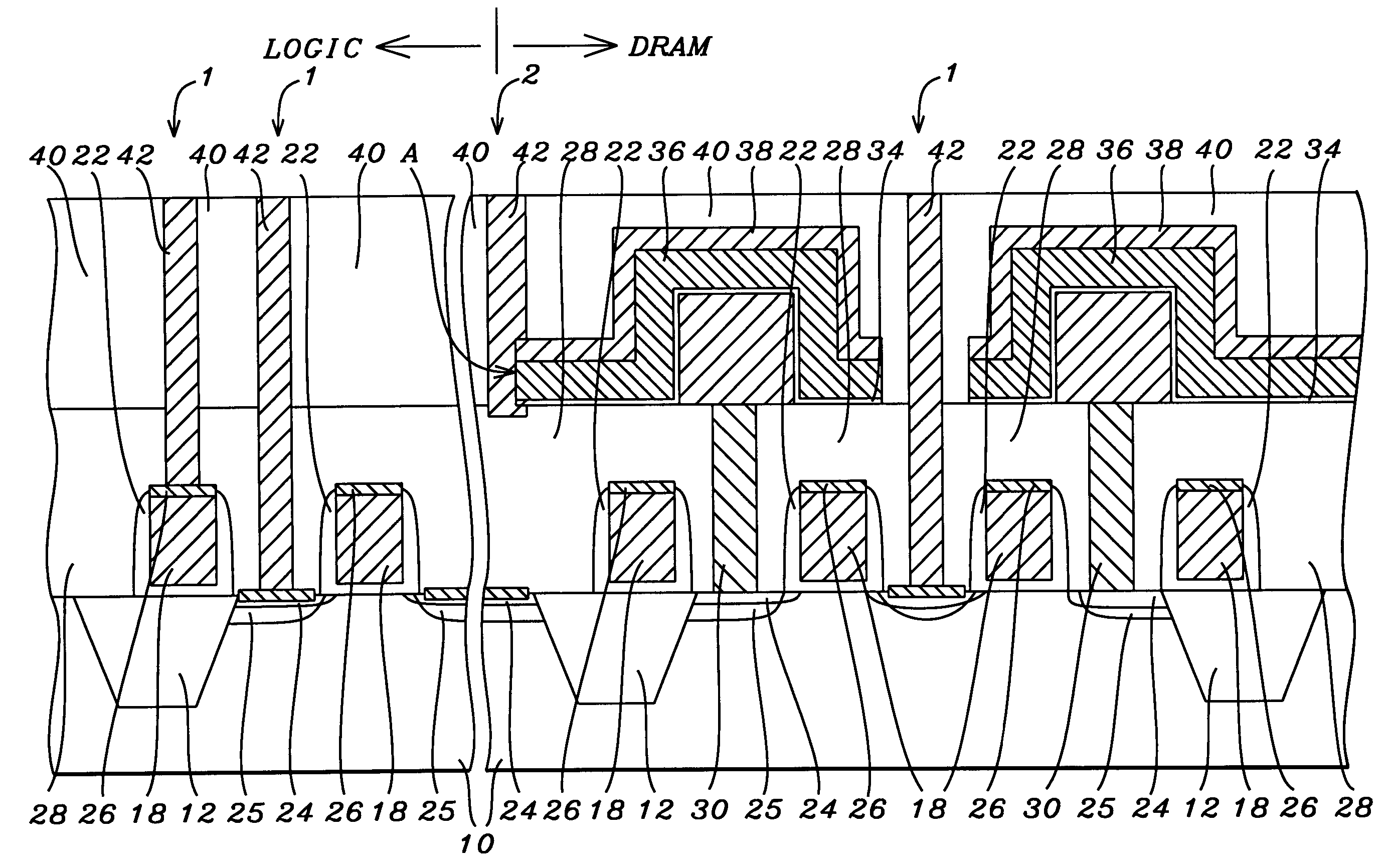

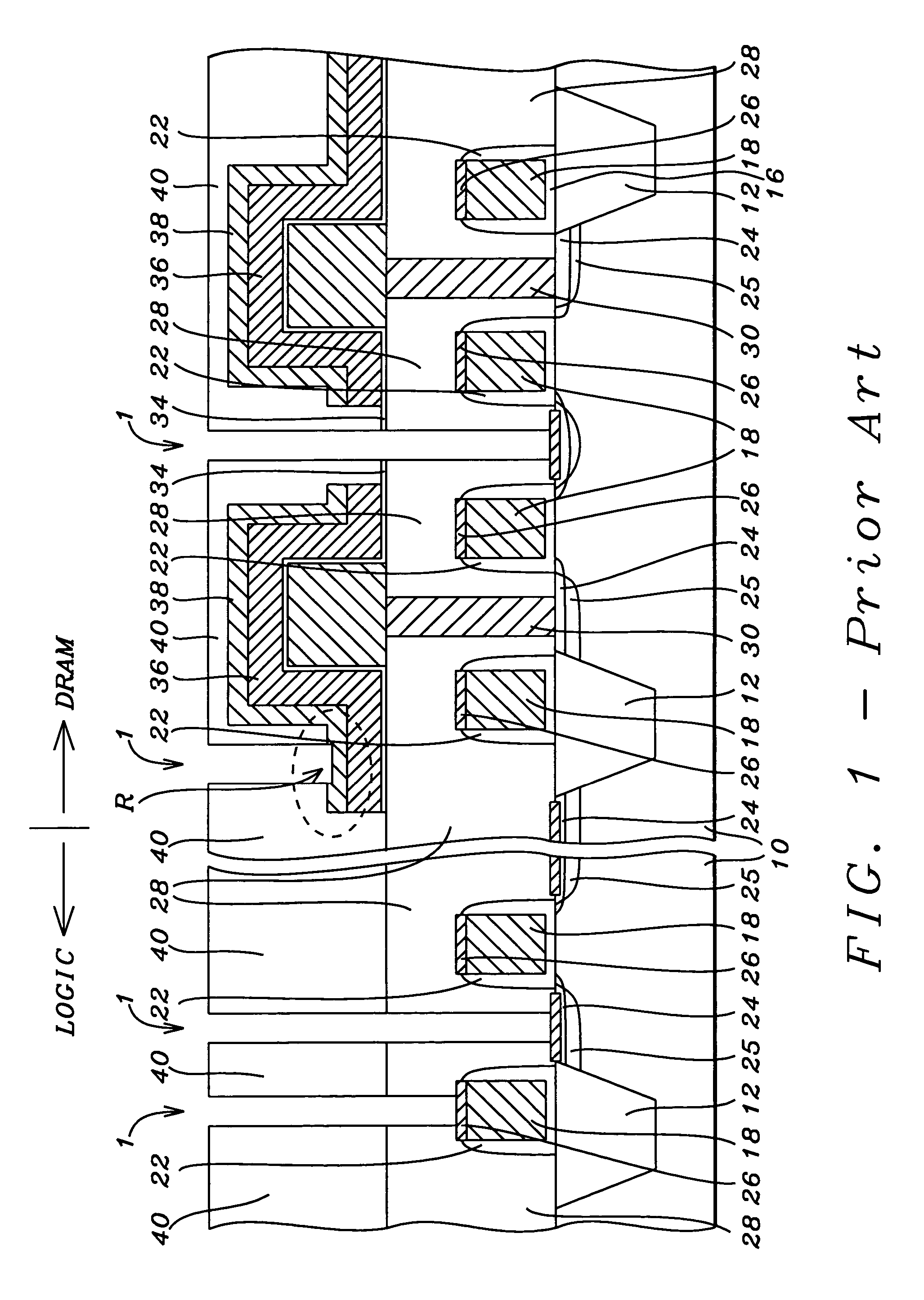

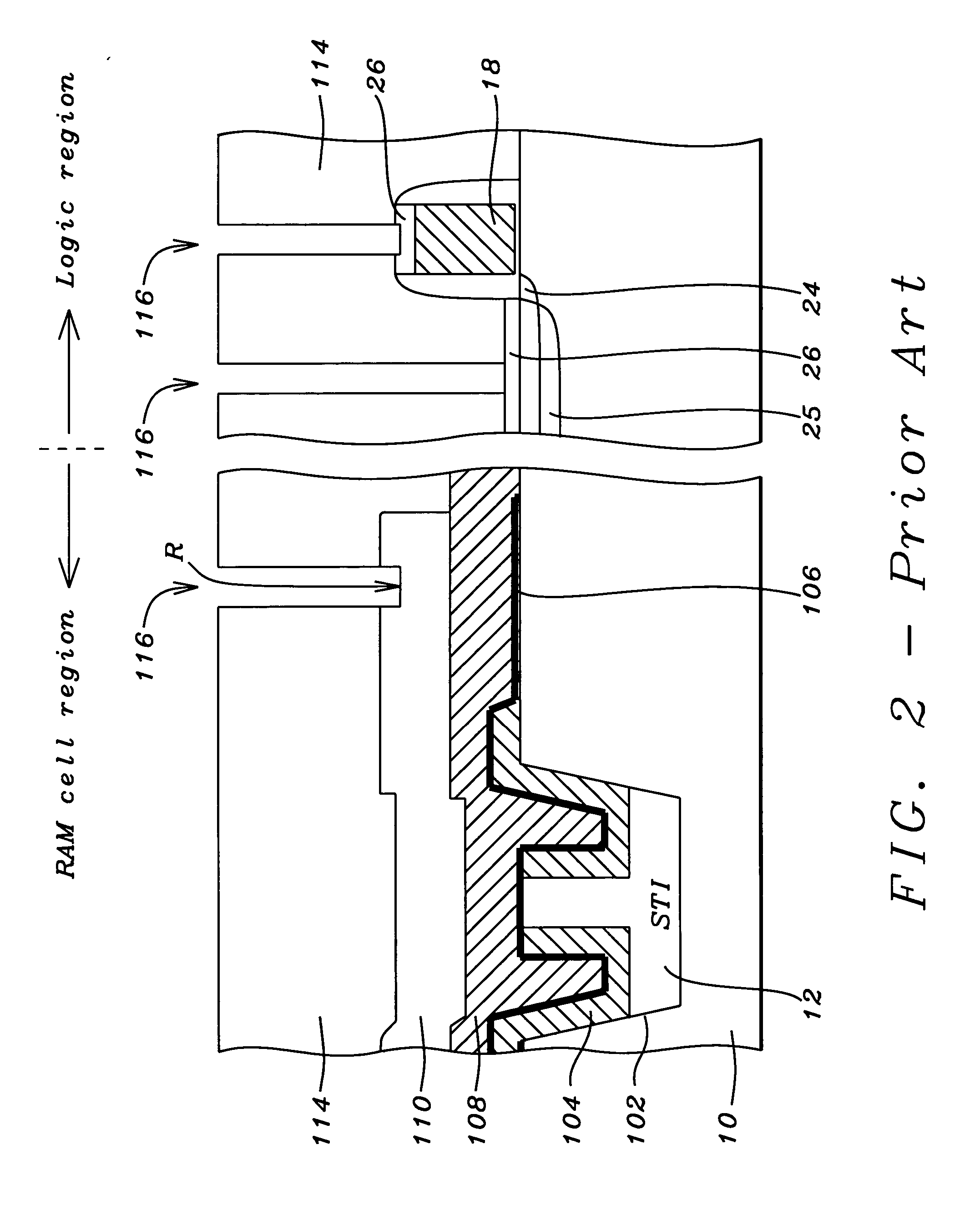

Structure for reducing leakage currents and high contact resistance for embedded memory and method for making same

ActiveUS20050093147A1More alignment toleranceReduce manufacturing costTransistorSemiconductor/solid-state device detailsDrain currentCapacitor

A method for fabricating an insulating layer having contact openings of varying depths for logic / DRAM circuits is achieved using a single mask and etch step. After forming stacked or trench capacitors, a planar insulating layer is formed. Contact openings are etched in the planar insulating layer to the substrate, and contact openings that extend over the edge of the stacked or trench capacitor top electrode, having an ARC, are etched using a novel mask design and a single etching step. This allows one to make contacts to the substrate without overetching while making low-resistance contacts to the sidewall of the capacitor top electrode. In the trench capacitor open areas are formed to facilitate making contact openings that extend over the top electrode. A series of contact openings that are skewed or elongated also improve the latitude in alignment tolerance.

Owner:TAIWAN SEMICON MFG CO LTD

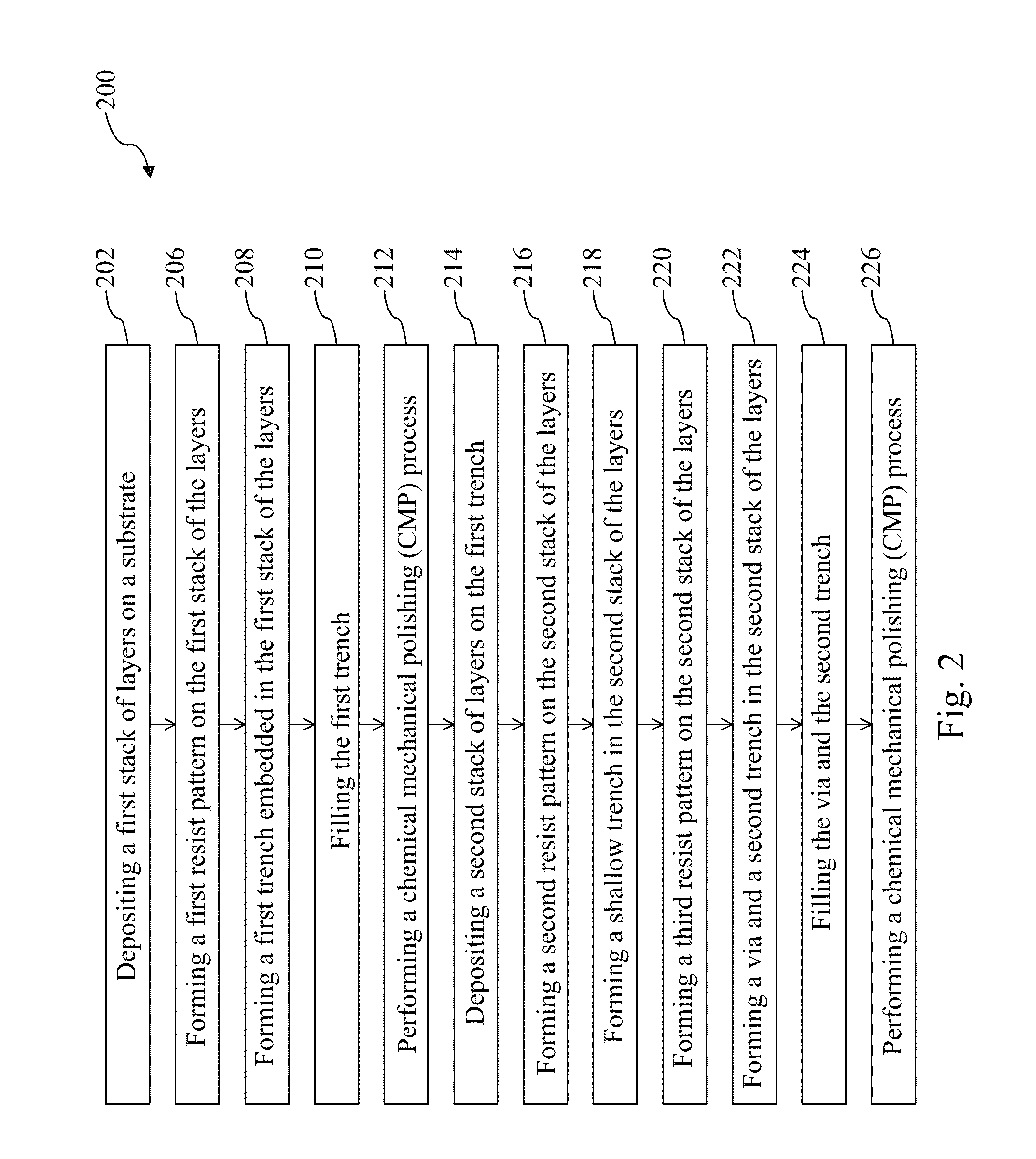

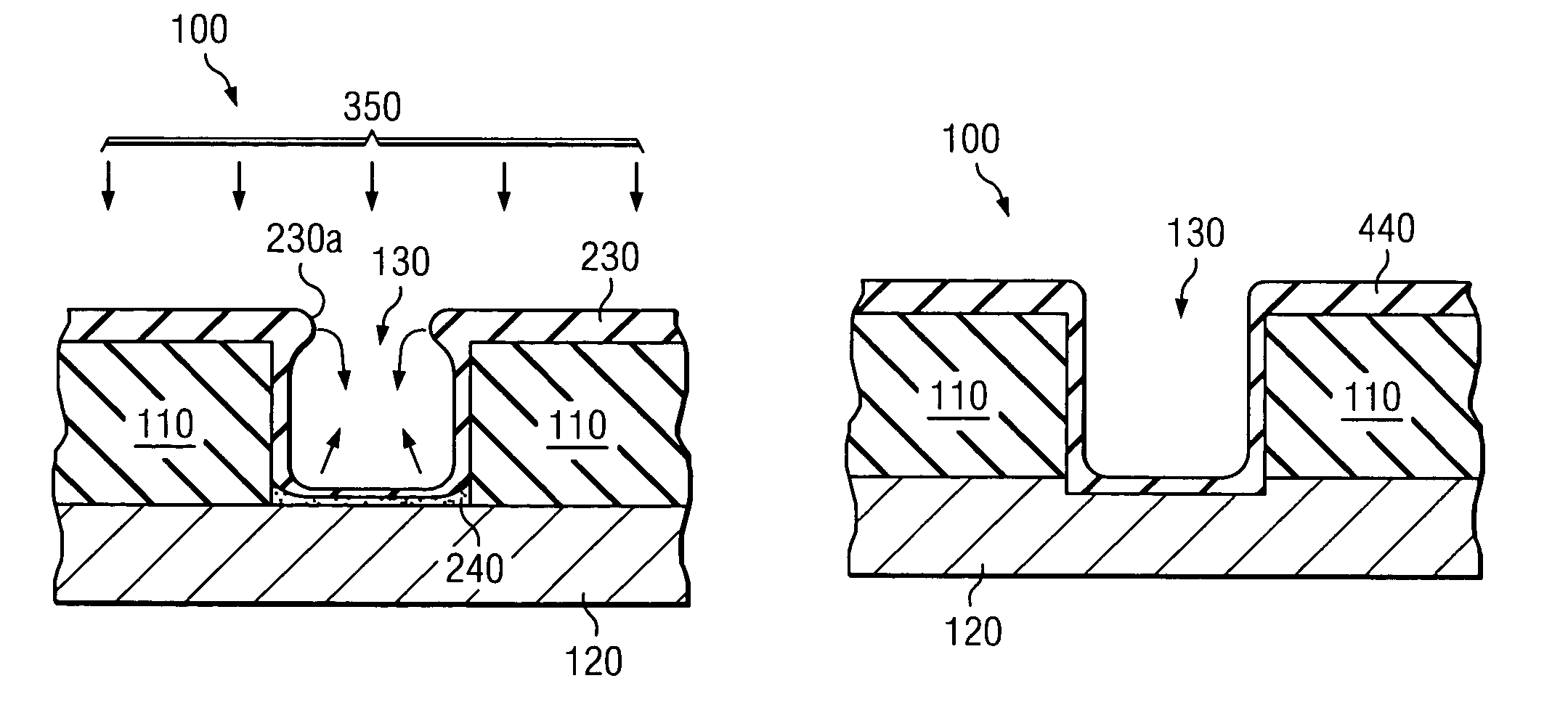

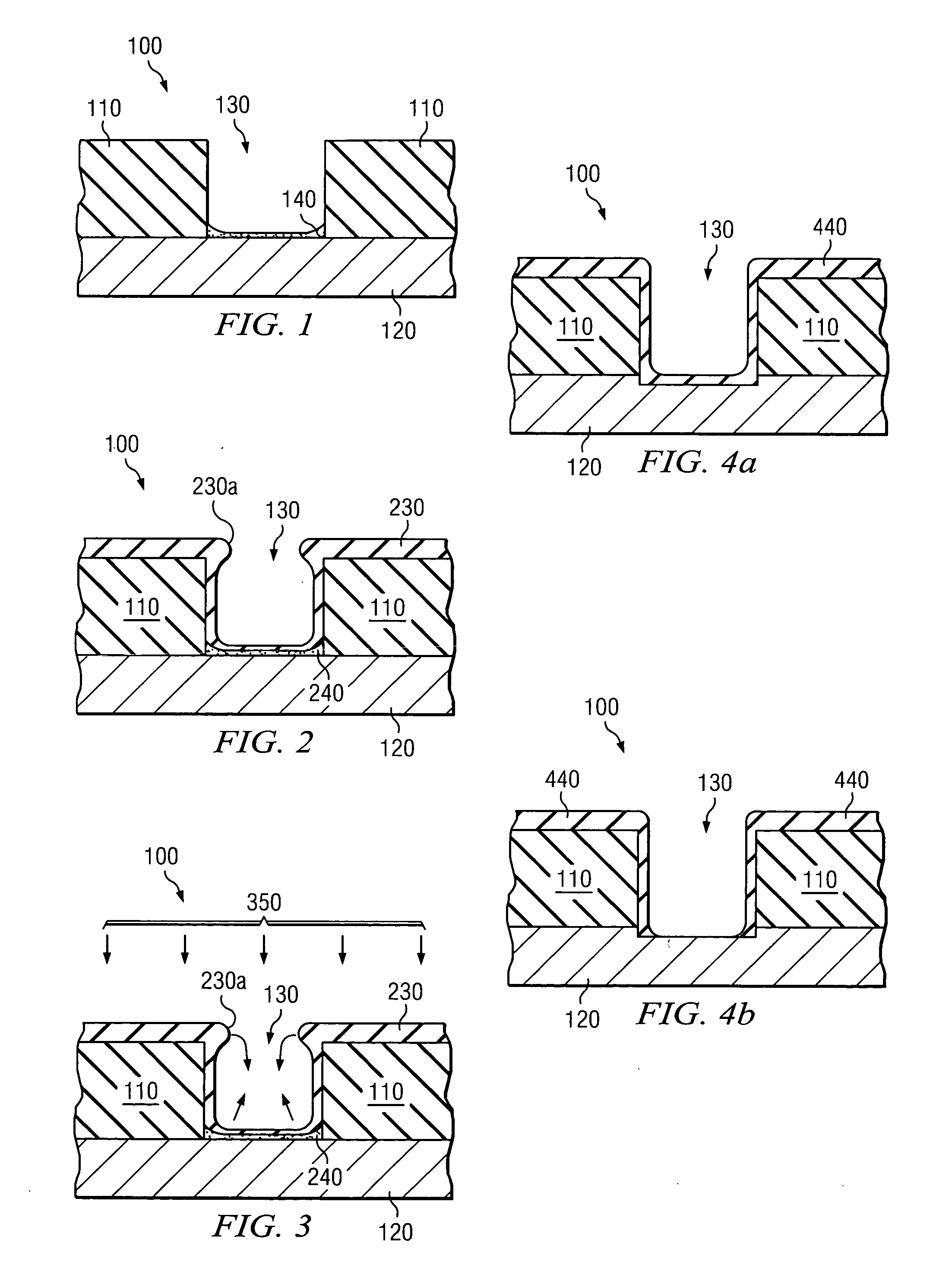

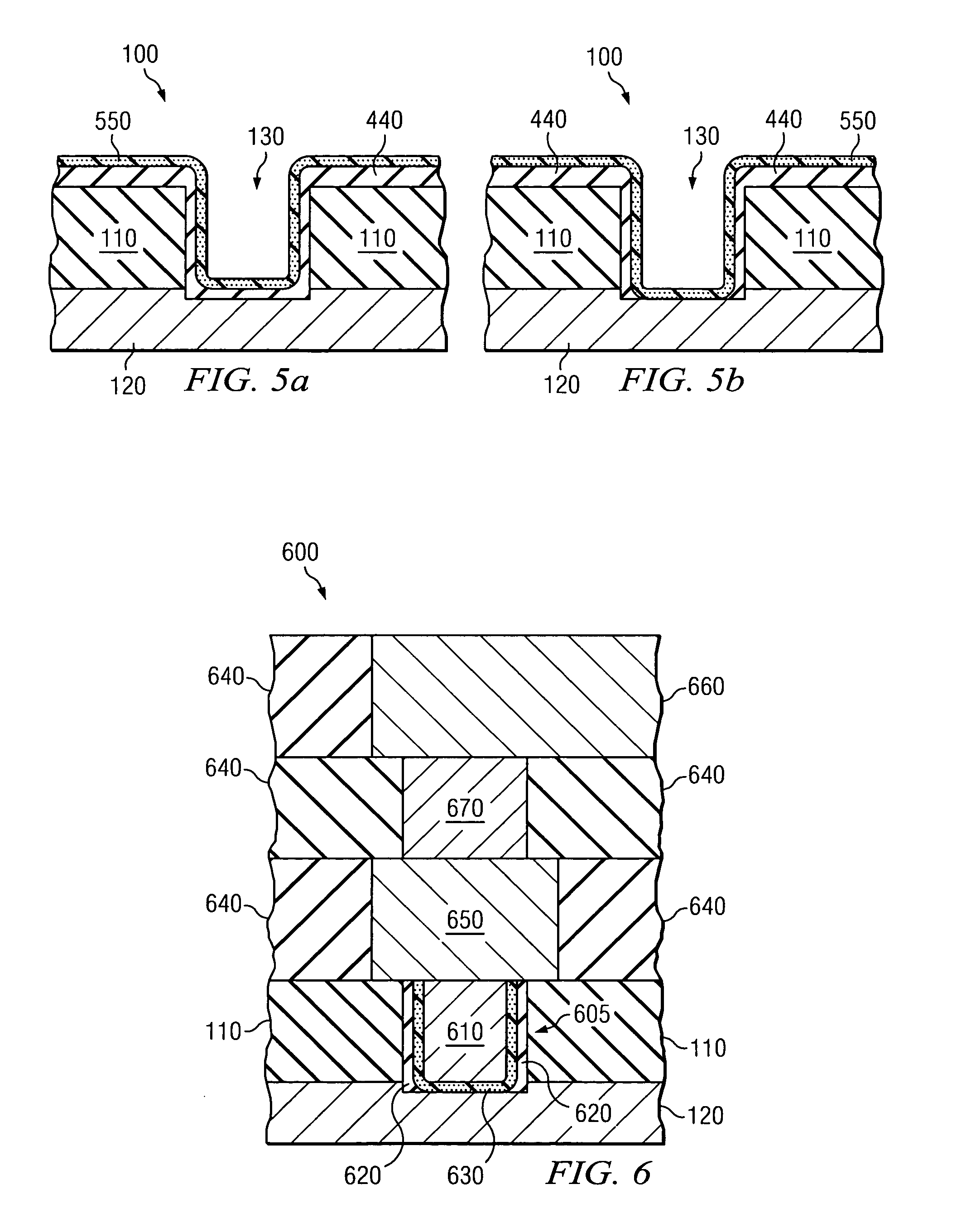

Contact resistance reduction by new barrier stack process

ActiveUS20060121724A1Reduce reentrant profileSemiconductor/solid-state device manufacturingEtchingEngineering

The present invention provides a method for forming an interconnect on a semiconductor substrate 100. The method includes forming an opening 230 over an inner surface of the opening 130, the depositing forming a reentrant profile near a top portion of the opening 130. A portion of barrier 230 is etched, which removes at least a portion of the barrier 230 to reduce the reentrant profile. The etching also removes at least a portion of the barrier 230 layer at the bottom of the opening 130.

Owner:TEXAS INSTR INC

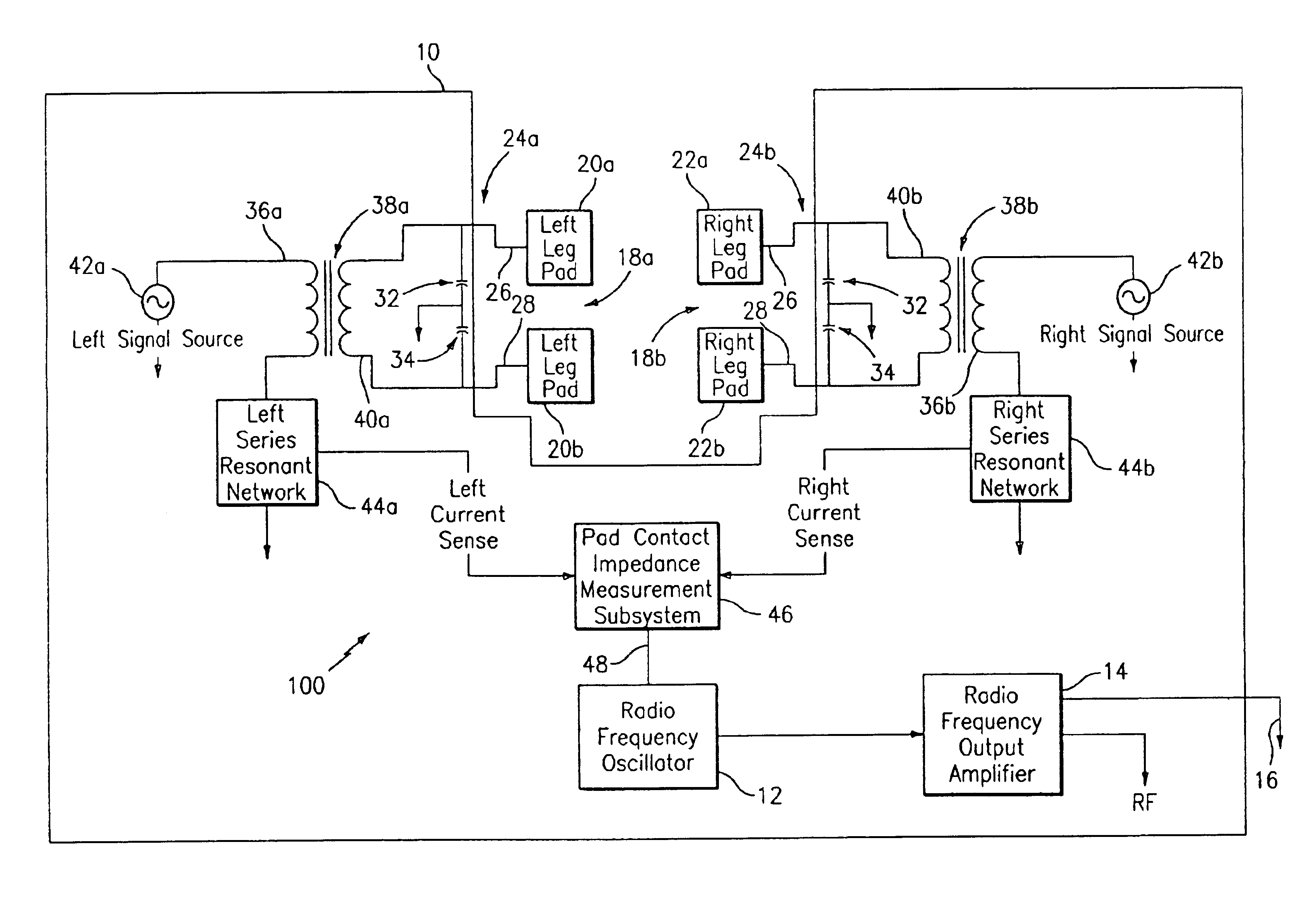

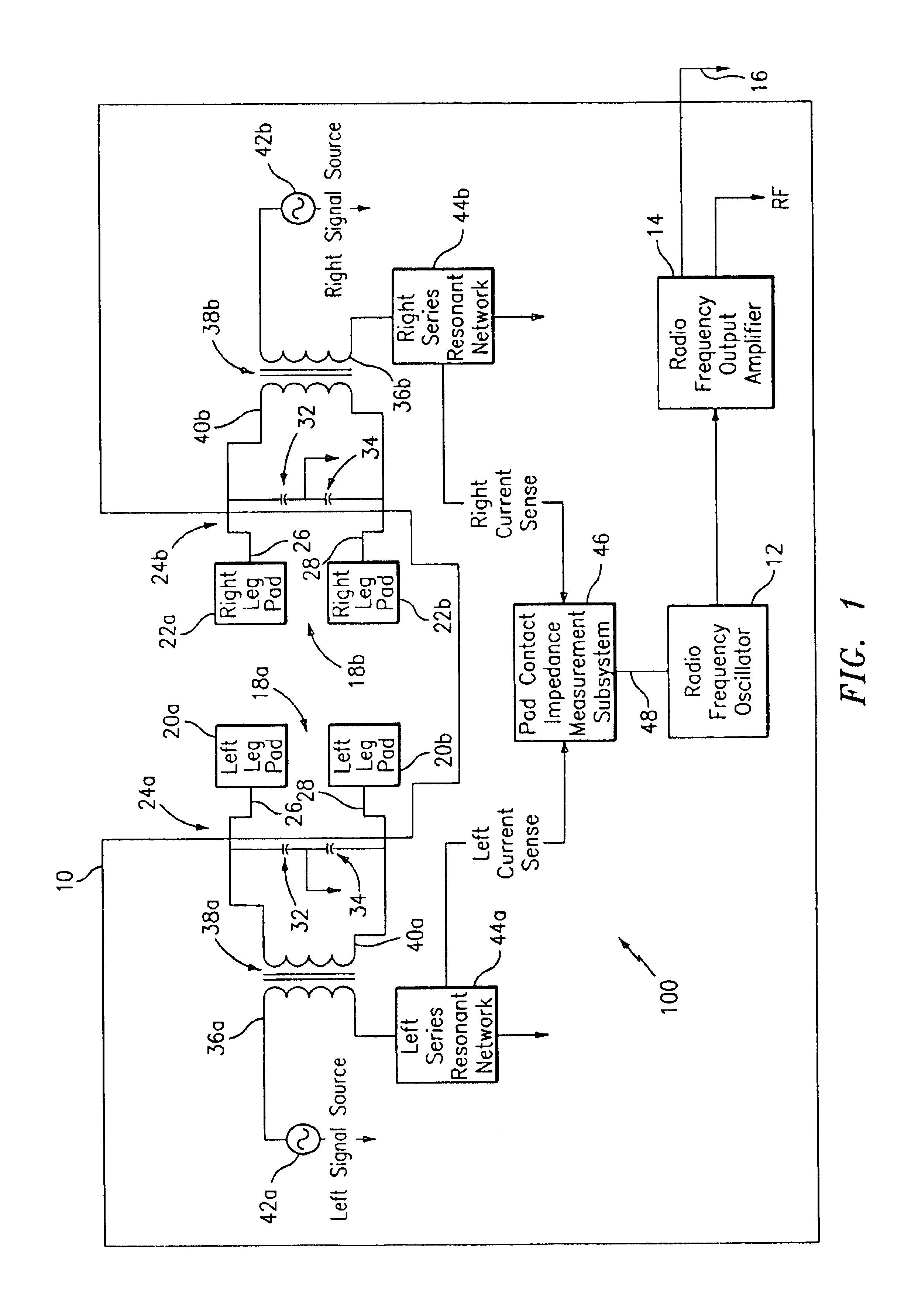

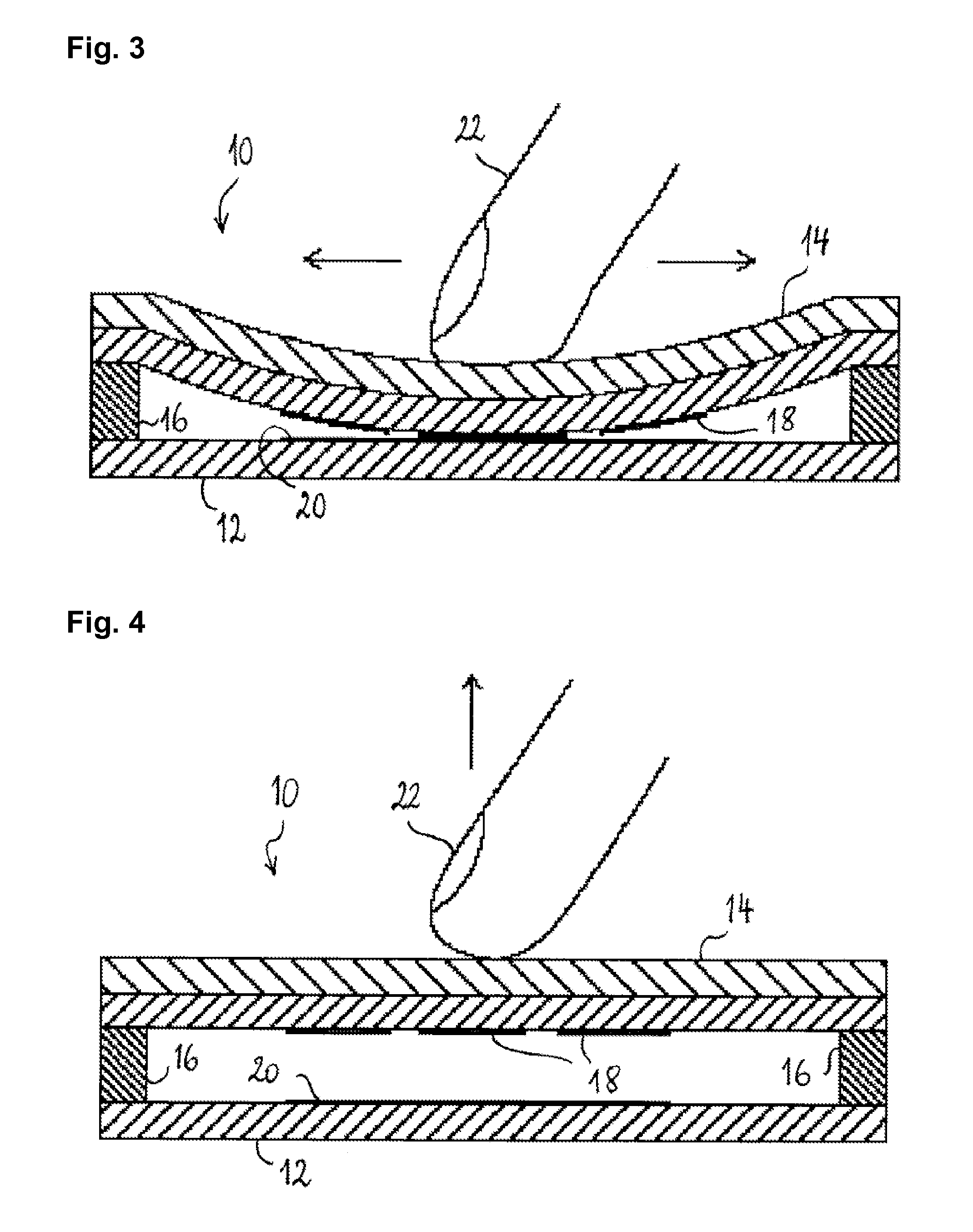

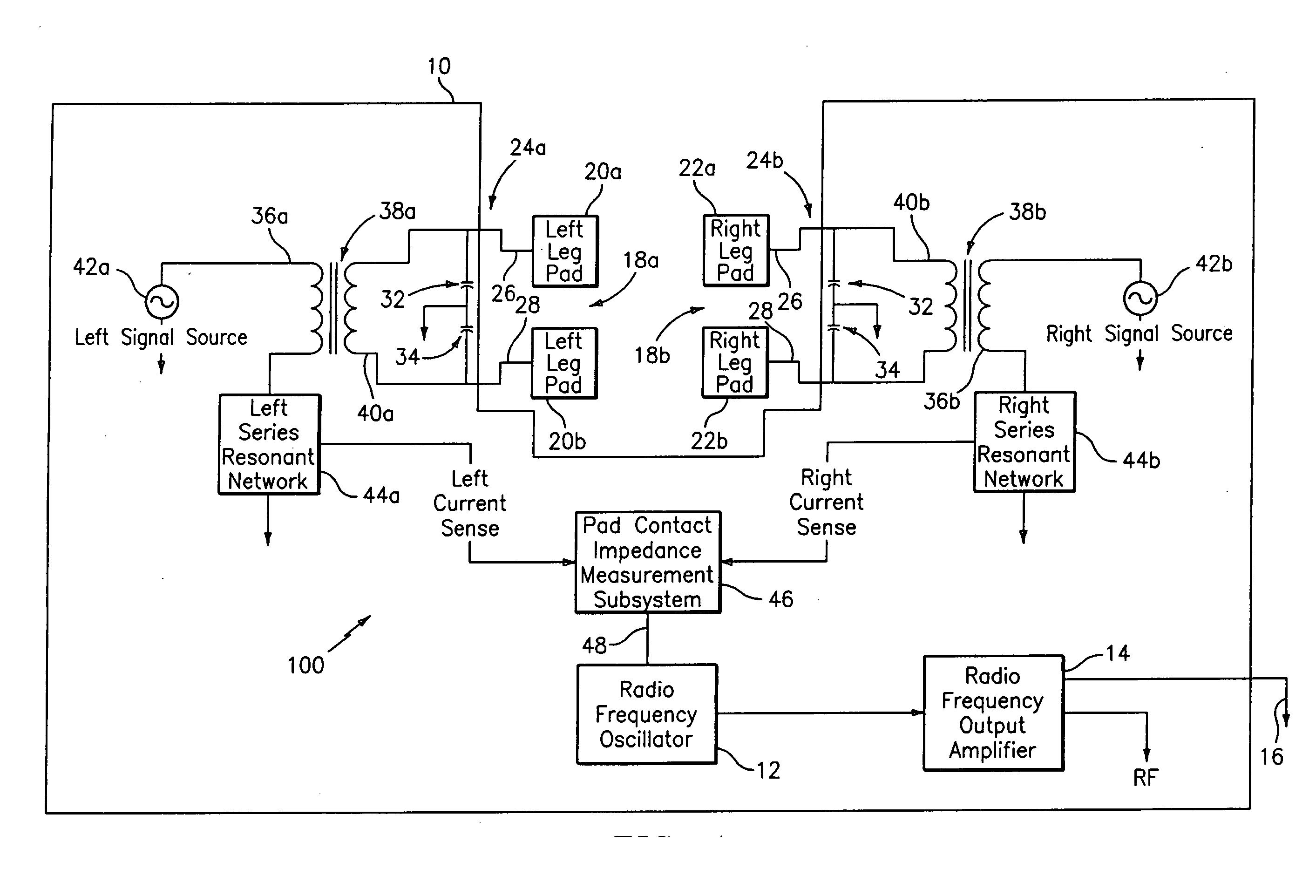

Multiple RF return pad contact detection system

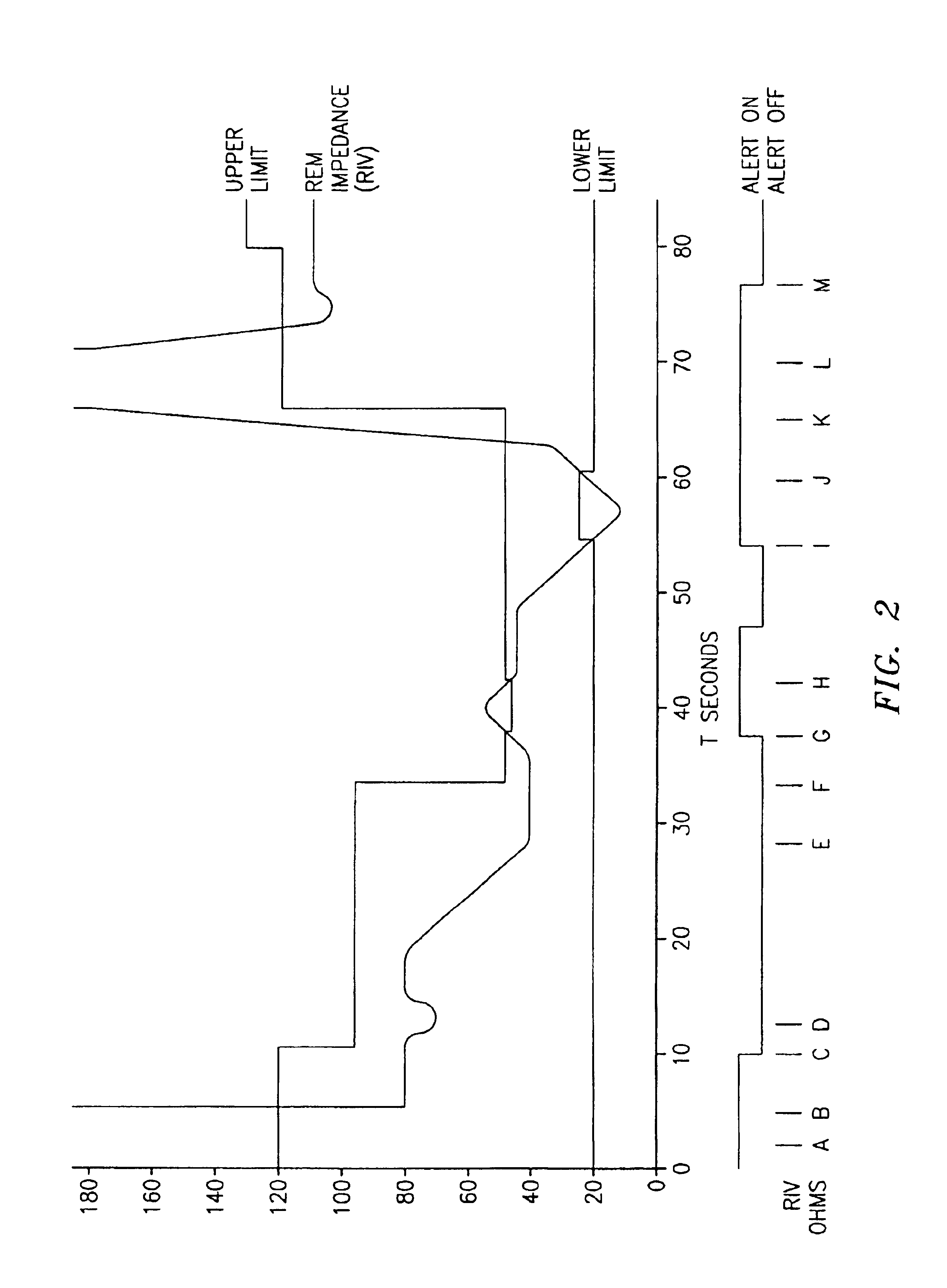

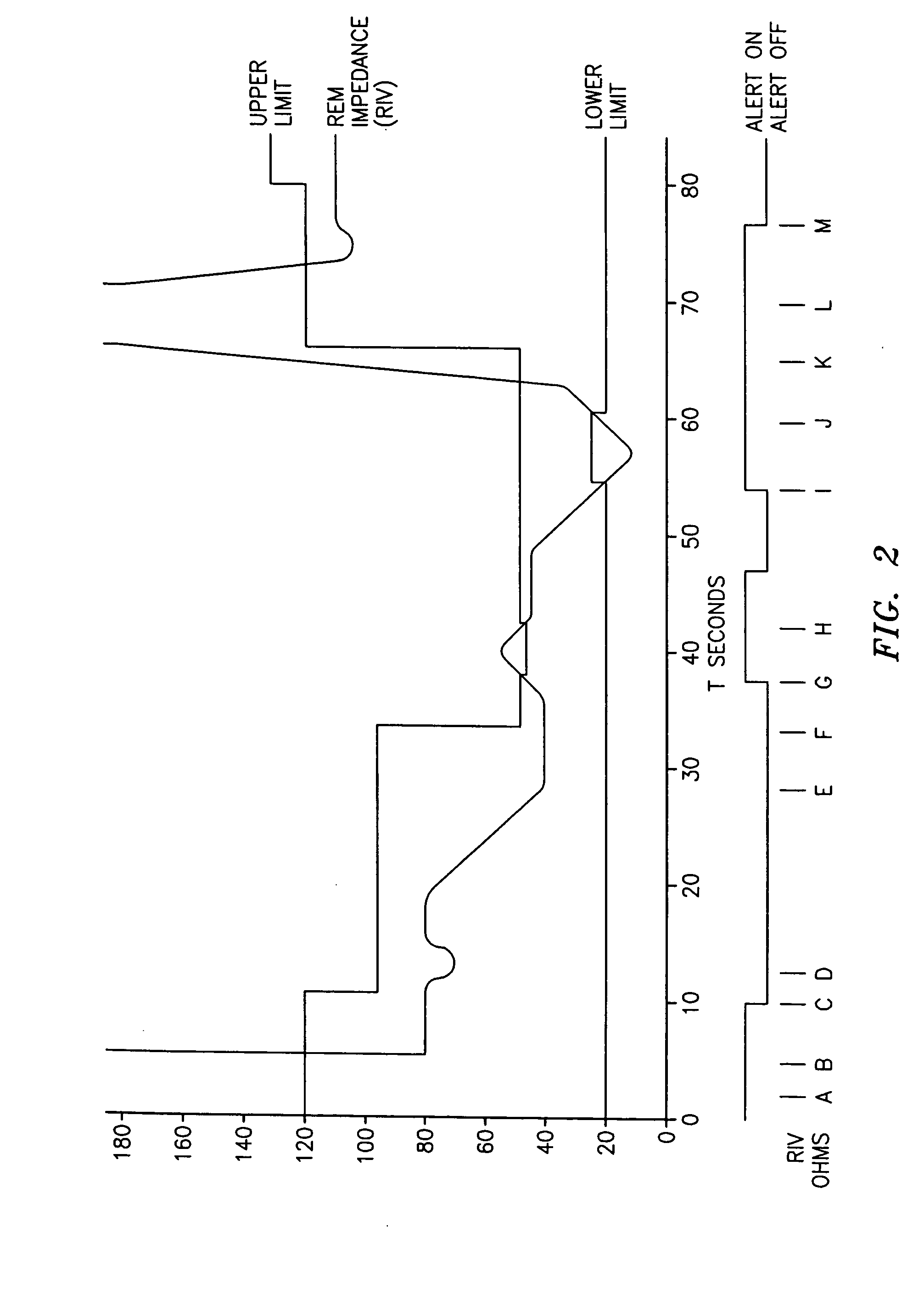

InactiveUS6860881B2Eliminating and minimizing riskCharacteristic is differentSurgical instruments for heatingElectrical resistance and conductanceContact impedance

A multiple RF return pad contact detection system is provided which is adaptive to different physiological characteristics of patients without being susceptible to electrosurgical current interference (e.g., interference or measurement interaction between components of the detection system). The detection system can measure or sense the contact resistance or impedance between the patient and pairs of RF return pads or return electrodes where multiple pairs of RF return pads are utilized due to the high current frequently needed during electrosurgery while eliminating or minimizing the risk of measurement interaction between the RF return pad pairs. The system allows for the independent and simultaneous measurement of the pad contact impedance for each pair of RF return pads. If the impedance of any pad pair is above a predetermined limit, the system turns off or reduces the electrosurgical output of the electrosurgical generator to prevent excess heating. The system eliminates or minimizes interference or measurement interaction between the pad pairs by providing a different signal source frequency for each pad contact pair, but a frequency which matches an associated series resonant network frequency. The current that flows in the series resonant network is a direct reflection or function of the pad impedance of the corresponding pad pair.

Owner:COVIDIEN AG

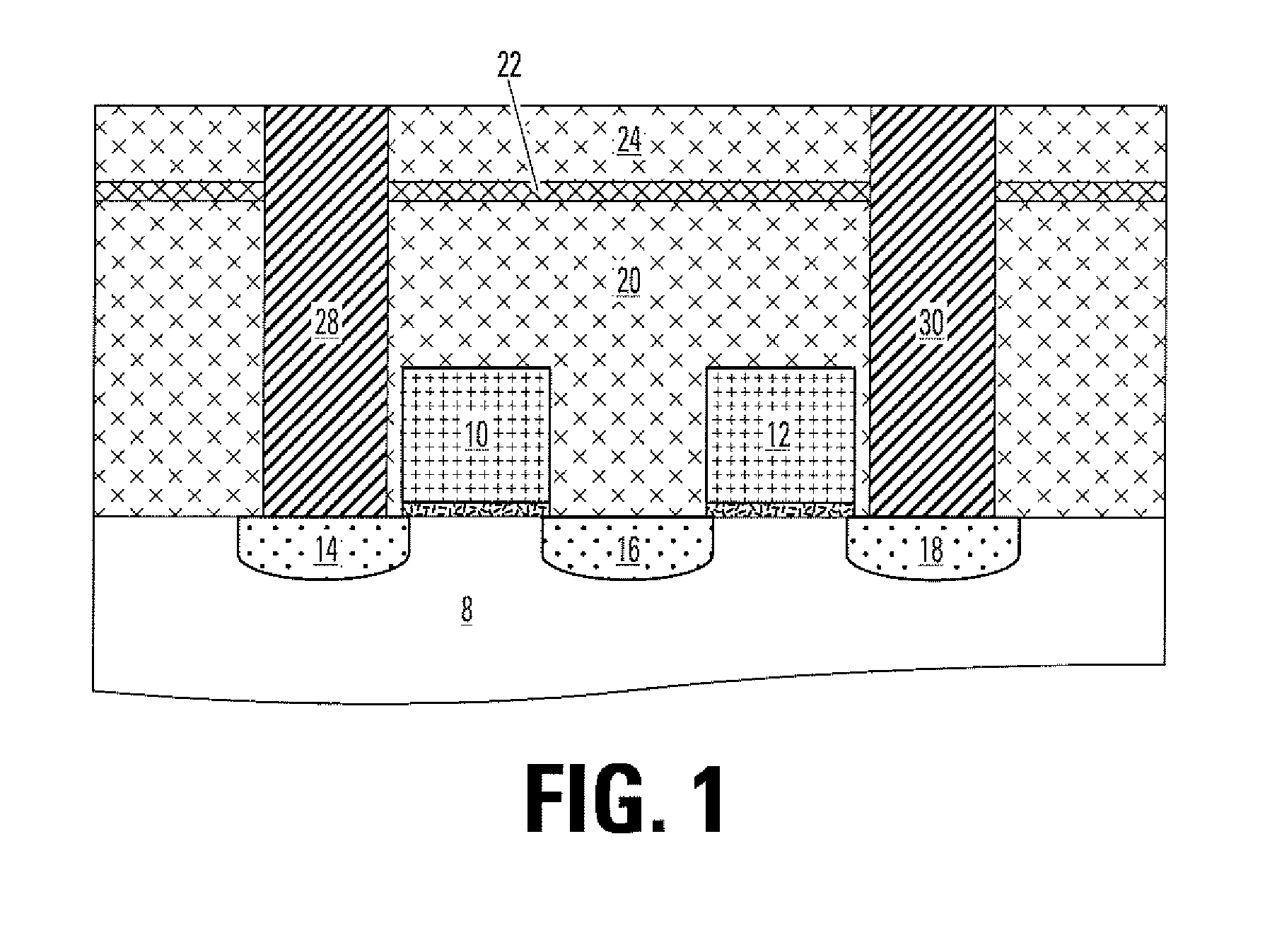

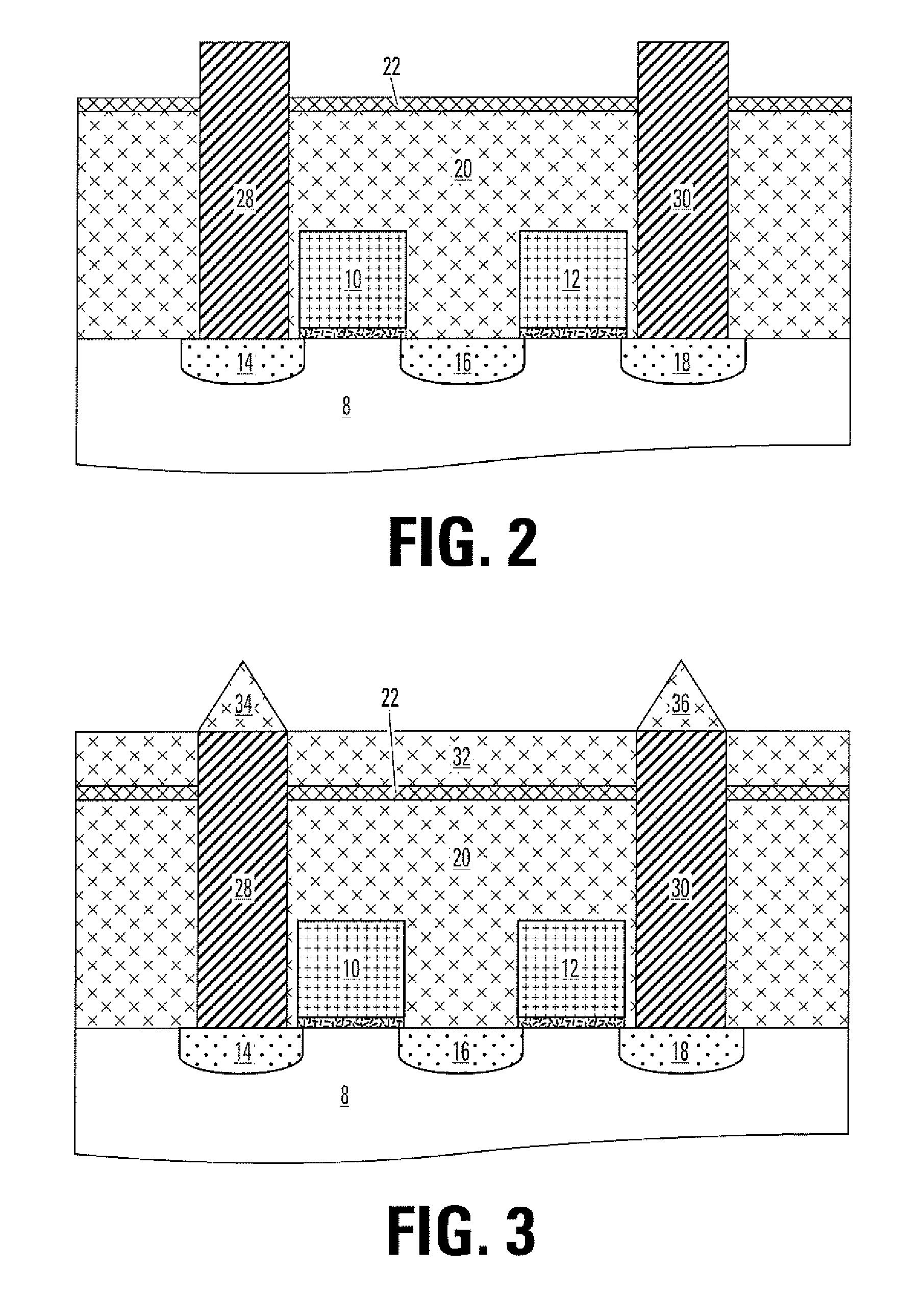

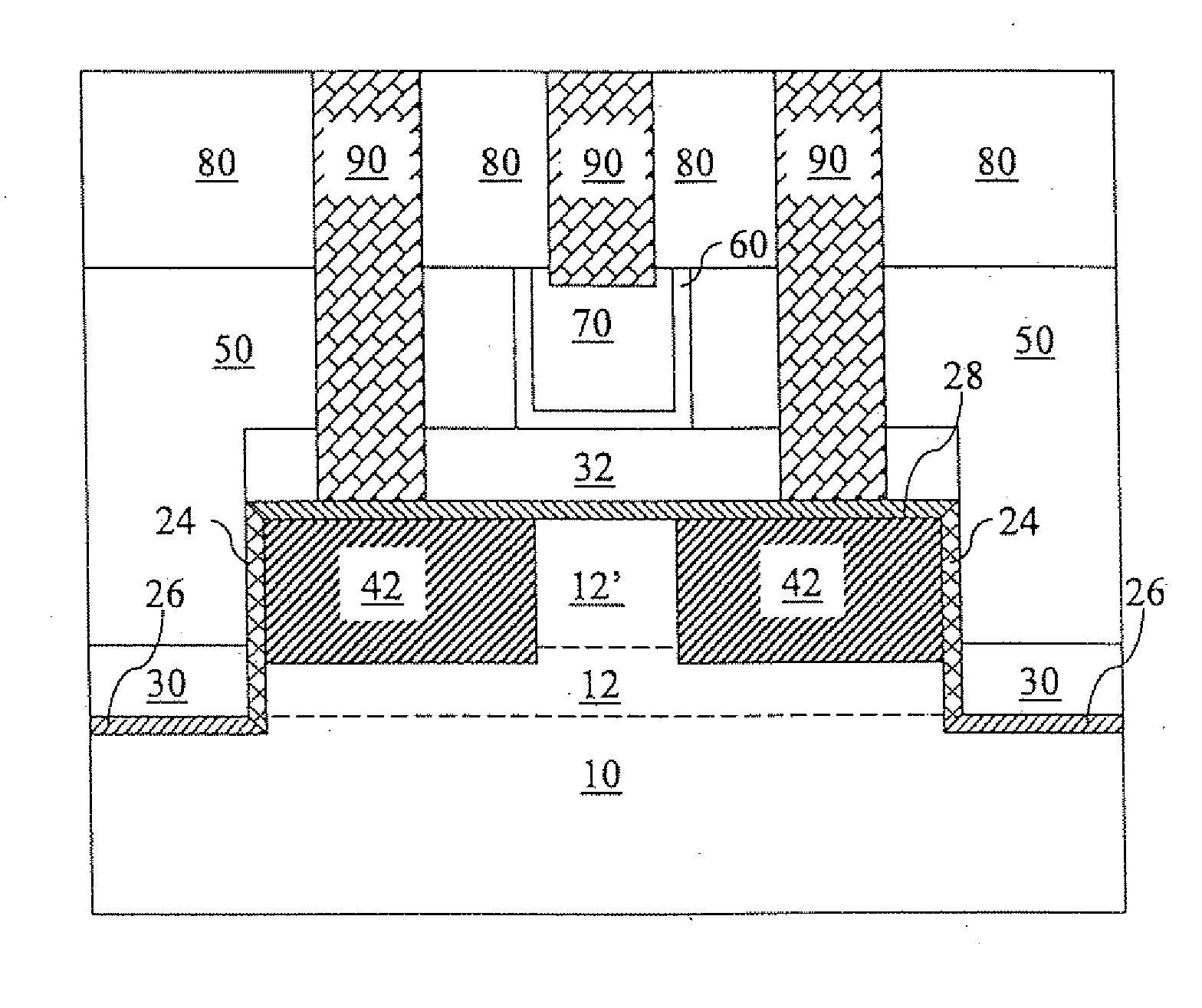

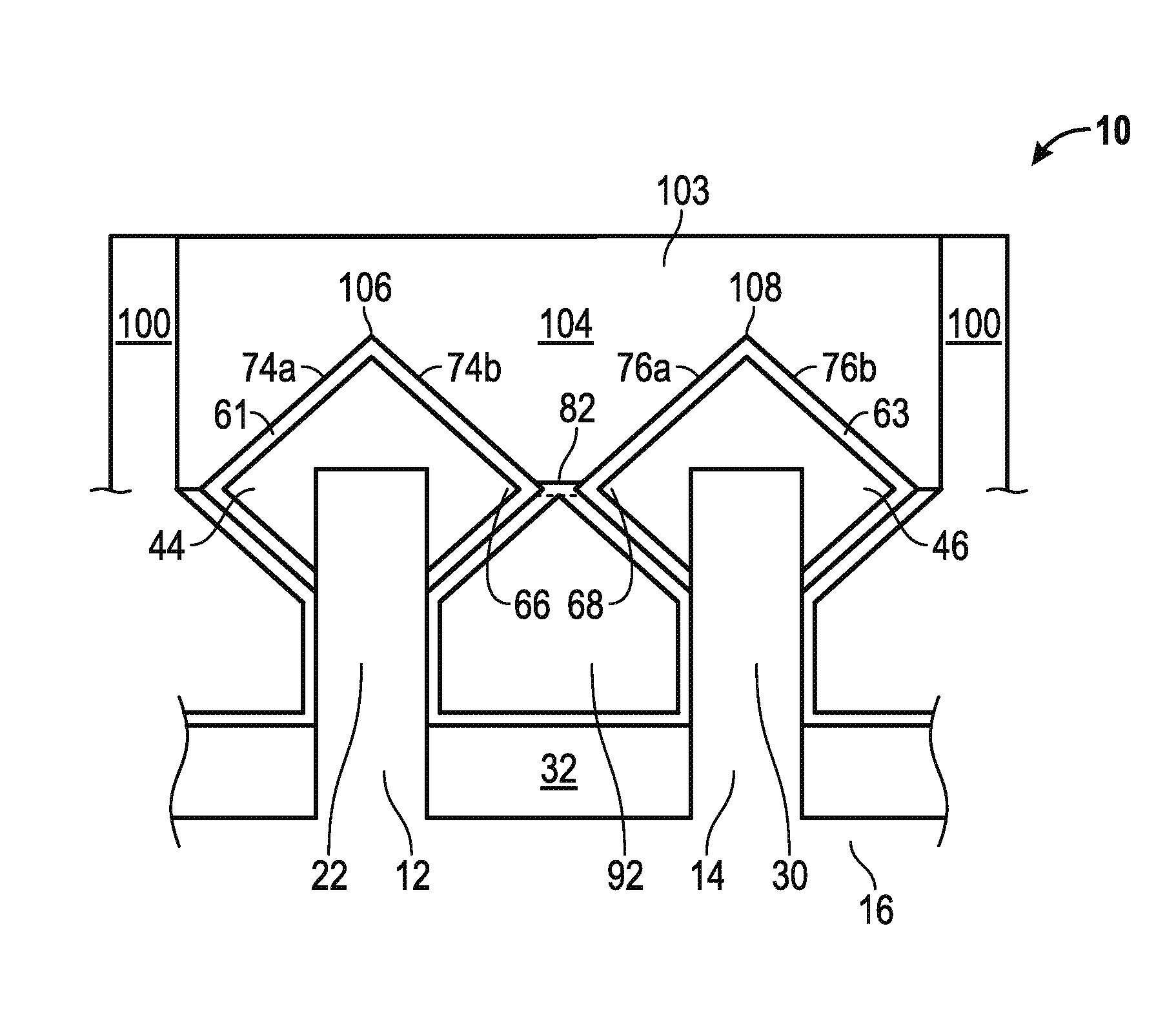

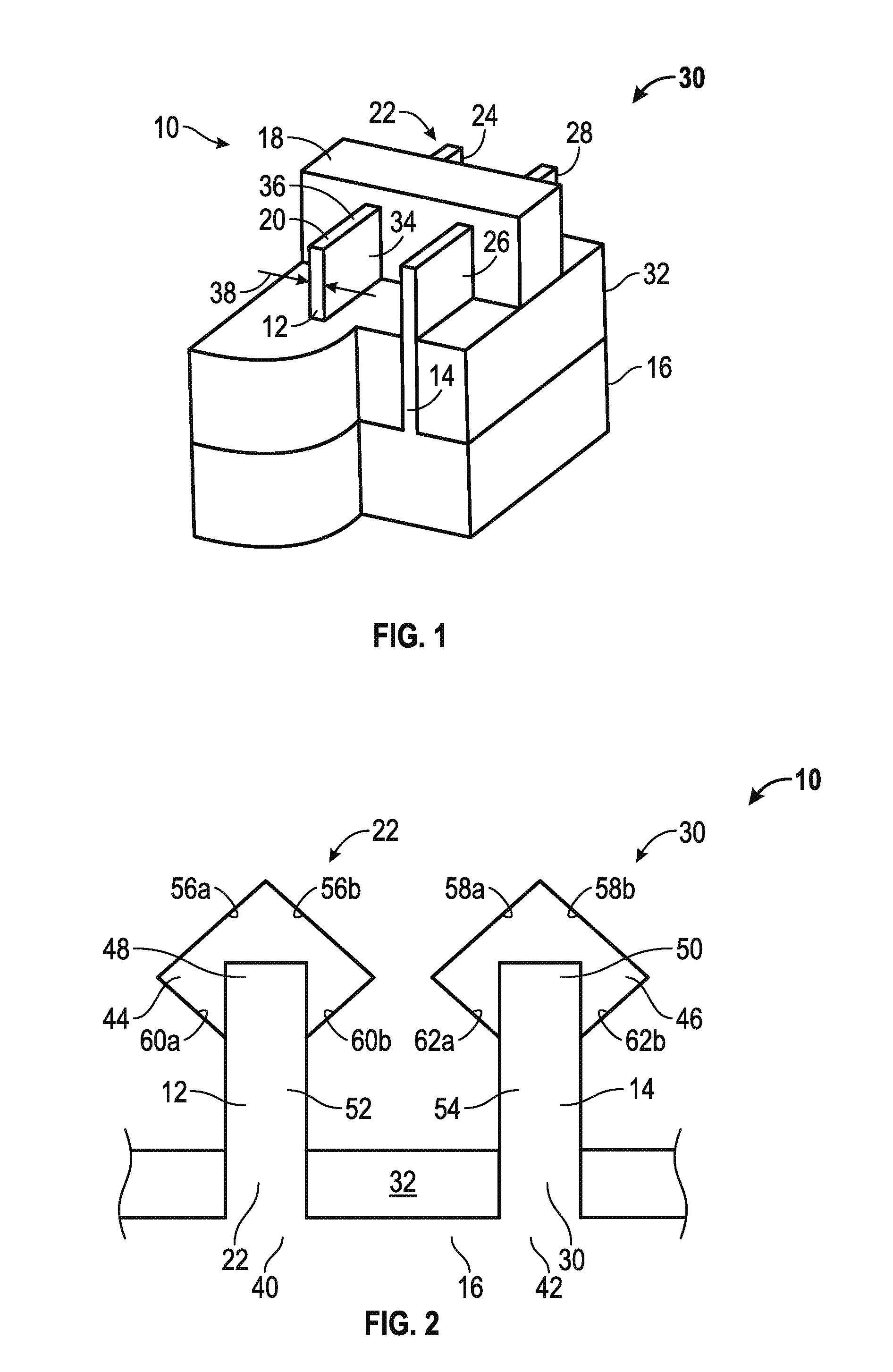

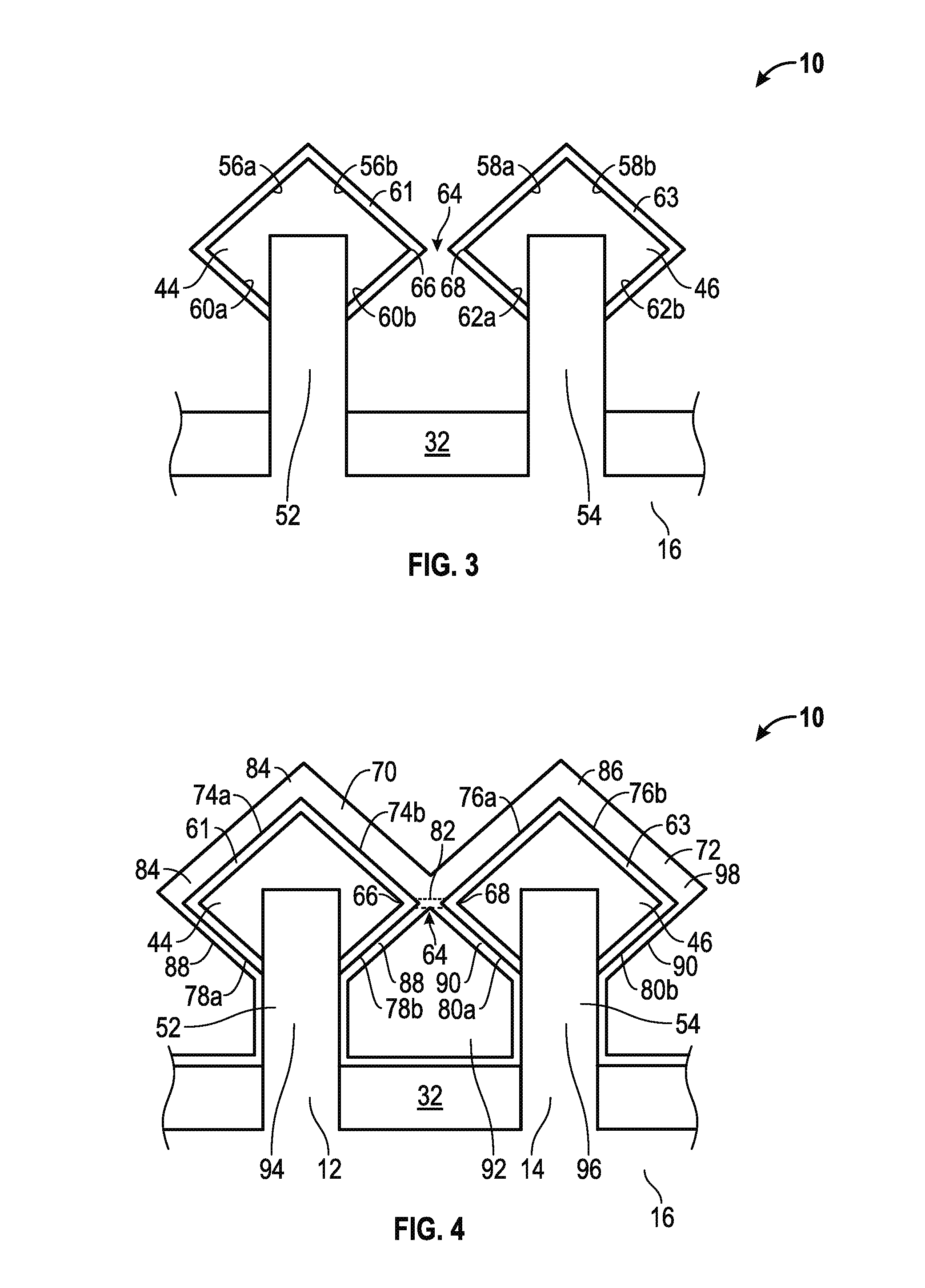

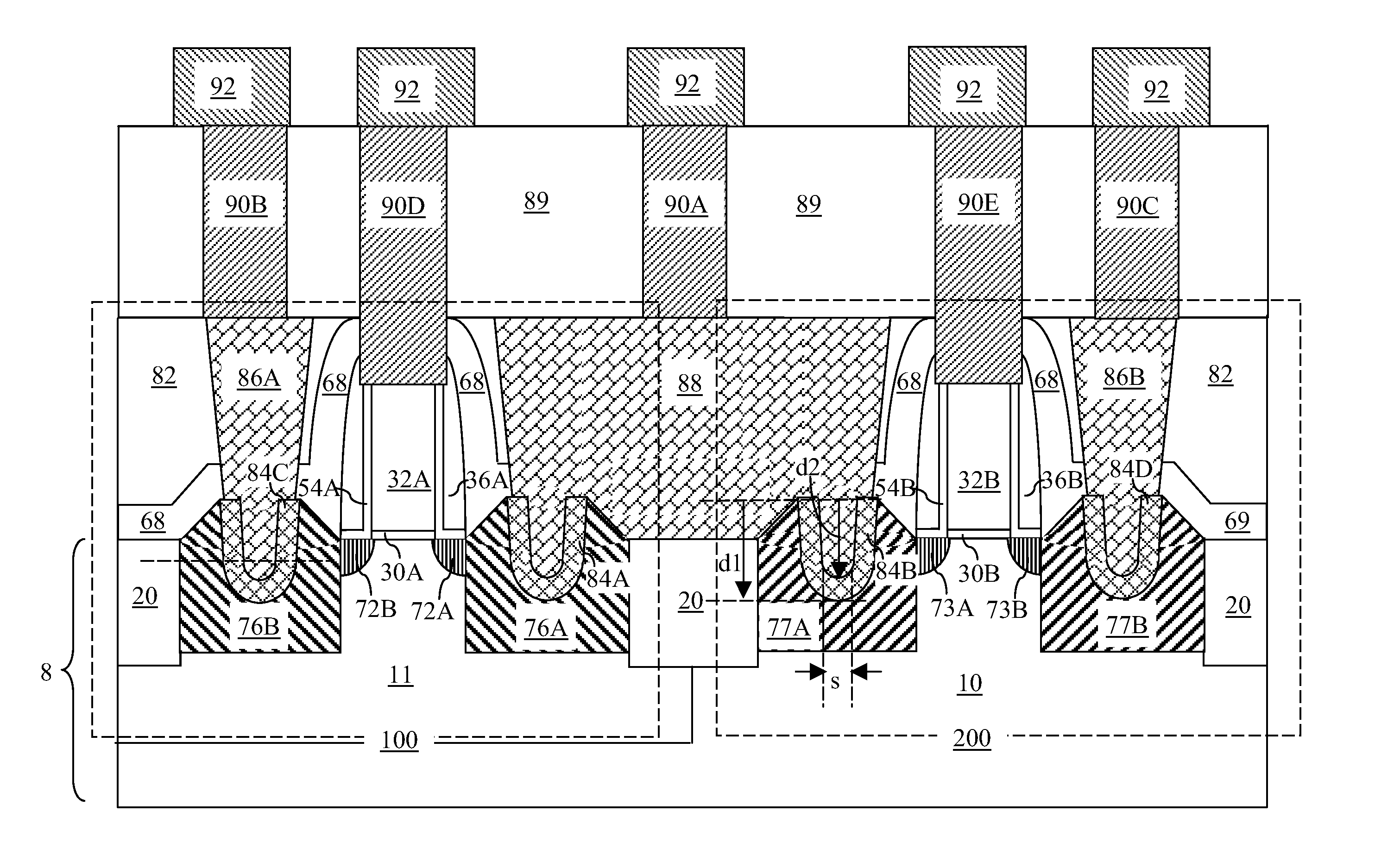

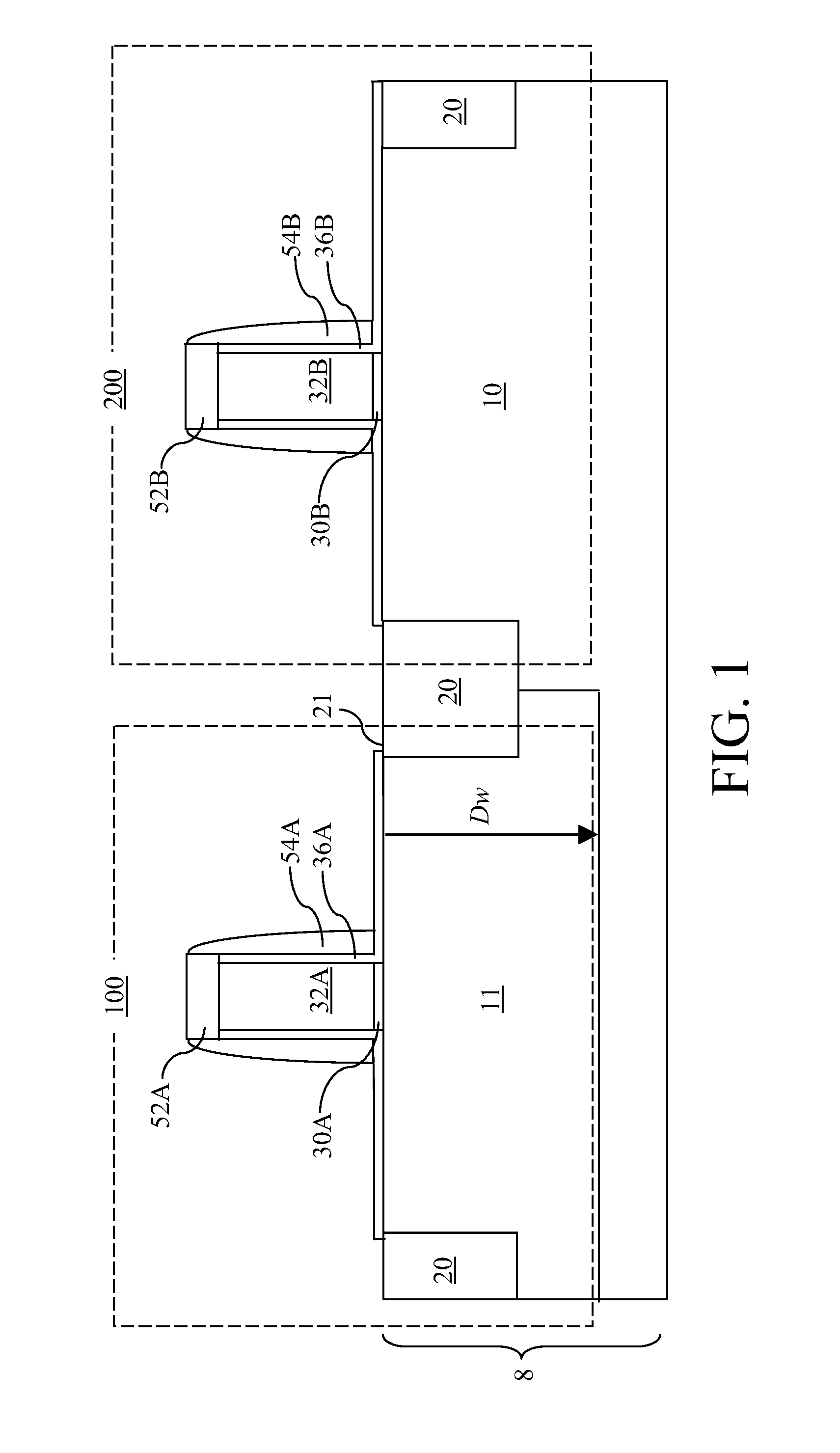

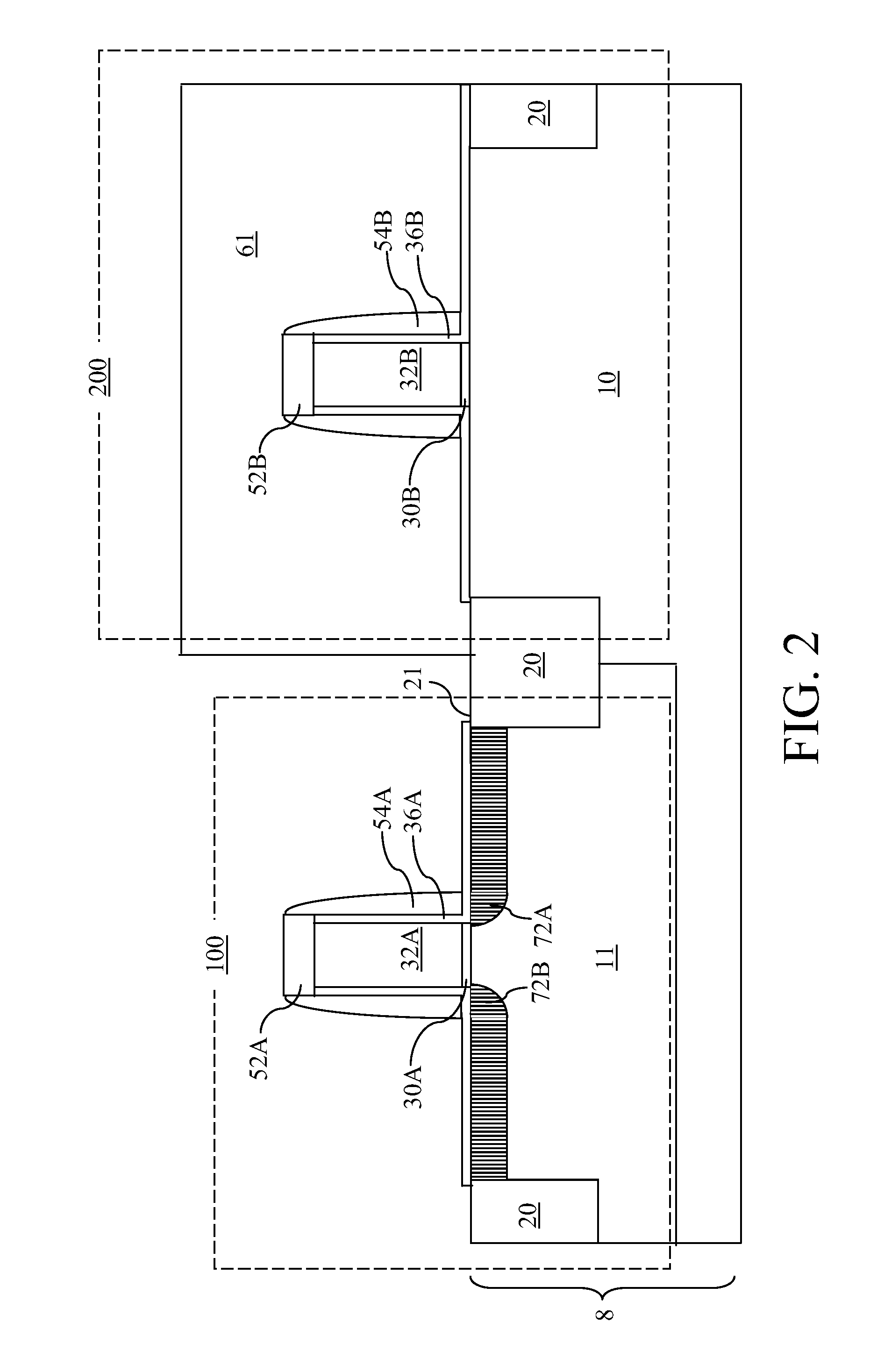

Integrated circuits including finfet devices with lower contact resistance and reduced parasitic capacitance and methods for fabricating the same

Integrated circuits and methods for fabricating integrated circuits are provided. In one example, an integrated circuit includes a semiconductor substrate. A first fin and a second fin are adjacent to each other extending from the semiconductor substrate. The first fin has a first upper section and the second fin has a second upper section. A first epi-portion overlies the first upper section and a second epi-portion overlies the second upper section. A first silicide layer overlies the first epi-portion and a second silicide layer overlies the second epi-portion. The first and second silicide layers are spaced apart from each other to define a lateral gap. A dielectric spacer is formed of a dielectric material and spans the lateral gap. A contact-forming material overlies the dielectric spacer and portions of the first and second silicide layers that are laterally above the dielectric spacer.

Owner:IBM CORP +1

Method for forming an integrated circuit

ActiveUS7402872B2Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

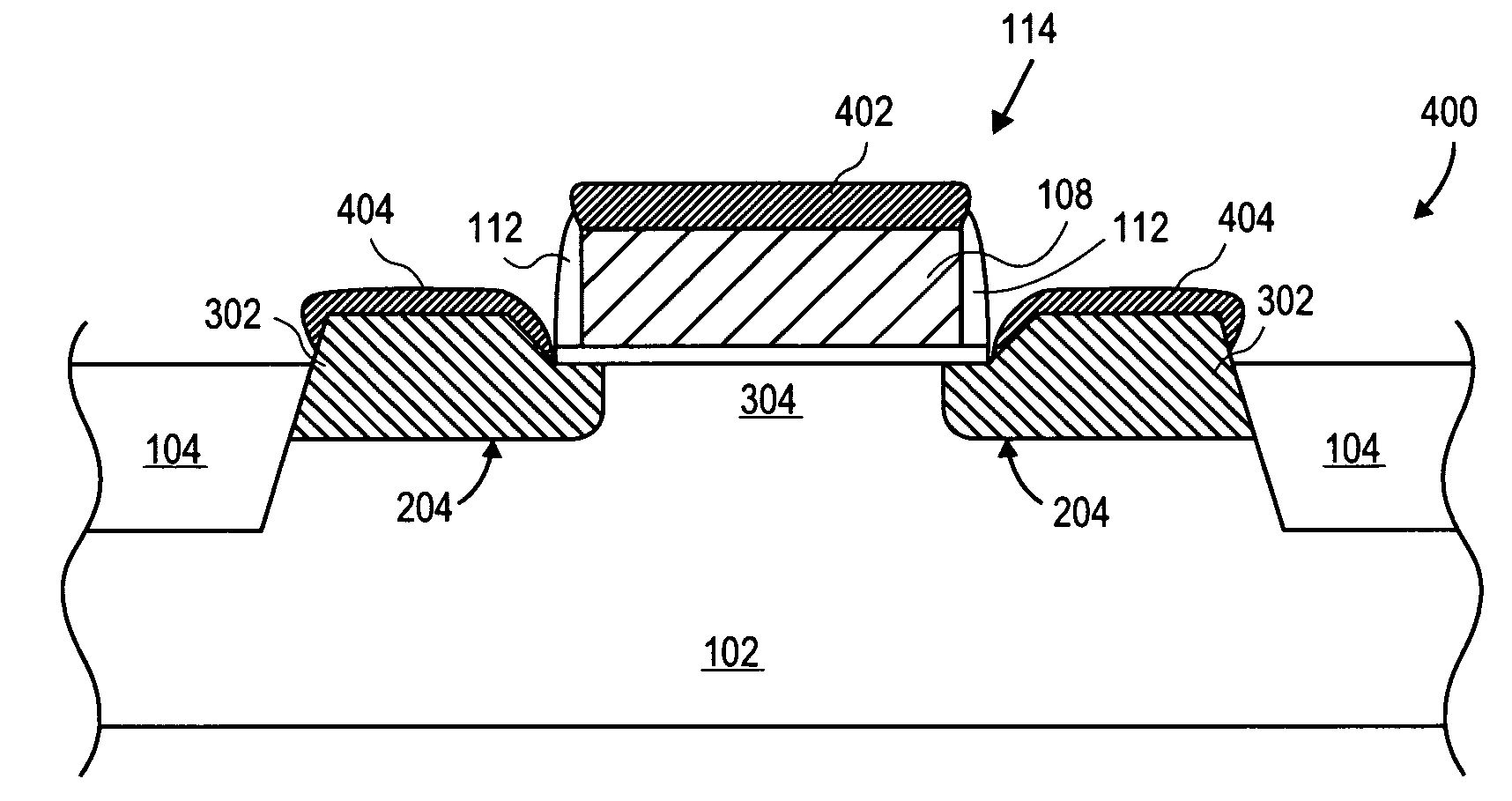

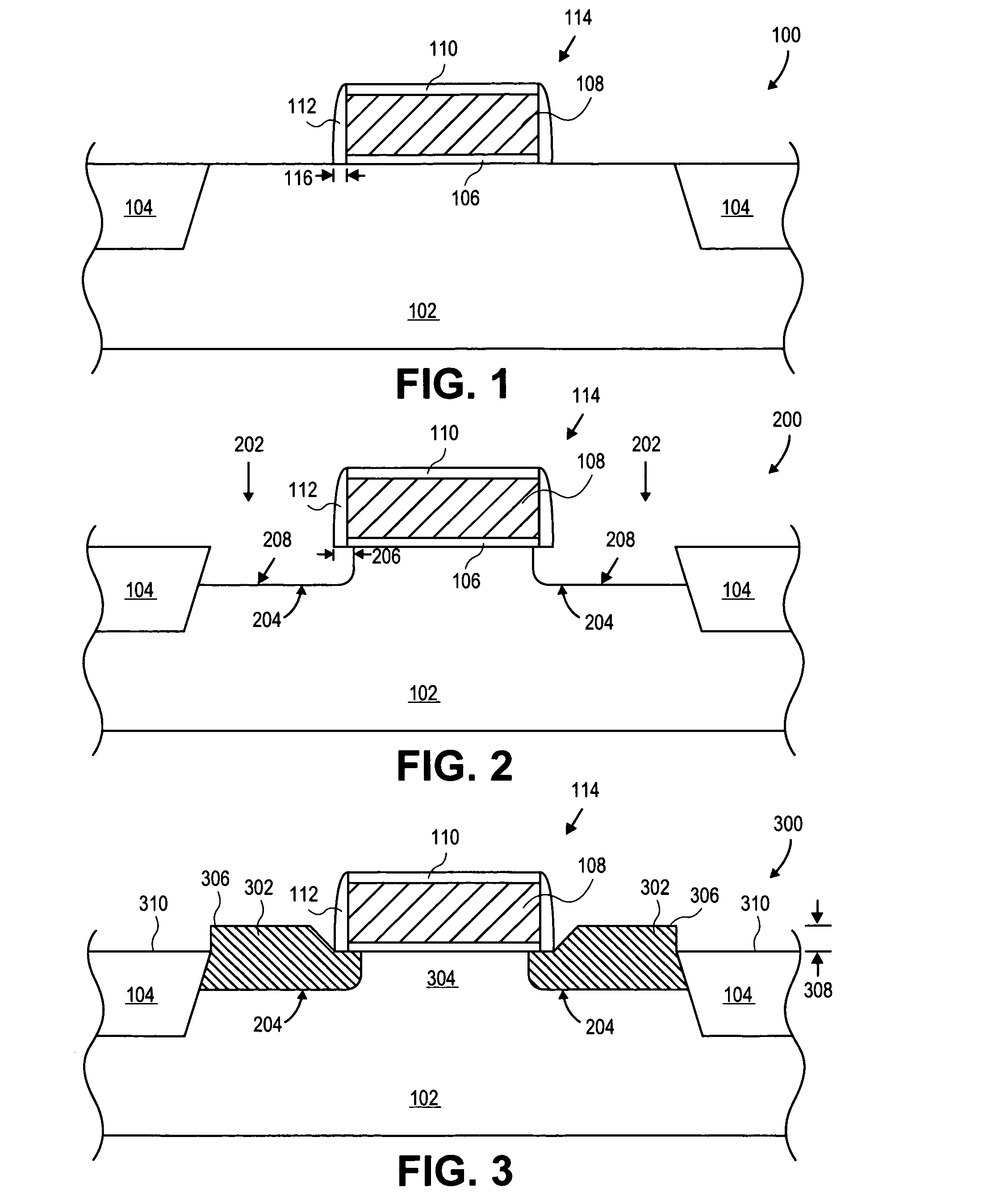

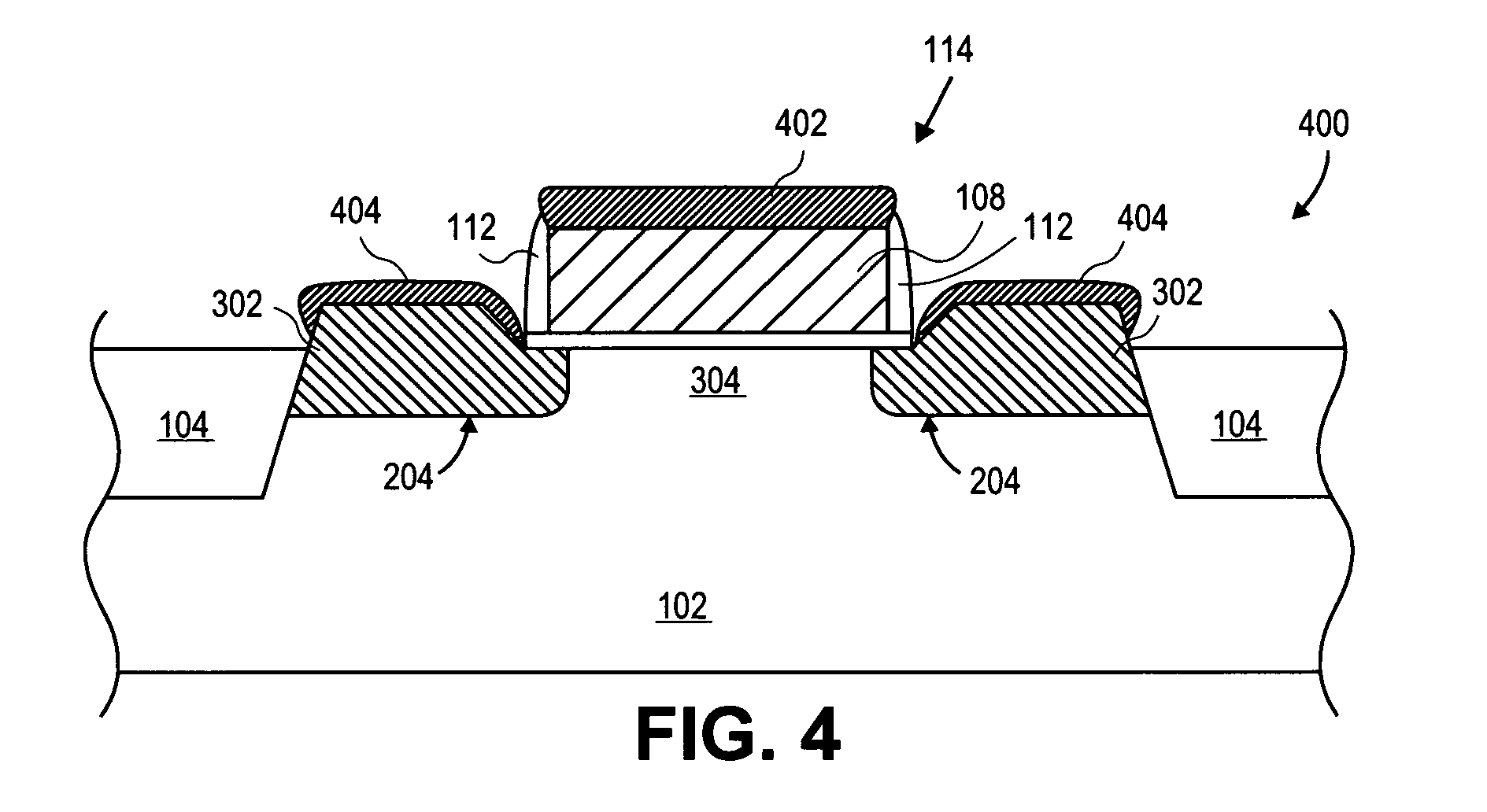

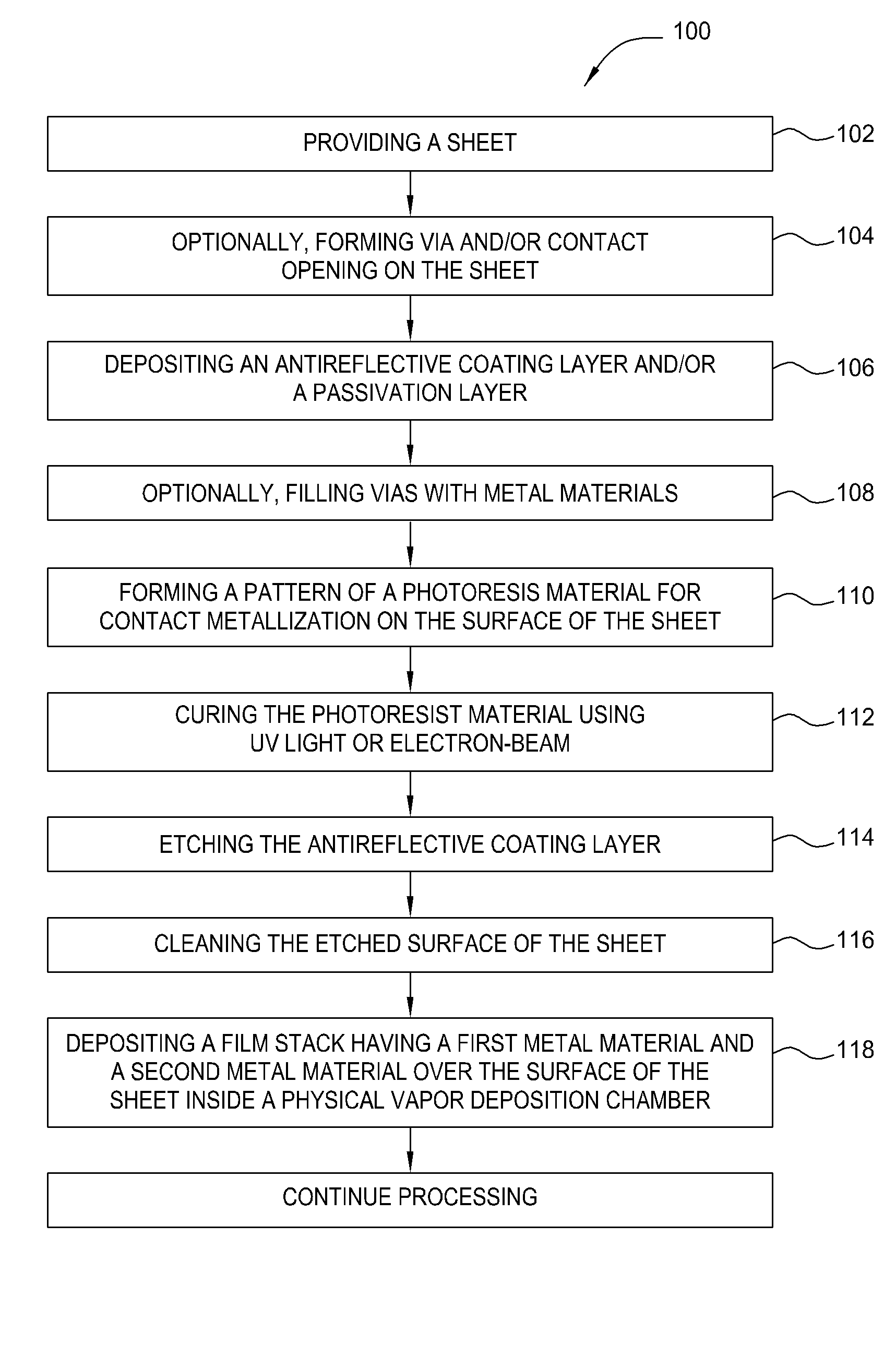

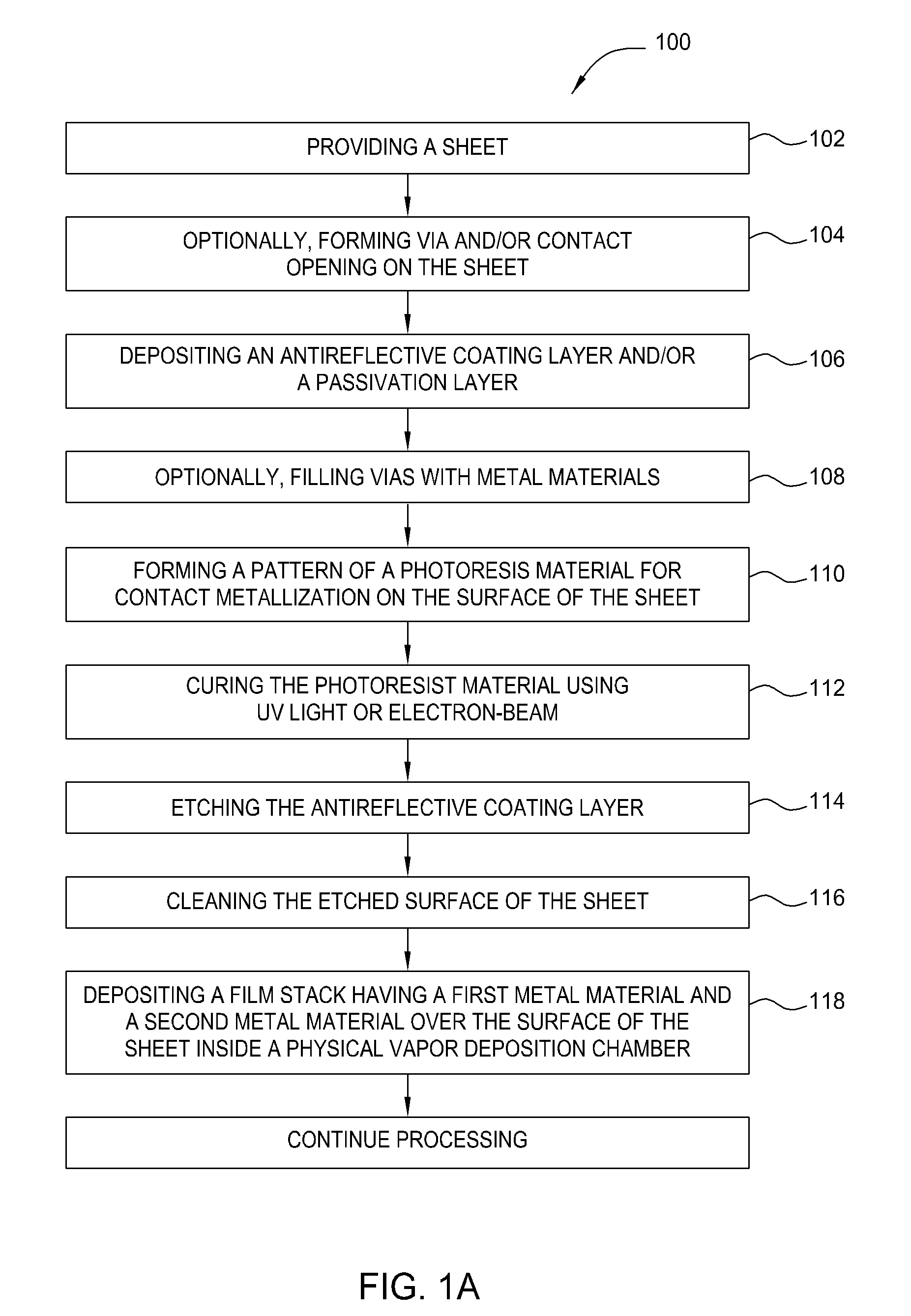

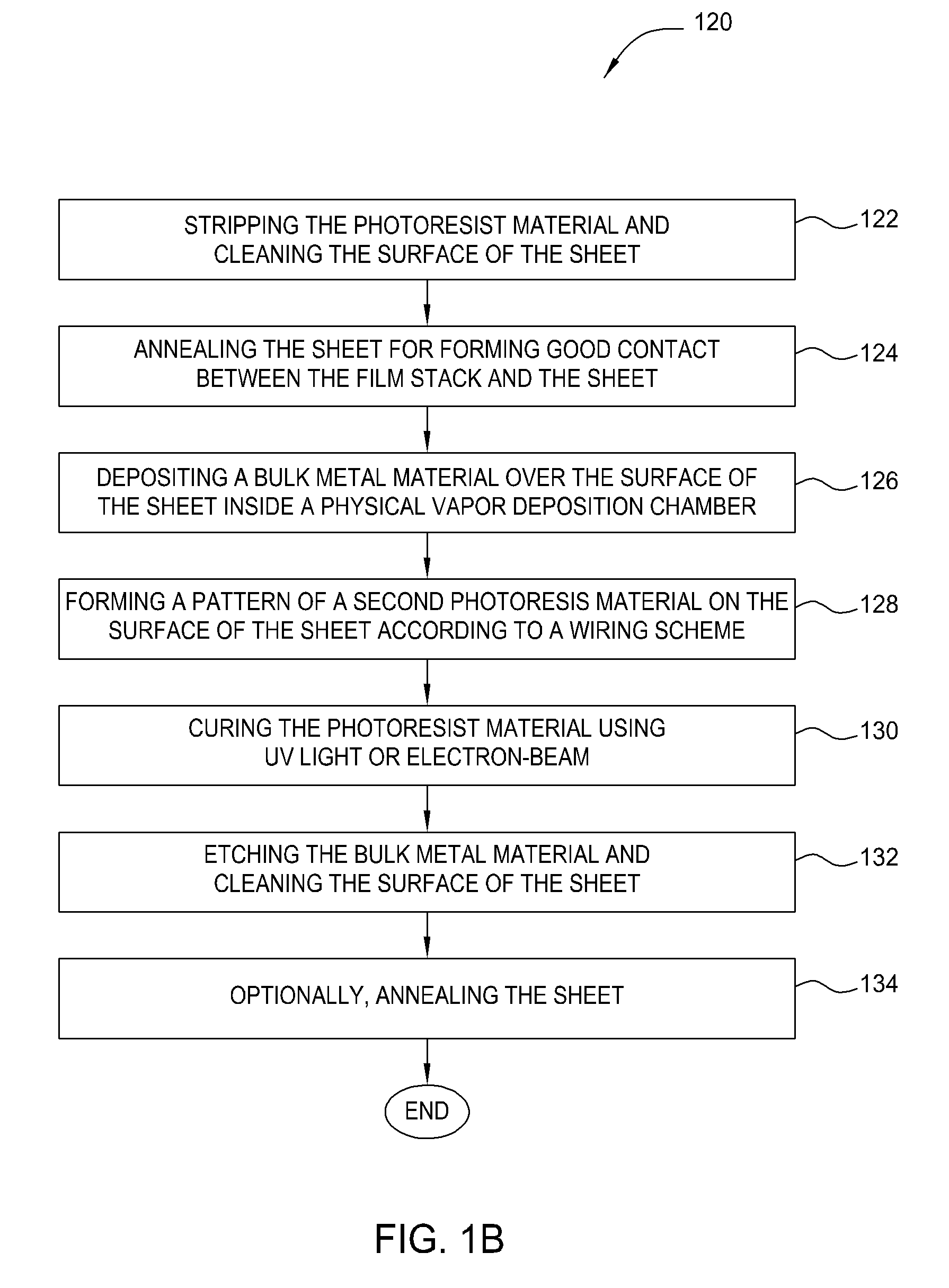

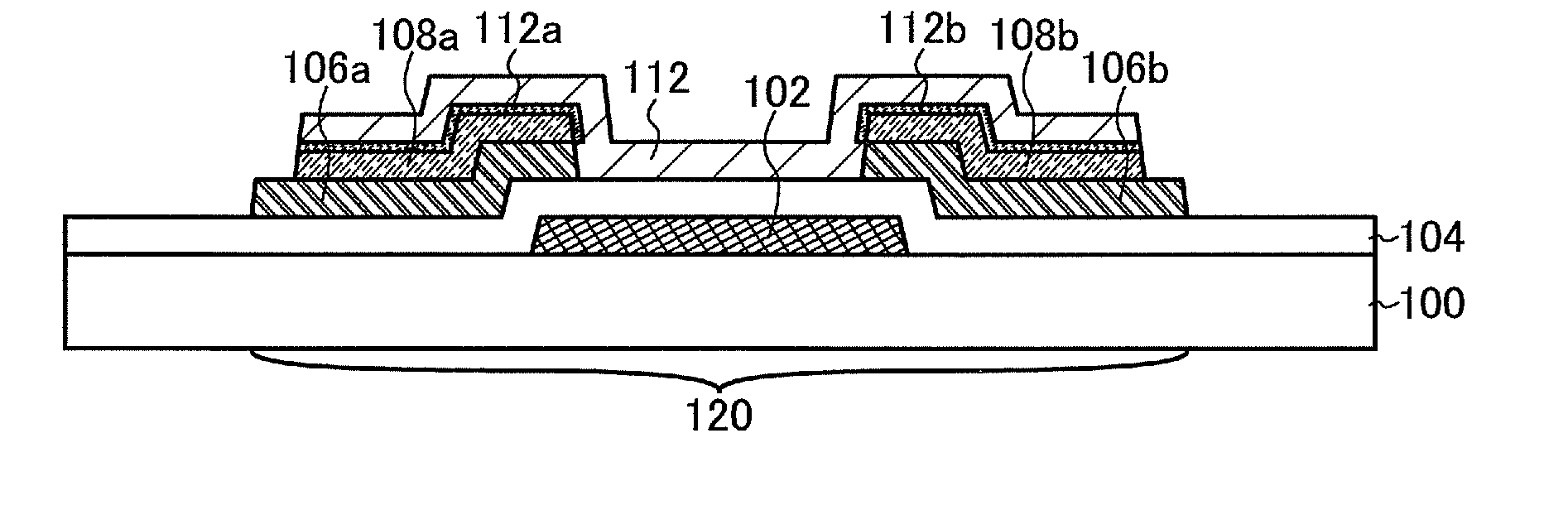

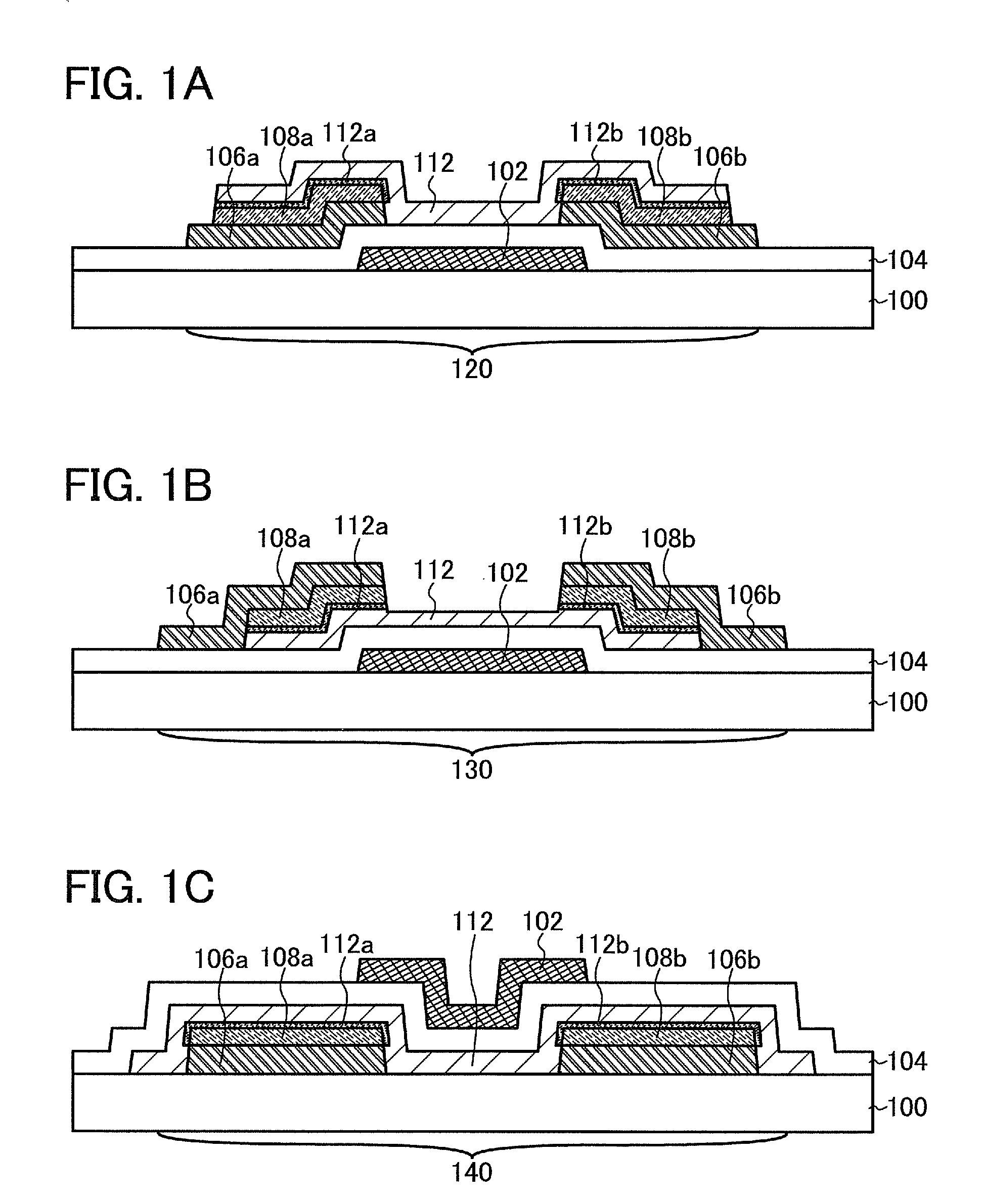

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

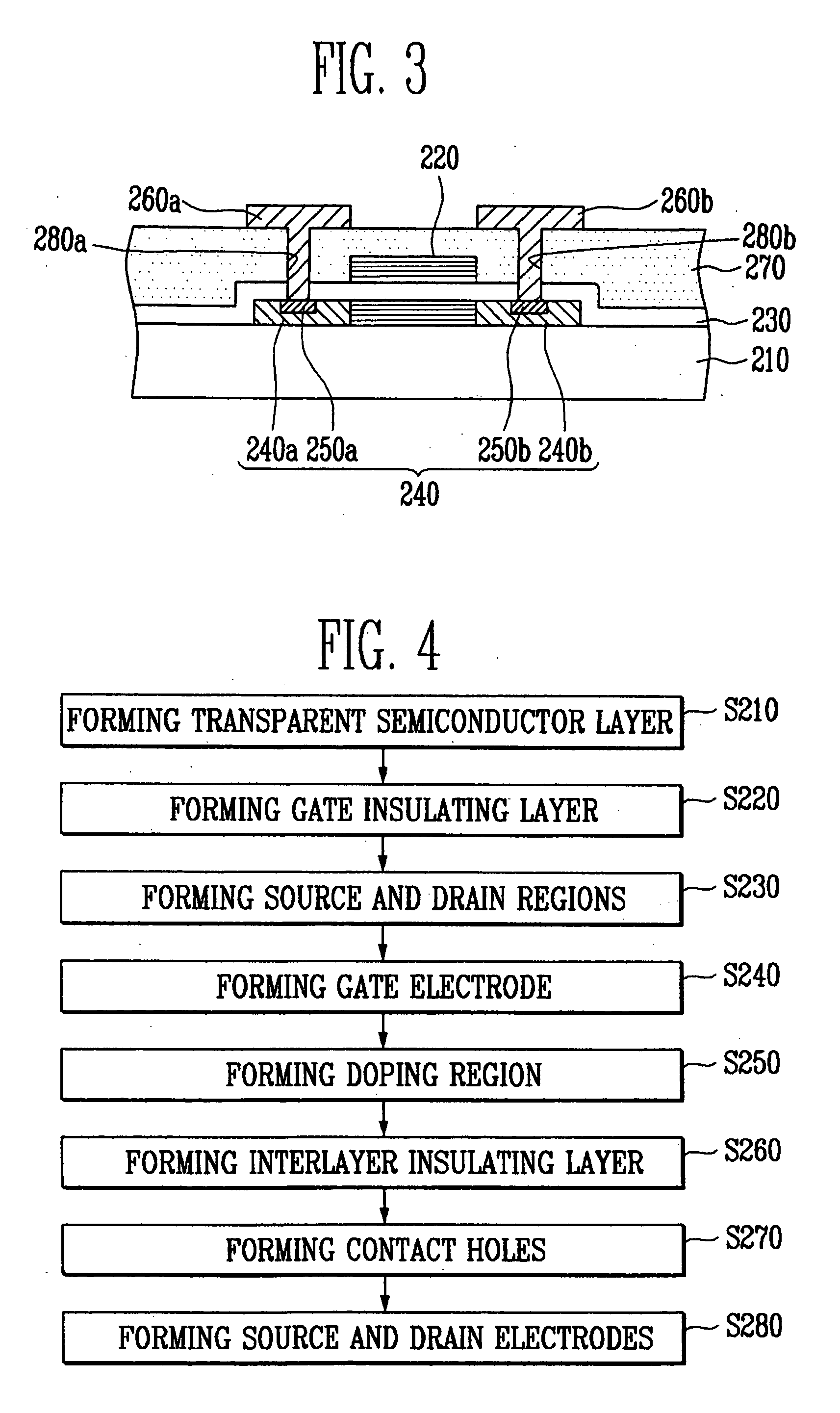

Transistor and method for manufacturing the transistor

ActiveUS20100193782A1Reduce variationContact resistanceTransistorSolid-state devicesCrystal structureSemiconductor

It is an object to reduce characteristic variation among transistors and reduce contact resistance between an oxide semiconductor layer and a source electrode layer and a drain electrode layer, in a transistor where the oxide semiconductor layer is used as a channel layer. In a transistor where an oxide semiconductor is used as a channel layer, at least an amorphous structure is included in a region of an oxide semiconductor layer between a source electrode layer and a drain electrode layer, where a channel is to be formed, and a crystal structure is included in a region of the oxide semiconductor layer which is electrically connected to an external portion such as the source electrode layer and the drain electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

Metal semiconductor alloy structure for low contact resistance

InactiveUS20120032275A1TransistorSemiconductor/solid-state device detailsSemiconductor materialsSemiconductor alloys

Contact via holes are etched in a dielectric material layer overlying a semiconductor layer to expose the topmost surface of the semiconductor layer. The contact via holes are extended into the semiconductor material layer by continuing to etch the semiconductor layer so that a trench having semiconductor sidewalls is formed in the semiconductor material layer. A metal layer is deposited over the dielectric material layer and the sidewalls and bottom surface of the trench. Upon an anneal at an elevated temperature, a metal semiconductor alloy region is formed, which includes a top metal semiconductor alloy portion that includes a cavity therein and a bottom metal semiconductor alloy portion that underlies the cavity and including a horizontal portion. A metal contact via is formed within the cavity so that the top metal semiconductor alloy portion laterally surrounds a bottom portion of a bottom portion of the metal contact via.

Owner:IBM CORP

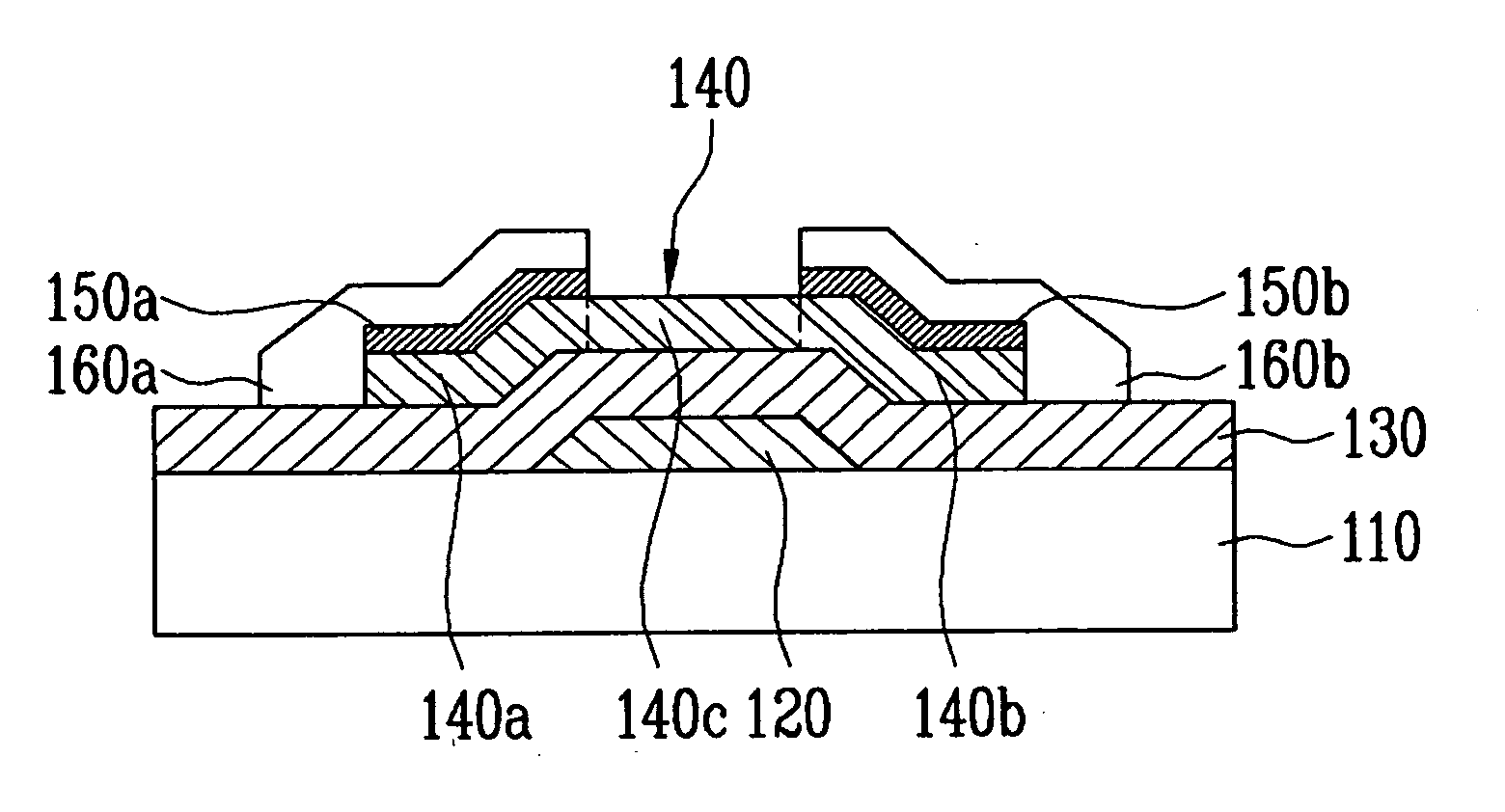

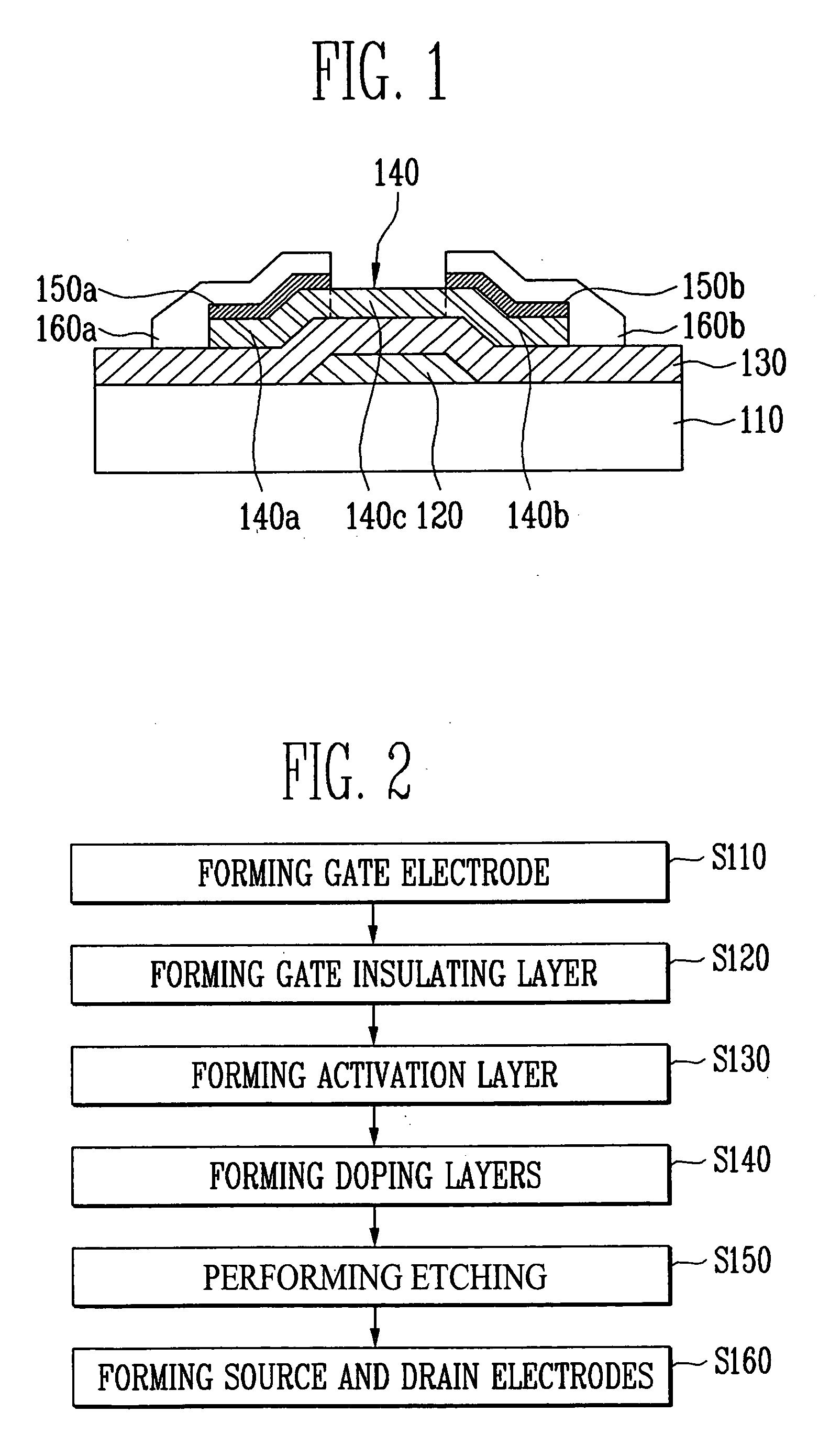

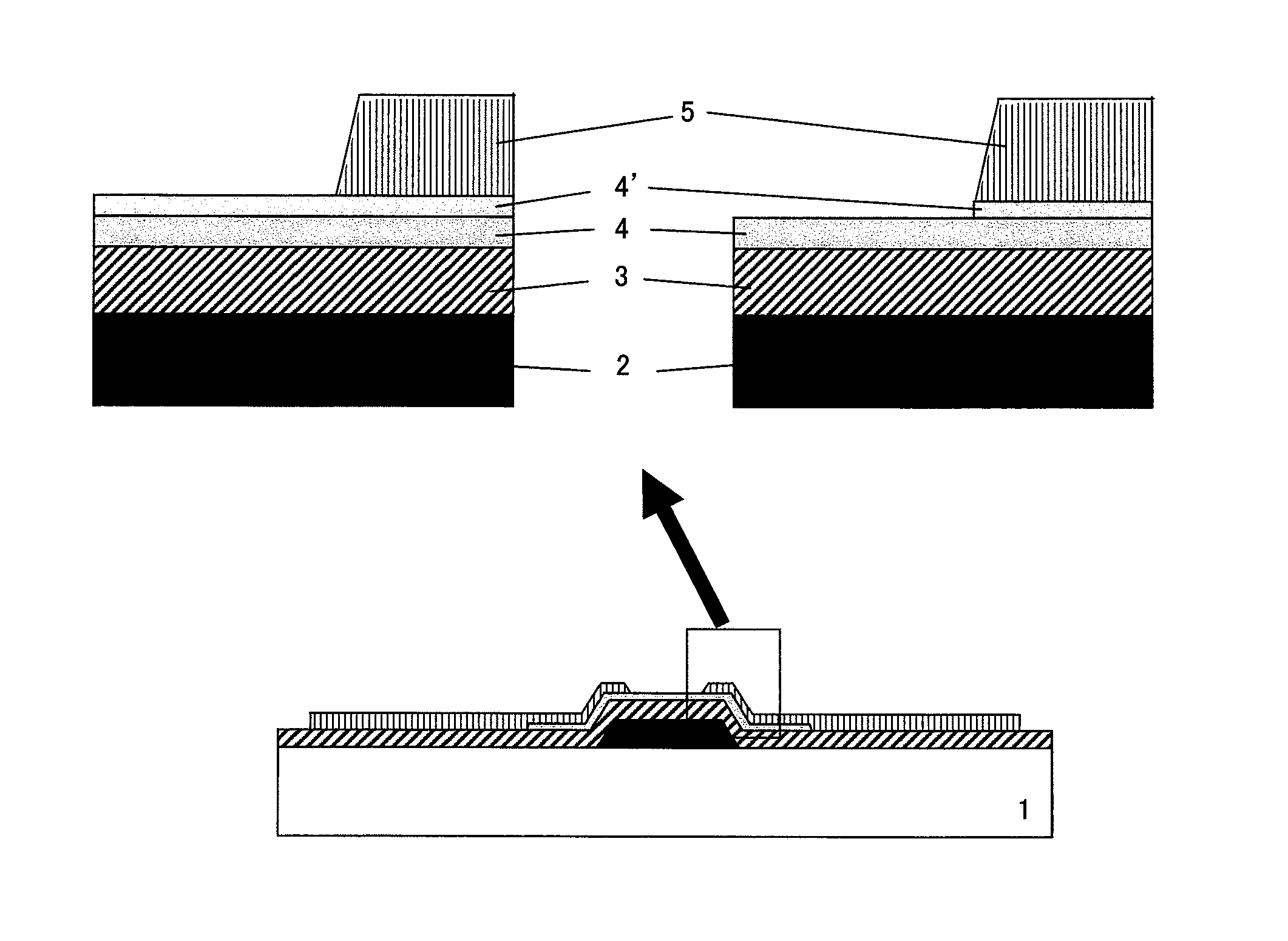

Transparent thin film transistor (TFT) and its method of manufacture

InactiveUS20070069209A1Eliminate the problemGood ohmic contactSemiconductor devicesOhmic contactBiological activation

A transparent thin film transistor (TFT) and a method of fabricating the same are provided. The transparent TFT includes transparent source and drain electrodes formed of transparent material, a transparent semiconductor activation layer that contacts the source and drain electrodes, that is formed of transparent semiconductor, and in which source and drain regions are formed, and a doping section provided between the transparent source and drain electrodes and the transparent activation layer to have the same doping type as that of the source and drain regions and to have doping concentration different from that of the source and drain regions. At this time, doping during the formation of the doping section is performed by an in-situ method in which a gas containing impurities is sprayed in the same apparatus as the apparatus used for the previous step. Therefore, it is possible to reduce high contact resistance generated when the transparent semiconductor activation layer contacts the transparent electrodes and to thus form ohmic contact.

Owner:SAMSUNG DISPLAY CO LTD

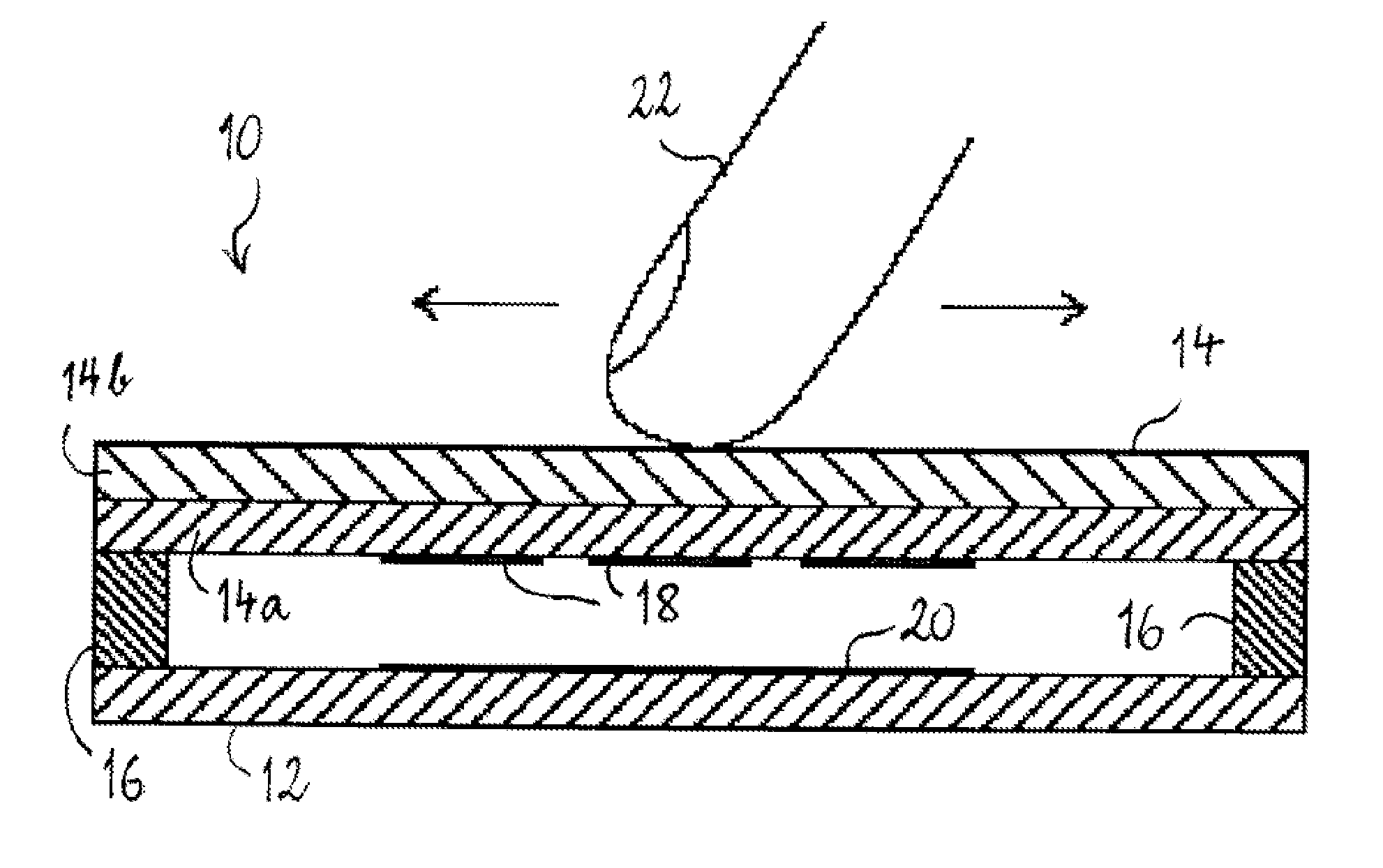

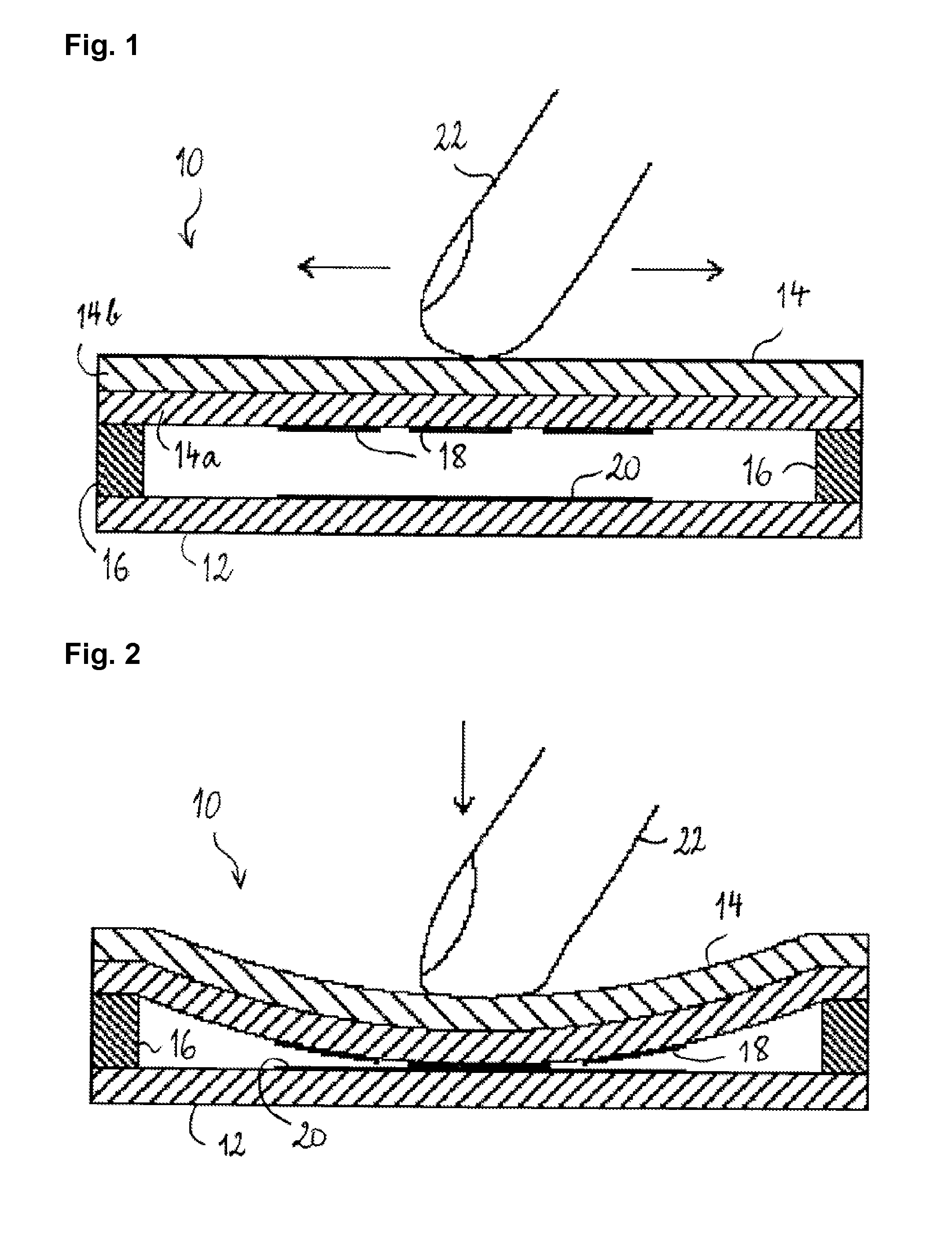

Touchpad with strip-shaped input area

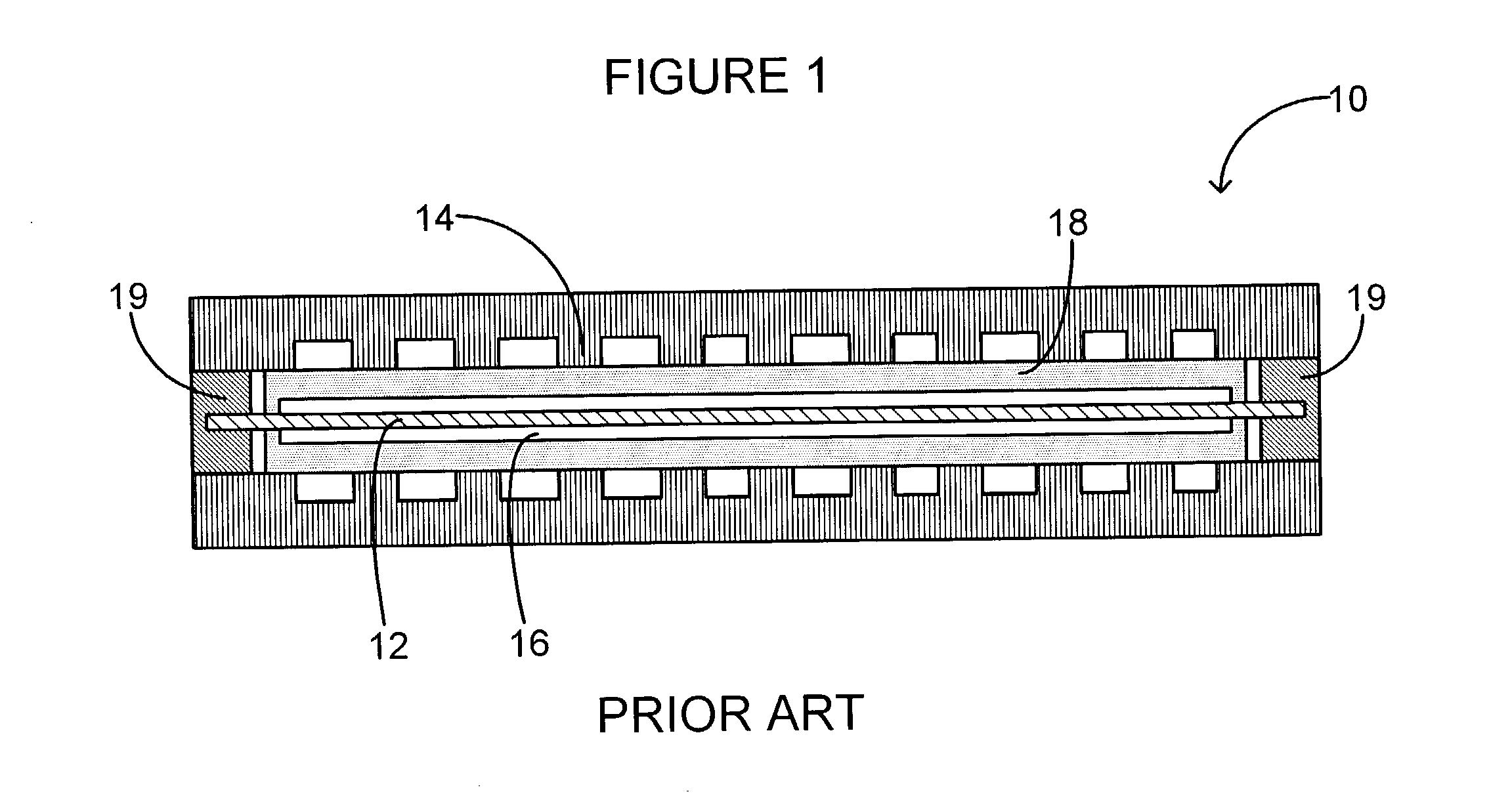

InactiveUS20110267300A1Simple structureLow production costElectronic switchingCathode-ray tube indicatorsEngineeringContact resistance

A touchpad with an input area having a straight or curved main line of extension comprises a support element, a cover having a first surface facing away from the support element and a second surface facing towards the support element and one or more spacers arranged at a periphery of the input area. The one or more spacers mount the cover on the support element in such a way that the cover spans over the support plate in the input area while it is depressible towards the support element by a force acting on the input area of the touchpad. A resistive trace is so arranged on the support element that it extends along the main line of extension of the input area. At least one terminal contacts the resistive trace at a particular point of the main line of extension of the input area and a set of detection electrodes is arranged on the second surface of the cover in facing relationship with the resistive trace. The detection electrodes are configured and arranged for capacitively detecting a position of a user's finger or stylus when the user's finger or stylus is in proximity of or in light touch with the first surface of the cover, and for resistively detecting a position of a user's finger or stylus when the user's finger or stylus depresses the cover and so brings at least one of the detection electrodes into electrical contact with the resistive trace.

Owner:IEE INT ELECTRONICS & ENG SA

Multiple RF return pad contact detection system

InactiveUS20050021022A1Eliminating and minimizing riskCharacteristic is differentSurgical instruments for heatingElectrical resistance and conductanceContact impedance

A multiple RF return pad contact detection system is provided which is adaptive to different physiological characteristics of patients without being susceptible to electrosurgical current interference (e.g., interference or measurement interaction between components of the detection system). The detection system can measure or sense the contact resistance or impedance between the patient and pairs of RF return pads or return electrodes where multiple pairs of RF return pads are utilized due to the high current frequently needed during electrosurgery while eliminating or minimizing the risk of measurement interaction between the RF return pad pairs. The system allows for the independent and simultaneous measurement of the pad contact impedance for each pair of RF return pads. If the impedance of any pad pair is above a predetermined limit, the system turns off or reduces the electrosurgical output of the electrosurgical generator to prevent excess heating. The system eliminates or minimizes interference or measurement interaction between the pad pairs by providing a different signal source frequency for each pad contact pair, but a frequency which matches an associated series resonant network frequency. The current that flows in the series resonant network is a direct reflection or function of the pad impedance of the corresponding pad pair.

Owner:COVIDIEN AG

Semiconductor device and method for manufacturing the same, and electric device

InactiveUS20060163743A1Simple stepsHighly integratedSemiconductor/solid-state device detailsElectroluminescent light sourcesElectrical resistance and conductanceLongest Diameter

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

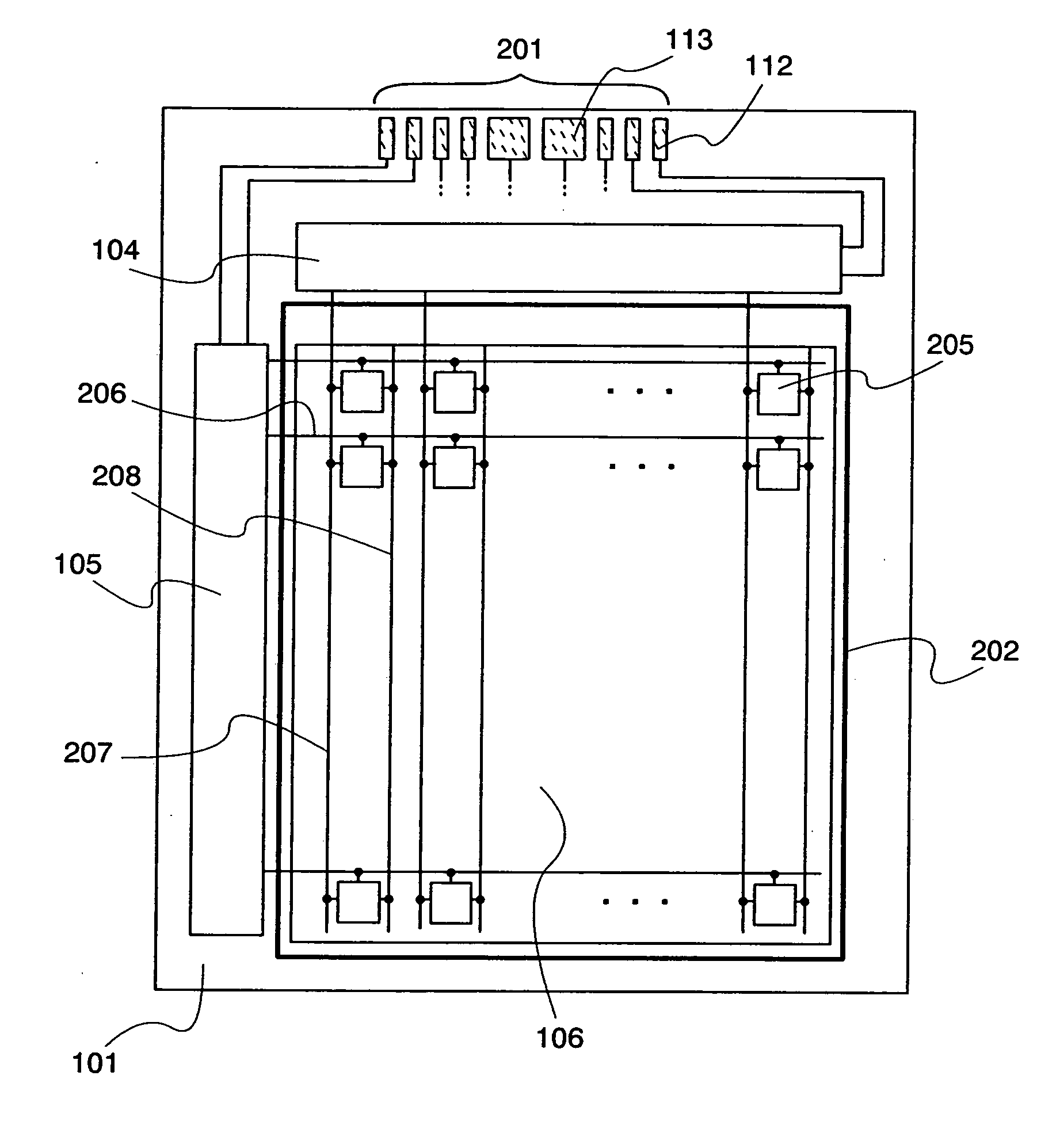

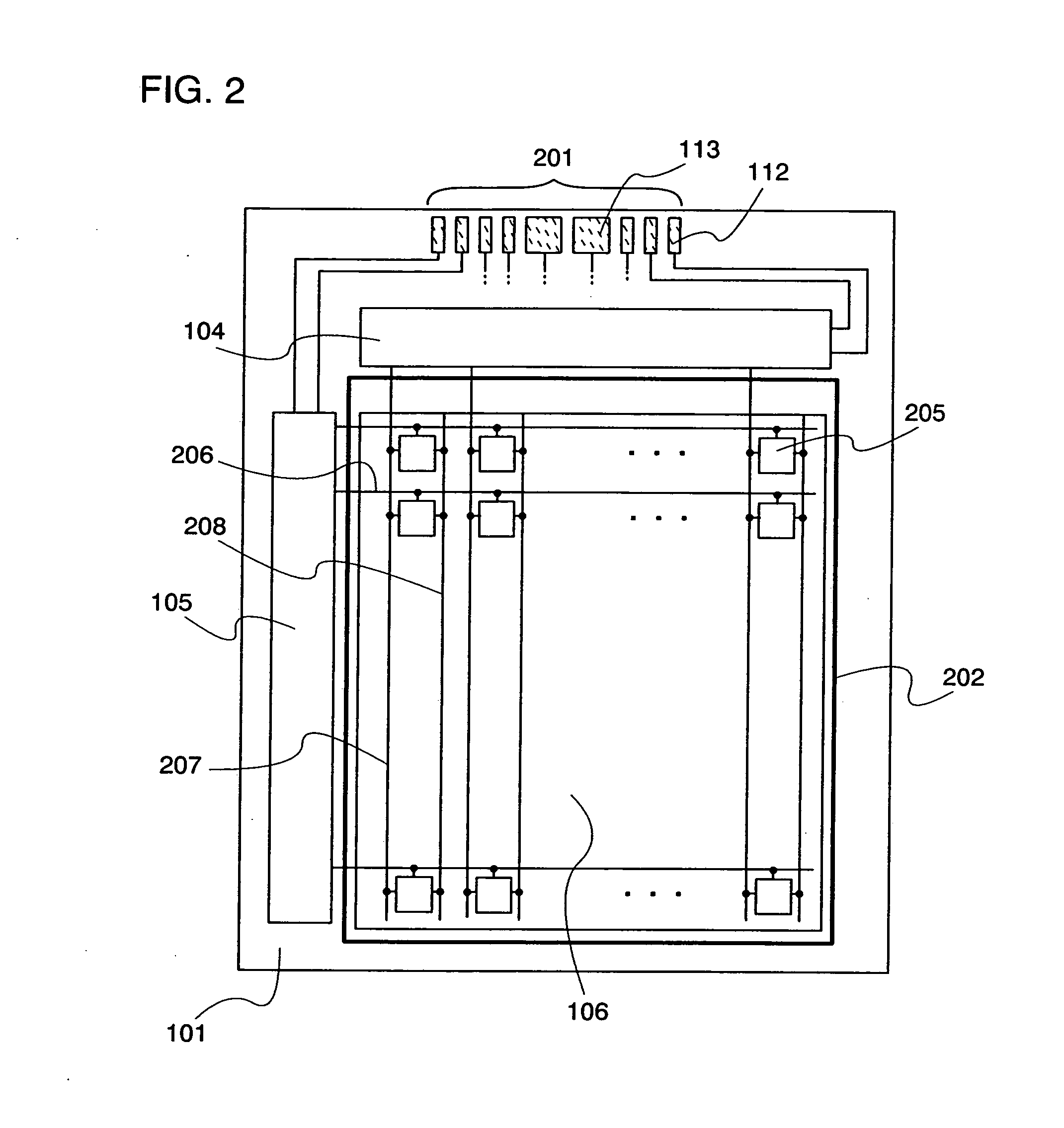

Semiconductor device and display device

InactiveUS20060244741A1Reduce resistanceSuppression pressure dropPrinted circuit aspectsSolid-state devicesElectrical resistance and conductanceDevice material

If misalignment in a line width direction of an electrode (pad) of a connection terminal is caused in attachment of a substrate and an FPC, a connection area of the FPC terminal and the connection terminal becomes smaller and contact resistance is increased. In particular, an increase in contact resistance of the connection terminal to which a power supply potential serving as a power source is inputted is a cause of defective display. In view of the above, an object of the present invention is to decrease the resistance of a power supply line, to suppress a voltage drop in the power supply line, and to prevent defective display. A connection terminal portion includes a plurality of connection terminals. The plurality of connection terminals is provided with a plurality of connection pads which is part of the connection terminal. The plurality of connection pads includes a first connection pad and a second connection pad having a line width different from that of the first connection pad. Pitches between the plurality of connection pads are equal to each other.

Owner:SEMICON ENERGY LAB CO LTD

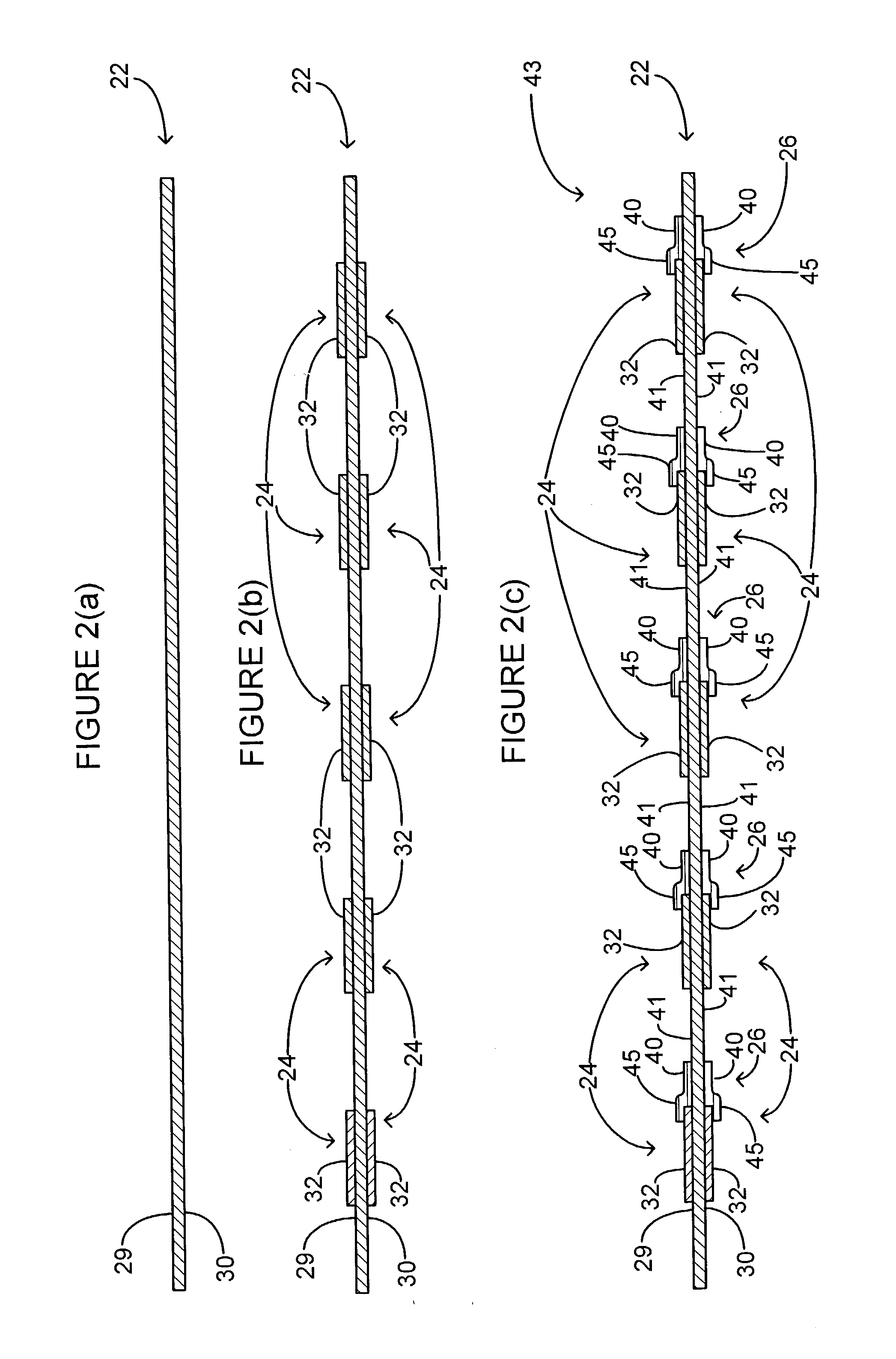

Method of fabricating fuel cells and membrane electrode assemblies

InactiveUS20040053100A1Low production costOvercome limitationsFuel cells groupingCell electrodesElectrical resistance and conductancePower battery

The application relates to a method of fabricating micro fuel cells and membrane electrode assemblies by thin film deposition techniques using a dimensionally stable proton exchange membrane as a substrate. The application also relates to membrane electrode assemblies and fuel cells fabricated in accordance with the method. The method includes the steps of successively depositing catalyst, current collector and flow management layers on the membrane substrate in predetermined patterns. Since the fuel cell is formed layer by layer, the need for assembly and sealing of discrete components is avoided. The method improves the contact resistance between the current collectors and catalyst layers and reduce ohmic losses, thereby avoiding the need for end plates or other compressive elements. This in turn reduces the overall thickness of the manufactured fuel cell. Since the fuel cell layers are optionally flexible, the devices may be fabricated using a continuous roller process or other automated means. The method minimizes production costs and costs of non-essential materials and is particularly suitable for low power battery replacement applications.

Owner:NAT RES COUNCIL OF CANADA

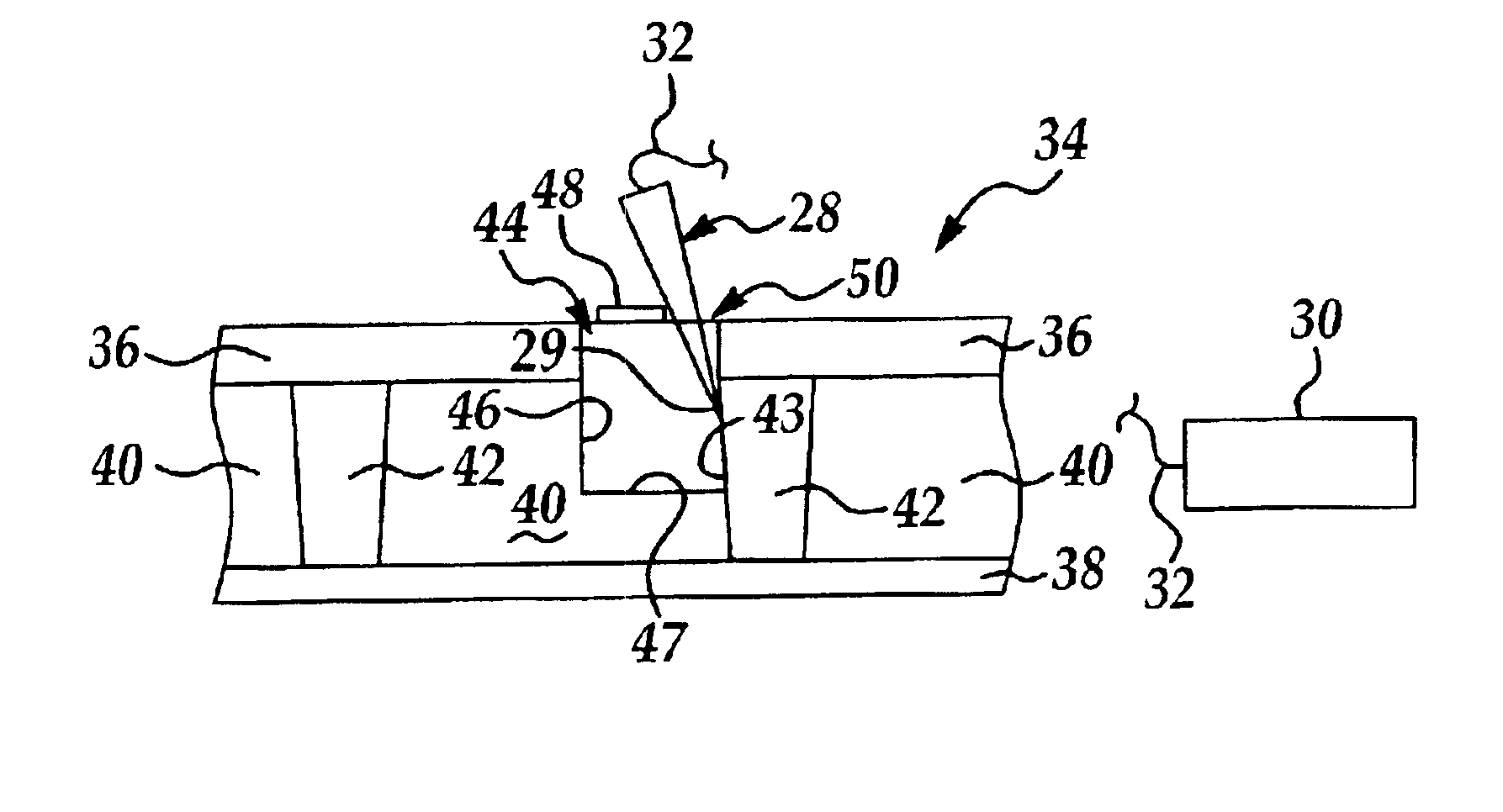

Probing of device elements

InactiveUS6902941B2Reduce contact resistanceAvoid Particle ContaminationSemiconductor/solid-state device testing/measurementElectronic circuit testingDielectricElectricity

A new and improved method for the probing of integrated circuits (ICs) and is particularly suitable for probing various elements of an IC for failure analysis or other electrical testing and / or measurement of the IC. The method includes providing a probe access trench in the IMD (intermetal dielectric) or other substrate adjacent to the circuit element to be tested and then providing direct electrical contact between the test probe and the sidewall of the element through the trench, during the testing process. Such direct electrical contact between the test probe and the sidewall of the element prevents excessively high contact resistance which may otherwise occur in the use of a probing pad between the test probe and the element.

Owner:TAIWAN SEMICON MFG CO LTD

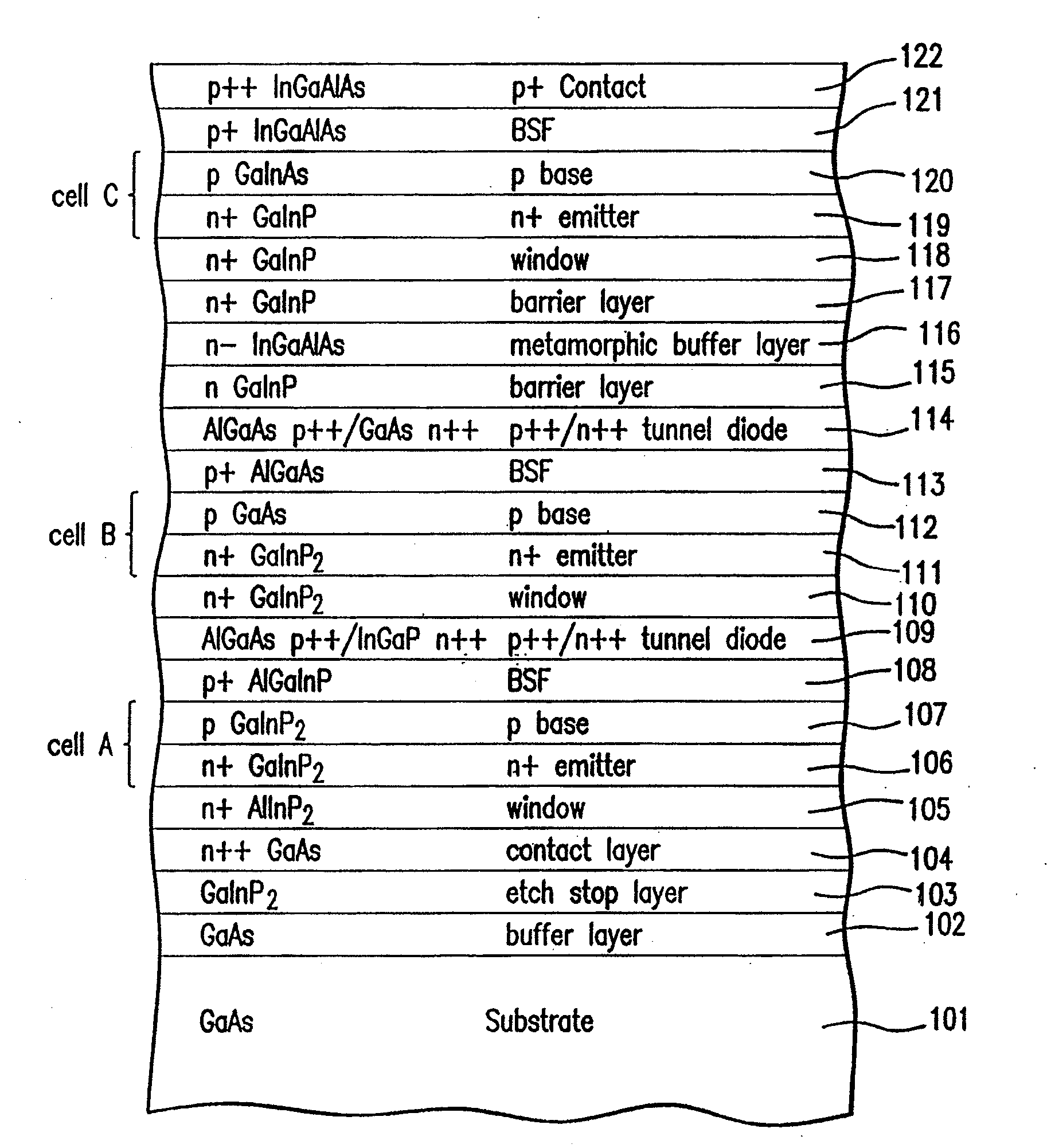

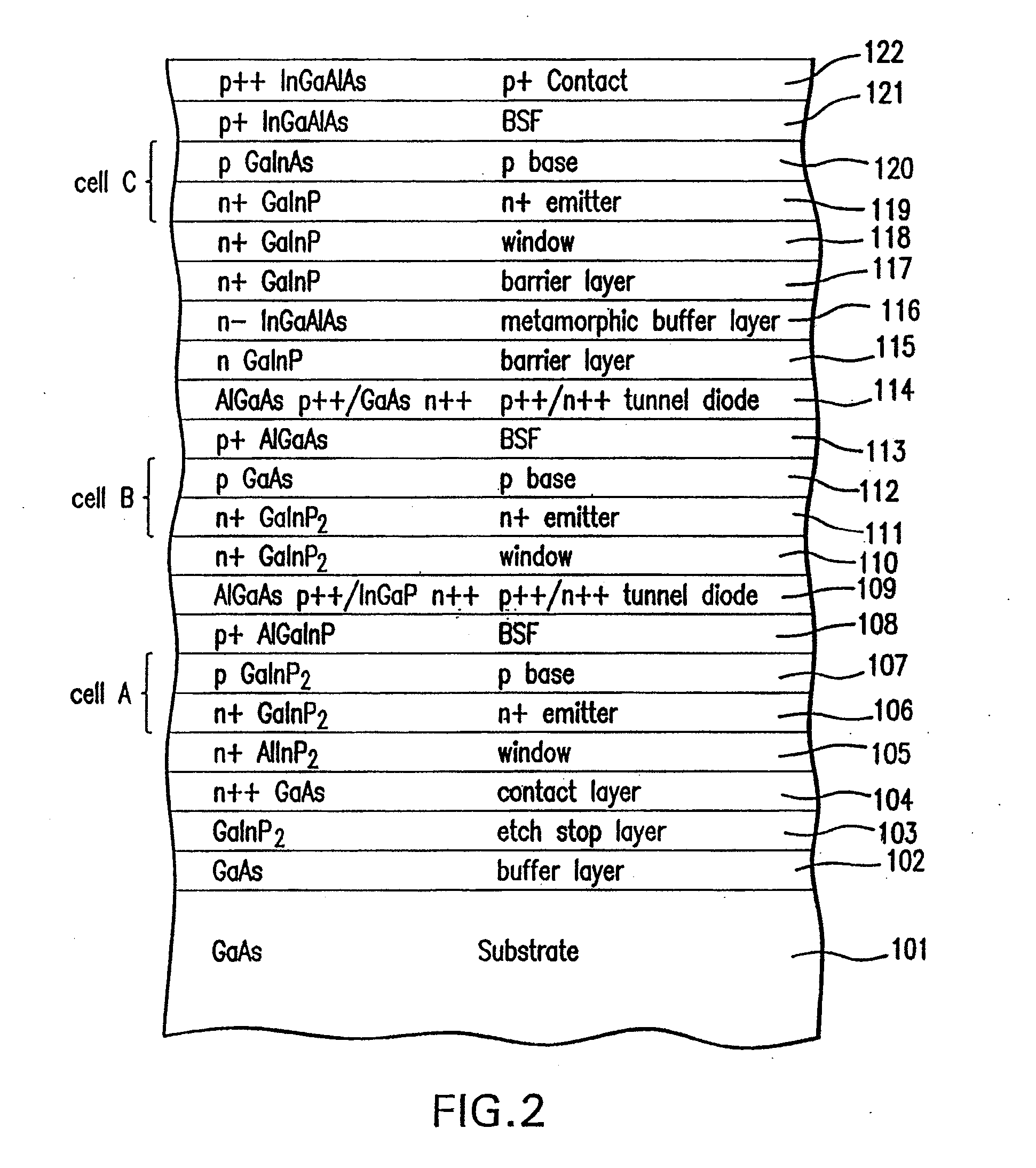

Ohmic n-contact formed at low temperature in inverted metamorphic multijunction solar cells

InactiveUS20100012175A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationSemiconductor materialsLattice mismatch

A method of forming a multifunction solar cell including an upper subcell, a middle subcell, and a lower subcell by providing a substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a graded interlayer over the second subcell, the graded interlayer having a third band gap greater than the second band gap; forming a third solar subcell over the graded interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell; and forming a contact composed of a sequence of layers over the first subcell at a temperature of 280° C. or less and having a contact resistance of less than 5×10−4 ohms-cm2.

Owner:EMCORE SOLAR POWER

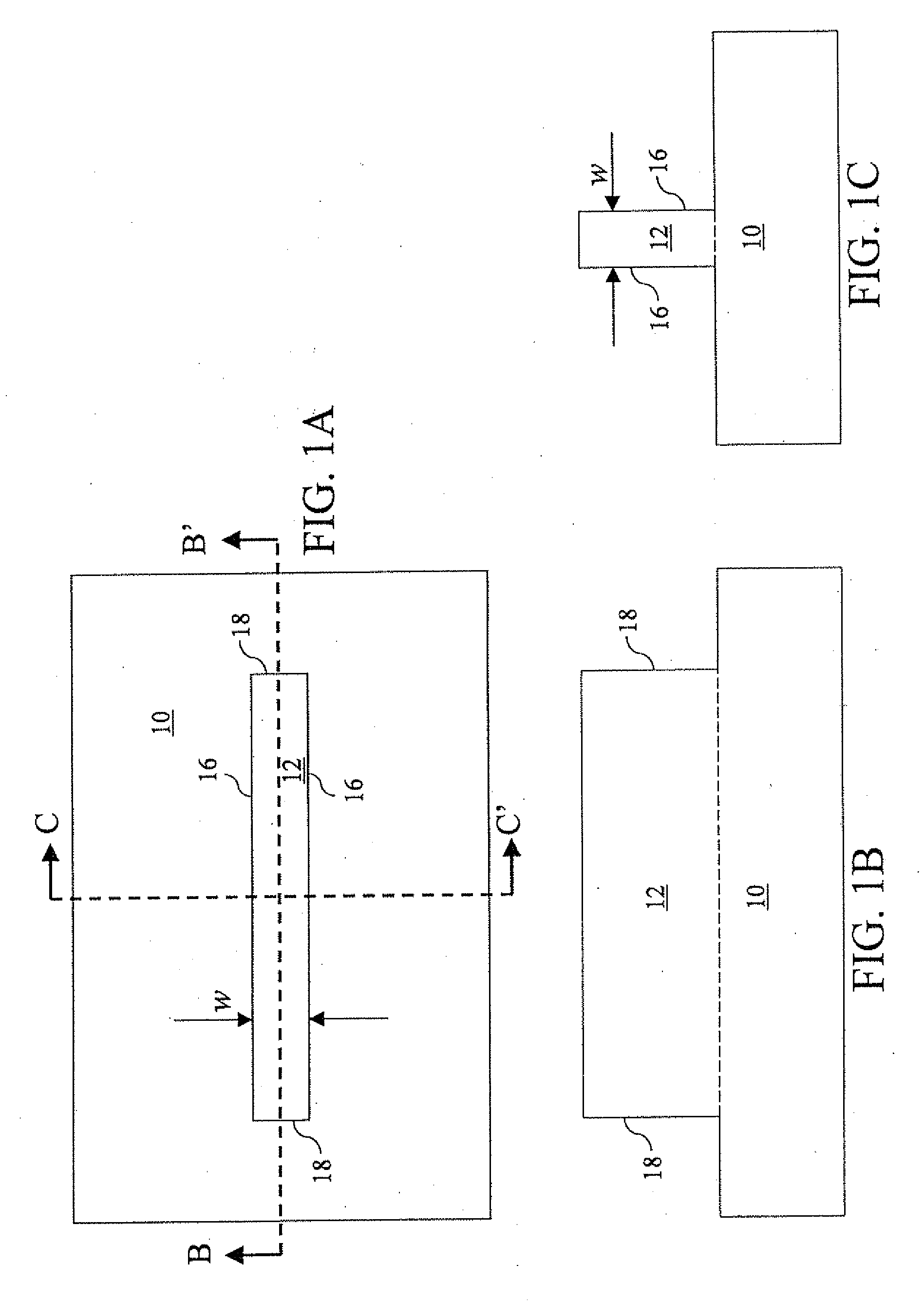

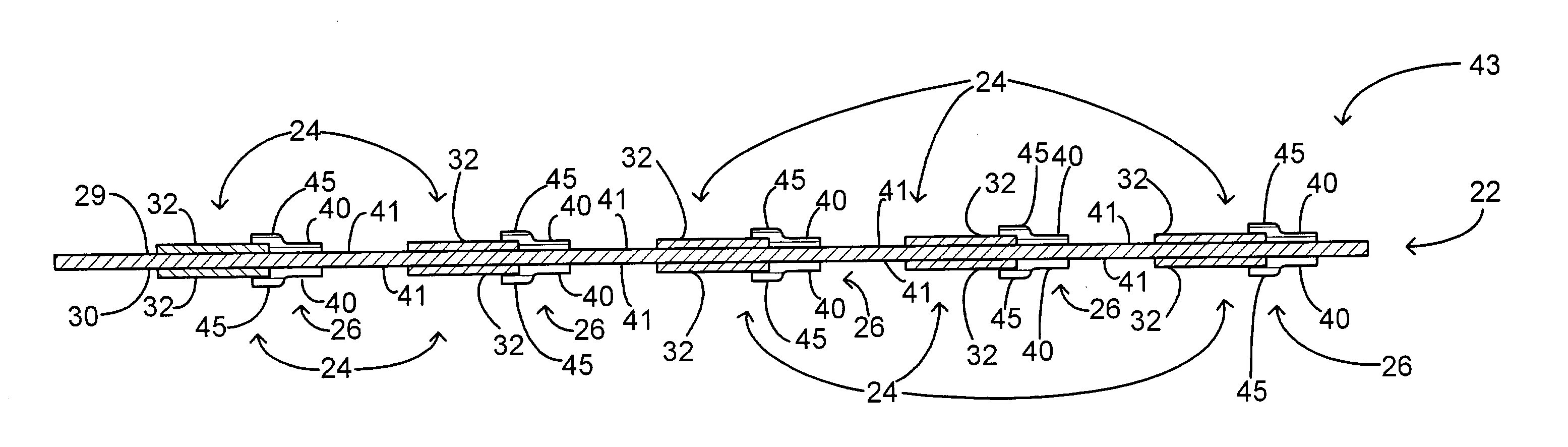

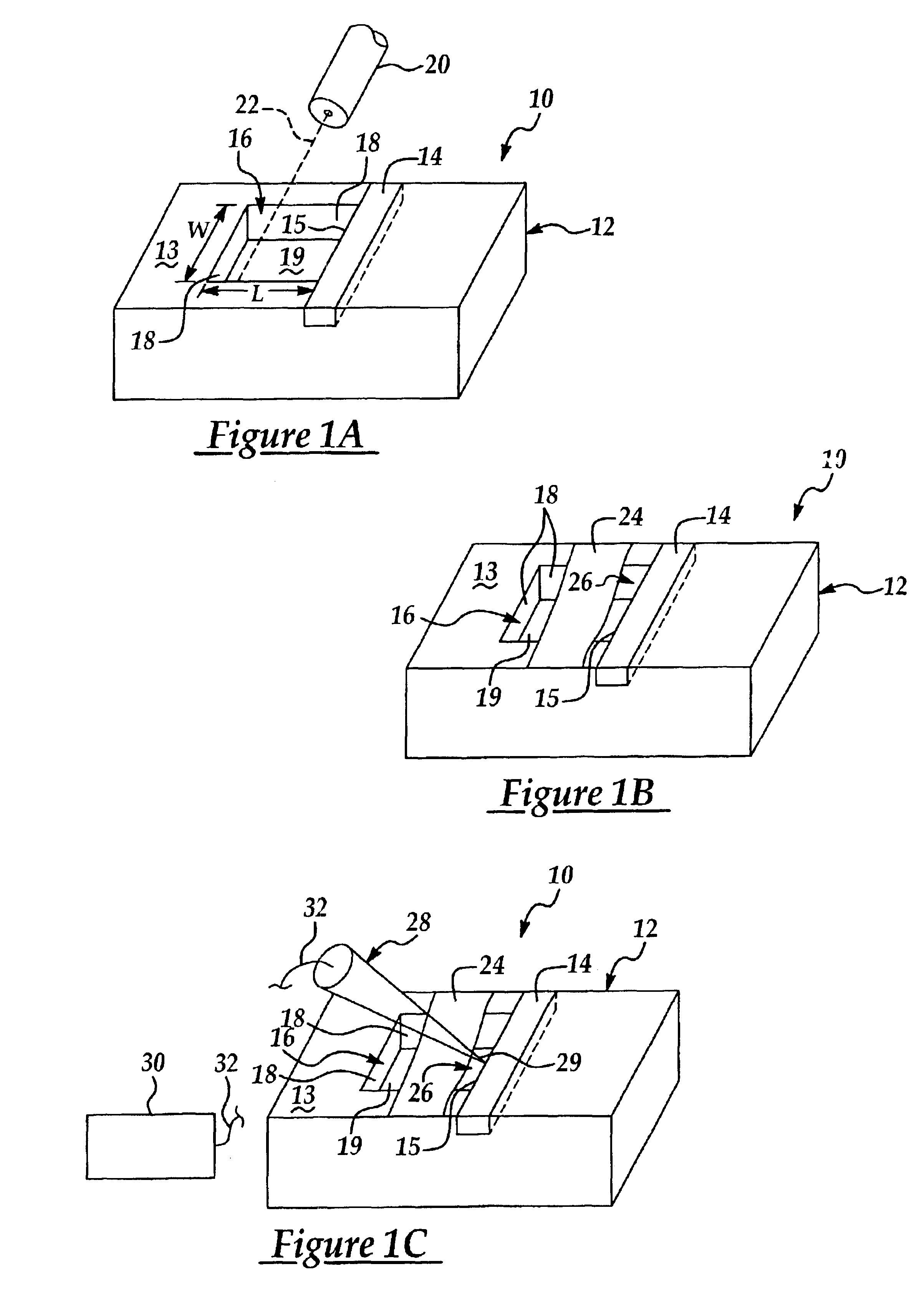

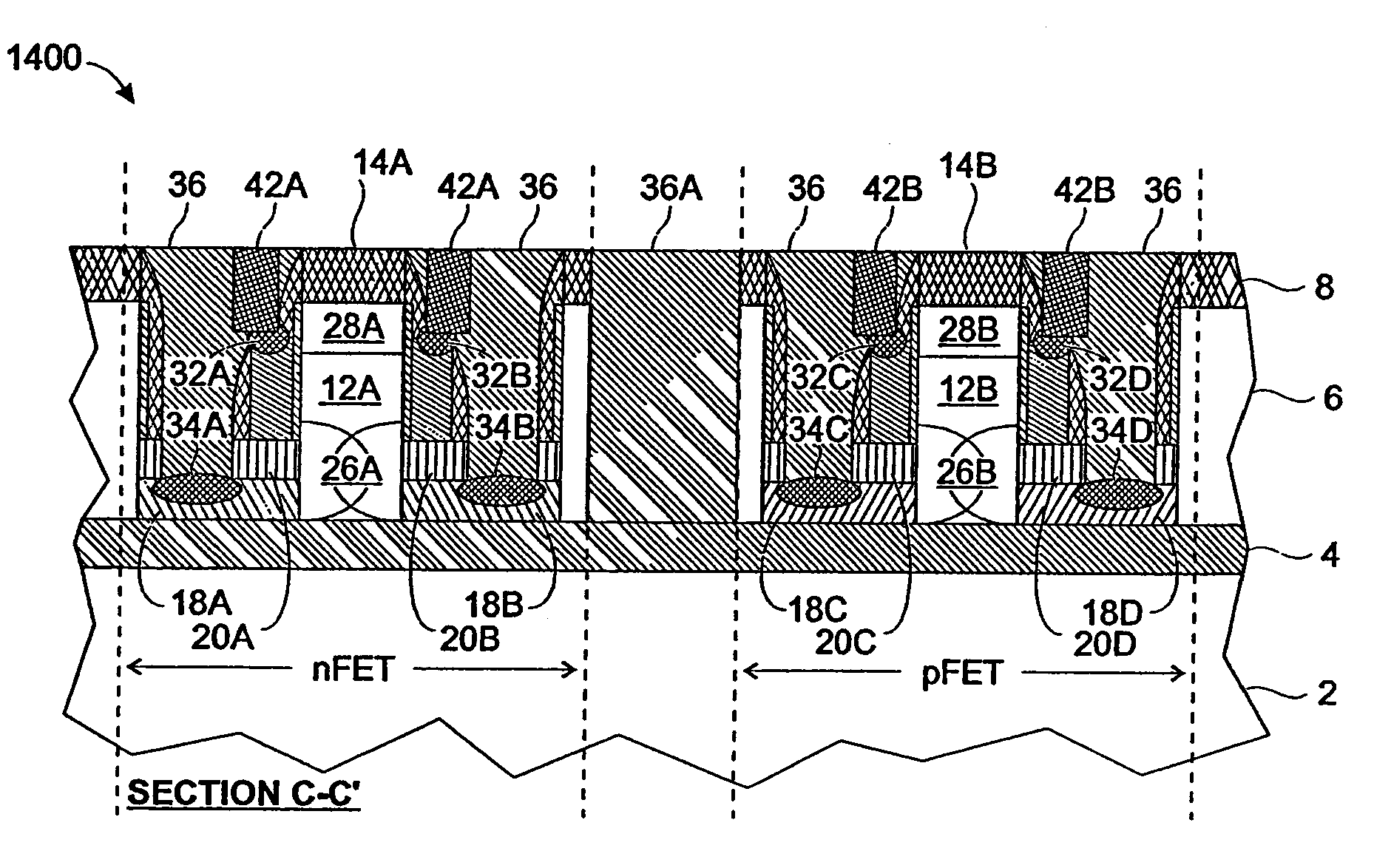

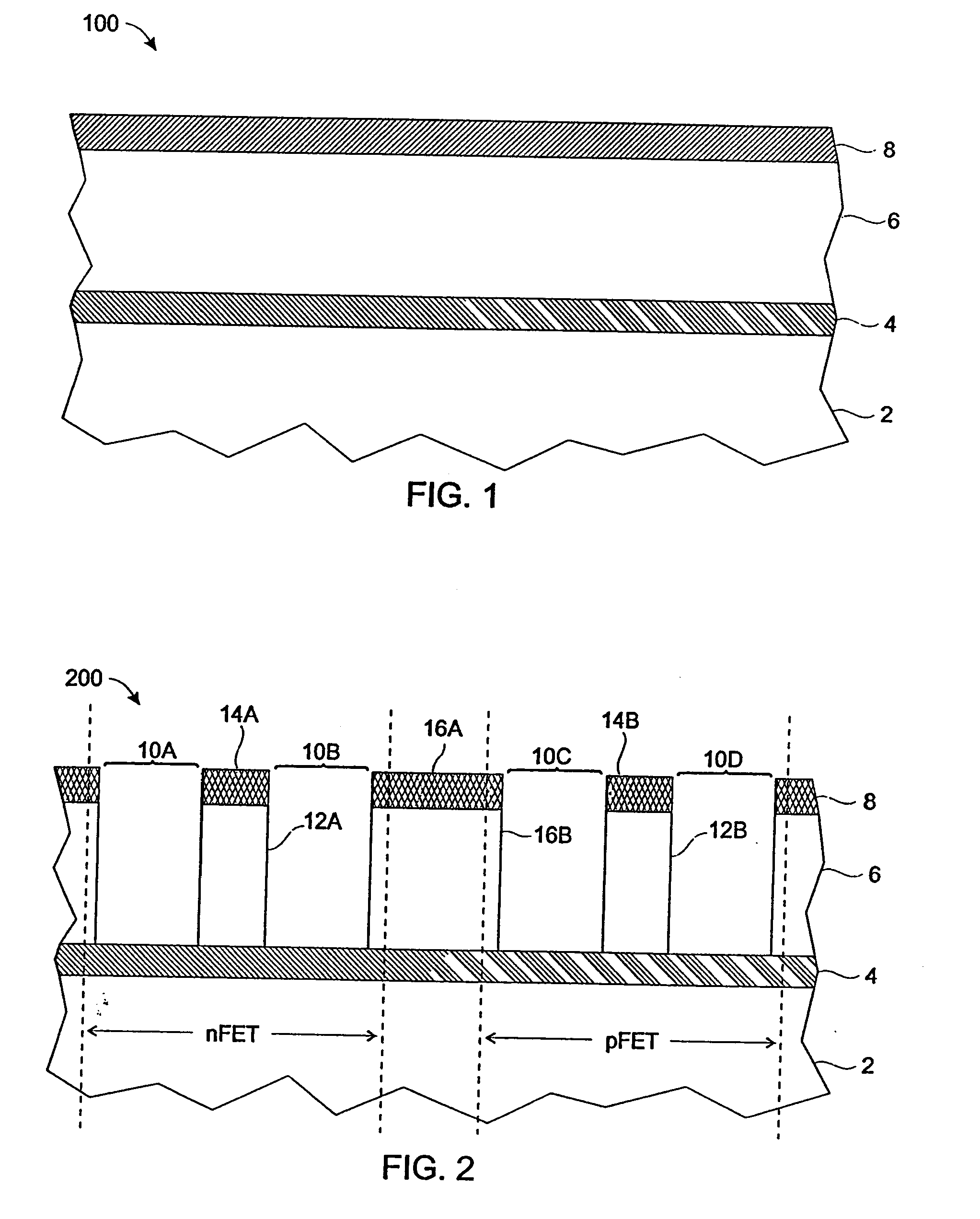

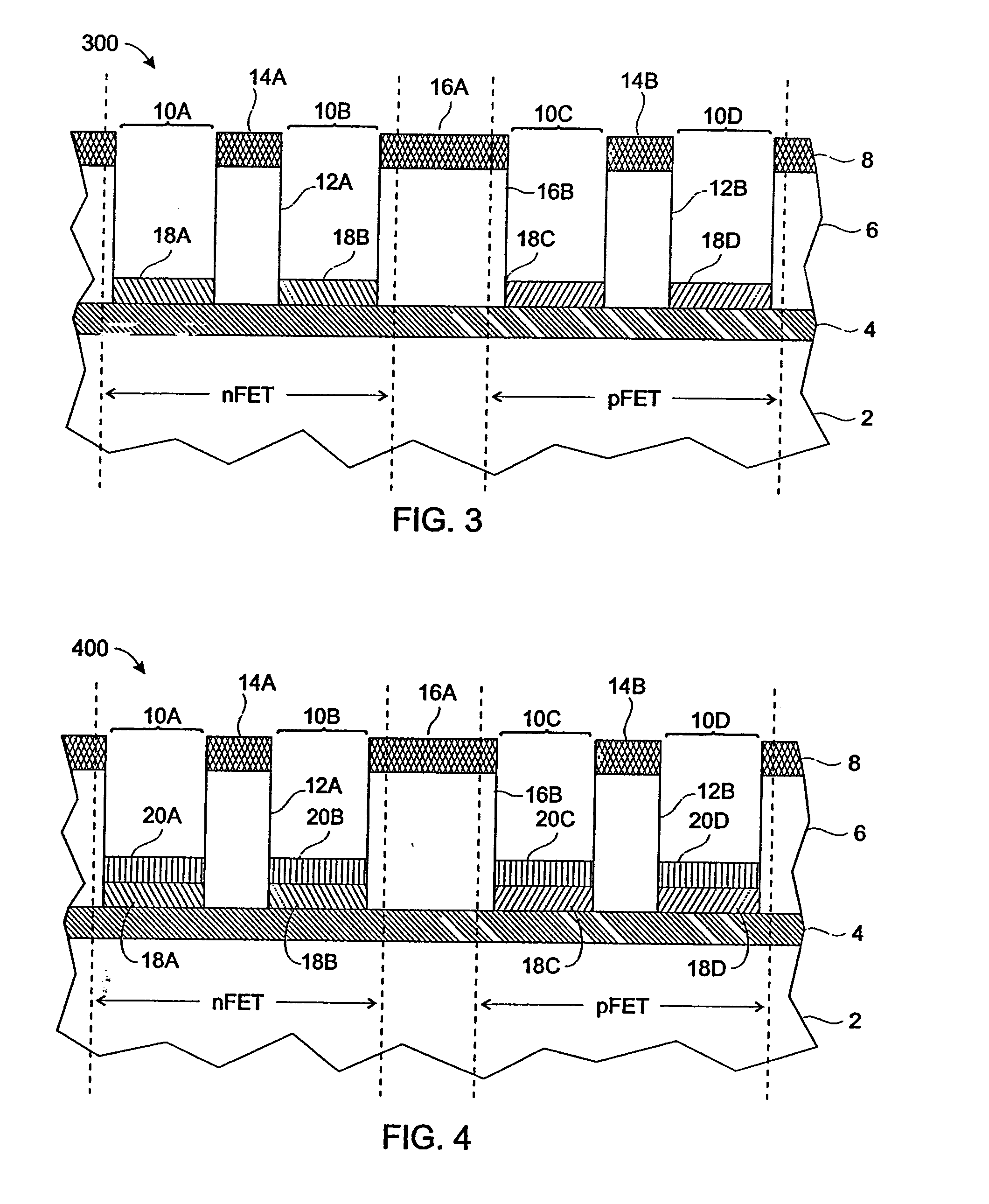

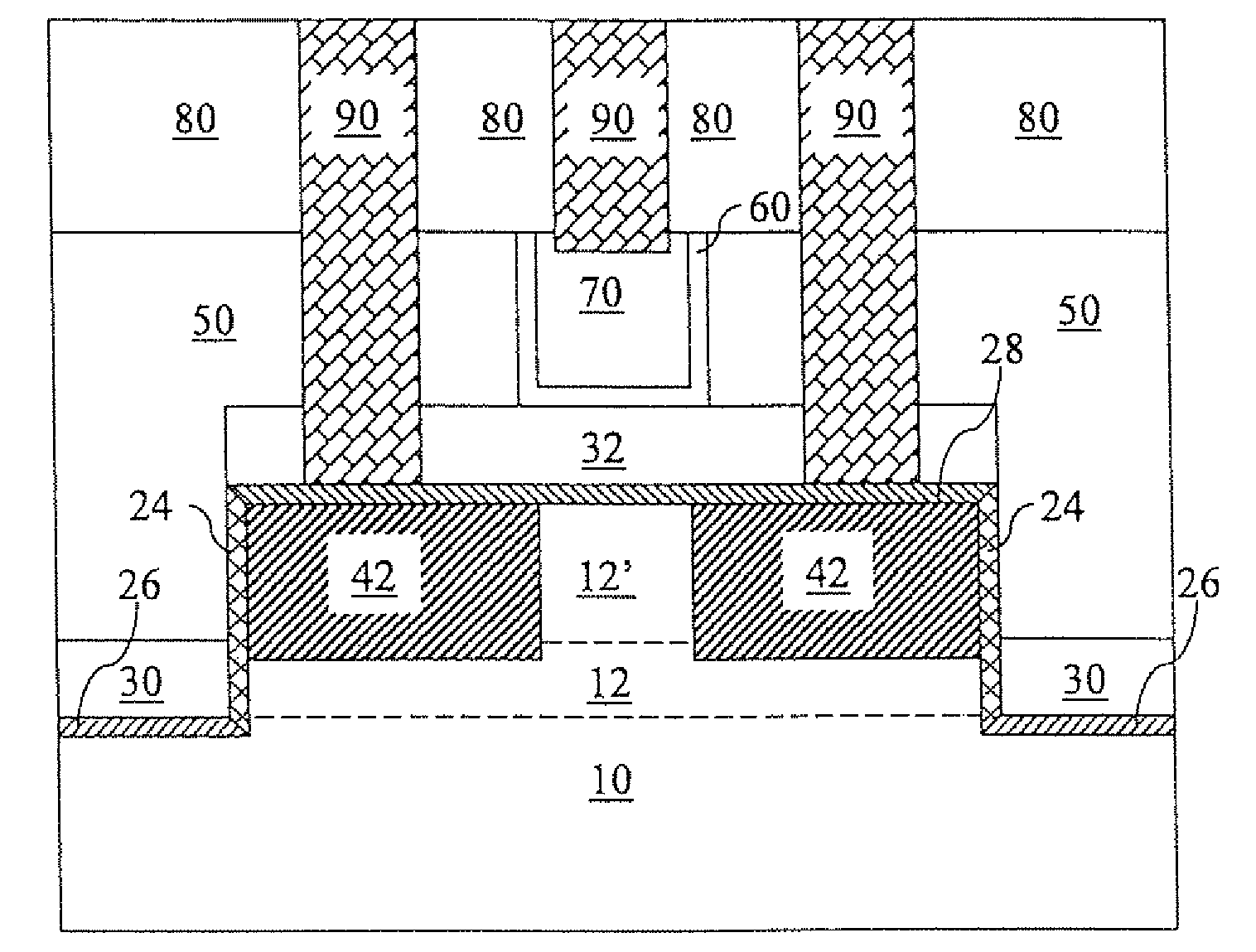

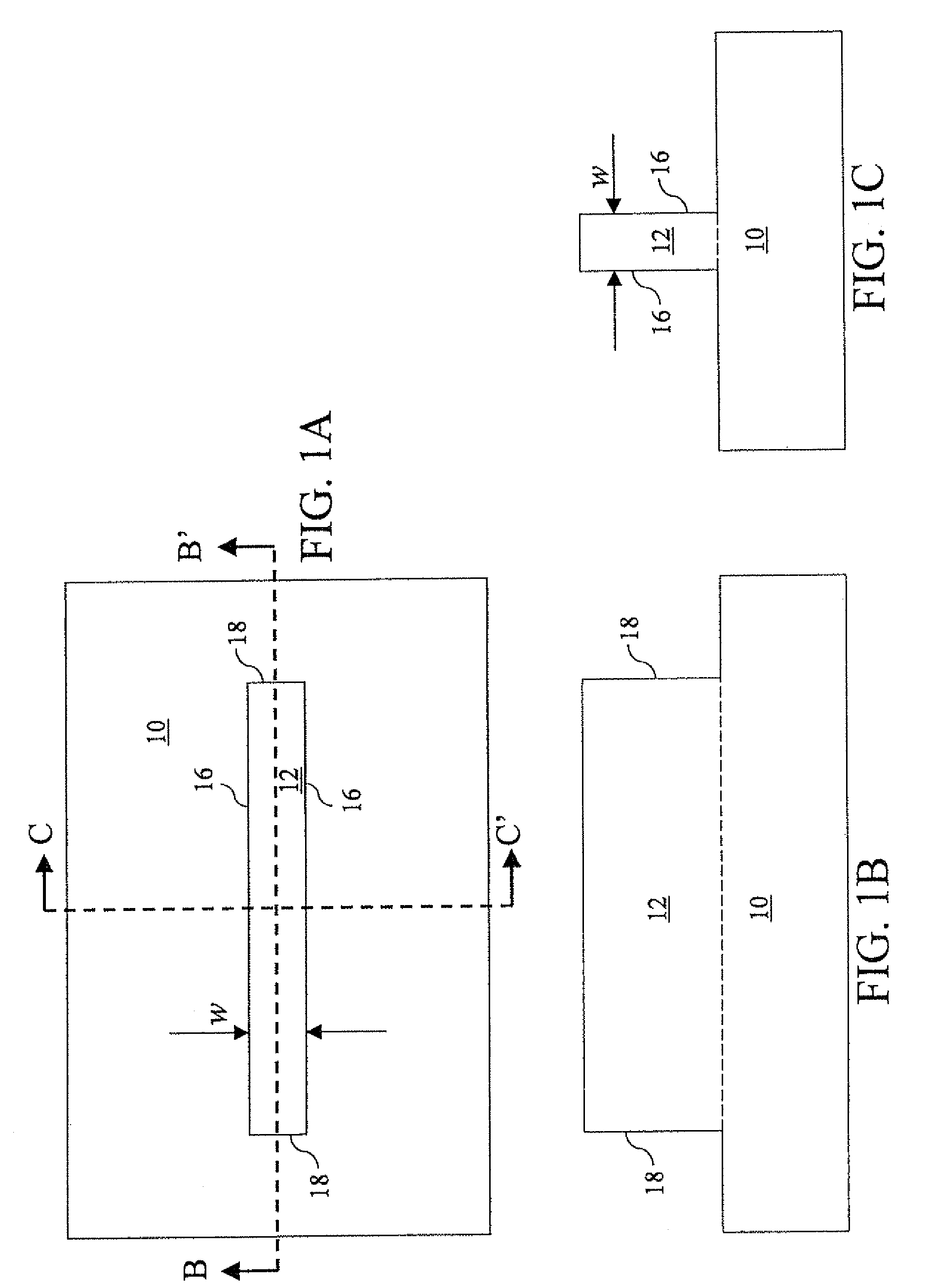

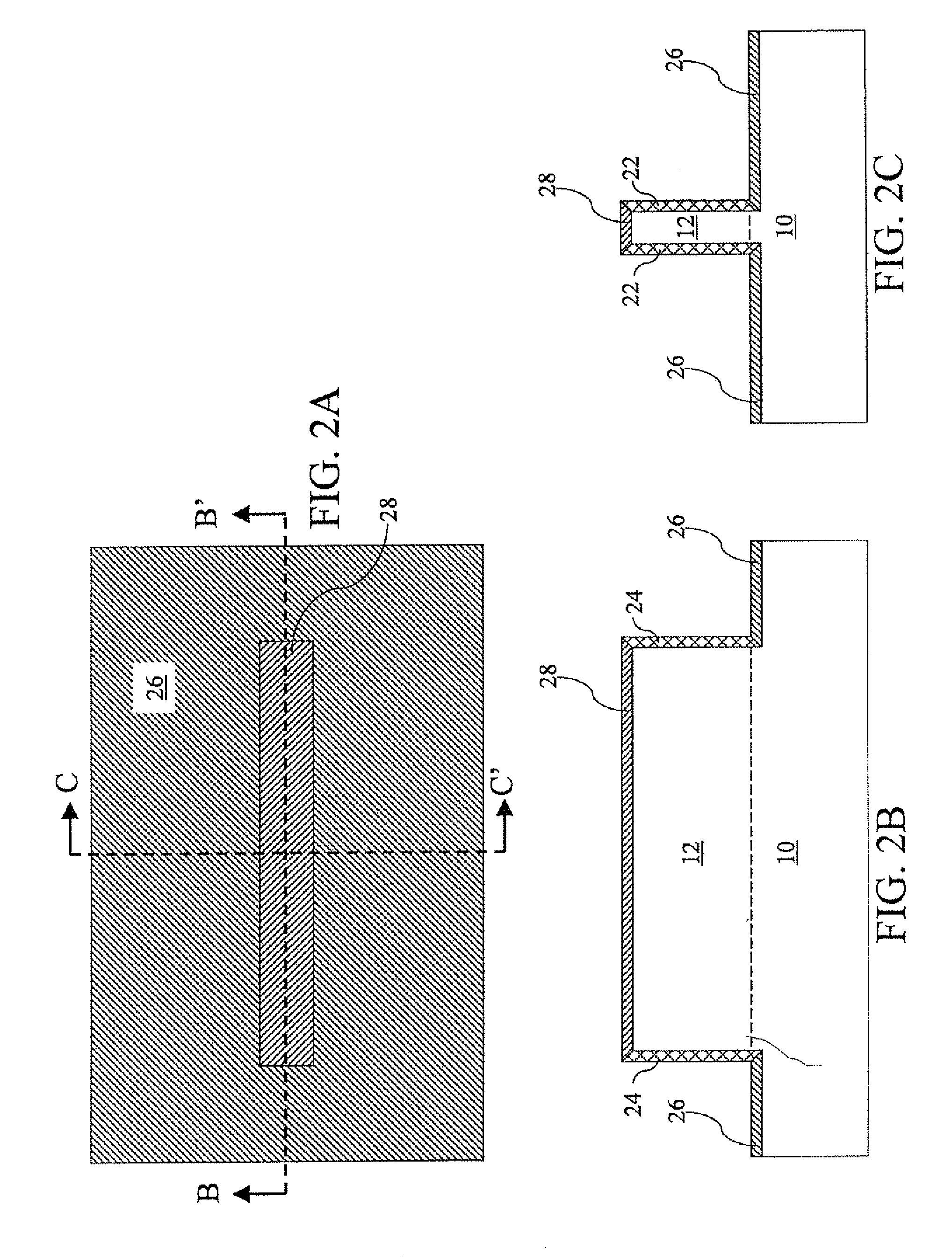

Vertical fin-fet mos devices

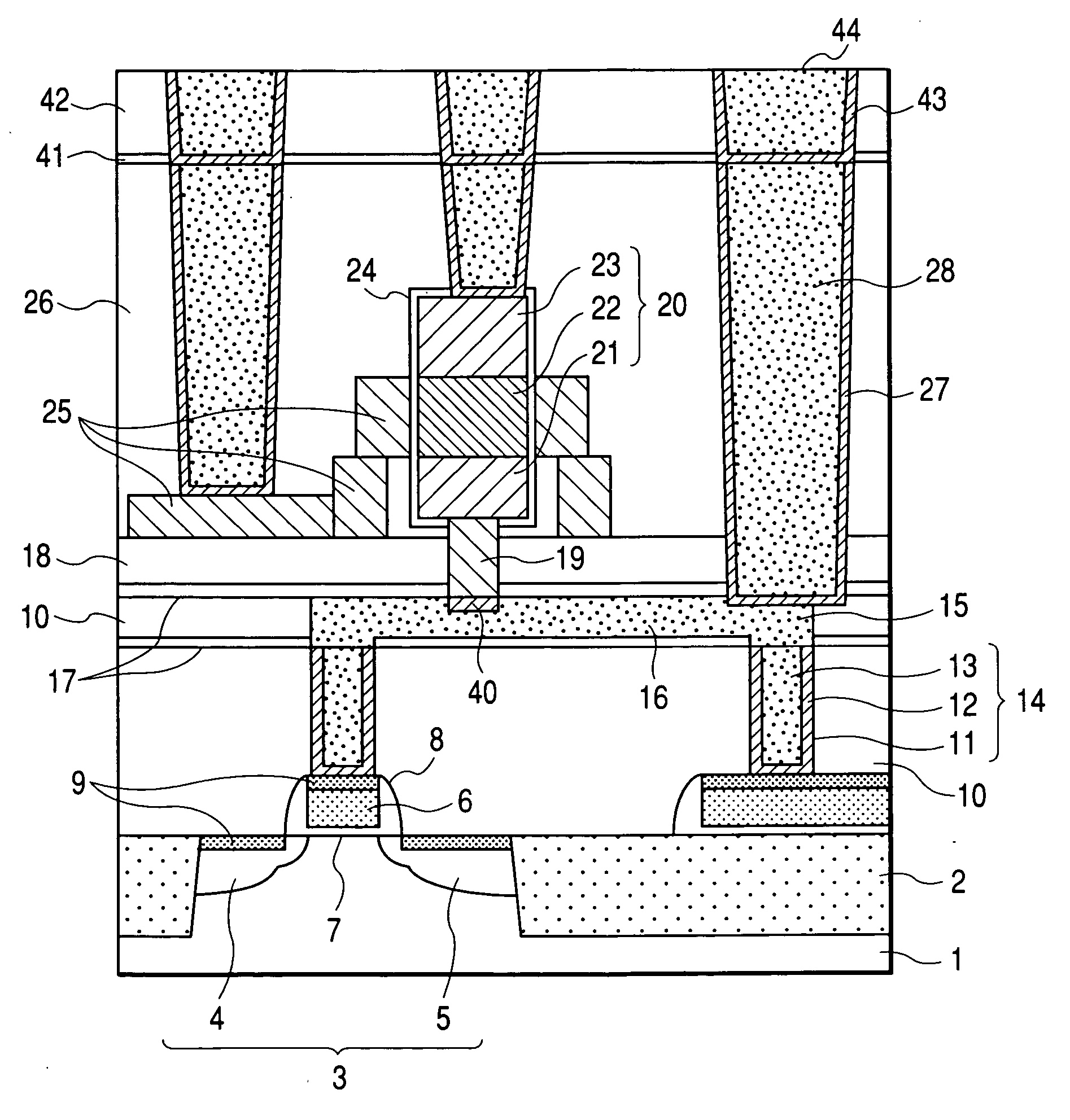

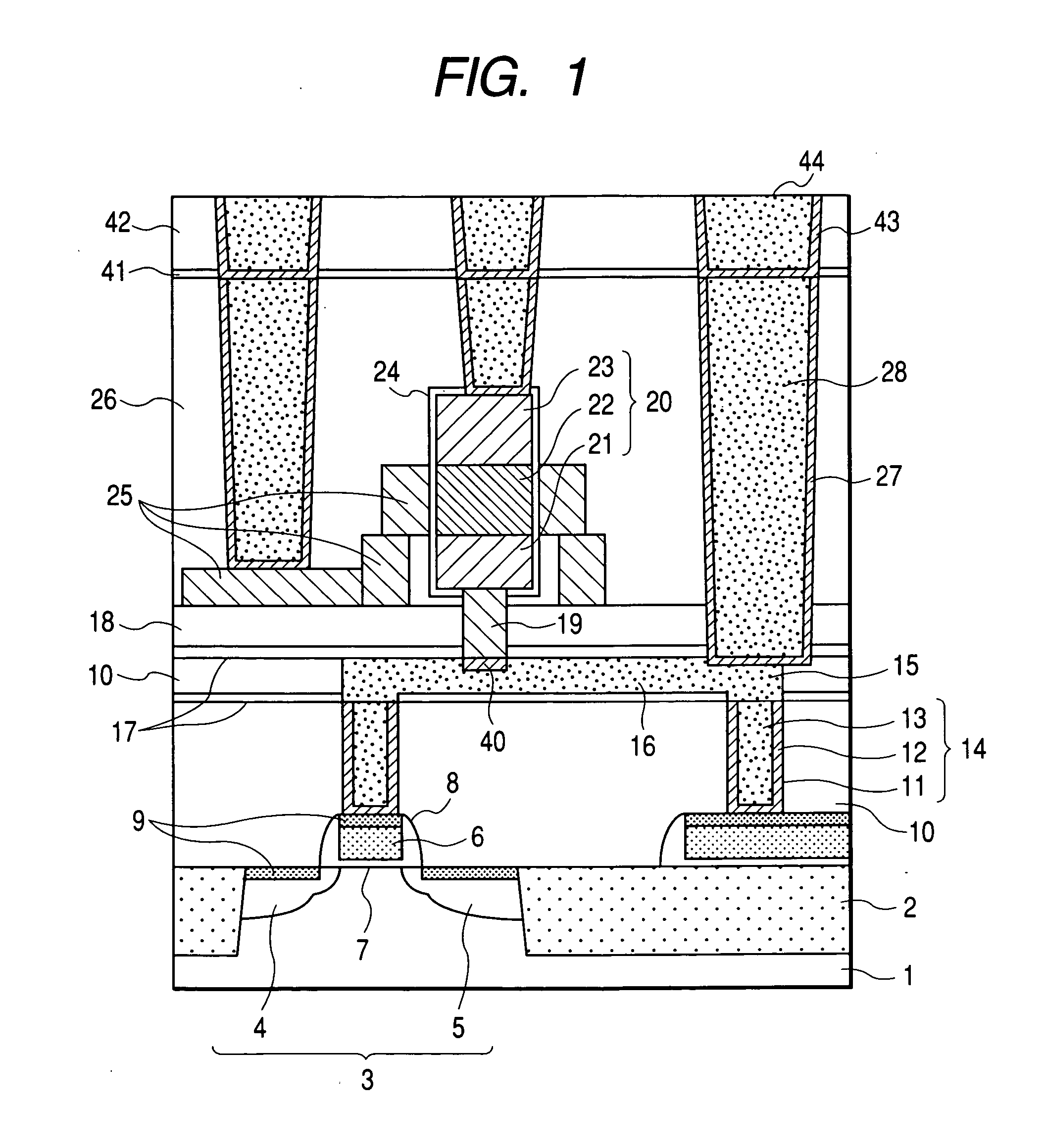

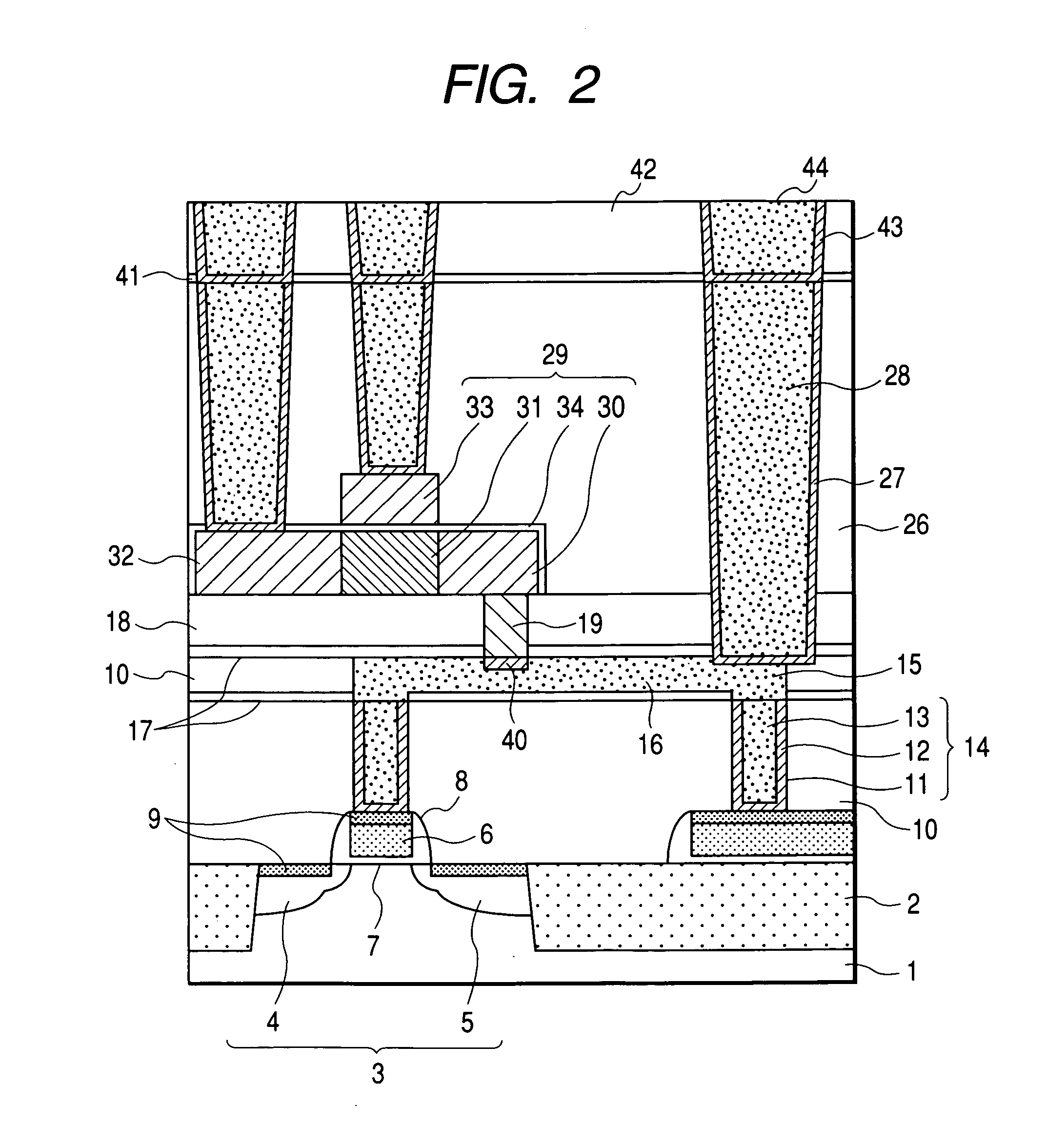

ActiveUS20090200604A1Reduce contact resistanceImprove current carrying capacityTransistorSolid-state devicesElectrical resistance and conductanceHigh density

A new class of high-density, vertical Fin-FET devices that exhibit low contact resistance is described. These vertical Fin-FET devices have vertical silicon “fins” (12A) that act as the transistor body. Doped source and drain regions (26A, 28A) are formed at the bottoms and tops, respectively, of the fins (12A). Gates (24A, 24B) are formed along sidewalls of the fins. Current flows vertically through the fins (12A) between the source and drain regions (26A, 28A) when an appropriate bias is applied to the gates (24A, 24B). An integrated process for forming pFET, nFET, multi-fin, single-fin, multi-gate and double-gate vertical Fin-FETs simultaneously is described.

Owner:GLOBALFOUNDRIES US INC

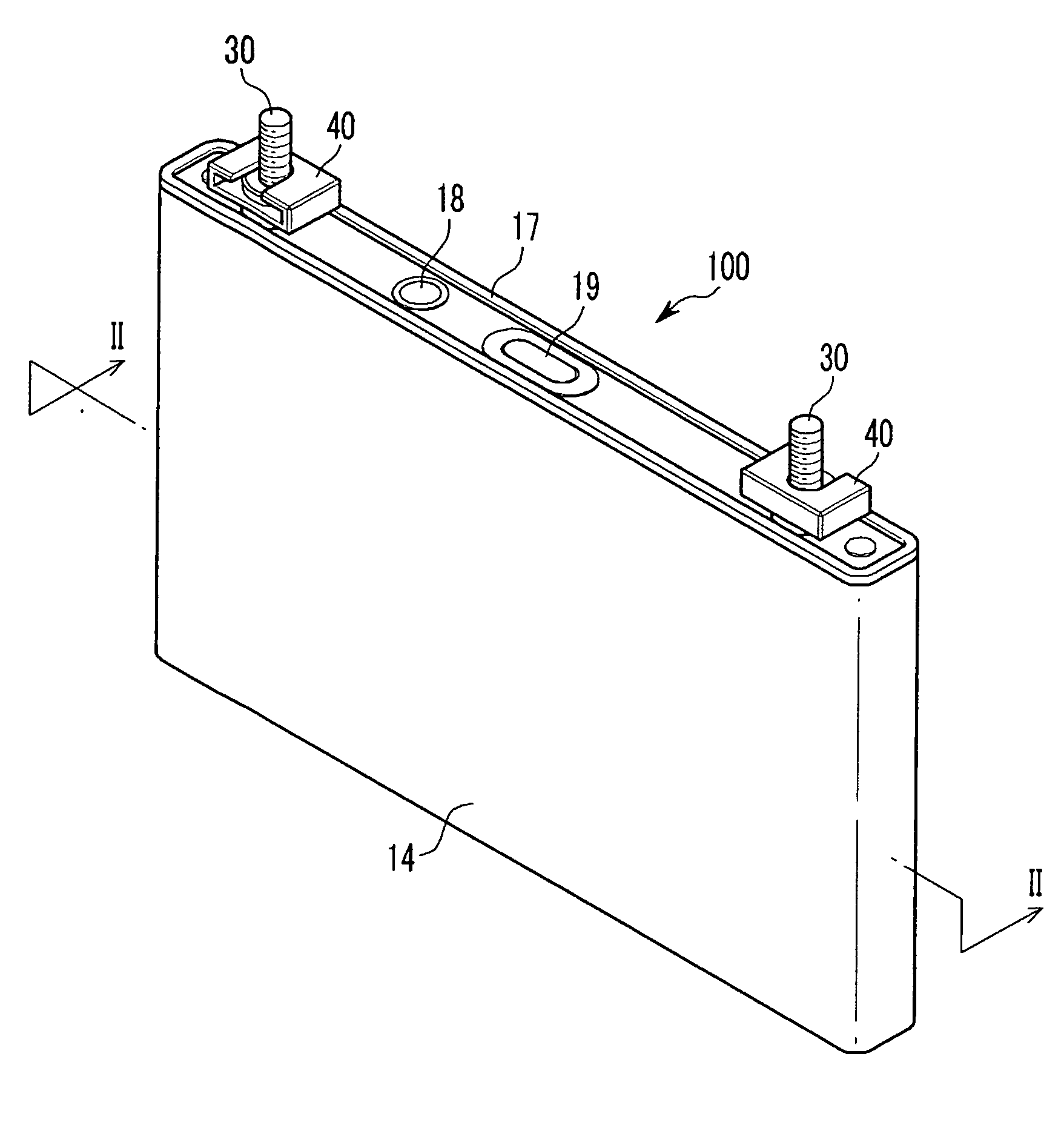

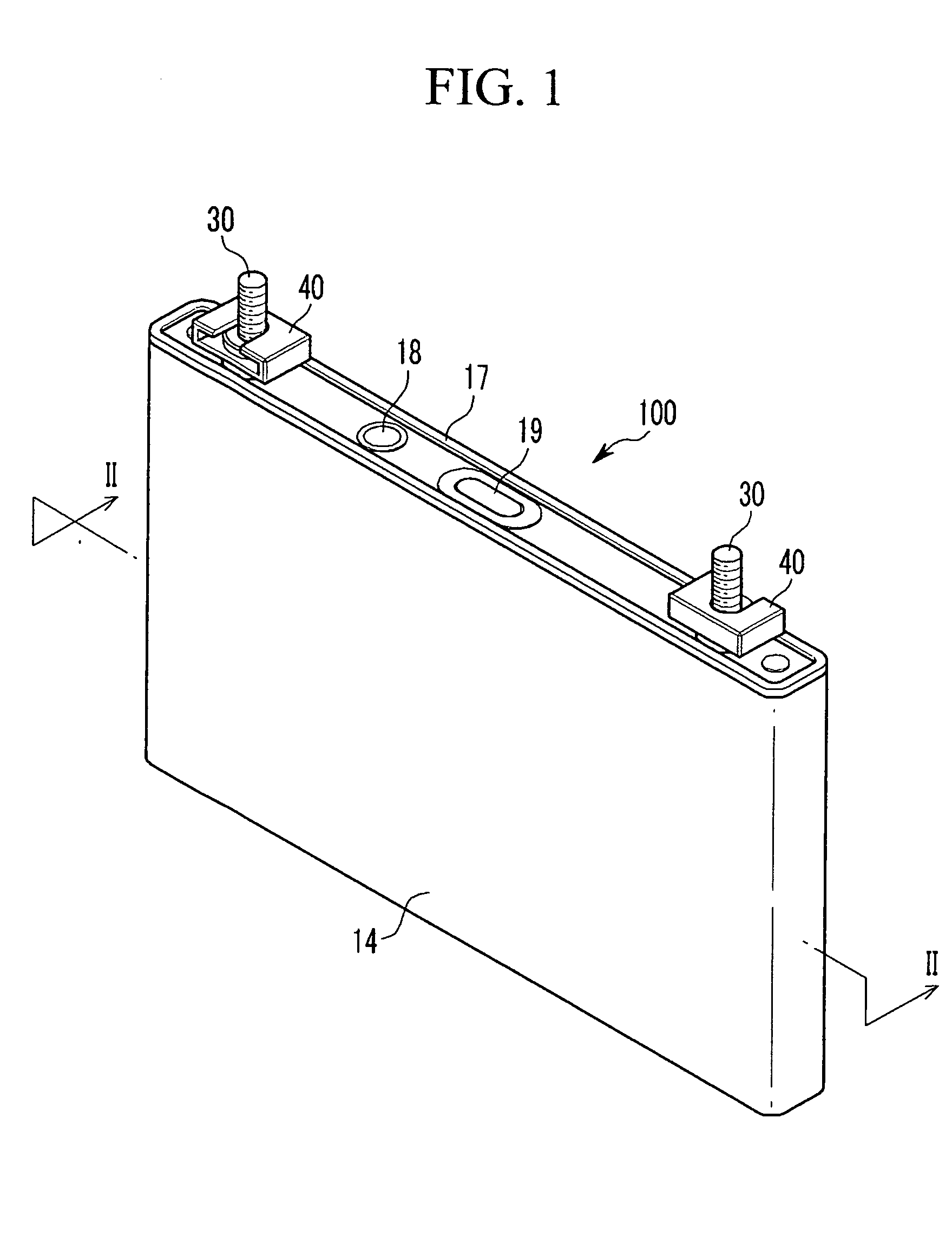

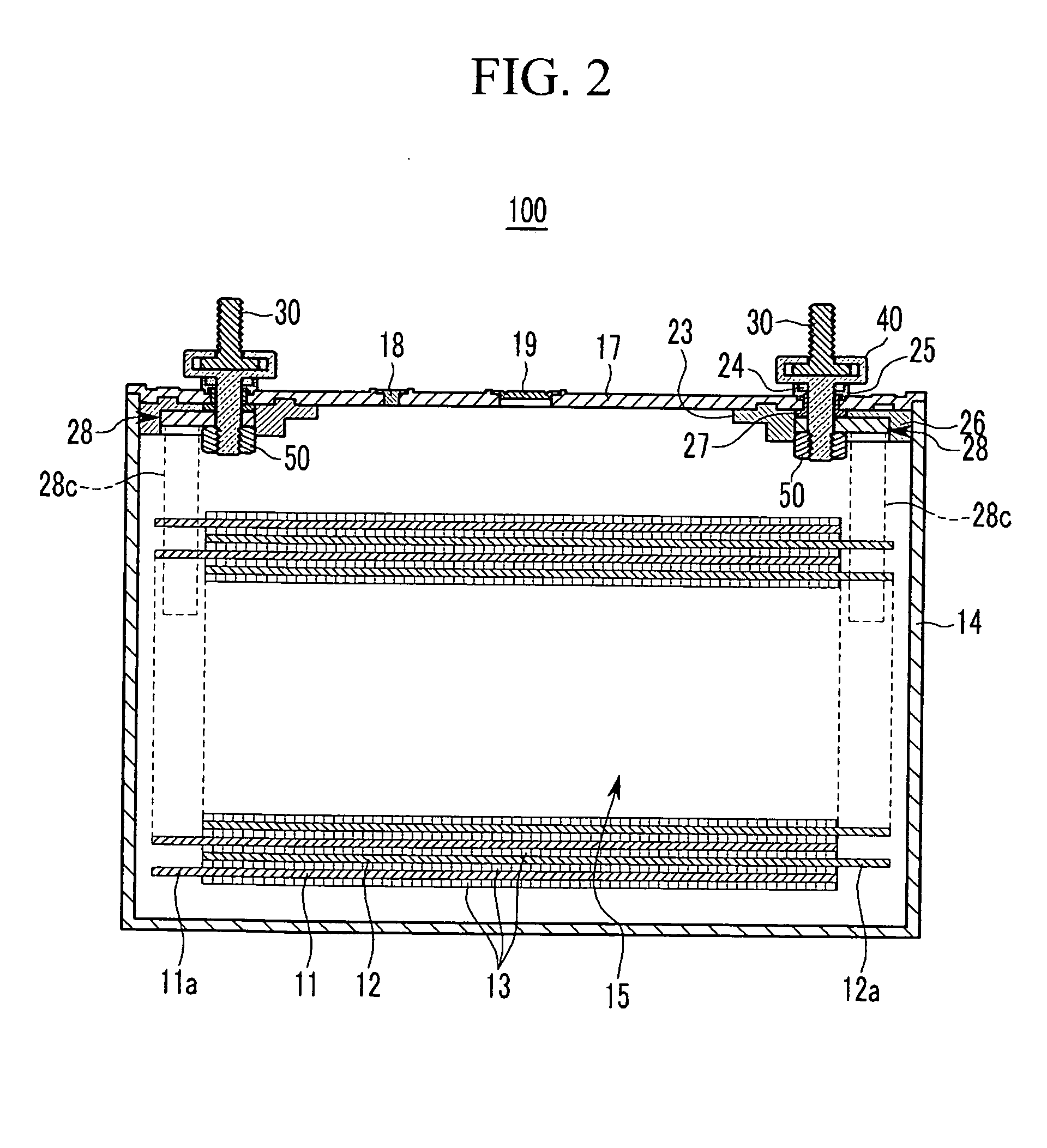

Rechargeable battery and battery module using the same

ActiveUS20100143786A1Reduce materialEasily releasing heatPrimary cell to battery groupingSmall-sized cells cases/jacketsElectricityRechargeable cell

A rechargeable battery includes an electrode group for producing electricity, a case for housing the electrode group, a cap plate combined with the case, an electrode terminal electrically coupled to the electrode group, and a fixing member disposed inside the case and combined to the support shaft portion. The electrode terminal includes a head portion disposed outside the case, and a support shaft portion protruding from the head portion and penetrating the cap plate. Contact resistance of the rechargeable battery can be reduced with this configuration. A battery module includes a plurality of rechargeable batteries and bus bars electrically connecting at least two of the rechargeable batteries, wherein each rechargeable battery includes a case with an internal space, a cap plate combined with the case, an electrode terminal including a head portion caught on the cap plate and a support shaft portion protruding from the head portion and penetrating the cap plate, and a fixing member disposed inside the case and combined to the support shaft portion.

Owner:SAMSUNG SDI CO LTD

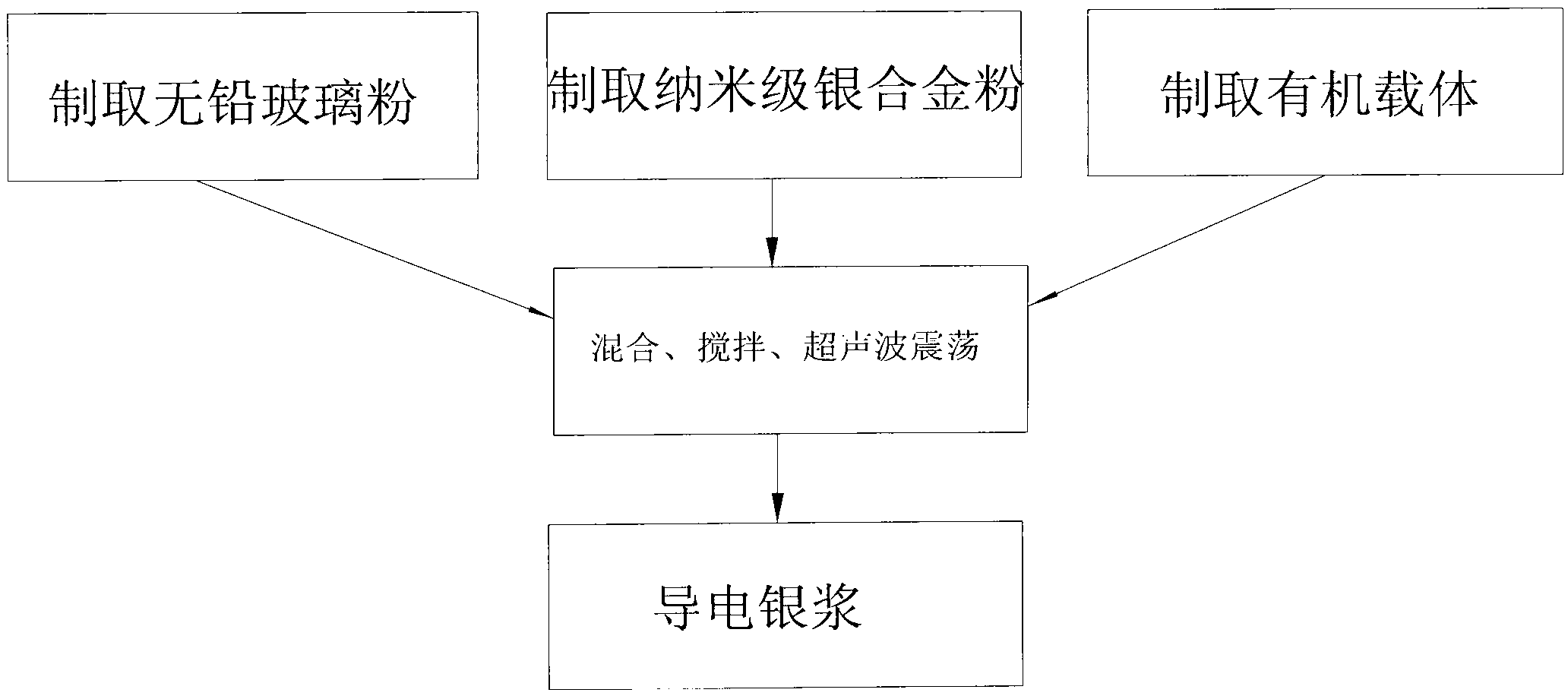

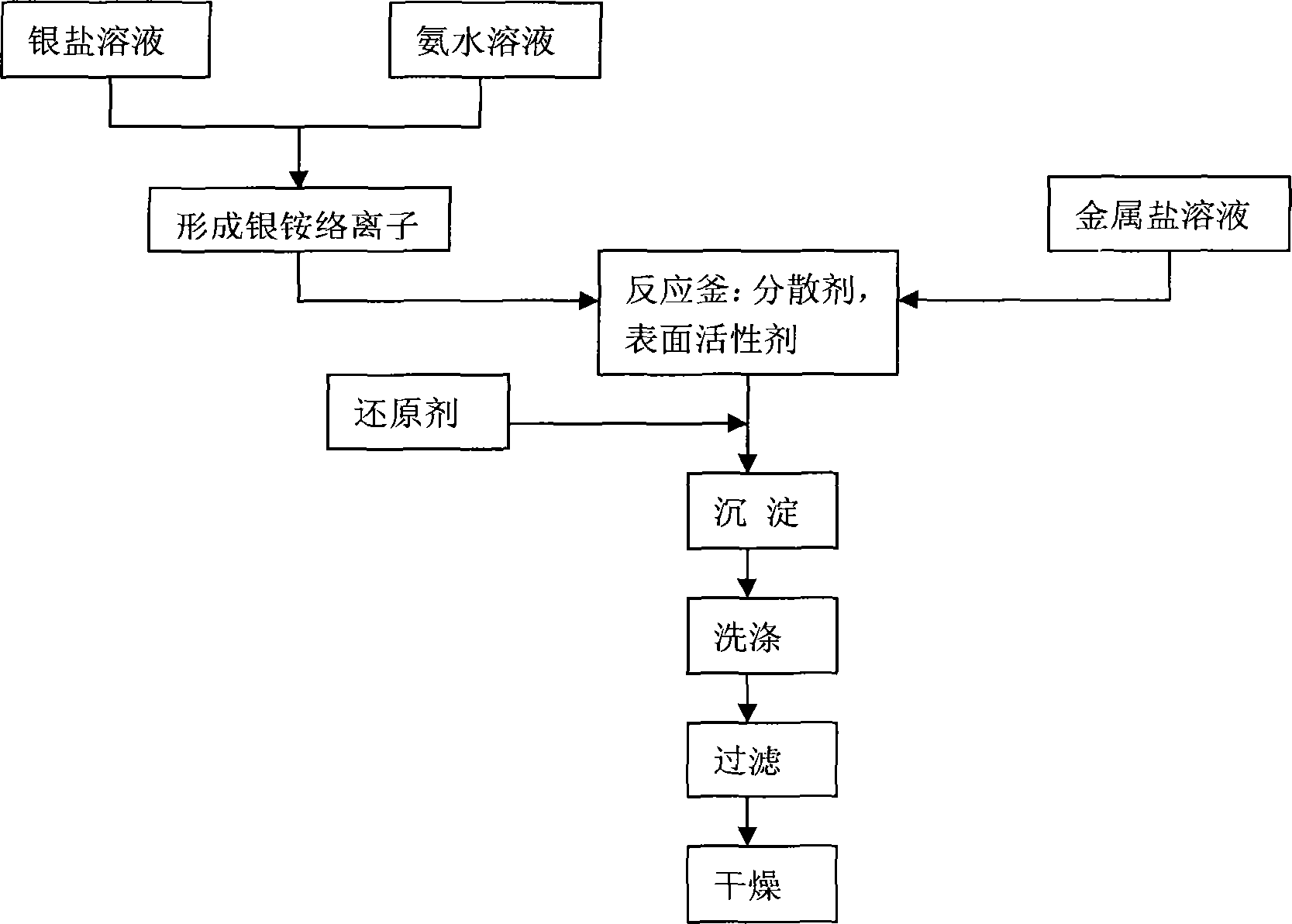

Electric conductive silver paste and manufacturing method thereof

ActiveCN103258584AEnhanced interconnectionIncrease contact areaNon-conductive material with dispersed conductive materialCable/conductor manufactureSilver pasteMetal alloy

The invention discloses electric conductive silver paste and a manufacturing method of the electric conductive silver paste. The electric conductive silver paste comprises, by mass percentage, 35 - 65 % of micron-sized silver powder, 1-10 % of nanometer-sized silver powder of or 1-20 % of nanometer-sized silver and other metal alloy powder, and 1-10 % of an organic carrier; for ceramics, solar cell silver paste comprises 2-15 % of unleaded glass powder, each component is manufactured in parts, weighed, mixed and stirred or mixed and rapidly scattered, and ultrasonic-vibrated or fine adjusted of viscosity of solvent, and therefore the electric conductive silver paste is obtained. Due to the fact that the nanometer-sized silver powder or the nanometer-sized silver alloy powder is mixed with the micron-sized silver powder, intensity of conductivity and a circuit is improved, adhesive force of crushing resistance and a base plate is improved, at the same time unleaded slurry good in thixotropy, low in contacting resistance and low in piece-needed slurry amount replaces lead slurry materials, the electric conductive silver paste is used for manufacturing crystalline silicon solar cells, improves photoelectric conversion efficiency, accords with environmental-protection ideas, and can be produced in large scales continuously.

Owner:SHENZHEN CHENGGONG CHEM

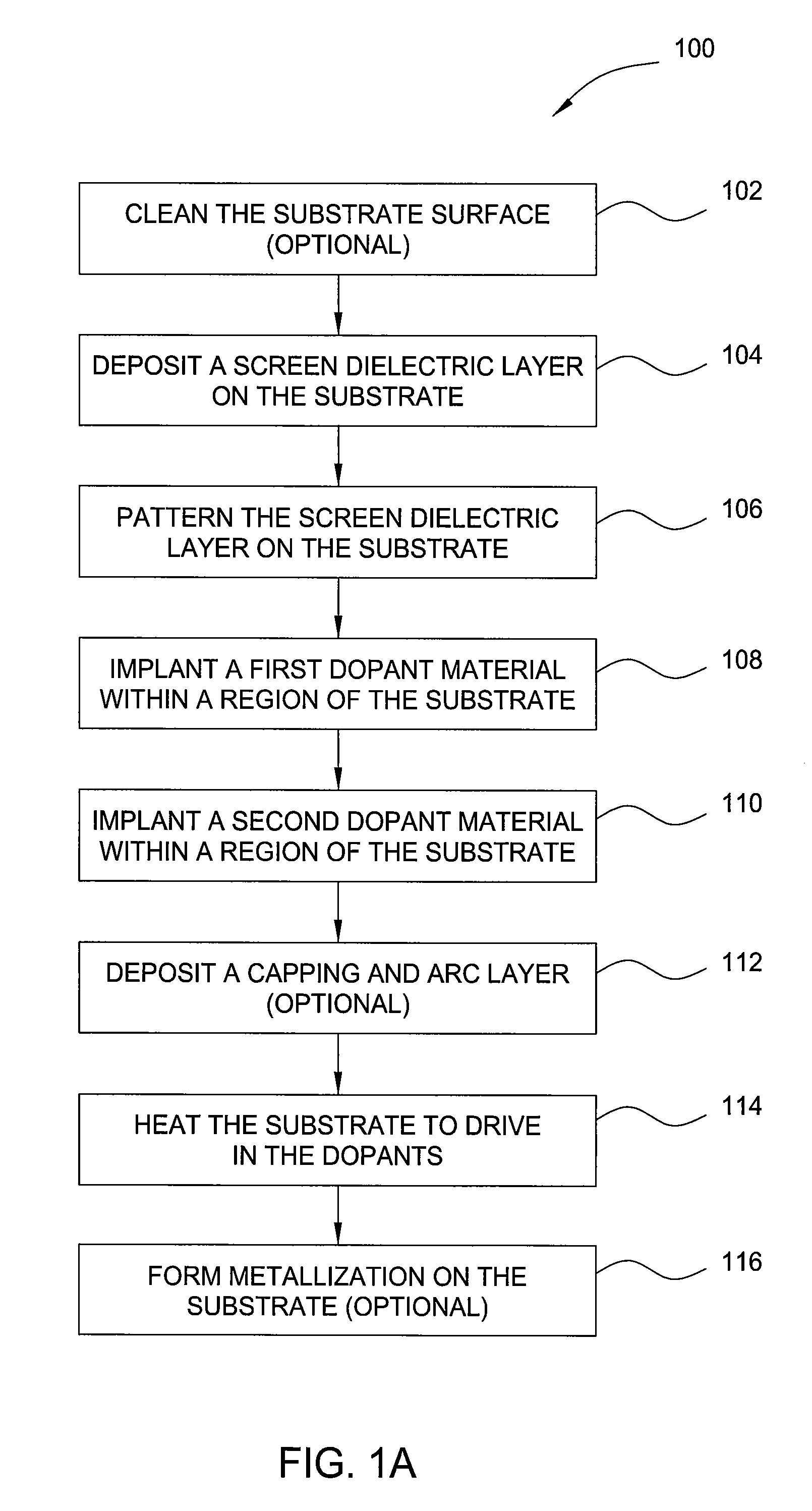

Methods of emitter formation in solar cells

InactiveUS20090068783A1Final product manufactureSemiconductor/solid-state device manufacturingDopantElectrical resistance and conductance

Embodiments of the invention contemplate high efficiency emitters in solar cells and novel methods for forming the same. One embodiment of the improved emitter structure, called a high-low type emitter, optimizes the solar cell performance by equally providing low contact resistance to minimize ohmic losses and isolation of the high surface recombination metal-semiconductor interface from the junction to maximize cell voltage. Another embodiment, called an alternating doping type emitter, provides regions of alternating doping type for use with point contacts in the back-contact solar cells. One embodiment of the methods includes depositing and patterning a doped or undoped dielectric layer on a surface of a substrate, implanting a fast-diffusing dopant and / or a slow-diffusing dopant into the substrate either simultaneously or sequentially, and annealing the substrate to drive in the dopants. Another embodiment of the methods includes using a physical mask to form a patterned dopant distribution in a substrate.

Owner:APPLIED MATERIALS INC

Oxide semiconductor device and method of manufacturing the same and active matrix substrate

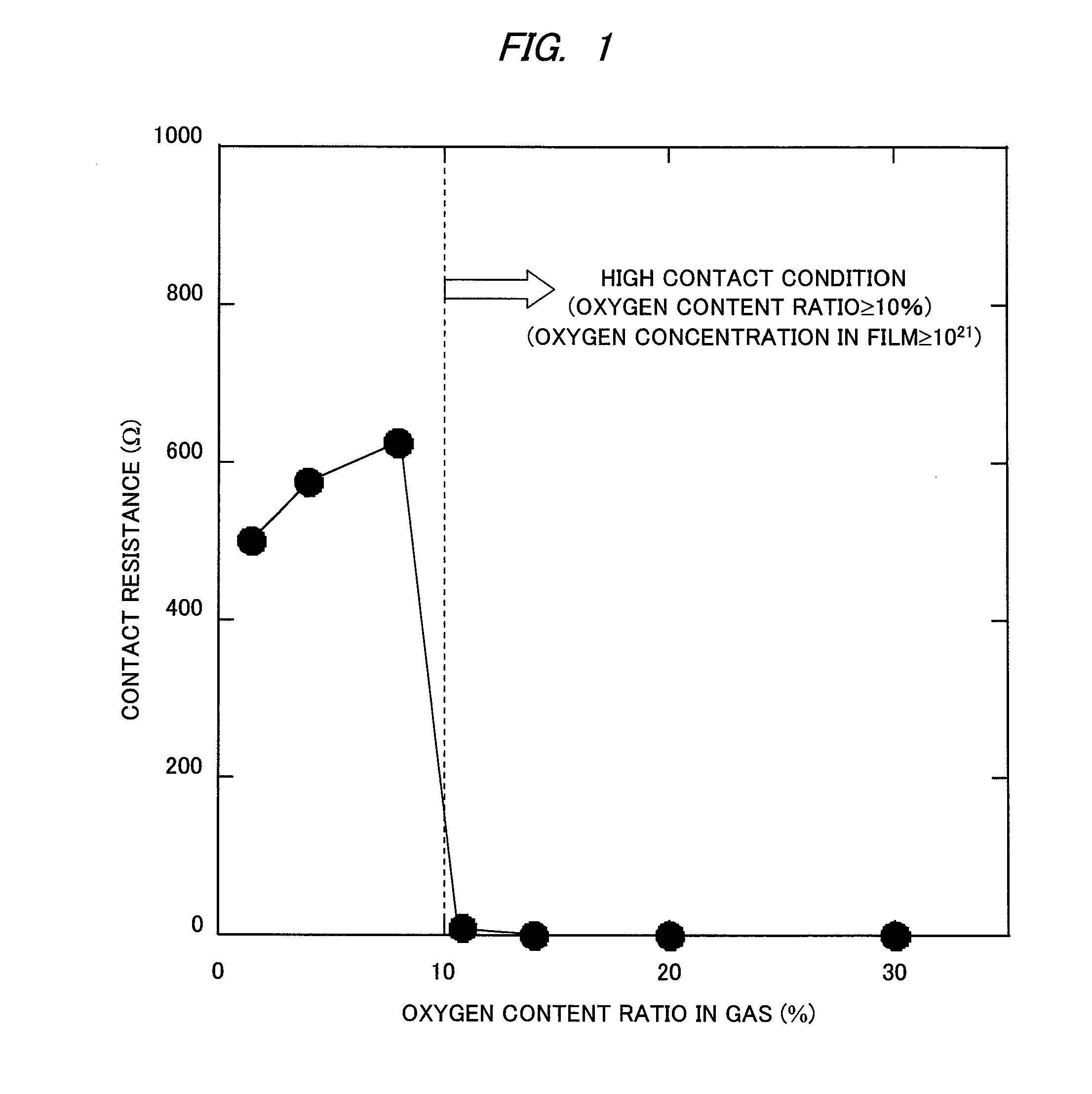

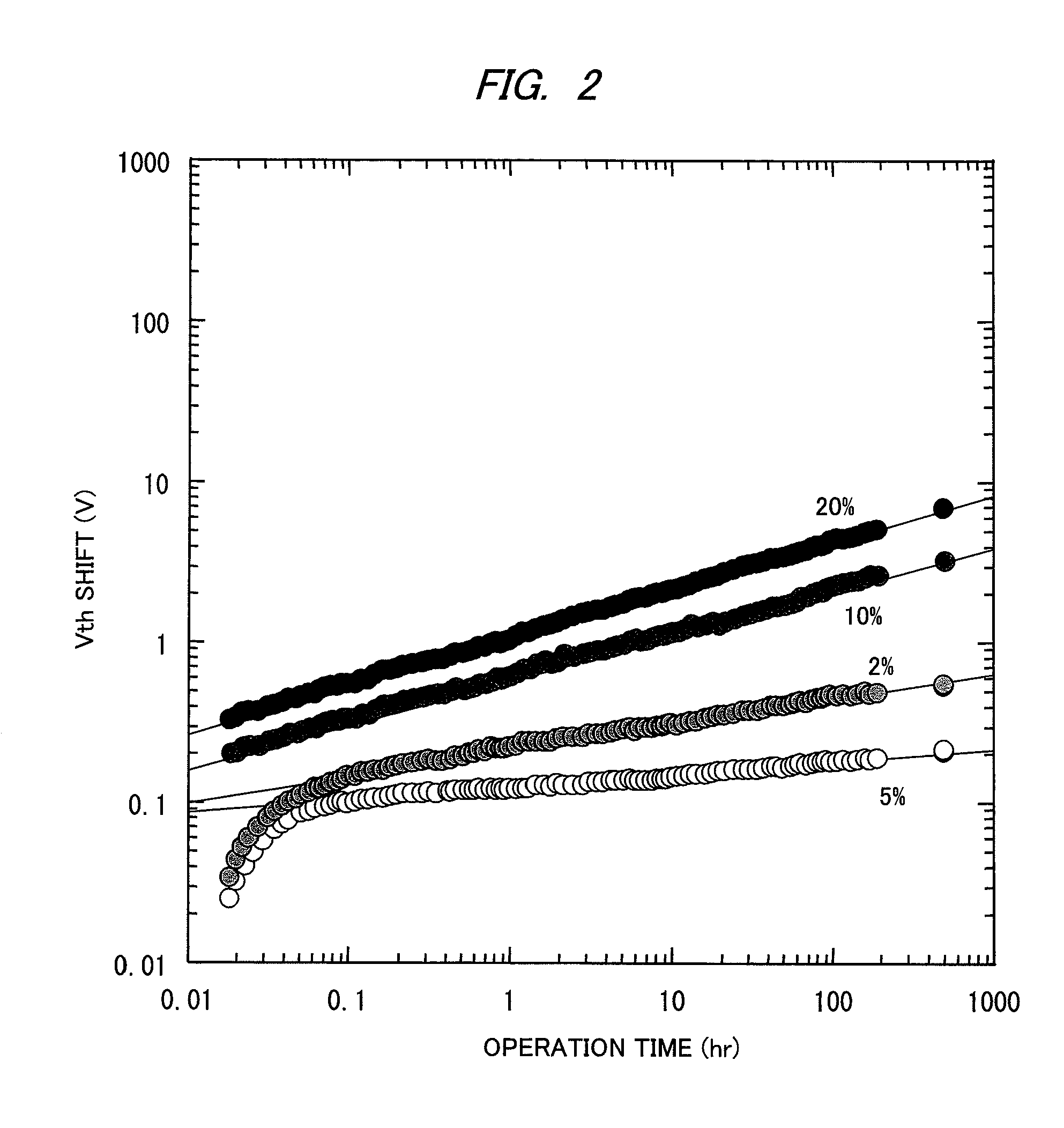

InactiveUS20100140614A1High content ratioImprove contact effectTransistorSolid-state devicesActive matrixThreshold potential

A phenomenon of change of a contact resistance between an oxide semiconductor and a metal depending on an oxygen content ratio in introduced gas upon depositing an oxide semiconductor film made of indium gallium zinc oxide, zinc tin oxide, or others in an oxide semiconductor thin-film transistor. A contact layer is formed with an oxygen content ratio of 10% or higher in a region from a surface, where the metal and the oxide semiconductor are contacted, down to at least 3 nm deep in depth direction, and a region to be a main channel layer is further formed with an oxygen content ratio of 10% or lower, so that a multilayered structure is formed, and both of ohmic characteristics to the electrode metal and reliability such as the suppression of threshold potential shift are achieved.

Owner:HITACHI LTD

Graphene-based transistor

ActiveUS7732859B2Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A graphene layer is formed on a surface of a silicon carbide substrate. A dummy gate structure is formed over the fin, in the trench, or on a portion of the planar graphene layer to implant dopants into source and drain regions. The dummy gate structure is thereafter removed to provide an opening over the channel of the transistor. Threshold voltage adjustment implantation may be performed to form a threshold voltage implant region directly beneath the channel, which comprises the graphene layer. A gate dielectric is deposited over a channel portion of the graphene layer. After an optional spacer formation, a gate conductor is formed by deposition and planarization. The resulting graphene-based field effect transistor has a high carrier mobility due to the graphene layer in the channel, low contact resistance to the source and drain region, and optimized threshold voltage and leakage due to the threshold voltage implant region.

Owner:GLOBALFOUNDRIES U S INC