Patents

Literature

19733results about "Electronic circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

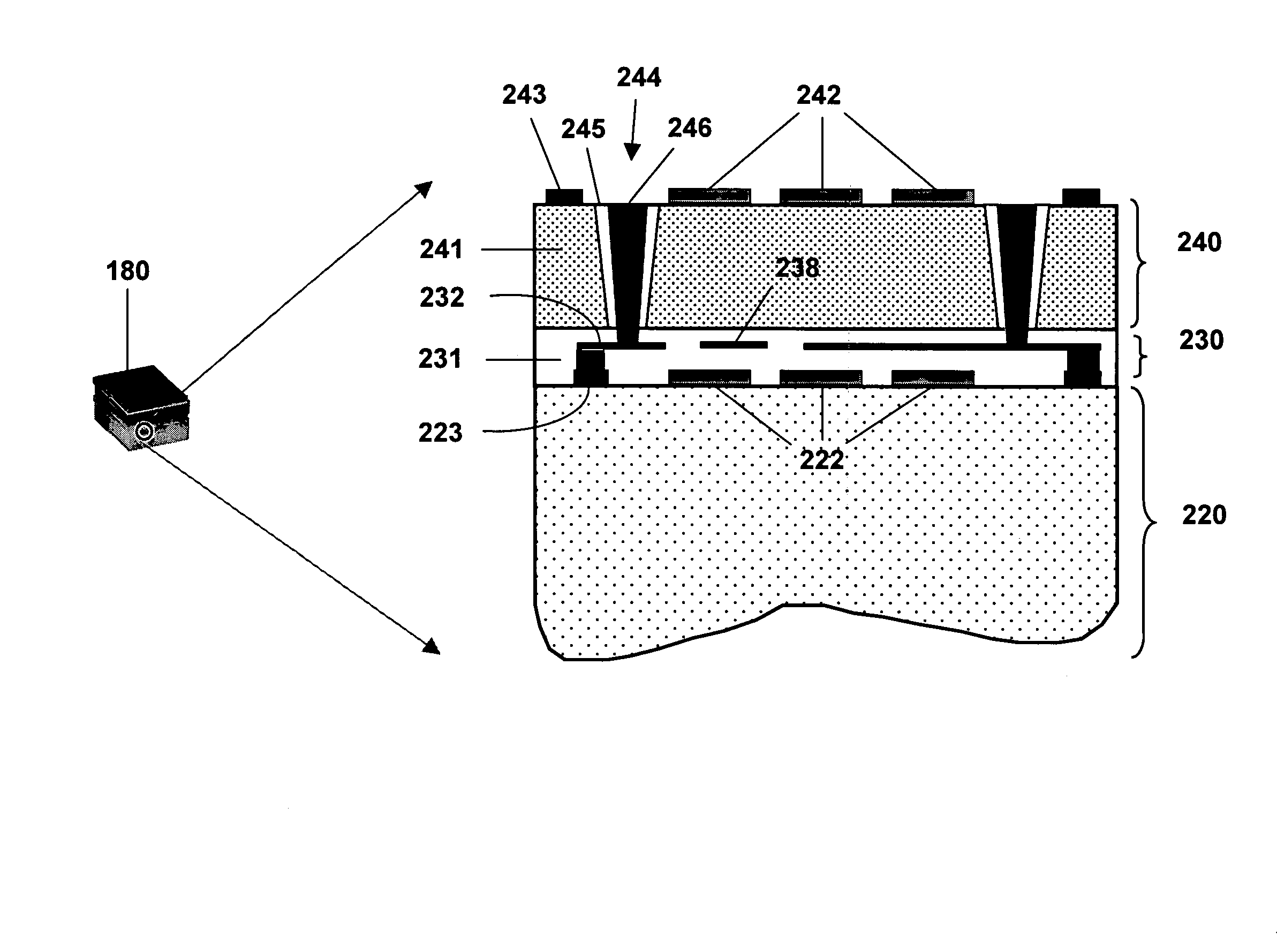

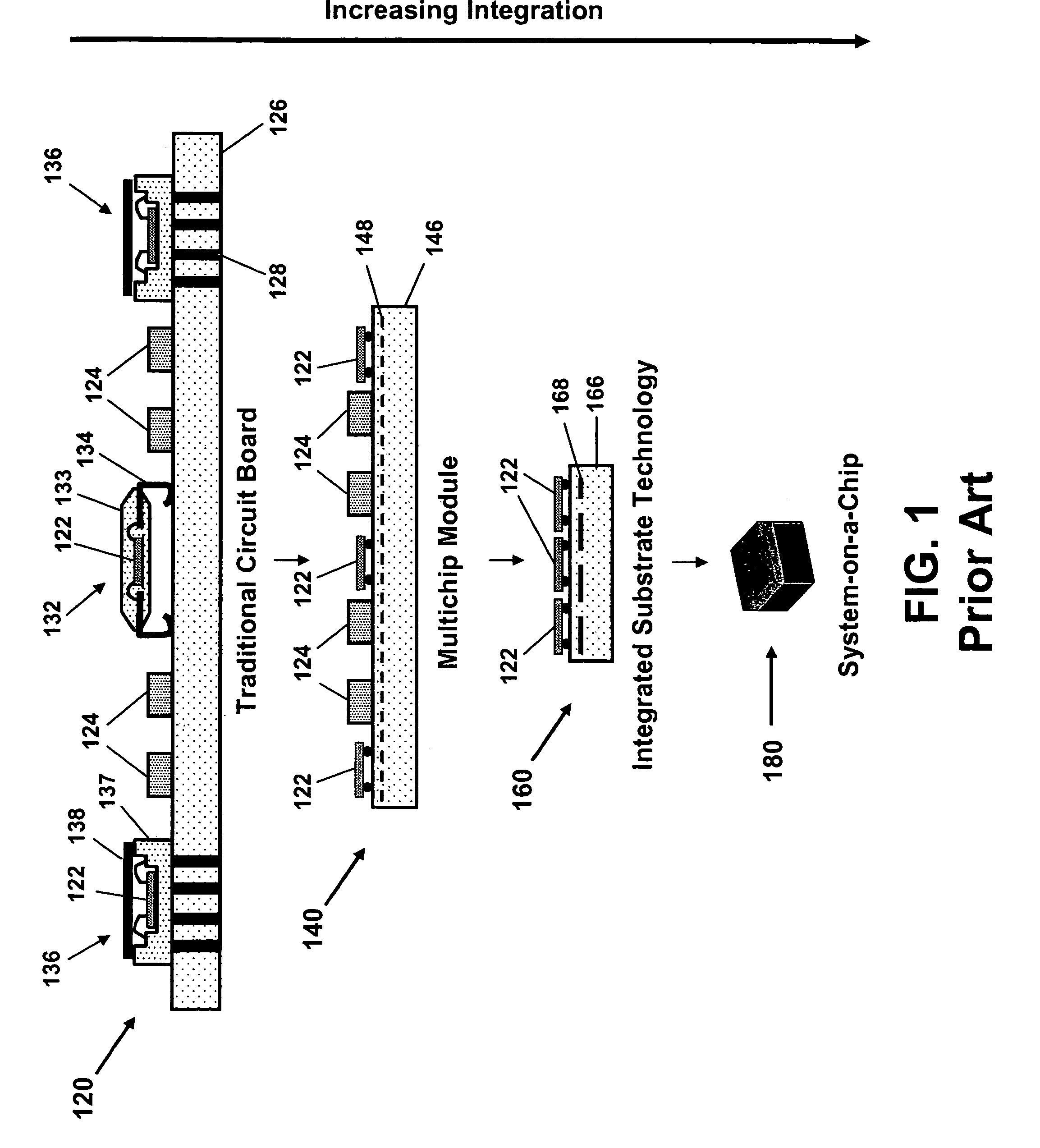

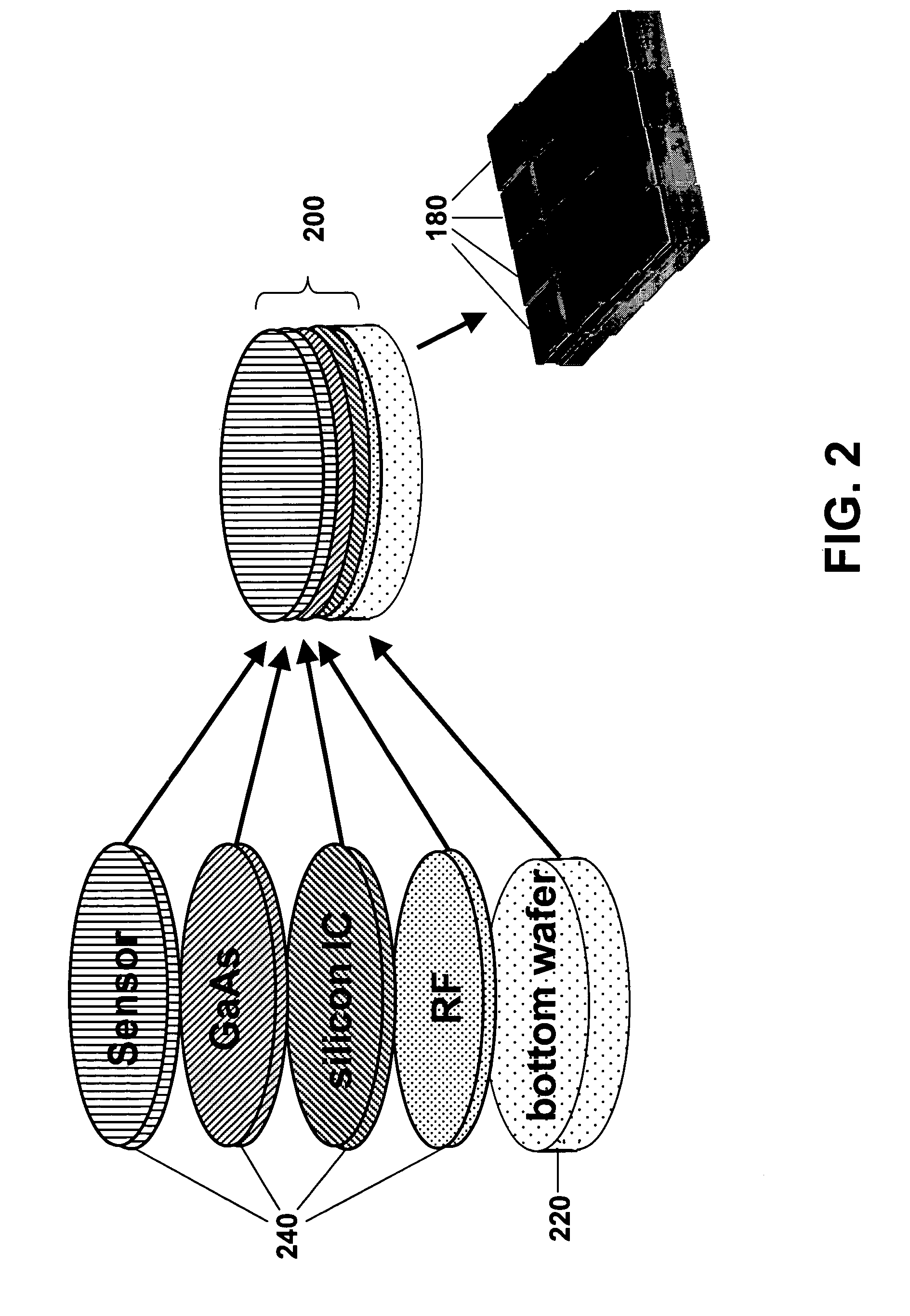

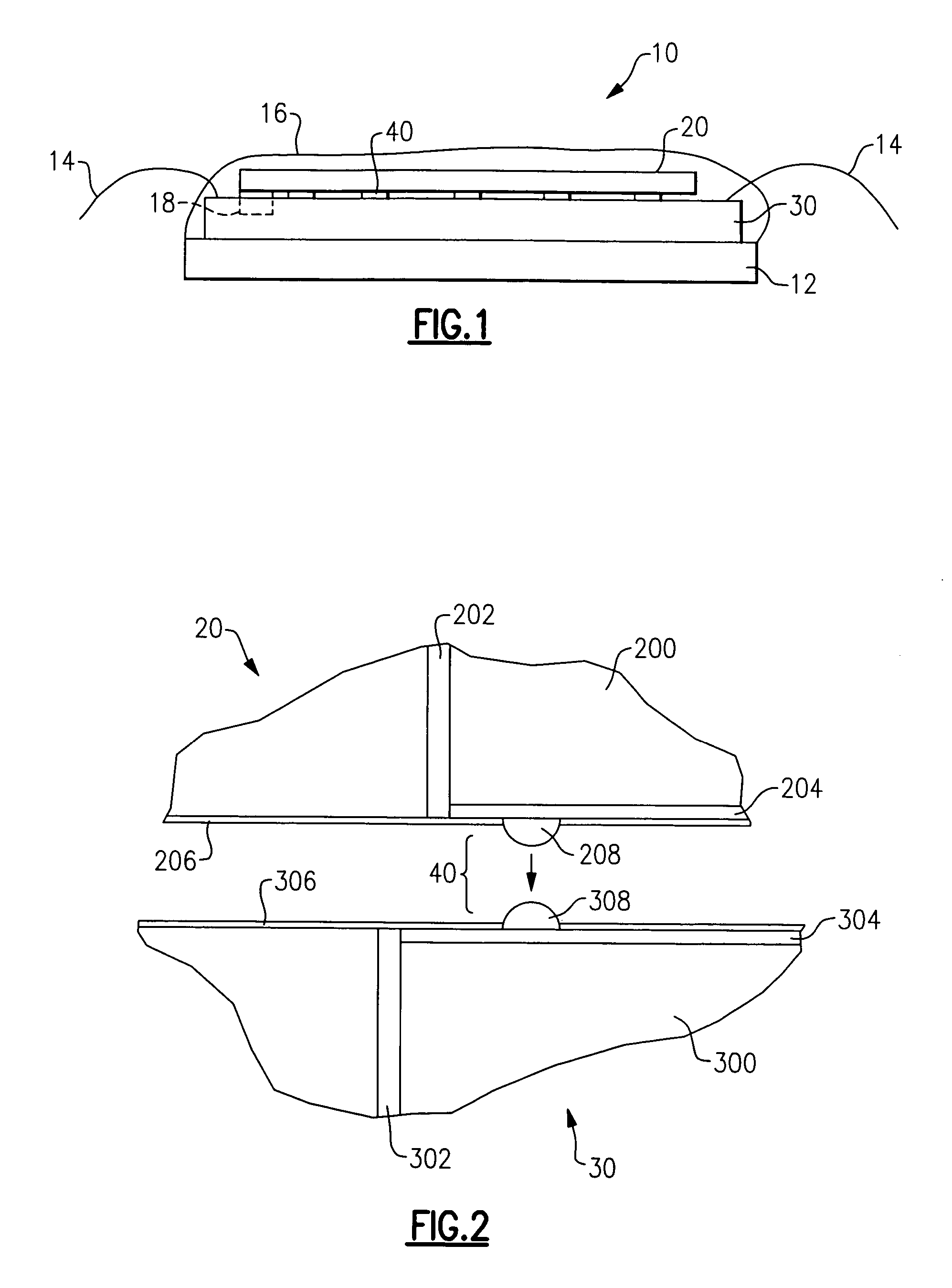

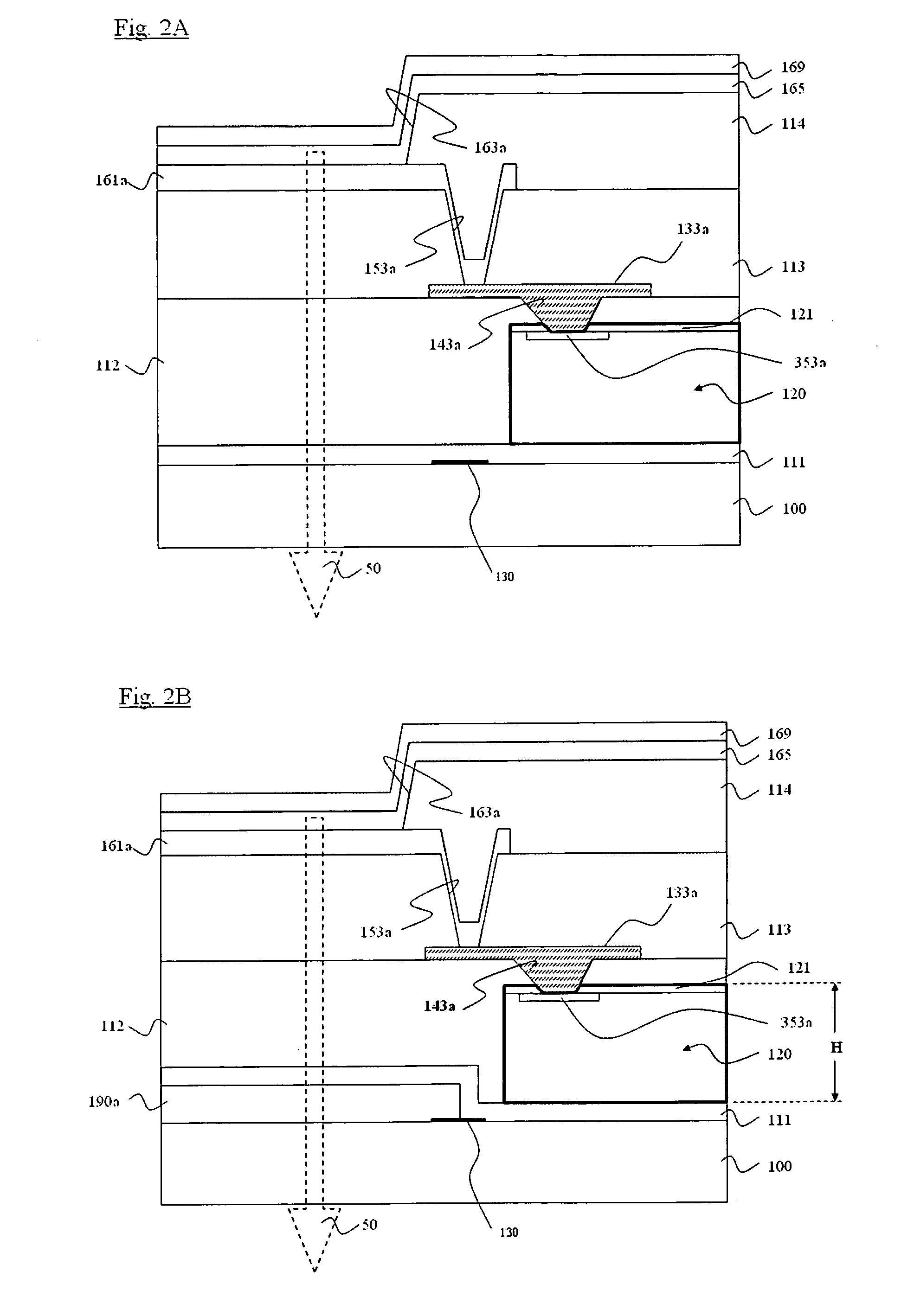

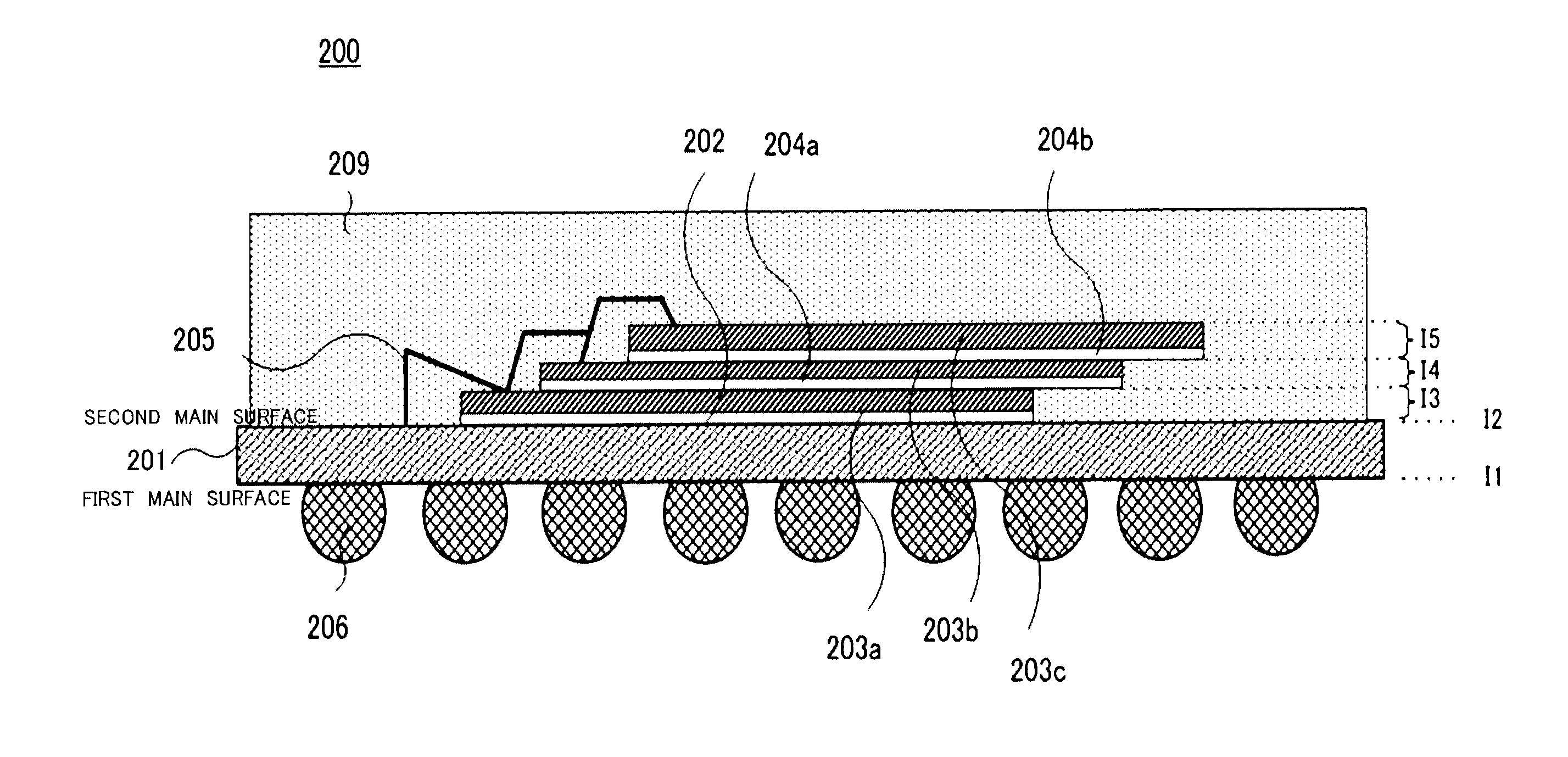

Heterogeneously integrated microsystem-on-a-chip

ActiveUS7335972B2Electronic circuit testingSemiconductor/solid-state device detailsMiniaturizationInterconnection

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

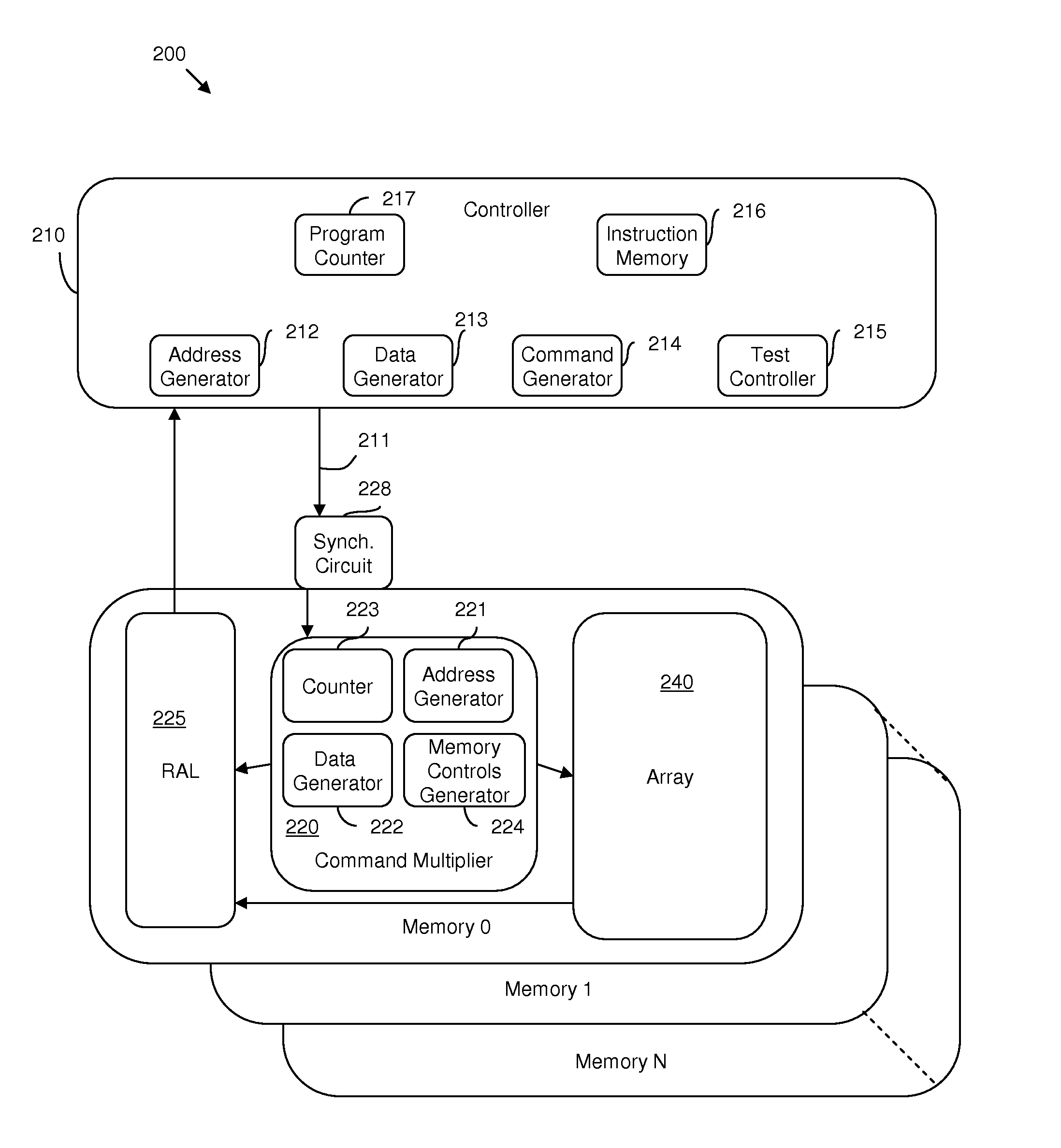

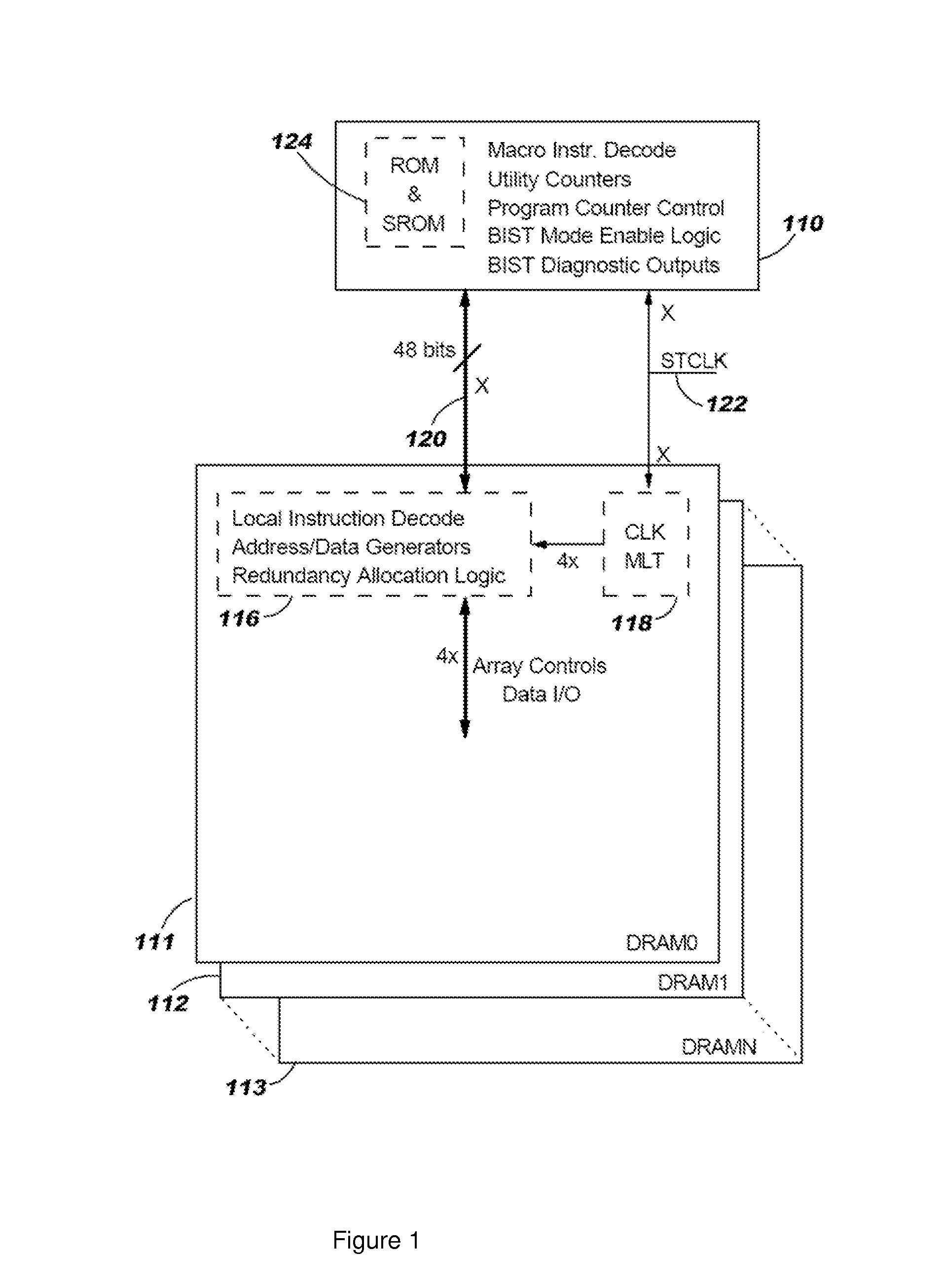

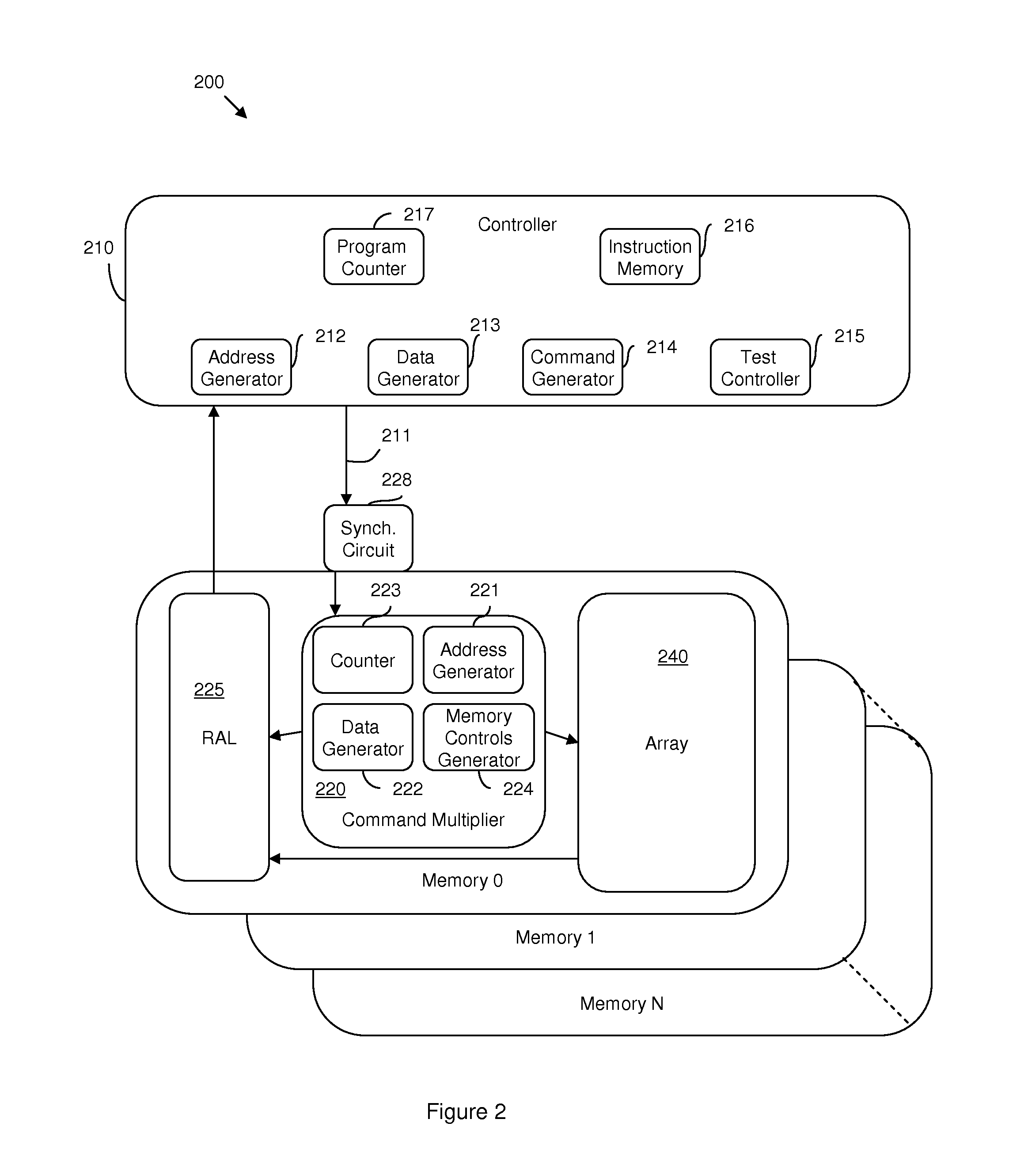

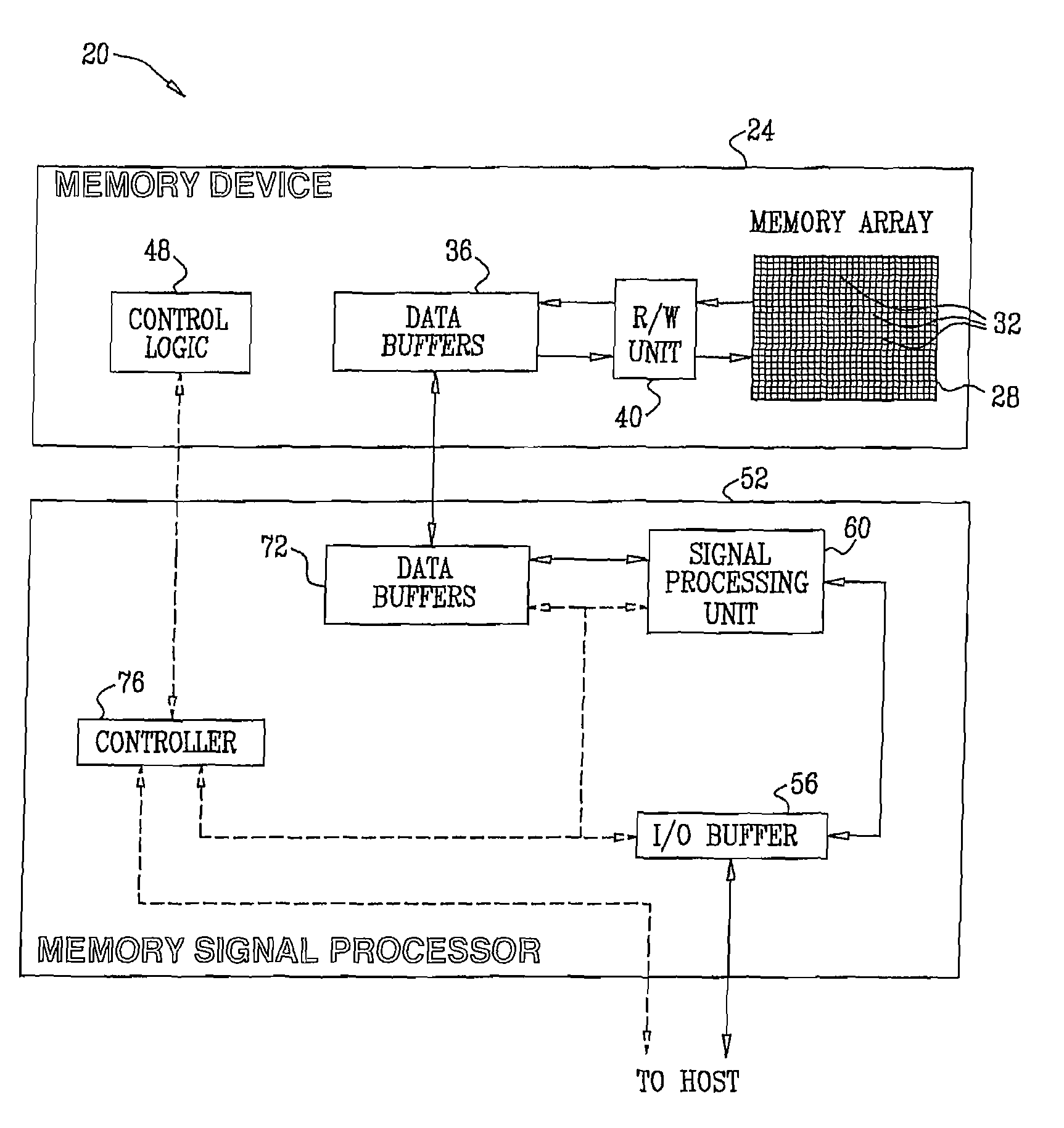

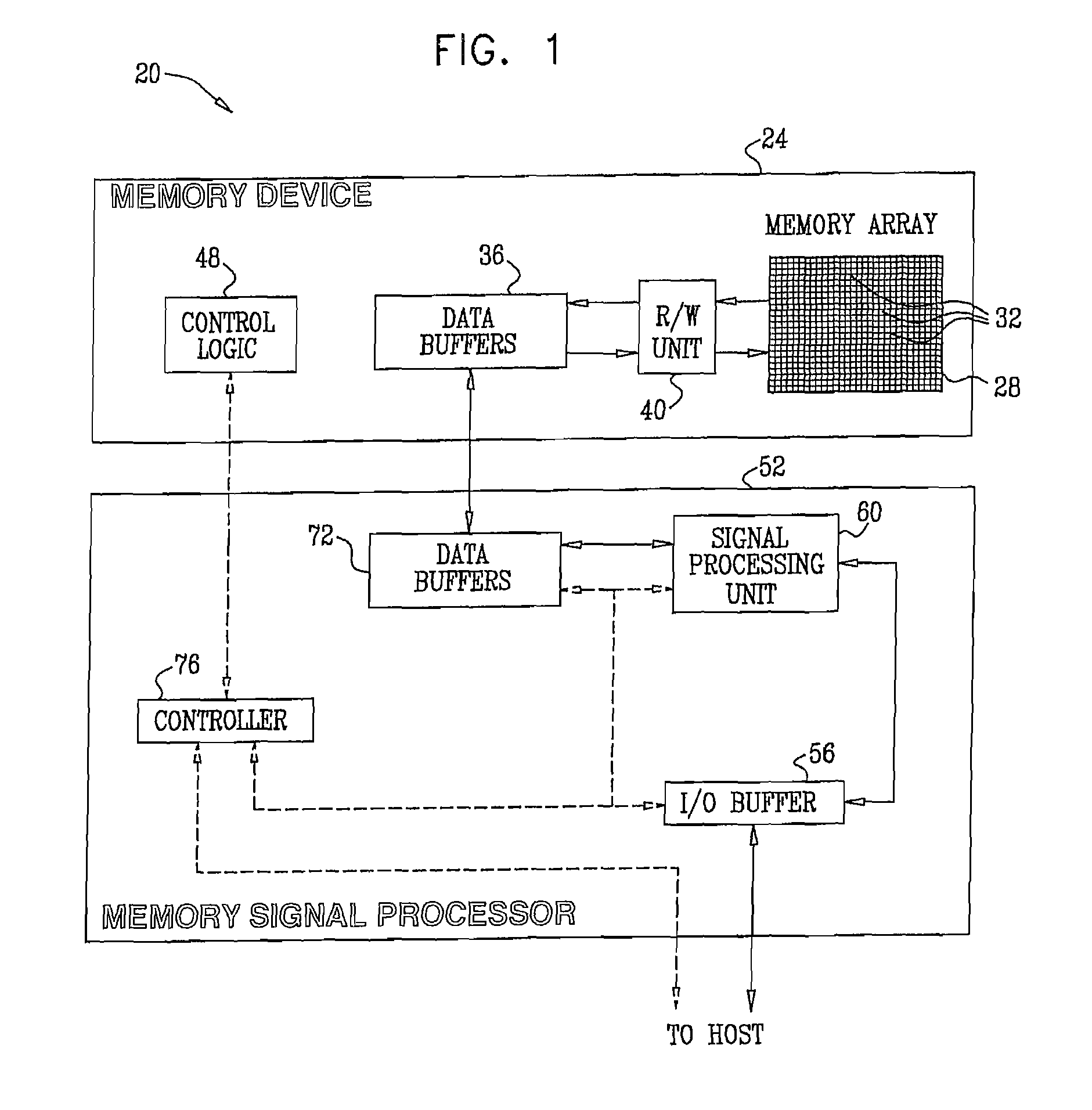

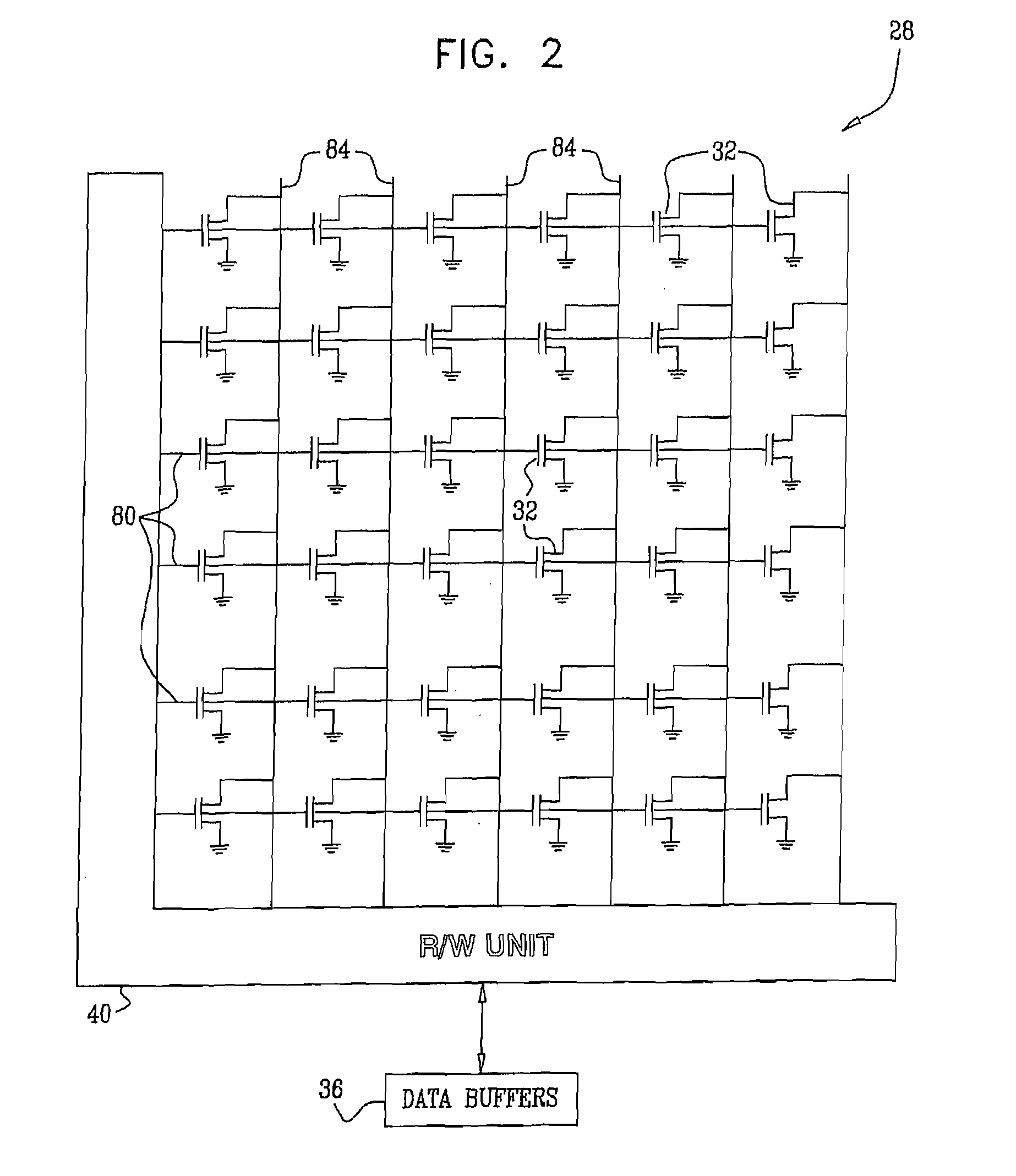

Hybrid built-in self test (BIST) architecture for embedded memory arrays and an associated method

ActiveUS20080178053A1Reduce frequencyMore test pattern flexibilityElectronic circuit testingFunctional testingSpecific testNormal mode

Disclosed are embodiments of a built-in self-test (BIST) architecture that incorporates a standalone controller that operates at a lower frequency to remotely perform test functions common to a plurality of embedded memory arrays. The architecture also incorporates command multipliers that are associated with the embedded memory arrays and that selectively operate in one of two different modes: a normal mode or a bypass mode. In the normal mode, instructions from the controller are multiplied so that memory array-specific test functions can be performed locally at the higher operating frequency of each specific memory array. Whereas, in the bypass mode, multiplication of the instructions is suspended so that memory array-specific test functions can be performed locally at the lower operating frequency of the controller. The ability to vary the frequency at which test functions are performed locally, allows for more test pattern flexibility.

Owner:META PLATFORMS INC

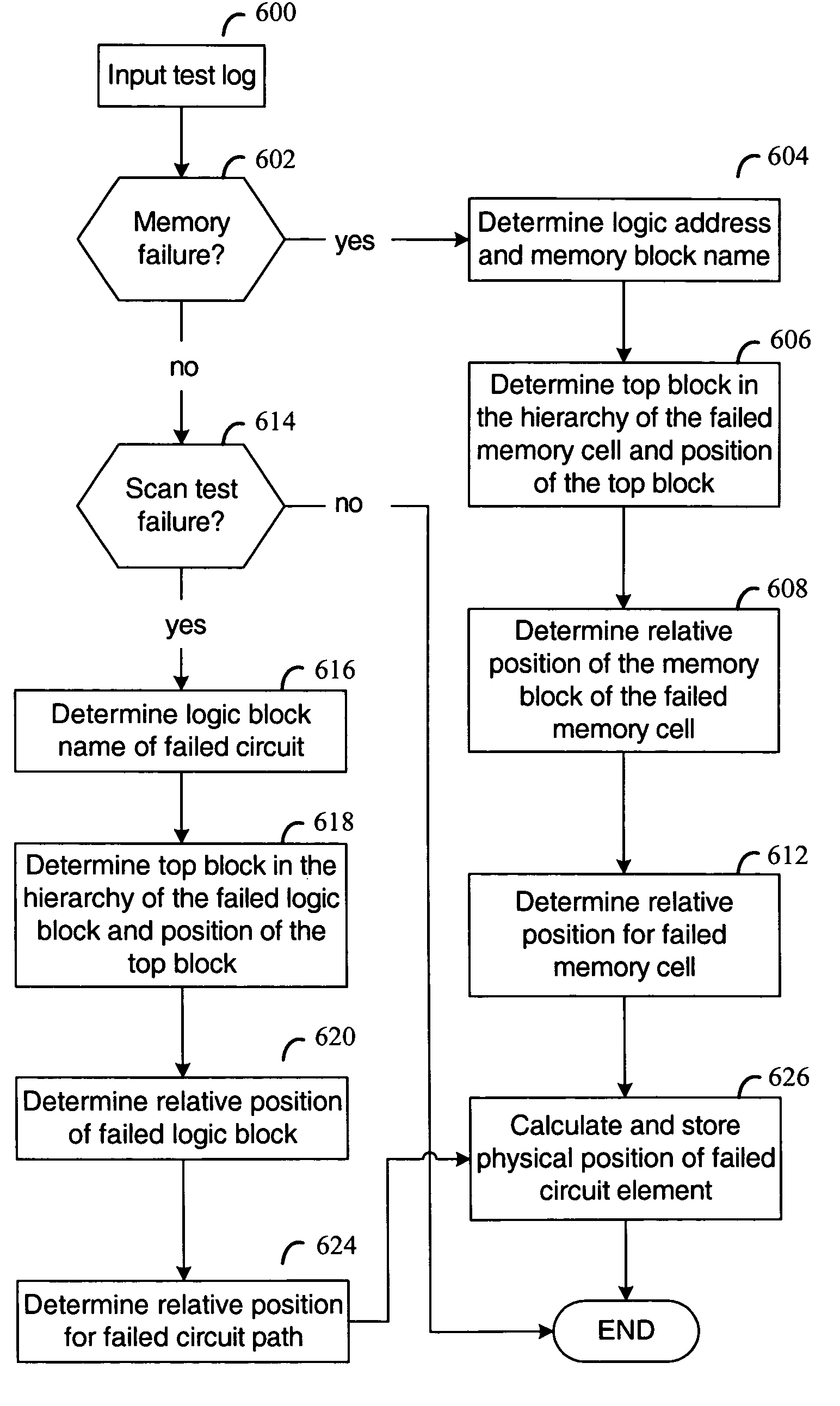

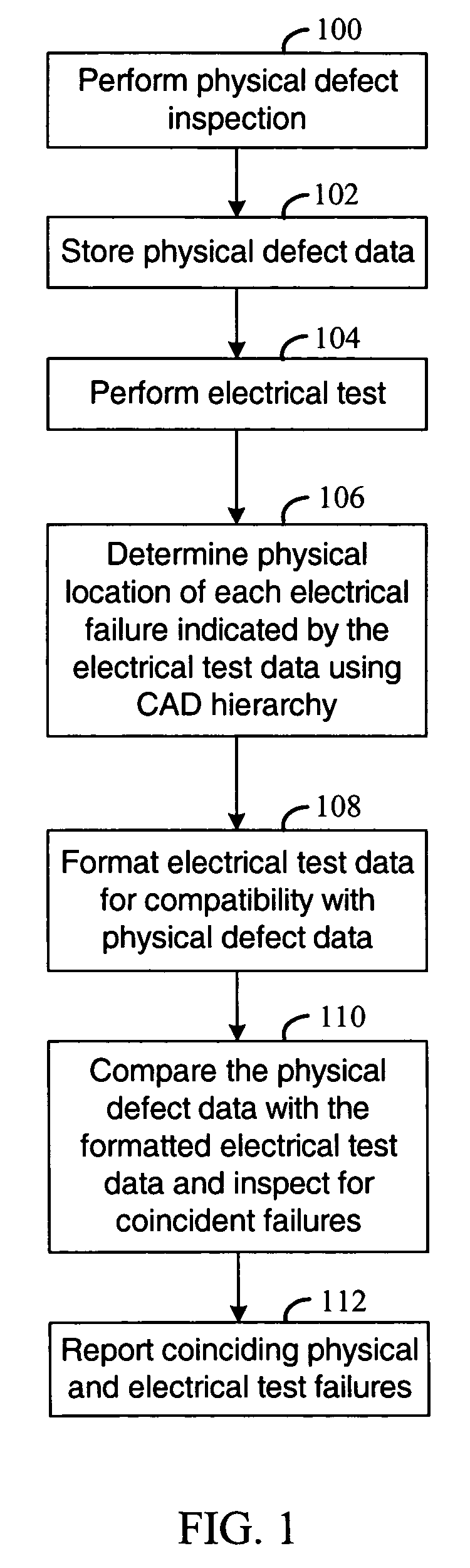

Correlation of electrical test data with physical defect data

ActiveUS6950771B1Improve yield analysisEasy to analyzeResistance/reactance/impedenceElectronic circuit testingData setDesign testing

Method and apparatus are disclosed for analyzing defect data produced in testing a semiconductor chip from a logic design. In various embodiments, input for processing is a first inspection data set that identifies a first set of physical locations that are associated with defects detected during fabrication of the chip. Also input is a second test data set that includes one or more identifiers associated with failing circuitry in the chip. A second set of physical locations is determined from the one or more identifiers of failing circuitry, hierarchical relationships between blocks of the design, and placement information associated with the blocks. Each of the one or more identifiers is associated with at least one of the blocks. Correspondences are identified between physical locations in the first inspection data set and the second set of physical locations.

Owner:XILINX INC

Multi-Level Striping and Truncation Channel-Equalization for Flash-Memory System

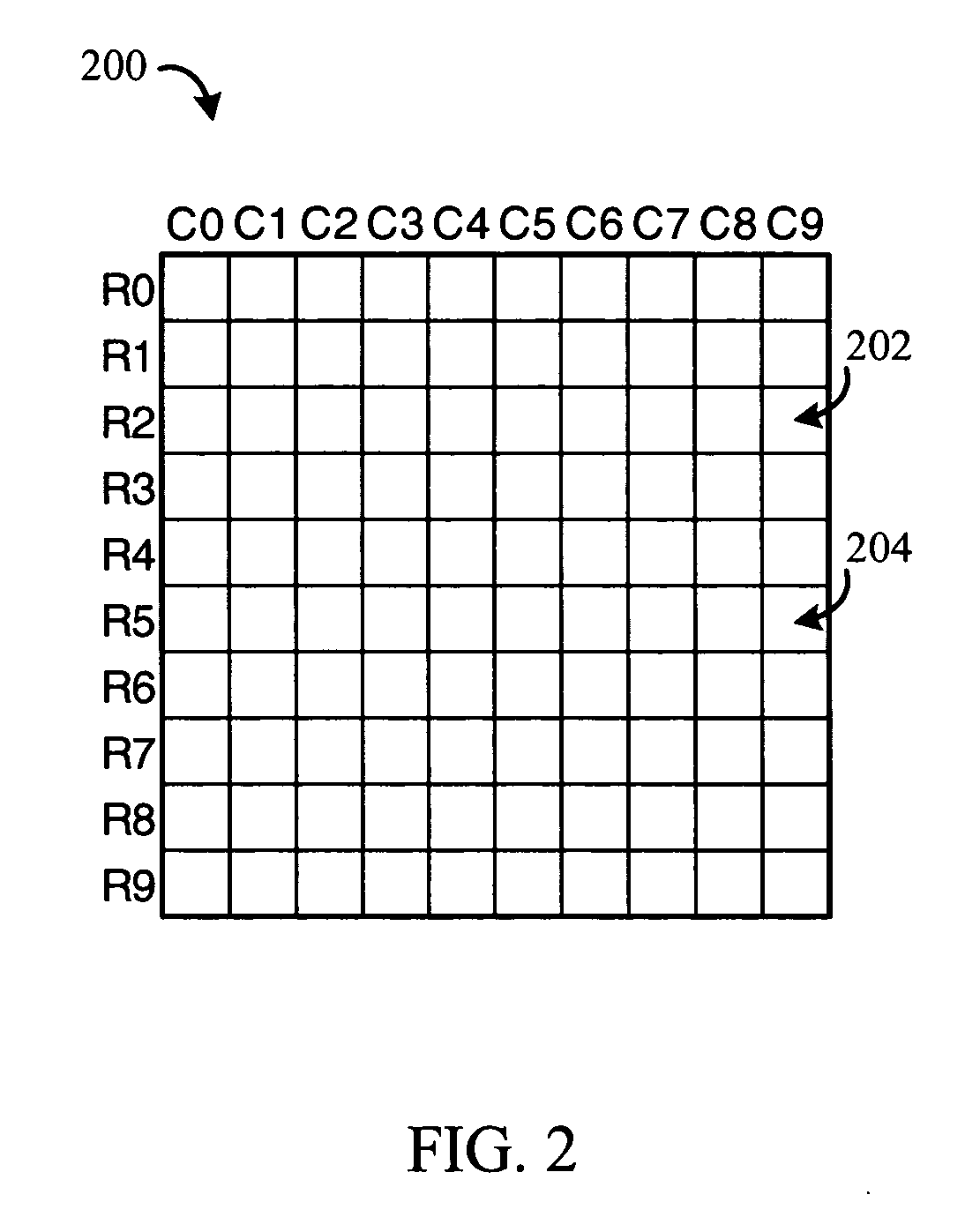

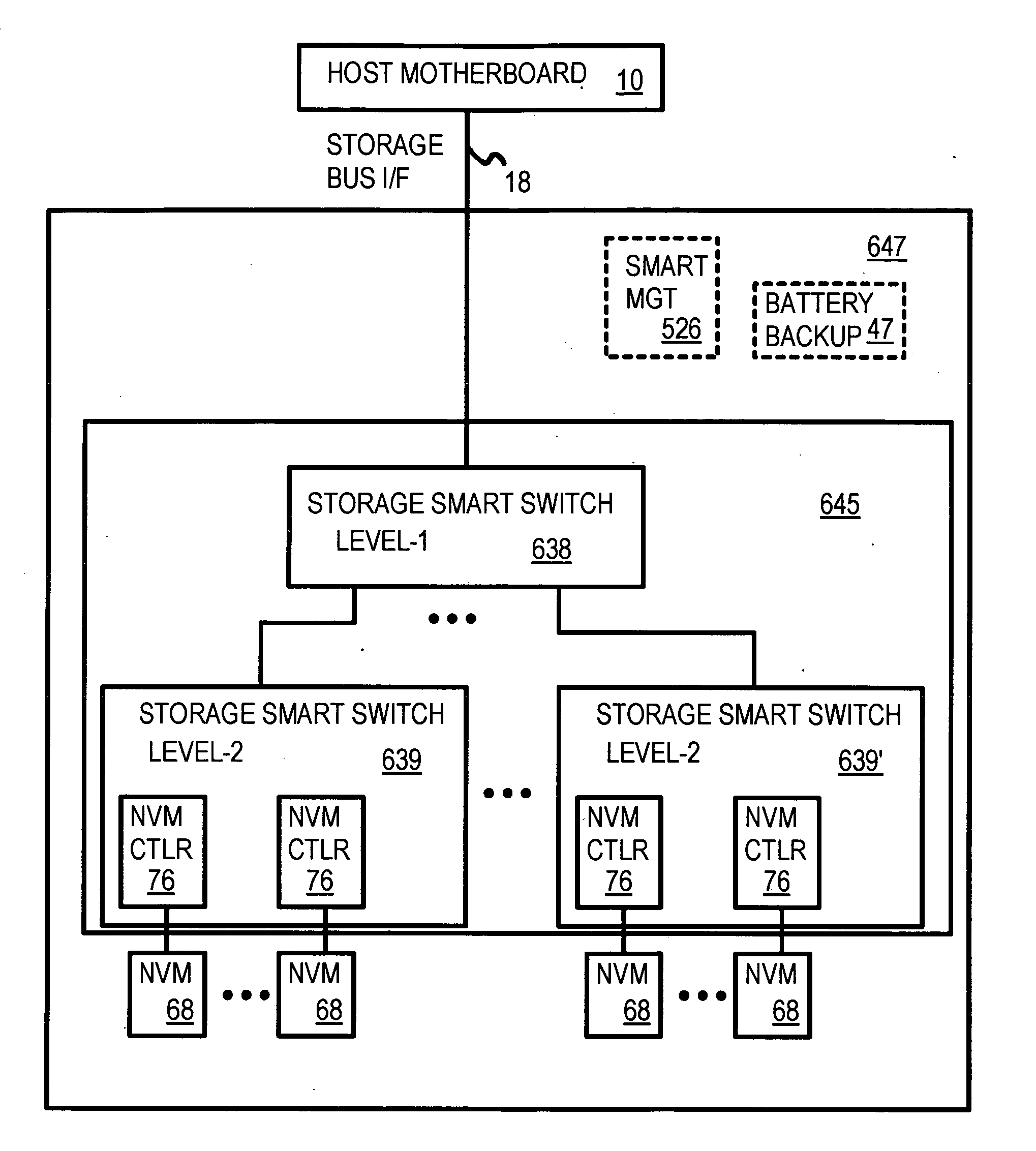

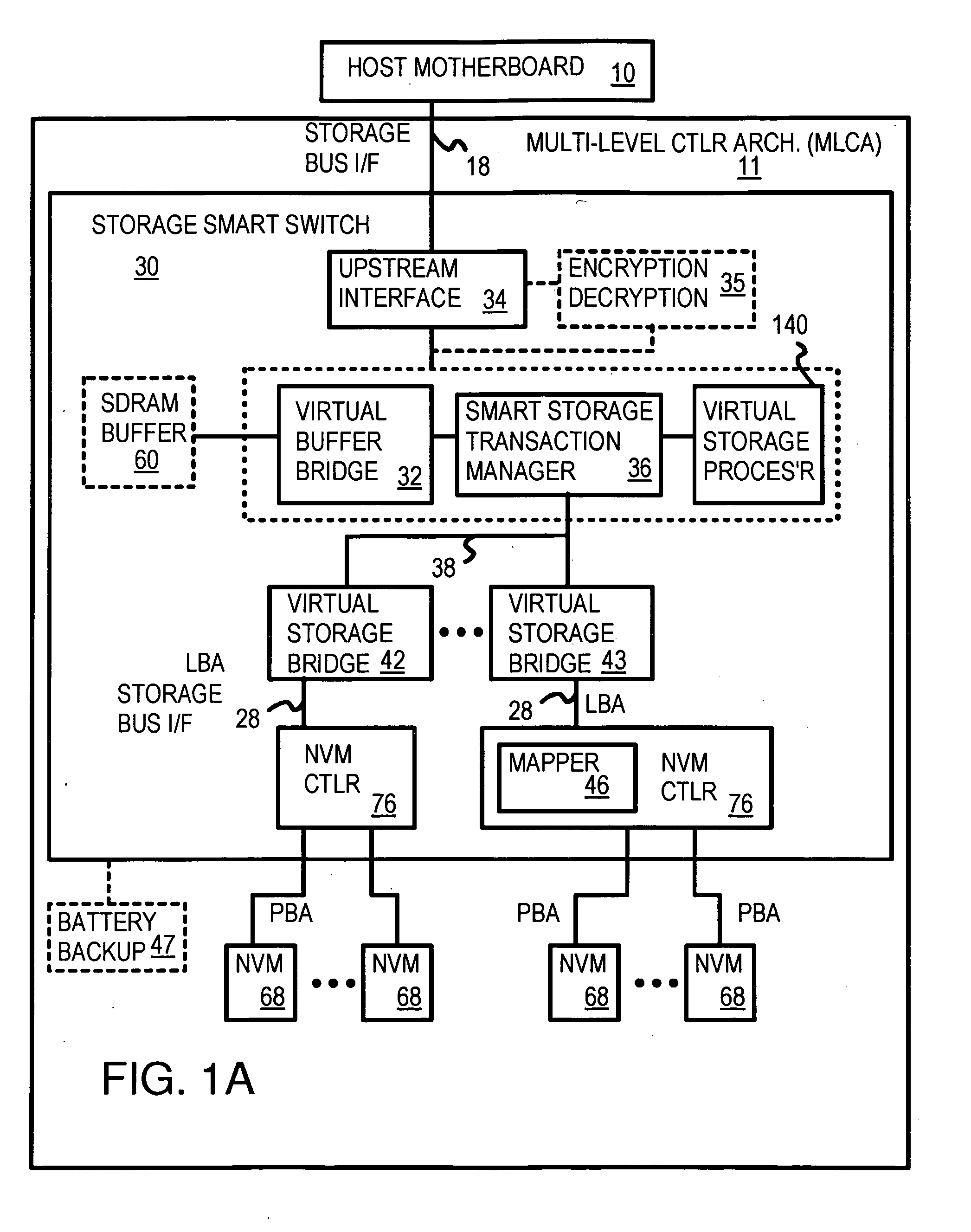

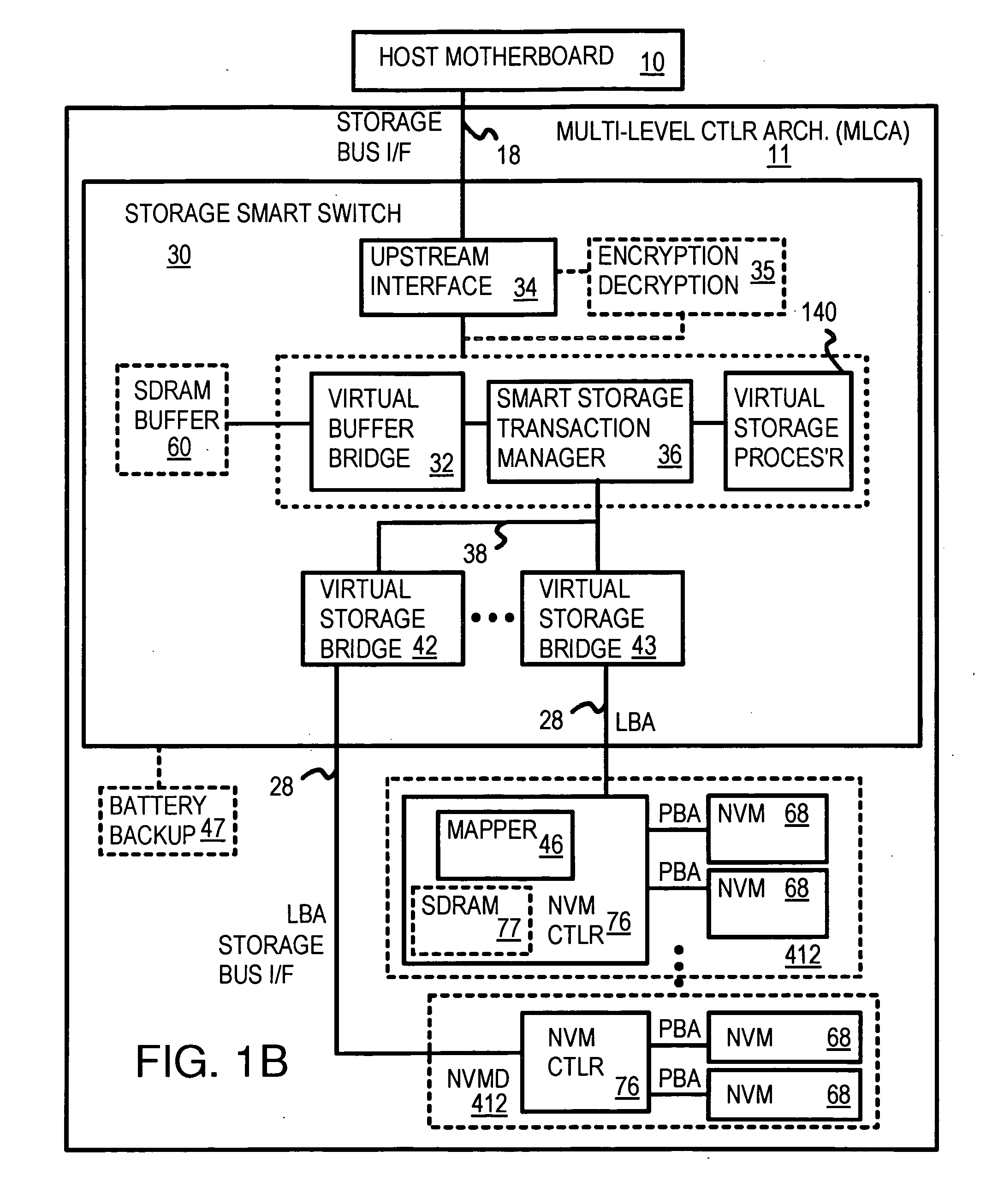

InactiveUS20090240873A1Memory architecture accessing/allocationError preventionLogical block addressingData access

Truncation reduces the available striped data capacity of all flash channels to the capacity of the smallest flash channel. A solid-state disk (SSD) has a smart storage switch salvages flash storage removed from the striped data capacity by truncation. Extra storage beyond the striped data capacity is accessed as scattered data that is not striped. The size of the striped data capacity is reduced over time as more bad blocks appear. A first-level striping map stores striped and scattered capacities of all flash channels and maps scattered and striped data. Each flash channel has a Non-Volatile Memory Device (NVMD) with a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory in the NVMD. Wear-leveling and bad block remapping are preformed by each NVMD. Source and shadow flash blocks are recycled by the NVMD. Two levels of smart storage switches enable three-level controllers.

Owner:SUPER TALENT TECH CORP

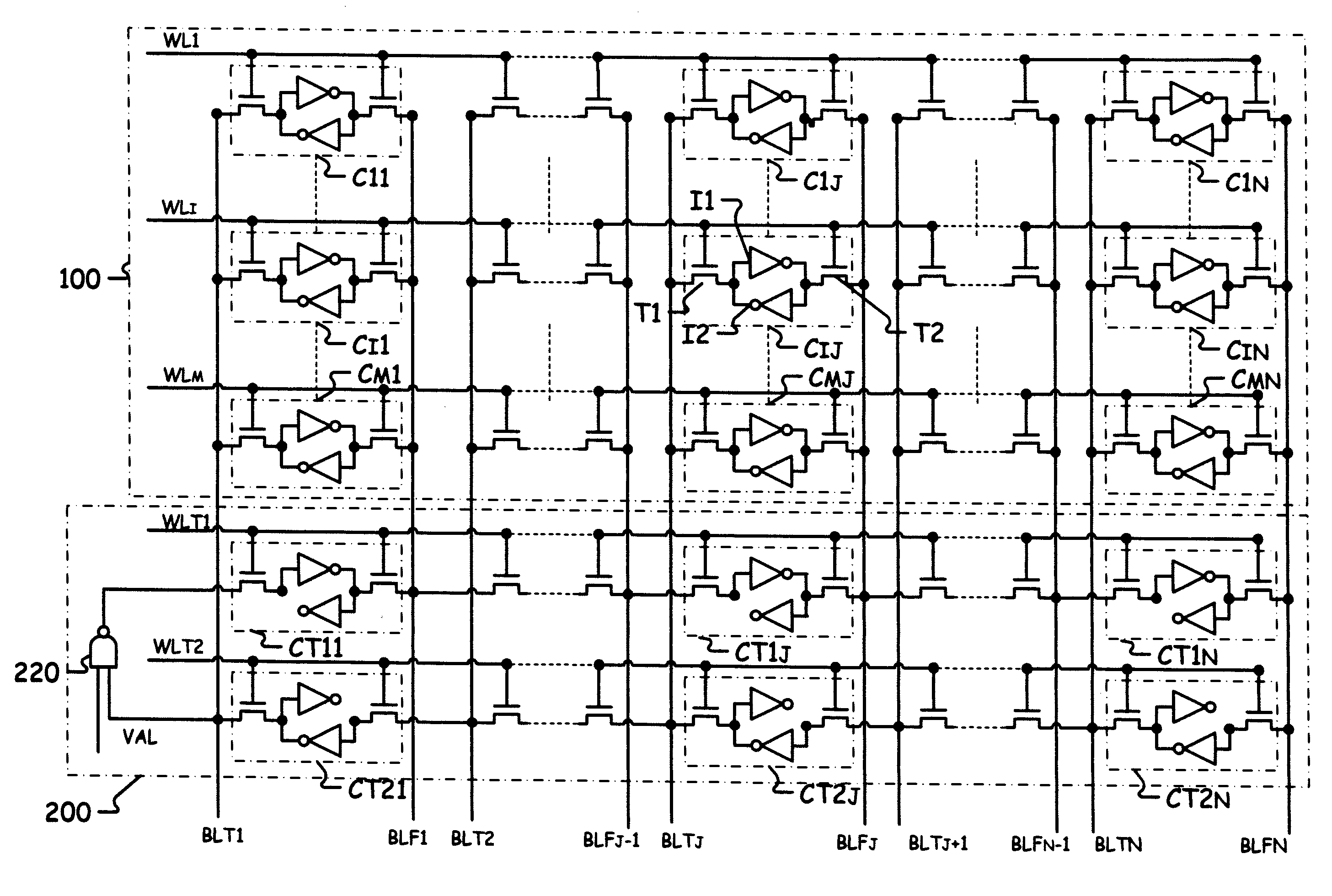

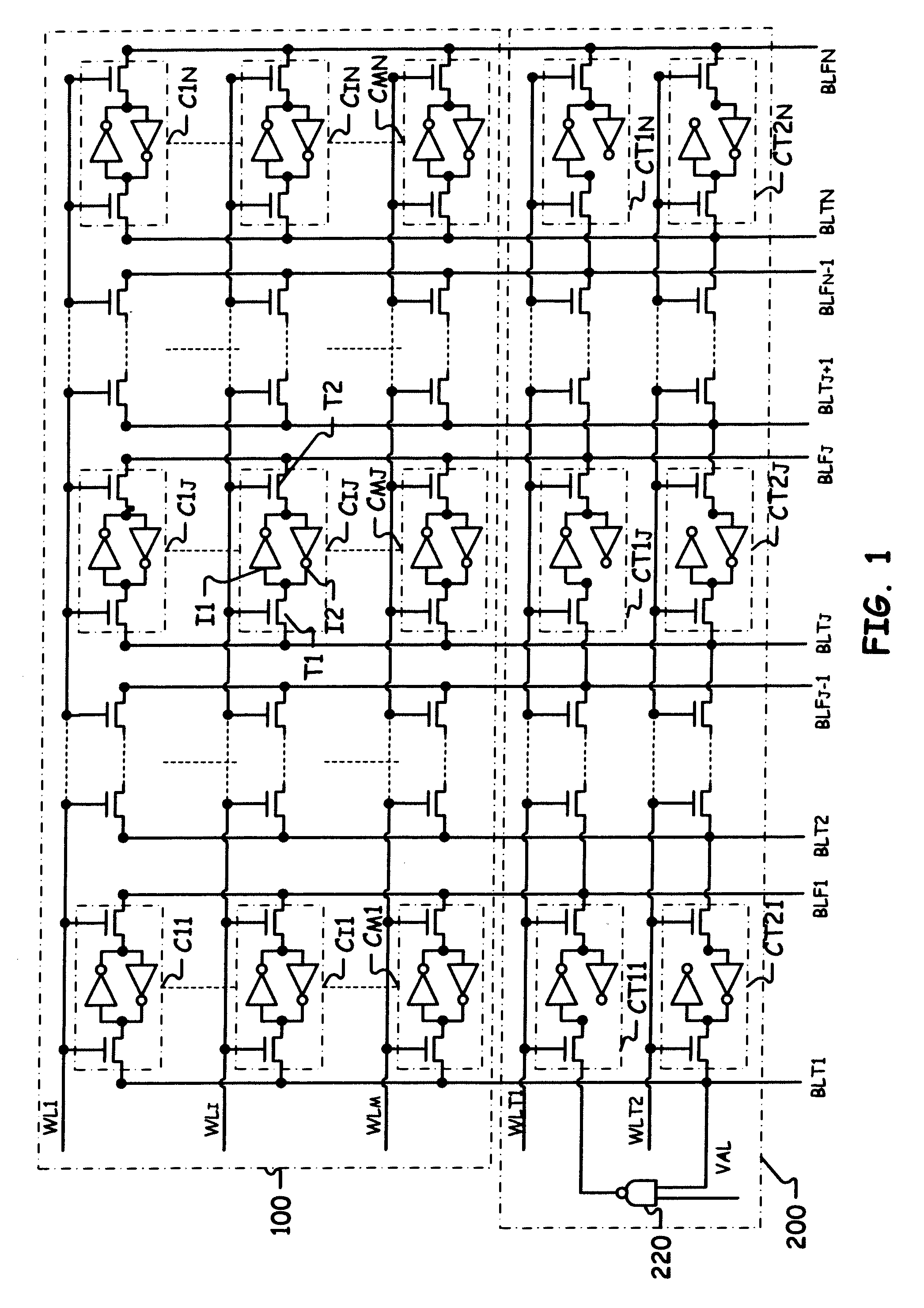

Memory including a performance test circuit

ActiveUS20090154273A1Easy to manufactureLimit memory consumptionElectronic circuit testingError detection/correctionBit lineTerm memory

A memory includes a plurality of memory cells each including a true data input connected to a true bit line and complementary data input connected to a complementary bit line, and two inverters connected head-to-tail firstly to the true data input and secondly to the complementary data input. The memory also includes a test circuit includes a plurality of test cells, each test cell includes a true data input connected to a complementary data input of the preceding test cell and a complementary data input connected to the true data input of the following test cell, the complementary data input of the last test cell being connected to the true data input of the first test cell, each test cell comprising a first inverter connected between the true data input and the complementary data input. The looped chain thus formed propagates a signal whose period is a function of the performance of the storage cells.

Owner:STMICROELECTRONICS SRL

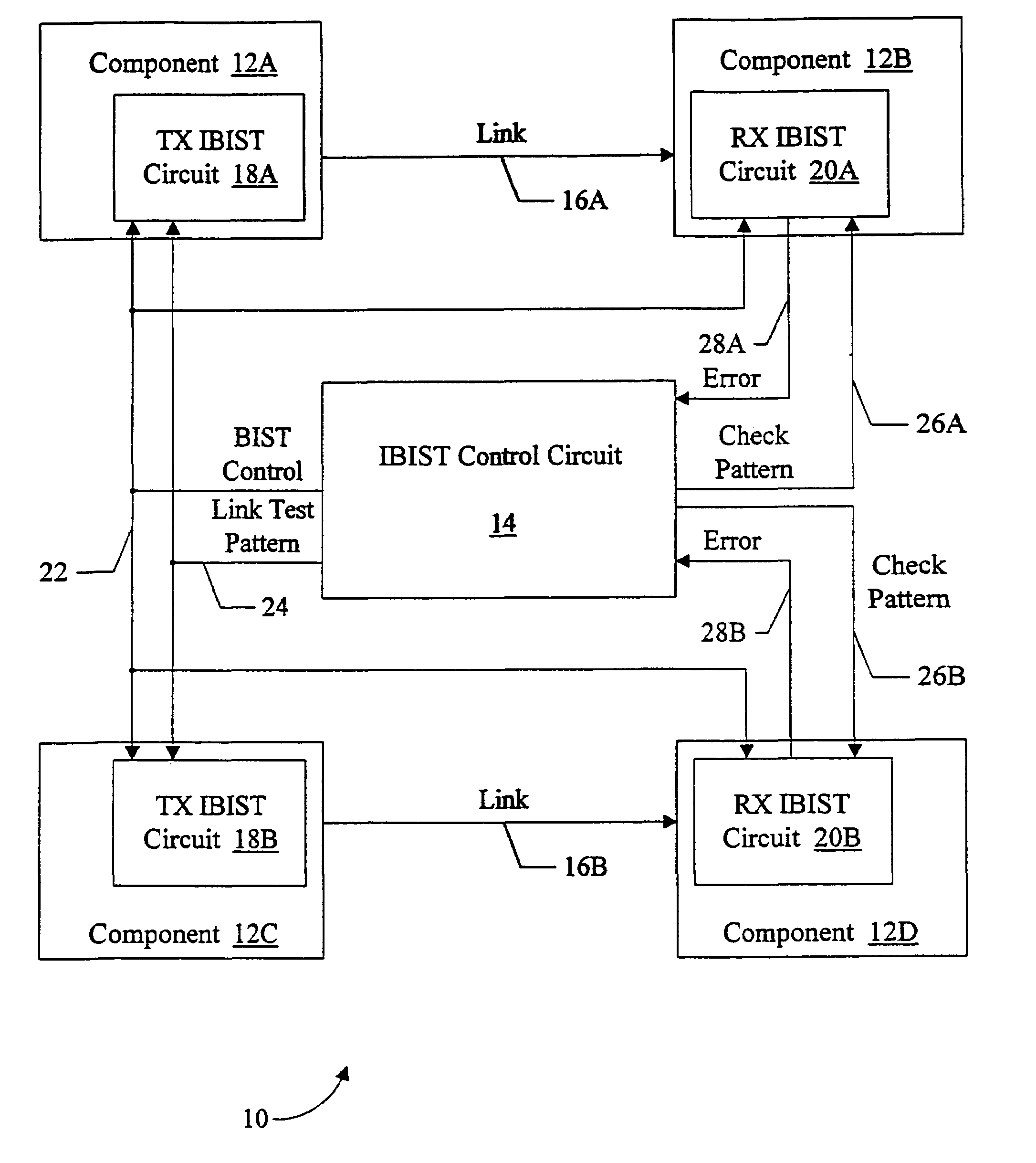

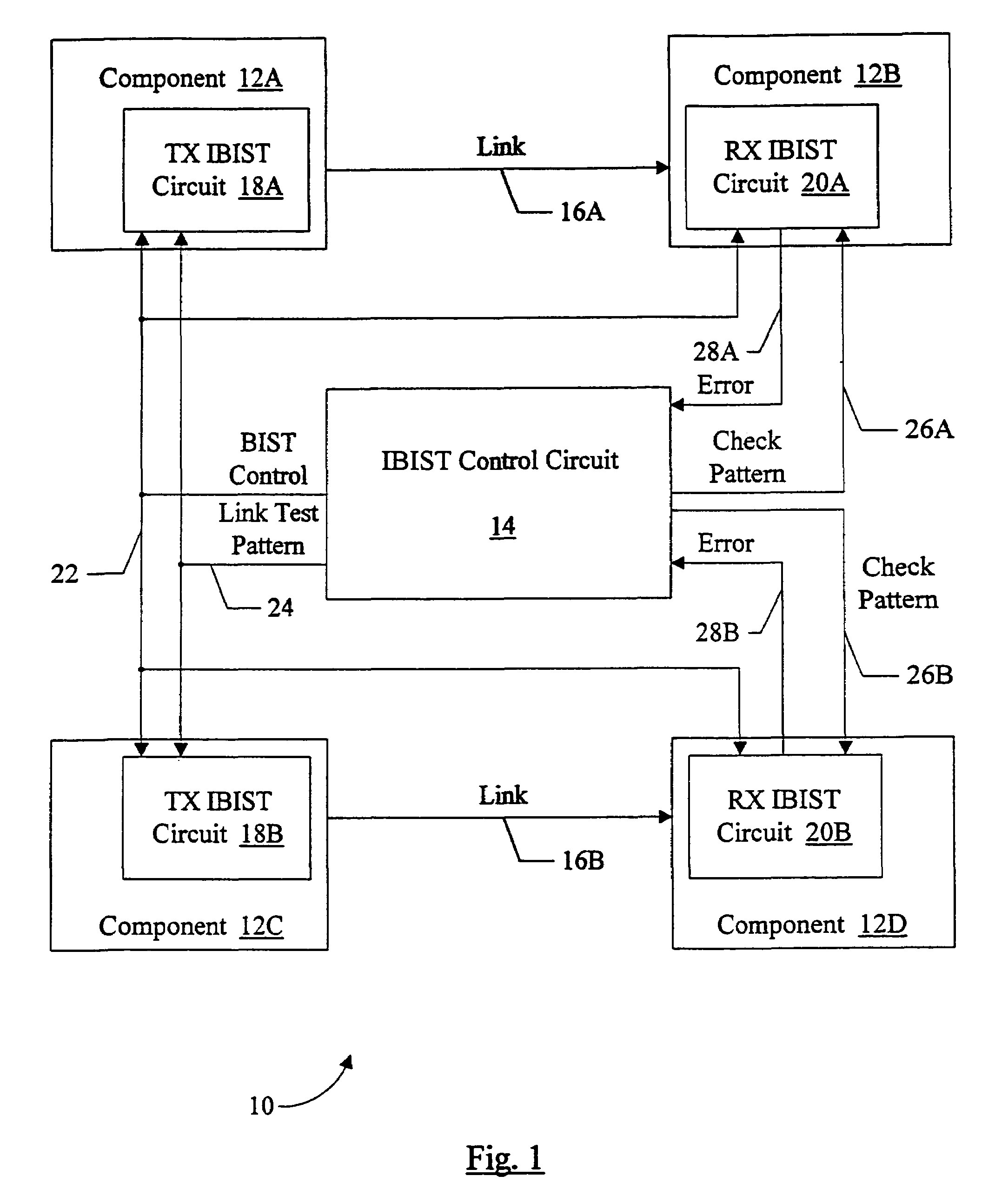

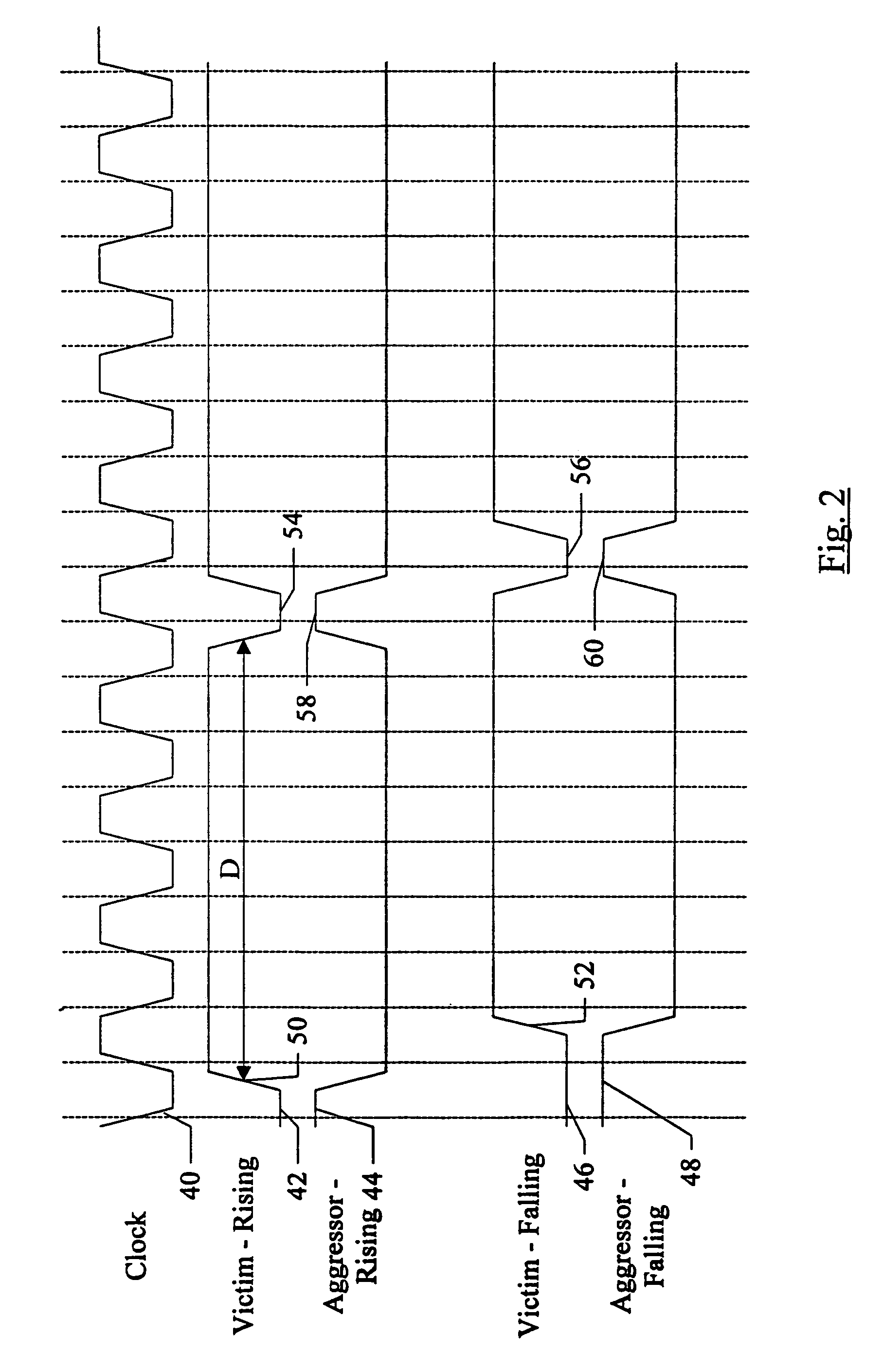

Source synchronous link integrity validation

InactiveUS6965648B1Flexible implementationCorrect operation testingElectronic circuit testingElectrical polaritySource-synchronous

A system may perform interconnect BIST (IBIST) testing on source synchronous links. The system may perform, at normal operating frequency, a source synchronous link test that tests a victim line on the source synchronous link using a transition weave pattern. The transition weave pattern causes interaction between a data transition on the victim line, previous transitions on the victim line, and transitions on the other lines of the link (the “aggressor” lines). The interaction caused may be: (i) a first crossing pulse on the victim line; (ii) a second crossing pulse of the opposite polarity on each aggressor line concurrent with the first crossing pulse on the victim line; and (iii) a reflection in the opposite direction of the first transition of the first crossing pulse, wherein the reflection results from a previous transition on the victim line.

Owner:ORACLE INT CORP

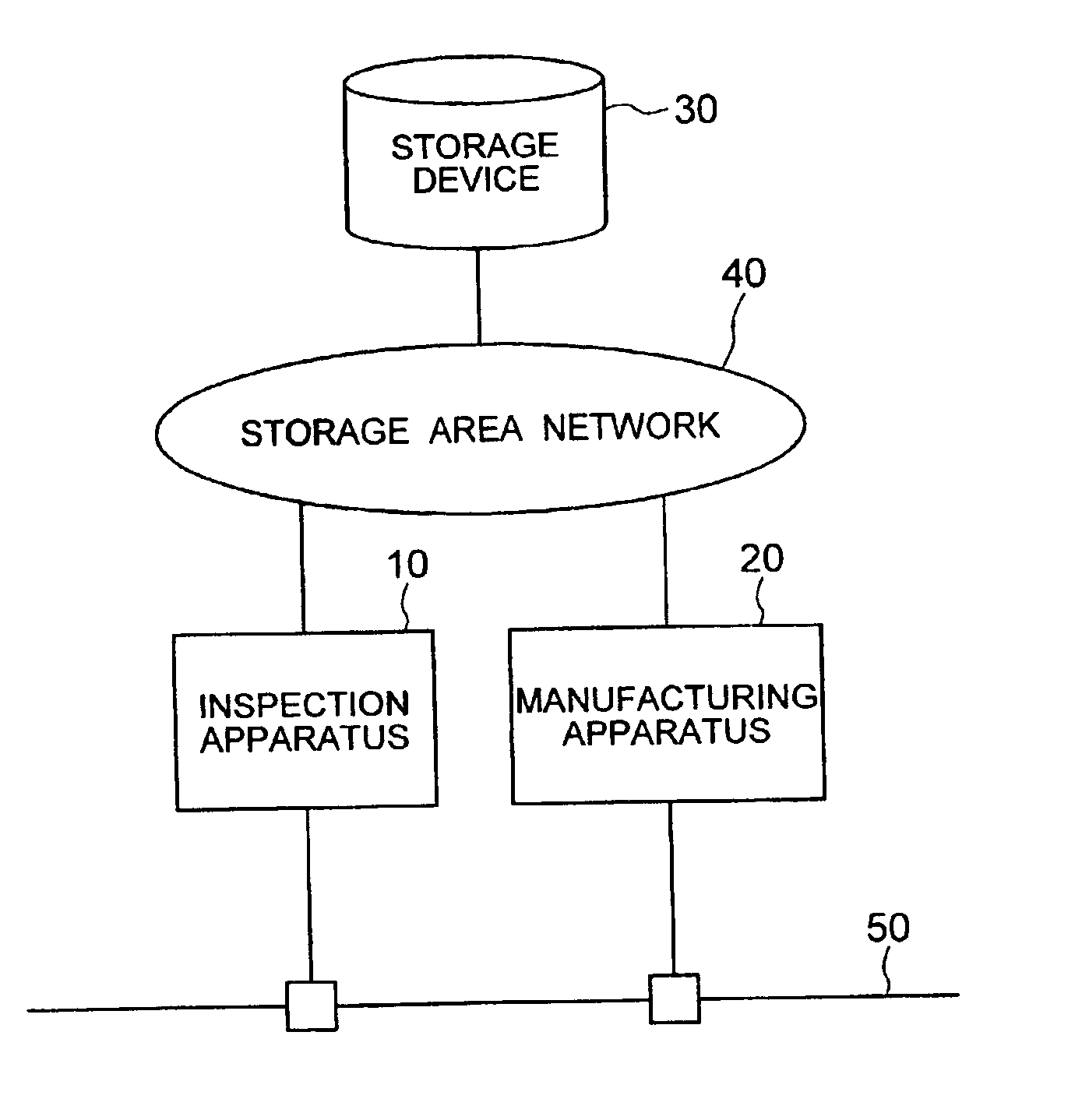

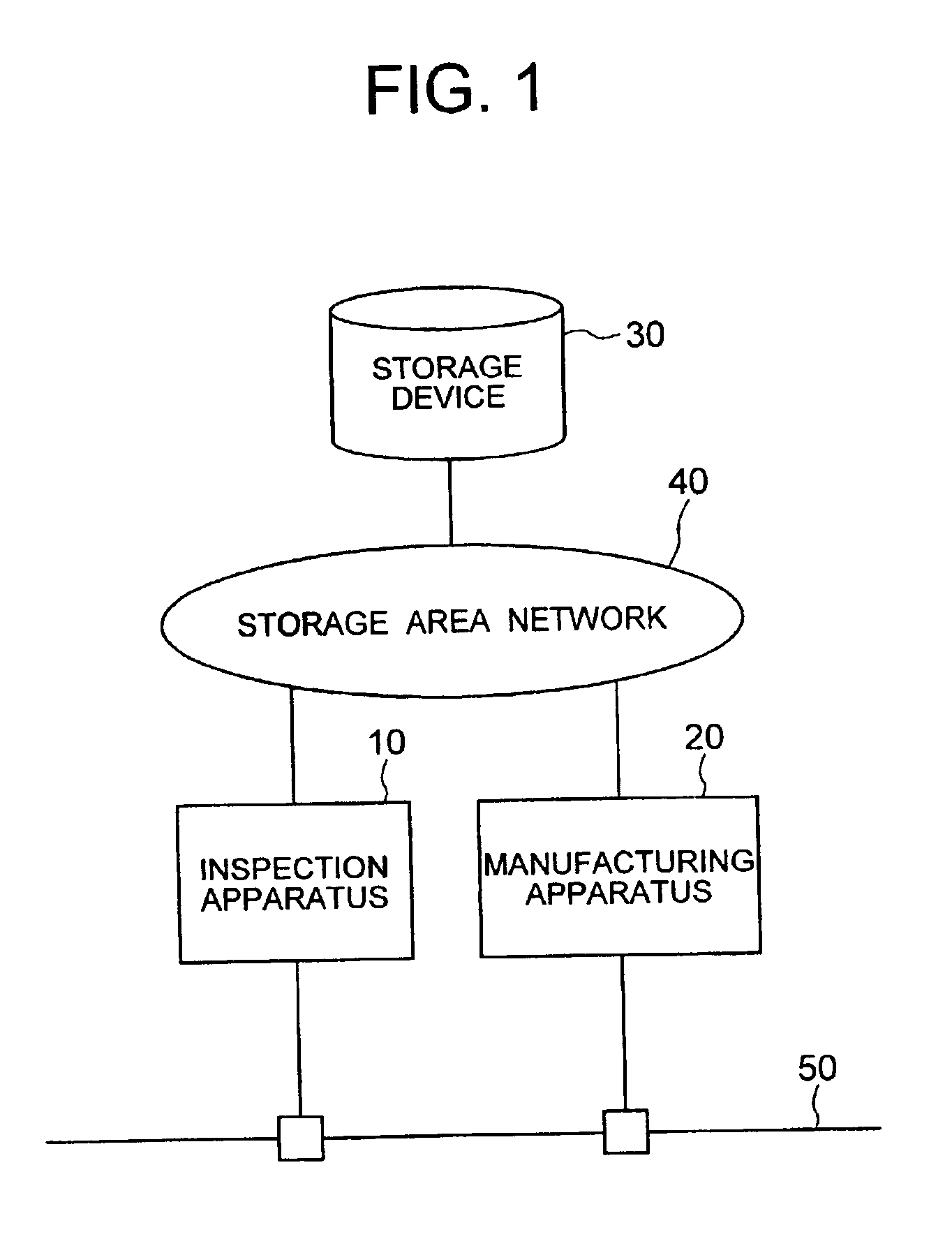

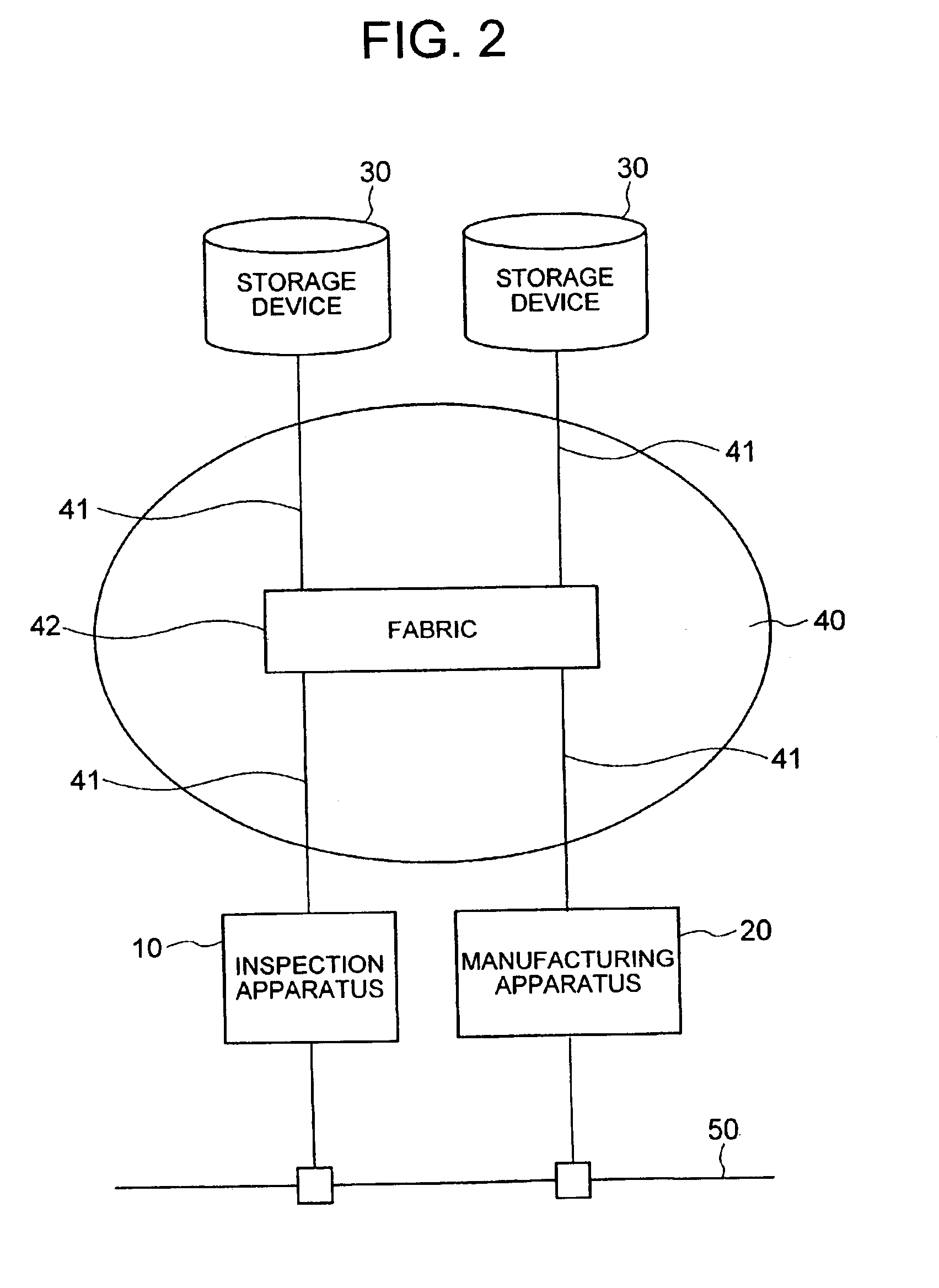

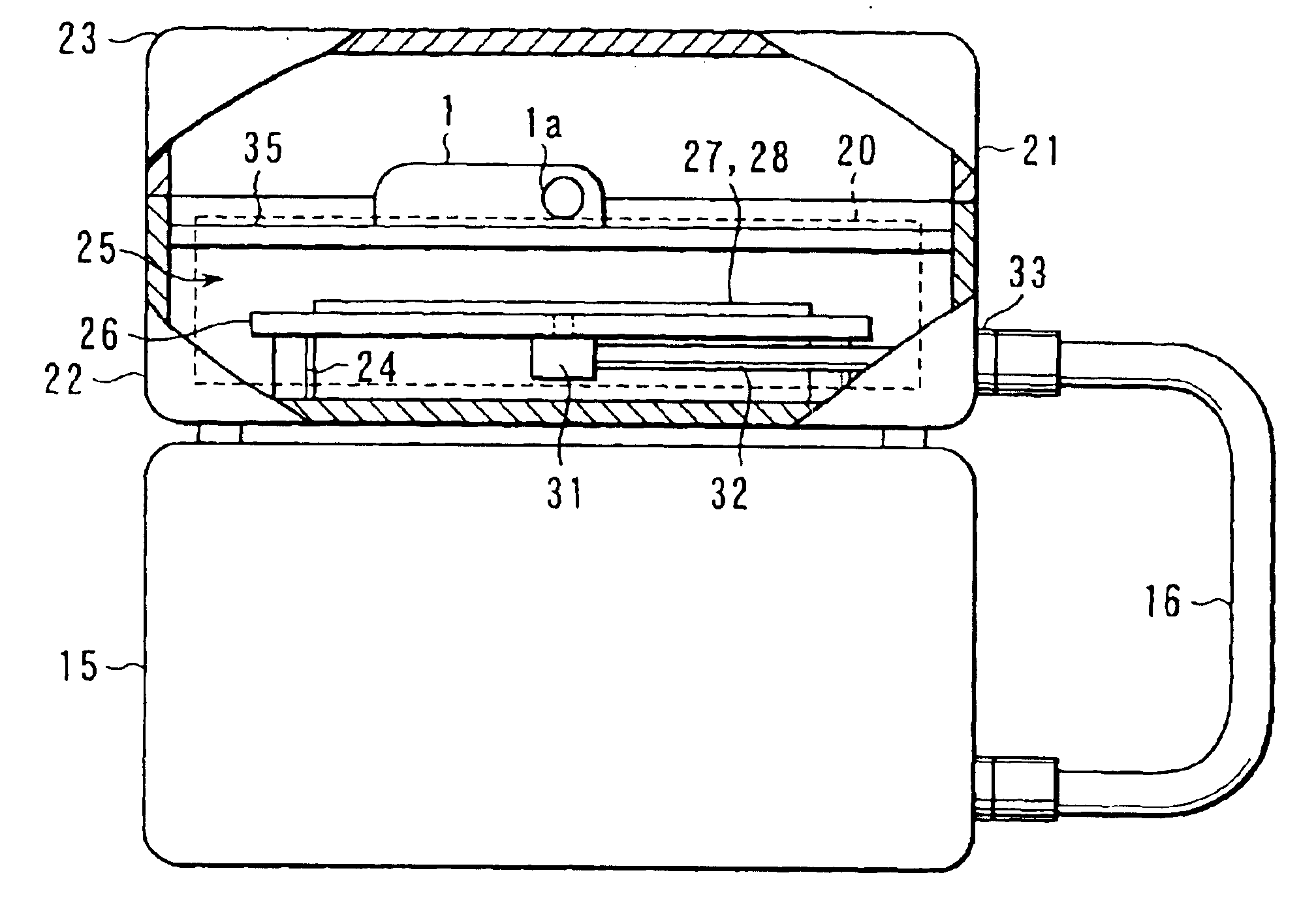

Semiconductor production system

InactiveUS6850854B2Improve system throughputIncrease in sizeSemiconductor/solid-state device testing/measurementElectronic circuit testingStorage area networkObservation unit

A semiconductor production system has a semiconductor manufacturing apparatus having an exposure unit, a control unit for controlling the exposure unit and a storage device; a semiconductor inspection apparatus having an observation unit, a control unit for controlling the observation unit and a storage device; and a storage device commonly used by the semiconductor manufacturing apparatus and the semiconductor inspection apparatus. The manufacturing apparatus, the inspection apparatus and the commonly used storage device are interconnected via a storage area network. With the semiconductor manufacturing apparatus and the storage device linked together via the storage area network, a large volume of image data or design data can be communicated at high speed, thus improving the system throughput.

Owner:HITACHI LTD

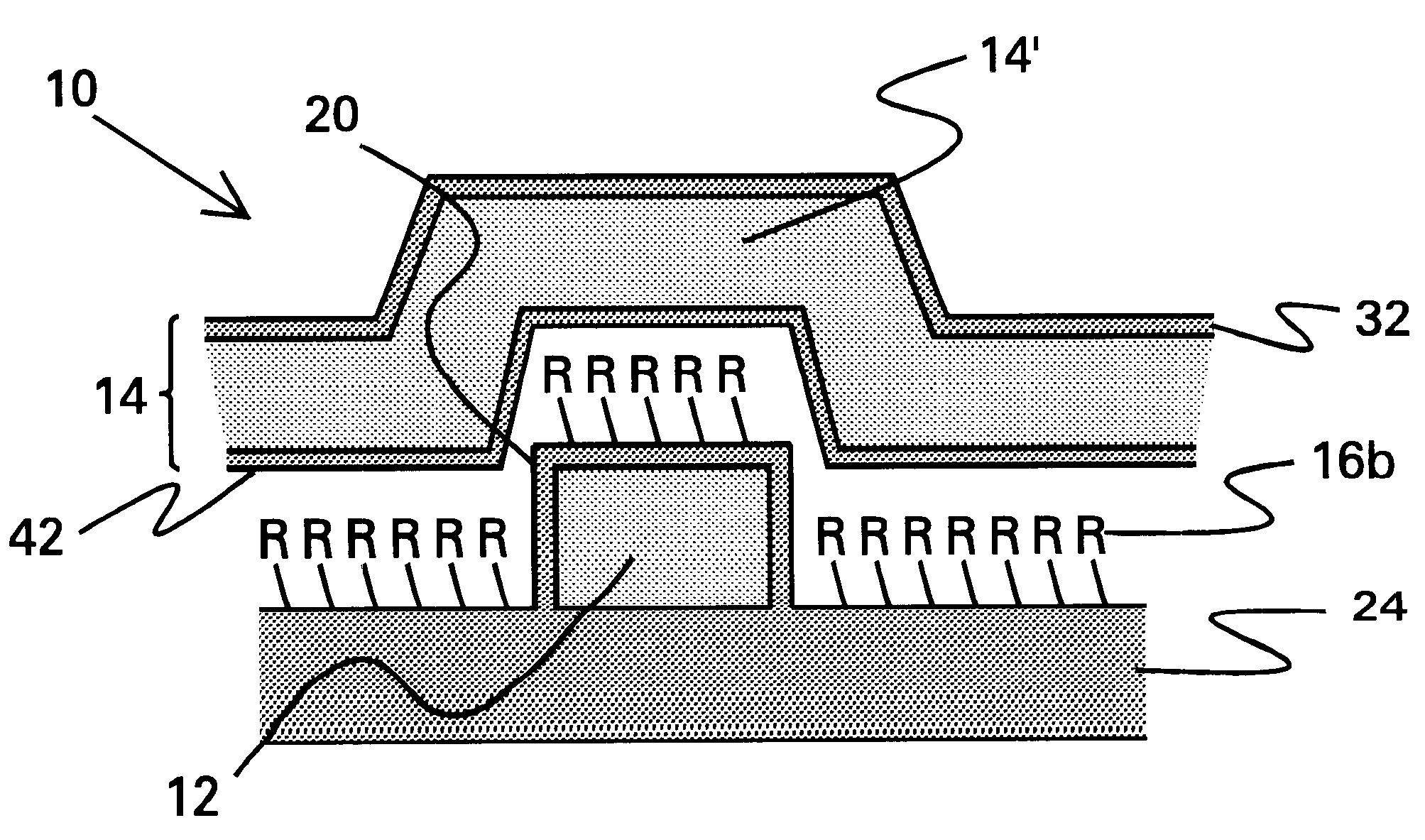

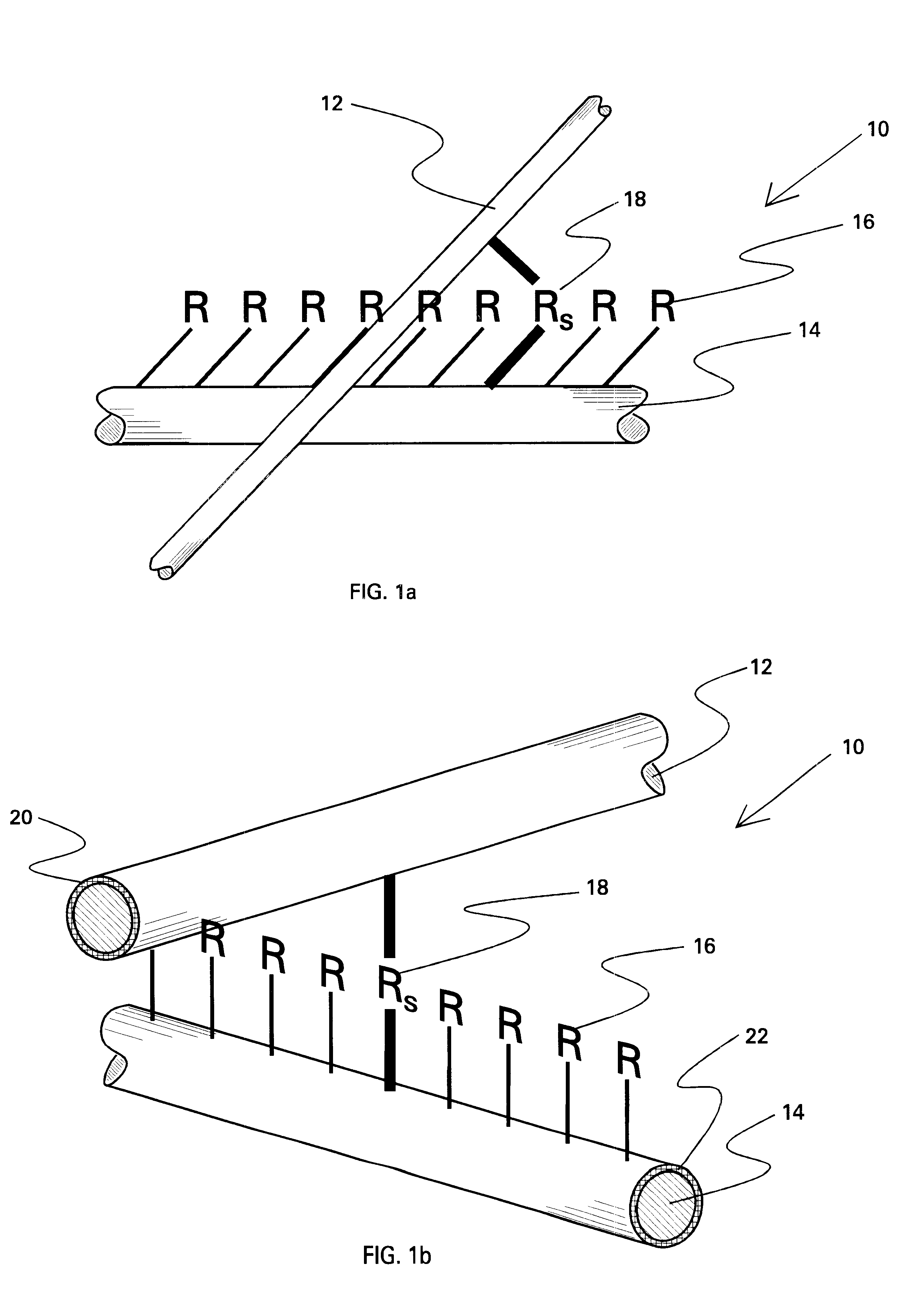

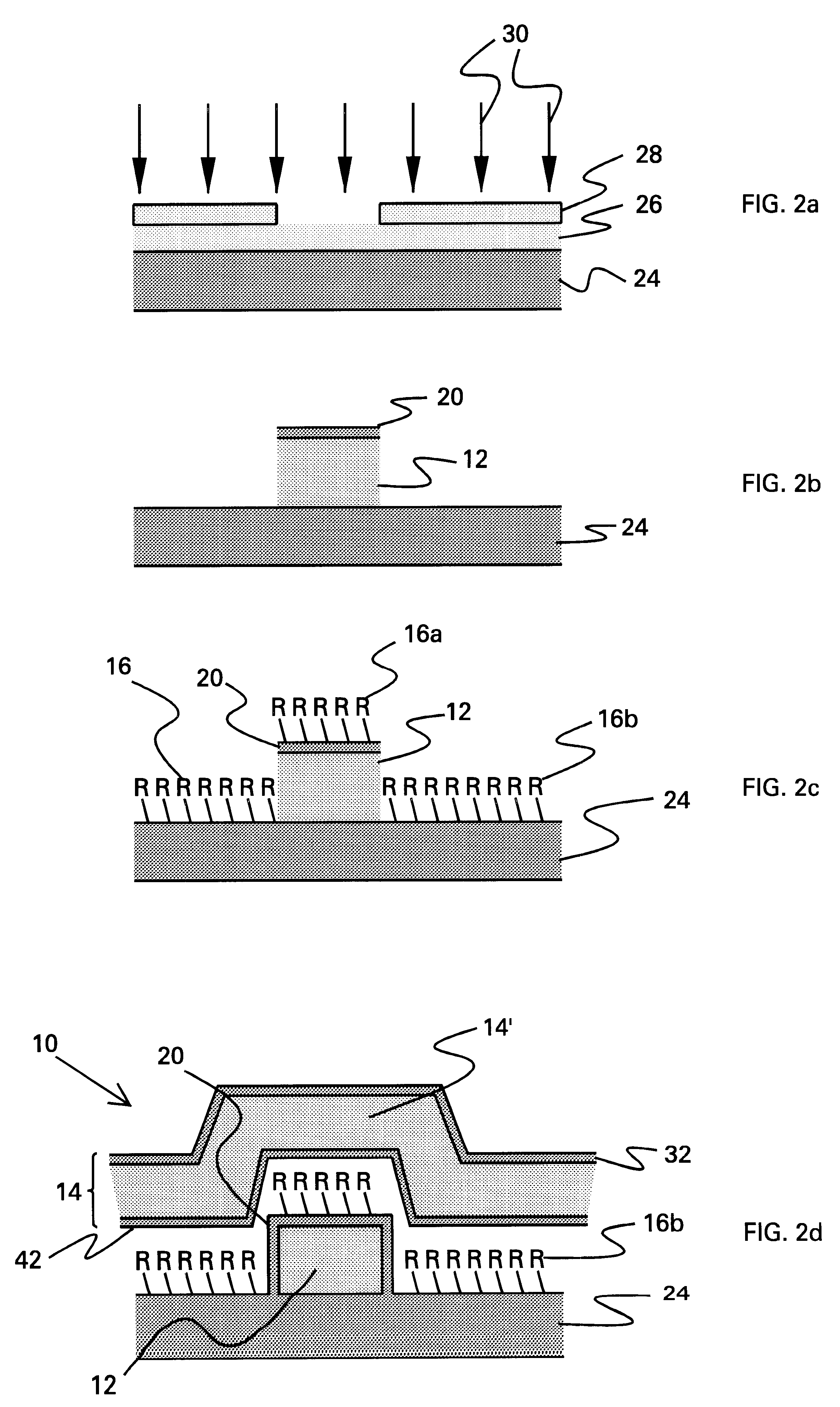

Chemically synthesized and assembled electronics devices

InactiveUS6459095B1Simple and inexpensive implementationMaterial nanotechnologyElectronic circuit testingCrossbar switchChemical synthesis

A route to the fabrication of electronic devices is provided, in which the devices consist of two crossed wires sandwiching an electrically addressable molecular species. The approach is extremely simple and inexpensive to implement, and scales from wire dimensions of several micrometers down to nanometer-scale dimensions. The device of the present invention can be used to produce crossbar switch arrays, logic devices, memory devices, and communication and signal routing devices. The present invention enables construction of molecular electronic devices on a length scale than can range from micrometers to nanometers via a straightforward and inexpensive chemical assembly procedure. The device is either partially or completely chemically assembled, and the key to the scaling is that the location of the devices on the substrate are defined once the devices have been assembled, not prior to assembly.

Owner:HEWLETT PACKARD CO +1

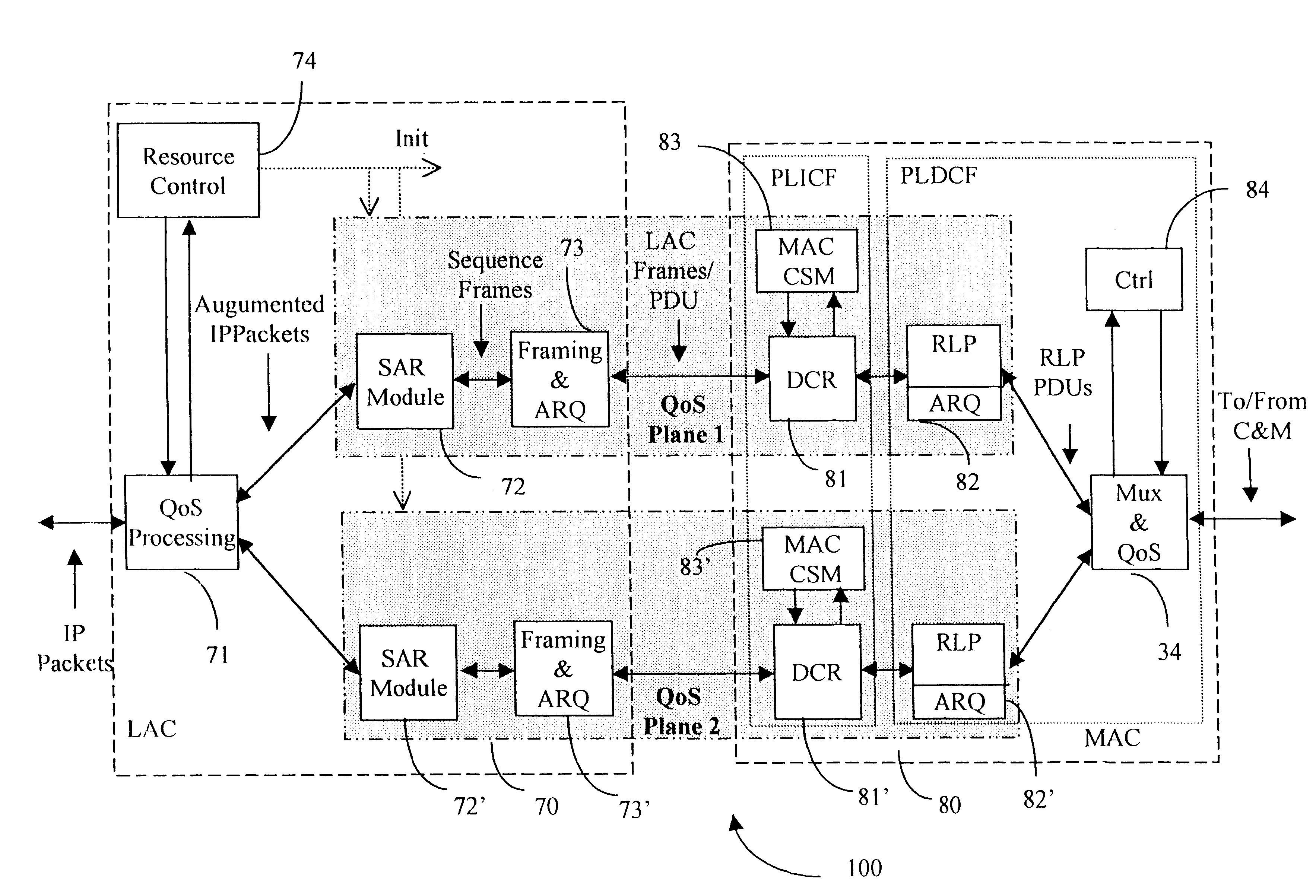

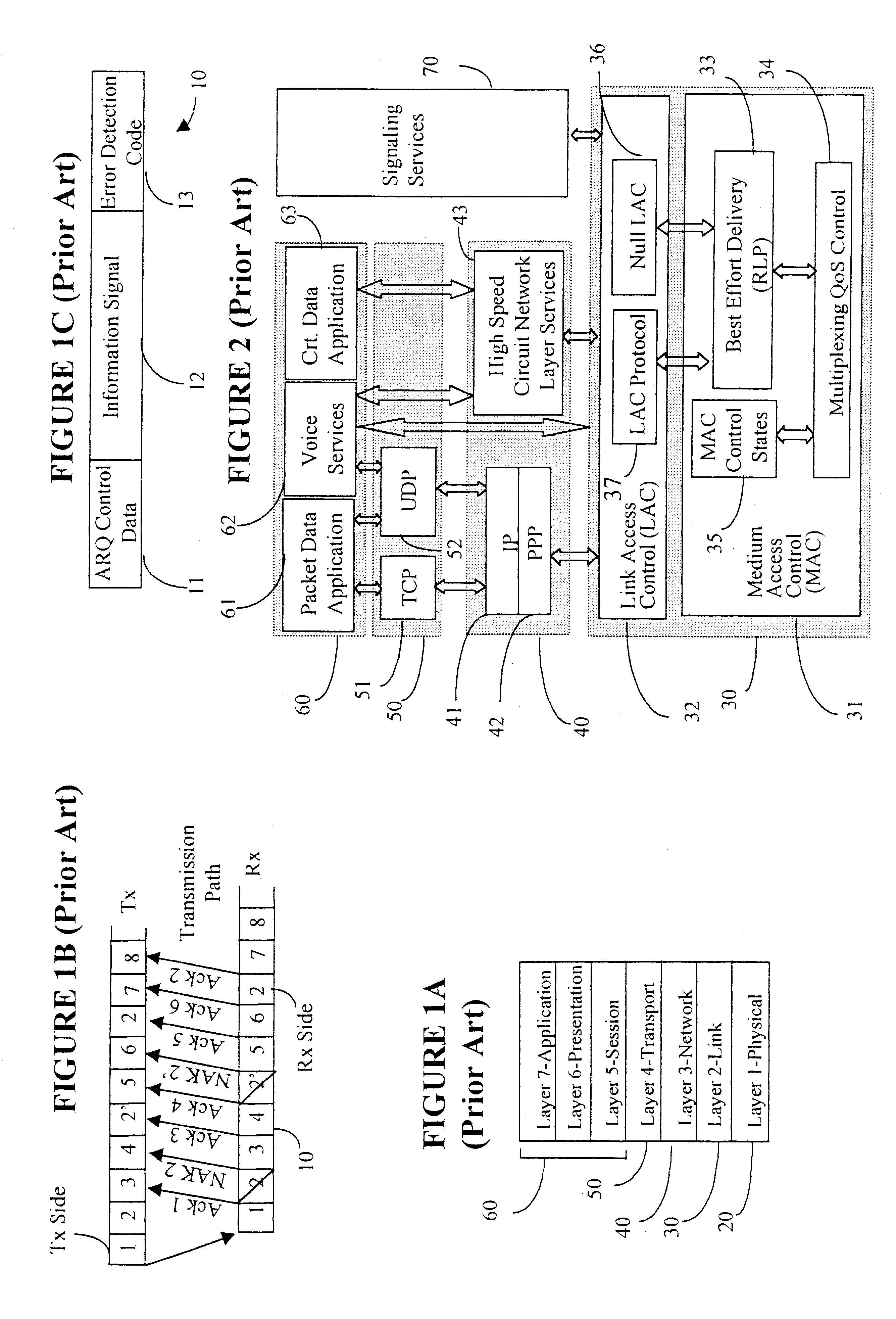

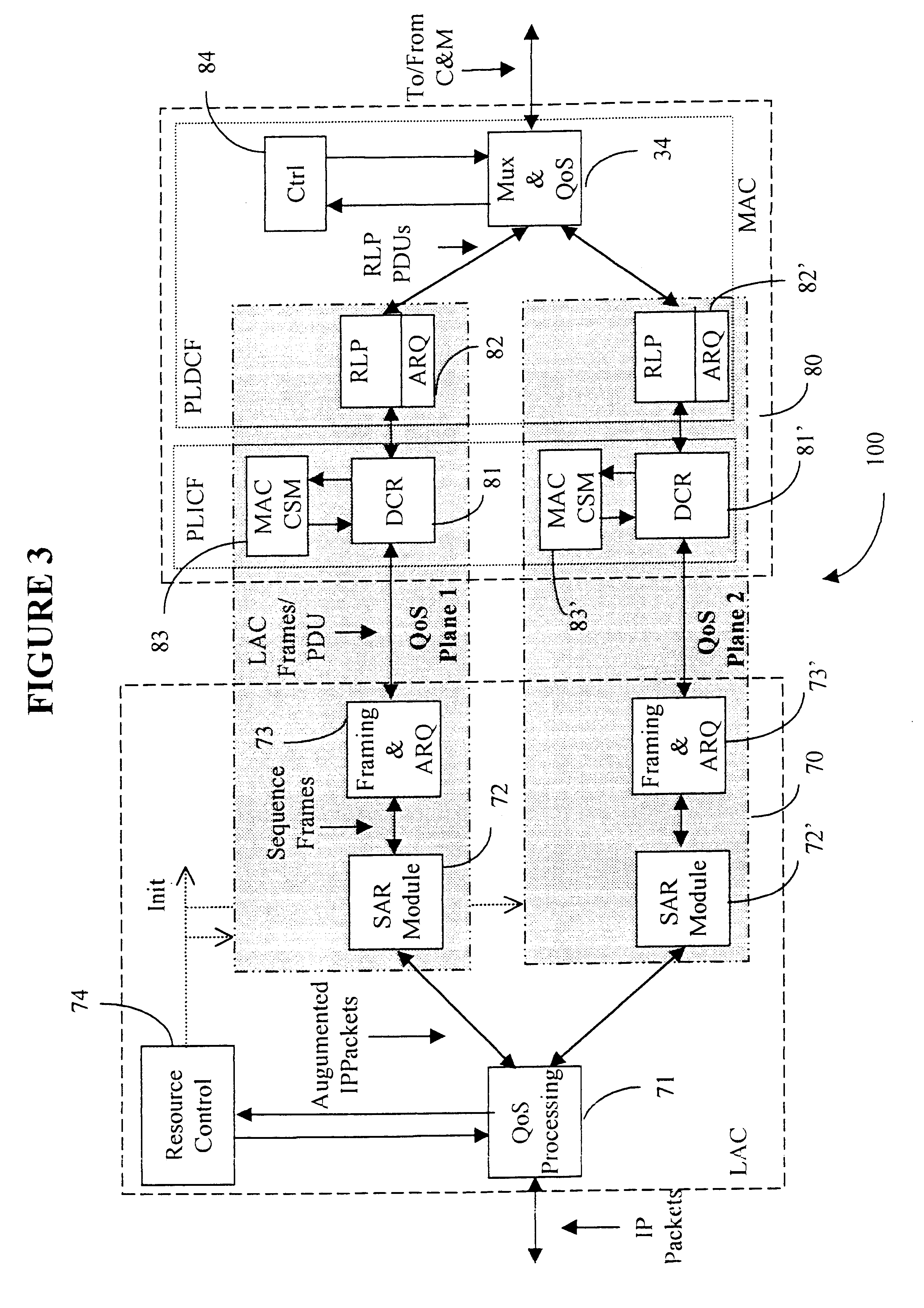

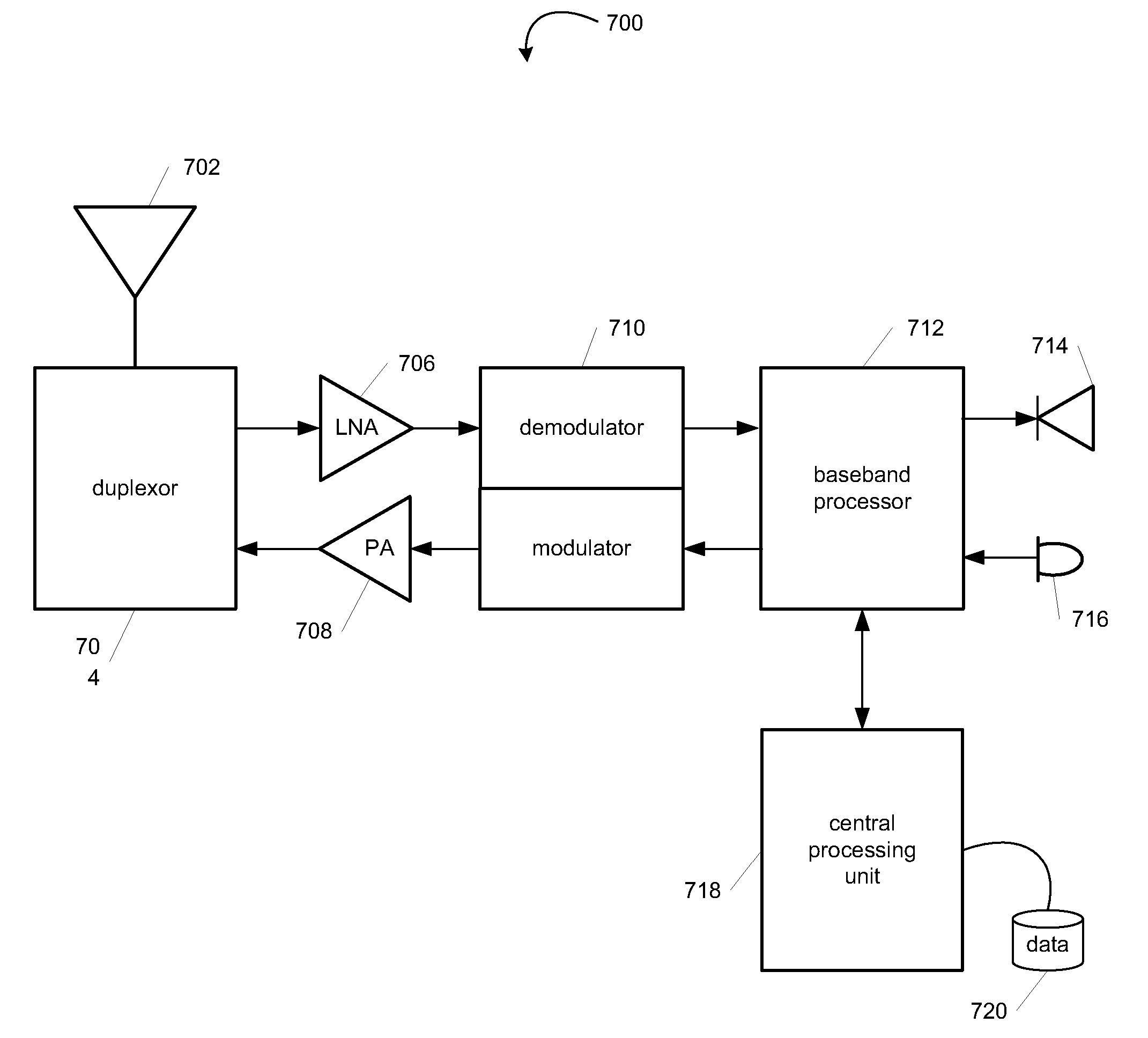

Data link control proctocol for 3G wireless system

InactiveUS6542490B1Error prevention/detection by using return channelElectronic circuit testingTelecommunications linkDual mode

A Data Link Control protocol for 3G wireless communication system for direct support for network layer protocols, e.g. the Internet Protocol (IP), is provided. The Link Layer disclosed comprises a Link Access Control (LAC) sublayer and a Medium Access Control (MAC) sublayer. At a transmit end of the wireless system, a plurality of Quality of Service (QoS) data planes are created to directly support the IP QoS. Each QoS data plane is optimized to handle QoS requirements for a corresponding Class of Service (CoS). Data packets received at the LAC sublayer are directed to a QoS data plane according to the particular QoS information they contain and processed according to the particular QoS requirement to generate variable size LAC frames. The variable size LAC frames are transmitted to the MAC sublayer for generating radio link protocol data units (RLP PDUs) to be transmitted to a receiving end. A new level of error correction is provided at the LAC sublayer as the size of the LAC PDUs can be dynamically adjusted in response to the conditions of the communication link. A dual mode ARQ is provided at the MAC sublayer to improve the quality of the air transmission for bursty as well as non-bursty traffic conditions.

Owner:ALCATEL LUCENT SAS

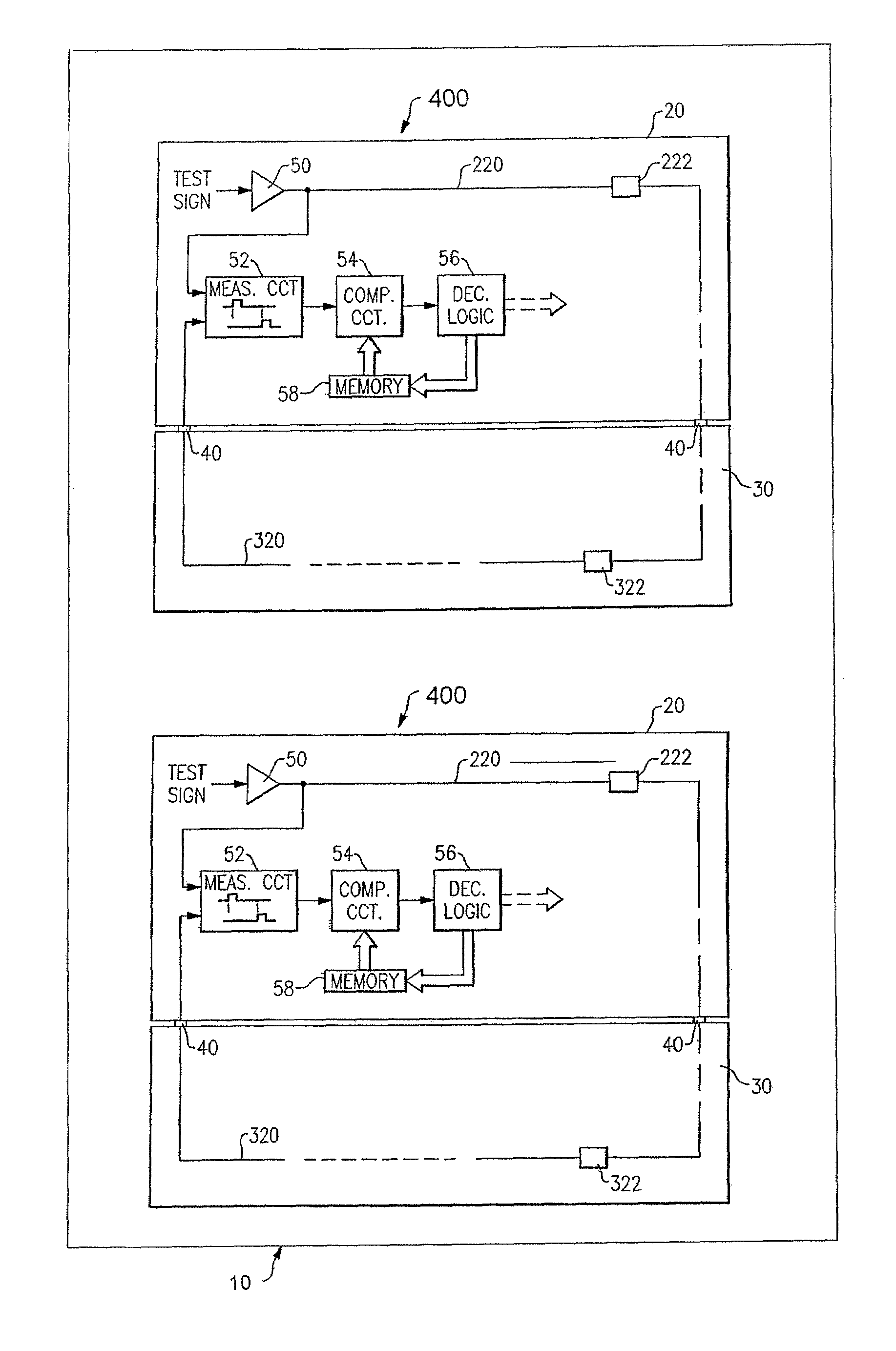

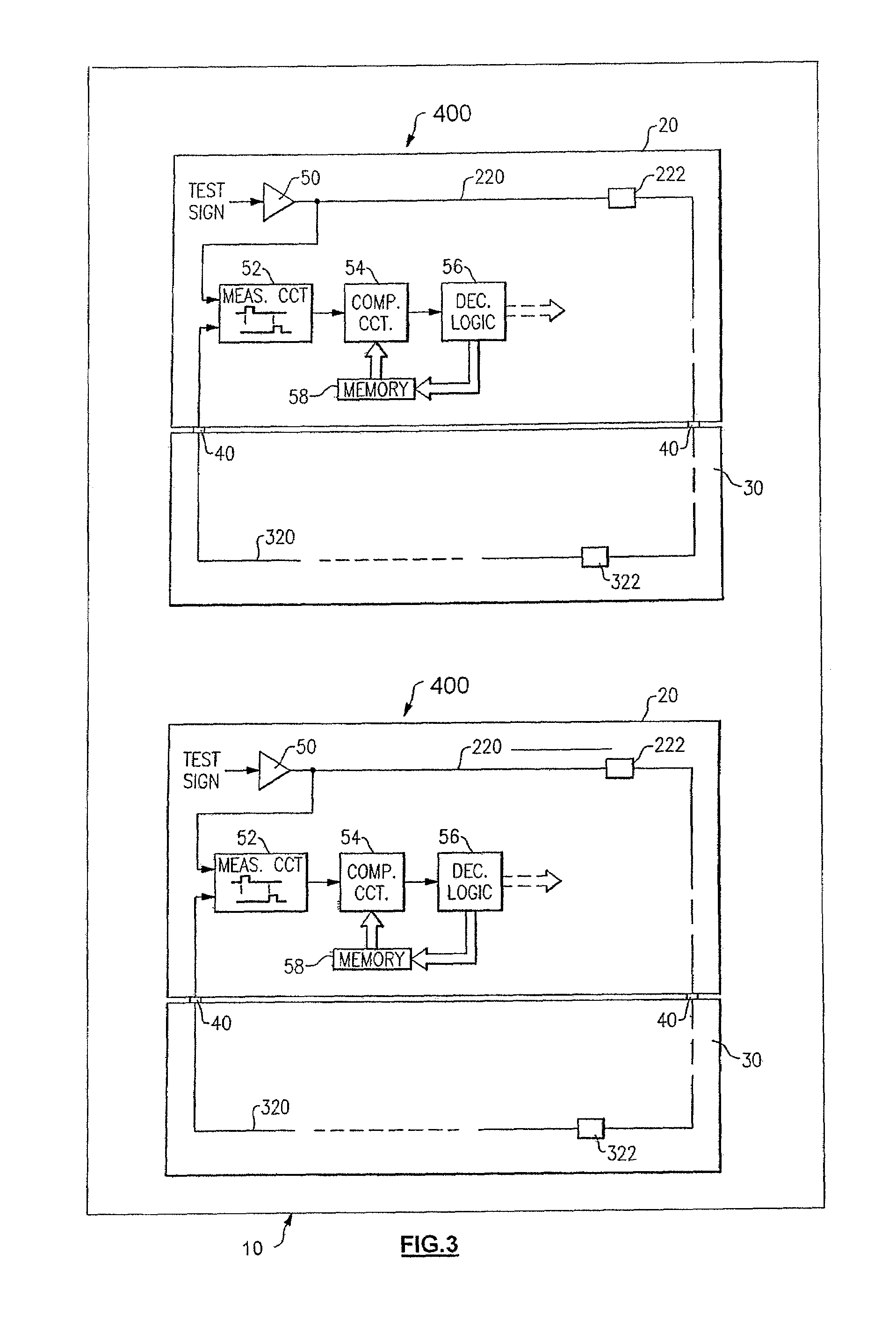

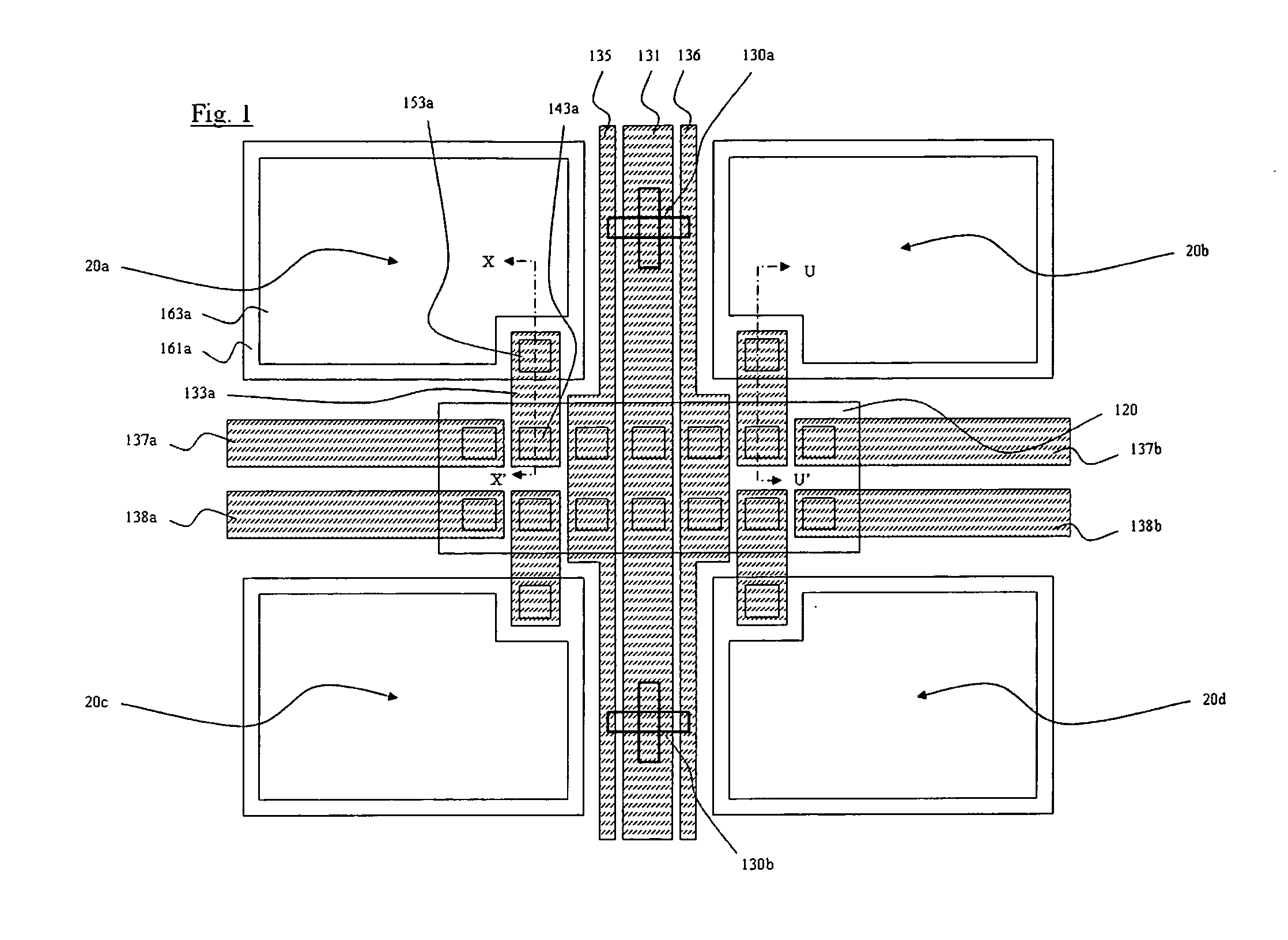

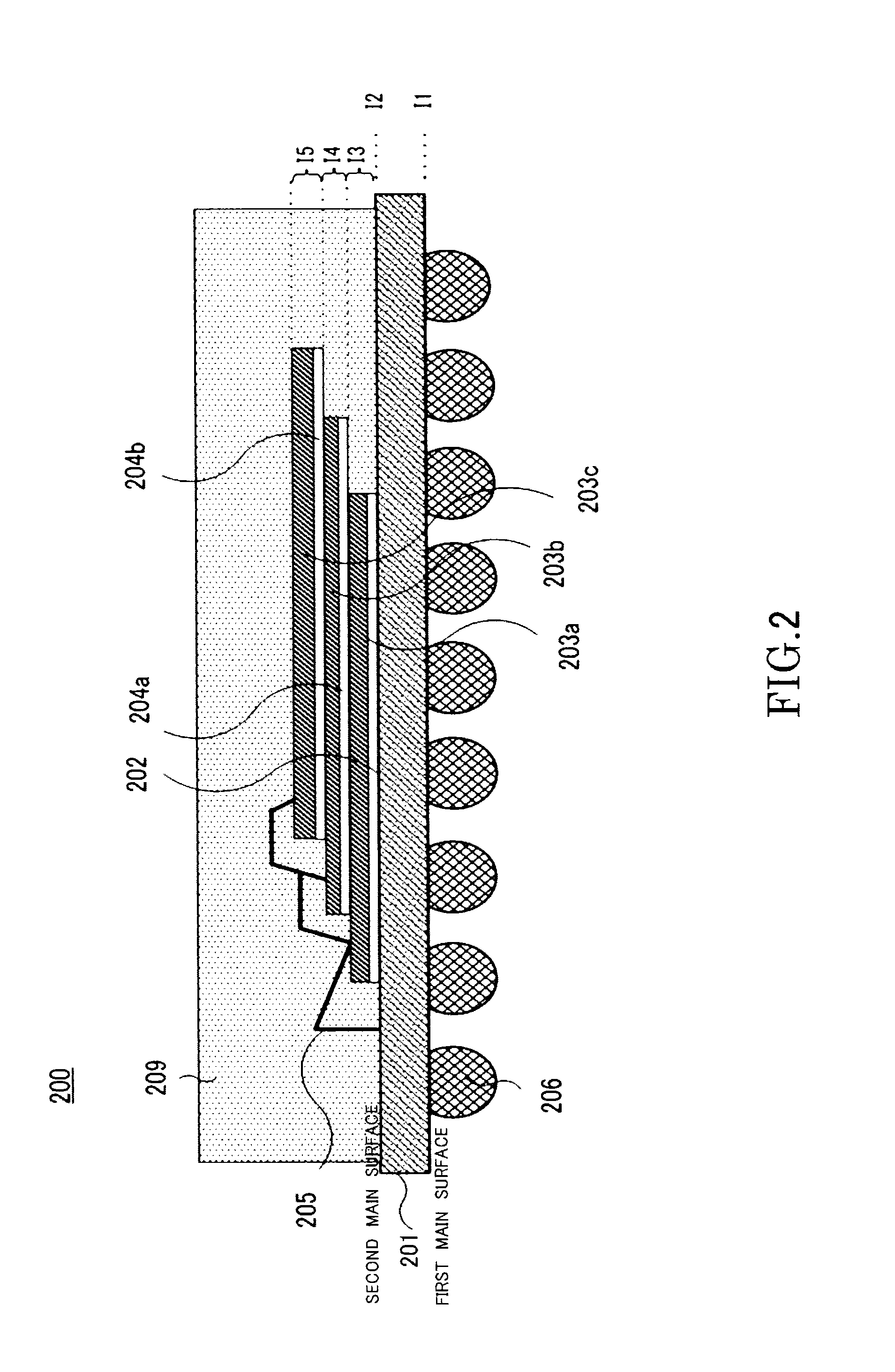

Stacked chip security

InactiveUS7557597B2Semiconductor/solid-state device testing/measurementElectronic circuit testingSemiconductor chipInterconnection

The present invention is directed to an integrated circuit module device. The device includes a first semiconductor chip having a first circuit layer and at least one first interconnection element disposed on a first chip surface. The at least one first interconnection element is electrically coupled to the first circuit layer. A second semiconductor chip includes a second circuit layer and at least one second interconnection element disposed on a second chip surface. The at least one second interconnection element is electrically coupled to the second circuit layer. The at least one first interconnection element is connected to the at least one second interconnection element to establish electrical continuity between the first circuit layer and the second circuit layer. The first surface is adjoined to the second surface. At least one ring delay circuit includes a first ring delay path partially disposed on the first circuit layer and a second ring delay path partially disposed on the second circuit layer. The first ring delay path and the second ring delay path form a signal path having a predetermined measurement signature. The ring delay circuit compares the predetermined measurement signature to a test measurement signature.

Owner:INT BUSINESS MASCH CORP

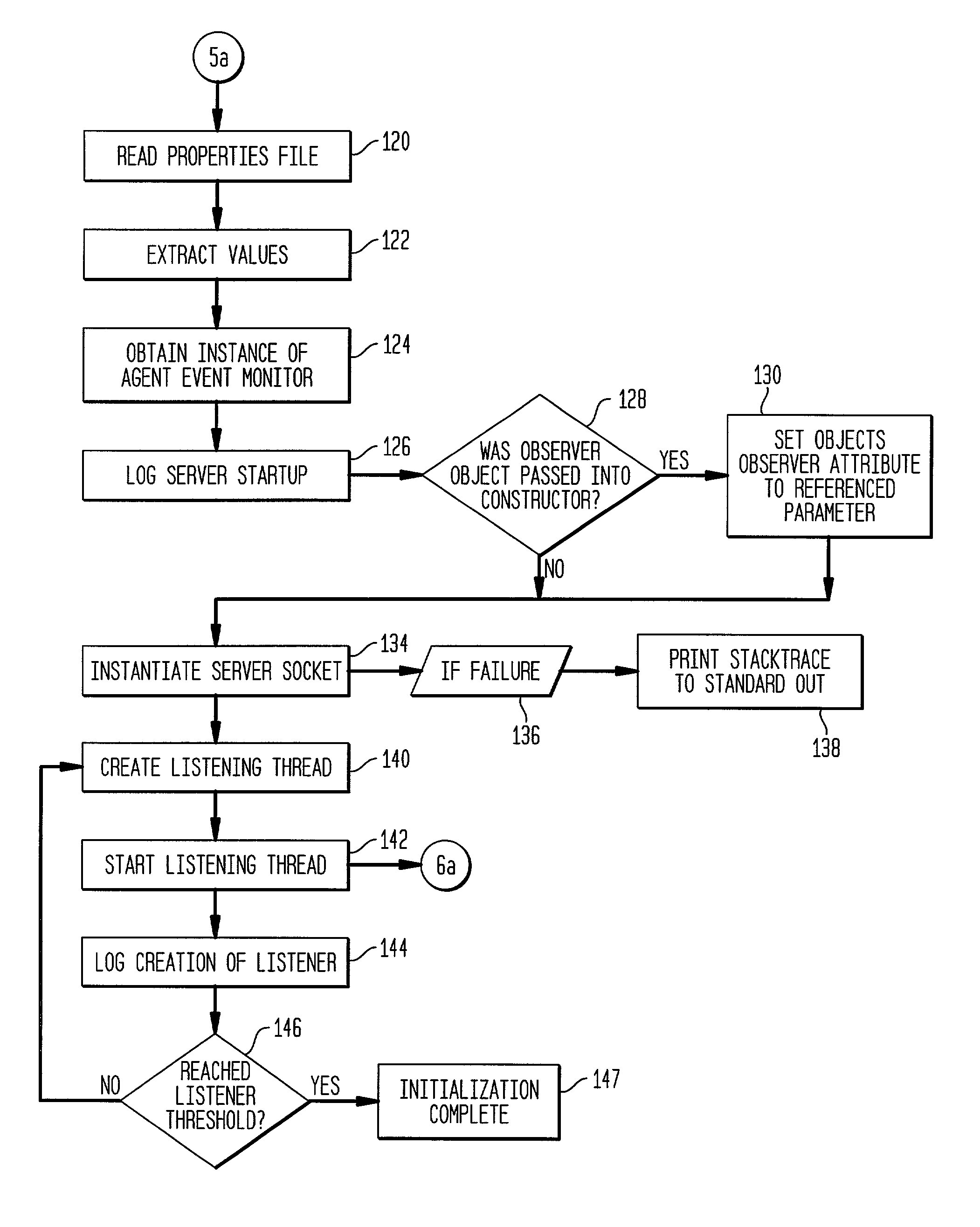

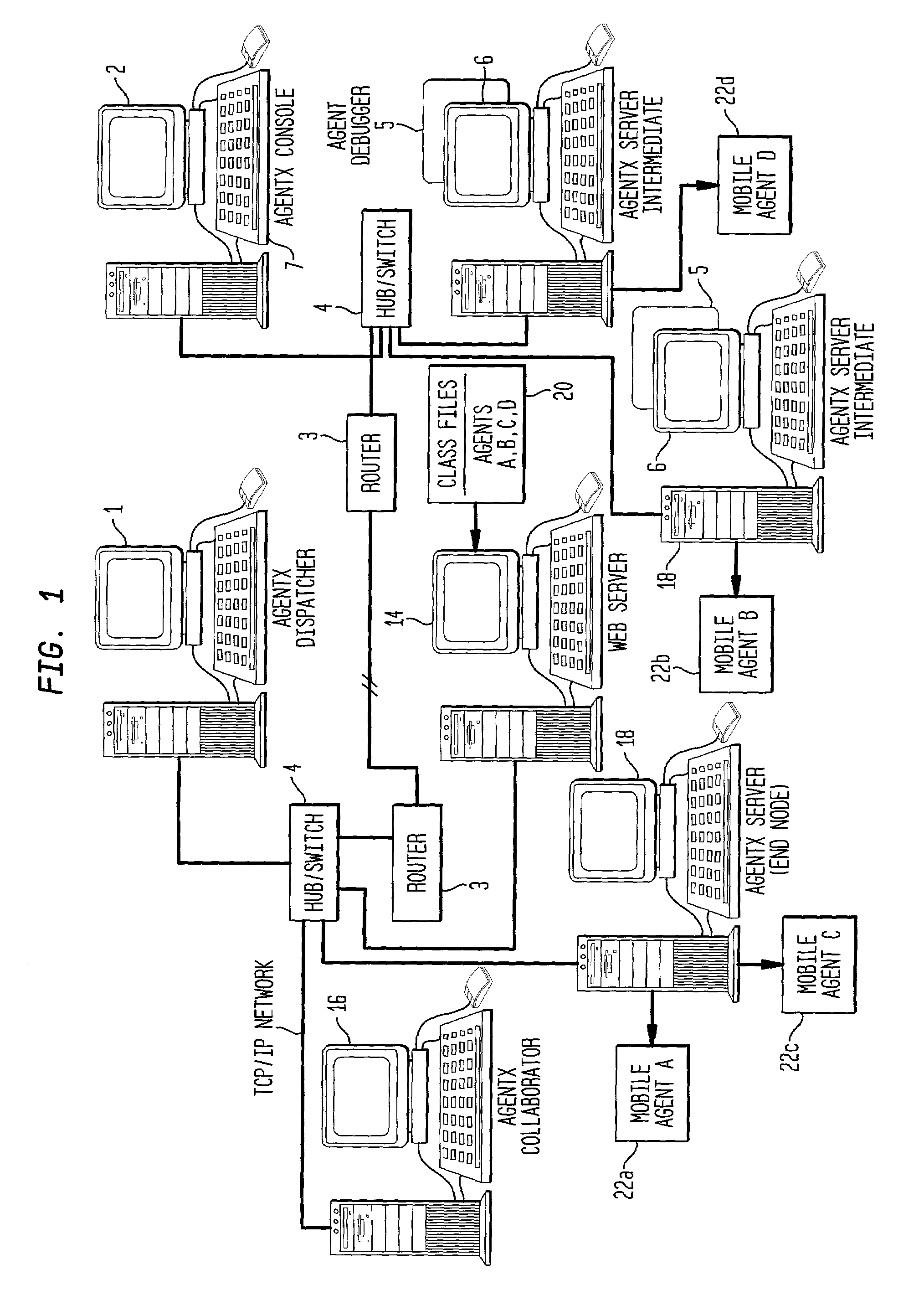

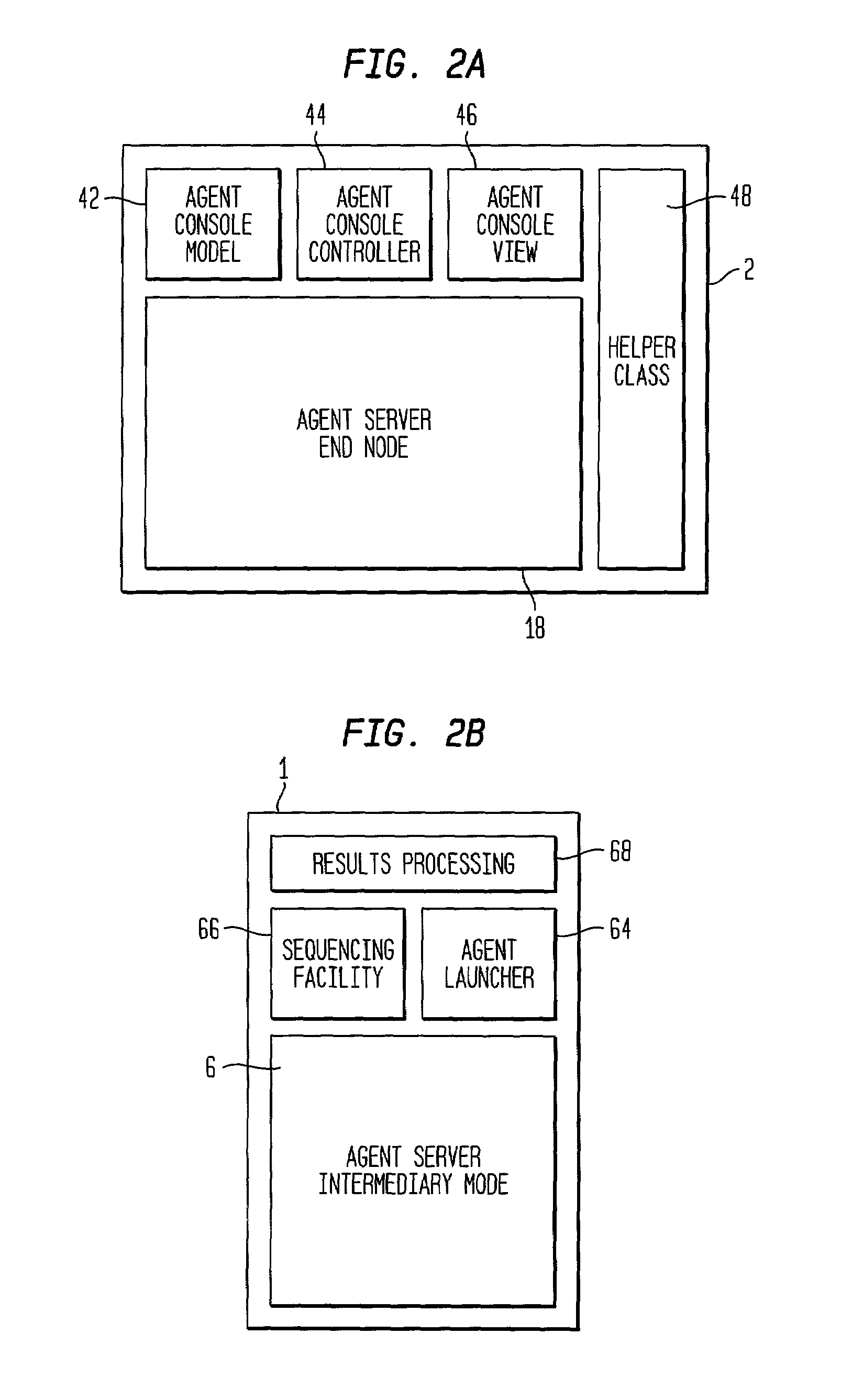

Method and apparatus for breaking down computing tasks across a network of heterogeneous computer for parallel execution by utilizing autonomous mobile agents

InactiveUS7082604B2Ease of parallel processingProgram initiation/switchingResource allocationApplication softwareLarge applications

A method and apparatus is provided for breaking down computing tasks within a larger application and distributing such tasks across a network of heterogeneous computers for simultaneous execution. The heterogeneous computers may be connected across a wide or local area network. The invention supports mobile agents that are self-migrating and can transport state information and stack trace information as they move from one host to another, continuing execution where the mobile agents may have left off. The invention includes a server component for providing an execution environment for the agents, in addition to sub-components which handle real-time collaboration between the mobile agents as well as facilities monitoring during execution. Additional components provide realistic thread migration for the mobile agents. Real-time stack trace information is stored as the computing tasks are executed, and if over-utilization of the computing host occurs, execution of the computing task can be halted and the computing task can be transferred to another computing hosts where execution can be seamlessly resumed using the stored, real-time state information and stack trace information.

Owner:MOBILE AGENT TECH

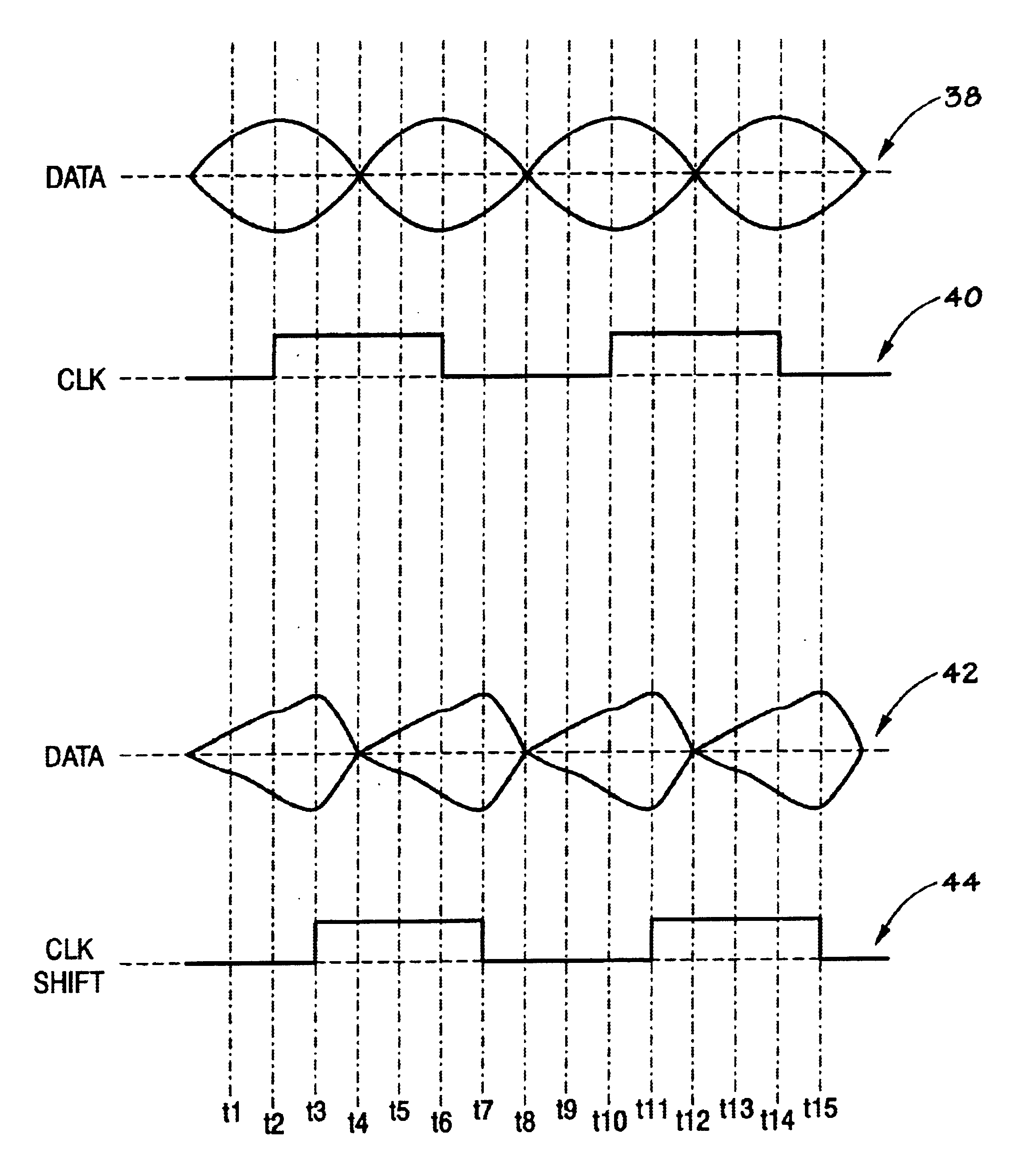

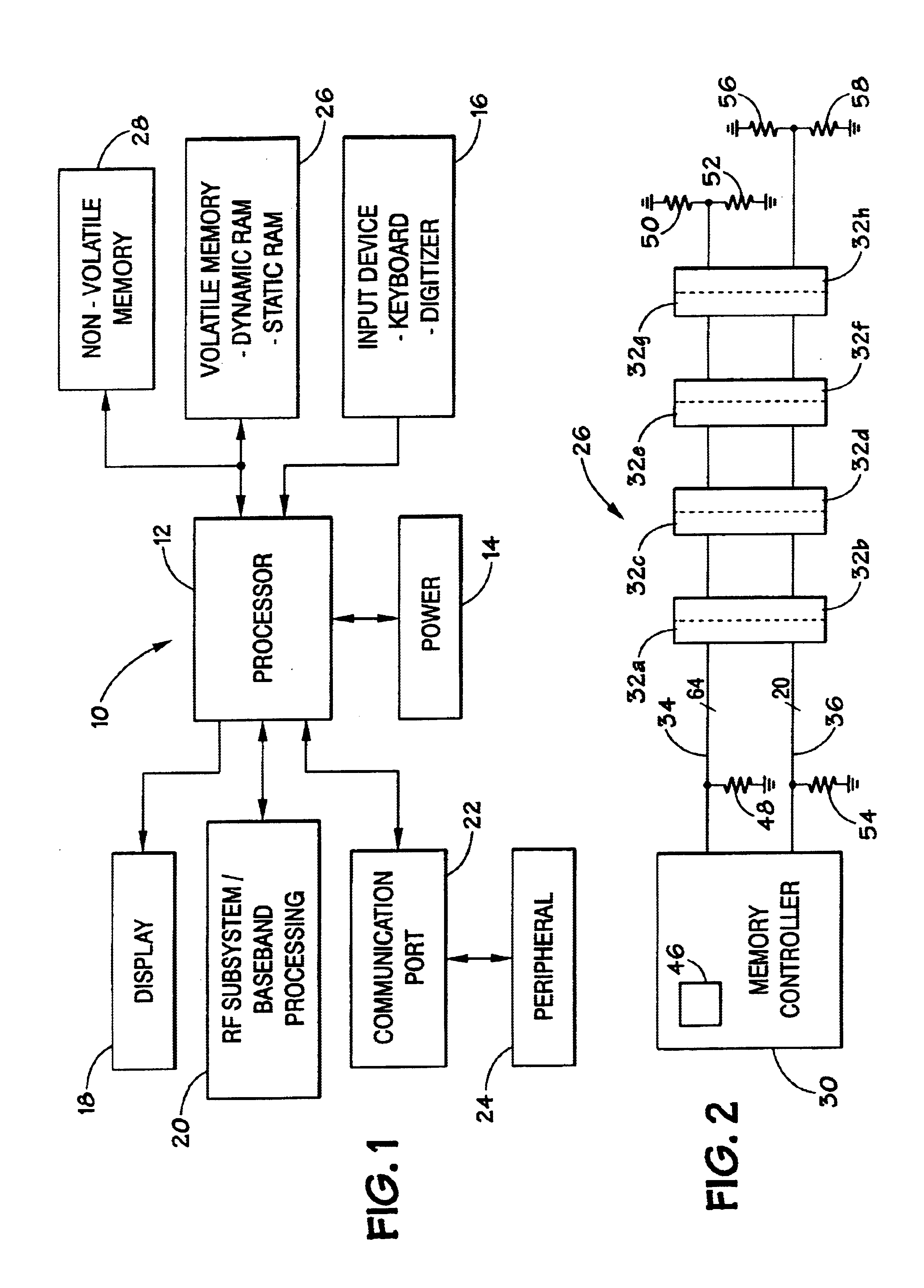

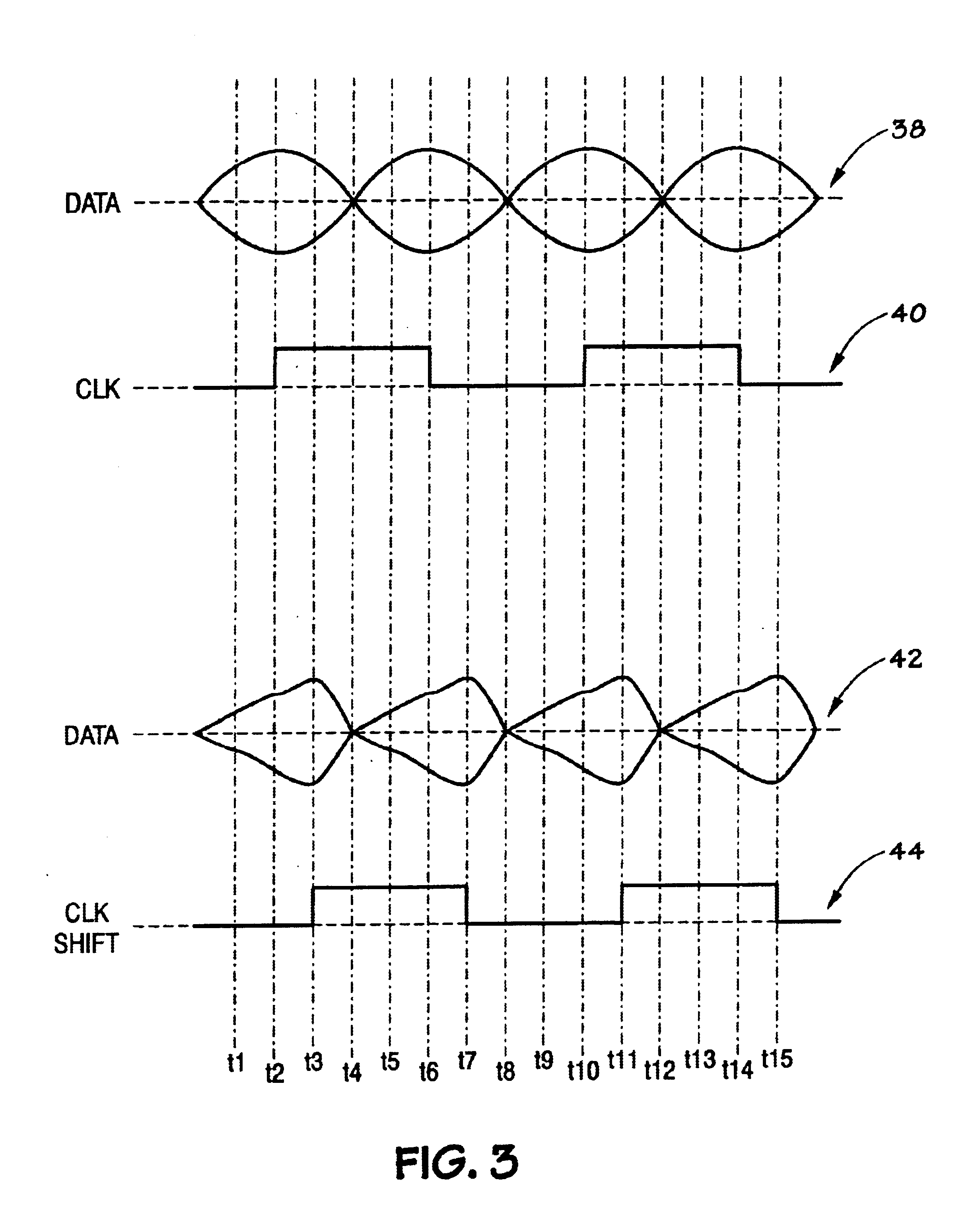

Write clock and data window tuning based on rank select

A configuration register used to adjust a clock or request signal with respect to the other. Specifically, a look-up table is provided in the memory controller. The look-up table is filled at bootup such that it contains test information from a master look-up table in the system BIOS, for instance. The look-up table in the memory controller stores current test data correlative to optimal sampling times for the current configuration. Adjustable delay elements or adjustable load elements may be used to change the relative sampling time of the request signal correlative to the values stored in the memory controller look-up table.

Owner:MICRON TECH INC

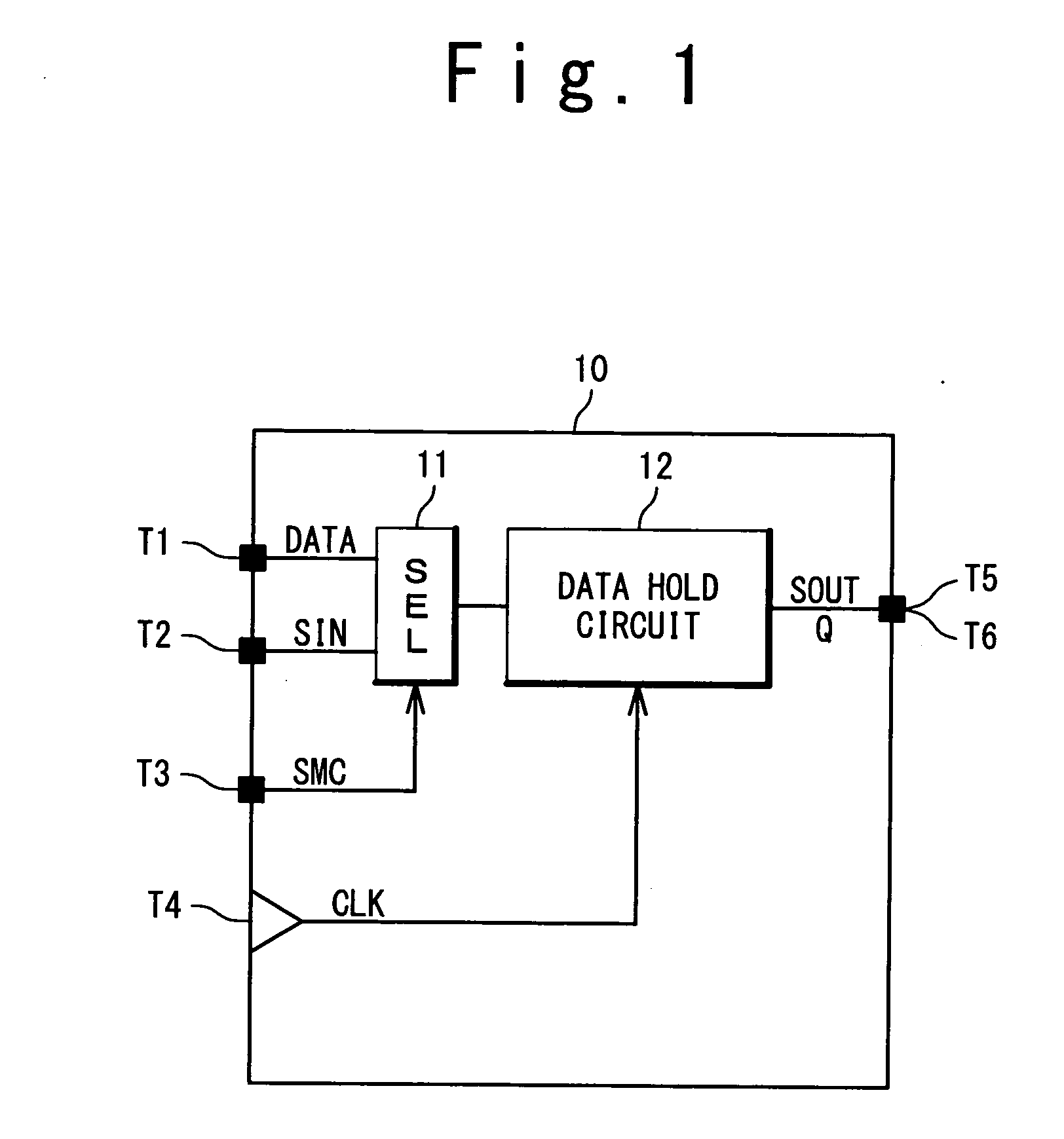

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

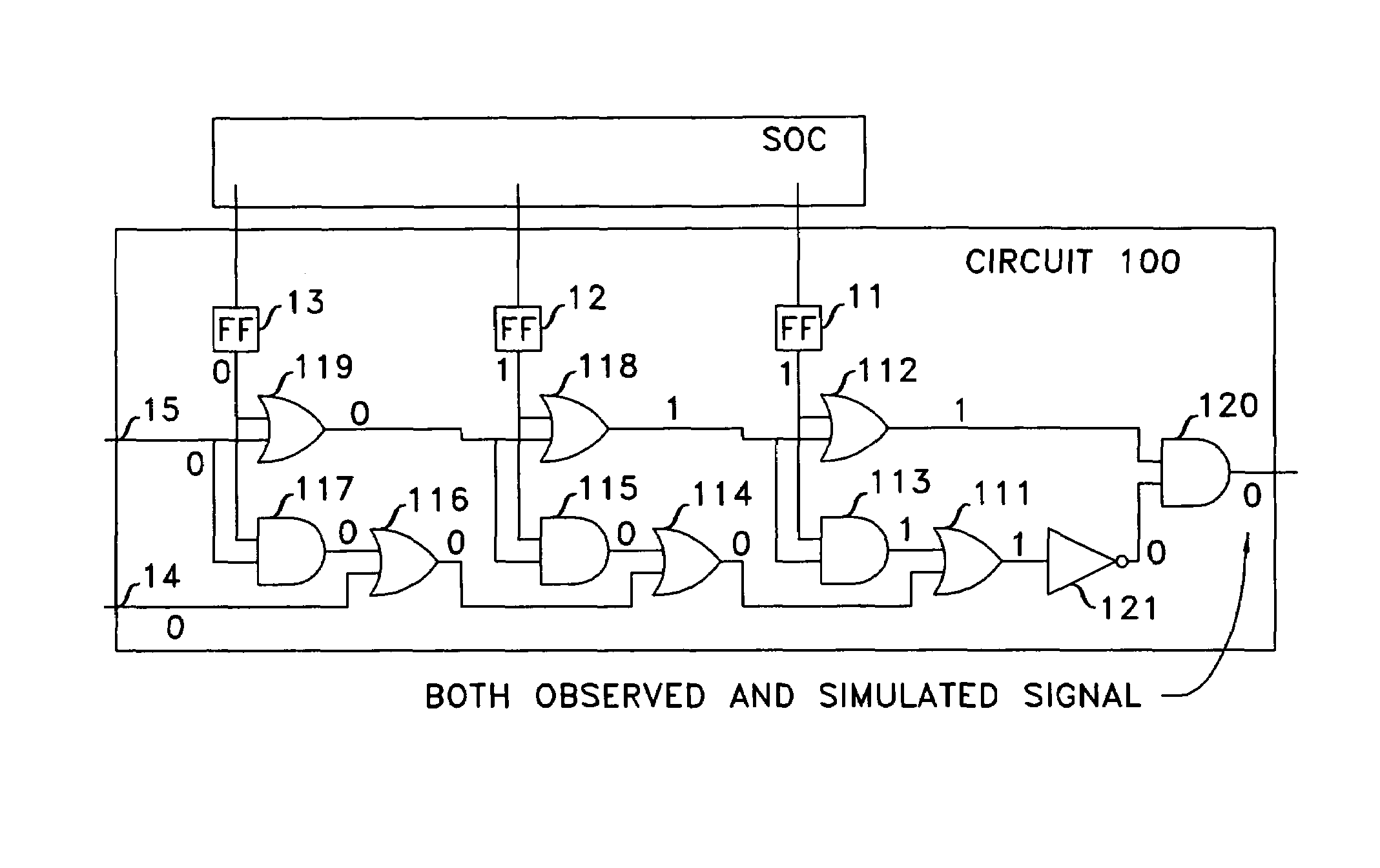

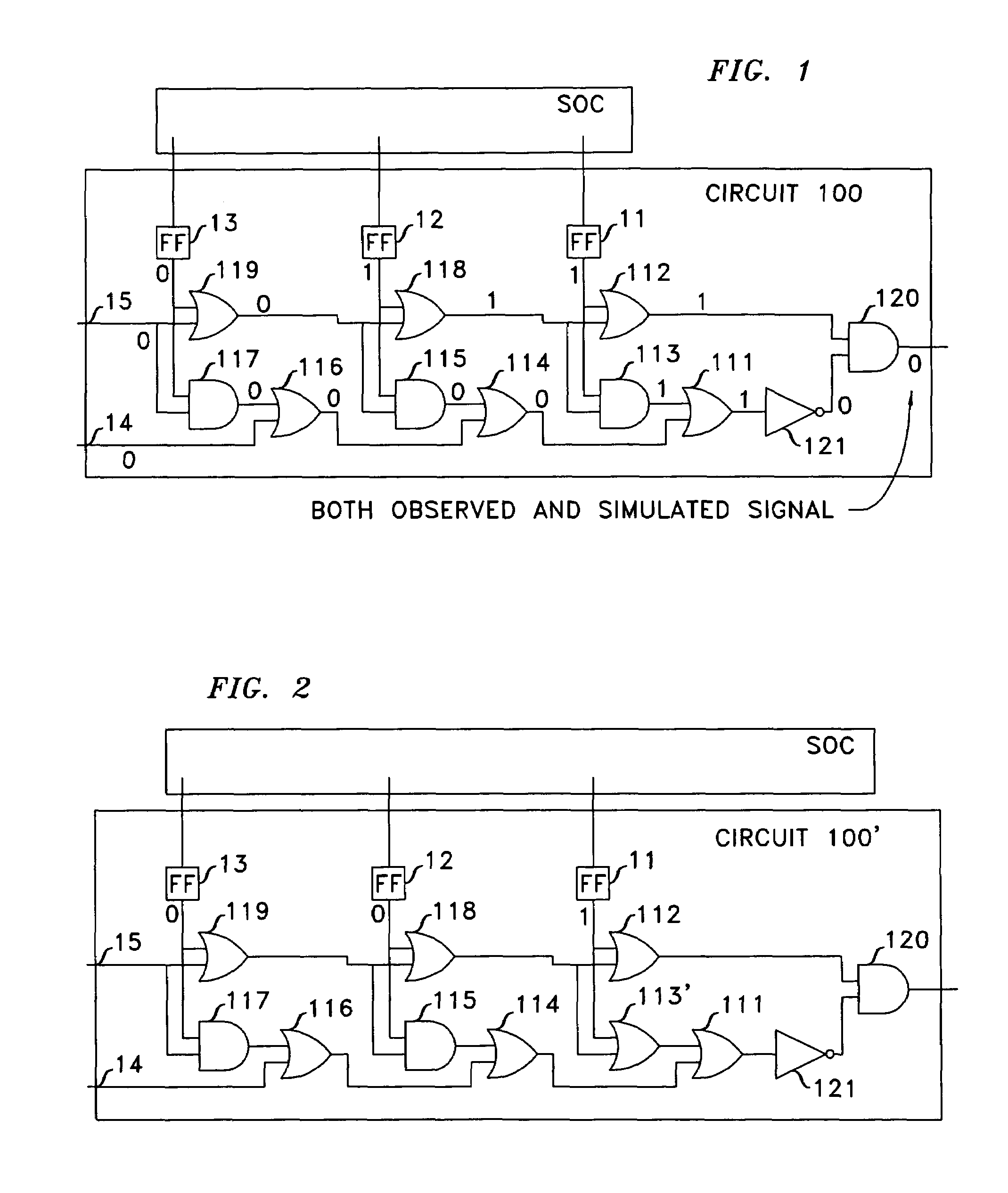

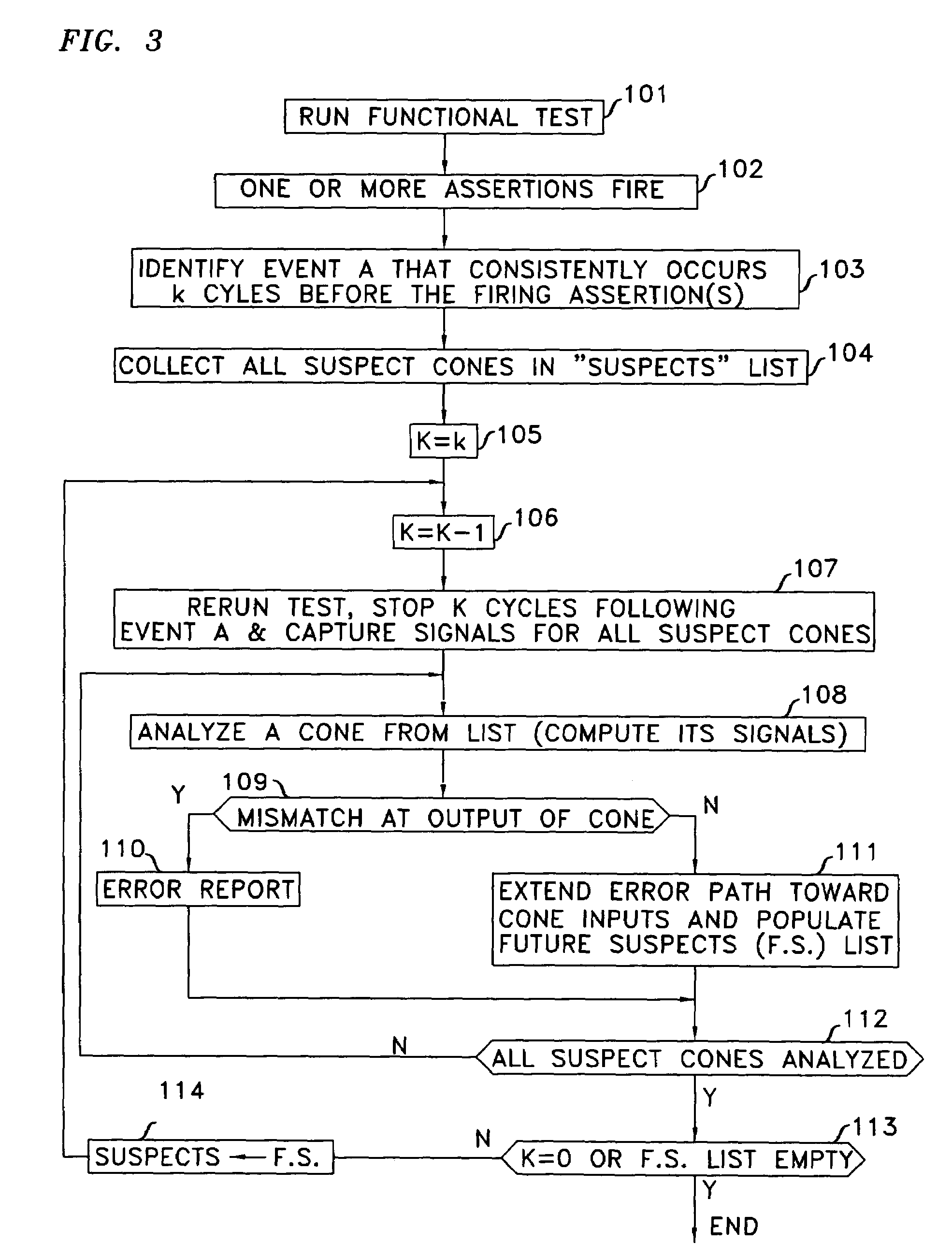

Method to locate logic errors and defects in digital circuits

When, in the course of an integrated circuit's functional test an assertion fires at clock k, the operational clock is stopped, the sequence is reapplied to capture inputs to the assertion circuit that fired, signals within the assertion circuit are computed, and the error is backtraced. Once one or more inputs of the assertion circuit are identified as potentially the source of the error, the process of backtracing is performed for each such input. When the input that is potentially the source of the error emanates from a memory circuit, the fanin cone of the memory circuit is identified and the process of backtracing through the last-identified fanin cone is undertaken for clock k−1. This is repeated iteratively until either a module of the integrated circuit is found to be the source of the error, or the error is extended to inputs of the SoC.

Owner:DAFCA

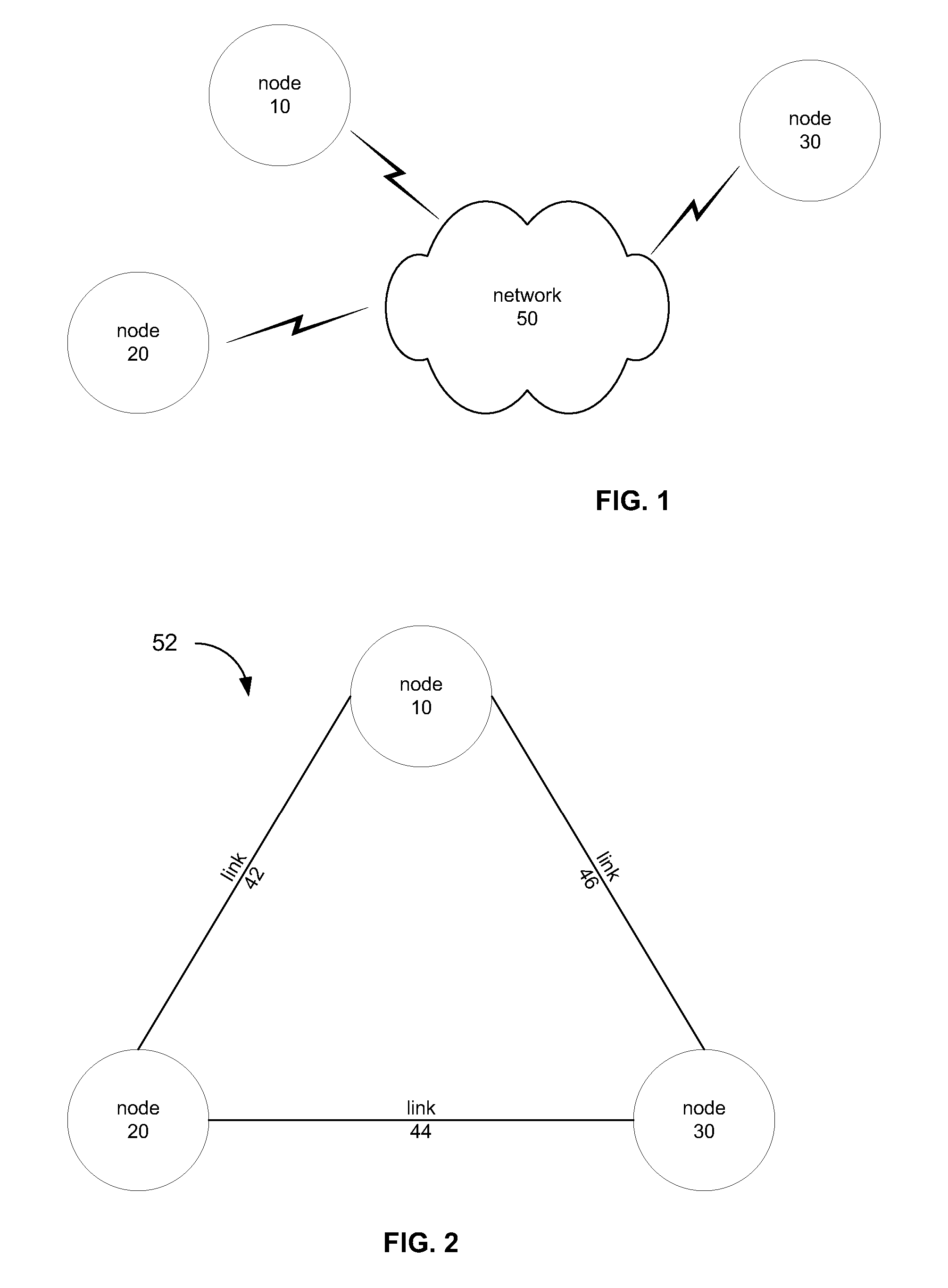

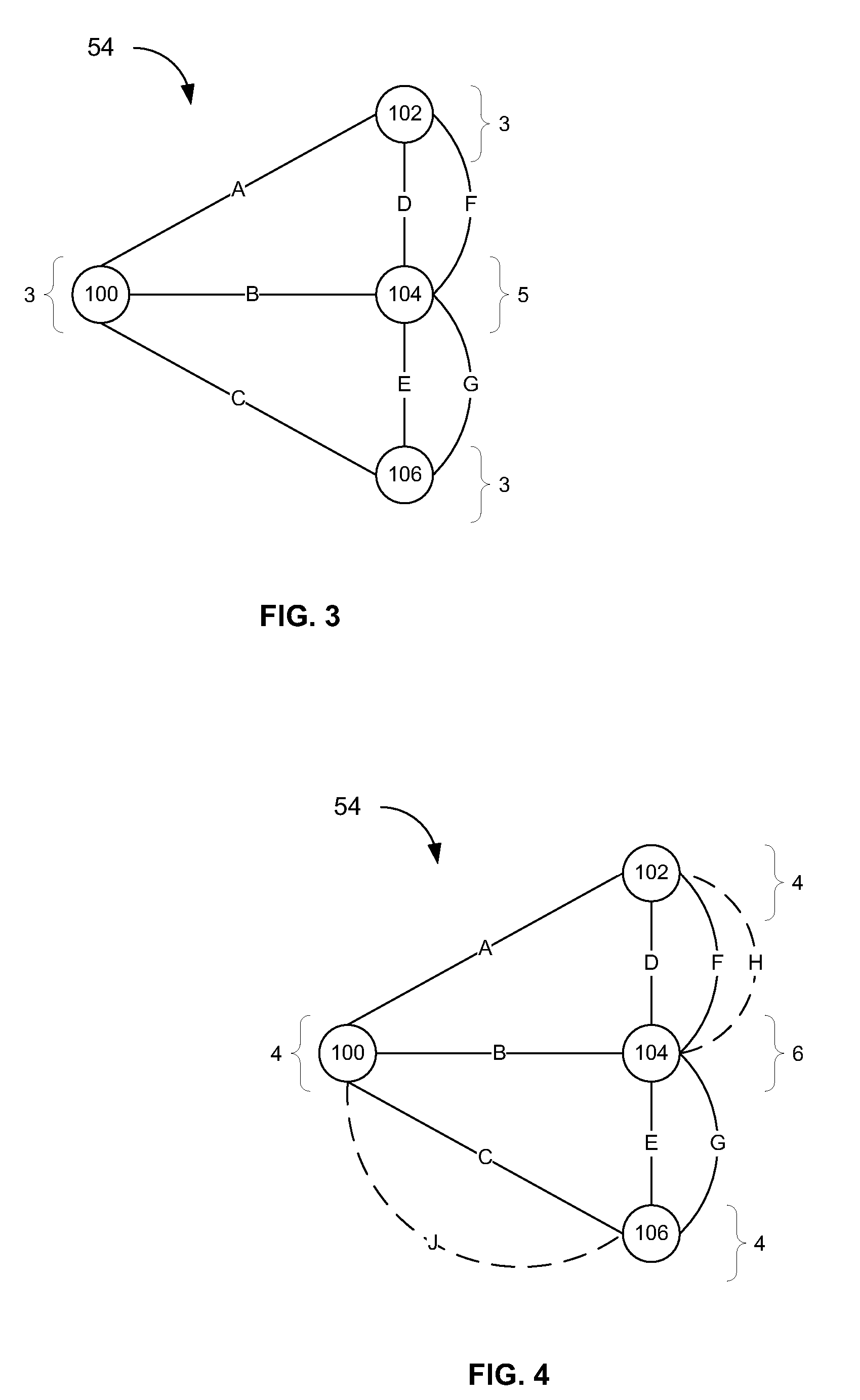

System and method for identifying nodes in a wireless network

InactiveUS7451365B2Blocking in networkAvoids a circular dependency on routing tablesElectronic circuit testingNetwork topologiesComputer hardwareWireless mesh network

Systems and methods for providing a boundary scan test of a wired or wireless network having a plurality of network nodes are presented. The system includes a test station communicatively coupled with the network. The test station creates a MAC layer scan test route sequence that includes each link in the network and is independent of the routing mechanism and protocol used for the network. The test station also creates a test agent that is configured to traverse each link in the scan test route sequence. The test agent is then deployed on the network and information about a link is reported back to the test station after the test agent examines the link. The scan test route sequence can be created by sending out a series of broadcast messages from one or more nodes in the network, sequentially applying a network tour to cover the entire network, or performing a depth first search on the entire network.

Owner:UNWIRED BROADBAND INC

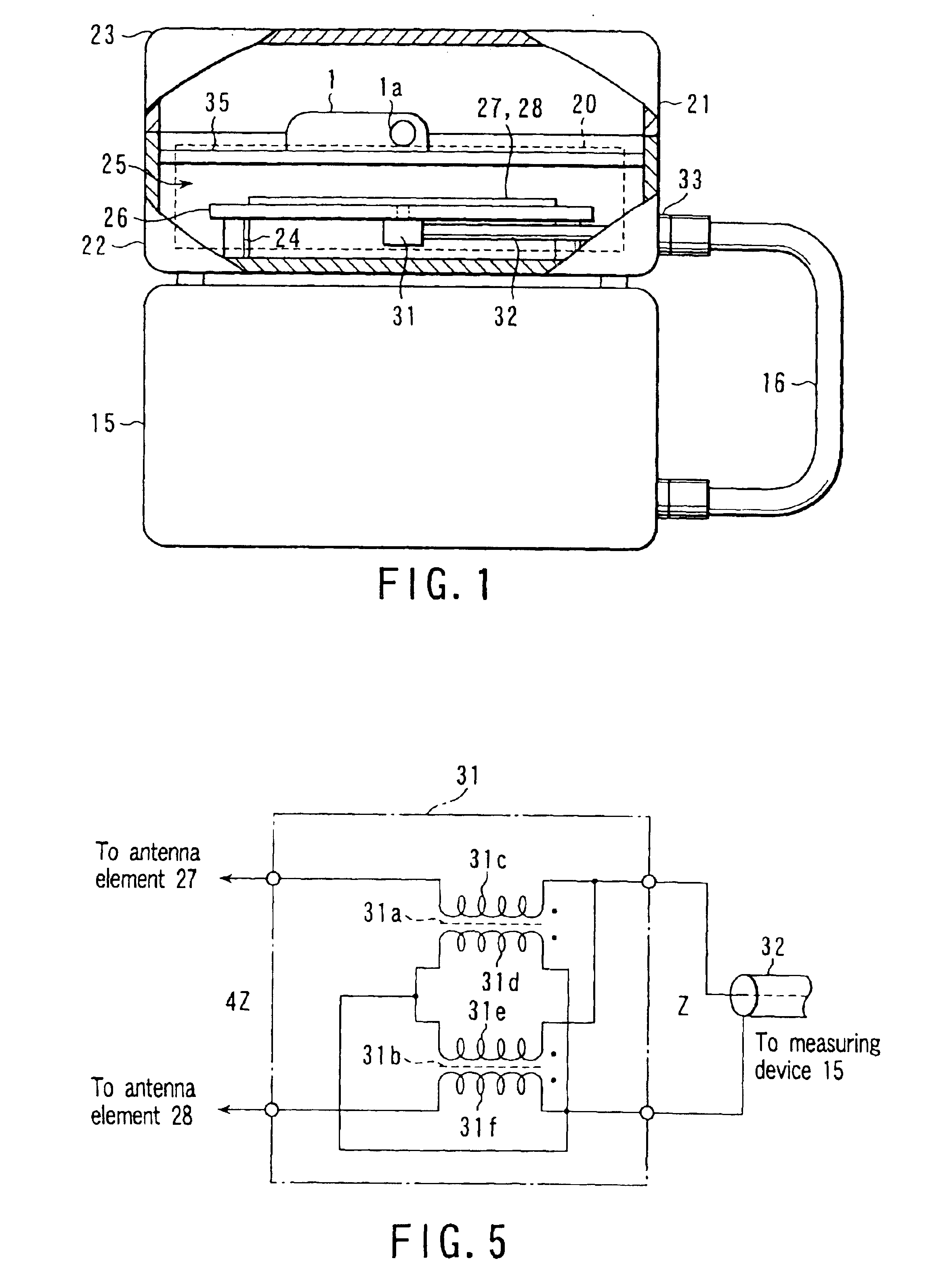

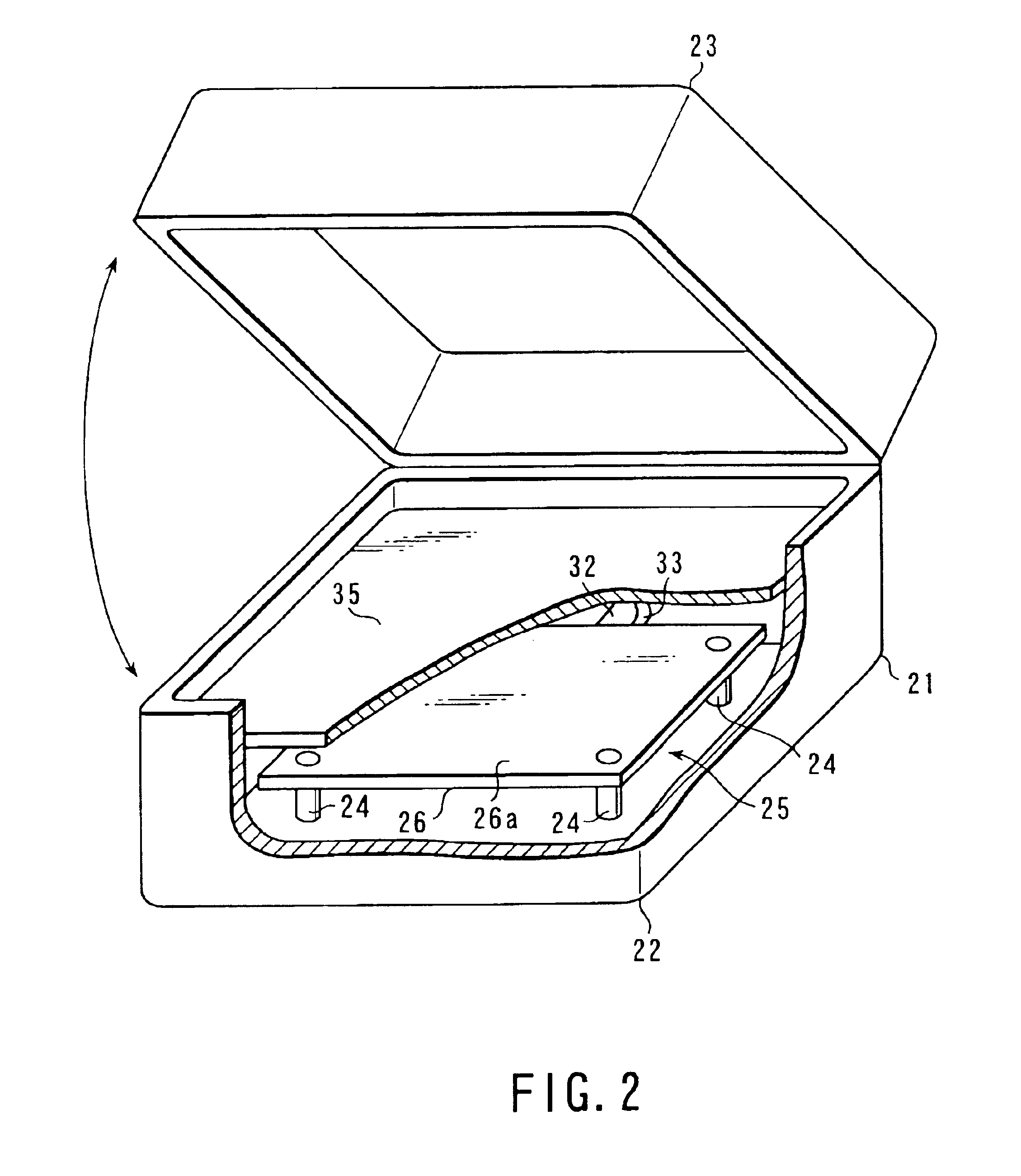

Protable radio terminal testing apparatus using single self-complementary antenna

InactiveUS6839032B2Simple structureEasy to operateTransmitters monitoringPower managementCouplingImpedance transformer

Owner:ANRITSU CORP

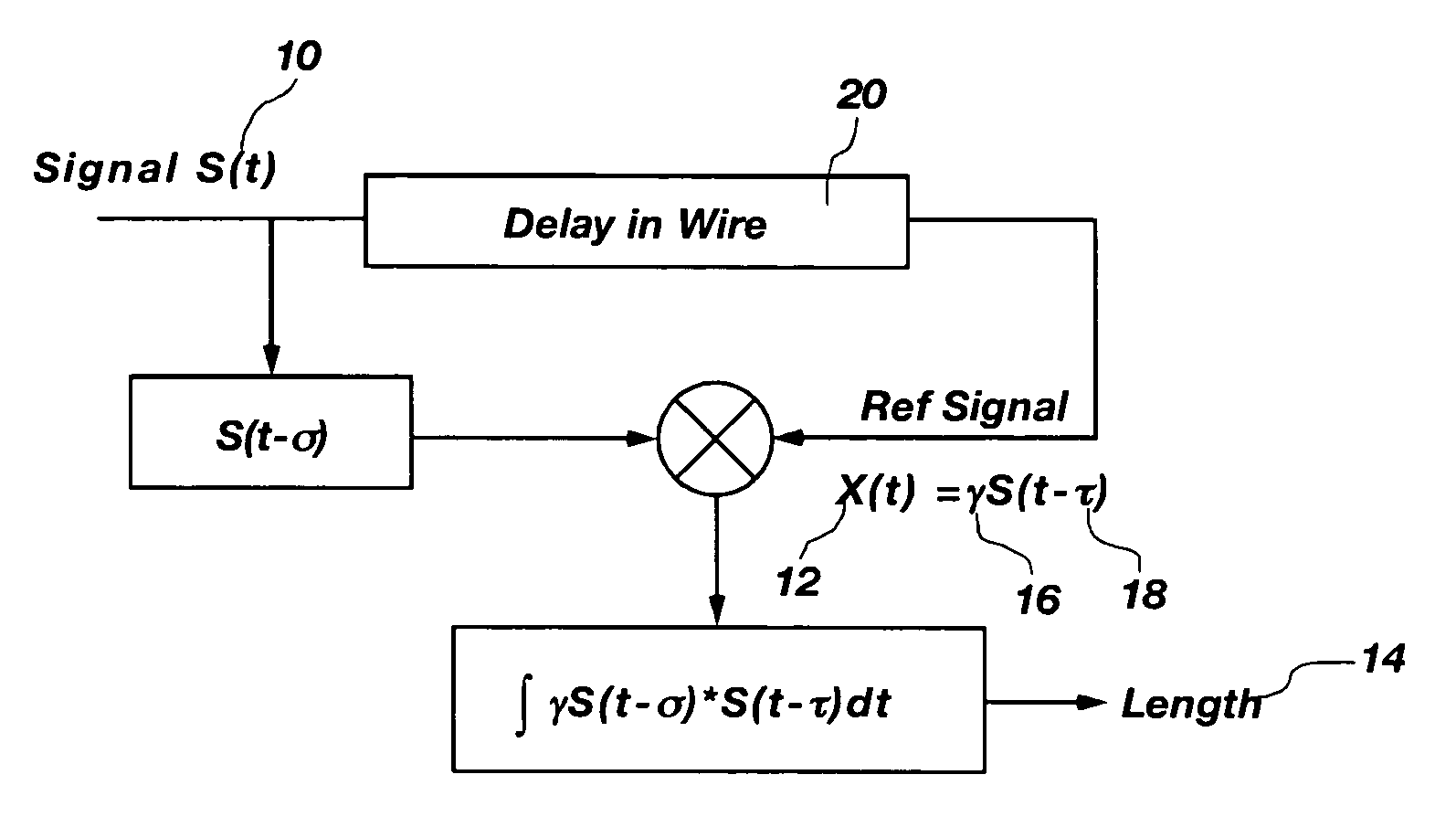

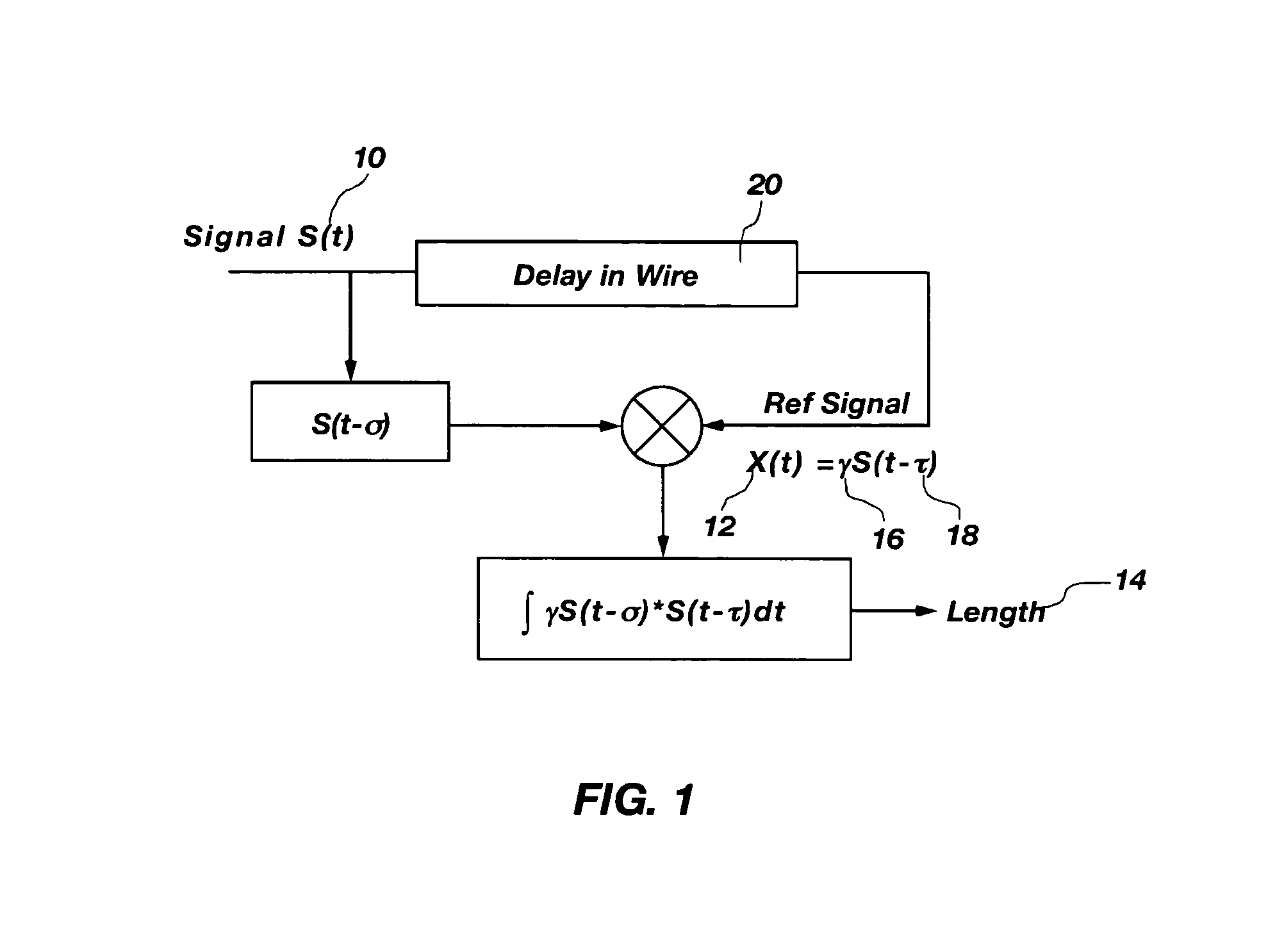

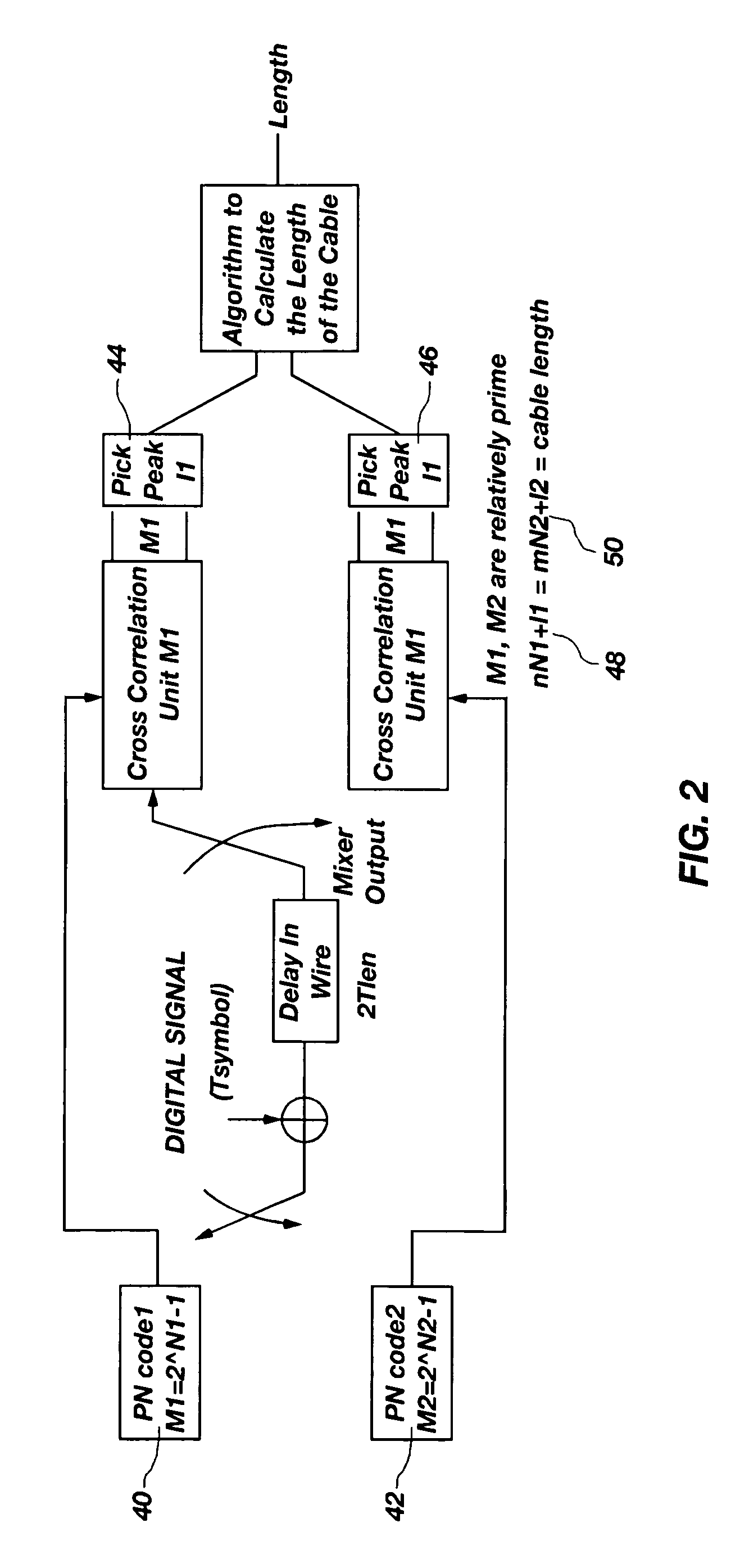

Digital spread spectrum methods and apparatus for testing aircraft wiring

InactiveUS7069163B2Efficient implementationElectronic circuit testingTesting electric installations on transportOriginal dataData signal

A system and method that utilizes direct sequence spread spectrum signal (DSSS) encoding to enable testing of a live wire, wherein an original data signal is modified and then transmitted along the wire, and a reflected signal is collected and analyzed using correlation techniques to determine characteristics of the live wire, including the location of a fault.

Owner:UTAH STATE UNIVERSITY

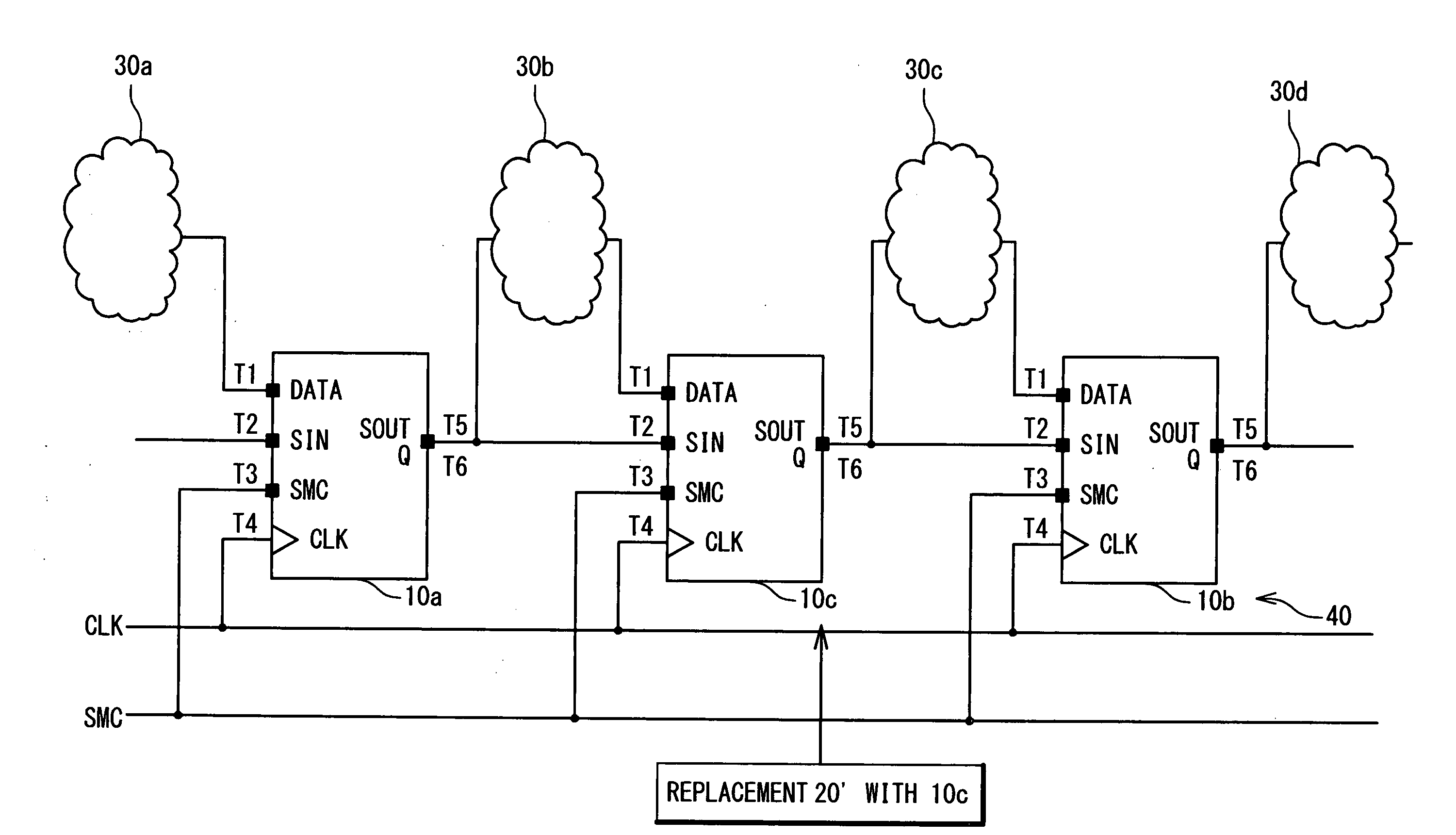

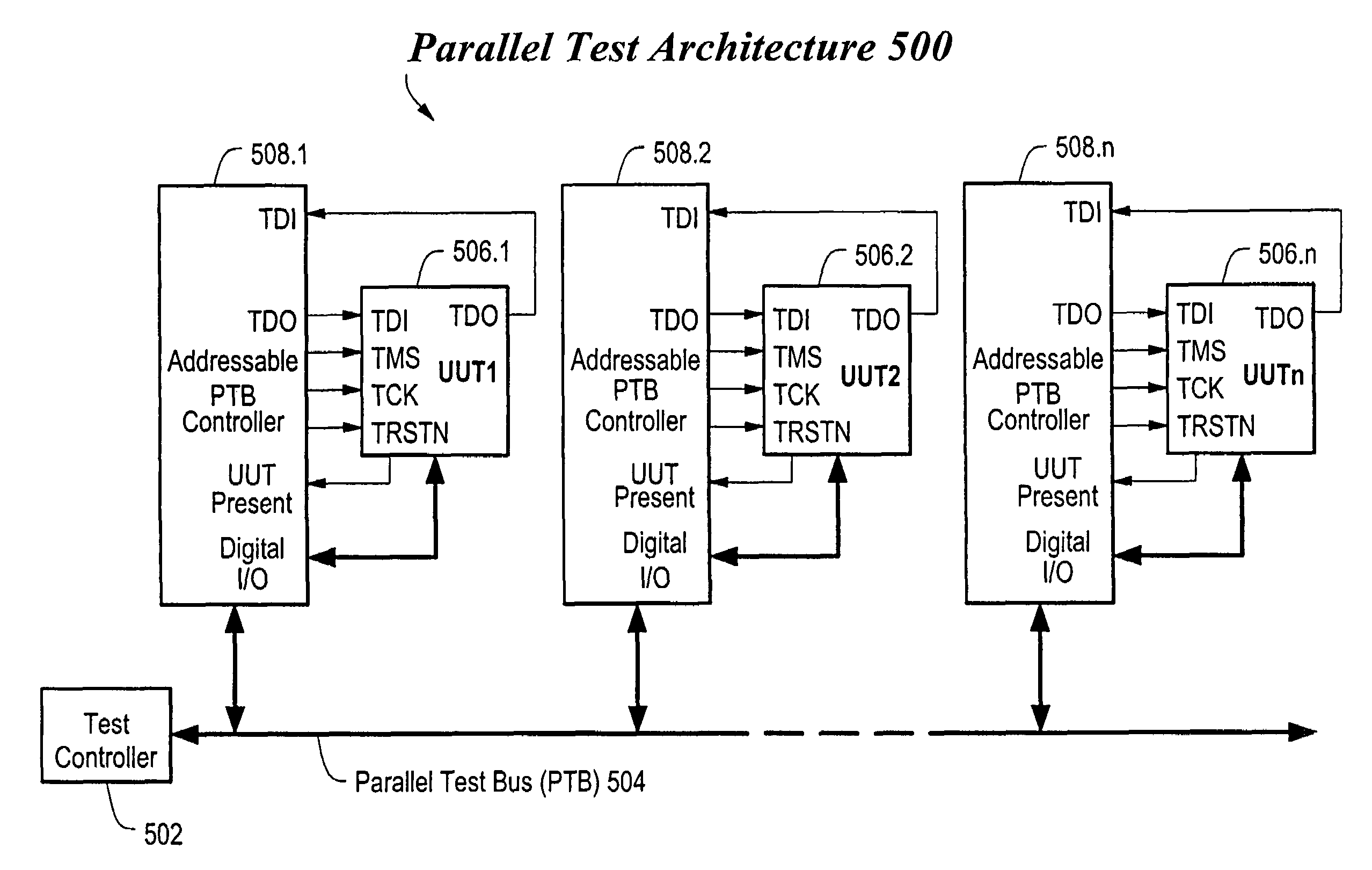

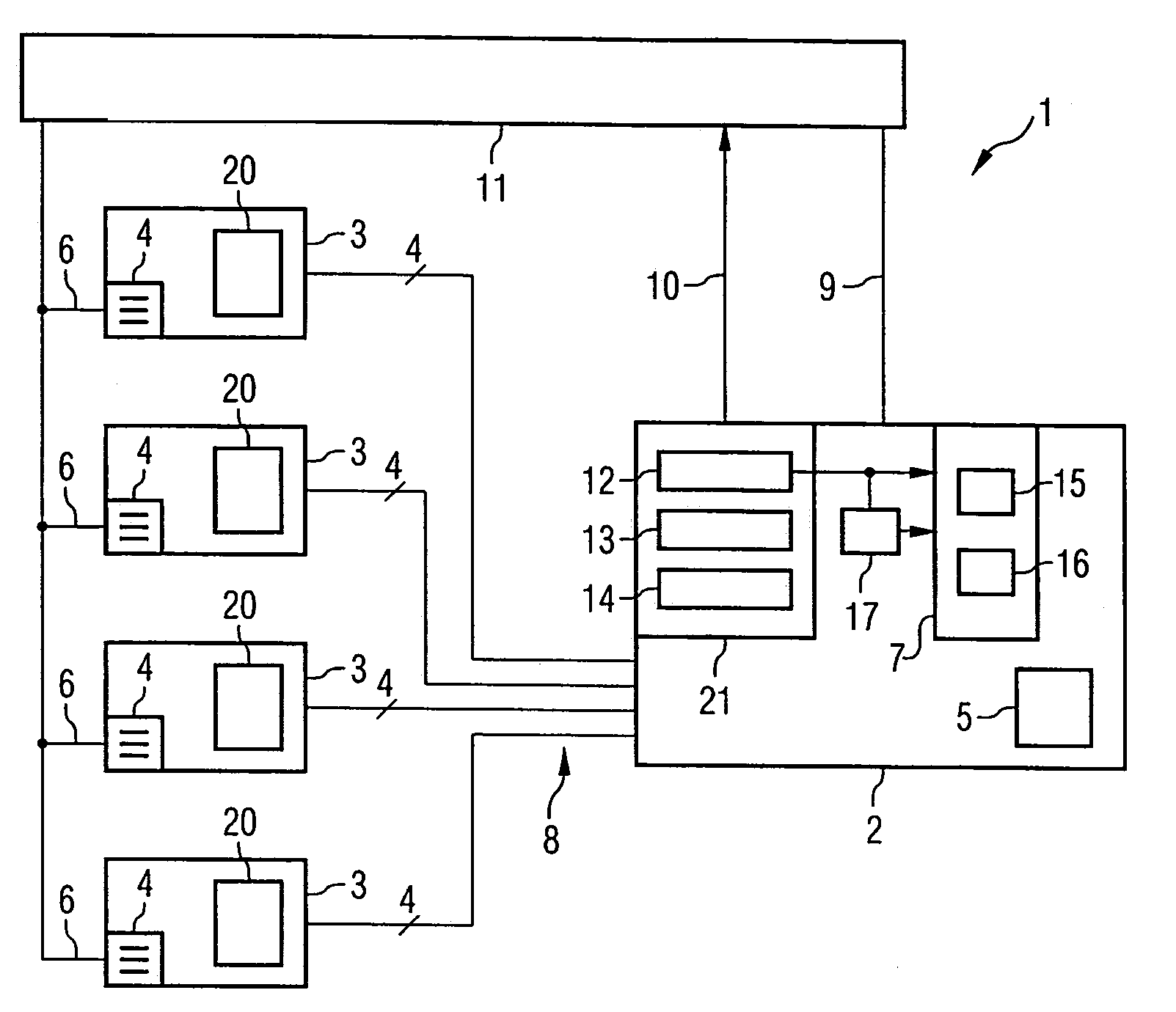

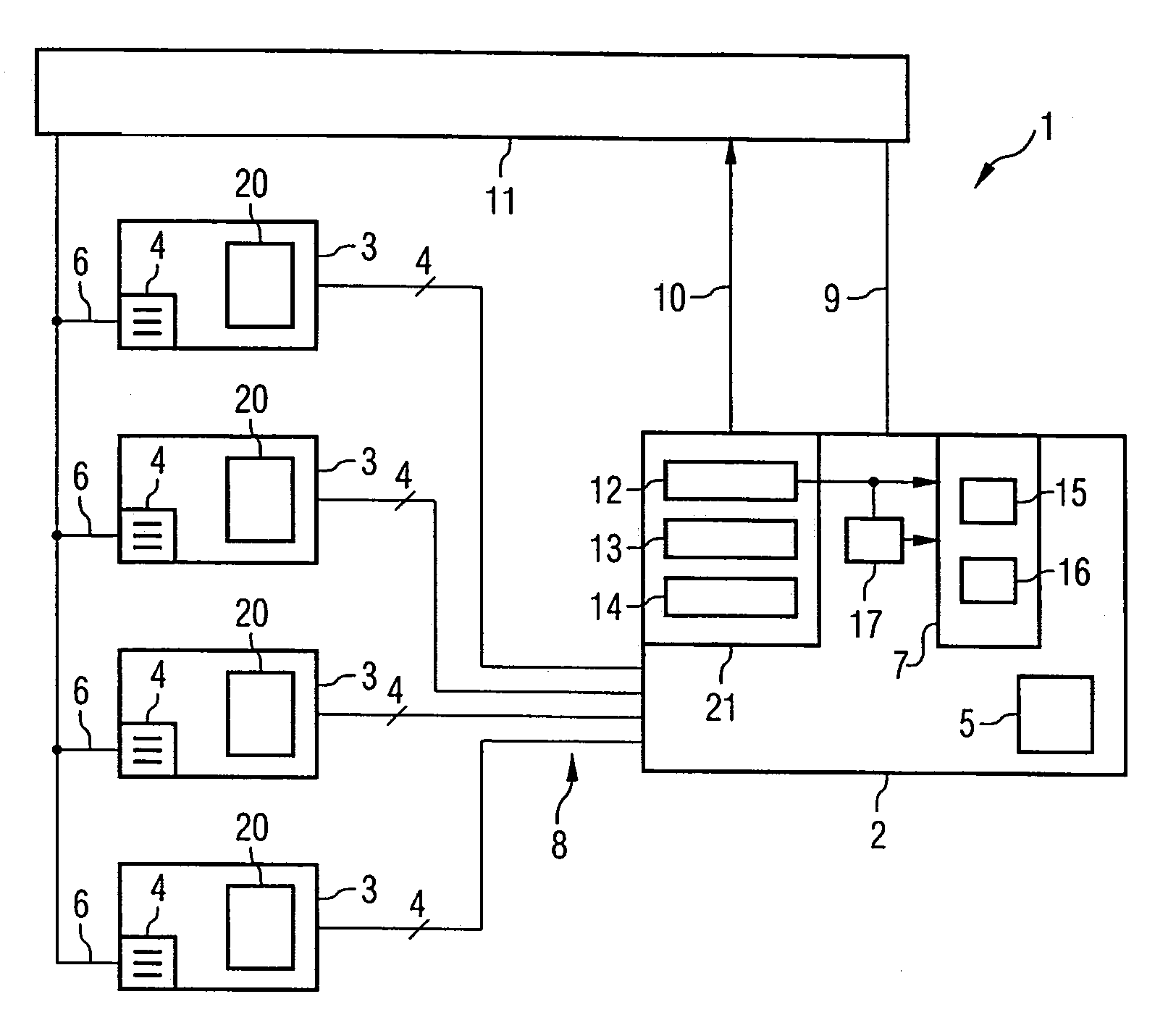

Method and apparatus for optimized parallel testing and access of electronic circuits

InactiveUS6988232B2Easy accessIncreased “ parallel ” testingElectronic circuit testingDetecting faulty computer hardwareEngineeringElectronic circuit

An architecture that provides stimulus data and verifies the response of multiple electronic circuits substantially in parallel for optimized testing, debugging, or programmable configuration of the circuits. The architecture includes a test bus, a primary test controller connected to the bus, and a plurality of local test controllers connected to the bus, in which each local test controller is coupleable to a respective circuit. The primary test controller sends stimulus data and expected response data over the bus to the respective local test controllers to perform parallel testing, debugging or programmable configuration of the circuits. Each local test controller applies the stimulus data and verifies the circuit response against the expected response data. Further, each local test controller stores the result of the verification for later retrieval by the primary test controller.

Owner:INTELLITECH INC

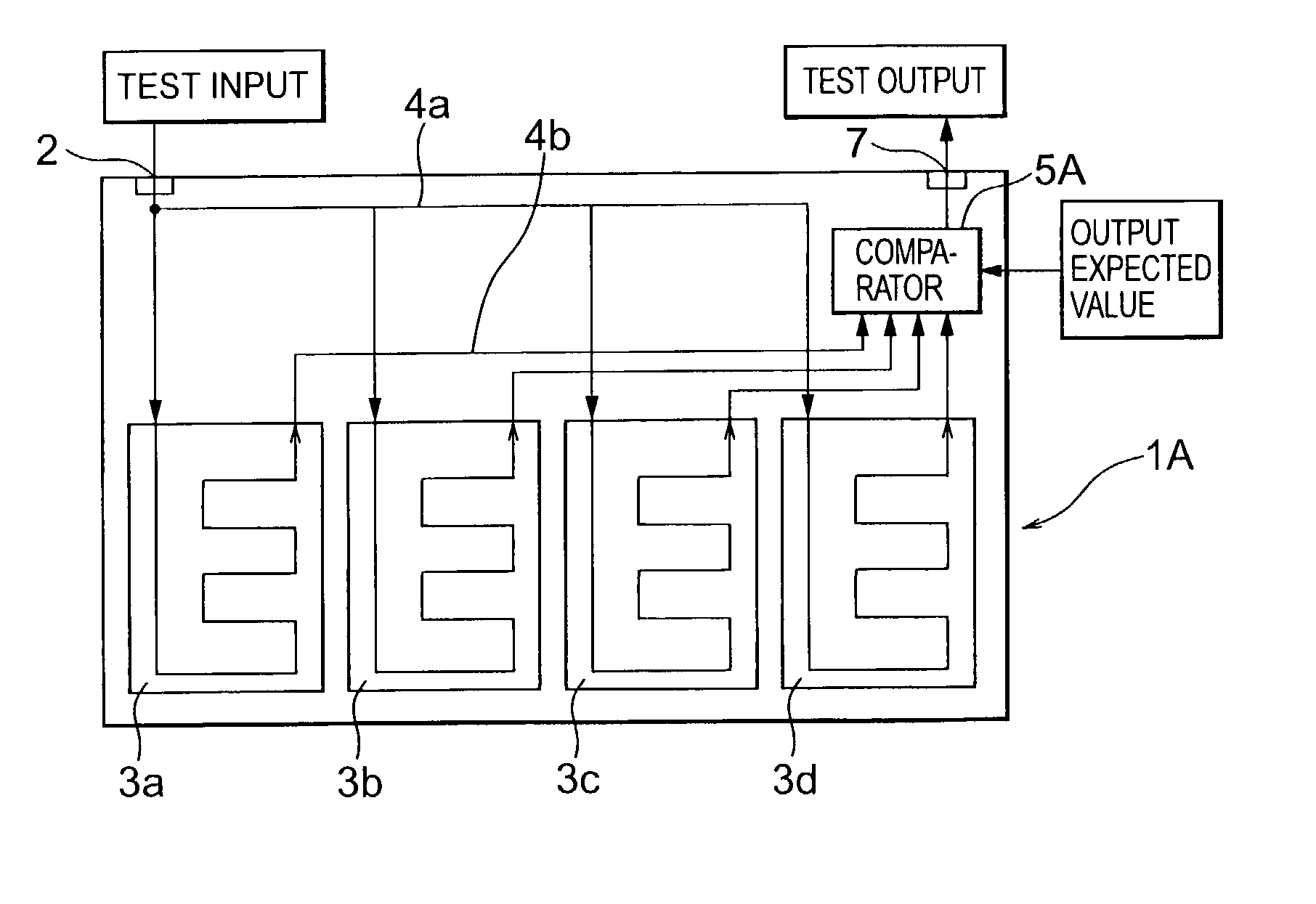

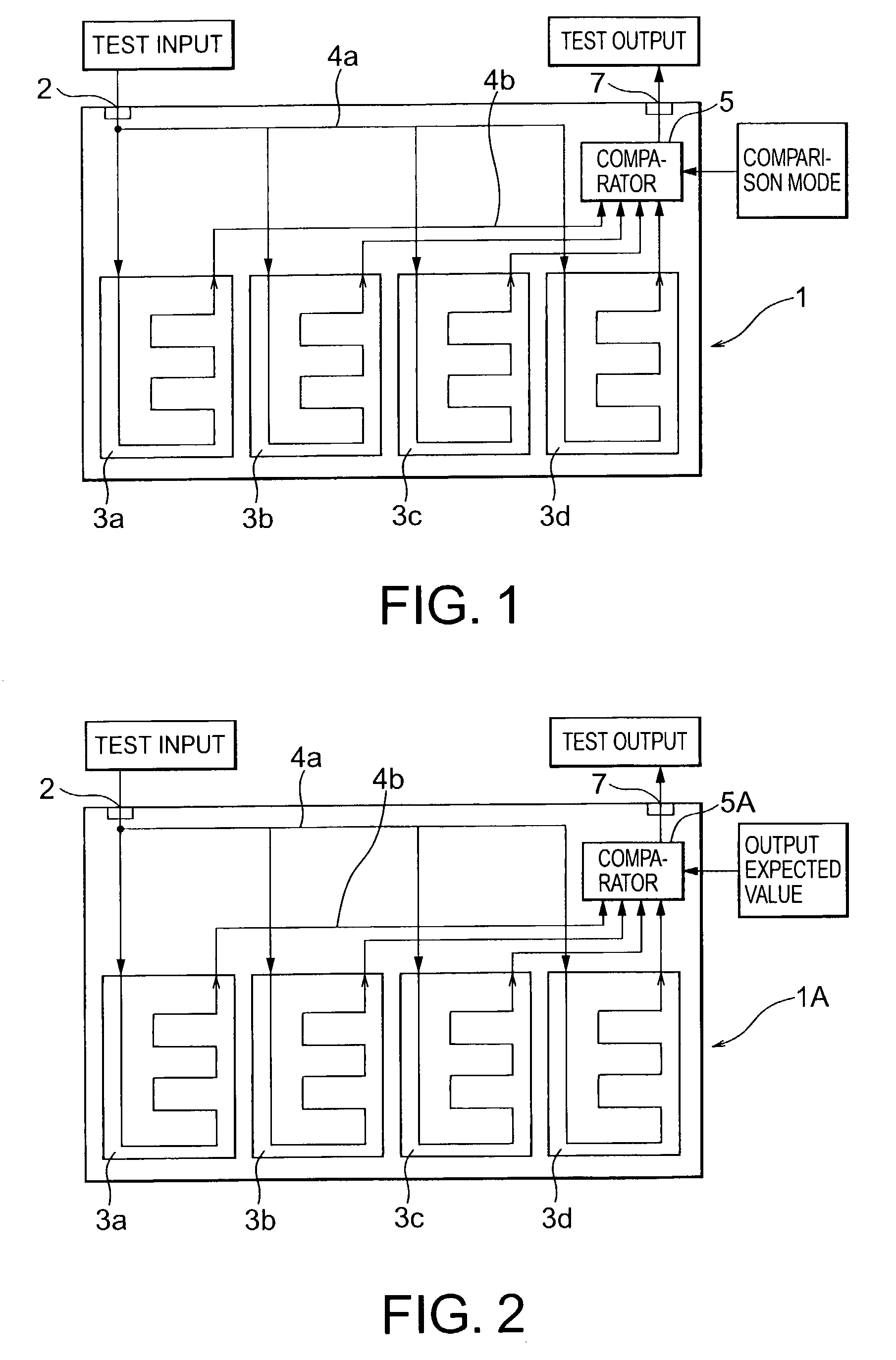

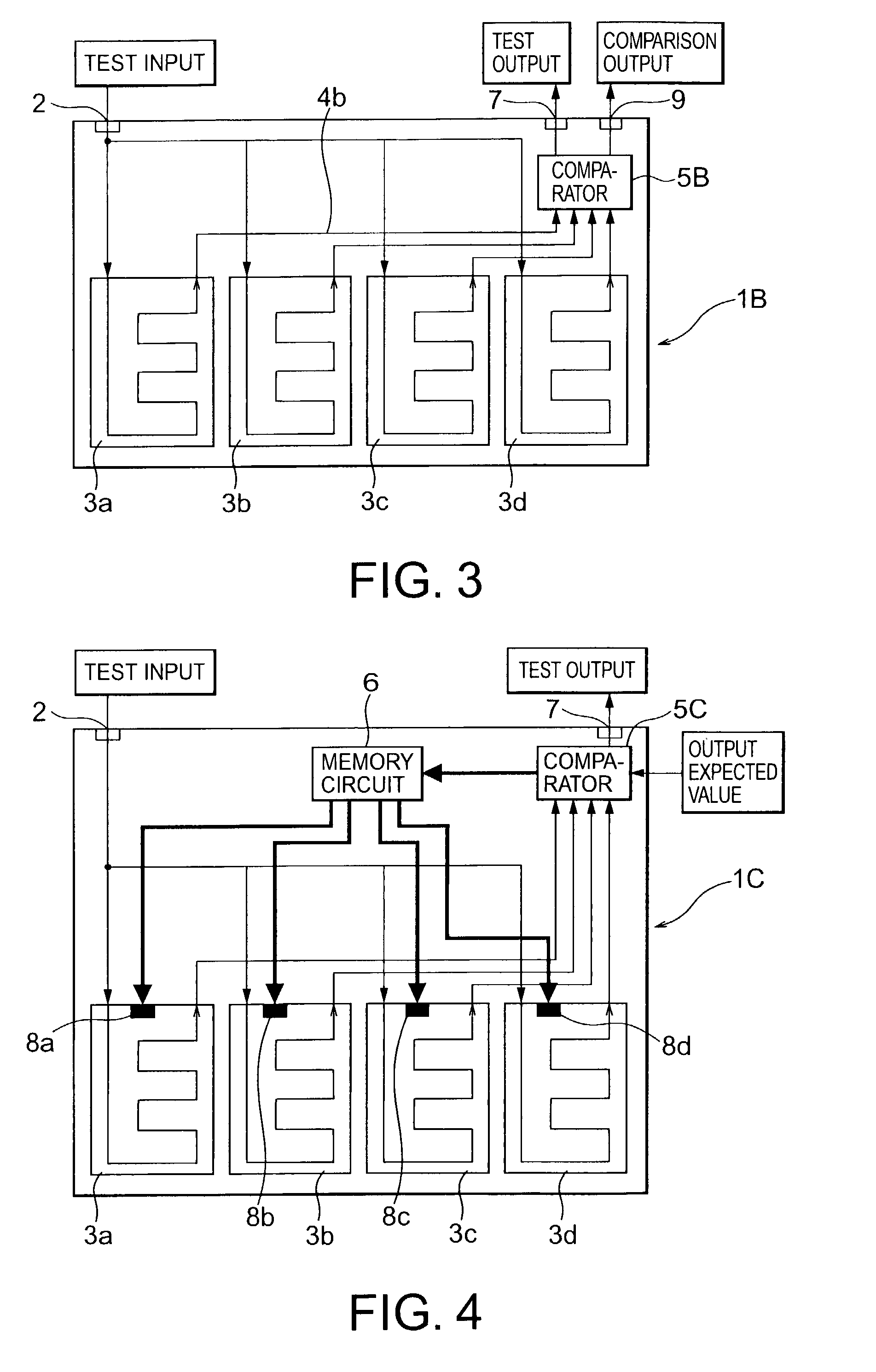

Semiconductor integrated circuit

InactiveUS20030061555A1Semiconductor/solid-state device testing/measurementElectronic circuit testingComparative testSemiconductor

A semiconductor integrated circuit includes: a plurality of circuits to be tested, each having the same structure; test paths each provided for one of the circuits to be tested; and a comparator receiving, via the test paths, test outputs sent from the circuits to be tested, comparing the test outputs, and determining whether the test outputs match with each other or not.

Owner:KK TOSHIBA

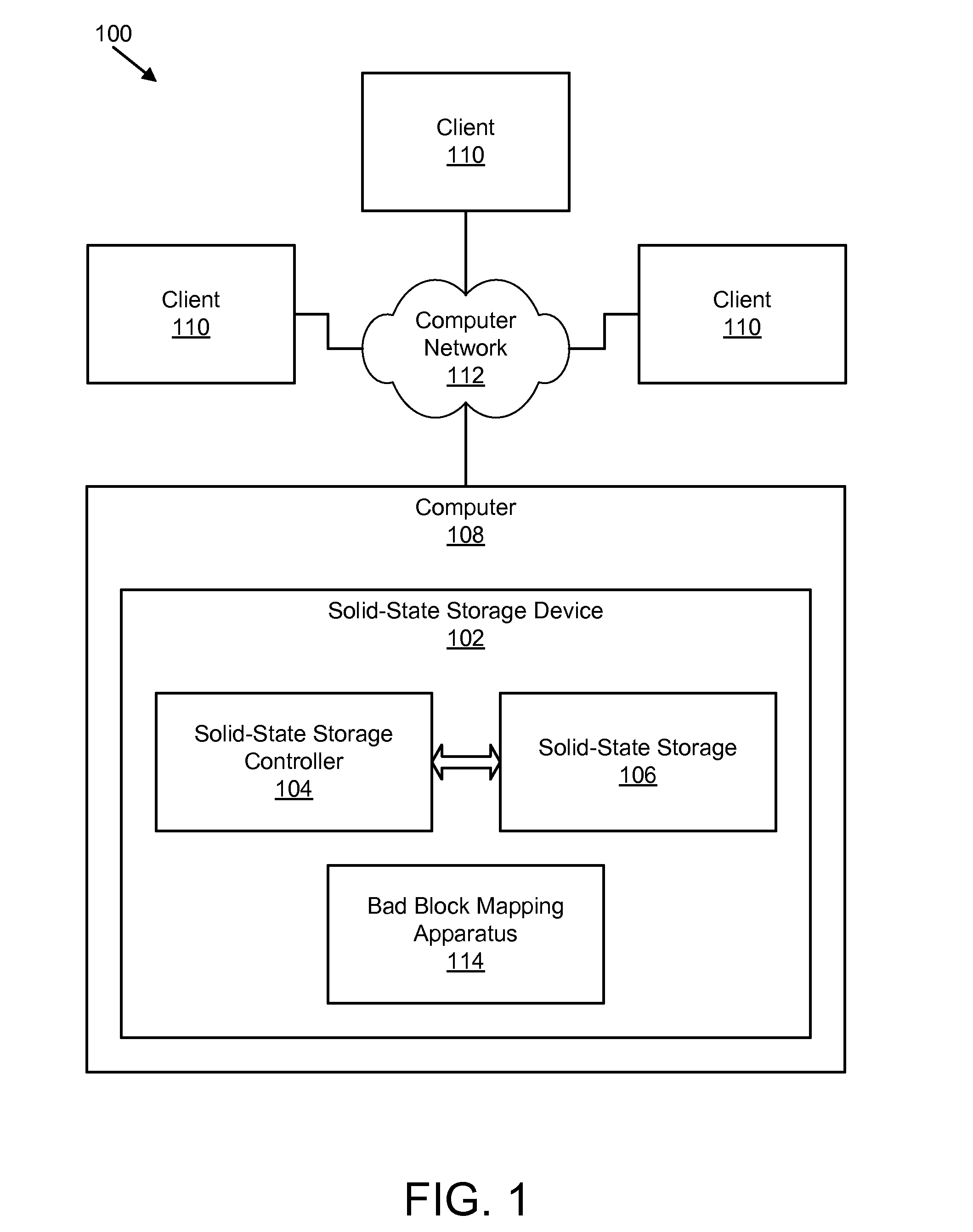

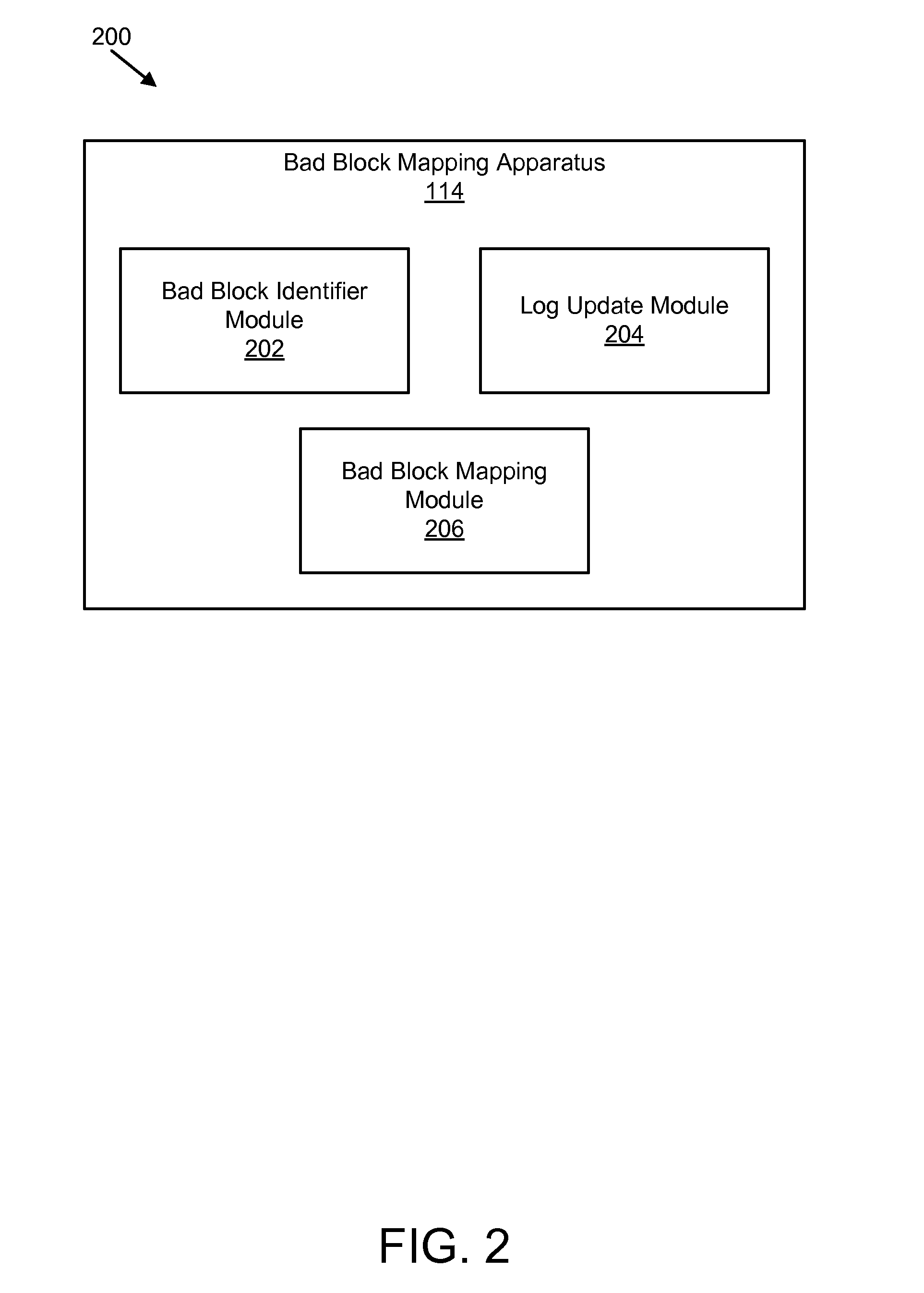

Apparatus, system, and method for bad block remapping

ActiveUS20090282301A1Improve reliabilityAvoid managementMemory architecture accessing/allocationError preventionSolid-state storageParallel computing

An apparatus, system, and method are disclosed for bad block remapping. A bad block identifier module identifies one or more data blocks on a solid-state storage element as bad blocks. A log update module writes at least a location of each bad block identified by the bad block identifier module into each of two or more redundant bad block logs. A bad block mapping module accesses at least one bad block log during a start-up operation to create in memory a bad block map. The bad block map includes a mapping between the bad block locations in the bad block log and a corresponding location of a replacement block for each bad block location. Data is stored in each replacement block instead of the corresponding bad block. The bad block mapping module creates the bad block map using one of a replacement block location and a bad block mapping algorithm.

Owner:SANDISK TECH LLC

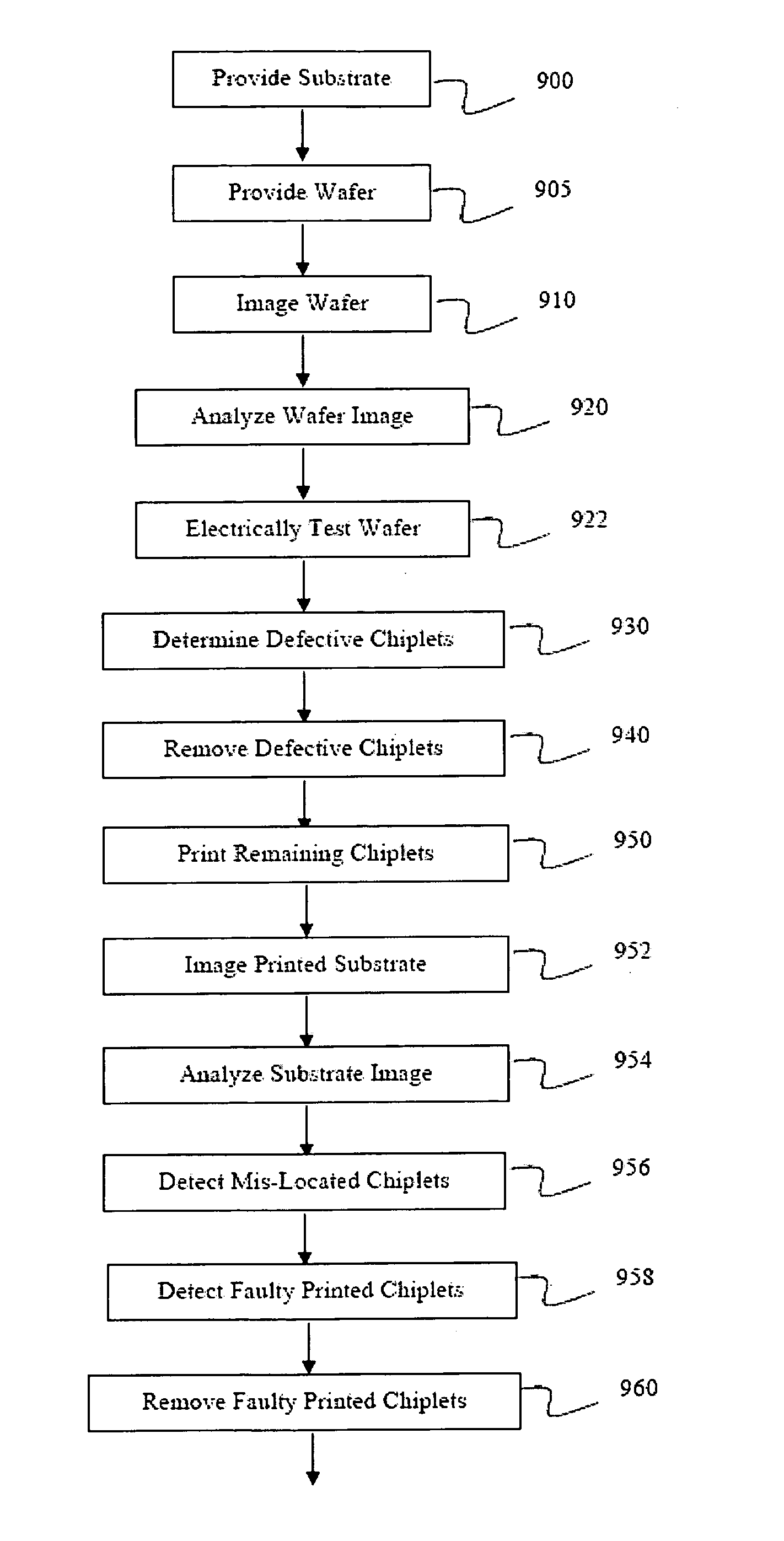

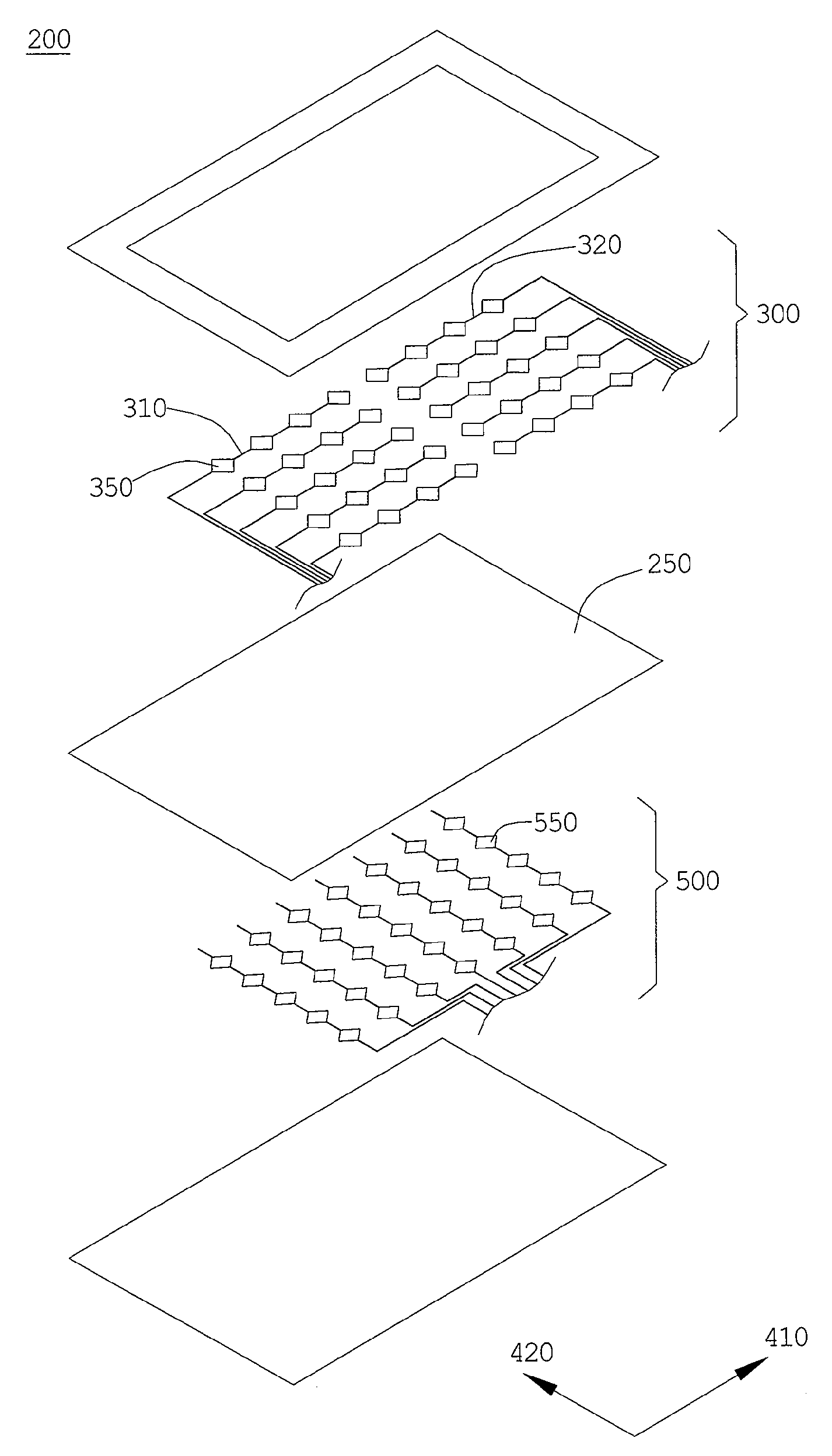

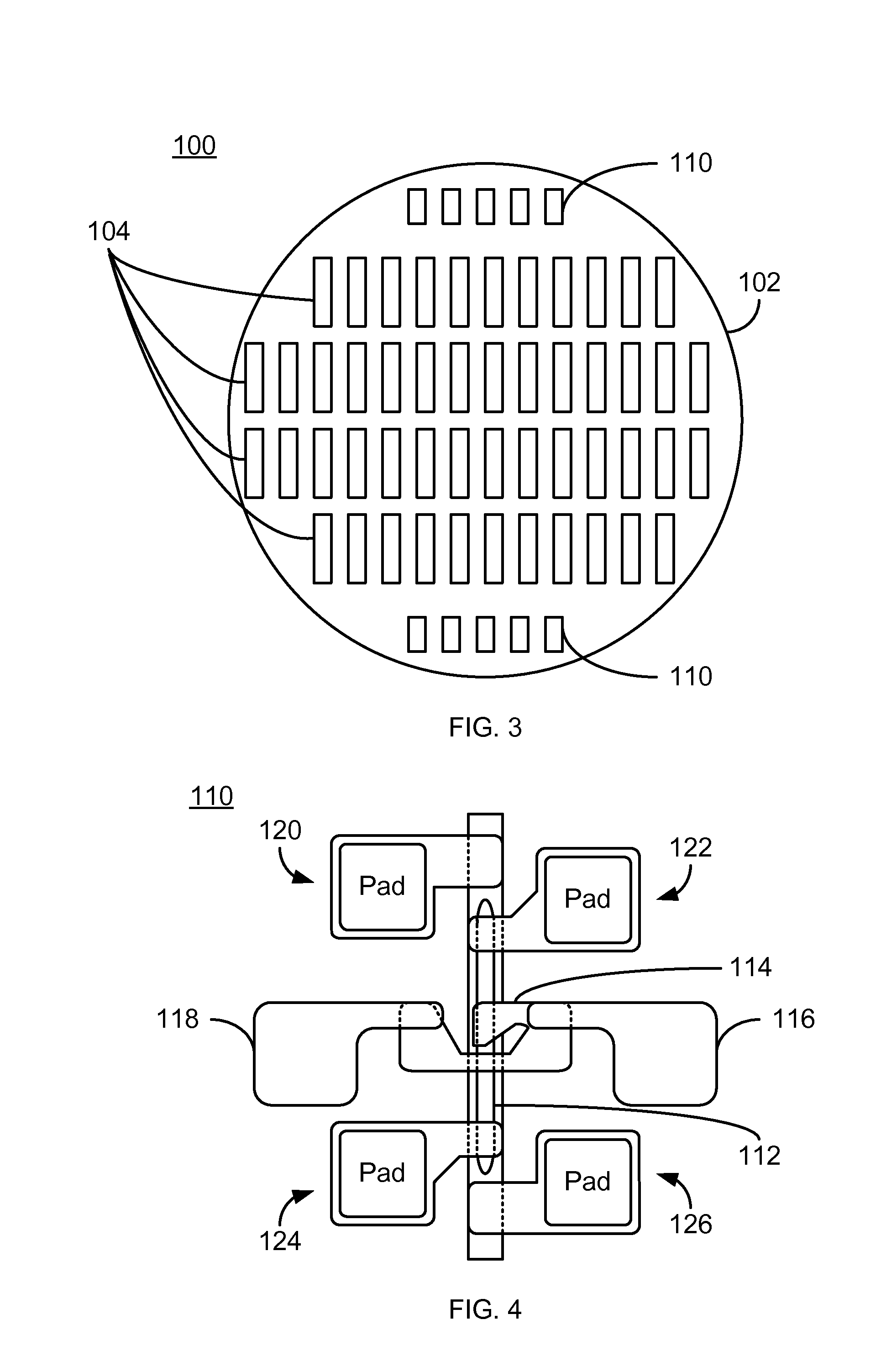

High-yield fabrication of large-format substrates with distributed, independent control elements

ActiveUS20120228669A1Semiconductor/solid-state device testing/measurementElectronic circuit testingElectrical and Electronics engineeringWafering

A large-format substrate with distributed control elements is formed by providing a substrate and a wafer, the wafer having a plurality of separate, independent chiplets formed thereon; imaging the wafer and analyzing the wafer image to determine which of the chiplets are defective; removing the defective chiplet(s) from the wafer leaving remaining chiplets in place on the wafer; printing the remaining chiplet(s) onto the substrate forming empty chiplet location(s); and printing additional chiplet(s) from the same or a different wafer into the empty chiplet location(s).

Owner:X DISPLAY CO TECH LTD

Method of making an auto-calibrating test sensor

InactiveUS20080105024A1Electronic circuit testingMaterial analysis by electric/magnetic meansAnalyteCalibration test

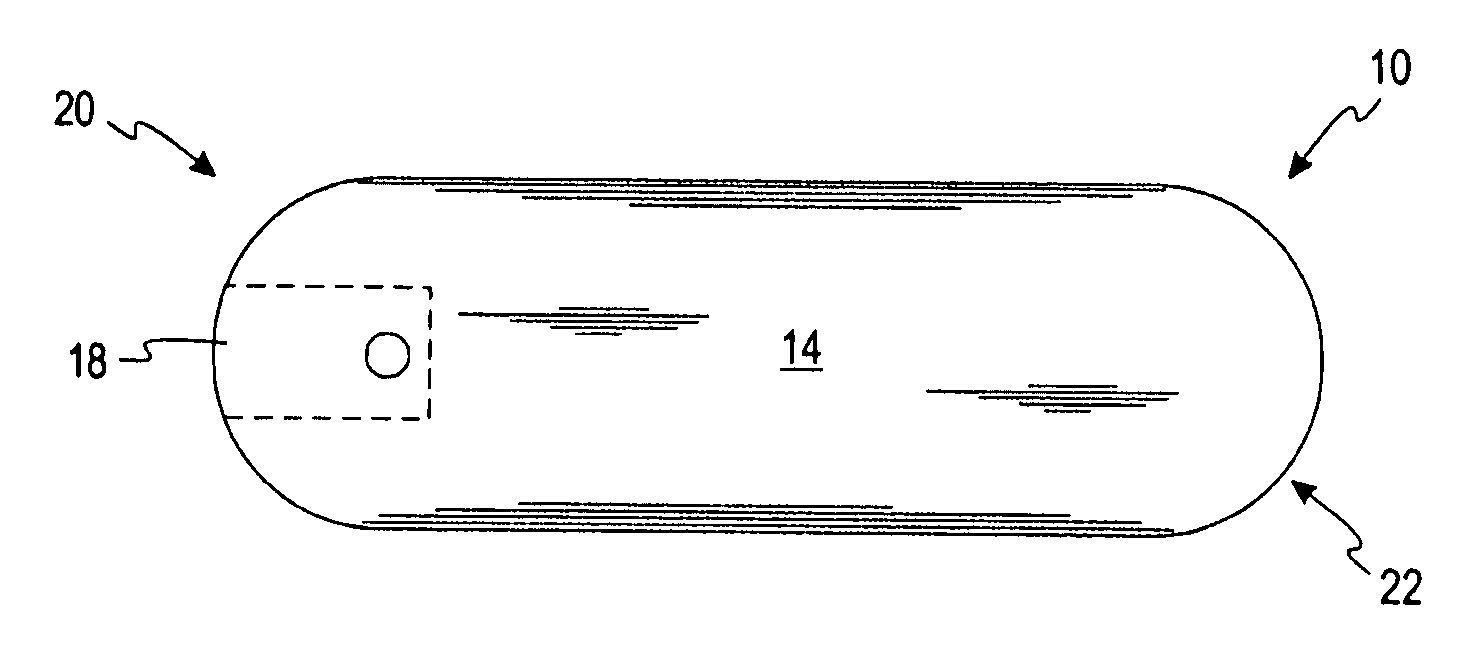

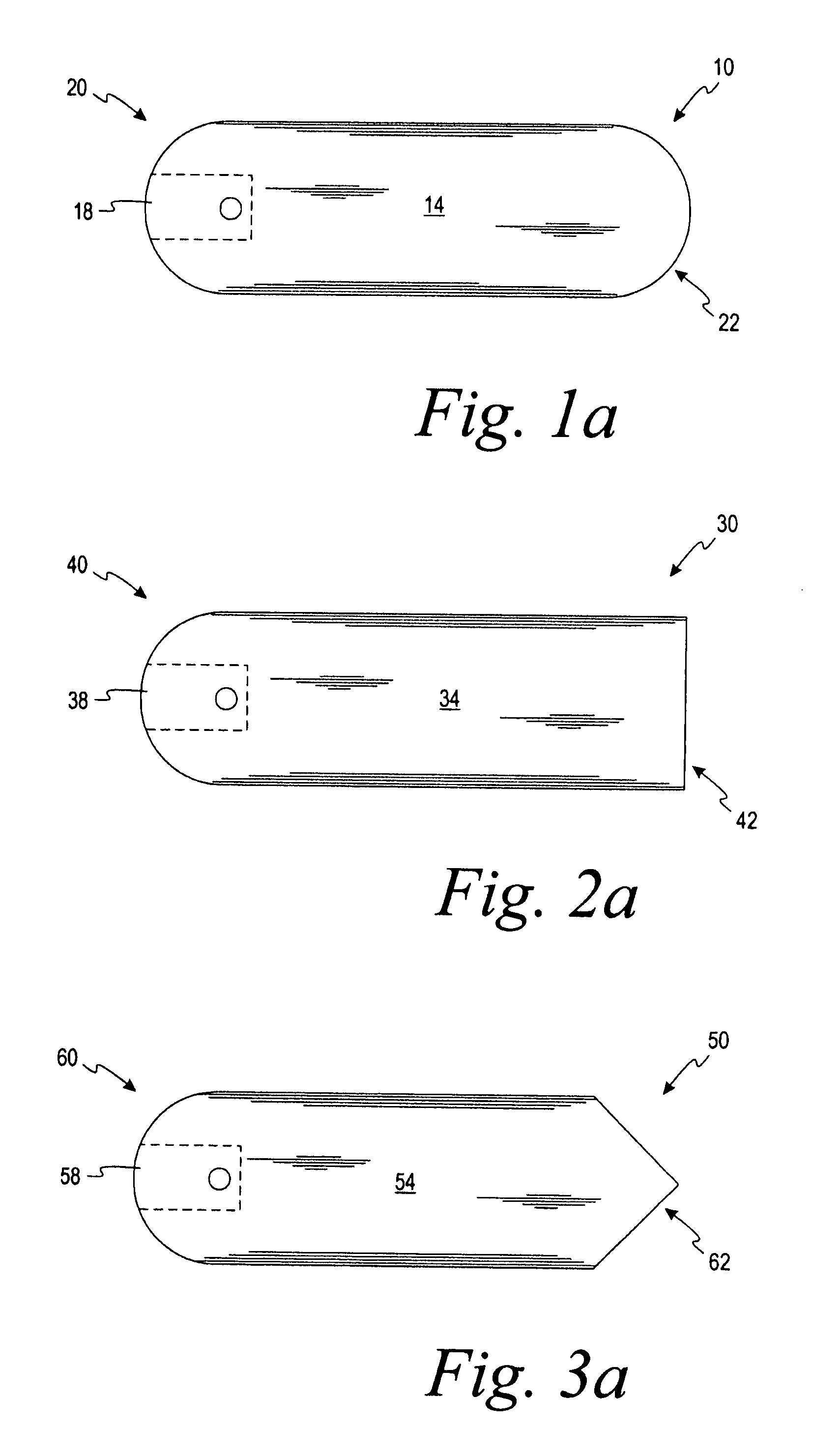

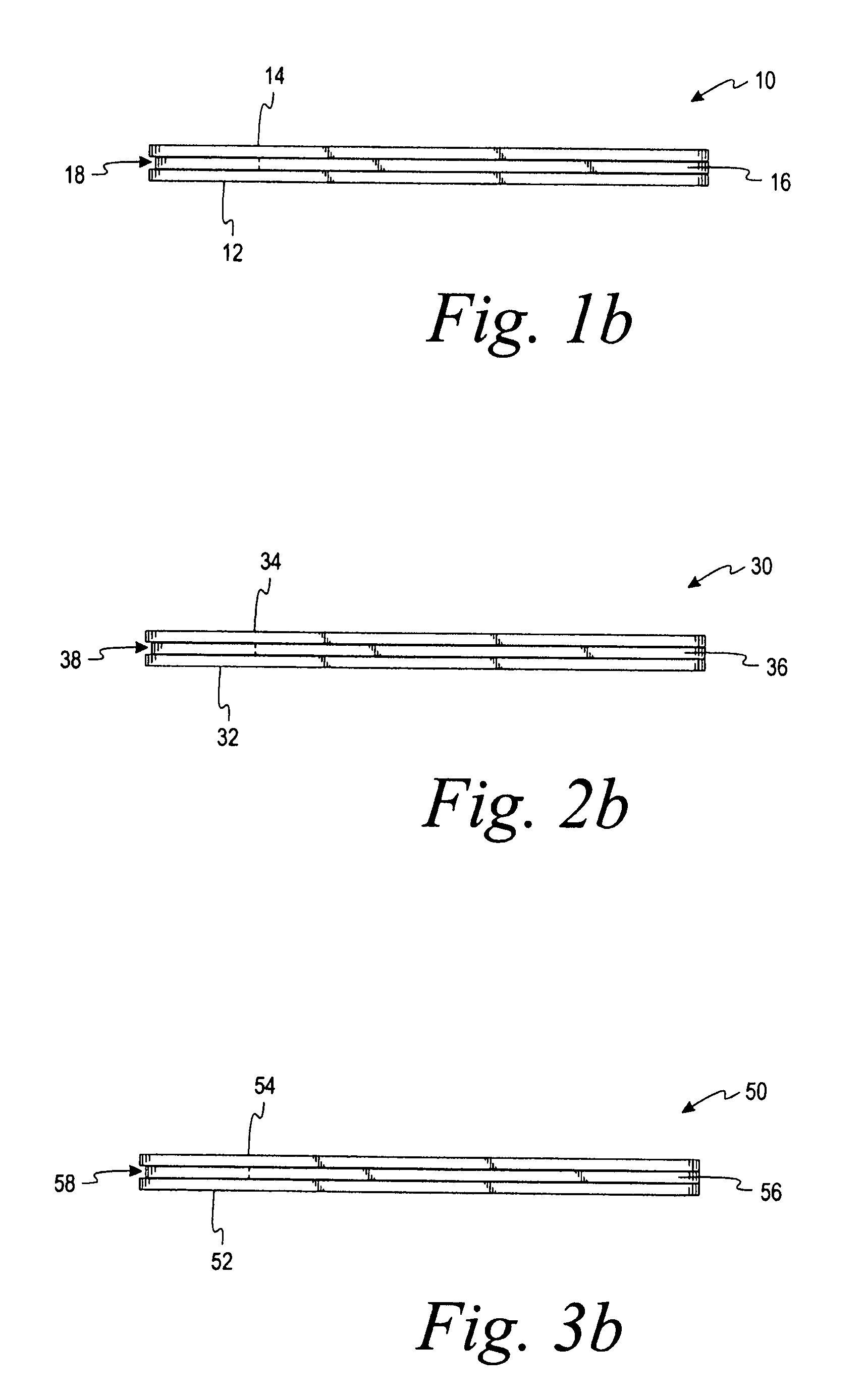

A test sensor is made that is adapted to assist in determining the concentration of an analyte in a fluid sample. The method includes providing a lid and providing a base. The lid is attached to the base to form an attached lid-base structure. The lid-base structure has a first end adapted to receive the fluid sample and a second opposing end adapted to be placed into a meter. Auto-calibration information is assigned to the lid-base structure. The second opposing end is formed such that the shape of the second opposing end corresponds to the auto-calibration information.

Owner:BAYER HEALTHCARE LLC

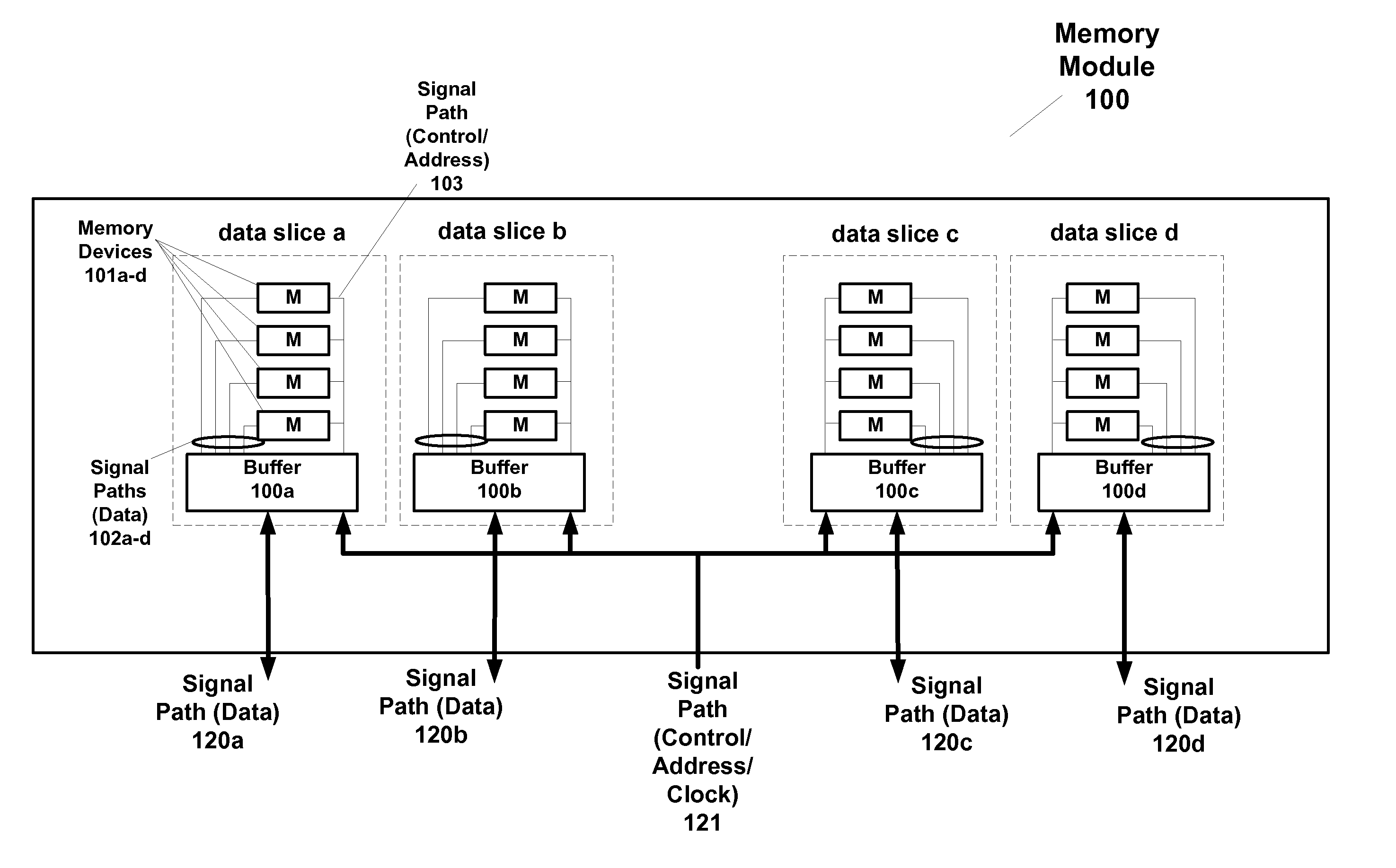

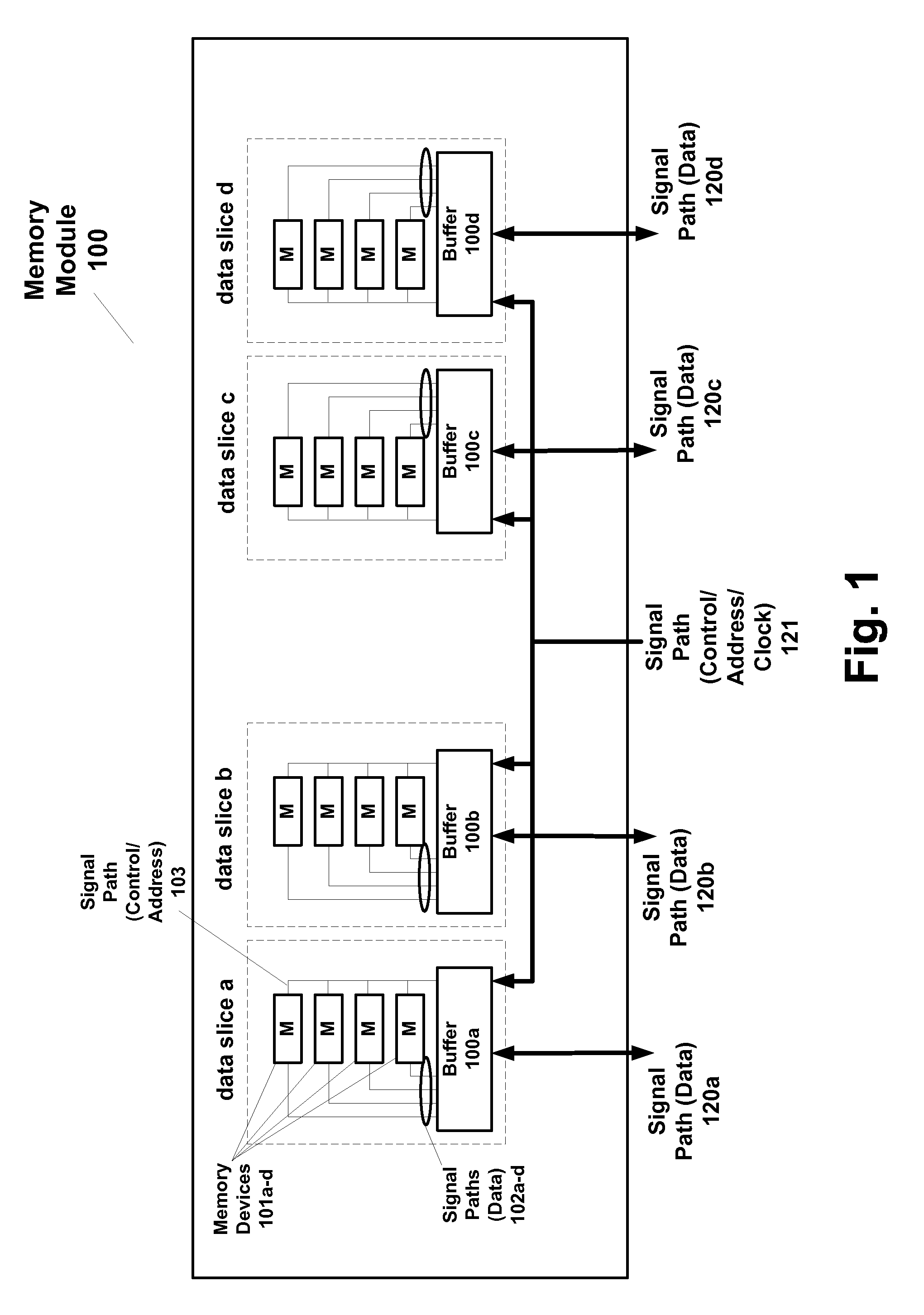

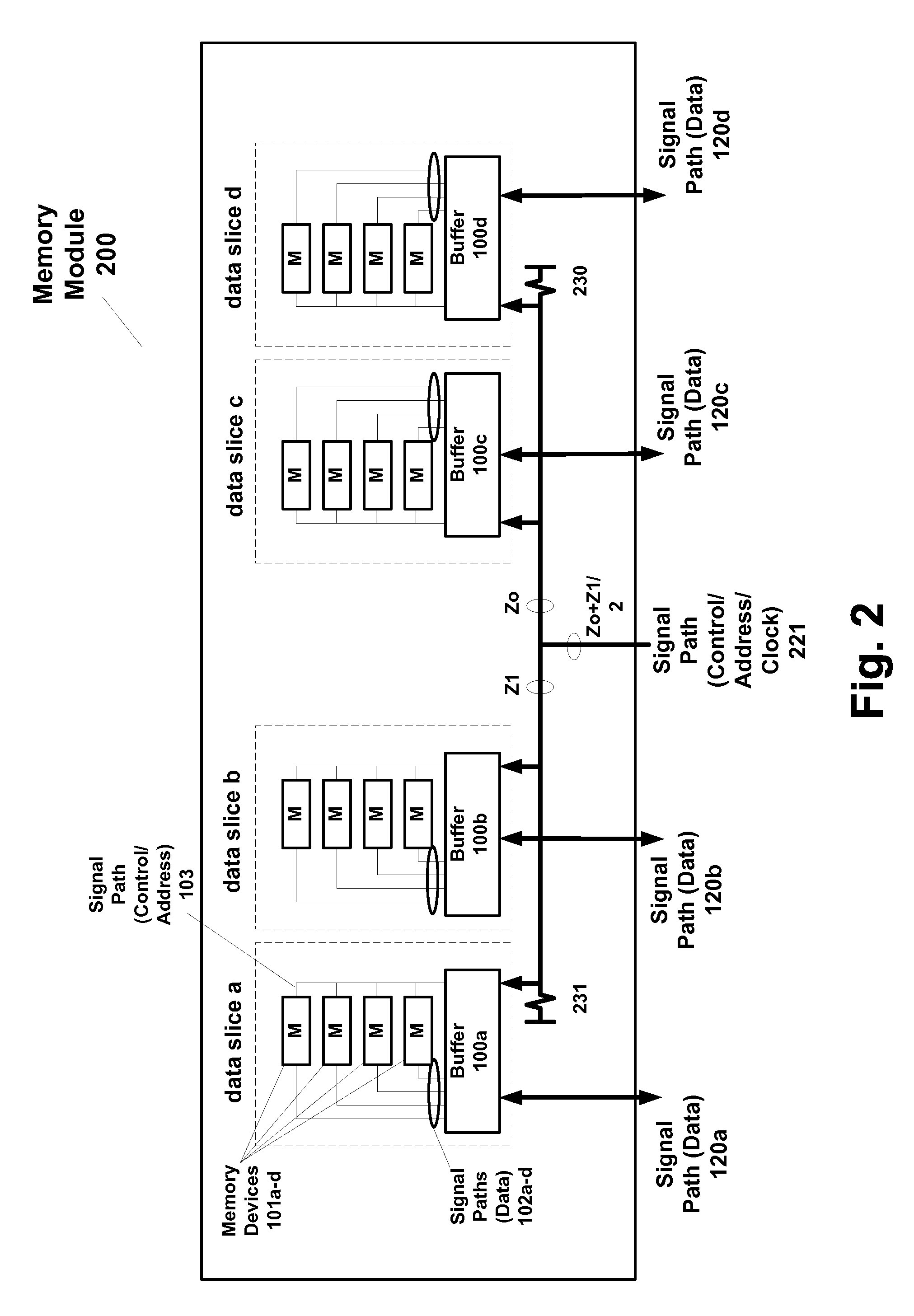

System including a buffered memory module

According to embodiments, a system includes a master device and a first memory module having a plurality of integrated circuit memory devices and a plurality of integrated circuit buffer devices that operate in first and second modes of operation (bypass mode). In a first mode of operation, a first memory module provides read data from the plurality of integrated circuit memory devices (via a integrated circuit buffer device) on a first signal path to the master and a second memory module simultaneously provides read data from its plurality of integrated circuit memory devices (via another integrated circuit buffer device on the second module) on a third signal path coupled to the master device. In a second mode of operation, the first memory module provides first read data from its plurality of integrated circuit memory devices (via the integrated circuit buffer device) on the first signal path and second read data from its plurality of integrated circuit memory devices (via the integrated circuit buffer device) on a second signal path that is coupled to a second memory module. An integrated circuit buffer device in the second memory module then bypasses the second read data from the second signal path and provides the second read data on a third signal path coupled to the master device.

Owner:RAMBUS INC

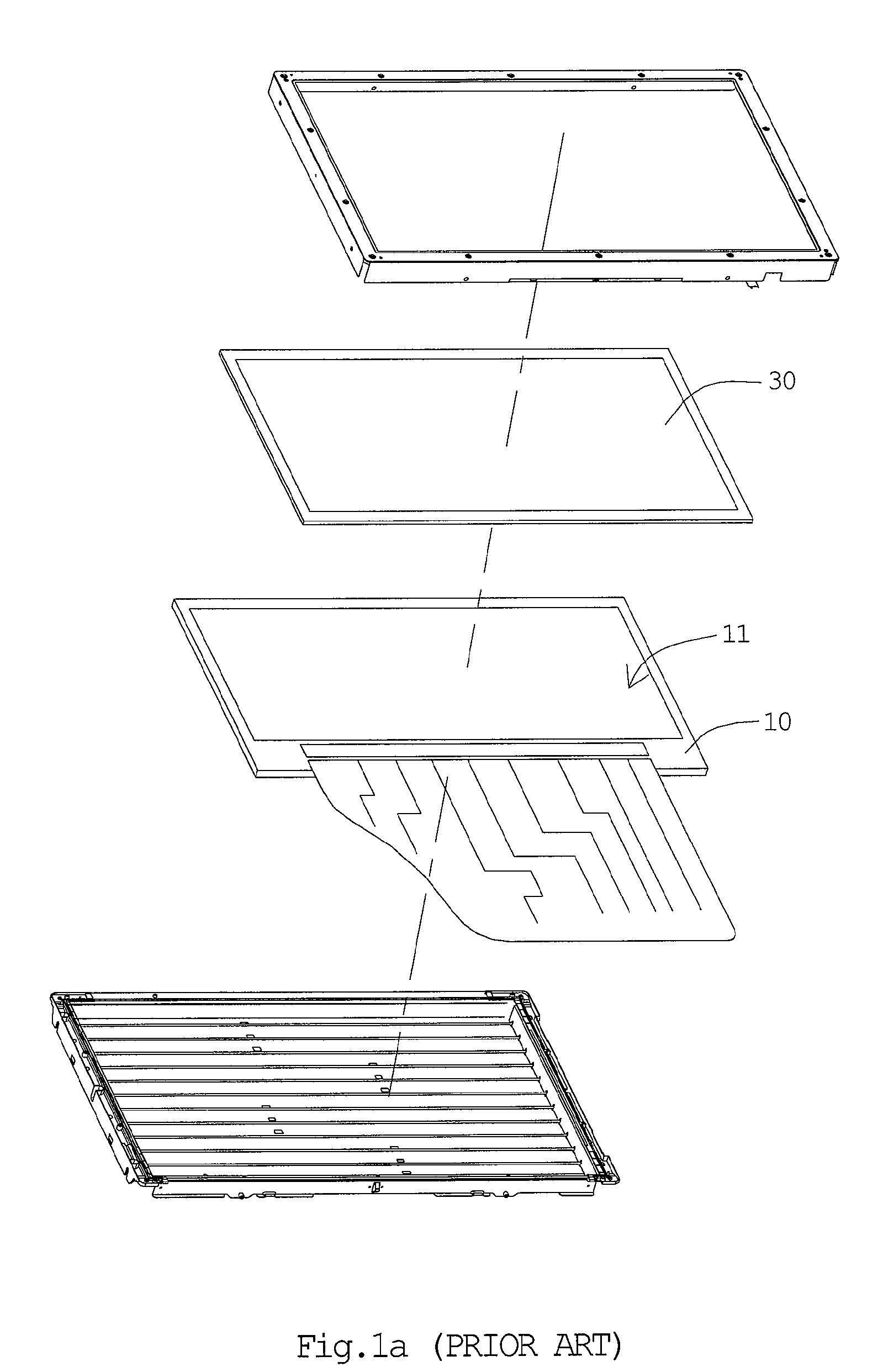

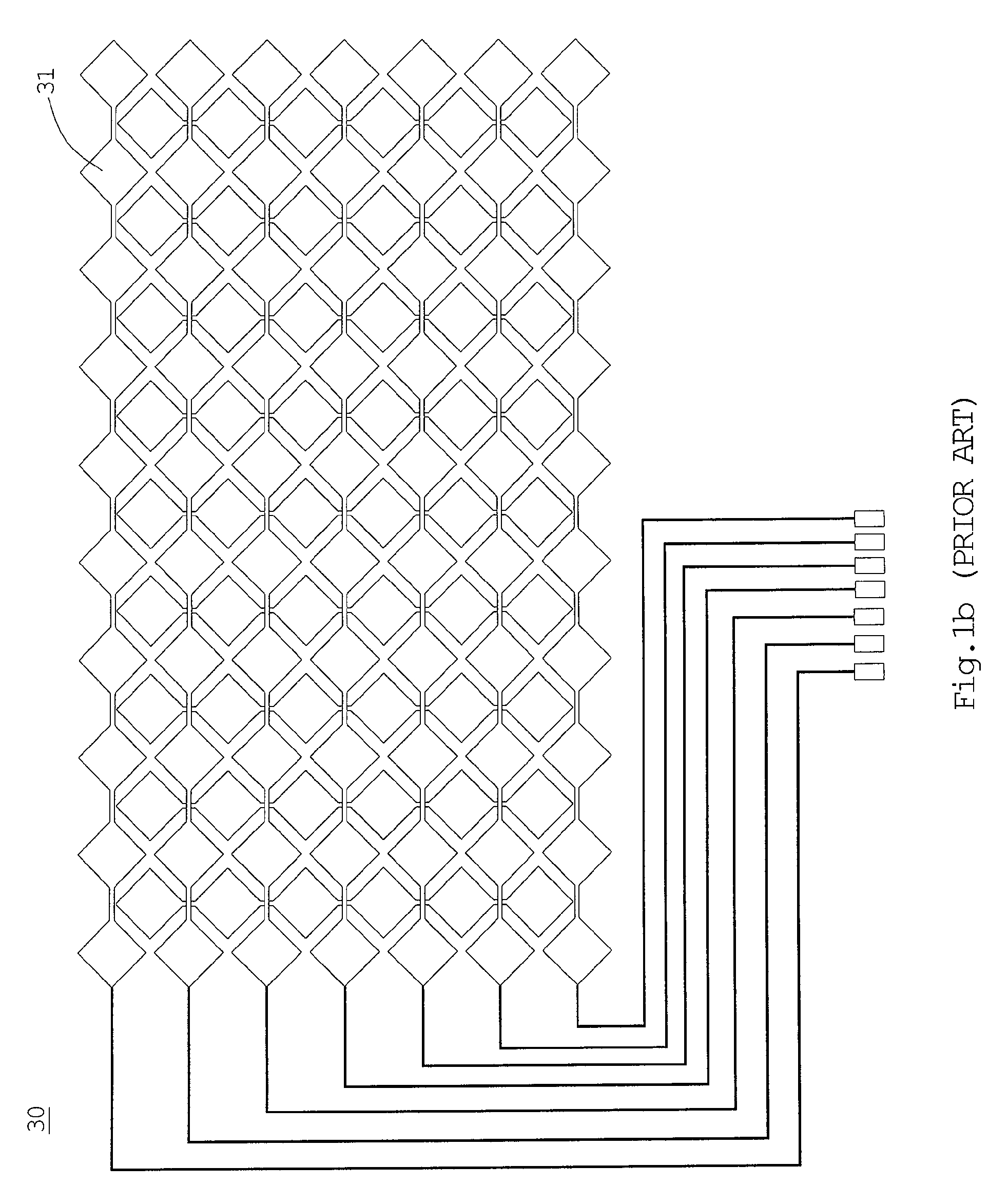

Capacitive Touch Panel with Low Impedance

ActiveUS20090085891A1Reduce resistanceSystem coupling capacitance and resistanceElectronic circuit testingStatic indicating devicesDisplay deviceDielectric layer

A capacitive touch panel and a display device using the capacitive touch panel are provided. The capacitive touch panel includes a first electrode layer, a second electrode layer, and a dielectric layer disposed between two layers. The first electrode layer has a plurality of first A electrode strings and first B electrode strings extended along a first direction. The first A electrode string and the first B electrode string respectively has a plurality of first direction electrodes. The second electrode layer has a plurality of second direction electrodes connected in series along a second direction. The first A and B electrode strings are disconnected in the first electrode layer while they are simultaneously detected for presence of signal variation.

Owner:AU OPTRONICS CORP

Memory module, test system and method for testing one or a plurality of memory modules

InactiveUS7231562B2Shorten the timeImprove throughputElectronic circuit testingCode conversionComputer scienceMemory module

The invention relates to an integrated memory module having a memory unit and a self-test circuit, the self-test circuit being embodied in such a way as to make available test data and test addresses for testing memory areas in the memory unit and to generate defect data depending on the detection of a defect, a test circuit being provided in order to receive defect data from one or a plurality of connectable memory modules to be detected, the test circuit being configured in such a way as to store the received defect data depending on addresses assigned thereto in the memory unit.

Owner:POLARIS INNOVATIONS LTD

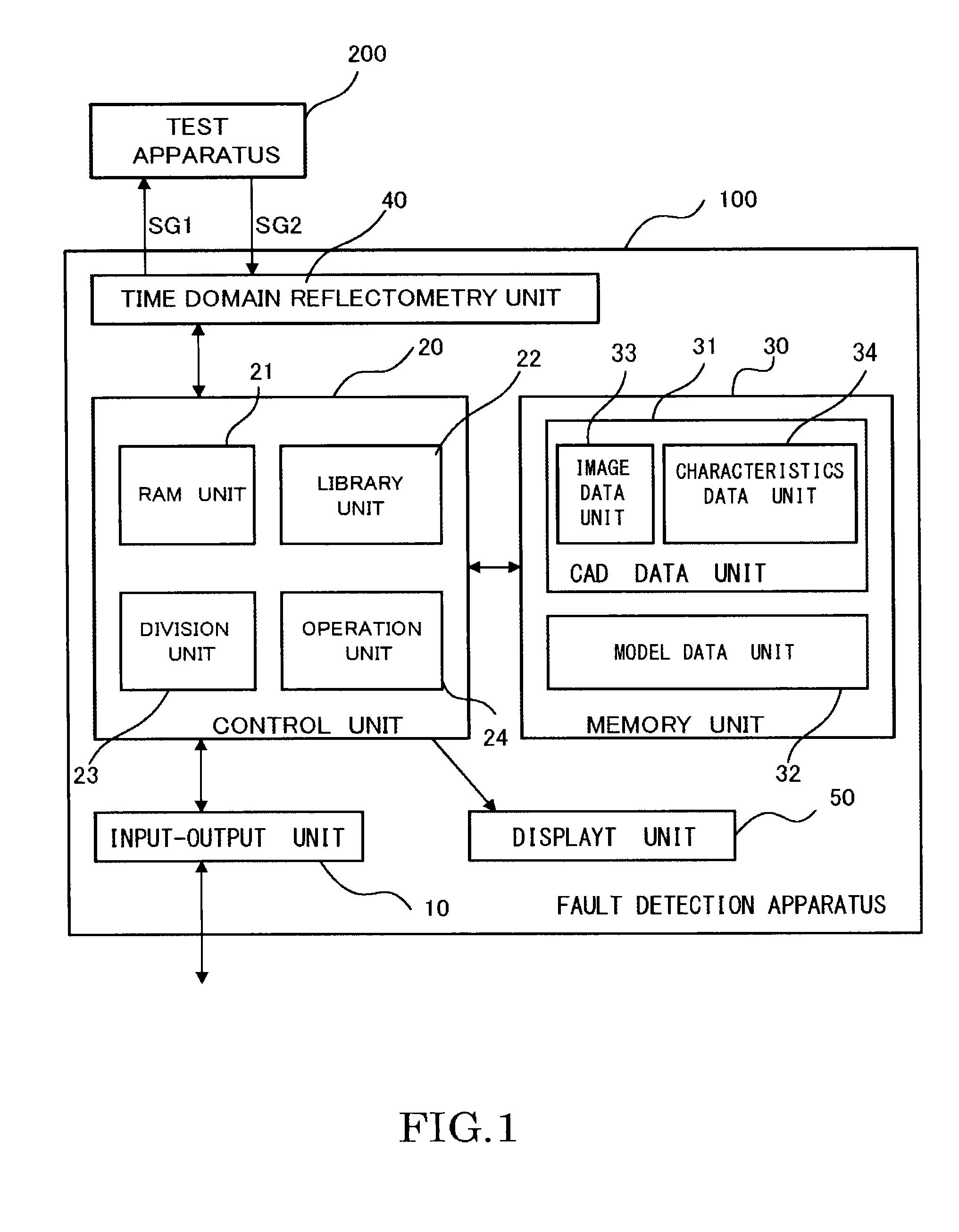

Fault detection apparatus

InactiveUS20140372068A1Improve accuracyElectronic circuit testingElectric connection testingTest objectComputer science

A fault detection apparatus according to an embodiment is provided with a measurement unit, a memory unit, a control unit, and a display unit. The measurement unit measures a first time period taken until a reflection signal reflected on a fault of a test apparatus is received after a first signal is transmitted to the test apparatus. The memory unit includes a CAD data unit having CAD data of the test apparatus, and a model data unit to store model data indicating a relation between the first time period and a predicted conduction distance of the first signal according to the CAD data. The control unit calculates a range of a test object selected in the test apparatus based on the CAD data, calculates the predicted conduction distance from the first time period based on the model data, and specifies a position of a fault of the test apparatus which is separated by the predicted conduction distance from the measurement unit in the range of the test object. The display unit displays the position of the fault in the CAD data.

Owner:TOSHIBA MEMORY CORP

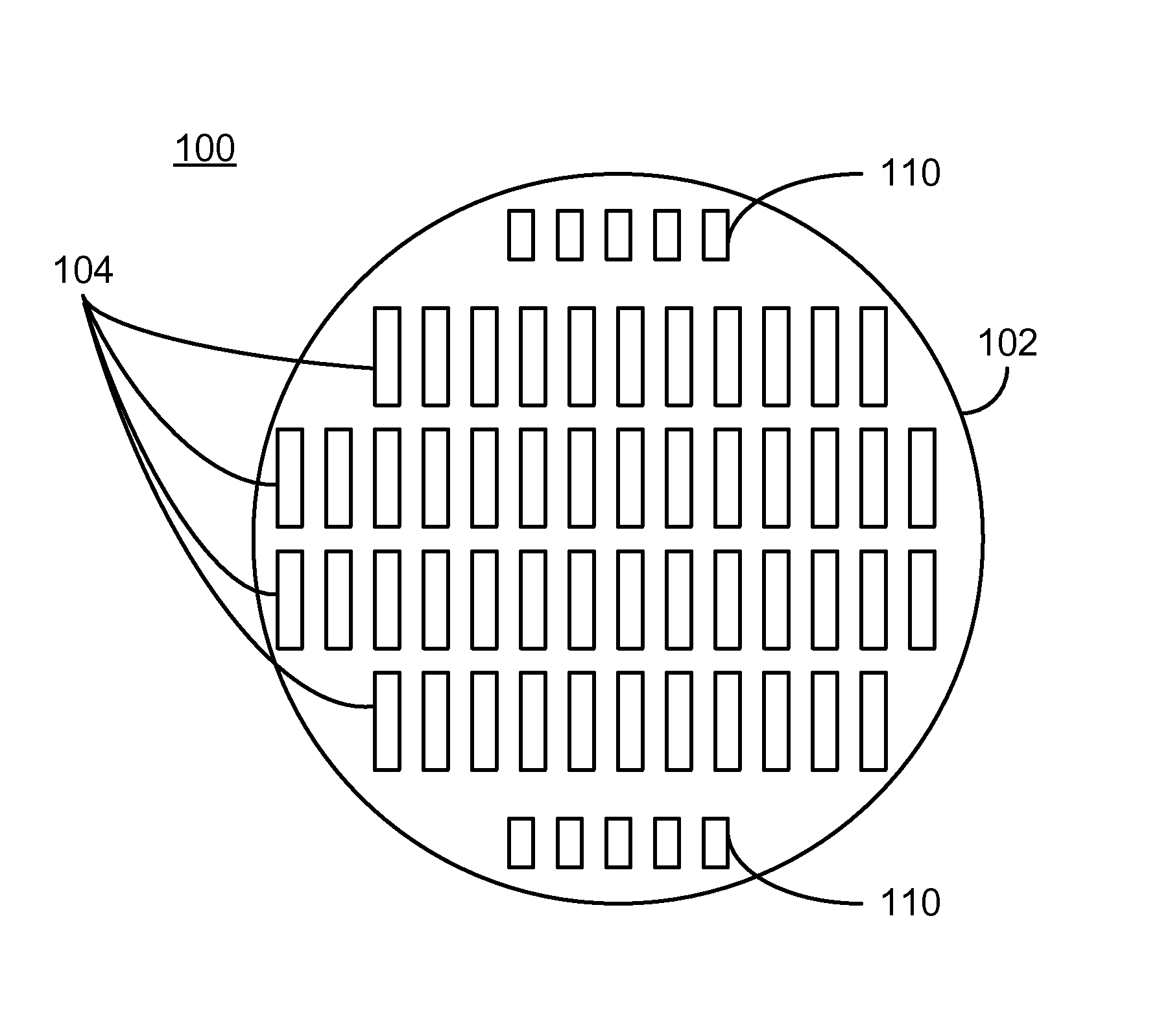

Method and system for performing on-wafer testing of heads

InactiveUS20130257421A1Electronic circuit testingMagnetic property measurementsPhysicsTest structure

A method and system for testing a read transducer are described. The read transducer includes a read sensor fabricated on a wafer. A system includes a test structure that resides on the wafer. The test structure includes a test device and a heater. The test device corresponds to the read sensor. The heater is in proximity to the test device and is configured to heat the test device substantially without heating the read sensor. Thus, the test structure allows for on-wafer testing of the test device at a plurality of temperatures above an ambient temperature.

Owner:WESTERN DIGITAL TECH INC

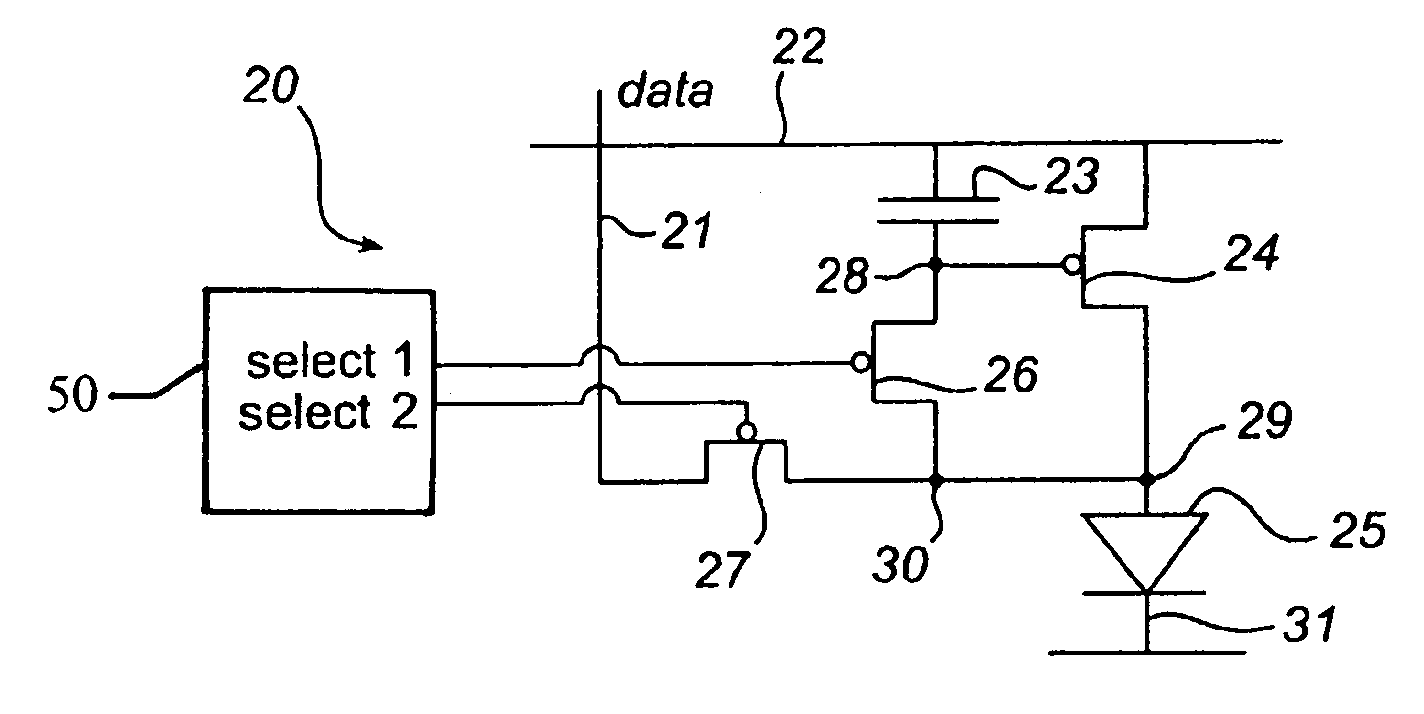

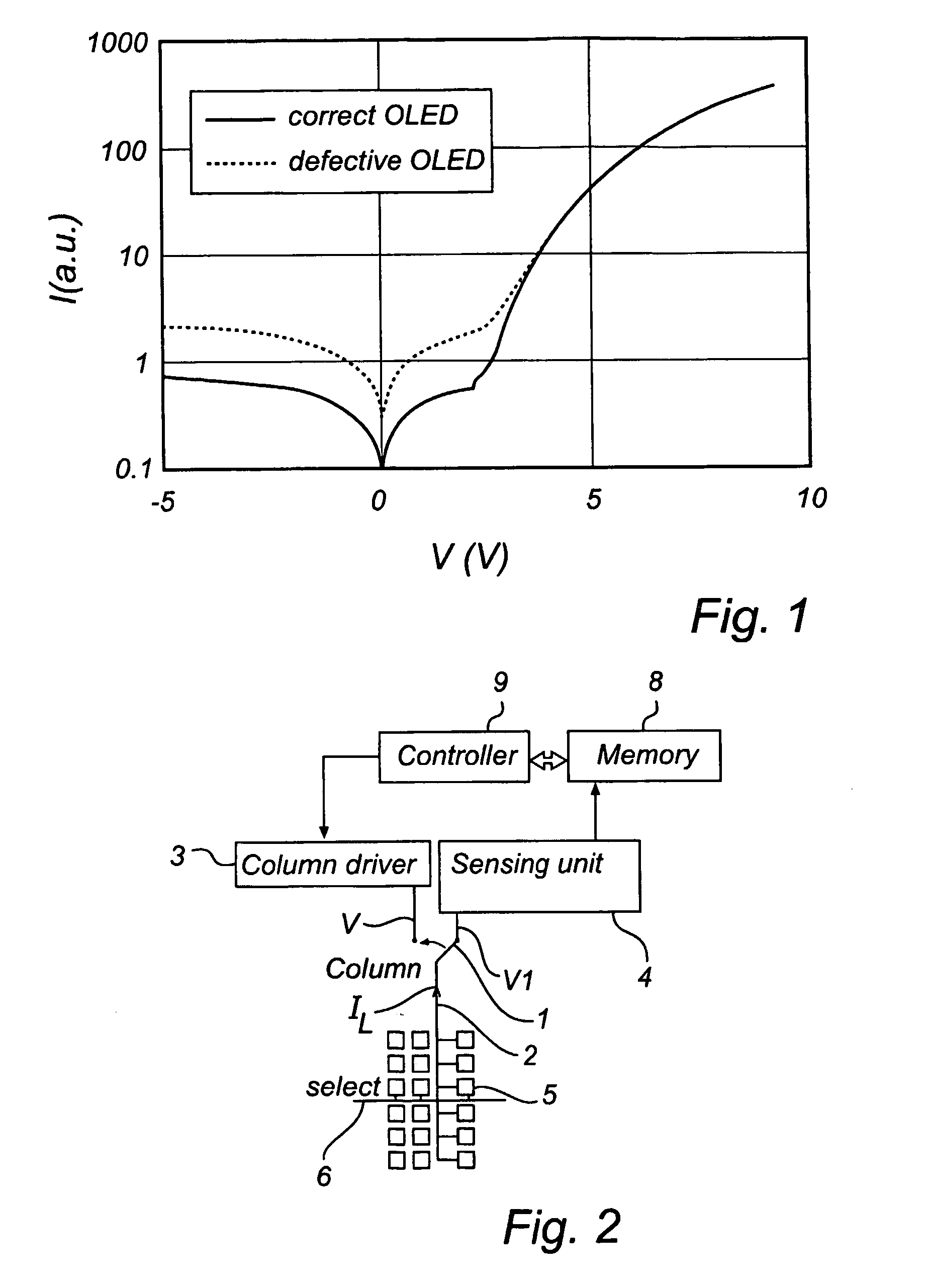

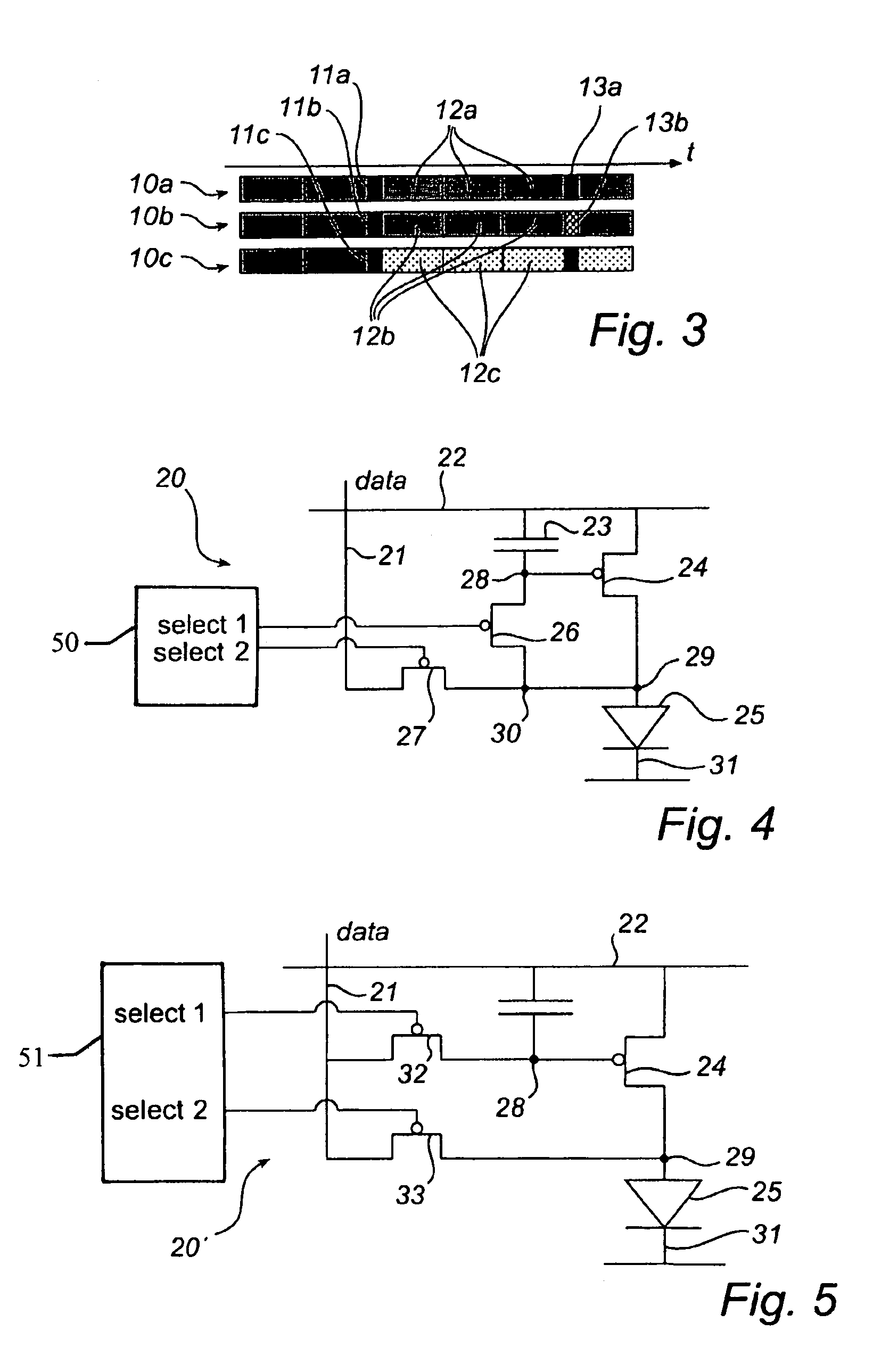

Light emissive element having pixel sensing circuit

ActiveUS7423617B2Improved reverse biasingElectronic circuit testingStatic indicating devicesActive matrixReverse bias

A method for sensing a light emissive element in an active matrix display pixel cell further including a data line connectable to a drive element and to a first electrode of the emissive element. The data line is connected to the anode of the emissive element, and a sensing voltage to reverse bias the emissive element, and detecting any leakage current flowing through the emissive element.

Owner:INNOLUX CORP

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

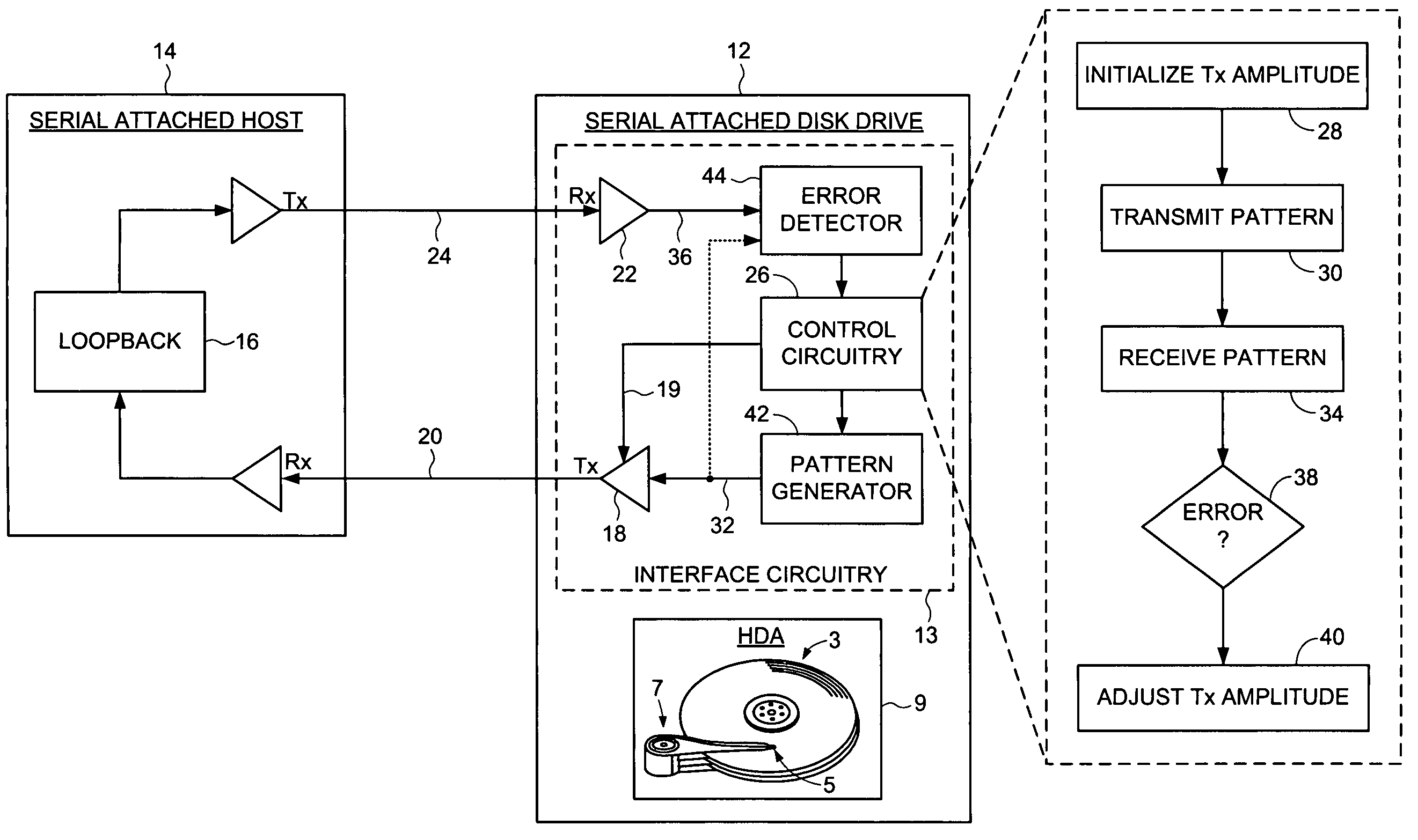

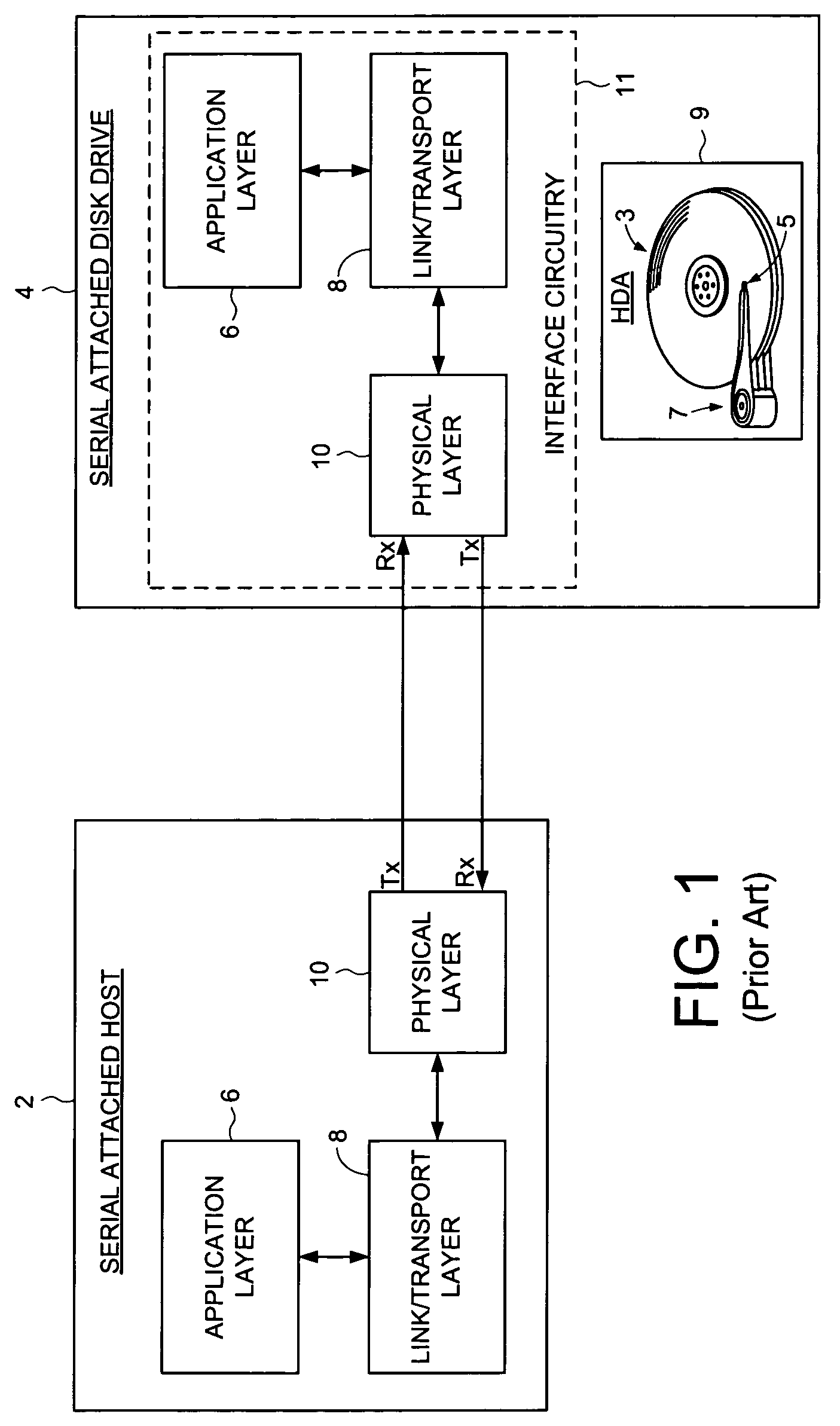

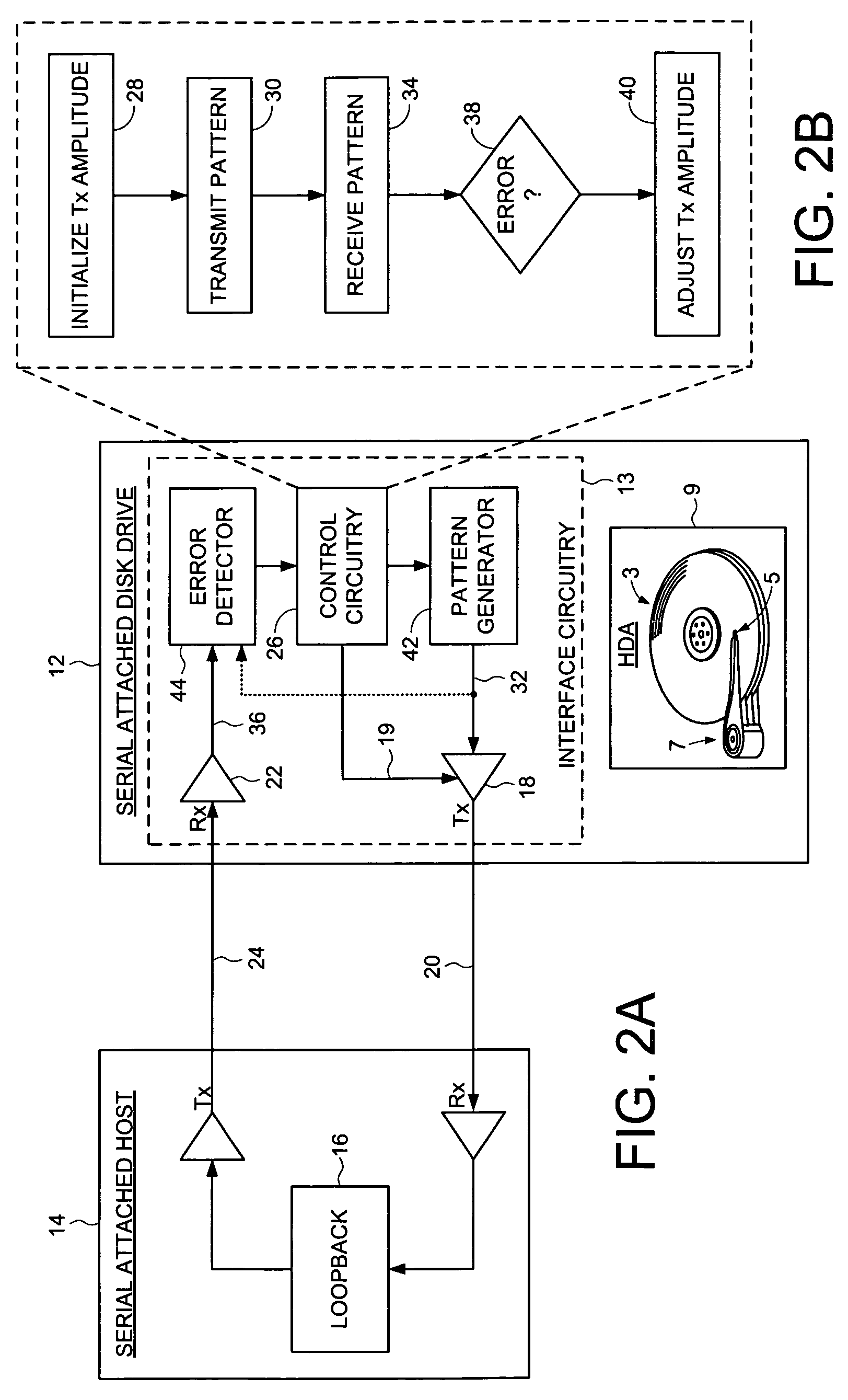

Disk drive using loopback to calibrate transmission amplitude

InactiveUS7280302B1Electronic circuit testingFilamentary/web record carriersTransmission amplitudeLoopback

A disk drive is disclosed for connecting to a host, the host comprising loopback circuitry operable to loop a pattern received from the disk drive back to the disk drive. The disk drive comprises interface circuitry including a transmitter driver operable to transmit transmission signals at a transmission amplitude, and a receiver driver operable to receive reception signals. The transmitter driver is configured to transmit at an initial transmission amplitude, and a calibration pattern is transmitted to the host through the transmitter driver. The reception signals received by the receiver driver are monitored to detect a loopback pattern representing a loopback of the calibration pattern. The loopback pattern is processed to detect an error, and the transmission amplitude is adjusted in response to the error.

Owner:WESTERN DIGITAL TECH INC