Patents

Literature

538 results about "Crossbar switch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

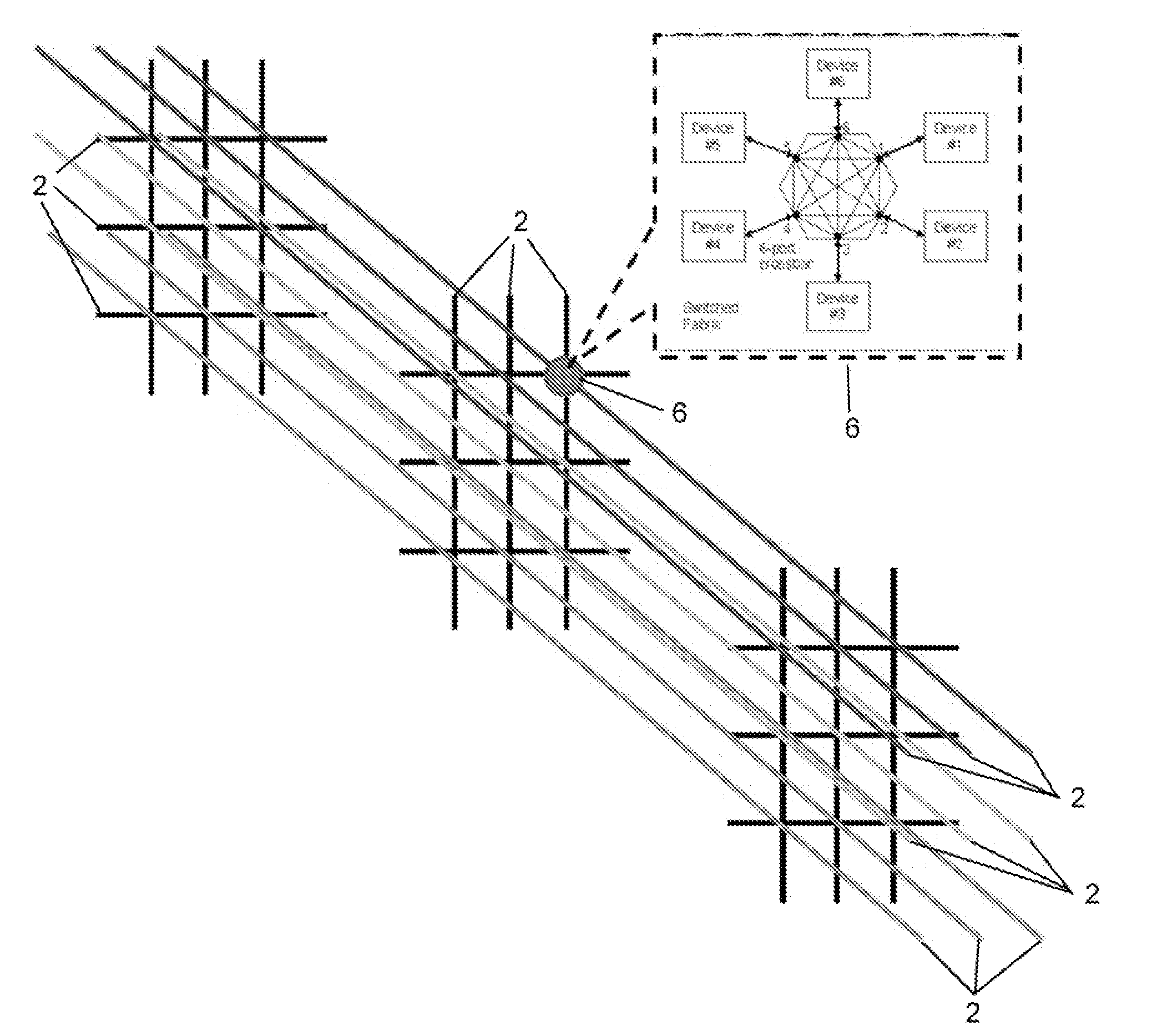

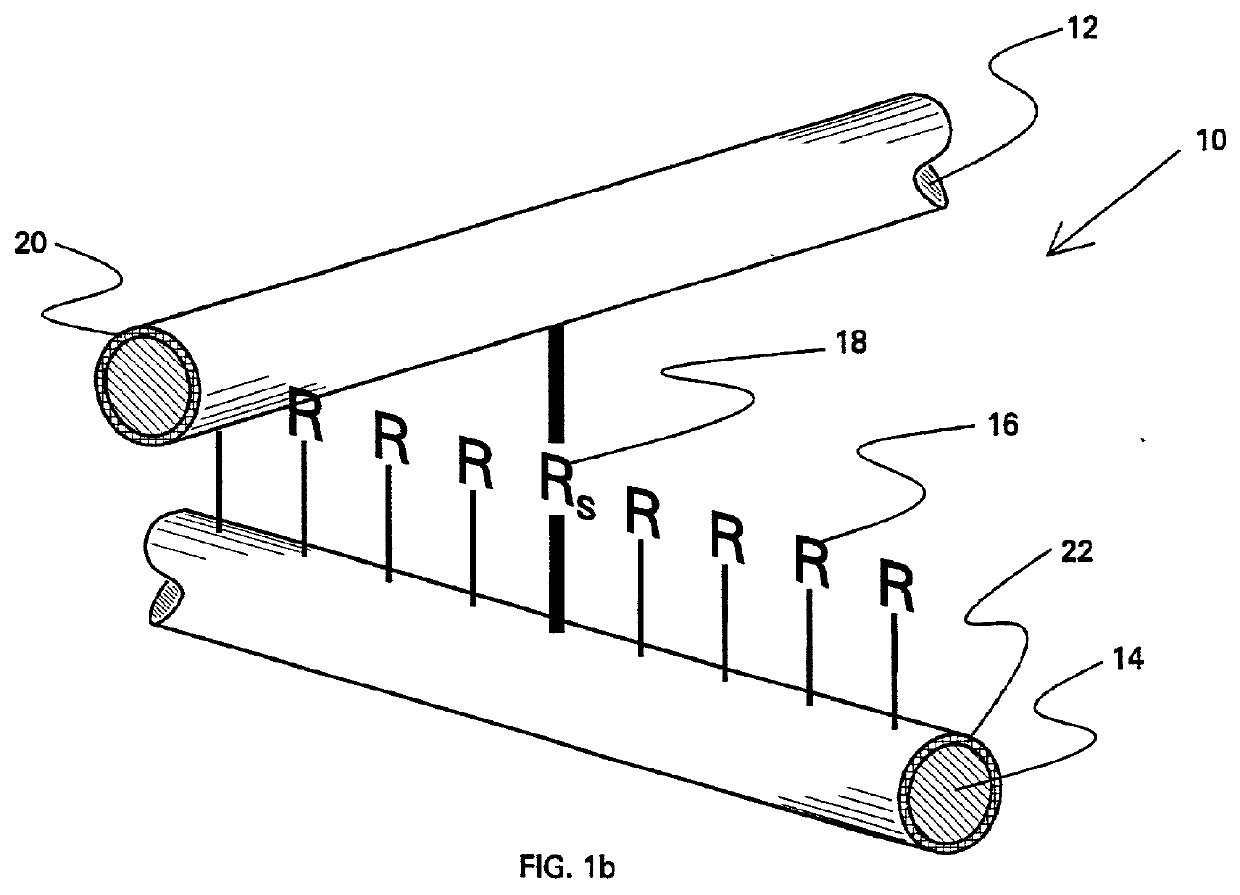

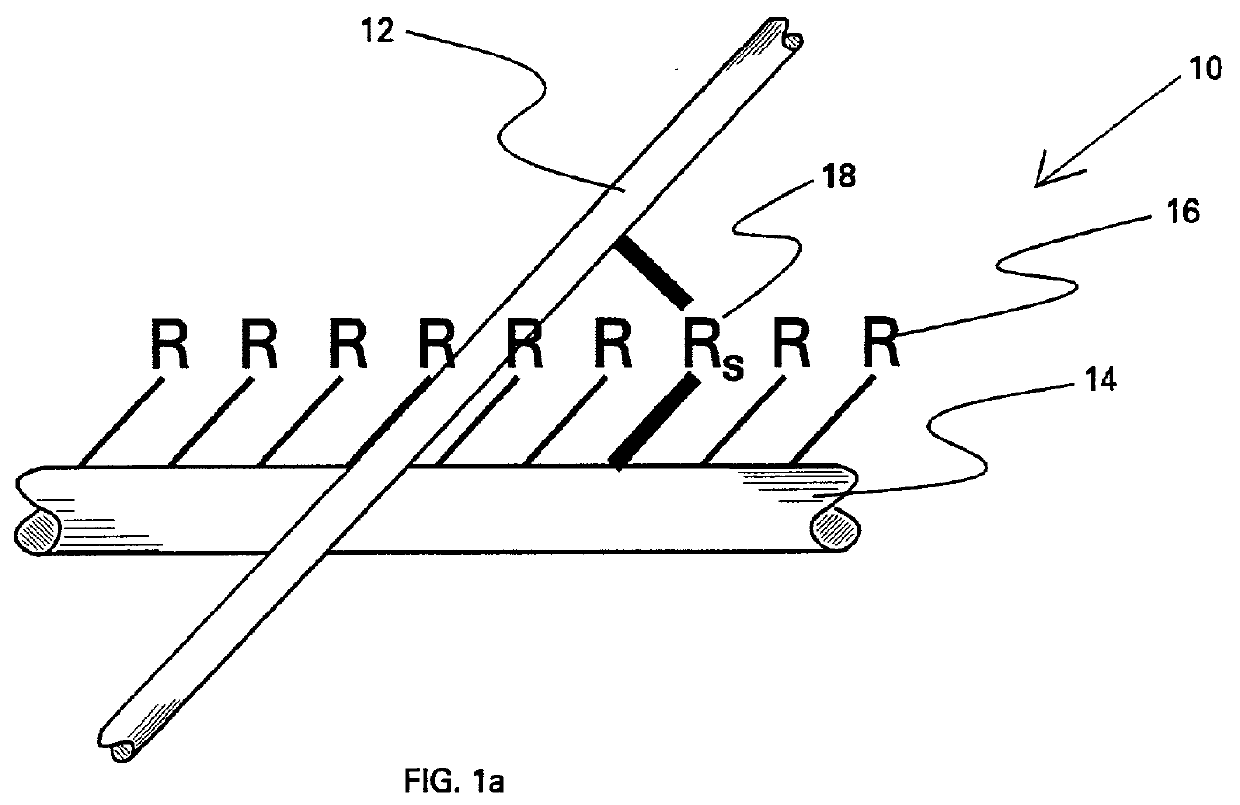

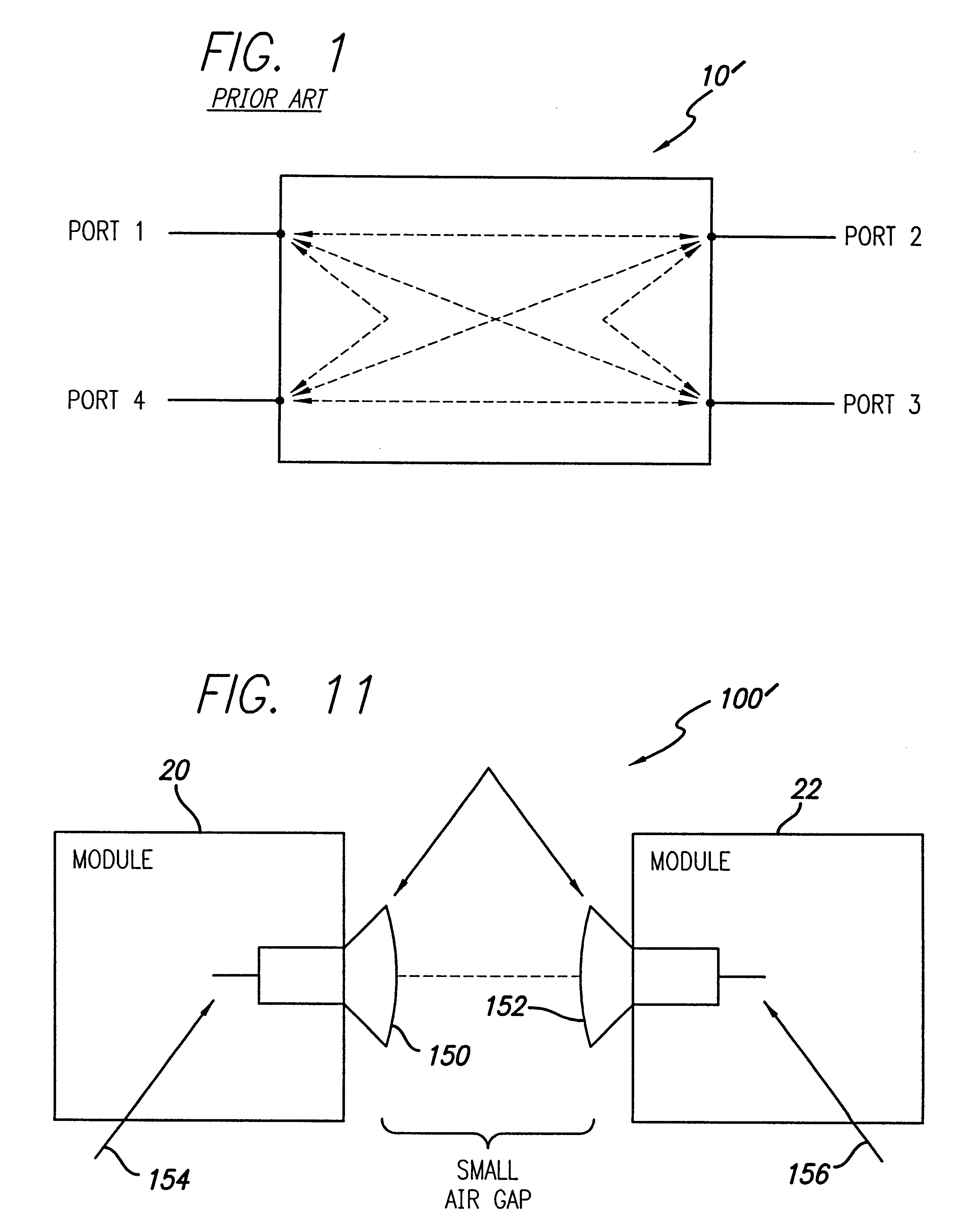

In electronics, a crossbar switch (cross-point switch, matrix switch) is a collection of switches arranged in a matrix configuration. A crossbar switch has multiple input and output lines that form a crossed pattern of interconnecting lines between which a connection may be established by closing a switch located at each intersection, the elements of the matrix. Originally, a crossbar switch consisted literally of crossing metal bars that provided the input and output paths. Later implementations achieved the same switching topology in solid state semiconductor chips. The cross-point switch is one of the principal switch architectures, together with a rotary switch, memory switch, and a crossover switch.

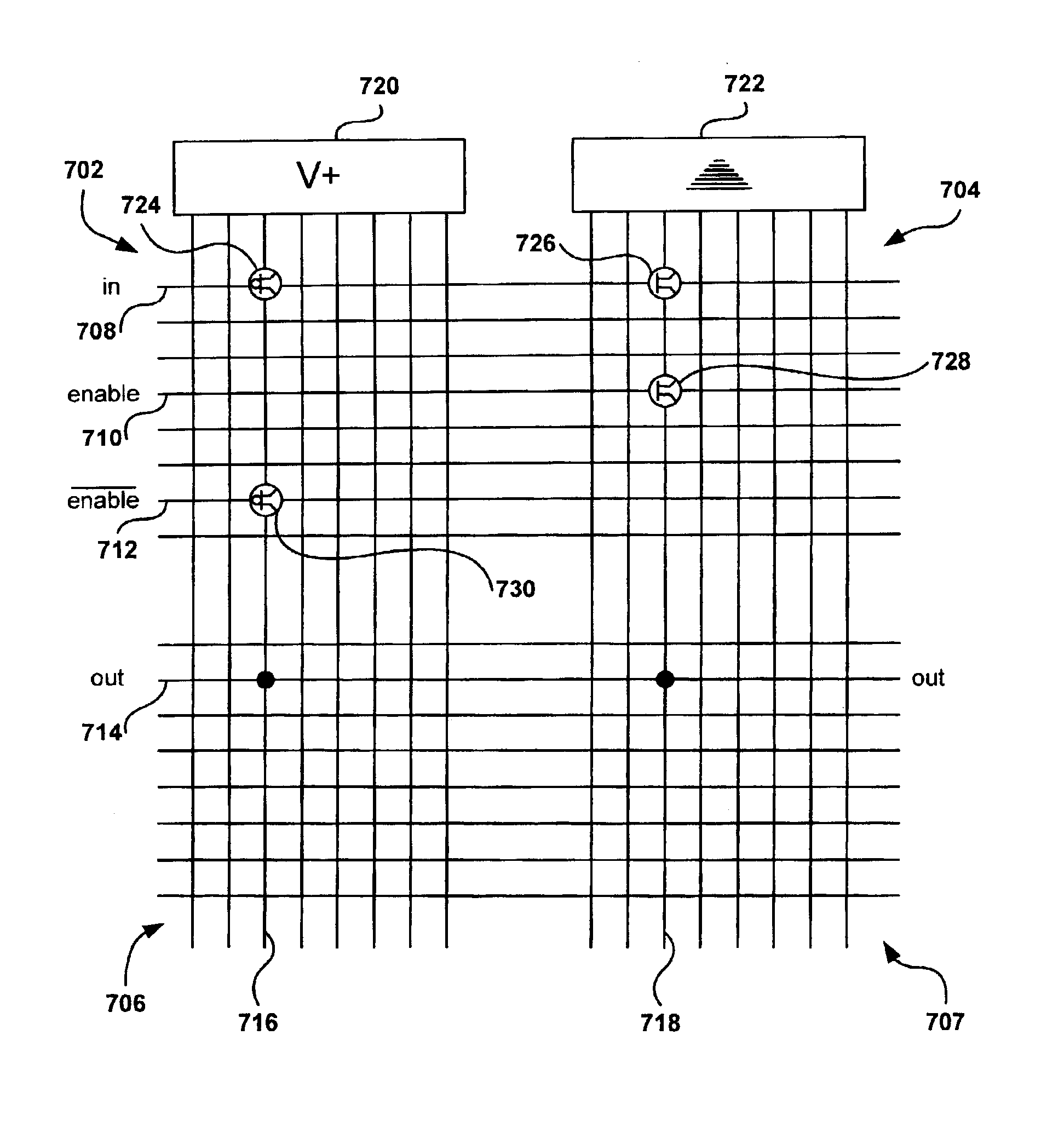

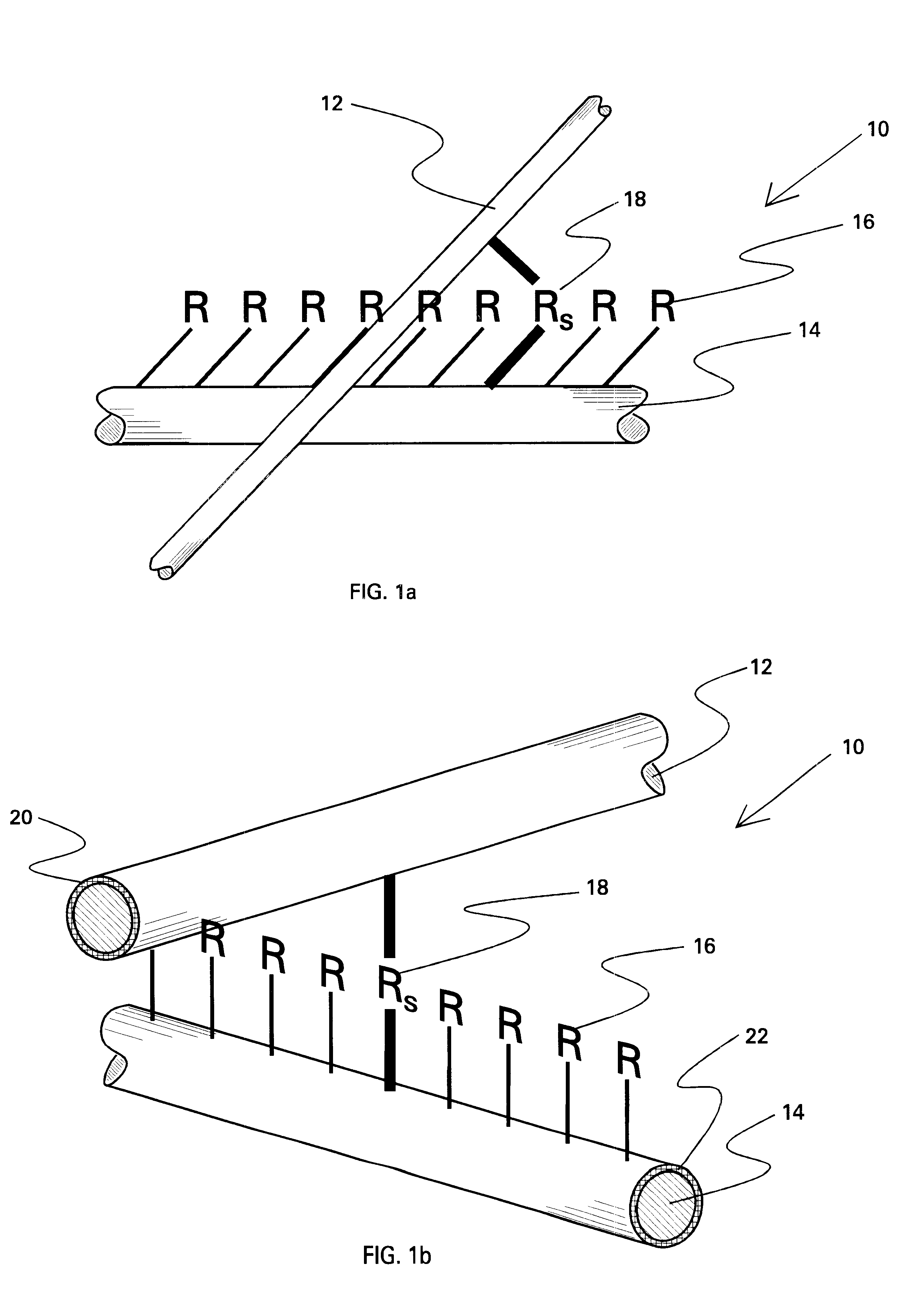

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

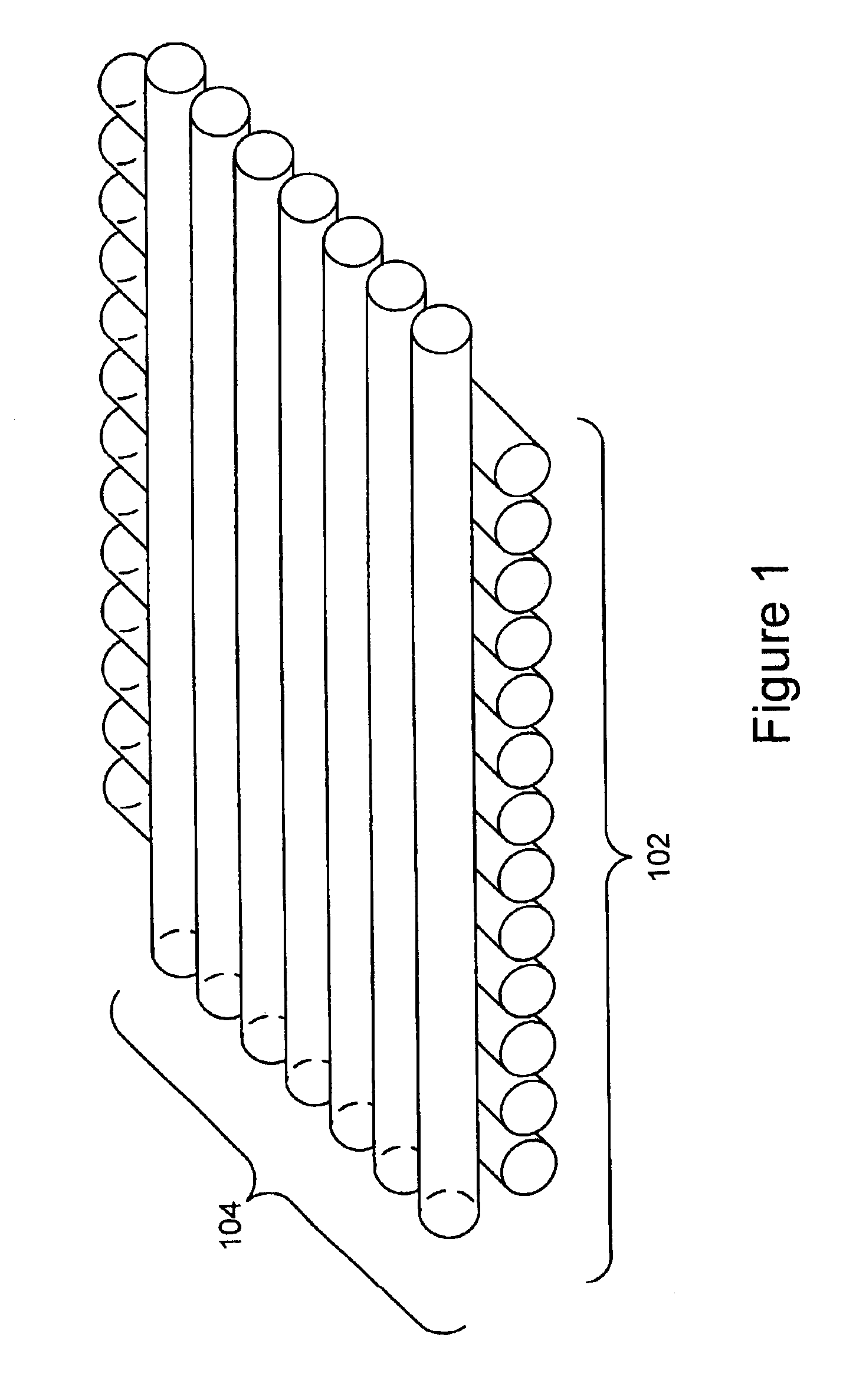

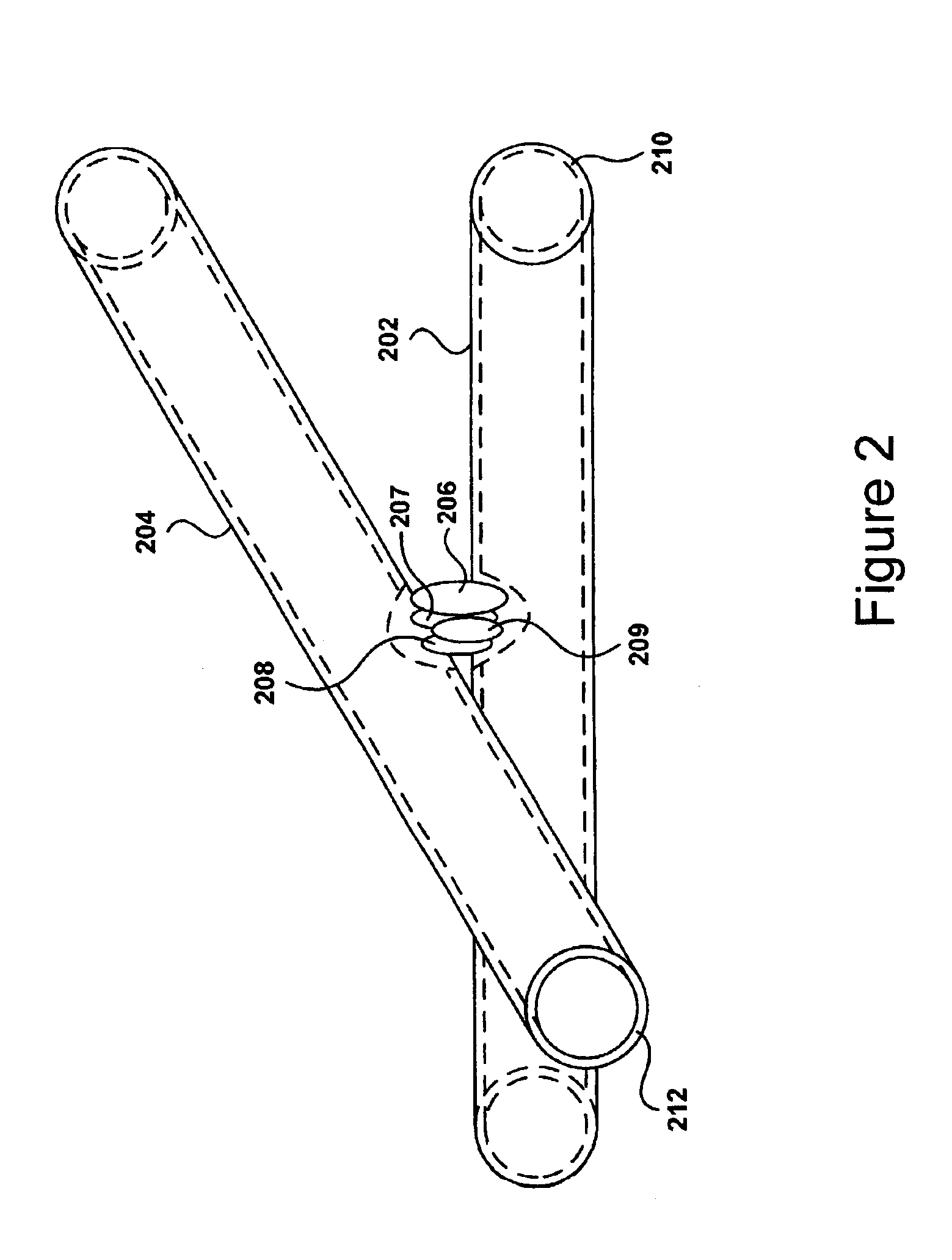

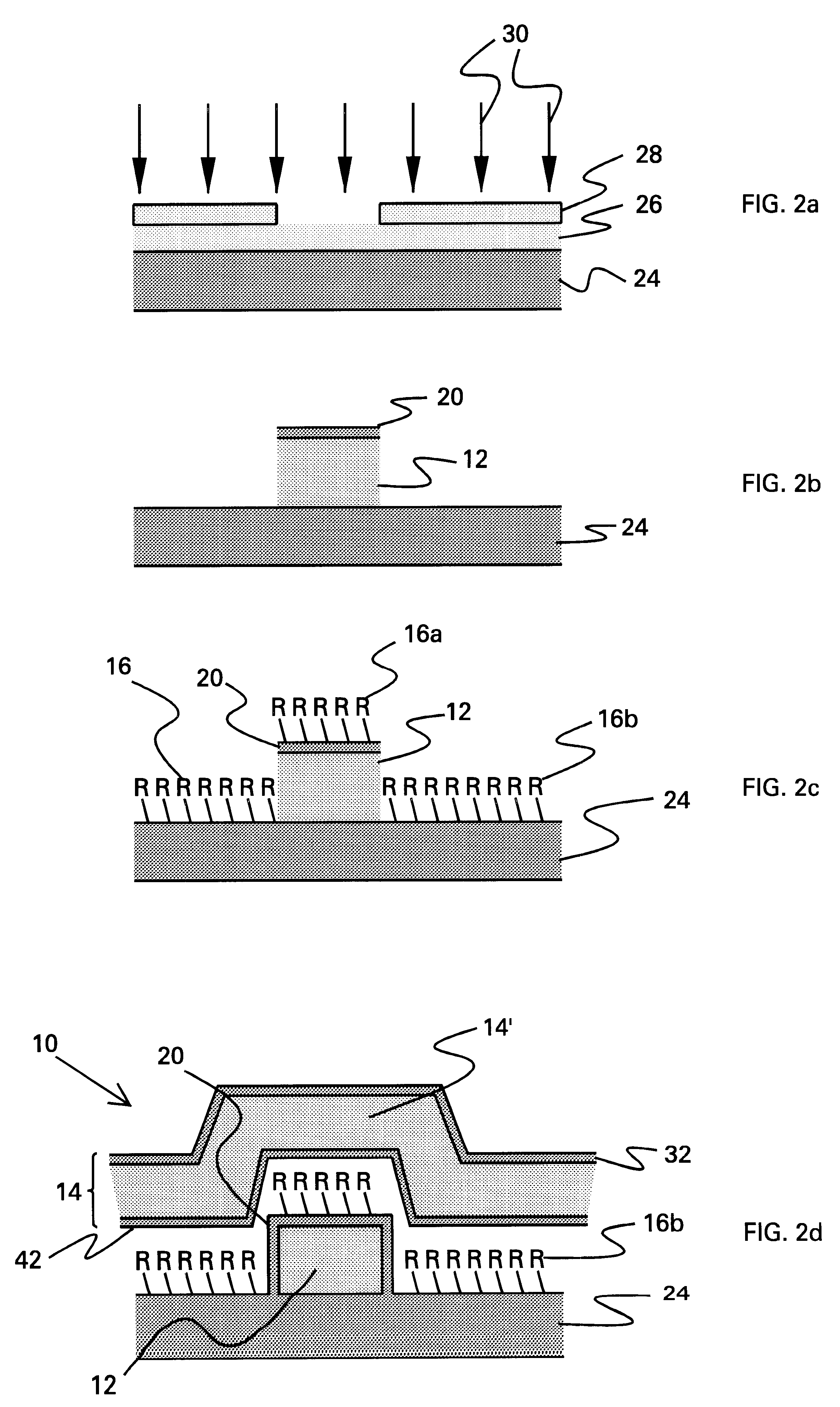

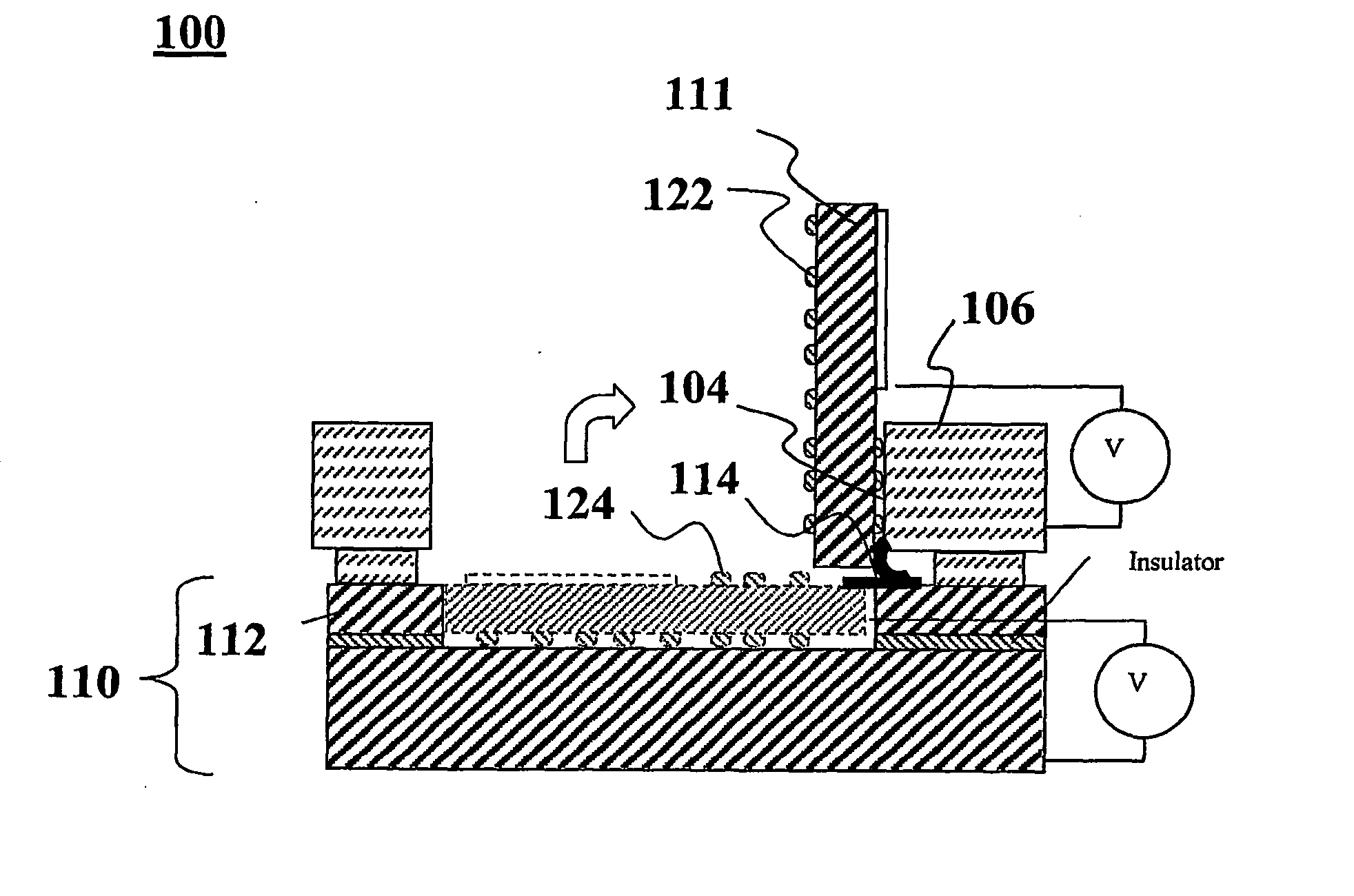

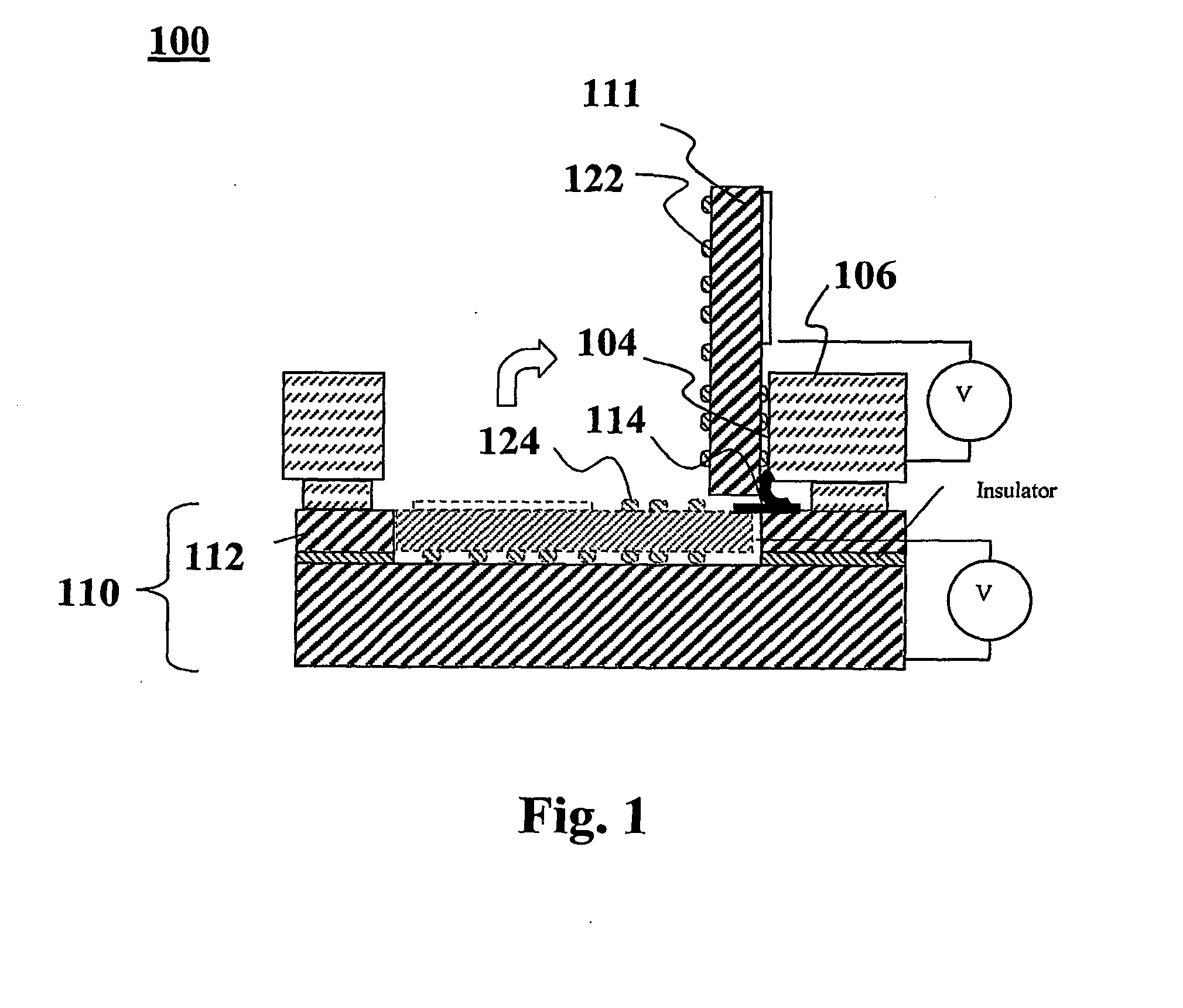

Chemically synthesized and assembled electronics devices

InactiveUS6459095B1Simple and inexpensive implementationMaterial nanotechnologyElectronic circuit testingCrossbar switchChemical synthesis

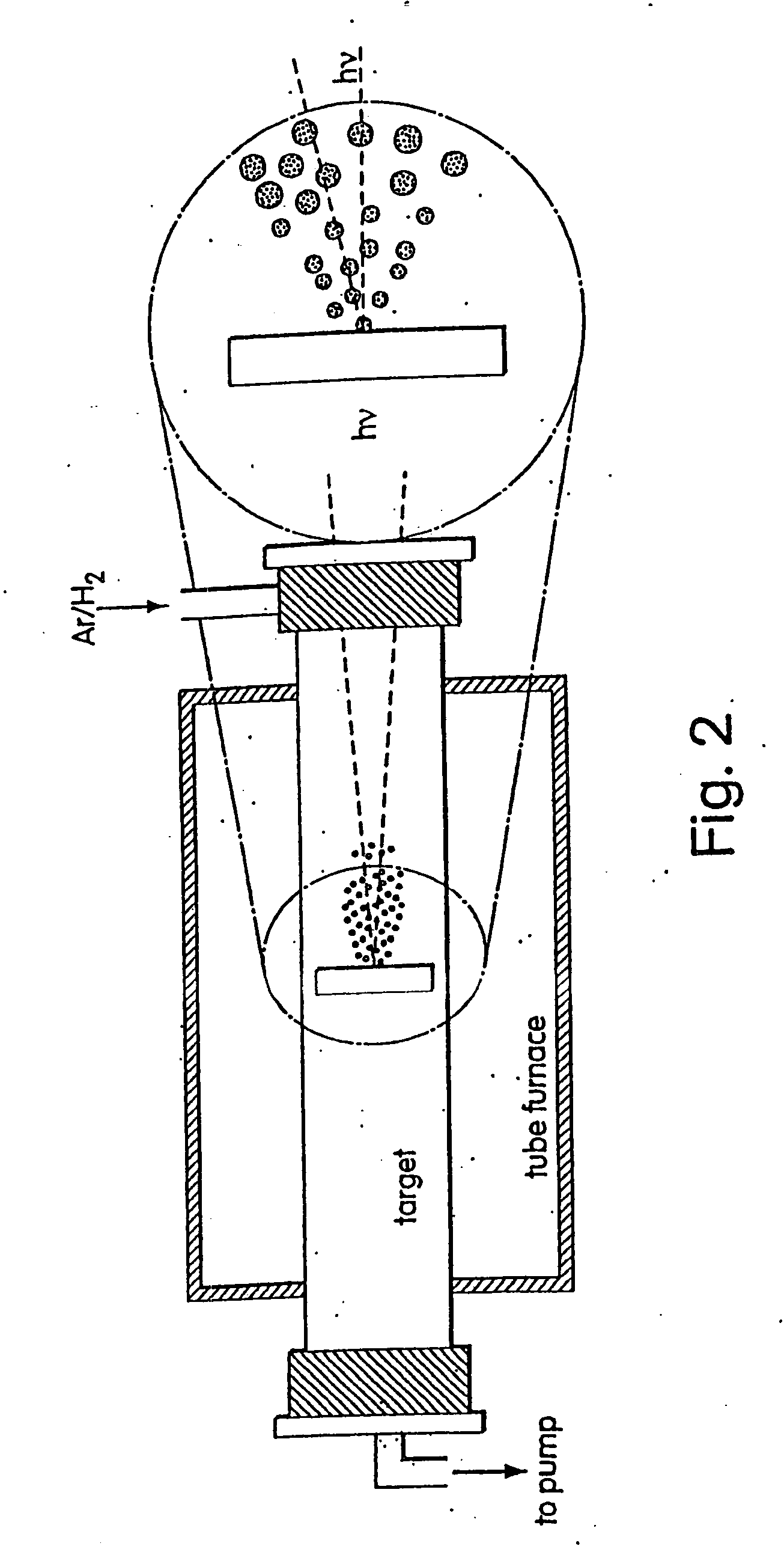

A route to the fabrication of electronic devices is provided, in which the devices consist of two crossed wires sandwiching an electrically addressable molecular species. The approach is extremely simple and inexpensive to implement, and scales from wire dimensions of several micrometers down to nanometer-scale dimensions. The device of the present invention can be used to produce crossbar switch arrays, logic devices, memory devices, and communication and signal routing devices. The present invention enables construction of molecular electronic devices on a length scale than can range from micrometers to nanometers via a straightforward and inexpensive chemical assembly procedure. The device is either partially or completely chemically assembled, and the key to the scaling is that the location of the devices on the substrate are defined once the devices have been assembled, not prior to assembly.

Owner:HEWLETT PACKARD CO +1

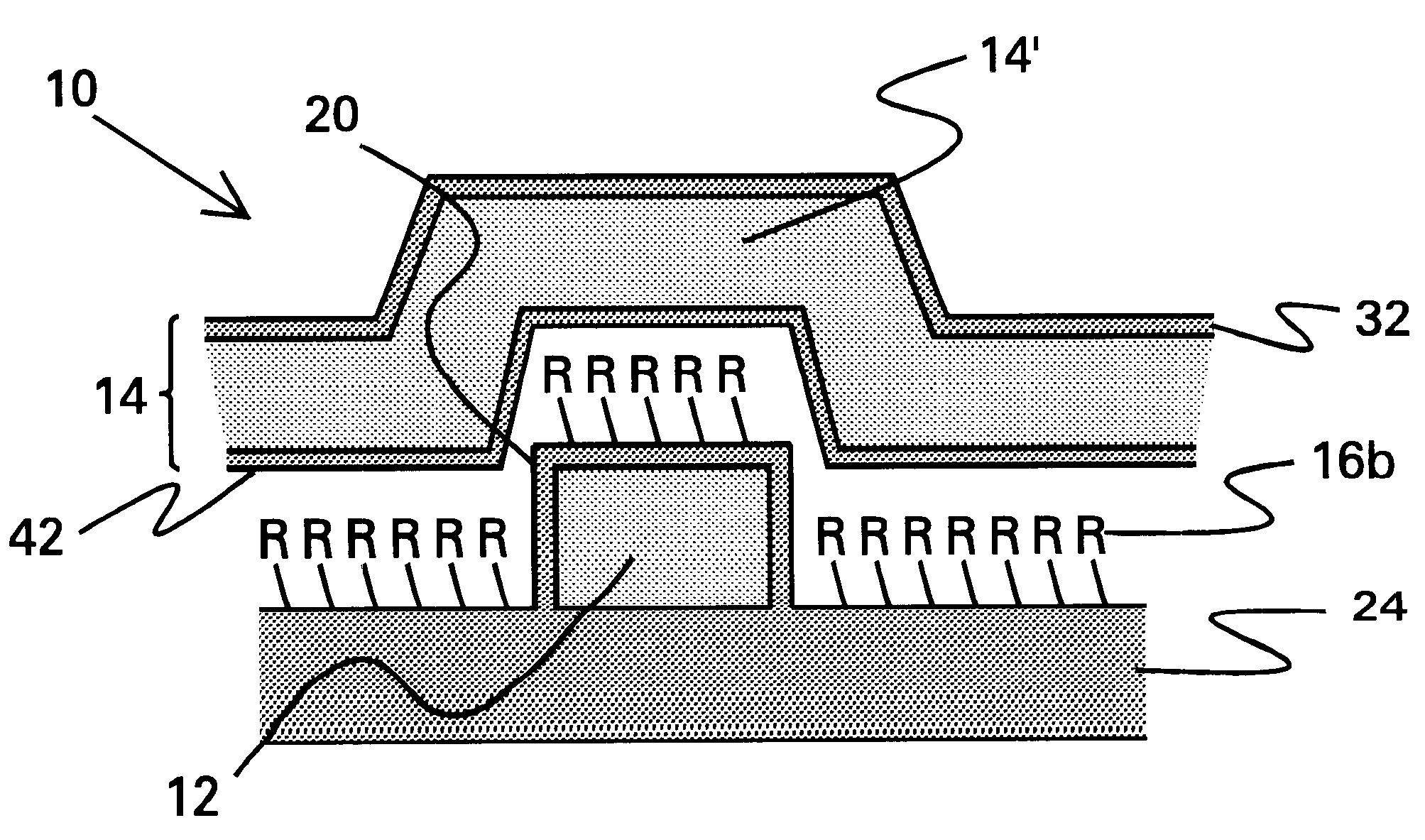

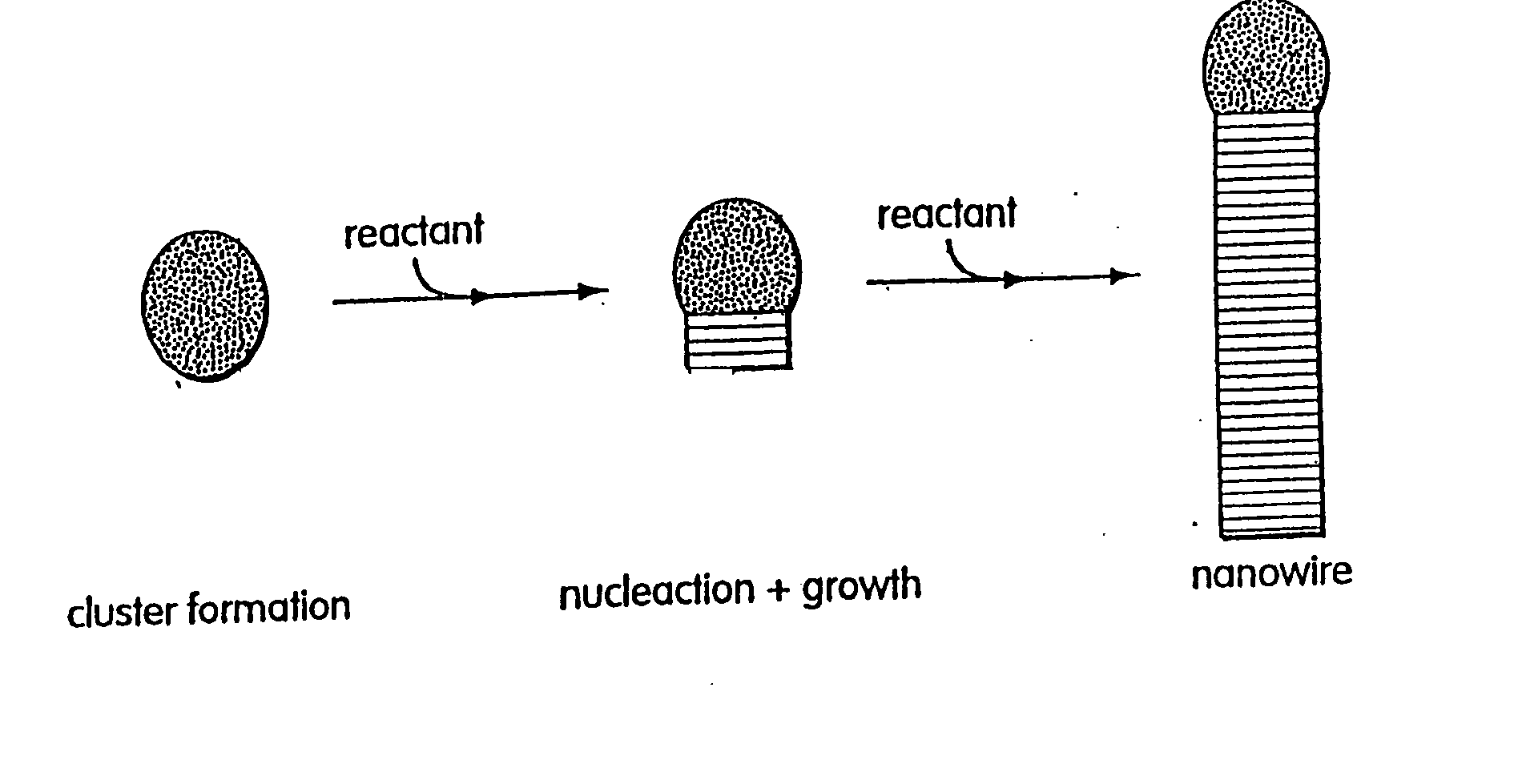

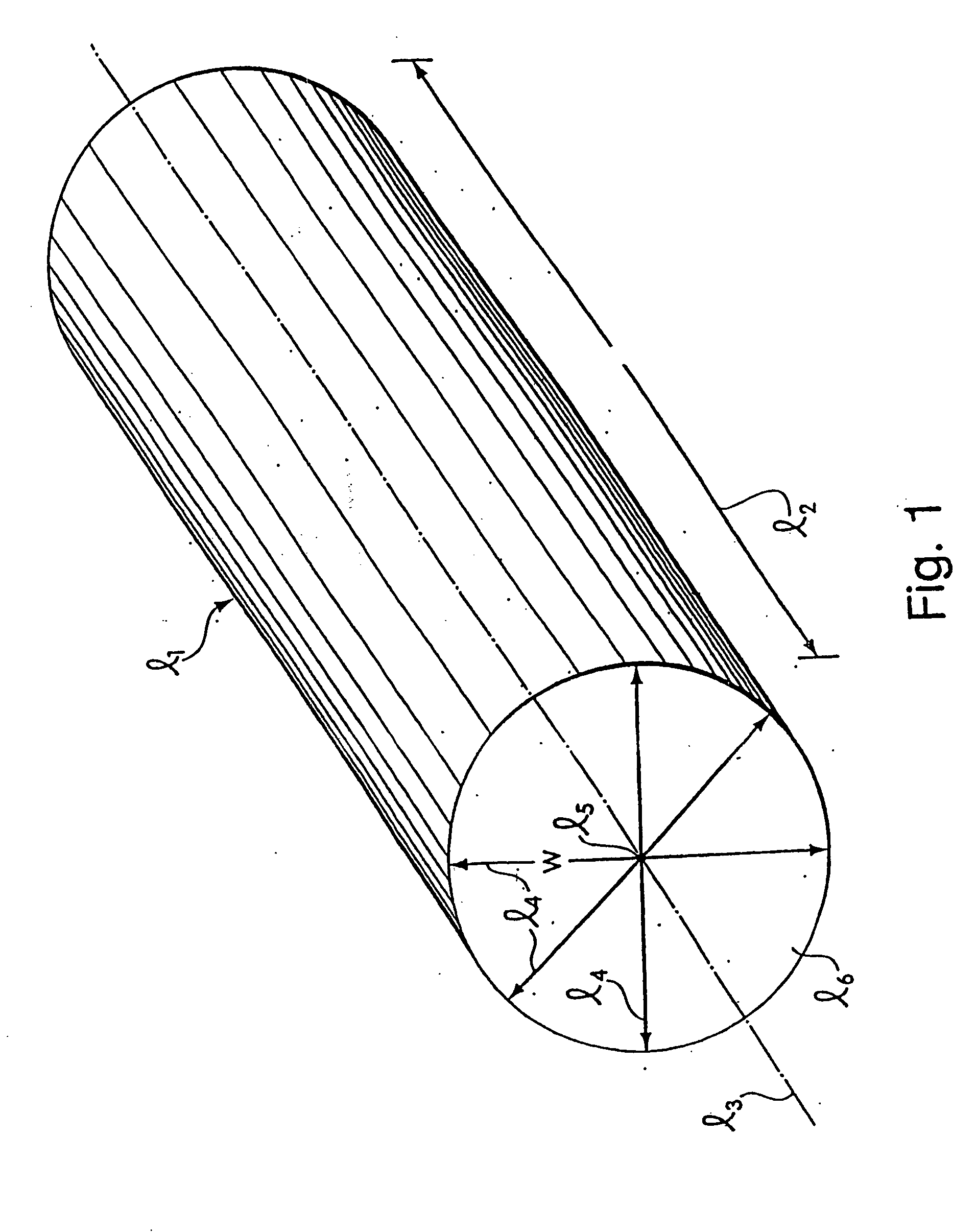

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

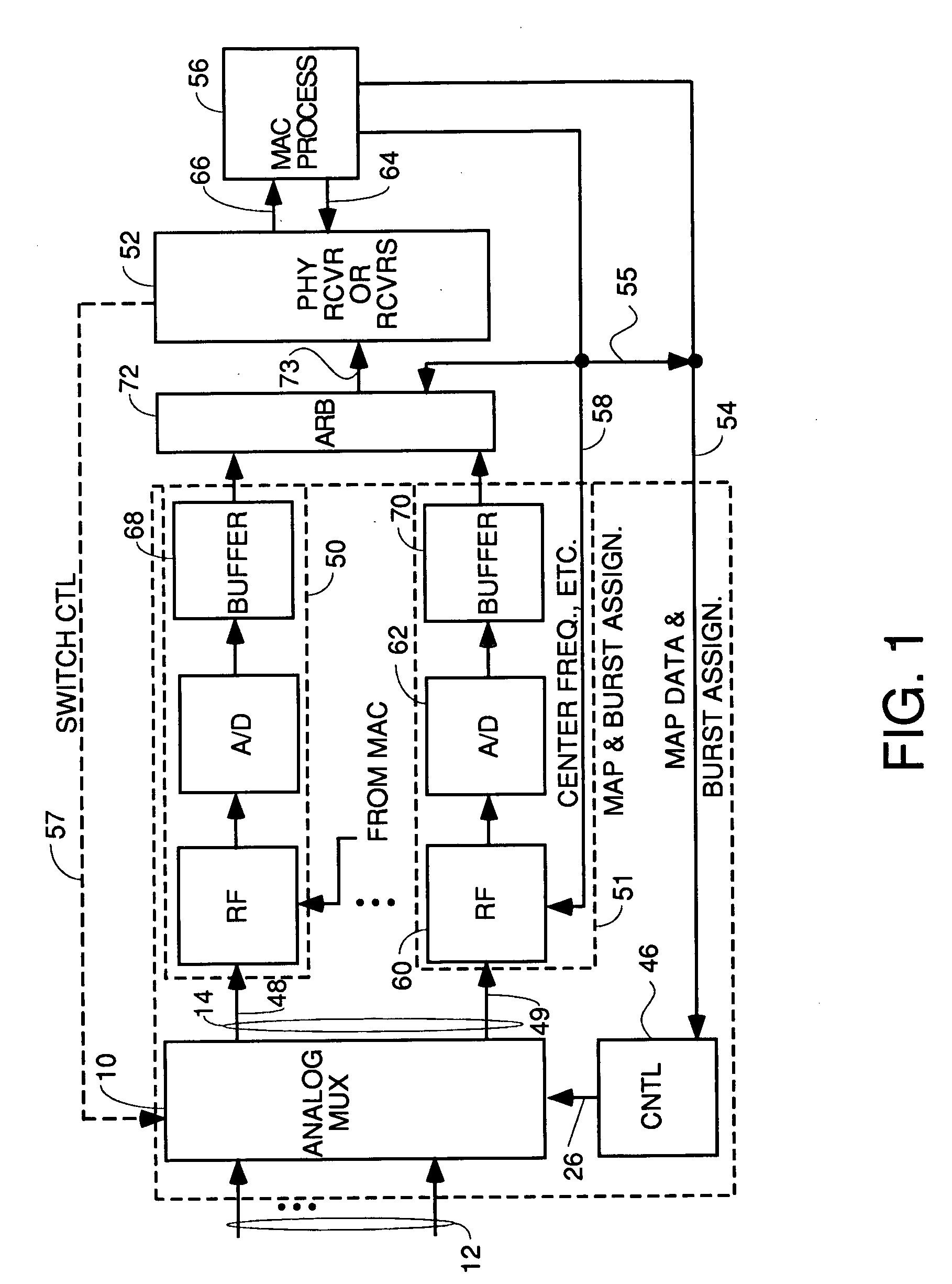

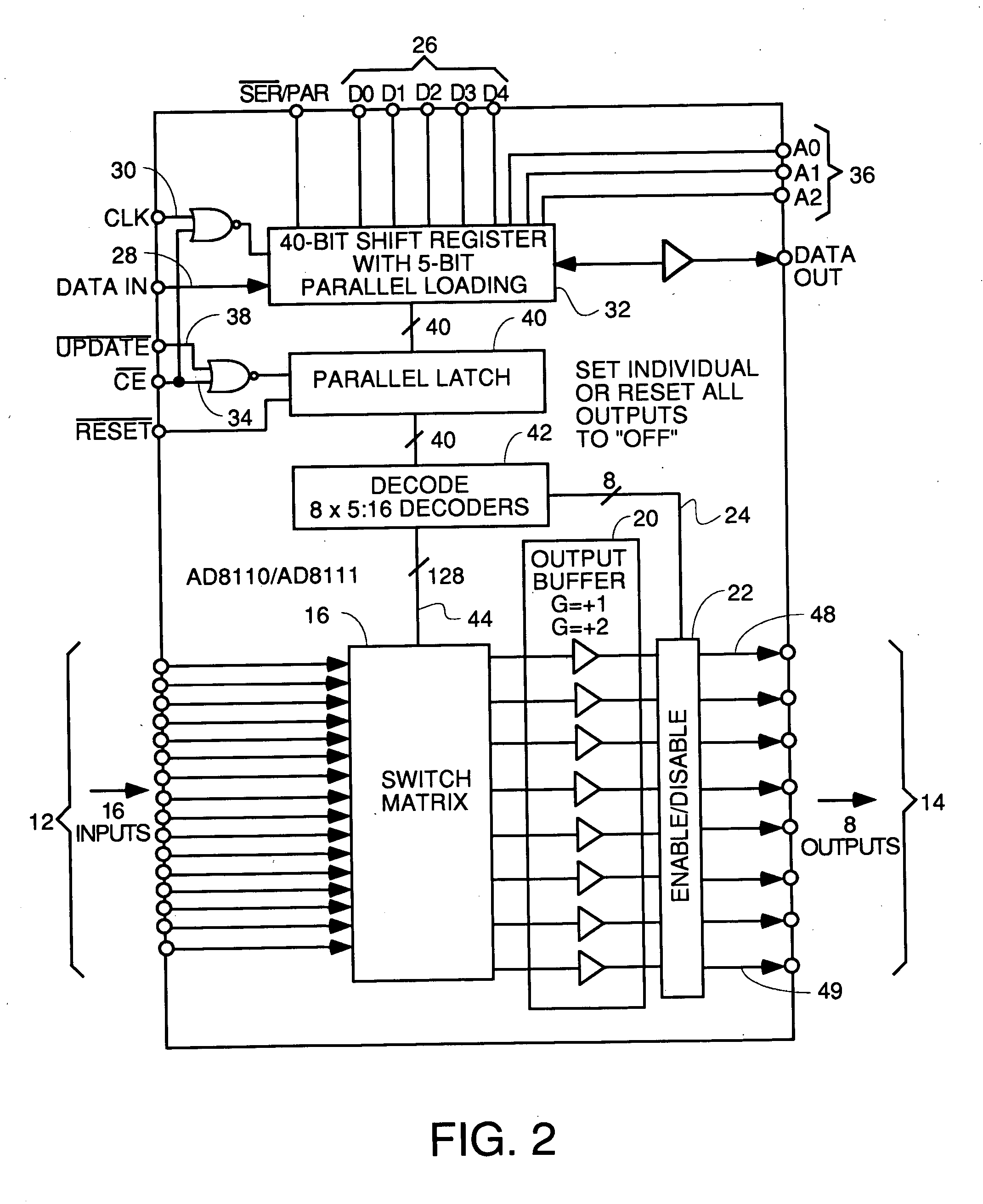

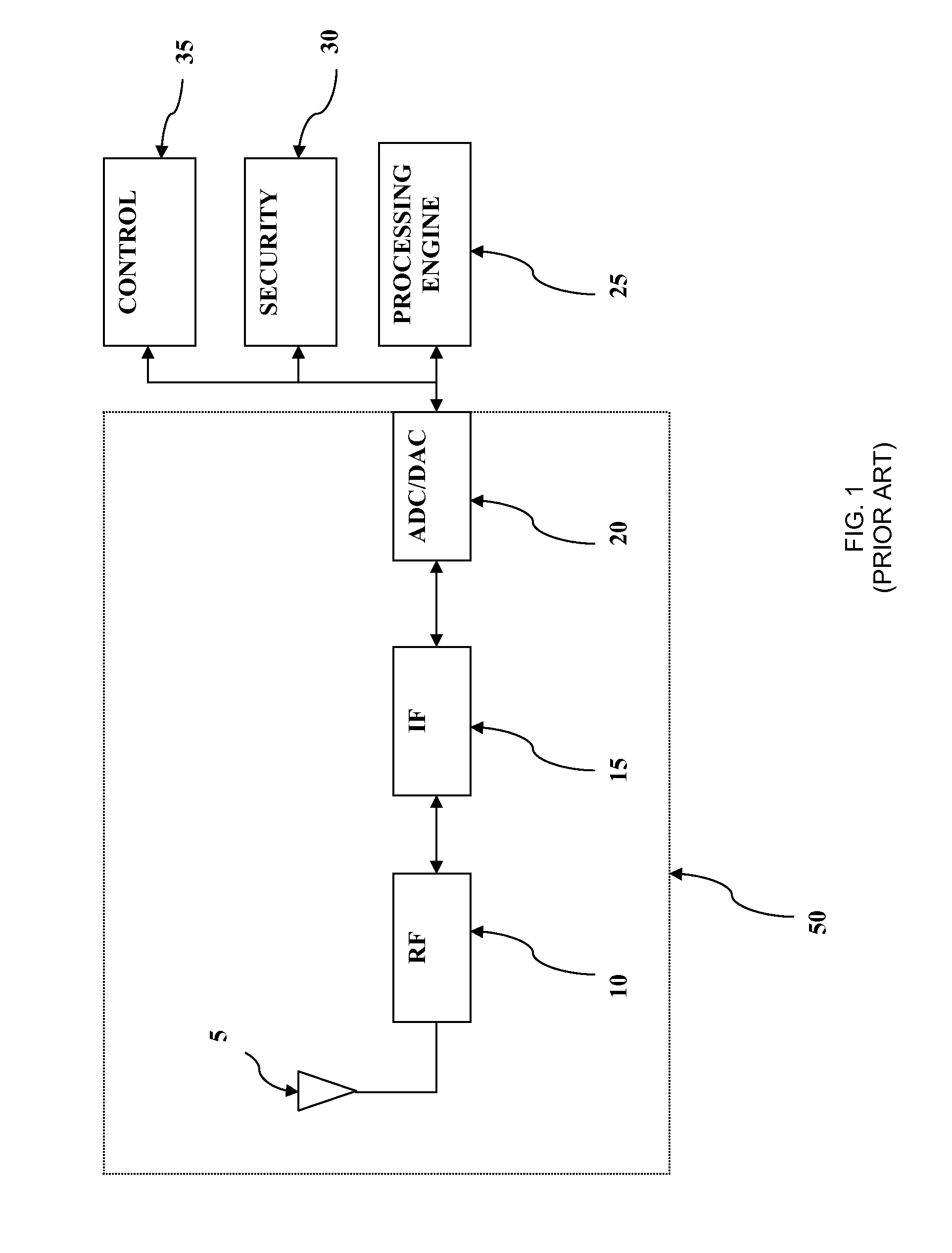

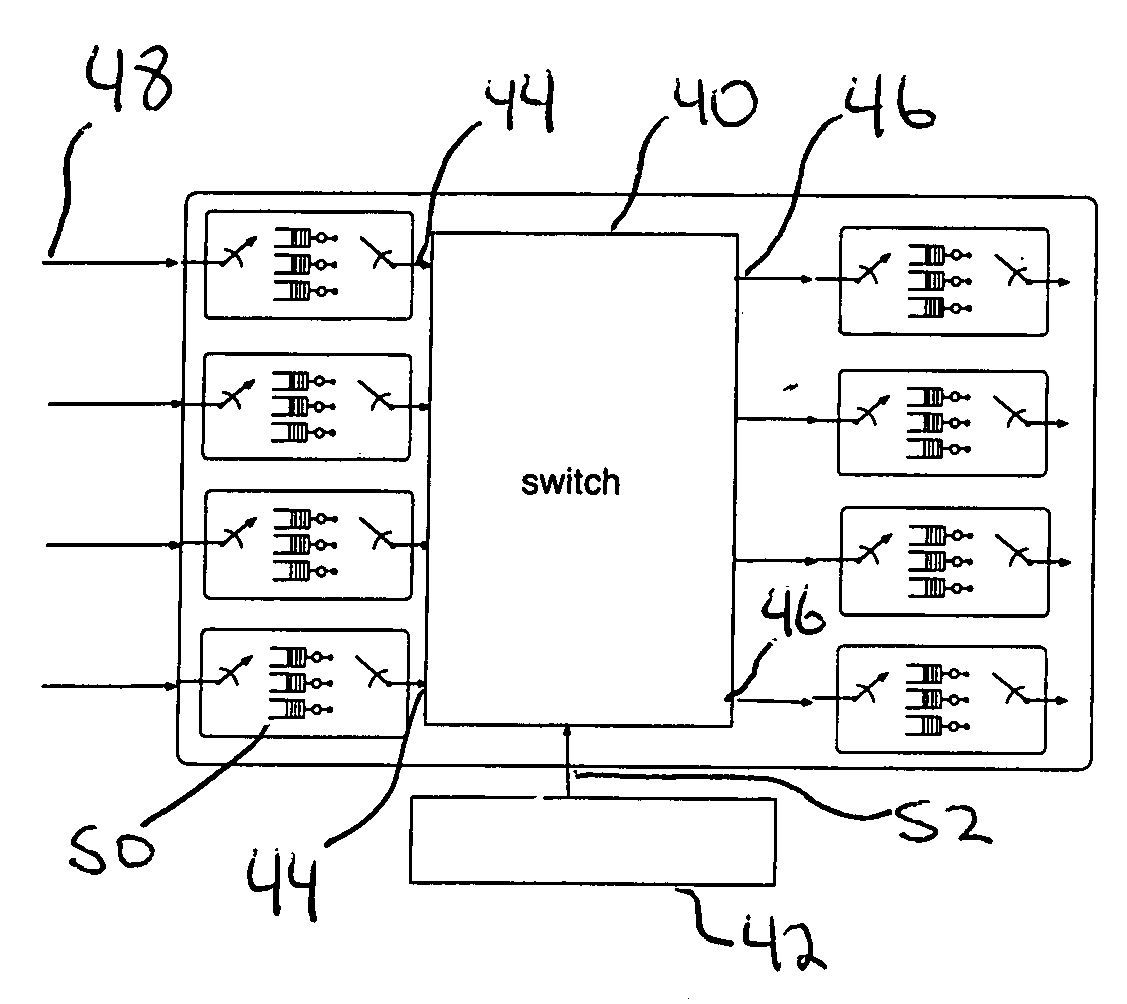

Upstream only linecard with front end multiplexer for CMTS

InactiveUS20050010958A1Easy to addMaximize Utilization EfficiencyMultiplex system selection arrangementsBroadband local area networksCrossbar switchMultiplexer

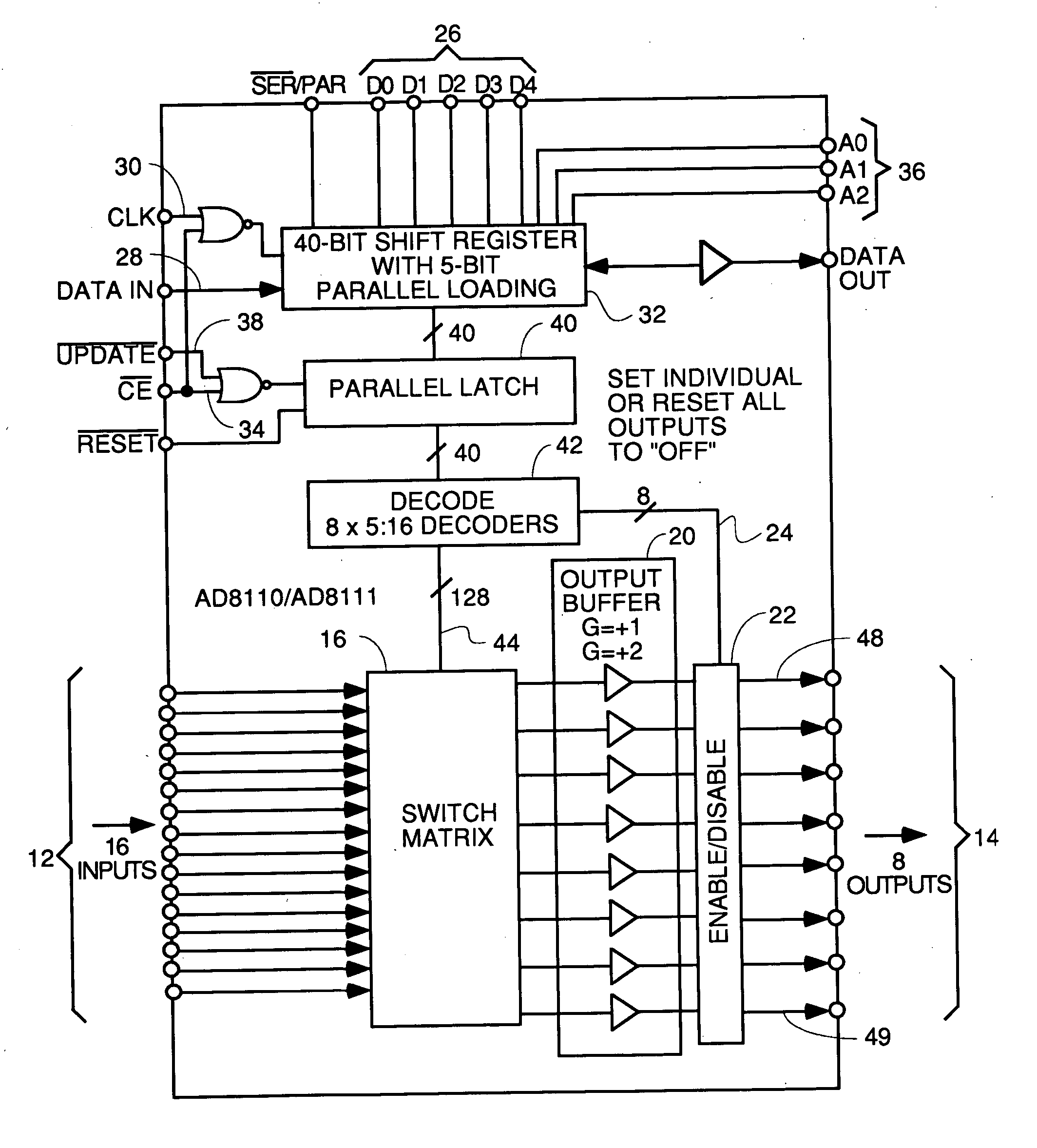

An upstream line card including a digital or analog multiplexer front end circuit for a Cable Modem Termination System. Each upstream line card has only upstream receivers and allows a CMTS to share one or a handful of receiver chips to receive and recover data from a larger number of input cables coupled to the front end multiplexer. A control circuit for the multiplexer uses MAP data and burst assignment data and upstream mini-slot counts for each of the input cables to determine when a burst is about to arrive on a cable and cause appropriate switching by the multiplexer or crossbar switch. In some embodiments, there is only one RF channel circuit coupled to the output of the multiplexer, so the multiplexer is controlled to couple the input cable upon which the burst is expected to the single RF channel. In other embodiments, there are multiple RF channels coupled to the inputs of the multiplexer so the multiplexer is controlled to connect each input cable on which a burst is expected to an available RF channel. In some embodiments, the sample data generated by each RF channel is buffered and an arbiter picks one burst at a time for application to the input of a CMTS receiver or doles out bursts to different receivers. In other embodiments, no buffers or arbiter are used, and each RF channel has its own dedicated CMTS receiver.

Owner:GOOGLE TECH HLDG LLC

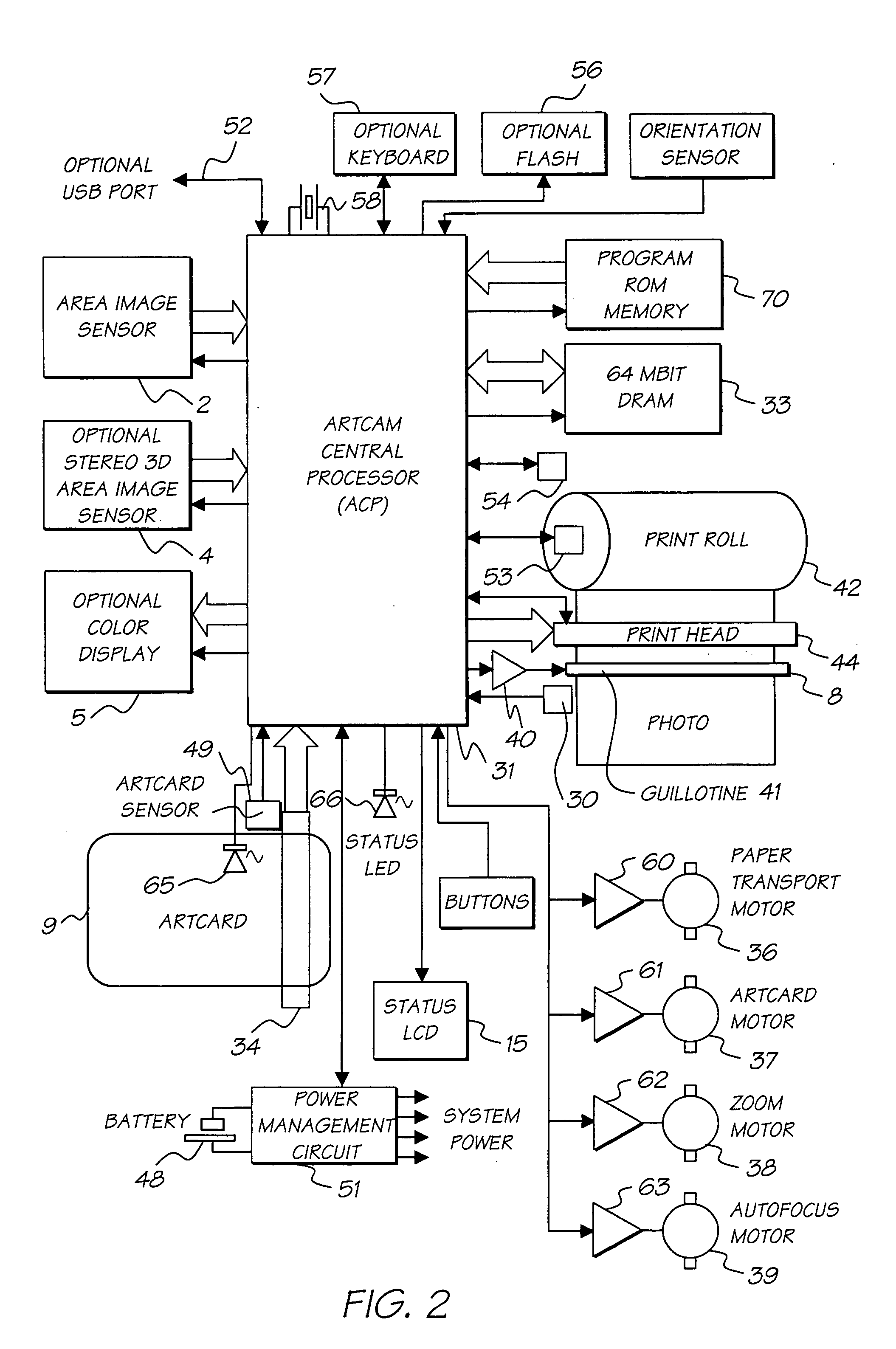

Digital camera system containing a VLIW vector processor

InactiveUS6879341B1Material nanotechnologyTelevision system detailsCrossbar switchArithmetic logic unit

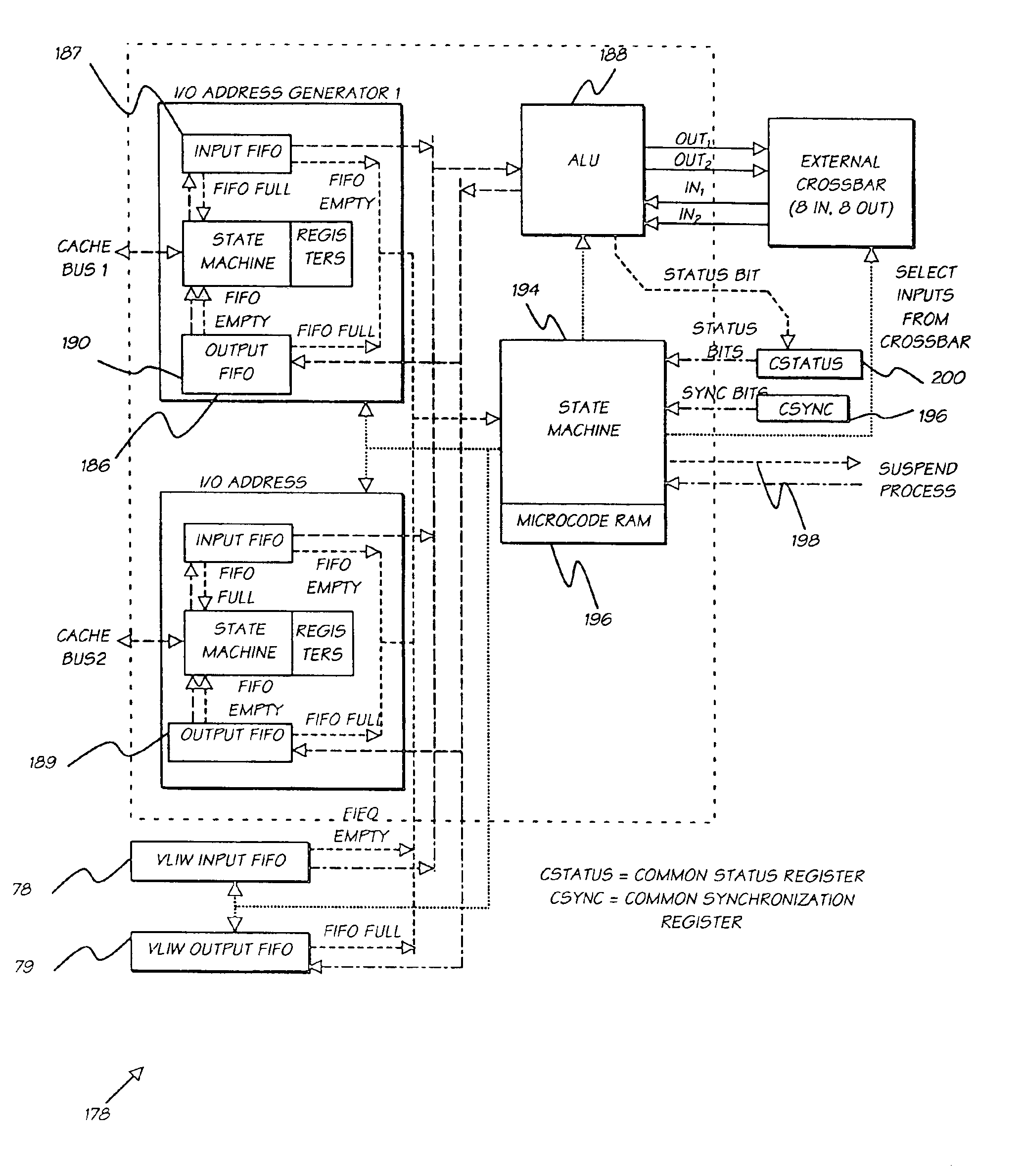

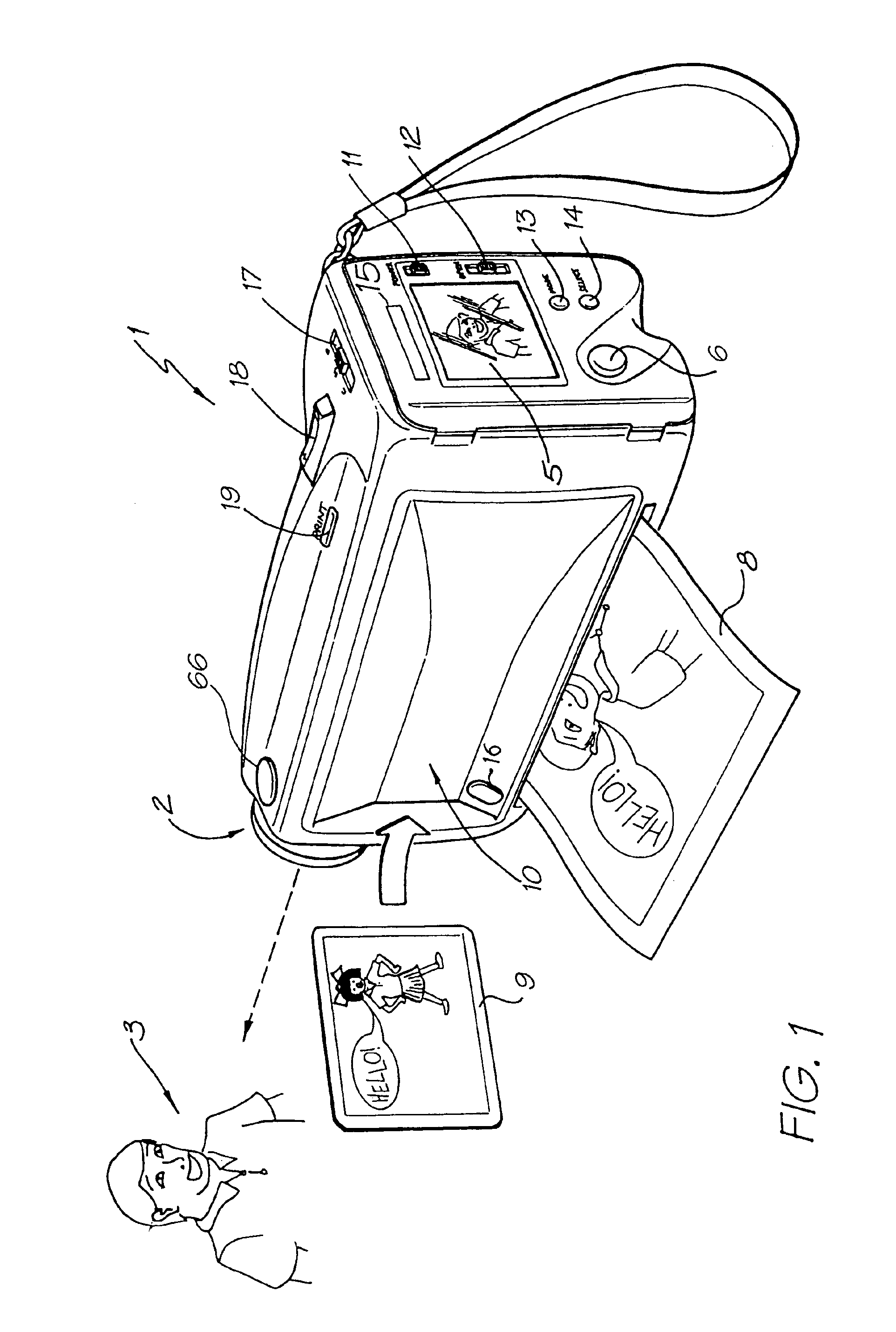

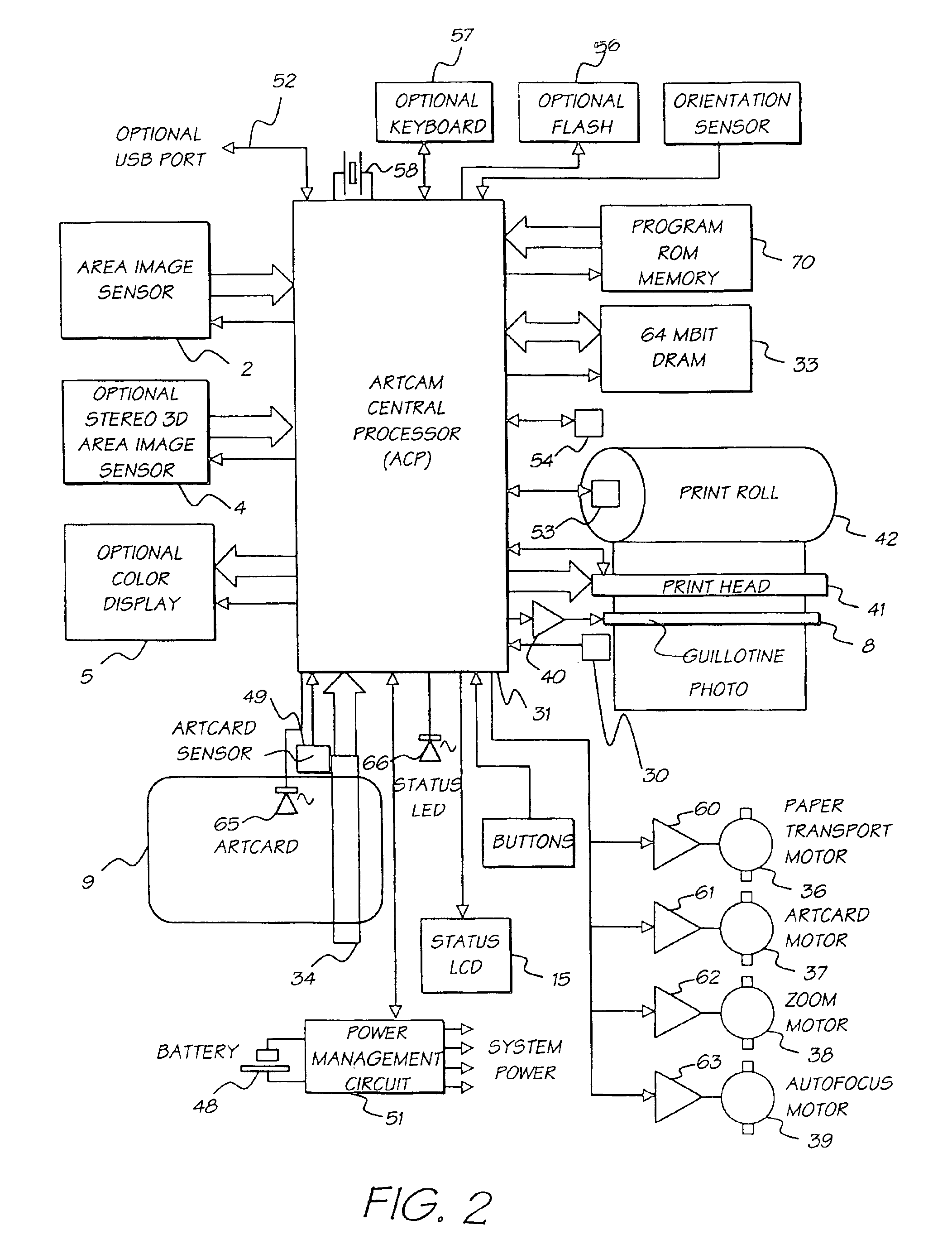

A digital camera has a sensor for sensing an image, a processor for modifying the sensed image in accordance with instructions input into the camera and an output for outputting the modified image where the processor includes a series of processing elements arranged around a central crossbar switch. The processing elements include an Arithmetic Logic Unit (ALU) acting under the control of a writeable microcode store, an internal input and output FIFO for storing pixel data to be processed by the processing elements and the processor is interconnected to a read and write FIFO for reading and writing pixel data of images to the processor. Each of the processing elements can be arranged in a ring and each element is also separately connected to its nearest neighbors. The ALU receives a series of inputs interconnected via an internal crossbar switch to a series of core processing units within the ALU and includes a number of internal registers for the storage of temporary data. The core processing units can include at least one of a multiplier, an adder and a barrel shifter. The processing elements are further connected to a common data bus for the transfer of a pixel data to the processing elements and the data bus is interconnected to a data cache which acts as an intermediate cache between the processing elements and a memory store for storing the images.

Owner:GOOGLE LLC

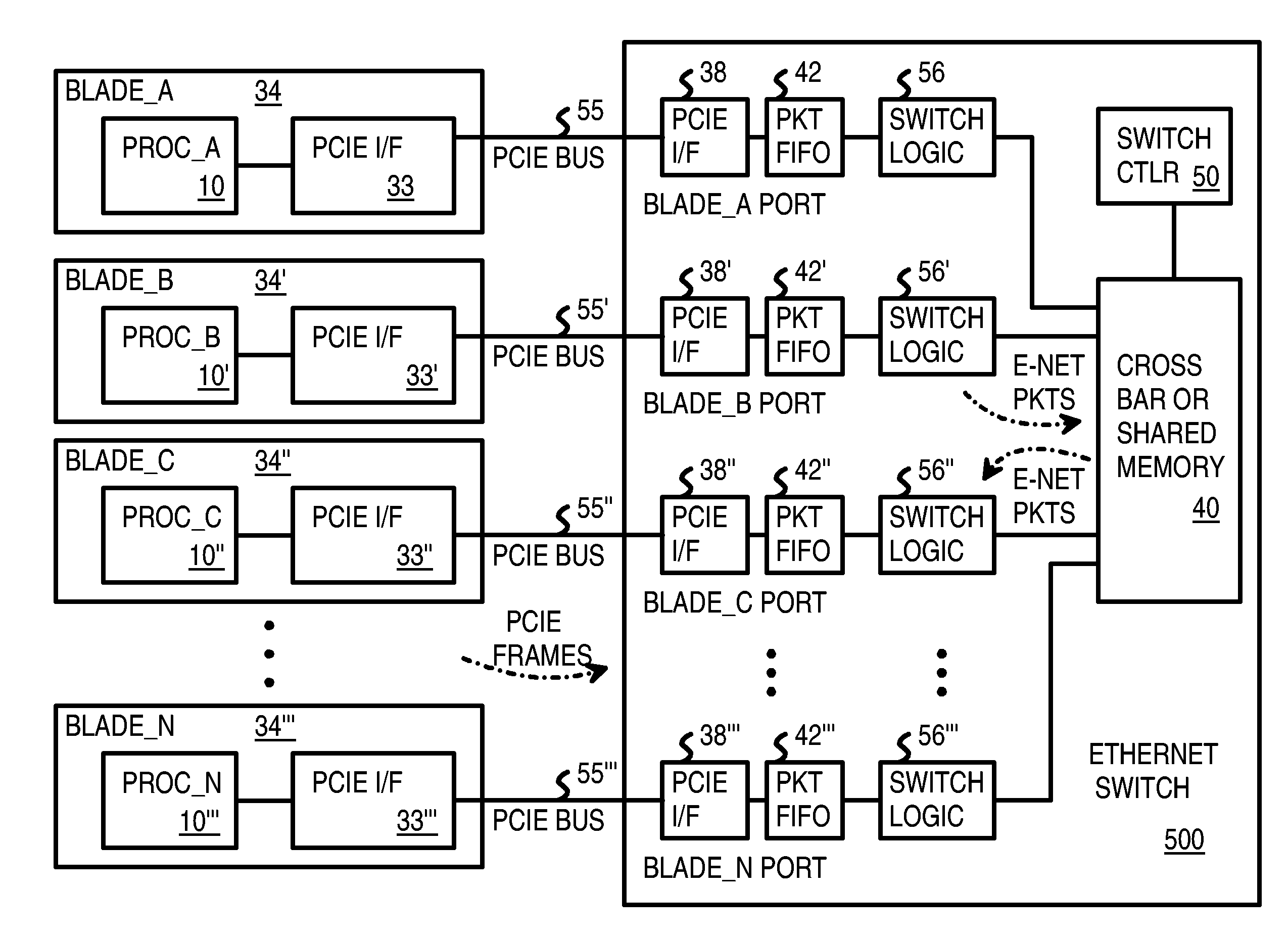

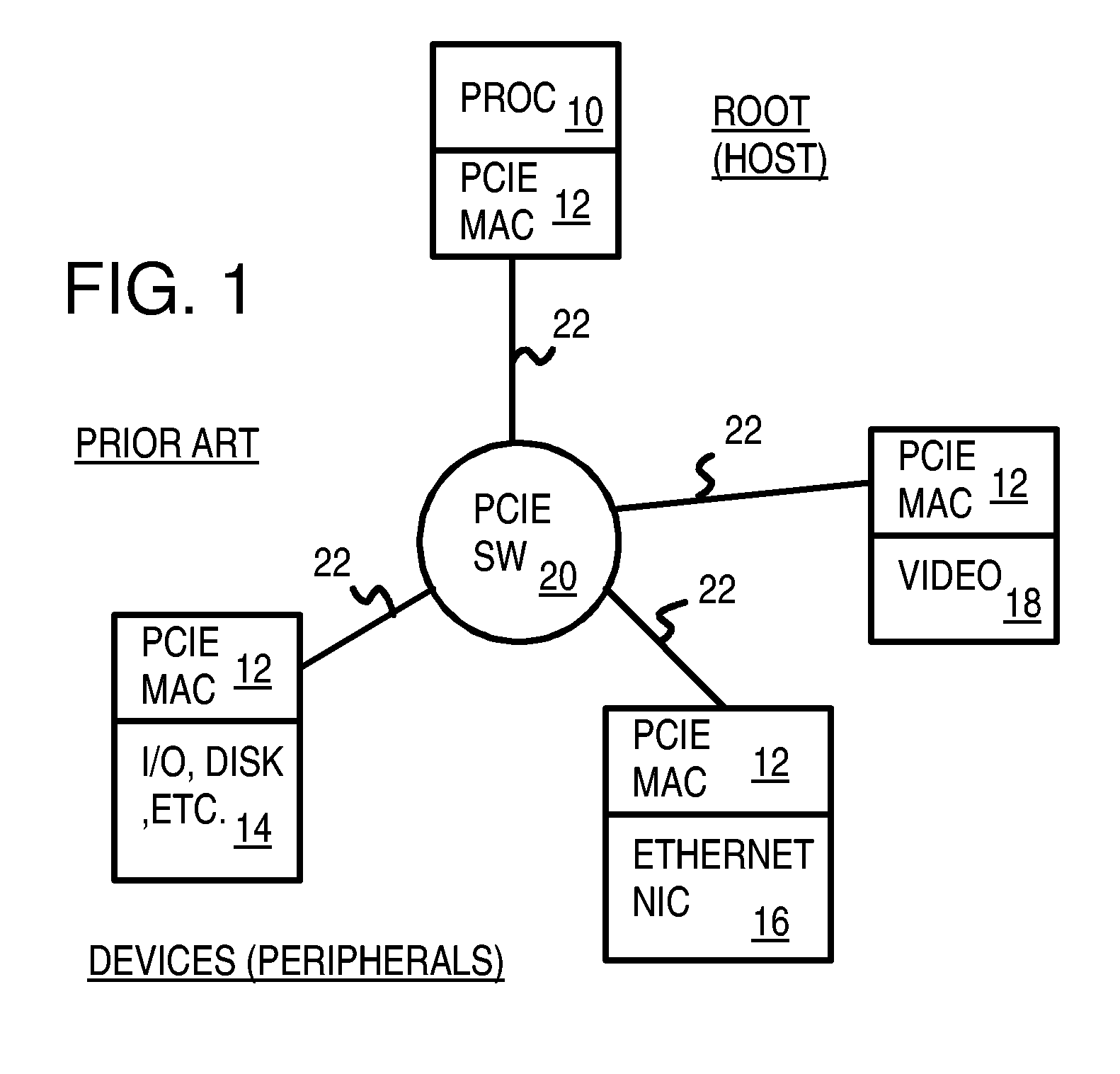

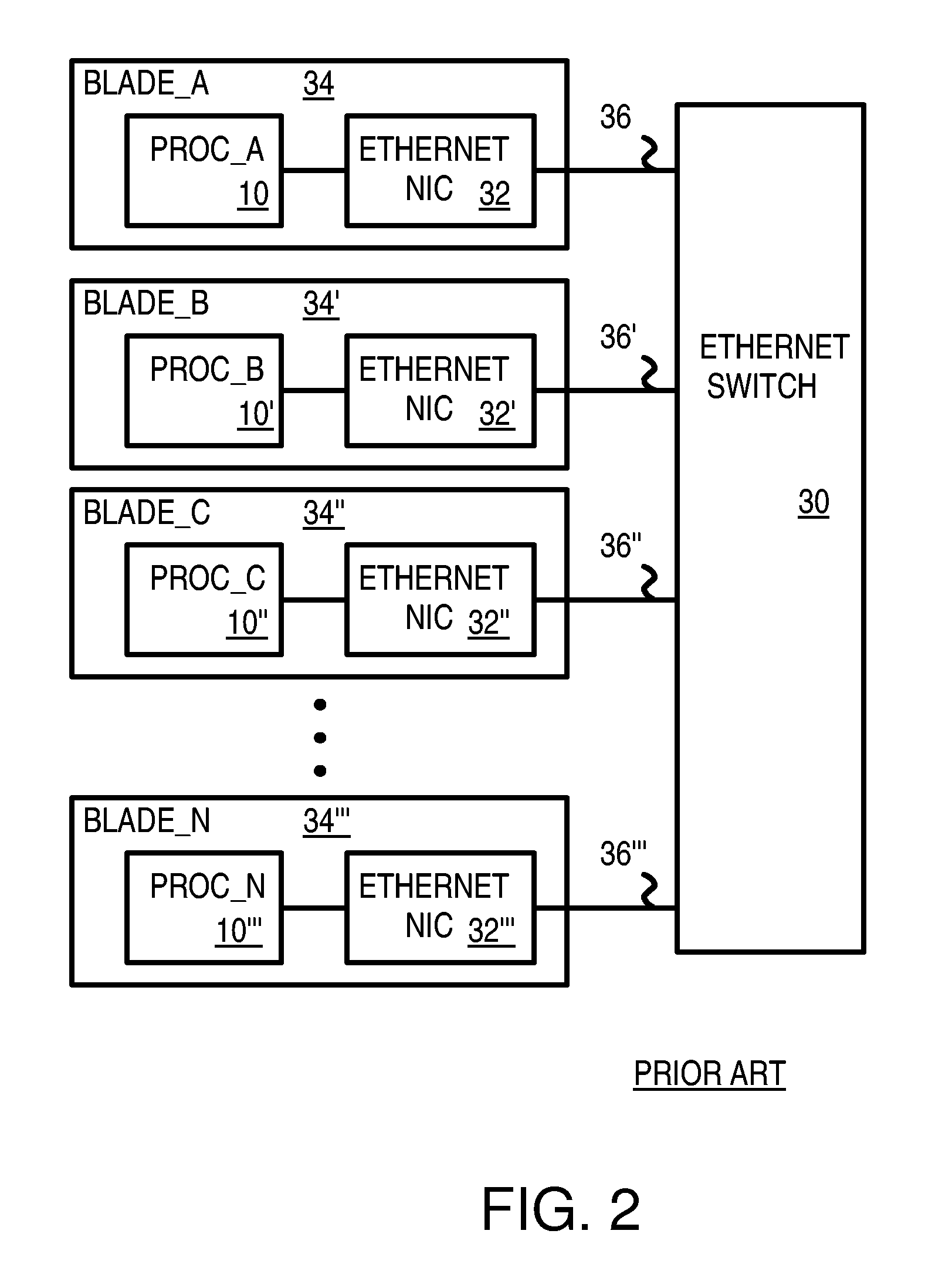

Pseudo-ethernet switch without ethernet media-access-controllers (MAC's) that copies ethernet context registers between PCI-express ports

A Pseudo-Ethernet switch has a routing table that uses Ethernet media-access controller (MAC) addresses to route Ethernet packets through a switch fabric between an input port and an output port. However, the input port and output port have Peripheral Component Interconnect Express (PCIE) interfaces that read and write PCI-Express packets to and from host-processor memories. When used in a blade system, host processor boards have PCIE physical links that connect to the PCIE ports on the Pseudo-Ethernet switch. The Pseudo-Ethernet switch does not have Ethernet MAC and Ethernet physical layers, saving considerable hardware. The switch fabric can be a cross-bar switch or can be a shared memory that stores Ethernet packet data embedded in the PCIE packets. Write and read pointers for a buffer storing an Ethernet packet in the shared memory can be passed from input to output port to perform packet switching.

Owner:DIODES INC

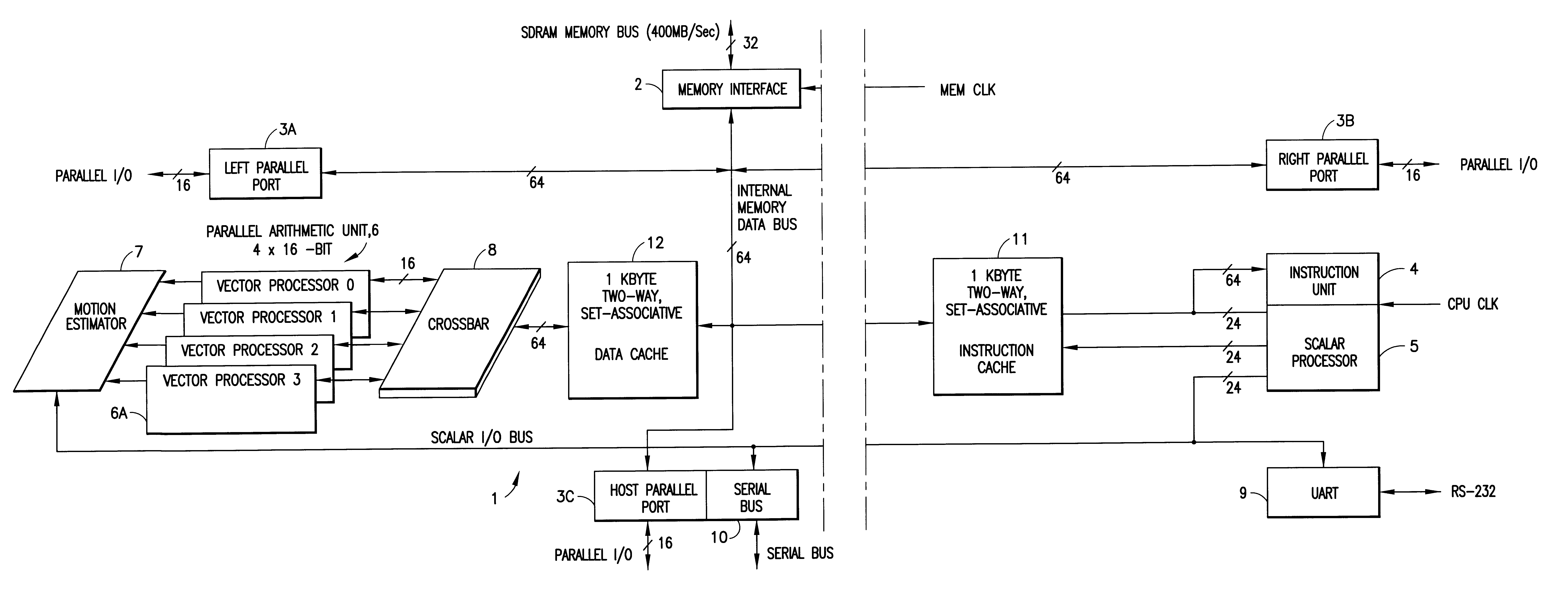

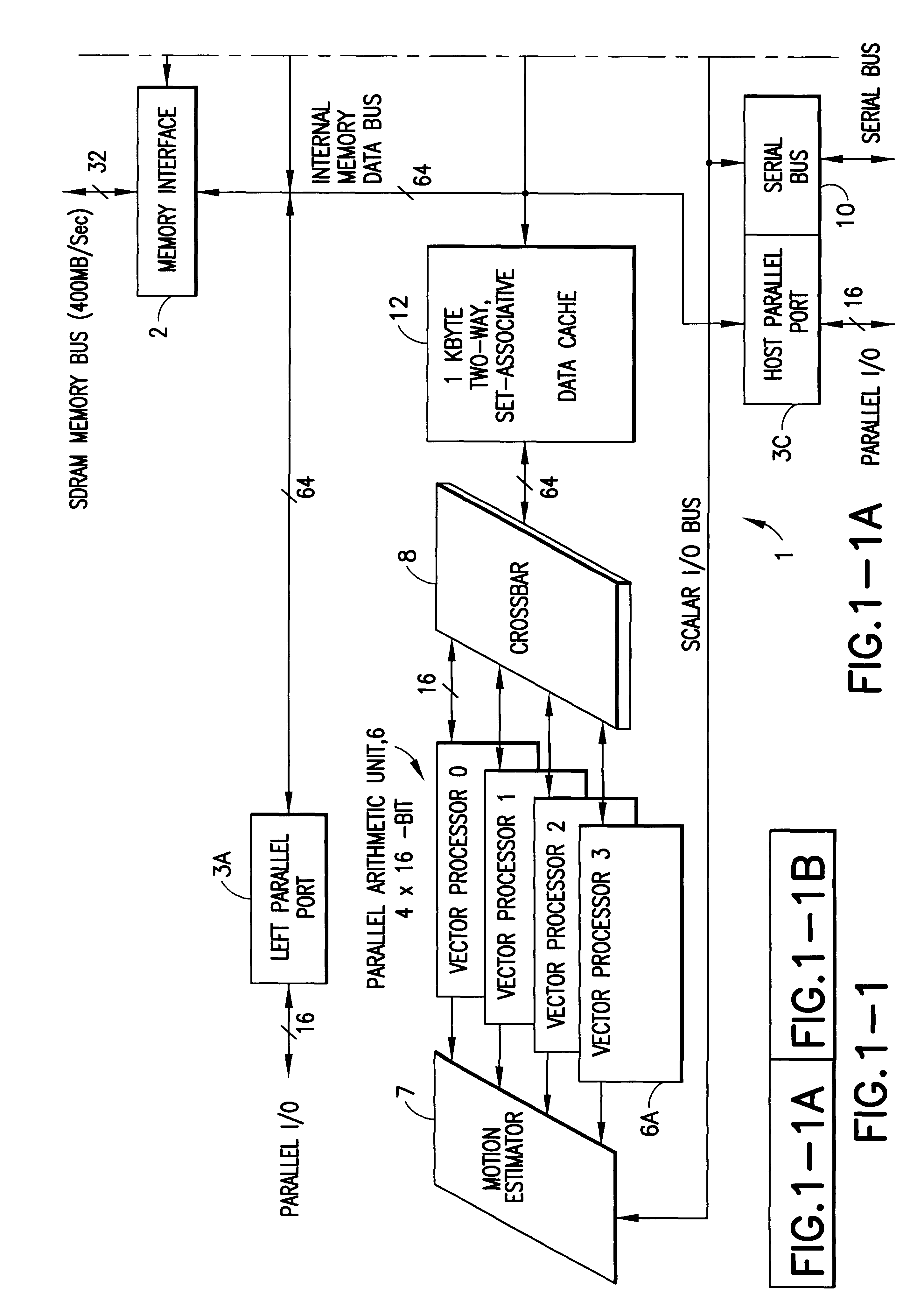

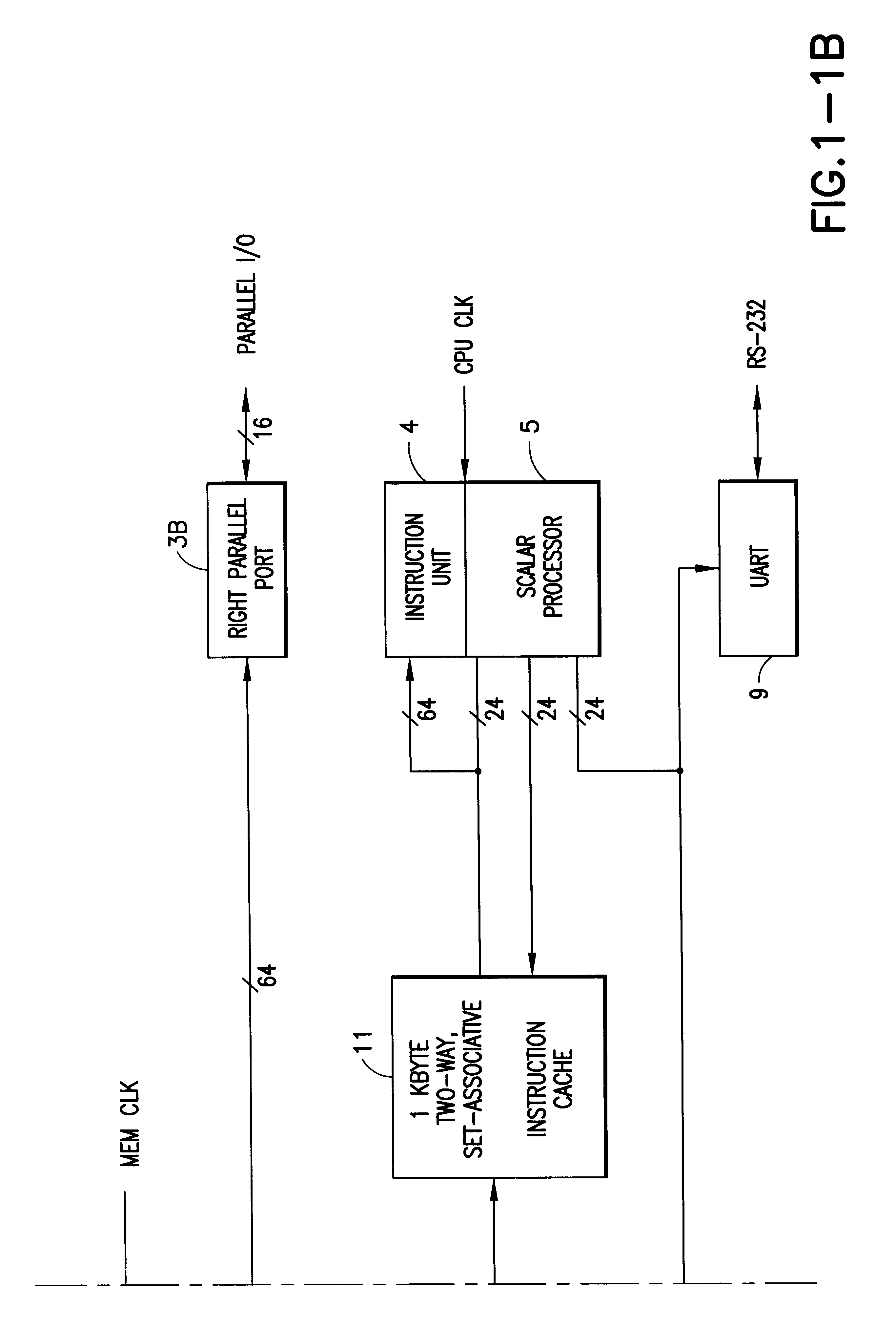

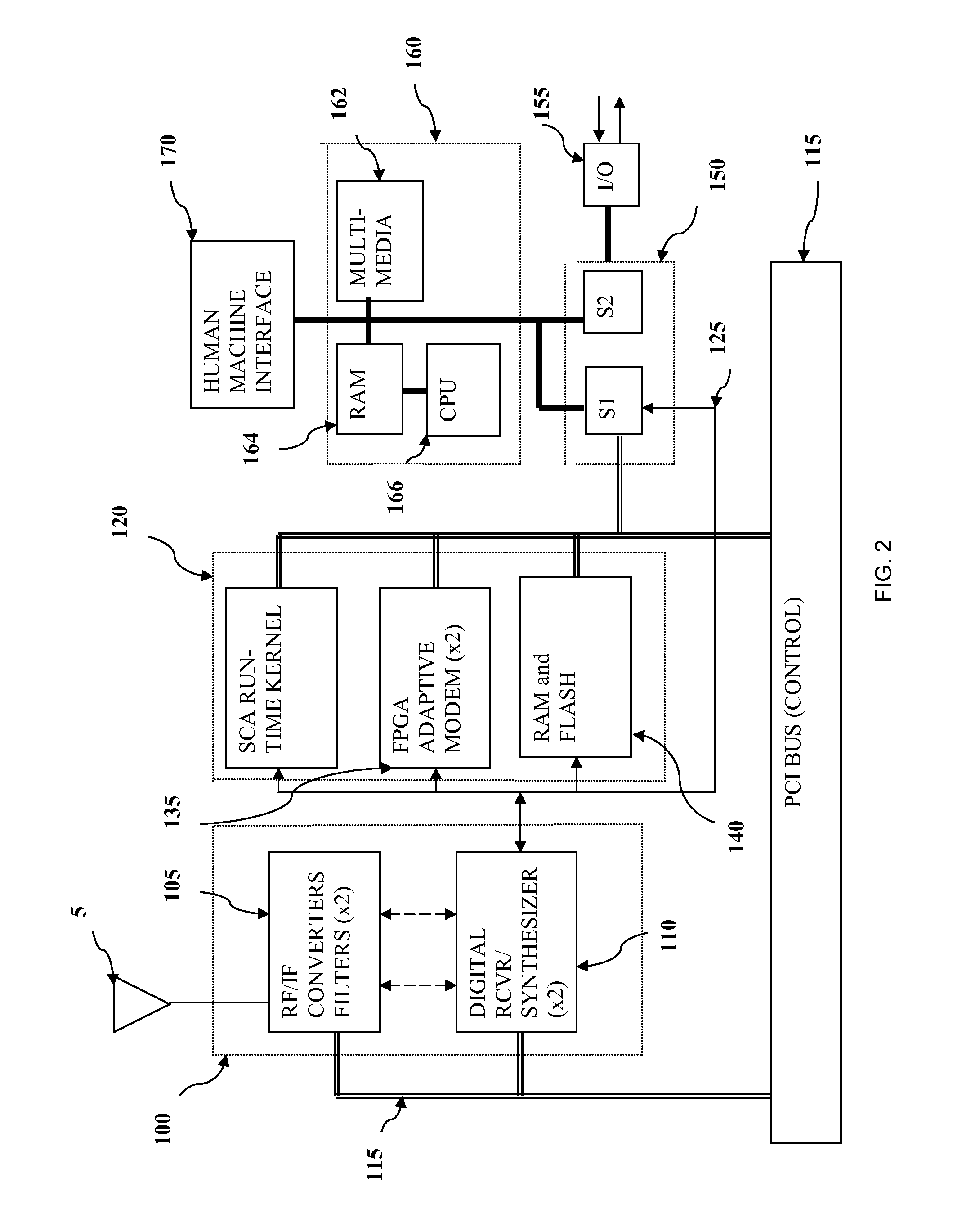

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

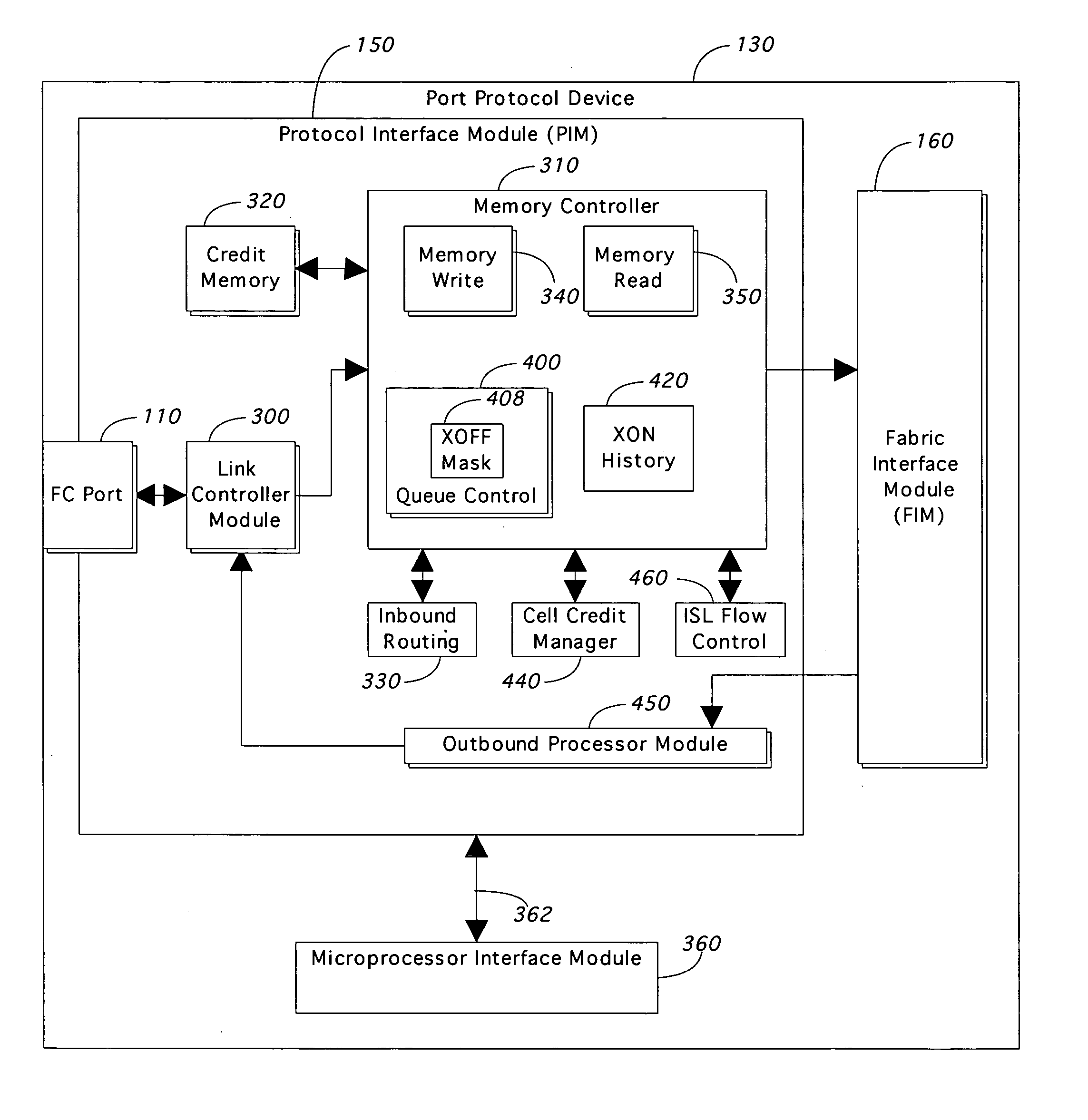

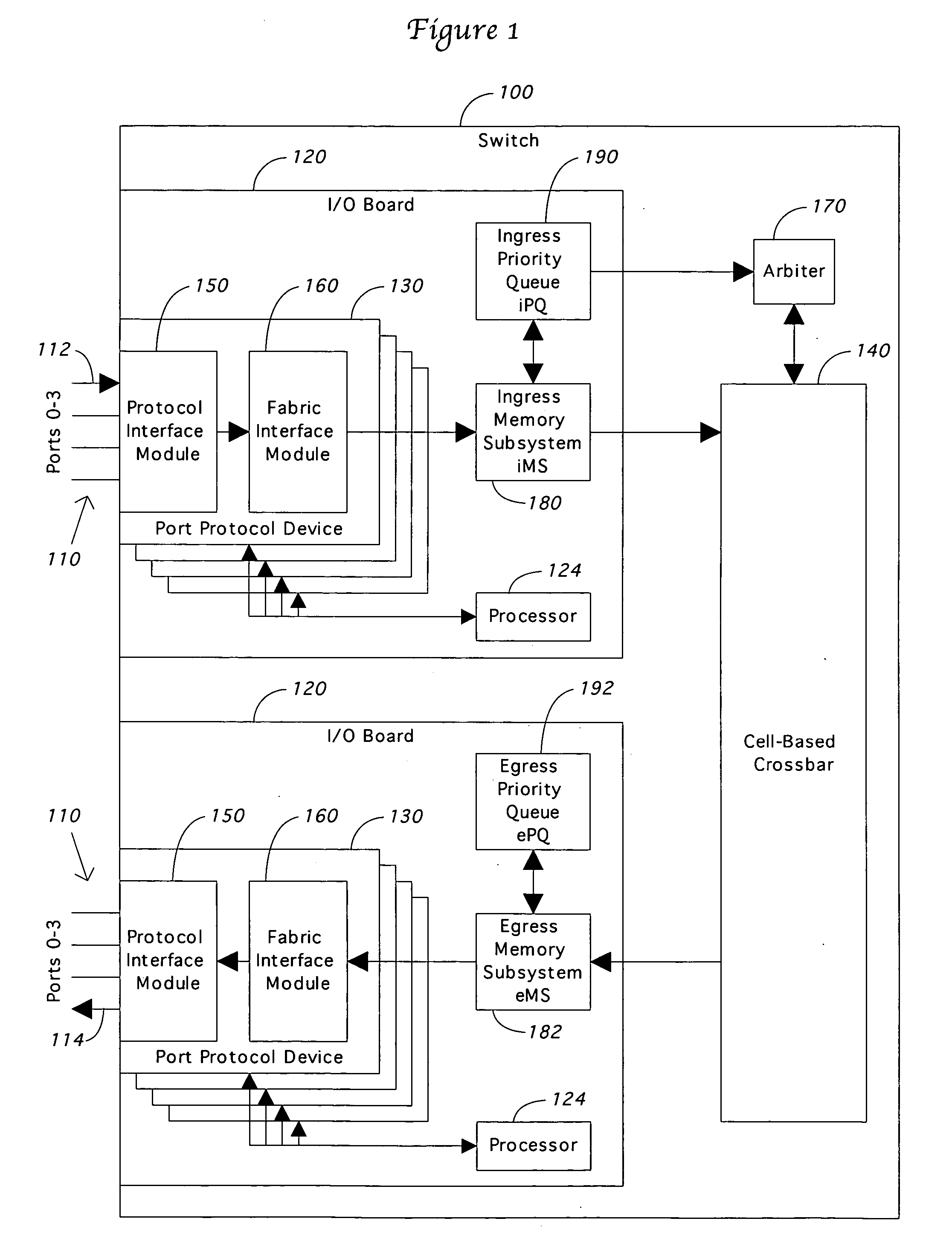

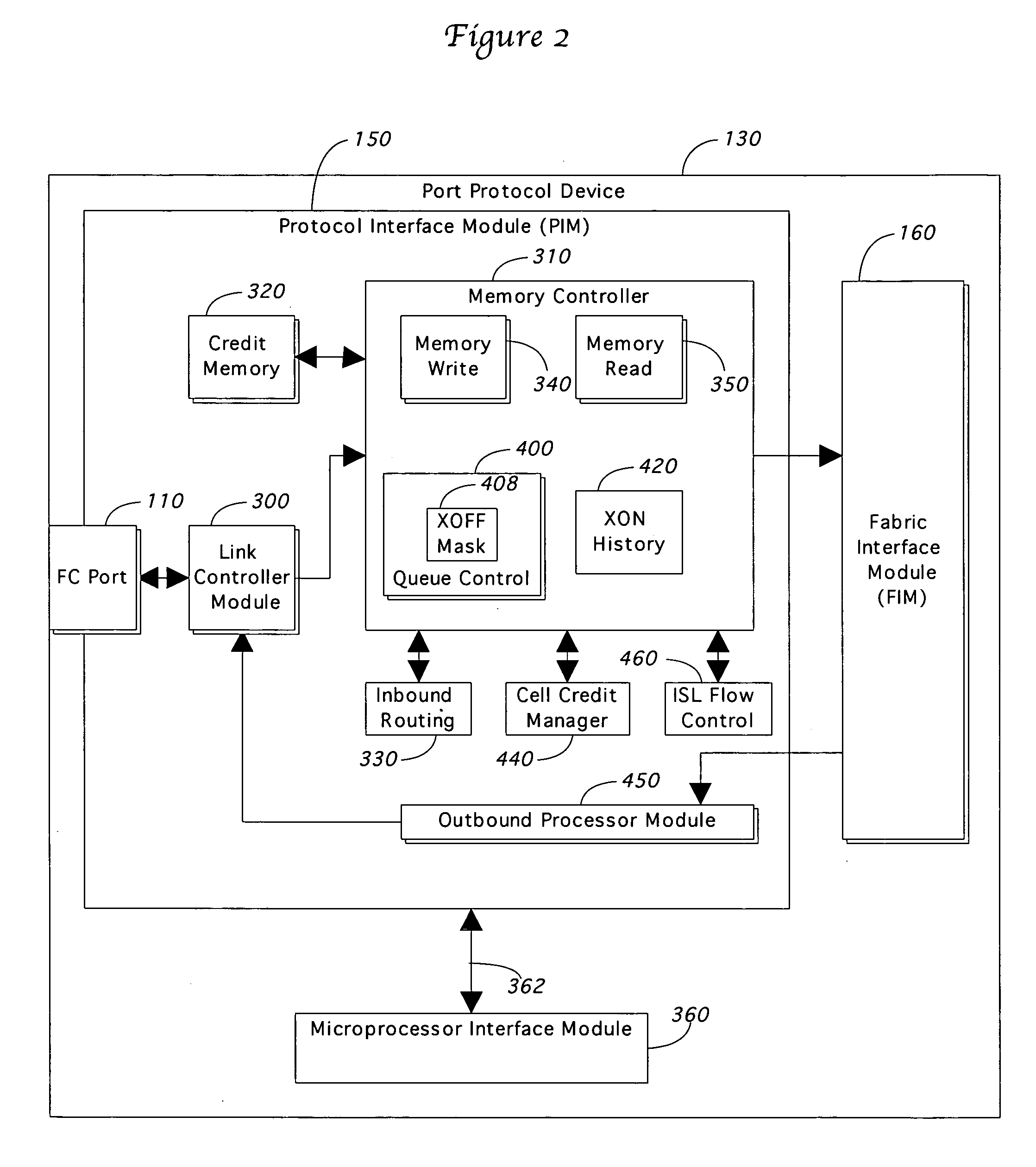

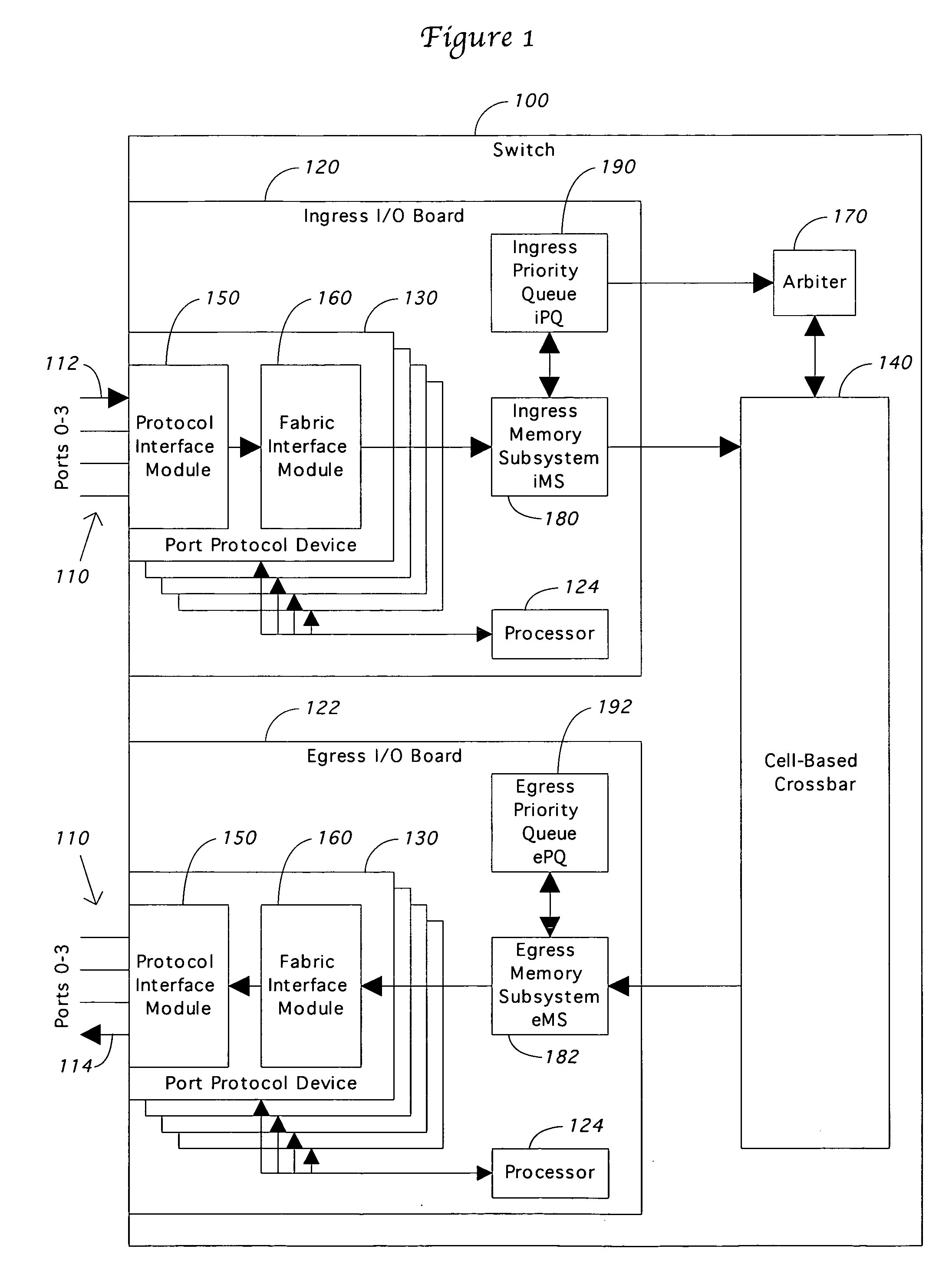

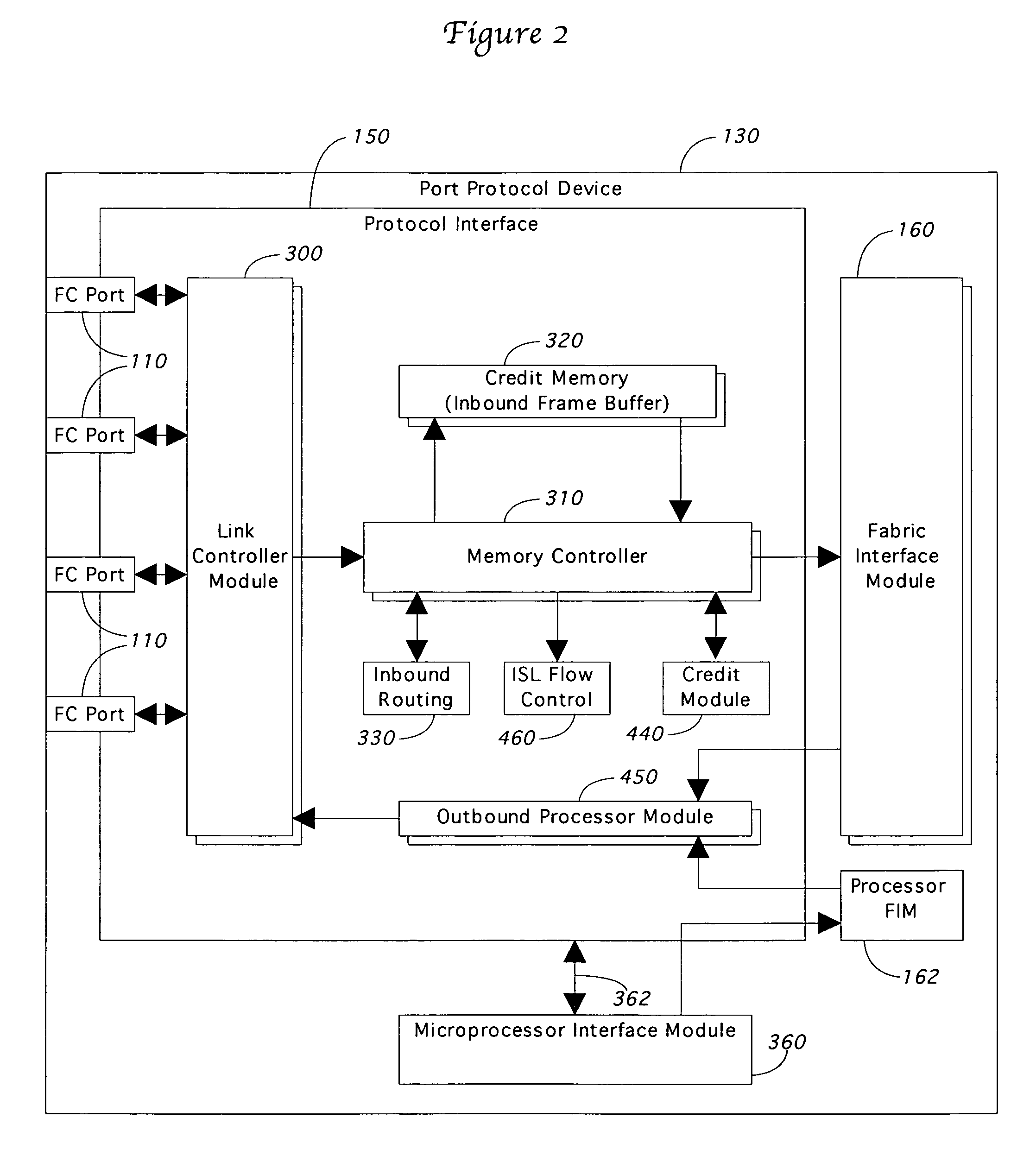

Fibre channel switch

InactiveUS20050047334A1Error preventionFrequency-division multiplex detailsCrossbar switchWire speed

A Fibre Channel switch is presented that tracks the congestion status of destination ports in an XOFF mask at each input. A mapping is maintained between virtual channels on an ISL and the destination ports to allow changes in the XOFF mask to trigger a primitive to an upstream port that provides virtual channel flow control. The XOFF mask is also used to avoid sending frames to a congested port. Instead, these frames are stored on a single deferred queue and later processed in a manner designed to maintain frame ordering. A routing system is provided that applies multiple routing rules in parallel to perform line speed routing. The preferred switch fabric is cell based, with techniques used to manage path maintenance for variable length frames and to adapt to varying transmission rates in the system. Finally, the switch allows data and microprocessor communication to share the same crossbar network.

Owner:MCDATA SERVICES CORP +1

Programmable logic device with embedded switch fabric

InactiveUS20080278197A1Telephonic communicationBootstrappingCrossbar switchProgrammable logic device

The invention in the simplest form is a programmable logic device consisting of gate arrays, external I / O endpoints, and an embedded switch fabric configurable for connecting gates to gates, endpoints to endpoints and gates to endpoints. The architecture may employ a fabric interface of non-blocking crossbar switches for making complex bus connections of multiple devices to facilitate high speed processing.

Owner:TECNICA

Port congestion notification in a switch

A congestion notification mechanism provides a congestion status for all destinations in a switch at each ingress port. Data is stored in a memory subsystem queue associated with the destination port at the ingress side of the crossbar. A cell credit manager tracks the amount of data in this memory subsystem for each destination. If the count for any destination exceeds a threshold, the credit manager sends an XOFF signal to the XOFF masks. A lookup table in the XOFF masks maintains the status for every switch destination based on the XOFF signals. An XON history register receives the XOFF signals to allow queuing procedures that do not allow a status change to XON during certain states. Flow control signals directly from the memory subsystem are allowed to flow to each XOFF mask, where they are combined with the lookup table status to provide a congestion status for every destination.

Owner:MCDATA SERVICES CORP

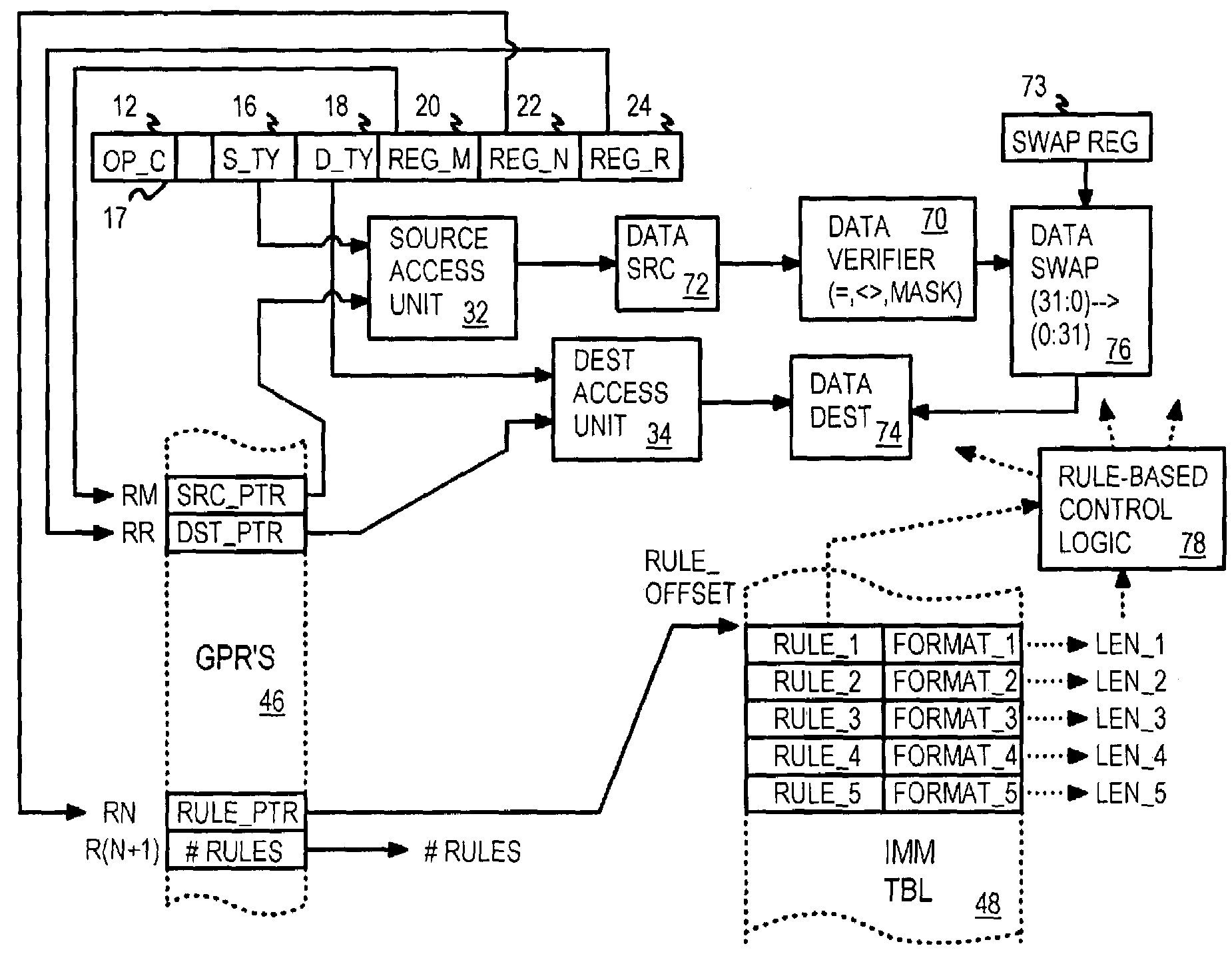

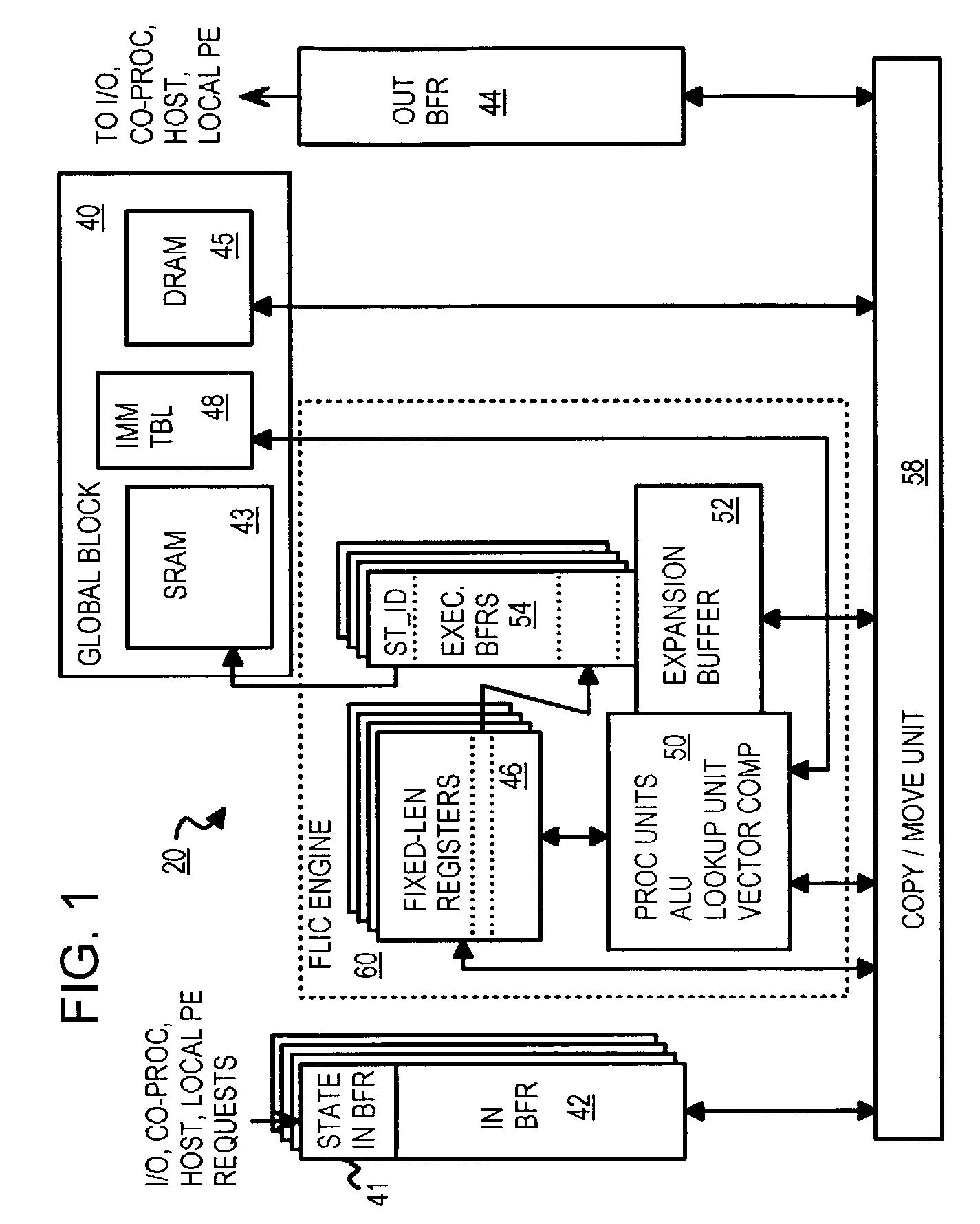

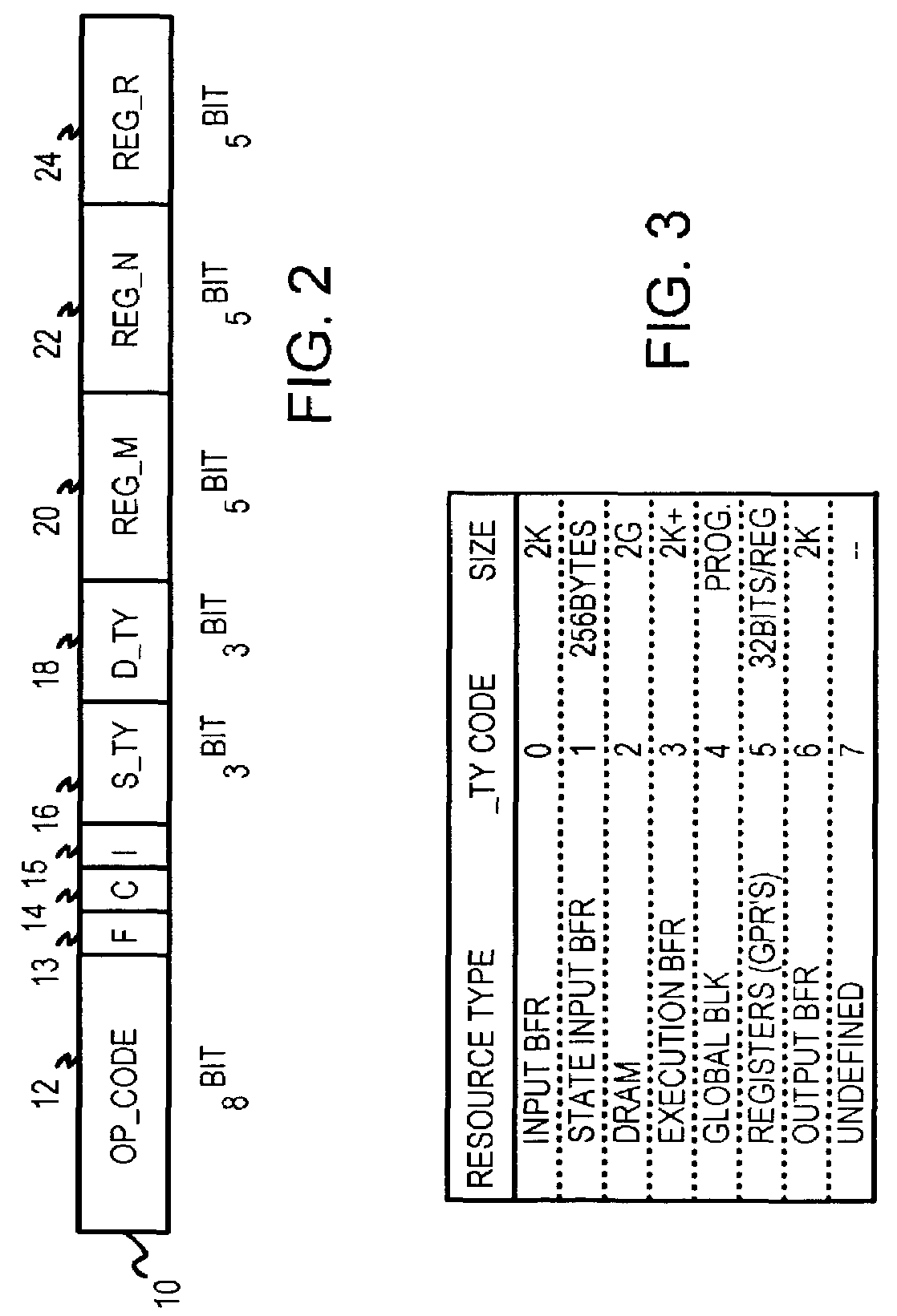

Native copy instruction for file-access processor with copy-rule-based validation

InactiveUS7191318B2Digital computer detailsSpecific program execution arrangementsCrossbar switchGeneral purpose

A copy instruction executed by a functional-level instruction-set computing (FLIC) processor copies a variable-length data block from one resource to another resource through a cross-bar switch. Resources include general-purpose registers, input, output, and execution buffers, DRAM, SRAM, and other memory. A copy-with-validate instruction has an operand pointing to a first rule in an immediate rule table. The first rule controls validation of a first data-item in the data being copied. Validation includes range and equality checking of the data-item. The value of the data-item or the current offset can be written to a register. A format field in the rule indicates the size of the data-item, or the size is read from the data-item for variable-size formats. The current offset is incremented by the size. The next data-item is validated by a next rule, and other rules in the immediate table control validation of other data-items in the data block.

Owner:RPX CORP

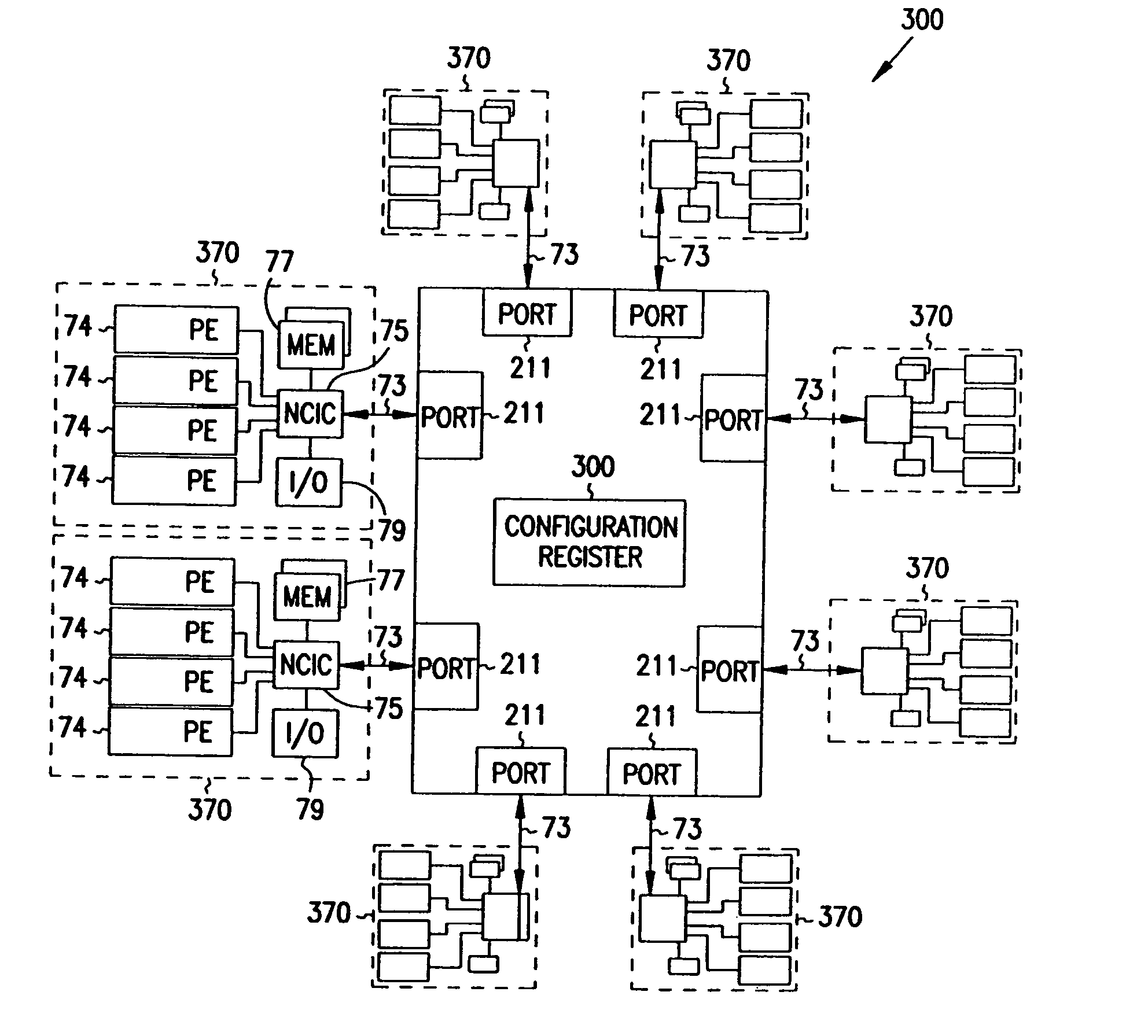

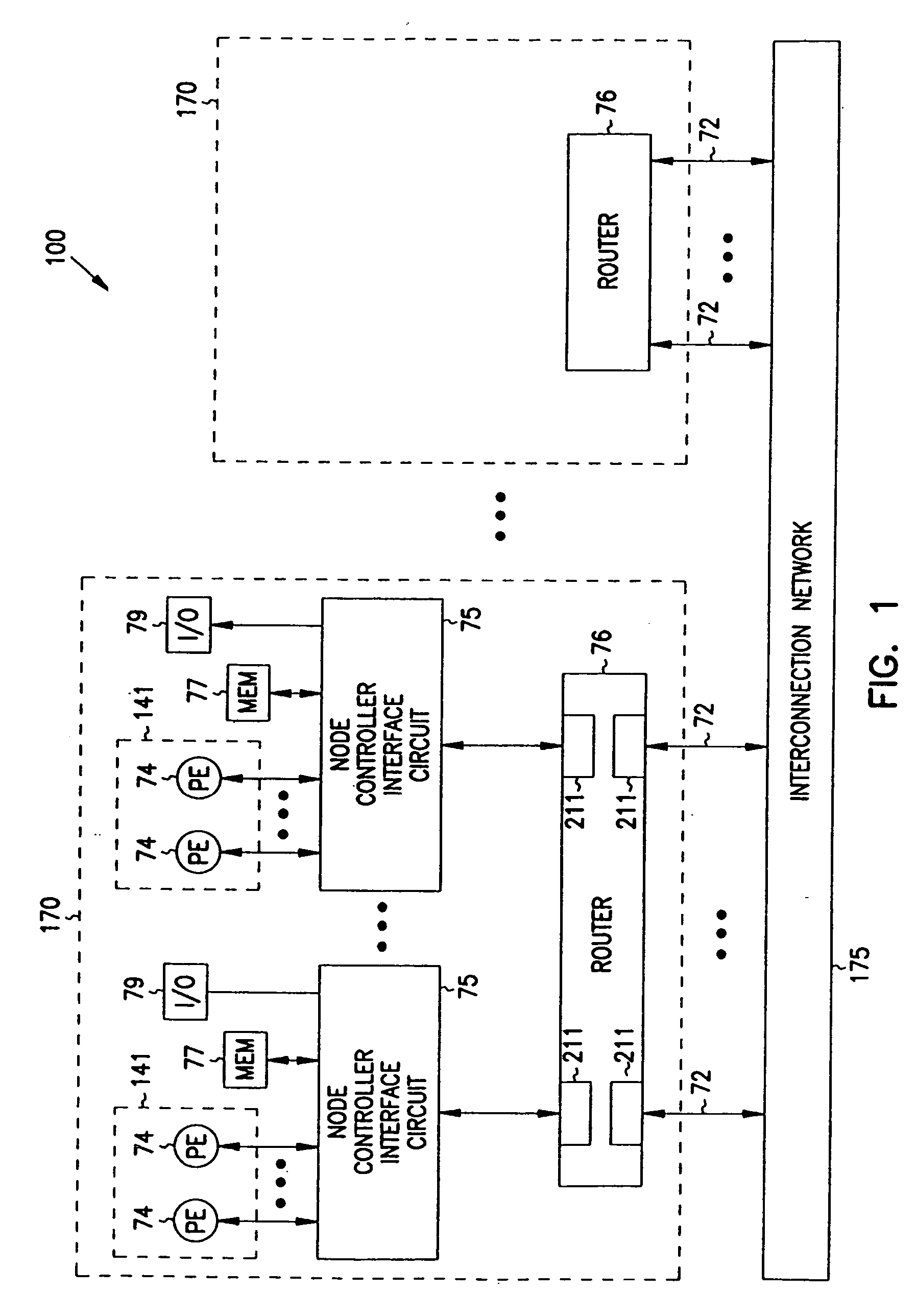

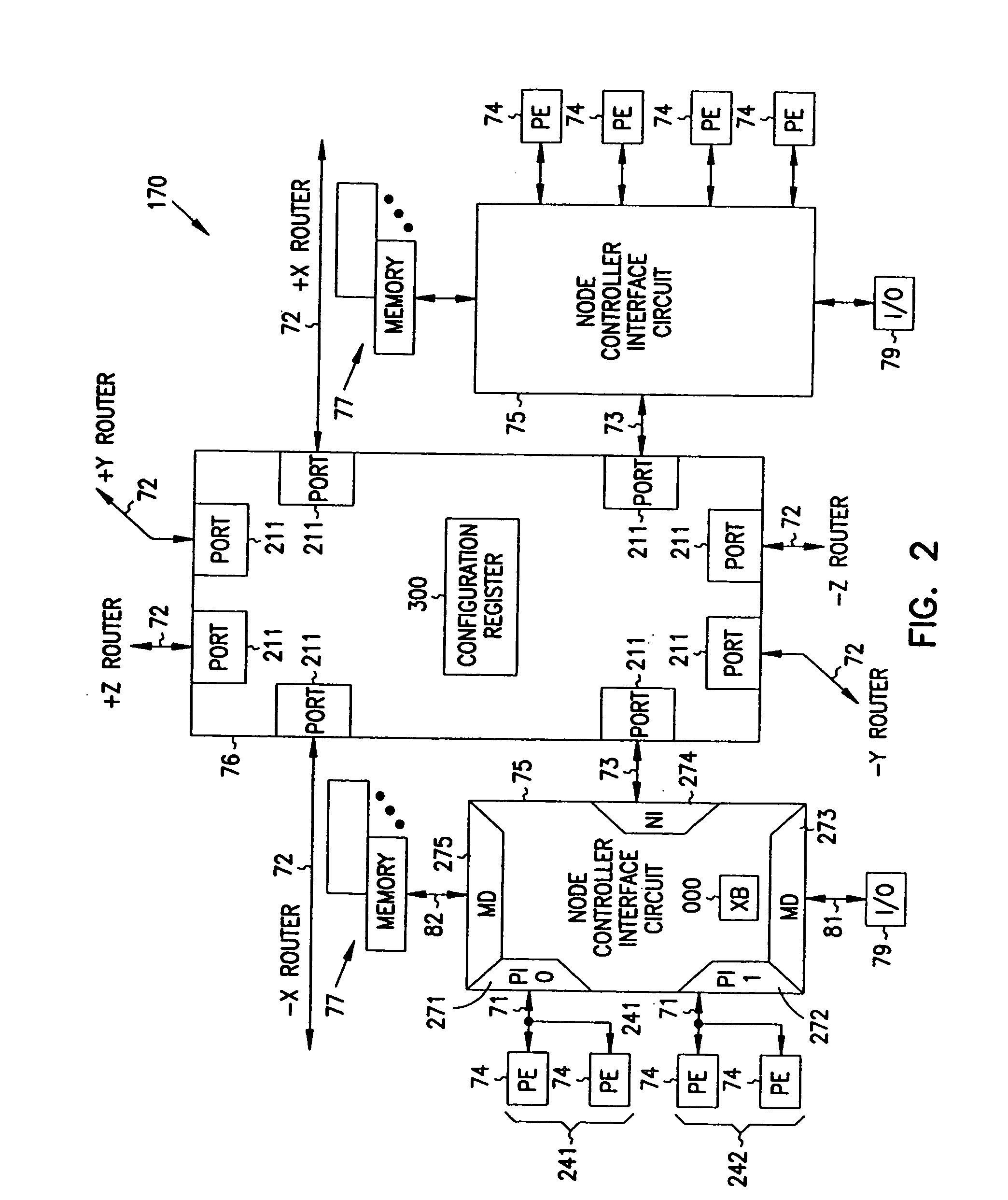

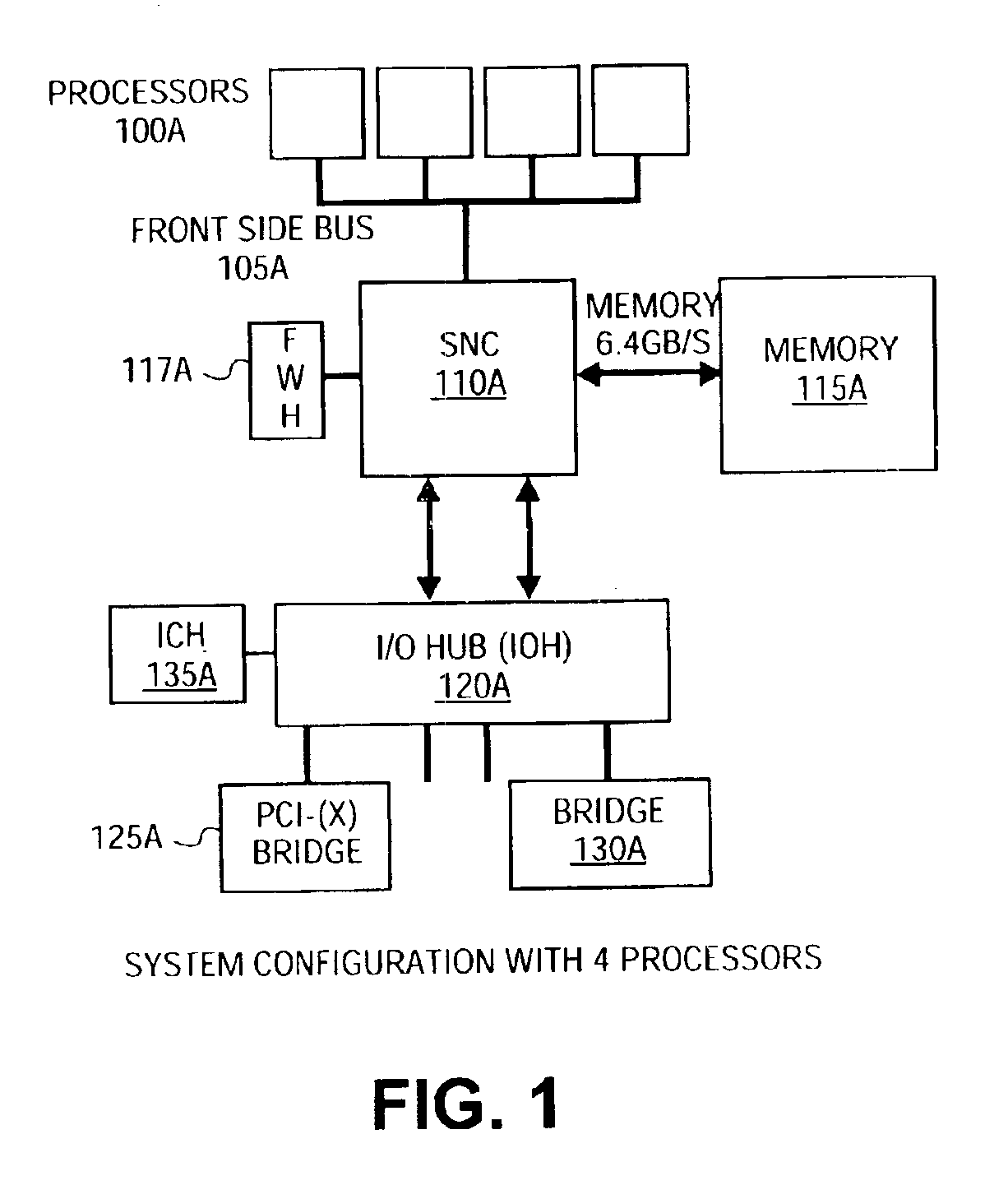

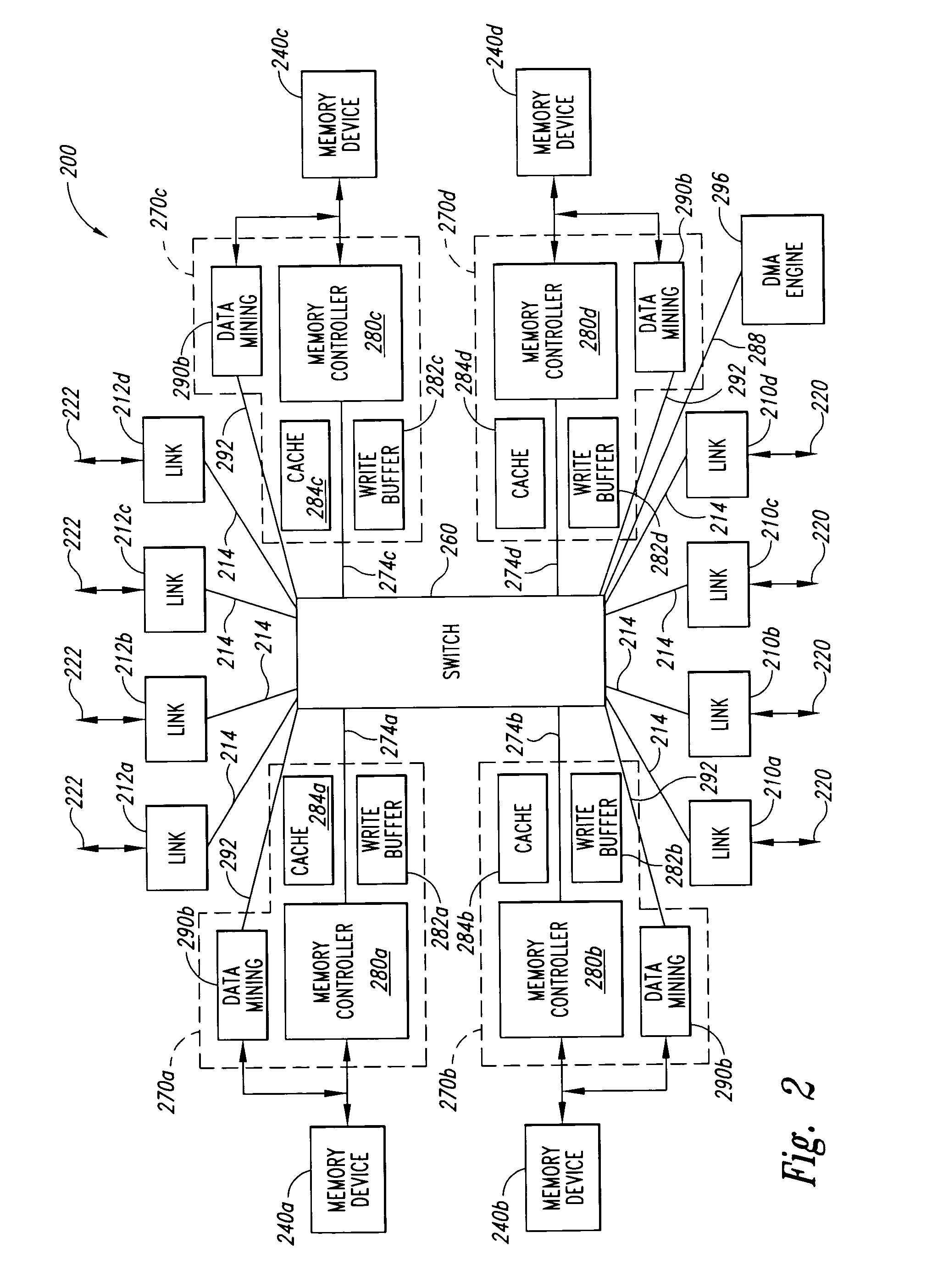

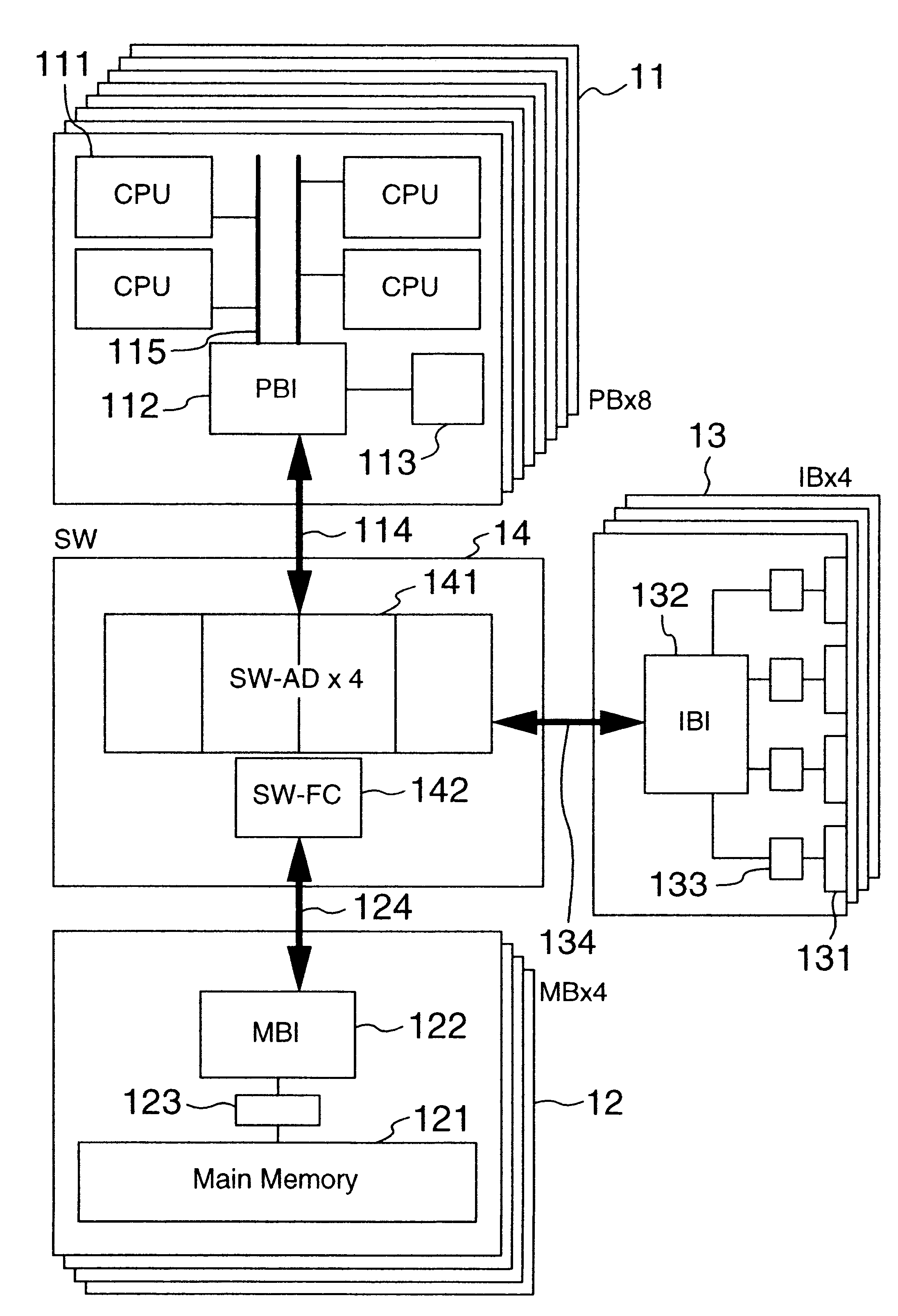

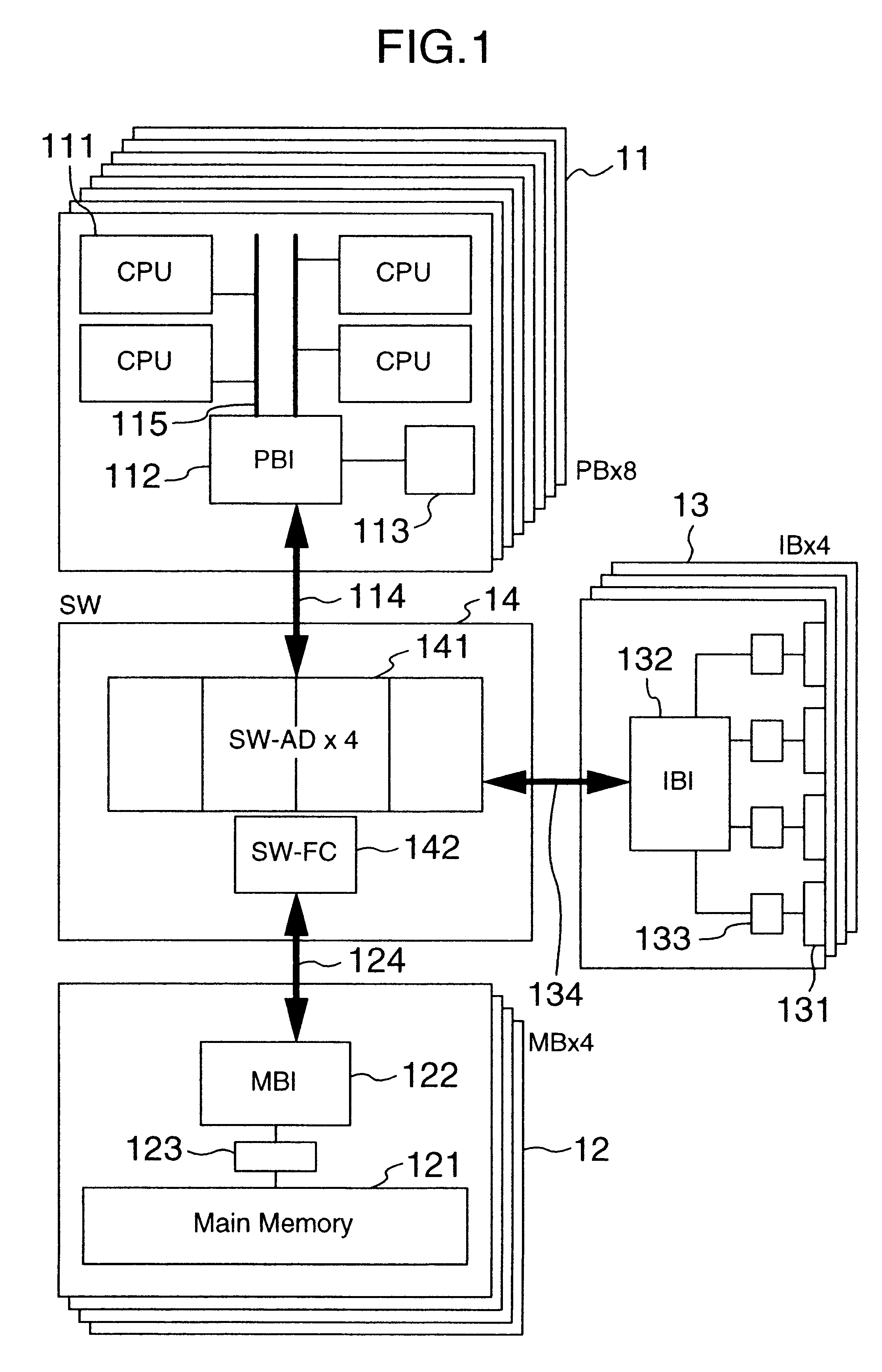

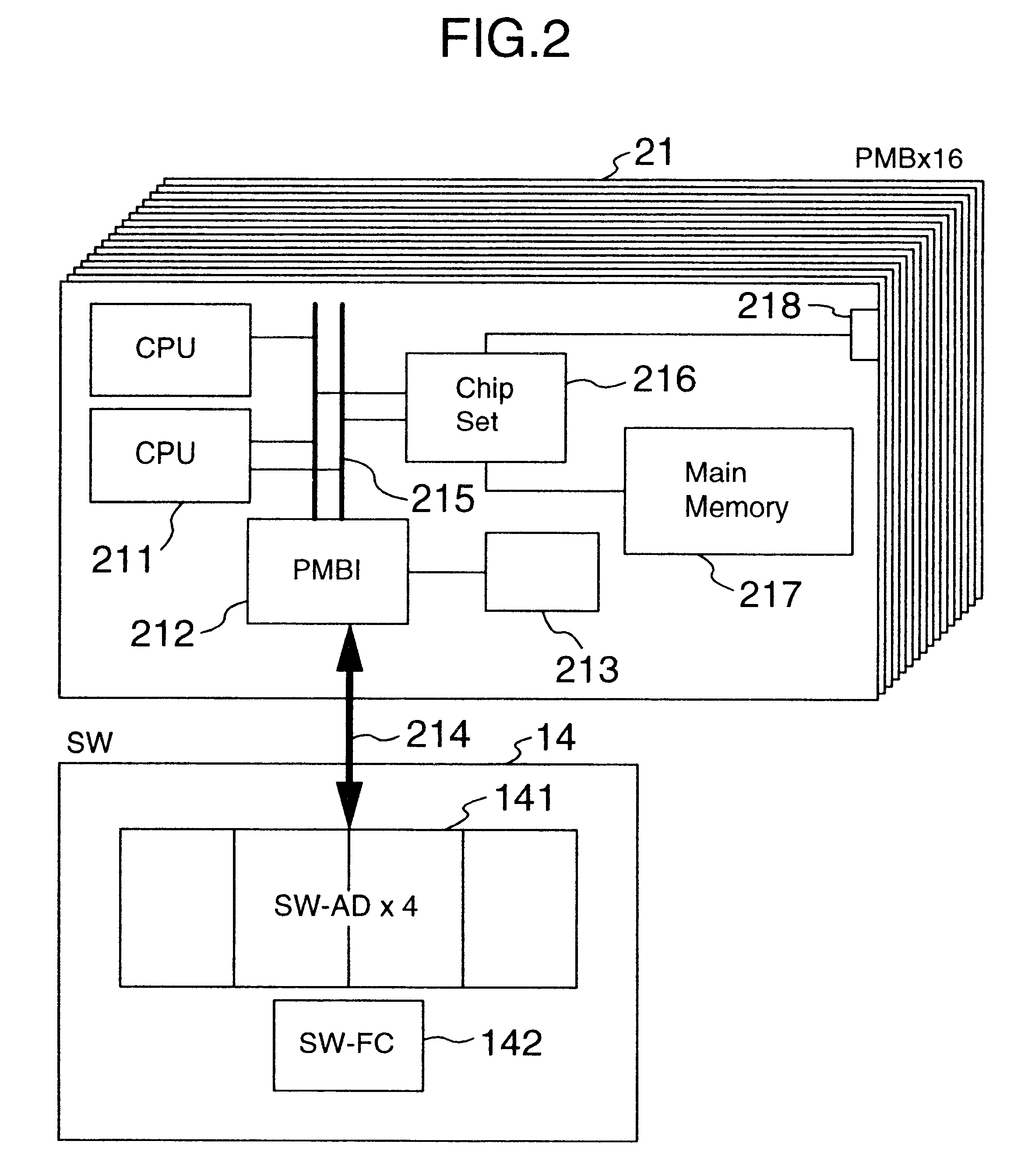

Multiprocessor node controller circuit and method

InactiveUS20050053057A1Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressCrossbar switch

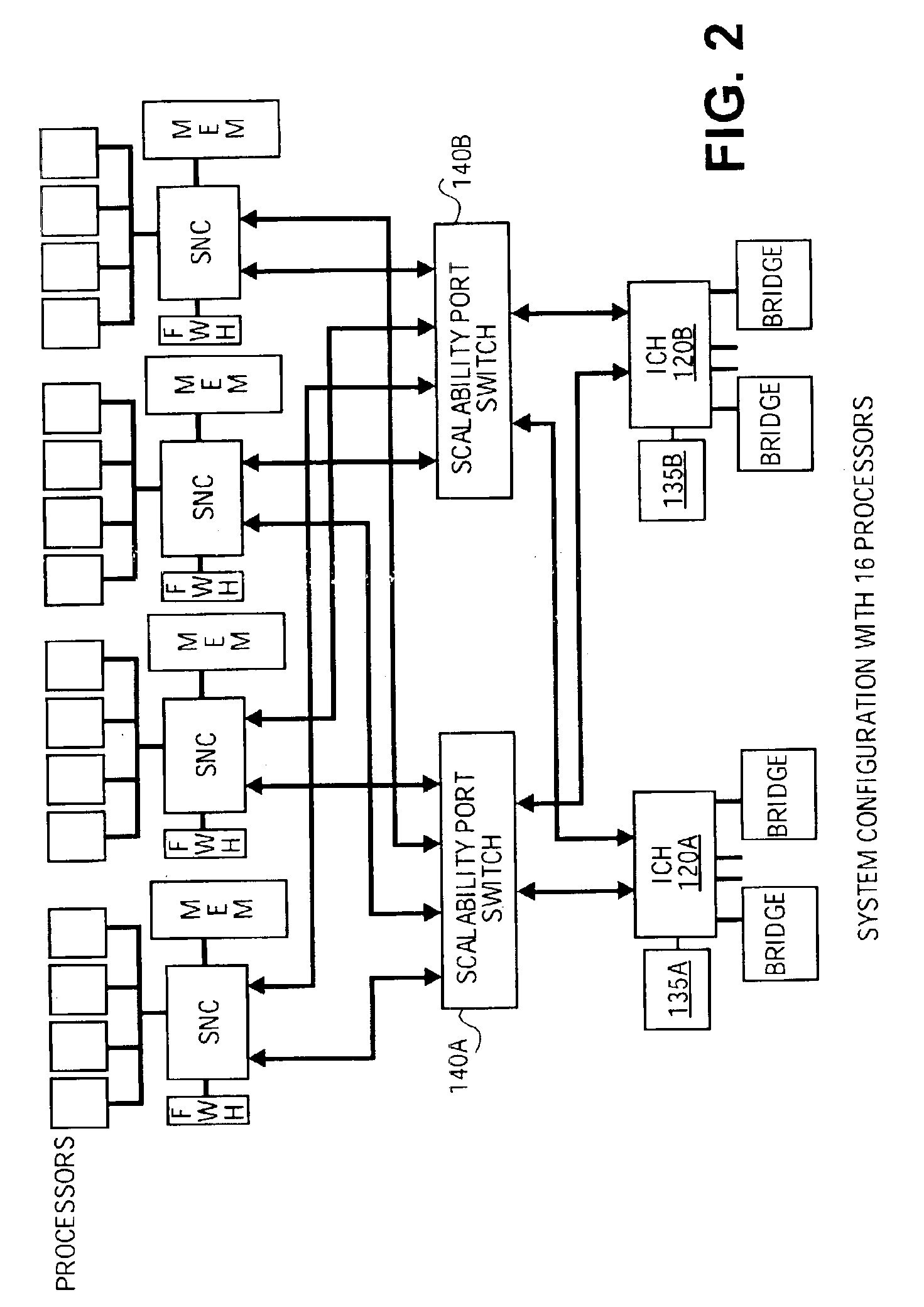

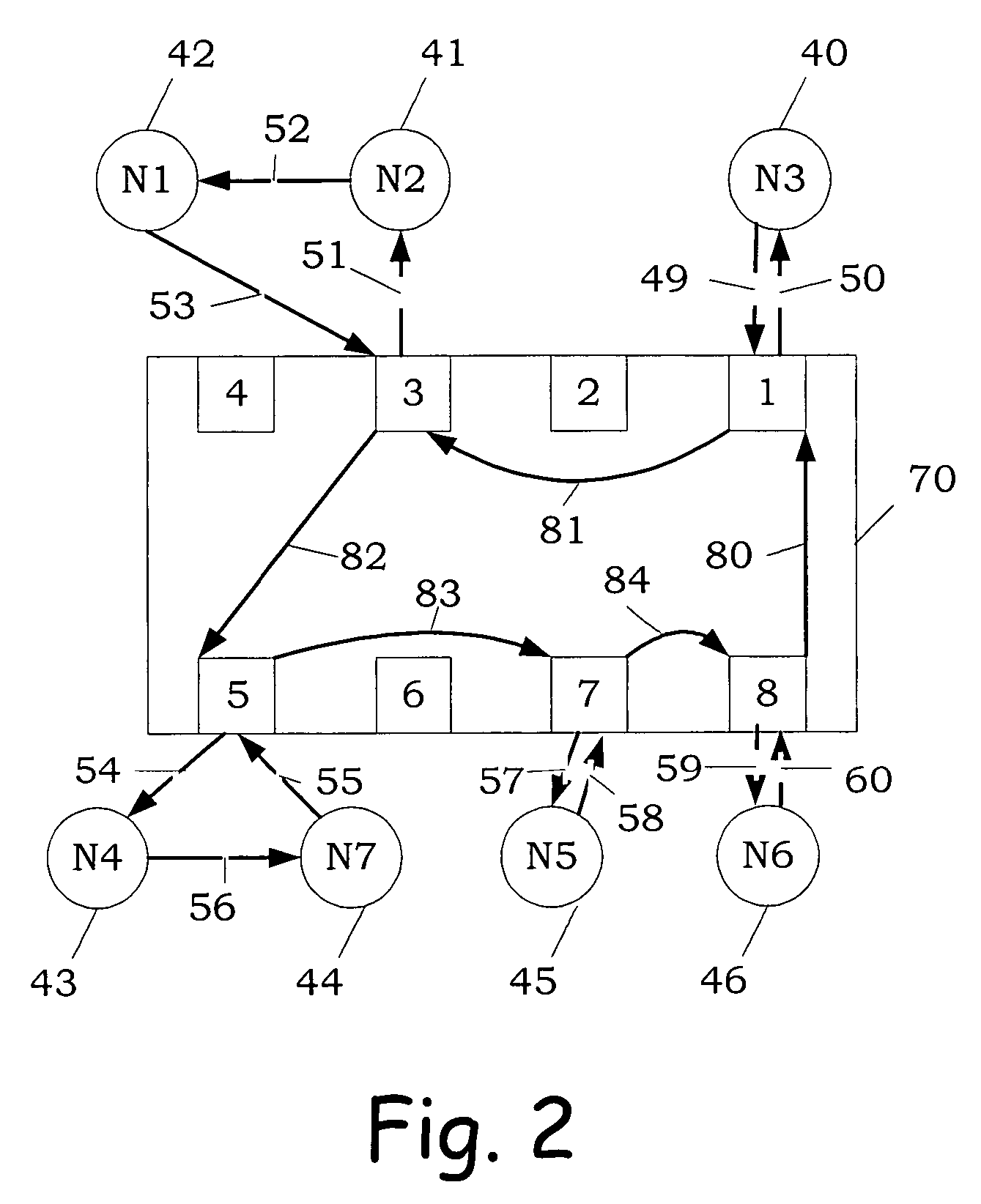

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

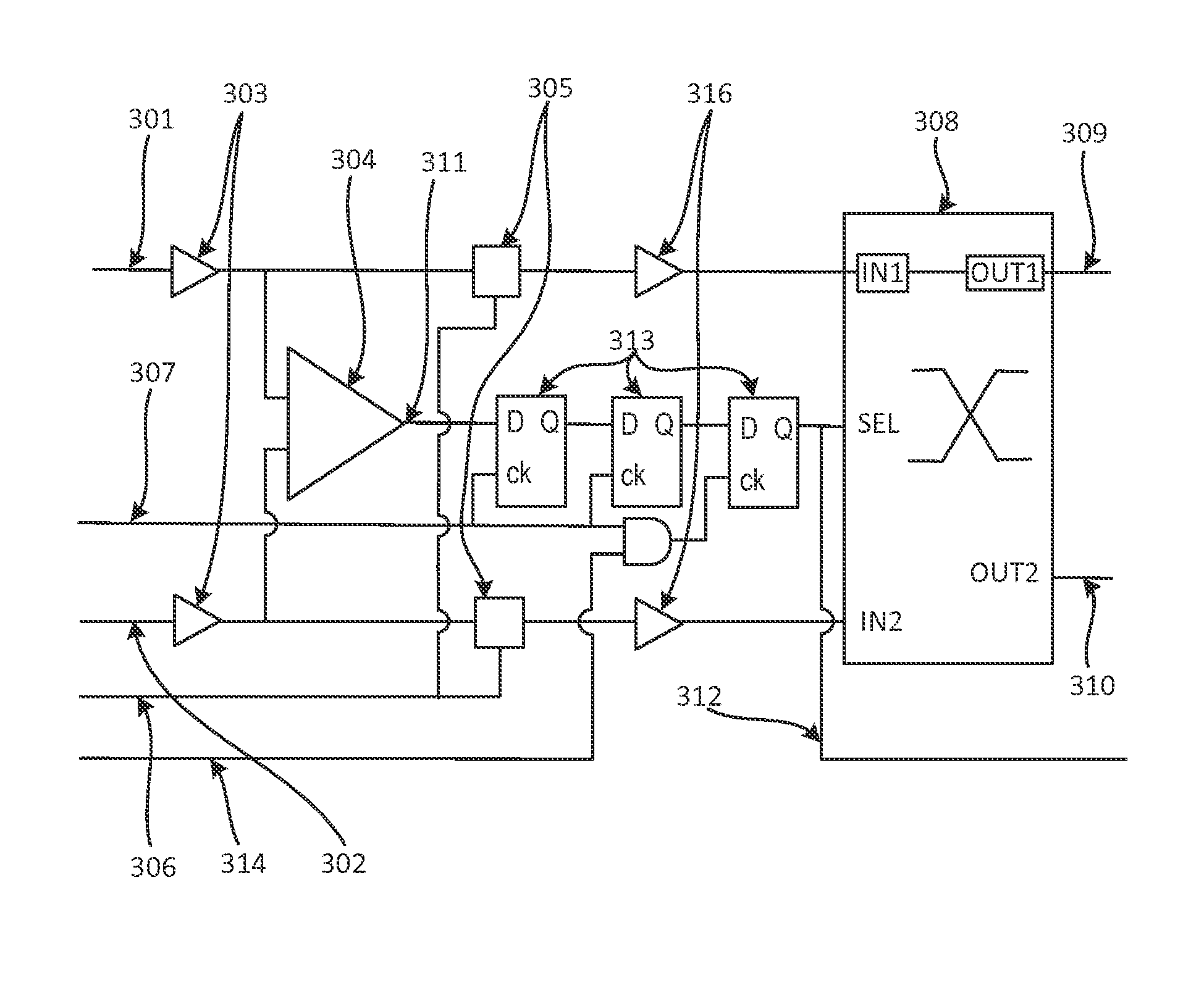

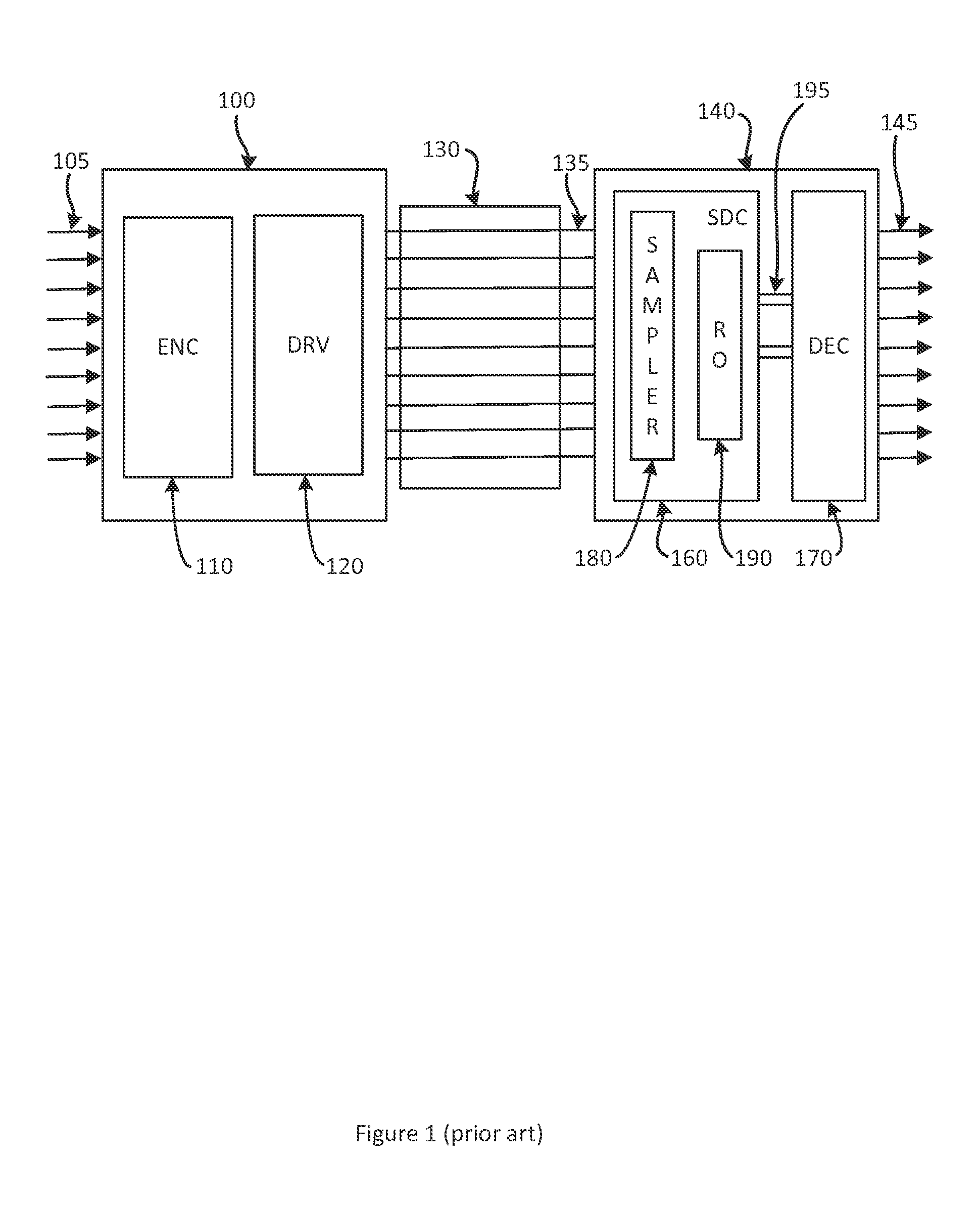

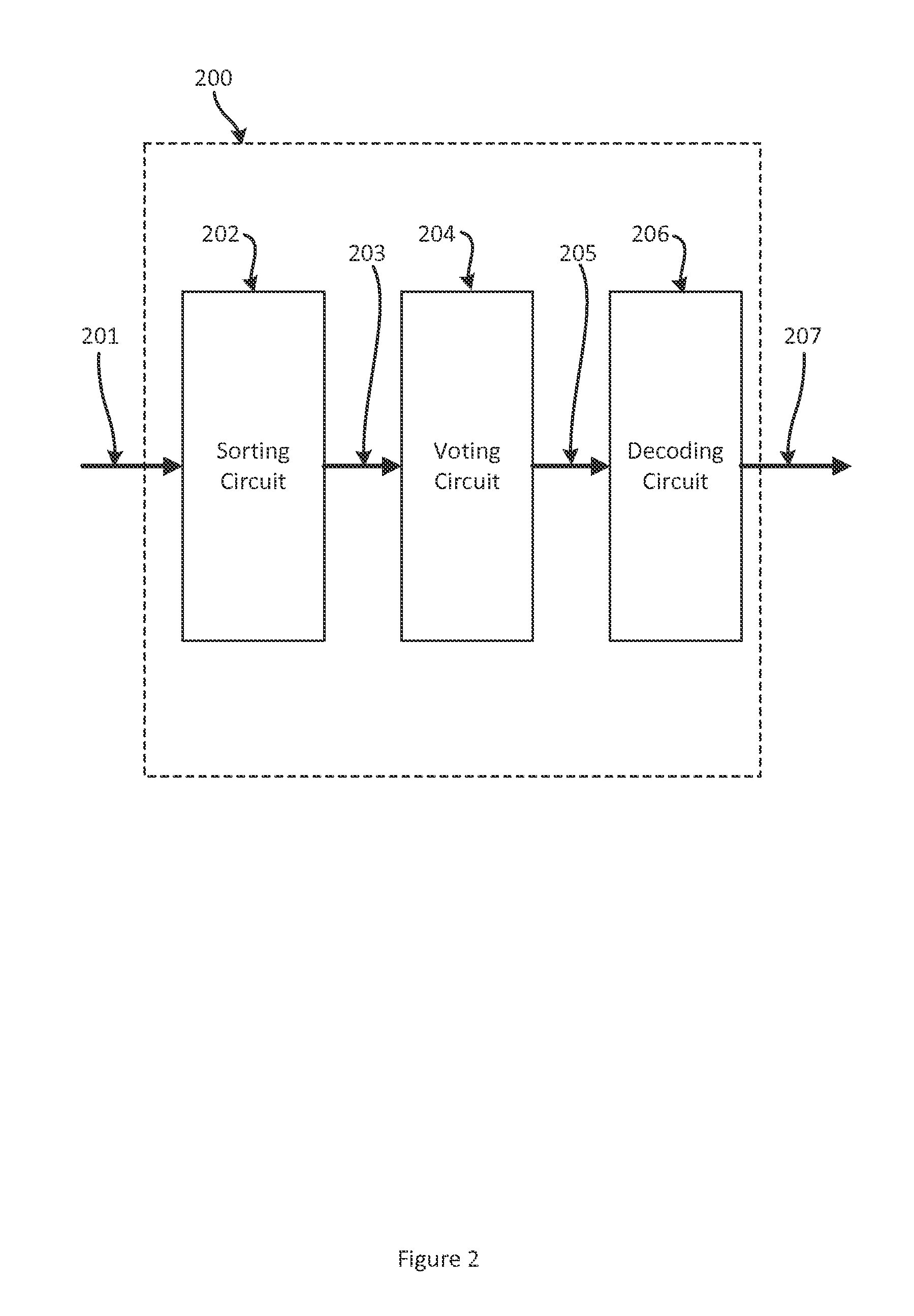

Crossbar switch decoder for vector signaling codes

ActiveUS8989317B1Efficient and effectiveAmplitude demodulation by homodyne/synchrodyne circuitsAmplitude-modulated carrier systemsCrossbar switchData set

An efficient decoding of vector signaling codes is obtained using a circuit that ranks received signal levels, designates ranked values as representing particular code elements, and translates those particular code elements into a decoded result. An optimized ranking circuit combines analog crossbar switching of signal values with comparators that provide digital results. These elements may be repetitively tiled into processing arrays capable of larger ranking operations, or iteratively applied to selected portions of the data set under control of a sequencer or controller.

Owner:KANDOU LABS

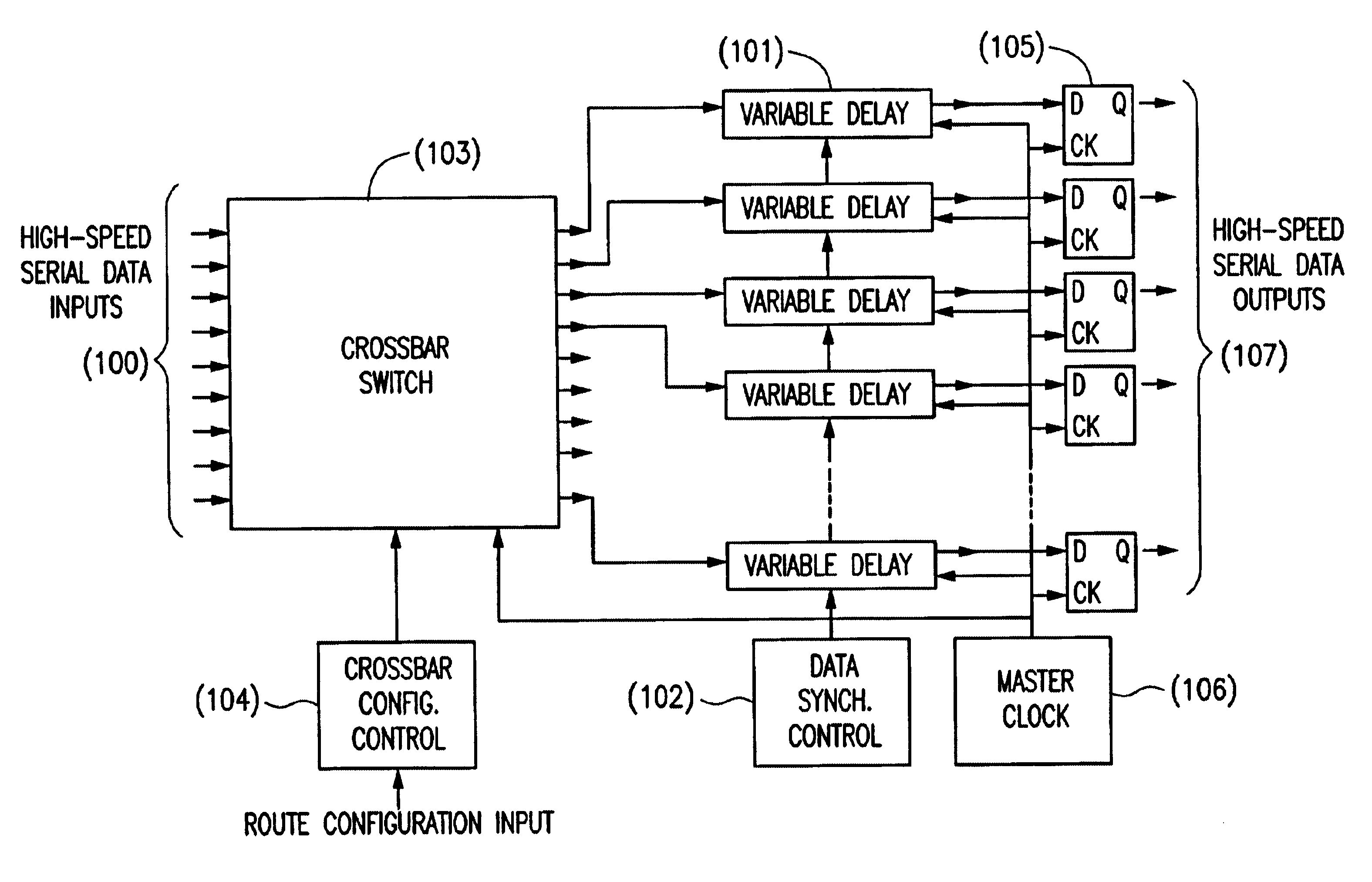

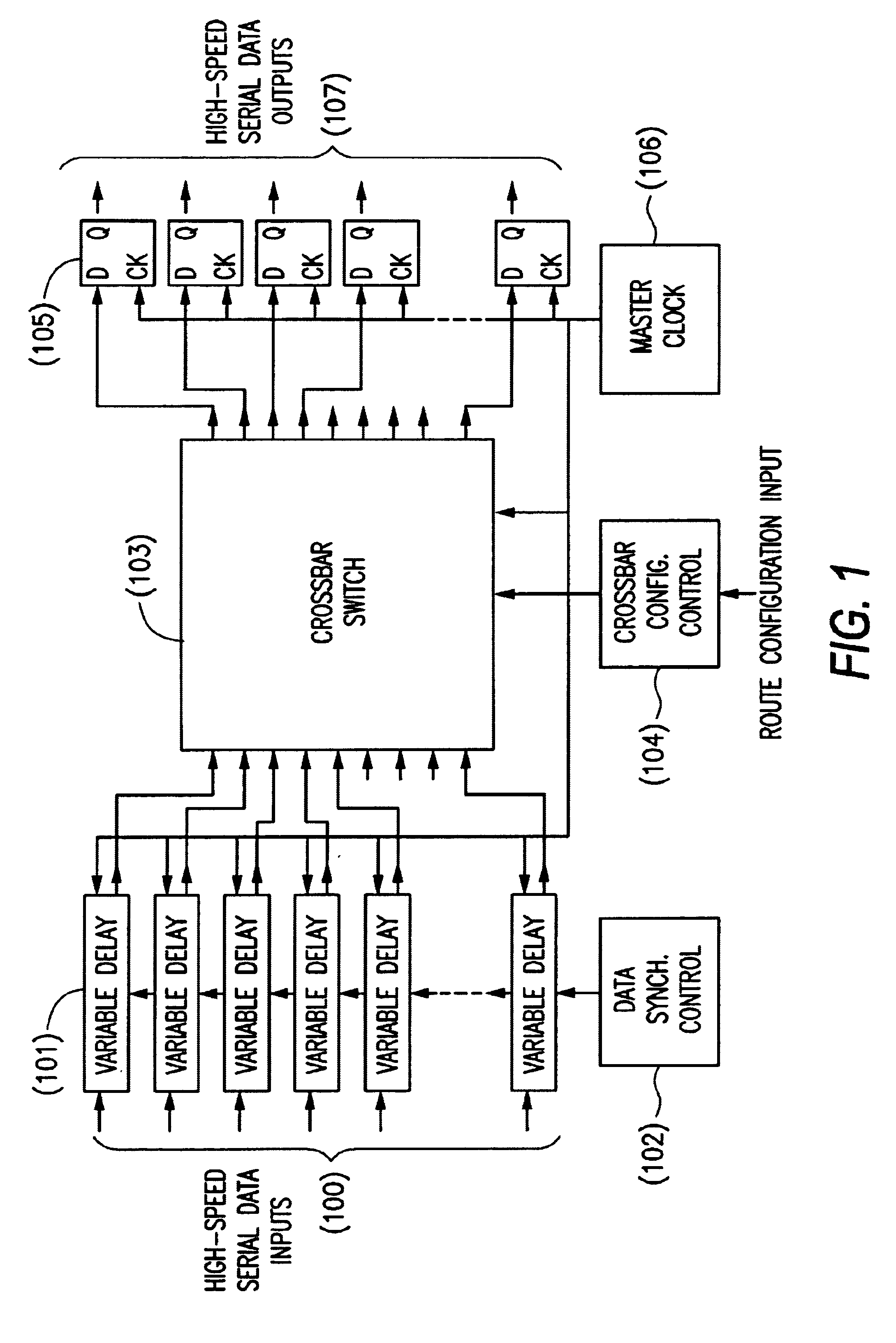

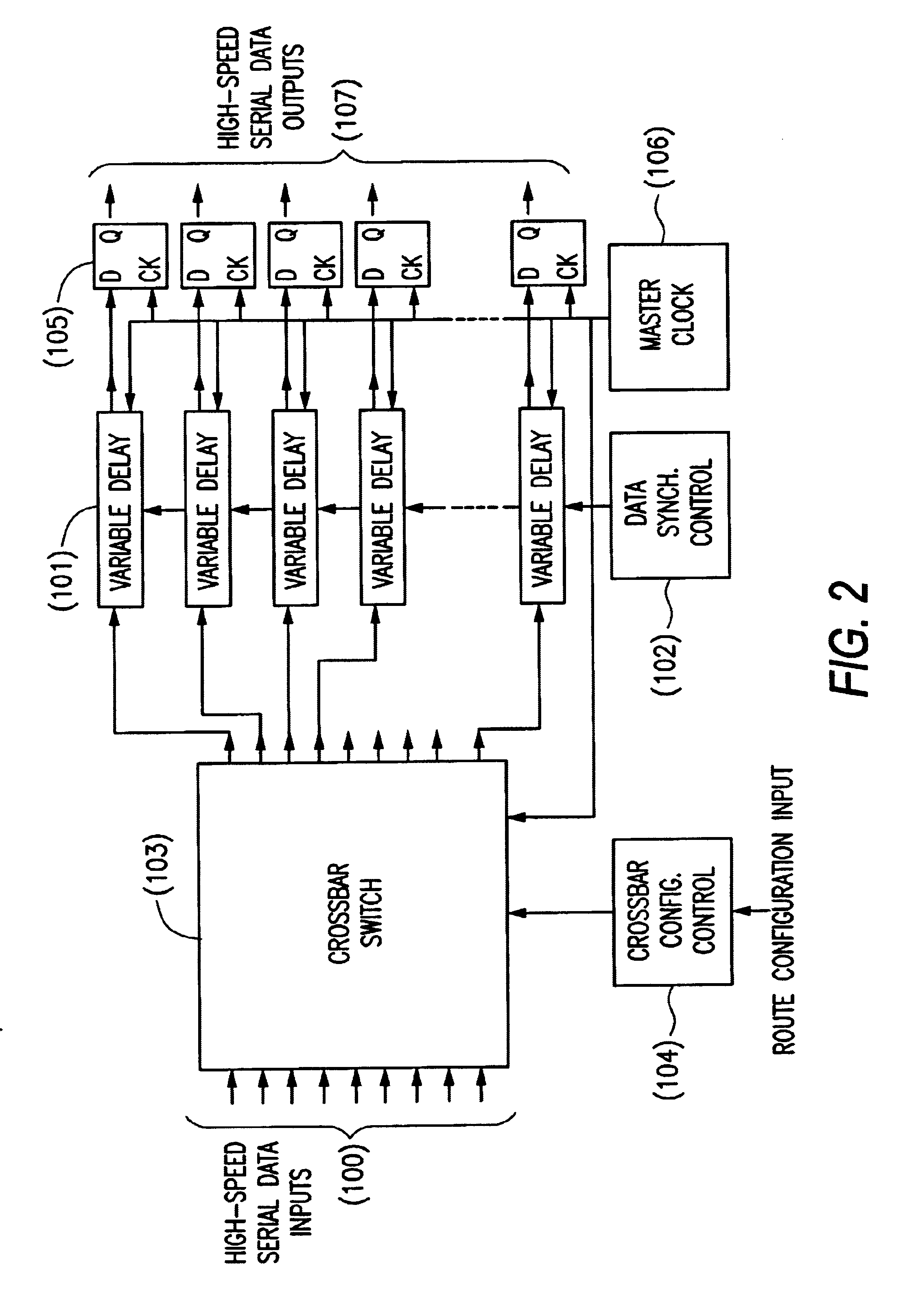

Crossbar switch and control for data networks switching

InactiveUS6636932B1Error preventionFrequency-division multiplex detailsCrossbar switchNetwork switch

A modified version of a switching / routing device commonly known as a crossbar switch which is optimized to switch and reroute very high speed synchronous data communication signals without interruptions and / or excessive transition time shifts.

Owner:ROUND ROCK RES LLC

Shared bypass bus structure

InactiveUS6912612B2Error preventionFrequency-division multiplex detailsCrossbar switchLatency (engineering)

A shared bypass bus structure for low-latency coherency controller access in a coherent scalable switch. In a coherent scalable switch with multiple coherent interconnect ports, distributed coherency control structures, and a crossbar interface between them, a shared bypass bus permits data transfer between the coherent interconnect ports and the coherency control structures while bypassing the crossbar interface. Some embodiments may comprise scalable switches to support one or more sets of processors with substantially independent snoop or cache coherency paths or arrangements.

Owner:INTEL CORP

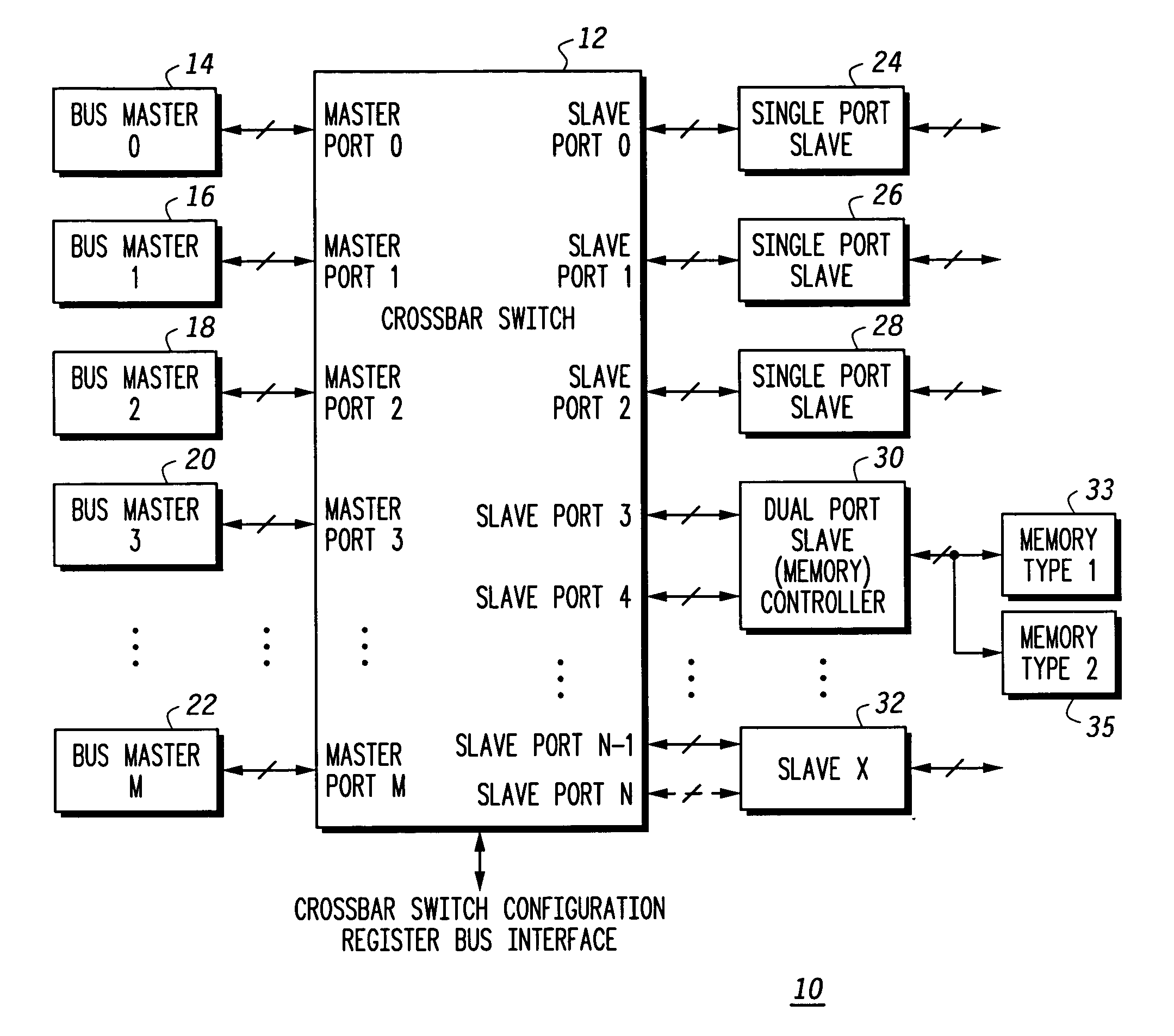

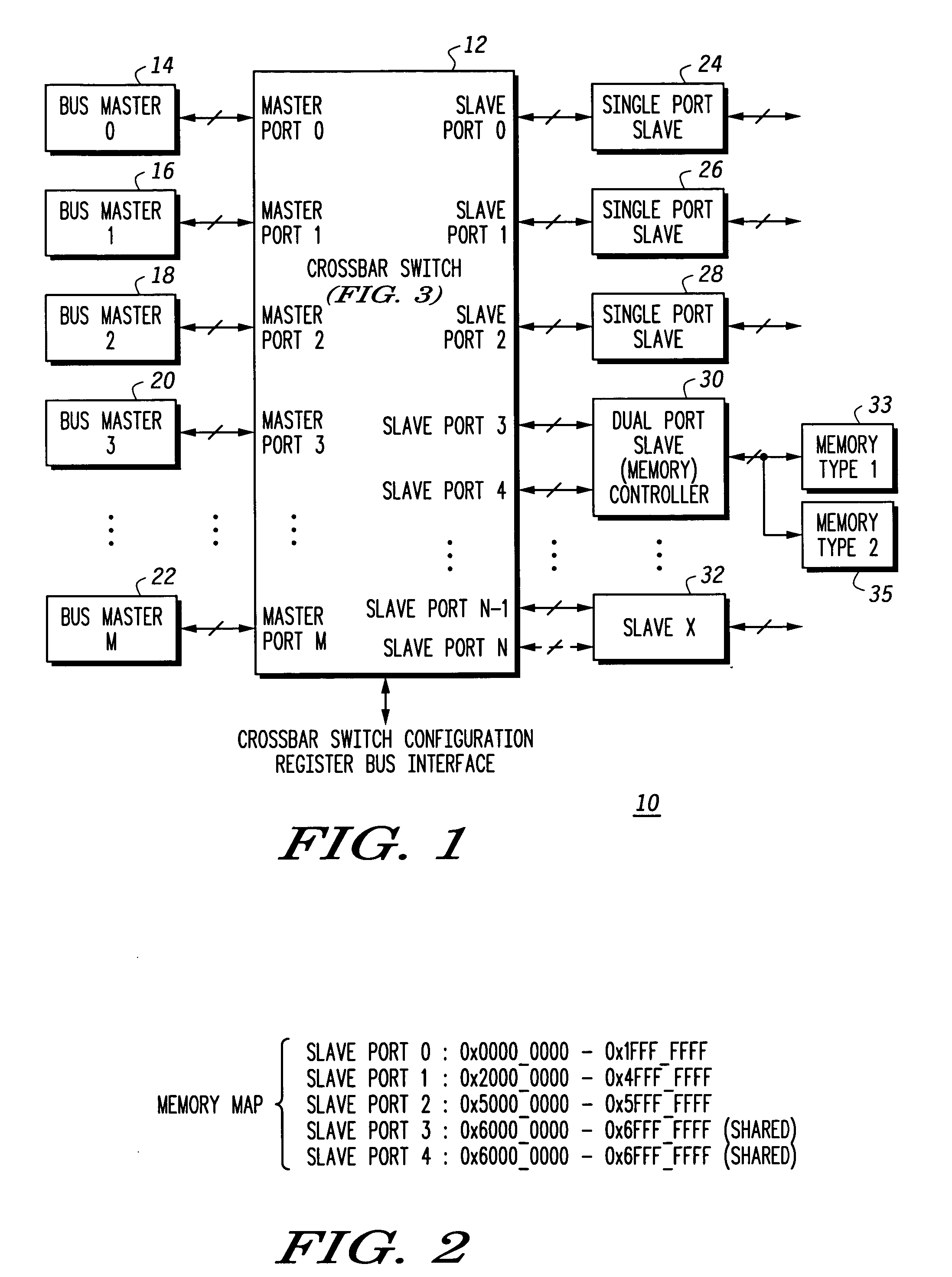

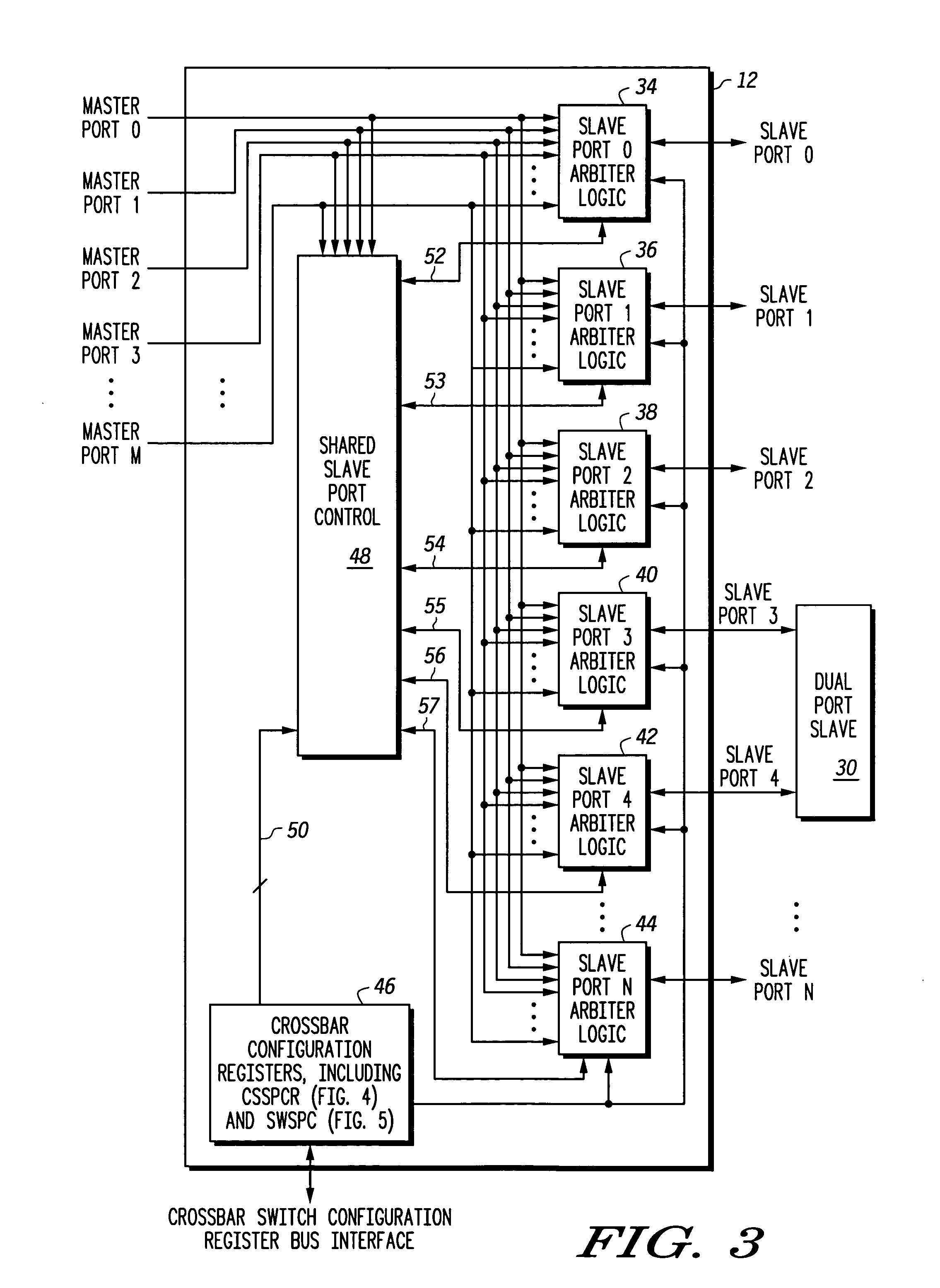

Crossbar switch that supports a multi-port slave device and method of operation

A crossbar switch (12) arbitrates for access from multiple bus masters (14, 16, 18, 20 and 22) to multiple addressed slave ports (3 and 4) that have overlapping address ranges. In one form, the address ranges are the same address range. The crossbar switch (12) uses shared slave port control circuitry (48), configuration registers (46) and slave port arbiter logic (34, 36, 38, 40, 42 and 44) to arbitrate for access when all the addressed ports are busy. A determination is made as to whether new access requests are higher or lower in priority than existing accesses. A determination on where to direct a new access request is made based upon a prediction of which of certain multiple accesses will complete first based on various factors including the number of data beats requested as well as wait state information. In one mode, the wait state information is determined dynamically.

Owner:NXP USA INC

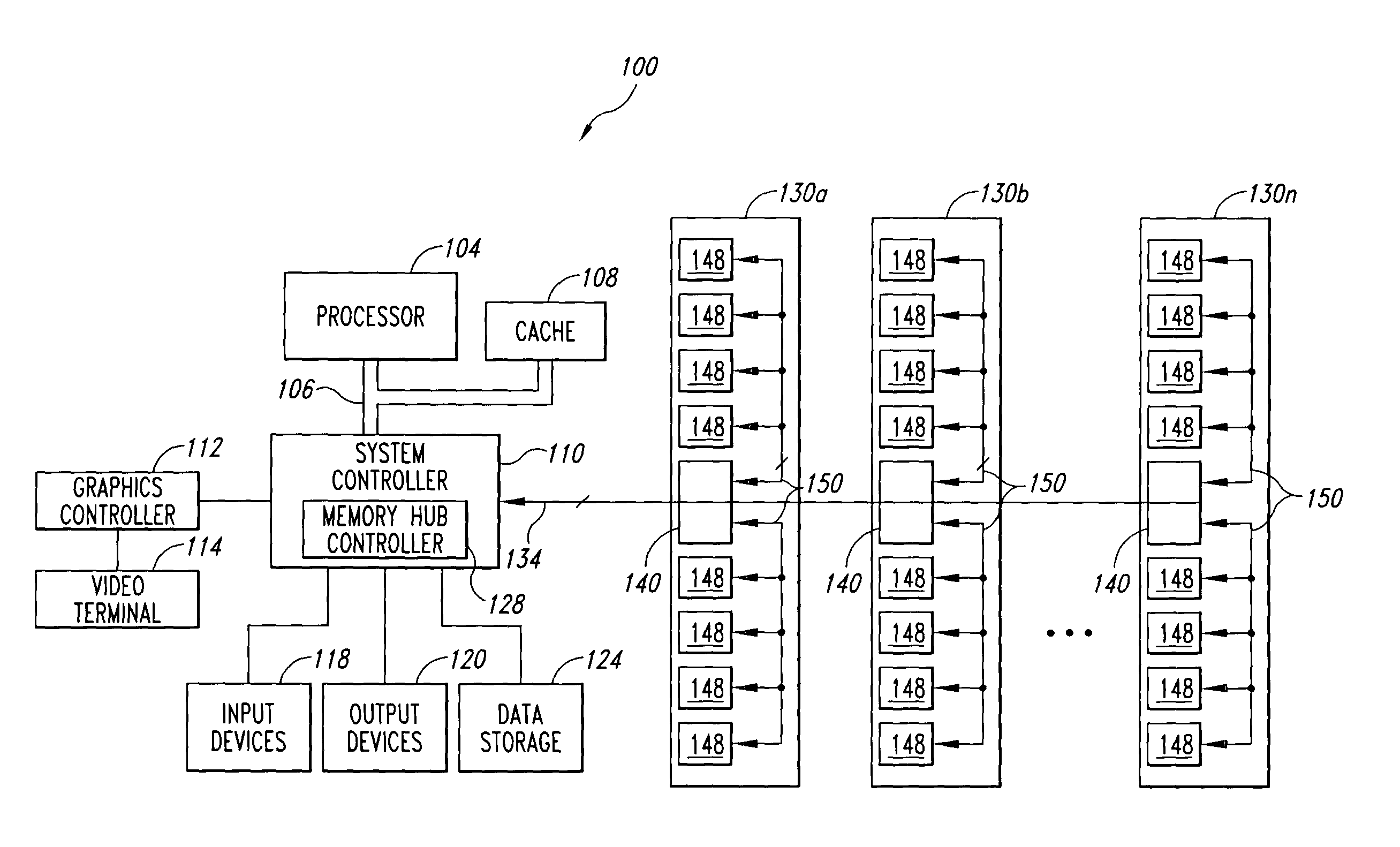

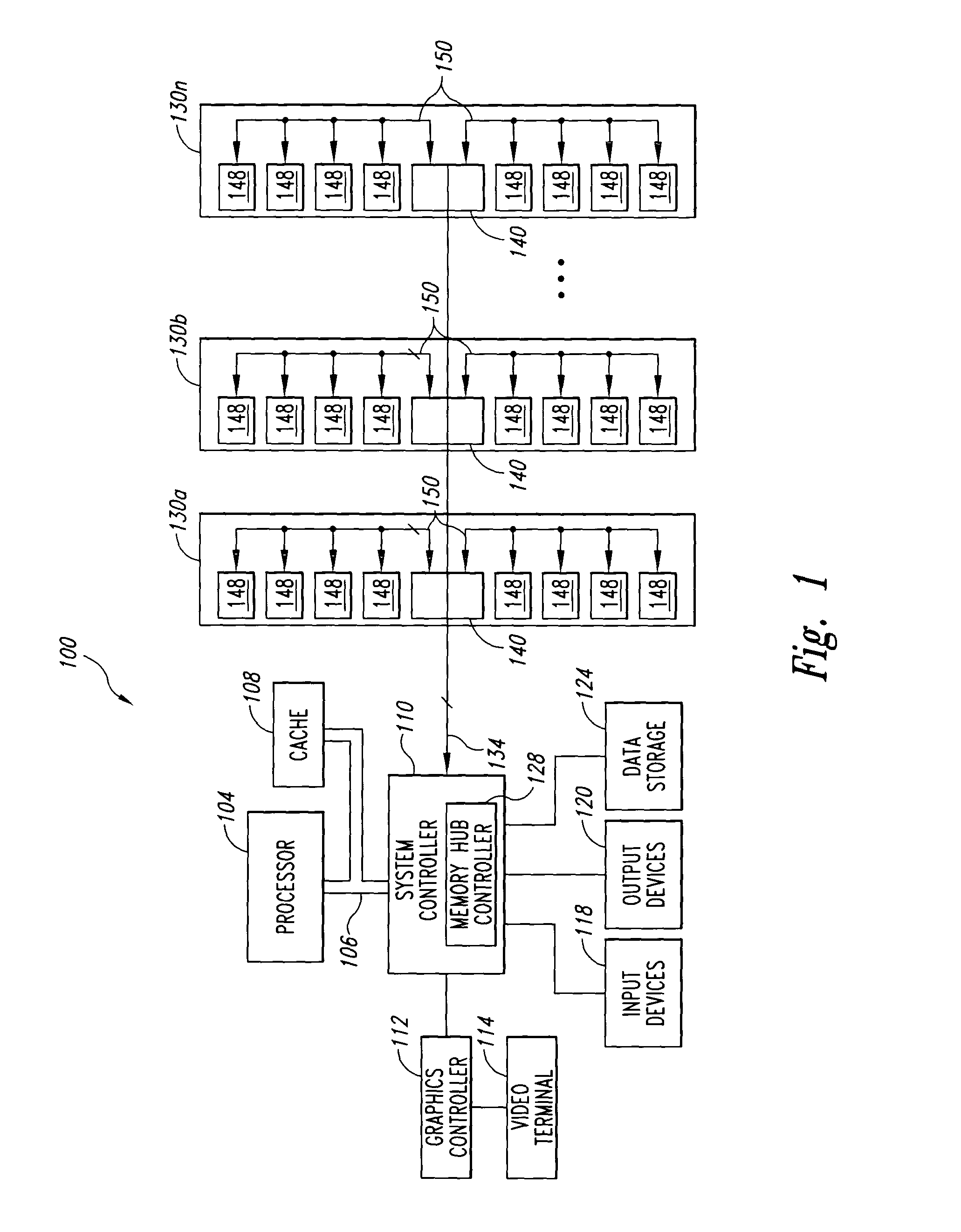

Memory module and method having on-board data search capabilities and processor-based system using such memory modules

InactiveUS20050050237A1Faster rateDigital data information retrievalStatic storageCrossbar switchWrite buffer

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory interfaces coupled to respective memory devices, and a cross-bar switch coupling any of the link interfaces to any of the memory interfaces. Each memory interface includes a memory controller, a write buffer, a read cache, and a data mining module. The data mining module includes a search data memory that is coupled to the link interface to receive and store at least one item of search data. A comparator receives both the read data from the memory device and the search data. The comparator then compares the read data to the respective item of search data and provides a hit indication in the event of a match.

Owner:MICRON TECH INC

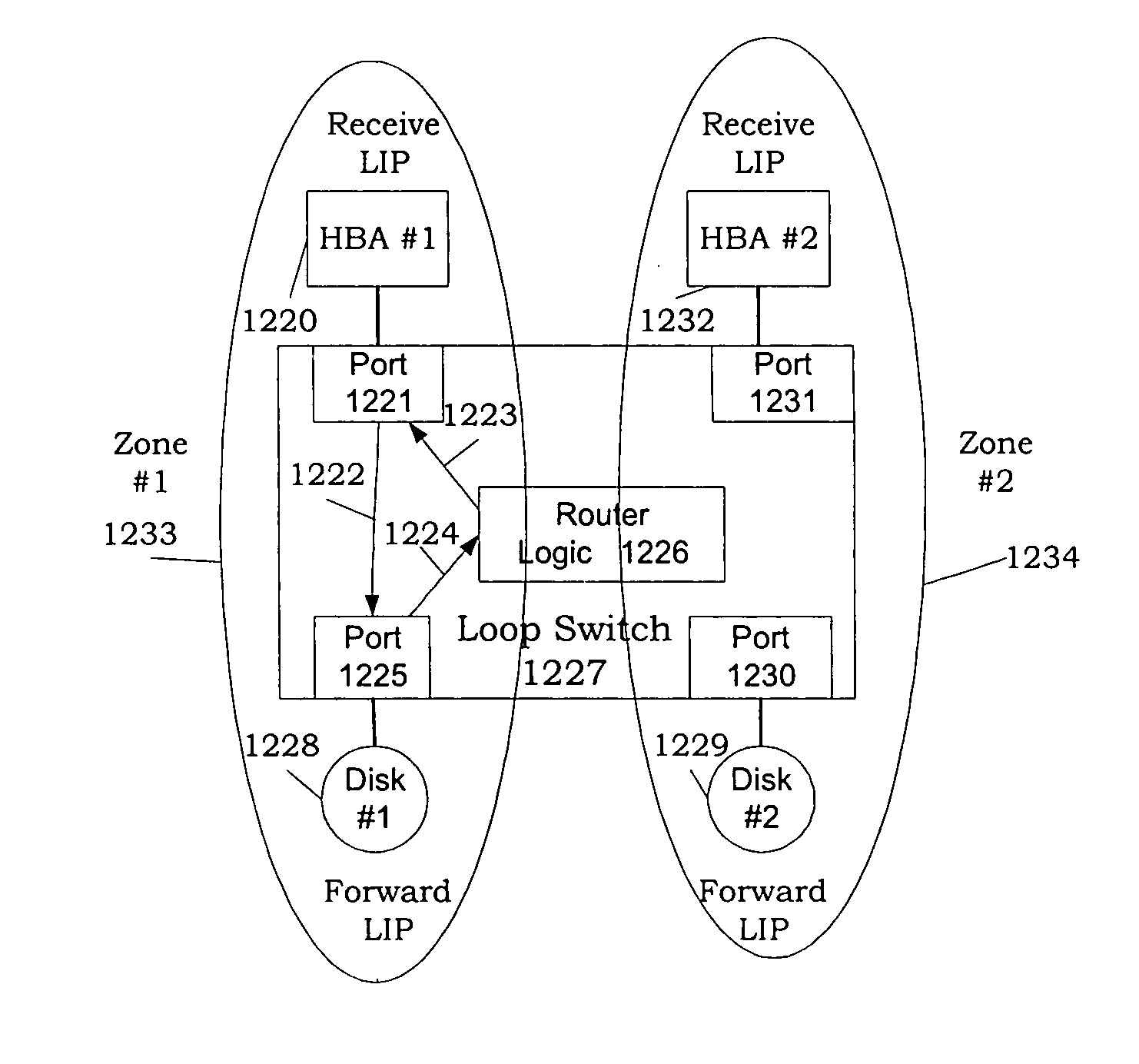

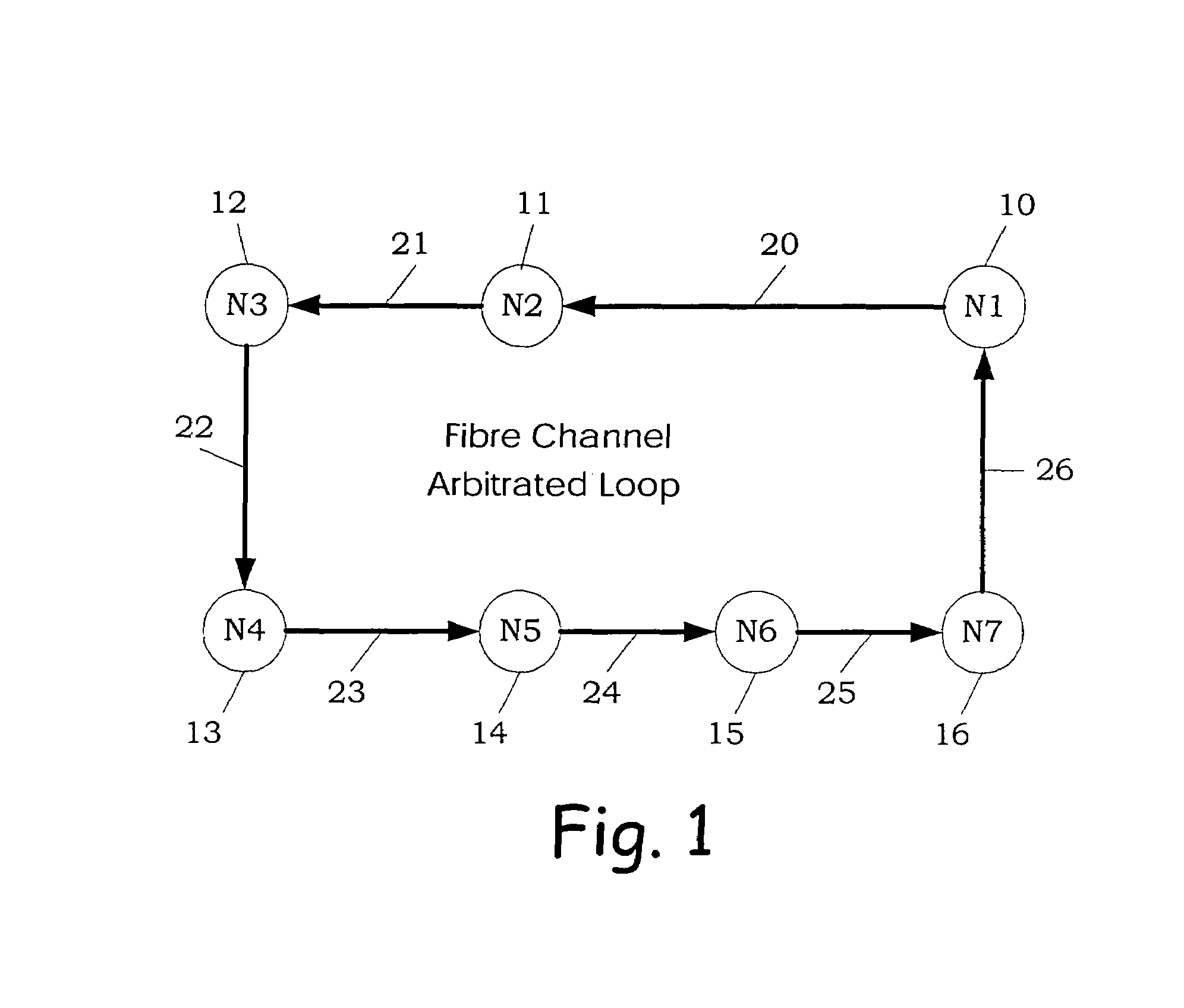

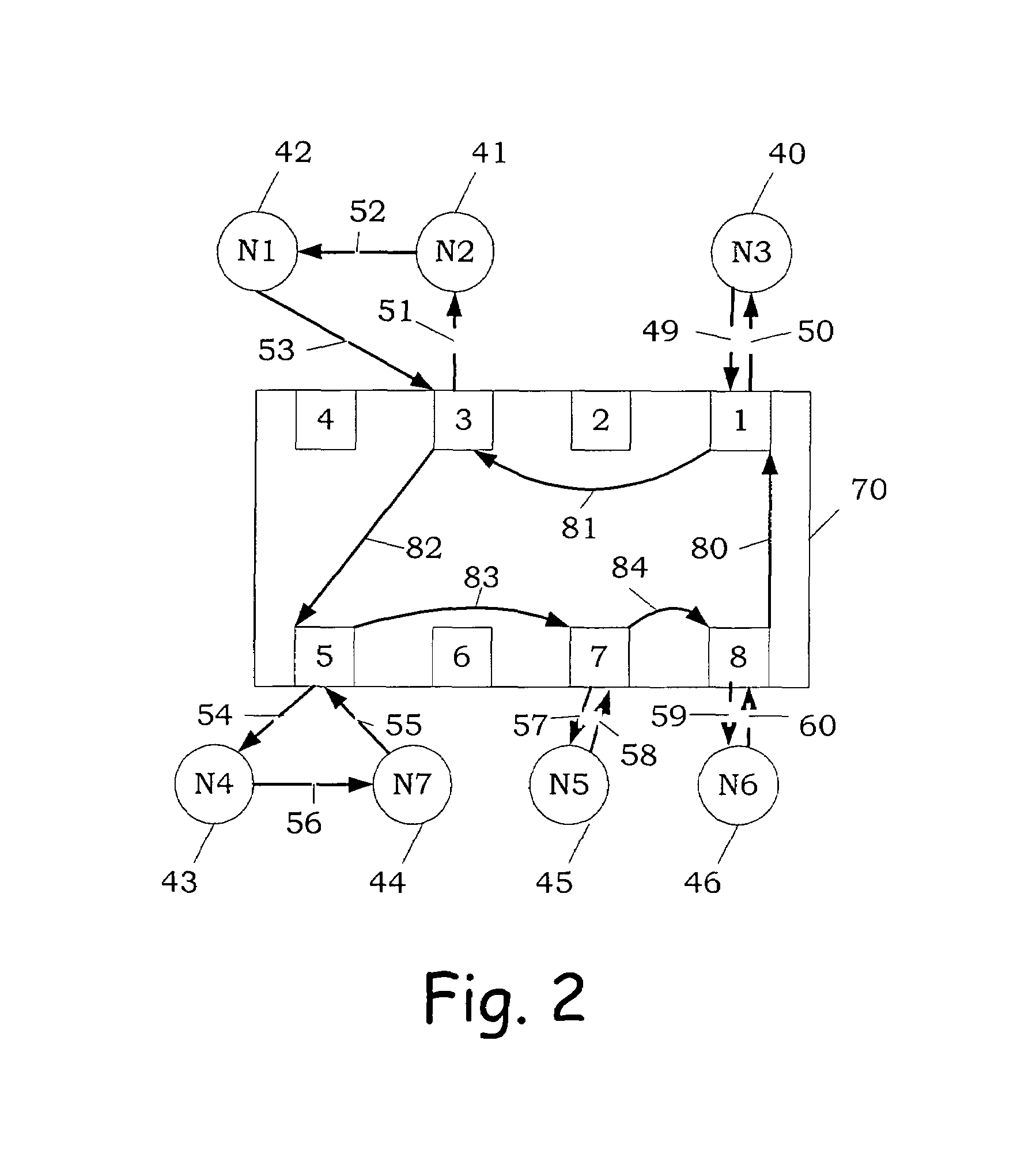

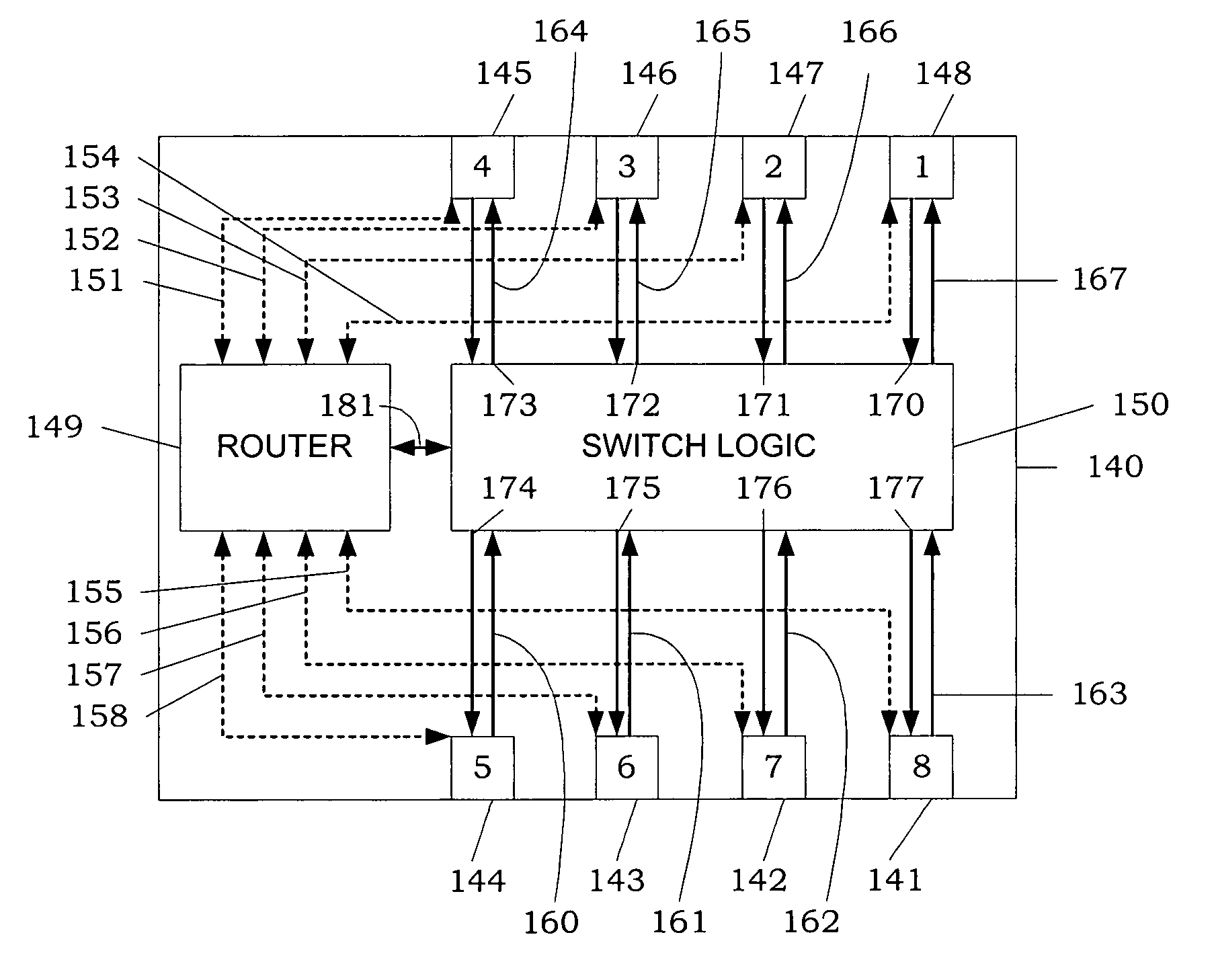

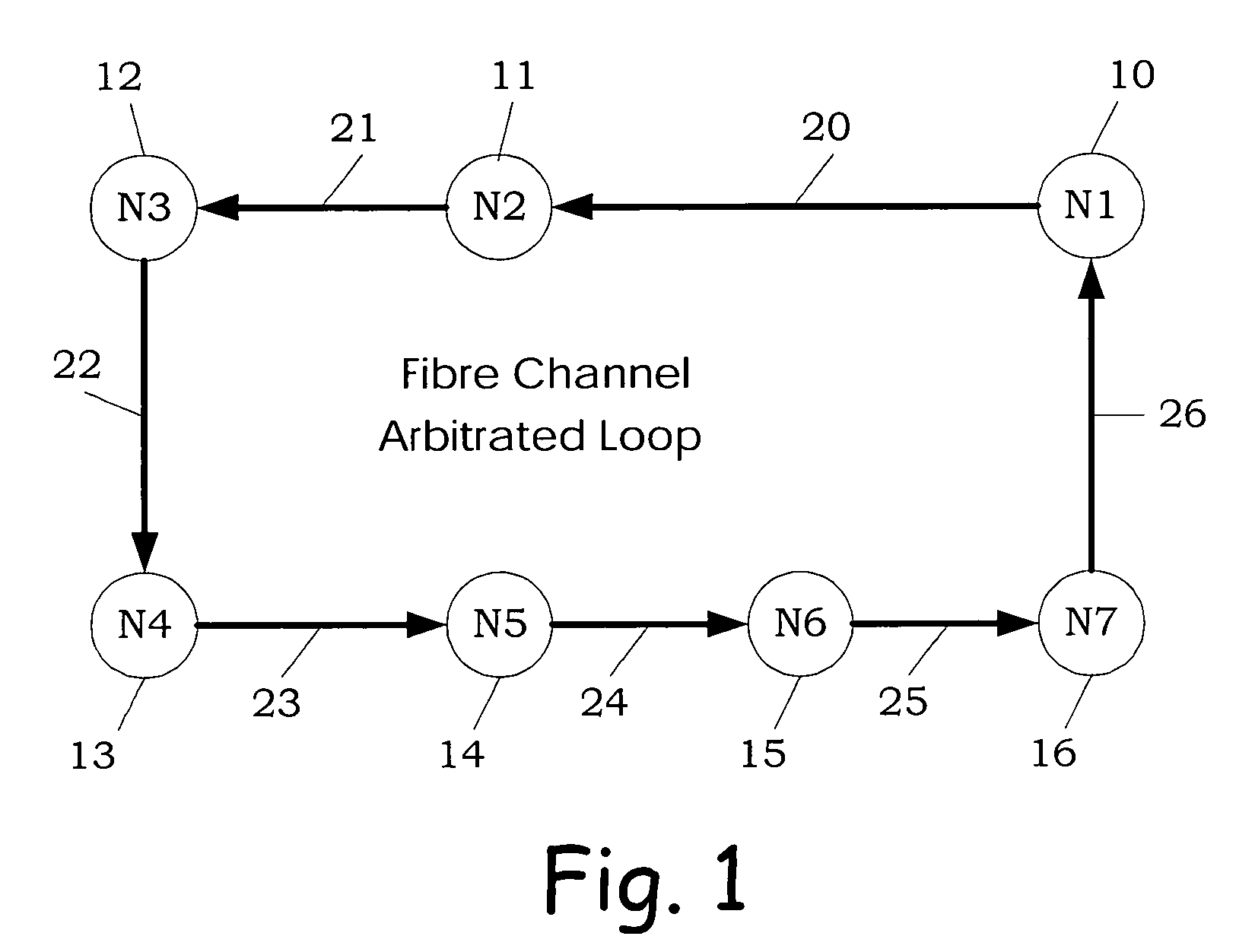

Methods and apparatus for device zoning in fibre channel arbitrated loop systems

ActiveUS7397788B2Effectively and efficiently switchImproved device access fairnessError preventionFrequency-division multiplex detailsCrossbar switchRouting table

Methods and apparatus for switching Fibre Channel Arbitrated Loop Systems is provided between a plurality of Fibre Channel Loop devices. In one aspect of the invention, the system switches based at least in part on arbitrated loop primitives. An exemplary interconnect system may include a first port and a second port, both including port logic to monitor certain arbitrated loop primitives, a connectivity apparatus, a route determination apparatus including a routing table consisting of ALPA addresses and their associated ports, the route determination apparatus coupled to each port and the connectivity apparatus, where the connectivity apparatus creates paths between the ports based on arbitrated loop primitives. In one embodiment, the connectivity apparatus is a crossbar switch. Examples of the arbitrated loop primitives that cause the switch to create paths between ports includes one or more of the following: ARB, OPN and CLS. In yet other aspects, the system ensures device access fairness through one or more techniques, including a rotating priority system, a counter to count the number of OPNs, especially sequential OPNs, and / or priority based on port type. Device zoning may be implemented. In one implementation, the system includes trunking such that frames may be transferred on multiple ports.

Owner:AVAGO TECH INT SALES PTE LTD

Optical cross-connect system

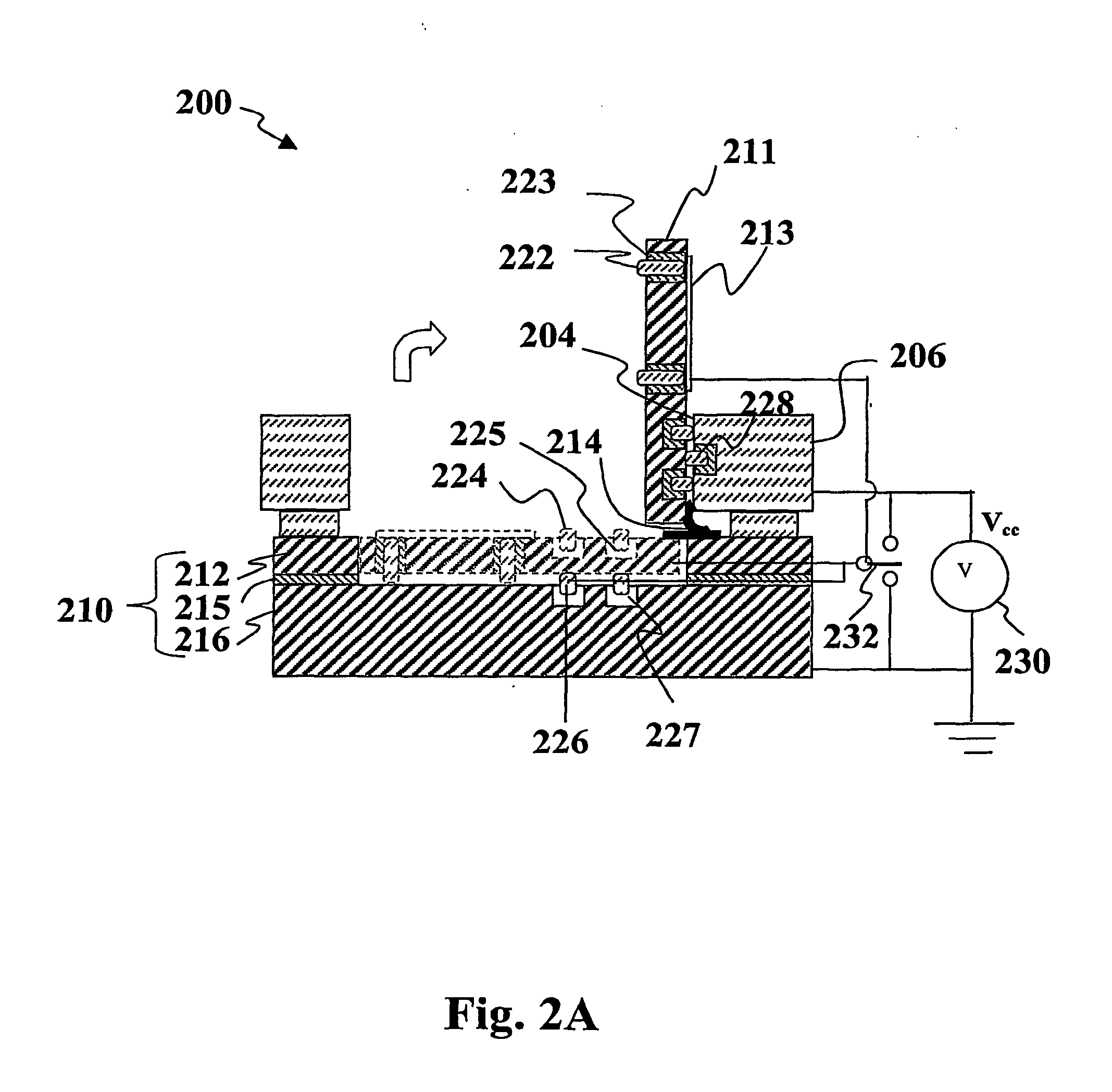

InactiveUS20060049826A1Overcome disadvantagesSemiconductor/solid-state device detailsSolid-state devicesCrossbar switchOptical cross-connect

An optical cross-connect switch comprises a base (216), a flap (211) and one or more electrically conductive landing pads (222) connected to the flap (211). The flap (211) has a bottom portion that is movably coupled to the base (216) such that the flap (211) is movable with respect to a plane of the base (216) from a first orientation to a second orientation. The one or more landing pads (222) are electrically isolated from the flap (211) and electrically coupled to be equipotential with a landing surface.

Owner:ANALOG DEVICES INC

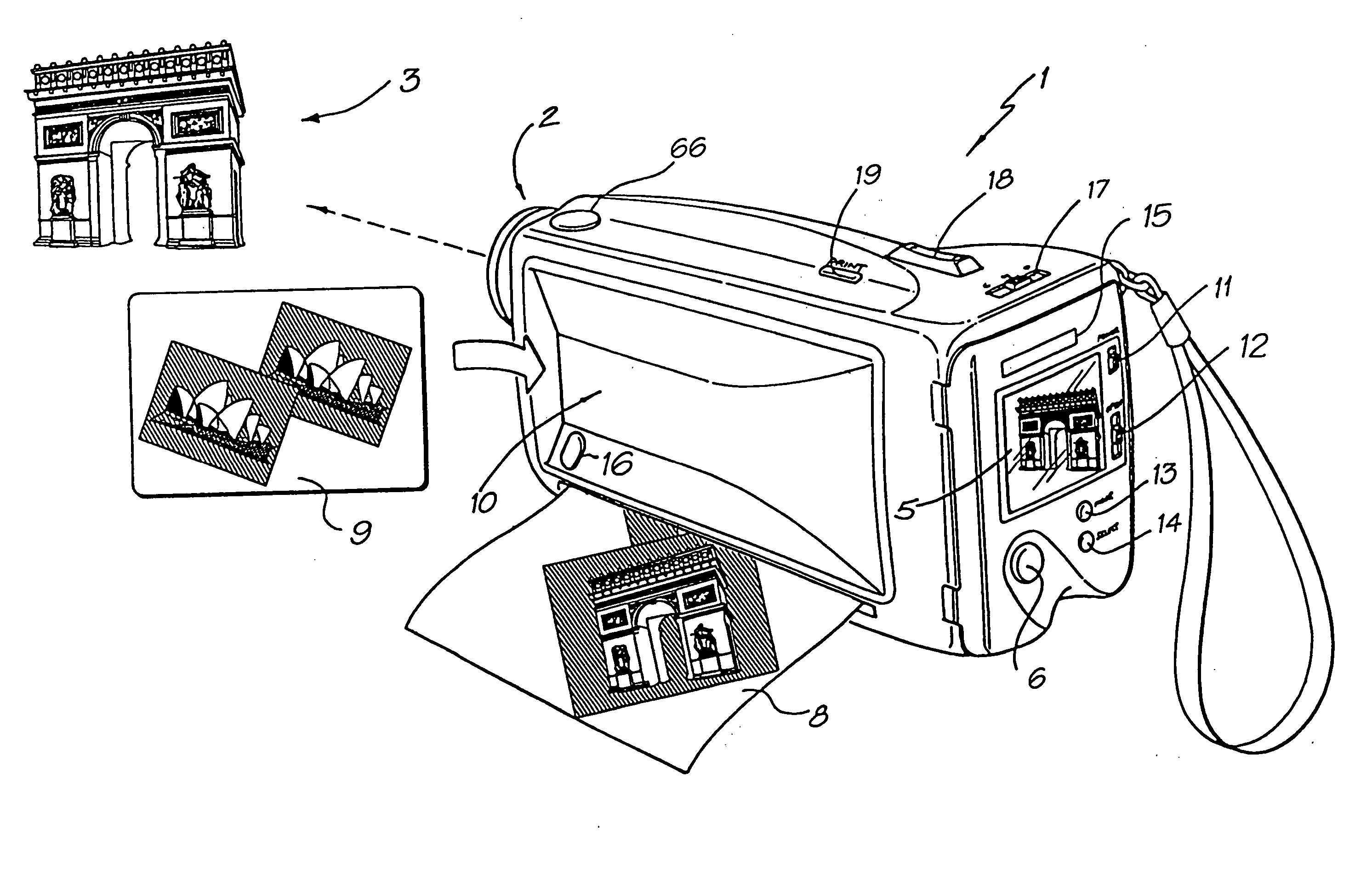

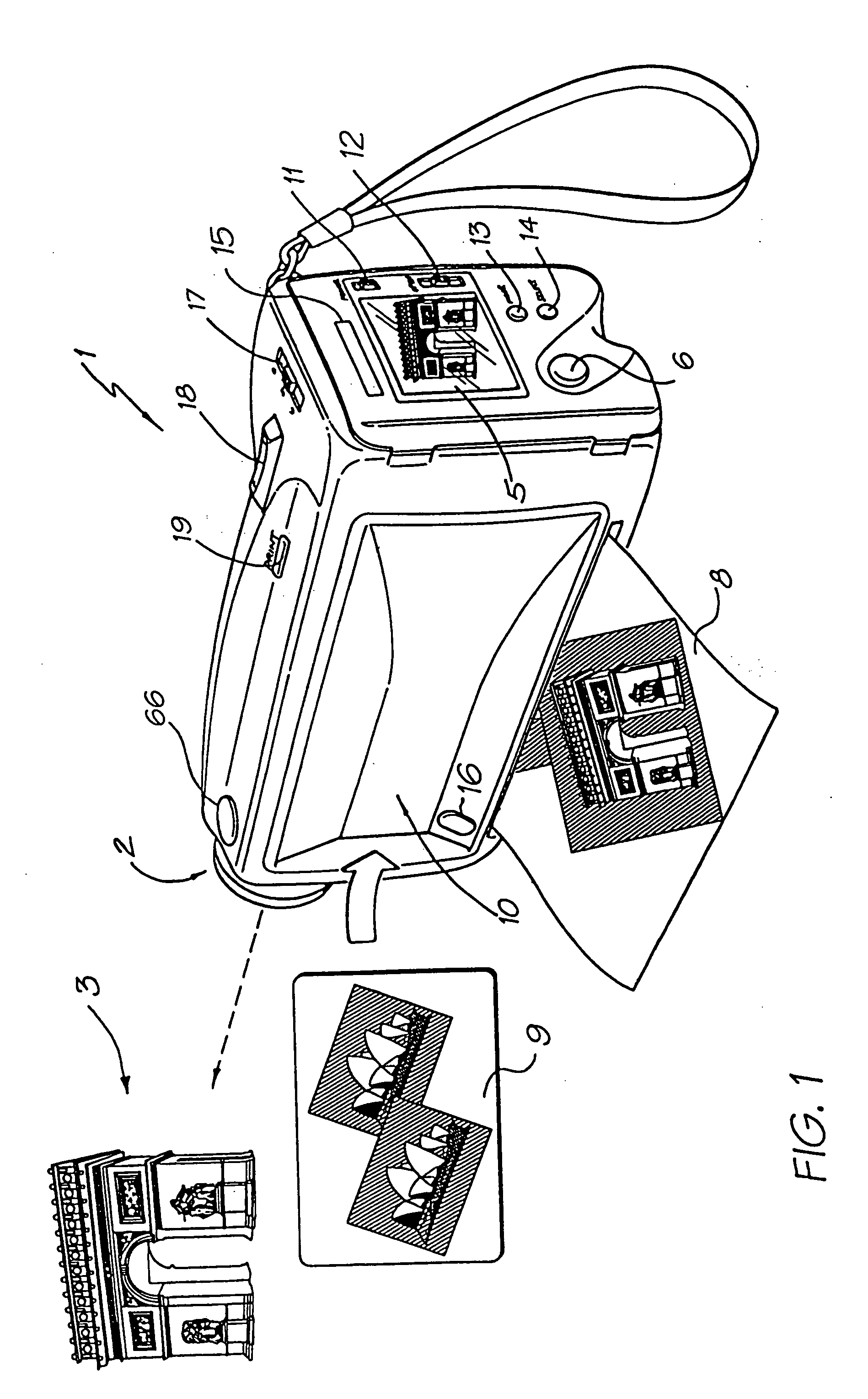

Digital camera having functionally interconnected image processing elements

InactiveUS20050179781A1Material nanotechnologyTelevision system detailsCrossbar switchImaging processing

A hand-held digital camera is provided comprising image sensing means for sensing an image, input means for receiving an input to modify the sensed image, image processing means for modifying the sensed image in accordance with the input and output means for outputting the modified image. The image processing means includes a plurality of processing elements functionally interconnected to each other via a crossbar switch. The crossbar switch is selectively configurable to pass data of the sensed image directly between the processing elements.

Owner:GOOGLE LLC

Chemically synthesized and assembled electronic devices

InactiveUS20010054709A1Simple and inexpensive implementationMaterial nanotechnologyElectronic circuit testingSignal routingChemical synthesis

A route to the fabrication of electronic devices is provided, in which the devices consist of two crossed wires sandwiching an electrically addressable molecular species. The approach is extremely simple and inexpensive to implement, and scales from wire dimensions of several micrometers down to nanometer-scale dimensions. The device of the present invention can be used to produce crossbar switch arrays, logic devices, memory devices, and communication and signal routing devices. The present invention enables construction of molecular electronic devices on a length scale than can range from micrometers to nanometers via a straightforward and inexpensive chemical assembly procedure. The device is either partially or completely chemically assembled, and the key to the scaling is that the location of the devices on the substrate are defined once the devices have been assembled, not prior to assembly.

Owner:HEWLETT PACKARD CO +1

System and method for virtualizing PCIe devices

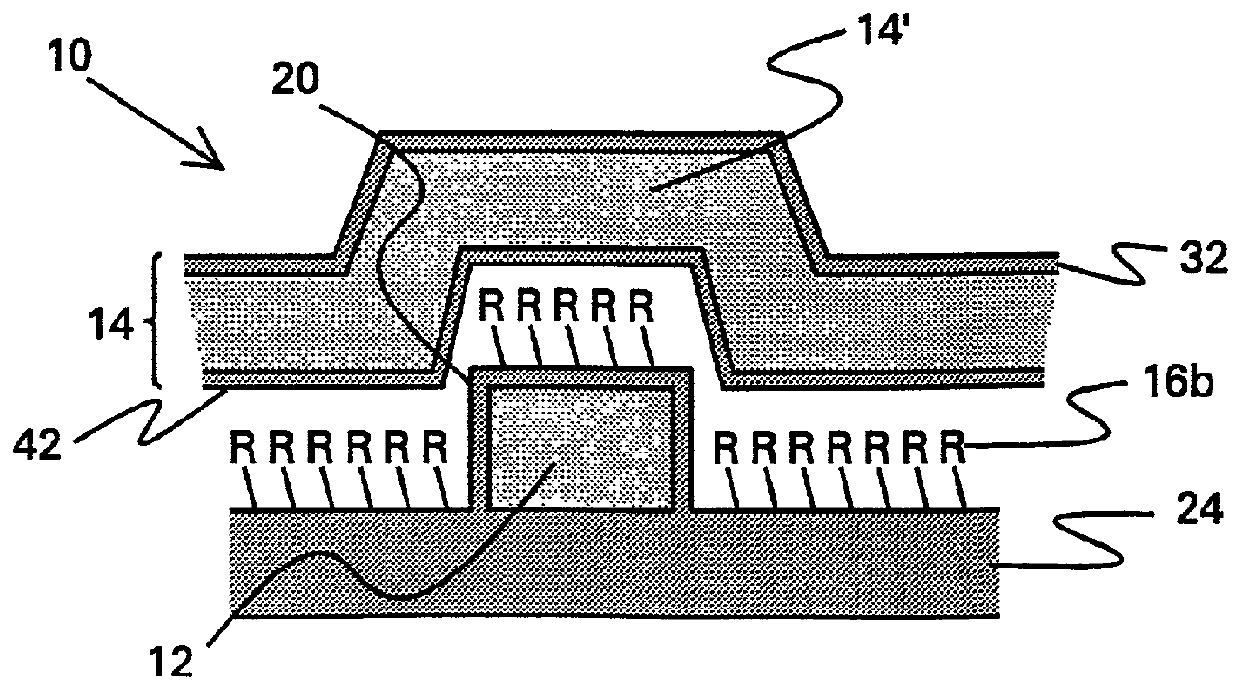

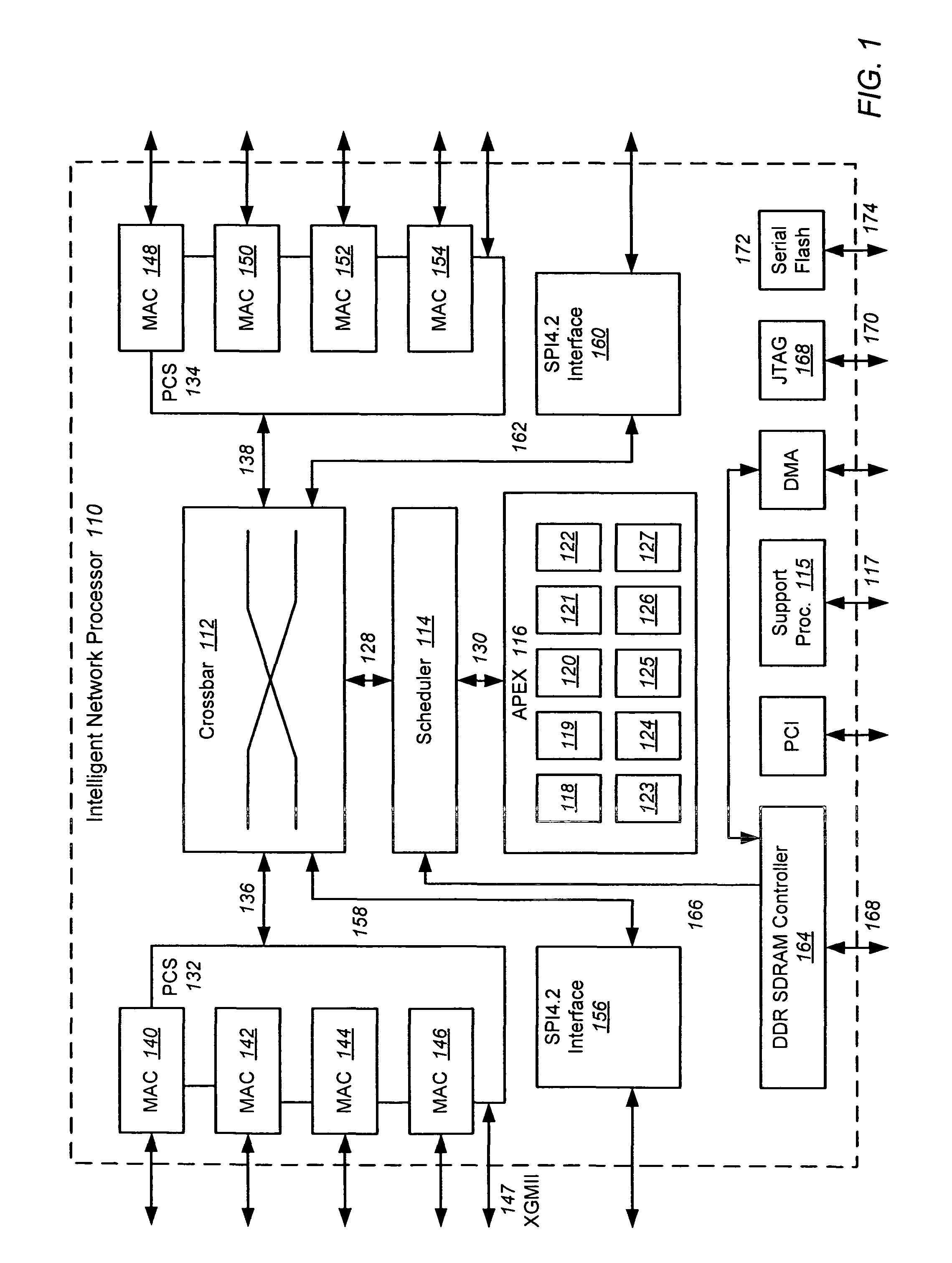

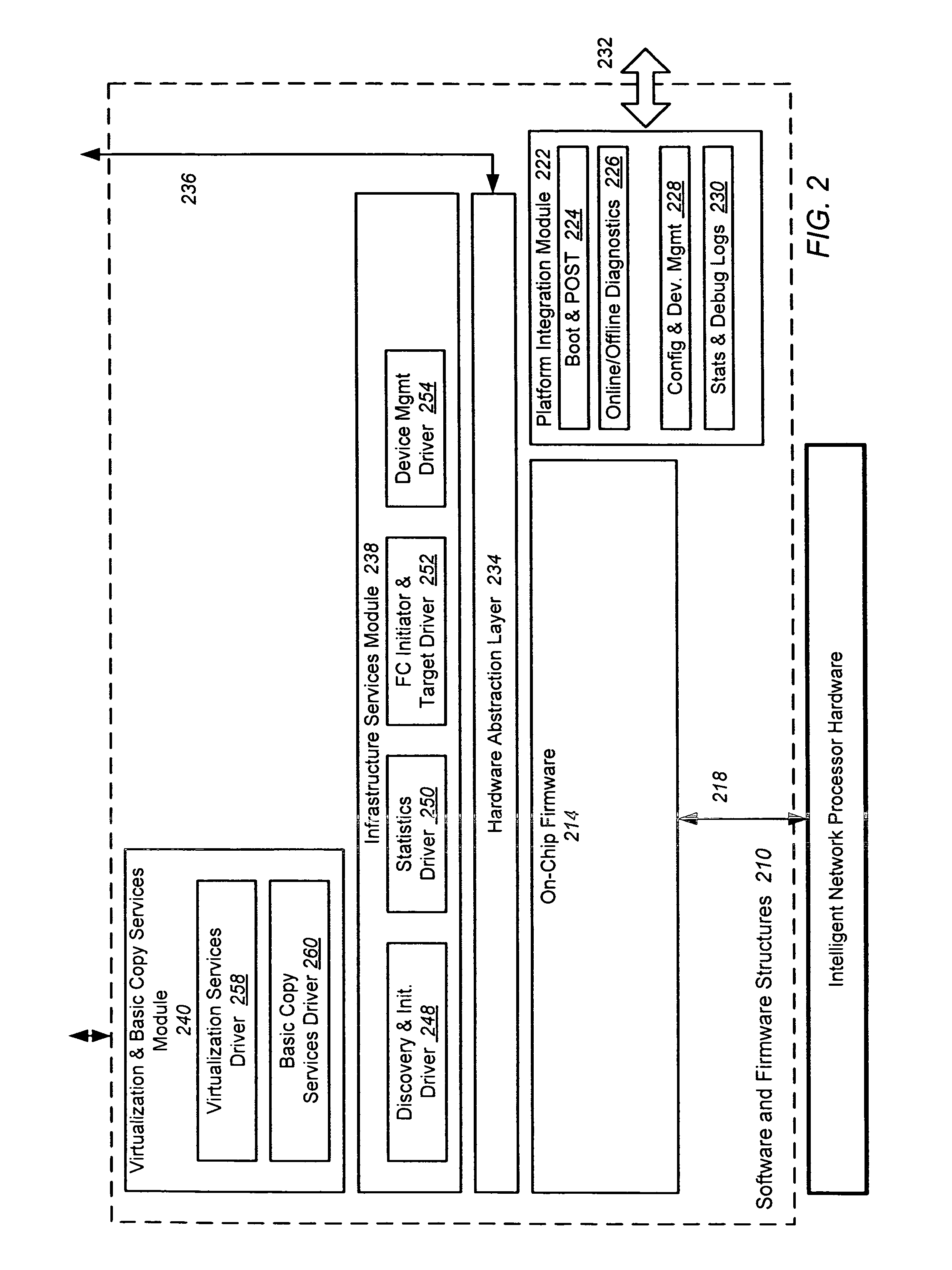

ActiveUS7743197B2Efficient accessImprove creditMultiple digital computer combinationsData switching networksCrossbar switchIntelligent Network

An intelligent network processor is disclosed that provides a PCI express (PCIe) host bus adapter with firmware selectable hardware capabilities and firmware enabled emulation of capabilities not supported by hardware. Support for Fibre Channel (FC) and Gigabit Ethernet (GbE) protocols are provided through the same fabric ports, including multiple port trunking for both protocols. On chip protocol conversion is provided for switching and routing between FC and GbE ports. Switching using the same crossbar module is provided for both FC and GbE protocols. The crossbar module is coupled to directly access external DDR memory so that messages from FC, GbE, and PCIe interfaces may be switched directly to the DDR memory.

Owner:EMULEX COMM CORP

Methods and apparatus for switching fibre channel arbitrated loop systems

InactiveUS7382790B2Effectively and efficiently switchImproved device access fairnessNetworks interconnectionElectric digital data processingCrossbar switchRouting table

Methods and apparatus for switching Fibre Channel Arbitrated Loop Systems is provided between a plurality of Fibre Channel Loop devices. In one aspect of the invention, the system switches based at least in part on arbitrated loop primitives. An exemplary interconnect system may include a first port and a second port, both including port logic to monitor certain arbitrated loop primitives, a connectivity apparatus, a route determination apparatus including a routing table consisting of ALPA addresses and their associated ports, the route determination apparatus coupled to each port and the connectivity apparatus, where the connectivity apparatus creates paths between the ports based on arbitrated loop primitives. In one embodiment, the connectivity apparatus is a crossbar switch. Examples of the arbitrated loop primitives that cause the switch to create paths between ports includes one or more of the following: ARB, OPN and CLS. In yet other aspects, the system ensures device access fairness through one or more techniques, including a rotating priority system, a counter to count the number of OPNs, especially sequential OPNs, and / or priority based on port type. Device zoning may be implemented. In one implementation, the system includes trunking such that frames may be transferred on multiple ports.

Owner:AVAGO TECH INT SALES PTE LTD

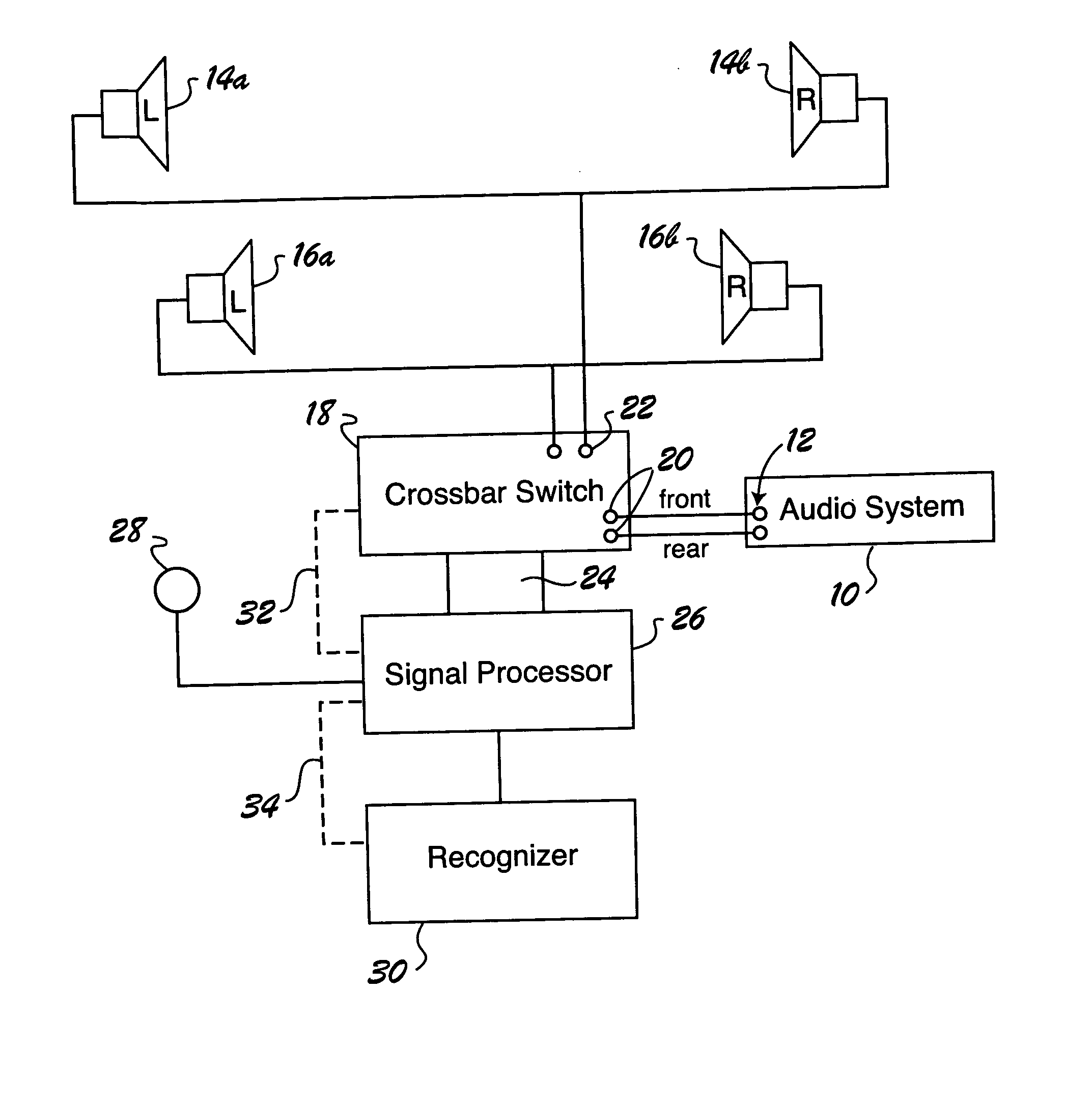

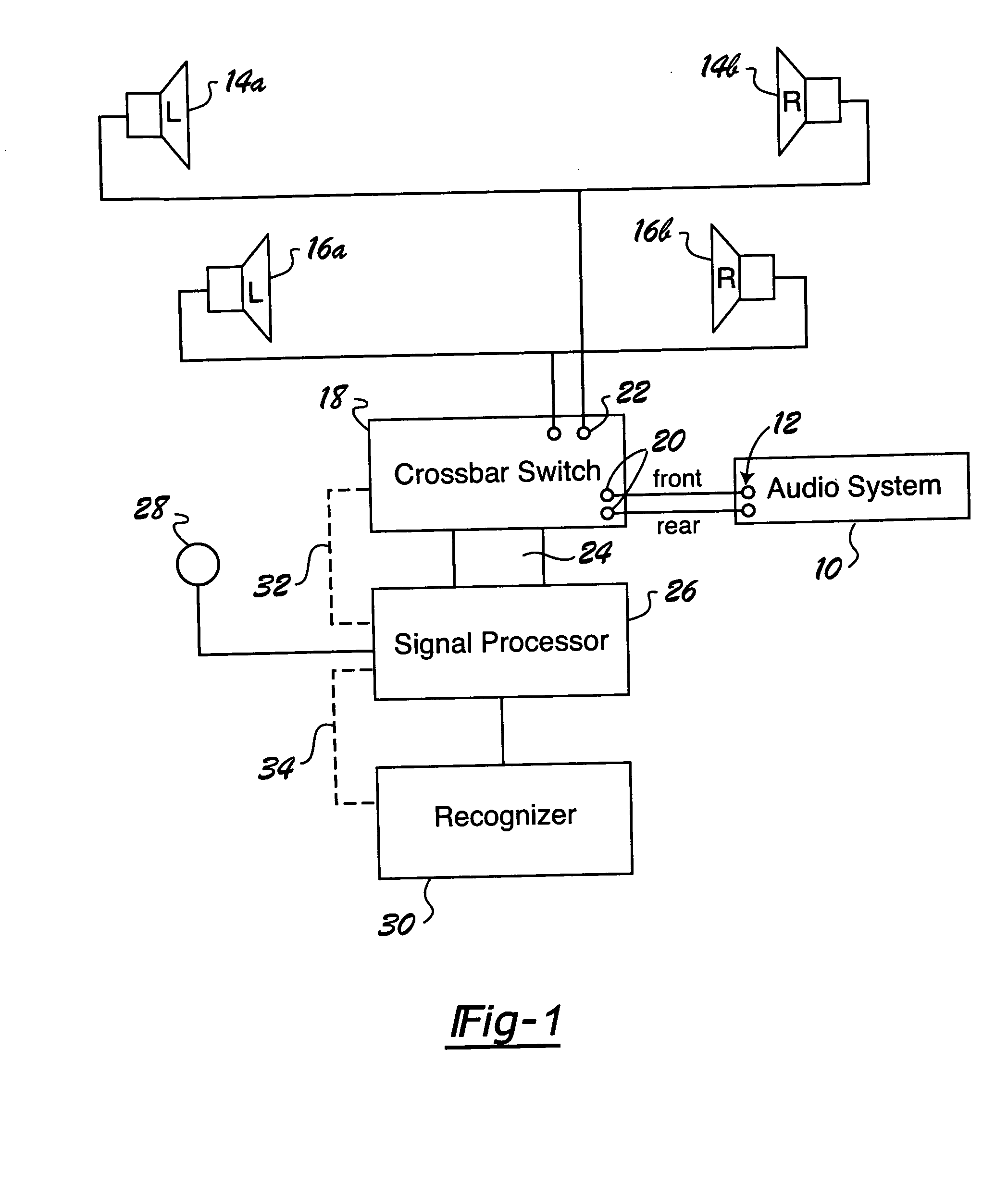

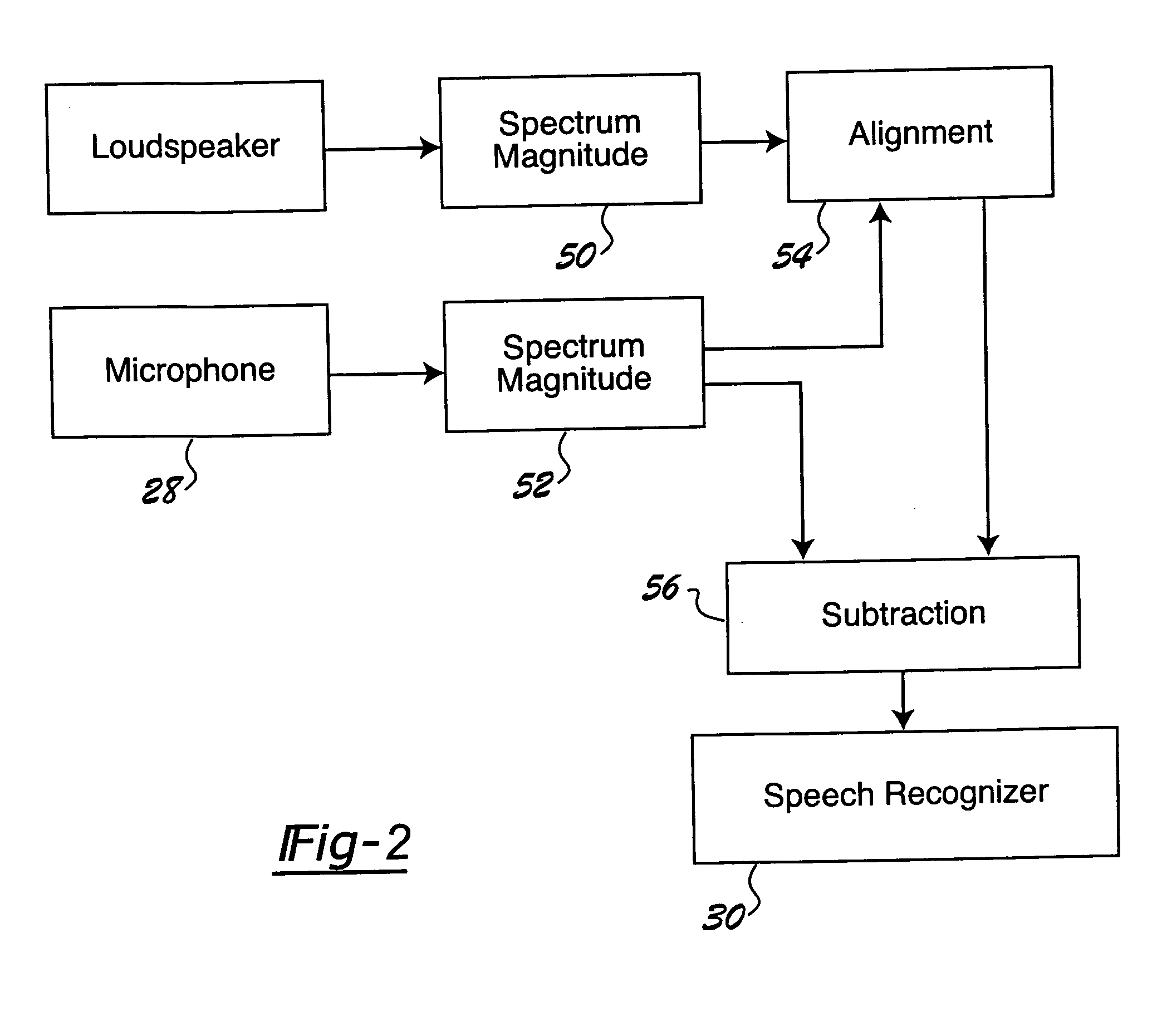

Speech recognizer performance in car and home applications utilizing novel multiple microphone configurations

System speakers are switched to function as sound input transducers to improve recognizer performance and to support recognizer features. A crossbar switch is selectively activated, either manually or under software control, to allow system loudspeakers to function as sound input transducers that supplement the recognition system microphone or microphone array. Using loudspeakers as “microphones” improves speech recognition in noisy environments, thus attaining better recognition performance with little added system cost. The loudspeakers, positioned in physically separate locations also provide spatial information that can be used to determine the location of the person speaking and thereby offer different functionality for different persons. Acoustic models are selected based on environmental and vehicle operating conditions and may be adapted dynamically using ambient information obtained using the loudspeakers as sound input transducers.

Owner:SOVEREIGN PEAK VENTURES LLC

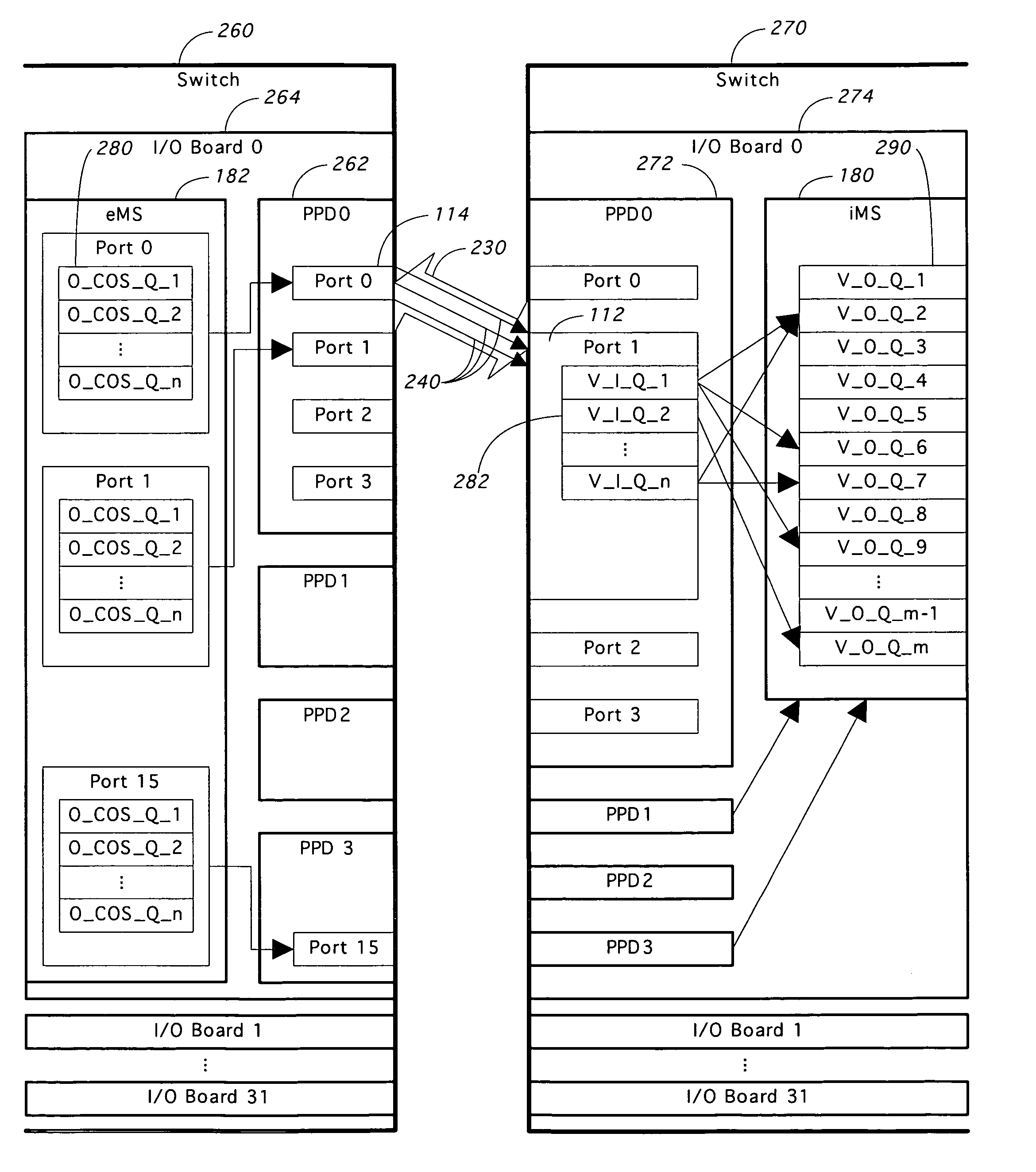

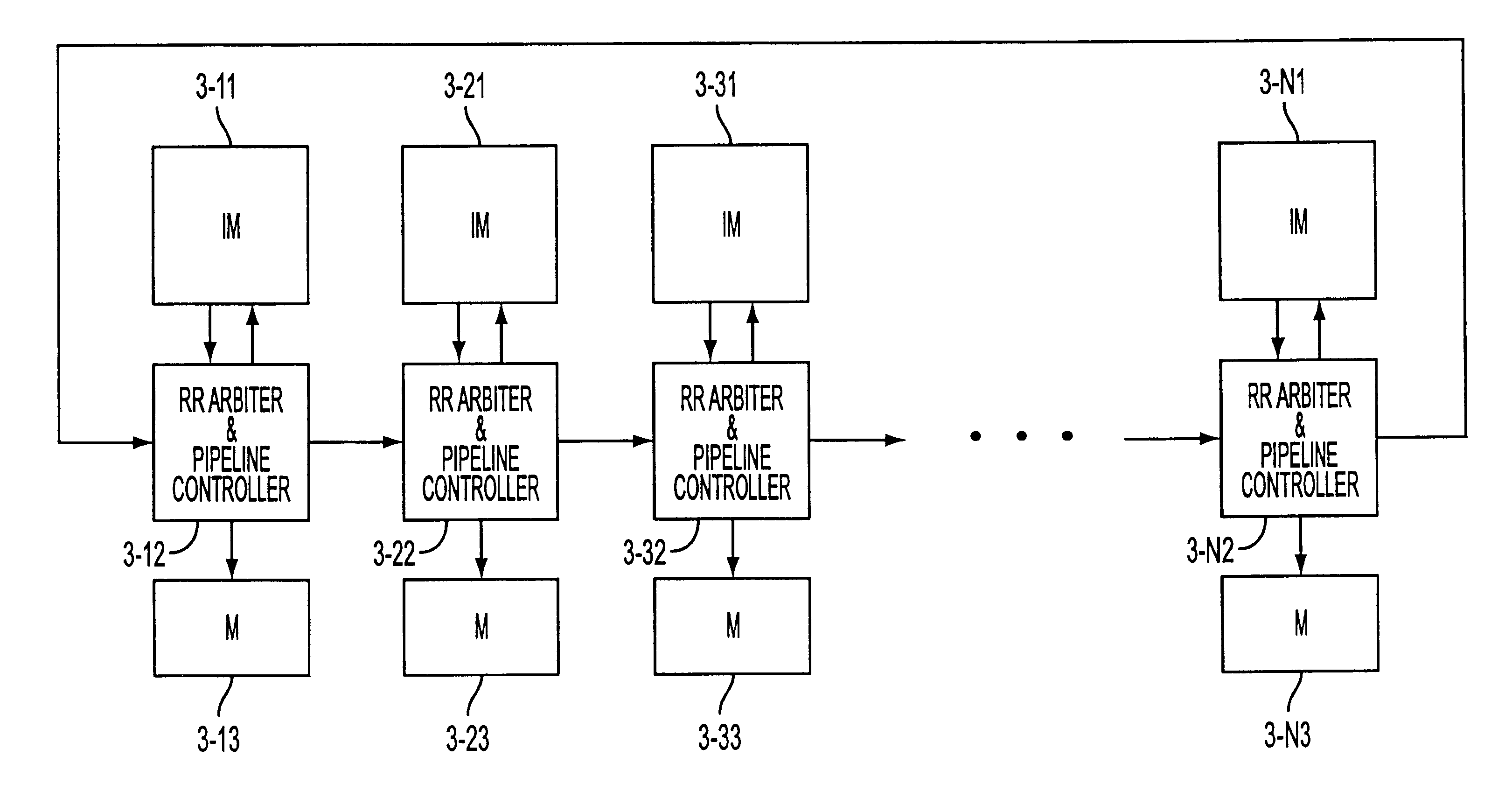

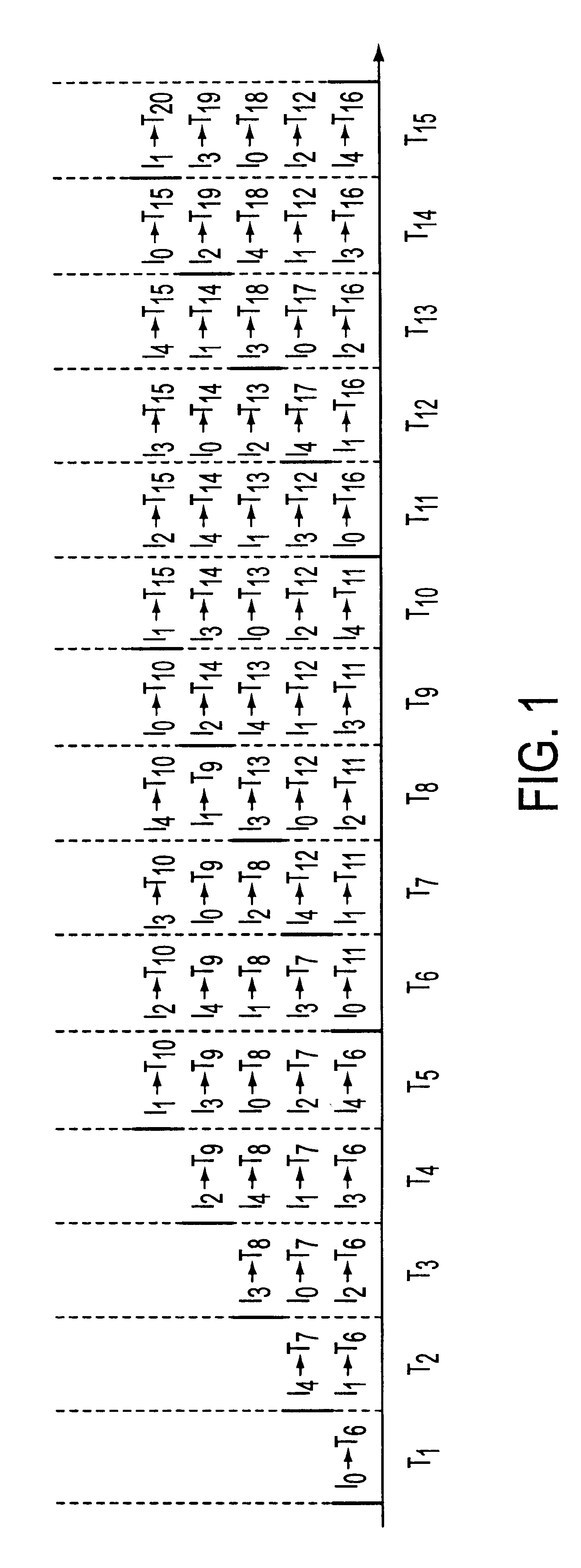

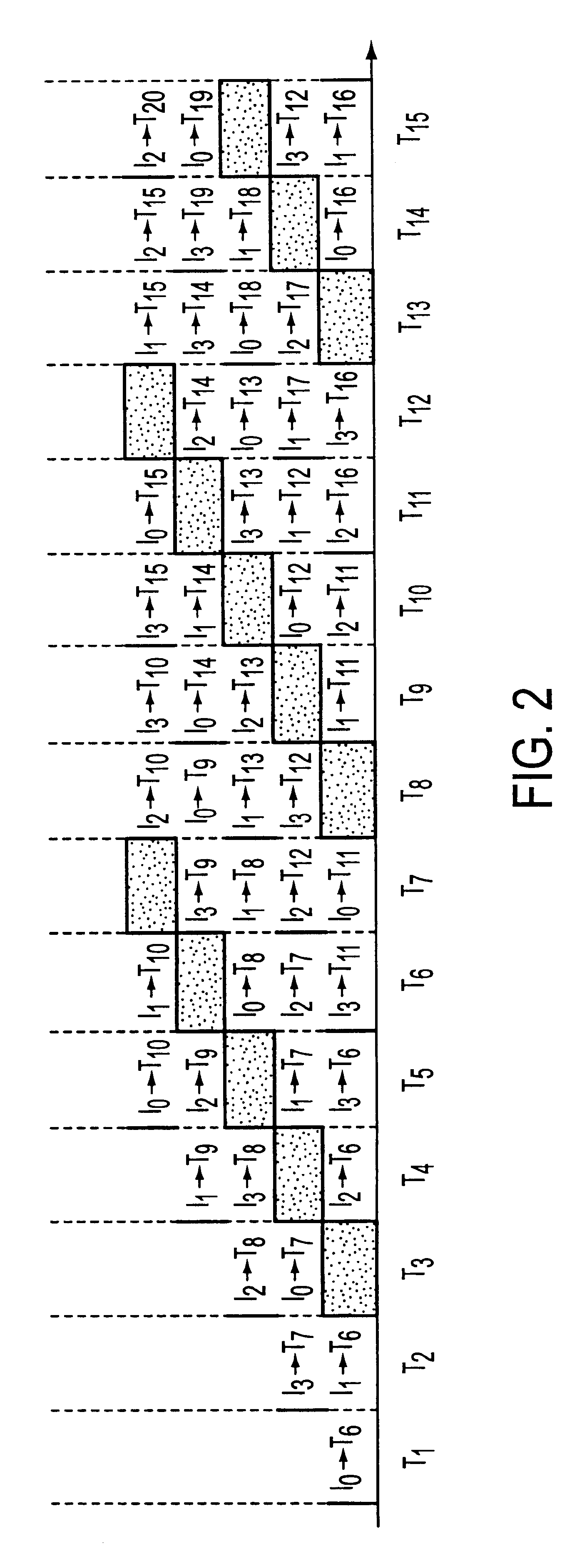

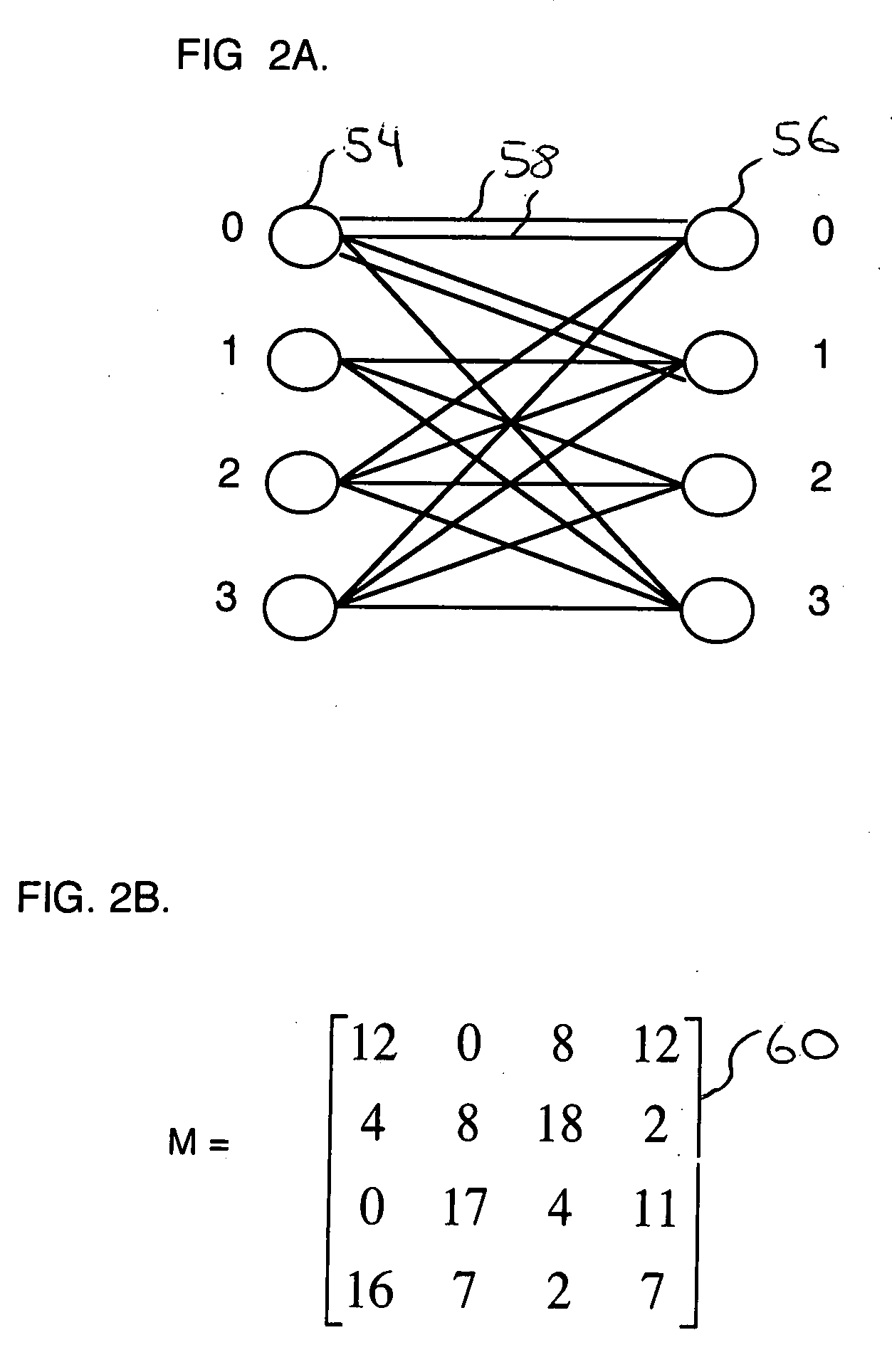

RRGS-round-robin greedy scheduling for input/output terabit switches

InactiveUS6618379B1Easy to useImprove performanceTime-division multiplexLoop networksCrossbar switchOptimal scheduling

A novel protocol for scheduling of packets in high-speed cell based switches is provided. The switch is assumed to use a logical cross-bar fabric with input buffers. The scheduler may be used in optical as well as electronic switches with terabit capacity. The proposed round-robin greedy scheduling (RRGS) achieves optimal scheduling at terabit throughput, using a pipeline technique. The pipeline approach avoids the need for internal speedup of the switching fabric to achieve high utilization. A method for determining a time slot in a NxN crossbar switch for a round robin greedy scheduling protocol, comprising N logical queues corresponding to N output ports, the input for the protocol being a state of all the input-output queues, output of the protocol being a schedule, the method comprising: choosing input corresponding to i=(constant-k-1)mod N, stopping if there are no more inputs, otherwise choosing the next input in a round robin fashion determined by i=(i+1)mod N; choosing an output j such that a pair (i,j) to a set C={(i,j)| there is at least one packet from I to j}, if the pair (i,j) exists; removing i from a set of inputs and repeating the steps if the pair (i,j) does not exist; removing i from the set of inputs and j from a set of outputs; and adding the pair (i,j) to the schedule and repeating the steps.

Owner:NEC CORP

Method and apparatus to schedule packets through a crossbar switch with delay guarantees

ActiveUS20070280261A1Minimize delay jitterMeet bandwidth requirementsMultiplex system selection arrangementsData switching by path configurationCrossbar switchDifferentiated services

A method for scheduling cell transmissions through a switch with rate and delay guarantees and with low jitter is proposed. The method applies to a classic input-buffered N×N crossbar switch without speedup. The time axis is divided into frames each containing F time-slots. An N×N traffic rate matrix specifies a quantized guaranteed traffic rate from each input port to each output port. The traffic rate matrix is transformed into a permutation with NF elements which is decomposed into F permutations of N elements using a recursive and fair decomposition method. Each permutation is used to configure the crossbar switch for one time-slot within a frame of size F time-slots, and all F permutations result in a Frame Schedule. In the frame schedule, the expected Inter-Departure Time (IDT) between cells in a flow equals the Ideal IDT and the delay jitter is bounded and small. For fixed frame size F, an individual flow can often be scheduled in O(logN) steps, while a complete reconfiguration requires O(NlogN) steps when implemented in a serial processor. An RSVP or Differentiated Services-like algorithm can be used to reserve bandwidth and buffer space in an IP-router, an ATM switch or MPLS switch during a connection setup phase, and the proposed method can be used to schedule traffic in each router or switch. Best-effort traffic can be scheduled using any existing dynamic scheduling algorithm to fill the remaining unused switch capacity within each Frame. The scheduling algorithm also supports multicast traffic.

Owner:SZYMANSKI TED HENRYK

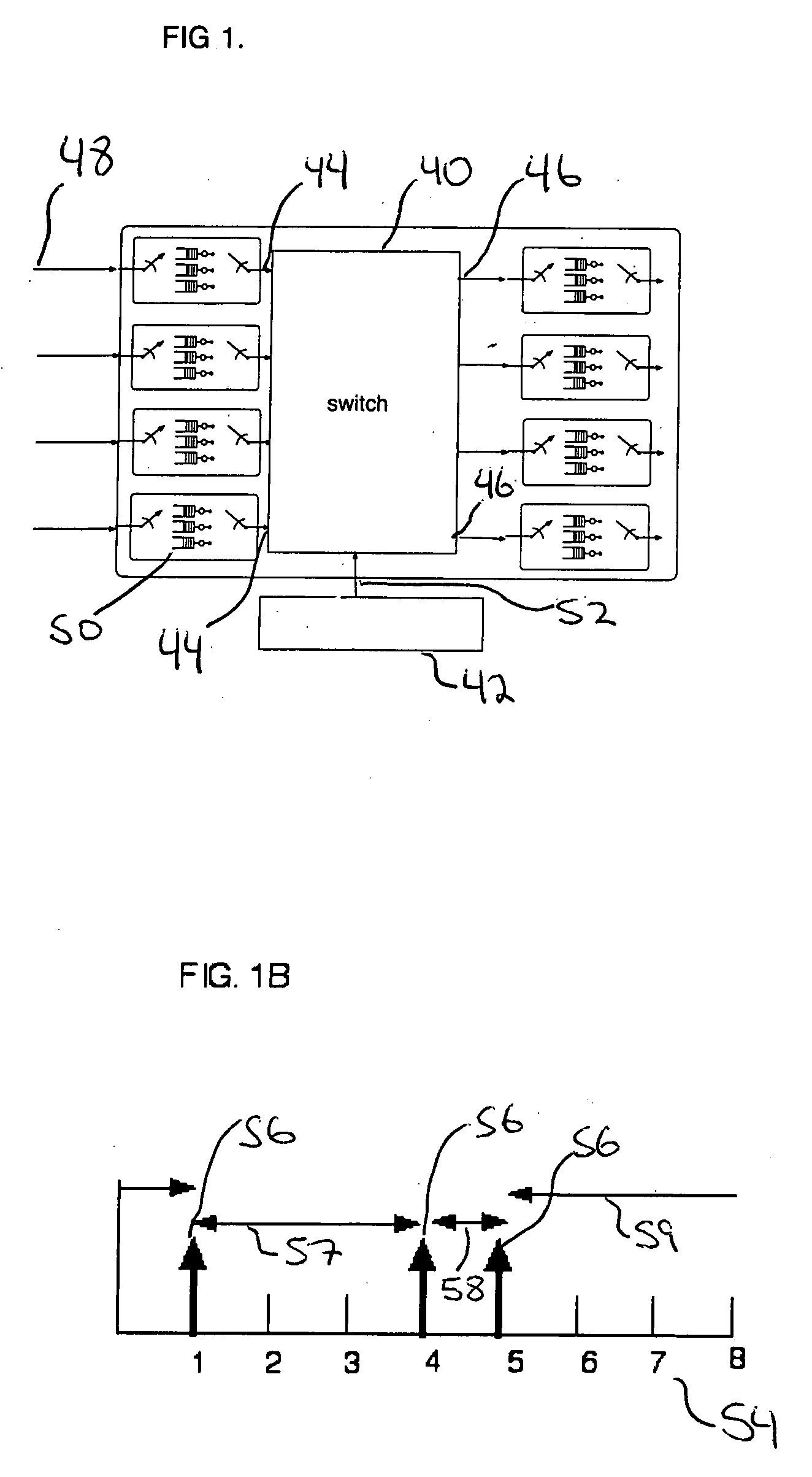

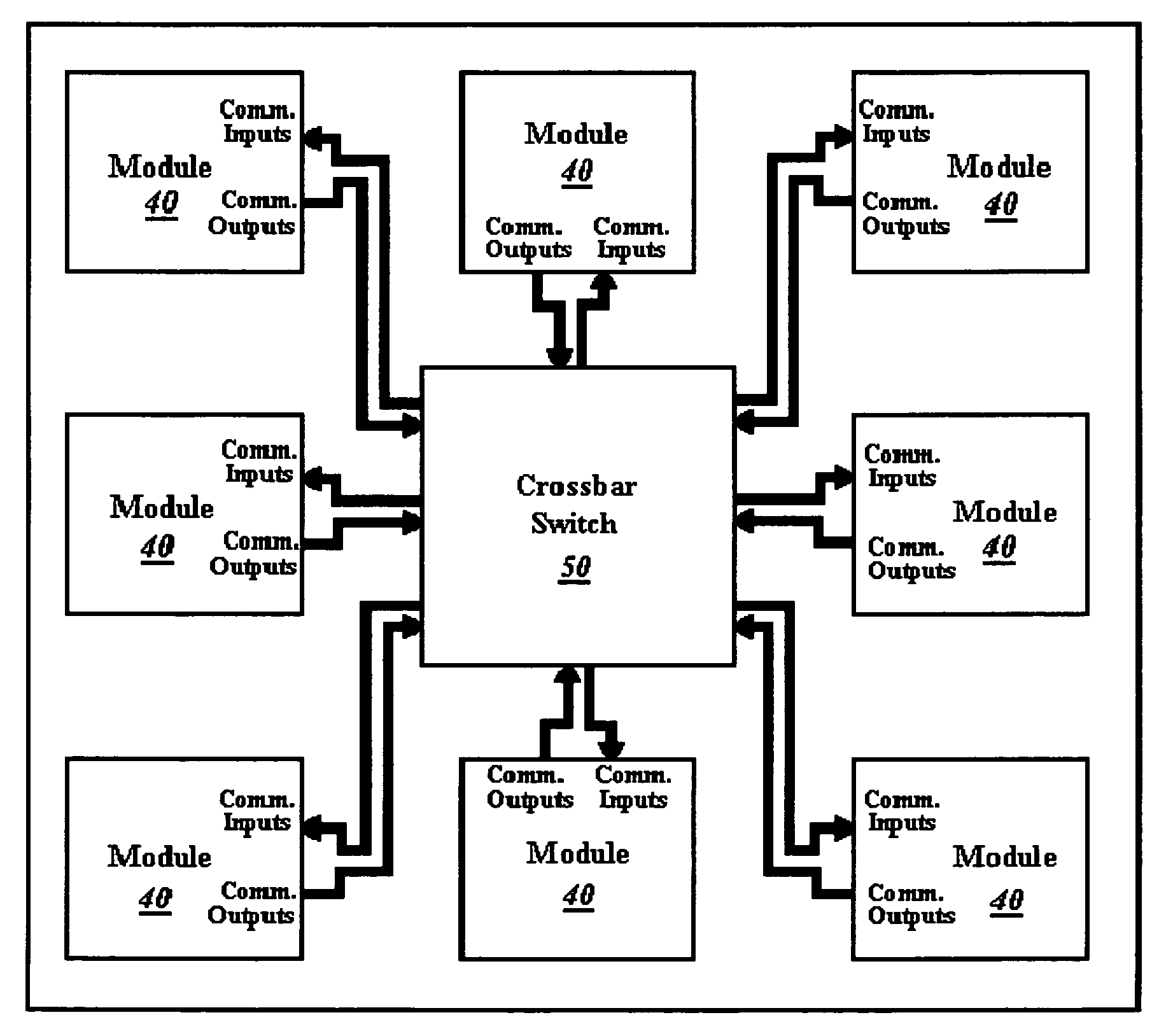

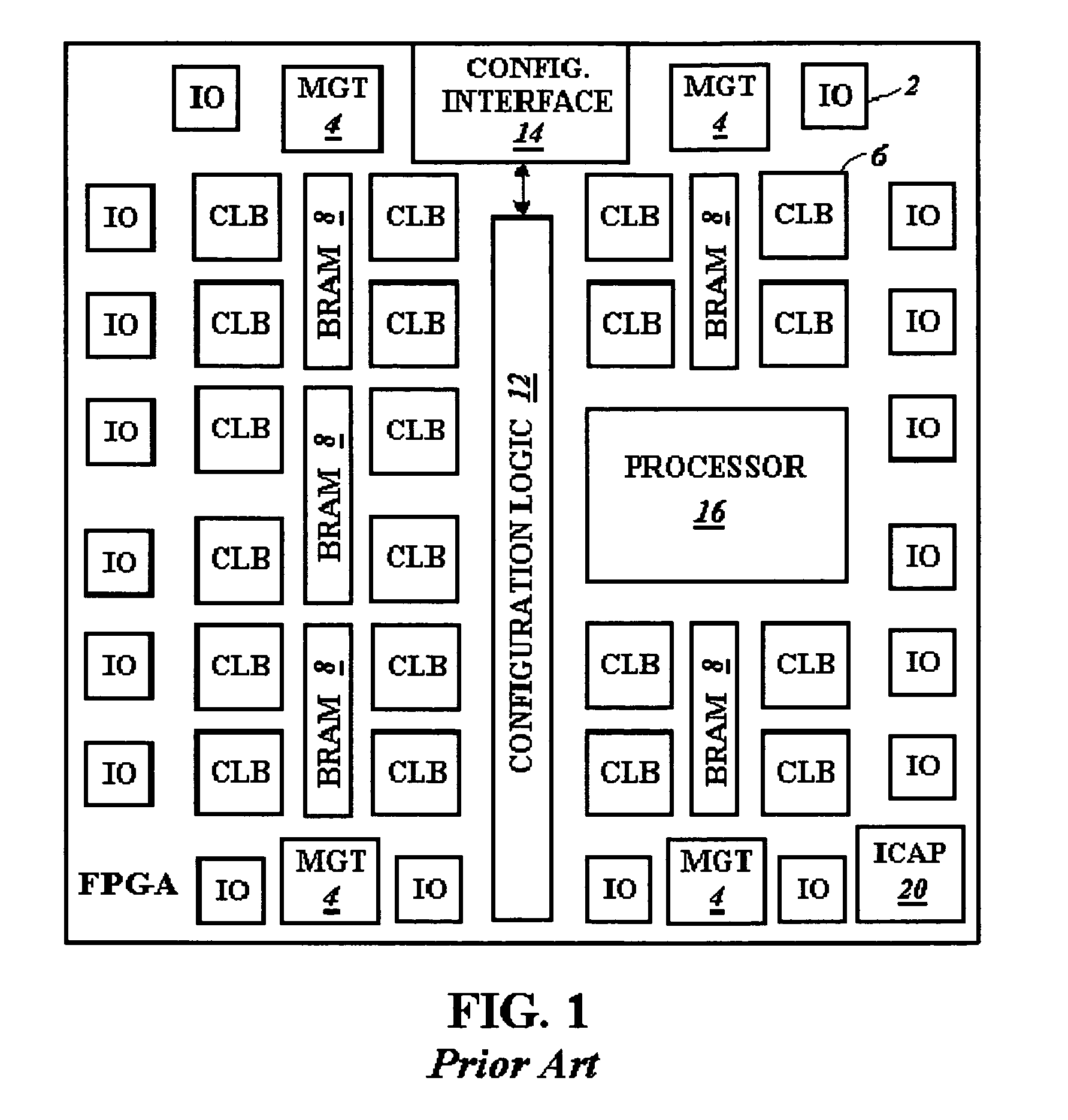

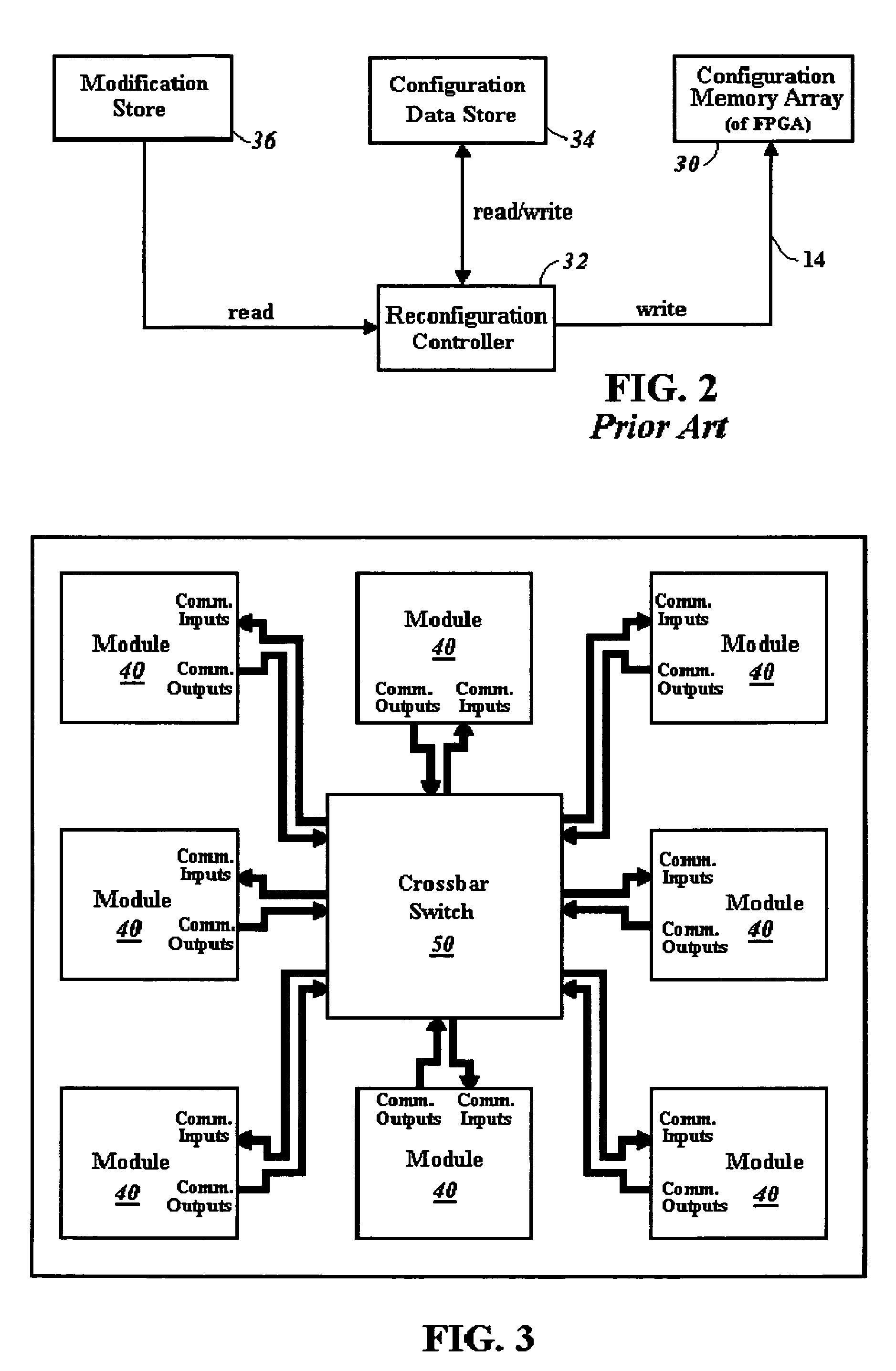

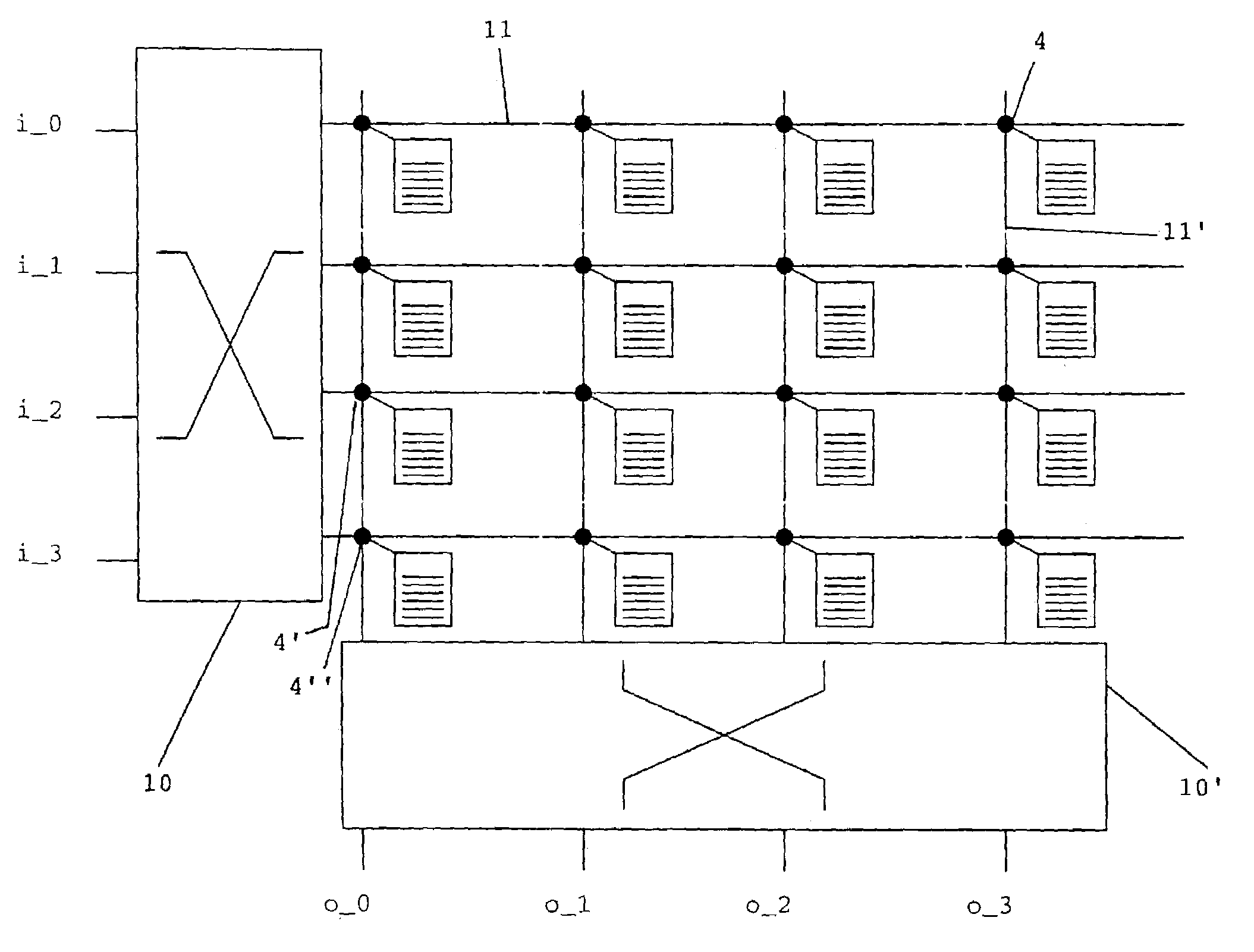

High bandwidth reconfigurable on-chip network for reconfigurable systems

ActiveUS7224184B1Quickly reconfiguredReduce necessarySolid-state devicesLogic circuits using elementary logic circuit componentsCrossbar switchAsynchronous communication

A crossbar switch (50) is implemented in a reconfigurable circuit, such as a FPGA, instantiated with a number of modules (40), the crossbar switch (50) providing communication links between the modules (40). The modules (40) and crossbar switch (50) can be easily updated in a partial reconfiguration process changing only portions of modules (40) and the crossbar switch (50) while other portions remain active. The crossbar switch (50) uses individual wiring to independently connect module outputs and inputs so that asynchronous communications can be used. The crossbar switch (50) can be implemented in different embodiments including a Clos crossbar switch, and a crossbar switch connecting each module output only to a corresponding module input, allowing for a reduction in the amount of FPGA resources required to create the crossbar switches.

Owner:XILINX INC

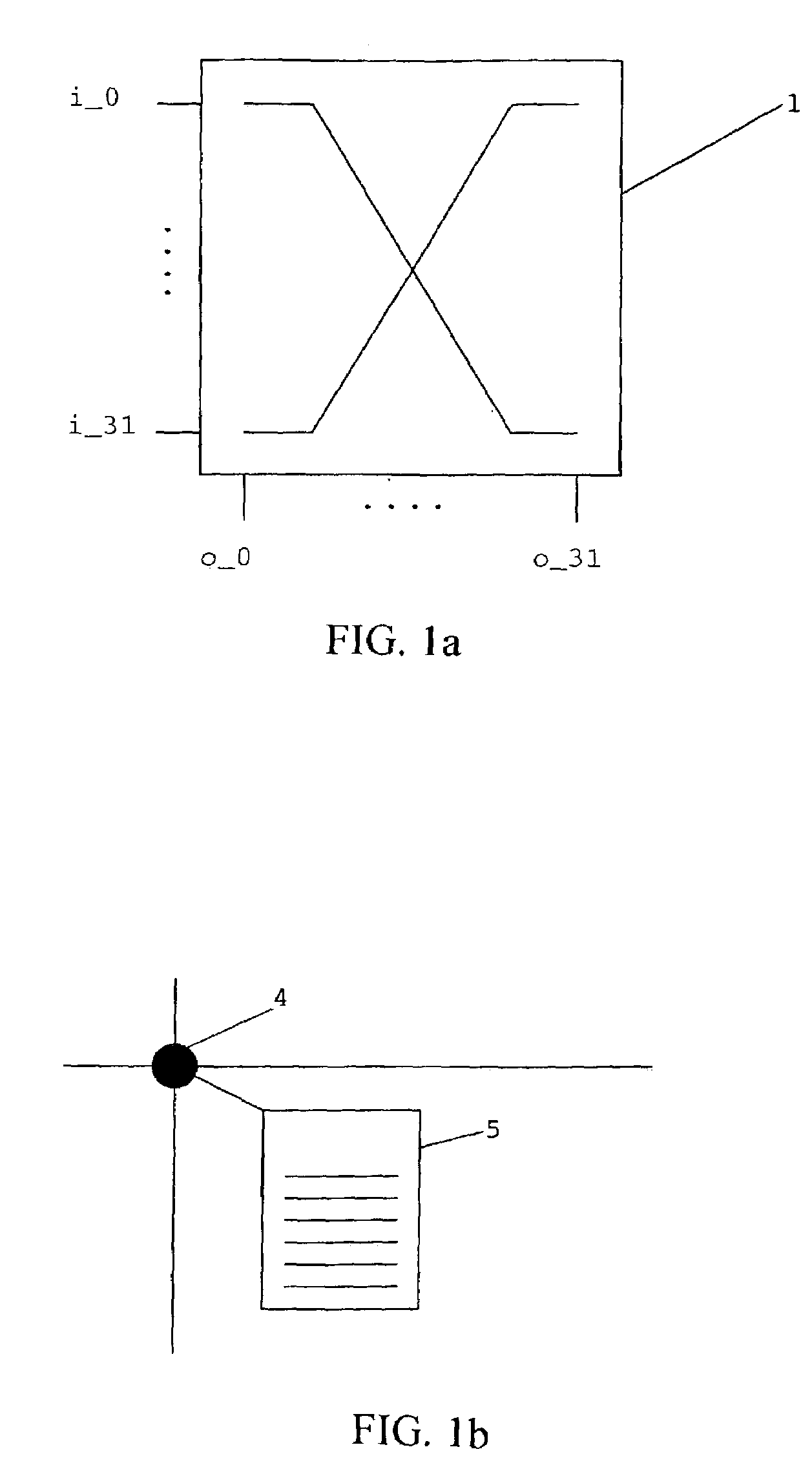

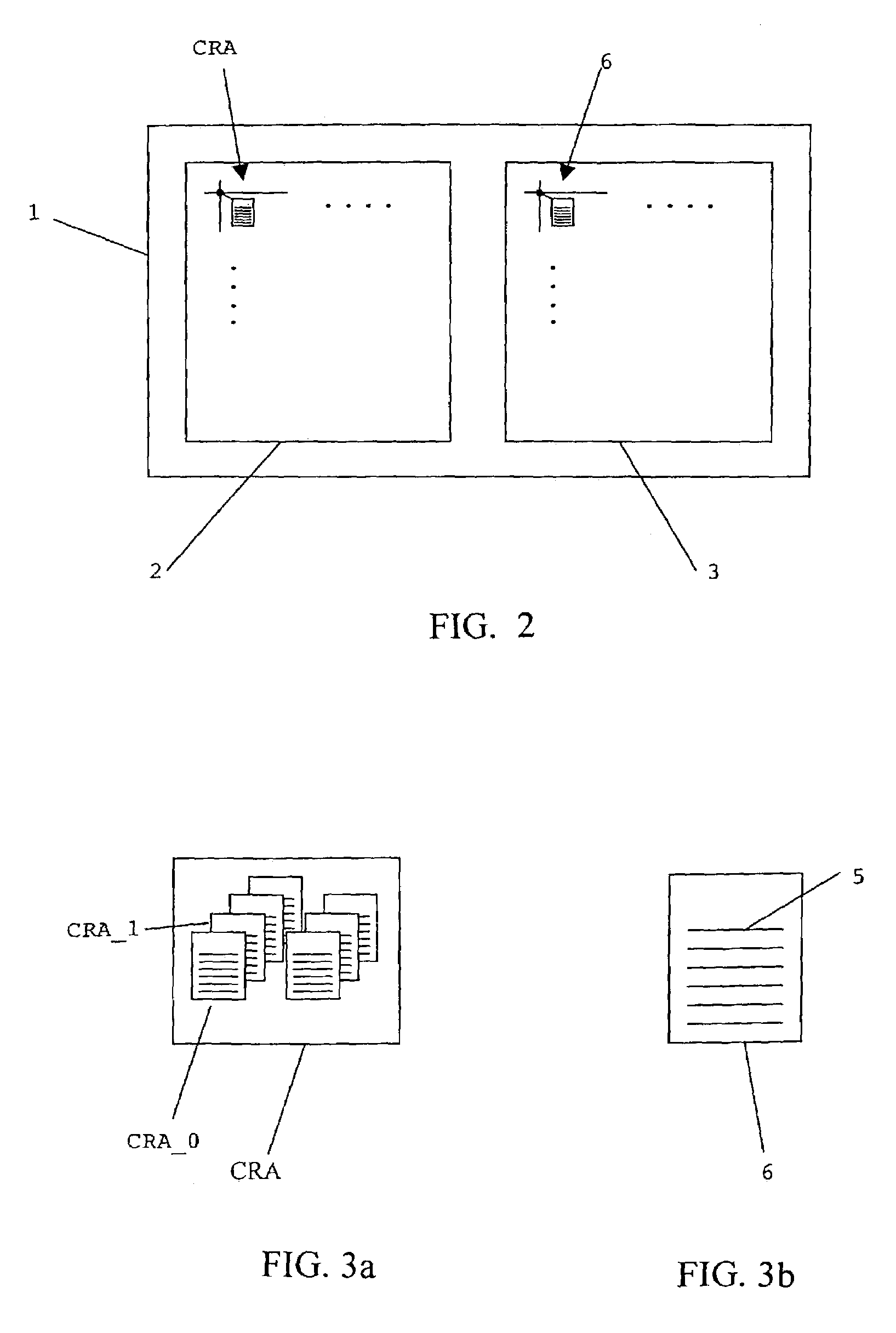

Method of operating a crossbar switch

The present invention relates to a method of operating a crossbar switch (1) having a control logic (2) and n input ports (i—0, . . . , i_n-1) and m output ports (o—0, . . . , o_m-1), wherein information packets of p different priority levels are routed from said n input ports (i—0, . . . , i_n-1) to said m output ports (o—0, . . . , o_m-1). Within said control logic (2), a pool (CRA) of buffers (CRA—0, CRA—1, . . . ) is provided for each crosspoint (4) for temporarily storing address information related to said information packets.

Owner:INT BUSINESS MASCH CORP

Switch control method and apparatus in a system having a plurality of processors

InactiveUS6378021B1Multiprogramming arrangementsMultiple digital computer combinationsInformation processingCrossbar switch

In an information processing apparatus having a crossbar switch, registers are provided for logical division of a connection of the crossbar switch into a plurality of groups, in order to allow a system to change the group division configuration while the system is in an ordinary operation. As an application of this, in a hot standby system, when a fault occurs in an active partition and the active partition is replaced by a standby partition, the standby partition is allowed to include system resources used by the active partition such as CPU's and memories.

Owner:HITACHI LTD

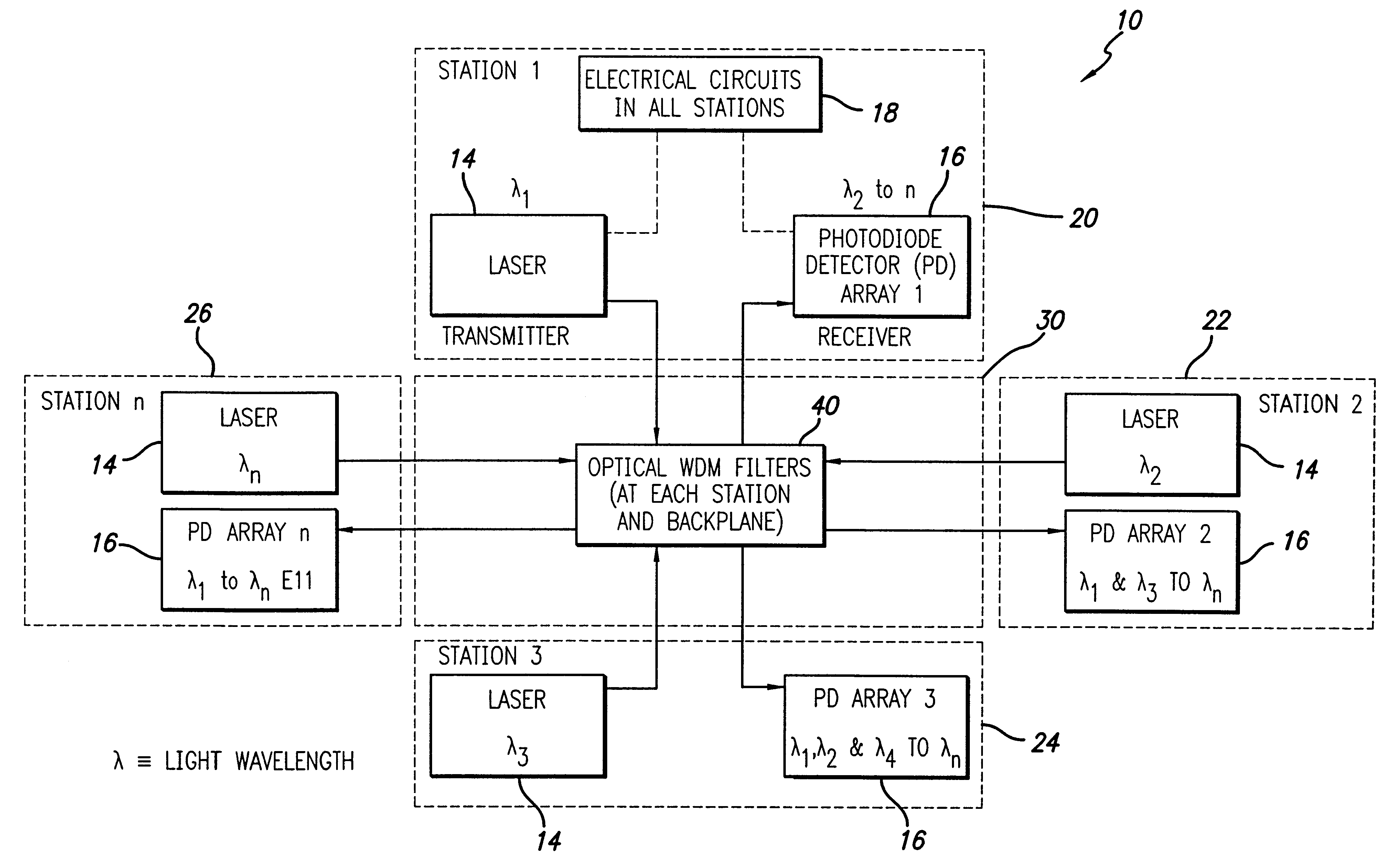

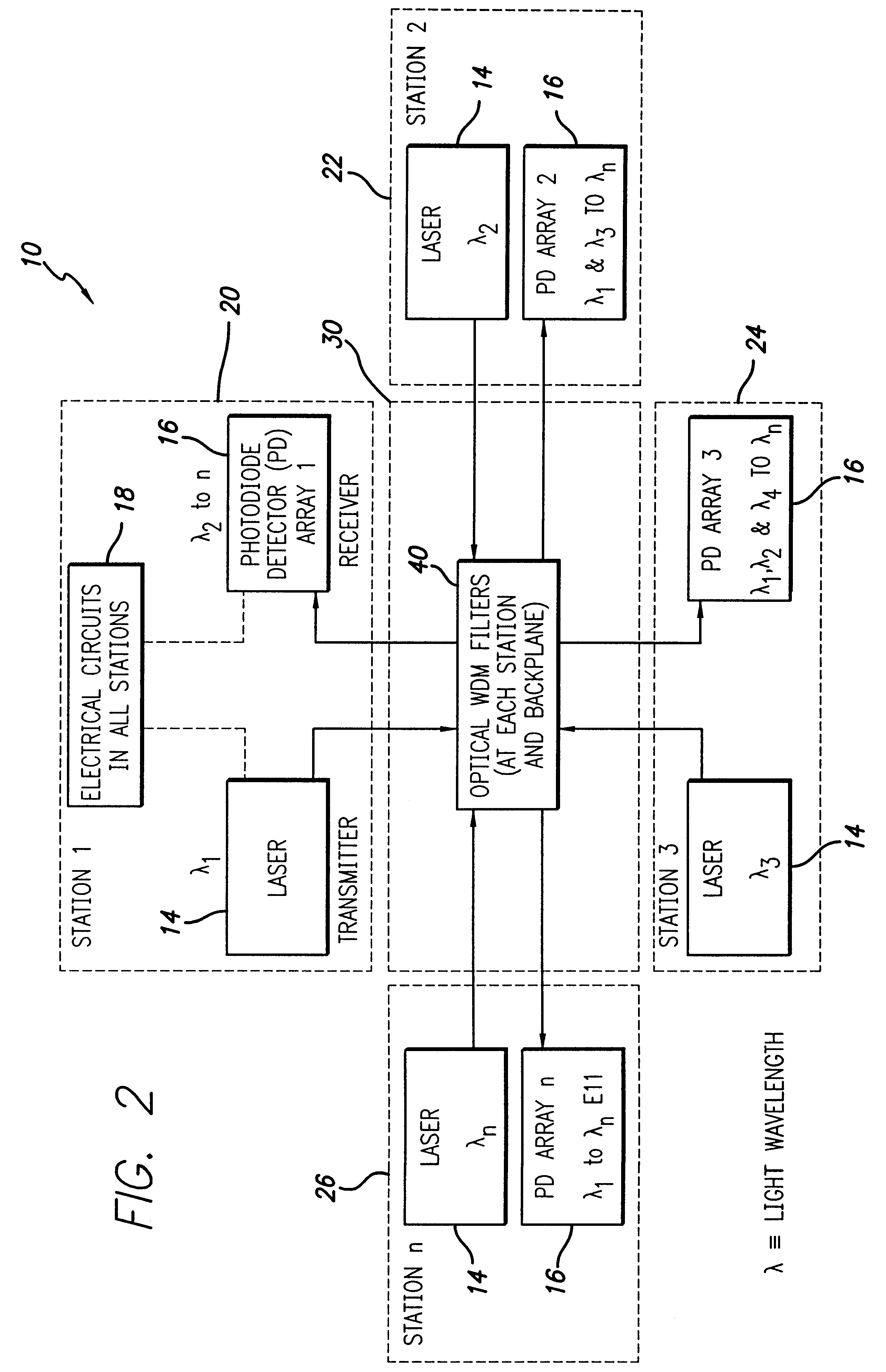

Opto-electronic distributed crossbar switch

InactiveUS6597824B2Multiplex system selection arrangementsCoupling light guidesCrossbar switchLaser transmitter

The invention is an optoelectronic (OE) crossbar switch (10) for both digital and analog signals, used either separately or combined, whose functions are reconfigurable and distributed. The invention allows multiple senders to be connected with multiple receivers simultaneously. The invention uses optical filters for wavelength division multiplexing and demultiplexing (WDM and WDD). A single fiber module input / output port carries multiple bi-directional signals that are optically filtered out in the module using WDM / WDD filters (12) at each sender / receiver and then selected after optical filtering using photodiode detectors (15) as detectors and switches. Laser transmitters (14), photodiode detectors (15), and smart electronics (18) are used to implement the crossbar switch functions. In addition to optical filters, the use of time division multiplexing (TDM) and code division multiple access (CDMA) implemented either electrically or optically are taught to increase the number of independent users that the distributed switch handles. The switch can be cascaded with other switches using optical bridging circuits (100) to create a scaleable interconnect fabric. An arbitration technique can be used which allows signals to be sent only when the intended receiver is capable of accepting these signals.

Owner:RAYTHEON CO