Patents

Literature

957 results about "Wait state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

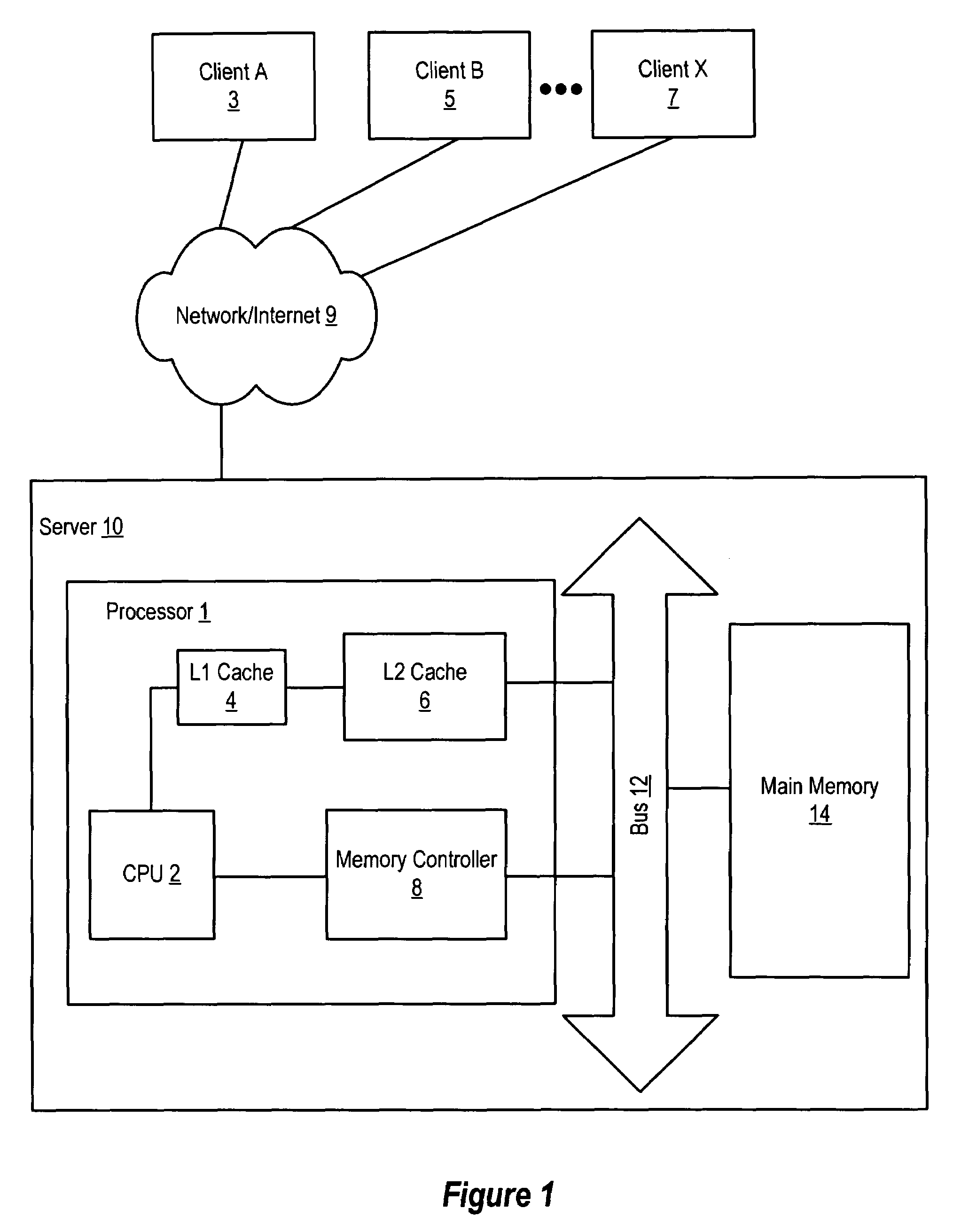

A wait state is a delay experienced by a computer processor when accessing external memory or another device that is slow to respond. Computer microprocessors generally run much faster than the computer's other subsystems, which hold the data the CPU reads and writes. Even memory, the fastest of these, cannot supply data as fast as the CPU could process it. In an example from 2011, typical PC processors like the Intel Core 2 and the AMD Athlon 64 X2 run with a clock of several GHz, which means that one clock cycle is less than 1 nanosecond (typically about 0.3 ns to 0.5 ns on modern desktop CPUs), while main memory has a latency of about 15–30 ns. Some second-level CPU caches run slower than the processor core.

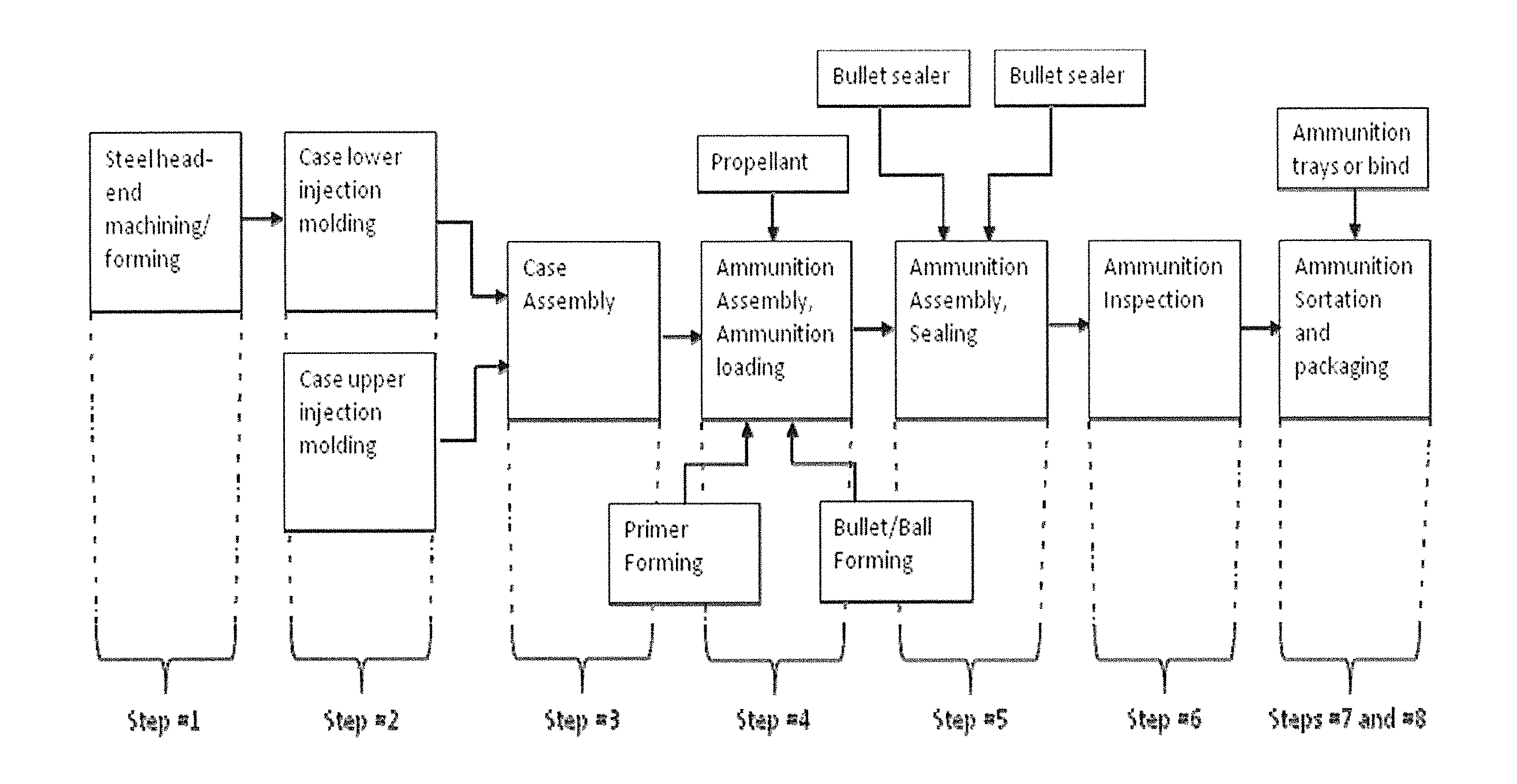

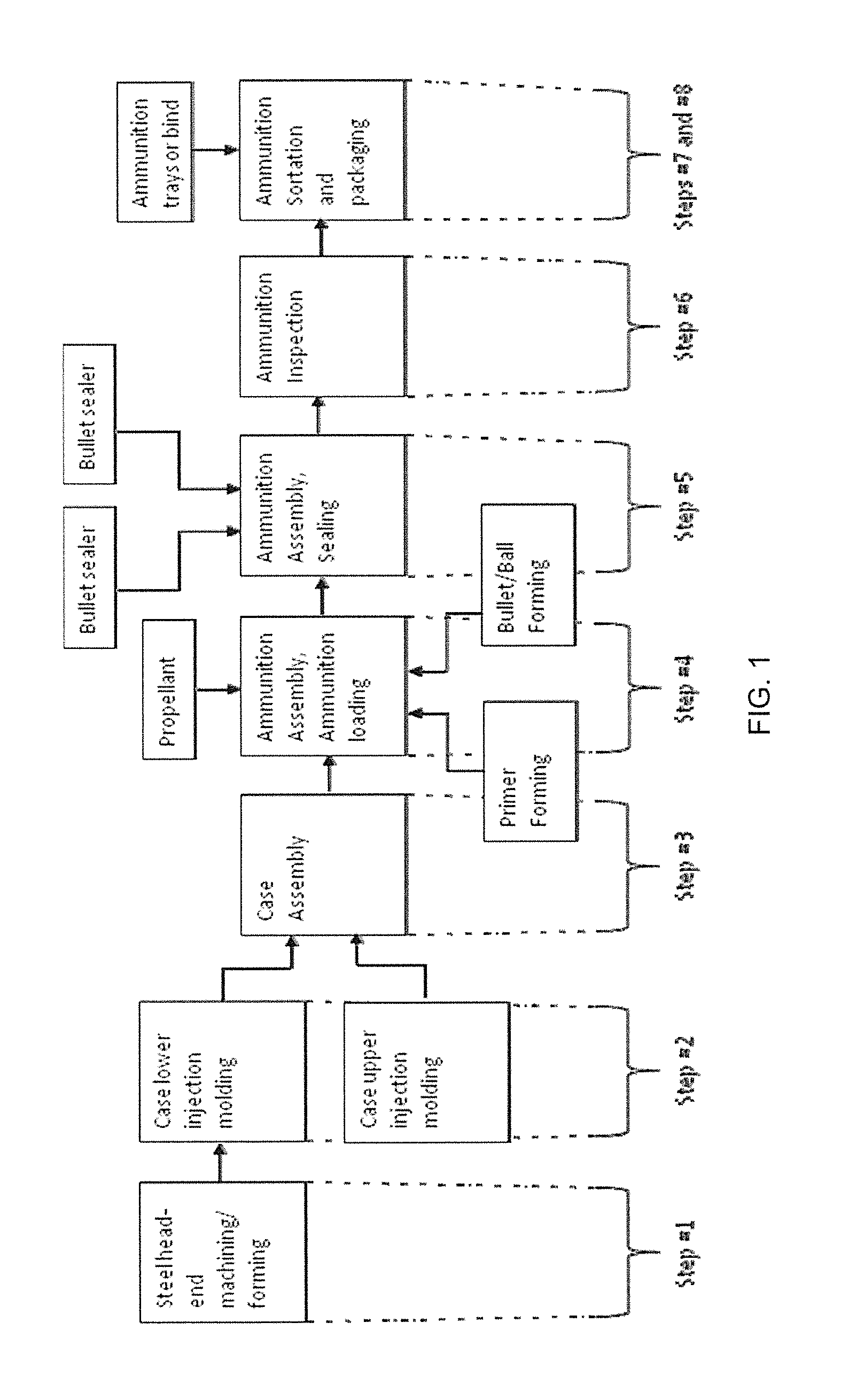

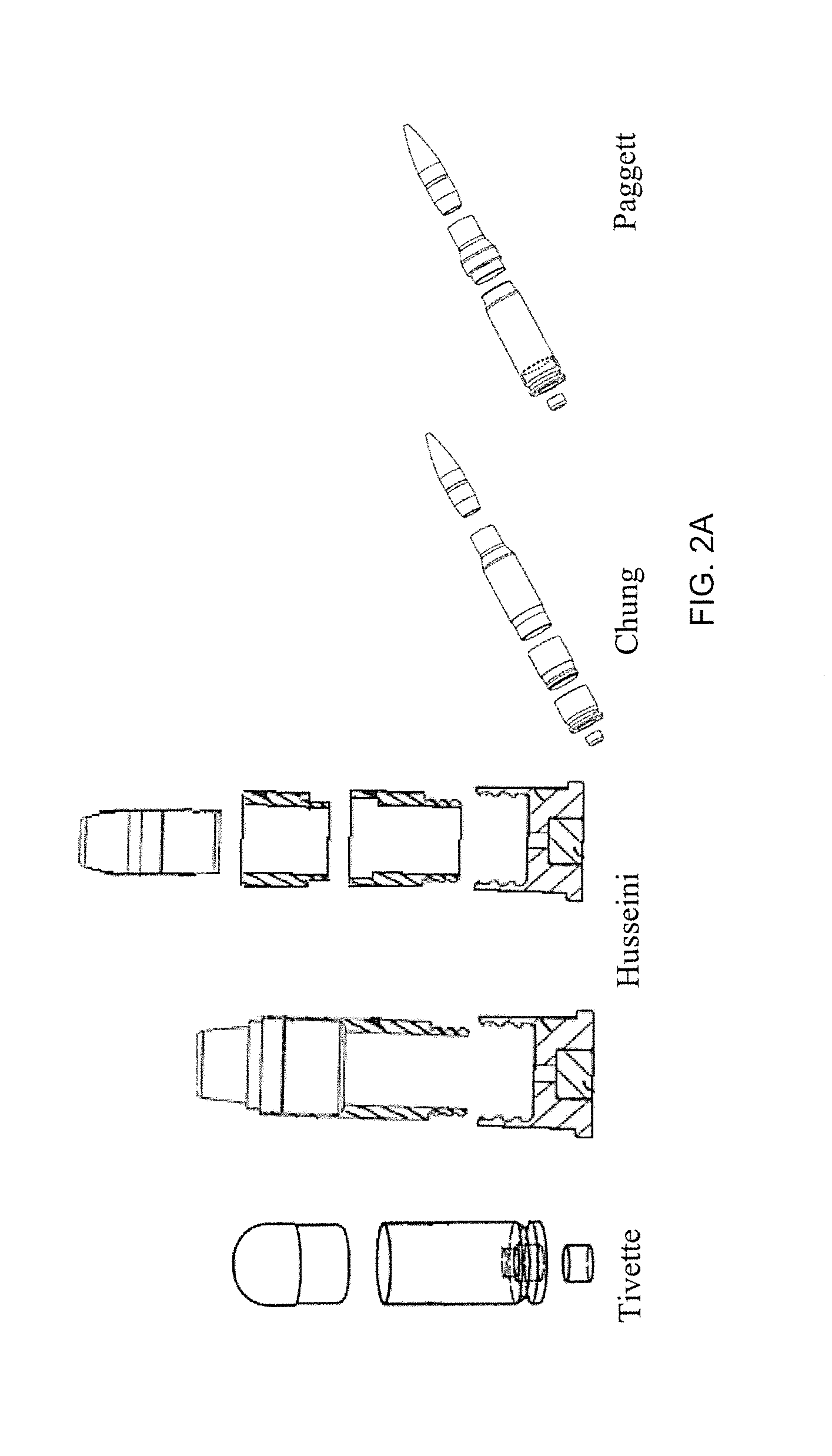

Integrated polymer and metal case ammunition manufacturing system and method

A fully automated, integrated, end-to-end synchronized and compact manufacturing system produces polymer or metal case ammunition. Manufacturing stations support case assembly, sealing (gluing / welding), final product inspection, cartridge packaging or binning, and loading. Station modularity facilitates rapid changeover to accommodate ammunition of differing calibers. Sensors and apparatus may be provided to place a manufacturing cell in a wait state until all components or materials are received in a preferred orientation for proper assembly. The system may join and use multipart cases, each including a lower portion with a head end attached thereto and at least one upper portion having a necked-down transition to the open top end. Elevator feeders, vibratory bowl feeders, and robotic pick-and-place feeders may be used to deliver components for assembly.

Owner:CYBERNET SYST

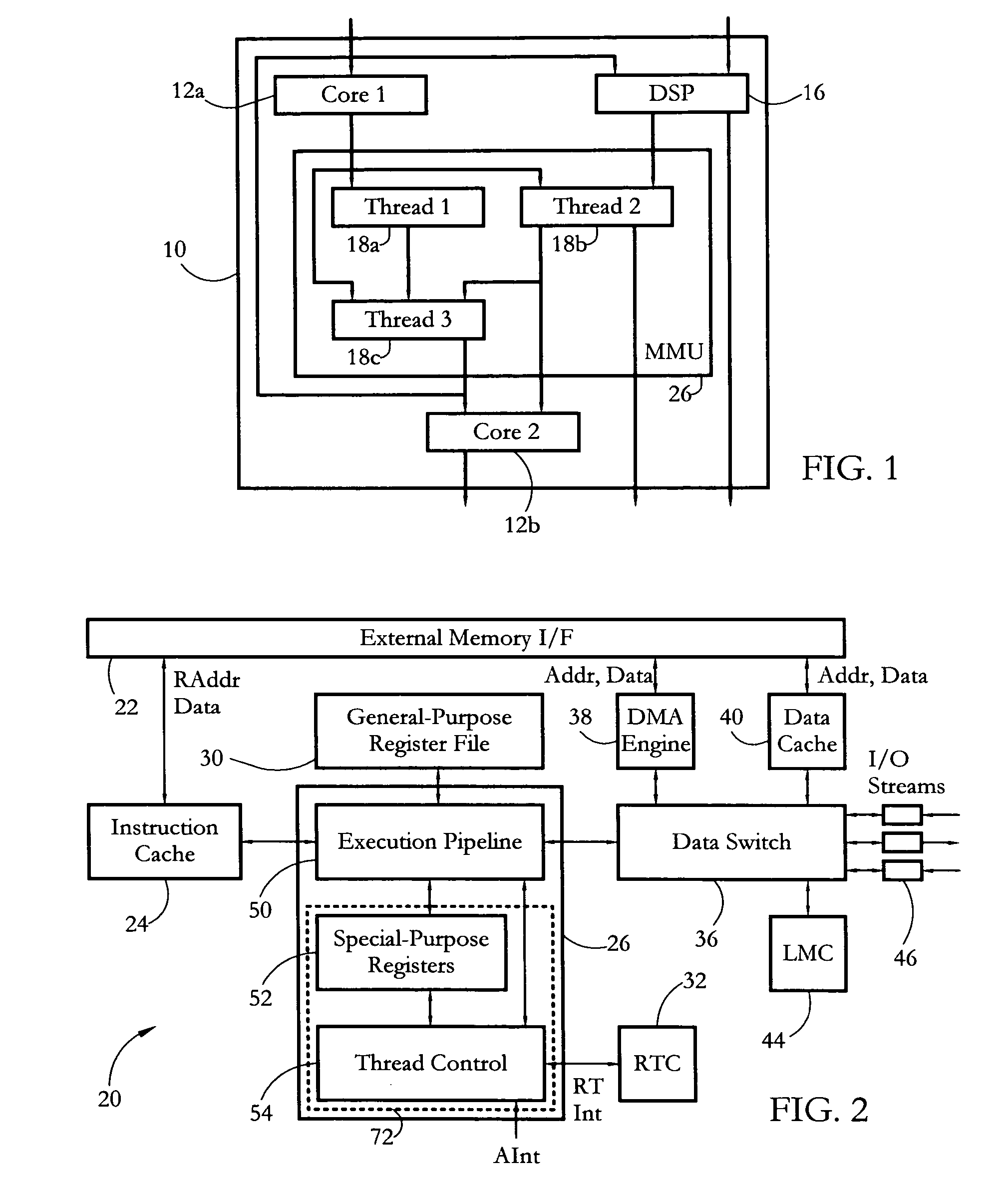

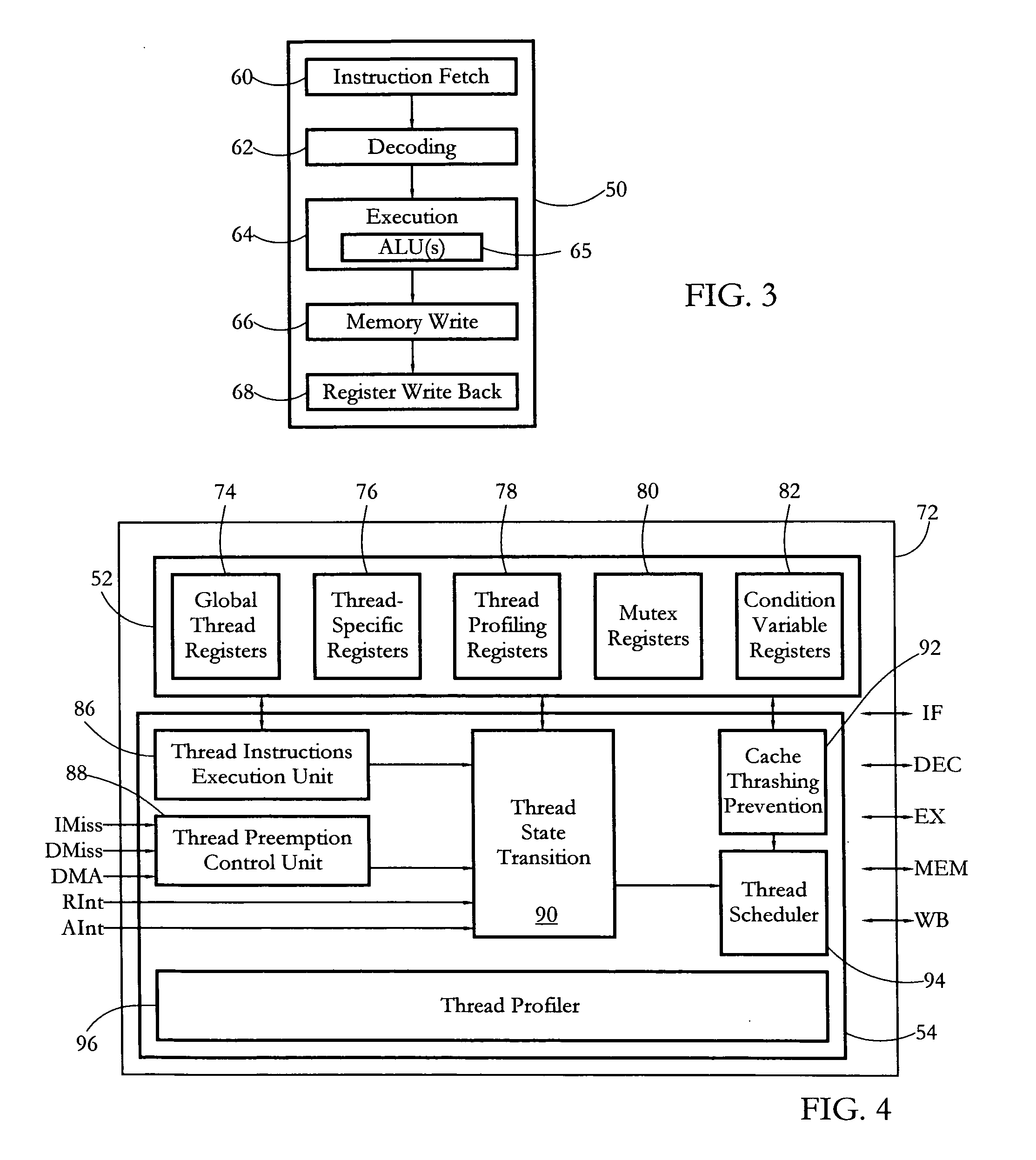

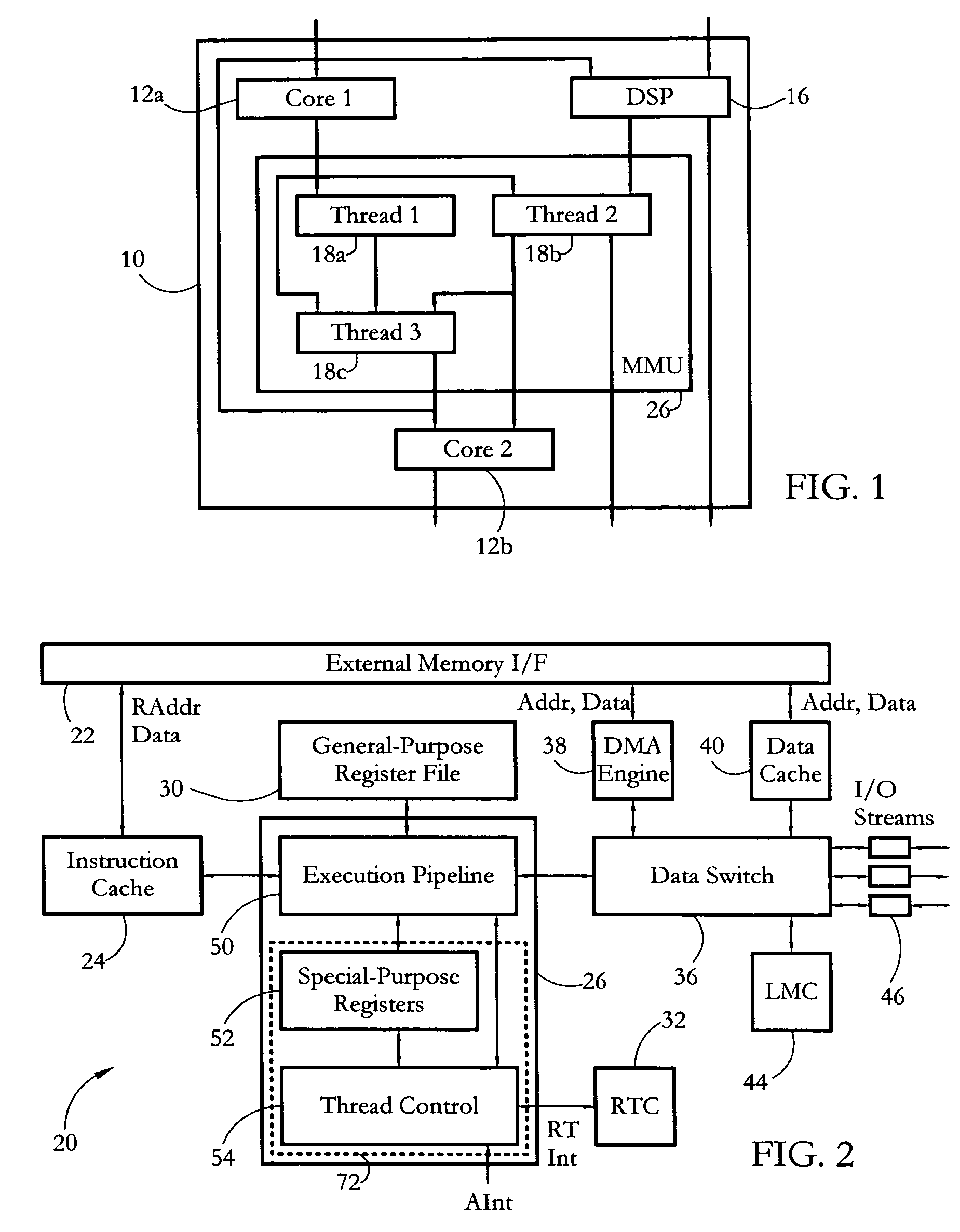

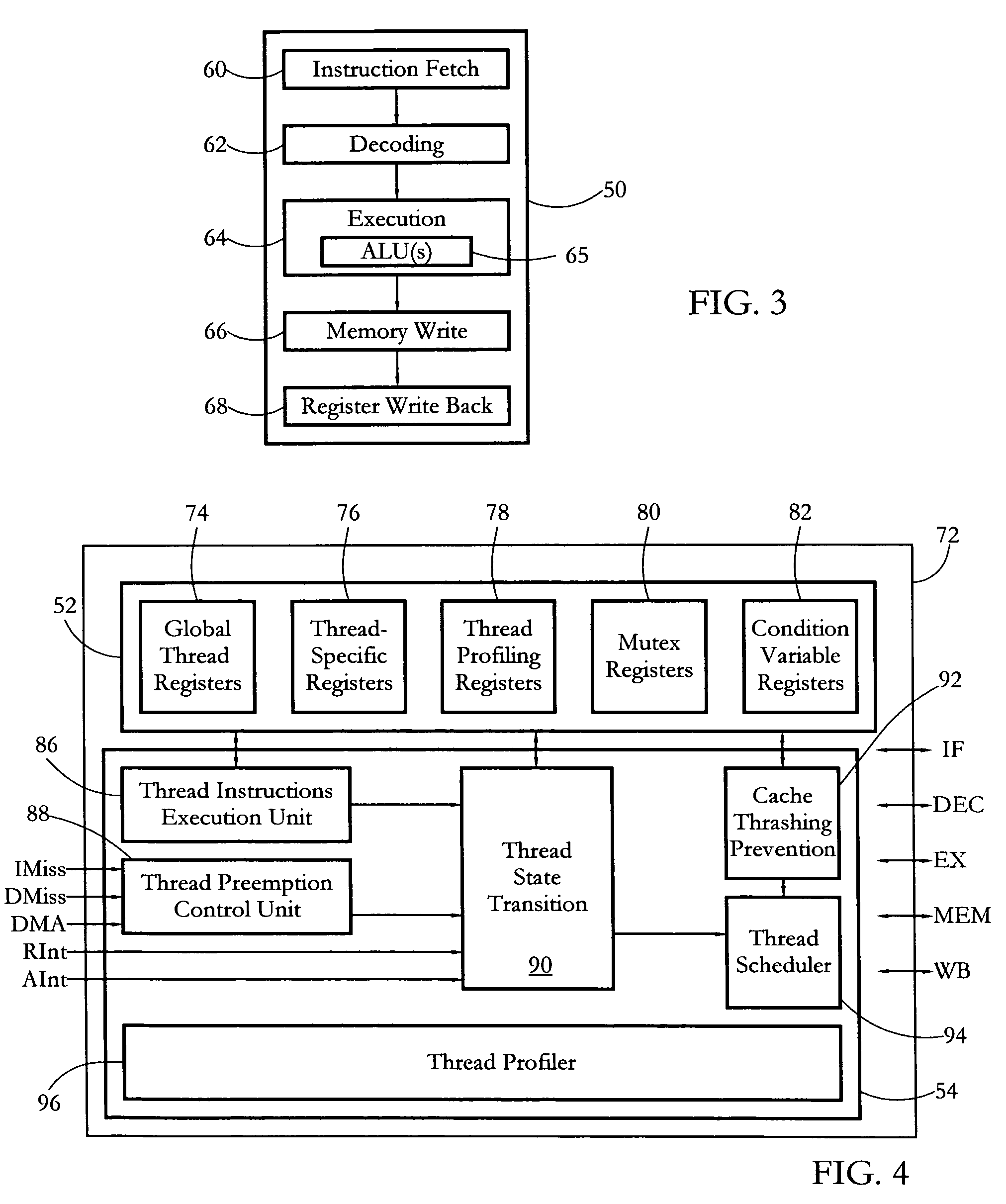

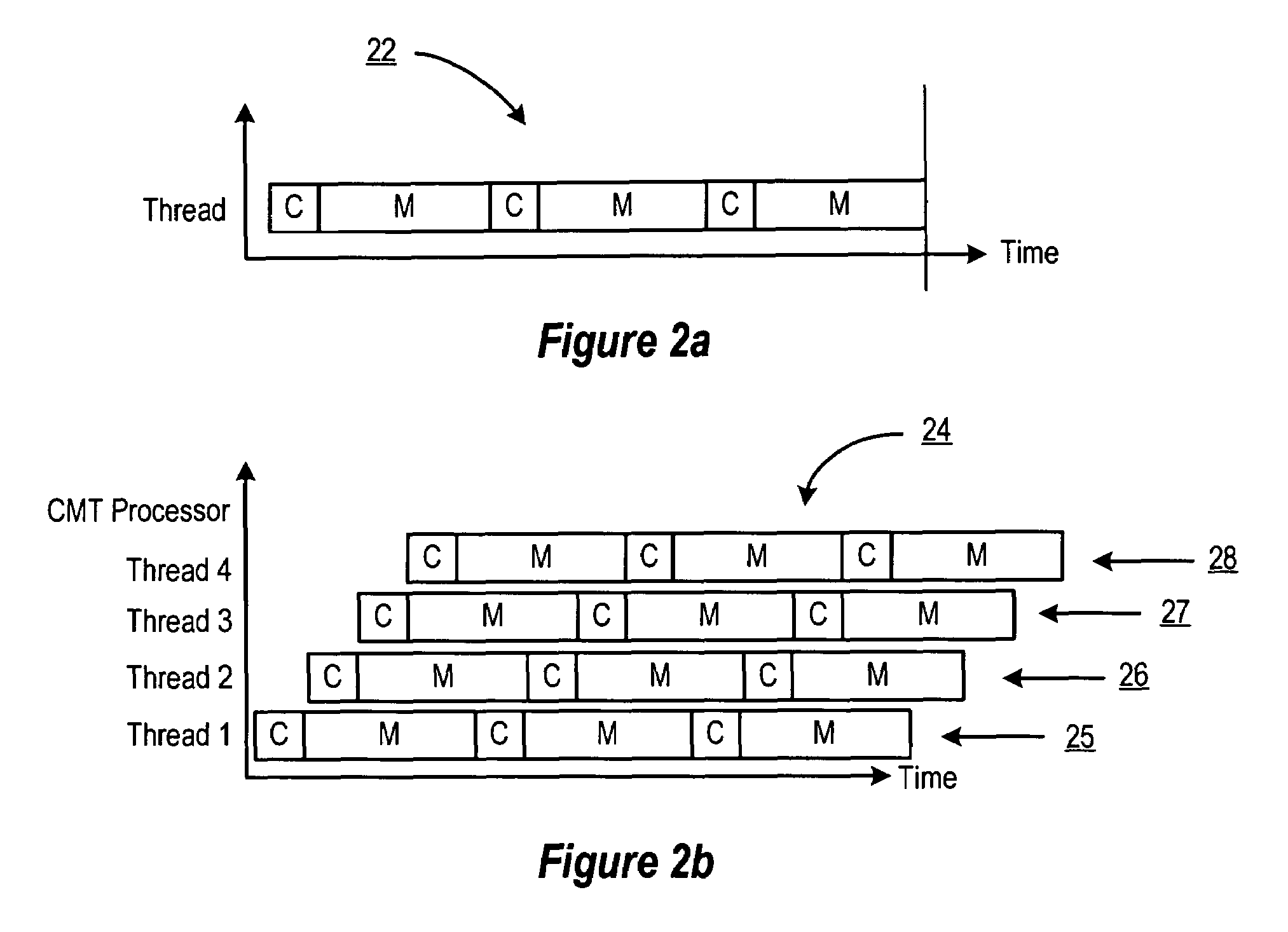

Hardware multithreading systems and methods

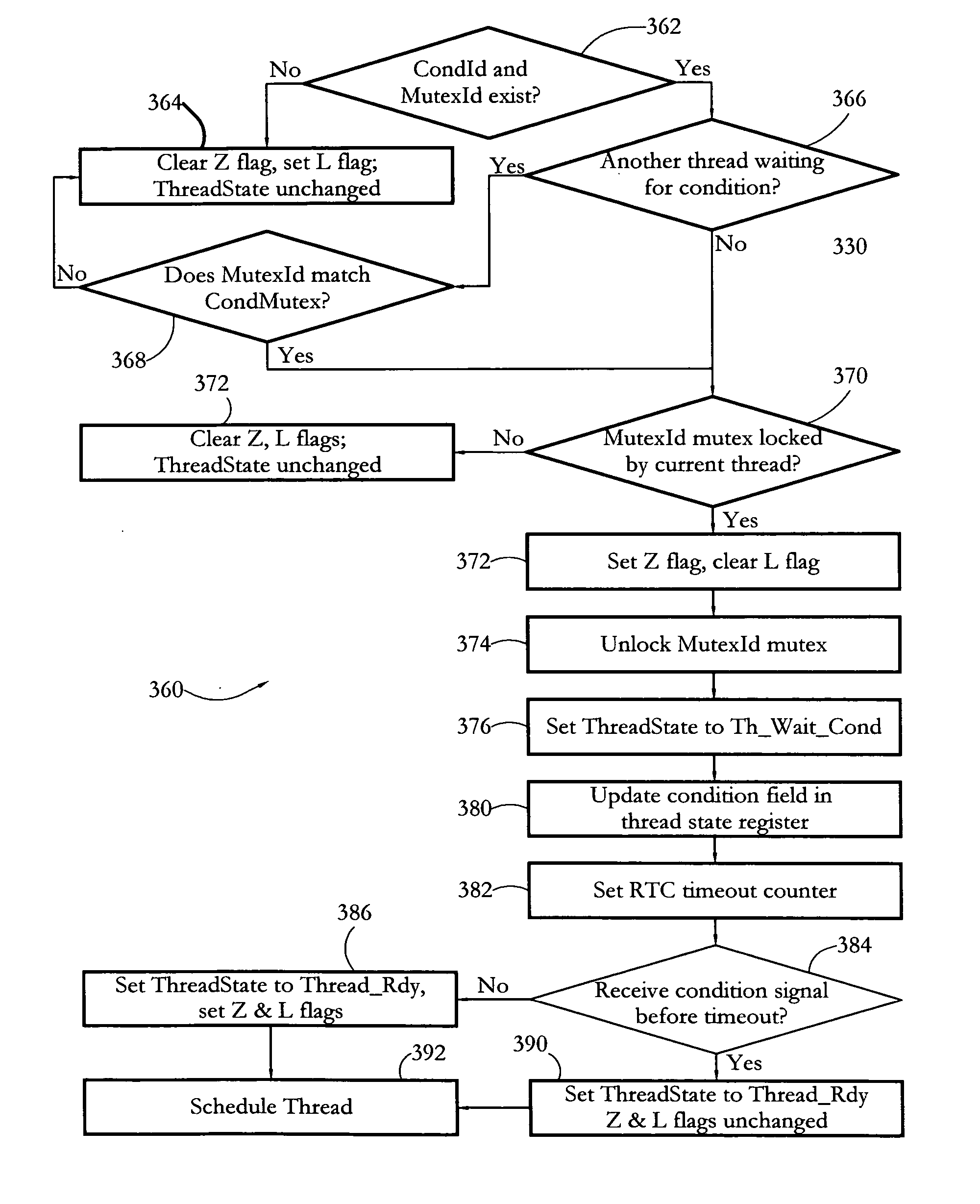

According to some embodiments, a multithreaded microcontroller includes a thread control unit comprising thread control hardware (logic) configured to perform a number of multithreading system calls essentially in real time, e.g. in one or a few clock cycles. System calls can include mutex lock, wait condition, and signal instructions. The thread controller includes a number of thread state, mutex, and condition variable registers used for executing the multithreading system calls. Threads can transition between several states including free, run, ready and wait. The wait state includes interrupt, condition, mutex, I-cache, and memory substates. A thread state transition controller controls thread states, while a thread instructions execution unit executes multithreading system calls and manages thread priorities to avoid priority inversion. A thread scheduler schedules threads according to their priorities. A hardware thread profiler including global, run and wait profiler registers is used to monitor thread performance to facilitate software development.

Owner:GEO SEMICONDUCTOR INC

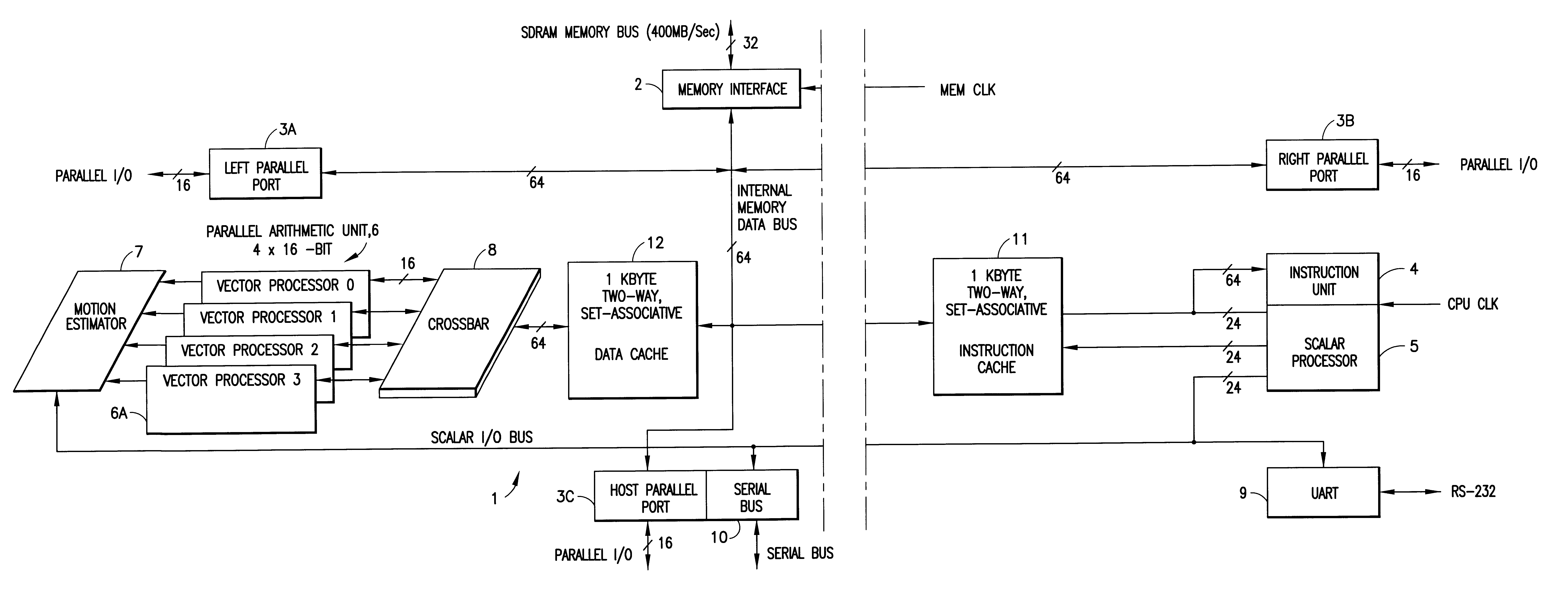

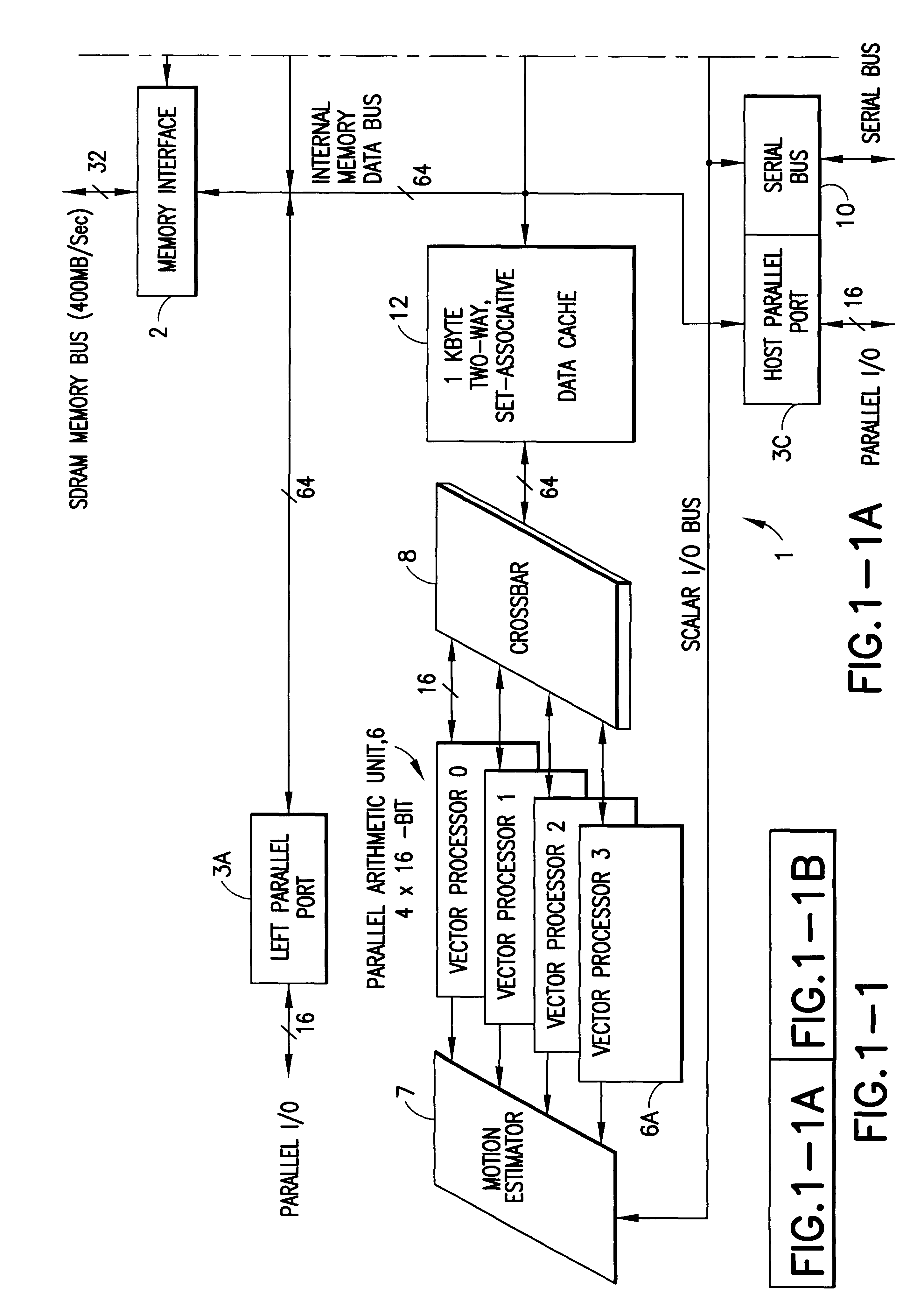

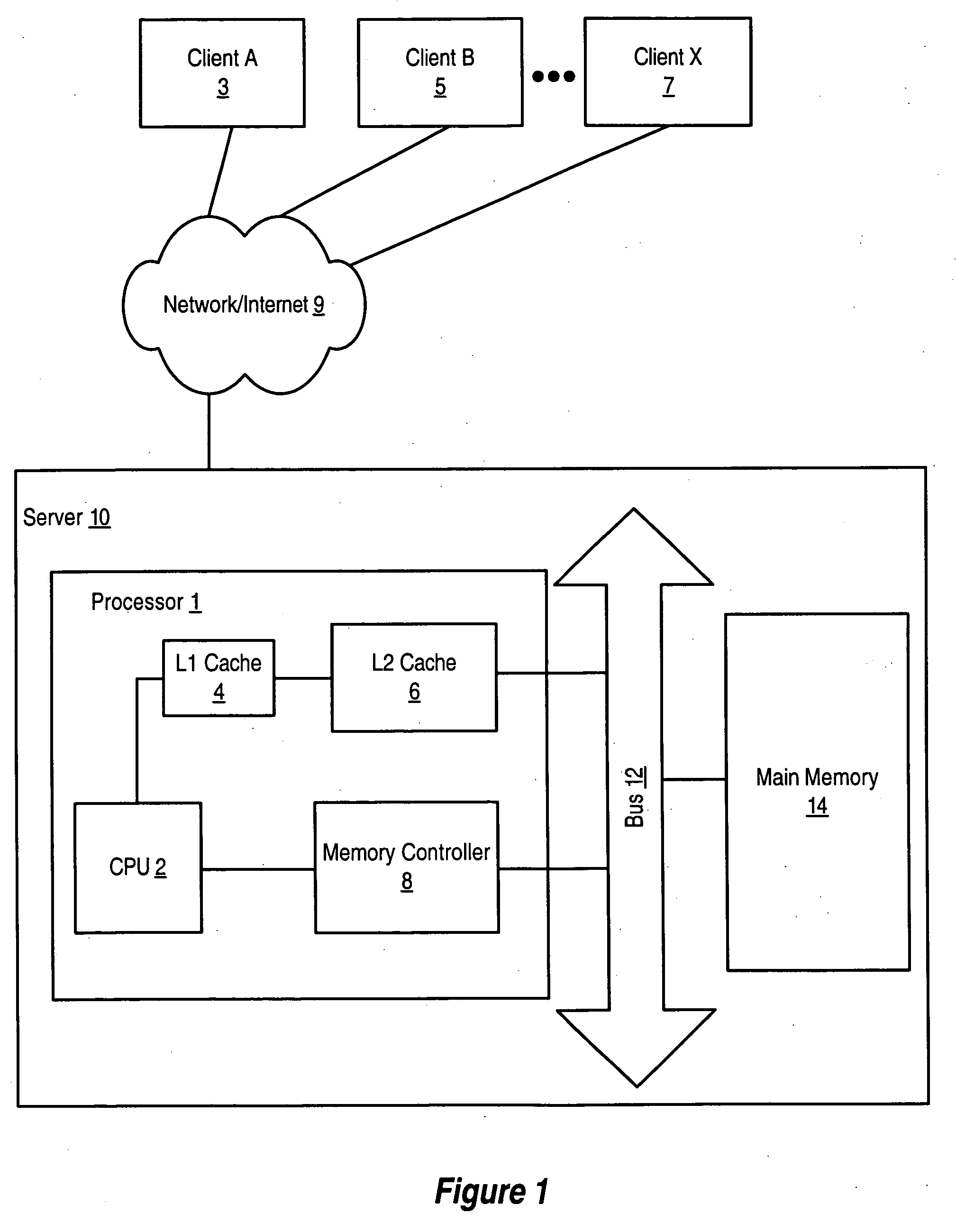

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

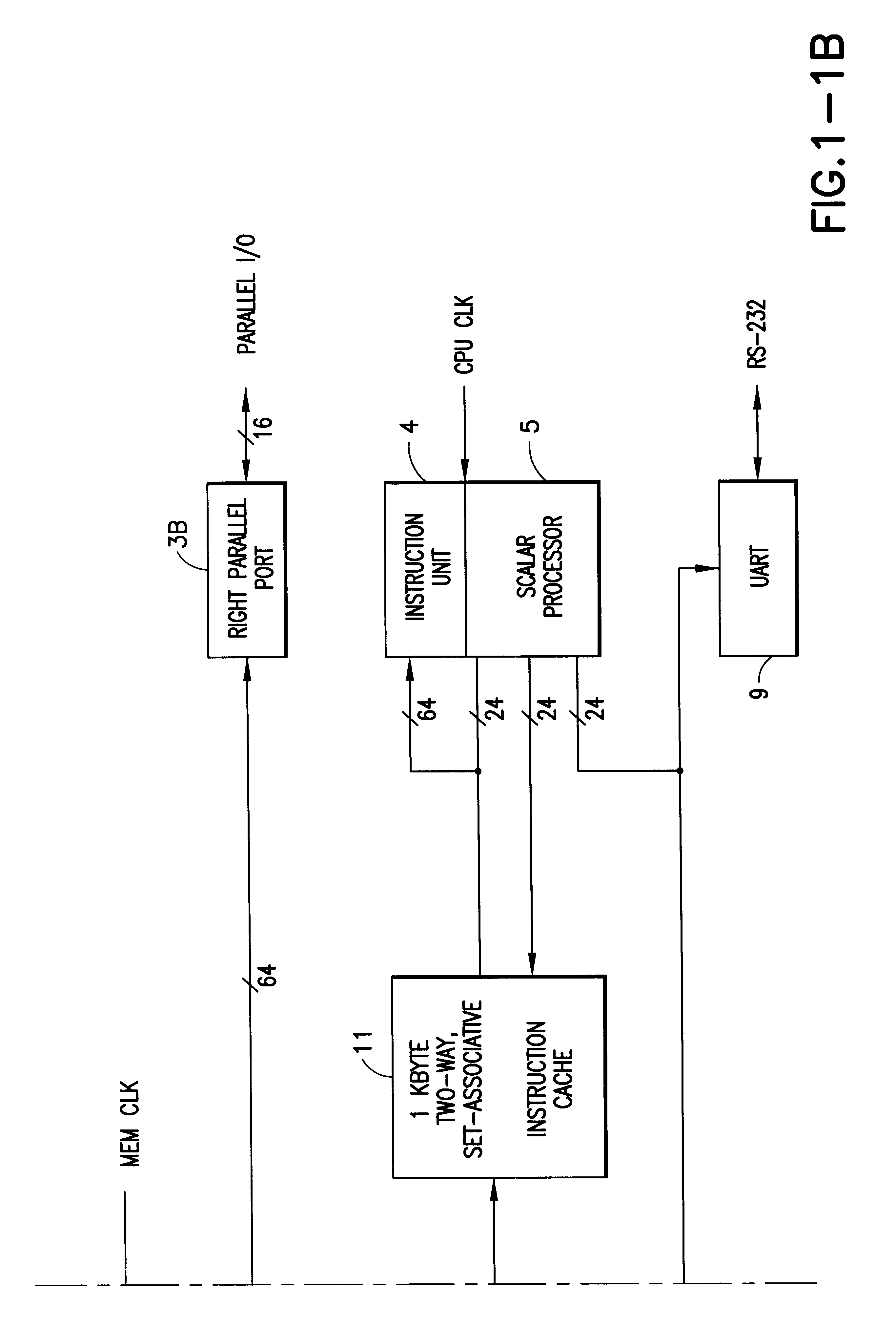

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

Ipnet gateway

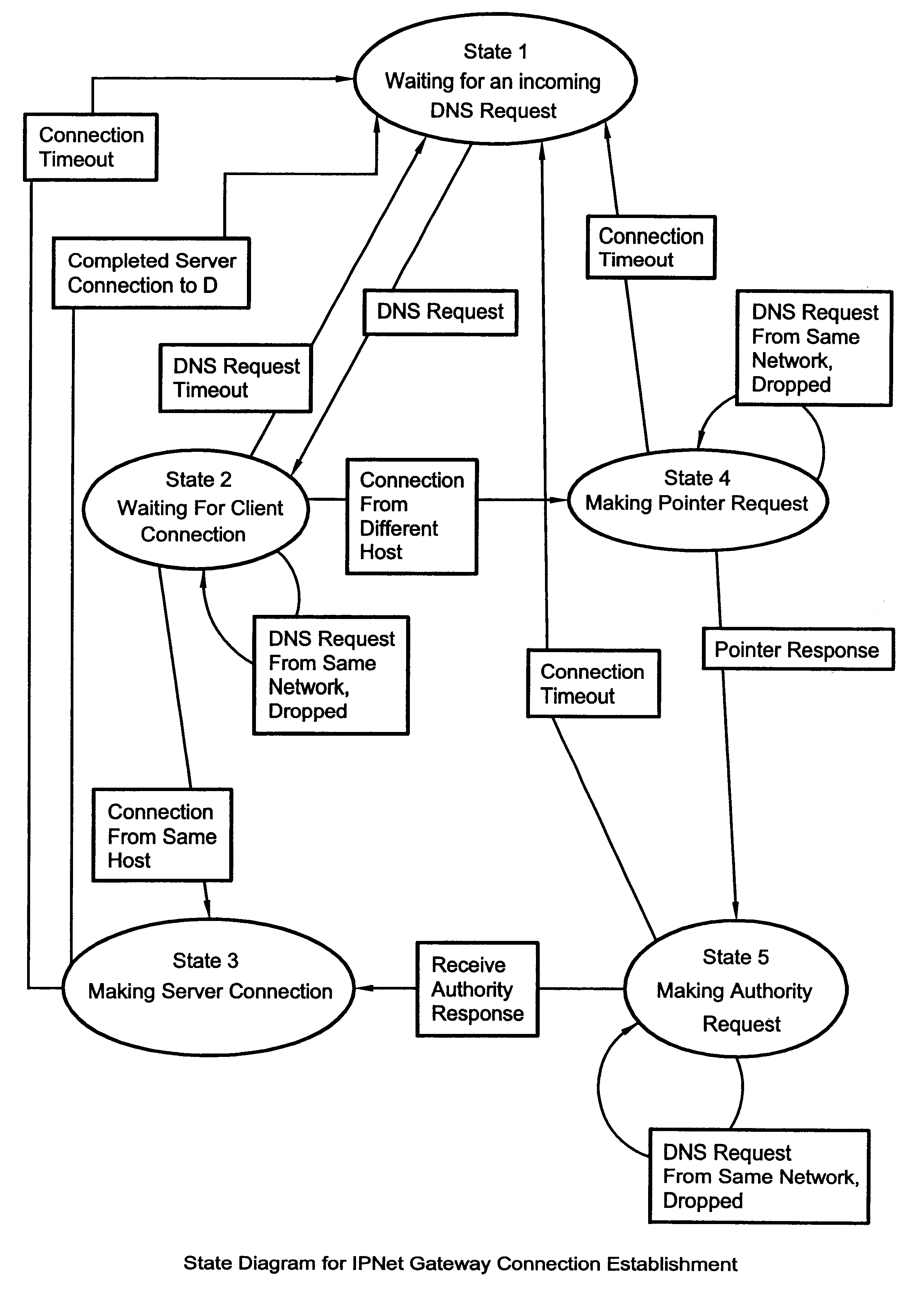

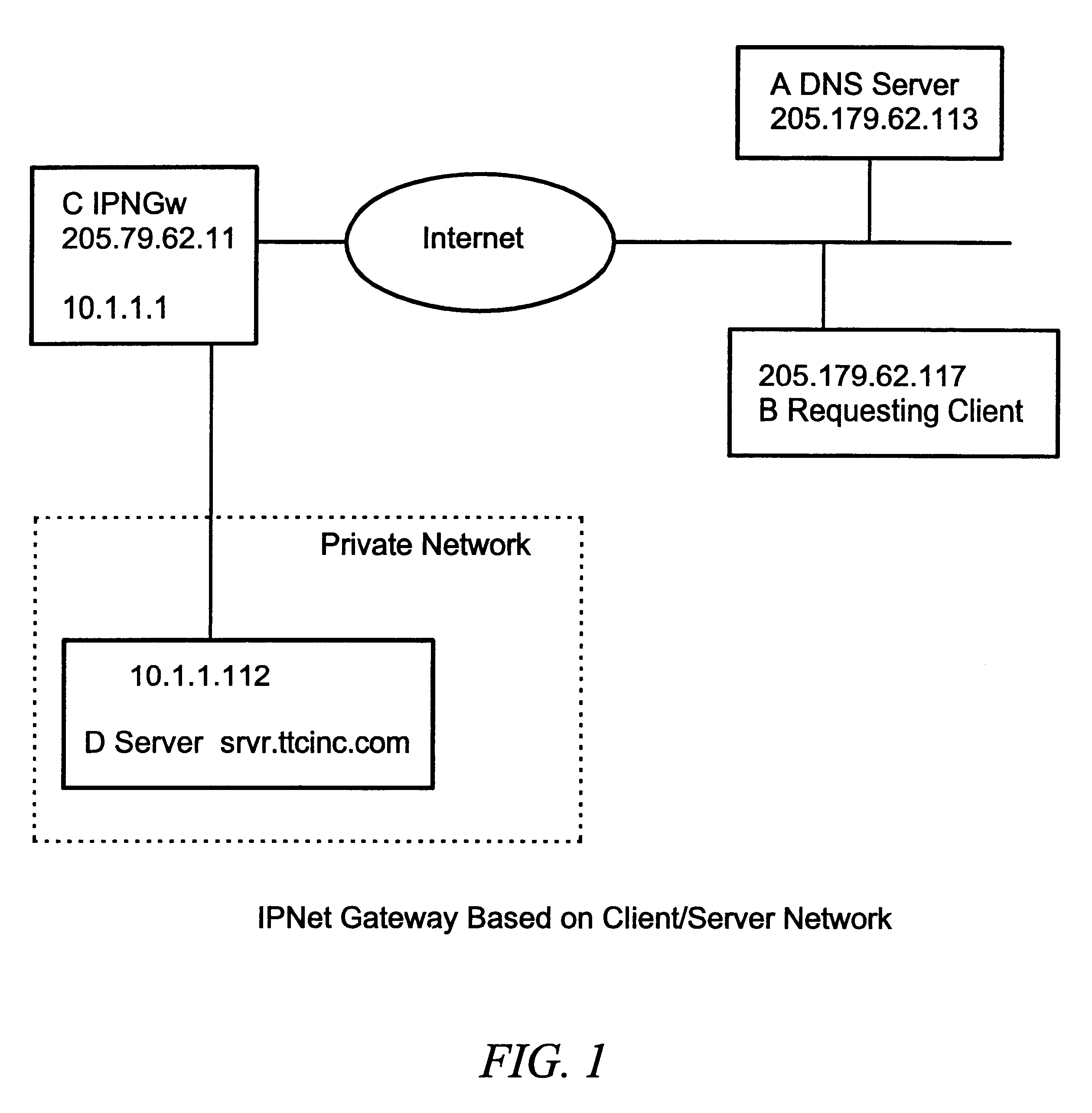

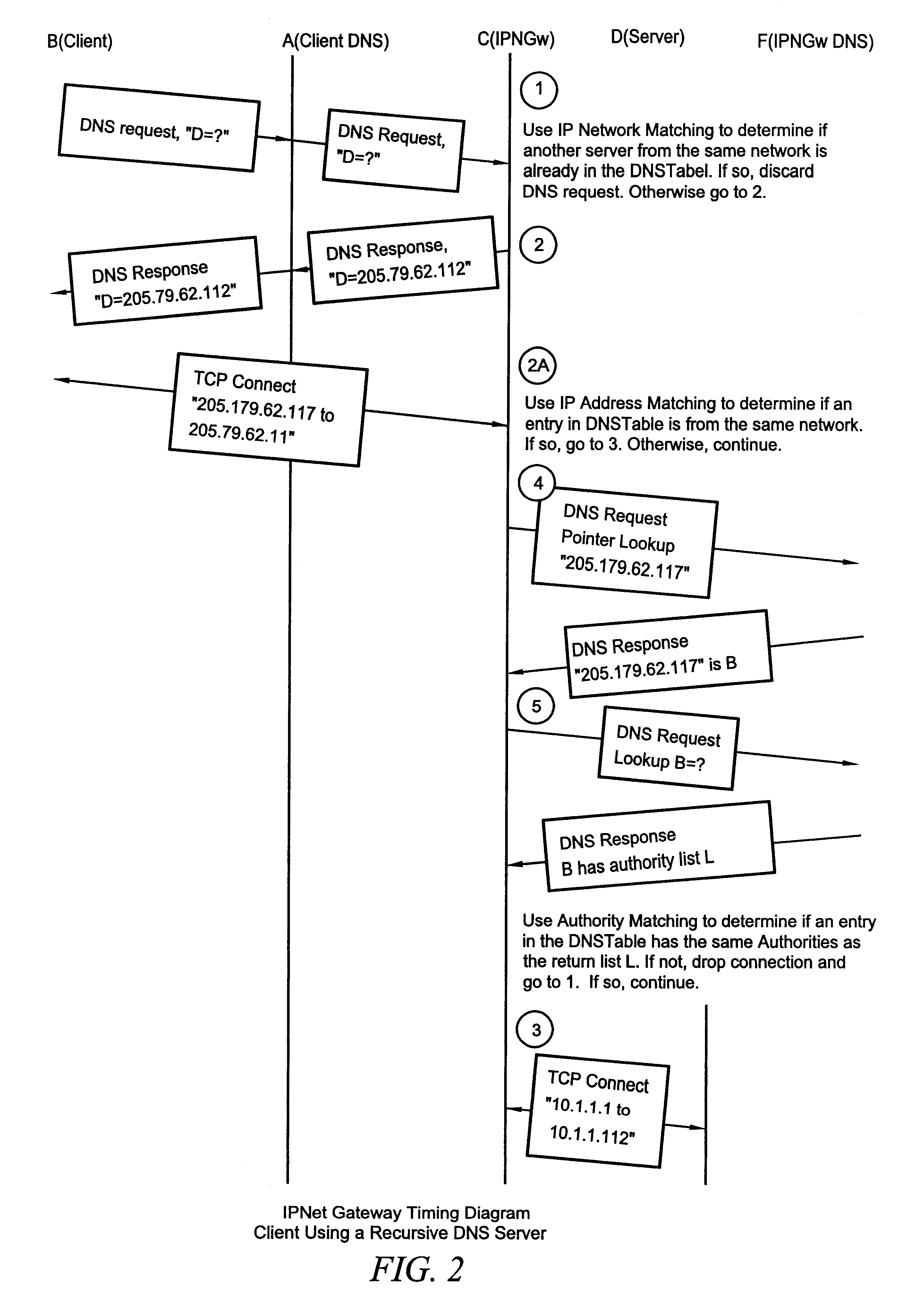

The IPNet Gateway (IPNGw) is a new technology that maps multiple servers on a private IP network to a single IP address on the Internet. As requests come in for DNS resolution of the server's domain name, the IPNet Gateway records the domain of the requesting client and the name of the requested server, and returns its own address as the destination address for the requested domain name. This DNS response is set as non-cacheable to prevent the association between the IPNGw IP address and the domain name of the target server beyond the anticipated following transaction from the client. As soon as the IPNGw responds to the DNS request it enters into a waiting state anticipating a connection from the client to the specific server identified in the DNS request. Subsequently, the client establishes a connection with the IPNGw, which in turn relays the connection request to the server.

Owner:LONGHORN HD LLC

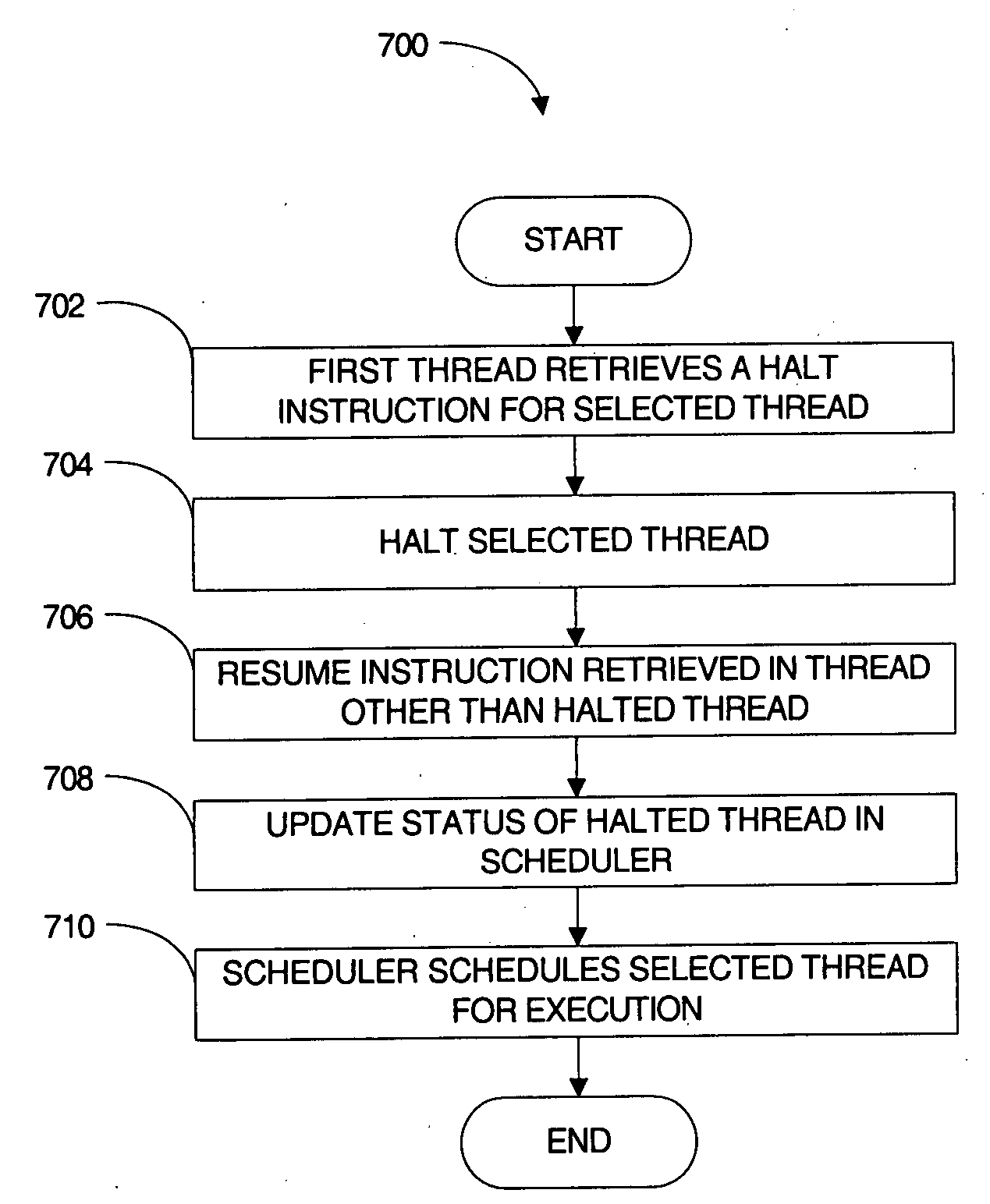

System and method for controlling thread suspension in a multithreaded processor

InactiveUS20060136919A1Energy efficient ICTMultiprogramming arrangementsProcessing coreParallel computing

A multi-thread processor including a processing core. The processing core including multiple threads and a scheduler. The scheduler includes a thread state register. The thread state register being capable of storing a selective wait state for a selected one of the threads. A method of scheduling threads in a multi-thread processor is also disclosed.

Owner:SUN MICROSYSTEMS INC

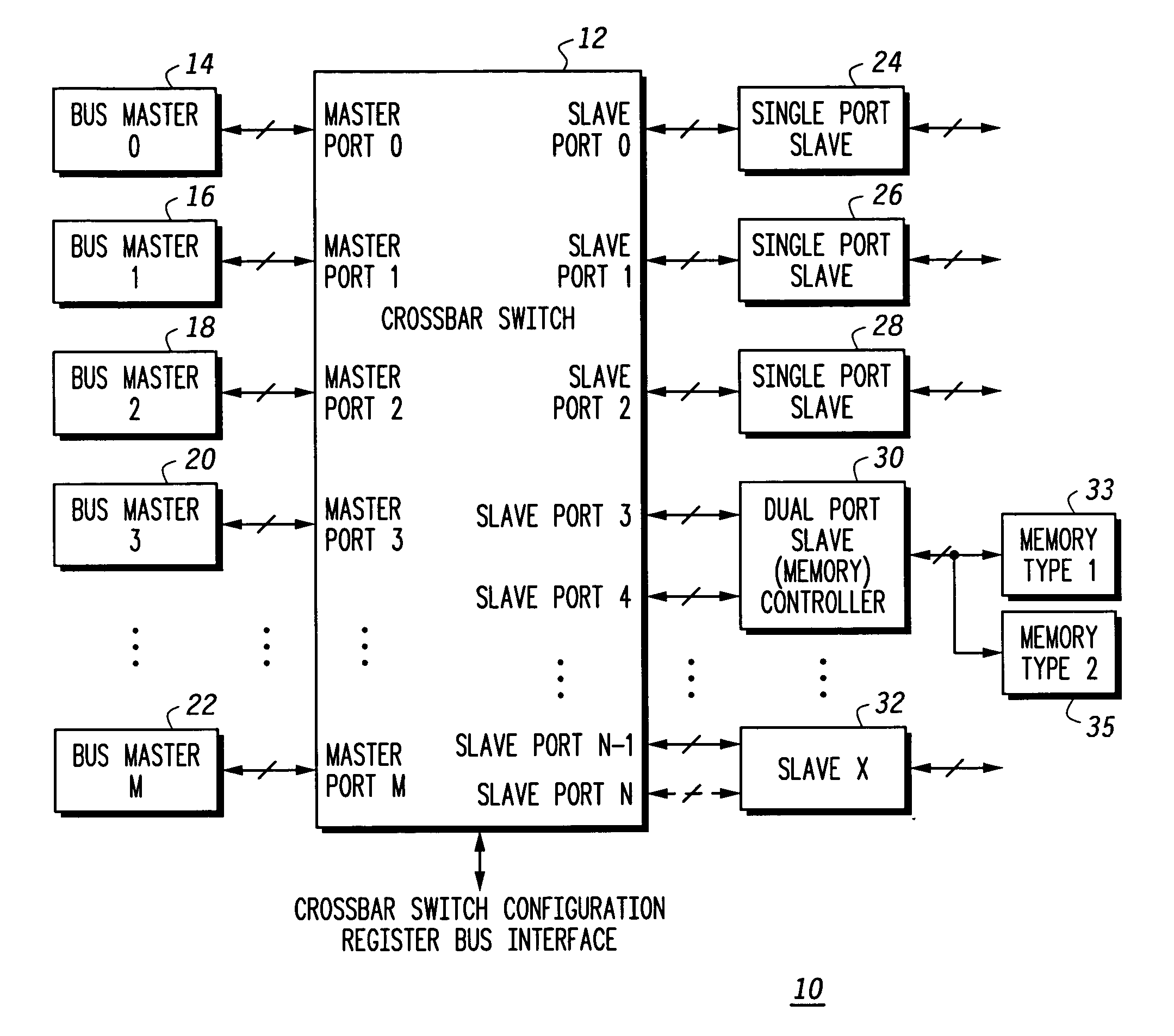

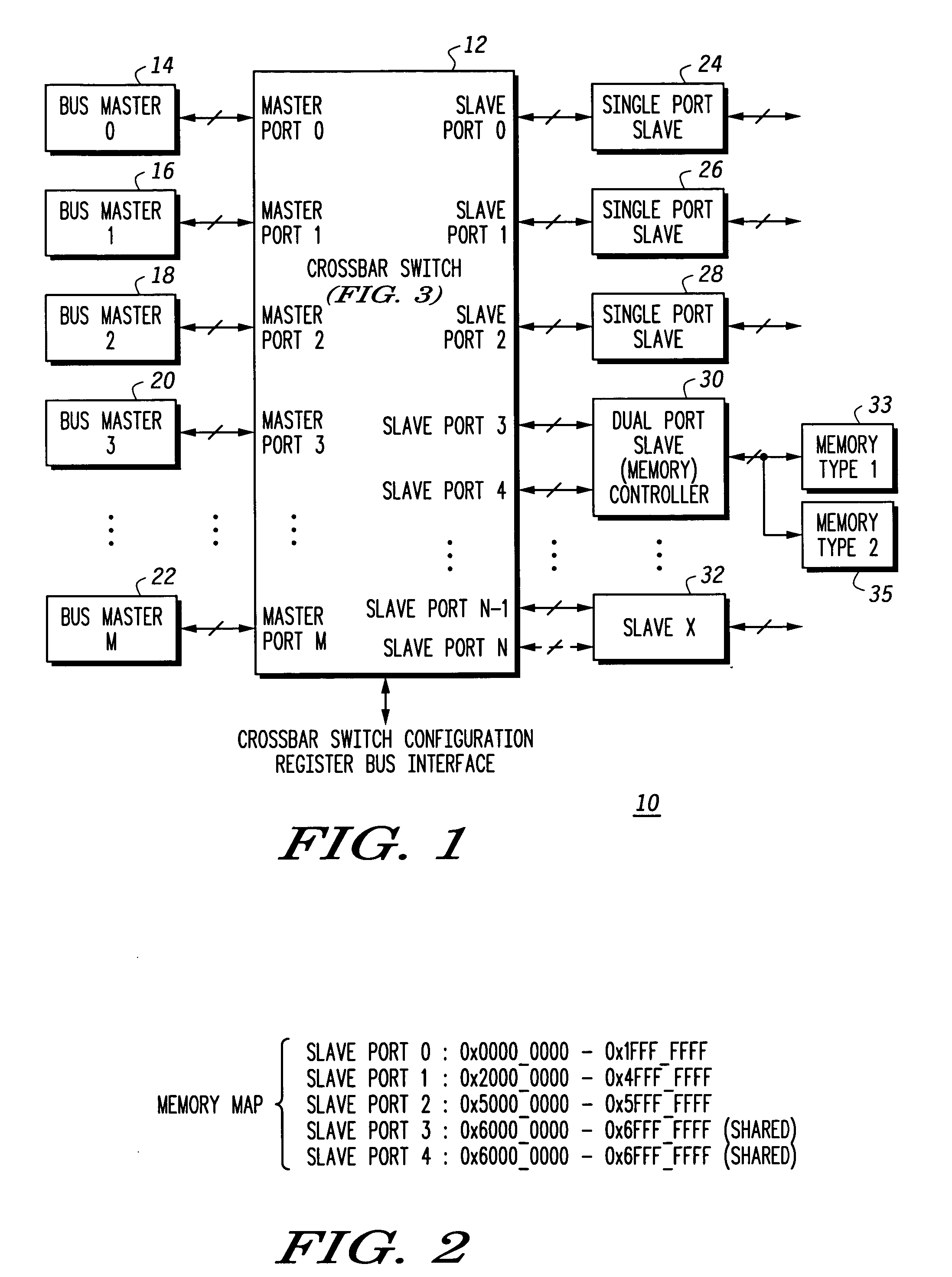

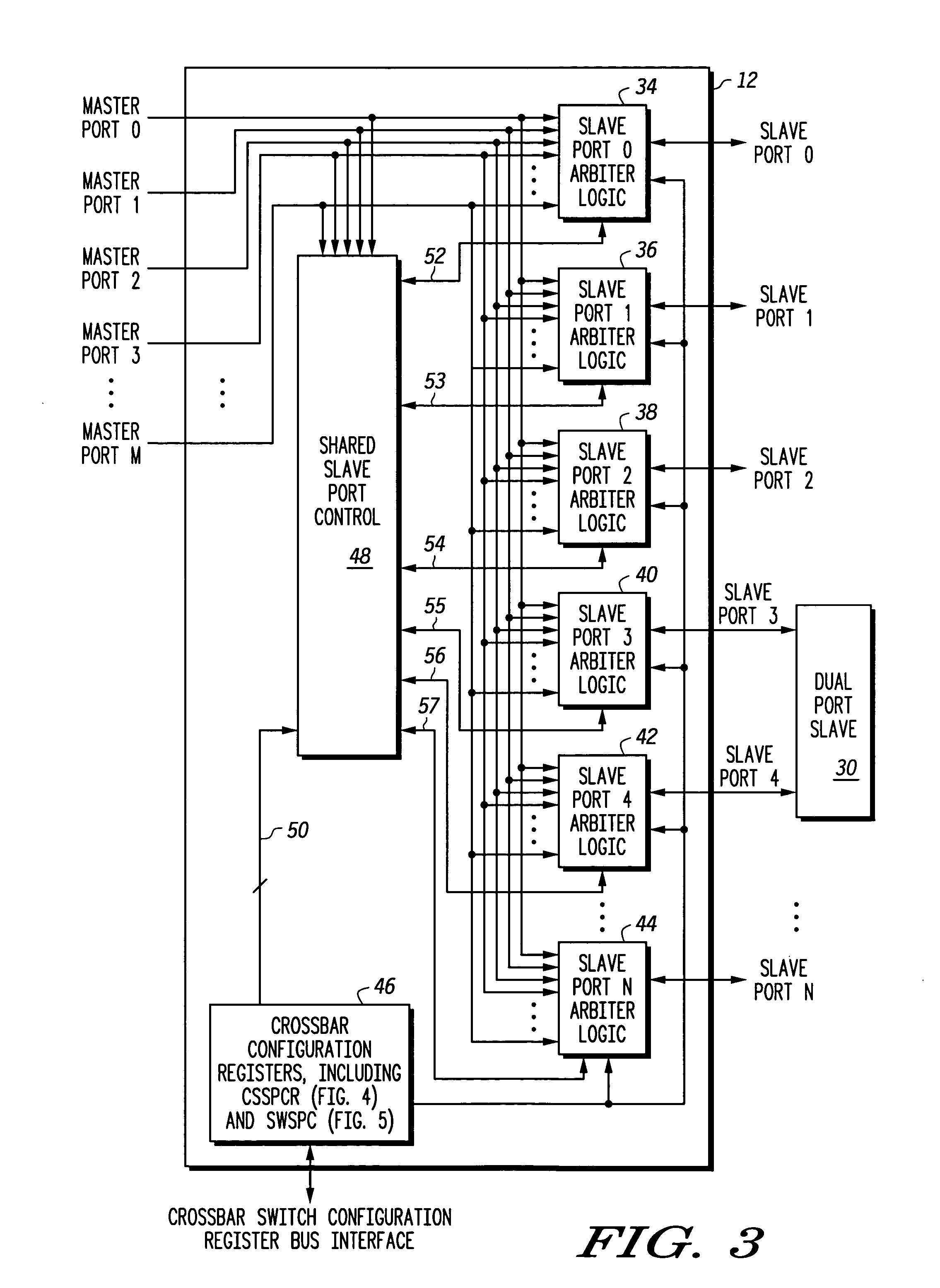

Crossbar switch that supports a multi-port slave device and method of operation

A crossbar switch (12) arbitrates for access from multiple bus masters (14, 16, 18, 20 and 22) to multiple addressed slave ports (3 and 4) that have overlapping address ranges. In one form, the address ranges are the same address range. The crossbar switch (12) uses shared slave port control circuitry (48), configuration registers (46) and slave port arbiter logic (34, 36, 38, 40, 42 and 44) to arbitrate for access when all the addressed ports are busy. A determination is made as to whether new access requests are higher or lower in priority than existing accesses. A determination on where to direct a new access request is made based upon a prediction of which of certain multiple accesses will complete first based on various factors including the number of data beats requested as well as wait state information. In one mode, the wait state information is determined dynamically.

Owner:NXP USA INC

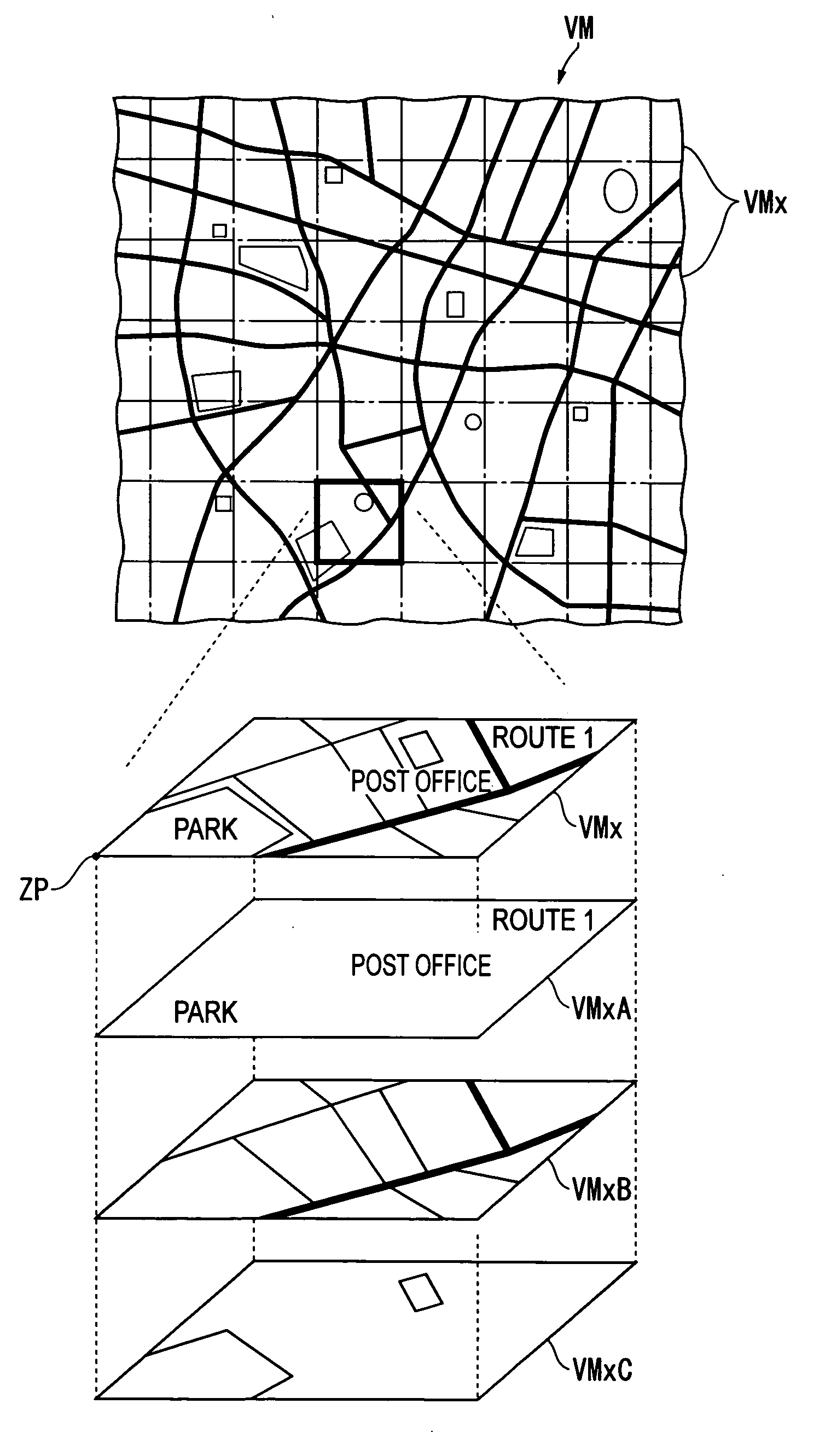

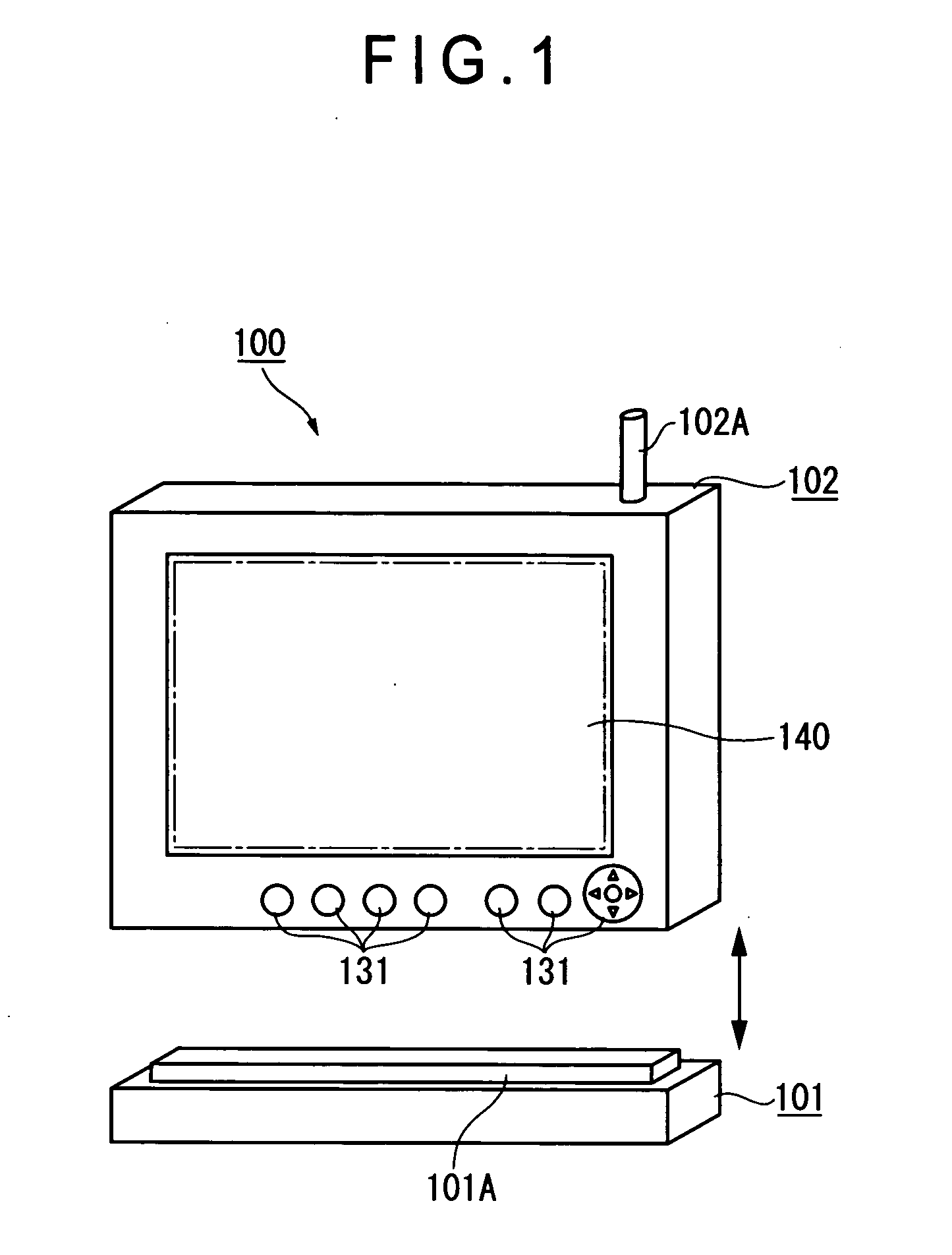

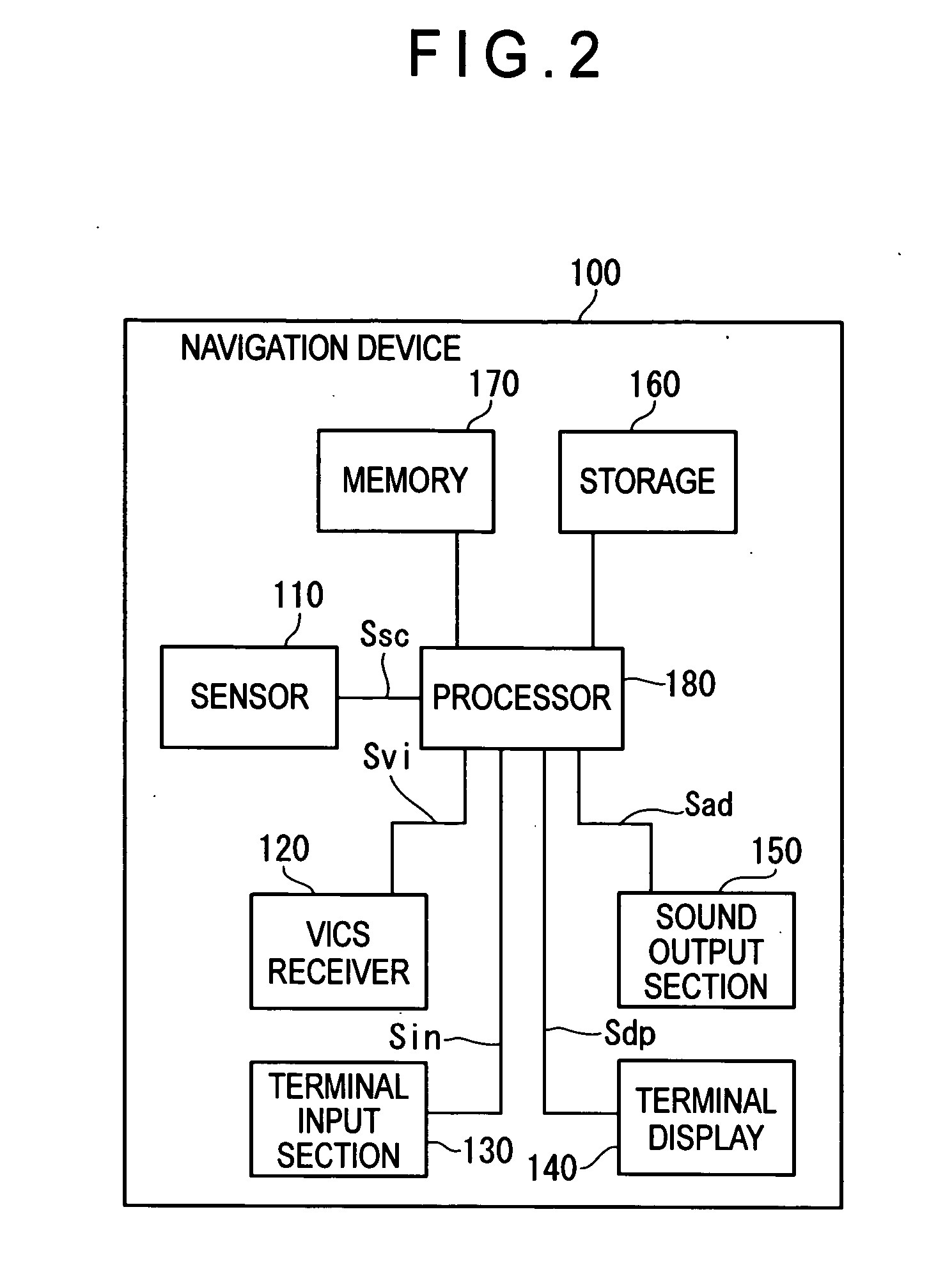

Guiding device, system thereof, method thereof, program thereof and recording medium storing the program

InactiveUS20050131631A1Instruments for road network navigationRoad vehicles traffic controlInformation searchingWait state

A route processor searches for a travel route based on current-position information, destination information and traffic information with use of map information. Predicted required time to arrive at a destination from a current-position of a vehicle is calculated based on the set travel route. Predicted departure time for the vehicle to leave is calculated based on scheduled time to arrive at the destination and the predicted required time. According to departure waiting state of the vehicle, time to notify departure guidance for encouraging the departure of the vehicle is set, and the departure guidance is notified at the set time. With this configuration, departure guidance for arriving at the destination at the scheduled time without arriving at the destination too early or late can be appropriately notified

Owner:PIONEER CORP +1

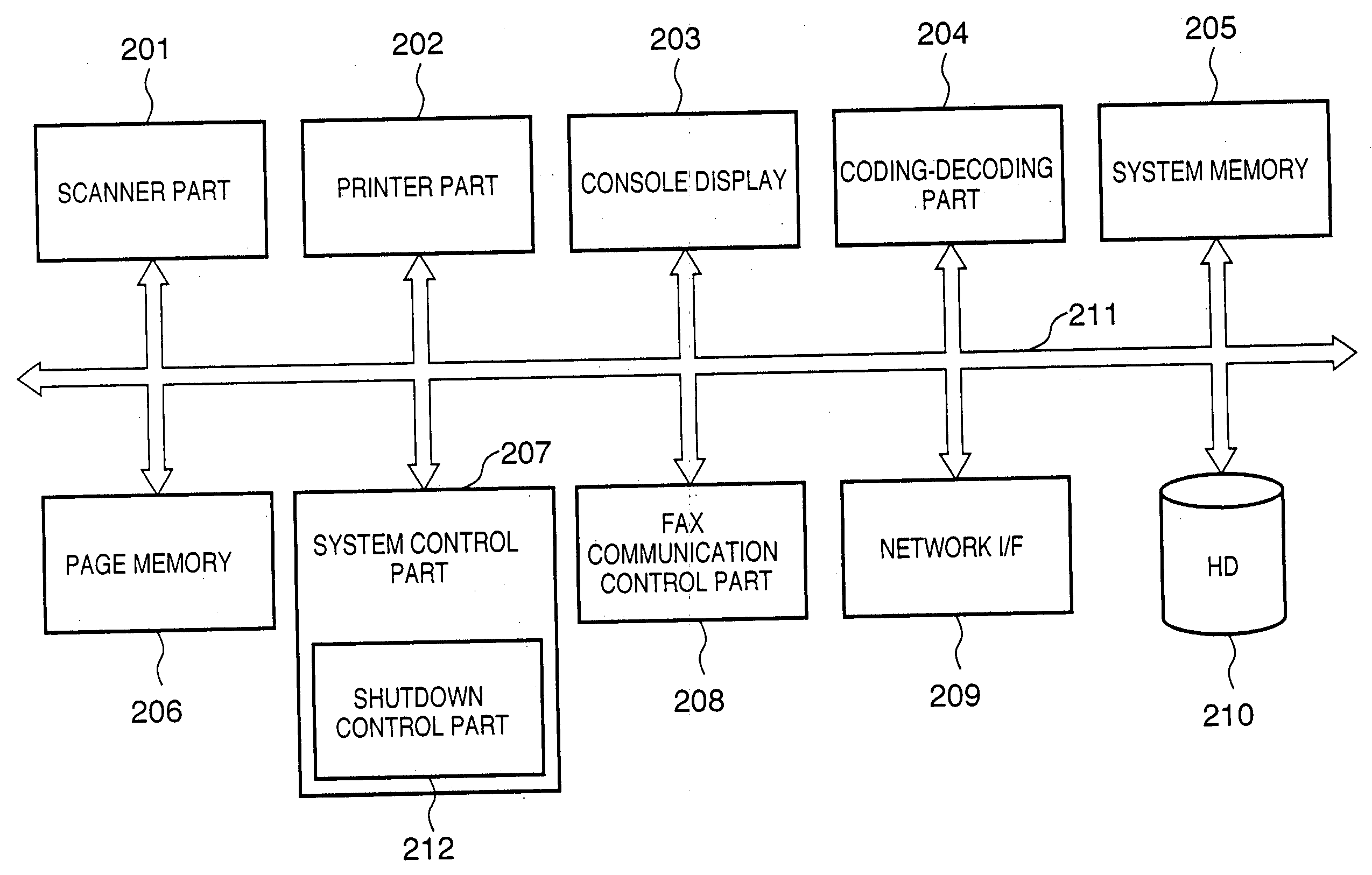

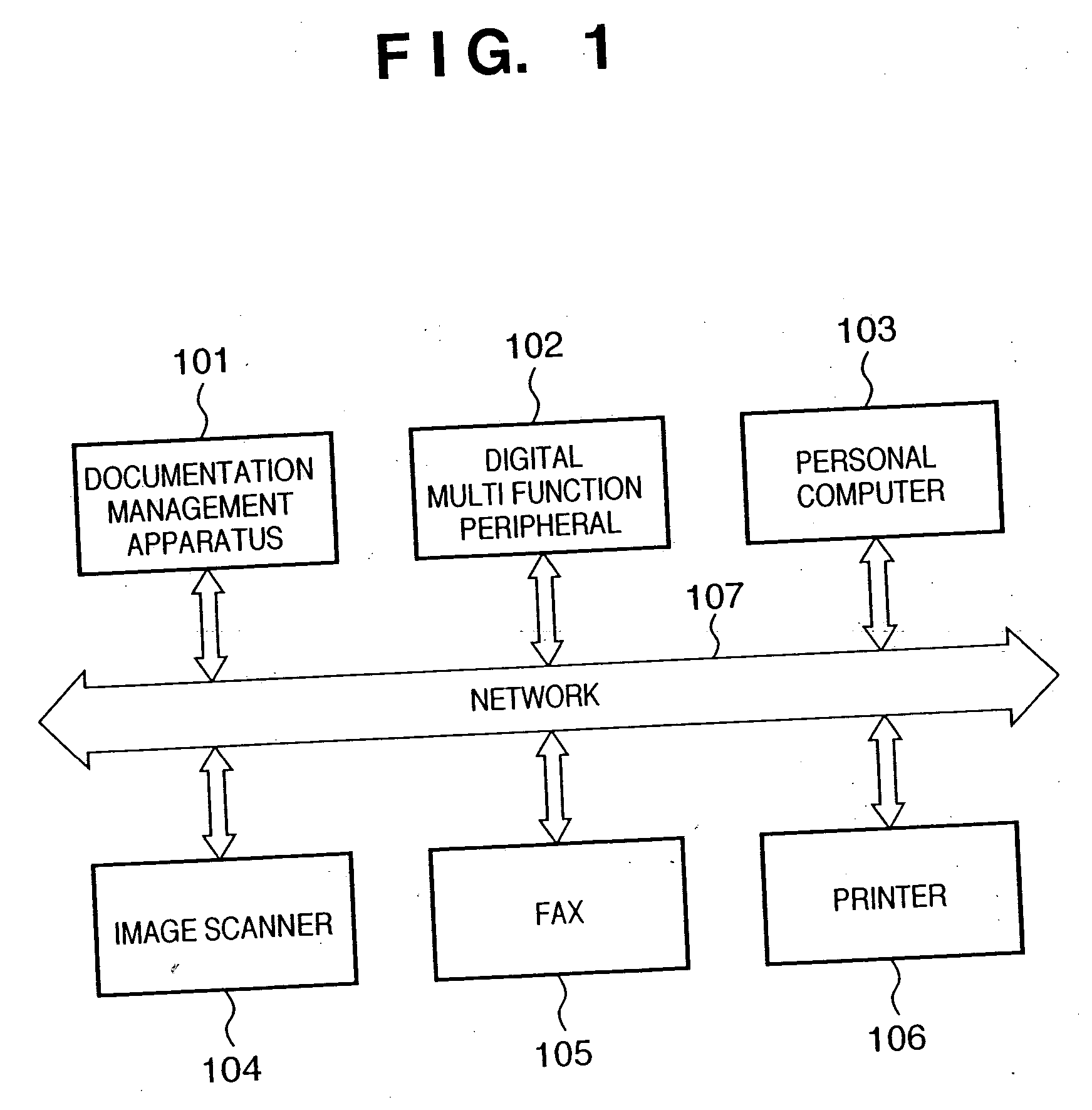

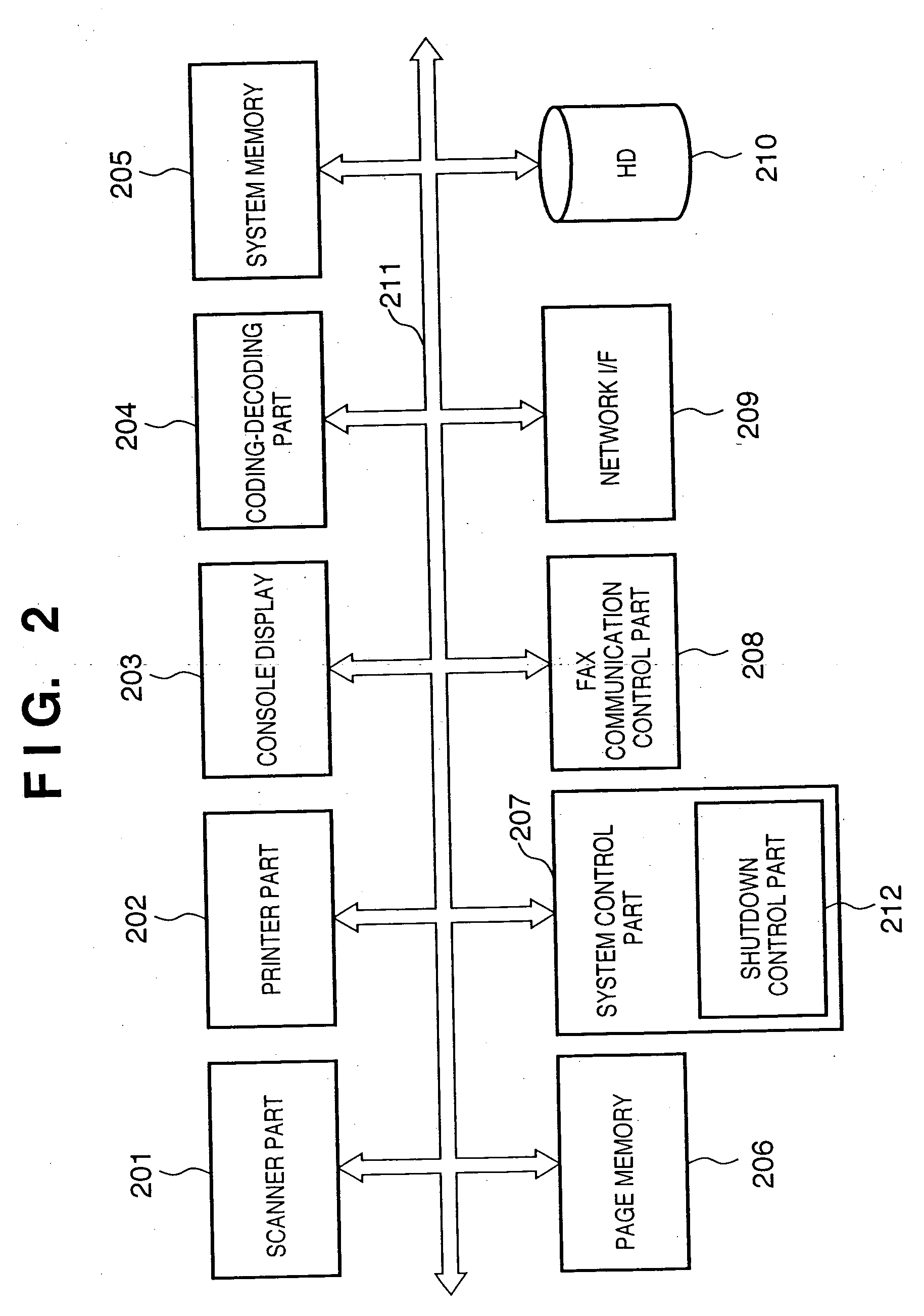

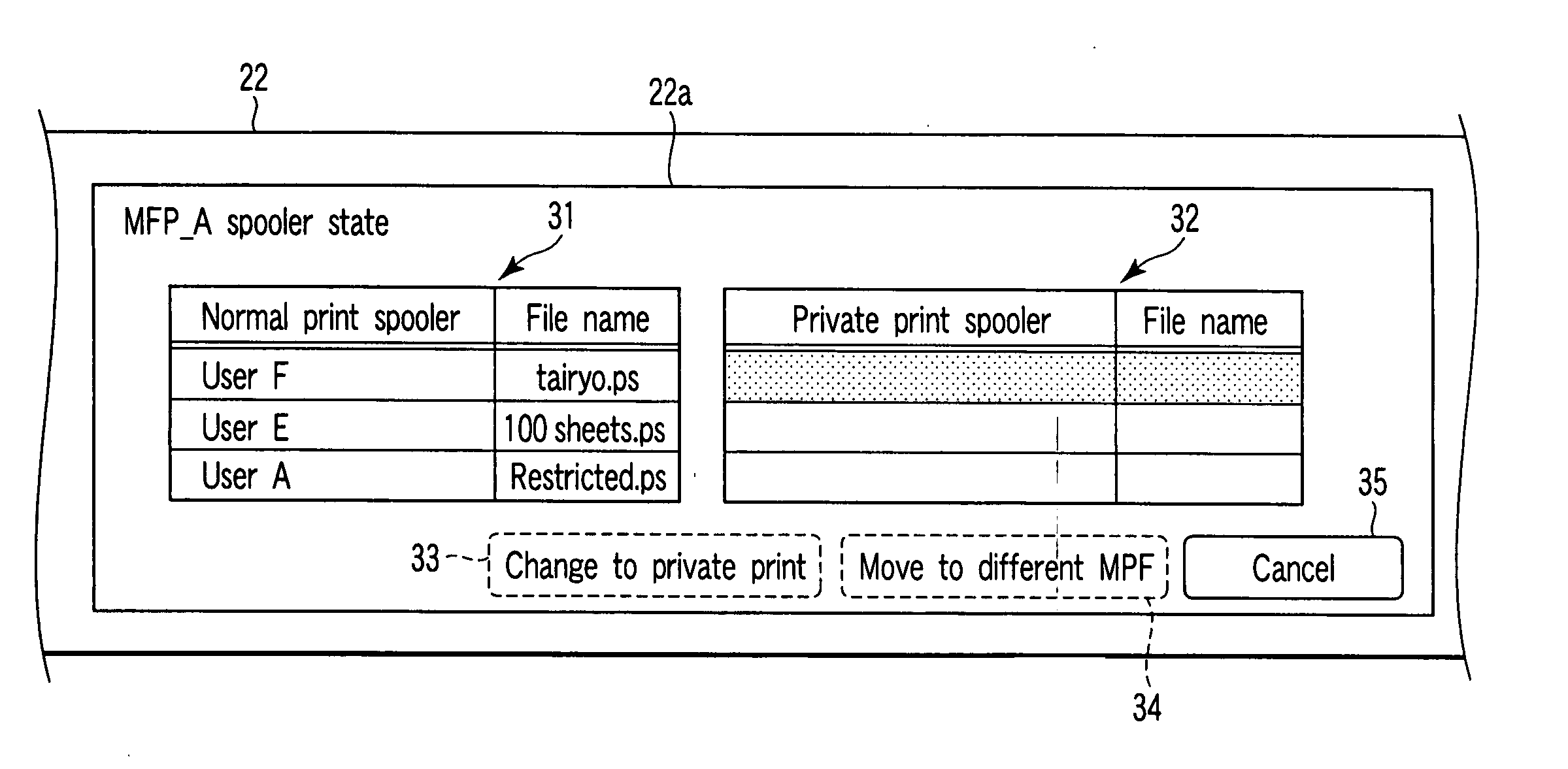

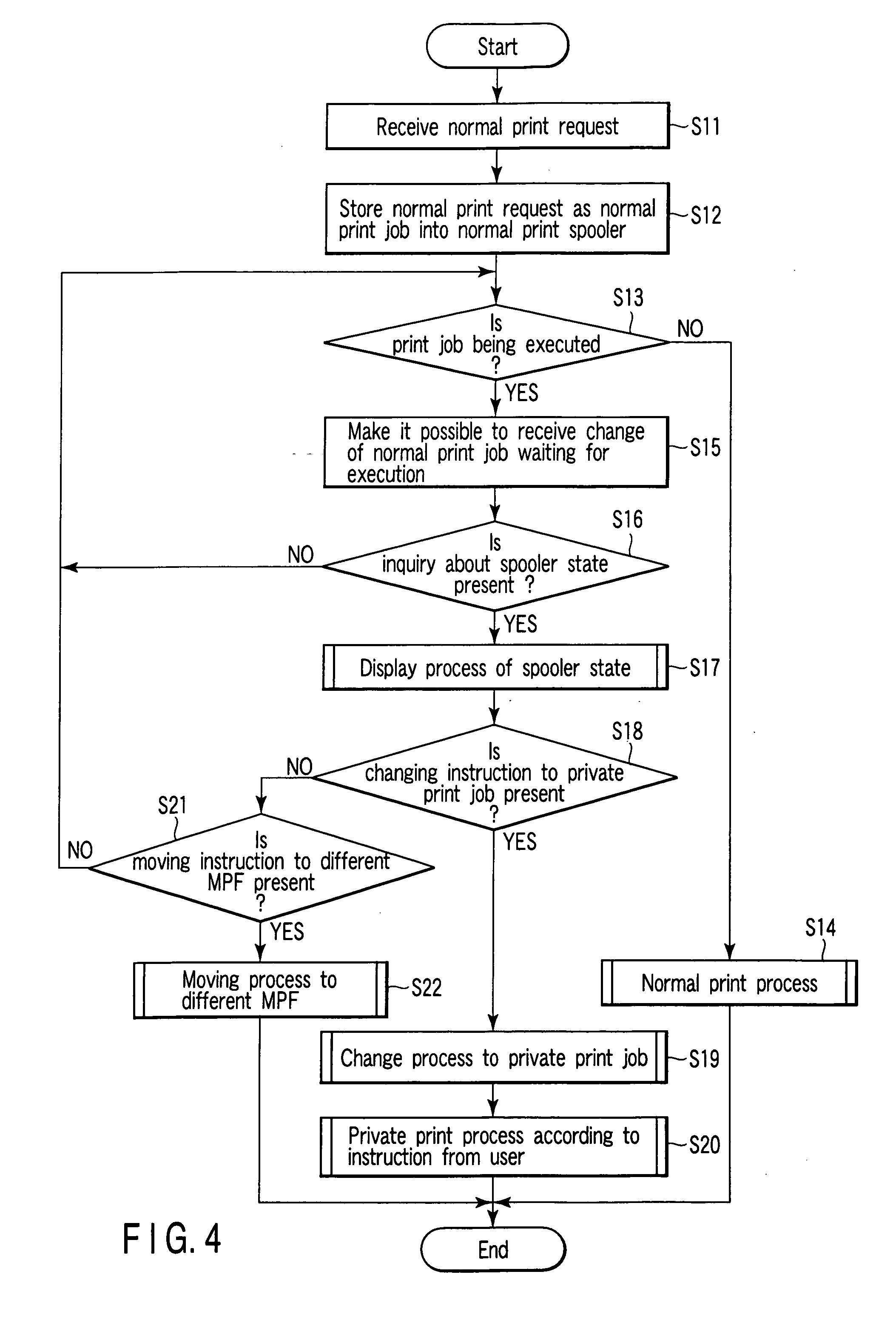

Job processing method of image forming apparatus and image forming apparatus

InactiveUS20060007469A1Easy to identifyDigital computer detailsVisual presentationImage formationMethod of images

In an image forming apparatus capable of processing data of a plurality of jobs that include at least any one of a copy function job, a sending function job and a print function job, when data of jobs currently processed and / or jobs in a waiting state for processing by the image forming apparatus are stored in a storage unit storing a plurality of data at the time an operation relating to powering off the image forming apparatus is performed by an operator, the fact that the jobs currently processed and / or the jobs in a waiting state exist is notified as information that can be confirmed by the operator.

Owner:CANON KK

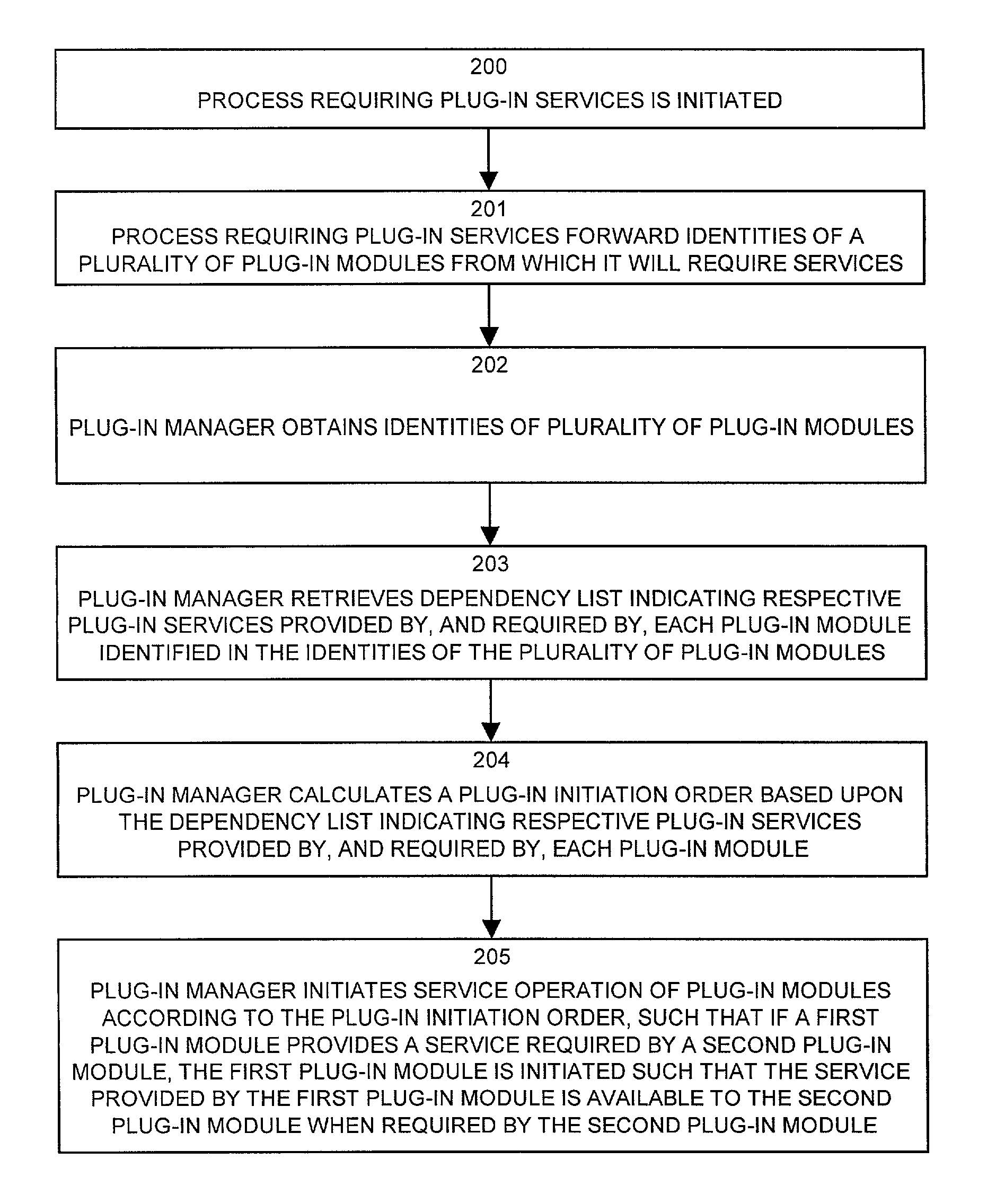

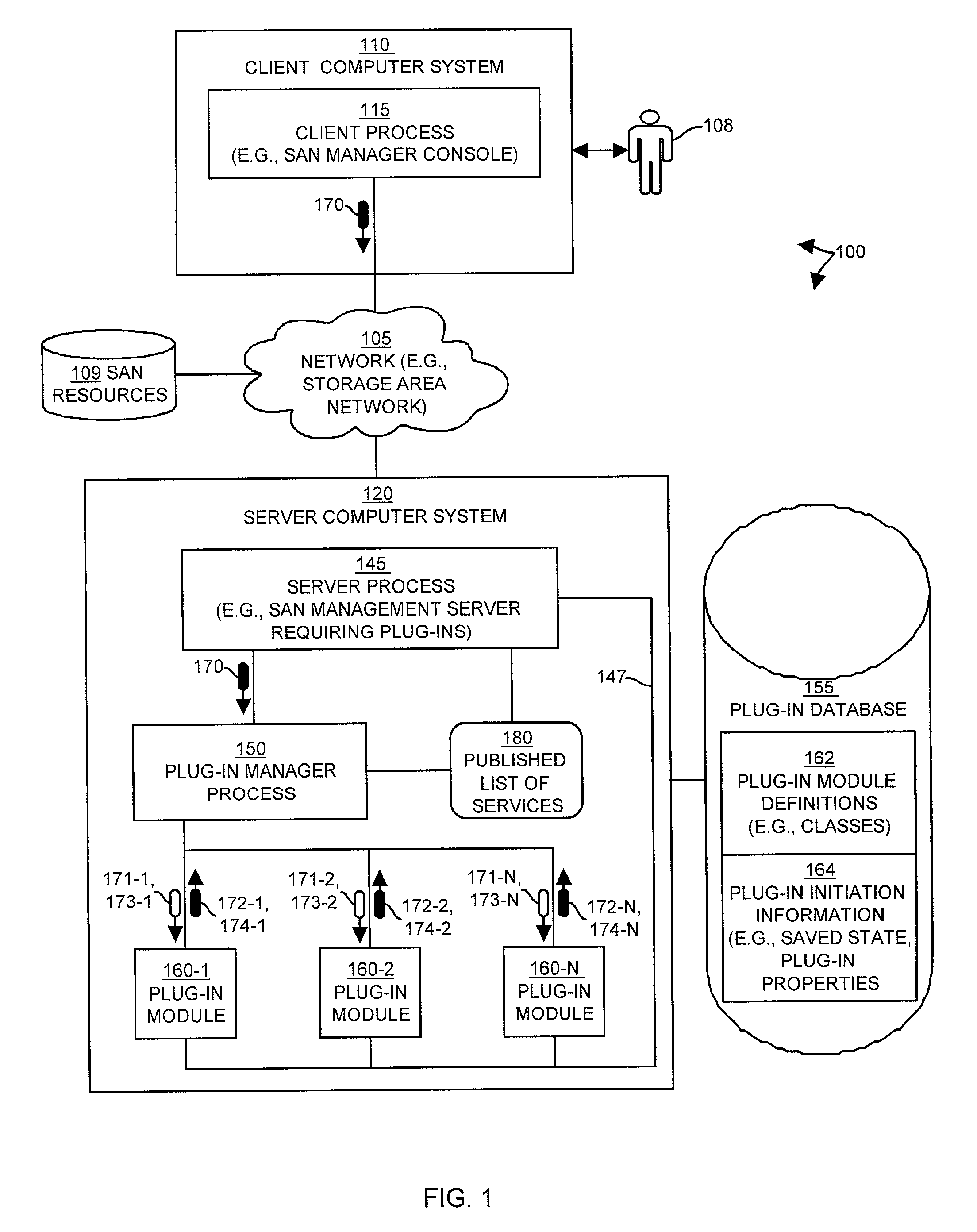

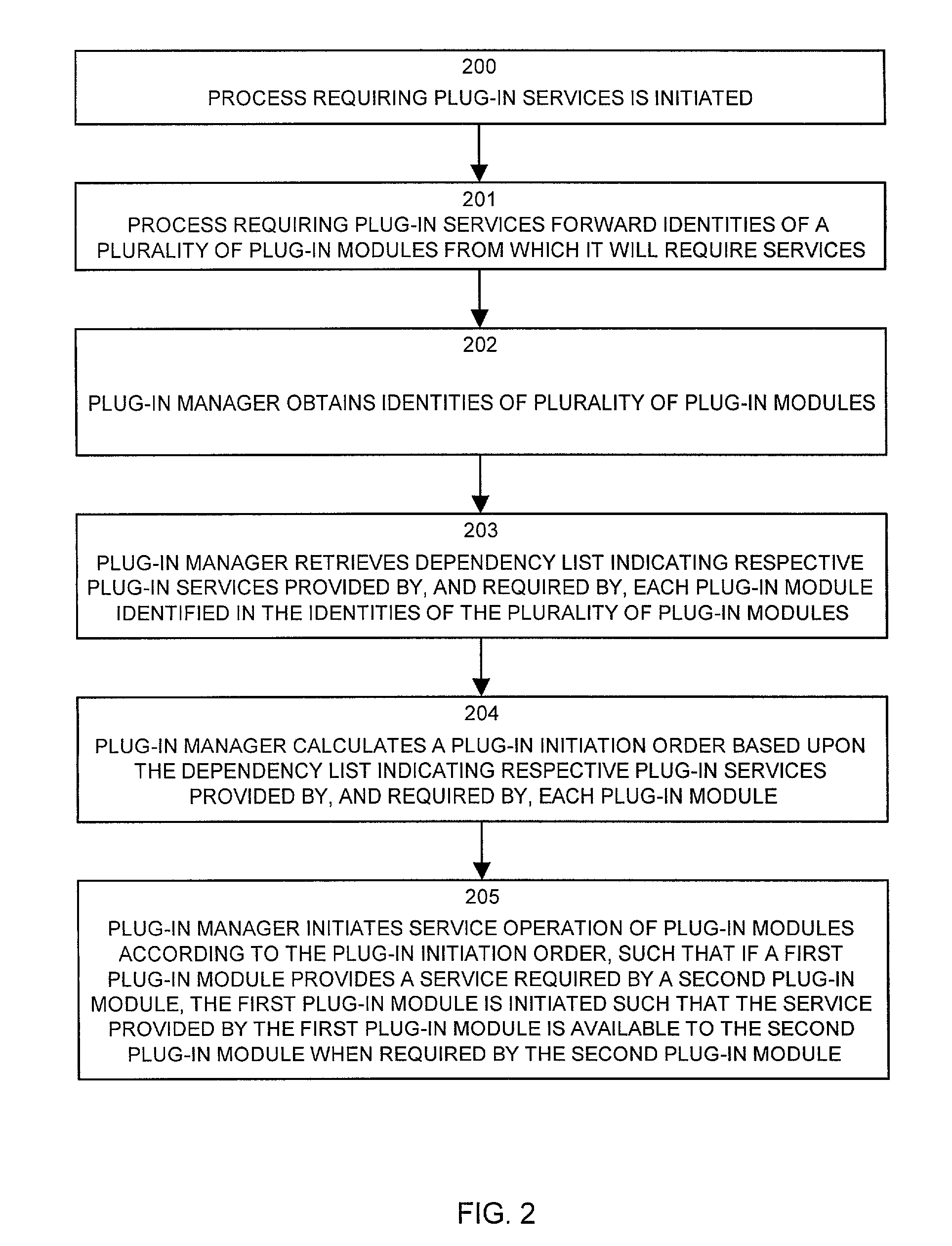

Methods and apparatus for managing plug-in services

ActiveUS7254814B1Avoid deadlockMultiprogramming arrangementsSpecific program execution arrangementsComputerized systemWait state

Methods and apparatus operate in a computer system to manage initiation and operation of plug-in modules providing plug-in services. The plug-in manager obtains identities of a plurality of plug-in modules and retrieves a dependency list indicating respective plug-in services provided by, and required by, each plug-in module identified in the identities of the plug-in modules. The plug-in manager then calculates a plug-in initiation order based upon the dependency list indicating respective plug-in services provided by, and required by, each plug-in module. The plug-in manager then initiates service operation of plug-in modules according to the plug-in initiation order, such that if a first plug-in module provides a service required by a second plug-in module, the first plug-in module is initiated such that the service provided by the first plug-in module is available to the second plug-in module when required by the second plug-in module. In addition, the plug-in manager can operate a wait state operation within plug-in modules that provide services that depend upon each other in order to avoid service deadlocked situations.

Owner:EMC IP HLDG CO LLC

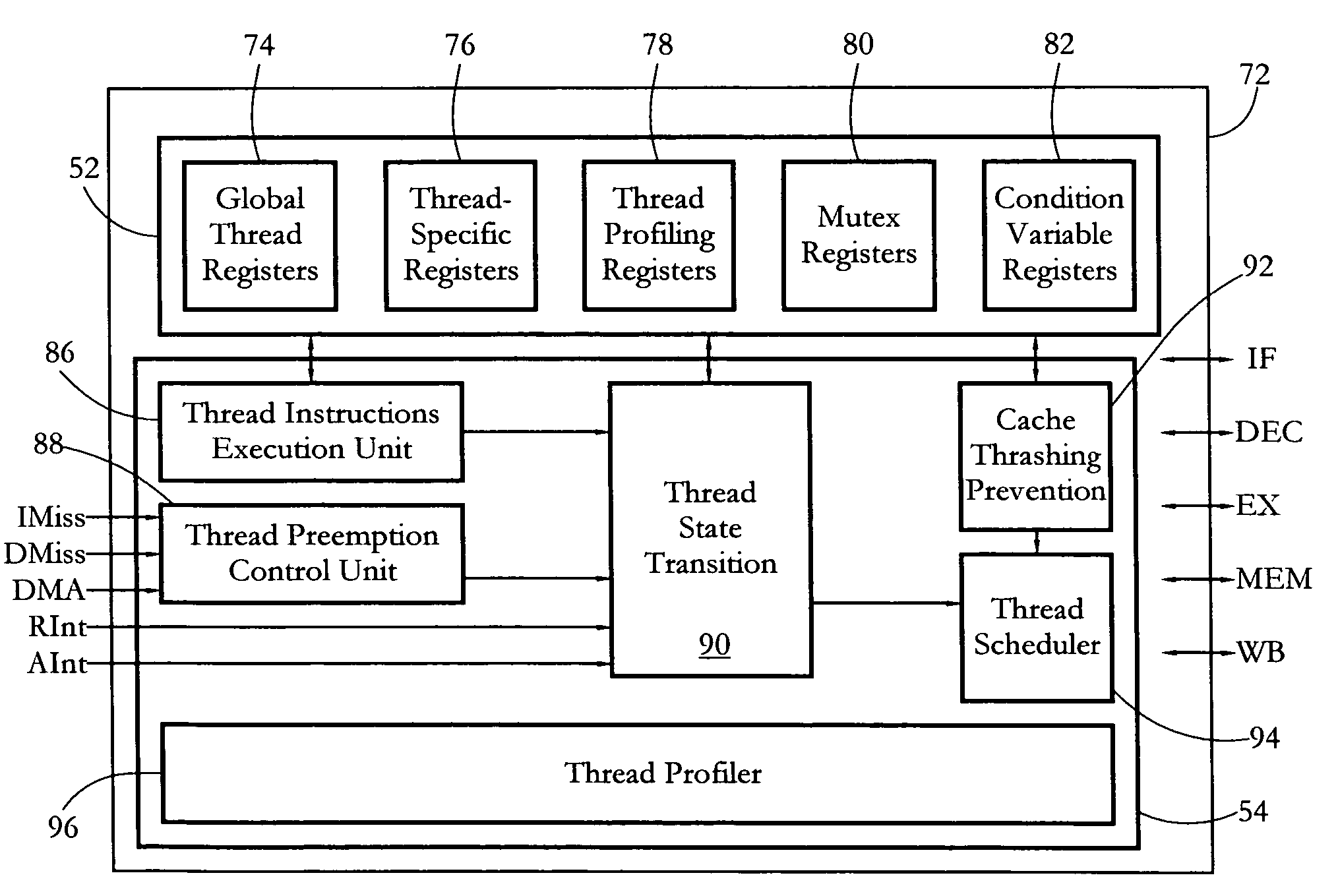

Hardware multithreading systems with state registers having thread profiling data

According to some embodiments, a multithreaded microcontroller includes a thread control unit comprising thread control hardware (logic) configured to perform a number of multithreading system calls essentially in real time, e.g. in one or a few clock cycles. System calls can include mutex lock, wait condition, and signal instructions. The thread controller includes a number of thread state, mutex, and condition variable registers used for executing the multithreading system calls. Threads can transition between several states including free, run, ready and wait. The wait state includes interrupt, condition, mutex, I-cache, and memory substates. A thread state transition controller controls thread states, while a thread instructions execution unit executes multithreading system calls and manages thread priorities to avoid priority inversion. A thread scheduler schedules threads according to their priorities. A hardware thread profiler including global, run and wait profiler registers is used to monitor thread performance to facilitate software development.

Owner:GEO SEMICONDUCTOR INC

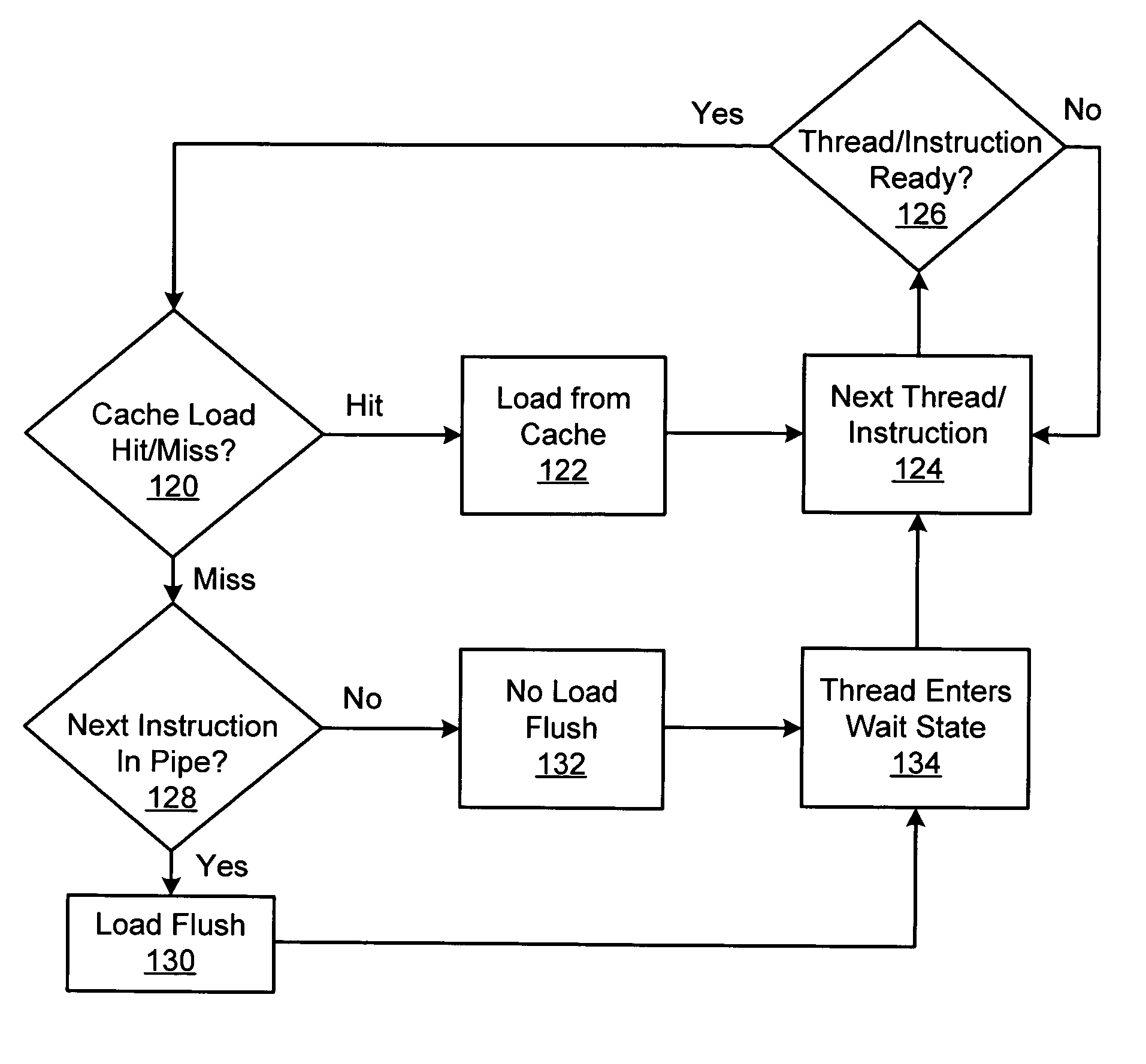

Handling cache misses by selectively flushing the pipeline

ActiveUS7509484B1Eliminate operationHigh bandwidthDigital computer detailsSpecific program execution arrangementsLoad instructionParallel computing

An apparatus and method for efficiently managing data cache load misses is described in connection with a multithreaded, pipelined multiprocessor chip. A CMT processor keeps track of load misses for each thread by issuing a load miss signal each time a load instruction to the data cache misses. A detection logic functionality in the IFU responds the load miss signal to determine if a valid instruction from the thread is at the one of the pipeline stages. If no instructions from the thread are detected in the pipeline, then no flush is required and the thread is placed in a wait state until the requested data is returned from higher order memory. If any instruction from the thread is detected in the pipeline, the thread is flushed and the instruction is re-fetched.

Owner:ORACLE INT CORP

Methods and apparatus for task sharing among a plurality of processors

InactiveUS20070083870A1Reduce stepsReduce operating frequencyMultiprogramming arrangementsMemory systemsMulti processorParallel computing

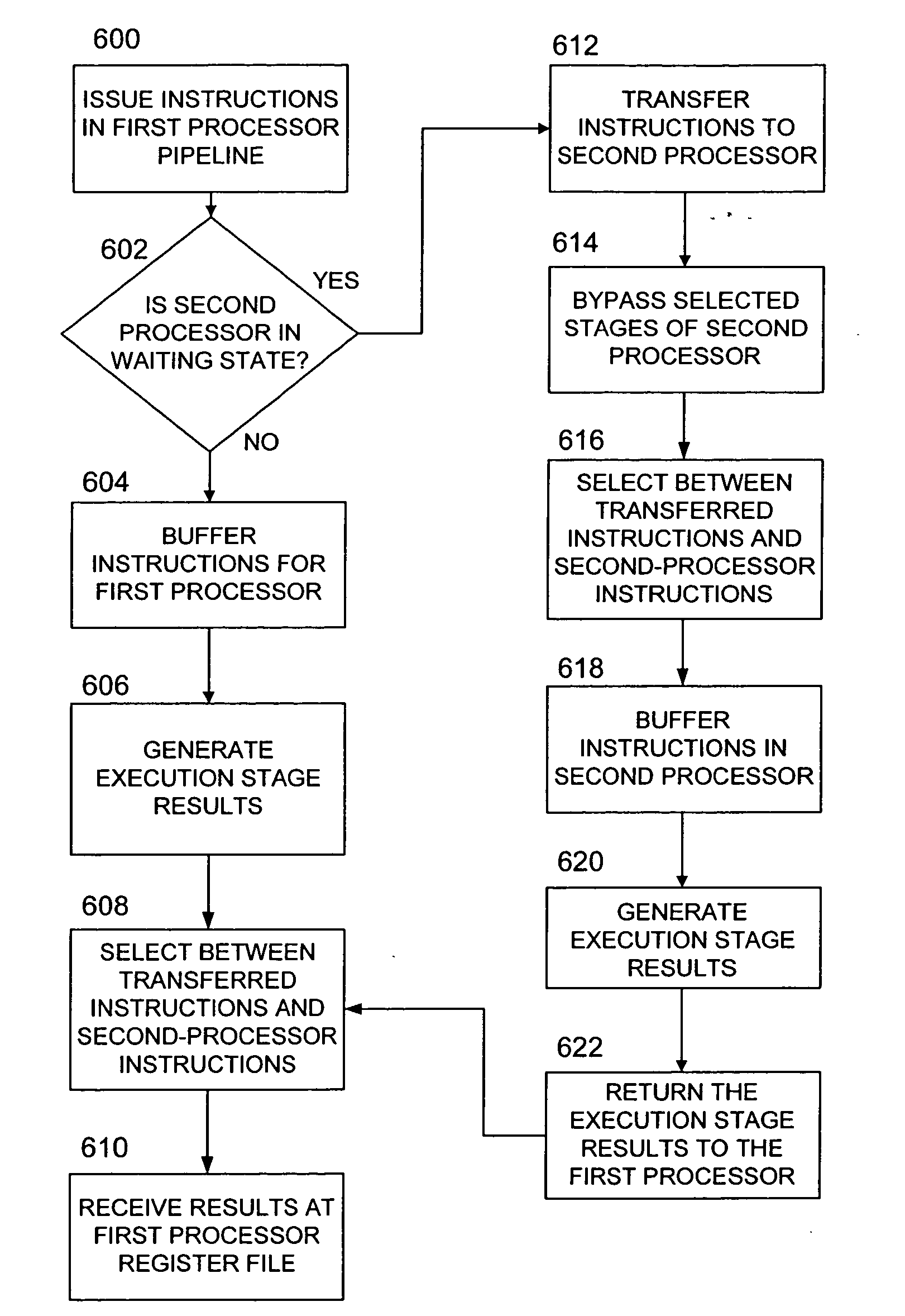

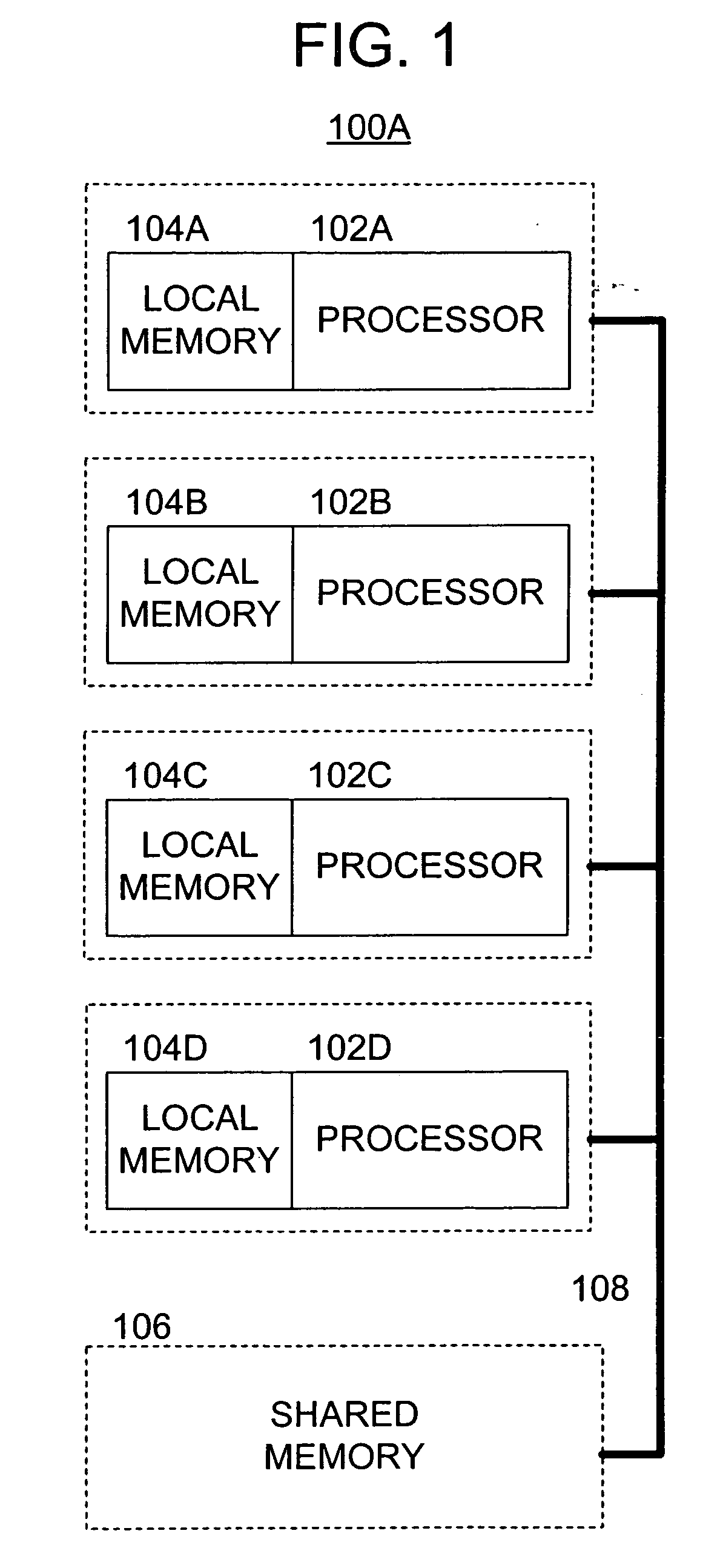

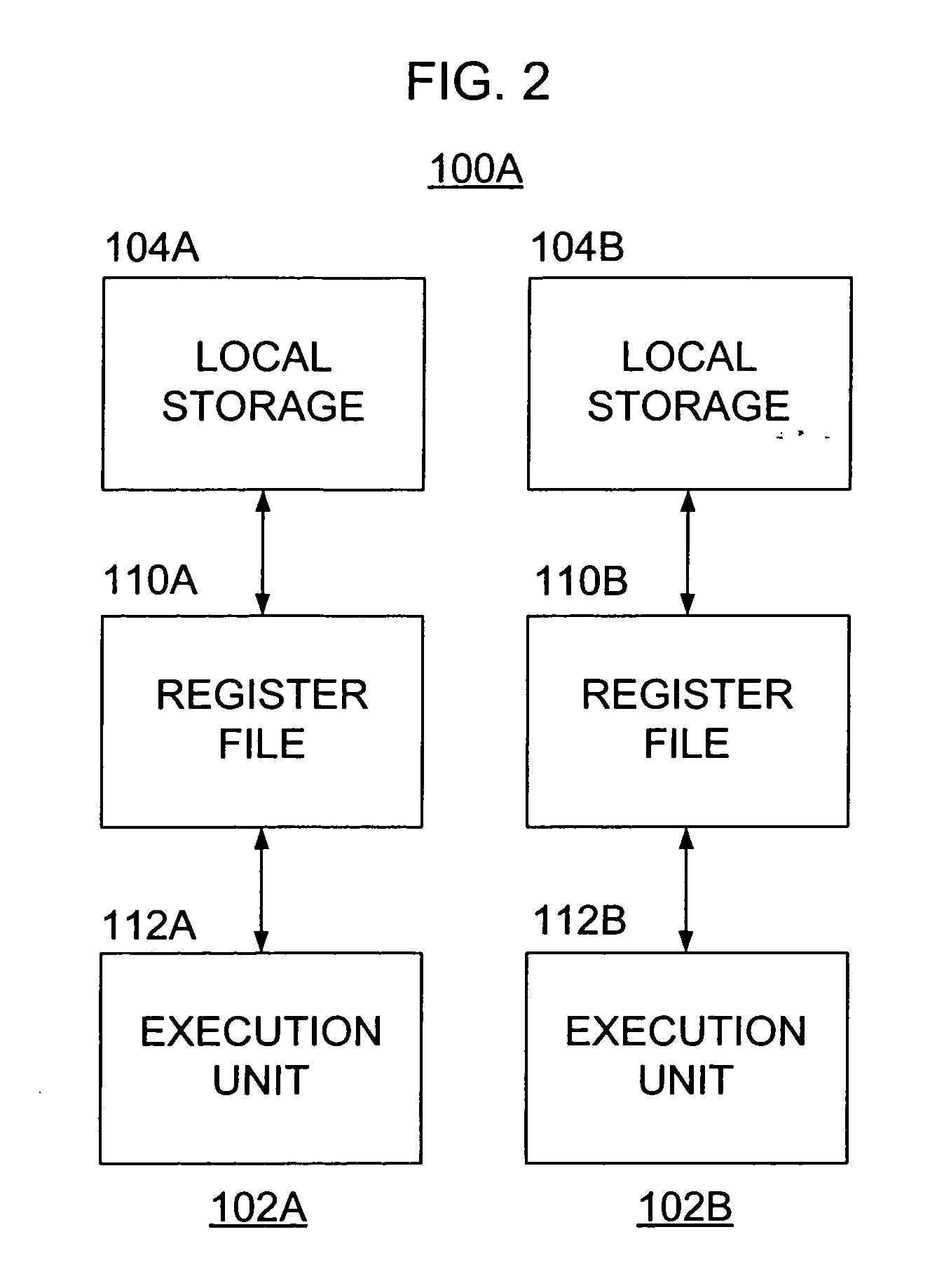

A method is disclosed which may include issuing a plurality of instructions in a processing pipeline of a first processor within a multiprocessor system; determining whether a second processor in the multiprocessor system is in at least one of a running state and a waiting state; and transferring at least one of the instructions to execution stages of a processing pipeline of the second processor and bypassing at least one earlier stage of the processing pipeline of the second processor, when the second processor is in the waiting state.

Owner:SONY COMPUTER ENTERTAINMENT INC

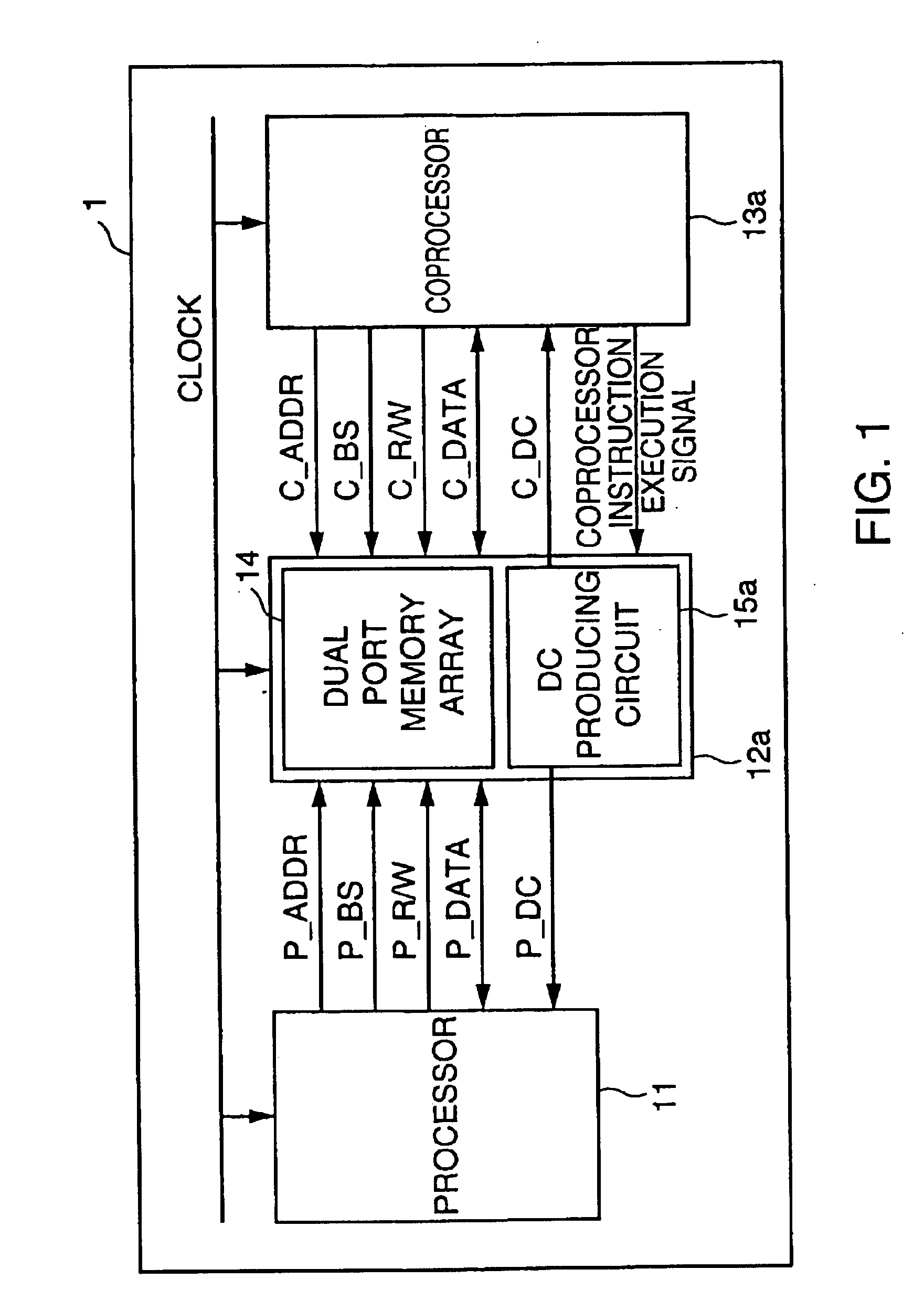

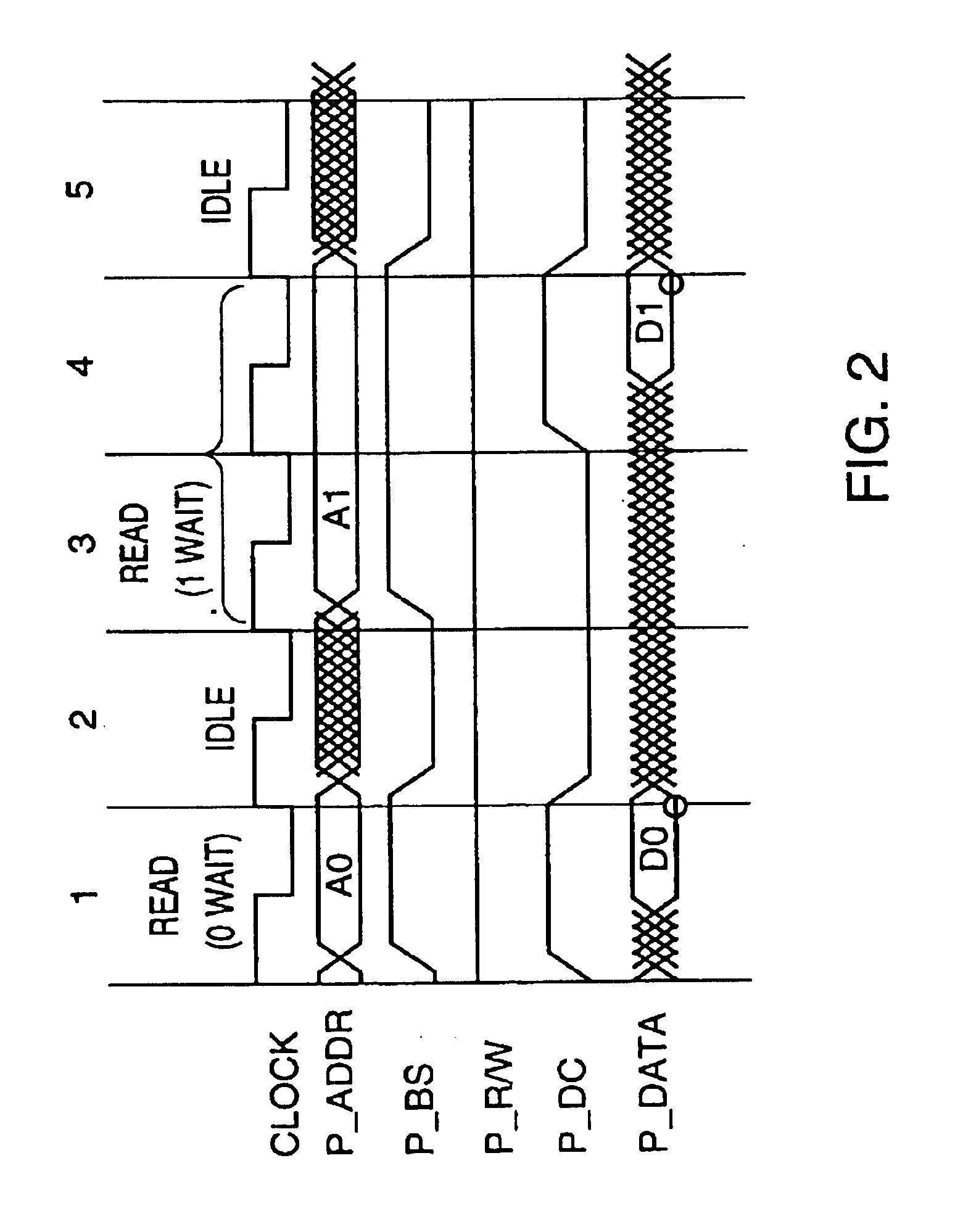

Synchronous signal producing circuit for controlling a data ready signal indicative of end of access to a shared memory and thereby controlling synchronization between processor and coprocessor

InactiveUS6928523B2Reduce overheadReduce power consumptionProgram synchronisationGeneral purpose stored program computerCoprocessorProcessor register

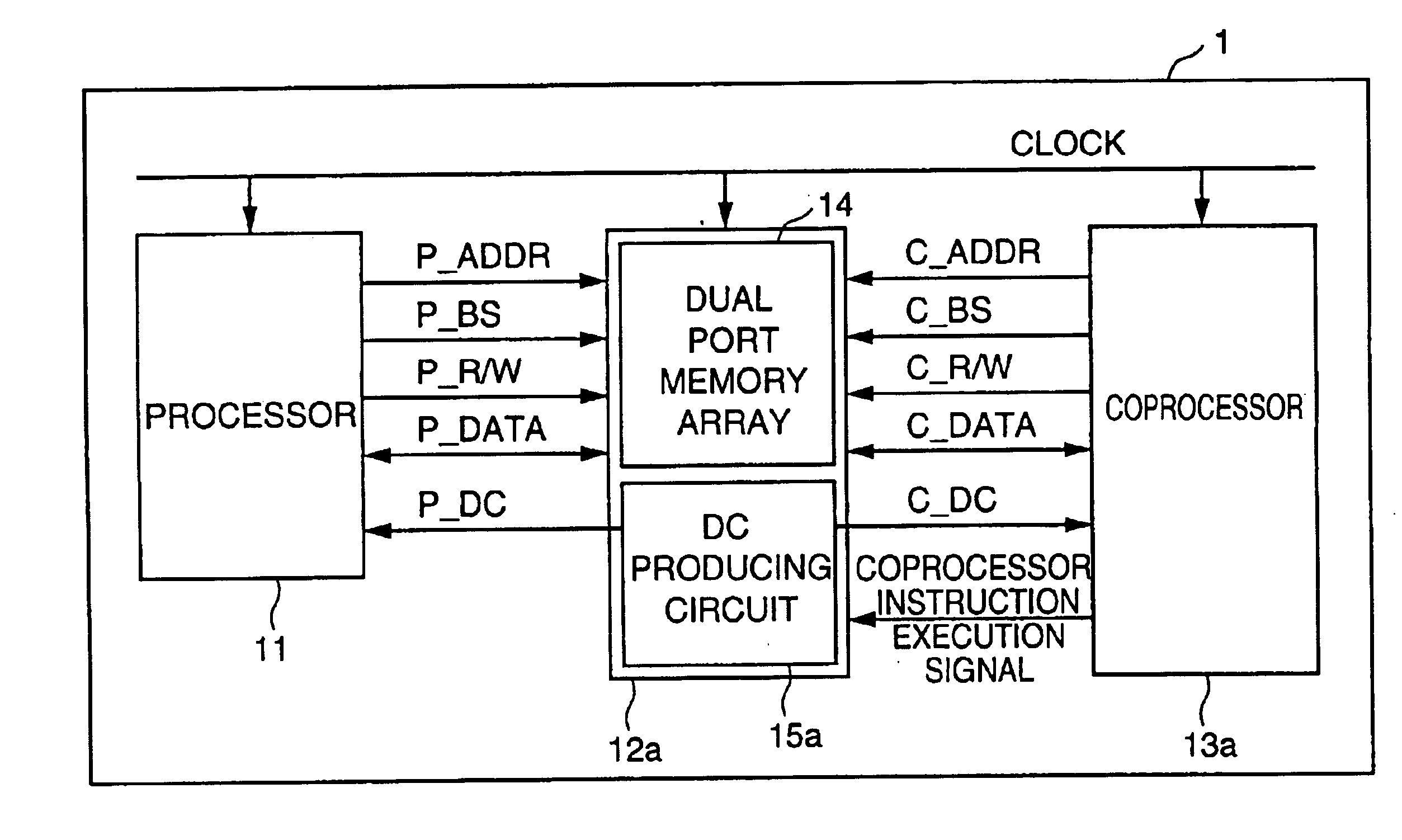

A synchronous signal producing circuit includes an access inhibit region register for designating an access inhibit region for a processor in a shared memory, a comparing circuit for detecting the access by the processor to the access inhibit region designated in the access inhibit region register, and a logic circuit for issuing a P_DC signal setting the processor to a wait state based on a coprocessor instruction execution signal and a result of the comparison by the comparing circuit.

Owner:RENESAS TECH CORP

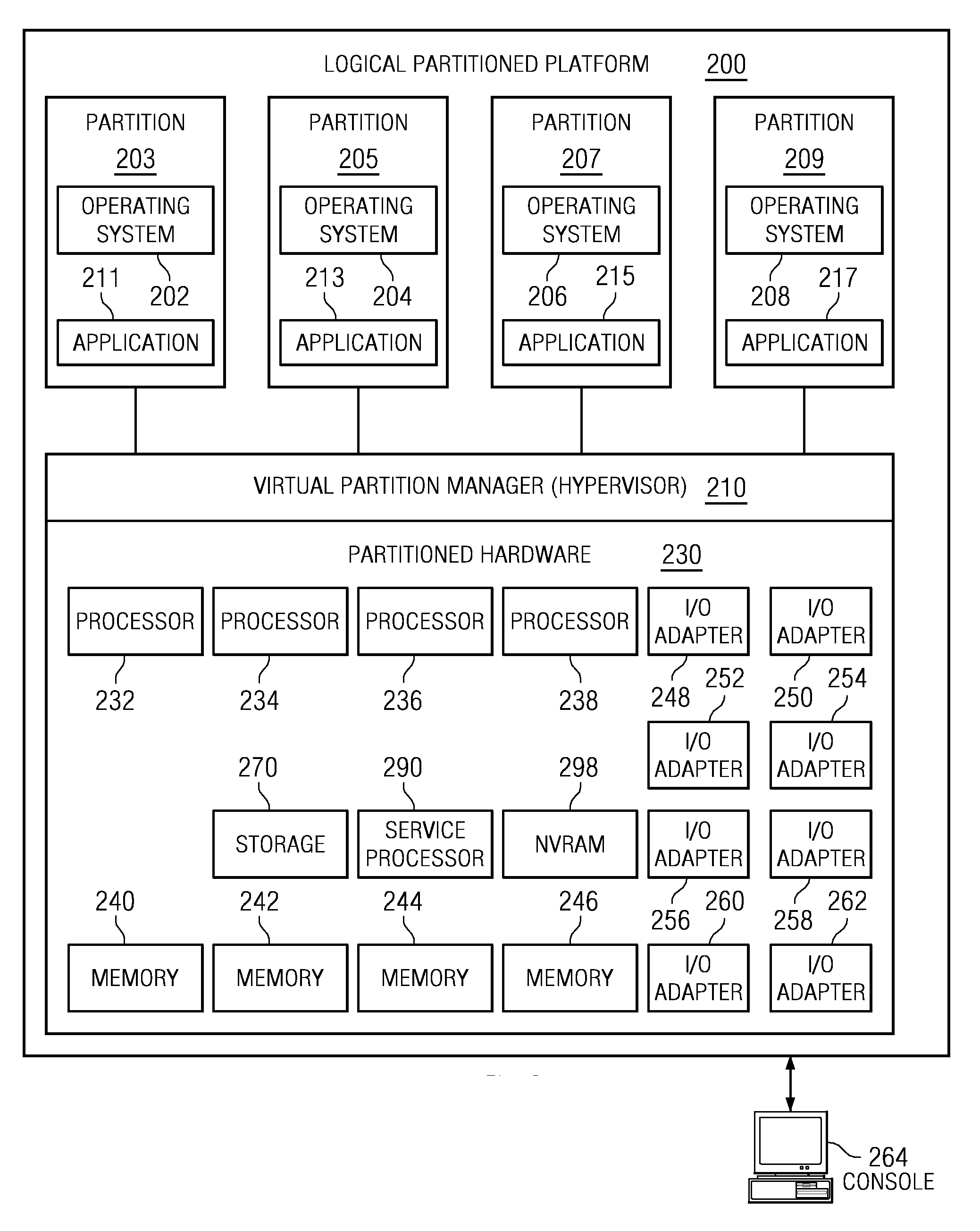

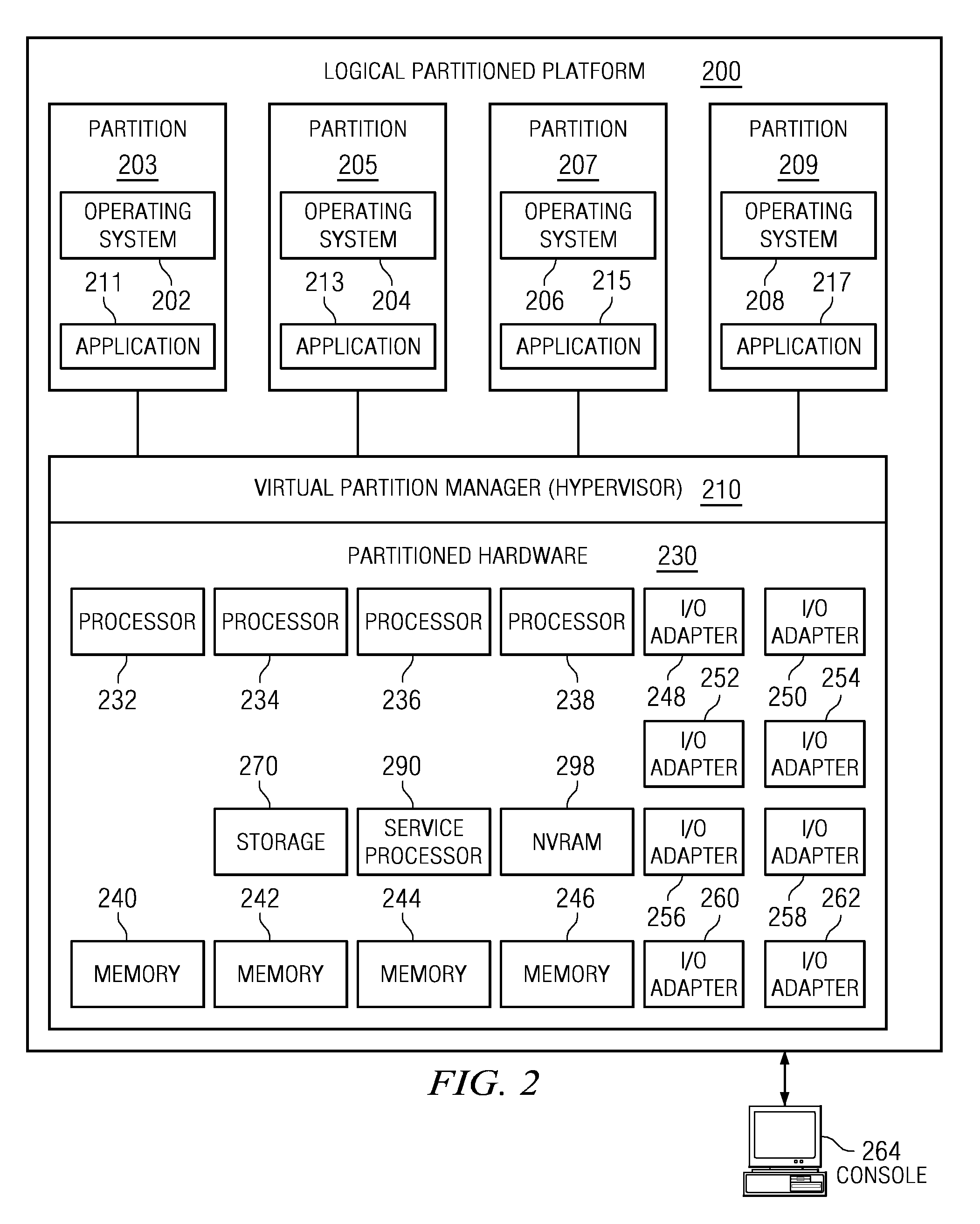

Optimizing System Performance Using Spare Cores in a Virtualized Environment

ActiveUS20110010709A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationVirtualizationProcessing core

A mechanism for optimizing system performance using spare processing cores in a virtualized environment. When detecting a workload partition needs to run on a virtual processor in the virtualized system, a state of the virtual processor is changed to a wait state. A first node comprising memory that is local to the workload partition is determined. A determination is also made as to whether a non-spare processor core in the first node is available to run the workload partition. If no non-spare processor core is available, a free non-spare processor core in a second node is located, and the state of the free non-spare processor core in the second node is changed to an inactive state. The state of a spare processor core in the first node is changed to an active state, and the workload partition is dispatched to the spare processor core in the first node for execution.

Owner:IBM CORP

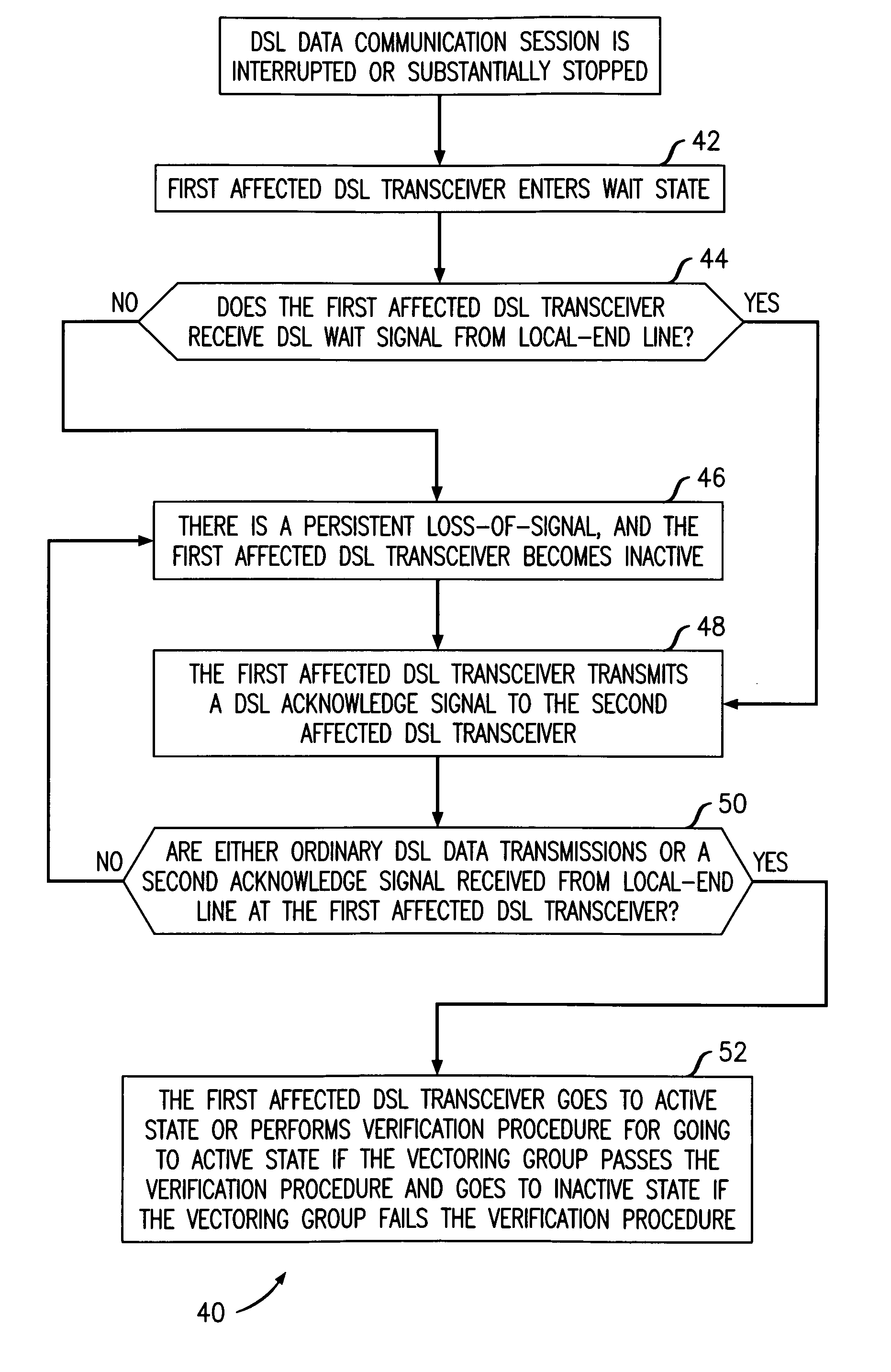

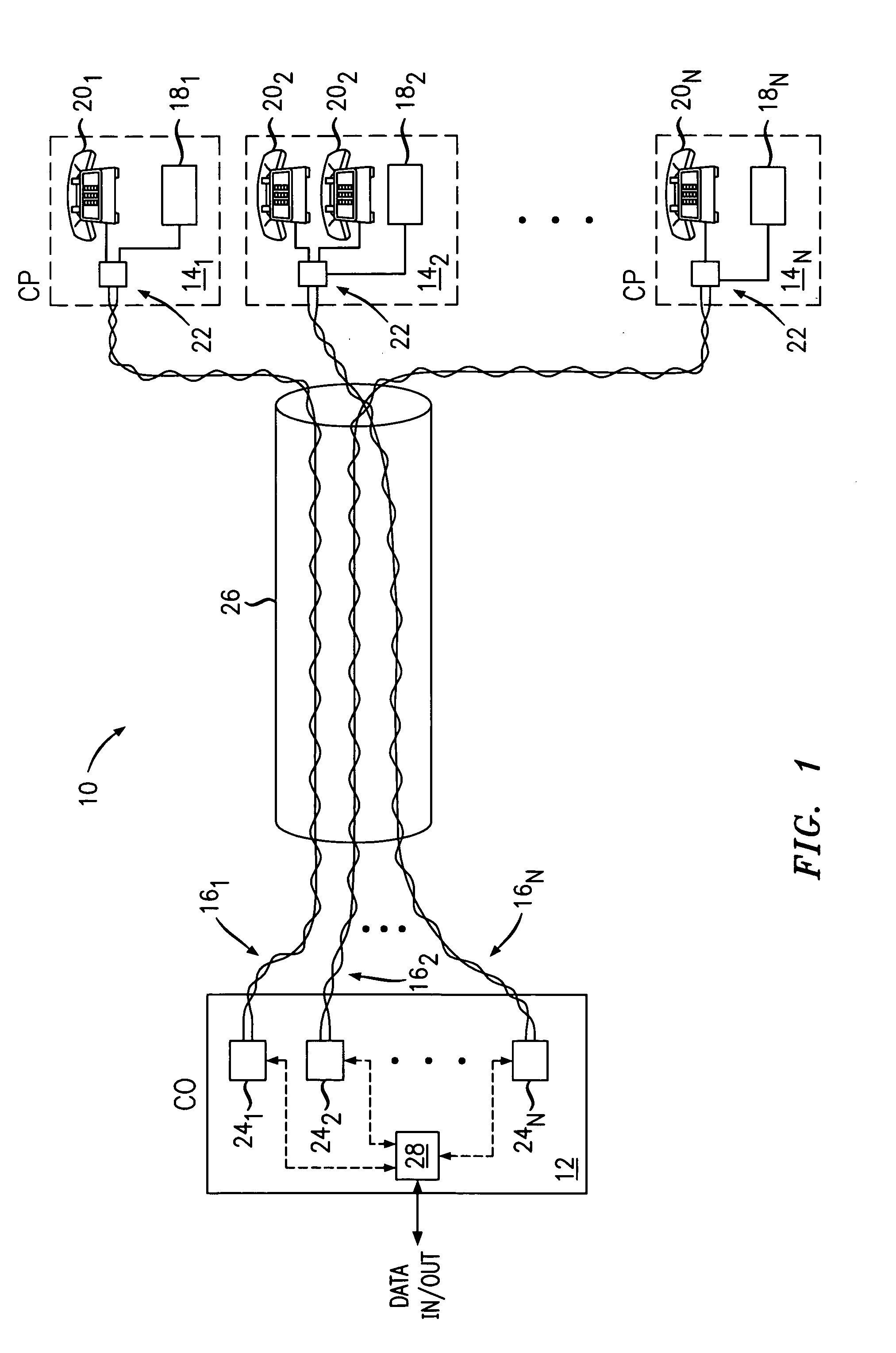

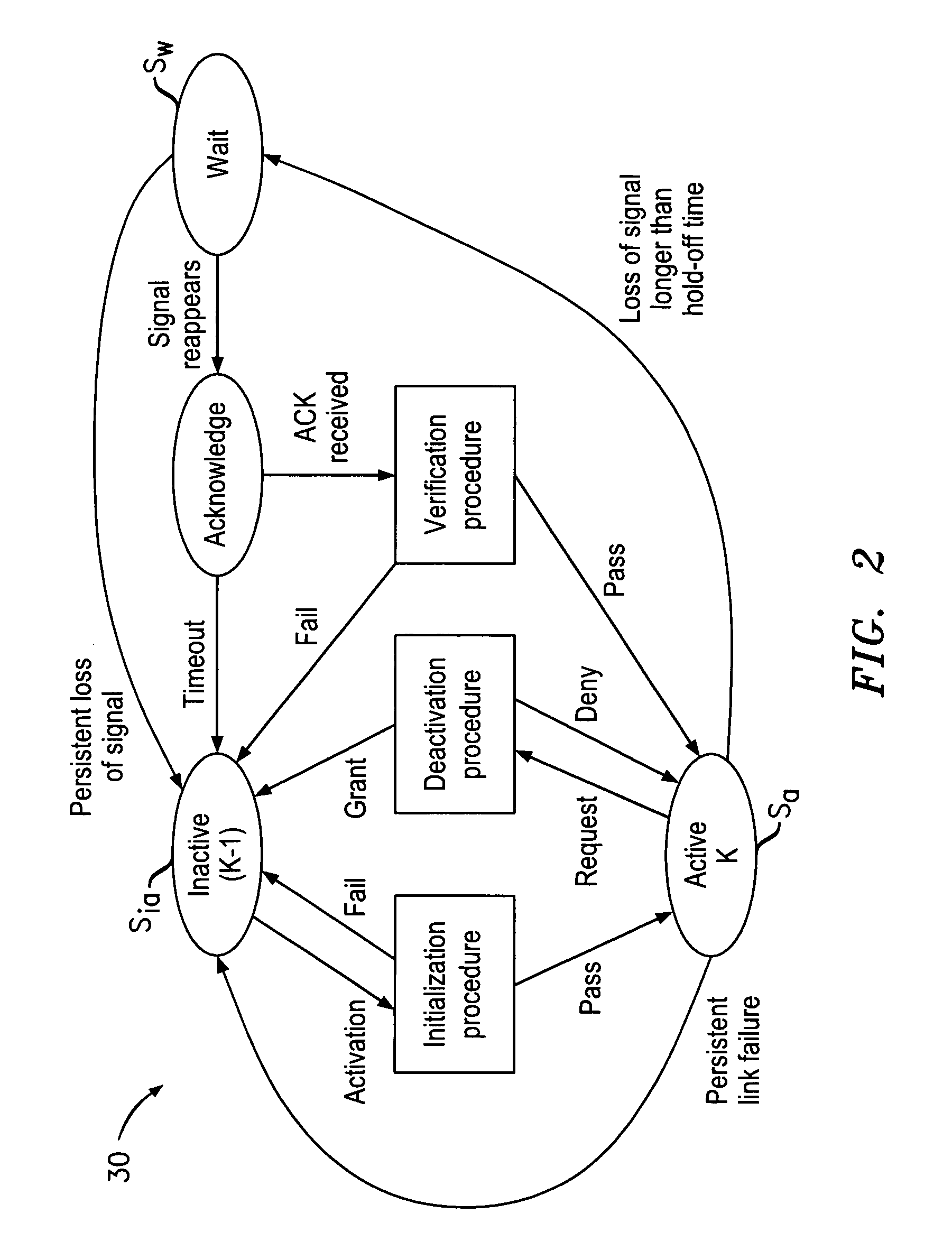

Validated signal resumption in DSL systems

ActiveUS20100278222A1Reduce power levelReduce crosstalkMultiplex system selection arrangementsError prevention/detection by using return channelTransceiverEngineering

An apparatus includes a DSL transceiver configured to transit to a DSL wait state in which a power transmitted from the DSL transceiver to a local-end line is substantially reduced in response to an interruption or substantial stop at the DSL transceiver of reception of DSL communications from the local-end line. The DSL transceiver is configured to transmit to the local-end line a DSL acknowledge signal in response to receiving from the local-end line a DSL wait signal. The DSL transceiver is configured to resume to transmit DSL communications to the local-end line at a power substantially higher than the power transmitted thereto in the DSL wait state in response either to receiving from the local-end line DSL transmissions at a substantially higher power than received there from in the DSL wait state or to receiving from the local-end line a second DSL acknowledge signal.

Owner:RPX CORP

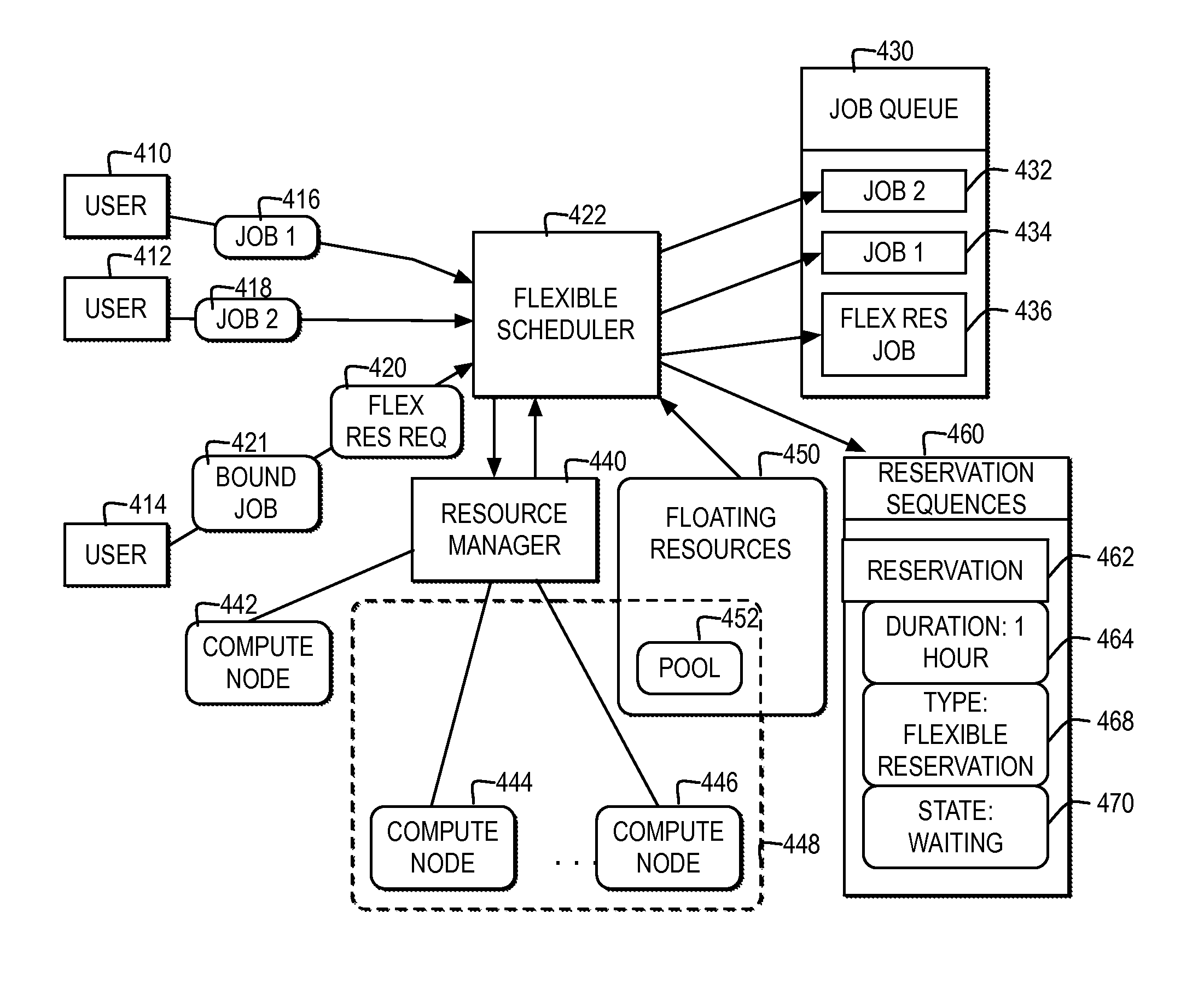

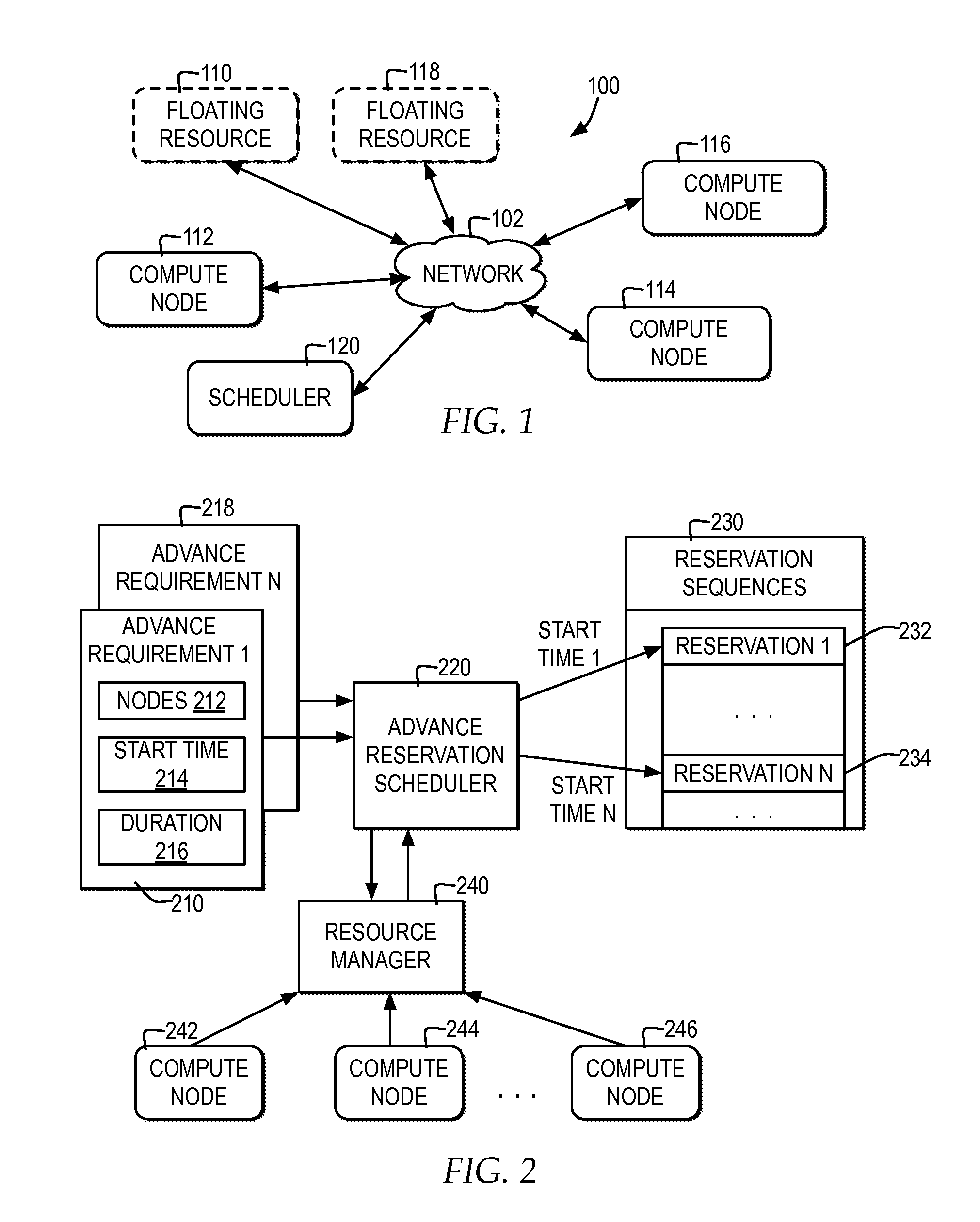

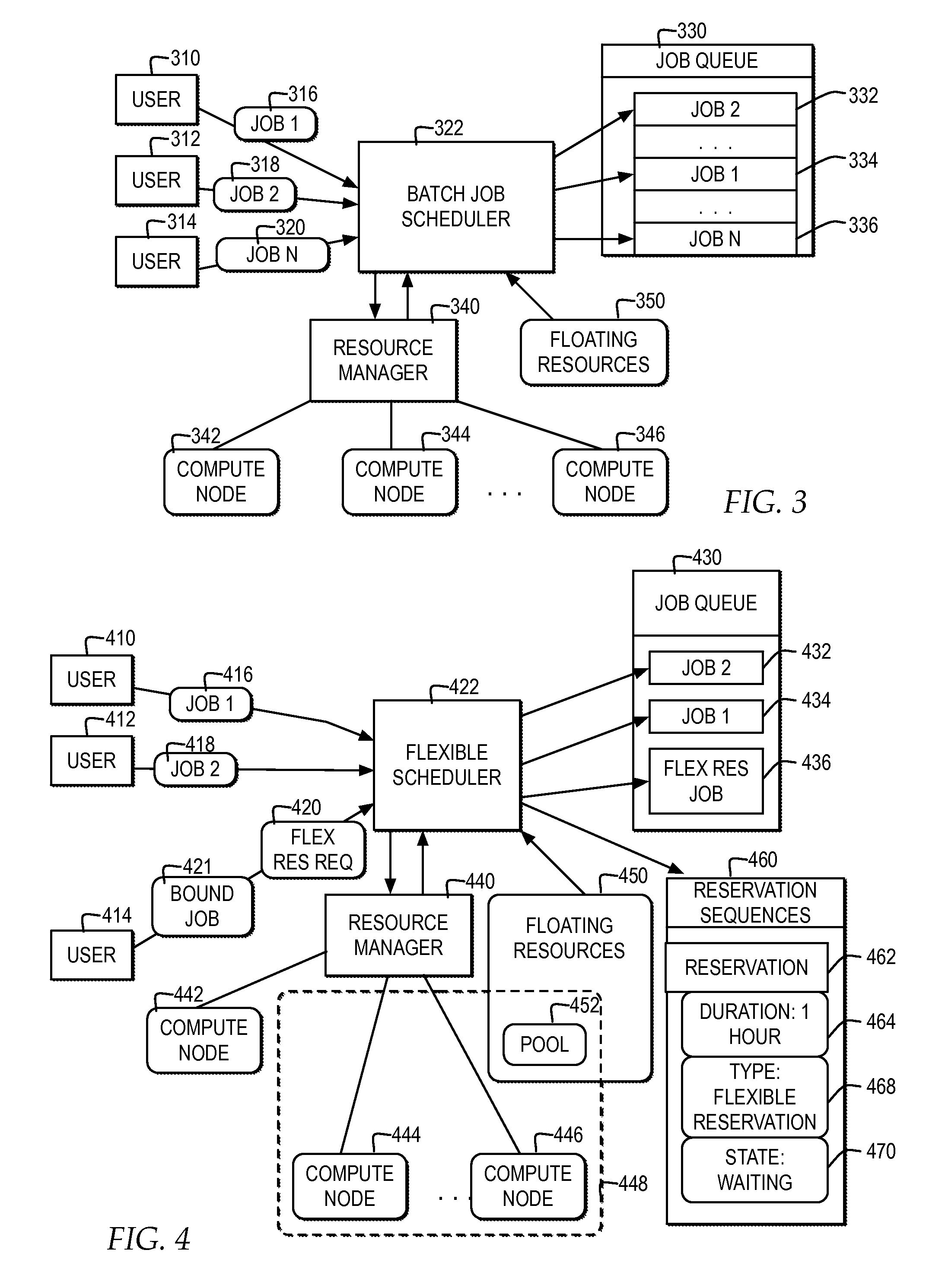

Workflow control of reservations and regular jobs using a flexible job scheduler

InactiveUS20120198462A1Efficiently managing workflowGeneral purpose stored program computerMultiprogramming arrangementsWait stateActive state

A scheduler receives at least one flexible reservation request for scheduling in a computing environment comprising consumable resources. The flexible reservation request specifies a duration and at least one required resource. The consumable resources comprise at least one machine resource and at least one floating resource. The scheduler creates a flexible job for the at least one flexible reservation request and places the flexible job in a prioritized job queue for scheduling, wherein the flexible job is prioritizes relative to at least one regular job in the prioritized job queue. The scheduler adds a reservation set to a waiting state for the at least one flexible reservation request. The scheduler, responsive to detecting the flexible job positioned in the prioritized job queue for scheduling next and detecting a selection of consumable resources available to match the at least one required resource for the duration, transfers the selection of consumable resources to the reservation and sets the reservation to an active state, wherein the reservation is activated as the selection of consumable resources become available and has uninterrupted use of the selection of consumable resources for the duration by at least one job bound to the flexible reservation.

Owner:IBM CORP

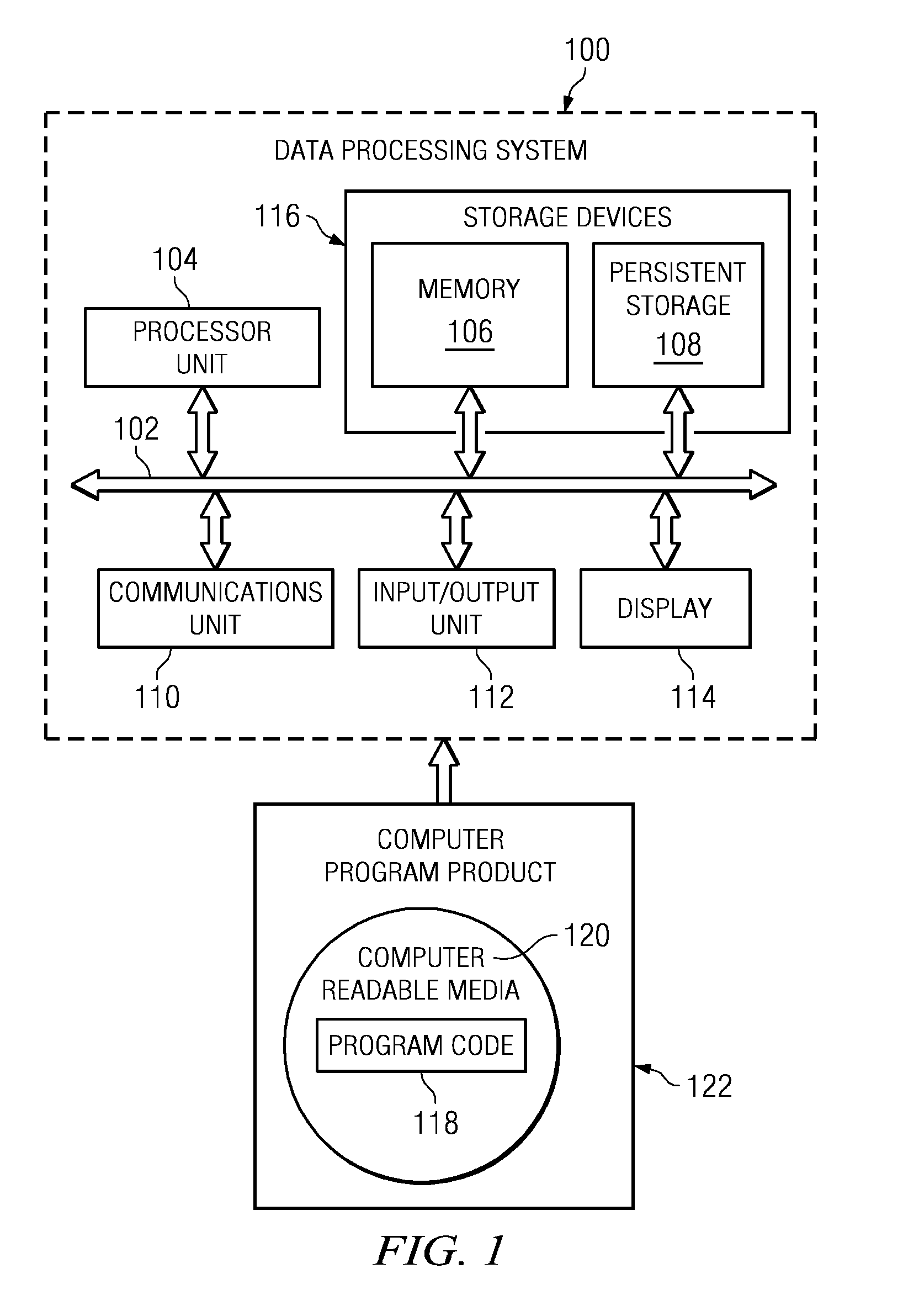

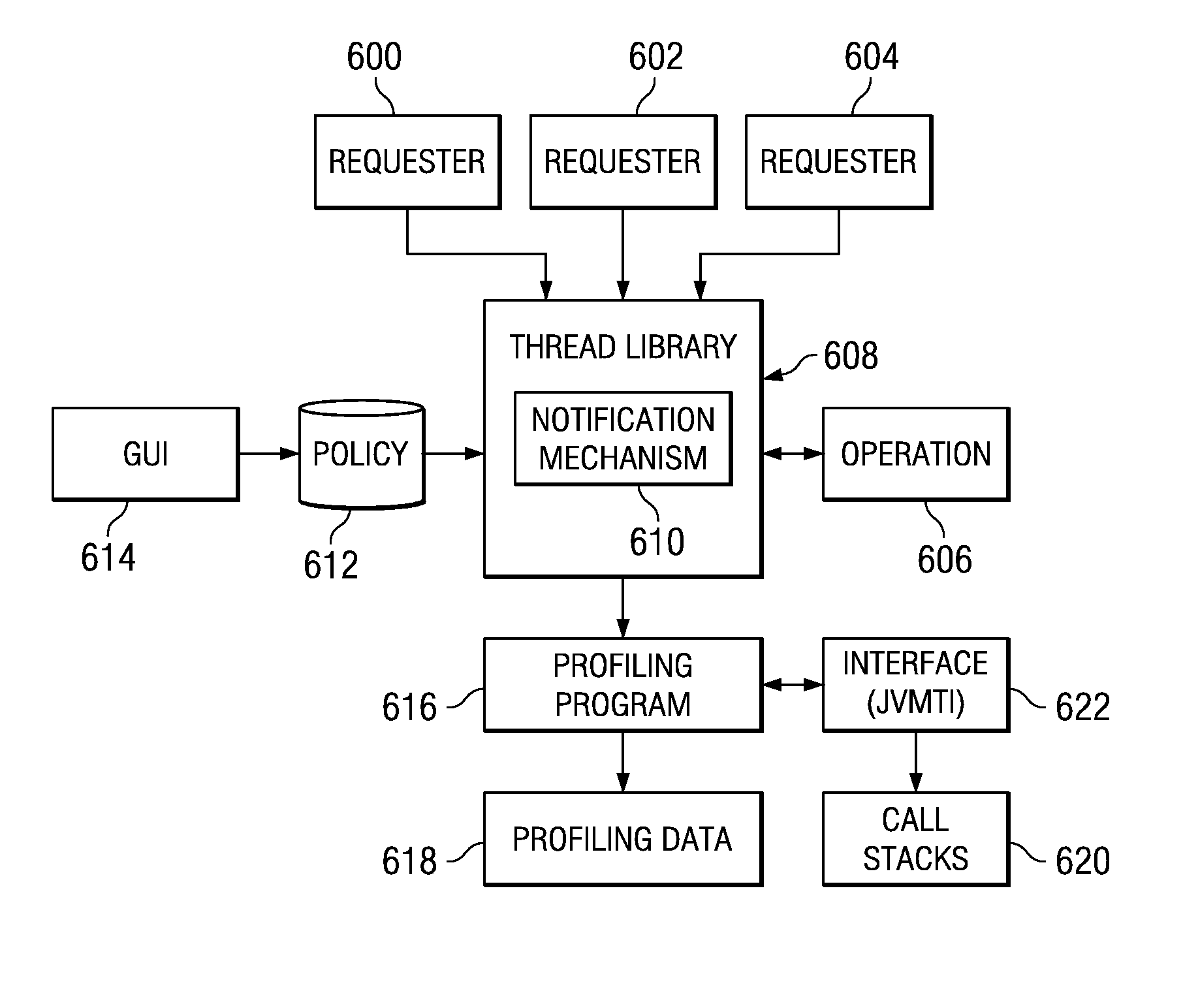

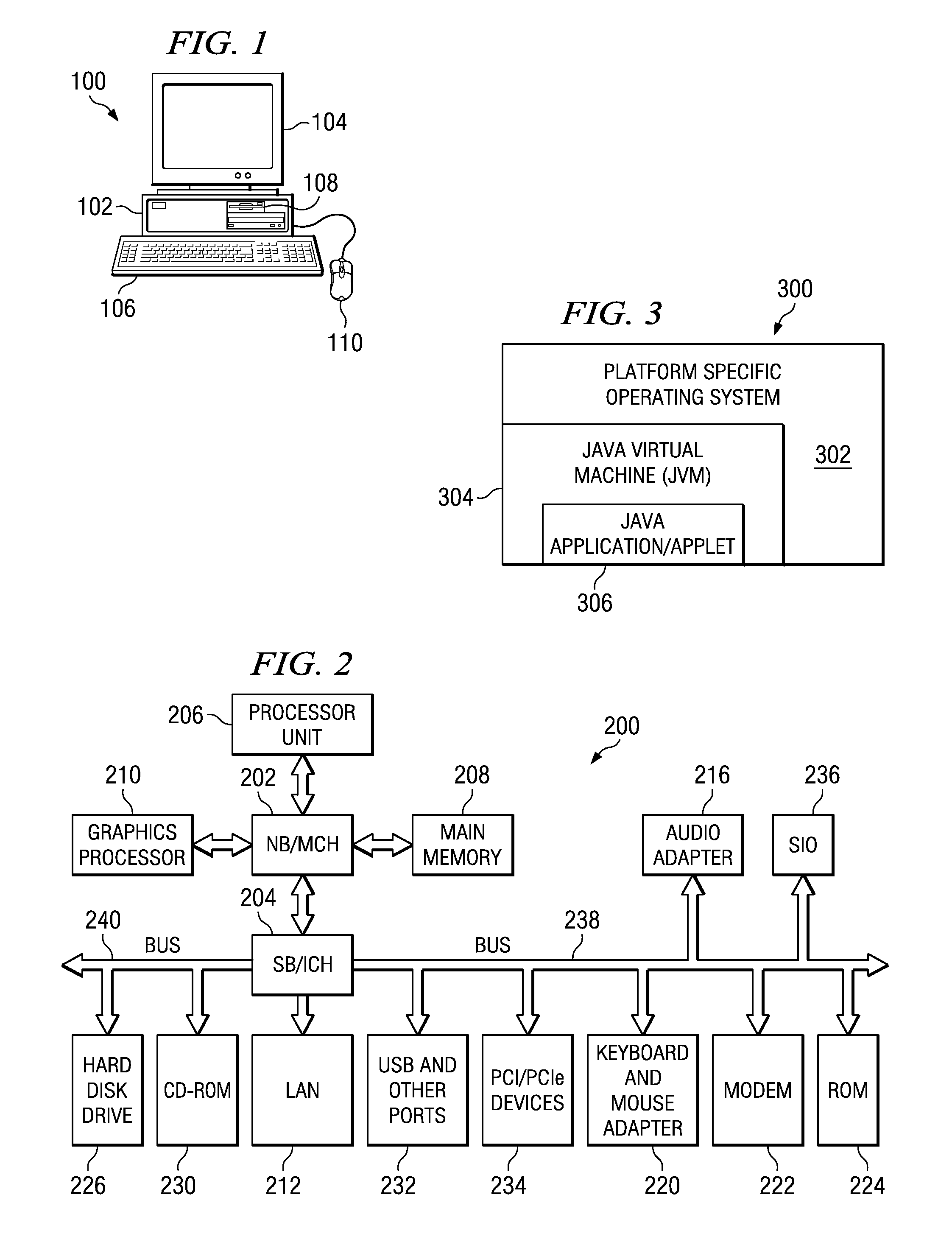

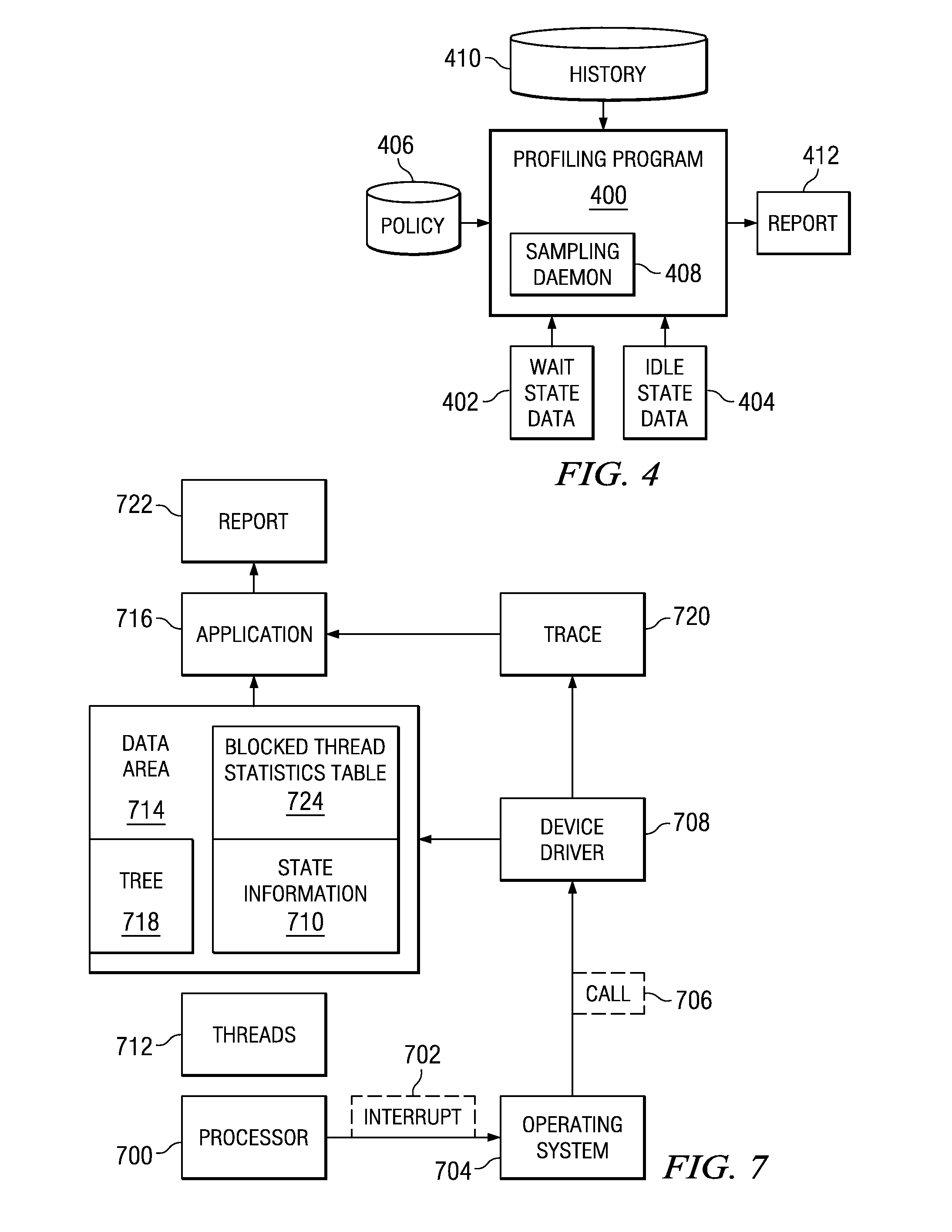

Method and Apparatus for Analyzing Wait States in a Data Processing System

ActiveUS20070220515A1Error detection/correctionMultiprogramming arrangementsData processing systemAnalysis data

A computer implemented method, apparatus, and computer usable program code for collecting information about threads. A thread entering a wait state is detected. Information is selectively obtained about a set of threads in the wait state using a policy to produce an action in response to the thread entering the wait state. A history containing the collected data may be saved and used to determine changes to patterns.

Owner:IBM CORP

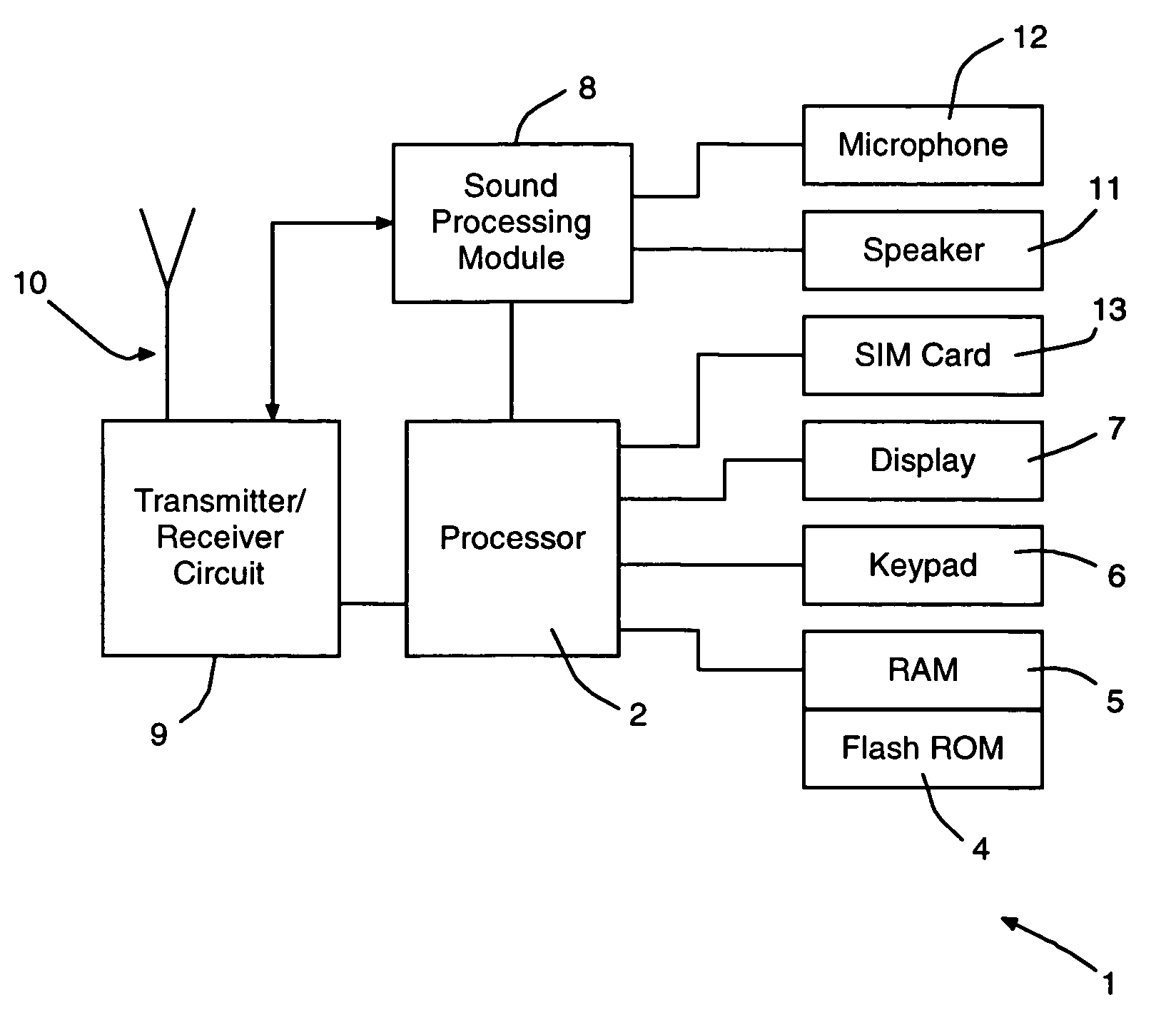

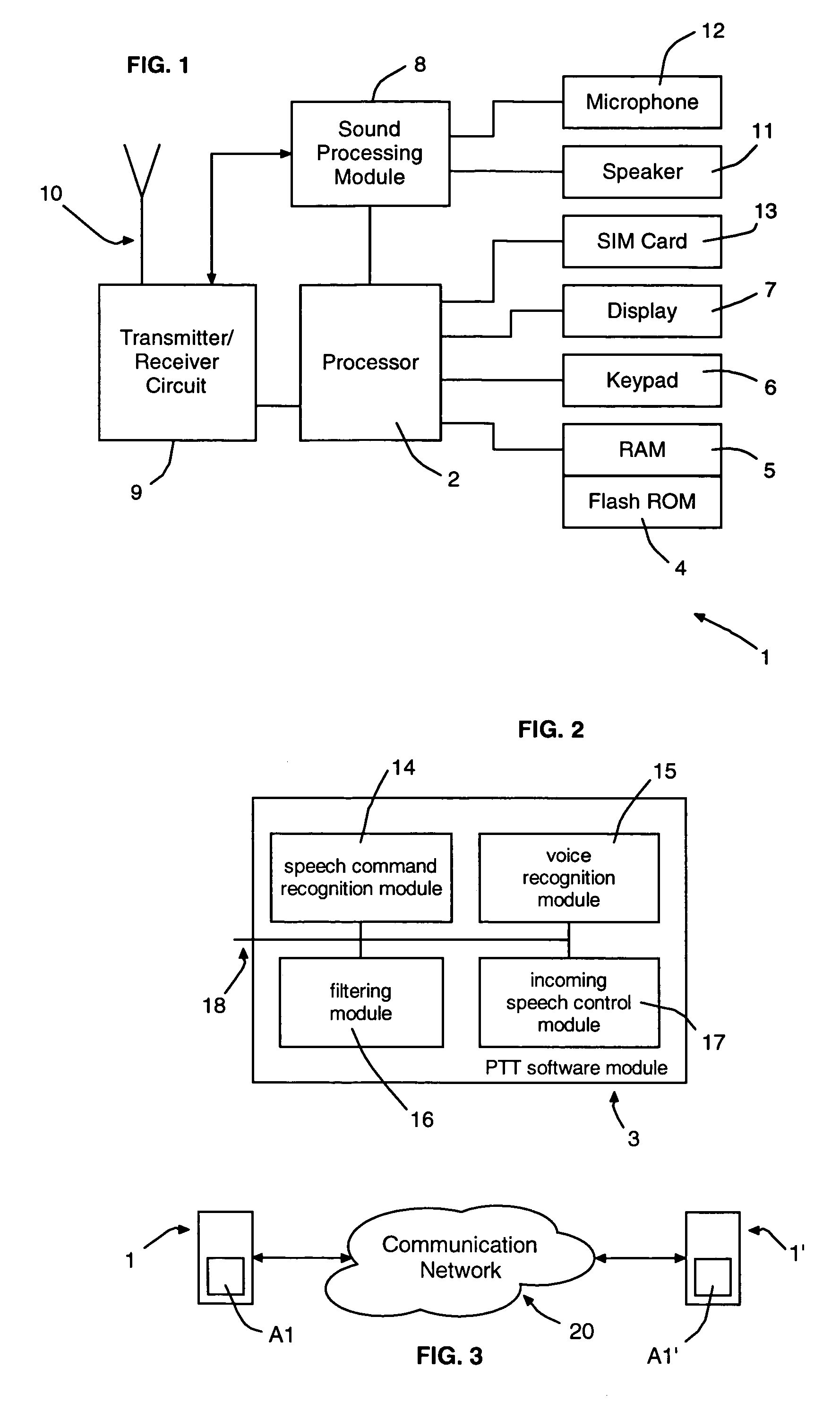

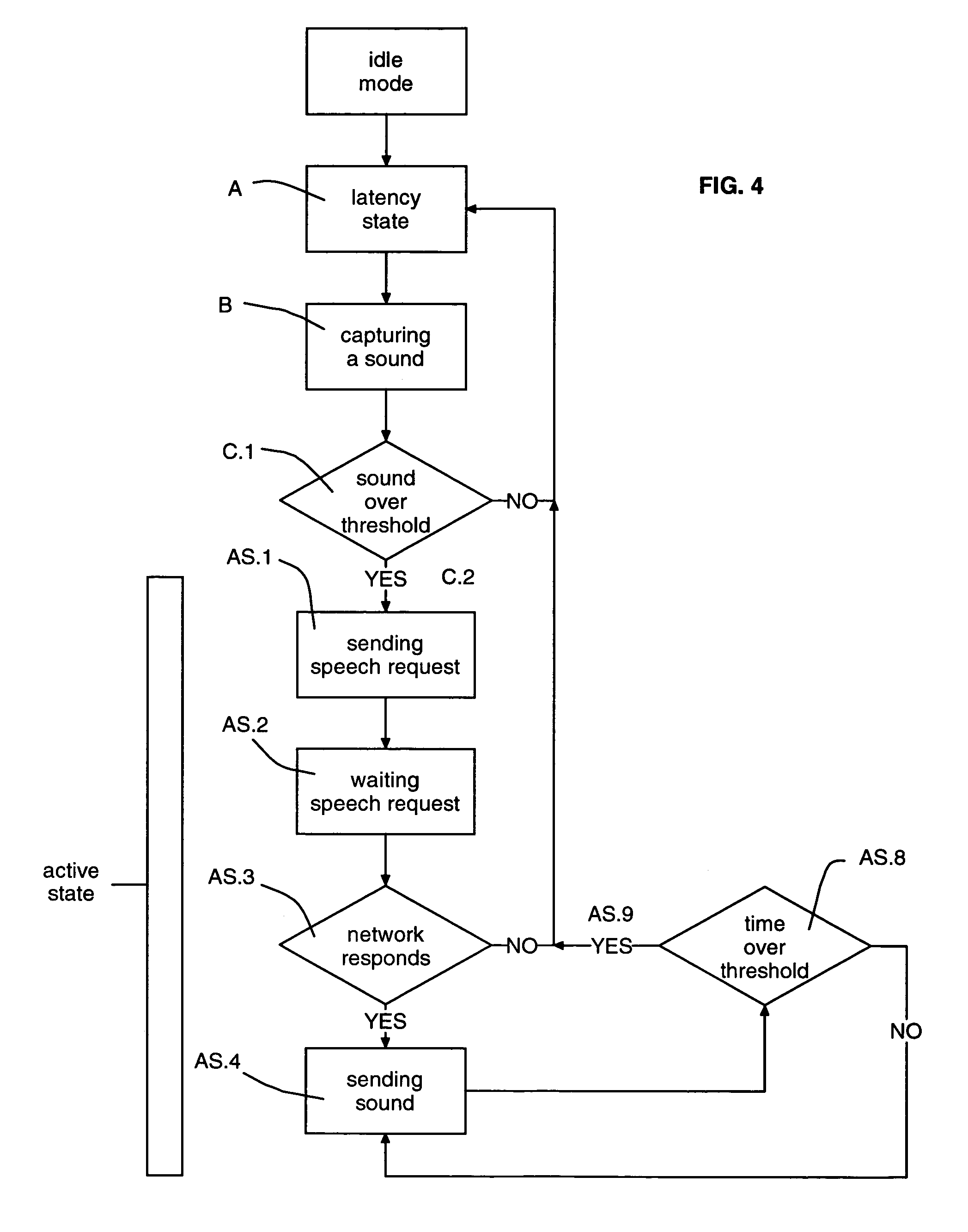

Push-to-talk mobile communication terminals

ActiveUS7366535B2Overcome problemsAvoid captureNetwork topologiesConnection managementPush-to-talkWait state

Mobile communication terminals comprising a processor unit, a microphone, and a sound processing module for processing sounds captured by the microphone. The processor unit is configured to operate the terminal for a push-to-talk communication with at least one other mobile communication terminal via the communication network, and to operate the terminal during said push-to-talk communication in a latency state or in an active state in which sound captured by the microphone is processed by the sound processing module and sent to the at least one other mobile communication terminal. The processor unit is also configured to change from the latency state to the active state in dependence of the sound captured by the microphone.

Owner:III HLDG 3

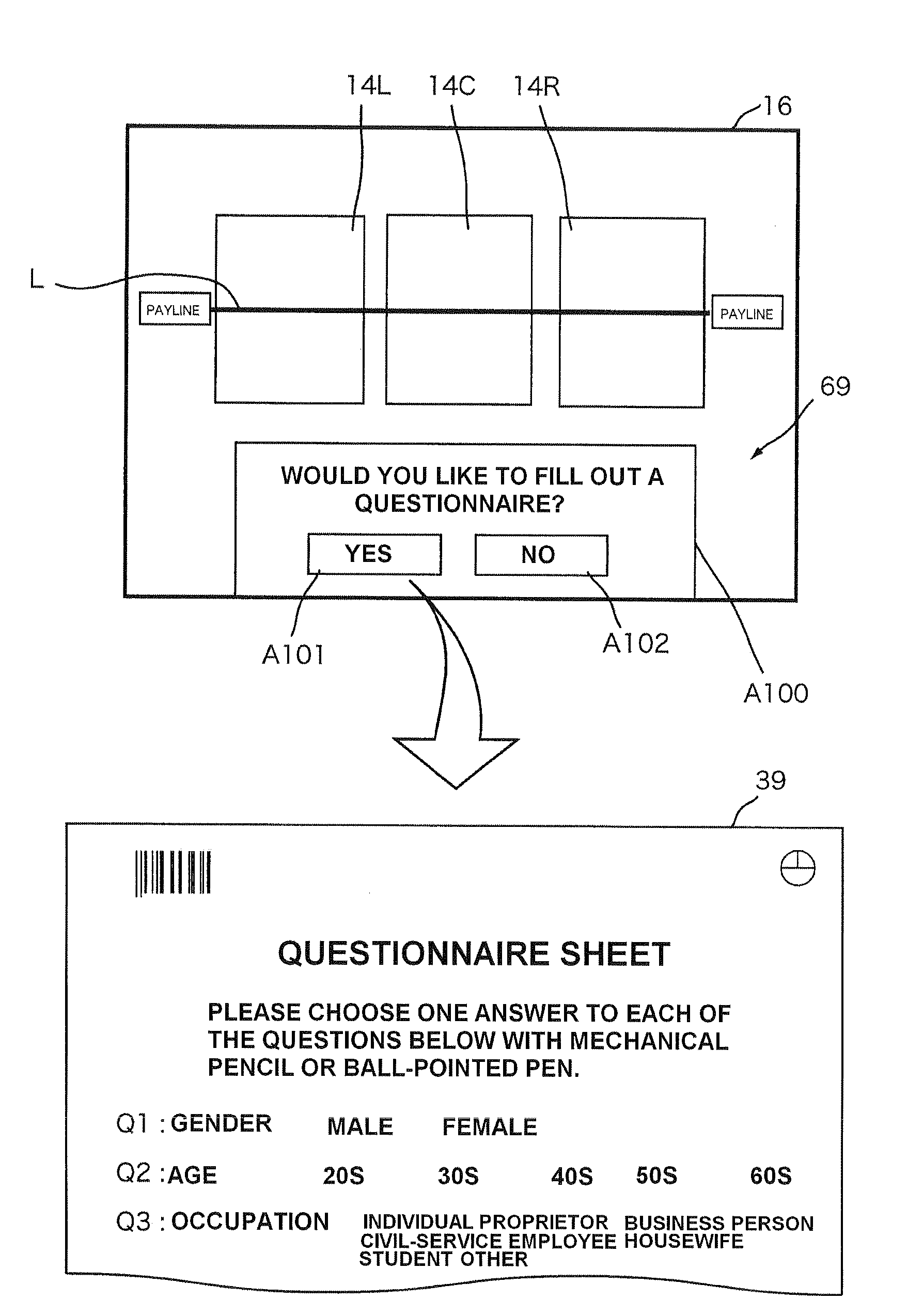

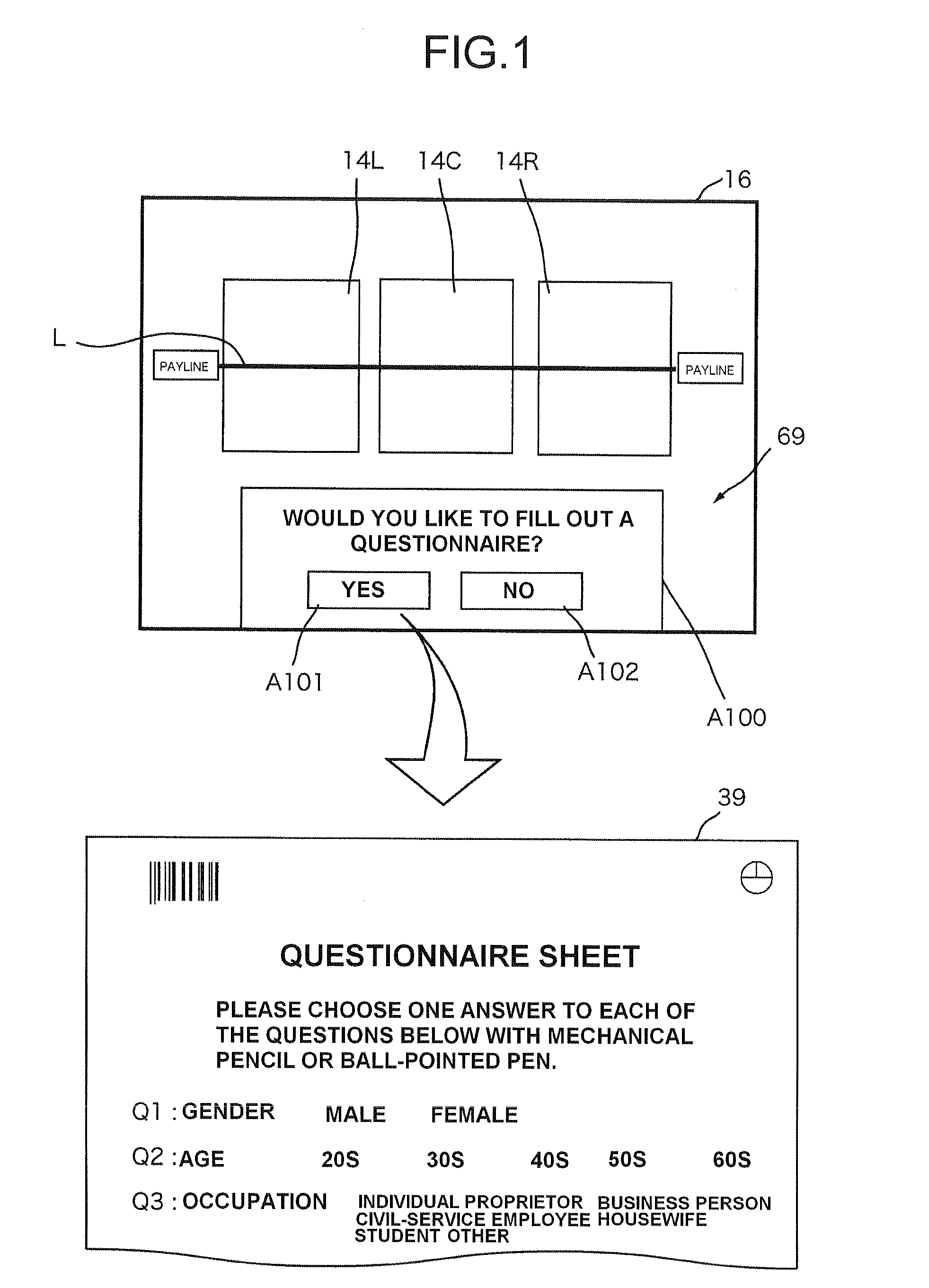

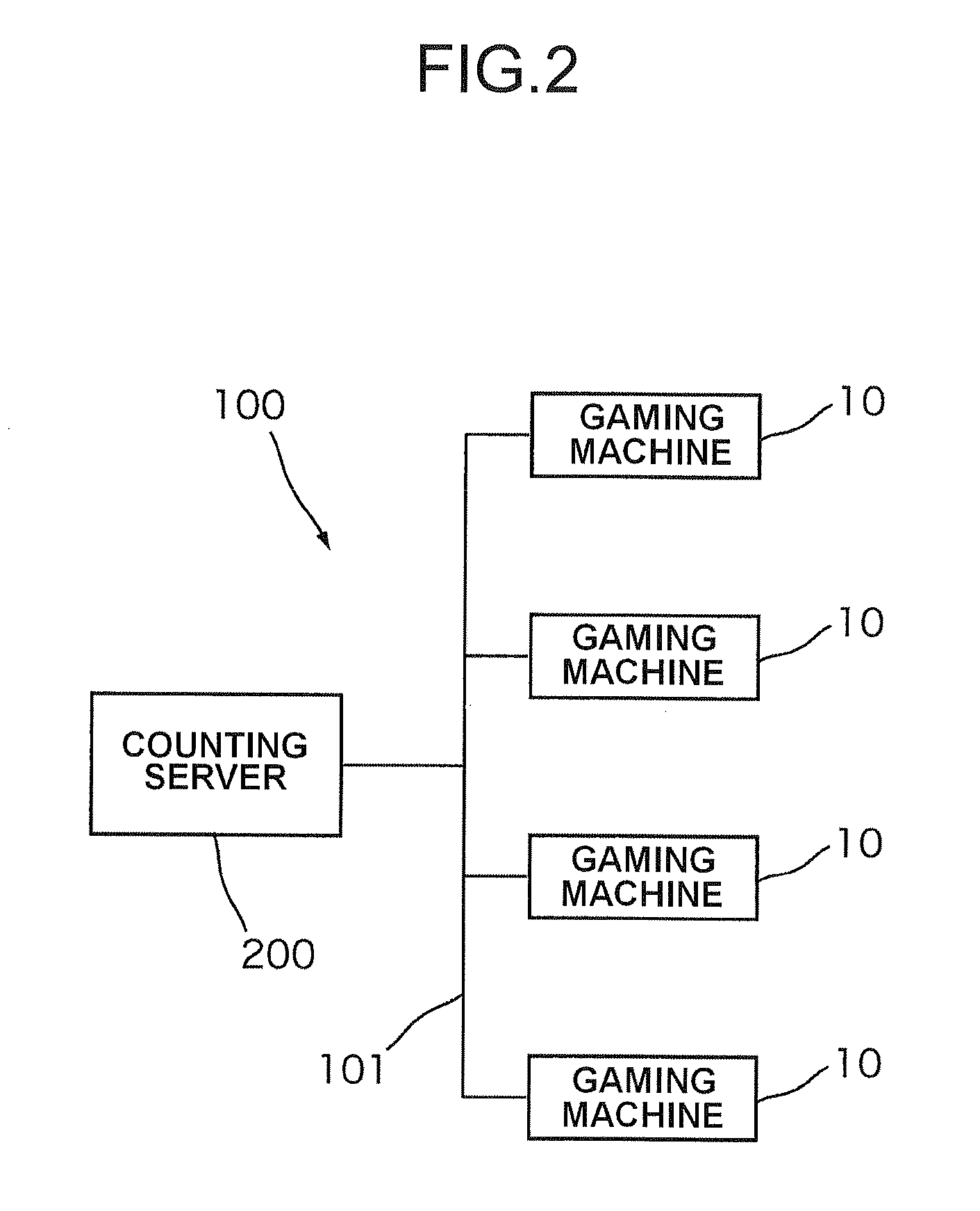

Gaming Machine Having Questionnaire Function And Control Method Thereof

InactiveUS20090253477A1Improve reliabilityMaintain interestApparatus for meter-controlled dispensingVideo gamesWait stateData storing

A gaming machine of the present invention includes: a controller which executes a process of starting a game while it is triggered that a predetermined condition has been met, a process of counting the number of times of executing the game, and a process of judging whether or not the counted number of times of executing the game has reached a predetermined value; a stocker for stocking a form on which questions to be answered are printed; an ejection device which is capable of ejecting the form stocked in the stocker in a case where it is judged that the number of times of executing the game has reached a predetermined value by the controller; a re-collection device for re-collecting the form that is ejected by the ejection device and in which answers to questions are entered; a reading device which reads the form in which answers to questions are entered and which data-converts the read answer; a memory which stores the data-converted answers by the reading device and plural types of video data and audio data; and a reproduction device which reproduces video data or audio data stored in the memory. The controller executes a process of transfer to a waiting state waiting for re-collection of the form in which answers to questions have been entered, after ejecting the form by the ejection device, a process of associating an answer data-converted from the form re-collected after transfer to the waiting state, with a game history obtained until transfer to the waiting state, and storing the associated answer in the memory, and a process of selecting video data and audio data from the memory in accordance with the answer and game history stored in the memory. The reproduction device reproduces the video data and audio data selected by the controller.

Owner:ARUZE GAMING AMERICA

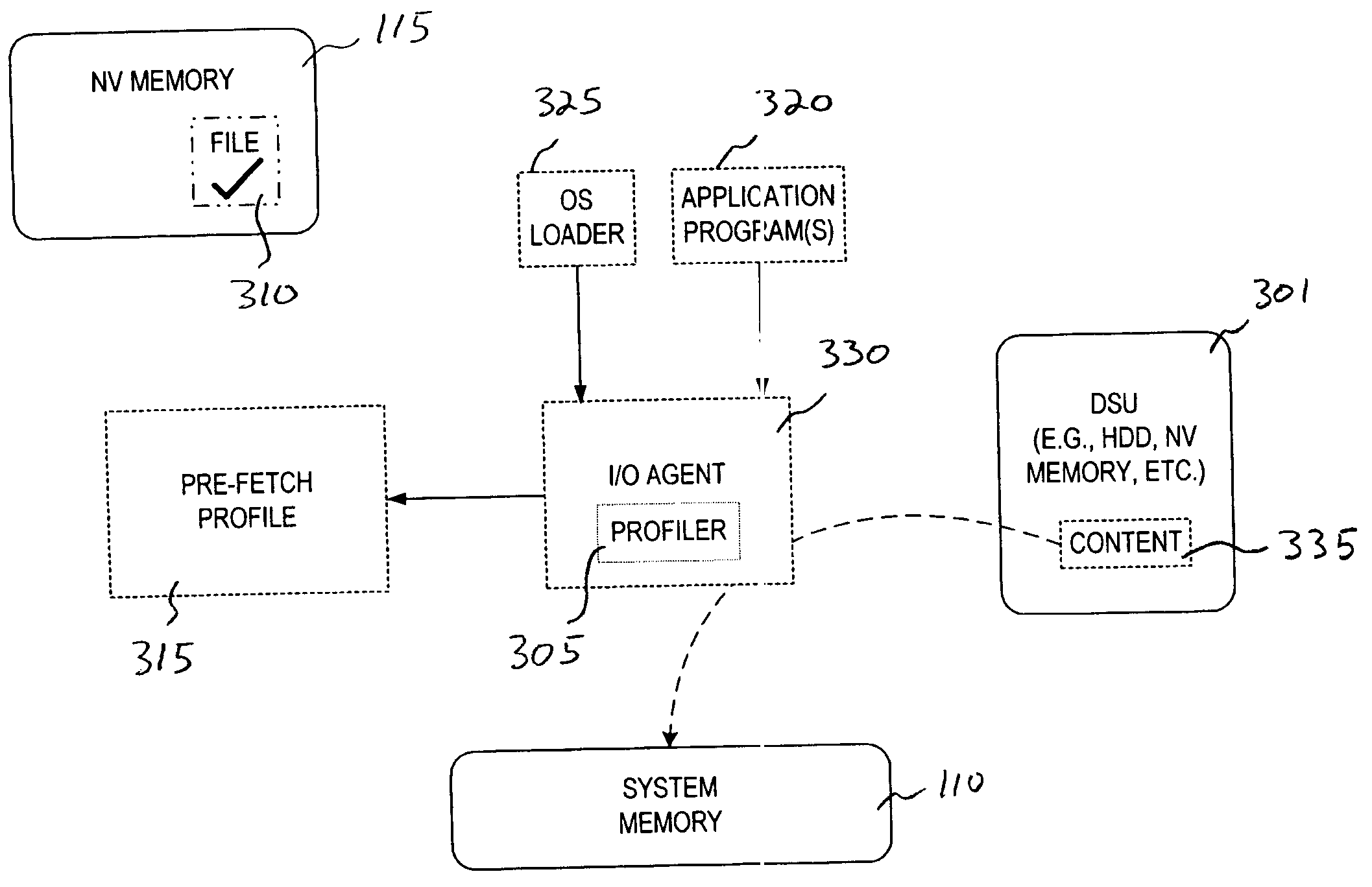

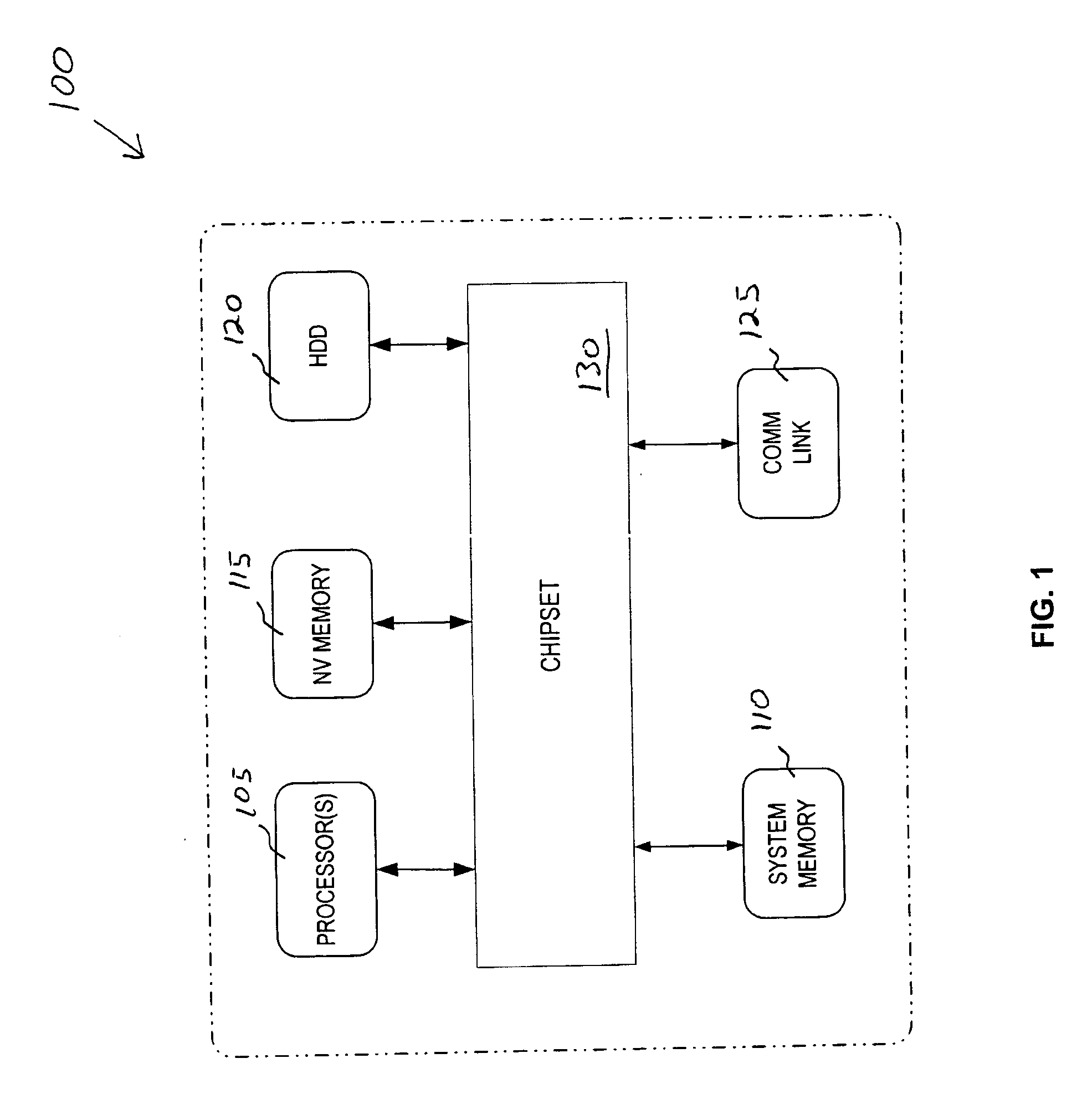

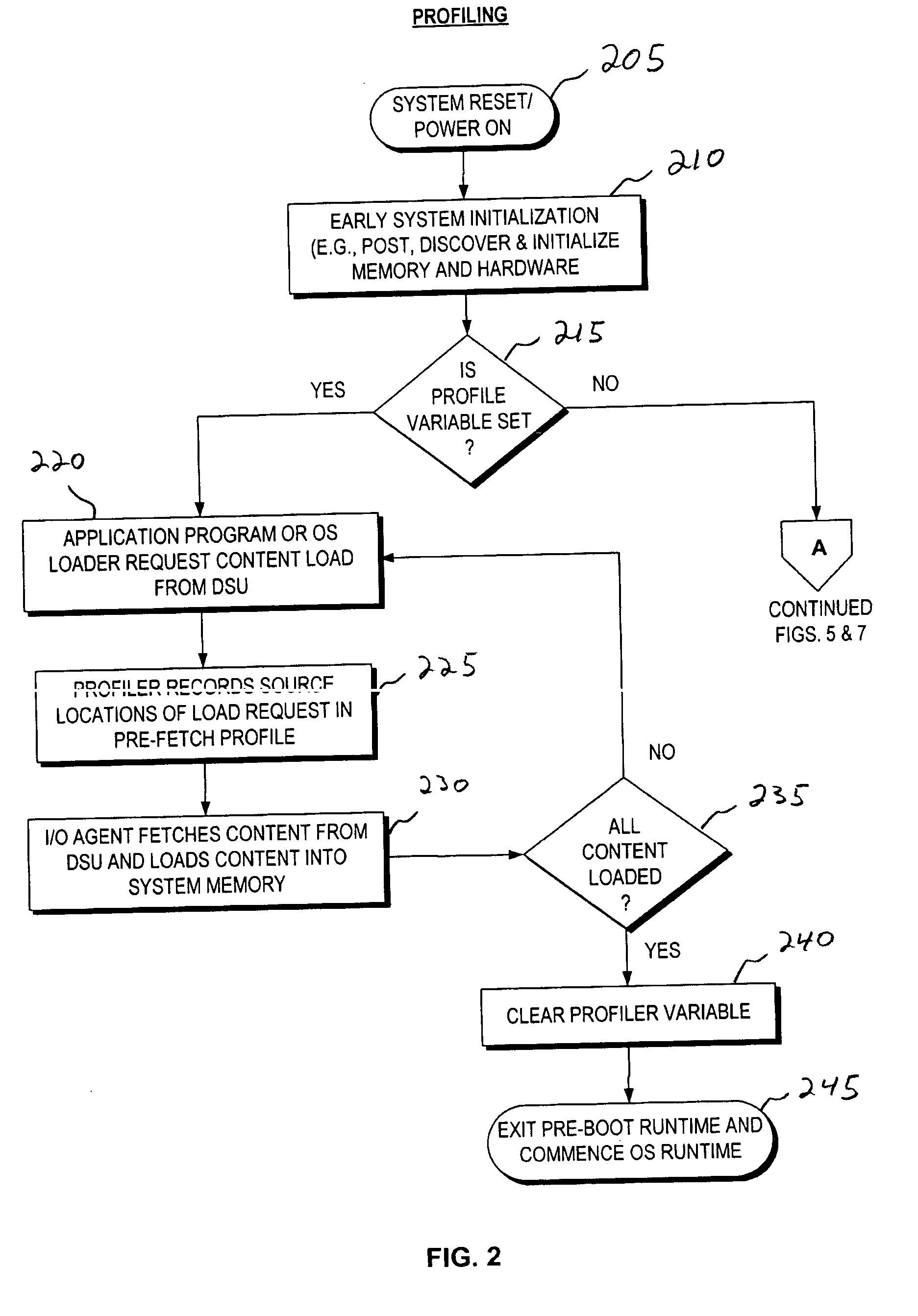

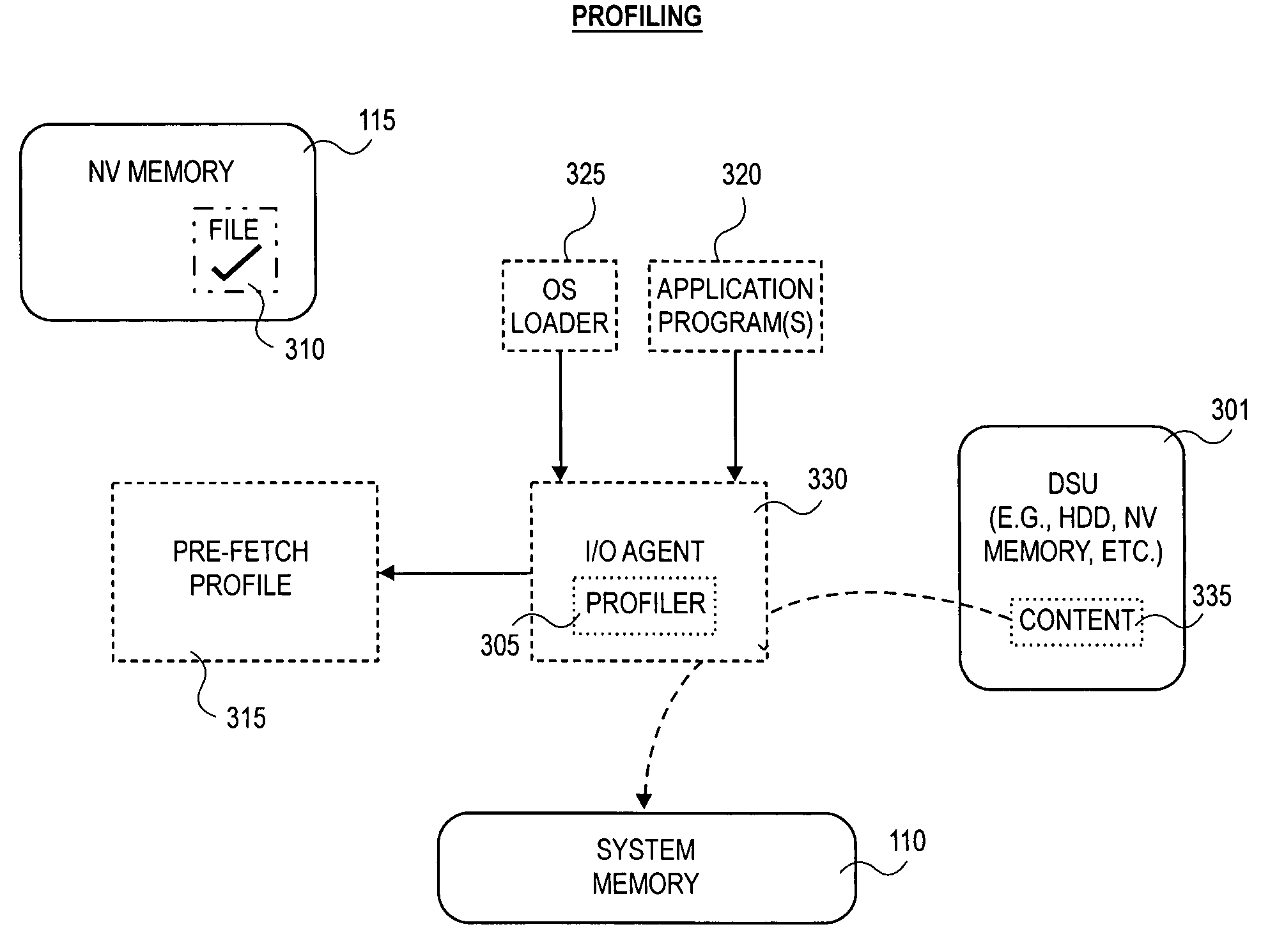

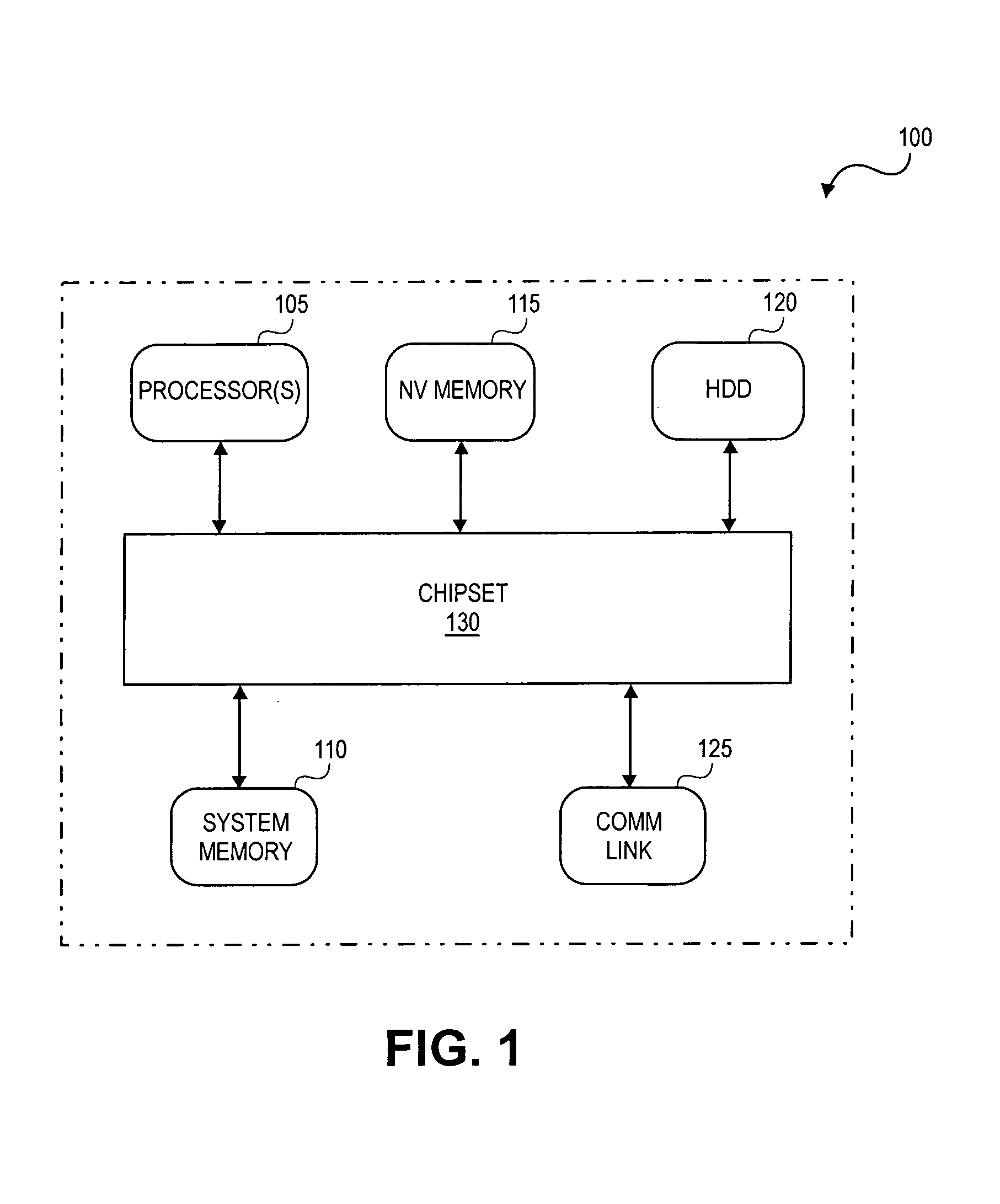

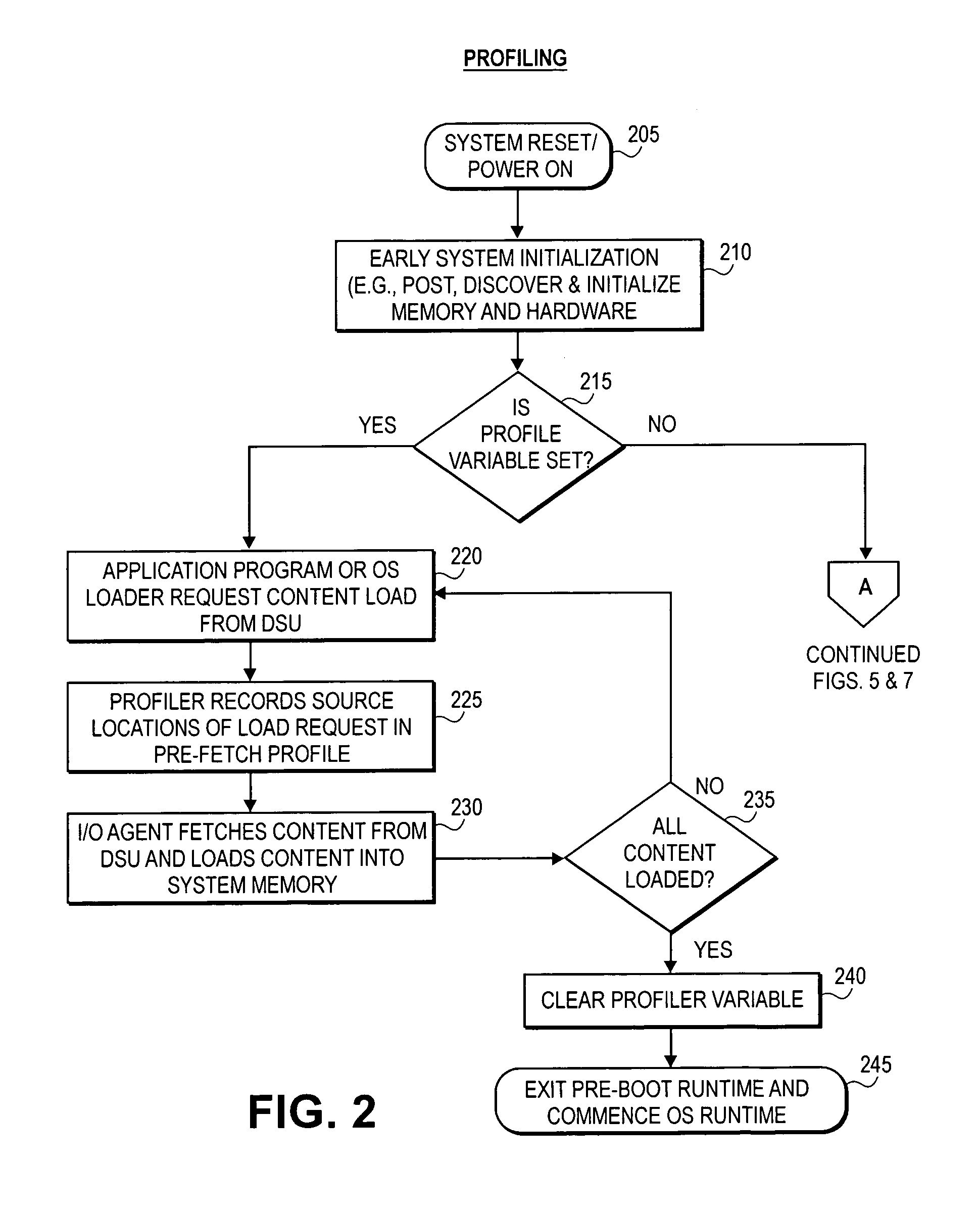

Aggressive content pre-fetching during pre-boot runtime to support speedy OS booting

A method and system for content pre-fetching during a processing system pre-boot runtime. First, it is determined when a processor of a processing system is in one of a busy wait state and an idle state during a pre-boot runtime of the processing system. Then, content is pre-fetched from a data storage unit of the processing system. The content is pre-fetched based upon a pre-fetch profile. The content is loaded into system memory of the processing system.

Owner:INTEL CORP

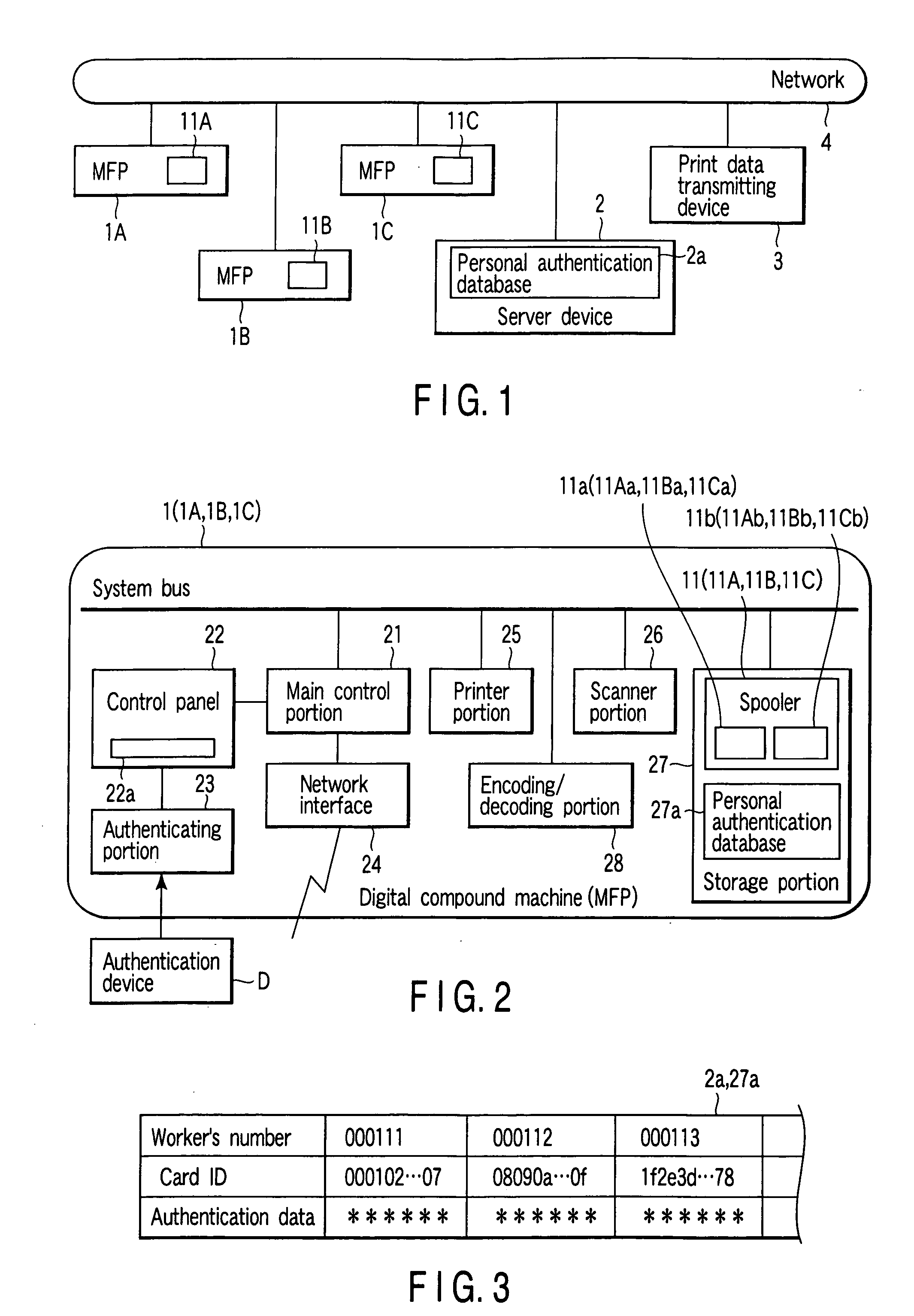

Image forming apparatus

ActiveUS20070133033A1Computer security arrangementsVisual presentationImage formationUser authentication

Owner:KK TOSHIBA +1

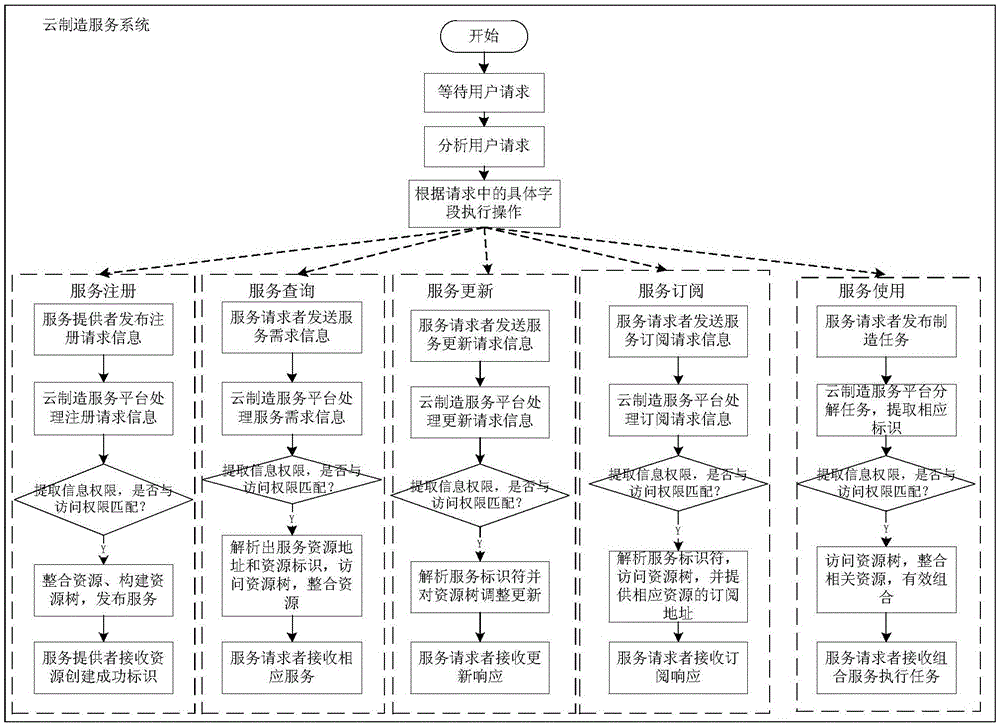

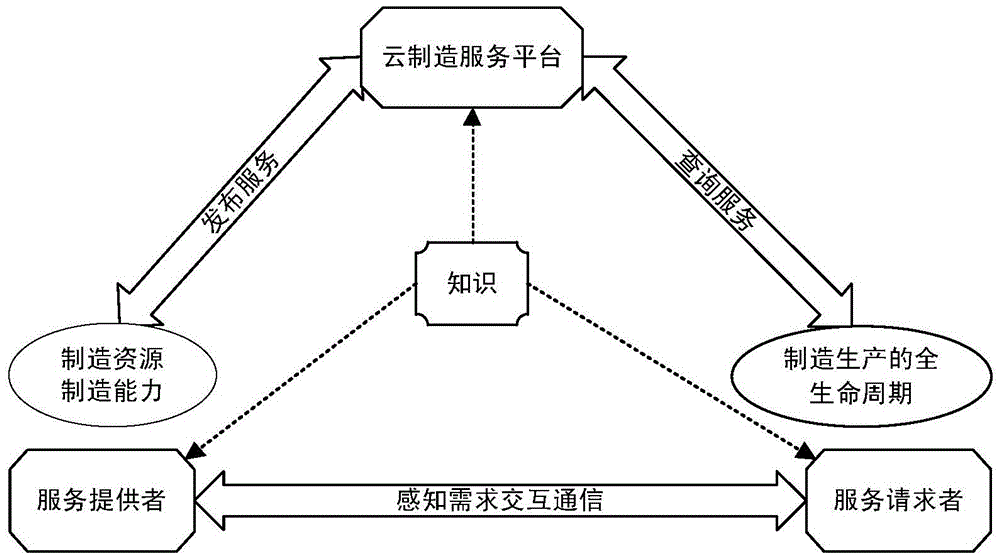

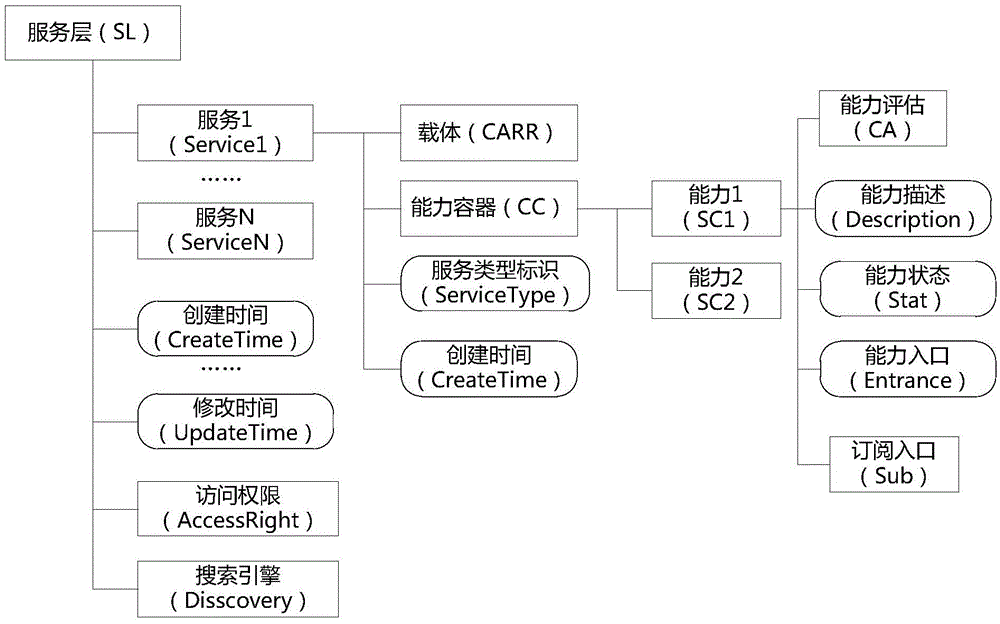

Organization and management and using method and system for cloud manufacturing service

InactiveCN105635283AEffective organizational managementActive service registrationTransmissionResource utilizationManagement efficiency

The invention discloses an organization and management and using method and system for a cloud manufacturing service. According to the method, on the basis of the internet of things technology and the cloud computing technology, interaction among a service provider, a service requester, and a cloud manufacturing service platform is described by using correlated network technologies like an XML language or an HTTP protocol; and modeling is carried out on the service based on description of the network technologies and a resource tree is constructed, so that the management efficiency and the resource utilization rate are effectively improved. Therefore, high-efficiency sharing of the resources and capabilities is realized; repeated building of the same kind of manufacturing resources and capability can be avoided; and the manufacturing energy and cost can be effectively saved. In a cloud manufacturing service system, a server is set to be in a user request waiting state; when a user request is received, the user request is analyzed; and corresponding operations of service registration, querying, updating, subscription, and usage are executed based on specific fields in the request.

Owner:NANJING UNIV OF POSTS & TELECOMM

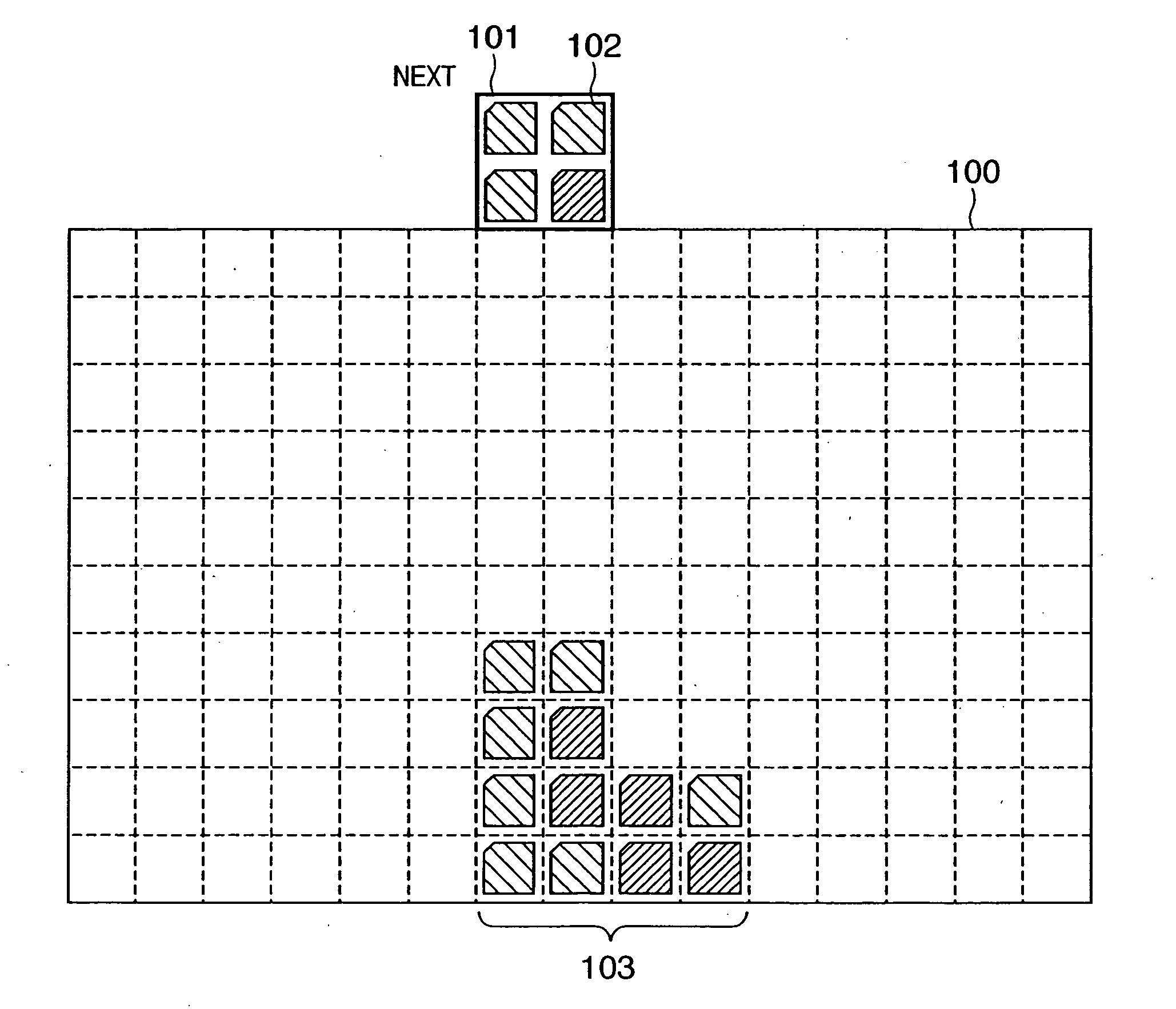

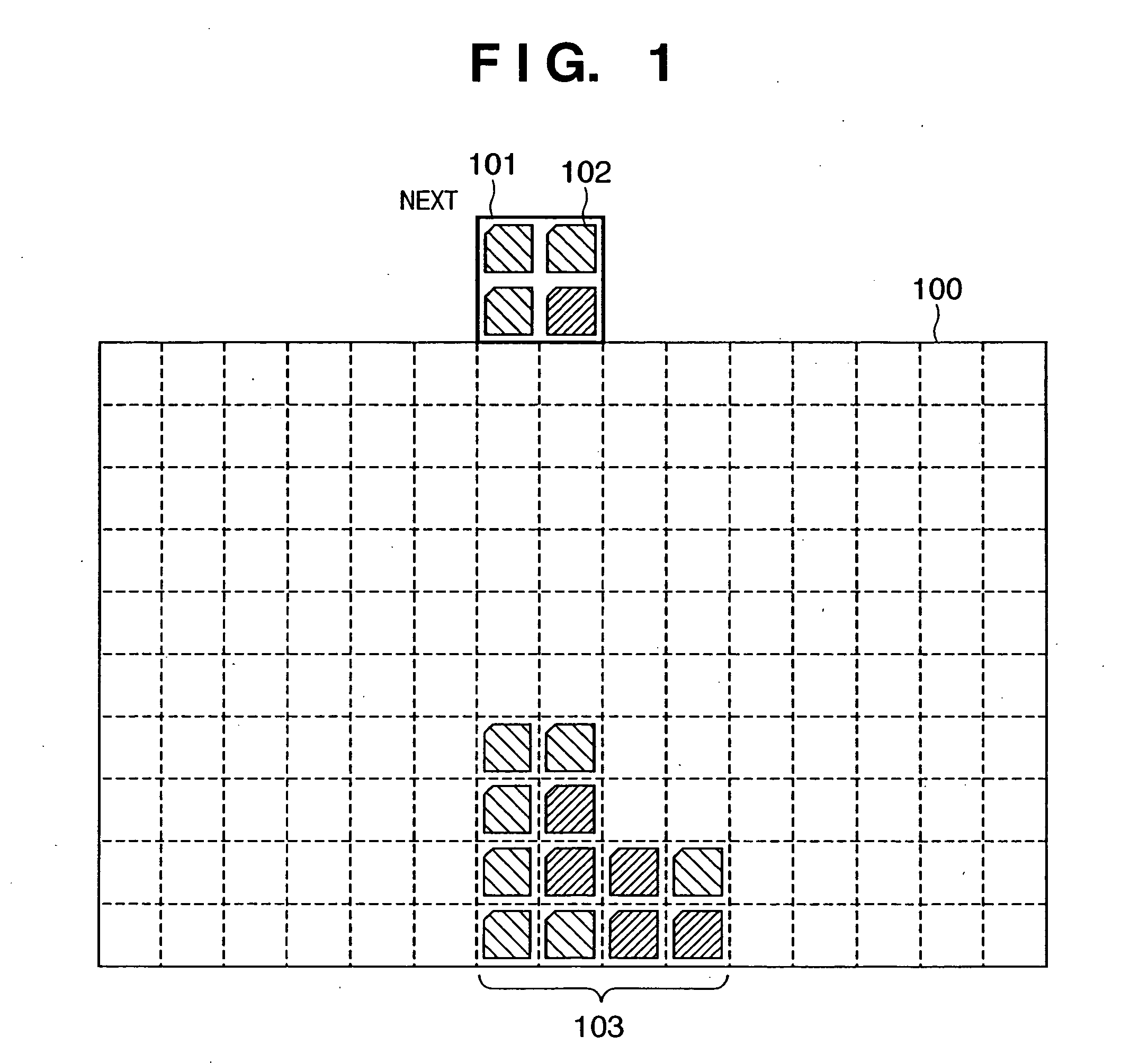

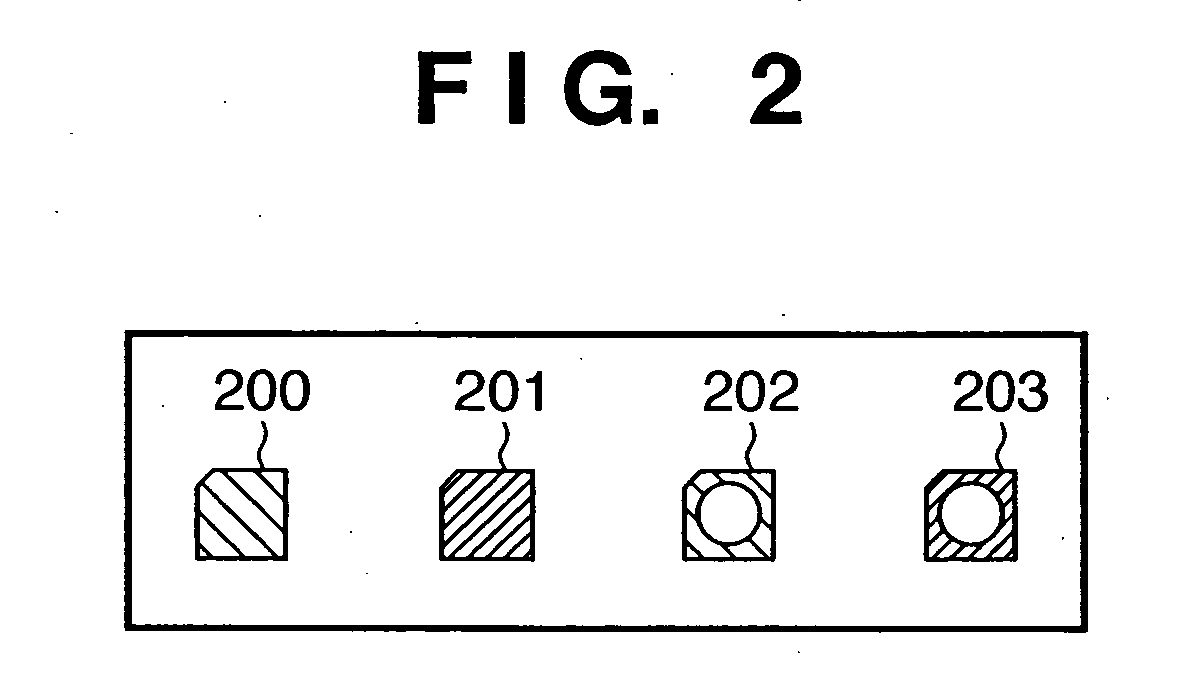

Game apparatus and control method therefor

ActiveUS20050266908A1Difficult to levelEasy to understandVideo gamesSpecial data processing applicationsWait stateSynchronism

A computer game which makes the player operate a falling object that falls in a predetermined display area, and clears the falling object and falling stop objects by combining the falling object and falling stop objects under a predetermined condition. If falling stop objects including blocks that stop falling include a group of blocks which meet a predetermined clear condition, the group of blocks are registered as blocks to be cleared, and the control waits for a clear waiting state. Even in this waiting state, the next falling object begins to fall. After that, when a sequence bar (701) which moves vertically or horizontally in synchronism with a music output along with the progress of the game has passed the blocks to be cleared, these blocks are cleared.

Owner:RESONAIR INC +2

Aggressive content pre-fetching during pre-boot runtime to support speedy OS booting

A method and system for content pre-fetching during a processing system pre-boot runtime. First, it is determined when a processor of a processing system is in one of a busy wait state and an idle state during a pre-boot runtime of the processing system. Then, content is pre-fetched from a data storage unit of the processing system. The content is pre-fetched based upon a pre-fetch profile. The content is loaded into system memory of the processing system.

Owner:INTEL CORP

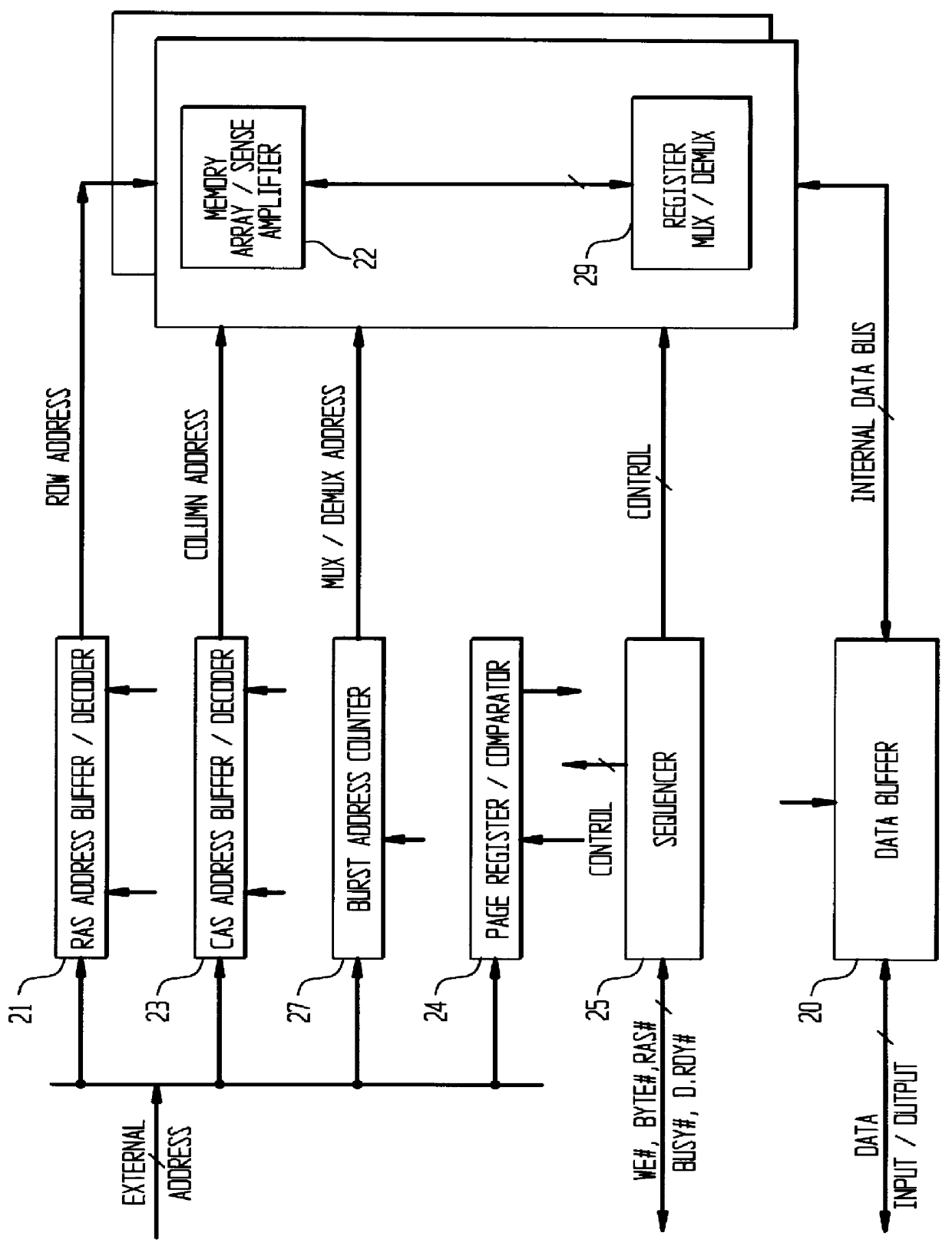

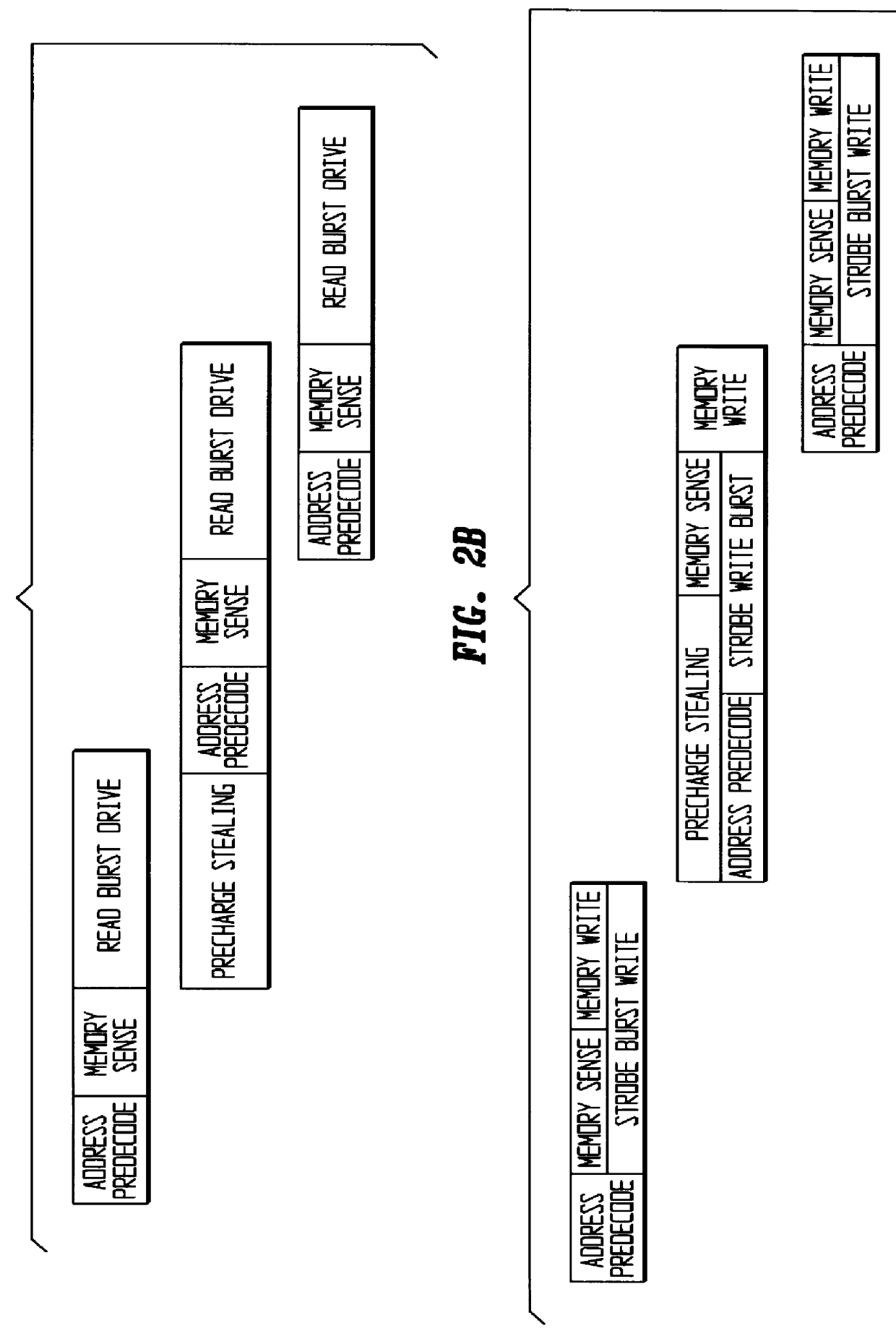

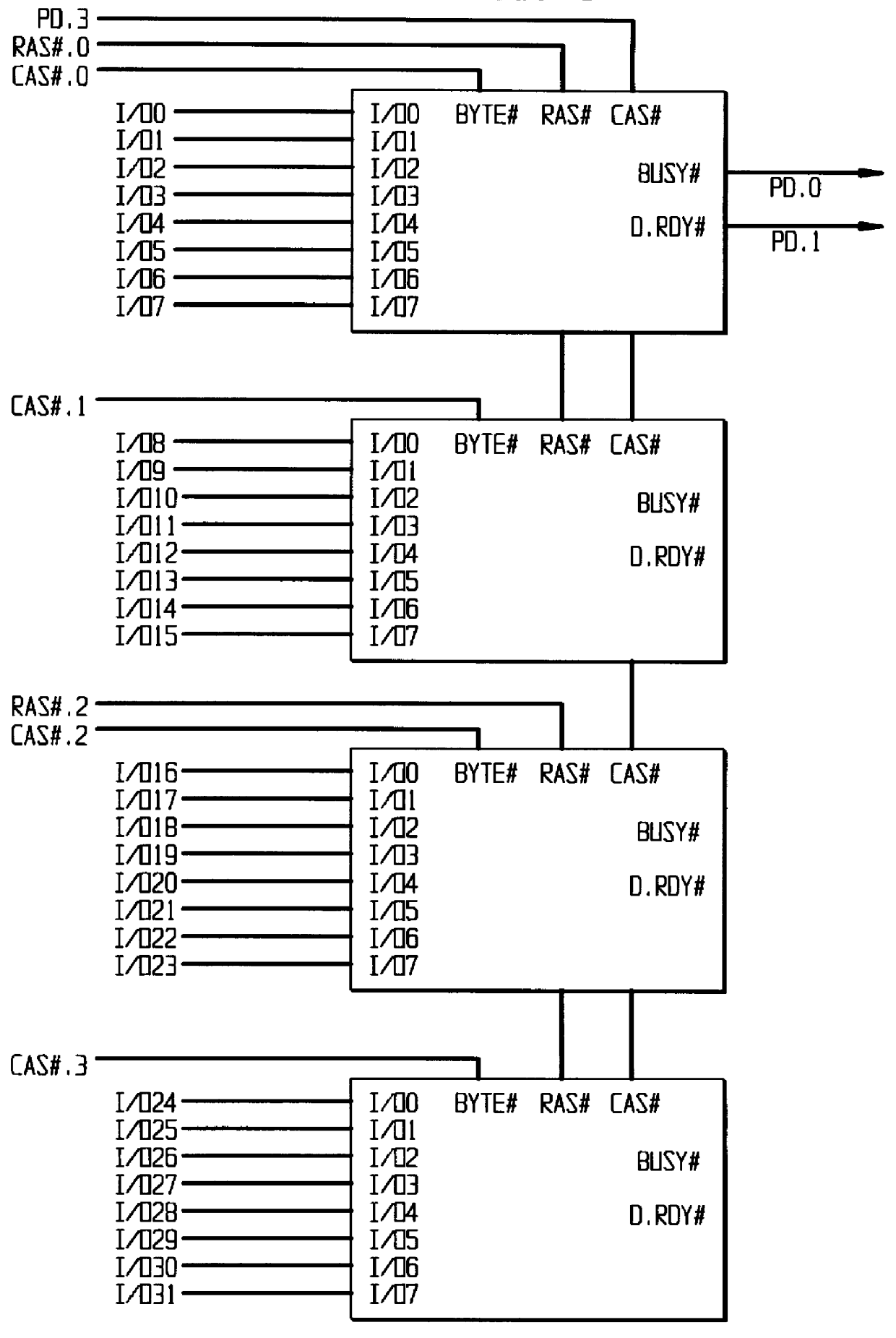

Hidden precharge pseudo cache DRAM

A new DRAM architecture, HPPC DRAM, is provided to support a high performance and low cost memory system. The HPPC DRAM has integrated the following concepts into a single DRAM chip. First, superset pin definitions backward-compatible to the traditional fast-page-mode DRAM SIMM. This allows one memory controller to support a memory system having both a traditional fast-page-mode DRAM and HPPC DRAM of this invention. Secondly, combining a memory array, a register of 4:1 Mux / Demux function, a RAS buffer / decoder, a CAS buffer / decoder, a burst address counter, a page register / comparator, a sequencer and a data buffer into a single DRAM IC chip. Using these intelligent peripheral circuits, the HPPC DRAM execute a pipeline cycle request and precharge cycle stealing. Thirdly, a precharge cycle stealing pipeline is implemented to the timing chain of read operation to eliminate the precharge cycle time which is achieved by executing read drive concurrently to the precharge cycle. This read timing chain shows that a zero wait state is sustained if there is a page-hit. Fourthly, a precharge cycle stealing pipeline is implemented to the timing chain of write operation to eliminate the precharge cycle time which is achieved by executing precharge cycle concurrently to address predecoding and data strobing.

Owner:TAIWAN SEMICON MFG CO LTD

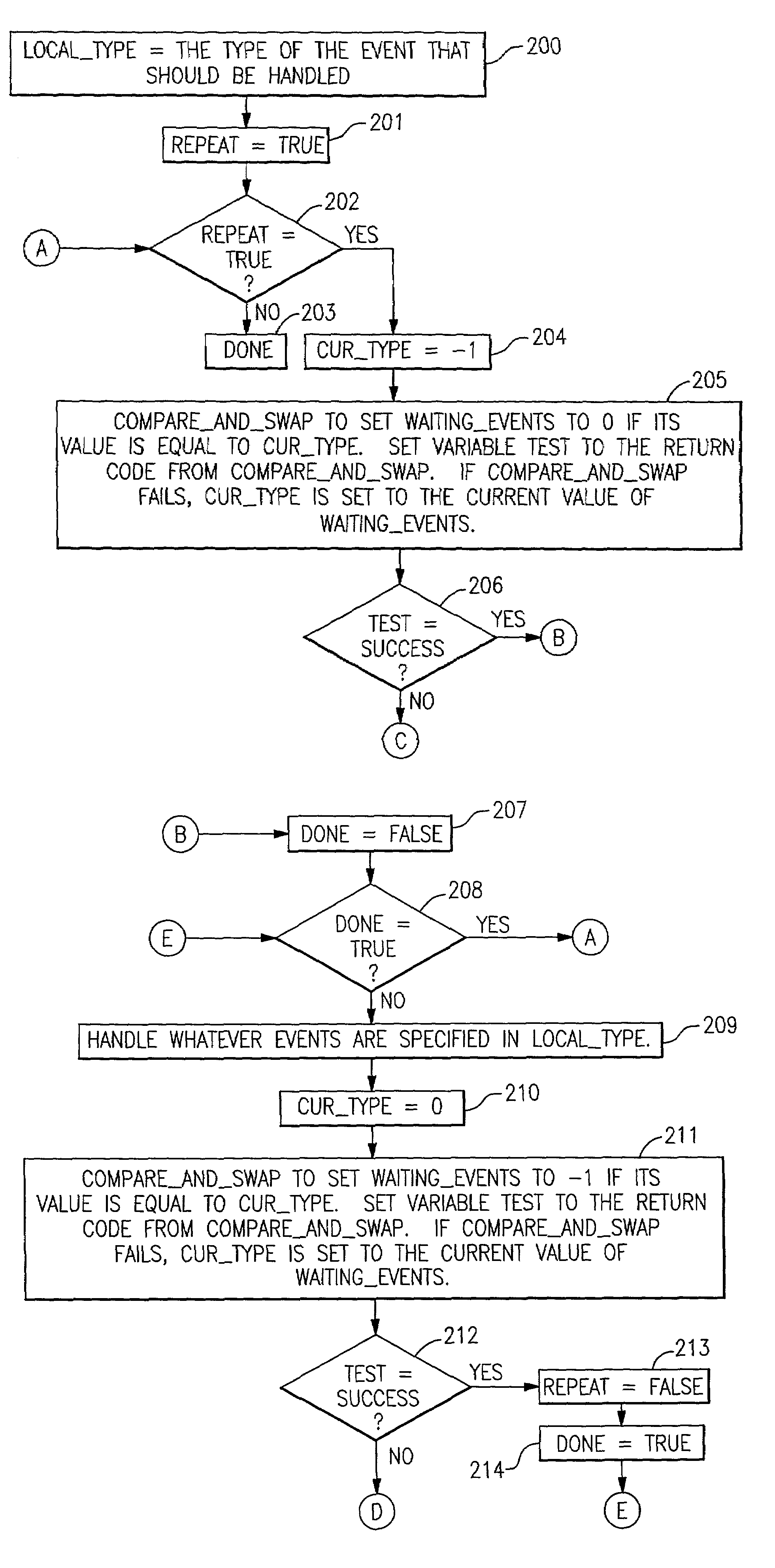

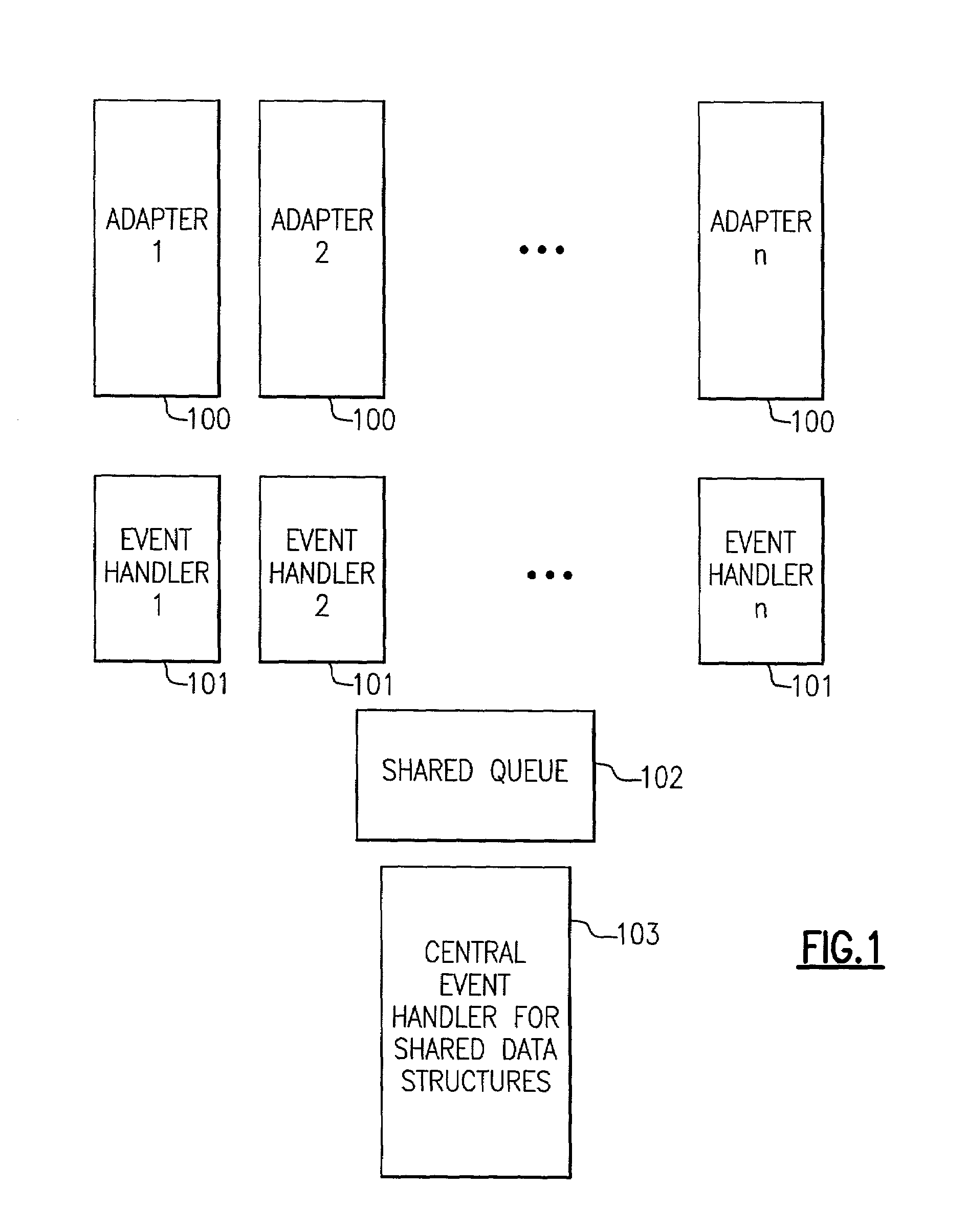

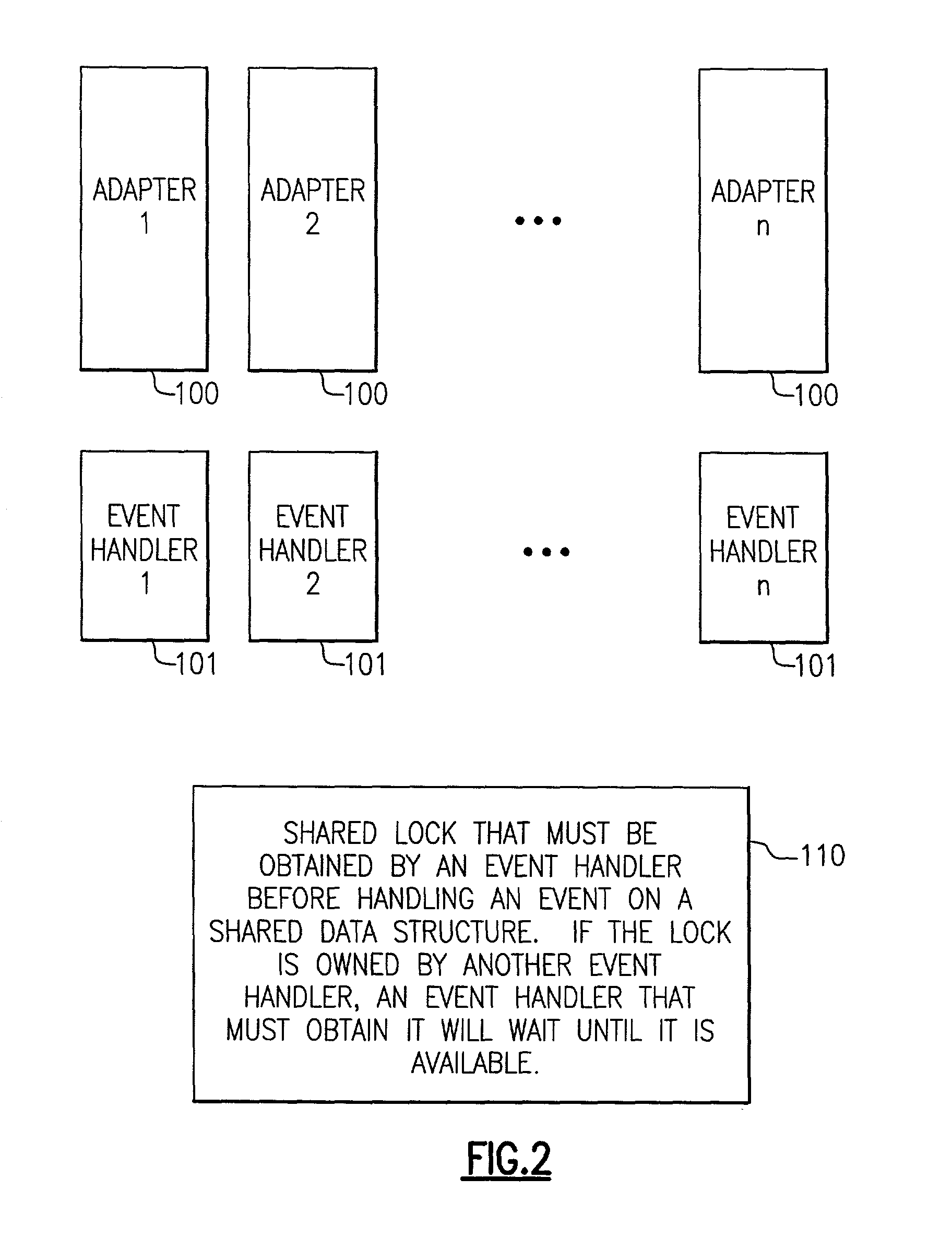

Serializing event handling in a threaded system with no wait states

InactiveUS7065765B2Increase speed and efficiencyDigital data processing detailsMultiprogramming arrangementsArray data structureBit array

Event handling in multinode data processing networks, in which data structures are shared between nodes and are subject to concurrent requests for access, is facilitated through the use of a separate small data structure (bit array or linked list) which permits an event handler to hand off the task of accessing the data structure to an event handler which is already accessing data from the same data structure. This eliminates the need for locking arrangements and / or the use of special coordinating event handlers.

Owner:IBM CORP

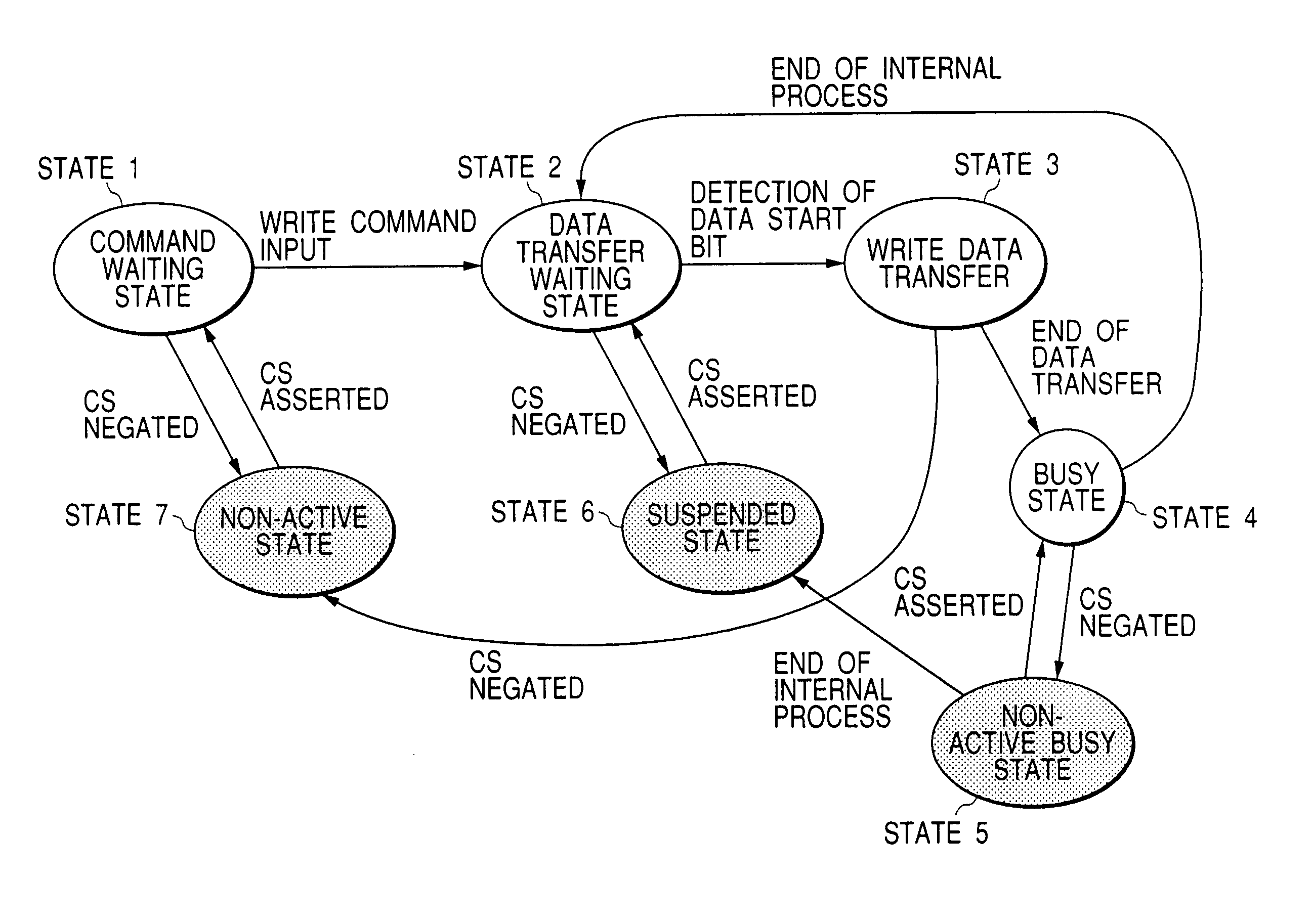

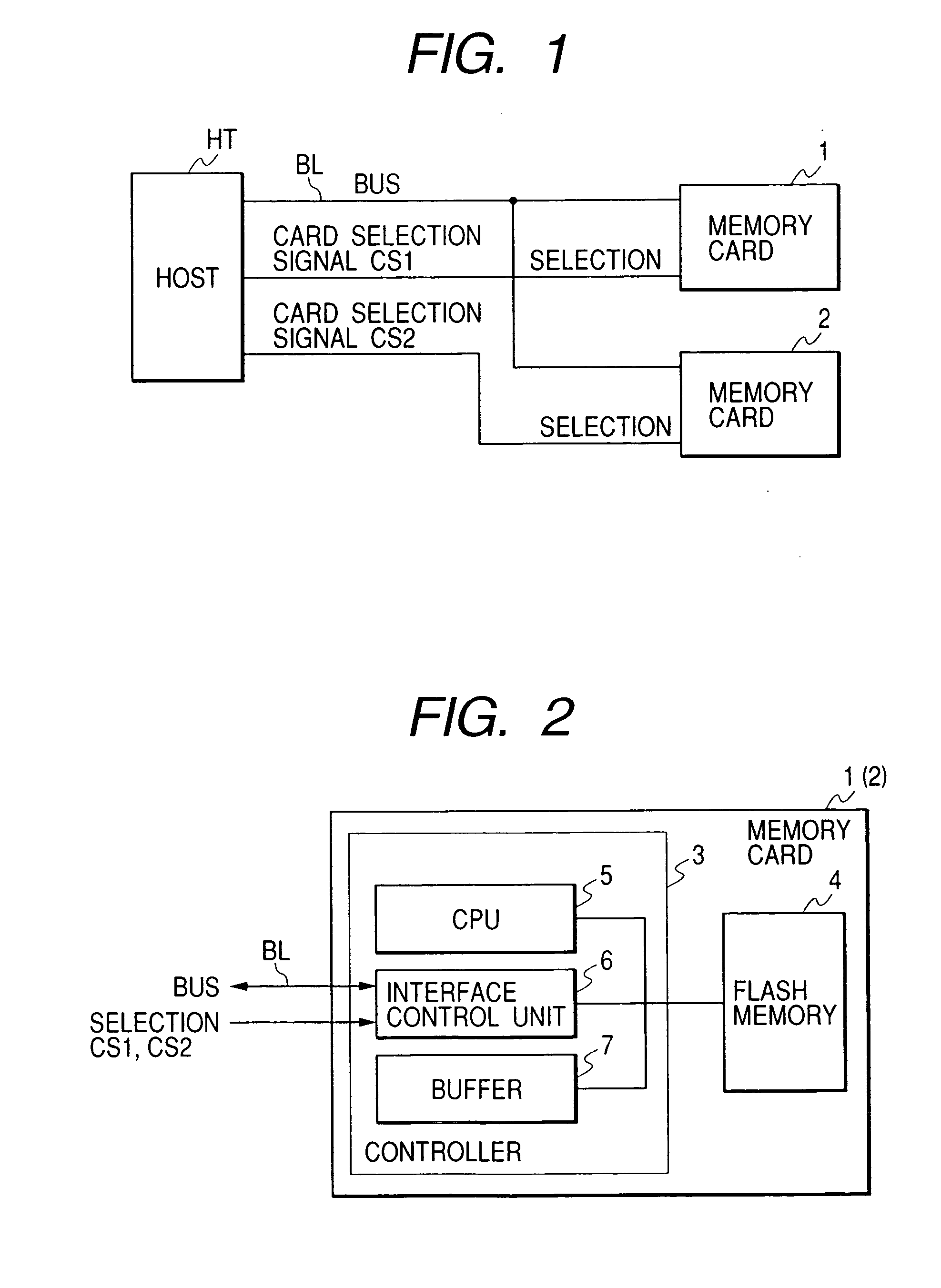

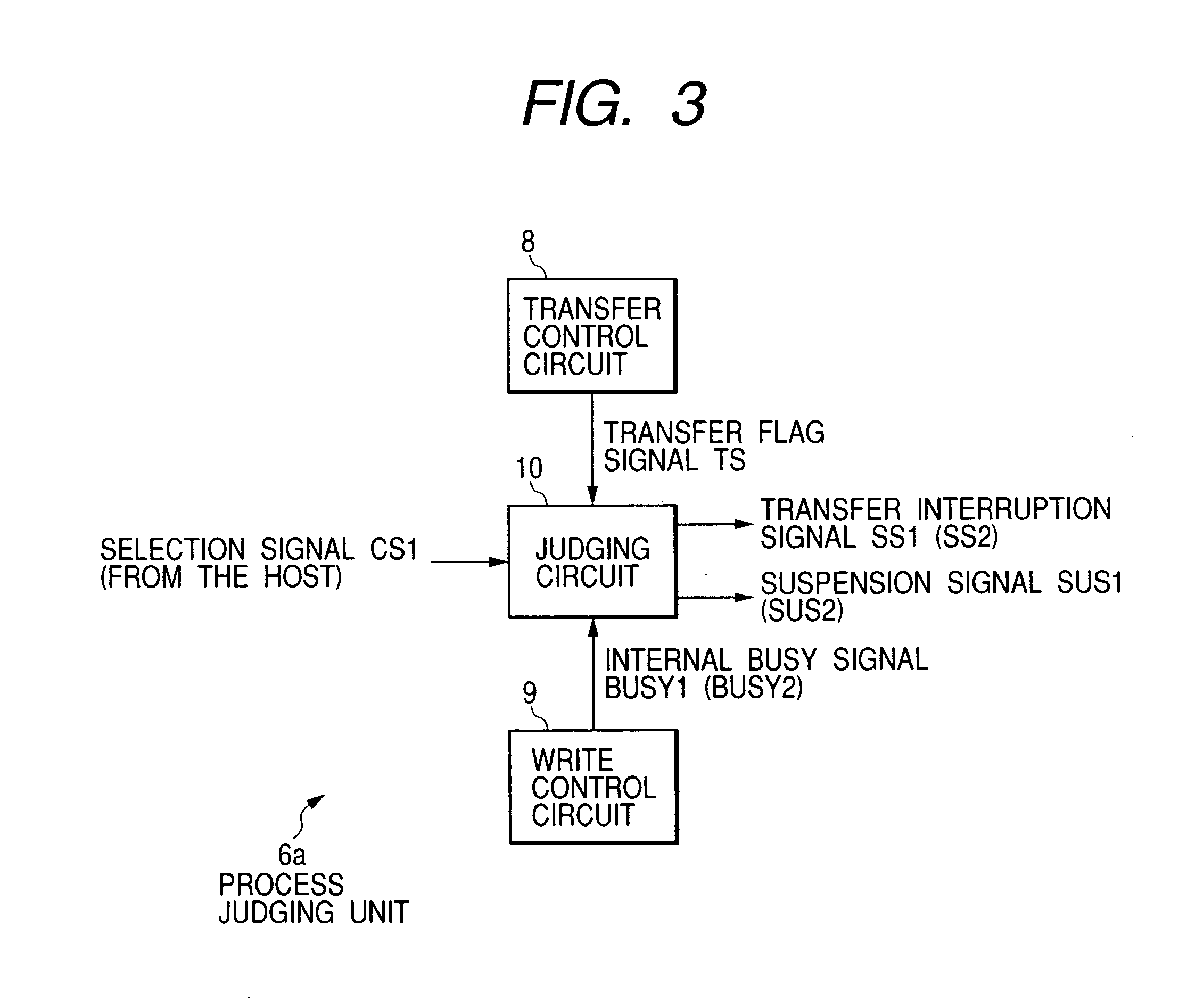

Non-volatile memory card and transfer interruption means

InactiveUS20070033334A1Easy to operateInput/output to record carriersRead-only memoriesTransfer procedureWait state

A memory card is provided with a transfer control circuit, a write control circuit and a judging circuit. The transfer control circuit outputs a transfer flag signal during the data transfer. The write control circuit outputs an internal busy signal during the data write operation. The judging circuit outputs a transfer interruption signal when a card selection signal of the host is negated during the input of the transfer flat signal and also outputs a suspension signal when the card selection signal is negated during the input of the internal busy signal. A CPU invalidates the data being transfer to interrupt the transfer process upon reception of the transfer interruption signal and completes, upon reception of the suspension signal, the process being executed and stays in the waiting condition. Consequently, even when the timing signal not conforming to the standards is transferred, the host can select the optimum processing operation from the internal processing conditions and thereby execute the selected operation.

Owner:RENESAS ELECTRONICS CORP

Vehicle traveling control device

ActiveUS20160304097A1Avoid traffic jamsEasy to changeRoad vehicles traffic controlCharacter and pattern recognitionEngineeringWait state

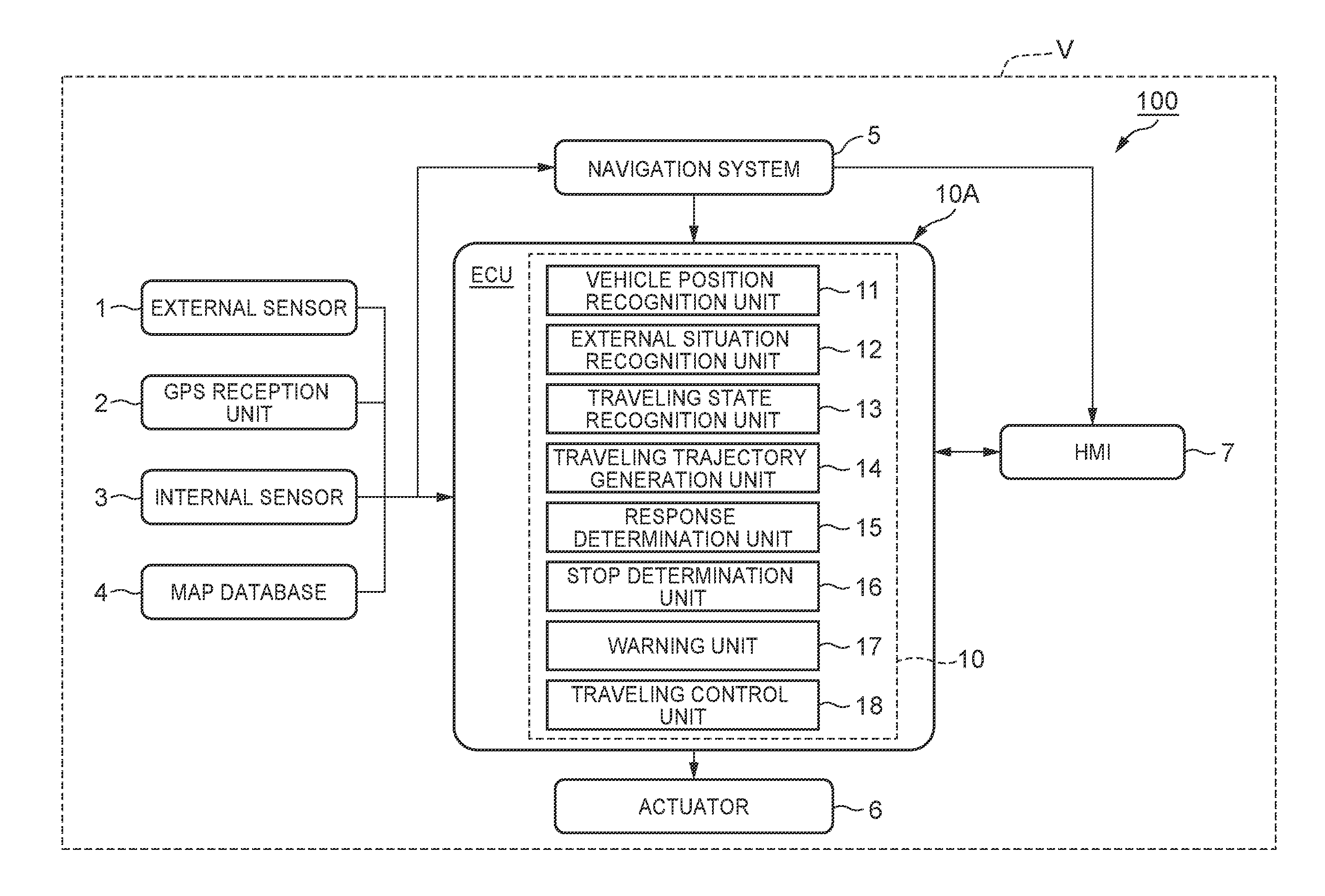

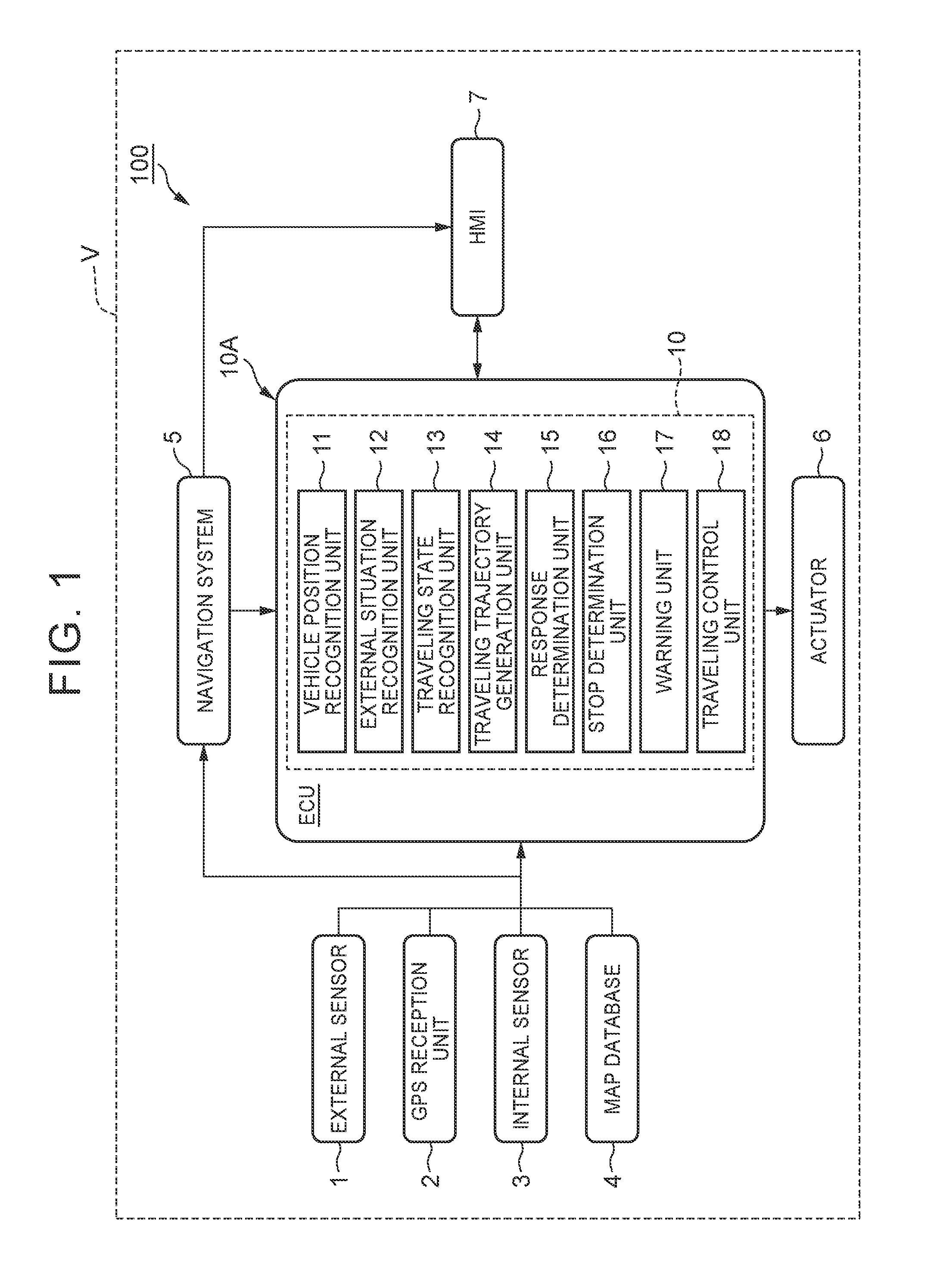

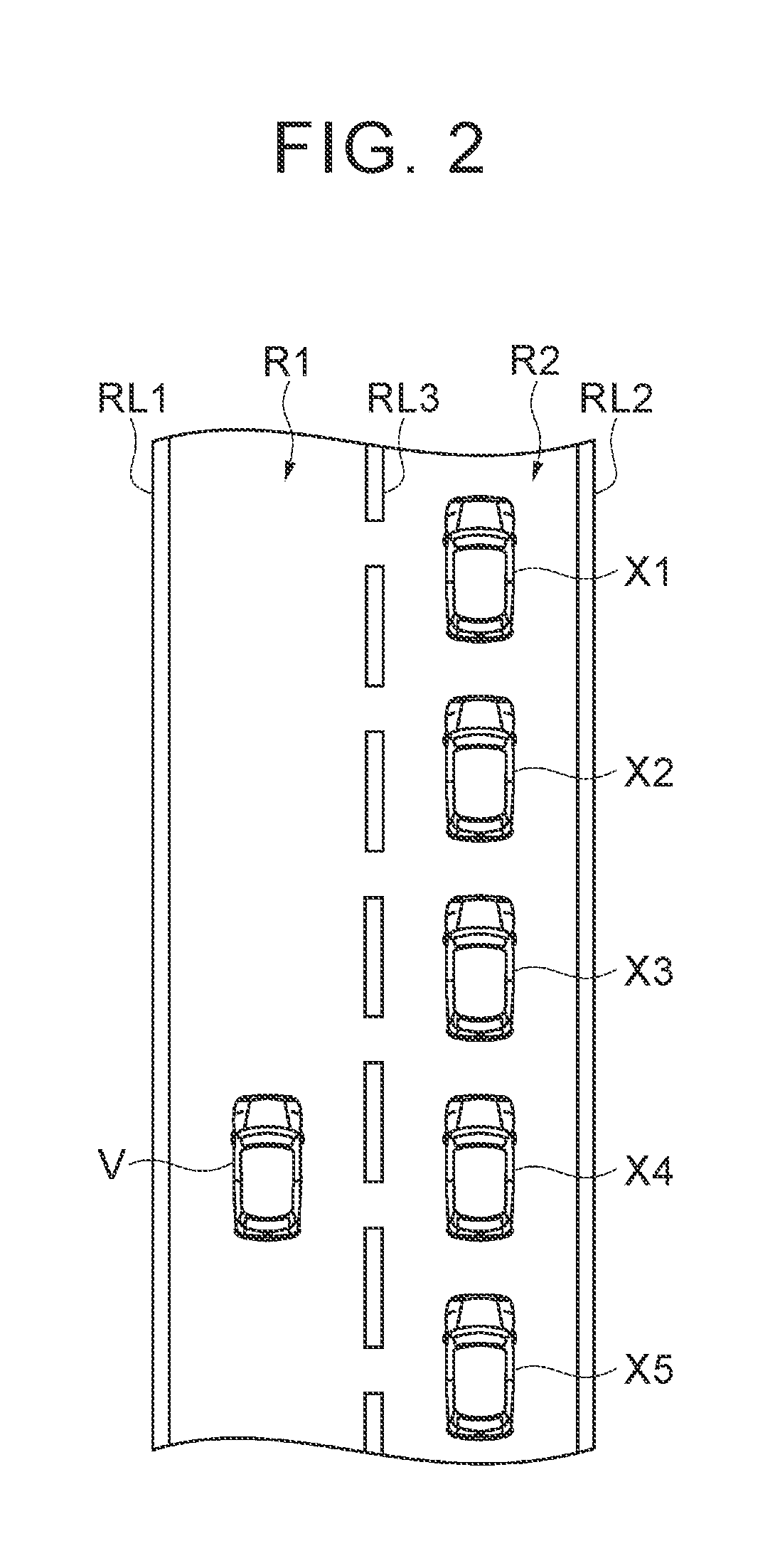

A vehicle traveling control device includes an acquisition unit that acquires surrounding information on the vehicle; an external situation determination unit that determines whether there is space, into which the vehicle will enter, in the adjacent lane based on the surrounding information on the vehicle; and a vehicle control unit that causes the vehicle to change the lane along a traveling trajectory predetermined to change the lane from the traveling lane to the adjacent lane. The vehicle control unit is configured to move the vehicle along the traveling trajectory and place the vehicle in a waiting state at a waiting position if the external situation determination unit determines that there is not the space, and is configured to move the vehicle from the waiting position to the space if the external situation determination unit determines that there is the space while the vehicle is placed in the waiting state.

Owner:TOYOTA JIDOSHA KK

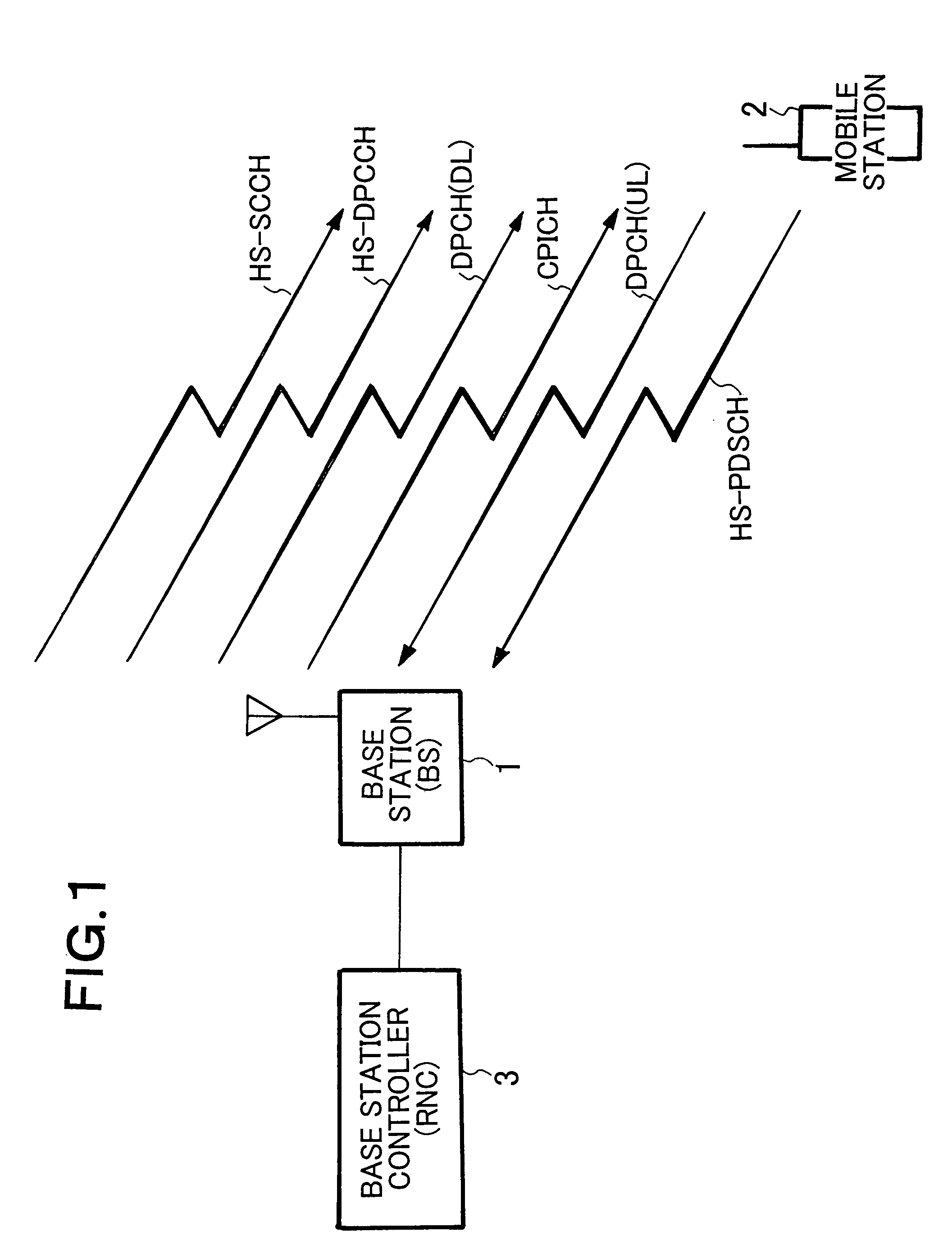

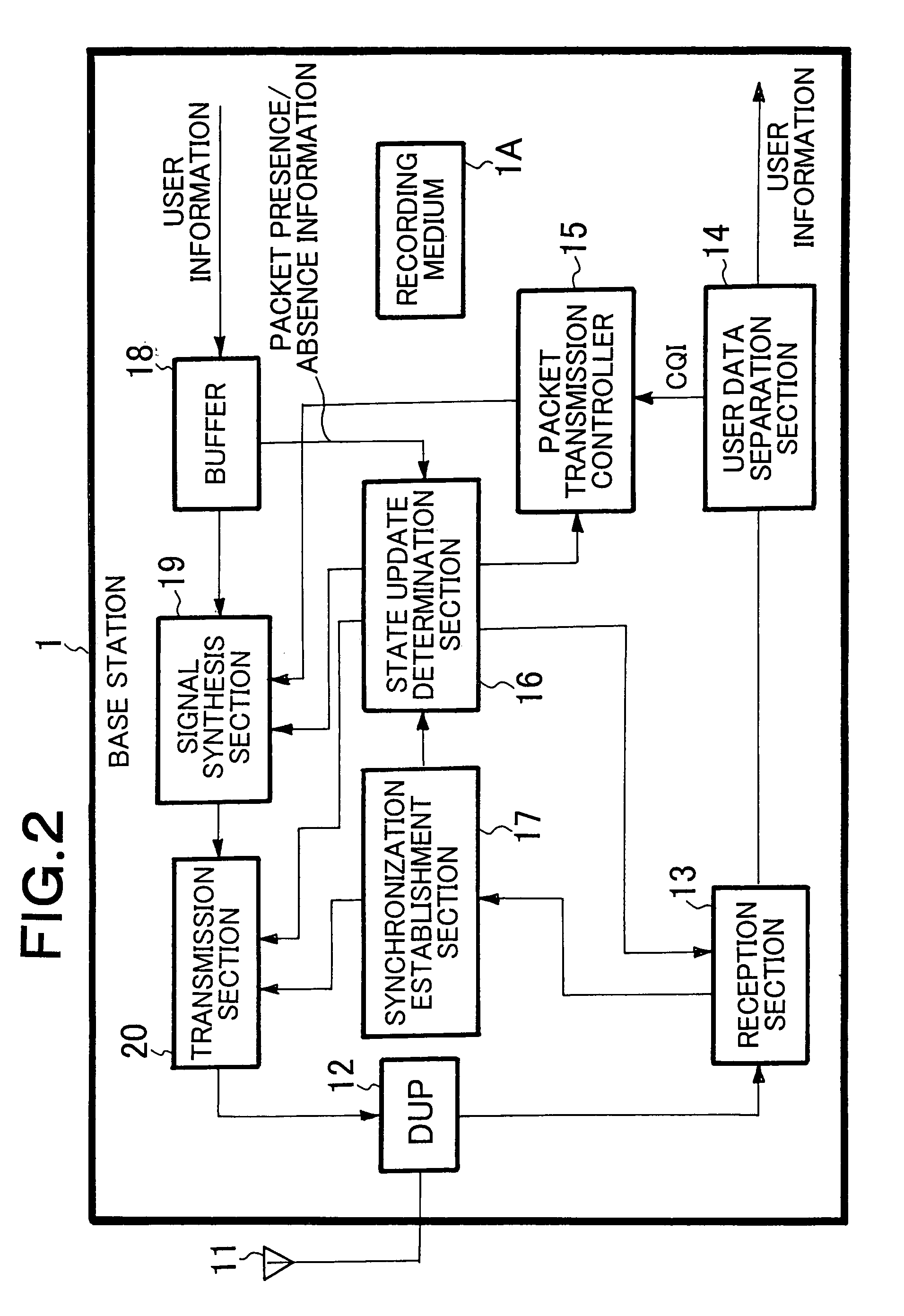

Synchronization establishment between a mobile station and base station system and method used for them

InactiveUS7403789B2Reduce power consumptionPromote disseminationEnergy efficient ICTSynchronisation arrangementStart timeControl signal

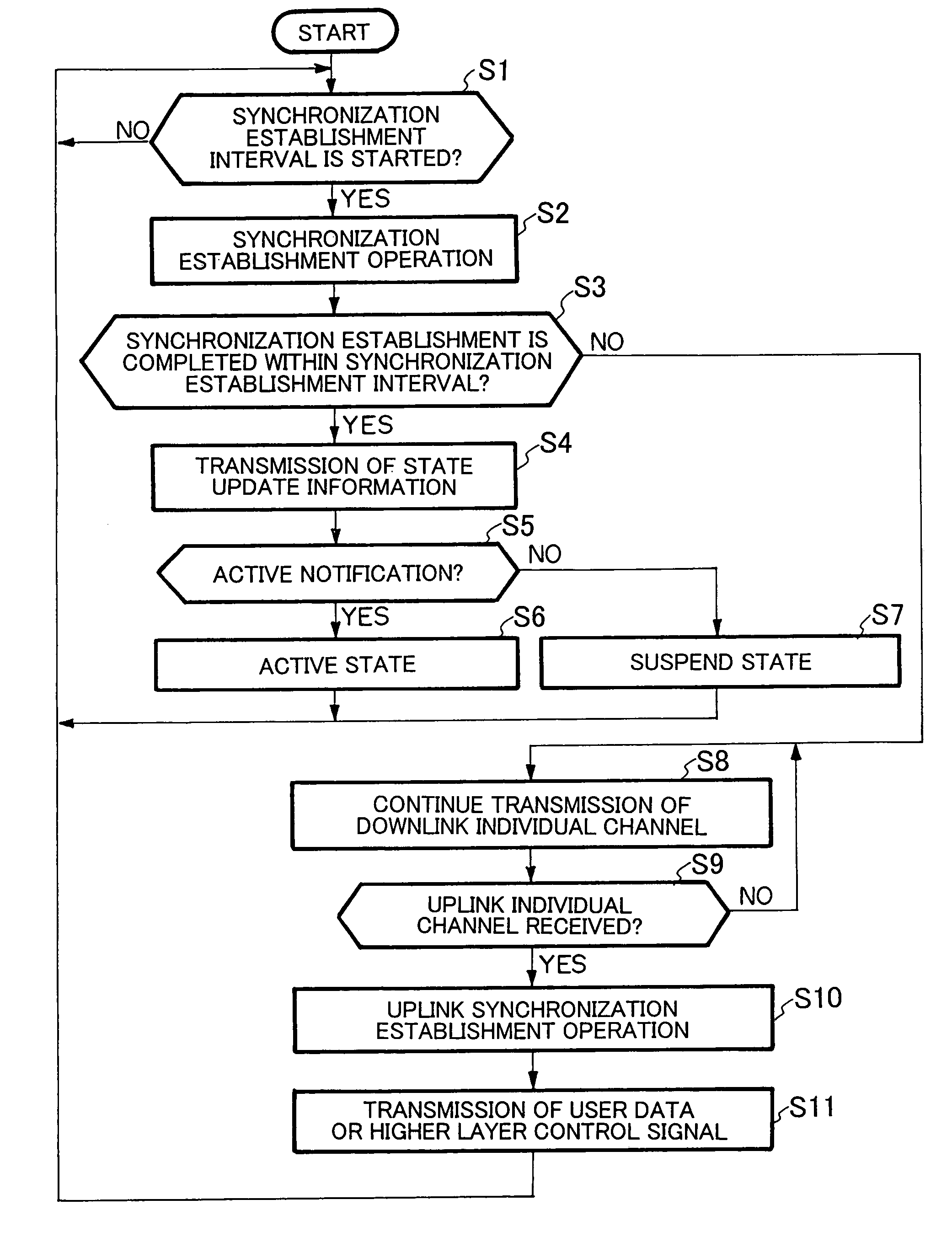

There is provided a mobile communication system capable of reducing the power consumption in the packet wait state and promptly transmitting a packet when data transmission is requested. At a predetermined synchronization establishment interval start time (T1), a base station starts transmission of DPCH (DL) which is a downlink individual channel. A mobile station receives the DPCH (DL) and starts synchronization establishment operation. If the synchronization of the DPCH (DL) is not established by the synchronization establishment interval end time (T2), the synchronization establishment operation is continued. If the base station cannot detect transmission of the DPCH (UL) which is an uplink individual channel from the base station by the synchronization establishment interval end time (T2), the base station continues transmission of the DPCH (DL) to the mobile station and suspends user data transmission in the state update information to the mobile station and DPCH (DL) to the mobile station and control signal transmission to an upper node layer until the DPCH (UL) transmission is detected.

Owner:NEC CORP

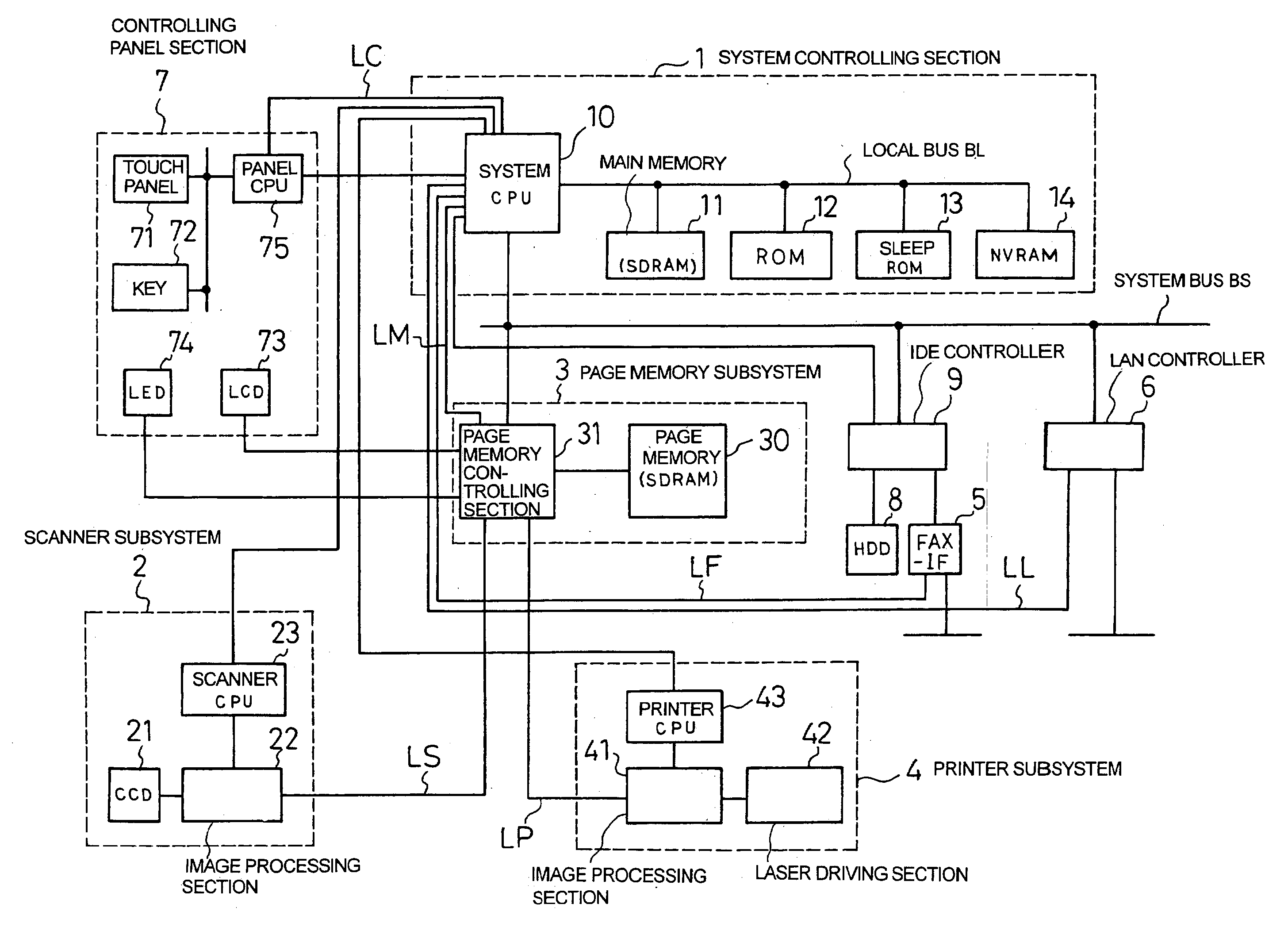

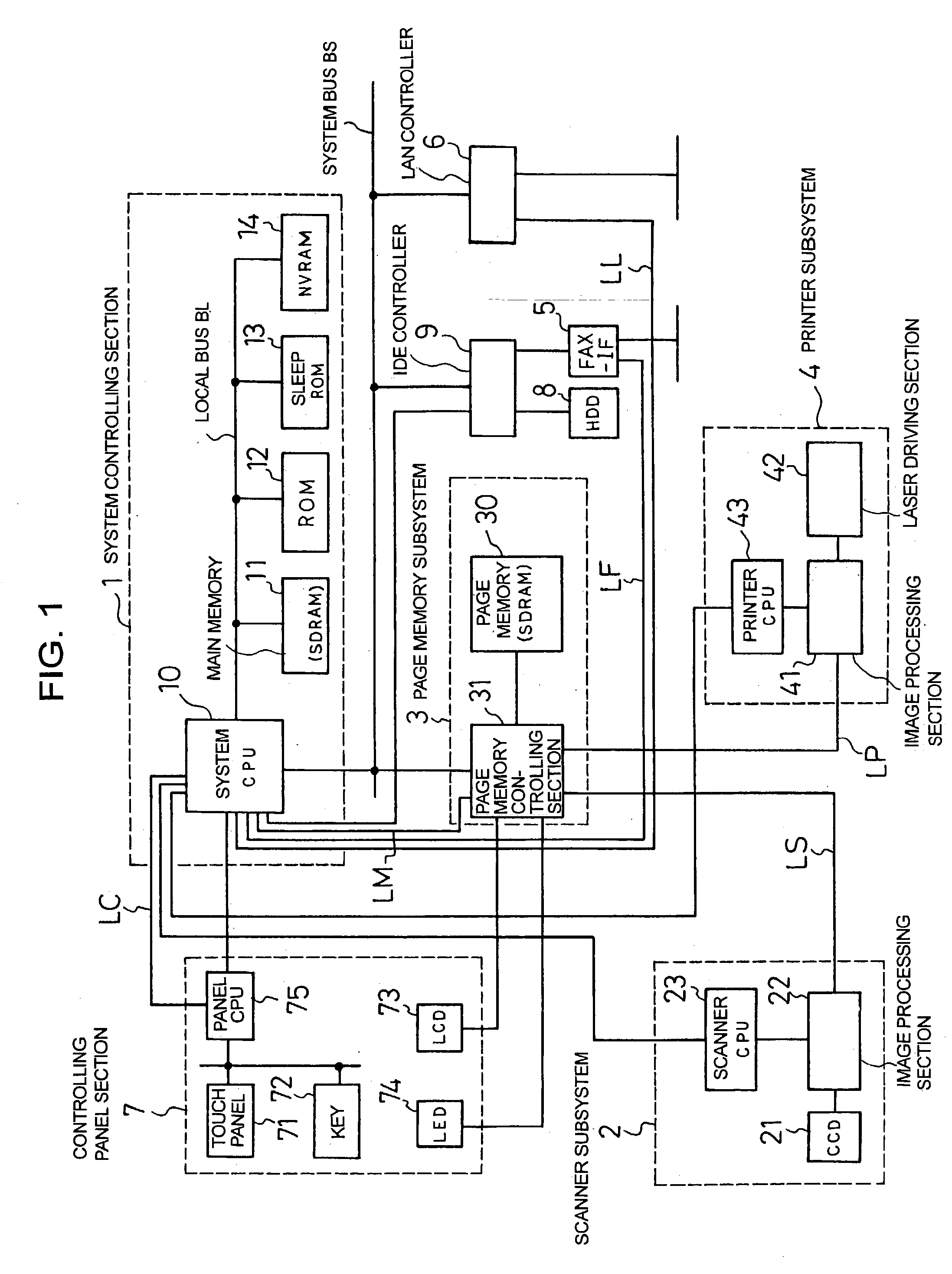

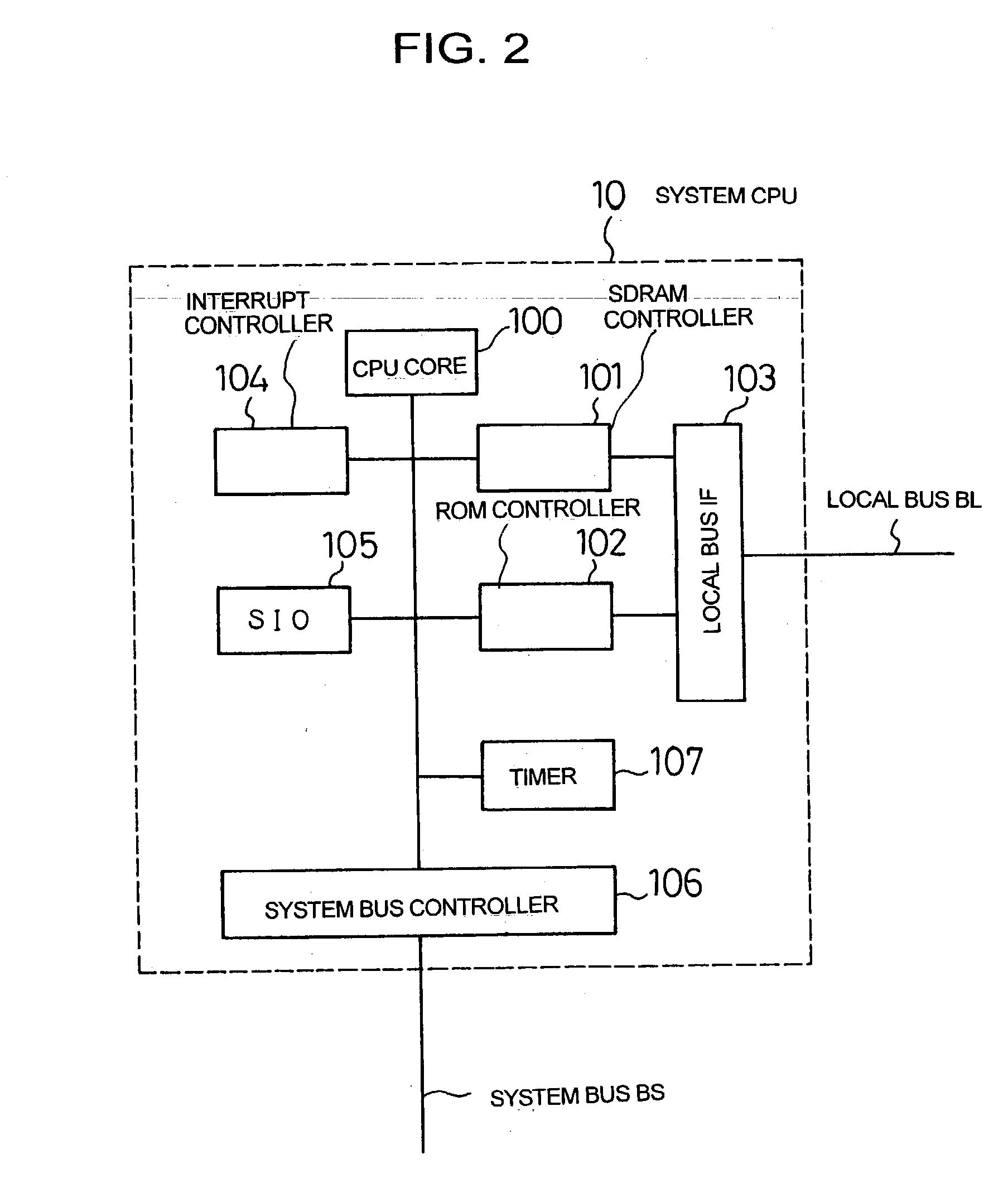

Information processing device with sleep mode function

InactiveUS20040073824A1Reduce power consumptionEnergy efficient ICTPower supply for data processingInformation processingSleep control

The present invention as disclosed hereby is to provide an information processing device with sleep mode function which is capable of running in a sleep mode, thereby reducing the power consumption for its accompanying device and main memory. In the information processing device with sleep mode function, its system CPU 10 during a normal operation mode loads a required control program from a ROM 12 to the main memory 11 and executes it to monitor an operating state of the accompanying device 2-9, and then executes a sleep controlling program stored in a sleep ROM 13 when it is detected that any operation request for the accompanying device has not been performed within a predetermined period of time. Upon execution of this sleep controlling program, the accompanying device is powered down with the exception of its reactivation-request generating function part and the clock supply to the main memory, the power supply to the main memory or both of them is(are) turned off, thereby allowing the information processing device to place in a waiting state for an interrupt from the accompanying device. Accordingly, the primary power for the accompanying device and the main memory is not wasted, thereby providing reduction of the power consumption.

Owner:KK TOSHIBA +1