Patents

Literature

183 results about "External memory interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An external memory interface is a bus protocol for communication from an integrated circuit, such as a microprocessor, to an external memory device located on a circuit board. The memory is referred to as external because it is not contained within the internal circuitry of the integrated circuit and thus is externally located on the circuit board.

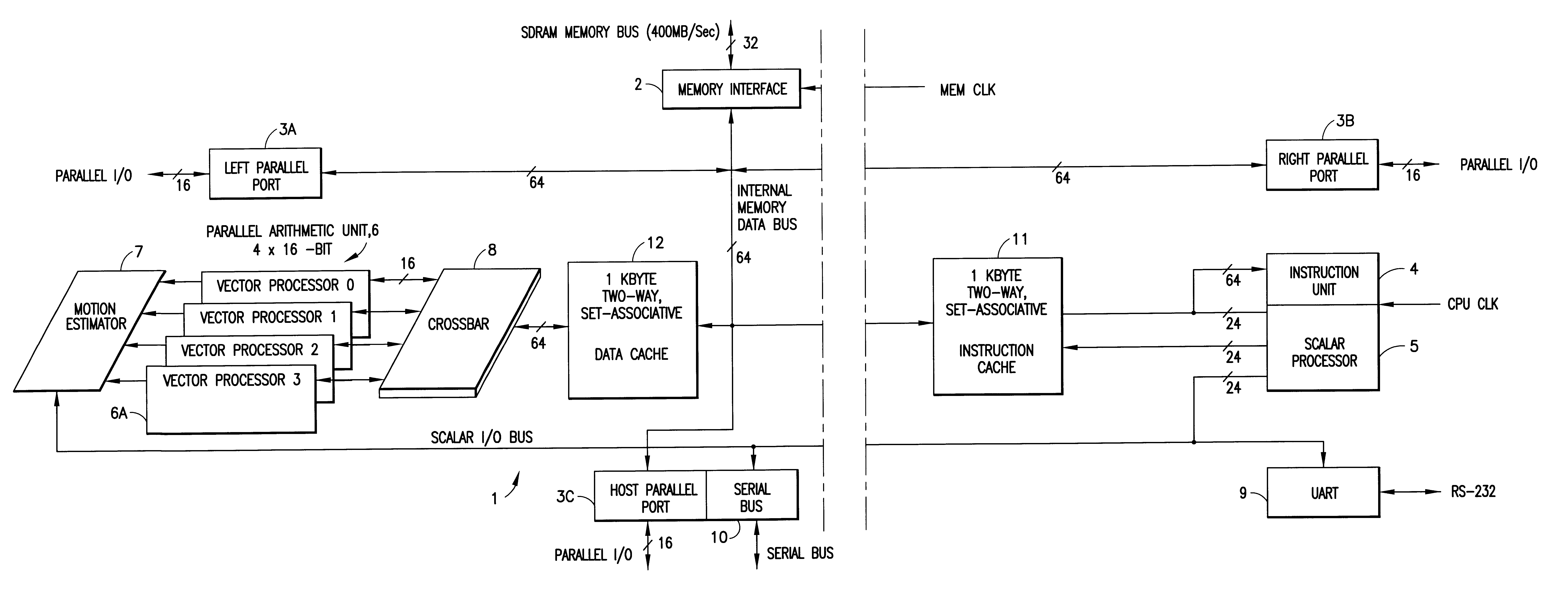

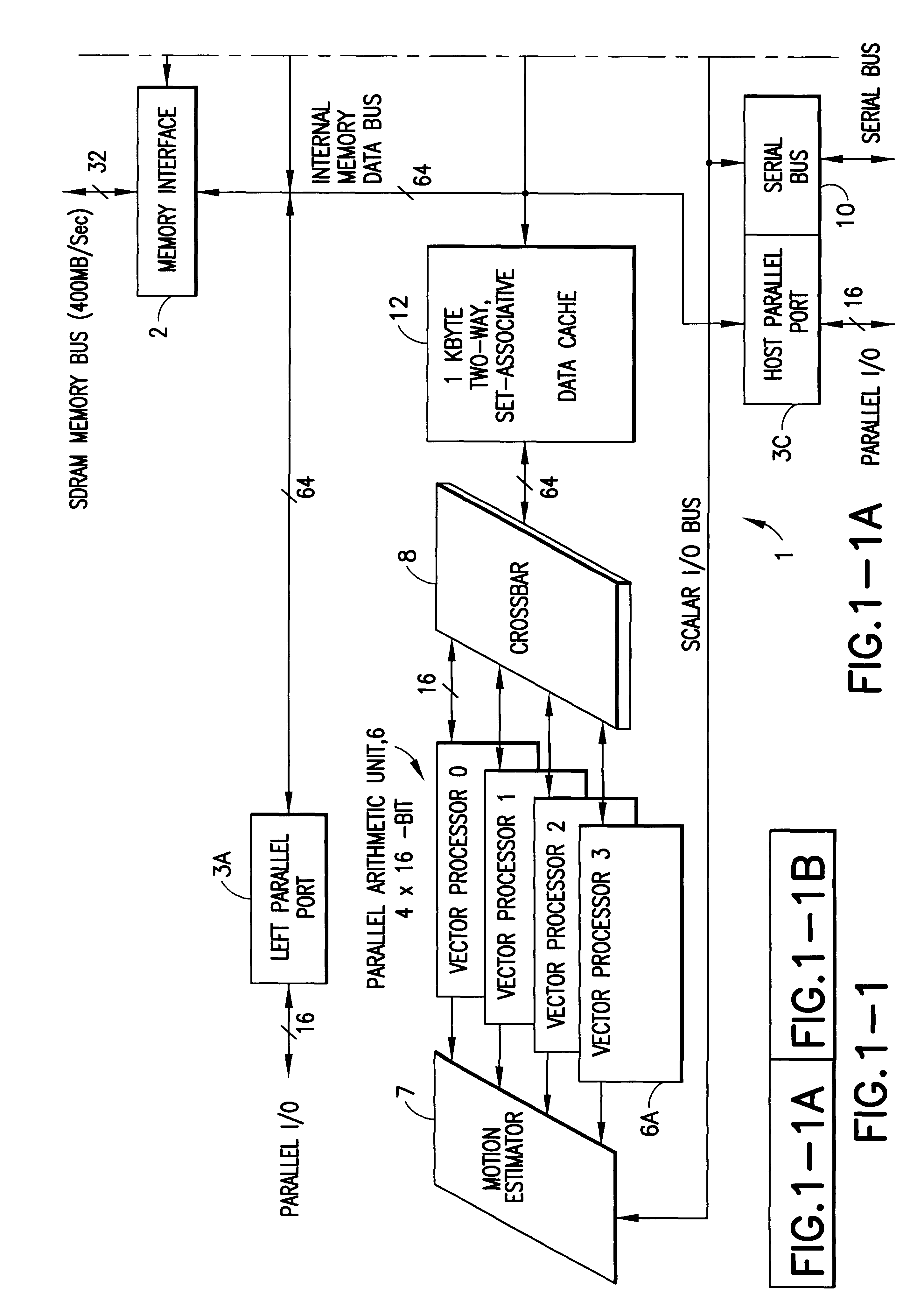

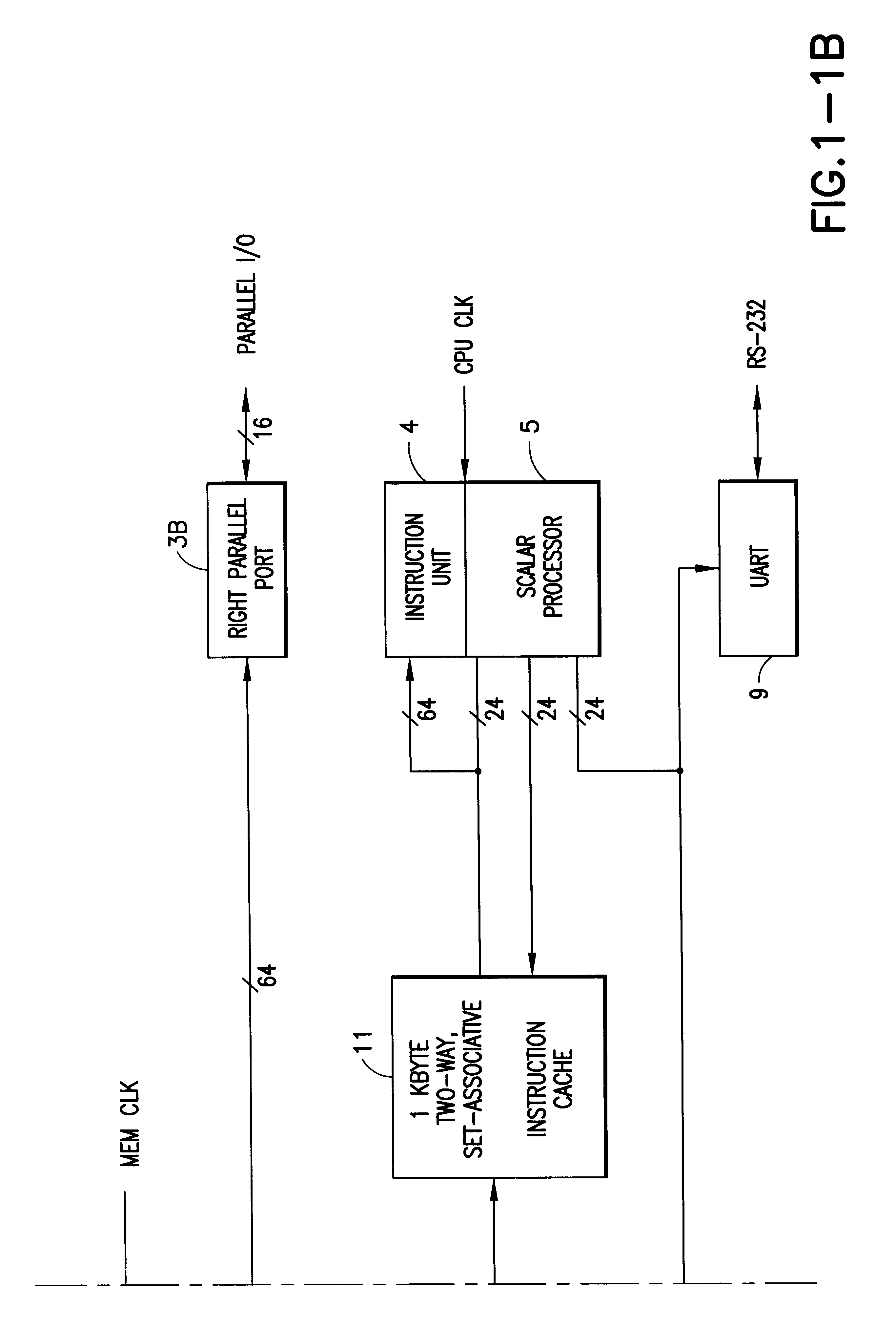

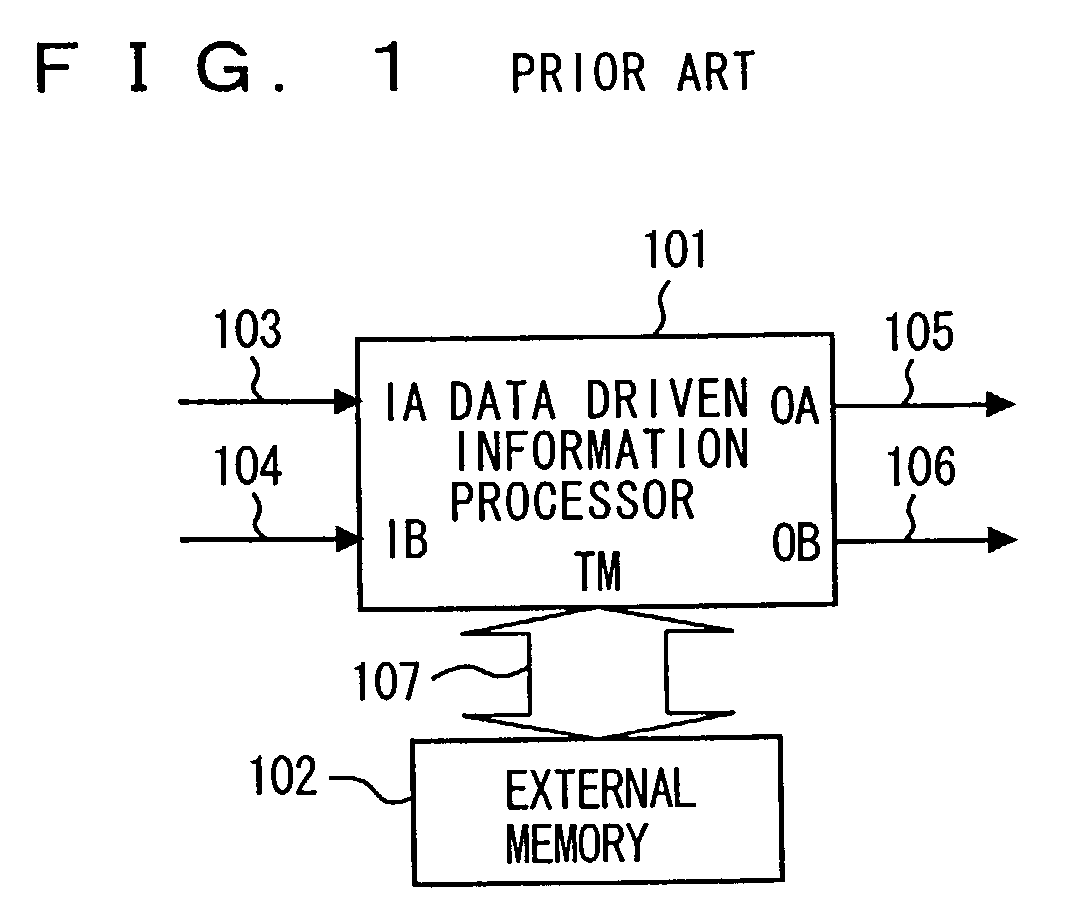

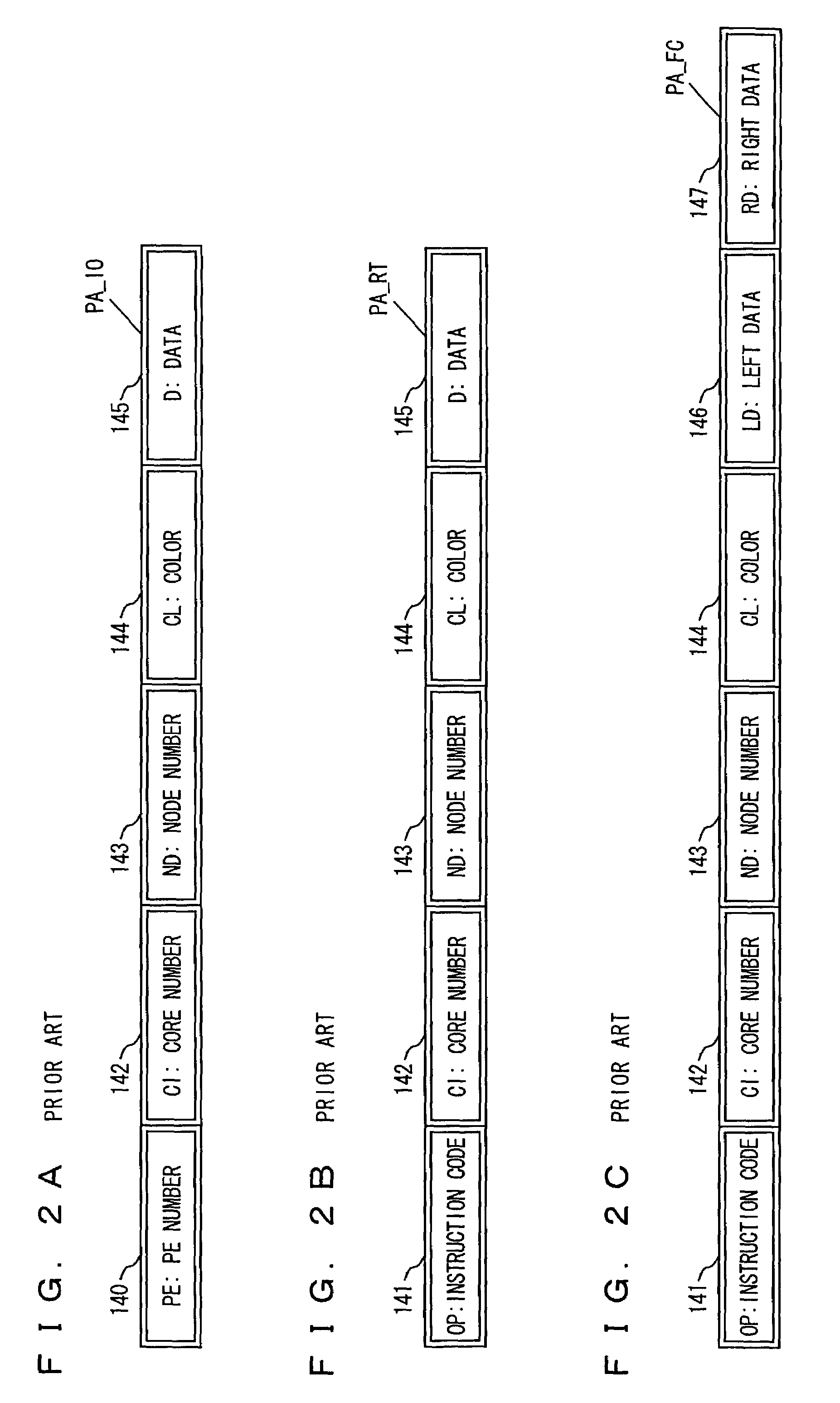

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

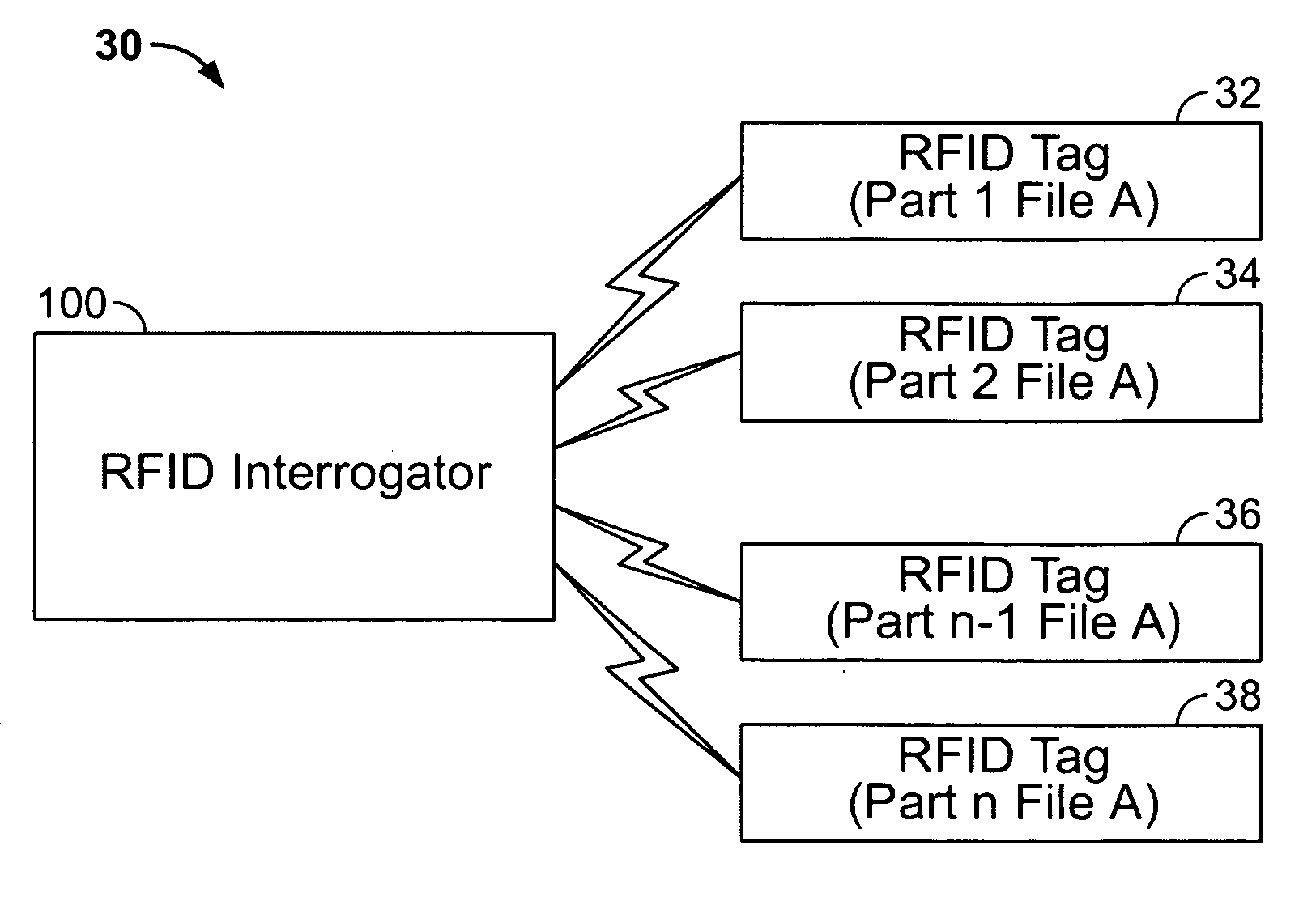

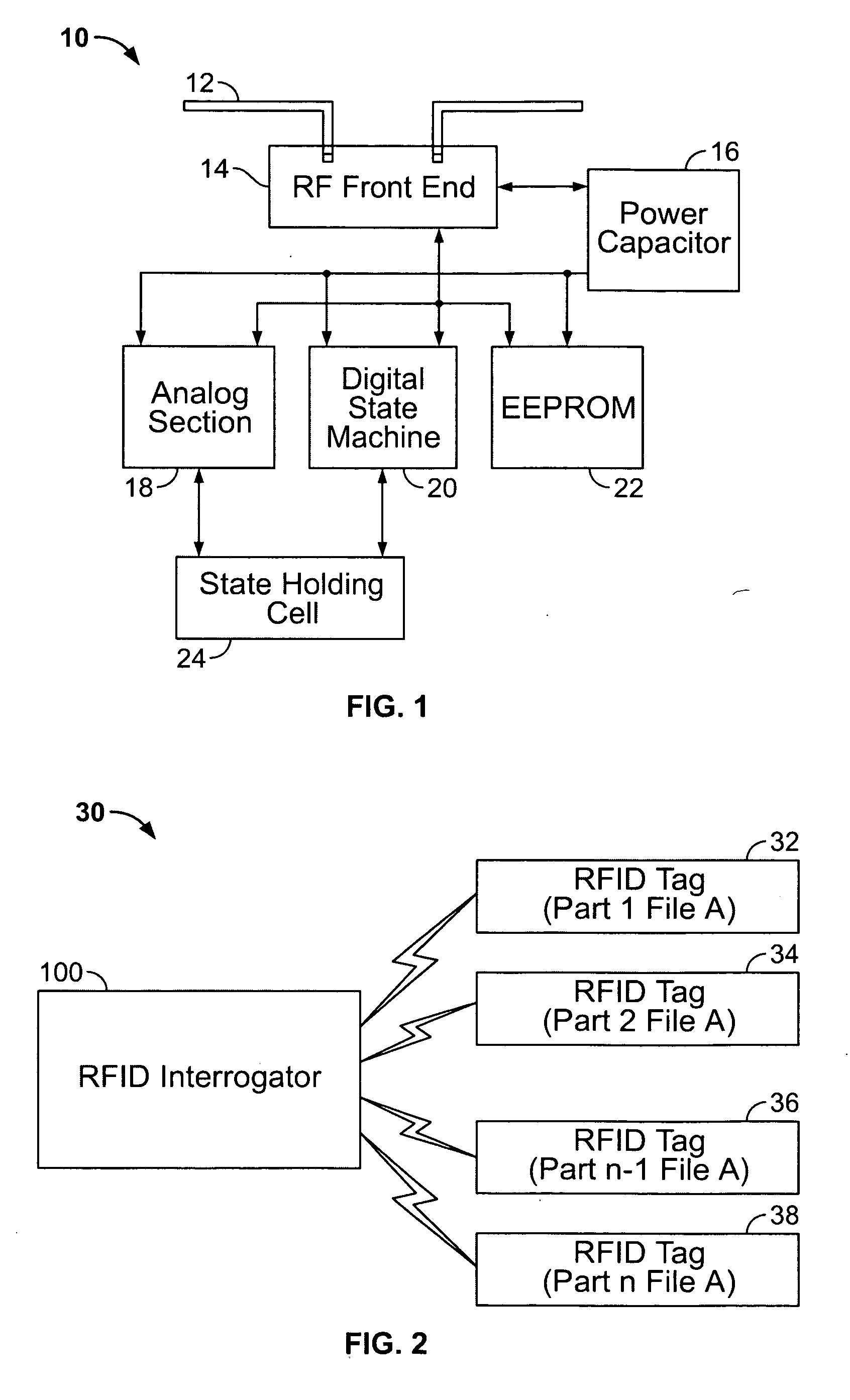

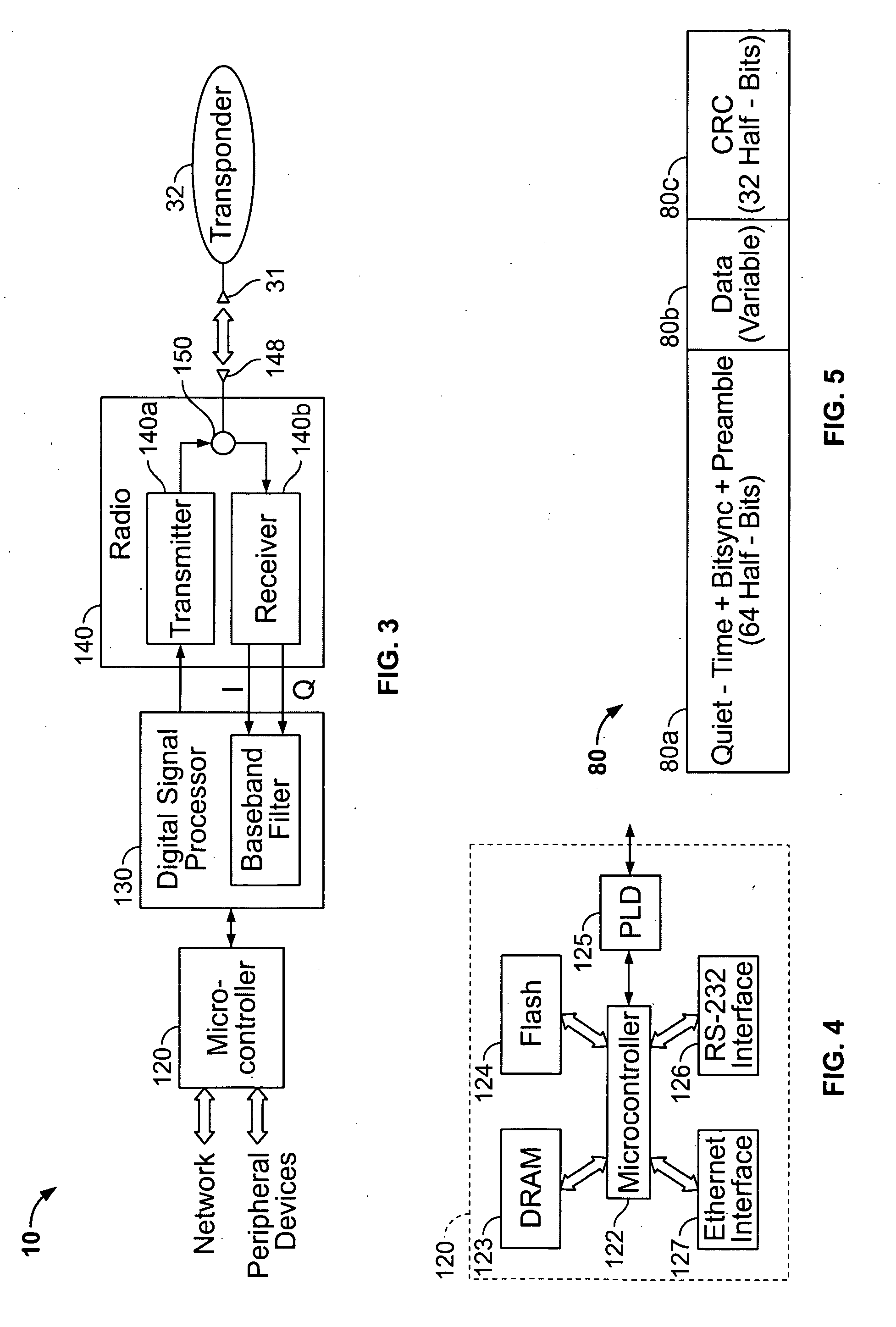

System for using RFID tags as data storage devices

InactiveUS20060279412A1Time-division multiplexCo-operative working arrangementsMicrocontrollerData file

The invention provides systems and methods for using radio frequency (RF) transponders interrogators for storing and retrieving data files. In one embodiment, the RF interrogator comprises a microcontroller module that retrieves a data file from a buffer memory space and breaks up the data file into multiple data packets, each data packet comprising a data file identifier and a sequence number. The present invention also provides a data storage device that comprises an RF transponder and a microcontroller that is in communication with the transponder via the external memory interface. In one embodiment, the transponder receives data over an RF broadcast, assigns an address to the data, and sends the data to the microcontroller via the external memory interface for storage at the assigned address.

Owner:INTERMEC IP

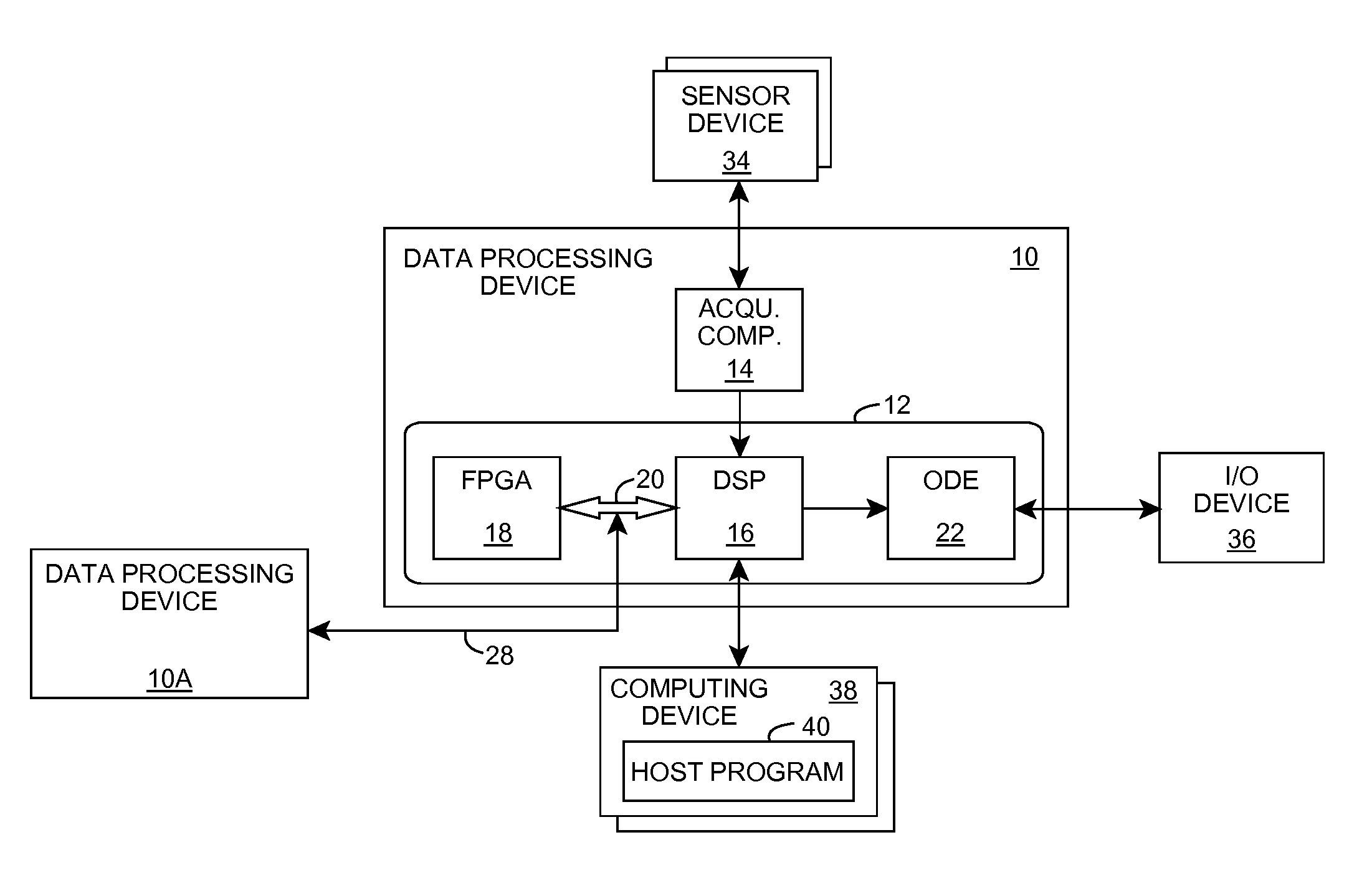

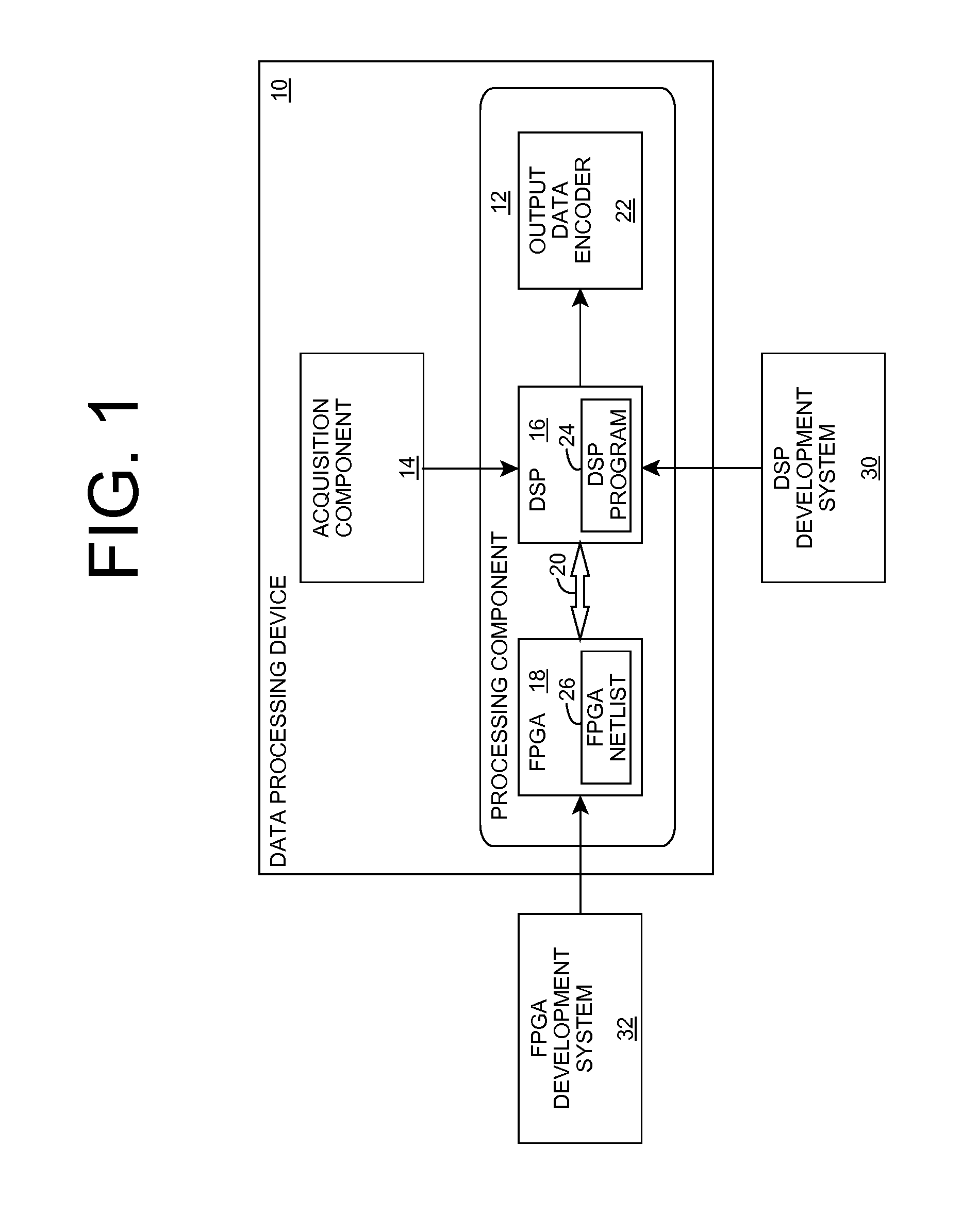

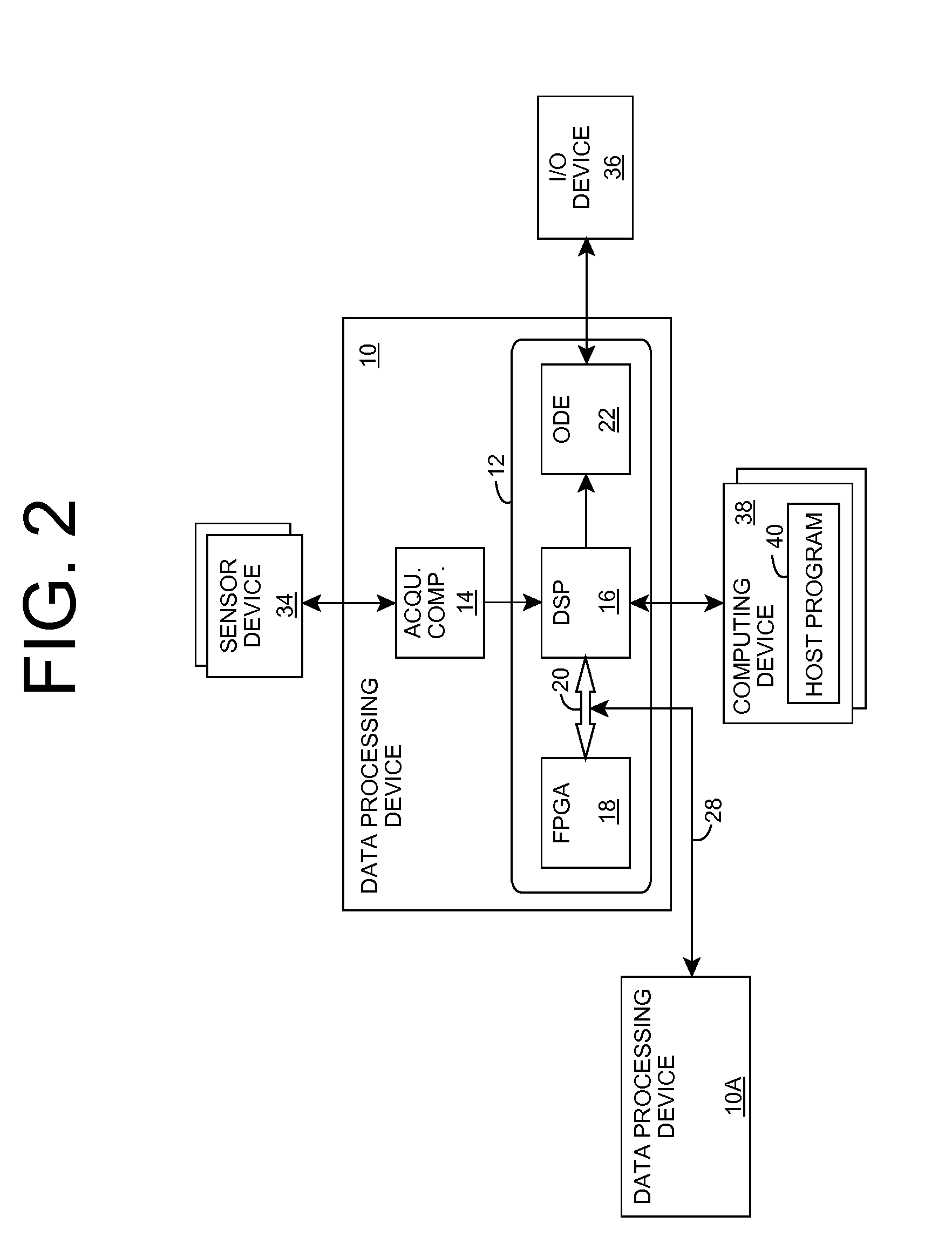

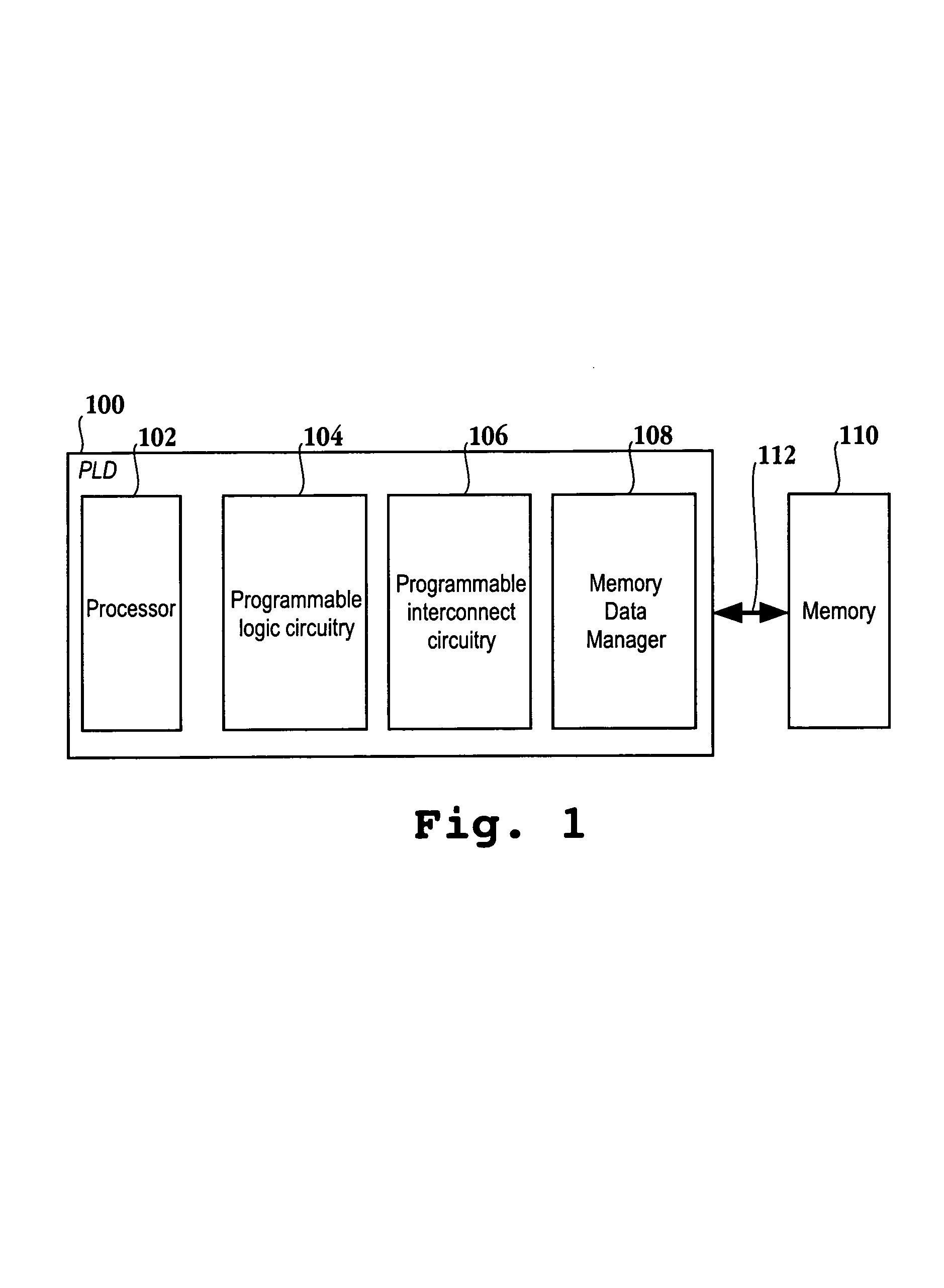

Sensor data processing using DSP and FPGA

InactiveUS20080177507A1Reduce the amount requiredReduce total powerAmplifier modifications to reduce noise influenceDigital computer detailsExternal memory interfaceField-programmable gate array

A system for managing sensor data, such as video data, includes a processing component for generating processed data based on the sensor data. The processing component can include a digital signal processor (DSP), the DSP including a computer usable medium for storing the processed data, a field programmable gate array (FPGA), and an external memory interface for transferring data between the DSP and the FPGA.

Owner:INT ELECTRONICS MACHINES

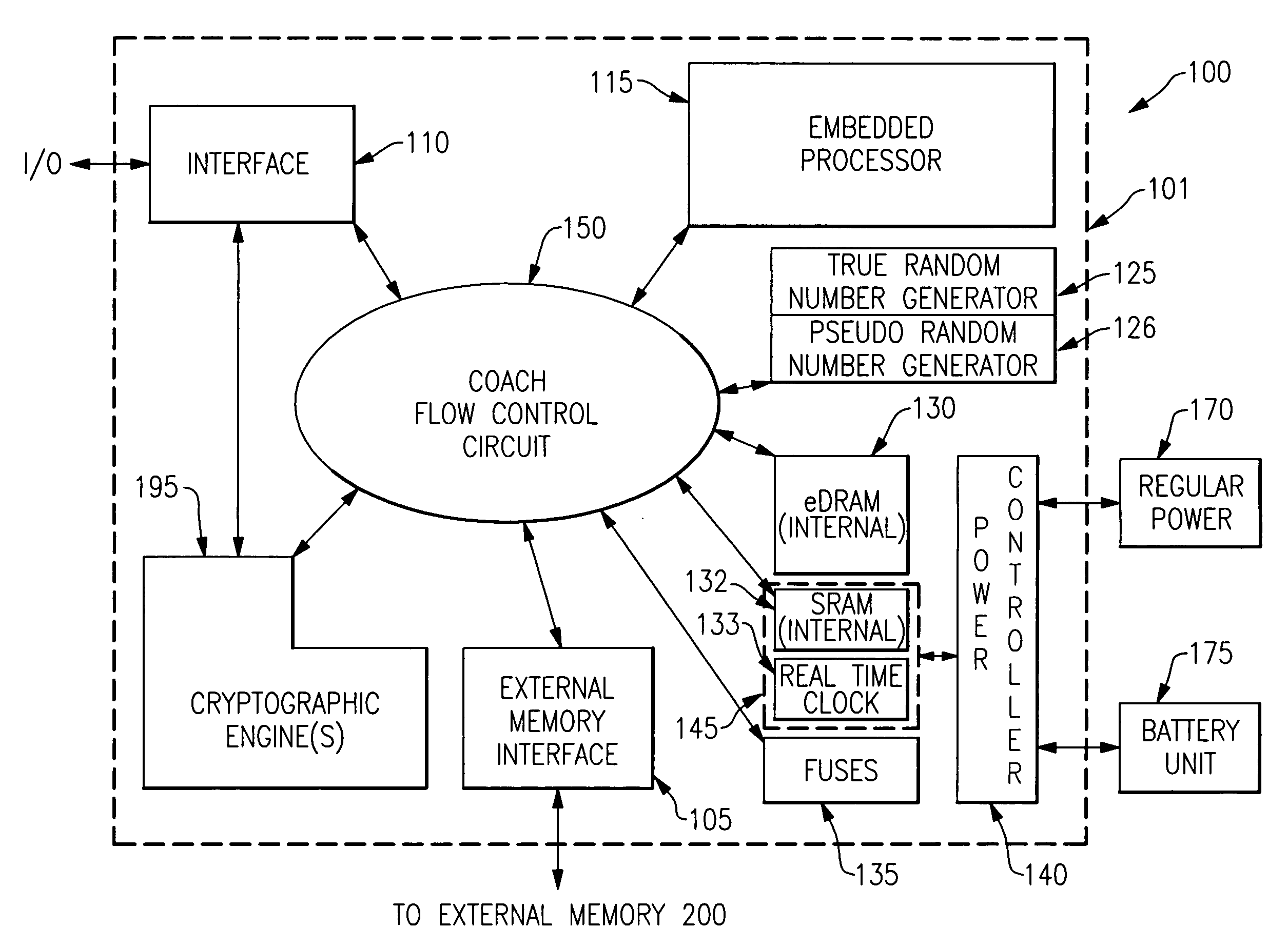

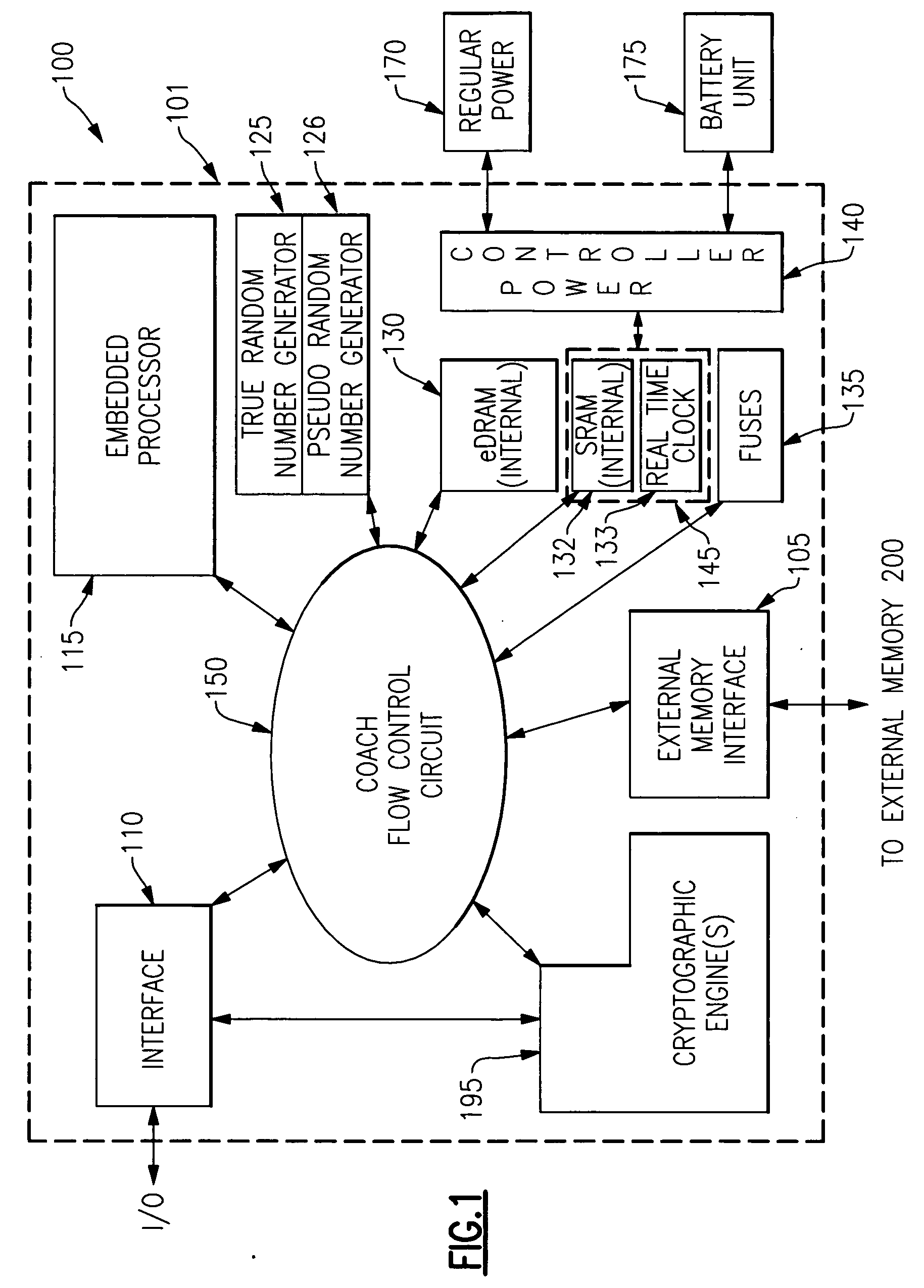

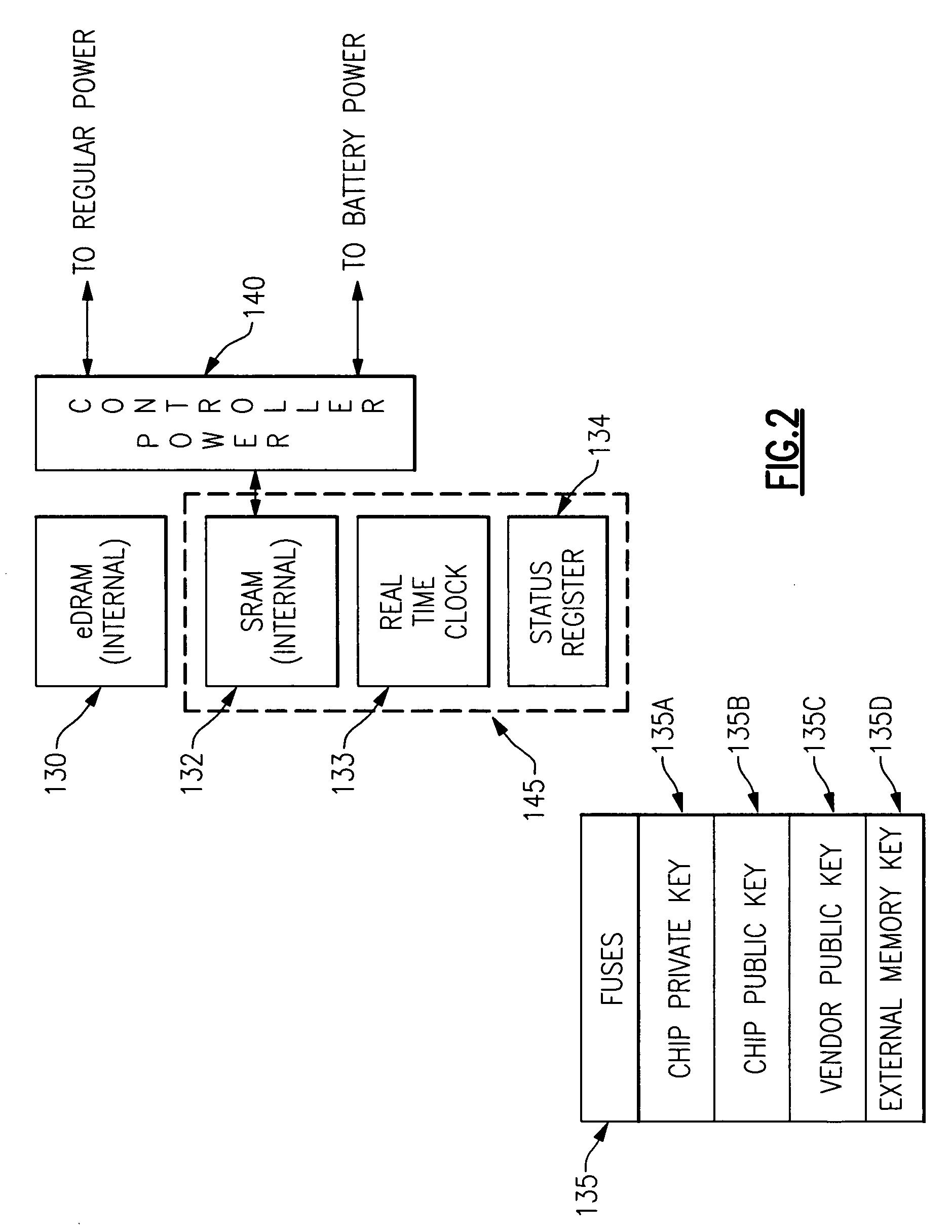

Circuit chip for cryptographic processing having a secure interface to an external memory

InactiveUS20060059369A1Improve process capabilityInhibit involvementUser identity/authority verificationUnauthorized memory use protectionInternal memoryStatic random-access memory

A mechanism is provided in which a secure chip for performing cryptographic and / or other functions is able to securely access a separate random access memory externally disposed with respect to a secure chip boundary. Addressing of the external memory is controlled so as to define certain regions therein which receive and store only encrypted information from the chip. Other regions of the external memory are set aside for the receipt and storage of unencrypted information. Access to the external memory is provided through a controlled interface which communicates with internal chip hardware which operates to control the flow of communication between various internal components such as cryptographic engines, data processors, internal memory of both the volatile and the nonvolatile variety and an external interface which provides the only other access to the chip. The internal chip hardware with which the external memory interface communicates is implemented as a combined ASIC and programmable hardware circuit, wherein the programmable hardware circuit is also securely configurable.

Owner:IBM CORP

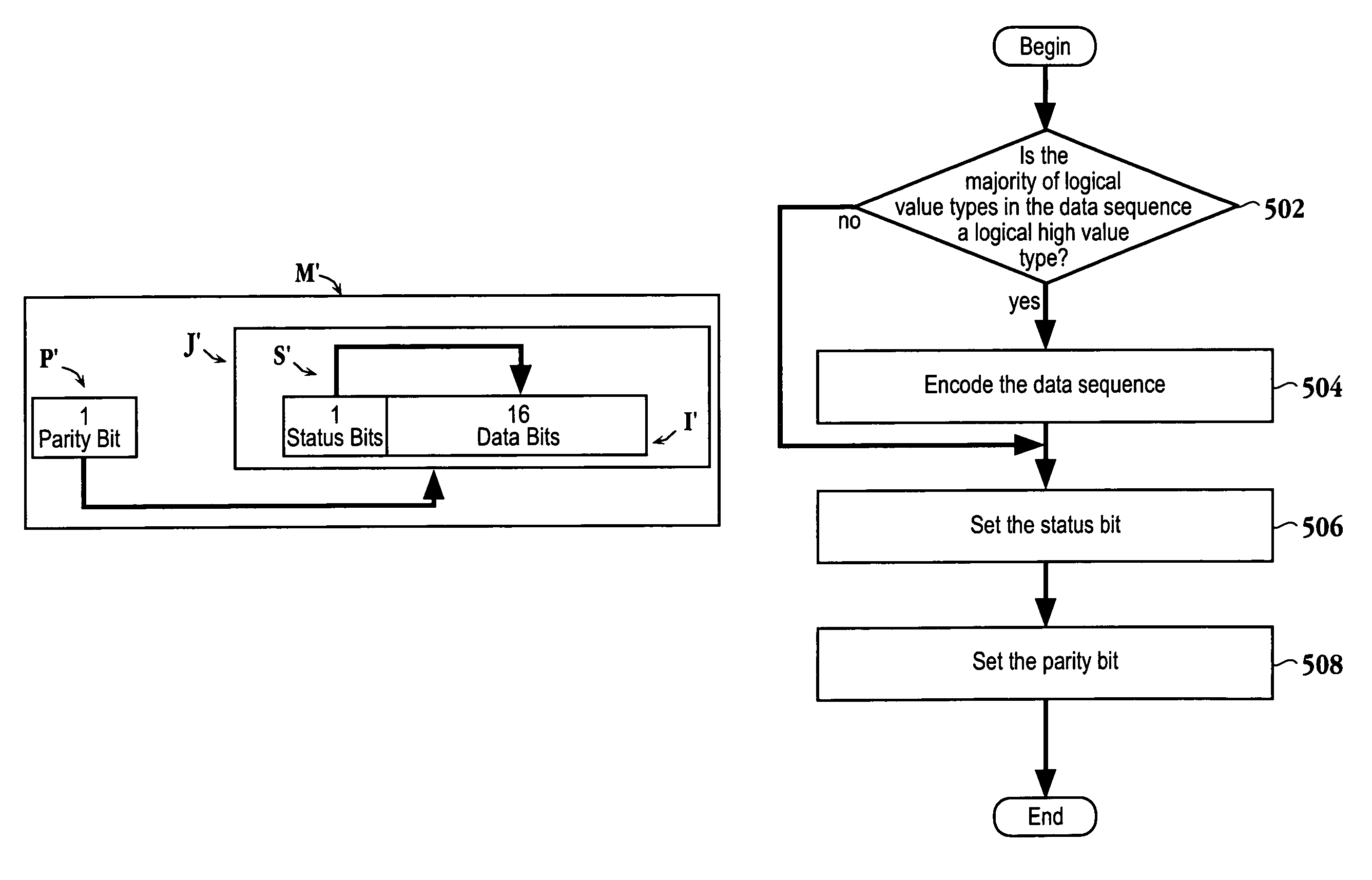

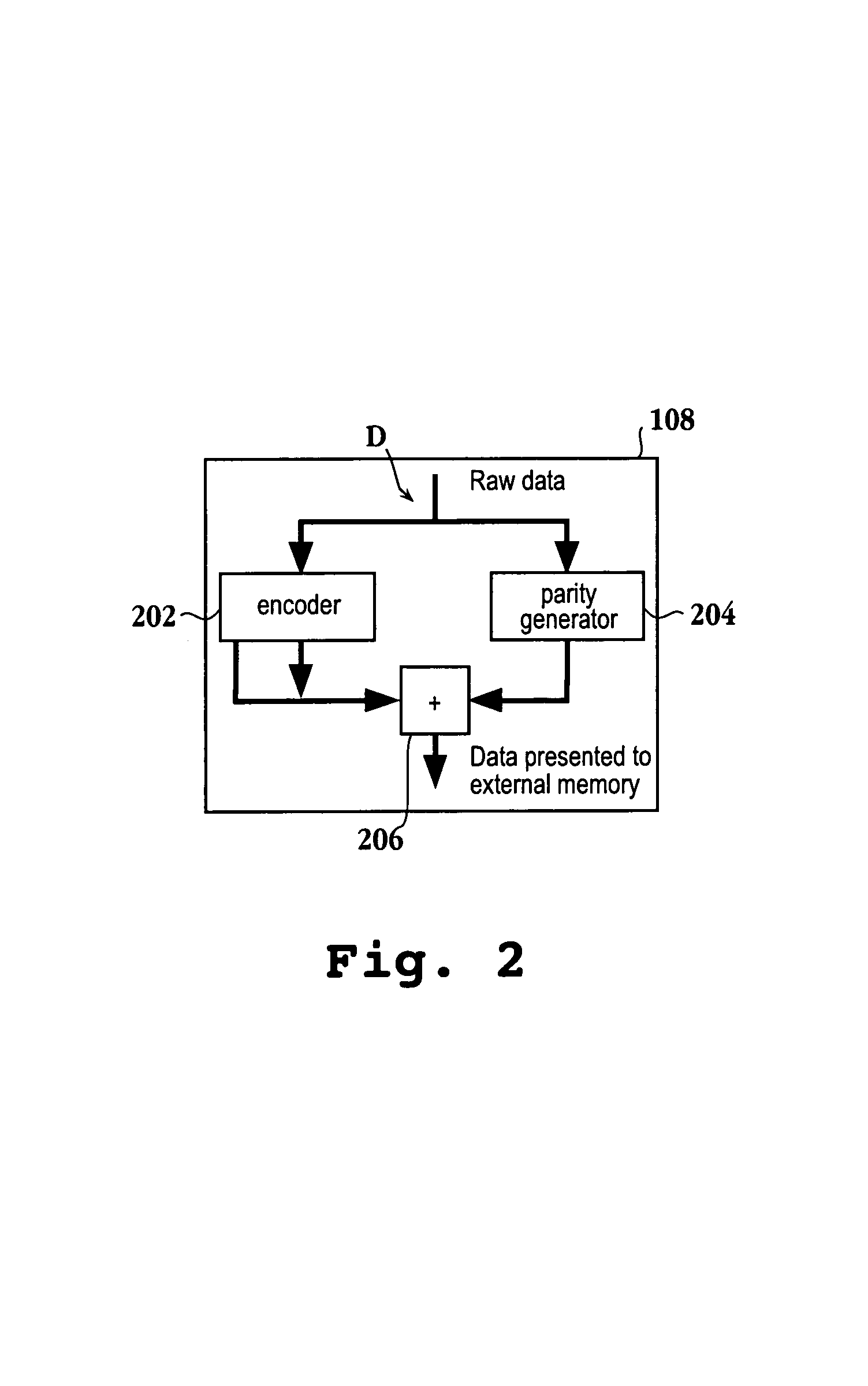

Method and system for improving memory interface data integrity in PLDs

InactiveUS7102544B1Reduces SSO effectDetecting errorError detection/correctionCode conversionData integrityExternal storage

An integrated circuit (IC) for optimizing data presentation to an external memory interface bus is provided. The IC is in communication with the external memory via the external memory interface bus. The IC includes an encoder that may encode the data that are being sent to an external memory. The encoder encodes the data based on the logic value of the majority of bits in the data. The encoder is capable of setting a status bit to indicate that the data are encoded. Further connected in series with the encoder is a parity generator that sets the parity bit logic value based on whether the number of logic 1s in the data, along with the status bit, is even or odd. The IC also includes a parity checker to detect whether any error occurred in the data during transmission. The decoder within the IC decodes the data to the original data.

Owner:TAHOE RES LTD

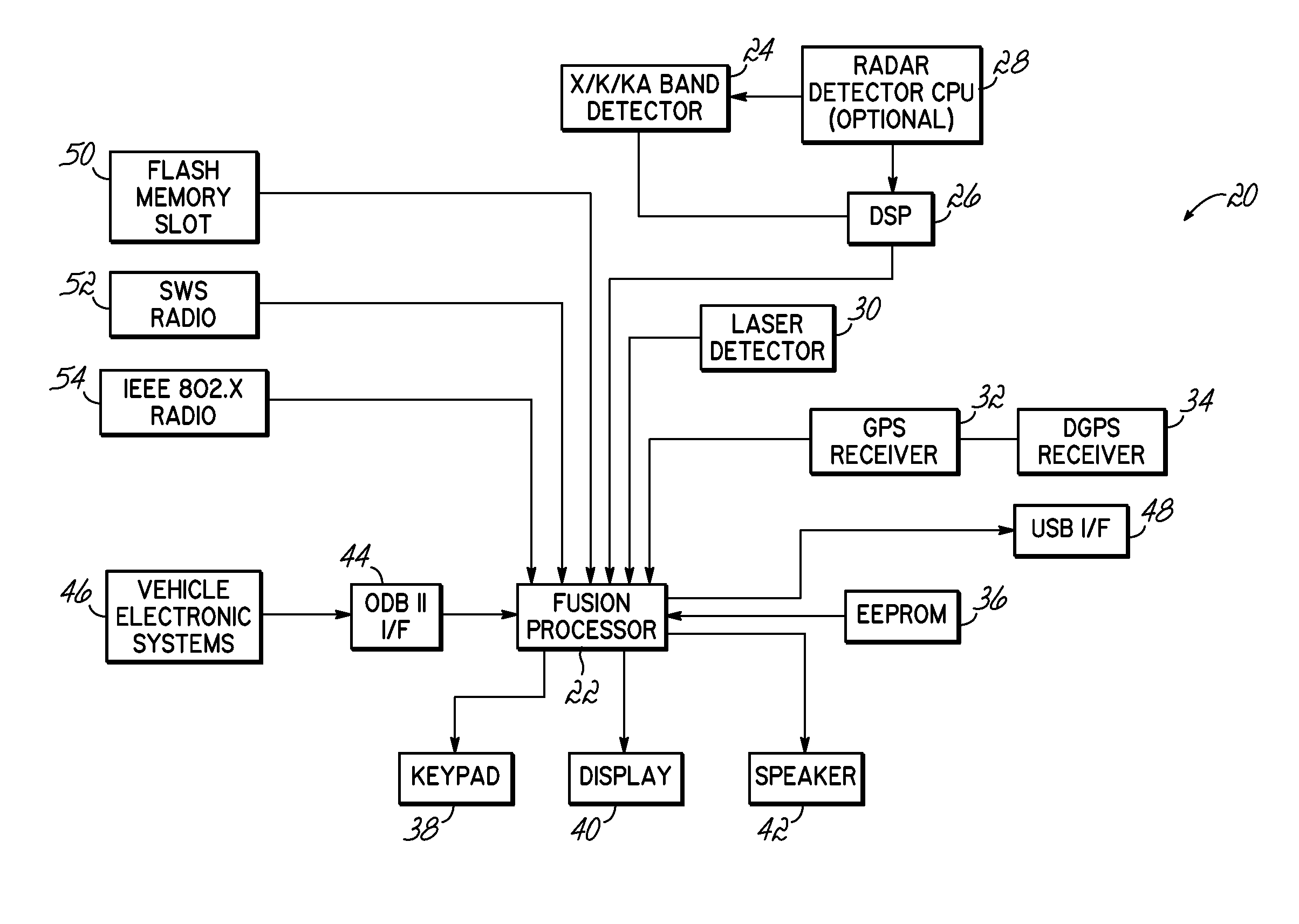

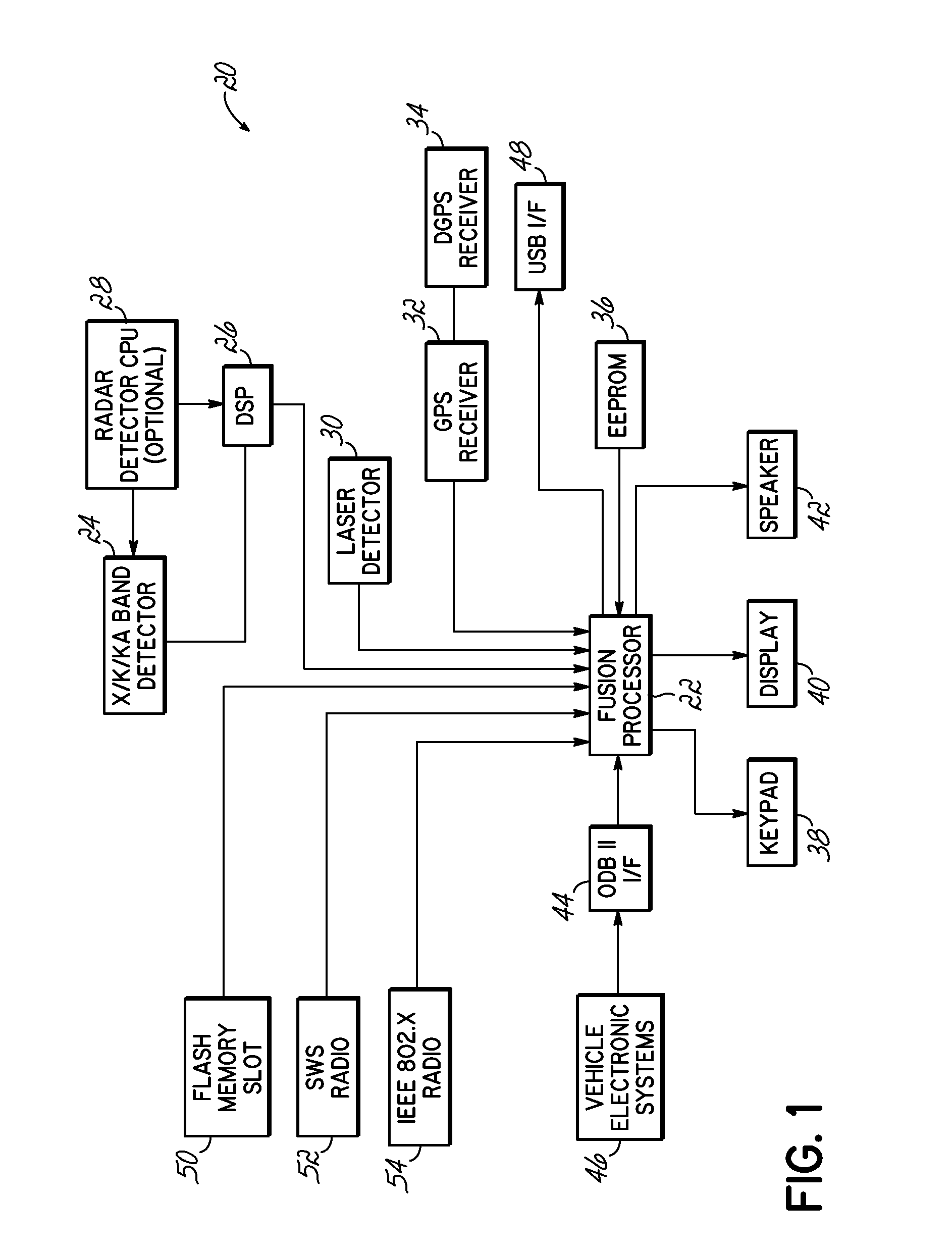

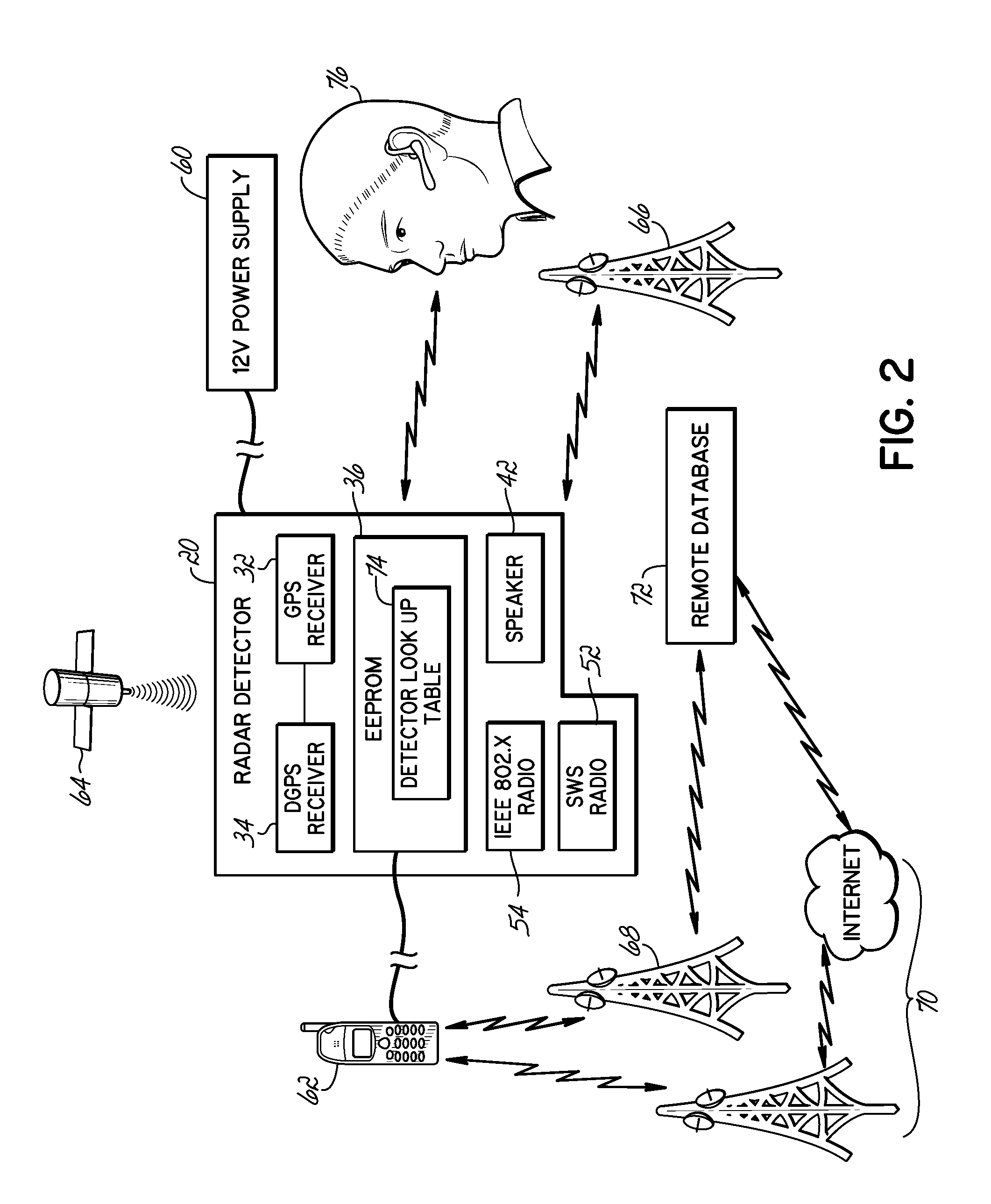

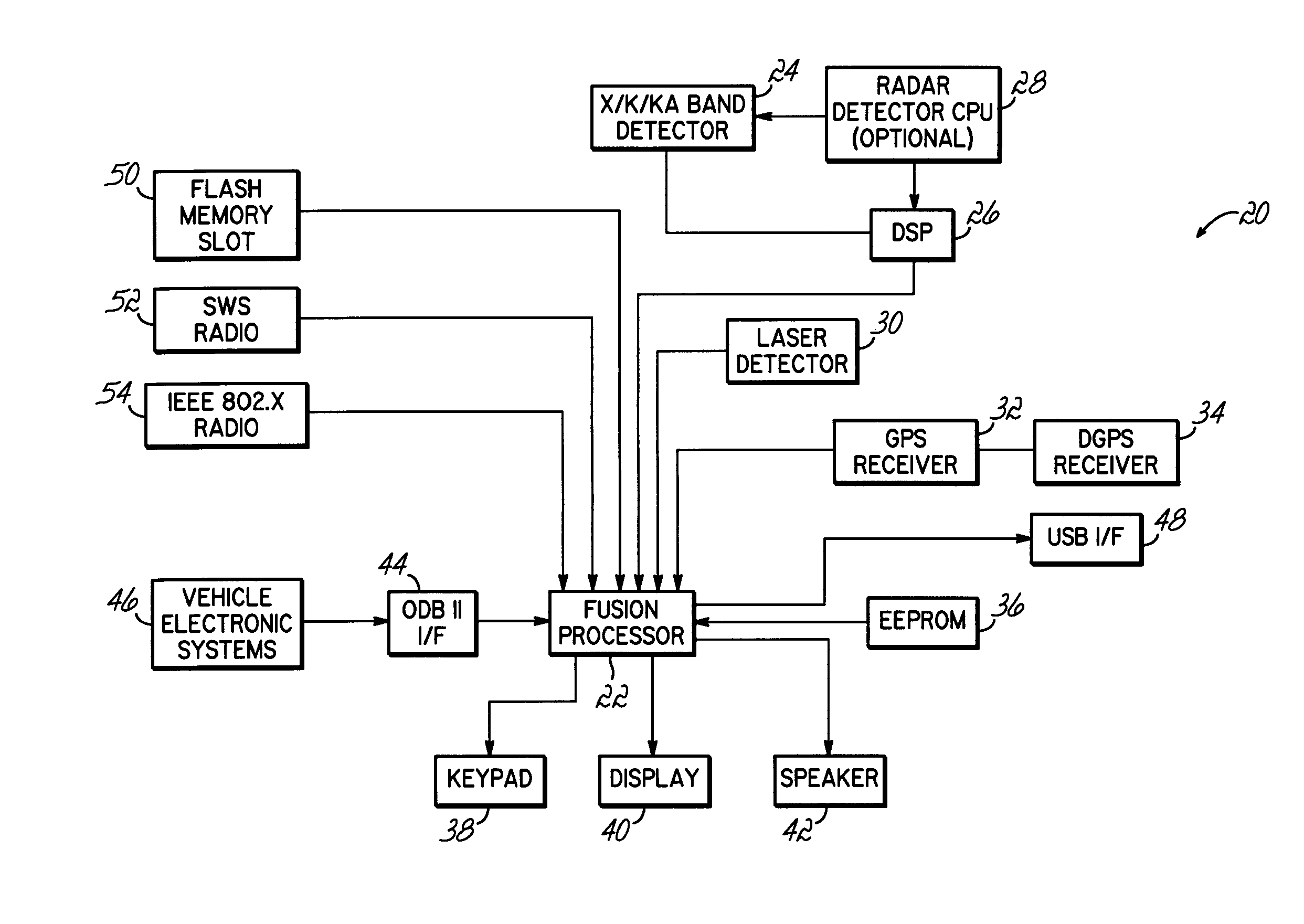

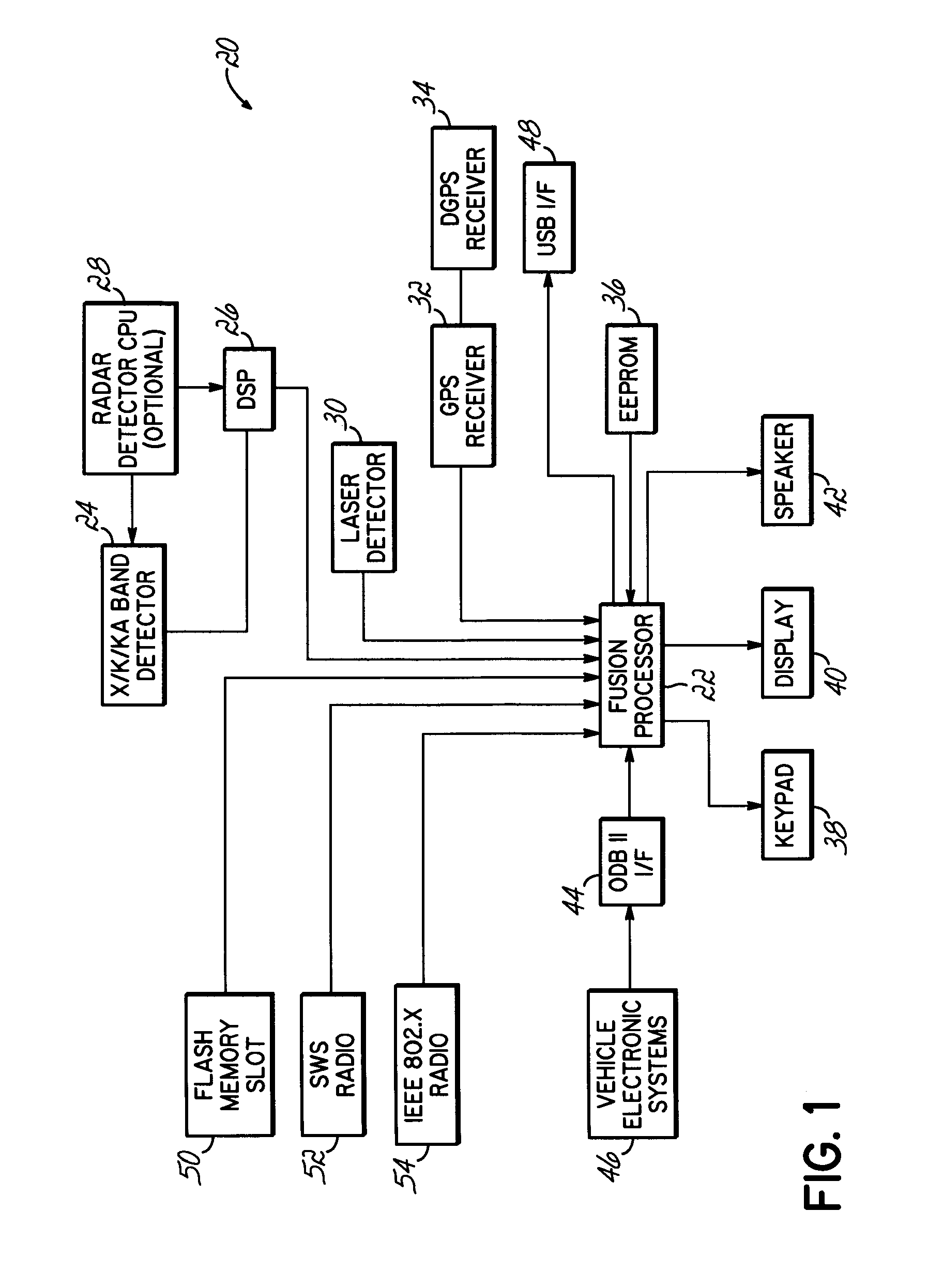

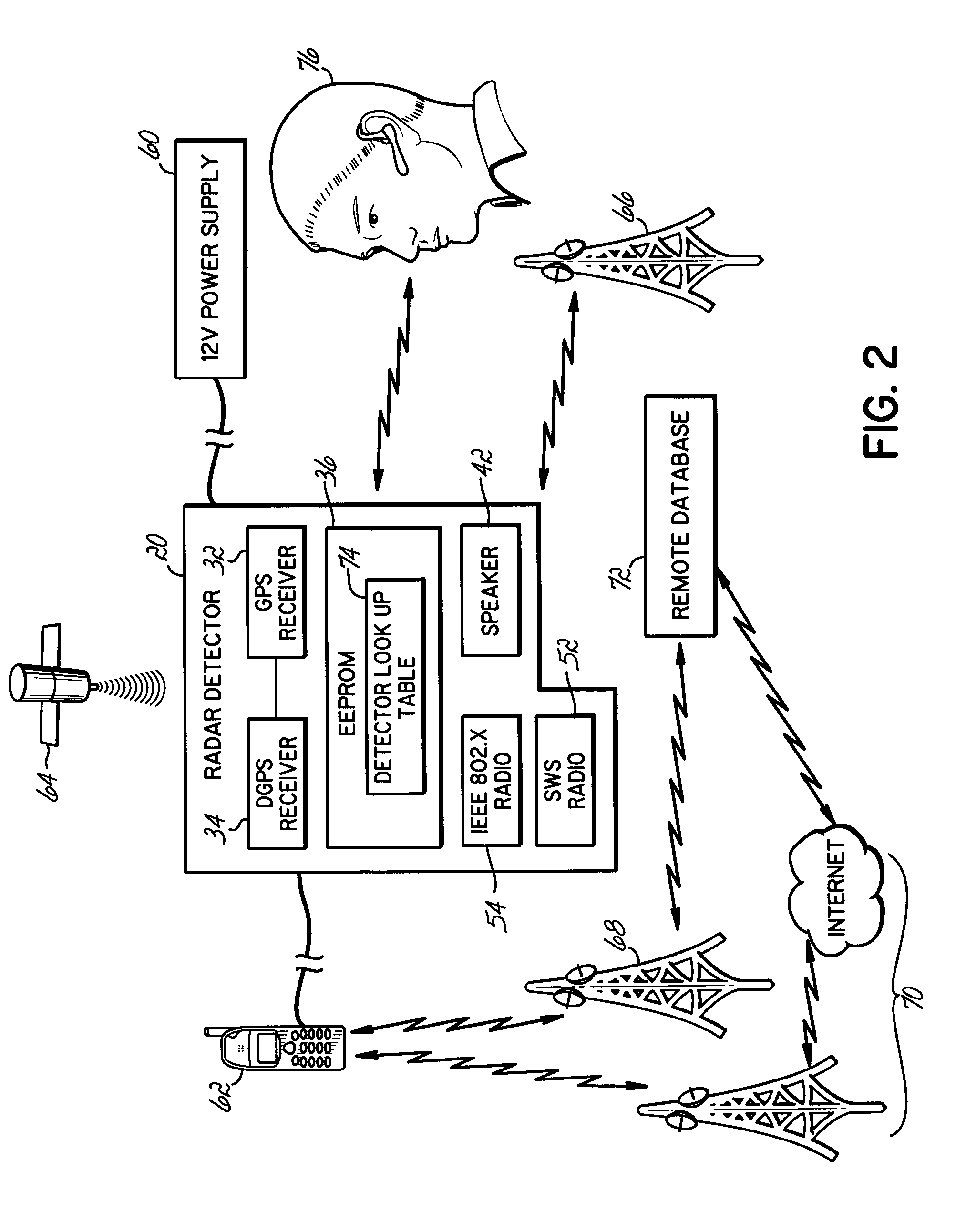

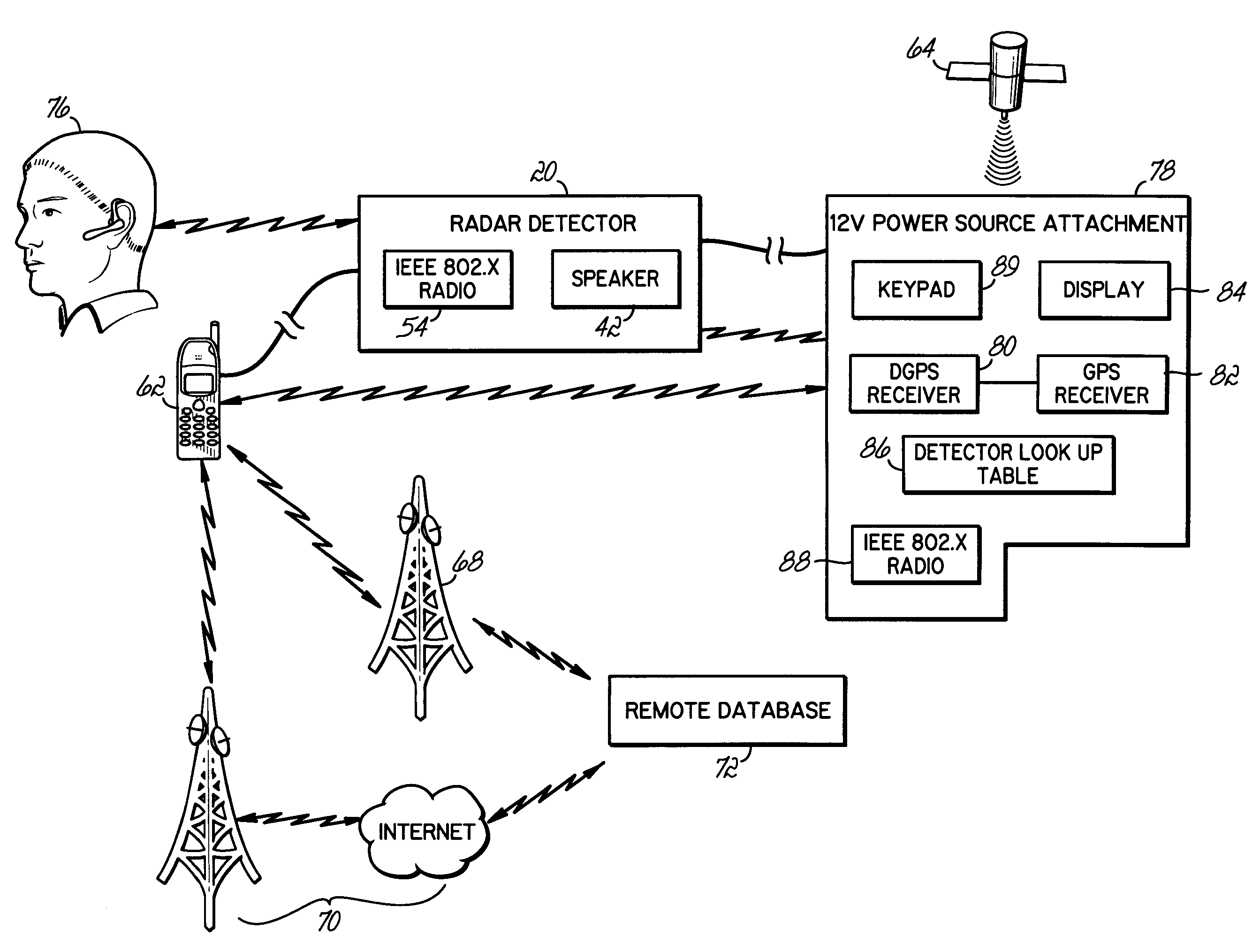

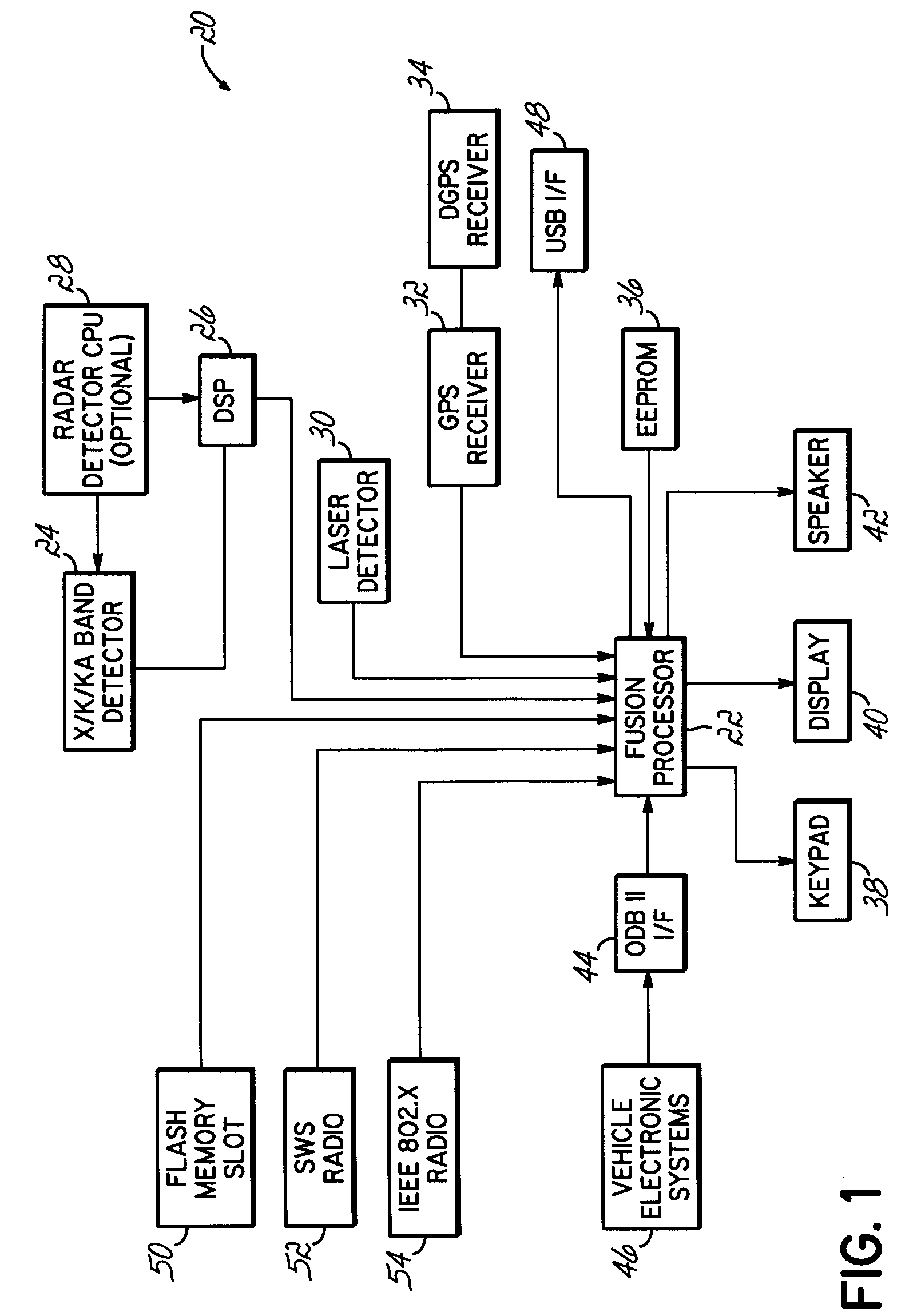

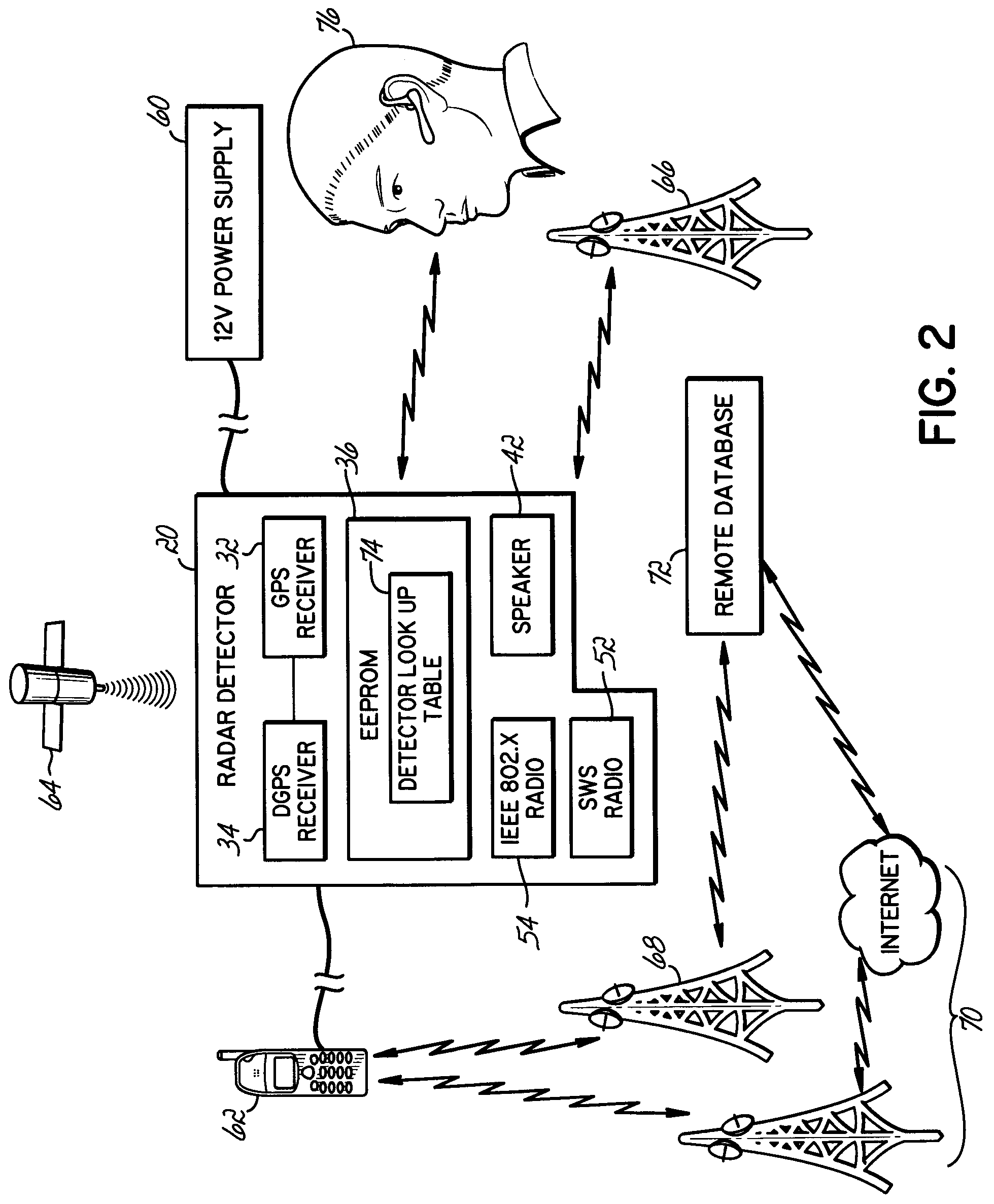

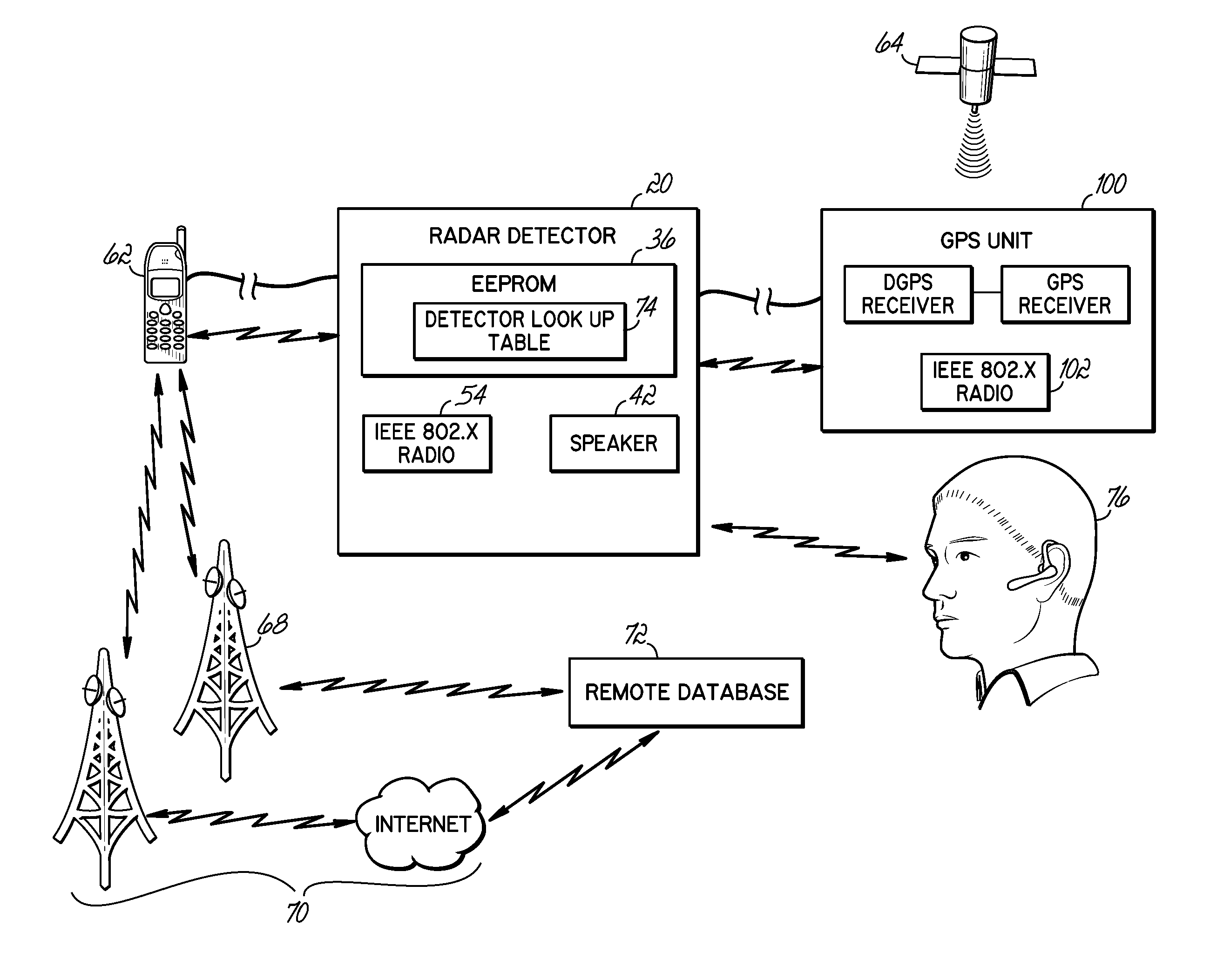

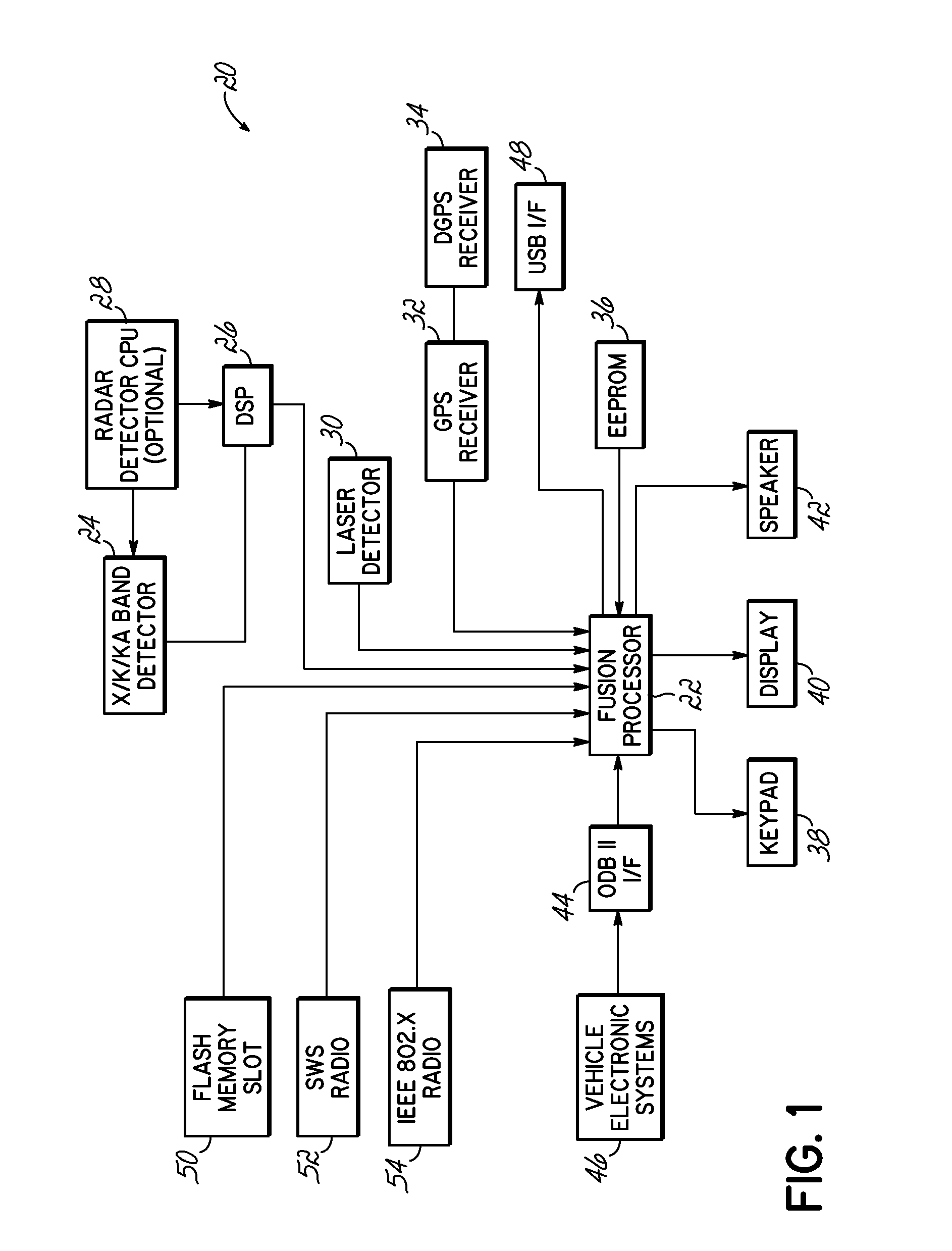

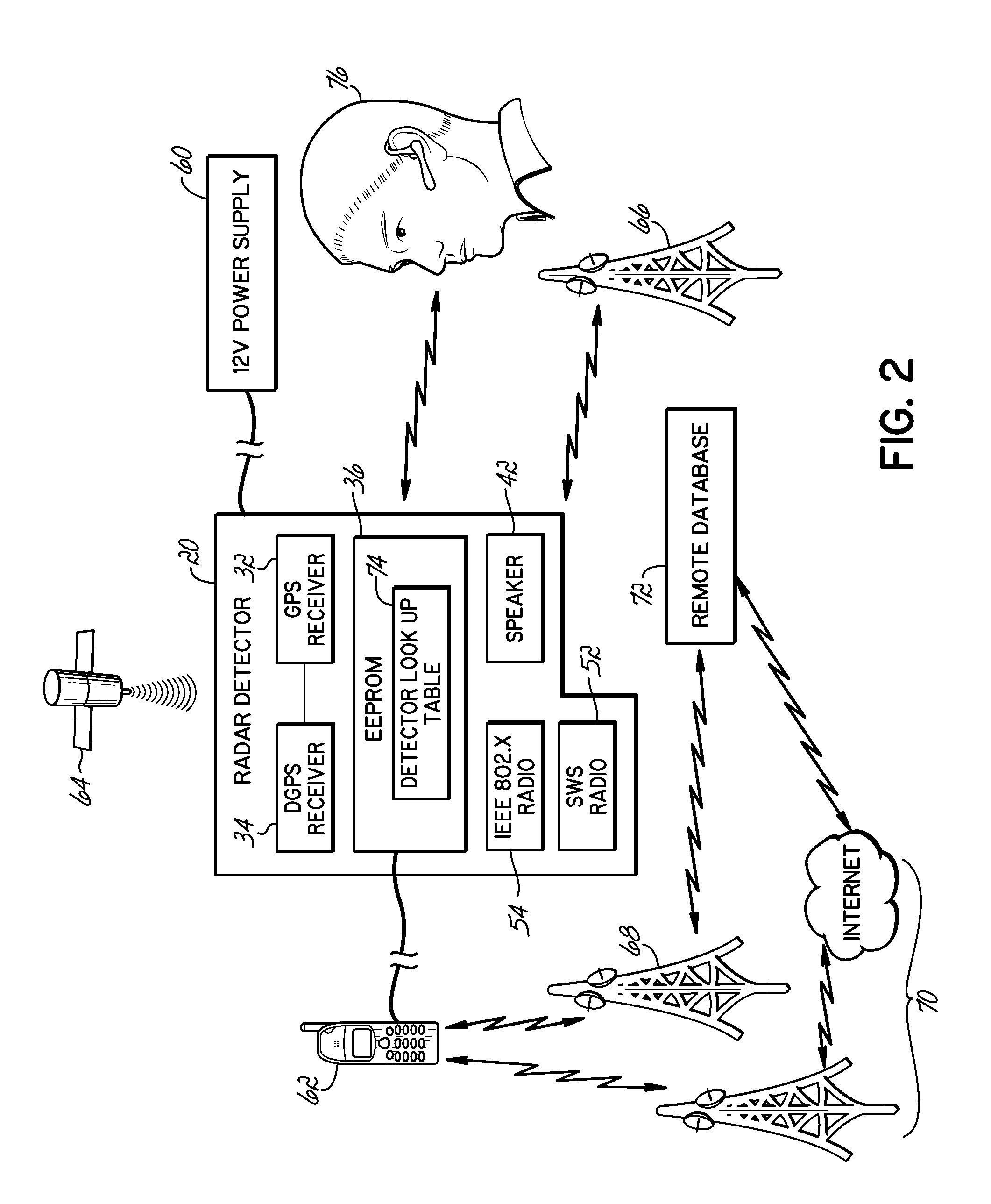

Wireless Connectivity in a Radar Detector

ActiveUS20100214149A1Wave based measurement systemsRoad vehicles traffic controlData connectionNetwork Communication Protocols

Wireless and other external connectivity technology is used in various ways to enhance or improve upon existing radar detector and police activity detection systems. External memory interfaces, such as SD cards or USB, provide external storage. Wireless interfaces such as Bluetooth, Zigbee, 802.11, and wireless personal area network communication protocols, allow a detector processor to interact wirelessly with external devices, such as a Bluetooth headset, a cellular network device providing a server connection, or toggle buttons used to indicate the presence of police activity at a current position. Further, radar detectors are upgraded to provide GPS capabilities, using the existing power / data connector of the radar detector.

Owner:ESCORT INC

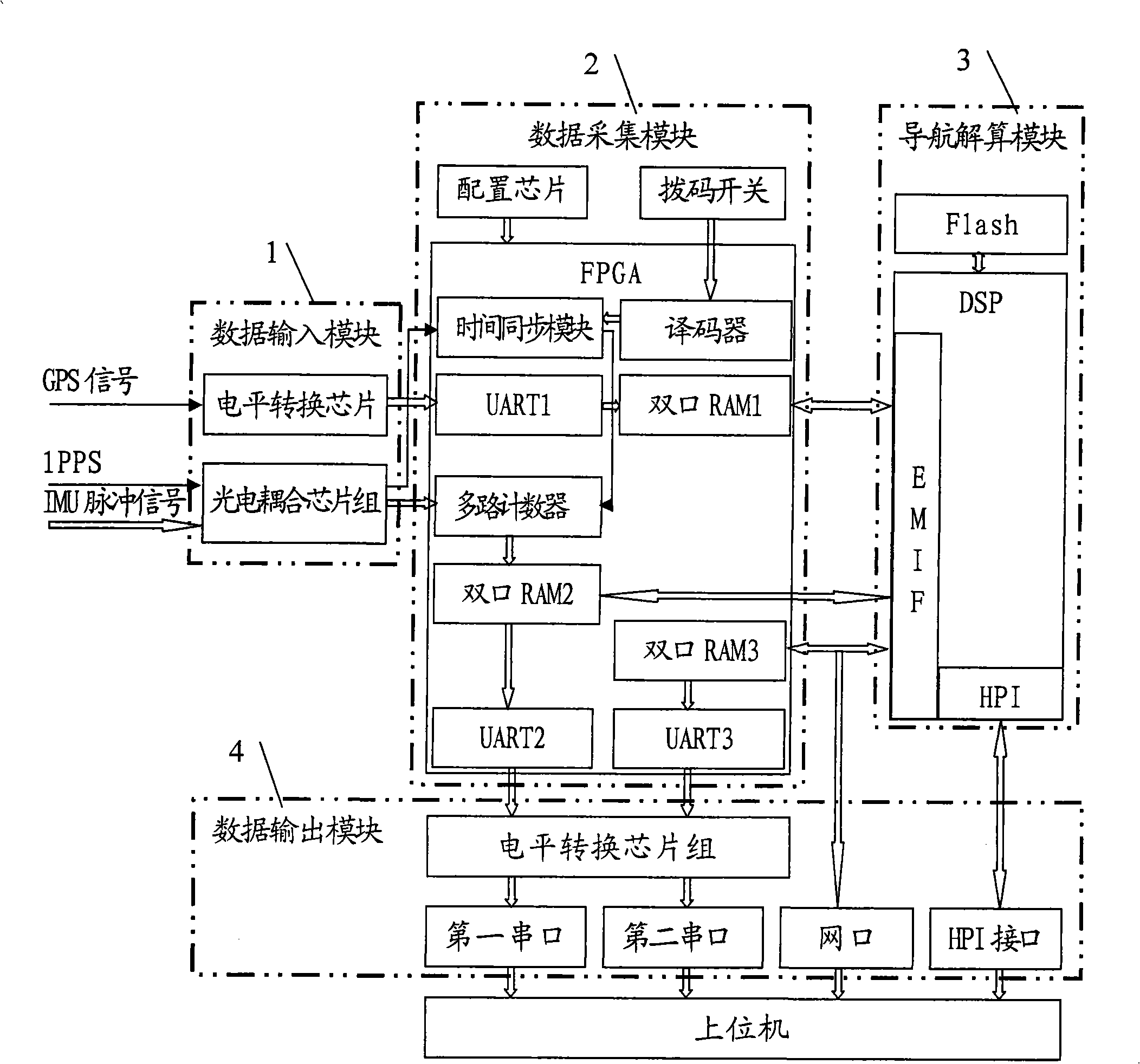

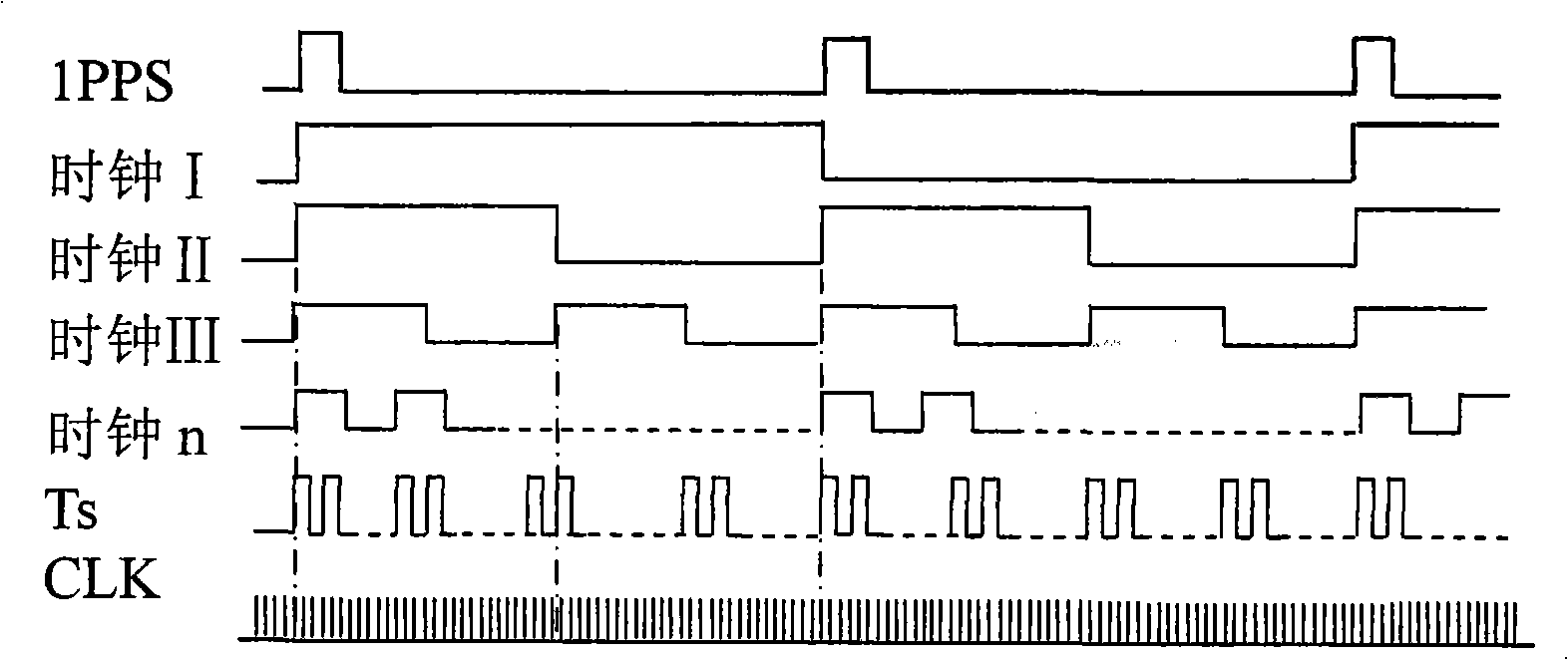

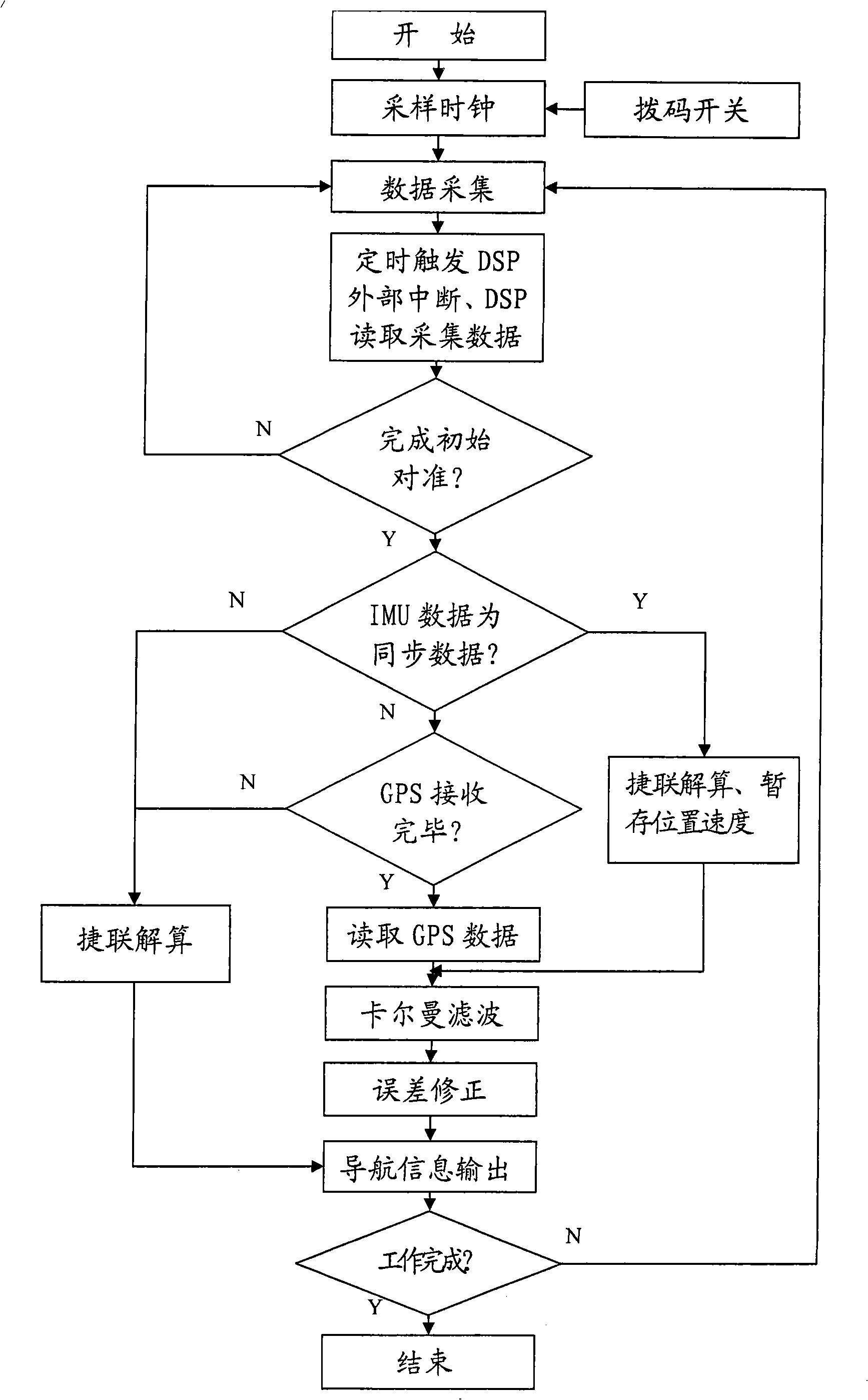

Integrated navigation computer based on DSP and FPGA

InactiveCN101261129AHighly integratedReduce volumeNavigational calculation instrumentsNavigation by speed/acceleration measurementsGround vehiclesFloating point

The invention provides an integrated navigation computer based on DSP and FPGA and used for integrated navigation of GPS and an inertial navigation system, consisting of a data input module, a data collecting module, a navigation solution module and a data output module. The data input module realizes the level conversion of input signals; the data collecting module utilizes the FPGA to realize the synchronous collection of IMU pulse signals and GPS signals; the navigation solution module concurrently read the data collected by the data collecting module by the external memory interface of a high-speed floating-point type DSP and completes the real-time integrated navigation of inertia or GPS; the navigation result is output by the data output module; furthermore, the output information has the characteristic of multi-redundancy. The navigation computer has high integration, small volume, light weight, low power loss, good real-time performance, strong expansibility, convenient system updating, and can be widely applied to the navigation of moving carriers such as aircrafts, ships and ground vehicles, etc.

Owner:BEIHANG UNIV

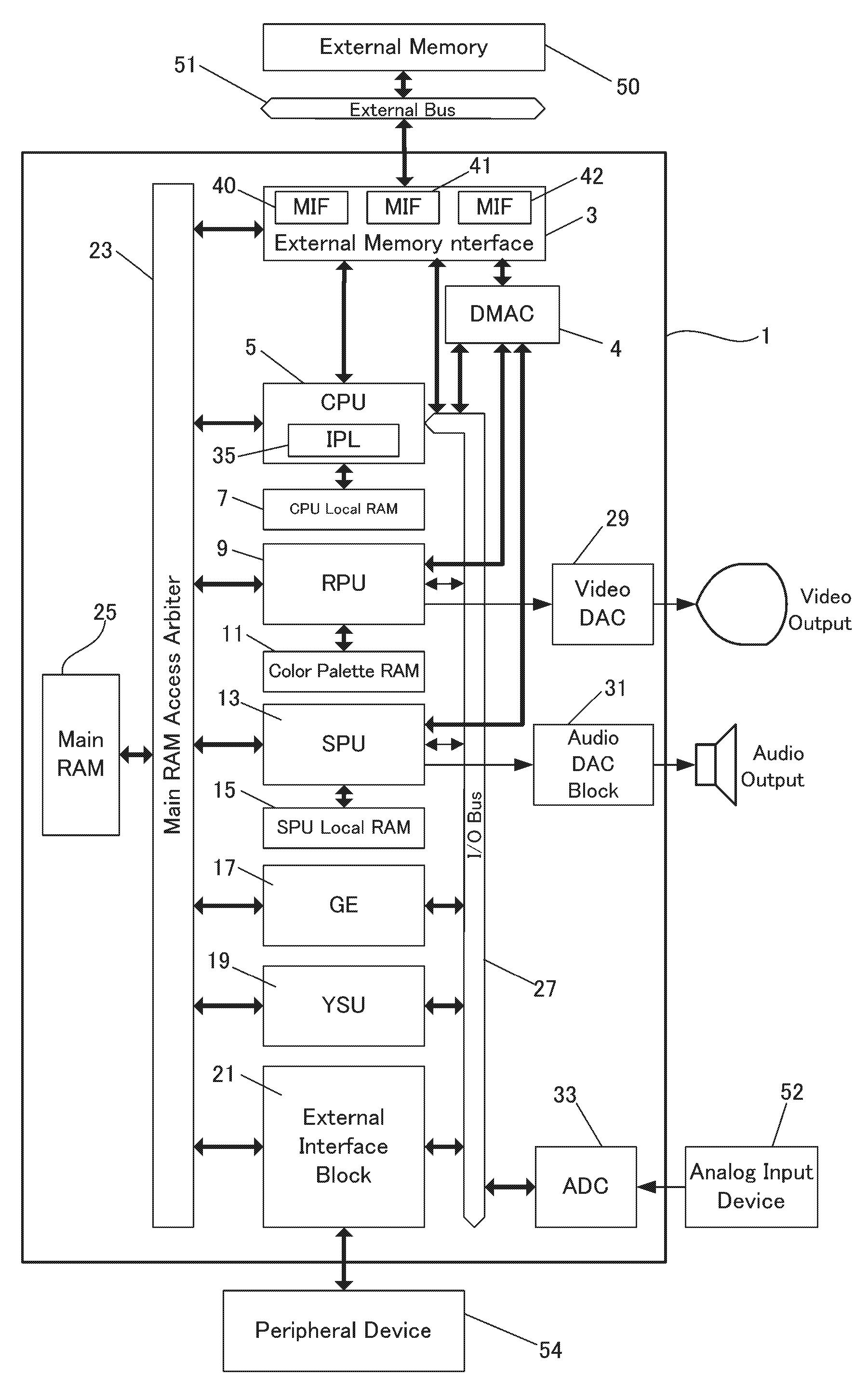

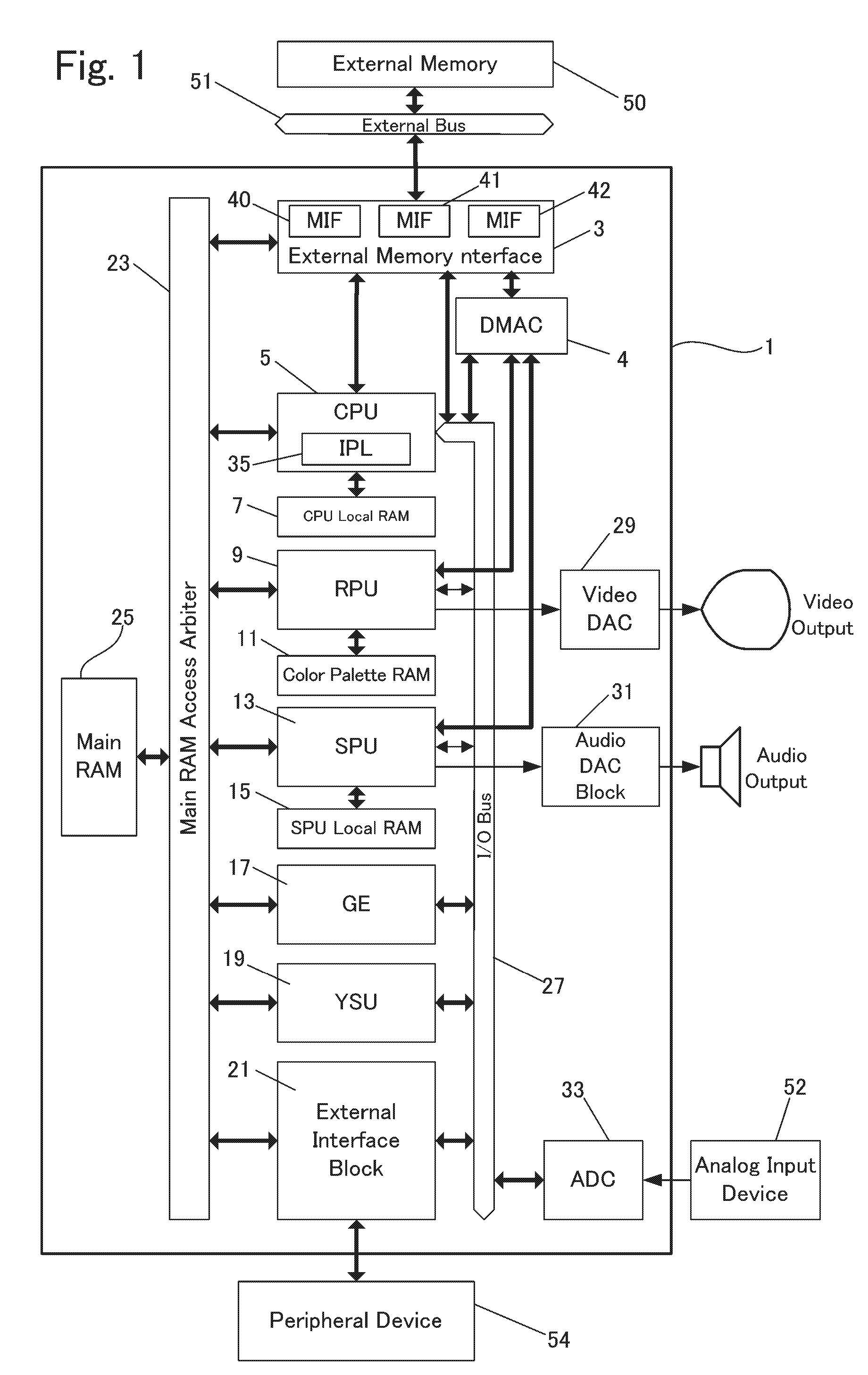

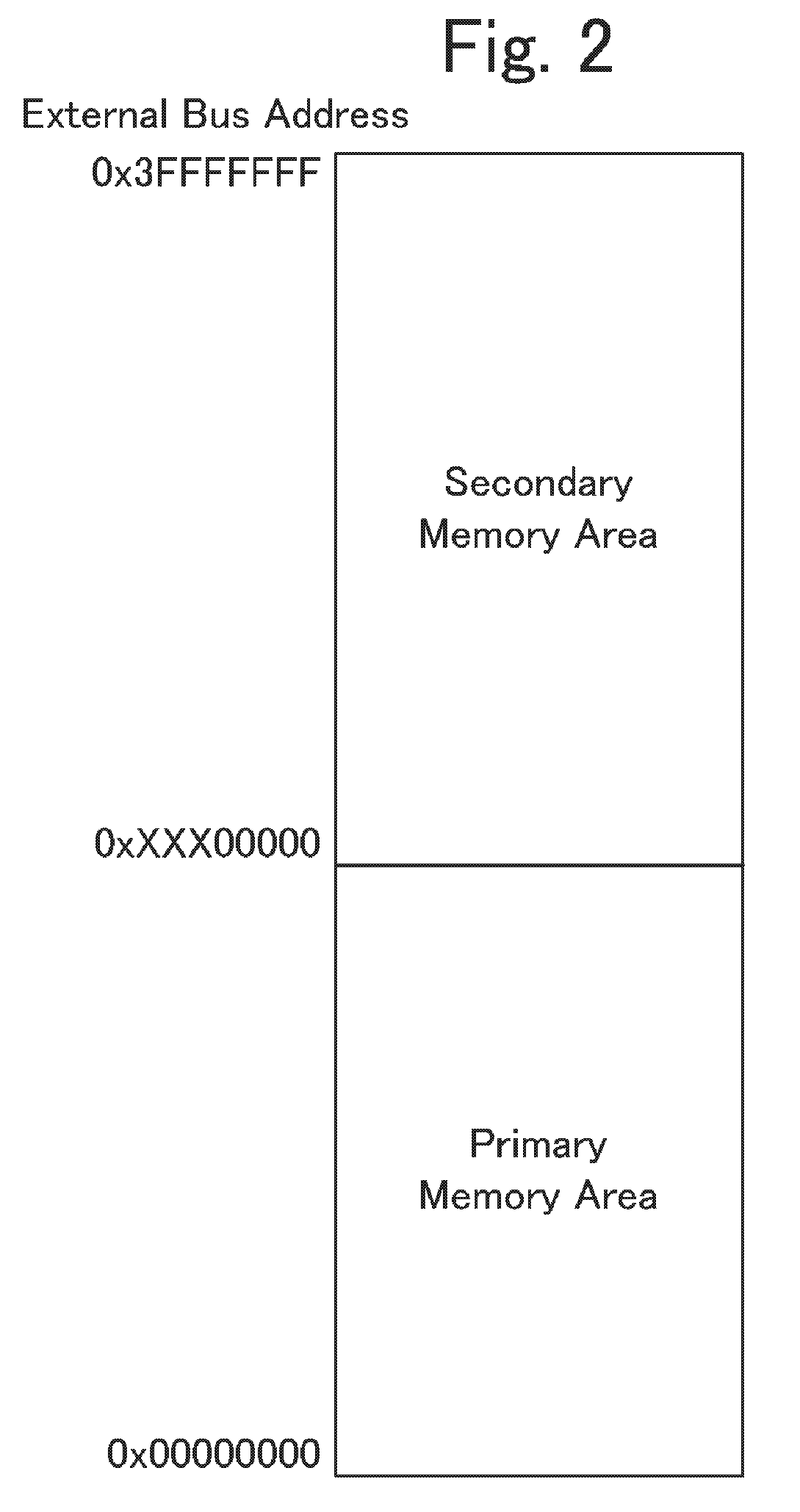

Multi-processor, direct memory access controller, and serial data transmitting/receiving apparatus

InactiveUS20090259789A1Reduce memory capacityIncrease the length of timeMemory systemsInput/output processes for data processingDirect memory accessManagement unit

A CPU 5 is provided with both the functionality of issuing an external bus access request directly to an external memory interface 3 and the functionality of issuing a DMA transfer request to a DMAC 4. Accordingly, in the case where data is randomly accessed at discrete addresses, an external bus access request is issued directly to the external memory interface 3, and in the case of data block transfer or page swapping as requested by a virtual memory management unit or the like, a DMA transfer request is issued to the DMAC 4, so that it is possible to effectively access the external memory 50.

Owner:SHINSEDAI KK

Wireless connectivity in a radar detector

ActiveUS20100214148A1Road vehicles traffic controlCommunication jammingData connectionNetwork Communication Protocols

Wireless and other external connectivity technology is used in various ways to enhance or improve upon existing radar detector and police activity detection systems. External memory interfaces, such as SD cards or USB, provide external storage. Wireless interfaces such as Bluetooth, Zigbee, 802.11, and wireless personal area network communication protocols, allow a detector processor to interact wirelessly with external devices, such as a Bluetooth headset, a cellular network device providing a server connection, or toggle buttons used to indicate the presence of police activity at a current position. Further, radar detectors are upgraded to provide GPS capabilities, using the existing power / data connector of the radar detector.

Owner:ESCORT INC

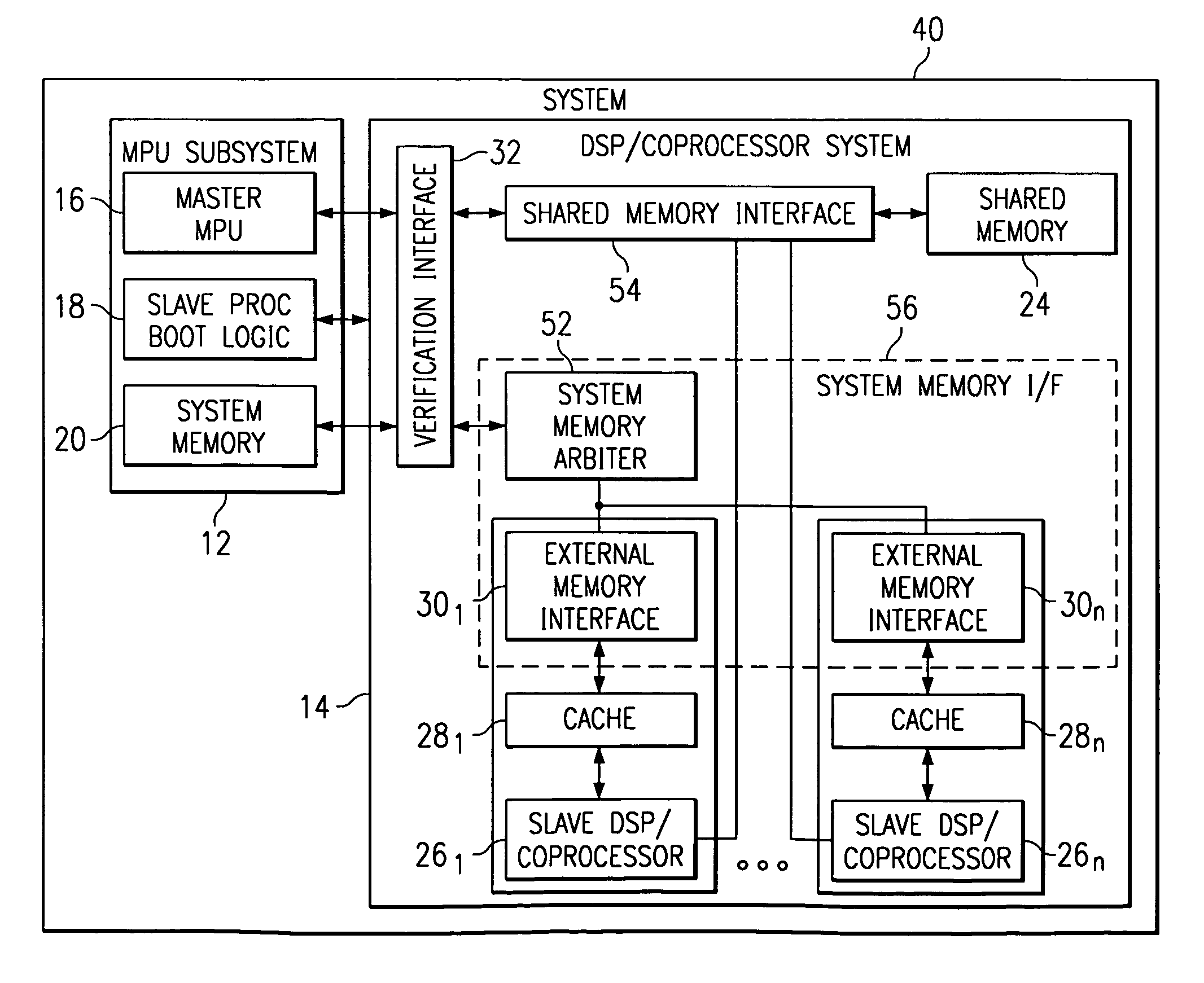

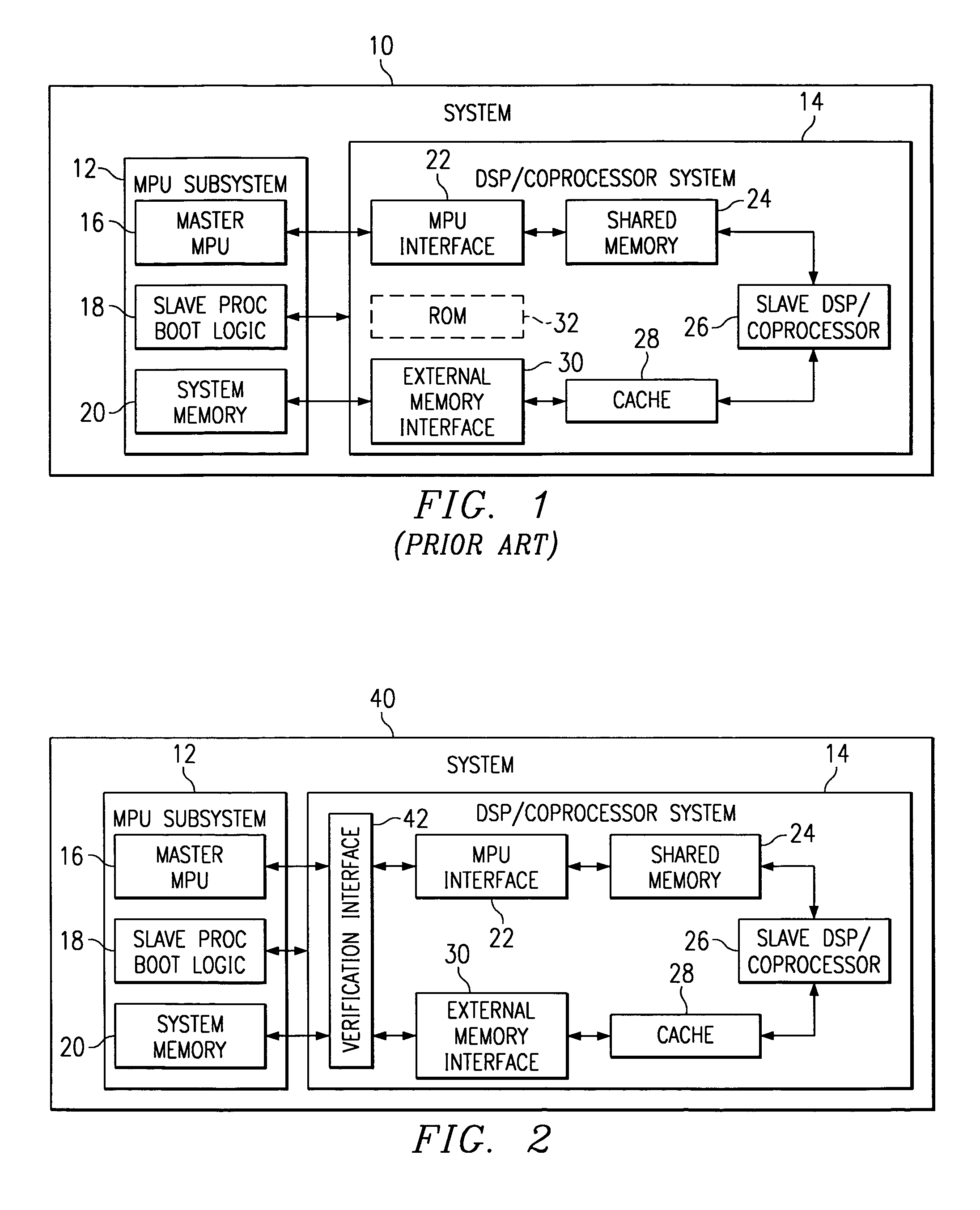

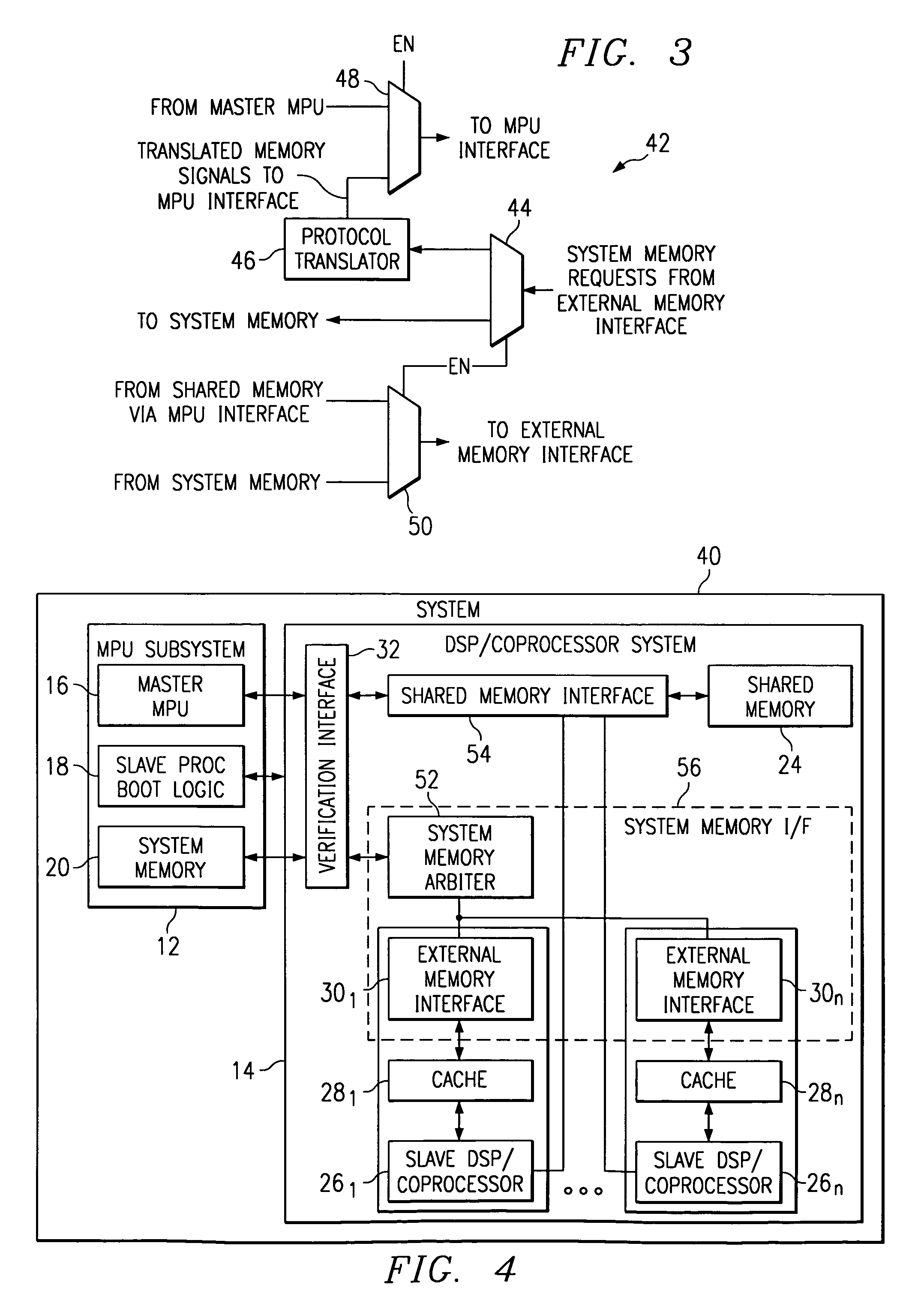

Multi-processor system verification circuitry

ActiveUS7469273B2Improve rendering capabilitiesImprove fault coverageFunctional testingMultiple digital computer combinationsCoprocessorSystem verification

A multiprocessor system (40) includes a MPU subsystem (12), with master MPU (16) and shared memory (24), and a DSP / Coprocessor subsystem (14), with one or more slave DSP / Coprocessors (26). The system memory (20) is accessed by each DSP / Coprocessor subsystem (14) through a cache (28) and external memory interface (30). A verification interface (42) is used in verification mode to isolate the DSP / Coprocessor subsystem (14) from the MPU subsystem (12) and to translate system memory requests from the external memory interfaces (30) (through an arbiter (52), where multiple external memory interfaces are used) to a protocol which can be used to access the data from the shared memory (24).

Owner:TEXAS INSTR INC

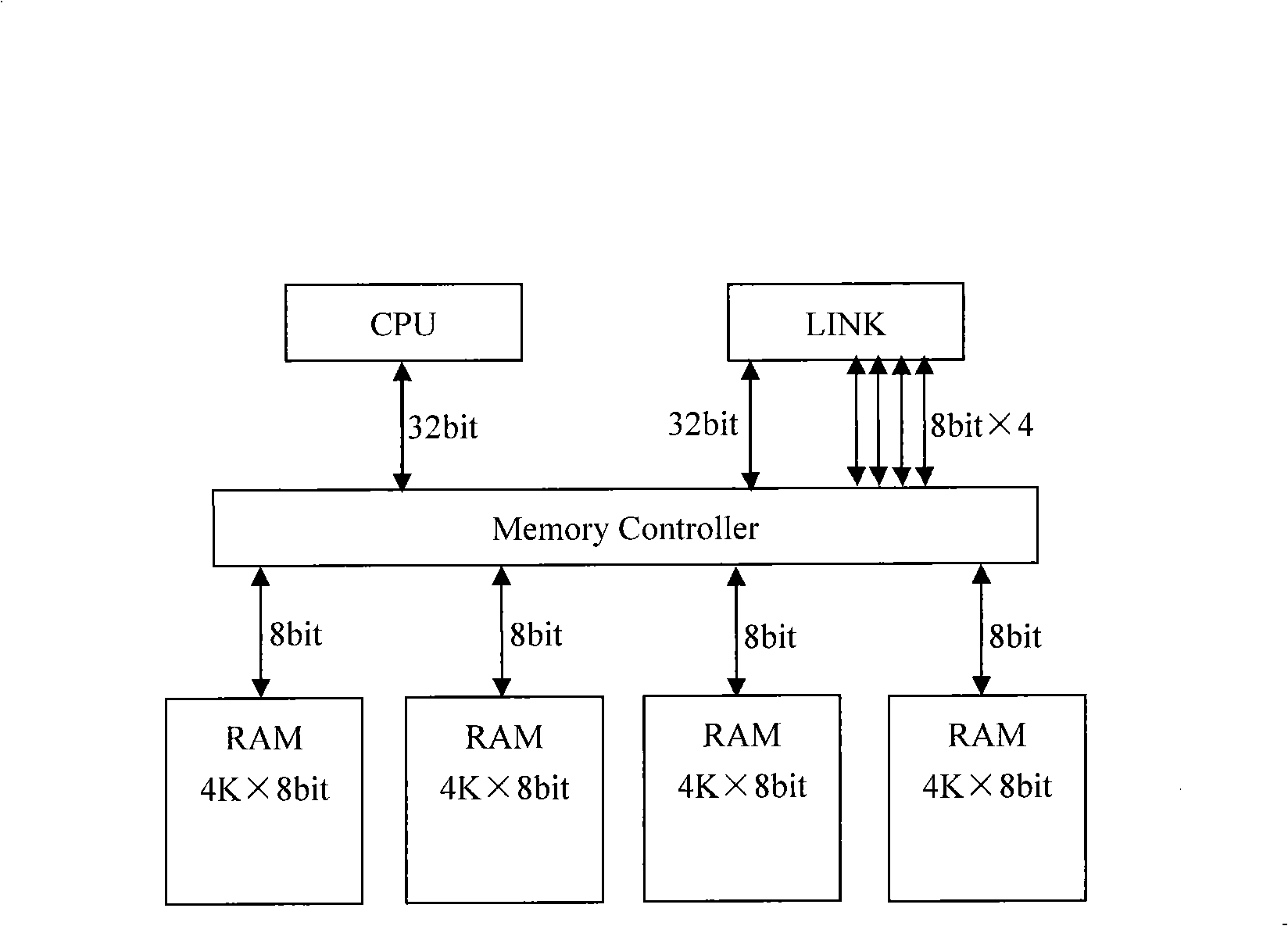

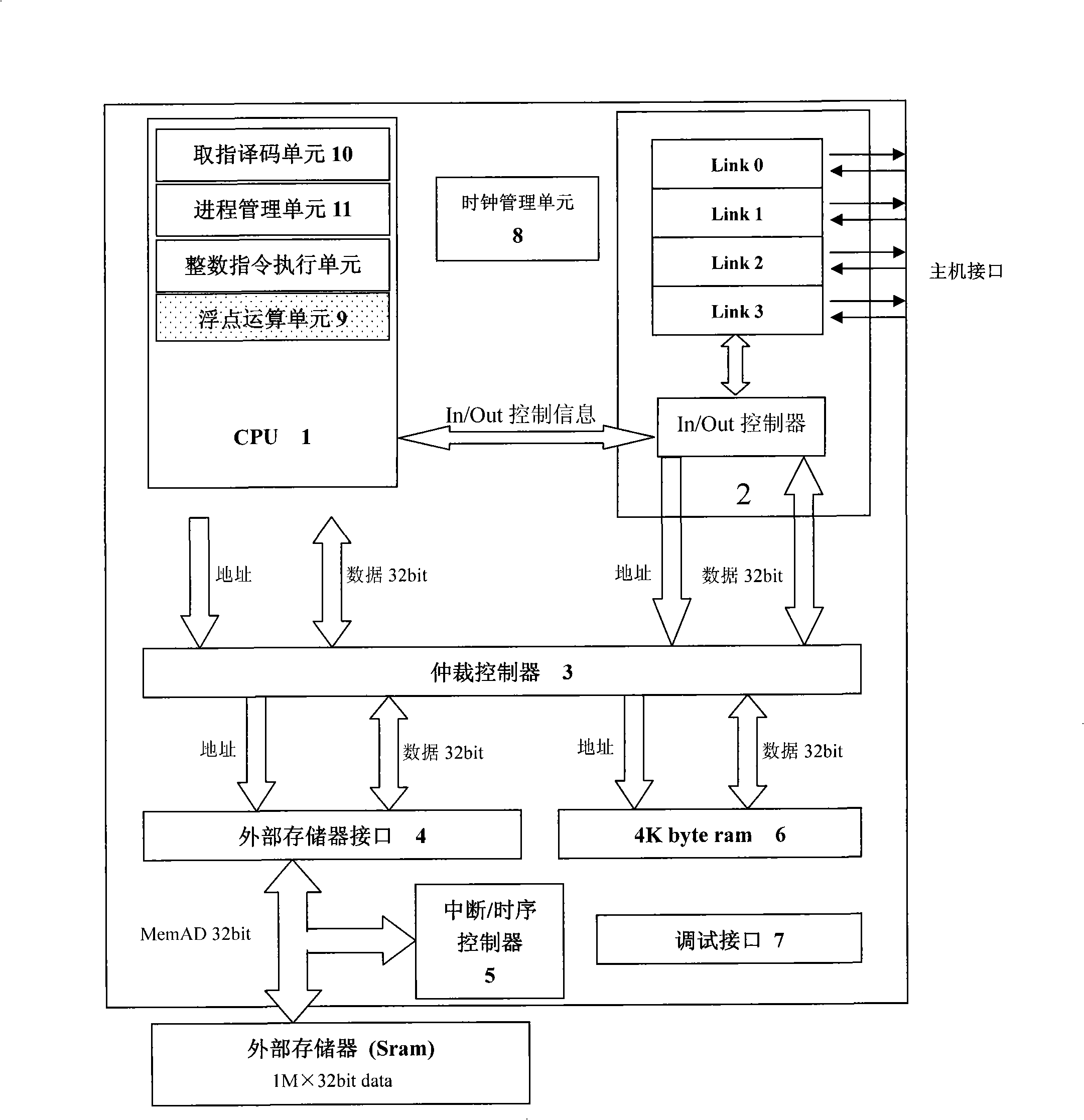

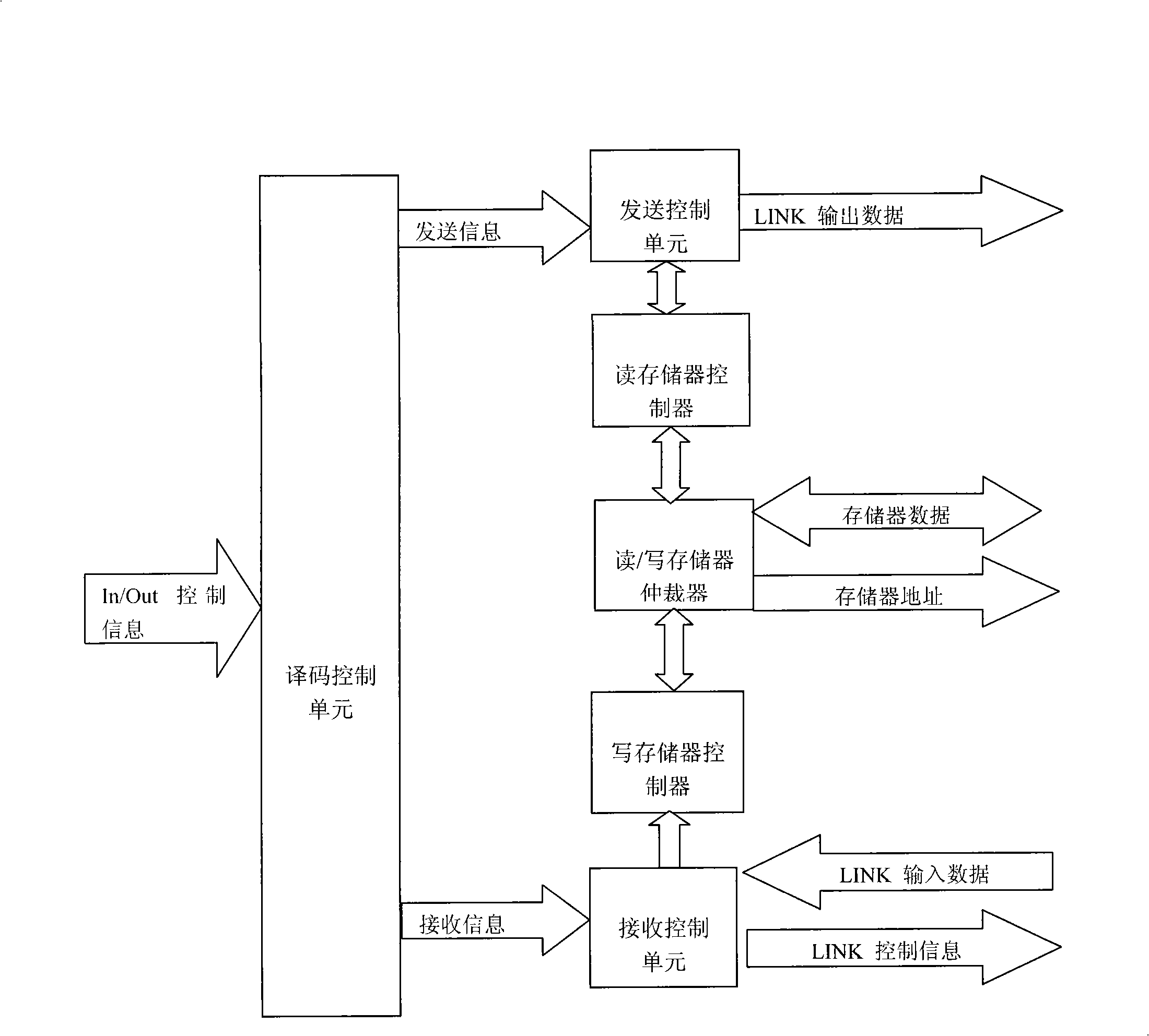

Paralleling microprocessor and its realization method

ActiveCN101334766ALow costEasy to modifyProgram initiation/switchingDigital data processing detailsInternal memoryParallel computing

The invention relates to a parallel microprocessor and a corresponding realization method which are based on FPGA development. The parallel microprocessor comprises a CPU which is a 32-bit fixed-point CPU formed by a fetch decoding unit, a process management unit and an integer instruction execution unit; a communication module formed by a plurality of units of LINK channels and In / Out controllers; an arbitration controller used for arbitrating internal and external address buses and a data bus of the CPU; an external memory interface used for providing reading / writing time-sequence logic for an external memory; an interruption / time-sequence controller used for providing timing and interruption for the CPU; an internal memory used for providing the instructions of the CPU and quickly accessing data. The CPU is also provided with a floating point unit (FPU) combining the 32-bit fixed-point CPU to form a 64-bit floating point CPU. The 32-bit fixed-point parallel microprocessor and the 64-bit floating point parallel microprocessor provided by the invention work stably, bring convenience for system modification and debugging, accelerate verification speed and provide a low-cost operation platform for programs written in OccamII language.

Owner:NEUSOFT MEDICAL SYST CO LTD

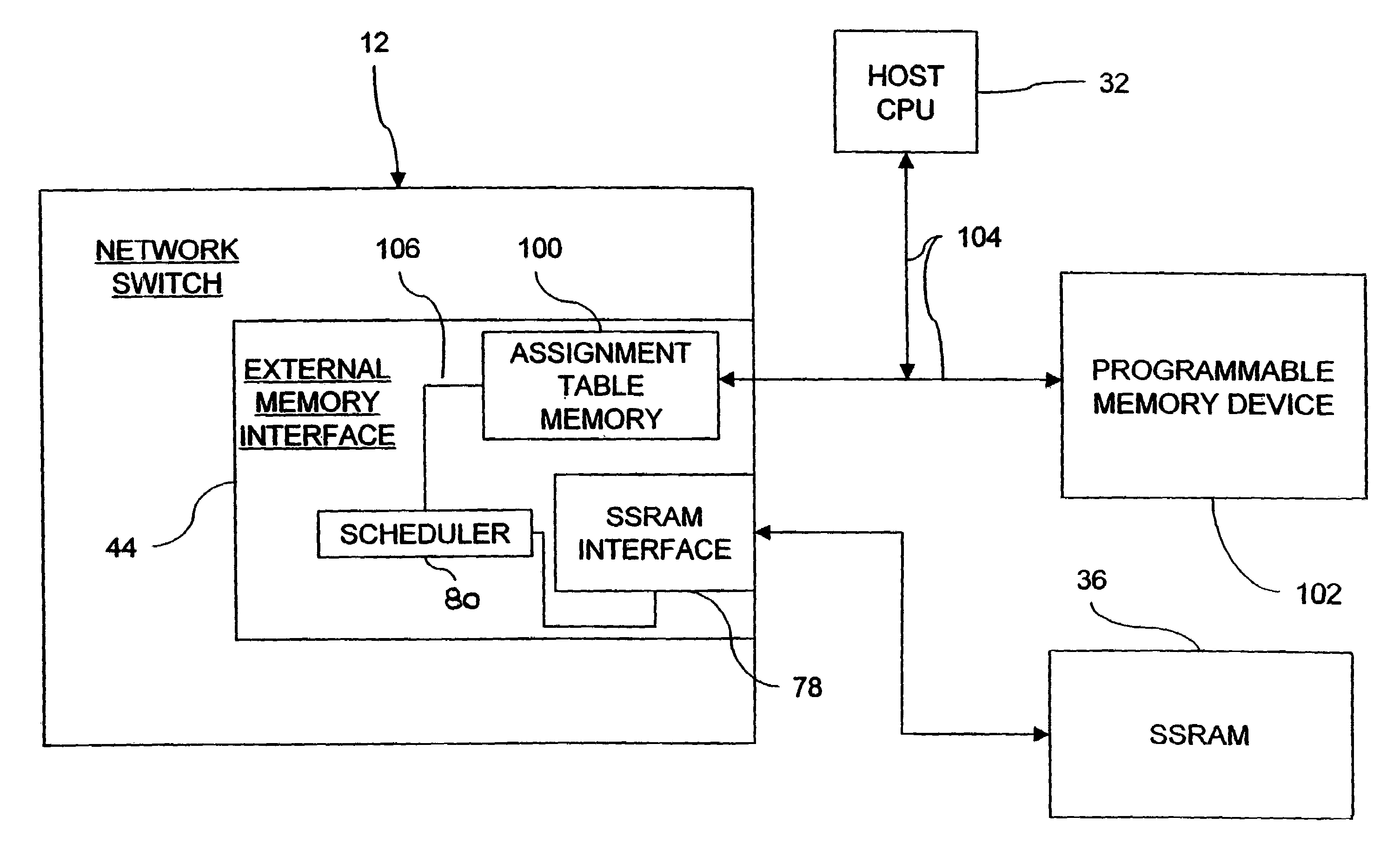

Apparatus and method for programmable memory access slot assignment

InactiveUS7031305B1Eliminate needTime-division multiplexStar/tree networksExternal storageNetwork switch

A network switch having switch ports for full-duplex communication of data packets with respective network nodes according to Ethernet (IEEE 802.3) protocol that flexibly assigns memory access slots to access an external memory according to programmable information. A scheduler within an external memory interface assigns the memory access slots to the respective network switch ports according to a programmed sequence written into an assignment table memory from an external programmable data storage device.

Owner:GLOBALFOUNDRIES INC

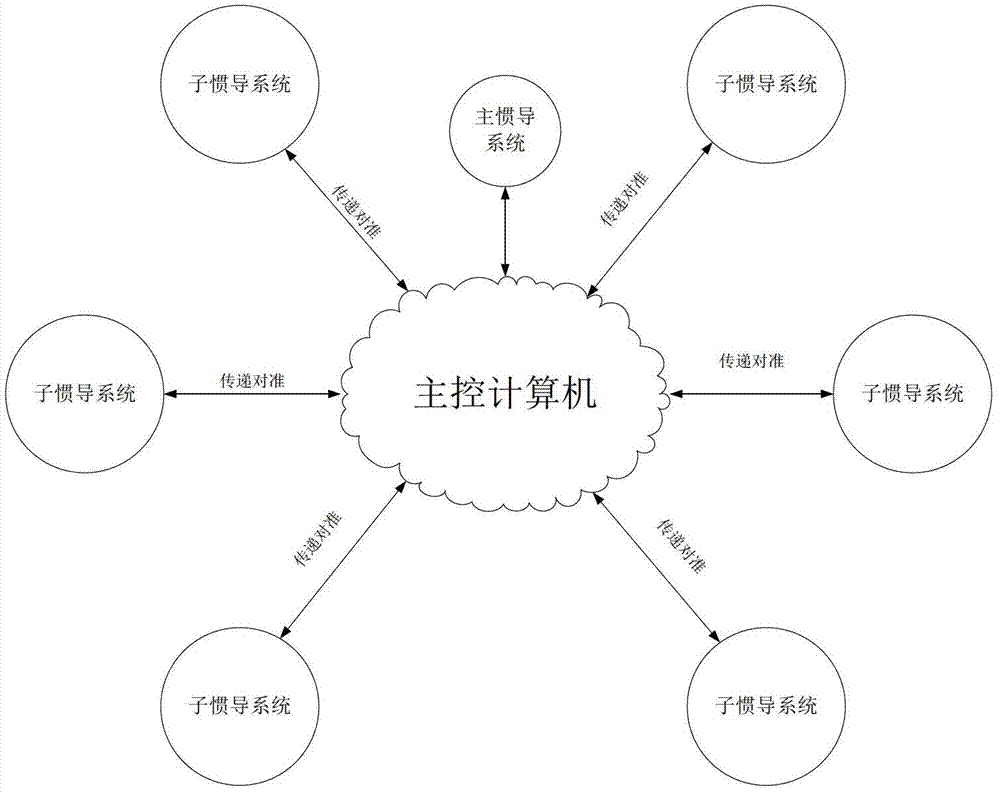

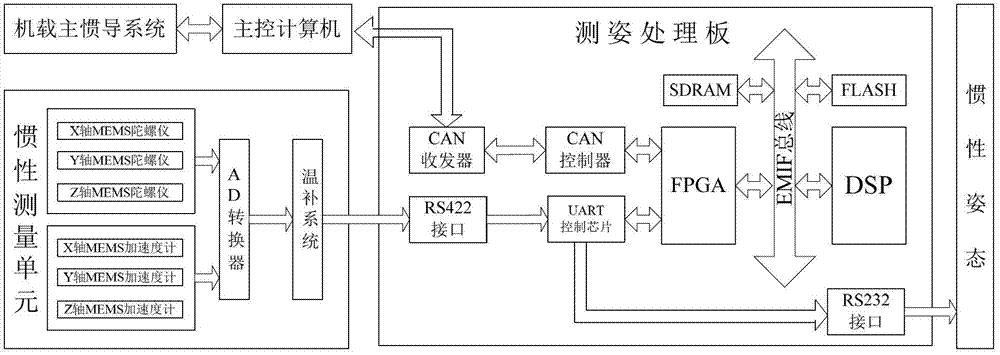

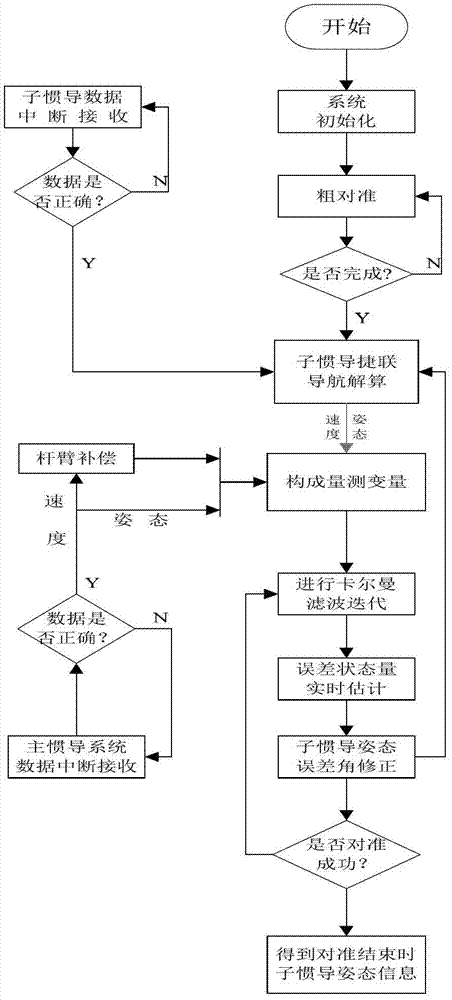

Airborne distributed inertial attitude measurement system and transfer alignment method of airborne distributed inertial attitude measurement system

ActiveCN103196448ALow costReduce volumeNavigation by speed/acceleration measurementsLN-3 Inertial Navigation SystemControl area

The invention relates to an airborne distributed inertial attitude measurement system and a transfer alignment method of the airborne distributed inertial attitude measurement system. The airborne distributed inertial attitude measurement system comprises a master inertial navigation system, a main control computer, and six slave inertial navigation systems connected with the main control computer, wherein each slave inertial navigation system respectively comprises an inertial measurement unit and an attitude measurement processing board, each inertial measurement unit is connected with an RS_422 interface of the corresponding attitude measurement processing board, each RS_422 interface is connected with an FPGA (Field Programmable Gate Array) chip through a UART (Universal Asynchronous Receiver / Transmitter) control chip, each FPGA chip is connected with a DSP (Digital Signal Processor) chip through an EMIF (External Memory Interface) bus and also connected with the master inertial navigation system through a CAN (Control Area Network) controller and a CAN transceiver, and the main control computer is connected with the master inertial navigation system. The transfer alignment method between the master inertial navigation system and each slave inertial navigation system of the airborne distributed inertial attitude measurement system comprises the steps of: by taking the speed information error and the attitude information error of the master inertial navigation system and the slave inertial navigation systems as measuring variables, correcting speed information and attitude information calculated by the slave inertial navigation systems after carrying out Kalman filtering iteration, and finally obtaining stable and accurate navigation attitude information.

Owner:NANJING UNIV OF SCI & TECH

Wireless connectivity in a radar detector

ActiveUS8373588B2Road vehicles traffic controlCommunication jammingData connectionNetwork Communication Protocols

Wireless and other external connectivity technology is used in various ways to enhance or improve upon existing radar detector and police activity detection systems. External memory interfaces, such as SD cards or USB, provide external storage. Wireless interfaces such as Bluetooth, Zigbee, 802.11, and wireless personal area network communication protocols, allow a detector processor to interact wirelessly with external devices, such as a Bluetooth headset, a cellular network device providing a server connection, or toggle buttons used to indicate the presence of police activity at a current position. Further, radar detectors are upgraded to provide GPS capabilities, using the existing power / data connector of the radar detector.

Owner:ESCORT INC

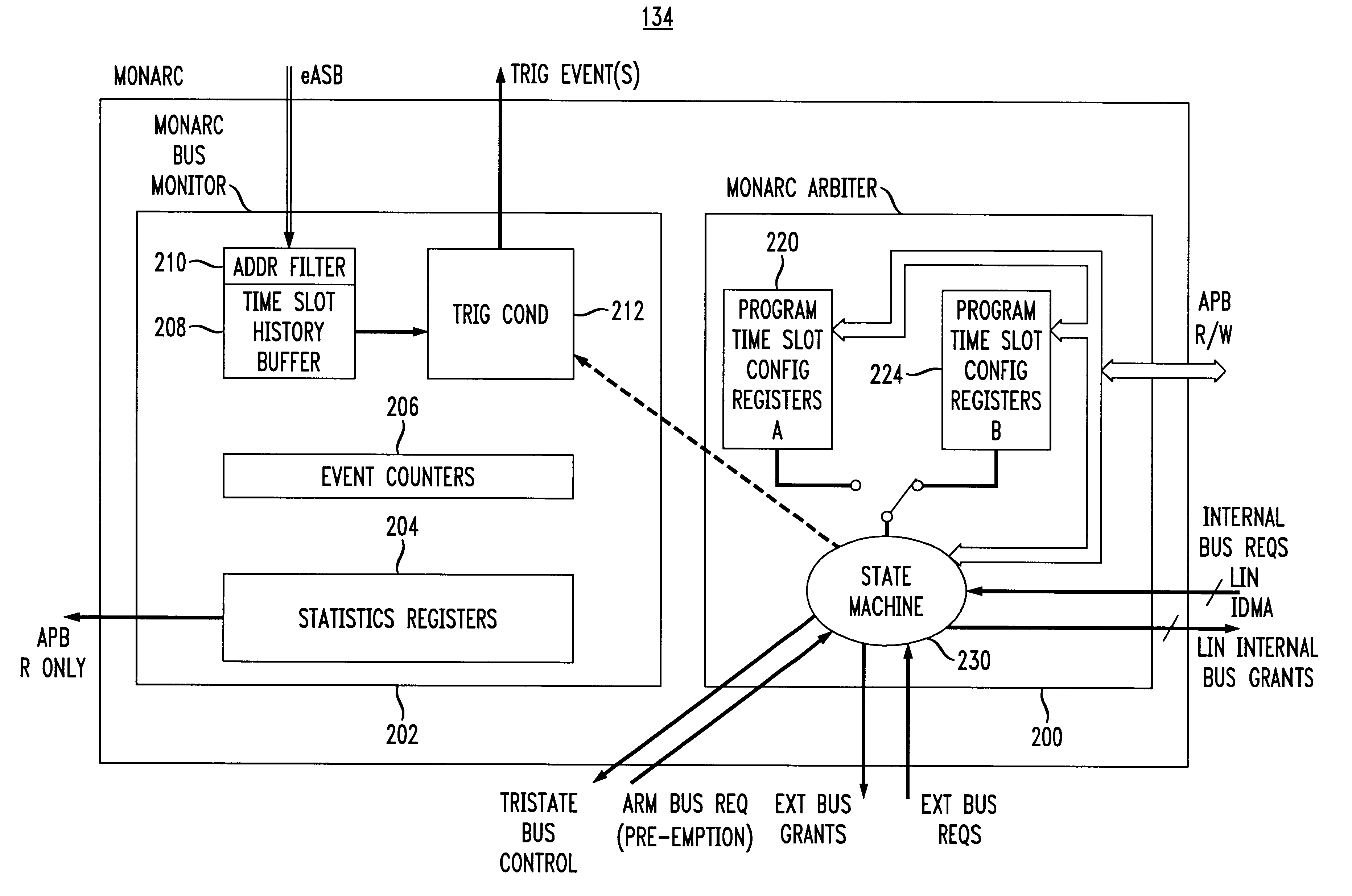

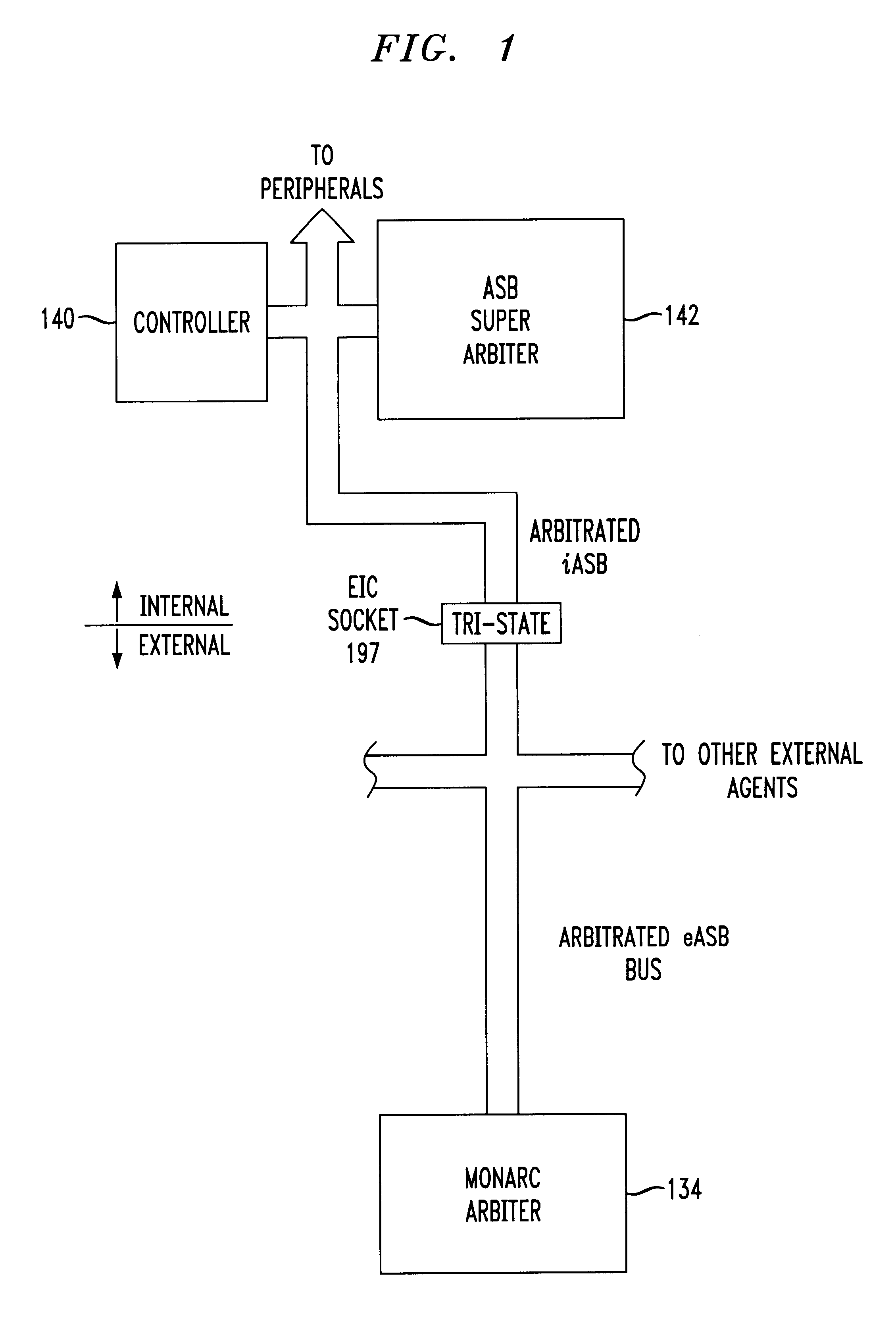

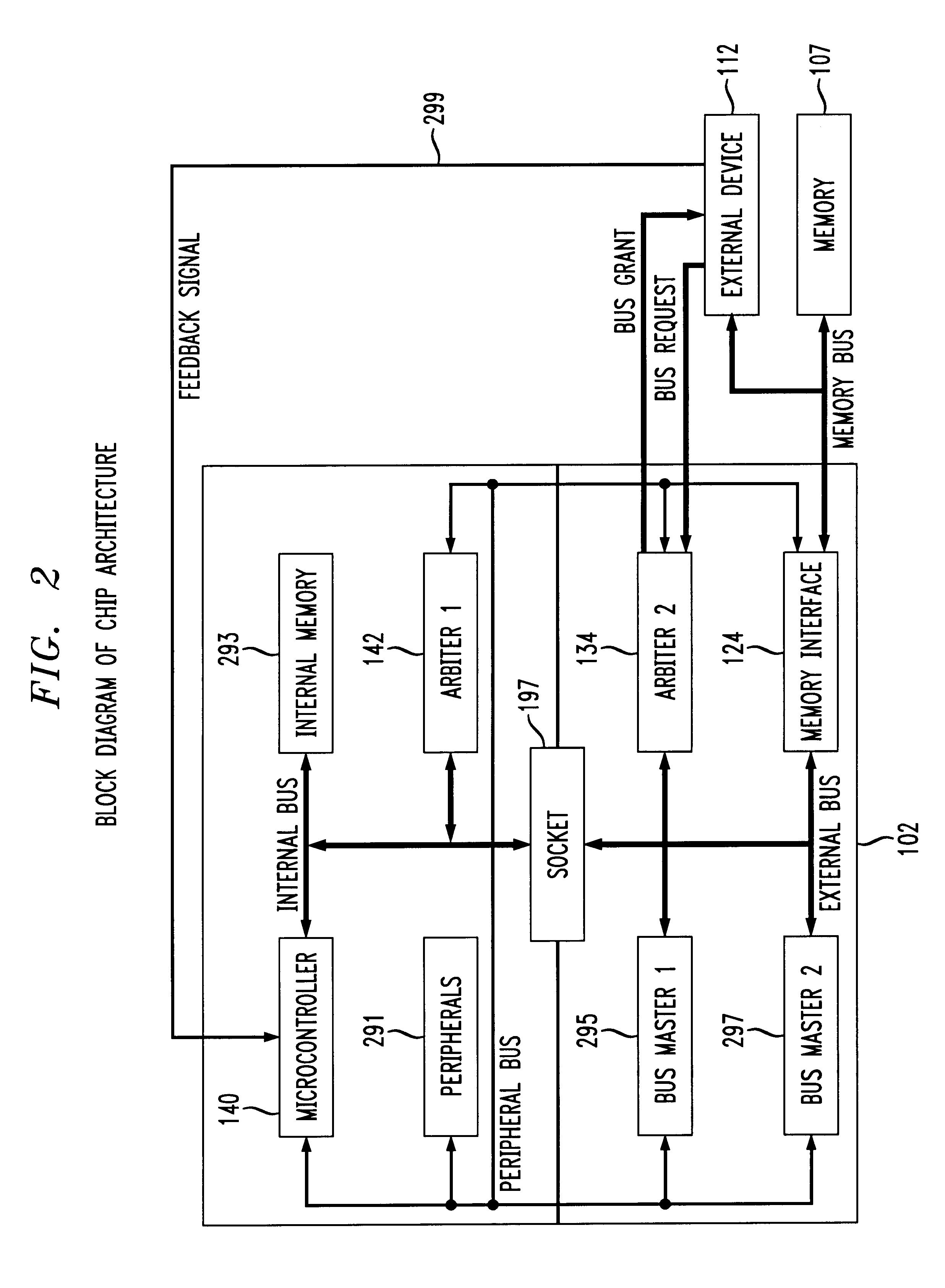

Shared devices and memory using split bus and time slot interface bus arbitration

A method and apparatus allowing efficient access control to a common data bus by including an isolation device to separate the common data bus, a priority-based arbiter to control access to the internal portion of the common data bus including a processor or other bus master, and a time slot arbiter to control access to the external portion of the common data bus including multiple bus masters, an external memory interface, etc. The common external memory may be allocated for exclusive or non-exclusive use by the various devices utilizing either portion of the isolated common data bus. External devices accessing the external memory may communicate directly with one or more bus masters, e.g., on the internal portion of the common data bus.

Owner:LUCENT TECH INC

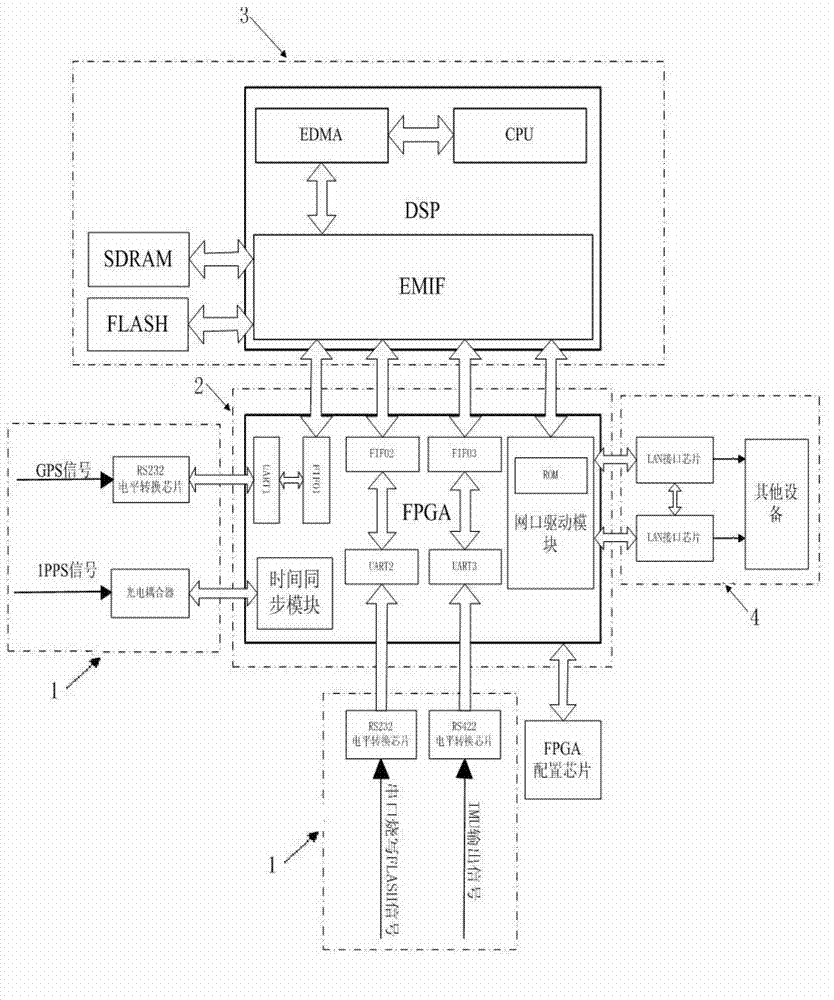

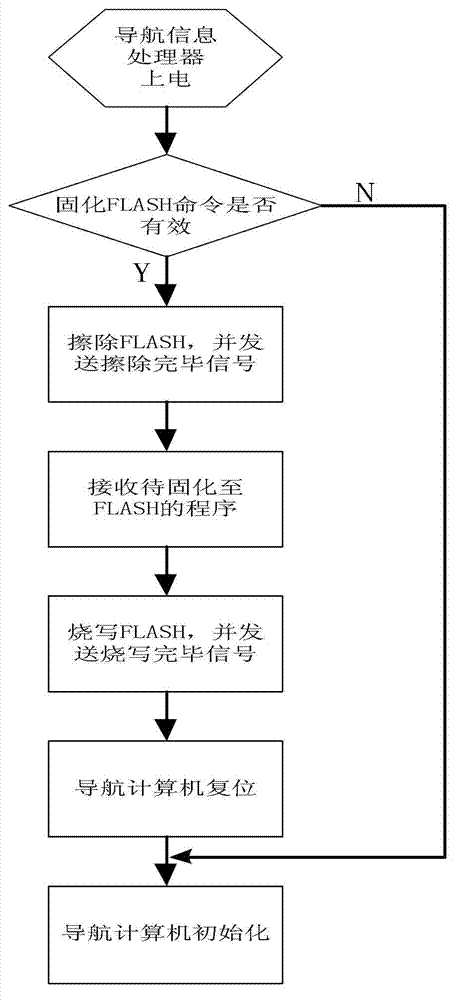

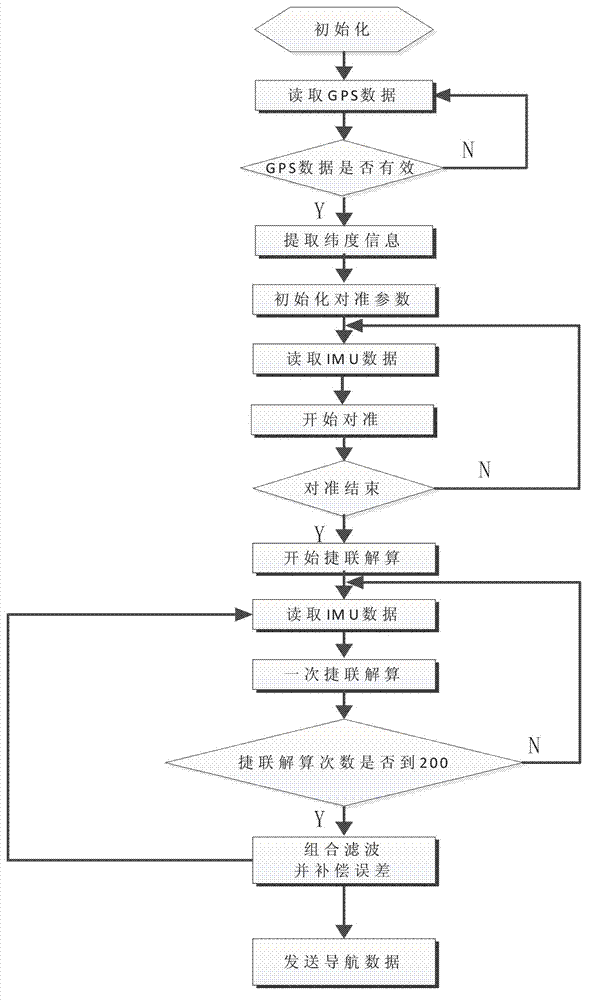

Embedded type navigation information processor based on DSP (digital signal processor) and FPGA (field programmable gata array)

ActiveCN103116175AQuick debuggingImprove debugging efficiencySatellite radio beaconingFilter algorithmData acquisition

The invention discloses an embedded type navigation information processor based on a DSP (digital signal processor) and an FPGA (field programmable gata array). The navigation information processor comprises a data acquisition module, a logic control management module, a navigation data processing module, a navigation data output module and a Flash program solidification module. The DSP of the navigation data processing module is connected with a Flash, an SDRAM (synchronous dynamic random access memory) and the FPGA outside the DSP through an EMIF (external memory interface). The Flash program solidification module is connected with an external development computer through a serial port. The data acquisition module acquires data and synchronizing signals output by an IMU (inertial measurement unit) and a GNSS (global navigation satellite system). Address decoding and time synchronization are carried out through the logic control management module, and the results are input to an SDRAM (synchronous dynamic random access memory) of the DSP. Strapdown calculating and filtering algorithm are carried out by the navigation data processing module. Navigation information data are sent to other application devices in the form of network messages through the navigation data processing module. The navigation information processor is a special navigation information processor hardware platform applicable to a strapdown inertial navigation system, and meets the requirements for miniaturization, low power consumption and high accuracy of an SINS (ship's inertial navigation system) / GNSS integrated navigation system.

Owner:SOUTHEAST UNIV

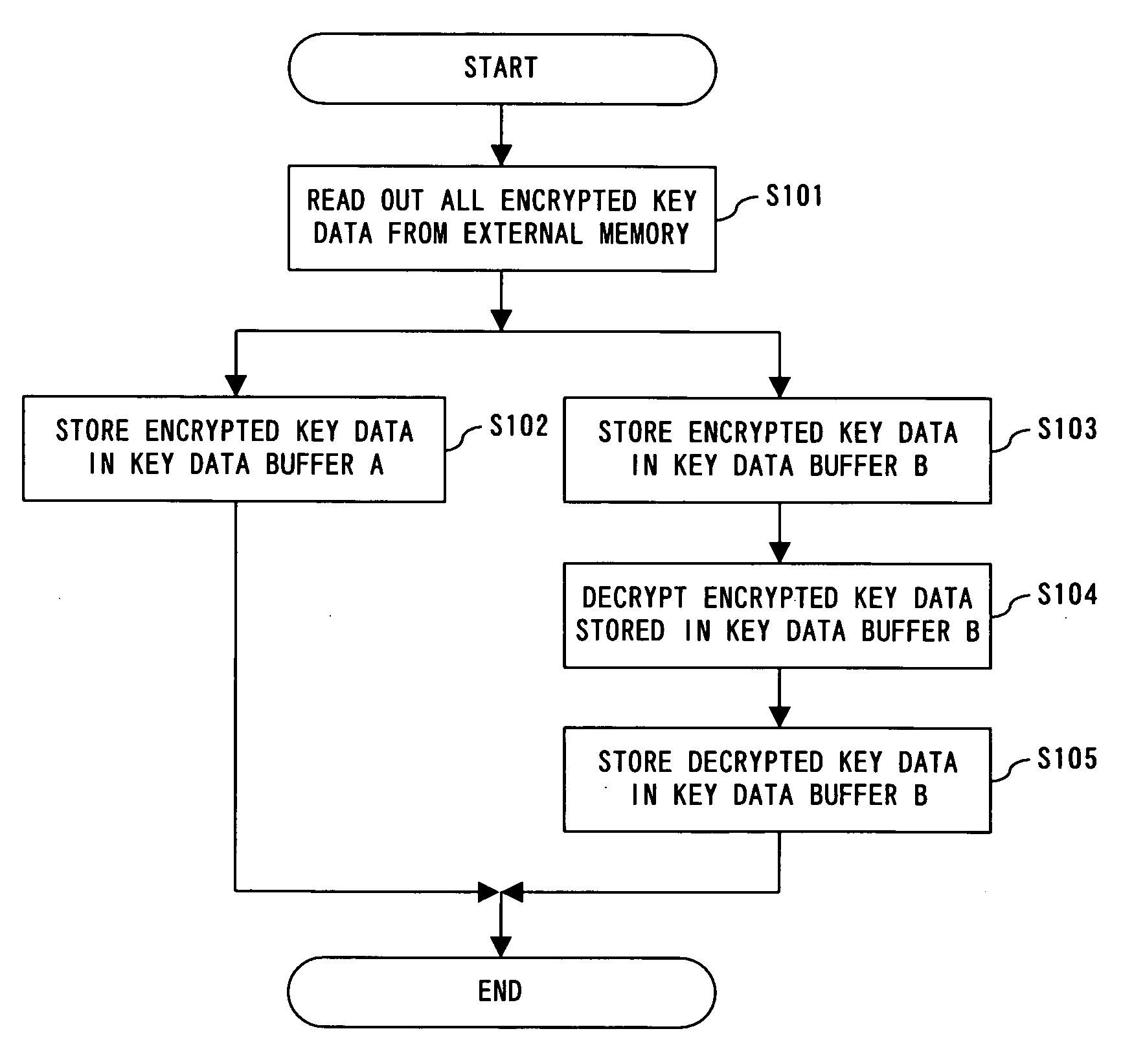

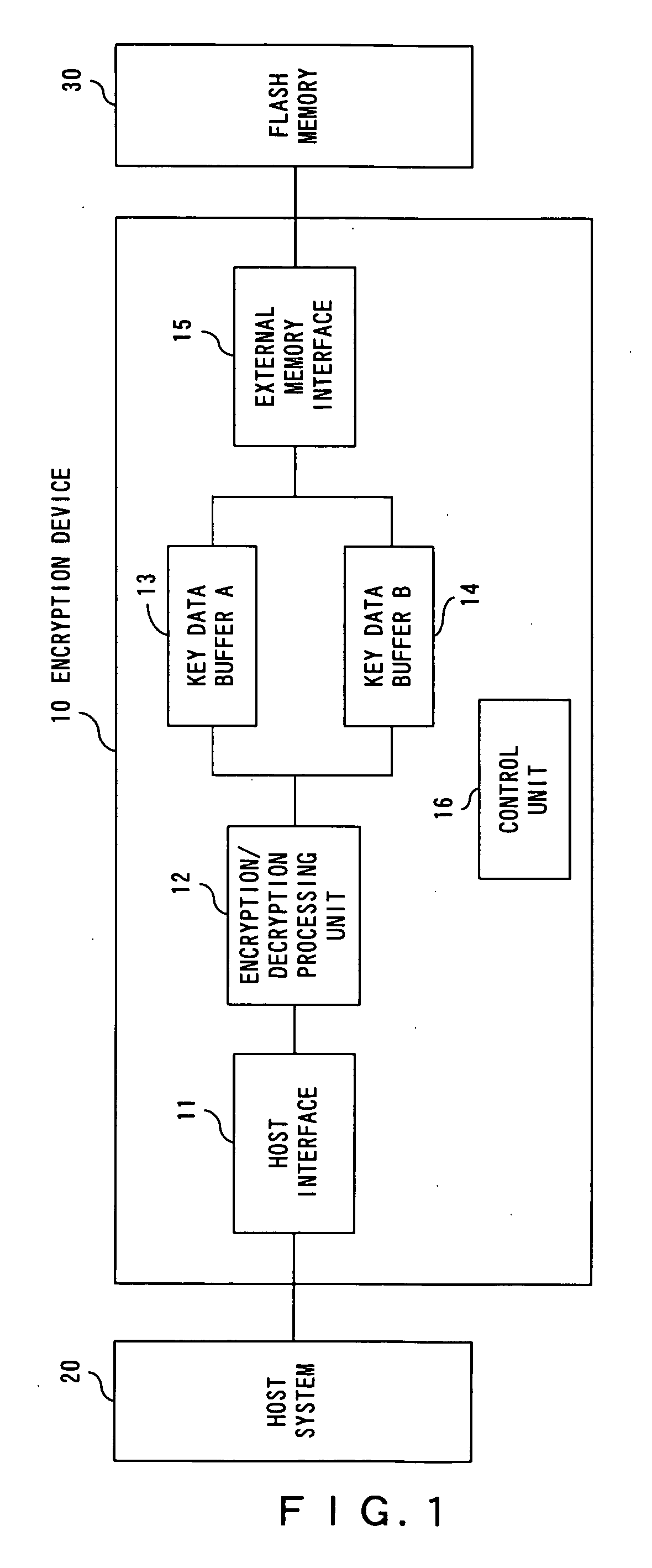

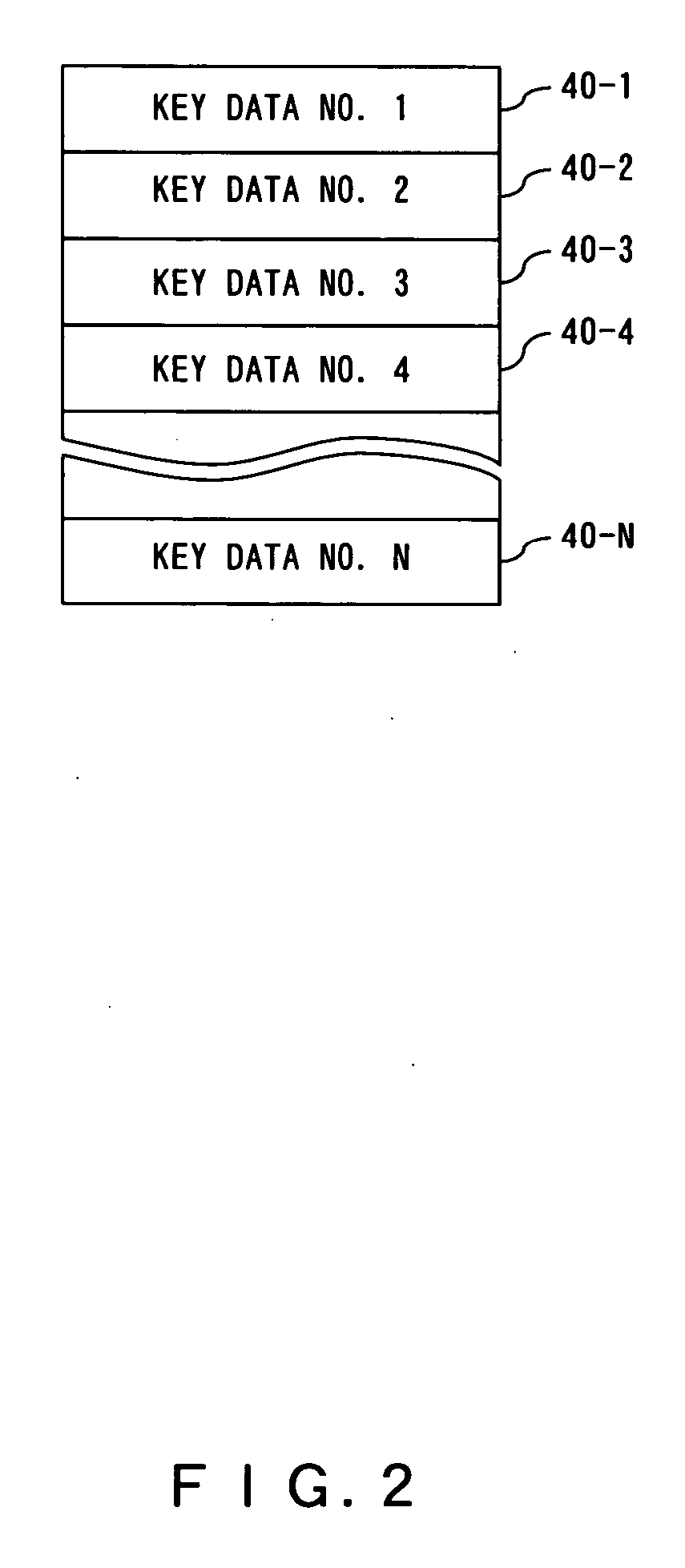

Encryption device

InactiveUS20070165864A1Processing speedReduce processing stepsKey distribution for secure communicationUnauthorized memory use protectionEncryption decryptionData storing

An encryption / decryption processing unit performs encryption / decryption processing of data transmitted from a host system, and encryption / decryption processing of key data used for encryption / decryption of the data. A key data buffer temporarily stores encrypted key data. A key data buffer temporarily stores unencrypted key data. An external memory interface controls flash memory attached outside, and reads / writes encrypted key data stored in the key data buffer.

Owner:SOCIONEXT INC

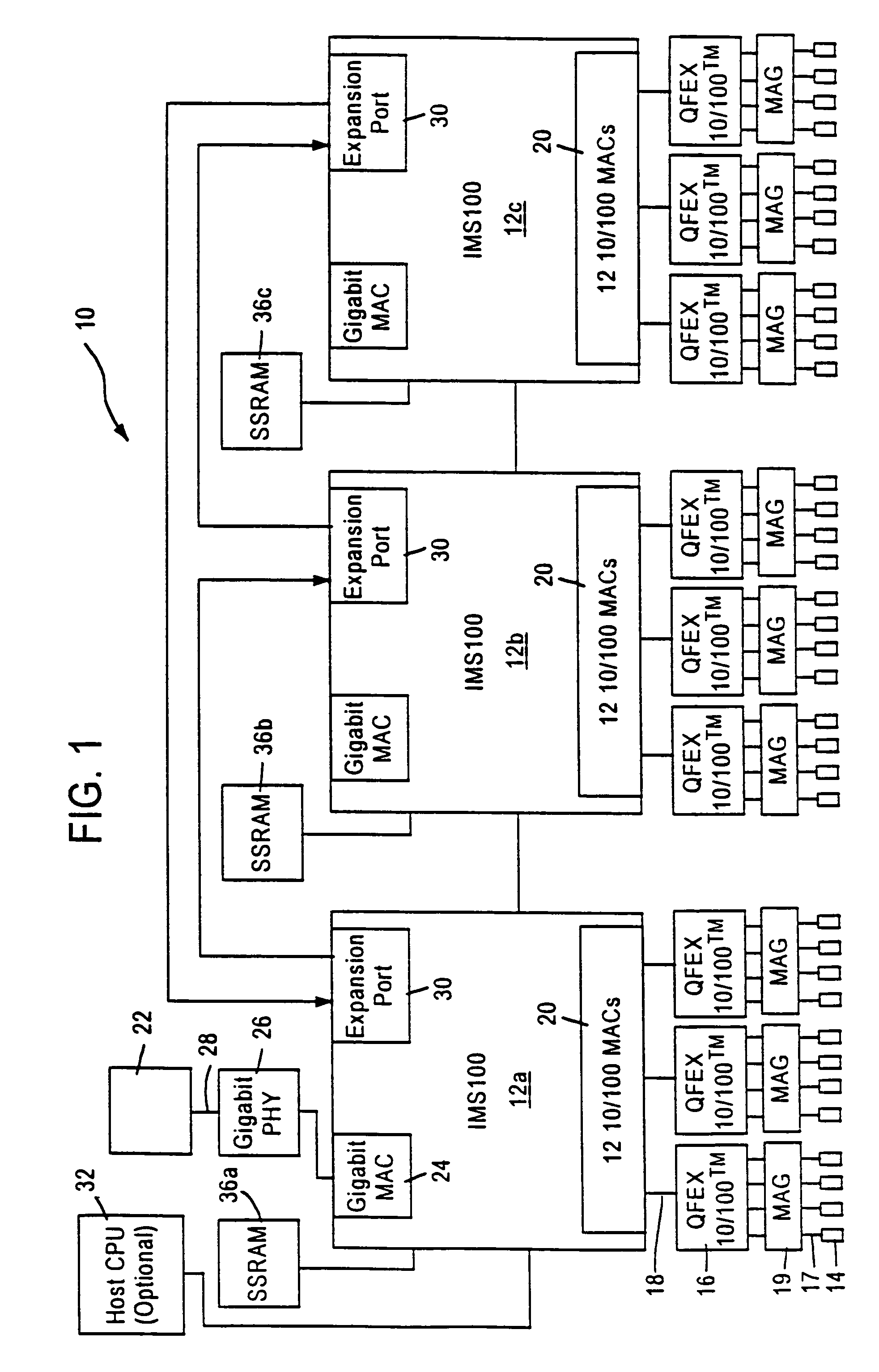

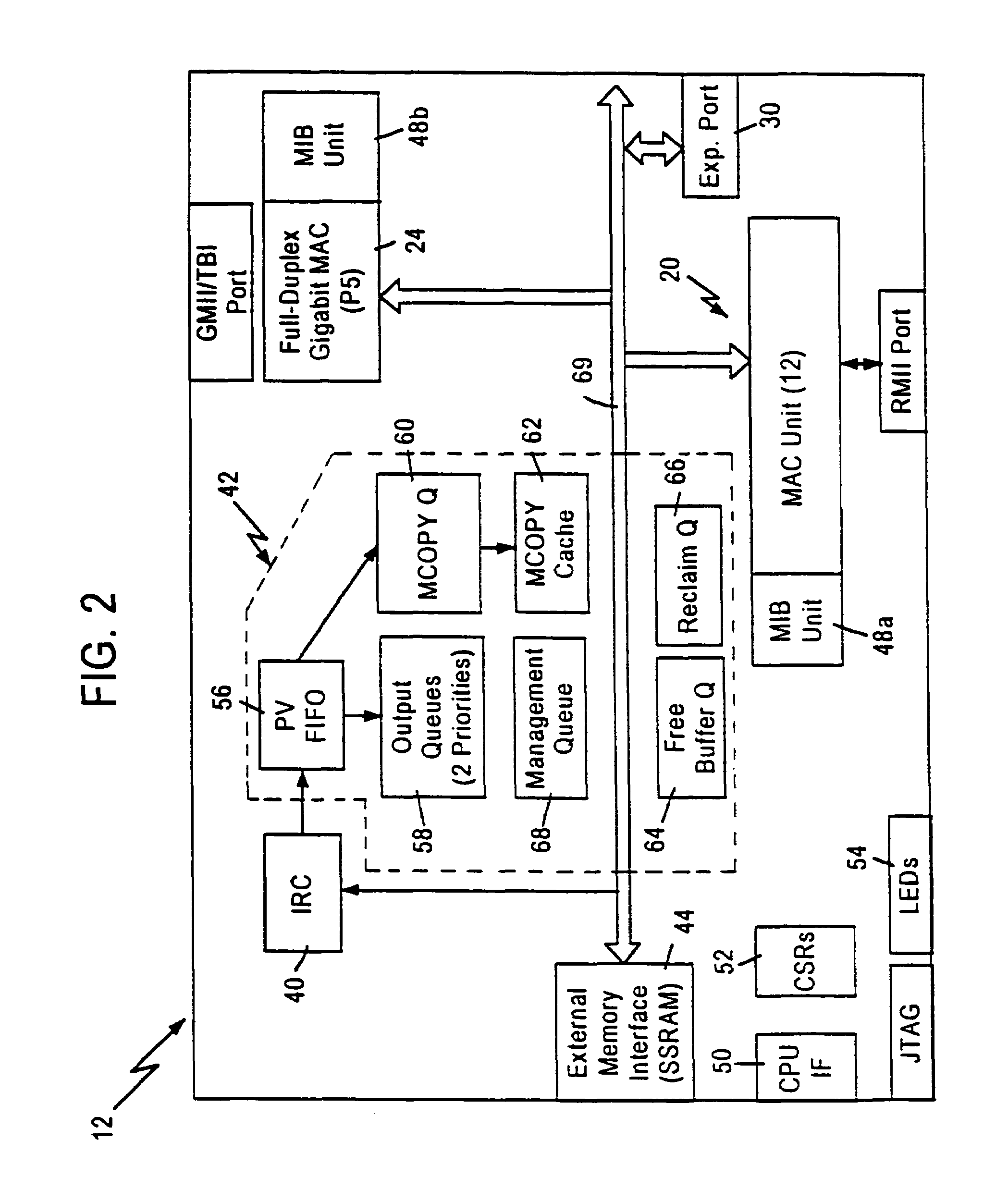

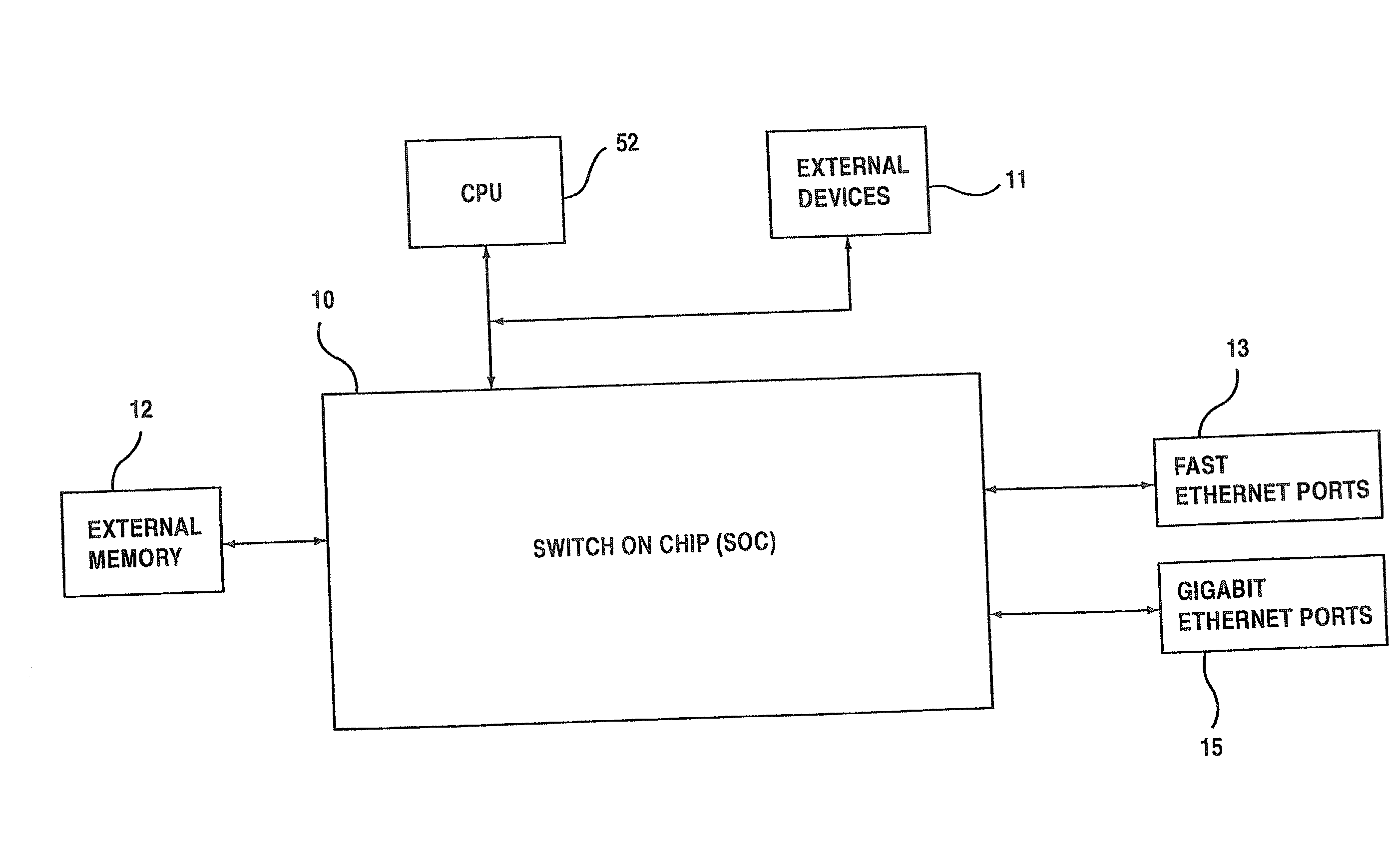

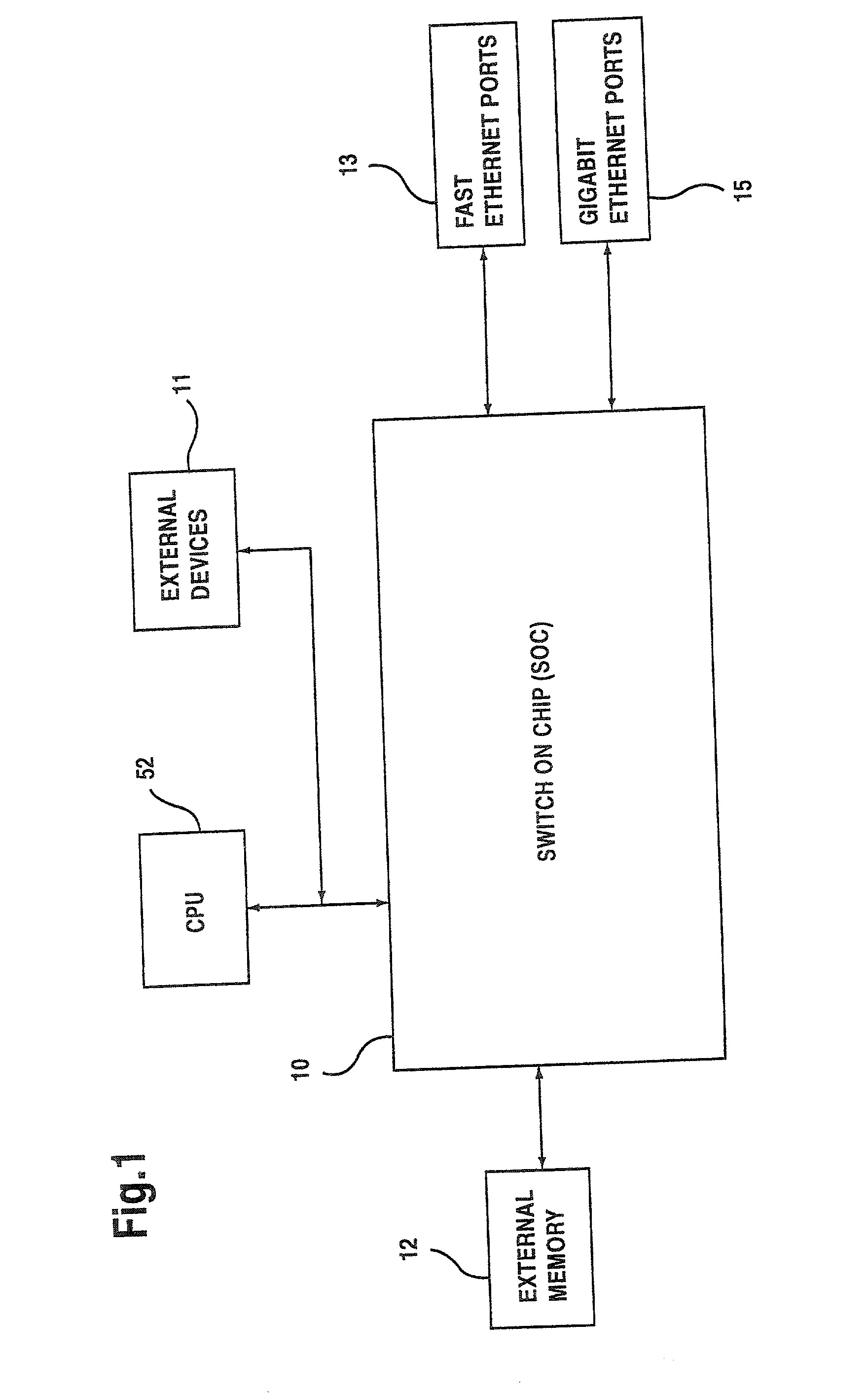

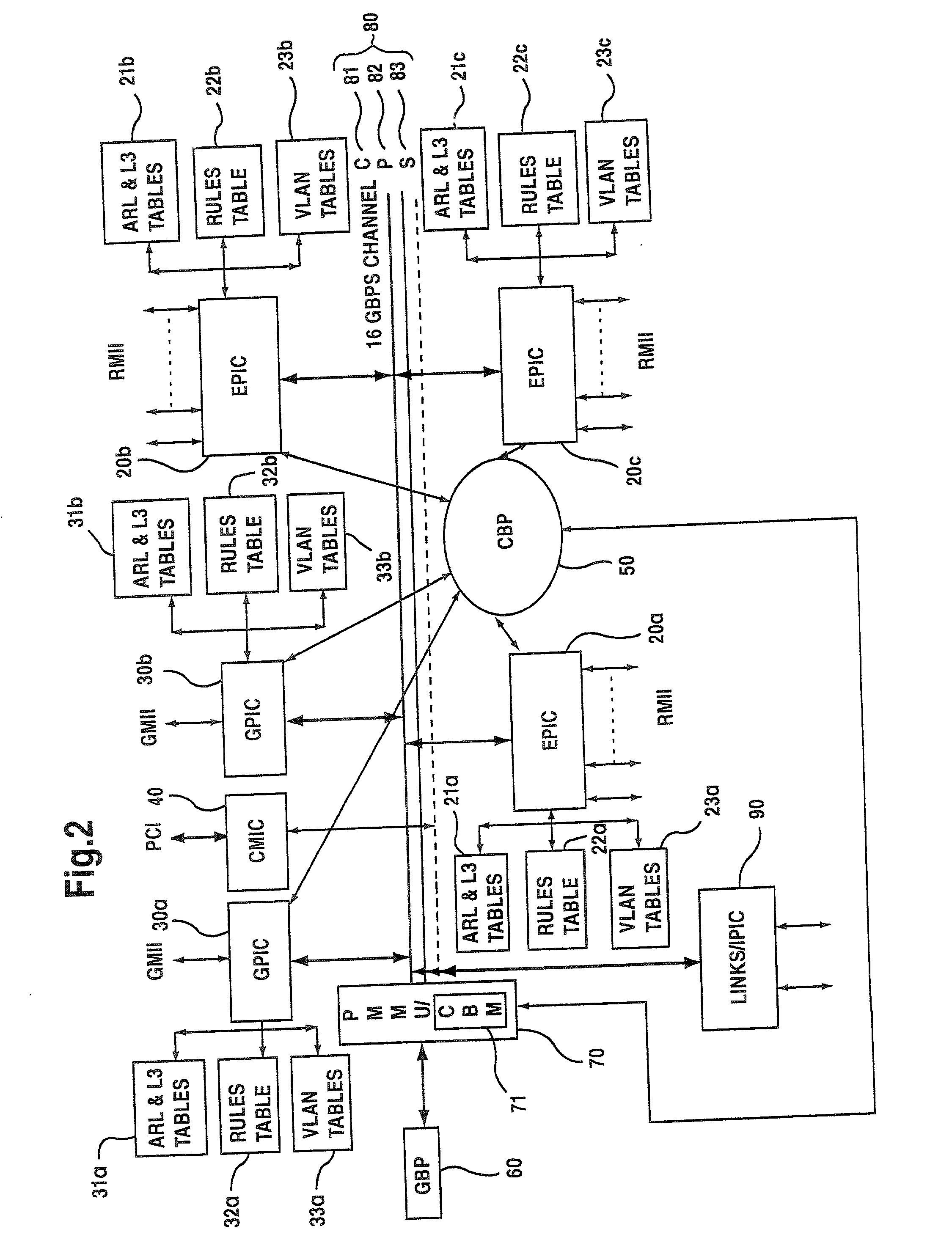

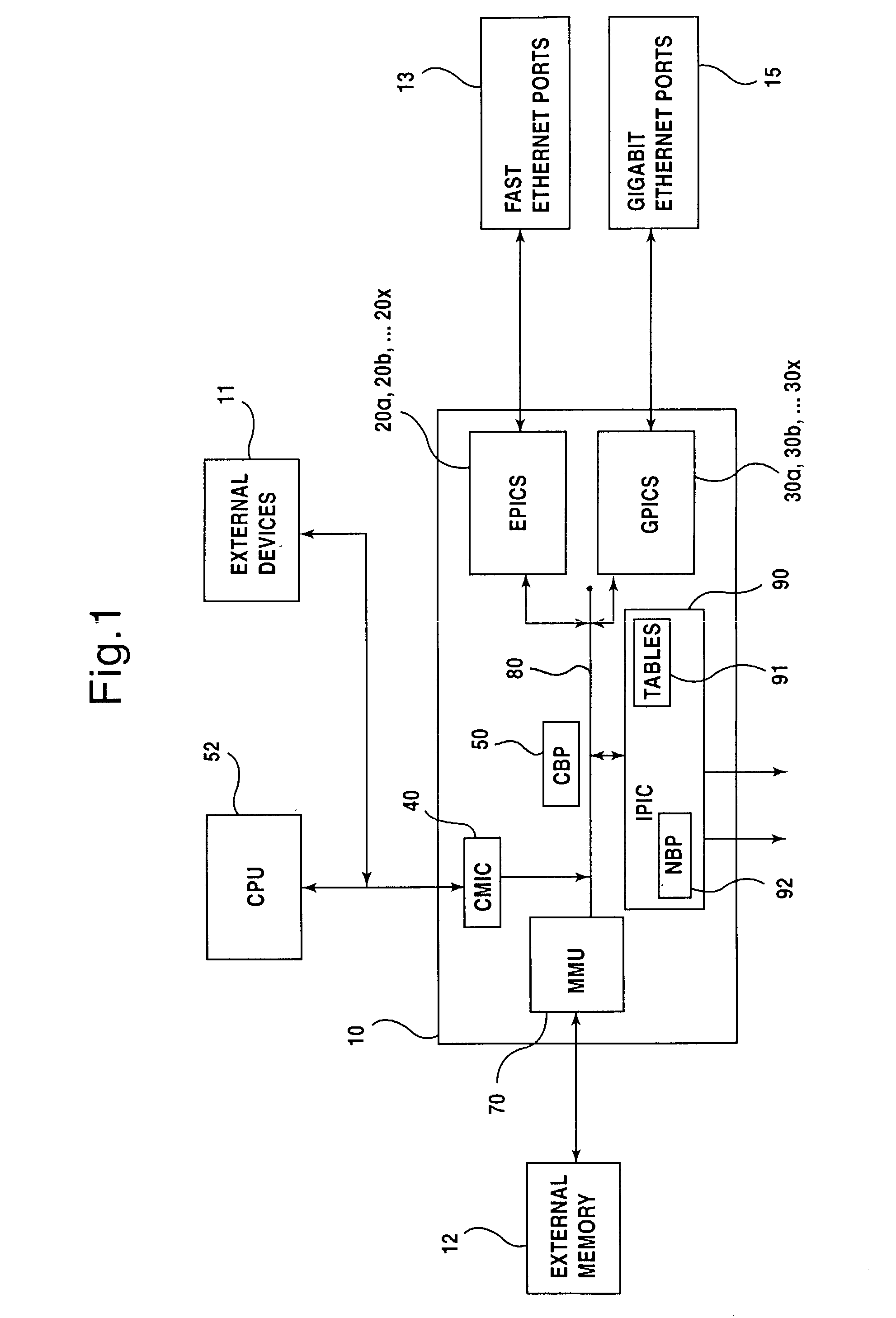

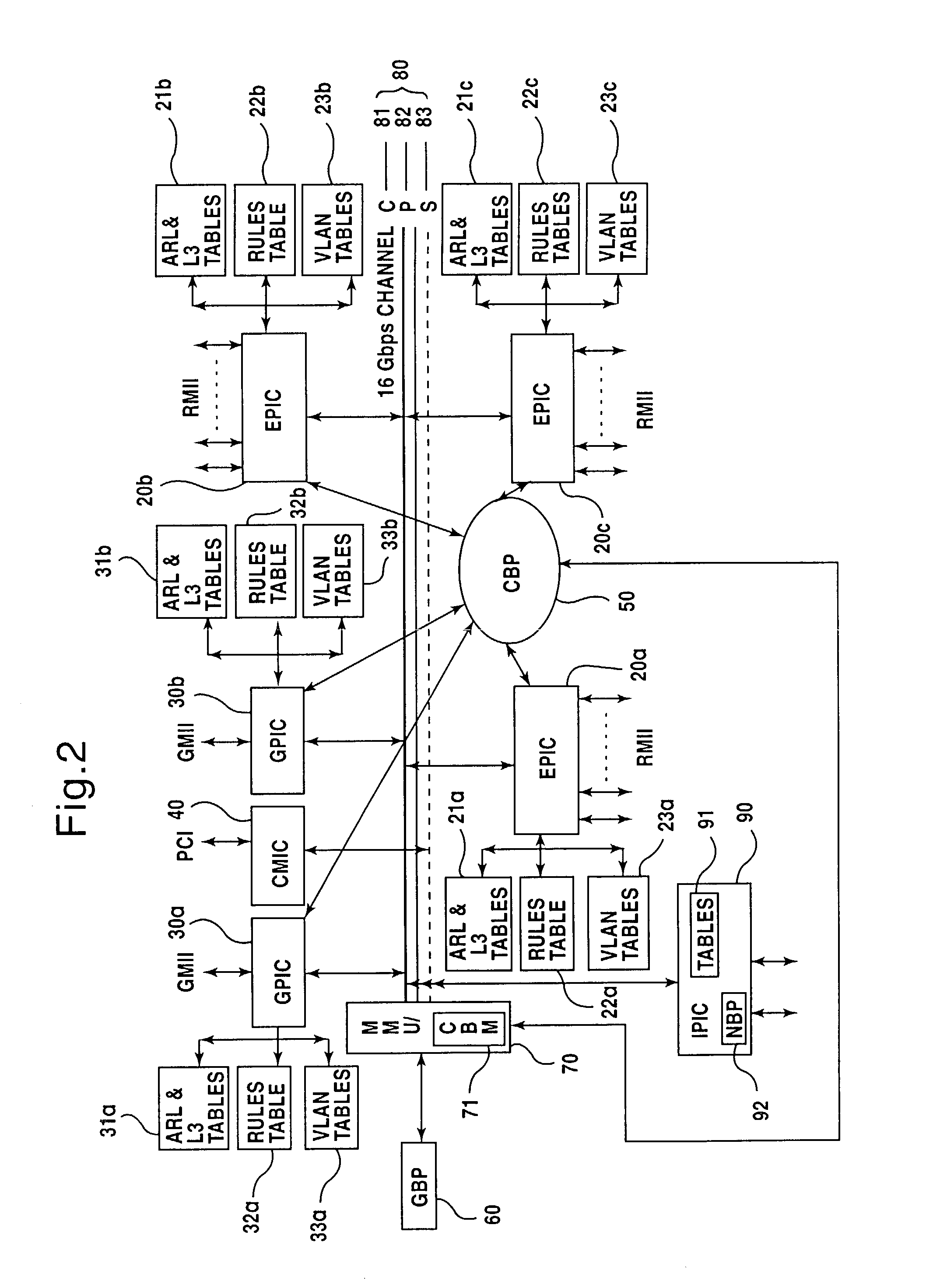

Network switching architecture with fast filtering processor

InactiveUS20020054604A1Special service provision for substationEnergy efficient ICTInternal memoryManagement unit

A network switch for network communications includes a first data port interface supporting a plurality of data ports transmitting and receiving data at a first data rate. A second data port interface supports a plurality of data ports transmitting and receiving data at a second data rate. A CPU interface is configured to communicate with a CPU, and an internal memory communicates with the first data port interface and the second data port interface. A memory management unit is provided, including an external memory interface, for communicating data from at least one of the first data port interface and the second data port interface and an external memory. A communication channel is provided, for communicating data and messaging information between the first data port interface, the second data port interface, the internal memory, and the memory management unit. One data port interface of the first data port interface and the second data port interface includes a fast filtering process, with the fast filtering processor filtering packets coming into the one data port interface. Selective filter action is taken based upon a filtering result.

Owner:AVAGO TECH INT SALES PTE LTD

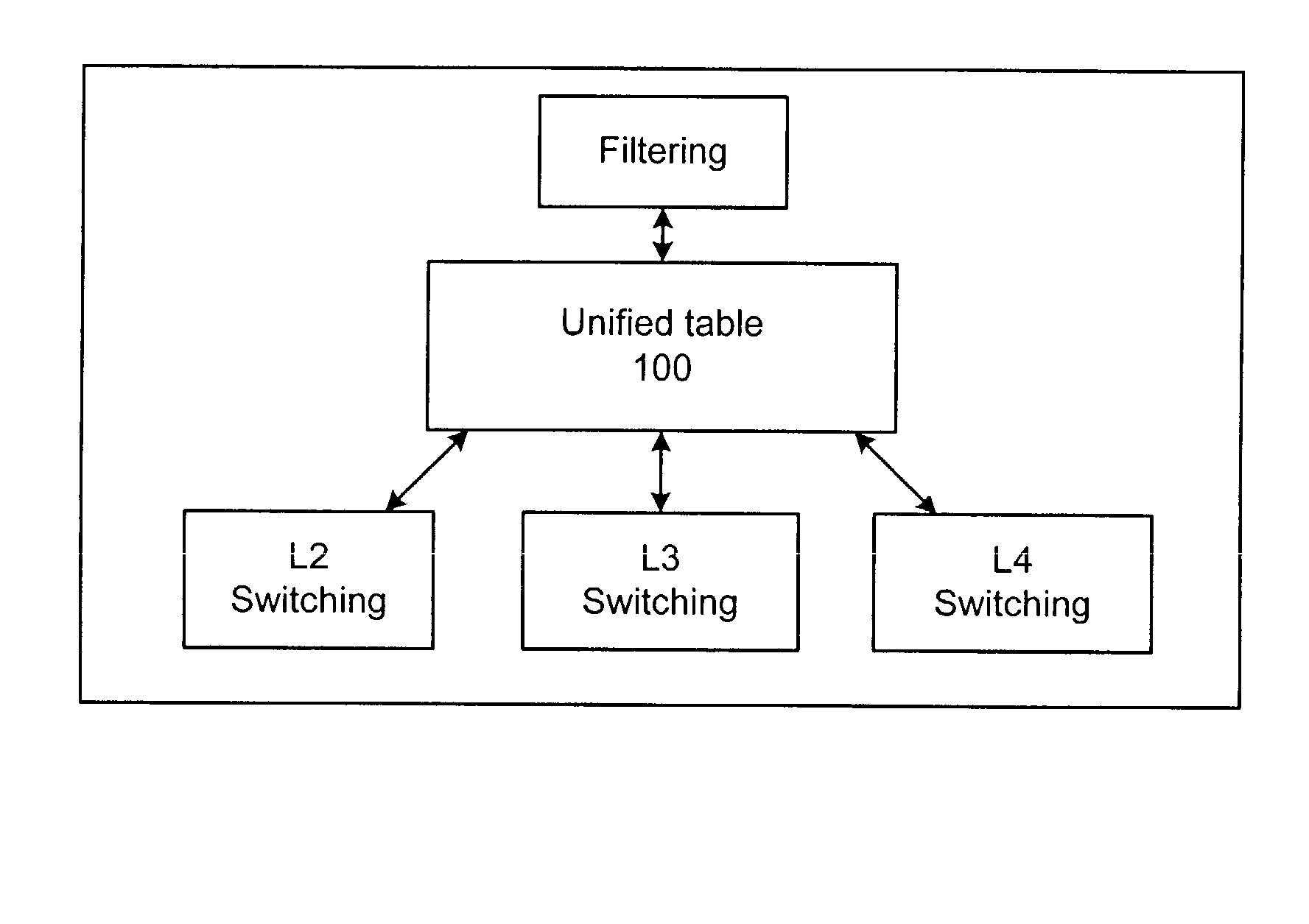

Unified table for L2, L3, L4, switching and filtering

InactiveUS7103055B2Special service provision for substationStore-and-forward switching systemsInternal memoryExternal storage

A network switch for network communications, wherein the network switch includes at least one data port interface supporting a plurality of data ports transmitting and receiving data at a first data rate and a second data rate. The at least one data port interface includes an ingress logic circuit in communication with the at least one data port interface for generating at least one of an ingress address resolution and a filtering search request. A CPU interface is provided and configured to communicate with a CPU. A shared hierarchical memory structure including an internal memory in communication with the at least one data port interface, and an external memory in communication with a memory management unit via an external memory interface is provided. A communication channel is provided for communicating data between the at least one data port interface, the internal memory, the CPU interface, and the memory management unit. Additionally, a unified table is provided, wherein the unified table is in connection with the communication channel, and the at least one data port interface. The unified table contains packet handling data for the network switch.

Owner:AVAGO TECH INT SALES PTE LTD

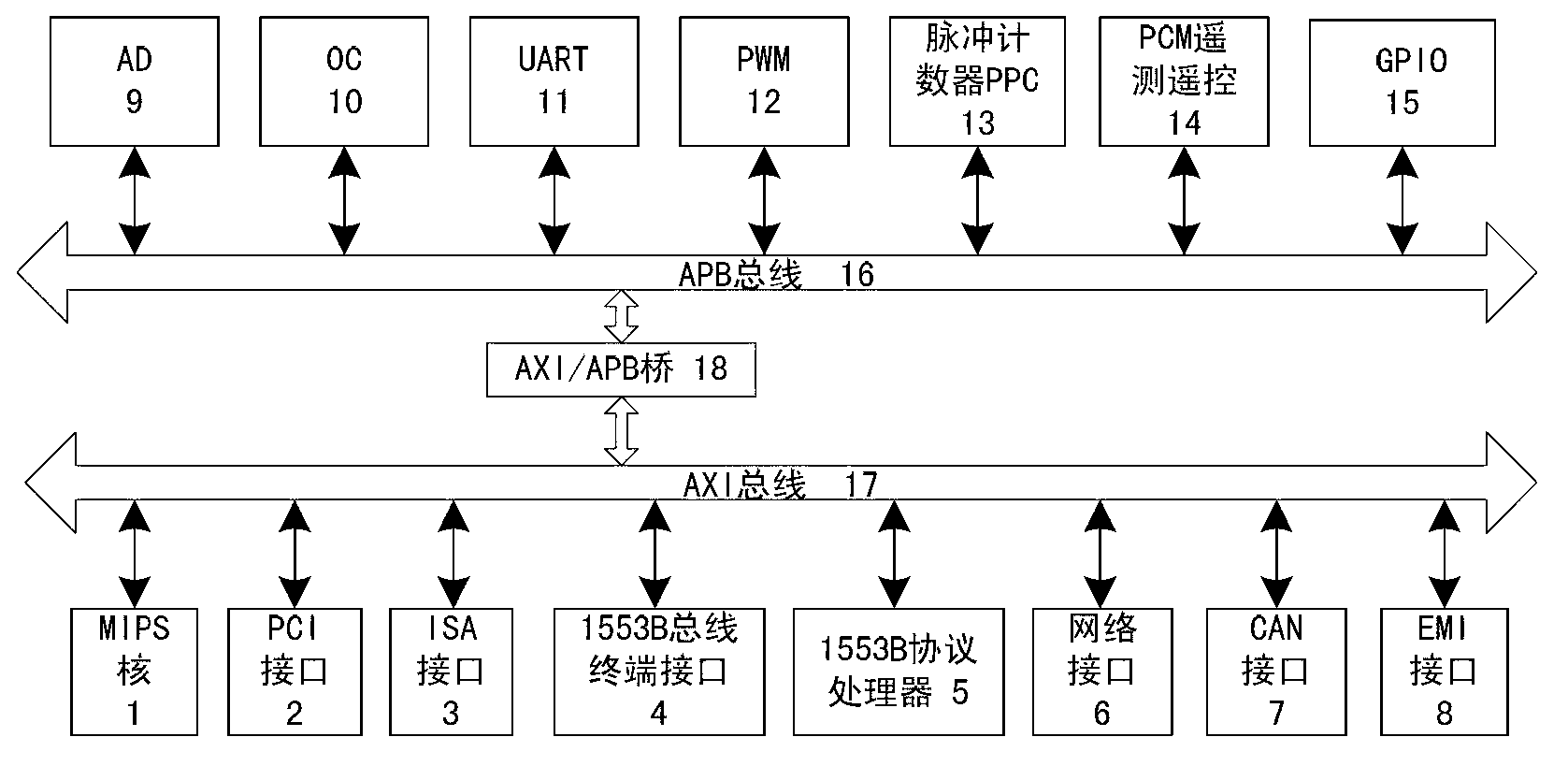

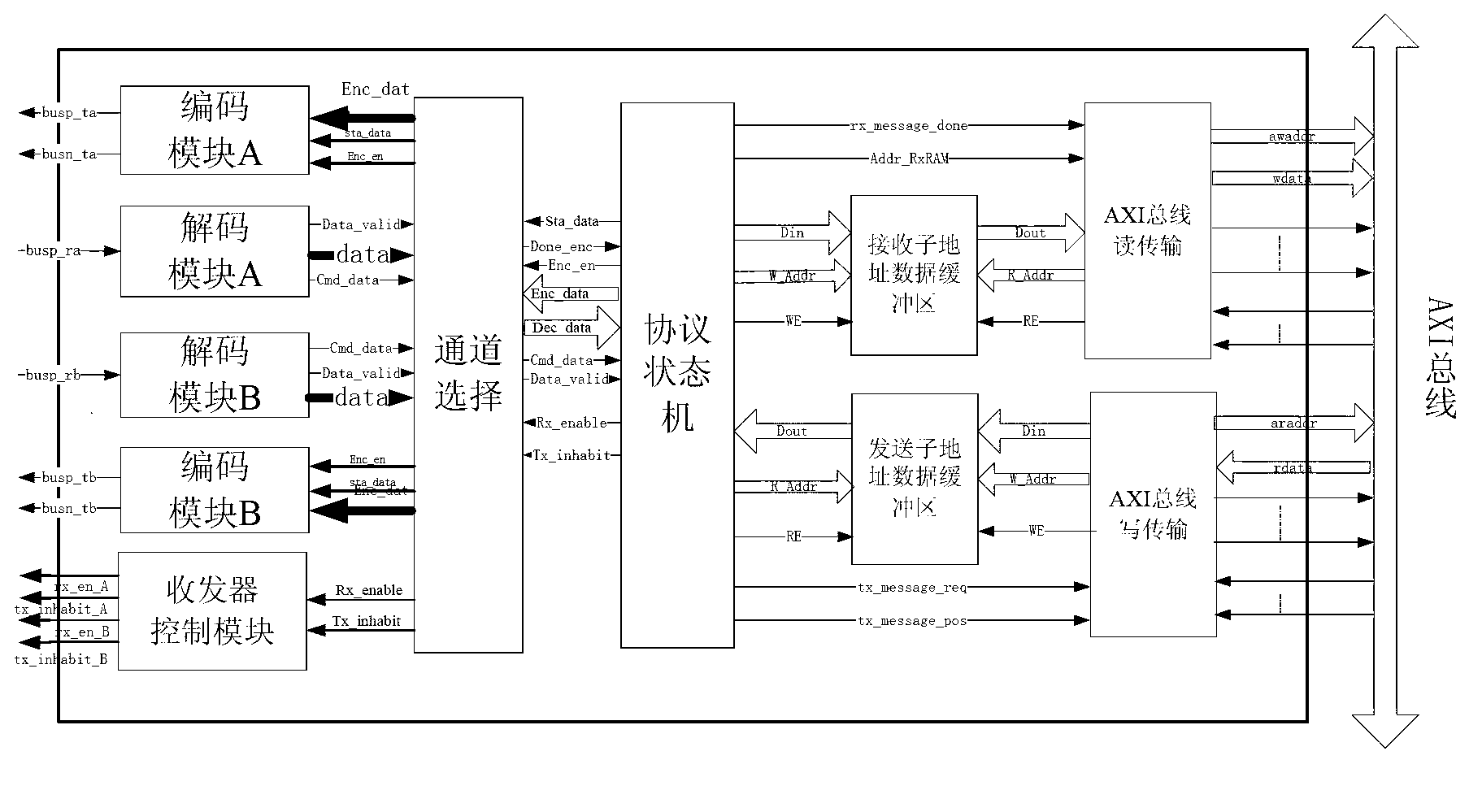

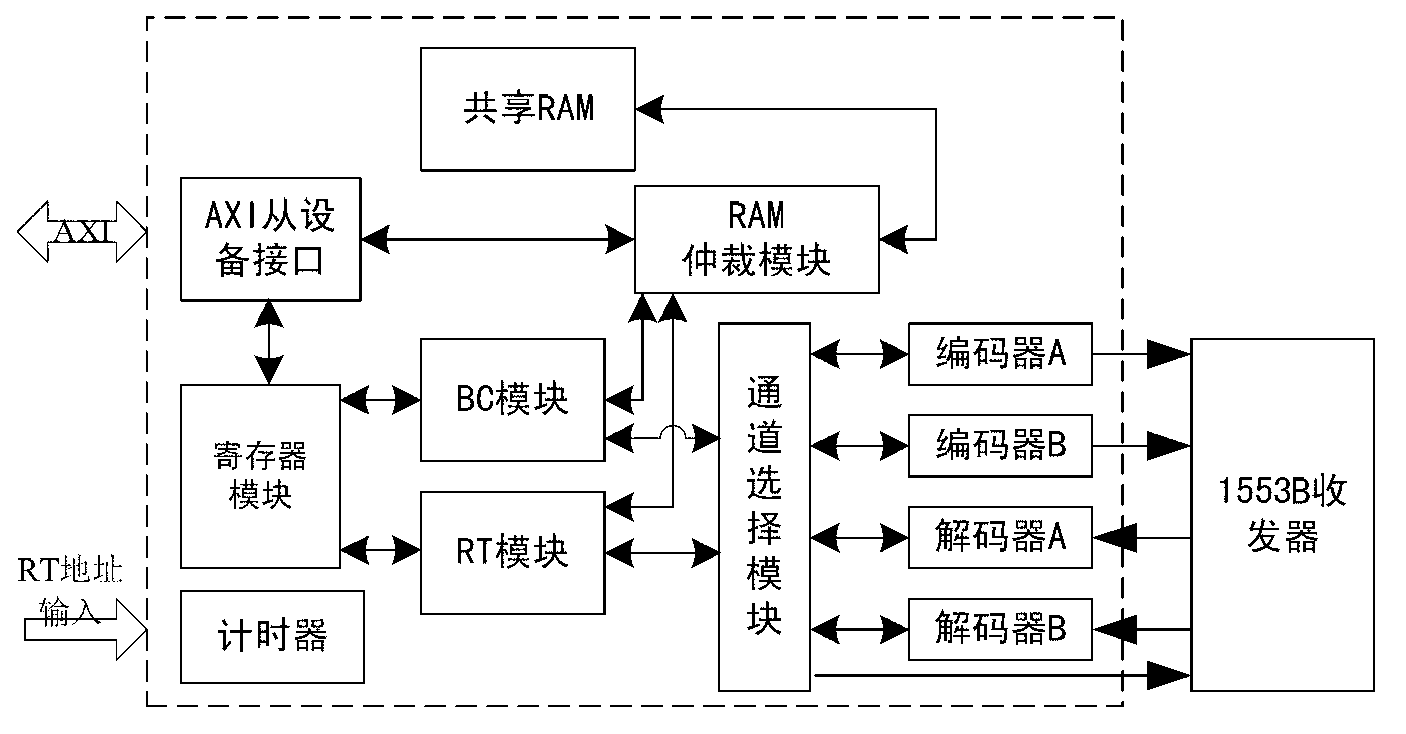

Special ASIC (Application Specific Integrated Circuit) chip system for spaceflight

ActiveCN102929836AHigh degree of integrationReduce mass volume power consumptionGeneral purpose stored program computerArea networkAdvanced Microcontroller Bus Architecture

The invention relates to a special ASIC (Application Specific Integrated Circuit) chip system for spaceflight. The special ASIC chip system comprises a MIPS (Million Instructions Per Second) nucleus, a PCI (Programmable Communications Interface) bus interface, an ISA (Internet Security And Acceleration) bus interface, a 1553B bus terminal interface, a 1553B protocol processor, a network interface, a CAN (Controller Area Network) interface, an EMI (External Memory Interface), AD acquisition control logic, OC door control logic, UART (Universal Asynchronous Receiver / Transmitter) serial port, PWM (Pulse Width Modulation) interface, a pulse counter PPC, PCM (Pulse Code Modulation) telemetry remote control module and a general input / output module, wherein the MIPS nucleus, the PCI bus interface, the ISA bus interface, the 1553B bus terminal interface, the 1553B protocol processor, a network interface, the CAN interface and the EMI are connected to an AMBA AXI (Advanced Microcontroller Bus Architecture Advanced eXtensible Interface) bus; and the AD acquisition control logic, the OC door control logic, the UART serial port, the PWM interface, the pulse counter PPC, the PCM telemetry remote control module and the general input / output module are connected to an AMBA APB (All Points Bulletin) bus; and the AMBA AXI bus is connected with the AMBA APB bus through an AXI / APB bridge.

Owner:NAT SPACE SCI CENT CAS

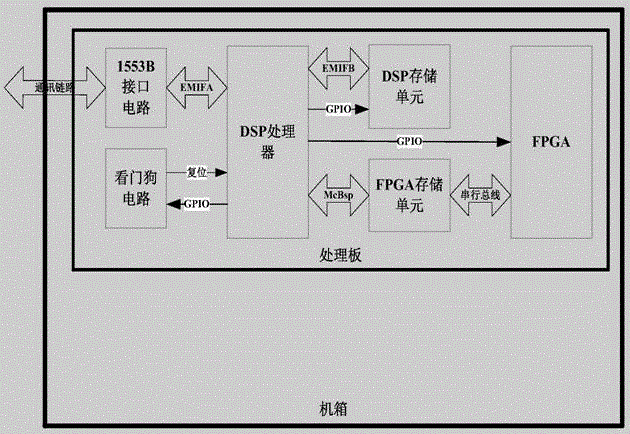

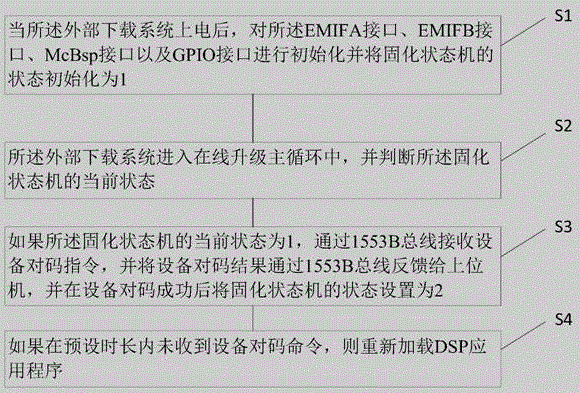

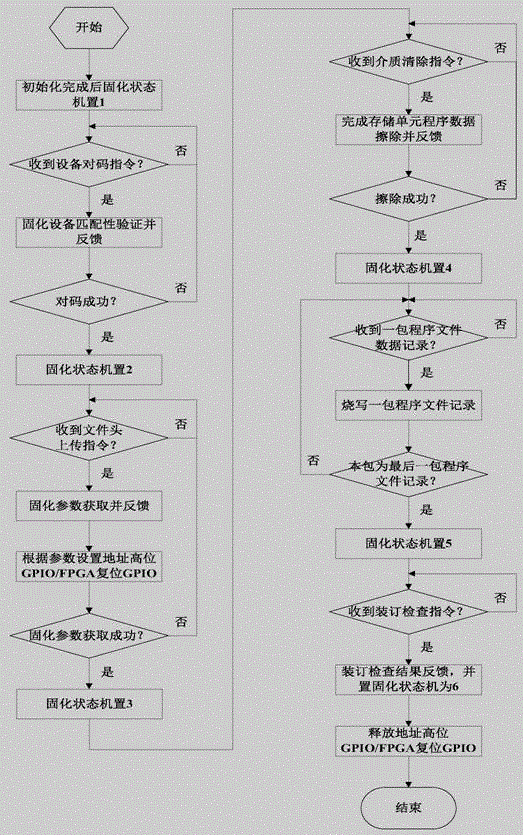

Method and system for external download of DSP (digital signal processor) program and FPGA (field programmable gate array) program

InactiveCN106547574AIncrease storage spaceImprove reliabilityVersion controlProgram documentationFpga field programmable gate arrayDsp processor

The invention provides a method and a system for external download of a DSP (digital signal processor) program and an FPGA (field programmable gate array) program. The system comprises a 1553B interface circuit, a DSP processor, a DSP storage unit, a watchdog circuit, an FPGA and an FPGA storage unit. The 1553B interface circuit is connected with the DSP processor through an EMIFA (external memory interface A), the watchdog circuit is connected with the DSP processor through a GPIO (general purpose input / output) interface, and the DSP storage unit is connected with the DSP processor through an EMIFB (external memory interface B) and a GPIO interface. The FPGA storage unit is connected with the DSP processor through a McBsp interface, the DSP processor is connected with the FPGA through a GPIO interface, and the FPGA storage unit is connected with the FPGA through a serial bus. The method and the system for external download of the DSP program and the FPGA program have the advantage that practicability, reliability and real-time performance of the system for external download can be improved.

Owner:SPACE STAR TECH CO LTD

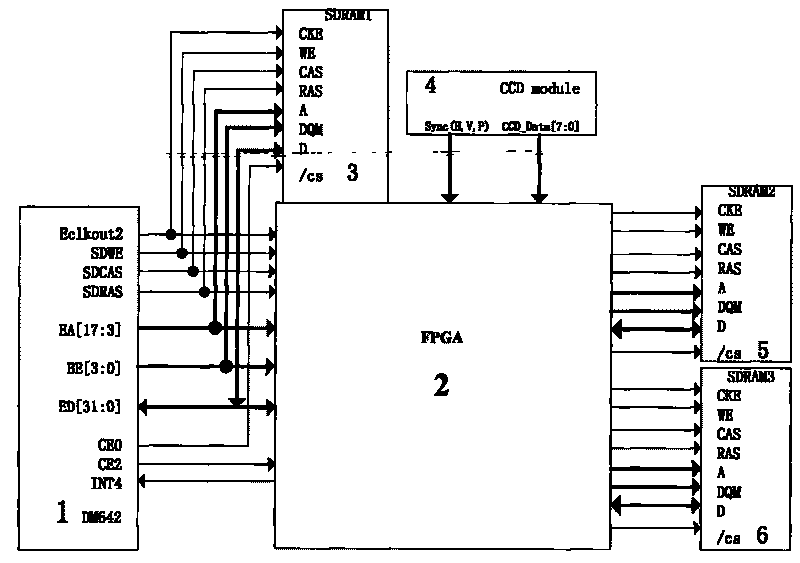

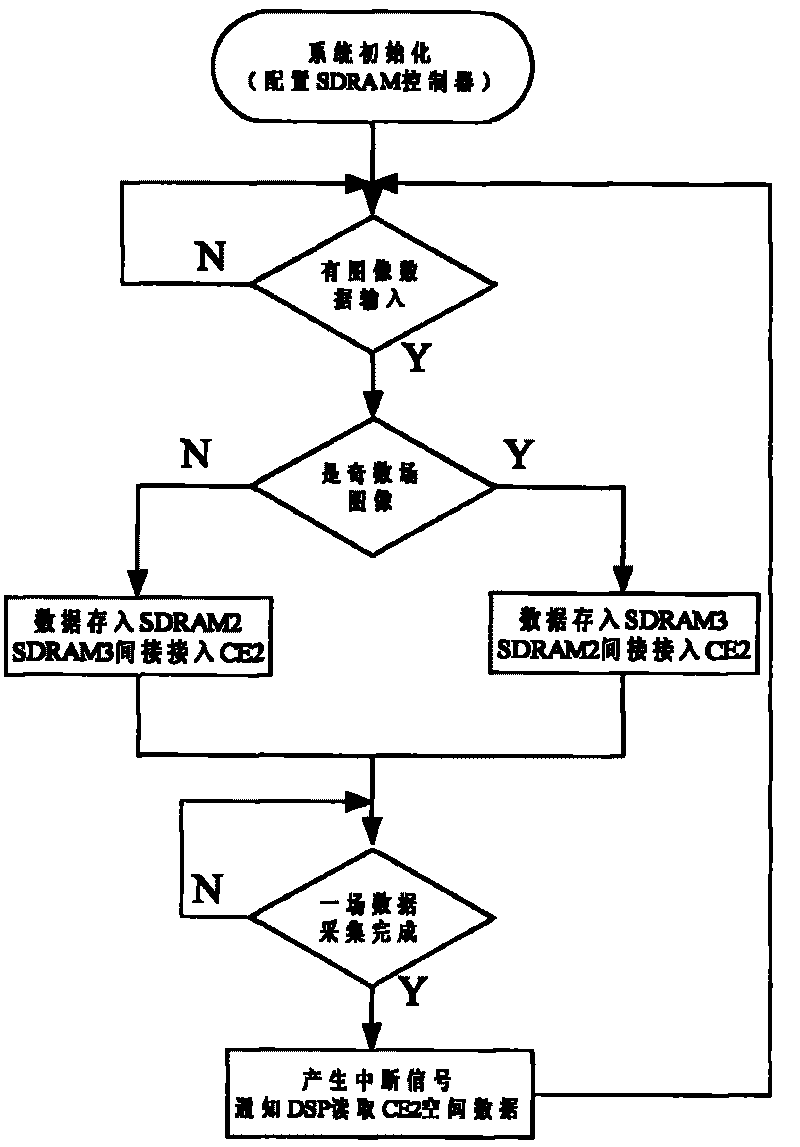

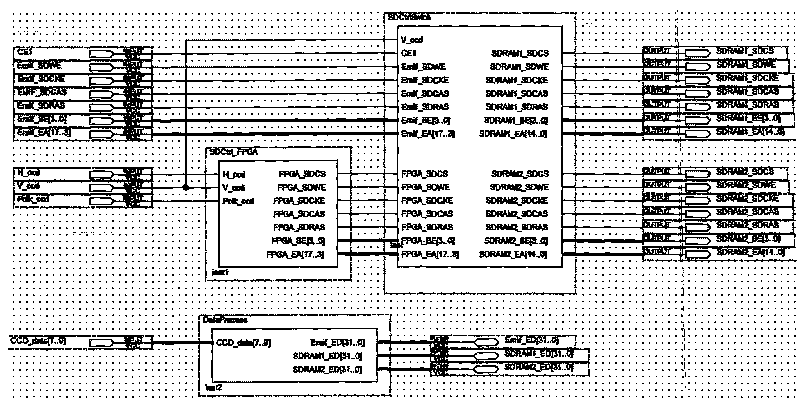

Structure and method for improving speed of external memory interface of high-definition image real-time collecting system DSP

InactiveCN101694609AImprove transmission efficiencyShorten the timeTelevision system detailsInput/output to record carriersControl signalMemory interface

The invention relates to a structure and a method for improving the speed of an external memory interface of a high-definition image real-time collecting system DSP. The structure comprises a system core processor DM642, a FPGA, a CCD collecting module and three memory devices. The method comprises the steps that the data bus between the DSP and two SDRAMs is alternatively switched by the FPGA so as to realize the dual-cache ping-pong operation of the image data, and a writing control signal is generated by the FPGA so as to directly write the CCD data in the two SDRAMs. The structure and the method complete the real-time collecting task of the high-definition images and greatly improve the switching speed of the EMIF bus data.

Owner:上海凯意电子科技有限公司

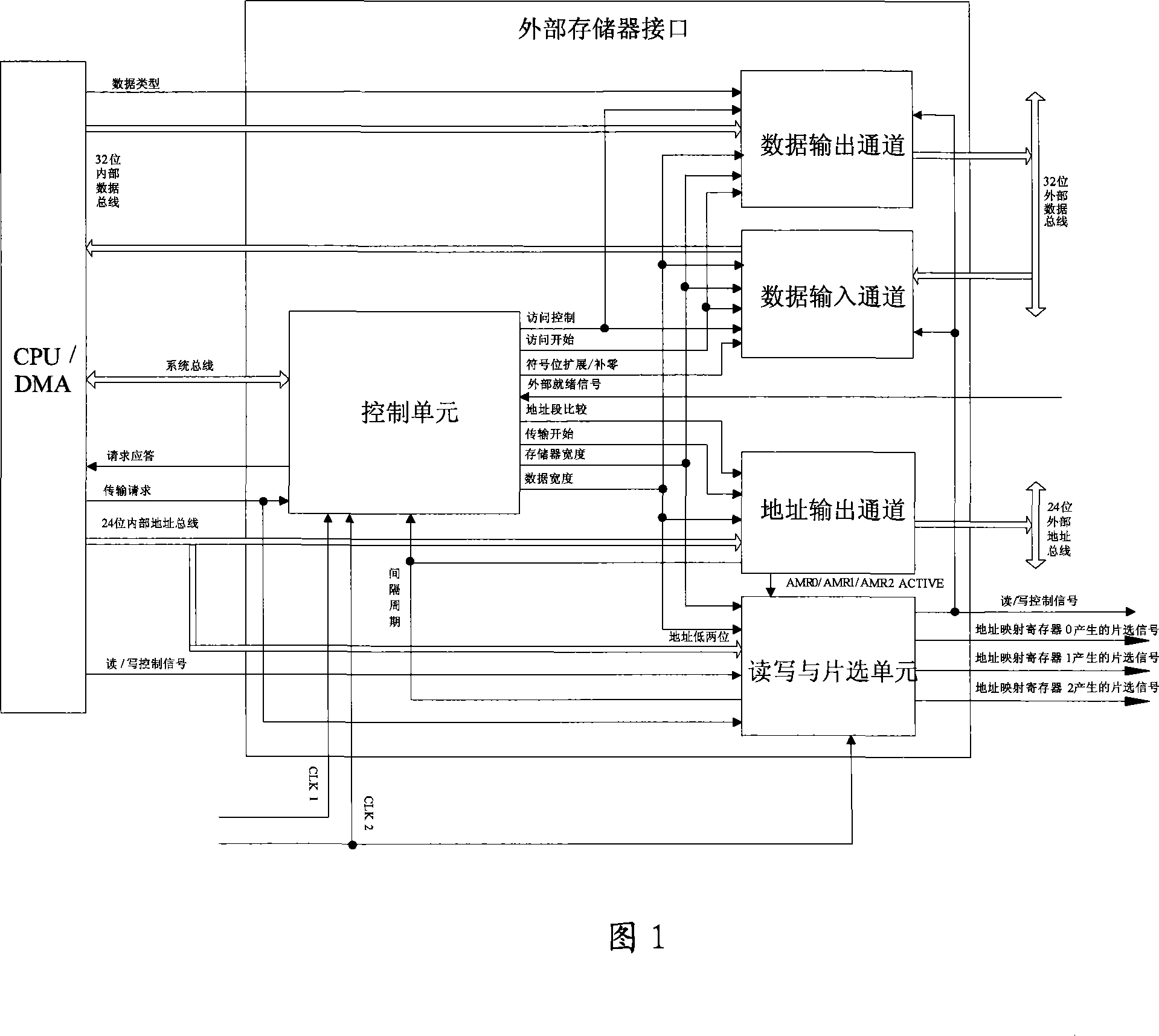

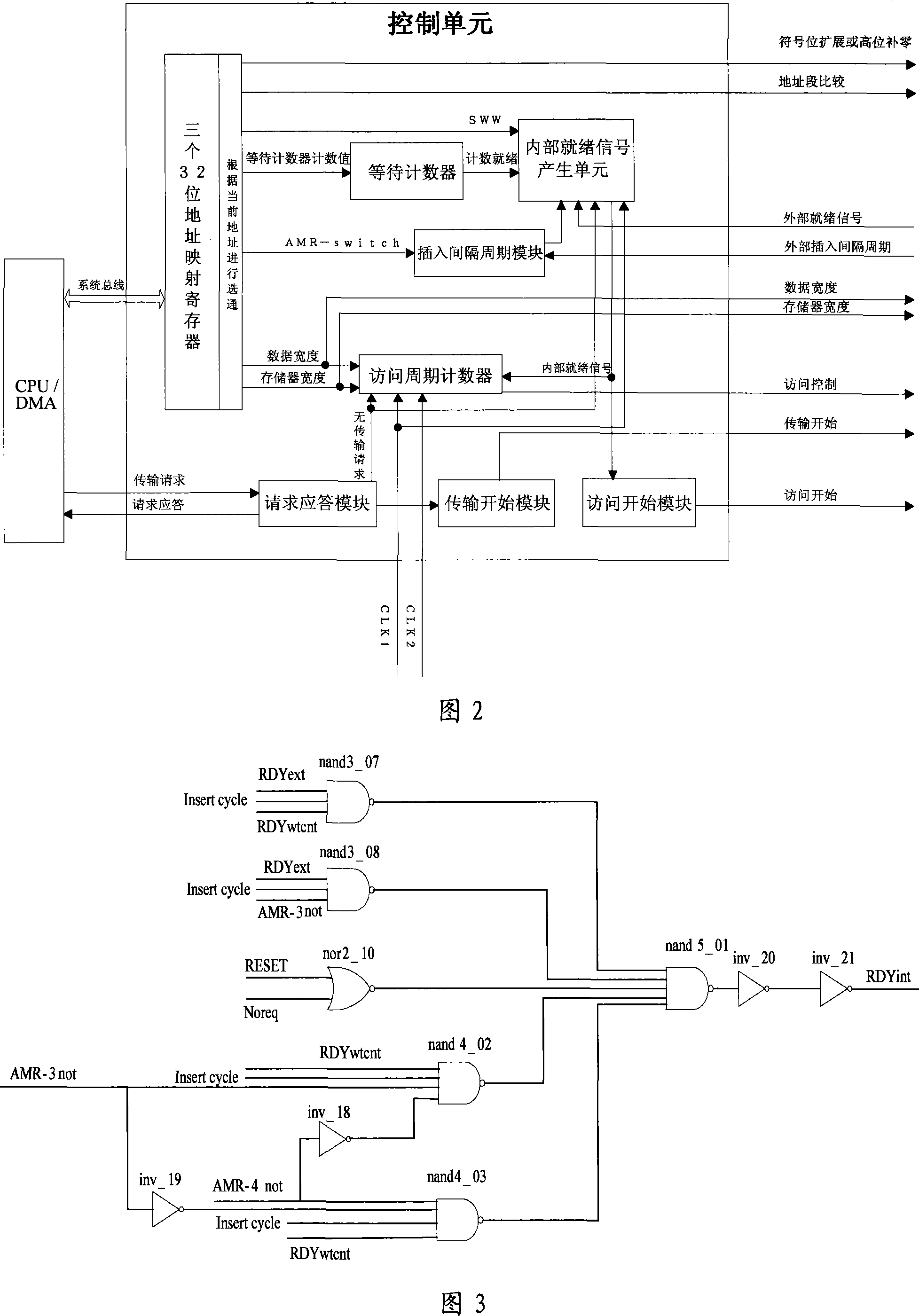

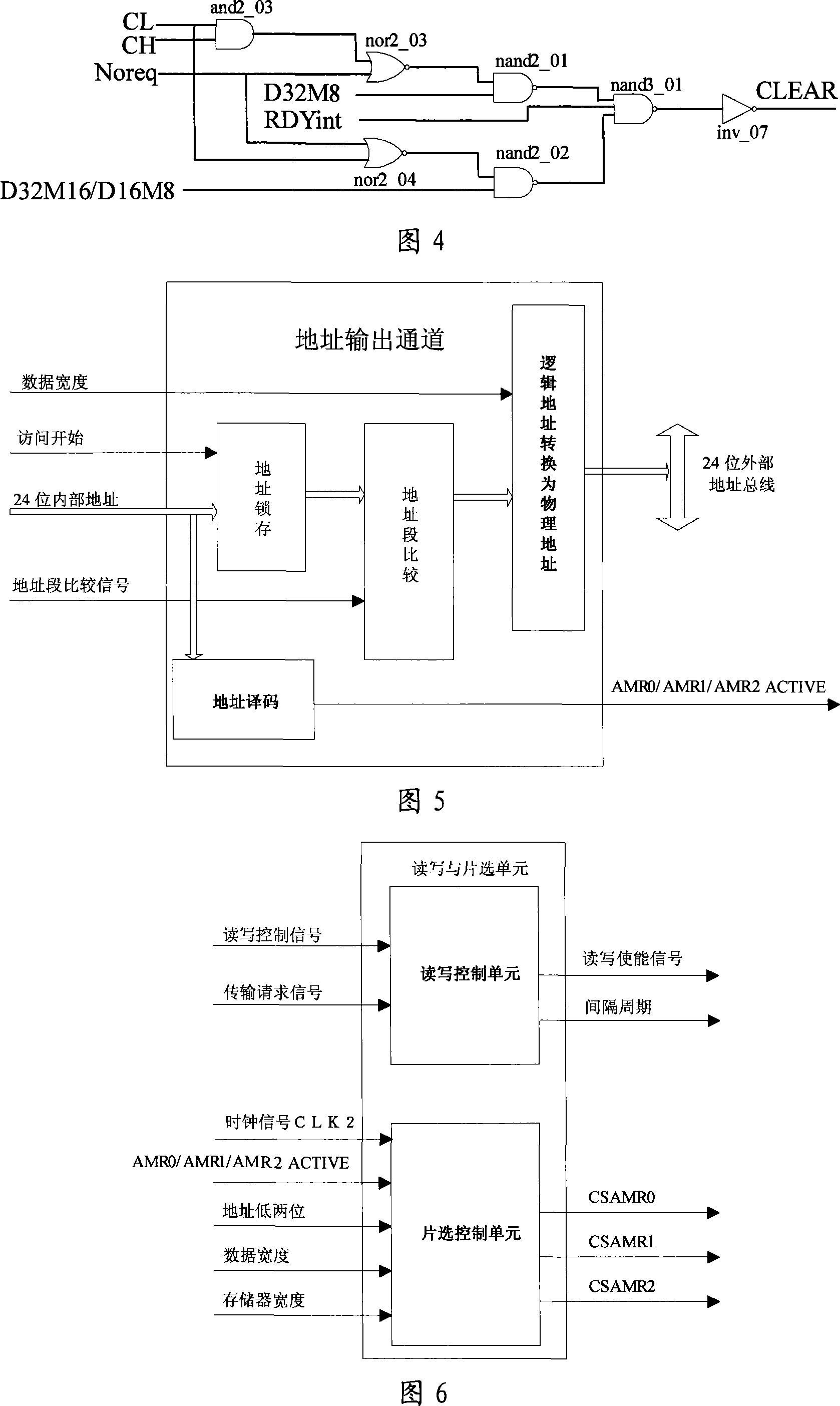

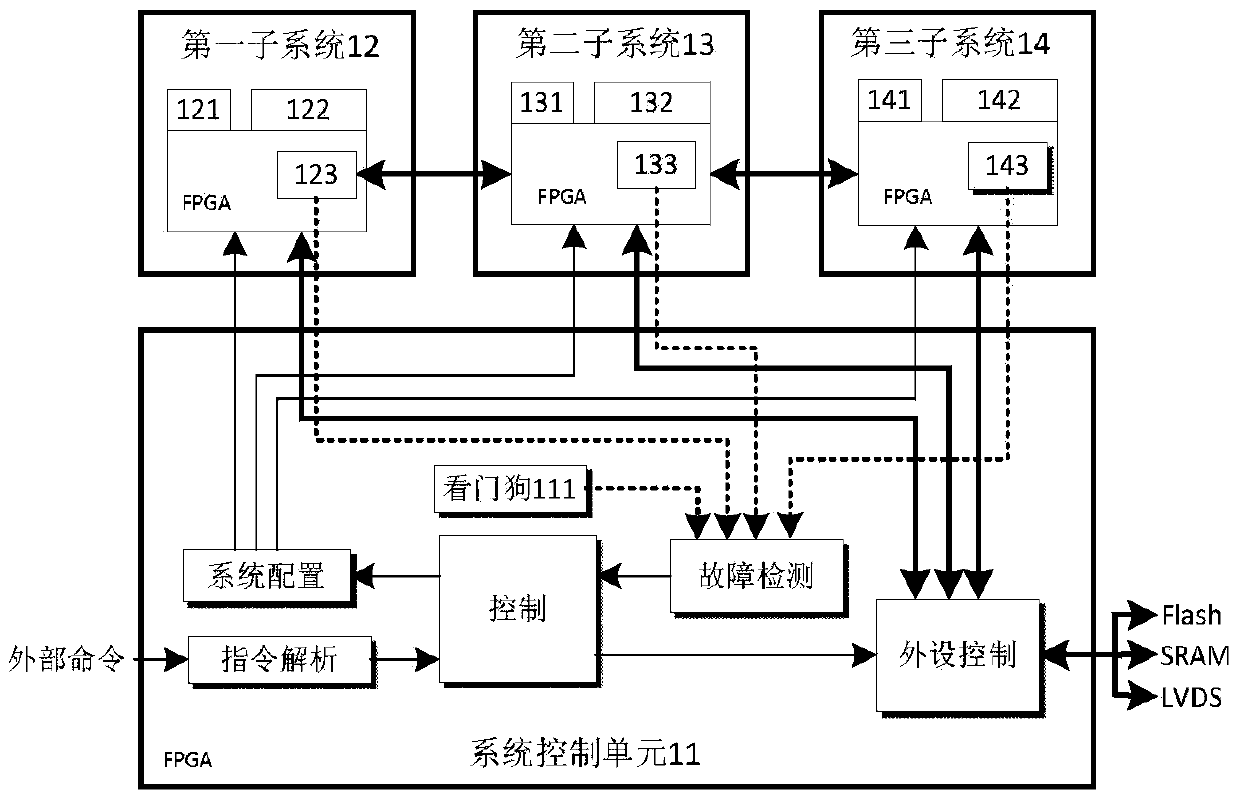

External memory storage interface

InactiveCN101221542AImprove acceleration performanceImprove work flexibilityElectric digital data processingExtensibilityExternal storage

The invention discloses an external memory interface consisting of a control unit, an address output channel, a reading-writing and chip-selection unit, a data input channel and a data output channel, wherein, the three 32-bit address mapped registers are designed in the control unit, which ensures that a 32-bit digital signal processor has the ability of interacting with a multiple bit-width external memory. The interface can synchronously make access operations to an 8-bit external memory, a 16-bit external memory and a 32-bit external memory, thereby improving the extensibility and the working flexibility of the 32-bit digital signal processor; at the same time, the interface has a simple structure, is easy to control and miniaturize, and is convenient to be realized on the chips.

Owner:BEIJING MXTRONICS CORP +1

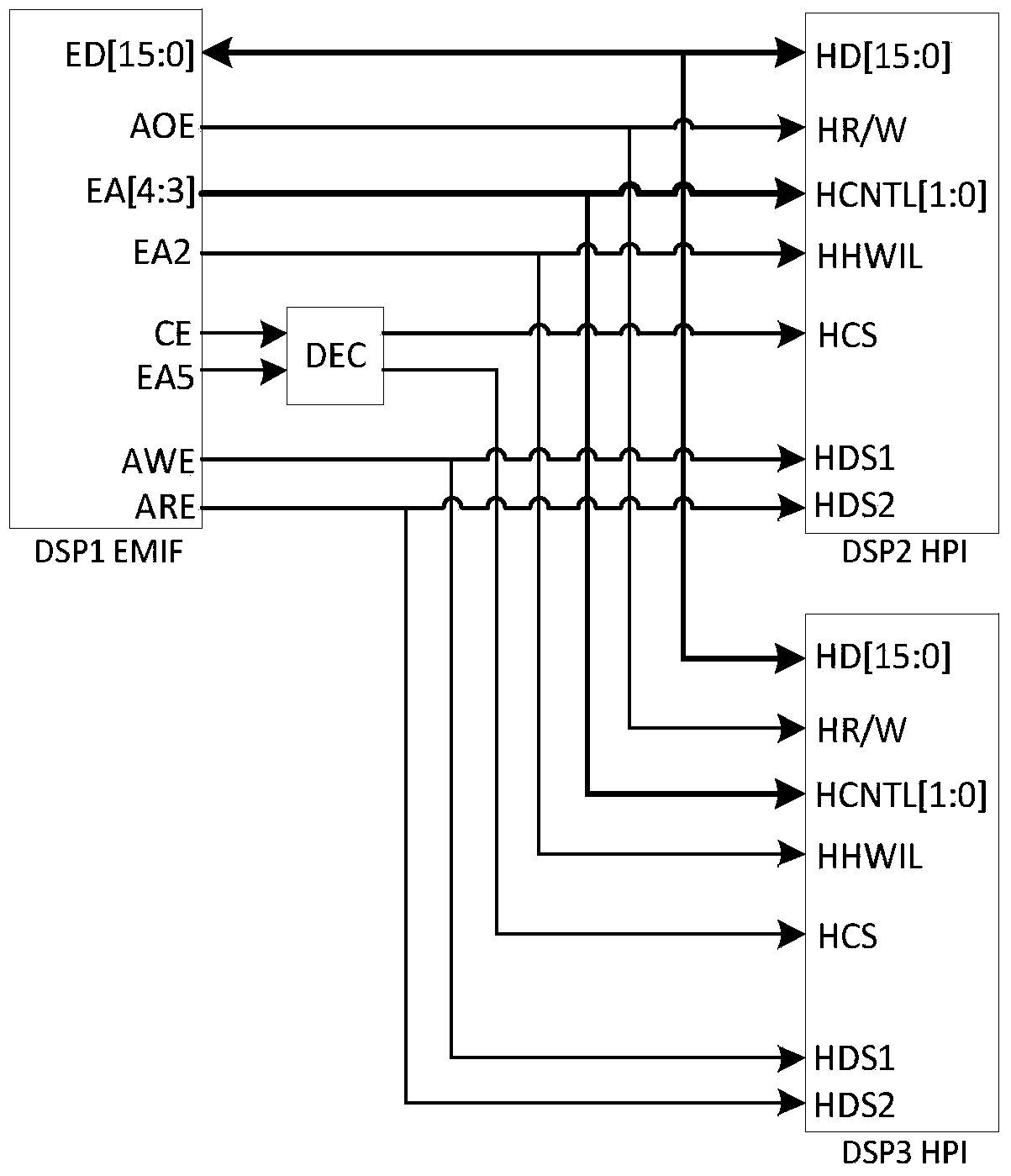

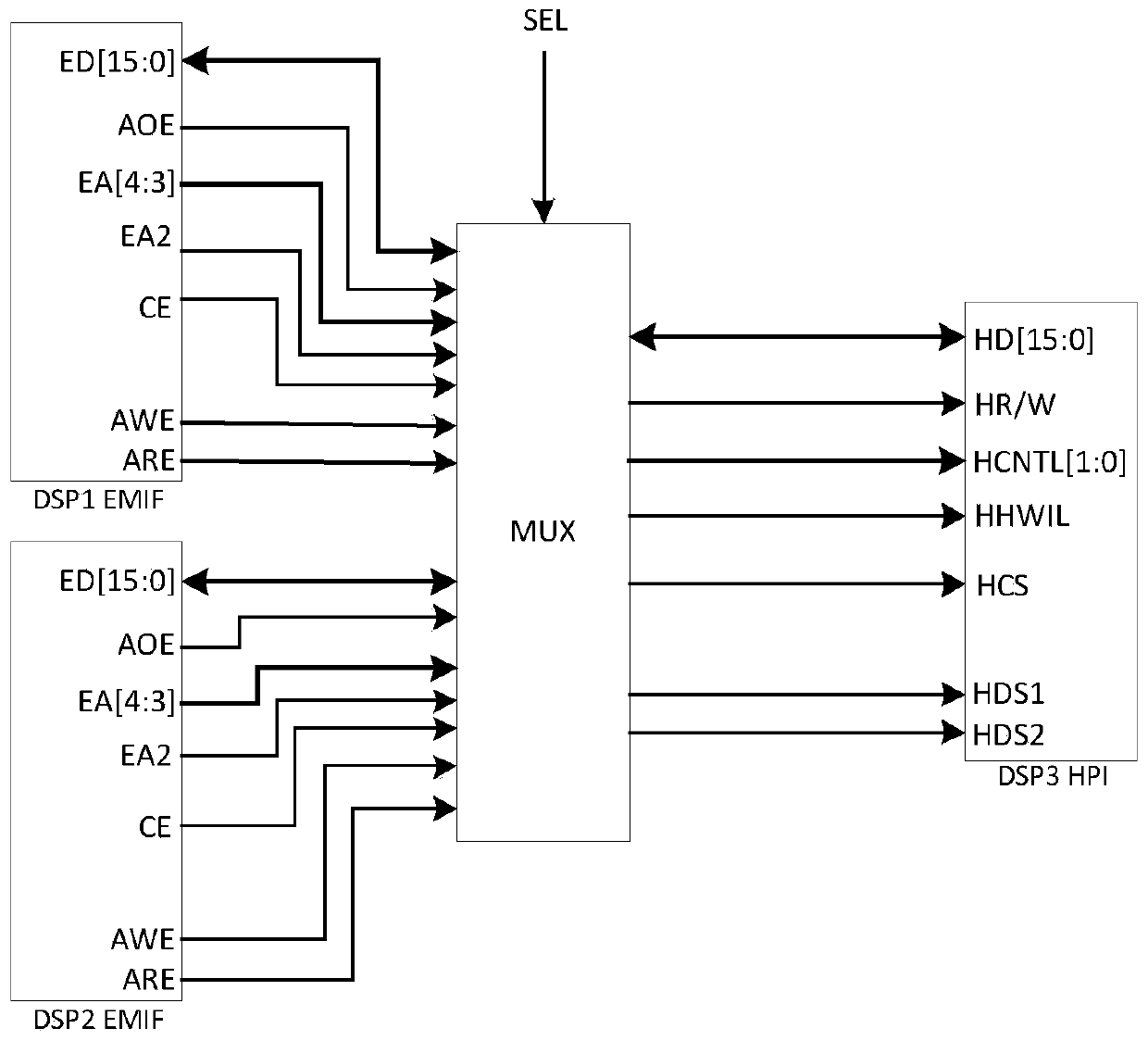

Radiation resistance and reinforcement parallel on-board computer system and use method thereof

ActiveCN103744754AImprove reliability and performanceMultiprogramming arrangementsRedundant hardware error correctionOn boardComputerized system

The invention relates to a radiation resistance and reinforcement parallel on-board computer system and a use method thereof, belongs to the field of on-board computer radiation resistance and reinforcement, and is realized through three DSP (Digital Signal Processor) chips and four FPGA (Field Programmable Gate Array) chips. The system consists of a system control unit and three same subsystems, wherein the system control unit is realized on one FPGA, and each subsystem comprises one DSP and one FPGA, and is connected with the system control unit. The system adopts a '2 parallel + 1 backup' structure, the two DSPs carry out parallel processing of on-board tasks, and the rest DSP serves as a backup DSP, and the backup DSP replaces the failed DSP when the DSP carrying out concurrent working has unrecoverable faults. The three DSPs are all interconnected through an external memory interface (EMIF) and a hardware platform interface (HPI). The system selects different backup mechanisms which comprise a fixed backup mechanism, a rotary backup mechanism and a preprocessing backup mechanism according to requirements of the on-board tasks.

Owner:SHANGHAI JIAO TONG UNIV

Wireless connectivity in a radar detector

ActiveUS8624771B2Wave based measurement systemsRoad vehicles traffic controlData connectionNetwork Communication Protocols

Owner:ESCORT INC

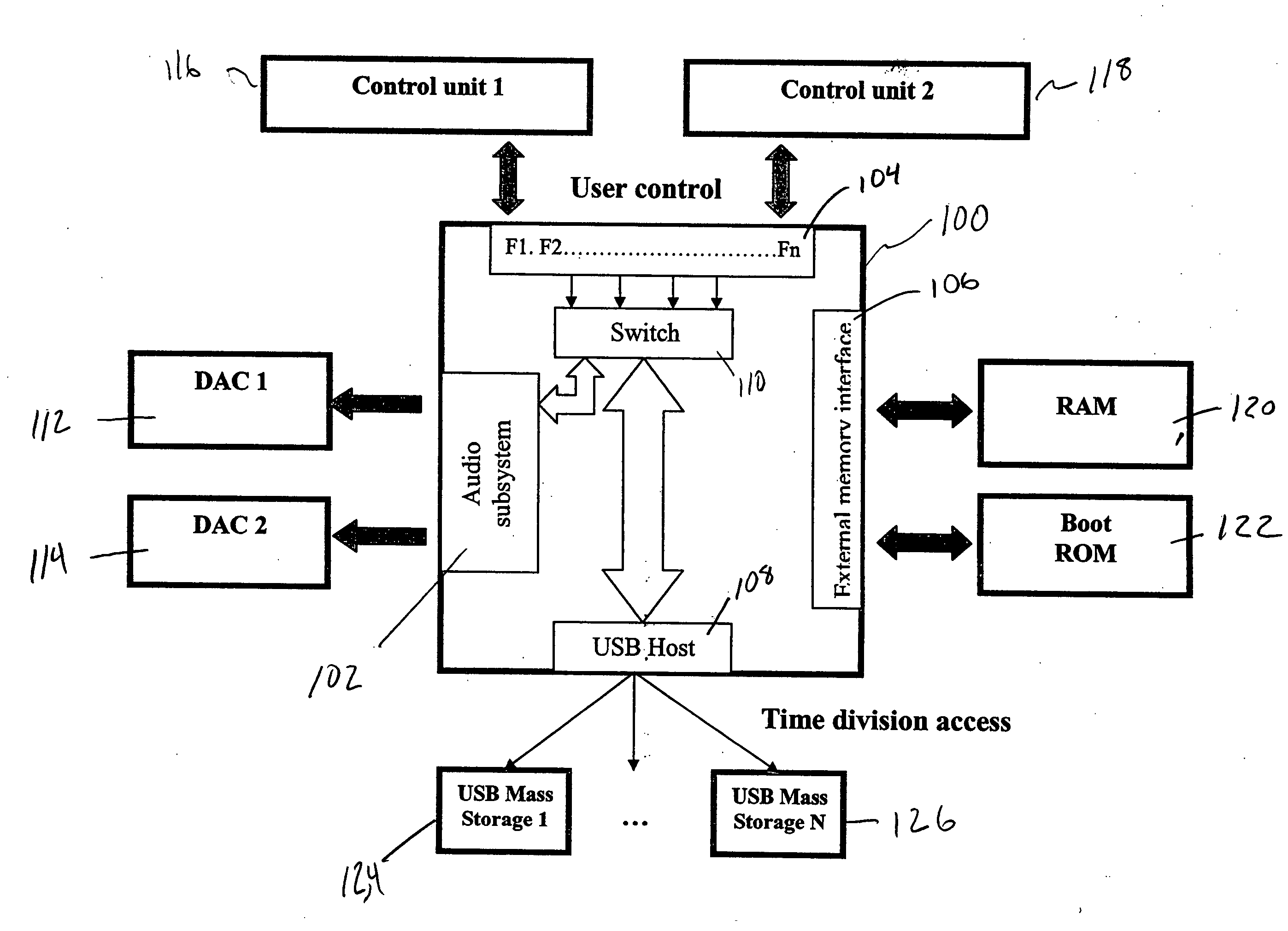

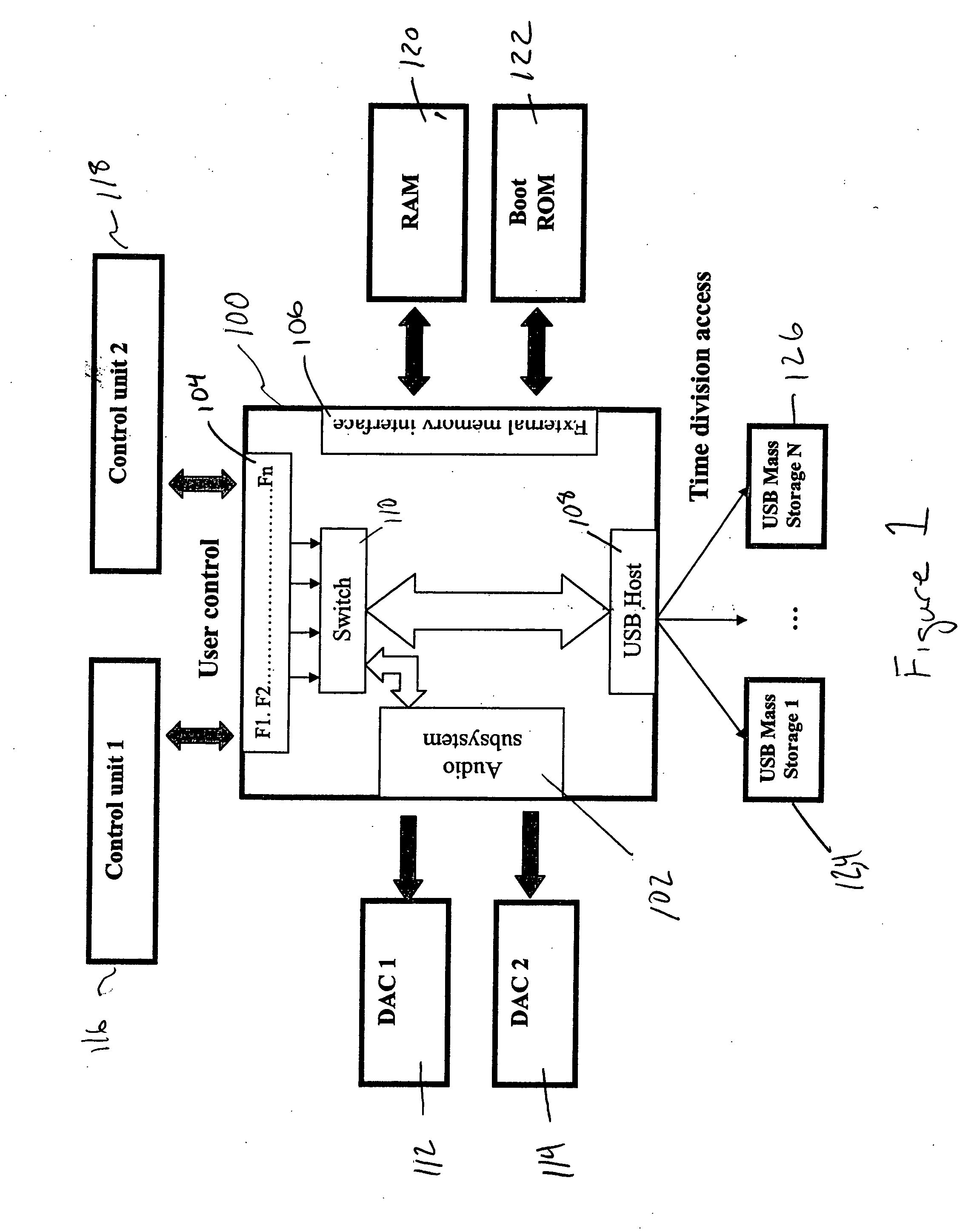

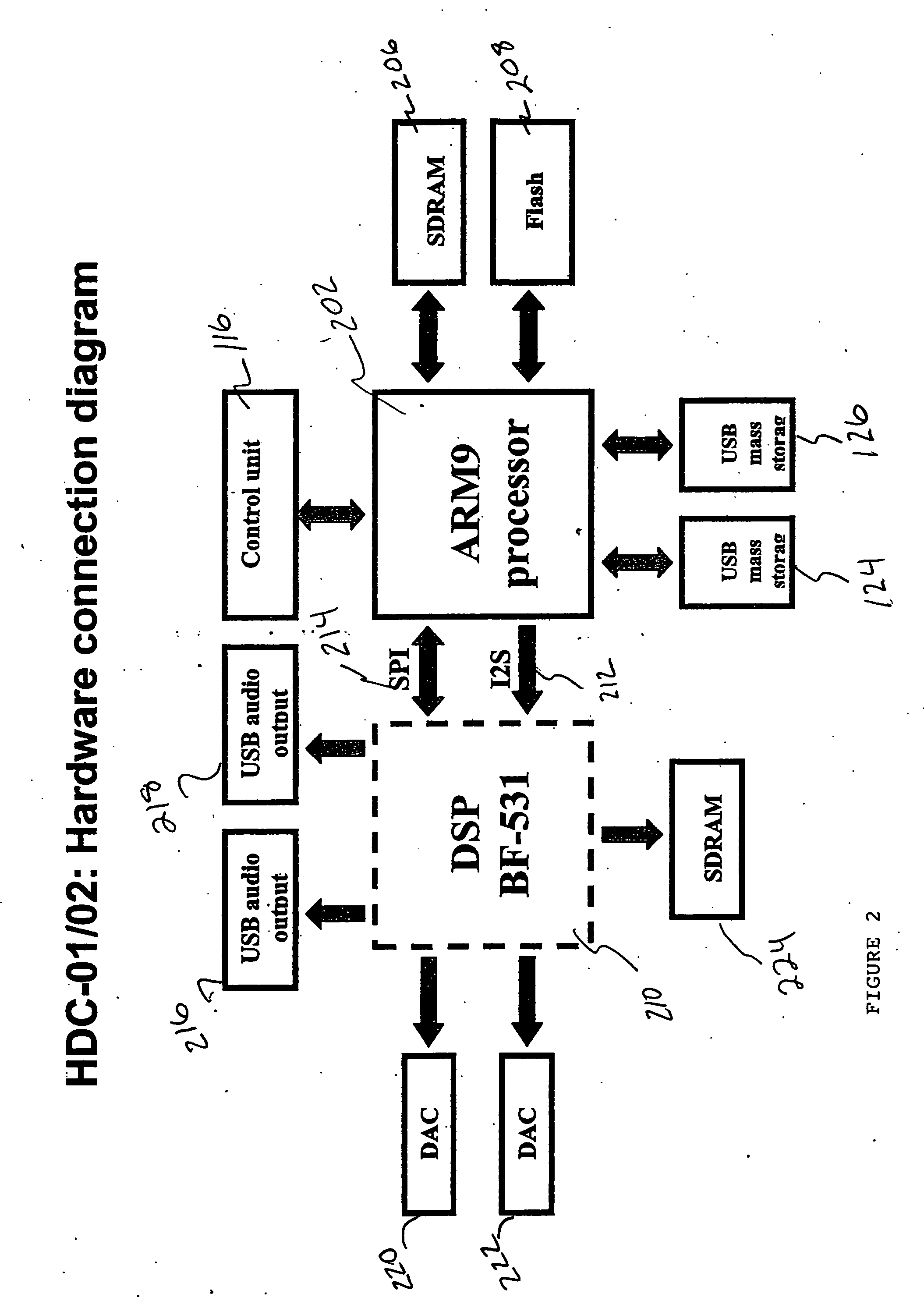

Digital media DJ mixer

InactiveUS20080121092A1Overcomes shortcomingImprove convenienceElectrophonic musical instrumentsElectronic editing digitised analogue information signalsMass storageOperational system

The present invention provides a music playback and manipulation system for generating audio playback of digital musical comprising; a user control device having an external memory interface for providing access to random access memory and read only memory, a mass storage host controller for providing access to and control of data from, a user controller interface and an audio subsystem interface; a mass storage device for storing a plurality of audio files; and a user control device for varying playback parameters of said audio files.

Owner:CABASSO ARTIE +2

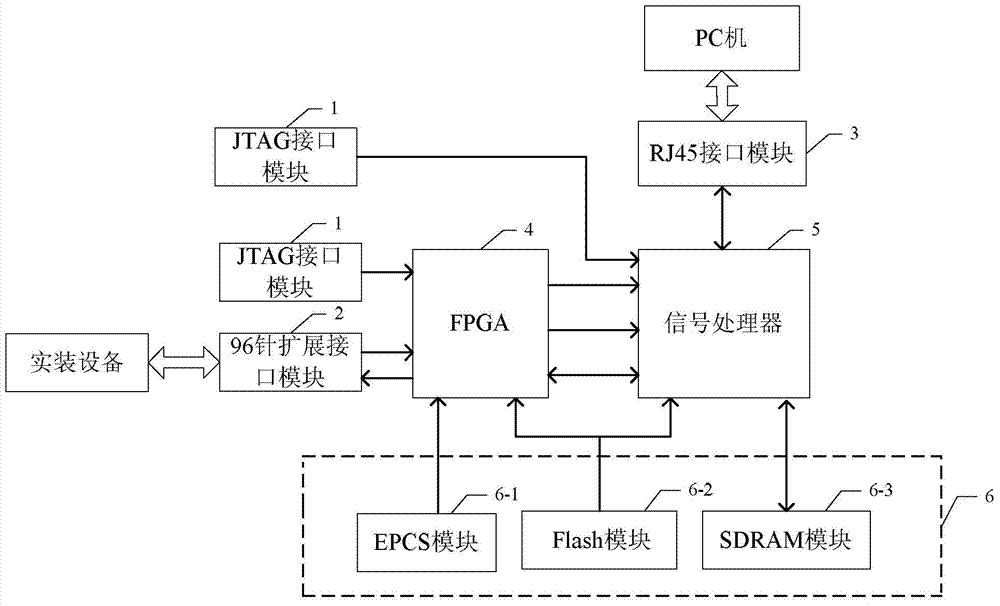

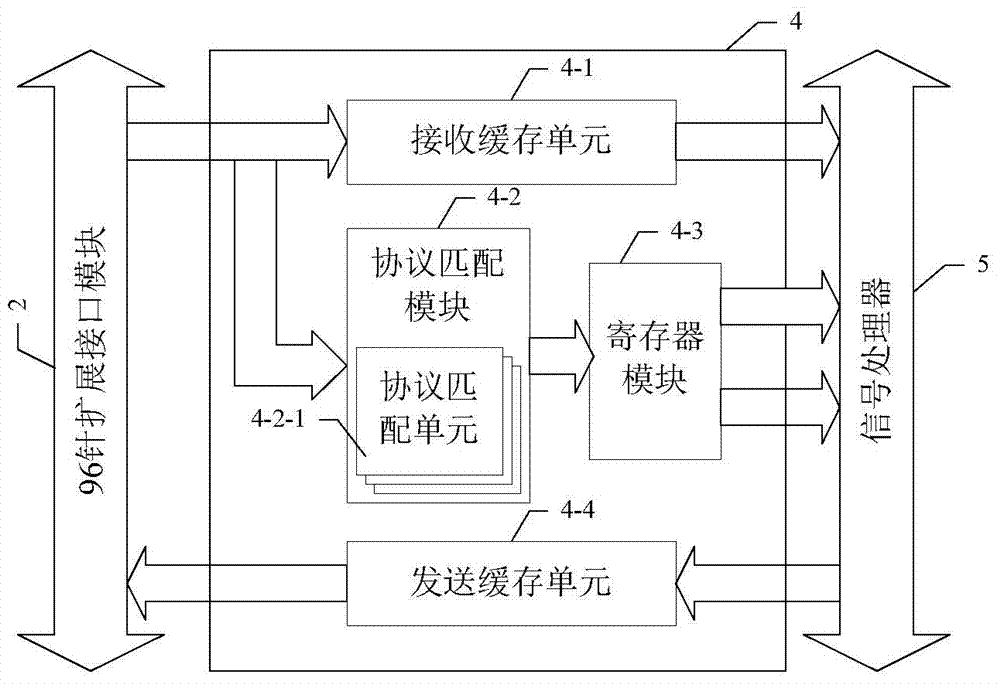

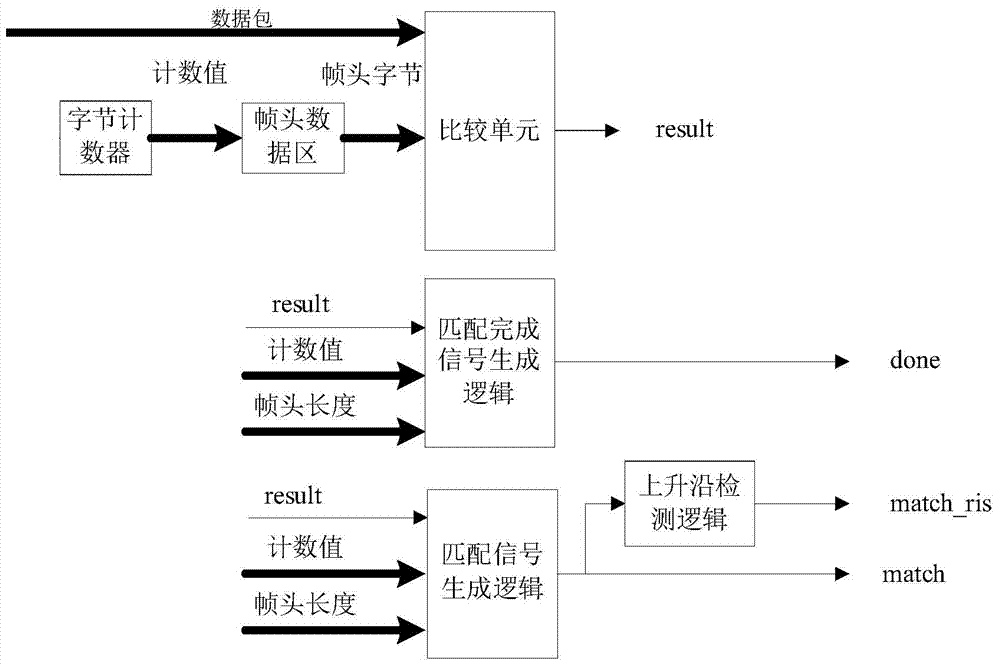

Universal device and method for protocol conversion

InactiveCN103685292AImprove conversion efficiencyImprove conversion accuracyTransmissionProcessor registerComputer module

The invention relates to a universal device and a universal method for protocol conversion, which belong to the field of virtual simulation tests. The existing problem of low conversion efficiency and precision in the protocol conversion by software is solved. The device comprises two JTAG interface modules, a 96-pin extension interface module, an RJ45 interface module, an FPGA, a signal processor and a memory, wherein the FPGA comprises a receiving buffer unit, a protocol matching module, a register module and a sending buffer unit. The FPGA stores the protocol data input by a 96-pin extension interface module into a receiving buffer unit and meanwhile sends to a protocol matching module for matching, the result is stored in a register module after the protocol matching module completes protocol matching, and the data in a receiving buffer unit and the information in a register region can be accessed by a signal processor through an external memory interface; the protocol conversion is performed through the signal processor and the conversion result is sent out through the signal processor. The universal device and the method are specifically applied in the field of protocol conversion.

Owner:HARBIN INST OF TECH

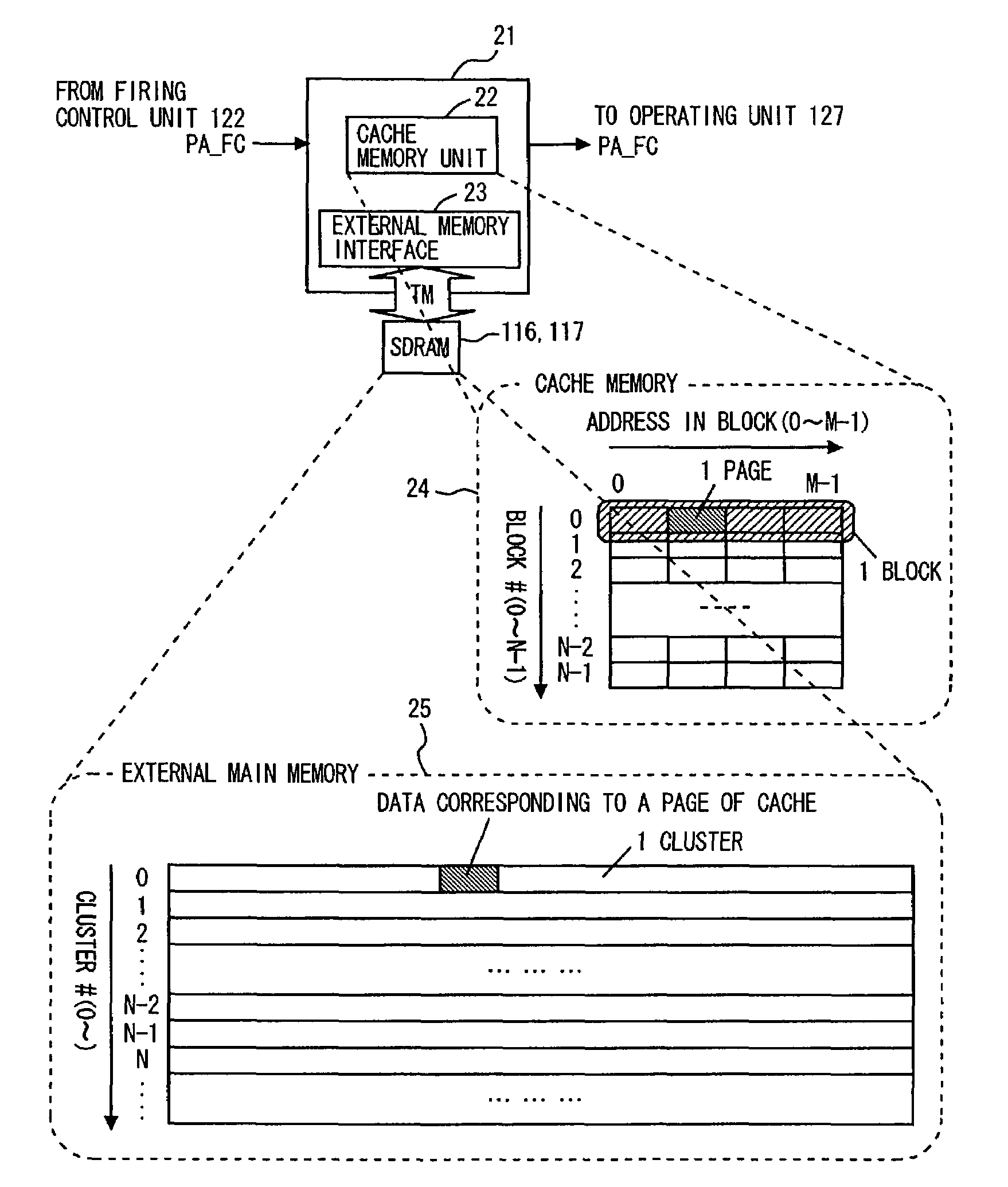

External memory control device regularly reading ahead data from external memory for storage in cache memory, and data driven type information processing apparatus including the same

InactiveUS7082499B2Prevents degradation of parallel processing capability of processingReduction of hardwareMemory adressing/allocation/relocationDigital computer detailsInformation processingExternal storage

When the cache memory unit reads the last word of a page of the cache memory, the external memory interface reads ahead data of a prescribed number of pages ahead of the relevant page. Thus, data corresponding to the access request to the external main memory is always held in the cache memory. This prevents degradation of parallel processing capability of the data driven type information processing apparatus.

Owner:SHARP KK

Multi-mode startup embedded system

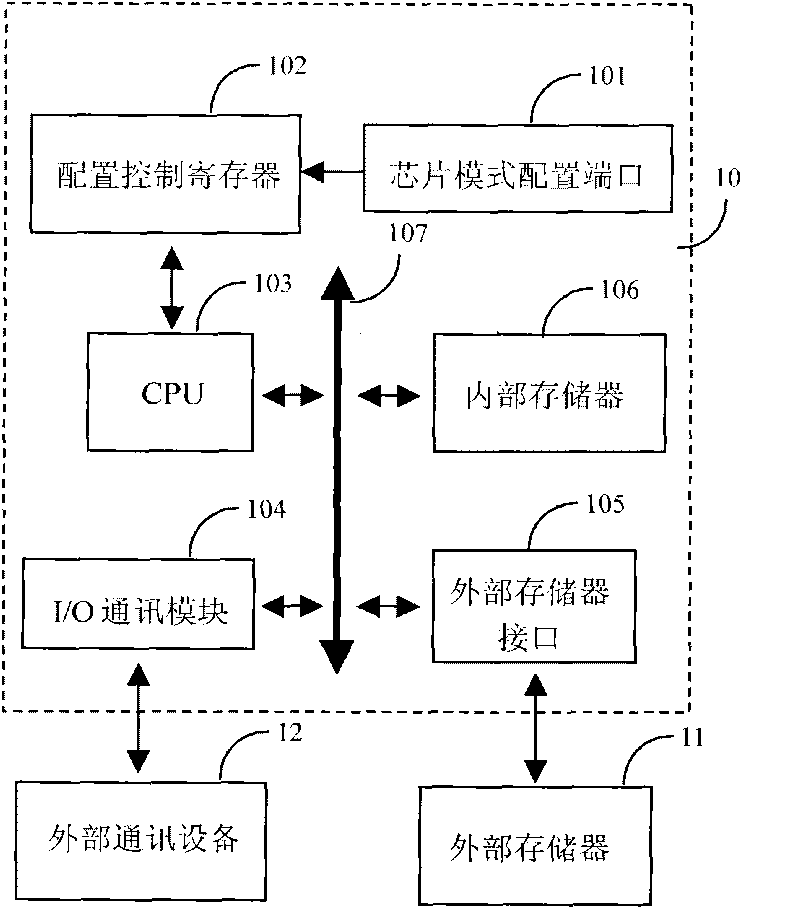

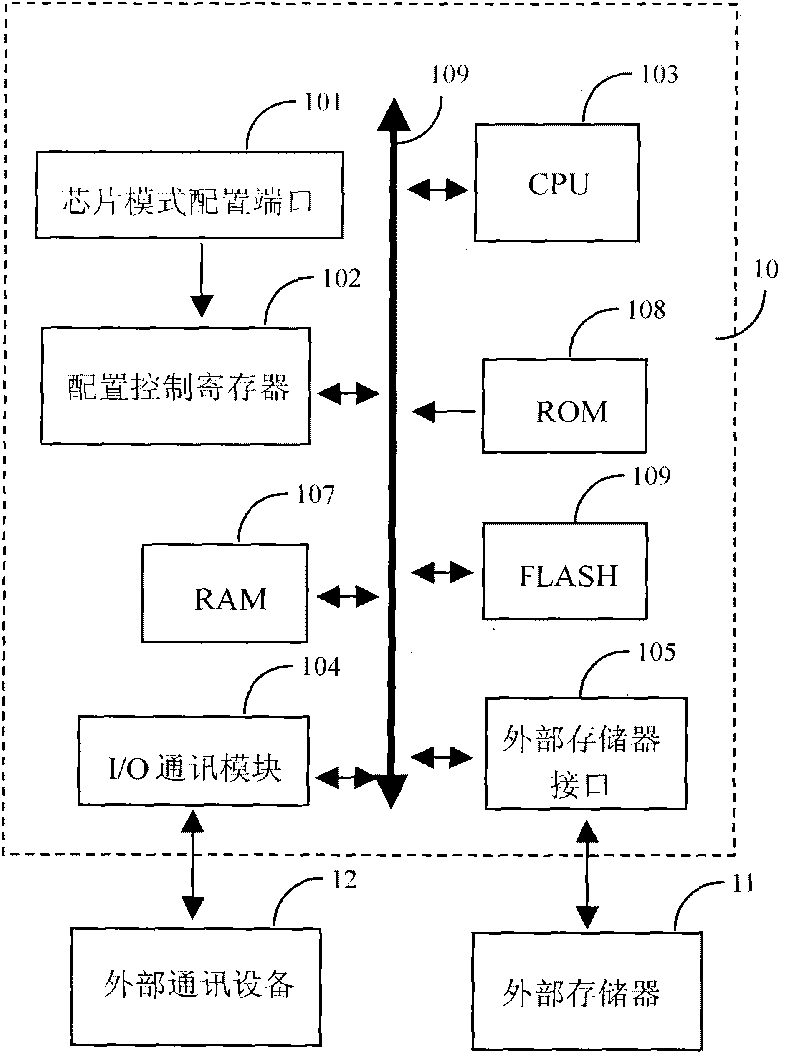

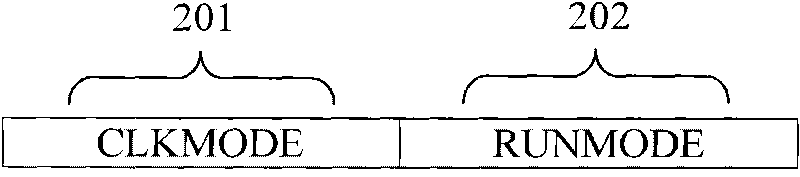

ActiveCN101699402AComplete and safe loadingIncrease fault toleranceProgram loading/initiatingMultiple applicationsExternal memory interface

The invention discloses a multi-mode startup embedded system, comprising a chip mode configuration port (101), a configuration control register (102), an internal memory (106), an external memory interface (105), an I / O communication module (104), a CPU (103) and a system bus (107). After the system is electrified, the startup mode of the system is determined according to information of the chip configuration port, wherein the startup mode of the system comprises startup from the internal memory, startup from the external memory, startup from the external communication equipment and the like. Users can select the startup mode of the embedded system through the chip mode configuration port. The invention not only can realize multi-mode startup of the embedded system, but also can realize multimode upgrading of system firmware, and meets the requirement of upgrading once again and multiple applications on the embedded system currently.

Owner:苏州国芯科技股份有限公司

Off-chip Nor Flash bus interface hardware encryption device

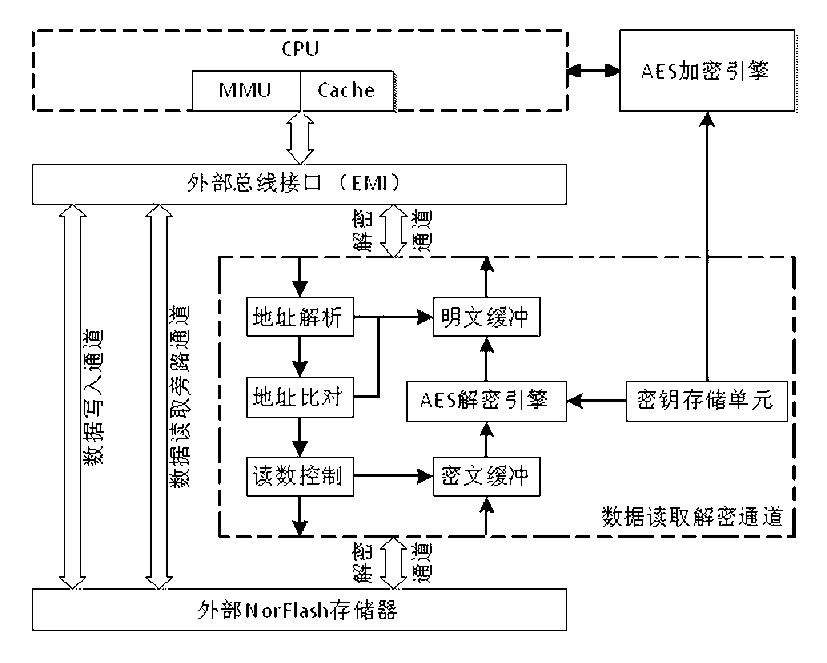

InactiveCN103258172AIncrease flexibilitySimple designDigital data protectionInternal/peripheral component protectionExtensibilityPlaintext

The invention relates to an off-chip Nor Flash bus interface hardware encryption device which comprises an EMI (external memory interface), a data reading decryption passage, a data reading bypass passage, a data writing passage and an AES (advanced encryption standard) encryption engine, wherein the EMI is used for CPU (central processing unit) extensible external memories, the three passages connects the EMI with external Nor Flash memories, the AES encryption engine is connected between a CPU and the data reading decryption passage and used for plaintext data encryption, and the data reading decryption passage comprises an address analyzing unit, an address comparing unit, an indication control unit, a cipher text buffer unit, an AES decryption engine, a plaintext buffer unit and a secret key storage unit. Hardware-software combination is used to provide data encryption for off-chip Nor Flash memories. The device supports a bypass function, data can be written into off-chip Nor Flash memories in plaintext and read in plaintext, so that data storage flexibility is achieved. By the device which is flexible in extensibility, easy to design, high in reliability and safety and the like, Nor Flash bus interface encryption is achieved.

Owner:福建睿矽微电子科技有限公司