Patents

Literature

990 results about "Parity bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

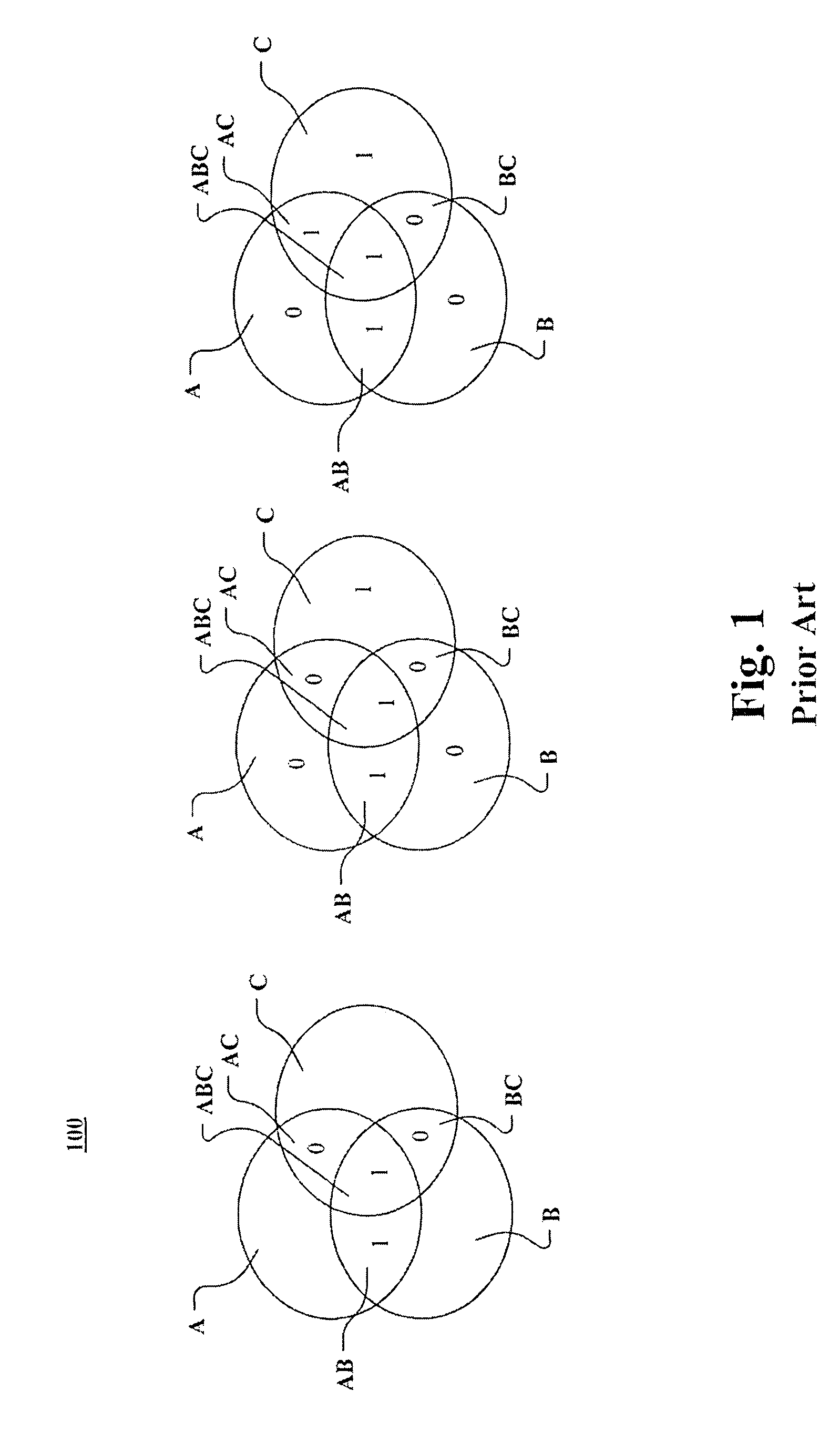

A parity bit, or check bit, is a bit added to a string of binary code to ensure that the total number of 1-bits in the string is even or odd. Parity bits are used as the simplest form of error detecting code.

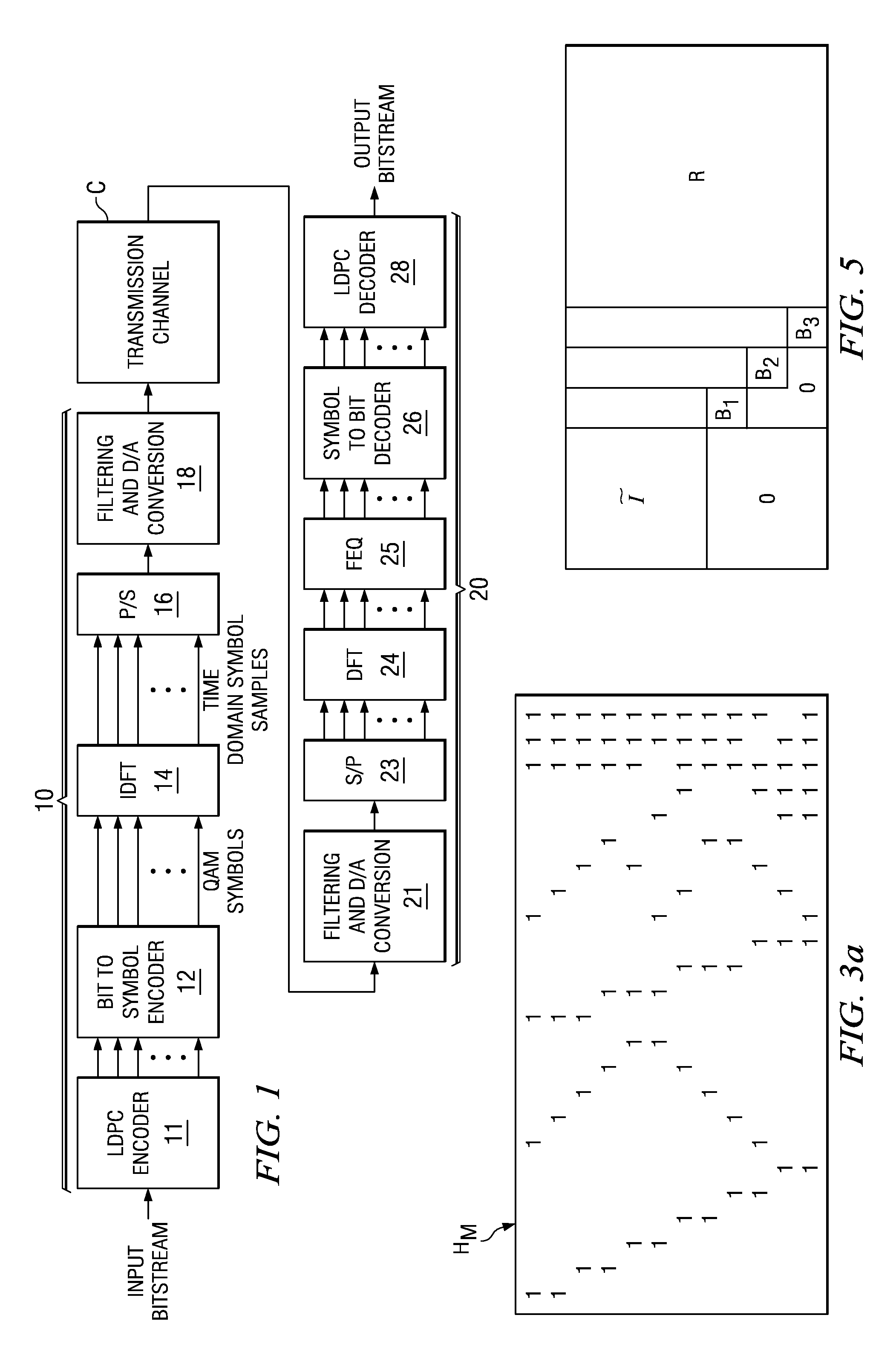

Data processing apparatus and method

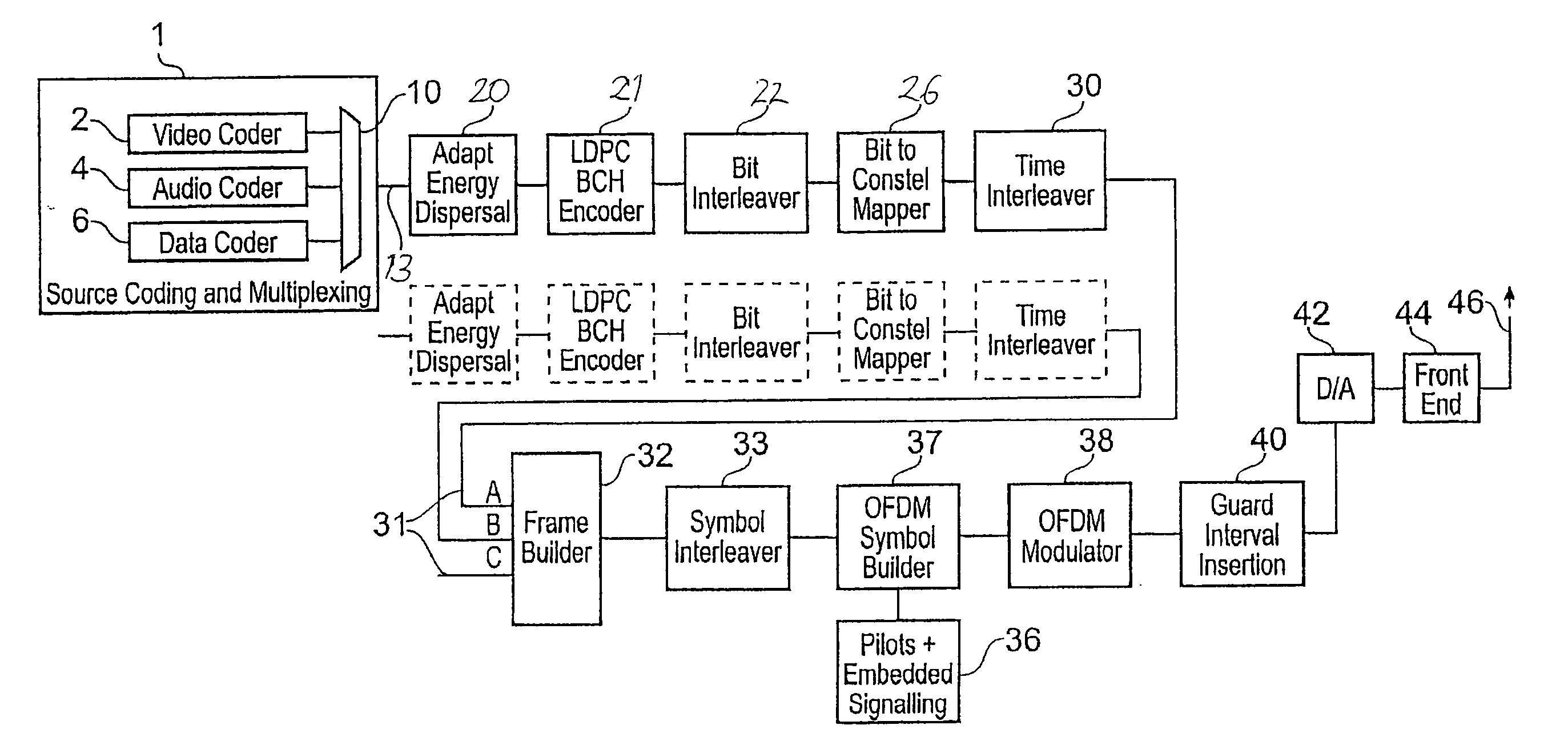

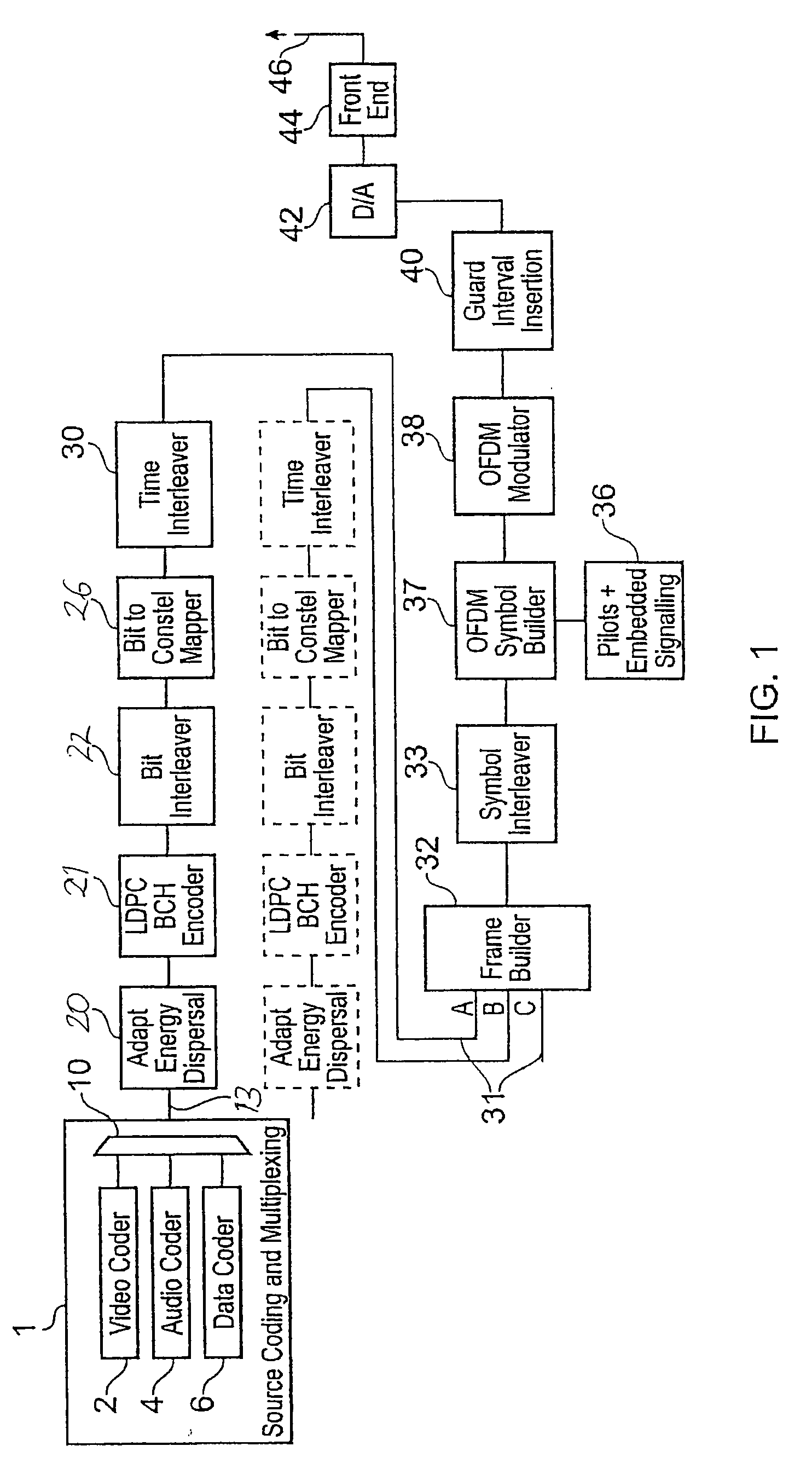

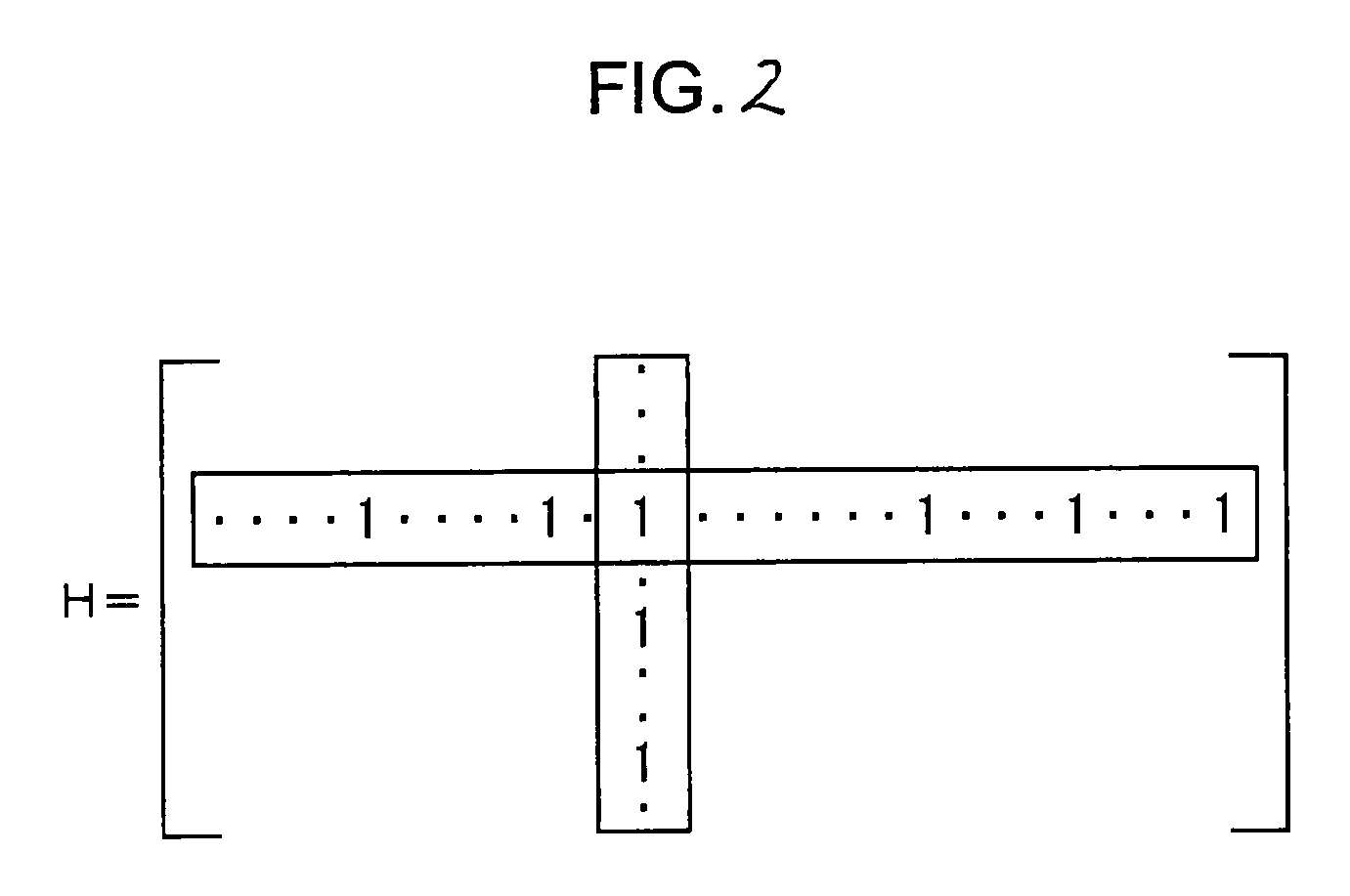

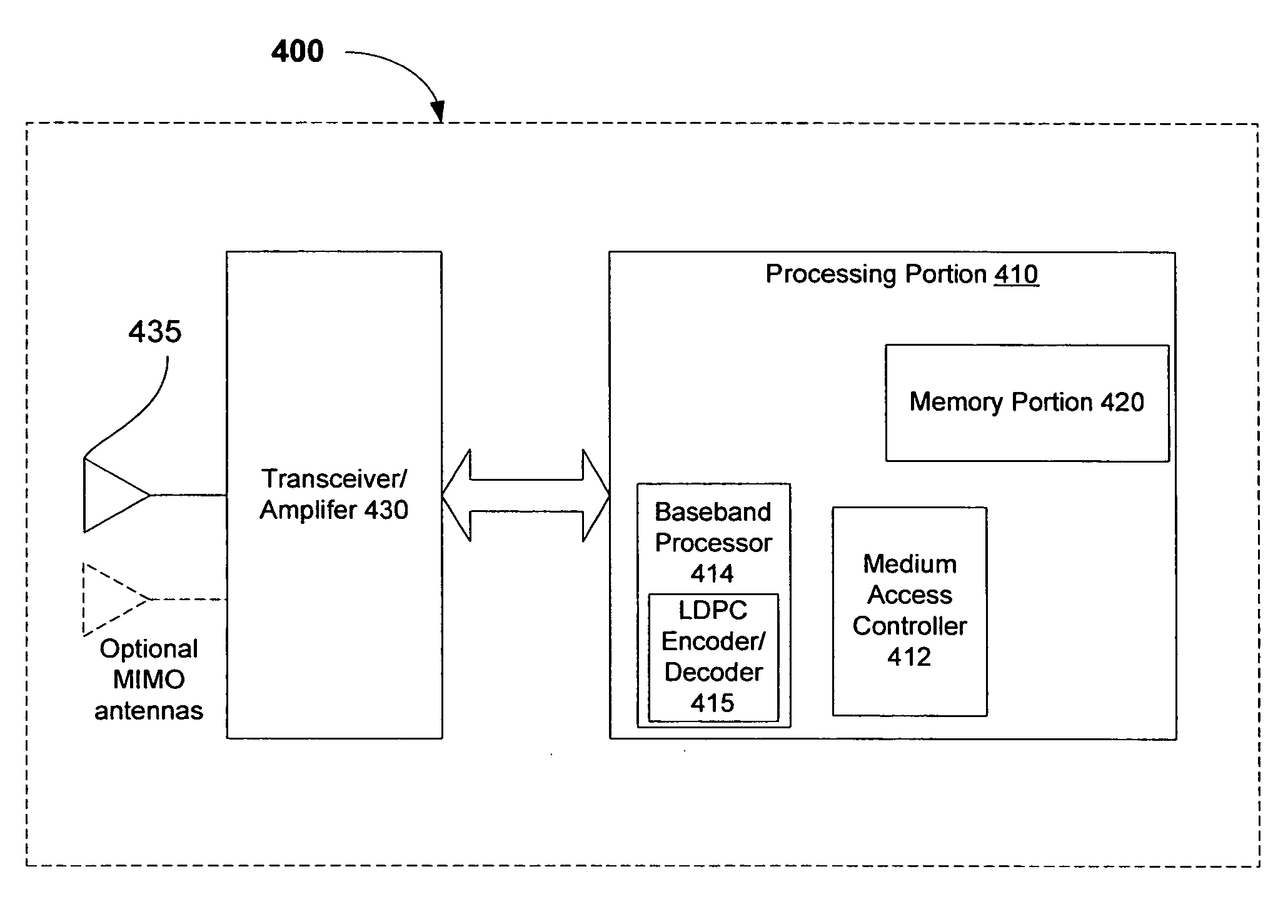

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

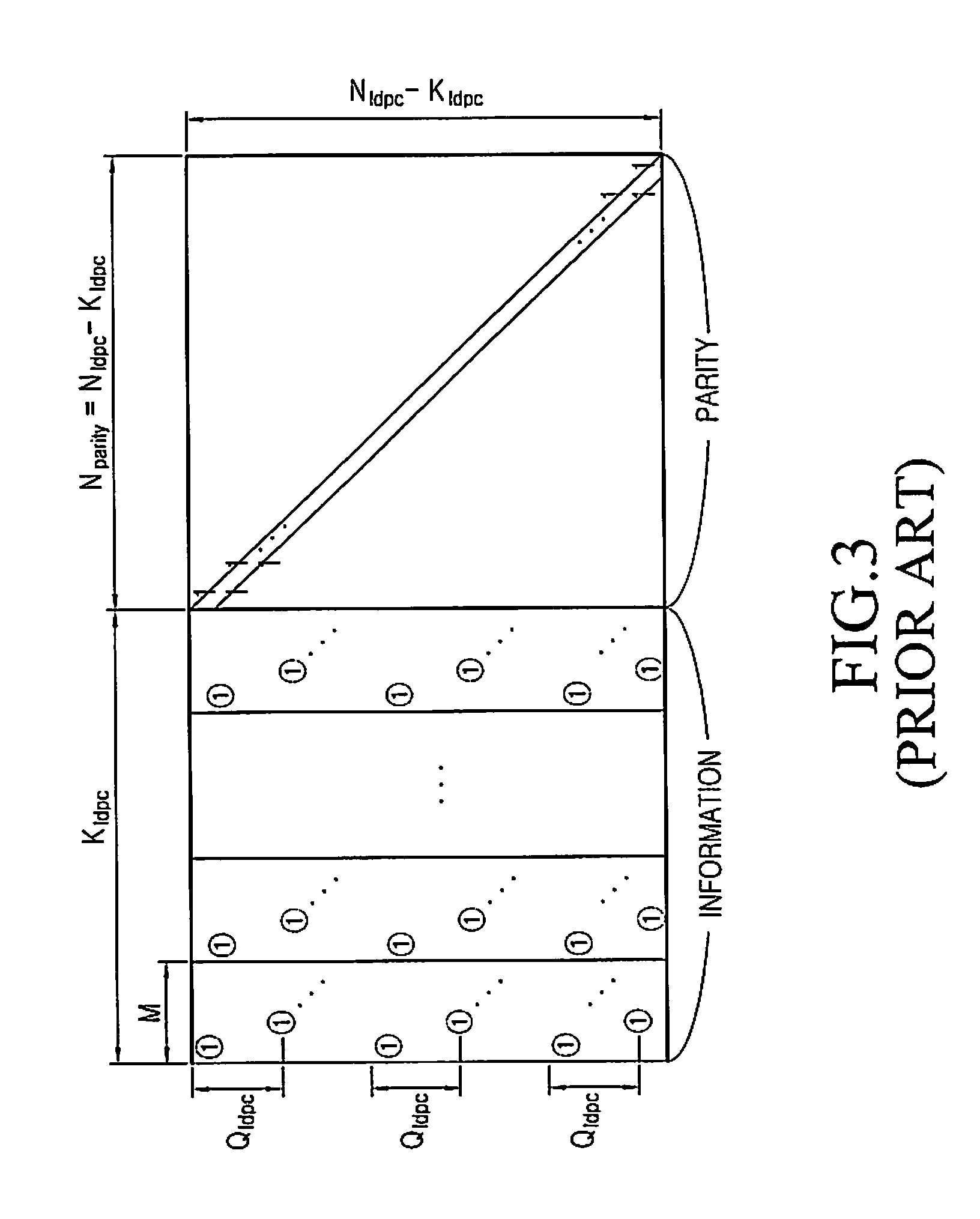

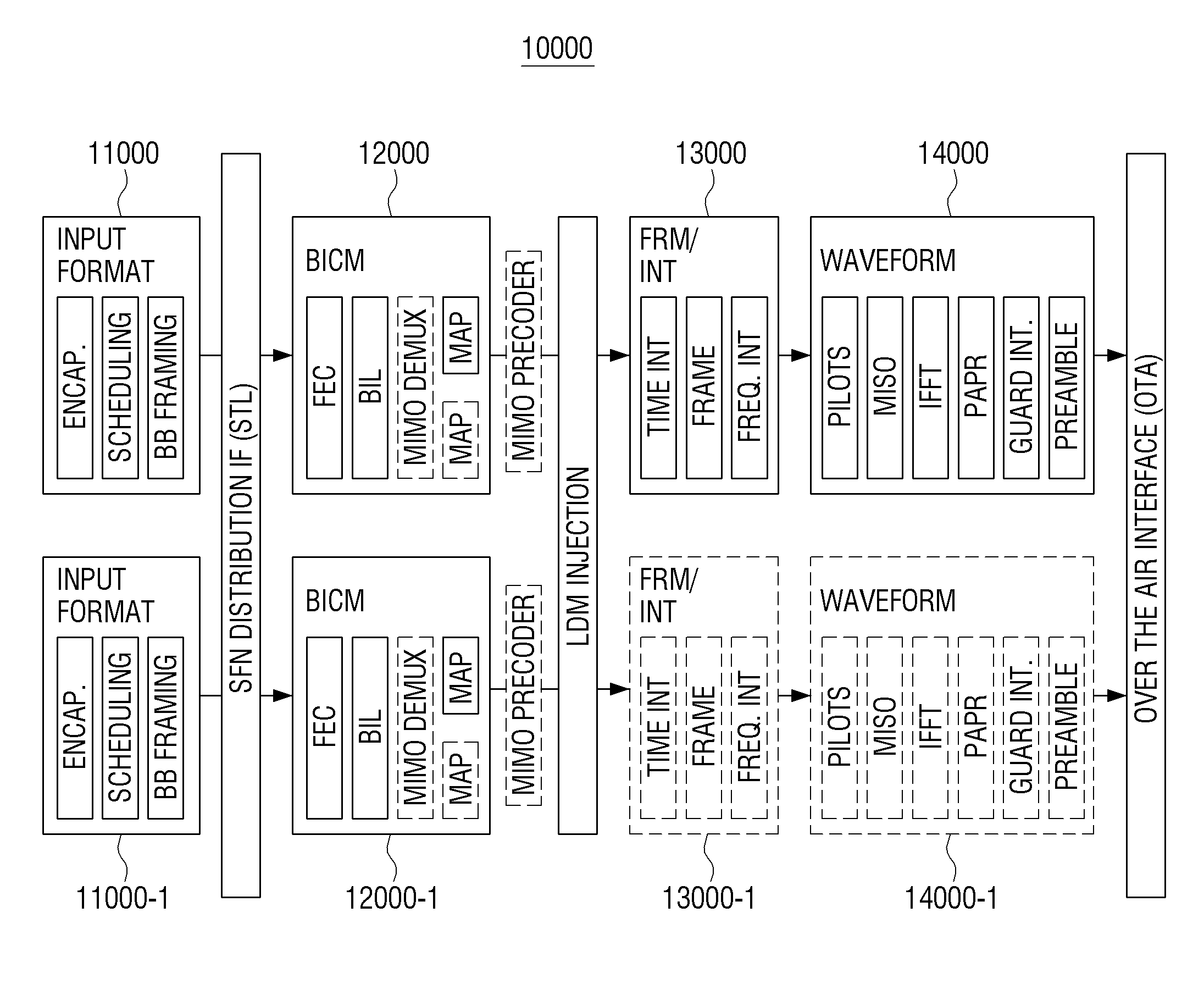

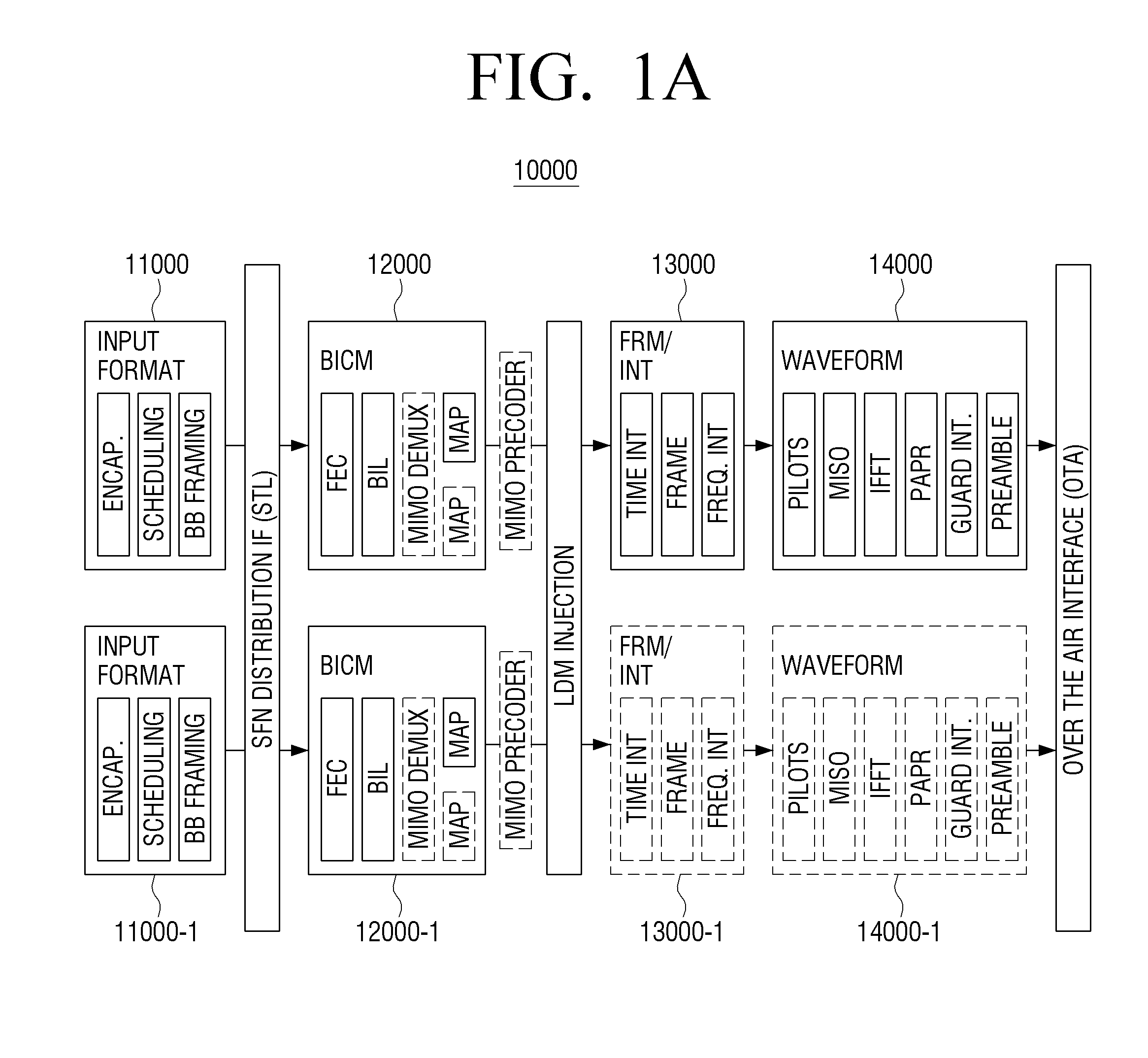

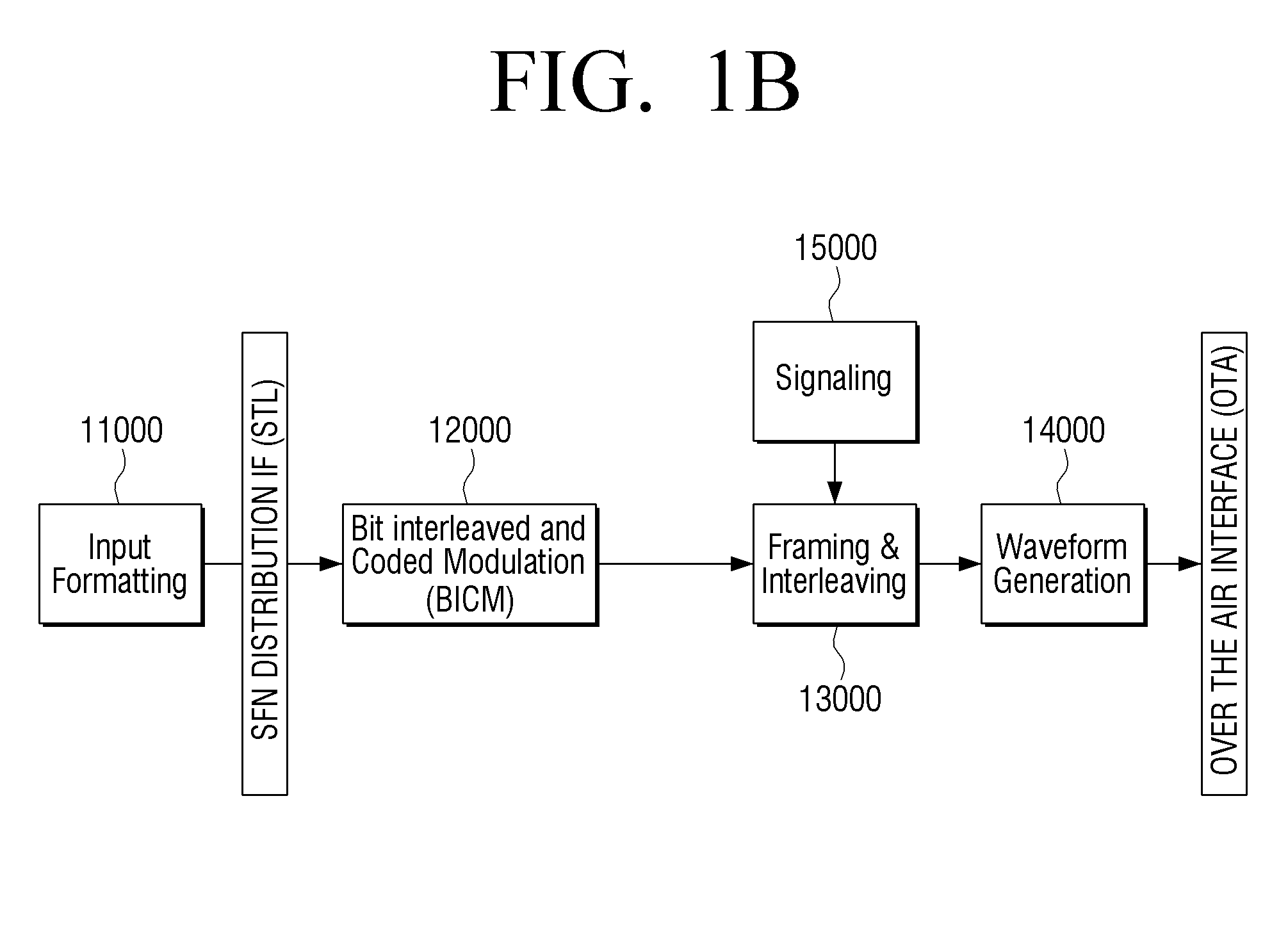

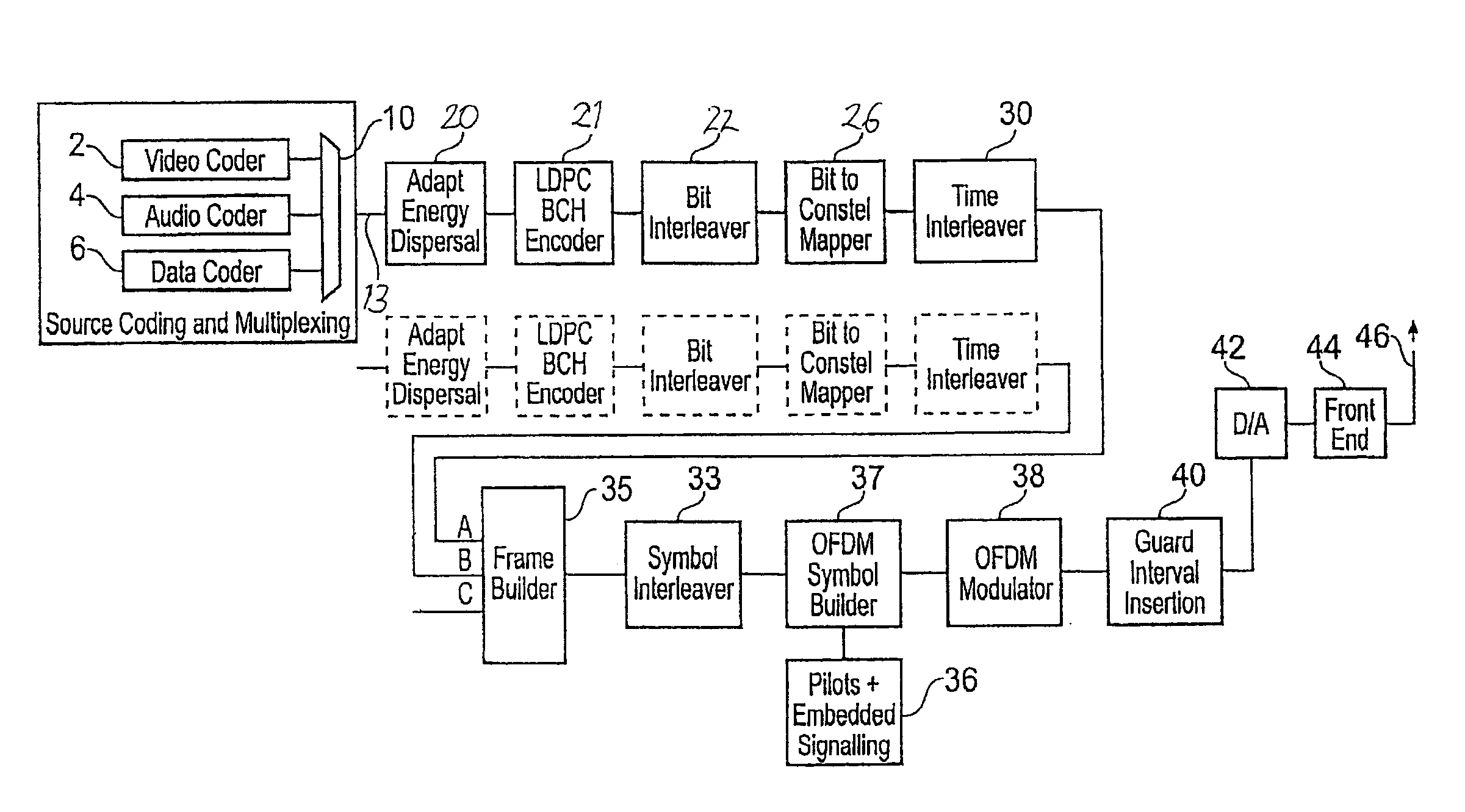

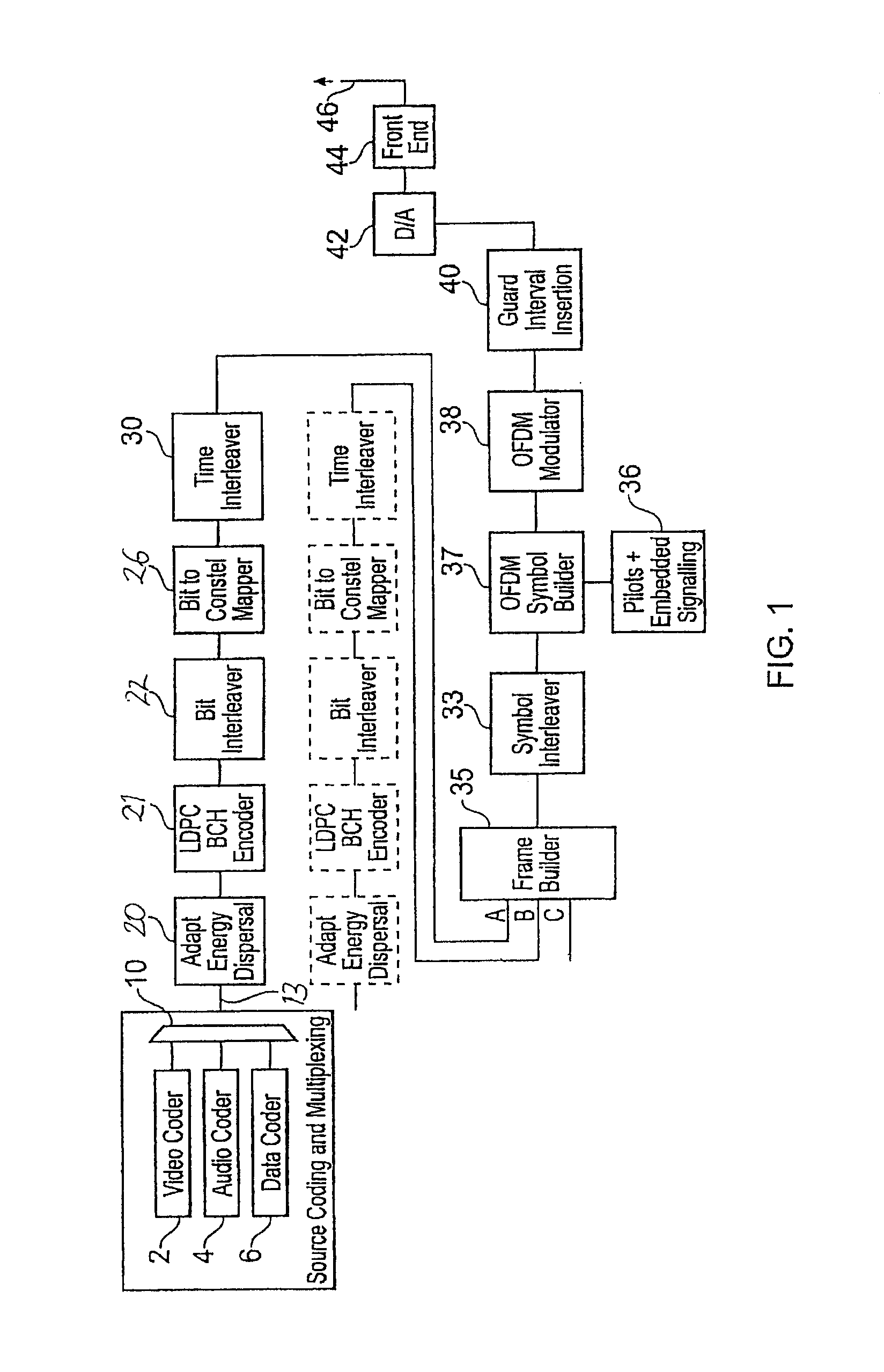

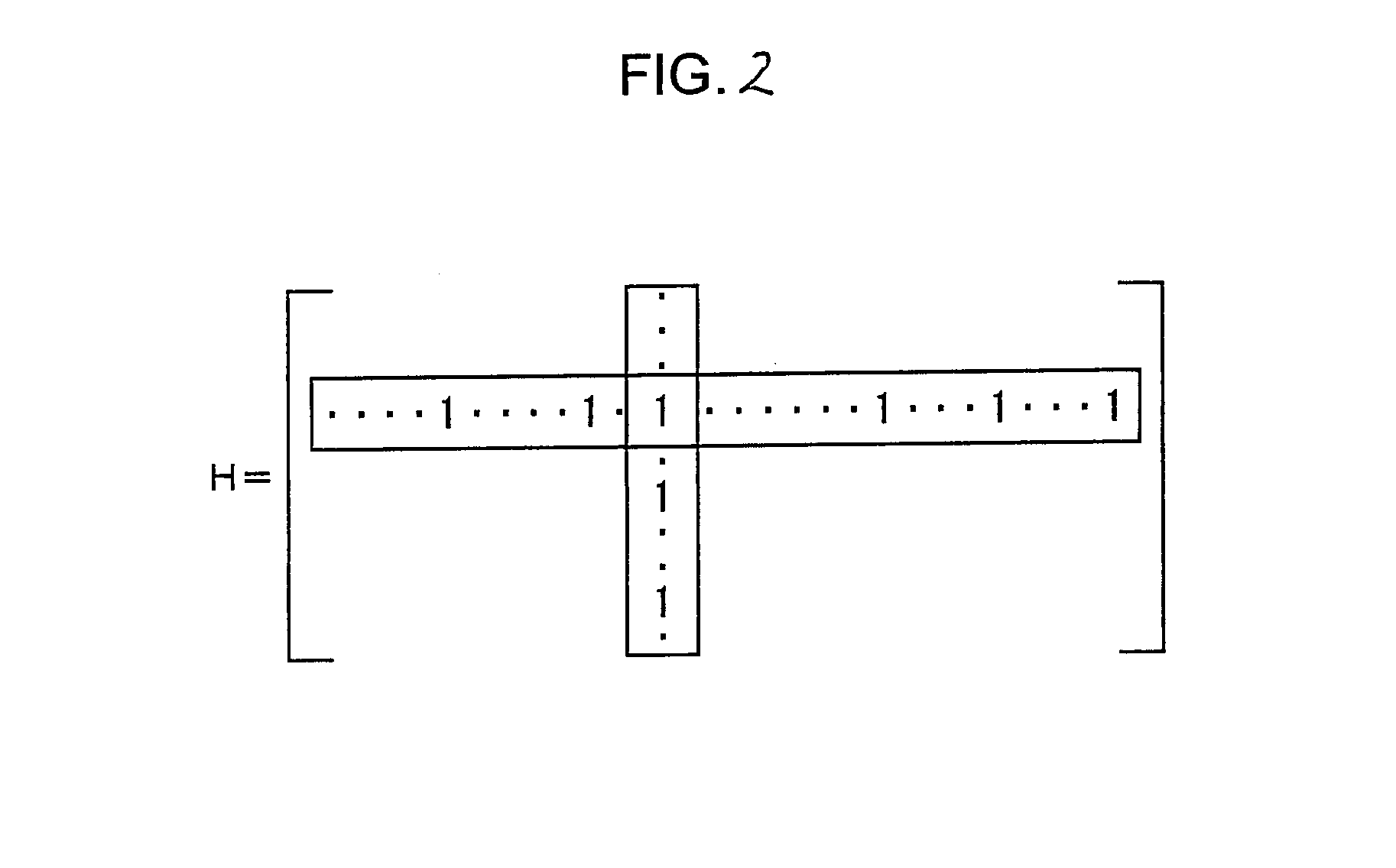

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

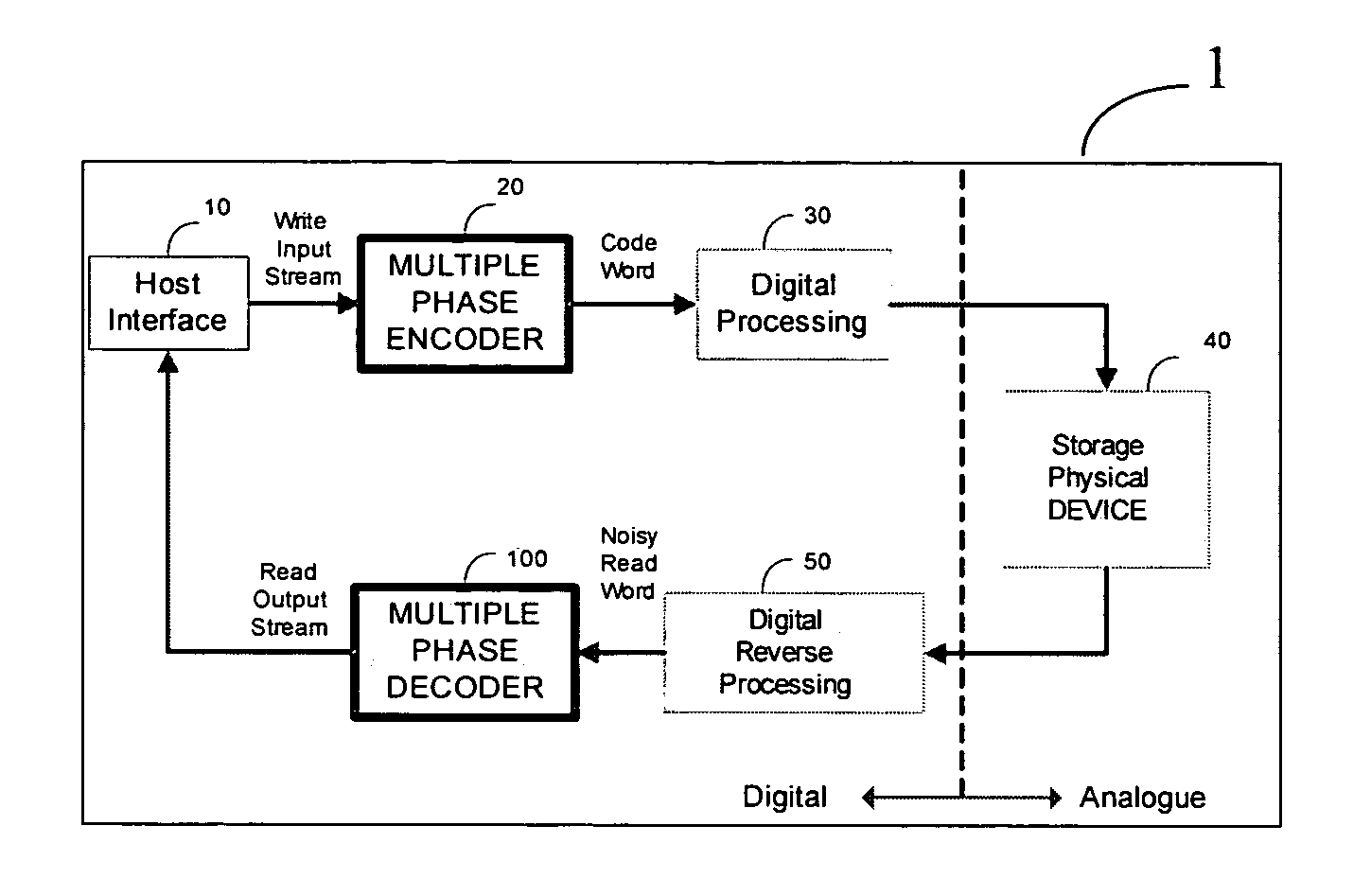

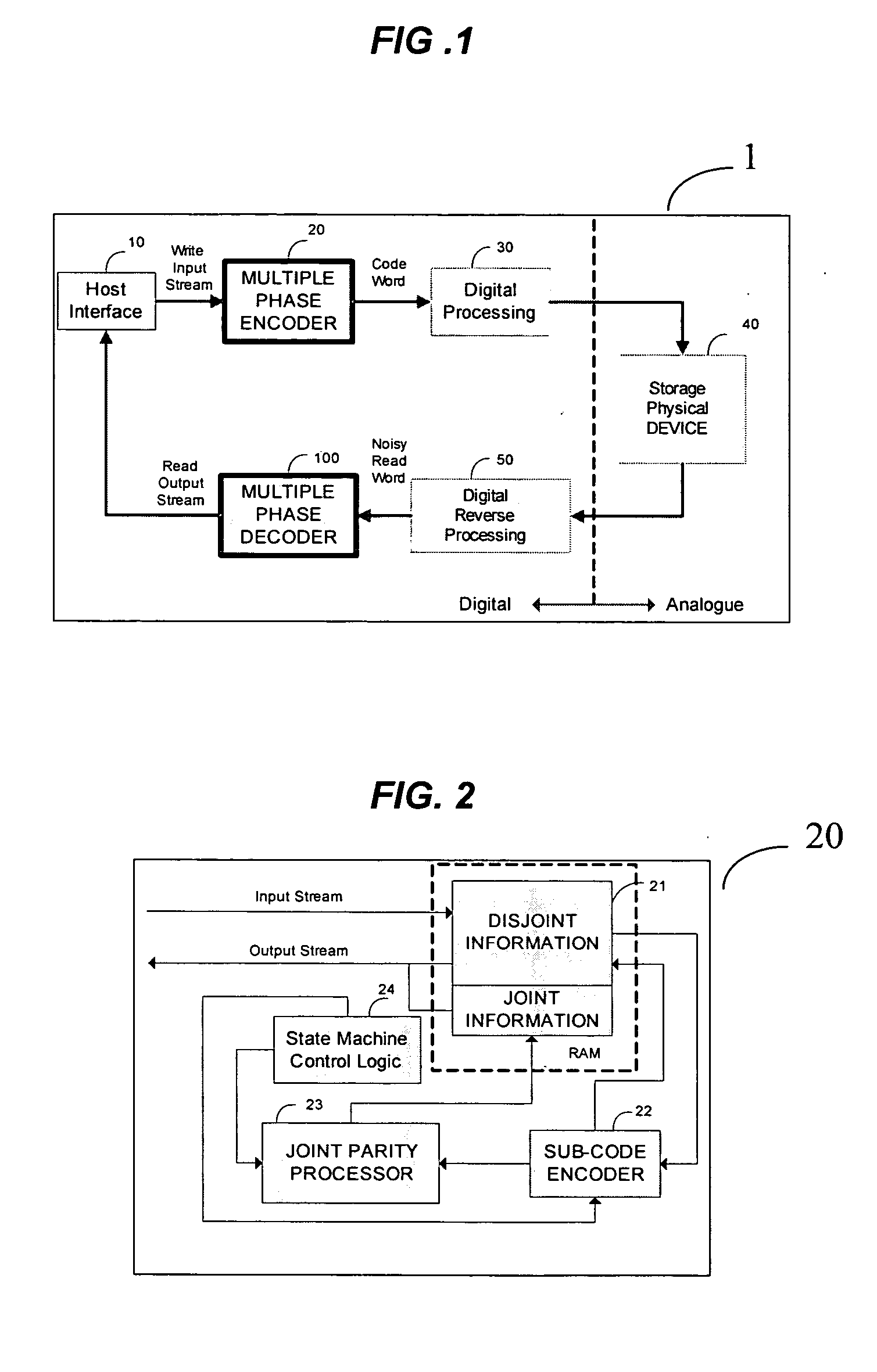

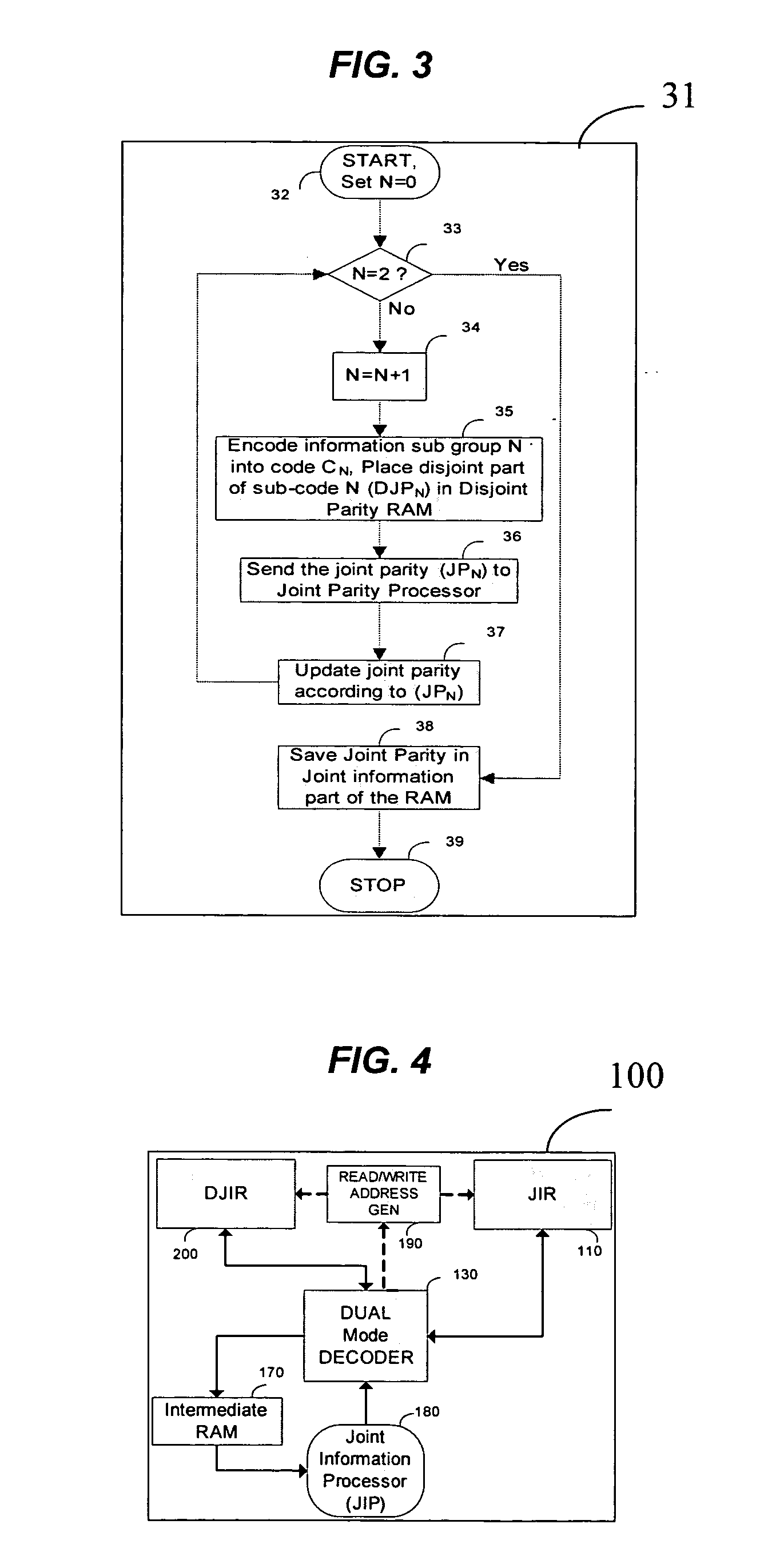

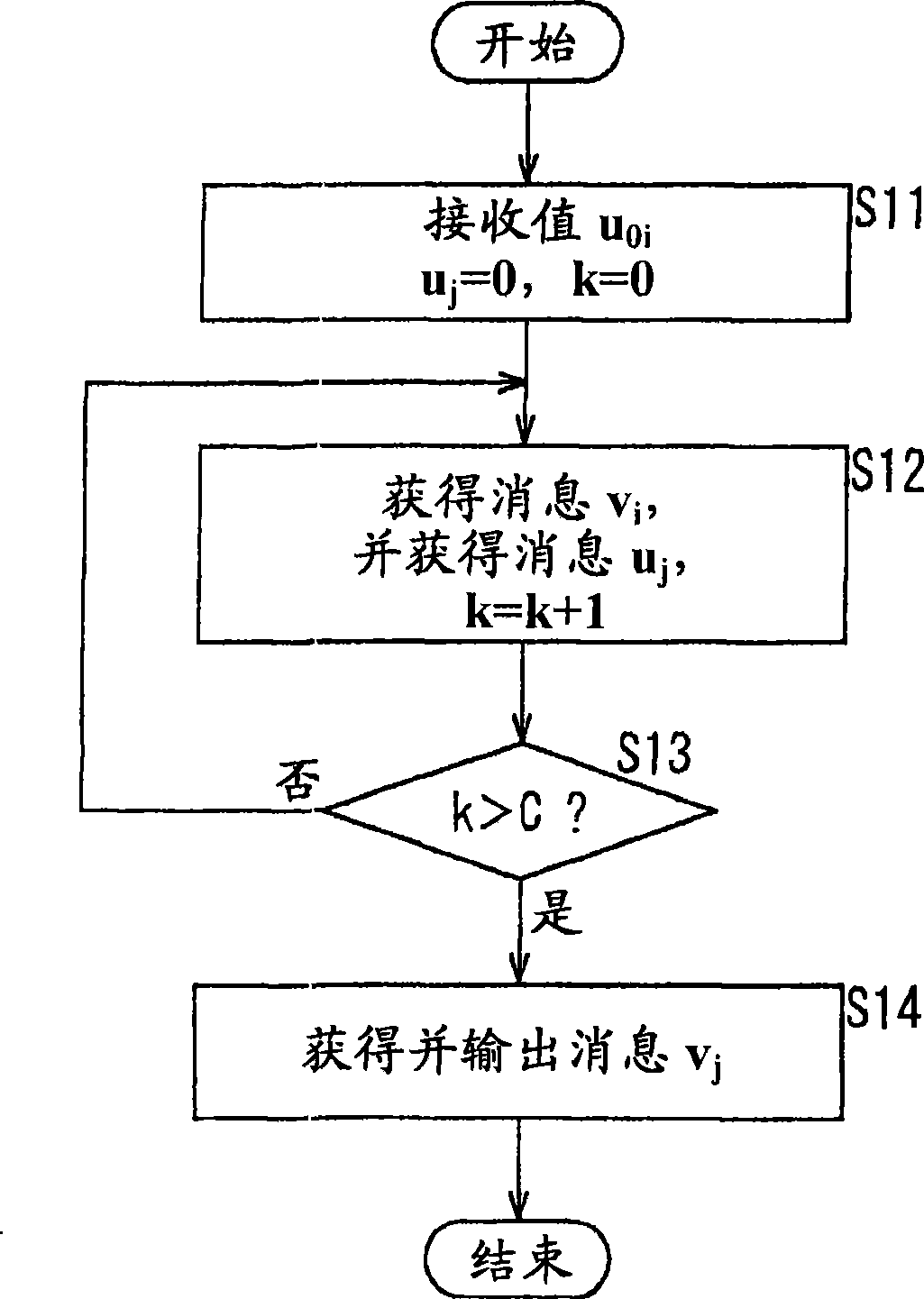

Method and device for multi phase error-correction

InactiveUS20070124652A1Error detection/correctionCode conversionTheoretical computer scienceMulti phase

Data bits to be encoded are split into a plurality of subgroups. Each subgroup is encoded separately to generate a corresponding codeword. Selected subsets are removed from the corresponding codewords, leaving behind shortened codewords, and are many-to-one transformed to condensed bits. The final codeword is a combination of the shortened codewords and the condensed bits. A representation of the final codeword is decoded by being partitioned to a selected subset and a plurality of remaining subsets. Each remaining subset is decoded separately. If one of the decodings fails, the remaining subset whose decoding failed is decoded at least in part according to the selected subset. If the encoding and decoding are systematic then the selected subsets are of parity bits.

Owner:RAMOT AT TEL AVIV UNIV LTD

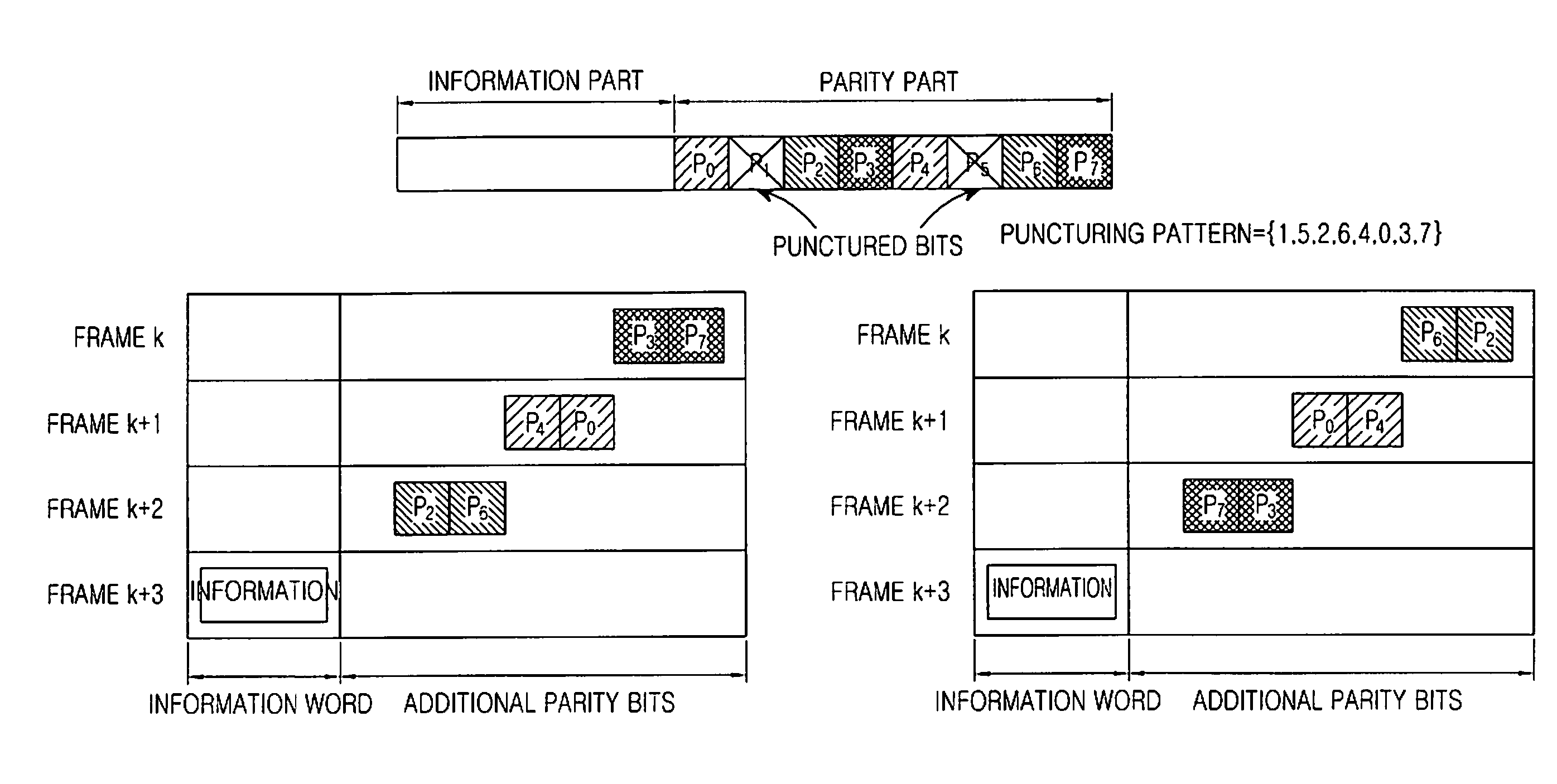

Method and apparatus for transmitting and receiving data in a communication system

ActiveUS20110119568A1Data representation error detection/correctionCode conversionCommunications systemComputer science

A method is provided for transmitting data, which improves a diversity effect in a communication system. The method includes transmitting an information word including a codeword in a (k+s)-th frame, generating s groups based on parity bits obtained by encoding the information word, and transmitting the s groups in s frames preceding the (k+s)-th frame, in a distributed manner.

Owner:SAMSUNG ELECTRONICS CO LTD

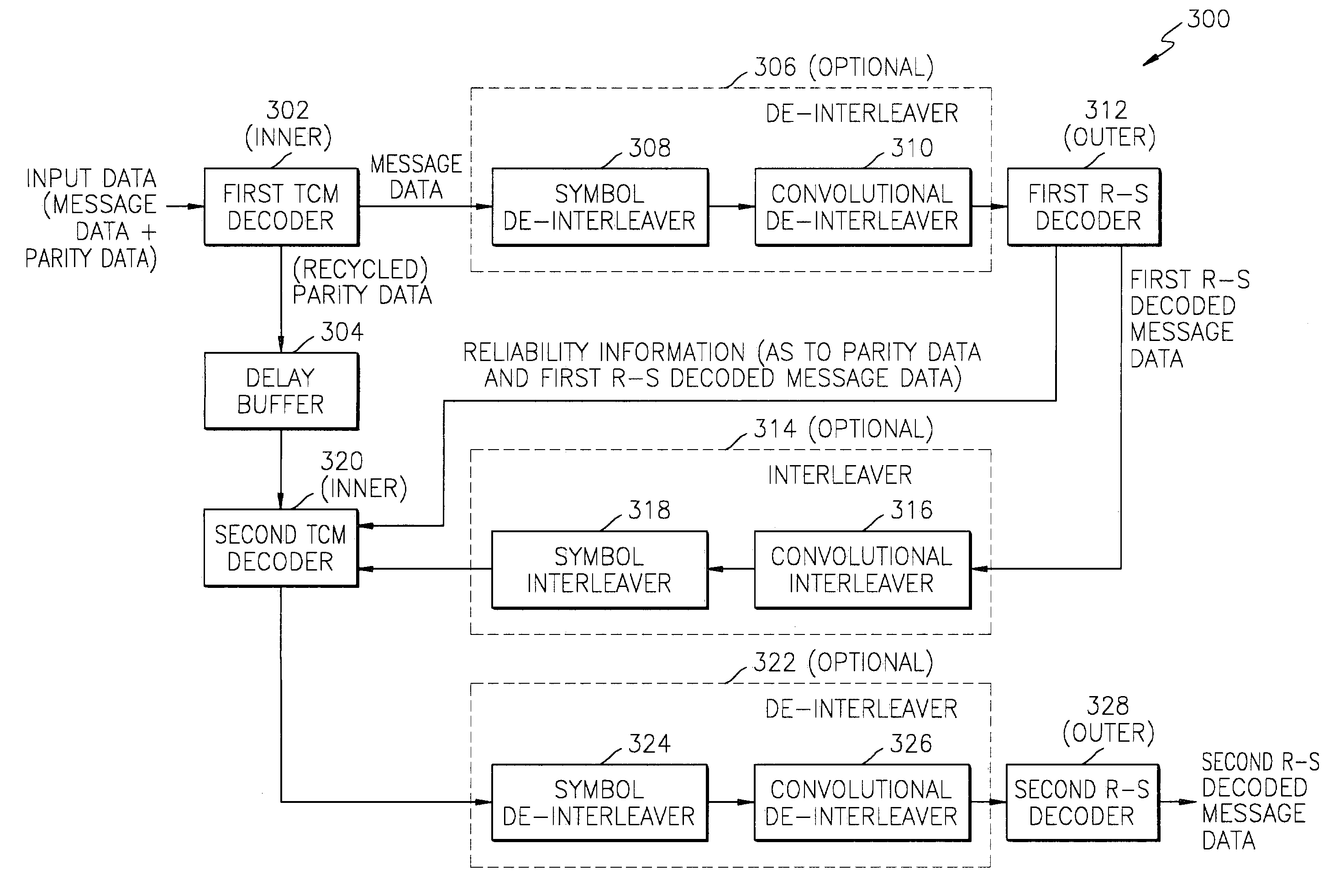

Decoding concatenated codes via parity bit recycling

Owner:SAMSUNG ELECTRONICS CO LTD

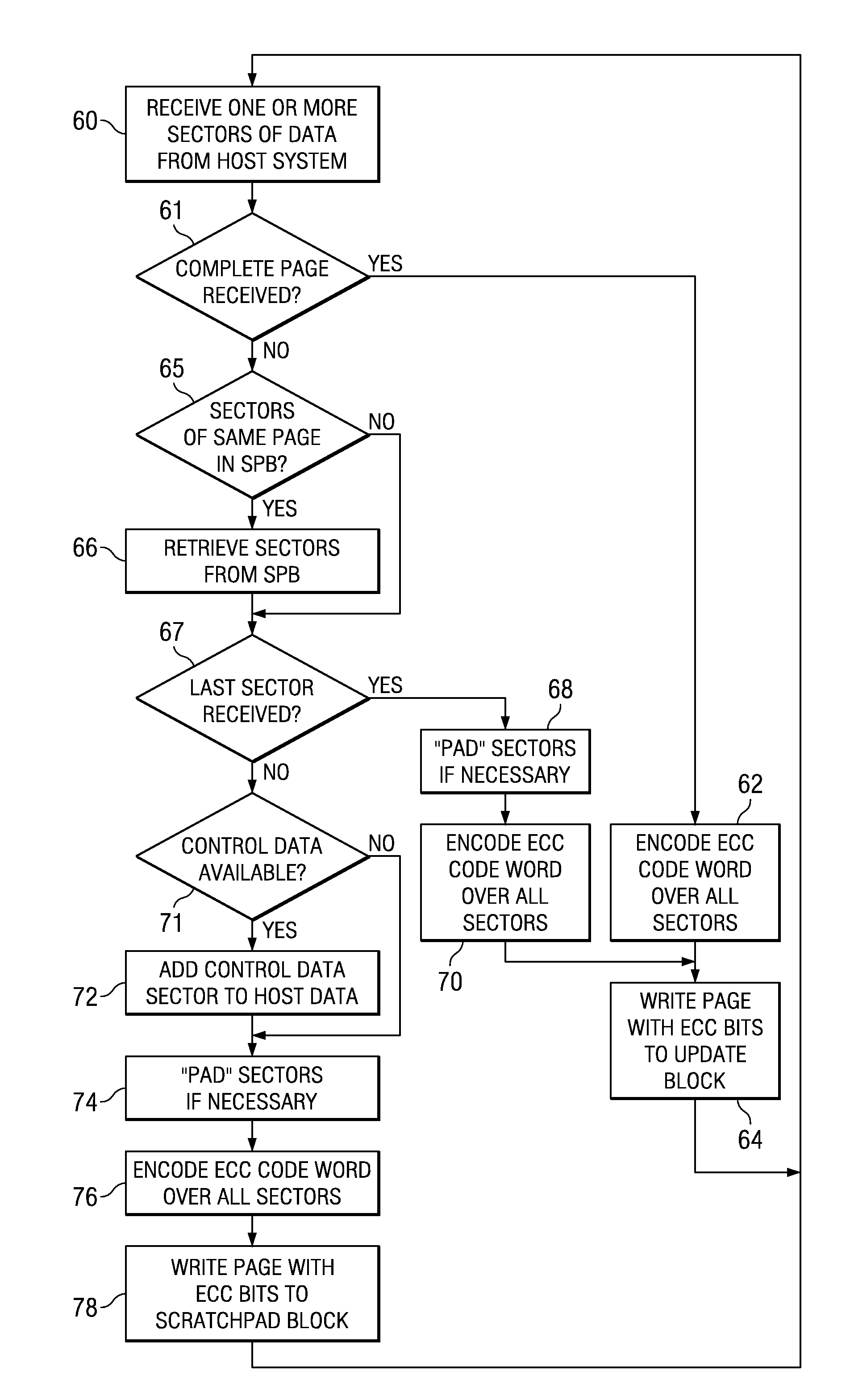

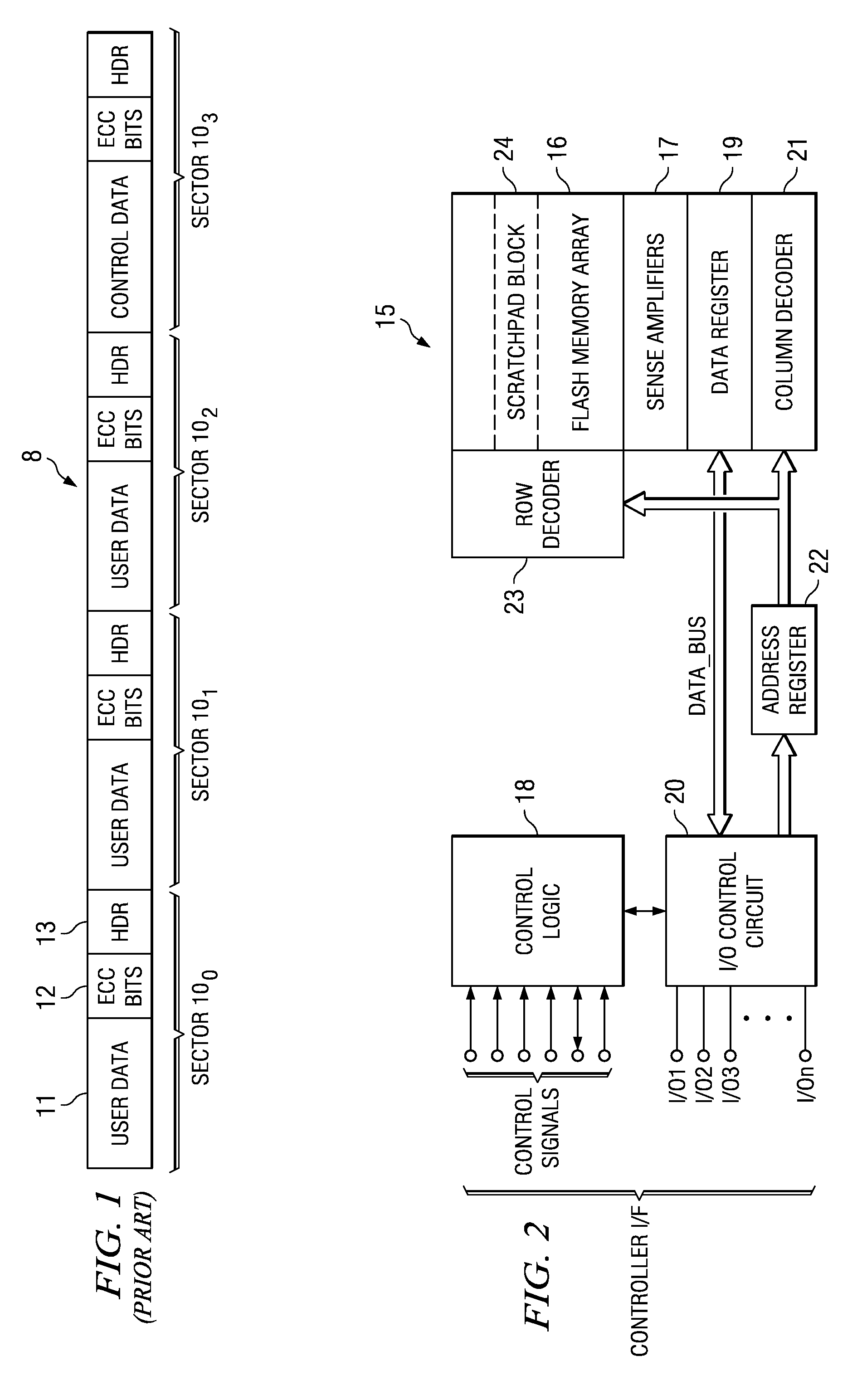

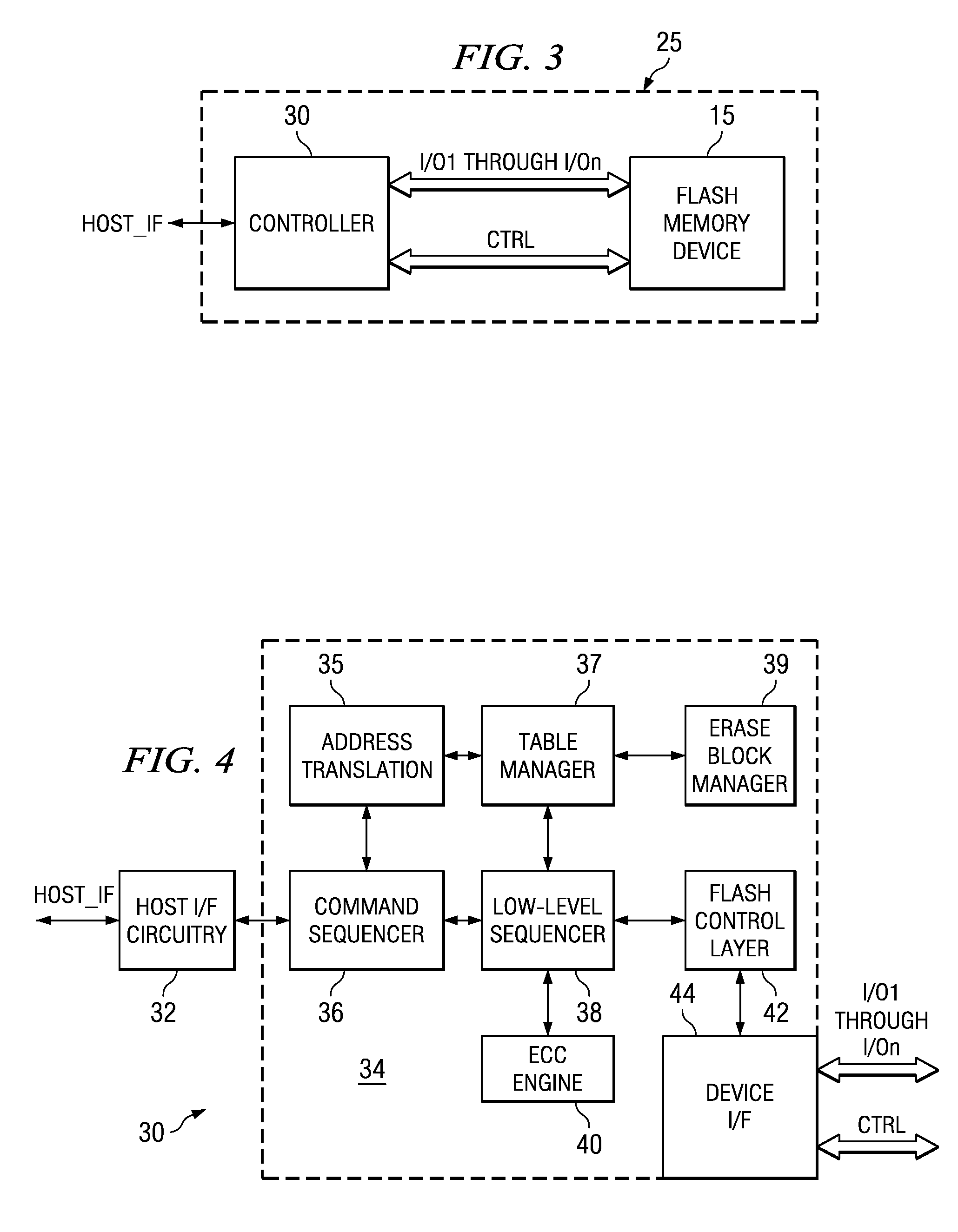

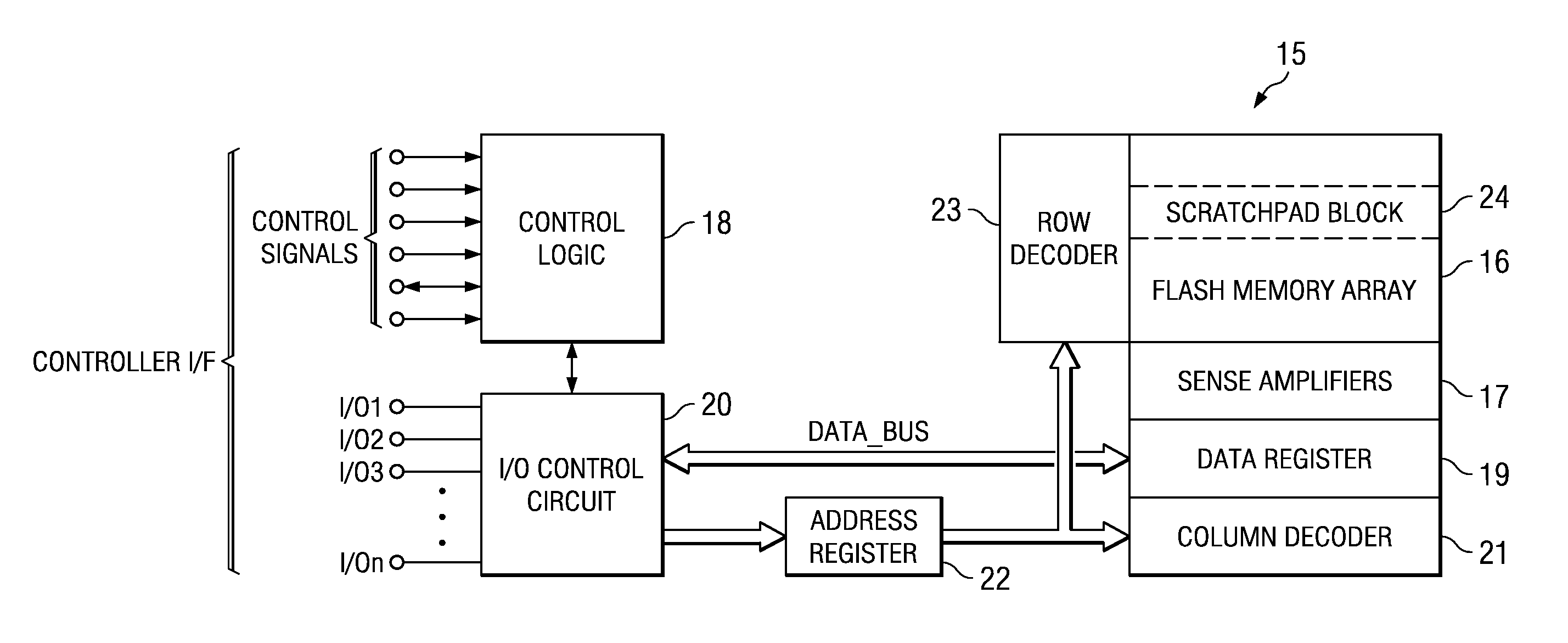

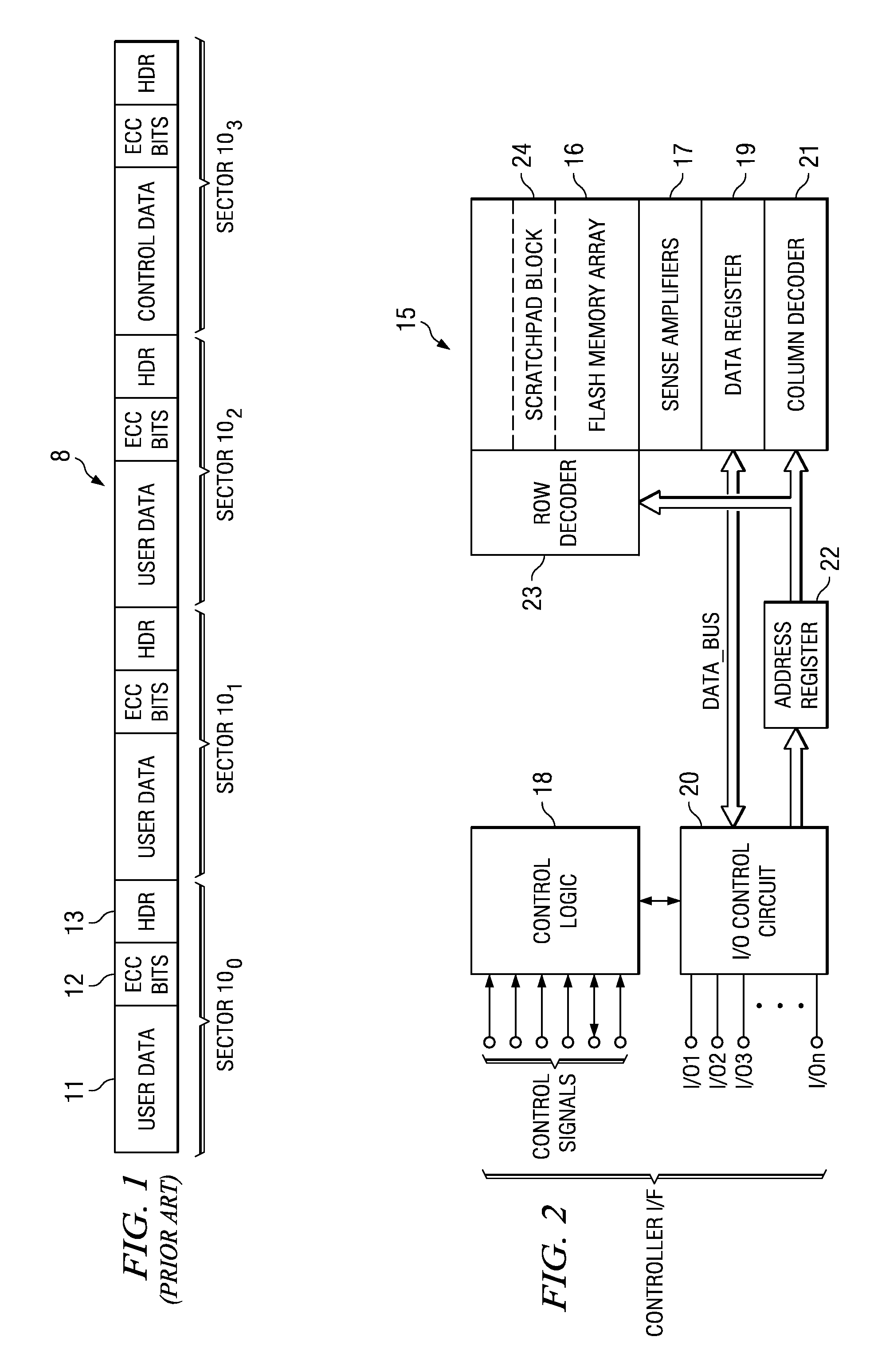

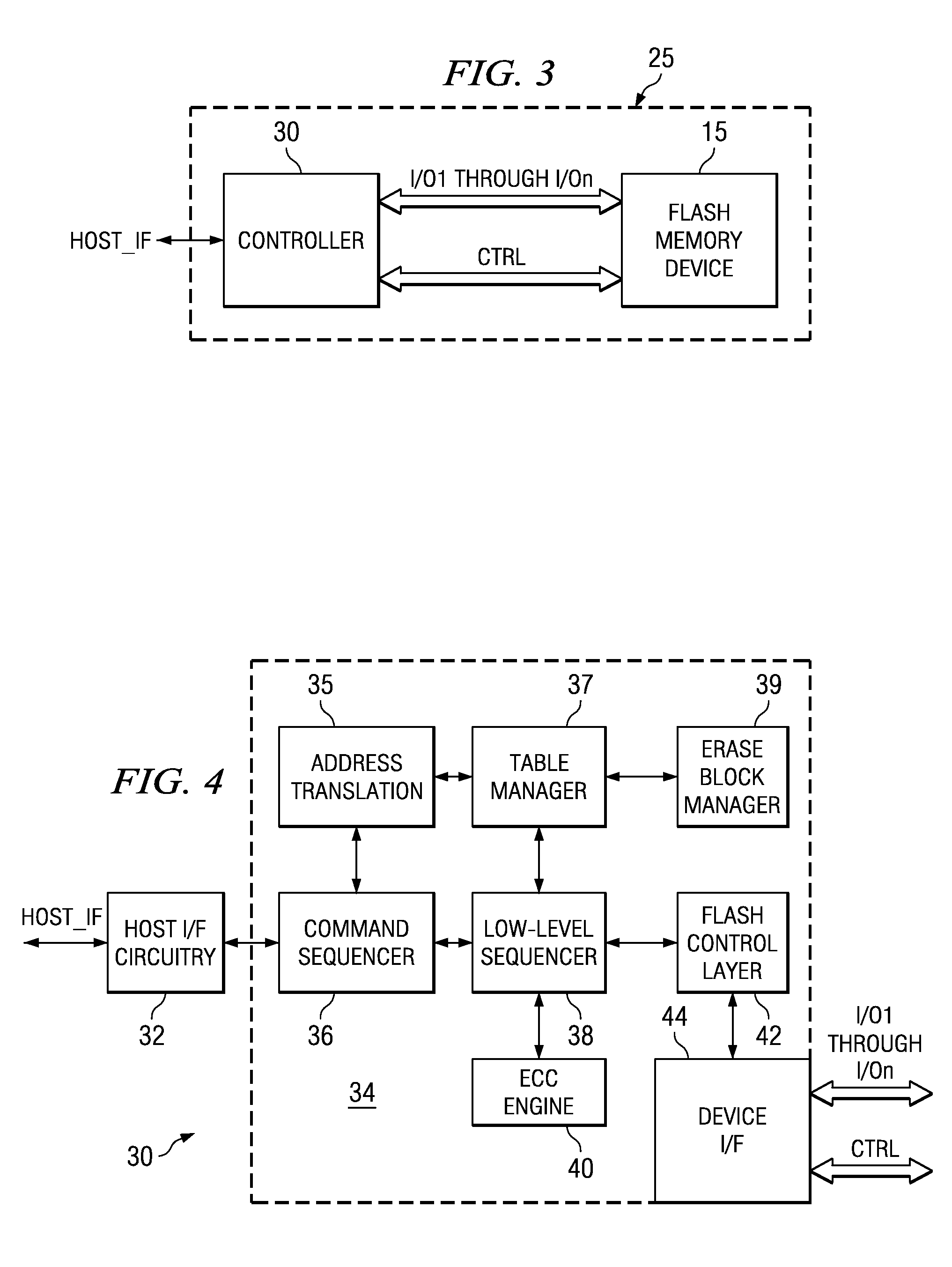

Method of Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

InactiveUS20070300130A1Efficient error correctionError detection/correctionRead-only memoriesControl dataDependability

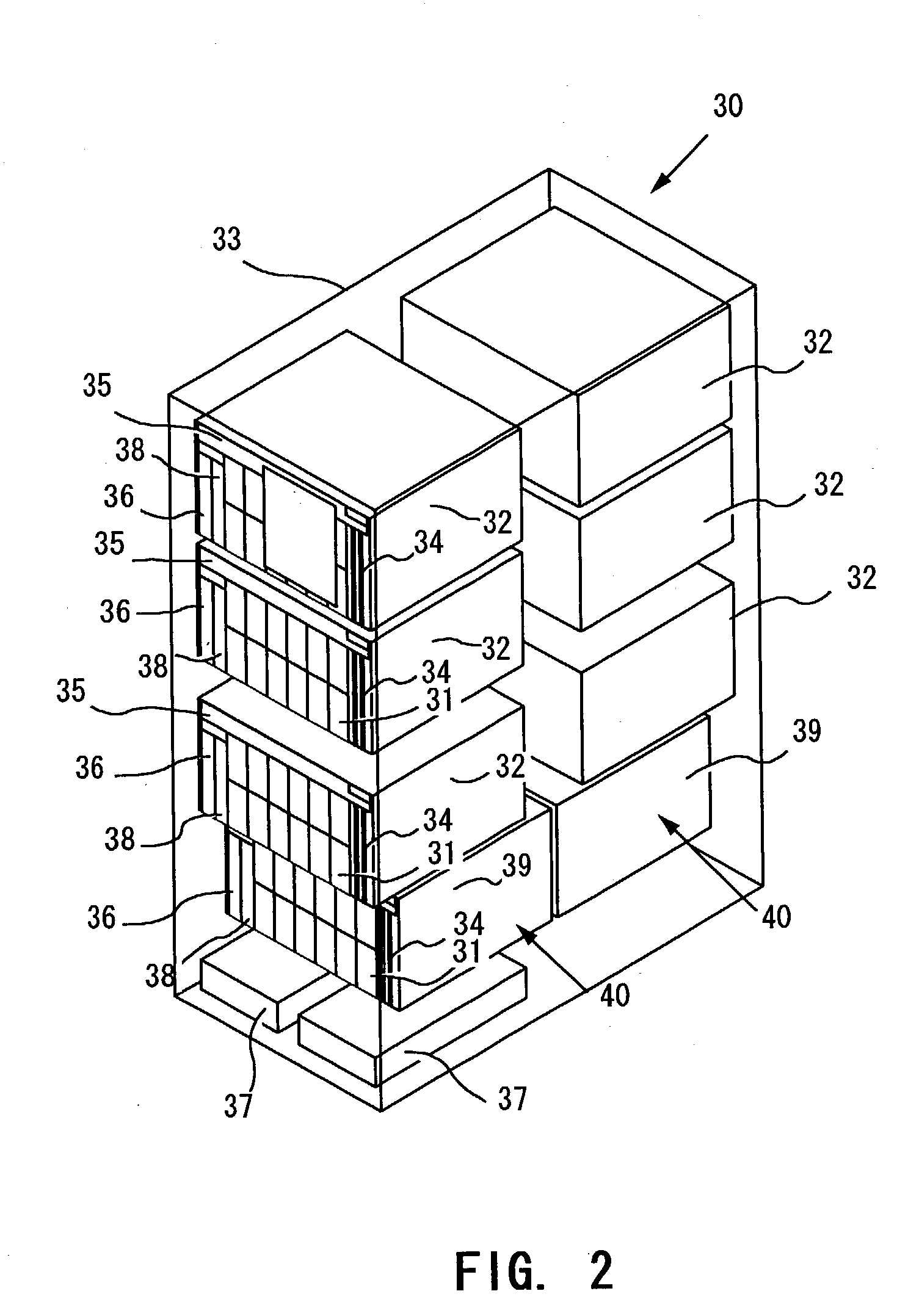

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

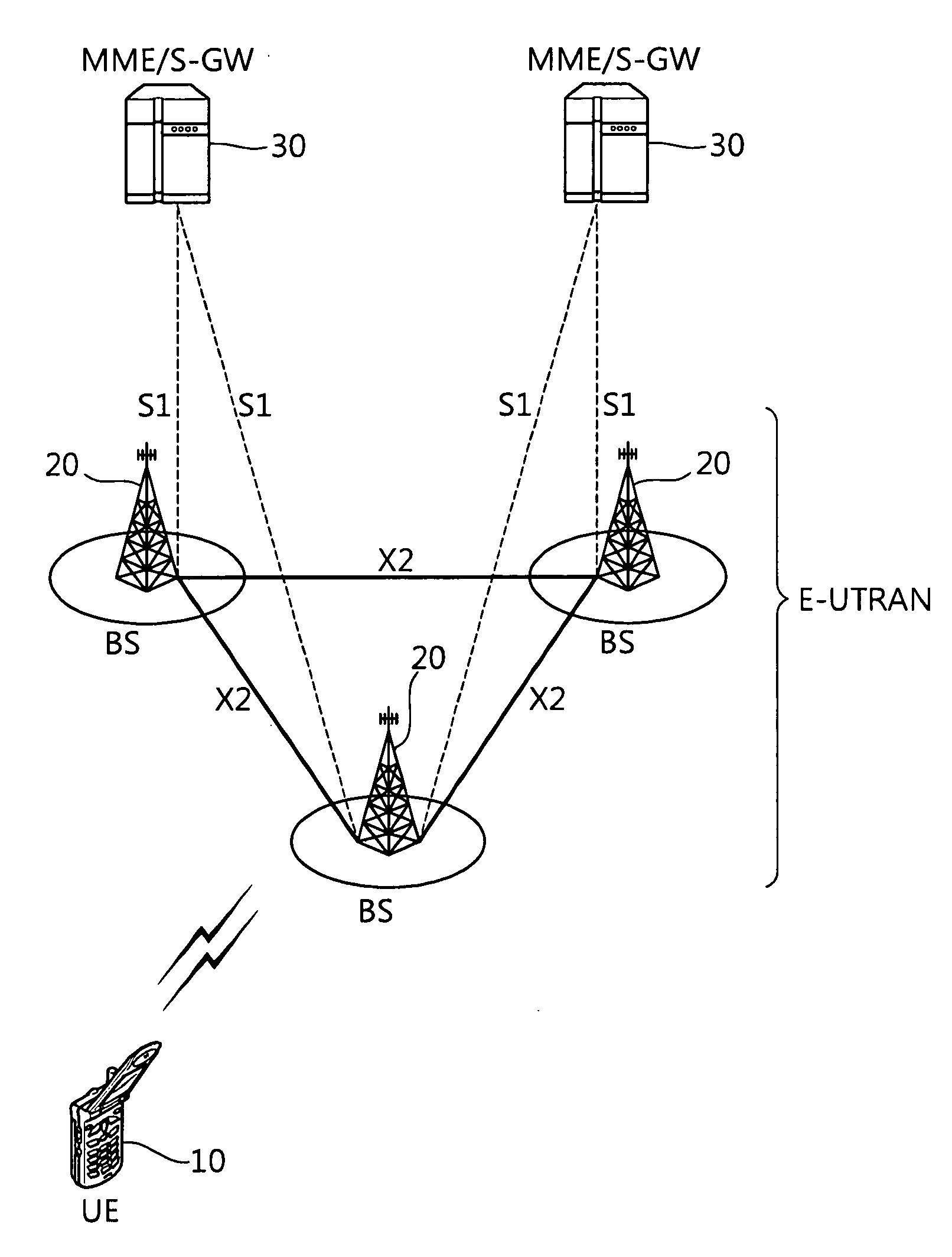

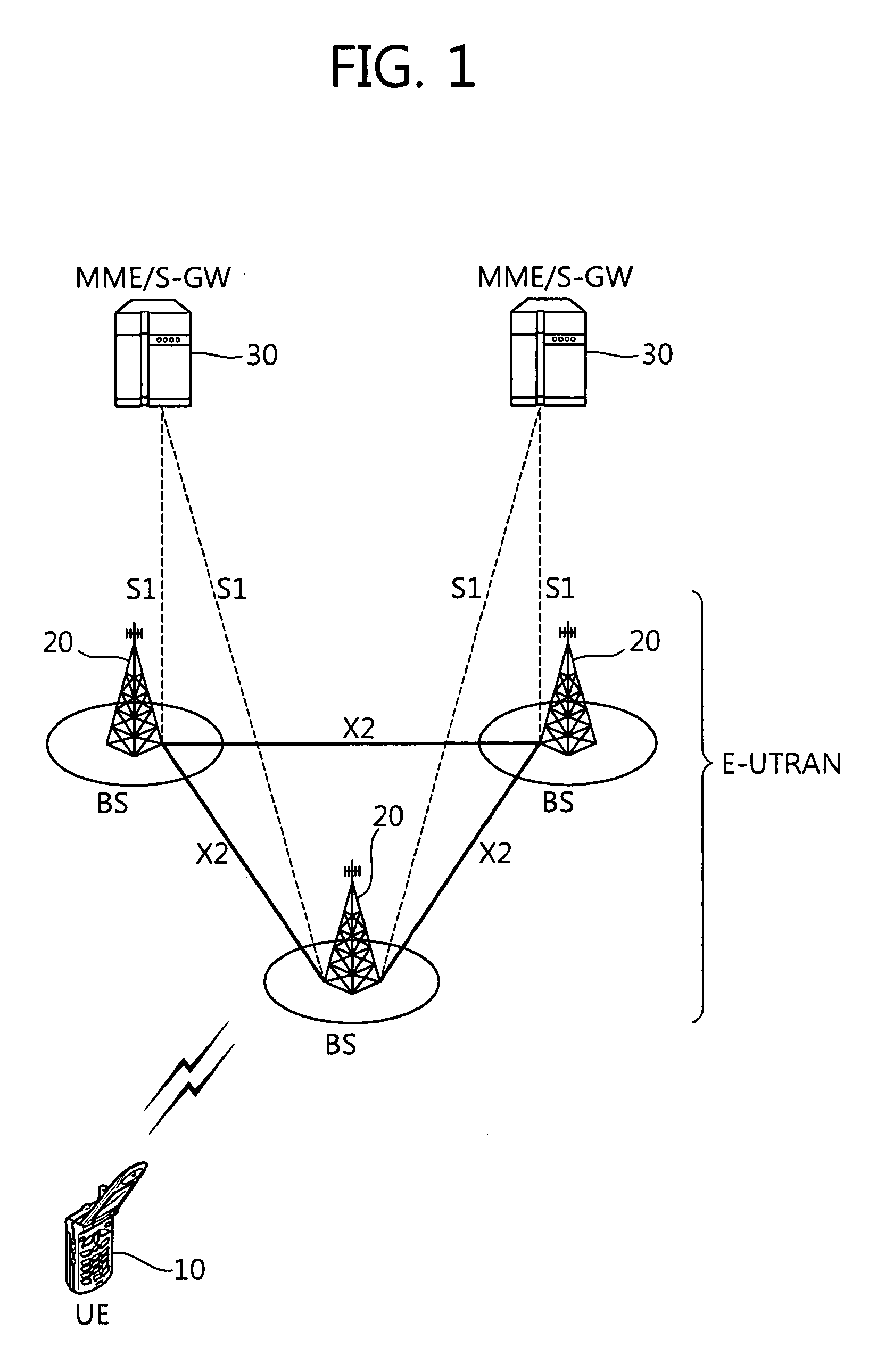

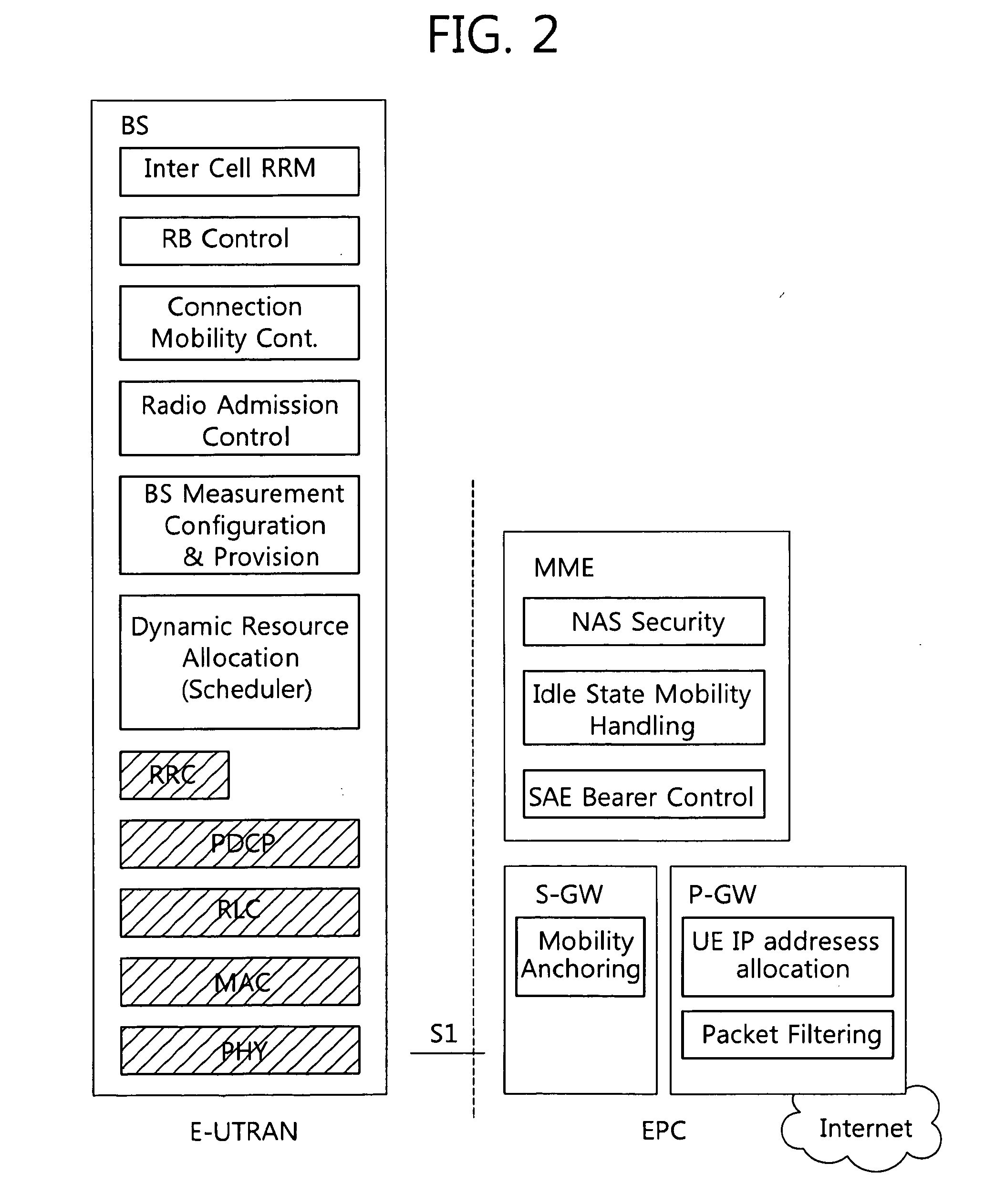

Method of controlling transmit power of uplink channel

A method of controlling a transmit power of an uplink channel is provided. Downlink control information of which Cyclic Redundancy Check (CRC) parity bits are masked with a TPC identifier is received on a downlink control channel. The transmit power of the uplink channel is adjusted based on a TPC command in the downlink control information.

Owner:LG ELECTRONICS INC

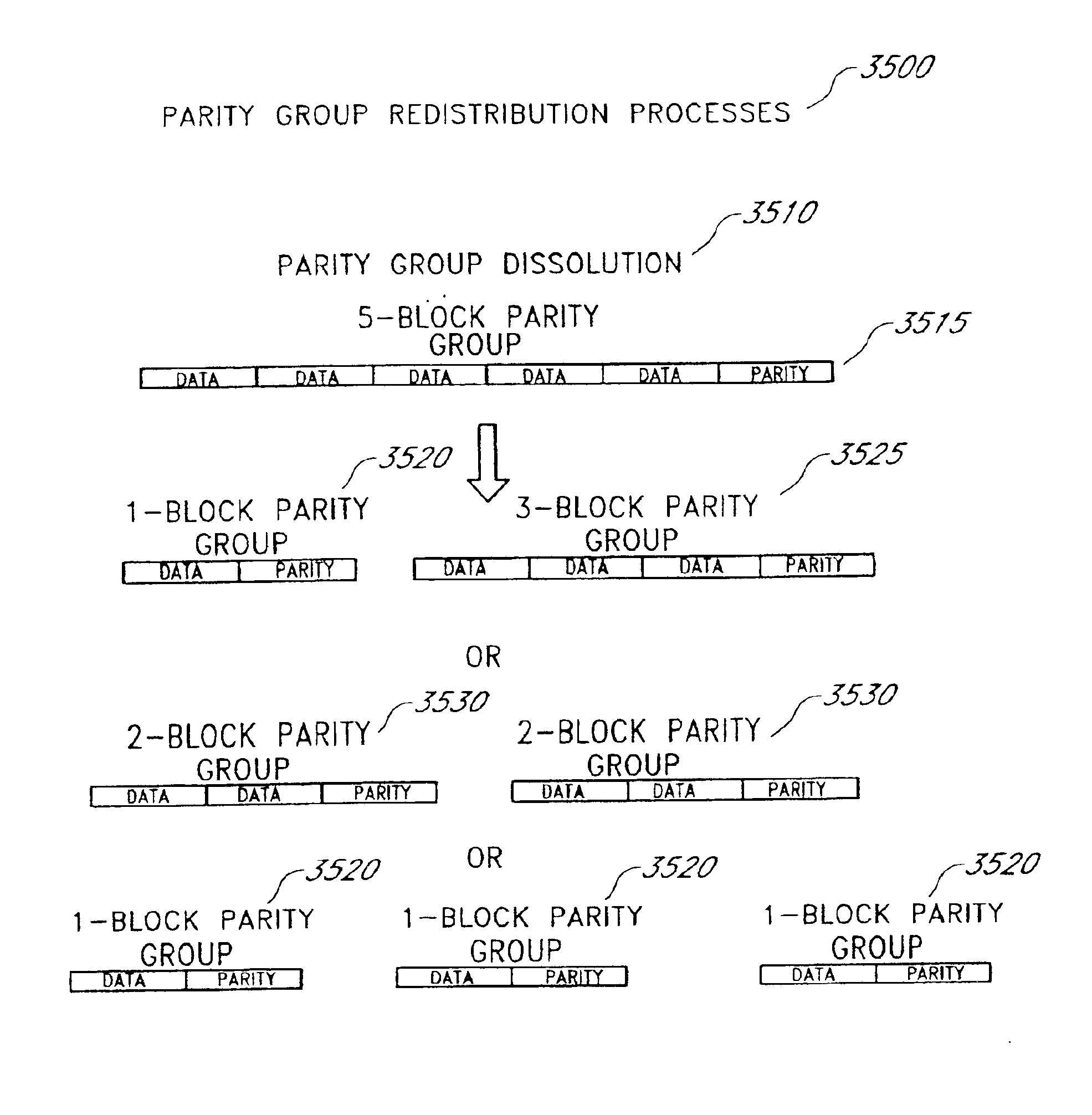

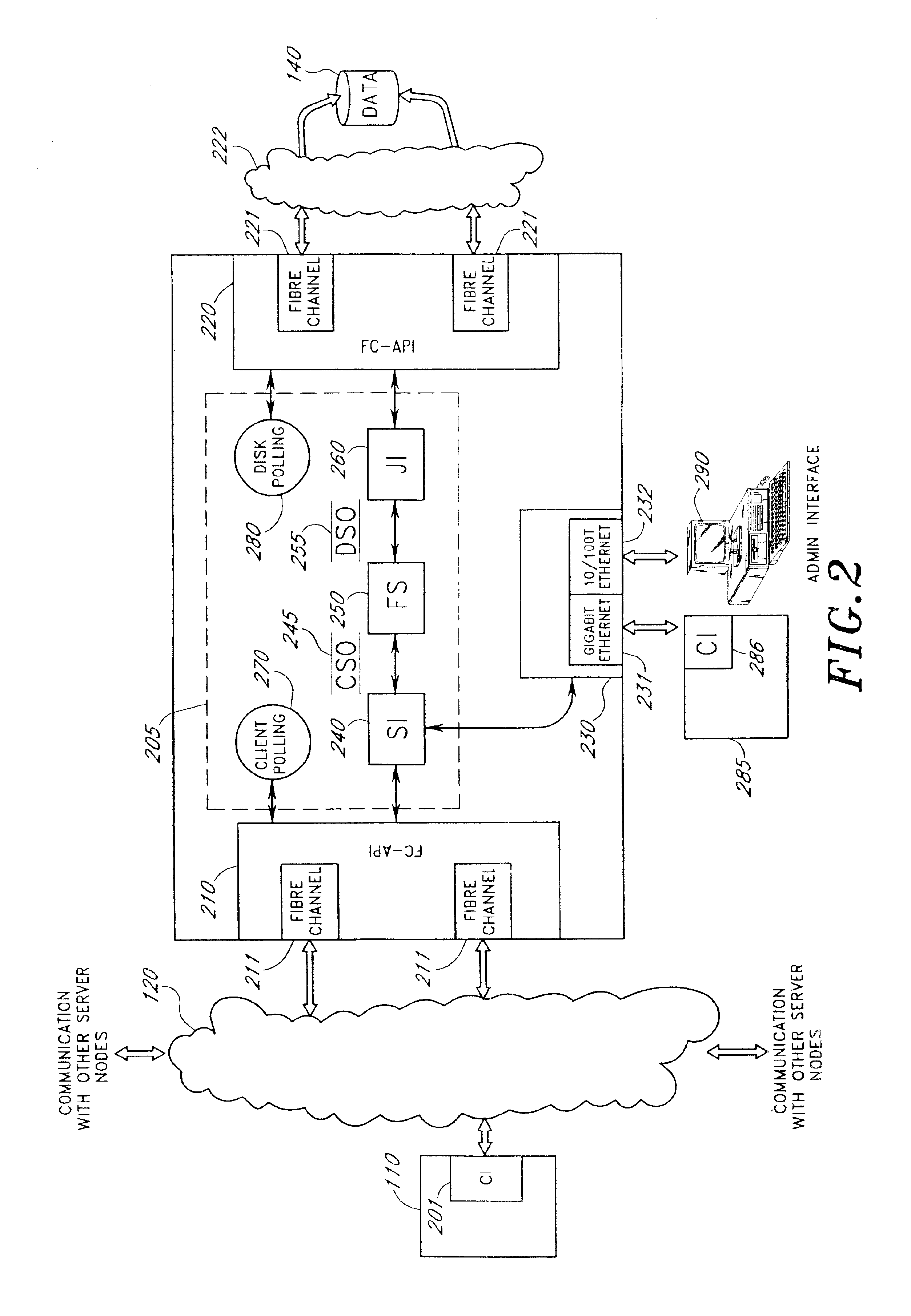

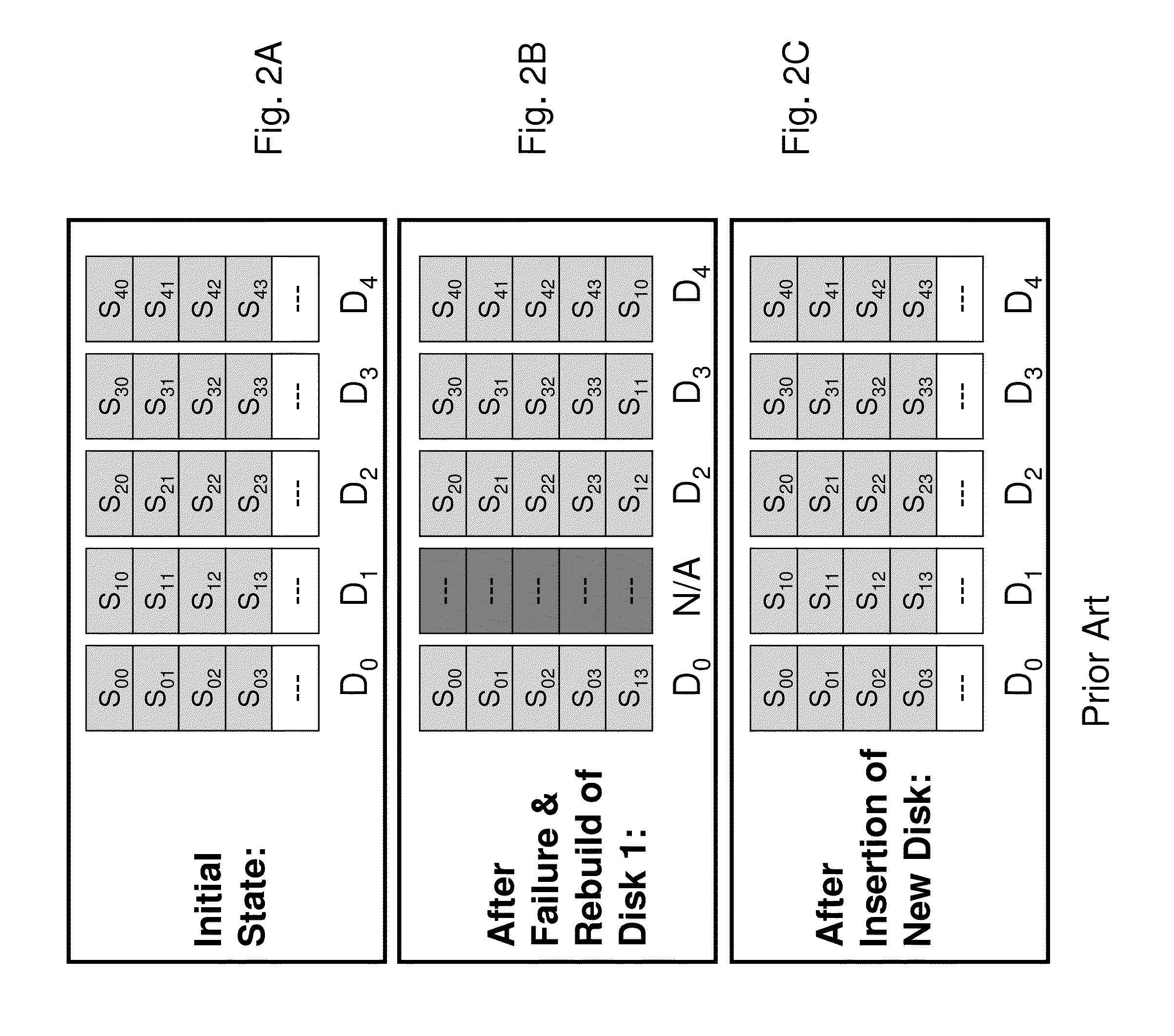

Dynamic data recovery

InactiveUS6871295B2Increase capacityImprove throughputMemory loss protectionDigital data processing detailsDynamic dataData recovery

A system and method for dynamic data recovery is described. The system and method for dynamic data recovery operates on a computer storage system that includes a plurality of disk drives for storing parity groups. Each parity group includes storage blocks. Each of the storage blocks is stored on a separate disk drive such that no two storage blocks from a given parity set reside on the same disk drive. The computer storage system further includes a recovery module to dynamically recover data that is lost when at least a portion of one disk drive in the plurality of disk drives becomes unavailable. The recovery module is configured to produce a reconstructed block by using information in the remaining storage blocks of a parity set that corresponds to an unavailable storage block. The recovery module is further configured to split the parity group corresponding to an unavailable storage block into two parity groups if the parity group corresponding to the unavailable storage block spanned all of the drives in the plurality of disk drives.

Owner:OVERLAND STORAGE

Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

ActiveUS20070271494A1Memory architecture accessing/allocationError detection/correctionControl dataDependability

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

Hybrid automatic repeat request system and method

InactiveUS7000174B2Uniform puncturingError prevention/detection by using return channelTransmission systemsTheoretical computer scienceLow density

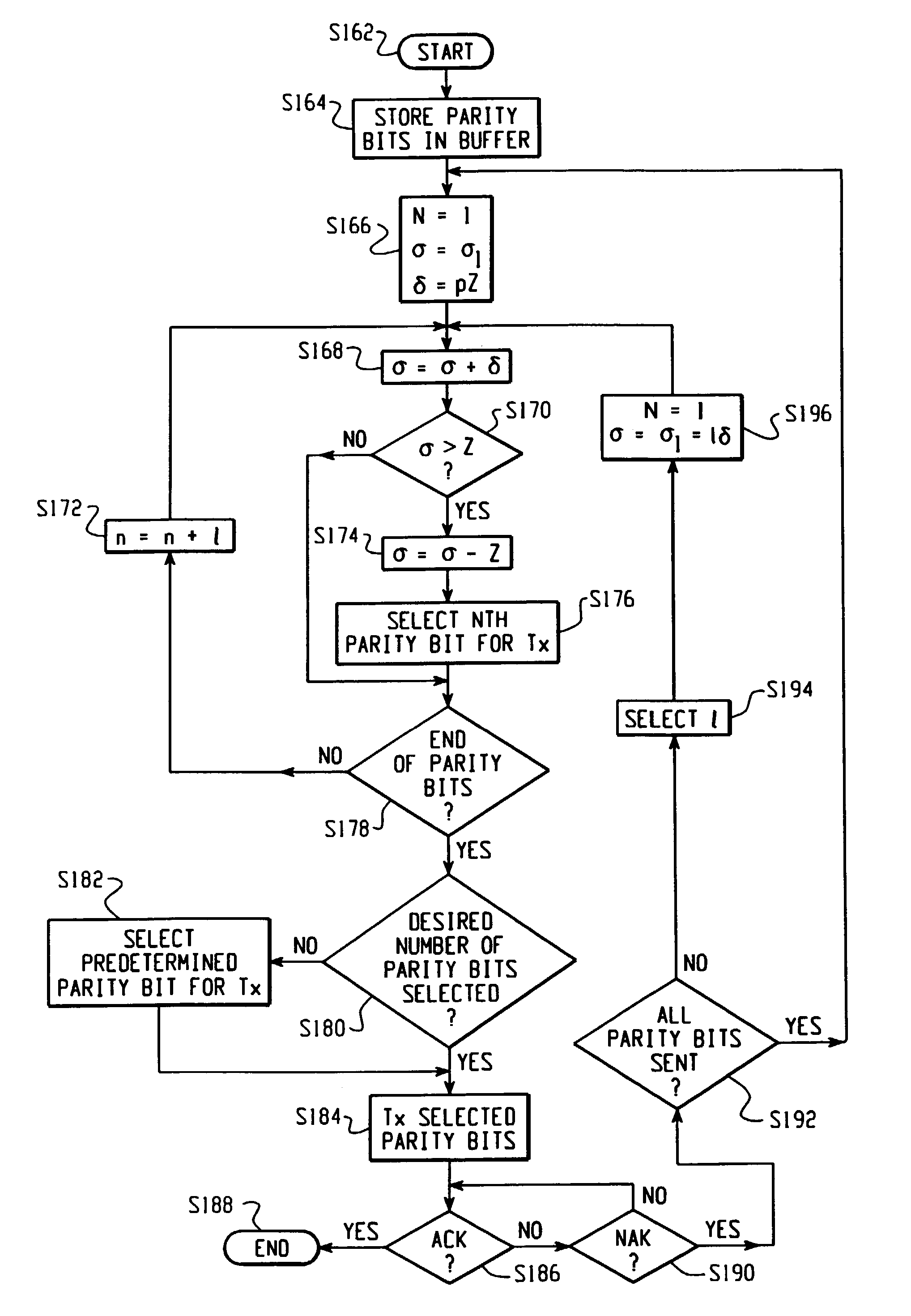

A data communication method and system for uniform arbitrary puncturing of parity bits generated by an encoder. The parity bits are stored in a buffer, and an a-bit accumulator is incremented to a predetermined initial value. For each parity bit in the buffer, the following steps are performed: the accumulator is incremented by a predetermined increment value, and if the accumulator overflows, the parity bit is selected for transmission. The predetermined initial value and the predetermined increment value are selected to achieve a desired amount of puncturing. In a further hybrid automatic repeat request (HARQ) communication method and system, the parity bits are generated by a low density parity check (LDPC) coder.

Owner:MALIKIE INNOVATIONS LTD

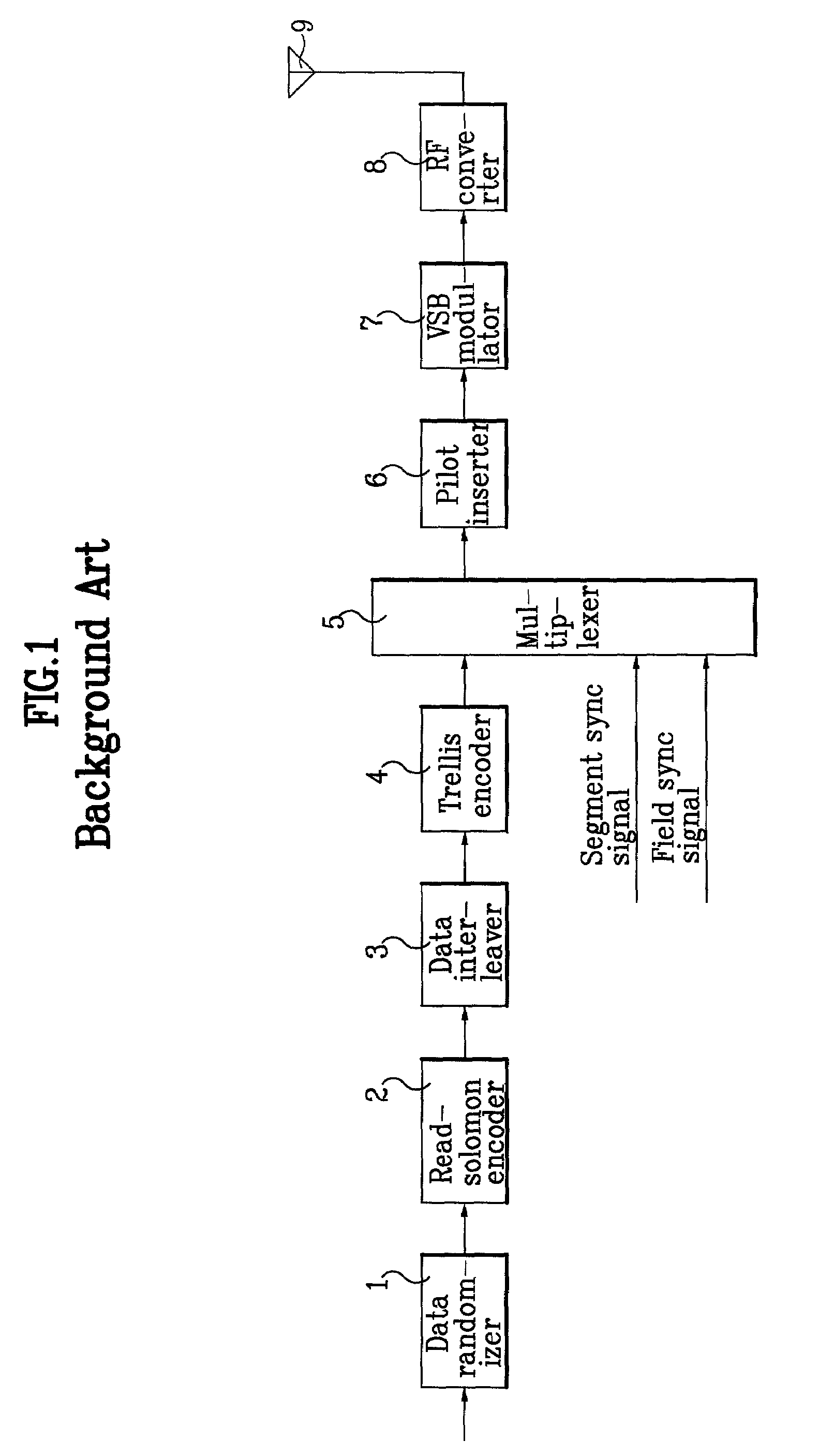

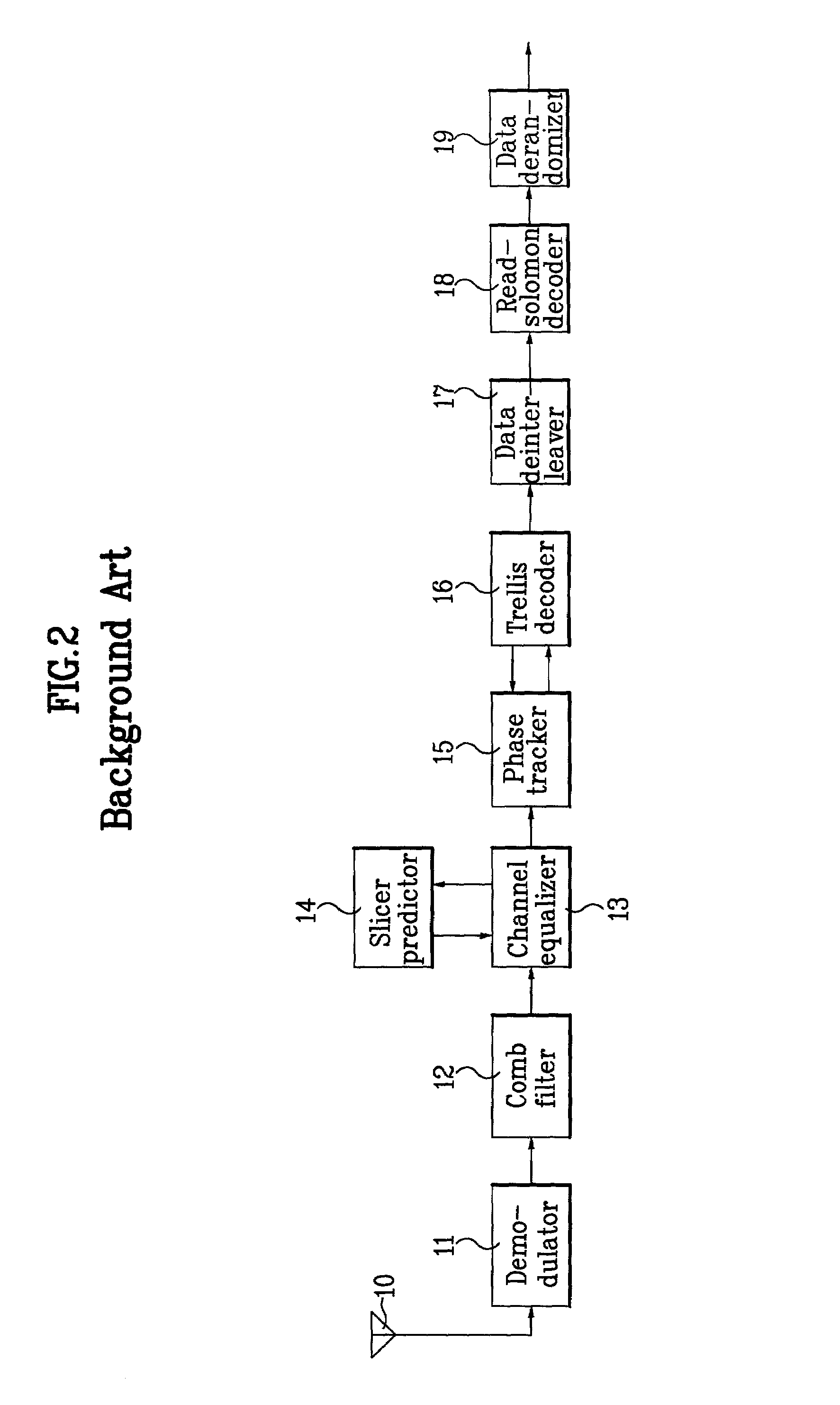

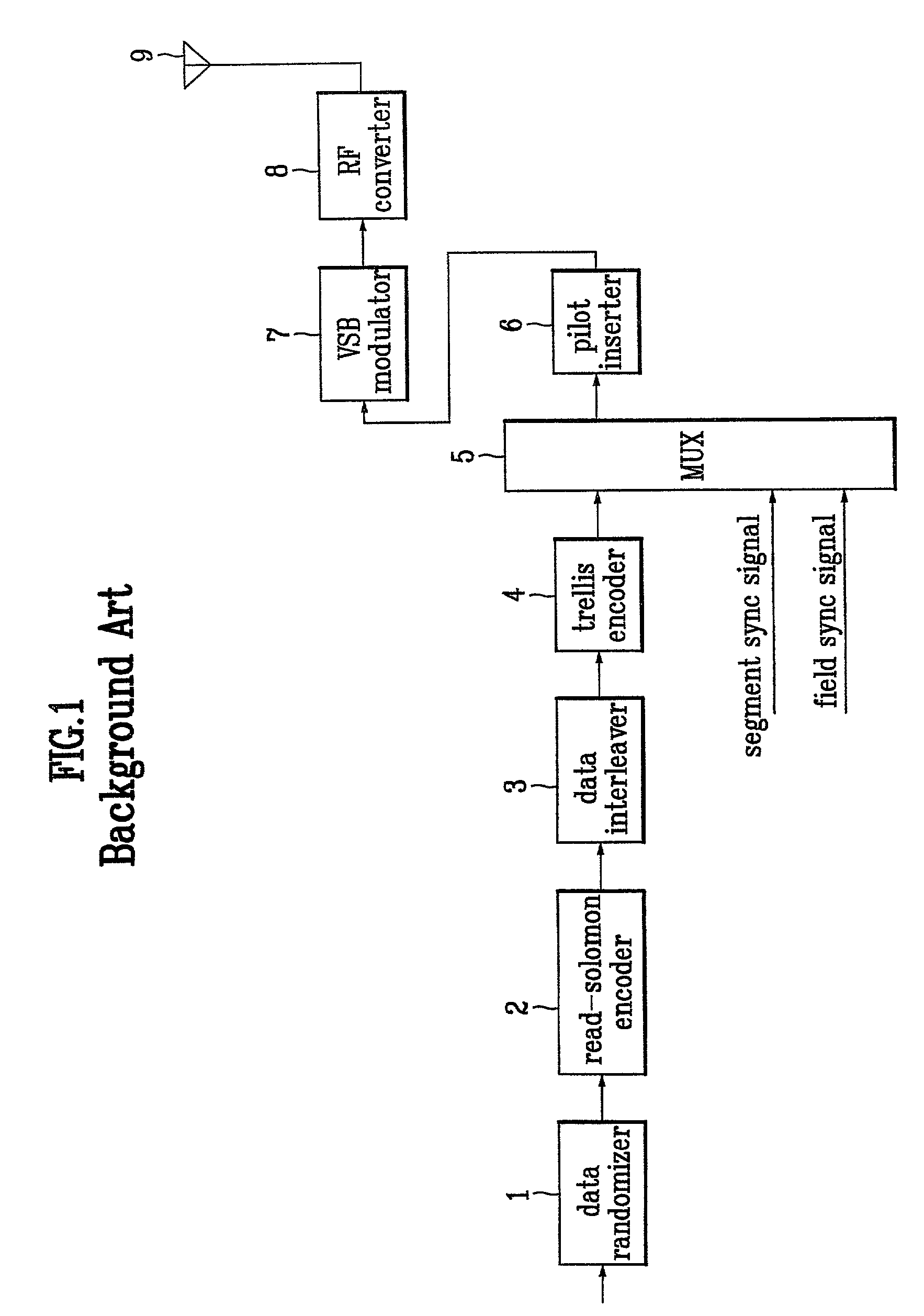

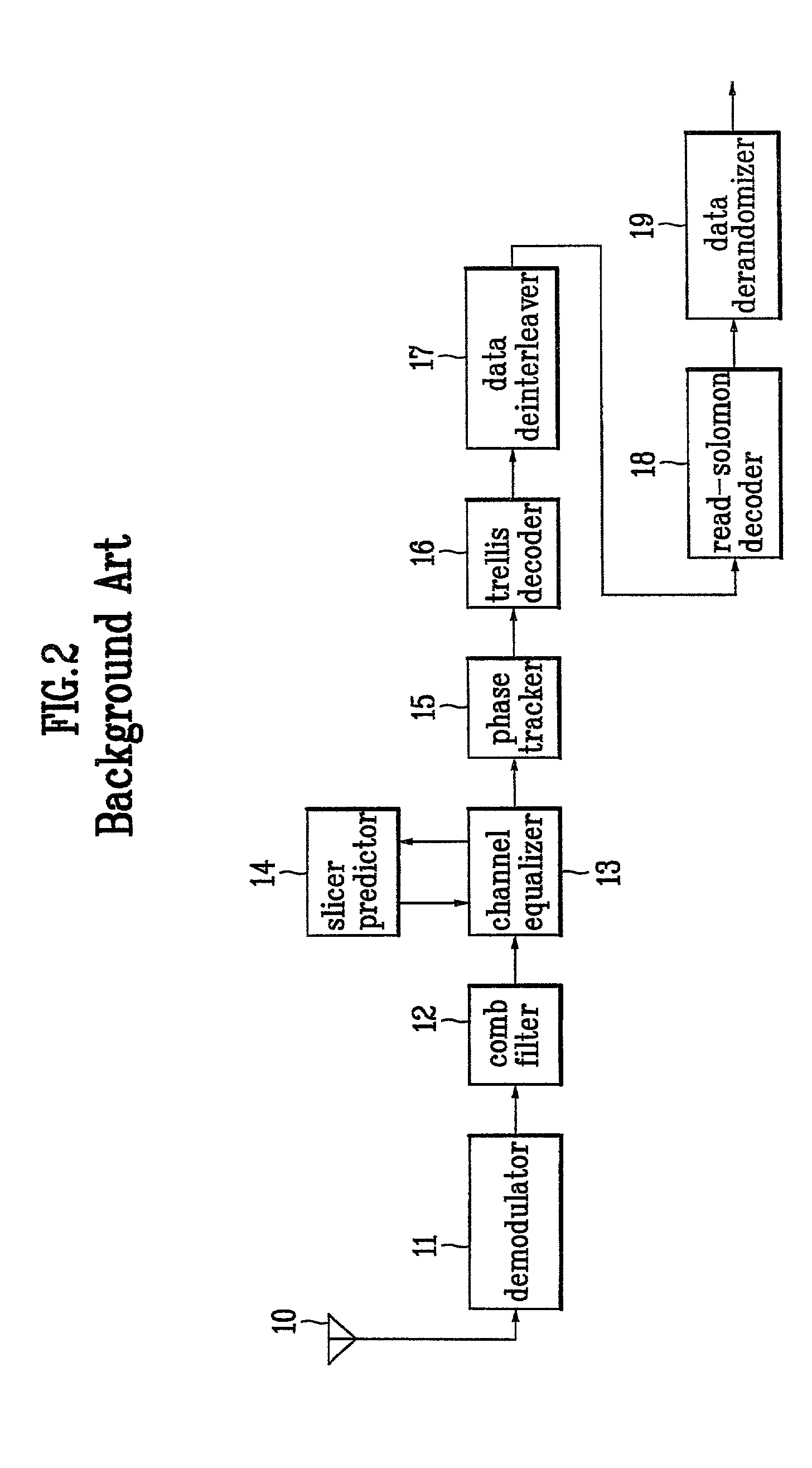

Digital VSB transmission system

InactiveUS6980603B2Noise robustData representation error detection/correctionCode conversionNoise levelComputer science

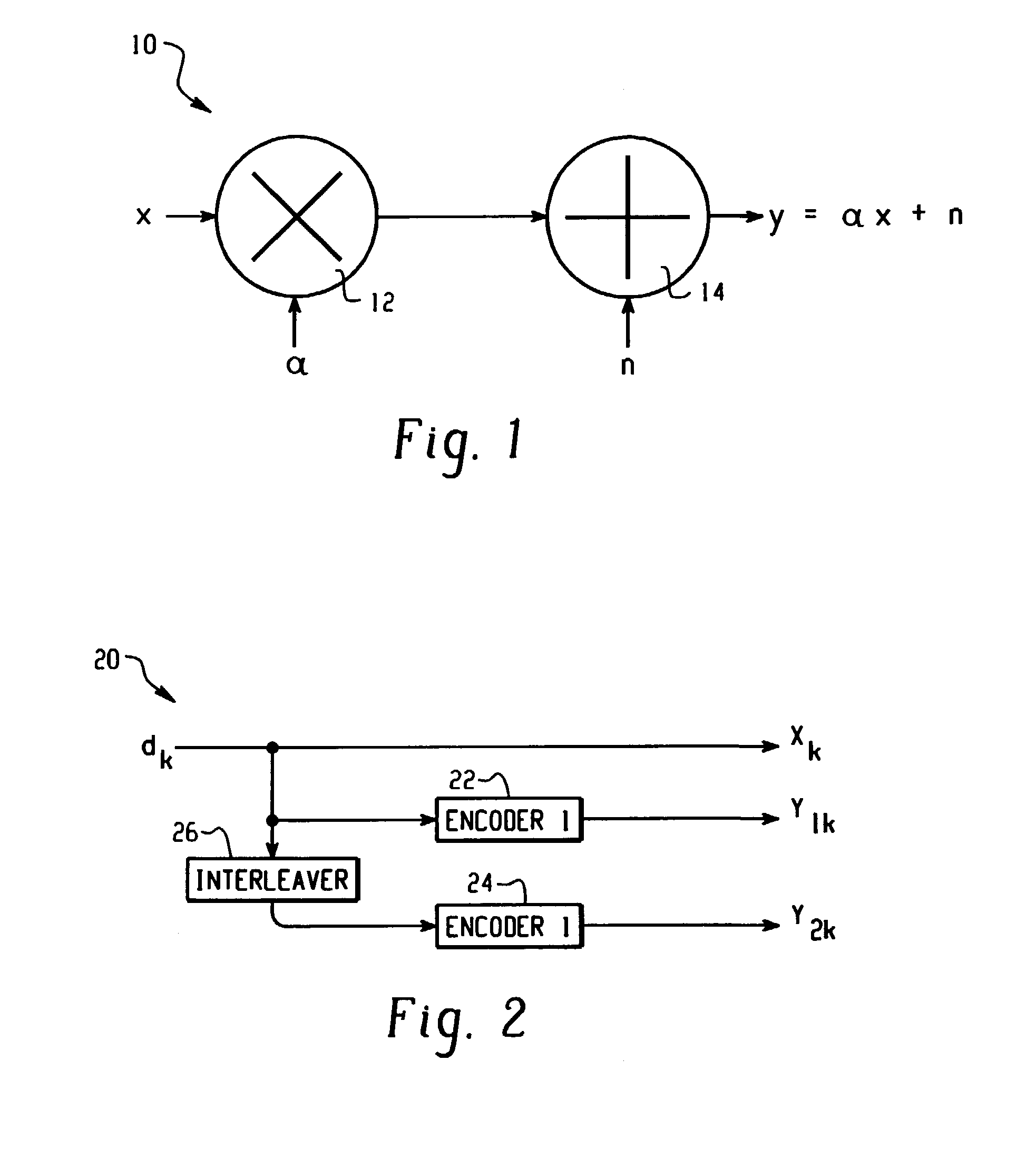

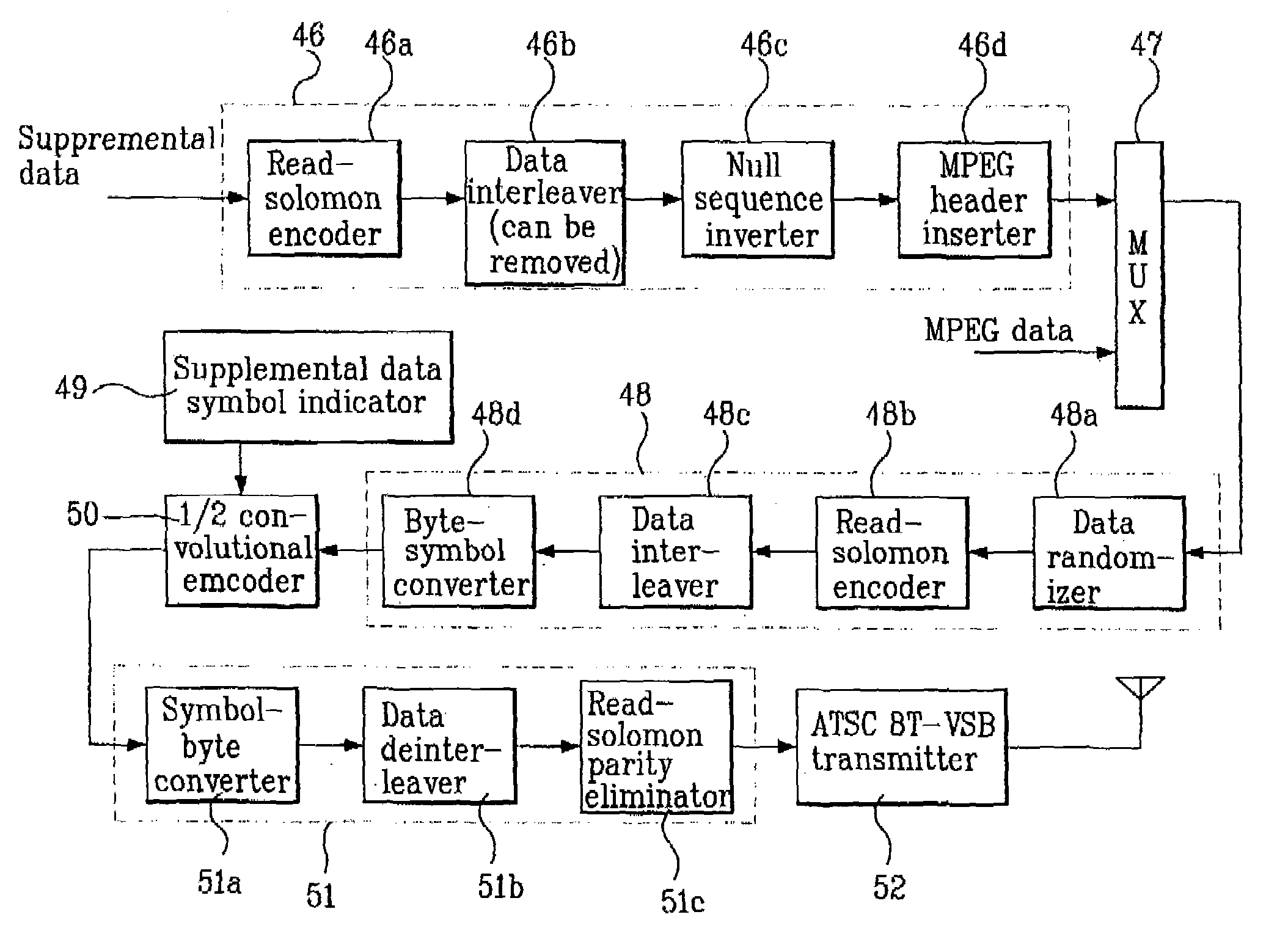

A digital VSB transmission system in disclosed. The system is compatible with the existing ATSC 8T-VSB receiver and able to transmit additional supplemental data as well as MPEG image / sound data. It initially encodes the information bit of the supplemental data with a ½ encoding rate in order to produce a parity bit and sends the parity bit together with the information bit. Therefore, both of the MPEG image / sound data and the supplemental data can be transmitted properly even through a channel having a high ghost and / or noise level. Particularly, it can significantly improve performances of the slicer predictor and trellis decoder of the VSB receiver.

Owner:LG ELECTRONICS INC

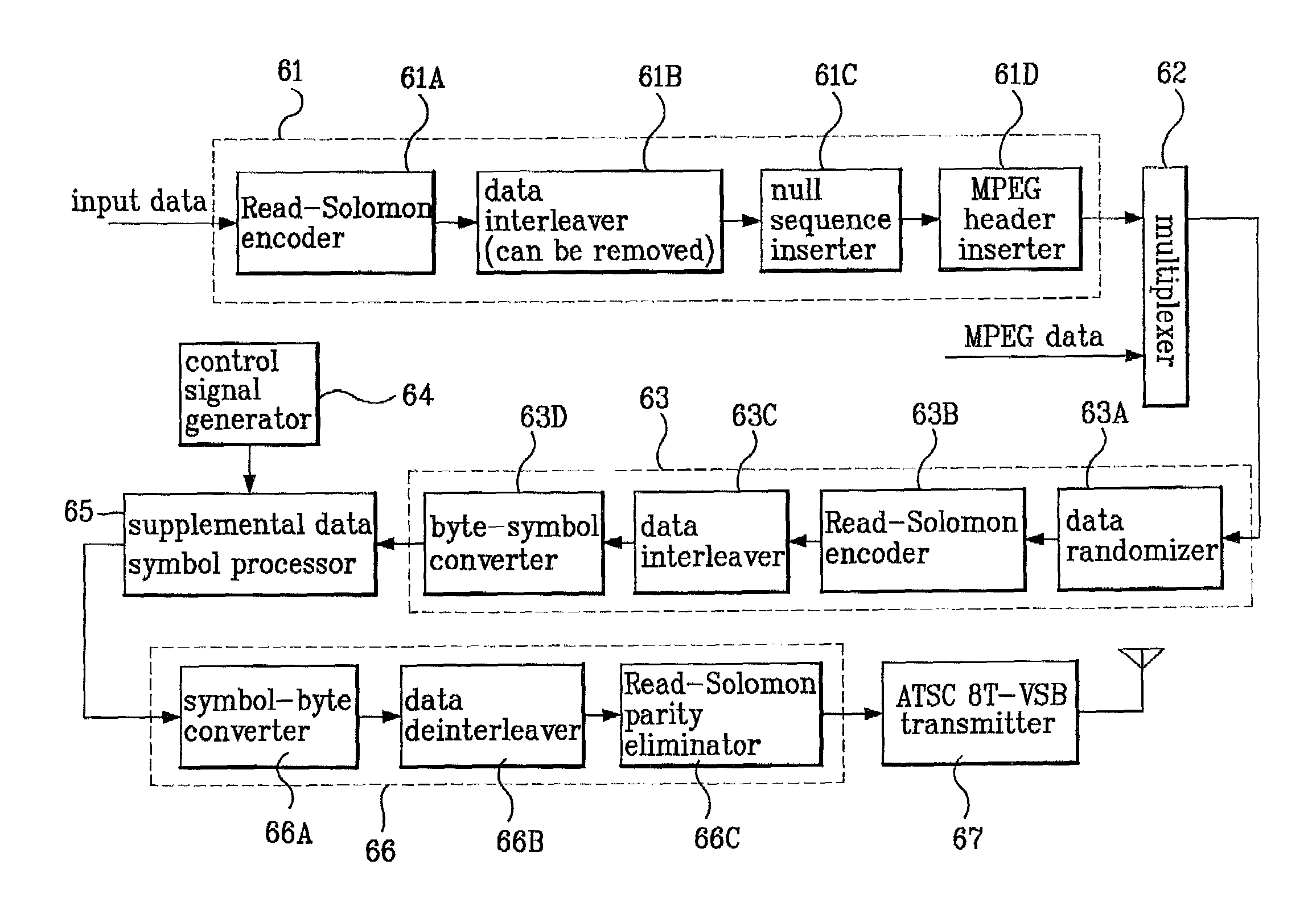

Digital VSB transmission system

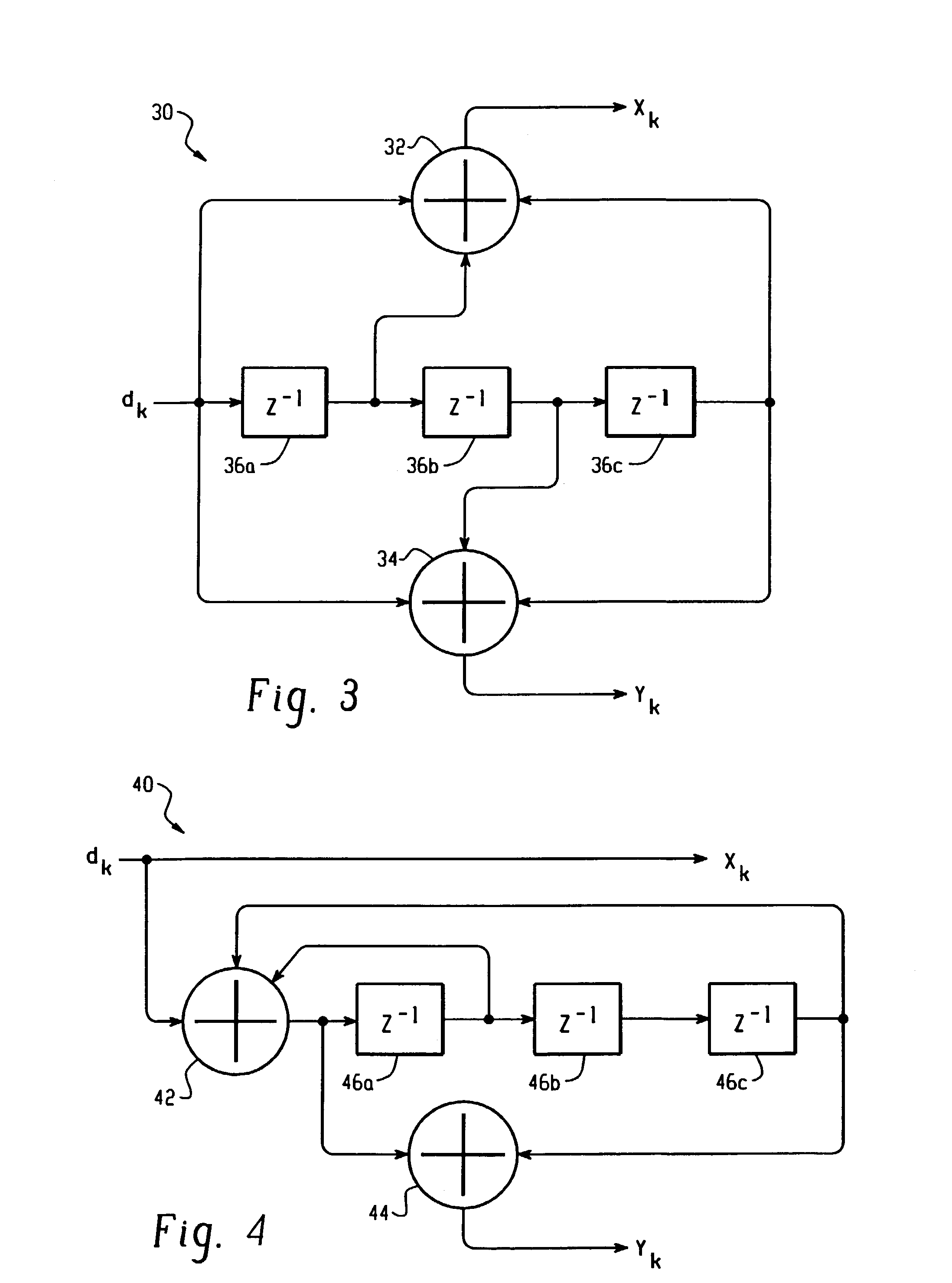

InactiveUS7092455B2Improve robustnessGreat encoding gainPulse modulation television signal transmissionModulation with suppressed carrierTransfer systemSupplementary data

A digital VSB transmission system that is able to send supplemental data along with MPEG image / sound data is enclosed. The system initially encodes the supplemental data symbol to generate a parity bit, and it multiplexes the parity bit with a predefined sequence and transmits the multiplexed data to a receiver. The system is compatible with the existing ATSC 8T-VSB receivers that are already on the market. It can have advantages over the other type of VSB transmission systems that transmit only the predefined sequence. In addition, the system according the to the present invention results a improved robustness against ghost and noise signals in a channel compared to systems using only the ½ rate convolutional encoding.

Owner:LG ELECTRONICS INC

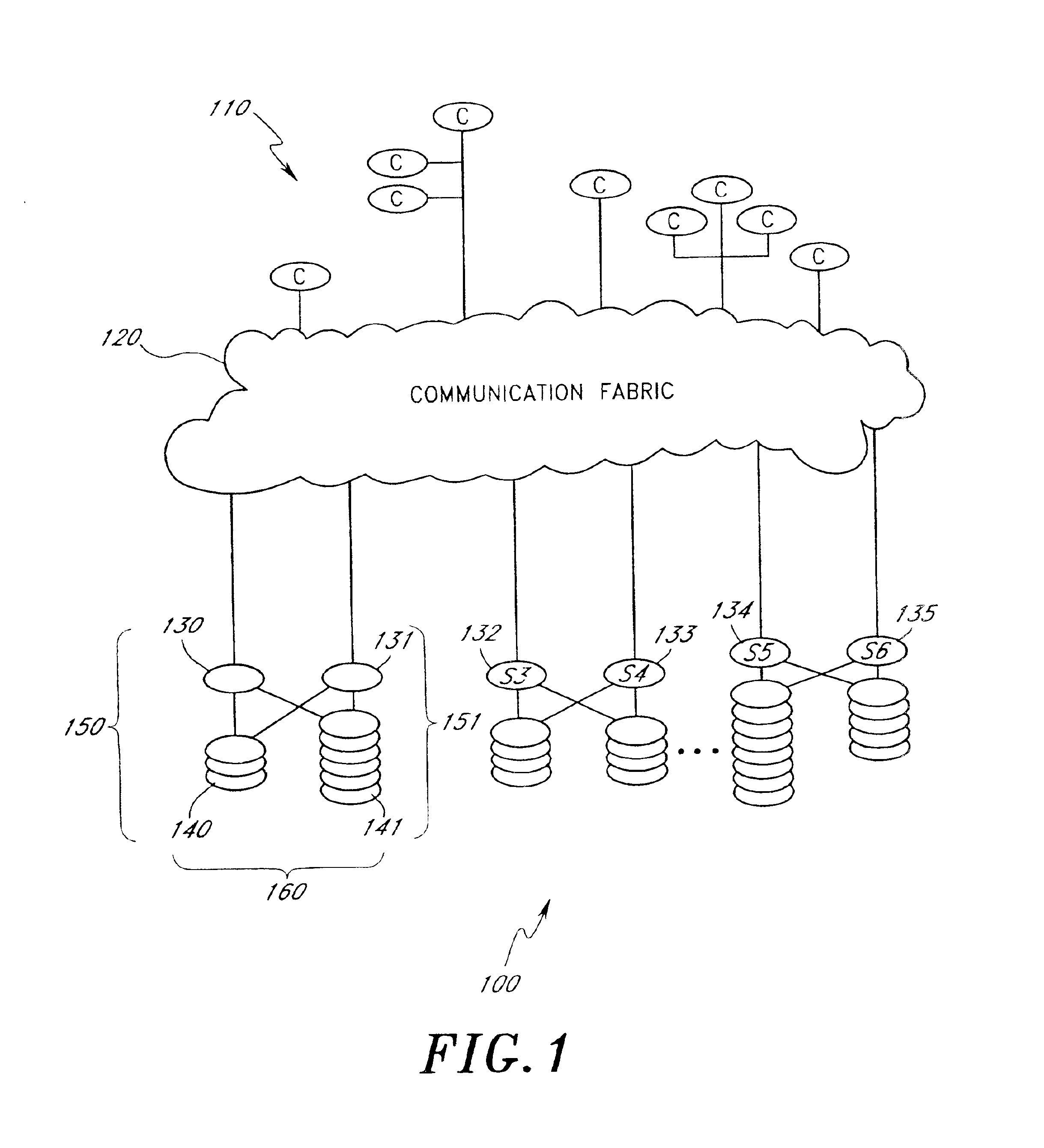

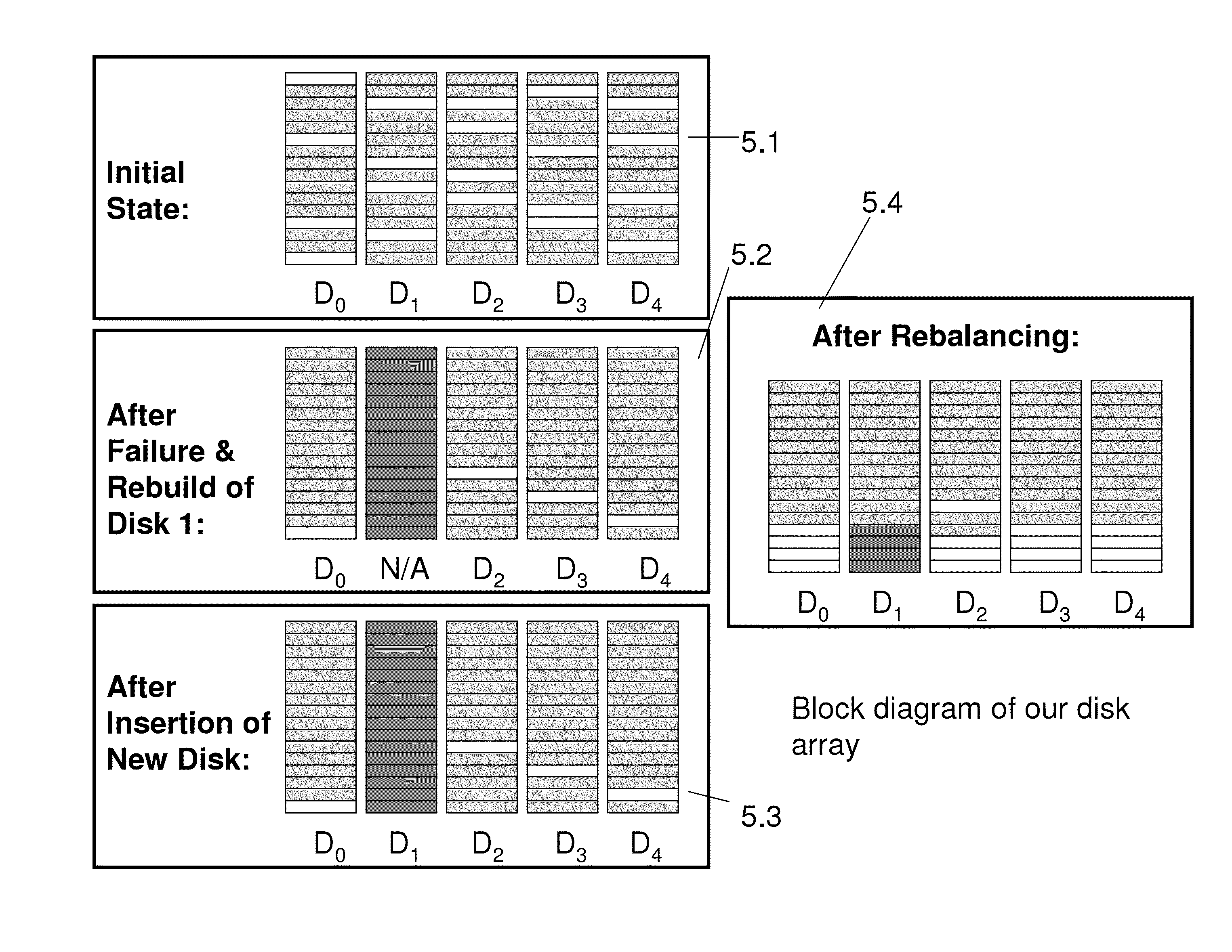

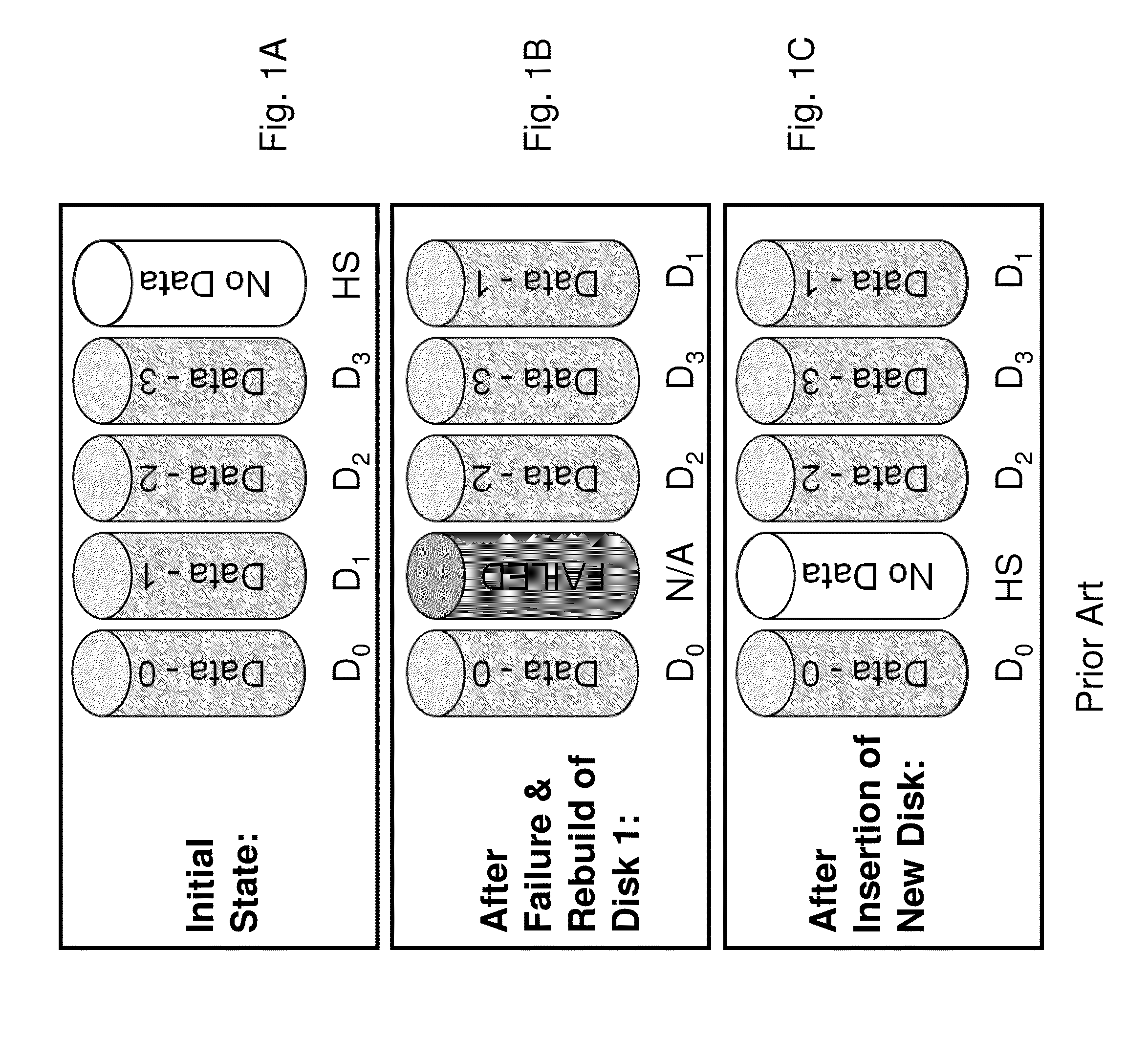

Data protection in a random access disk array

ActiveUS20130173955A1Variable performanceMaximize sharingMemory architecture accessing/allocationMemory loss protectionParity bit

A disk array memory system comprises: a plurality of disks in a disk array for storage of content data and parity data in stripes, content data in a same stripe sharing parity bits of said parity data, each disk having a spare disk capacity including at least some of a predefined array spare capacity, said array spare capacity providing a dynamic space reserve over said array to permit data recovery following a disk failure event; a cache for caching content data prior to writing to said disk array; and a controller configured to select a stripe currently having a largest spare stripe capacity, for a current write operation of data from said cache, thereby to write all said data of said current write operation on a same stripe, thereby to maximize sharing of parity bits per write operation and minimize separate parity write operations.

Owner:EMC IP HLDG CO LLC

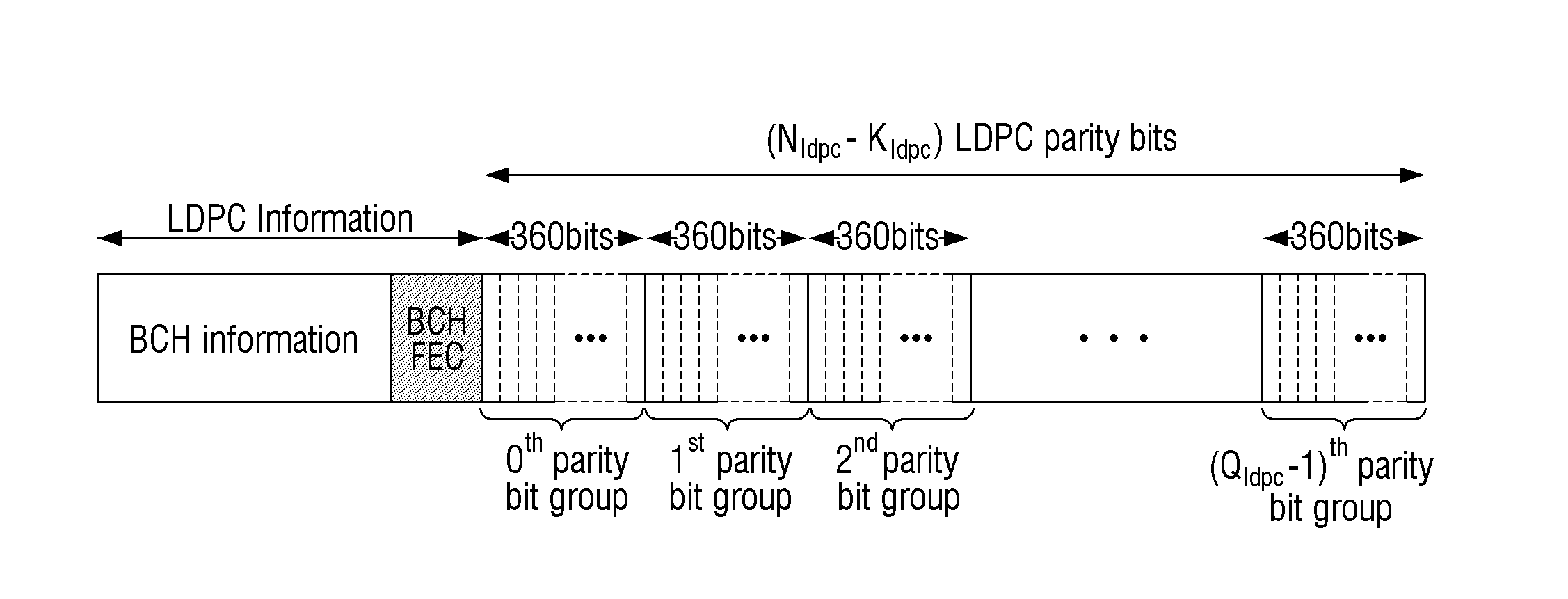

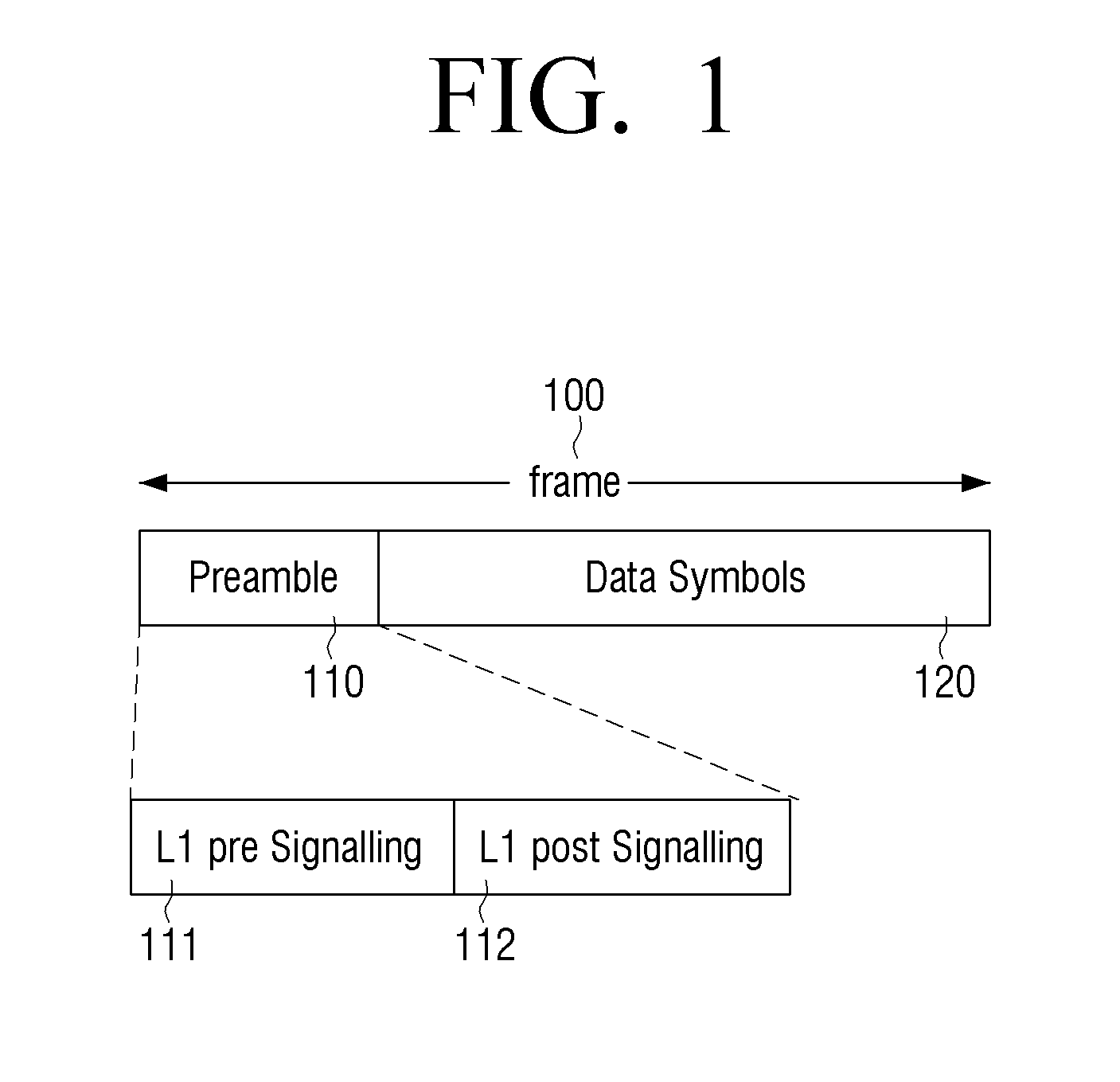

Transmitting apparatus and interleaving method thereof

ActiveUS20150341052A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError detection/correctionParity-check matrixComputer engineering

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to perform a low-density parity check (LDPC) encoding on input bits using a parity check matrix to generate an LDPC codeword comprising information word bits and parity bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Data processing device and method

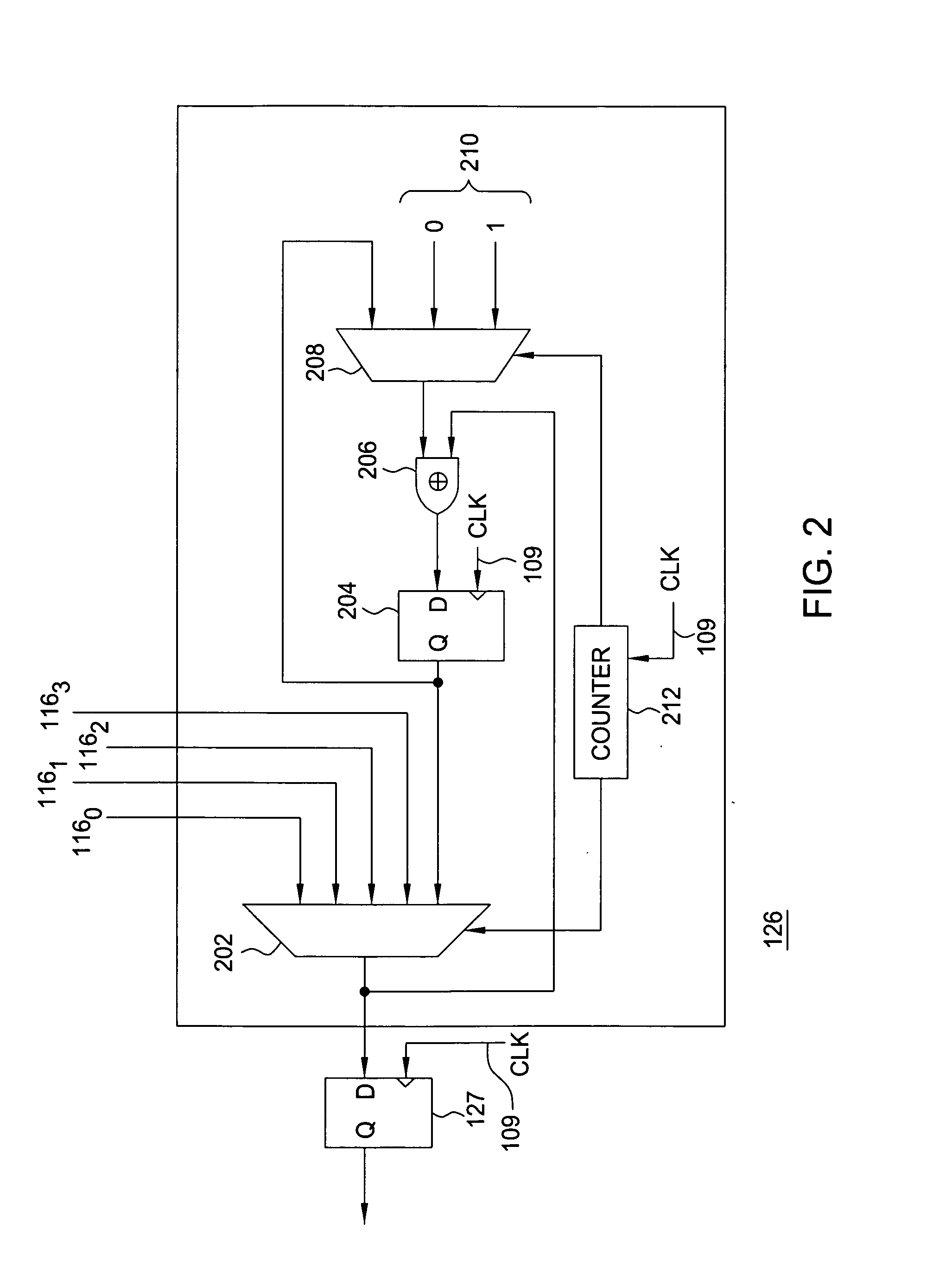

ActiveCN101510865APulse modulation television signal transmissionError preventionAddress generatorCarrier signal

A data processing device transmits the data bits on the predetermined quantity carrying wave signal of the OFDM sign. The data processing device comprises a parity interweaver for operating the pairs of LDPC coding data. The data bits are obtained by the parity matrix LDPC detecting with the LDPC code. The parity matrix has a ladder-type structure interweaving the LDPC code data to the different parity bit position. The mapping unit maps the parity interweaving bit to the data signs corresponding to the modulating signs of the solution. The sign interweaver reads the quantity signs to the sign interweaving store, carrying out the data sig of the sign interweaving store reading the order with different reading; the order address set is confirmed. The address set is generated by the address generator.

Owner:SONY CORP

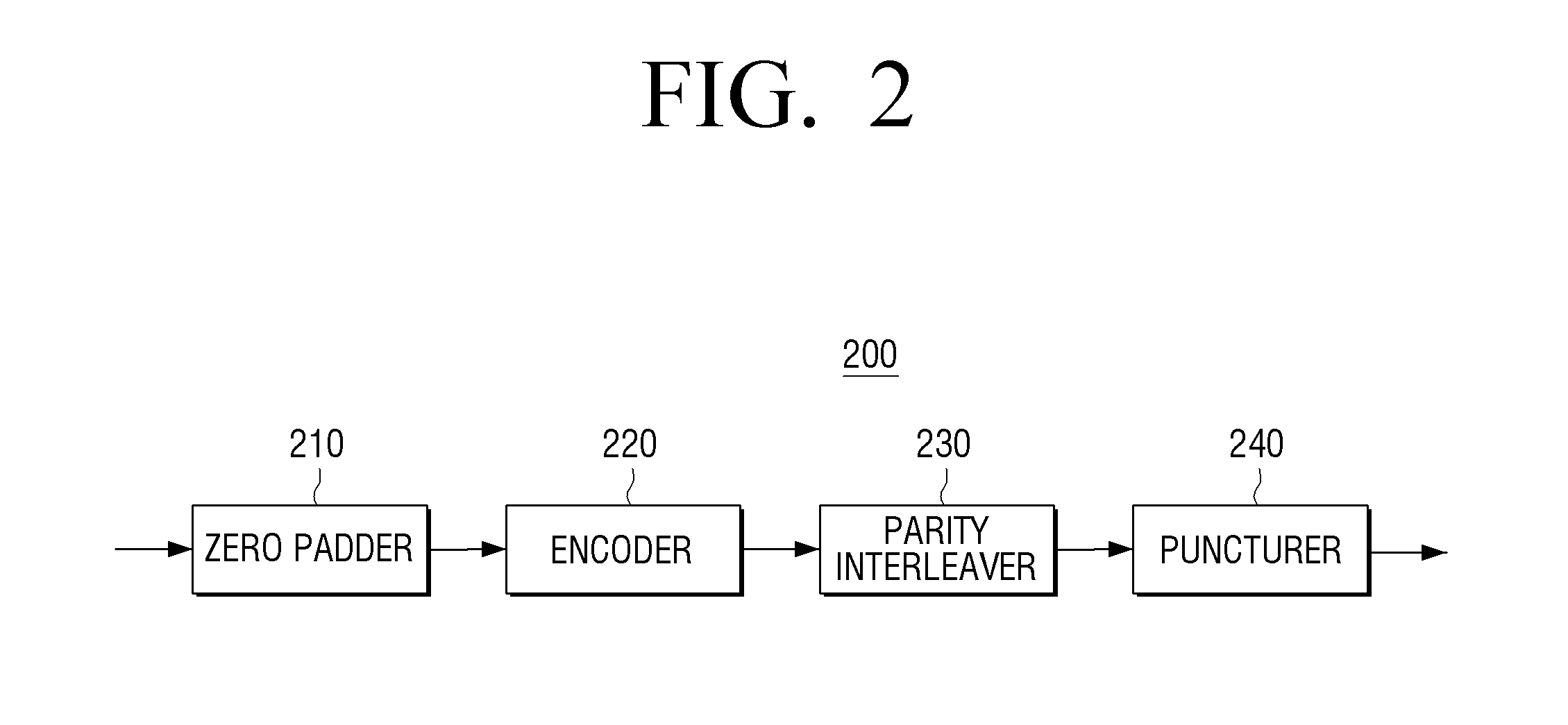

Transmitting apparatus and puncturing method thereof

InactiveUS20150082118A1Improve decoding performanceError correction/detection using multiple parity bitsCode conversionLow-density parity-check codeLow density

Provided are a transmitting apparatus, a receiving apparatus and methods of puncturing and depuncturing of parity bits. The transmitting apparatus includes: a zero padder configured to pad at least one zero bit to input bits; an encoder configured to generate a Low Density Parity Check (LDPC) codeword by performing LDPC encoding with respect to the bits to which the at least one zero bit is padded; a parity interleaver configured to interleave LDPC parity bits constituting the LDPC codeword; and a puncturer configured to puncture at least a part of the interleaved LDPC parity bits based on a pre-set puncturing pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

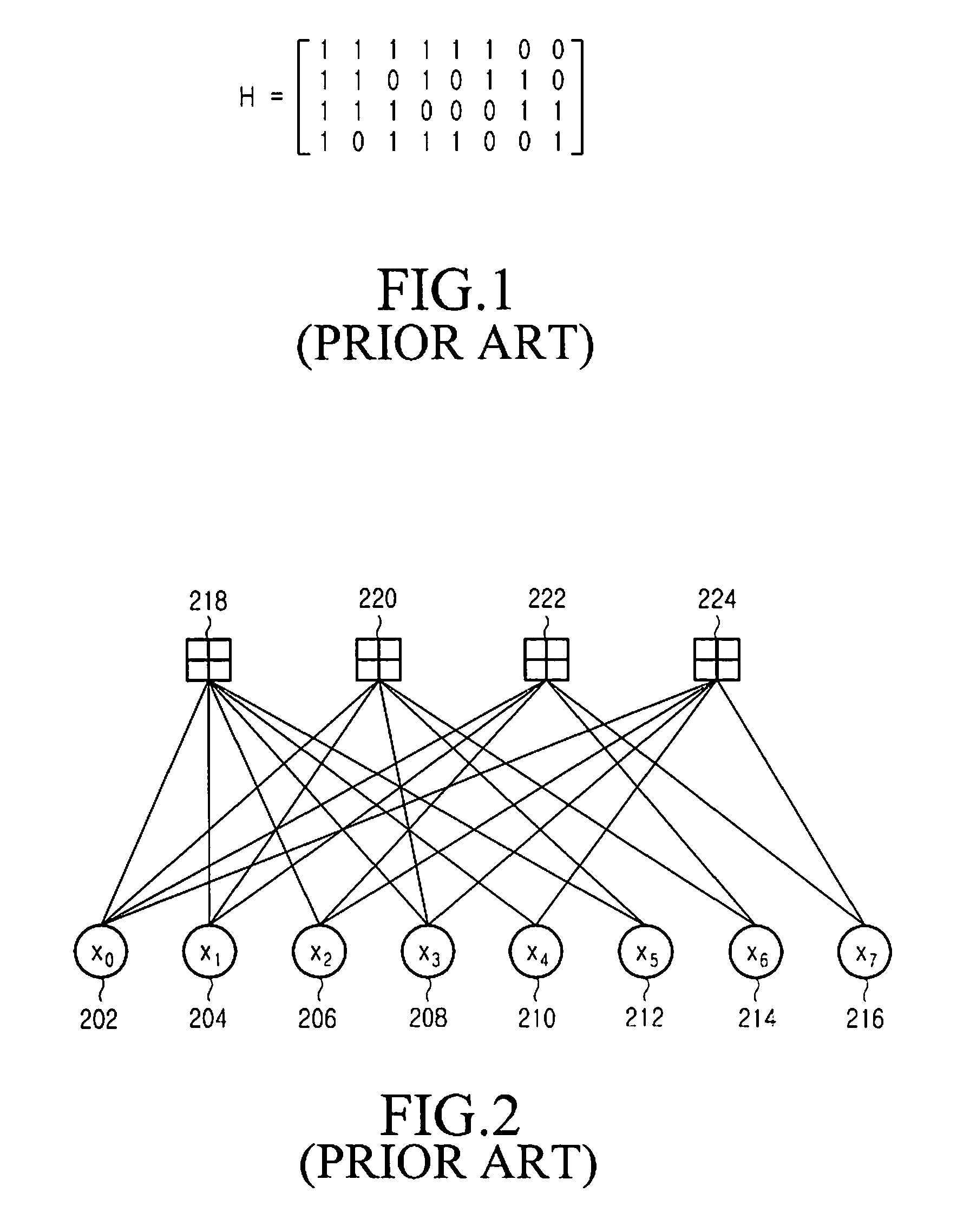

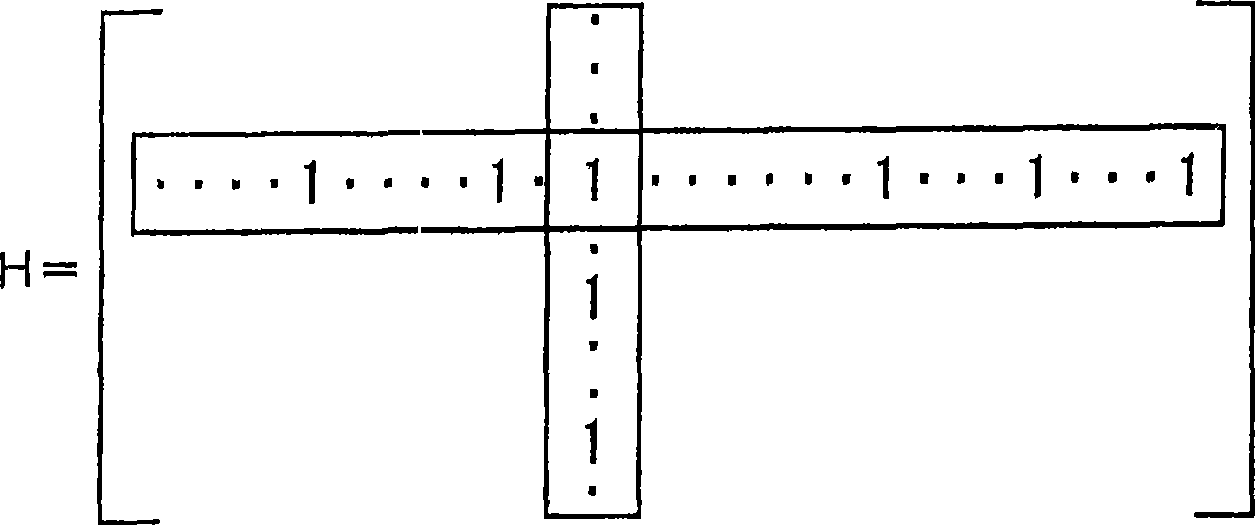

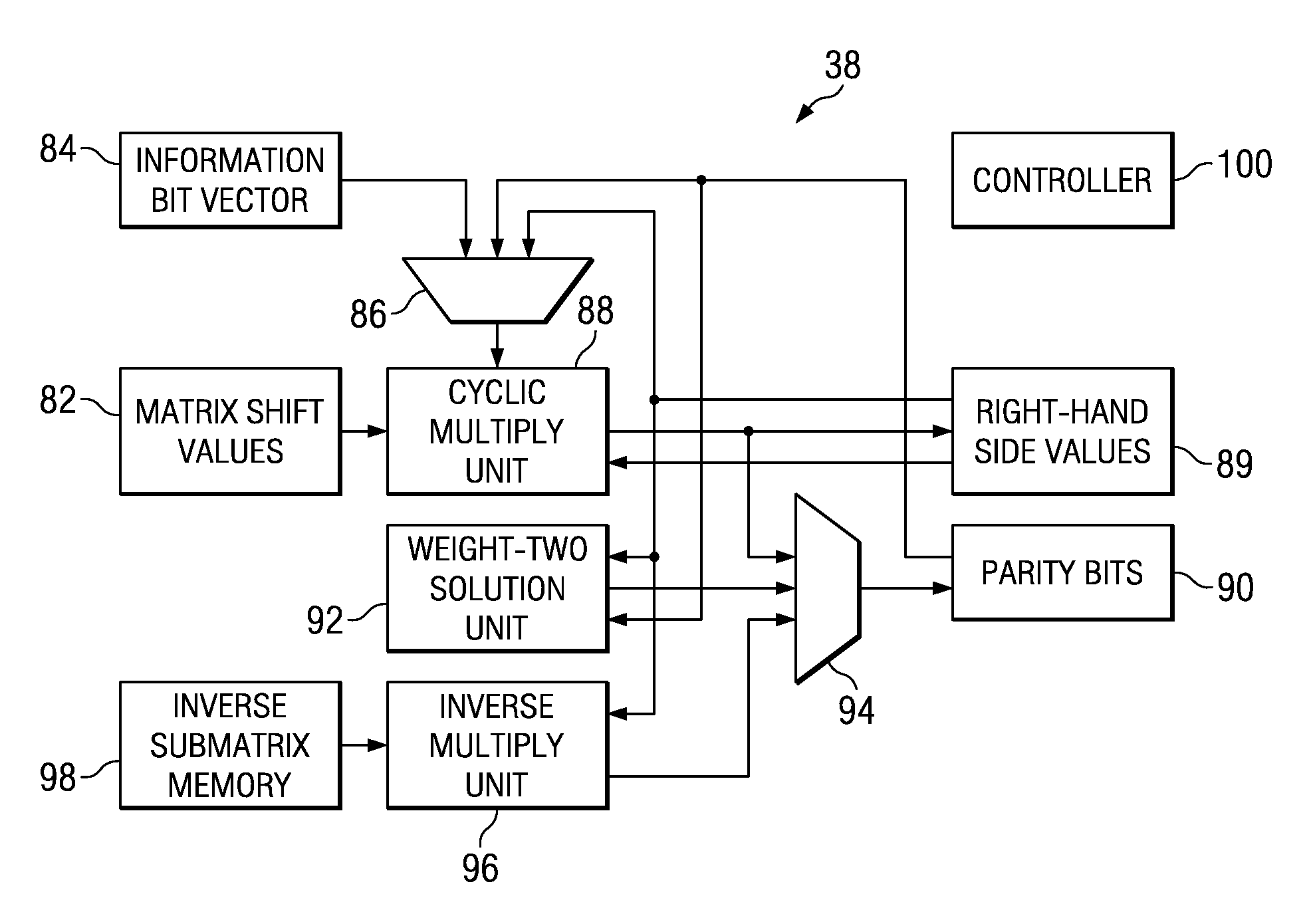

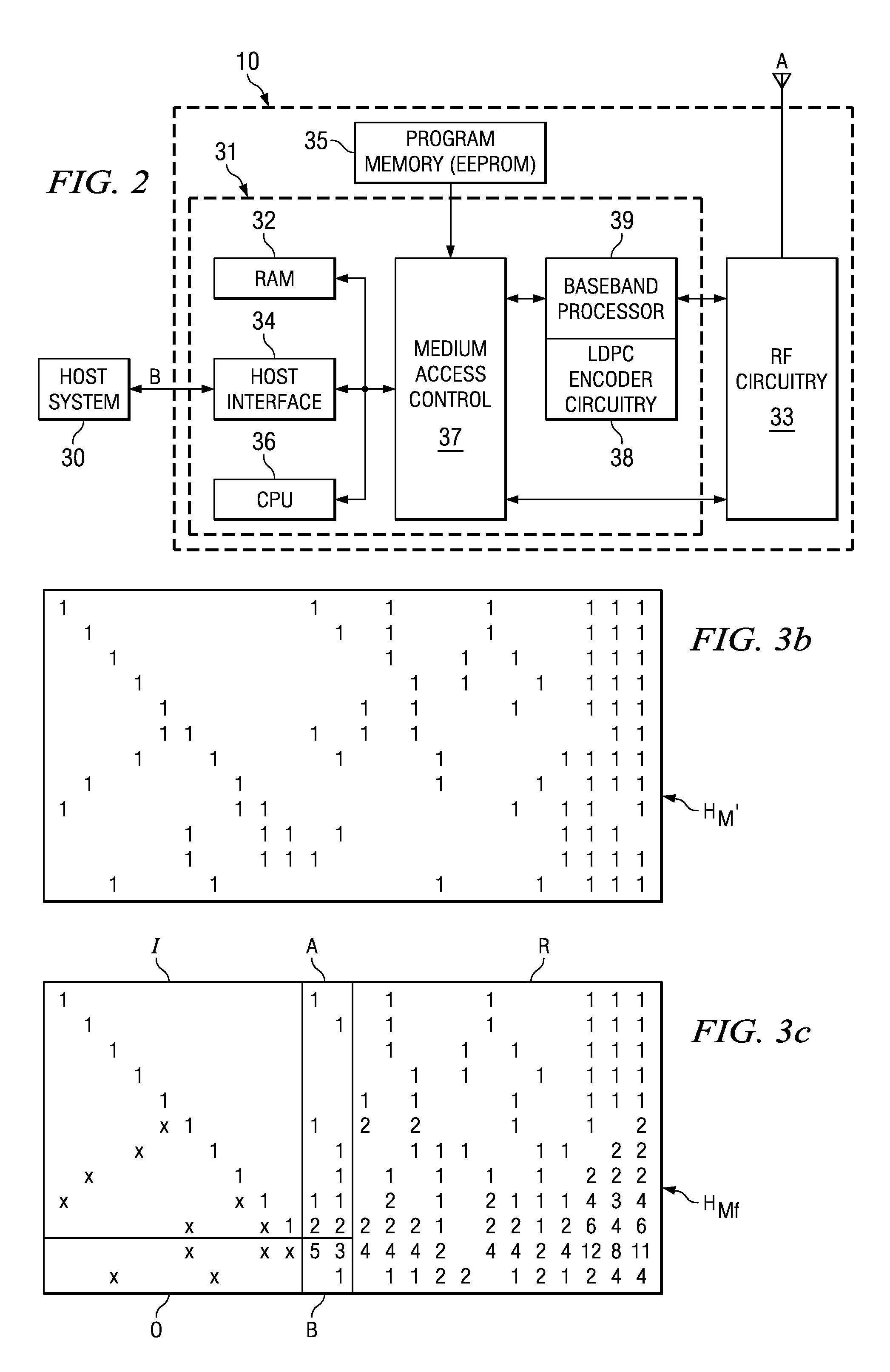

Efficient encoder for low-density-parity-check codes

ActiveUS7162684B2Improve efficiencyLow implementation costError detection/correctionError correction/detection using multiple parity bitsDiagonalParity-check matrix

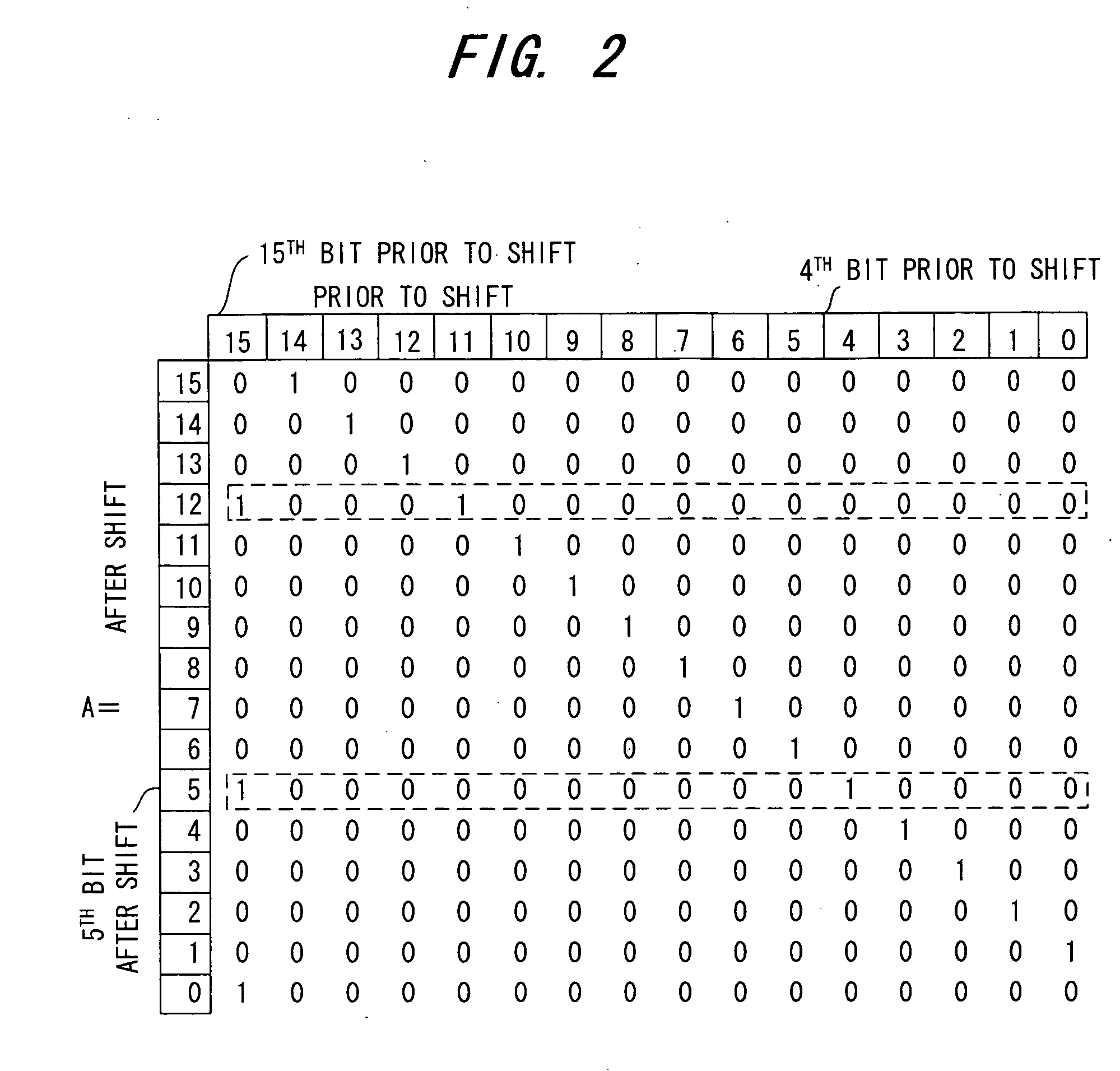

Encoder circuitry for applying a low-density parity check (LDPC) code to information words is disclosed. The encoder circuitry takes advantage of a macro matrix arrangement of the LDPC parity check matrix in which a left-hand portion of the parity check matrix is arranged as an identity macro matrix, each entry of the macro matrix corresponding to a permutation matrix having zero or more circularly shifted diagonals. The encoder circuitry includes a cyclic multiply unit, which includes a circular shift unit for shifting a portion of the information word according to shift values stored in a shift value memory for the matrix entry, and a bitwise exclusive-OR function for combining the shifted entry with accumulated previous values for that matrix entry. Circuitry for solving parity bits for row rank deficient portions of the parity check matrix is also included in the encoder circuitry.

Owner:TEXAS INSTR INC

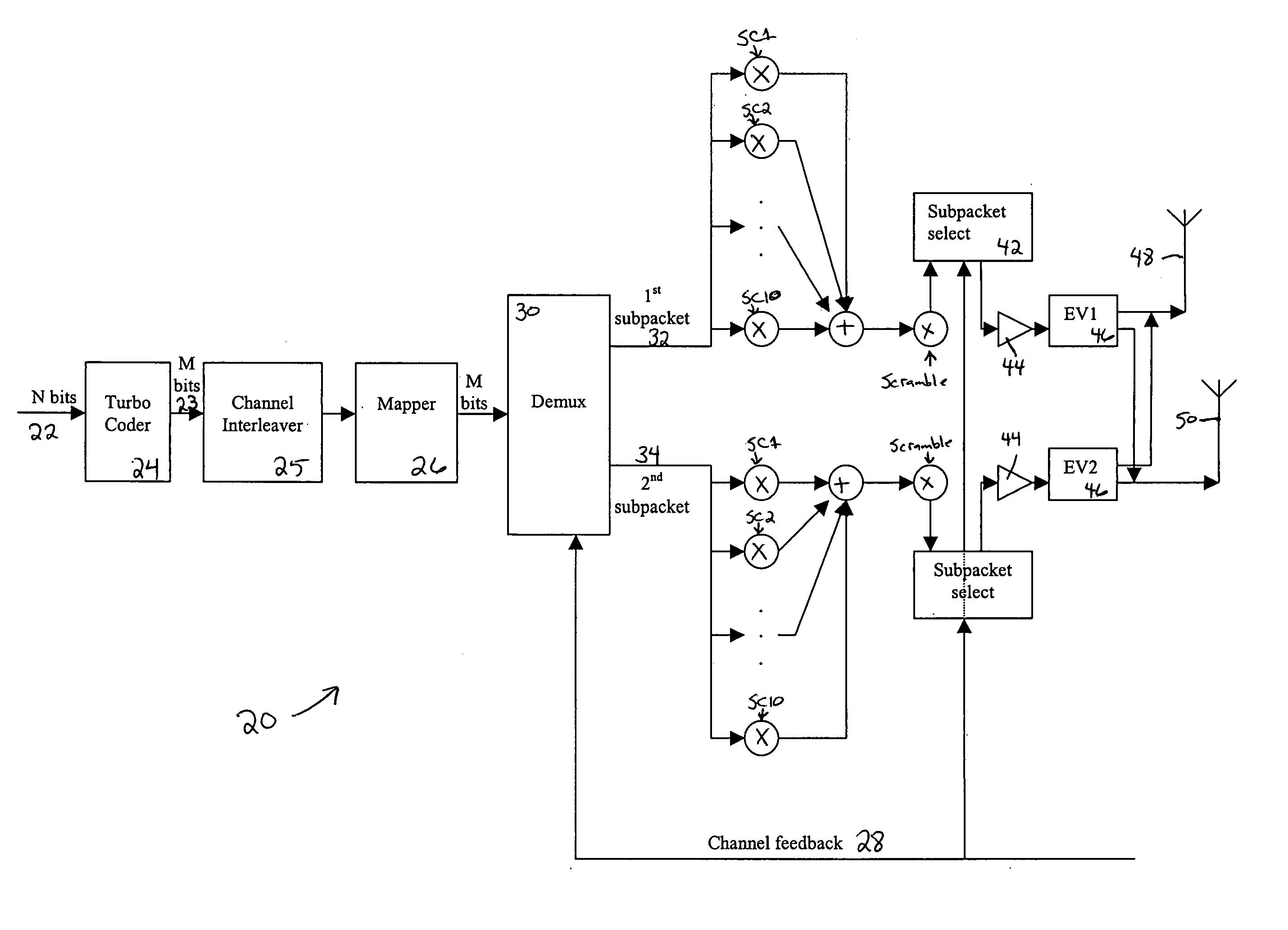

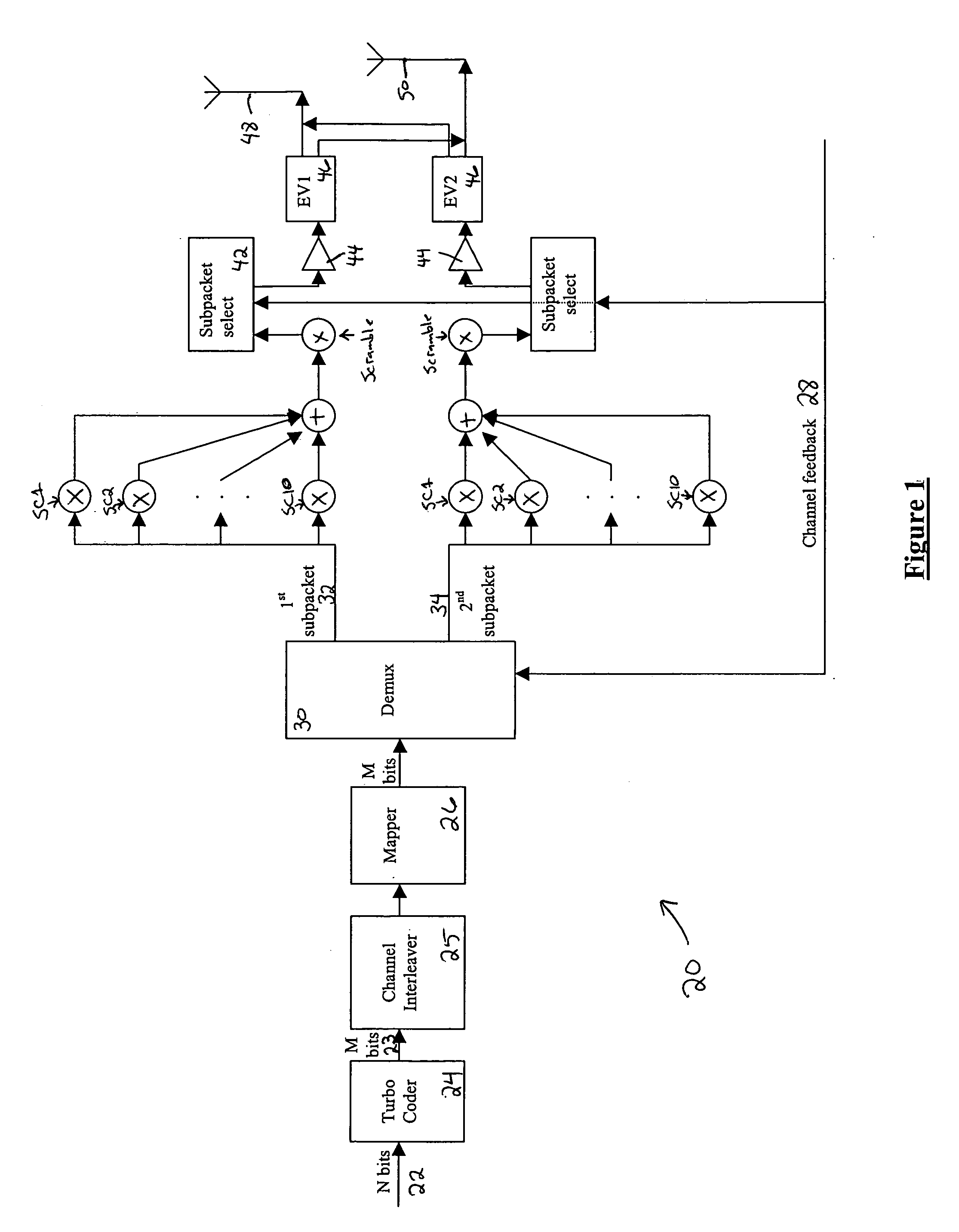

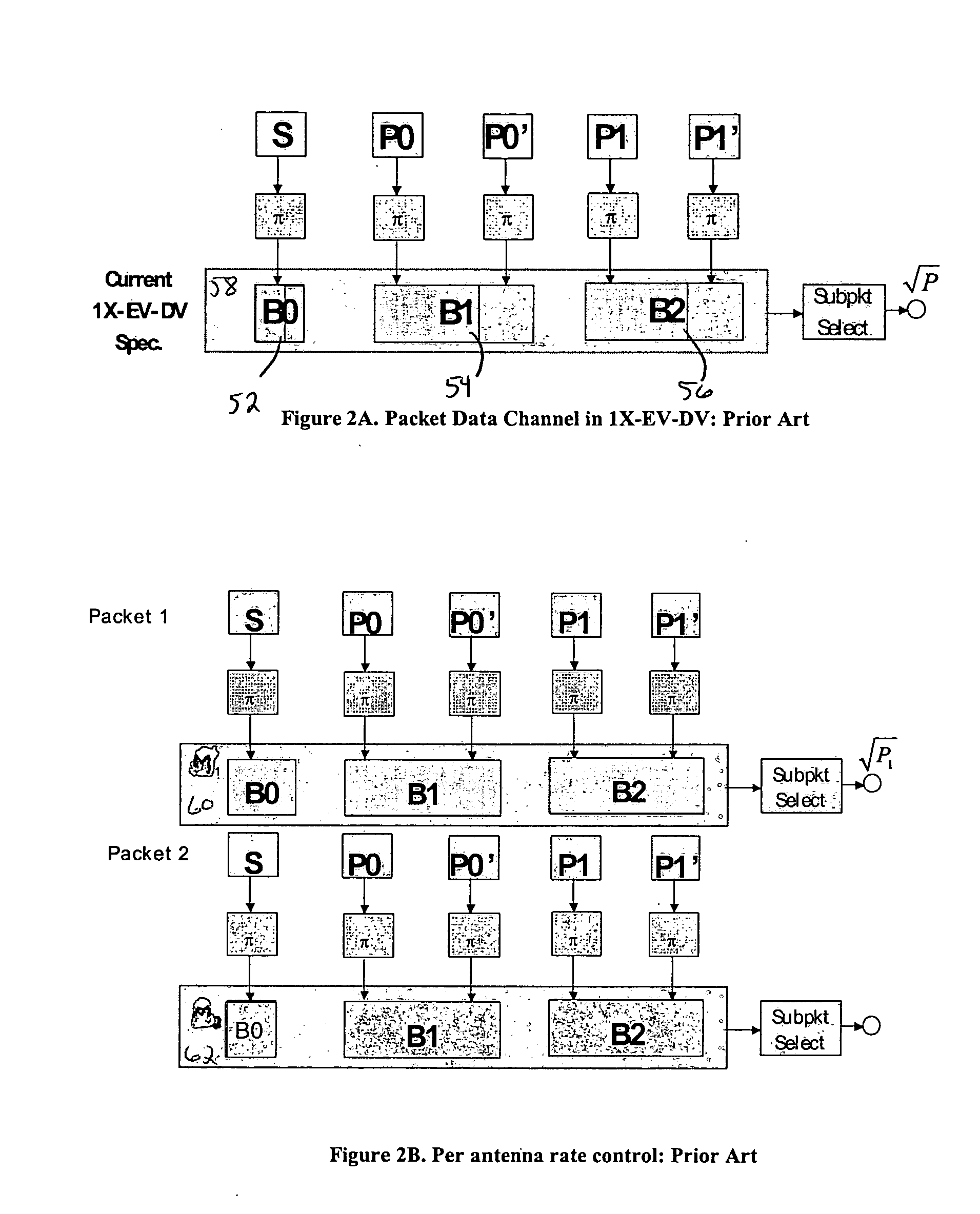

Flexible rate split method for MIMO transmission

InactiveUS20050111376A1Wide diversityReduce error rateSpatial transmit diversityFrequency-division multiplex detailsMimo transmissionSelection system

A method for transmitting a packet of N input bits includes encoding all of the N bits as a single entity, such as with an interleaver of length N within a turbo coder, outputting M encoded bits, channel interleaving the M bits, splitting the M encoded bits into a parallel first and second portion, and transmitting them over separate channels to achieve spatial diversity. The size of the first and second portion is determined based on a closed feedback loop that provides some knowledge of the channel, preferably a measure of channel capacity. The feedback loop may also provide channel knowledge to a subpacket selector associated with each transmit antenna, which determines an appropriate rate for that channel and selects subpackets to fill a transmission packet for that channel. The subpacket selectors choose a subpacket of systematic bits and fill the remaining transmission packet size with subpackets of parity bits. Eigenvectors may be employed to transmit each transmission packet over more than one channel with a power disparity between the channels. A transmitter according to the present invention is also described.

Owner:NOKIA CORP

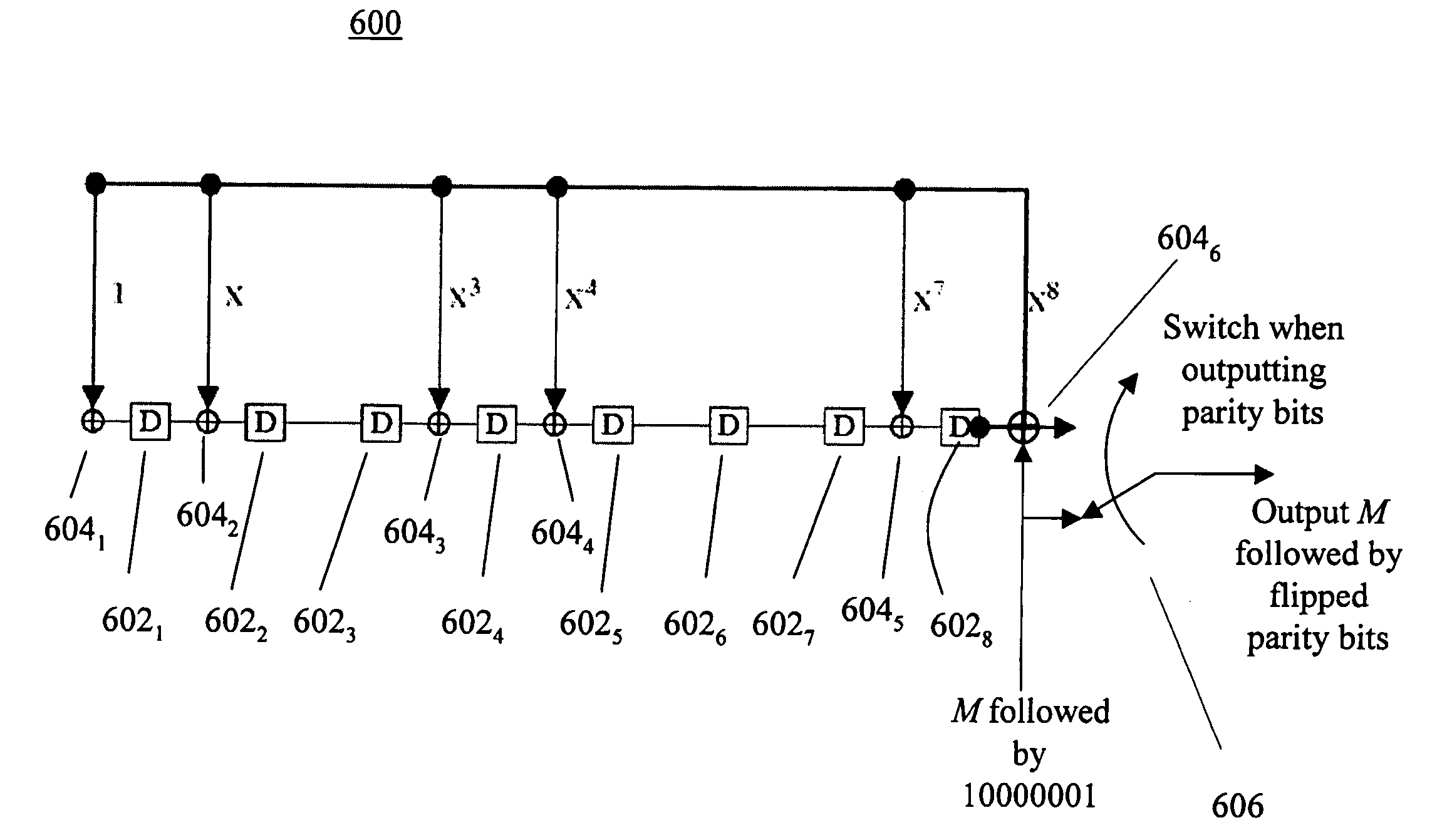

Cyclic redundancy check modification for message length detection and error detection

ActiveUS20050257118A1Reduce probabilityCode conversionError detection onlyMessage lengthCommunications system

In a method for a variable-length communications system including encoding a message and decoding a data bit stream, the message includes a plurality of message blocks. A message block of the message is encoded by generating a parity check bit stream, flipping the parity check bit stream, and appending the flipped parity check bit stream to the end of the message block. When a data bit stream is received, a guessed message block and a guessed flipped parity check bit stream are extracted based on a guessed message block length. A parity check bit stream is generated for the guessed message block and then flipped. If the flipped parity check bit stream is the same as the guessed flipped parity check bit stream, the message block has been identified. Otherwise, the guessed message block length is increased by 1 and the above step is repeated.

Owner:NAT CHIAO TUNG UNIV +1

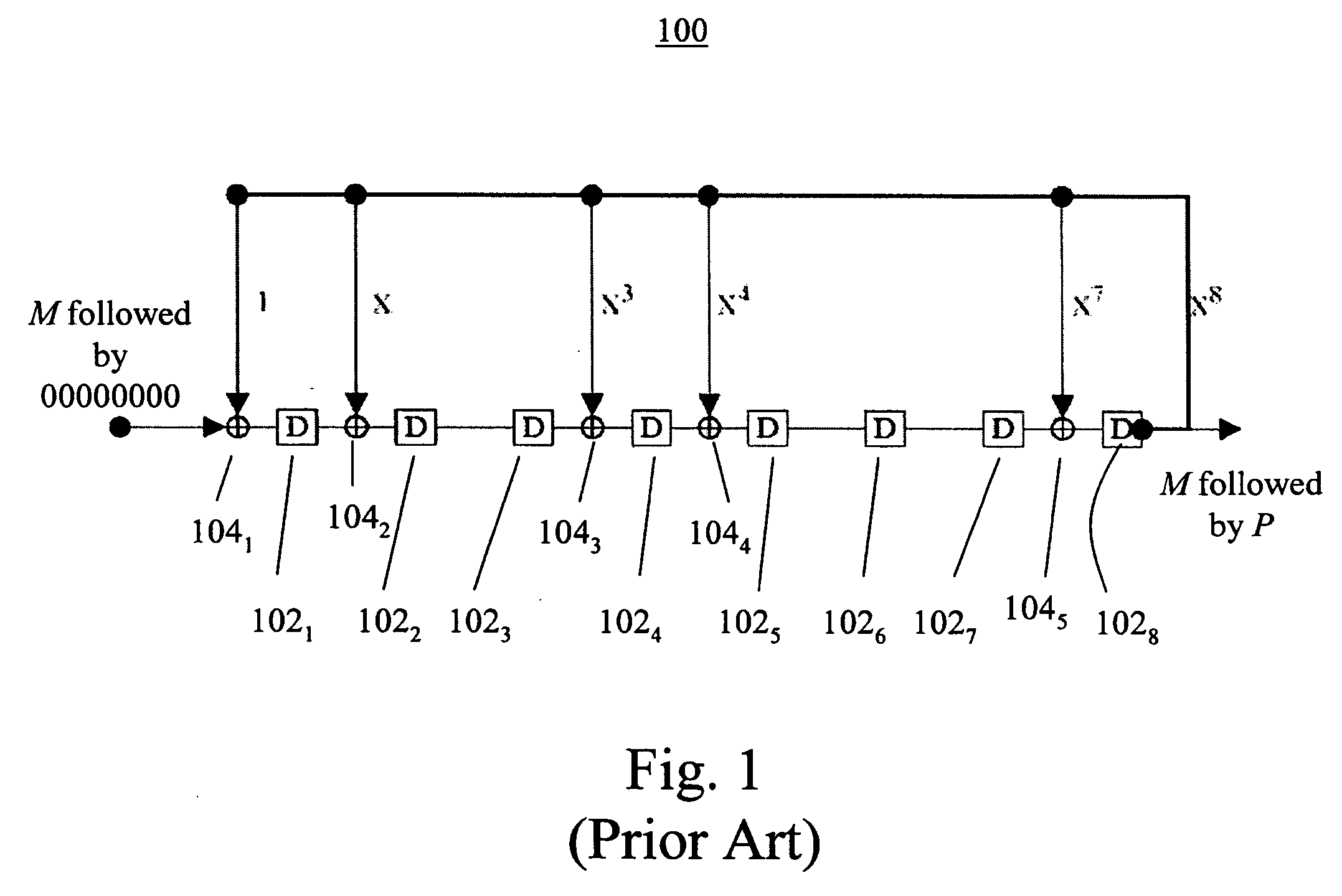

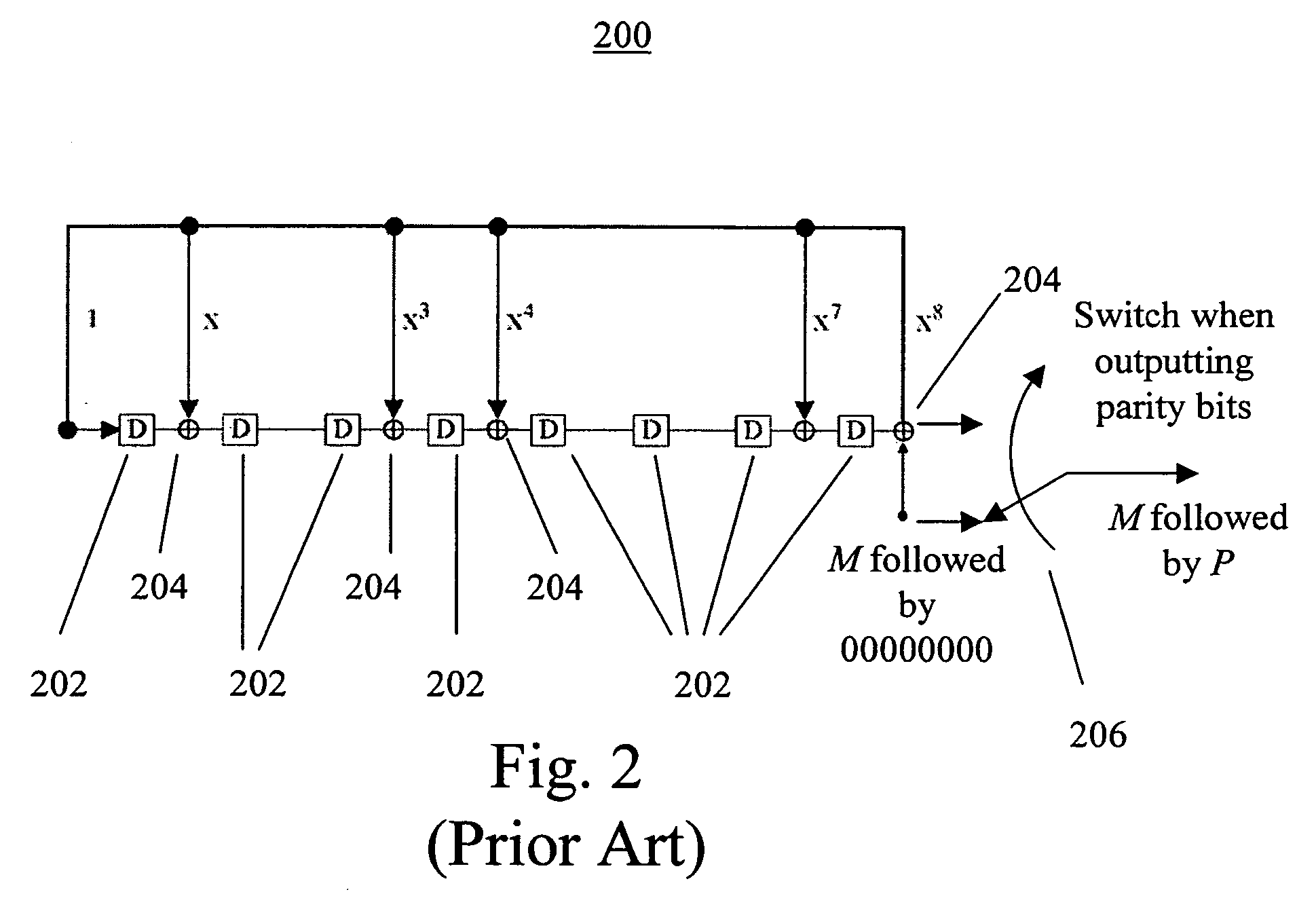

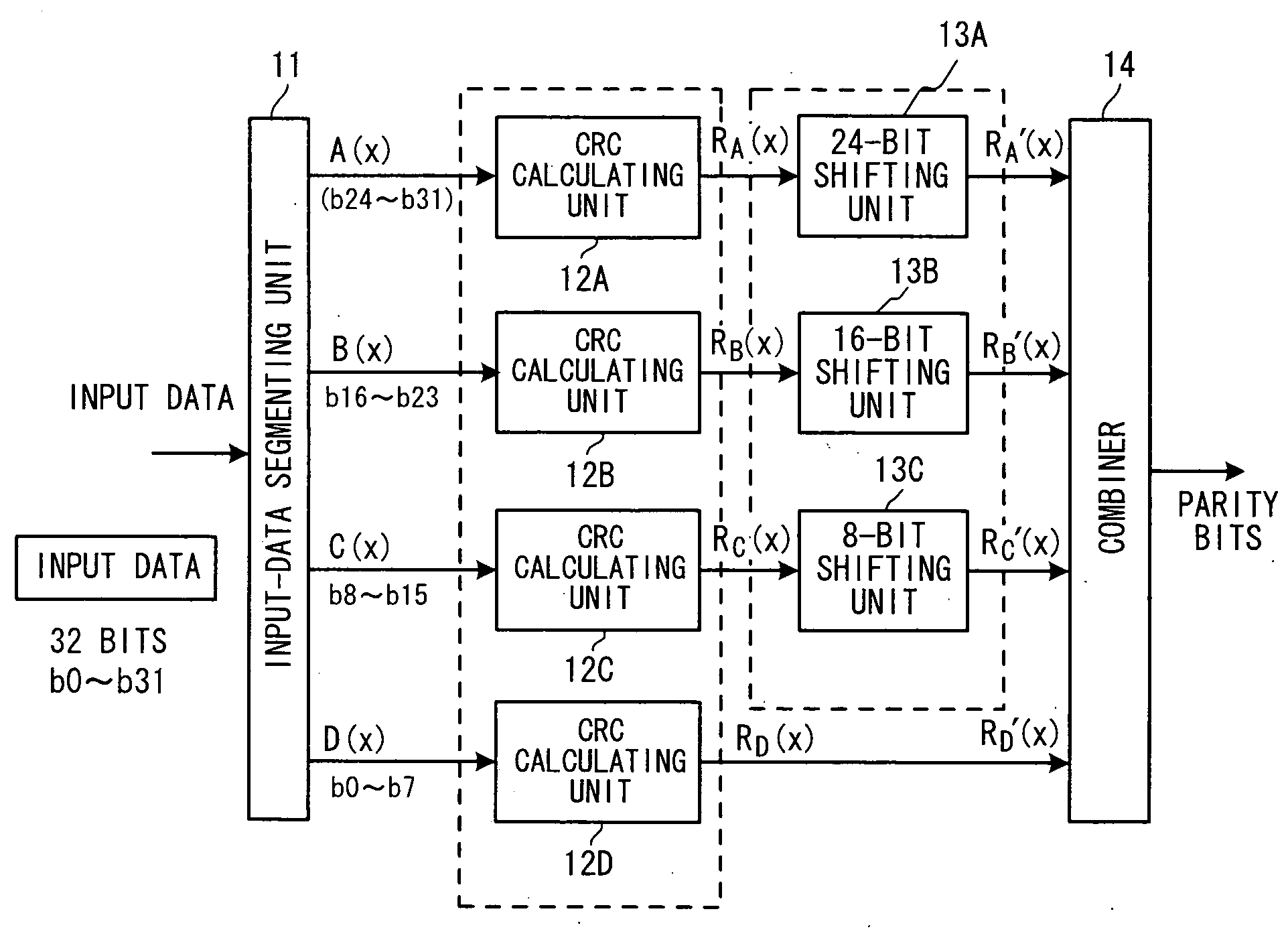

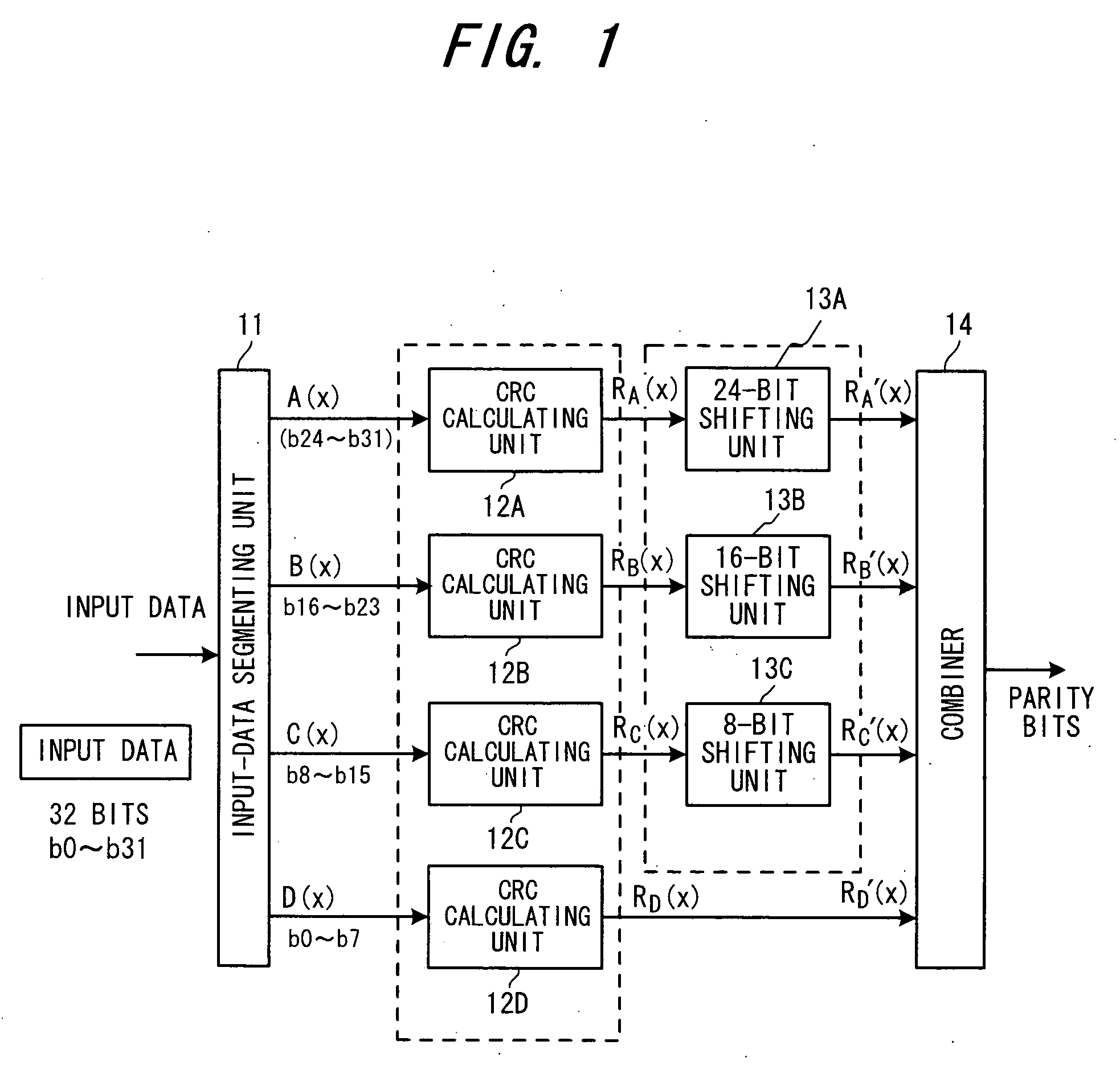

Error-detecting encoding and decoding apparatus and dividing apparatus

InactiveUS20050097432A1Shorten the timeReduce latencyError preventionError detection/correctionArtificial intelligenceError detection coding

Disclosed are an error-detecting encoding apparatus for creating parity bits by error-detecting encoding processing, appending the parity bits to an input data string and encoding the data string, and an error-detecting decoding apparatus for detecting error using these parity bits. Data segmenting means segments an input data string, which is to undergo error-detecting encoding, into a plurality of sub-data strings, dividing means divides the segmented sub-data strings by a polynomial, which is for generating an error-detecting code, and calculates remainders, converting means applies conversion processing, which conforms to a segmentation position of the sub-data strings, to the remainders on a per-remainder basis, and combining means combines converted values, which have been obtained by the conversion processing, and outputs parity bits. An encoder appends this parity to a data string, and a decoder detects error using this parity.

Owner:FUJITSU LTD

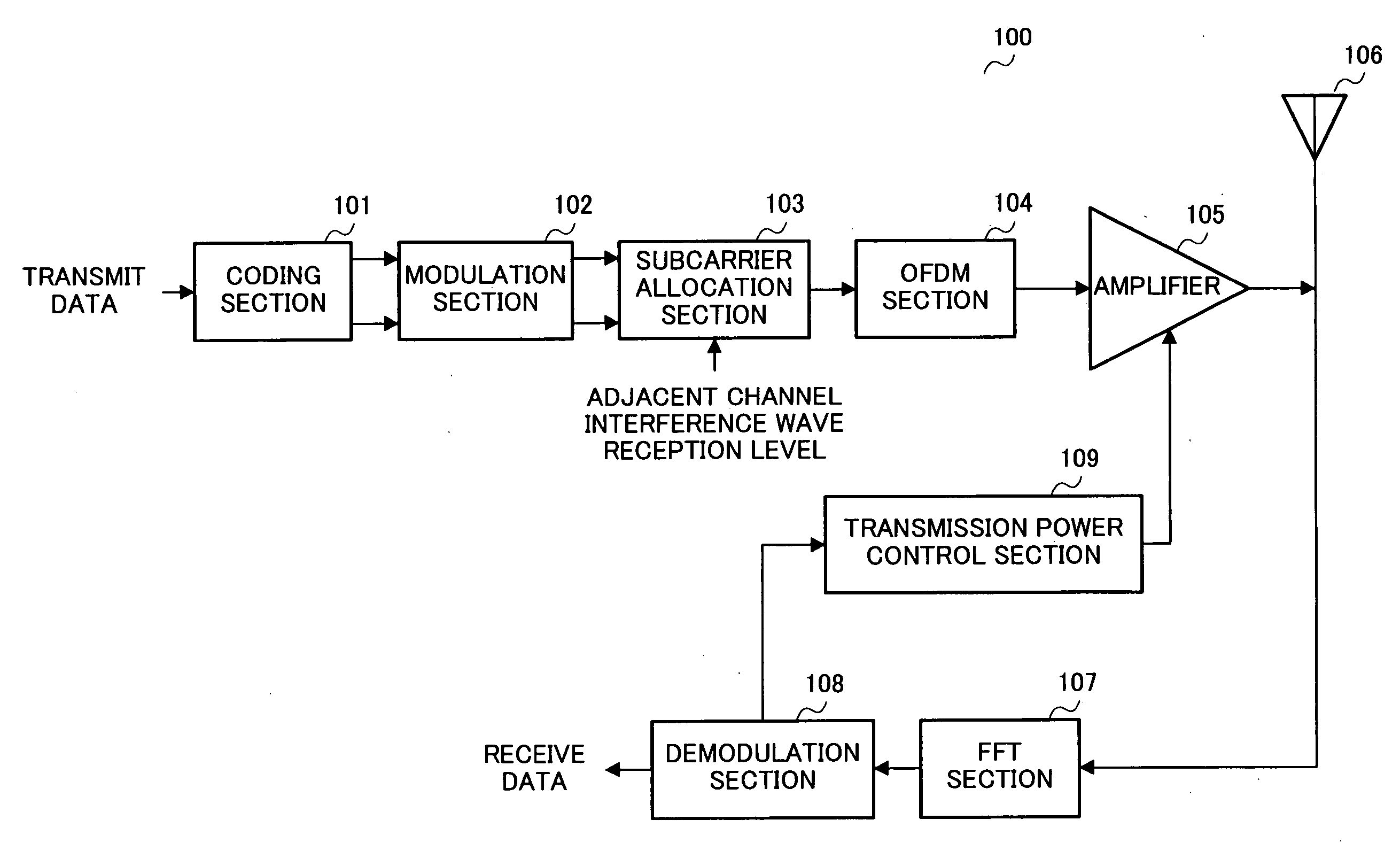

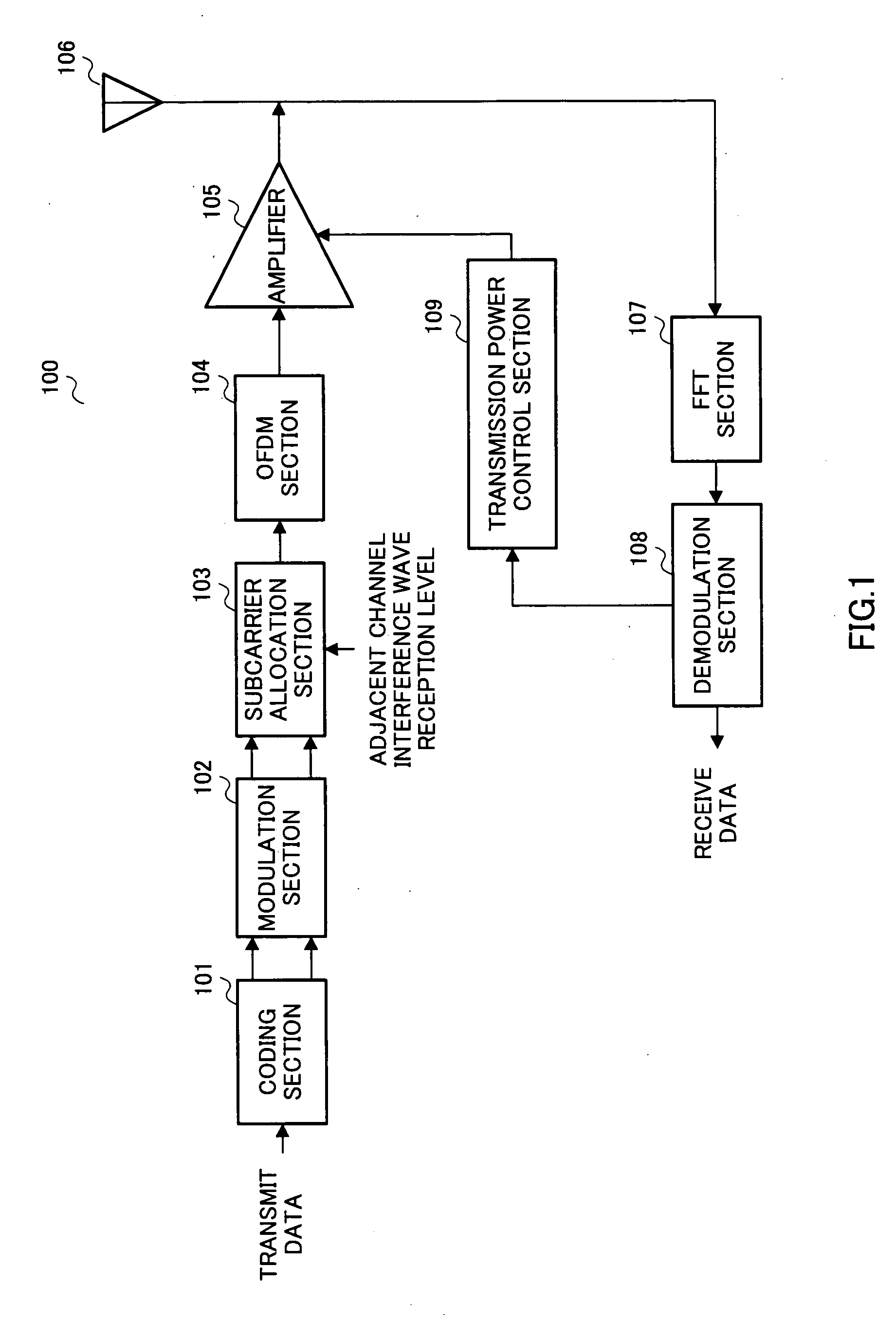

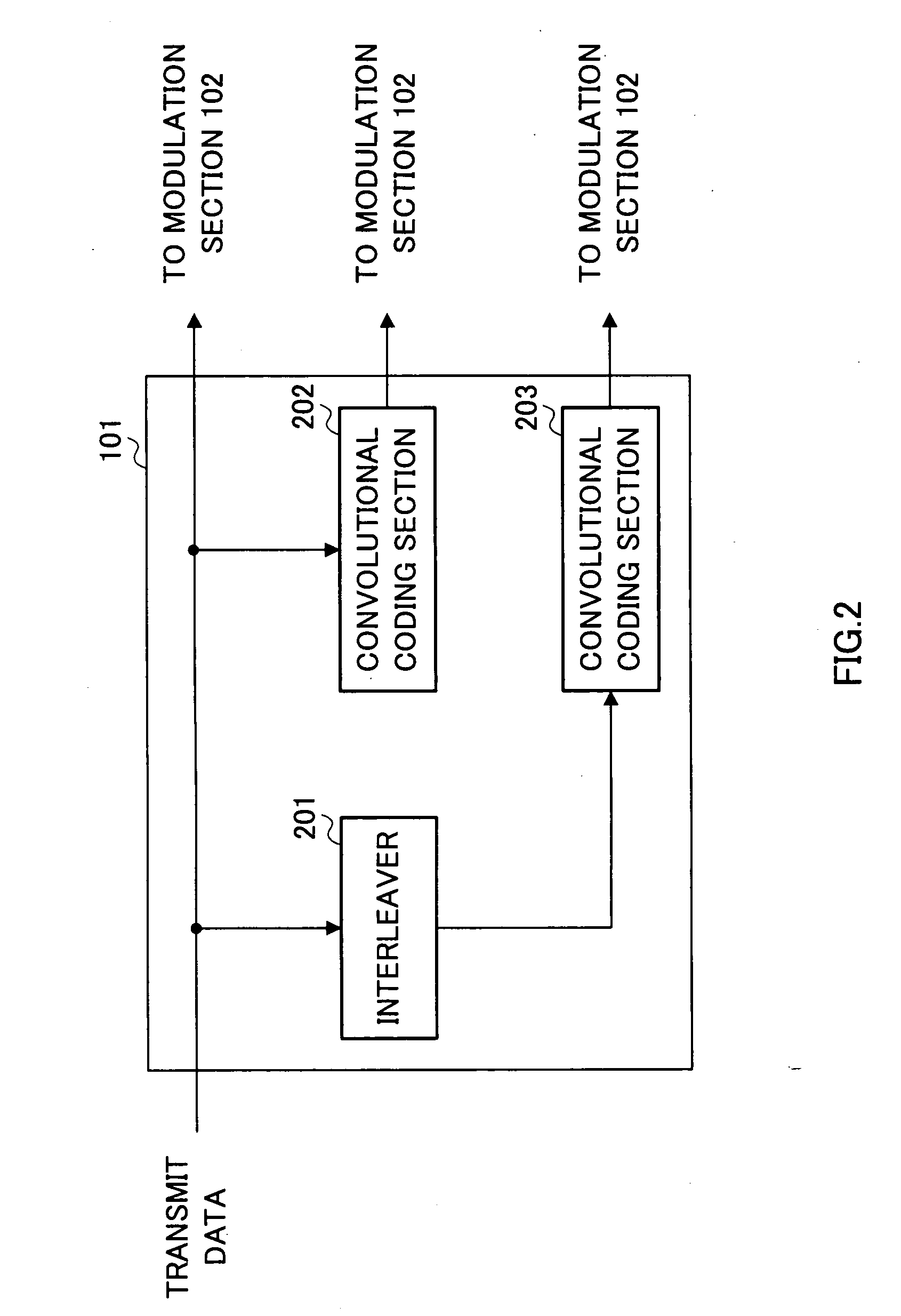

Multi-carrier transmitting apparatus and multi-carrier transmitting method

ActiveUS20060160498A1Prevent degradationImprove significantly the error rate characteristics of transmit dataOther decoding techniquesTransmission path divisionCarrier signalTurbo coded

A coding section 101 turbo-codes transmit data and outputs parity bit data, and systematic bit data for which good quality is required. A modulation section 102 modulates the parity bit data and systematic bit data. A subcarrier allocation section 103 rearranges the transmit data so that systematic bit data is allocated to subcarriers in the vicinity of the center frequency and parity bit data is allocated to subcarriers in the vicinity of both ends. An OFDM section 104 performs orthogonal frequency division multiplexing of the transmit data, and allocates parity bit data and systematic bit data to respective subcarriers. By this means, it is possible to improve significantly the error rate characteristics of transmit data for which good quality is required, and prevent degradation of the quality of transmit data for which good quality is required.

Owner:OPTIS WIRELESS TECH LLC

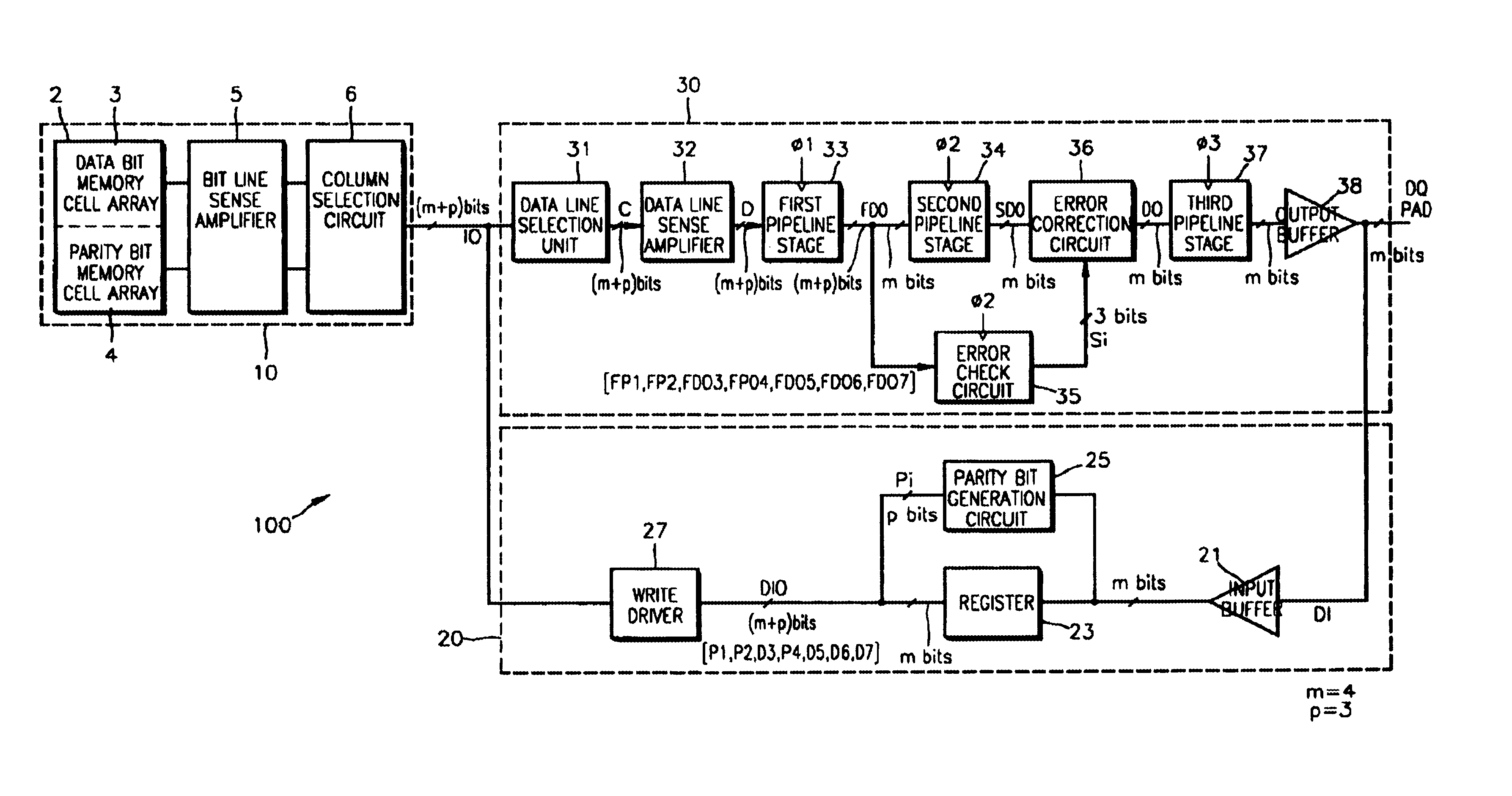

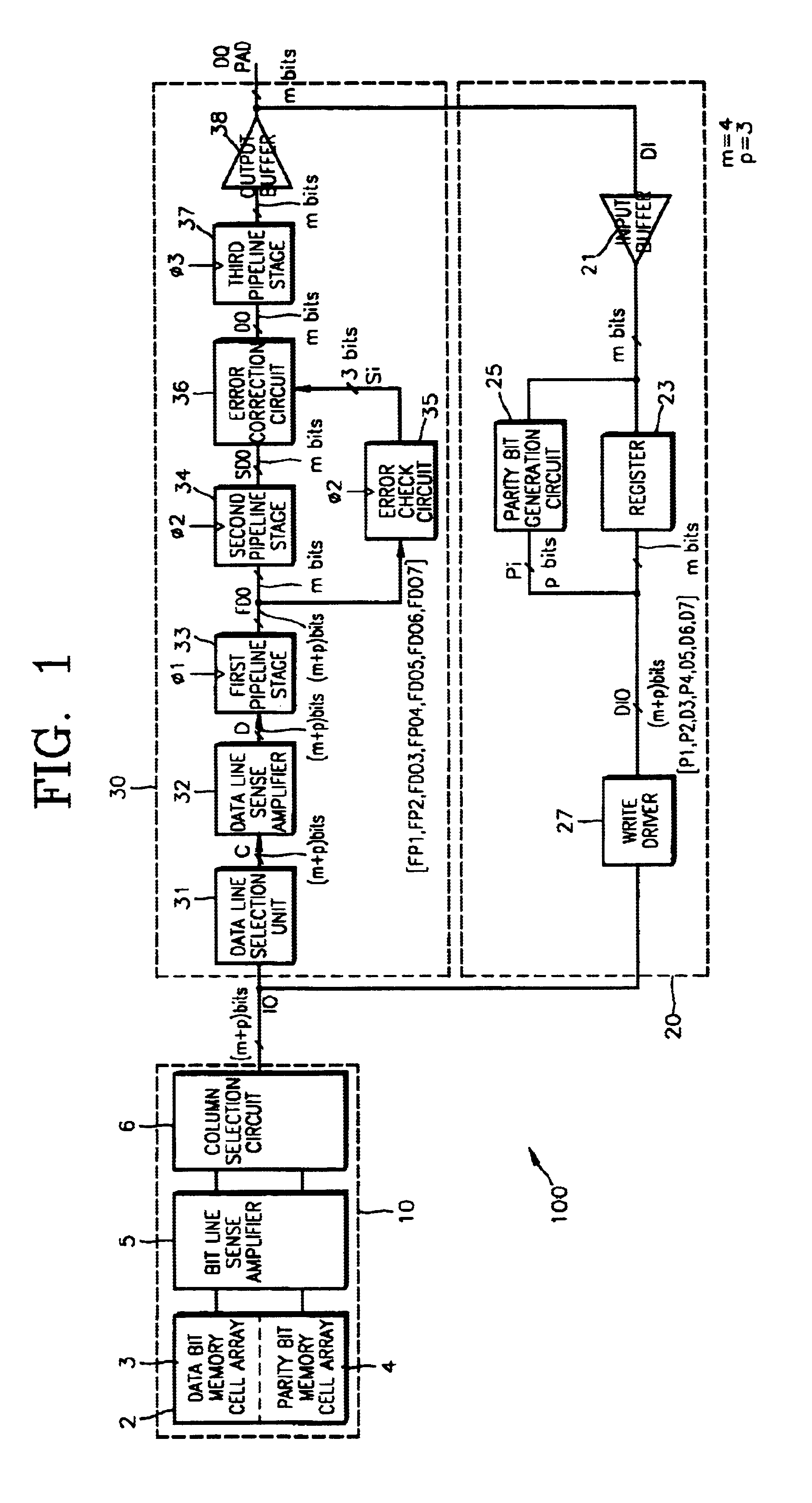

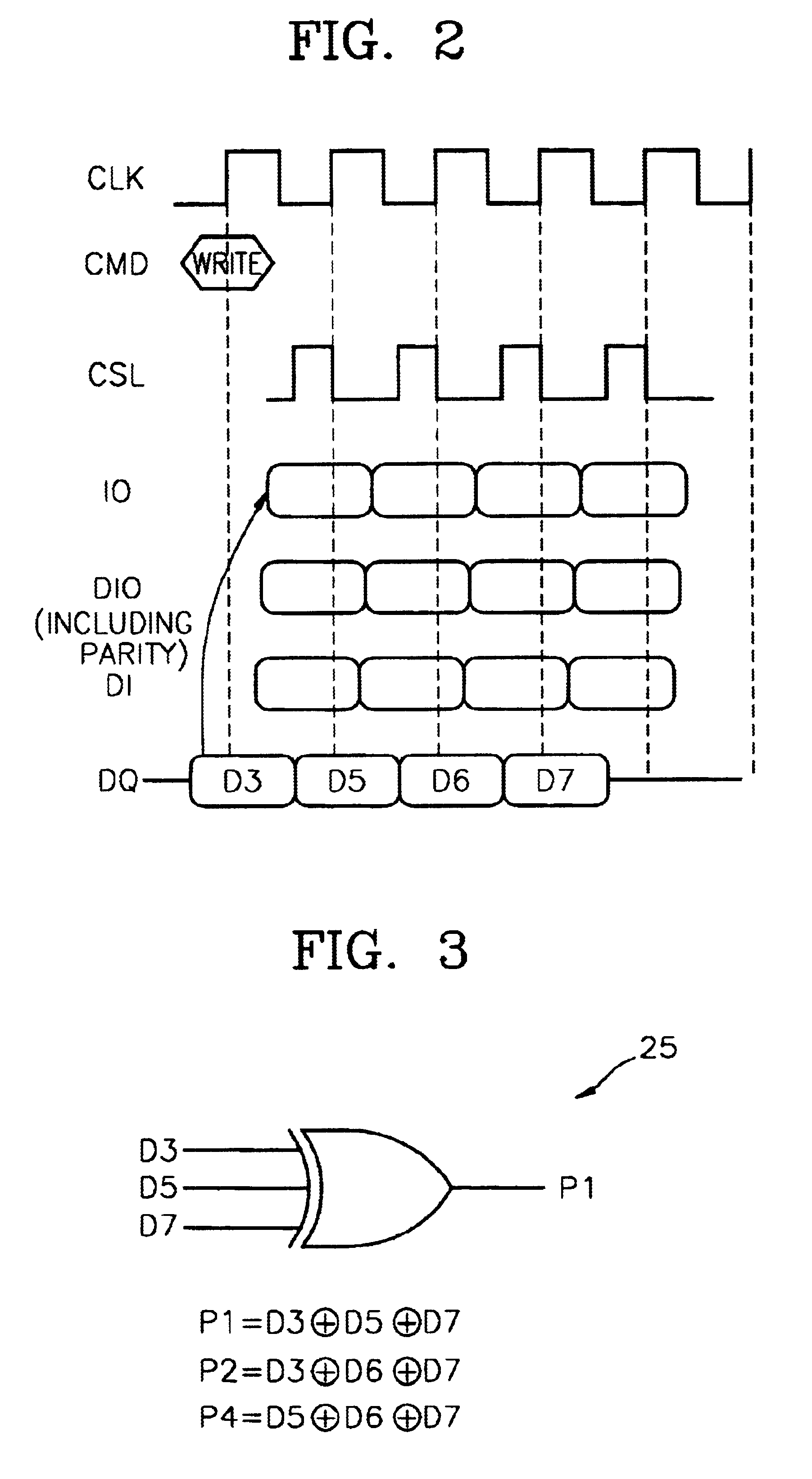

Integrated circuit memory devices having error checking and correction circuits therein and methods of operating same

Integrated circuit memory devices include a memory cell array having therein a plurality of stored data bits and a plurality of parity bits generated from a plurality of write data bits received by the memory device during a write operation. The plurality of stored data bits and the plurality of parity bits may collectively form a word having a length of m+p bits, where m and p are integers. An error check circuit is provided that converts the plurality of stored data bits and the plurality of parity bits into a plurality of syndrome bits (e.g., Si) that designate a location of a bit error in the plurality of stored data bits when compared against the original write data bits. An error correction circuit is provided that uses the plurality of syndrome bits to correct an error in the plurality of stored data bits and generate a plurality of read data bits that match the plurality of original write data bits.

Owner:SAMSUNG ELECTRONICS CO LTD

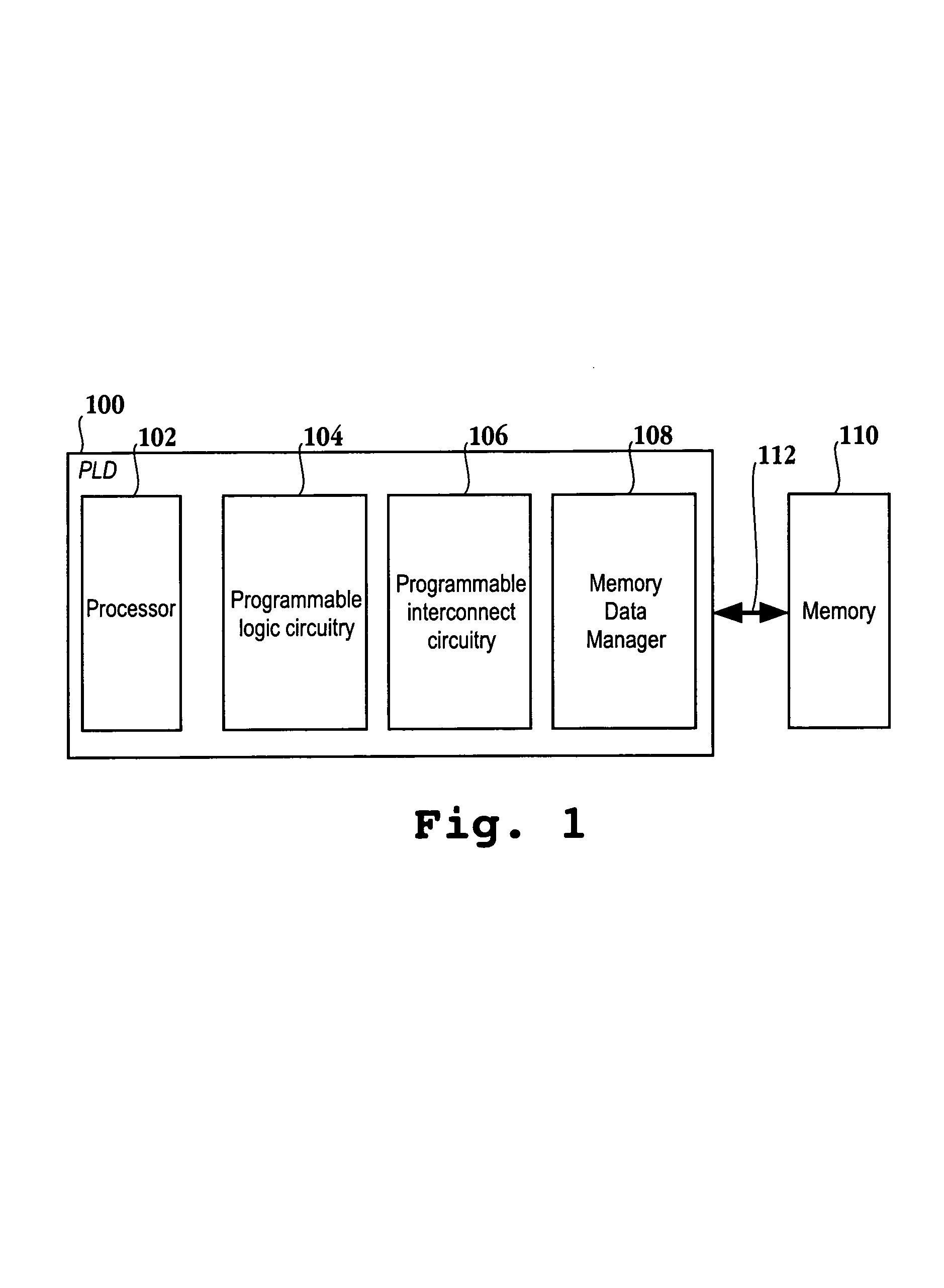

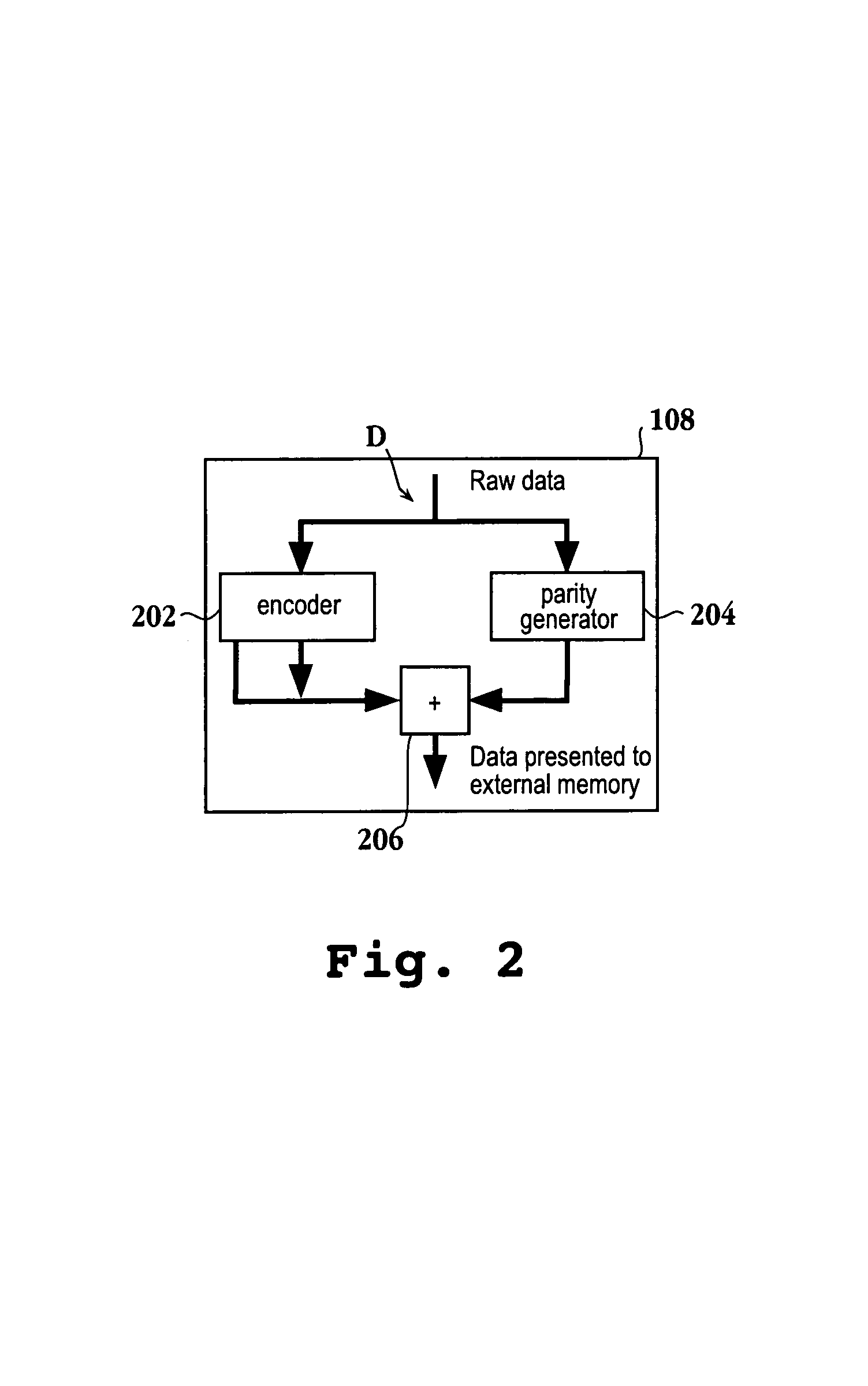

Method and system for improving memory interface data integrity in PLDs

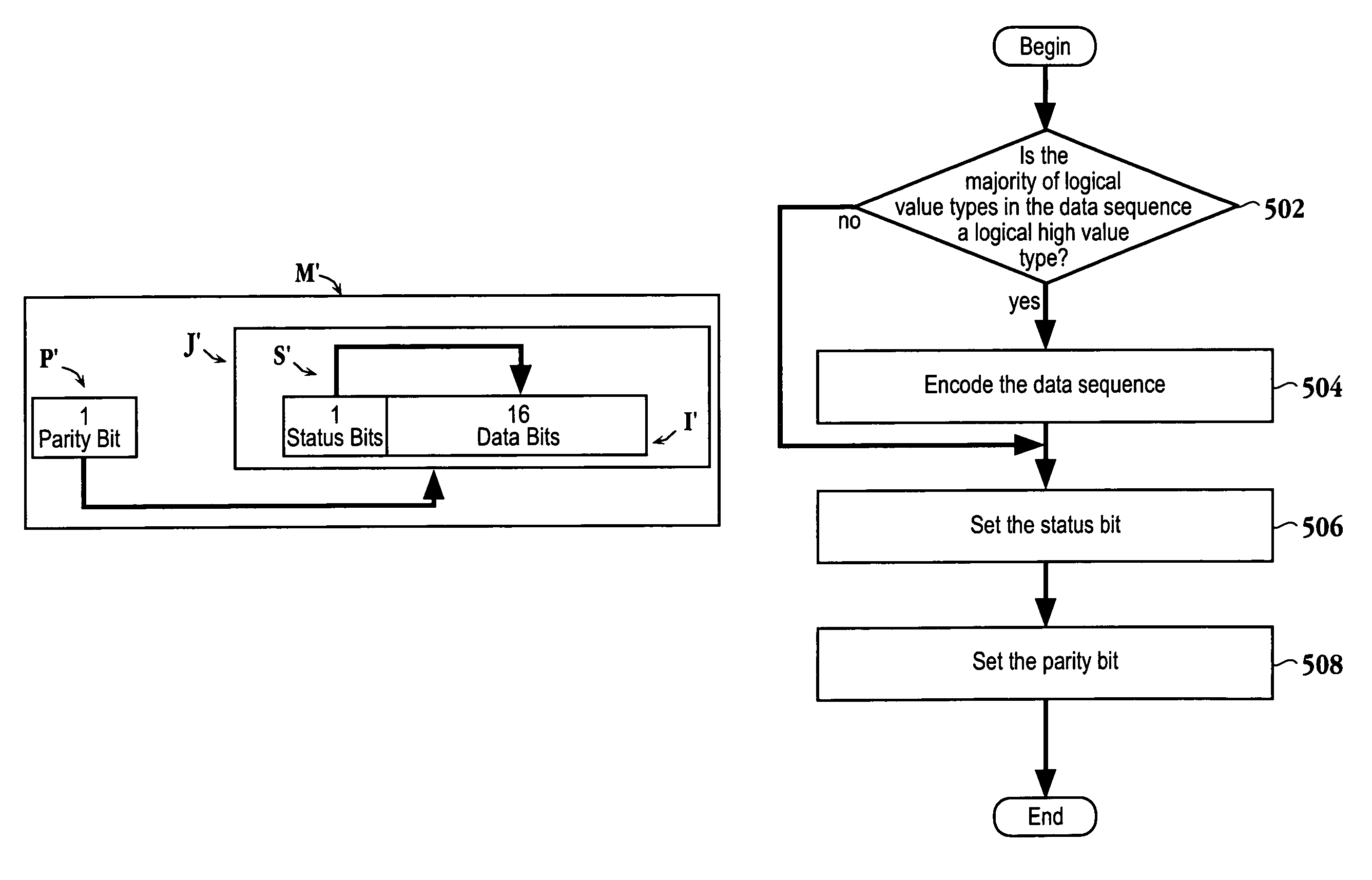

InactiveUS7102544B1Reduces SSO effectDetecting errorError detection/correctionCode conversionData integrityExternal storage

An integrated circuit (IC) for optimizing data presentation to an external memory interface bus is provided. The IC is in communication with the external memory via the external memory interface bus. The IC includes an encoder that may encode the data that are being sent to an external memory. The encoder encodes the data based on the logic value of the majority of bits in the data. The encoder is capable of setting a status bit to indicate that the data are encoded. Further connected in series with the encoder is a parity generator that sets the parity bit logic value based on whether the number of logic 1s in the data, along with the status bit, is even or odd. The IC also includes a parity checker to detect whether any error occurred in the data during transmission. The decoder within the IC decodes the data to the original data.

Owner:TAHOE RES LTD

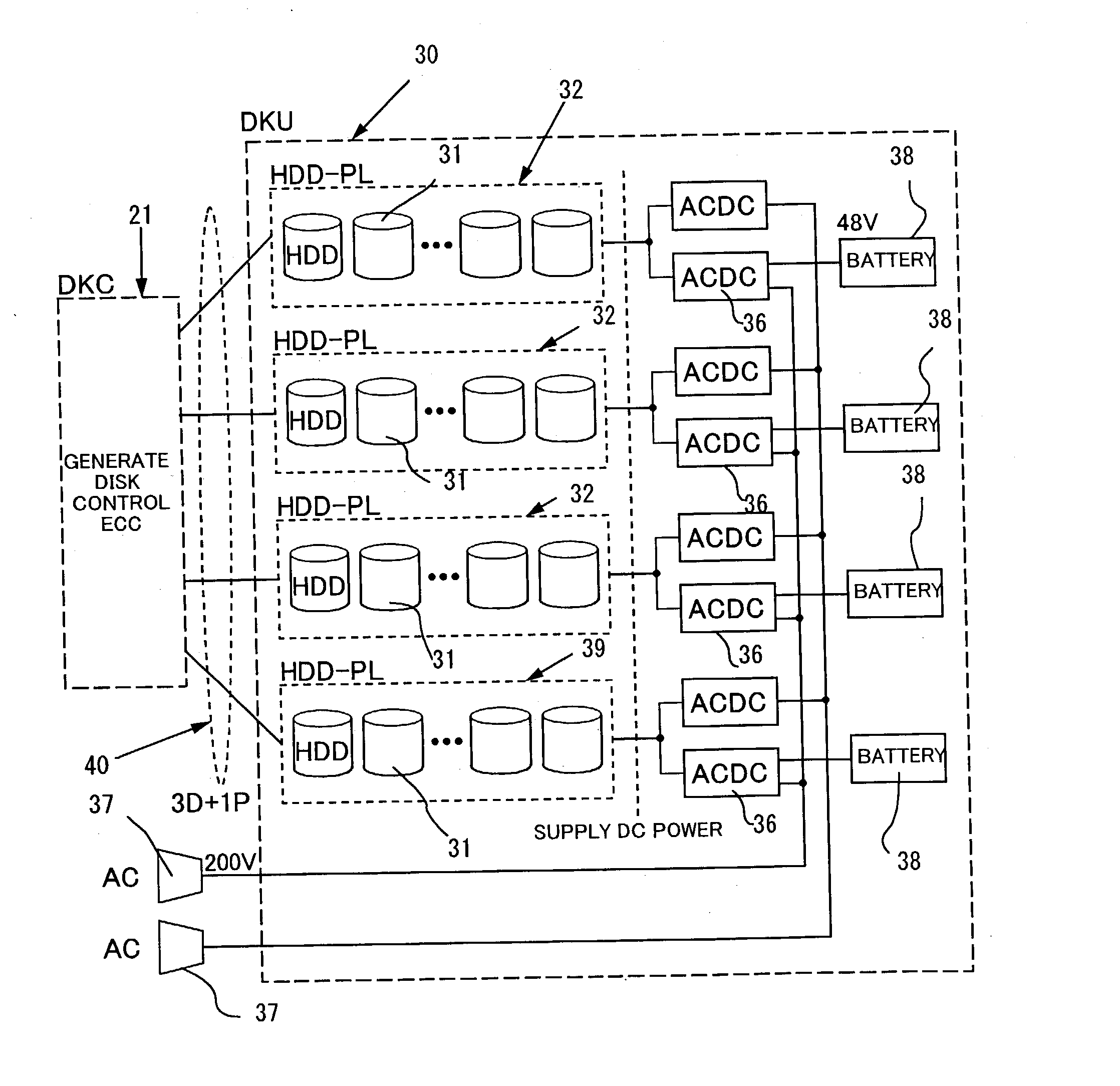

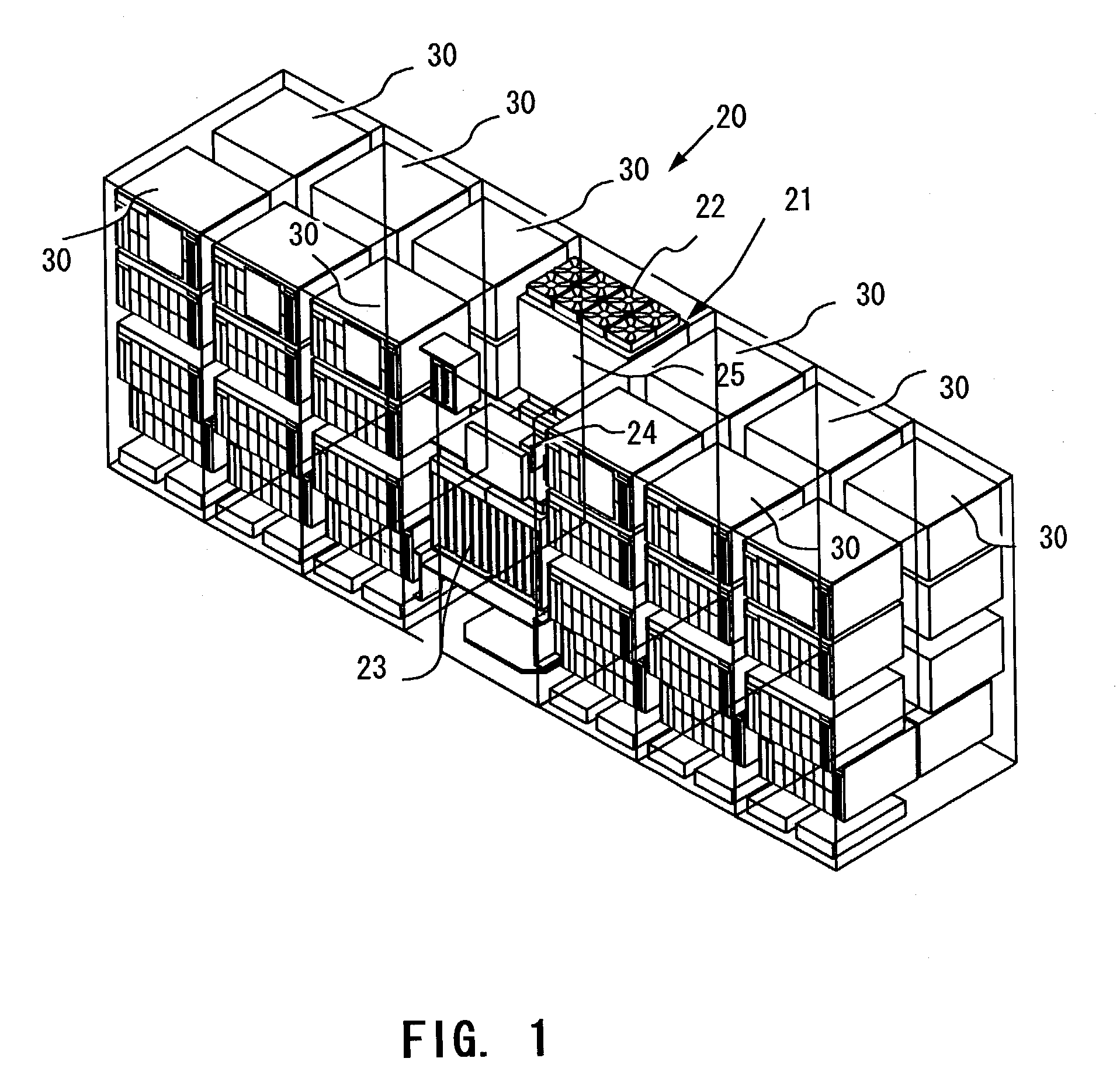

Method for backing up power supply of disk array device and system thereof

InactiveUS20030217300A1Volume/mass flow measurementPower supply for data processingDisk arrayEmbedded system

A disk array device having two or more disk units, each disk unit including at least one disk drive, at least either of said disk units having parity bits carrying data recovery information, comprises at least one backup battery provided for each of said disk unit.

Owner:HITACHI LTD

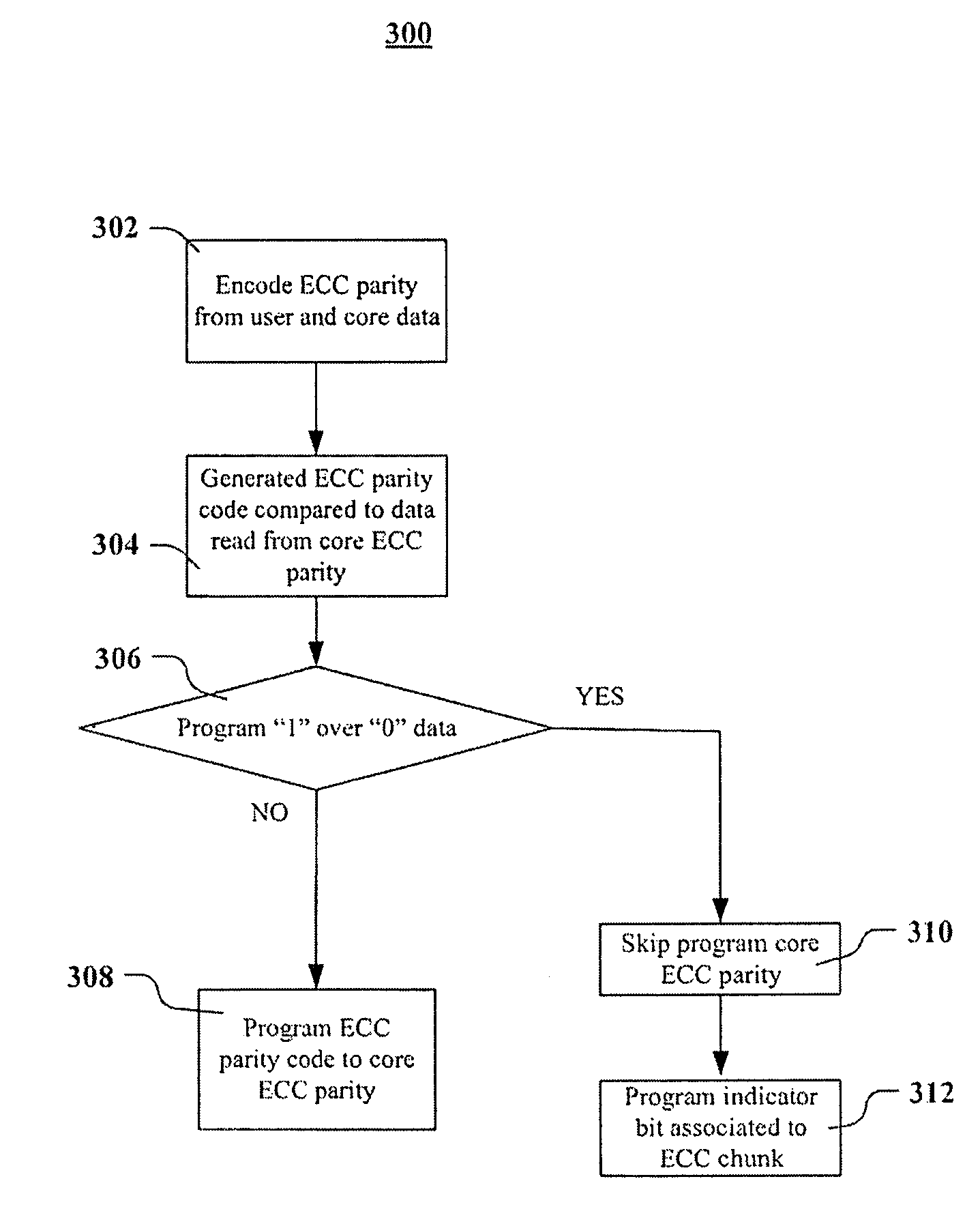

Implementation of recycling unused ECC parity bits during flash memory programming

Methods for recycling unused error correction code (ECC) during flash memory programming, comprise generating ECC from user data to form a syndrome and storing the syndrome into volatile memory. ECC is re-encoded corresponding to the syndrome read from the memory with new user data. Re-encoding ECC comprises comparing new ECC with the most recent ECC of the previous syndrome, correcting a bit error in the new ECC, and indicating if the new ECC has failed.

Owner:VALLEY DEVICE MANAGEMENT

Transmitting apparatus and interleaving method thereof

ActiveUS20150341053A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

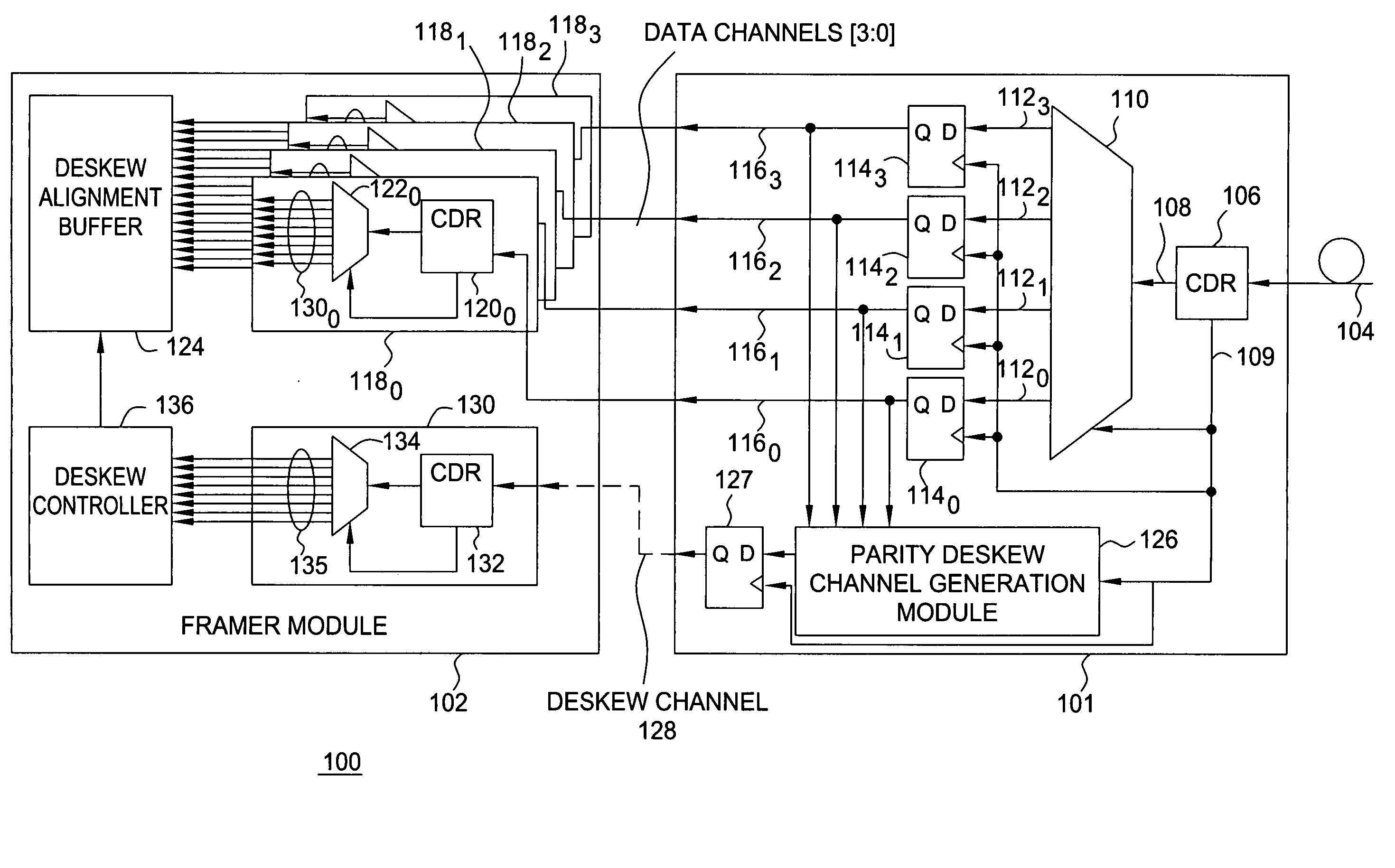

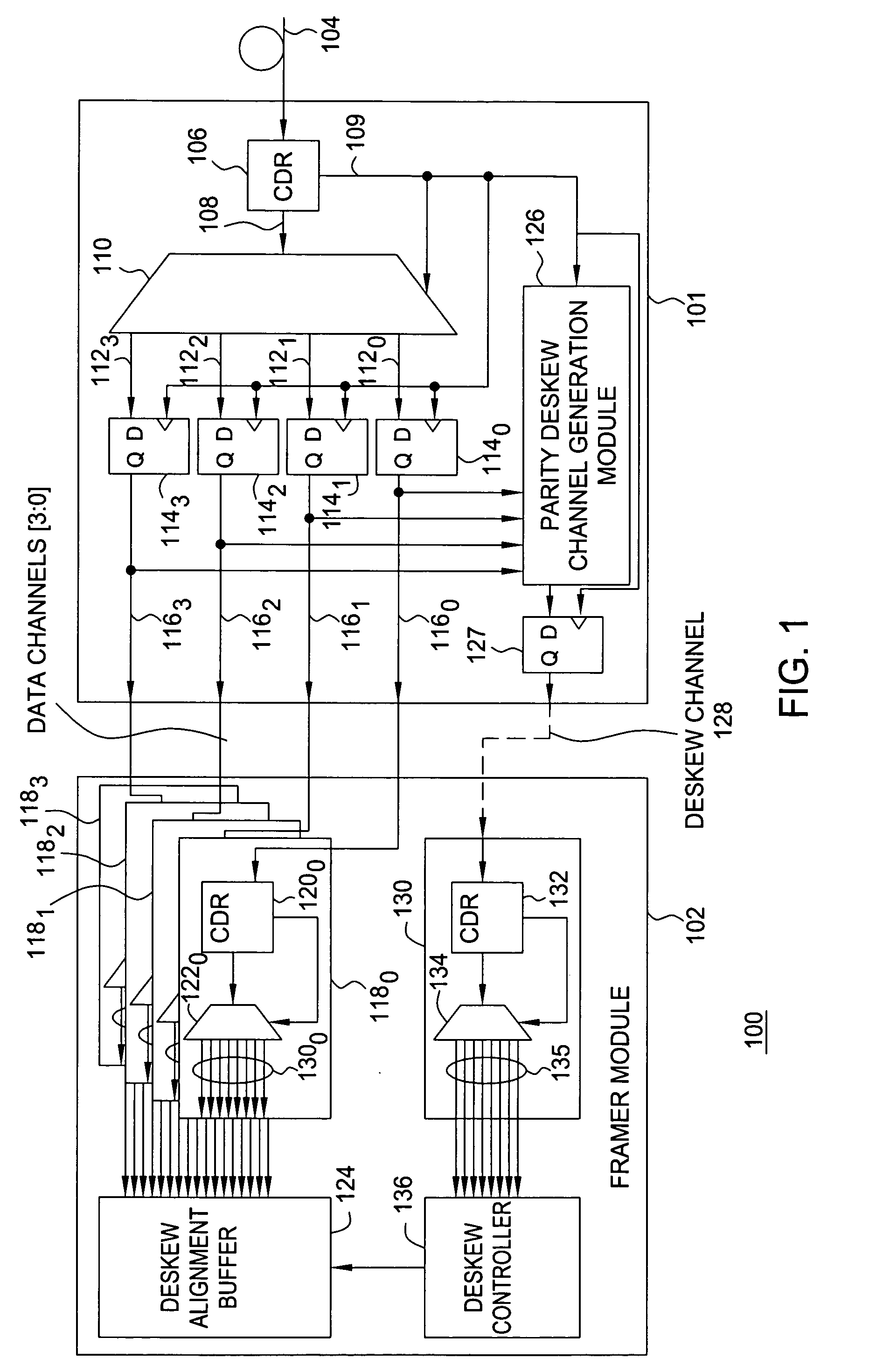

Method and apparatus for synchronizing data channels using an alternating parity deskew channel

ActiveUS20070006053A1Reduce skewSimpler and efficient and reliable and cost-effectiveChannel dividing arrangementsError detection/correctionChannel useParity bit

The invention includes a method and apparatus for aligning a plurality of data channels using a deskew bitstream. The method includes receiving the deskew bitstream, identifying an aligned deskew frame by processing the deskew bitstream, identifying a data channel alignment position associated with each of the plurality of data channels by comparing a deskew channel comparison bit from the aligned deskew frame to a data channel comparison bit from each of the plurality of data channels, and selecting the plurality of data channel alignment positions associated with the respective plurality of data channels for aligning the plurality of data channels. The plurality of data channels are aligned in a manner for substantially reducing skew associated with the data channels. The deskew bitstream comprises a plurality of data bits associated with the data channels and a plurality of parity bits generated using at least a portion of the data bits.

Owner:ALCATEL-LUCENT USA INC

LOW DENSITY PARITY CHECK (LDPC) CODING FOR A 32k MODE INTERLEAVER IN A DIGITAL VIDEO BROADCASTING (DVB) STANDARD

ActiveUS20120189079A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError correction/detection using LDPC codesParity-check matrixCarrier signal

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals.

Owner:SONY CORP

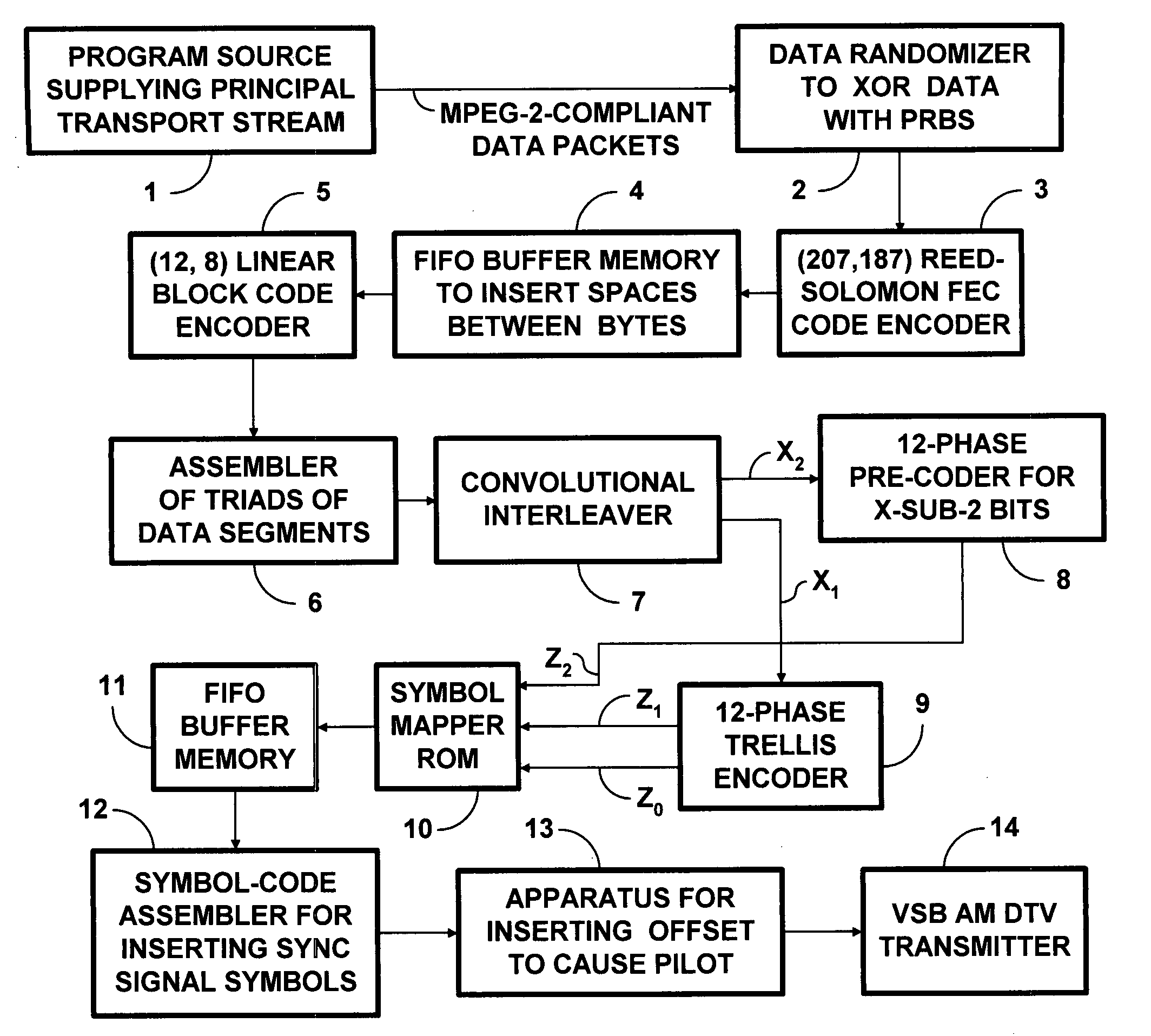

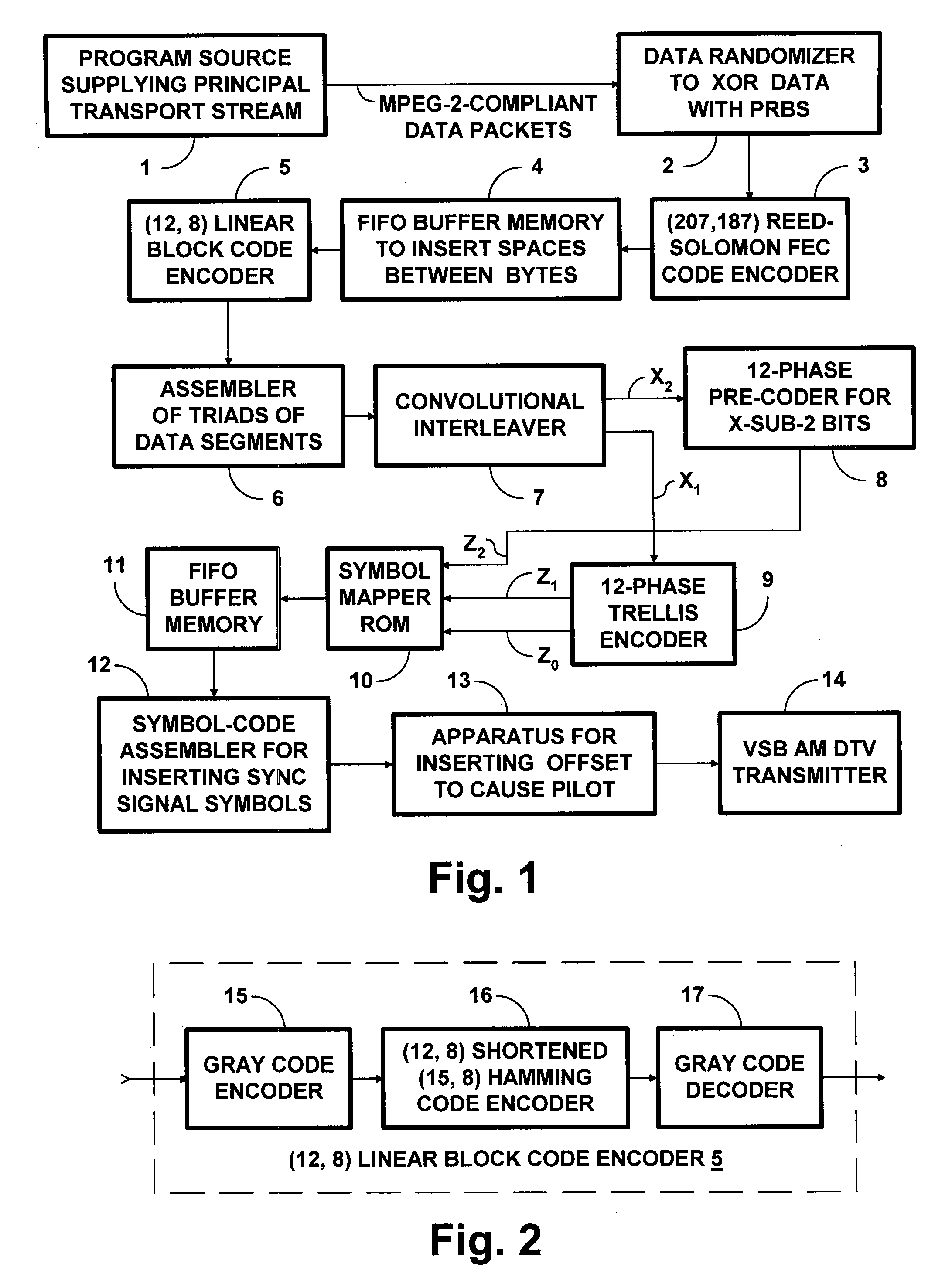

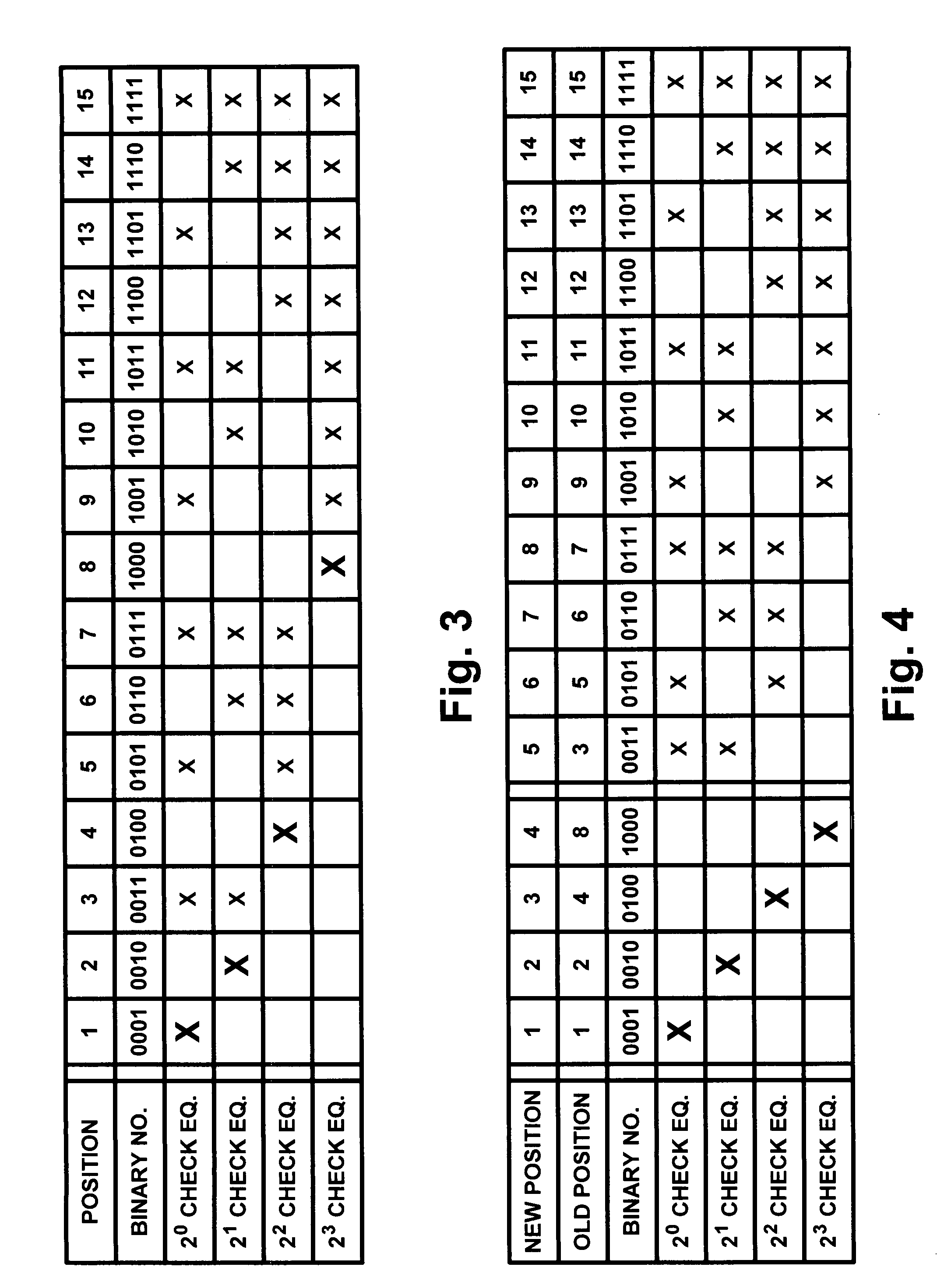

Robust DTV signals transmitted at two thirds the code rate of ordinary 8VSB DTV signals

Owner:LIMBERG ALLEN LEROY

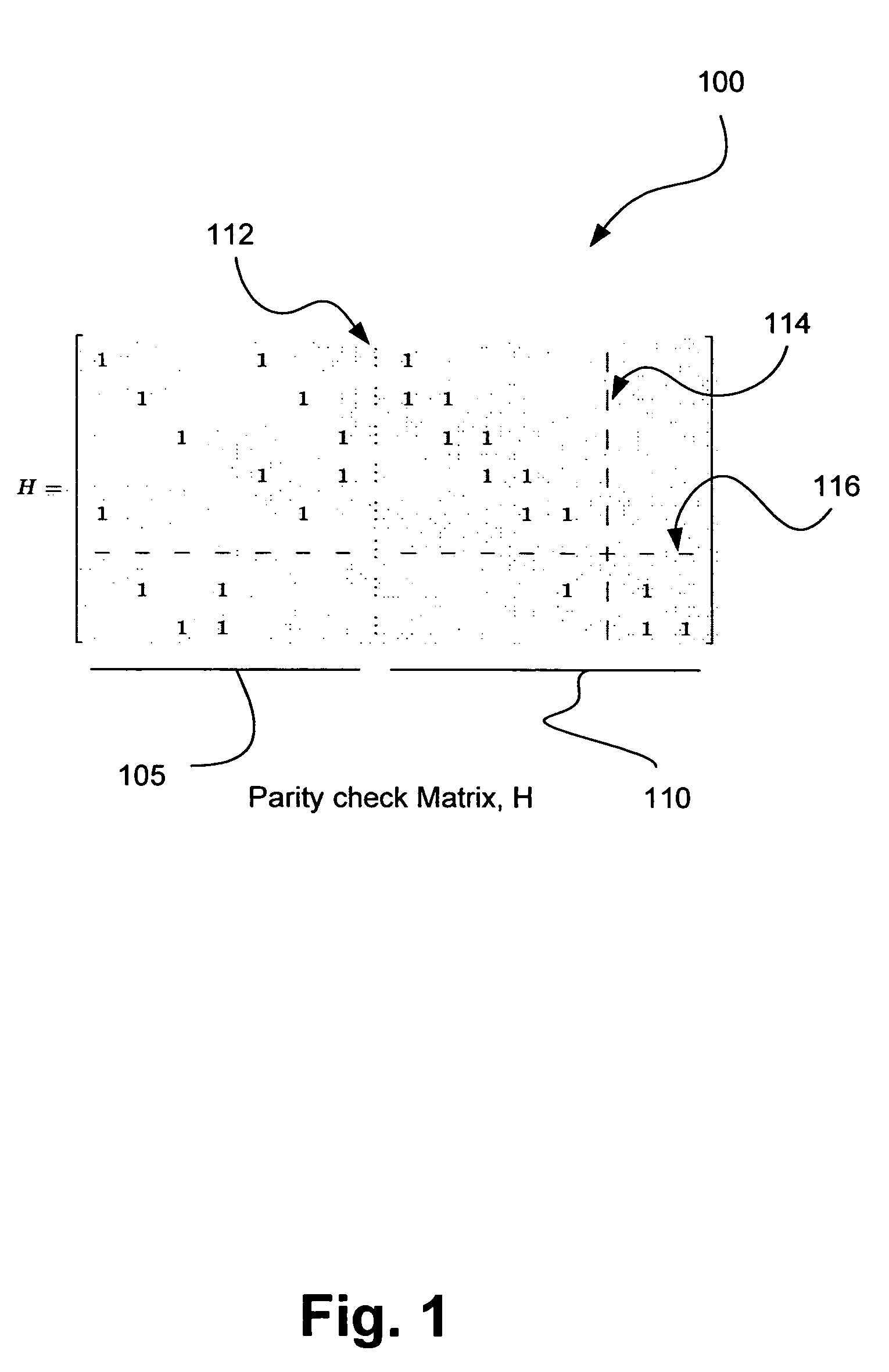

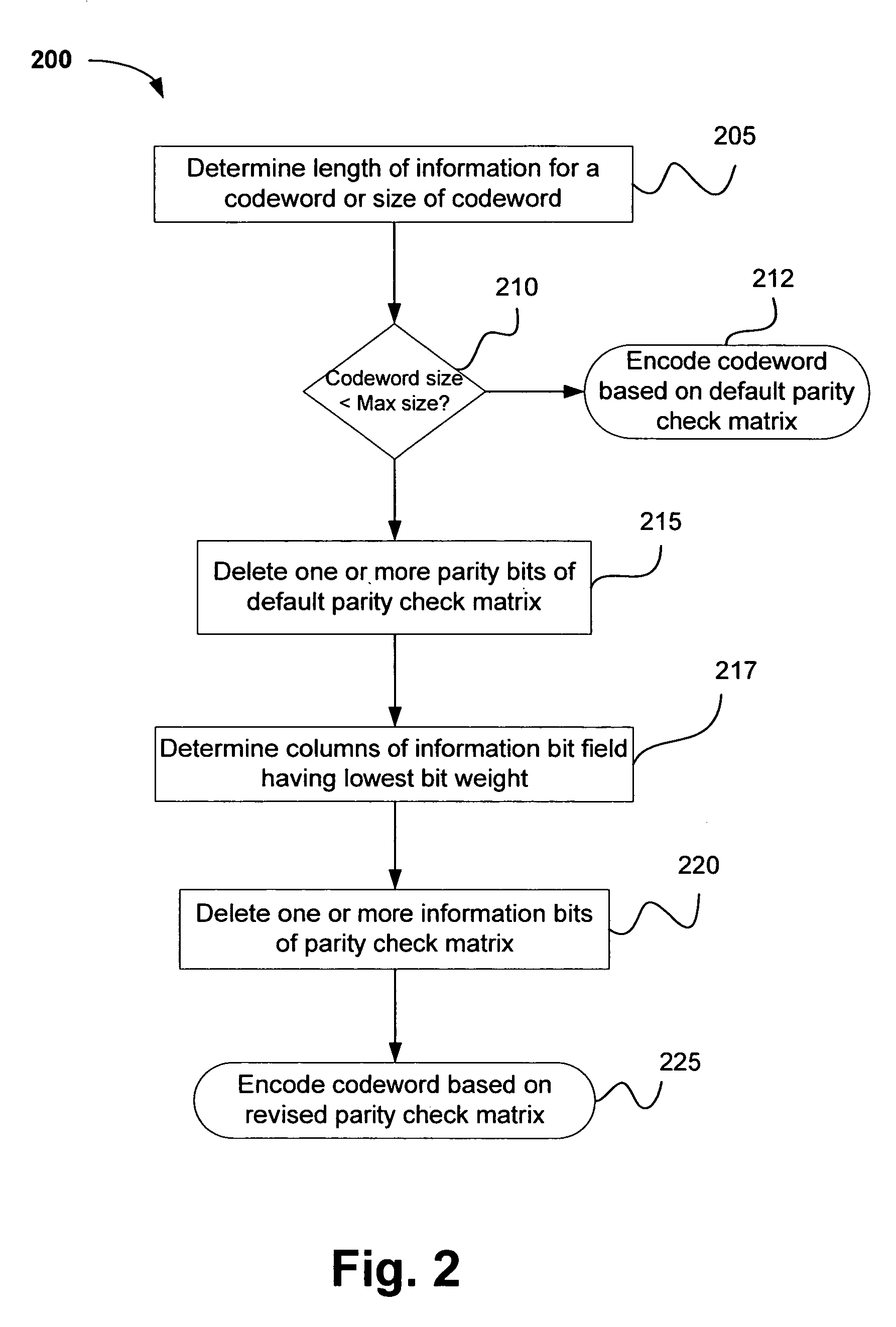

Method and apparatus for varying lengths of low density party check codewords

ActiveUS7263651B2Error preventionNetwork traffic/resource managementParity-check matrixTheoretical computer science

A method and apparatus for encoding / decoding information using low density parity check (LDPC) codewords of varying lengths. In one implementation, an encoder / decoder uses a parity check matrix having a size that corresponds to a length of information for each codeword. In one example, the size of the parity check matrix may be retrieved from multiple stored matrices having different sizes. In other examples, a mother code matrix may be dynamically adjusted by puncturing parity bits and / or deleting information bits. Other inventive embodiments and adaptations are also disclosed.

Owner:APPLE INC

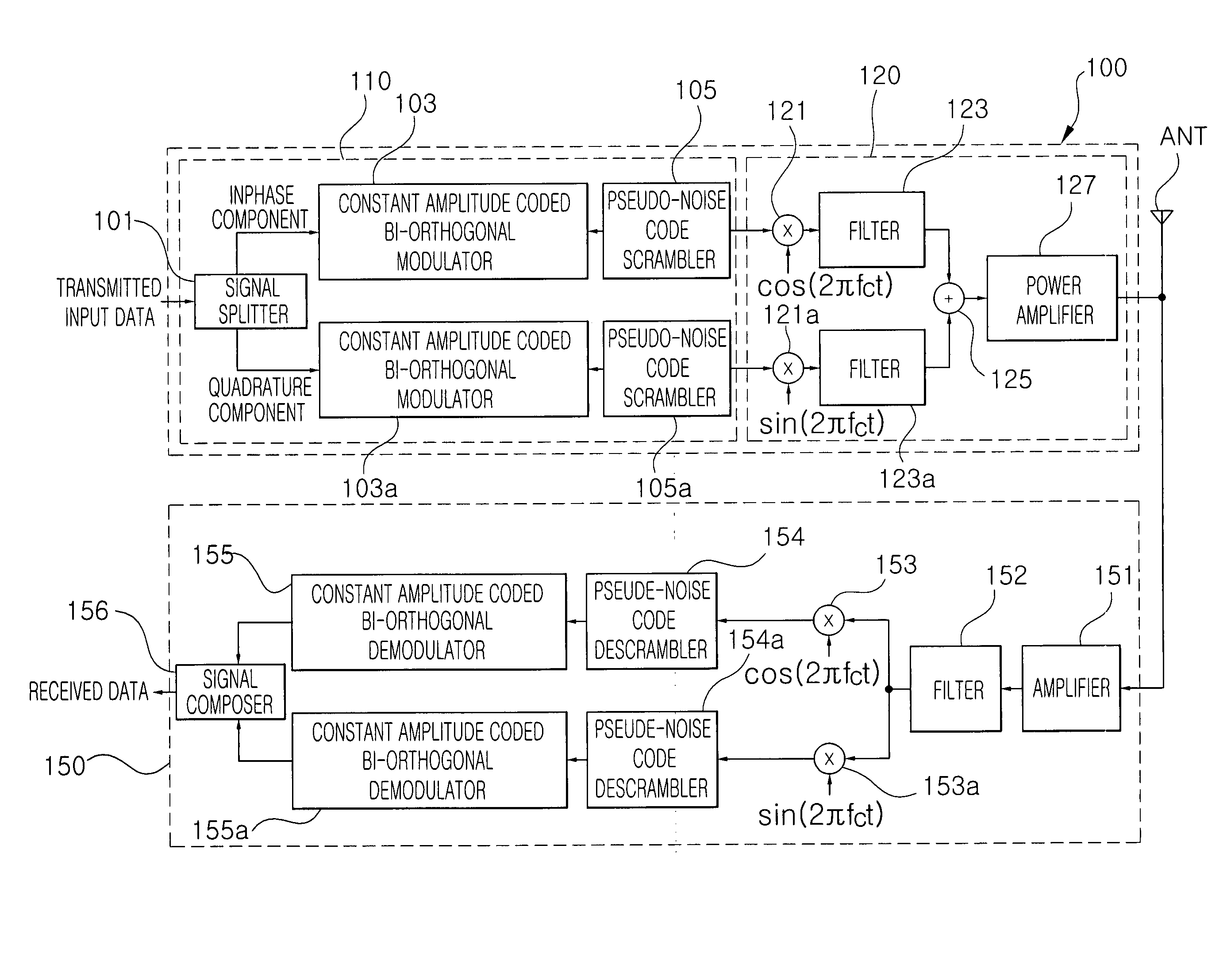

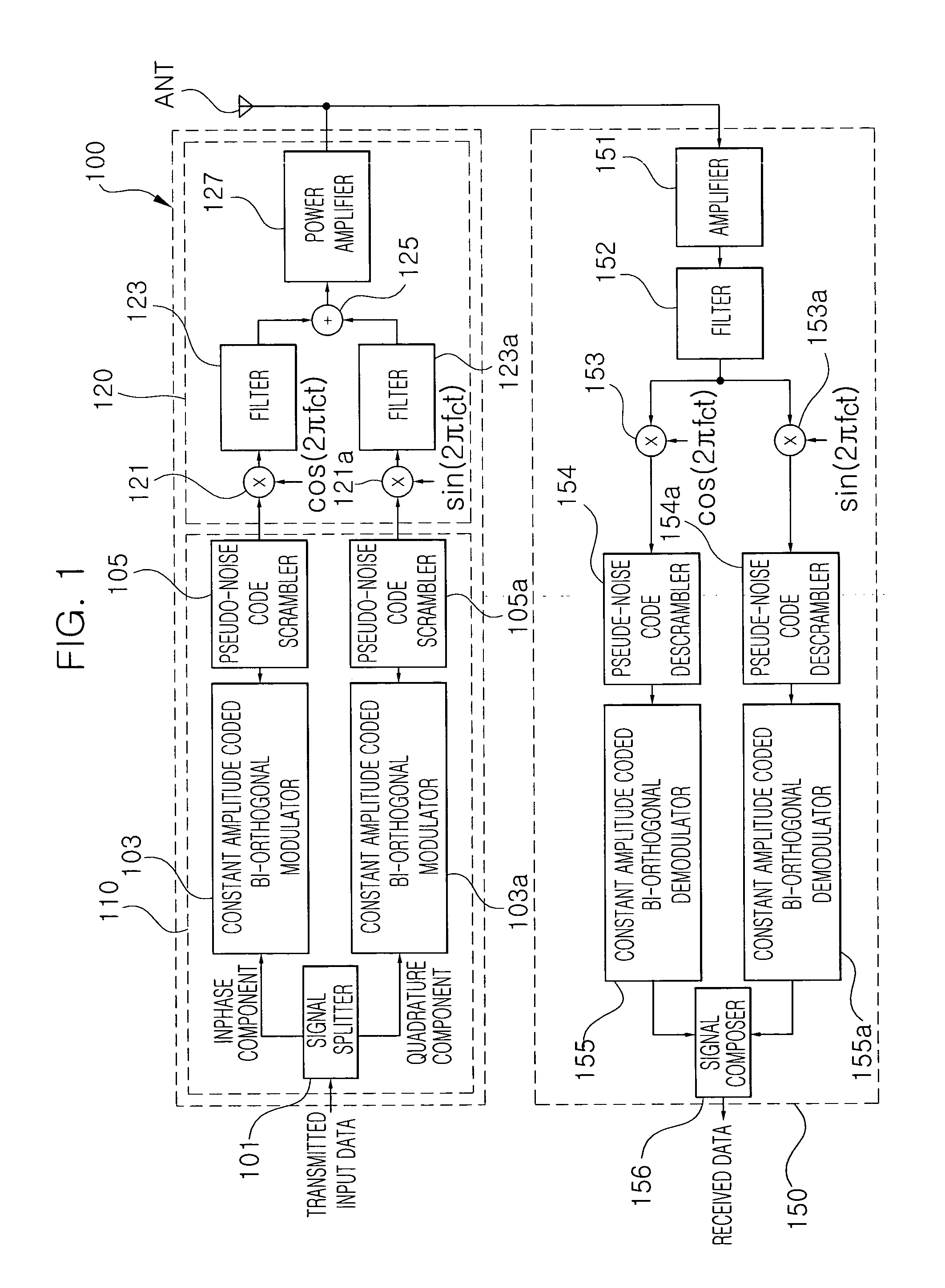

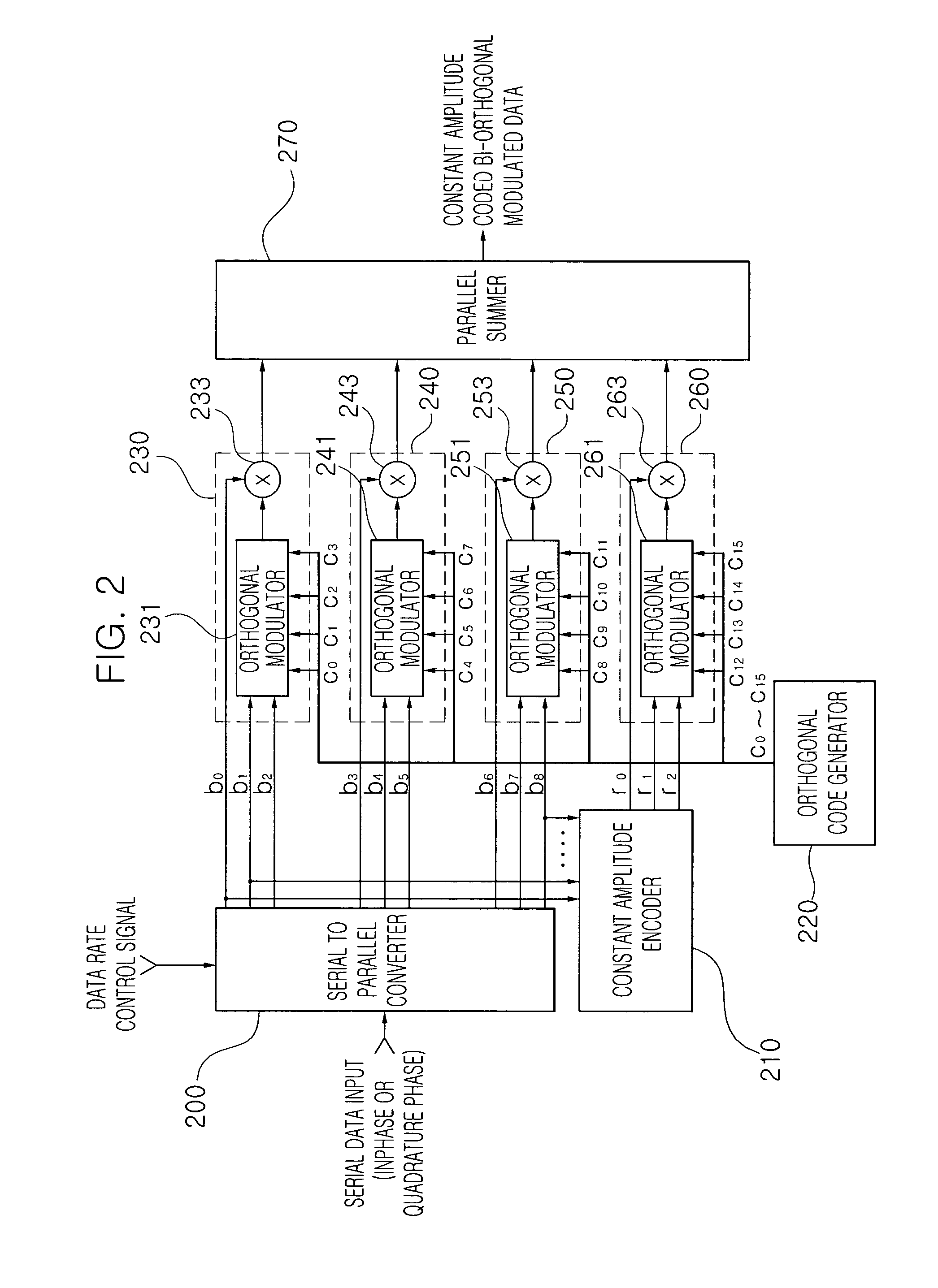

Apparatus for constant amplitude coded bi-orthogonal demodulation

ActiveUS20040146116A1Improve performanceEnsure correct executionError preventionCode conversionAudio power amplifierQuadrature modulation

A constant amplitude coded bi-orthogonal demodulator demodulates the received constant amplitude bi-orthogonal modulated data, cancels the parity bits to generate the serial data, detects the occurrence of an error by dividing the demodulated data into a plurality of groups of data, outputs the serial data as demodulated data if an error does not occur, sequentially converts bit polarities of data of groups in which an error occurs if the error detector detects the error, compares distances between the received bi-orthogonal modulated data and the constant amplitude coded bi-orthogonal modulated data, and selects, as demodulated data, data of which corresponding bit polarities are changed according to the comparison results. According to the present invention, power consumption is reduced, a power amplifier can be manufactured at an inexpensive cost, interference robustness can be ensured, and data can be transmitted at a high transmission rate and a variable transmission rate.

Owner:KOREA ELECTRONICS TECH INST