Patents

Literature

4519 results about "Static random-access memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Static random-access memory (static RAM or SRAM) is a type of semiconductor random-access memory (RAM) that uses bistable latching circuitry (flip-flop) to store each bit. SRAM exhibits data remanence, but it is still volatile in the conventional sense that data is eventually lost when the memory is not powered.

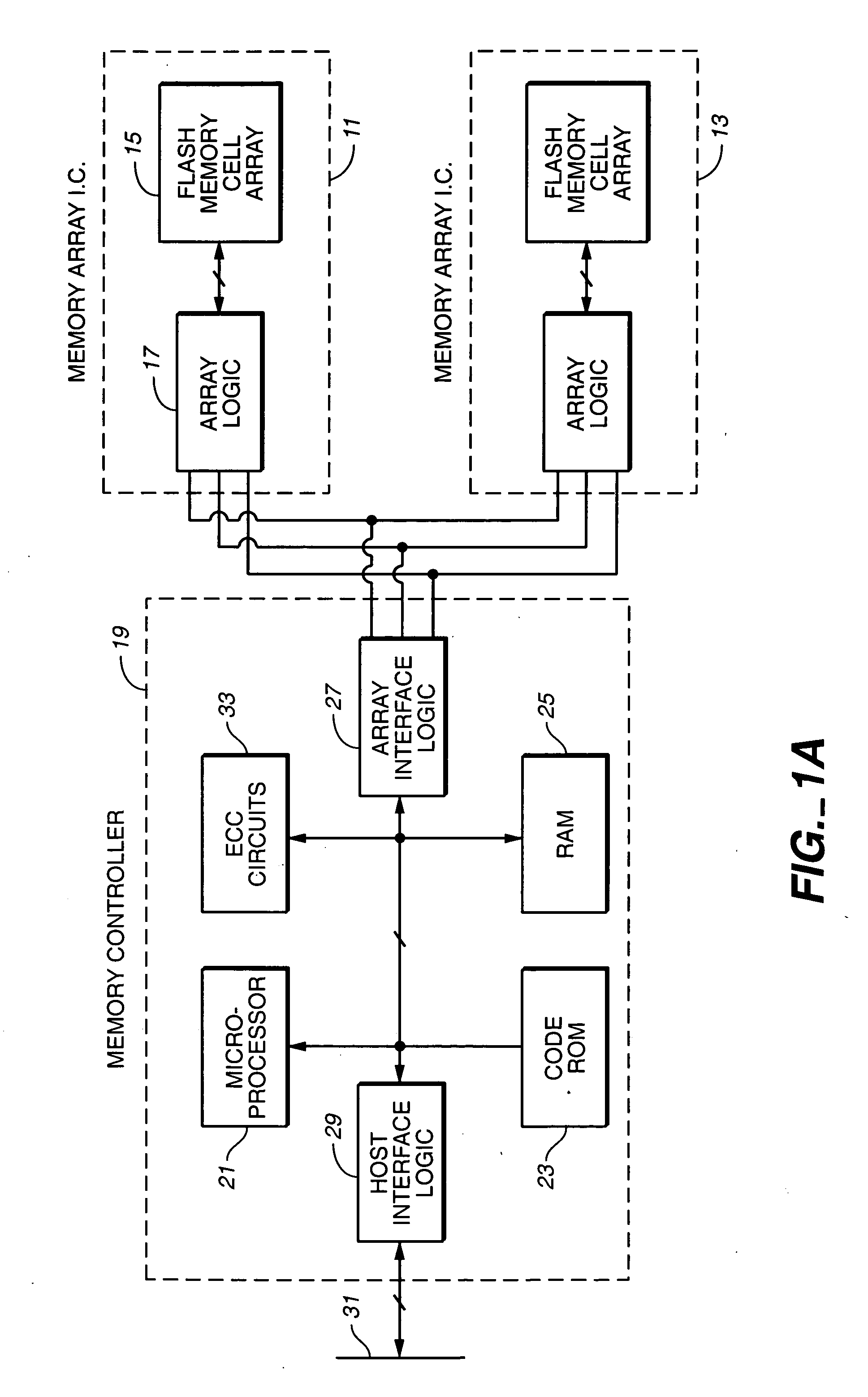

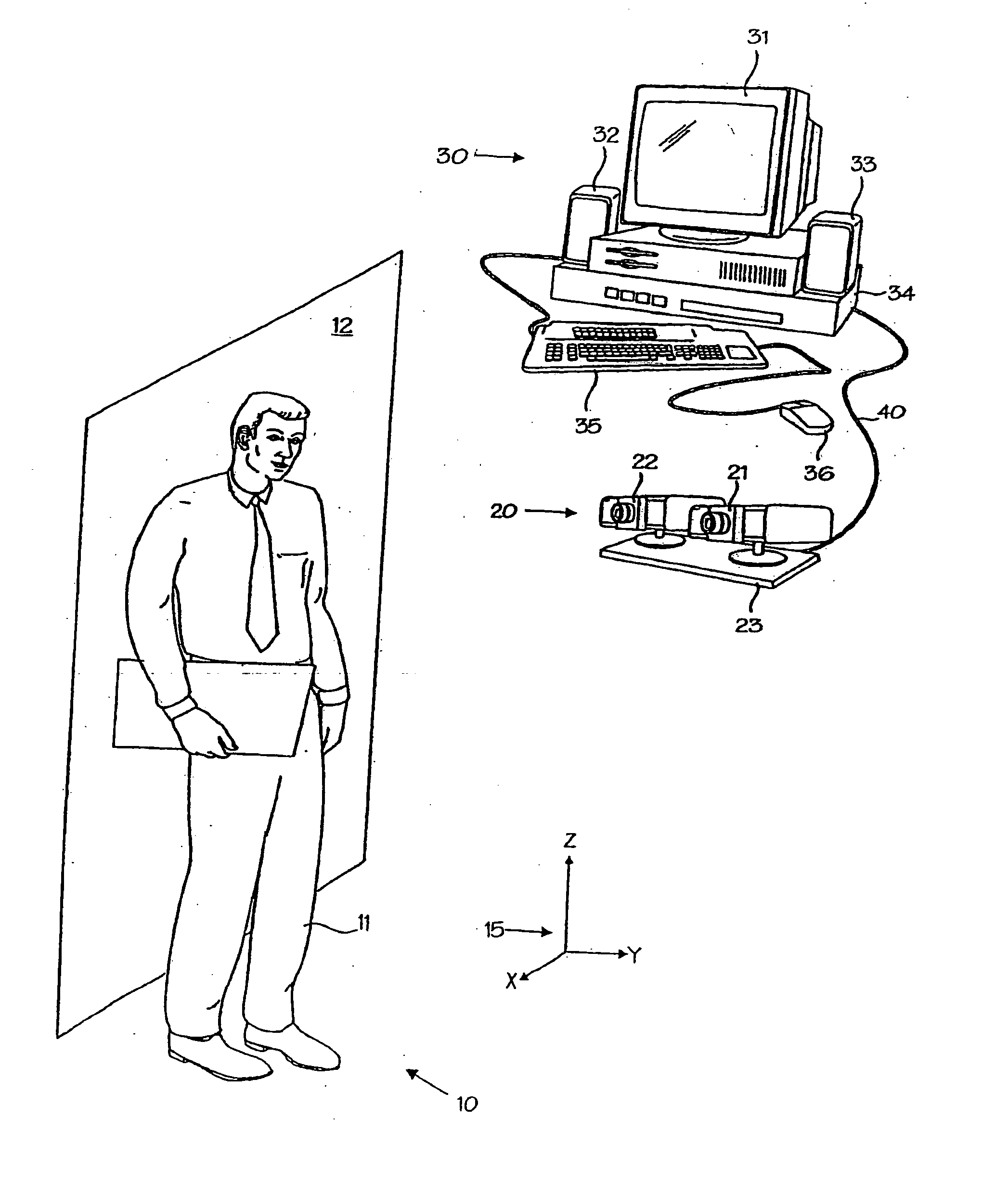

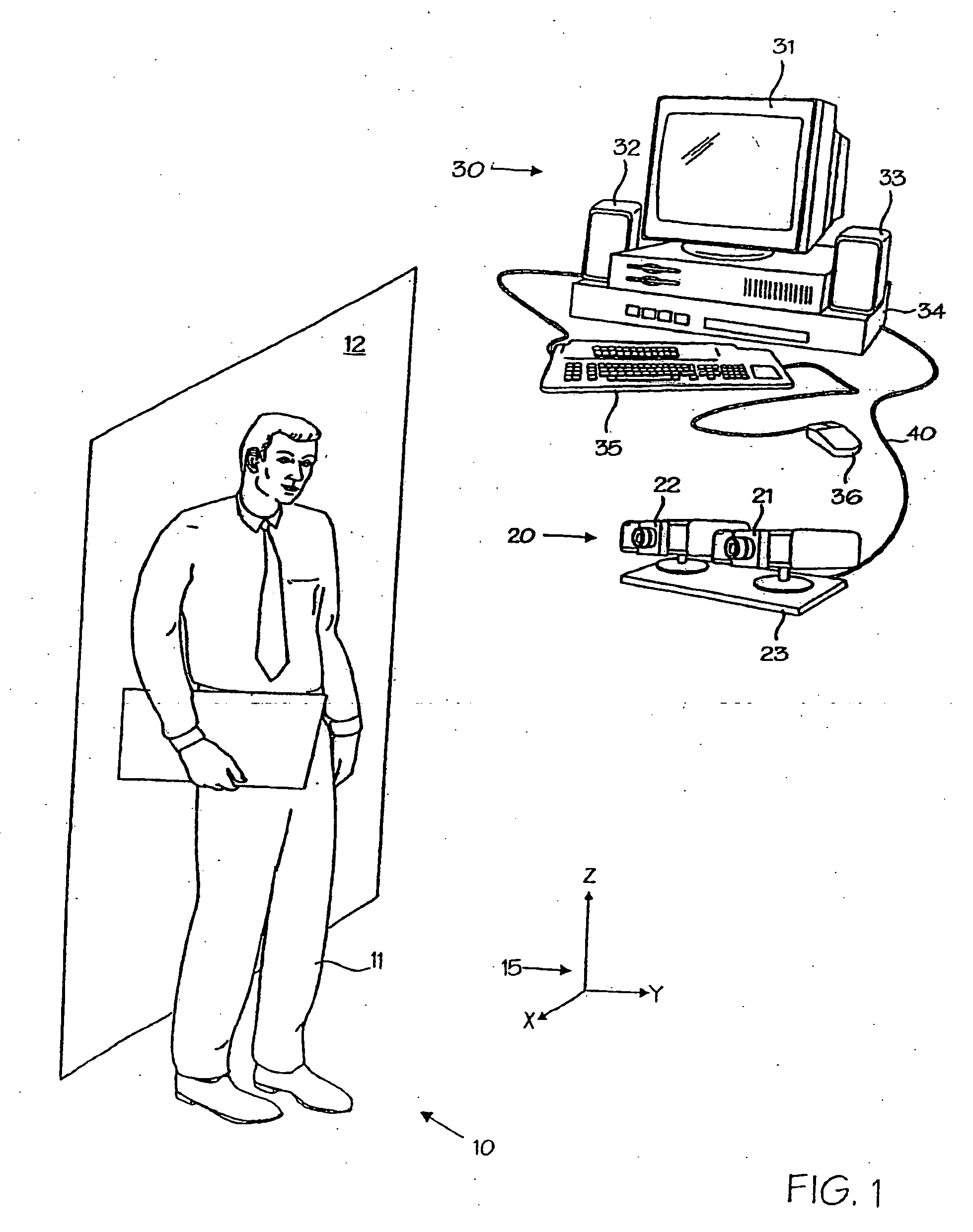

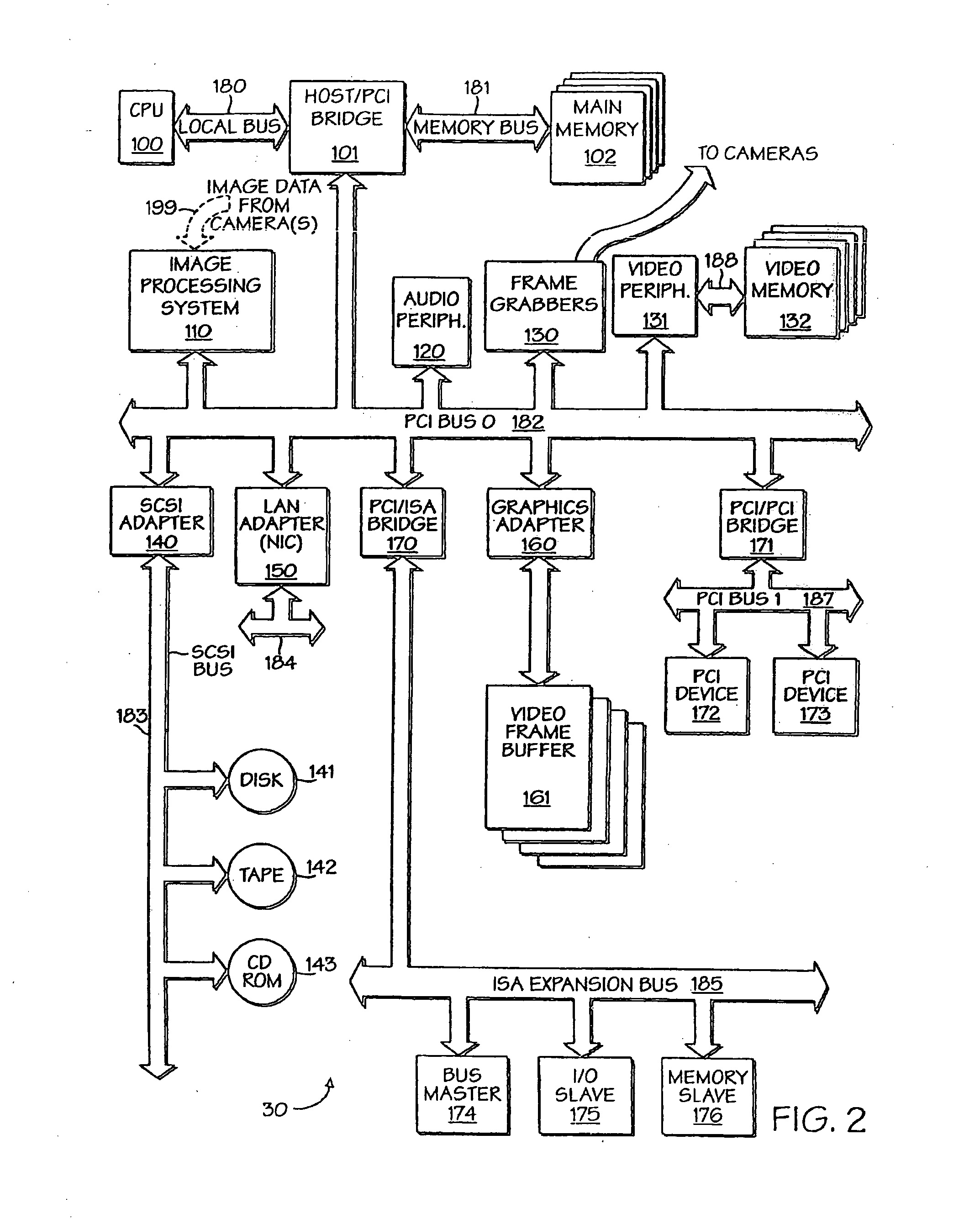

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

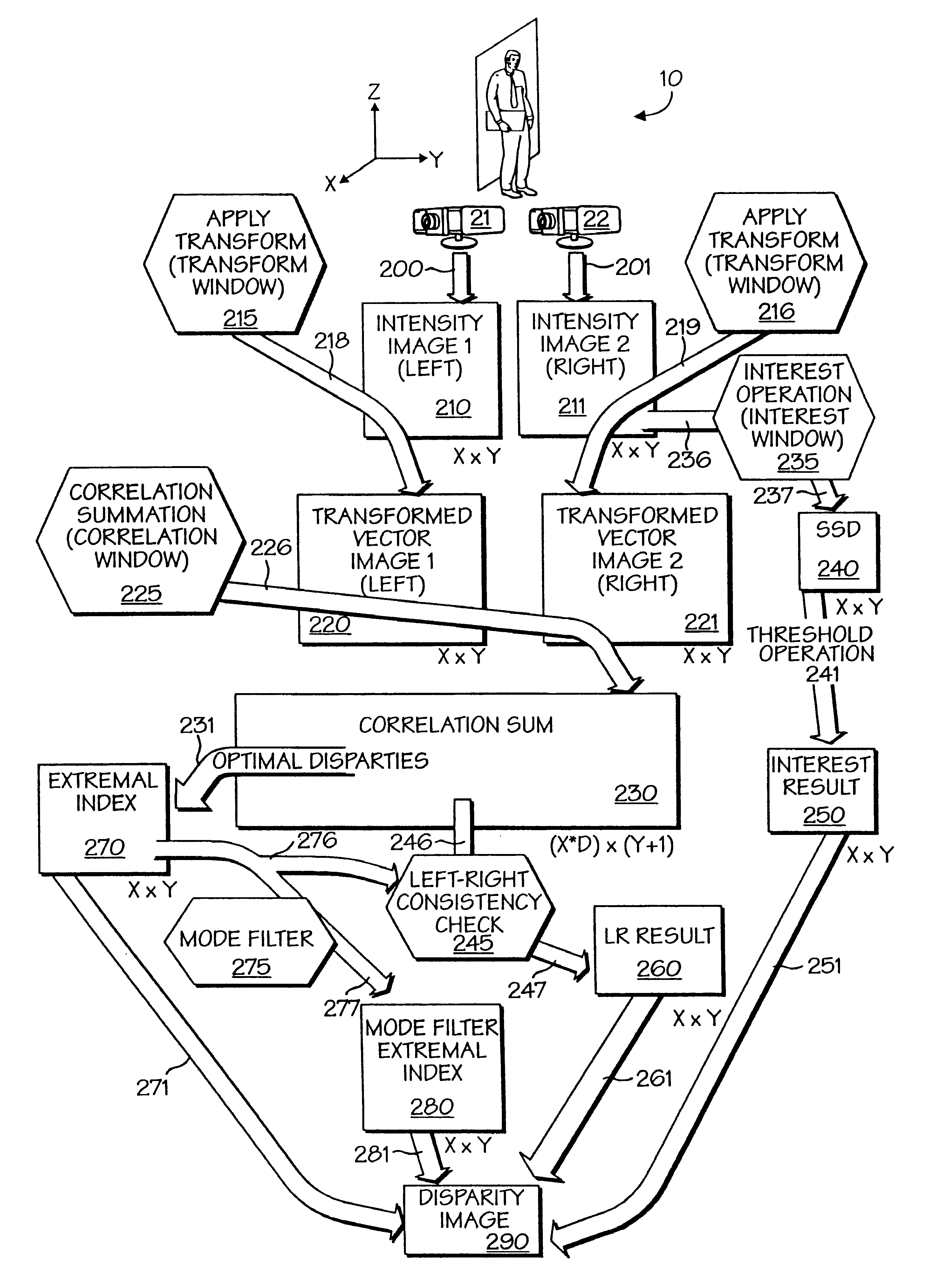

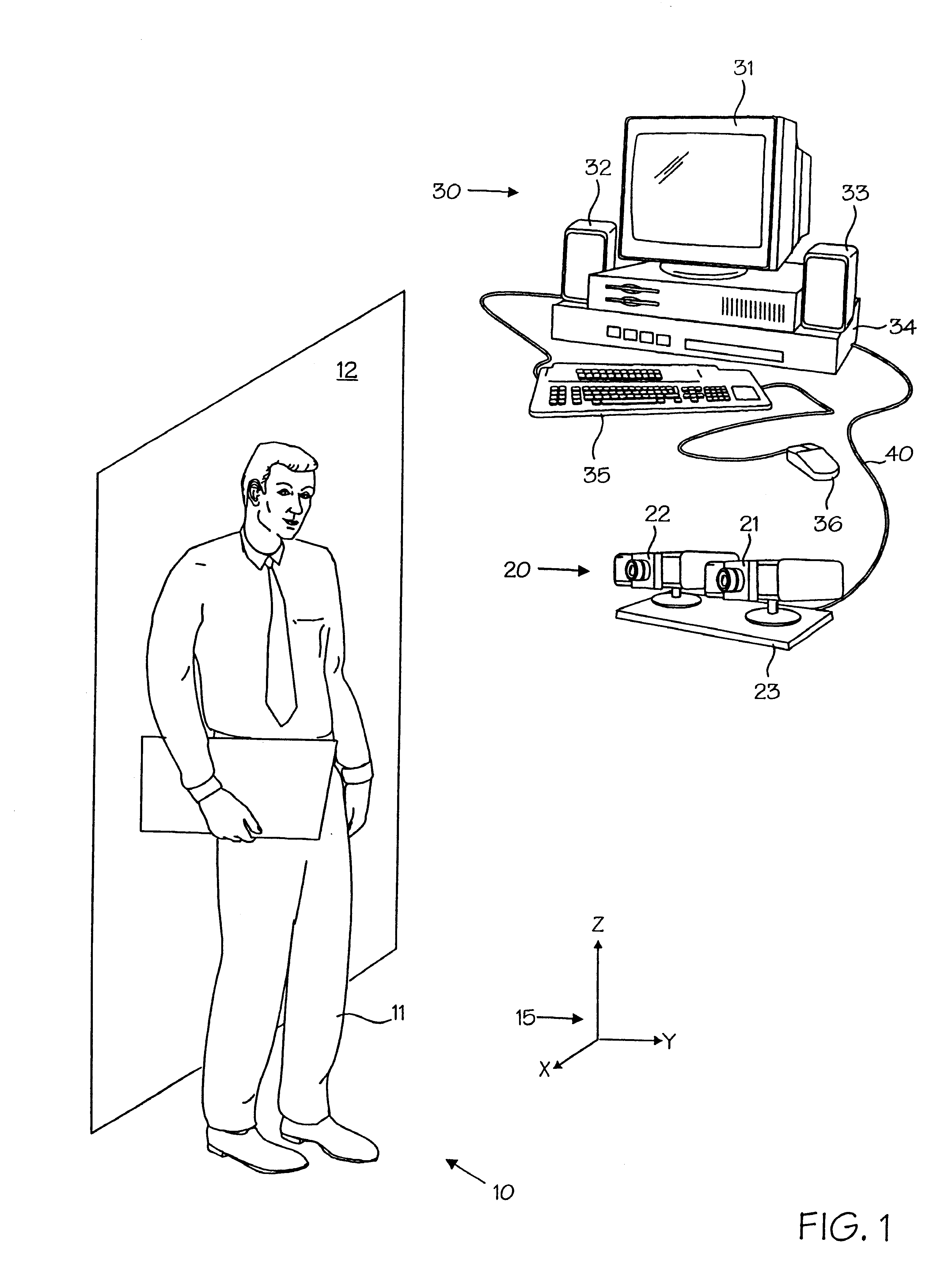

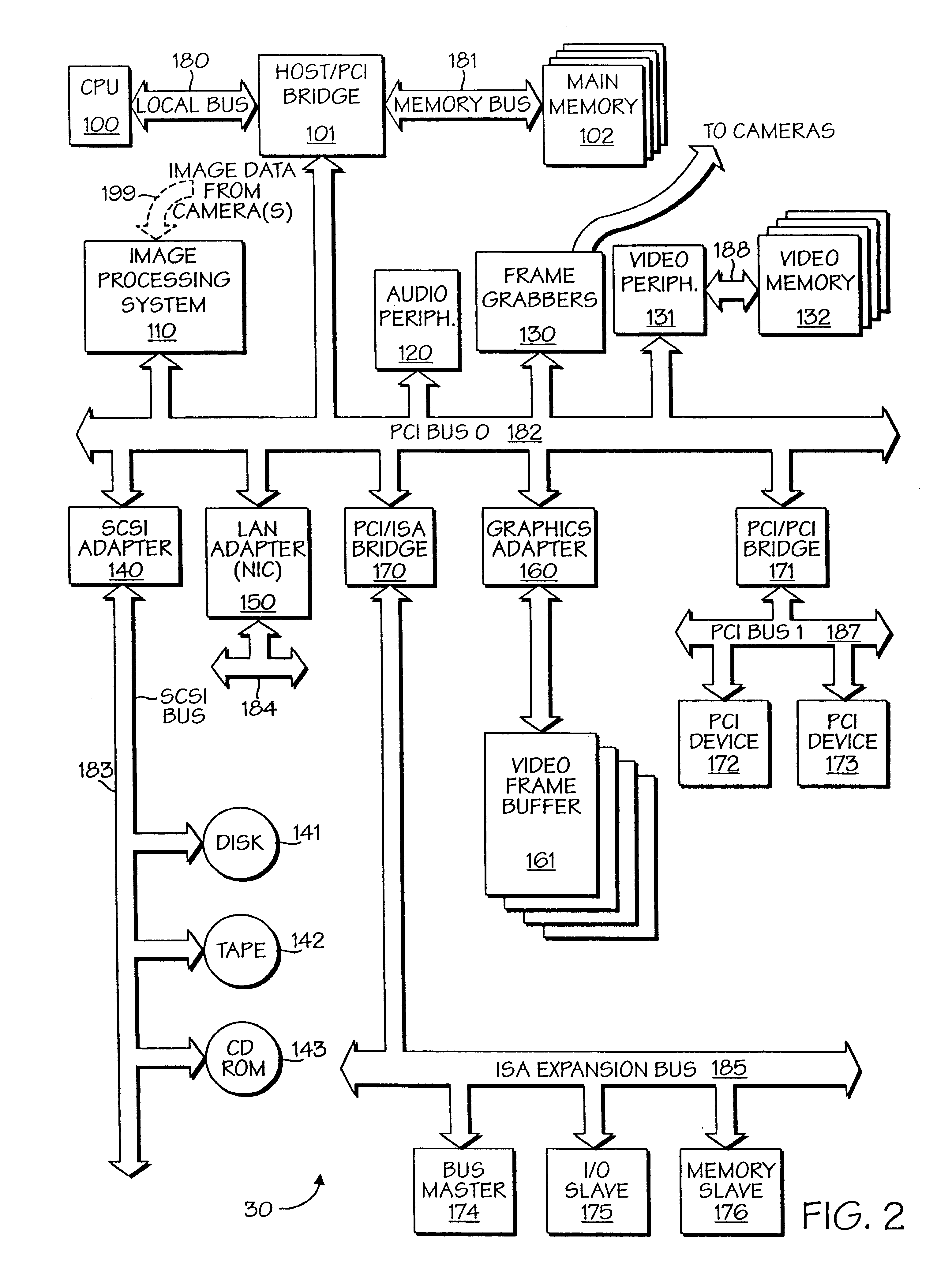

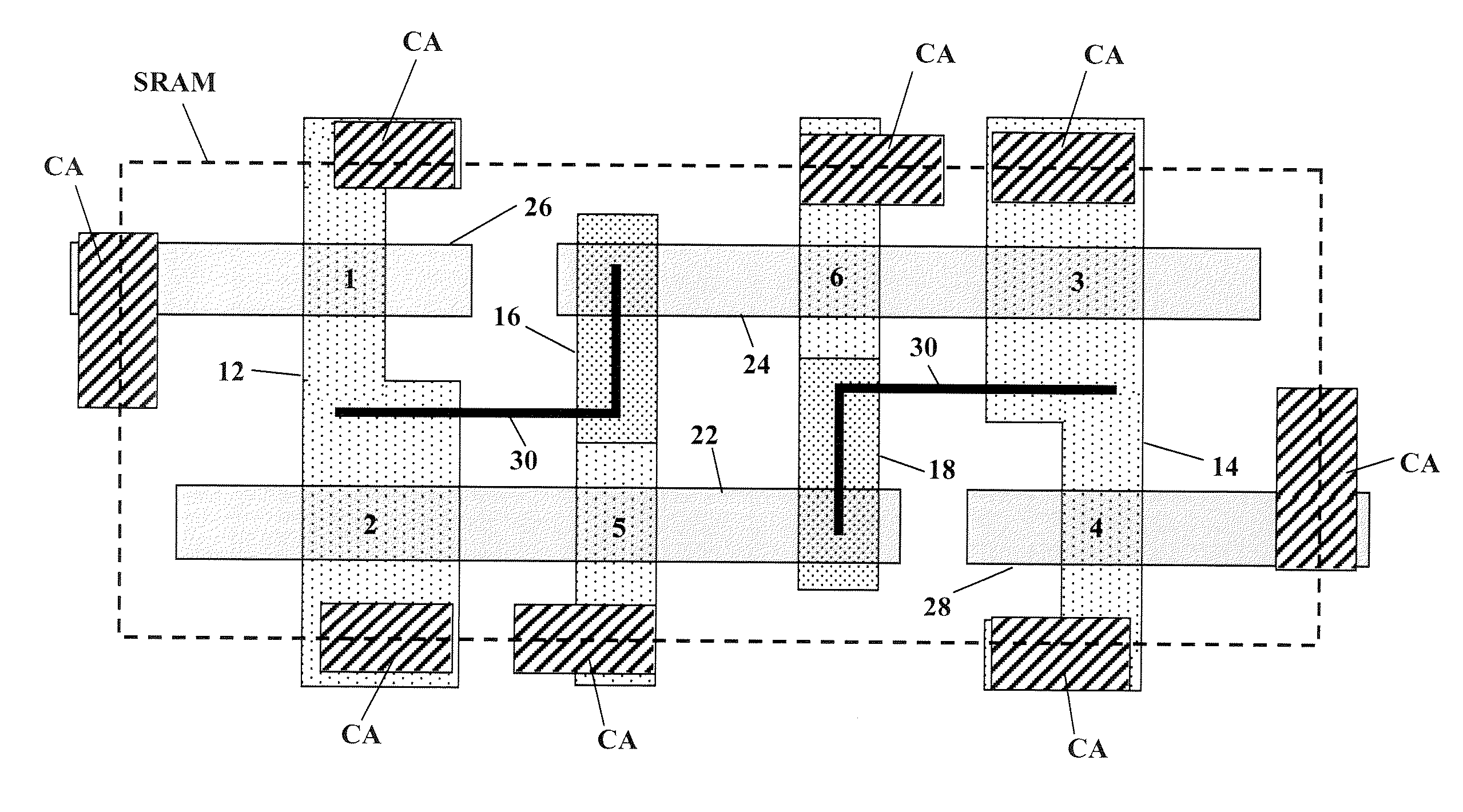

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

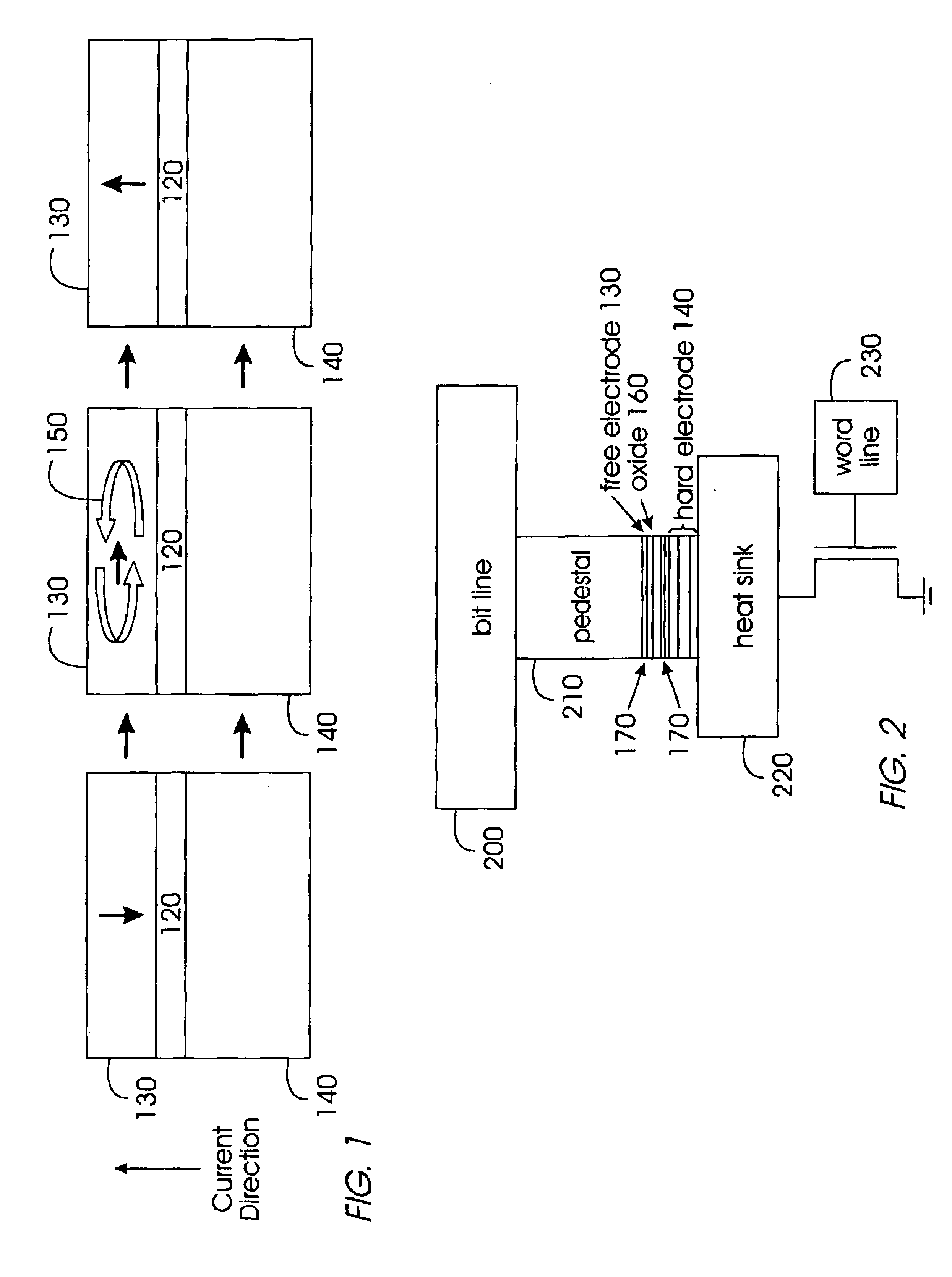

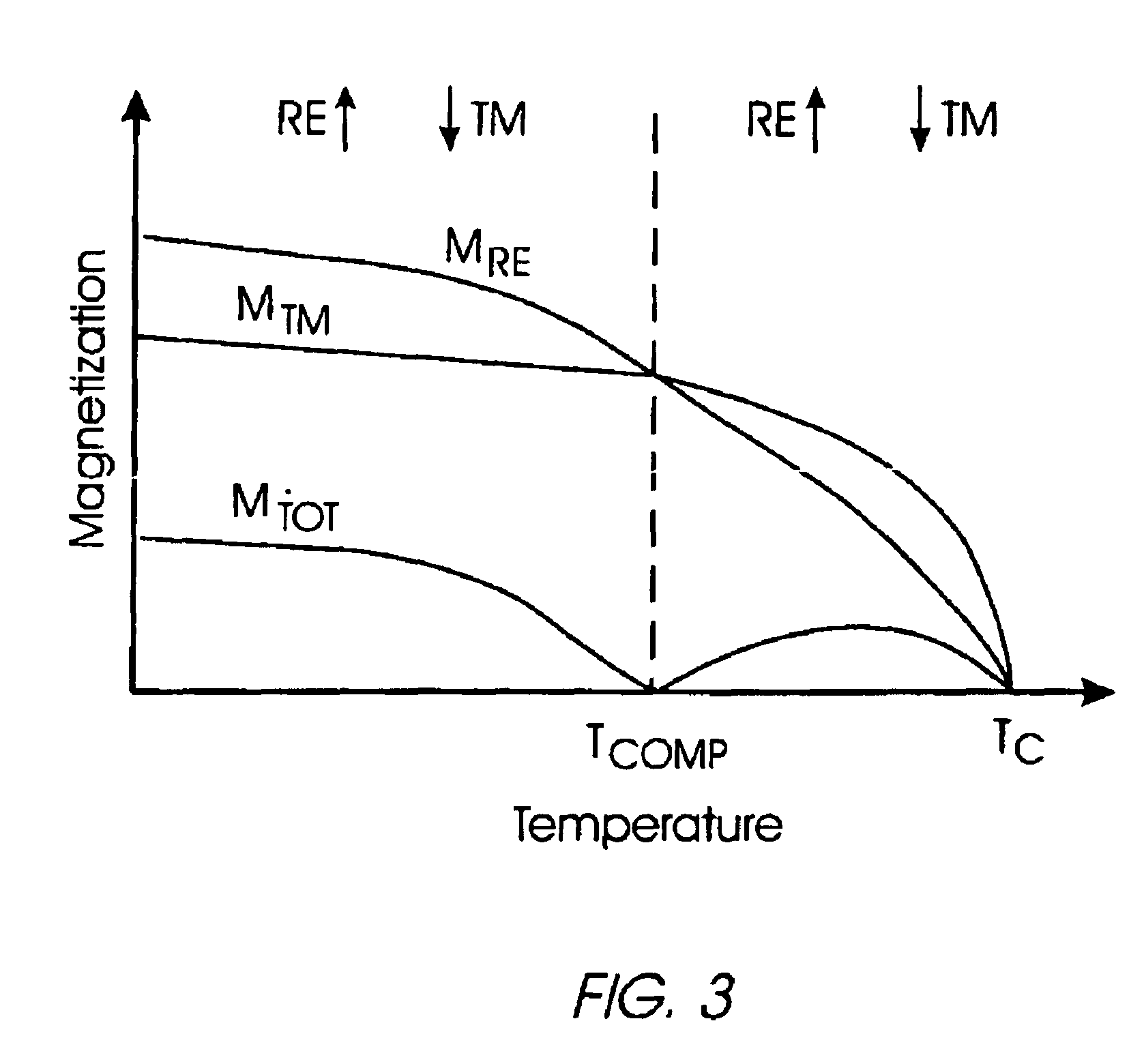

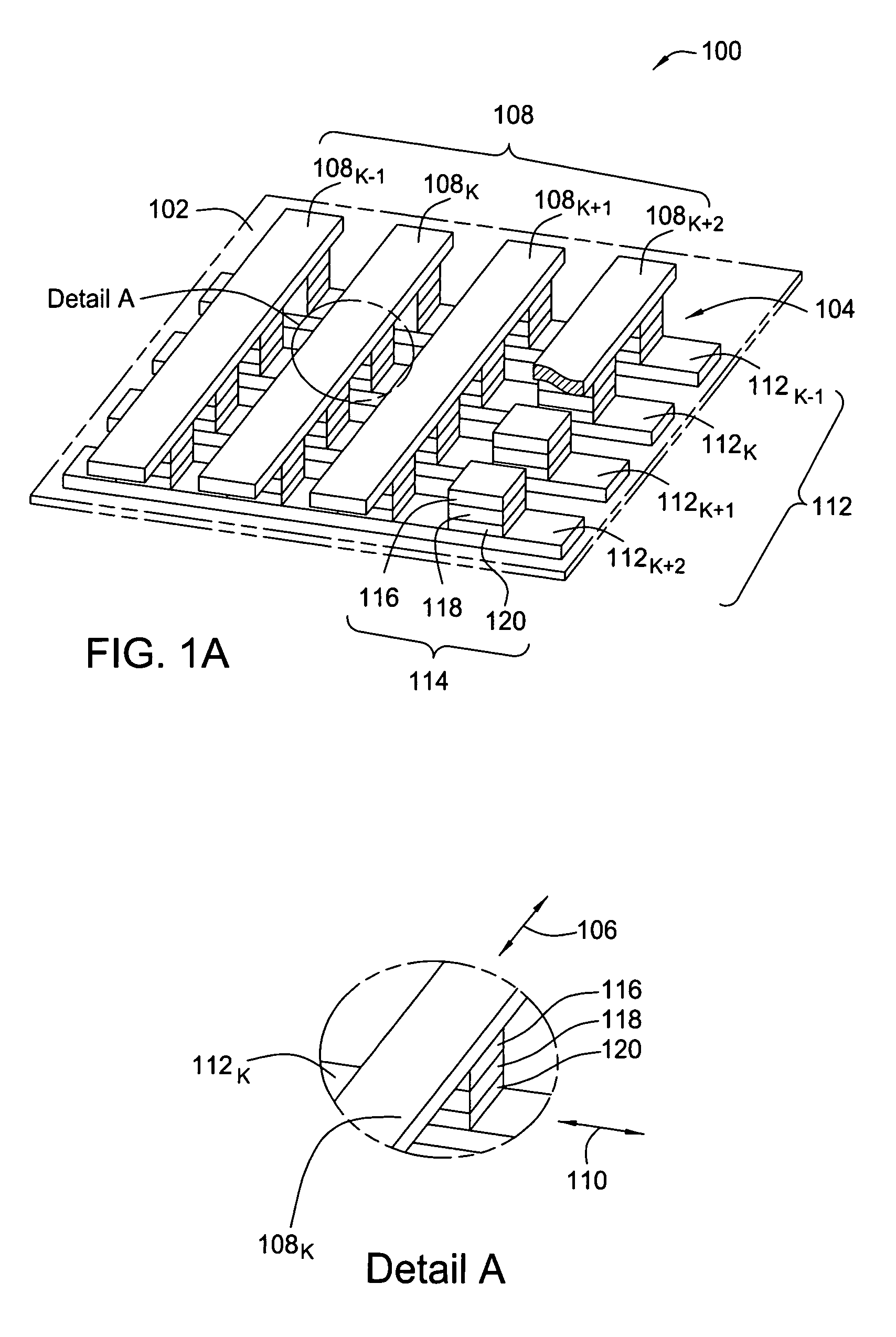

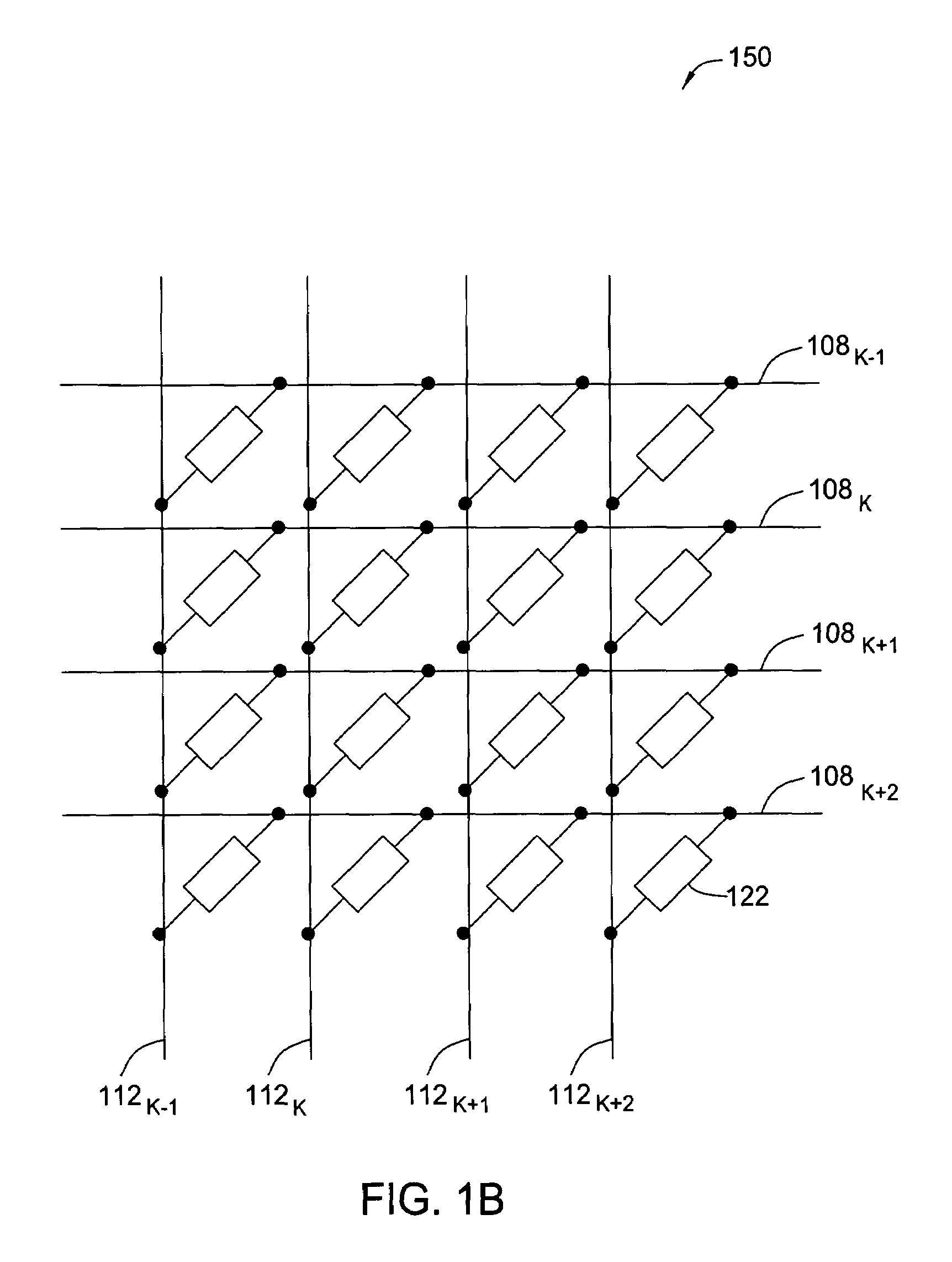

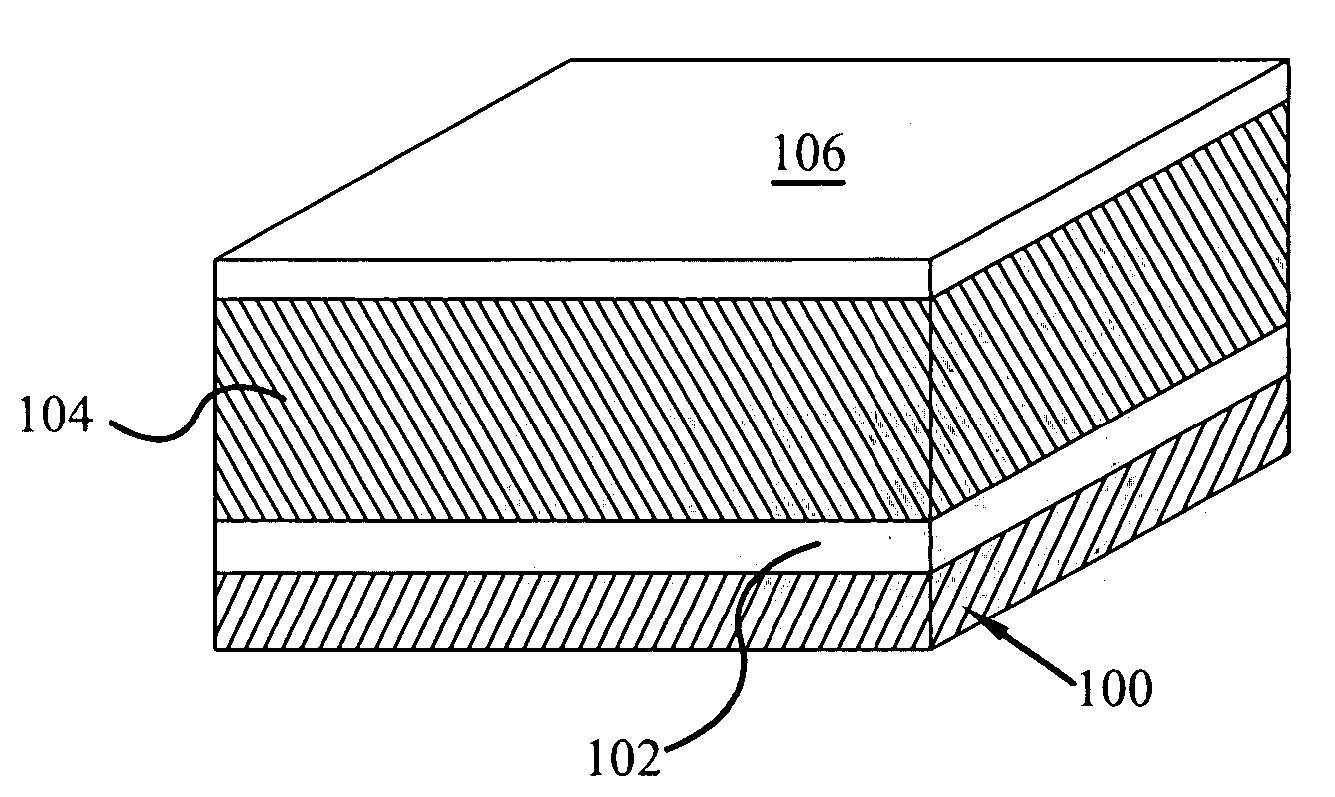

Thermally-assisted magnetic random access memory (MRAM)

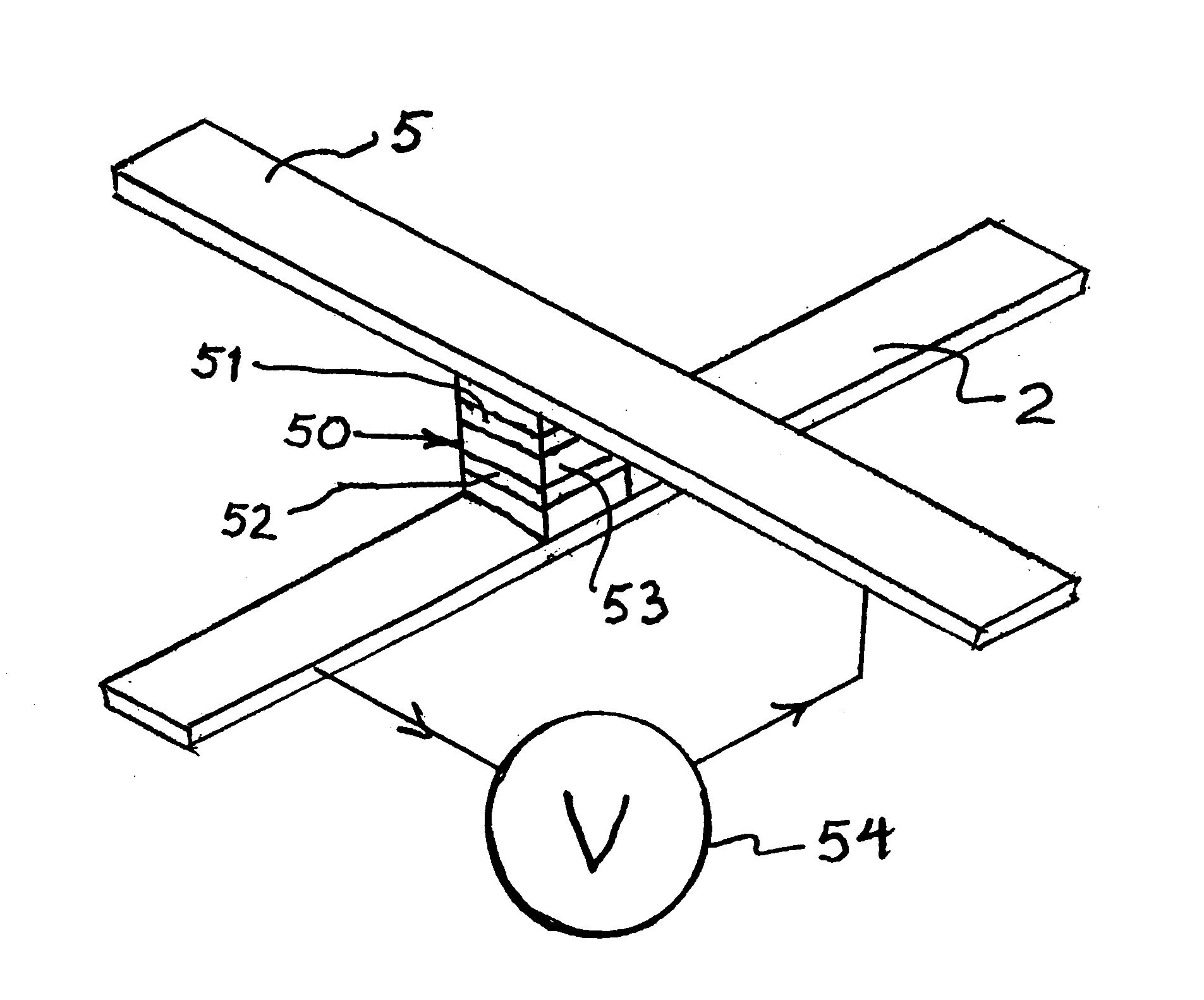

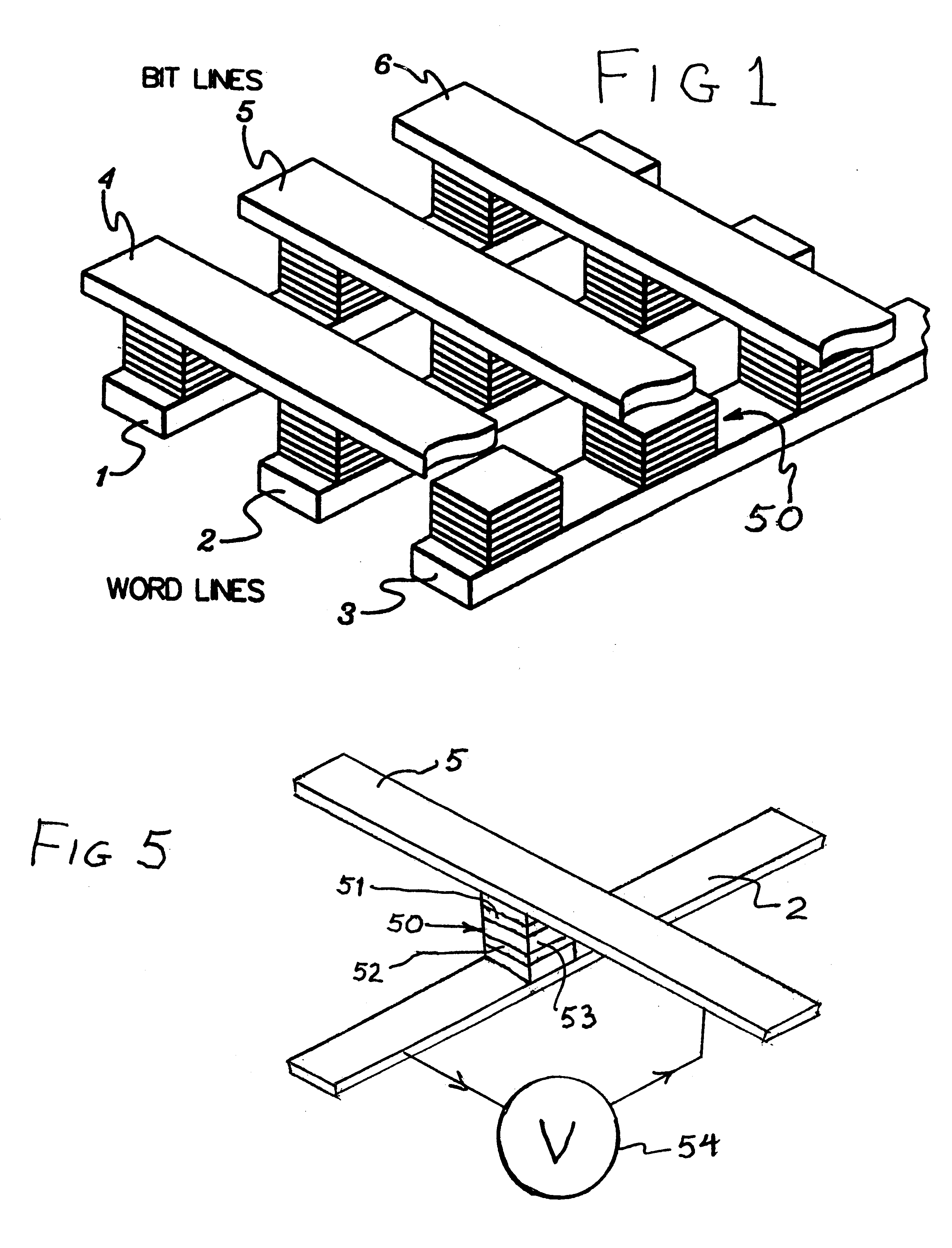

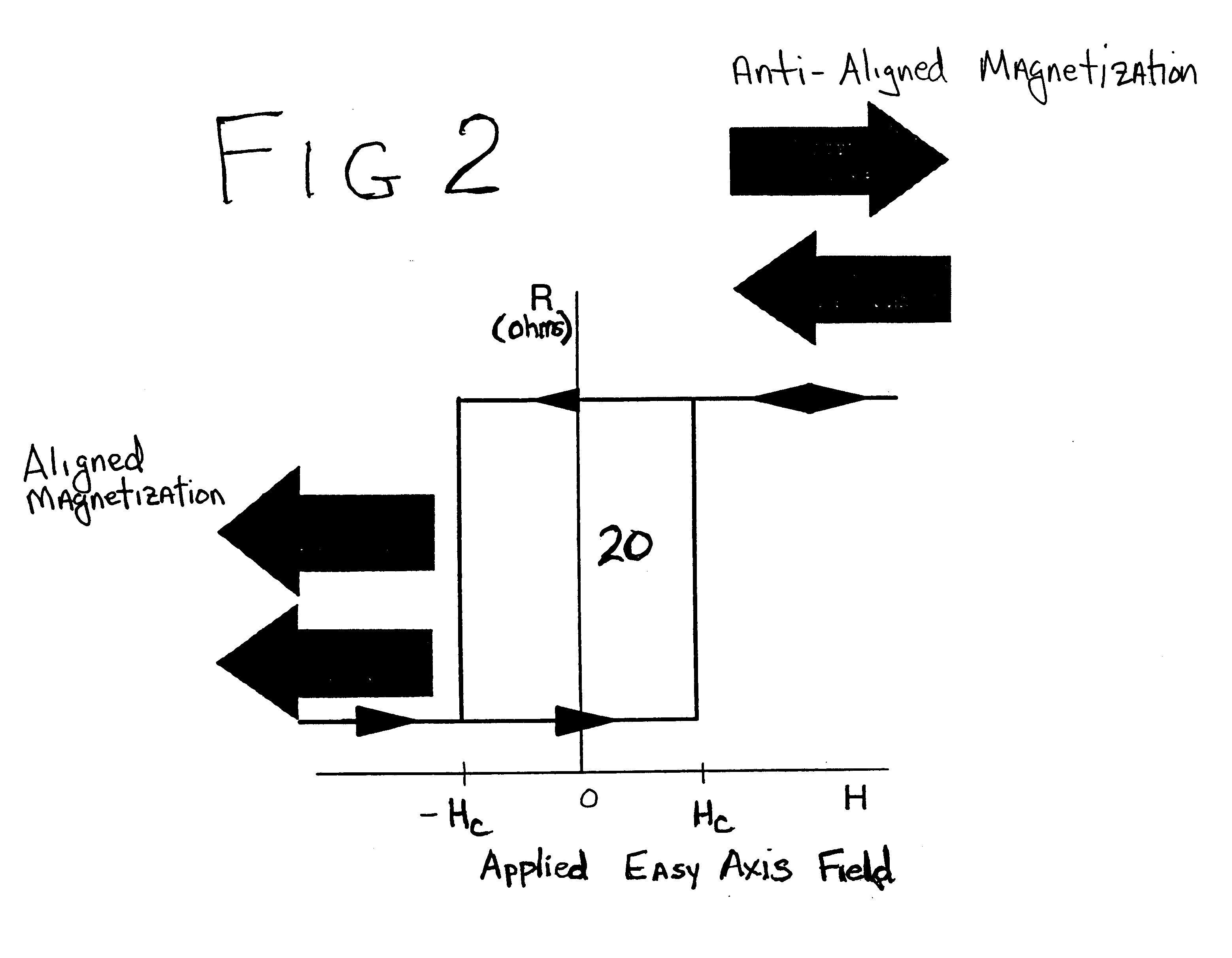

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

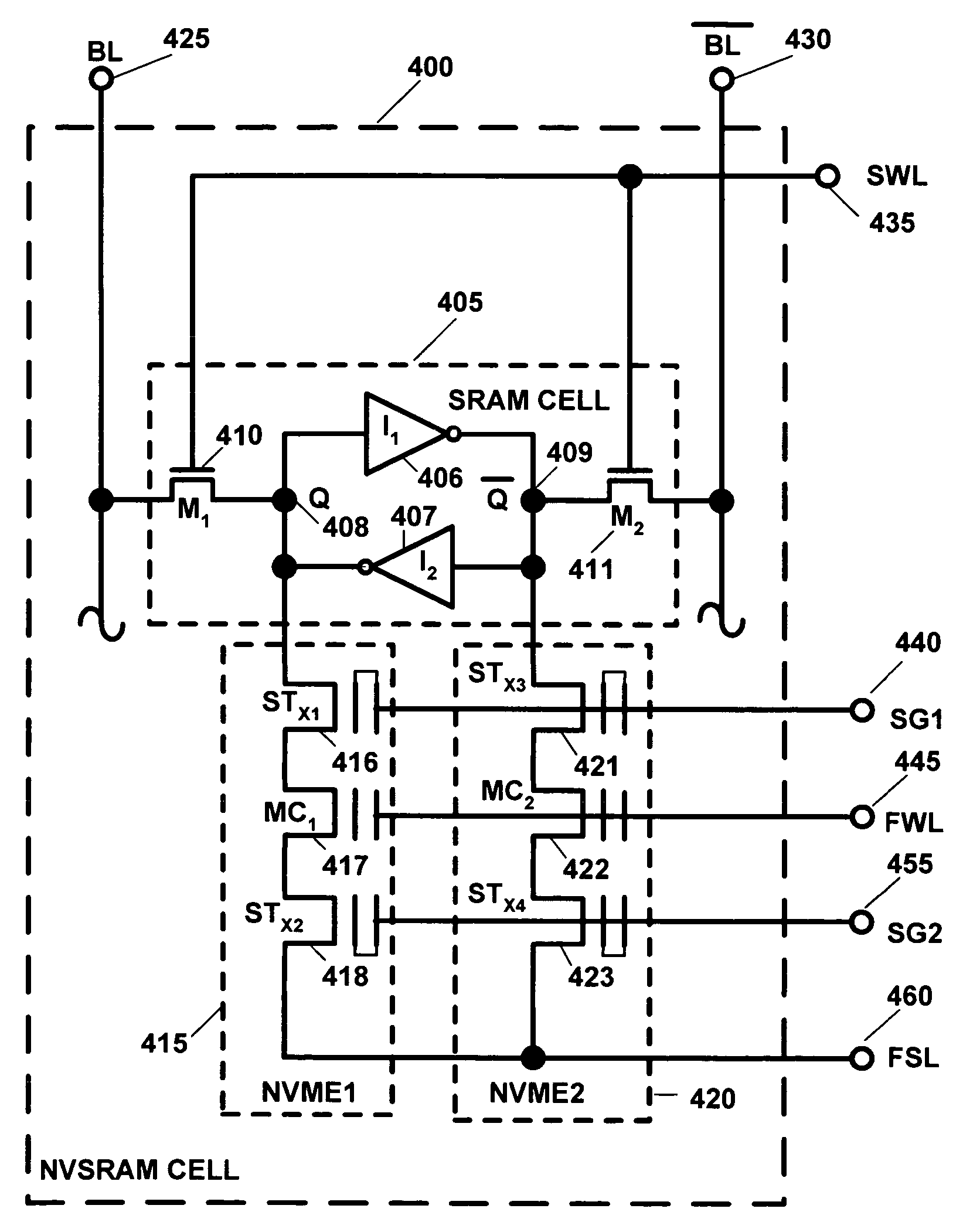

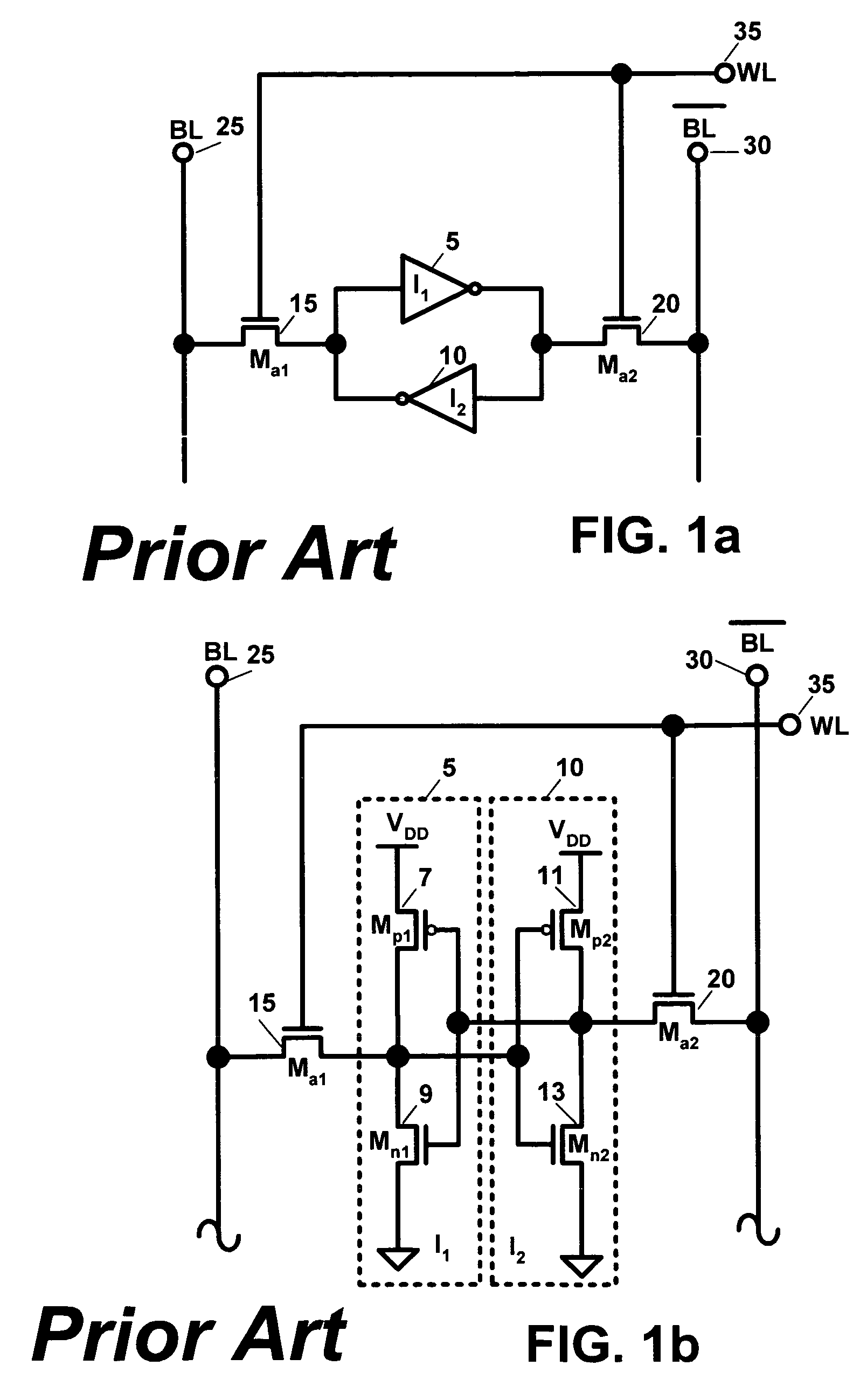

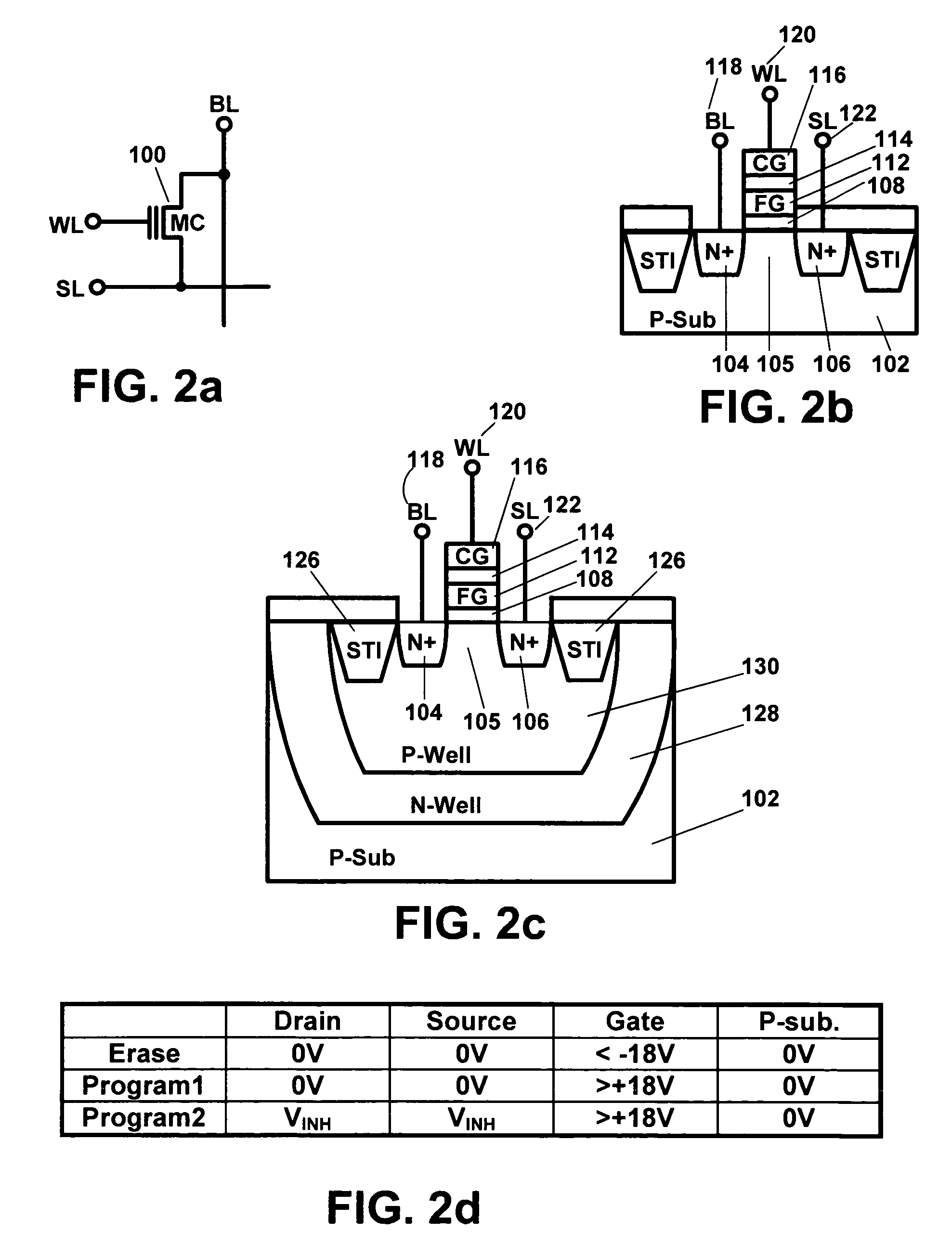

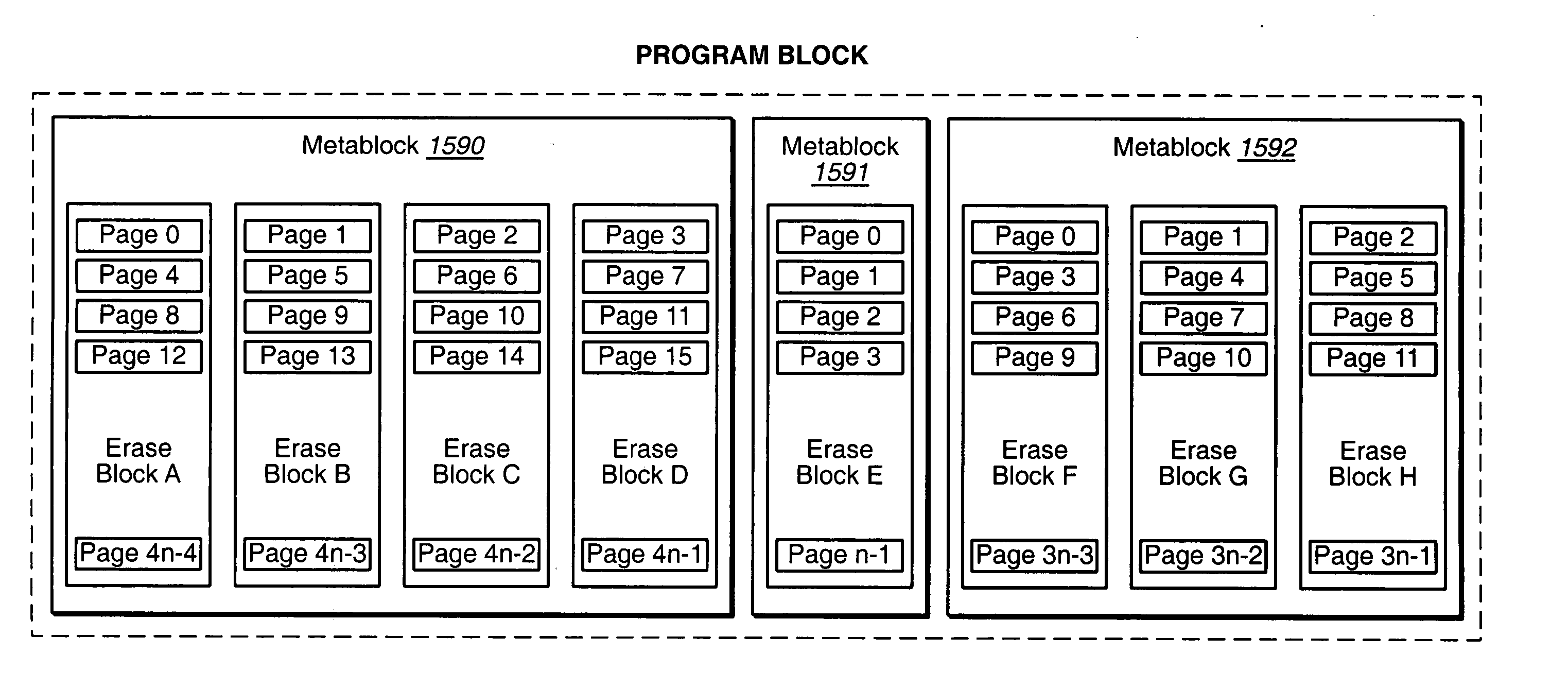

NVRAM memory cell architecture that integrates conventional SRAM and flash cells

A nonvolatile SRAM array has an array of integrated nonvolatile SRAM circuits arranged in rows and columns on a substrate. Each of the integrated nonvolatile SRAM circuits includes an SRAM cell, a first and second nonvolatile memory element. The SRAM cell has a latched memory element in communication first and second nonvolatile memory elements to receive and permanently retain the digital signal from the latched memory element. A power detection circuit detects a power interruption and a power initiation and communicates the detection of the power interruption and power initiation to the plurality of integrated nonvolatile SRAM circuits. The SRAM cell, upon detection of the power interruption, transmits the digital signal to the first and second nonvolatile memory elements. The SRAM cell of each of the nonvolatile static random access memories upon detection of the power initiation, receives the digital signal from the first and second nonvolatile memory elements.

Owner:ABEDNEJA ASSETAB L L C

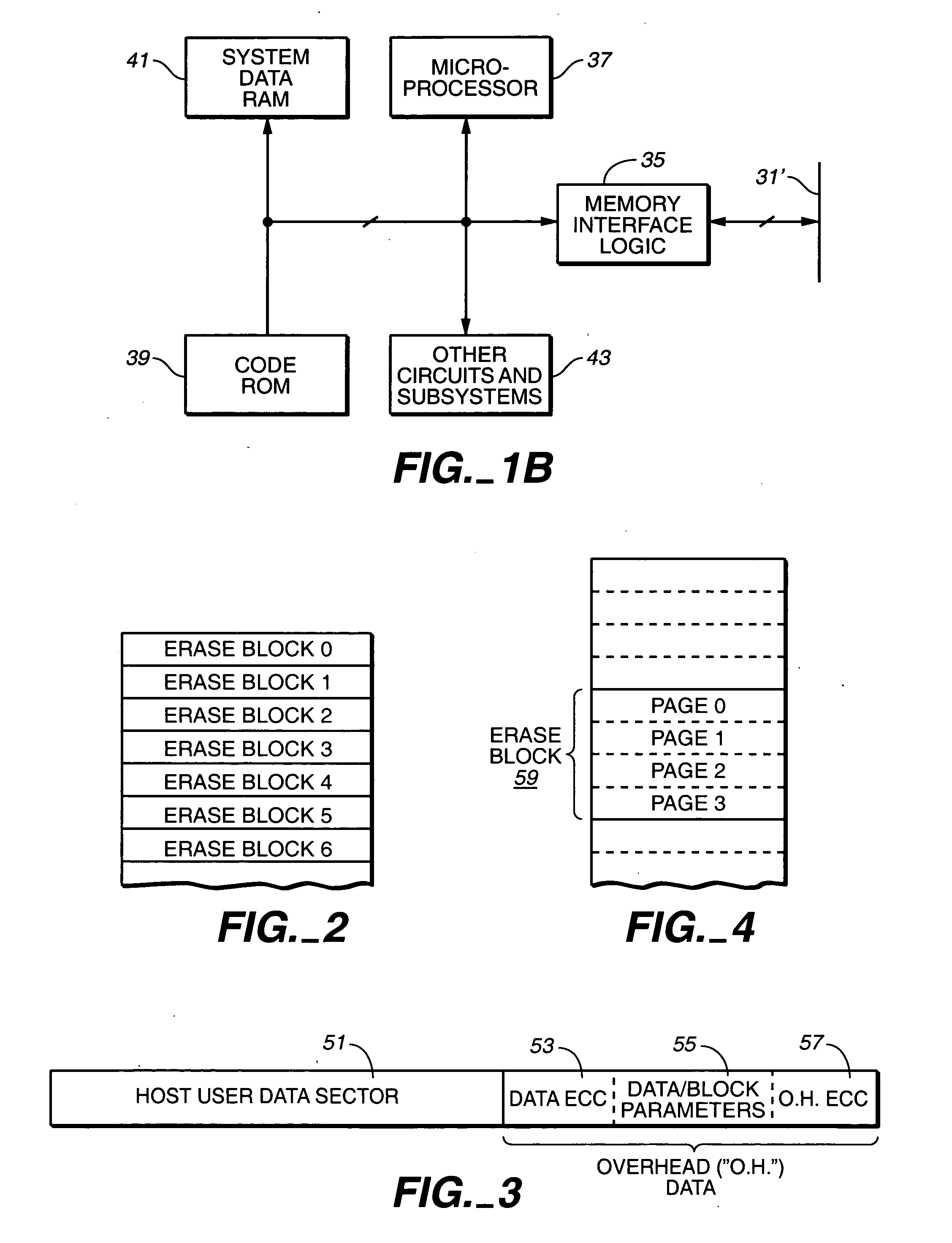

Data boundary management

InactiveUS20050144363A1Reduce the impactReduce impactMemory architecture accessing/allocationMemory adressing/allocation/relocationStatic random-access memoryRandom access memory

Data may be stored in a non-volatile memory array in adaptive metablocks that are configured according to the locations of data boundaries in the data. Data may be stored in an intermediate format and later copied to adaptive metablocks configured for the data. Data in intermediate format may be stored in non-volatile random access memory or in a portion of the non-volatile memory array.

Owner:SANDISK TECH LLC

Resistive random access memory and method for manufacturing the same

ActiveUS20100112810A1Improve the immunityReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesStatic random-access memoryRandom access memory

A resistive random access memory including, an insulating layer, a hard mask layer, a bottom electrode, a memory cell and a top electrode is provided. The insulating layer is disposed on the bottom electrode. The insulating layer has a contact hole having a first width. The hard mask layer has an opening. A portion of the memory cell is exposed from the opening and has a second width smaller than the first width. The top electrode is disposed on the insulating layer and is coupled with the memory cell.

Owner:MACRONIX INT CO LTD

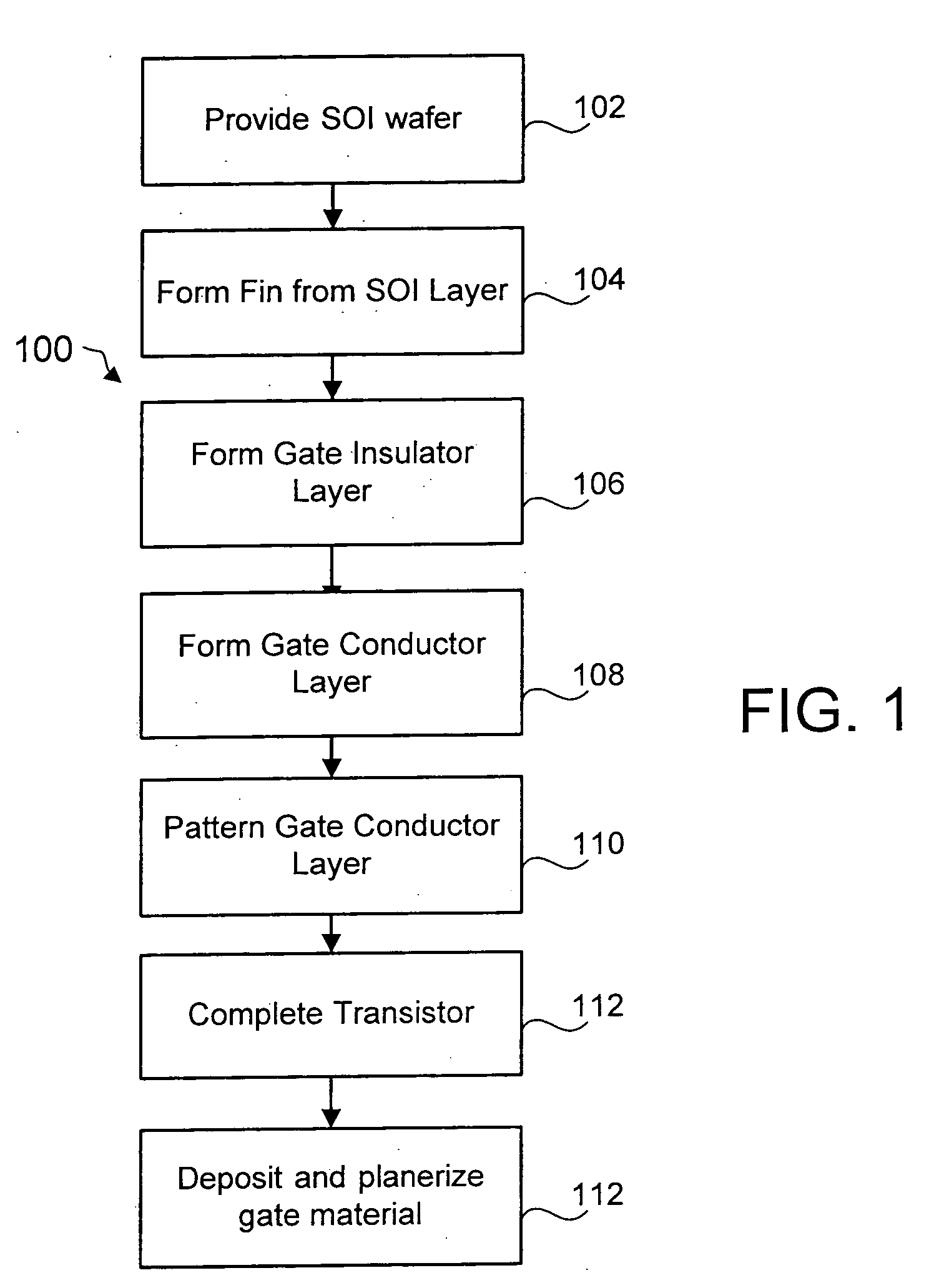

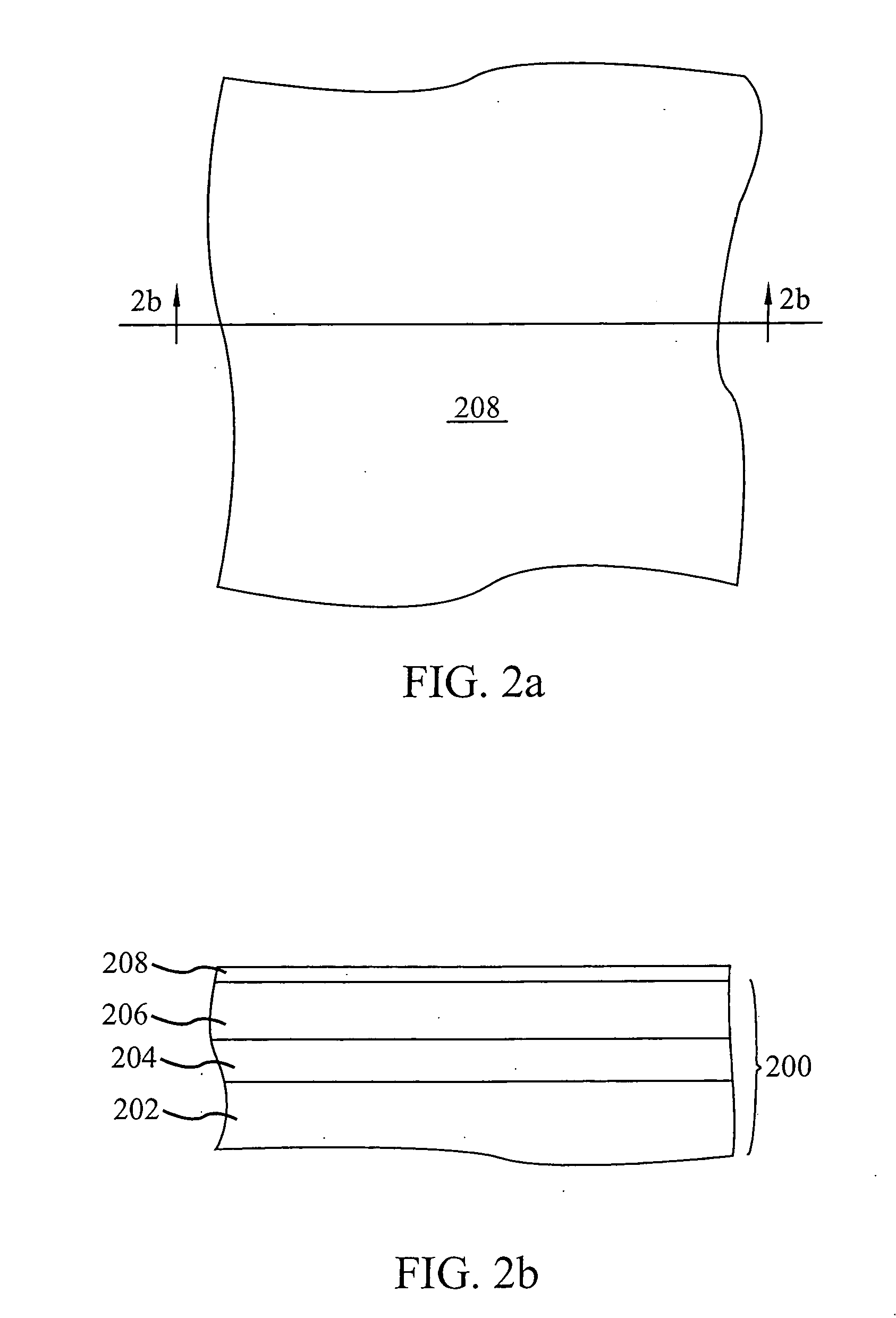

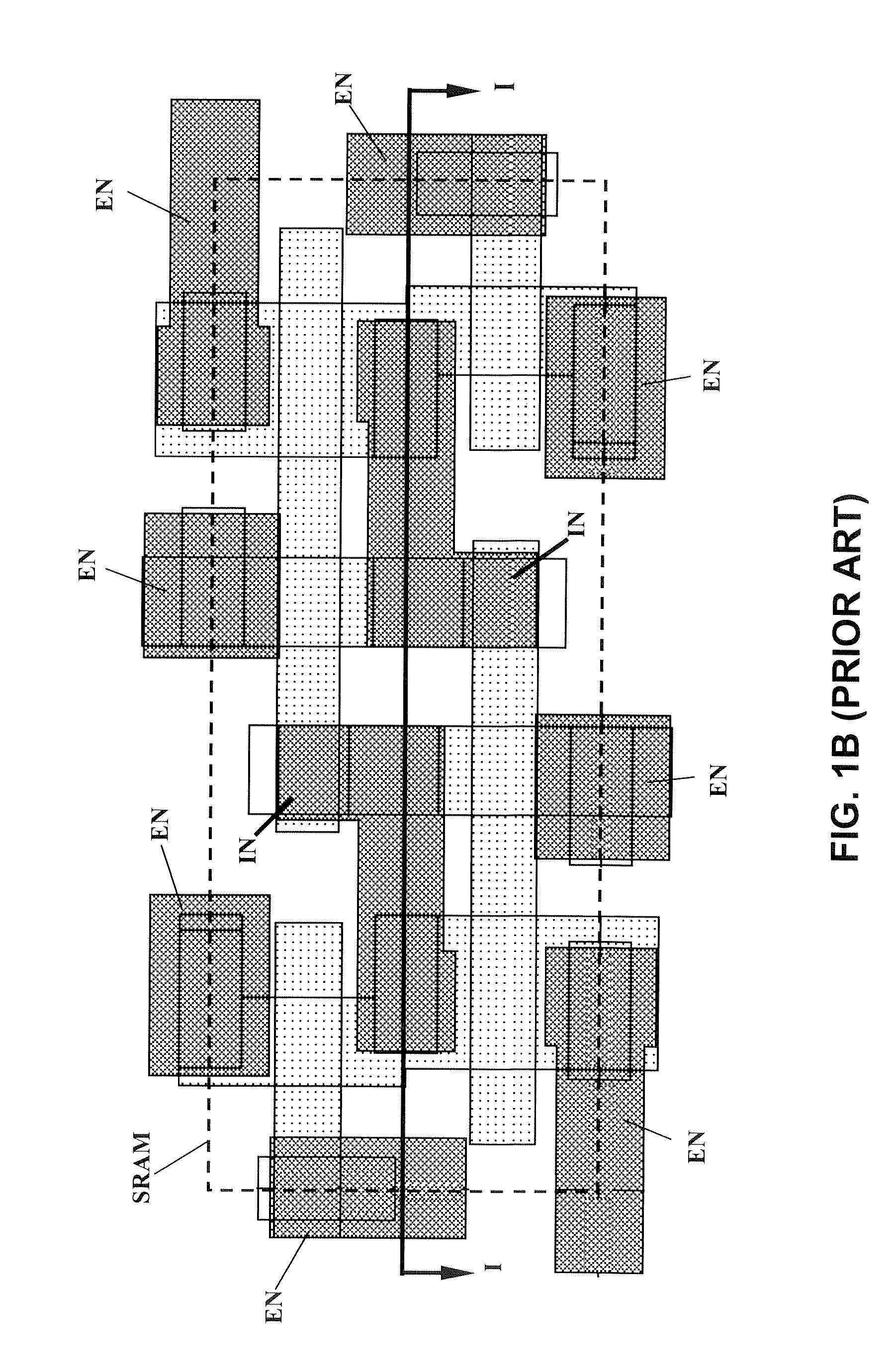

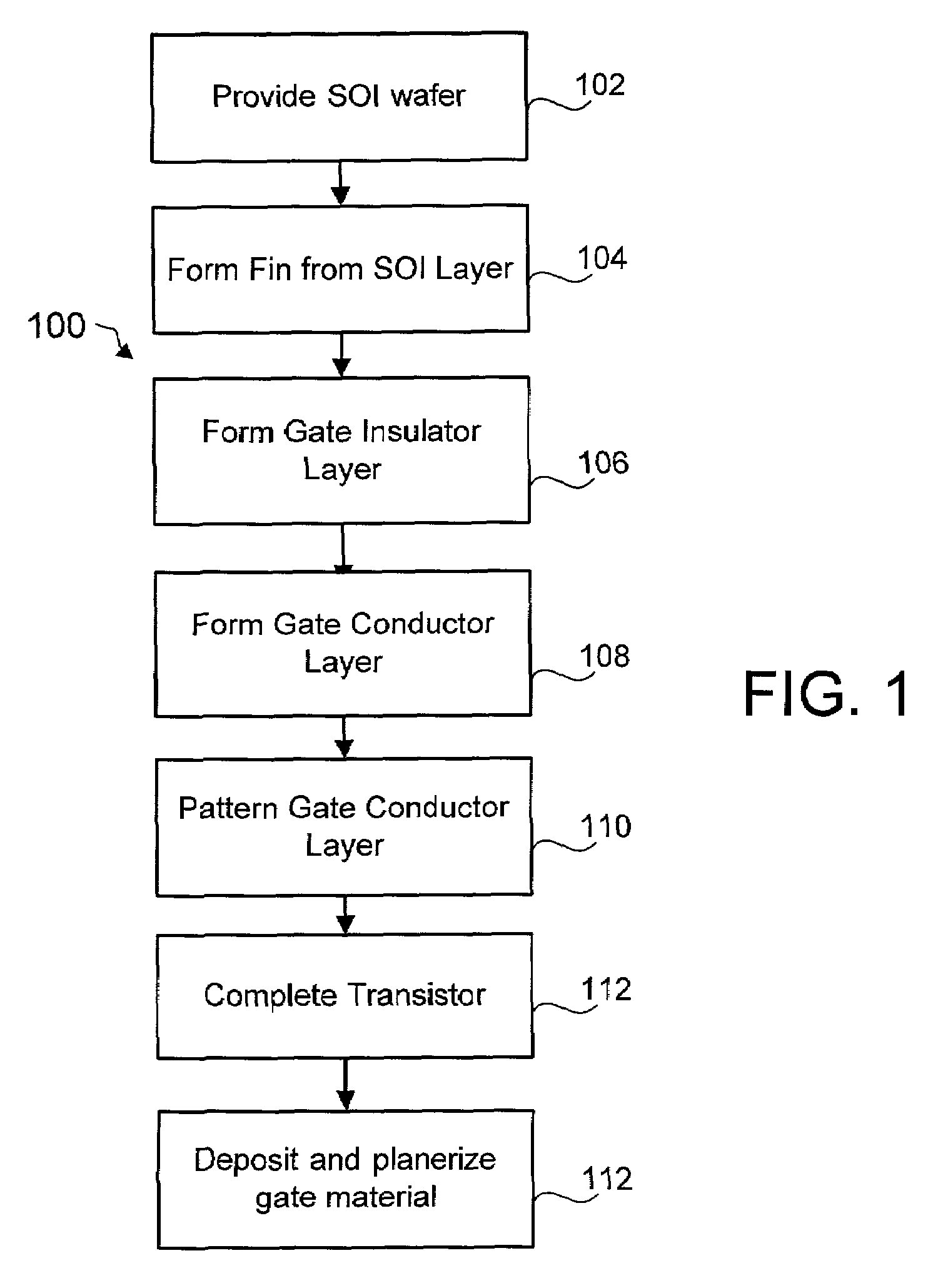

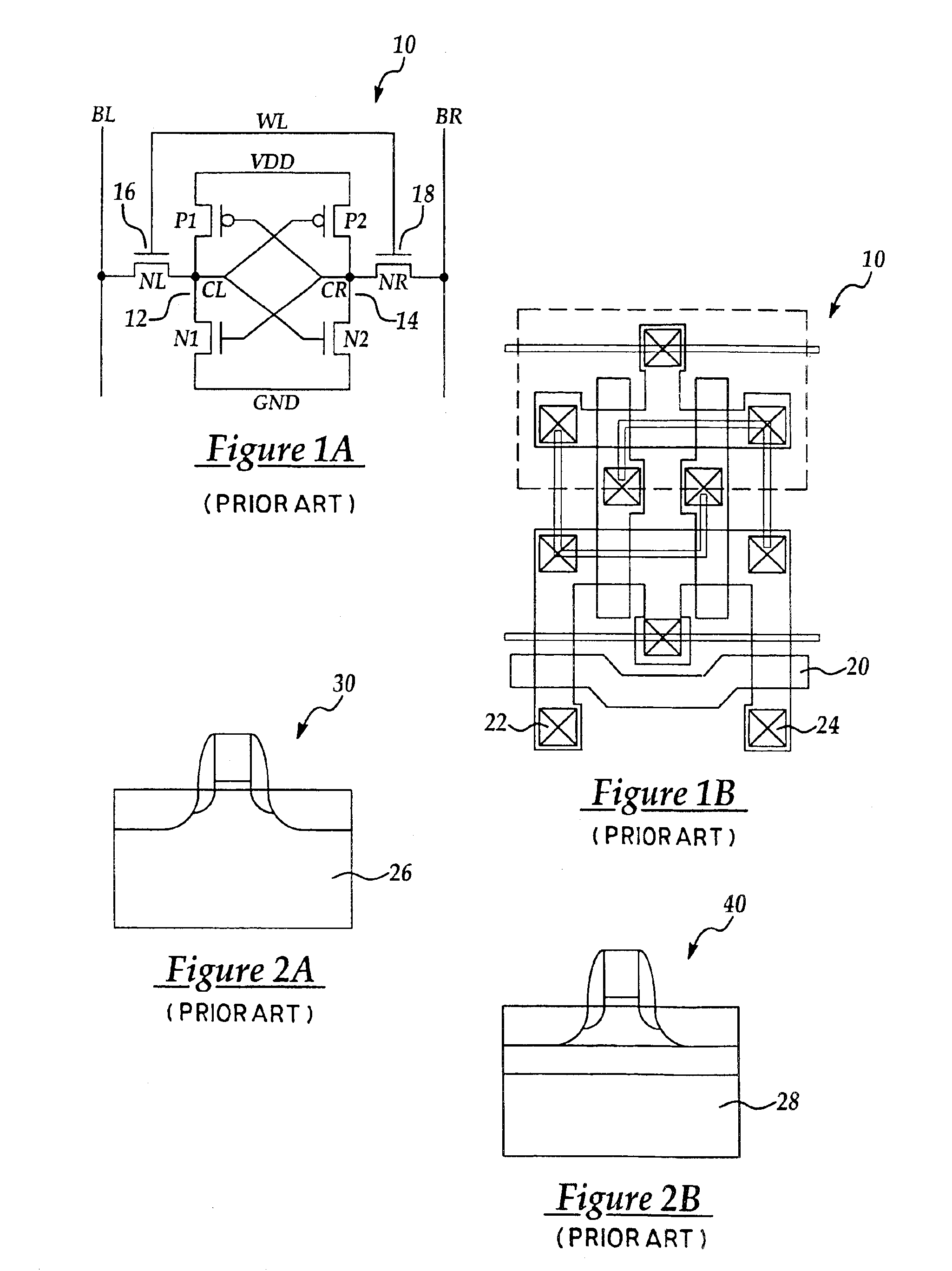

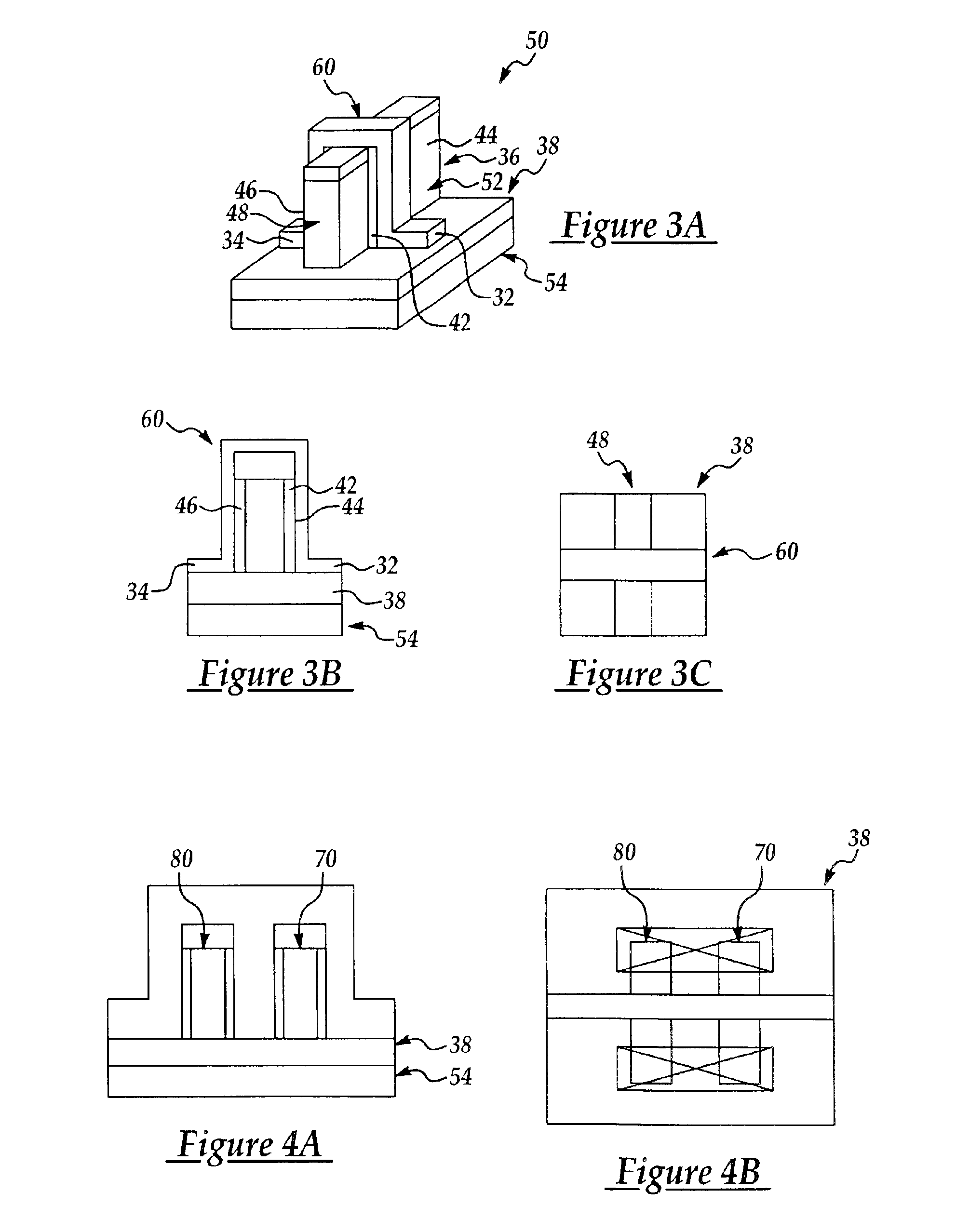

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS20050121676A1High gainAccurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation

Owner:GLOBALFOUNDRIES INC

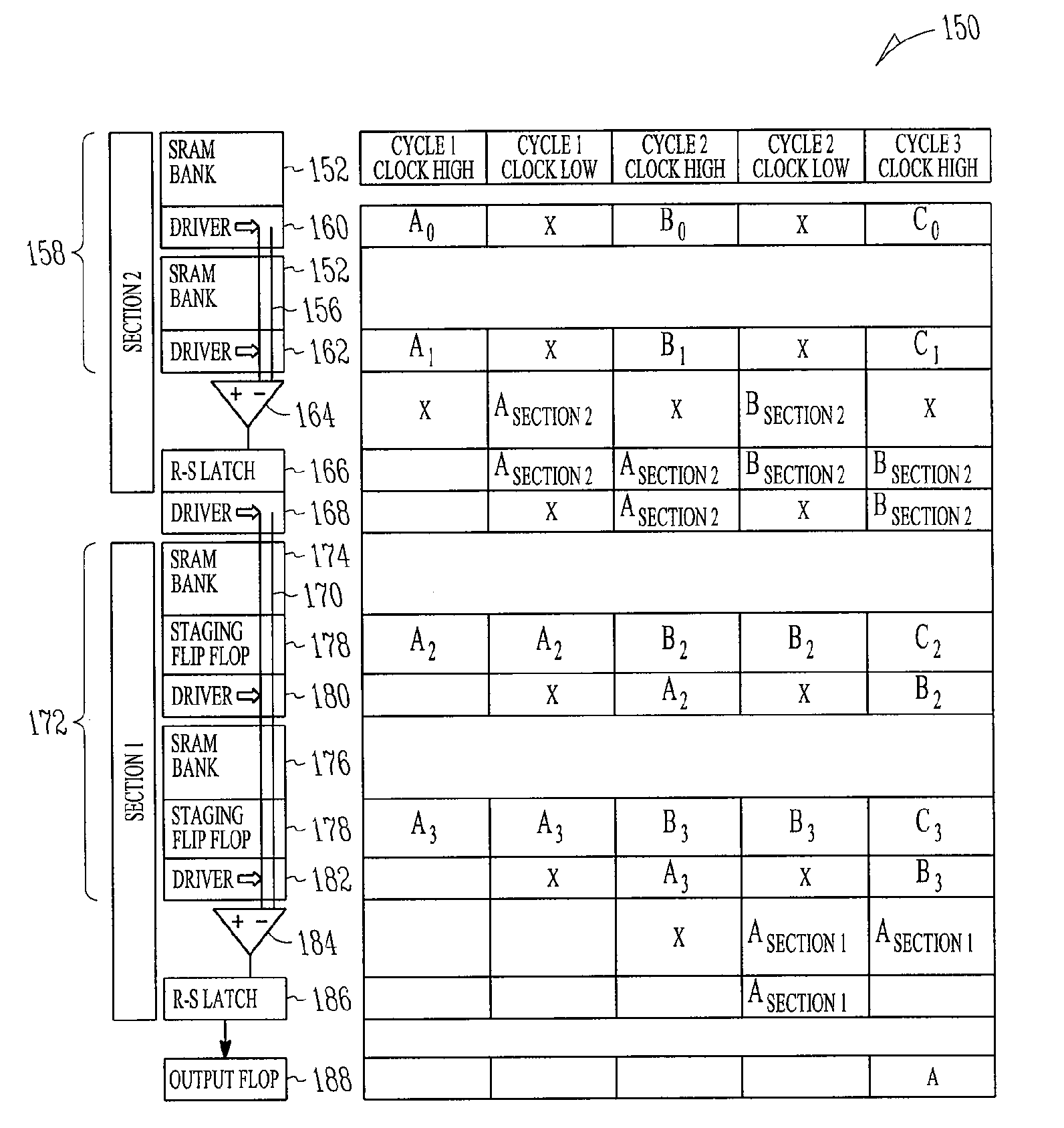

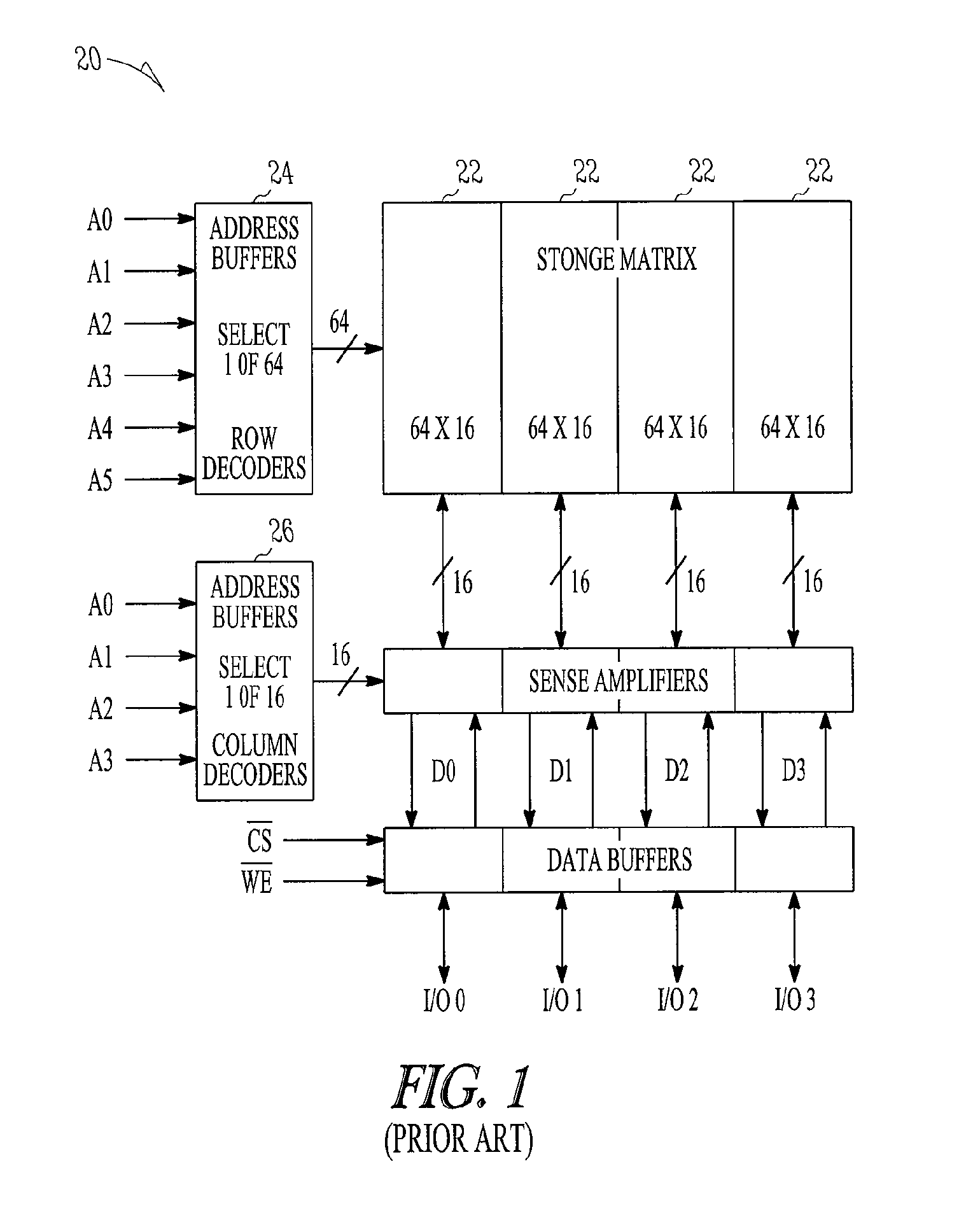

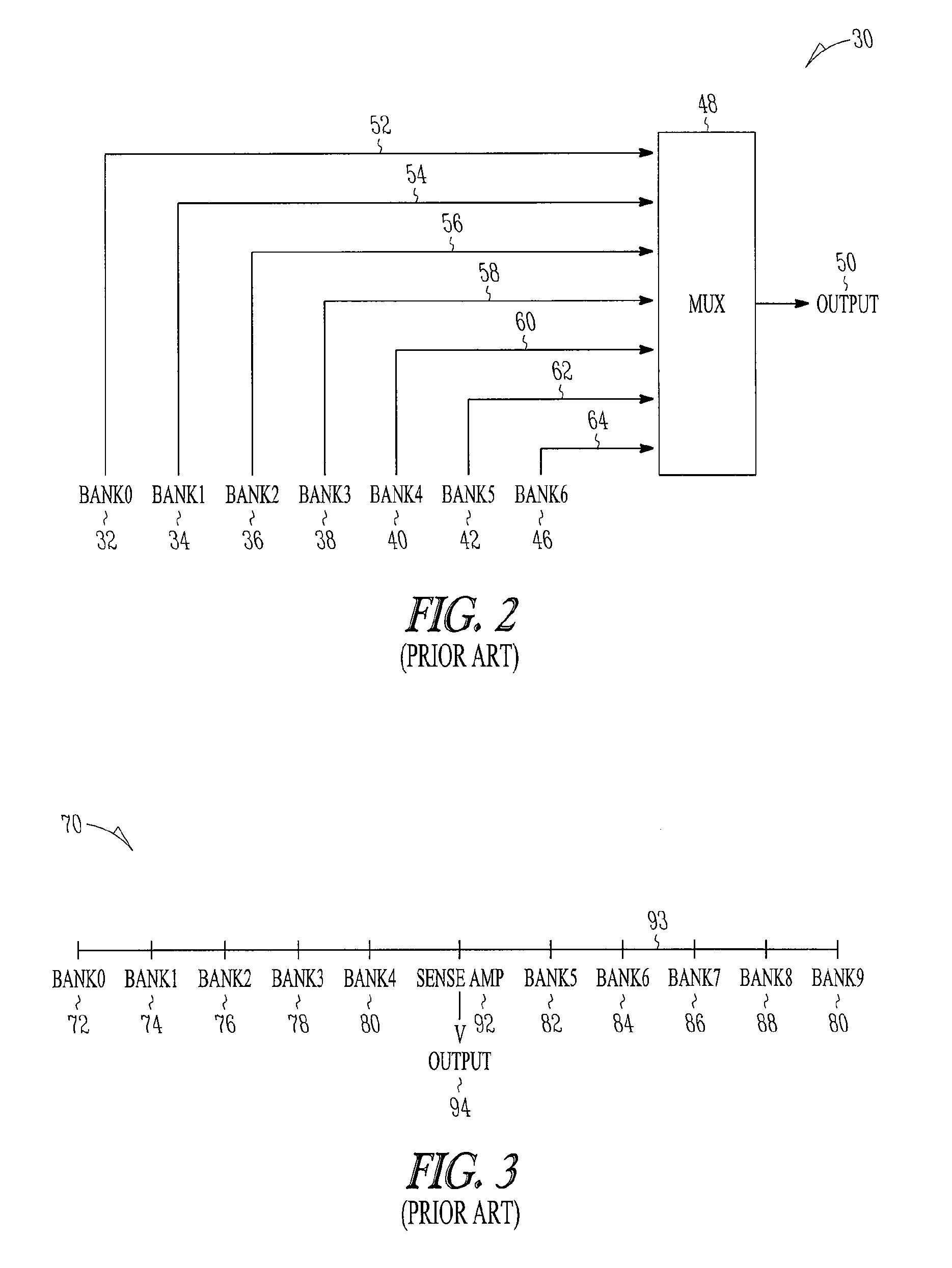

Static random access memory architecture

An architecture for a semiconductor static random access memory (SRAM) is described. In one example, a first set or group or stage of SRAM banks are coupled to a first data bus formed using bit line pairs, and a second set or group or stage of SRAM banks are coupled to a second data bus formed using other bit line pairs. The number of banks coupled to each bit line pair is determined by the SRAM's operating frequency and size. Each data bus is coupled to a sense amplifier. The output from the sense amplifier is then coupled to the bit line pair of a group of SRAM banks. This adjacent group has staging logic coupled to each SRAM bank to store the output of the SRAM bank until the contents from the first group is placed on the bit line of the adjacent stage of SRAM banks. The output from either the first stage or from one of the SRAM banks in the adjacent stage's SRAM banks, which had been stored in the adjacent stage's staging logic, is driven to the sense amplifier coupled to the adjacent stage. Successive stages of SRAM banks can be coupled together until an arbitrary number of stages of SRAM banks have been coupled together.

Owner:CISCO TECH INC

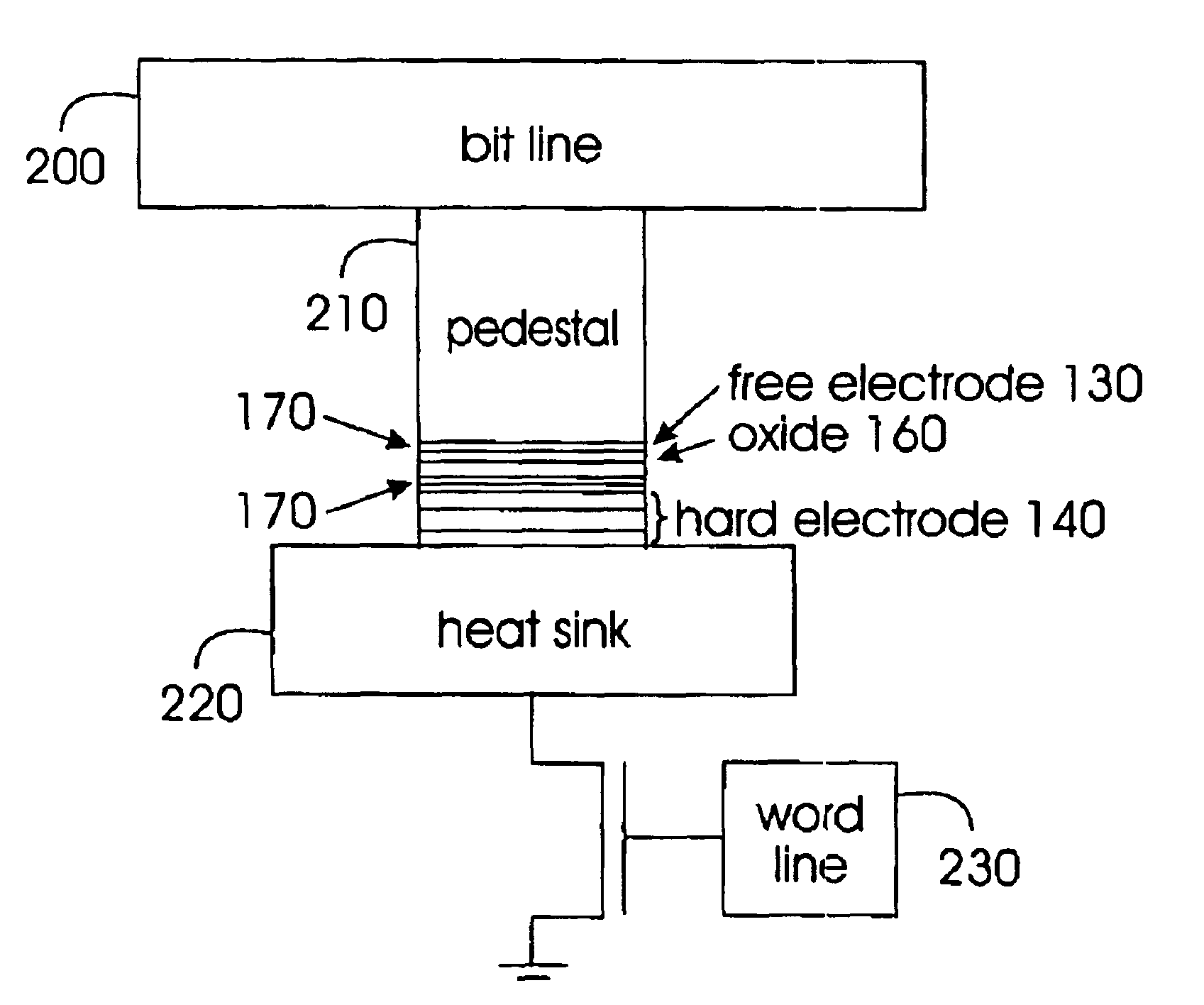

Thermally-assisted magnetic writing using an oxide layer and current-induced heating

InactiveUS6771534B2Increase in sizeIncrease in coercivityNanostructure applicationNanomagnetismElectrical resistance and conductanceElectrical conductor

A method and structure for a non-volatile magnetic random access memory (MRAM) device that has a stable magnetic electrode, an oxide layer adjacent the stable magnetic electrode, and a free magnetic electrode. The oxide layer is between the stable magnetic electrode and the free magnetic electrode. In the invention, a conductor is connected to a stable magnetic electrode. The oxide layer has a resistance at levels to allow sufficient power dissipation to lower the anisotropy of the free magnetic electrode through current induced heating. Current-induced heating is used in combination with spin-transfer torque or a magnetic field to switch the free magnetic electrode.

Owner:GLOBALFOUNDRIES U S INC

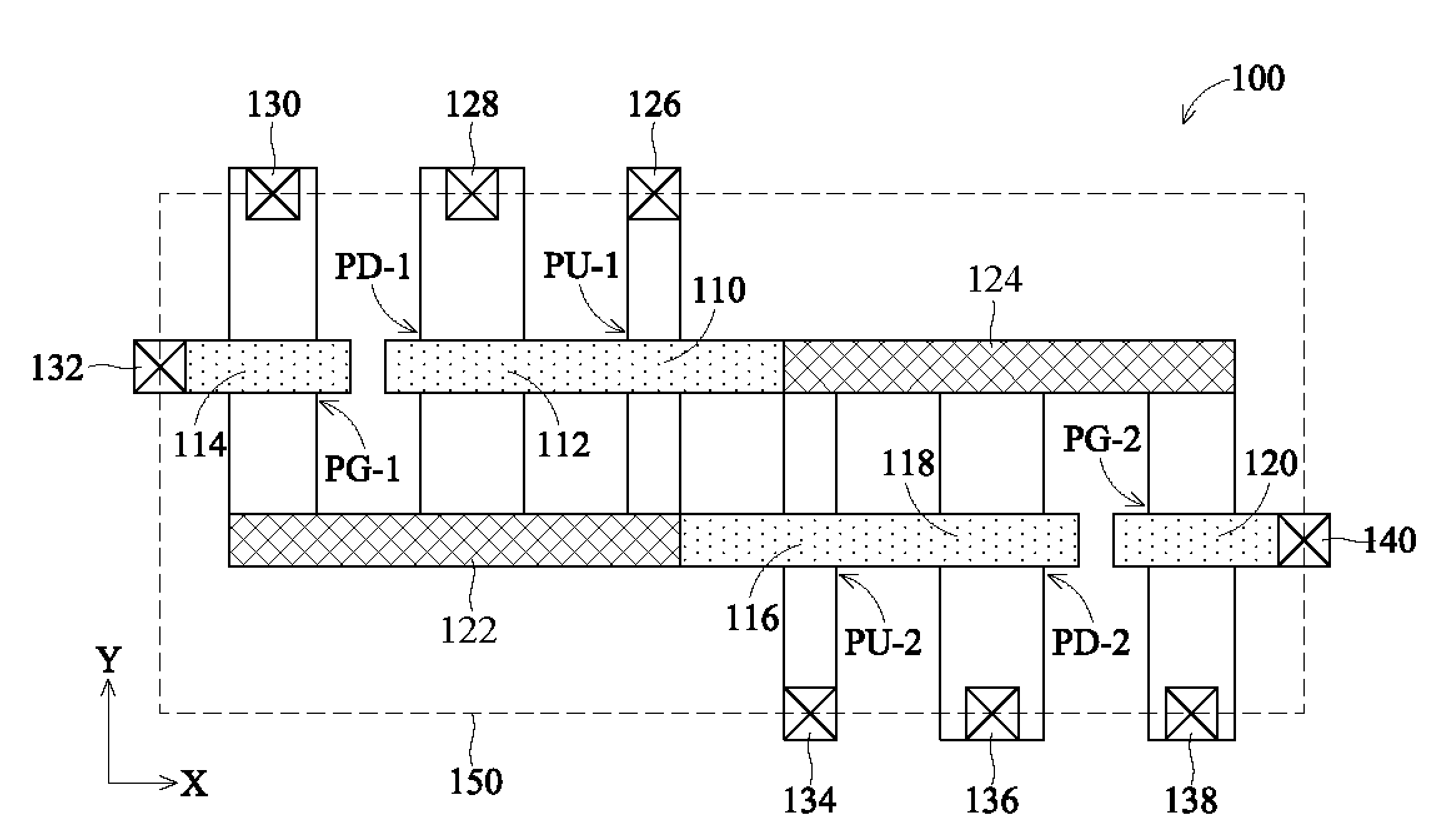

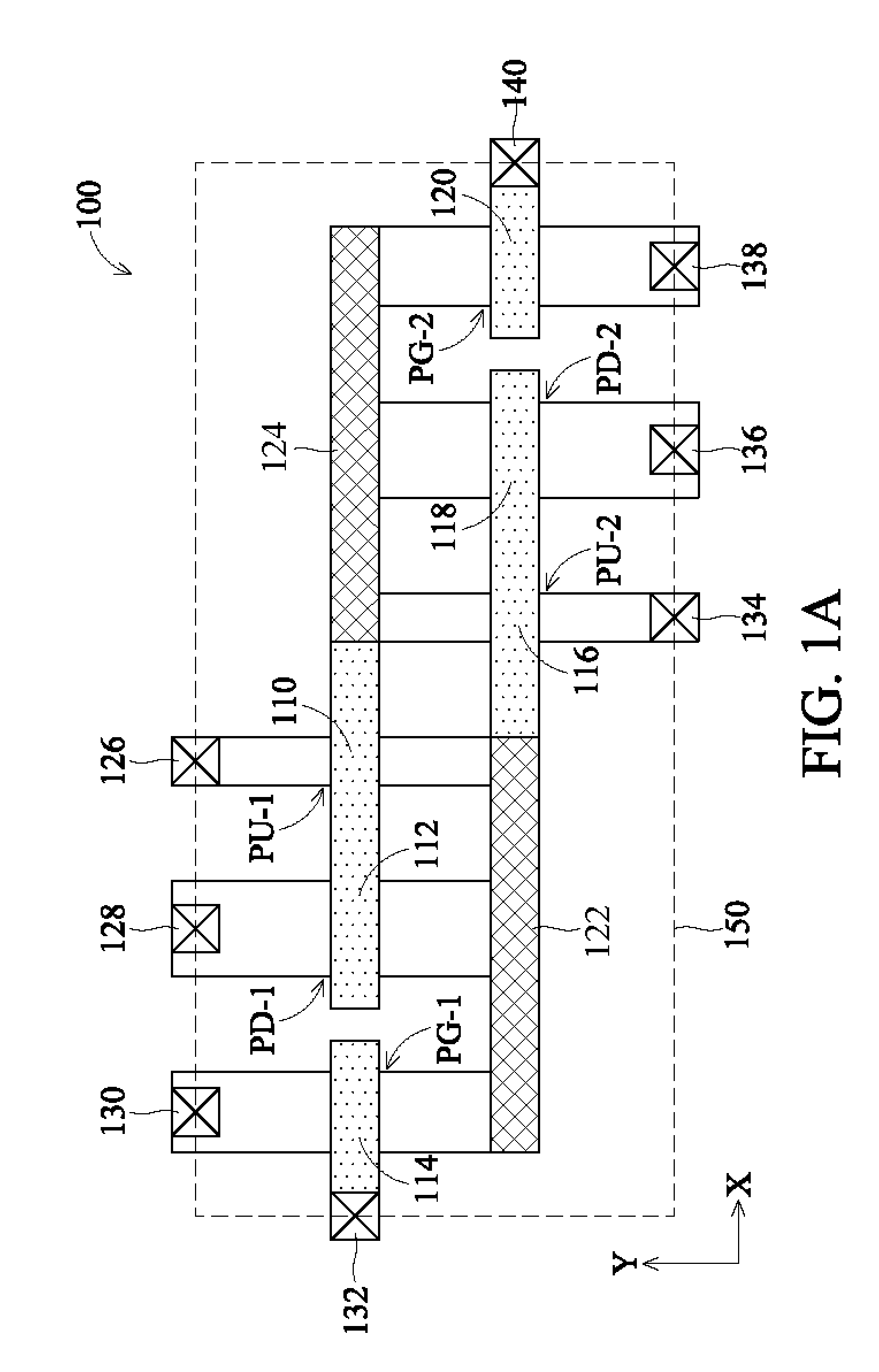

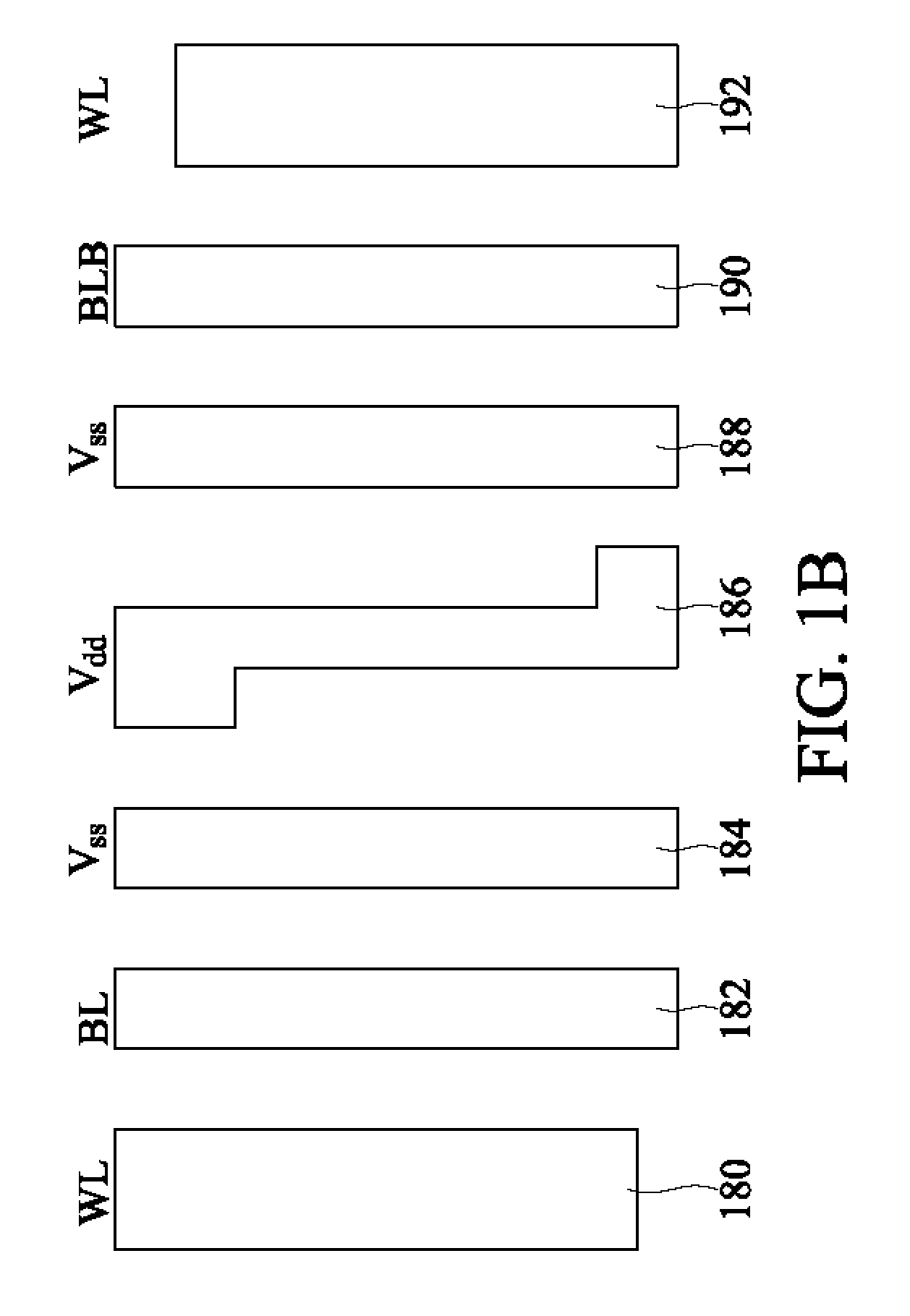

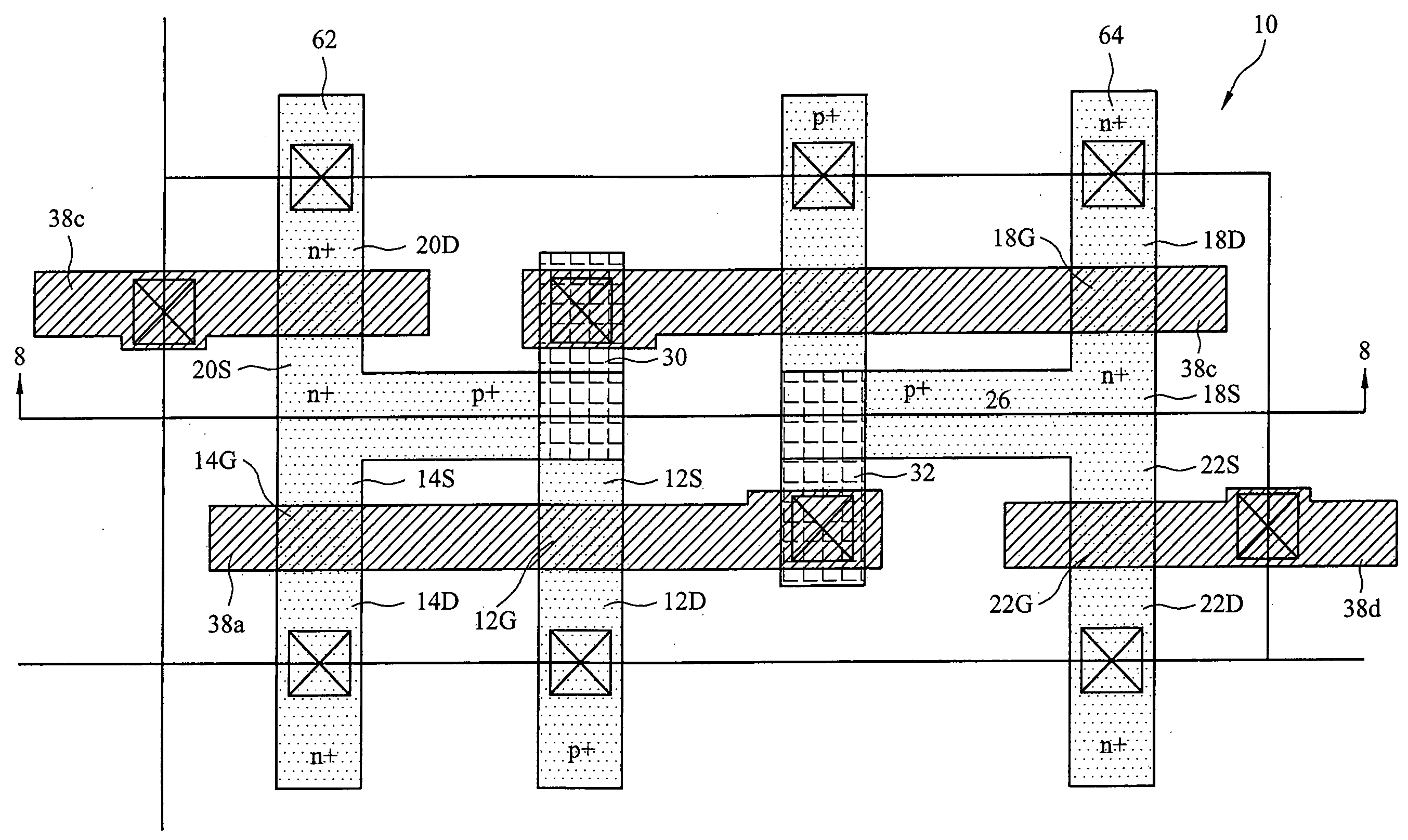

Static random access memory (SRAM) cell and method for forming same

InactiveUS8004042B2High densitySmall sizeTransistorSolid-state devicesStatic random-access memoryRandom access memory

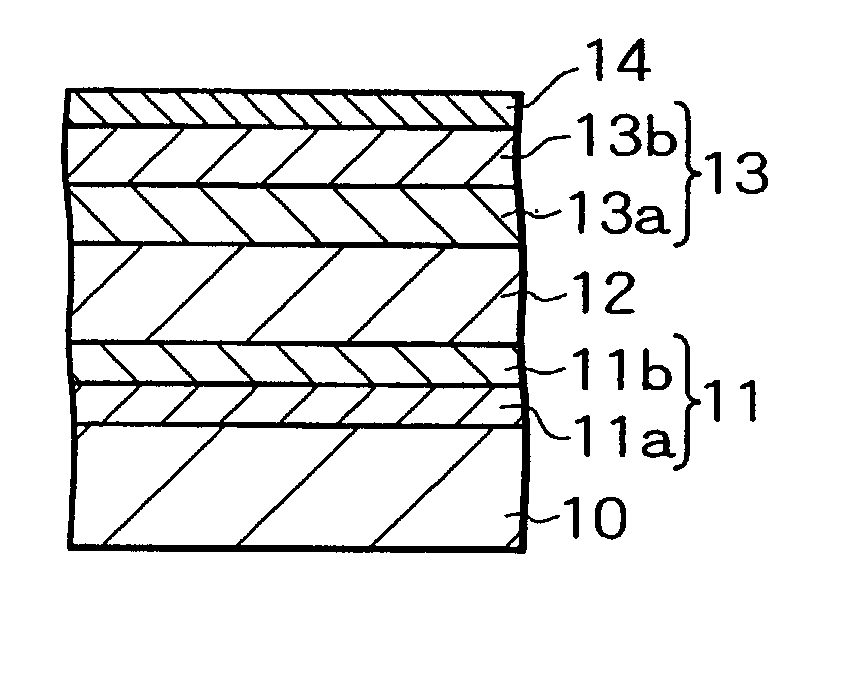

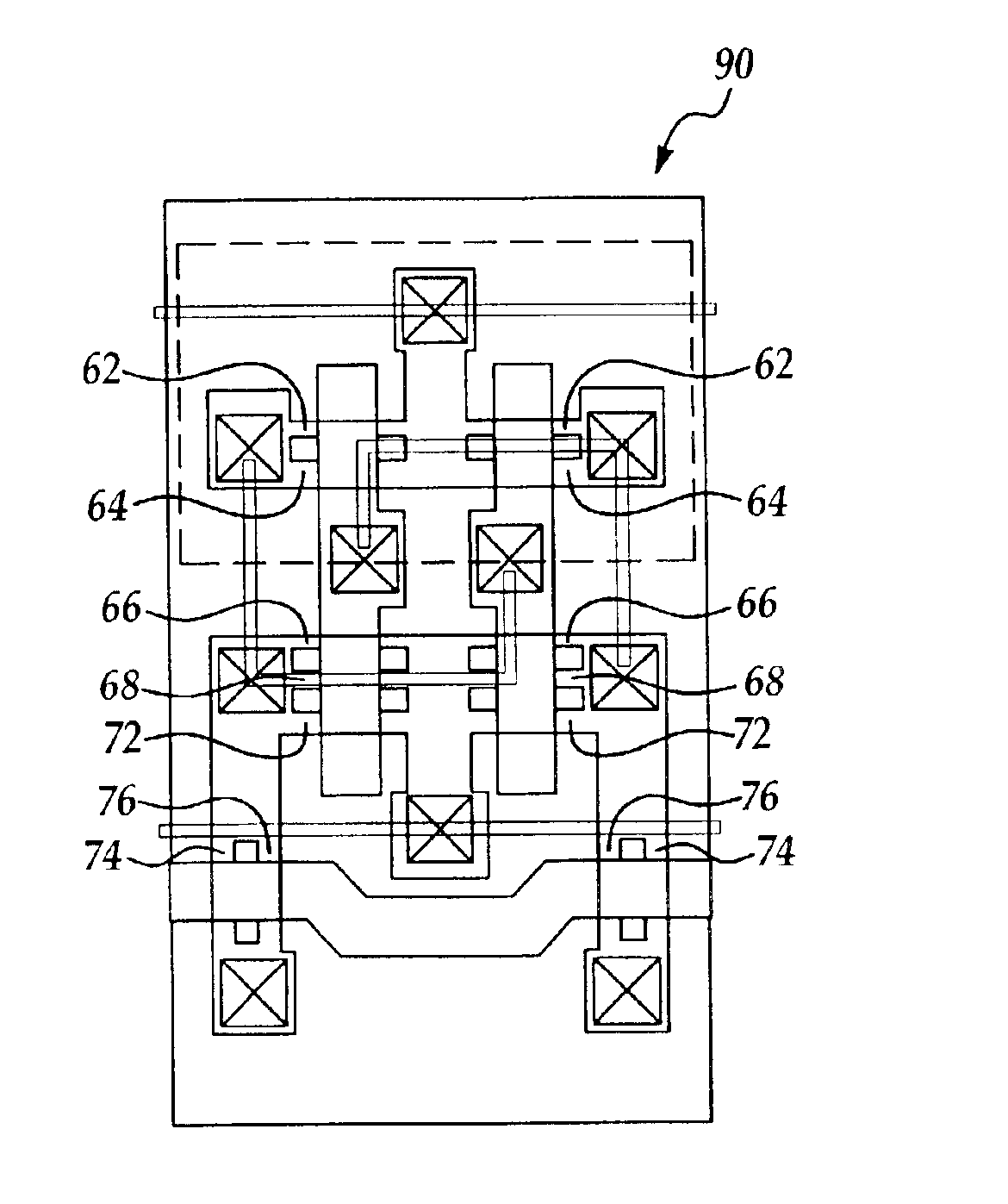

In accordance with an embodiment of the present invention, a static random access memory (SRAM) cell comprises a first pull-down transistor, a first pull-up transistor, a first pass-gate transistor, a second pull-down transistor, a second pull-up transistor, a second pass-gate transistor, a first linear intra-cell connection, and a second linear intra-cell connection. Active areas of the transistors are disposed in a substrate, and longitudinal axes of the active areas of the transistors are all parallel. The first linear intra-cell connection electrically couples the active area of the first pull-down transistor, the active area of the first pull-up transistor, and the active area of the first pass-gate transistor to a gate electrode of the second pull-down transistor and a gate electrode of the second pull-up transistor. The second linear intra-cell connection electrically couples the active area of the second pull-down transistor, the active area of the second pull-up transistor, and the active area of the second pass-gate transistor to a gate electrode of the first pull-down transistor and a gate electrode of the first pull-up transistor.

Owner:TAIWAN SEMICON MFG CO LTD

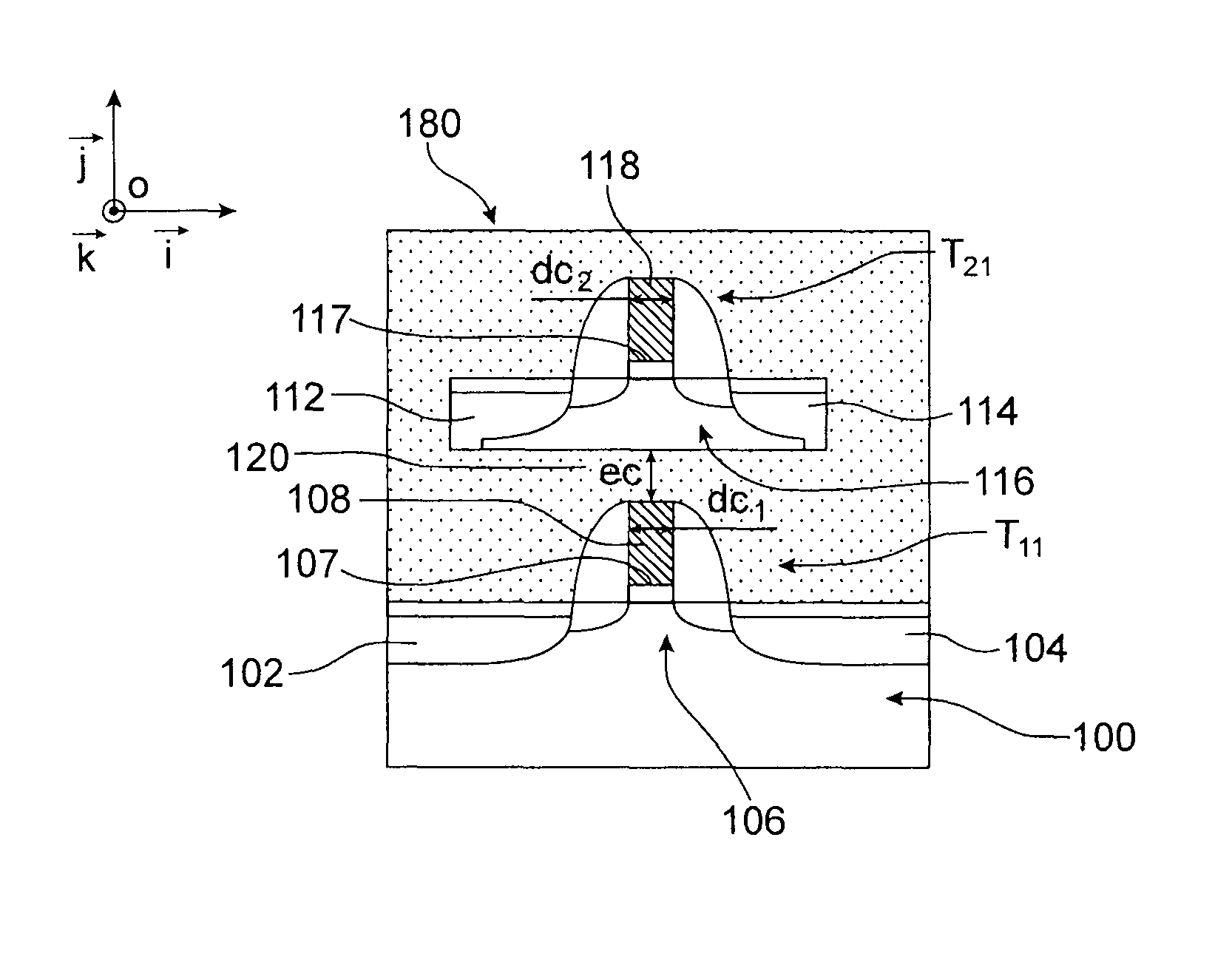

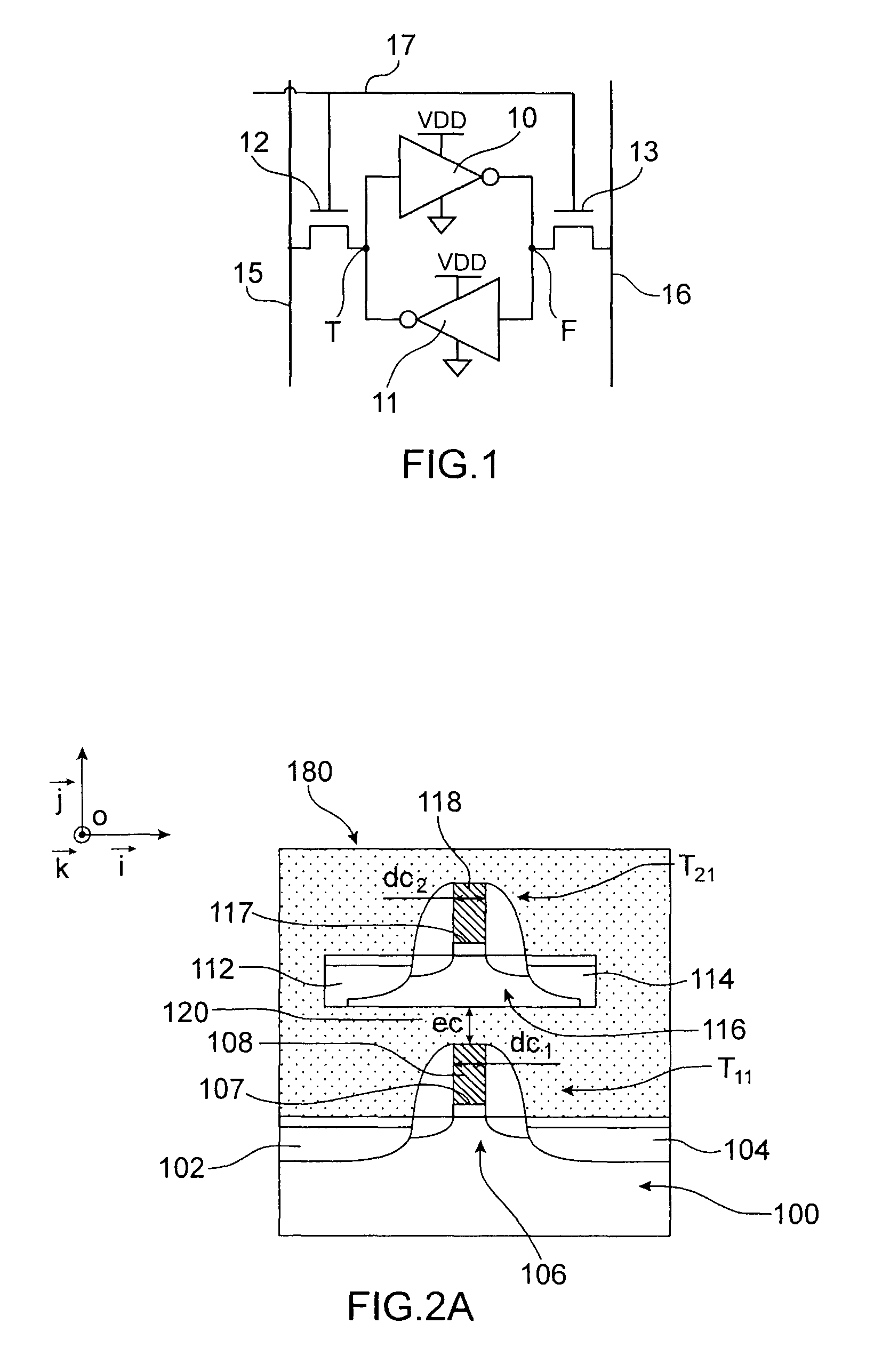

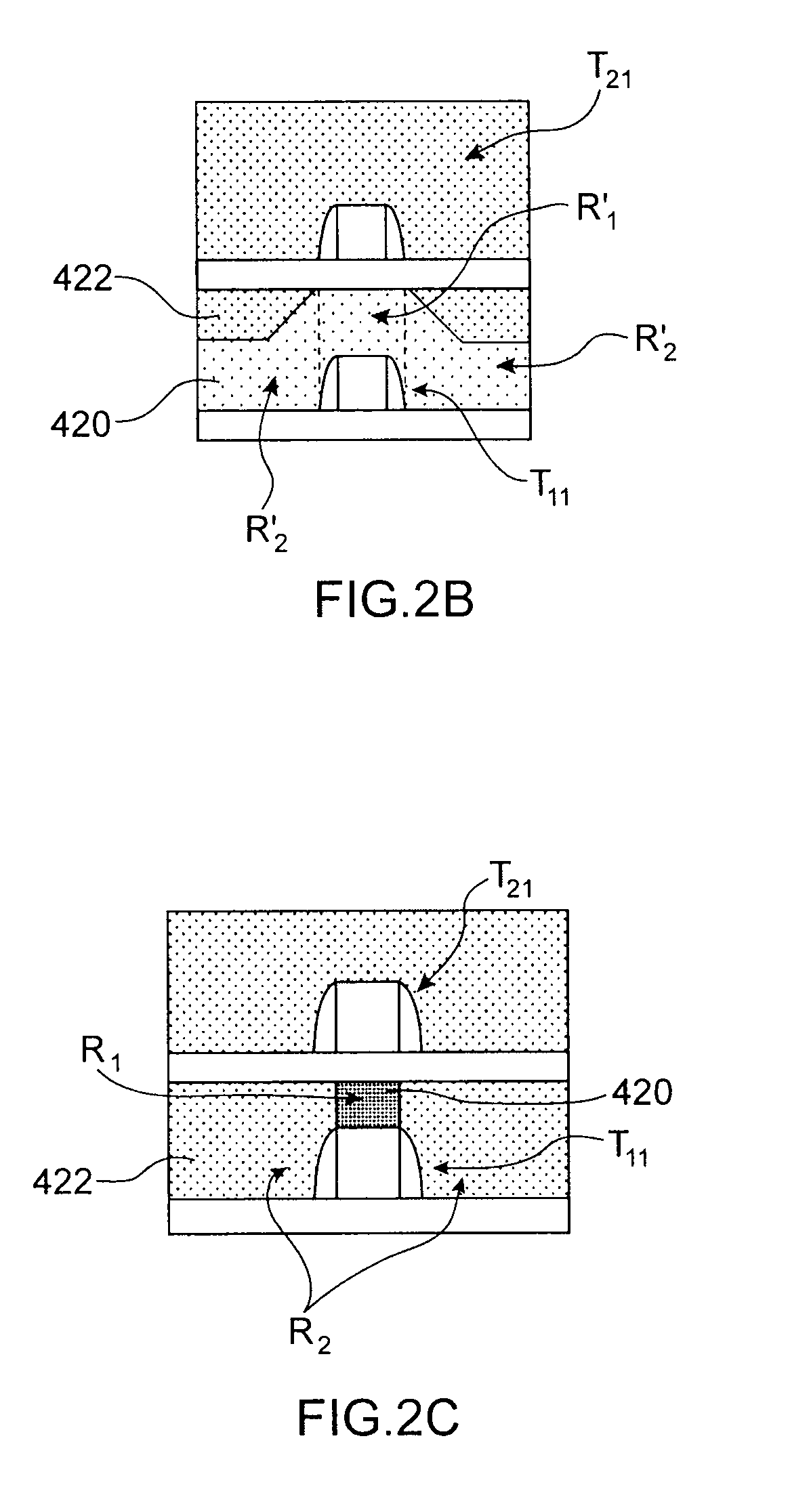

SRAM memory cell having transistors integrated at several levels and the threshold voltage VT of which is dynamically adjustable

InactiveUS8013399B2Improved integration density and electrical performanceTransistorSolid-state devicesBit lineStatic random-access memory

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

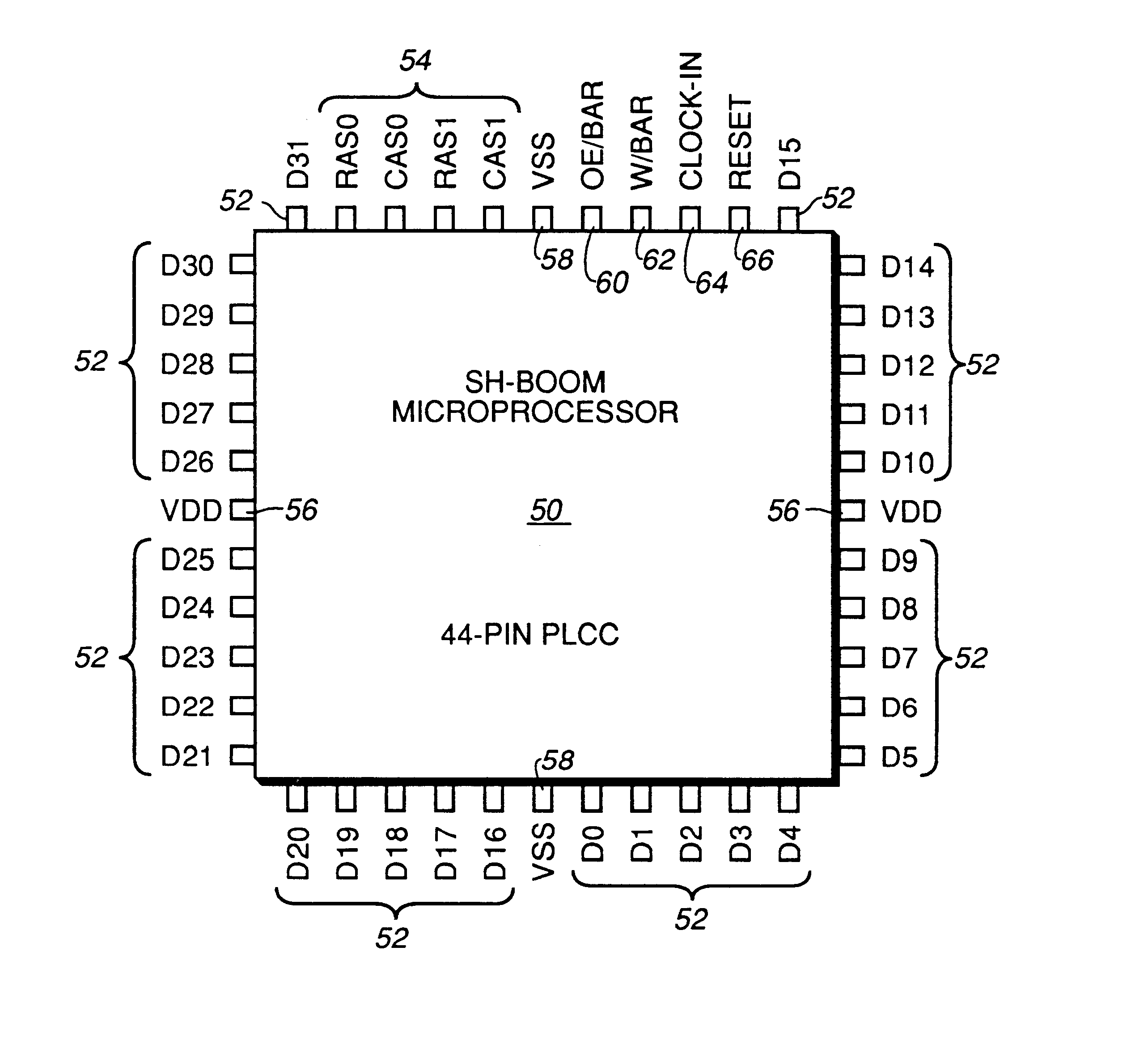

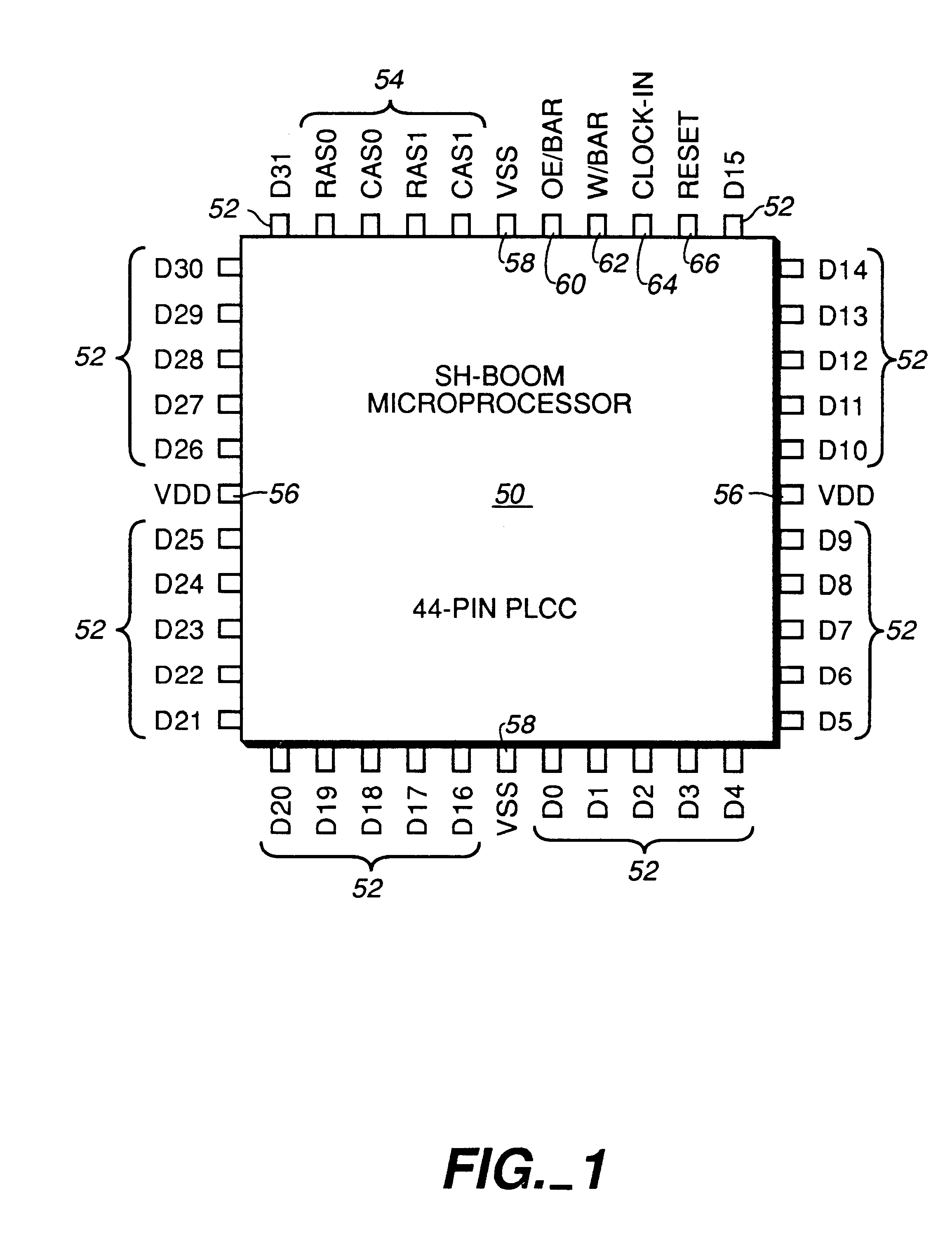

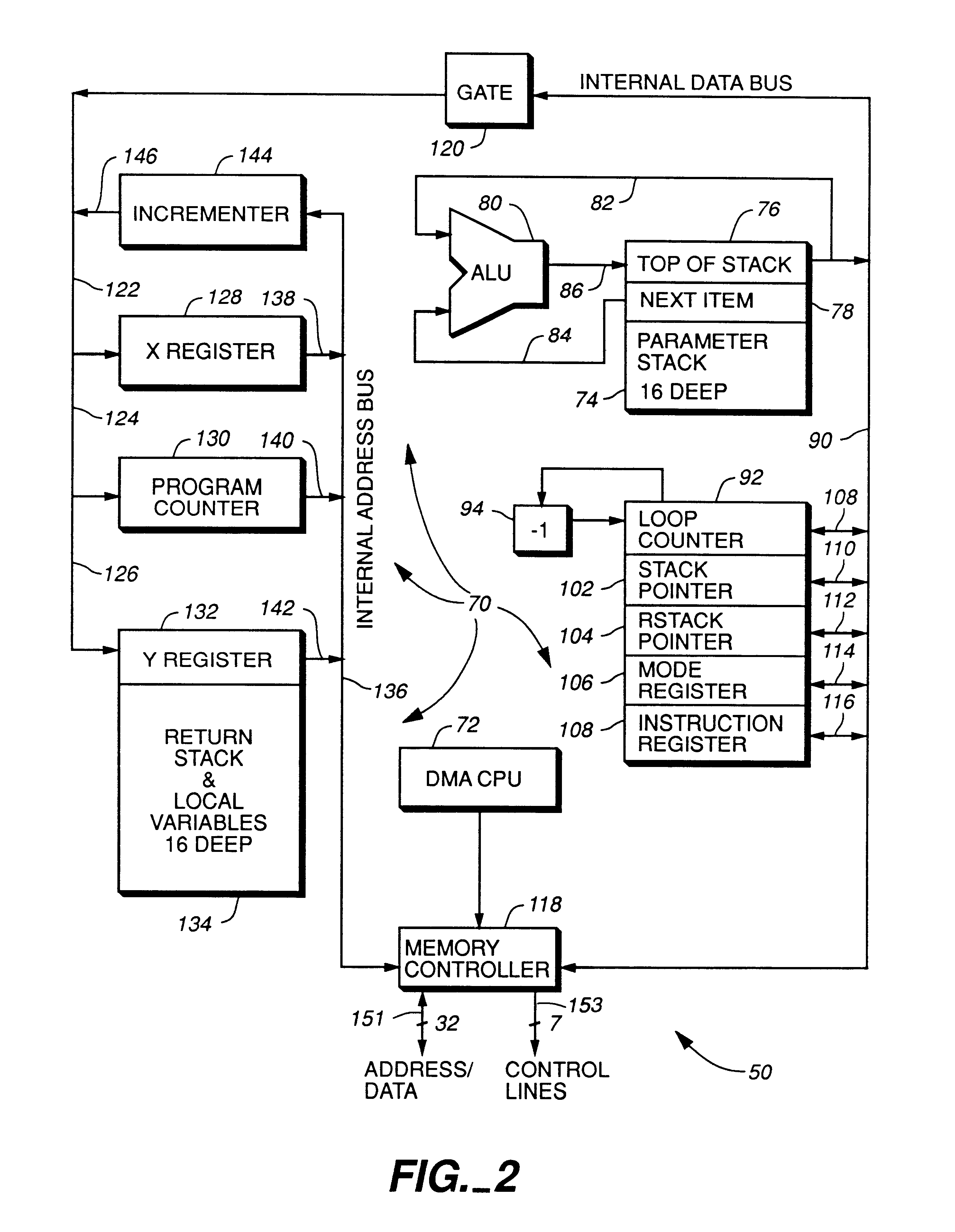

High performance microprocessor having variable speed system clock

InactiveUS6598148B1Improve performanceWithout sacrificing microprocessor speedRandom number generatorsInstruction analysisComputer architectureStatic random-access memory

A microprocessor integrated circuit including a processing unit disposed upon an integrated circuit substrate is disclosed herein. The processing unit is designed to operate in accordance with a predefined sequence of program instructions stored within an instruction register. A memory, capable of storing information provided by the processing unit and occupying a larger area of the integrated circuit substrate than the processing unit, is also provided within the microprocessor integrated circuit. The memory may be implemented using, for example dynamic or static random-access memory. A variable output frequency system clock, such as generated by a ring oscillator, is also disposed on the integrated circuit substrate.

Owner:MOORE CHARLES H TTE UTD 03 21 2006 THE EQUINOX TRUST

Data processing system and method

InactiveUS20060013473A1Eliminate informationImage enhancementImage analysisStatic random-access memoryHigh memory

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

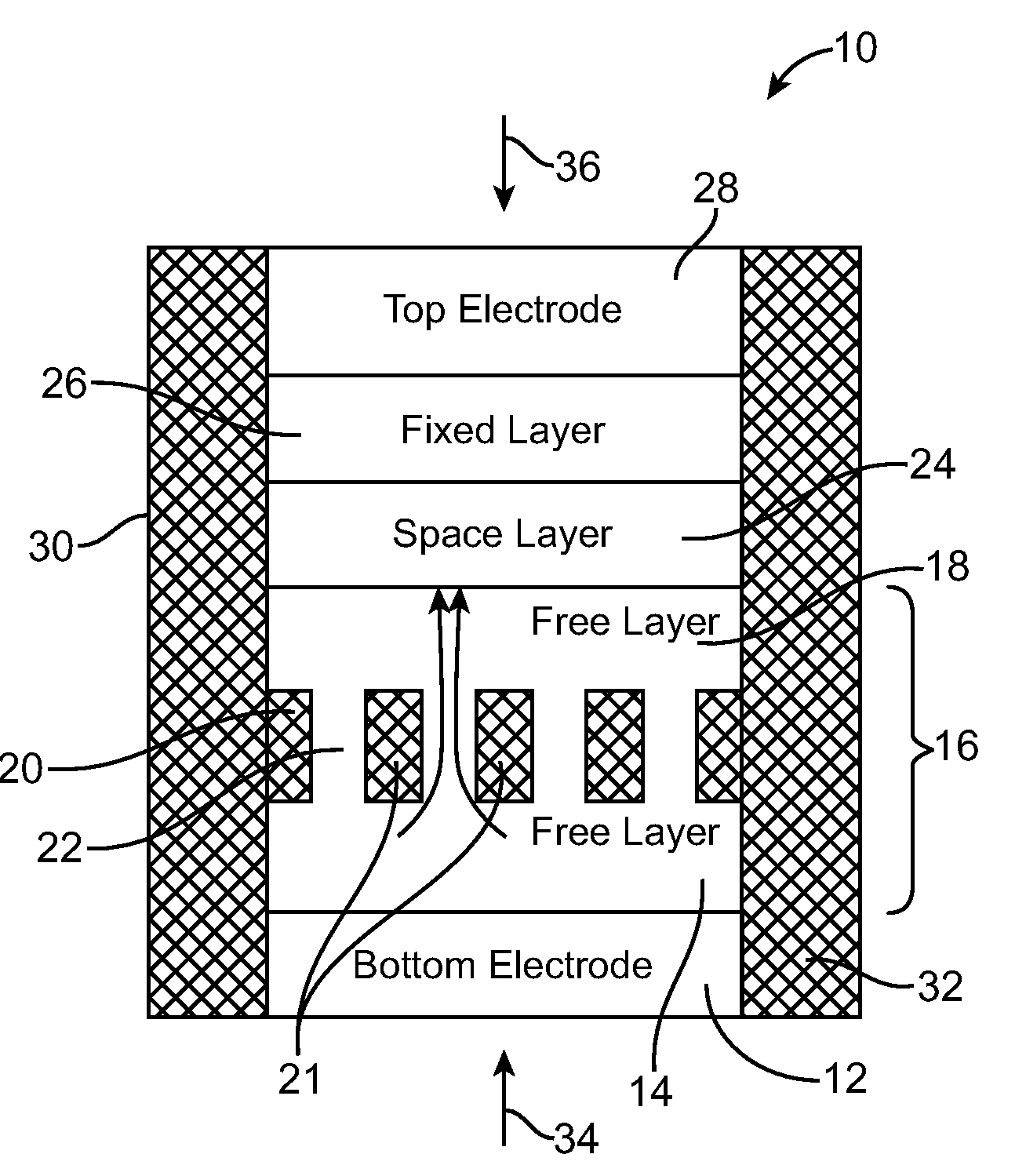

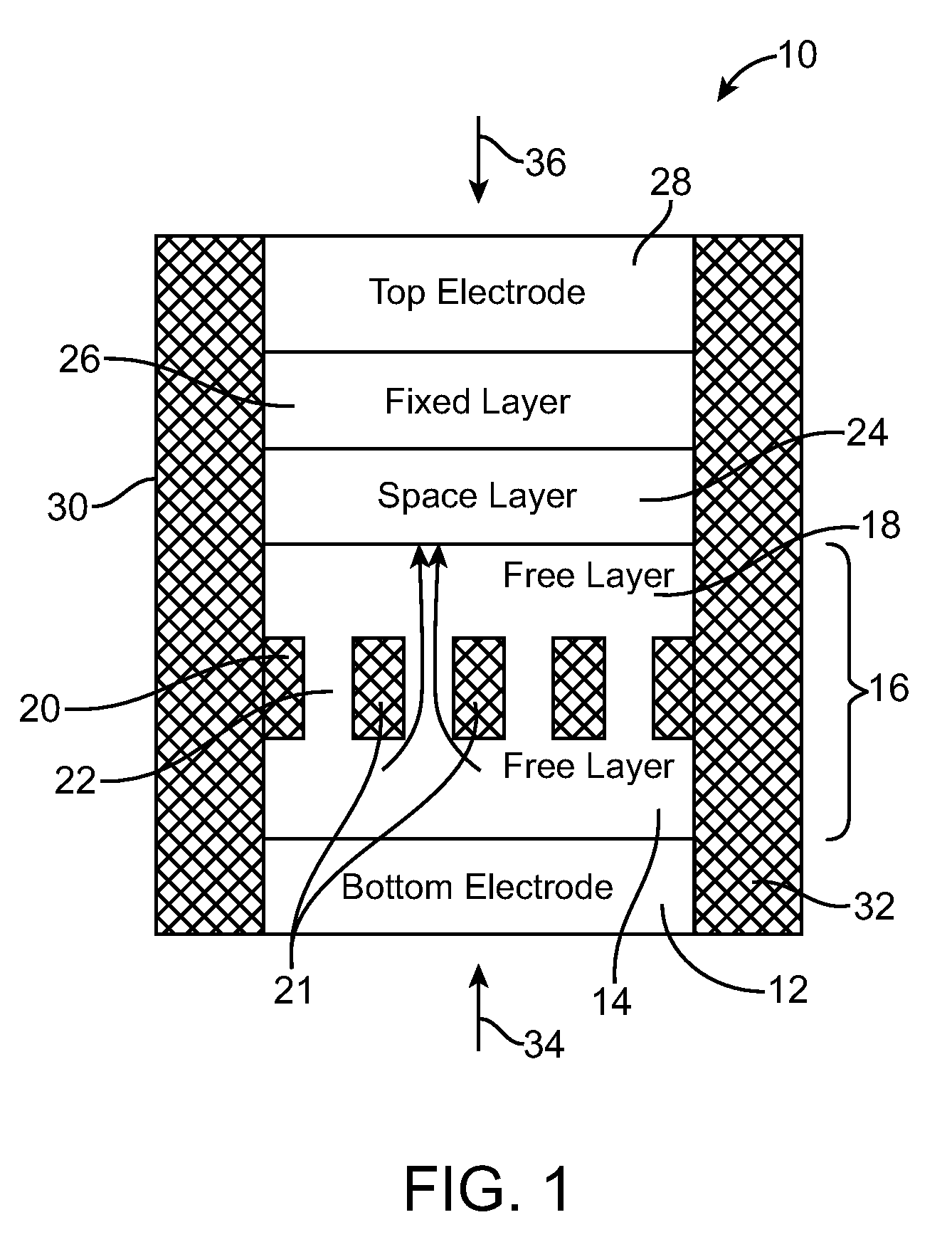

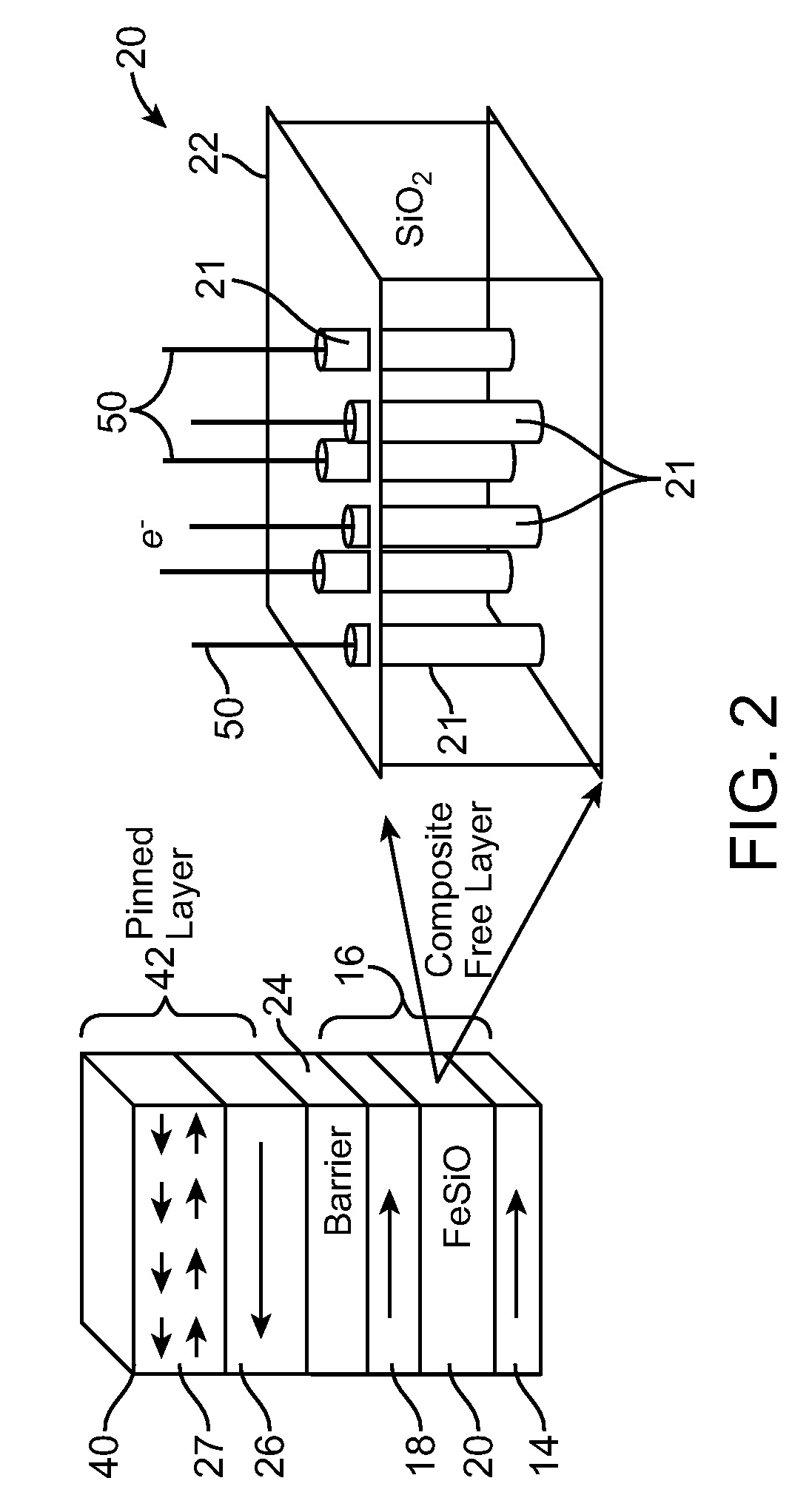

Current-confined effect of magnetic nano-current-channel (NCC) for magnetic random access memory (MRAM)

ActiveUS7732881B2Magnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingCurrent limitingCurrent channel

One embodiment of the present invention includes a memory element having a composite free layer including a first free sub-layer formed on top of the bottom electrode, a nano-current-channel (NCC) layer formed on top of the first free sub-layer, and a second free sub-layer formed on top of the NCC layer, wherein when switching current is applied to the memory element, in a direction that is substantially perpendicular to the layers of the memory element, local magnetic moments of the NCC layer switch the state of the memory element.

Owner:AVALANCHE TECH

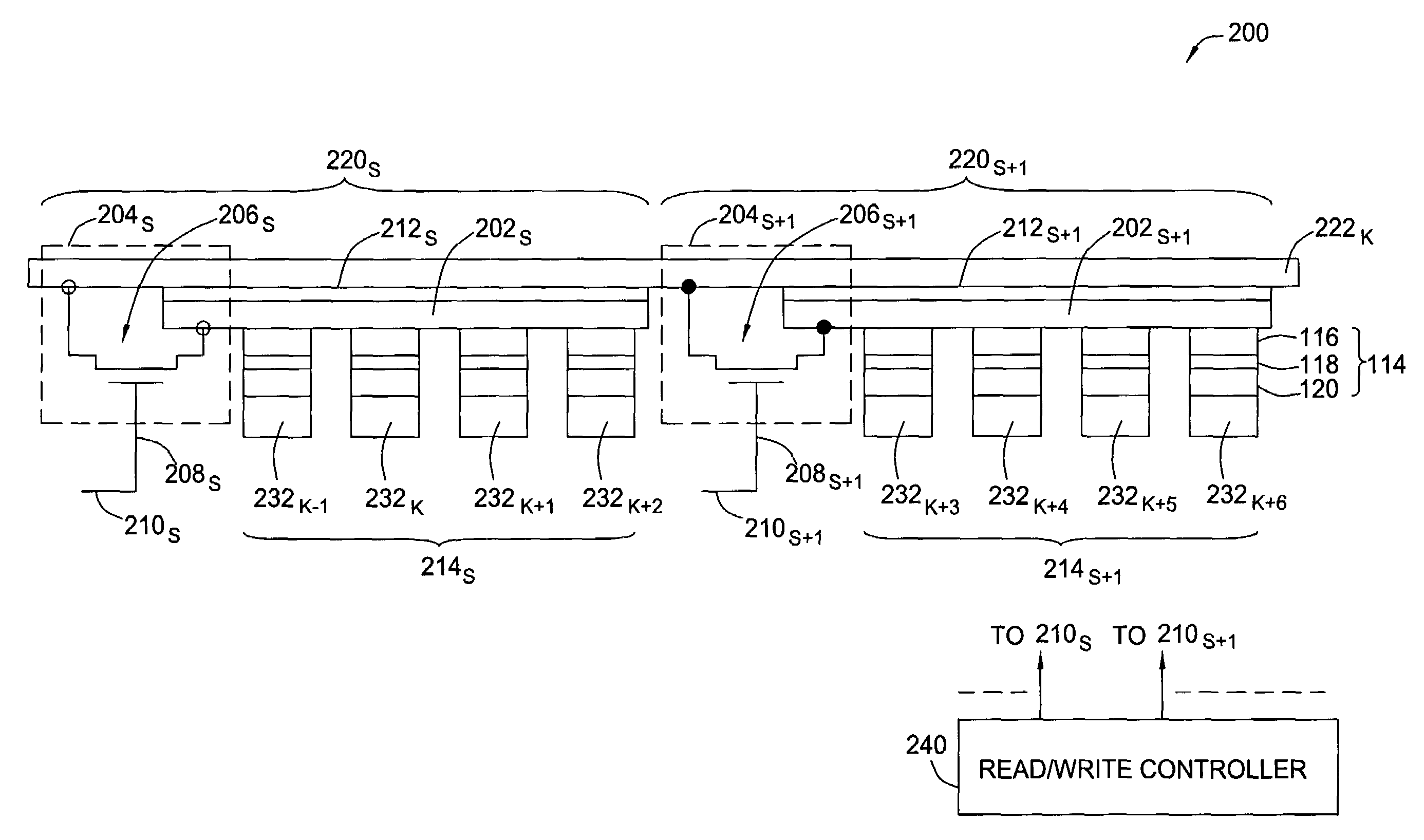

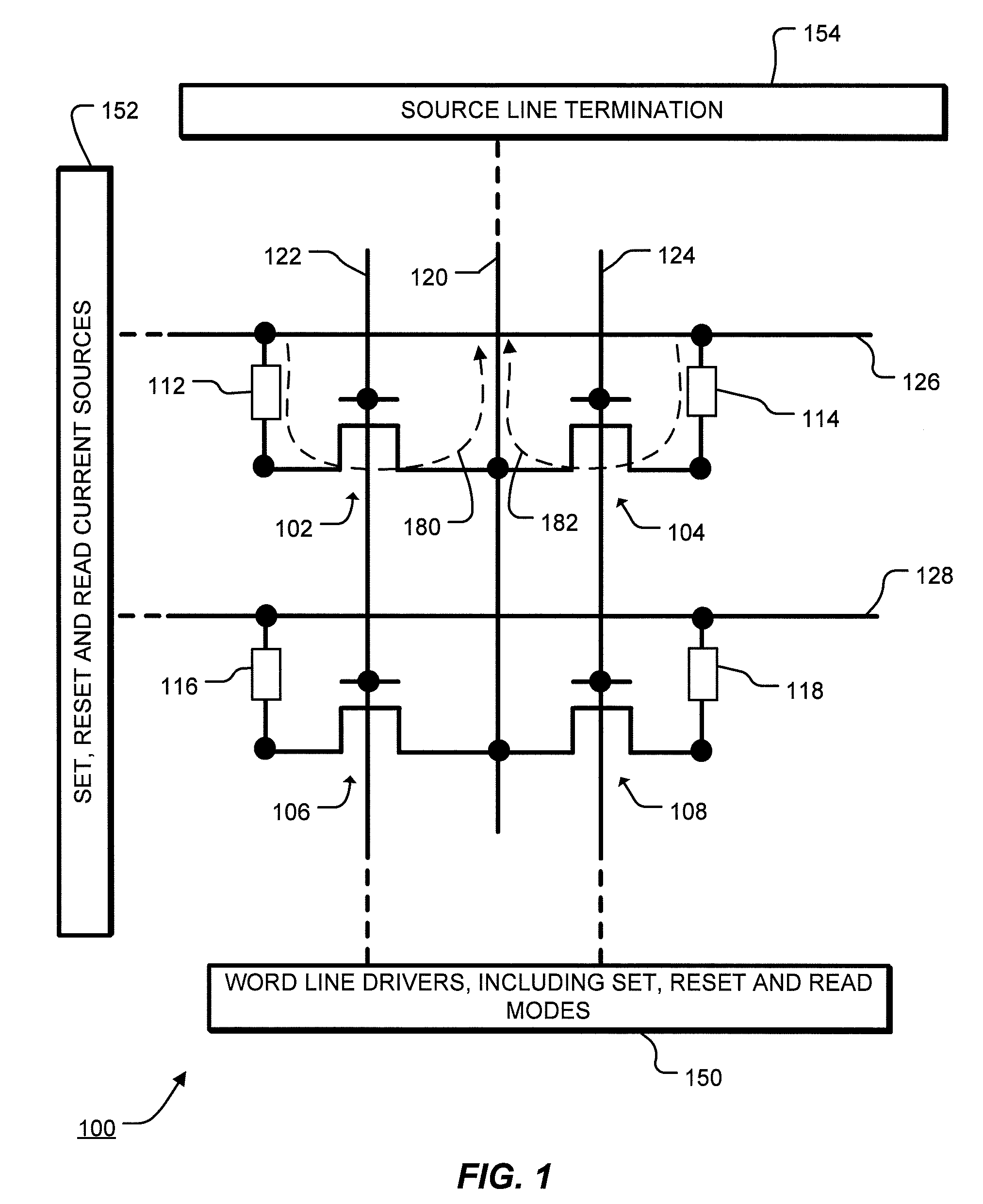

MRAM array having a segmented bit line

InactiveUS6982902B2Reduce leakage currentRaise the ratioDigital storageBit lineStatic random-access memory

A magneto-resistive random access memory (MRAM) array comprises global bit lines segmented using a plurality of local bit lines. A read / write controller is connected to the switches. Switches couple the global bit line to the local bit lines. The MRAM array has low leakage currents and facilitates a high signal-to-noise (S / N) ratio of read and write operations.

Owner:IBM CORP +1

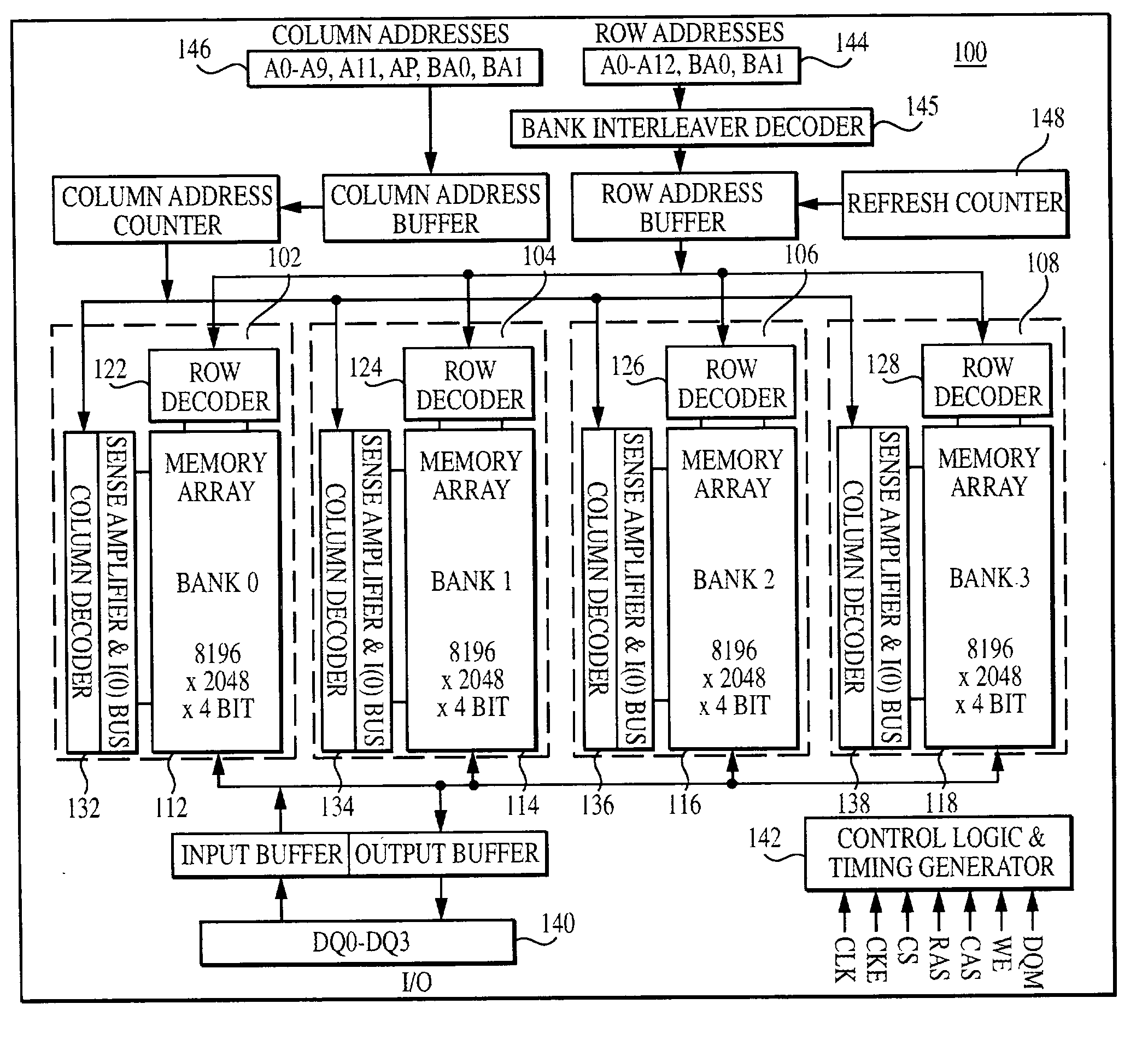

Combined command set

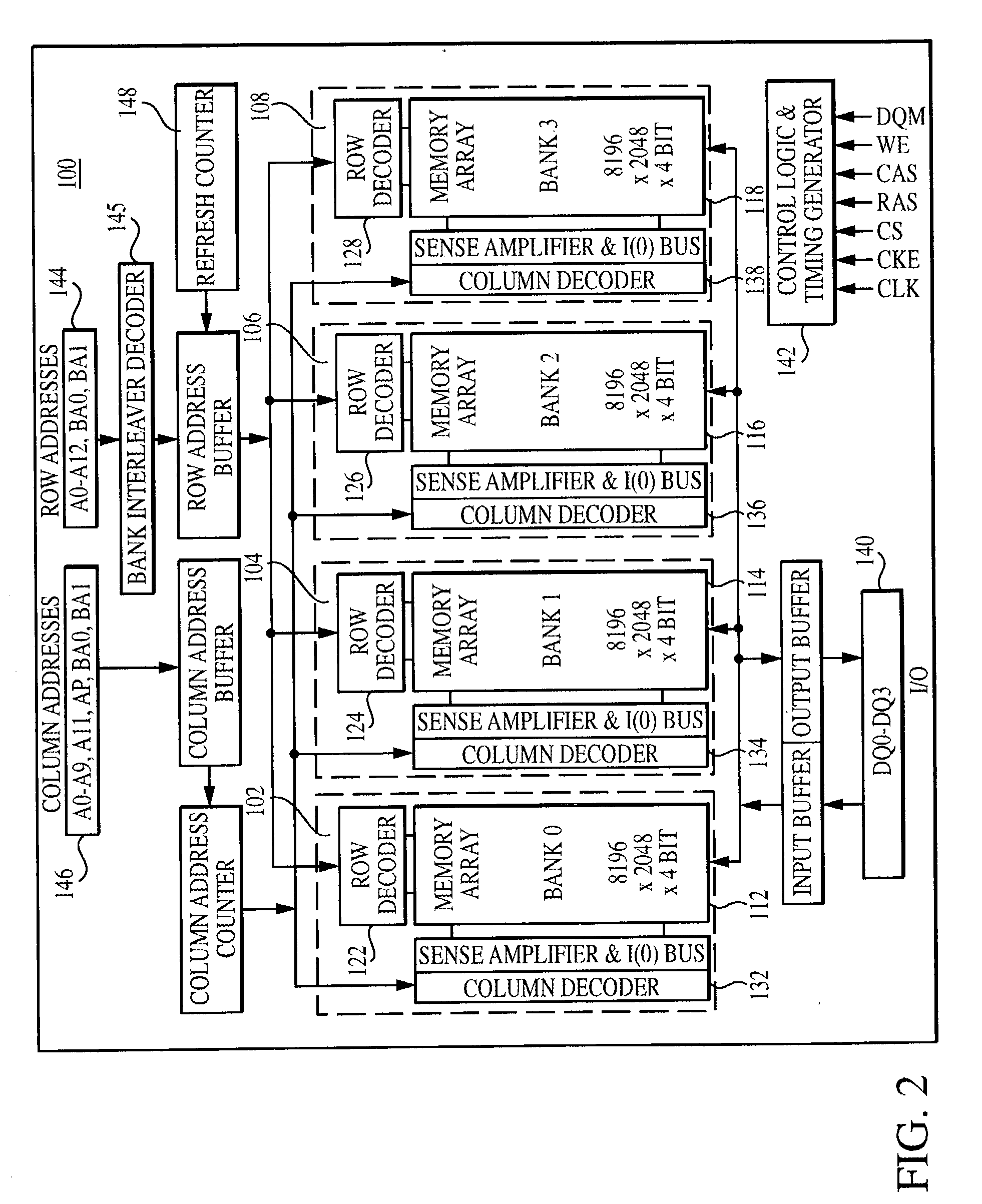

InactiveUS20030217223A1Memory adressing/allocation/relocationDigital storageStatic random-access memoryMemory bank

A circuit and method of operation for combining commands in a DRAM (dynamic random access memory) are revealed. The method applies to DRAMs having a plurality of memory banks or arrays. The method combines commands to rows on different memory banks, and the method also combines row and column commands on different memory banks. The method eliminates steps in a sequence of commands, and may significantly increase speed of input / output to a DRAM.

Owner:INFINEON TECH AG

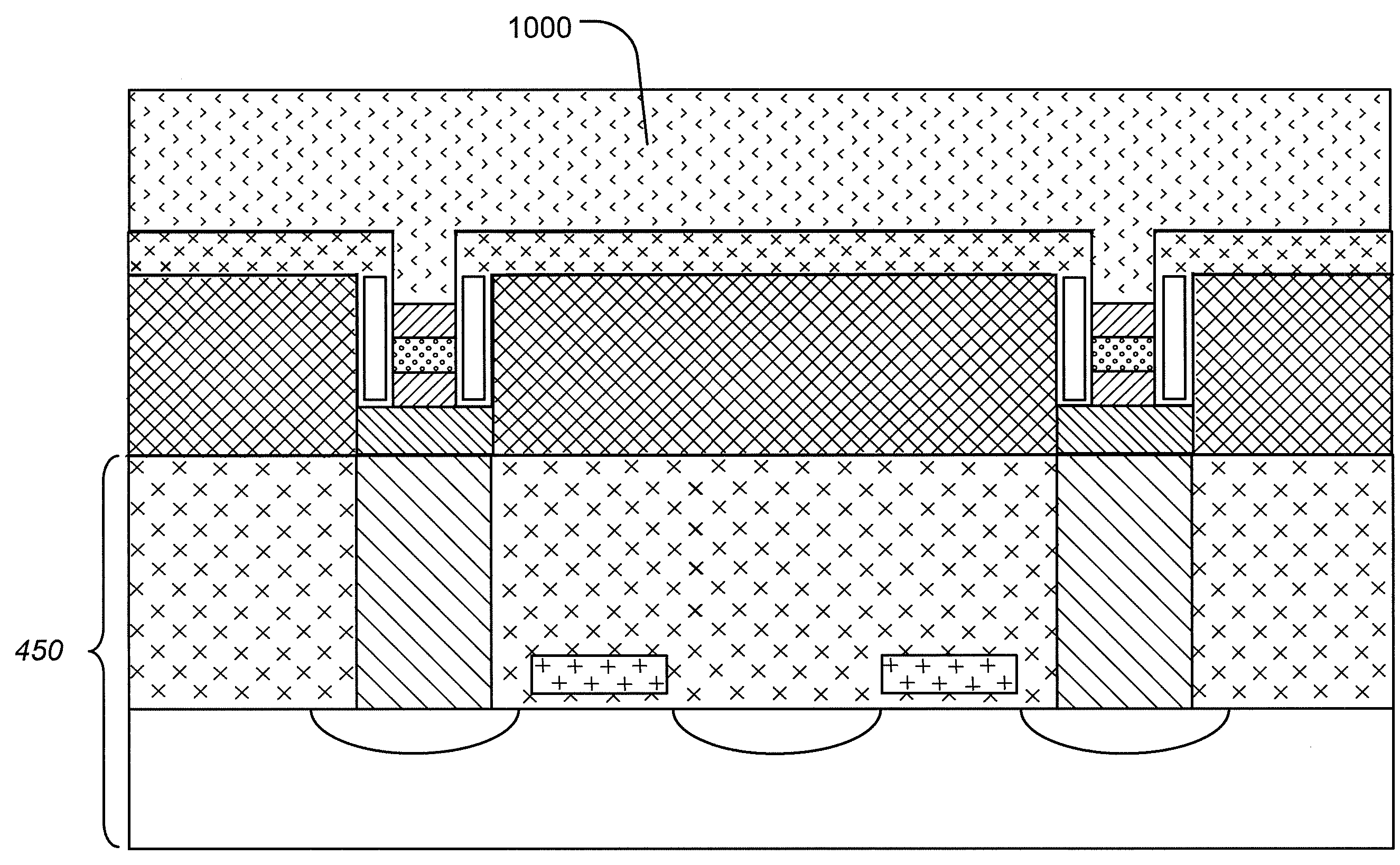

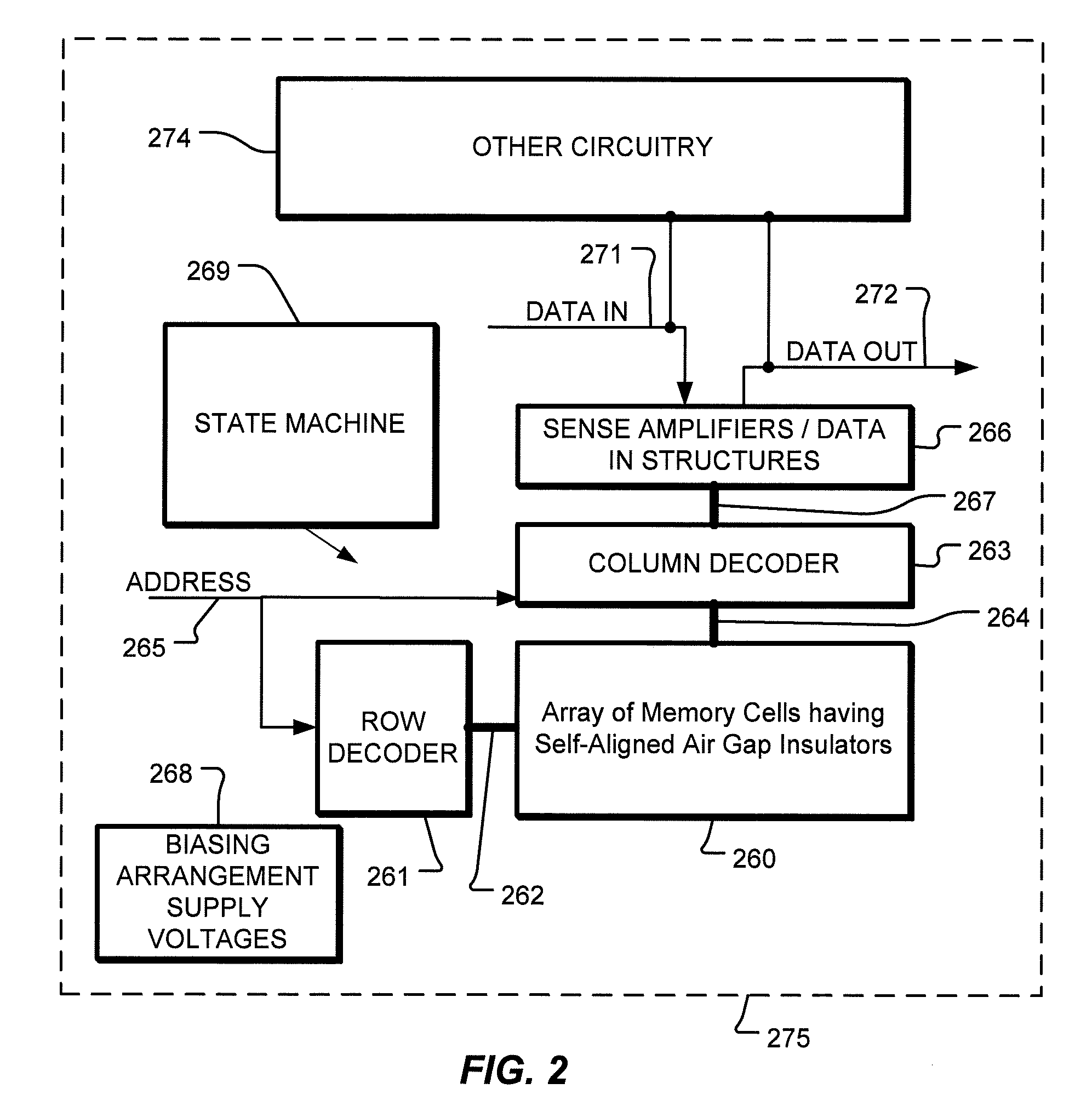

Method for manufacturing a resistor random access memory with a self-aligned air gap insulator

ActiveUS20090101883A1Reduce the amount requiredReduce heat dissipationSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesStatic random-access memoryRandom access memory

Owner:MACRONIX INT CO LTD

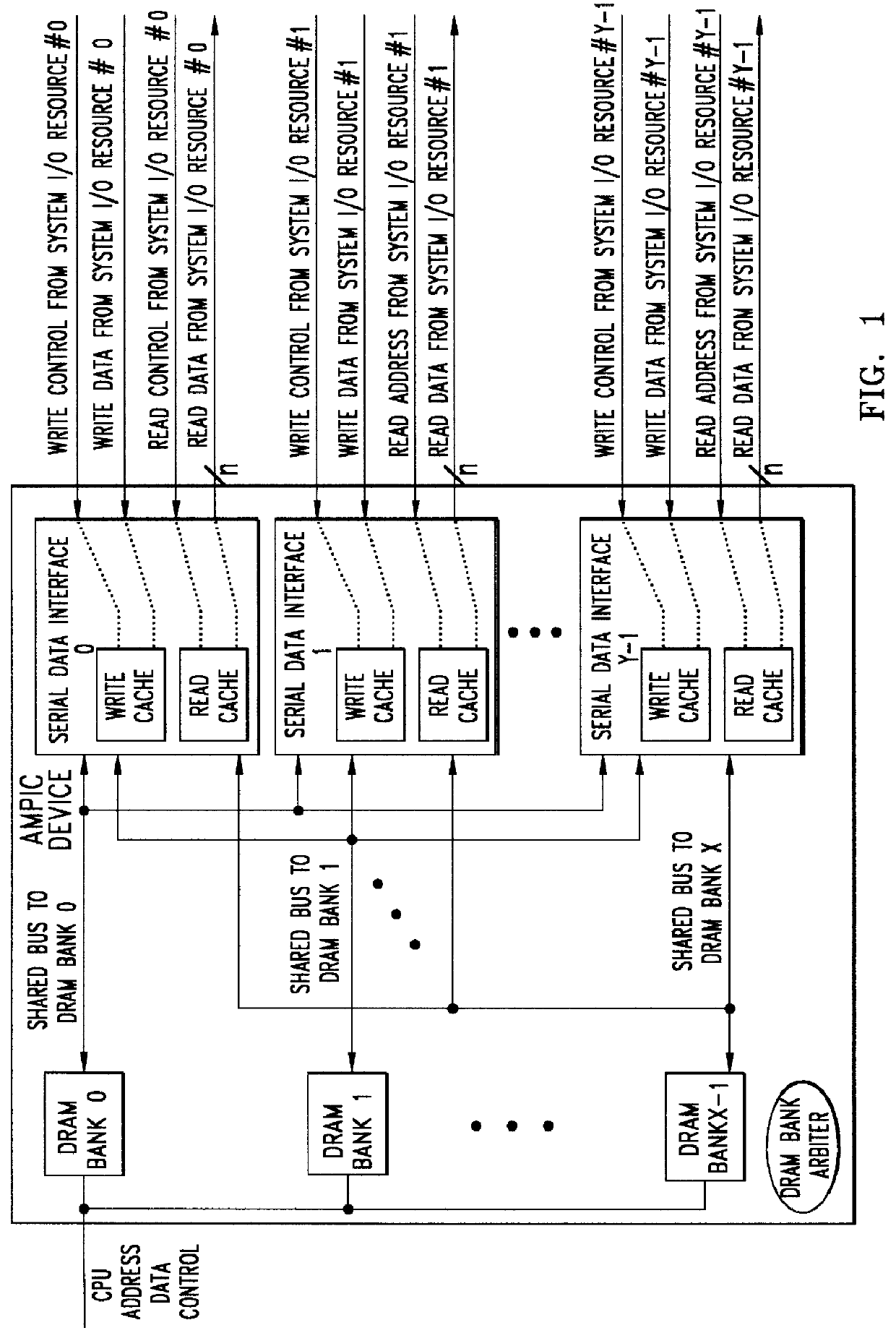

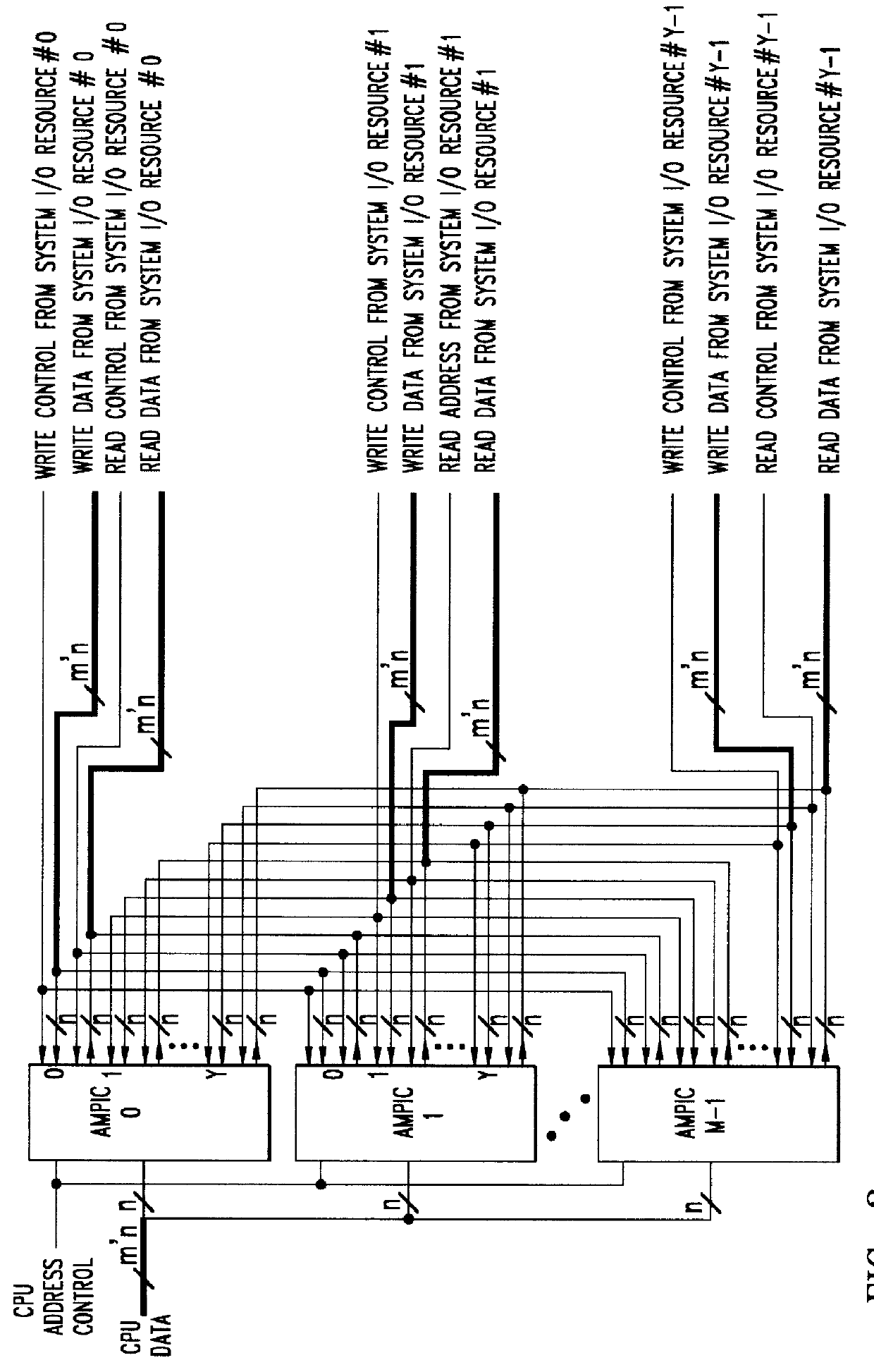

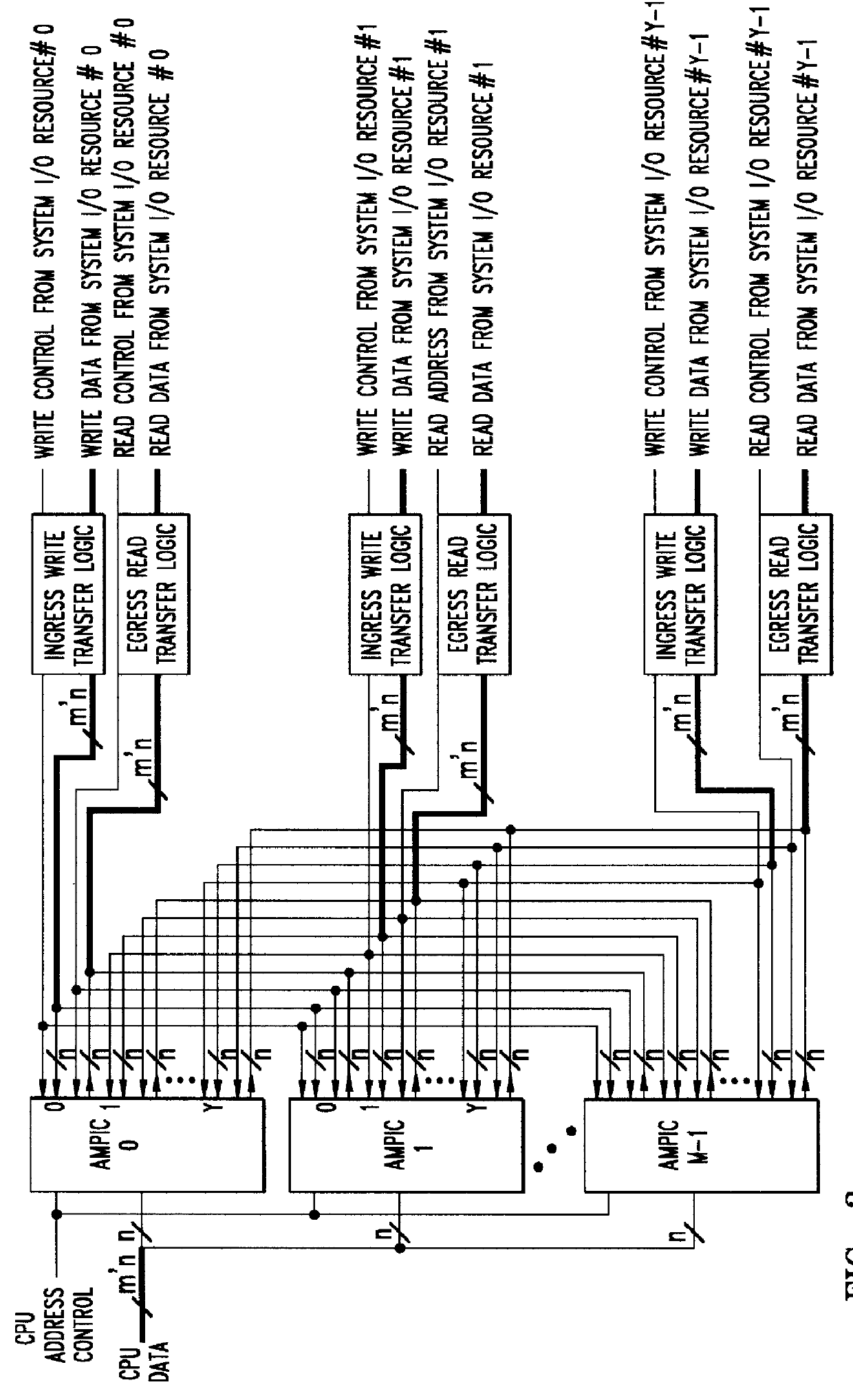

Method of and apparatus for validating data read out of a multi port internally cached dynamic random access memory (AMPIC DRAM)

InactiveUS6085290AEliminates race conditionMemory architecture accessing/allocationMemory adressing/allocation/relocationData validationStatic random-access memory

An apparatus for and method of enhancing the performance of a multi-port internal cached DRAM (AMPIC DRAM) by providing an internal method of data validation within the AMPIC memories themselves to guarantee that only valid requested data is returned from them, or properly marked invalid data. A modified technique for identifying bad data that has been read out of AMPIC memory devices in the system.

Owner:NEXABIT NETWORKS +1

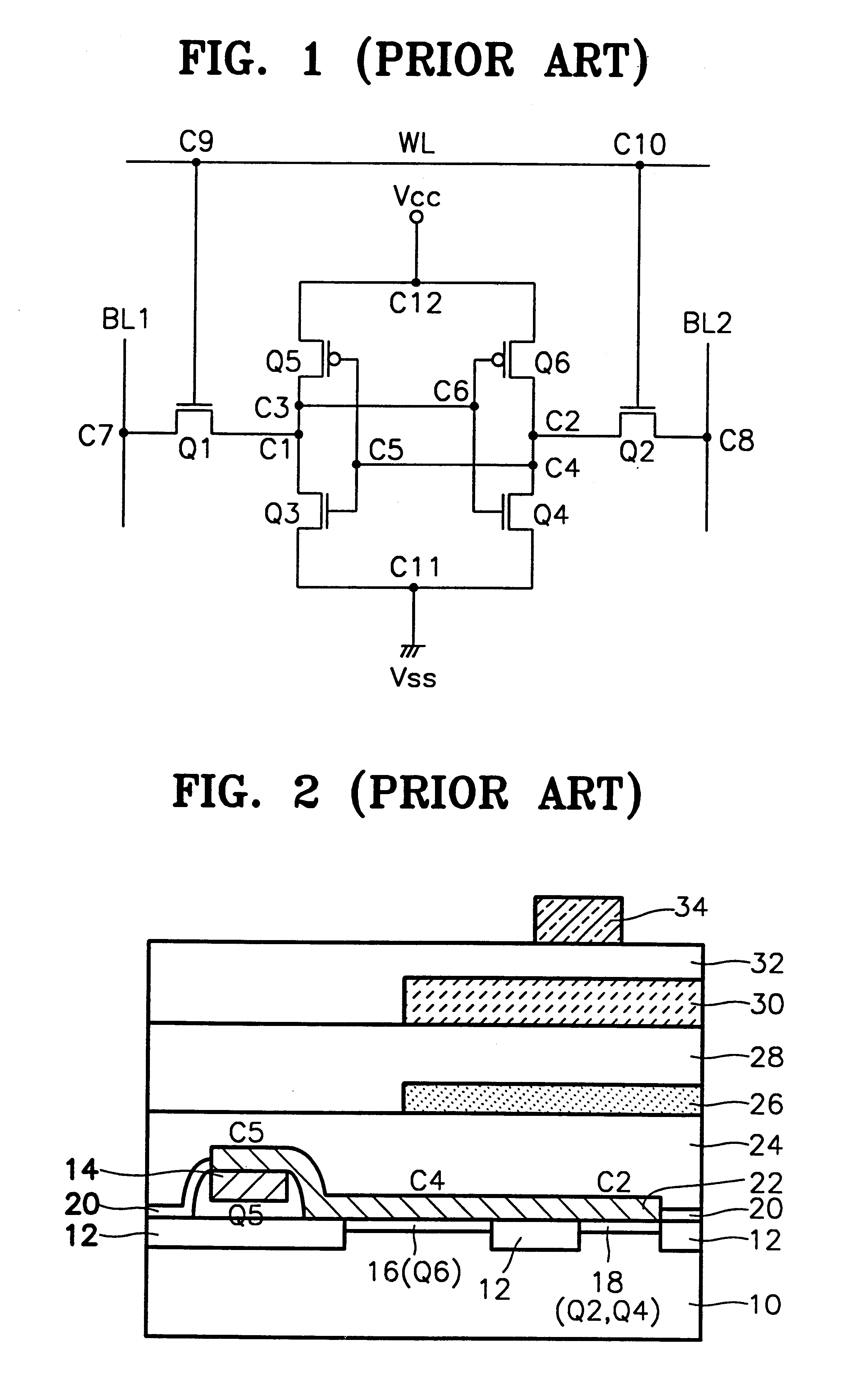

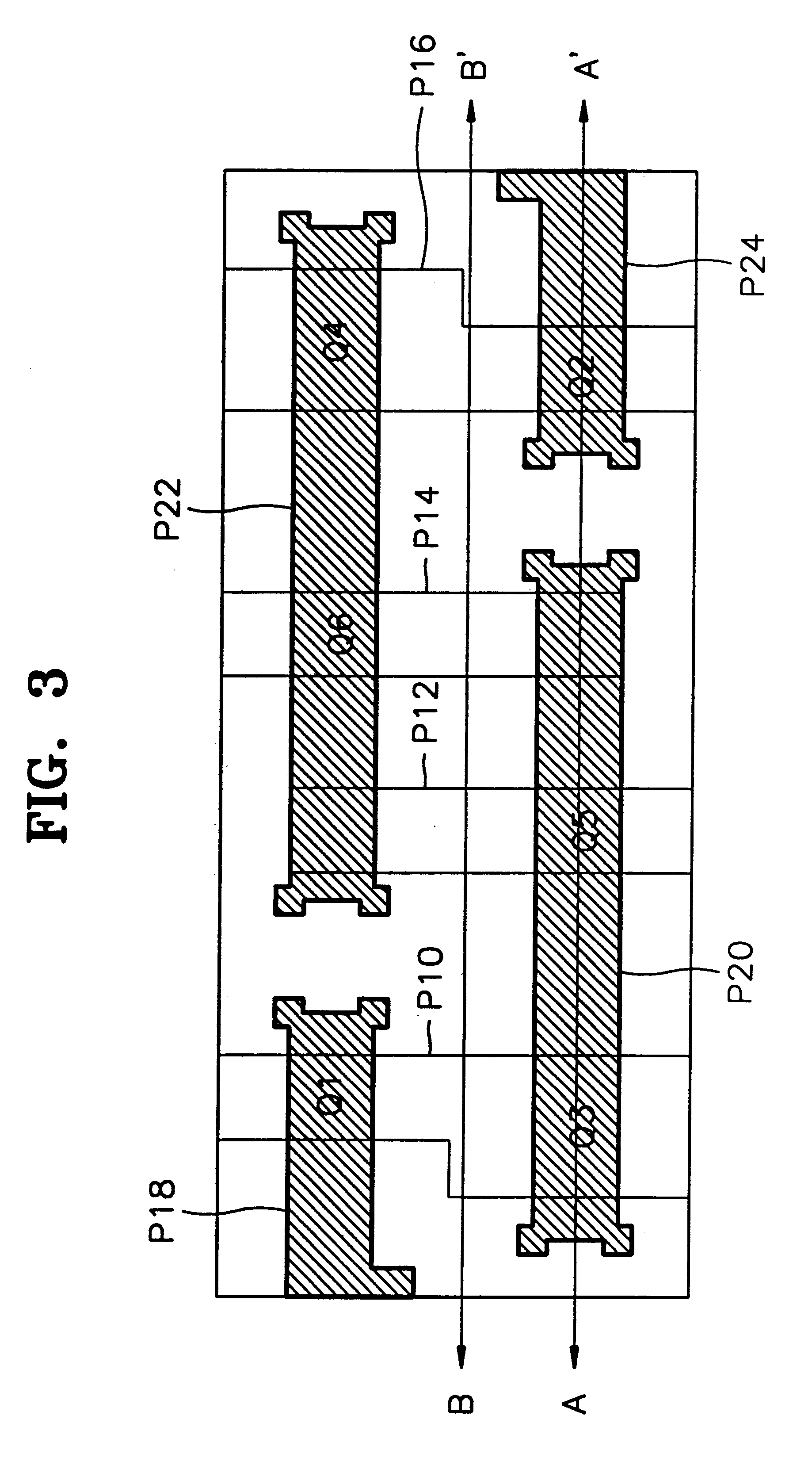

Static random access memory device and method for manufacturing the same

A static random access memory (SRAM) device and a method for manufacturing the same are disclosed. In the SRAM device including a flip-flop circuit including two access transistors and a pair of inverters, connection lines for connecting the inputs and outputs of the inverters, and a word line, power supply lines and bit lines are formed of a metal interconnection. The resistance of interconnection can be reduced and the SRAM device manufacturing process can be performed along with CMOS standard logic manufacturing process.

Owner:SAMSUNG ELECTRONICS CO LTD

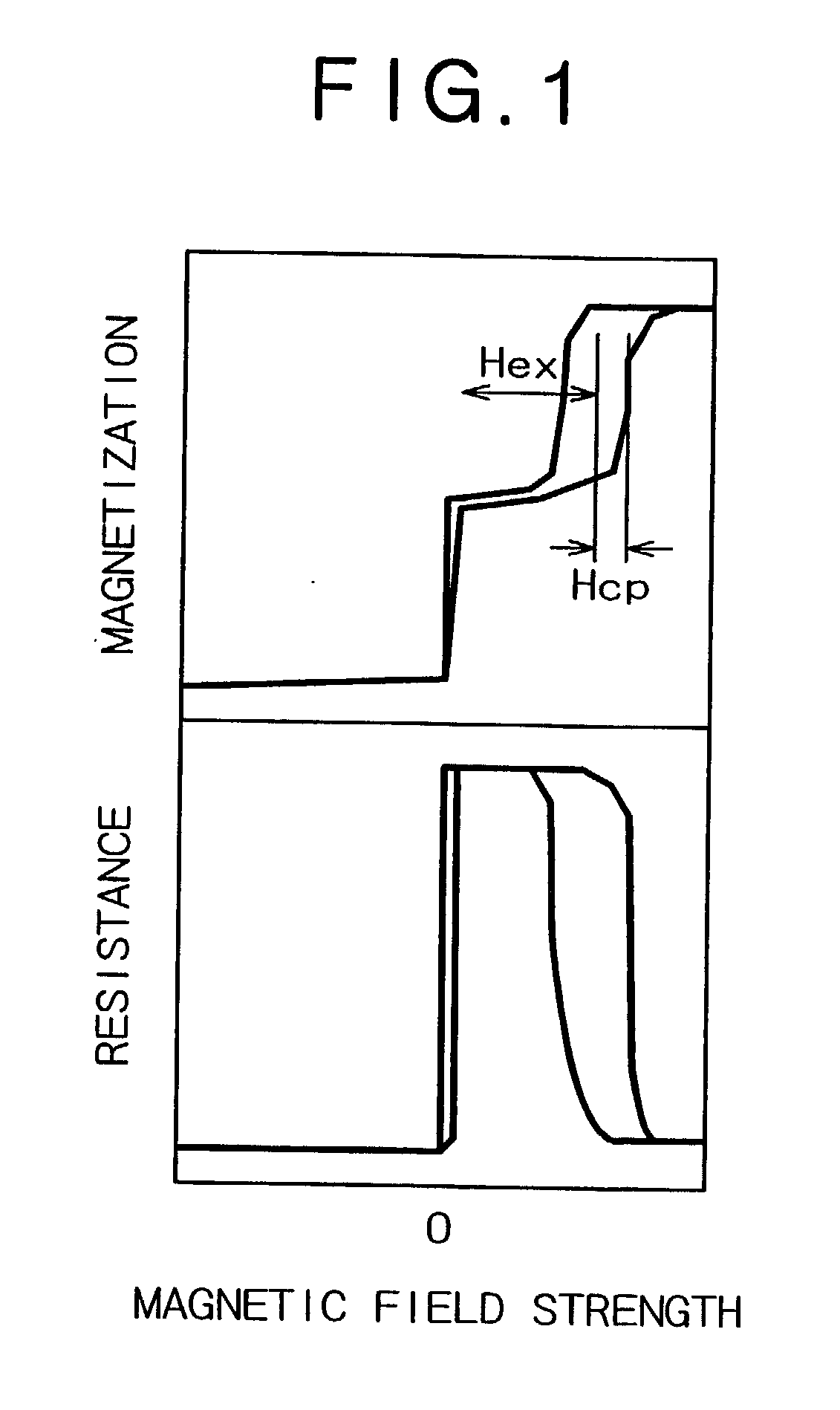

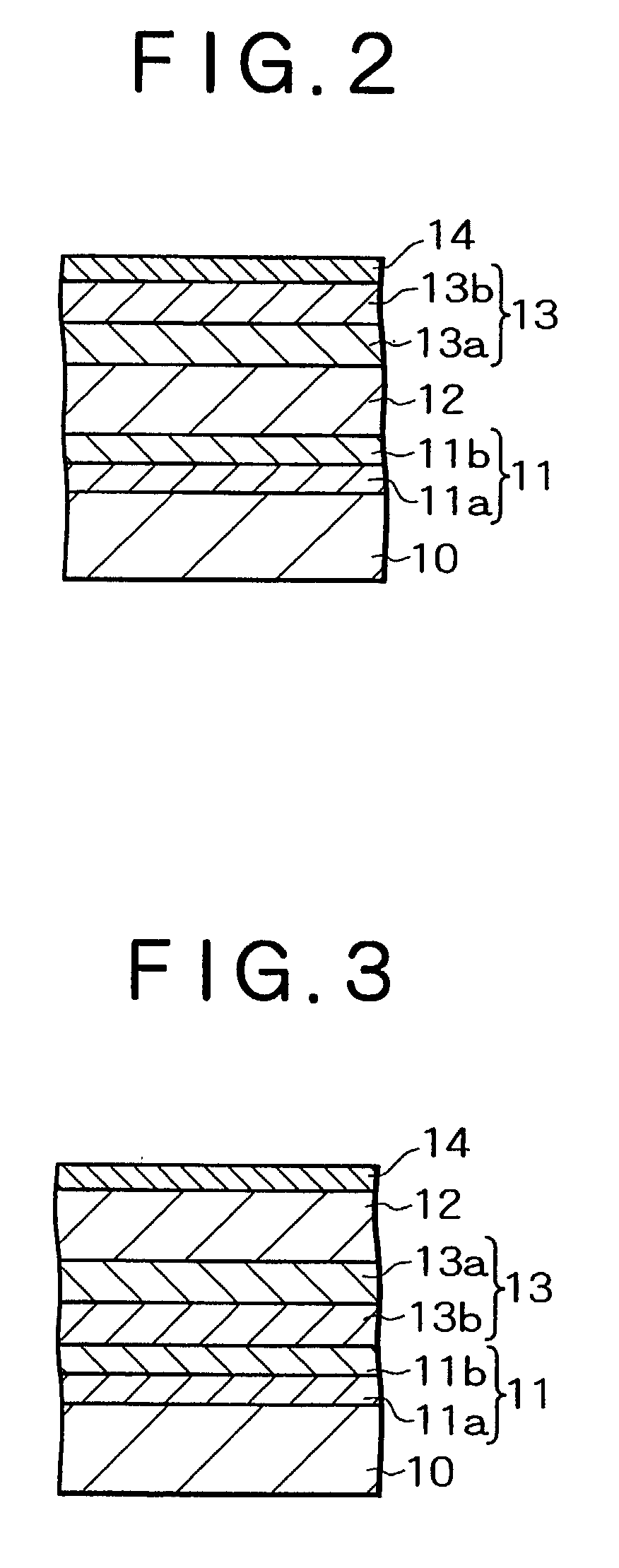

Exchange coupling film, magneto-resistance effect device, magnetic head, and magnetic random access memory

A foundation layer increasing adhesive properties to a substrate, another foundation layer controlling orientation of an antiferromagnetic layer, the antiferromagnetic layer including a disordered alloy of IrMn, a pinning layer, and a cap protection layer are formed in the order on the substrate. The pinning layer includes two layers having an exchange coupling giving layer which exchange-couples to the antiferromagnetic layer and an exchange coupling enhancement layer which enhances the exchange coupling, the exchange coupling giving layer is made of a ferromagnetic material including Co or a Co100-XFeX alloy (O<=X<25) having face-centered cubic structure. The exchange coupling enhancement layer is made of Fe or a Co100-YFeY alloy (25<=Y<=100) having body-centered cubic structure.

Owner:NEC CORP

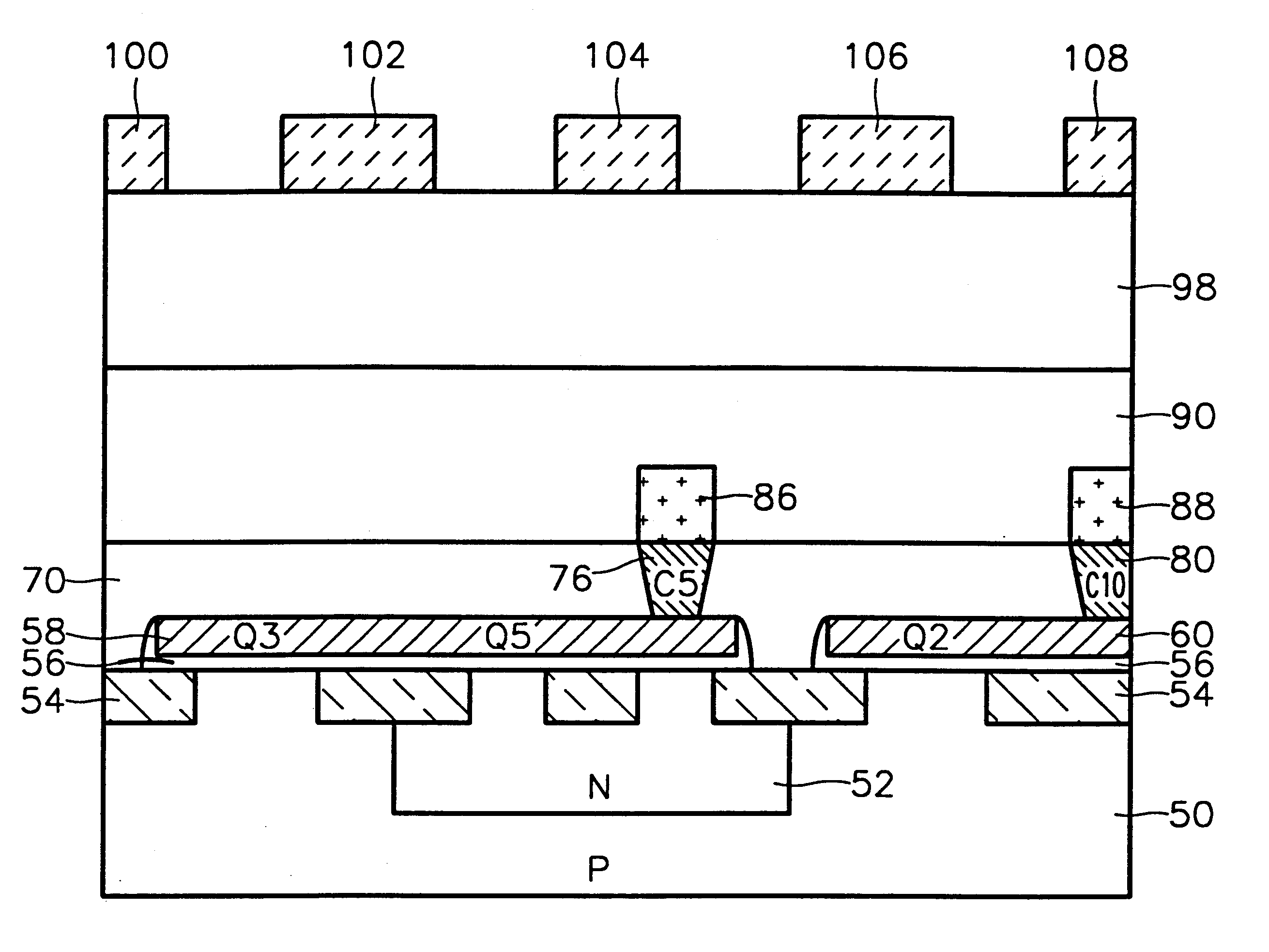

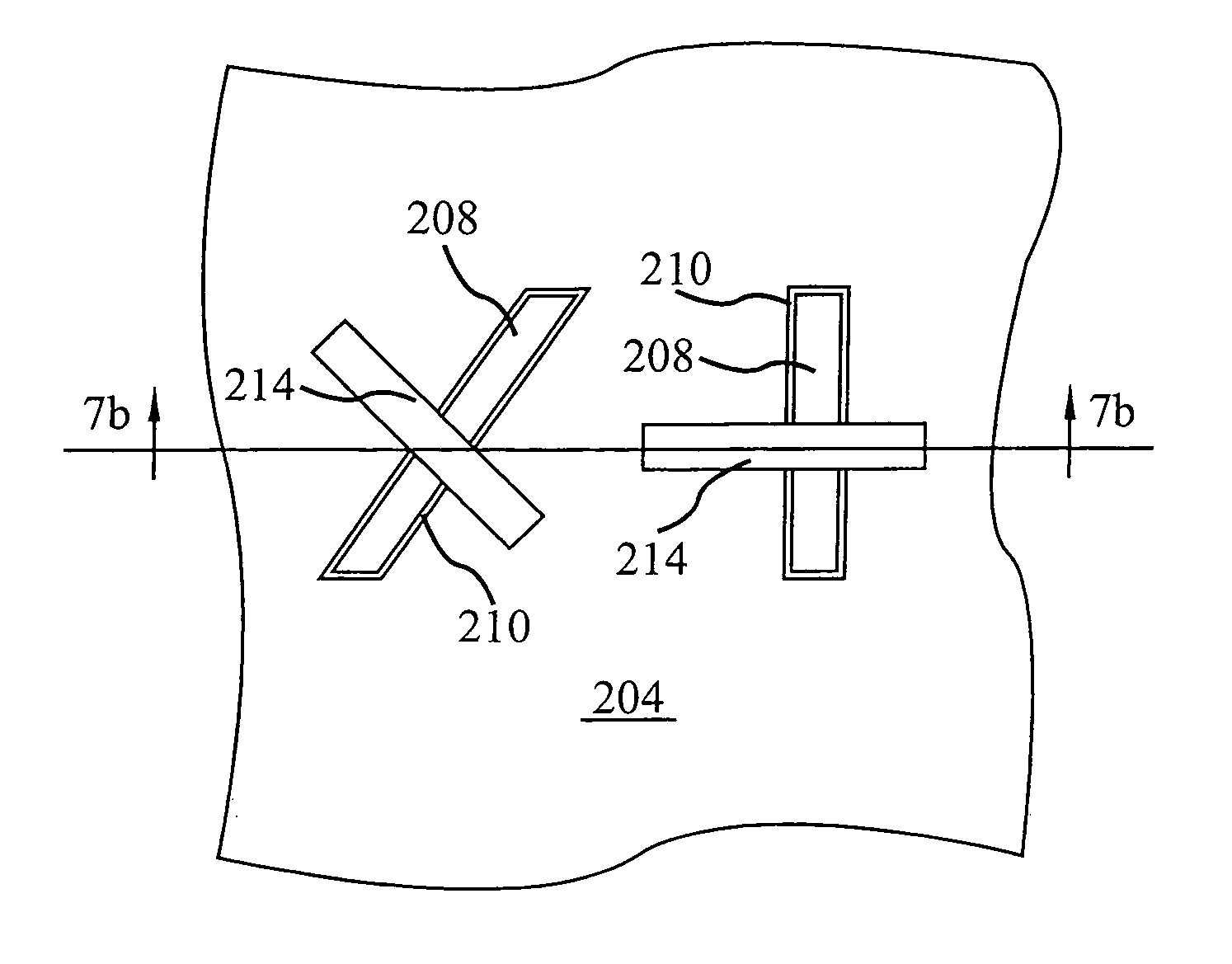

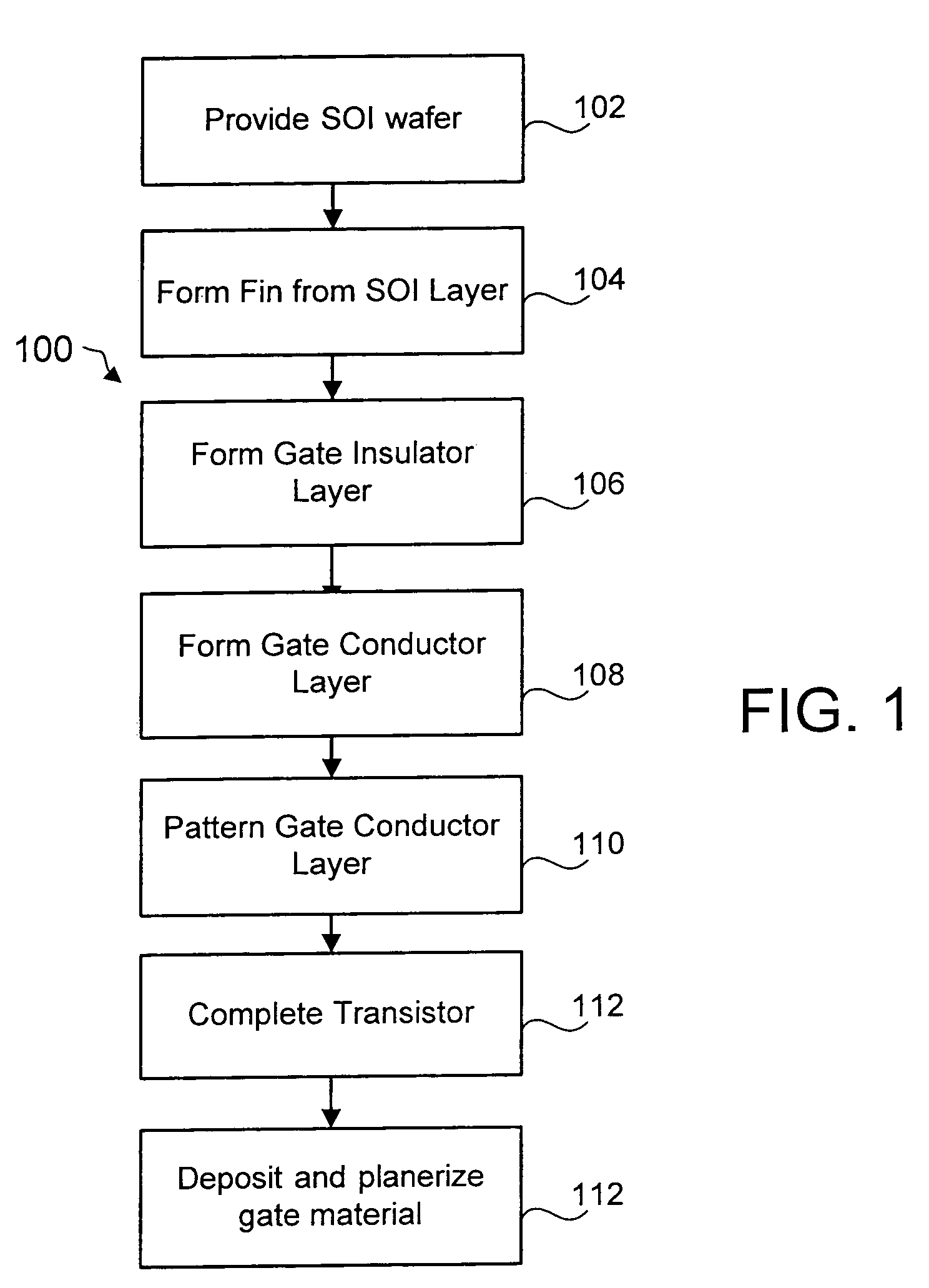

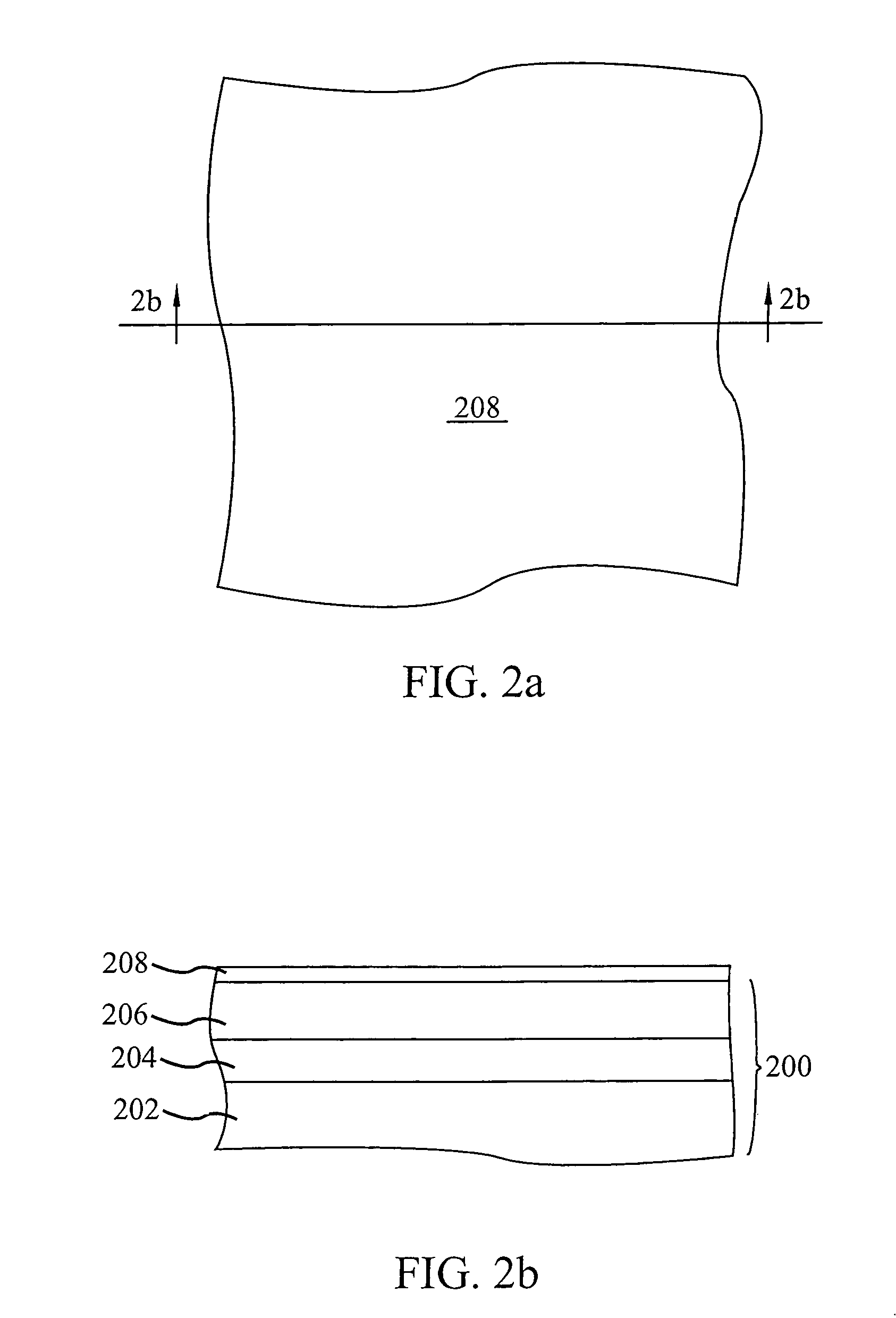

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS7087477B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES INC

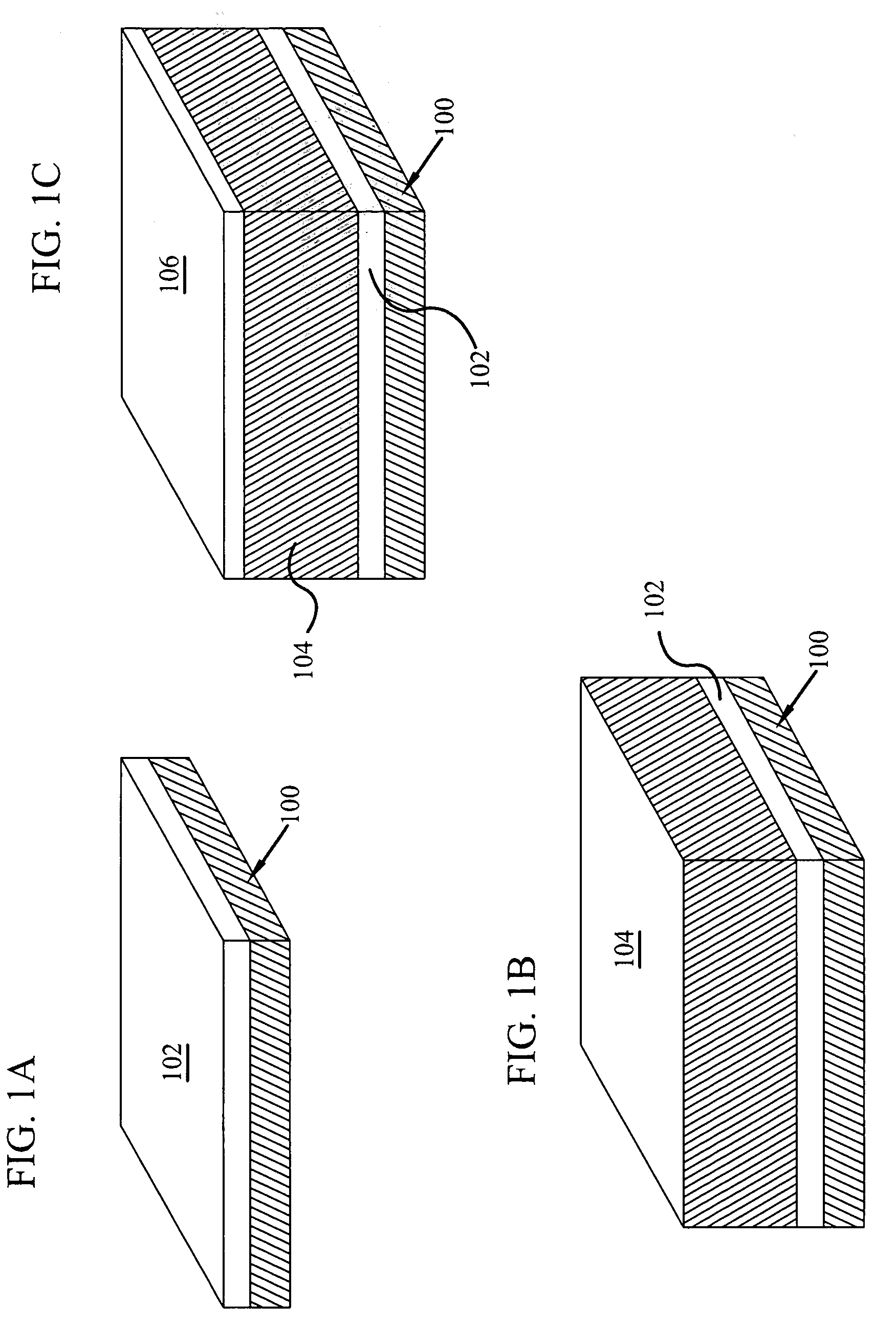

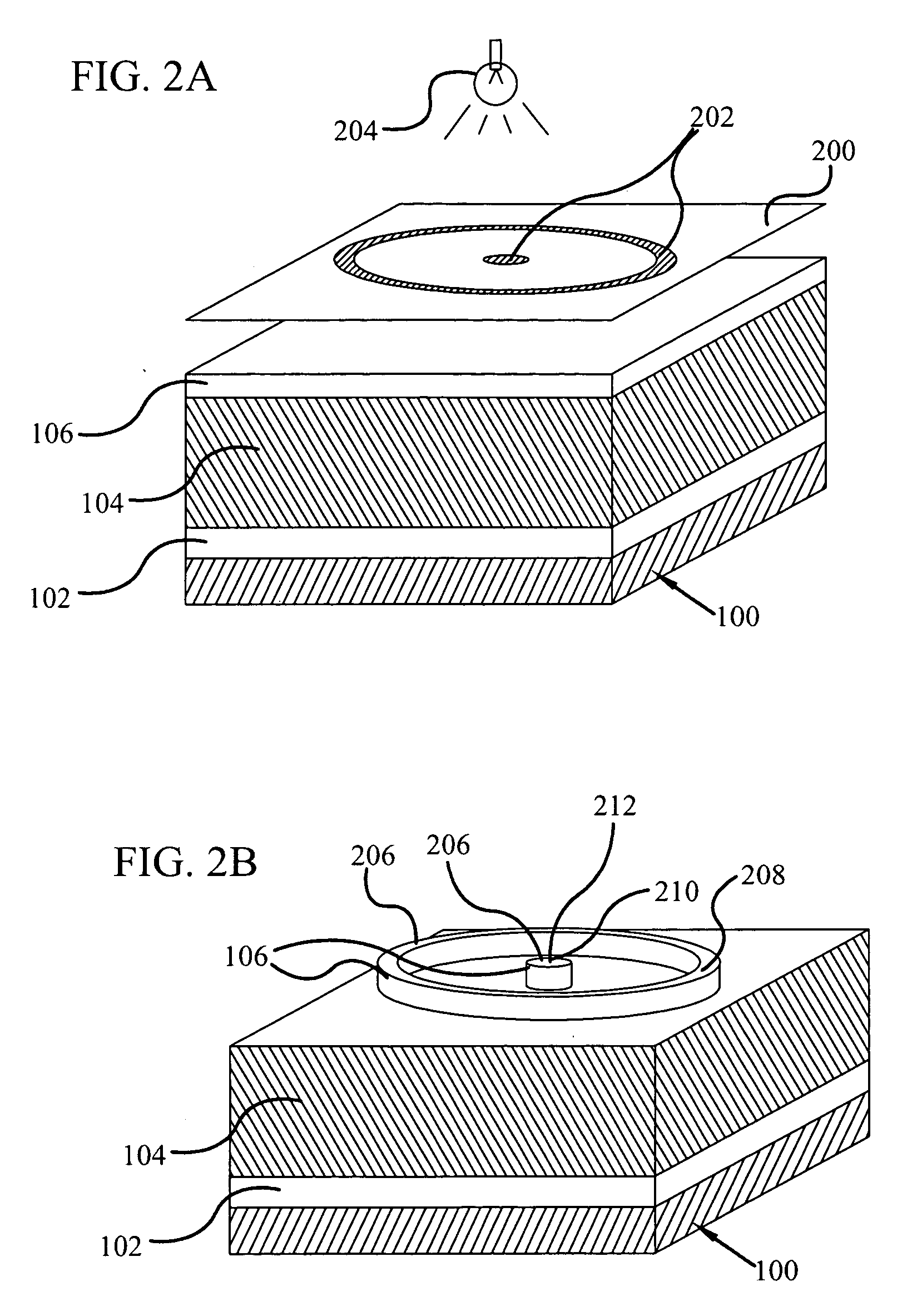

Method of making toroidal MRAM cells

InactiveUS20050158881A1Semiconductor/solid-state device manufacturingDigital storageDielectricStatic random-access memory

This invention provides a method of making nano-scaled toroidal magnetic memory cells, such as may be used, for example, in magnetic random access memory (MRAM). In a particular embodiment a semiconductor wafer substrate is prepared and a conductor layer is provided upon the wafer. A hard layer is deposited upon the first conductor. From the hard layer, ion etching is employed to form an annular wall about a pillar, the wall and pillar defining an annular slot. A ferromagnetic data layer is deposited within the annular slot and a junction stack is then provided upon at least a portion of the data layer. A dielectric is applied to insulate the structure and then planarized to expose the pillar.

Owner:DATA QUILL

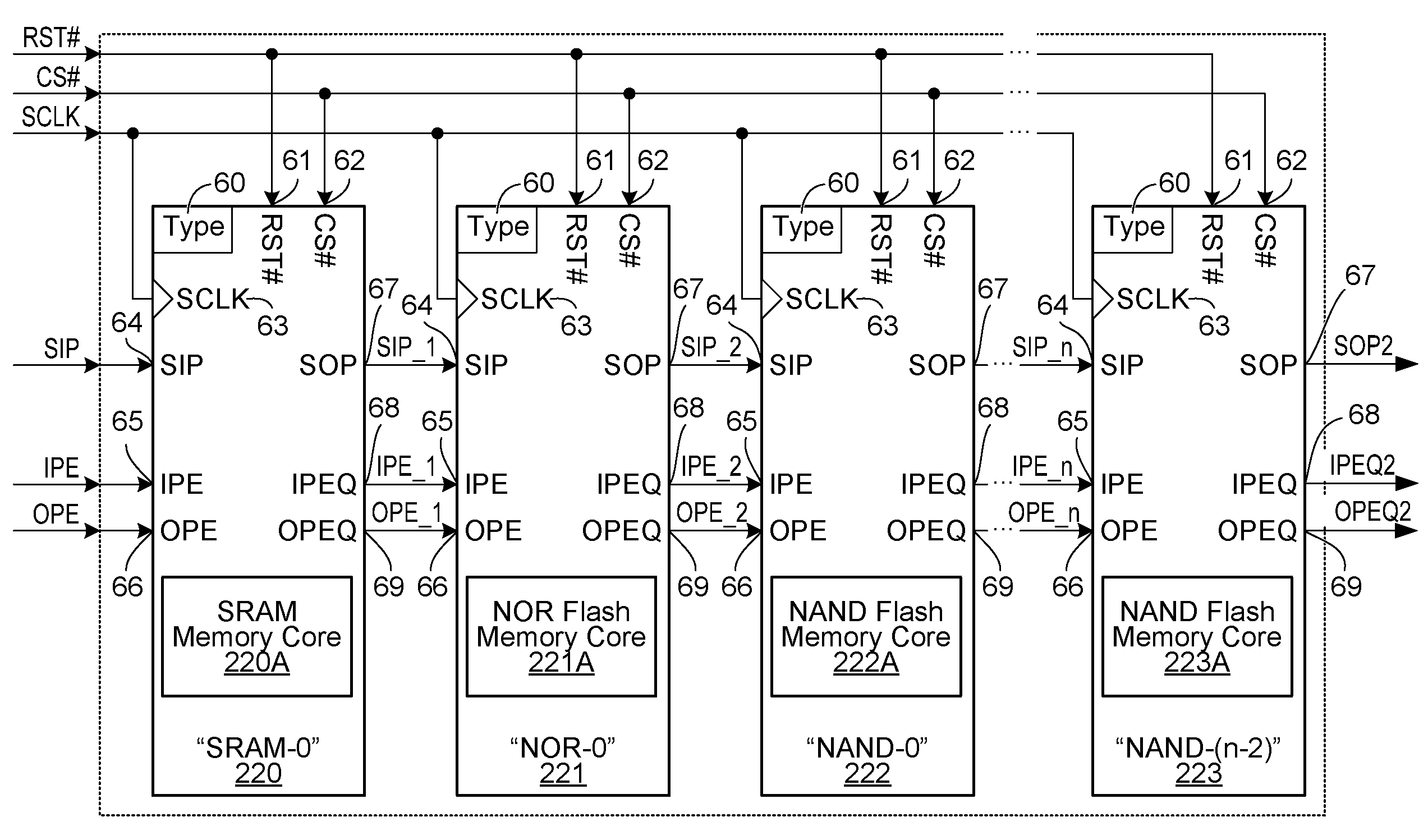

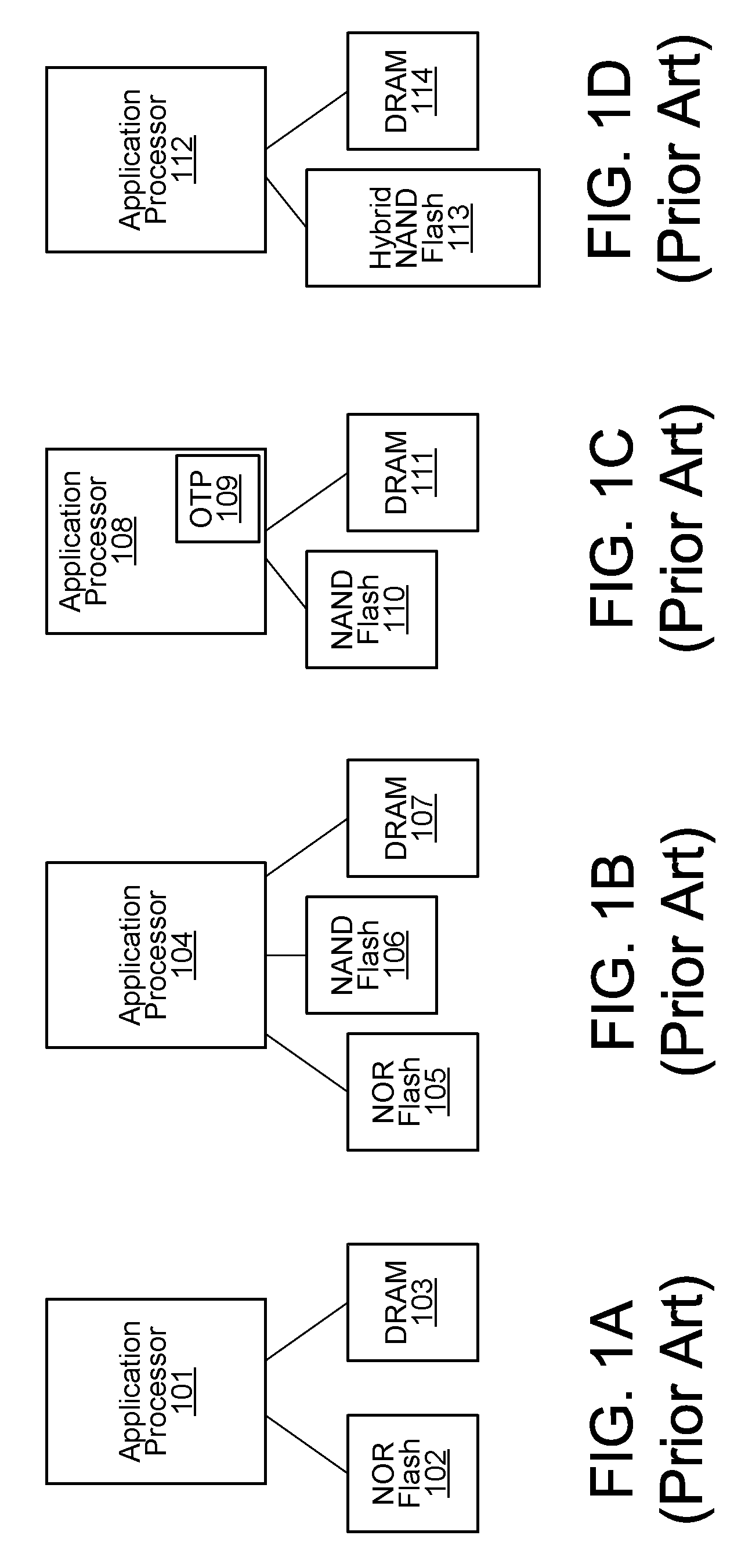

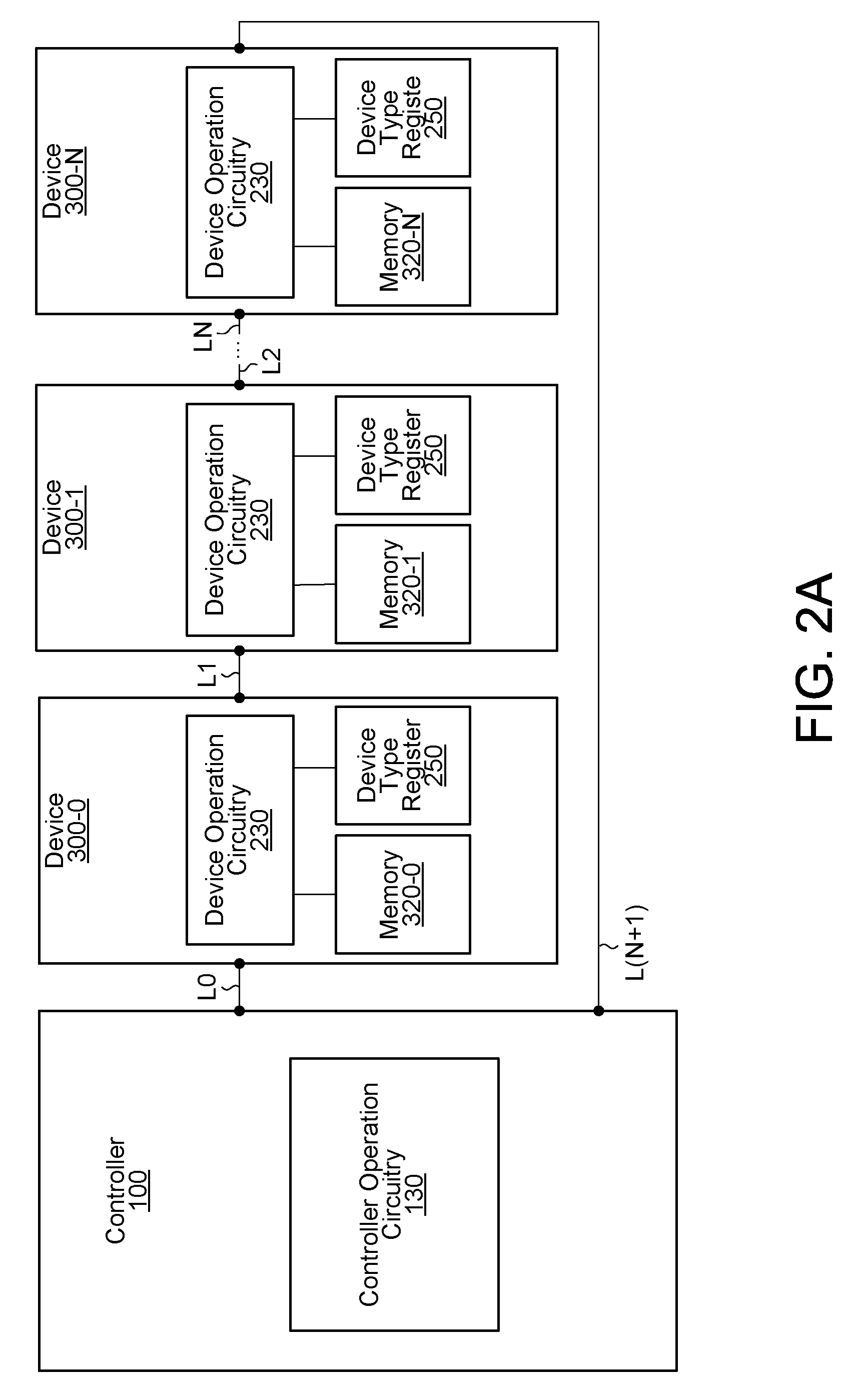

System and method of operating memory devices of mixed type

InactiveUS20080140916A1Memory adressing/allocation/relocationRead-only memoriesHybrid typeStatic random-access memory

A memory system architecture is provided in which a memory controller controls memory devices in a serial interconnection configuration. The memory controller has an output port for sending memory commands and an input port for receiving memory responses for those memory commands requisitioning such responses. Each memory device includes a memory, such as, for example, NAND-type flash memory, NOR-type flash memory, random access memory and static random access memory. Each memory command is specific to the memory type of a target memory device. A data path for the memory commands and the memory responses is provided by the interconnection. A given memory command traverses memory devices in order to reach its intended memory device of the serial interconnection configuration. Upon its receipt, the intended memory device executes the given memory command and, if appropriate, sends a memory response to a next memory device. The memory response is transferred to the memory controller.

Owner:CONVERSANT INTPROP MANAGEMENT INC

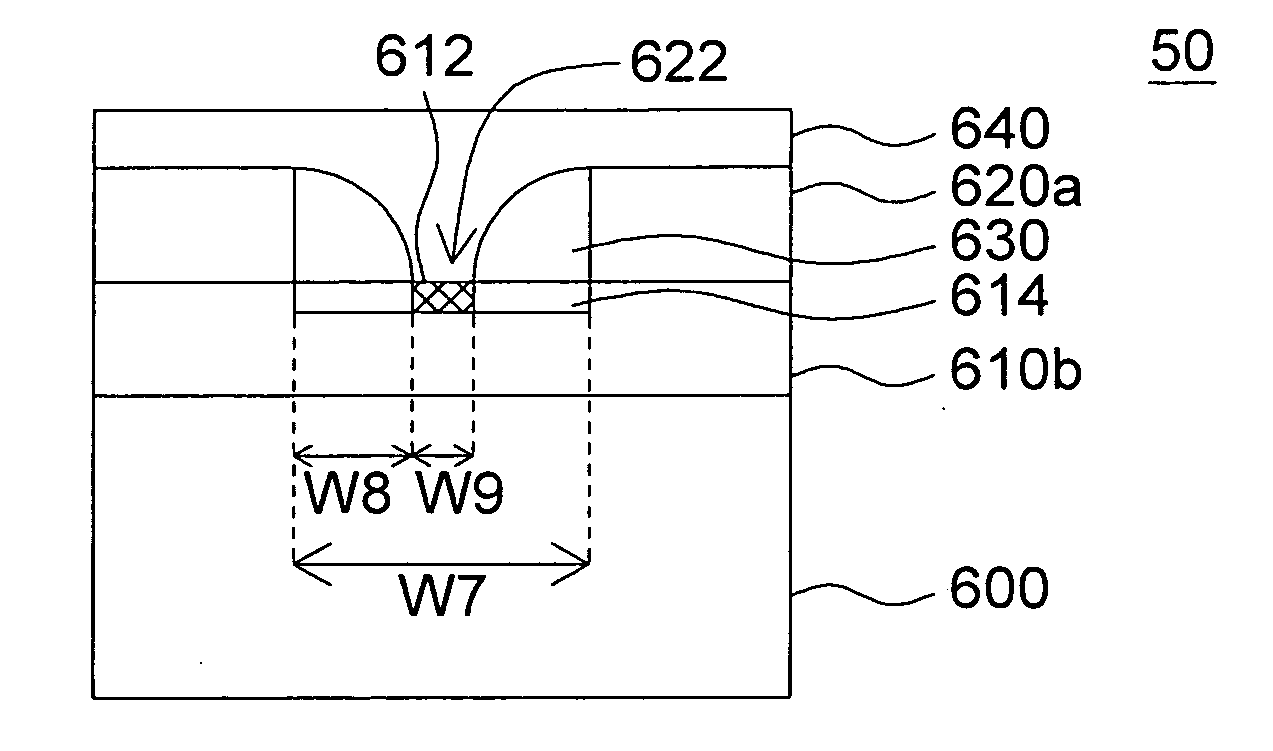

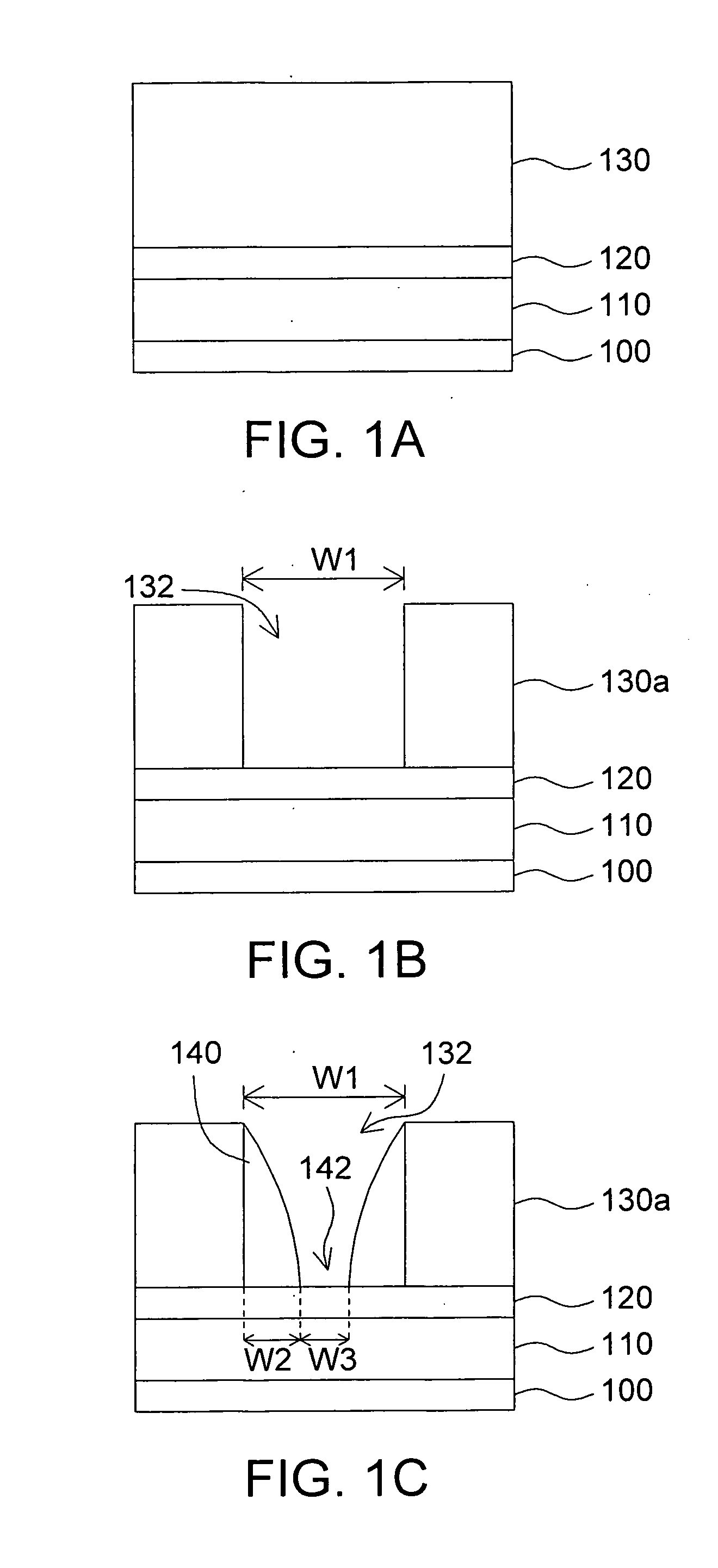

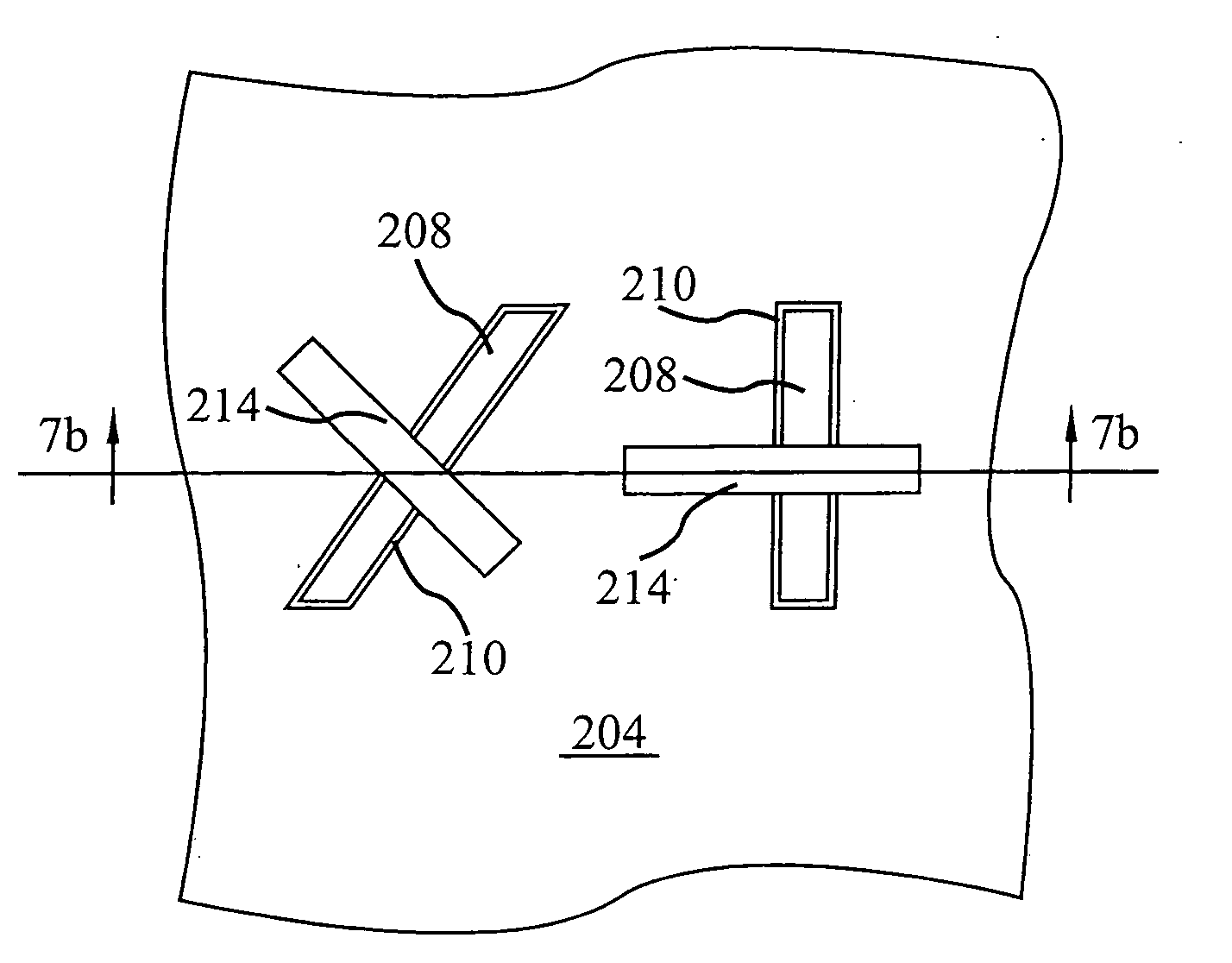

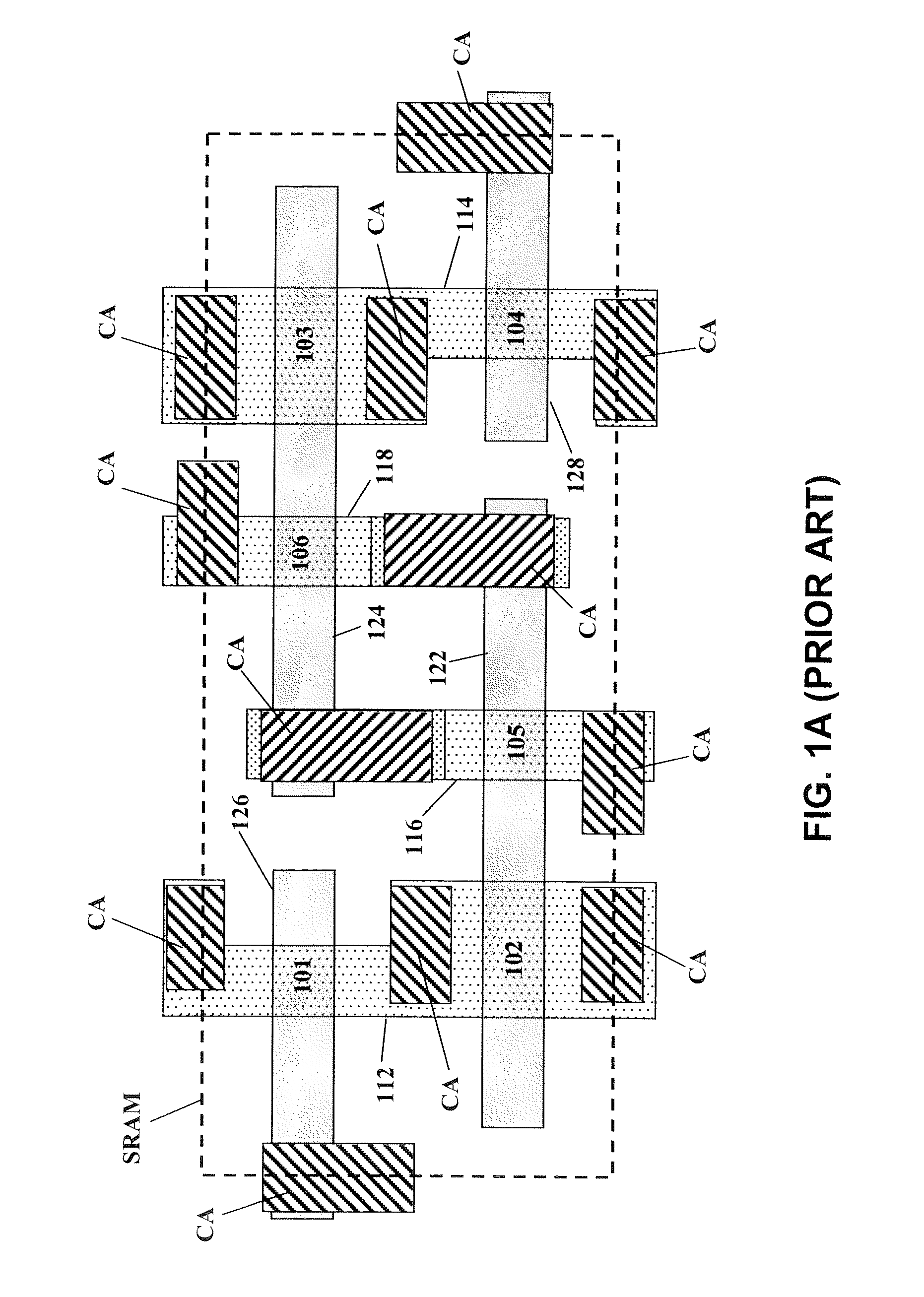

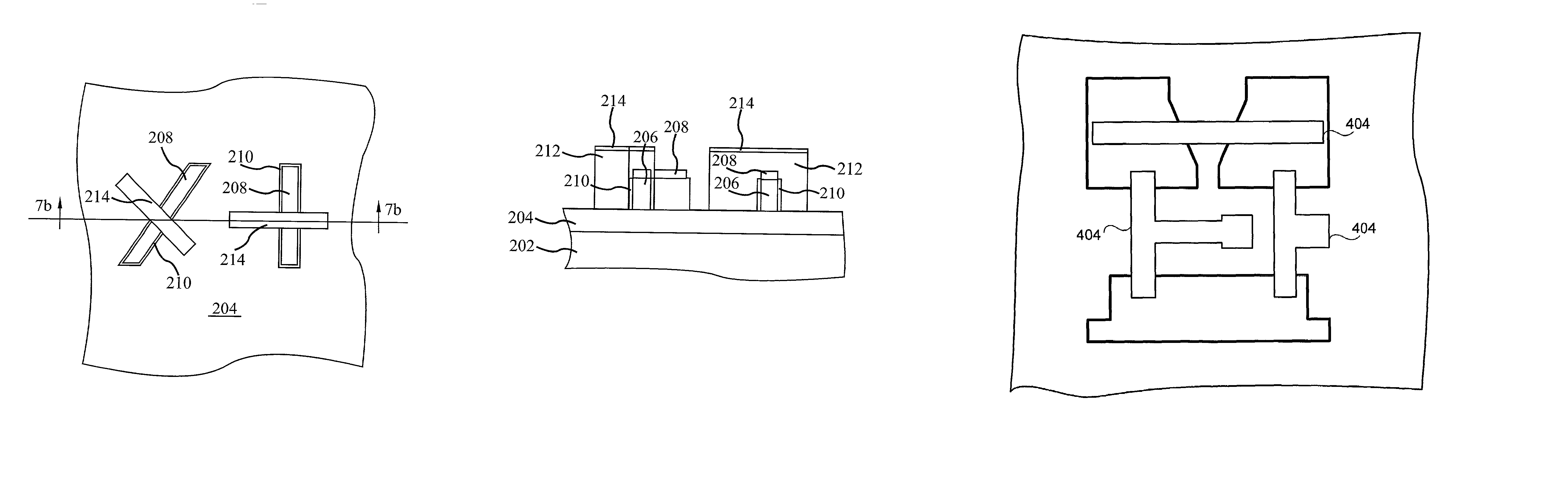

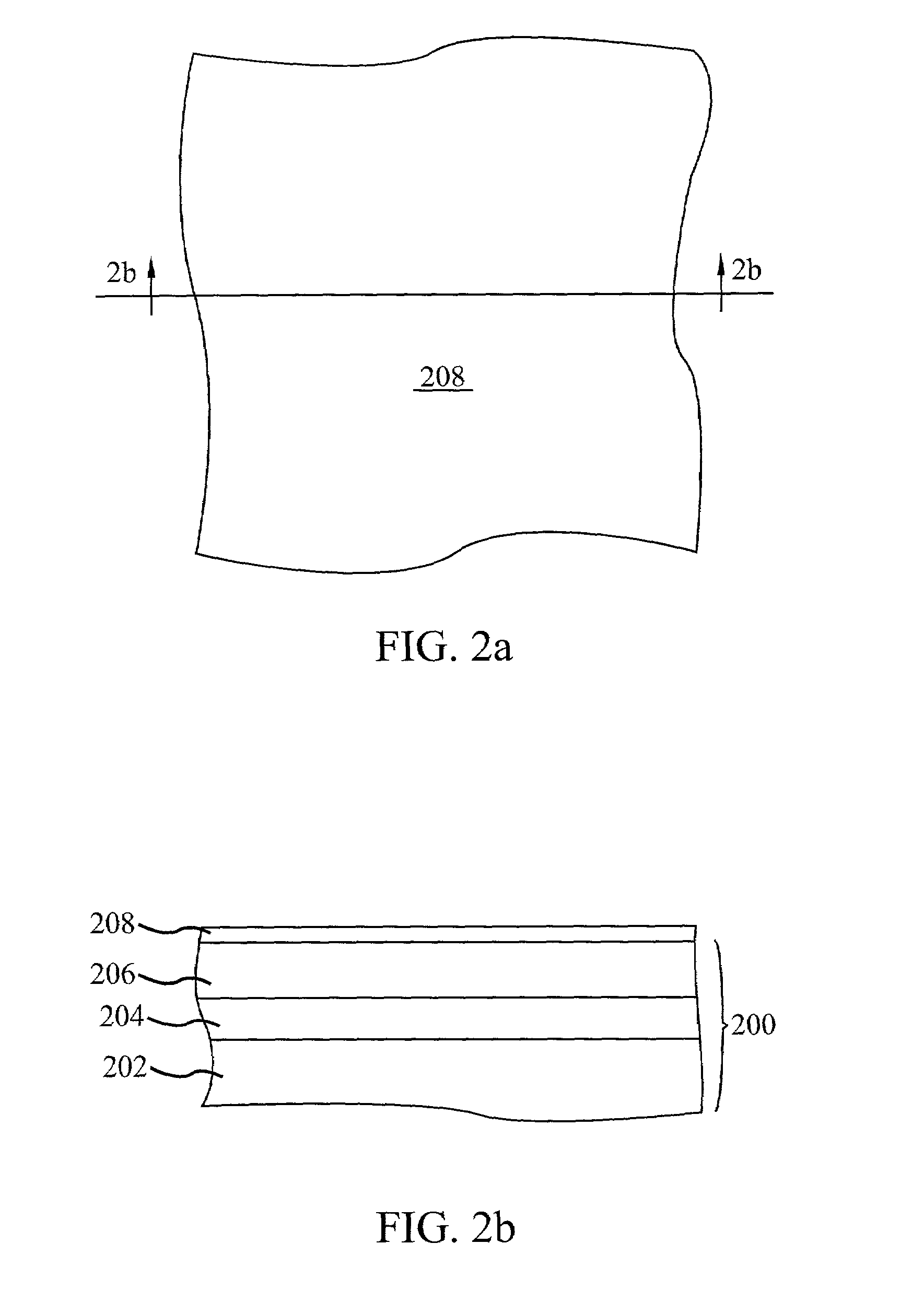

Sub-lithographic local interconnects, and methods for forming same

InactiveUS20080083991A1Achieve scaleReduce in quantityTransistorSemiconductor/solid-state device detailsStatic random-access memorySram cell

The present invention relates to a semiconductor device having first and second active device regions that are located in a semiconductor substrate and are isolated from each other by an isolation region therebetween, while the semiconductor device contains a first sub-lithographic interconnect structure having a width ranging from about 20 nm to about 40 nm for connecting the first active device region with the second active device region. The semiconductor device preferably contains at least one static random access memory (SRAM) cell located in the semiconductor substrate, and the first sub-lithographic interconnect structure directly cross-connects a pull-down transistor of the SRAM cell with a pull-up transistor thereof without any metal contact therebetween. The first sub-lithographic interconnect structure can be readily formed by lithographic patterning of a mask layer, followed by formation of sub-lithographic features using either self-assembling block copolymers or dielectric sidewall spacers.

Owner:IBM CORP

Finfet SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS6967351B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES U S INC

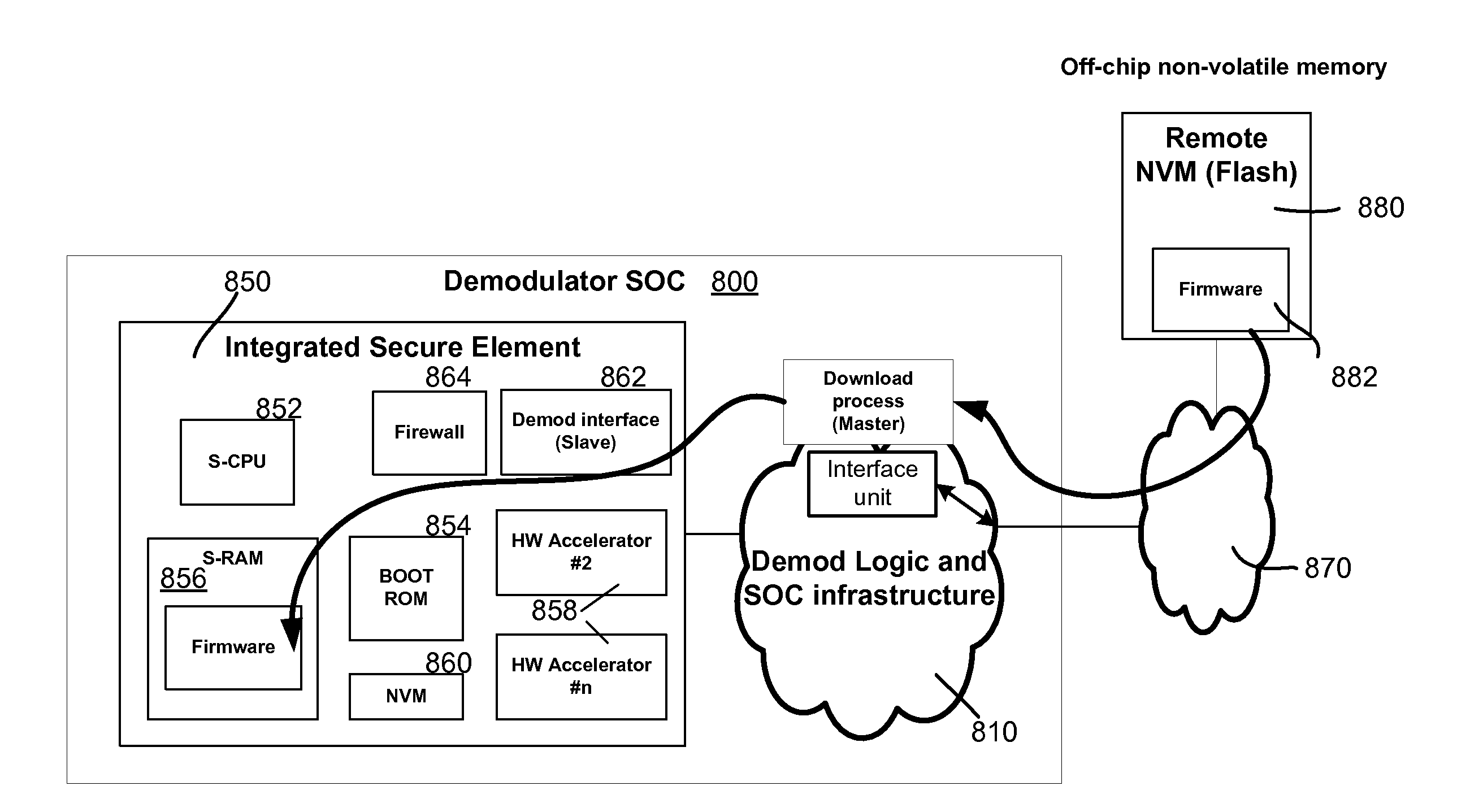

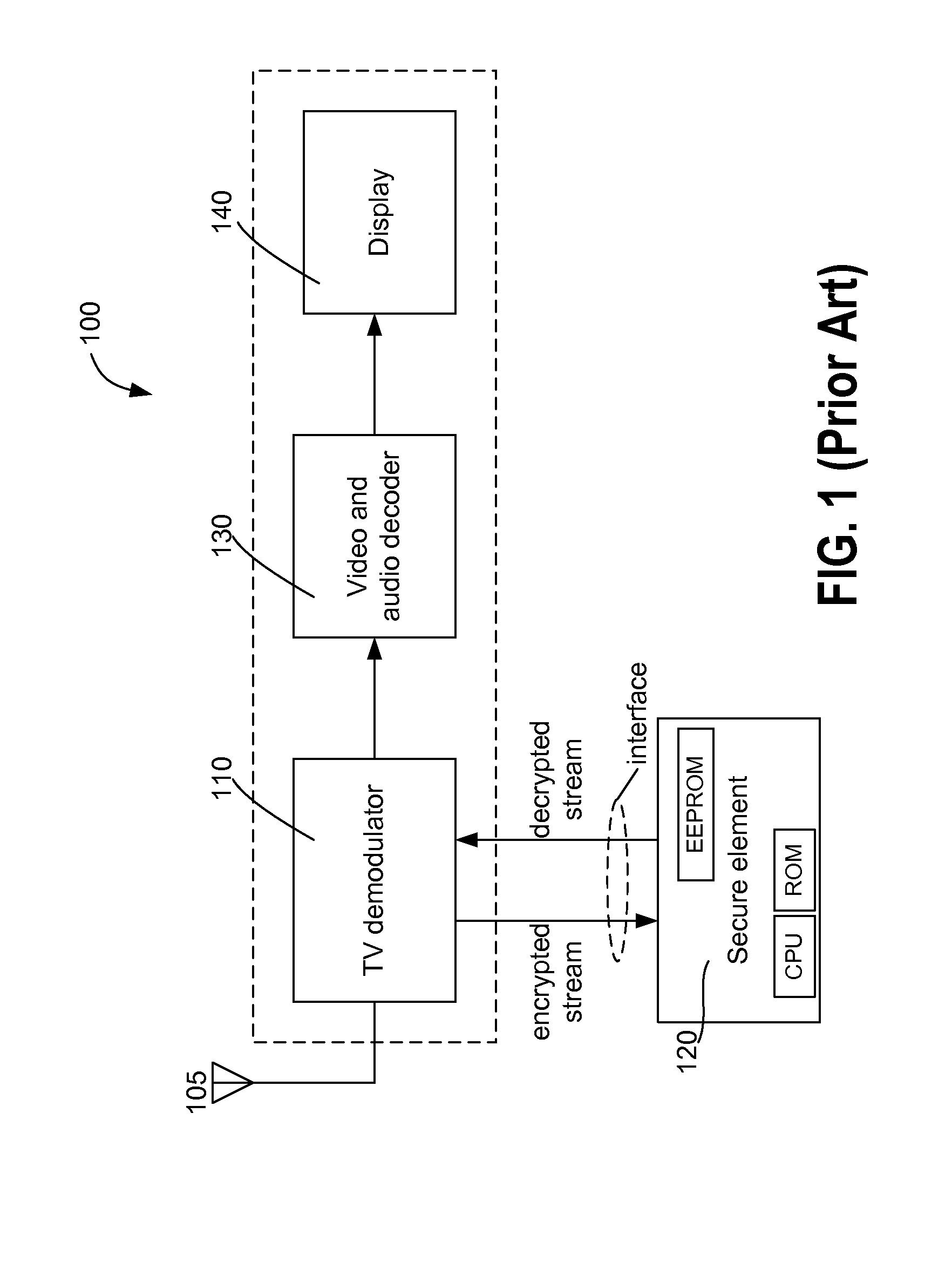

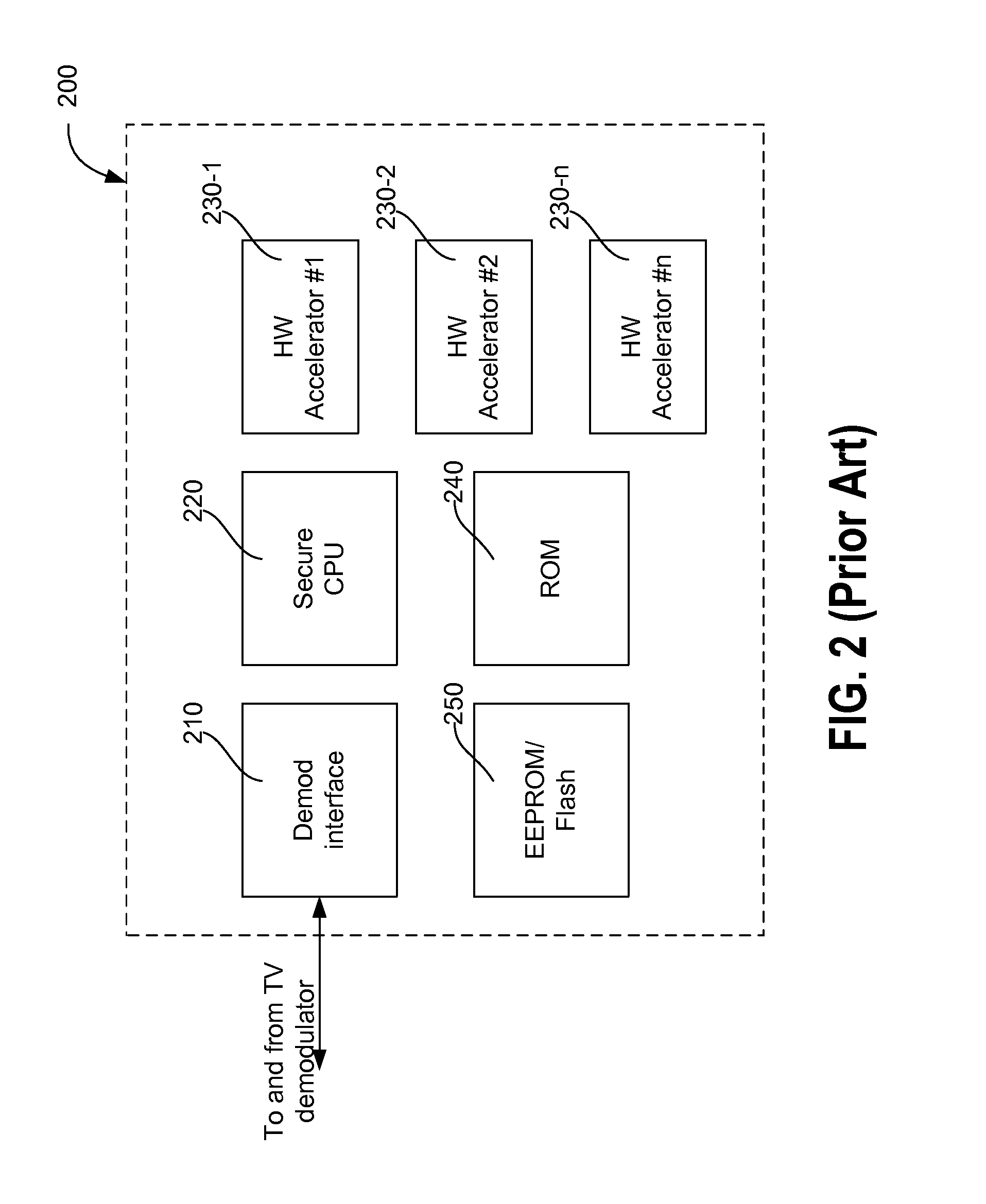

Firmware Authentication and Deciphering for Secure TV Receiver

InactiveUS20120079287A1Unauthorized memory use protectionHardware monitoringStatic random-access memoryTelevision receivers

A method for authenticating and deciphering an encrypted program file for execution by a secure element includes receiving the program file and a digital certificate that is associated with the program file from an external device. The method stores the program file and the associated certificate in a secure random access memory disposed in the secure element and hashes the program file to obtain a hash. The method authenticates the program file by comparing the obtained hash with a checksum that is stored in the certificate. Additionally, the method writes runtime configuration information stored in the certificate to corresponding configuration registers disposed in the secure element. The method further generates an encryption key using a seed value stored in the certificate and a unique identifier disposed in the secure element and deciphers the program file using the generated encryption key.

Owner:RADIOXIO LLC

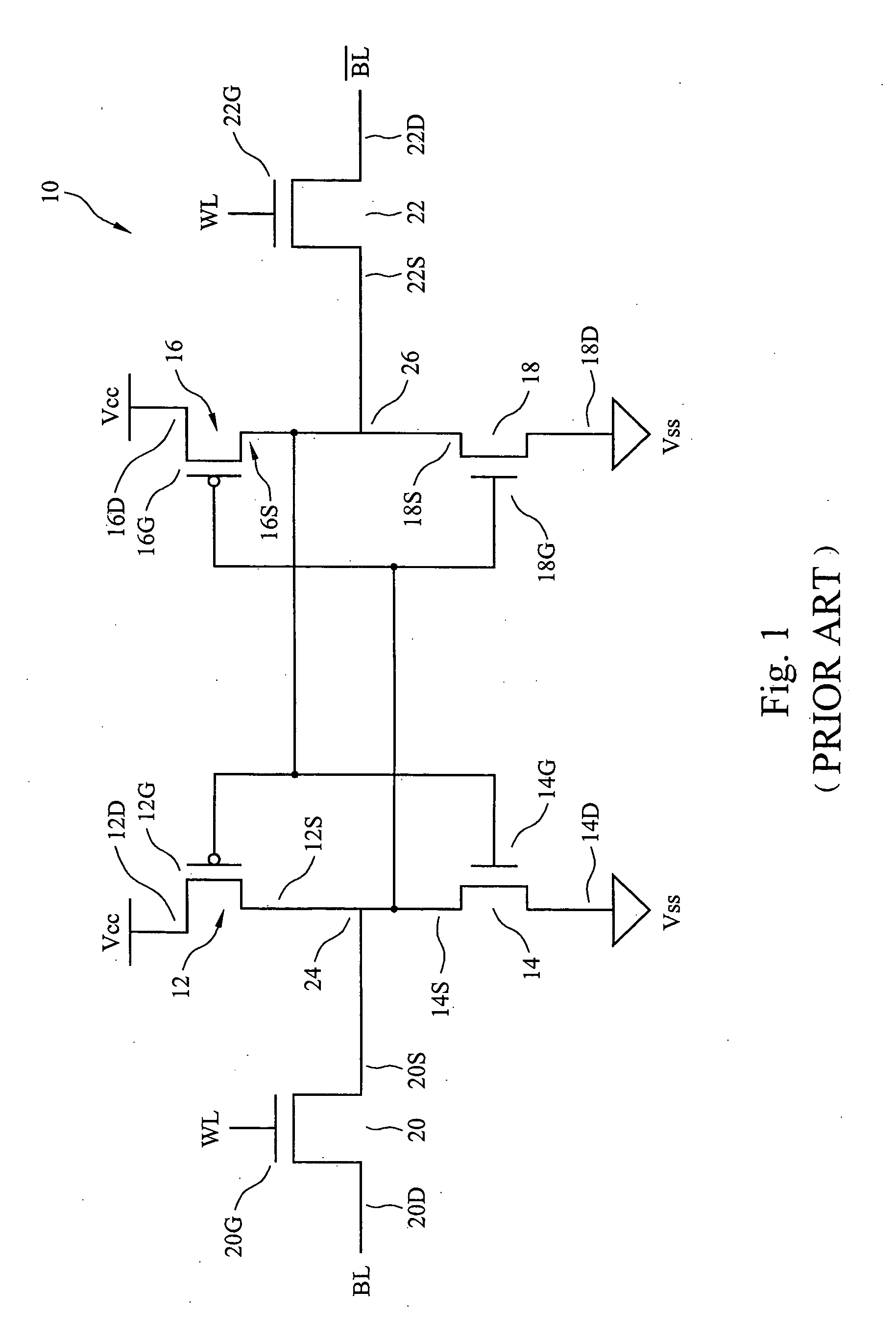

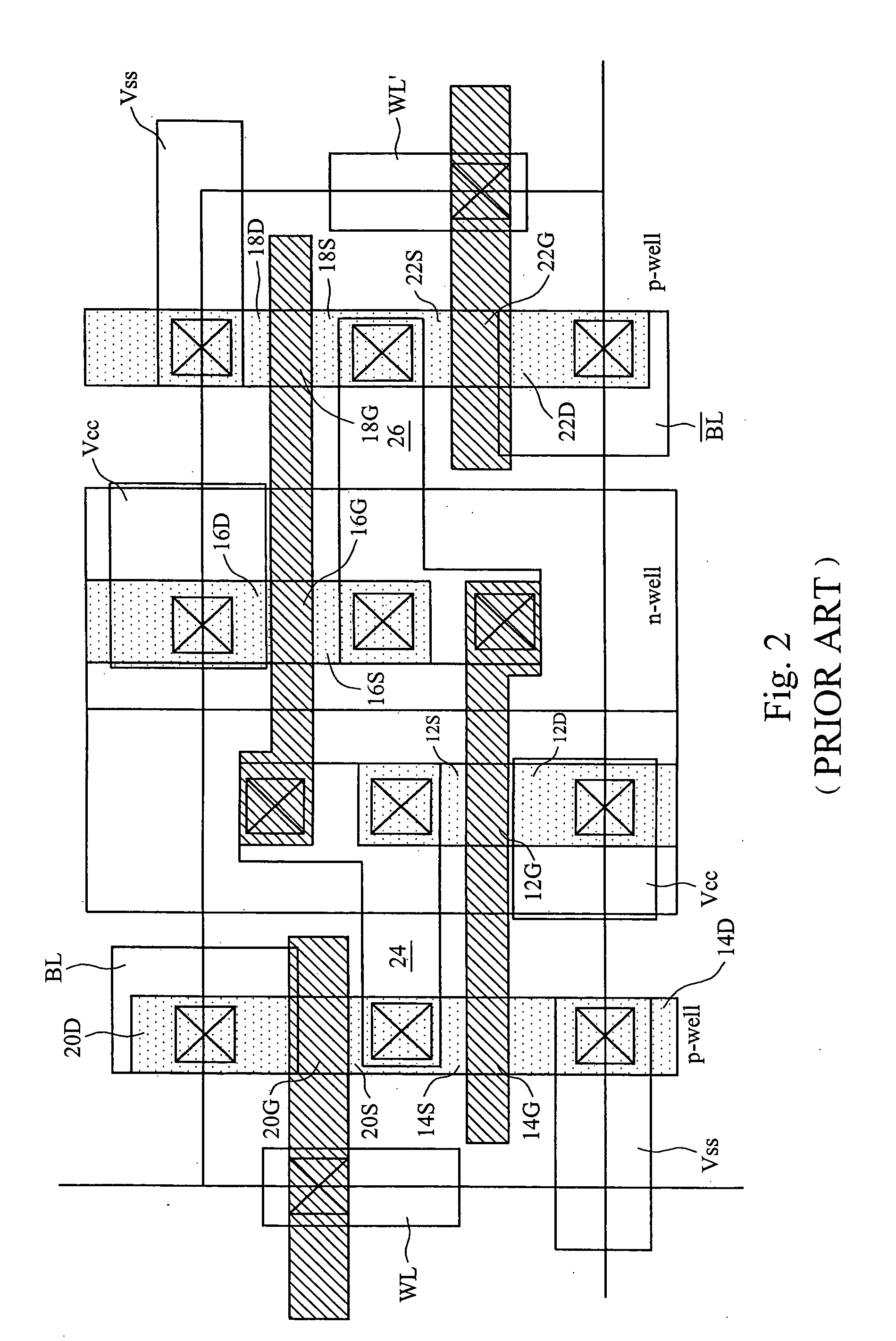

CMOS SRAM cell configured using multiple-gate transistors

InactiveUS6864519B2High dielectric constantSave layout area andTransistorSemiconductor/solid-state device detailsCMOSBit line

A complementary metal-oxide-semiconductor static random access memory cell that is formed by a pair of P-channel multiple-gate field-effect transistors (P-MGFETs), a pair of N-channel multiple-gate field-effect transistors (N-MGFETs), a second pair of N-MGFETs that has a drain respectively connected to a connection linking the respective drain of the N-MGFET of the first pair of N-MGFET to the drain of the P-MGFET of the pair of P-MGFETs; a pair of complementary bit lines, each respectively connected to the source of the N-MGFET of the second pair of N-MGFETS; and a word line connected to the gates of the N-MGFETs of the second pair of N-MGFETs.

Owner:TAIWAN SEMICON MFG CO LTD

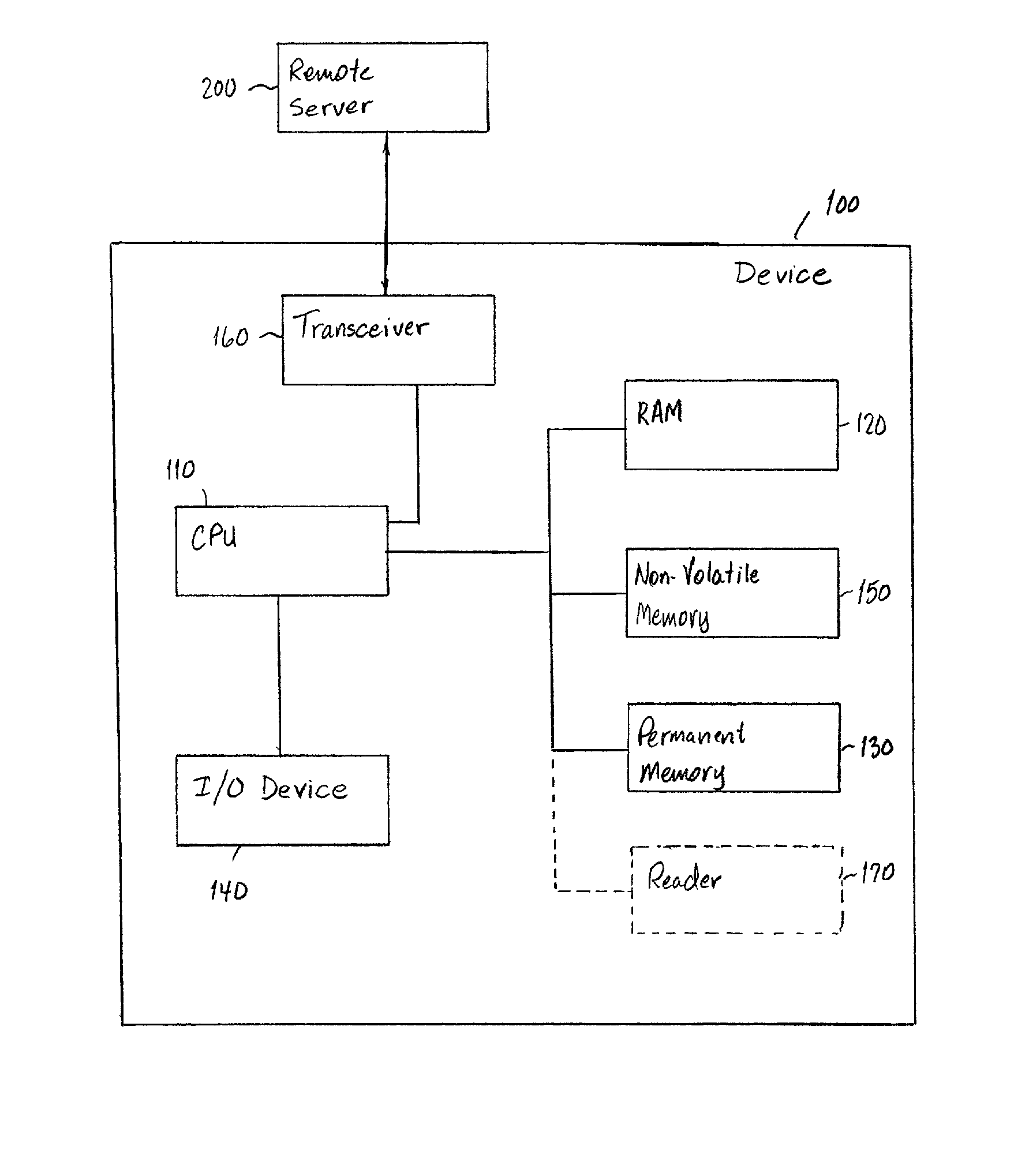

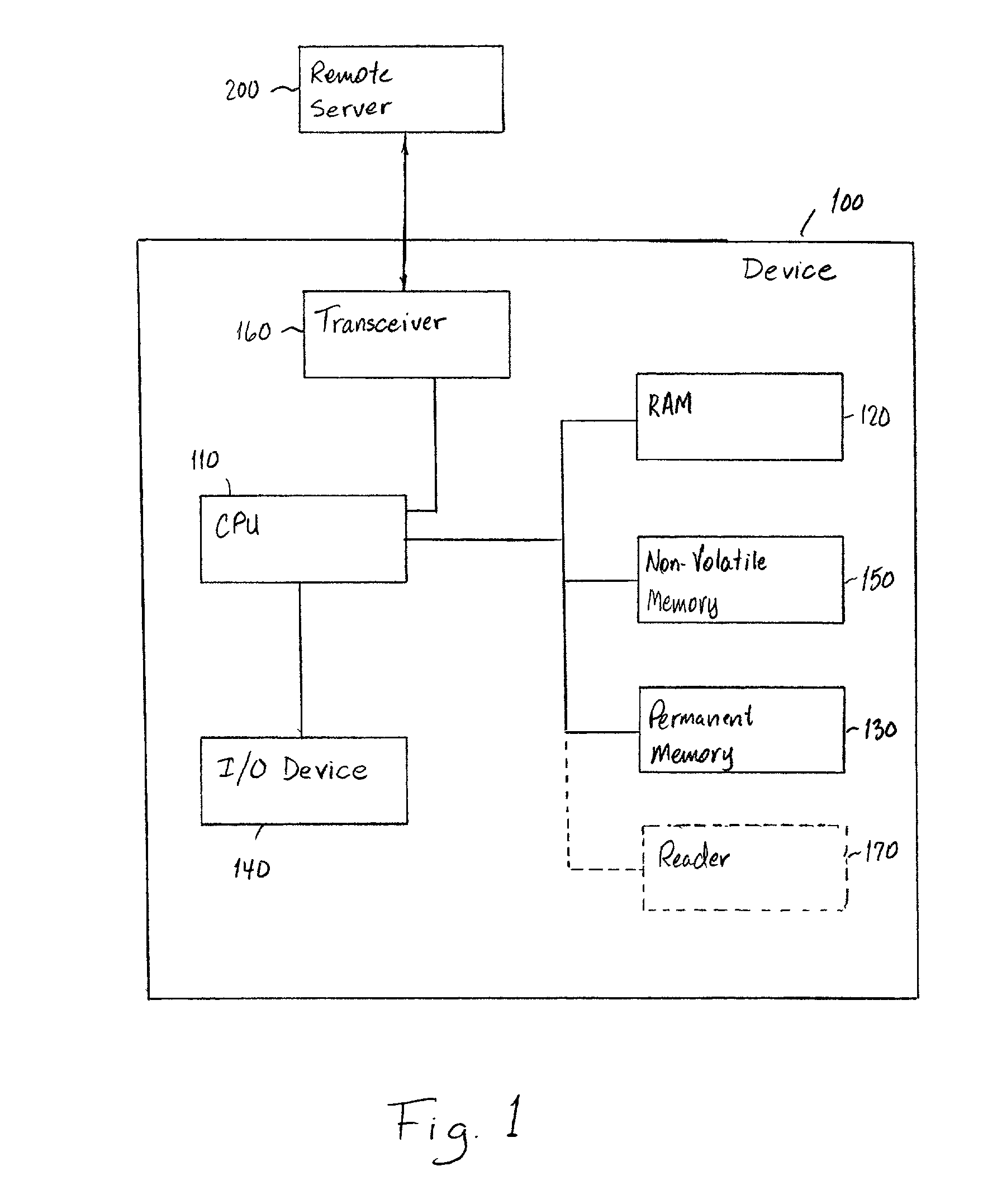

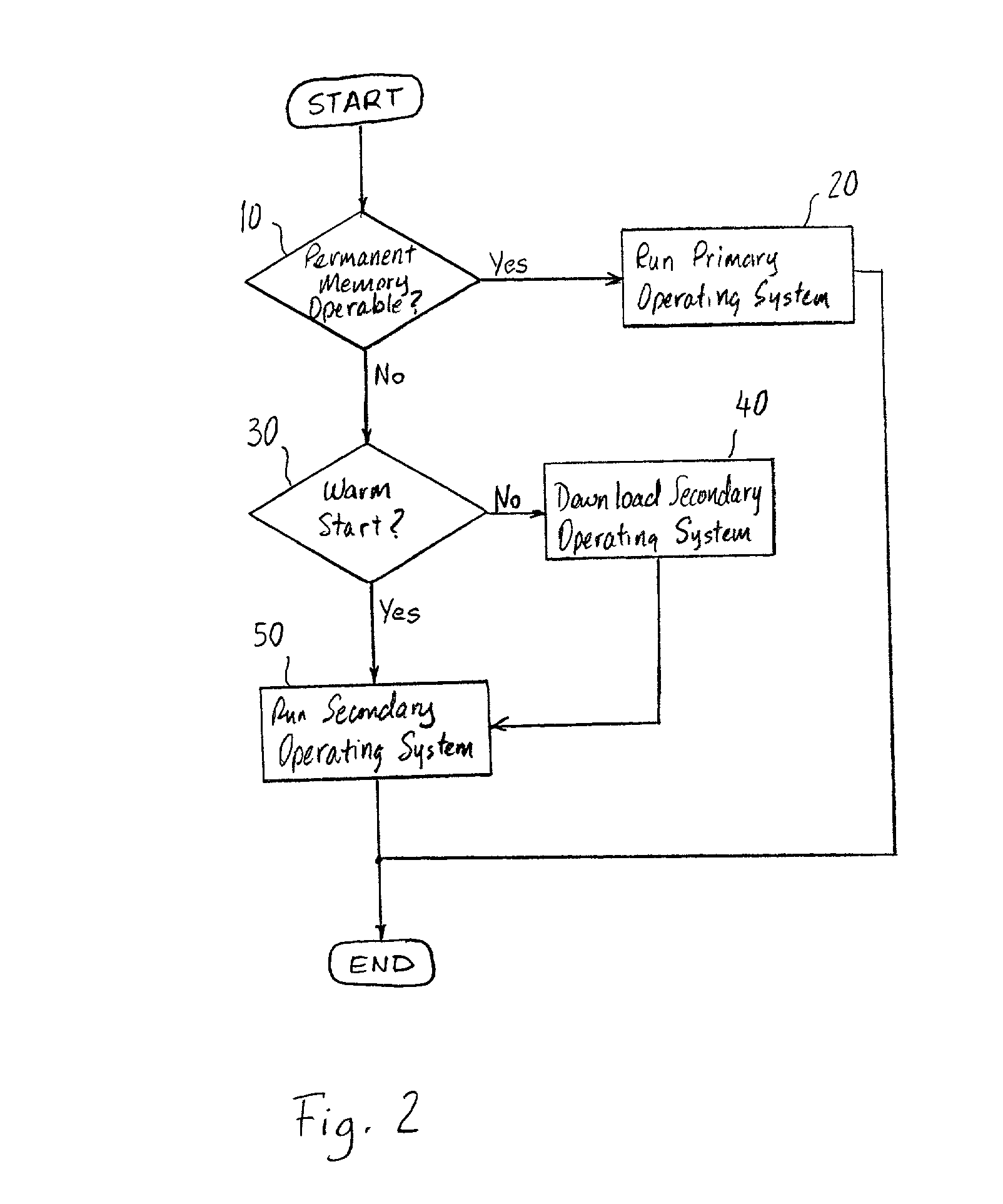

Crash recovery system

A set top box for a television includes a hard drive, a random access memory, and a non-volatile memory. To maintain functionality of the device after a crash of the hard drive, the non-volatile memory includes an executable program for downloading a secondary operating system from a remote server or other secondary storage during a startup when the primary operating system in the hard drive is not accessible. The secondary operating system is stored in the random access memory and is a functional subset of the primary operating system to allow the use of the primary functionality of the set top box until the hard disk drive is repaired or replaced.

Owner:NOKIA TECHNOLOGLES OY

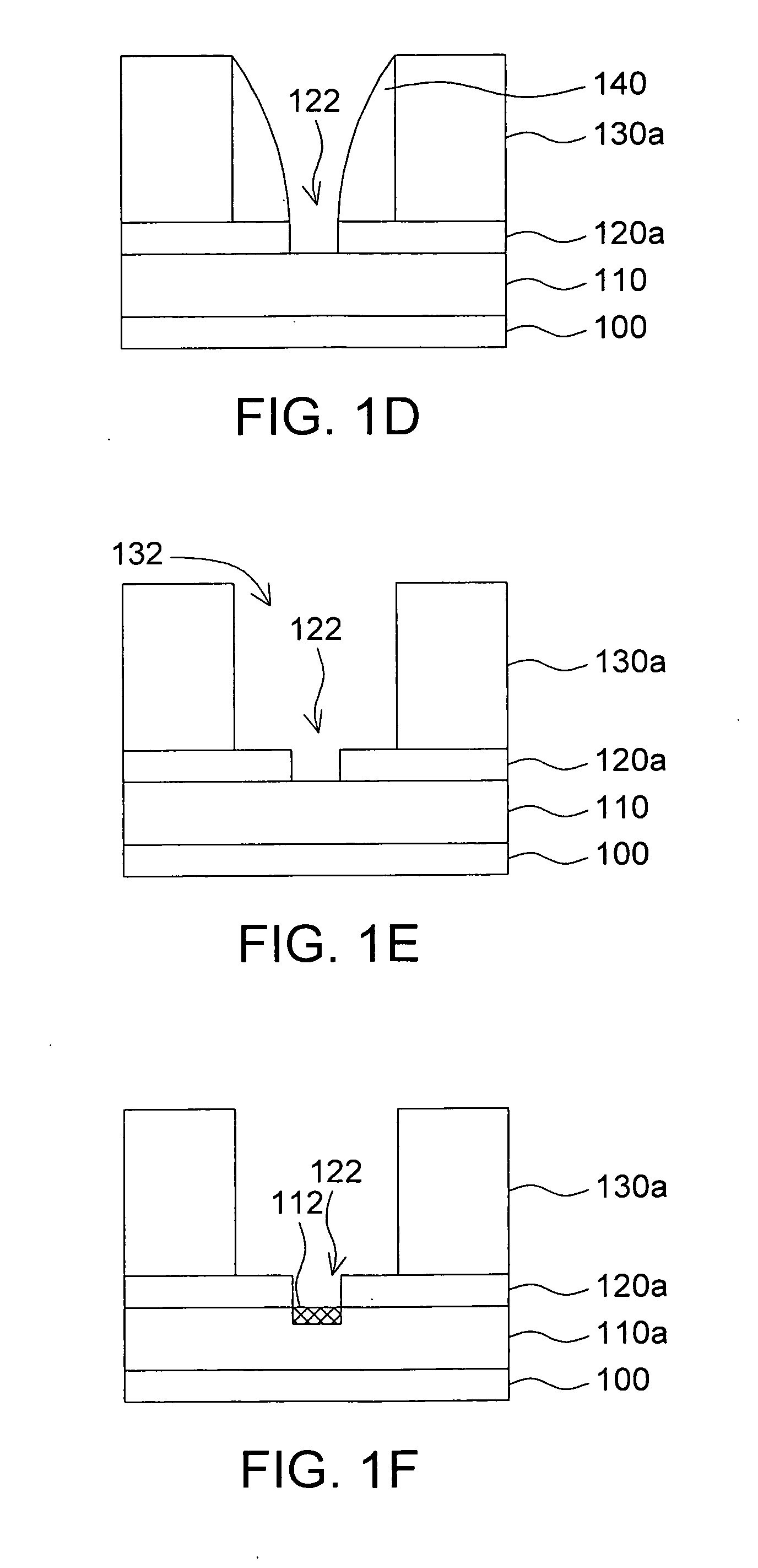

Method of forming a static random access memory with a buried local interconnect

ActiveUS20060019488A1Reduce the numberReduce spacingTransistorSolid-state devicesStatic random-access memoryEngineering

An SRAM cell includes six transistors. The storage nodes are implemented using local interconnects. A first level of metal overlies the interconnects but is electrically isolated therefrom. Contact plugs are formed to couple the cell to the first level of metal. The contact plugs are preferably formed in a different process step than the interconnects.

Owner:TAIWAN SEMICON MFG CO LTD

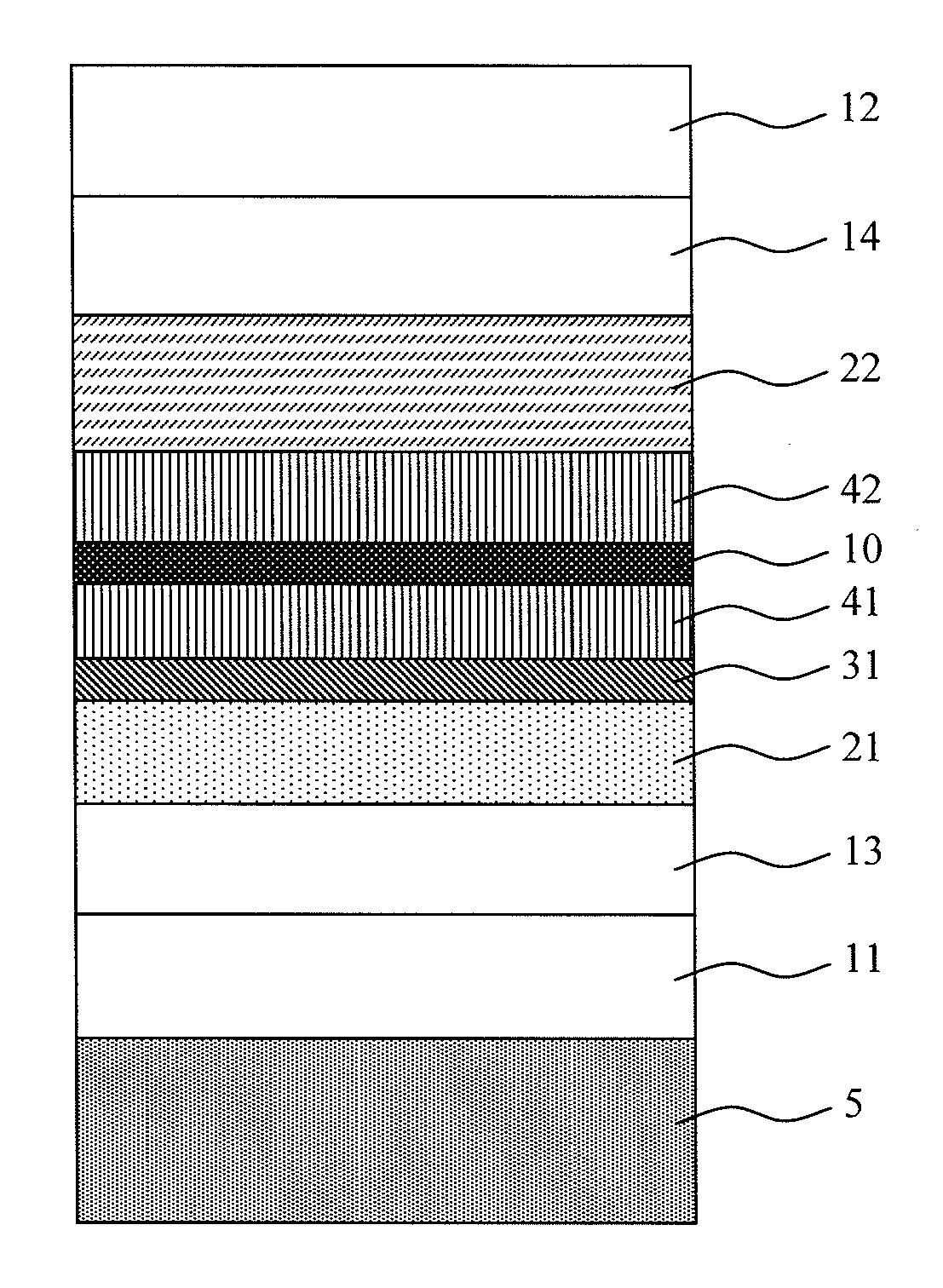

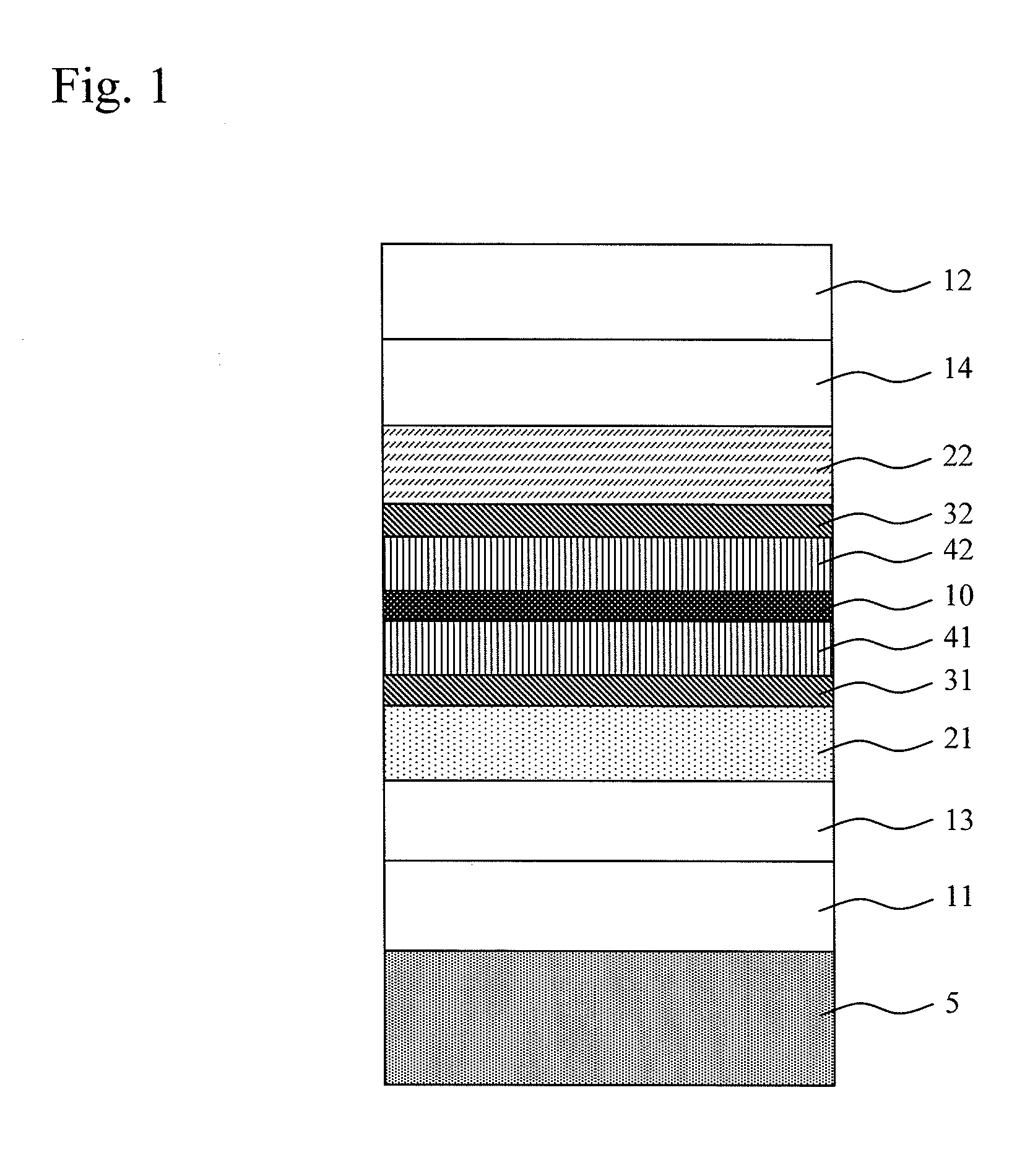

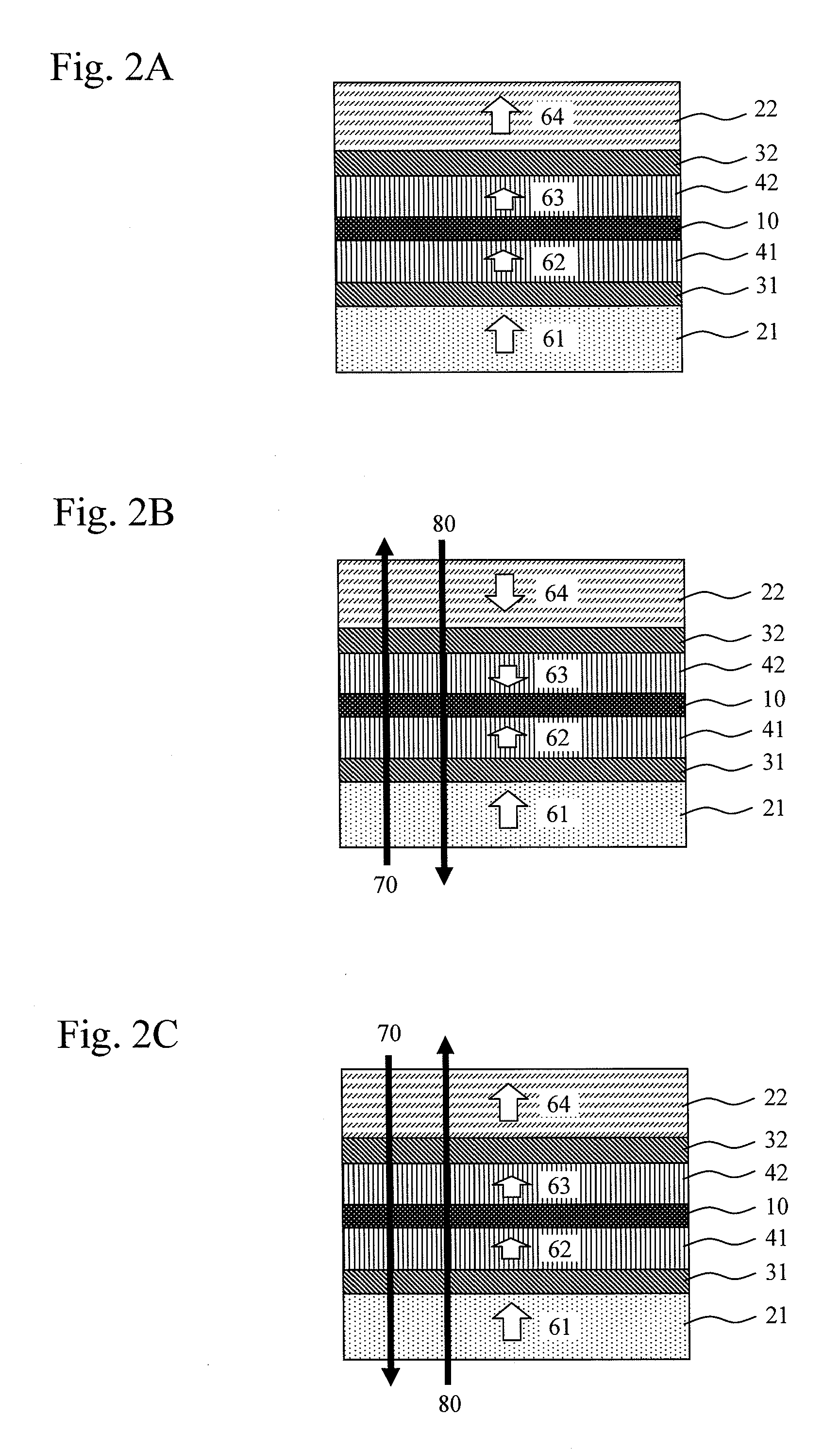

Magnetoresistive effect element, magnetic memory cell using same, and random access memory

ActiveUS20130028013A1Raise the ratioNanomagnetismMagnetic-field-controlled resistorsStatic random-access memoryRandom access memory

Provided is a magnetoresistive effect element which uses a perpendicularly magnetized material and has a high TMR ratio. Intermediate layers 31, 32 composed of an element metal having a melting point of 1600° C. or an alloy containing the metal on an outside of a structure consisting of a CoFeB layer 41, an MgO barrier layer 10, and a CoFeB layer 42. By inserting the intermediate layers 31, 32, crystallization of the CoFeB layer during annealing is advanced from an MgO (001) crystal side, so that the CoFeB layer has a crystalline orientation in bcc (001).

Owner:TOHOKU UNIV

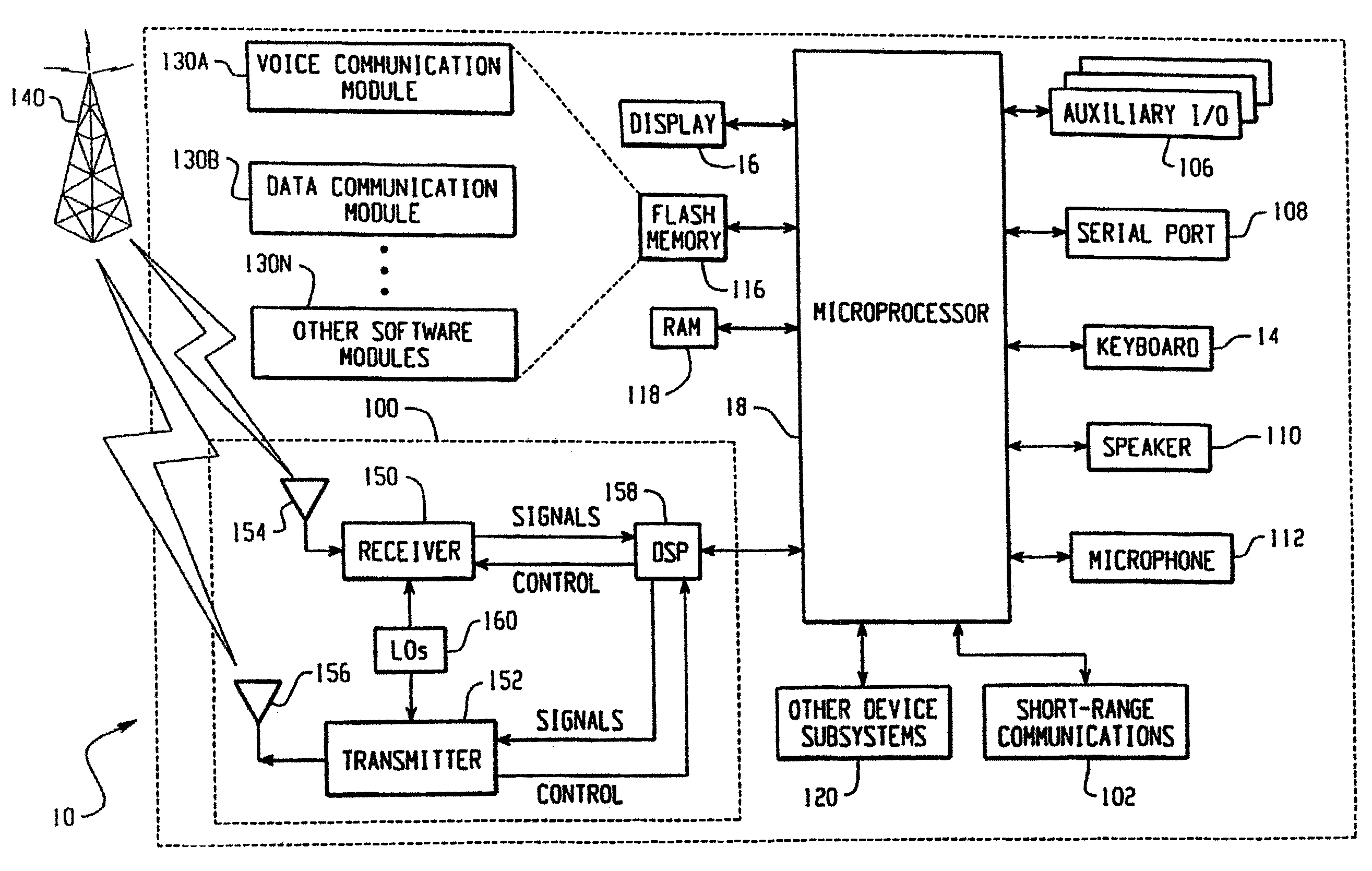

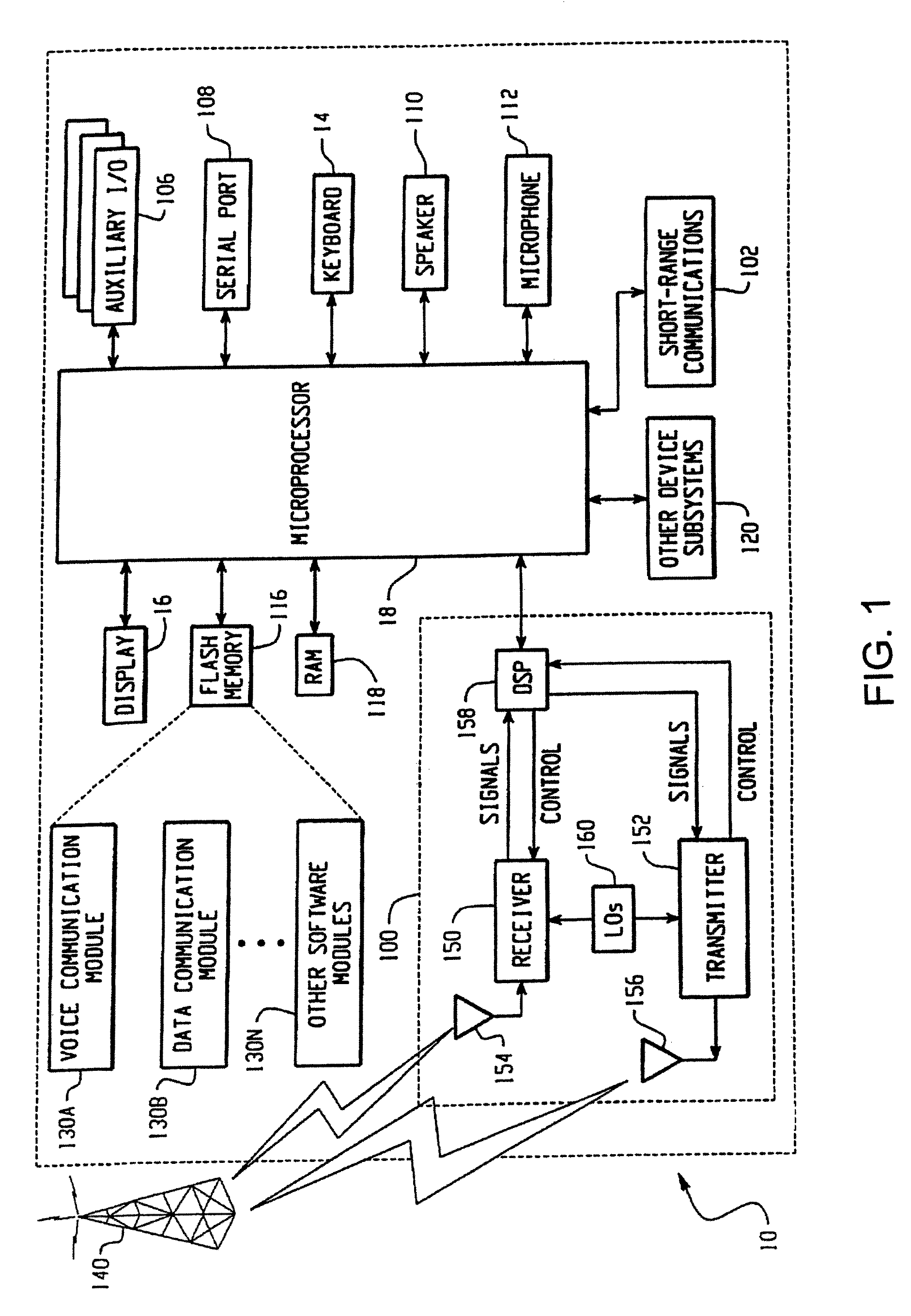

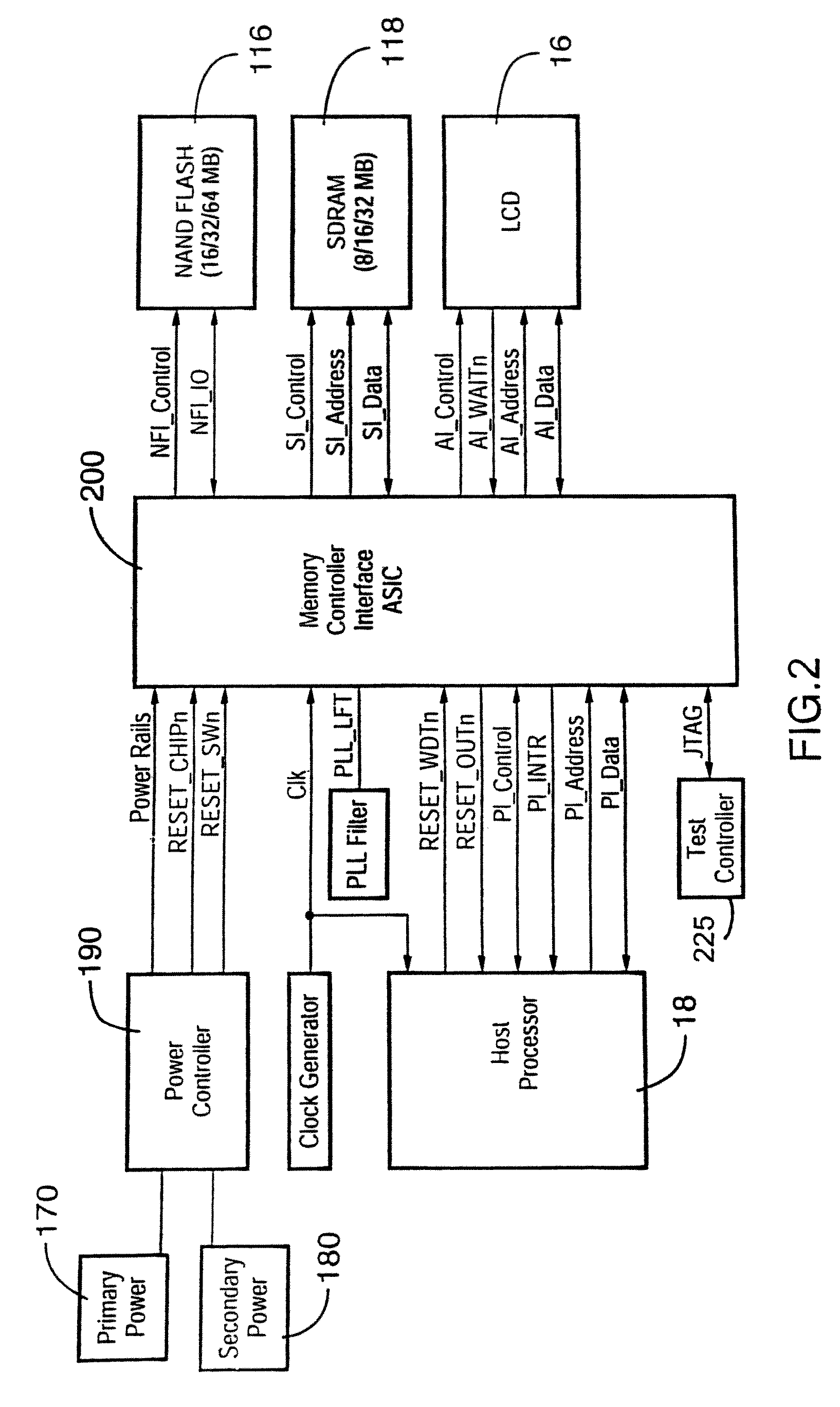

Memory controller interface

ActiveUS7610433B2Memory architecture accessing/allocationMemory loss protectionStatic random-access memoryMemory interface

A memory interface controller and method to allow a processor designed and configured to operate with NOR flash and static random access memory (SRAM) memory devices to instead operate using NAND flash and synchronous dynamic random access memory (SDRAM). The system accomplishes this by caching sectors out of NAND flash into SDRAM, where the data can be randomly accessed by the processor as though it were accessing data from NOR flash / SRAM. Sectors containing data required by the processor are read out of NAND flash and written into SDRAM, where the data can be randomly accessed by the processor.

Owner:MALIKIE INNOVATIONS LTD