Patents

Literature

1601 results about "Low leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electrolytic capacitors with a polymeric outer layer

ActiveUS6987663B2Reduce leakage currentLow ESRHybrid capacitor electrolytesSolid electrolytic capacitorsPolymer scienceElectrolysis

Electrolytic capacitors having low equivalent series resistance and low leakage current are described. The electrolytic capacitors include a solid electrolyte layer of a conductive material in particular a conductive polymer, and an outer layer that includes binders, polymeric anions and conductive polymers (e.g., polythiophenes). Also described is a method of preparing electrolytic capacitors that involves forming the conductive polymer of the solid electrolyte layer in situ by means of chemical oxidative polymerization or electrochemical polymerization. Electronic circuits that include the electrolytic capacitors are also described.

Owner:HERAEUS PRECIOUS METALS GMBH & CO KG

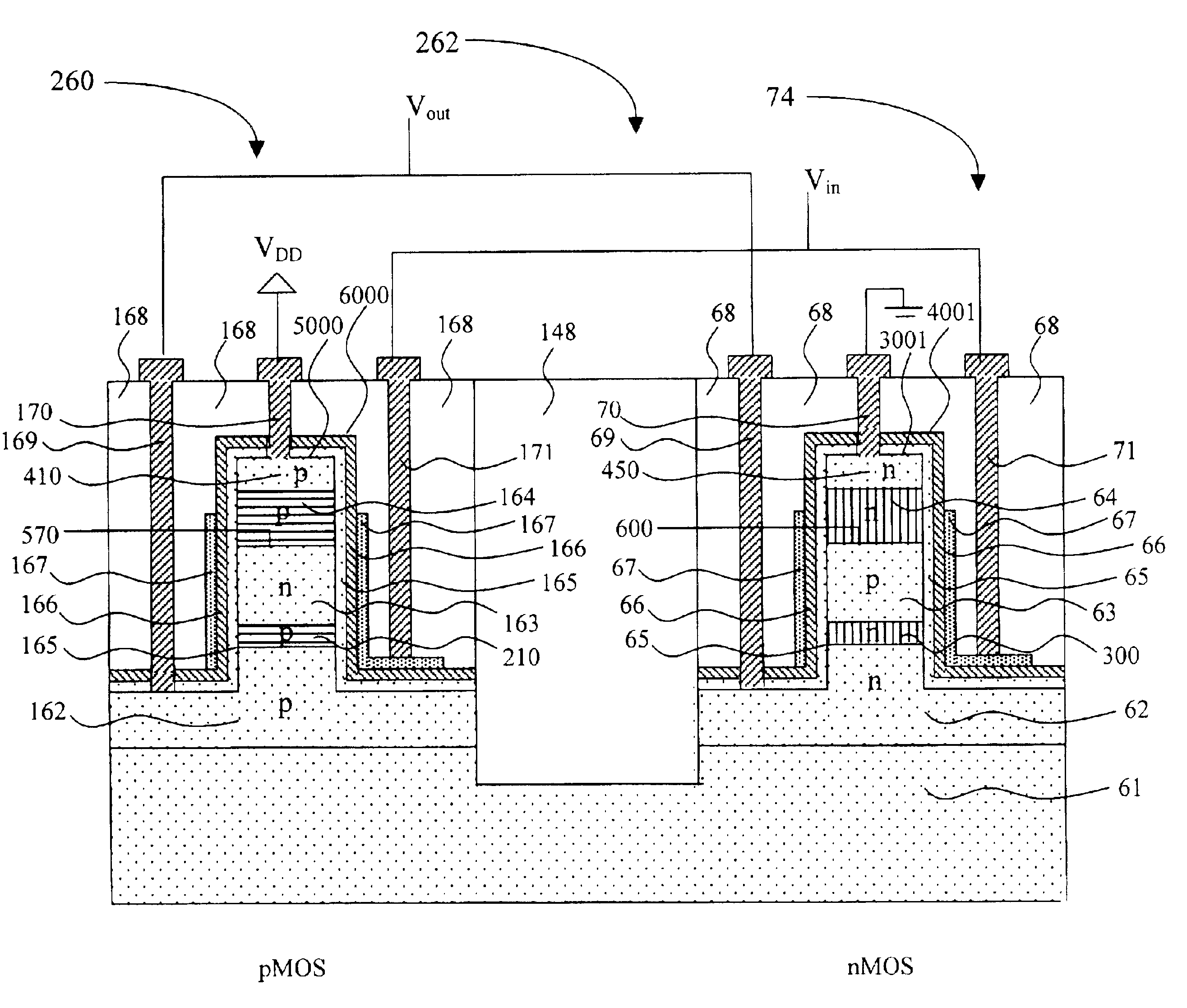

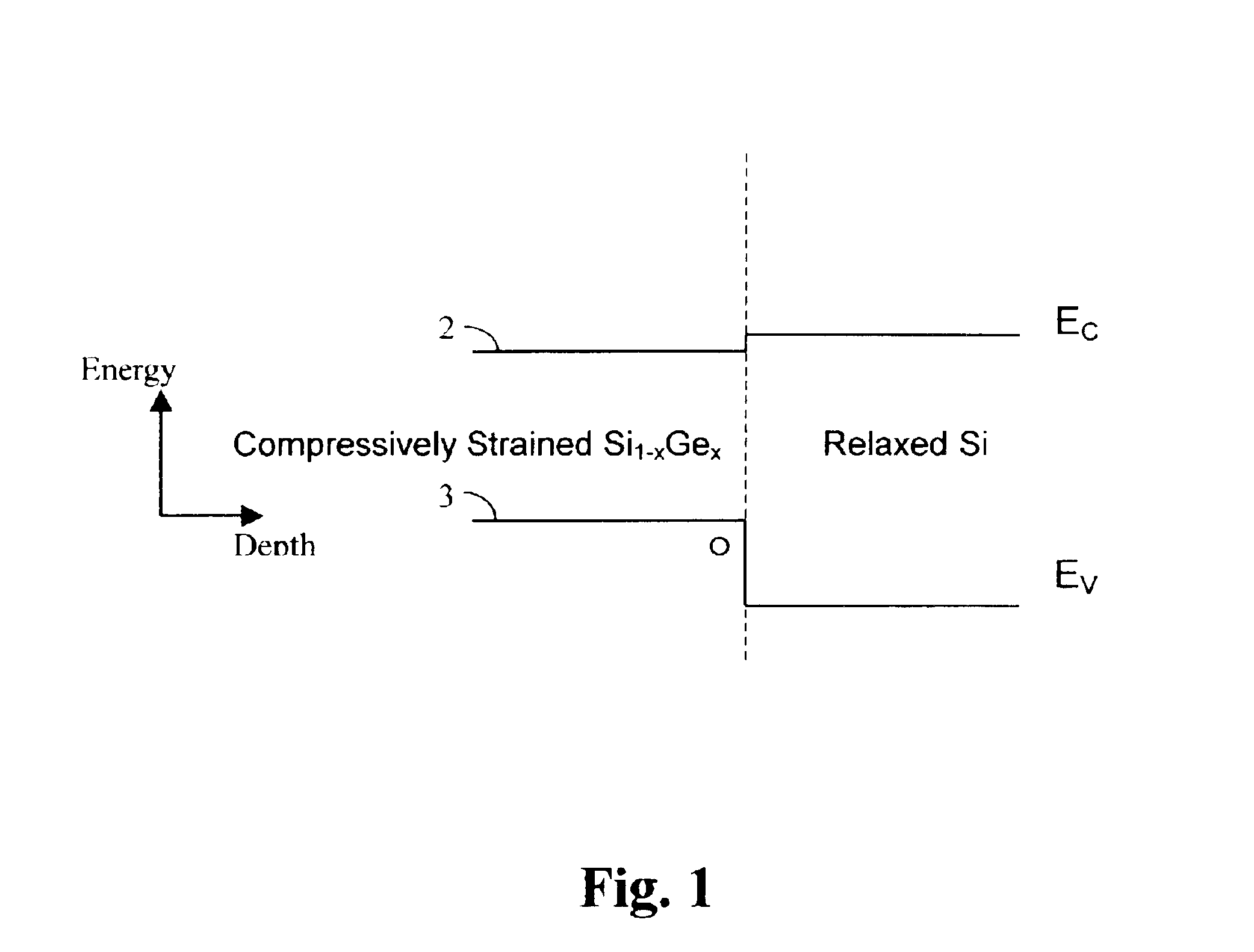

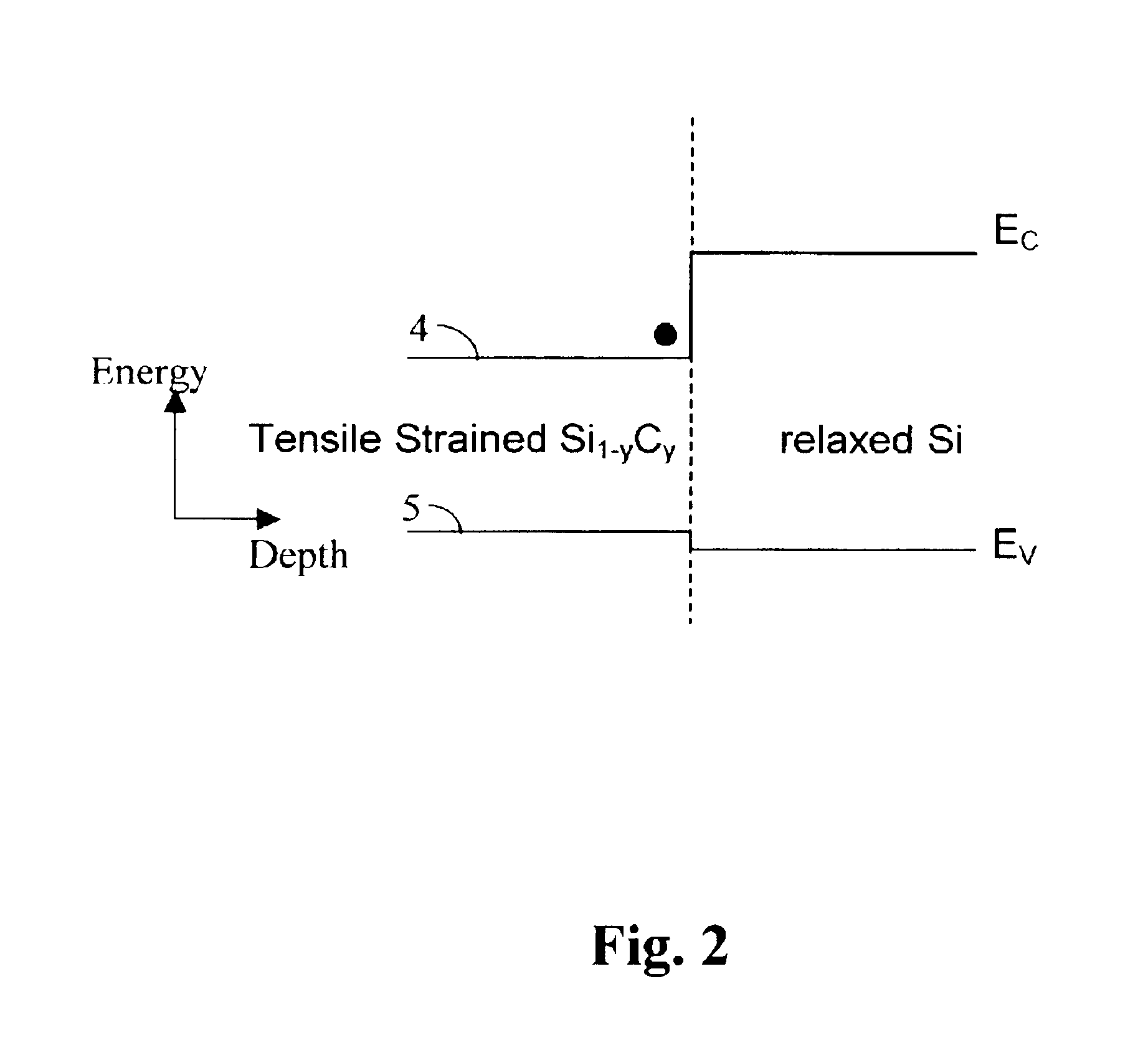

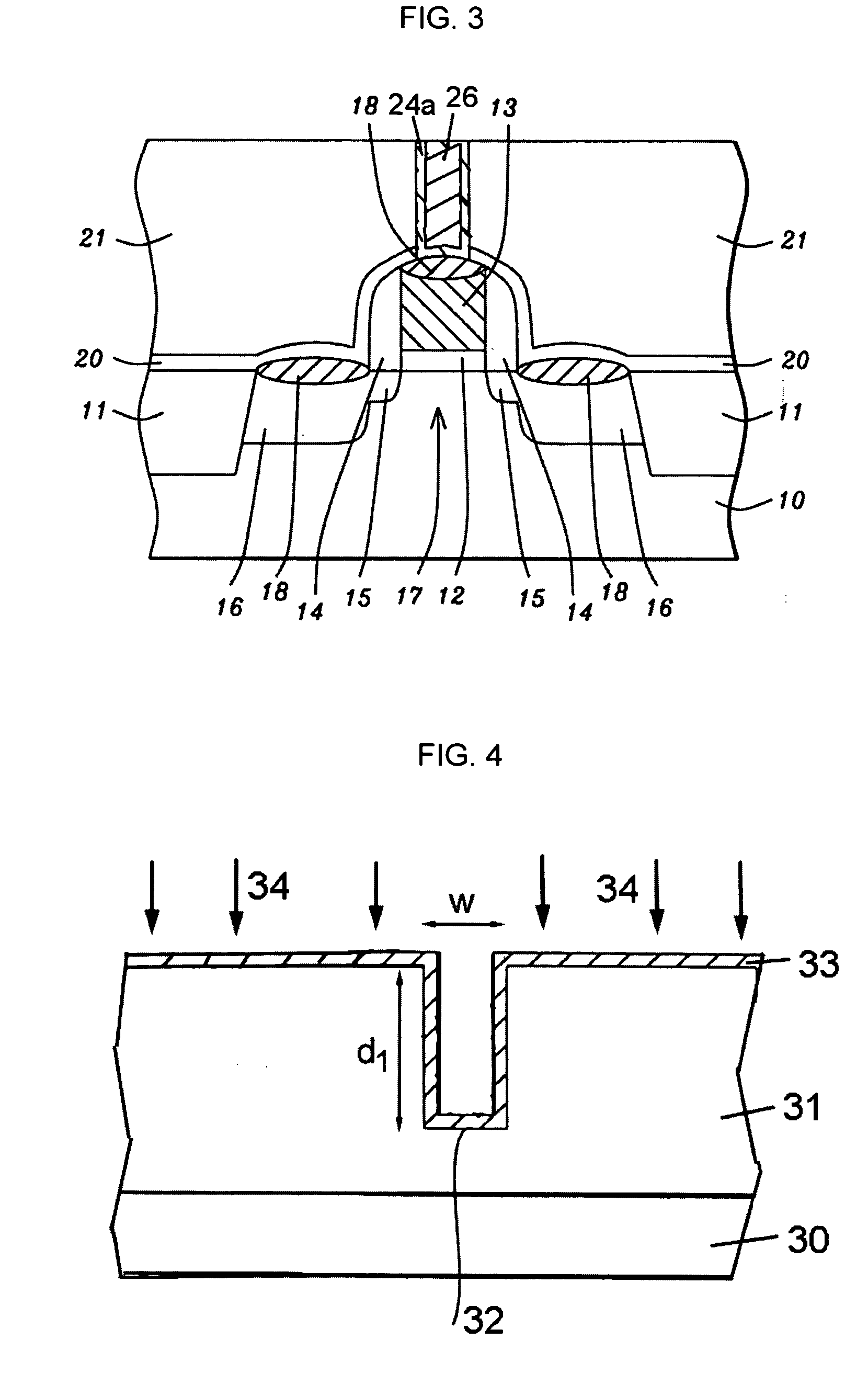

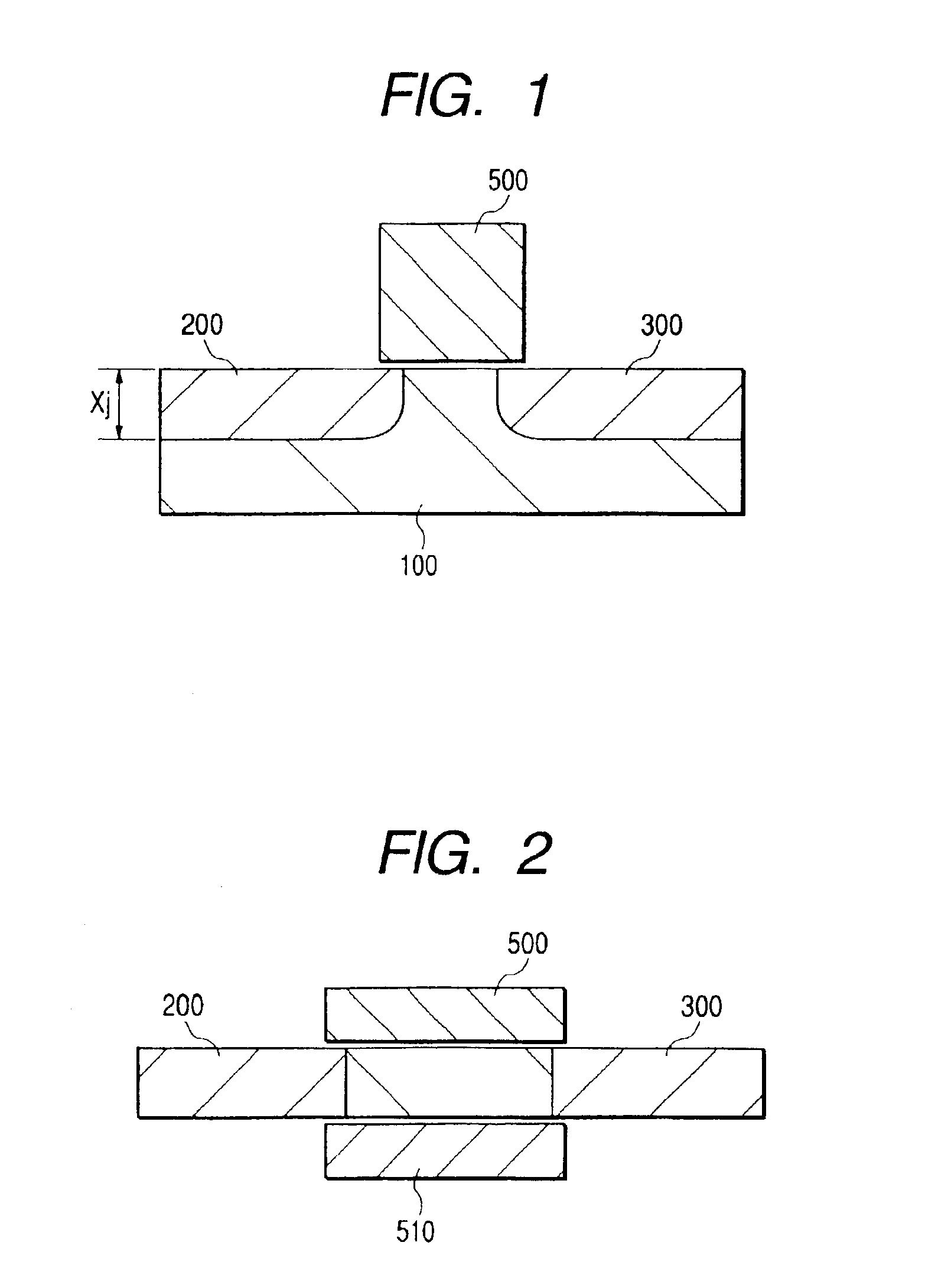

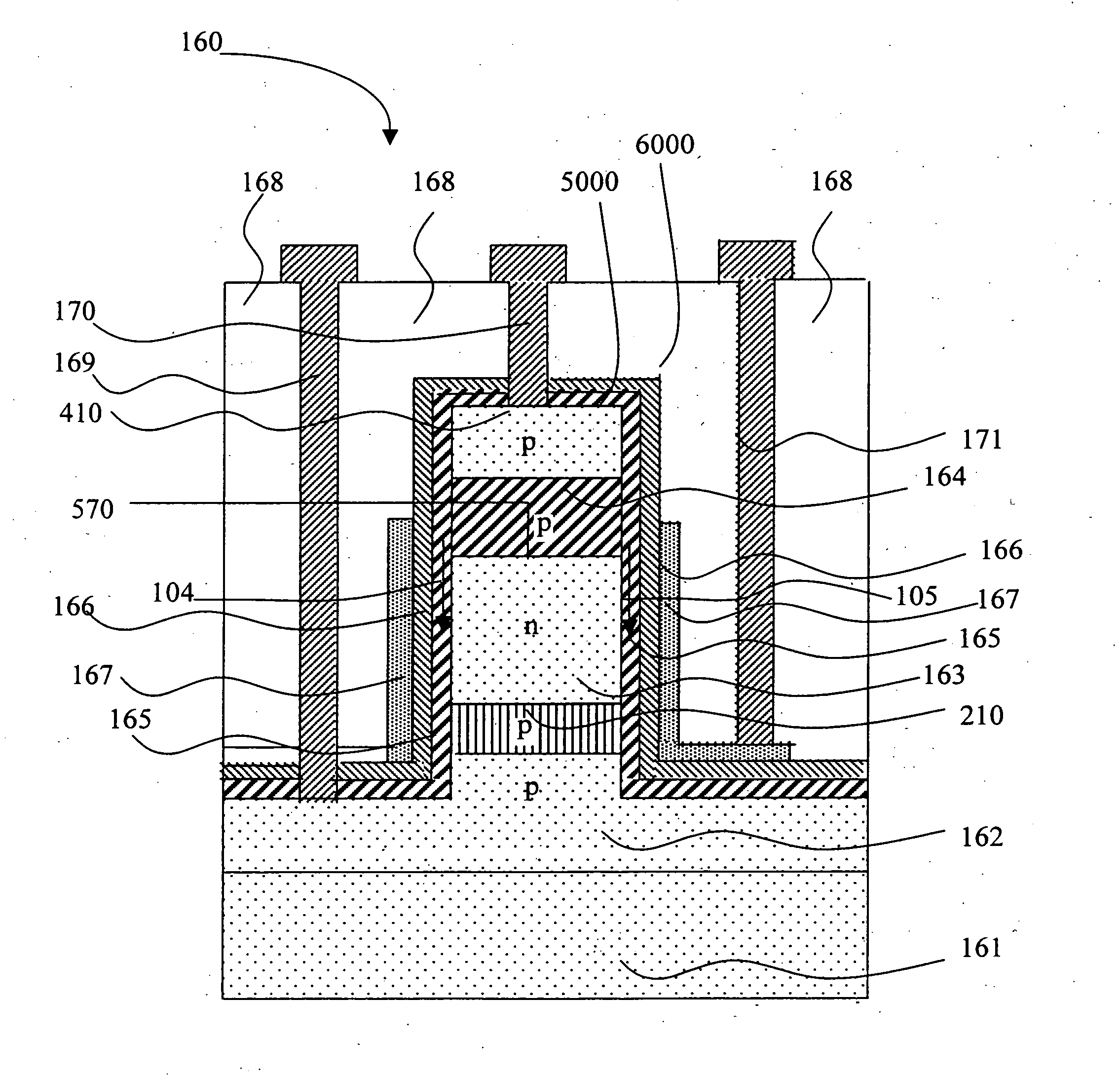

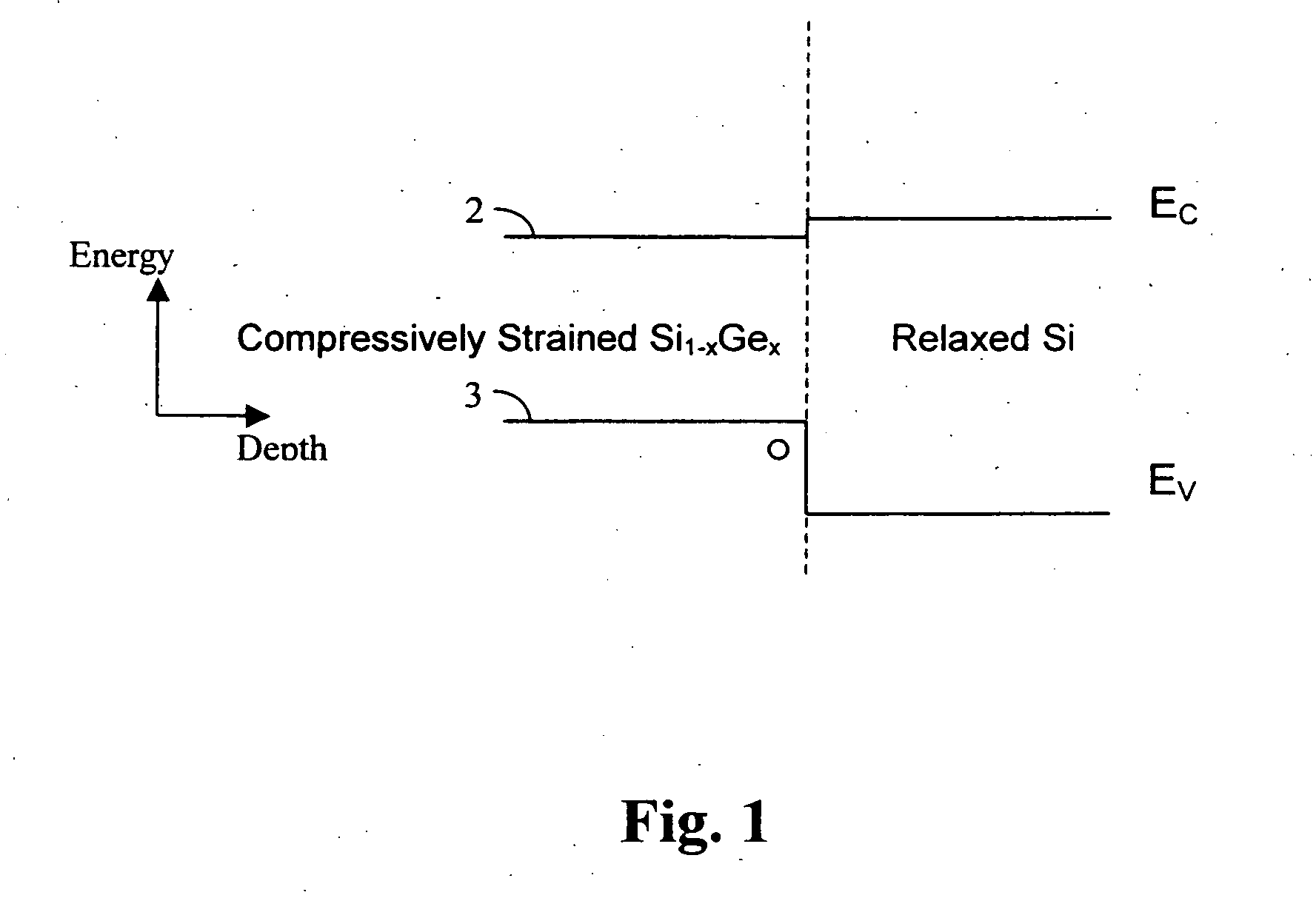

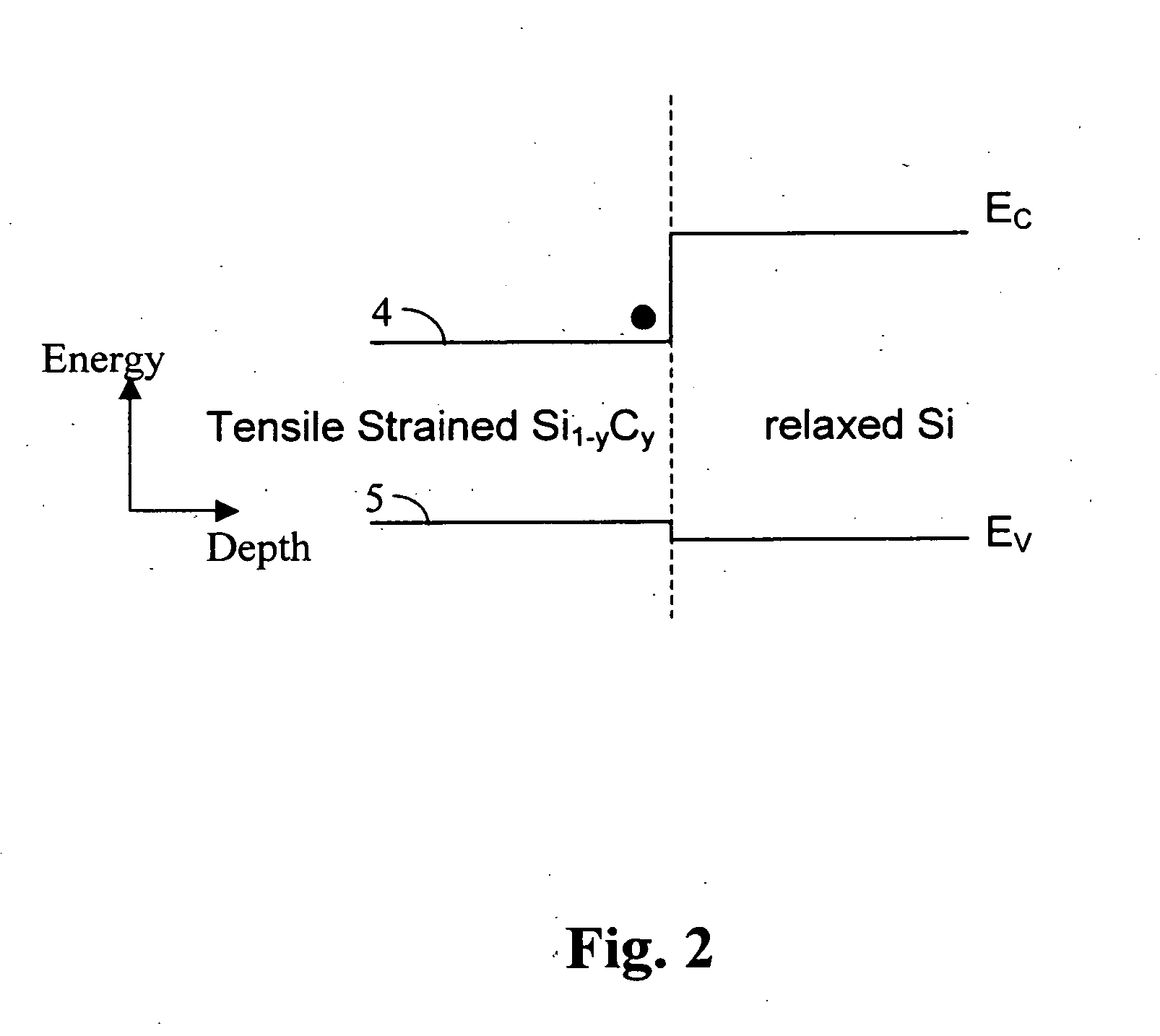

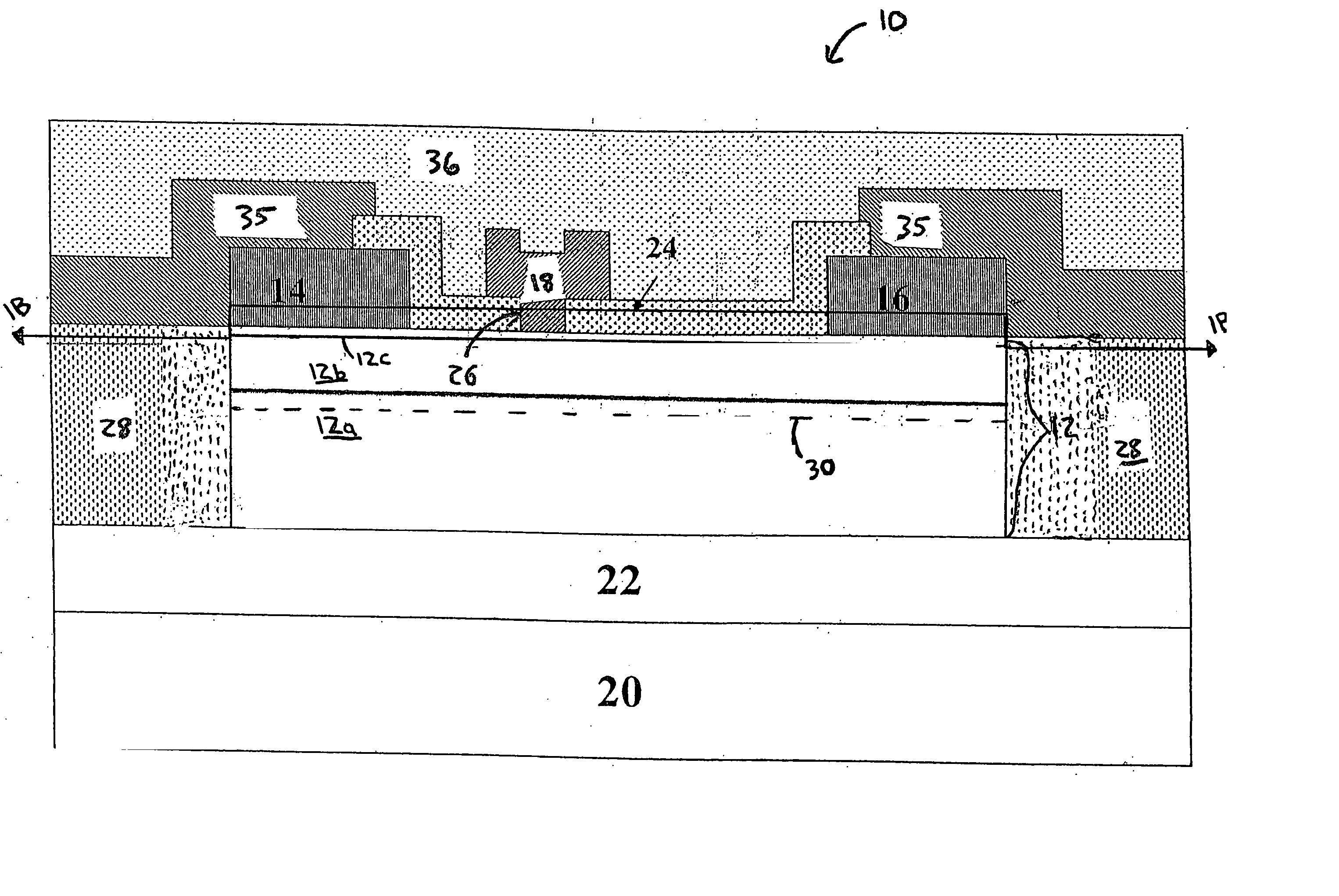

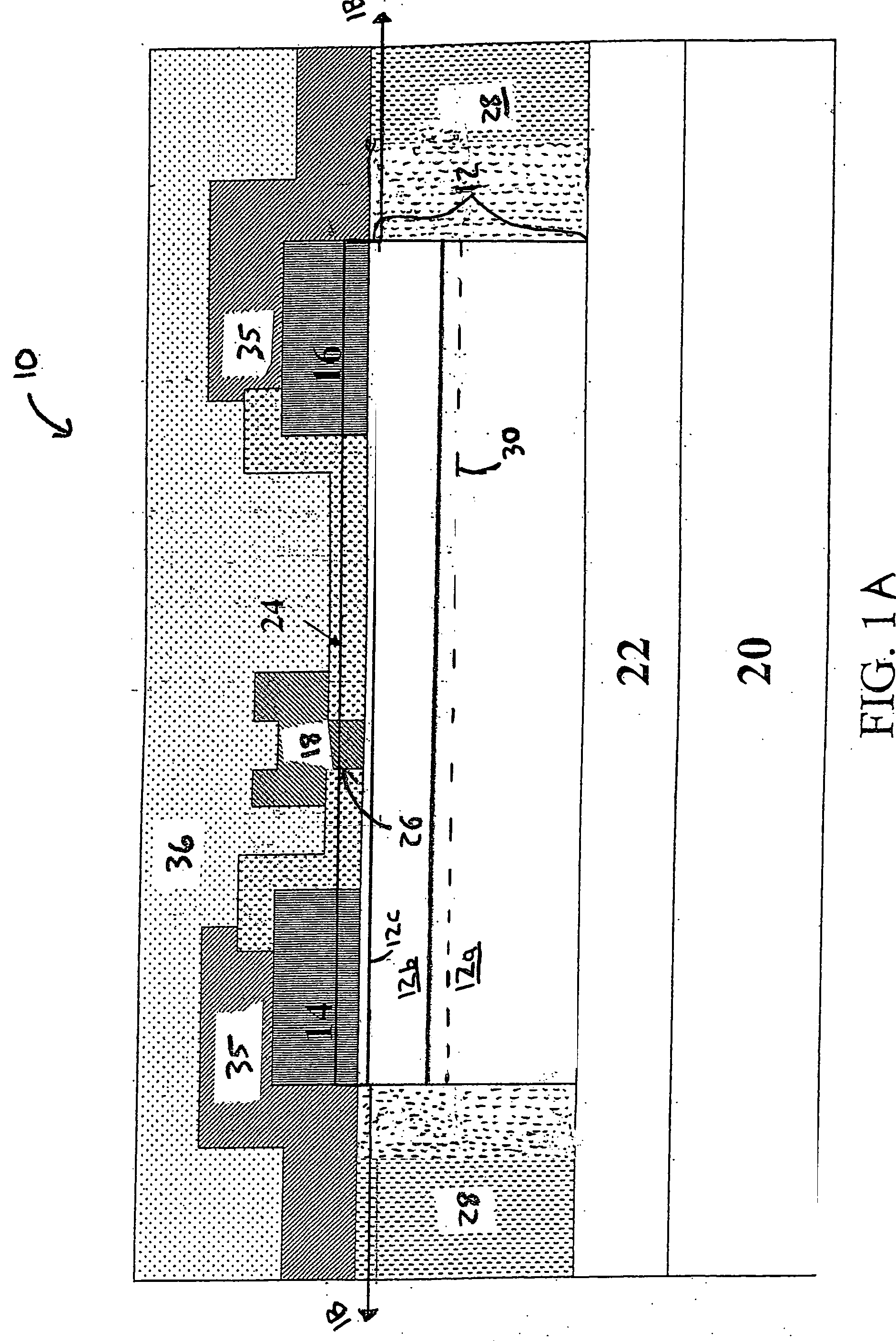

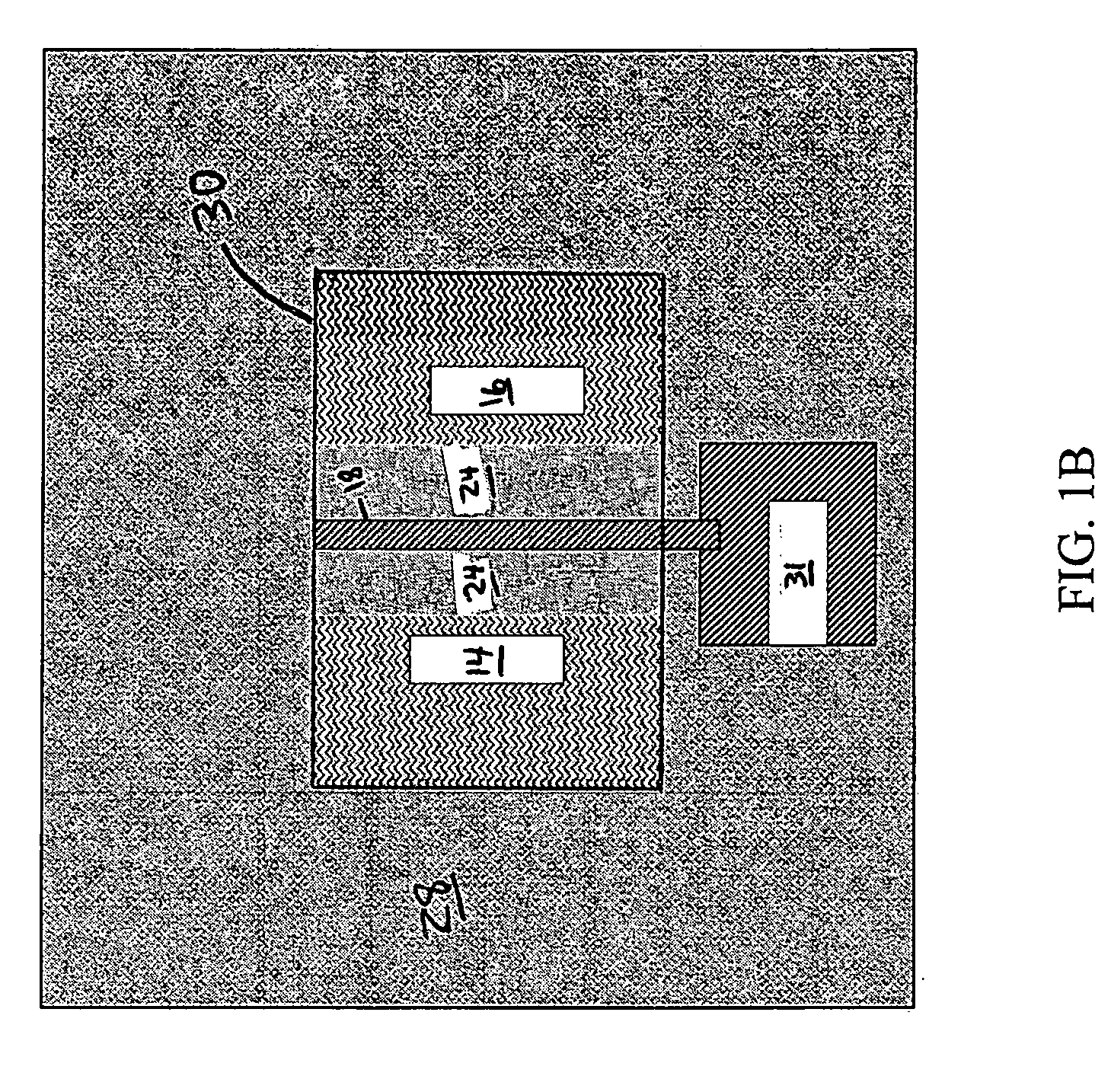

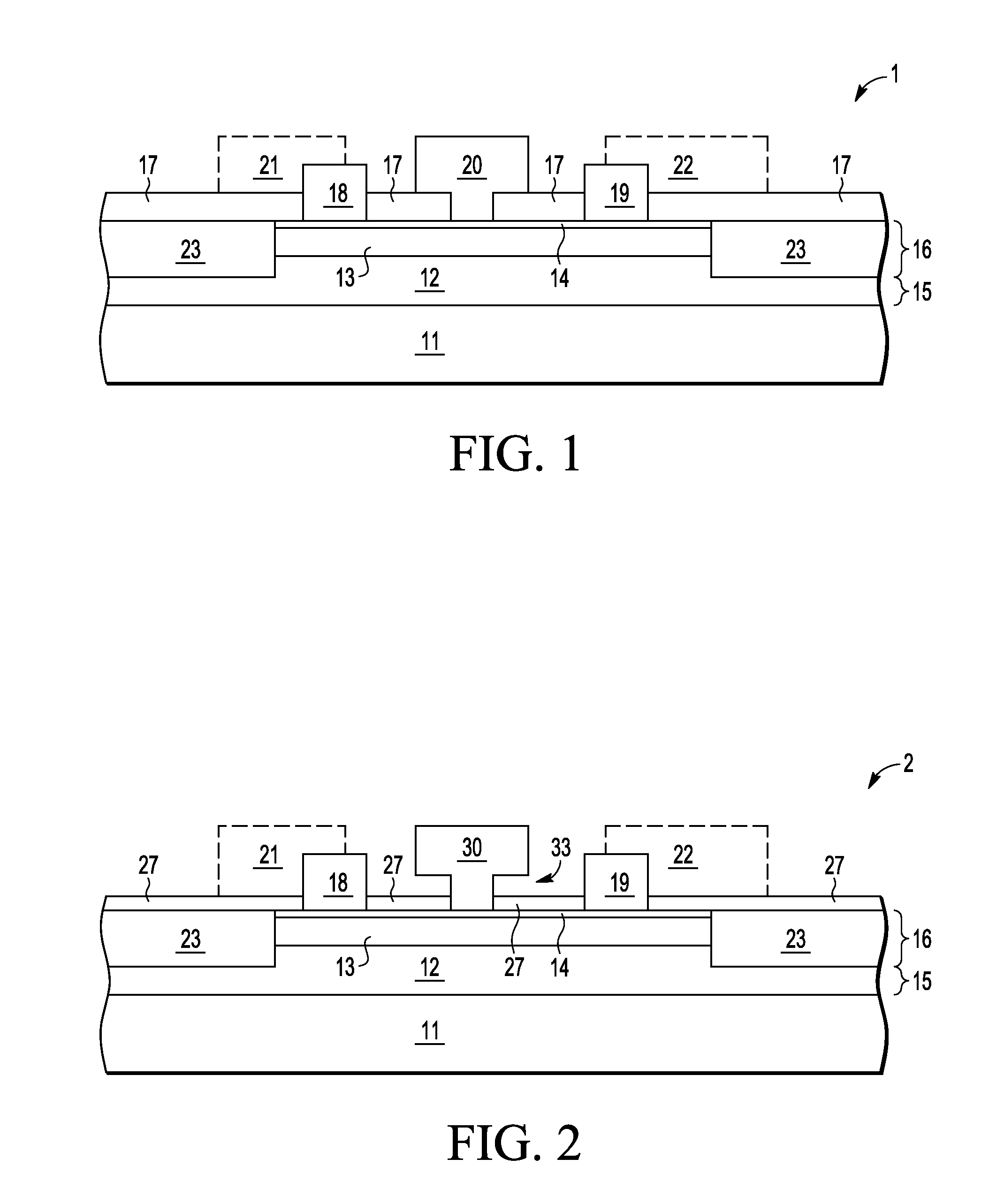

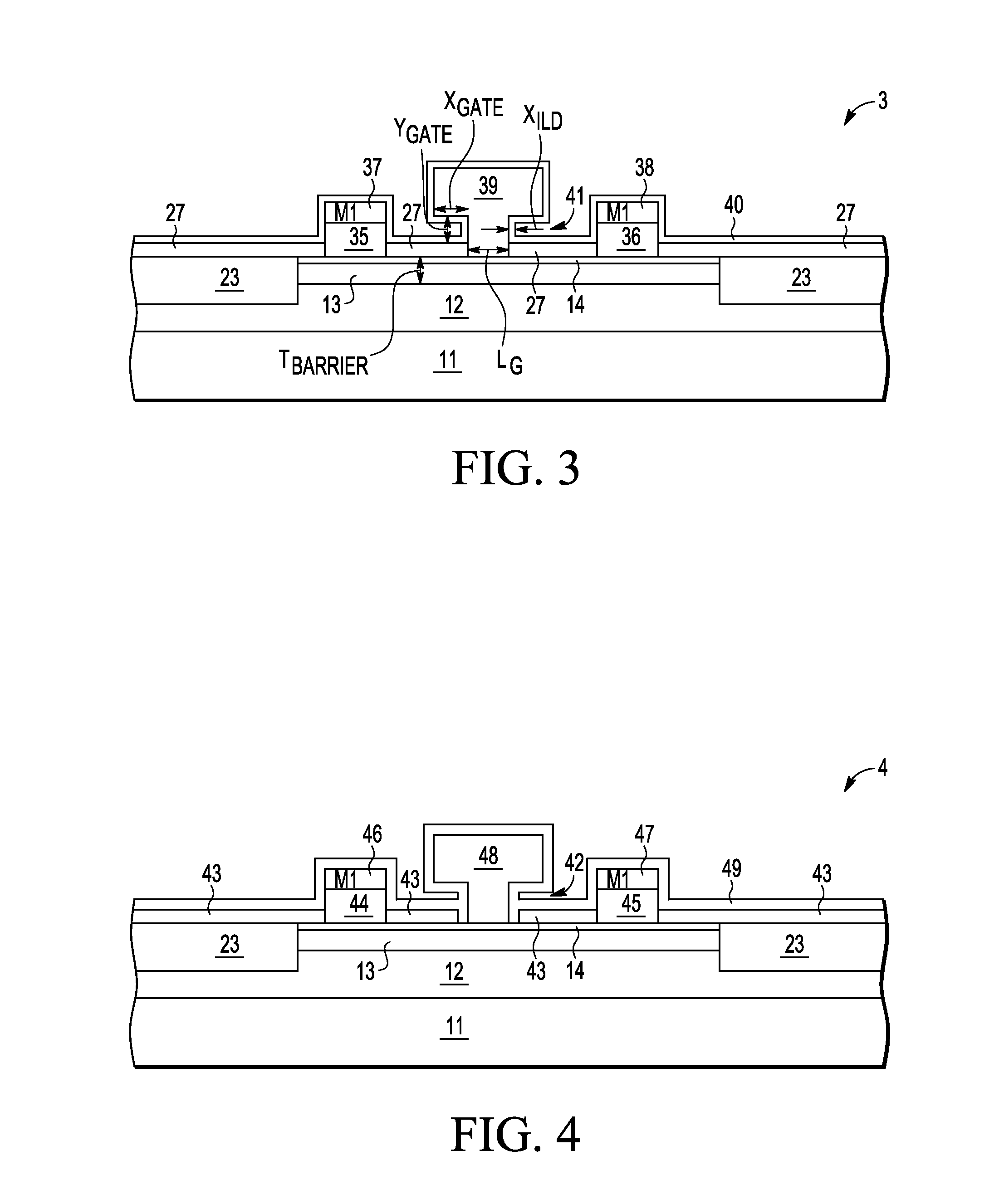

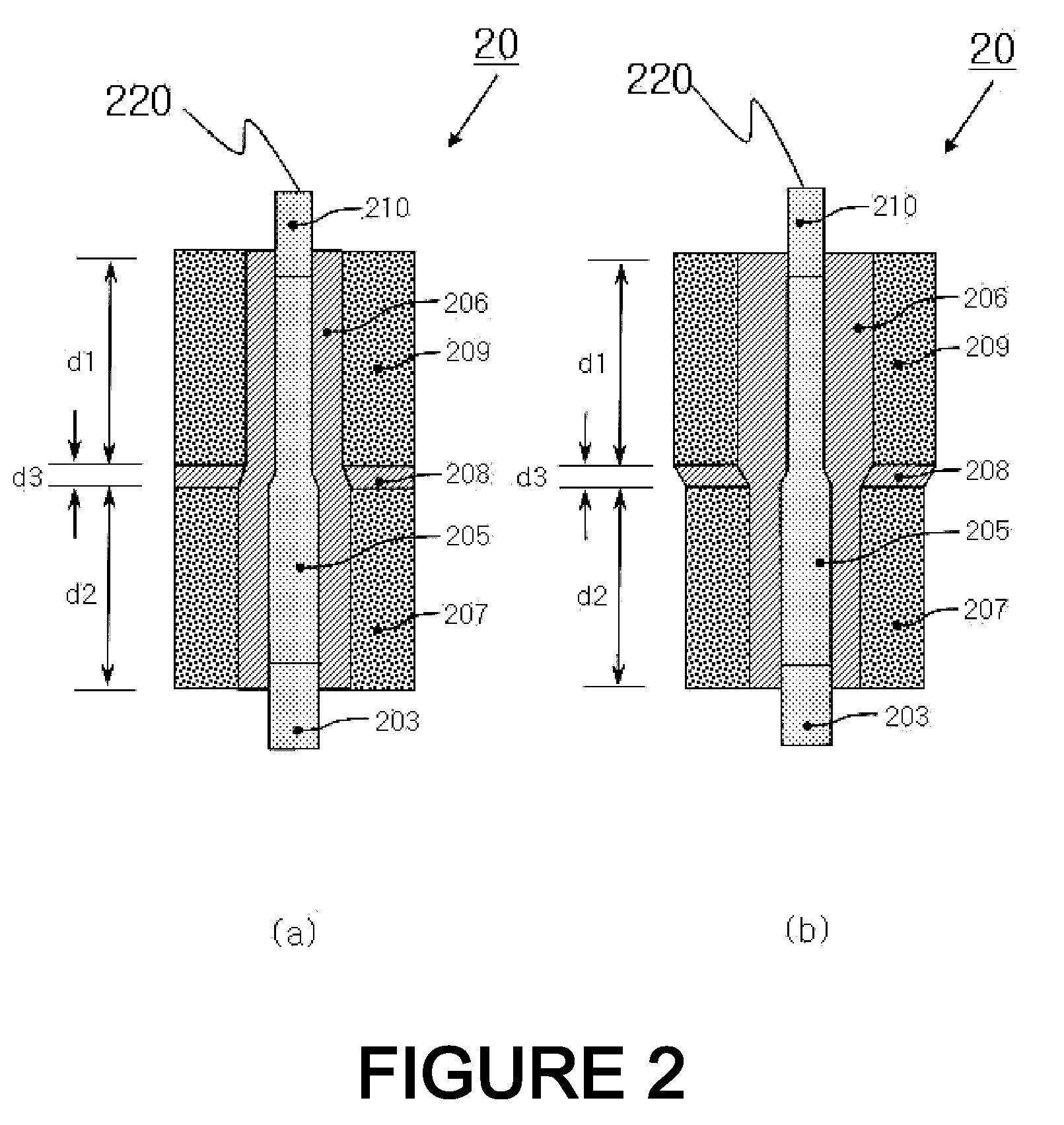

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

Method to form a robust TiCI4 based CVD TiN film

InactiveUS20050112876A1Low resistivityReduce stressSemiconductor/solid-state device manufacturingChemical vapor deposition coatingChlorideLow leakage

A method is described for a plasma treatment of a TiCl4 based CVD deposited TiN layer that reduces stress, lowers resistivity, and improves film stability. Resistivity is stable in an air ambient for up to 48 hours after the plasma treatment. A TiN layer is treated with a N-containing plasma that includes N2, NH3, or N2H4 at a temperature between 500° C. and 700° C. Optionally, H2 may be added to N2 in the plasma step which removes chloride impurities and densifies the TiN layer. The TiN layer may serve as a barrier layer, an ARC layer, or as a bottom electrode in a MIM capacitor. An improved resistance of the treated TiN layer to oxidation during formation of an oxide based insulator layer and a lower leakage current in the MIM capacitor is also achieved.

Owner:TAIWAN SEMICON MFG CO LTD

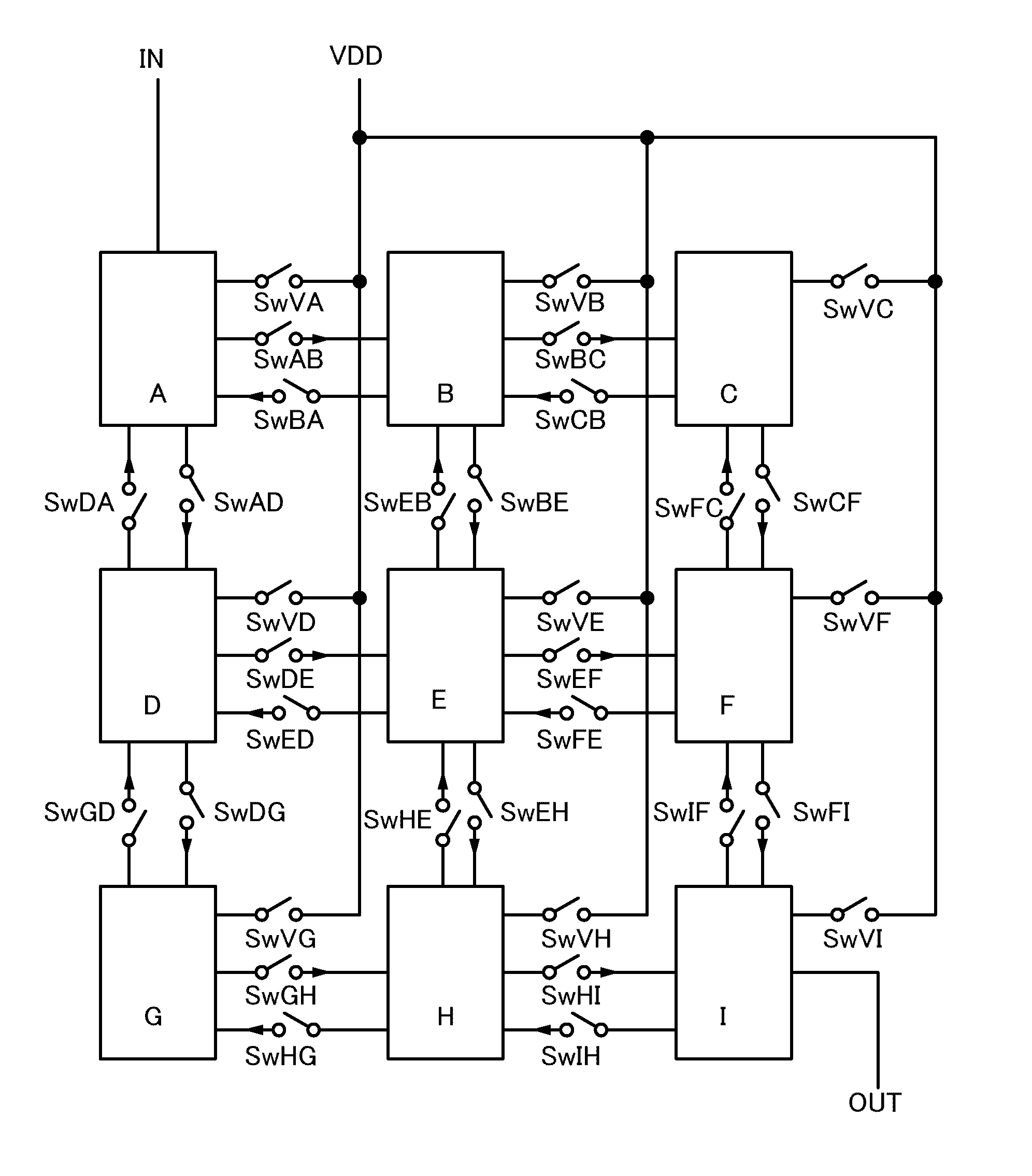

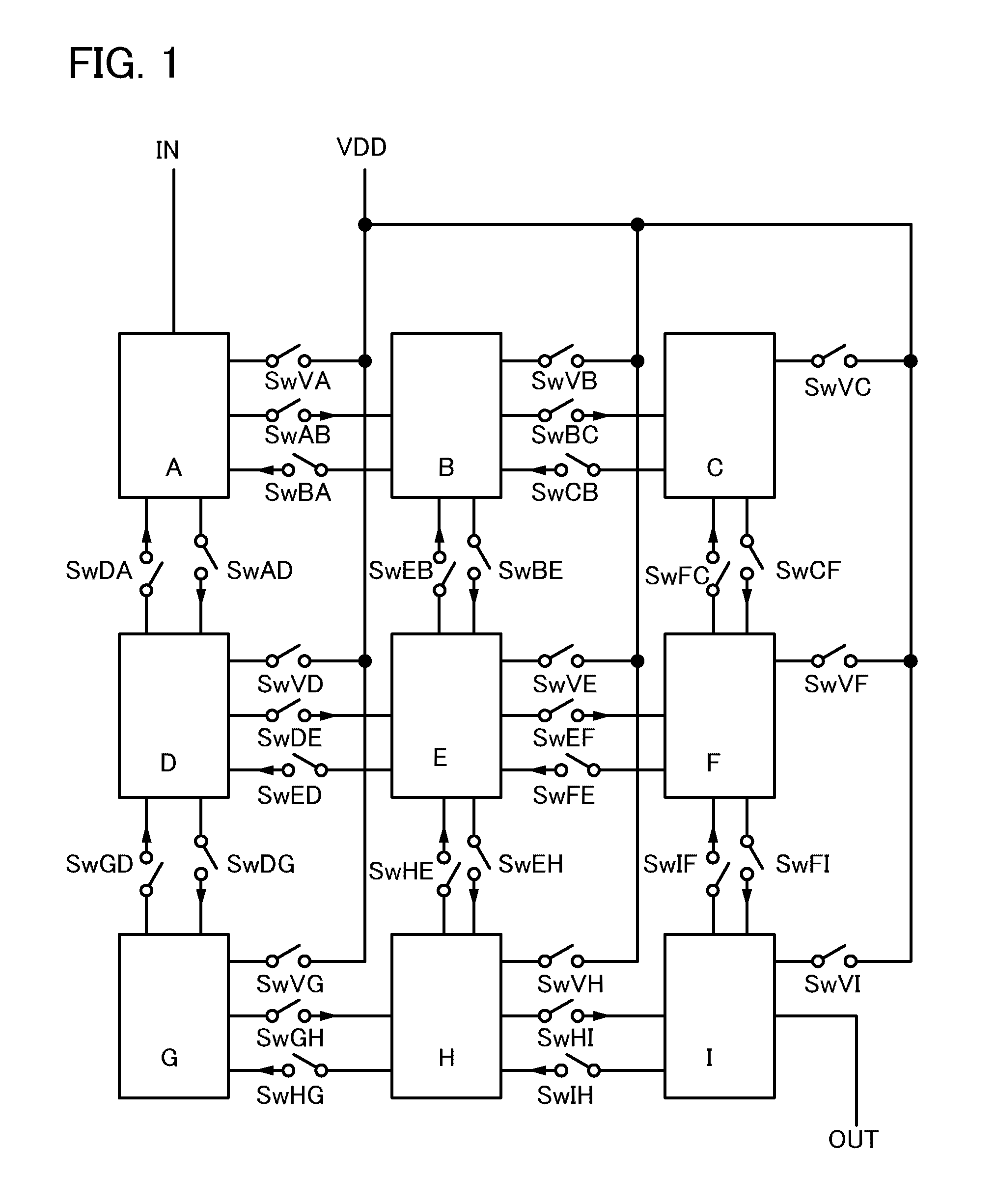

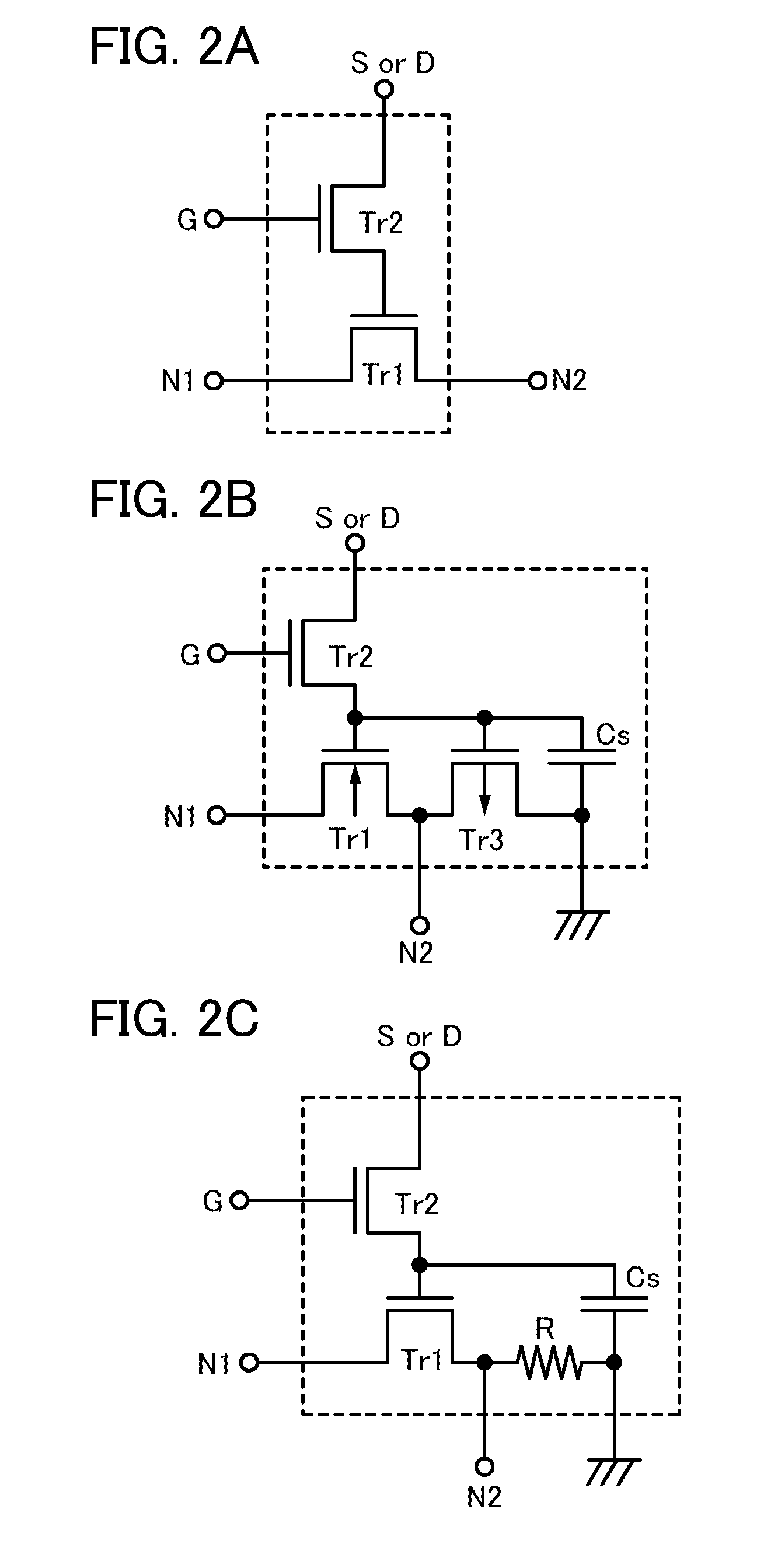

Semiconductor device

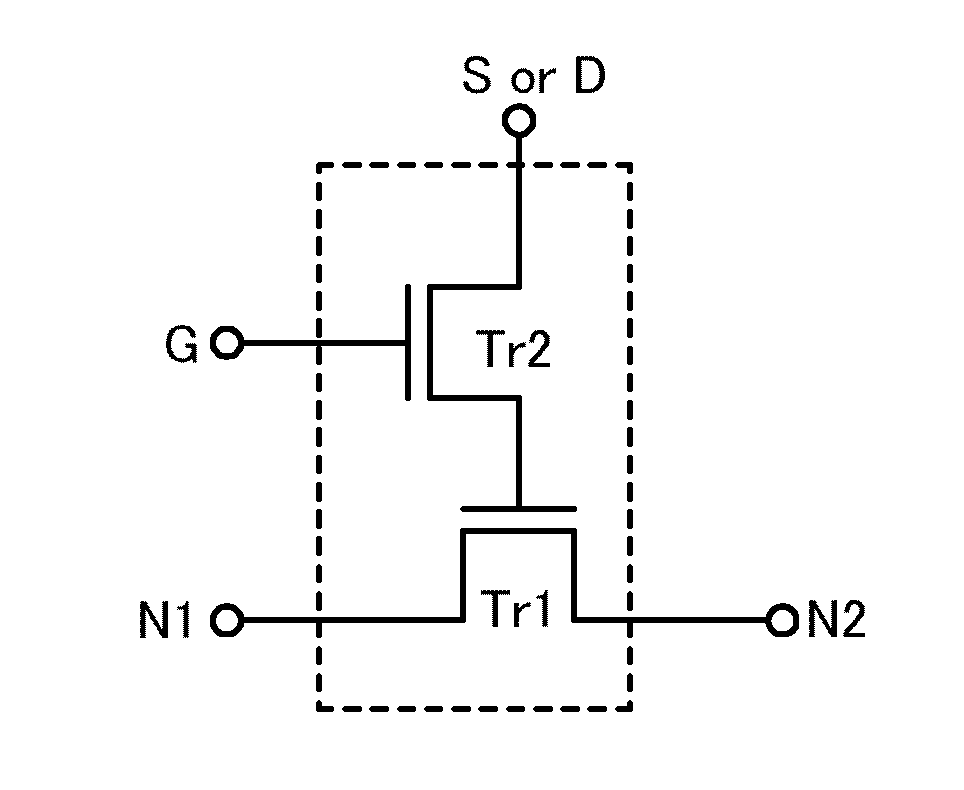

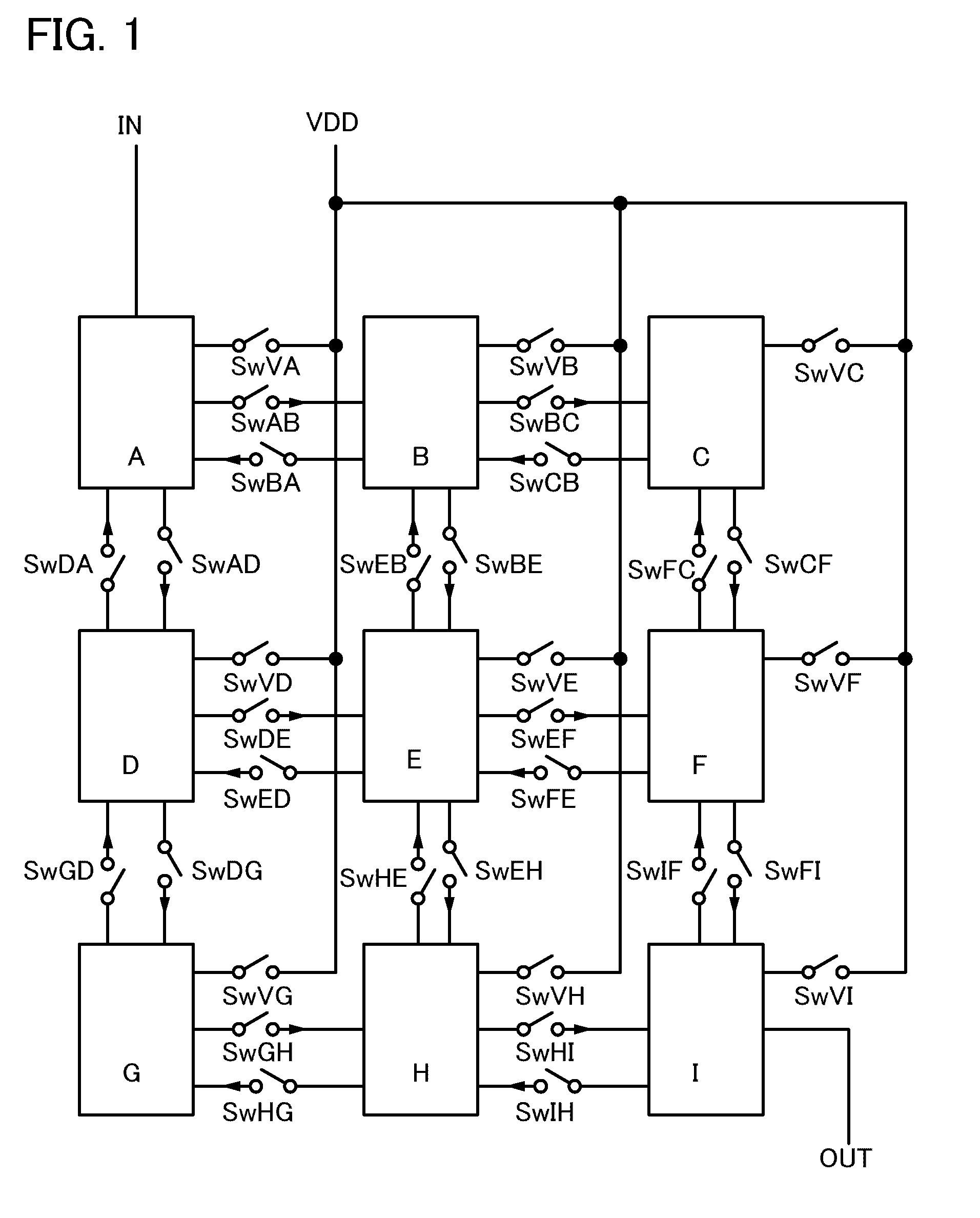

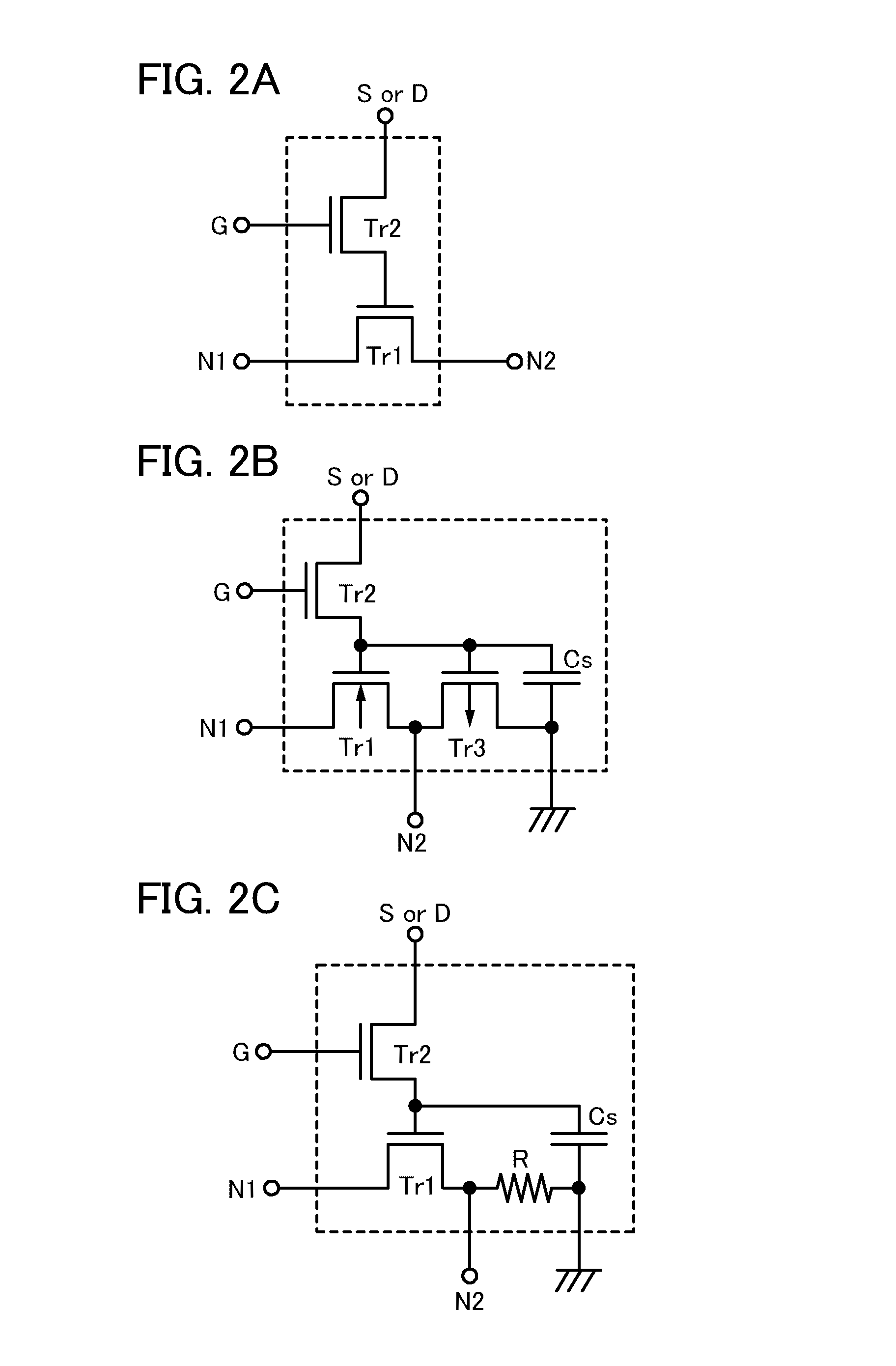

ActiveUS20110175646A1Suppress power consumptionPrevent degradationTransistorPower reduction in field effect transistorsProgrammable logic deviceLow leakage

It is an object to provide a semiconductor device in which power consumption can be reduced. It is another object to provide a highly reliable semiconductor device using a programming cell, such as a programmable logic device (PLD). In accordance with a change in a configuration of connections between basic blocks, power supply voltage furnishing to the basic blocks is changed. That is, when the structure of connections between the basic blocks is such that a basic block does not contribute to a circuit, the supply of the power supply voltage to this basic block is stopped. Further, the supply of the power supply voltage to the basic blocks is controlled using a programming cell formed using a field effect transistor whose channel formation region is formed using an oxide semiconductor, the field effect transistor having extremely low off-state current or extremely low leakage current.

Owner:SEMICON ENERGY LAB CO LTD

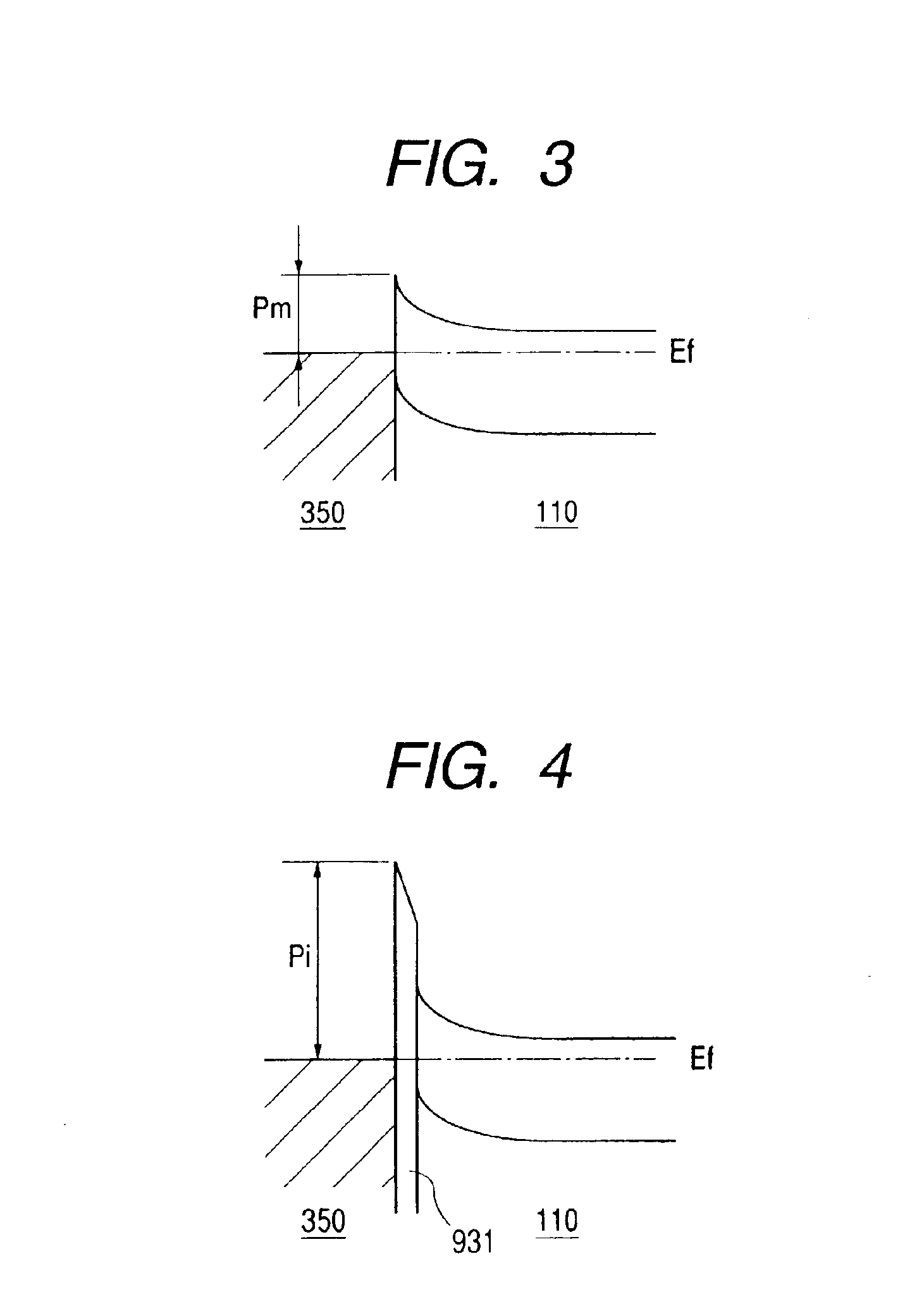

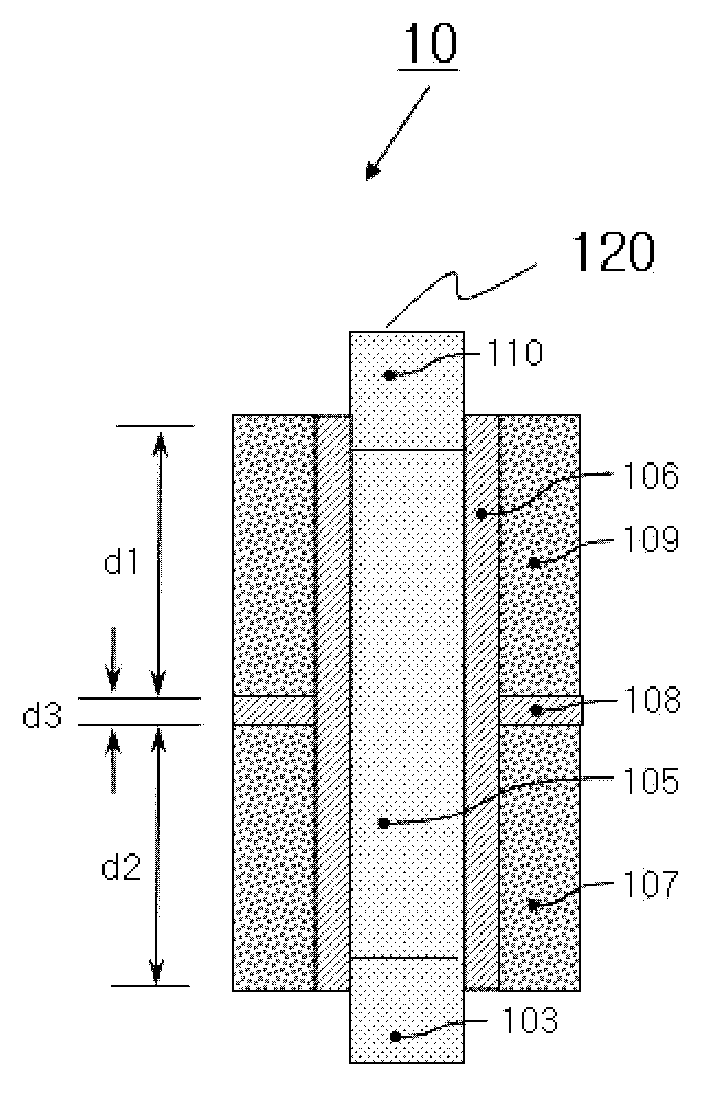

Vertical semiconductor device with tunnel insulator in current path controlled by gate electrode

InactiveUS6873009B2Suppress lowering of driving forceLower average currentTransistorSolid-state devicesGate leakage currentJunction leakage

It is an object of the present invention to provides a field effect transistor with extremely low leakage current. It is another object of the invention to provide a semiconductor memory device having an excellent information holding characteristic. It is a further object of the invention to provide a method for manufacturing in a simple manner a novel field effect transistor or semiconductor memory device with extremely low leakage current. According to a typical basic configuration of the present invention, a thin insulating film is inserted in a vertically disposed Schottky junction to form source and drain electrodes and a tunnel of the insulating film in the junction is controlled by a gate electrode. The gate electrode is disposed on each of both sides of a vertical channel, permitting a field effect to be exerted effectively on the junction, whereby a junction leakage in an OFF state can be made extremely low.

Owner:HITACHI LTD

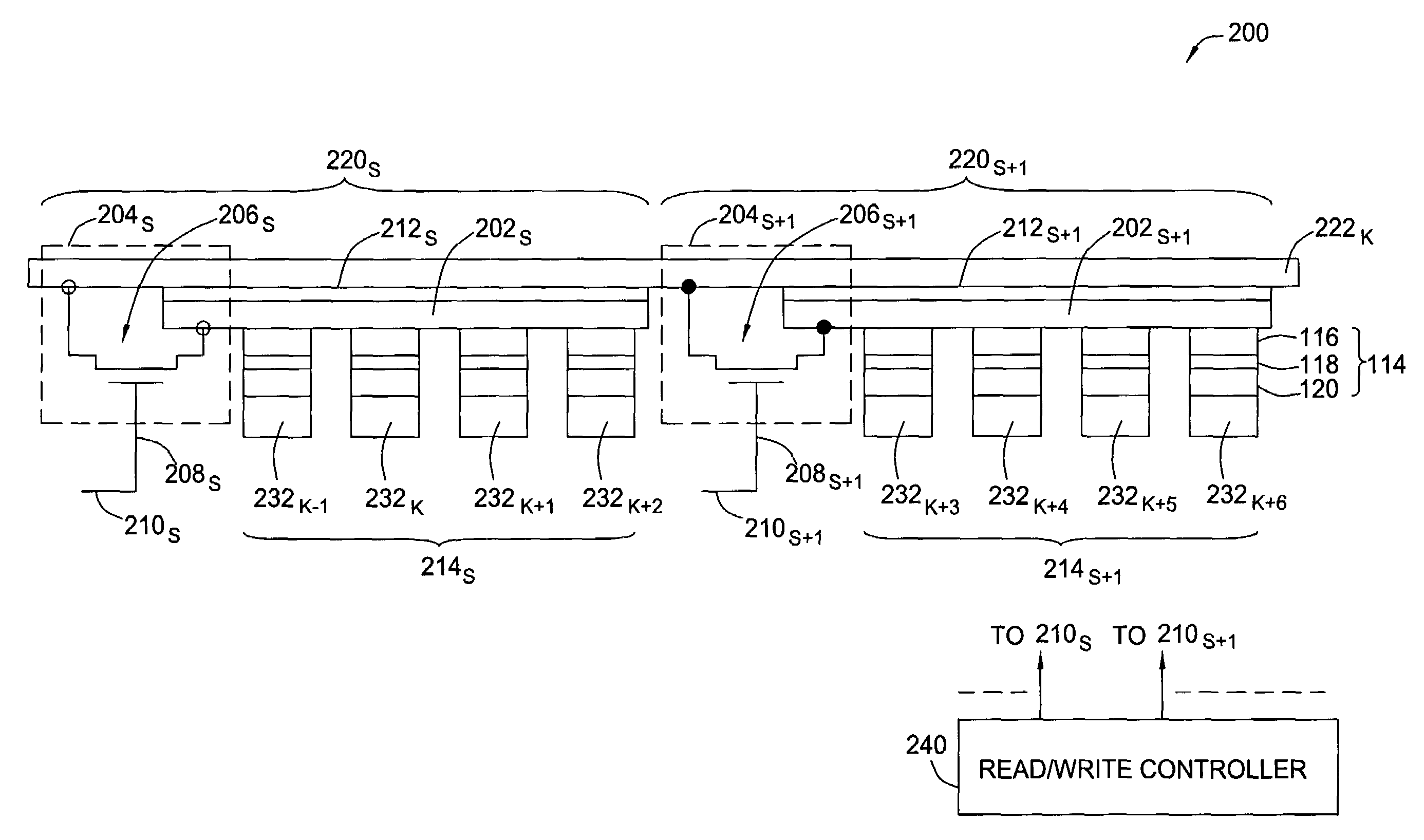

MRAM array having a segmented bit line

InactiveUS6982902B2Reduce leakage currentRaise the ratioDigital storageBit lineStatic random-access memory

A magneto-resistive random access memory (MRAM) array comprises global bit lines segmented using a plurality of local bit lines. A read / write controller is connected to the switches. Switches couple the global bit line to the local bit lines. The MRAM array has low leakage currents and facilitates a high signal-to-noise (S / N) ratio of read and write operations.

Owner:IBM CORP +1

Structure and method for making low leakage and low mismatch nmosfet

An improved SRAM and fabrication method are disclosed. The method comprises use of a nitride layer to encapsulate PFETs and logic NFETs, protecting the gates of those devices from oxygen exposure. NFETs that are used in the SRAM cells are exposed to oxygen during the anneal process, which alters the effective work function of the gate metal, such that the threshold voltage is increased, without the need for increasing the dopant concentration, which can adversely affect issues such as mismatch due to random dopant fluctuation, GIDL and junction leakage.

Owner:IBM CORP

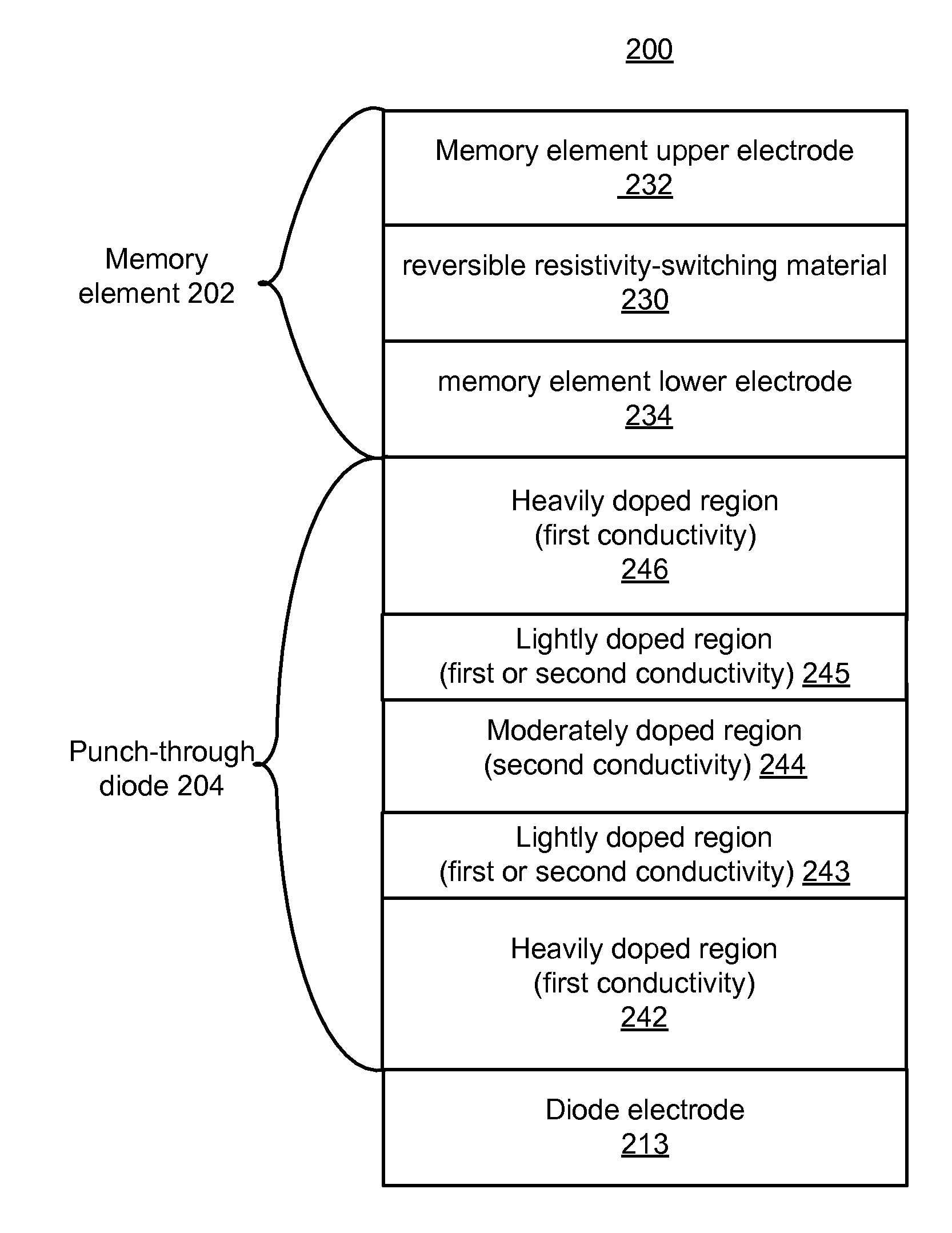

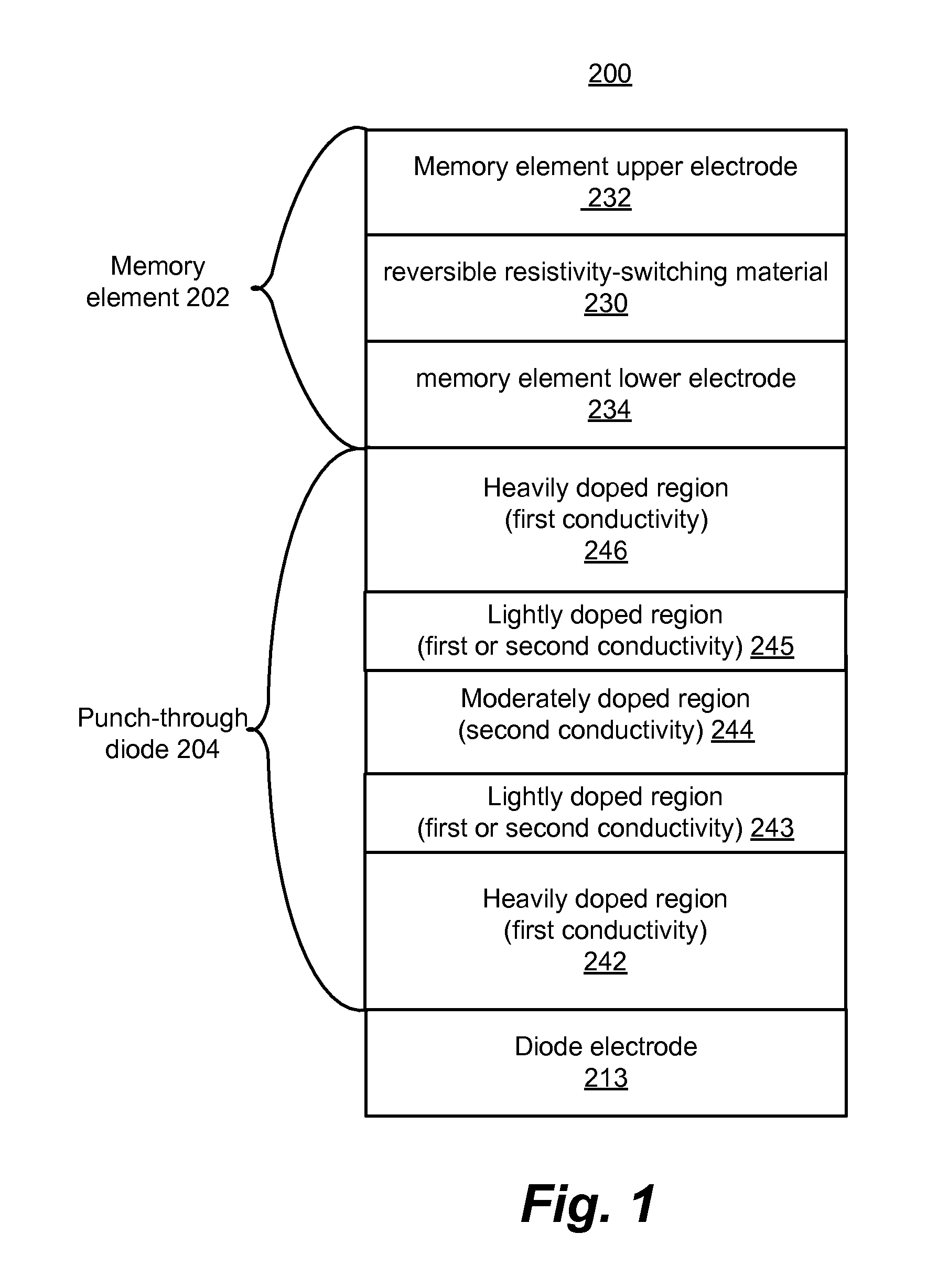

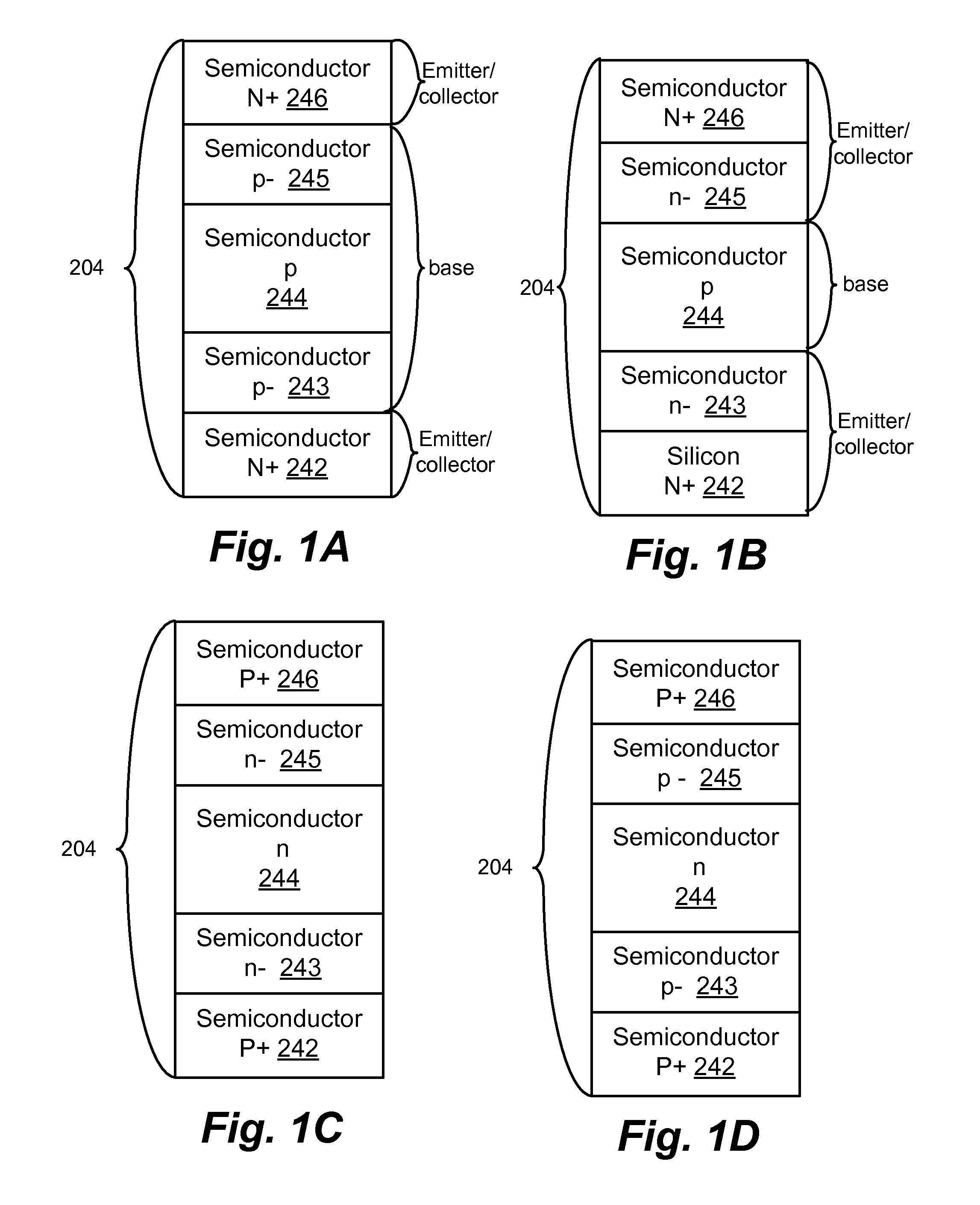

Punch-through diode steering element

ActiveUS20110089391A1Semiconductor/solid-state device detailsSolid-state devicesLow leakageEngineering

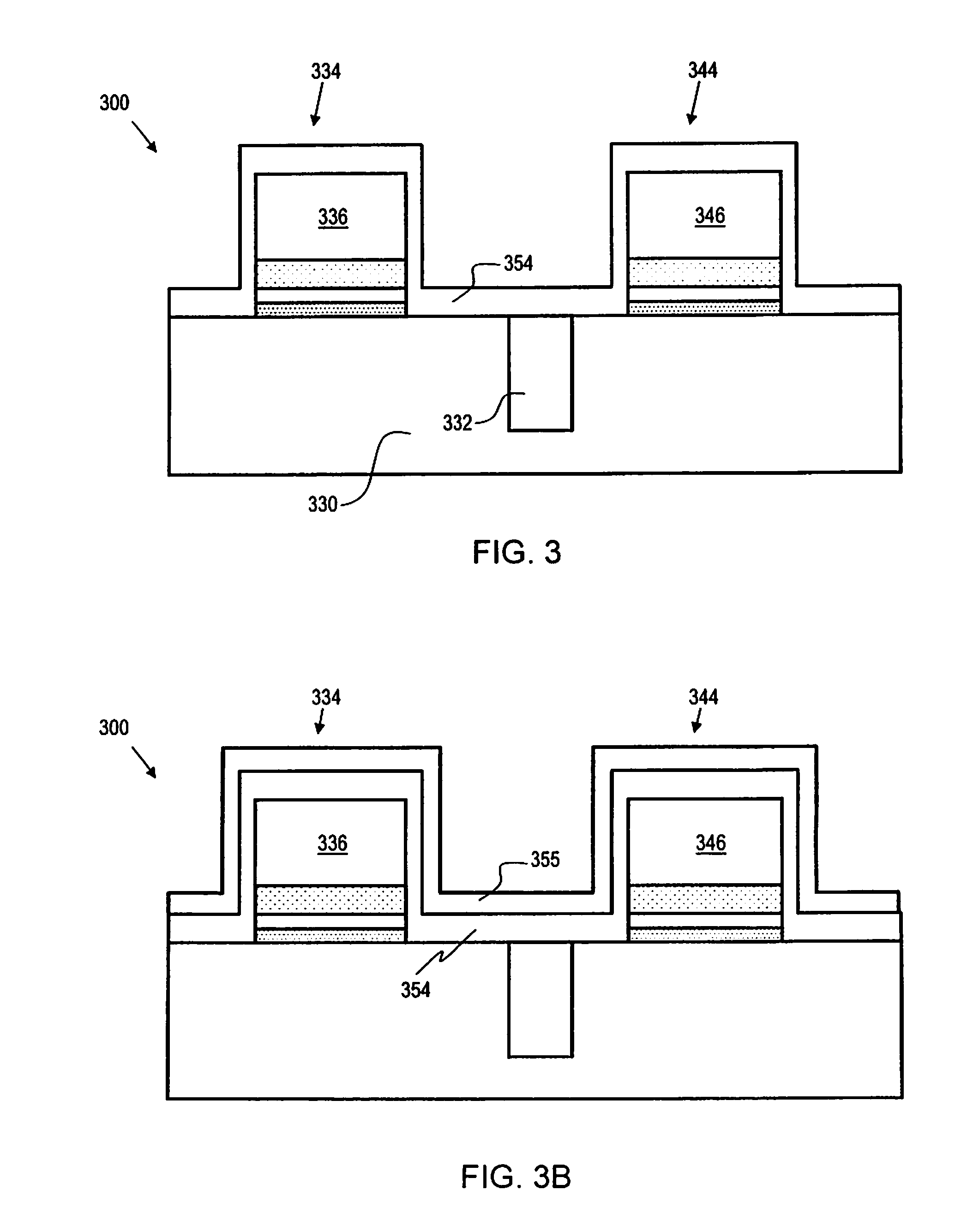

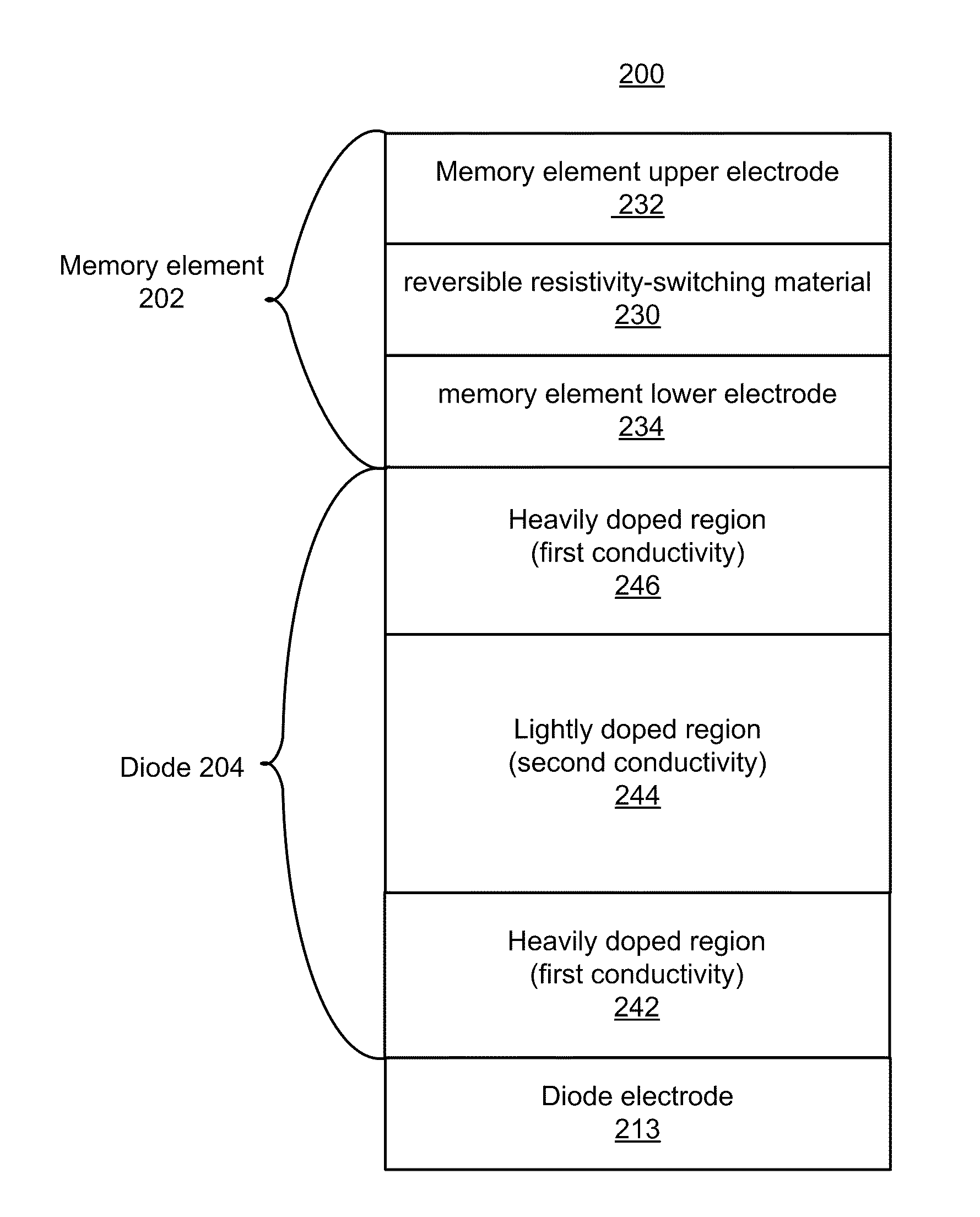

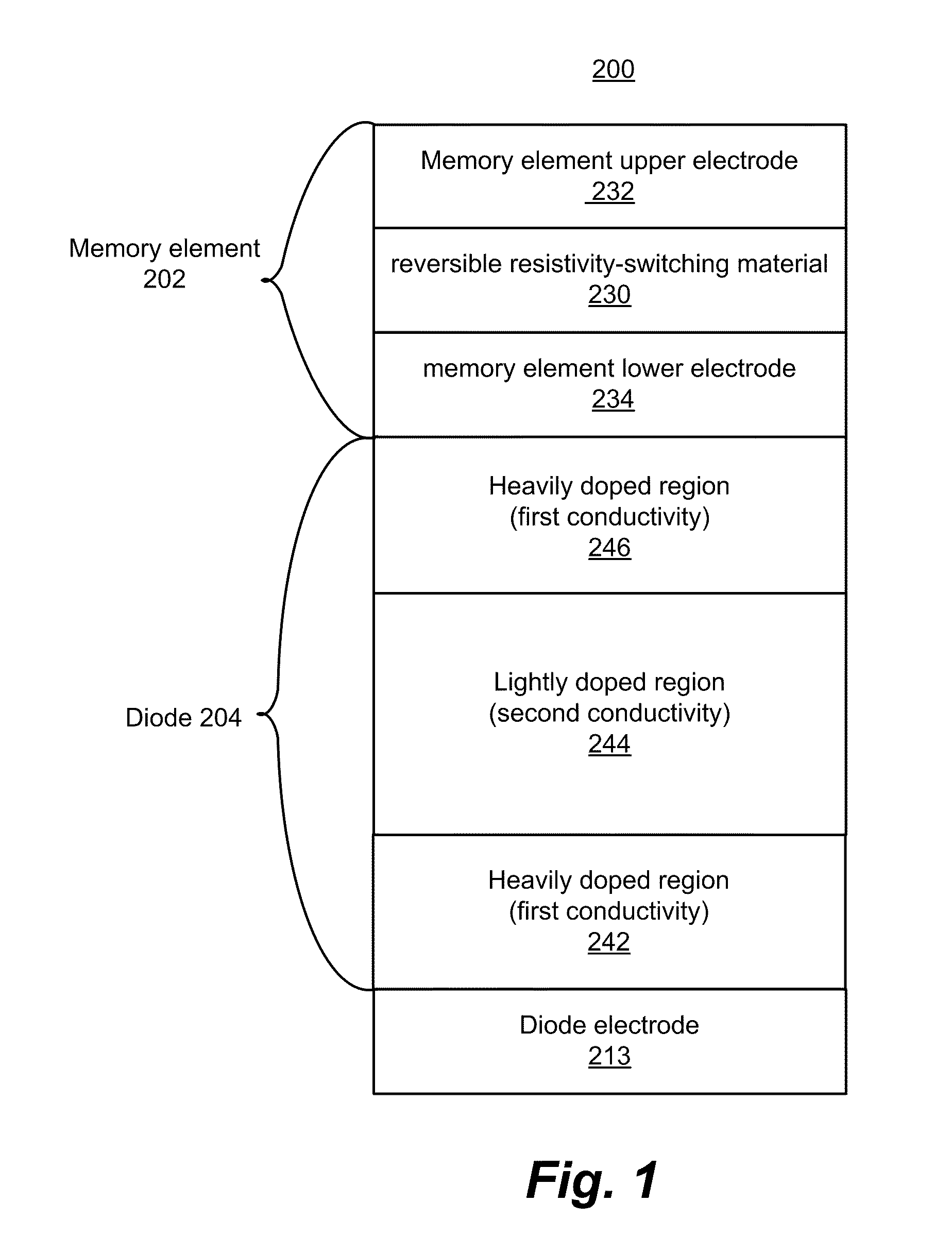

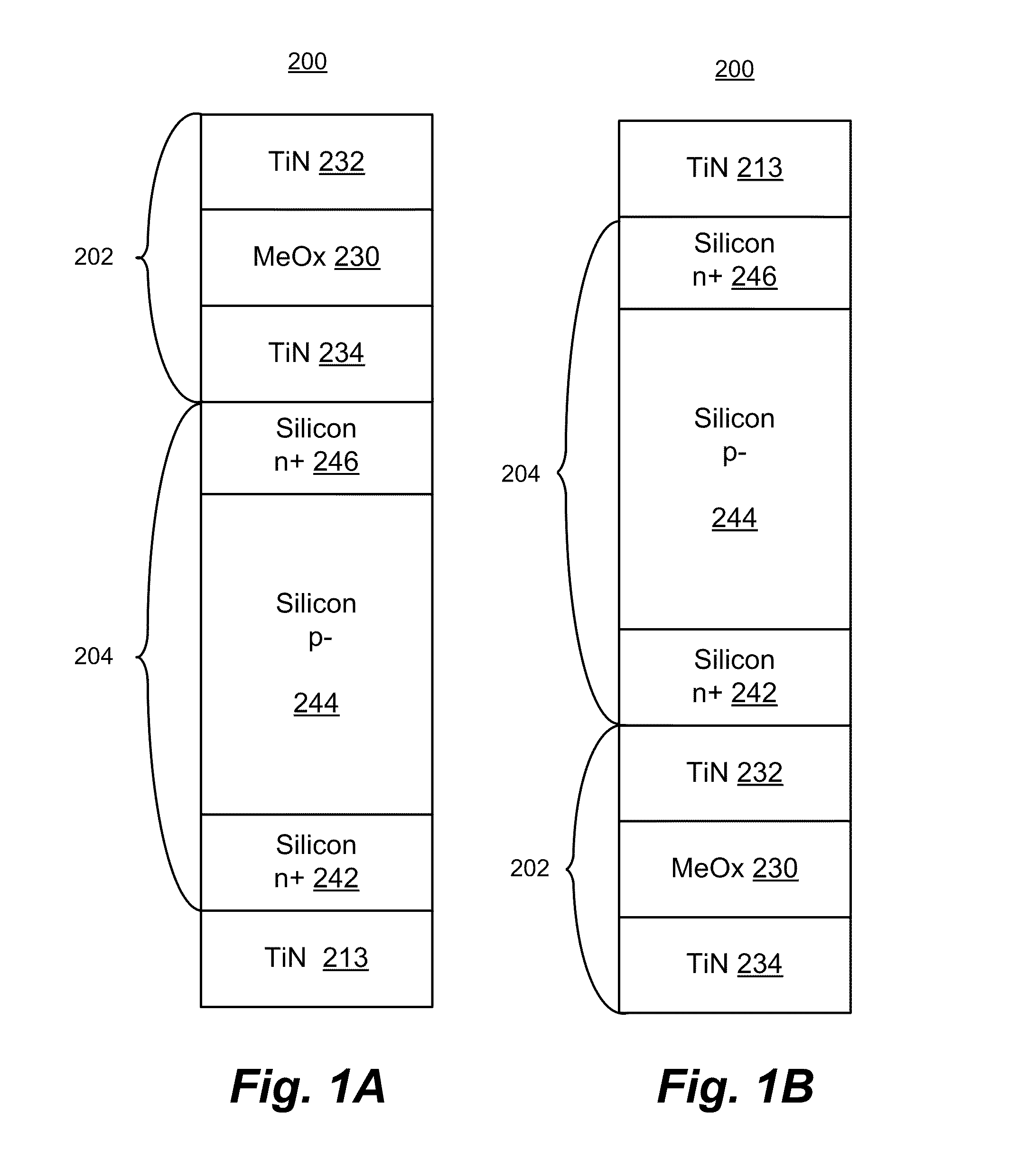

A storage system and method for forming a storage system that uses punch-through diodes as a steering element in series with a reversible resistivity-switching element is described. The punch-through diode allows bipolar operation of a cross-point memory array. The punch-through diode may have a symmetrical non-linear current / voltage relationship. The punch-through diode has a high current at high bias for selected cells and a low leakage current at low bias for unselected cells. Therefore, it is compatible with bipolar switching in cross-point memory arrays having resistive switching elements. The punch-through diode may be a N+ / P− / N+ device or a P+ / N− / P+ device.

Owner:SANDISK TECH LLC

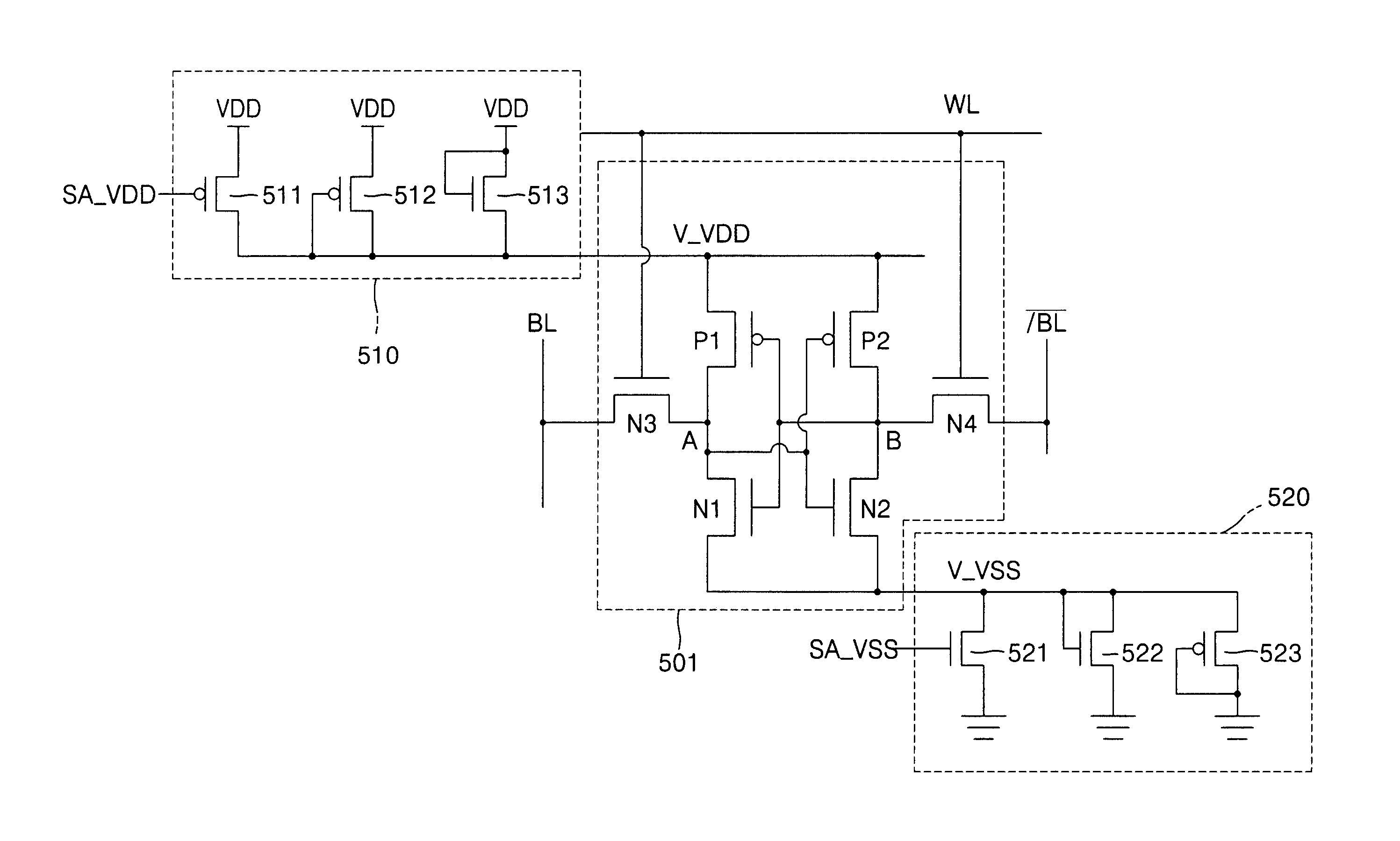

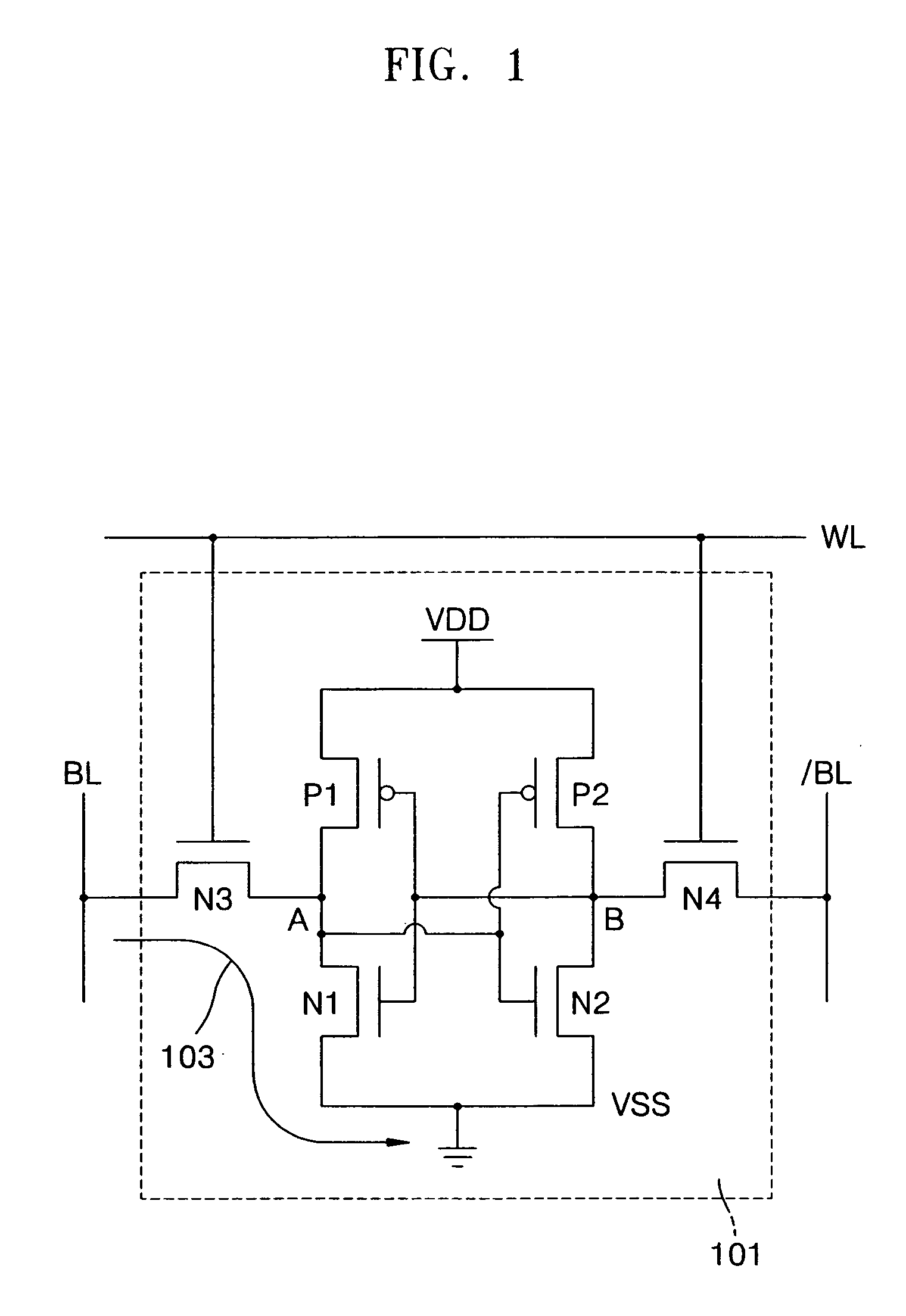

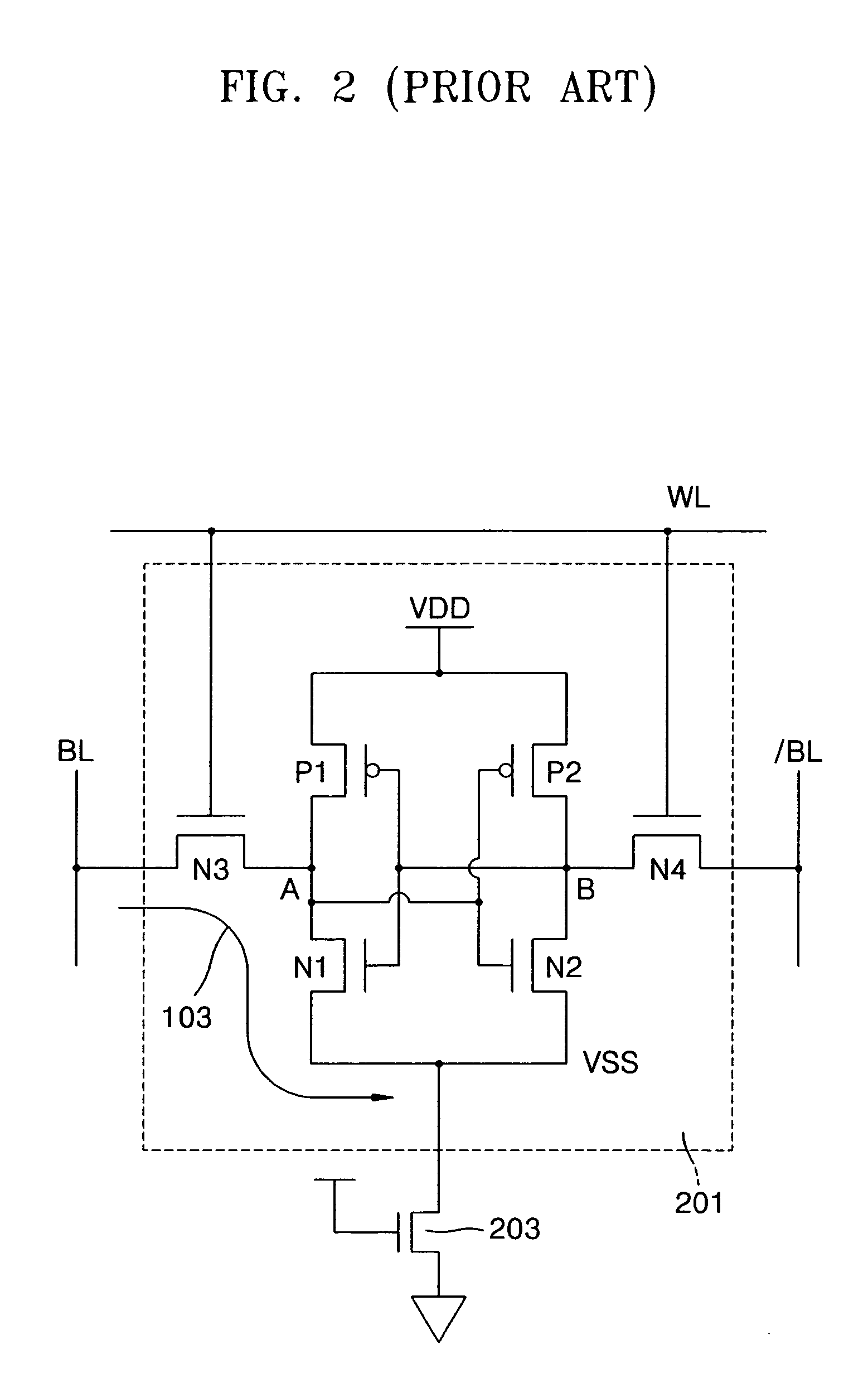

SRAM employing virtual rail scheme stable against various process-voltage-temperature variations

An SRAM employs a virtual rail configuration that is stable against process-voltage-temperature (PVT) variation. The SRAM provides a virtual power supply voltage to an SRAM cell that is obtained by lowering a power supply voltage by a threshold voltage of a transistor and a virtual ground voltage obtained by raising a ground voltage by a threshold voltage of a transistor. Due to the use of PMOS and NMOS transistors of diode types connected between the power supply voltage and the virtual power supply voltage and the use of NMOS and PMOS transistors of diode types connected between the ground voltage and the virtual ground voltage, a virtual power supply voltage level and a virtual ground voltage level that are stable even against various PVT variations are provided, so that low-leakage current characteristics are stable.

Owner:SAMSUNG ELECTRONICS CO LTD

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS20070148939A1Superb performanceSuperb scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

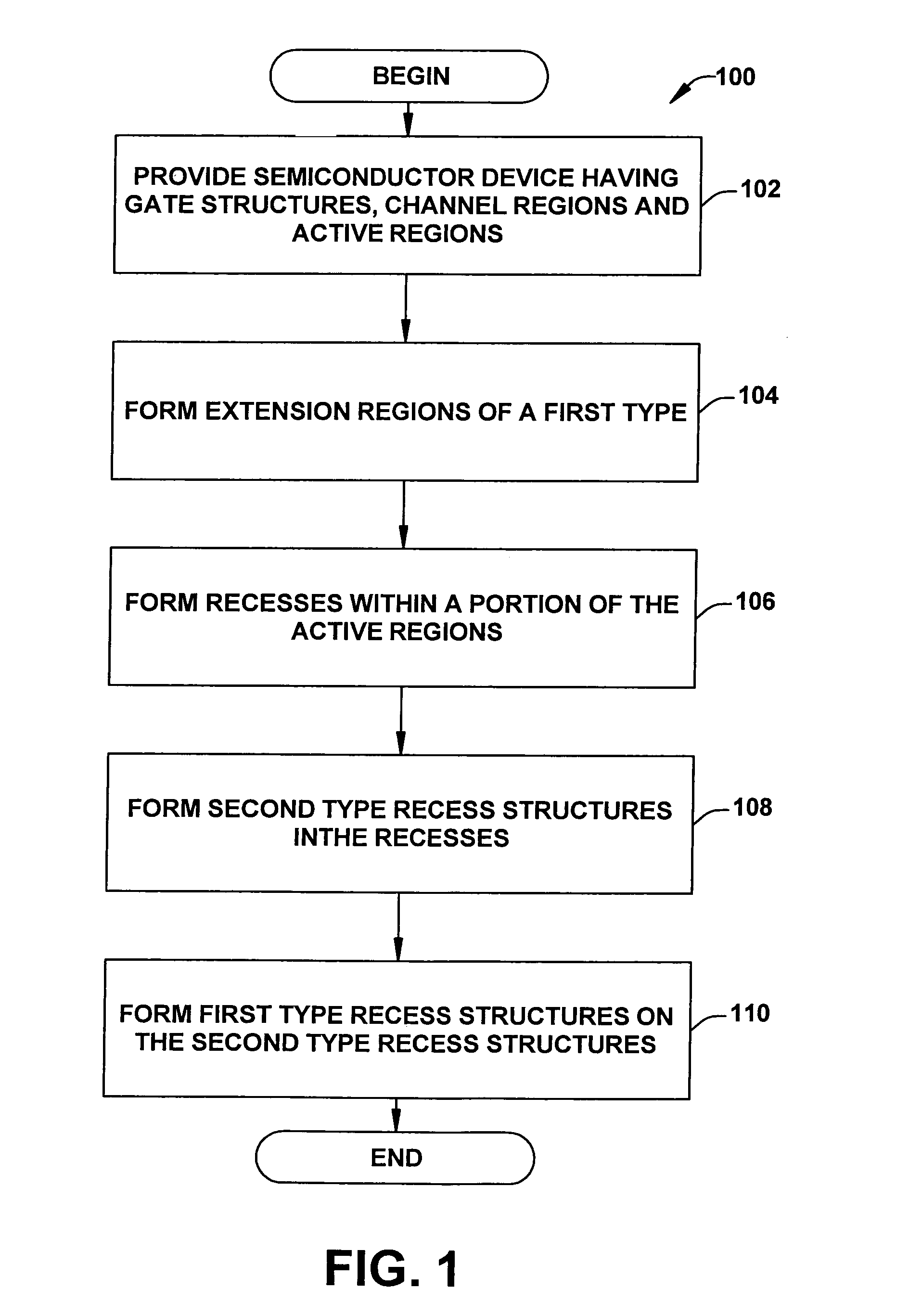

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

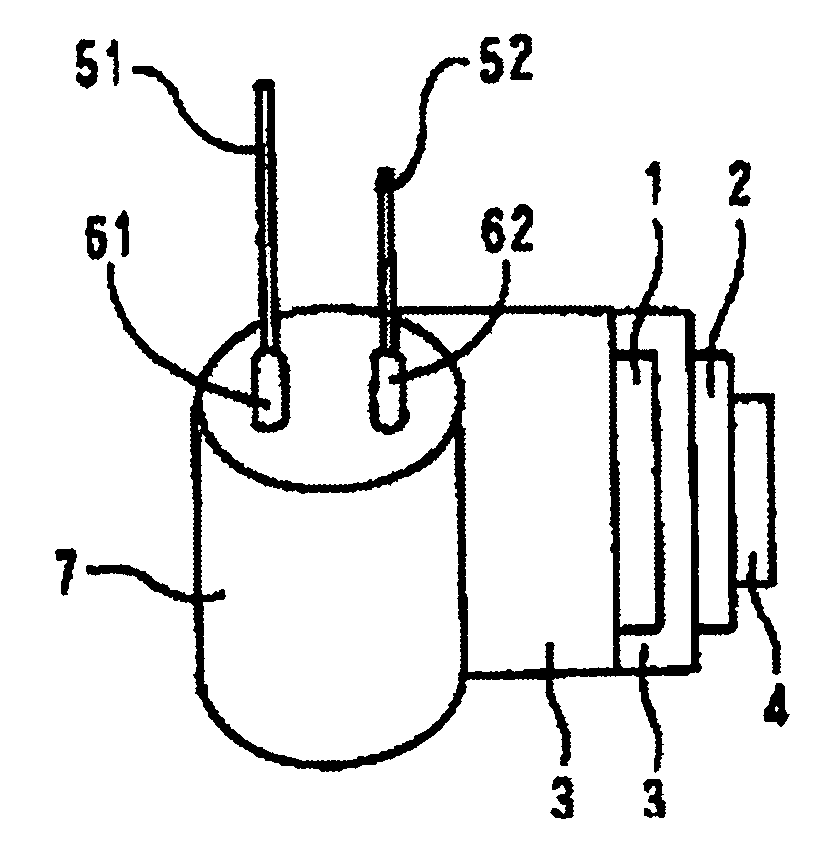

Method of manufacturing electrolytic capacitor and electrolytic capacitor

ActiveUS7497879B2Improve pressure resistanceSmall currentHybrid capacitor electrolytesSolid electrolytic capacitorsDielectricElectrolysis

A method of manufacturing an electrolytic capacitor including the following steps as well as an electrolytic capacitor manufactured by the method are provided. The method includes: a dispersion impregnation step of impregnating, with a dispersion containing electrically conductive solid particles or powder and a solvent, a capacitor element having an anode foil with a dielectric coating film formed thereon and an opposite cathode foil that are wound with a separator interposed therebetween; a dry step of evaporating the solvent after the dispersion impregnation step to form an electrically conductive solid layer on a surface of the dielectric coating film; and an electrolytic solution impregnation step of impregnating a gap in the electrically conductive solid layer with an electrolytic solution. Accordingly, an electrolytic capacitor that can be manufactured more easily that is excellent in voltage proofing property and that has a lower ESR and a lower leakage current is provided.

Owner:SANYO ELECTRIC CO LTD +1

Punch-through diode

ActiveUS20120145984A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringLow leakage

A punch-through diode and method of fabricating the same are disclosed herein. The punch-through diode may be used as a steering element in a memory device having a reversible resistivity-switching element. For example, a memory cell may include a reversible resistivity-switching element in series with a punch-through diode. The punch-through diode allows bipolar operation of a cross-point memory array. The punch-through diode may have a symmetrical non-linear current / voltage relationship. The punch-through diode has a high current at high bias for selected cells and a low leakage current at low bias for unselected cells. In other words, the ratio of Ion / Ioff is high. Therefore, the punch-through diode is compatible with bipolar switching in cross-point memory arrays having resistive switching elements.

Owner:SANDISK TECH LLC

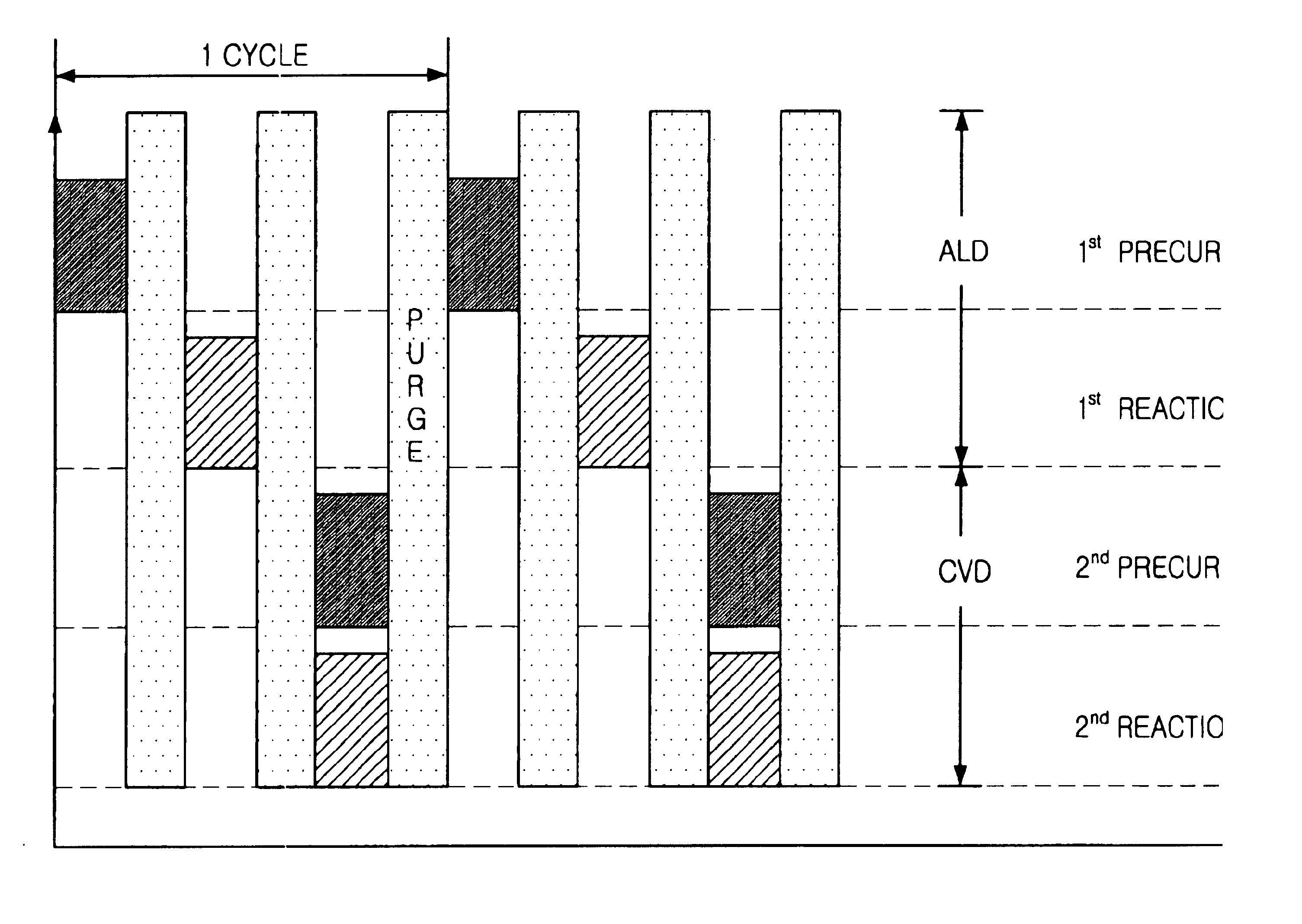

Method for forming polyatomic layers

InactiveUS6800567B2Reduce processing stepsIncrease speedSemiconductor/solid-state device manufacturingGas phaseLow leakage

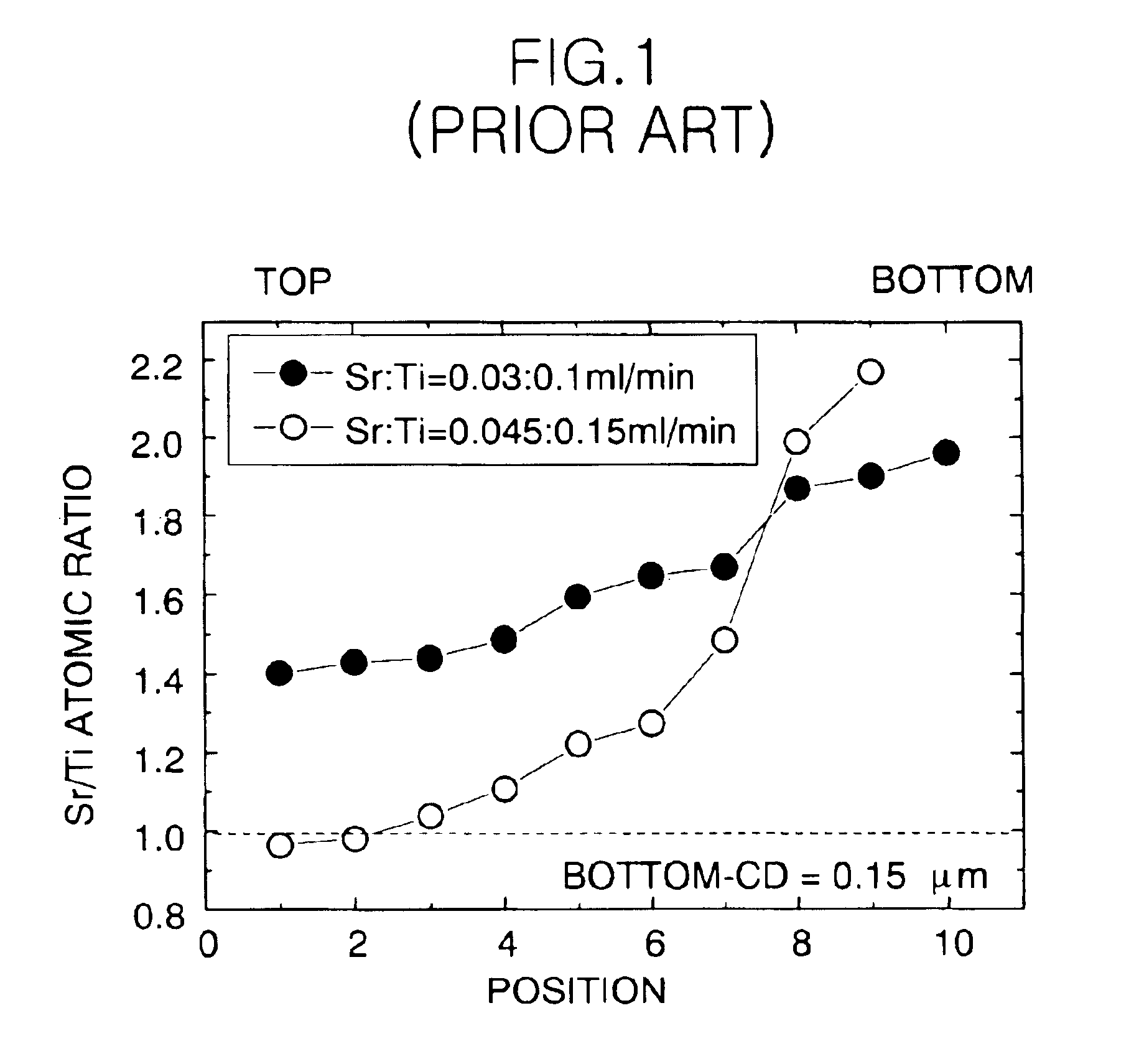

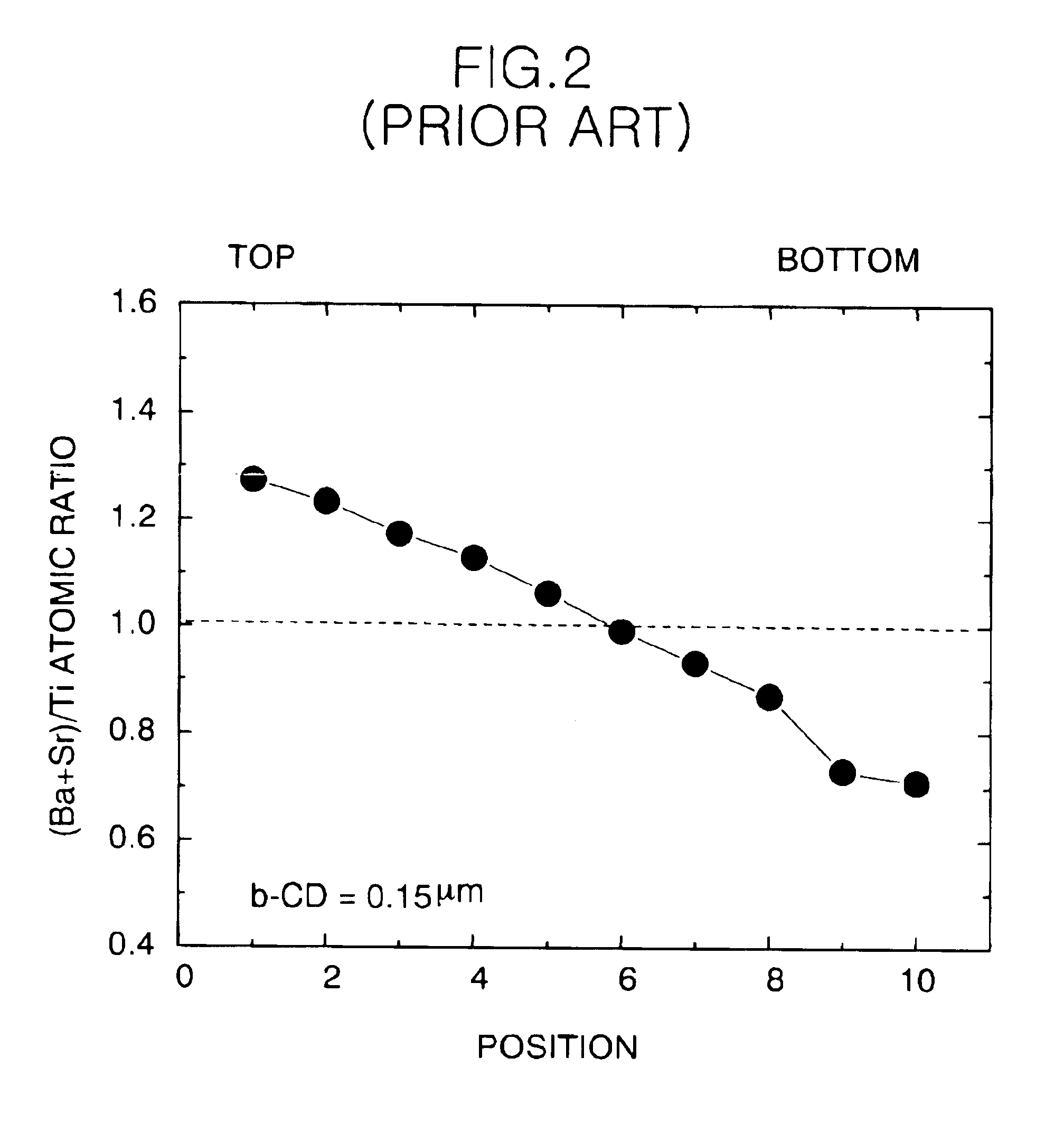

A method for forming a polyatomic layer with a mixed deposition method consisting of an atomic layer deposition method (ALD) and a chemical vapor deposition method. The mixed deposition method can be adopted to form a polyatomic high dielectric layer, such as BST or STO. Accordingly, it is possible to form a polyatomic high dielectric layer having a uniform composition distribution, and thereby also having a high dielectric characteristic and a low leakage current characteristic.

Owner:SK HYNIX INC

Semiconductor device

ActiveUS8547753B2Improve versatilityReduce designPower reduction in field effect transistorsTransistorProgrammable logic deviceHemt circuits

Owner:SEMICON ENERGY LAB CO LTD

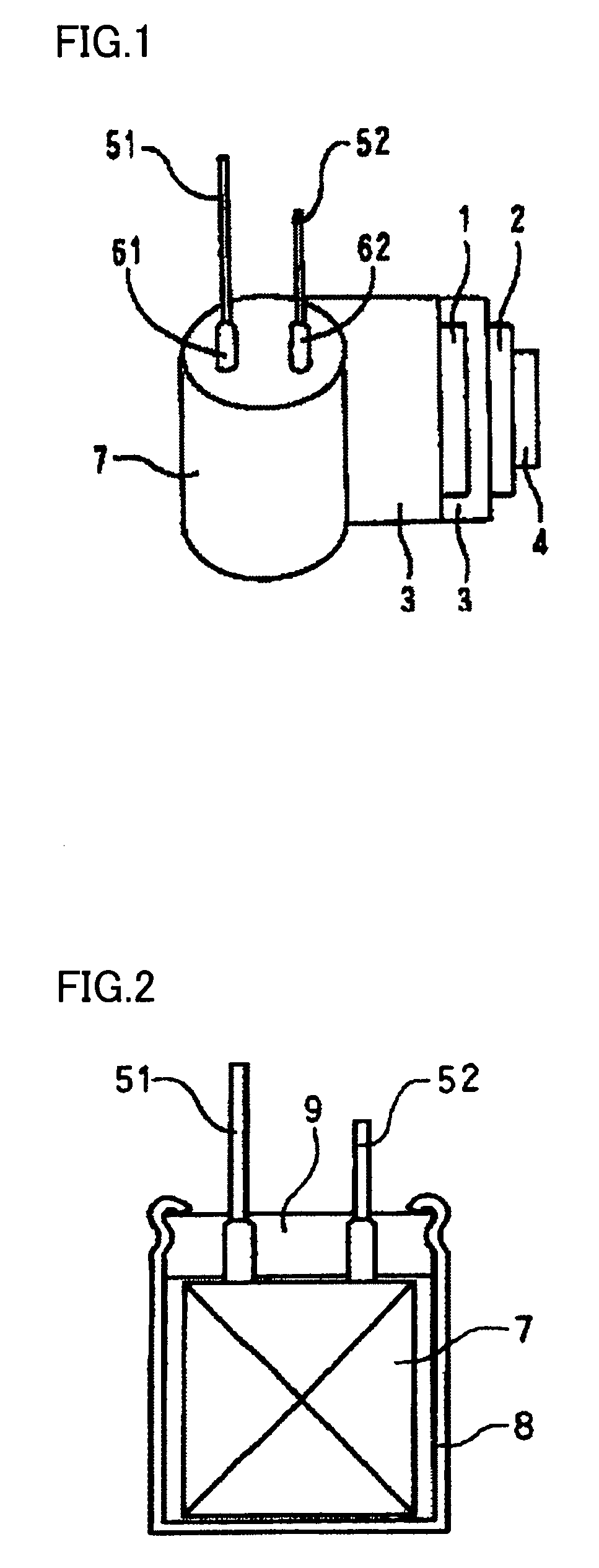

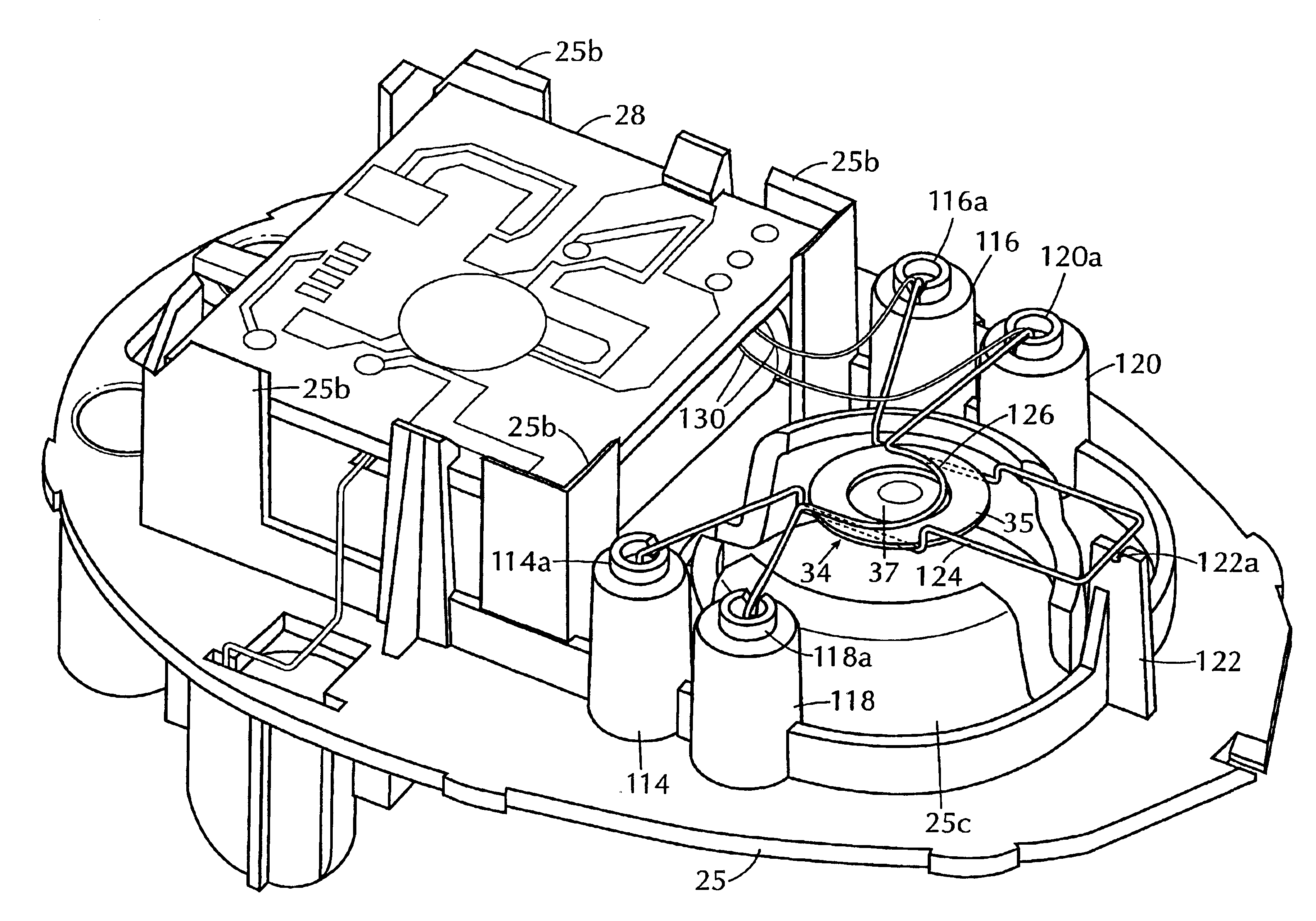

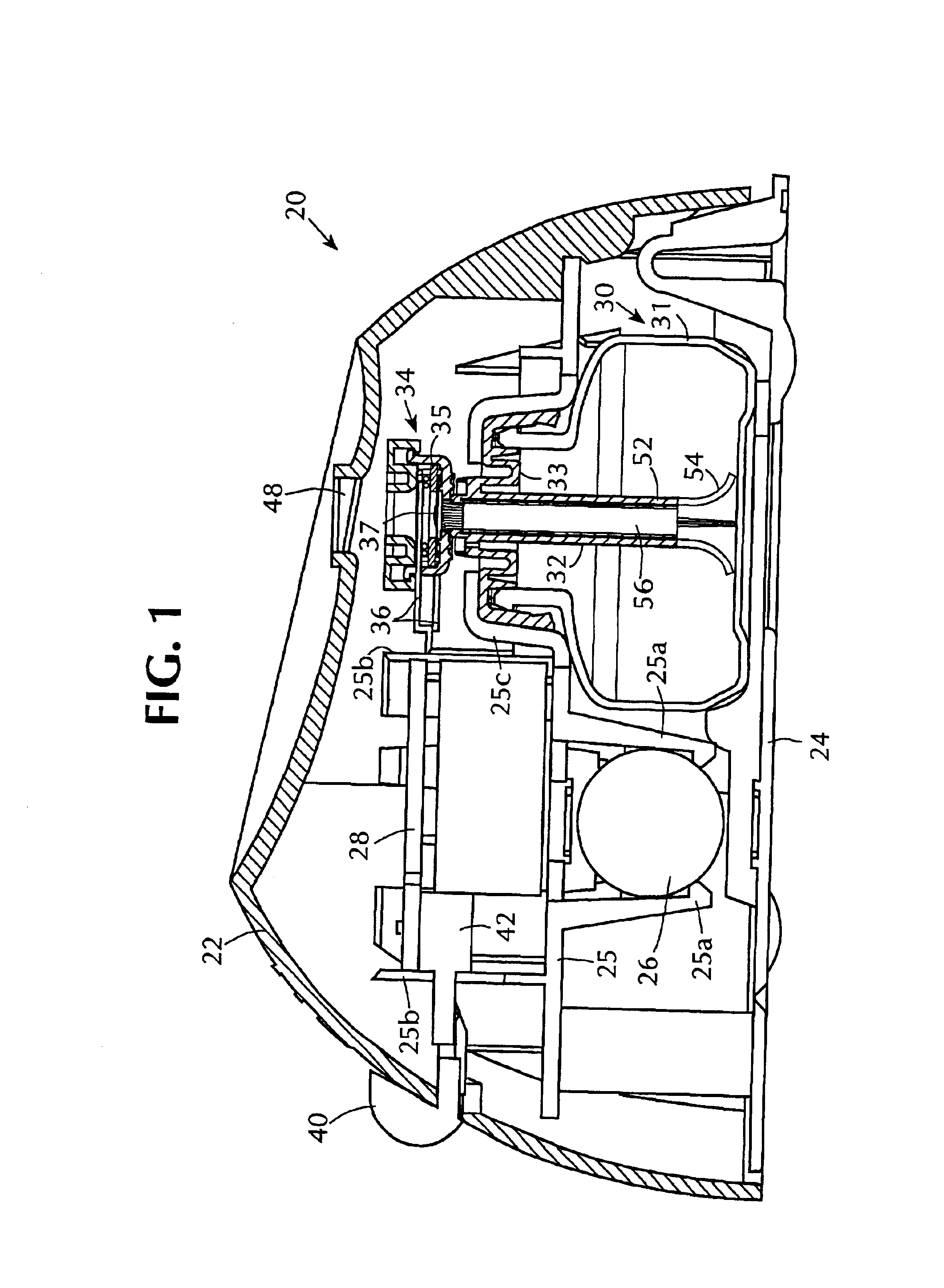

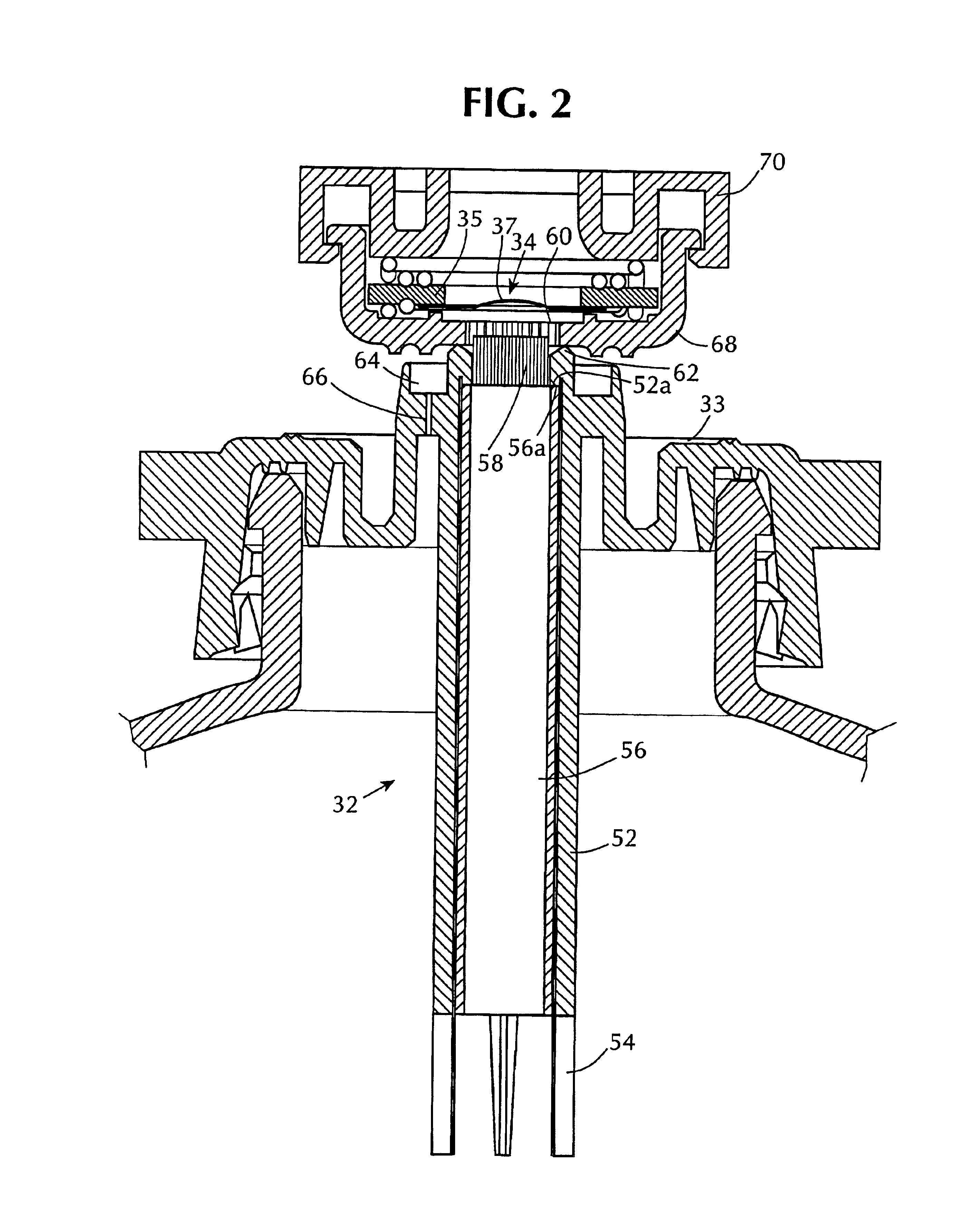

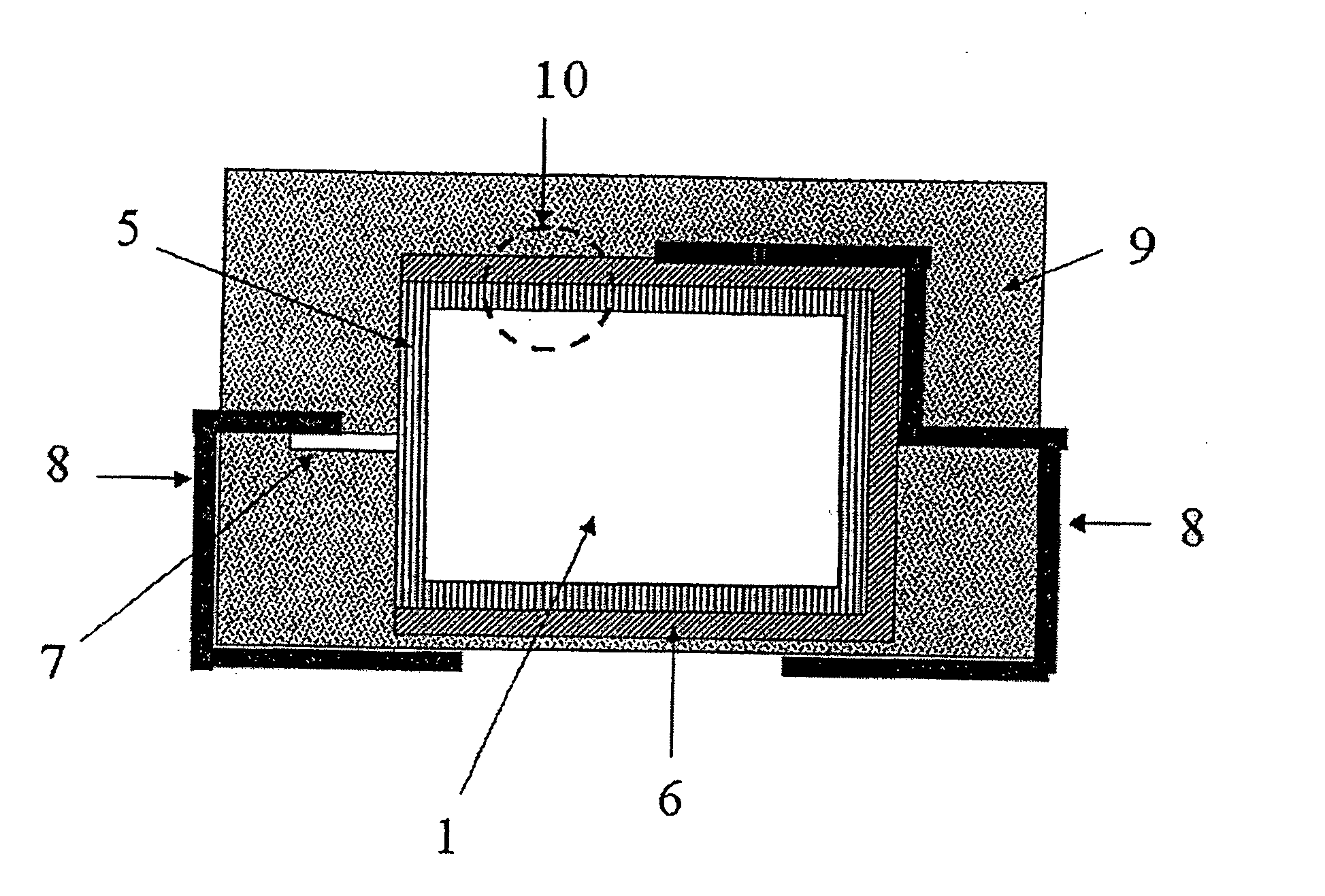

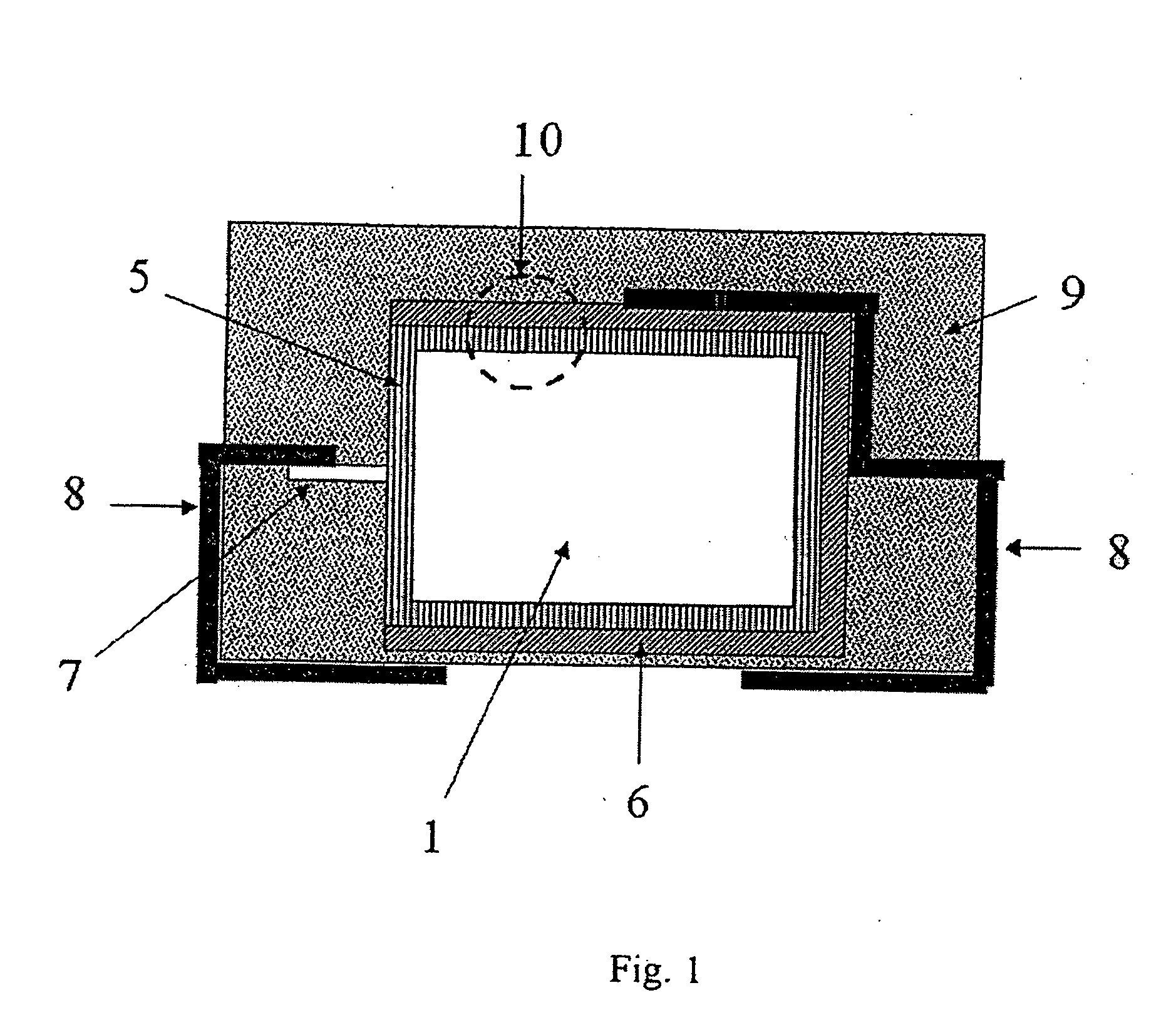

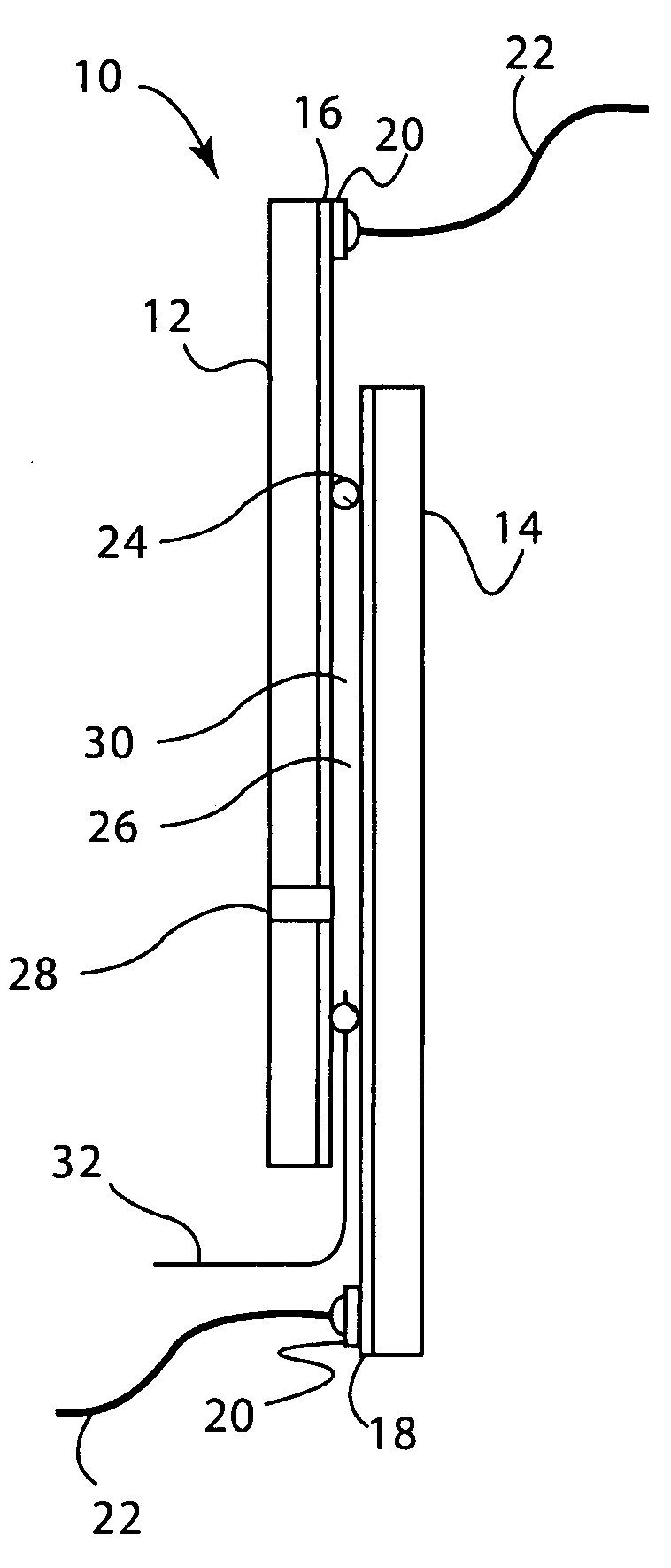

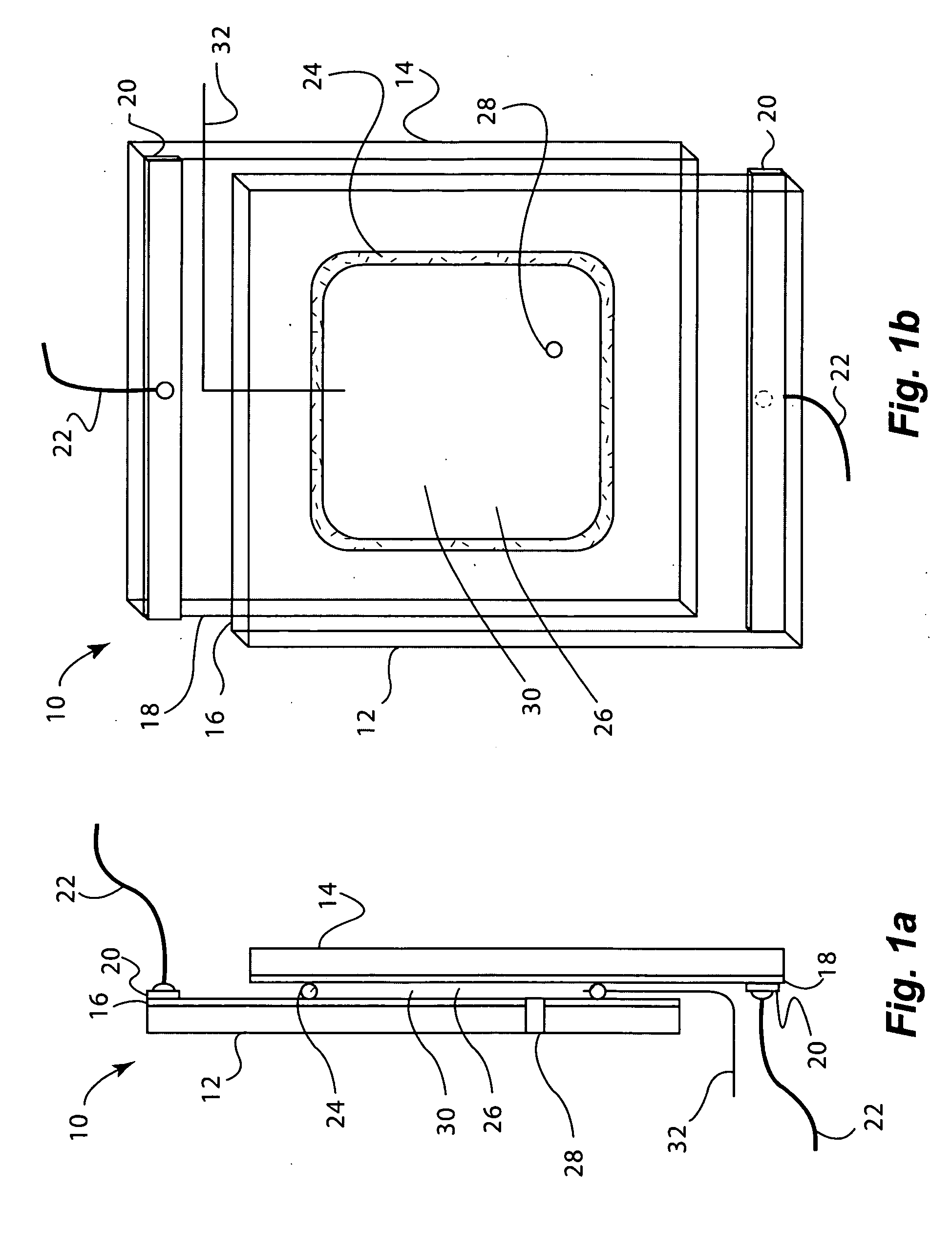

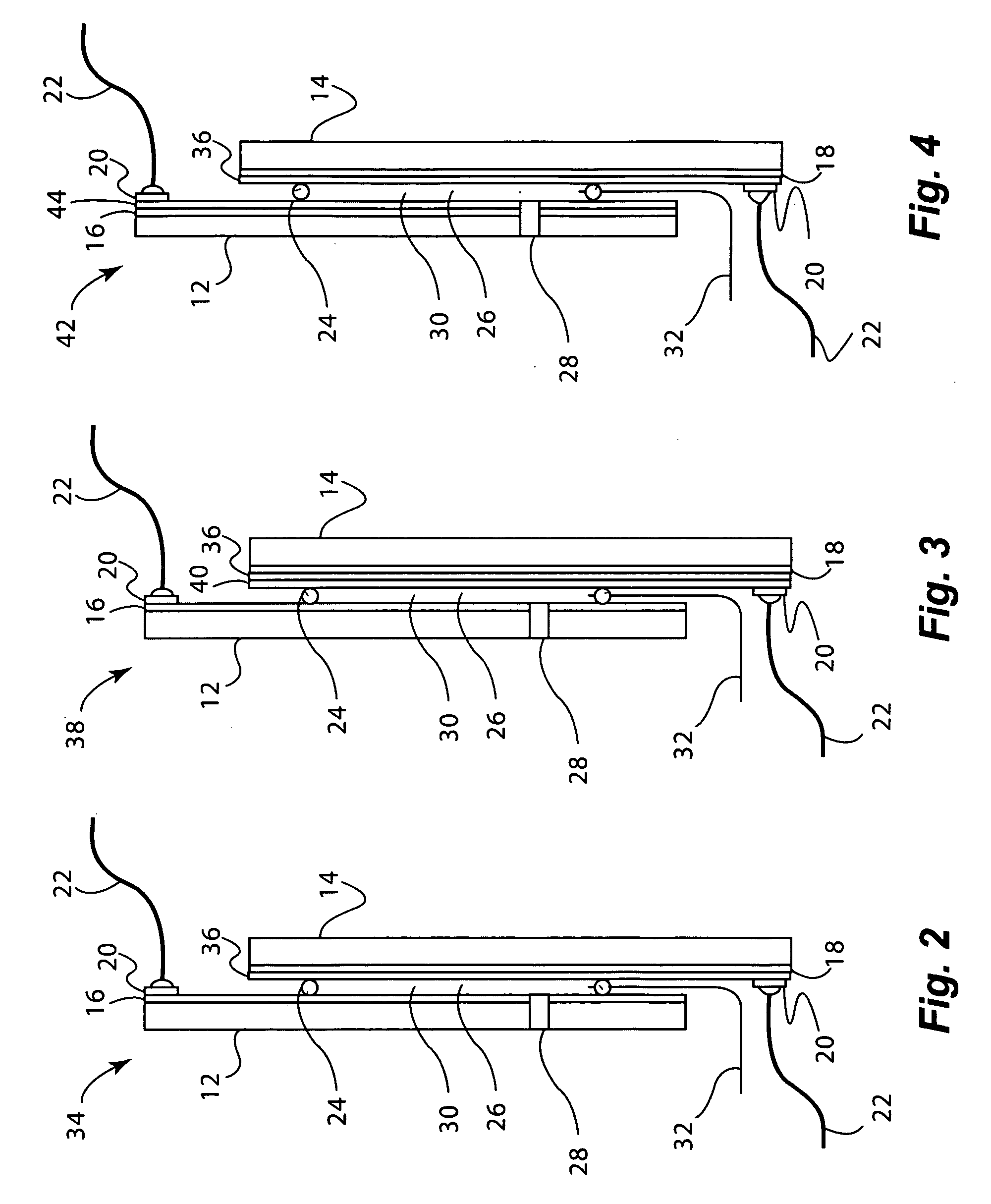

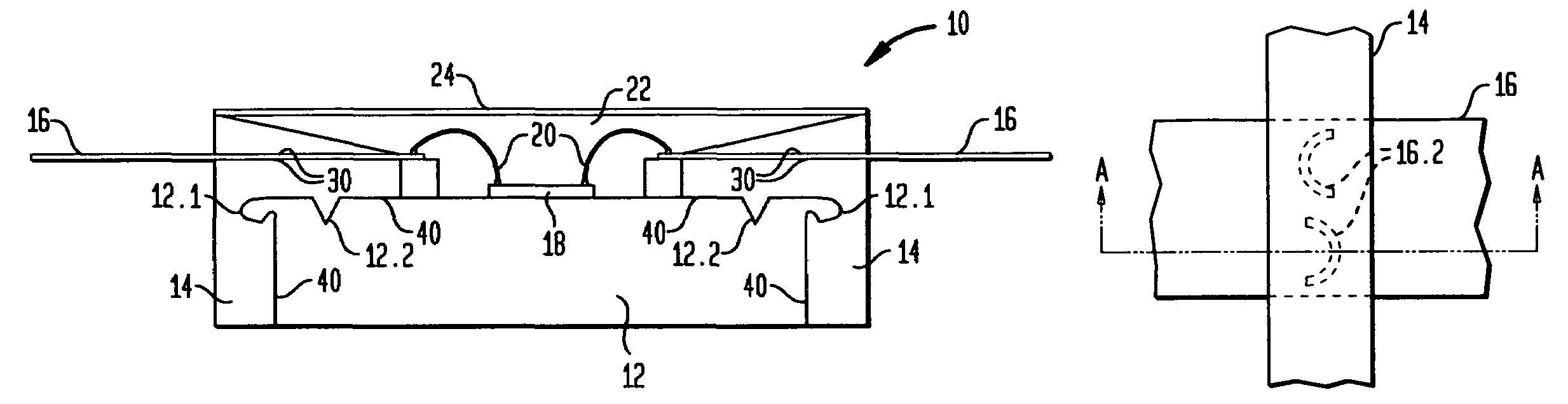

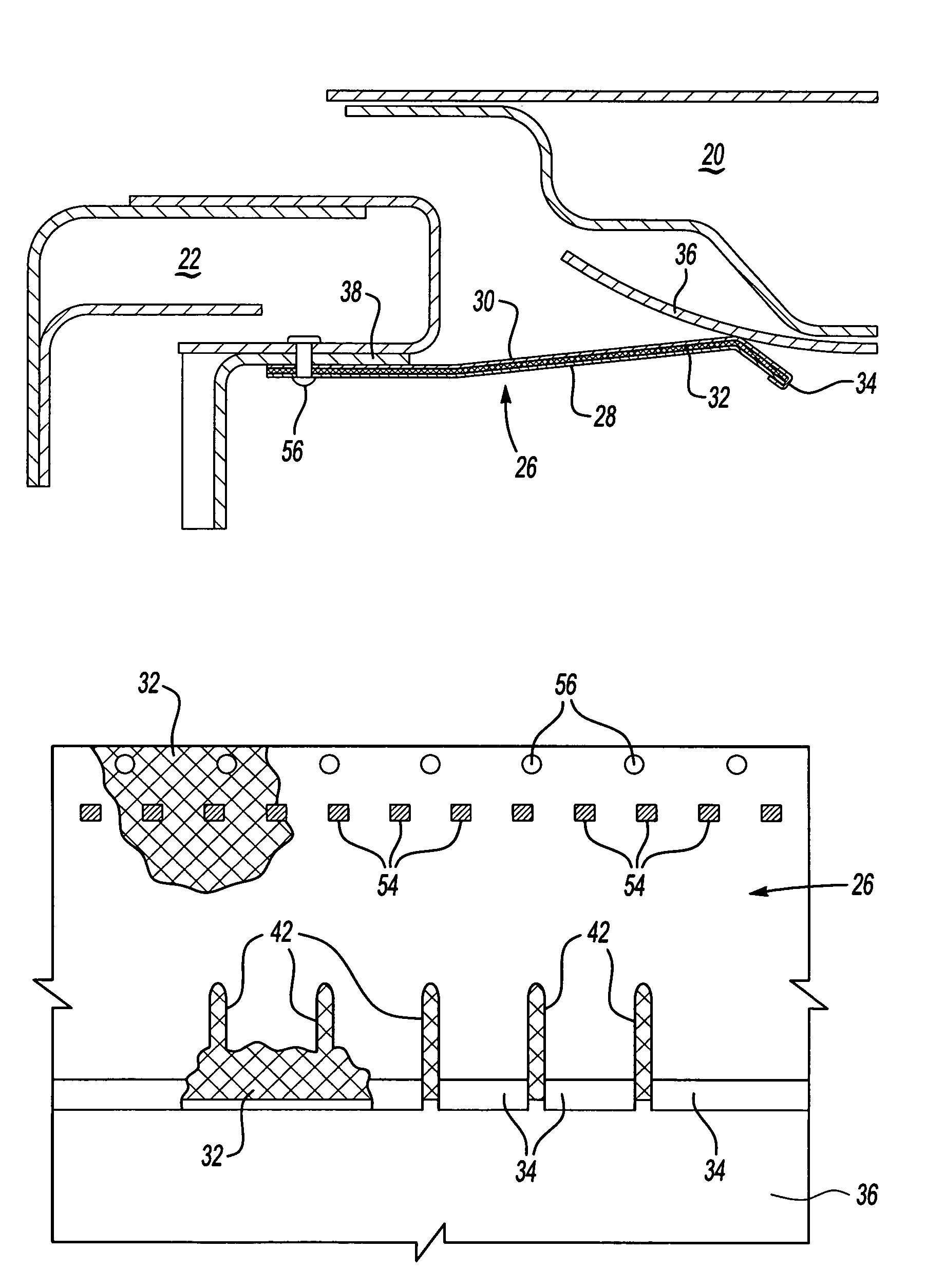

Low leakage liquid atomization device

InactiveUS6843430B2Minimize migrationImprove device performanceMovable spraying apparatusSpray nozzlesElectricityNebulizer

A battery operated atomizer device comprising, in a housing (22), a liquid reservoir (30) from which a capillary type liquid delivery system (38) extends to contact a piezoelectric actuator an atomization plate assembly (34), the assembly (34) being supported by means of wire-like elements (36) in cantilever fashion over the liquid delivery system, the liquid delivery system comprising an outer tubular member (52) and a solid rod (56) which have facing surfaces configured to define between them, longitudinal capillary liquid passages.

Owner:SC JOHNSON & SON INC

Gallium nitride material structures including isolation regions and methods

InactiveUS20050145851A1Improve leakage currentSemiconductor/solid-state device manufacturingDiodeLow leakageVolumetric Mass Density

Gallium nitride material structures, including devices, and methods associated with the same are provided. In some embodiments, the structures include one or more isolation regions which electrically isolate adjacent devices. One aspect of the invention is the discovery that the isolation regions also can significantly reduce the leakage current of devices (e.g., transistors) made from the structures, particularly devices that also include a passivating layer formed on a surface of the gallium nitride material. Lower leakage currents can result in increased power densities and operating voltages, amongst other advantages.

Owner:NITRONEX

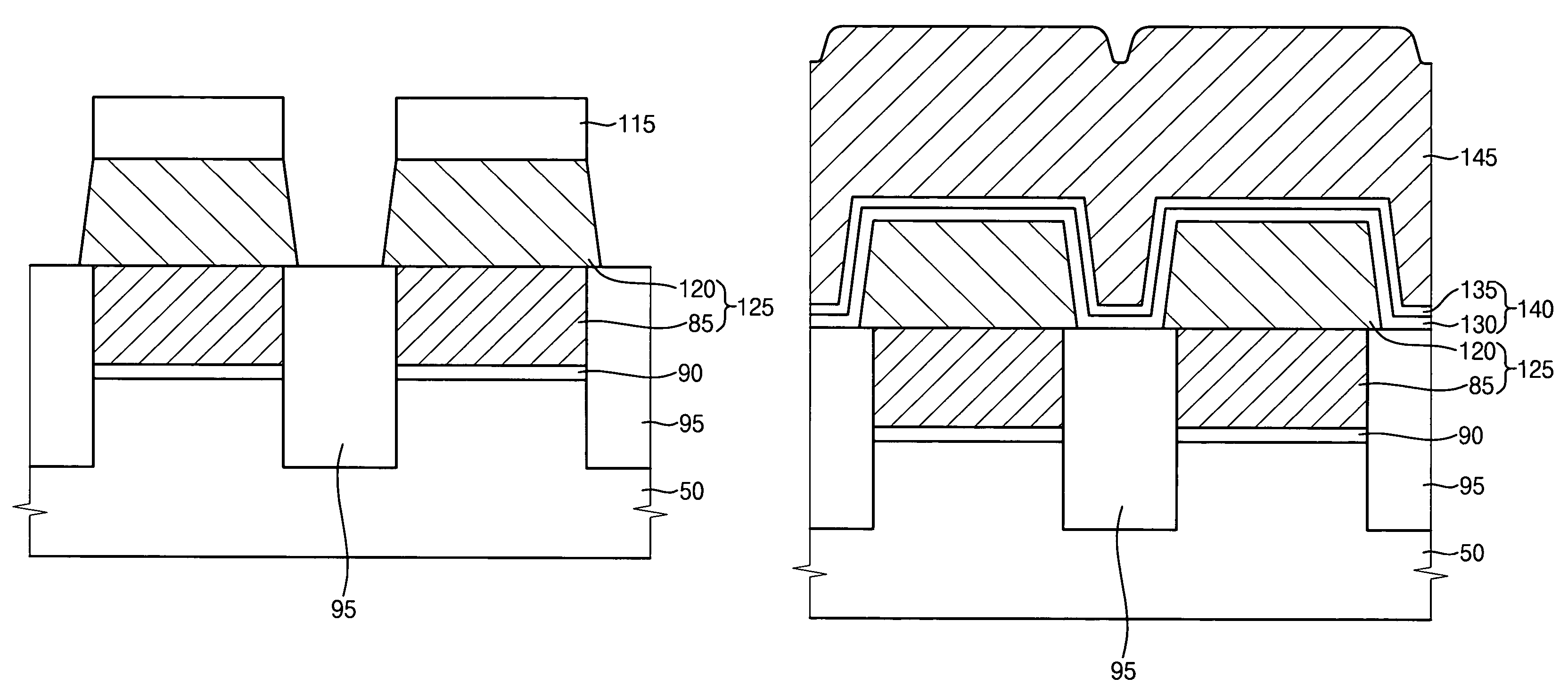

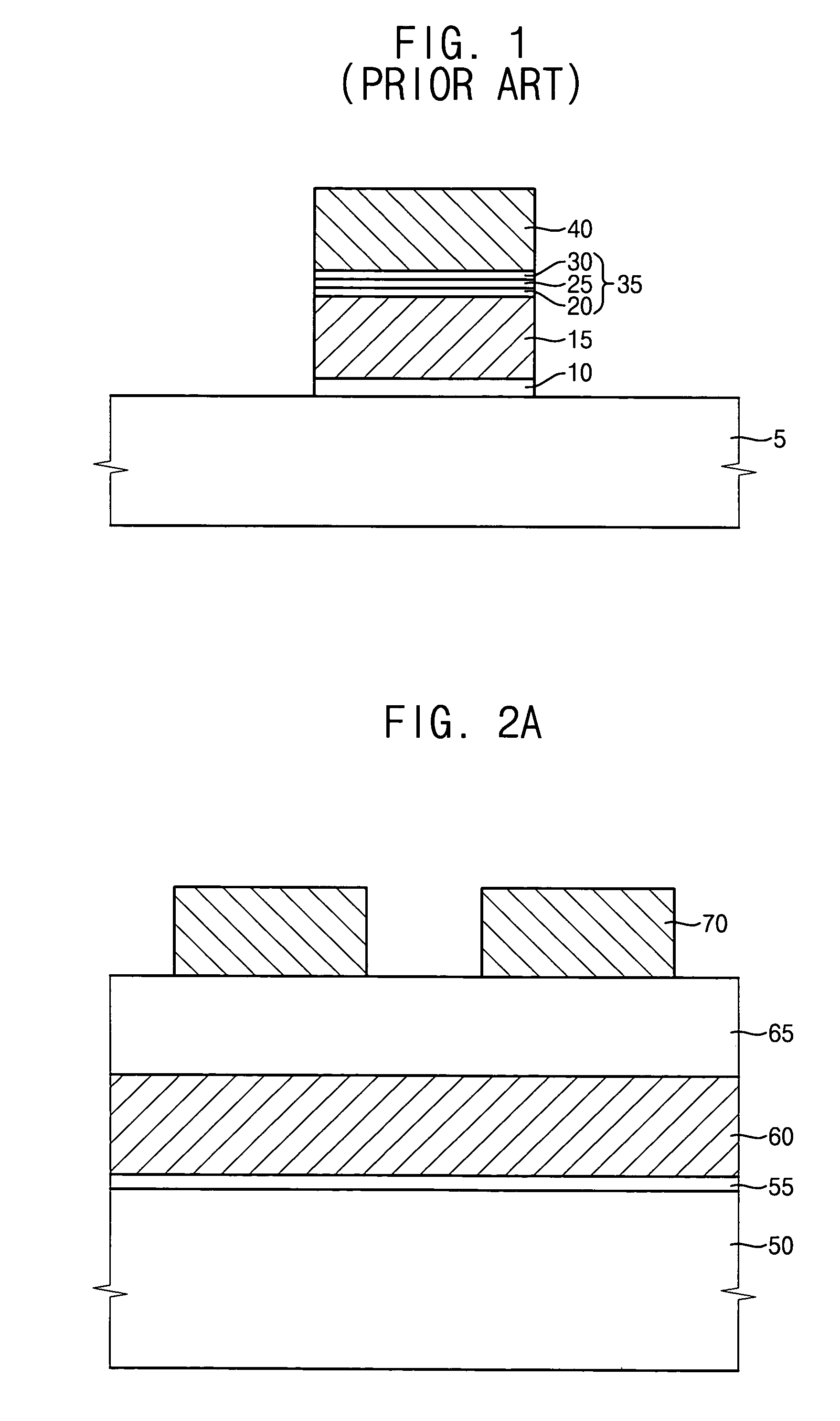

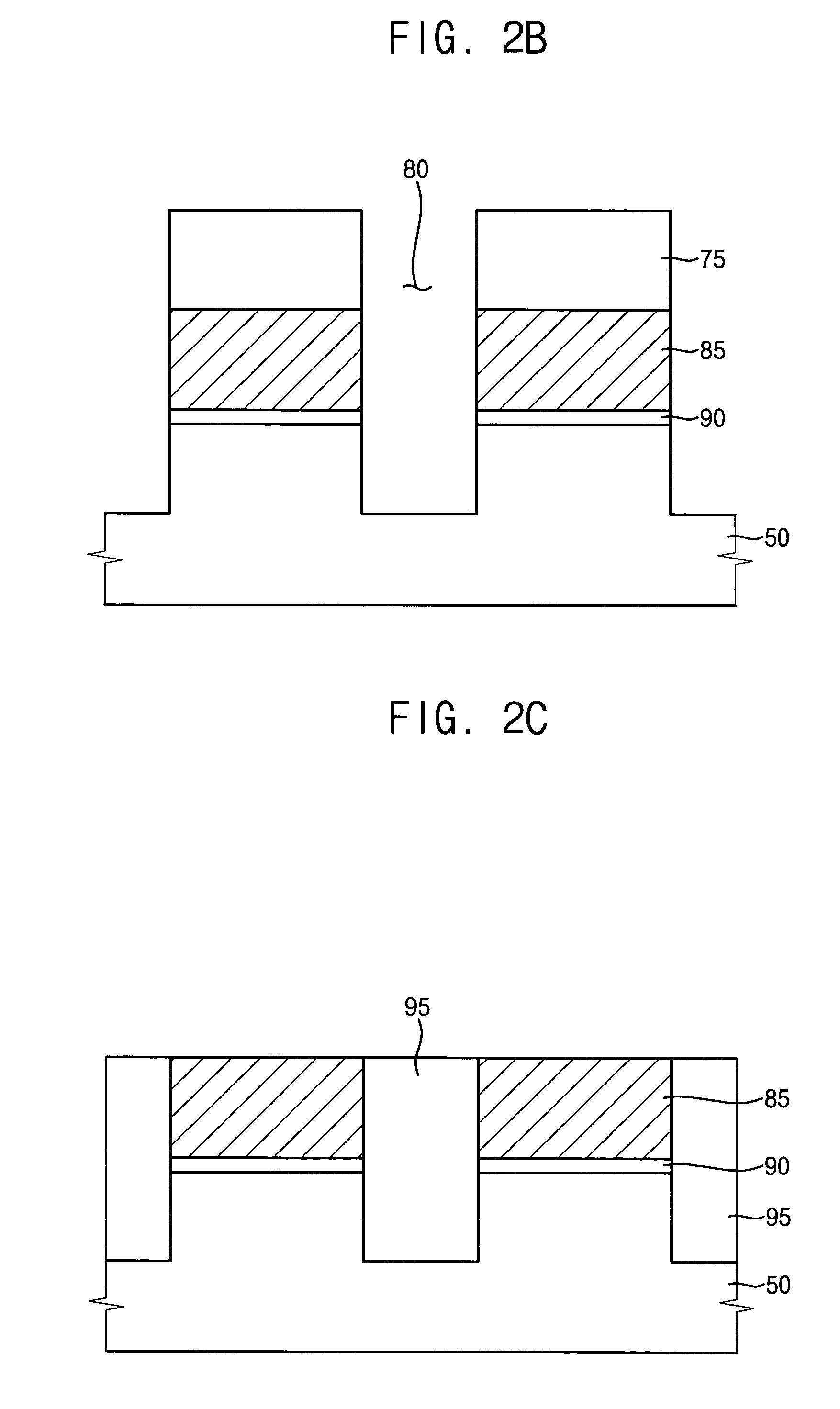

Dielectric structures having high dielectric constants, methods of forming the dielectric structures, non-volatile semiconductor memory devices having the dielectric structures and methods of manufacturing the non-volatile semiconductor memory devices

ActiveUS20060244147A1High dielectric constantImprove heat resistanceRoofingSemiconductor/solid-state device detailsCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

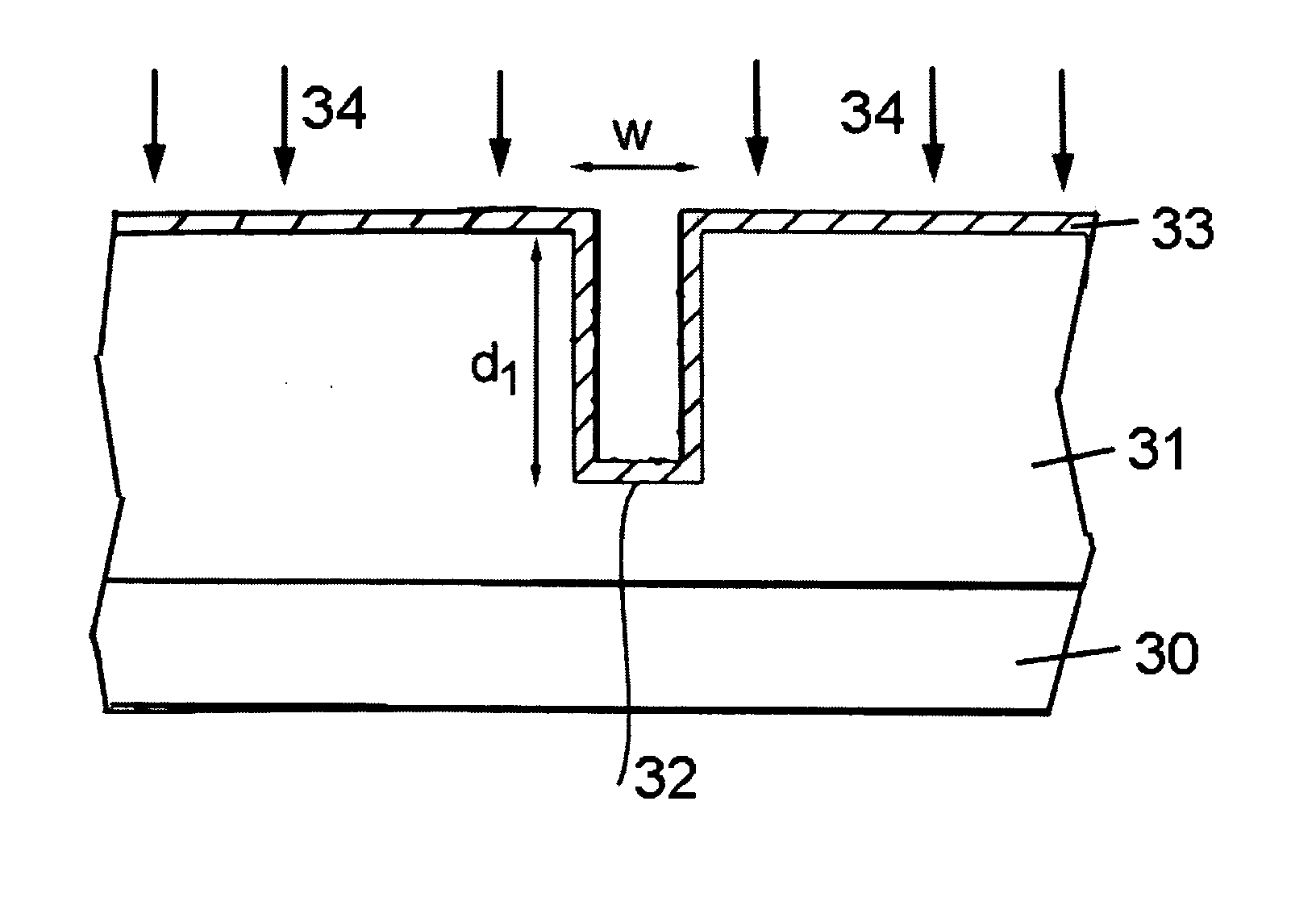

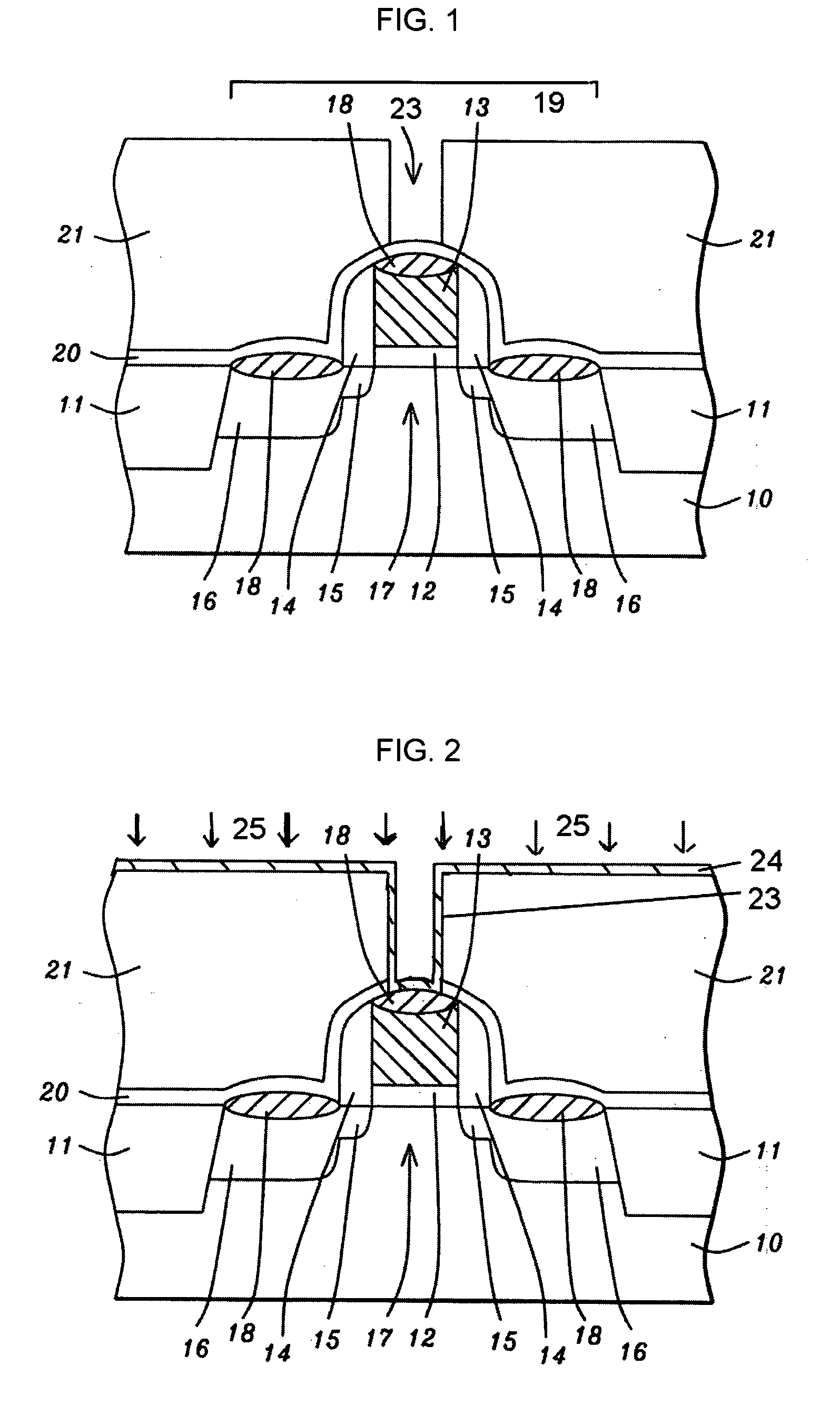

Systems and methods for low leakage strained-channel transistor

ActiveUS7026232B1Easy to manufactureSelectively applying strainSemiconductor/solid-state device manufacturingSemiconductor devicesLow leakageSemiconductor

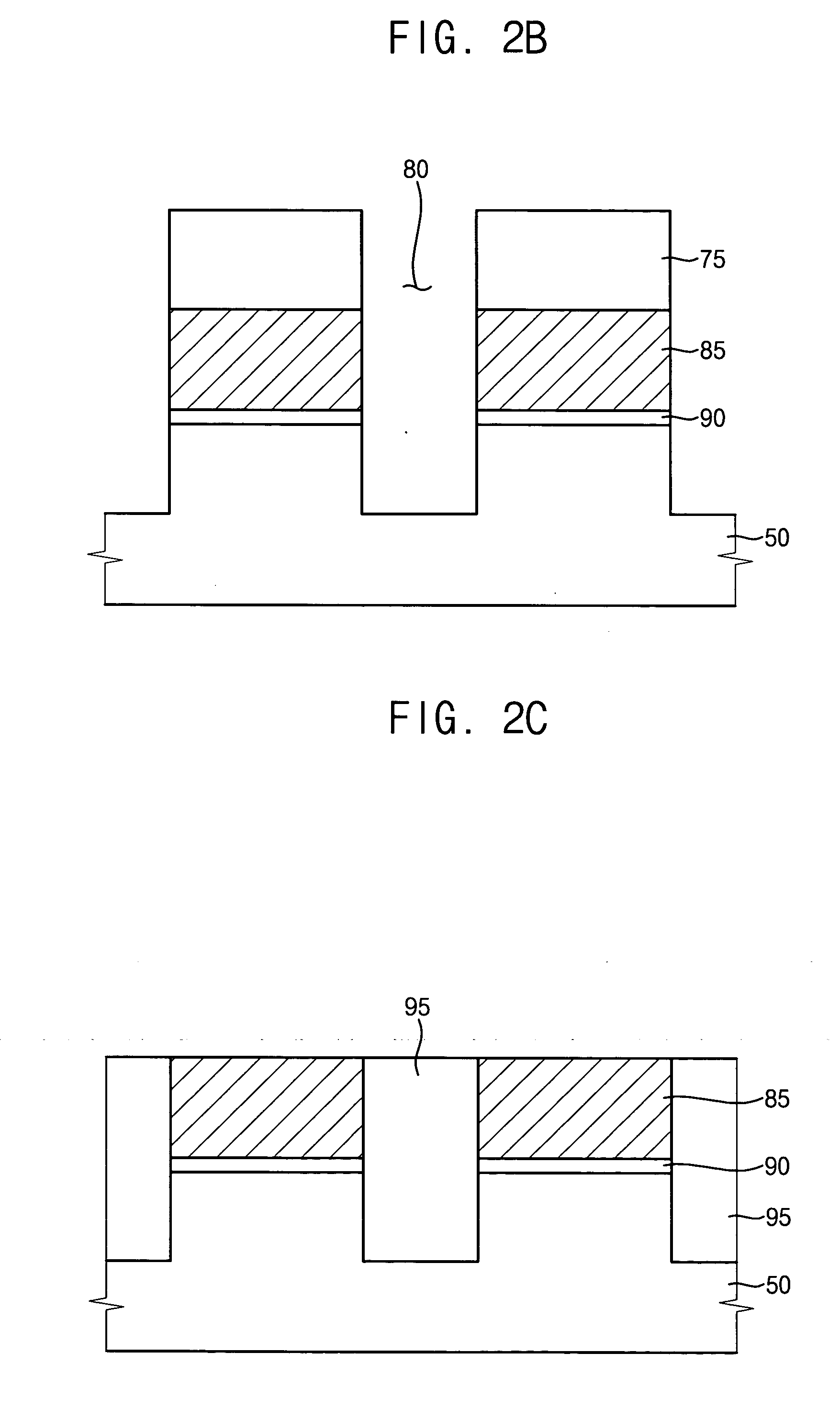

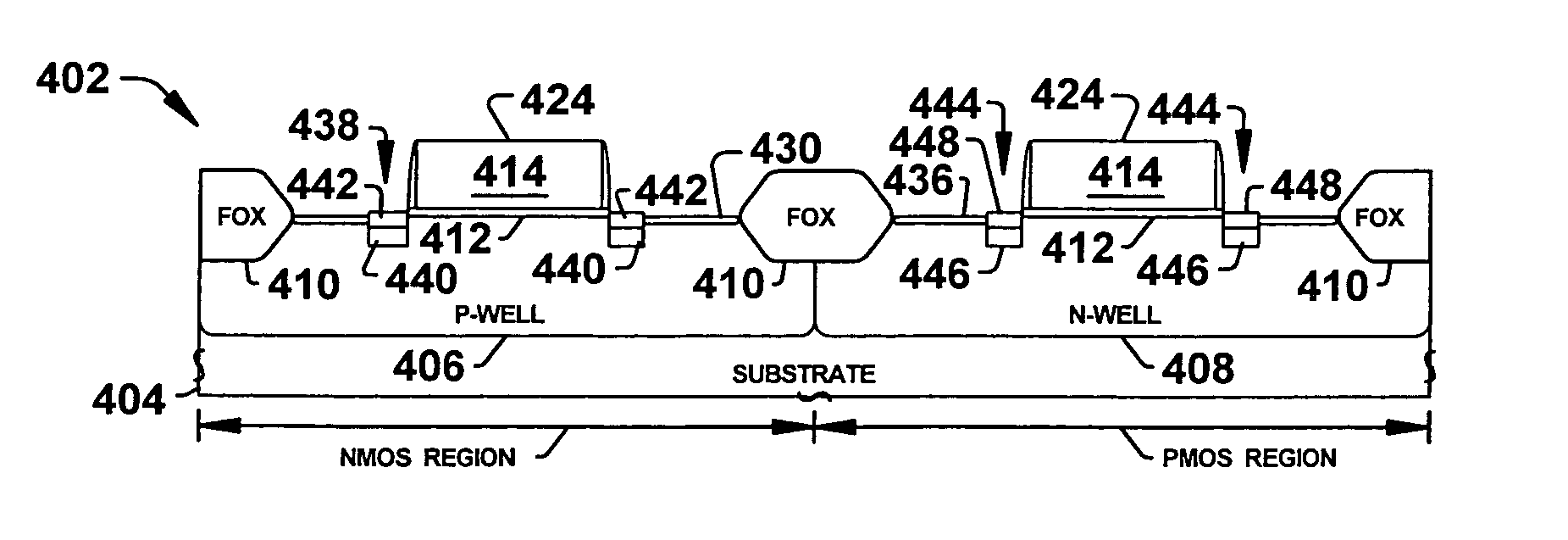

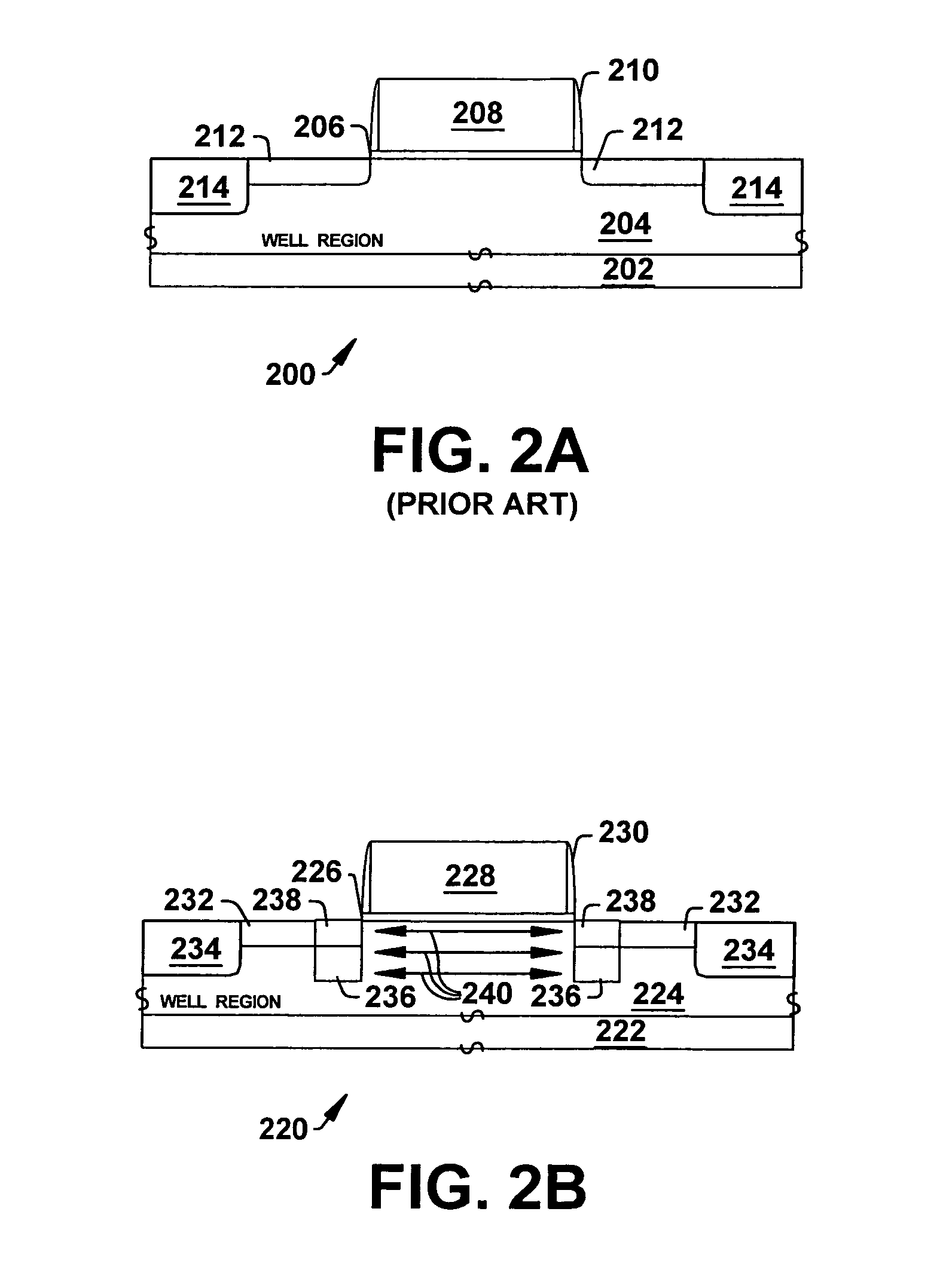

The present invention facilitates semiconductor fabrication by providing methods of fabrication that mitigate leakage and apply strain to channel regions of transistor devices. A semiconductor device having gate structures, channel regions, and active regions is provided (102). Extension regions of a first type of conductivity are formed within the active regions (104). Recesses are then formed within a portion of the active regions (106). Second type recess structures are formed (108) within the recesses, wherein the second type recess structures have a second type of conductivity opposite the first type and are comprised of a strain inducing material. Then, first type recess structures are formed (110) within the recesses and on the second type recess structures, wherein the first type recess structures have the first type of conductivity and are comprised of a strain inducing material.

Owner:TEXAS INSTR INC

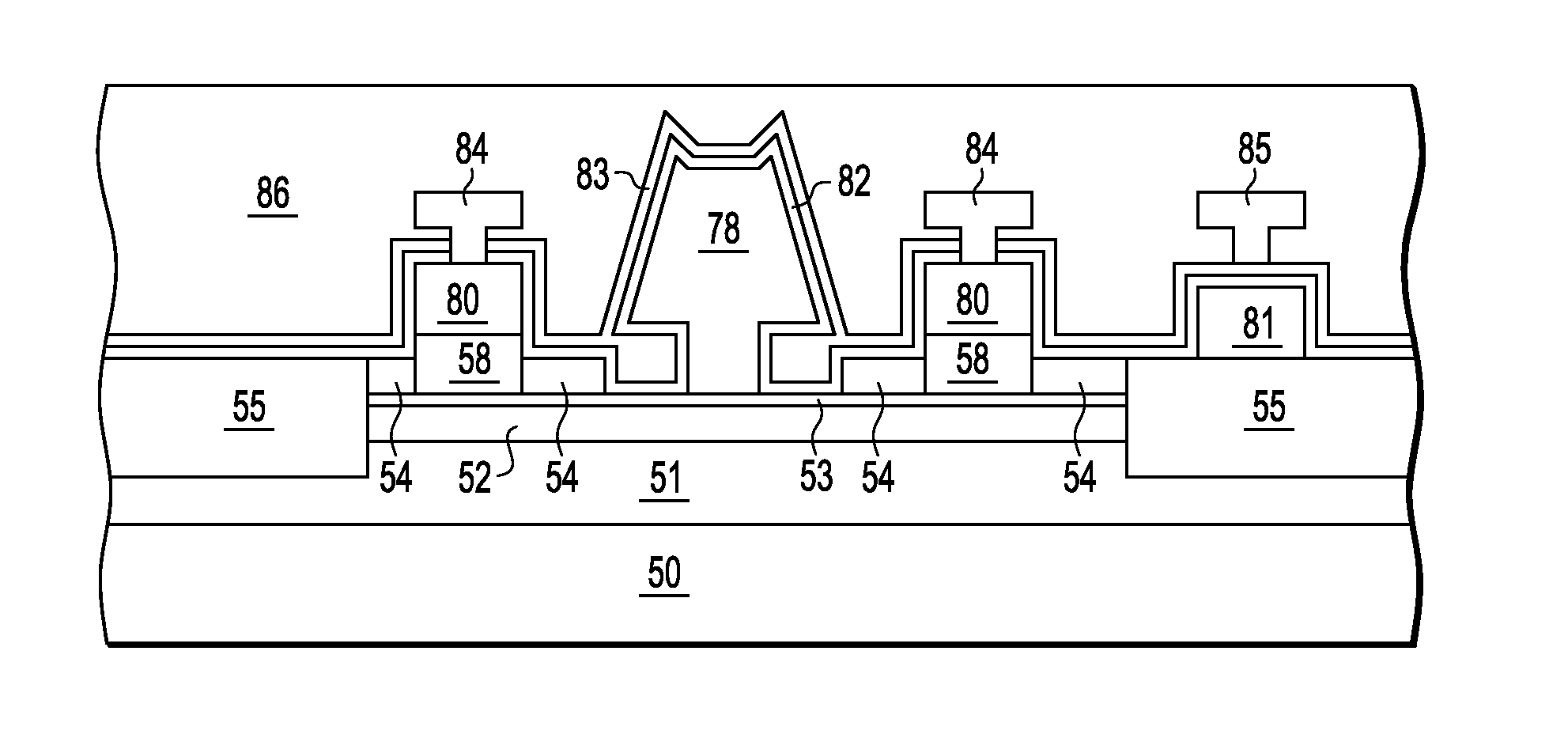

High Speed Gallium Nitride Transistor Devices

ActiveUS20130277680A1TransistorSemiconductor/solid-state device manufacturingSurface layerLow leakage

A low leakage current switch device (110) is provided which includes a GaN-on-Si substrate (11-13) covered by a passivation surface layer (43) in which a T-gate electrode with sidewall extensions (48) is formed and coated with a conformal passivation layer (49) so that the T-gate electrode sidewall extensions are spaced apart from the underlying passivation surface layer (43) by the conformal passivation layer (49).

Owner:NXP USA INC

Dielectric structures having high dielectric constants, and non-volatile semiconductor memory devices having the dielectric structures

ActiveUS7482677B2High dielectric constantImprove heat resistanceSemiconductor/solid-state device detailsRoofingCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

Electrolytic capacitors with a polymeric outer layer

ActiveUS20050111165A1Reduce leakage currentLow ESRHybrid capacitor electrolytesSolid electrolytic capacitorsElectrolysisCompound (substance)

Electrolytic capacitors having low equivalent series resistance and low leakage current are described. The electrolytic capacitors include a solid electrolyte layer of a conductive material in particular a conductive polymer, and an outer layer that includes binders, polymeric anions and conductive polymers (e.g., polythiophenes). Also described is a method of preparing electrolytic capacitors that involves forming the conductive polymer of the solid electrolyte layer in situ by means of chemical oxidative polymerization or electrochemical polymerization. Electronic circuits that include the electrolytic capacitors are also described.

Owner:HERAEUS PRECIOUS METALS GMBH & CO KG

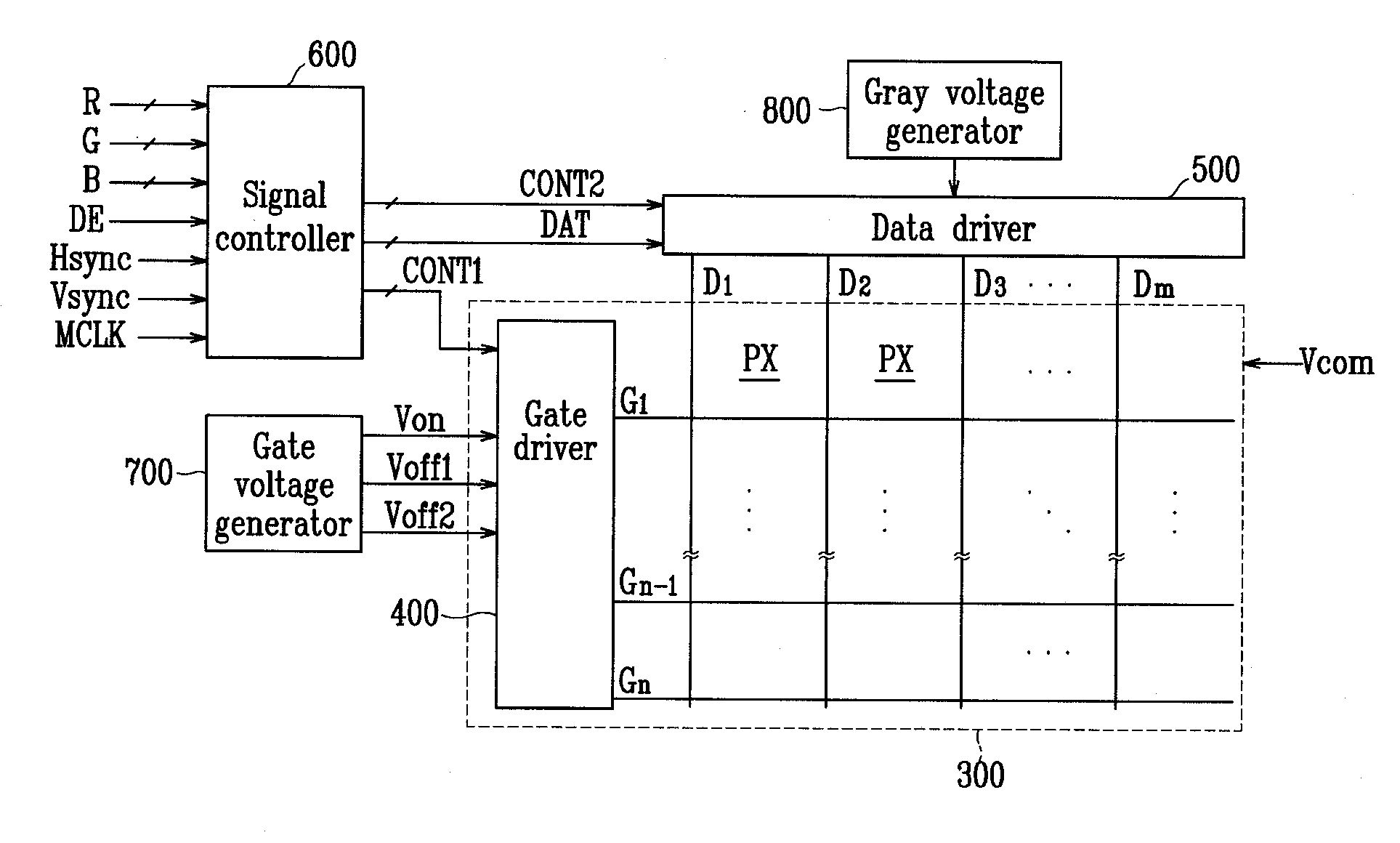

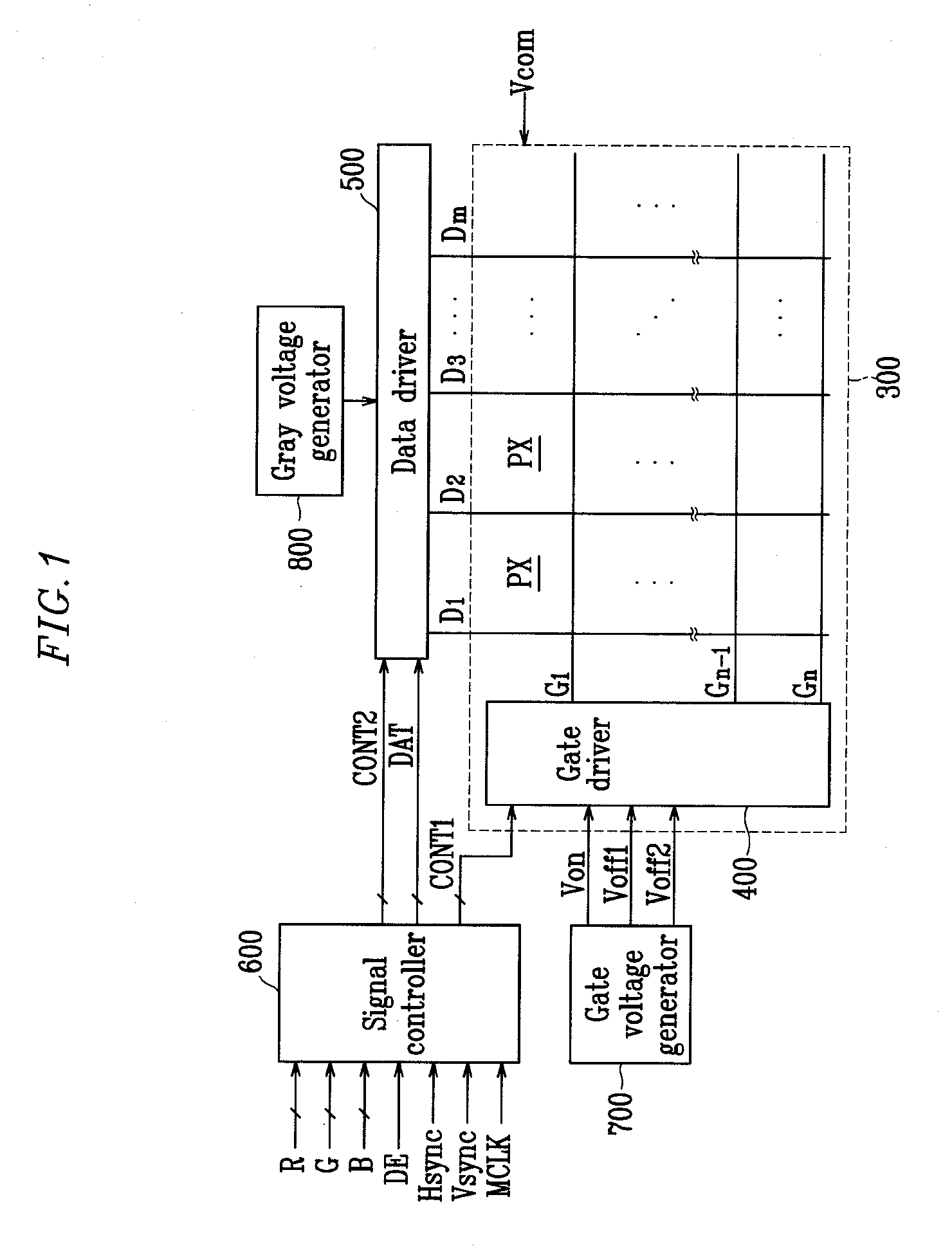

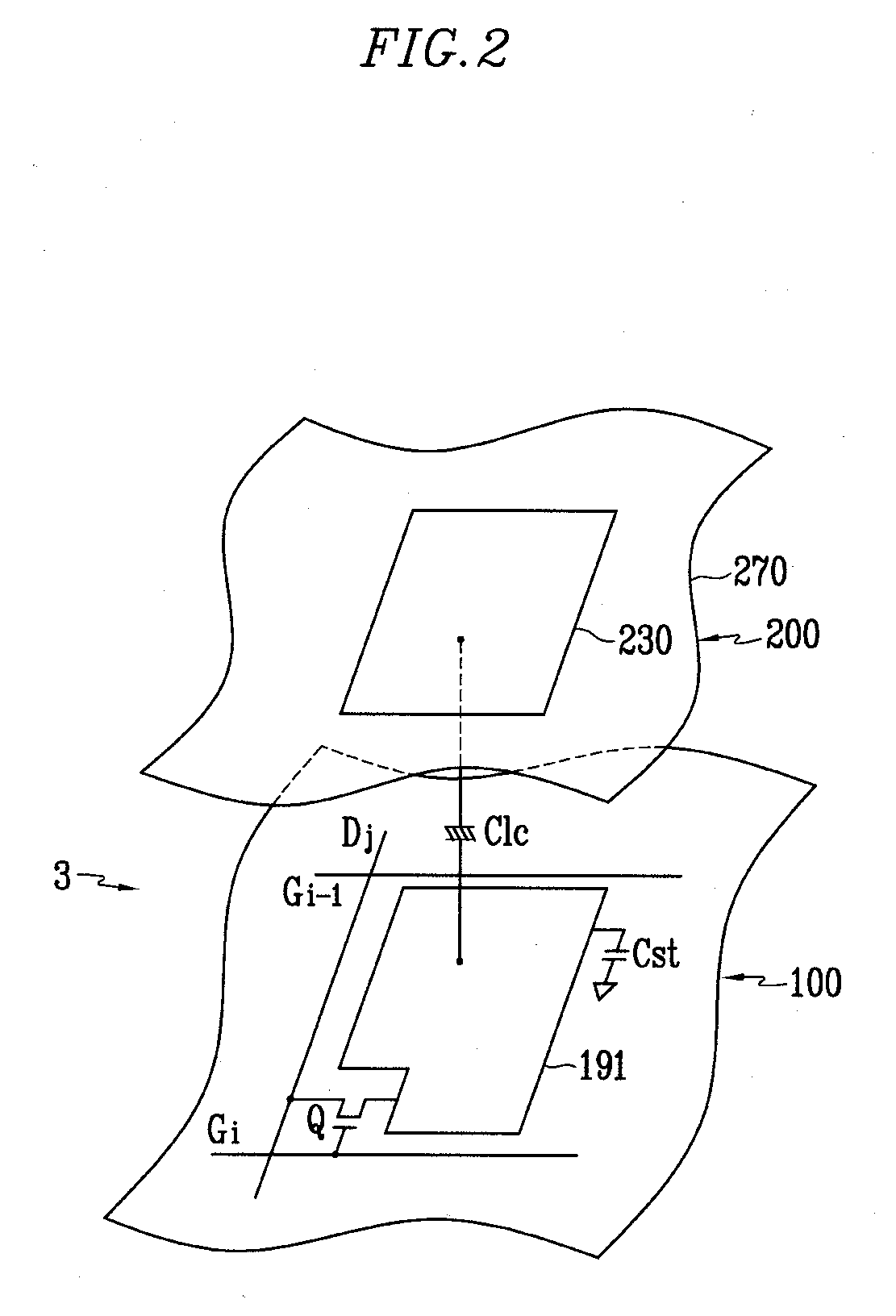

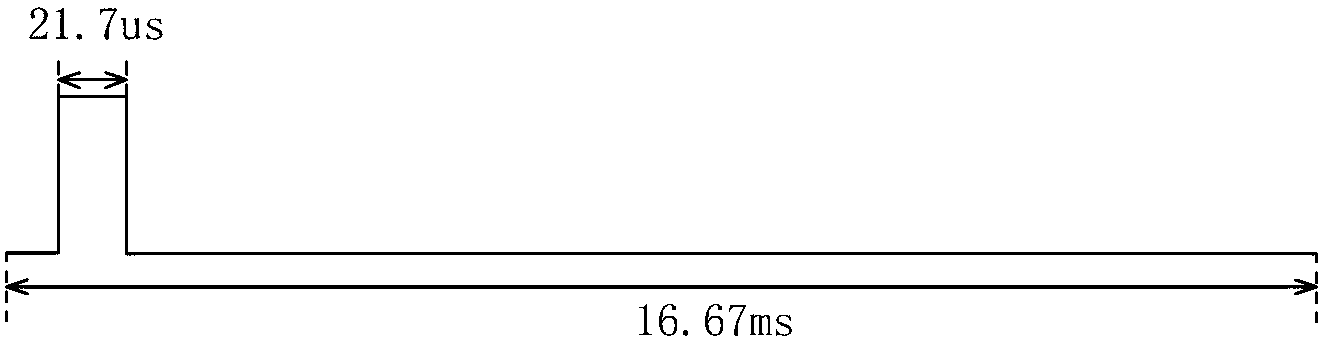

Low-leakage gate lines driving circuit for display device

ActiveUS20080079701A1Reduce leakage currentImprove reliabilityCathode-ray tube indicatorsDigital storageStart signalLow leakage

A gates-line driving circuit of a display device includes a plurality of stages that are serially connected to each other, where each stage includes a plurality of transistors and a plurality of capacitors and receives a scanning start signal, a plurality of clock signals, and first and second gate-off voltages Voff1 and Voff2 of different magnitudes, where some of the transistors are turned off with the first gate-off voltage, and others of the transistors are turned off with the second gate-off voltage.

Owner:SAMSUNG DISPLAY CO LTD

Durable electrooptic devices comprising ionic liquids

InactiveUS20080266642A1NanoopticsTenebresent compositionsElectrical conductorQuaternary ammonium cation

Electrolyte solutions for electrochromic devices such as rear view mirrors and displays with low leakage currents are prepared using inexpensive, low conductivity conductors. Preferred electrolytes include bifunctional redox dyes and molten salt solvents with enhanced stability toward ultraviolet radiation. The solvents include lithium or quaternary ammonium cations, and perfluorinated sulfonylimide anions selected from trifluoromethylsulfonate (CF3SO3−), bis(trifluoromethylsulfonyl)imide ((CF3SO2)2N−), bis(perfluoroethylsulfonyl)imide ((CF3CF2SO2)2N−) and tris(trifluoromethylsulfonyl)methide ((CF3SO2)3C−). Electroluminescent, electrochromic and photoelectrochromic devices with nanostructured electrodes include ionic liquids with bifunctional redox dyes. Some of the electrolyte solutions color to red when devices employing the solutions are powered, leading to red or neutral electrooptic devices.

Owner:TRIAD NAT SECURITY LLC +2

Semiconductor device package with reduced leakage

ActiveUS7224047B2Strong and low leakageReduce leakageSemiconductor/solid-state device detailsSolid-state devicesInterfacial bondSemiconductor package

Owner:BELL SEMICON LLC

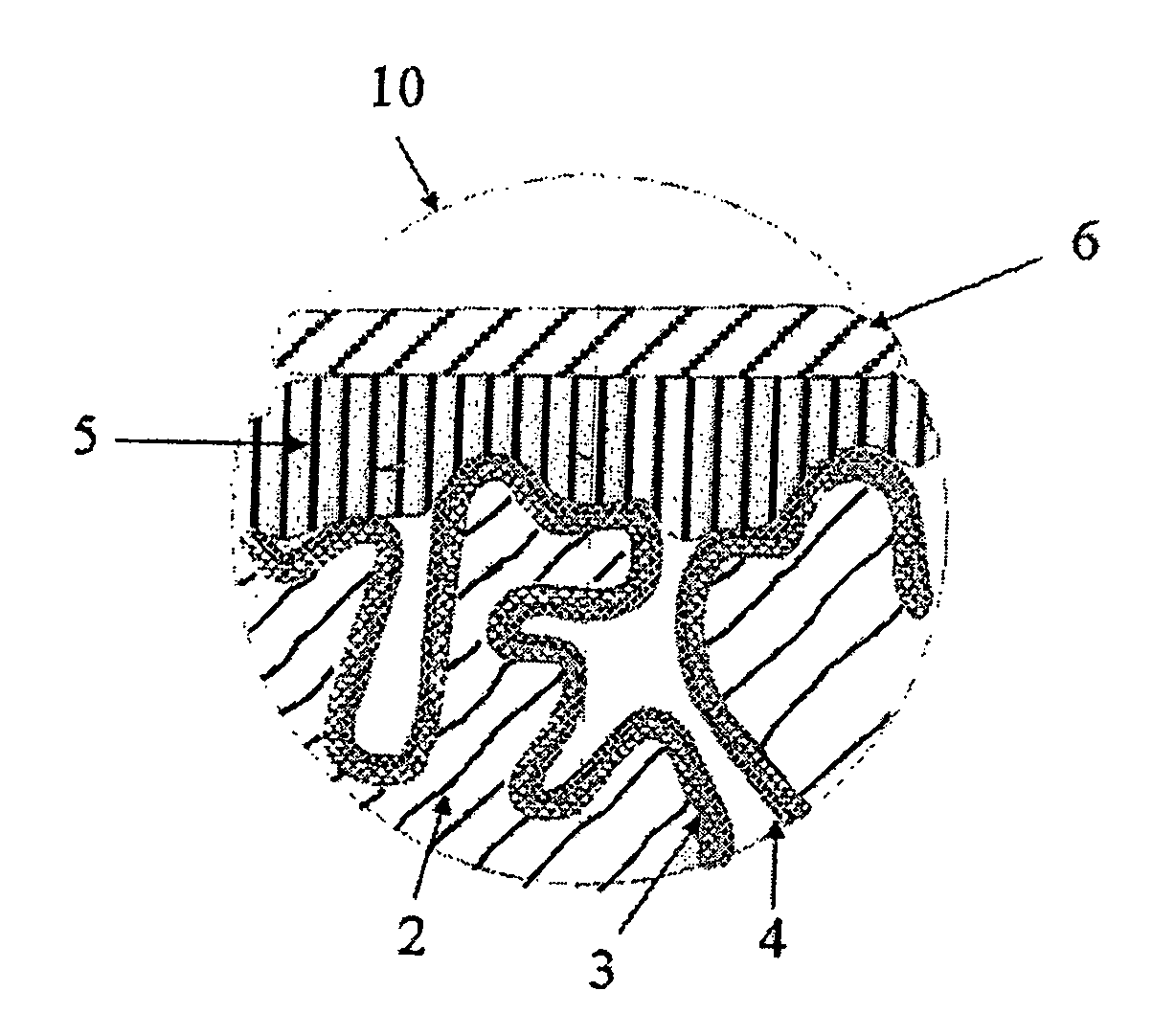

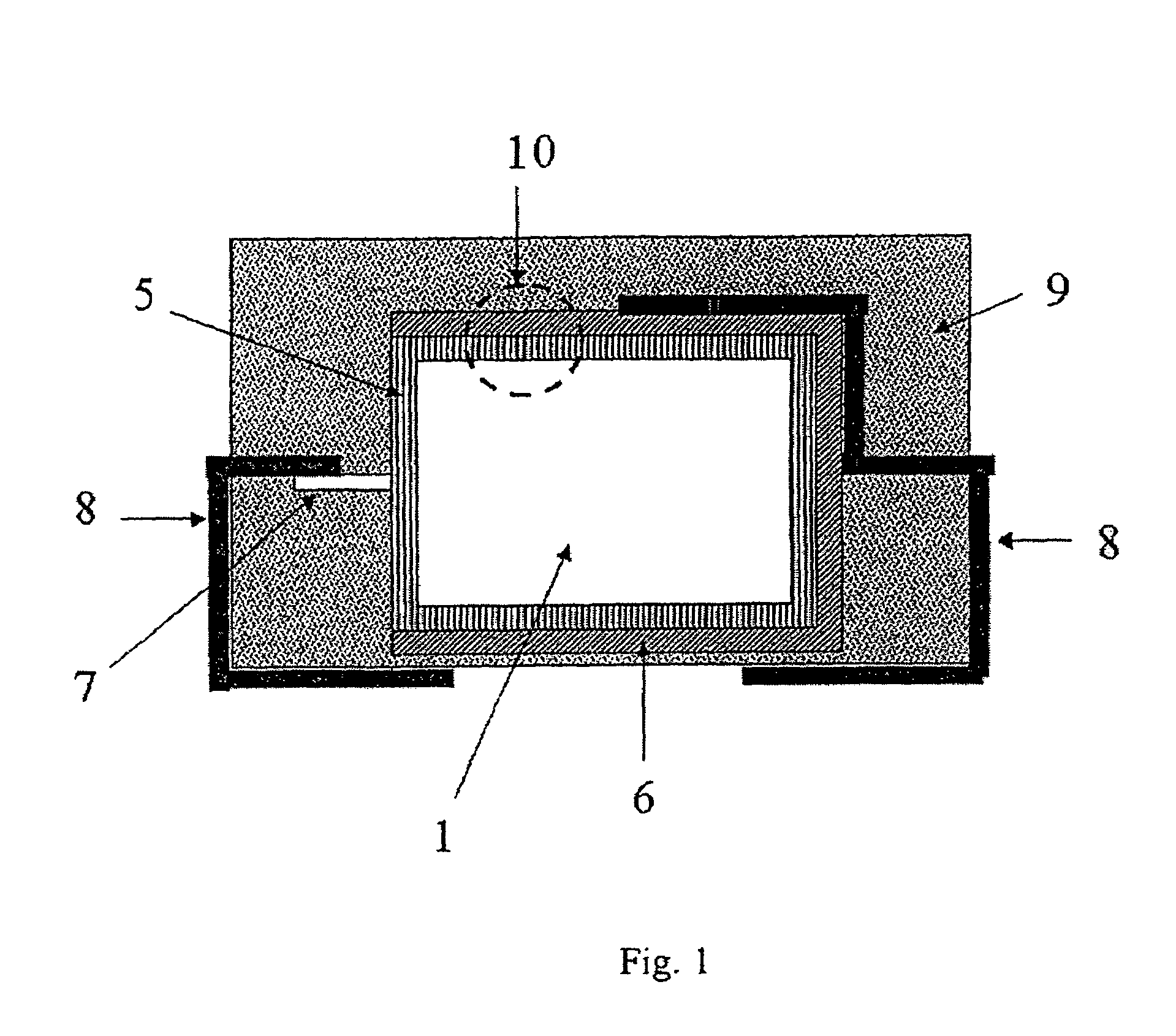

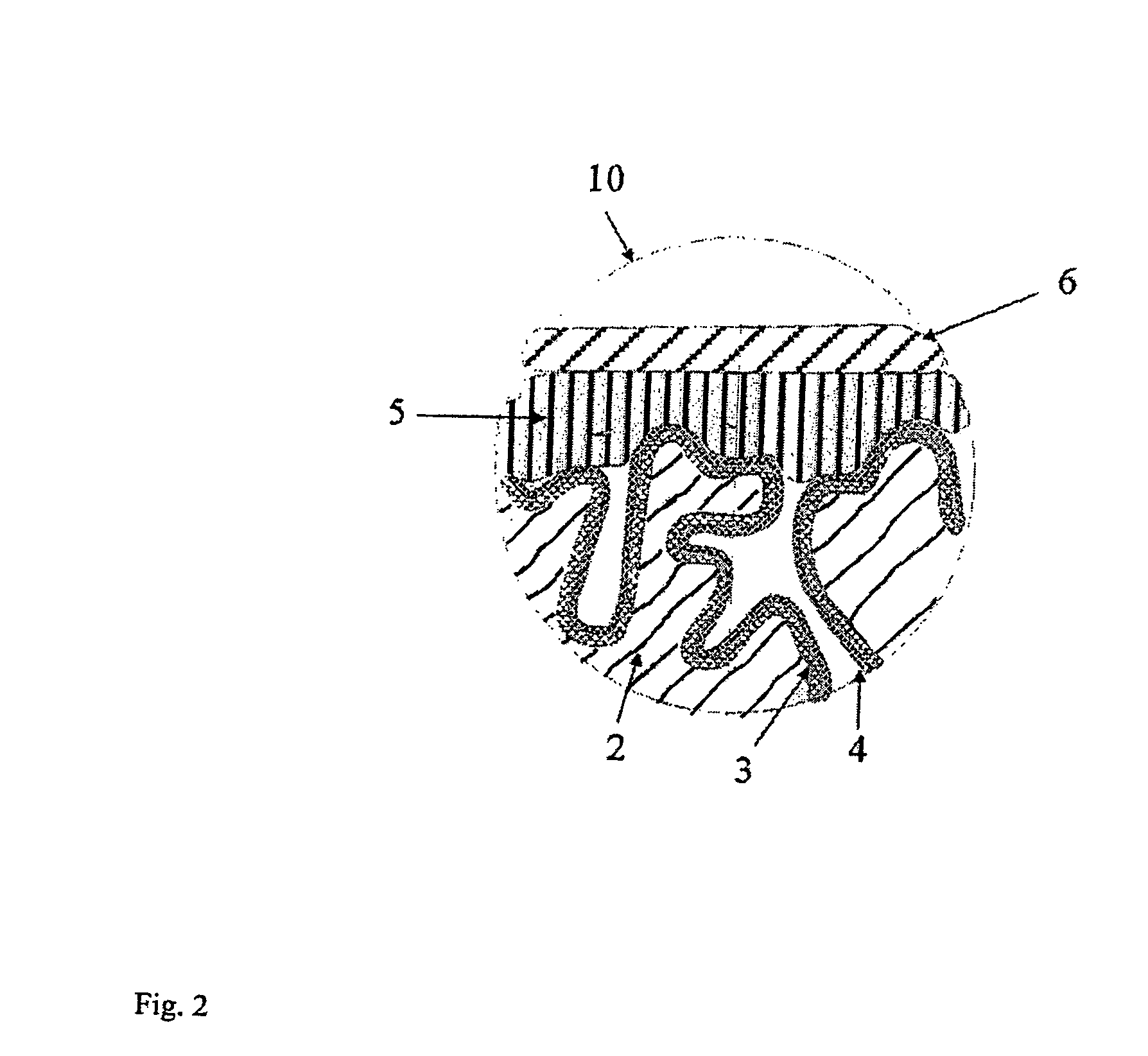

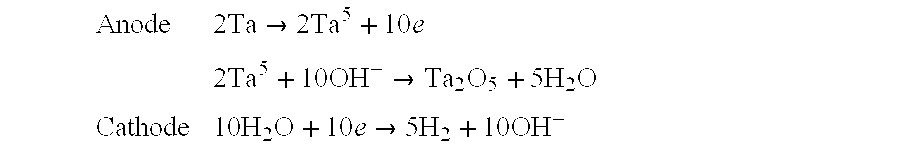

Protective coating for electrolytic capacitors

InactiveUS6864147B1Low dissipation factorLow leakage currentSolid electrolytic capacitorsSemiconductor/solid-state device manufacturingShellacElectrolysis

A solid electrolytic capacitor that comprises an anode that contains a valve-action metal (e.g., tantalum, niobium, and the like) and a dielectric film overlying the anode is provided. The capacitor also comprises a protective coating overlying the dielectric film, wherein the protective coating contains a relatively insulative, resinous material. For example, in one embodiment, the resinous material can be a drying oil, such as olive oil, linseed oil, tung oil, castor oil, soybean oil, shellac, and derivatives thereof. The capacitor also comprises a conductive polymer coating overlying the protective coating. As a result of the present invention, it has been discovered that a capacitor can be formed that can have a relatively low leakage current, dissipation factor, and equivalents series resistance.

Owner:KYOCERA AVX COMPONENTS CORP

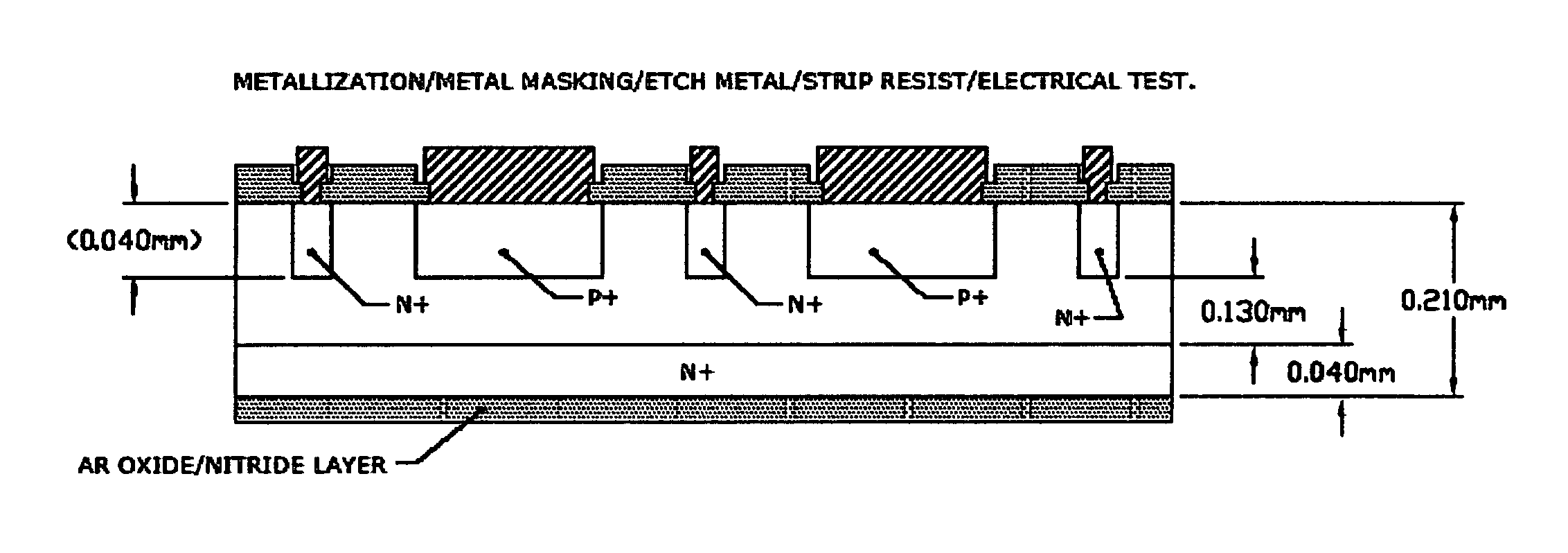

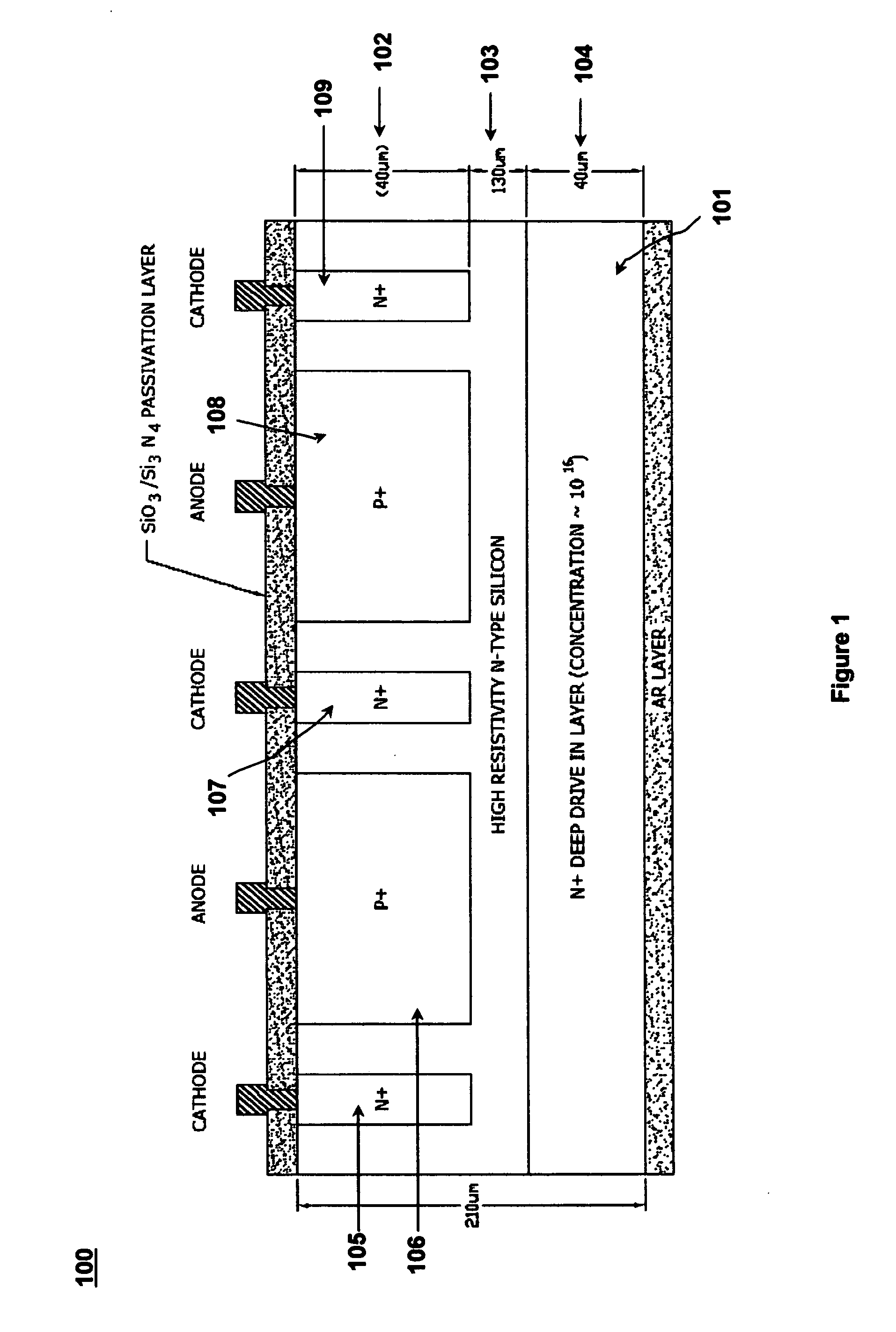

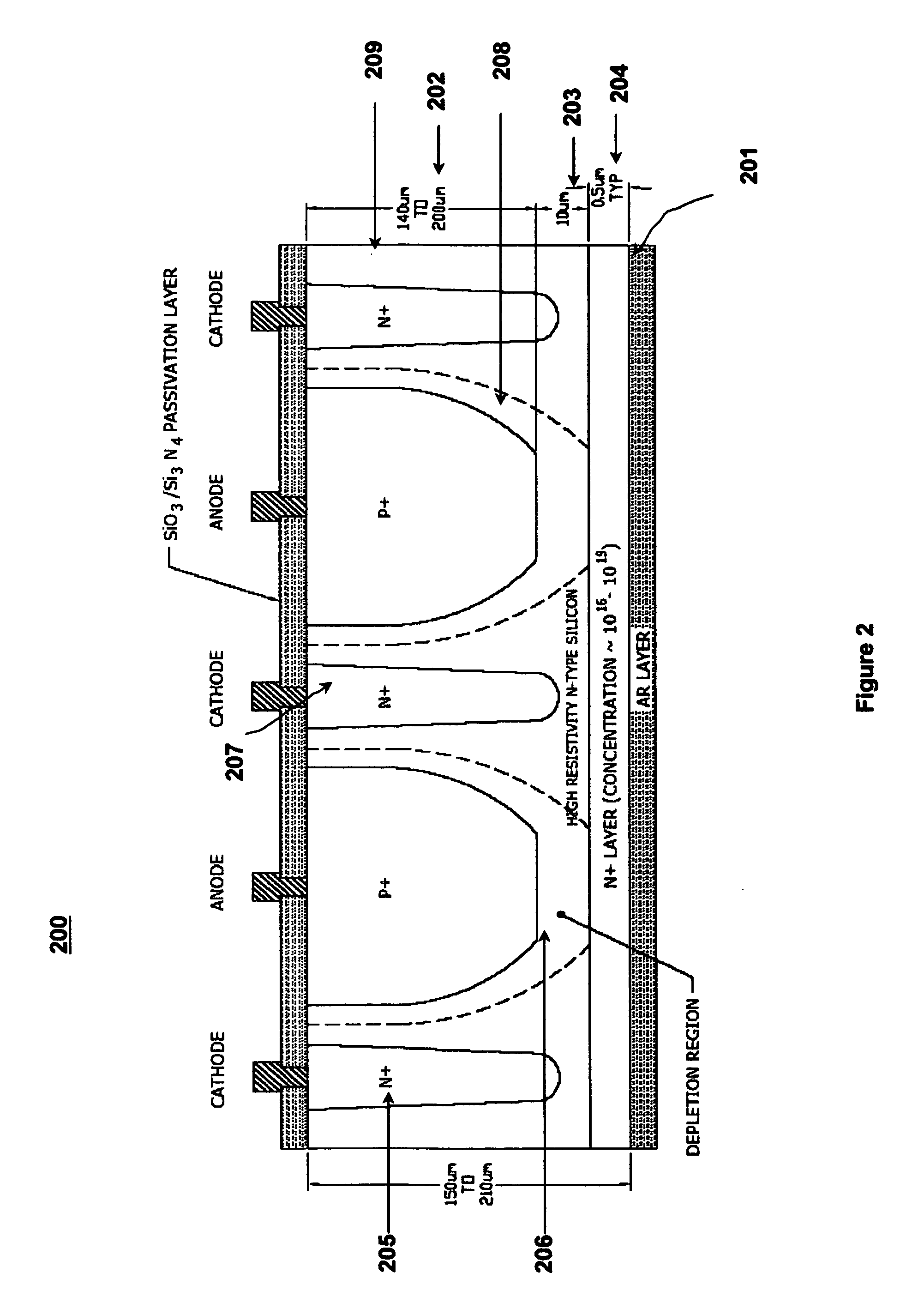

Deep diffused thin photodiodes

ActiveUS20070090394A1Improve device performanceReduce crosstalkThyristorSolid-state devicesLow leakageRadiation damage

This invention comprises photodiodes, optionally organized in the form of an array, including p+ deep diffused regions or p+ and n+ deep diffused regions. More specifically, the invention permits one to fabricate thin 4 inch and 6 inch wafer using the physical support provided by a n+ deep diffused layer and / or p+ deep diffused layer. Consequently, the present invention delivers high device performances, such as low crosstalk, low radiation damage, high speed, low leakage dark current, and high speed, using a thin active layer.

Owner:OSI OPTOELECTRONICS

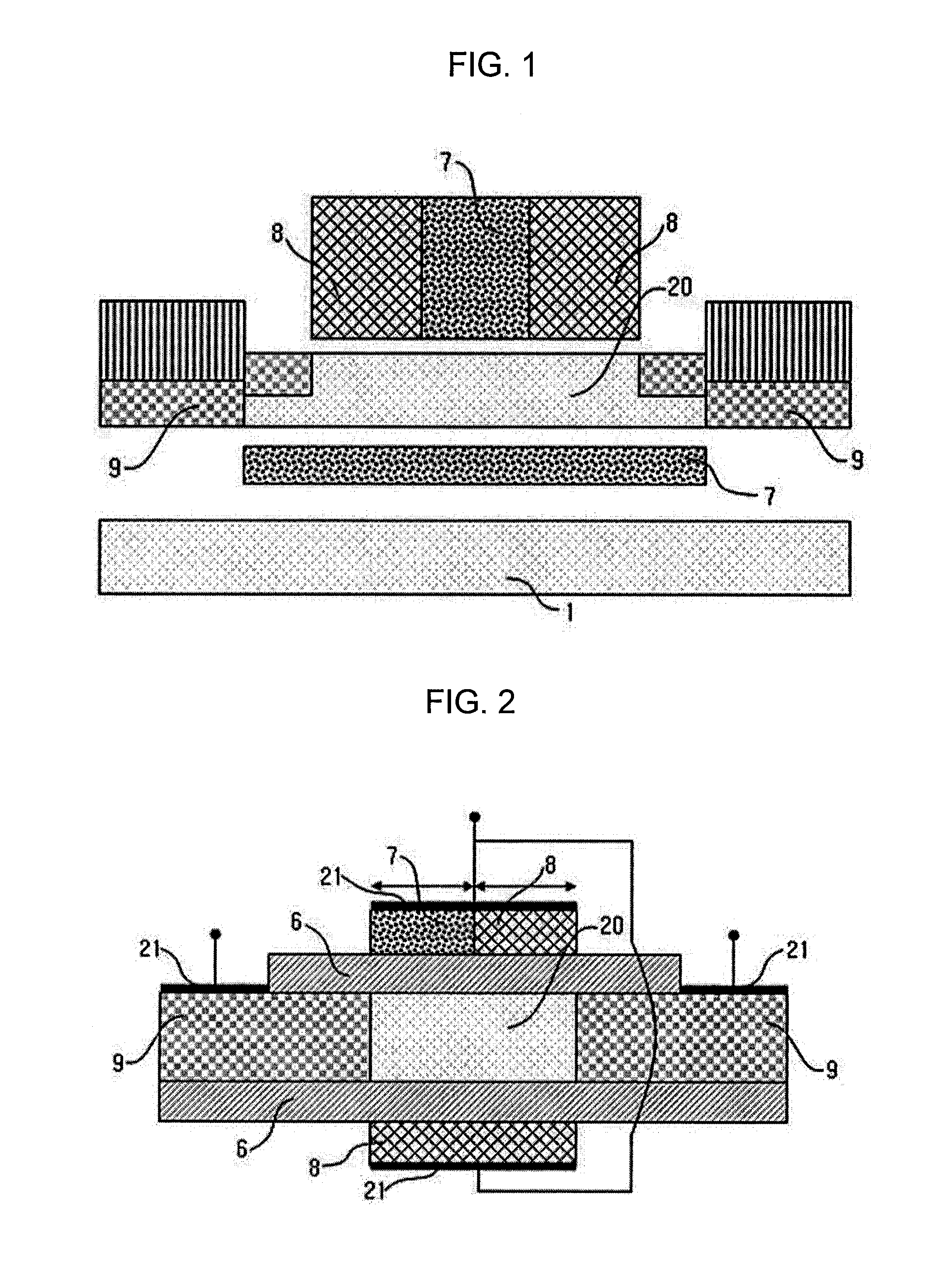

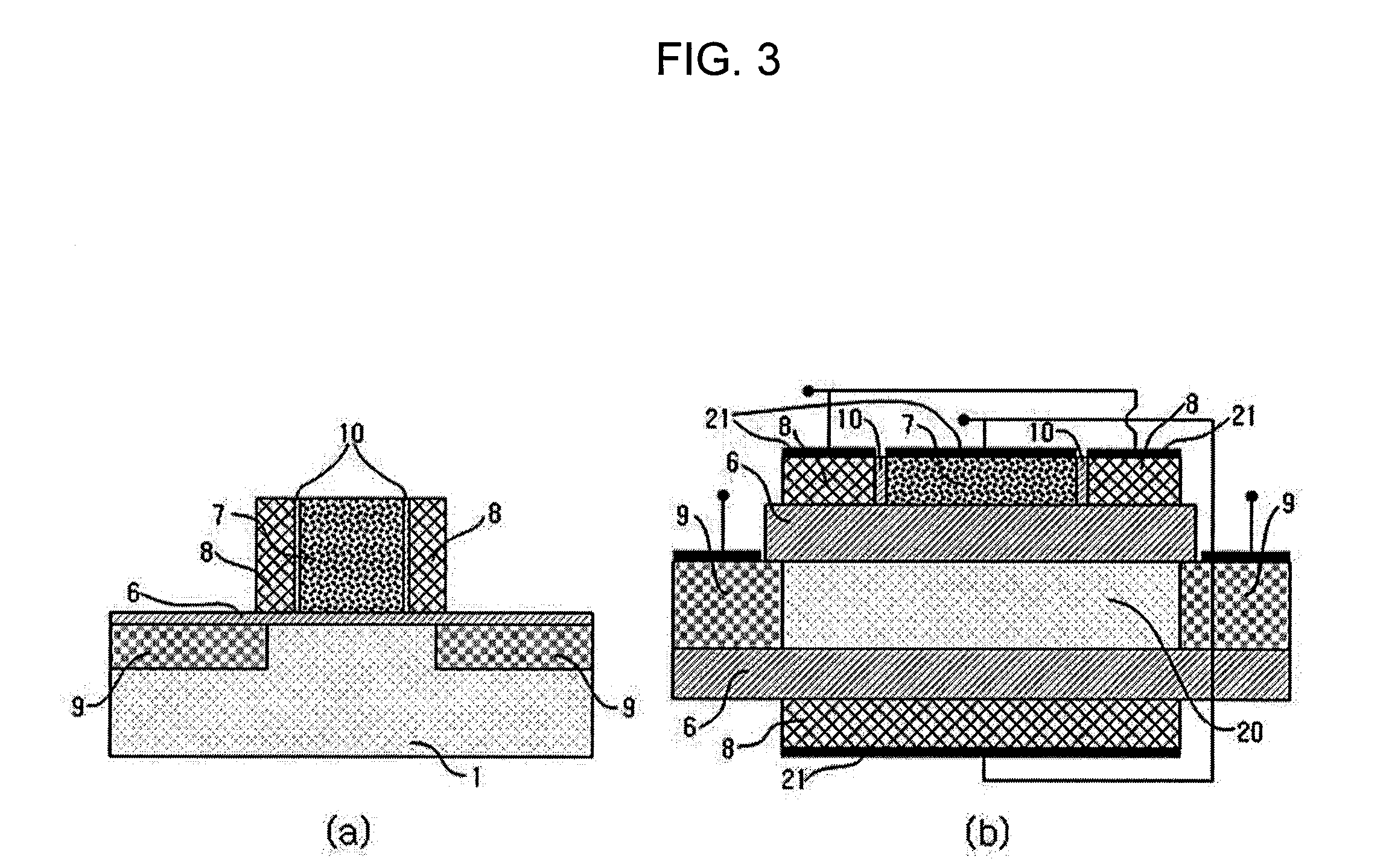

Fin field effect transistor having low leakage current and method of manufacturing the finfet

ActiveUS20100270619A1Reduce leakage currentHigh densityTransistorSolid-state devicesGate leakage currentEngineering

Provided is a fin field effect transistor (FinFET) having low leakage current and a method of manufacturing the same. The FinFET includes: a bulk silicon substrate; a fence-shaped body formed by patterning the substrate; an insulating layer formed on a surface of the substrate to a first height of the fence-shaped body; a gate insulating layer formed at side walls and an upper surface of the fence-shaped body at which the insulating layer is not formed; a gate electrode formed on the gate insulating layer; source / drain formed at regions of the fence-shaped body where the gate electrode is not formed. The gate electrode includes first and second gate electrodes which are in contact with each other and have different work functions. Particularly, the second gate electrode having a low work function is disposed to be close to the drain. As a result, the FinFET according to the present invention increases a threshold voltage by using a material having the high work function for the gate electrode and lowers the work function of the gate electrode overlapping with the drain, so that gate induced drain leakage (GIDL) can be reduced.

Owner:SEOUL NAT UNIV R&DB FOUND

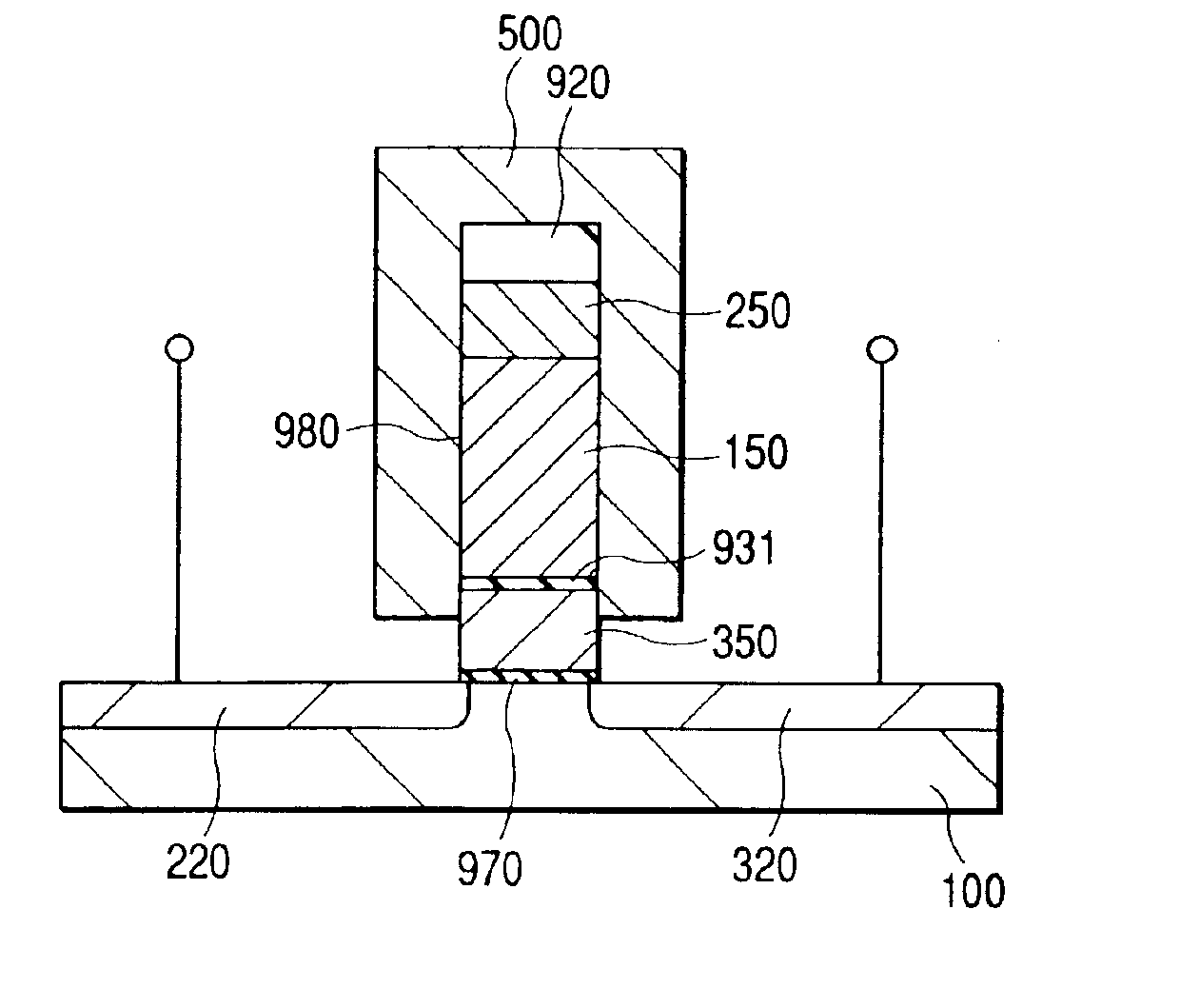

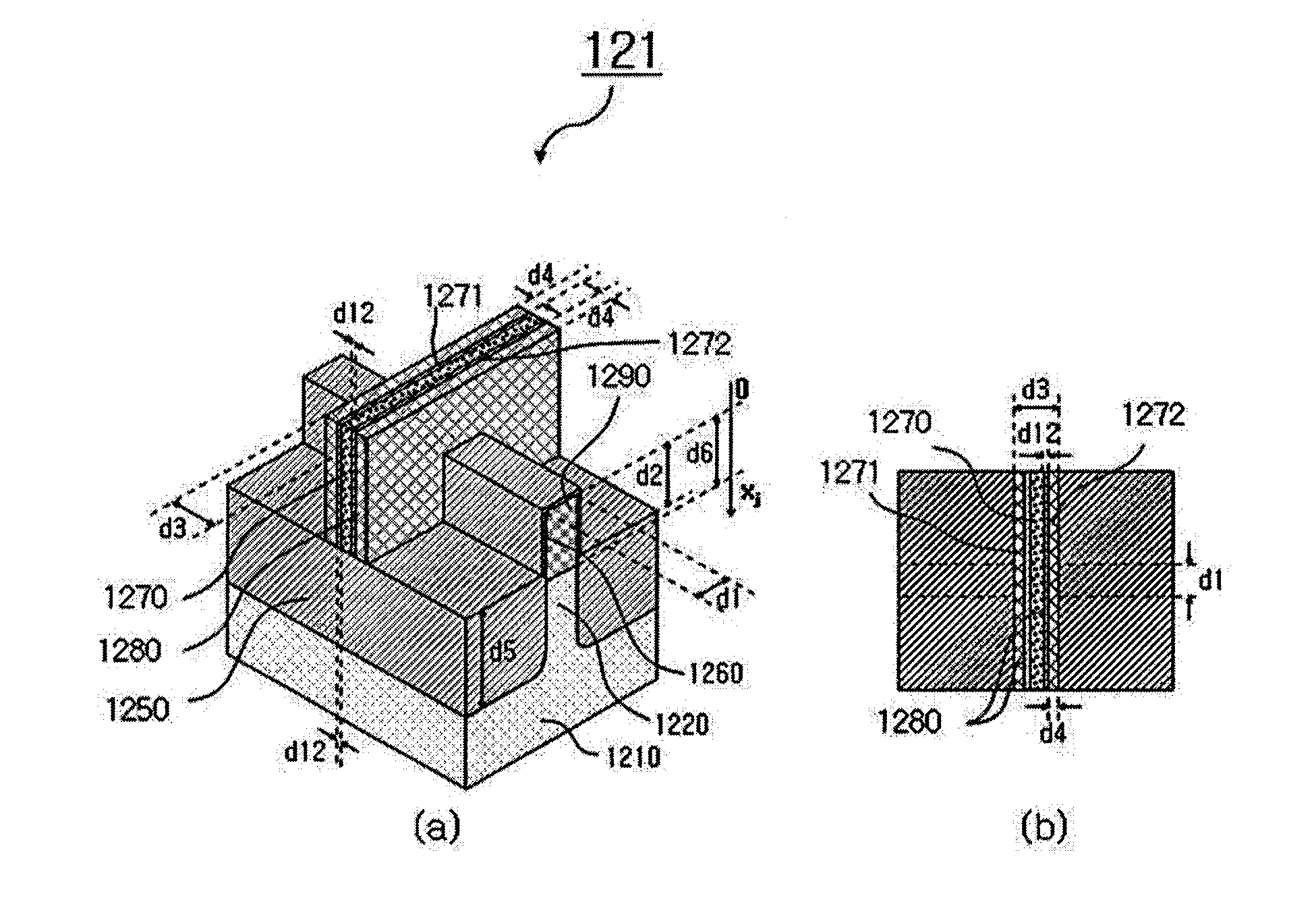

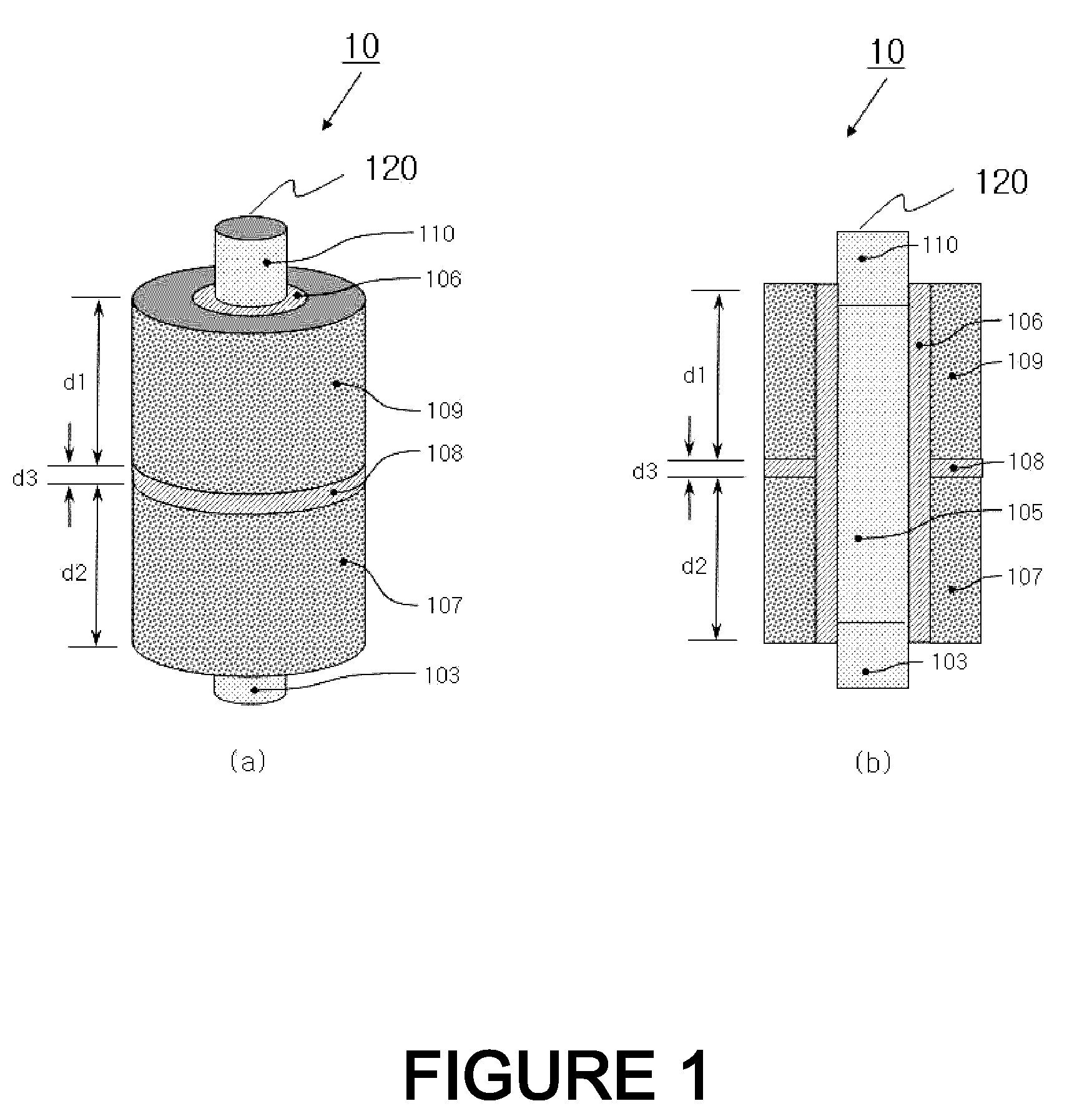

Pillar-type field effect transistor having low leakage current

InactiveUS20080251825A1Reduced cell device areaGood miniaturization characteristicTransistorSolid-state devicesGate leakage currentWork function

A pillar-type field effect transistor having low leakage current is provided. The pillar-type field effect transistor includes a semiconductor pillar, a gate insulating layer formed on a portion of a surface of the semiconductor pillar, a gate electrode formed on the gate insulating layer, and source / drain regions formed on portions of the semiconductor pillar where the gate electrode is not formed, in which the gate electrode includes a first gate electrode, a second gate electrode, and an inter-gate insulating layer, in which the first gate electrode has a work function higher than that of the second gate electrode, in which the inter-gate insulating layer is formed between the first gate electrode and the second gate electrode, and in which the first gate electrode and the second gate electrode are electrically connected by a contact or a metal interconnection line. A portion of the second gate electrode having the work function lower than that of the first gate electrode is overlapped by the drain region. Accordingly, the gate electrode of the pillar-type FET is formed using a material having a high work function, so that the threshold voltage can be increased and the work function of the portion of the gate electrode overlapped by the drain region can be decreased. Therefore, gate induced drain leakage is reduced, so that off-state leakage current can likewise be greatly reduced.

Owner:SEOUL NAT UNIV R&DB FOUND

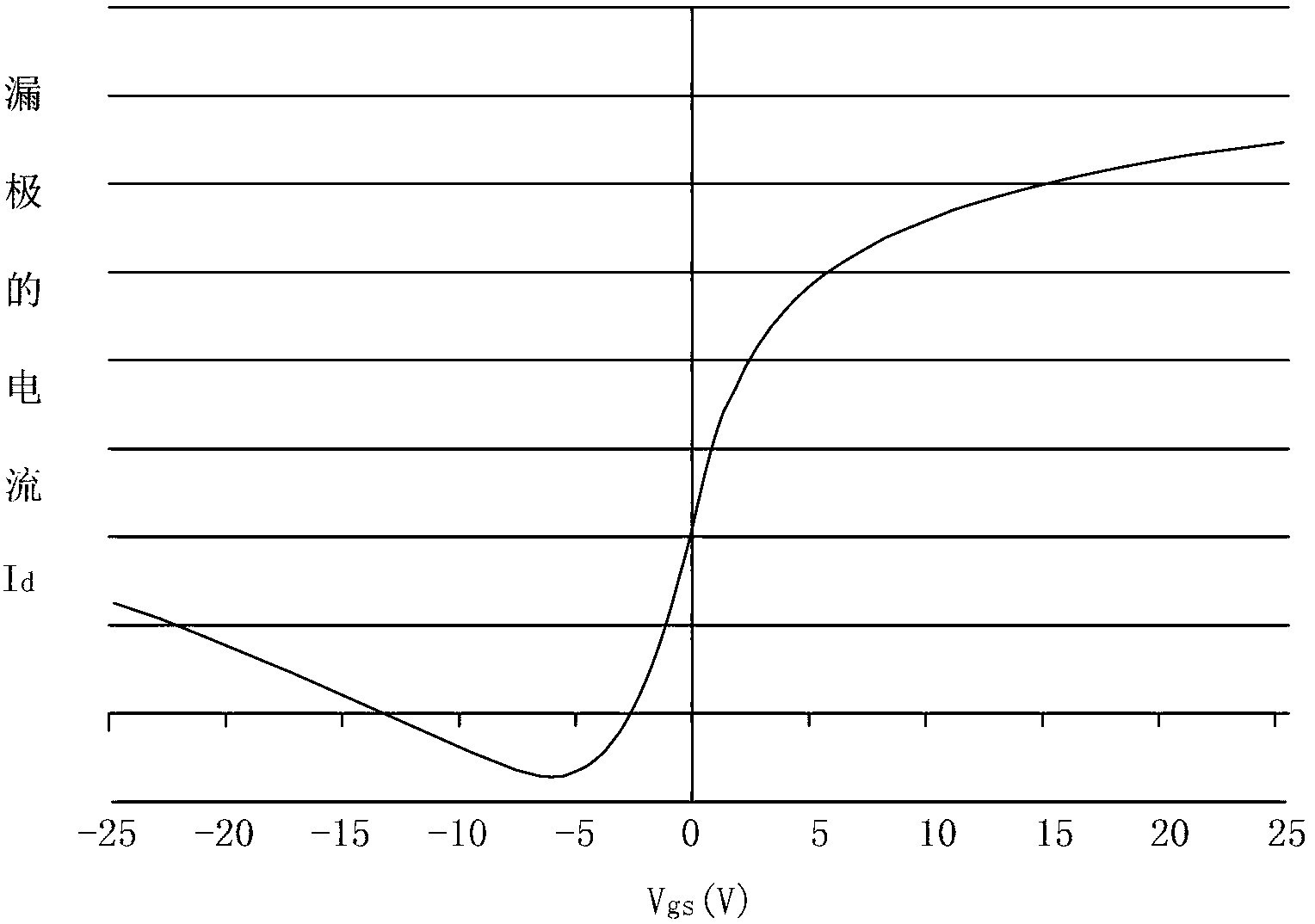

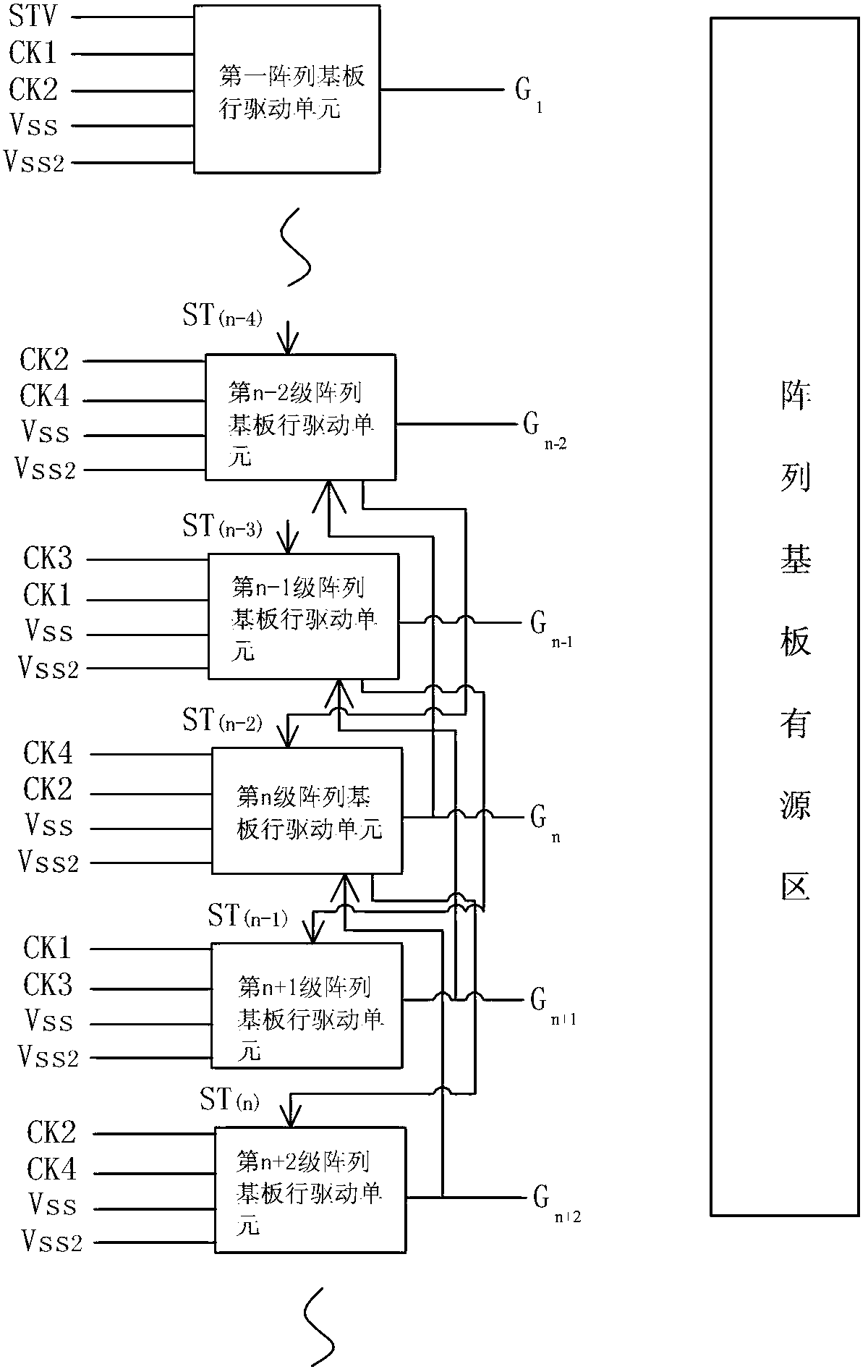

Array substrate row driving circuit

ActiveCN103310755AReduce leakage currentImprove display qualityStatic indicating devicesDigital storageEngineeringLow leakage

The invention provides an array substrate row driving circuit. The driving circuit comprises multiple array substrate row driving units, wherein an n-level array substrate row driving unit of the array substrate row driving circuit comprises an n-2 level signal input end (21), an n+2 level signal input end (22), a clock signal first input end (23), a clock signal second input end (24), a first low electric level input end (25), a second low electric level input end (26), a first output end (27), a second output end (28), a pull-up driving unit (32), a pull-up unit (34) and first to third pull-down units (36, 37 and 38). As a second low electric level signal is added, and the second low electric level is utilized to lower a voltage difference Vgs between a gate and a source of the first output end thin-film transistor, relatively low leakage current of the thin-film transistor is obtained, and precise control is achieved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

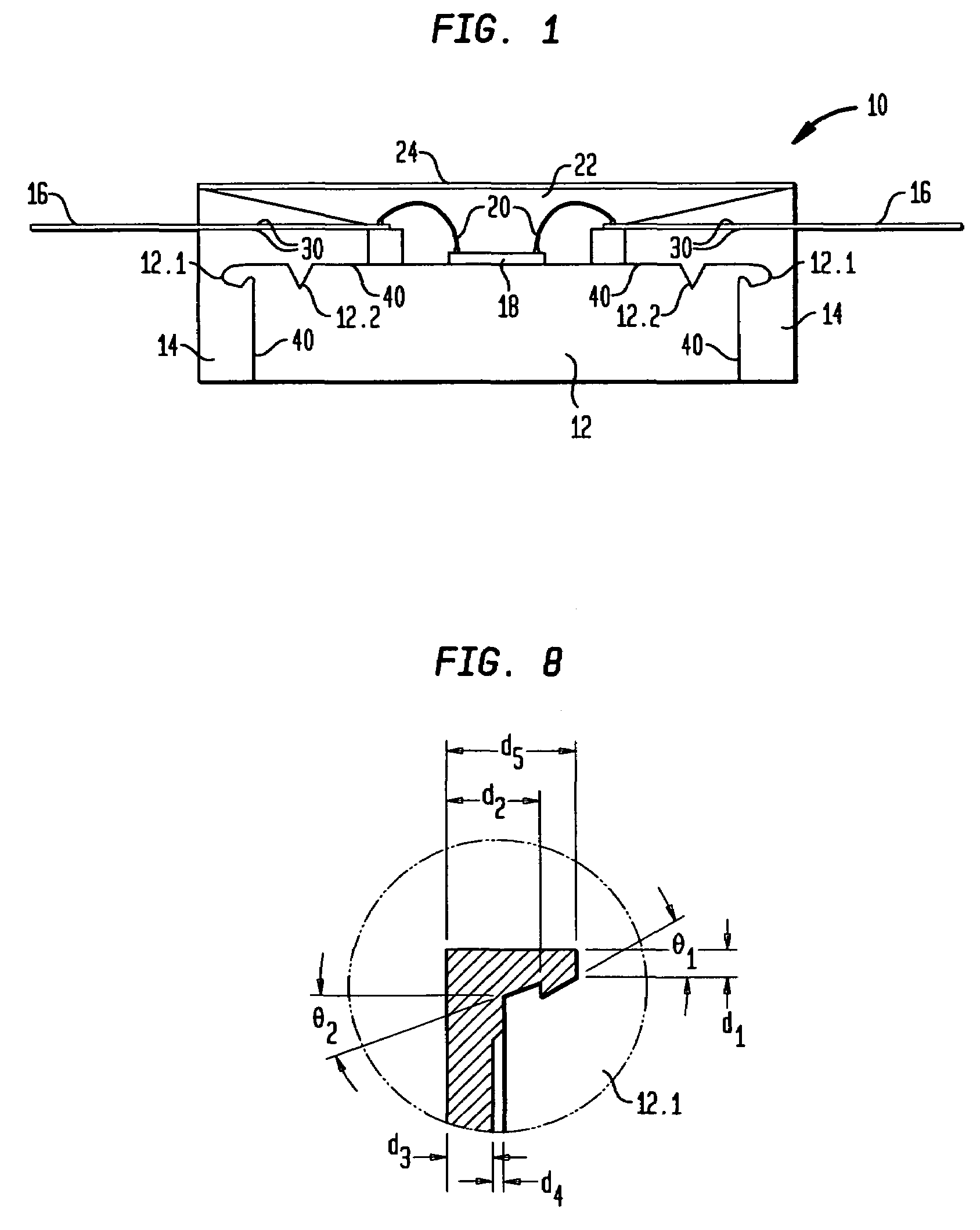

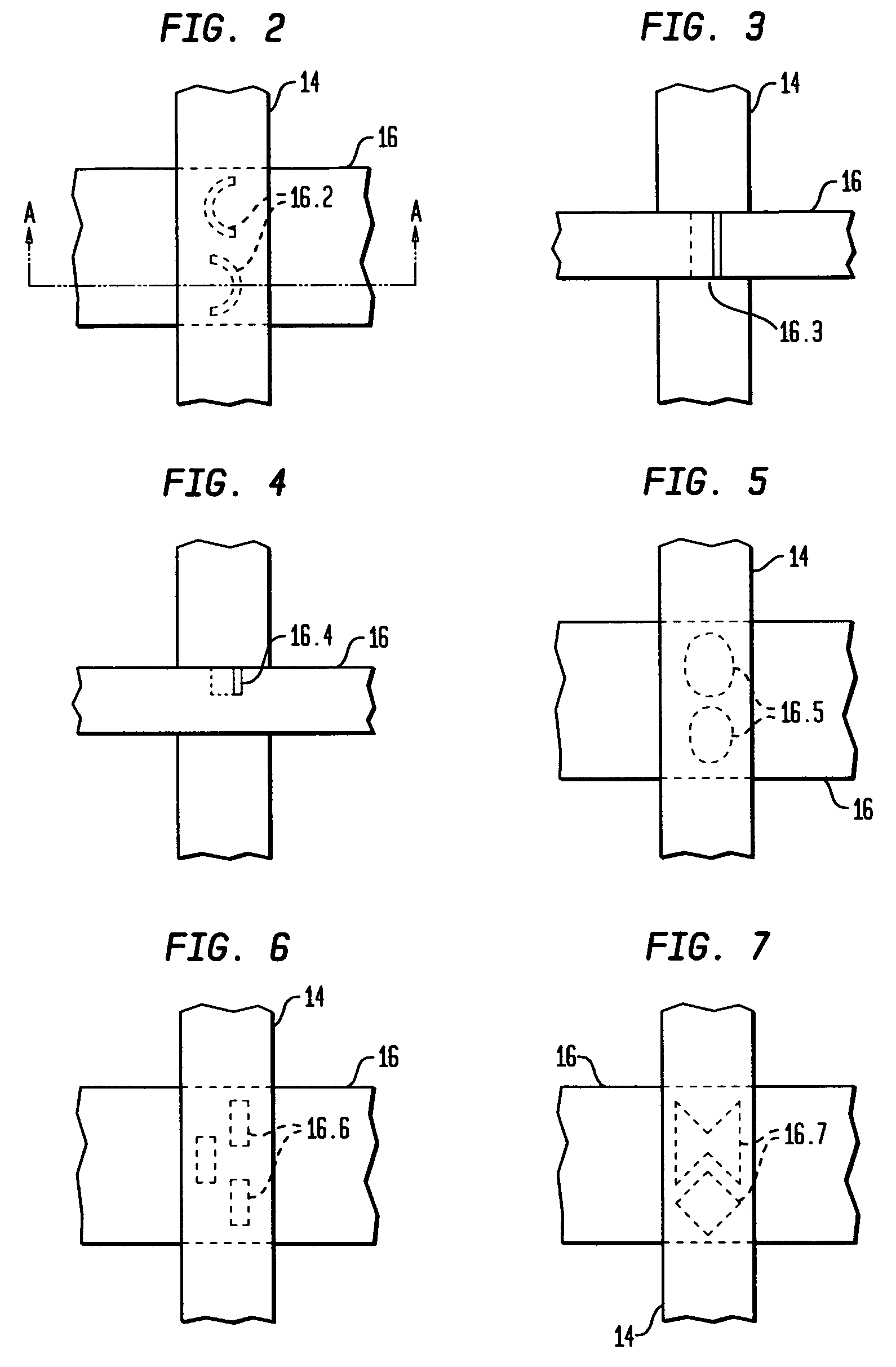

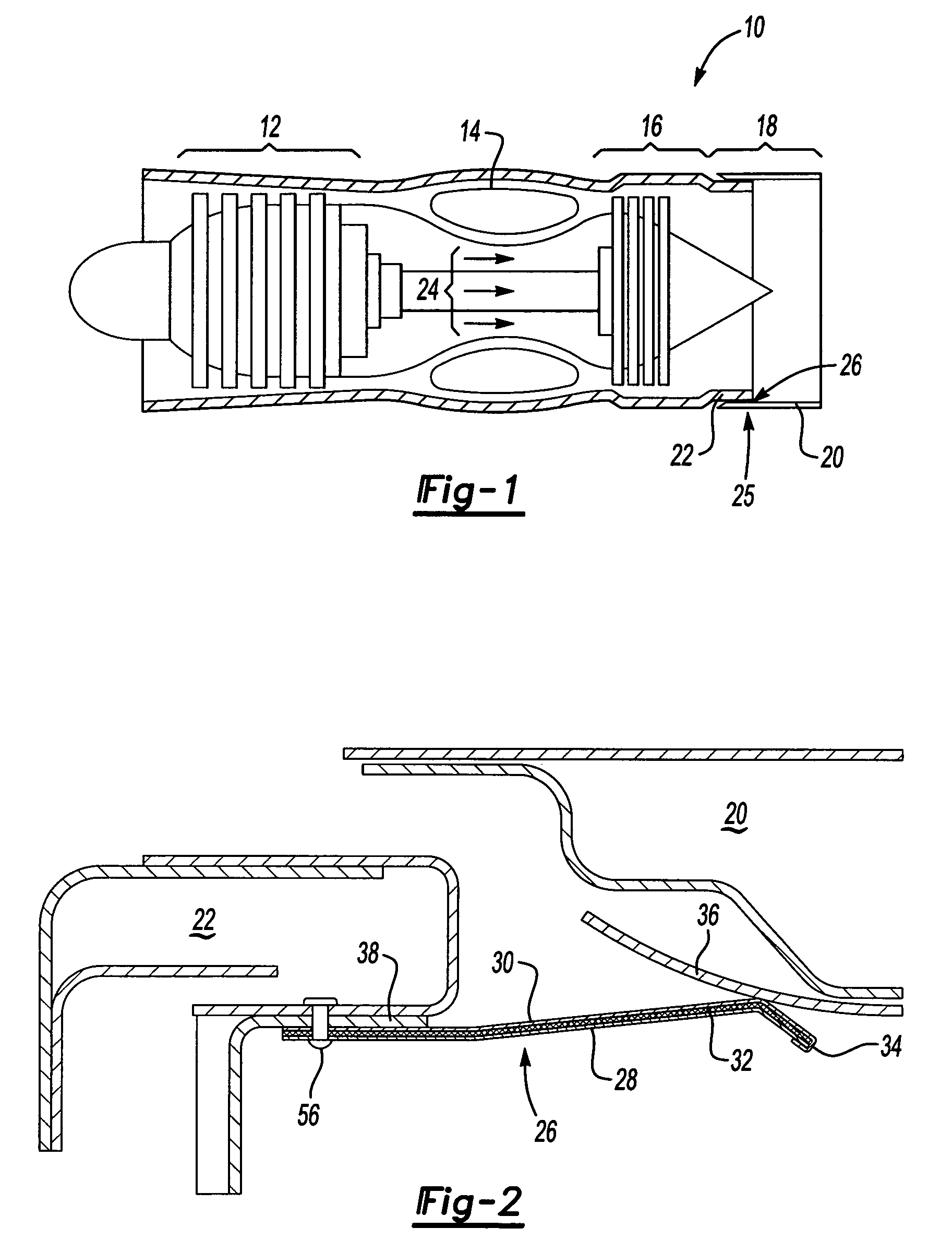

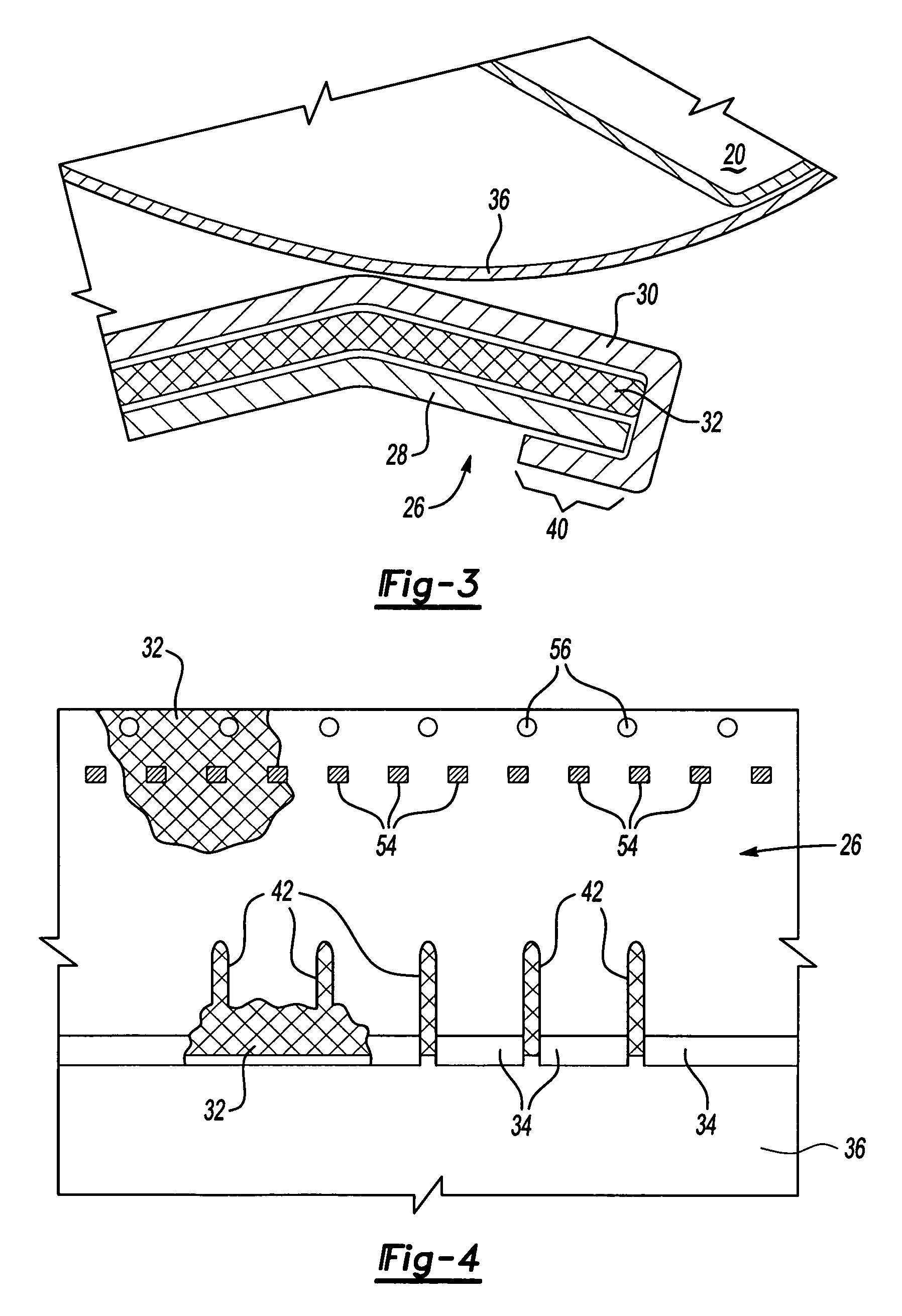

Low leakage finger seal

ActiveUS7367567B2Reduce gapEliminates gap and leak pathEngine sealsGas turbine plantsPliabilityLow leakage

A seal for an exhaust duct includes a metal mesh member sandwiched between an outer plate and an inner plate. The seal includes a plurality of flexible members defined by a plurality of slots in both the inner and outer plates. The flexible members provide for expansion and contraction along with creating flexibility in the region of contact between the seal land and the seal. The metal mesh member substantially eliminates gaps and leak paths created through the slots. The metal mesh member is composed of a plurality of interwoven wire strands impregnated with a high temperature elastomeric sealant. The impregnation of high temperature elastomeric sealant over the metal mesh member improves sealing while maintaining the desired flexibility of the seal.

Owner:RTX CORP