Patents

Literature

2607results about "Thyristor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

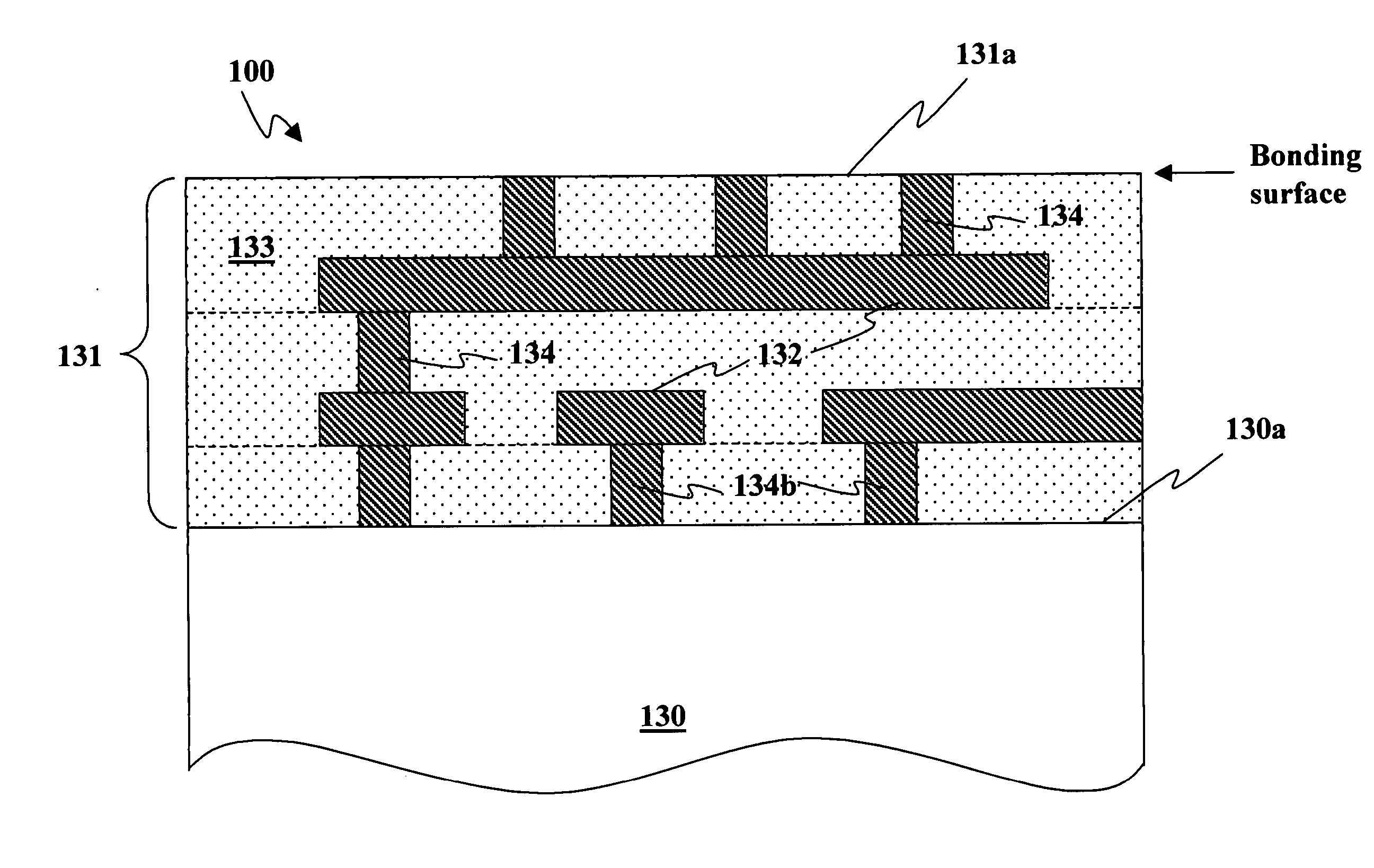

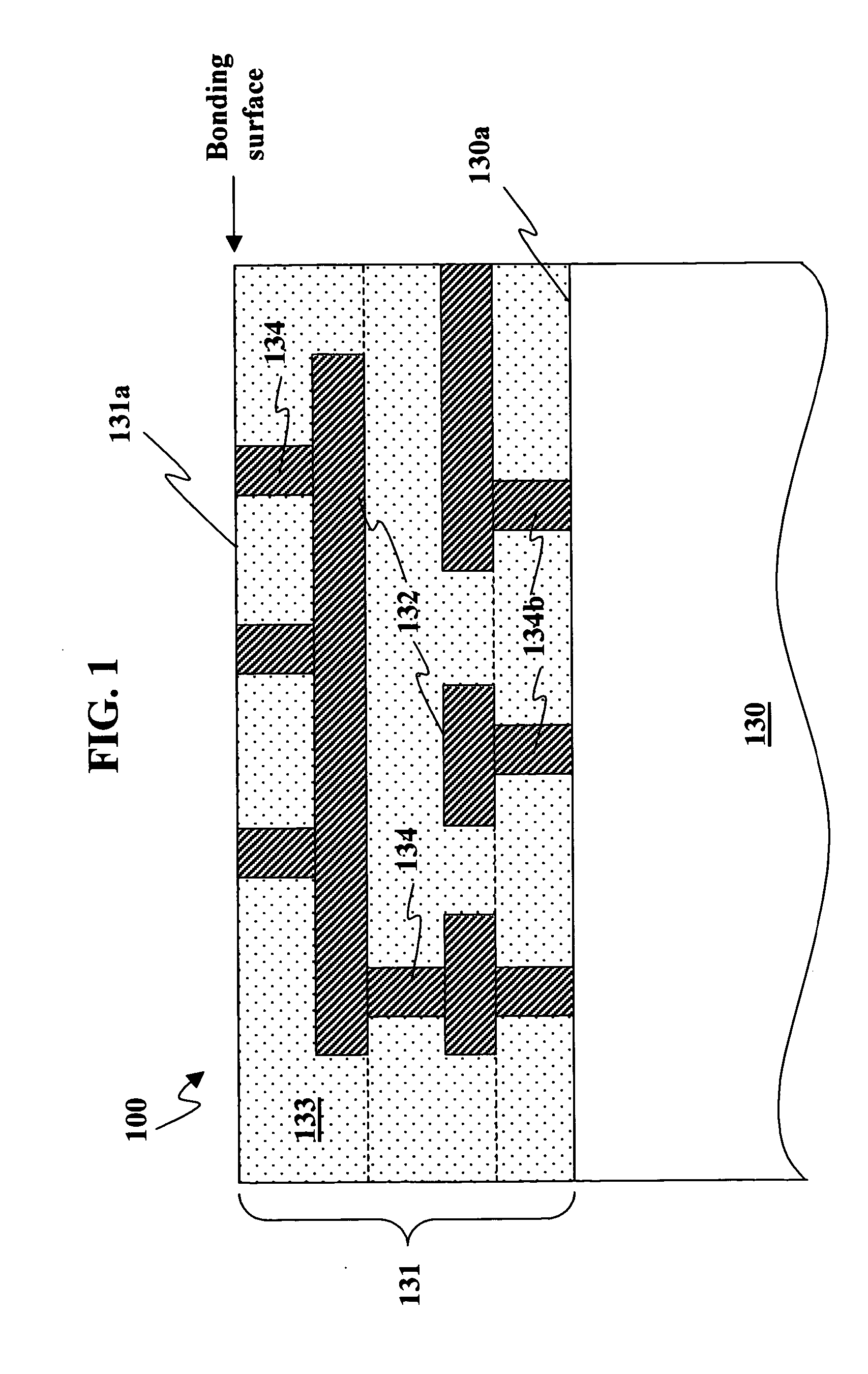

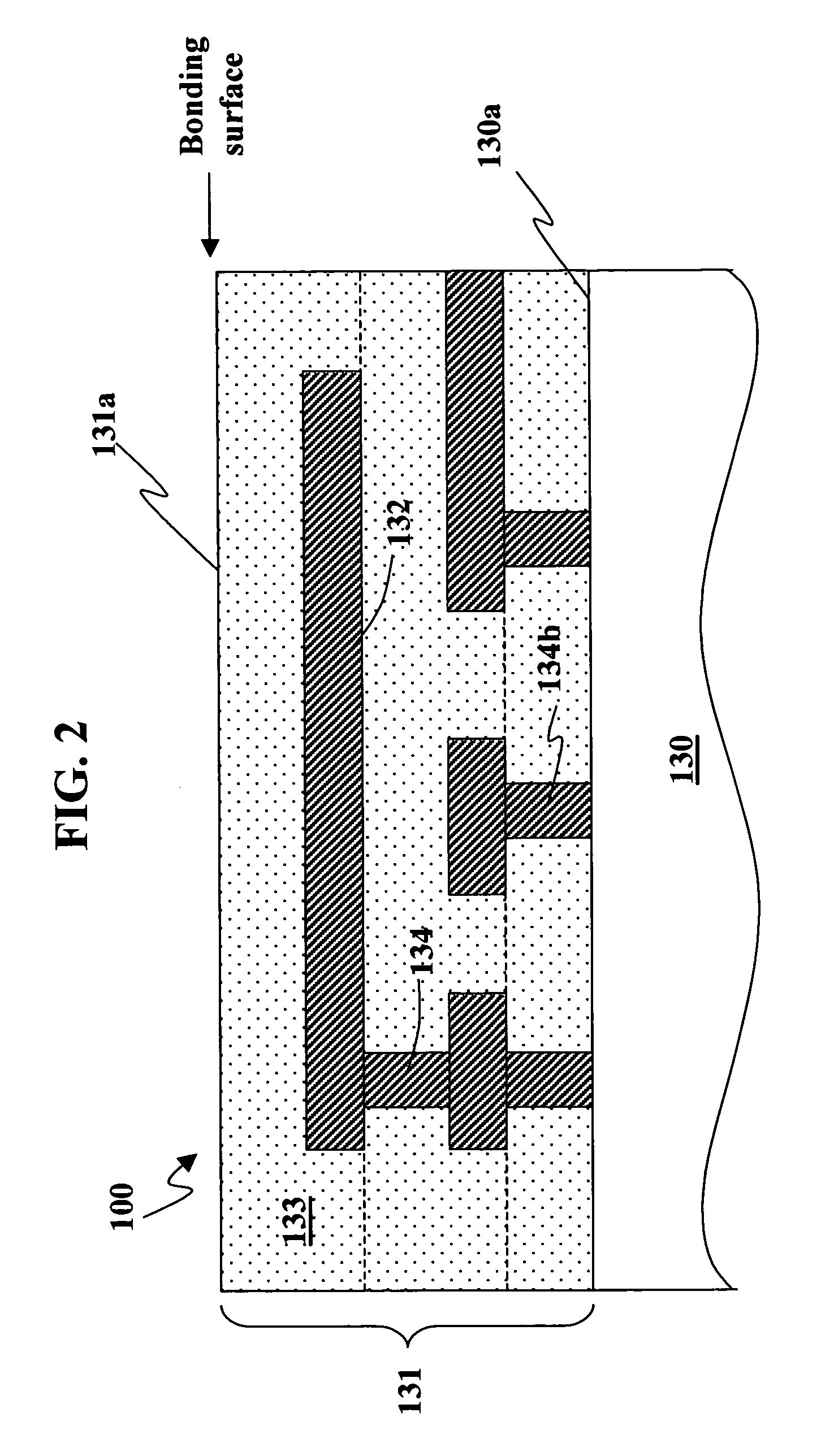

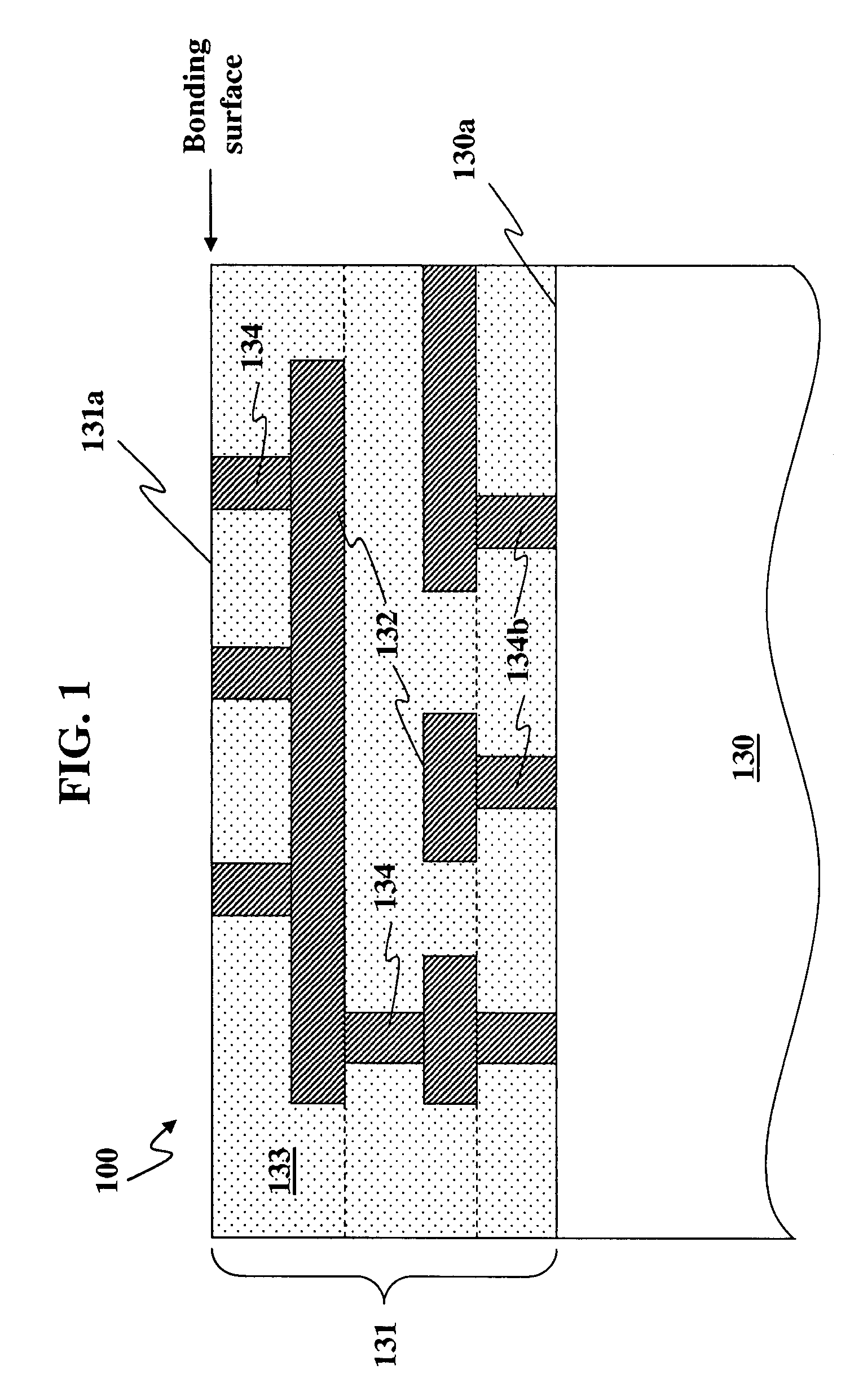

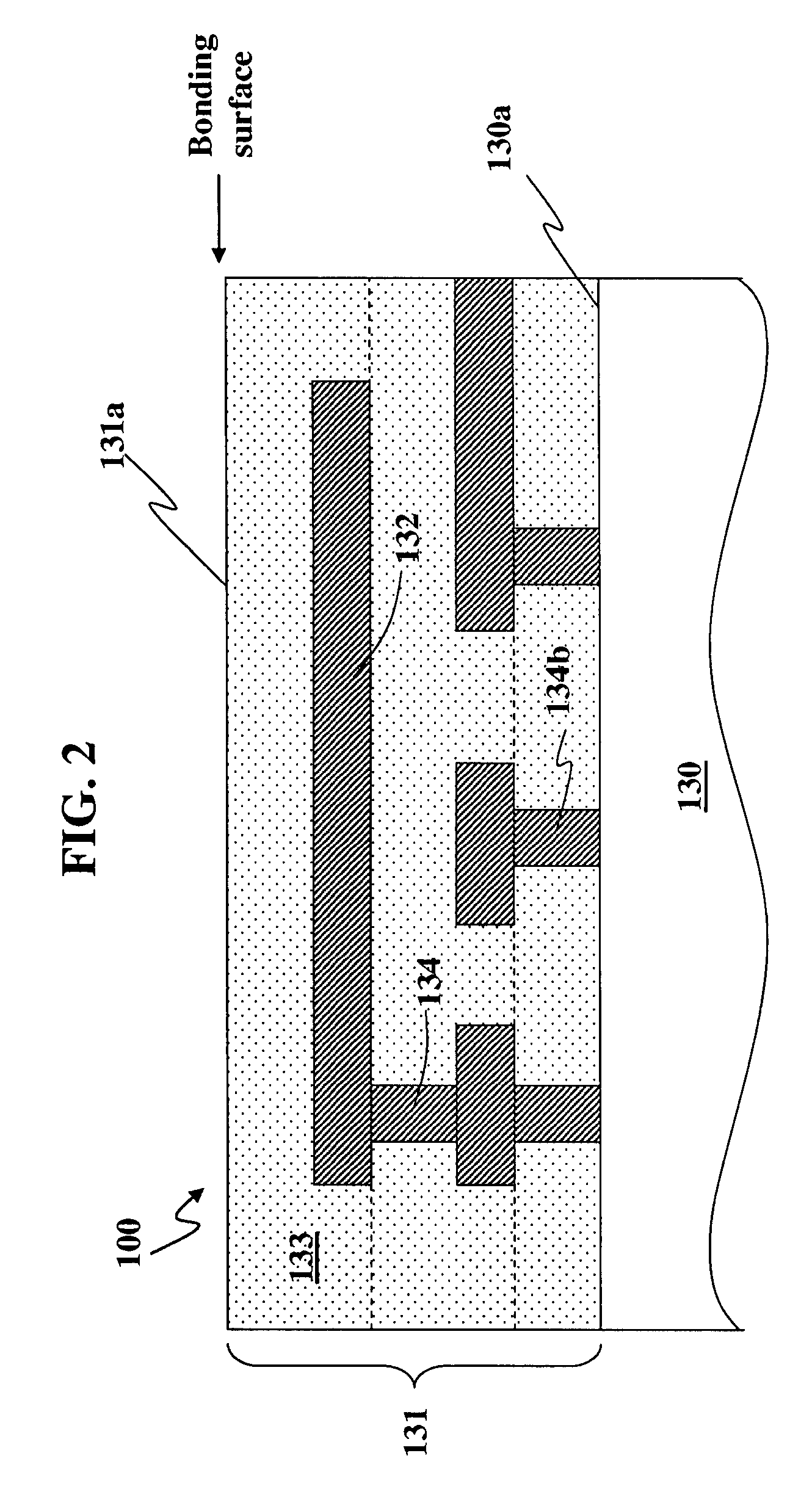

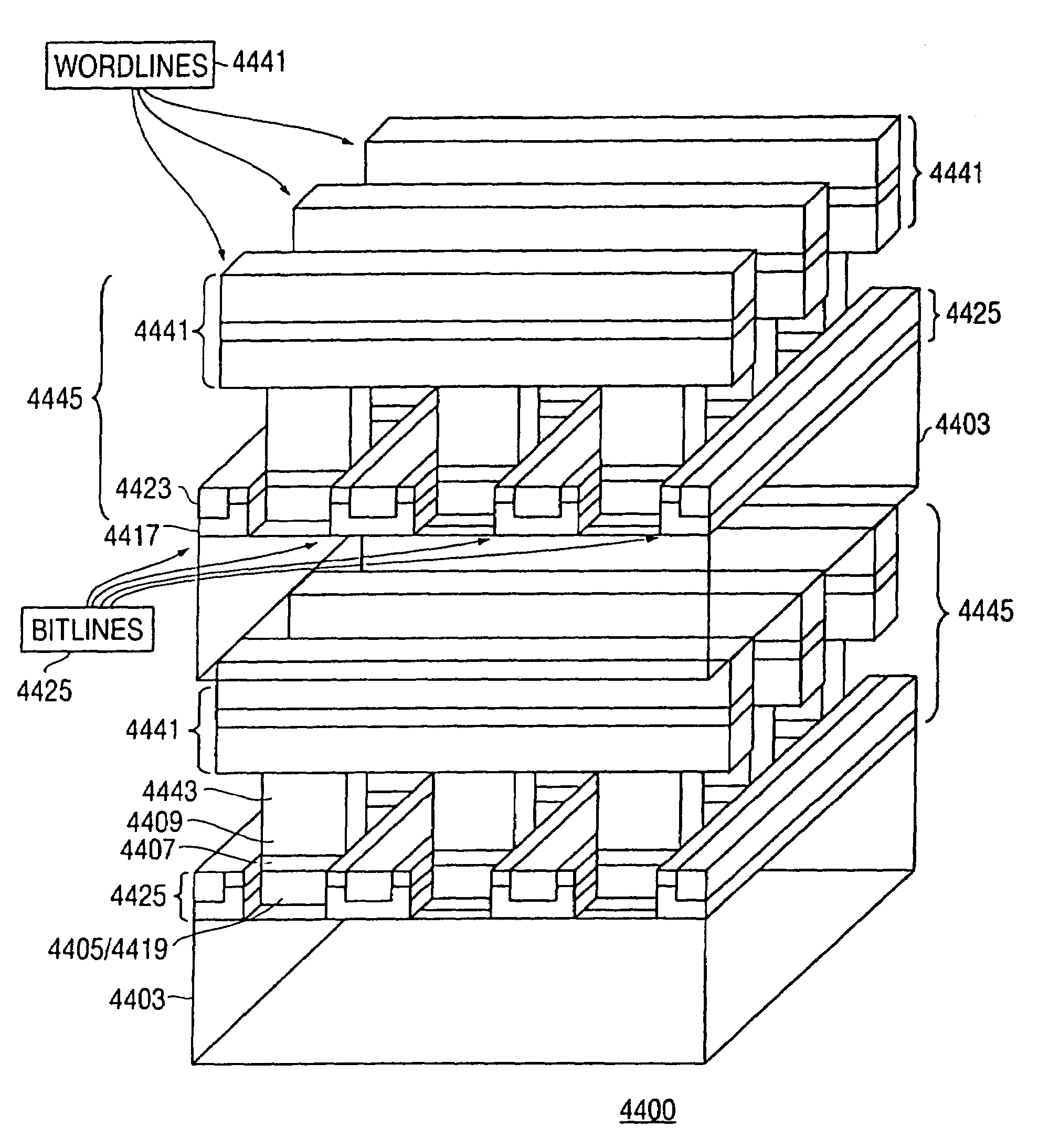

Monolithic three dimensional array of charge storage devices containing a planarized surface

There is provided a monolithic three dimensional array of charge storage devices which includes a plurality of device levels, wherein at least one surface between two successive device levels is planarized by chemical mechanical polishing.

Owner:WODEN TECH INC

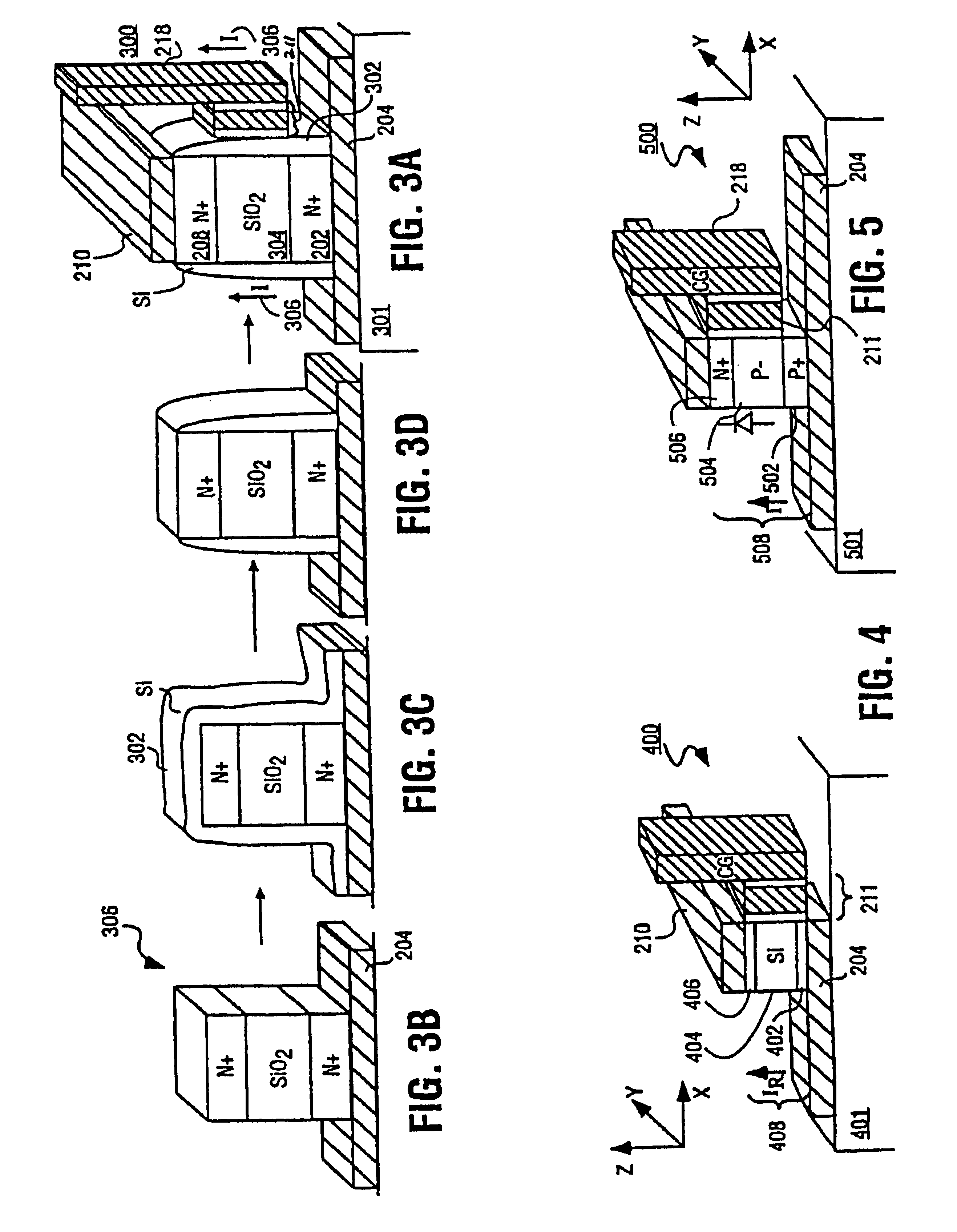

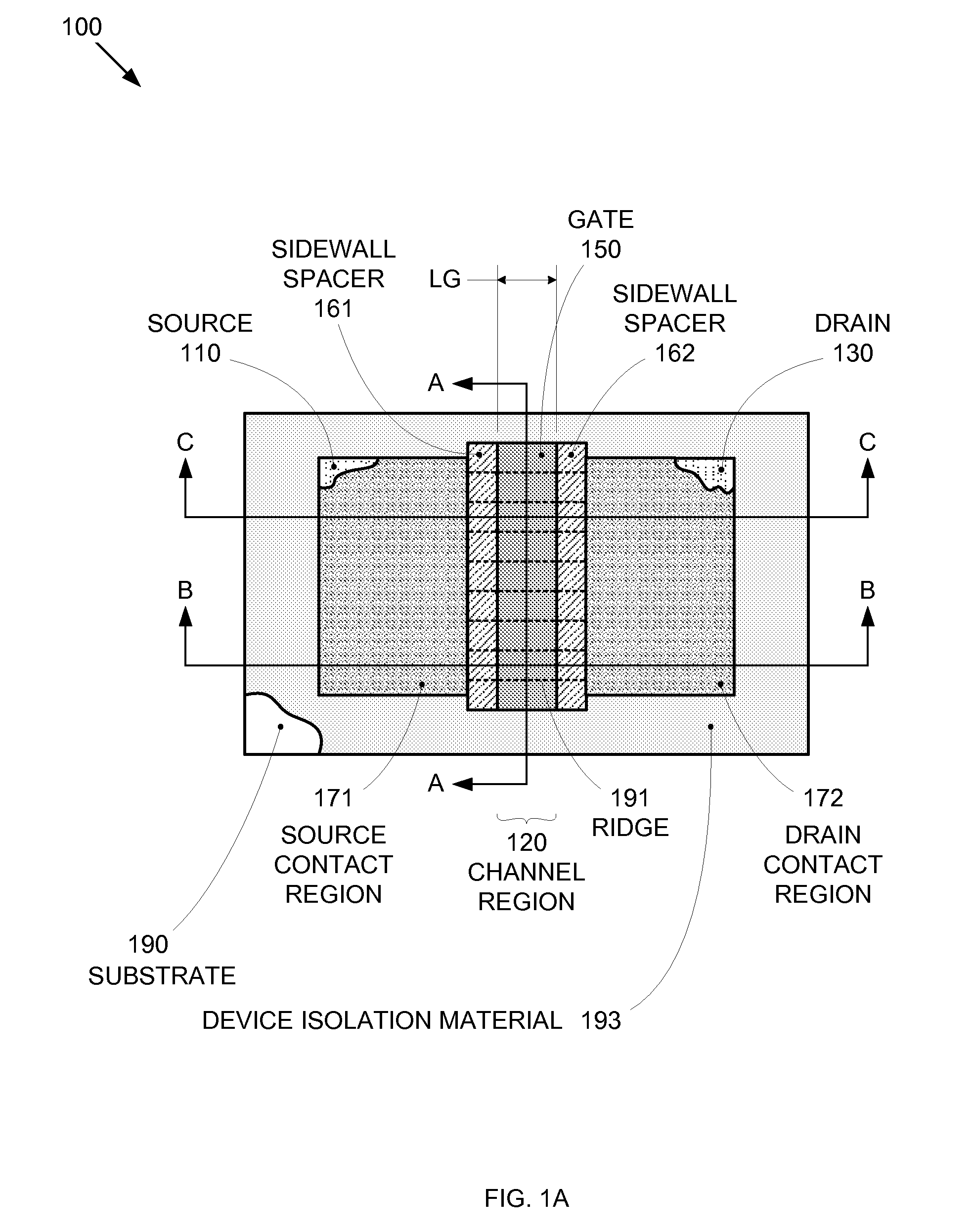

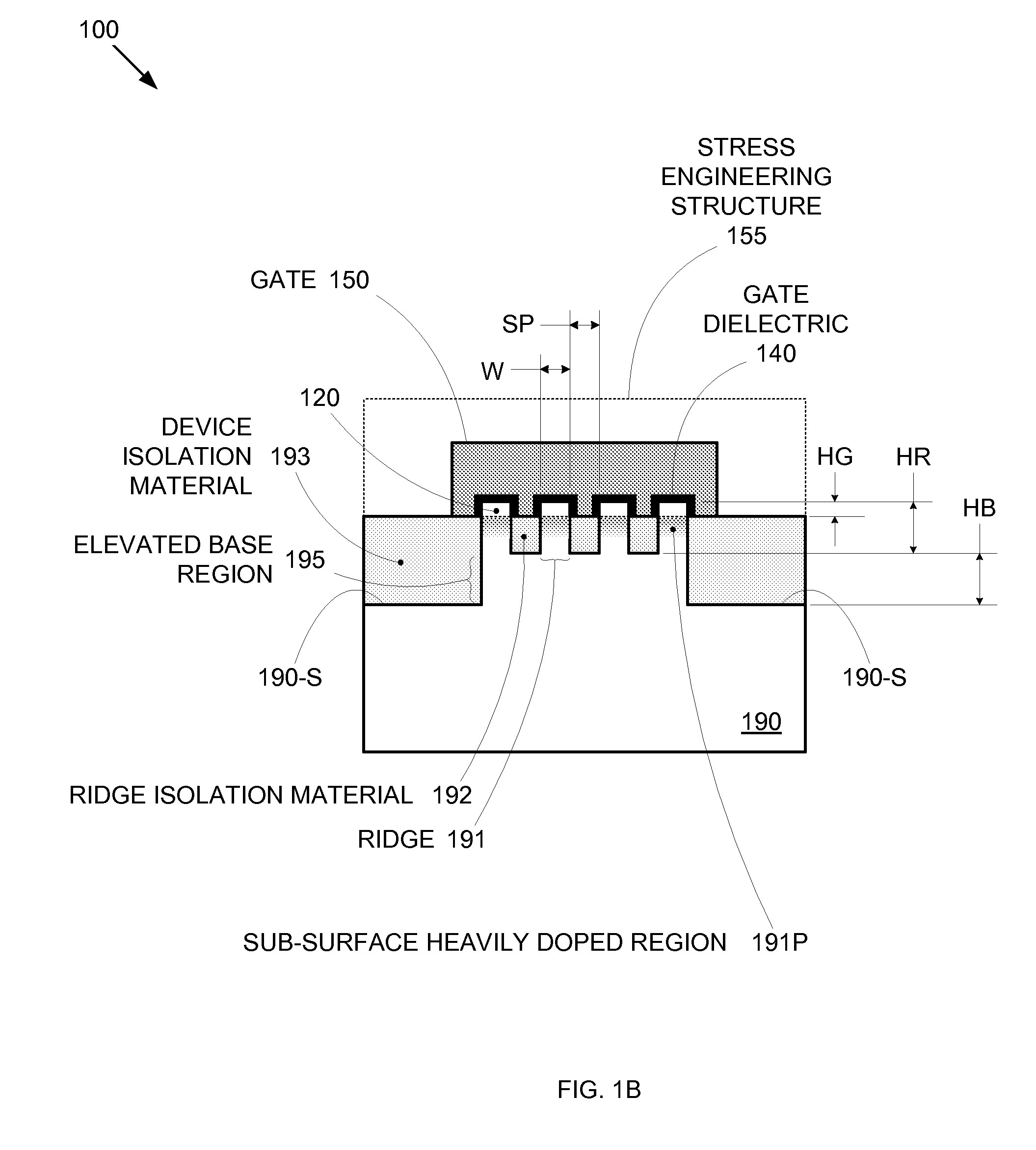

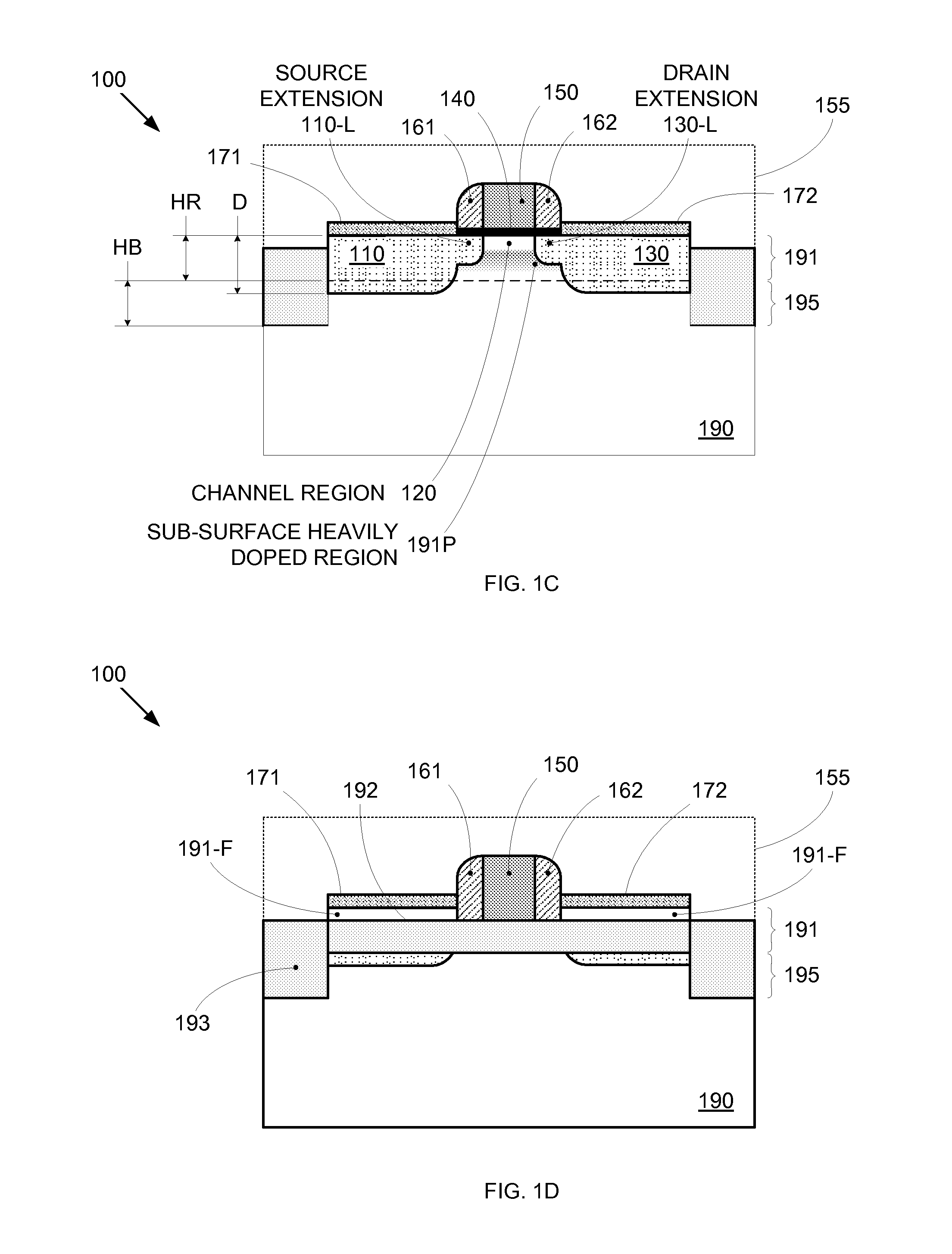

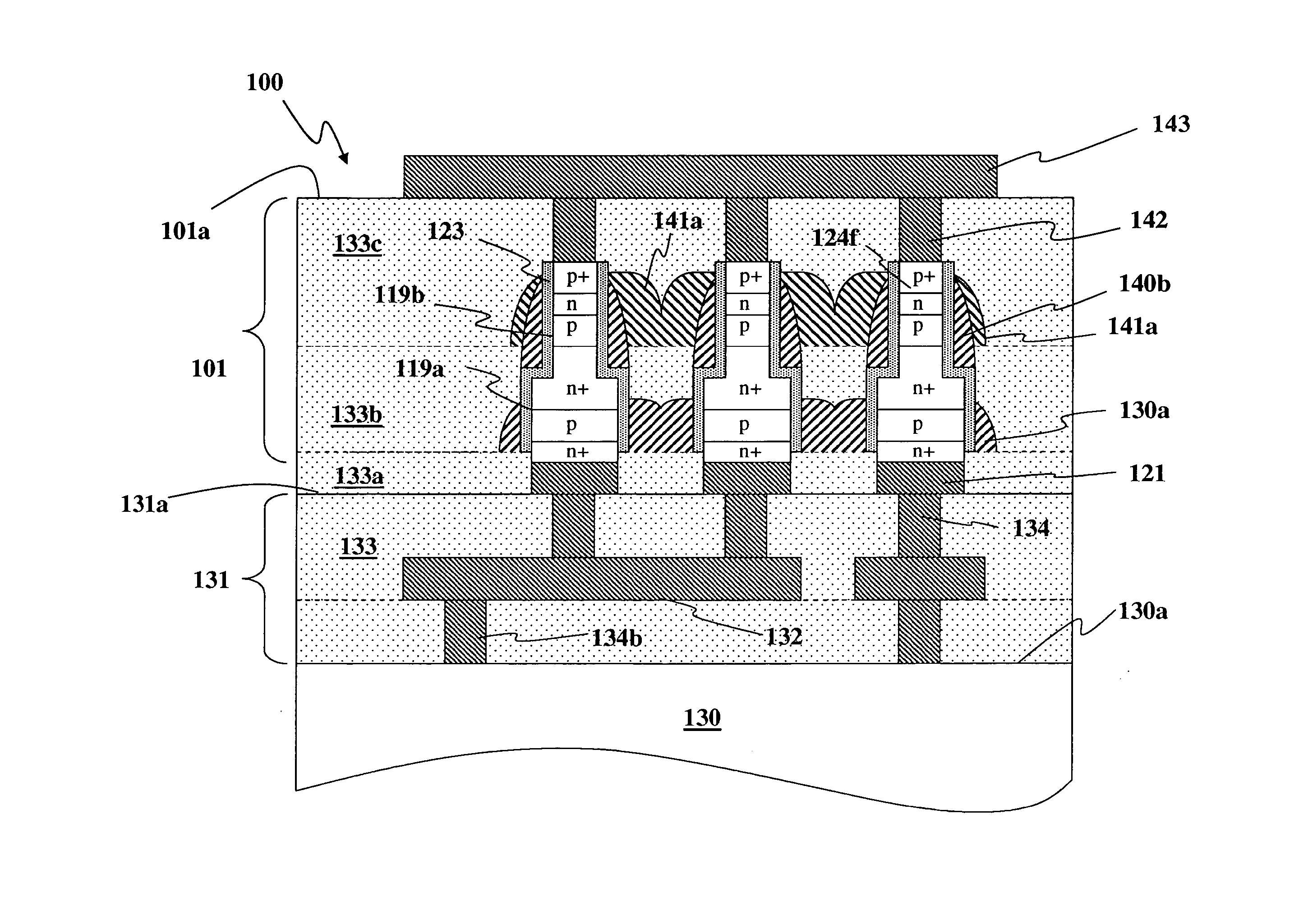

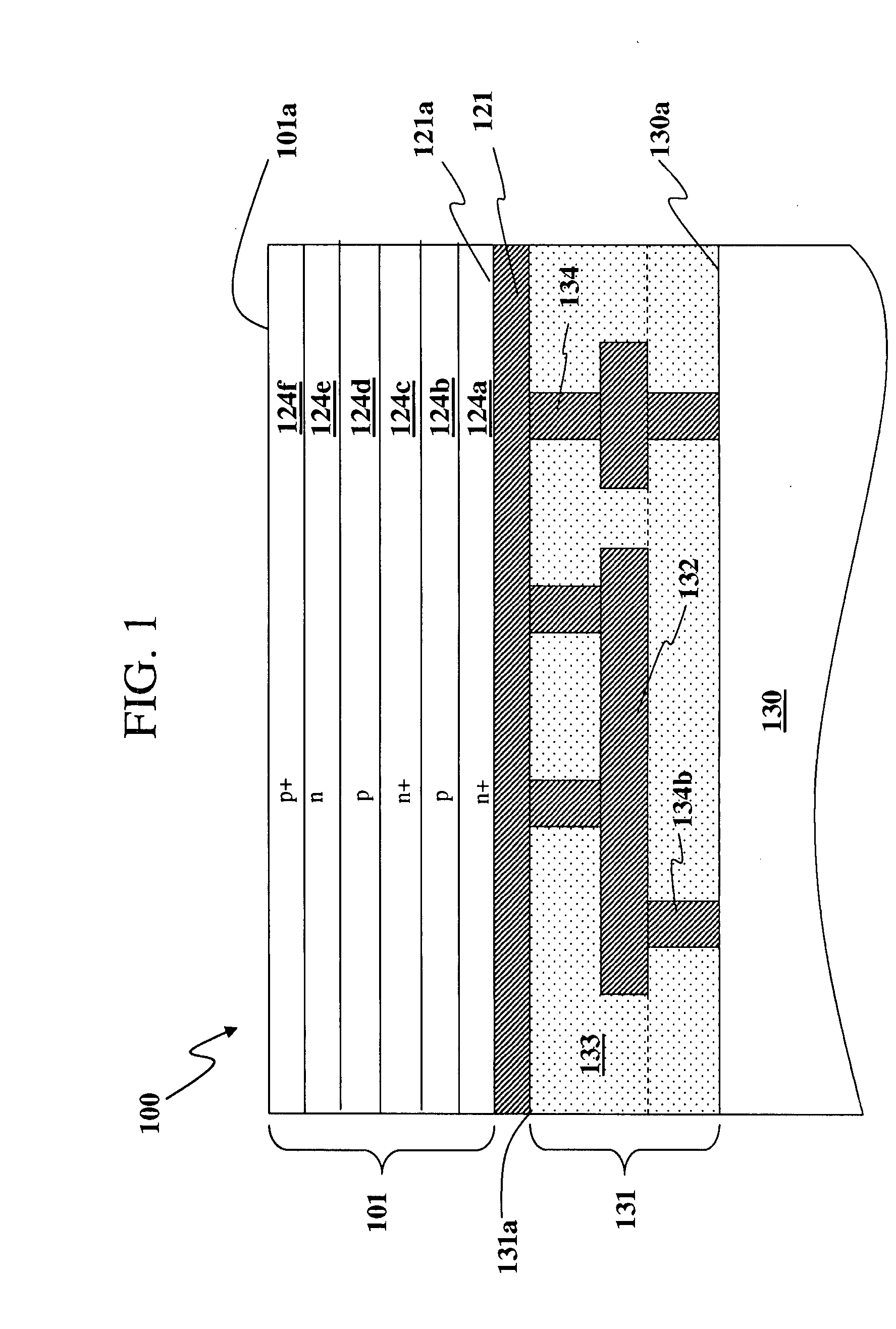

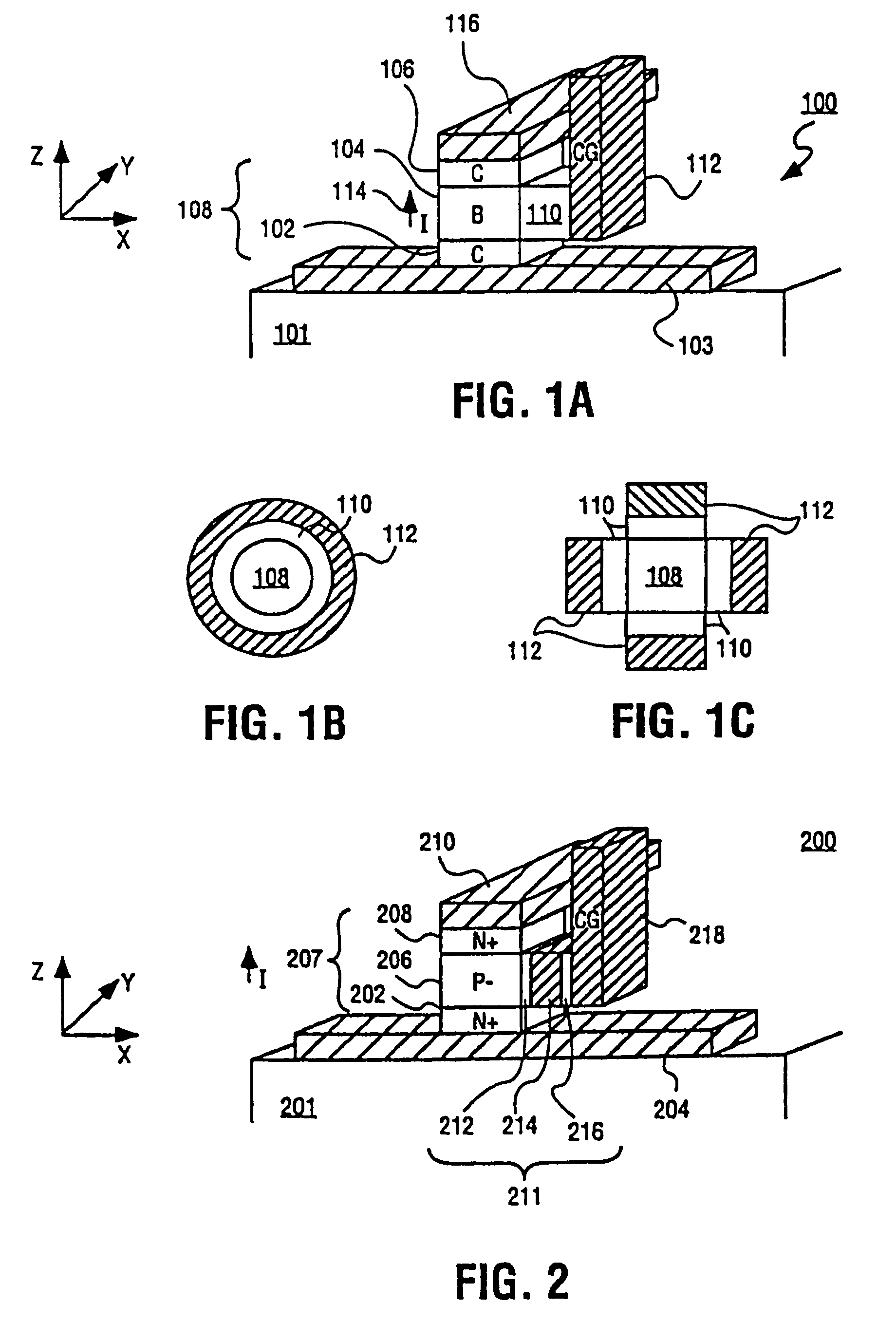

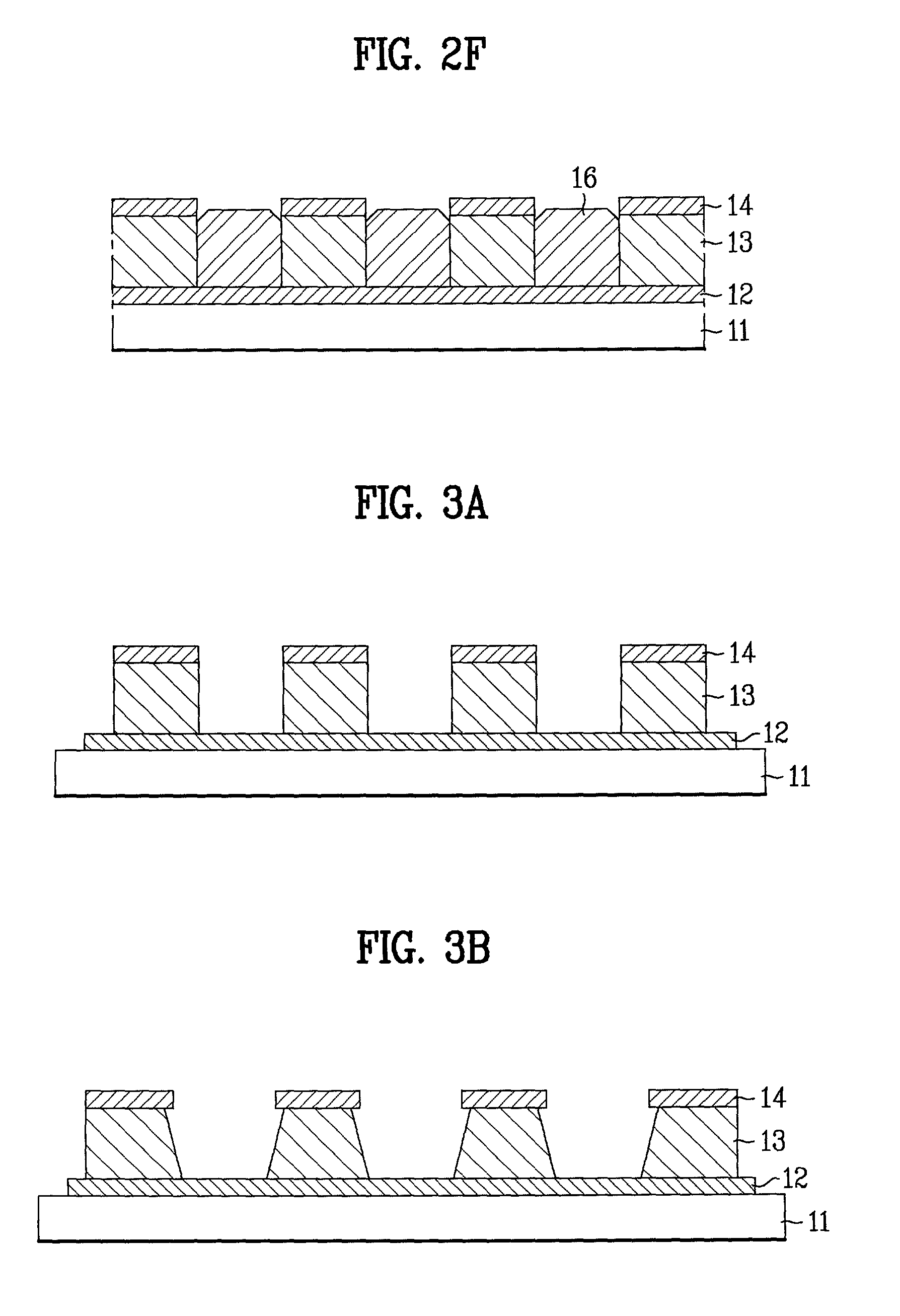

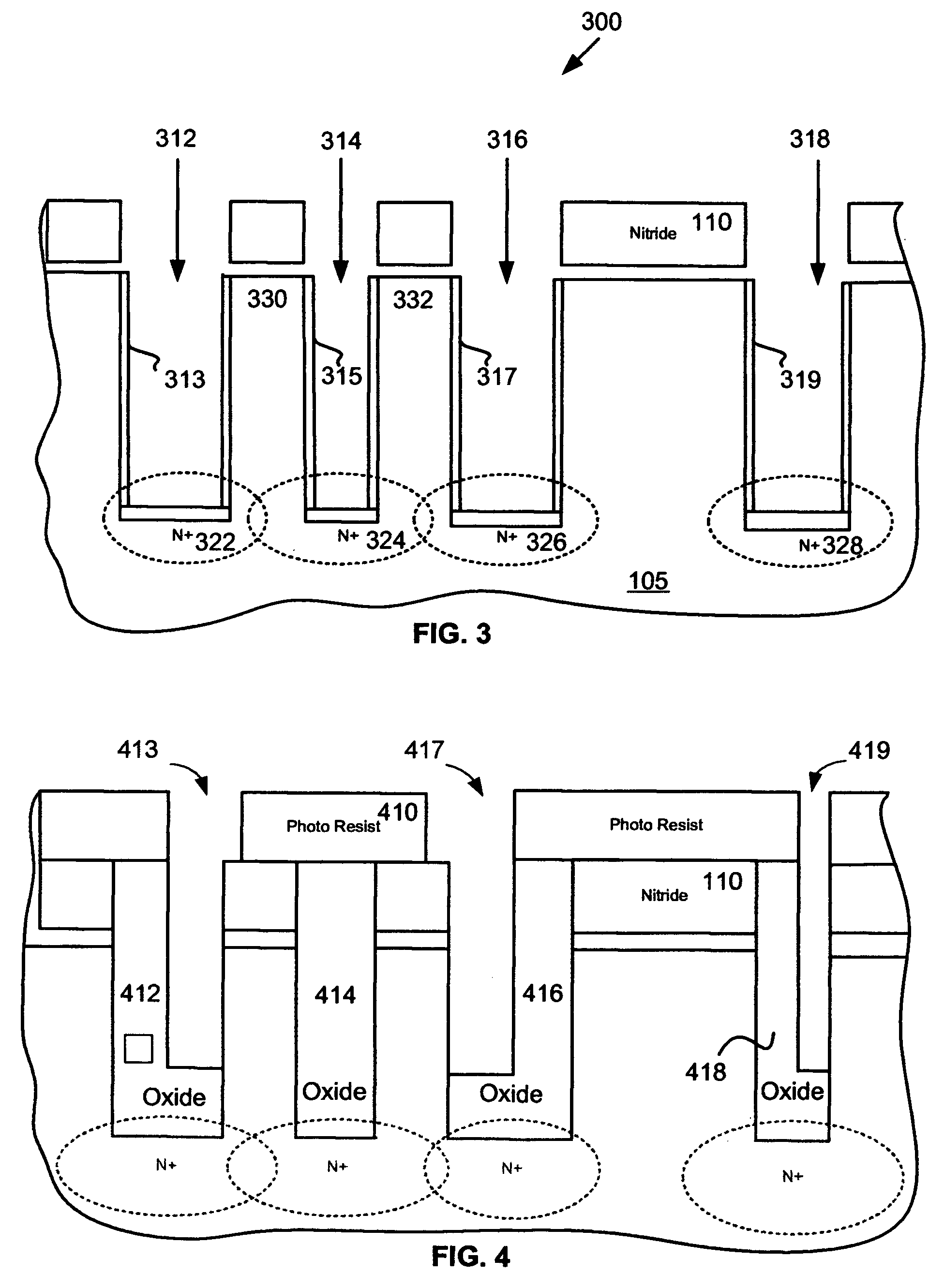

Enhanced Segmented Channel MOS Transistor with Narrowed Base Regions

ActiveUS20070128782A1Increase costImprove performanceThyristorSolid-state devicesPre-existingImage resolution

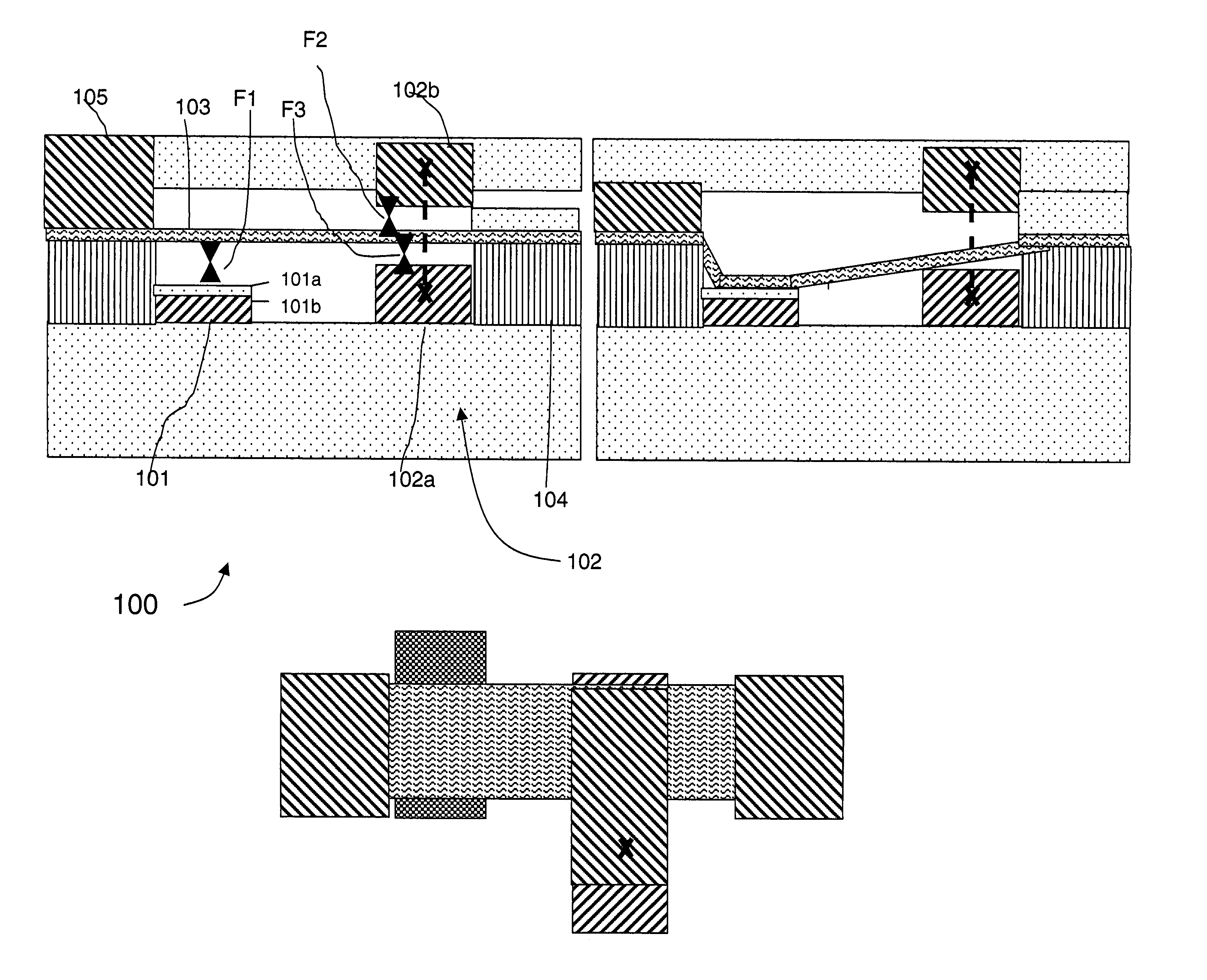

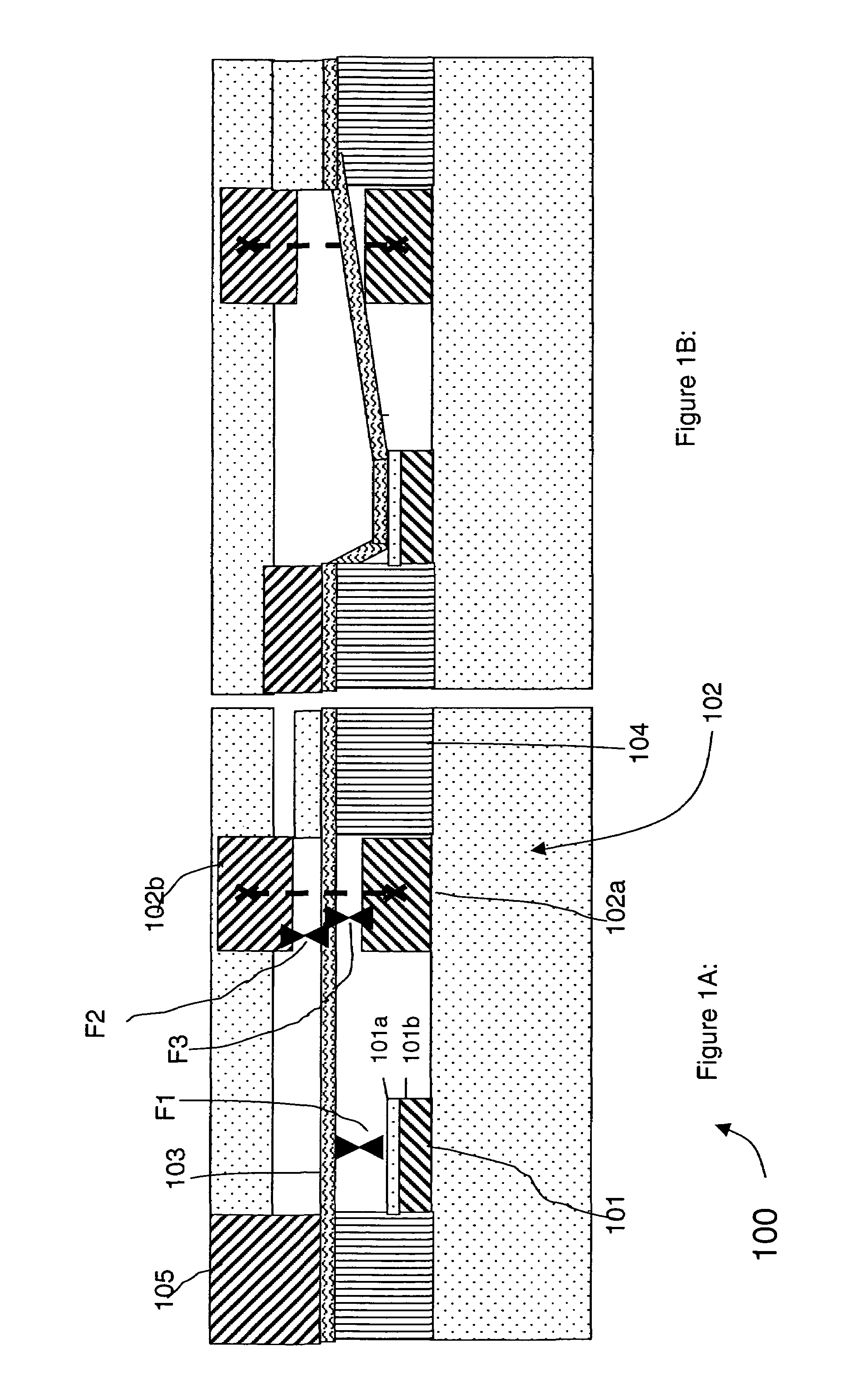

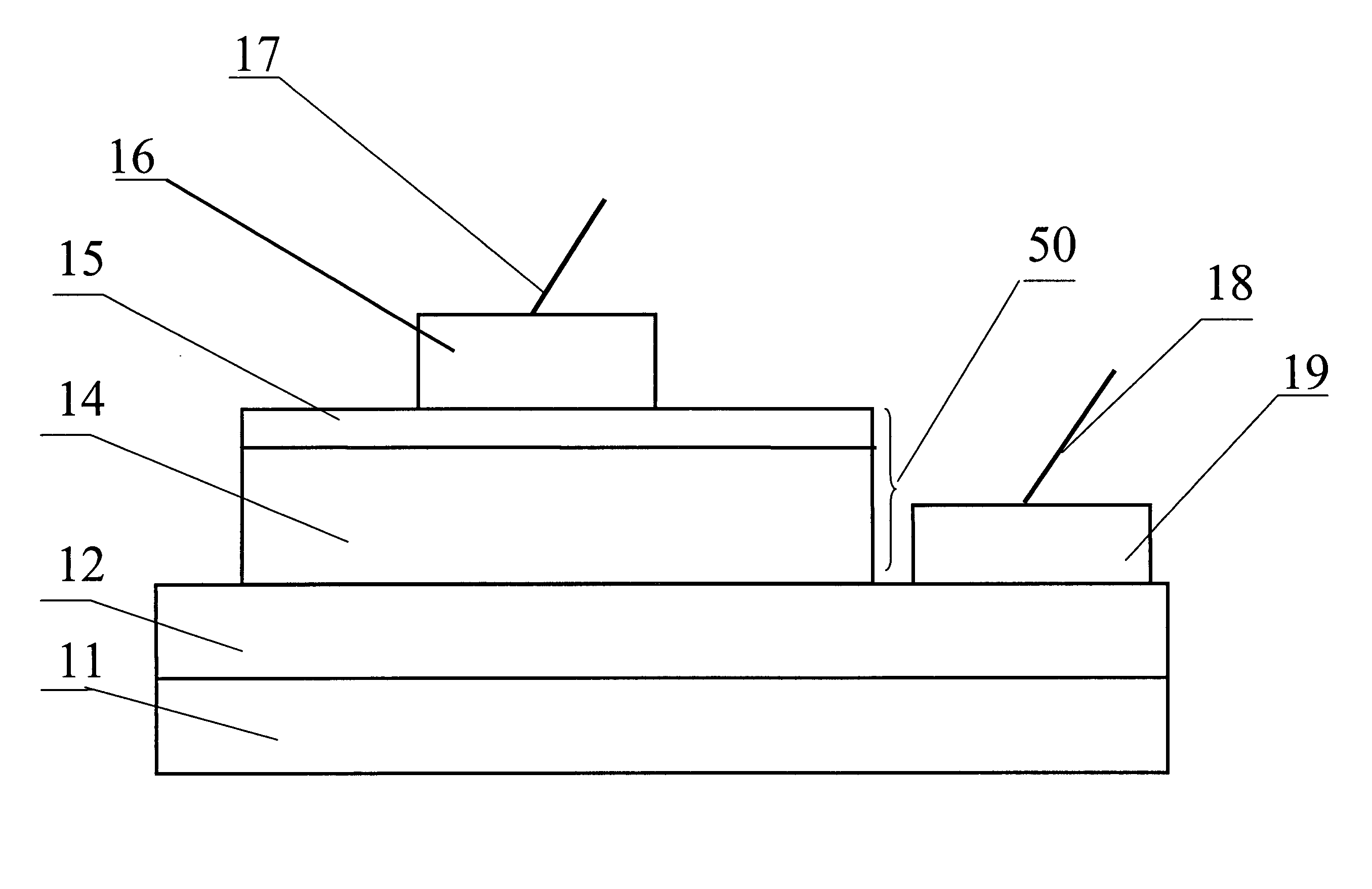

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

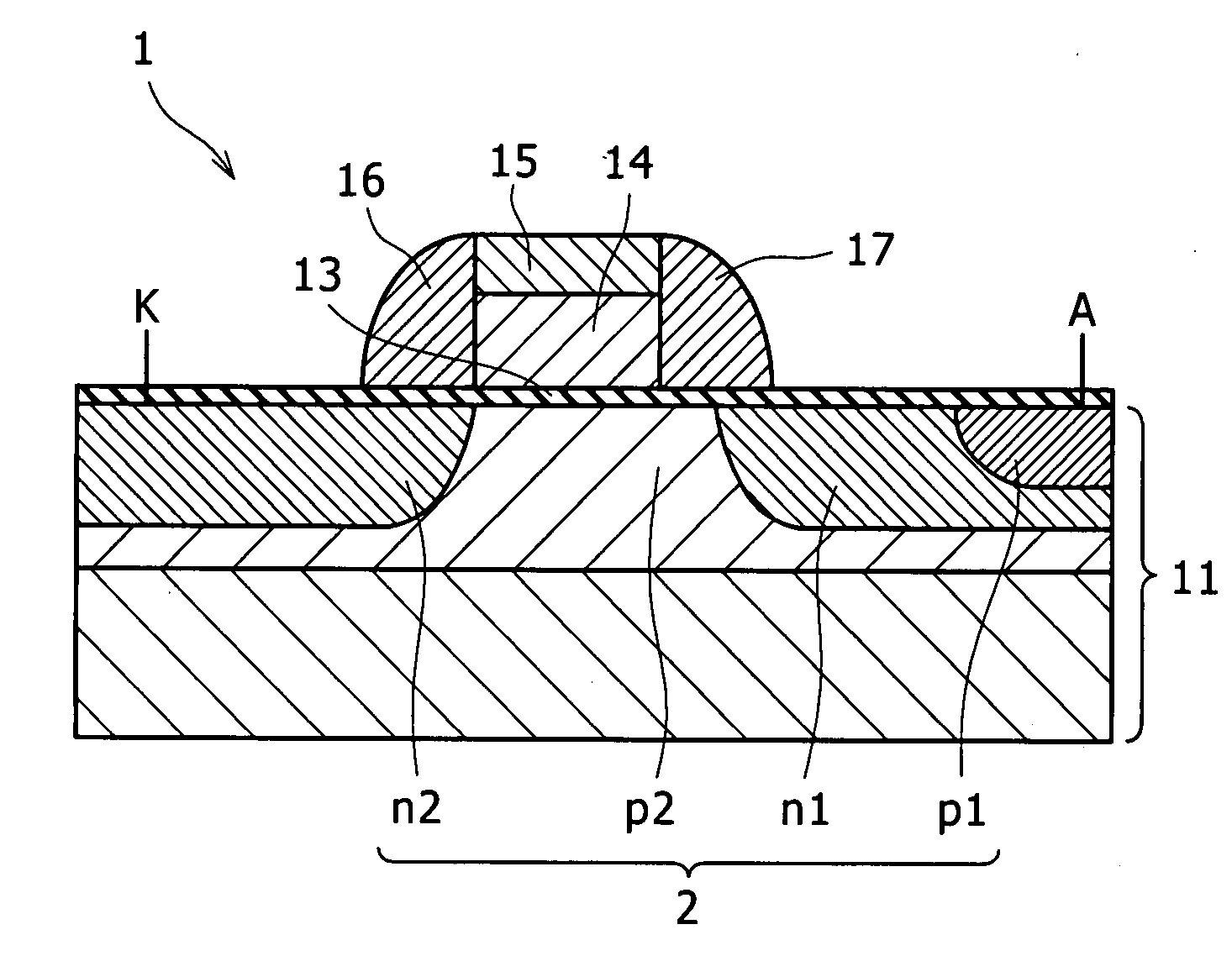

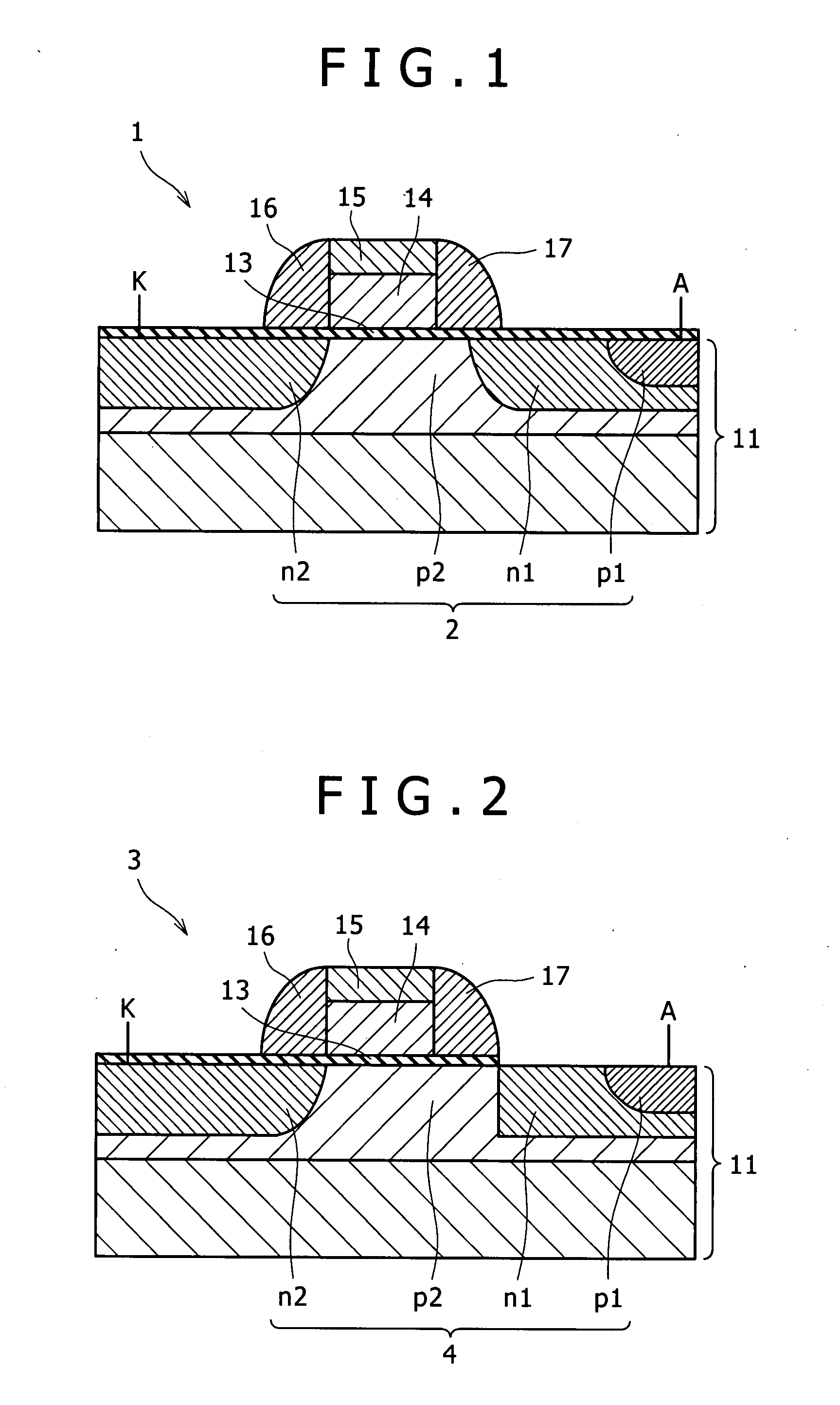

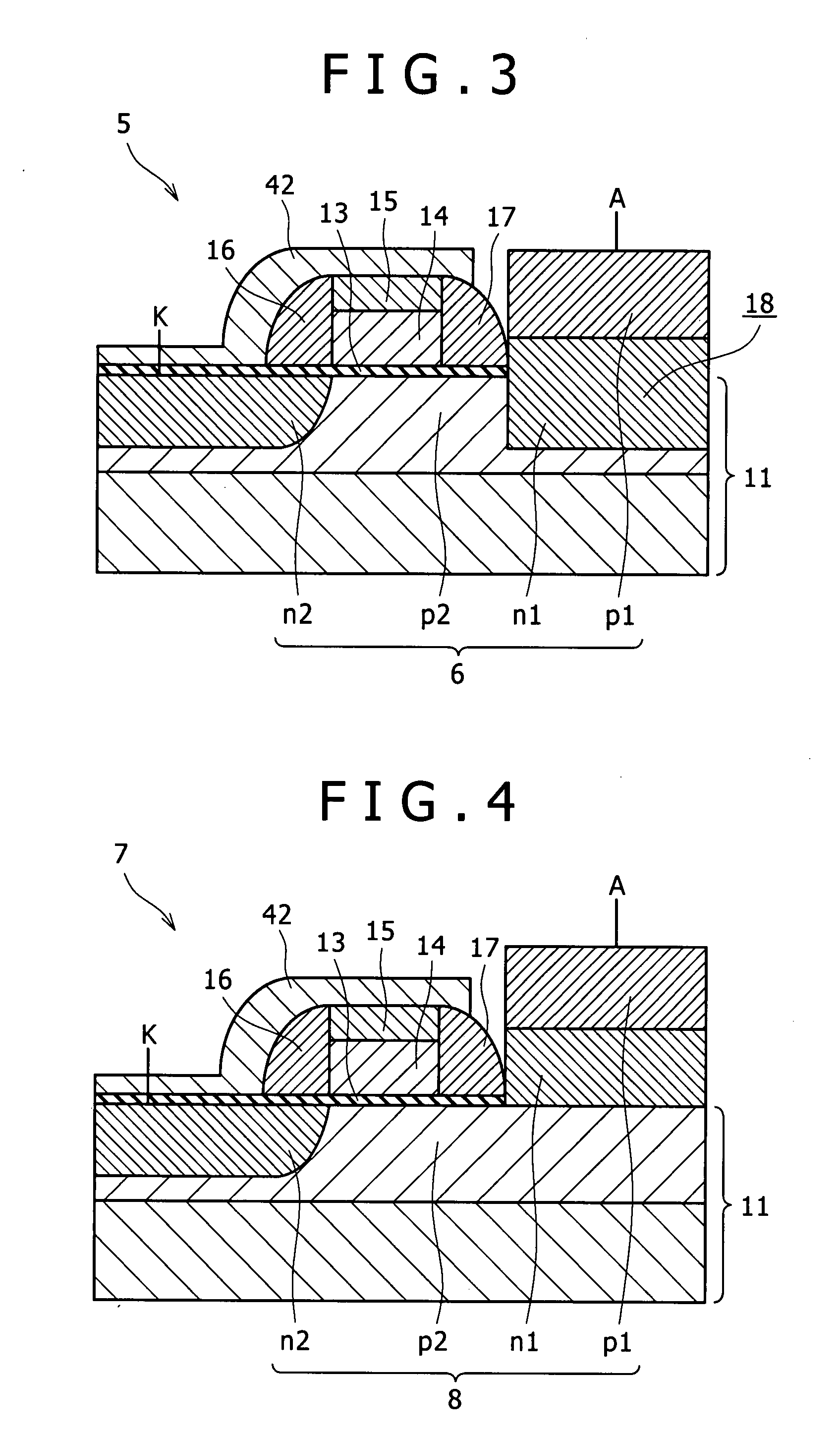

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20080042165A1Increase speedImprove mobilityThyristorSemiconductor/solid-state device manufacturingThyratronSemiconductor

A semiconductor device includes a thyristor configured to be formed through sequential joining of a first region of a first conductivity type, a second region of a second conductivity type opposite to the first conductivity type, a third region of the first conductivity type, and a fourth region of the second conductivity type, and have a gate formed over the third region. The first to fourth regions are formed in a silicon germanium region or germanium region.

Owner:SONY CORP

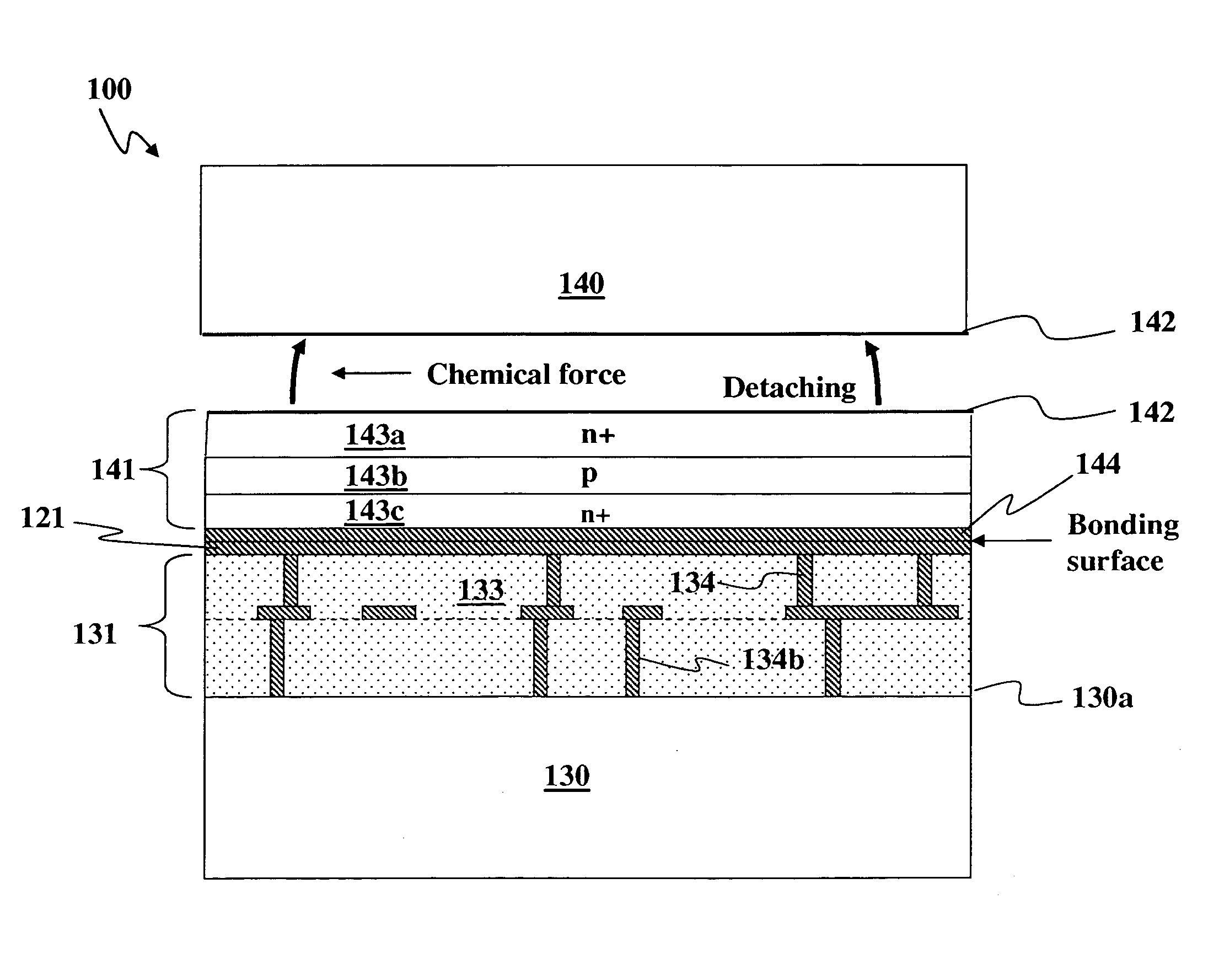

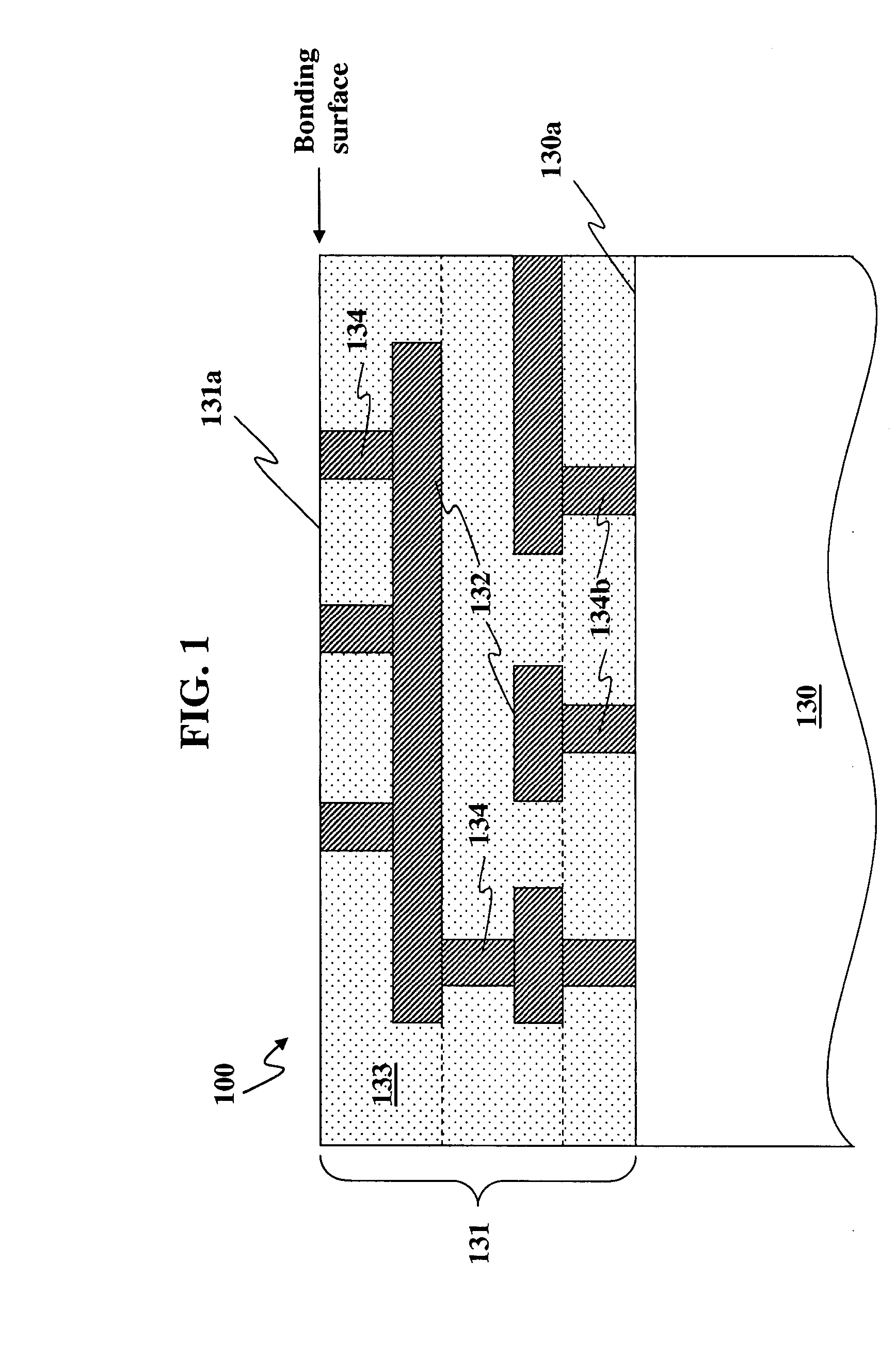

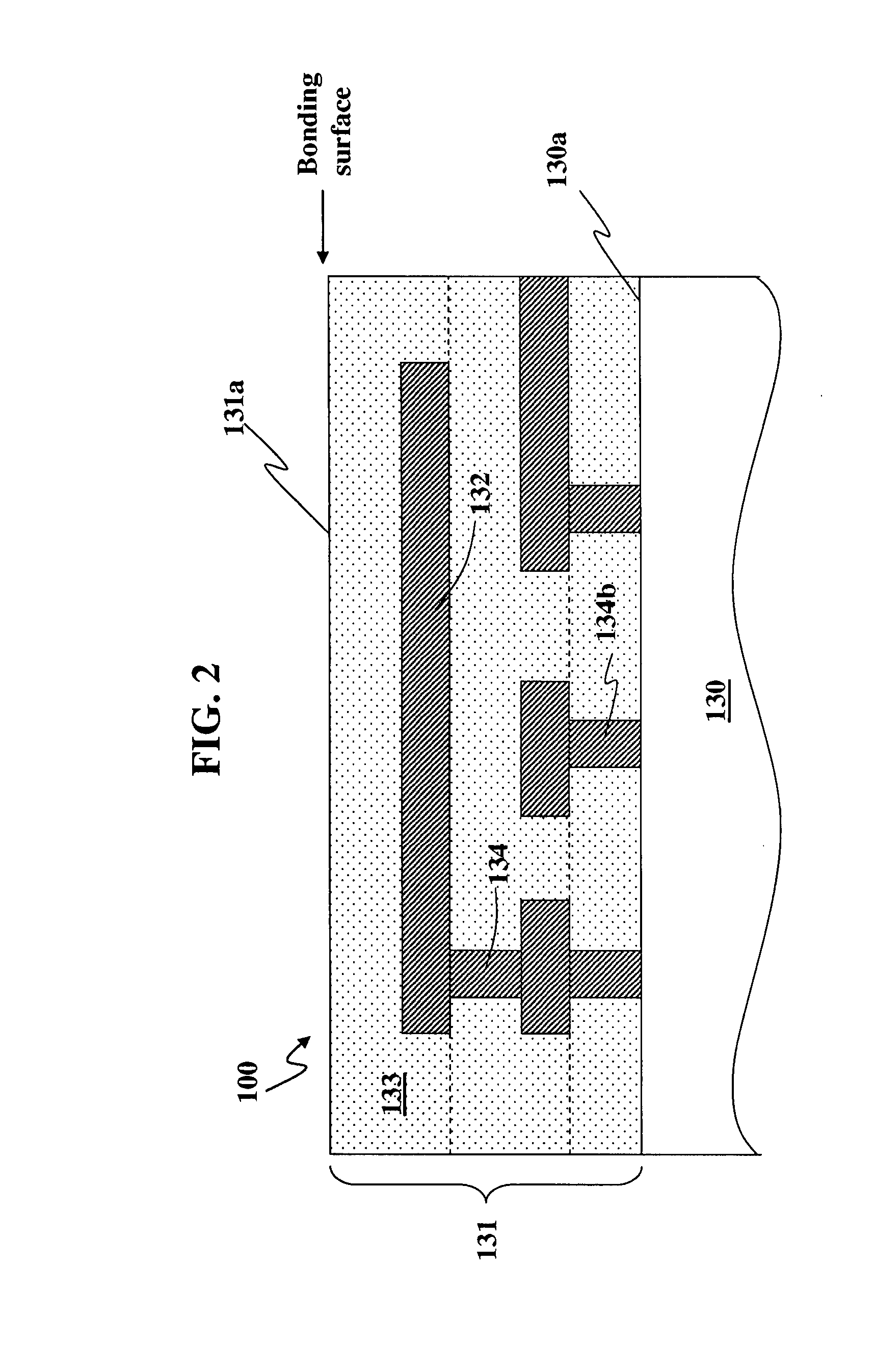

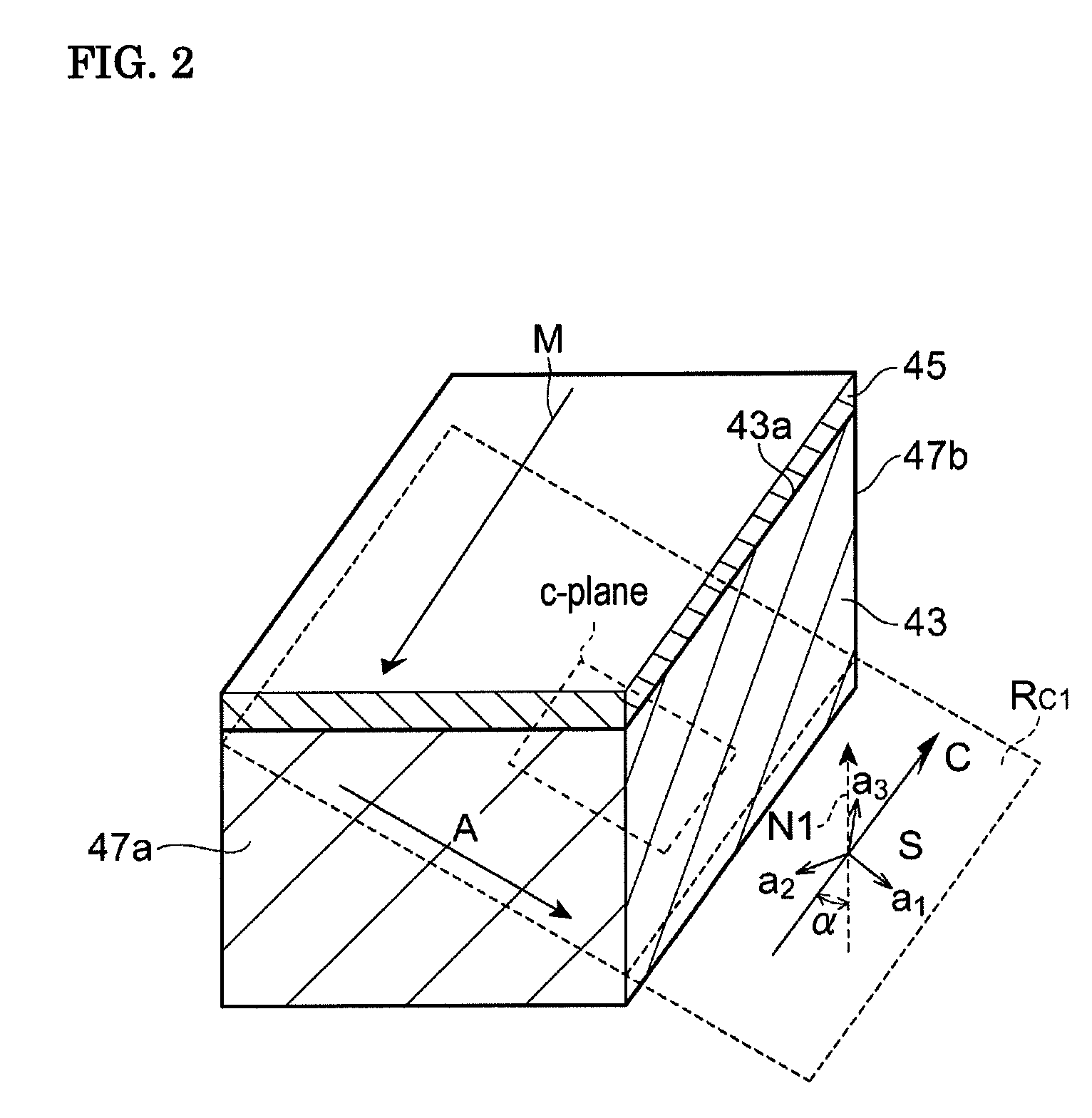

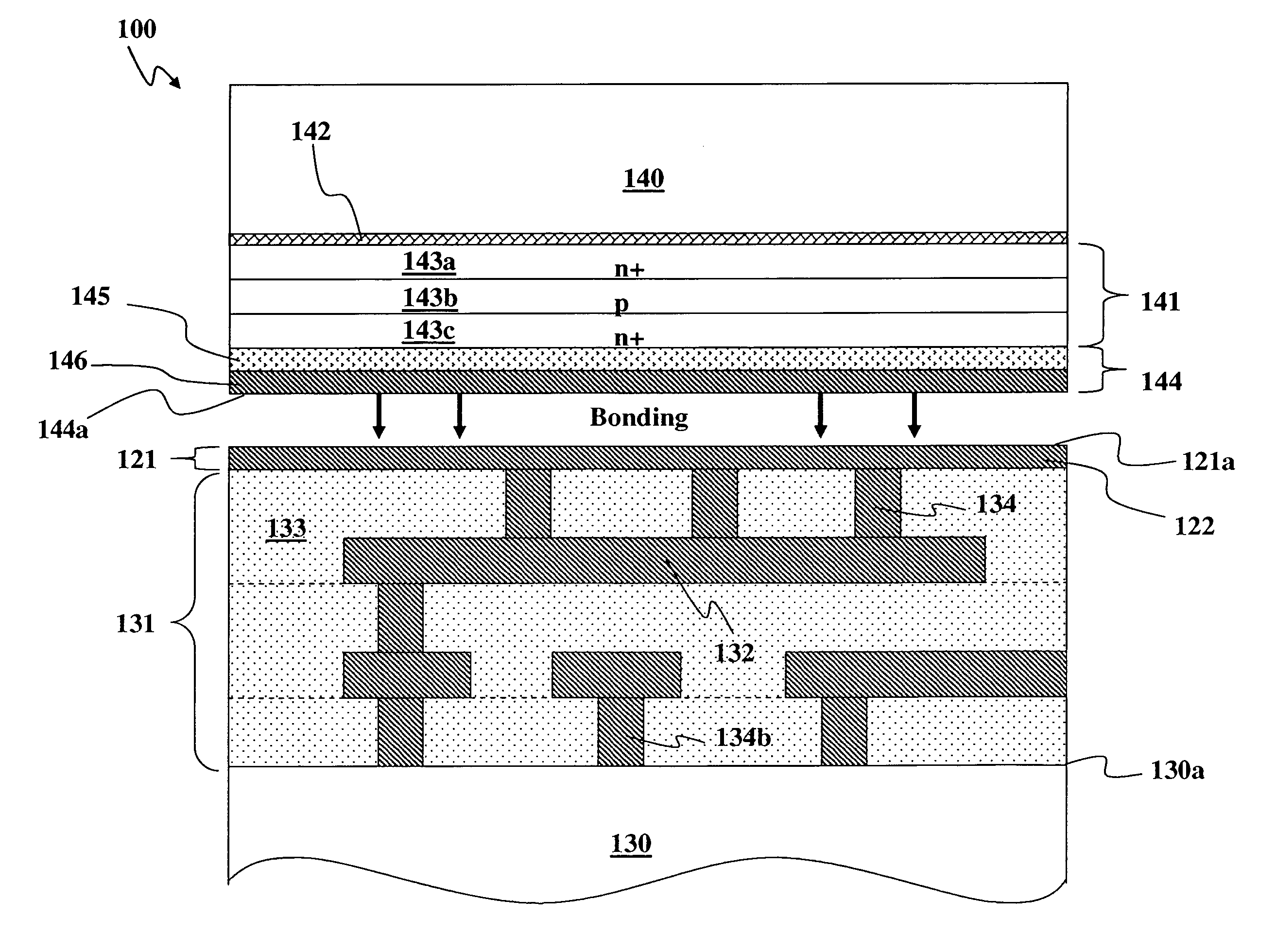

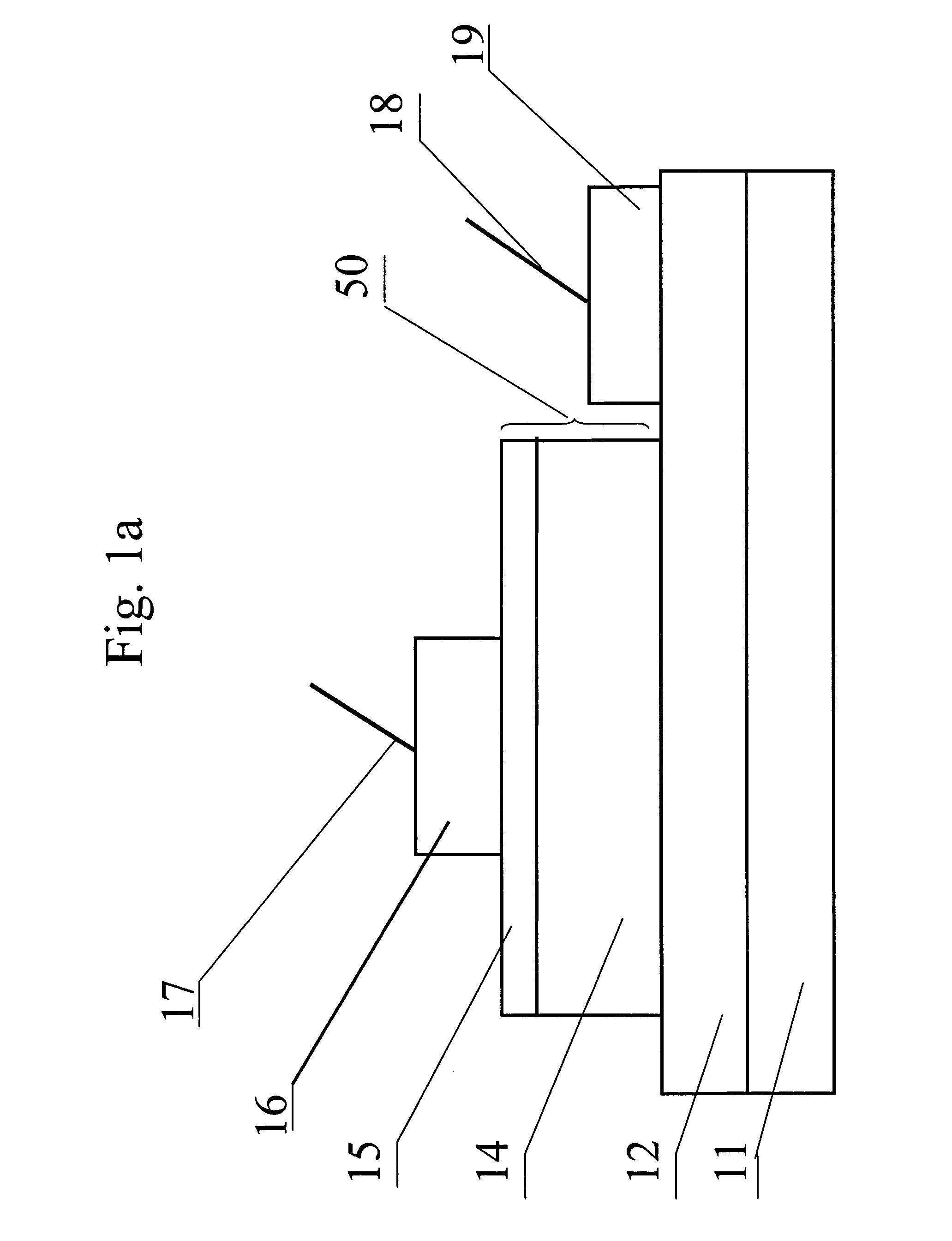

Semiconductor bonding and layer transfer method

The present invention provides a method of coupling substrates together. The method includes providing first and second substrates and then coupling the first and second substrates together. One of the first and second substrates includes devices with an interconnect region positioned thereon and the other substrate carries a device structure.

Owner:BESANG

Semiconductor bonding and layer transfer method

The present invention provides a method of coupling substrates together. The method includes providing first and second substrates and then coupling the first and second substrates together. One of the first and second substrates includes devices with an interconnect region positioned thereon and the other substrate carries a device structure.

Owner:BESANG

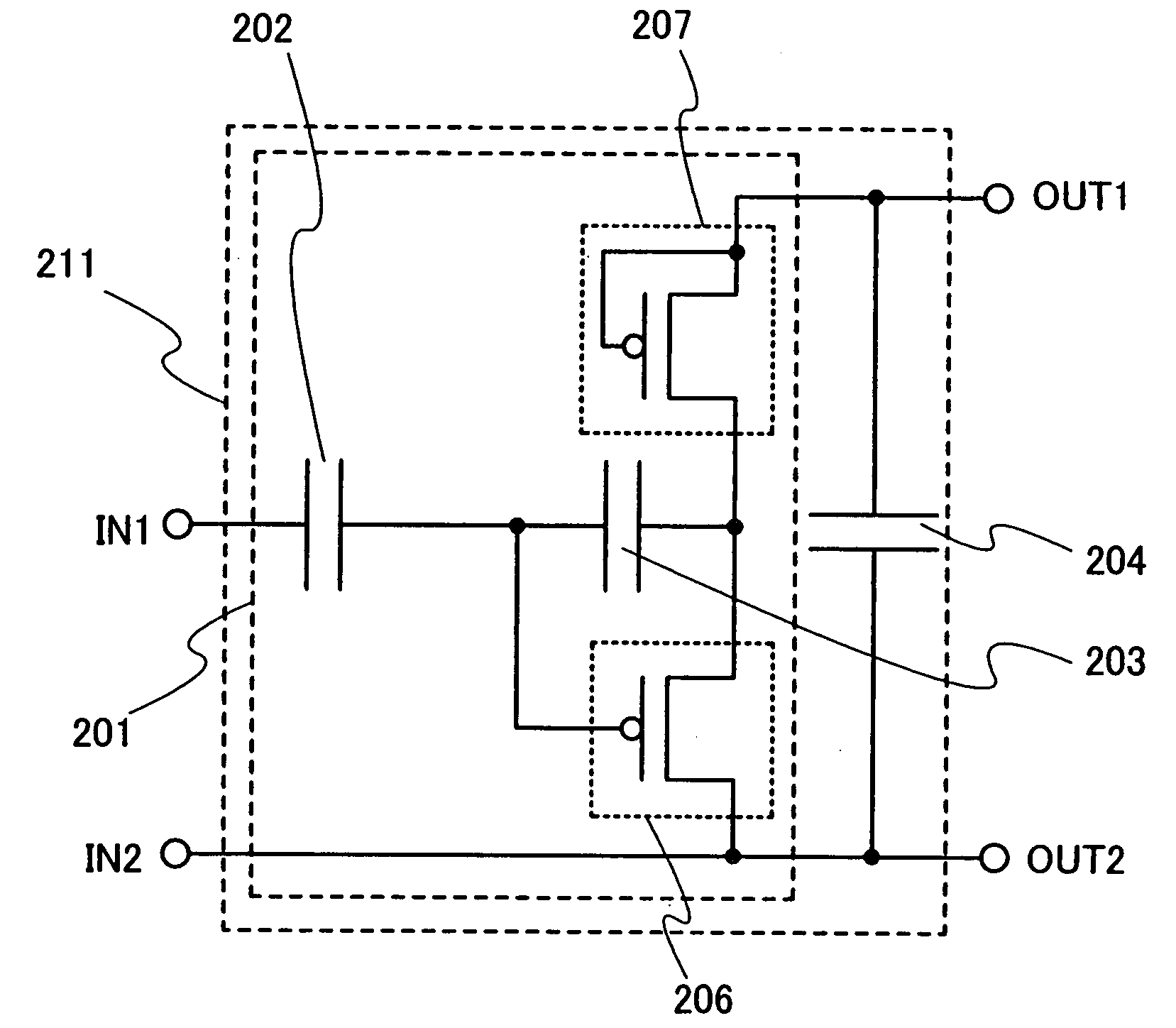

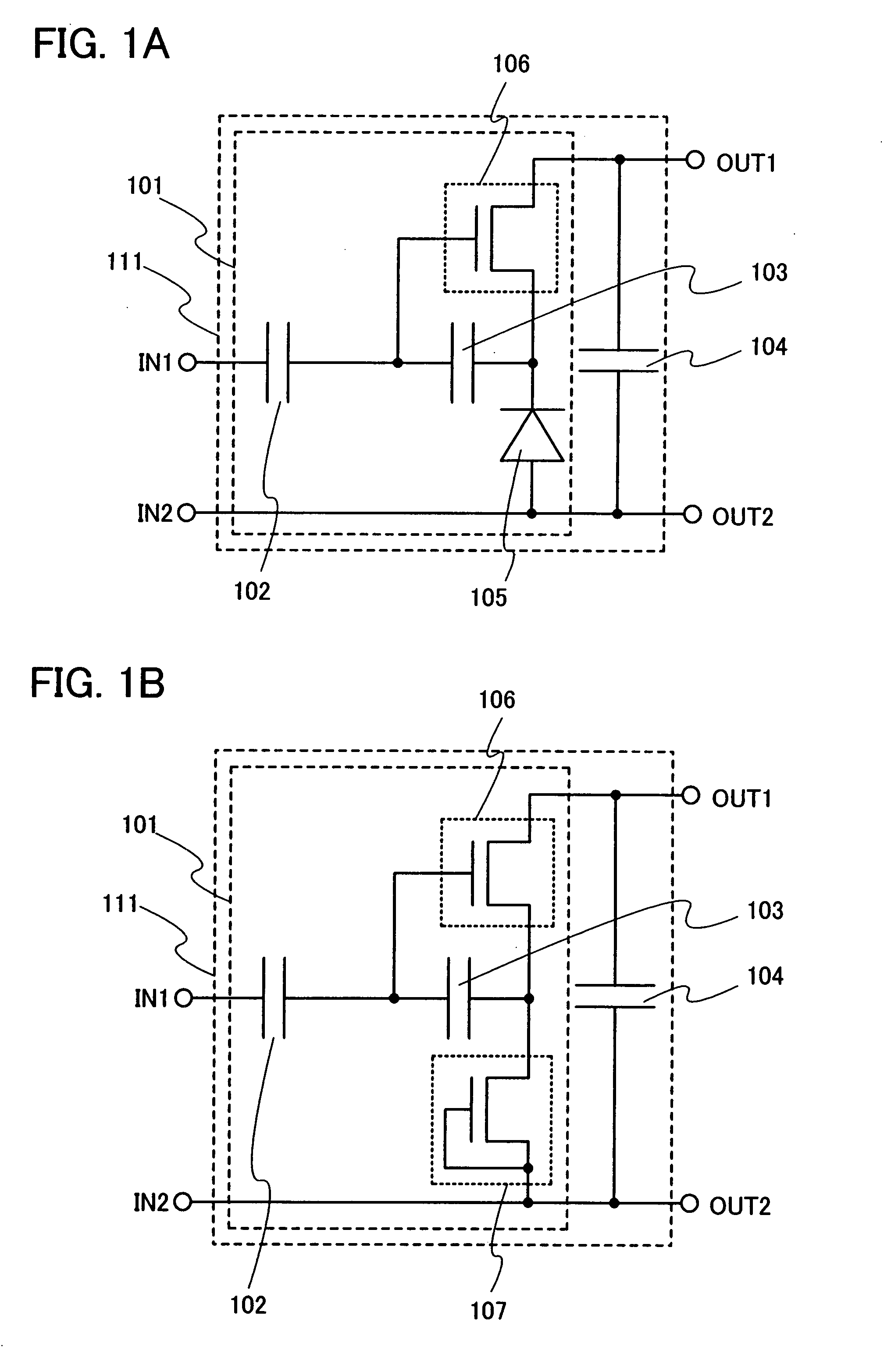

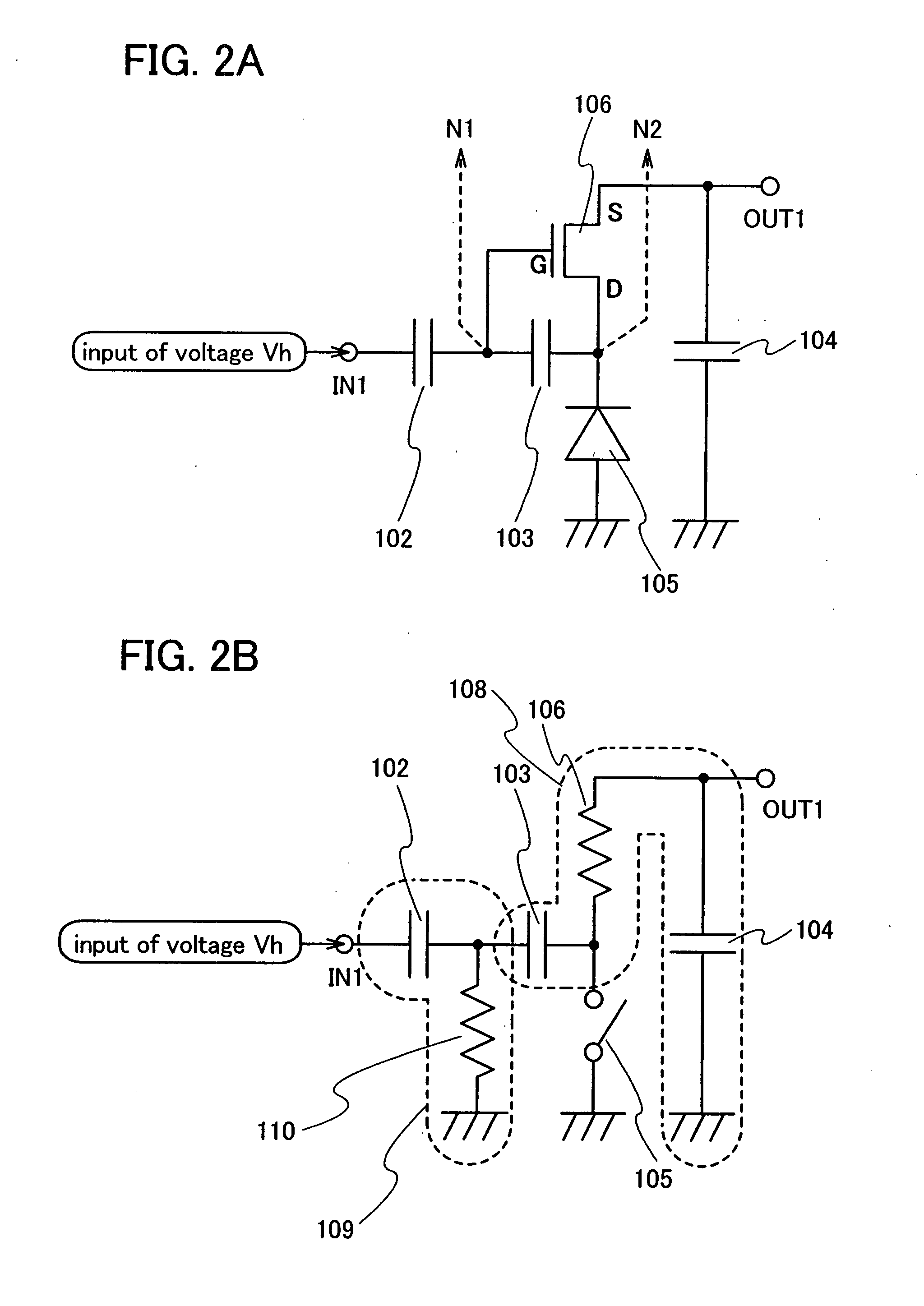

Rectifier circuit, power supply circuit, and semiconductor device

It is an object of the present invention to provide a rectifier circuit that can suppress deterioration or dielectric breakdown of a semiconductor element due to excessive current. A rectifier circuit of the present invention includes at least a first capacitor, a second capacitor, and a diode which are sequentially connected in series in a path which connects an input terminal and one of two output terminals, and a transistor. The second capacitor is connected between one of a source region and a drain region and a gate electrode of the transistor. Further, the other one of the source region and the drain region and the other one of two output terminals are connected each other.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory device

A method of forming a circuit includes providing a substrate; providing an interconnect region positioned on the substrate; bonding a device structure to a surface of the interconnect region; and processing the device structure to form a first stack of layers on the interconnect region and a second stack of layers on the first stack. The width of the first stack is different than the width of the second stack.

Owner:BESANG

Semiconductor memory device

A method of forming a circuit includes providing a substrate; providing an interconnect region positioned on the substrate; bonding a device structure to a surface of the interconnect region; and processing the device structure to form a first stack of layers on the interconnect region and a second stack of layers on the first stack. The width of the first stack is different than the width of the second stack.

Owner:BESANG

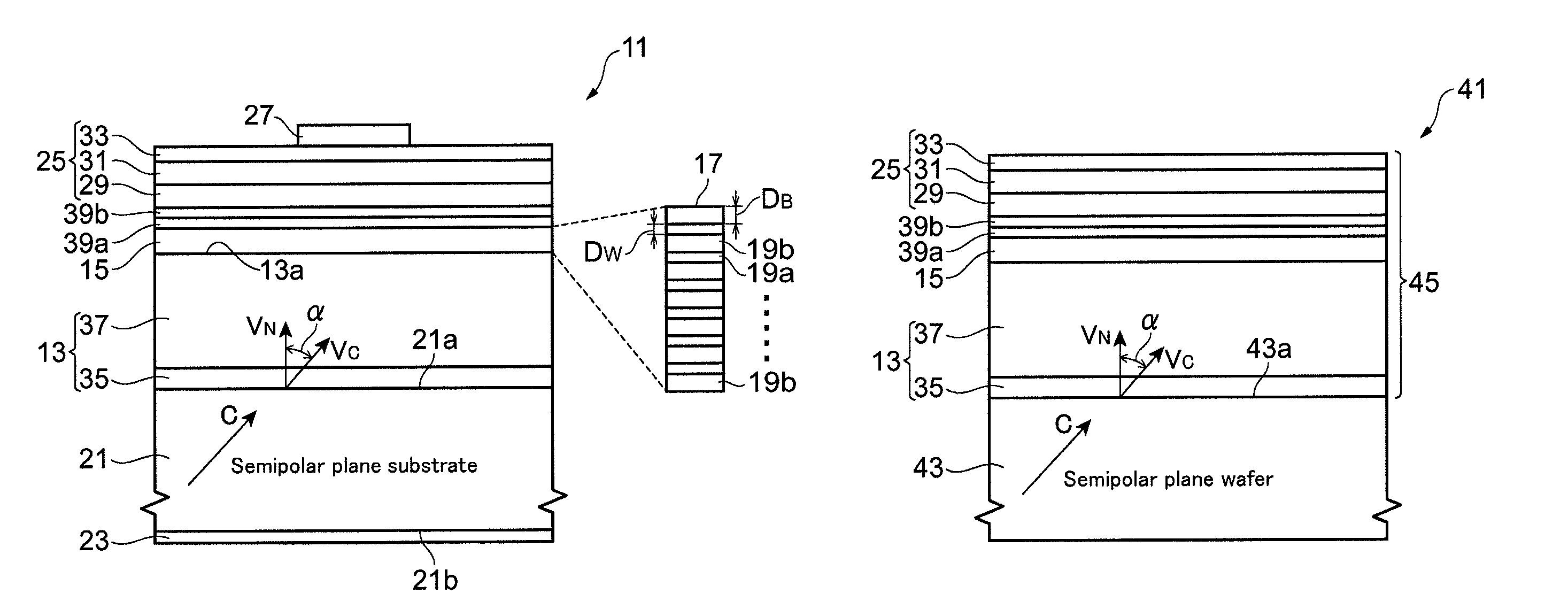

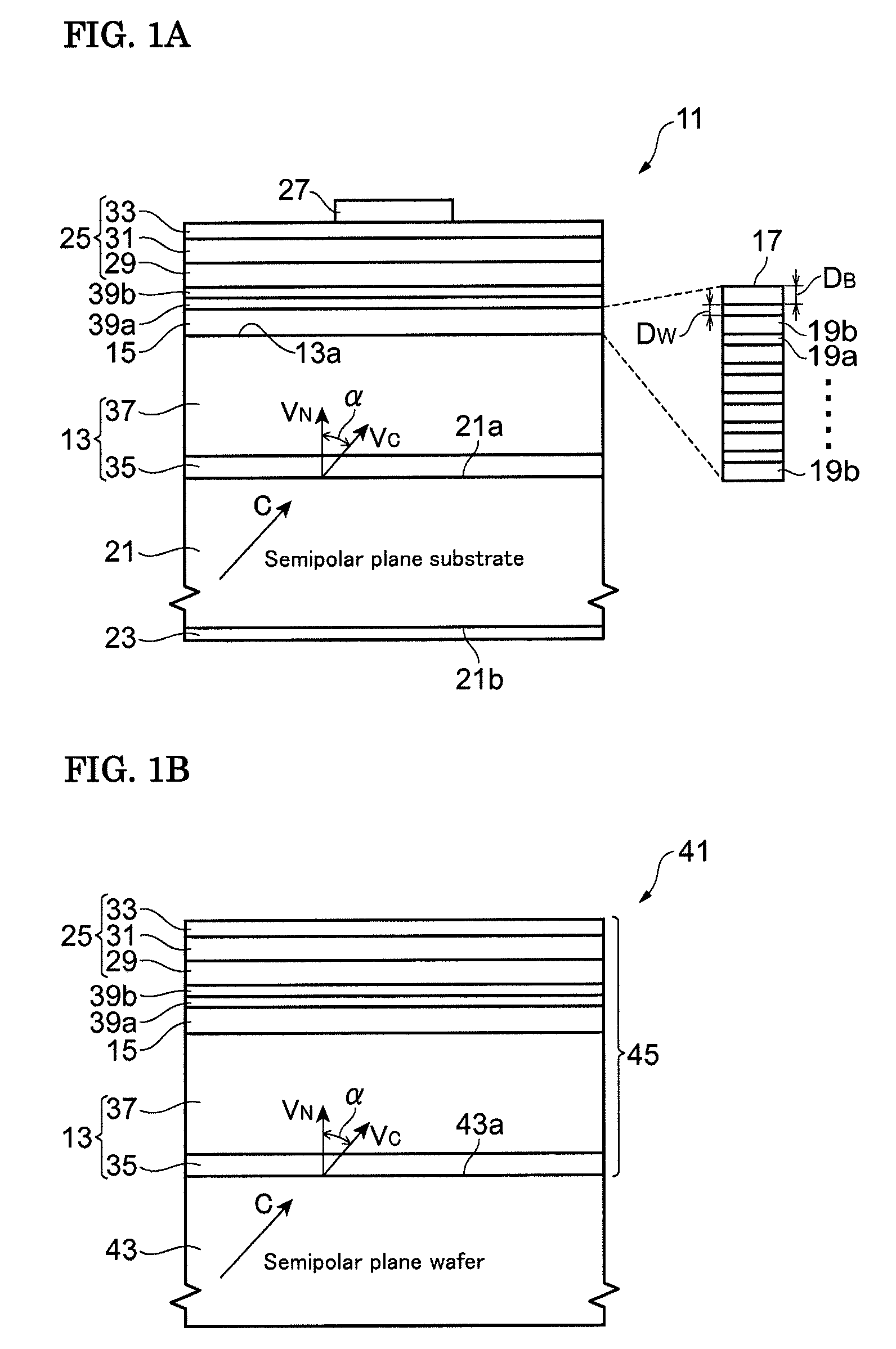

Group-III nitride light-emitting device

ActiveUS7968864B2Piezoelectric field is reducedLow efficiencyThyristorSolid-state devicesQuantum wellLength wave

A group-III nitride light-emitting device is provided. An active layer having a quantum well structure is grown on a basal plane of a gallium nitride based semiconductor region. The quantum well structure is formed in such a way as to have an emission peak wavelength of 410 nm or more. The thickness of a well layer is 4 nm or more, and 10 nm or less. The well layer is composed of InXGa1-XN (0.15≦X<1, where X is a strained composition). The basal plane of the gallium nitride based semiconductor region is inclined at an inclination angle within the range of 15 degrees or more, and 85 degrees or less with reference to a {0001} plane or a {000-1} plane of a hexagonal system group III nitride. The basal plane in this range is a semipolar plane.

Owner:SUMITOMO ELECTRIC IND LTD

Semiconductor bonding and layer transfer method

The present invention provides a method of coupling substrates together. The method includes providing first and second substrates and then coupling the first and second substrates together. One of the first and second substrates includes devices with an interconnect region positioned thereon and the other substrate carries a device structure.

Owner:BESANG

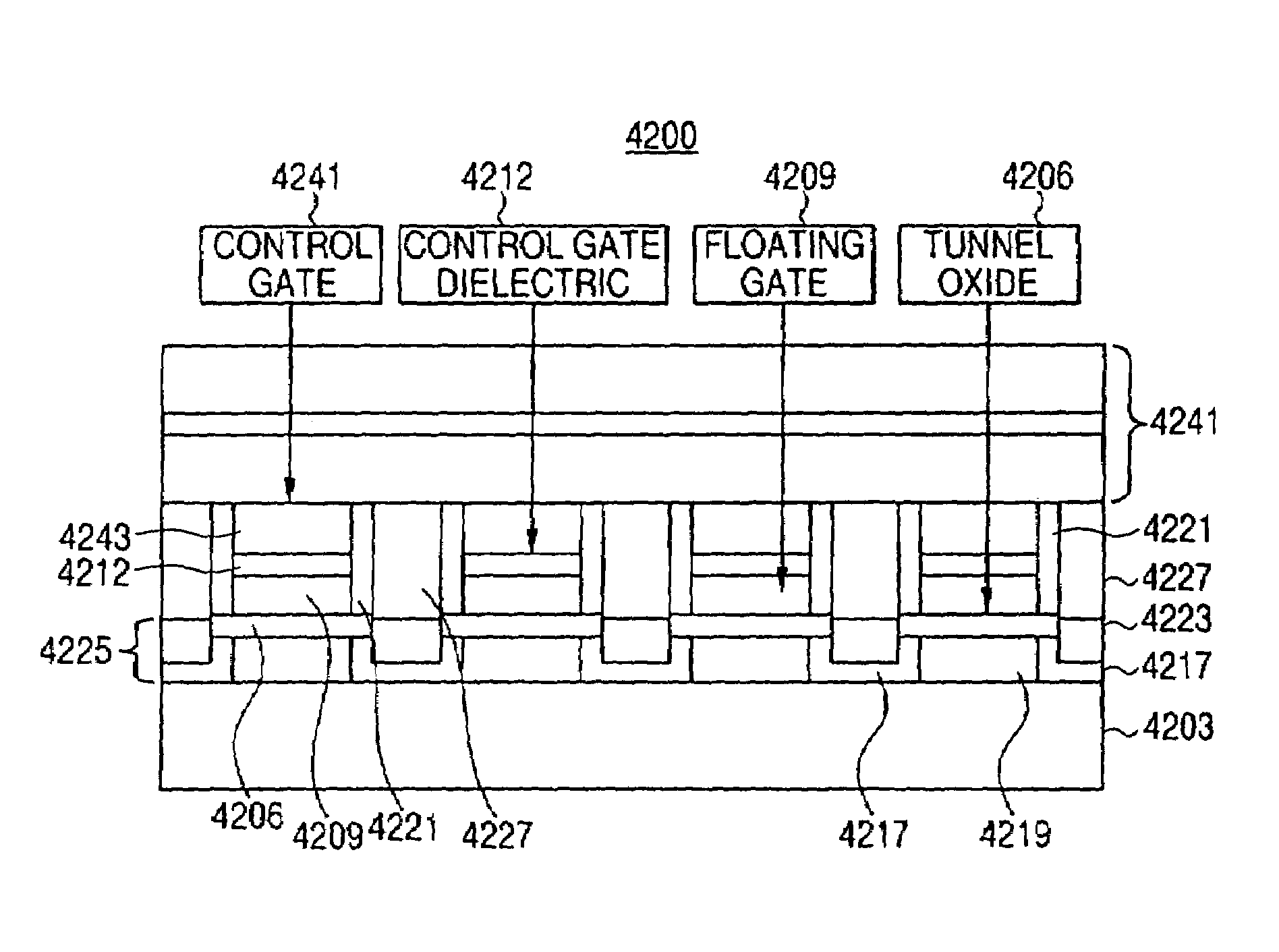

Dense arrays and charge storage devices

Owner:WODEN TECH INC

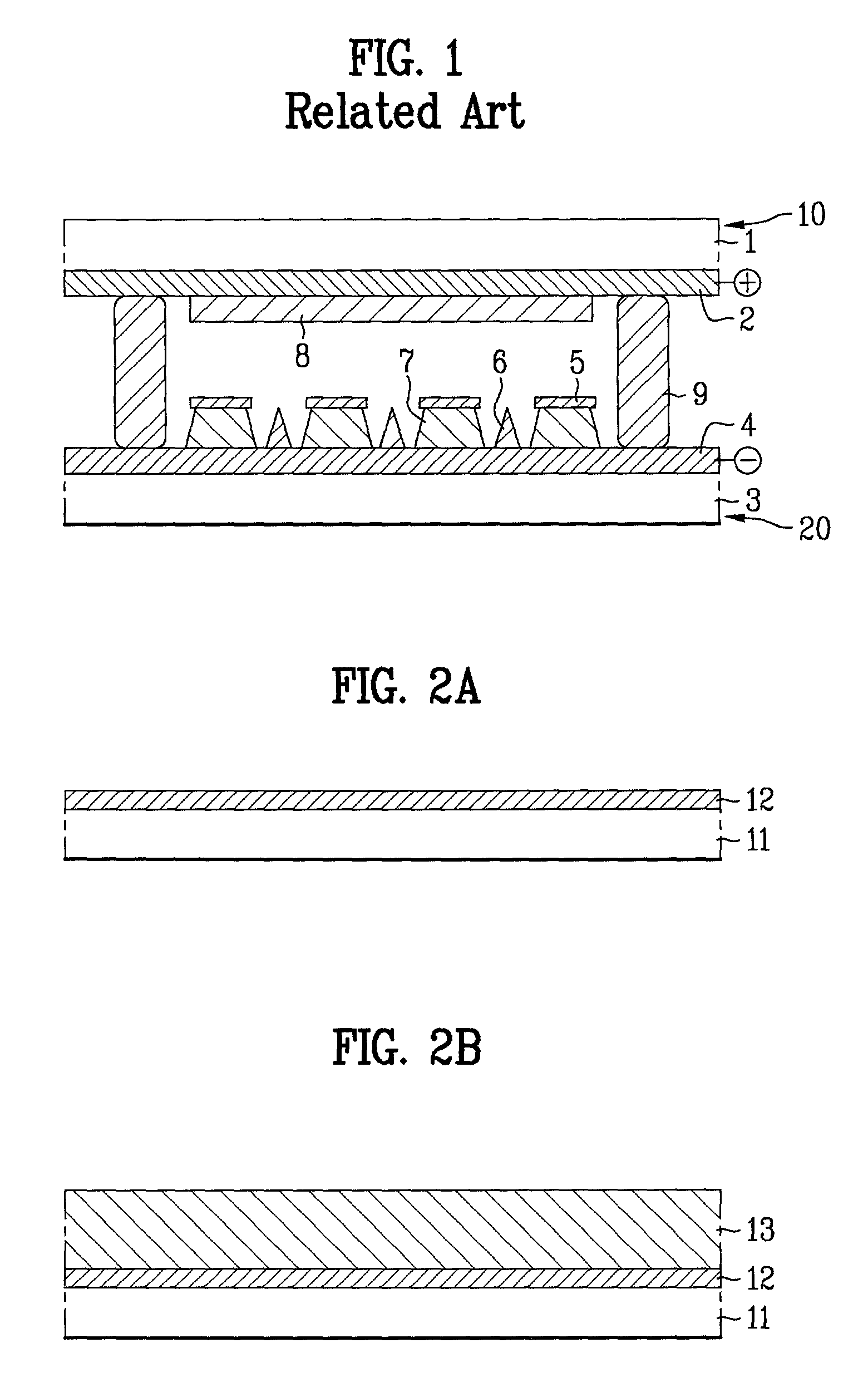

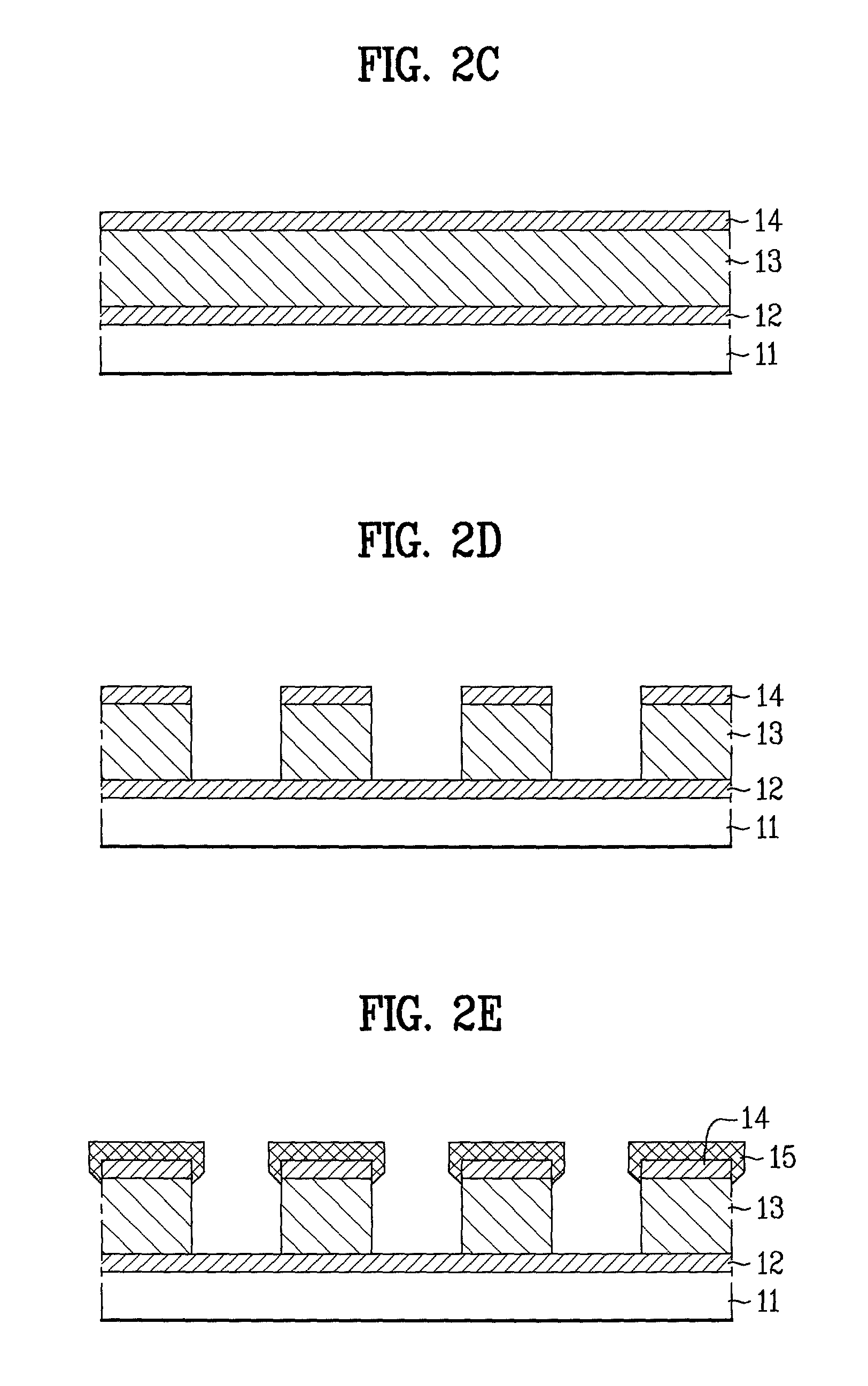

Field emission display and method for fabricating the same

InactiveUS20010004979A1Stable driving voltageUniform characteristicsMaterial nanotechnologyDecorative surface effectsLow voltageCarbon nanotube

Field emission display and method for fabricating the same, the field emission display including a cathode array having a cathode electrode formed on a substrate, insulating layers and carbon nanotube films for use as emitter electrodes formed alternately on the cathode electrode, and a gate electrode formed on the insulating layer, thereby permitting fabrication of a large sized cathode plate at a low cost because the film is formed by screen printing and exposure, which can reduce the cumbersome steps in fabrication of the related art Spindt emitter tip, and both a low voltage and a high voltage FEDs because the carbon nanotube film used as the emitter has a low work function, with an easy and stable electron emission capability.

Owner:LG ELECTRONICS INC

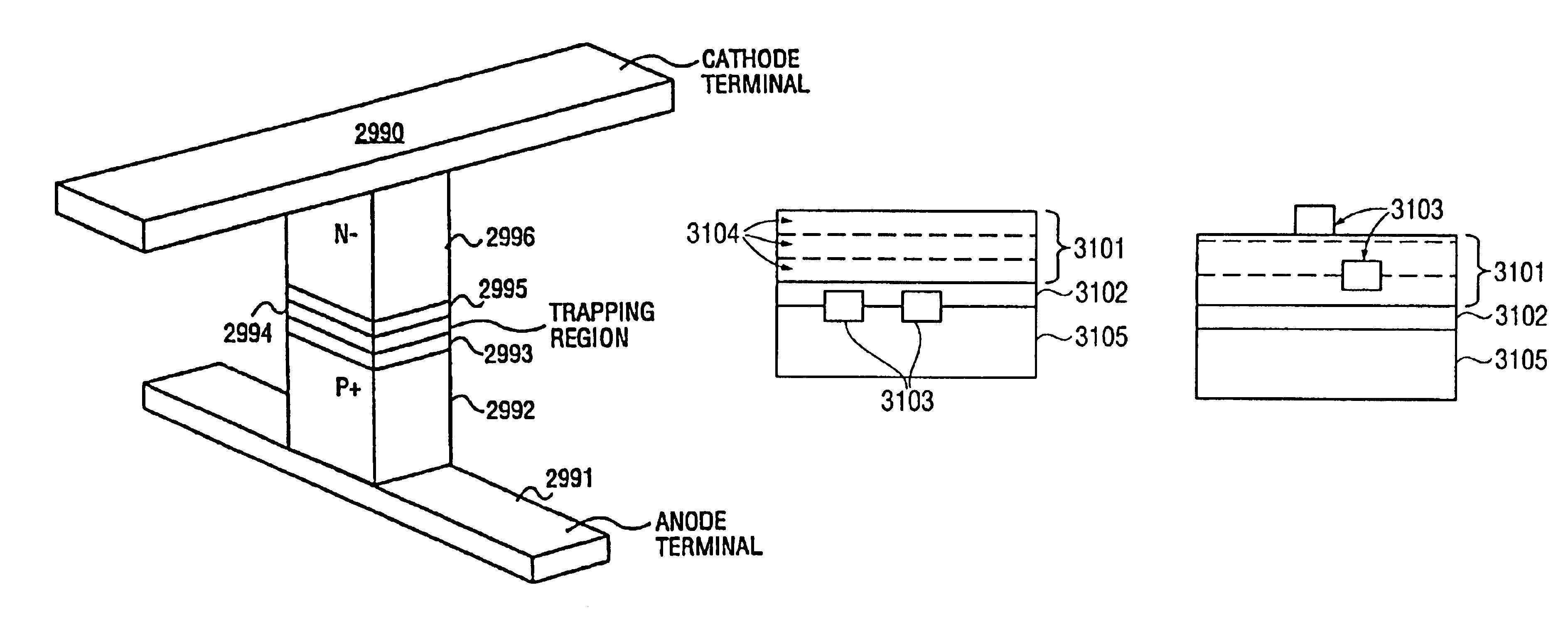

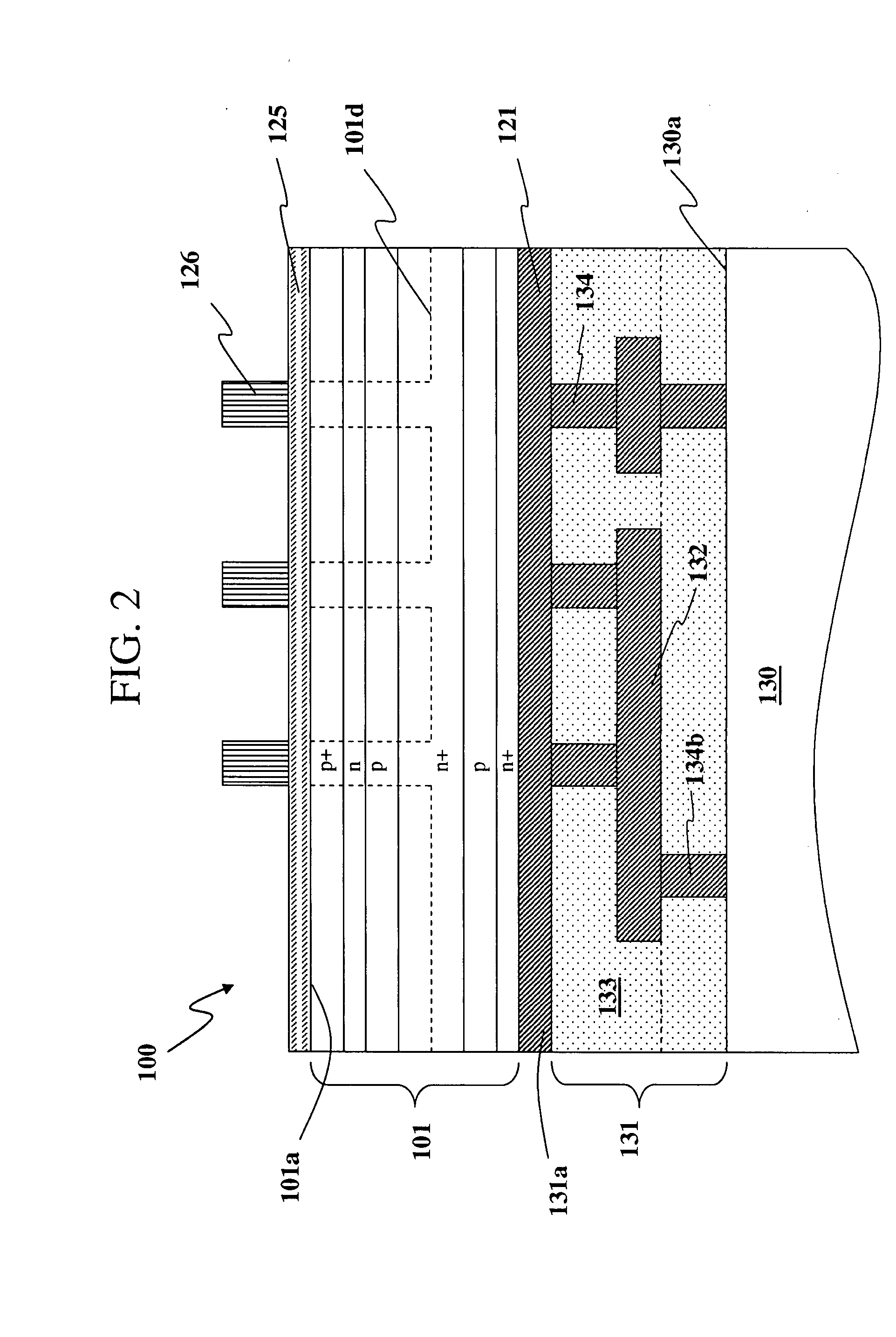

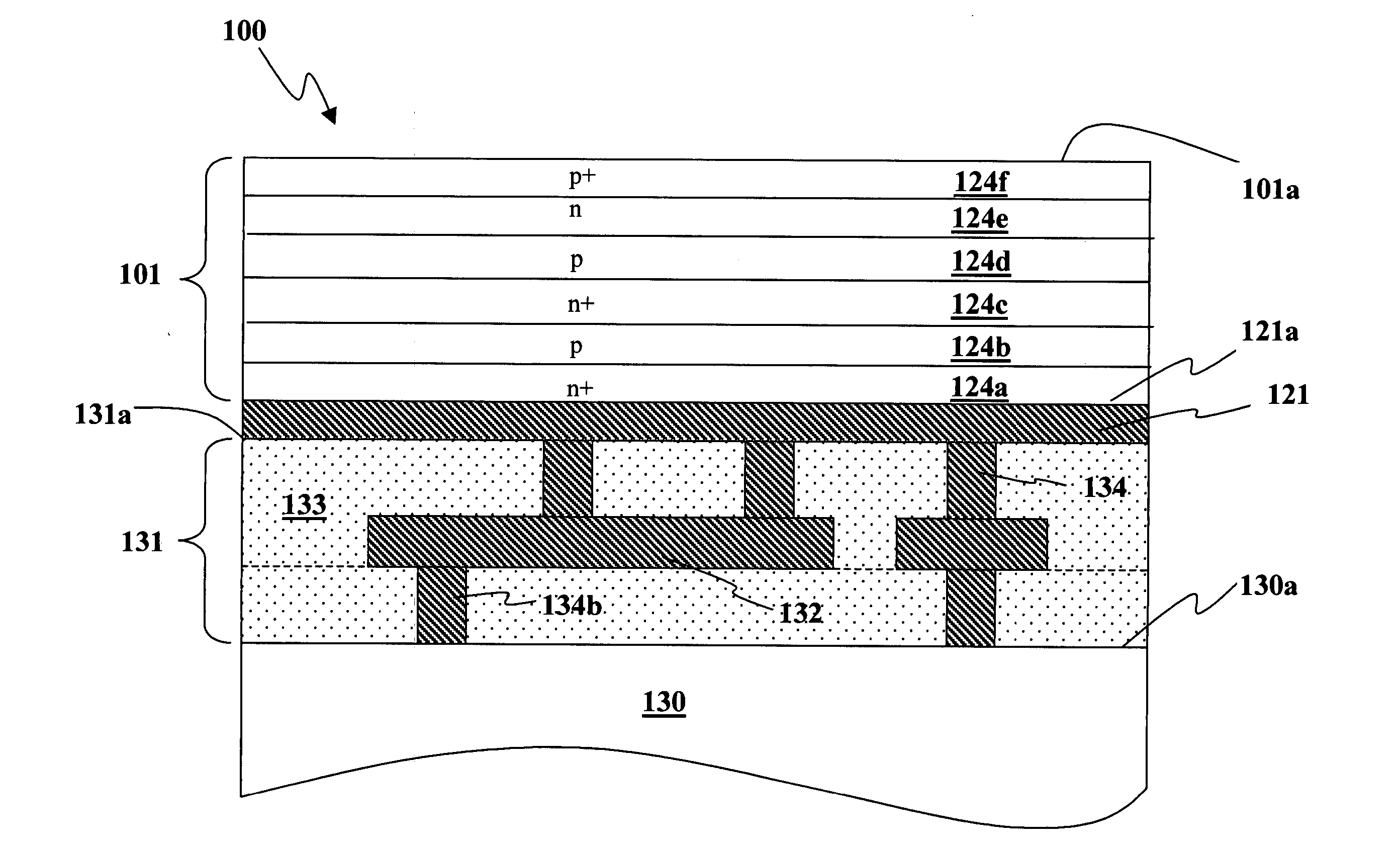

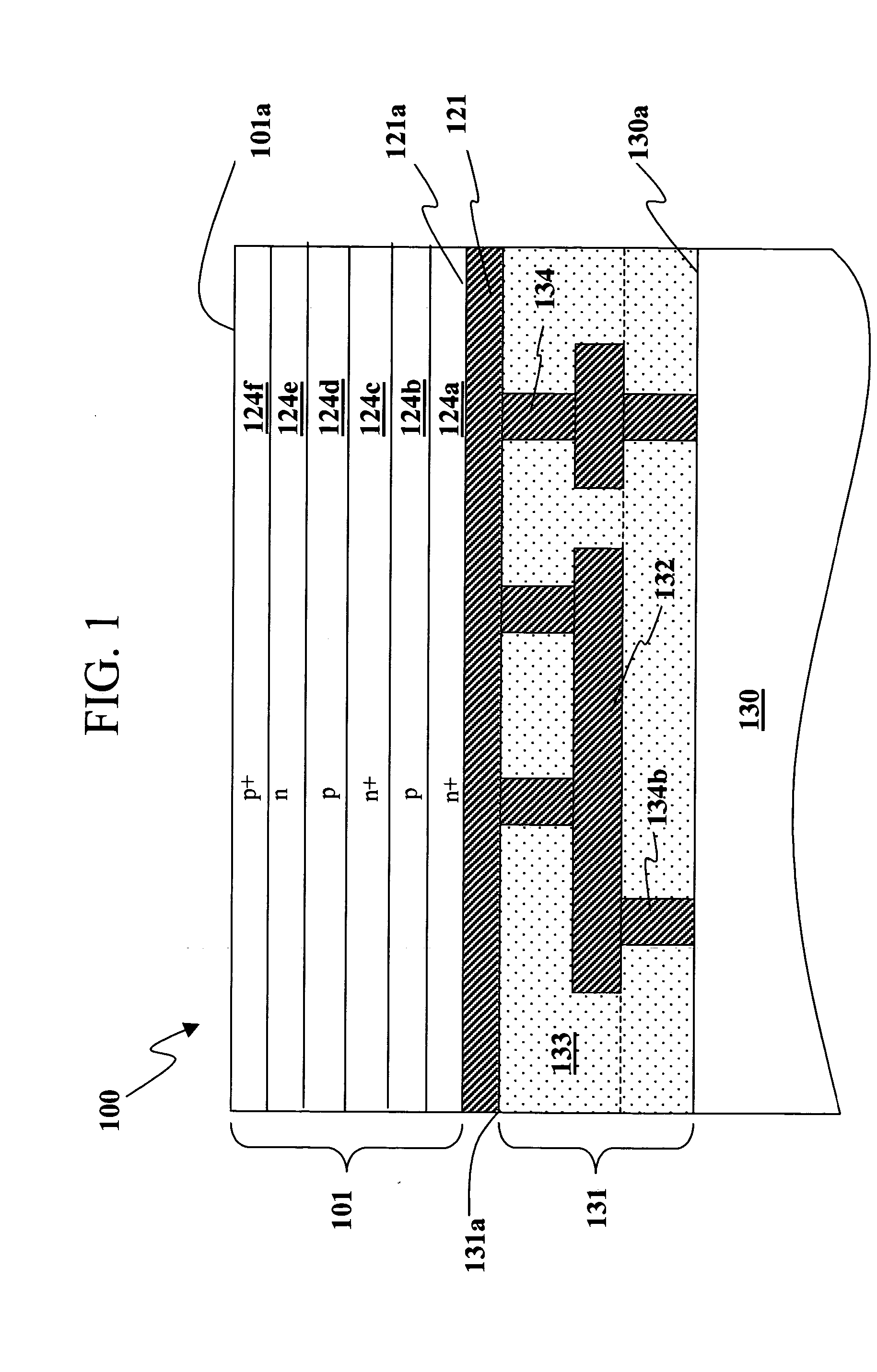

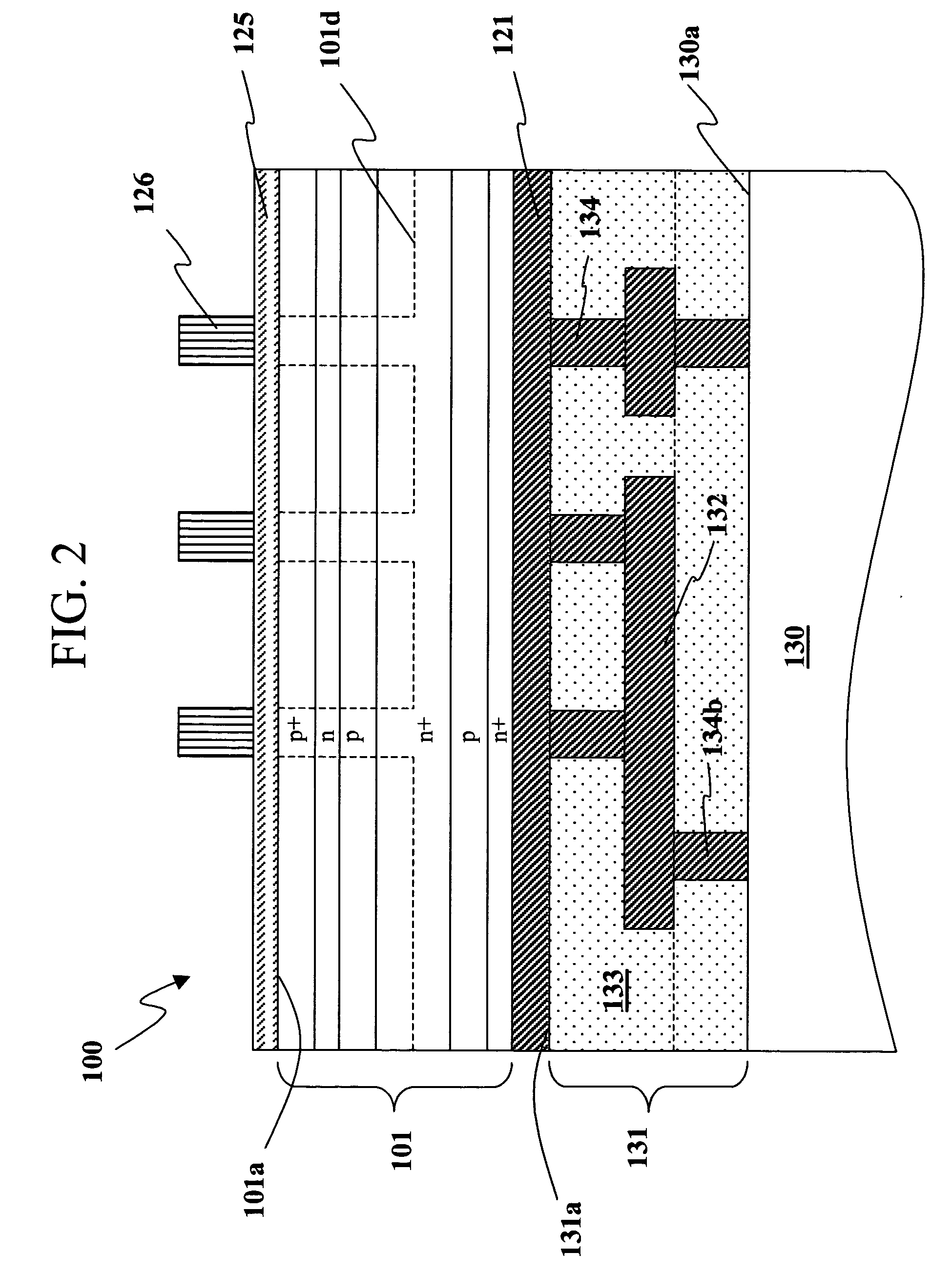

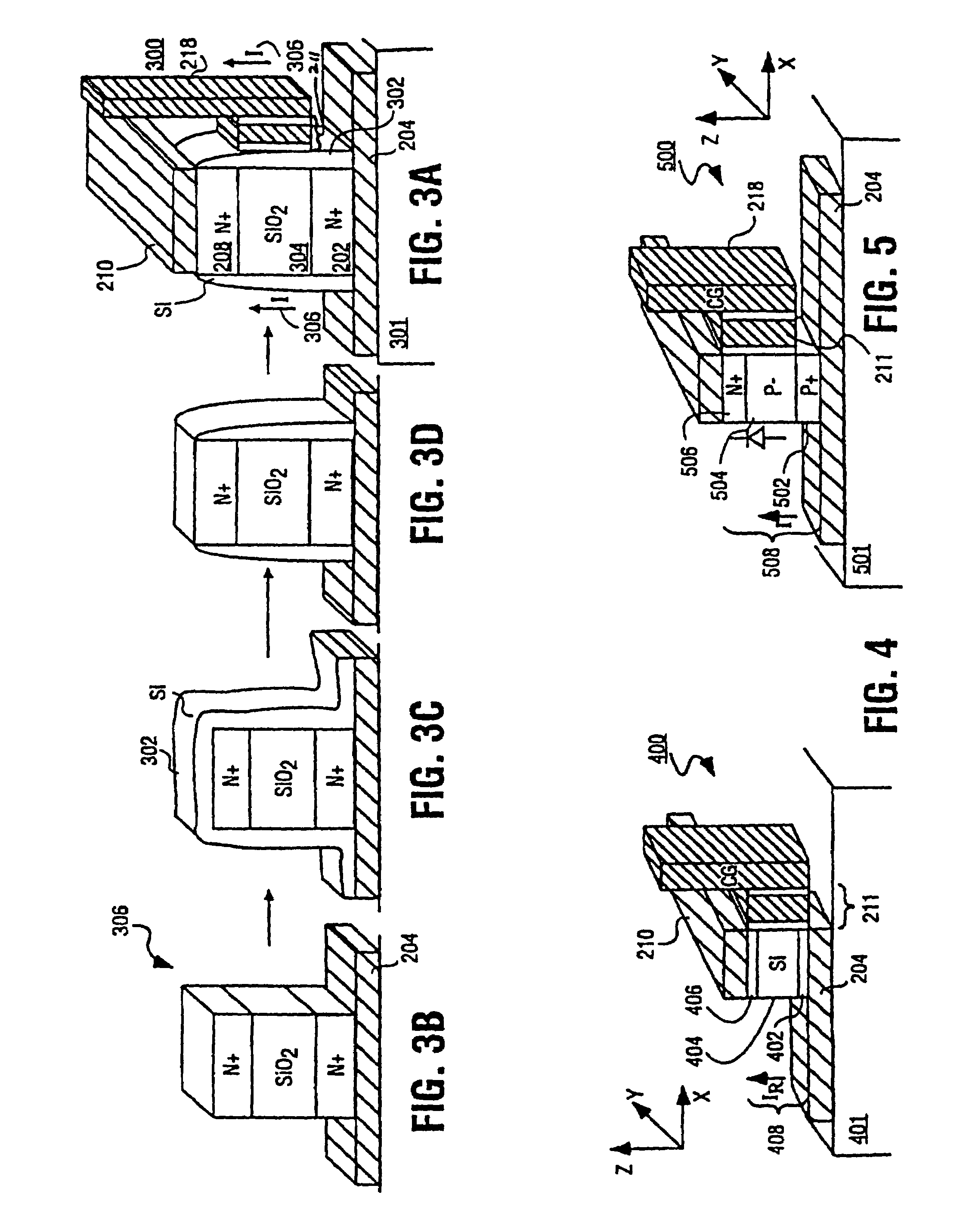

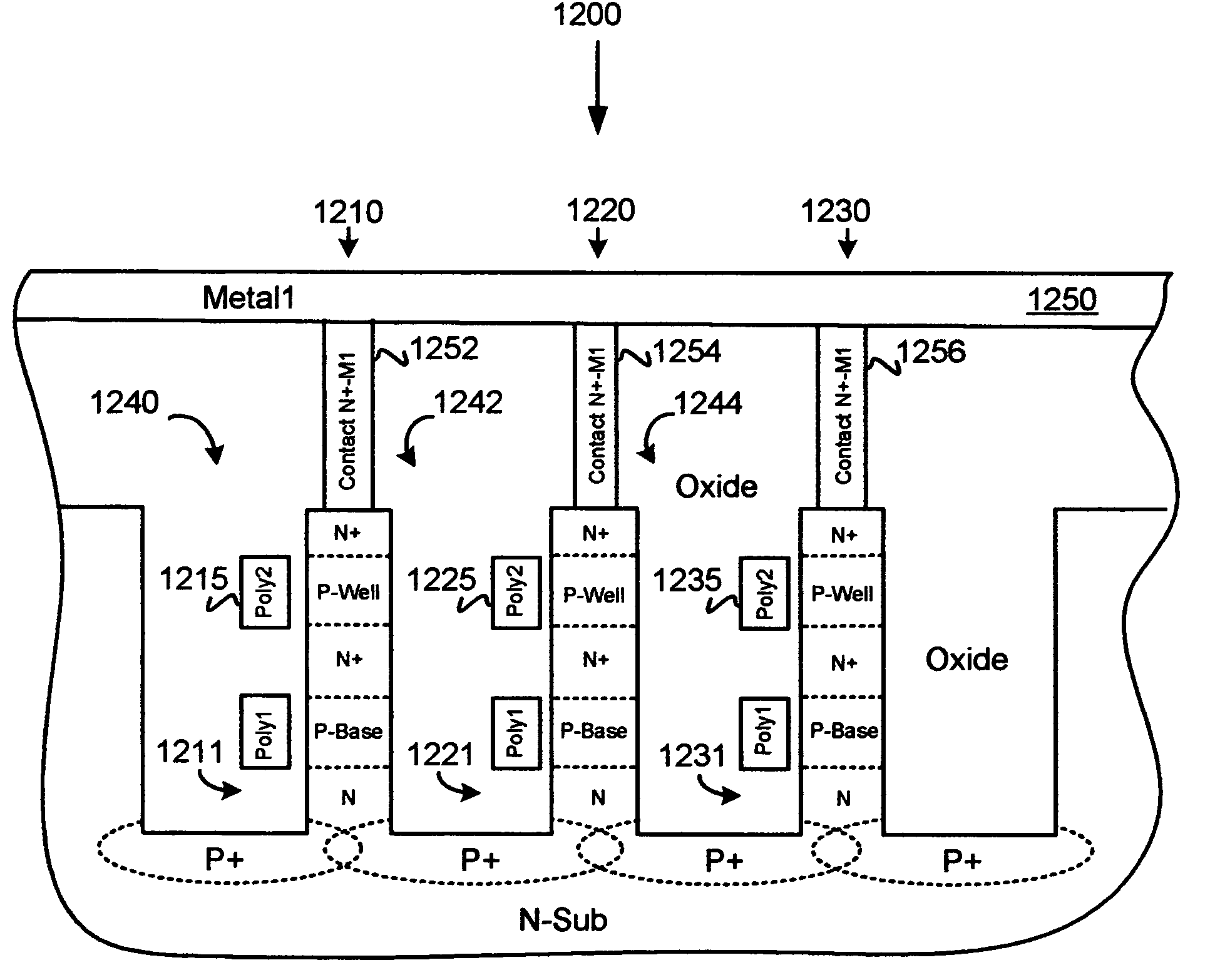

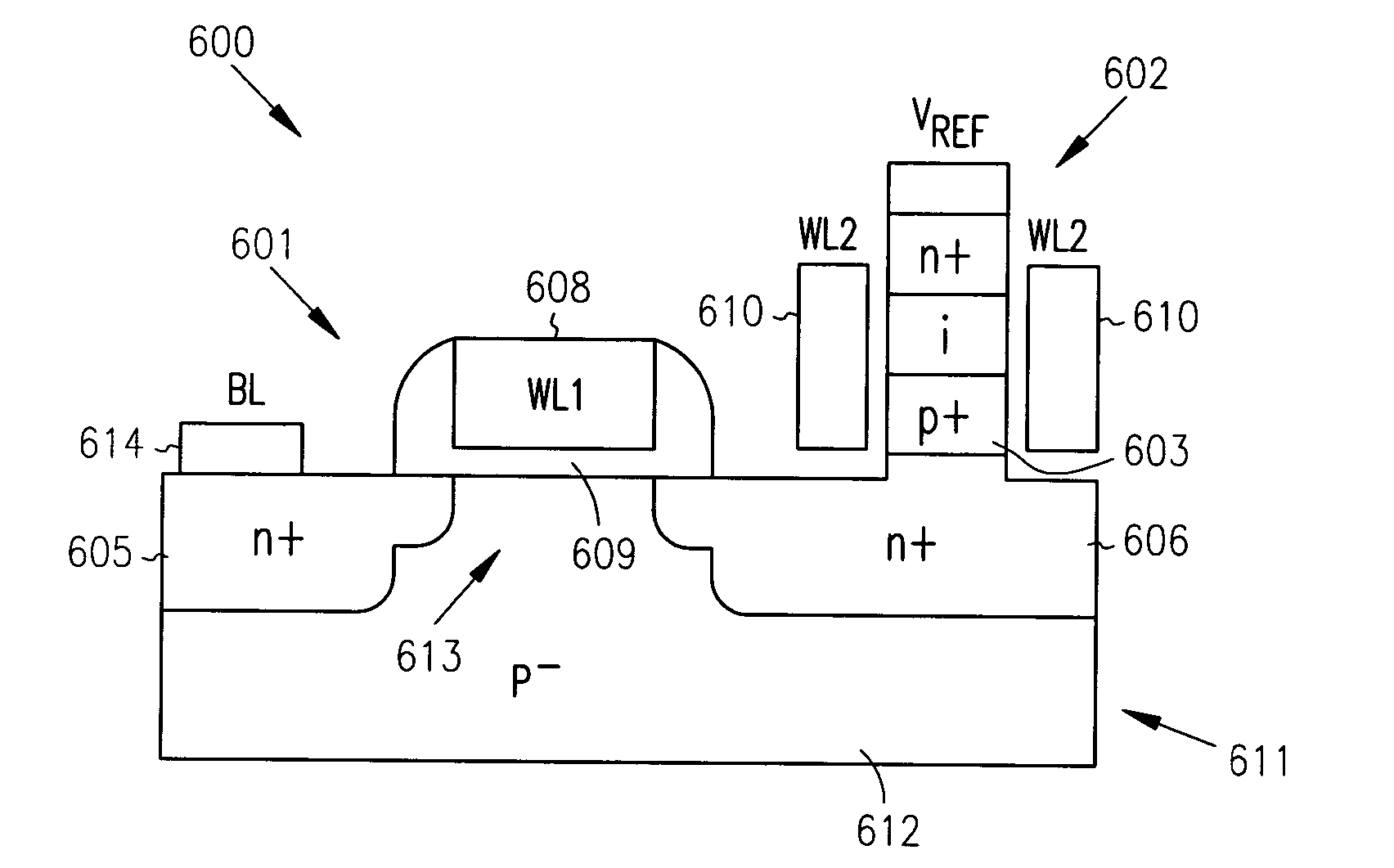

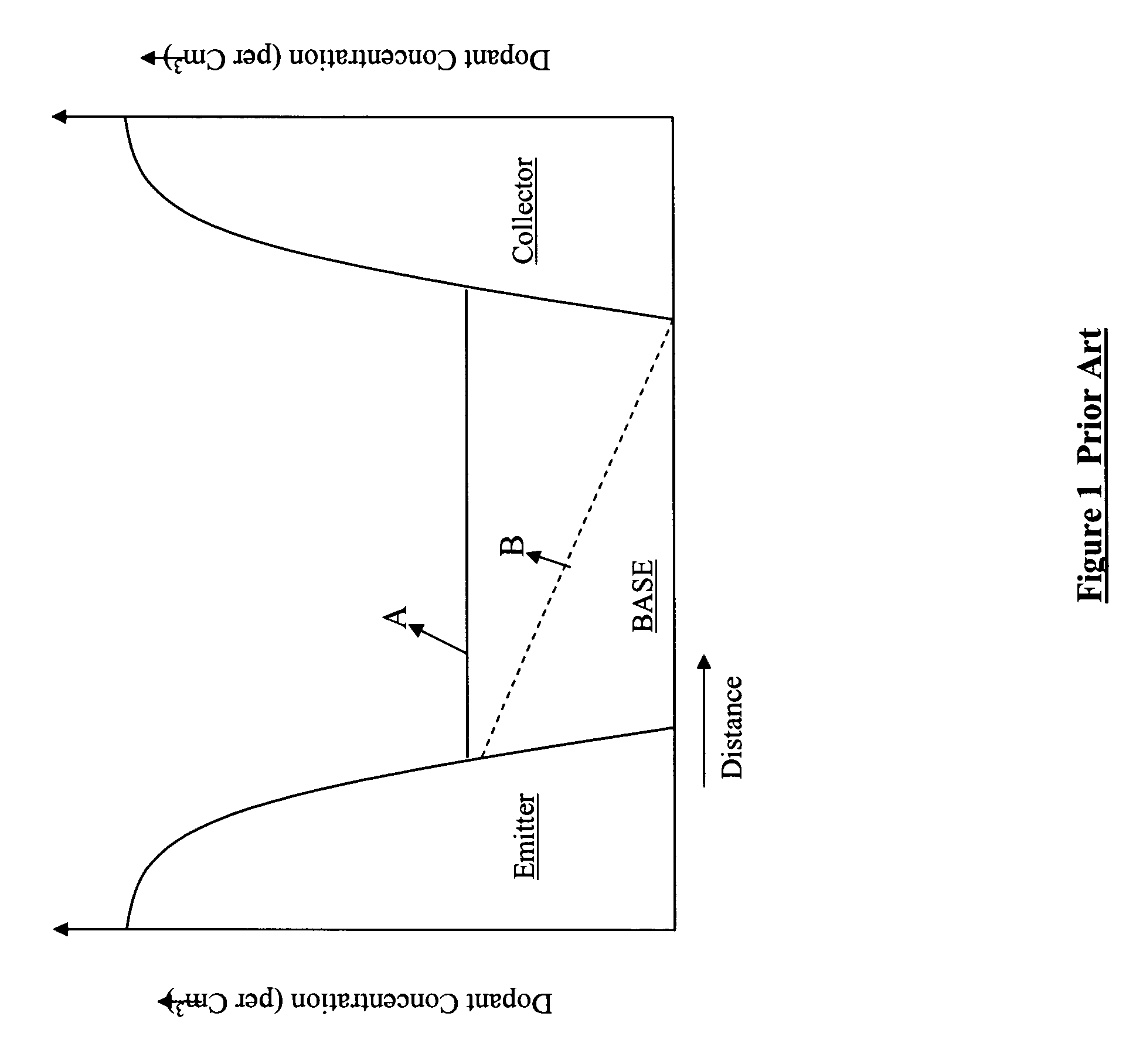

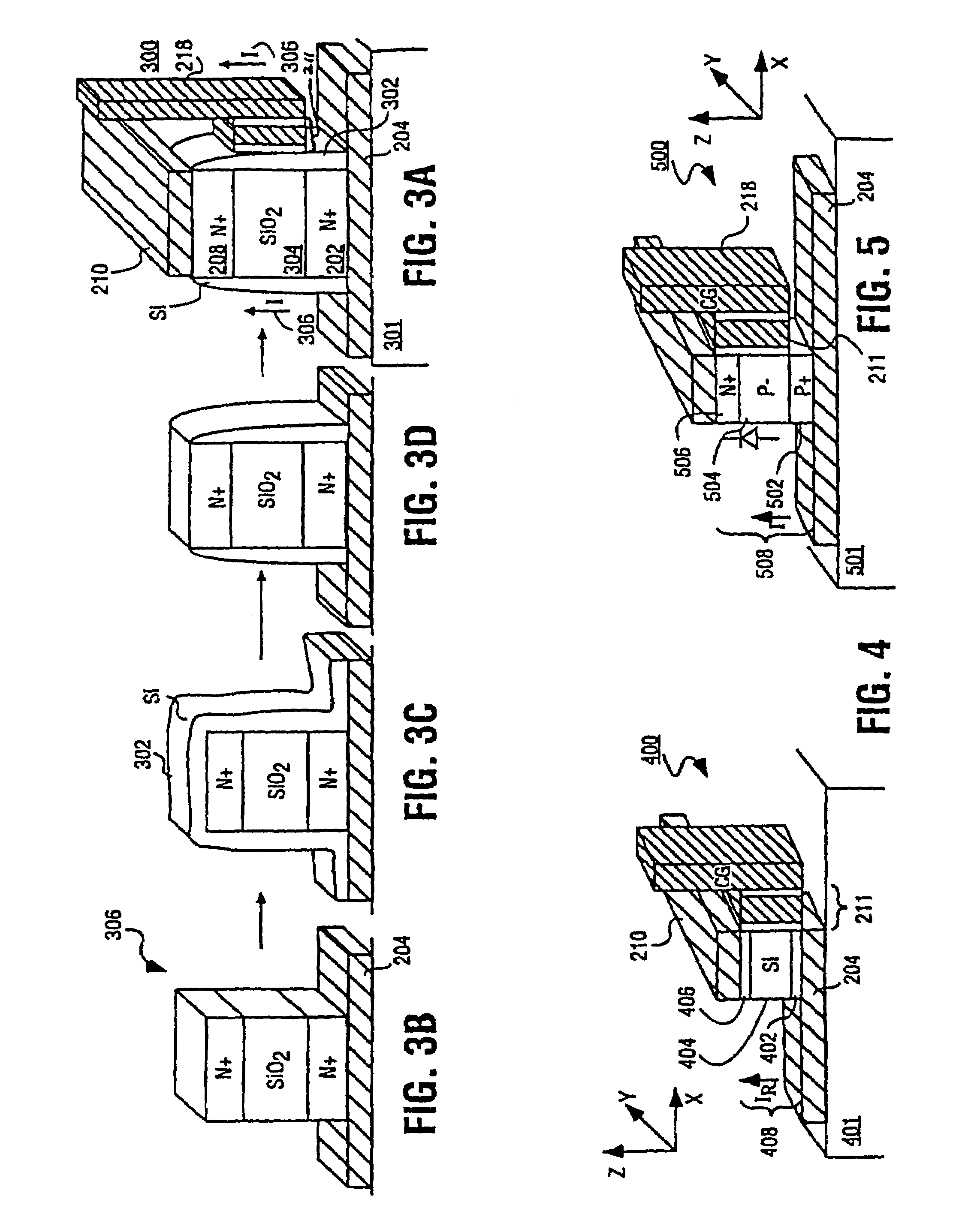

Vertical thyristor-based memory with trench isolation and its method of fabrication

InactiveUS7456439B1Avoid excessive distanceThyristorSolid-state devicesSemiconductor materialsDevice material

A semiconductor device may comprise a plurality of memory cells. A memory cell may comprise a thyristor, at least a portion of which is formed in a pillar of semiconductor material. The pillar may comprise sidewalls defining a cylindrical circumference of a first diameter. In a particular embodiment, the pillars associated with the plurality of memory cells may define rows and columns of an array. In a further embodiment, a pillar may be spaced by a first distance of magnitude up to the first diameter relative to a neighboring pillar within its row. In an additional further embodiment, the pillar may be spaced by a second distance of a magnitude up to twice the first diameter, relative to a neighboring pillar within its column.

Owner:T RAM ASSIGNMENT FOR THE BENEFIT OF CREDITORS LLC +1

Dynamic schottky barrier MOSFET device and method of manufacture

InactiveUS20050139860A1ThyristorSemiconductor/solid-state device manufacturingMOSFETSchottky barrier

A device for regulating a flow of electric current and its manufacturing method are provided. The device includes metal-insulator-semiconductor source-drain contacts forming Schottky barrier or Schottky-like junctions to the semiconductor substrate. The device includes an interfacial layer between the semiconductor substrate and a metal source and / or drain electrode, thereby dynamically adjusting a Schottky barrier height by applying different bias conditions. The dynamic Schottky barrier modulation provides increased electric current for low drain bias conditions, reducing the sub-linear turn-on characteristic of Schottky barrier MOSFET devices and improving device performance.

Owner:SPINNAKER SEMICON

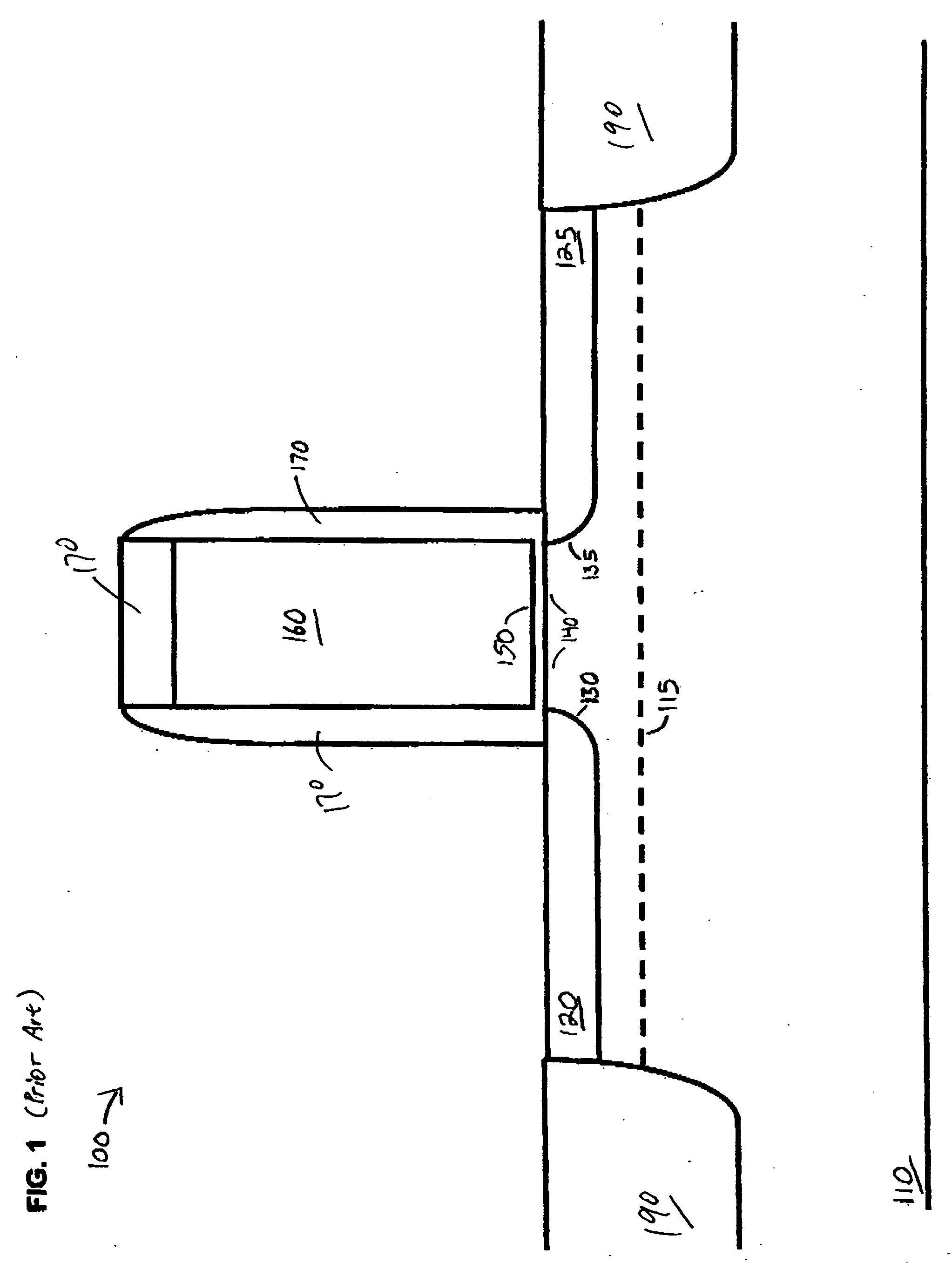

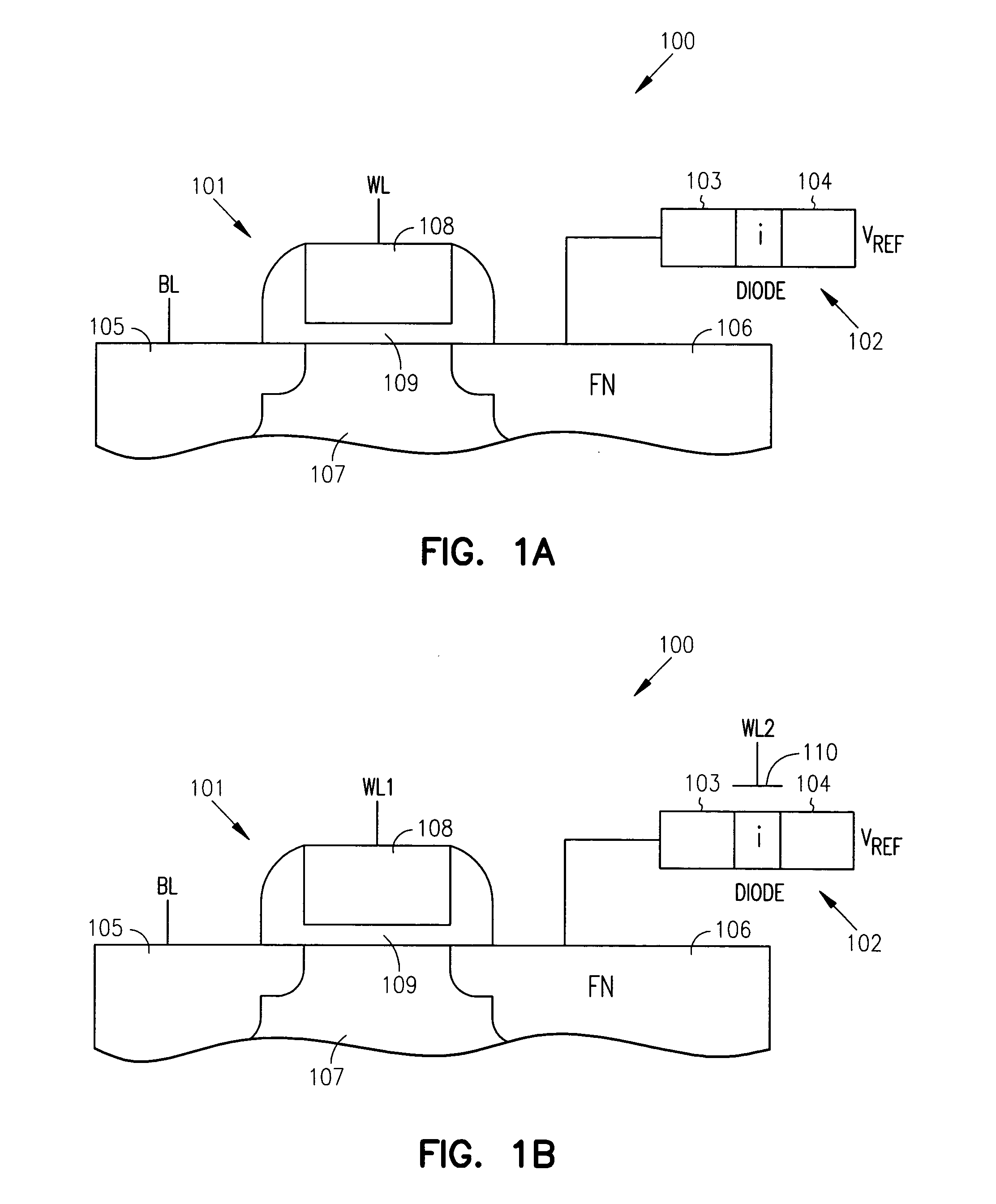

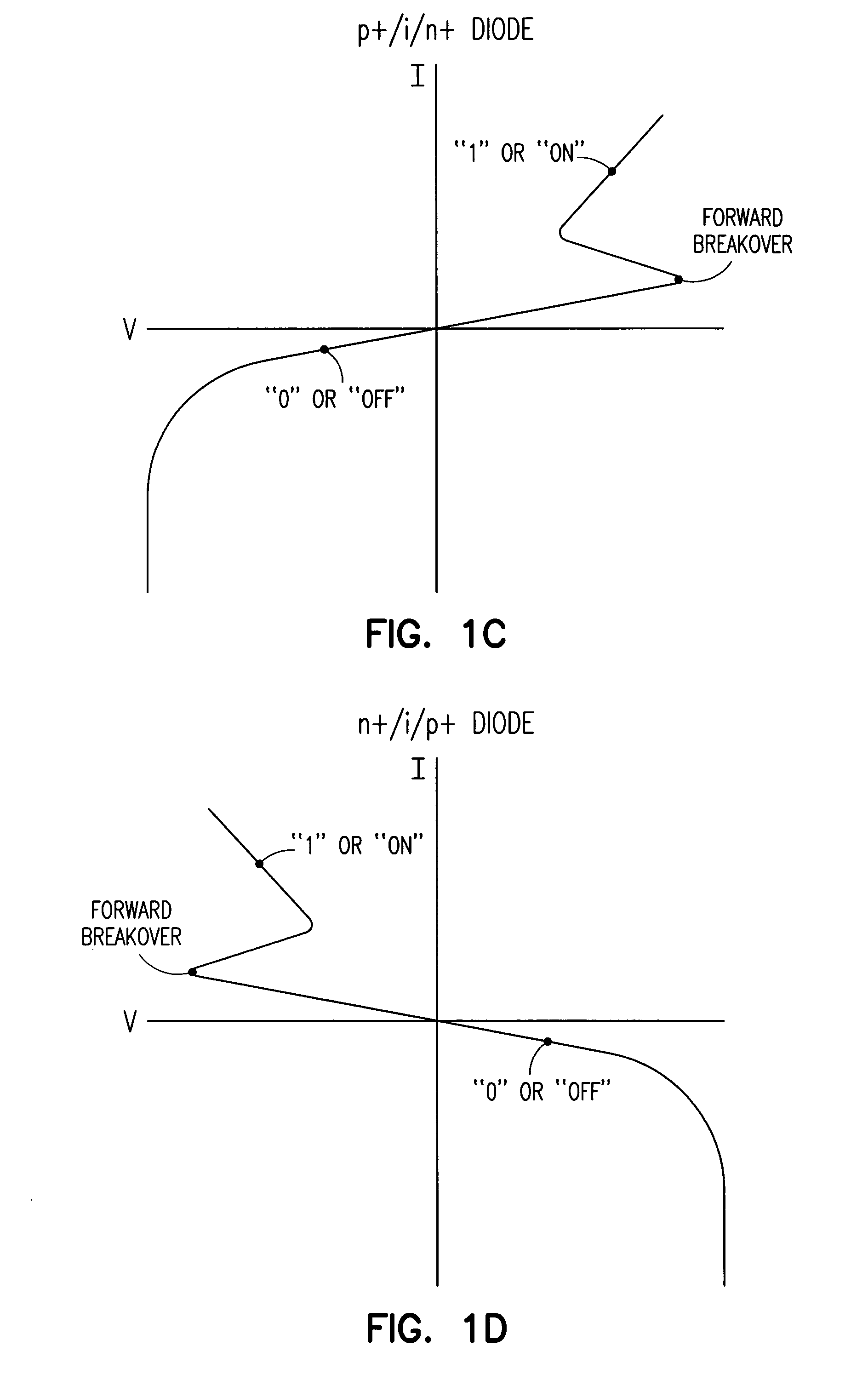

High-performance one-transistor memory cell

ActiveUS20050001232A1Reduce standby powerAddressing slow performanceTransistorThyristorCharge retentionSemiconductor

One aspect of this disclosure relates to a memory cell. In various embodiments, the memory cell includes an access transistor having a floating node, and a diode connected between the floating node and a diode reference potential line. The diode includes an anode, a cathode, and an intrinsic region between the anode and the cathode. A charge representative of a memory state of the memory cell is held across the intrinsic region of the diode. In various embodiments, the memory cell is implemented in bulk semiconductor technology. In various embodiments, the memory cell is implemented in semiconductor-on-insulator technology. In various embodiments, the diode is gate-controlled. In various embodiments, the diode is charge enhanced by an intentionally generated charge in a floating body of an SOI access transistor. Various embodiments include laterally-oriented diodes (stacked and planar configurations), and various embodiments include vertically-oriented diodes. Other aspects and embodiments are provided herein.

Owner:MICRON TECH INC

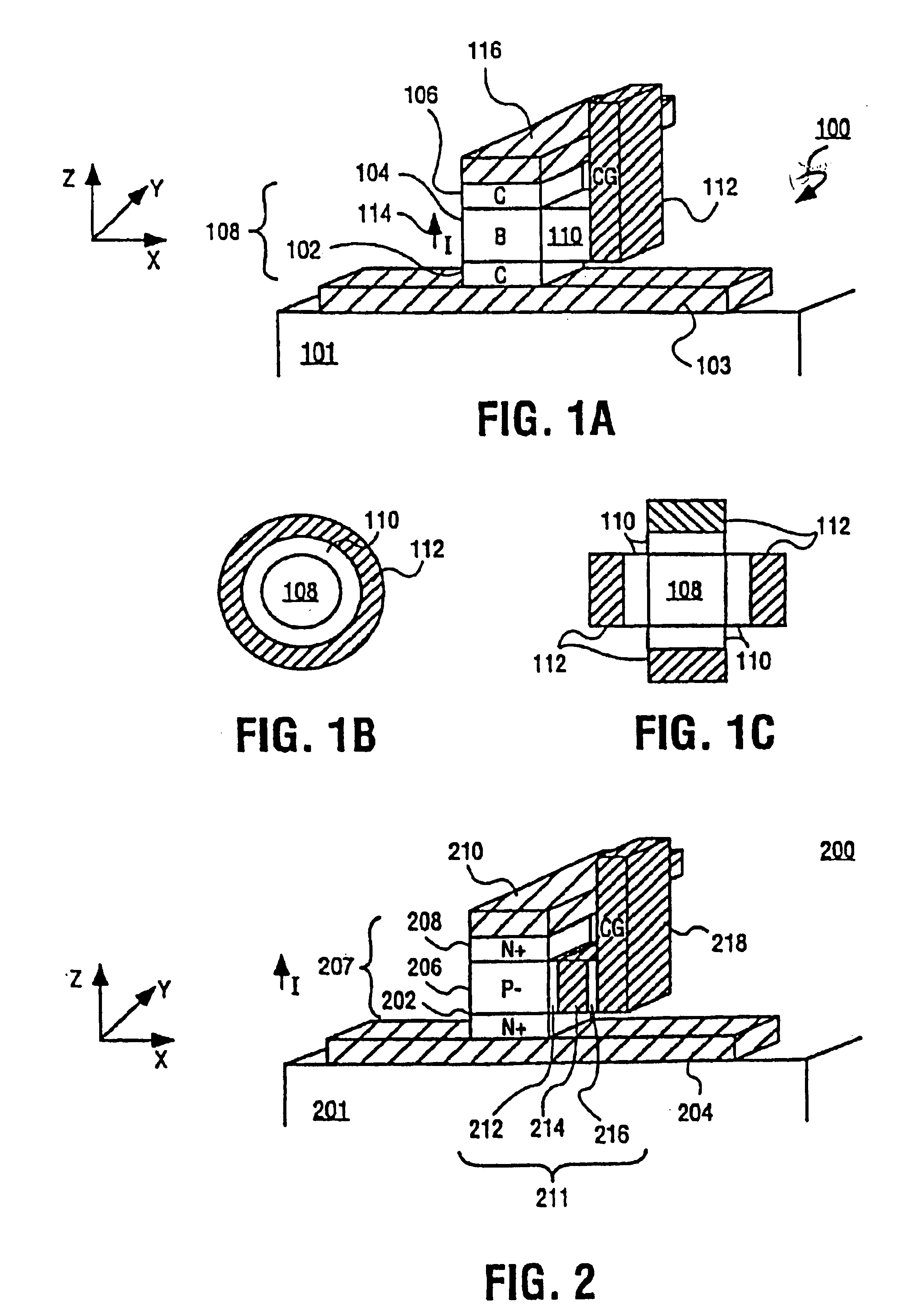

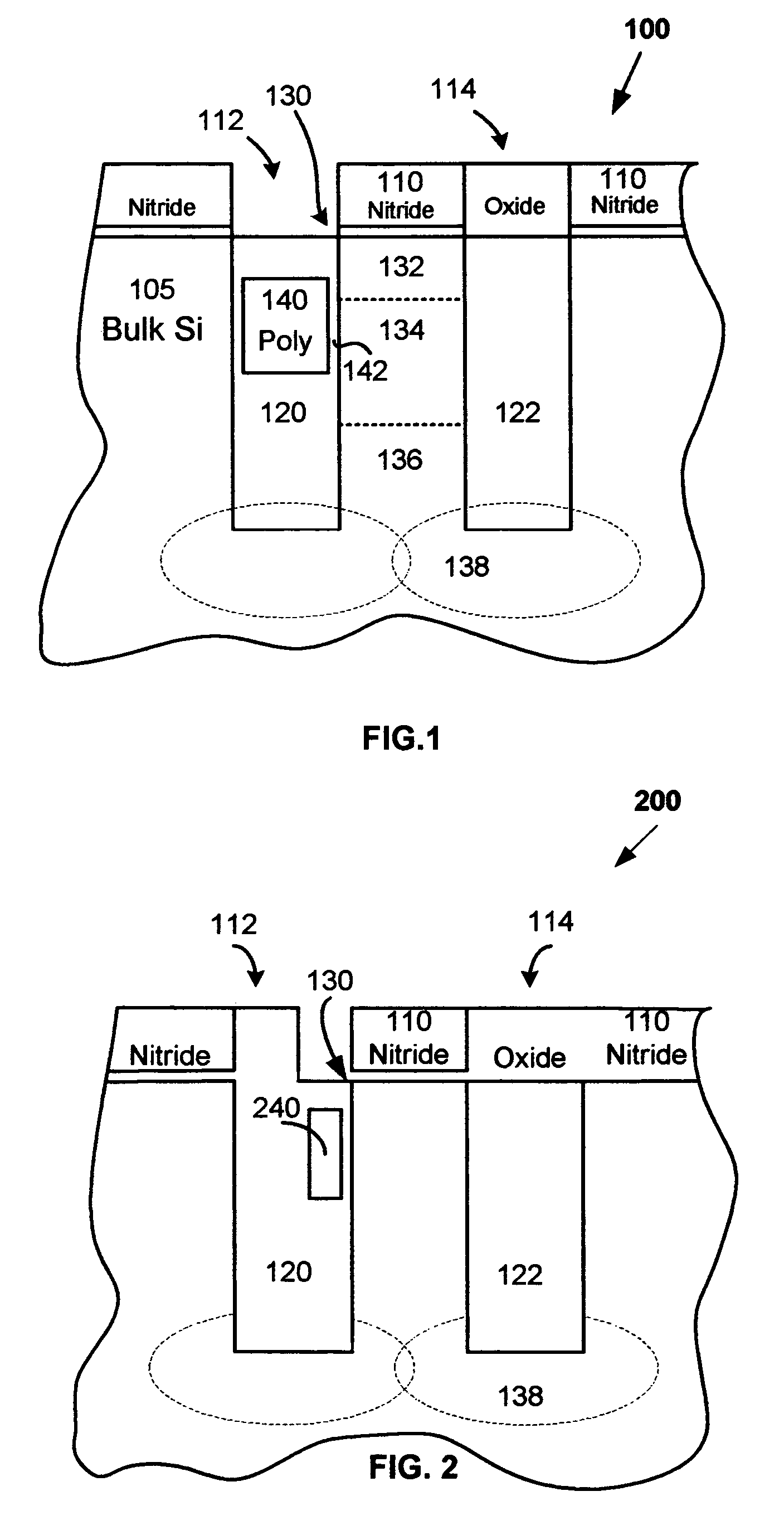

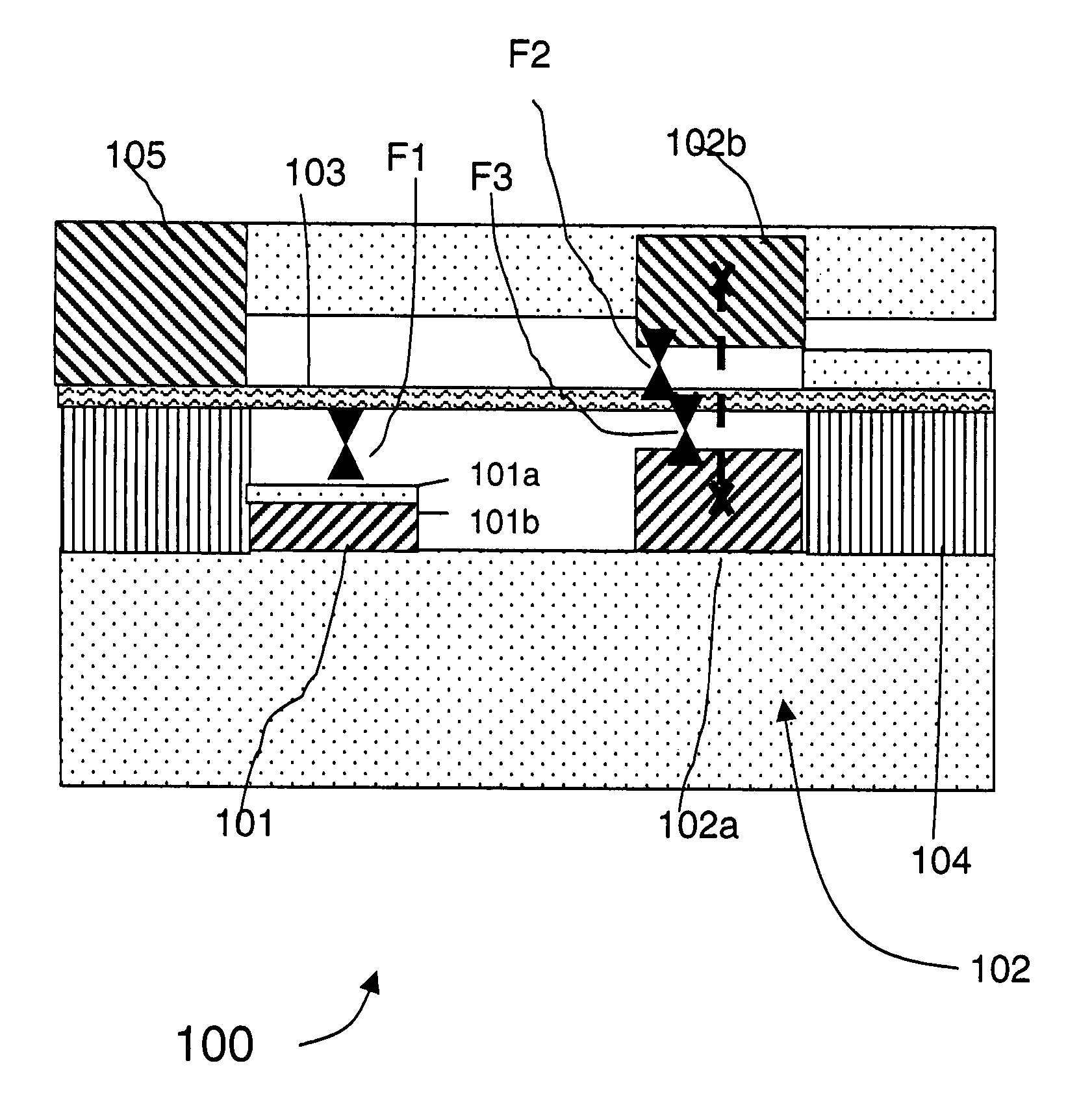

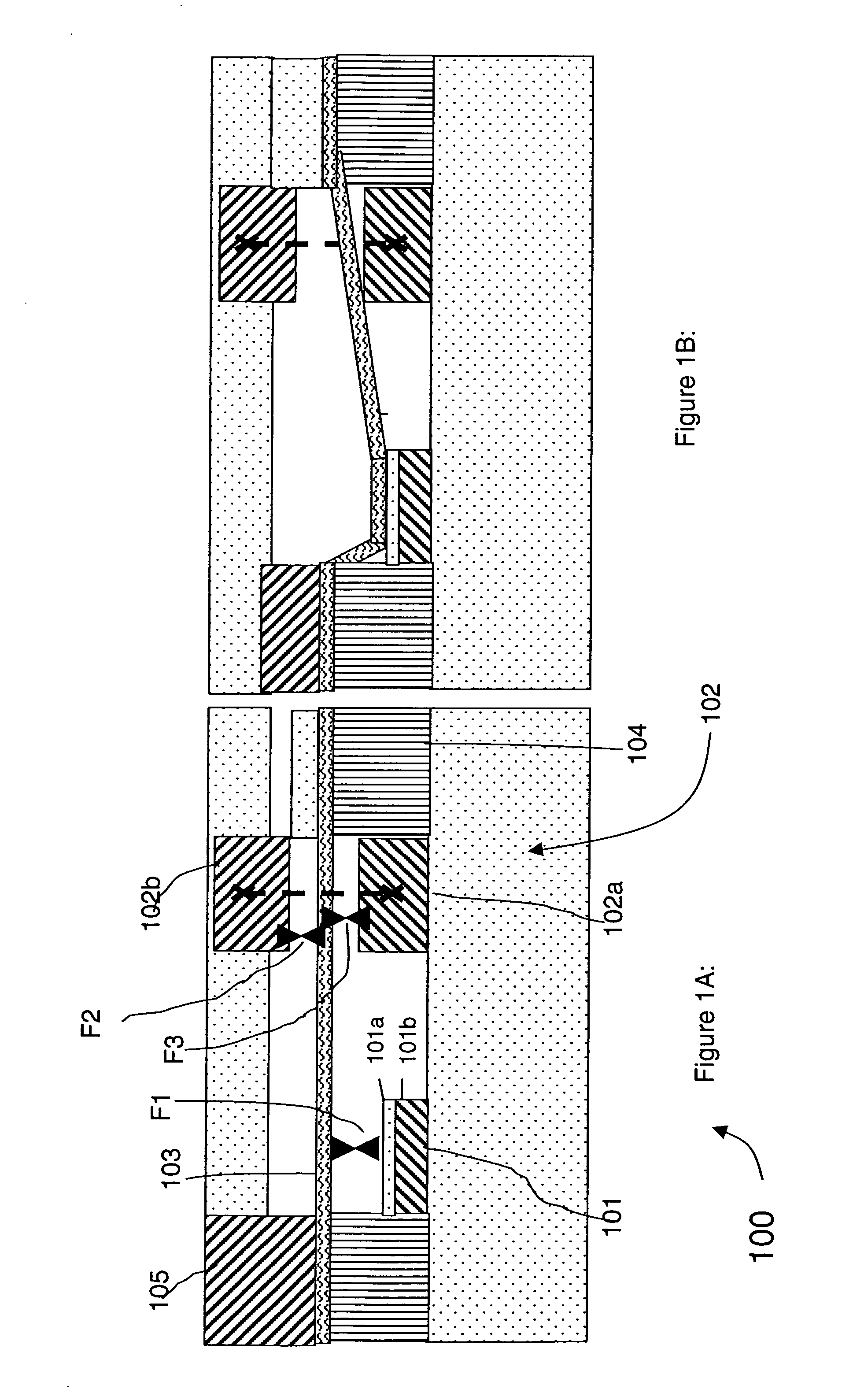

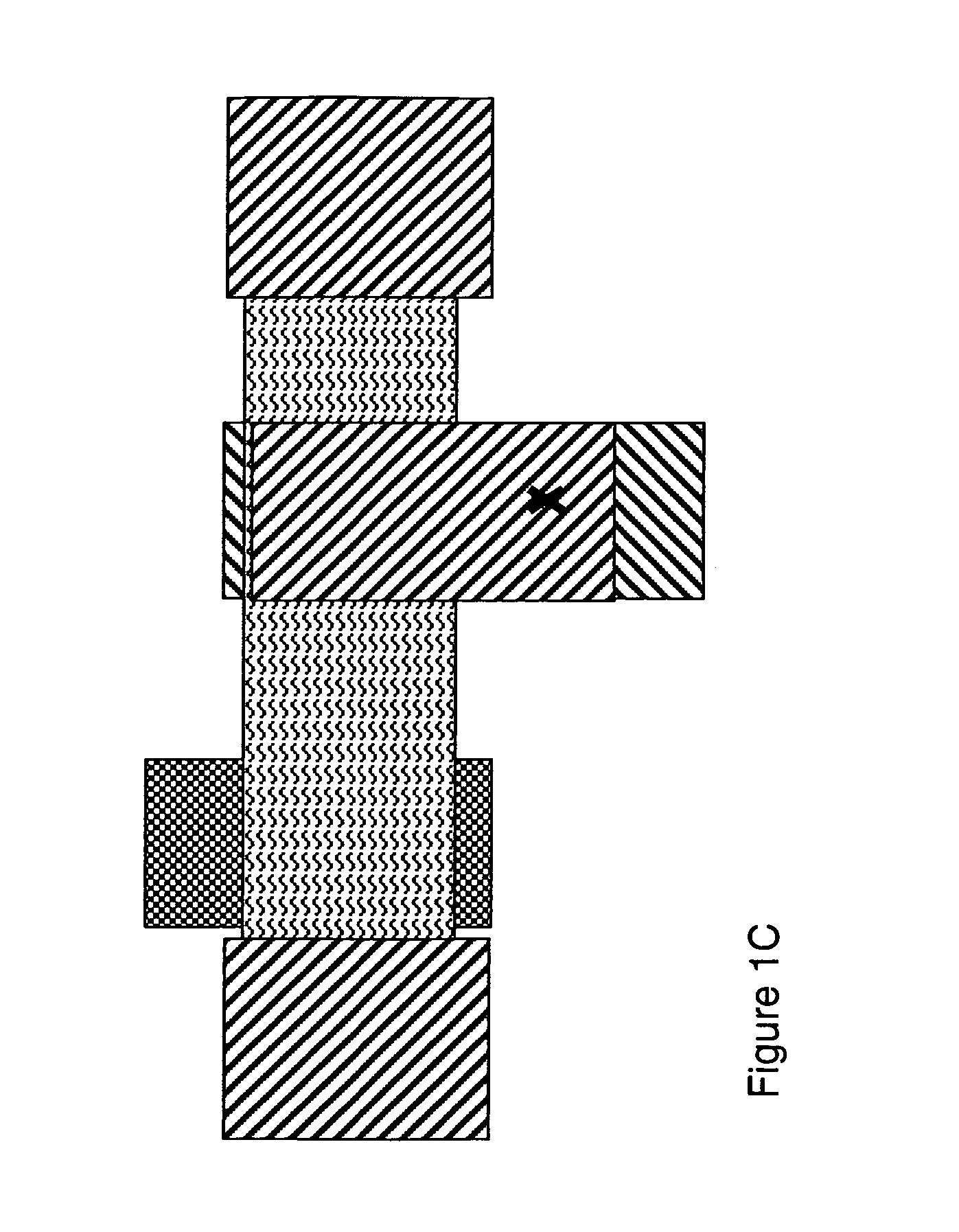

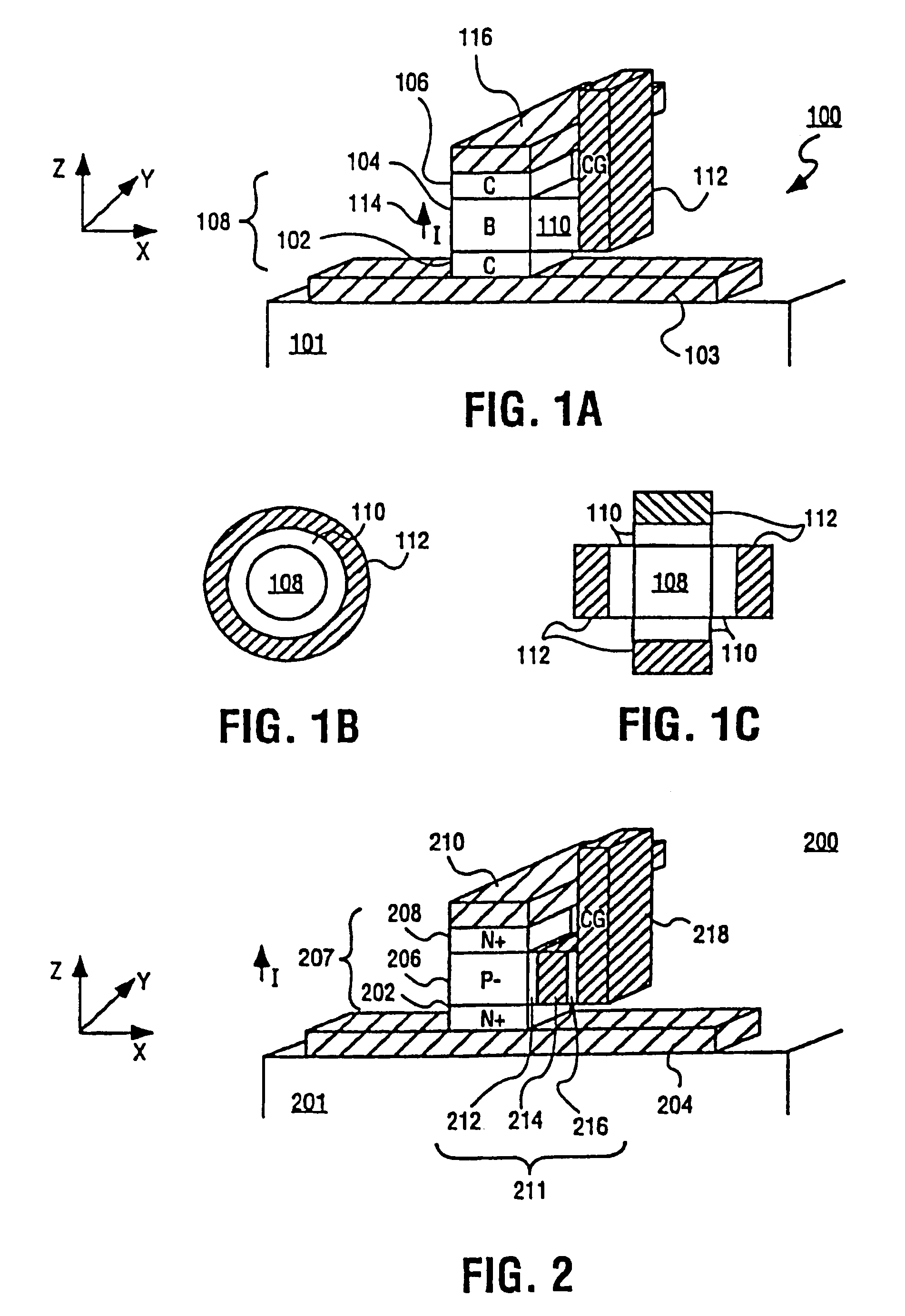

Semiconductor diode with reduced leakage

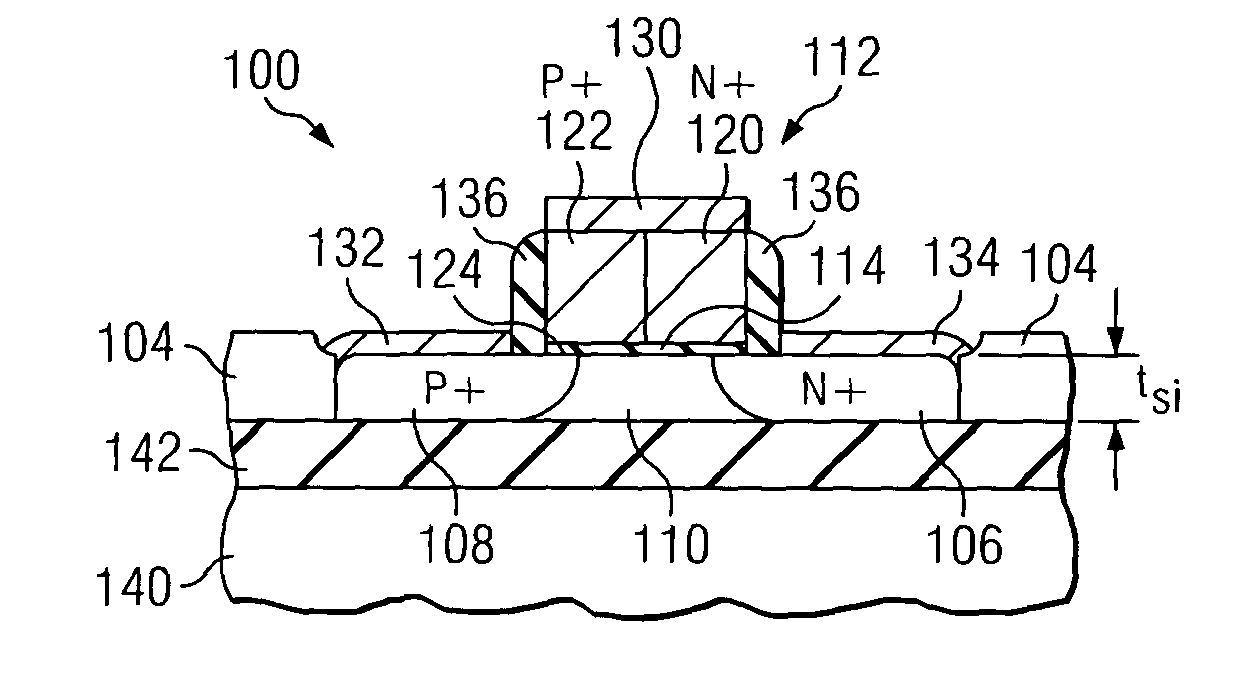

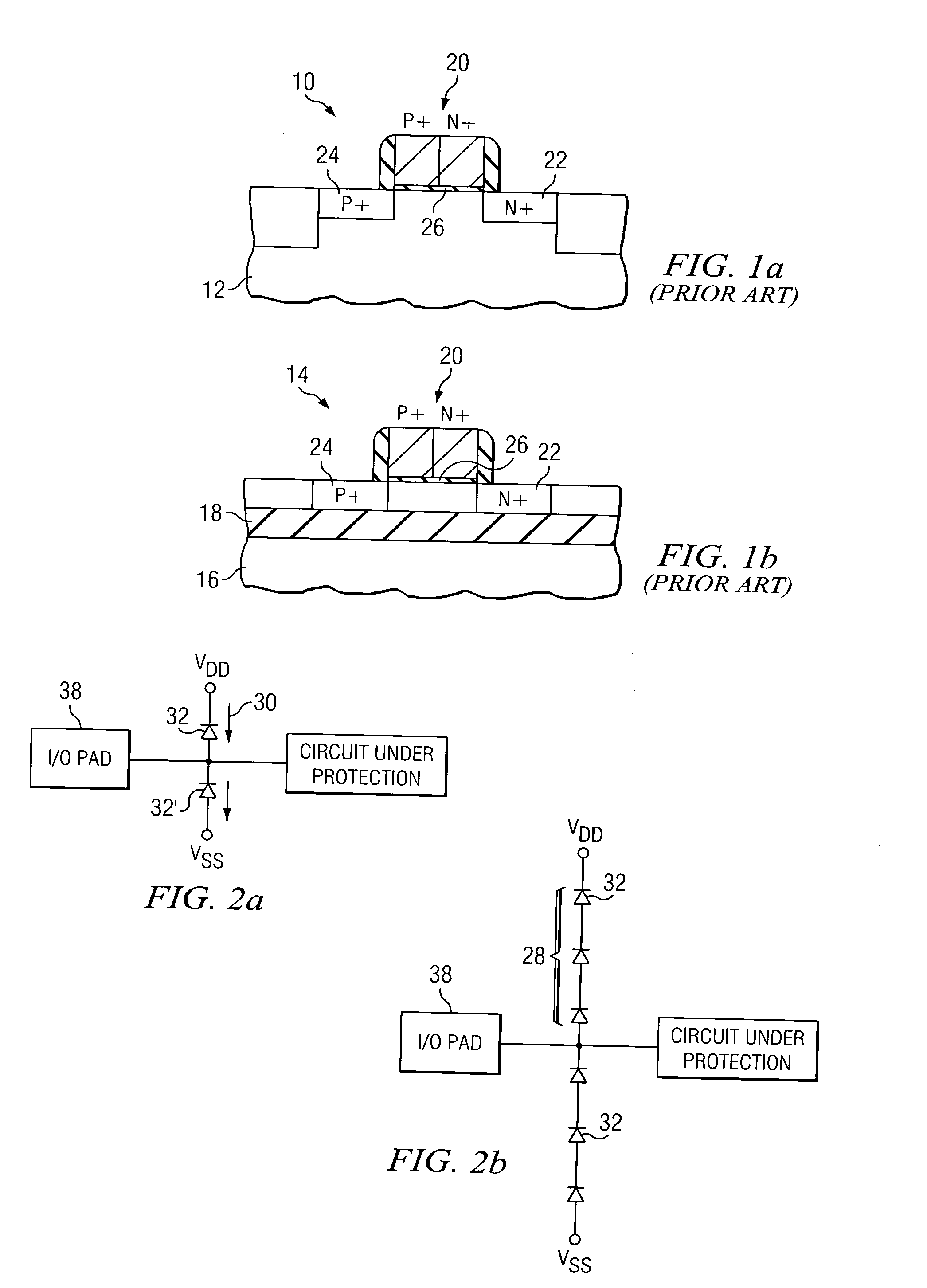

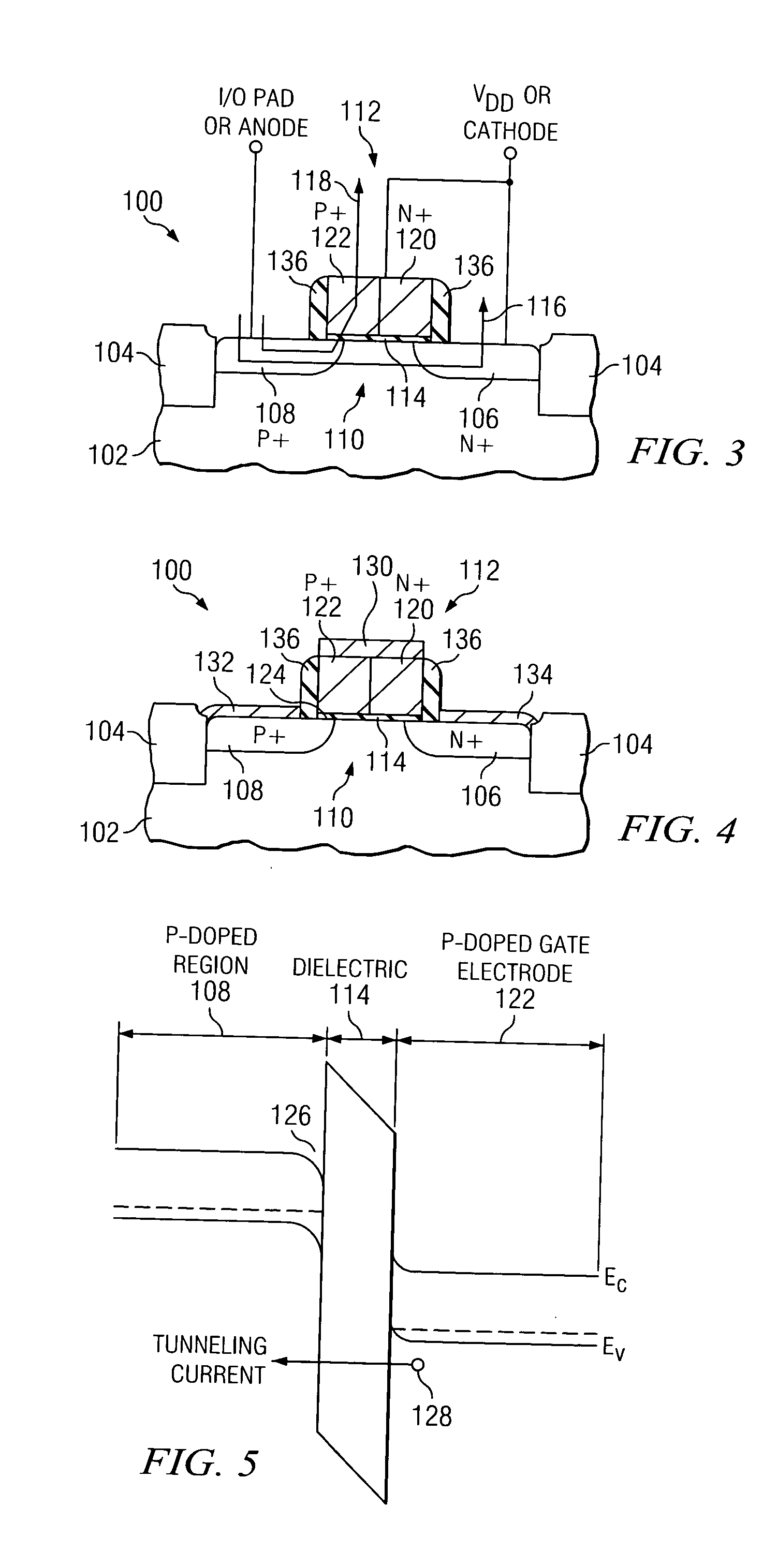

InactiveUS20050035410A1Reduce reverse leakage currentReduce leakage currentTransistorThyristorGate dielectricPermittivity

A diode 100 is formed on a silicon-on-insulator substrate that includes a silicon layer overlying an insulator layer 142. An active region is formed in the silicon layer and includes a p-doped region 108 and an n-doped region 106 separated by a body region 110. A high permittivity gate dielectric 114 overlies the body region 110 and a gate electrode 112 overlies the gate dielectric 114. As an example, the diode can be used for ESD protection.

Owner:TAIWAN SEMICON MFG CO LTD

Nanotube-based switching elements

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

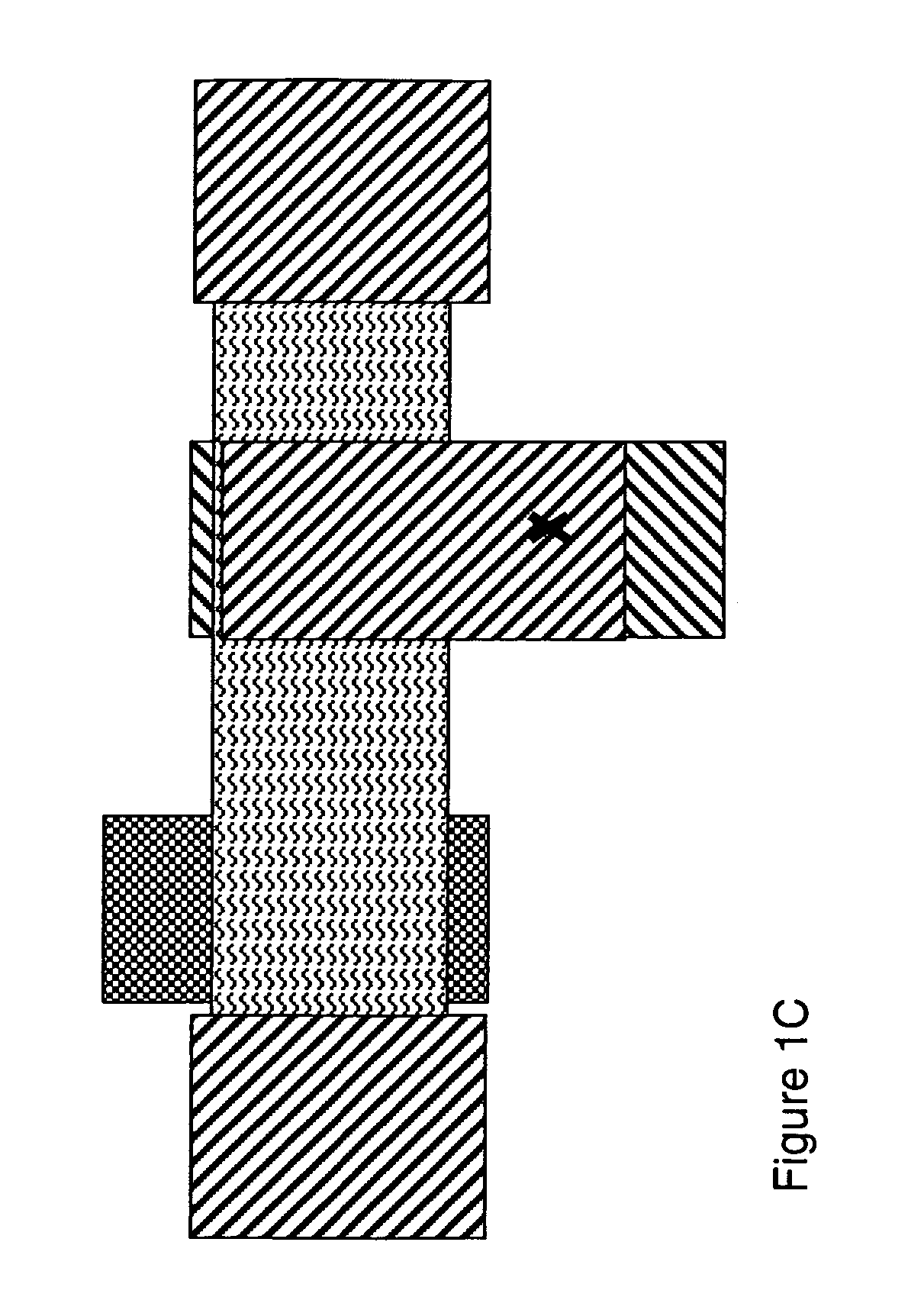

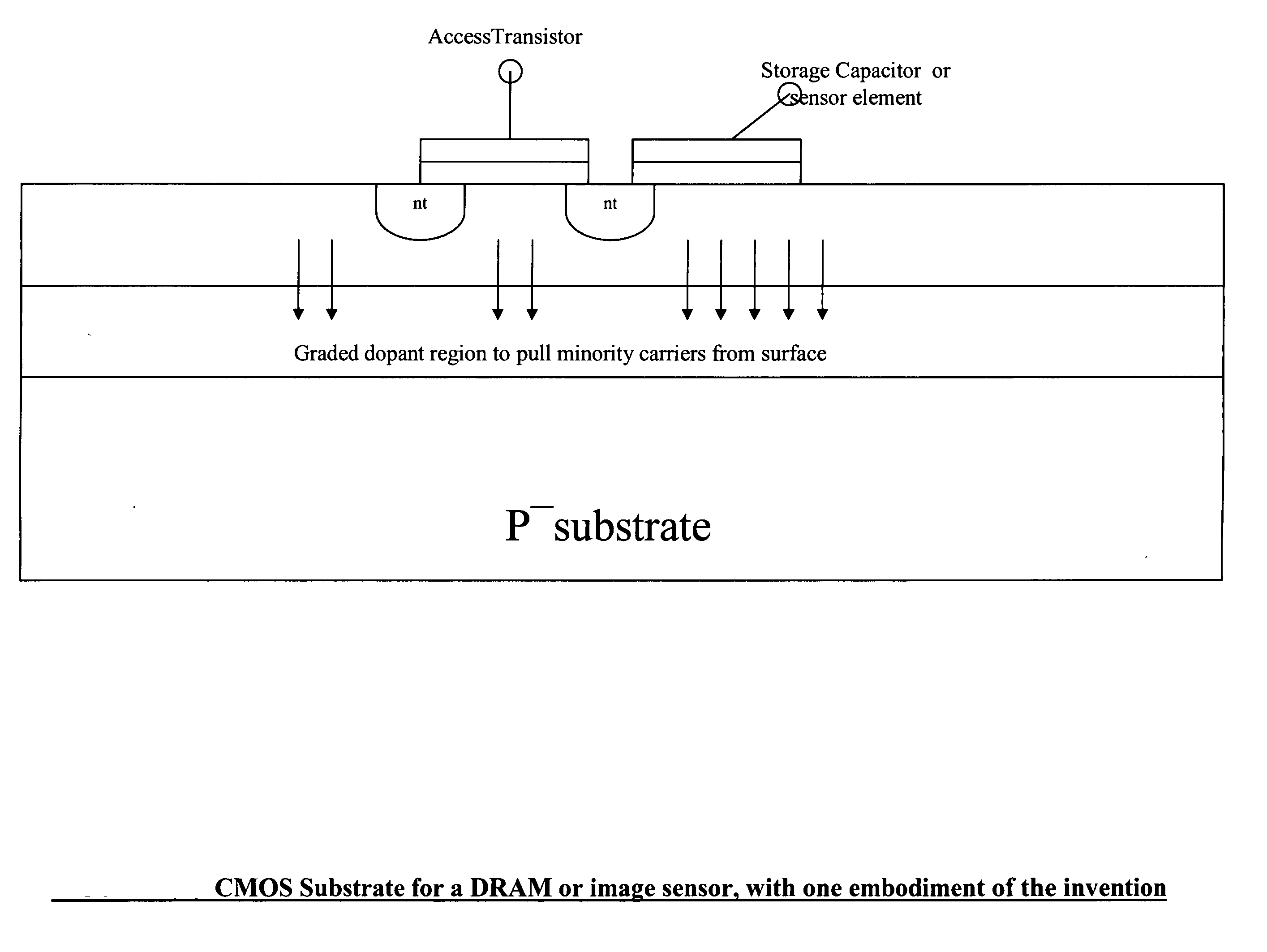

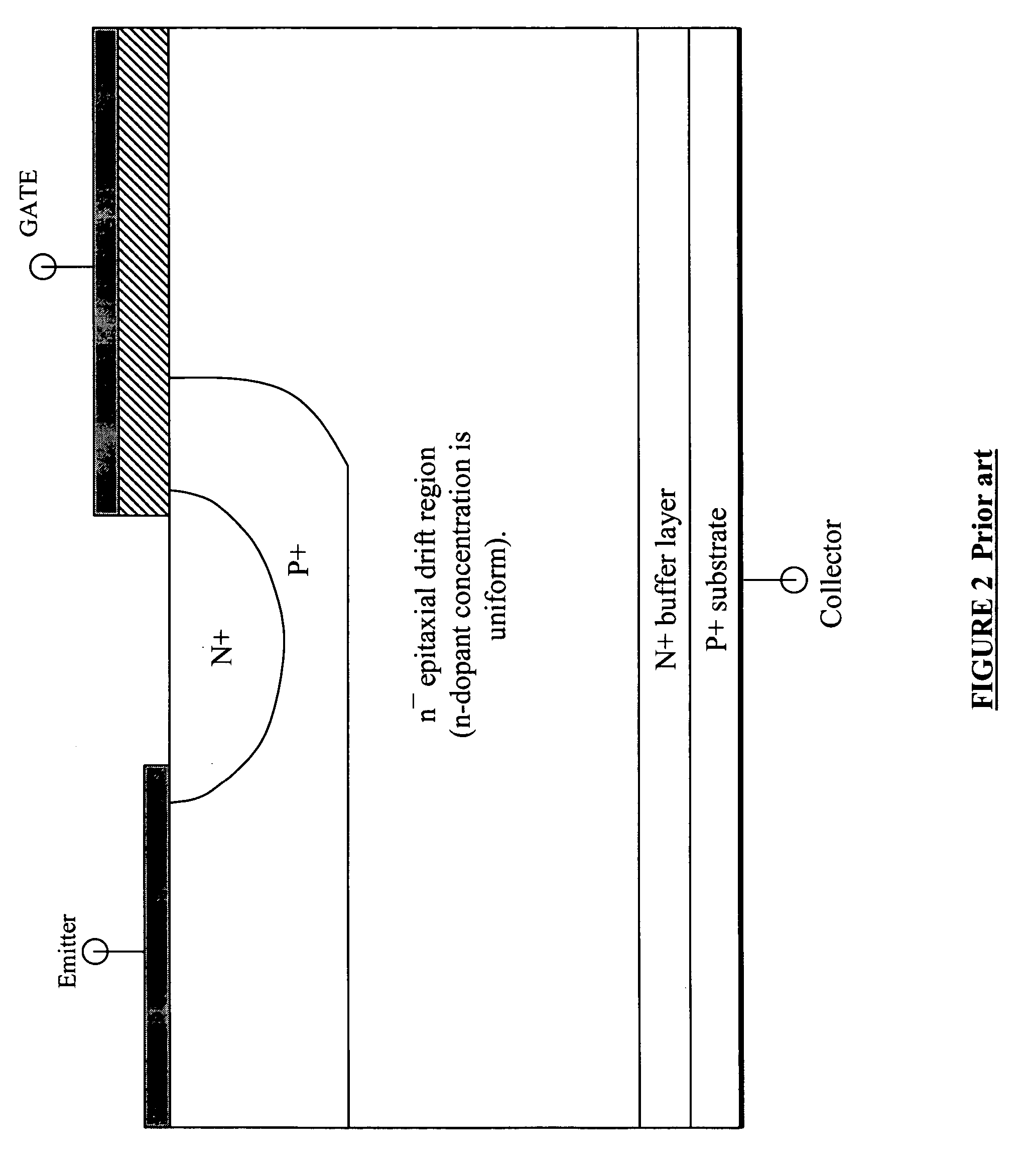

Semiconductor devices with graded dopant regions

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

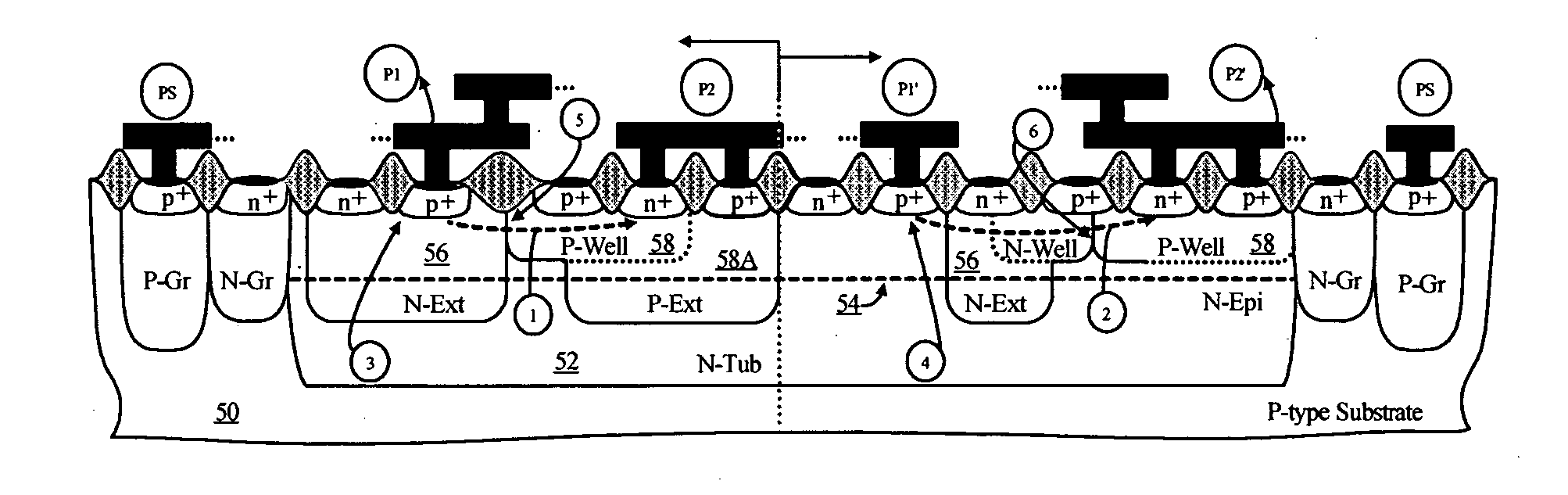

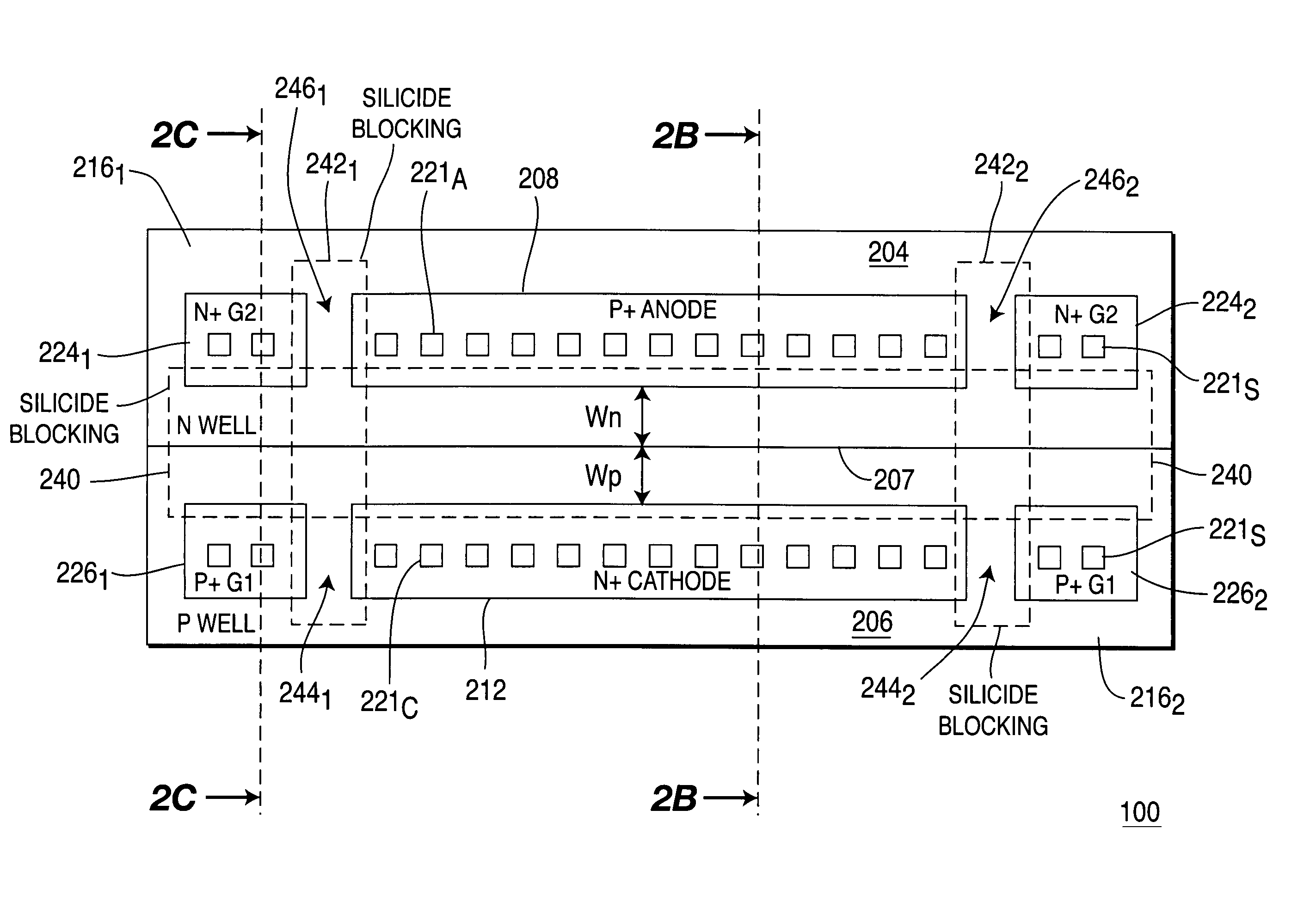

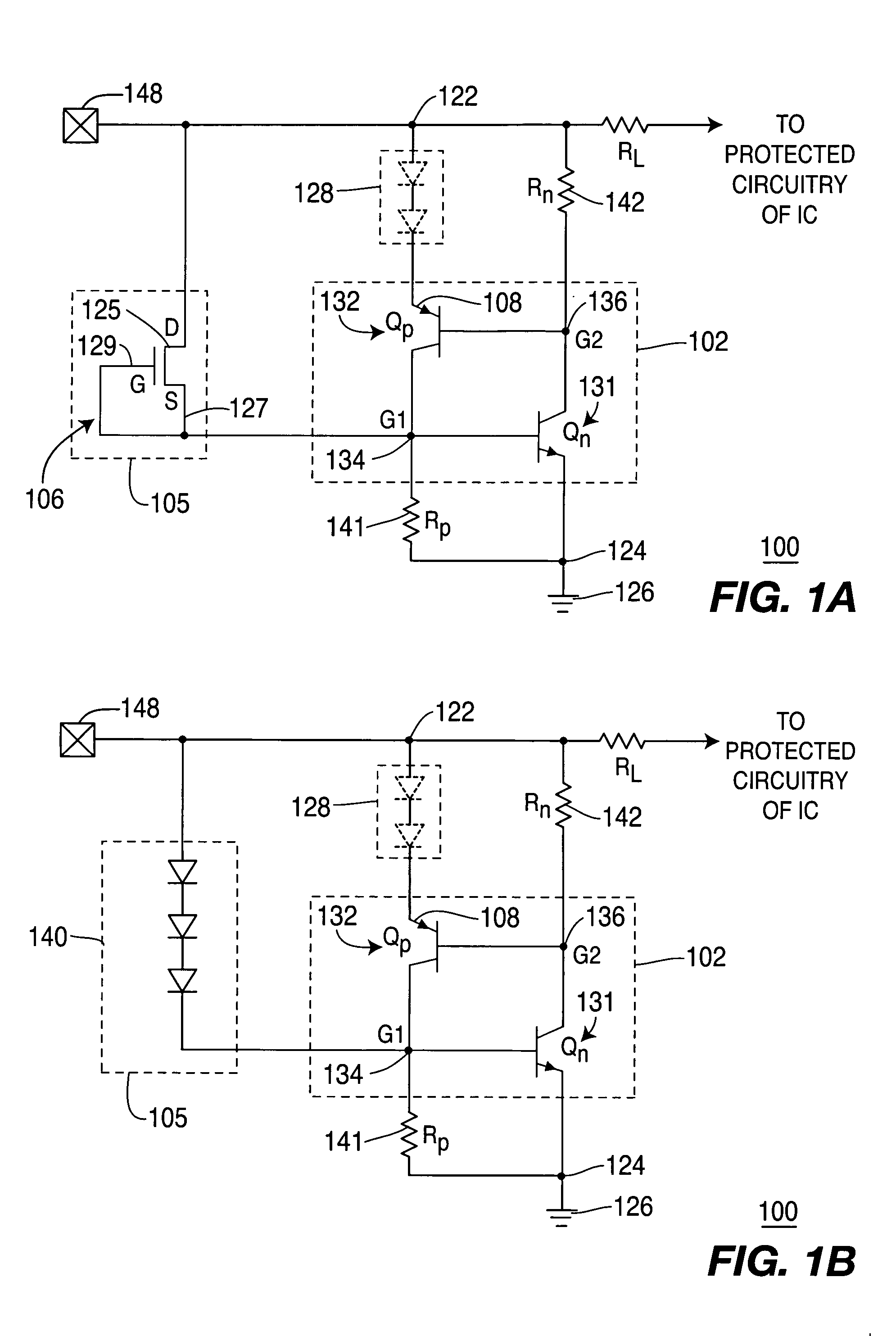

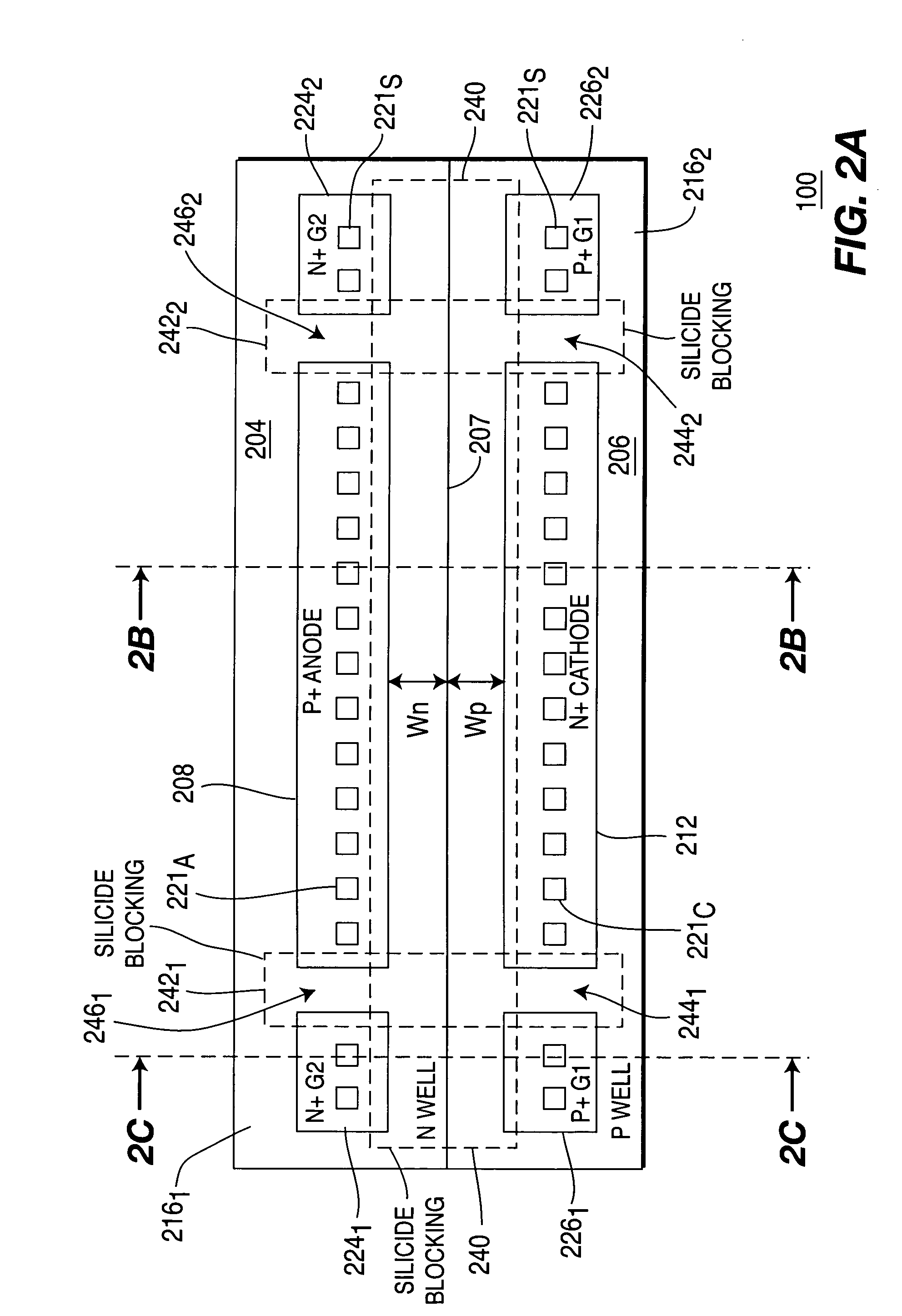

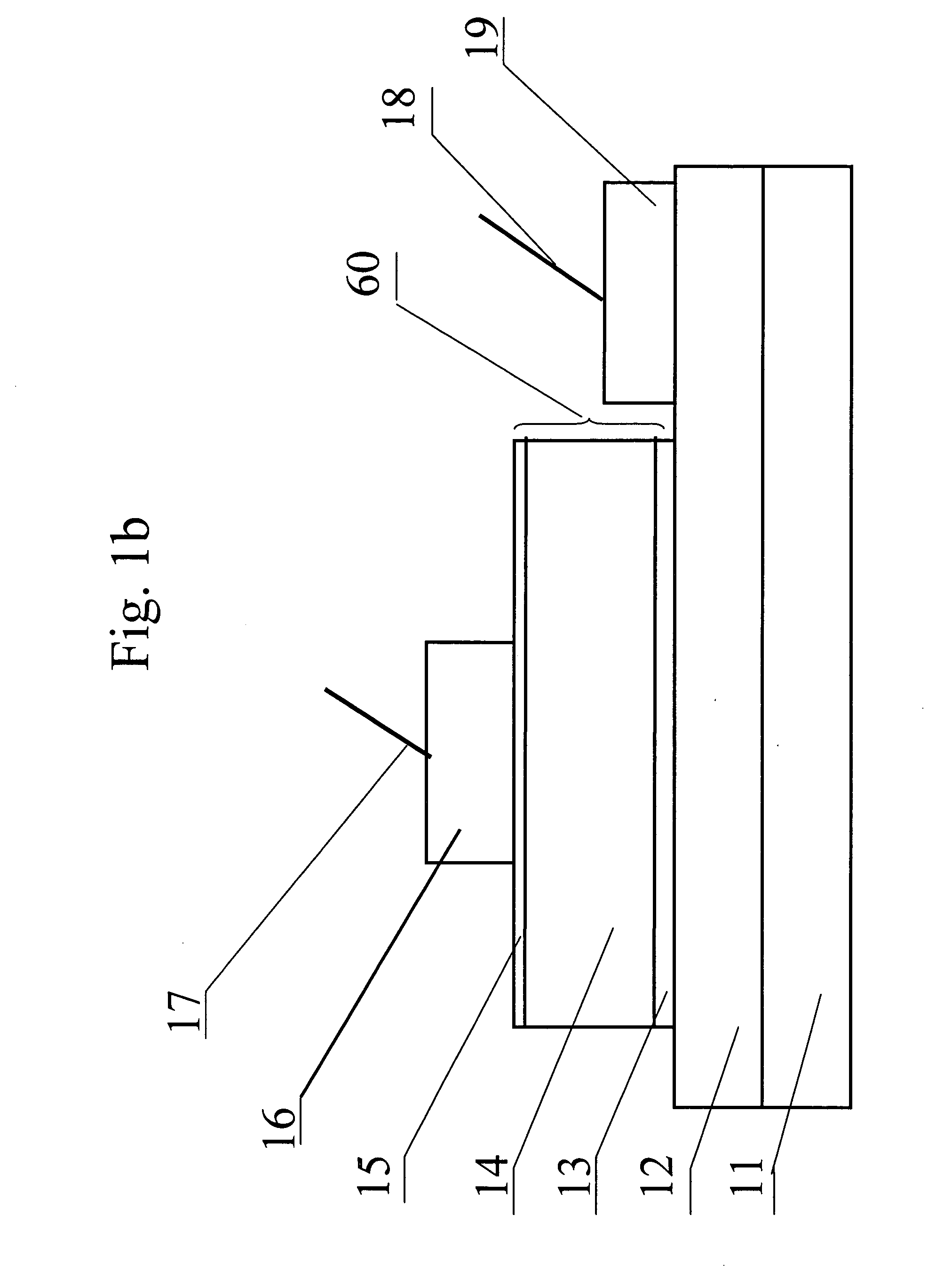

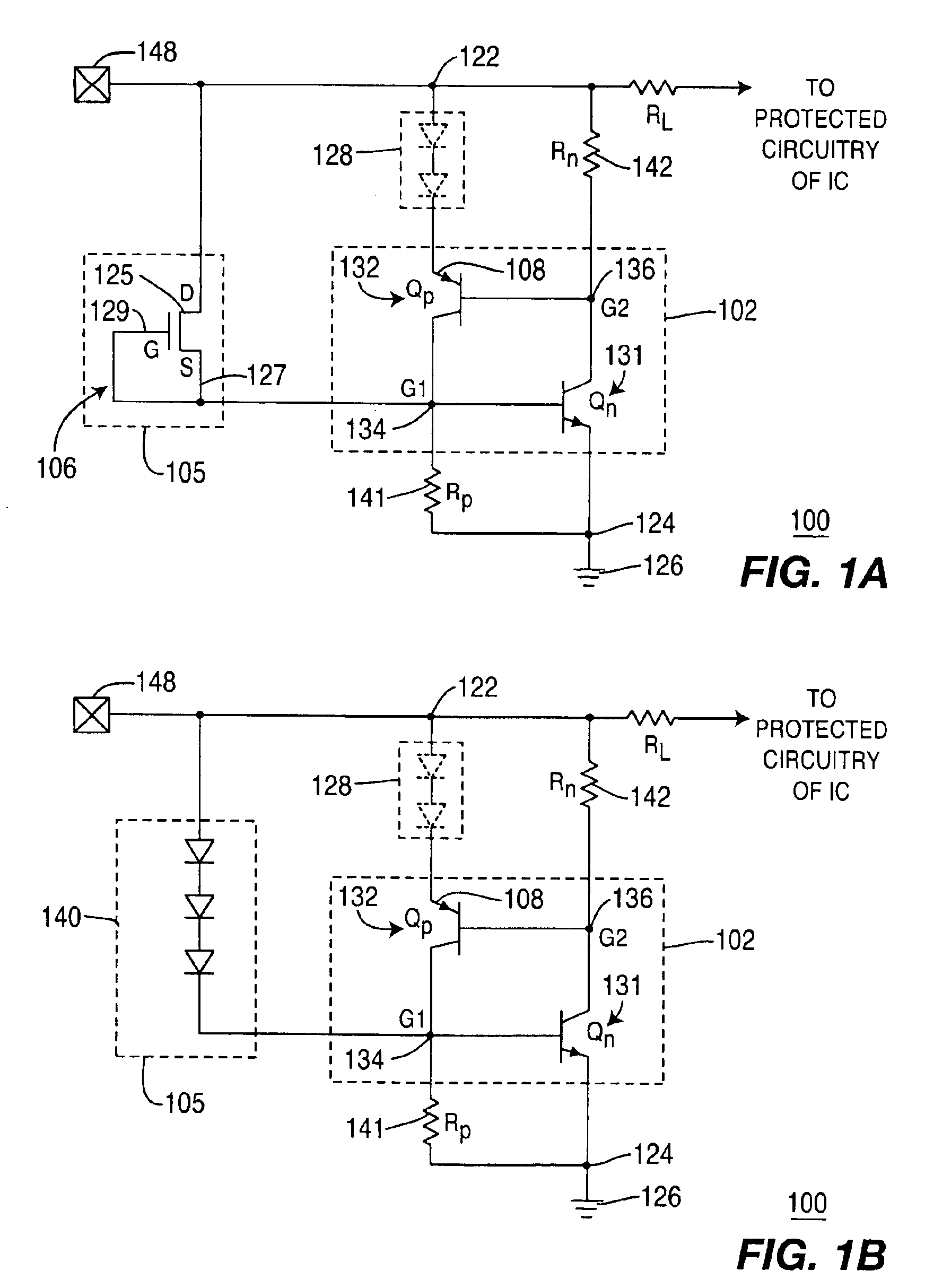

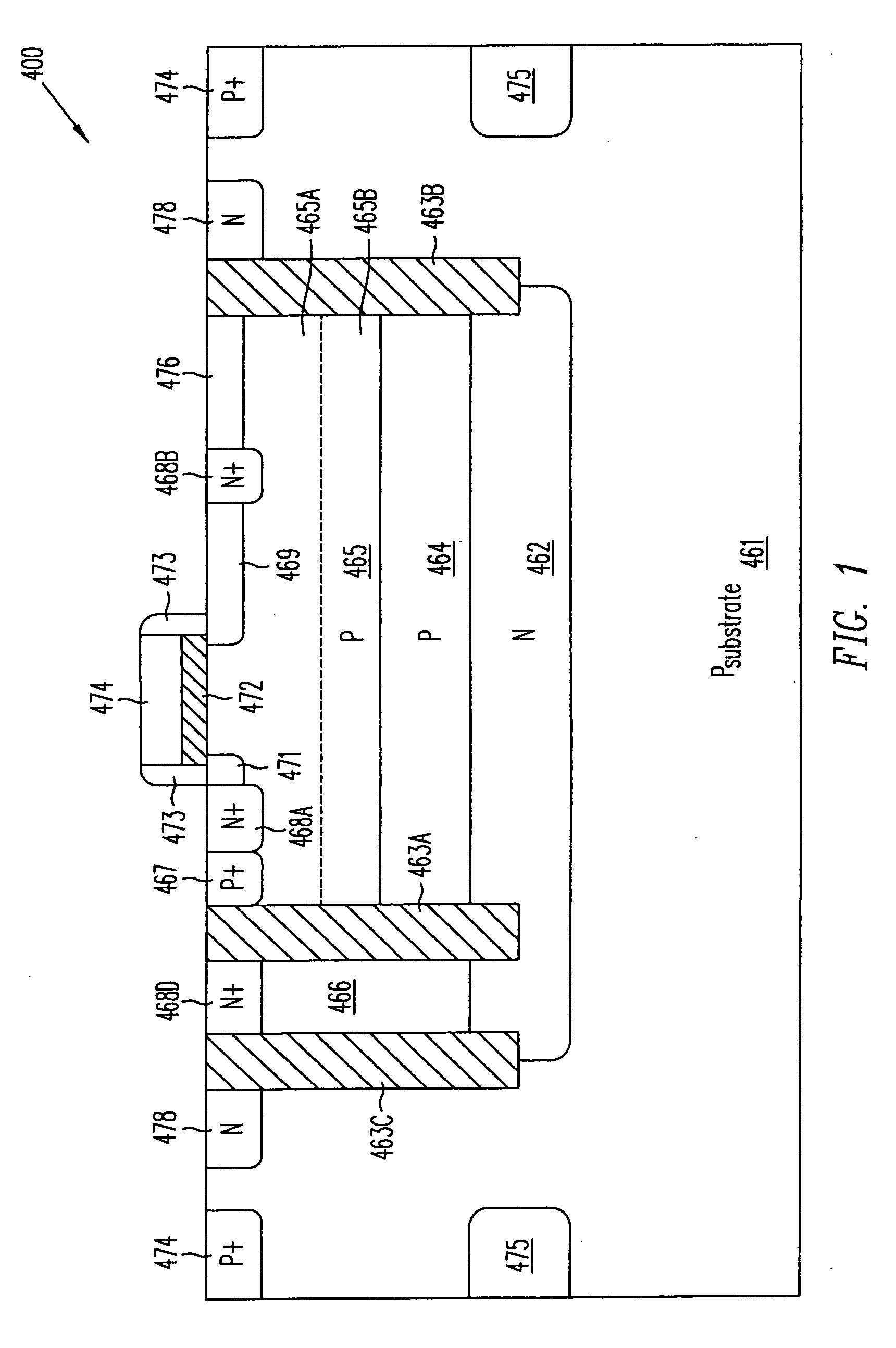

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

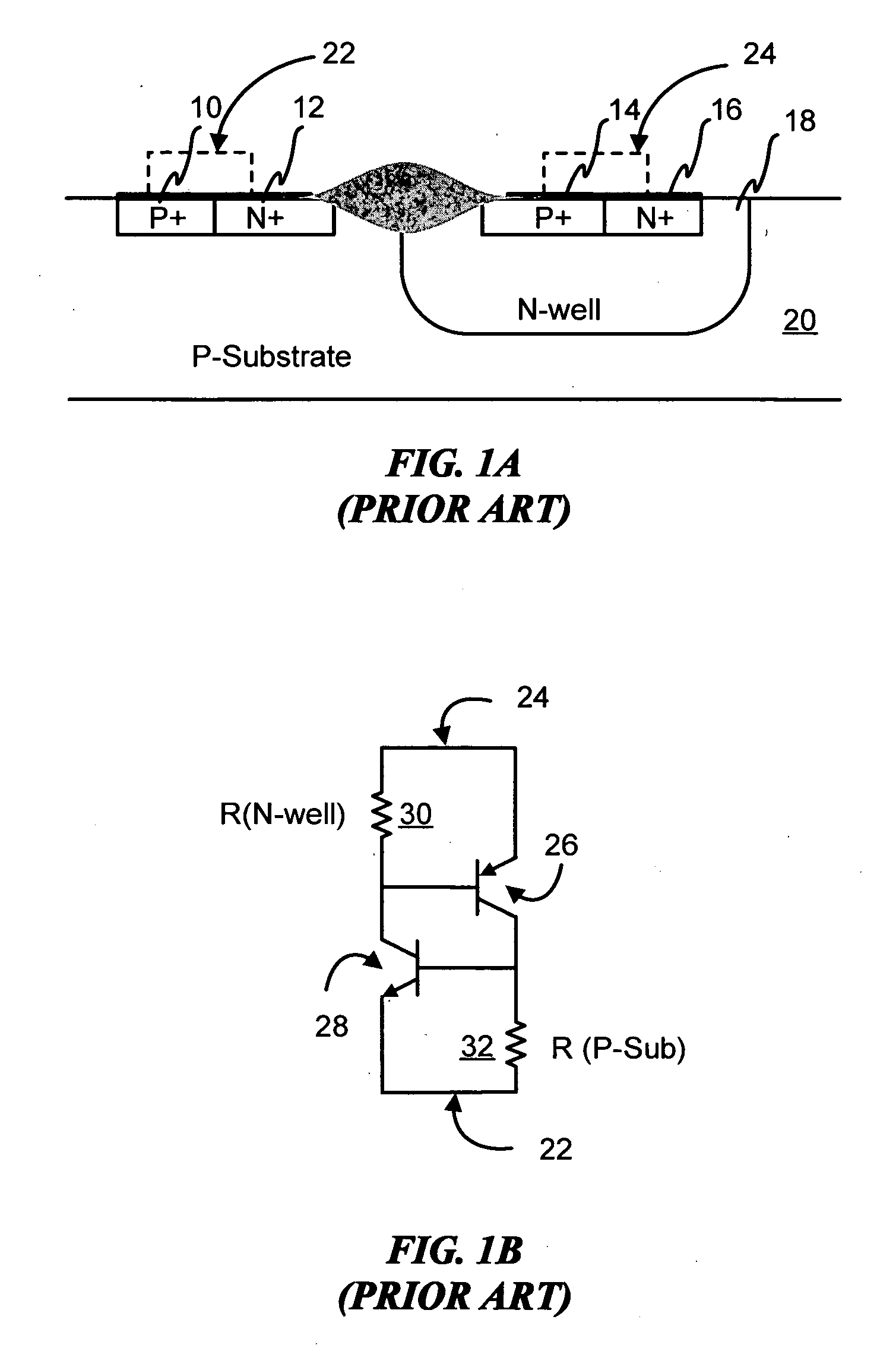

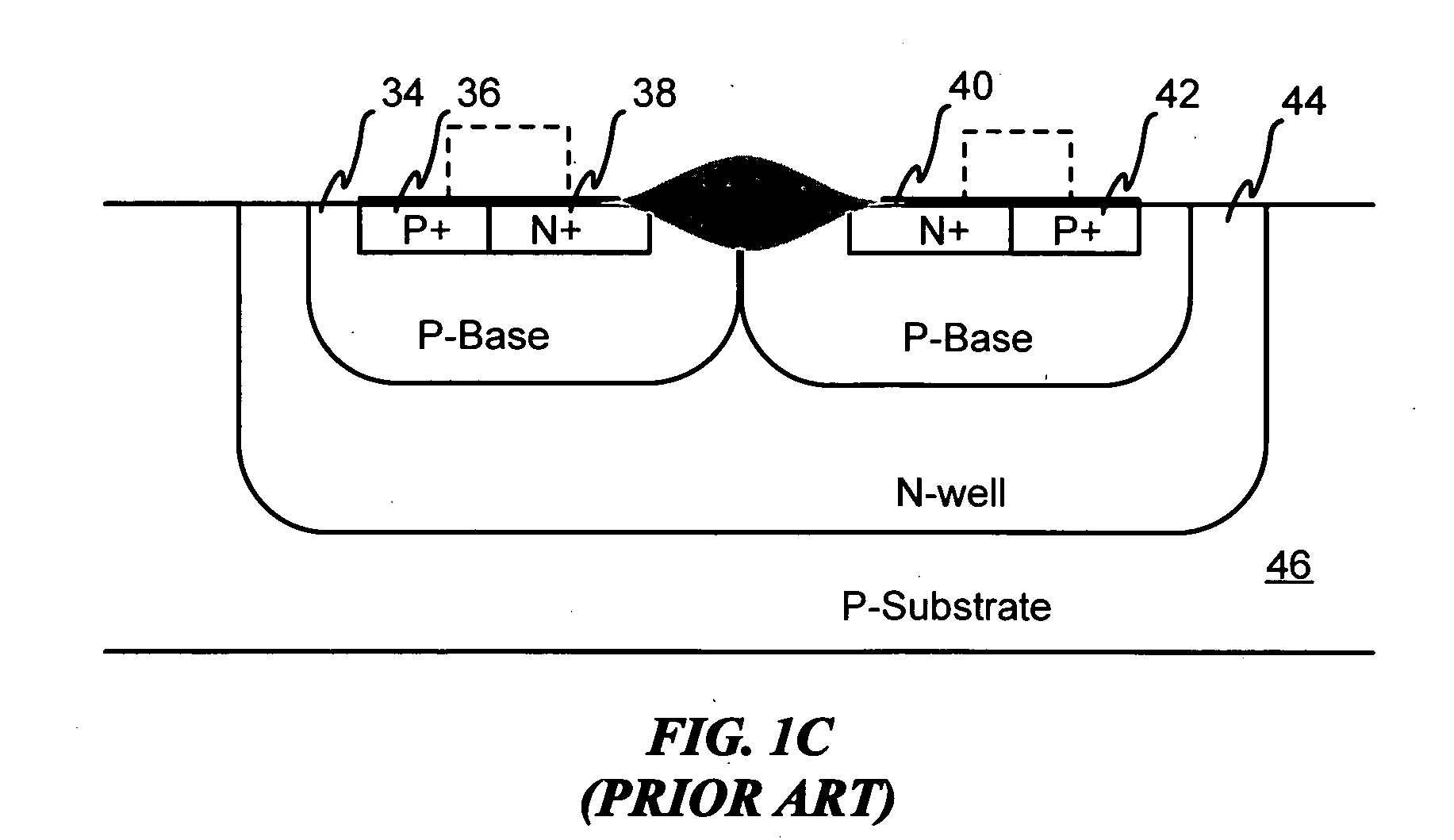

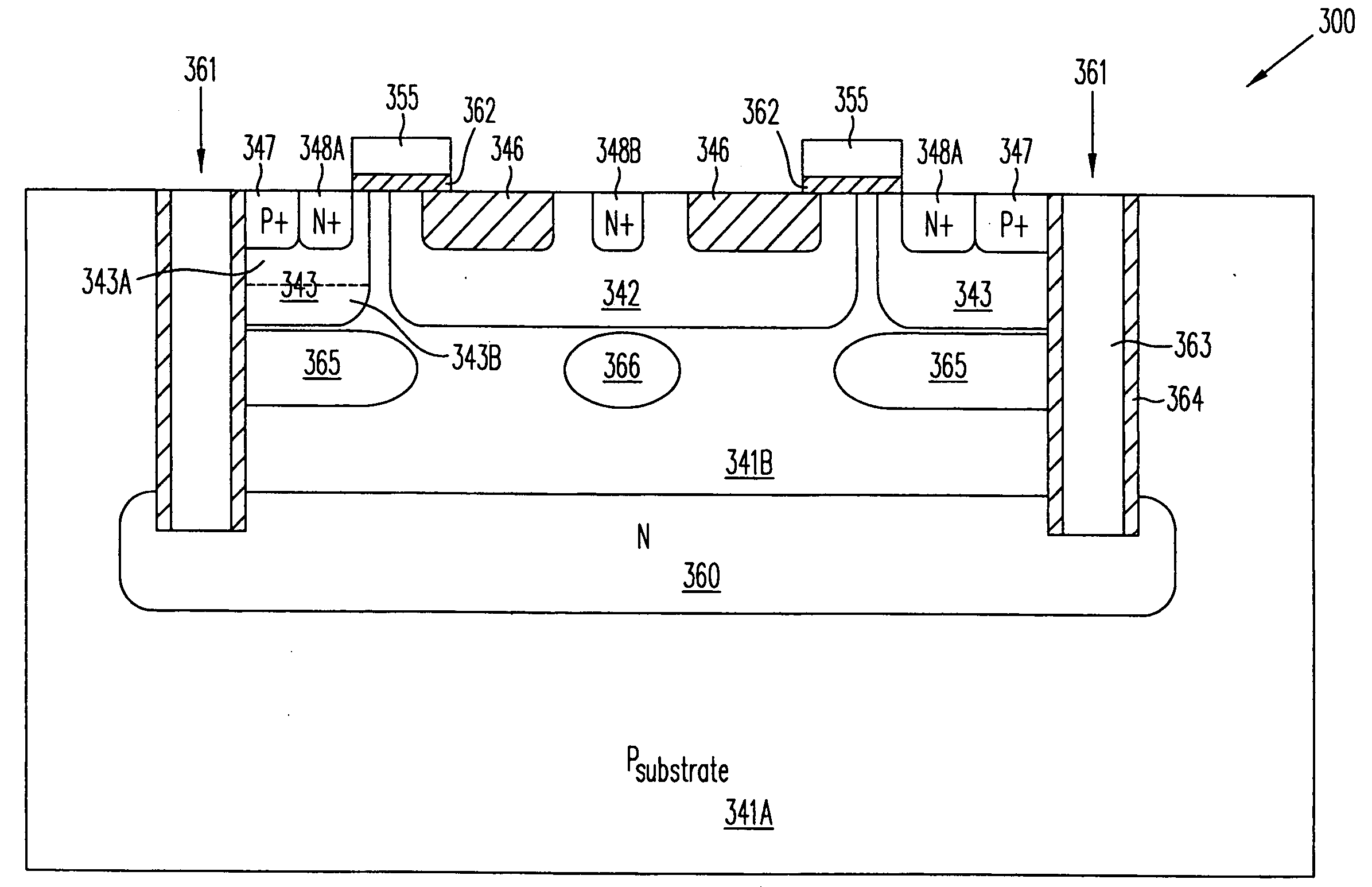

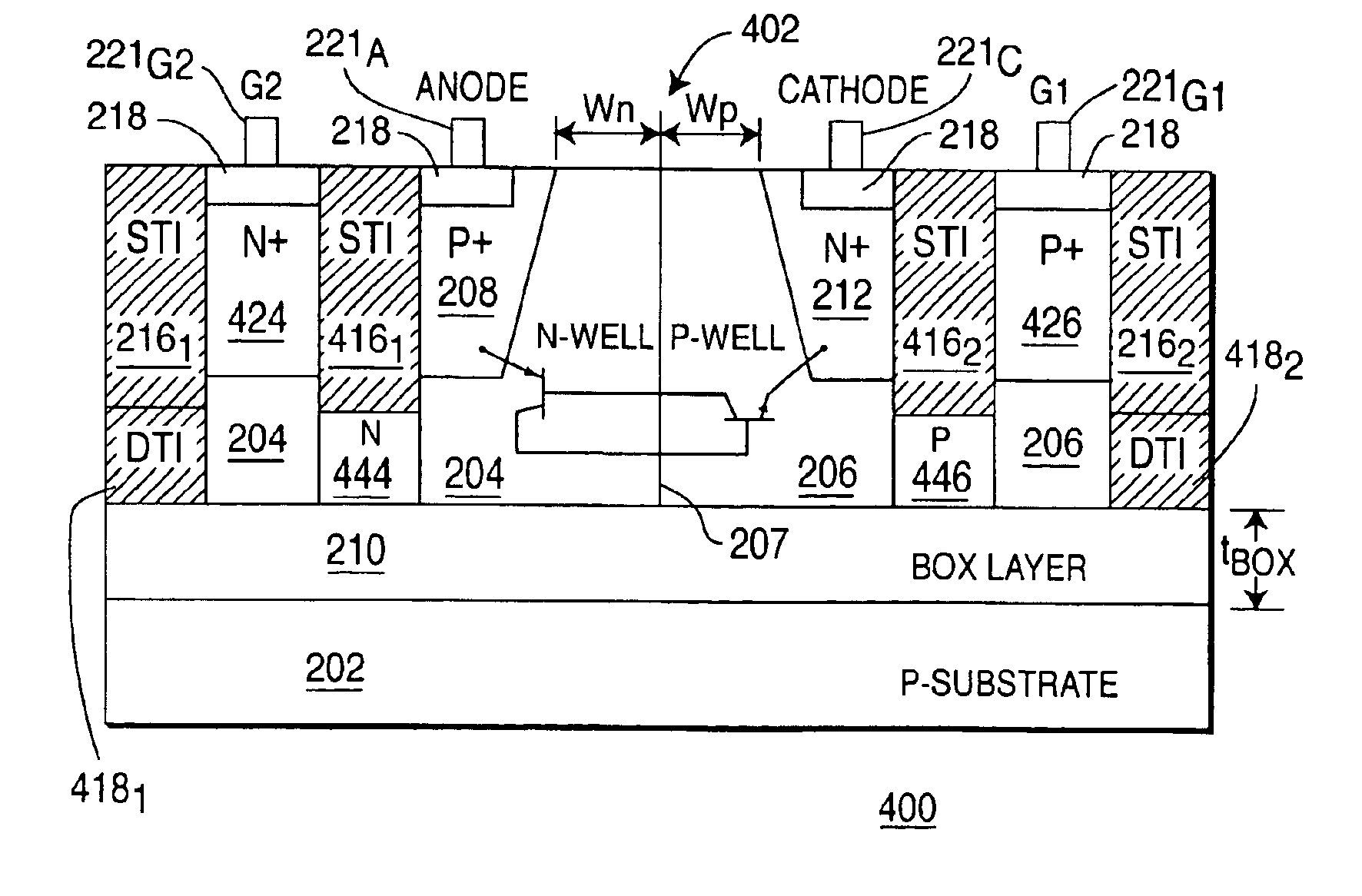

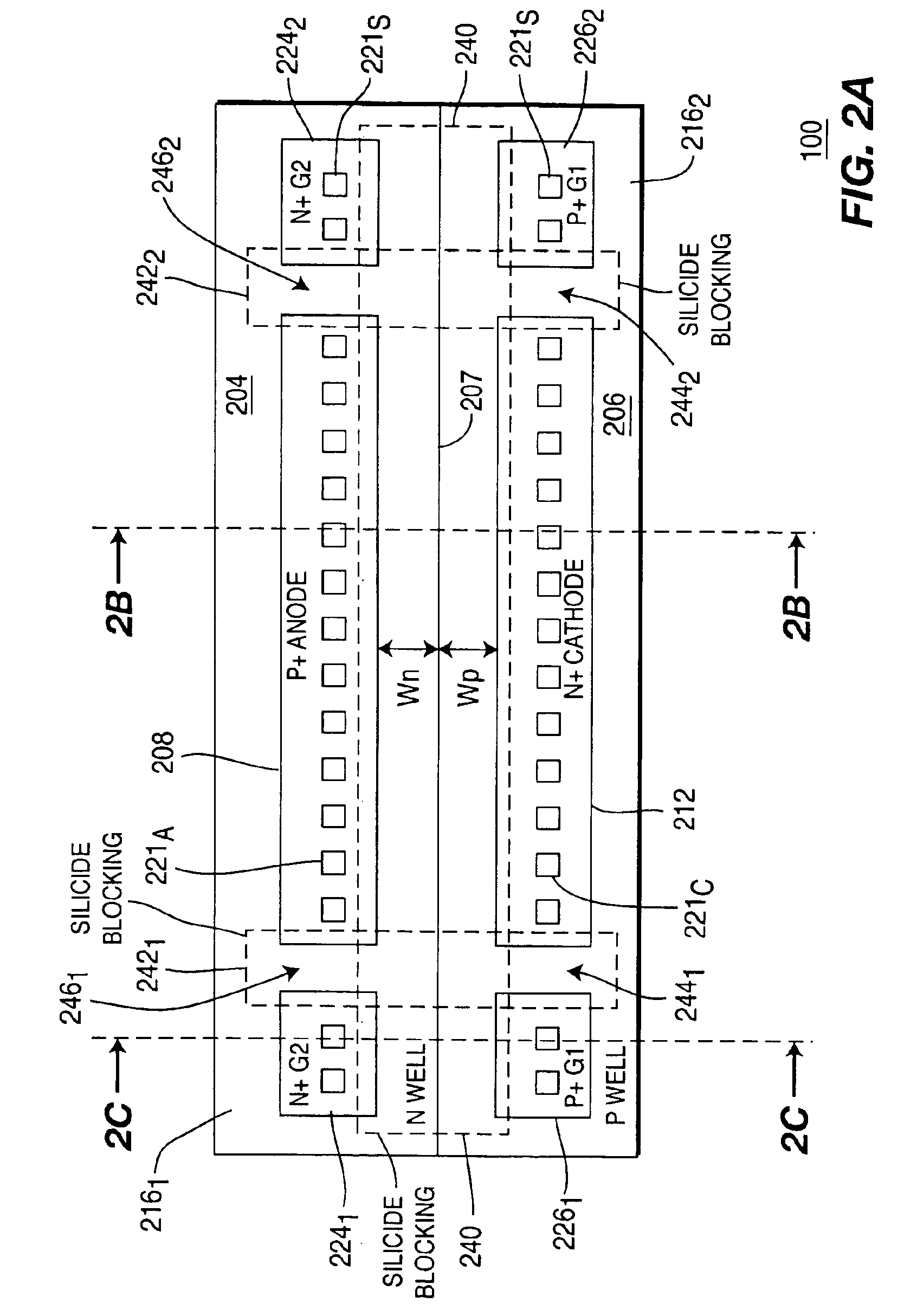

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

InactiveUS20050212051A1Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

Owner:SOFICS BVBA

Switchable resistive perovskite microelectronic device with multi-layer thin film structure

ActiveUS20050151156A1Lowered pulse voltageProtection of device being damagedThyristorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceMagnification

A switchable resistive device has a multi-layer thin film structure interposed between an upper conductive electrode and a lower conductive electrode. The multi-layer thin film structure comprises a perovskite layer with one buffer layer on one side of the perovskite layer, or a perovskite layer with buffer layers on both sides of the perovskite layer. Reversible resistance changes are induced in the device under applied electrical pulses. The resistance changes of the device are retained after applied electric pulses. The functions of the buffer layer(s) added to the device include magnification of the resistance switching region, reduction of the pulse voltage needed to switch the device, protection of the device from being damaged by a large pulse shock, improvement of the temperature and radiation properties, and increased stability of the device allowing for multivalued memory applications.

Owner:UNIV HOUSTON SYST

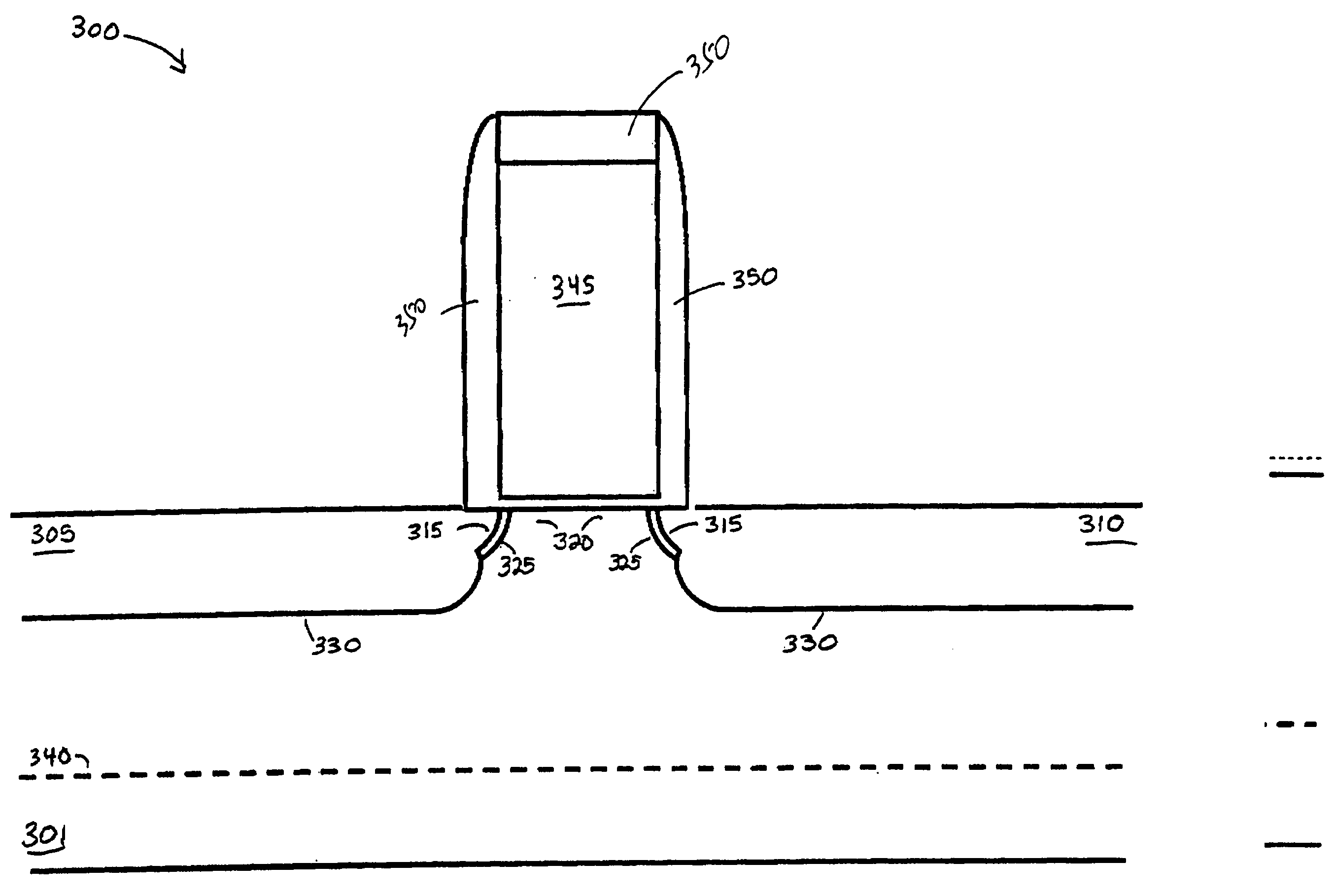

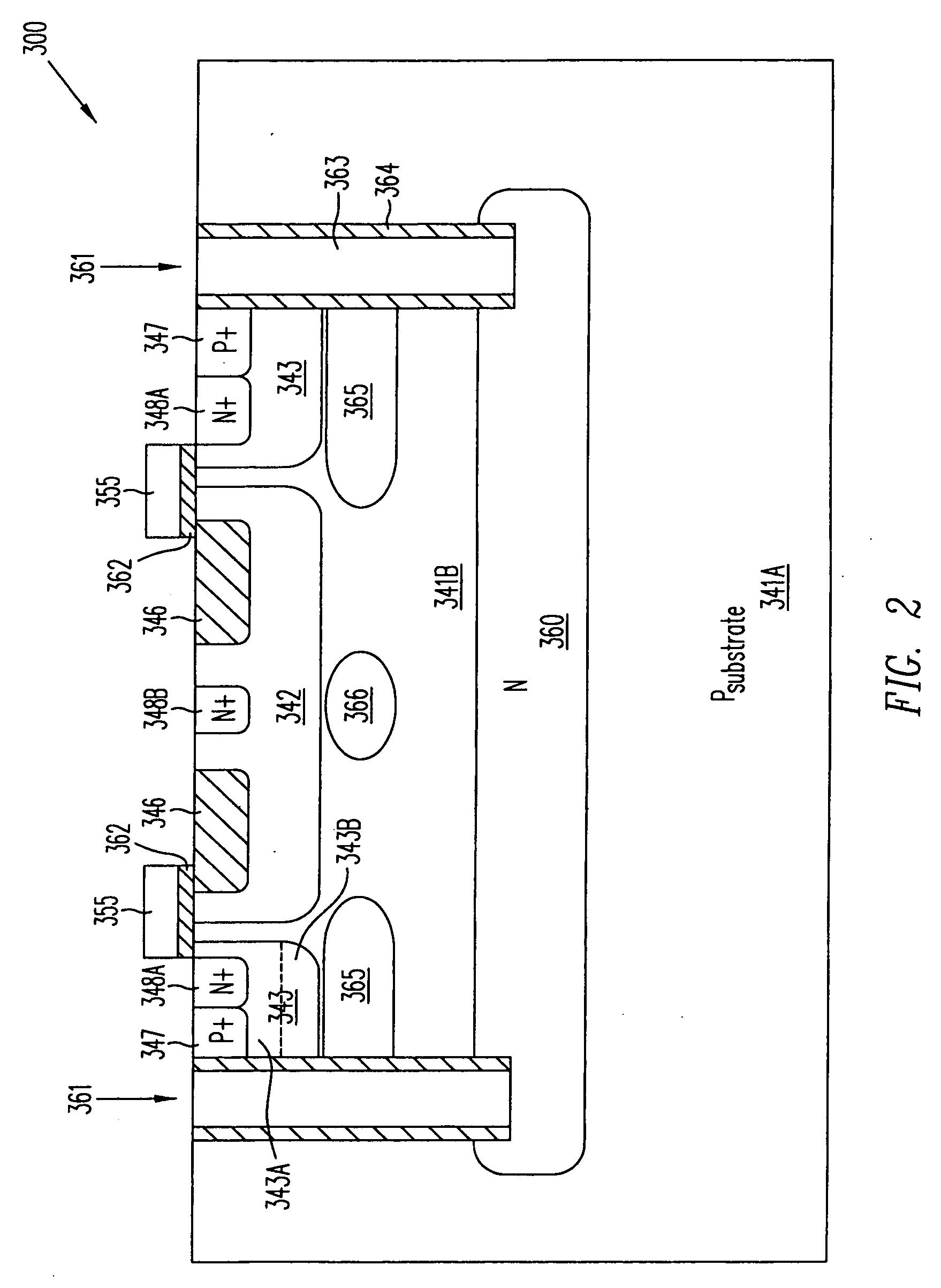

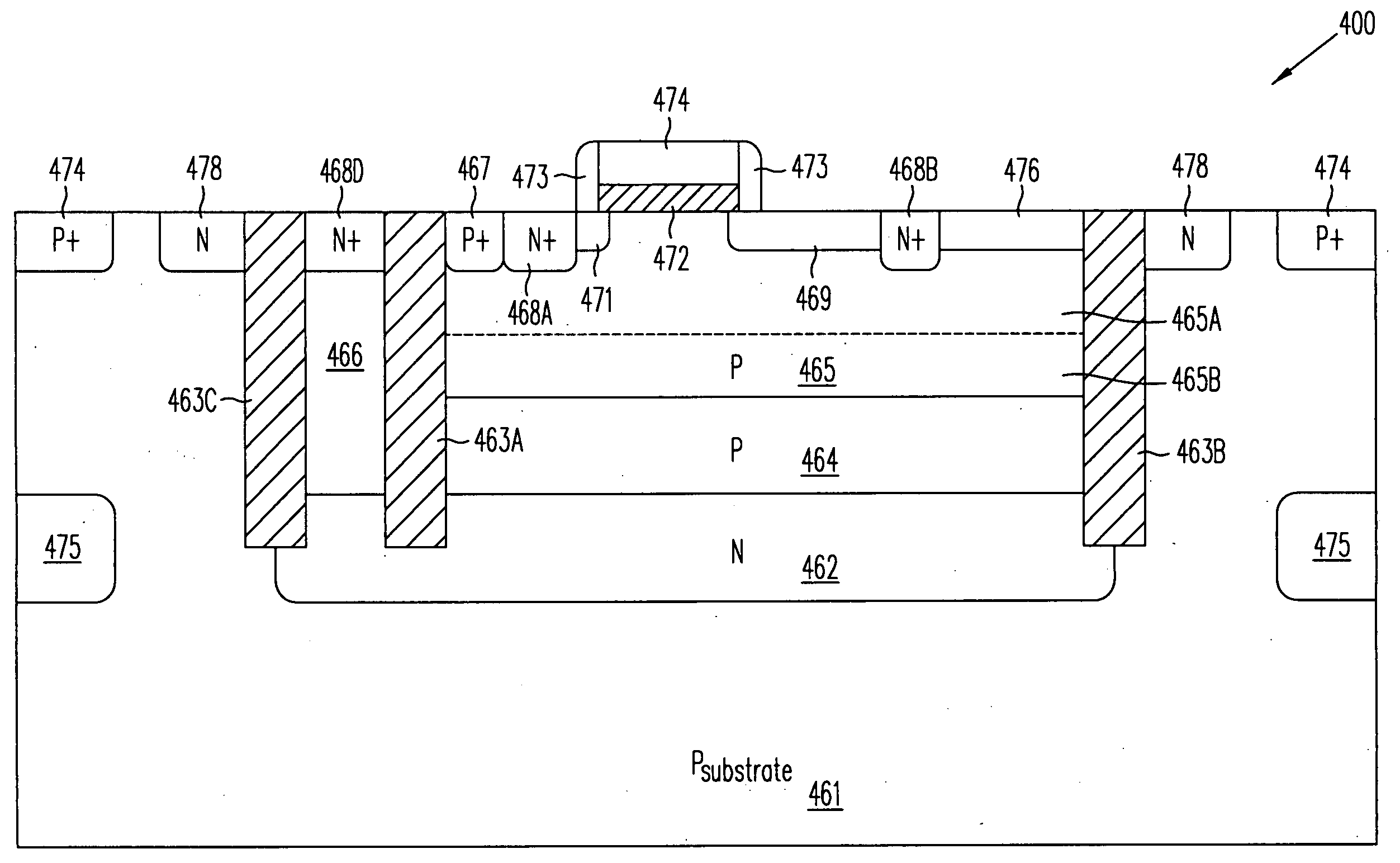

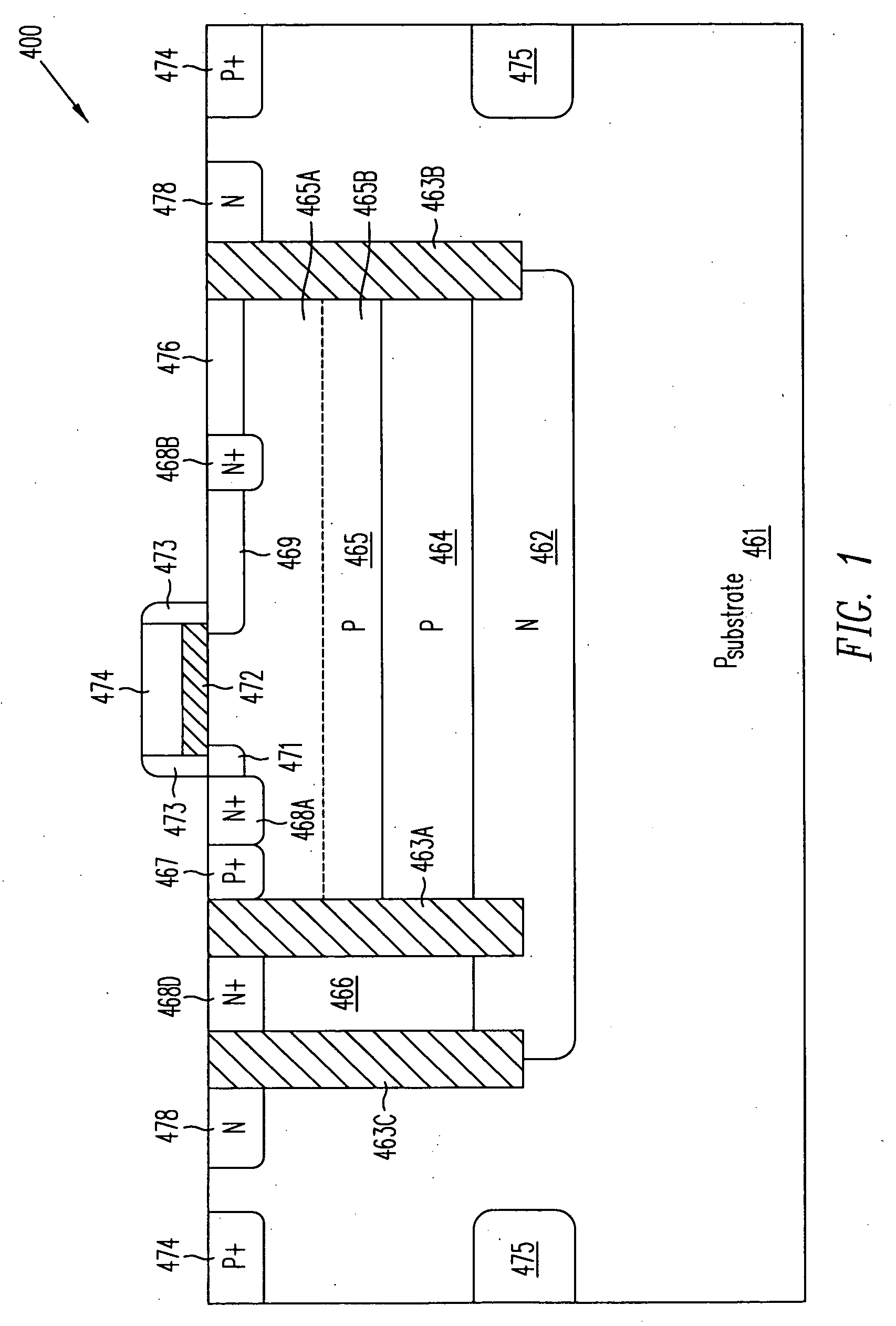

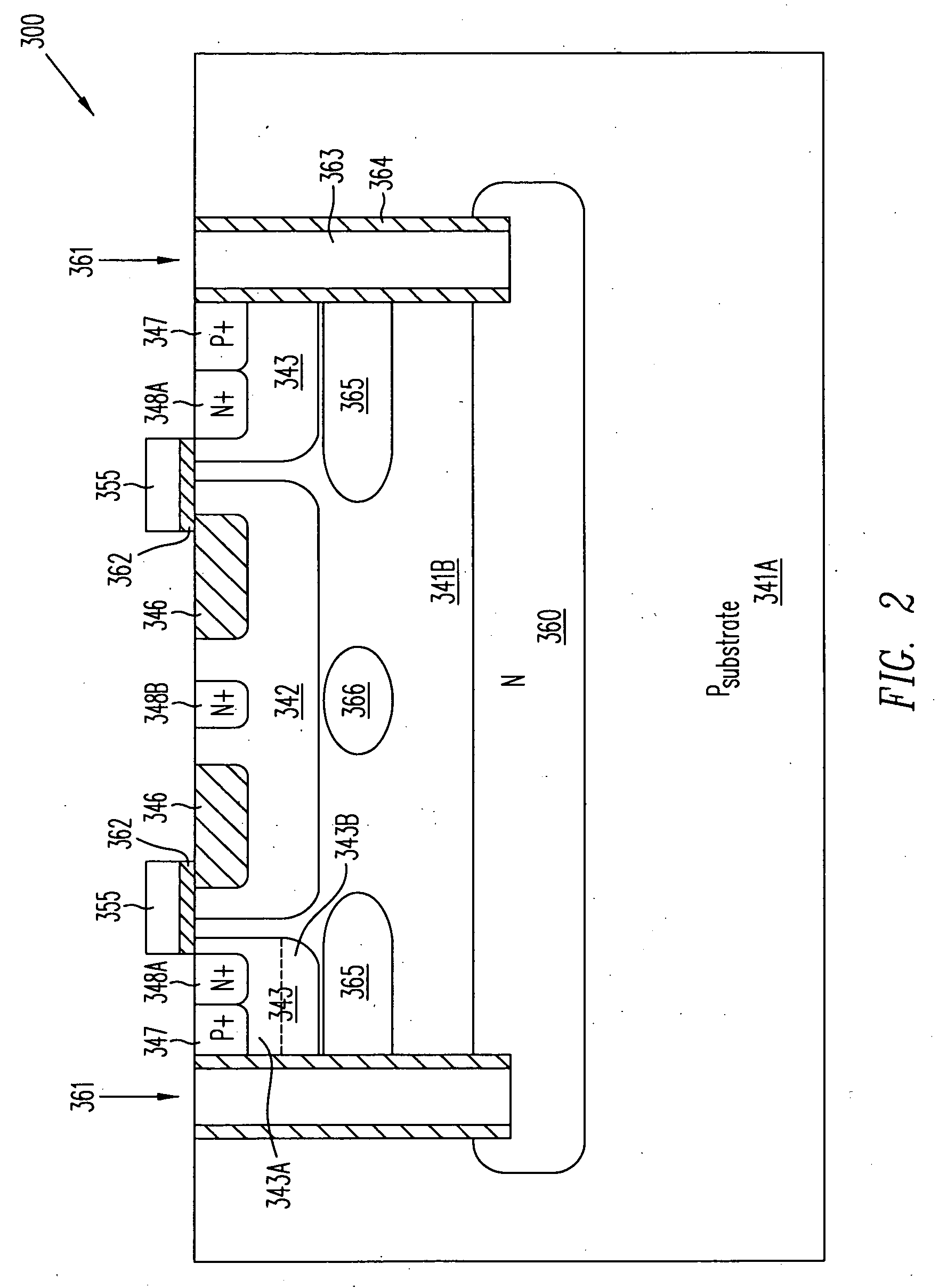

Isolated quasi-vertical DMOS transistor

Various integrated circuit devices, in particular a quasi-vertical DMOS transistor, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Nanotube-based switching elements

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

Rail stack array of charge storage devices and method of making same

There is provided a monolithic three dimensional array of charge storage devices which includes a plurality of device levels, wherein at least one surface between two successive device levels is planarized by chemical mechanical polishing.

Owner:WODEN TECH INC

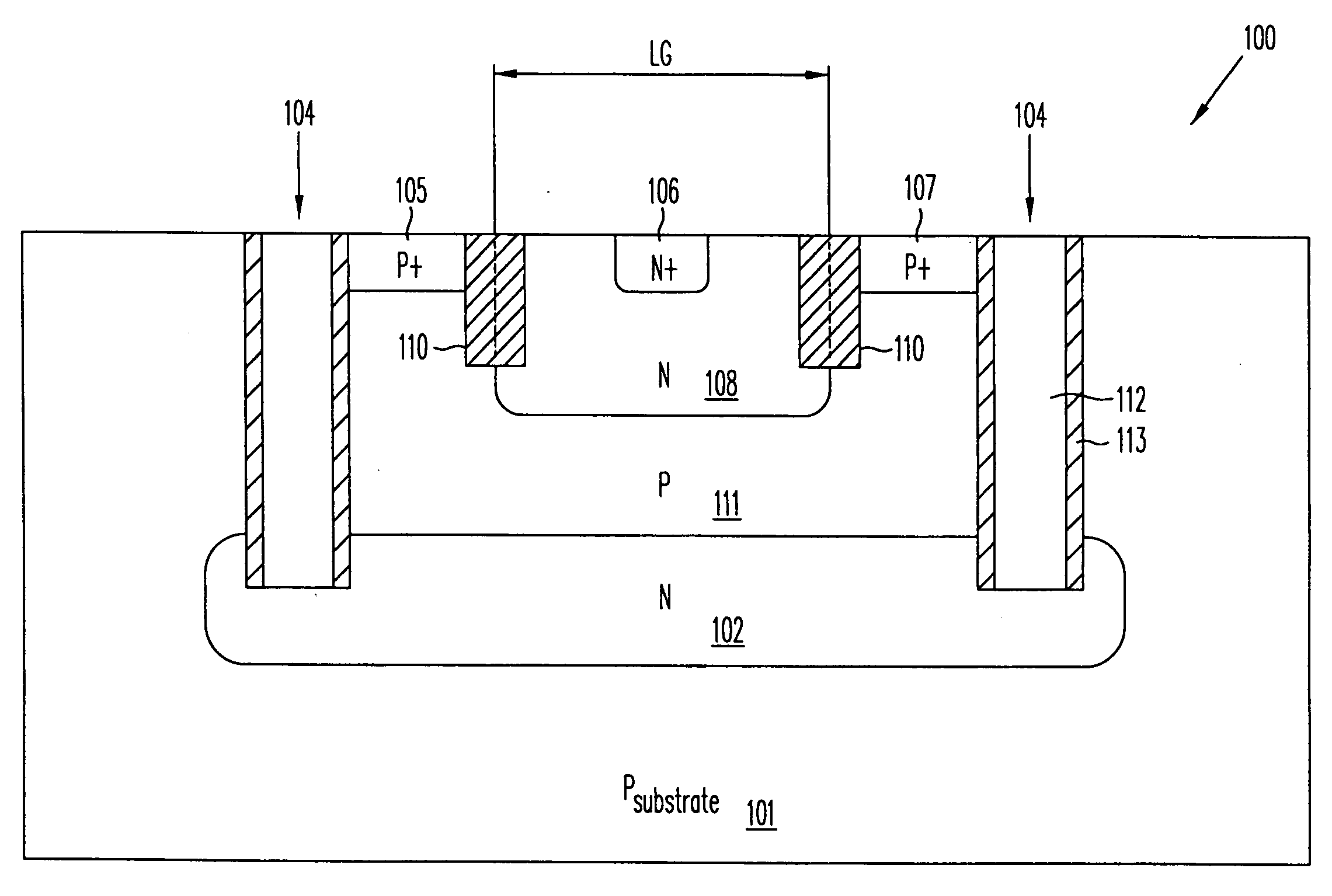

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

ActiveUS6909149B2Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

A silicon-on-insulator (SOI) electrostatic discharge (ESD) protection device that can protect very sensitive thin gate oxides by limiting the power dissipation during the ESD event, which is best achieved by reducing the voltage drop across the active (protection) device during an ESD event. In one embodiment, the invention provides very low triggering and holding voltages. Furthermore, the SOI protection device of the present invention has low impedance and low power dissipation characteristics that reduce voltage build-up, and accordingly, enable designers to fabricate more area efficient protection device

Owner:SOFICS BVBA

Isolated transistor

InactiveUS20080191277A1Reduce chargeReducing other time-dependent surface-related phenomenonTransistorThyristorConductive materialsDielectric layer

Various integrated circuit devices, in particular a transistor, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

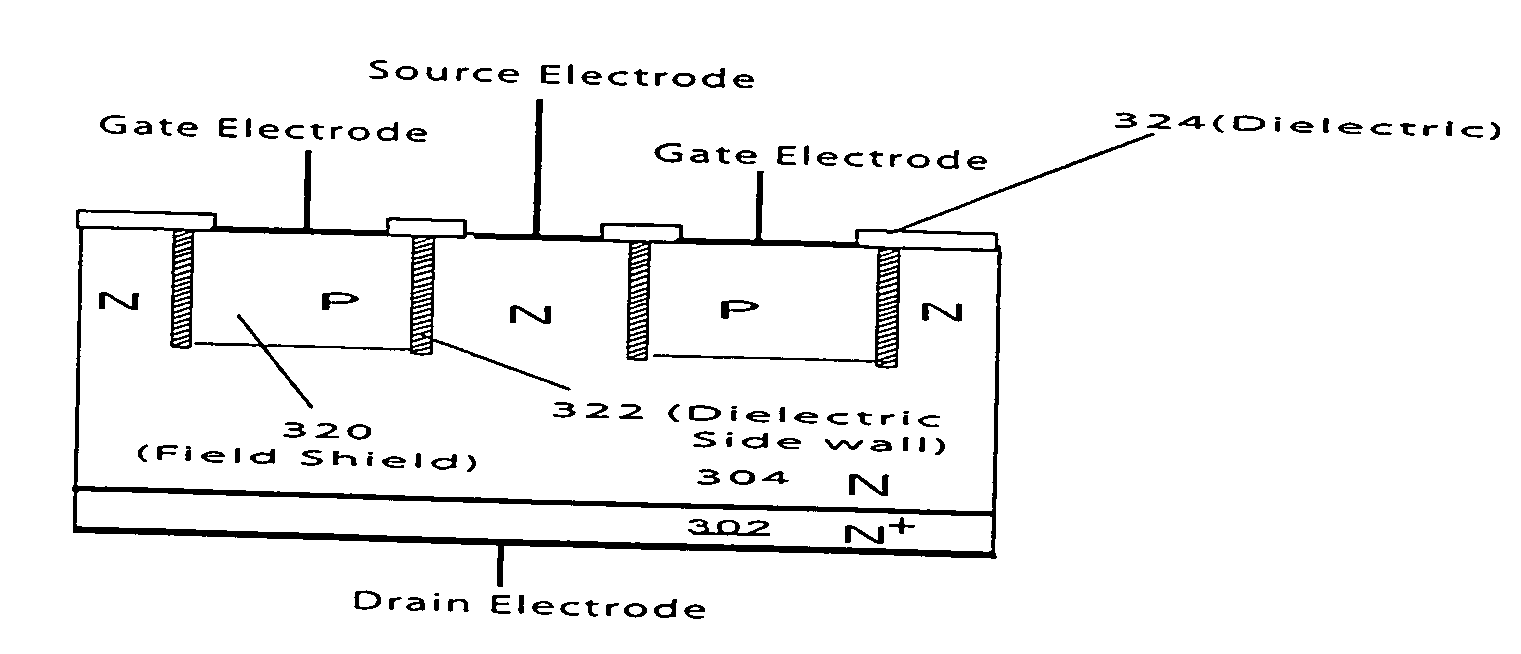

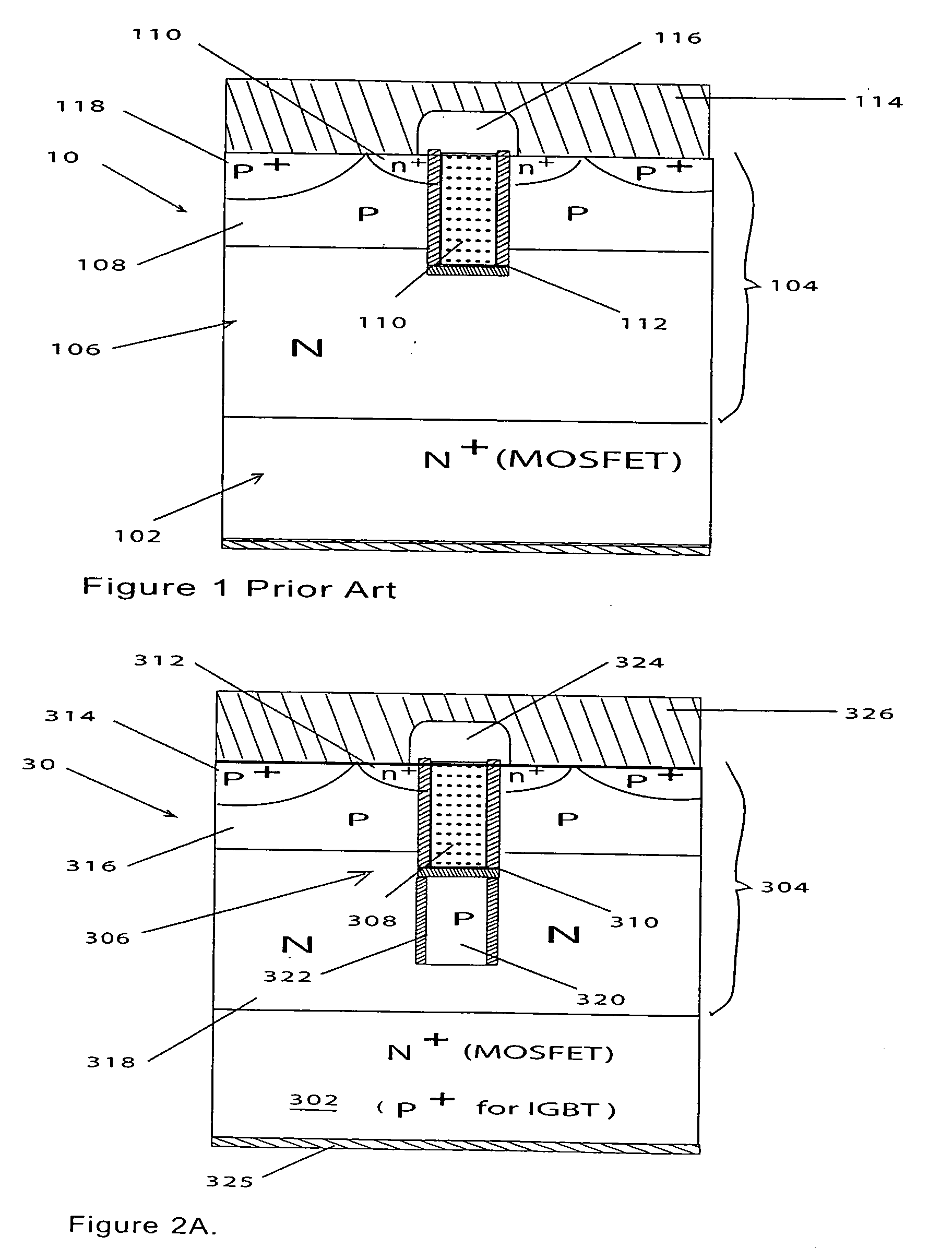

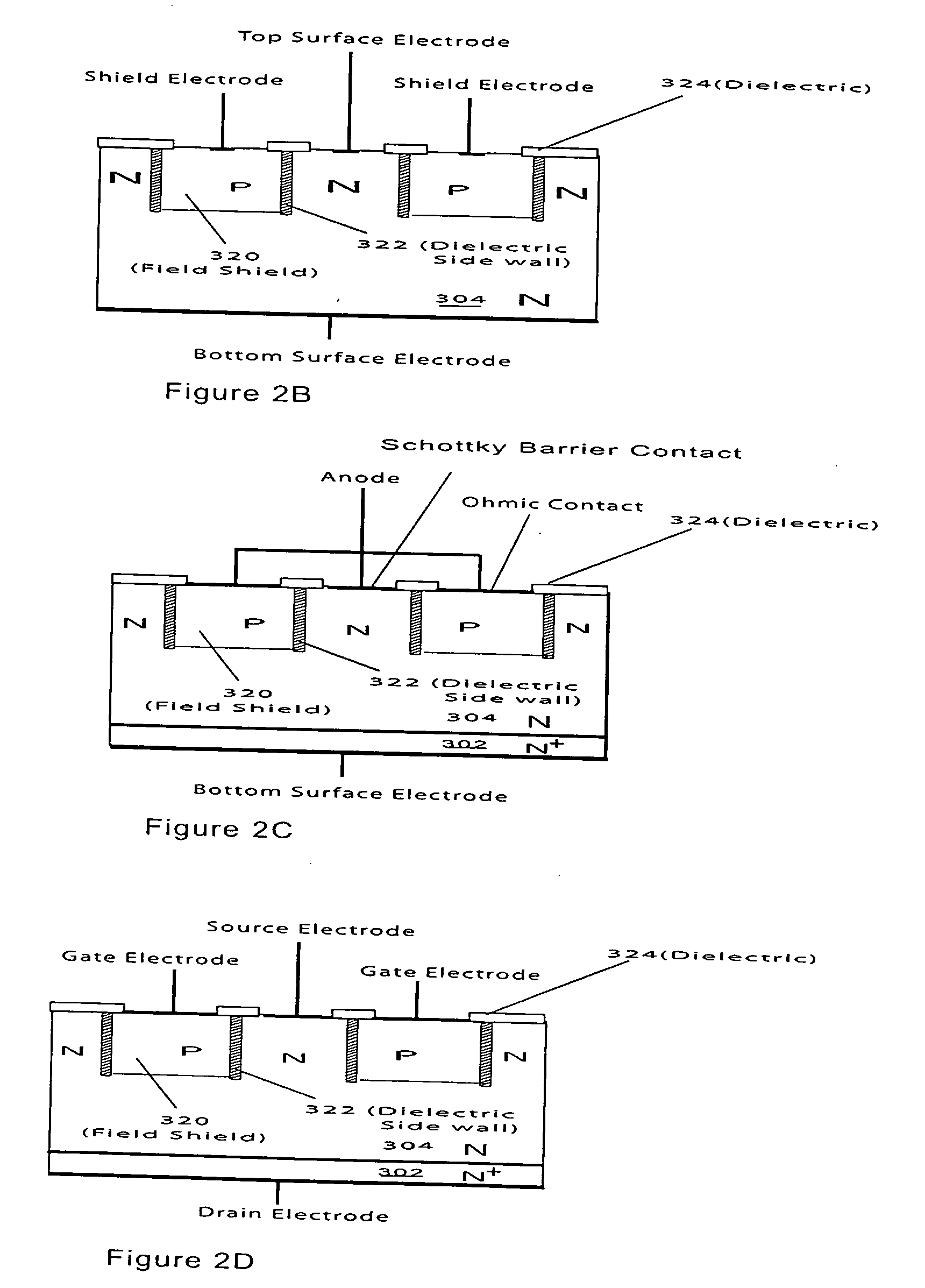

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

Warp-free semiconductor wafer, and devices using the same

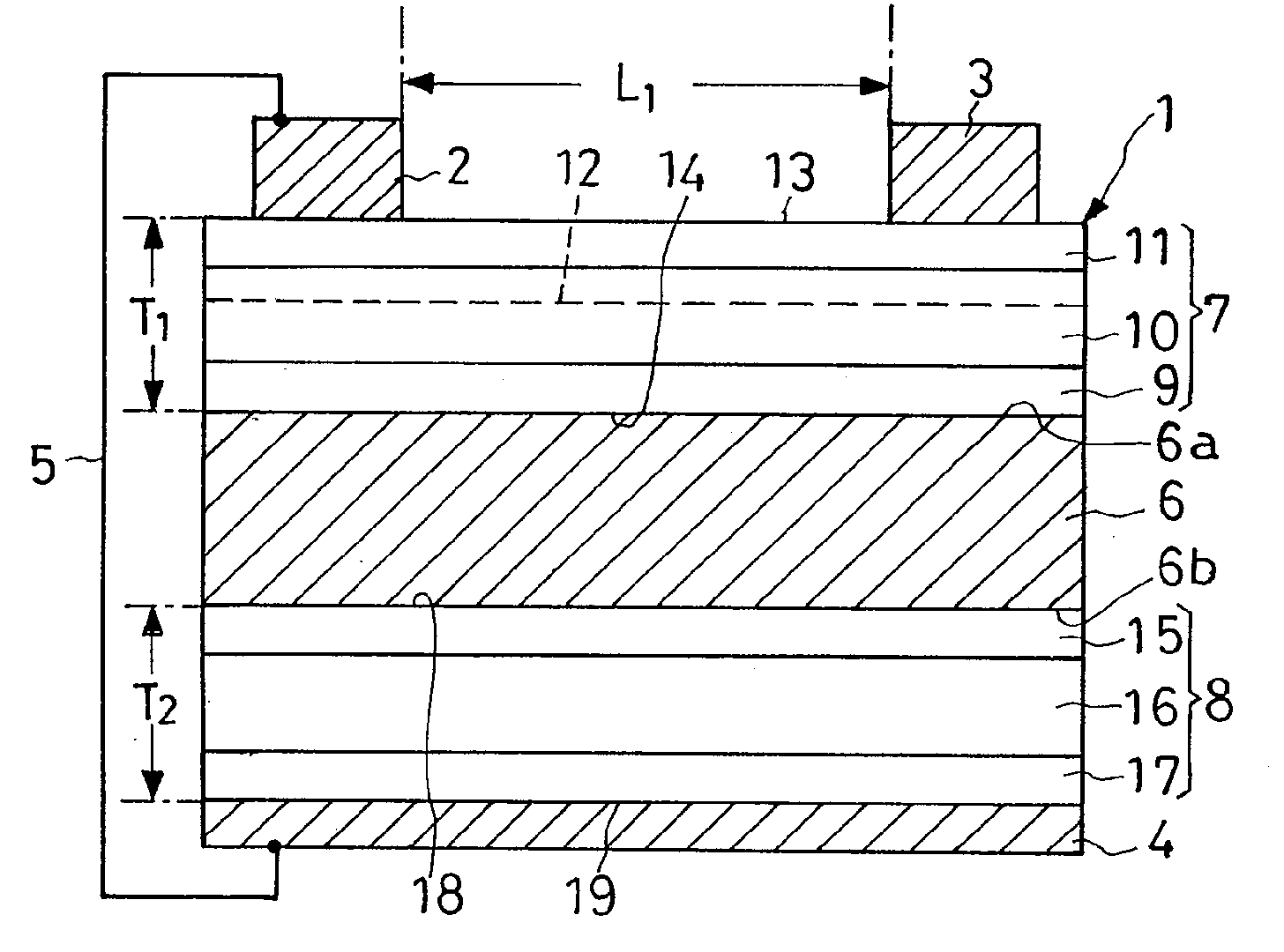

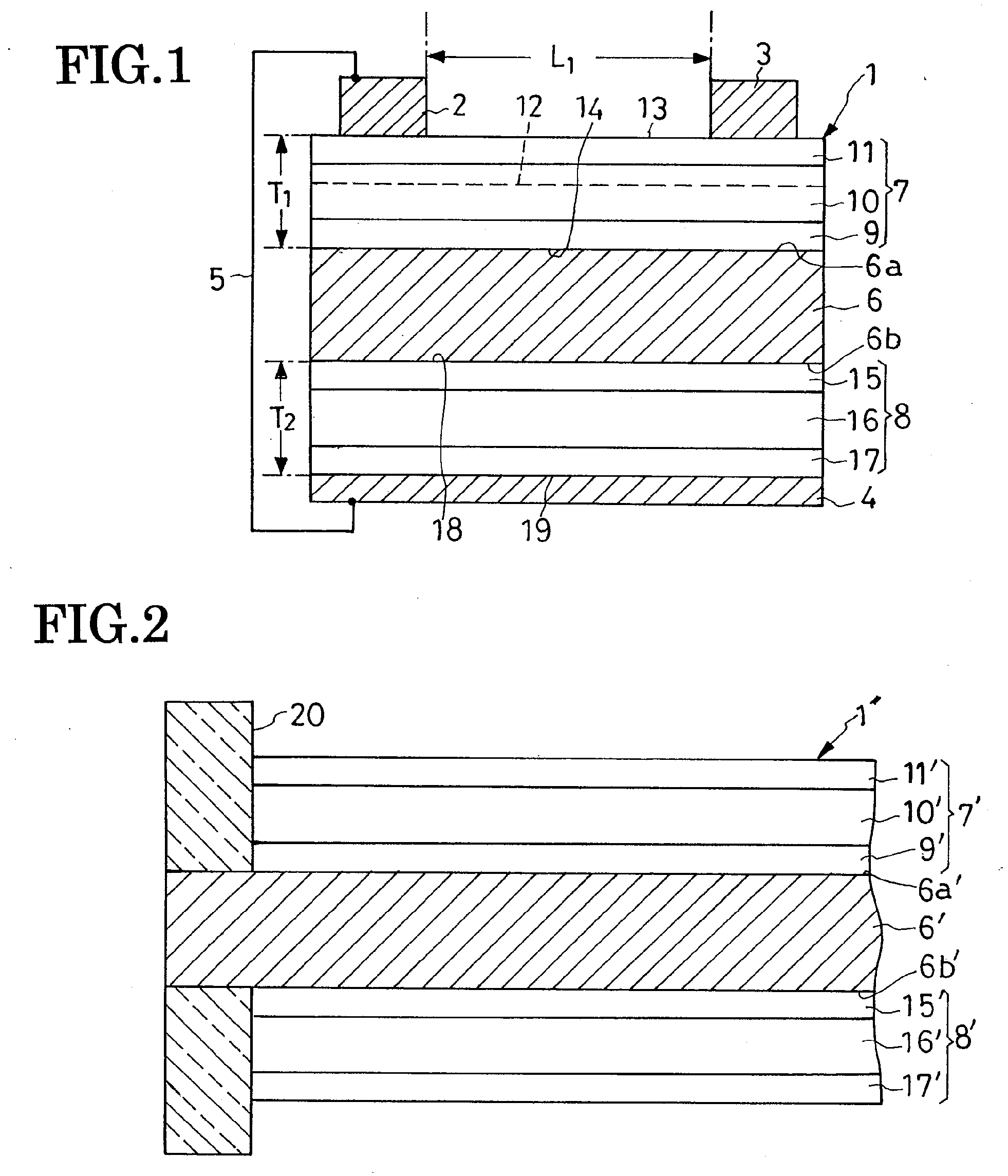

A semiconductor wafer to be diced into individual SBDs, HEMTs or MESFETs has a substrate with a main semiconductor region and counter semiconductor region formed on its opposite surfaces. The main semiconductor region is configured to provide the desired semiconductor devices. In order to counterbalance the warping effect of the main semiconductor region on the substrate, as well as to enhance the voltage strength of the devices made from the wafer, the counter semiconductor region is made similar in configuration to the main semiconductor region. The main semiconductor region and counter semiconductor region are arranged in bilateral symmetry as viewed in a cross-sectional plane at right angles with the substrate surfaces.

Owner:SANKEN ELECTRIC CO LTD

Isolated junction field-effect transistor

Various integrated circuit devices, in particular a junction field-effect transistor (JFET), are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

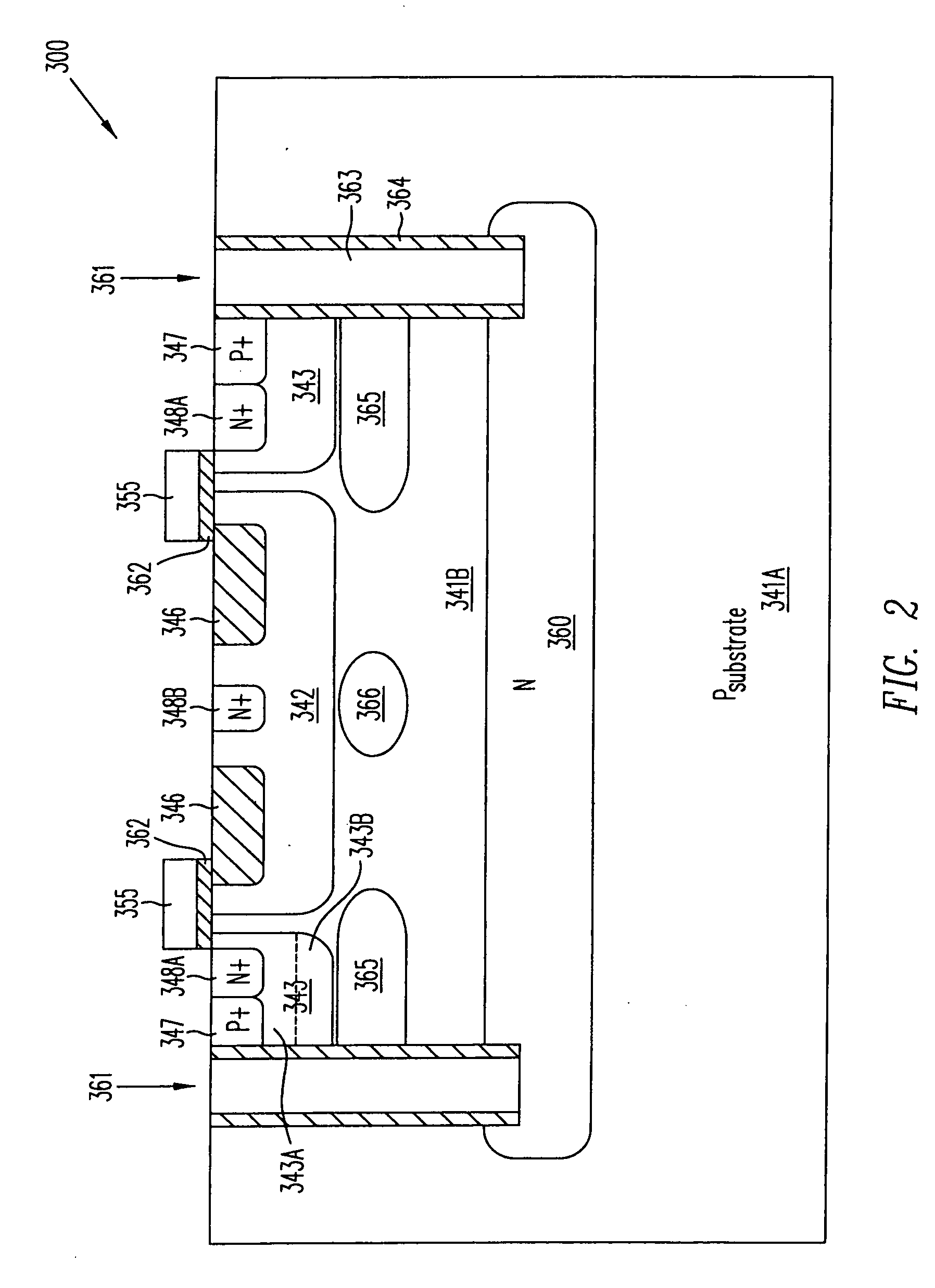

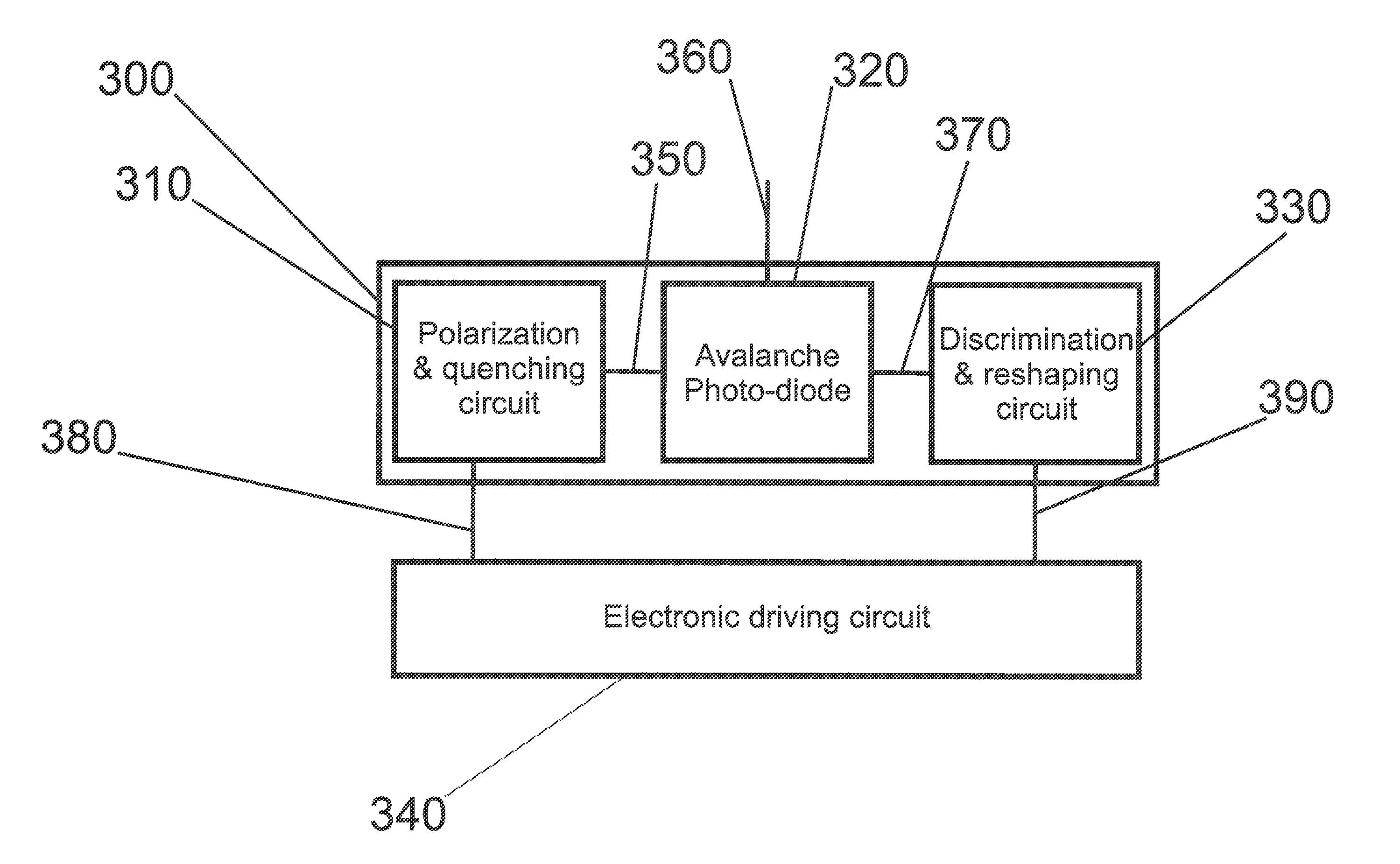

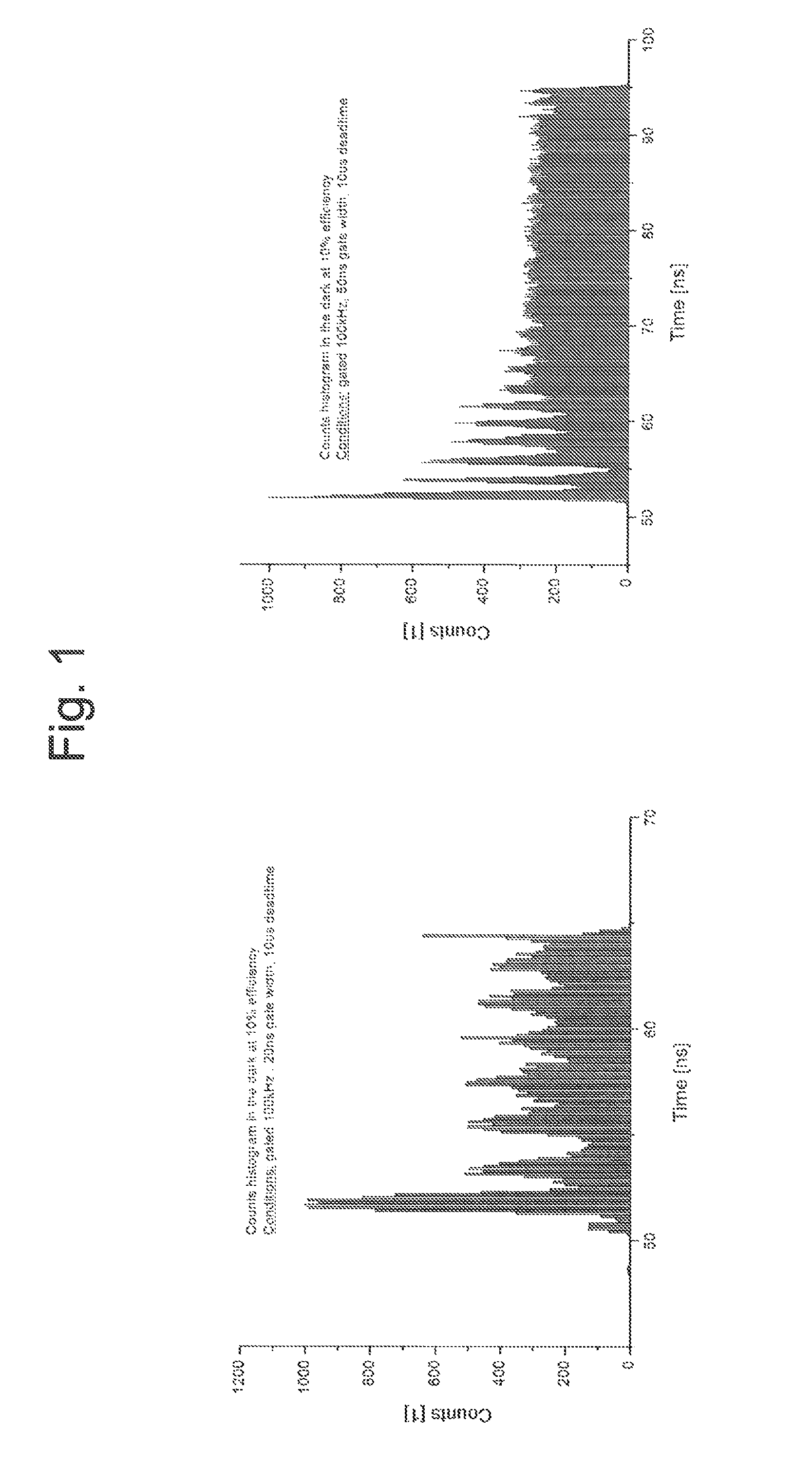

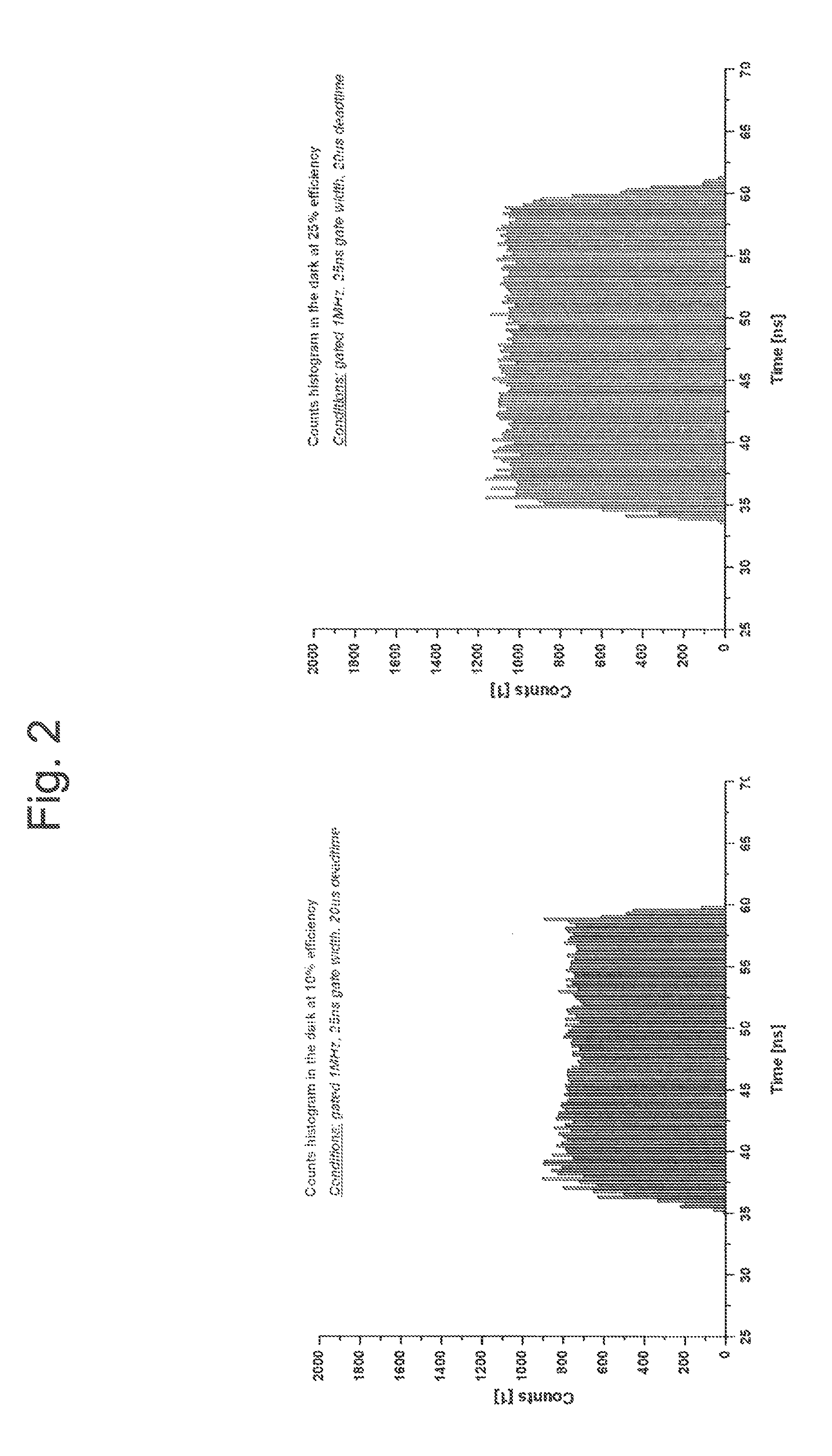

Apparatus and method for allowing avalanche photodiode based single-photon detectors to be driven by the same electrical circuit in gated and in free-running modes

An apparatus and method for allowing avalanche photodiode based single-photon detectors to be driven by the same electrical circuit in gated and in free-running modes is proposed. The high-performance working of all the running modes relies on the capability of tuning the rise-time value of the electrical pulse driver which activates the avalanche photodiode in Geiger mode.

Owner:ID QUANTIQUE SA