Patents

Literature

287results about How to "Reduce reverse leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor diode with reduced leakage

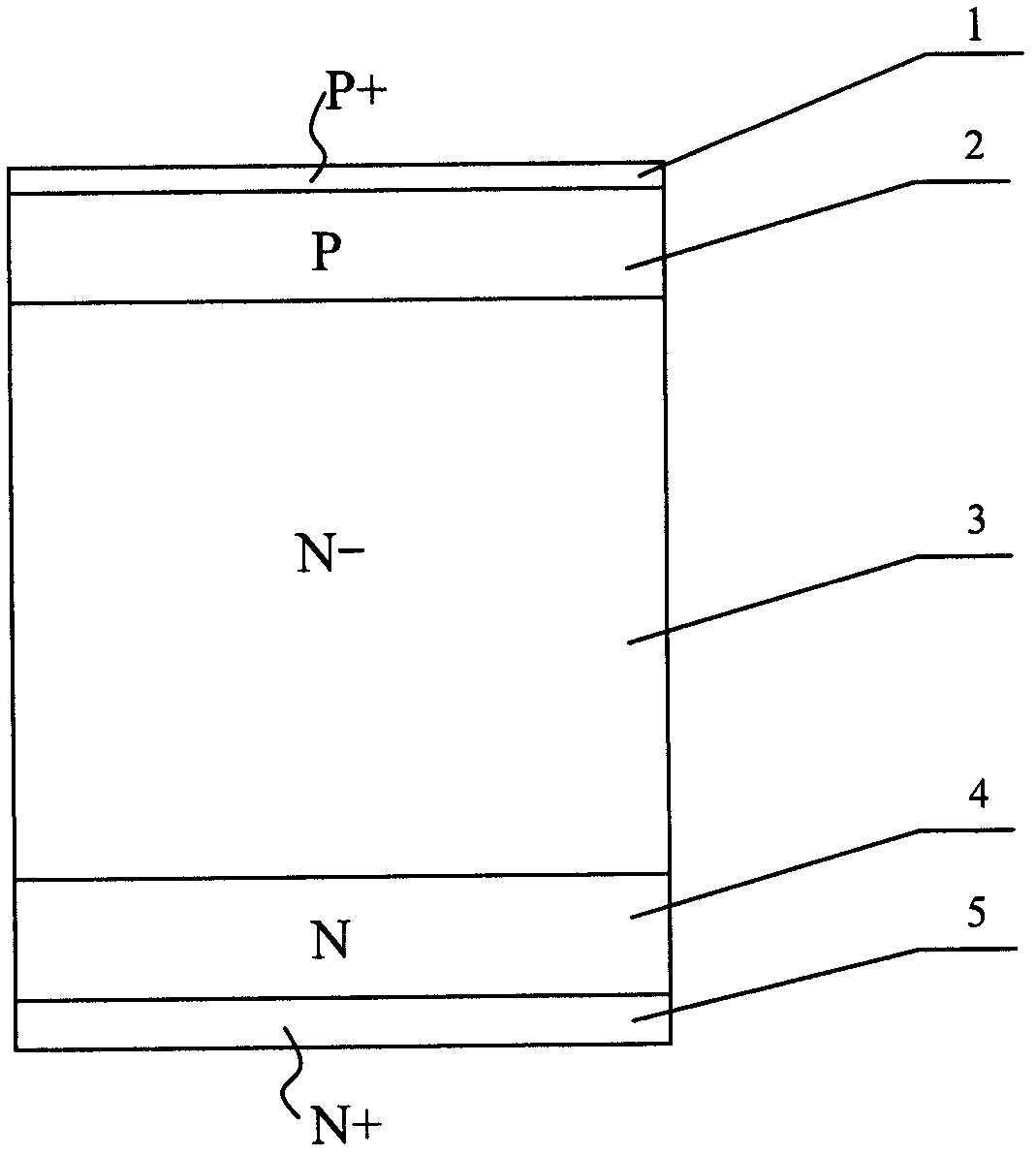

InactiveUS20050035410A1Reduce reverse leakage currentReduce leakage currentTransistorThyristorGate dielectricPermittivity

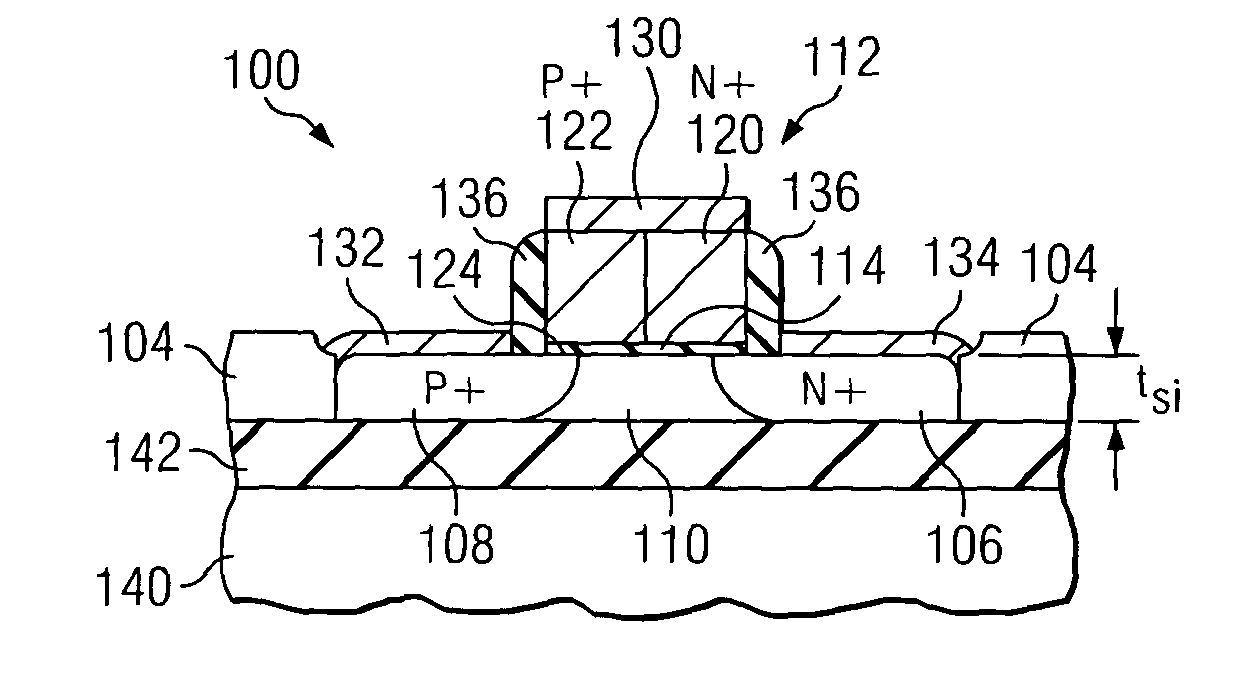

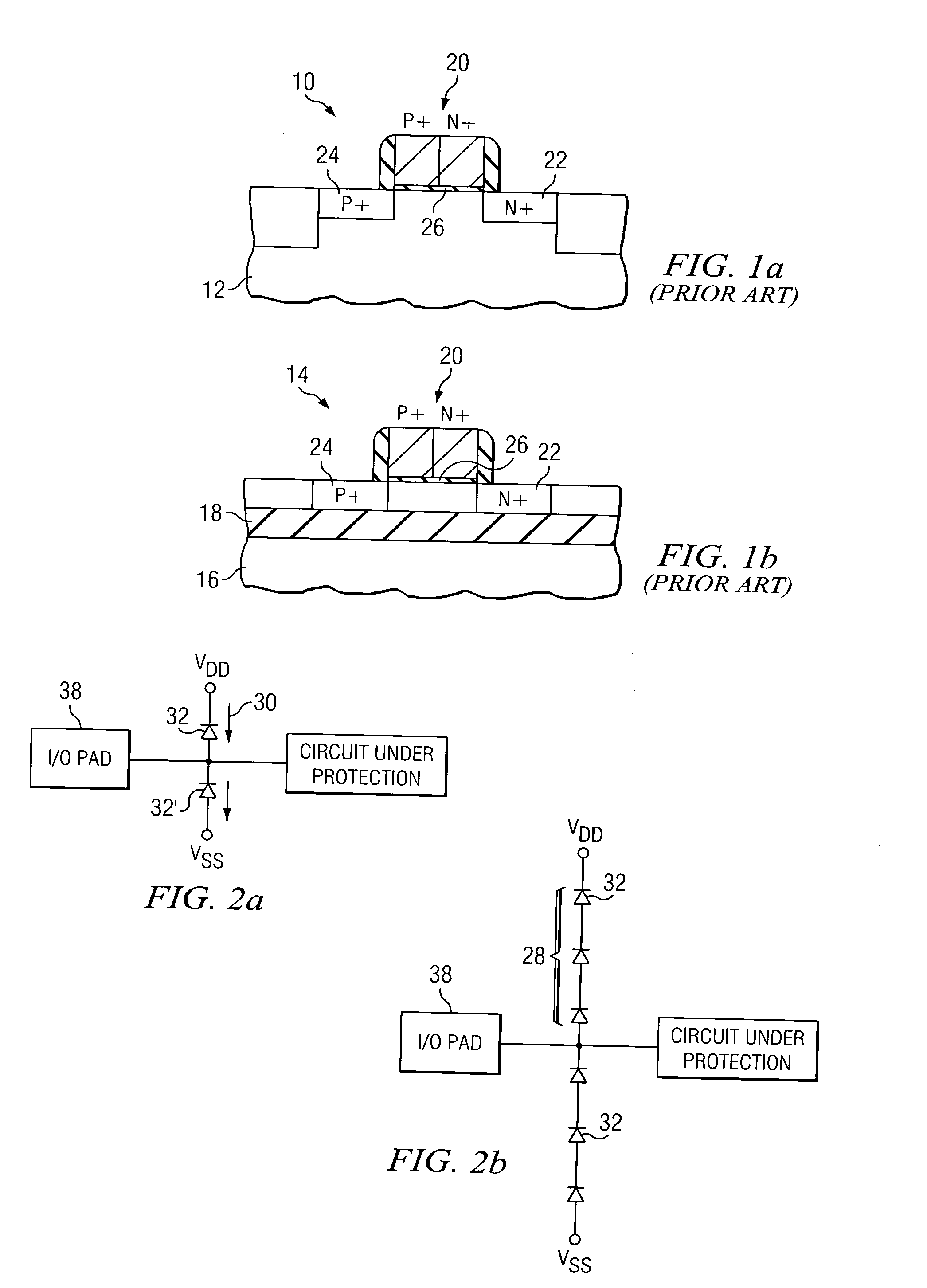

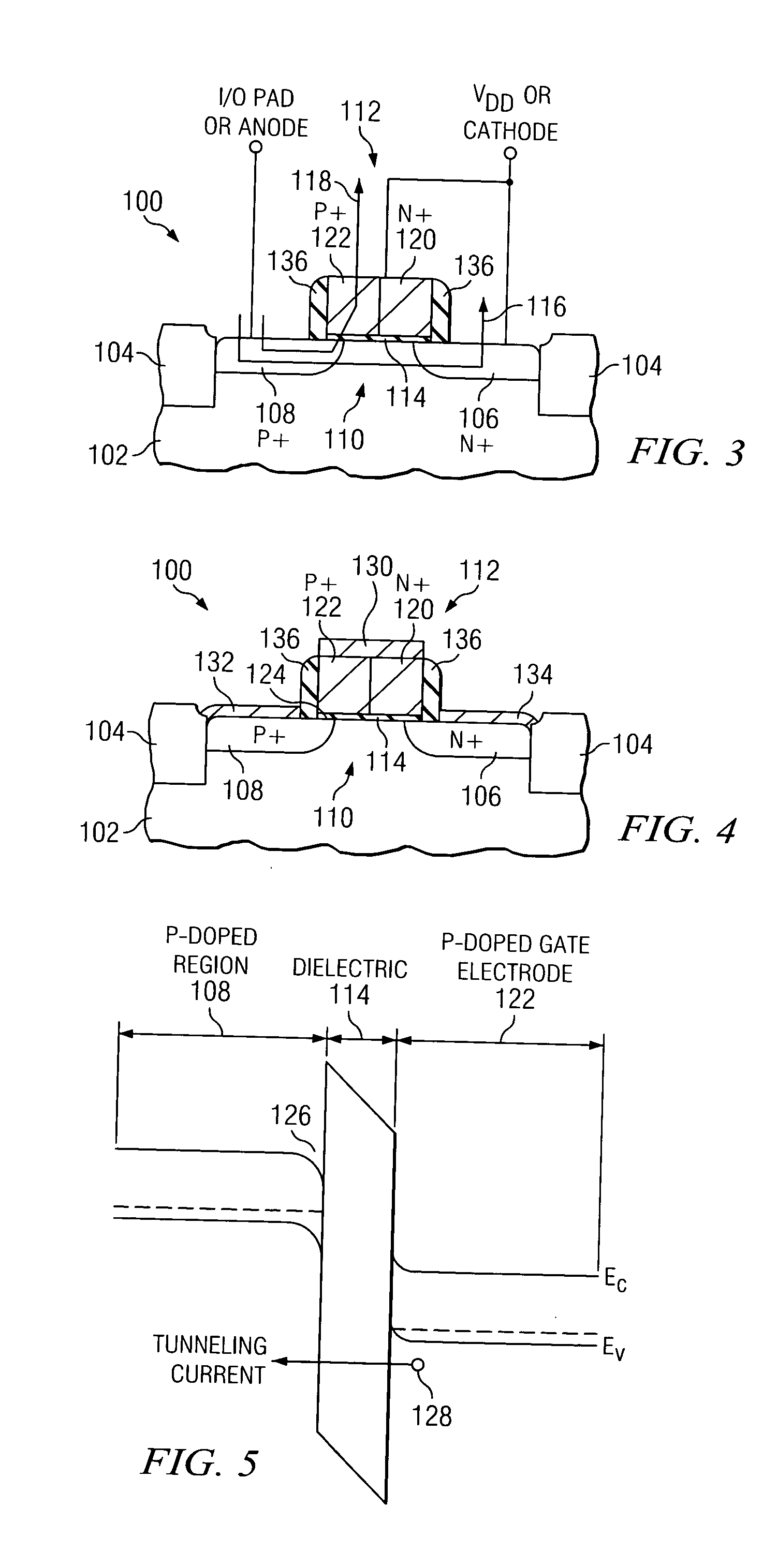

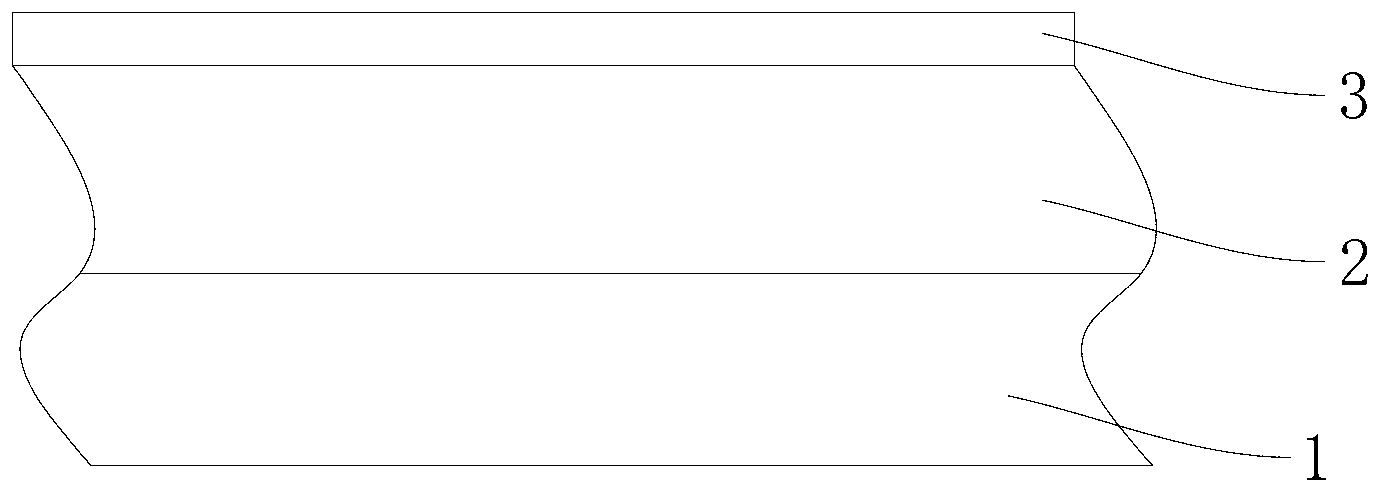

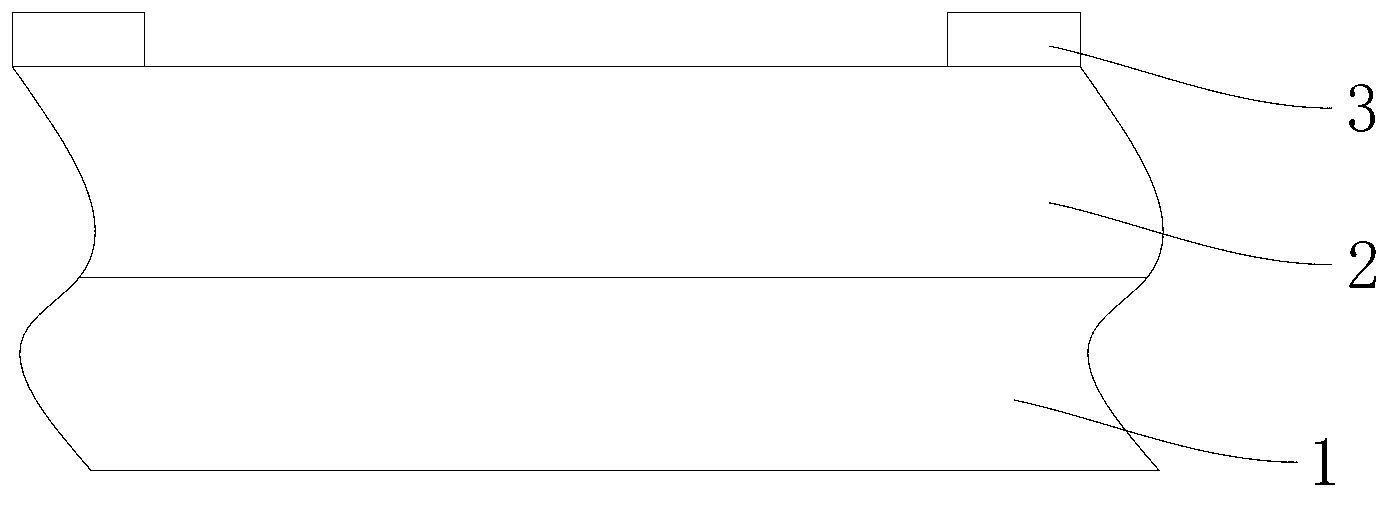

A diode 100 is formed on a silicon-on-insulator substrate that includes a silicon layer overlying an insulator layer 142. An active region is formed in the silicon layer and includes a p-doped region 108 and an n-doped region 106 separated by a body region 110. A high permittivity gate dielectric 114 overlies the body region 110 and a gate electrode 112 overlies the gate dielectric 114. As an example, the diode can be used for ESD protection.

Owner:TAIWAN SEMICON MFG CO LTD

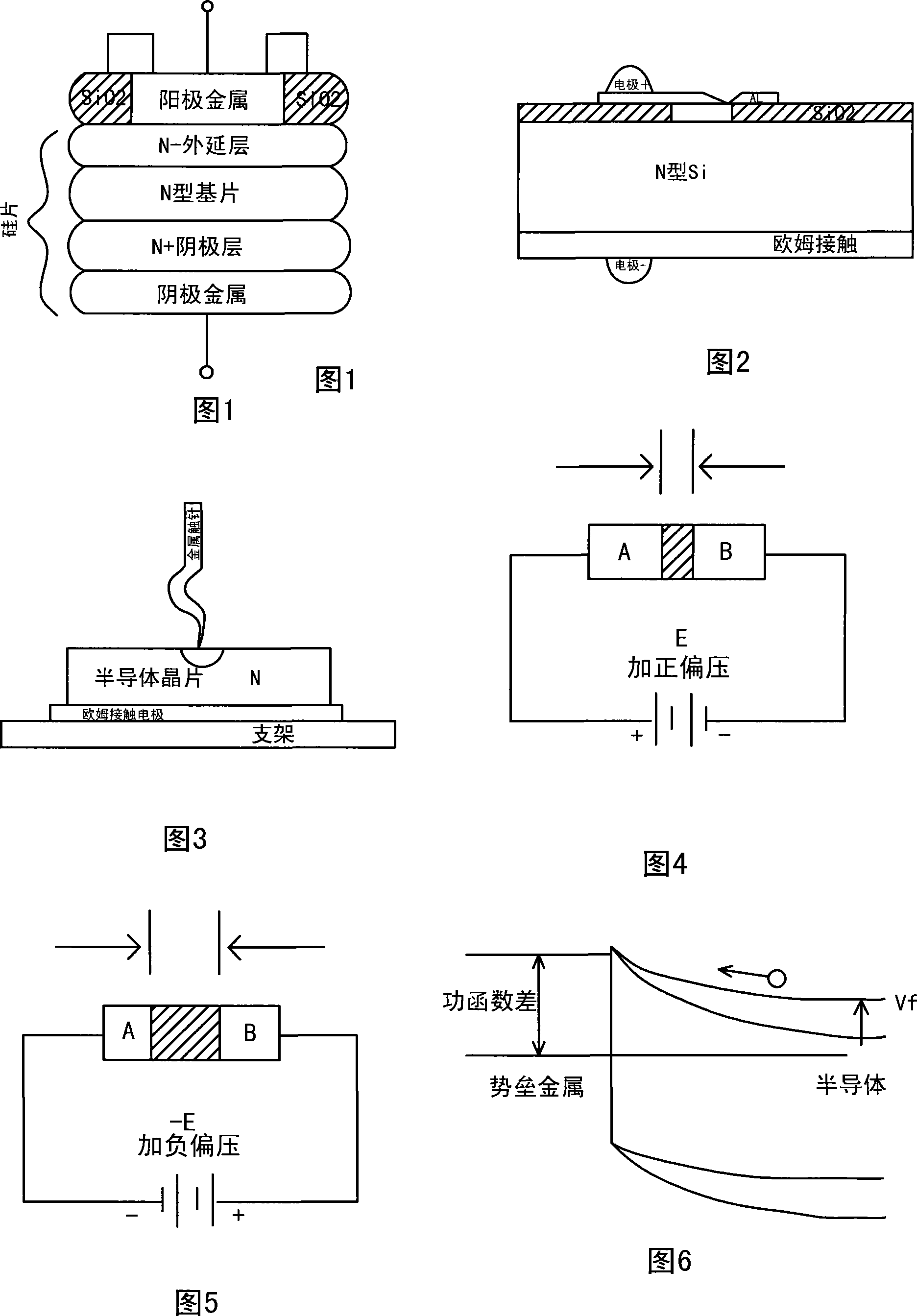

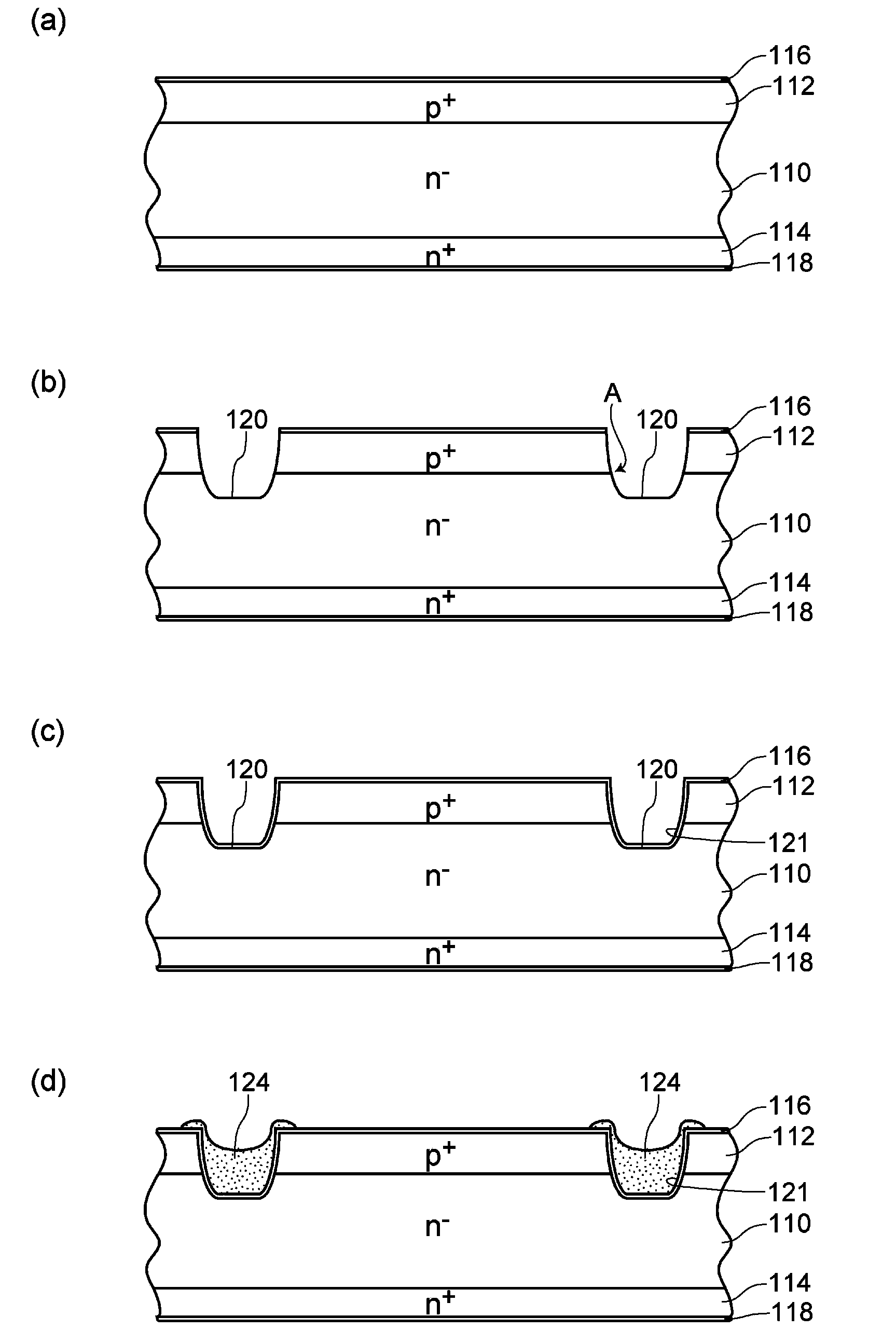

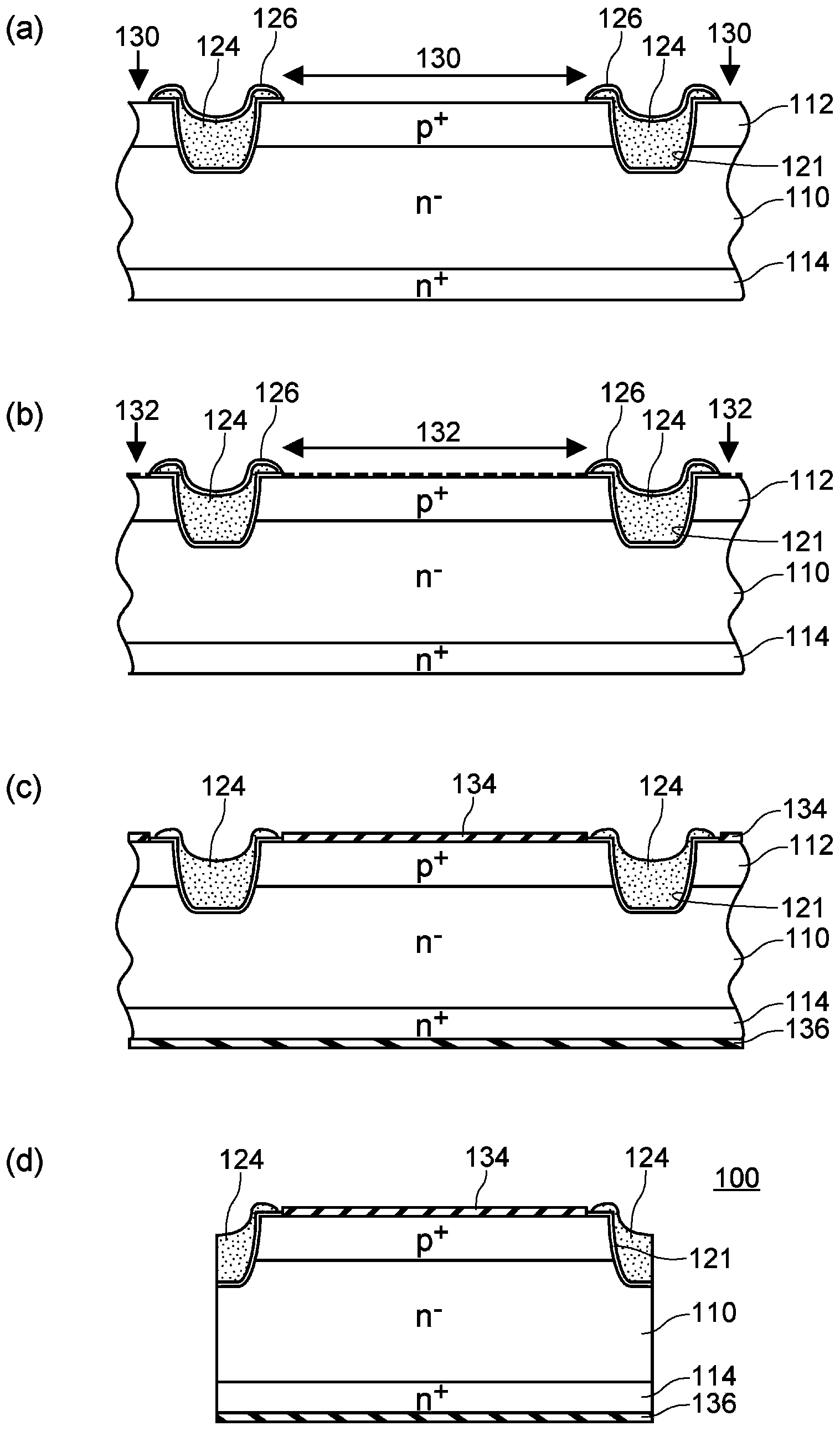

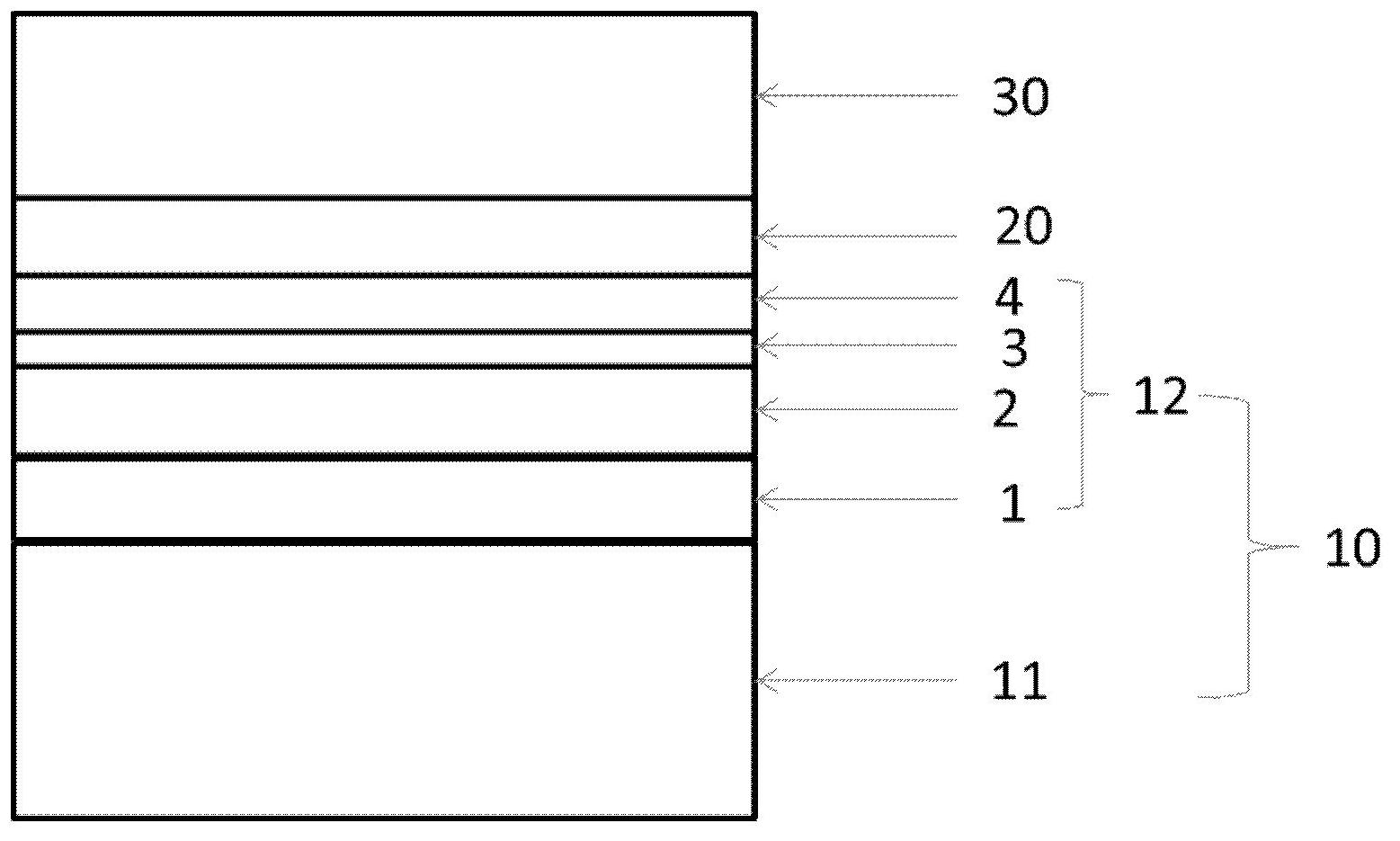

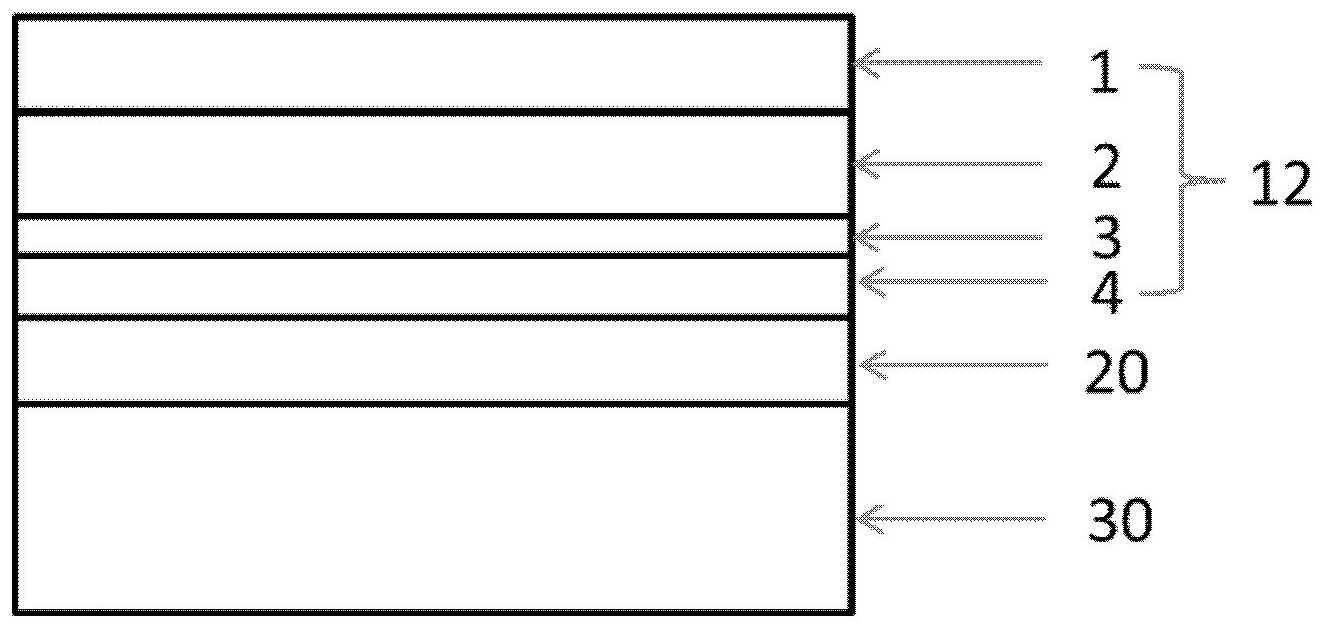

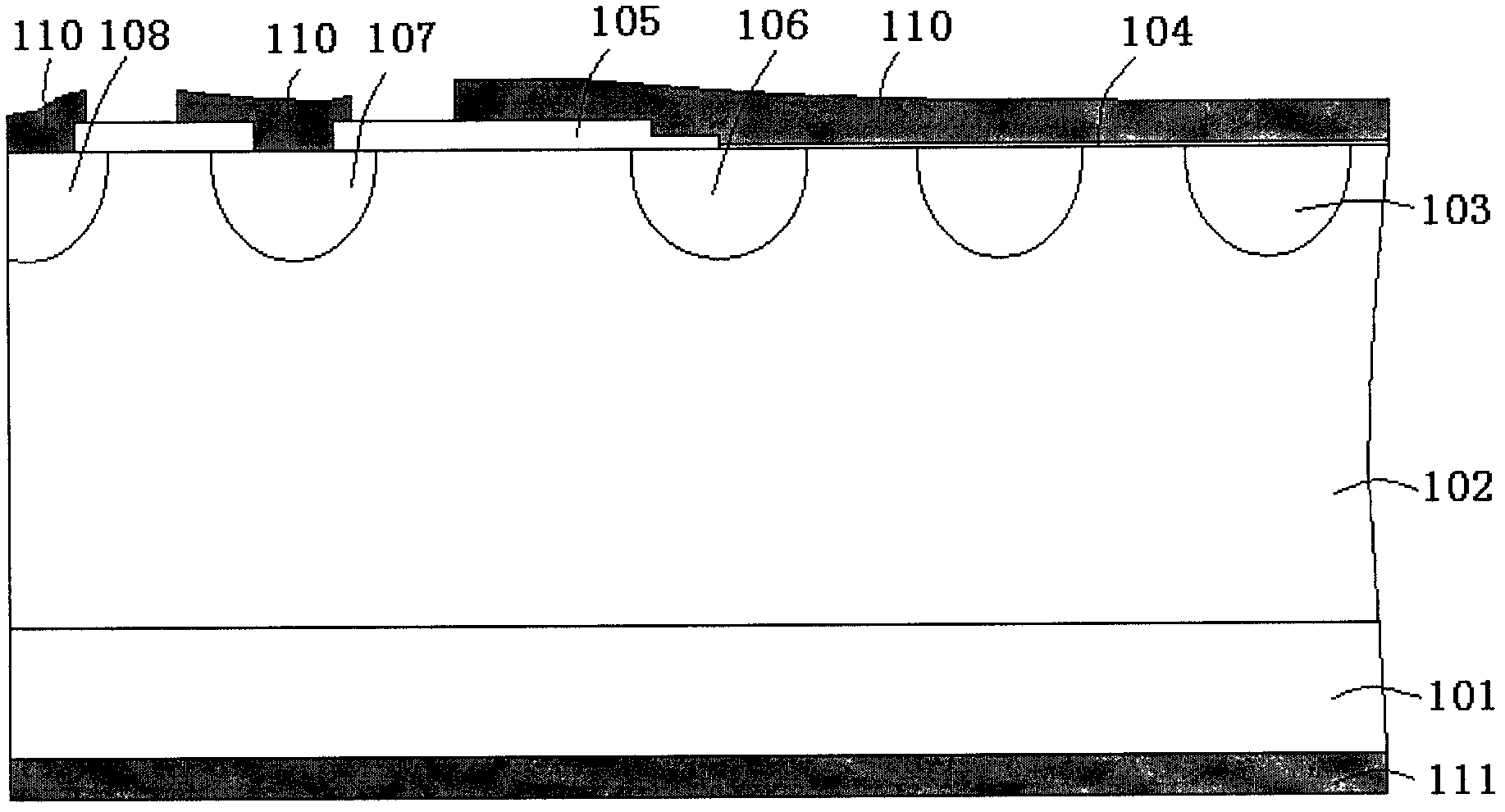

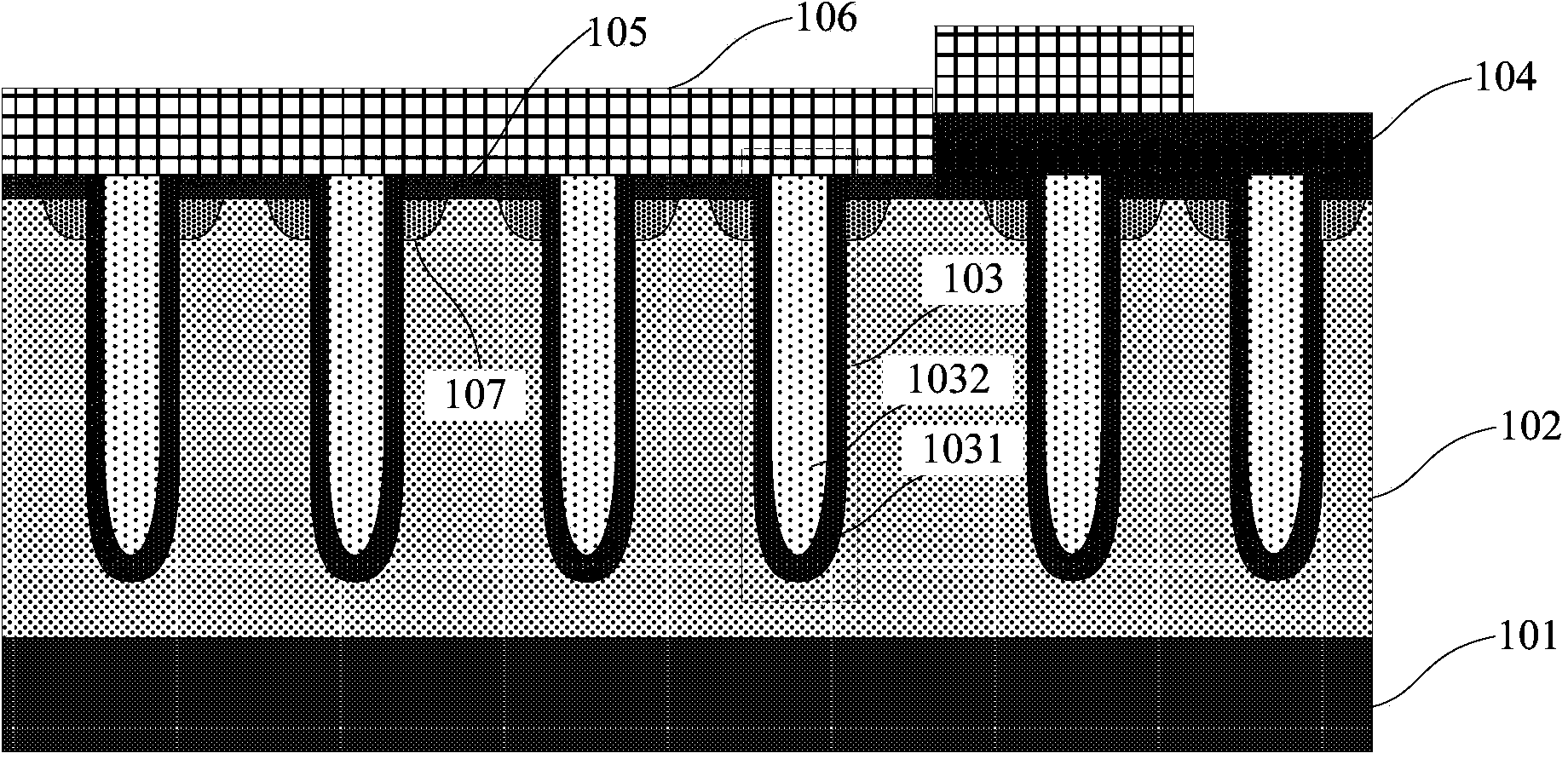

Trench schottky with multiple epi structure

InactiveUS20090309181A1Reduce doping concentrationIncrease the doping concentrationSemiconductor devicesDopantSchottky barrier

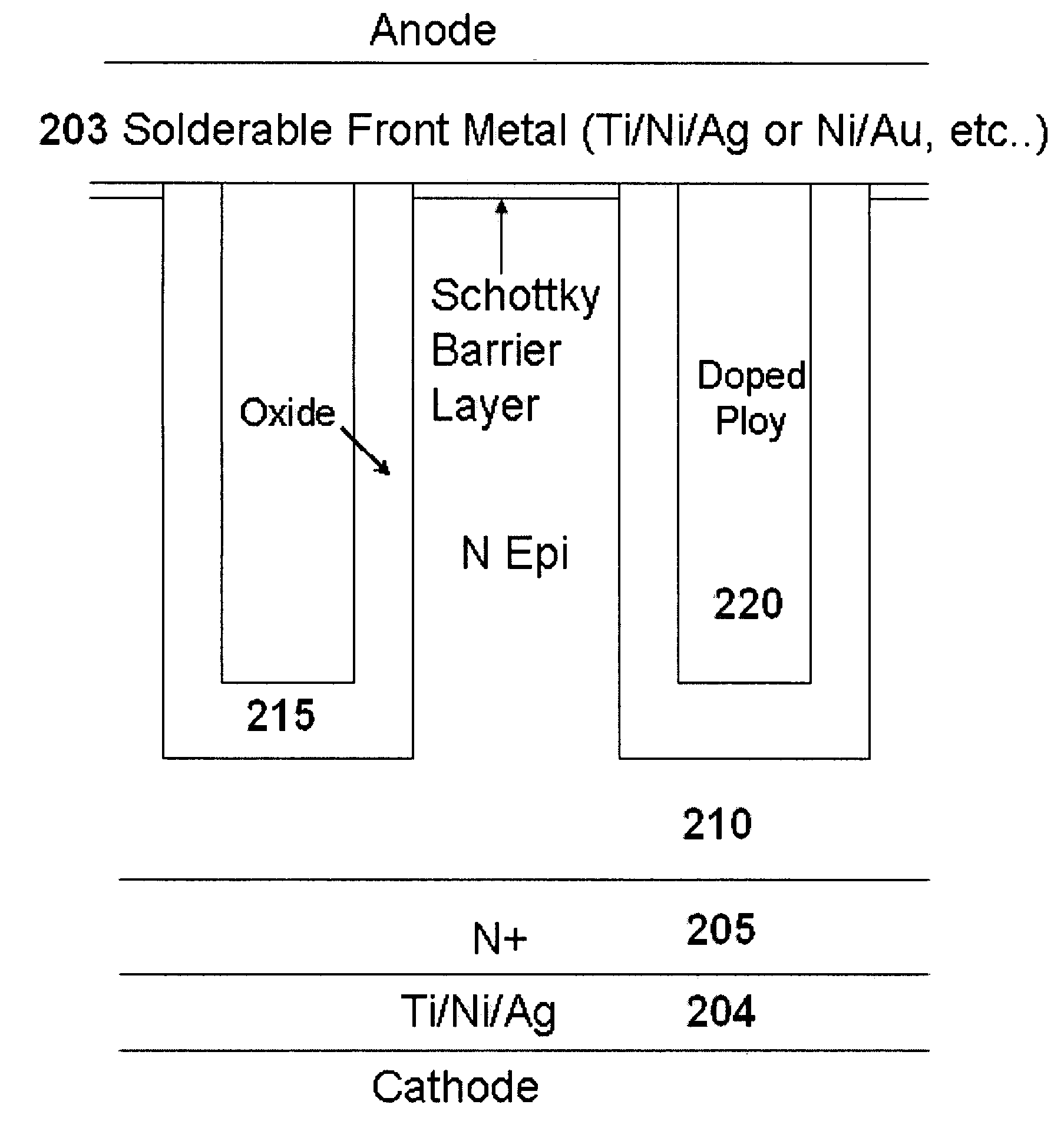

A trench Schottky barrier rectifier includes an cathode electrode at a face of a semiconductor substrate and an multiple epitaxial structure in drift region which in combination provide high blocking voltage capability with low reverse-biased leakage current and low forward voltage. The multiple structure of the drift region contains a concentration of first conductivity dopants therein which comprises two or three different uniform value from a Schottky rectifying junction formed between the anode electrode and the drift region. The thickness of the insulating region (e.g., SiO2) in the MOS-filled trenches is greater than 1000 Å to simultaneously inhibit field crowing and increase the breakdown voltage of the device. The multiple epi structure is preferably formed by epitaxial growth from the cathode region and doped in-situ.

Owner:FORCE MOS TECH CO LTD

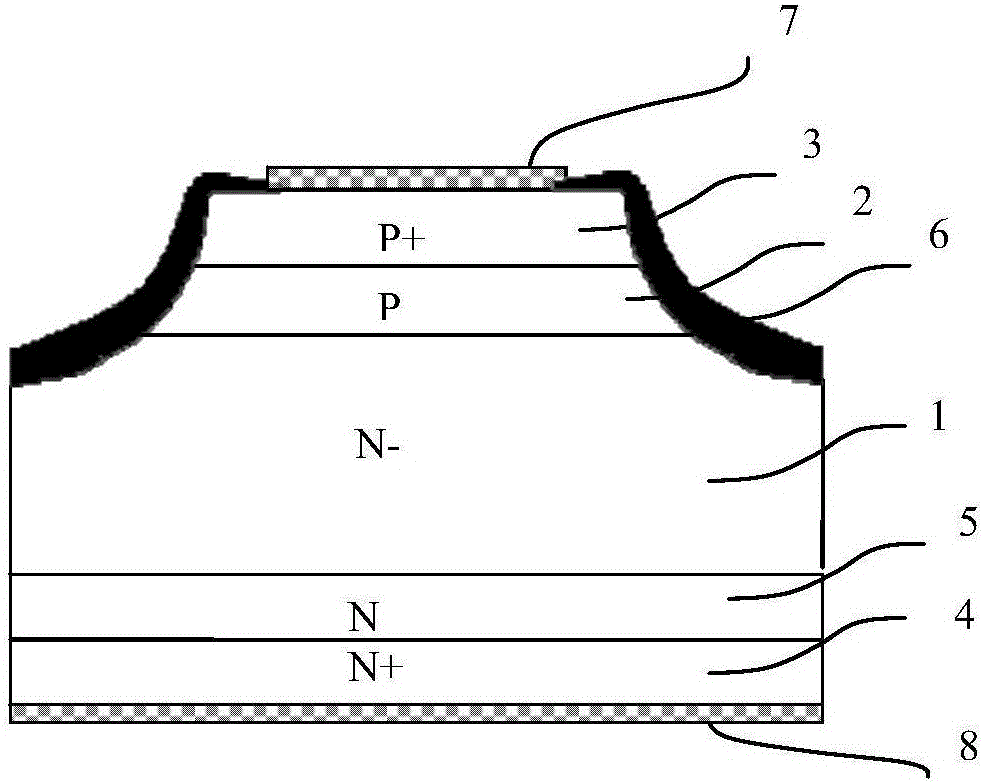

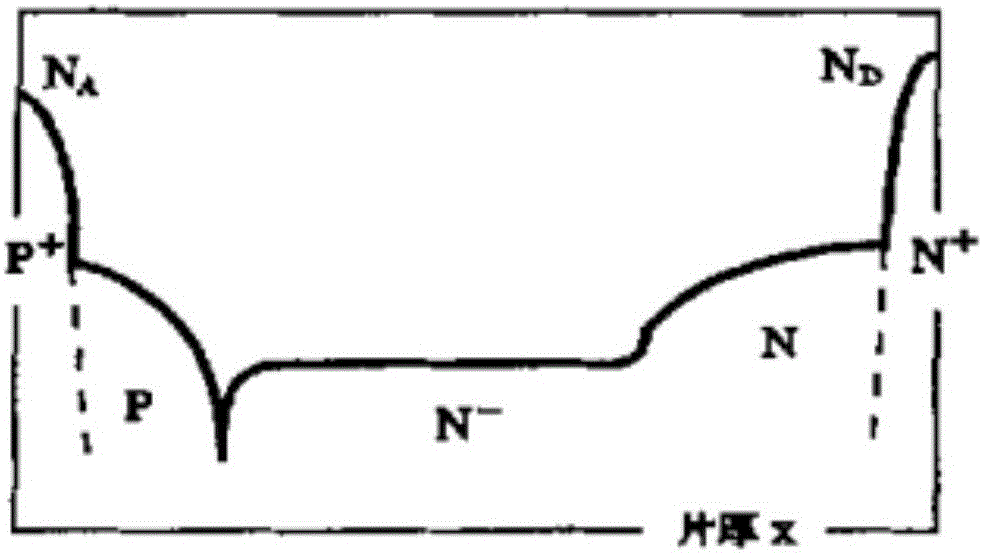

Method for manufacturing planar high-voltage ultrafast soft recovery diode

ActiveCN102569067ALow costMeet the requirements of mass productionSemiconductor/solid-state device manufacturingPlatinumLow leakage

The invention discloses a method for manufacturing a planar high-voltage ultrafast soft recovery diode. The method comprises the following steps of: oxidizing, and photoetching to form an active region and a field limiting ring; doping and pushing; manufacturing a polycrystalline silicon field plate; performing platinum diffusion; thinning; forming an N-type buffer layer; performing contact doping and annealing; and metalizing. The method can be used for manufacturing an ultrafast soft recovery diode chip which is low in cost and short in recovery time and has high-voltage resistance, low leakage current, low forward voltage drop and soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

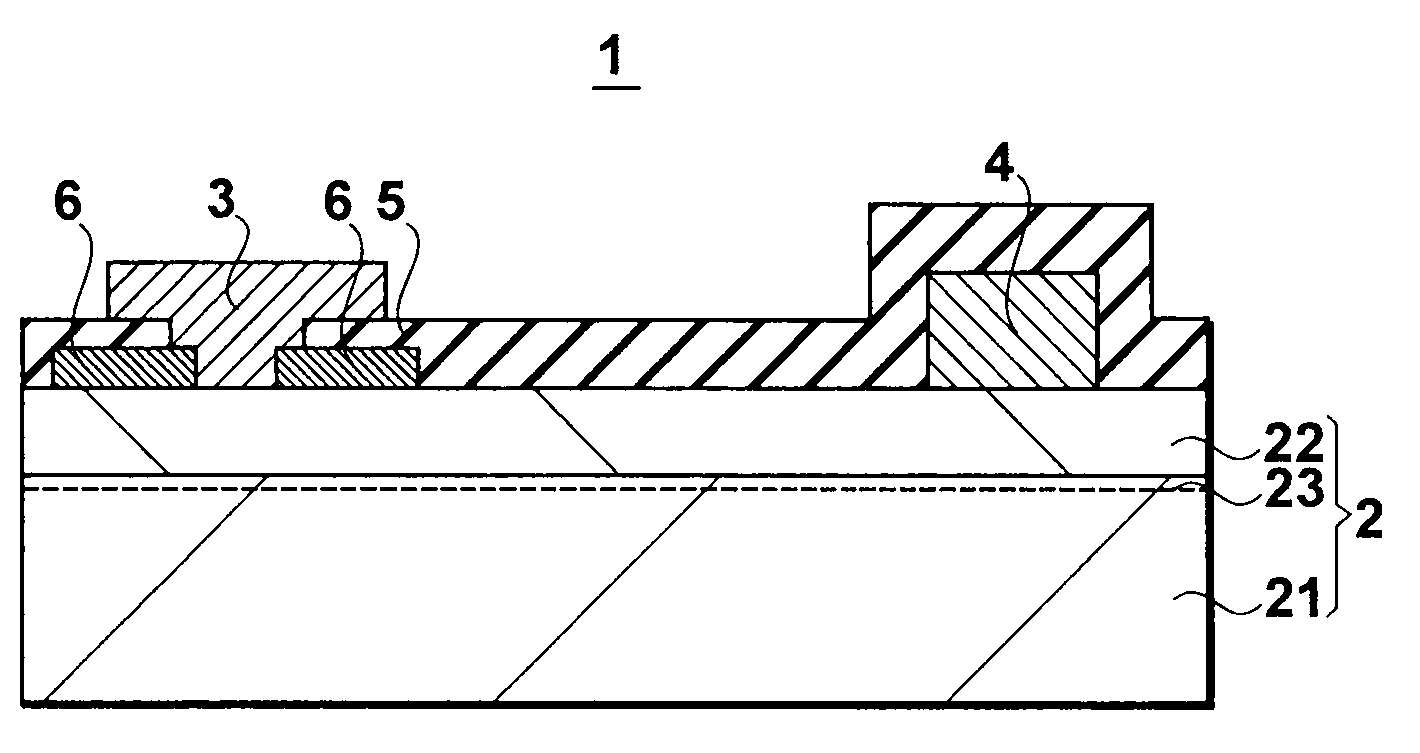

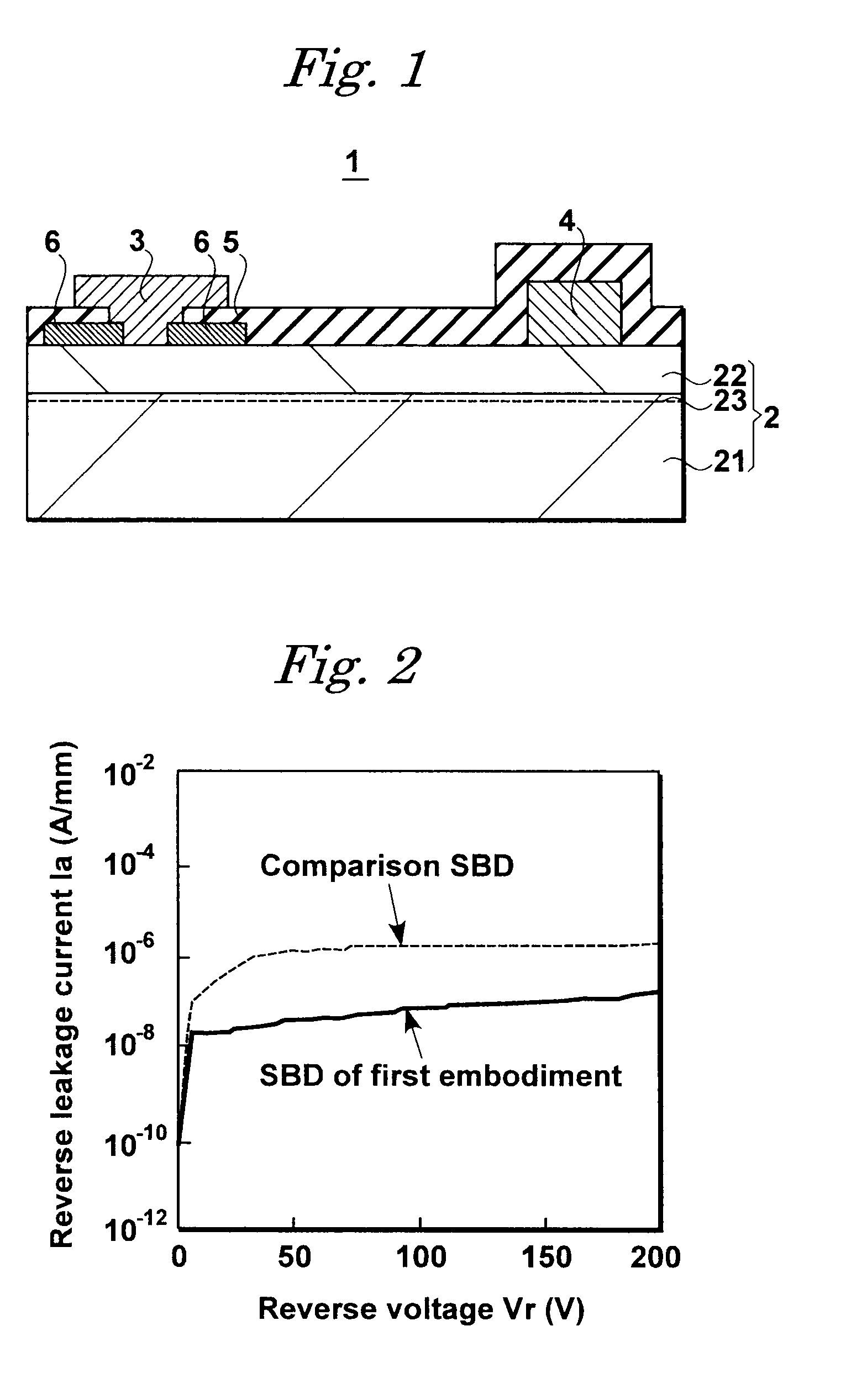

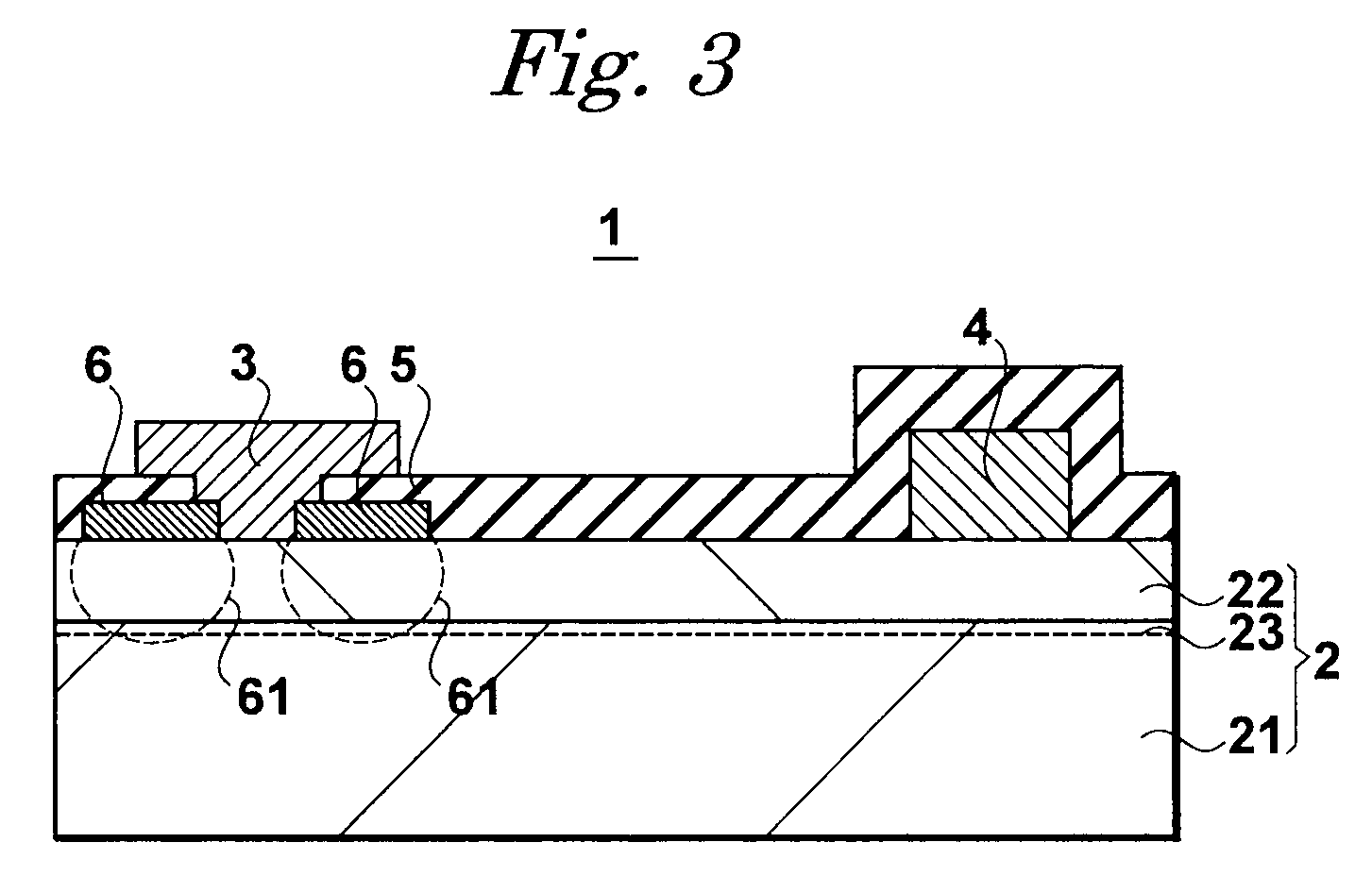

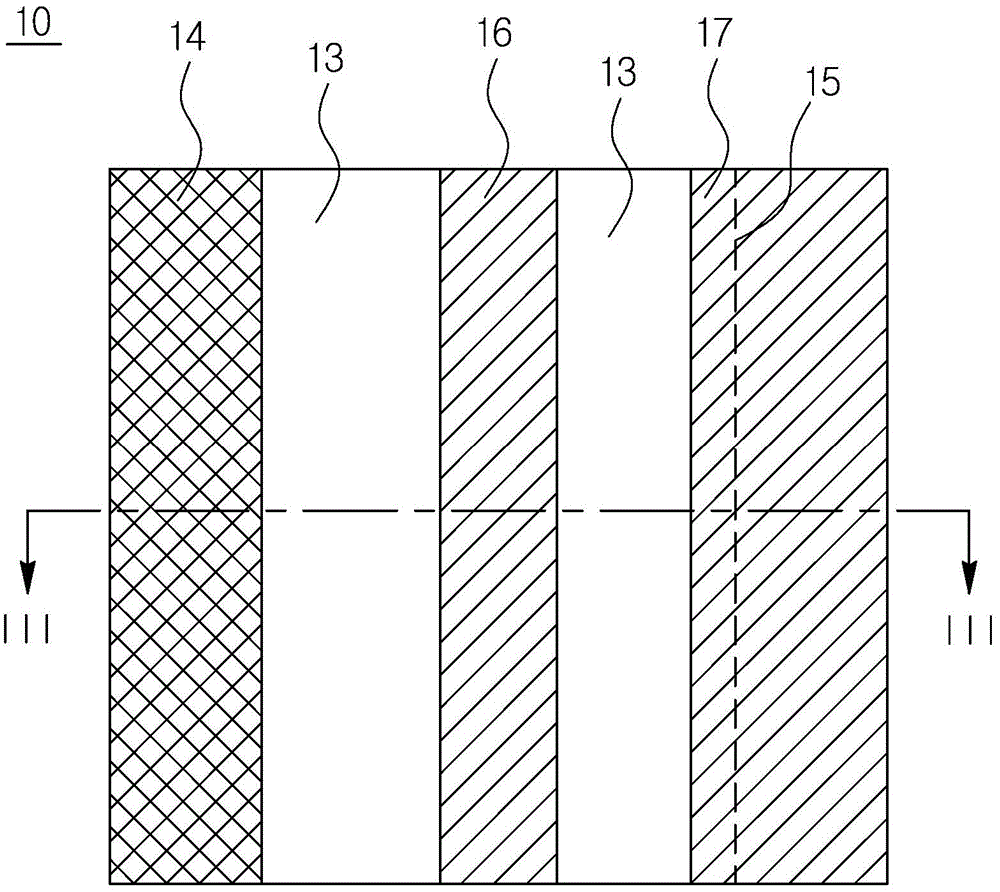

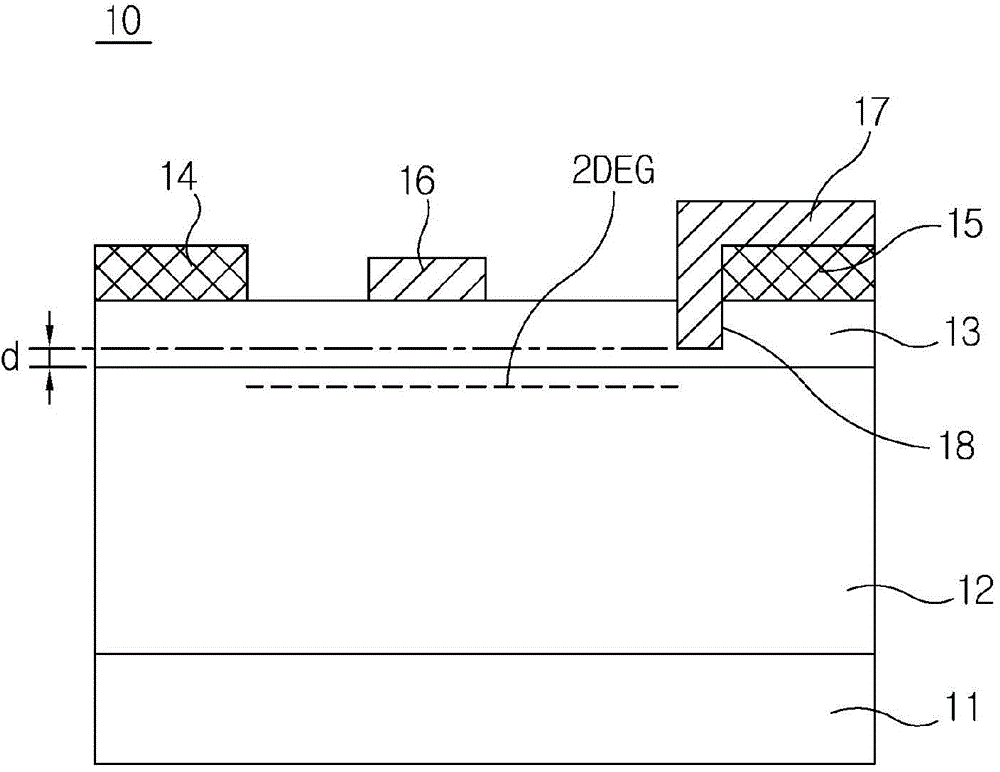

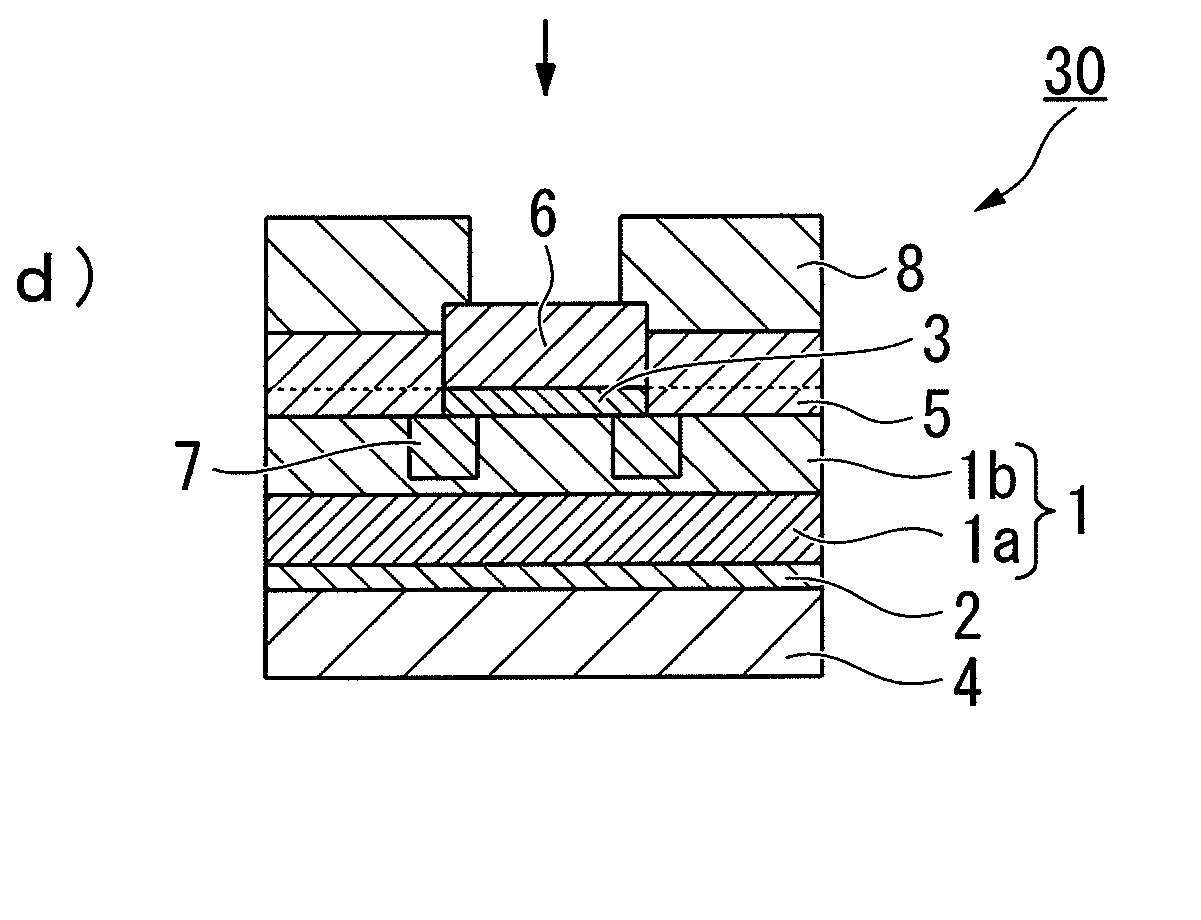

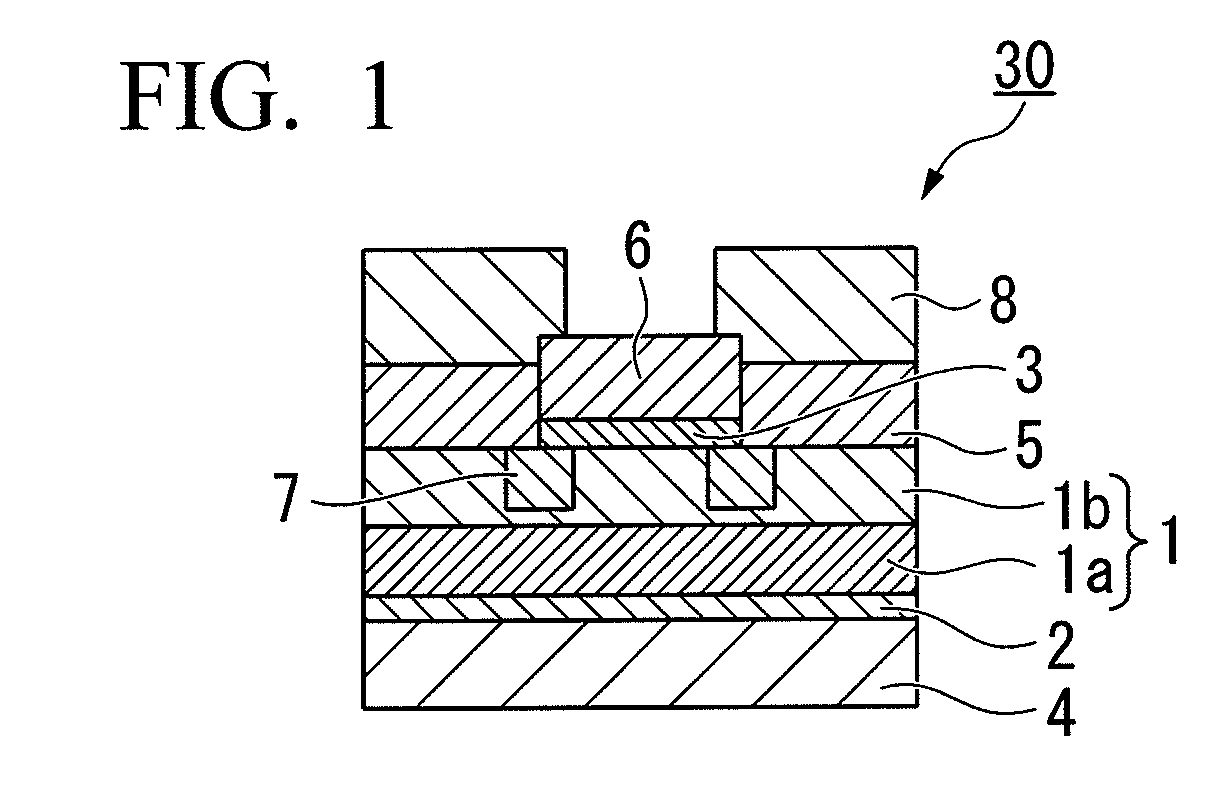

Semiconductor device

ActiveUS20100078683A1Maintain forward characteristicReduce reverse leakage currentSemiconductor devicesNitrideSemiconductor

A semiconductor device include: a nitride group semiconductor functional layer including a second nitride group semiconductor region on a first nitride group semiconductor region where a two-dimensional carrier gas layer is made, the second nitride group semiconductor region functioning as a barrier layer; a first main electrode electrically connected to one end of the two-dimensional carrier gas layer; a second main electrode electrically connected to the other end of the two-dimensional carrier gas layer; and metal oxide films placed between the first and second main electrodes, electrically connected to the first main electrode, and reducing a carrier density of the two-dimensional carrier gas layer.

Owner:SANKEN ELECTRIC CO LTD

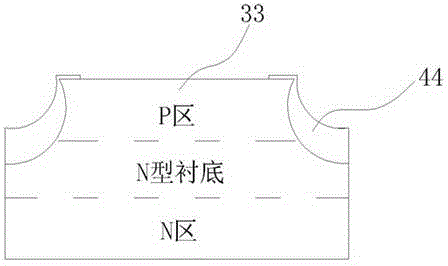

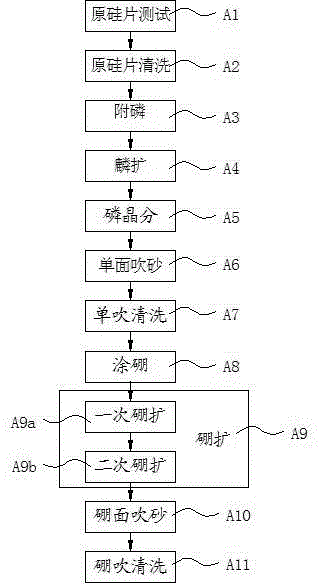

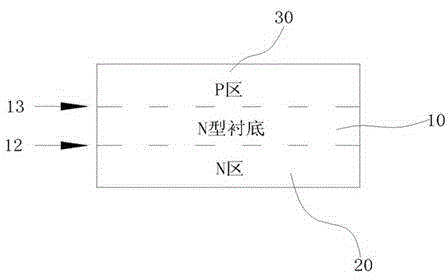

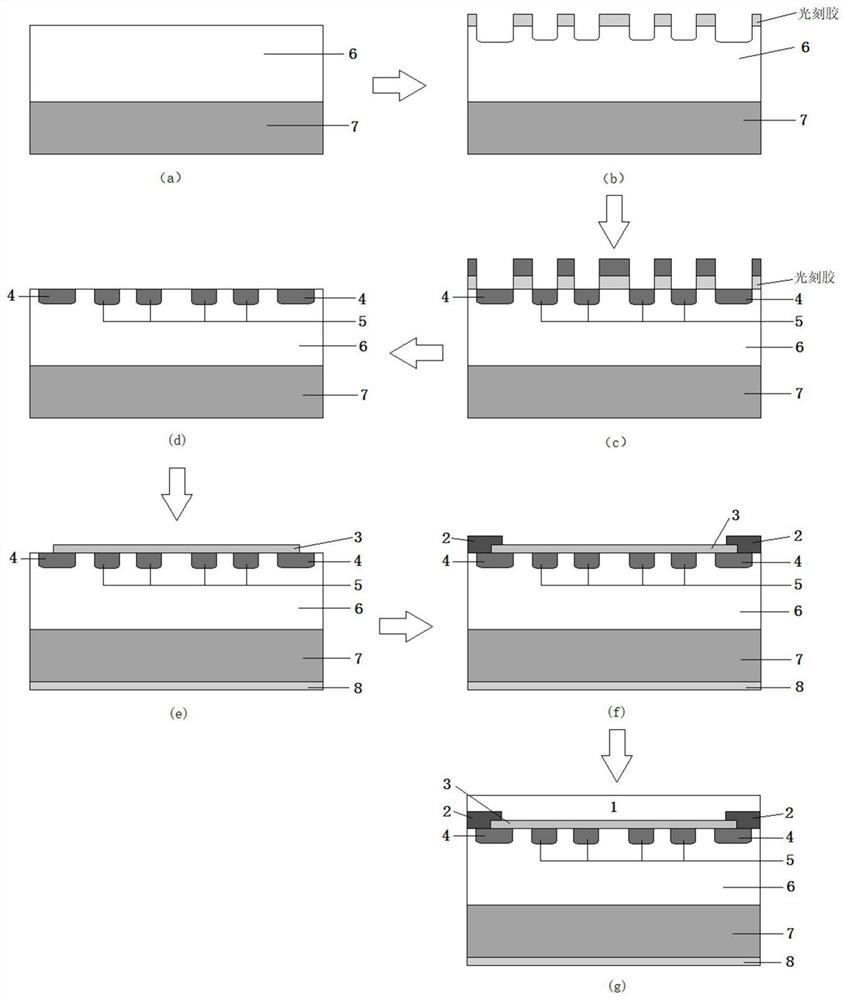

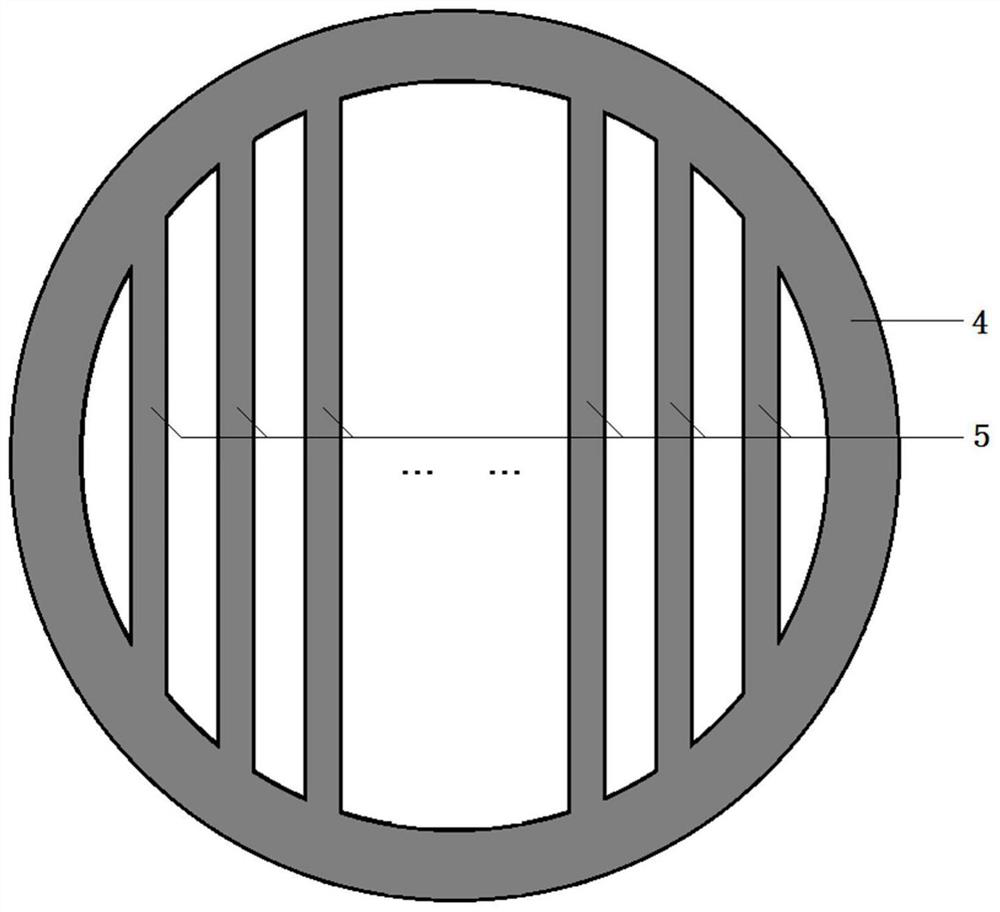

Manufacturing process of transient voltage suppression diode chip

ActiveCN103606521AStress reliefReduce defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a manufacturing process of a transient voltage suppression diode chip. The manufacturing process of the transient voltage suppression diode chip includes two production processes: a diffusion process and a GPP process. The steps of the diffusion process include original silicon wafer testing, original silicon wafer washing, phosphorus attachment, phosphorus diffusion, phosphorus wafer separation, single side sand blasting, single blasting washing, boron coating, boron diffusion, boron wafer separation, boron side sand blasting, and boron blasting washing, wherein the step of boron diffusion comprises primary boron diffusion and secondary boron diffusion; and the steps of the GPP process sequentially include oxidation, primary photoetching, groove etching, photoresist sintering, groove washing, SIPOS passive film formation, glassivation, secondary photoetching, surface etching, and nickel-gold plating. The manufacturing process of the transient voltage suppression diode chip in the invention reduces defects of the chip, enables voltage distribution to be relatively concentrated, and reduces reverse leakage current at the same time.

Owner:南通康芯半导体科技有限公司

Gallium nitride Schottky diode and manufacturing method thereof

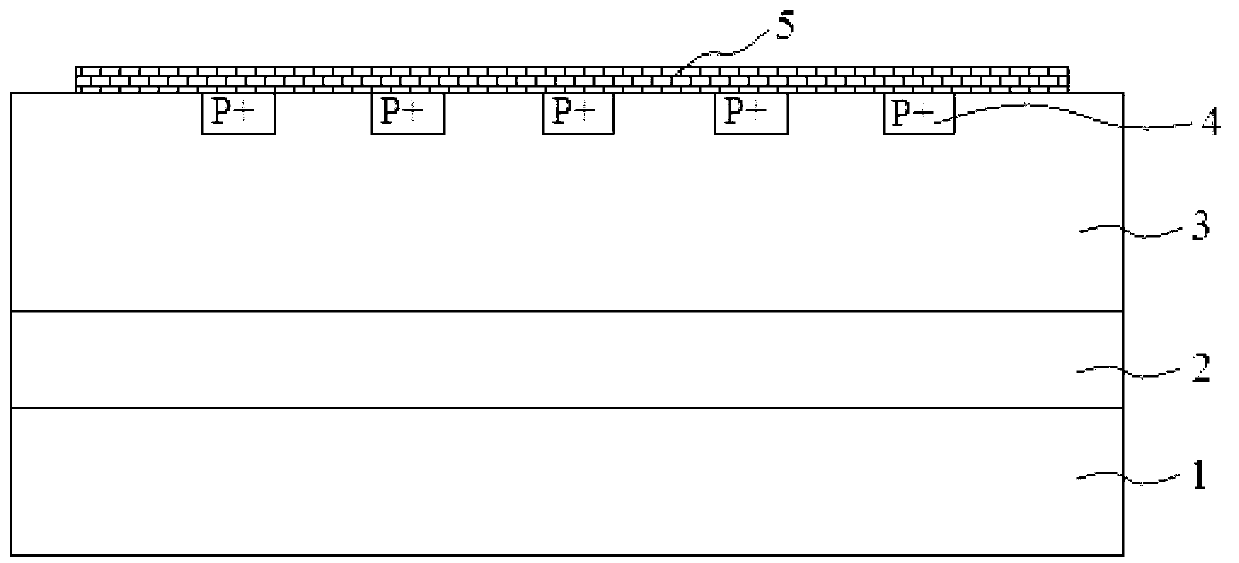

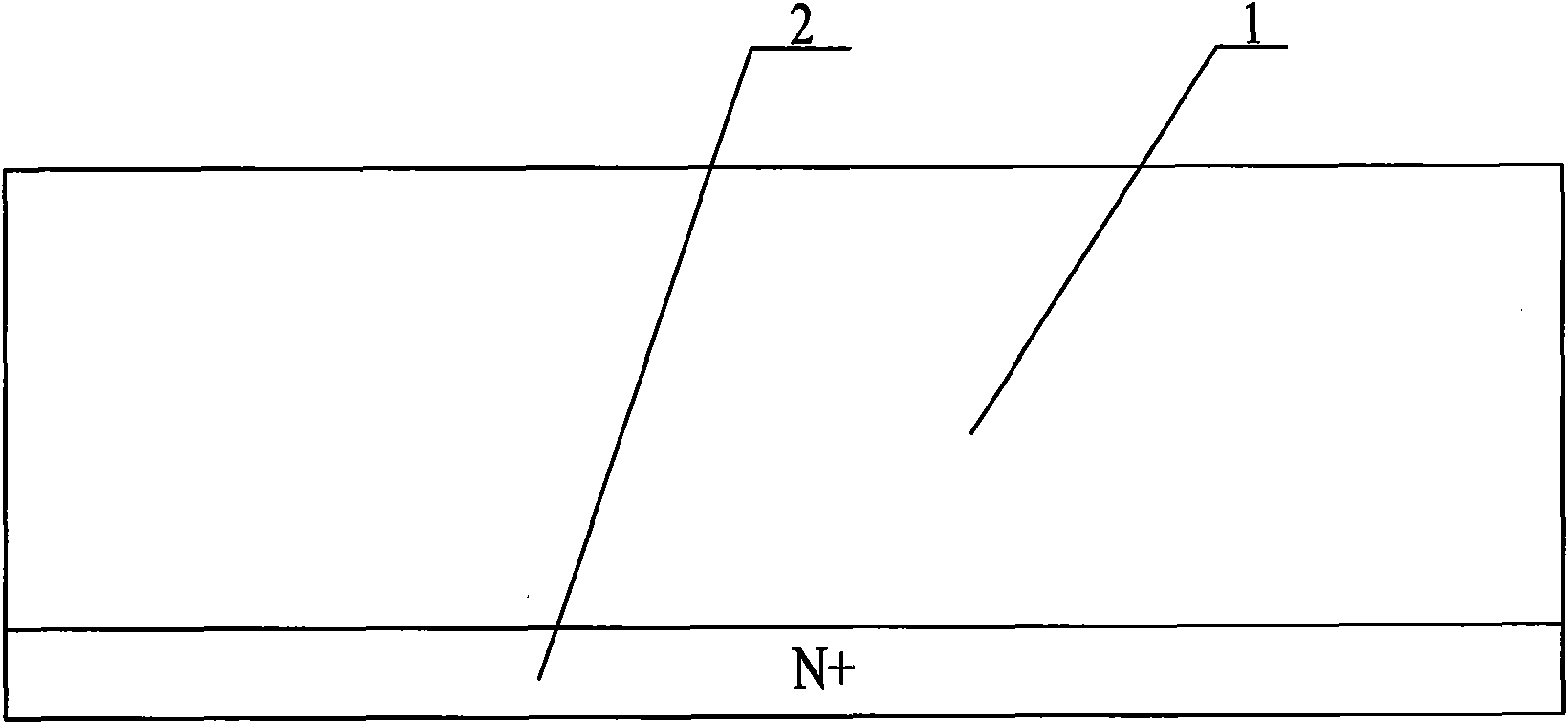

ActiveCN103346083ALow forward turn-on voltageReduce reverse leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGallium nitride

A manufacturing method of a GaN Schottky diode comprises the steps: providing a substrate; depositing a nucleating layer and / or a buffering layer on the substrate; depositing a heavy-doping n-type GaN layer on the nucleating layer and / or the buffering layer, and depositing a light-doping n-type GaN layer on the heavy-doping n-type GaN layer; arranging a plurality of p-type heavy-ion-doping GaN regions on the surface of the light-doping n-type GaN layer; depositing an insulation layer or a medium layer on the surface of the light-doping n-type GaN layer; defining a Schottky electrode region on the insulation layer, and trepanning the Schottky electrode region; depositing a Schottky electrode on the trepanned Schottky electrode region, wherein the Schottky electrode makes contact with the surface of the light-doping n-type GaN layer; defining an ohmic electrode region on the substrate, and trepanning the ohmic electrode region; depositing an ohmic electrode in the trepanned ohmic electrode region, wherein the ohmic electrode makes contact with the heavy-doping n-type GaN layer. The forward starting voltage of the Schottky diode is small, and a larger current can pass through in the forward direction; a leaked current in the backward direction is small, and larger voltage and power can be borne in the backward direction.

Owner:GPOWER SEMICON

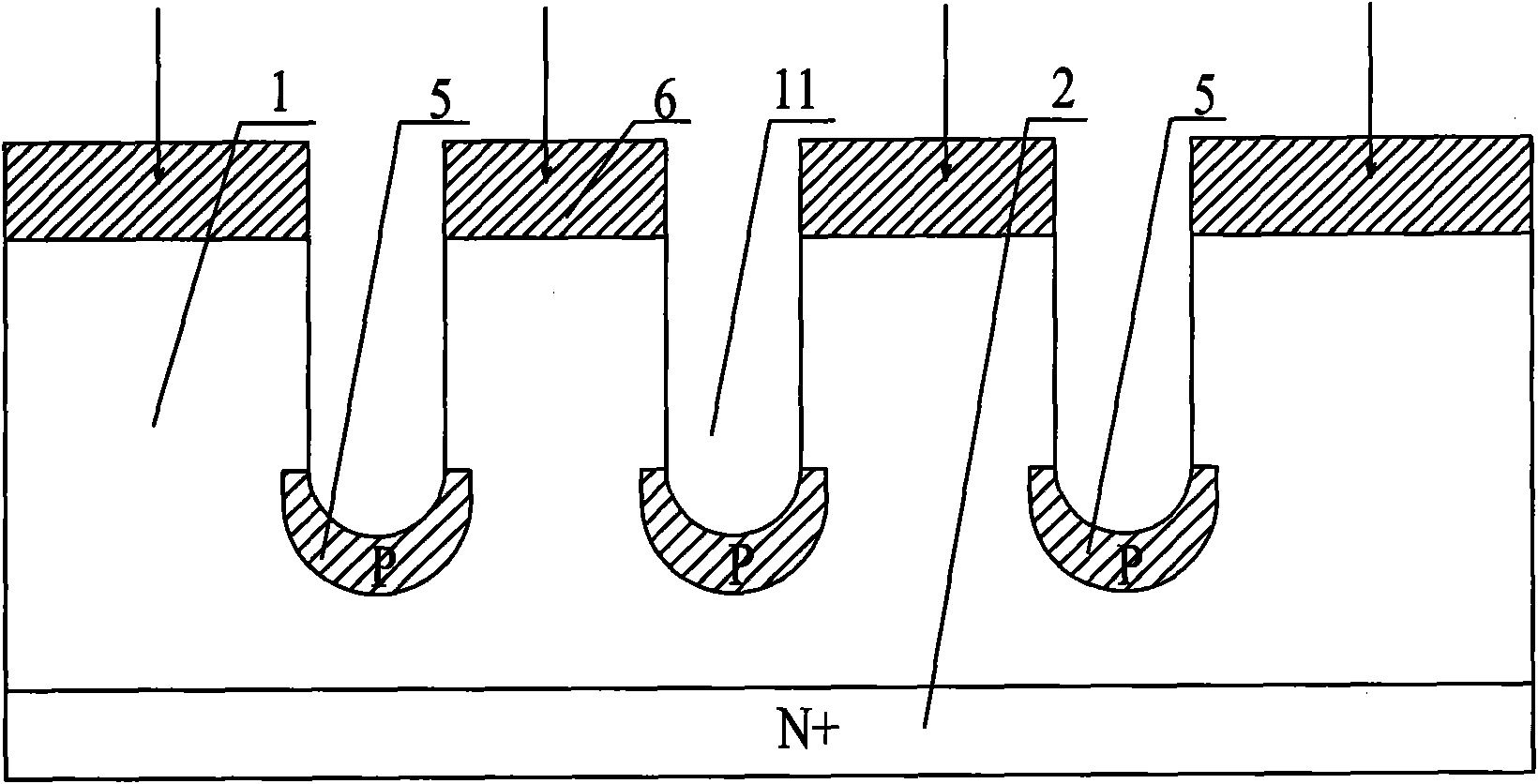

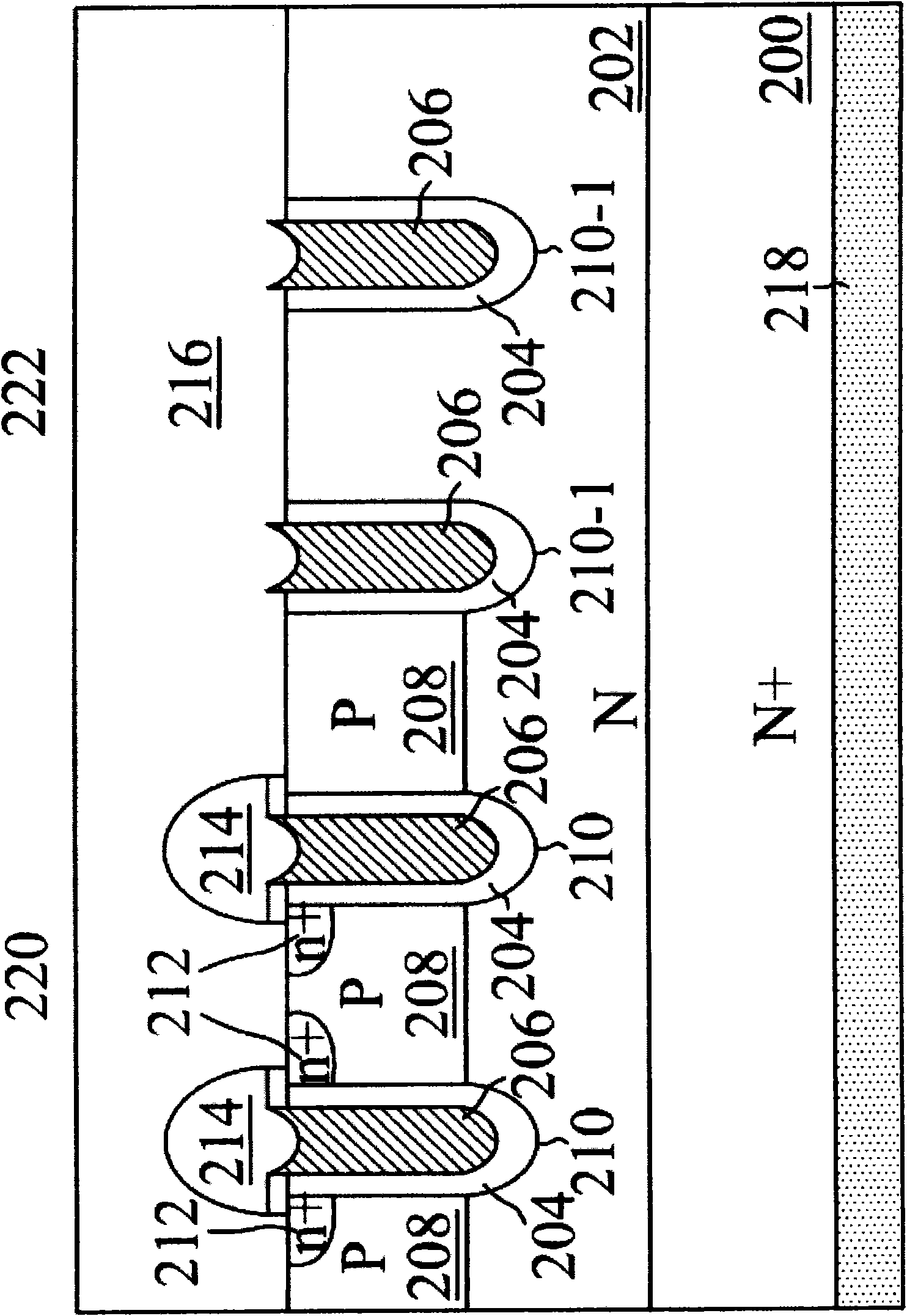

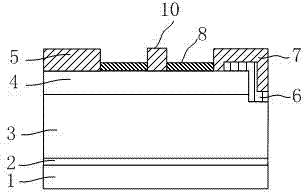

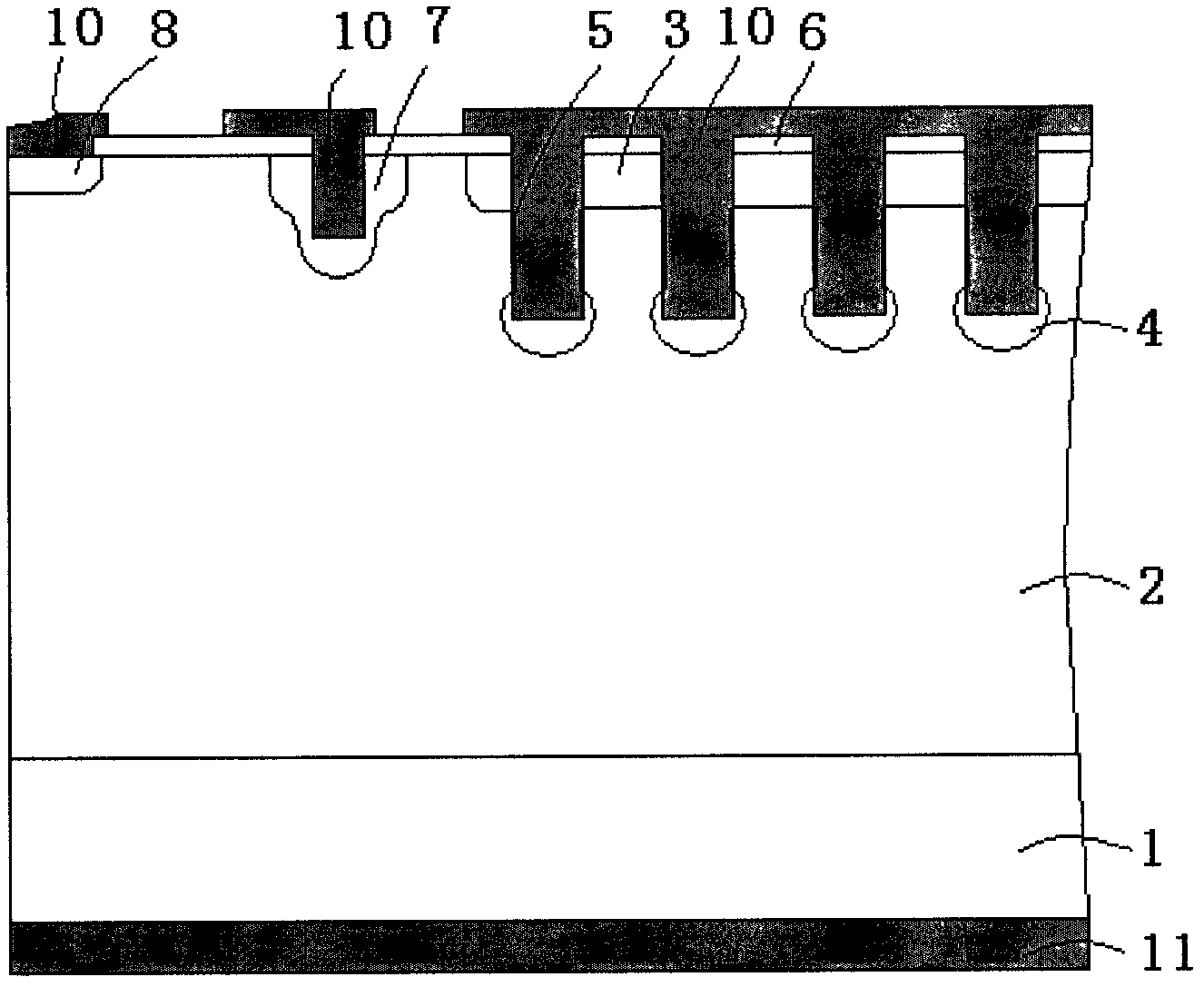

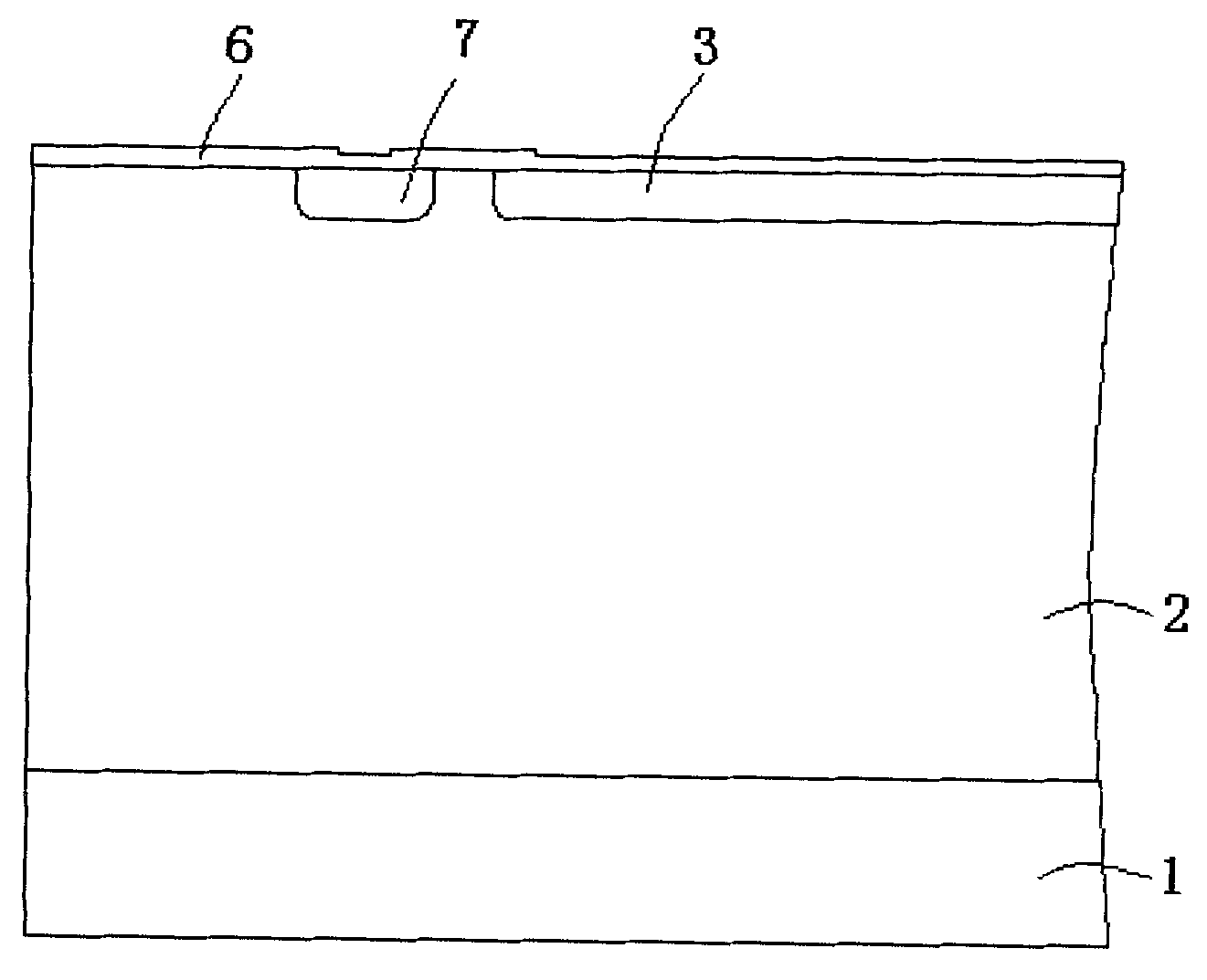

Grooved semiconductor rectifier and manufacturing method thereof

InactiveCN101783345AReduce forward voltage dropReduce reverse leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention relates to a grooved semiconductor rectifier and a manufacturing method thereof. The grooved semiconductor rectifier comprises a semiconductor baseplate, a first conduction type substrate and a first conduction type drift region, wherein one or more grooves extend from the first main plane to the first conduction type drift region, one or more mesa parts are limited at the upper part of the first conduction type drift region, and the upper part of the mesa part is provided with a first conduction type injection layer; the inner wall of the groove is covered with an insulation oxide layer, and a first electrode is deposited in the groove covered with the insulation oxide layer; the first conduction type drift region is provided with a second conduction type enclosure layer corresponding to the bottom of the groove, and the bottom of the groove is coated by the second conduction type enclosure layer; a first metal layer corresponding to the upper part of the first plane is deposited on the semiconductor baseplate; and the second plane of the semiconductor baseplate is covered with a second metal layer. The invention has the advantage of low manufacturing cost, and reduces the reverse leakage current and the forward conduction voltage drop of the Schottky rectifier.

Owner:无锡新洁能功率半导体有限公司

Schottky diode and manufacturing method for Schottky diode

InactiveCN104134704AIncrease widthReduce concentration effectSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSchottky diode

The invention provides a Schottky diode and a manufacturing method of the Schottky diode. The Schottky diode has the advantages that due to the fact that a groove structure with the wide upper portion and the narrow lower portion is mainly formed in a semiconductor layer, the concentration of two-dimensional electron gas below the Schottky metal inclined groove face can be effectively modulated, the Schottky barrier width and the Schottky barrier height can be increased, and therefore reverse electric leakage can be reduced; meanwhile, the concentration effect of an electric field at the edge of a groove can be further effectively improved, and the breakdown voltage of a device can be increased.

Owner:GPOWER SEMICON

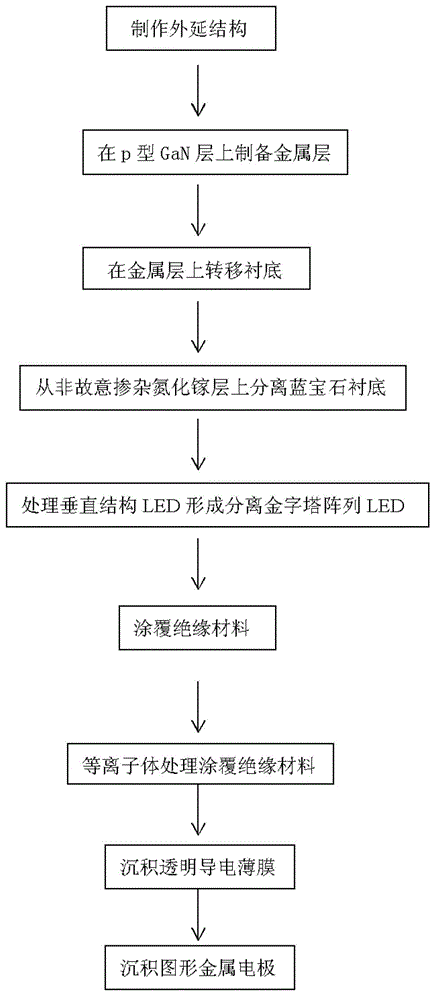

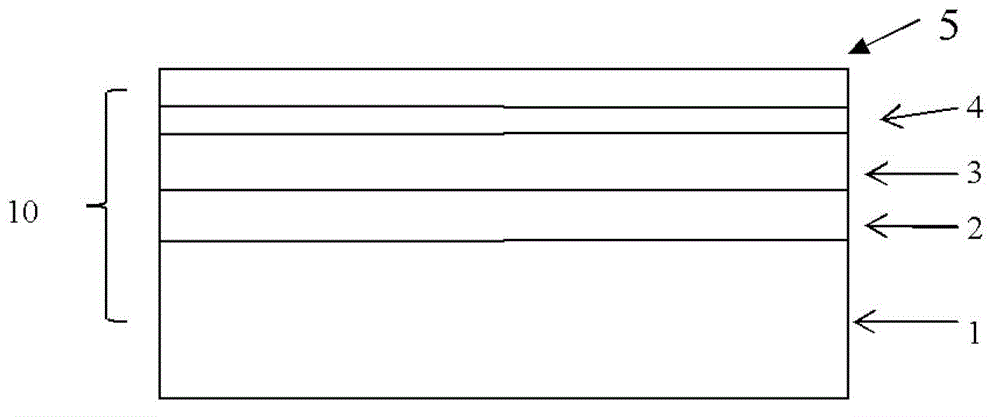

Method for manufacturing flexible pyramid array GaN-based semiconductor light-emitting diode

InactiveCN102983234AHigh light efficiencyReduce reverse leakage currentSemiconductor devicesQuantum wellEukaryotic plasmids

A method for manufacturing a flexible pyramid array GaN-based semiconductor light-emitting diode comprises the following steps: selecting an epitaxial structure, wherein the epitaxial structure comprises a sapphire substrate, as well as an unpremeditated doped gallium nitride layer, an n type GaN layer, a quantum well layer and a p type GaN layer which grow on the sapphire substrate sequentially; preparing a metal layer on the p type GaN layer; transferring a substrate on the metal layer; separating the sapphire substrate in the epitaxial structure from the unpremeditated doped gallium nitride layer; corroding, namely corroding the unpremeditated doped gallium nitride layer downwards to the metal layer to form a separated pyramid-shaped array; coating an insulating material on the side of the pyramid-shaped array; performing plasmid processing on the coated insulating material, so that the unpremeditated doped gallium nitride layer at the upper end of the pyramid-shaped array is exposed; depositing one layer of transparent conductive film on the coated insulating material and the unpremeditated doped gallium nitride layer; and depositing a graphic metal electrode on the transparent conductive film by a photoetching method to finish preparation.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

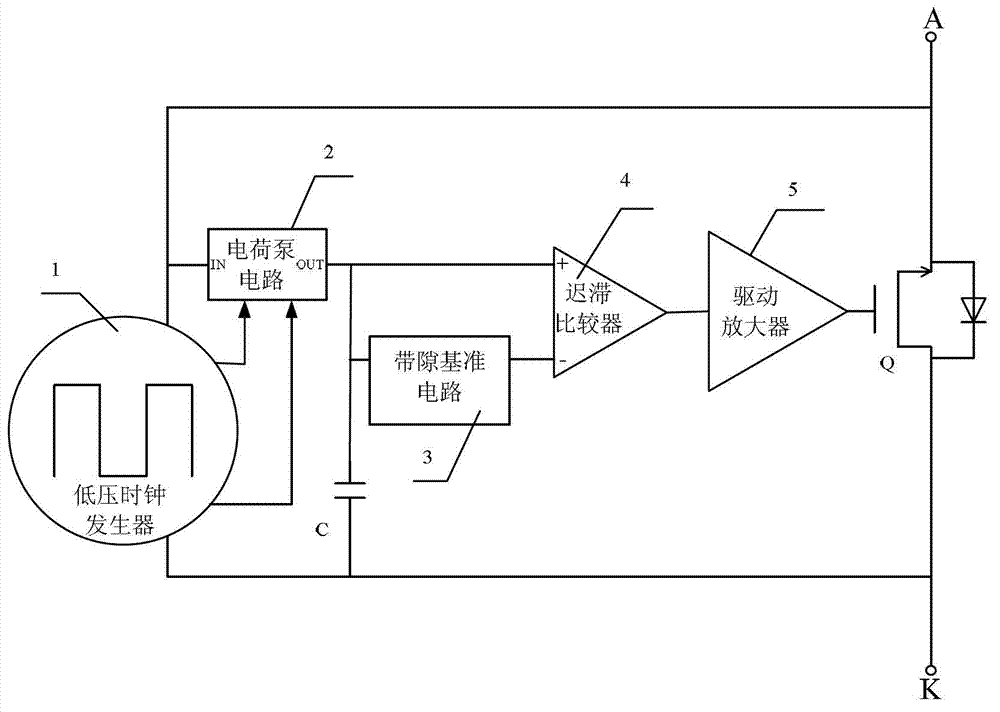

High-performance rectifier diode replaced circuit

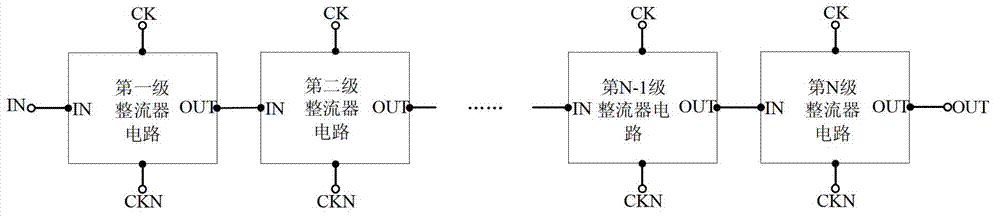

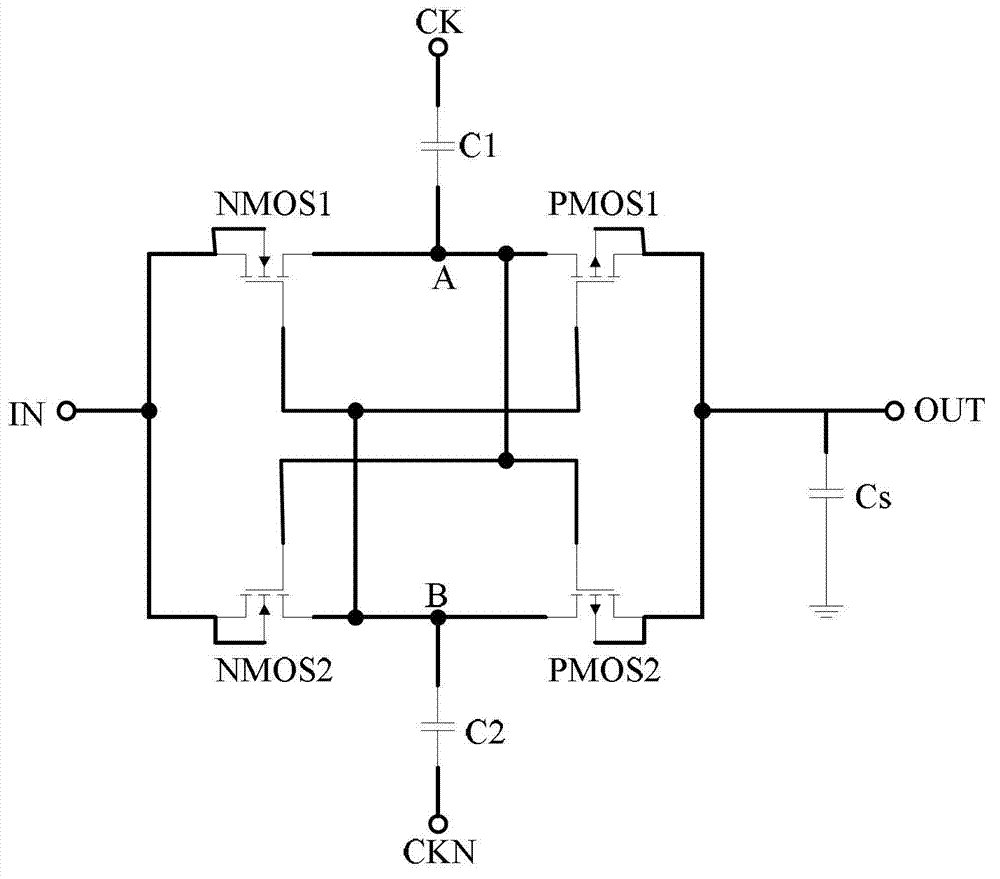

ActiveCN102904421AReduce forward voltage dropSolve excessive power consumptionAc-dc conversionApparatus without intermediate ac conversionAudio power amplifierLow voltage

The invention discloses a high-performance rectifier diode replaced circuit which comprises a capacitor, a low-voltage clock generator, a charge pump circuit, a band-gap reference circuit, a hysteresis comparator, a driving amplifier and a power metal oxide semiconductor (MOS) pipe and is characterized in that the low-voltage clock generator detects voltages at two ends of a diode pipe and generates clock signals to drive the charge pump circuit; the charge pump circuit detects the voltages at two ends of the diode pipe and stores the charges in the capacitor after the charges are amplified; the voltage stored on the capacitor and the standard voltage output by the band-gap reference circuit are respectively output to the hysteresis comparator for comparison; and when the voltage stored in the capacitor is larger than the standard voltage output by the band-gap reference circuit, the hysteresis comparator outputs starting signals which are amplified by the driving amplifier and then output to the power MOS pipe to drive the power MOS pipe to be conducted. The high-performance rectifier diode replaced circuit can achieve equivalent diode working characteristics through a pulse working mode and can totally replace original selective beacon radar (SBR) devices in performance and dimension.

Owner:CHONGQING SOUTHWEST INTEGRATED CIRCUIT DESIGN

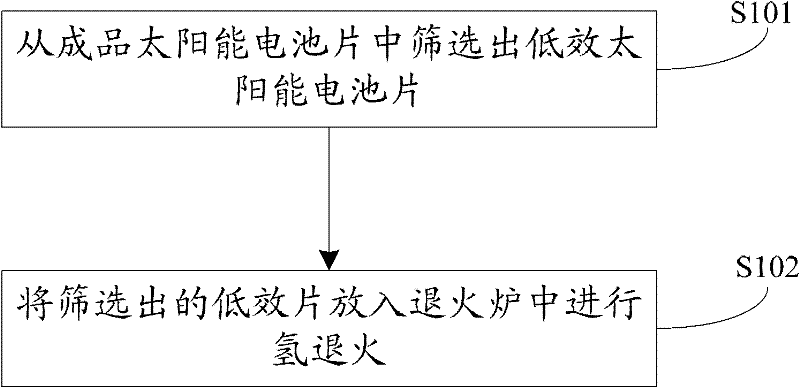

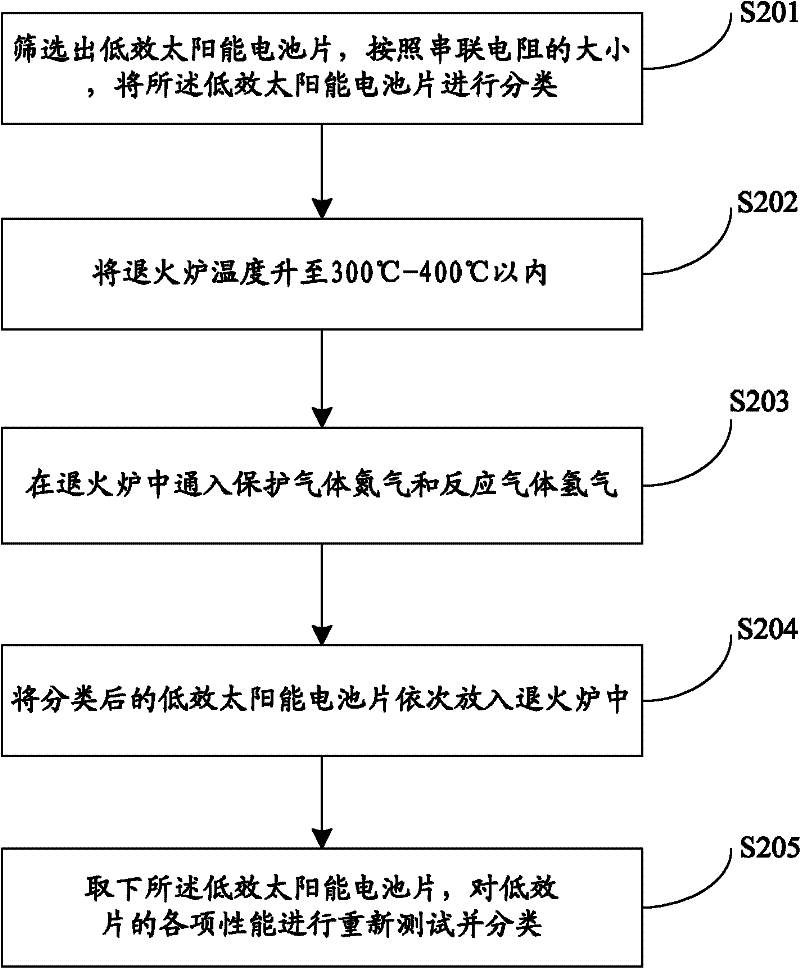

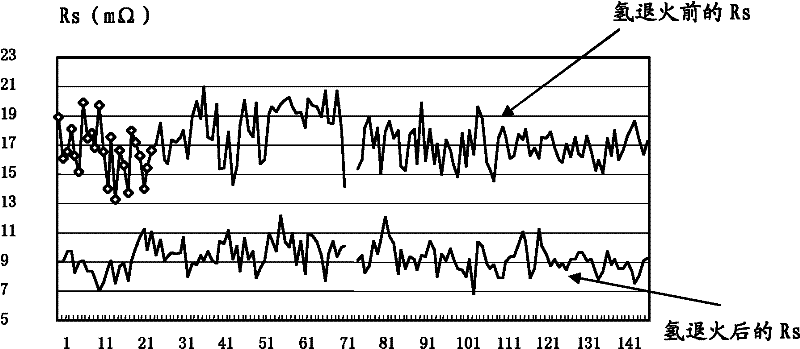

A processing method of inefficient solar cell sheets

InactiveCN102185008AReduce the series resistance RsImprove conductivityFinal product manufactureSemiconductor devicesSolar cellMetal electrodes

The invention discloses a processing method of inefficient solar cell sheets. The processing method comprises the steps of screening out inefficient solar cell sheets from solar cell sheet products, and disposing the inefficient solar cell sheets into an annealing furnace for annealing with hydrogen. In the embodiment of the invention, the inefficient cell sheets are annealed with hydrogen. Since hydrogen can reduce oxide on metal electrodes, the contact resistance between the metal electrodes and silicon is thereby reduced, and accordingly the total series resistance of the inefficient cell sheets is reduced. Moreover, since hydrogen possesses a passivation function, the electroactive impurities are passivated, the recombination rate of carriers on cell surfaces and the lifetime of minority carriers are prolonged. Therefore, the shunt resistance of the cell sheets is improved and the reverse leakage current density is reduced, accordingly the filling factors of the cell sheets are increased and the conversion efficiency is improved.

Owner:JETION SOLAR HLDG

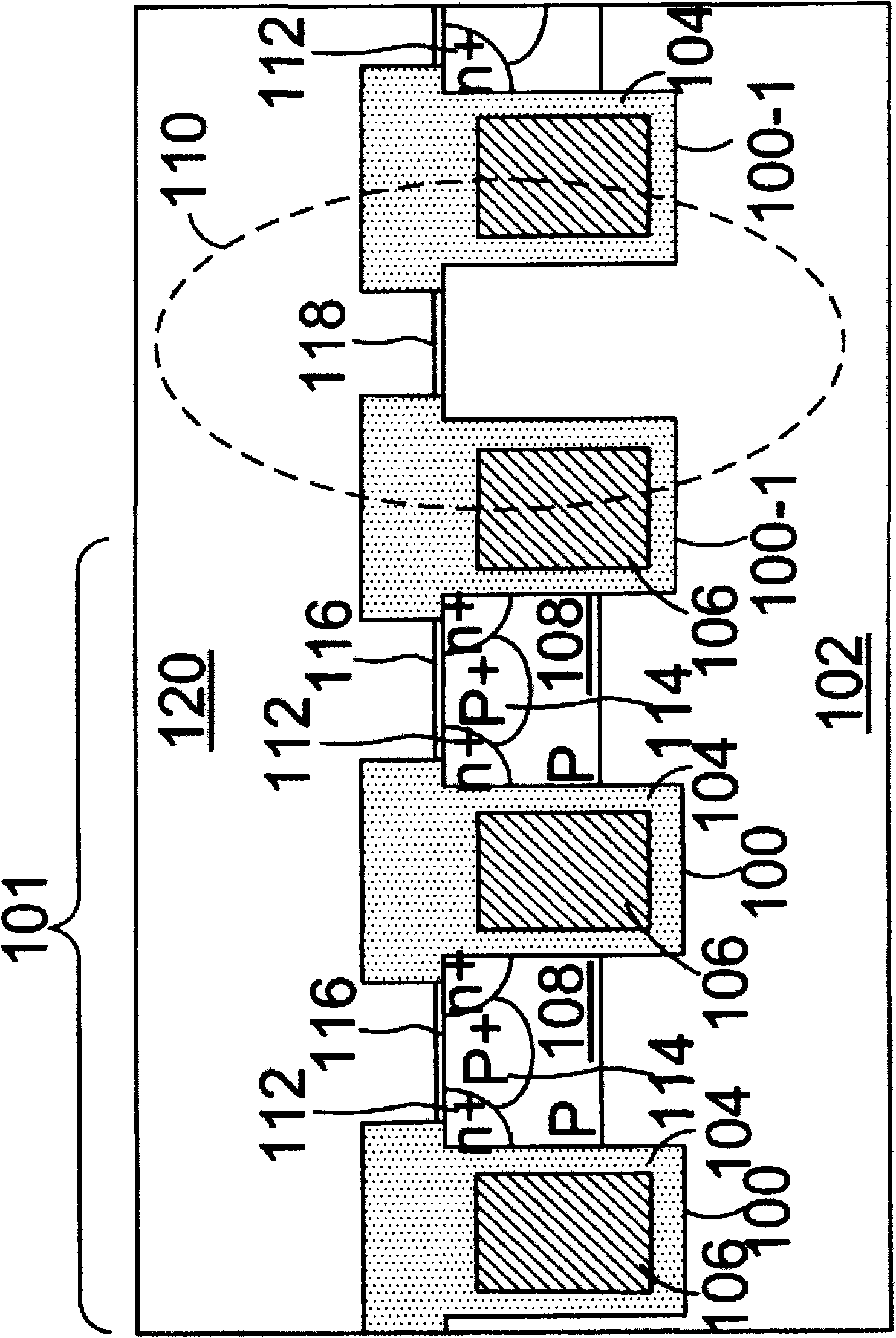

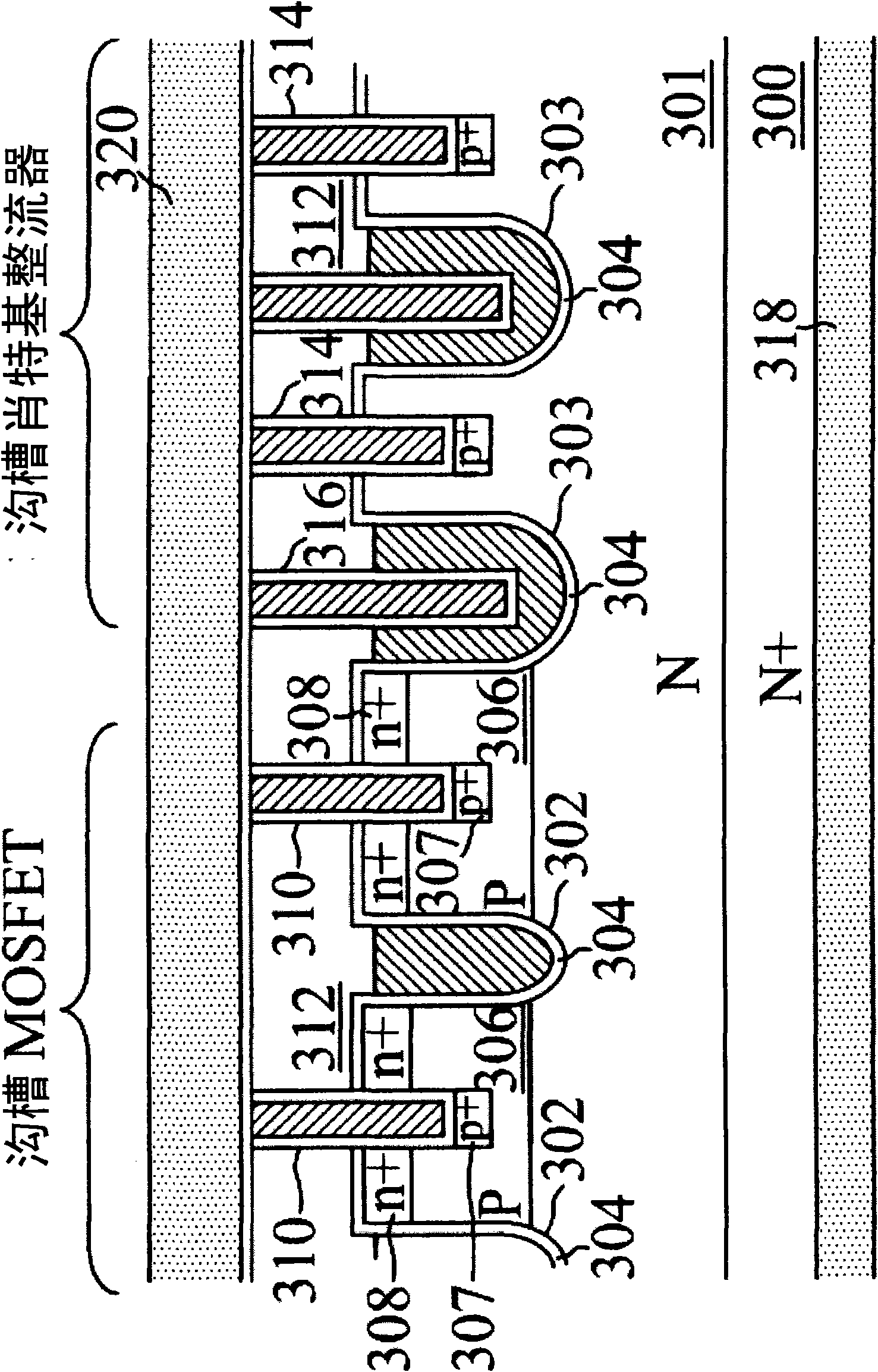

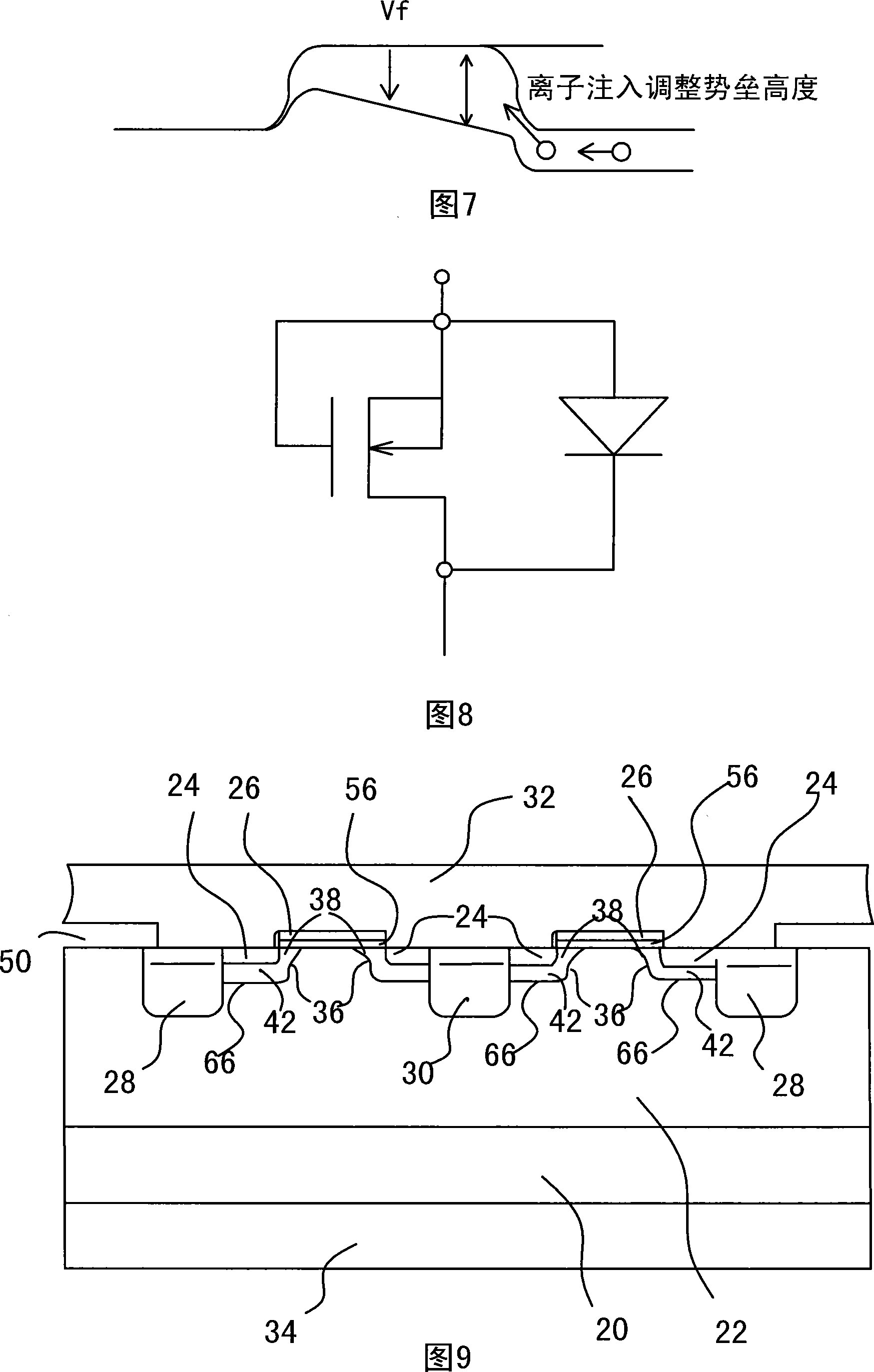

Semiconductor integrated circuit and manufacturing method thereof

InactiveCN102315220AReduce device sizeLower turn-on resistanceTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

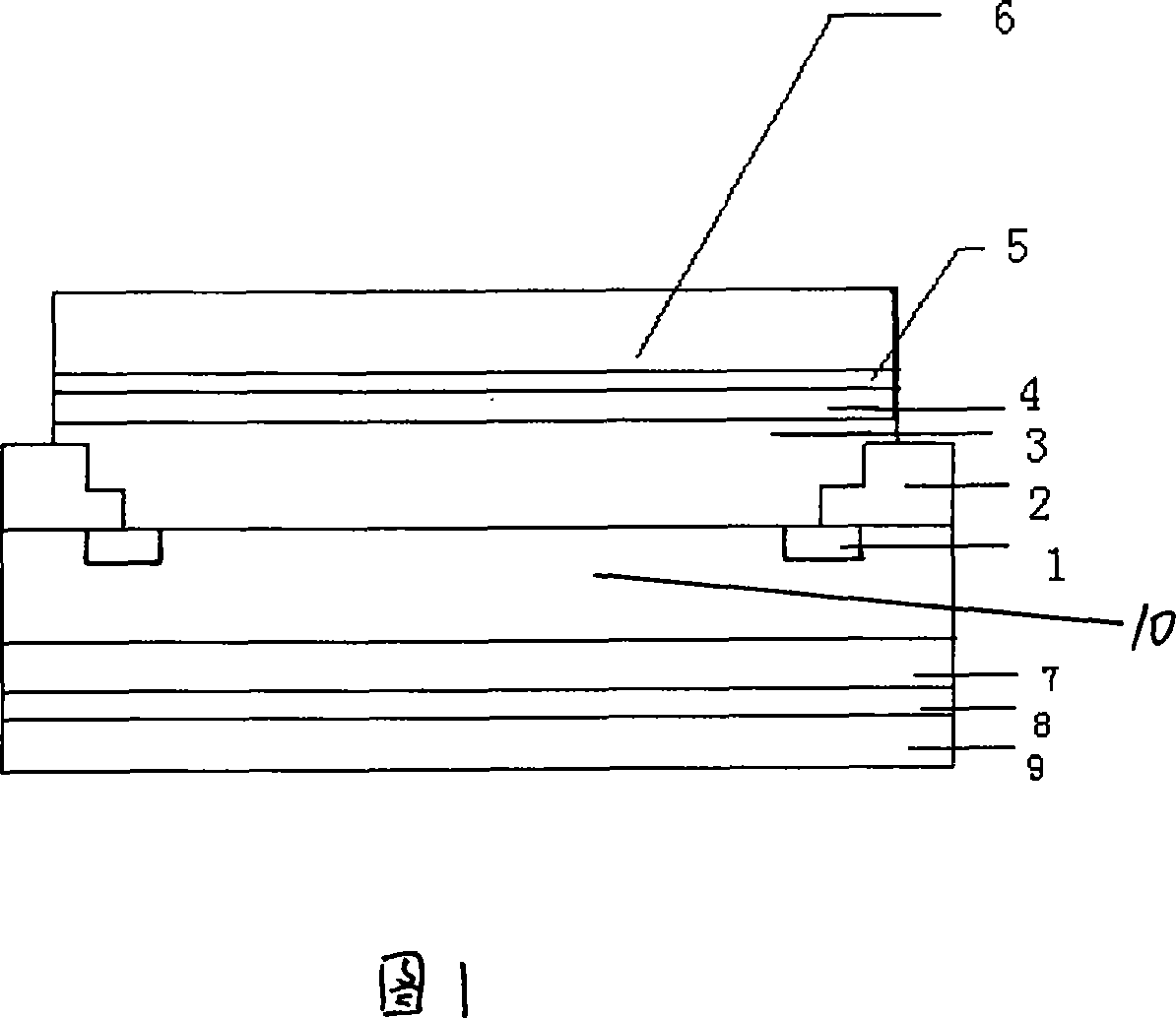

The invention discloses a semiconductor integrated circuit and a manufacturing method thereof. The semiconductor integrated circuit comprises a plurality of grooved metal oxide semiconductor field effect transistors and a plurality of grooved Schottky rectifiers which are positioned on a same substrate, wherein the plurality of grooved metal oxide semiconductor field effect transistors are provided with grooved source contact regions; and the plurality of grooved Schottky rectifiers are provided with grooved anode contact regions. By the semiconductor integrated circuit with the structure, grooved metal oxide semiconductor field effect transistors have lower starting resistance and Schottky rectifiers have lower pre-position voltage and low reverse leakage current.

Owner:FORCE MOS TECH CO LTD

Semiconductor rectifier device and manufacturing method thereof

InactiveCN101226883ASmall PN junction parasitic effectImprove junction characteristicsSemiconductor/solid-state device detailsSolid-state devicesEngineeringP–n junction

Disclosed are a semiconductor rectifier device and a method for preparation thereof. The device is composed of an equivalent PN junction and a vertical MOS pipe in parallel connection. And an upper source / drain area in the vertical MOS pipe is formed through the following procedures: a, performing N-type ion implantation for an area exposed from a first primary surface of silicon chips after procedures of photo-etching and corroding of a grid electrode, b, performing silicon controlled corrosion for the area exposed from the first primary surface of the silicon chips after implanted by N-type ions, rapidly annealing the N-type ions retained in an area bellow the lateral face of the grid electrode to form the upper source / drain area. The invention resolves the problems brought by the larger surface and unreasonable distribution of the upper source / drain N+ area of the existing vertical MOS pipe through the process of silicon controlled corrosion. For equivalent PN junction areas, a single PN junction is used to replace the original NPN pipe, and thereby the equivalent PN junction areas have fewer parasitic effect of the PN junction. For equivalent vertical MOS pipe areas, residual N-type ions are used to form the upper source / drain area via rapidly annealing, thereby largely reducing effective junction area of the upper source / drain area with smaller reverse leakage current.

Owner:SUZHOU SILIKRON SEMICON CO LTD

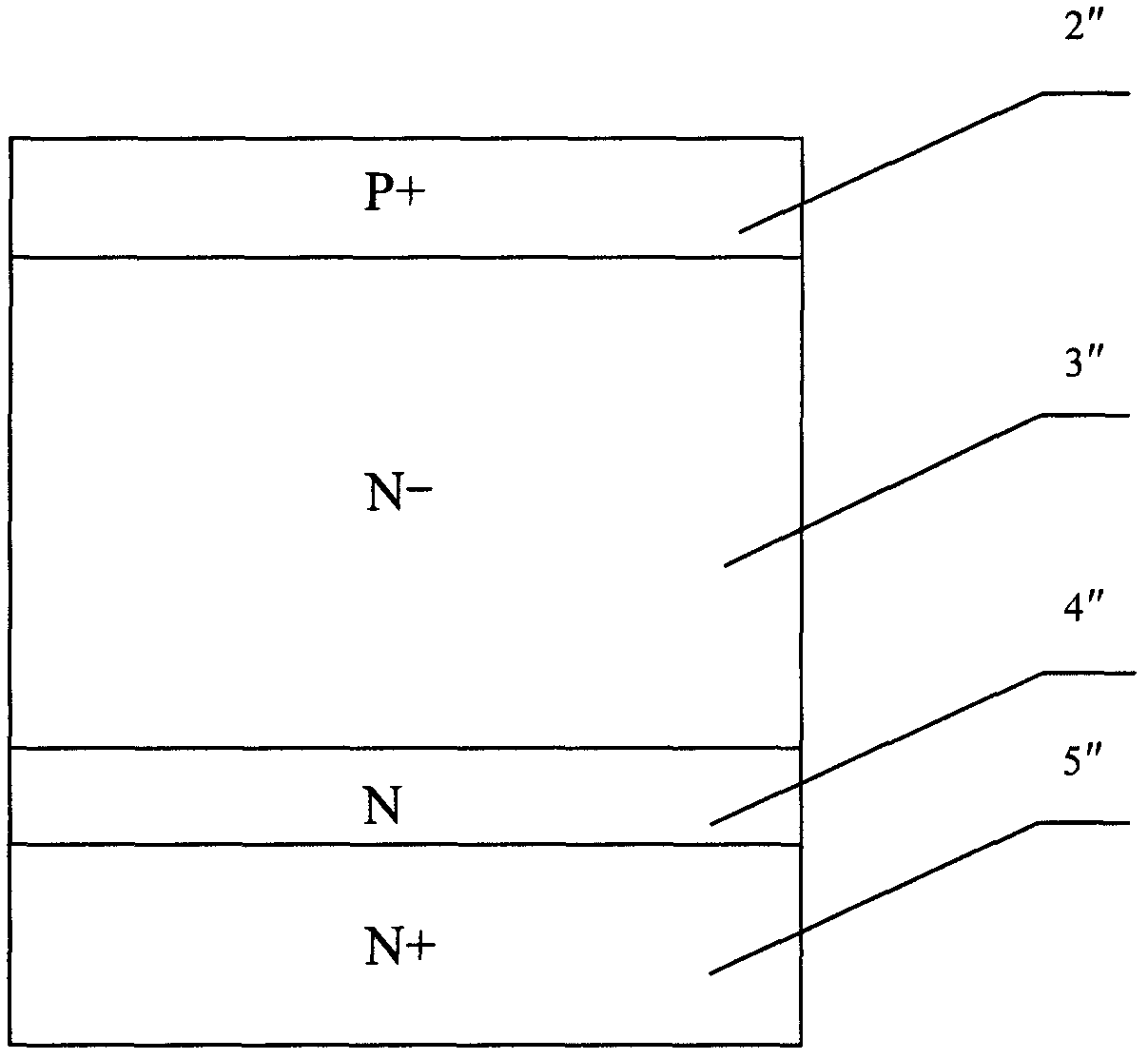

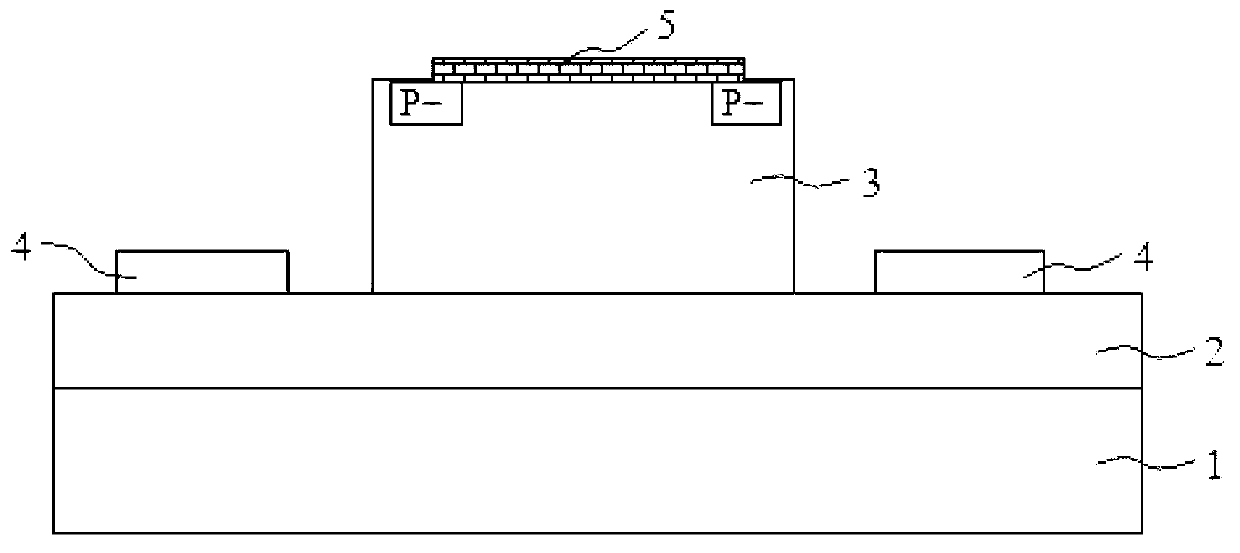

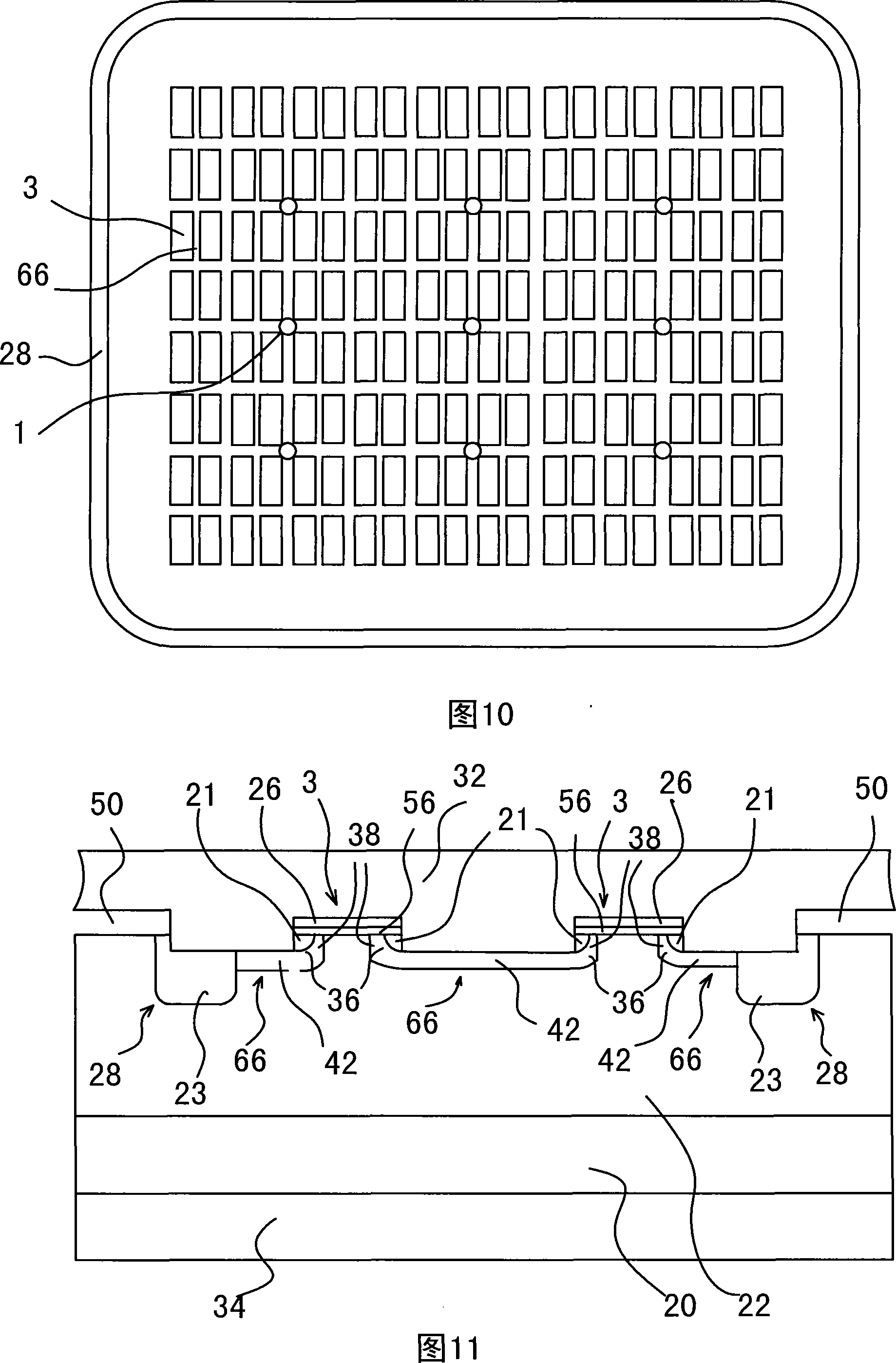

Diffusion-technology-based manufacture method for fast recovery diode chip having double buffering layers

ActiveCN105977154AShort recovery timeHas soft recovery propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyPeak current

The invention relates to a diffusion-technology-based manufacture method for a fast recovery diode chip having a double-buffer-layer structure. During a manufacture process, reverse recovery charges and reverse recovery time are reduced and effect of reverse recovery peak current is inhibited. The fast recovery diode is formed by adopting a phosphorus deep diffusion mode and a cathode structure formed by the diffusion is an N+N structure, an N area is a buffering layer which can block expansion of a space charge area, shortens a width of a base area and reduces forward on-state voltage drop; when the diode is reverse, an electric field between an N-N interface and an NN+ interface slows down carrier reverse drawing speed, which enables more charges to be used for recombination and softens the recovery characteristics. The diffusion-technology-based manufacture method adopts the diffusion mode to form the anode and the cathode of the fast recovery diode chip, combines with the platinum diffusion minority carrier life control technology, has a simple manufacture technology process and can manufacture the fast recovery diode chip which is low in cost, high in voltage resistance, short in recovery time and has soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

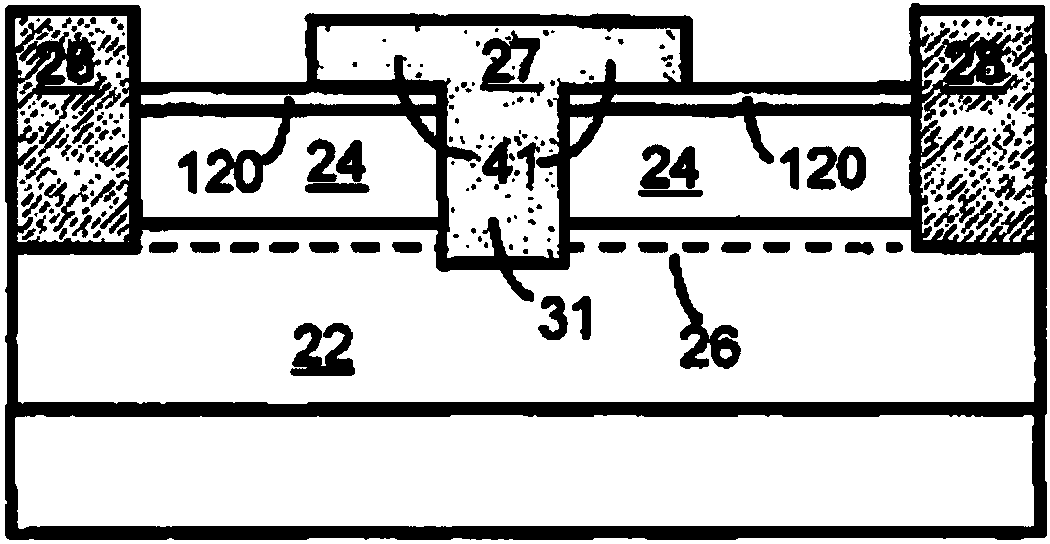

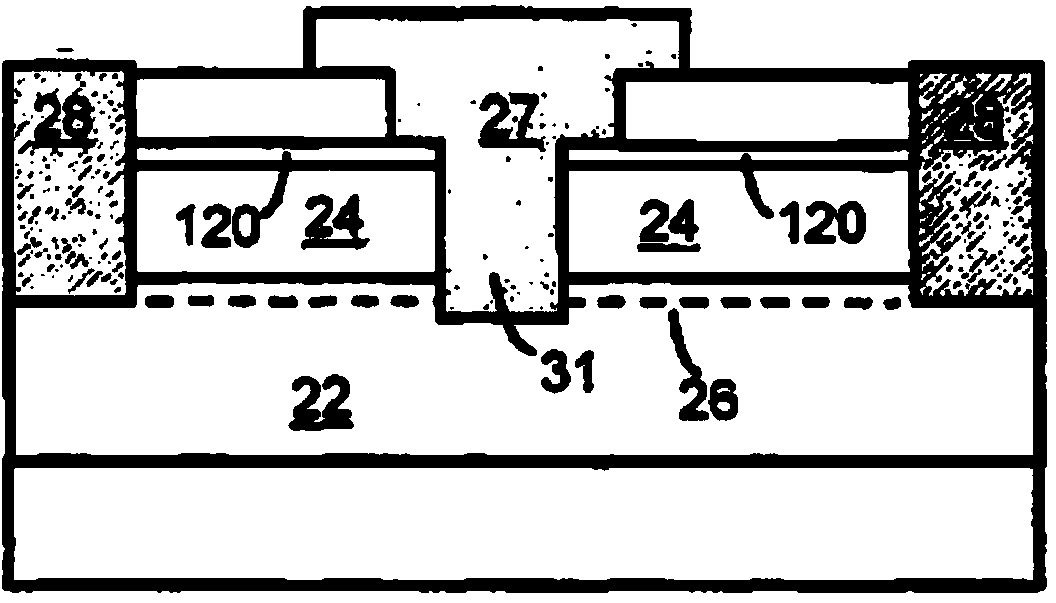

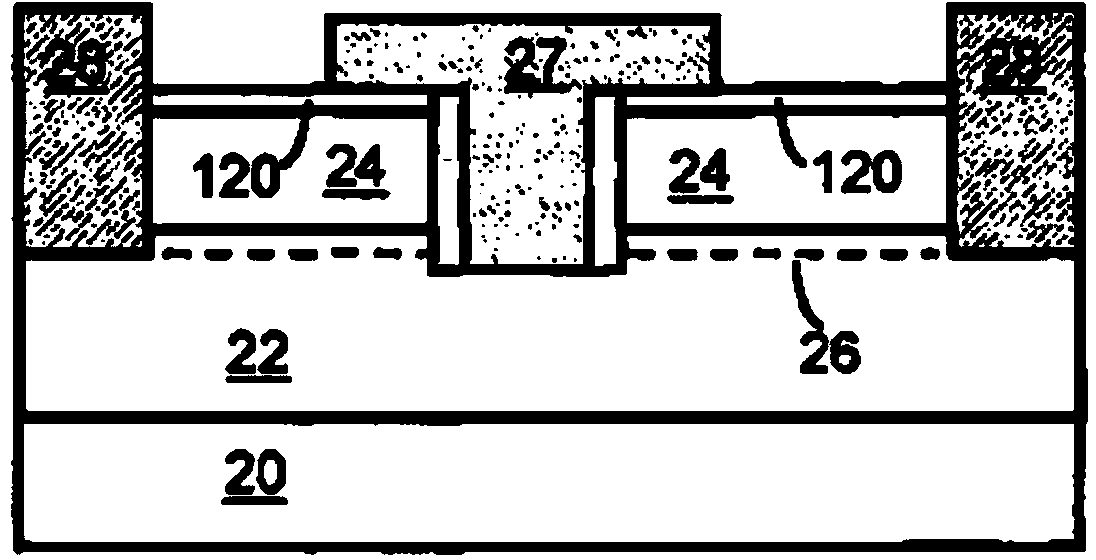

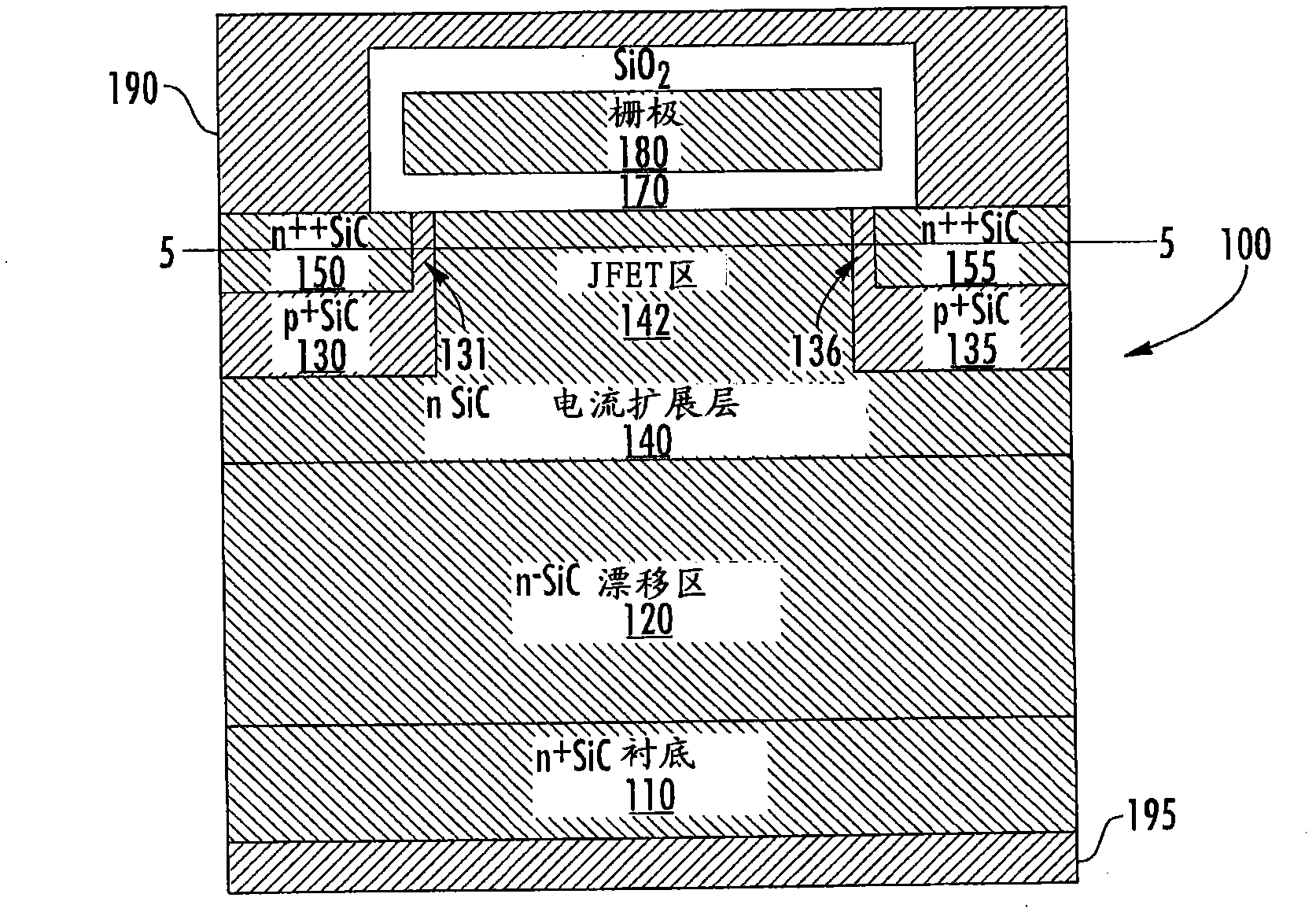

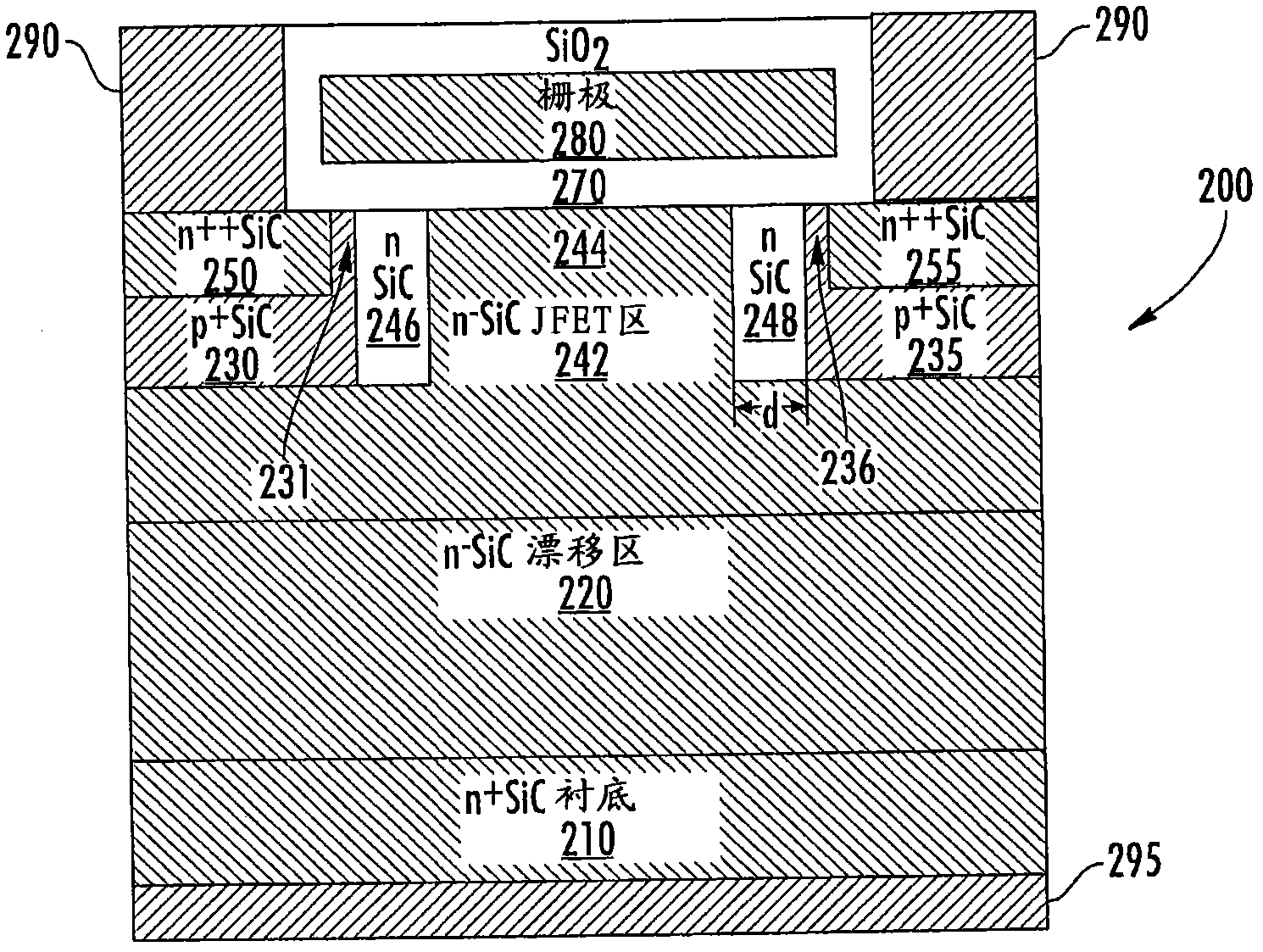

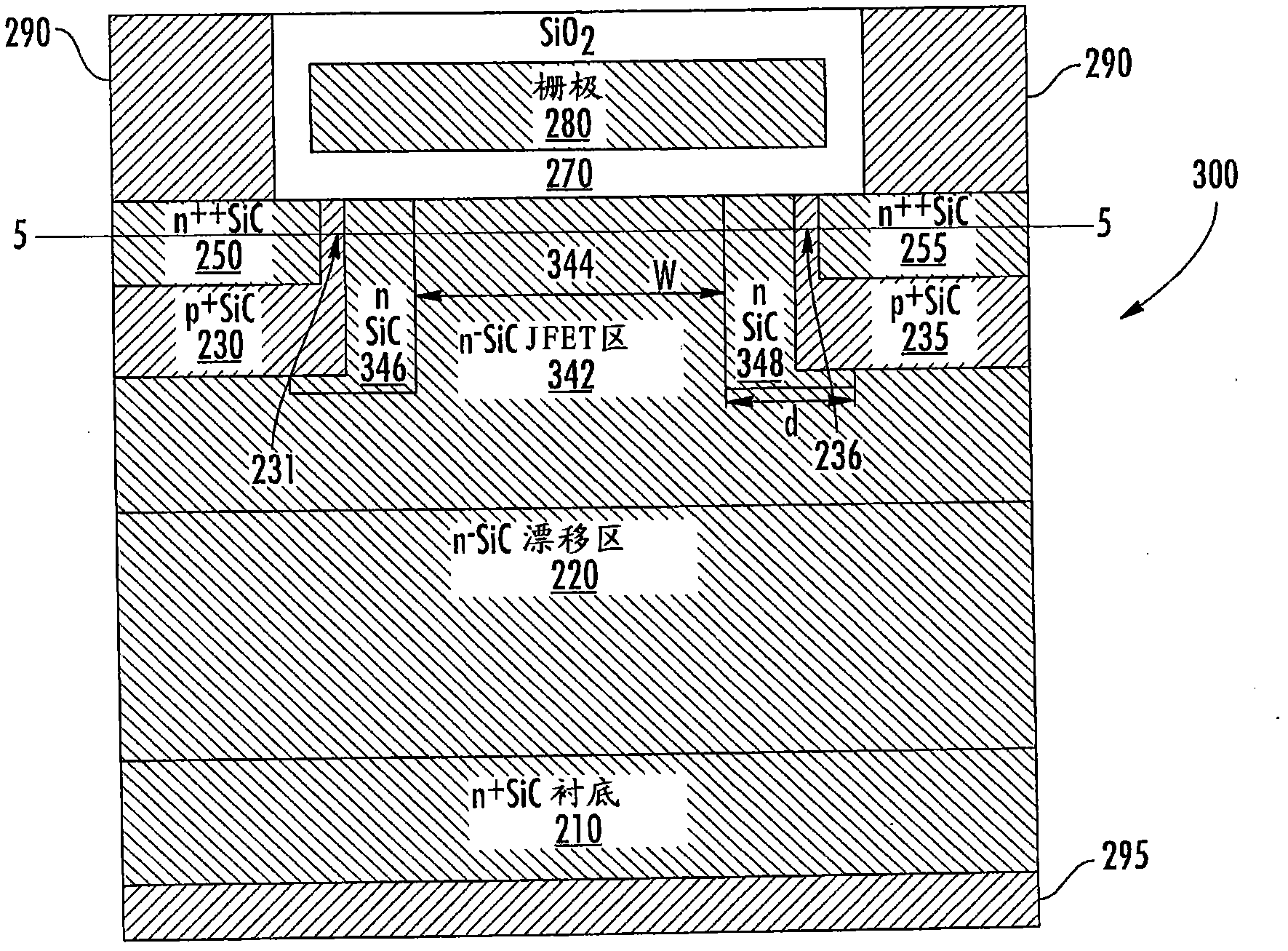

Power semiconductor devices having selectively doped JFET regions and related methods of forming such devices

ActiveCN102714224AImprove stabilityImprove manufacturing yieldTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceBroadband

Semiconductor switching devices include a wide band-gap drift layer having a first conductivity type (e.g., n-type), and first and second wide band-gap well regions having a second conductivity type (e.g., p-type) on the wide band-gap drift layer. First and second wide band-gap source / drain regions of the first conductivity type are on the first and second wide band-gap well regions, respectively. A wide band-gap JFET region having the first conductivity type is provided between the first and second well regions. This JFET region includes a first local JFET region that is adjacent a side surface of the first well region and a second local JFET region that is adjacent a side surface of the second well region. The local JFET regions have doping concentrations that exceed a doping concentration of a central portion of the JFET region that is between the first and second local JFET regions of the JFET region.

Owner:CREE INC

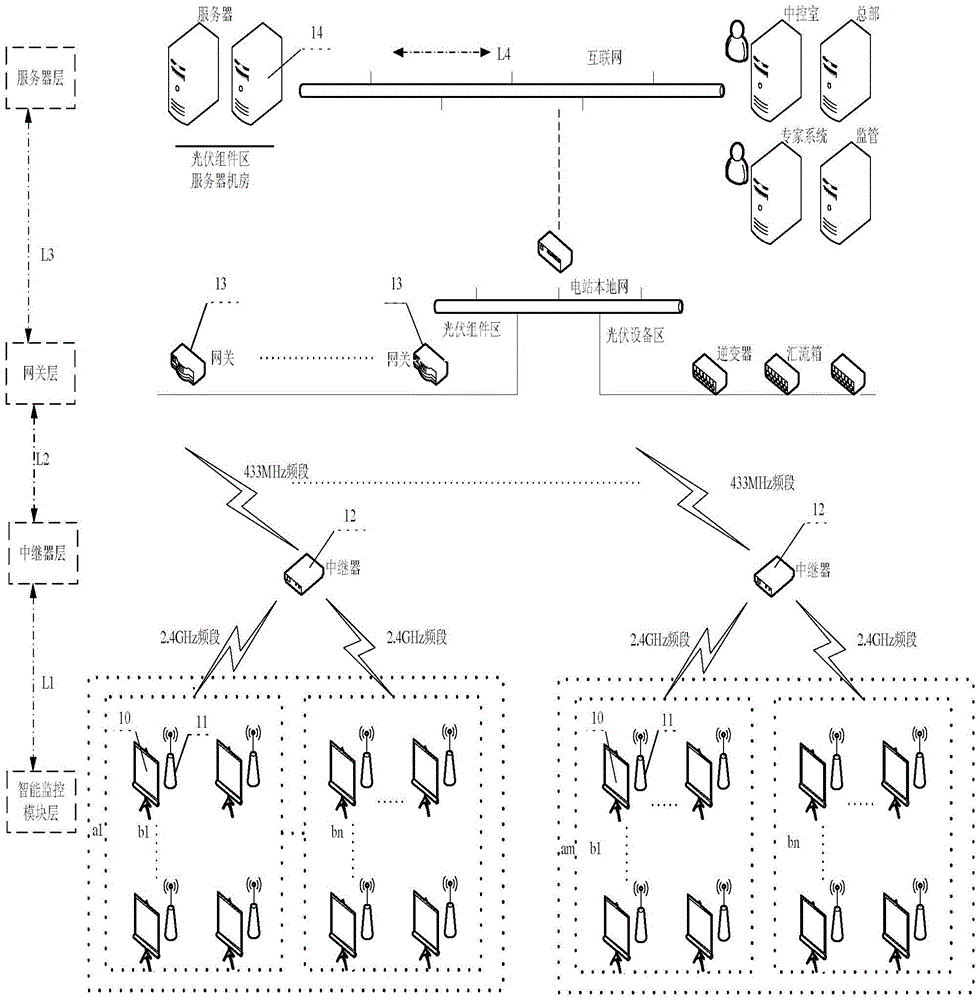

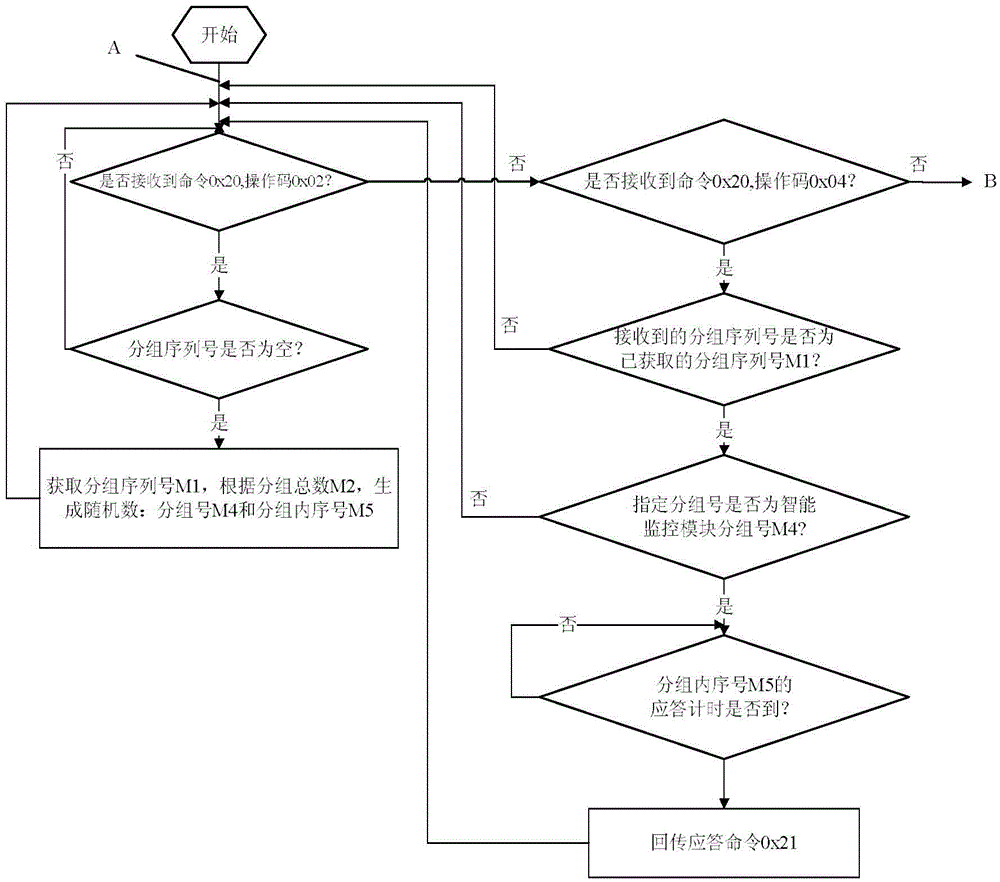

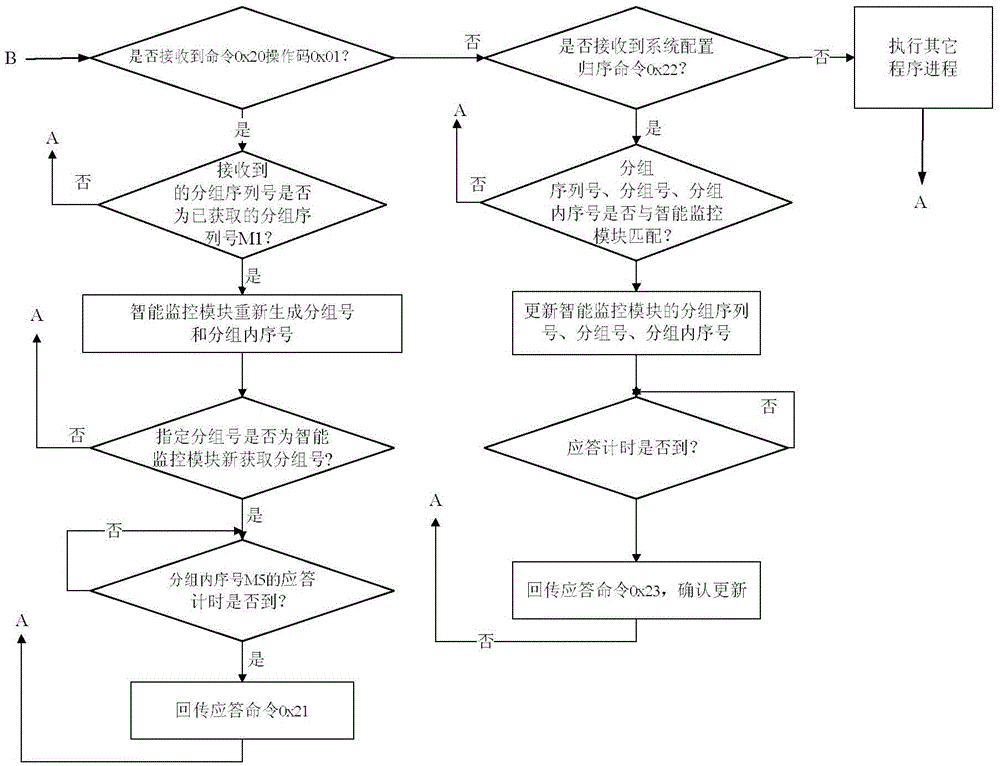

Wireless intelligent monitoring system and method for photovoltaic power station

ActiveCN105490388AHigh return on investmentFlexible architectureCircuit arrangementsInformation technology support systemMonitoring systemPhotovoltaic power station

The invention discloses a wireless intelligent monitoring system and method for a photovoltaic power station. The wireless intelligent monitoring system for the photovoltaic power station comprises a server layer, a gateway layer, a repeater layer and a monitoring module layer, wherein the server layer is the top layer; the monitoring module layer is the bottom layer; bidirectional communication is performed between each two adjacent layers; the server layer consists of multiple servers; the gateway layer consists of multiple gateways; the repeater layer consists of multiple repeater modules; the wireless intelligent monitoring system is characterized in that the monitoring module layer consists of a1-am grouping sequences, wherein m is less than or equal to 65536; each grouping sequence is divided into b1-bm groups, wherein n is a natural number less than or equal to 255; each group consists of i intelligent monitoring modules, wherein i is a natural number less than or equal to 183; each repeater performs wireless communication with all the intelligent monitoring modules in each grouping sequence; the repeaters and the gateways are in wireless communication; and the intelligent monitoring modules are used for detecting information of photovoltaic modules, and perform wireless communication with the repeaters. According to the wireless intelligent monitoring system and method for the photovoltaic power station, the electric energy utilization rate of the photovoltaic power station can be improved, and the wireless intelligent monitoring system and method are wide in application prospects.

Owner:CHONGQING SOUTHWEST INTEGRATED CIRCUIT DESIGN

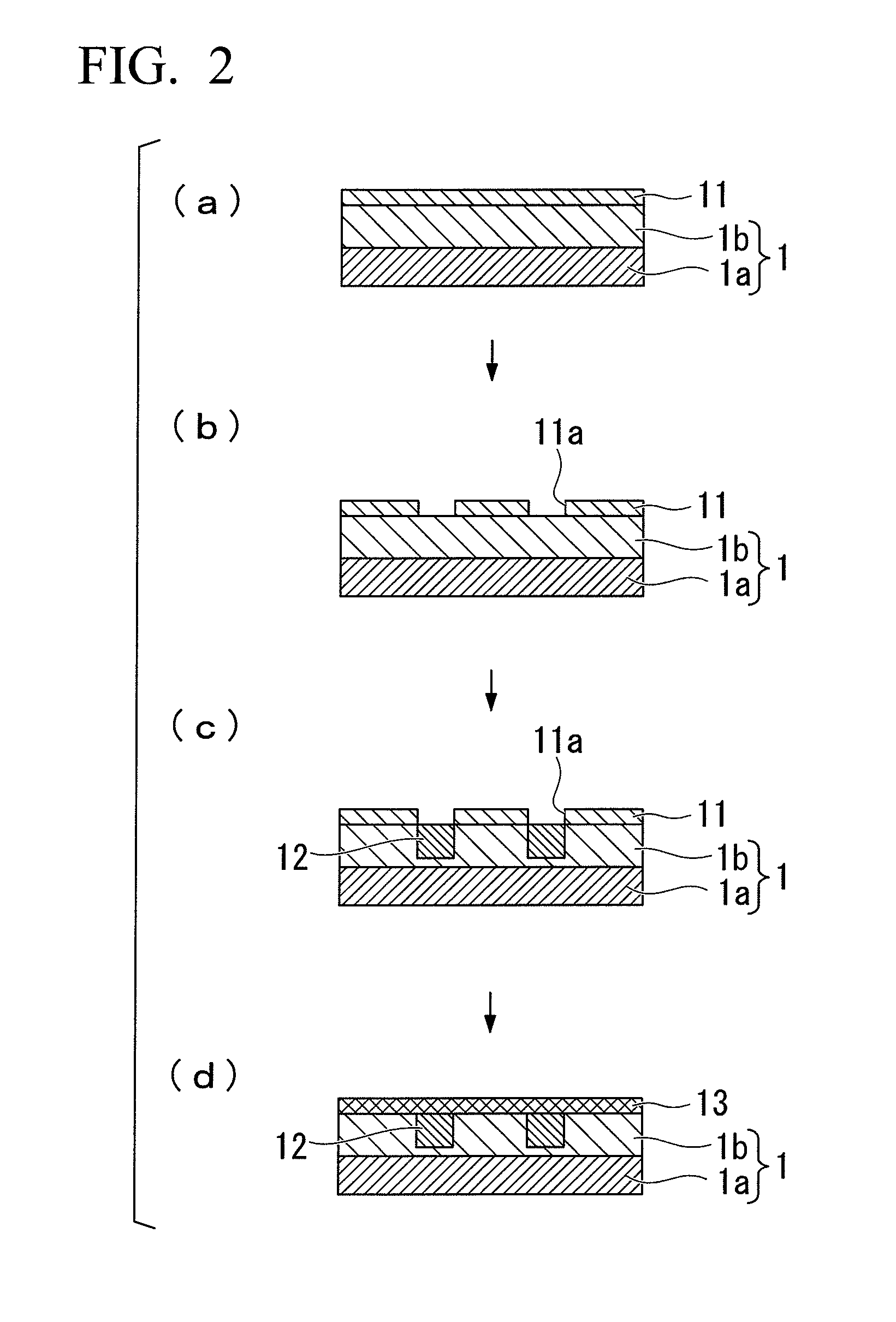

Semiconductor device production method and semiconductor device

ActiveCN103518254AResistantImprove insulation performanceThyristorSemiconductor/solid-state device detailsInsulation layerAlkaline earth metal

A semiconductor device production method including, in order: a first step in which a semiconductor element having a pn junction-exposed section is prepared; a second step in which an insulation layer is formed so as to cover the pn junction-exposed section; and a third step in which a layer comprising a glass composition for semiconductor junction protection is formed upon the insulation layer, and then a glass layer is formed upon the insulation layer by sintering the layer comprising the glass composition for semiconductor junction protection. The glass composition for semiconductor junction protection comprises glass fine particles prepared from a melt obtained by melting a raw material containing at least two alkali earth metal oxides from among at least SiO2, Al2O3, B2O3, ZnO, CaO, MgO, and BaO, and not substantially containing Pb, As, Sb, Li, Na, or K. In addition none of the raw material components are included as fillers. As a result, a semiconductor device having high pressure resistance similar to conventional semiconductor devices can be obtained using a glass material not including lead.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

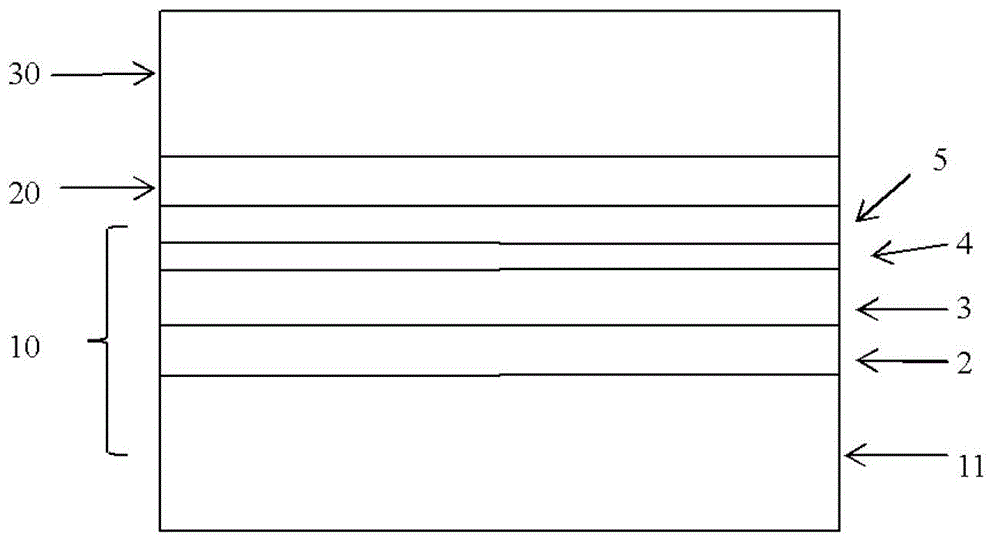

Method for manufacturing micro-nano pyramid gallium nitride based light-emitting diode array with vertical structure

InactiveCN102694093AImprove internal quantum efficiencyLarge specific surface areaSemiconductor devicesMicro nanoPlasma technology

The invention provides a method for manufacturing a micro-nano pyramid gallium nitride based light-emitting diode array with a vertical structure. The method comprises the following steps of: selecting an epitaxial structure, wherein the epitaxial structure comprises a sapphire substrate and a gallium nitride LED (Light-Emitting Diode) layer; the gallium nitride LED layer comprises an un-designed doped gallium nitride layer, an N-type gallium nitride layer, a quantum well layer and a p-type gallium nitride layer; depositing a metal layer on the p-type gallium nitride layer; transferring an epitaxial structure and the metal layer on the substrate to form a base sheet; separating the sapphire substrate in the epitaxial structure from the epitaxial structure by utilizing a laser stripping method; putting the base sheet into a solution to be corroded and forming a fragmented micro-nano pyramid structure on one face of the un-designed doped gallium nitride layer of the gallium nitride LED layer of the epitaxial structure; coating silica gel on the surface of the micro-nano pyramid structure; removing the silica gel at the tip of the micro-nano pyramid structure by utilizing a plasma technology and keeping the silica gel at the bottom of the micro-nano pyramid structure; depositing a transparent conductive layer on the surface of the micro-nano pyramid structure; and depositing an image metal electrode on the transparent conductive layer through a photoetching method so as to finish the preparation.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

GaN-based heterojunction schottky diode device and preparing method thereof

InactiveCN104332504AAchieve separationLower turn-on voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionReverse current

The invention relates to a GaN-based heterojunction schottky diode device and a preparing method thereof. The GaN-based heterojunction schottky diode device comprises a substrate and an epitaxial layer which grows on the substrate, wherein the epitaxial layer comprises a stress buffer layer, a GaN layer and a heterostructure barrier layer which are arranged from bottom to top. The anode area of the epitaxial layer is etched for forming a recessed trough. A low work function metal layer is plated on the recessed trough and partial surface of the heterostructure barrier layer through vapor plating. A high work function metal layer is plated above the low work function metal layer and the planar area of the heterostructure barrier layer through vapor plating. The high work function metal layer and the low work function metal layer form a mixed anode. Ohmic metal is plated on the cathode area through vapor plating for forming a cathode. The epitaxial layer is integrally covered by a passivation insulating layer. The insulating layer is etched for forming an electrode window. According to the GaN-based heterojunction schottky diode device, combination of mixed anode metal and anode recessed trough technique is realized; current under forward bias is activated in advance through the side wall of the anode recessed trough; reverse leakage current is cut off through the high work function metal layer on the surface of the heterostructure barrier layer under reverse bias, thereby realizing separation of forward and reverse current channels, and achieving a technical object of the GaN-based heterojunction schottky diode device with low turn-on voltage and low reverse leakage current.

Owner:SUN YAT SEN UNIV

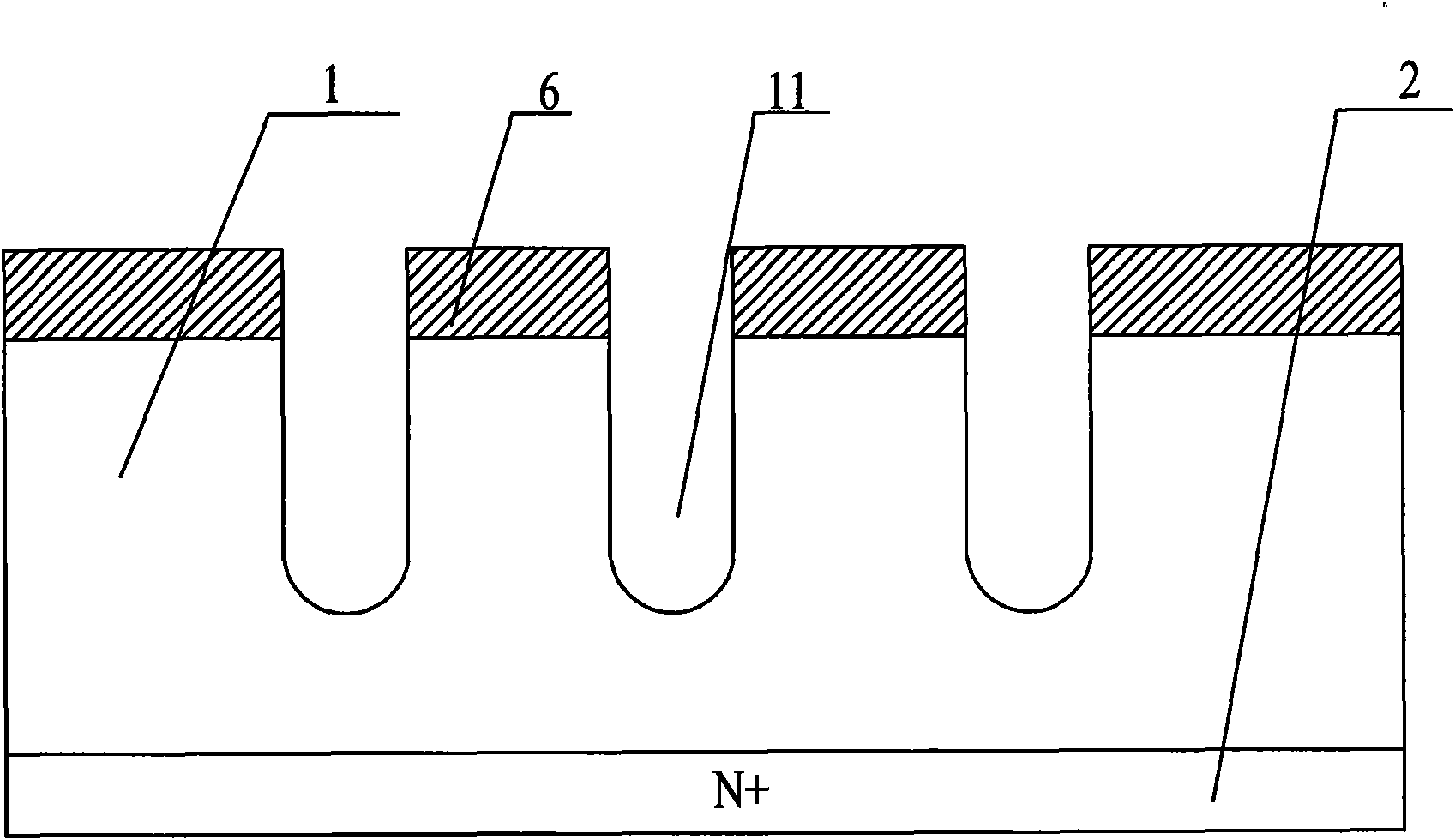

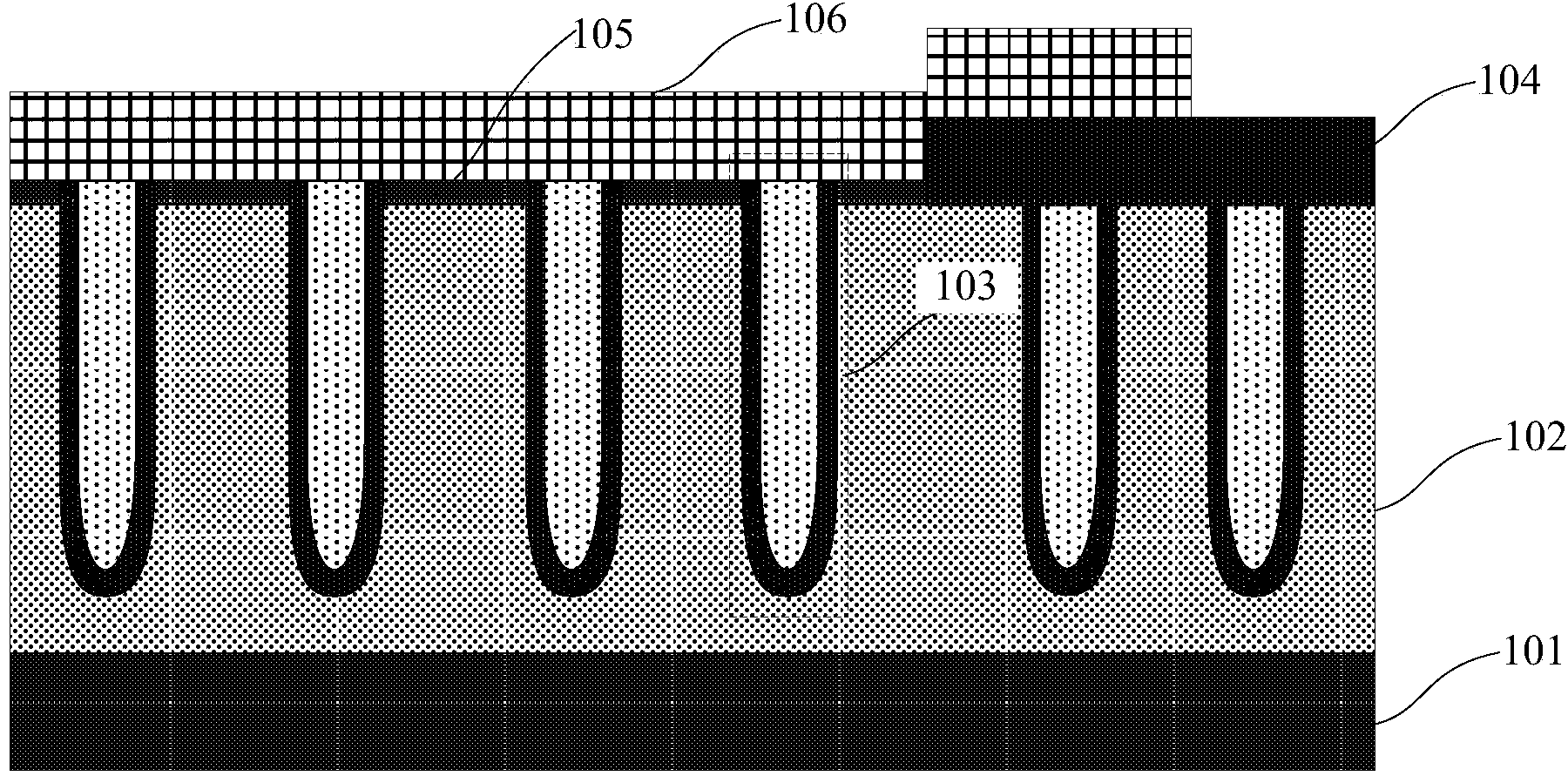

Silicon carbide groove MOS junction barrier Schottky diode and manufacturing method thereof

ActiveCN103928532AImprove reliabilityReduce reverse leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldConcentration effect

The invention discloses a silicon carbide groove MOS junction barrier Schottky diode and a manufacturing method of the silicon carbide groove MOS junction barrier Schottky diode. The problems of too low breakdown voltages, too low reliability and the like caused by the serious electric field concentration effect on the edge of a device and too high leakage currents are mainly solved. The silicon carbide groove MOS junction barrier Schottky diode and the manufacturing method are characterized in that a groove MOS structure is introduced on the basis of a traditional JBS device structure, and therefore the functions of relieving electric field concentration on a P-junction edge and lowering the leakage currents are achieved.

Owner:XIDIAN UNIV

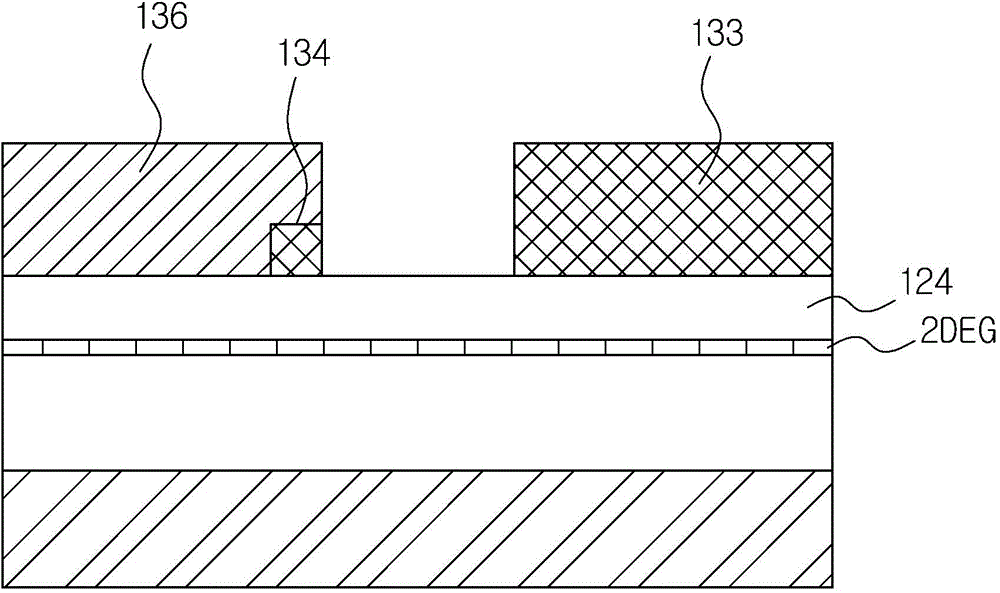

Nitride Semiconductor Device And Method Of Manufacturing The Same

InactiveCN104037212ALower threshold voltageReduce switching lossSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectrode Contact

Owner:SEOUL SEMICONDUCTOR

Fast recovery diode and manufacturing method thereof

InactiveCN102867849AIncreased Schottky areaReduce conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesHigh current densitySchottky barrier

The invention relates to a fast recovery diode device, and also relates to a manufacturing method of the fast recovery diode device. According to the invention, a groove structure is added into a traditional Schottky barrier rectifier (MPS) structure intruding into a PN junction. Compared with the traditional MPS device, the fast recovery diode device disclosed by the invention has the advantages of lower forward voltage drop and higher current density.

Owner:盛况

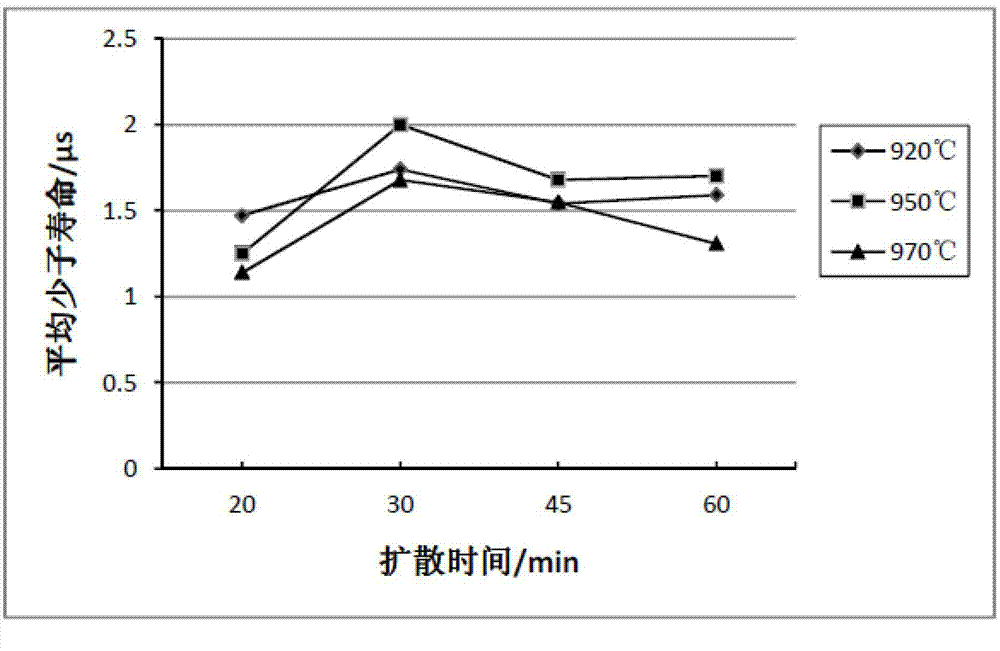

Phosphorous gettering method of metallurgy polycrystalline silicon wafer, silicon wafer and solar cell prepared by silicon wafer

InactiveCN103117328AImprove life expectancyEfficient removalRenewable energy productsSemiconductor devicesTime rangeOxygen

The invention provides a phosphorous gettering method of a metallurgy polycrystalline silicon wafer, a silicon wafer and a solar cell prepared by the silicon wafer The phosphorous gettering method includes: corroding to remove a damaged layer on the surface of the silicon wafer; rinsing the silicon wafer and drying; subjecting the silicon wafer to gettering heat treatment in a diffusion furnace, wherein the diffusion phosphorous source flow volume ranges from 650 to 700ml / min, dry oxygen flow volume ranges from 500 to 700ml / min, diffusing temperature ranges from 920 to 970 DEG C, and the diffusing time ranges from 30-45min; cooling the silicon wafer; corroding to remove a getter layer and PN junctions generated on the surface of the silicon wafer due to phosphorus diffusion; rinsing the silicon wafer and drying to obtain the gettered metallurgy polycrystalline silicon wafer. Service life of the silicon wafer is obviously prolonged, and reverse leakage current and light attenuation of the solar cell prepared by the silicon wafer are obviously reduced. The phosphorous gettering method is short in diffusing time, so that production period is shortened, energy consumption is reduced, and industrial production is suited.

Owner:INNER MONGOLIA RIYUE SOLAR ENERGY TECH

MOS super barrier rectifier device and manufacturing method thereof

InactiveCN103325839AGuaranteed depthLow costSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringImpurity

The invention discloses an MOS super barrier rectifier device which is provided with a groove, a second conduction type injection region wraps the groove, the structure can replace a protecting ring structure, a primary photomask is removed compared with the prior art, the depth of the second conduction type injection region is guaranteed, and good pressure proof functions are performed. In addition, the invention further discloses a manufacturing method. According to the method, after the groove is formed, the second conduction type injection region is injected and formed by carrying out heat treatment on activator impurities, the photomask needed when a protecting ring is formed and the processes of long-time trap pushing are removed, cost is saved, the damage, caused by injection by using macro-energy, to the surfaces of devices is avoided, transverse diffusion distance of micro-energy injection region is small, and the control over the length of a channel region and the distance between adjacent second conduction type injection regions is better.

Owner:ZHANGJIAGANG CASS SEMICON

Power schottky device barrier method

ActiveCN101051613AAvoid mutual expansionImprove positive characteristicsSemiconductor/solid-state device manufacturingEtchingAlloy

Characters of the method includes following steps: (1) oxidation; (2) first photo etching; (3) boron diffusion; (4) second photo etching; (5) sputtering barrier metal; (6) vaporizing multilayer of metal on face side; (7) third photo etching; (8) annealing; (9) thinning rear face; (10) vaporizing multilayer of metal on rear face; (11) alloying (12) testing and cutting to separate slices. Useful effects are: reducing influences from surface state, enhancing forward and backward characteristics as well as capability of inverted voltage resistant and anti burning, preventing oxidation of metal layer prolonging service life, avoiding interdiffusion between each metal and silicide, raising fatigue resistance, and reinforcing stability of parts.

Owner:JINAN JINGHENG ELECTRONICS

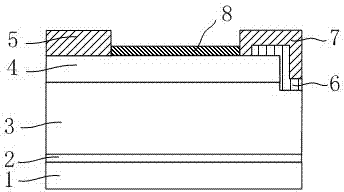

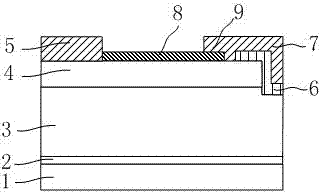

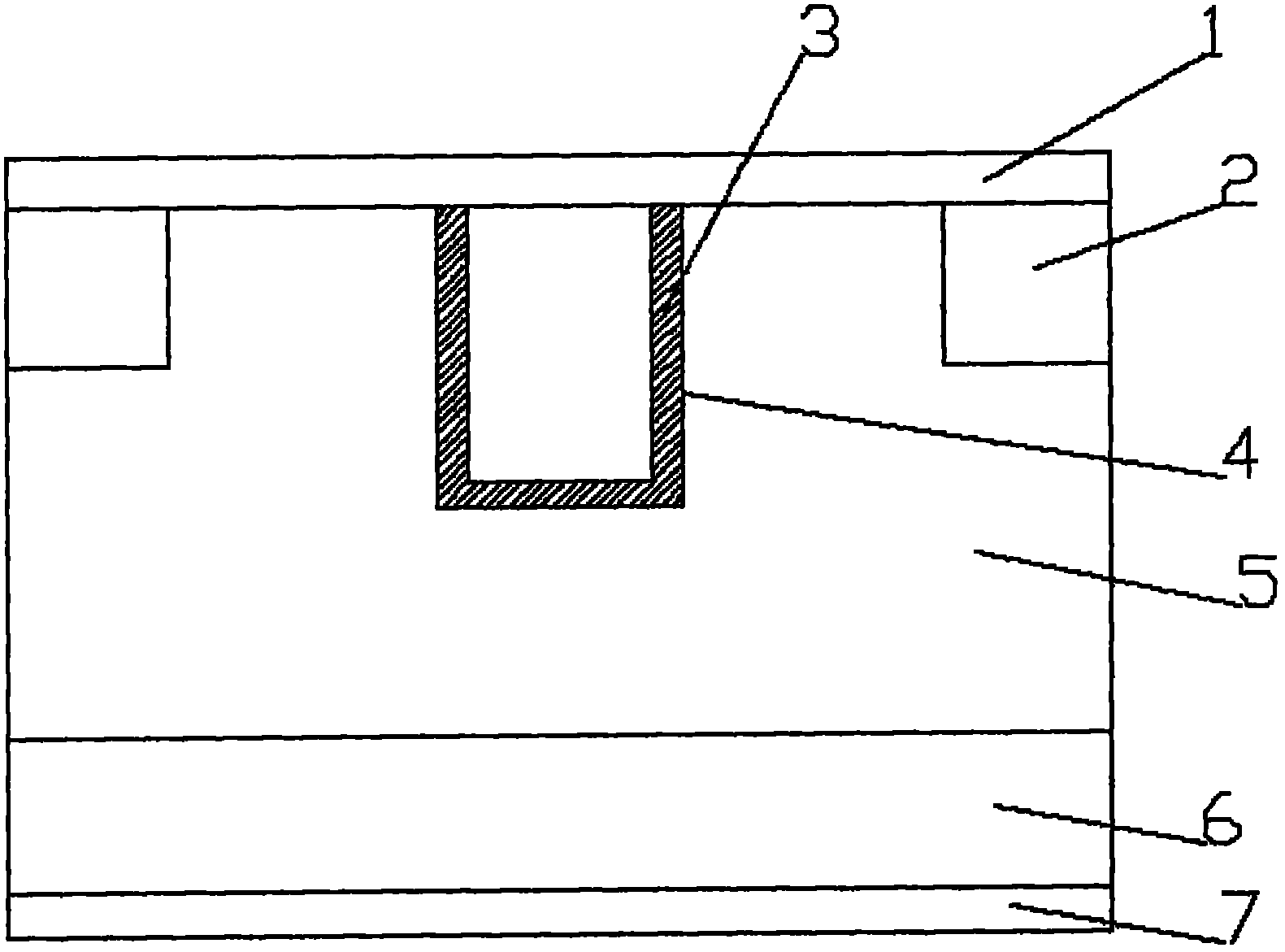

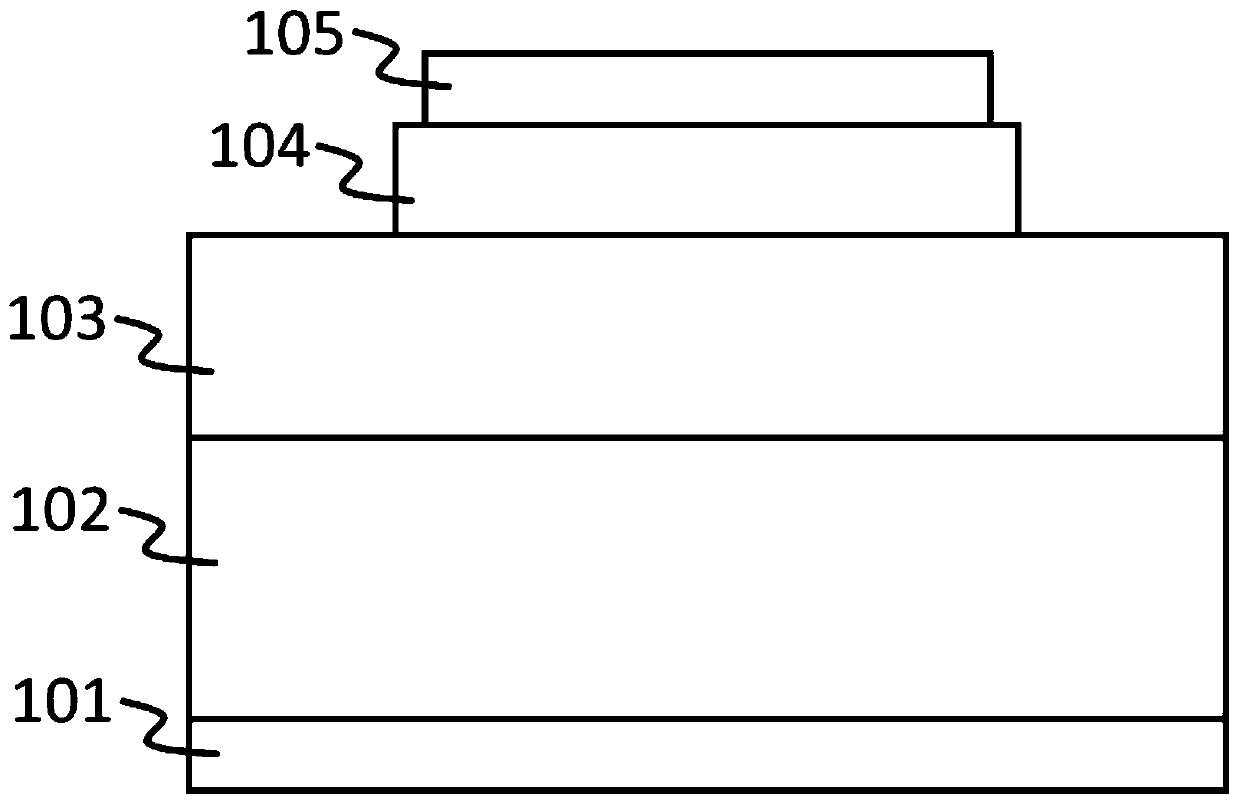

Gallium oxide junction barrier Schottky diode with field plate structure

InactiveCN112186032AReduce peakAlleviate the effect of electric field concentrationSemiconductor devicesHemt circuitsElectric current flow

The invention discloses a gallium oxide junction barrier Schottky diode with a field plate structure, and mainly solves the problems that an electric field concentration effect exists in an existing device and a P type is not easy to dope. The diode comprises a cathode metal layer (8), a substrate (7) and an epitaxial layer (6), the upper half part of the epitaxial layer is provided with a P-typeannular region (4) and a P-type gate region (5), the two P-type regions form a PN junction on the epitaxial layer, and the upper surface of the epitaxial layer is provided with an anode metal layer (3); the edge of the metal layer is arranged on the upper surface of the P-type annular region, the remaining upper surface of the P-type annular region is covered with a dielectric layer (2), the dielectric layer surrounds the edge of the anode metal layer and covers the edge of the upper surface of the anode metal layer, and anode field plates (1) are arranged on the upper surface of the anode metal layer and the upper surface of the dielectric layer to relieve the electric field concentration effect. According to the invention, the breakdown voltage is improved, the forward current of the device is increased, the reverse leakage current is reduced, and the device can be used for manufacturing high-power and high-frequency rectification, detection and frequency mixing circuits.

Owner:XIDIAN UNIV

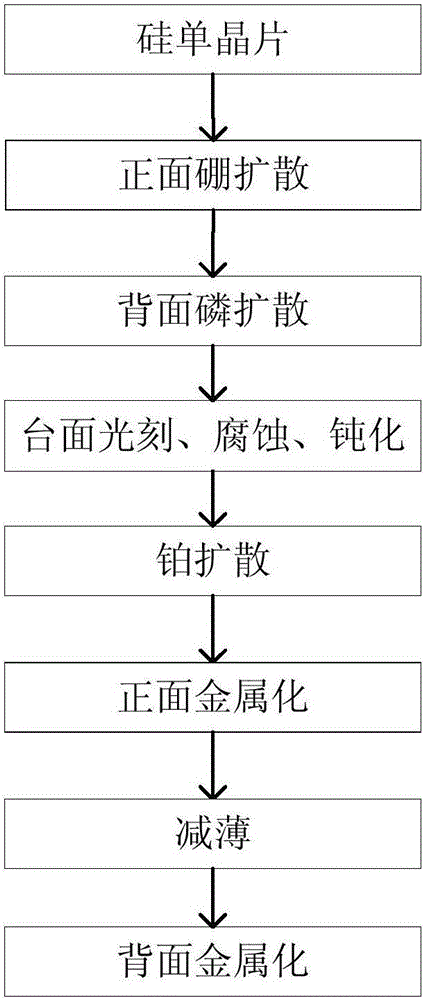

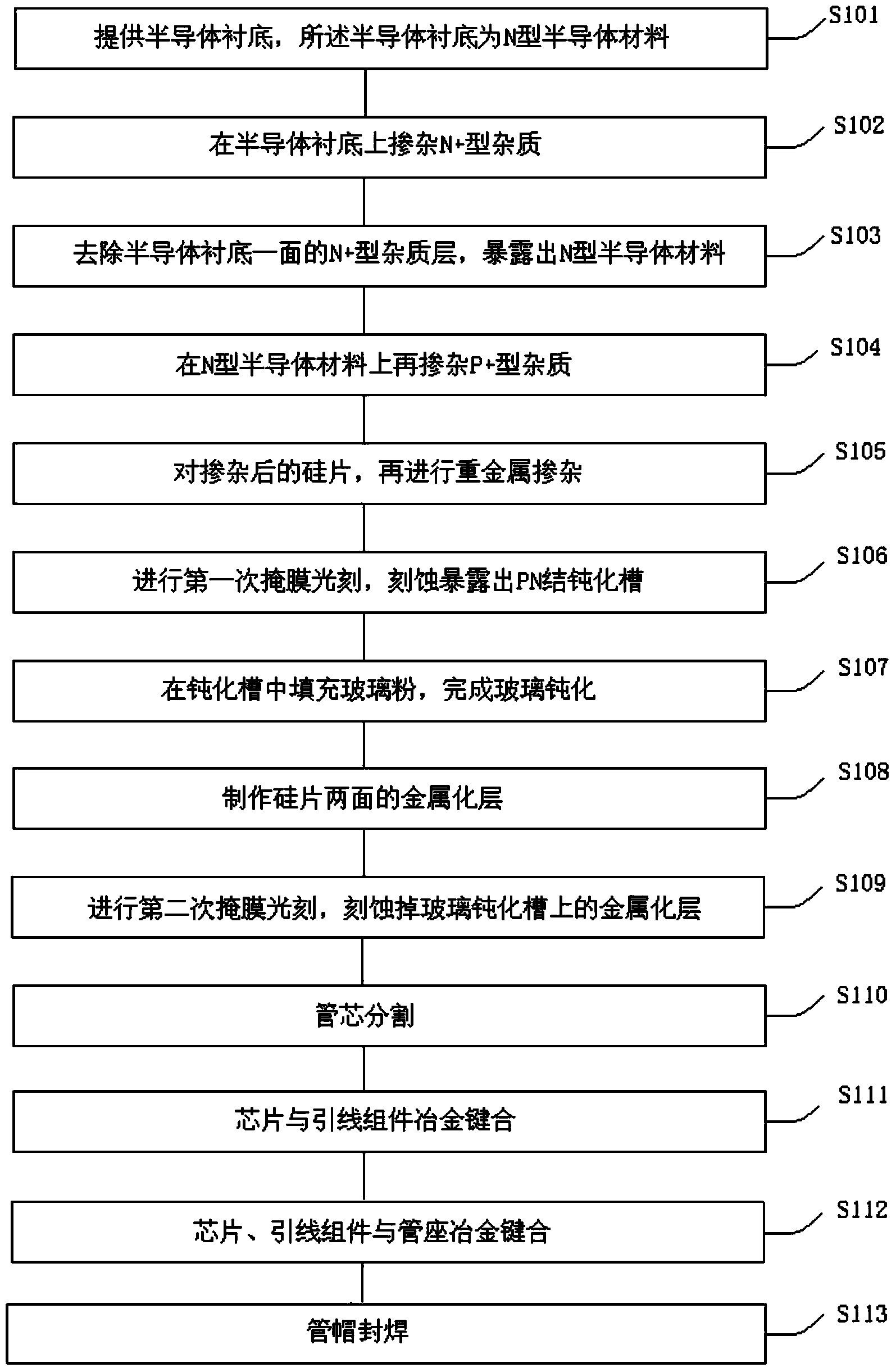

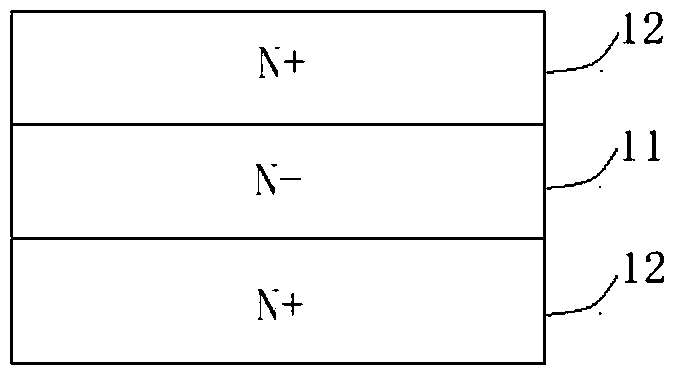

Method for manufacturing 50A high-current fast recovery diode

ActiveCN104269356AReduce reverse leakage currentImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDiffusion methodsSemiconductor materials

The invention discloses a method for manufacturing a 50A high-current fast recovery diode. The method for manufacturing the 50A high-current fast recovery diode comprises the steps that an N type semiconductor silicon material is provided to serve as a semiconductor substrate; the N type semiconductor substrate is doped with N+ type impurities; the N+ type impurity layer on one side of the semiconductor substrate is removed; an exposed N-type semiconductor material is doped with dual P+ type impurities; heavy metal platinum doping is conducted according to the high-temperature diffusion method; primary mask photoetching is conducted; glass powder is arranged in a passivation groove through knife coating, high-temperature sinter molding is conducted, and then PN junction glass passivation is completed; multiple metallization layers are manufactured on the two sides of a silicon wafer according to the vacuum sputtering method; secondary mask photoetching is conducted; the silicon wafer is divided into independent dies; a chip and a lead component are bonded together; the chip, the lead component and a diode holder are bonded together in a metallurgical mode through sintering; a diode cap and the diode holder are welded together in a sealed mode through percussion welding. According to the method for manufacturing the 50A high-current fast recovery diode, the manufacturing process based on the method is less influenced by the environment, the technology is mature, the stability and the repeatability are high, and the method can be widely used for volume production of high-current fast recovery diodes.

Owner:西安卫光科技有限公司

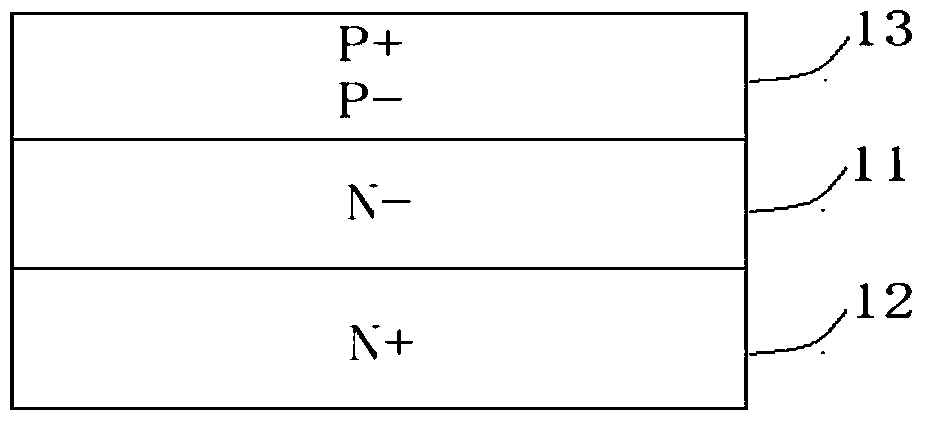

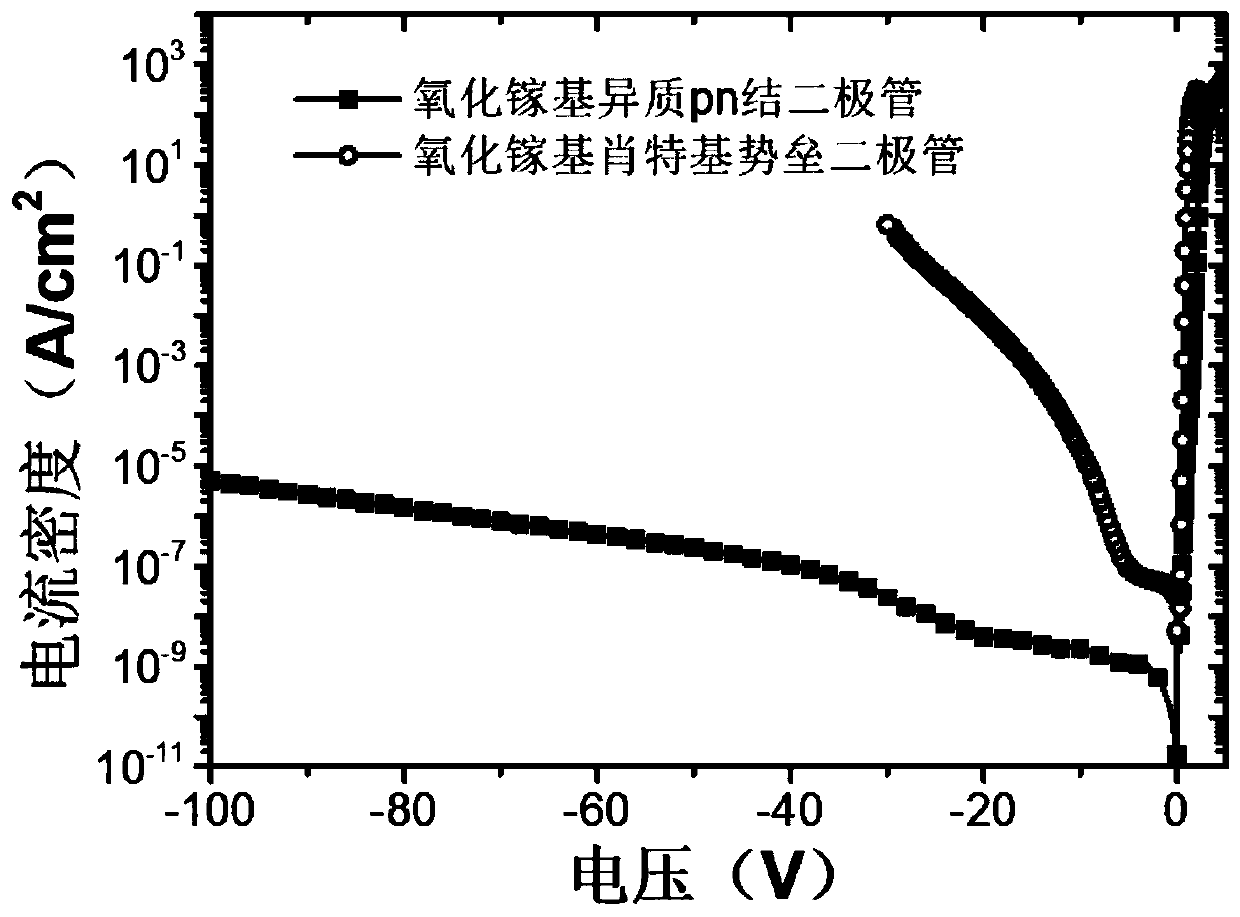

Gallium oxide-based heterogeneous PN junction diode and preparation method thereof

InactiveCN110085681AAvoiding p-type doping problemsImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalP type doping

The invention discloses a gallium oxide-based heterogeneous PN junction diode and a preparation method thereof, and relates to the technical field of semiconductor devices. In allusion to the shortcomings such as high reverse leakage current, low breakdown voltage and poor reliability of gallium-oxide-based diodes in the prior art, it is proposed that a p-type oxide semiconductor layer is arrangedbetween an n-type doped gallium oxide voltage resistant layer and an anode electrode. The amorphous or polycrystalline p-type oxide semiconductor layer and the single crystal n-type doped gallium oxide voltage resistant layer are adopted to form a heterogeneous PN junction, the advantage of high hole concentration of the amorphous or polycrystalline p-type oxide semiconductor layer is utilized while giving full play to the high voltage resistant advantage of the single crystal gallium oxide material, and the p-type doping problem of the gallium oxide material is skillfully avoided. The realized diode device has the advantages of low reverse leakage current, high voltage resistance and stable performance, and the preparation process is simple.

Owner:SUN YAT SEN UNIV

Schottky barrier diode device structure and manufacturing method thereof

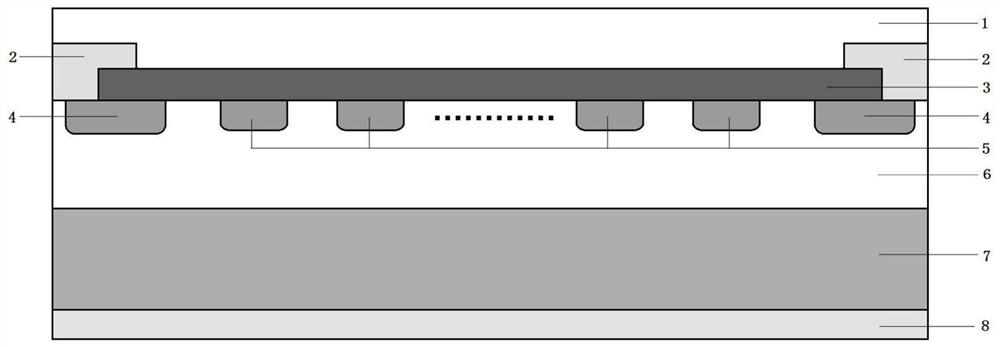

ActiveCN103943688AImprove reverse breakdown voltageReduce electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsDielectric layer

The invention provides a Schottky barrier diode device structure and a manufacturing method of the structure. The device structure comprises a first conductive type substrate, first conductive type epitaxial layers which are combined on the surface of the first conductive type substrate, a plurality of groove structures, second conductive type doping areas, a Schottky metal layer and an upper electrode. The groove structures comprise grooves formed in the first conductive type epitaxial layers, dielectric layers combined on the surfaces of the grooves, and conductive materials, the grooves are filled with the conductive materials, the second conductive type doping areas are formed at the positions, arranged on two sides of the groove structures, of the surfaces of the first conductive type epitaxial layers, and the Schottky metal layer is formed on the surfaces of the first conductive type epitaxial layers. The doping areas are added on two sides of the groove structures, the P / N knot is introduced, electric fields of the areas are reduced, and therefore reverse leakage currents are reduced. Meanwhile, JFET structures are introduced between the doping areas, reverse breakdown voltages of the Schottky barrier diode device structure are improved, and the reverse leakage currents are reduced.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

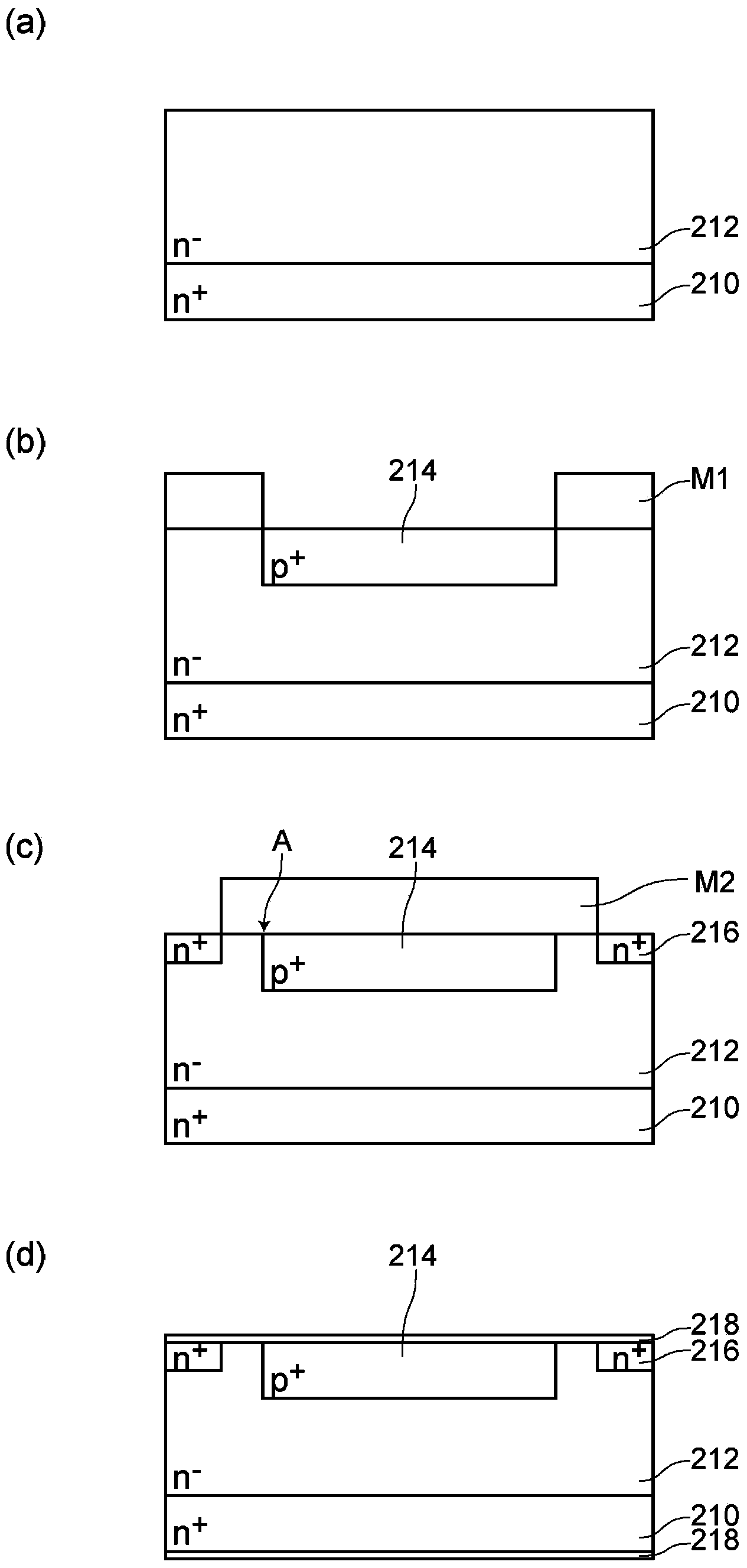

Method for manufacturing silicon carbide semiconductor device

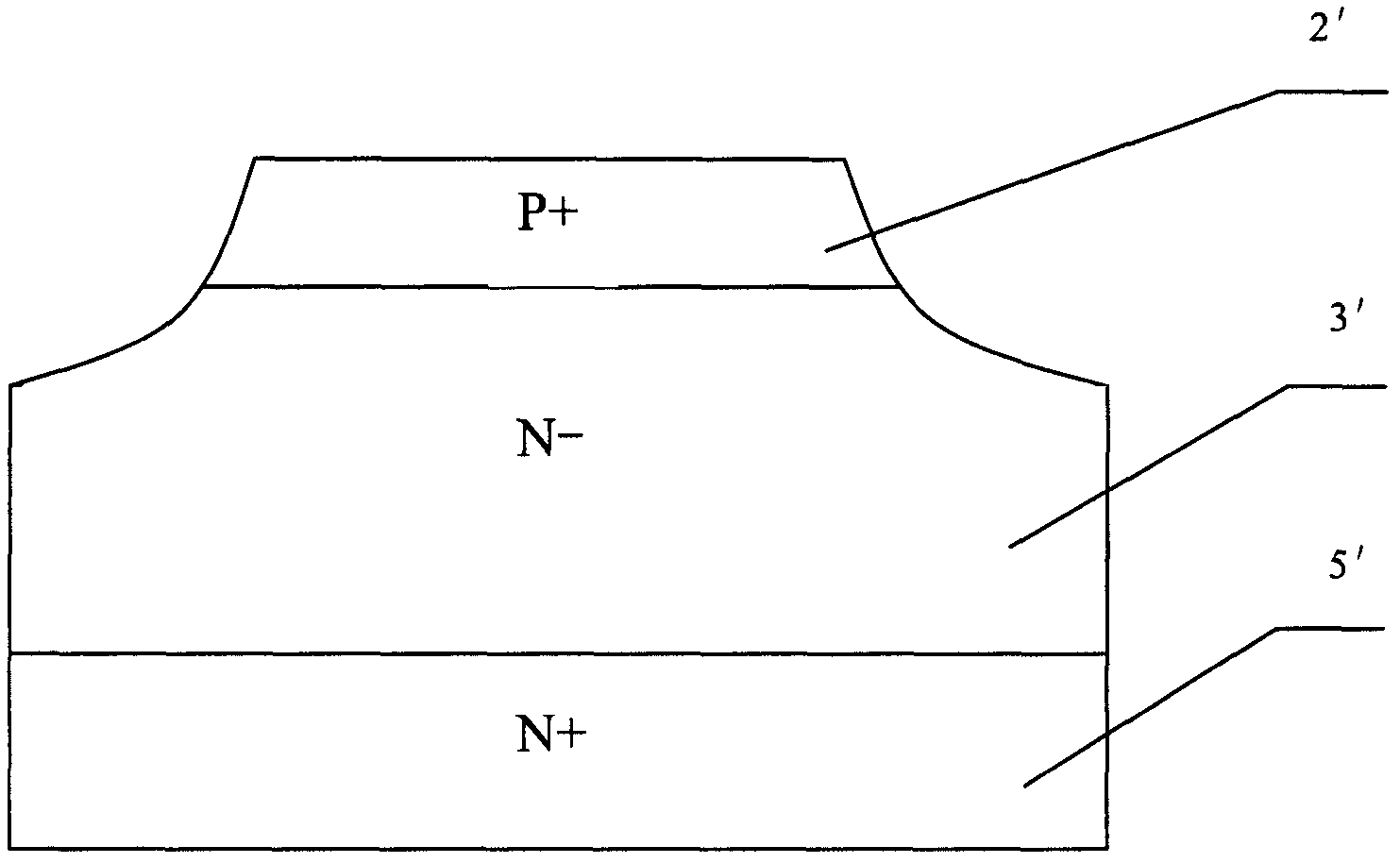

InactiveUS20110256699A1High forward currentReduce reverse leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowReverse leakage current

Provided is a method for manufacturing a silicon carbide semiconductor device which is capable of obtaining the silicon carbide semiconductor device having a high forward current and a low reverse leakage current by a simple method. The method for manufacturing a silicon carbide semiconductor device includes the steps of: forming a film made of a first electrode material on one surface of a silicon carbide substrate, and forming an ohmic electrode by performing heat treatment at a temperature range of 930 to 950° C.; and forming a film made of a second electrode material on the other surface of the silicon carbide substrate, and forming a Schottky electrode by performing heat treatment.

Owner:SHOWA DENKO KK