Patents

Literature

297results about How to "Reduce electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

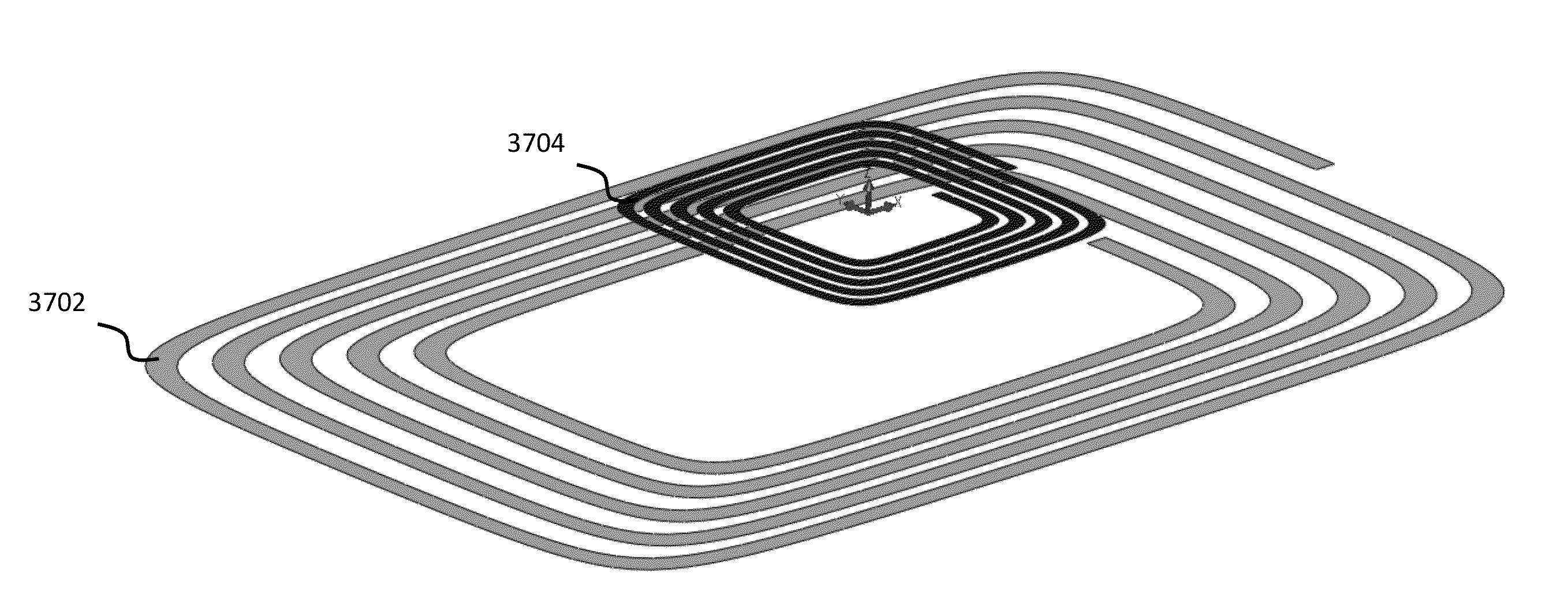

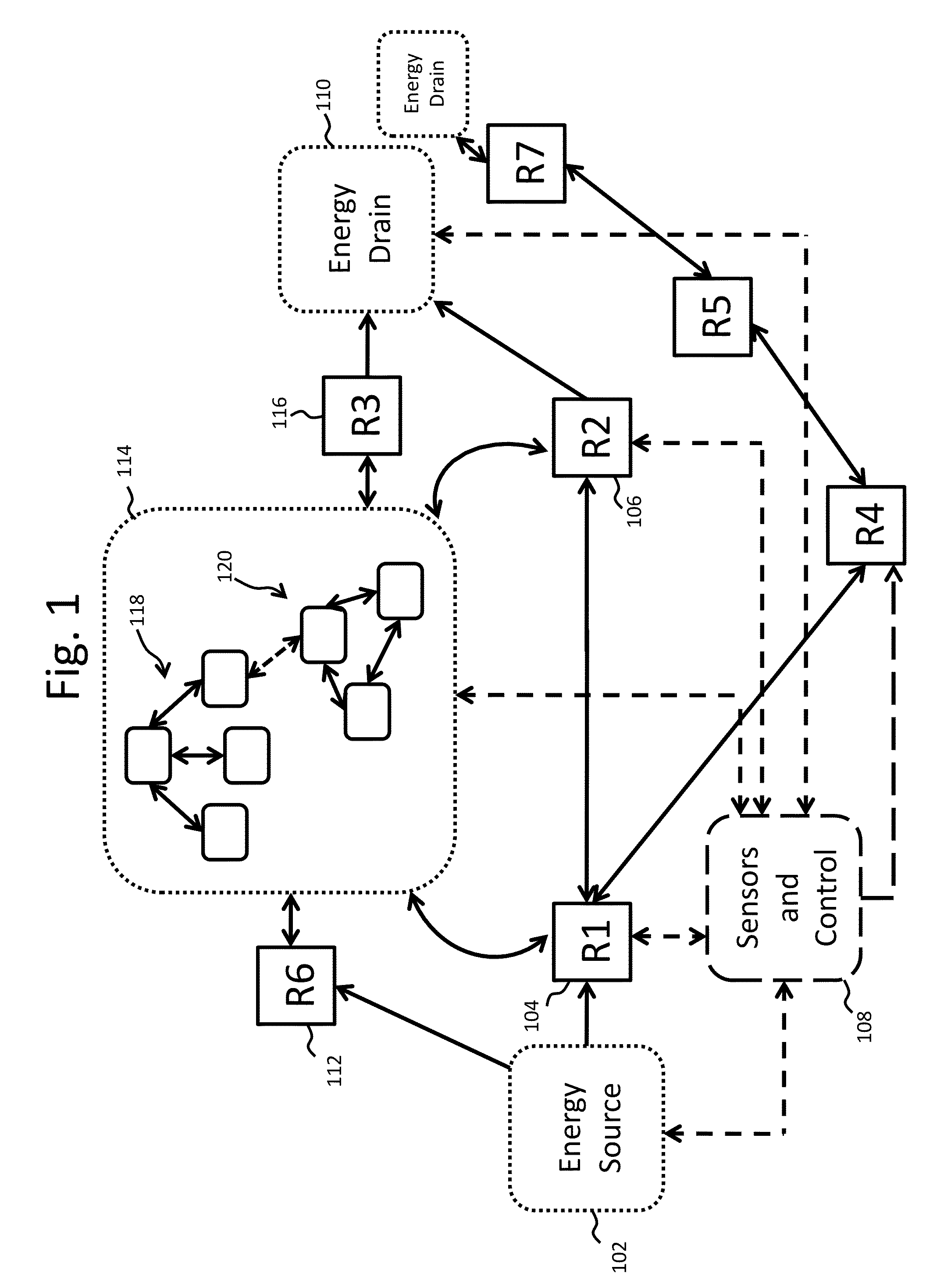

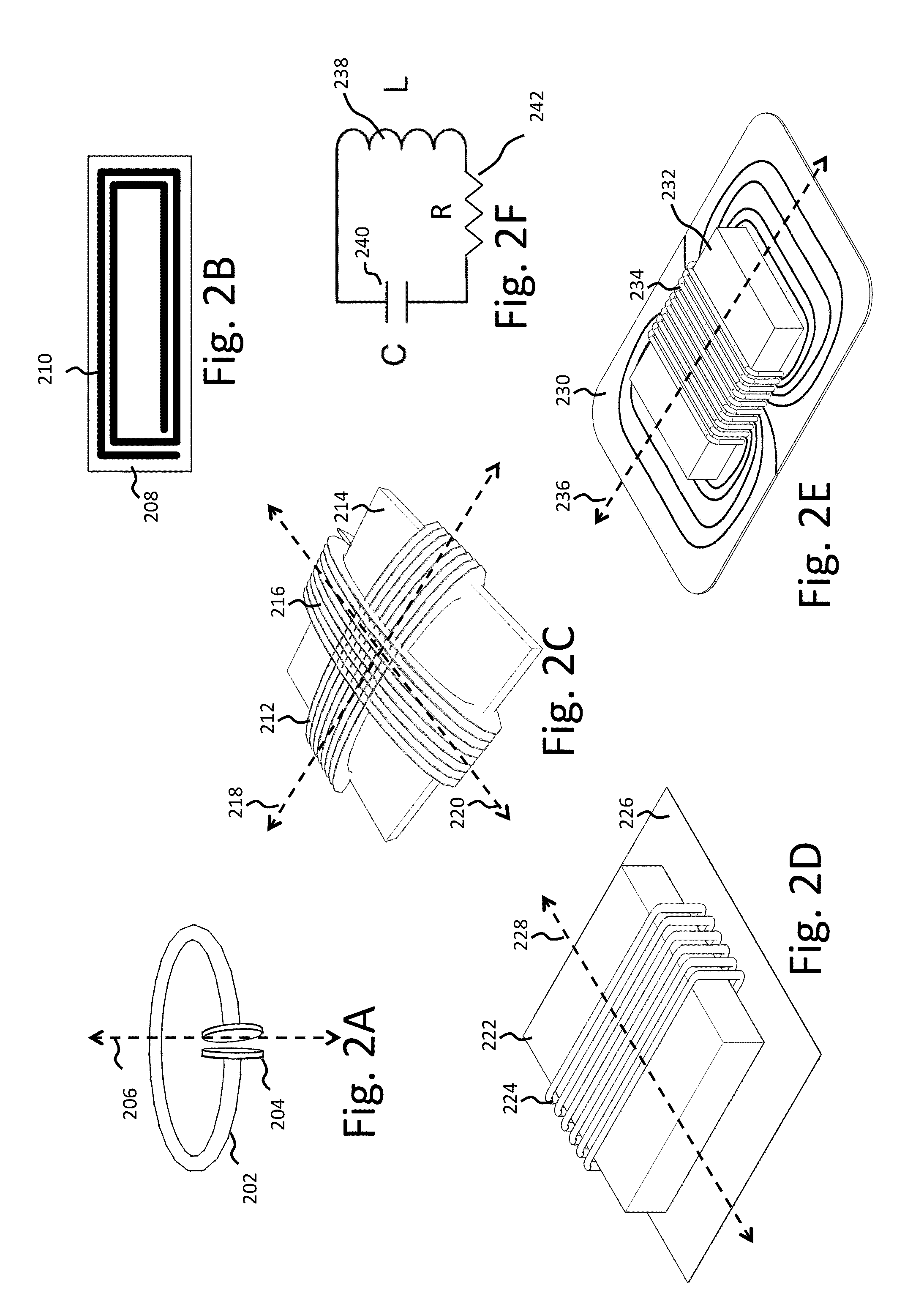

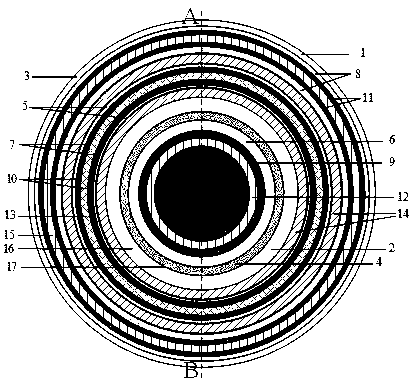

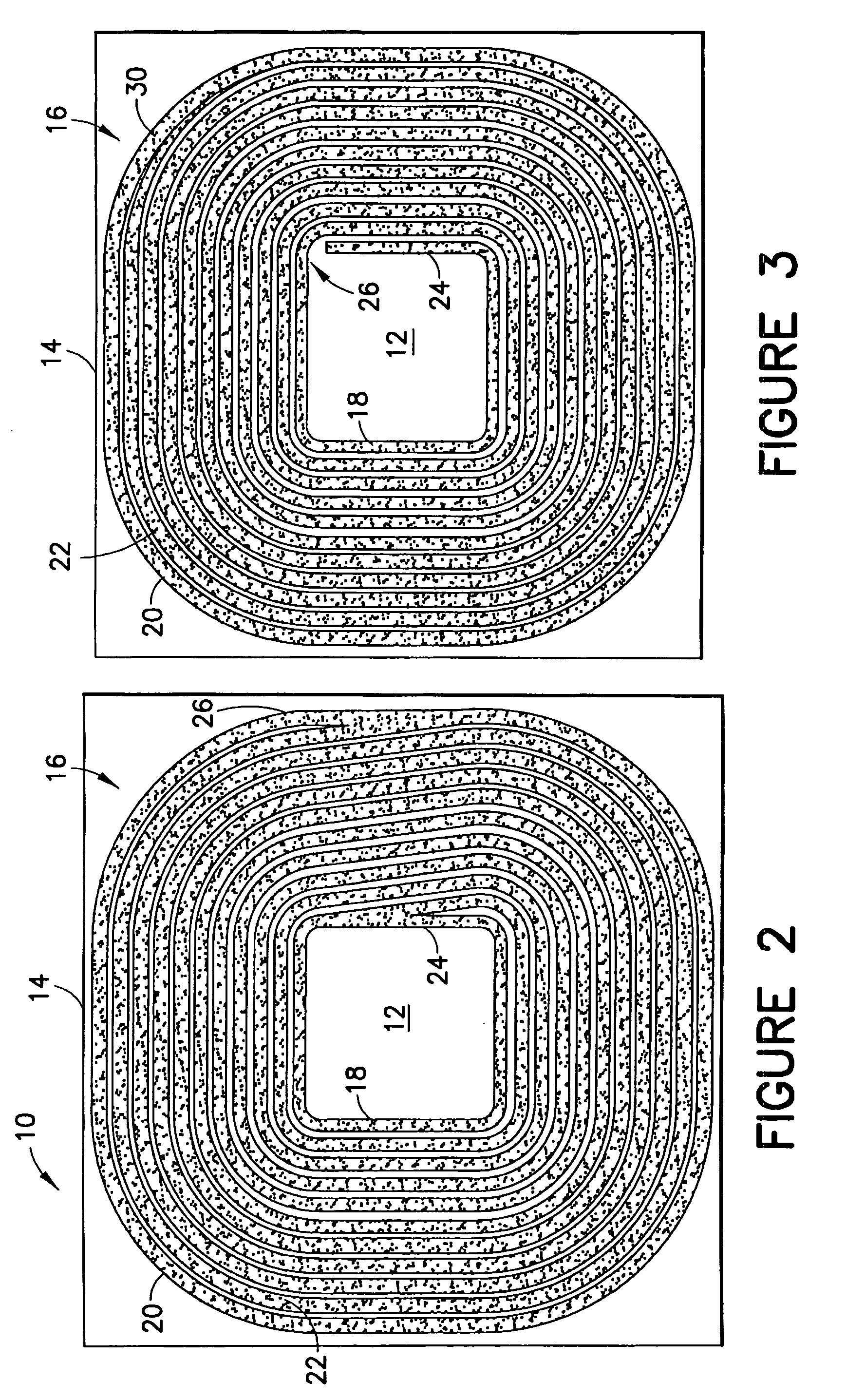

High frequency PCB coils

Described herein designs for high frequency printed circuit board (PCB) resonator coils. The resonator coils are printed or etched on a thin substrate. The number of loops of the resonator coil, the width of each trace, the spacing between the traces, and the like are adjusted to increase the quality factor Q of the resonator coils.

Owner:WITRICITY CORP

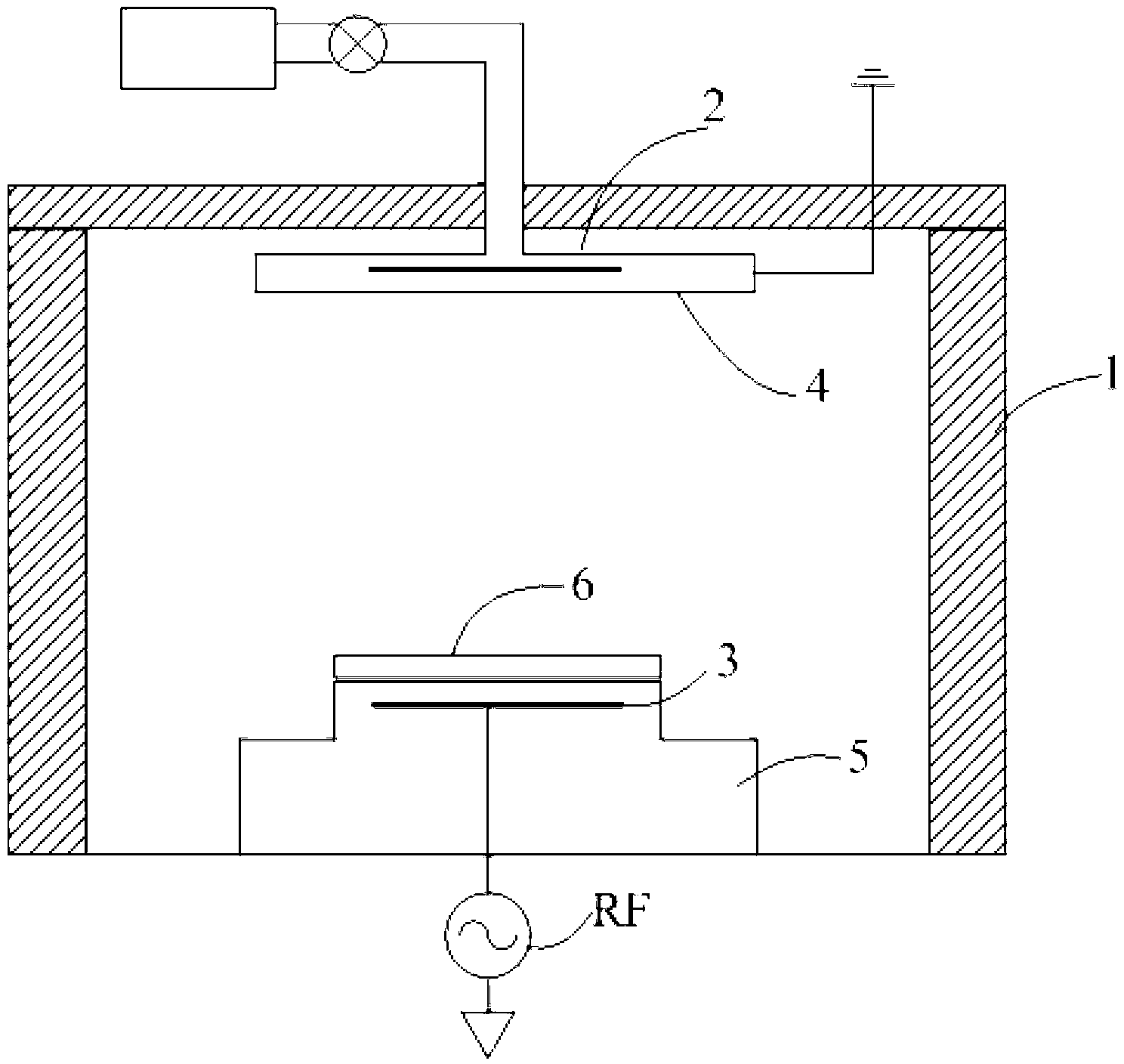

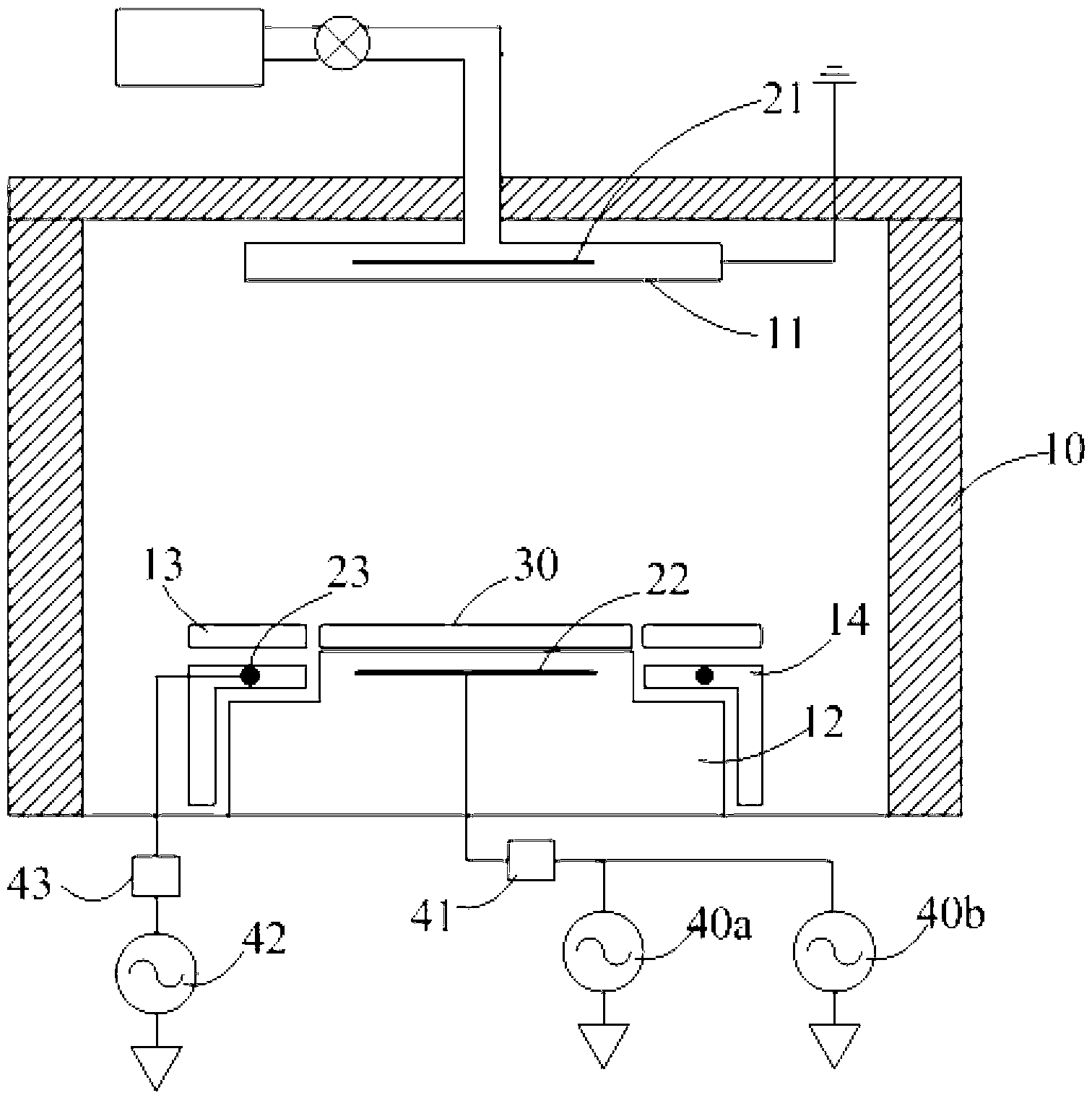

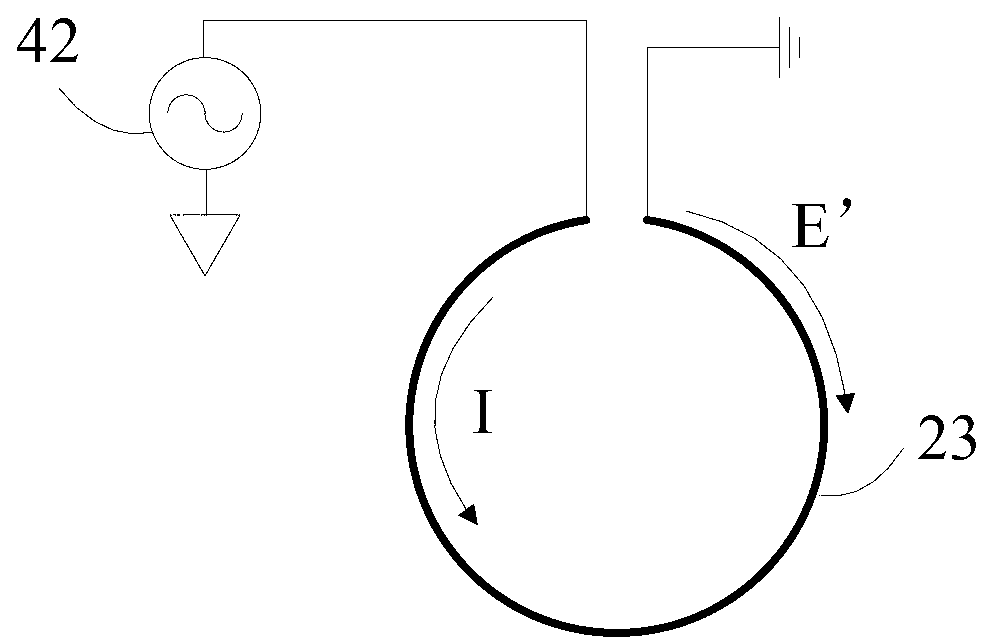

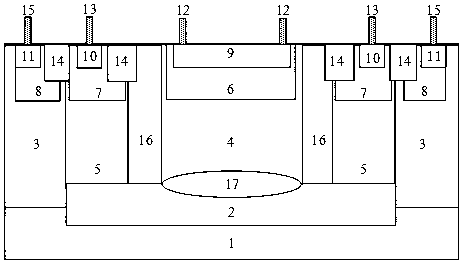

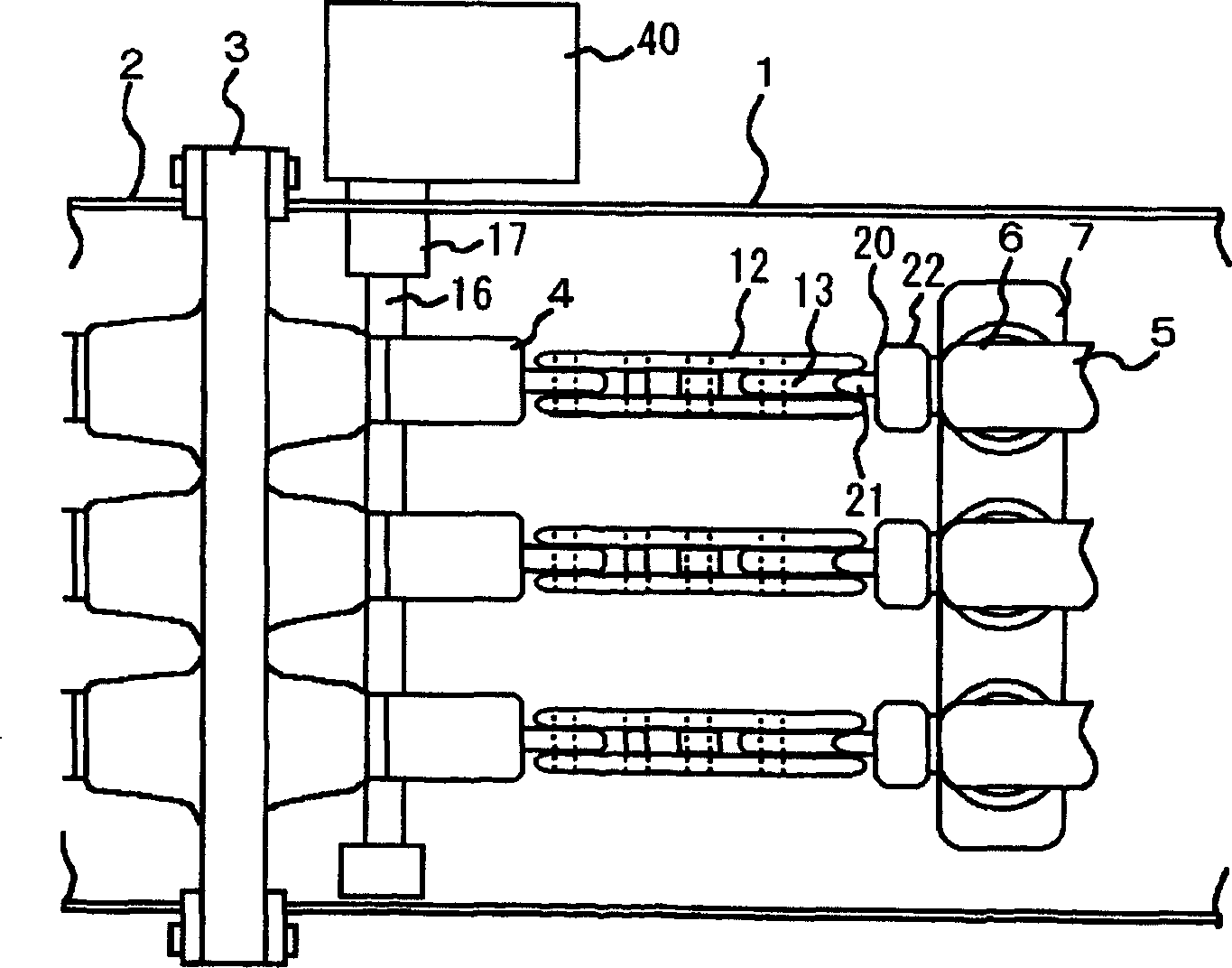

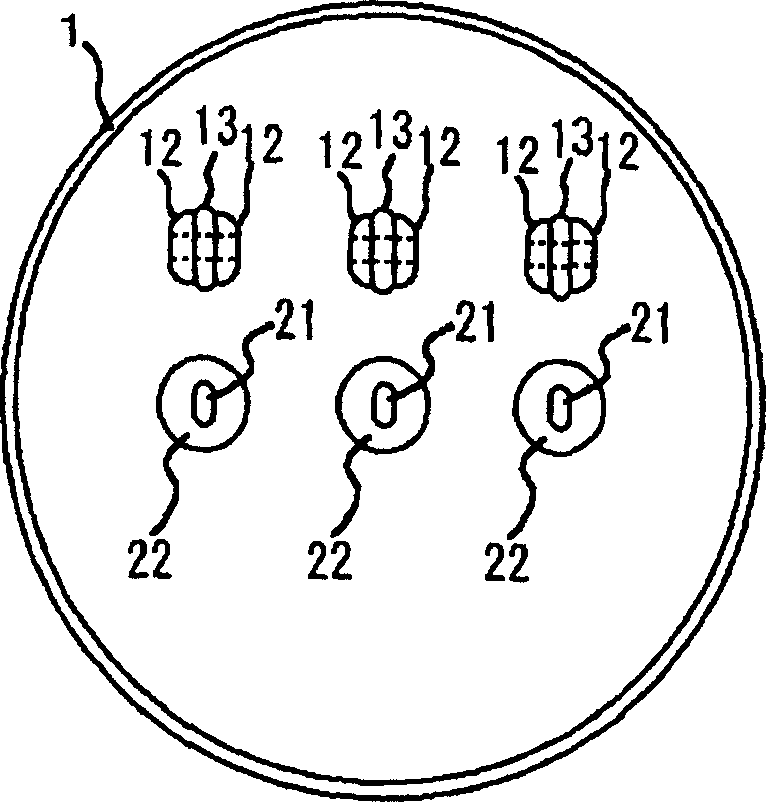

Plasma processing device

ActiveCN103227091AUniform treatment processViolent bombardmentElectric discharge tubesDensity distributionEngineering

The invention discloses a plasma processing device which comprises a reaction cavity, a first radio-frequency power source and a second radio-frequency power source, wherein the reaction cavity comprises an upper electrode and a lower electrode which are arranged in parallel, an annular insulator, and opening metal ring electrodes; the upper electrode is arranged in a gas spray header; the lower electrode is arranged in a static clamping chuck; the first radio-frequency power source is used for forming a perpendicular radio-frequency electric field between the upper and lower electrodes to generate plasma; the second radio-frequency power source is used for adjusting energy of the plasma; the annular insulator surrounds the static clamping chuck and / or an area above the static clamping chuck; the opening metal ring electrodes are wound by wires, and embedded into the annular insulator; and a radio-frequency current is supplied in the metal ring electrodes to generate a horizontal induction electric field. The plasma processing device can improve the uniformity of density distribution of the plasma in the reaction cavity effectively.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

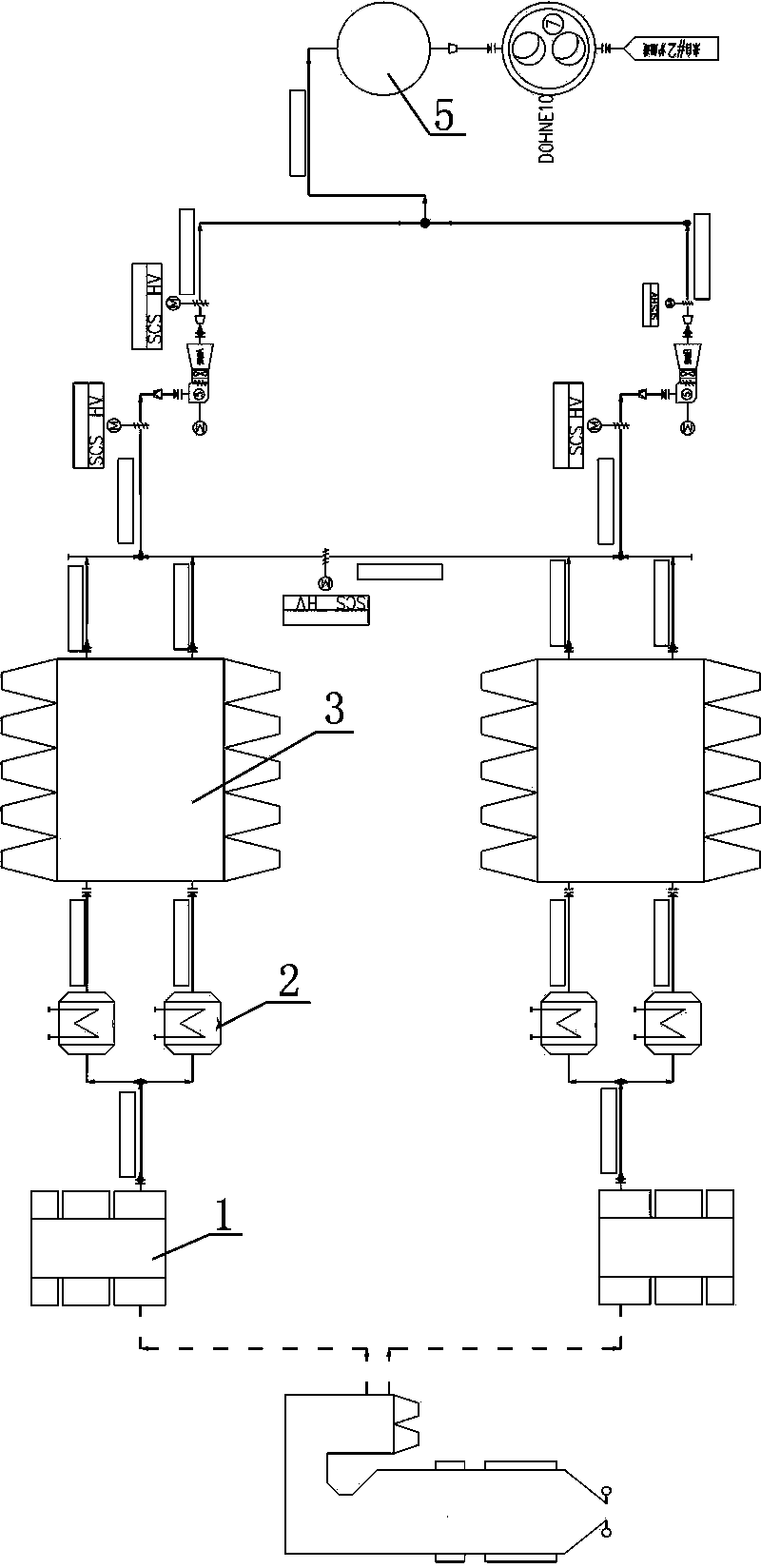

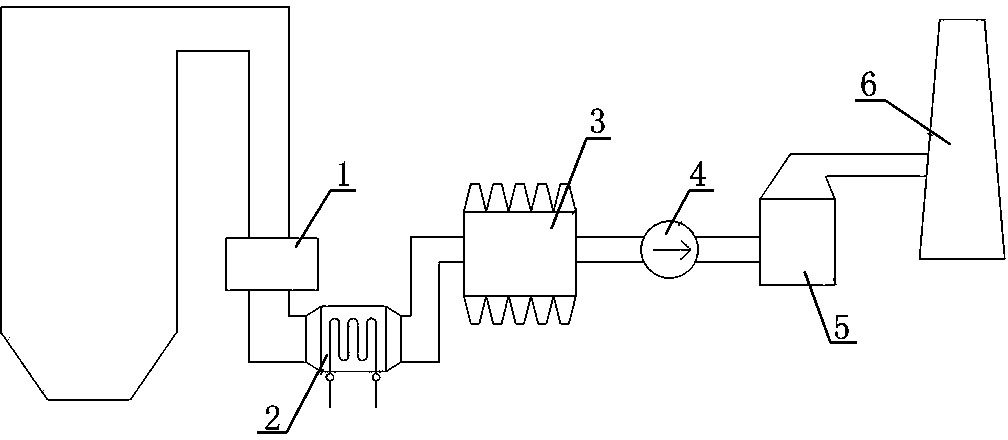

Low temperature electric precipitation system in fuel electric plant

InactiveCN103363536AImprove the dust collection rateMeet the requirements of emission standardsLighting and heating apparatusAir preheaterEnvironmental resistance

A low temperature electric precipitation system in a fuel electric plant comprises at least one air preheater, at least one electric precipitator and connecting pipes for connecting the air preheater and the electric precipitator together, a flue-gas heat exchanger for lowering the flue-gas temperature entering the electric precipitator to enable the flue-gas temperature to reach or be lower than flue-gas dew point at the temperature of 90 DEG C is arranged between the air preheater outlet and the electric precipitator inlet; the electric precipitator is communicated with a desulfuration absorption tower through an induced-draft fan; a chimney is connected with the rear part of the desulfuration absorption tower. The flue-gas heat exchanger adopts a backward flow heat exchange type; a vertical pipe heat exchange flow passage or a horizontal pipe heat exchange flow passage is arranged at the inner part of the flue-gas heat exchanger; the system has the characteristics that the project equipment investment is reduced; the auxiliary power ratio is lowered; the energy is saved; the consumption is reduced; the heat economy of the unit can be improved; the latest environment-friendly emission standard can be satisfied.

Owner:ZHEJIANG ELECTRIC POWER DESIGN INST +1

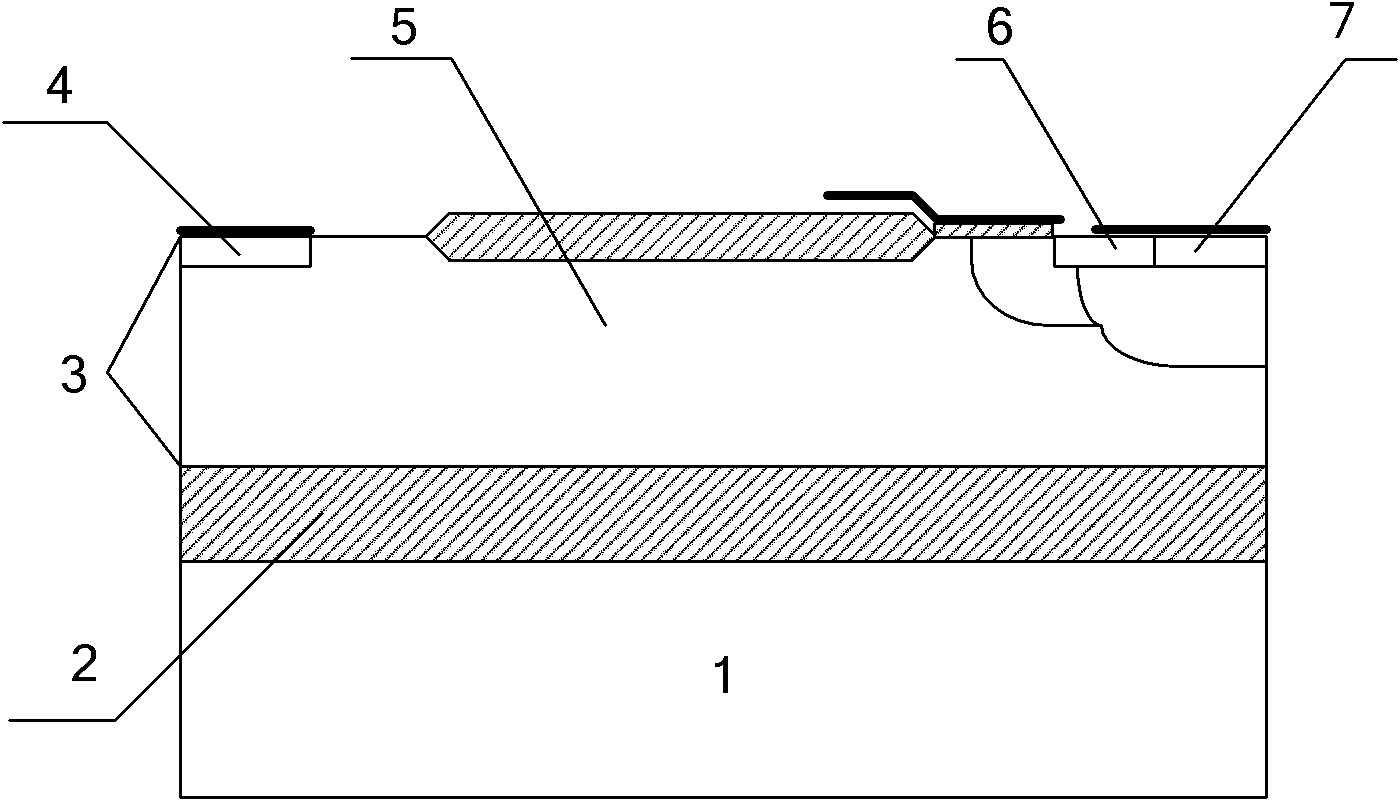

Silicon-based near-infrared single photon avalanche diode detector and manufacturing method thereof

InactiveCN110416335AImprove detection efficiencyReduce dark count rateFinal product manufactureSemiconductor devicesInfraredSingle-photon avalanche diode

The invention discloses a silicon-based near-infrared single photon avalanche diode detector, and belongs to the technical field of photoelectric detection. The single photon avalanche diode detectorcomprises a P-type epitaxial layer arranged above a P-type substrate, wherein the P-type substrate and the P-type epitaxial layer are provided with an N+ buried layer region therebetween, deep P wellregions are symmetrically arranged on the N+ buried layer region, a deep P well region is arranged on the N+ buried layer region at the central position, and an avalanche region is formed between thedeep P well region and the N+ buried layer region. According to the single photon avalanche diode detector, the deep avalanche region is formed between the deep P well and the N+ buried layer, the lightly-doped and uniformly distributed P-type epitaxial layer is utilized as a virtual protection ring at the same time to improve the near-infrared photon detection efficiency, the size of the device is reduced, and the dark counting noise is reduced. The manufacturing method can carry out manufacturing based on the standard silicon-based process, and has the advantages of low cost, high integration, low power consumption, near-infrared detection capability and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

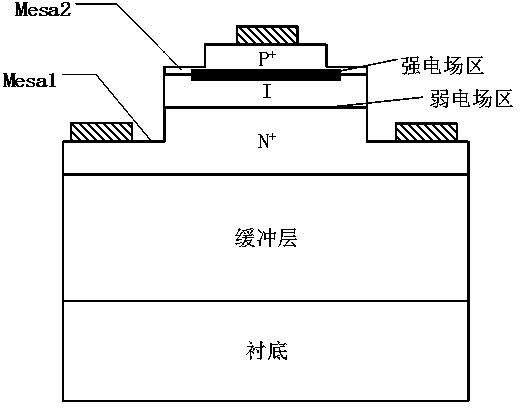

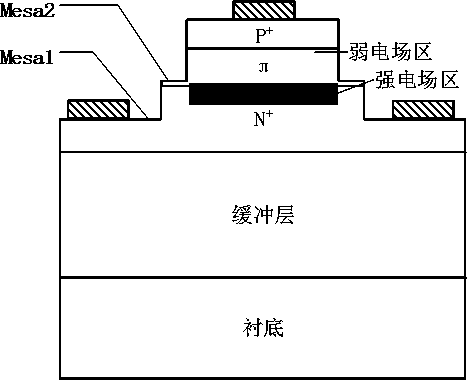

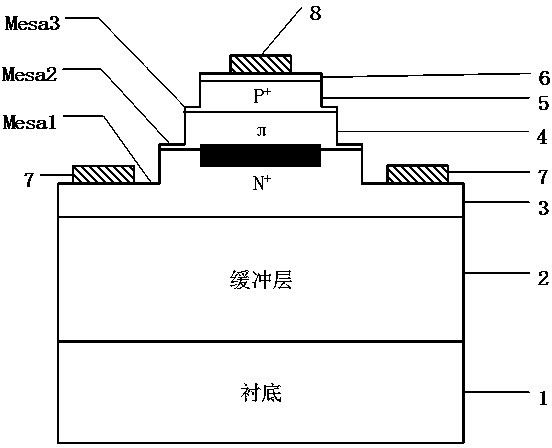

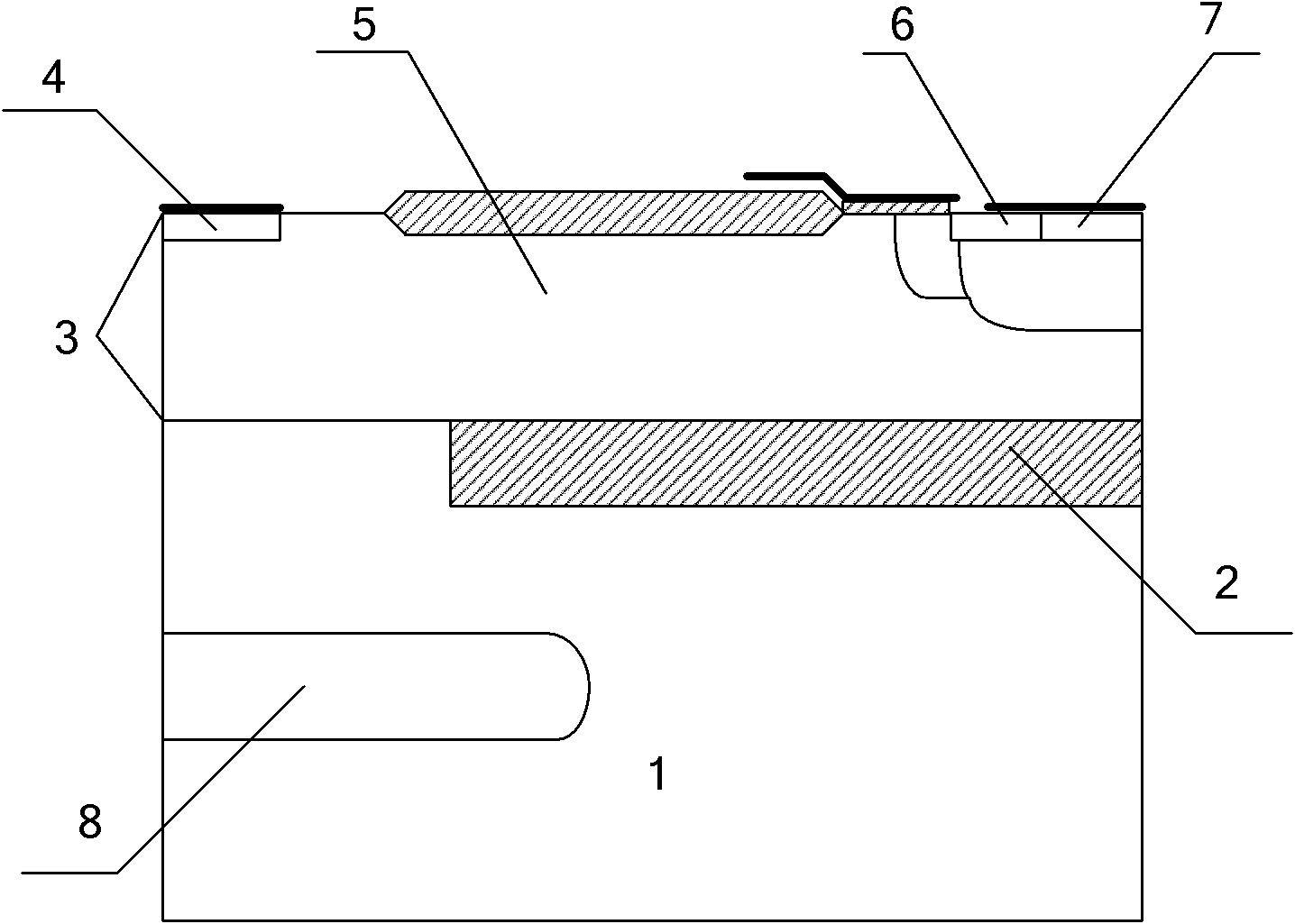

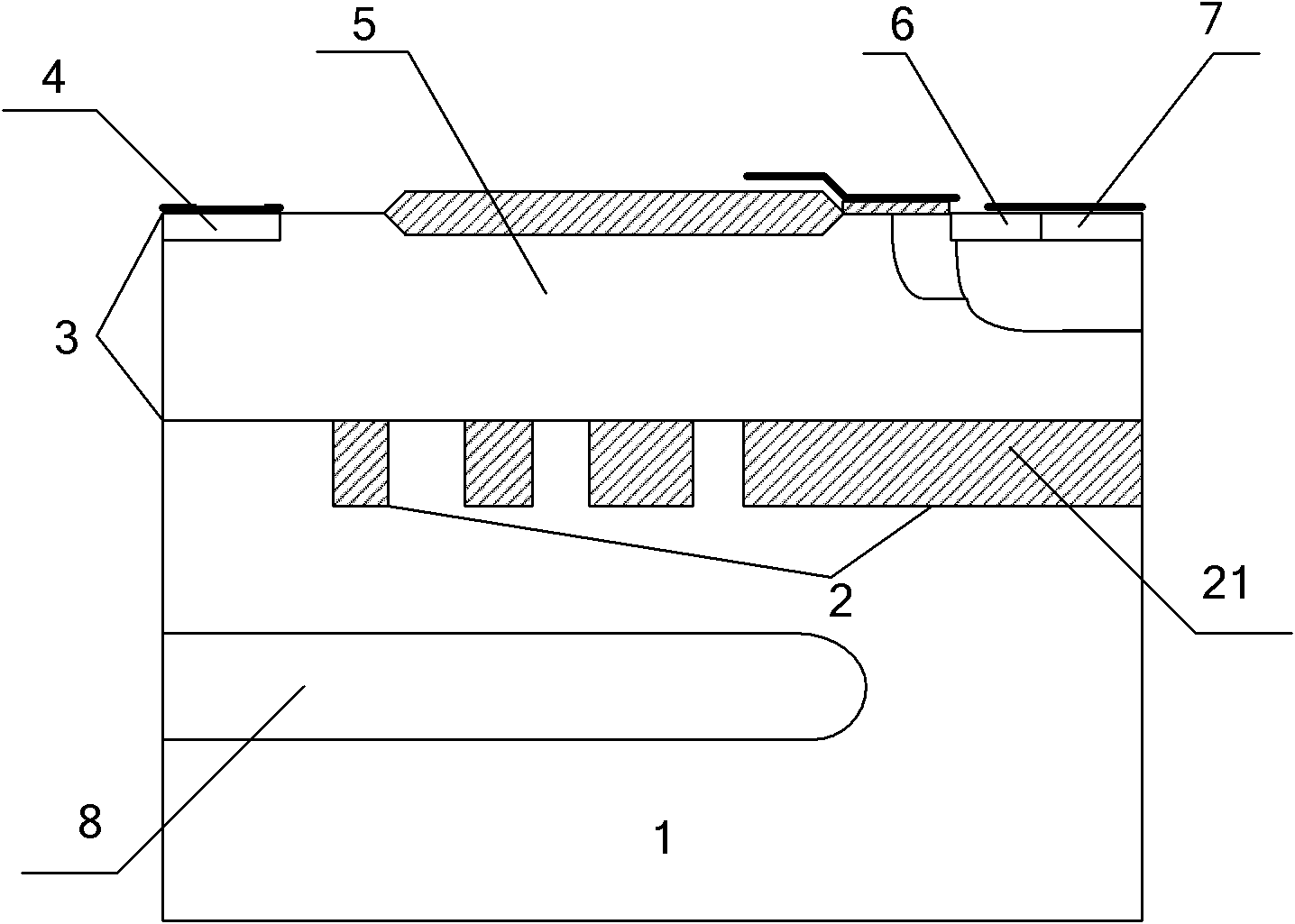

Three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector and preparation method thereof

InactiveCN104282793AAvoid premature breakdownSolve the problem of reverse premature breakdownFinal product manufactureSemiconductor devicesPhotodetectorElectrode Contact

The invention relates to the technical field of detectors, in particular to a three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector and a preparation method of the three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector. The three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector comprises a substrate, a buffer layer, an n-type doping nitride ohmic electrode contact layer, a Pi-type nitride active layer, a p-type doping nitride layer, a p-type heavy-doping nitride ohmic contact layer, n-type ohmic contact electrodes and a p-type ohmic contact electrode, wherein the buffer layer, the n-type doping nitride ohmic electrode contact layer, the Pi-type nitride active layer, the p-type doping nitride layer and the p-type heavy-doping nitride ohmic contact layer are sequentially grown on the substrate through epitaxial growth methods such as a molecular beam epitaxial method or an organometallic chemical vapor deposition epitaxial method; the n-type ohmic contact electrodes are manufactured on the n-type layer, and the p-type ohmic contact electrode is manufactured on the p-type layer. The three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector can solve the problems that a traditional p-i-n structured device leaks a large number of currents and the edge of the traditional p-i-n structured device can be broken through easily in advance; moreover, a three-mesa structure conducts double-suppression protection on edge electric fields of a strong electric field region and a weak electric field region of a p-Pi-n structured device, so that the edge electric field is effectively prevented from being broken through in advance.

Owner:SUN YAT SEN UNIV

CMOS (Complementary Metal-Oxide-Semiconductor) transistor and stress memory treatment method thereof

ActiveCN102097381AReduce the possibilityIncreasing the thicknessTransistorSemiconductor/solid-state device manufacturingCMOSProportion integration differentiation

The invention discloses a CMOS (Complementary Metal-Oxide-Semiconductor) transistor and a stress memory treatment method thereof. The method comprises the following steps of: providing a substrate with a formed CMOS transistor, wherein the lower surface of the substrate is provided with a silicon oxide layer corresponding to the inner layer of the side wall of a grid of the CMOS transistor and a silicon nitride layer corresponding to the outer layer of the side wall of the grid; sequentially depositing a buffer oxide layer and a stress silicon nitride layer on the upper surface of the CMOS transistor; removing the stress silicon nitride layer on the upper surface of a PMOS (P-channel Metal Oxide Semiconductor) transistor and annealing the substrate if the CMOS transistor comprises a NMOS (N-channel Metal Oxide Semiconductor) transistor and the PMOS transistor; directly annealing the substrate if the CMOS transistor comprises the NMOS transistor; and removing the stress silicon nitride layer on the upper surface of the NMOS transistor and the buffer oxide layer and keeping the silicon oxide layer and the silicon nitride layer, corresponding to the side wall of the grid, on the lower surface of the substrate. The stress memory treatment method in the invention is favorable for decreasing the occurrence probability of PID (Proportion Integration Differentiation) and saving cost, and is simple.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

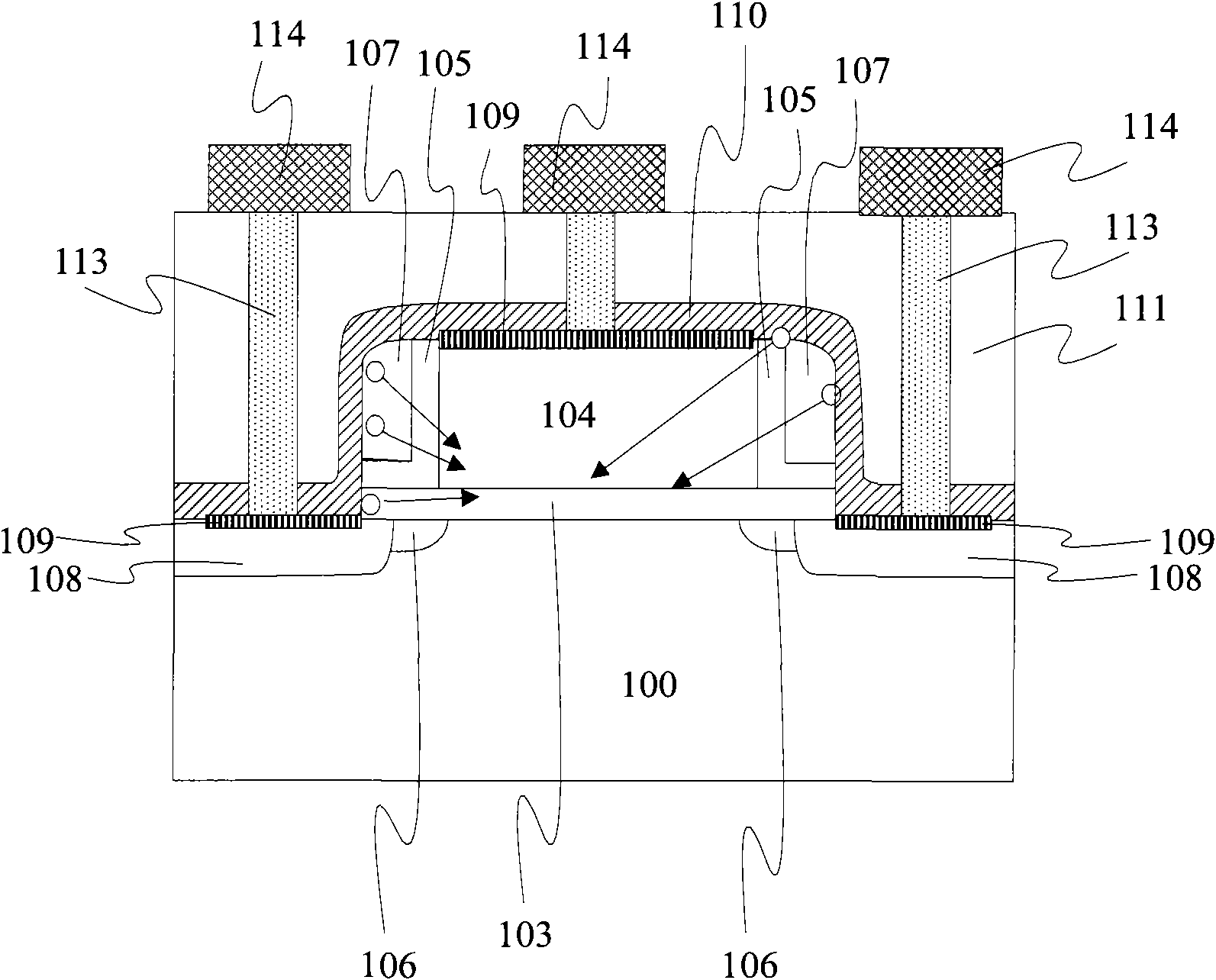

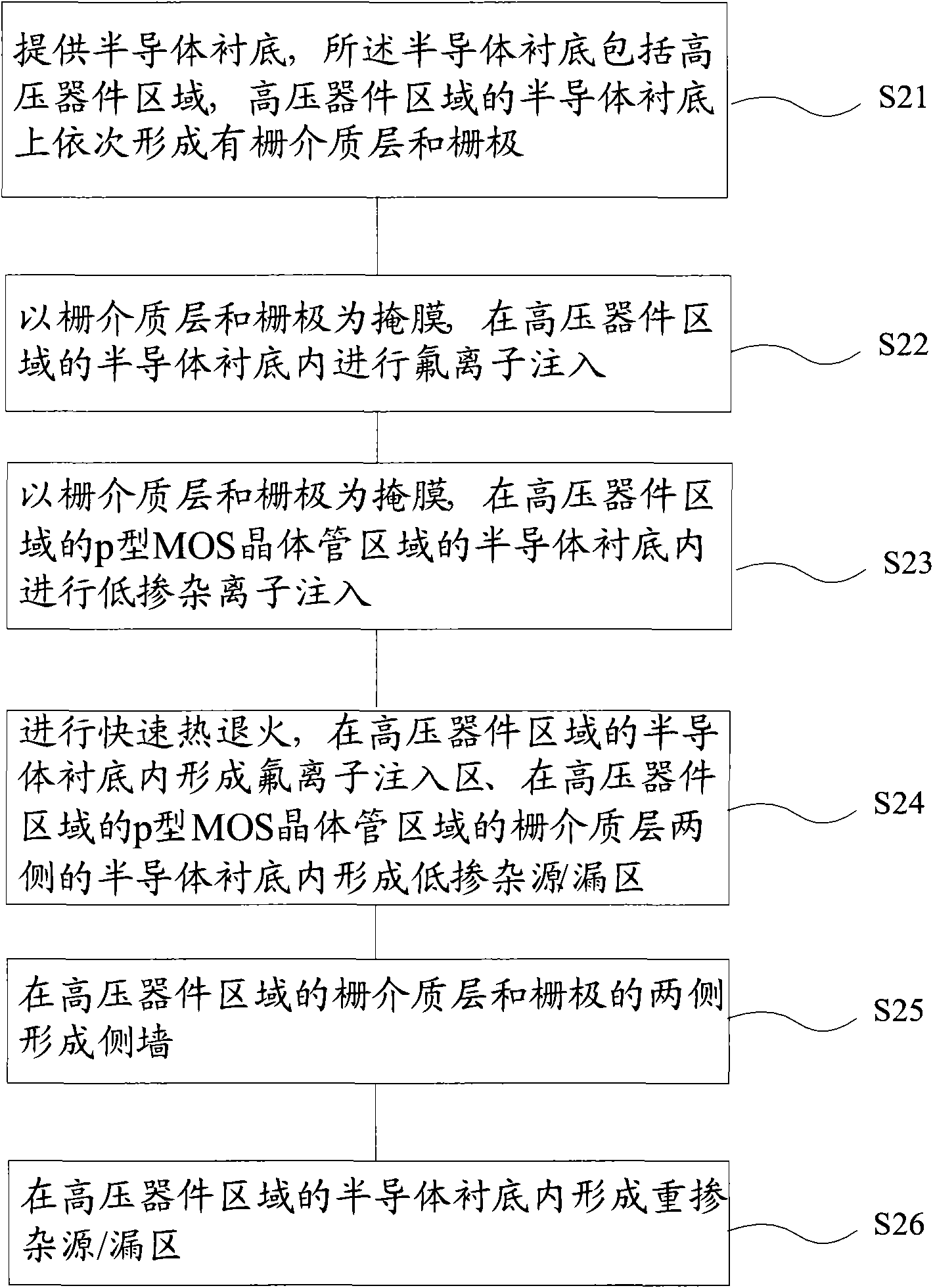

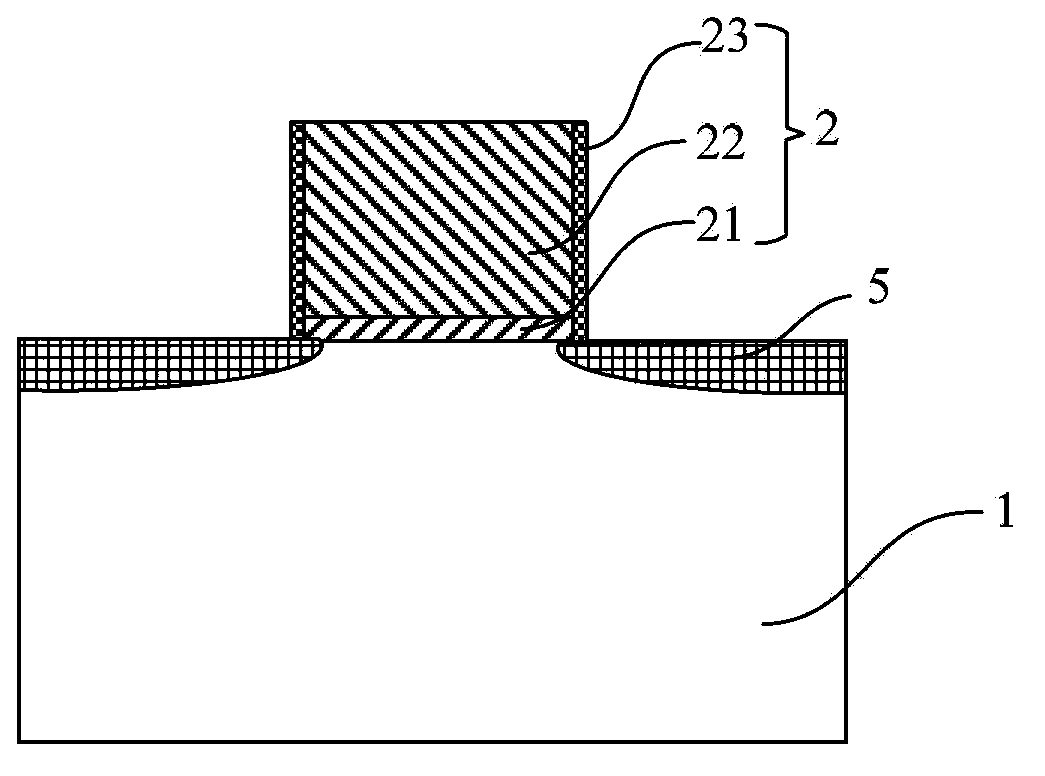

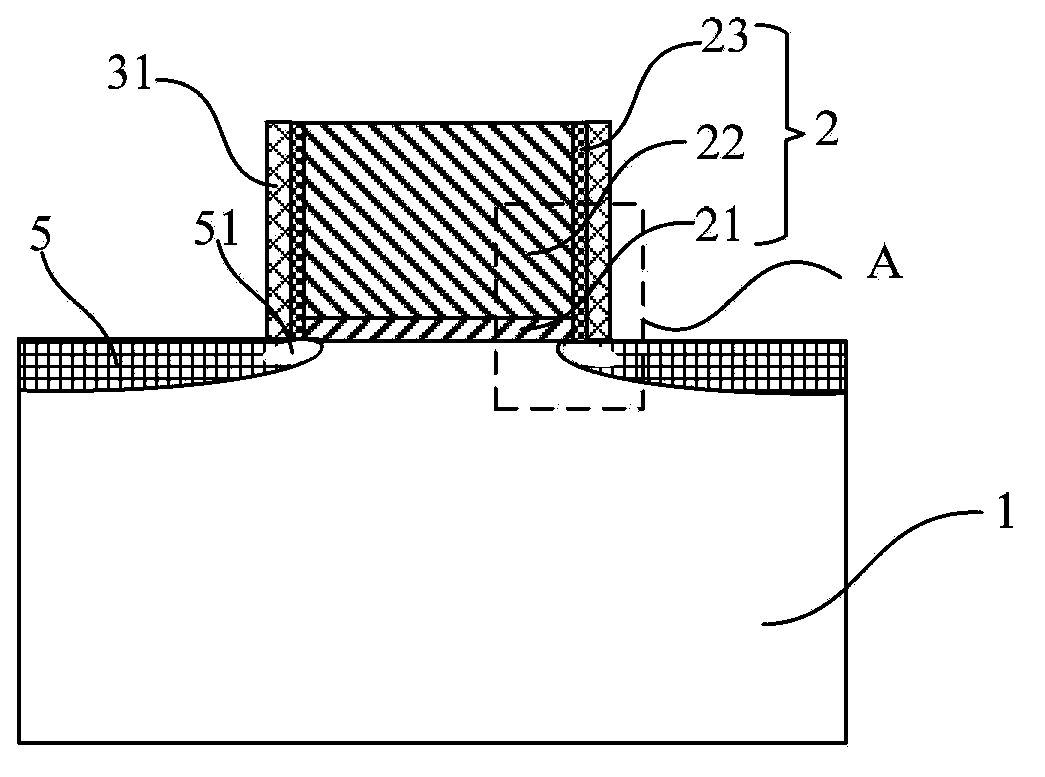

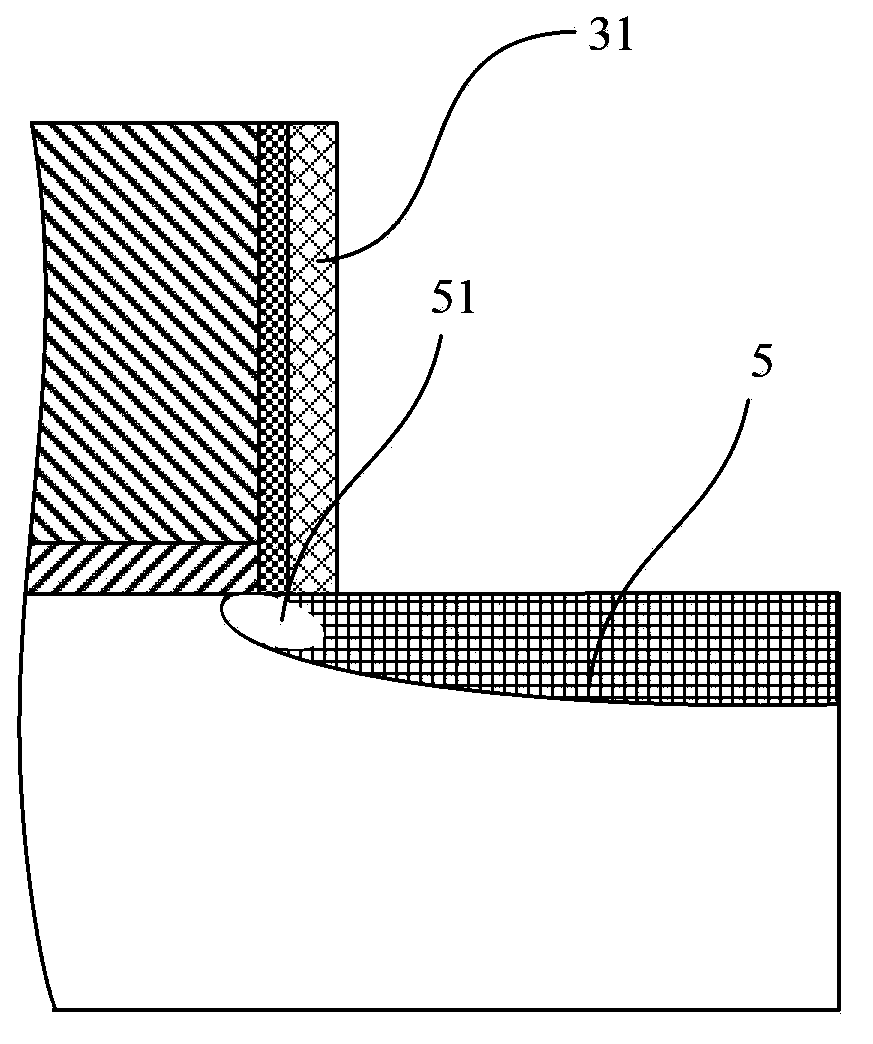

Semiconductor device, p-type MOS transistor and manufacturing method thereof

ActiveCN101572250AAvoid formingReduce dislocation defectsSolid-state devicesSemiconductor/solid-state device manufacturingHigh pressureMedia layer

The invention relates to a semiconductor device, a p-type MOS transistor and a manufacturing method thereof. The method for manufacturing the semiconductor device comprises the following steps: providing a semiconductor substrate; taking a grid medium layer and a grid electrode as masks, and implanting fluorine ions into a semiconductor substrate in a high-voltage device region; taking the grid medium layer and the grid electrode as the masks, and implanting low doped ions into a semiconductor substrate in the p-type MOS transistor region of the high-voltage device region; performing quick thermal annealing; forming side walls on both sides of the grid medium layer and the grid electrode in the high-voltage device region; and forming a heavy doping source / drain region in the semiconductor substrate of the high-voltage device region. The invention also provides the semiconductor device, the p-type MOS transistor and the manufacturing method thereof. The invention is favorable for restricting the influence of the NBTI effect on the MOS transistor by forming a fluorine ion implantation region on a low doping source / drain region in the p-type MOS transistor region of the high-voltage device region, and simultaneously can reduce the hot carrier injection effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

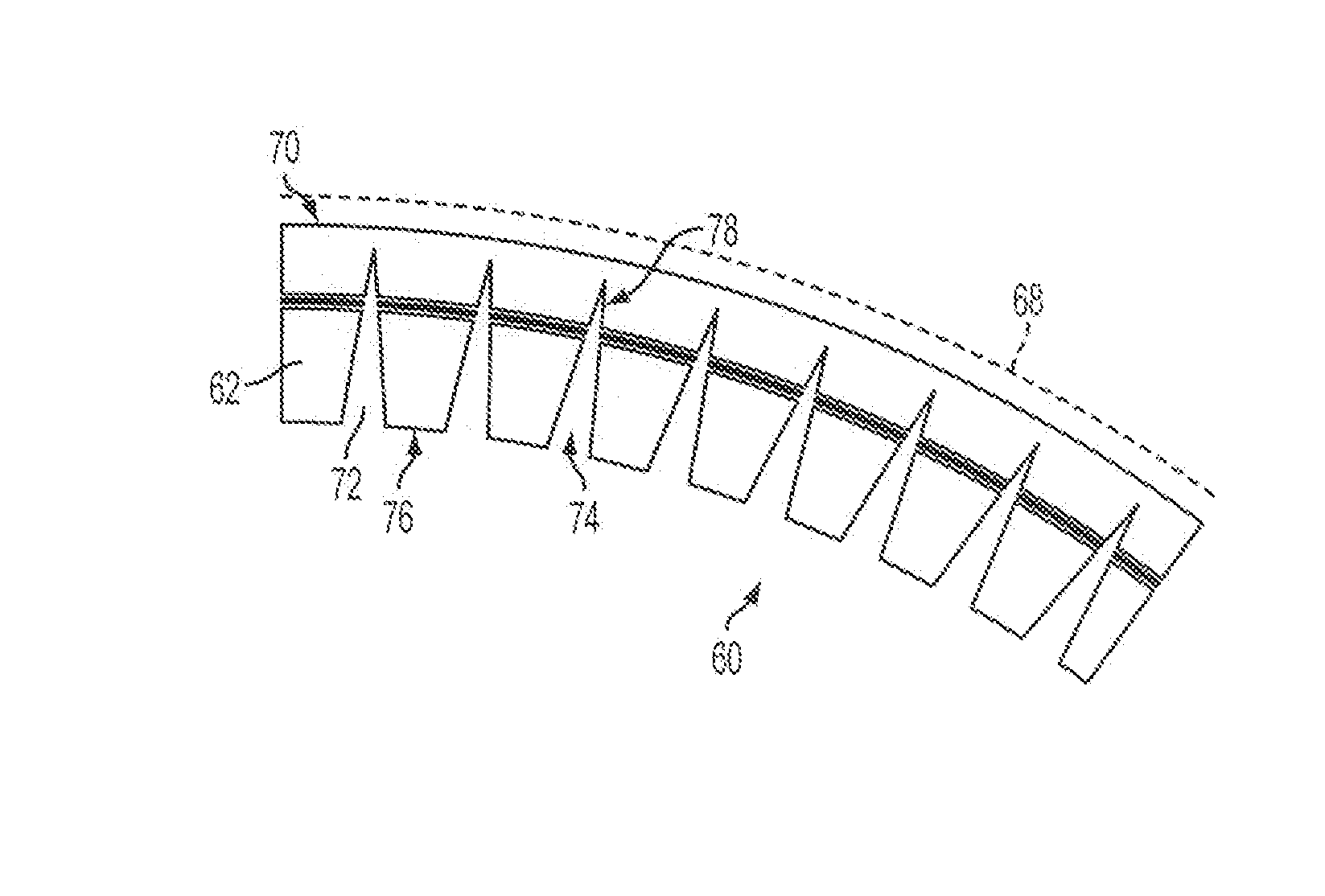

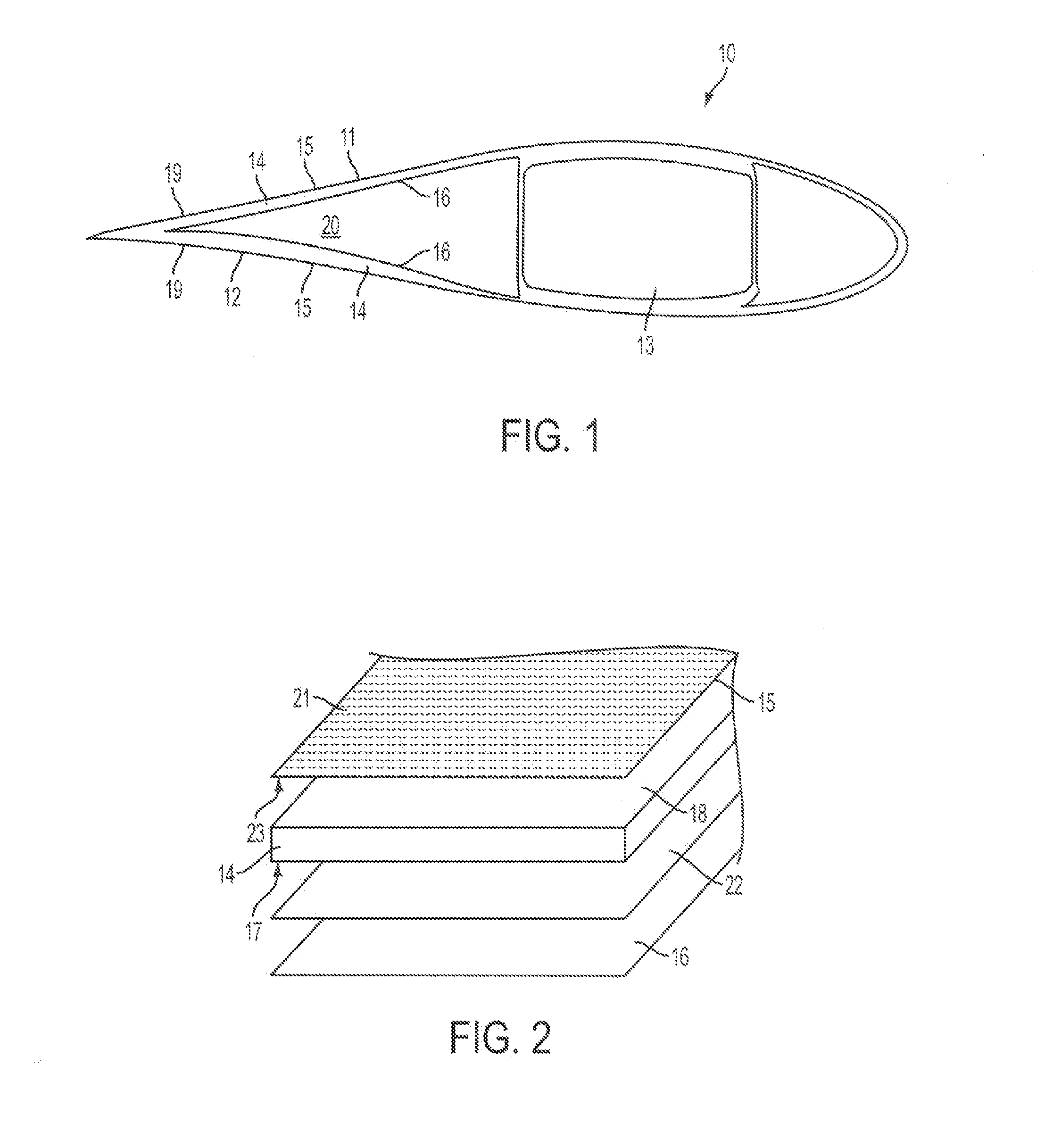

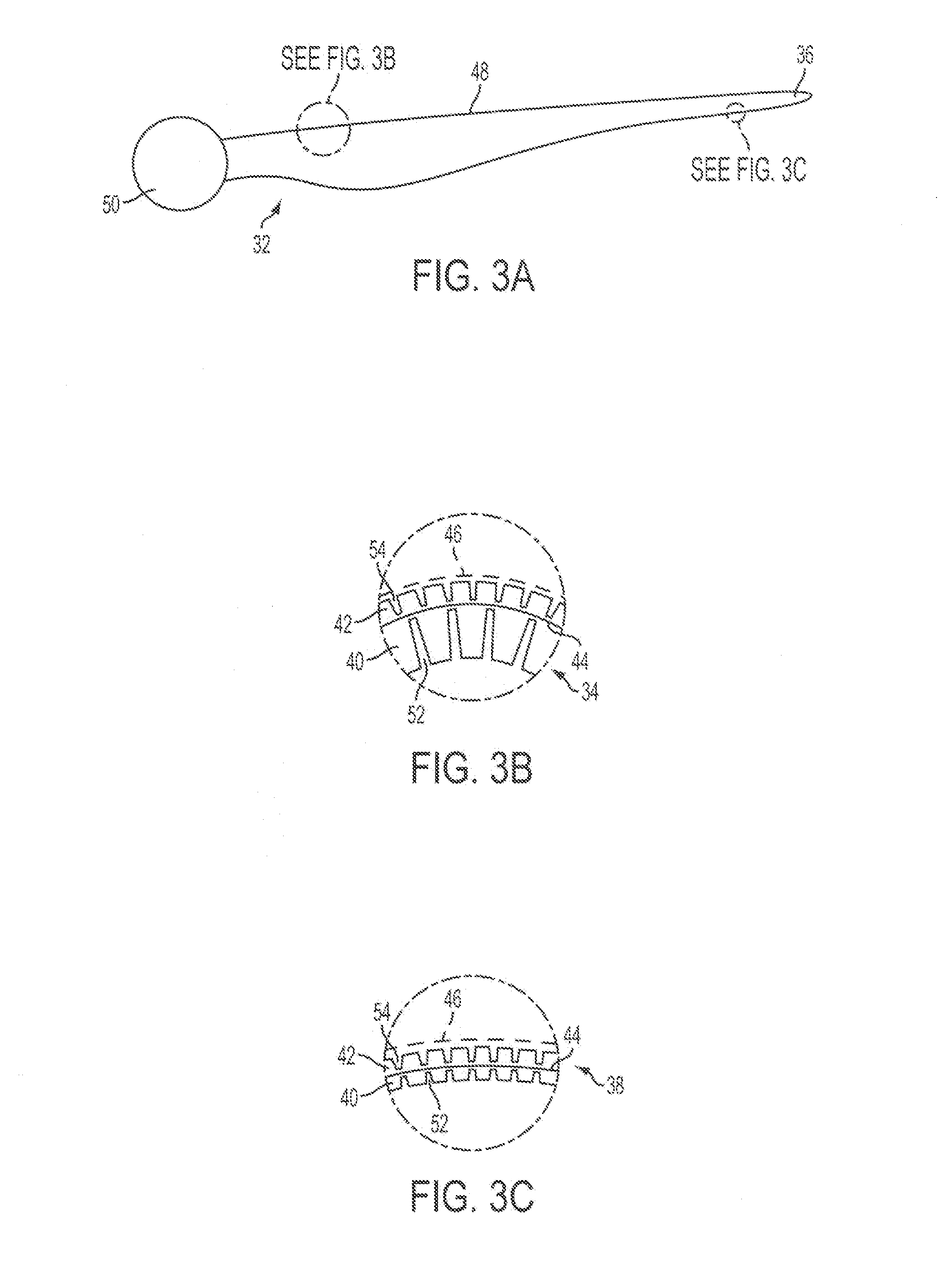

Core for a composite structure and method of fabrication thereof

ActiveUS20130294925A1Easy to hangIncreased flexibility/drapabilityPropellersFinal product manufactureTurbine bladeGround plane

A flexible core (60) for a composite structure is described. The core includes a first core layer (62), a second core layer (64), and a ground plane (66) between the first and second core layers. A plurality of slits (72) is provided in the core, and each slit extends through one of the first of second core layers and through the ground plane. The core may be the core of a sandwich panel, for example a sandwich panel of the type used in the composite construction of wind turbine blades (10).

Owner:VESTAS WIND SYST AS

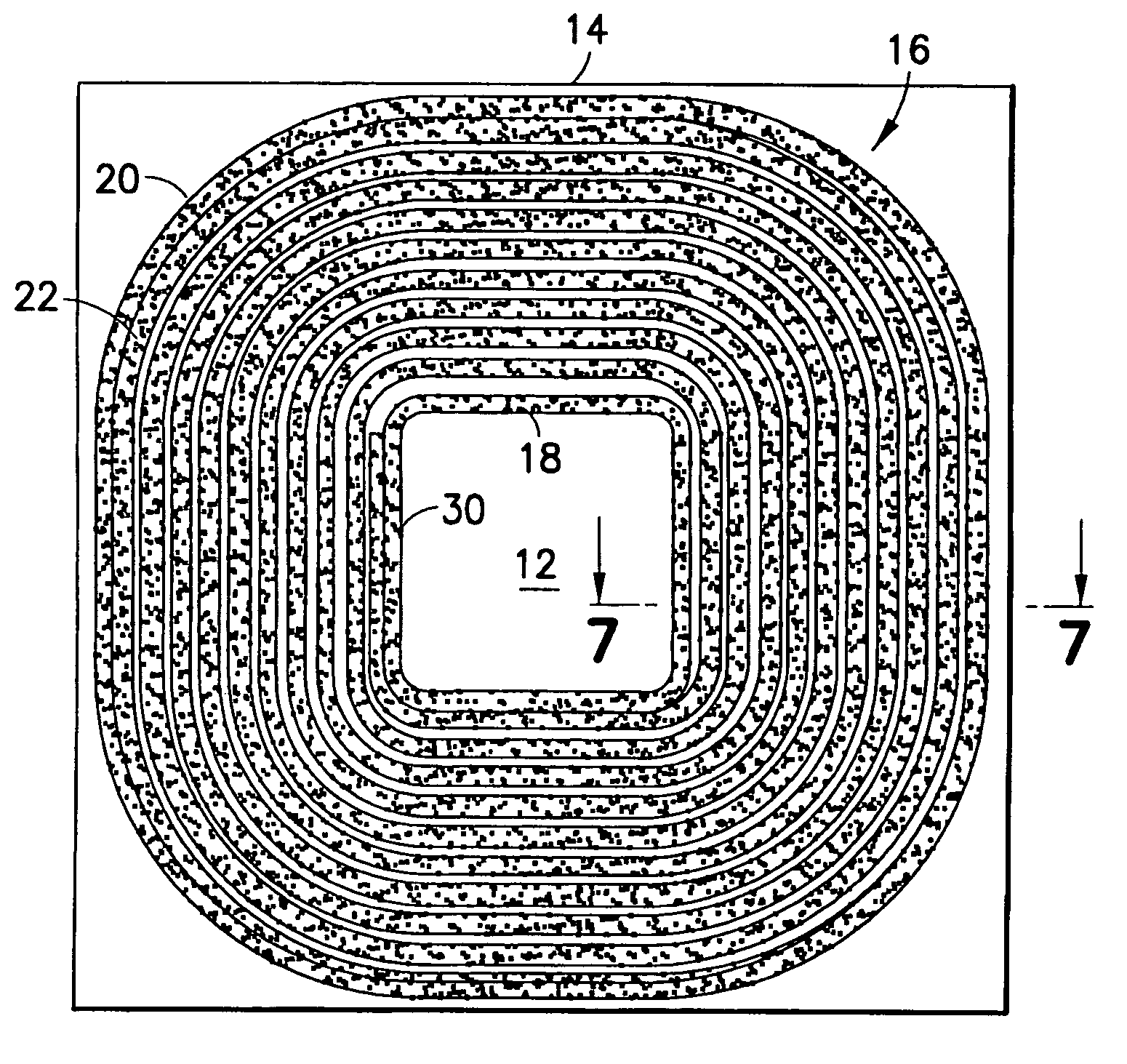

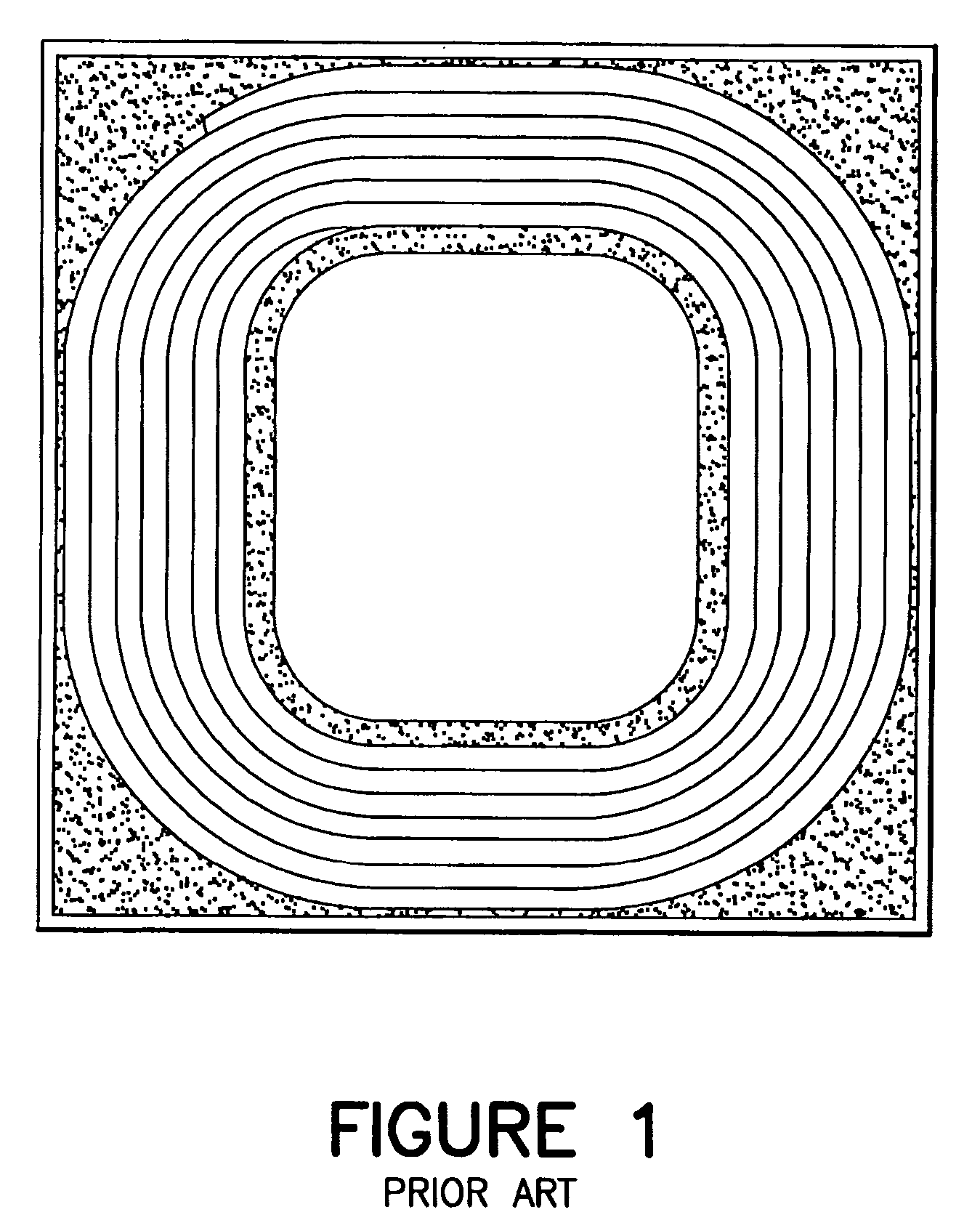

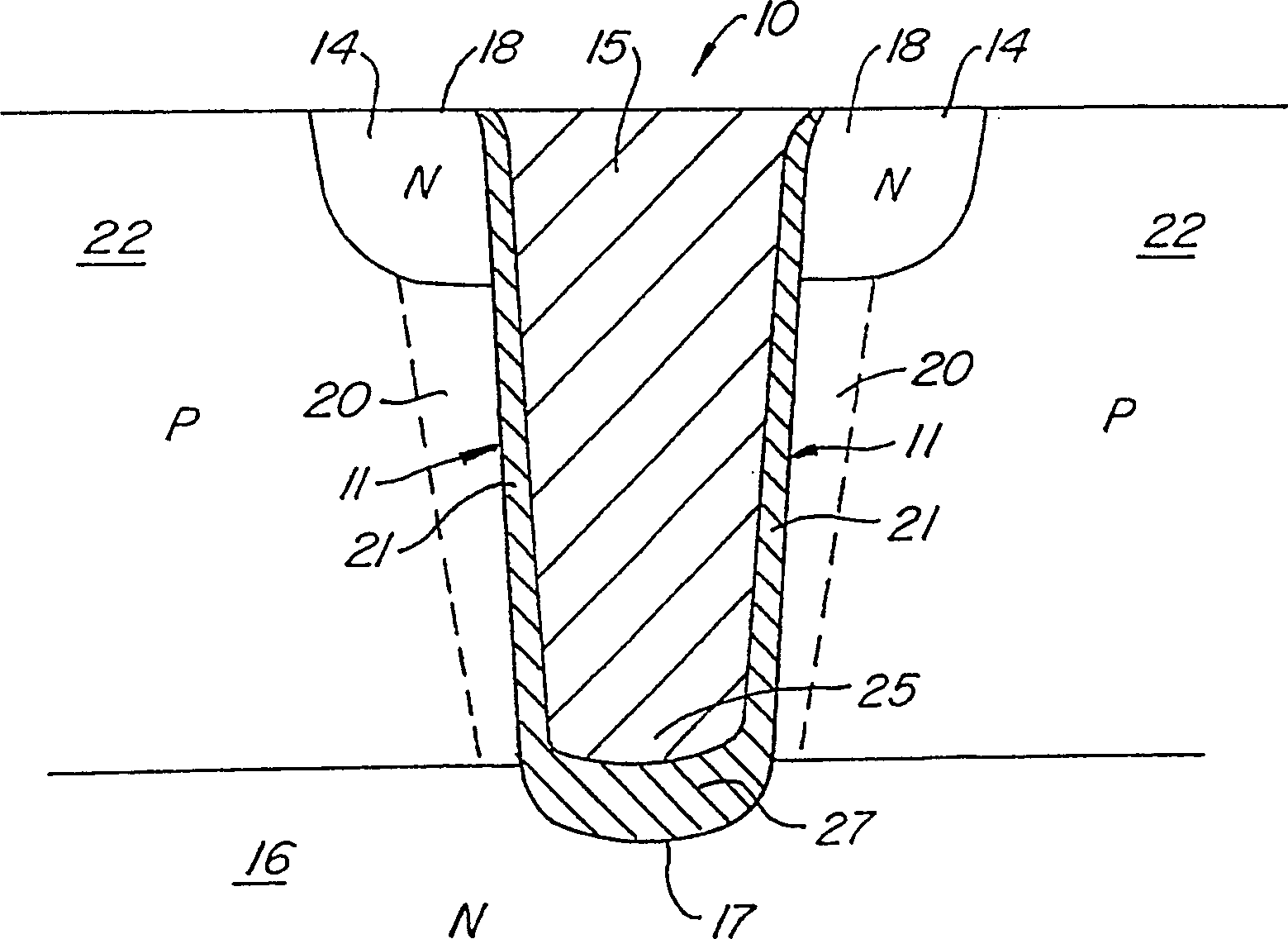

Passivation structure with voltage equalizing loops

ActiveUS7183626B2Reduce electric fieldConstant gainTransistorSemiconductor/solid-state device detailsClosed loopEngineering

Owner:INFINEON TECH AMERICAS CORP

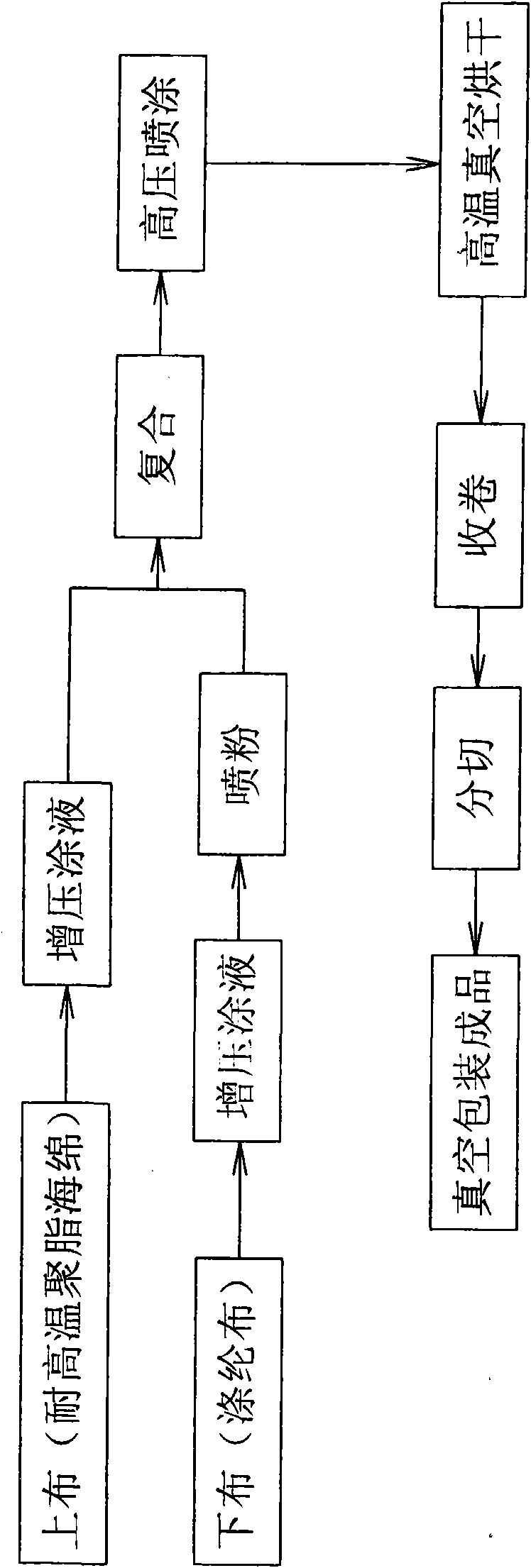

Production method of semi-conductive buffer water-blocking band

ActiveCN101567236AGood surface conductivityReduce surface resistanceFibre treatmentClimate change adaptationPolyesterVacuum pack

The invention relates to a production method of a water-blocking band, in particular to a production method of a semi-conductive buffer water-blocking band. The production method comprises the following steps: firstly, supercharging and soaking a high-temperature resistant polyester sponge and terylene cloth in conductive liquid, spraying high water-absorbent resin on the terylene cloth and compounding the high-temperature resistant polyester sponge and the terylene cloth; then, spraying the conductive liquid with a high-pressure spray gun and drying the high-temperature resistant polyester sponge and the terylene cloth which are compounded in vacuum at a high temperature; and finally, coiling, cutting and packaging the high-temperature resistant polyester sponge and the terylene cloth which are compounded in vacuum to be a finished semi-conductive buffer water-blocking band . Proved by detection, the semi-conductive buffer water-blocking band has the advantages of high intensity, thinness, rapid swelling in water, high water absorption, good water-blocking effect, high-temperature environment influence resistance, small surface resistance, low volume electric resistivity, European Union environmental protection accordance, and the like, can satisfy the water blocking and the electric field shielding among parts of power cables, and the like, maintains the safe use of the cables, can generate the semi-conductive shielding action so as to buffer an electric field, can be lined at the inner side of a metal protective sleeve to buffer the friction between the inner protective sleeve and the metal protective sleeve and can satisfy the normal working temperature of the cables.

Owner:YANG ZHOU TENGFEI ELECTRIC CABLE & APPLIANCE MATERIALS CO LTD

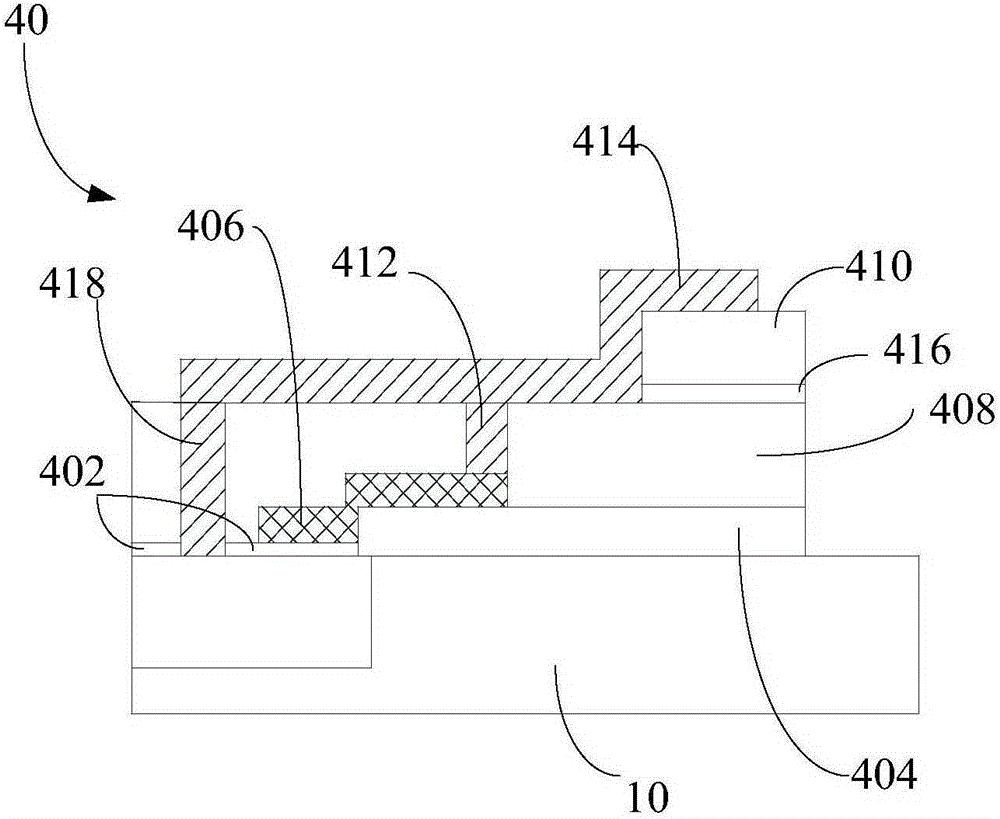

Power transistor and manufacturing method thereof

ActiveCN105185829AReduce electric fieldImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEngineering

The invention relates to a power transistor, which comprises a substrate, an active region and a terminal region, wherein the active region and the terminal region are formed on the substrate; the terminal region comprises a transition field limiting ring, field limiting rings, a cut-off ring and voltage-sharing protection structures; the transition field limiting ring, the field limiting rings and the cut-off ring are formed on the substrate and are sequentially arranged from inside to outside; gate oxidation layers in the voltage-sharing protection structures are formed on the surfaces of various doped regions; the field oxidation layers, first dielectric layers and second dielectric layers are formed on substrates at one side of various doped regions and are sequentially distributed upwards in a stepped form; the thickness of each field oxidation layer is greater than that of each gate oxidation layer; polysilicon field plates partially cover the gate oxidation layers and partially cover the field oxidation layers; first contact holes are formed in the first dielectric layers, run through the first dielectric layers and are connected to the polysilicon field plates; metal field plates partially cover the first dielectric layers and the second dielectric layers; and the metal field plates are connected with the polysilicon field plates through the first contact holes. The breakdown voltage of the power transistor is relatively high. The invention further relates to a manufacturing method of the power transistor.

Owner:深圳深爱半导体股份有限公司

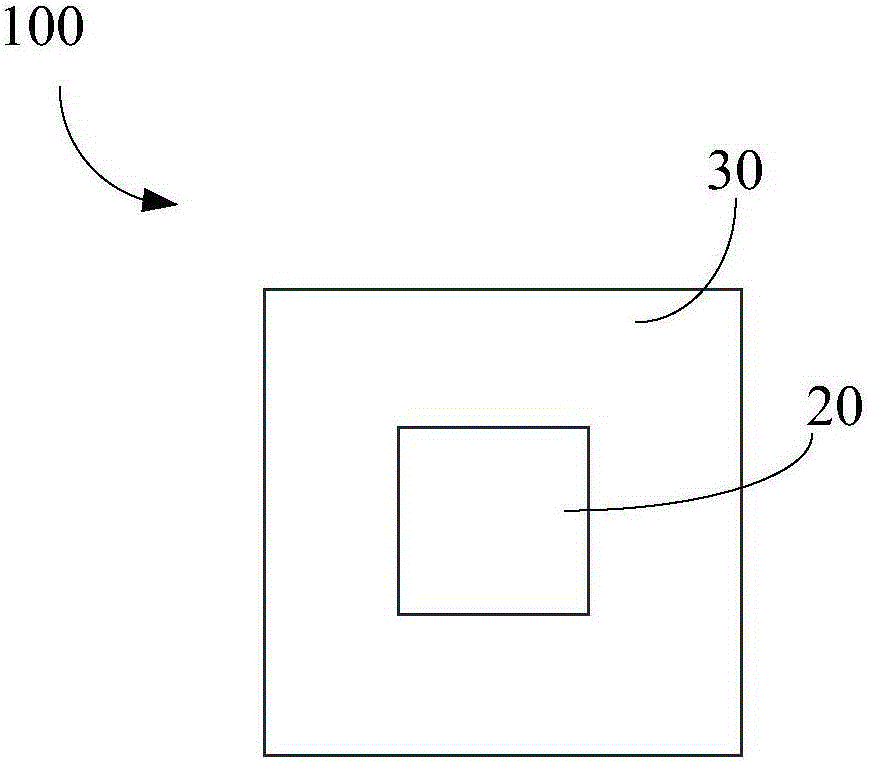

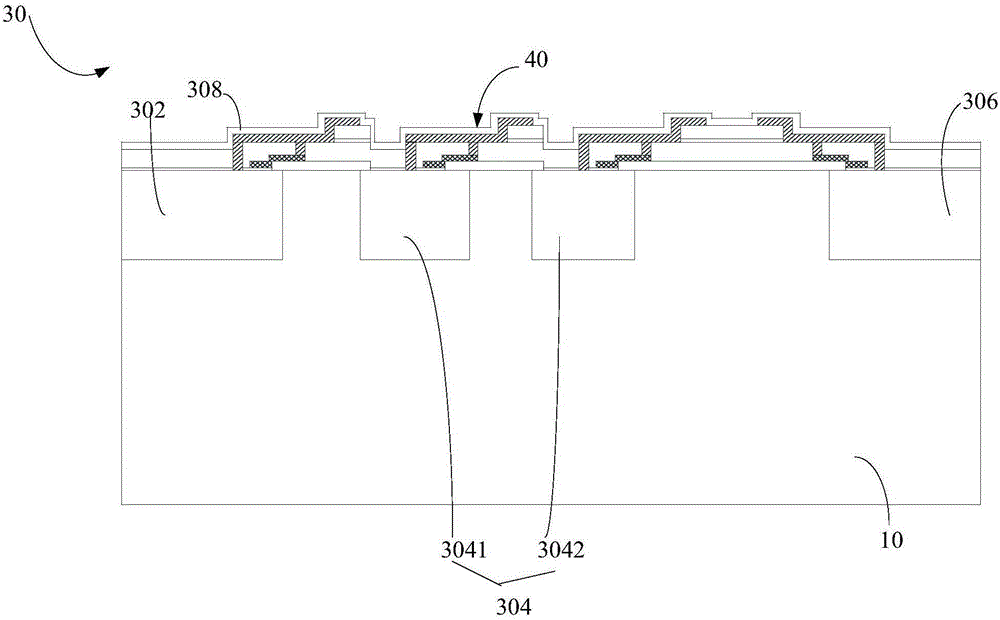

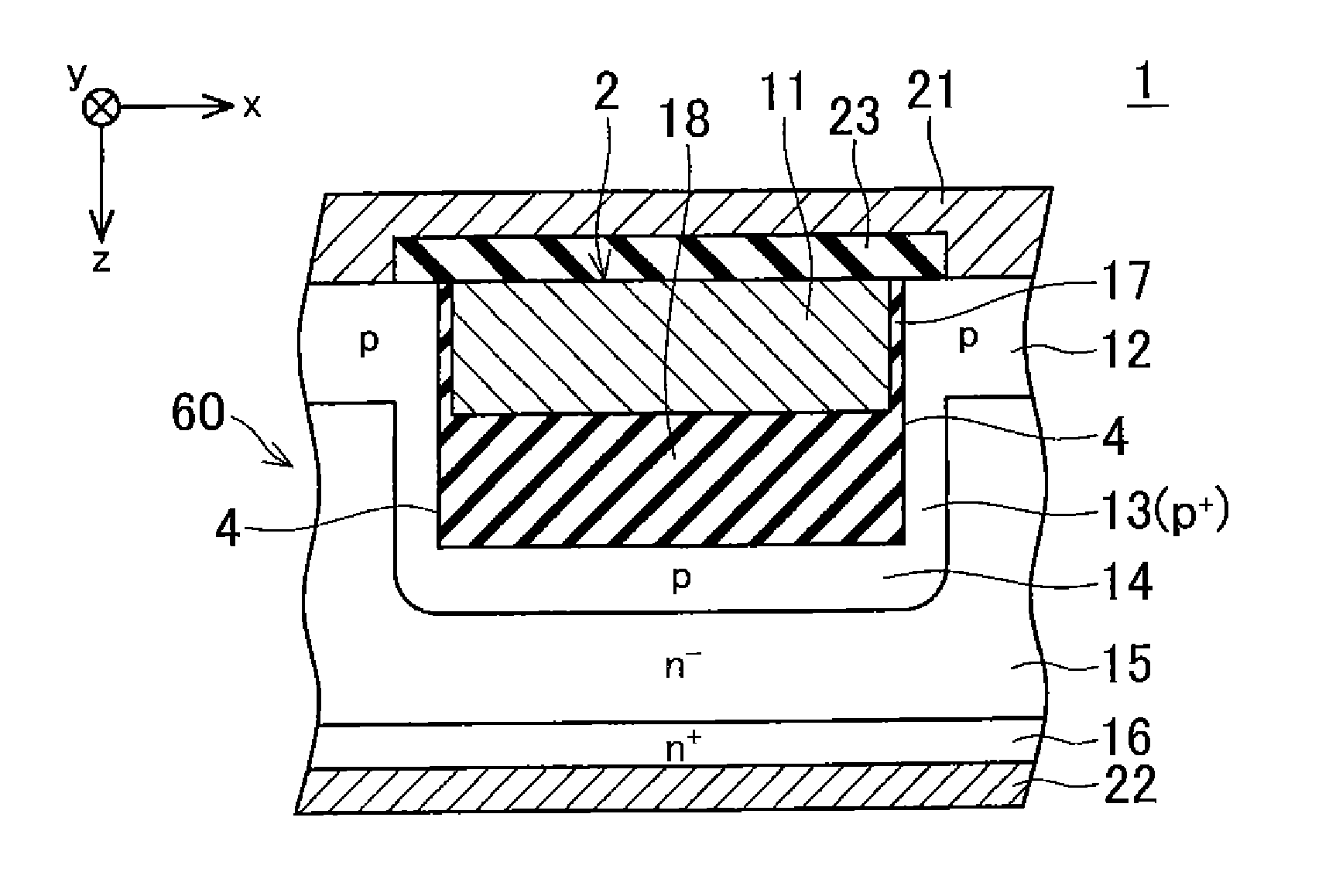

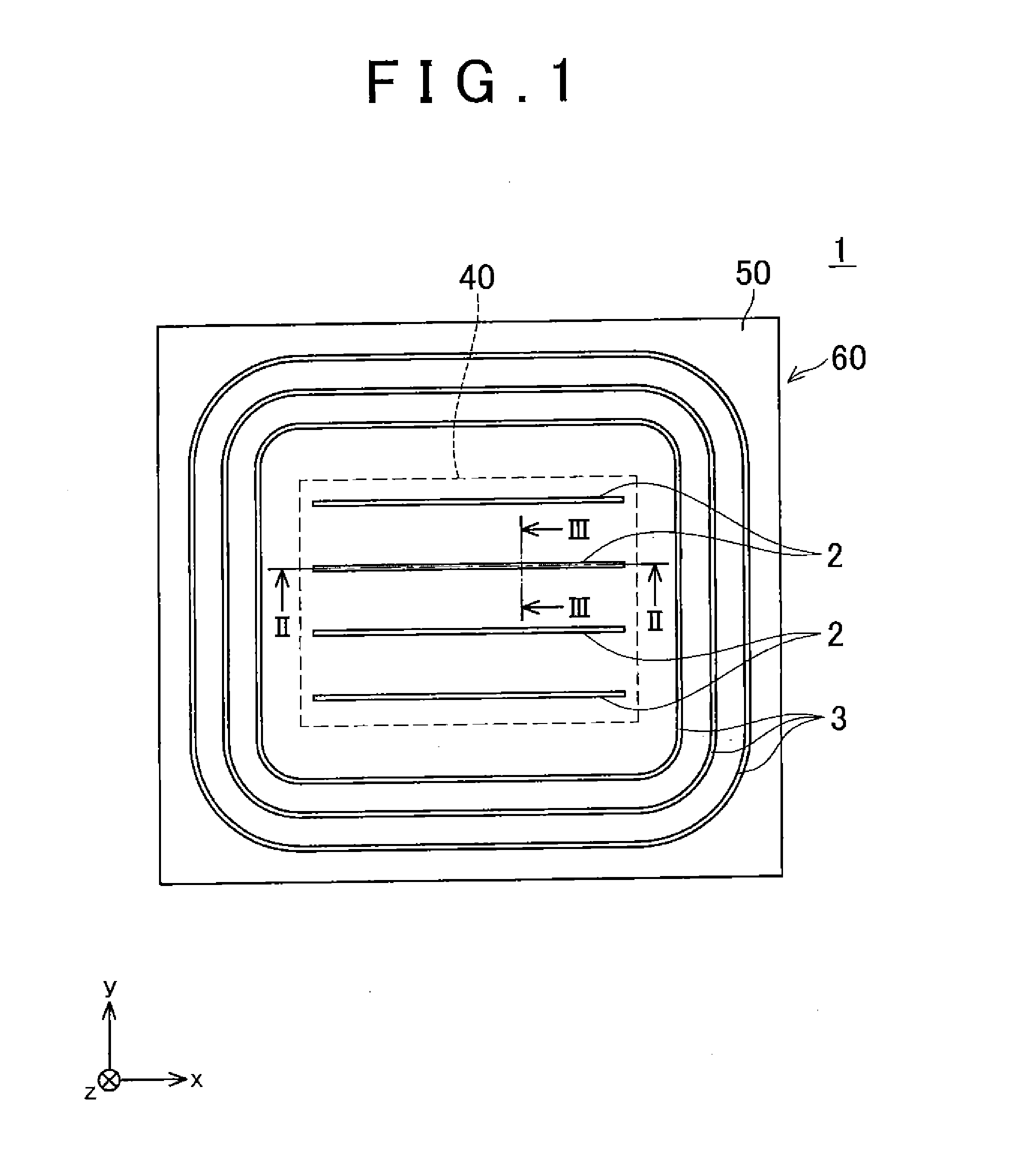

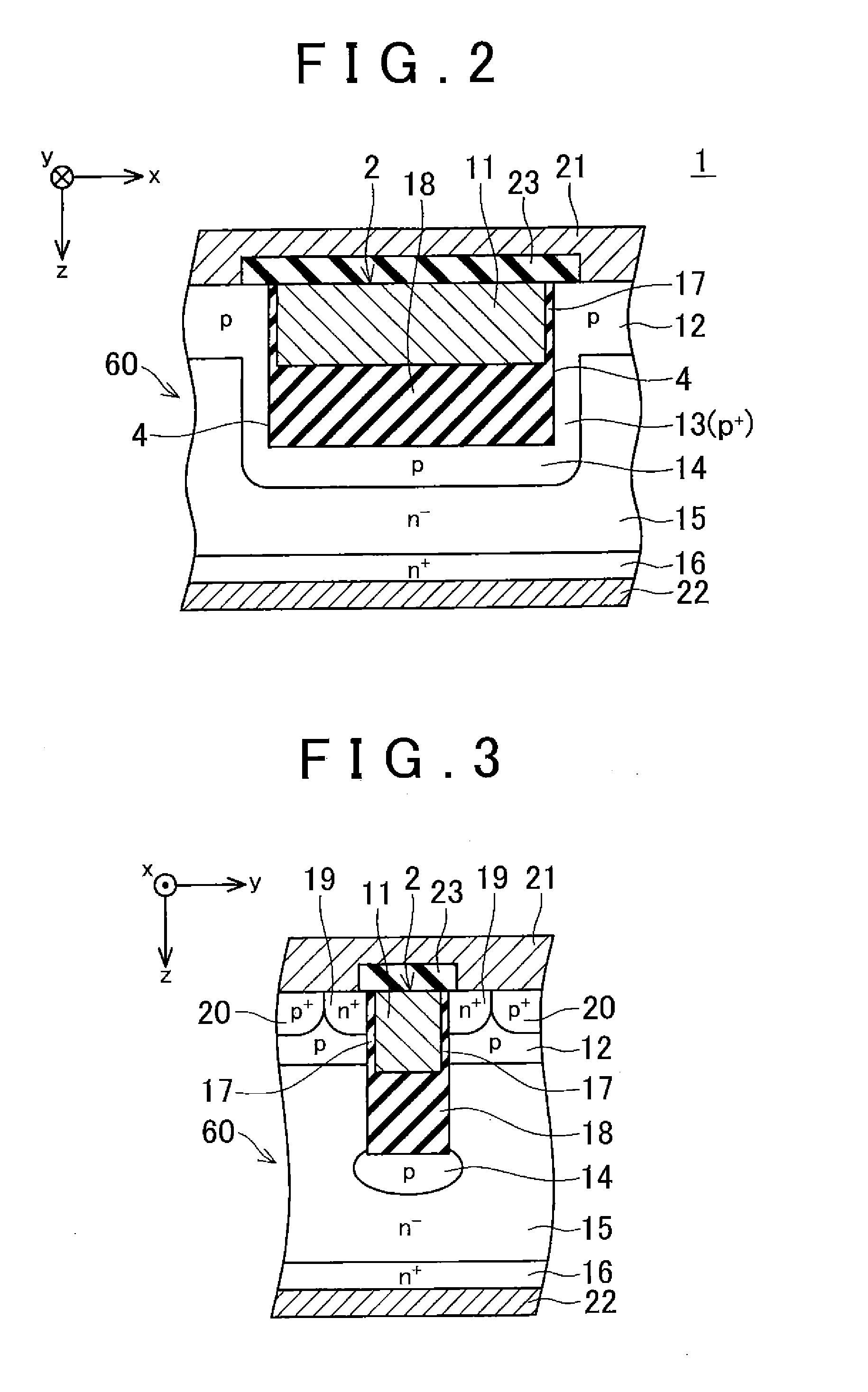

Semiconductor device

ActiveUS20150171175A1Reduce electric fieldReduce remarkably the electric field appliedSemiconductor devicesElectrical conductorTrench gate

A semiconductor device includes: a drift layer having a first conductivity type; a body layer having a second conductivity type; a first semiconductor region having the first conductivity type; a gate insulation film; a trench gate electrode; a first main electrode; a second semiconductor region having the second conductivity type; and a conductor region. The first main electrode is electrically connected with the body layer and the first semiconductor region. The second semiconductor region is disposed on a bottom part of the gate trench, and is surrounded by the drift layer. The conductor region is configured to electrically connect the first main electrode with the second semiconductor region and is configured to equalize, when the semiconductor device is in an off-state, a potential of the second semiconductor region and a potential of the first main electrode.

Owner:TOYOTA JIDOSHA KK +1

Method for manufacturing PMOS transistor

ActiveCN103985634AIncrease working currentImprove work performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowCharge carrier mobility

The invention provides a method for manufacturing a PMOS transistor. First of all, a second groove is formed through etching in a stress filling layer which is about to be predoped to prepare a source region and a drain region, the side wall of the second groove below a gate area being adjacent to a reserved part of a lightly doped source leakage extension area before the stress filling layer is formed, and afterwards, the second groove is filled so as to form an adjustment layer whose doping concentration is higher than that of the stress filling layer so that at the time when a source-drain area is prevented from generating break-through currents, the Ge and B doping concentrations on the surfaces of the source region and the drain region are improved; on one hand, the lost B doping impurities in the reserved part of the lightly doped source leakage extension area are supplemented, the B doping concentration of the lightly doped source leakage extension area is increased, the resistance of a channel region, the source region and the drain region is reduced, the electric field of the channel region is reduced, and the working currents are improved; and on the other hand, the stress applied to the channel region by the source region and the drain region is enhanced, the carrier mobility of the device channel region is improved, and the working currents of the PMOS transistor are increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

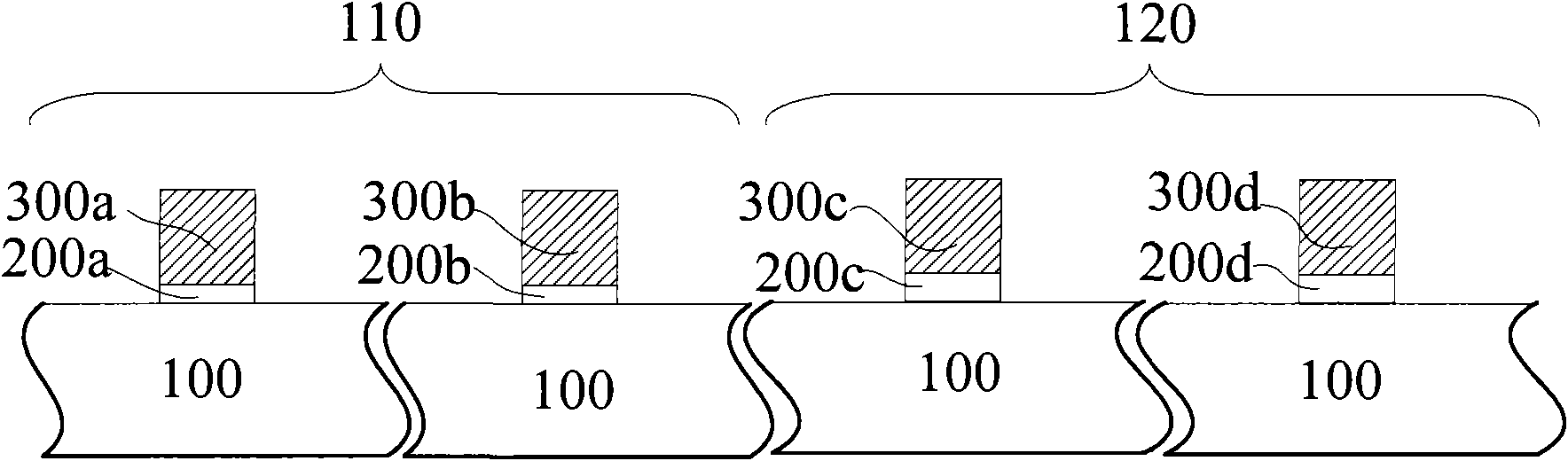

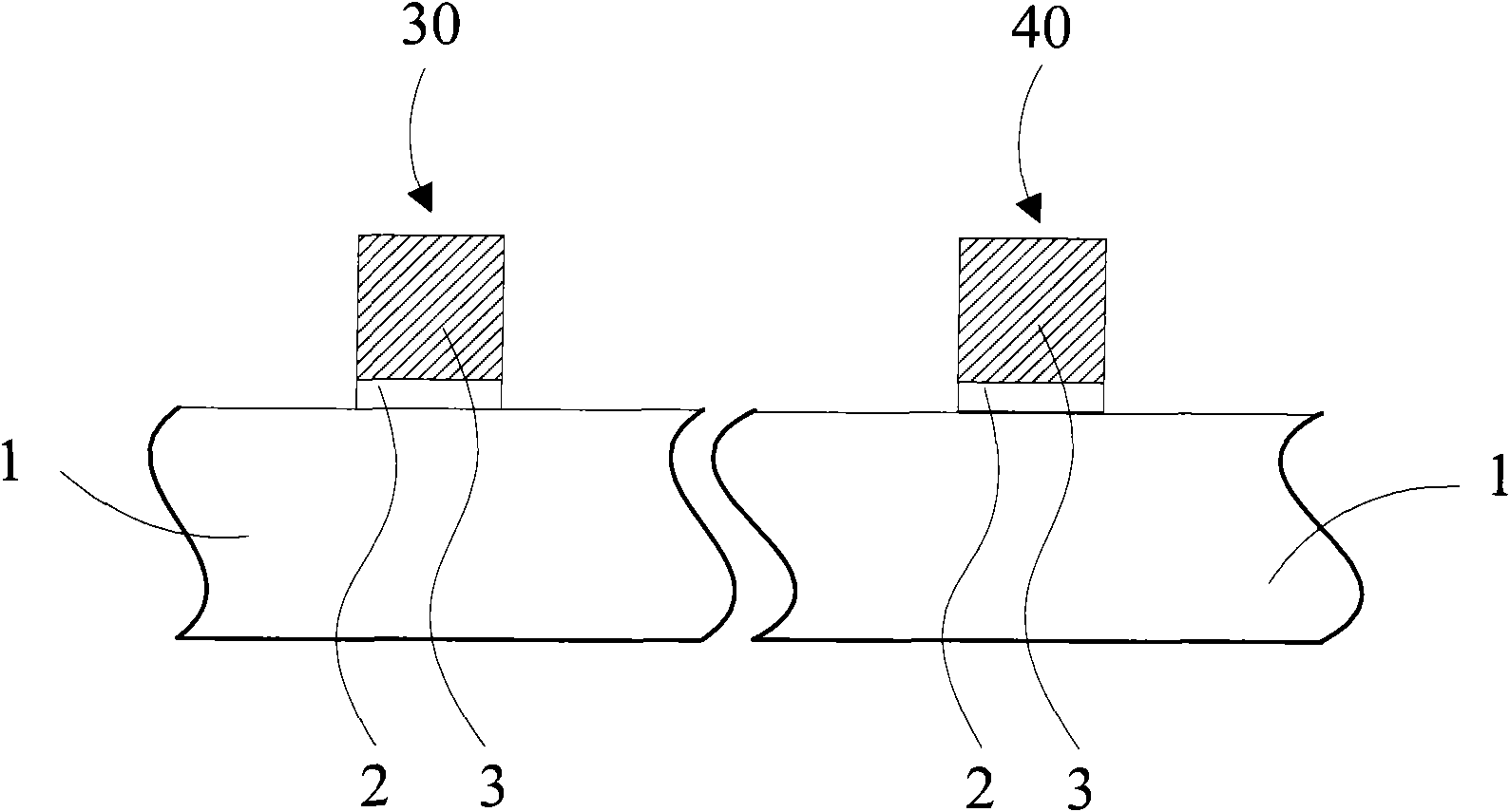

Semiconductor device, n-type MOS transistor and manufacturing method thereof

ActiveCN101572251AInhibition formationInhibition of agglomerationTransistorSemiconductor/solid-state device manufacturingHot carrier effectInput/output

The invention relates to a semiconductor device, an n-type MOS transistor and a manufacturing method thereof. The semiconductor device comprises a semiconductor substrate, a grid medium layer, a grid electrode, side walls, a light doping source / drain region, a heavy doping source / drain region, and a fluorine ion implantation region, wherein the gird medium layer, the grid electrode and the side wall are positioned inside an input / output device region of the semiconductor substrate; the low doping source / drain region and the heavy doping source / drain region are positioned inside semiconductor substrates in an n-type MOS transistor region and a p-type MOS transistor region of the input / output device region; and the fluorine ion implantation region is positioned inside a semiconductor substrate in the n-type MOS transistor region of the input / output device region. Correspondingly, the invention also provides a method for manufacturing the semiconductor device, the n-type MOS transistor and the method for manufacturing the n-type MOS transistor. The fluorine ion implantation region is formed in the low doping source / drain region of the n-type MOS transistor region, and fluorine ions in the fluorine ion implantation region and silicon in the semiconductor substrate form fluorine-silicon groups so as to prevent the formation of charge traps, prevent the aggregation of charges in the low doping source / drain region under the condition of additional voltage, and forming hot carrier effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

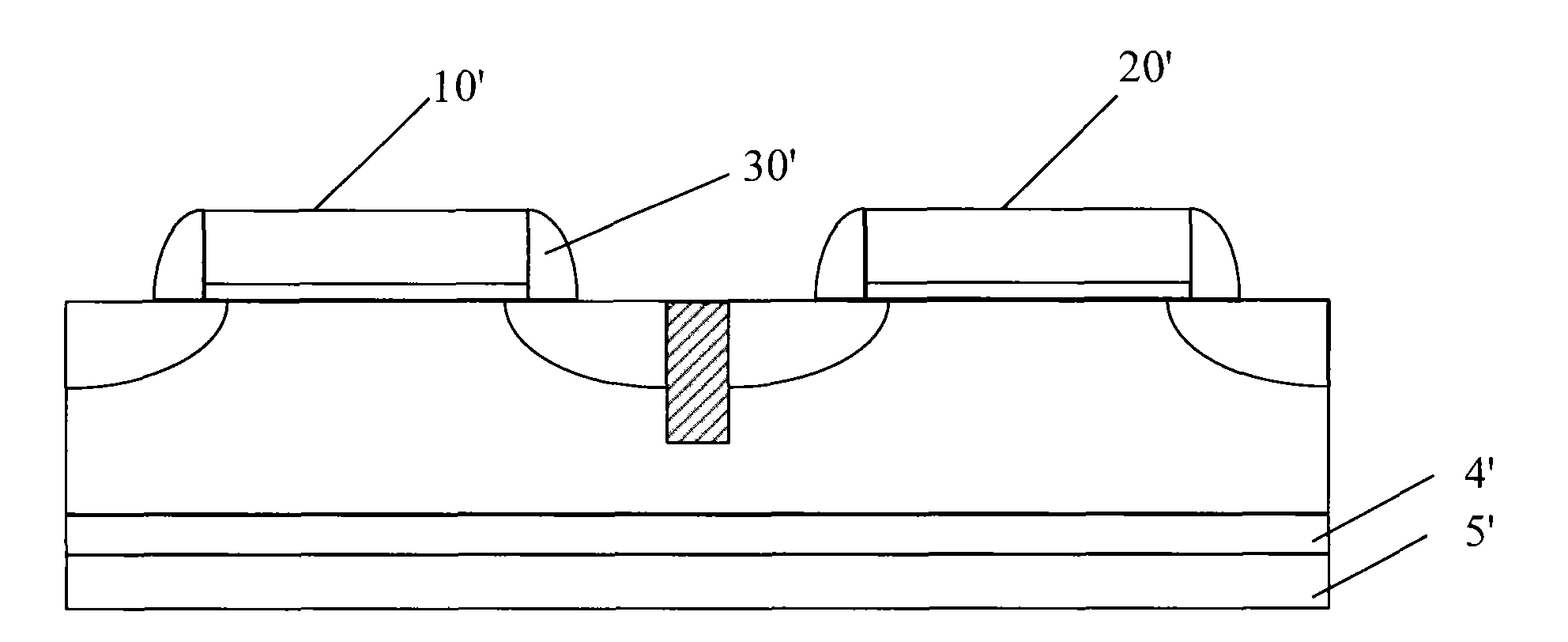

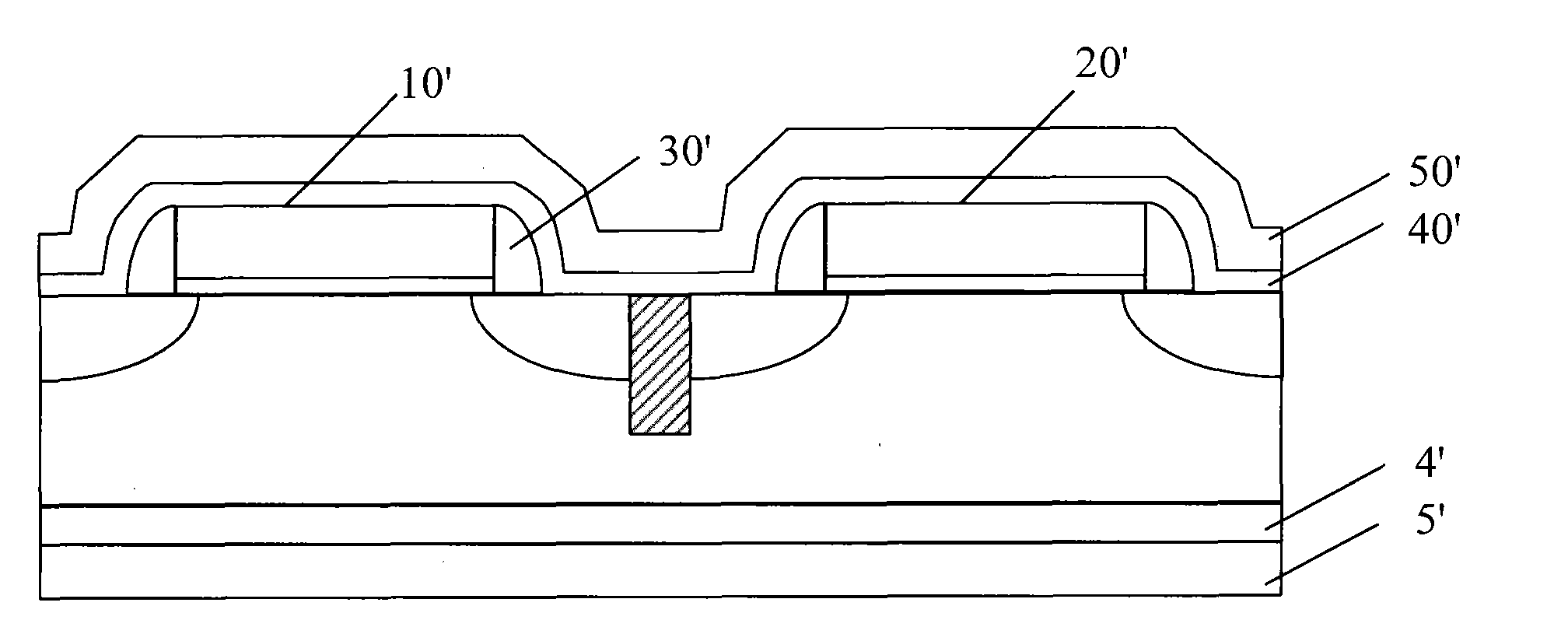

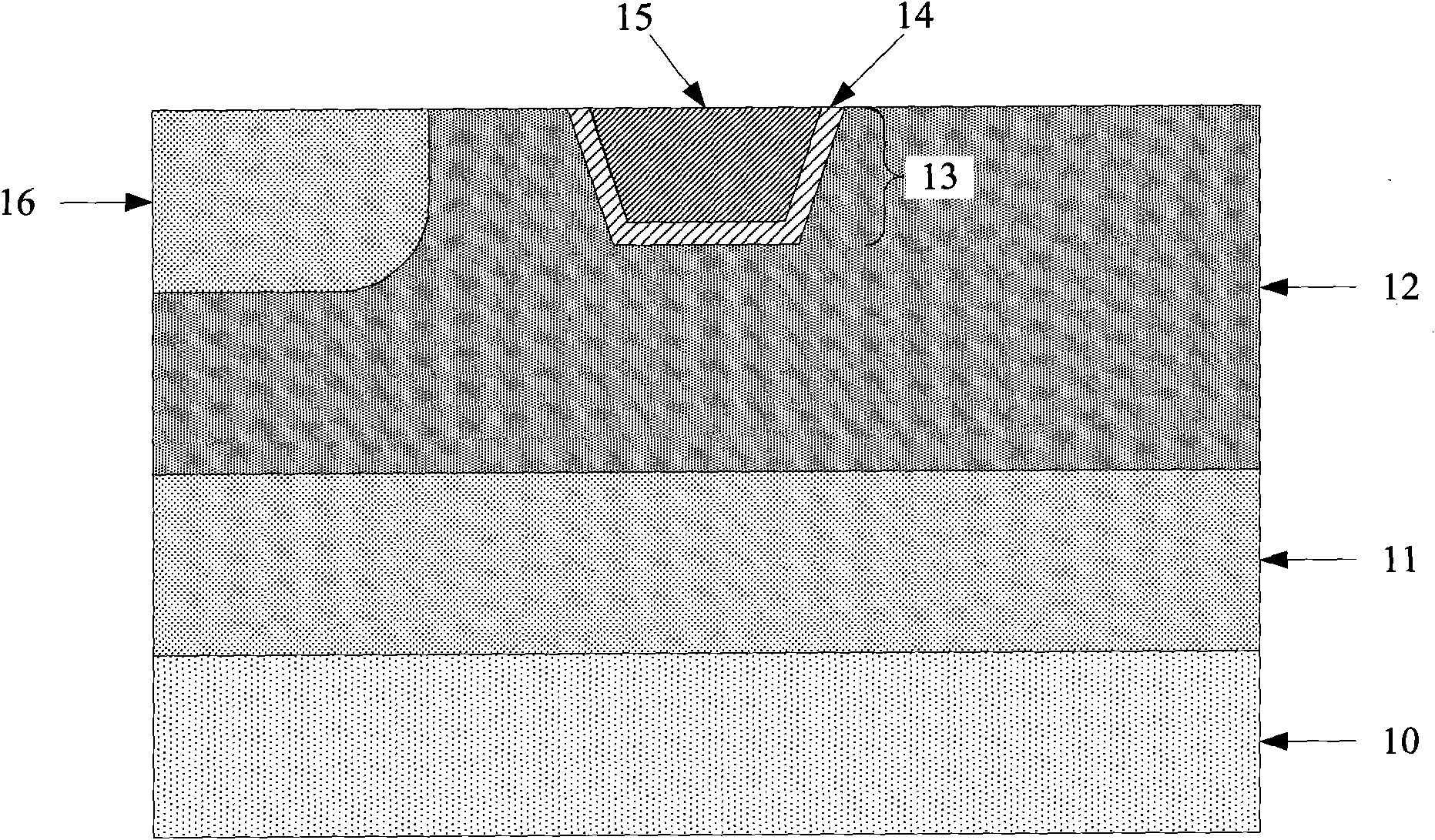

LDMOS (laterally diffused metal oxide semiconductor) and manufacturing method thereof

ActiveCN102054864AWork lessImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesElectron collisionOptoelectronics

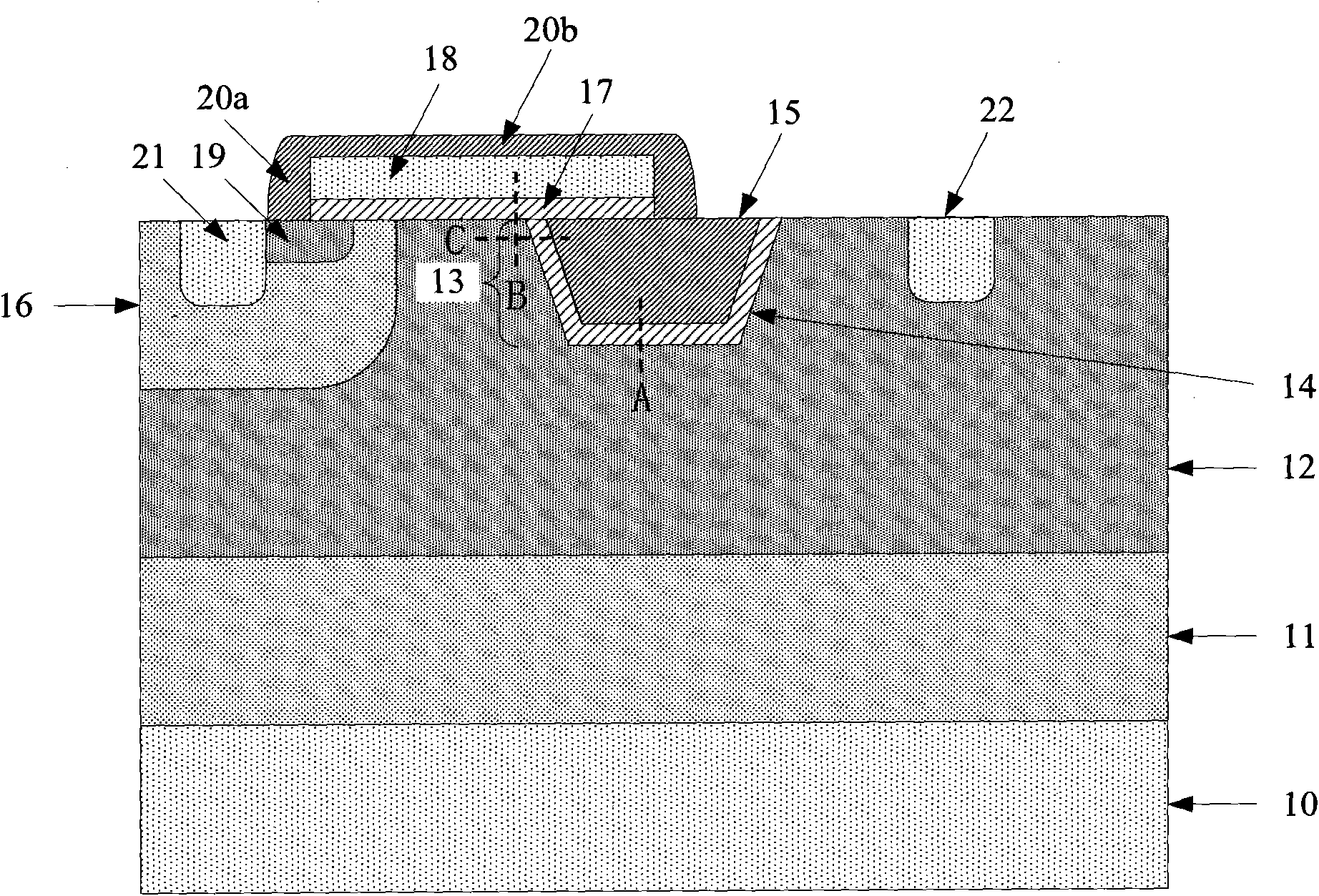

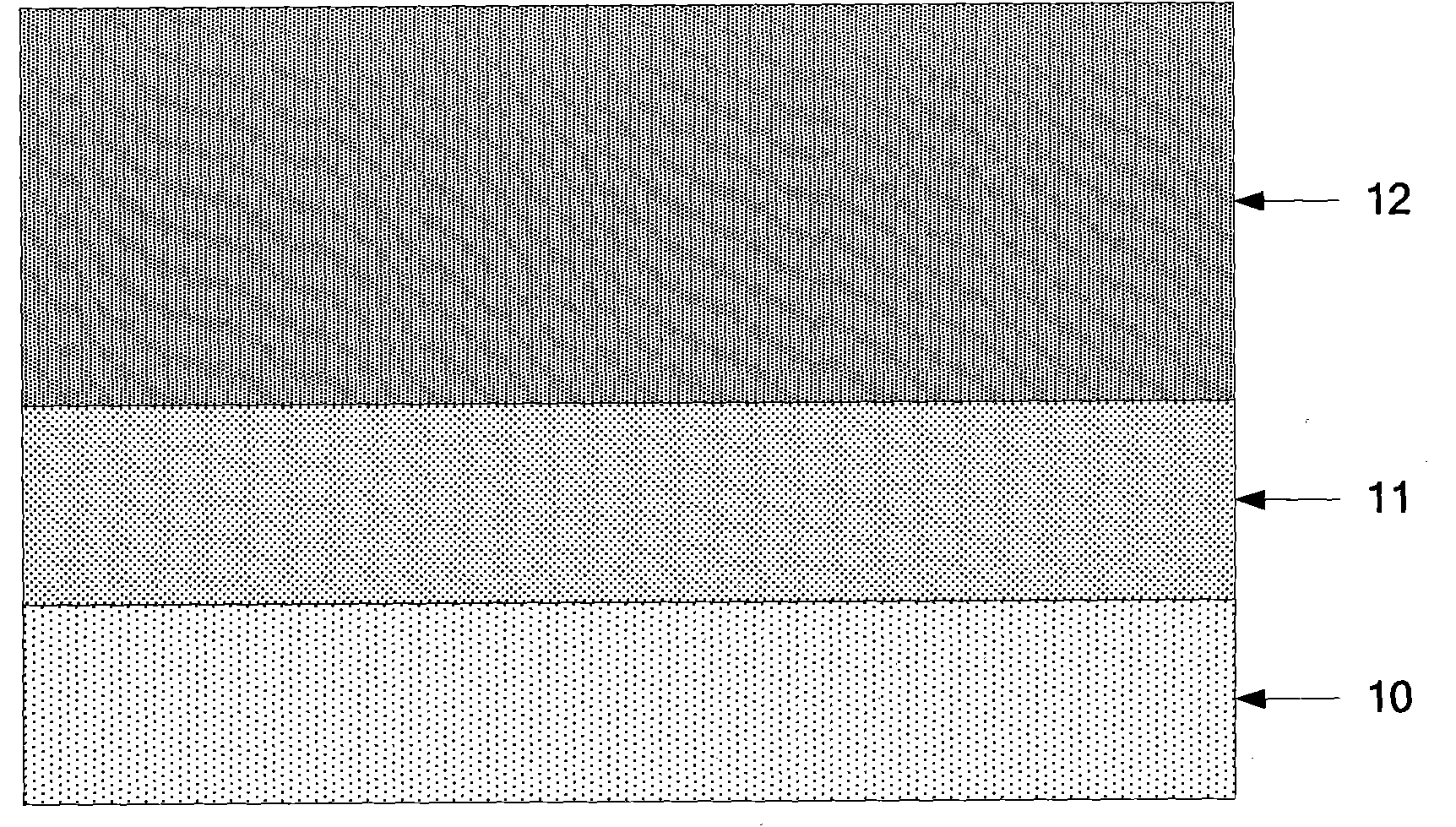

The invention discloses a LDMOS. Based on the traditional LDMOS (laterally diffused metal oxide semiconductor) structure, a light dope area (30) is arranged on the side wall and the bottom close to a groove (13) in a well (12). The doping types of the light dope area (30) and the well (12) are the same and the doping density of the light dope area (30) is lower. The invention also discloses a manufacturing method of an LDMOS. The shifting area of the traditional LDMOS is the well (12) but the shifting area of the LDMOS provided by the invention is the well (12) and the light dope area (30), so that the electric field along vertical and horizontal directions of the groove in the LDMOS provided by the invention is conveniently reduced, therefore reducing the electron collision strength in the shifting area, restraining the hot carrier injection effect, and increasing the safety working area and reliability of the LDMOS device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

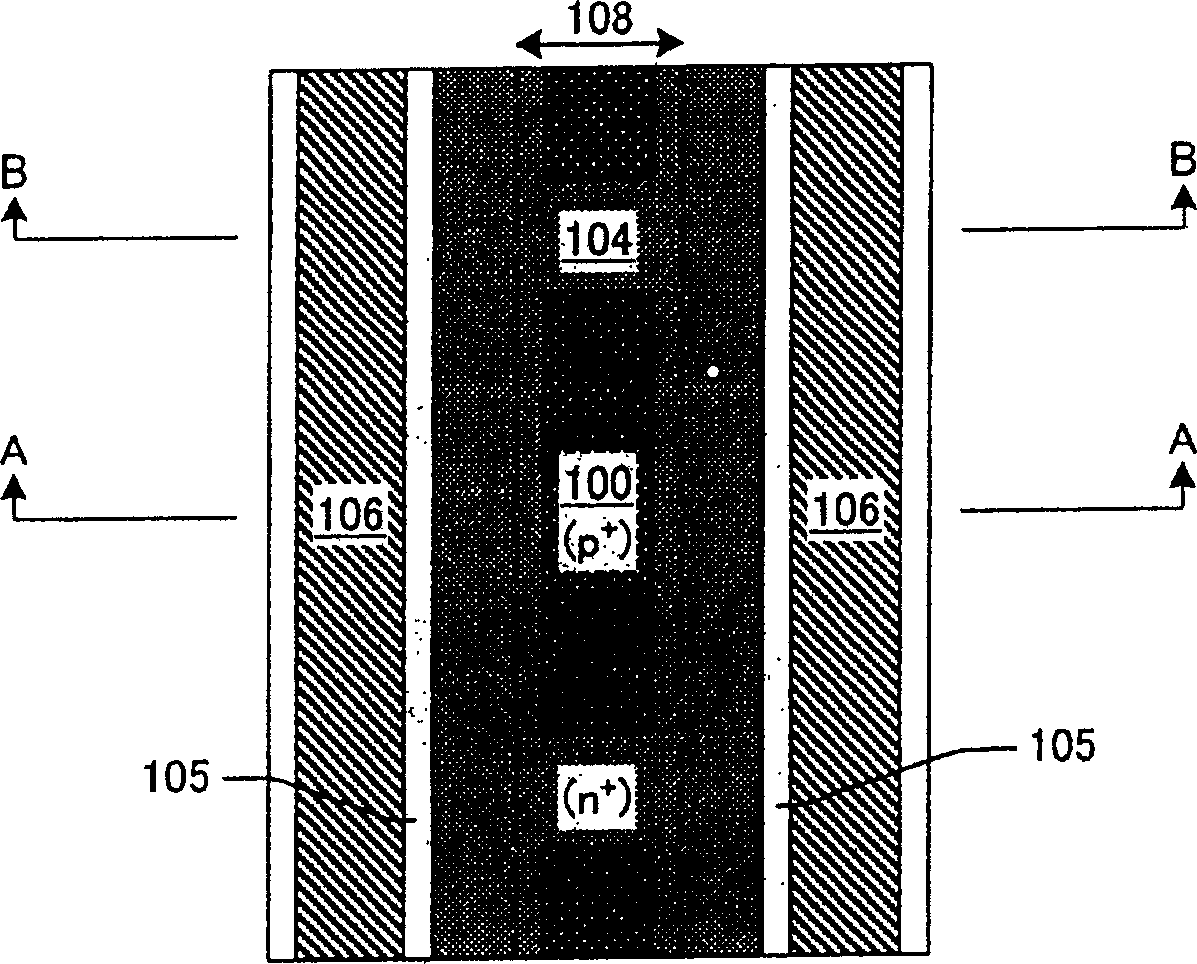

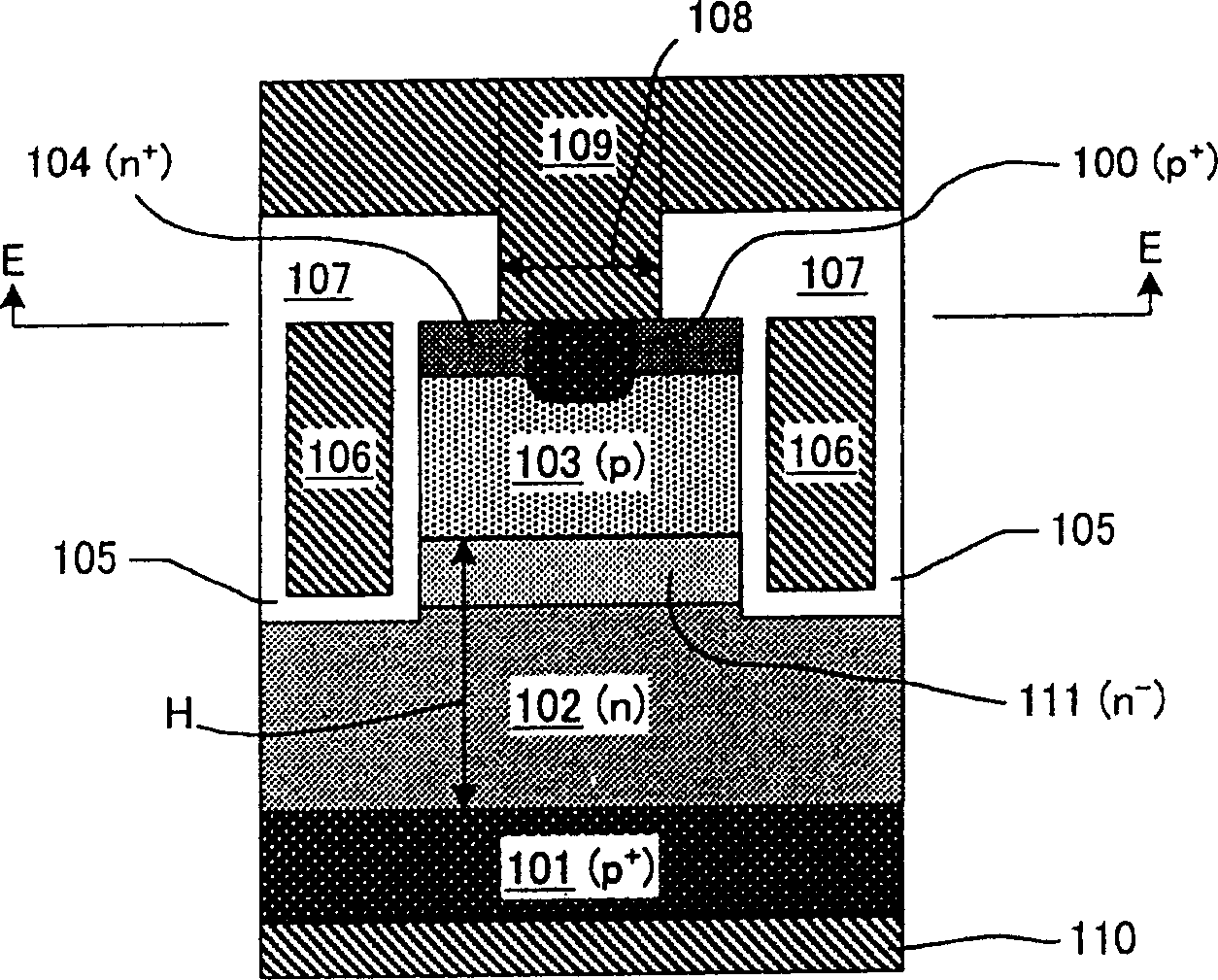

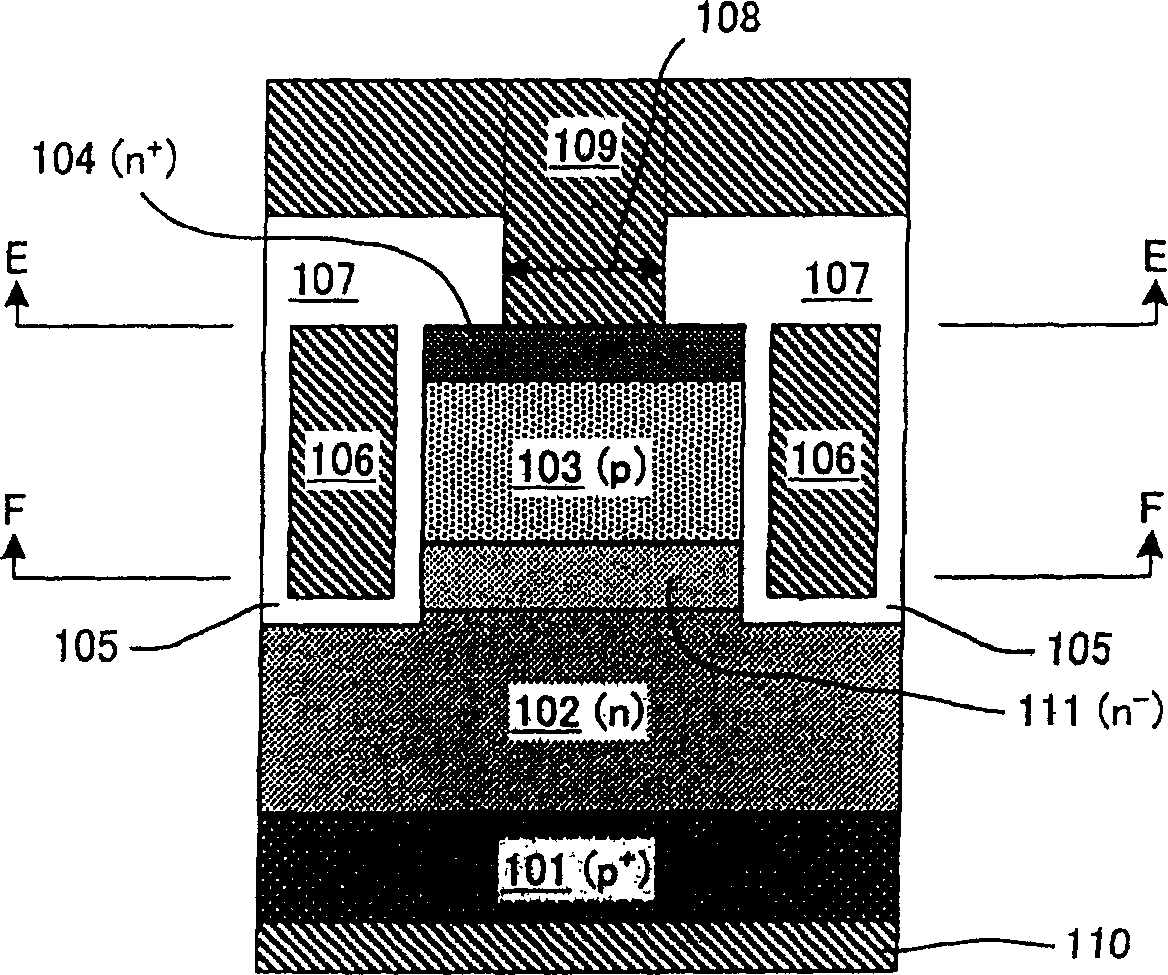

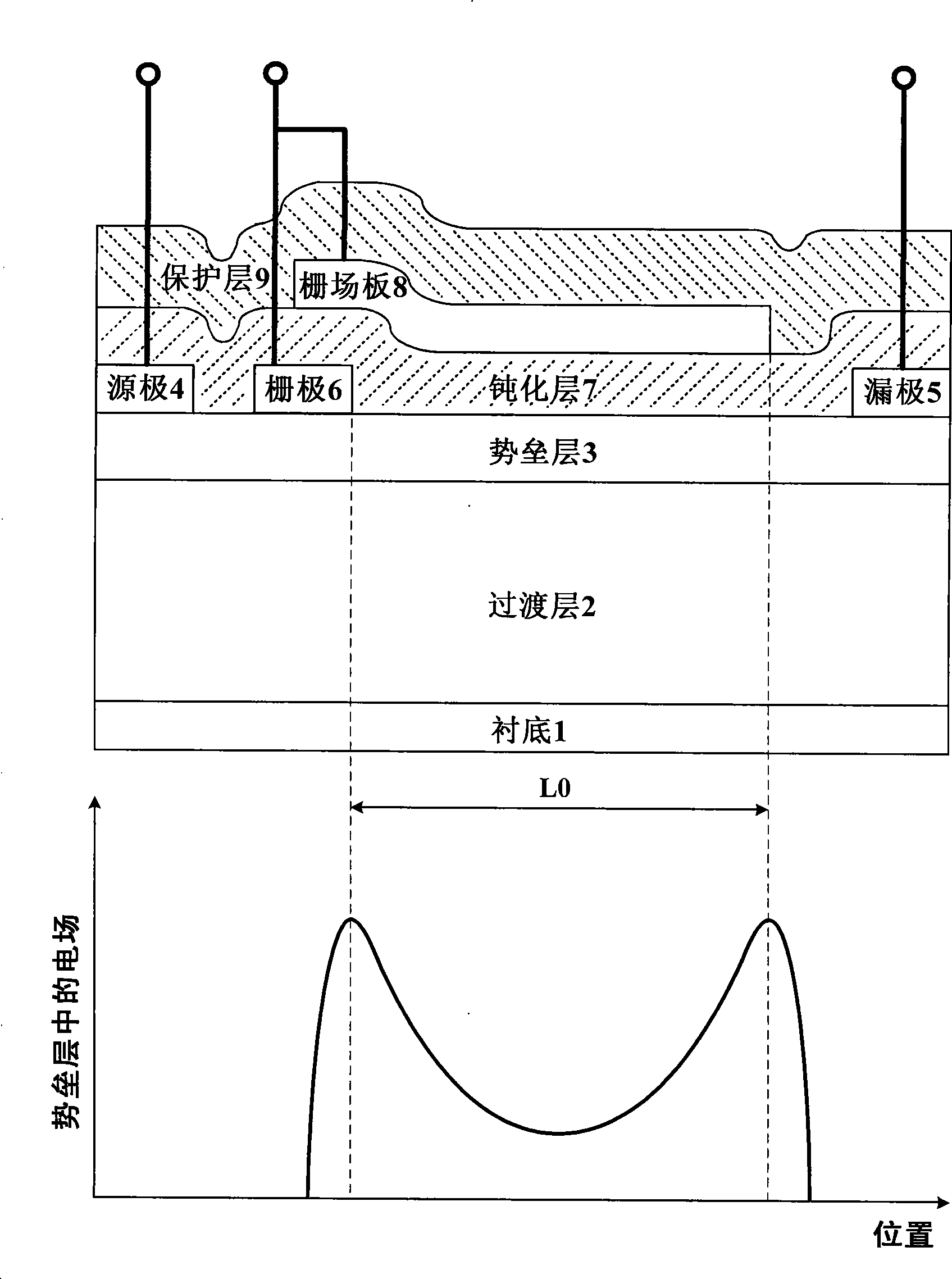

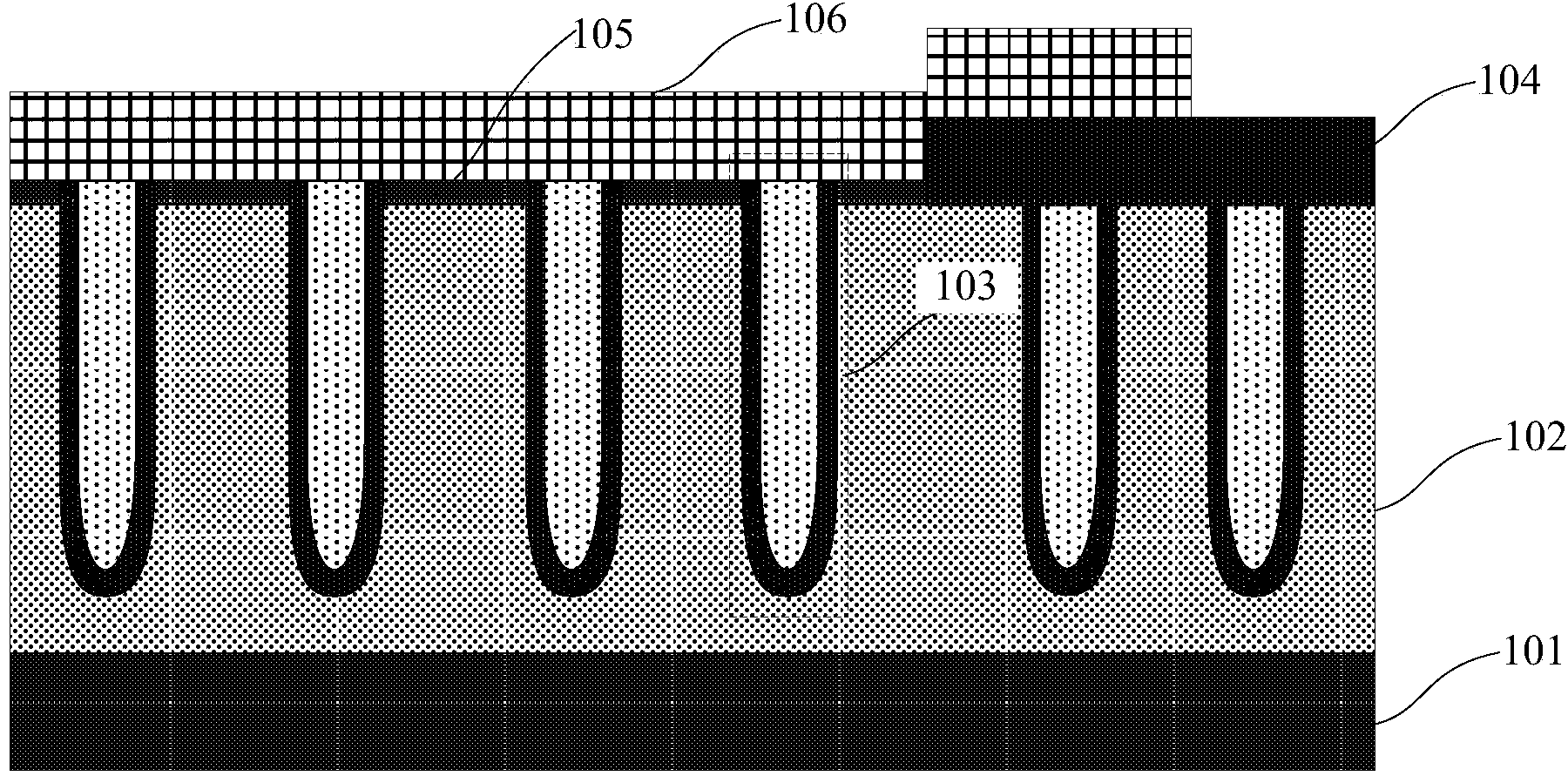

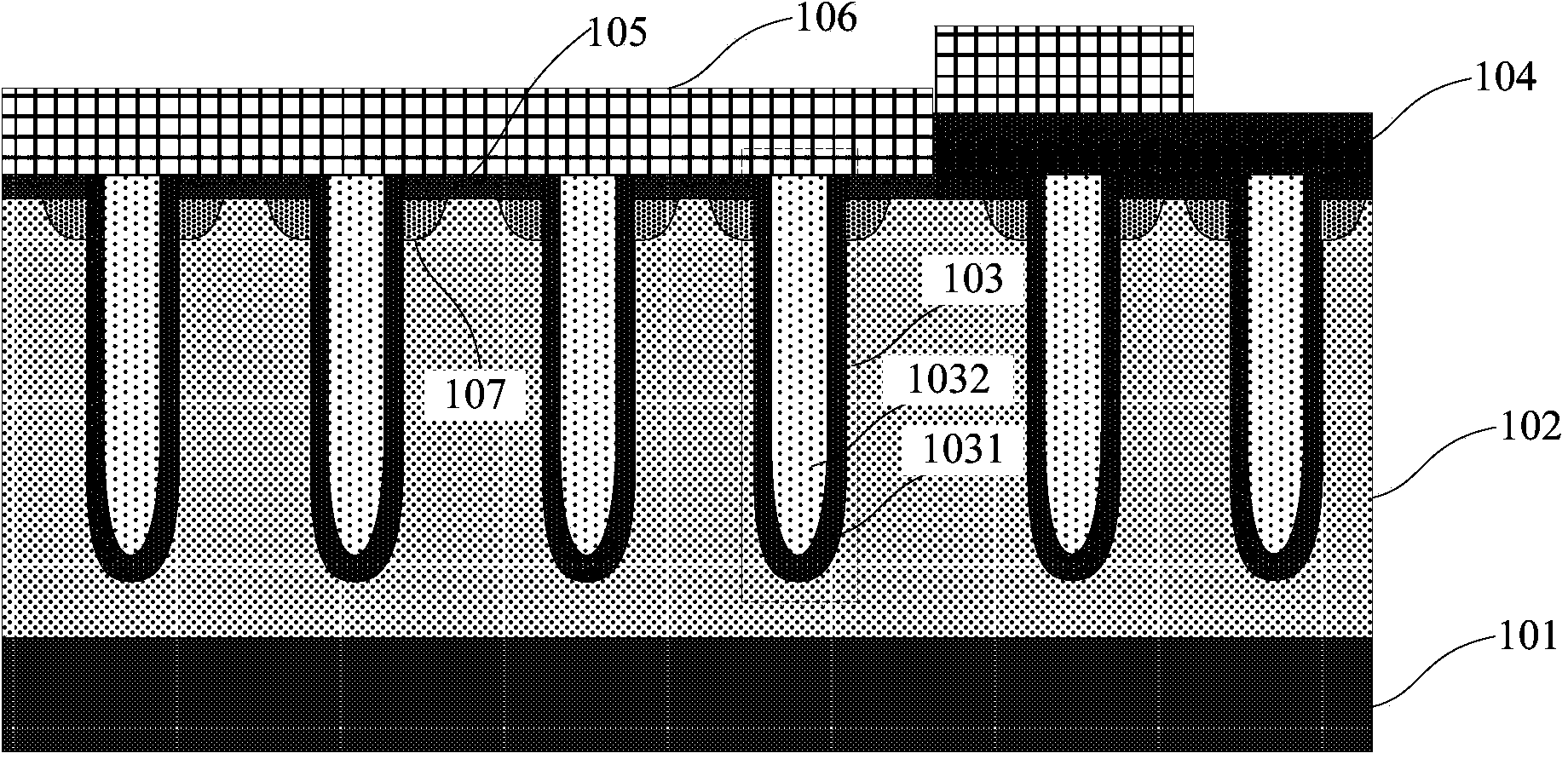

High withstand voltage field effect type semiconductor device

ActiveCN1525575AImprove pressure resistanceReduce electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesMiniaturizationVertical field

It is intended to provide a high withstand voltage vertical field effect type semiconductor device that relaxes electric fields in a semiconductor substrate without thickening thickness of a drift region and achieves withstand-ability against high voltage without sacrificing ON-voltage, switch-OFF characteristics, and miniaturization. A field effect type semiconductor device comprises emitter regions (100,104) and gate electrodes (106) and the like on a surface (upper surface in FIG.2), a collector region (101) and the like on the other surface (lo - -type field dispersion regions (111) of low impurity concentration are arranged between P-type body regions (103) facing to gate electrodes (106) and an N-type drift region (102) below P-type body regions (103). Thereby, the electric field between collector and emitter is relaxed and a high withstand voltage field effect type semiconductor device is realized. Another field dispersion region can be arranged between the N-type drift region (102) and P + -type collector region (101) below the N-type drift region (102).

Owner:TOYOTA JIDOSHA KK

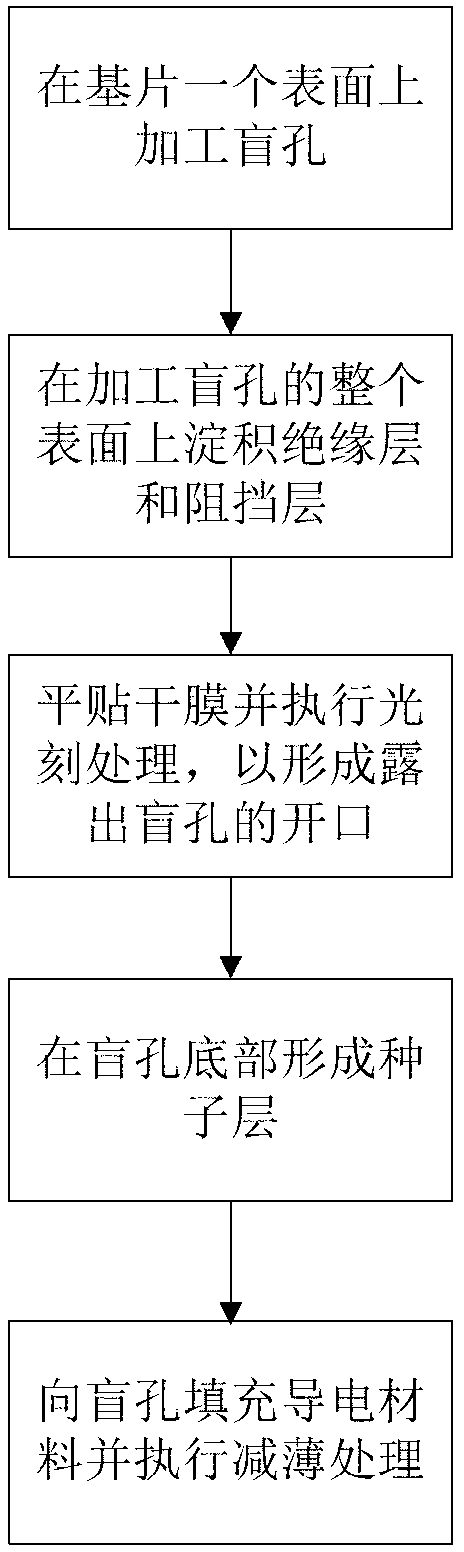

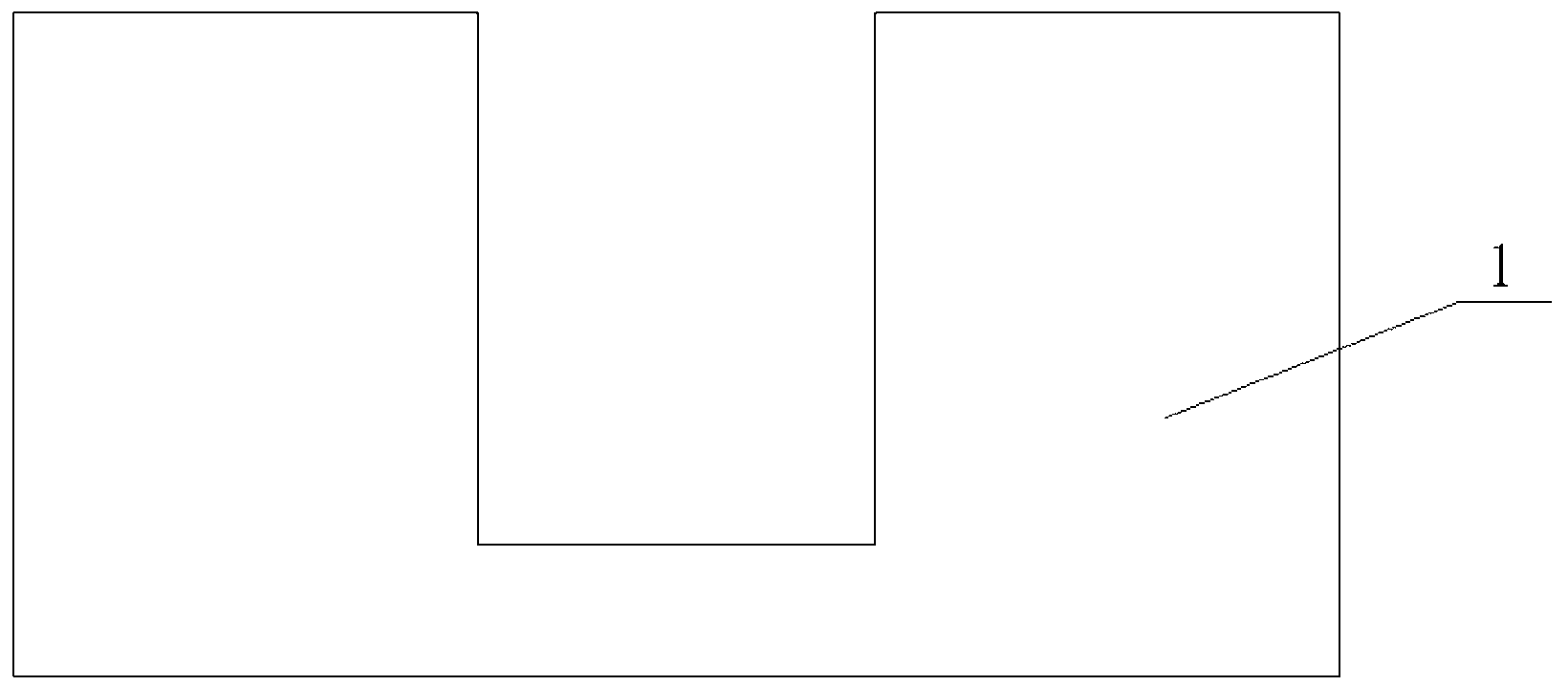

Manufacturing method of through hole interconnection structure and product of through hole interconnection structure

InactiveCN103258789AQuality improvementFilling high speedSemiconductor/solid-state device manufacturingInterconnectionEngineering

The invention discloses a manufacturing method of a through hole interconnection structure. The manufacturing method of the through hole interconnection structure comprises the following steps: (a) a blind hole is machined in one surface of a substrate; (b) an insulating layer and a barrier layer are deposited on the whole surface in sequence, where the blind hole is machined, of the substrate; (c) a light-sensitive dry film is paved on and attached to the surface, containing the barrier layer, of the substrate, and exposure imaging treatment is carried out on the surface, so that an opening exposed out of the blind hole is formed; (d) the dry film is used as a covering film, a seed layer is formed on the barrier layer on the bottom of the blind hole, and the seed layer is prevented from covering the barrier layer deposited on the lateral wall of the blind hole; (e) growth from bottom to top is achieved with the seed layer on the bottom of a through hole as guiding media, and the thickness of another surface of the substrate is reduced until the blind hole is machined to be the through hole. The invention further discloses a product of the through hole interconnection structure. According to the manufacturing method of the through hole interconnection structure and the product of the through hole interconnection structure, through hole electroplating which is convenient to control, low in cost, and high in efficiency can be achieved, and the product of the through hole interconnection structure and with better filling effect can be obtained.

Owner:HUAZHONG UNIV OF SCI & TECH

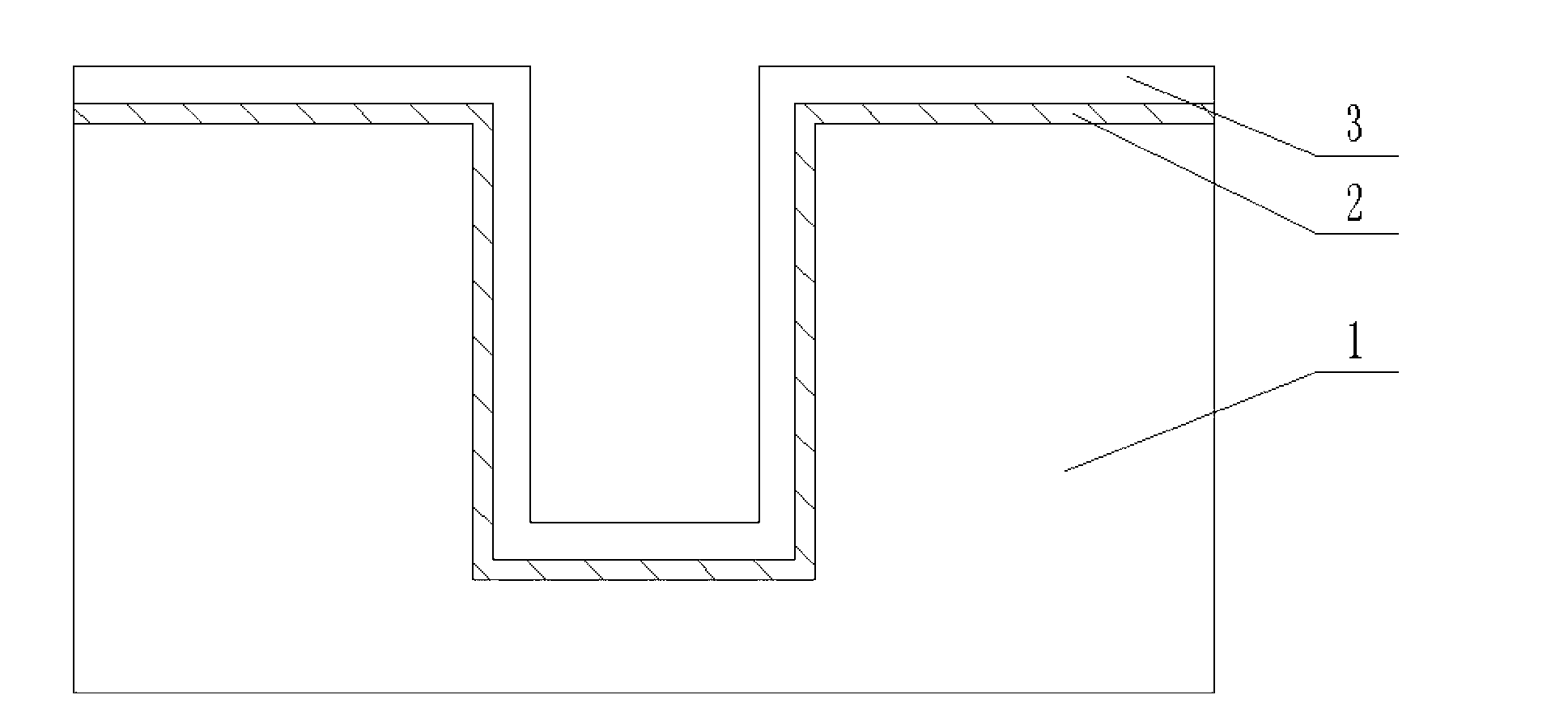

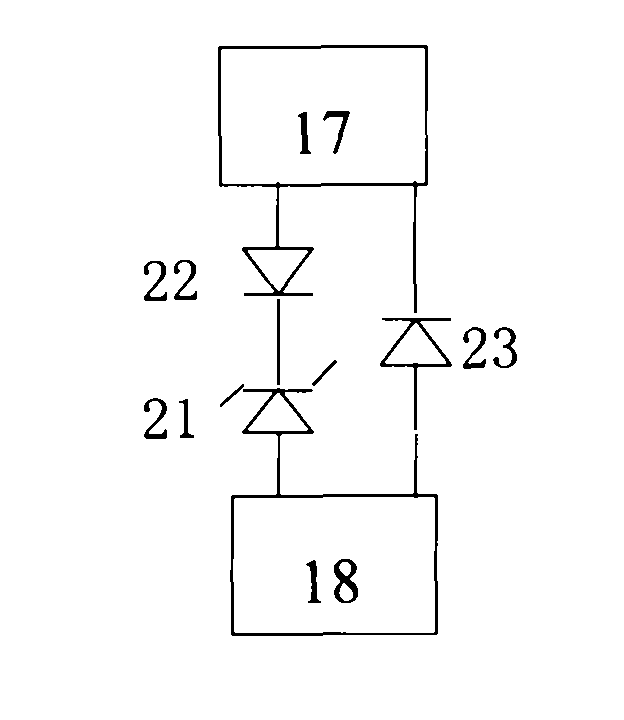

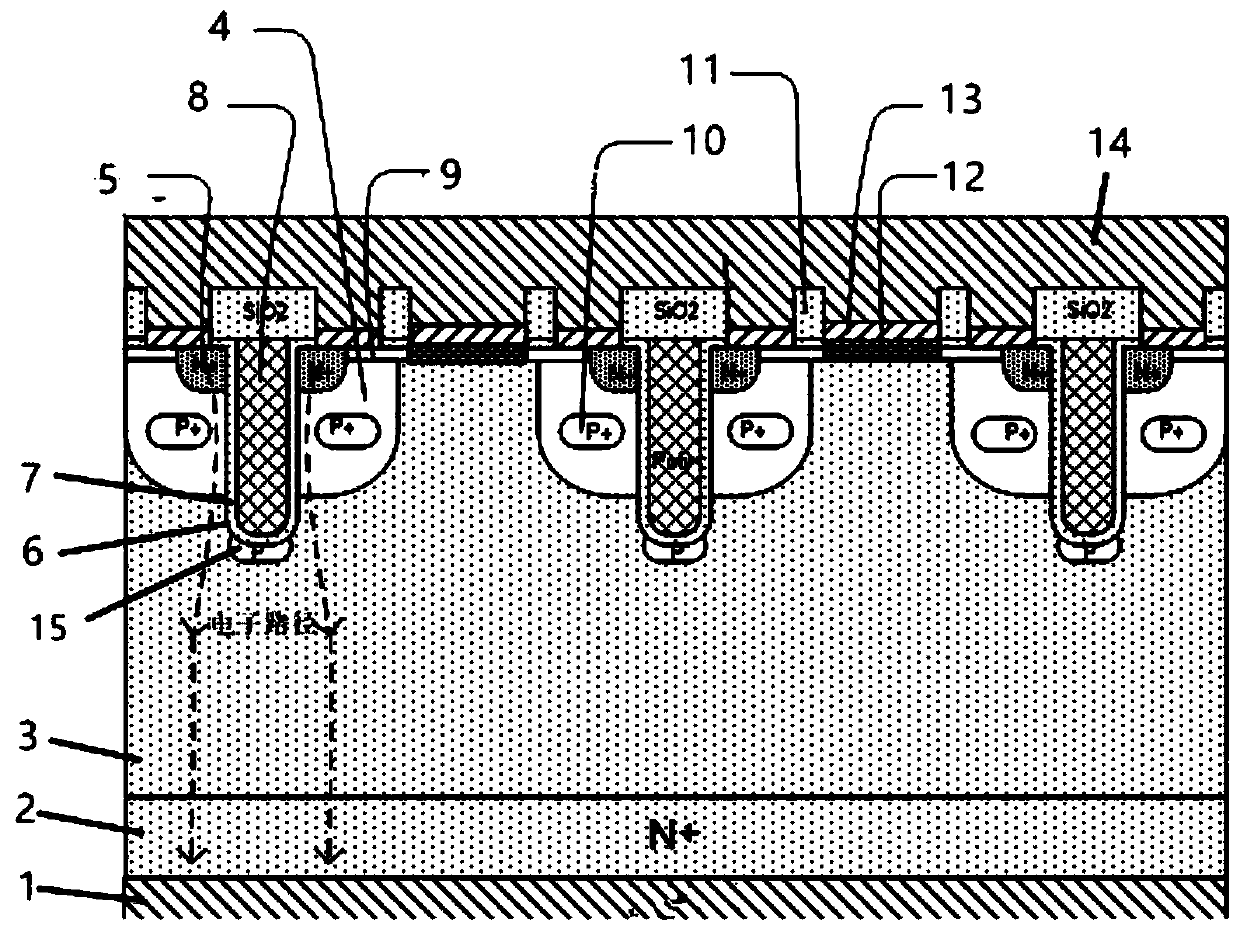

ESD (electrostatic discharge) protection circuit and manufacturing method thereof

InactiveCN102082148AReduce electric fieldMinimize injection effectSemiconductor/solid-state device detailsSolid-state devicesElectrostatic dischargeZener diode

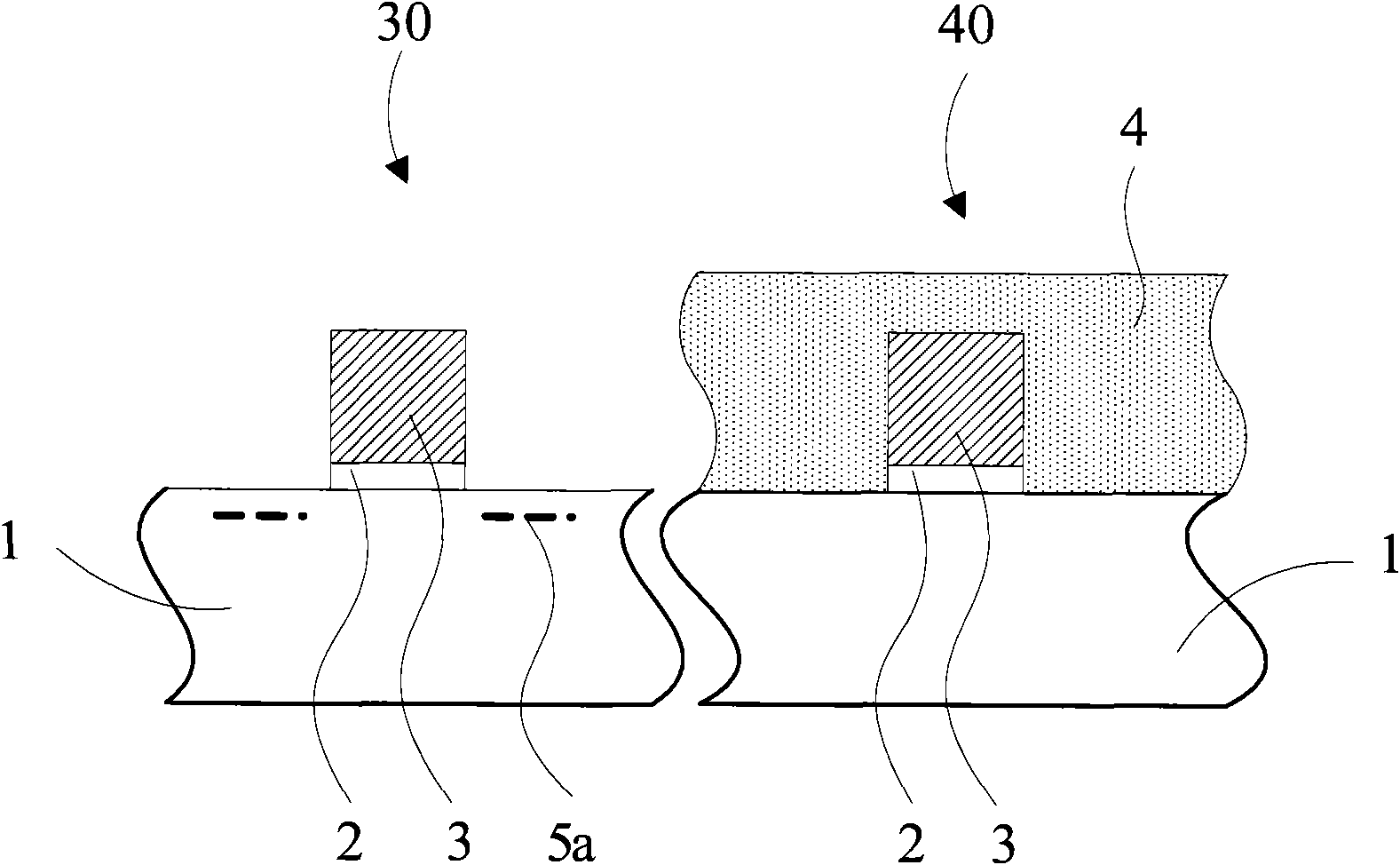

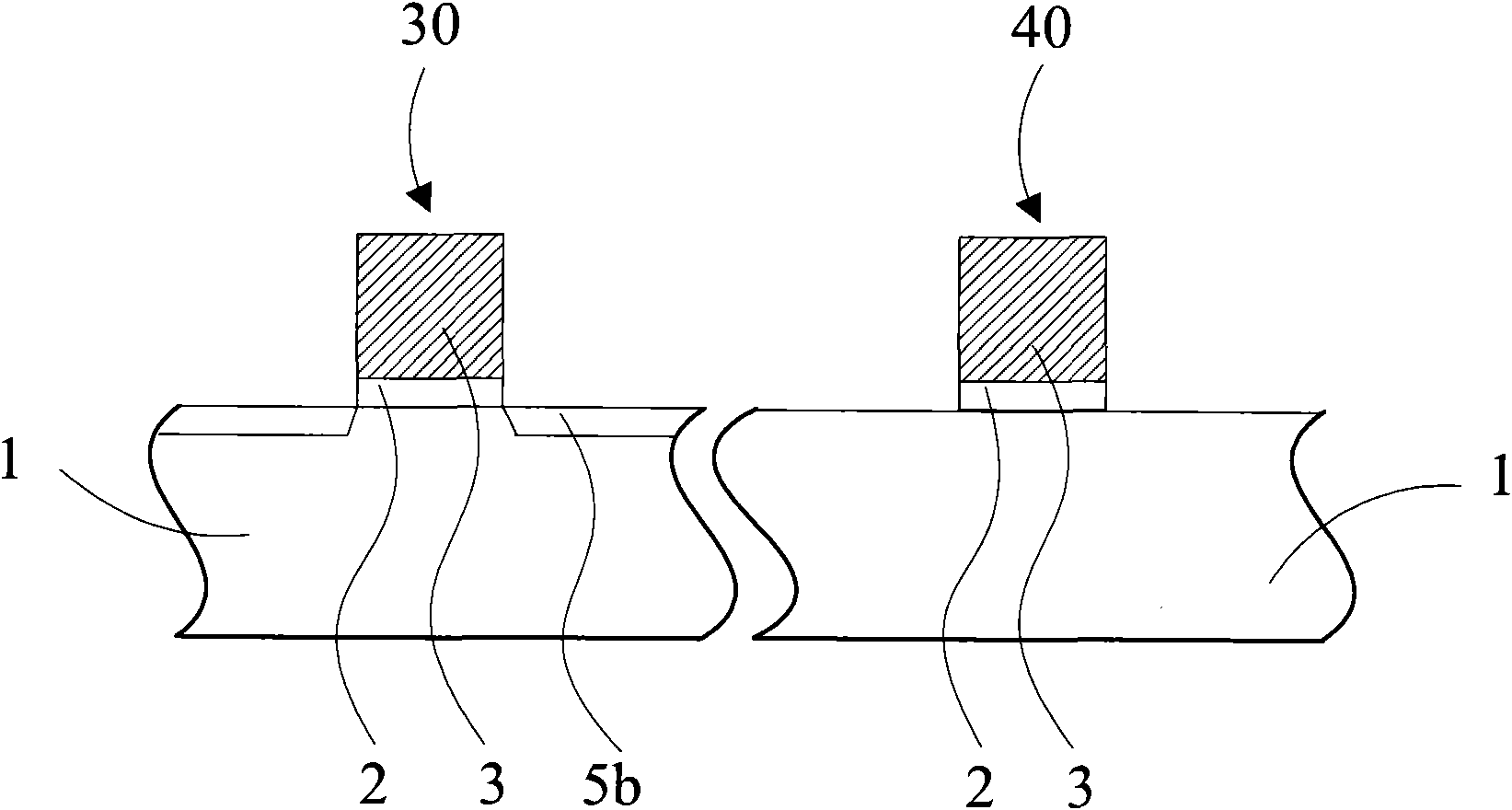

The invention discloses an ESD (electrostatic discharge) protection circuit. The protection circuit is composed of a first branch and a second branch which are connected in parallel, wherein the first branch is formed by connecting a Zener diode (21) with a first diode (22) in serials; and the second branch is a second diode (23). The protection circuit is characterized in that an n-type heavily doped Zener ion implantation region (11) and a p-type heavily doped substrate (10) form the Zener diode (21); a p-type heavily doped region (15a) and an n well (13a) form the first diode (22); and an n well (13b) and the p-type heavily doped substrate (10) form the second diode (23). The invention also discloses a manufacturing method of the ESD protection circuit. The ESD protection circuit has the advantages of low parasitic capacitance and high response speed, is simple to manufacture, and is especially suitable for protection of input / output ESD circuits with voltages lower than 5V.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

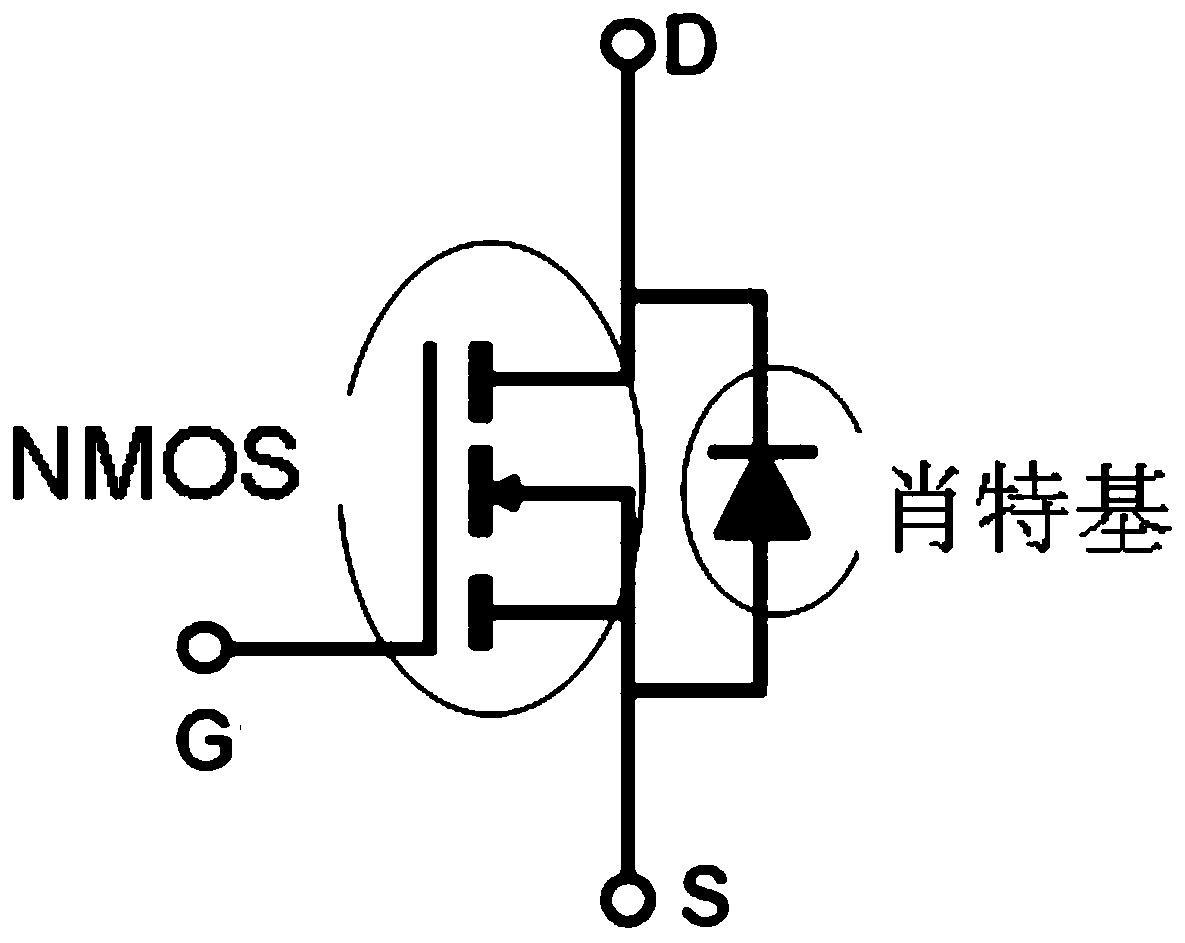

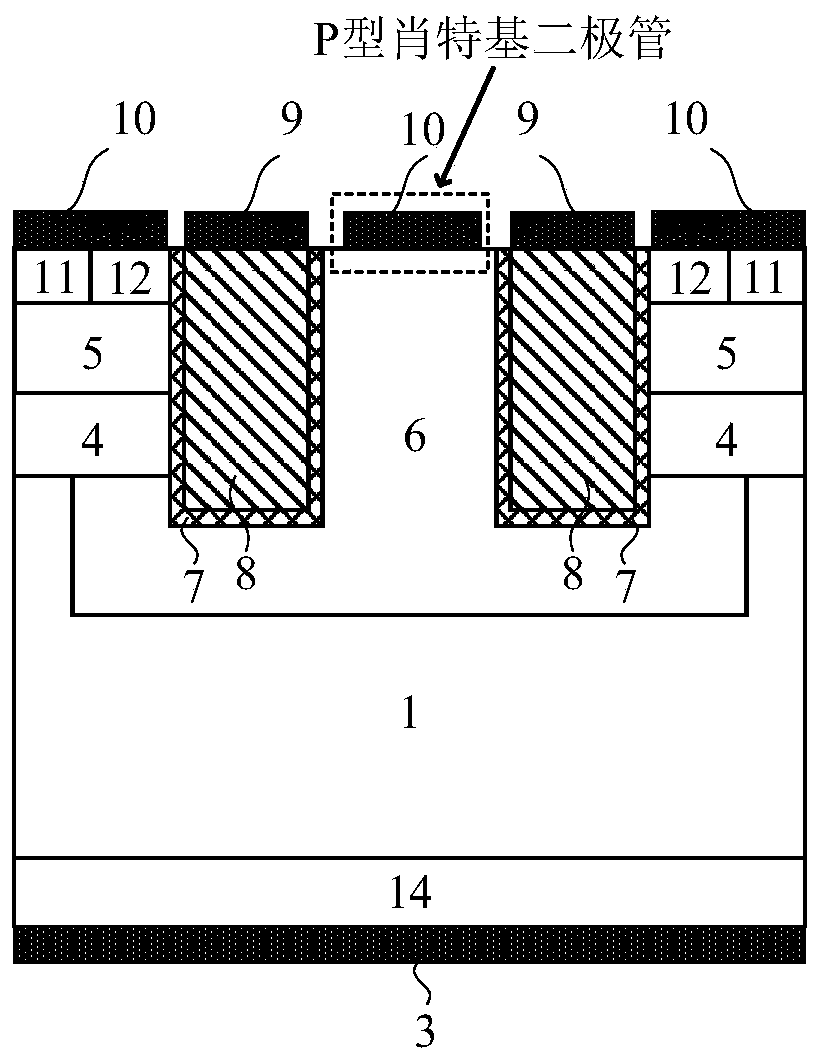

Enhanced silicon carbide MOSFET device and manufacturing method thereof

ActiveCN111081759AFast switching speedImprove performanceTransistorSolid-state devicesMOSFETSchottky barrier

The invention discloses an enhanced silicon carbide MOSFET device. The enhanced silicon carbide MOSFET device sequentially comprises back metal, an N+ type heavily doped SiC substrate, an N- epitaxiallayer, an insulating dielectric layer and front metal from bottom to top. According to the invention, a Schottky diode is integrated into the MOSFET device, and the area of a Schottky barrier metal layer is flexibly increased or decreased to adjust and adapt to the current and specification of the MOSFET and the Schottky diode, so that the effects of increasing the switching speed of the MOSFET,reducing the switching loss and the like are achieved, the performance and the reliability of the device can be greatly improved, and the application cost of the device is reduced. The enhanced silicon carbide MOSFET device adopts a trench SiC MOSFET design, and a conductive channel is changed from the traditional horizontal direction to the vertical direction, so that a JFET effect between primitive cells of the traditional MOSFET is eliminated, and the current capability of the device is improved. The gate bottom P region at the bottom of the trench can protect and weaken an electric field at the bottom of the trench, thereby playing a certain role in electrostatic shielding of gate oxide at the bottom of the trench, and improving the reliability of the device. Meanwhile, certain help isprovided for voltage resistance of the device.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

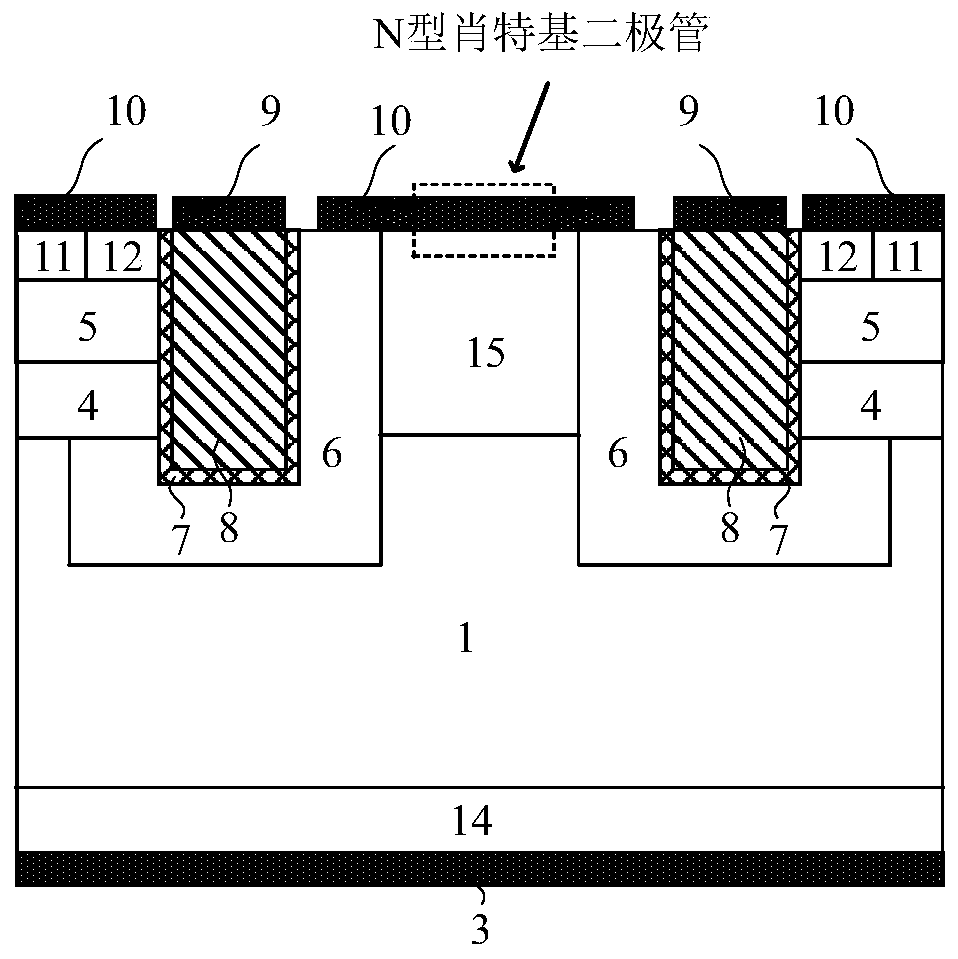

SiC power device

ActiveCN110767753ASmall pressure dropEliminate minority carrier injection effectDiodeHeterojunction diodeMinority carrier injection

The invention belongs to the field of power semiconductors, and particularly provides a SiC power device. The SiC power device comprises a SiC MOSFET and a SiC IGBT. For the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; forthe SiC MOSFET device integrated with an N-type Schottky diode or an integrated heterojunction diode, the voltage drop during reverse conduction of the MOSFET can be reduced, and the minority carrierinjection effect is eliminated, so that the conduction loss and reverse recovery loss of the diode are reduced; for the reverse conduction type SiC IGBT device integrated with the PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and moreover, for the reverse conduction type SiC IGBT device integrated with the N-type Schottky diode or the heterojunction diode, the voltage drop during reverse conduction of the reverse conduction IGBT can be reduced, the minority carrier injection effect is eliminated, and the conduction loss and reverse recovery loss of the diode are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

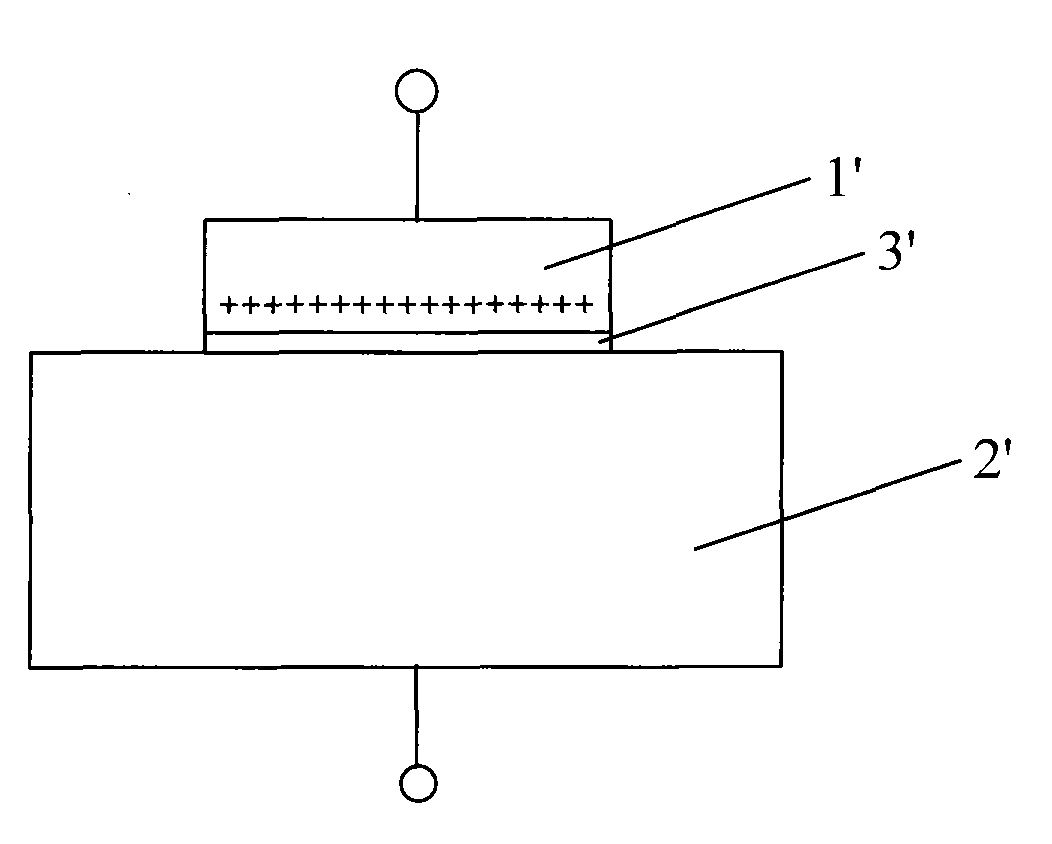

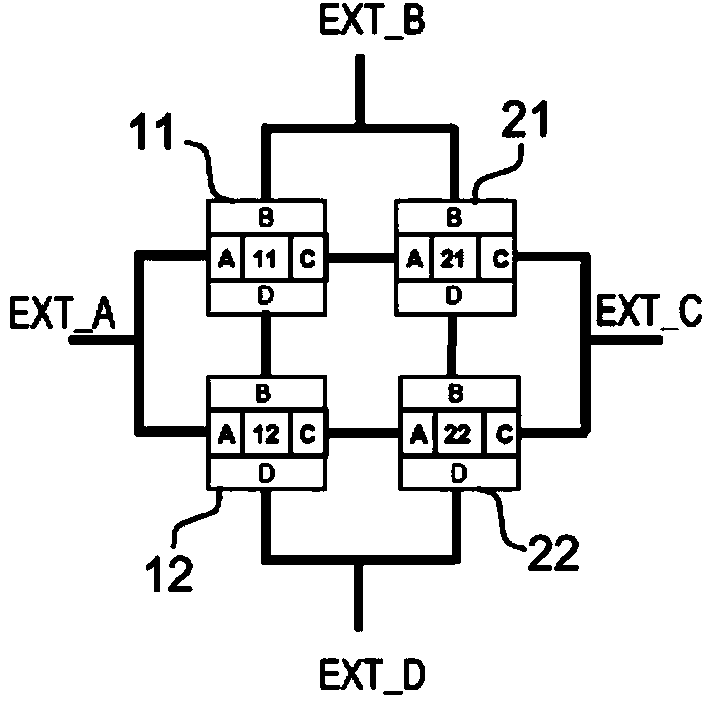

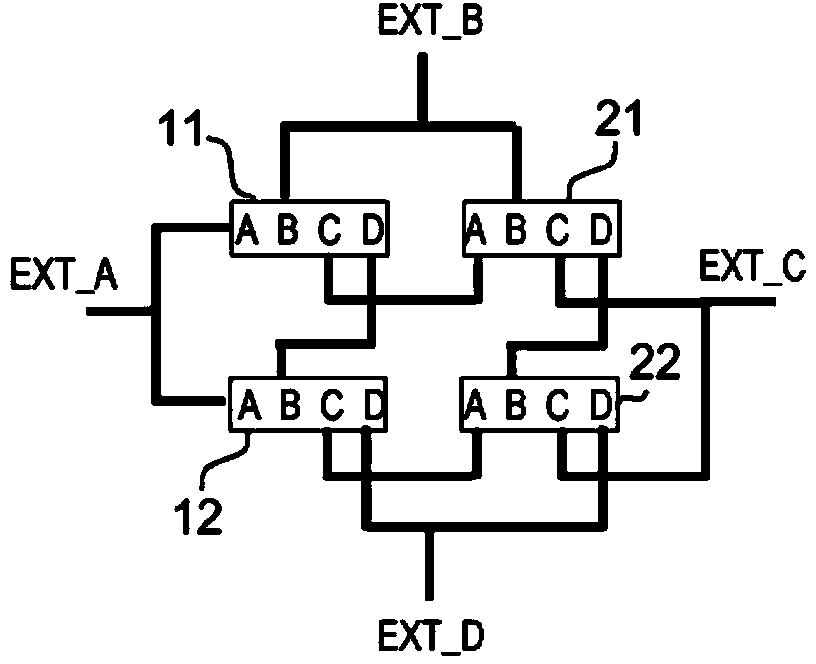

Hall sensor

ActiveCN103874929AReduce electric fieldReduce residual bias voltagePower measurement by galvanomagnetic effect devicesMagnetic sensor arraysPhysics

Owner:AMS AG

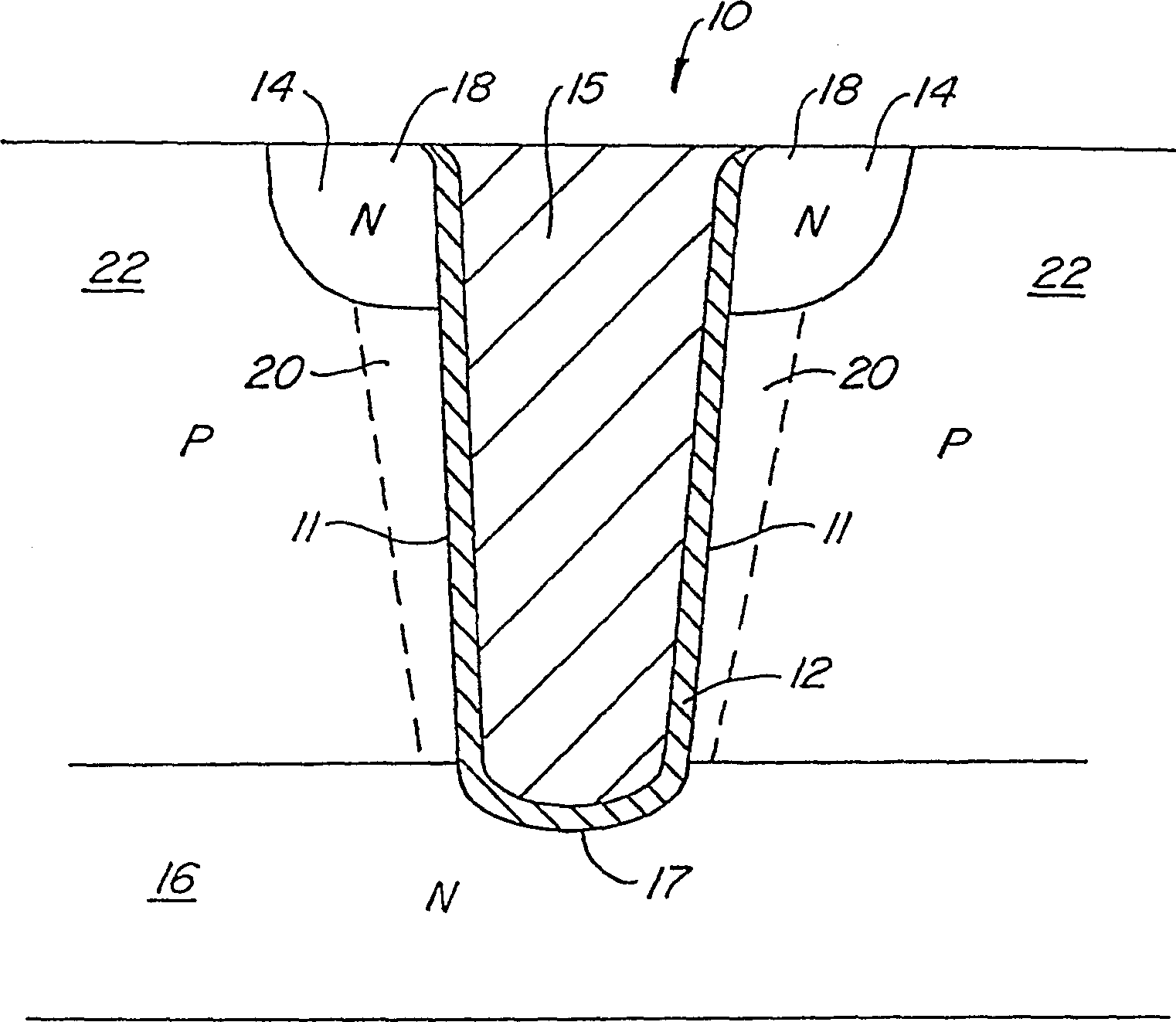

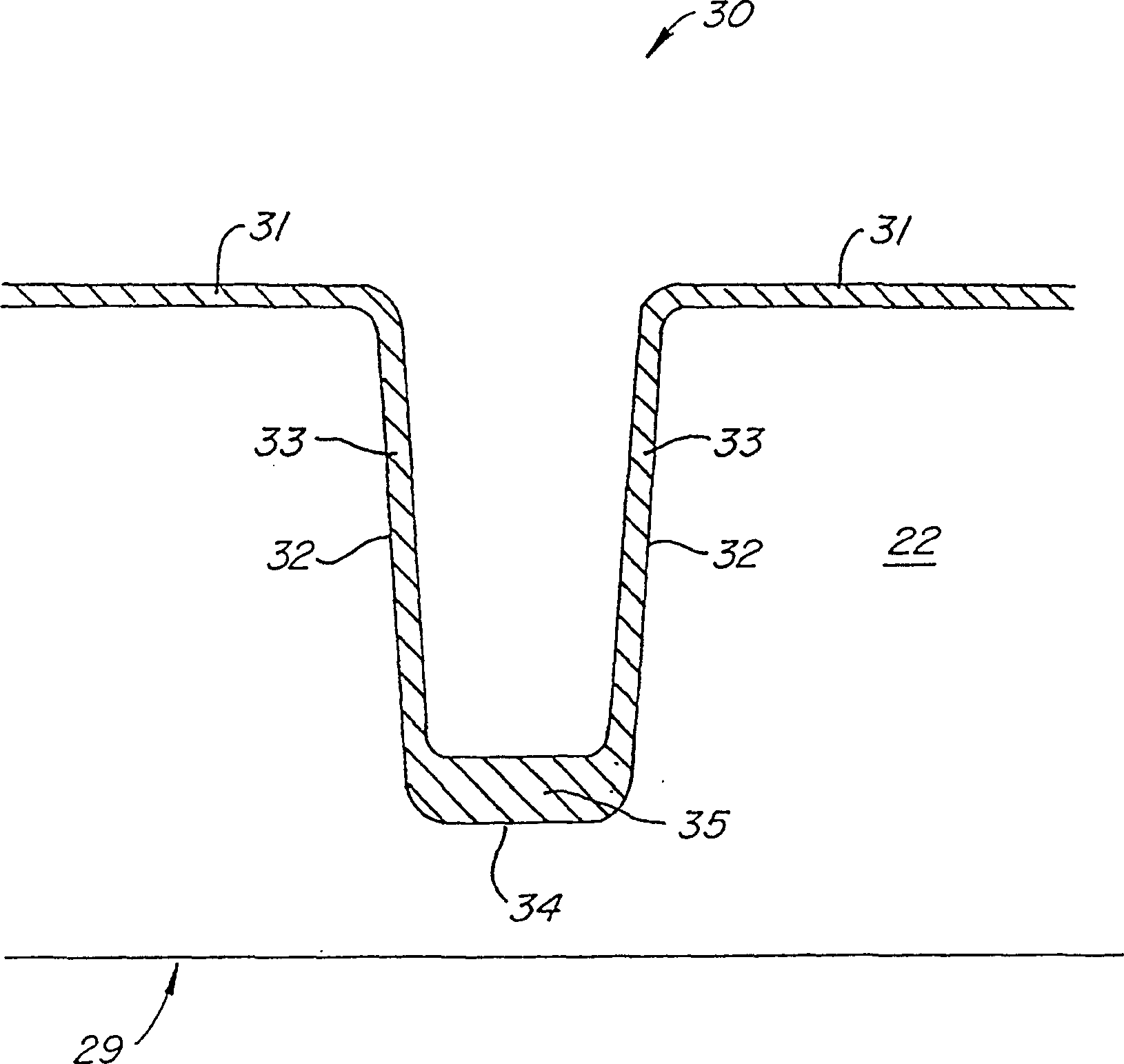

Thick oxide layer on botton of trench structure in silicon

InactiveCN1447986AInsulation etch defectsReduce electric fieldTransistorSemiconductor/solid-state device manufacturingCapacitanceDielectric layer

A gate isolation structure of a semiconductor device and method of making the same provides a trench in a silicon substrate, wherein a dielectric layer is formed on sidewalls and bottom of the trench, the dielectric layer having a first thickness on the sidewalls and a second thickness at the bottom that is greater than the first thickness. The thicker dielectric layer at the bottom substantially reduces gate charge to reduce the Miller Capacitance effect, thereby increasing the efficiency of the semiconductor device and prolonging its life.

Owner:FAIRCHILD SEMICON CORP

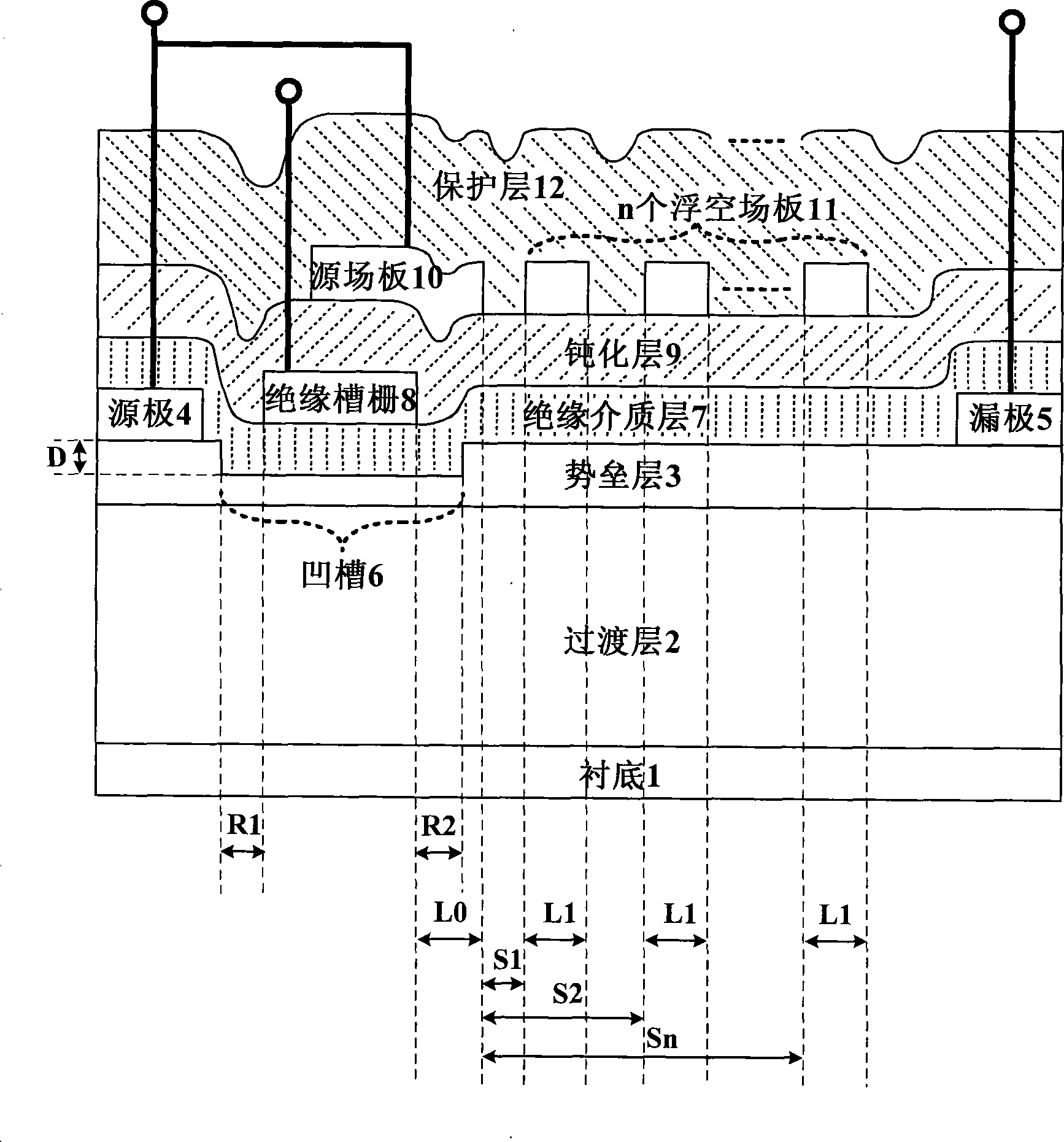

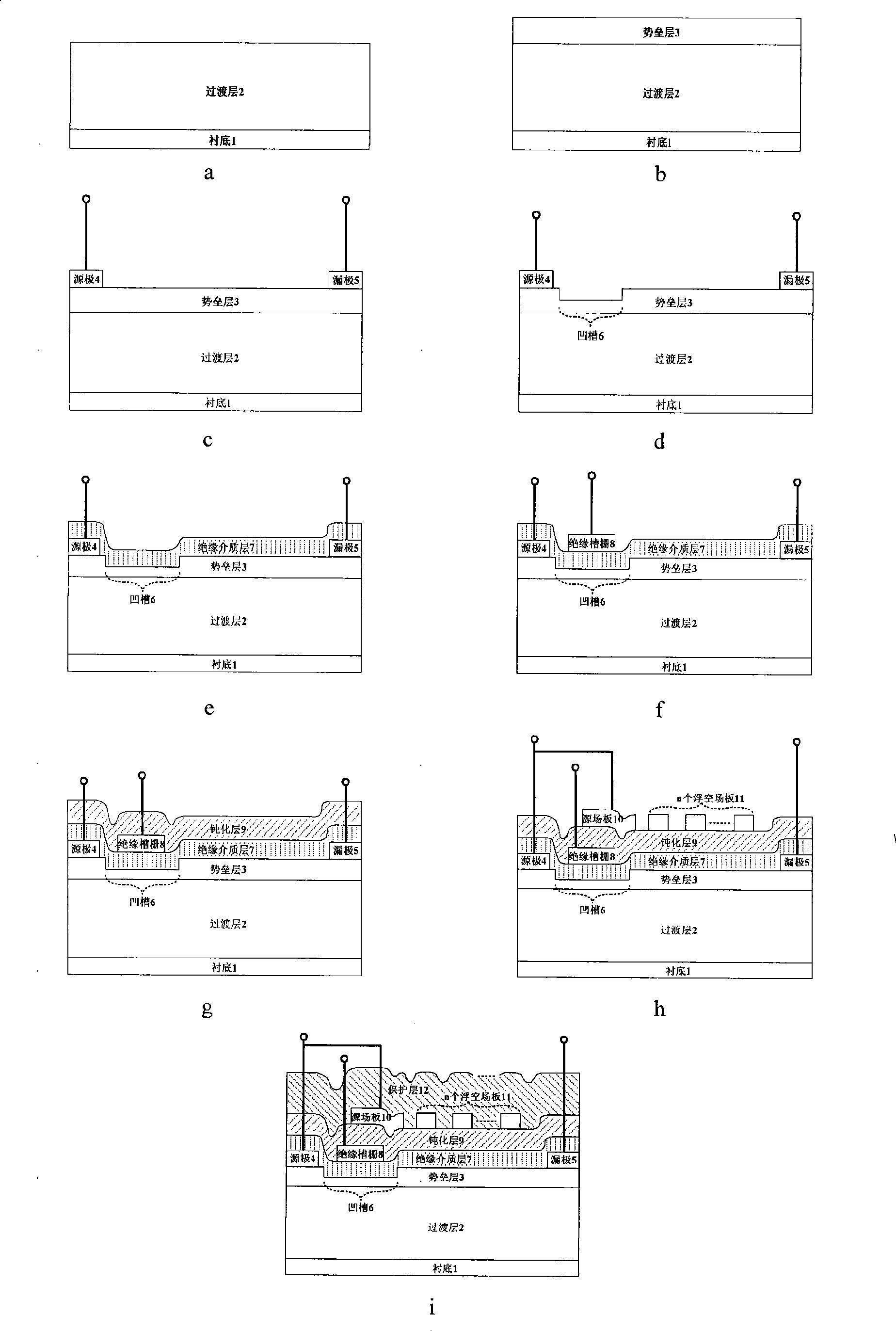

Heterojunction field effect transistor for groove insulated gate type multiple source field plate

InactiveCN101414634AImprove breakdown voltageLarge drain-source voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSource field

The invention discloses a heterojunction field effect transistor of a groove-insulated gate type composite source field plate. The transistor comprises a substrate, a transition layer, a barrier layer, a source electrode, a drain electrode, an insulation medium layer, an insulated groove gate, a passivation layer, a source field plate and a protection layer from bottom to top; a groove is opened on the barrier layer, the insulated groove gate is arranged on the insulation medium layer at the upper part of the groove, the source field plate is arranged on the passivation layer, and the source electrode is electrically connected with the source field plate, wherein, n floating field plates are deposited on the passivation layer arranged between the source field plate and the drain field plate. The floating field plates have the same size and are mutually independent, and the spacing between two adjacent floating field plates increases based on the number of the floating field plates arranged along the direction from the source field plate to the drain electrode. The n floating field plates are in floating state and completed together with the source field plate on the passivation layer by one-time process. The heterojunction field effect transistor has the advantages of simple process, good reliability, strong stability, good frequency characteristic and high output power, and can be used for fabricating microwave power devices based on III-V group compound semiconductor heterojunction structure.

Owner:XIDIAN UNIV

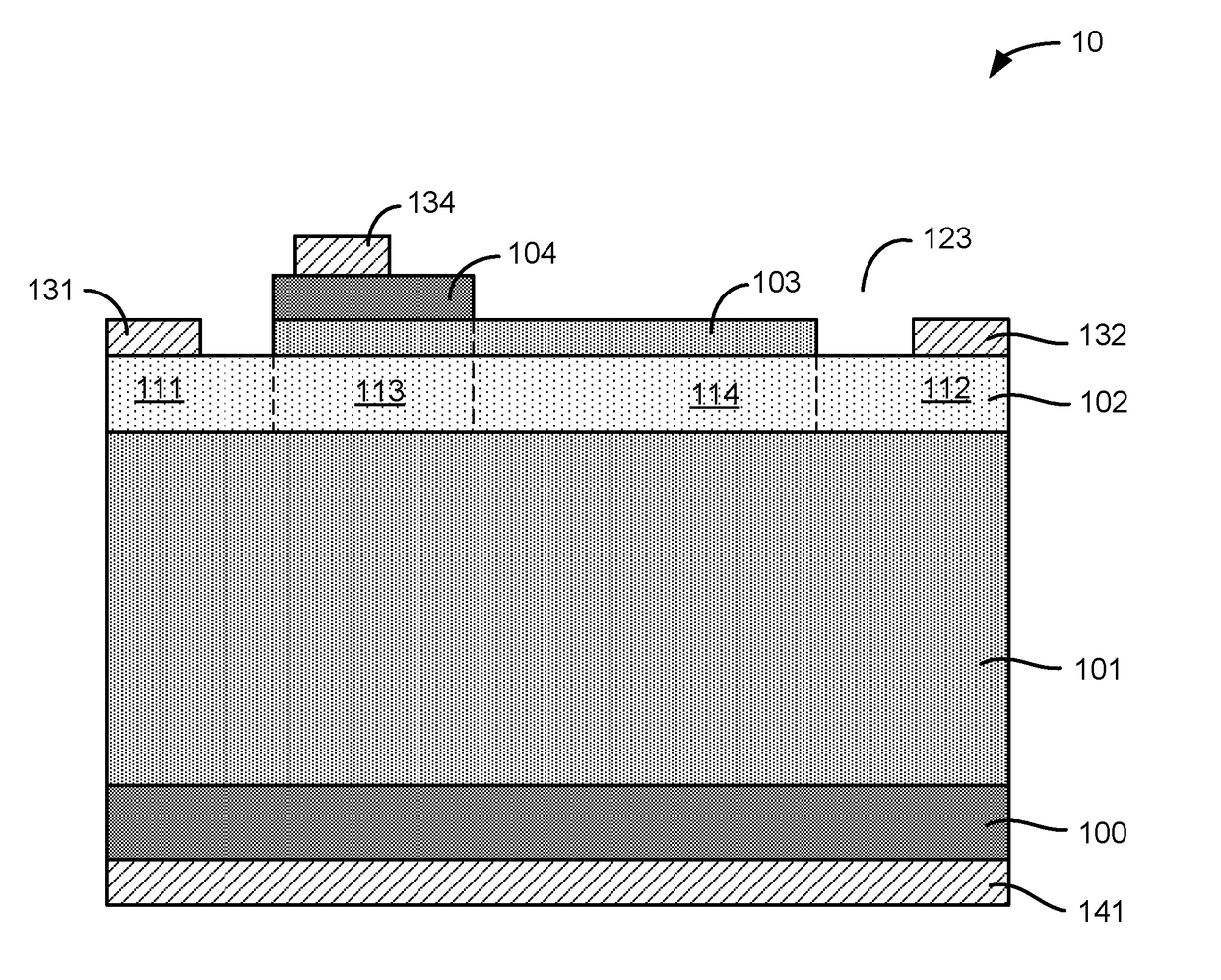

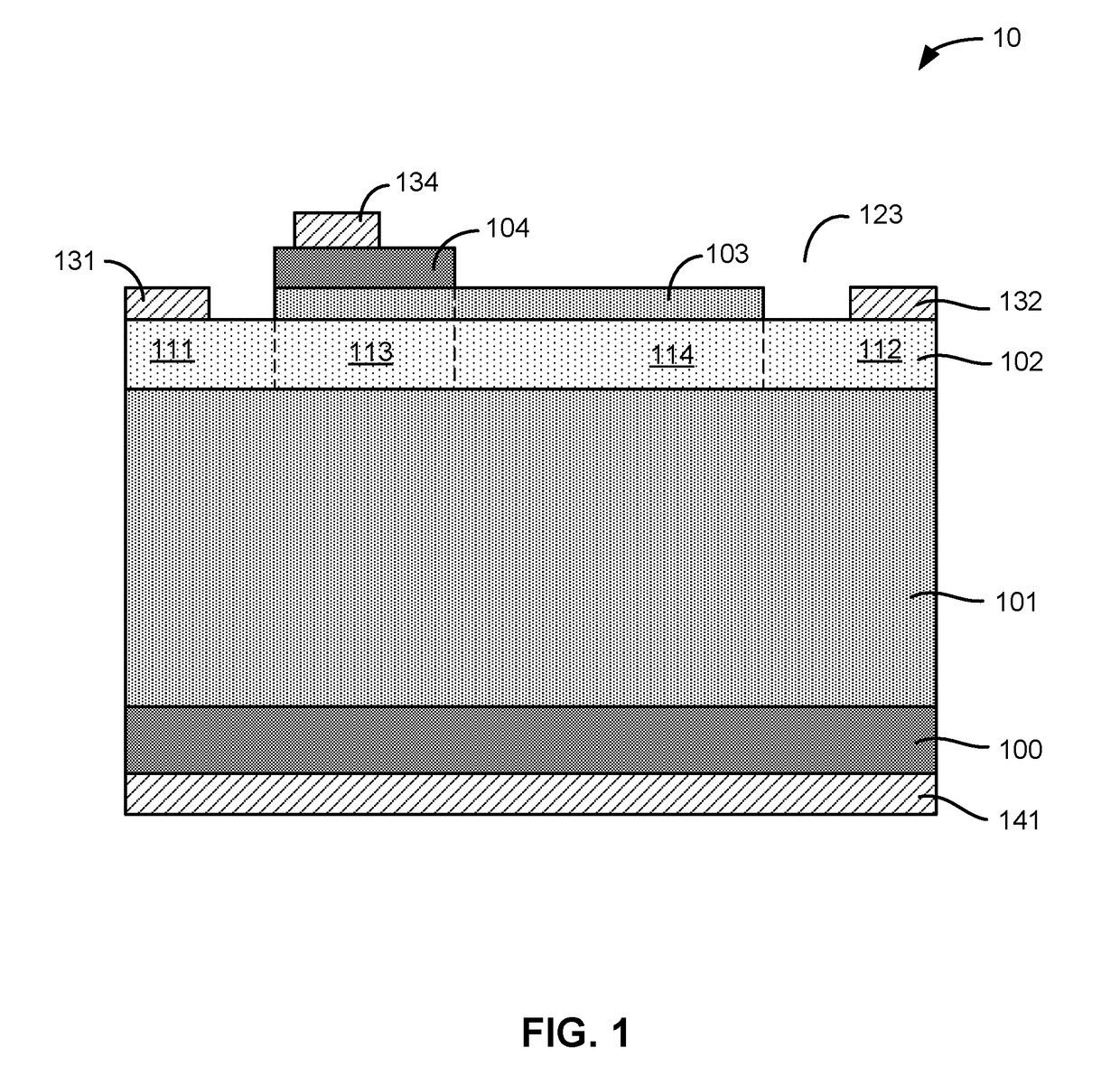

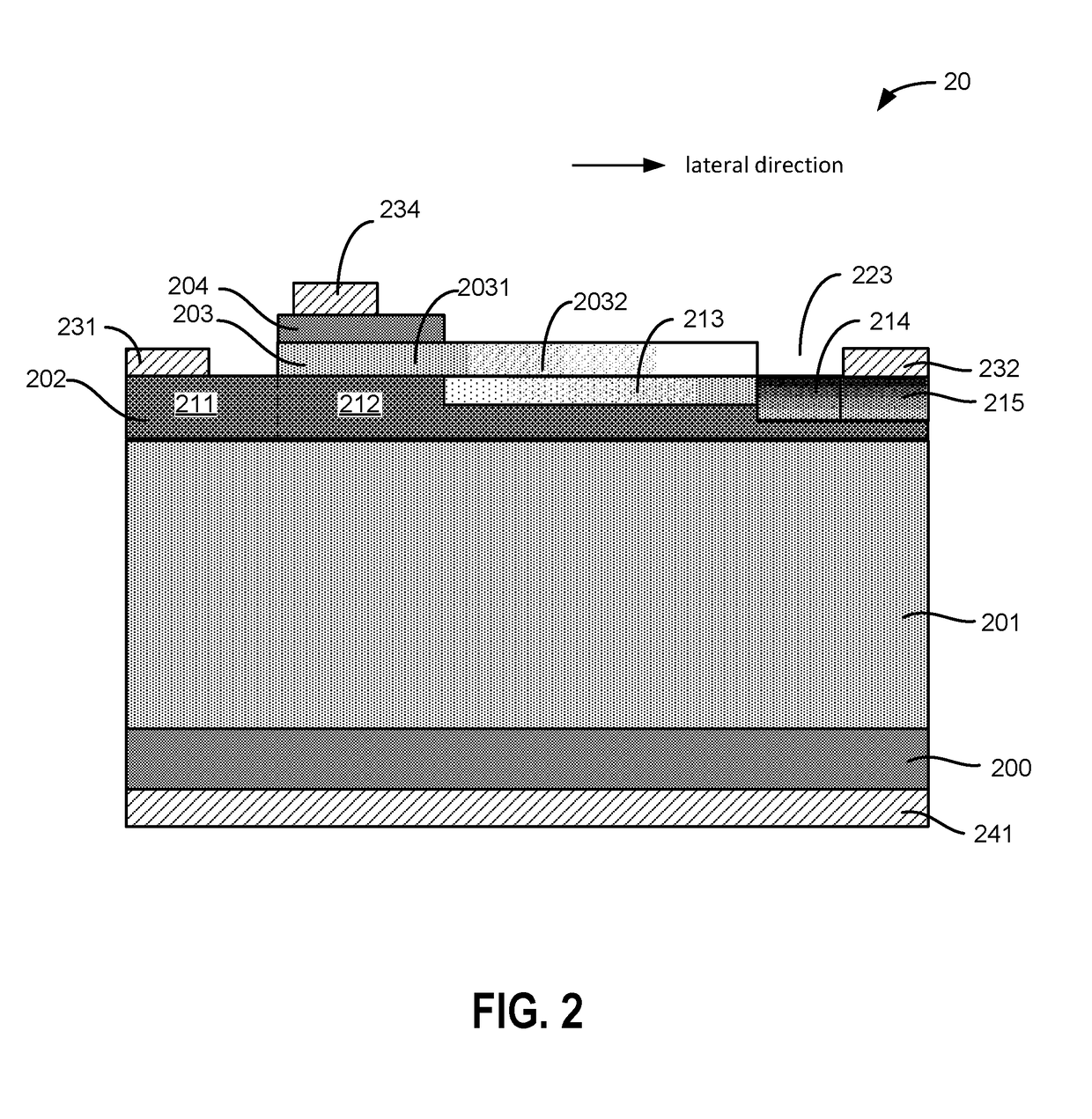

Lateral gallium nitride jfet with controlled doping profile

ActiveUS20180219106A1Reduce electric fieldImprove breakdown voltageSemiconductor devicesDopantElectrical conductor

A lateral junction field-effect transistor includes a substrate of a first conductivity type having a dopant concentration; a first semiconductor layer of the first conductivity type having a first dopant concentration lower than the dopant concentration and disposed on the substrate; a second semiconductor layer of a second conductivity type having a second dopant concentration, the second conductivity type being different from the first conductivity type, the second semiconductor layer disposed on the first semiconductor layer; a third semiconductor layer of the first conductivity type having a third dopant concentration, the third semiconductor layer disposed on the second semiconductor layer; a fourth semiconductor layer of the first conductivity type having a fourth dopant concentration lower than the dopant concentration, the fourth semiconductor layer disposed on the third semiconductor layer; a source region and a drain region disposed in the second semiconductor layer and on opposite sides of the third semiconductor layer.

Owner:QROMIS INC

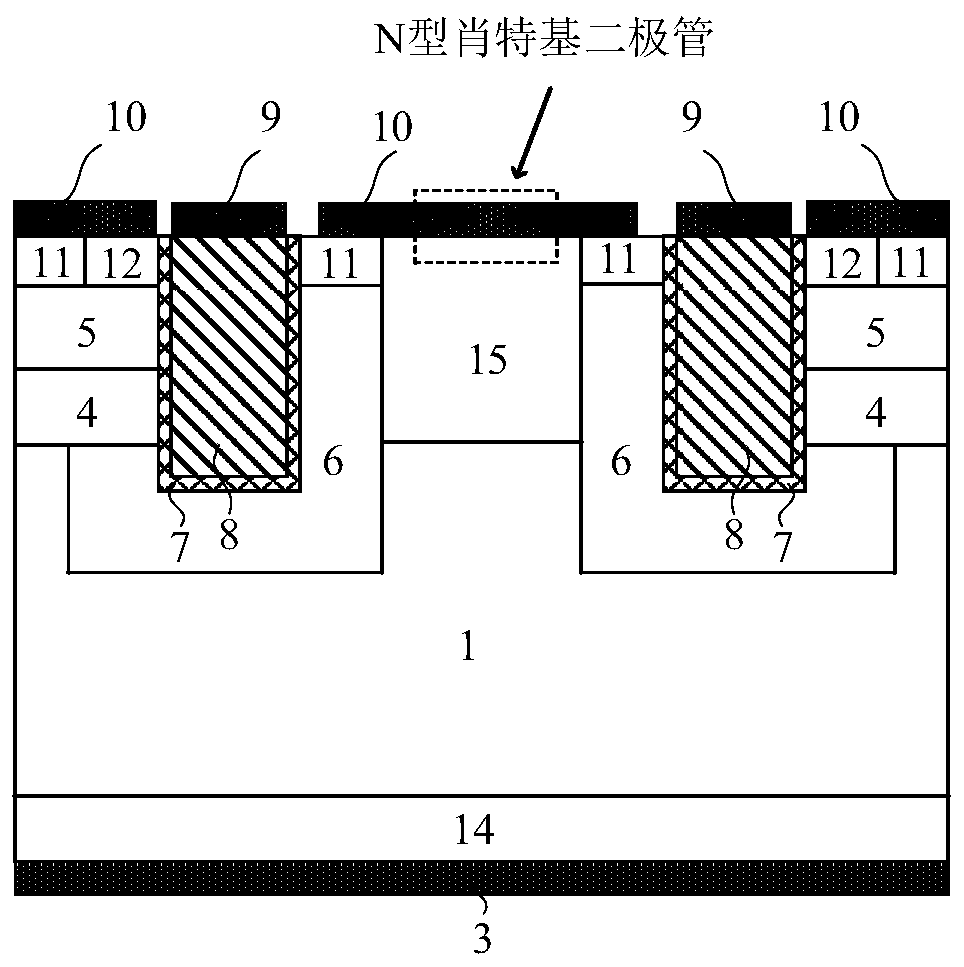

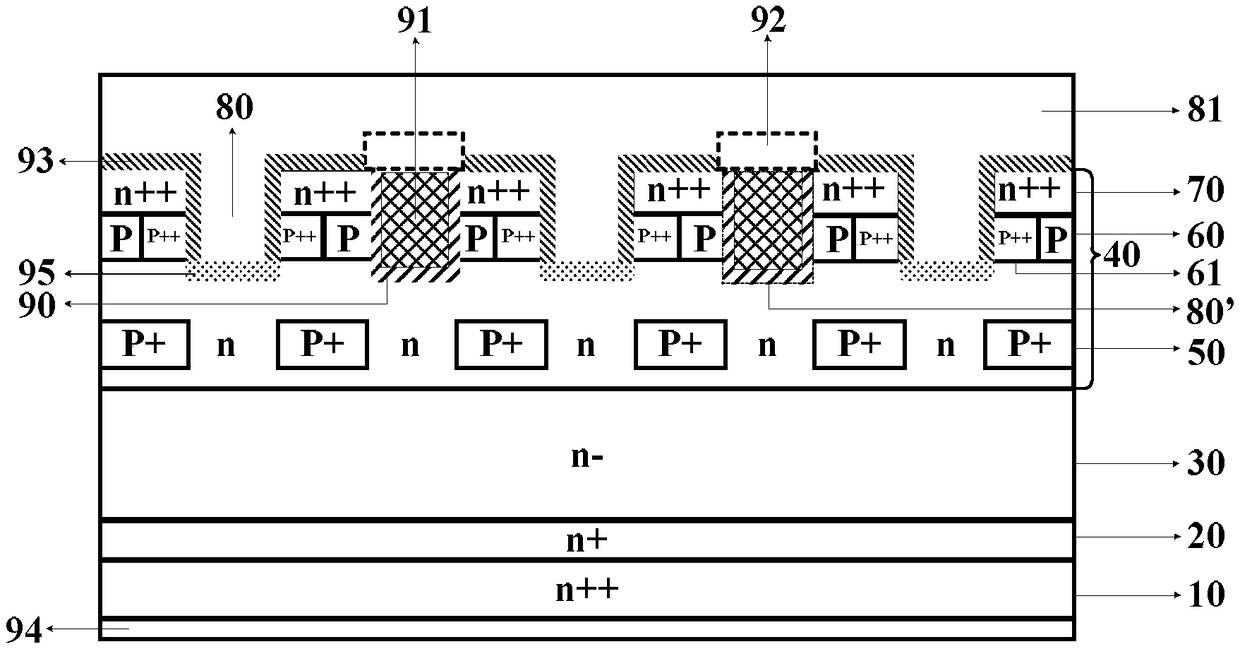

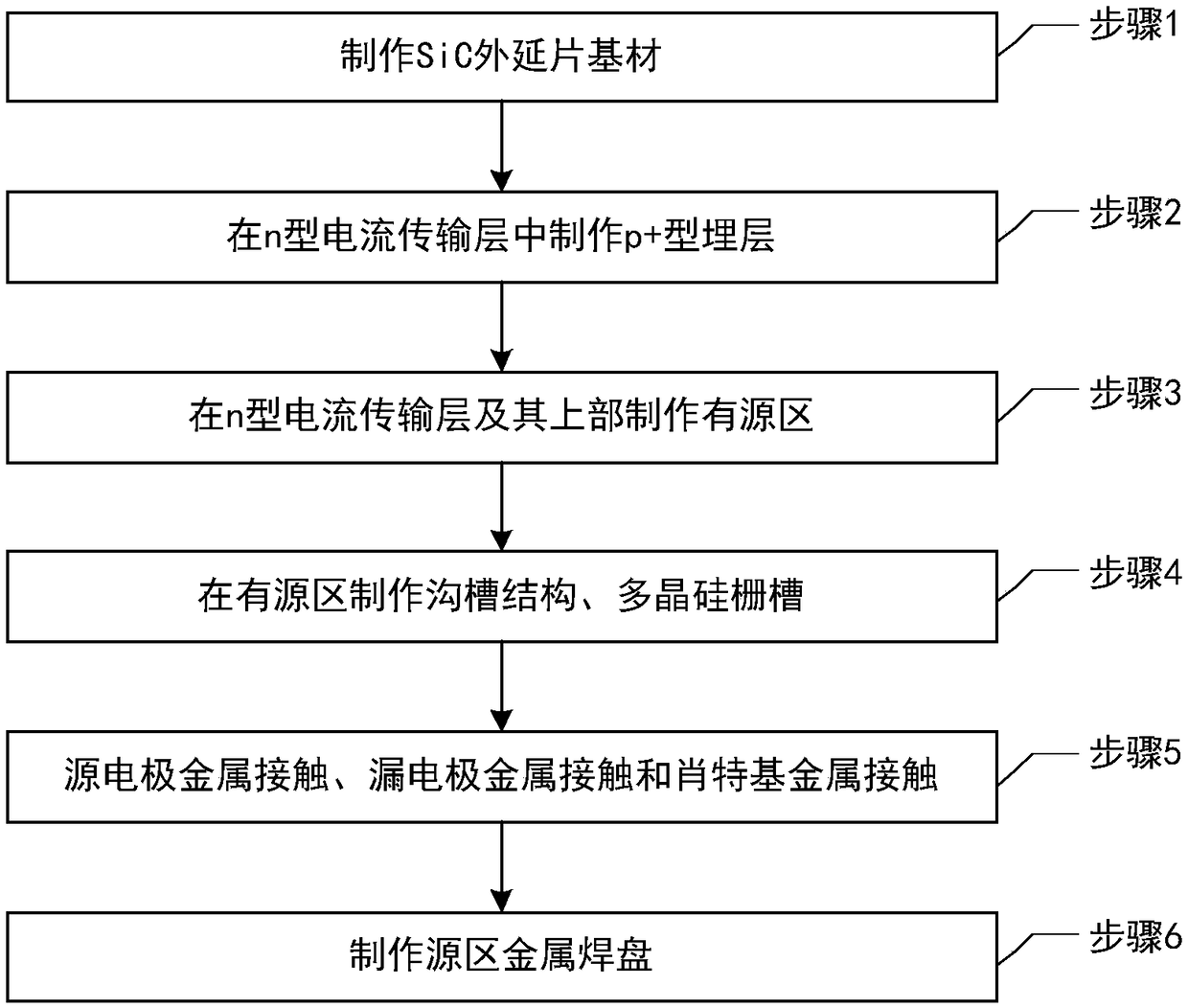

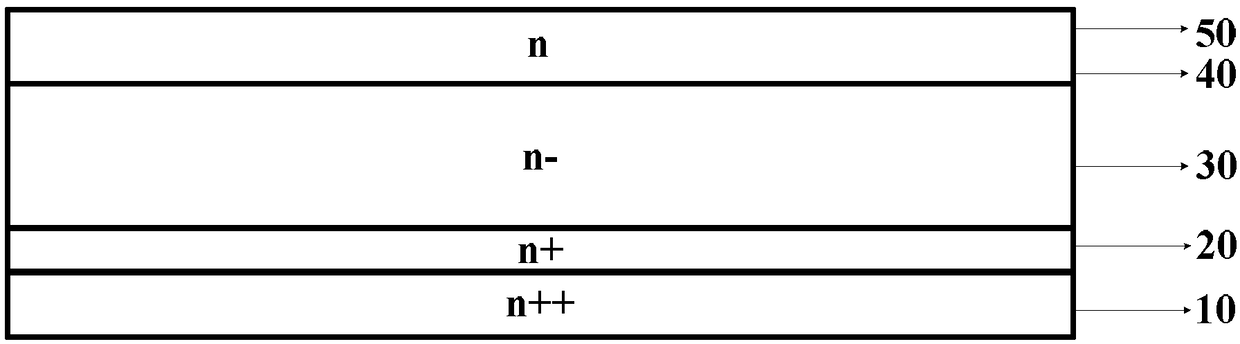

A structure of SiC UMOSFET integrated with SBD and a preparation method thereof

InactiveCN109065540AGood on-state characteristicsReduce dopingSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETField-effect transistor

The invention provides a silicon carbide trench gate metal oxide with semiconductor field effect transistor (SiC UMOSFET) structure integrated Schottky diode (SBD) and a method for manufacturing the same, The structure is characterized by, a p +-type bury layer (50) is formed on the n-type current transport layer (40) by implantation, and further an n-type current transport layer (40) is epitaxially formed so that the p +-type buried layer (50) floats, and the p +-type buried layer (50) can effectively reduce the electric field in the gate trench oxide and the electric field at the Schottky contact position in the blocking mode, so that the SBD integrated SiC UMOSFET has high blocking ability, and the high temperature and high field reliability of the device are greatly improved. At that same time, the relative position of the main trench (80), the main trench (80') and the p +-type buried layer (50) and the n-type current transport layer (40) are adjusted so that when the MOSFET is operated in the first quadrant, the conduction characteristic of the MOSFET does not degrade significantly; When the MOSFET is operated in the third quadrant, the conduction of the parasitic pn diode inthe MOSFET is effectively suppressed and the Schottky diode conduction mode is obtained. SiC UMOSFETs with integrated SBD have a lower total chip area than discrete SBD and MOSFET devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

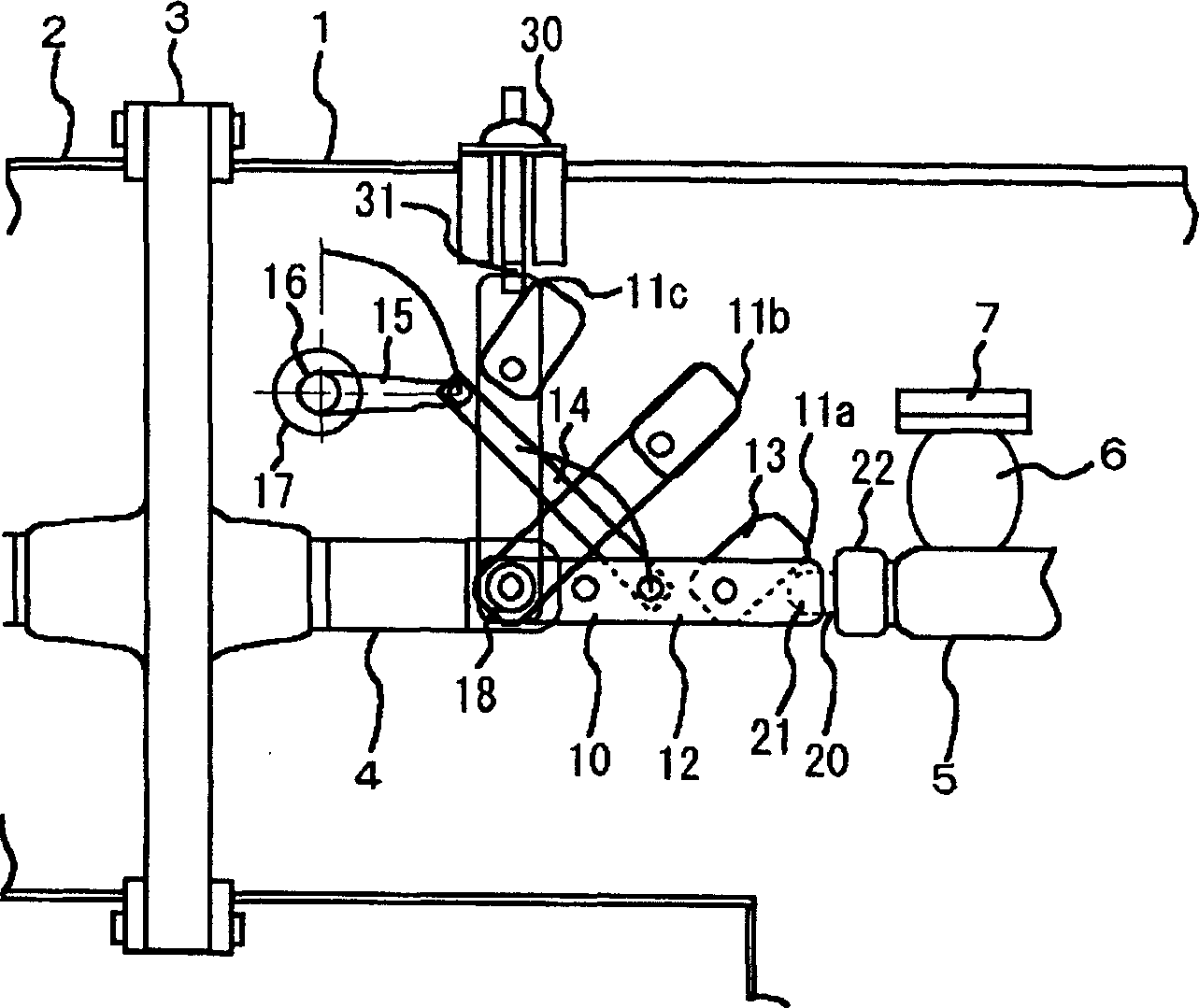

Switch device

InactiveCN1471208AGuaranteed Dielectric StrengthGood partition effectSwitches with movable electrical contactsAir-break switch detailsCharge currentExcitation current

In this switching device, a field relaxation electrode is provided on the movable contact of a disconnector so that the movable contact can be connected to a fixed contact by changing the position of the field relaxation electrode between an open state and a closed state. By providing the field relaxation electrode on the movable contact of the disconnector, the ground dielectric strength and interpolar dielectric strength in the open state position can be improved to reduce the size and cost of the equipment. By improving the charging current interrupting performance and exciting current interrupting performance, the applicable range on system of the equipment can be extended.

Owner:HITACHI LTD

Schottky barrier diode device structure and manufacturing method thereof

ActiveCN103943688AImprove reverse breakdown voltageReduce electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsDielectric layer

The invention provides a Schottky barrier diode device structure and a manufacturing method of the structure. The device structure comprises a first conductive type substrate, first conductive type epitaxial layers which are combined on the surface of the first conductive type substrate, a plurality of groove structures, second conductive type doping areas, a Schottky metal layer and an upper electrode. The groove structures comprise grooves formed in the first conductive type epitaxial layers, dielectric layers combined on the surfaces of the grooves, and conductive materials, the grooves are filled with the conductive materials, the second conductive type doping areas are formed at the positions, arranged on two sides of the groove structures, of the surfaces of the first conductive type epitaxial layers, and the Schottky metal layer is formed on the surfaces of the first conductive type epitaxial layers. The doping areas are added on two sides of the groove structures, the P / N knot is introduced, electric fields of the areas are reduced, and therefore reverse leakage currents are reduced. Meanwhile, JFET structures are introduced between the doping areas, reverse breakdown voltages of the Schottky barrier diode device structure are improved, and the reverse leakage currents are reduced.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

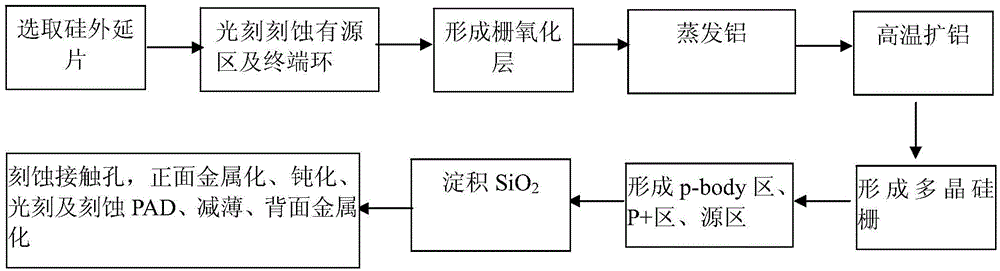

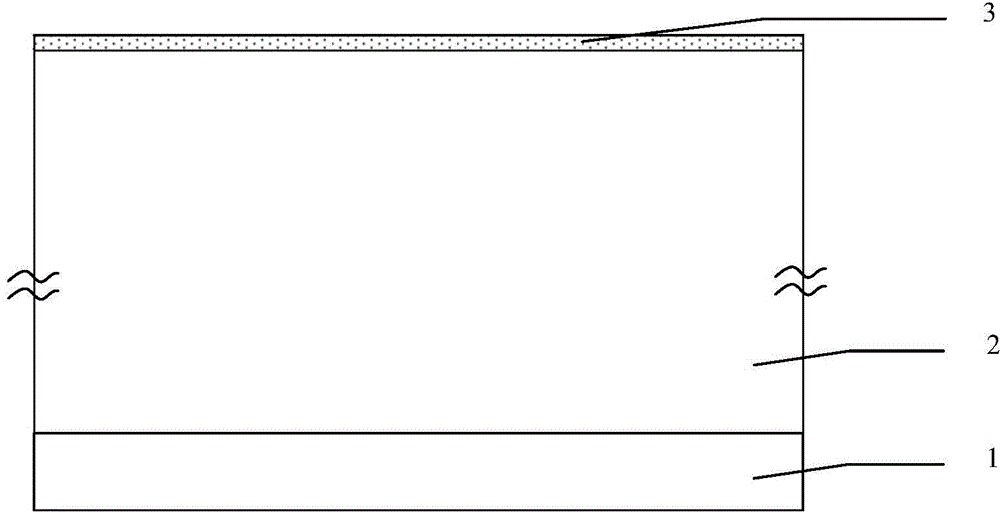

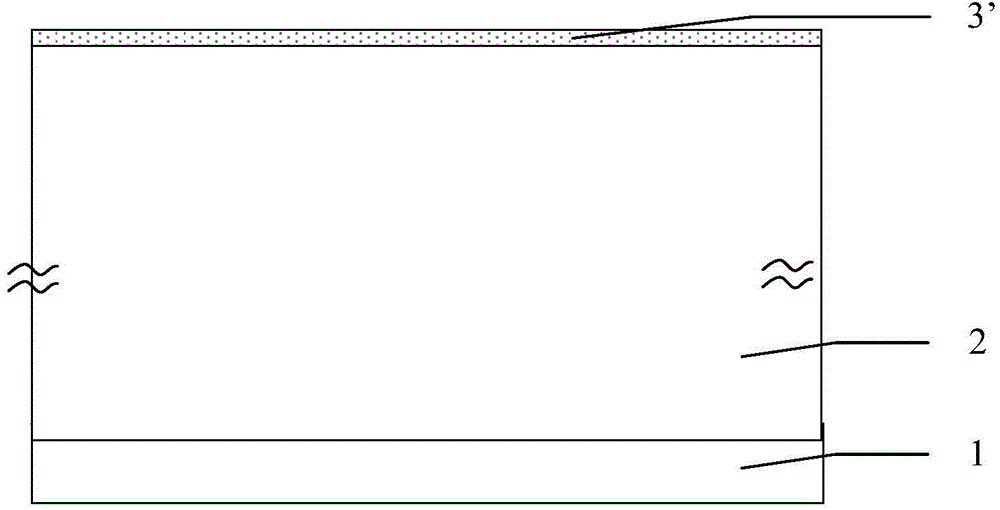

Manufacture method of VDMOS device with irradiation resistance

ActiveCN104576398ASimple processManufacturing process compatibleSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate oxide

The invention discloses a manufacture method of a VDMOS device with irradiation resistance. The manufacture method of the VDMOS device is characterized by forming a gate oxide layer, evaporating aluminum on the gate oxide layer, and then diffusing aluminum at high temperature to form a gate medium of an Si-O-Al structure. Positive charges accumulated in the gate medium can be reduced when the VDMOS device is irradiated; the resistance to total dose irradiation of the device is improved; meanwhile, compared with the conventional silicon dioxide gate medium, the gate medium of the Si-O-Al structure is higher in dielectric constant; the resistance to single event gate rupture of the device can be improved. The manufacture method can be used for effectively overcoming the contradiction of requirements on the thickness of the resistance to total dose irradiation and the single event gate rupture and optimizing the resistance to total dose irradiation and the single event gate rupture at the same time; the process is simple; the resistance to the irradiation of the VDMOS device is improved.

Owner:BEIJING MXTRONICS CORP +1

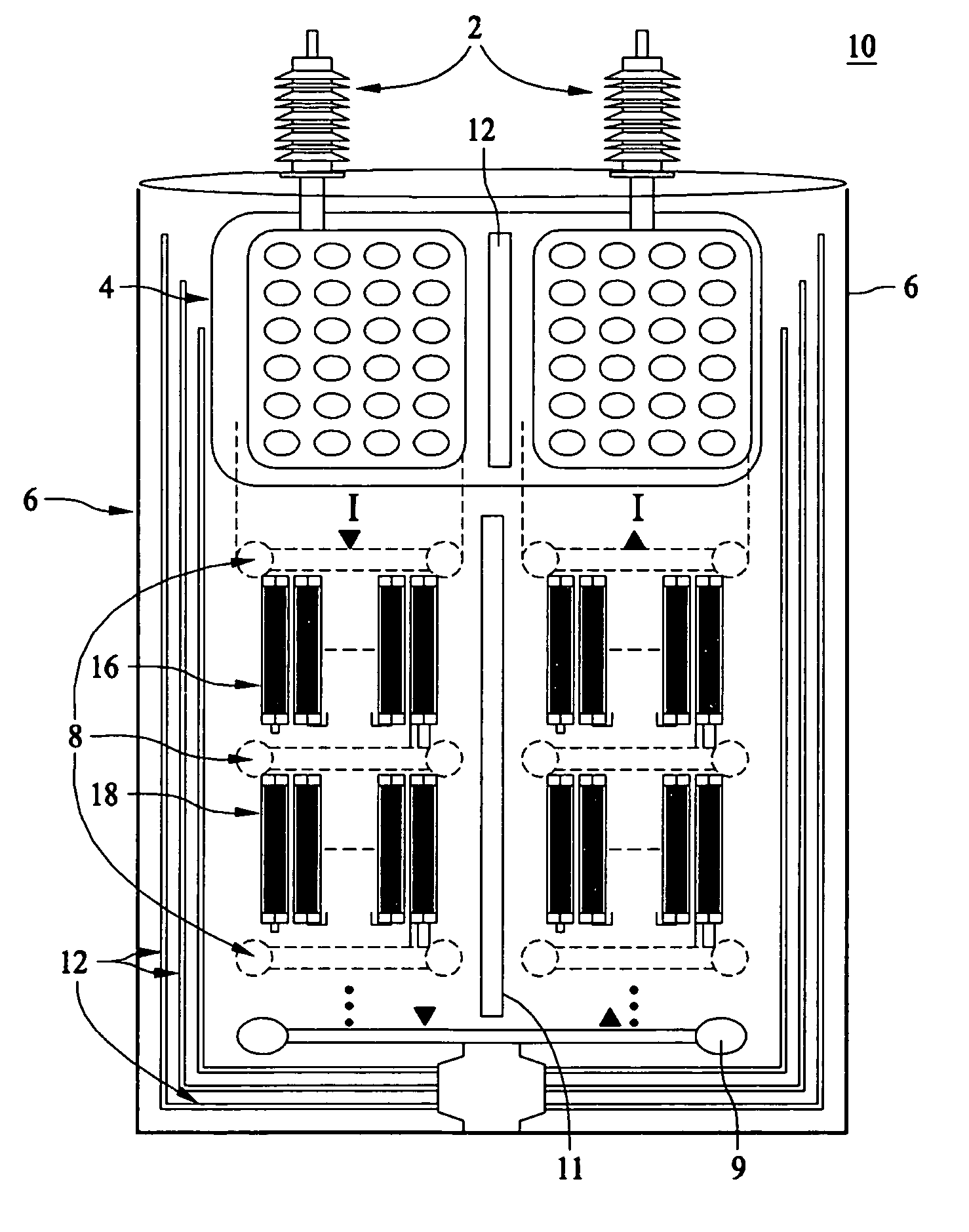

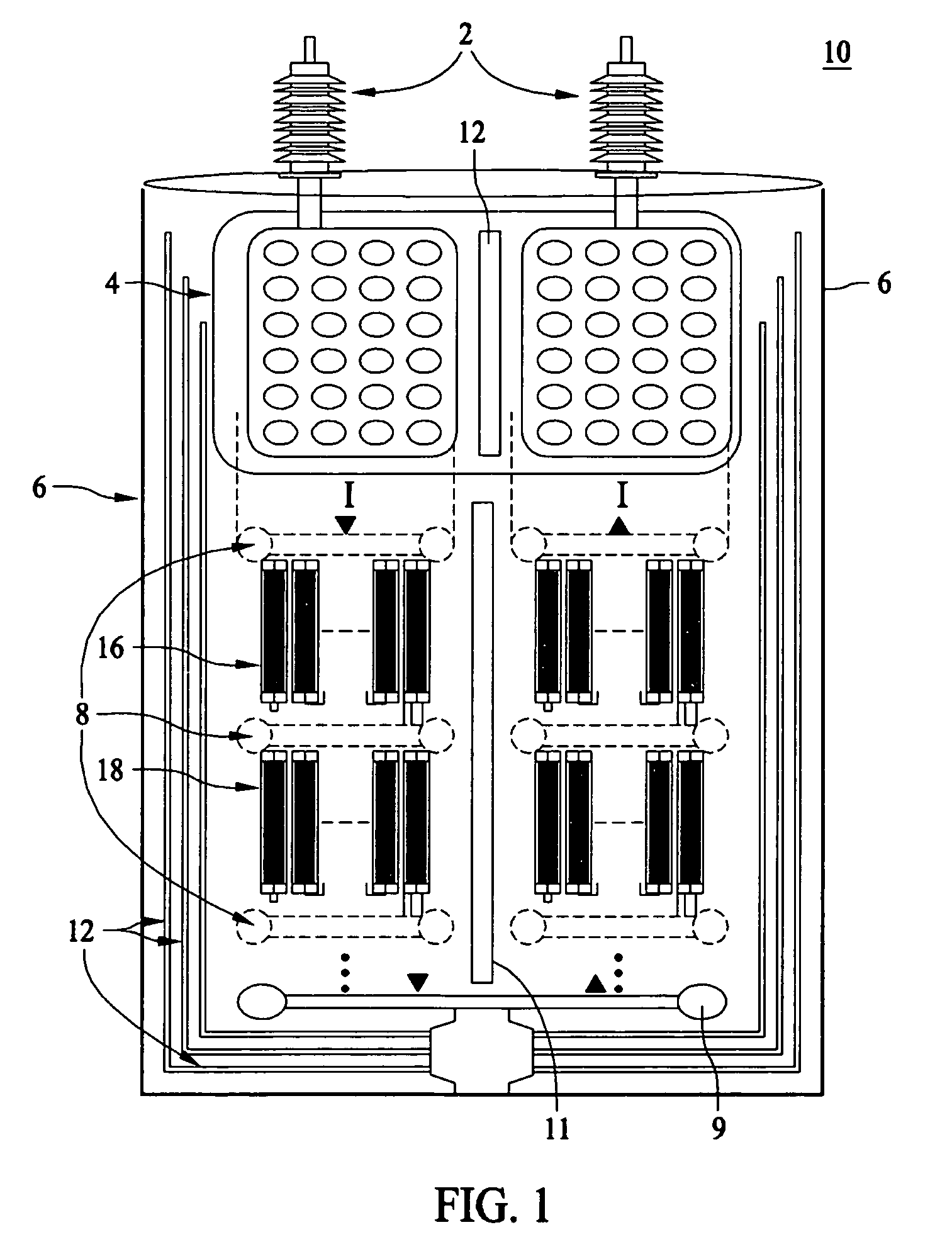

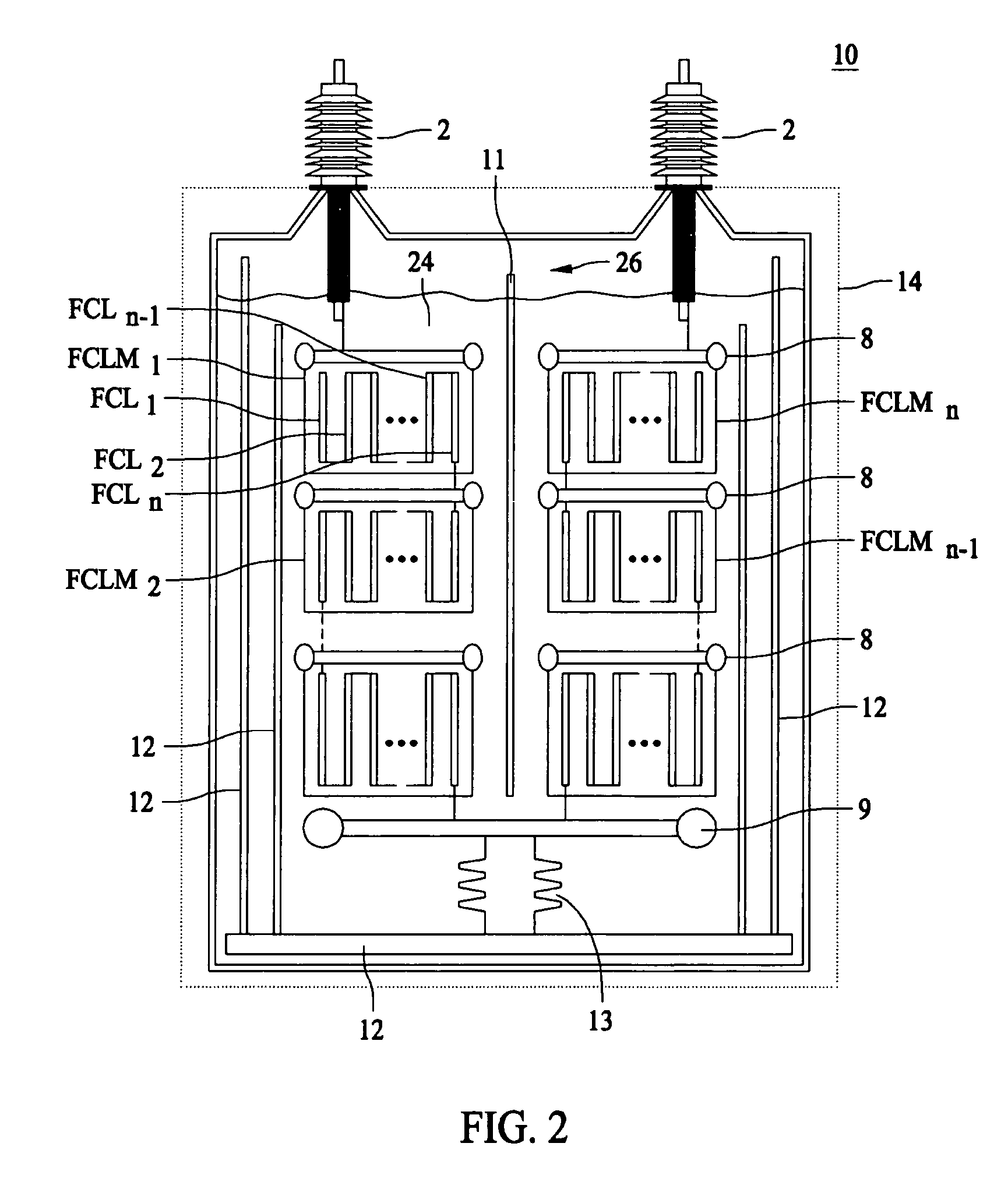

High voltage design structure for high temperature superconducting device

InactiveUS20070023680A1Reduce electric fieldReduce stressSuperconductors/hyperconductorsMaterial analysis by optical meansHigh temperature superconductingEngineering

In accordance with the present invention, modular corona shields are employed in a HTS device to reduce the electric field surrounding the HTS device. In a exemplary embodiment a fault current limiter module in the insulation region of a cryogenic cooling system has at least one fault current limiter set which employs a first corona shield disposed along the top portion of the fault current limiter set and is electrically coupled to the fault current limiter set. A second corona shield is disposed along the bottom portion of the fault current limiter set and is electrically coupled to the fault current limiter set. An insulation barrier is disposed within the insulation region along at least one side of the fault current limiter set. The first corona shield and the second corona shield act together to reduce the electric field surrounding the fault limiter set when voltage is applied to the fault limiter set.

Owner:SUPERPOWER INC

Partial SOI (silicon on insulator) traverse double-diffused device

ActiveCN102082169AEfficient deliveryReduce doping concentrationSemiconductor devicesNitrogenHeating effect

The invention relates to the SOI (silicon on insulator) technology. The invention solves the problem that the heating effect of the existing conventional SOI device is obvious, and provides a partial SOI traverse double-diffused device. The technical scheme of the invention is summarized as follows: one end of an oxide buried layer of the partial SOI traverse double-diffused device is arranged below a source electrode and is contacted with the edge of the device, the horizontal distance between the other end of the oxide buried layer and a drain type II impurity ohm contact area is not less than zero, a PN (phosphorus-nitrogen) junction is formed by the way that a type I impurity substrate is contacted with the silicon layer of the type II impurity top layer between the other end of the oxide buried layer and the edge of the device below the drain. The partial SOI traverse double-diffused device has the beneficial effects that the oxide buried layer is provided with an opening below the drain, the heat produced by an SOI device can be effectively transferred, and the partial SOI traverse double-diffused device is applicable to SOI devices.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD