Patents

Literature

86 results about "Heterojunction diode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

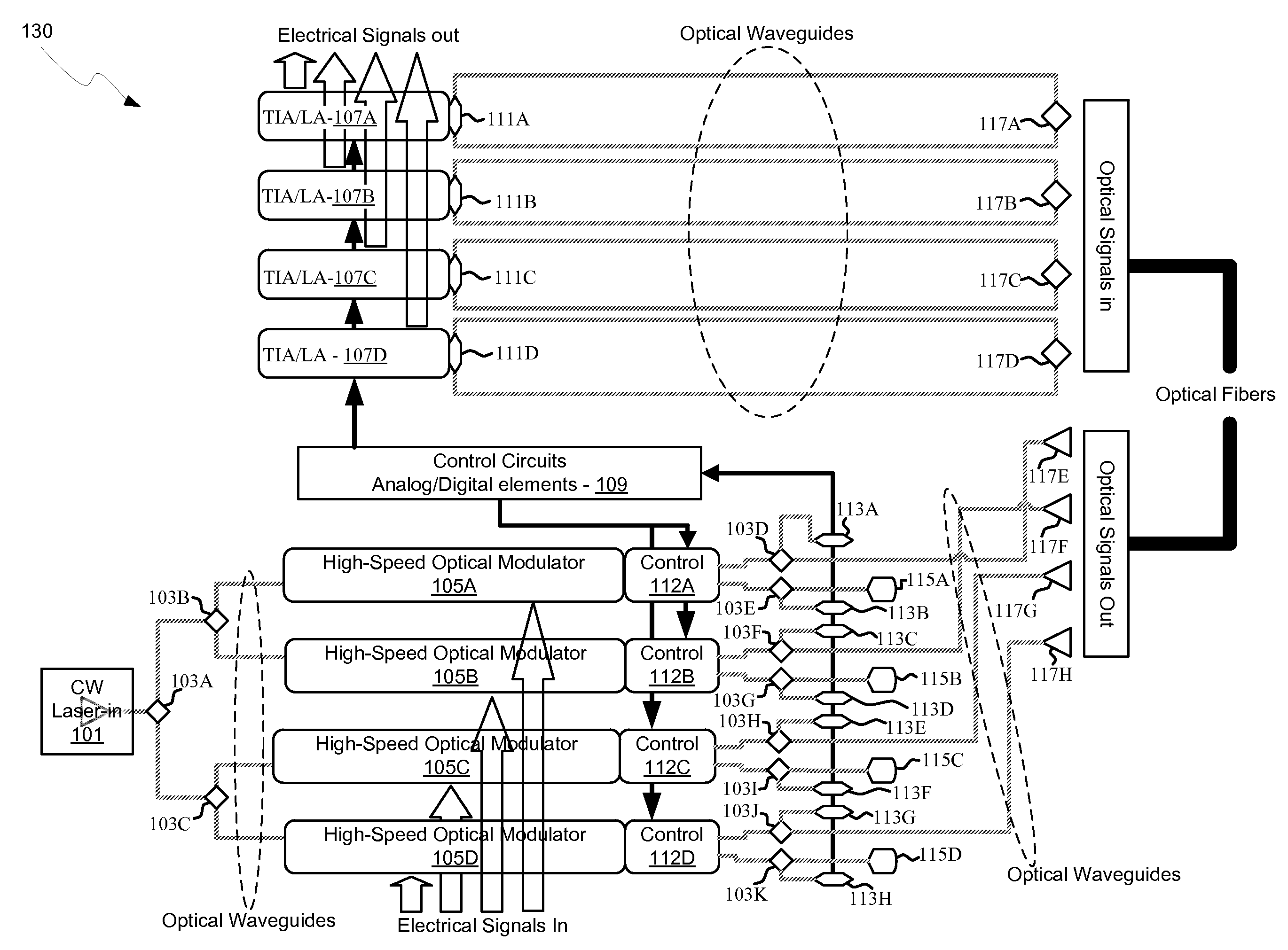

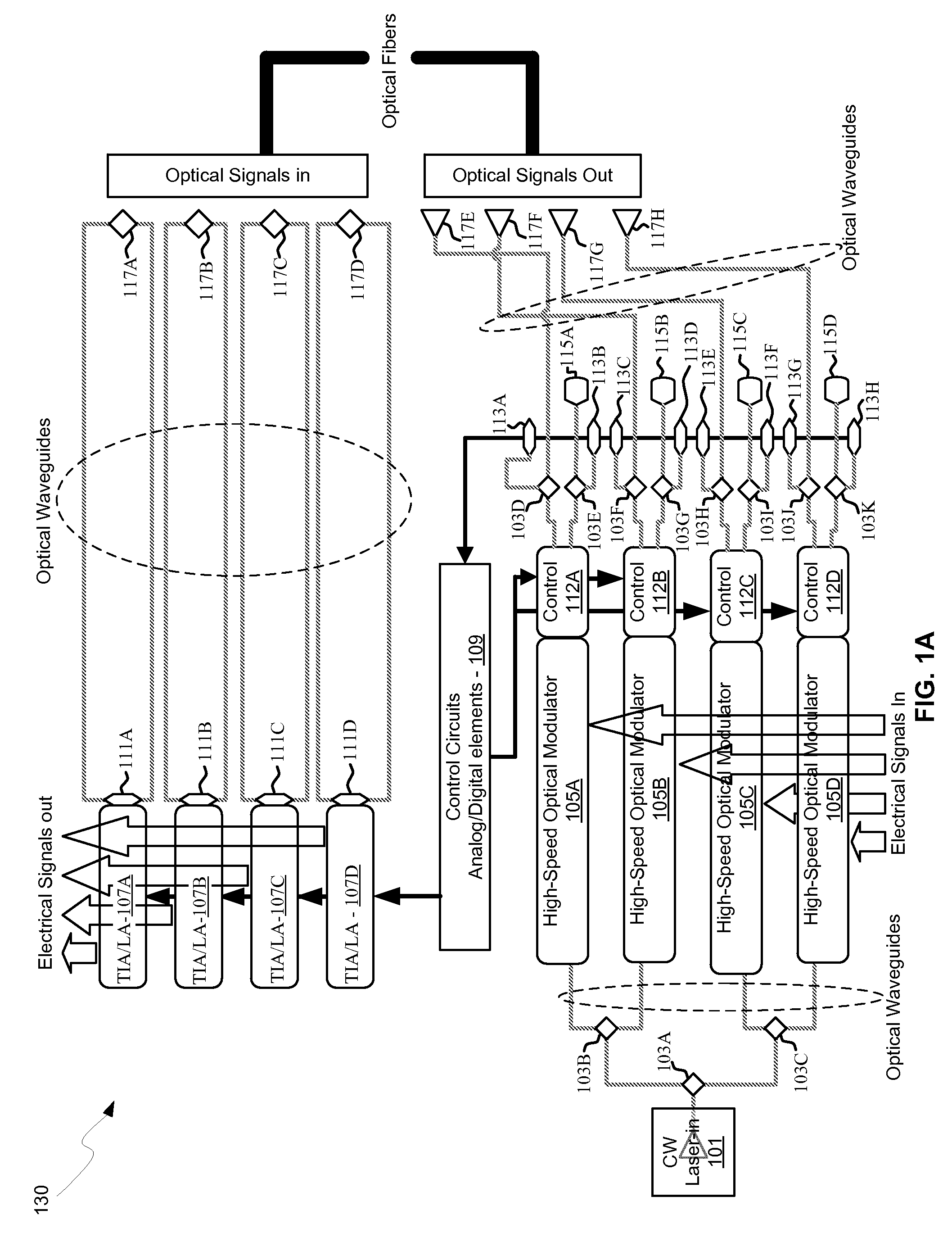

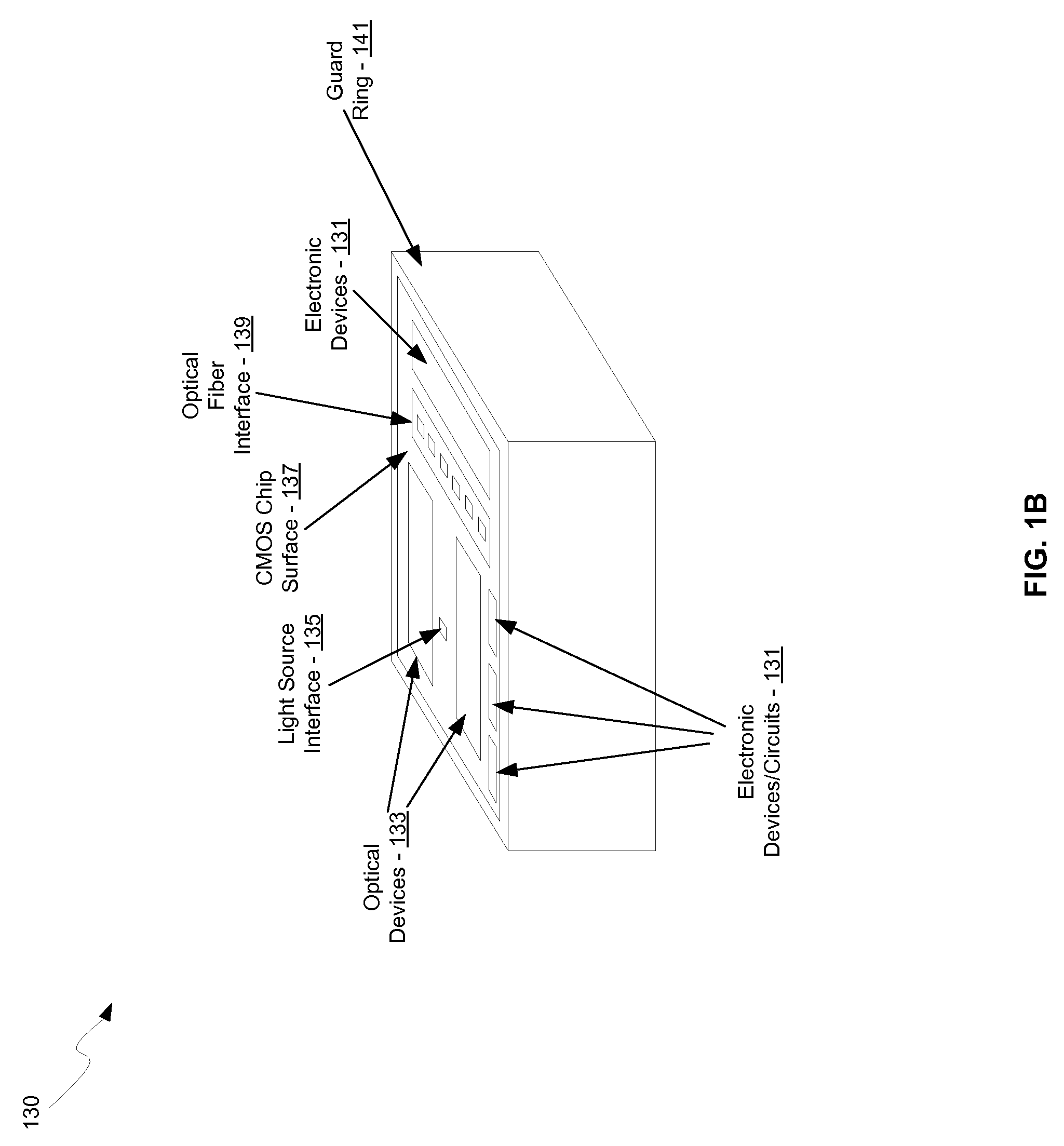

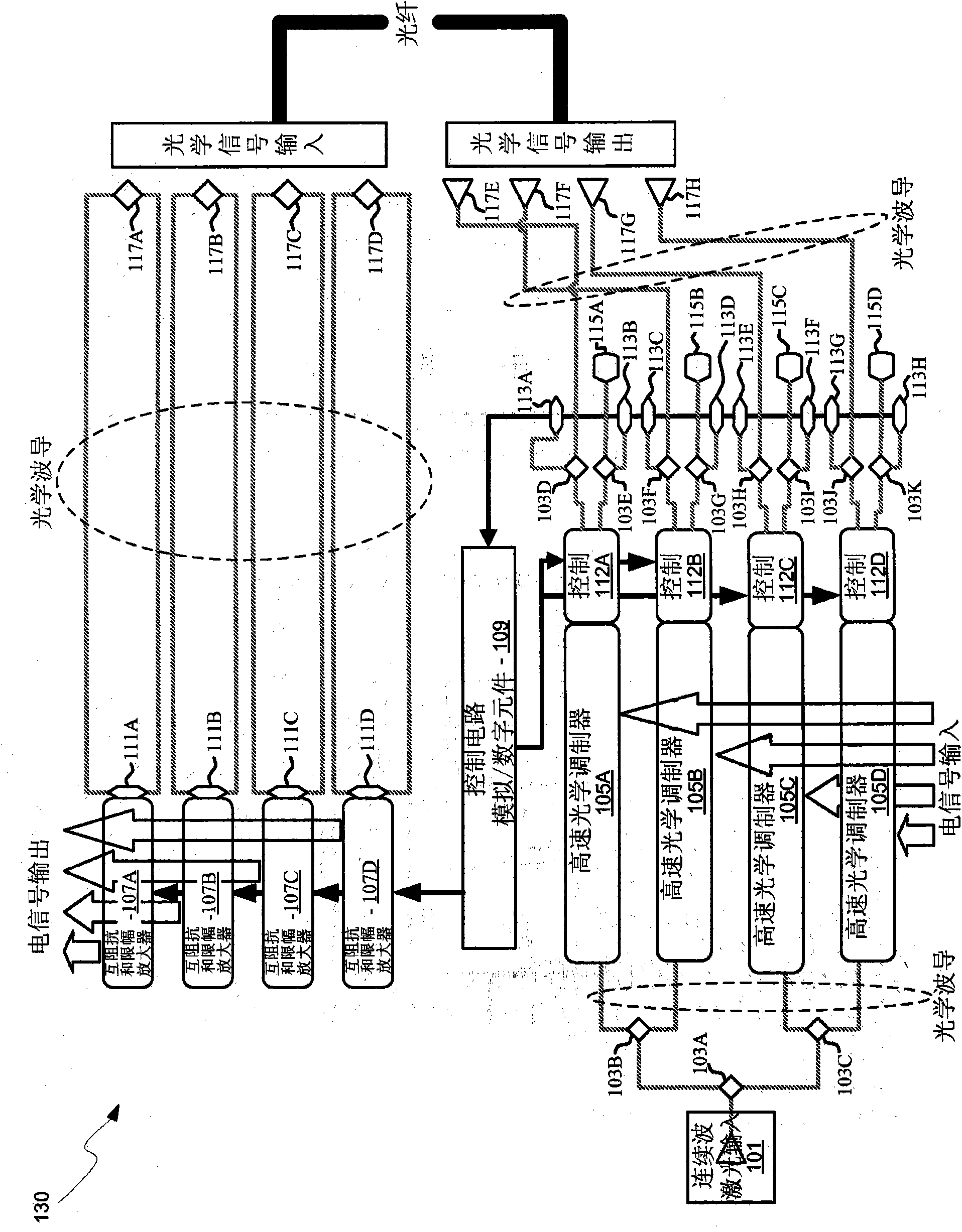

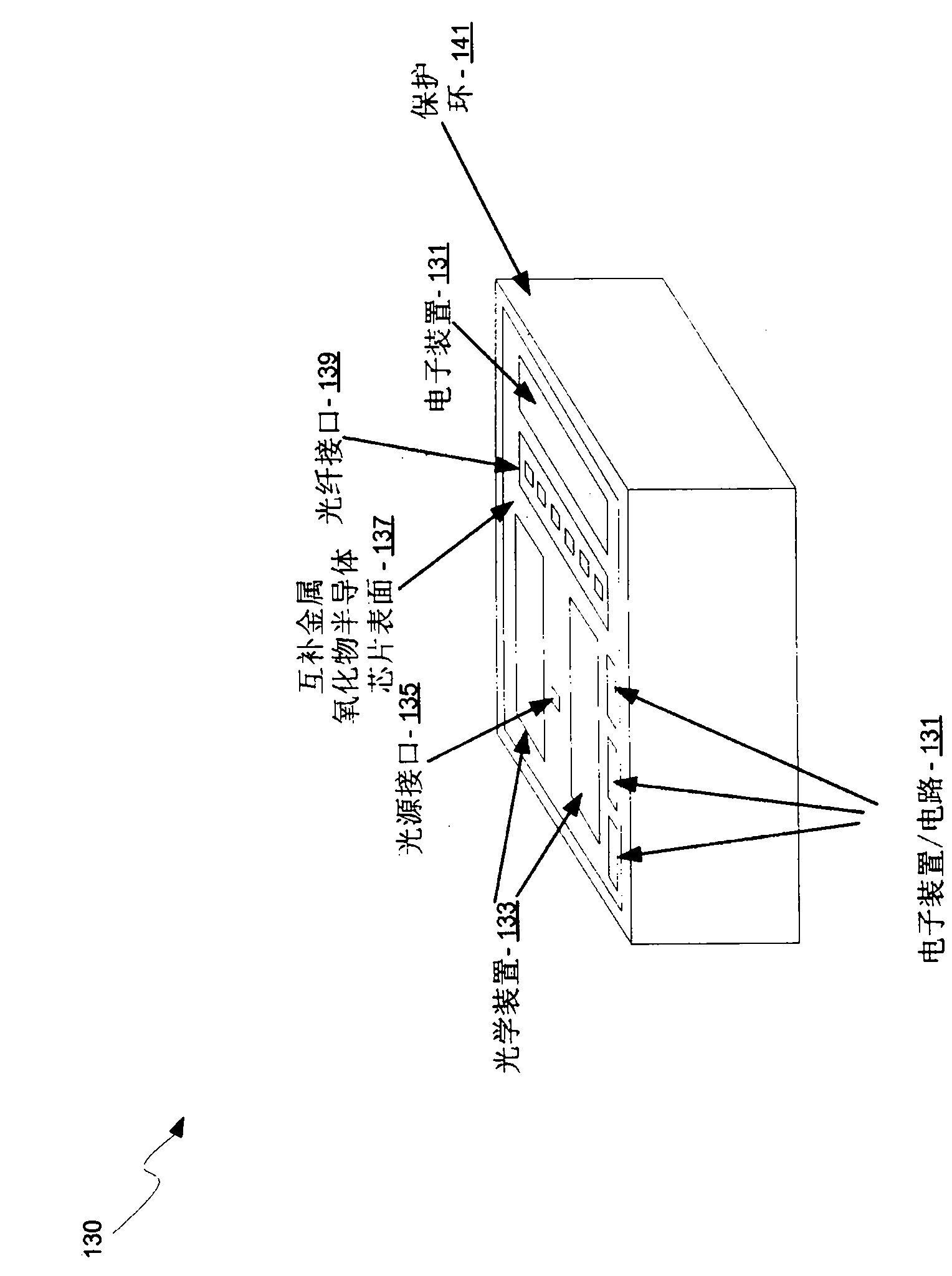

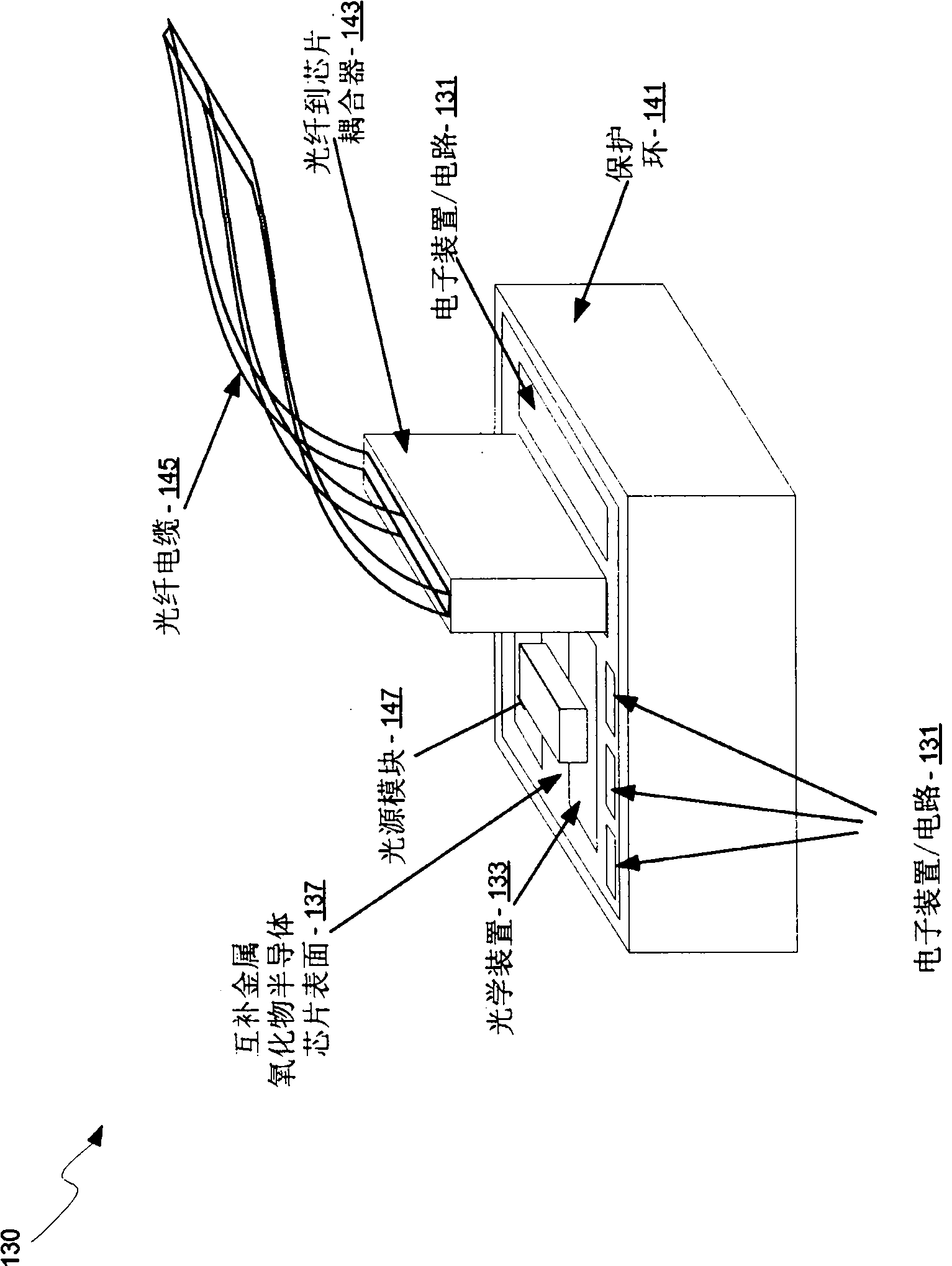

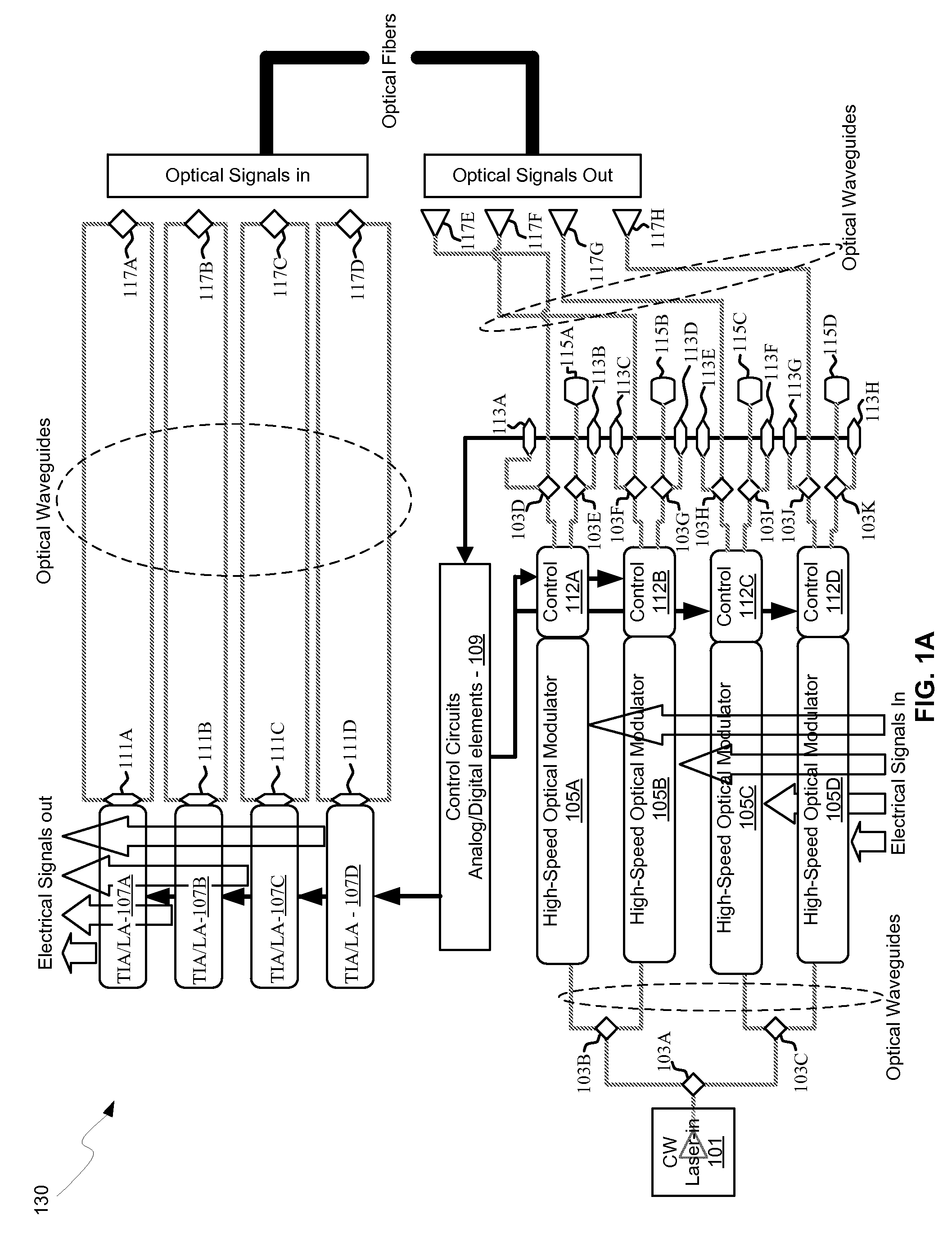

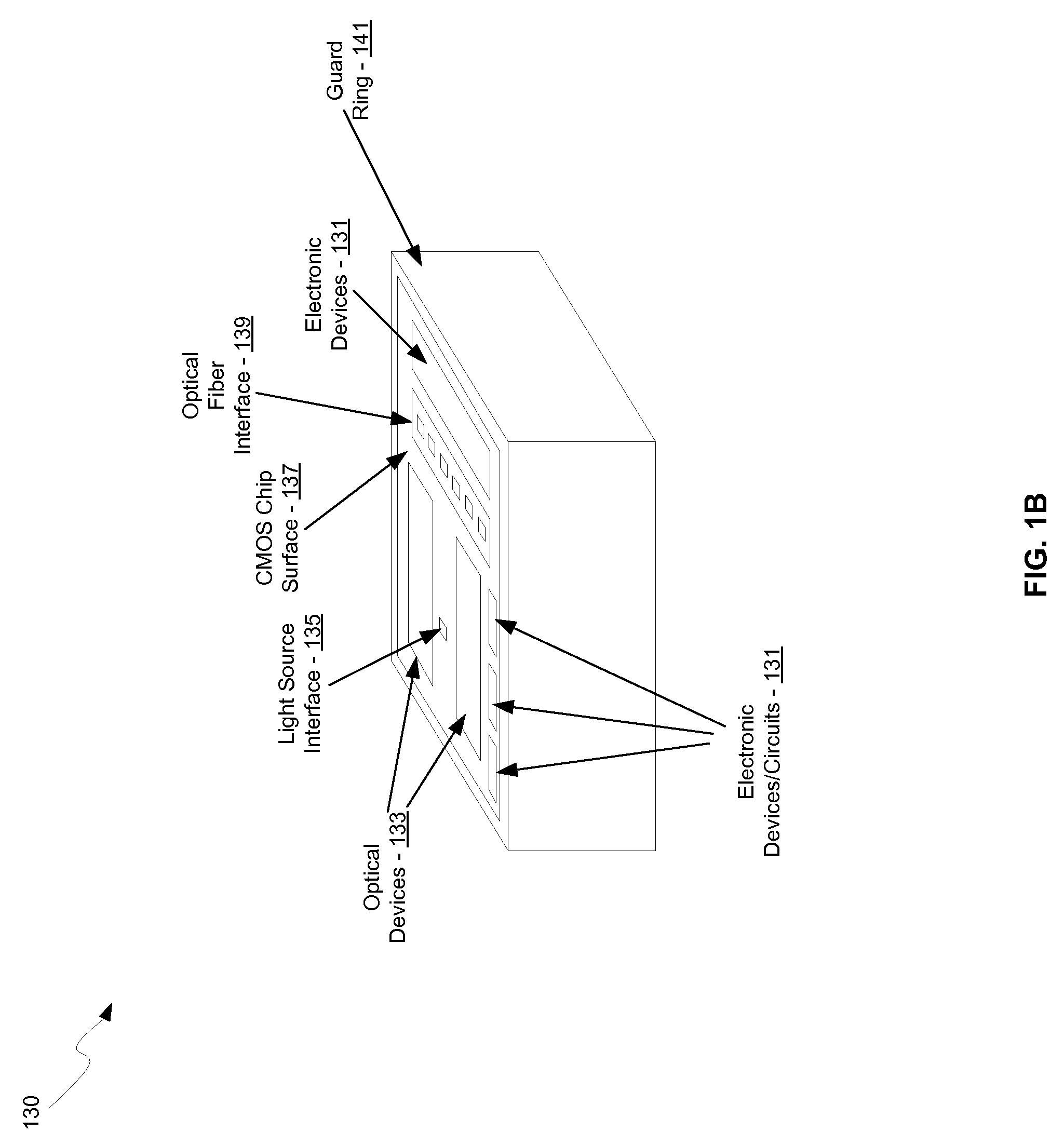

Method and system for optoelectronics transceivers integrated on a CMOS chip

Methods and systems for optoelectronics transceivers integrated on a CMOS chip are disclosed and may include receiving optical signals from optical fibers via grating couplers on a top surface of a CMOS chip, which may include a guard ring. Photodetectors may be integrated in the CMOS chip. A CW optical signal may be received from a laser source via grating couplers, and may be modulated using optical modulators, which may be Mach-Zehnder and / or ring modulators. Circuitry in the CMOS chip may drive the optical modulators. The modulated optical signal may be communicated out of the top surface of the CMOS chip into optical fibers via grating couplers. The received optical signals may be communicated between devices via waveguides. The photodetectors may include germanium waveguide photodiodes, avalanche photodiodes, and / or heterojunction diodes. The CW optical signal may be generated using an edge-emitting and / or a vertical-cavity surface emitting semiconductor laser.

Owner:CISCO TECH INC

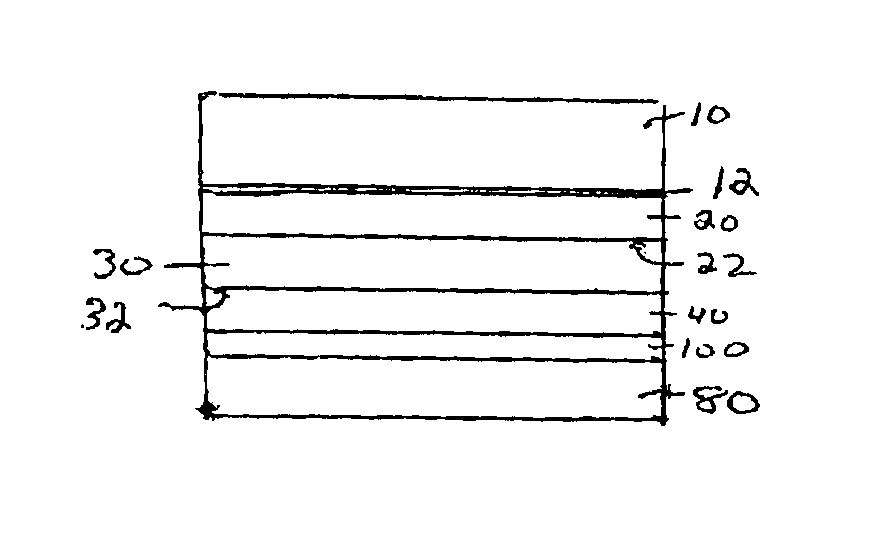

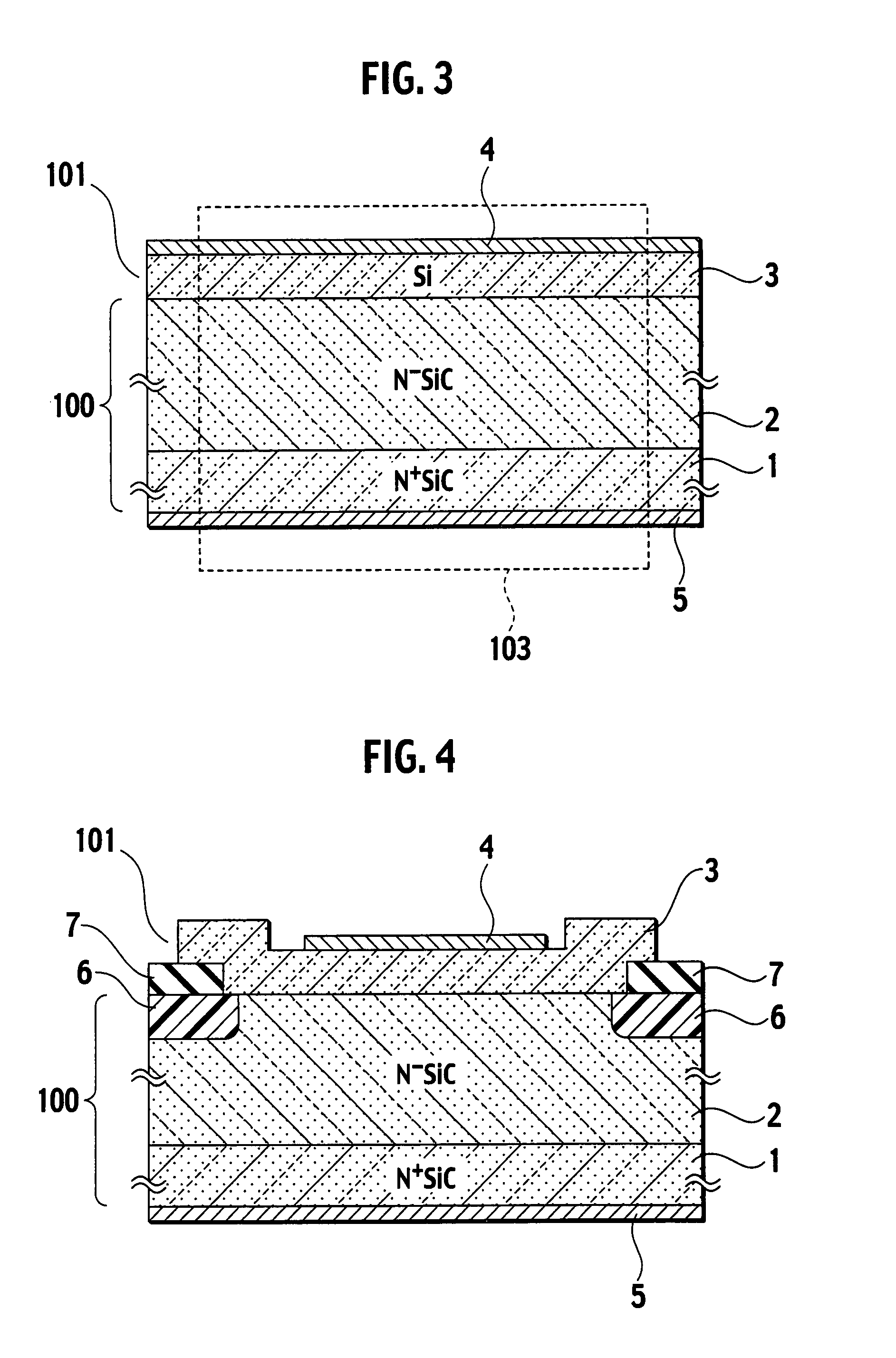

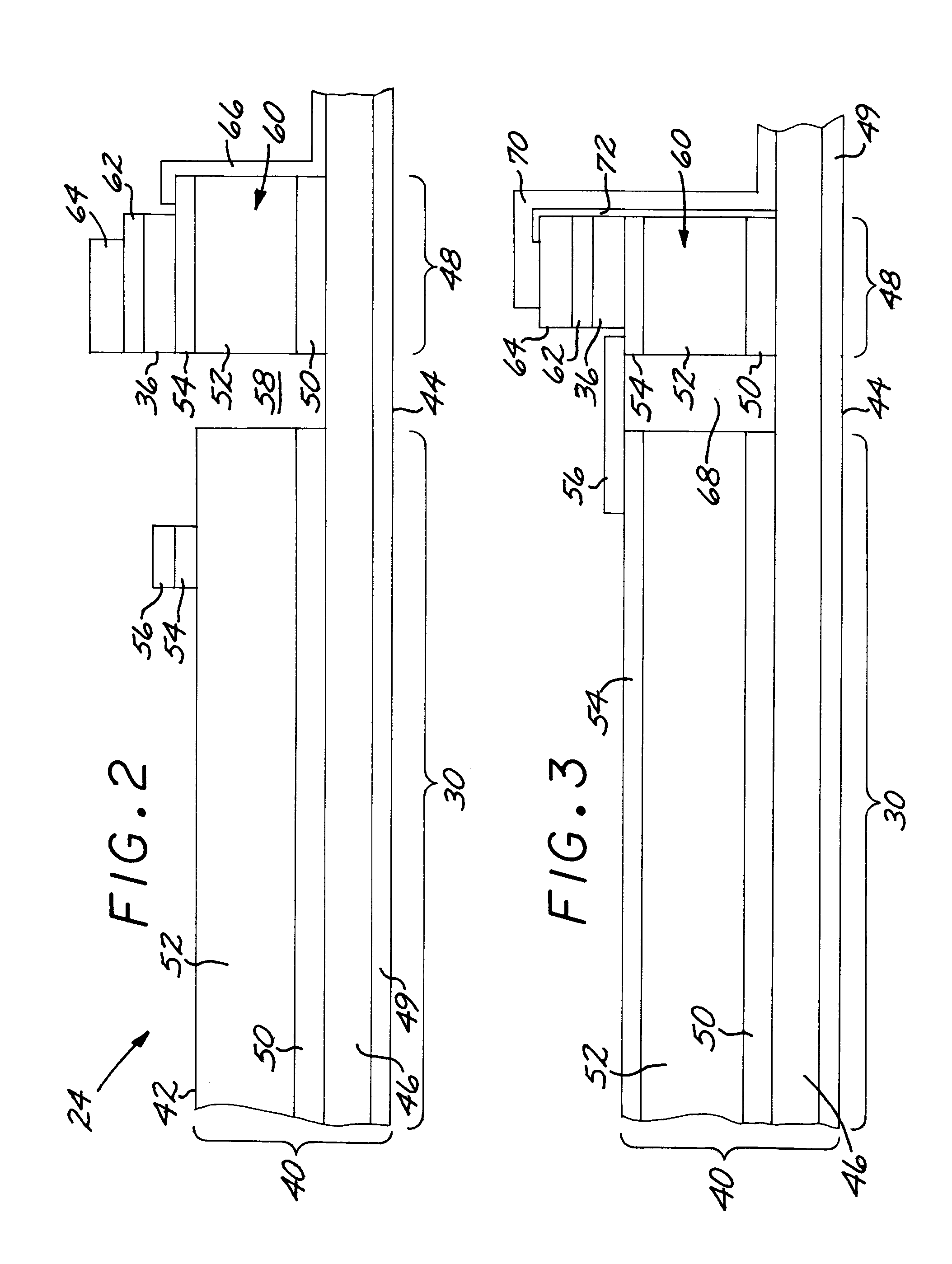

Layer transfer of low defect SiGe using an etch-back process

InactiveUS6890835B1Reduce defectsQuality improvementTransistorPolycrystalline material growthThermal treatmentSemiconductor

A method for forming strained Si or SiGe on relaxed SiGe on insulator (SGOI) or a SiGe on Si heterostructure is described incorporating growing epitaxial Si1-yGey layers on a semiconductor substrate, smoothing surfaces by Chemo-Mechanical Polishing, bonding two substrates together via thermal treatments and transferring the SiGe layer from one substrate to the other via highly seletive etching using SiGe itself as the etch-stop. The transferred SiGe layer may have its upper surface smoothed by CMP for epitaxial deposition of relaxed Si1-yGey, and strained Si1-yGey depending upon composition, strained Si, strained SiC, strained Ge, strained GeC, and strained Si1-yGeyC or a heavily doped layer to make electrical contacts of the SiGe / Si heterojunction diodes.

Owner:GLOBALFOUNDRIES INC

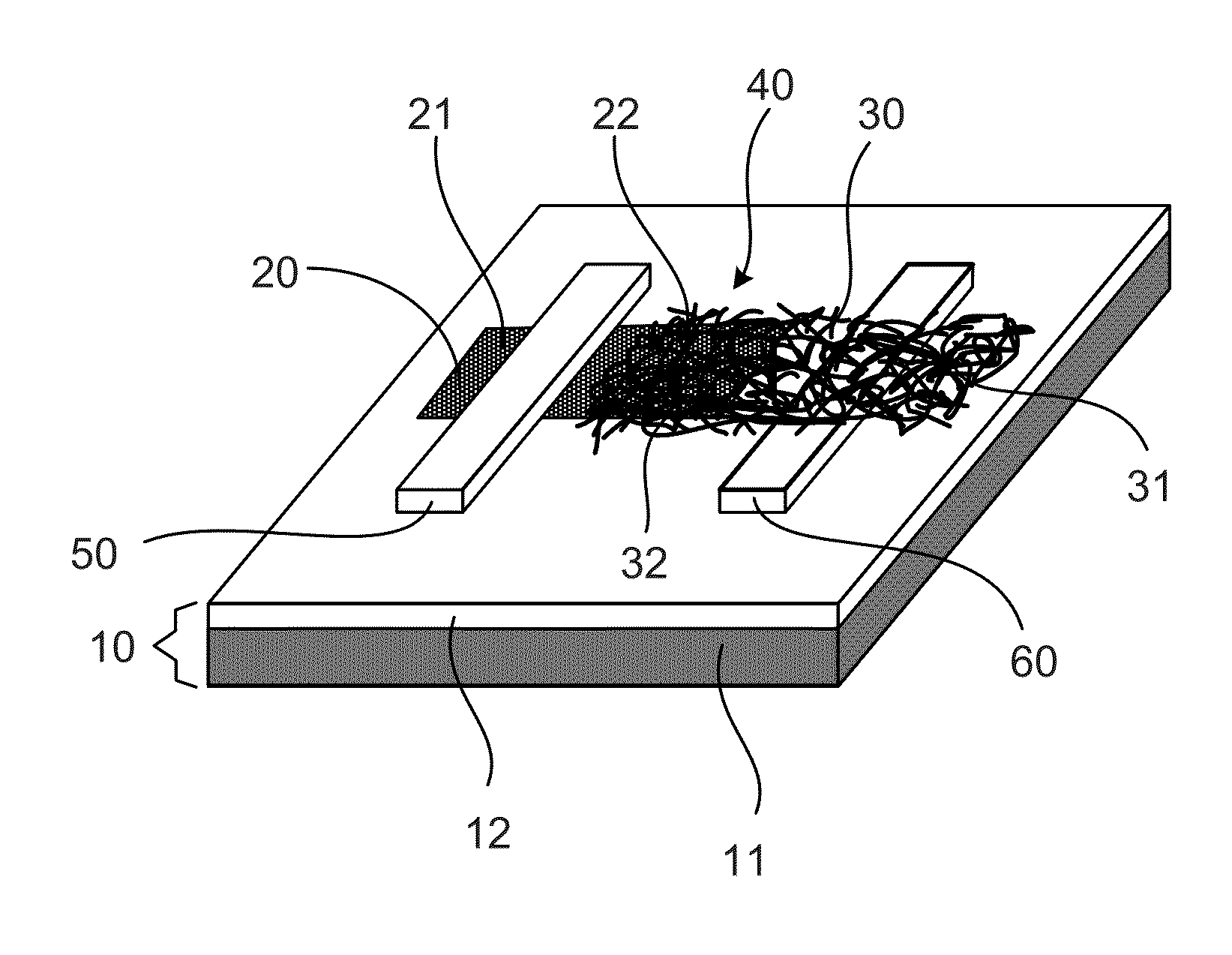

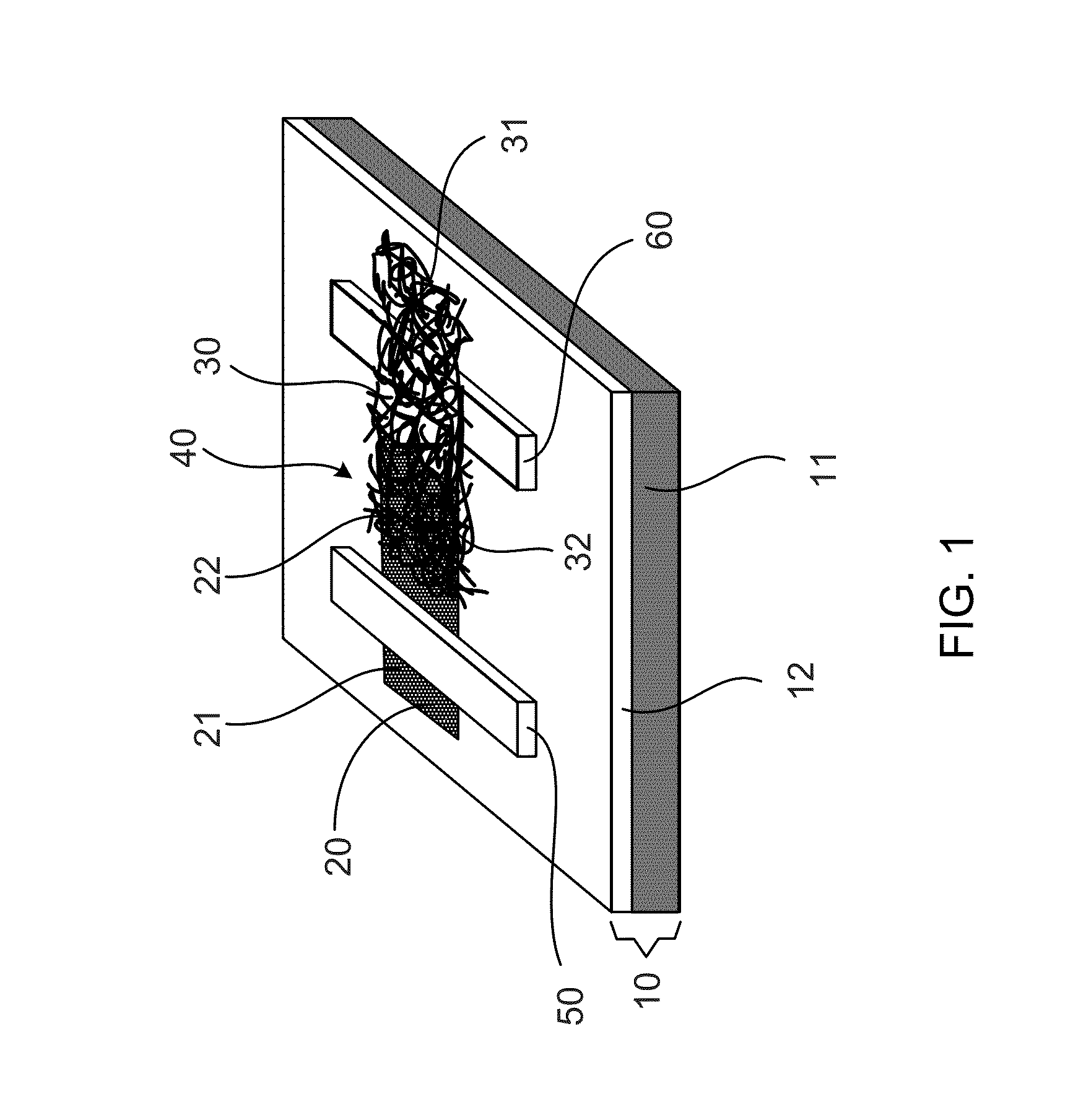

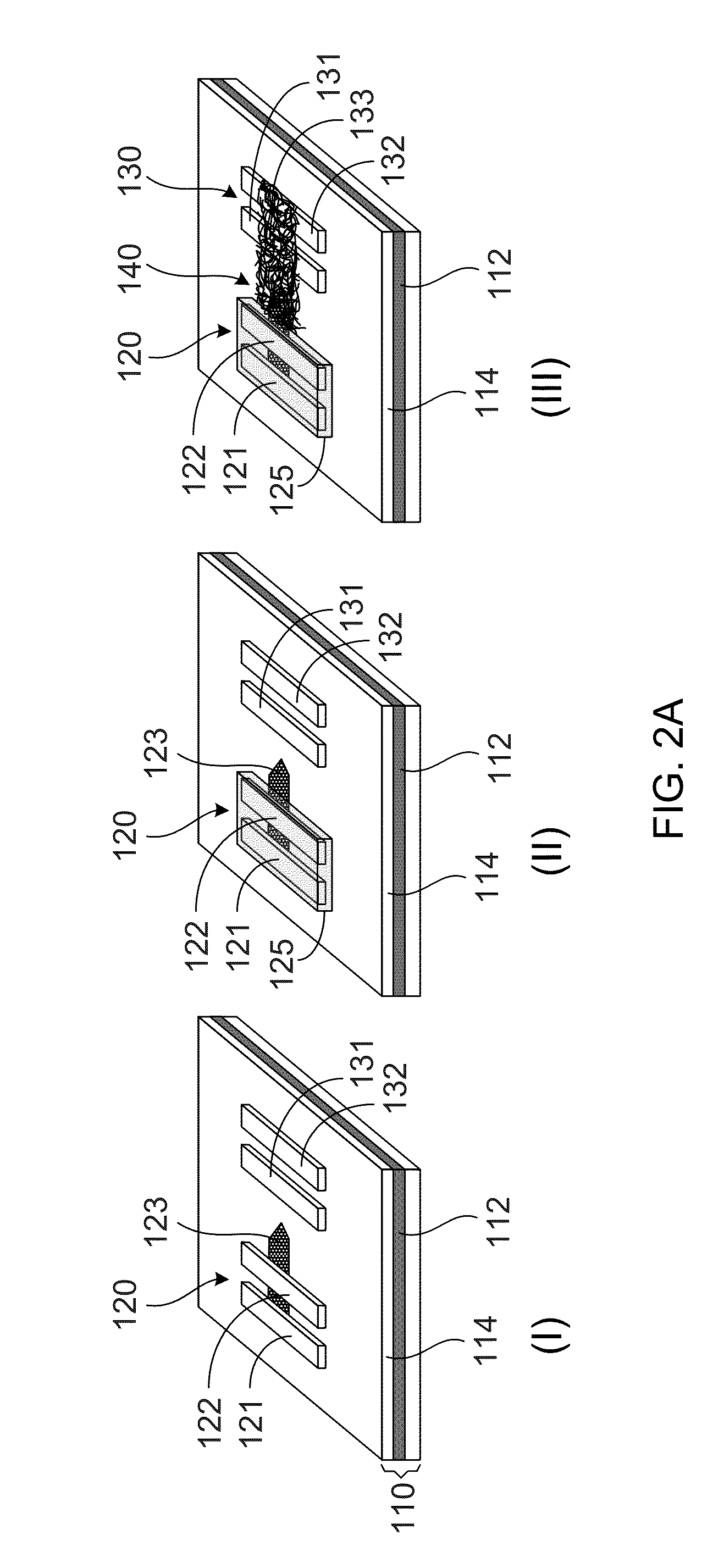

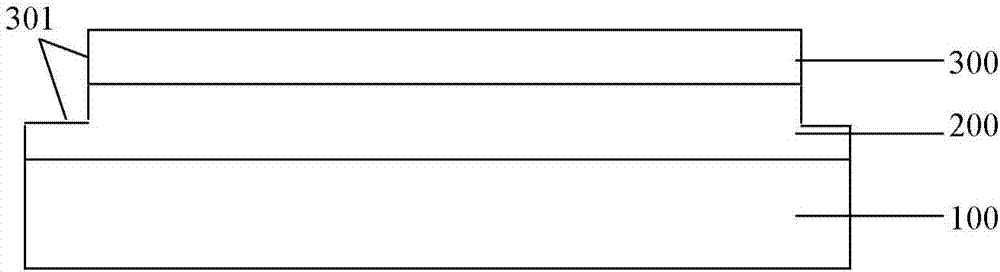

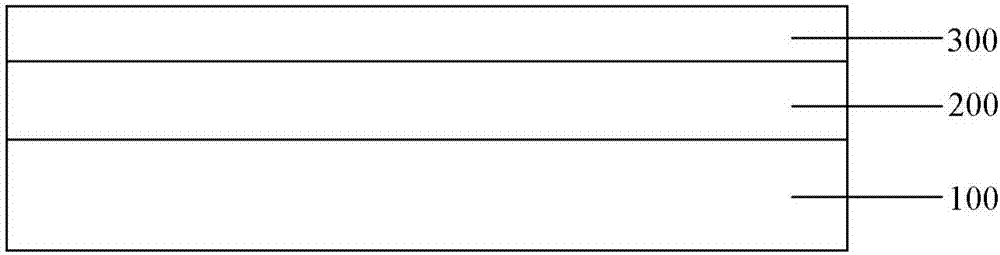

Gate-tunable p-n heterojunction diode, and fabrication method and application of same

ActiveUS20150034907A1Semiconductor/solid-state device manufacturingSemiconductor devicesCarbon nanotubeRectifier diodes

One aspect of the invention relates to a gate-tunable p-n heterojunction diode including a vertical stacked heterojunction of two ultrathin semiconductors. In one embodiment, single-layer molybdenum disulphide of an n-type semiconductor are stacked below semiconducting single-walled carbon nanotubes of a p-type semiconductor with each of them connected to a gold electrodes to form a p-n heterojunction. The electrical properties of the p-n heterojunction can be modulated by a gate voltage applied to a gate electrode and range from an insulator to a linear-response resistor to a highly rectifying diode. The gate tunability of the p-n heterojunction also allows spectral control over the photoresponse.

Owner:NORTHWESTERN UNIV

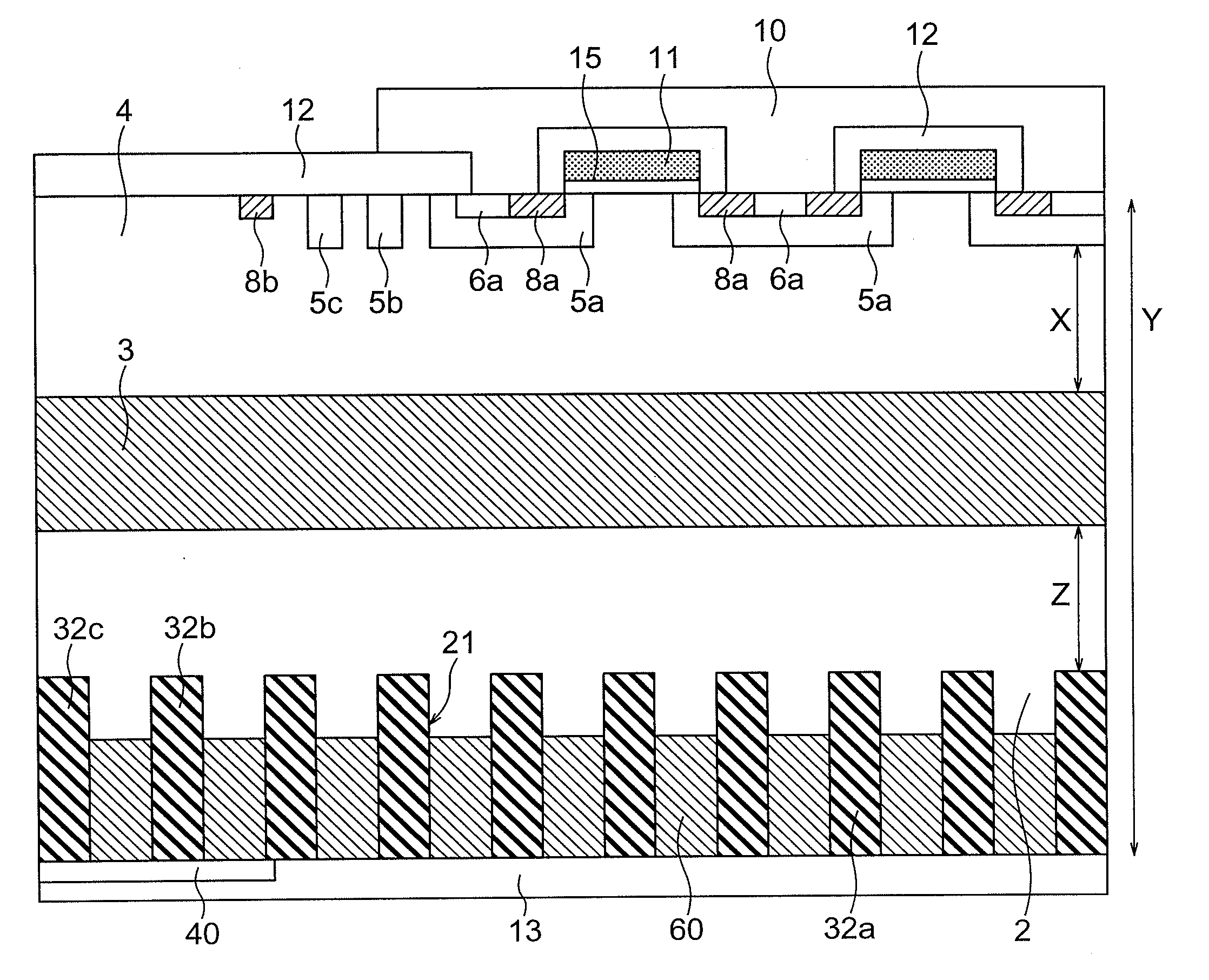

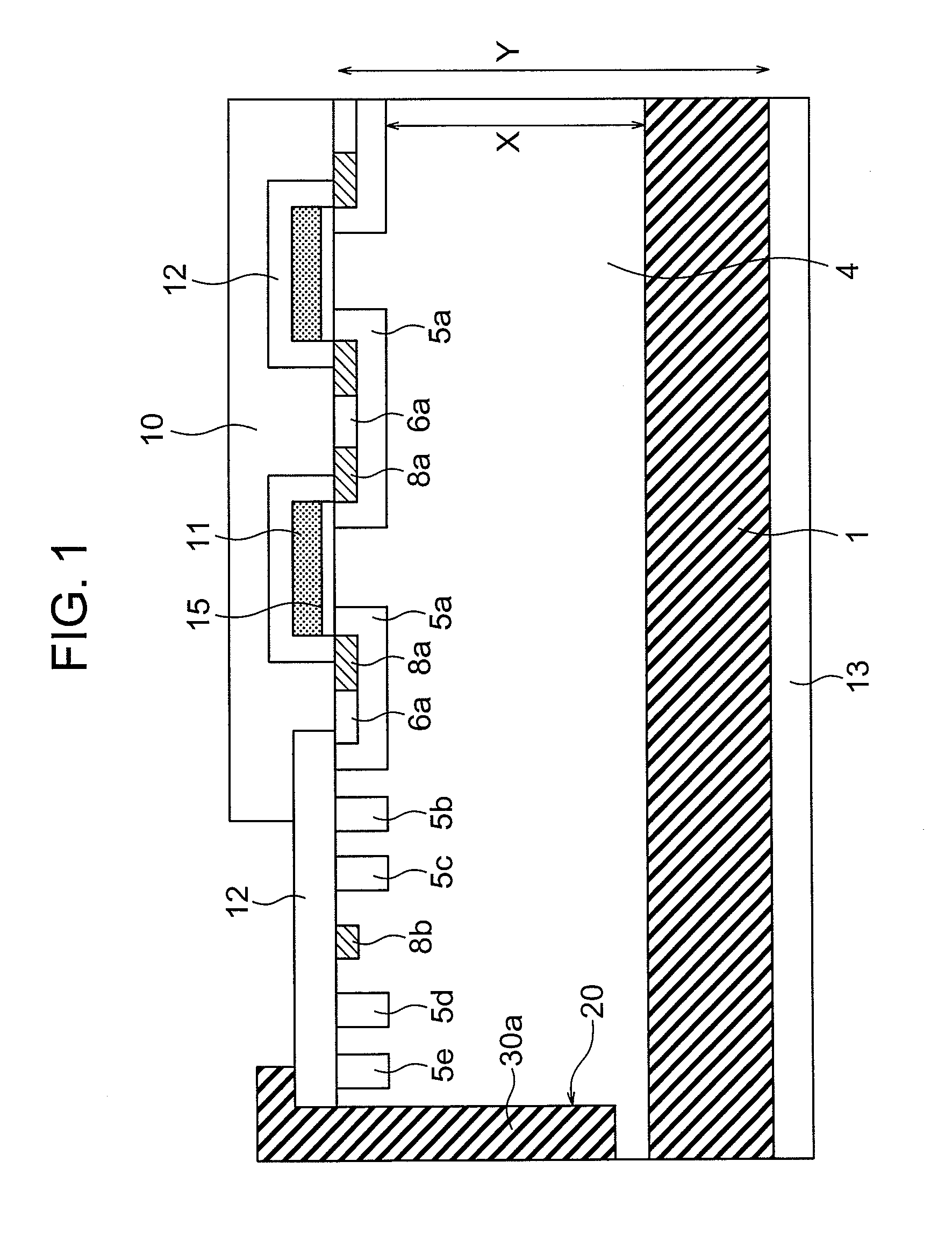

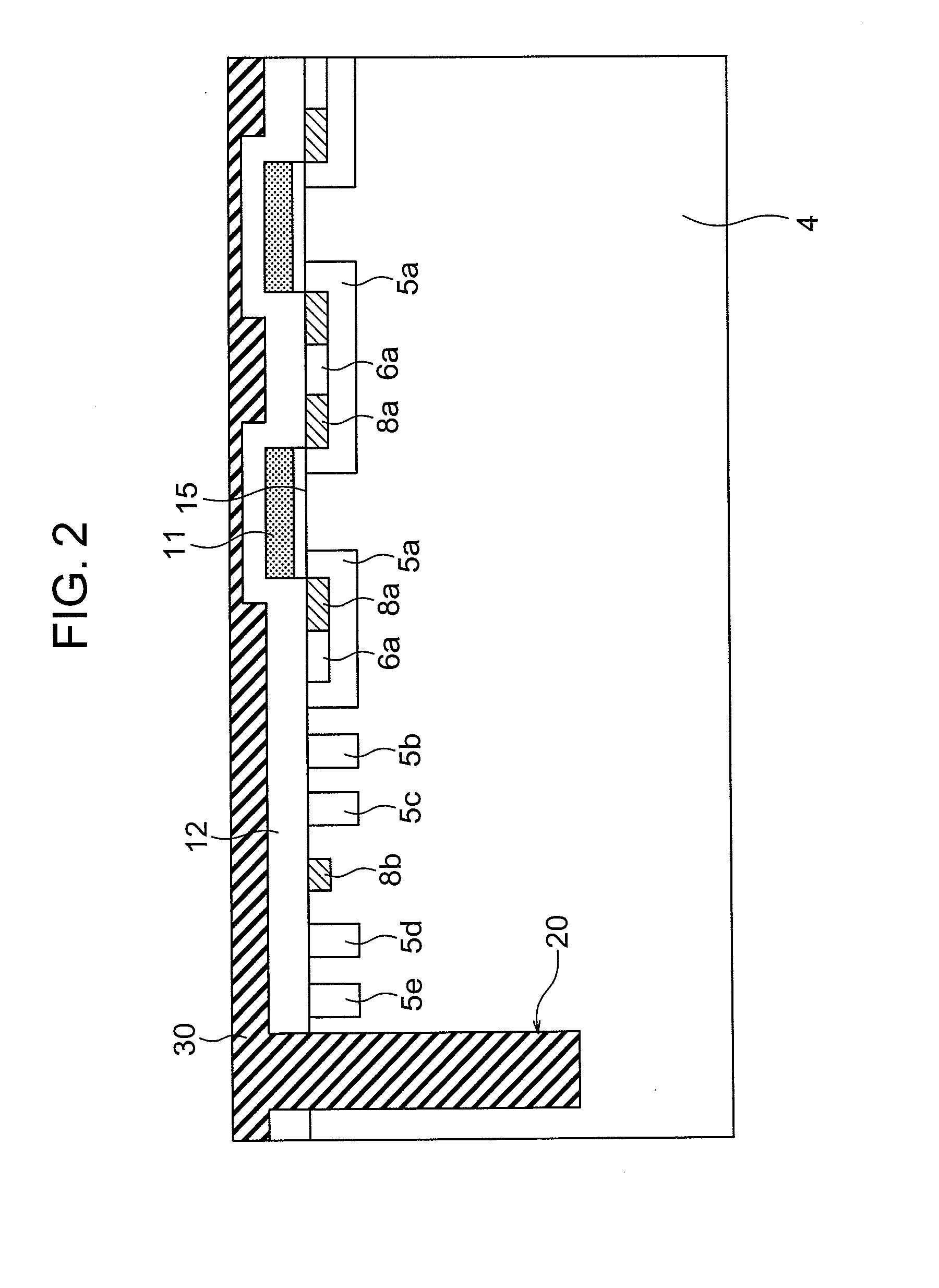

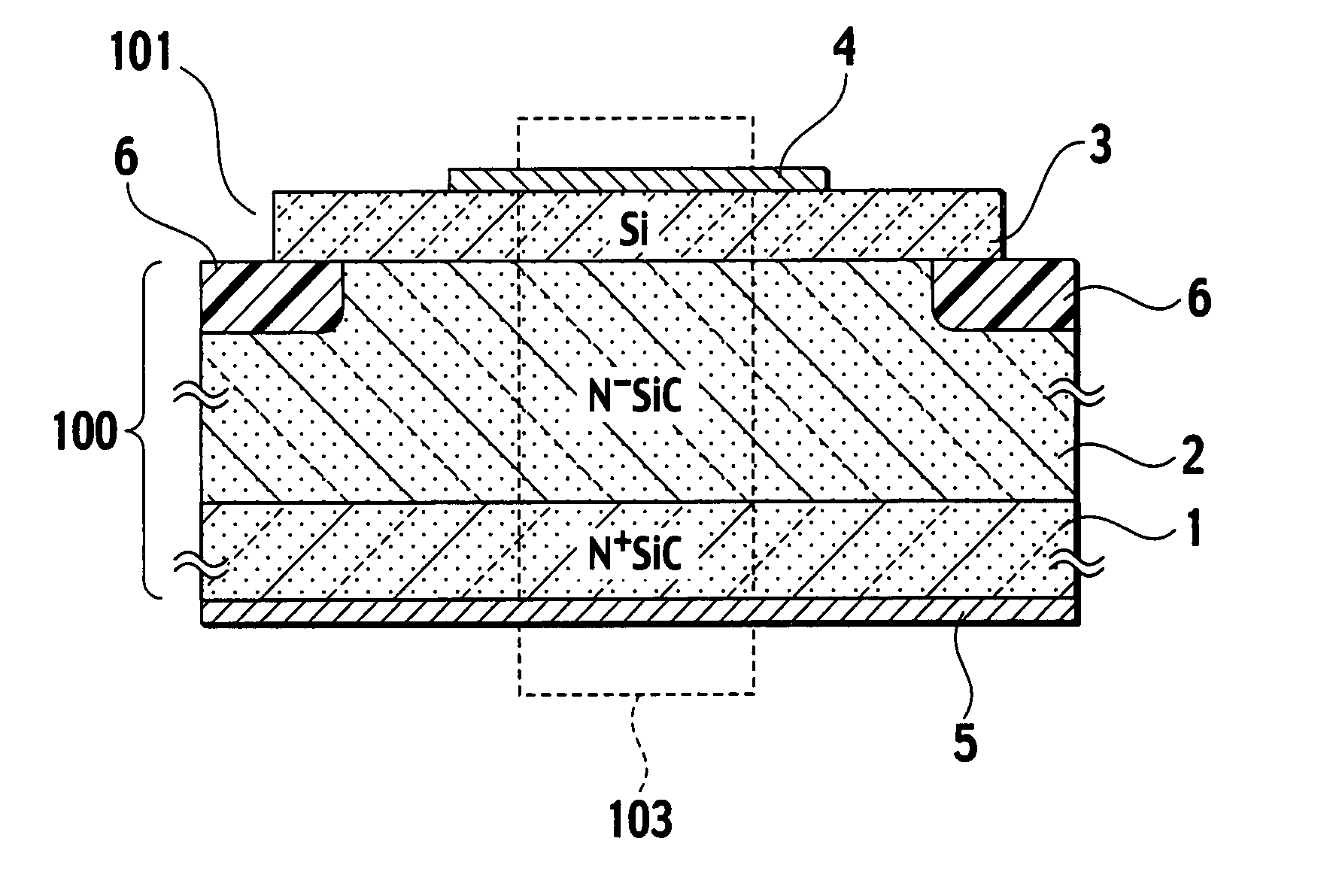

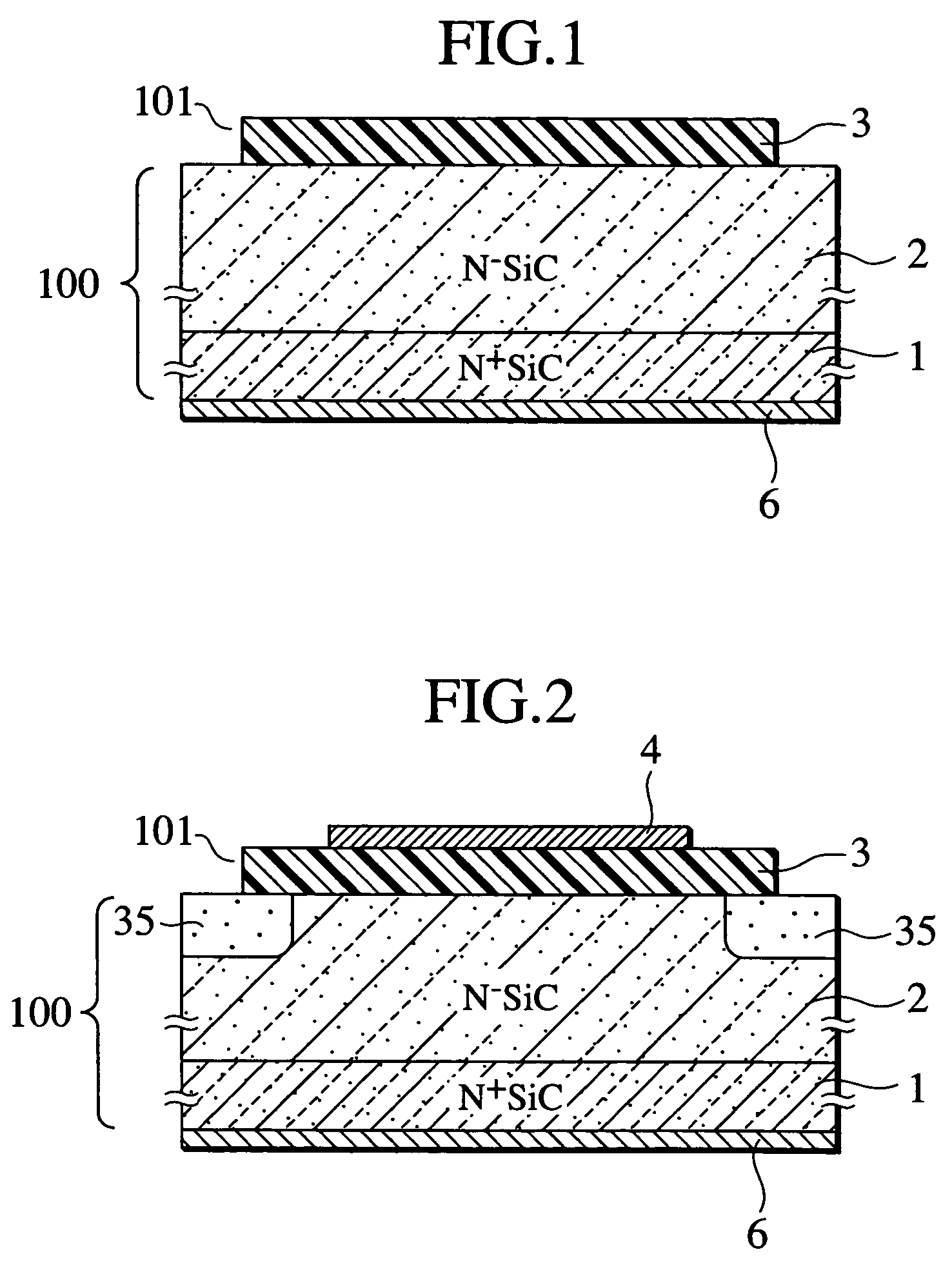

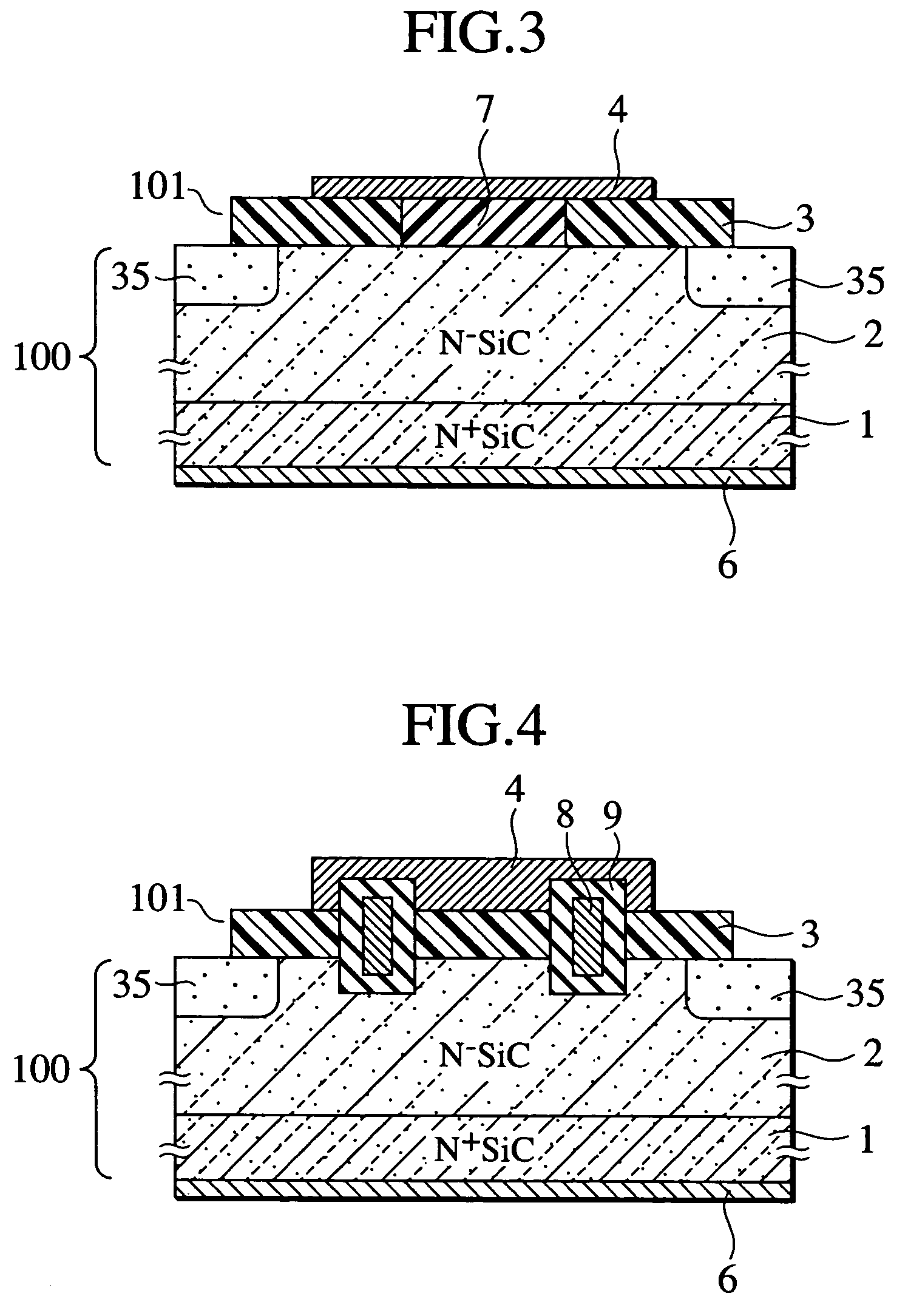

Semiconductor device

InactiveUS20070221953A1Reduce lossImprove pressure resistanceThyristorSolid-state devicesWide bandWideband

A semiconductor device such as a reverse blocking type switching element is provided with a switching element made of a wide band gap semiconductor on the side of a first major plane where a first terminal is formed, while the wide band gap semiconductor is operable at a high voltage and in low loss. In a reverse blocking type switching element having a hetero junction diode for blocking a reverse direction current on the side of a second major plane where a second terminal is formed, a silicon semiconductor region is provided in a side surface of the semiconductor so as to prevent a deterioration of a withstanding voltage of the hetero junction diode.

Owner:HITACHI LTD

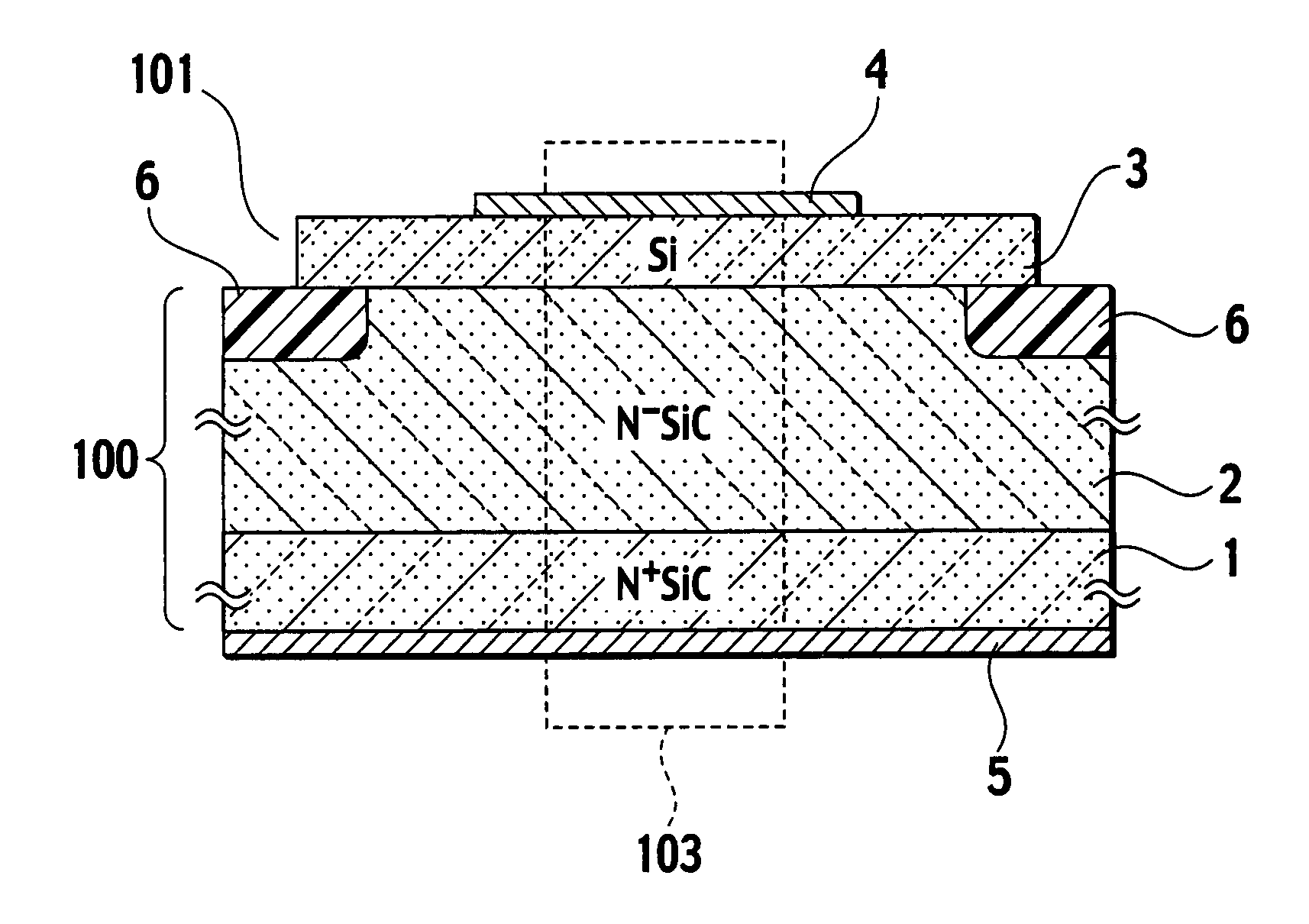

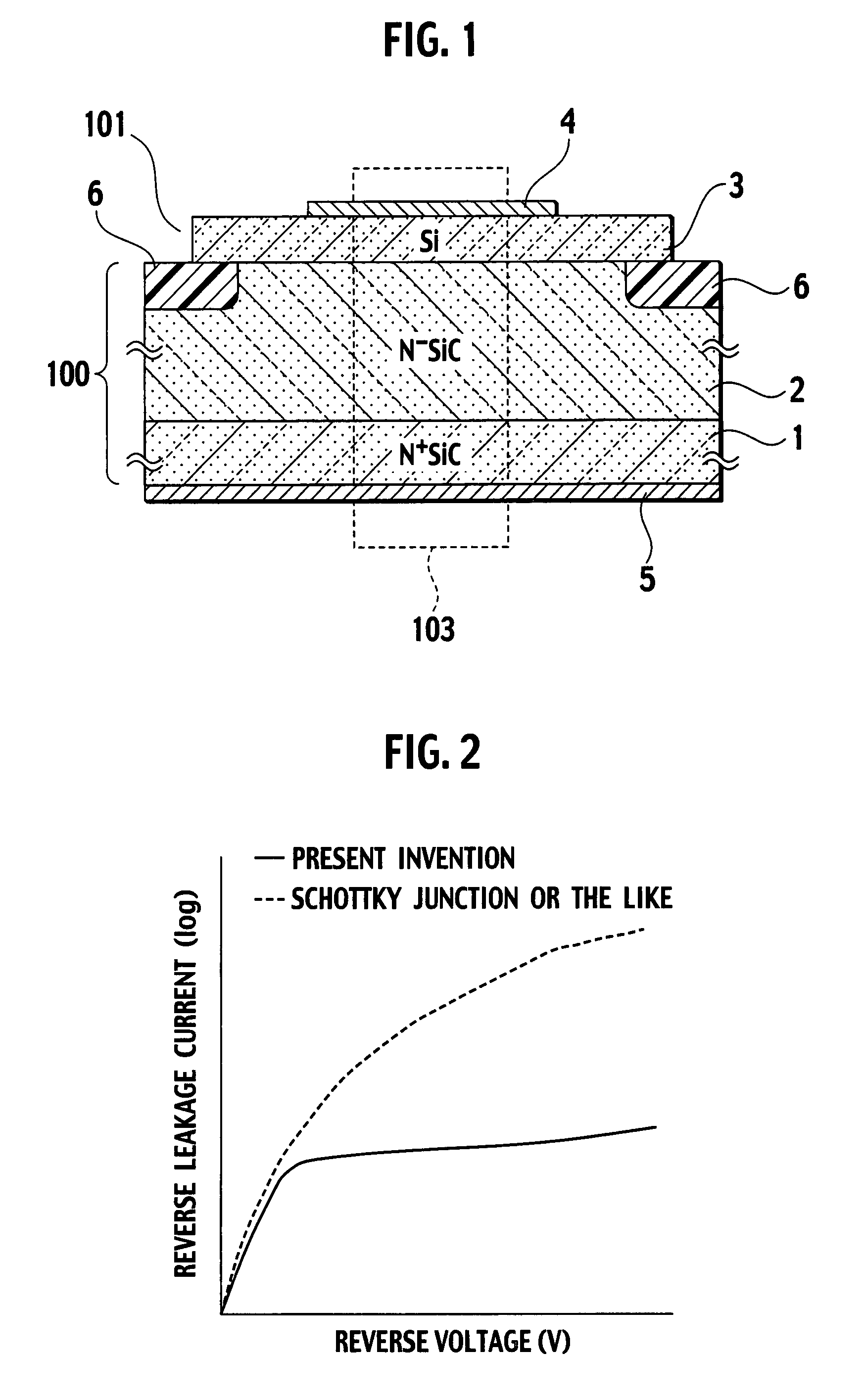

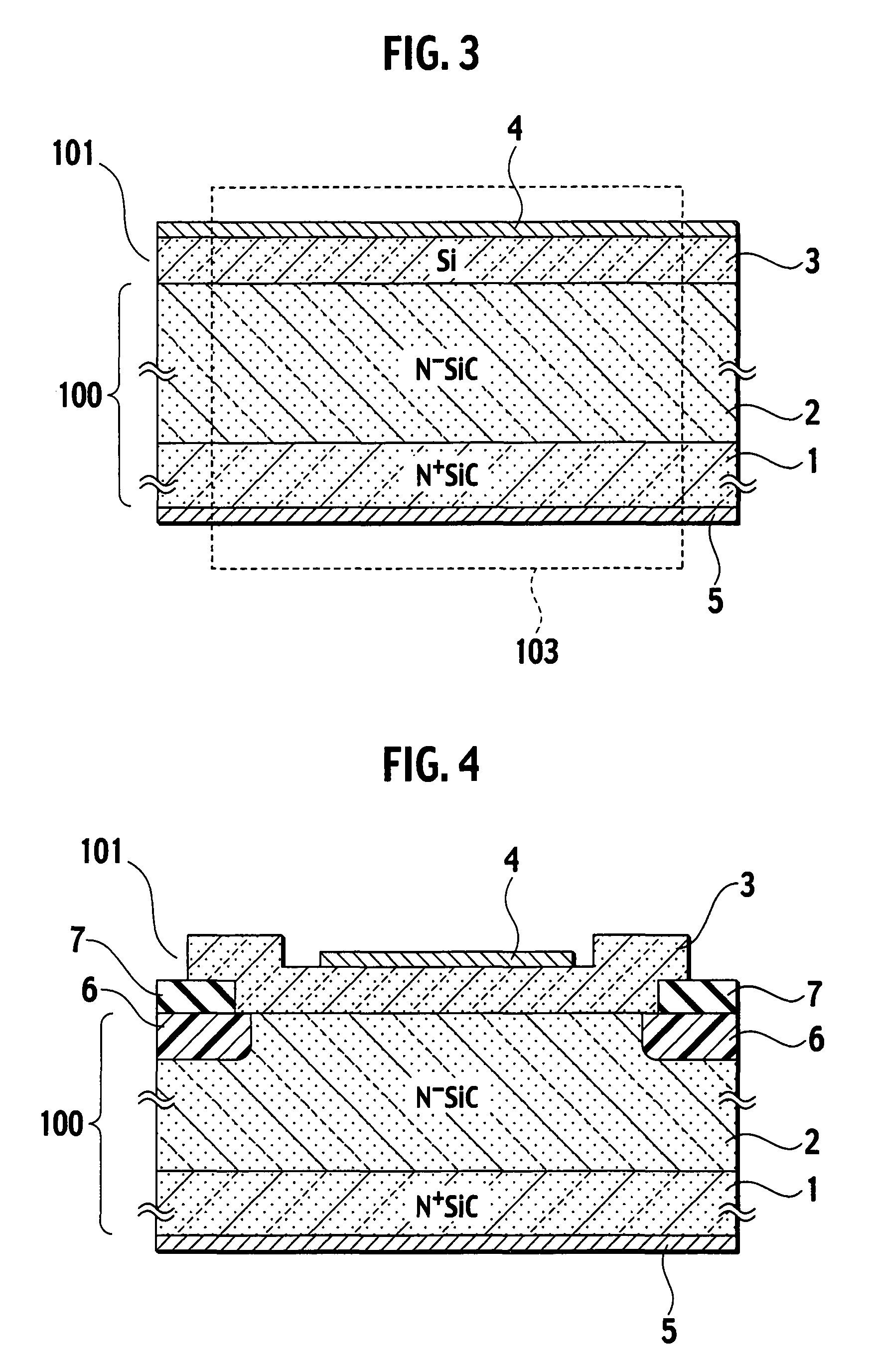

Semiconductor device and manufacturing method thereof

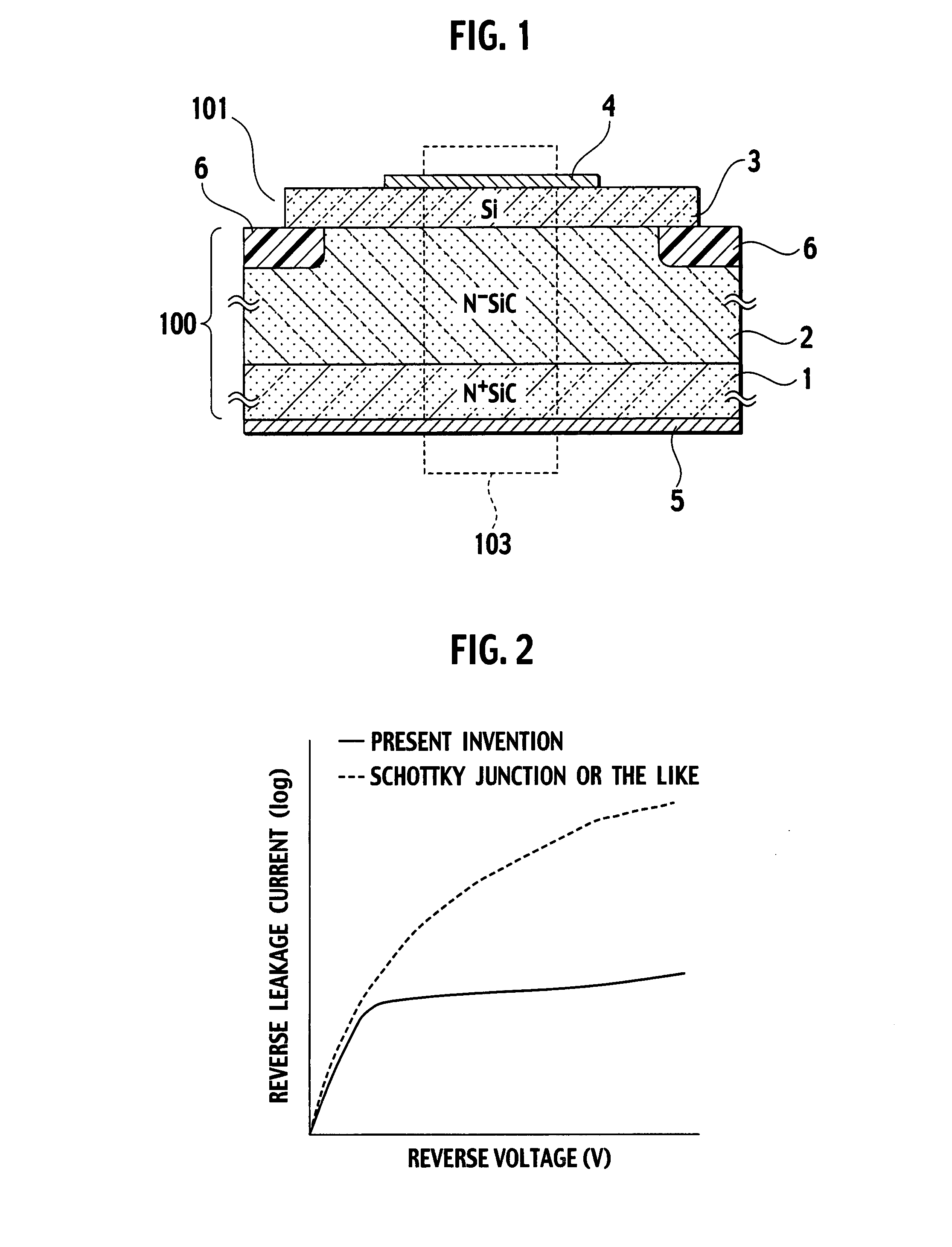

ActiveUS20070235745A1High avalanche resistance characteristicTransistorSemiconductor/solid-state device manufacturingEngineeringReverse bias

Impurity concentration of a second semiconductor region is set such that when a predetermined reverse bias is applied to a heterojunction diode configured by a first semiconductor region and the second semiconductor region, a breakdown voltage at least in a heterojunction region other than outer peripheral ends of the heterojunction diode is a breakdown voltage of a semiconductor device.

Owner:NISSAN MOTOR CO LTD

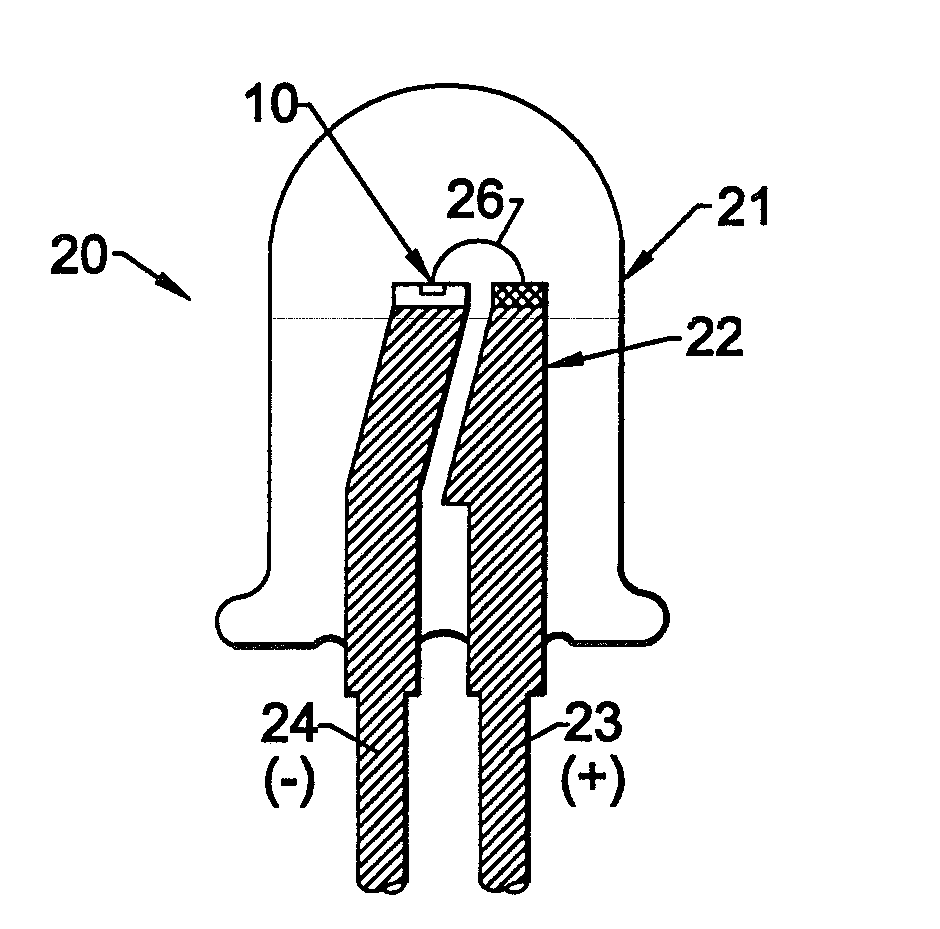

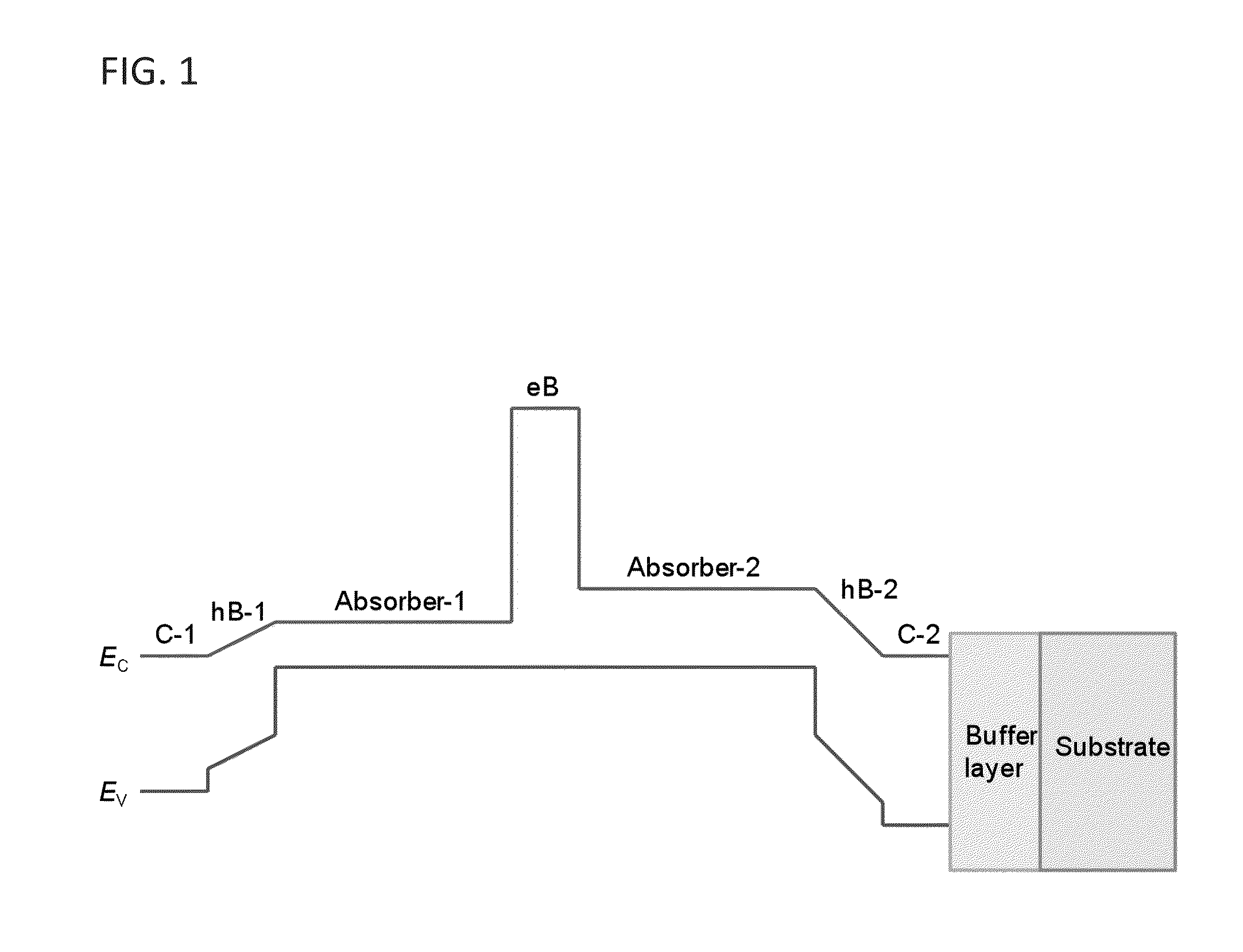

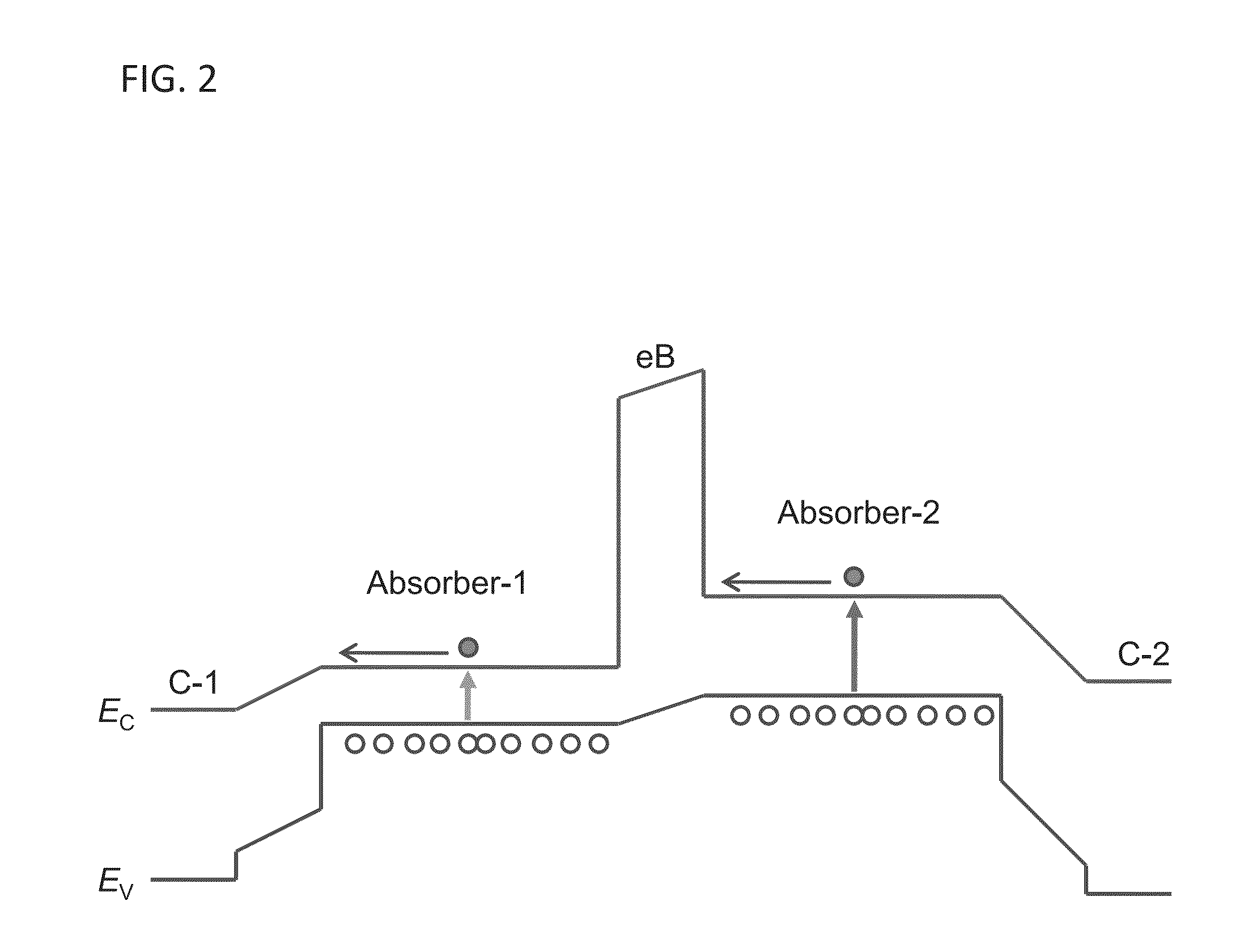

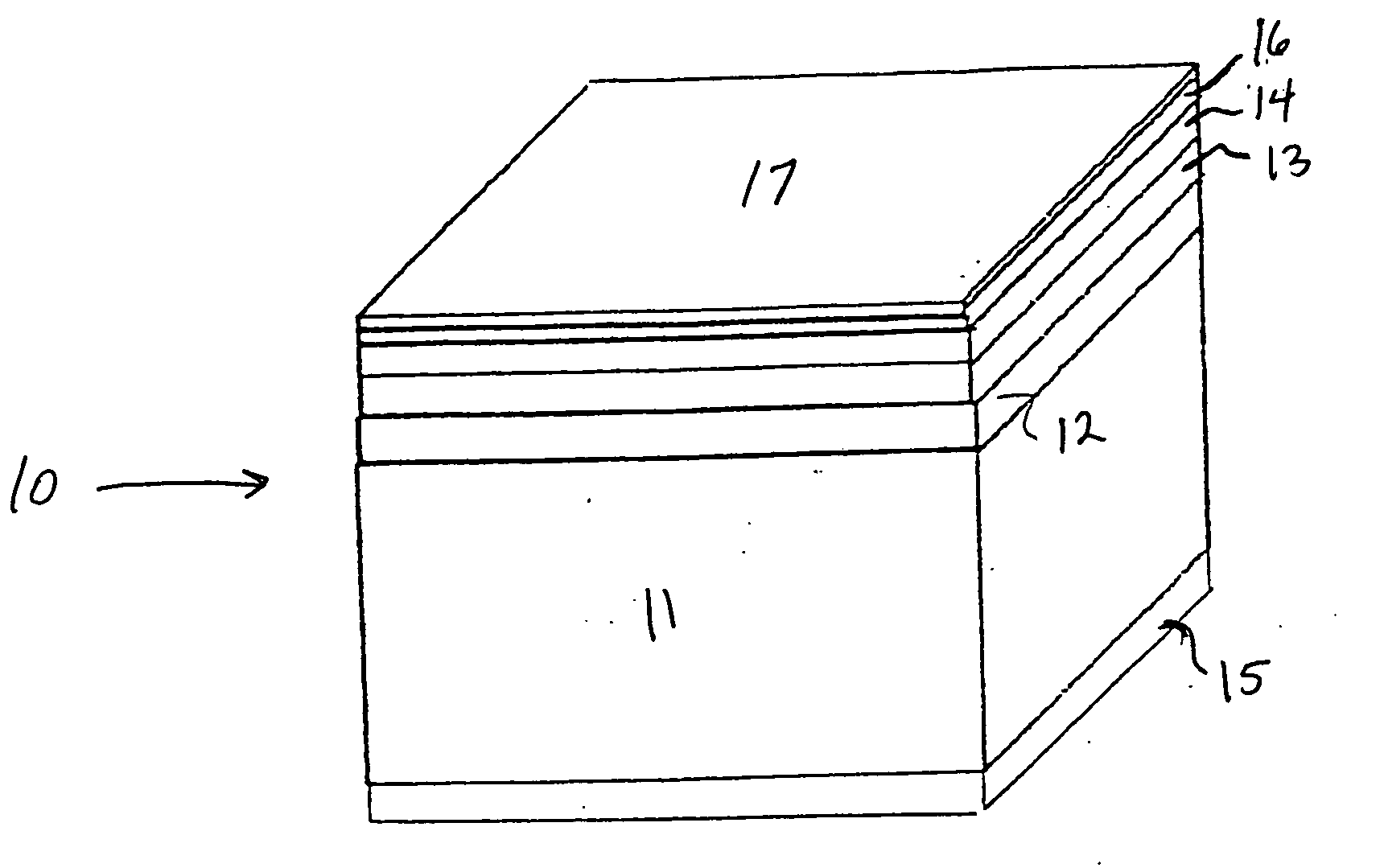

Robust Group III light emitting diode for high reliability in standard packaging applications

InactiveUS7125737B2Solid-state devicesSemiconductor/solid-state device manufacturingHigh humidityOhmic contact

A physically robust light emitting diode is disclosed that offers high-reliability in standard packaging and that will withstand high temperature and high humidity conditions. The diode comprises a Group III nitride heterojunction diode with a p-type Group III nitride contact layer, an ohmic contact to the p-type contact layer, and a sputter-deposited silicon nitride composition passivation layer on the ohmic contact. A method of manufacturing a light emitting diode and an LED lamp incorporating the diode are also disclosed.

Owner:CREE INC

Semiconductor device having a heterojunction diode and manufacturing method thereof

ActiveUS7781786B2High avalanche resistance characteristicSemiconductor/solid-state device manufacturingDiodeDevice materialEngineering

Impurity concentration of a second semiconductor region is set such that when a predetermined reverse bias is applied to a heterojunction diode configured by a first semiconductor region and the second semiconductor region, a breakdown voltage at least in a heterojunction region other than outer peripheral ends of the heterojunction diode is a breakdown voltage of a semiconductor device.

Owner:NISSAN MOTOR CO LTD

Normally-off field-controlled channel gan heterojunction diode

InactiveCN102280494AImplement field control featuresEfficient use ofSemiconductor devicesControl channelPositive power

A normally-off type field-controlled channel GaN heterojunction diode belongs to the technical field of semiconductor devices. The invention adopts the technology of combining insulating layer-groove, modulation doping and groove-modulation doping to change the conductive channel structure of the existing GaN heterojunction diode, and convert the original normally-on spontaneously polarized GaN heterojunction The junction conductive channel is changed into a normally-off field-controlled conductive channel combining spontaneous polarization and piezoelectric polarization in the present invention, which realizes the field-controlled characteristics of the GaN heterojunction diode conductive channel and reduces the forward conduction resistance and enhanced reverse cut-off capability. The invention has lower forward conduction resistance and power consumption, stronger reverse cut-off ability, and is compatible with AlGaN / GaN HEMT power switching device technology, which is beneficial to the application of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

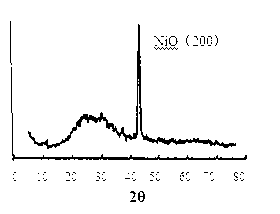

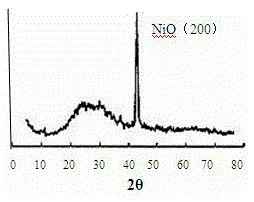

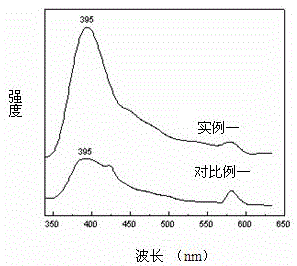

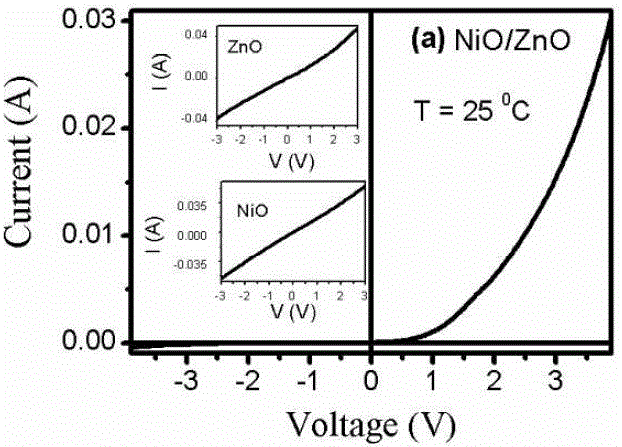

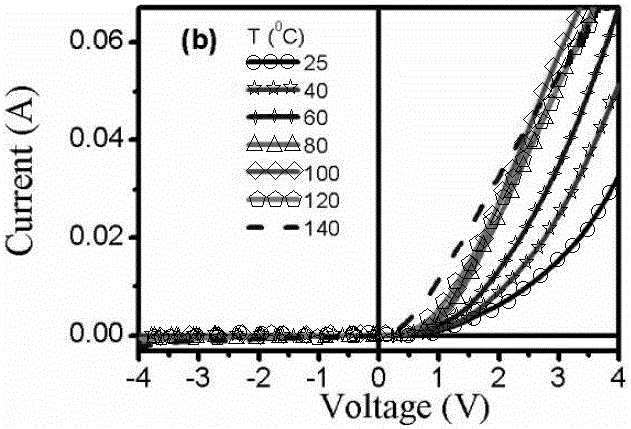

P-zinc oxide/N- nickel oxide heterogeneous PN junction ultraviolet laser diode and method for production

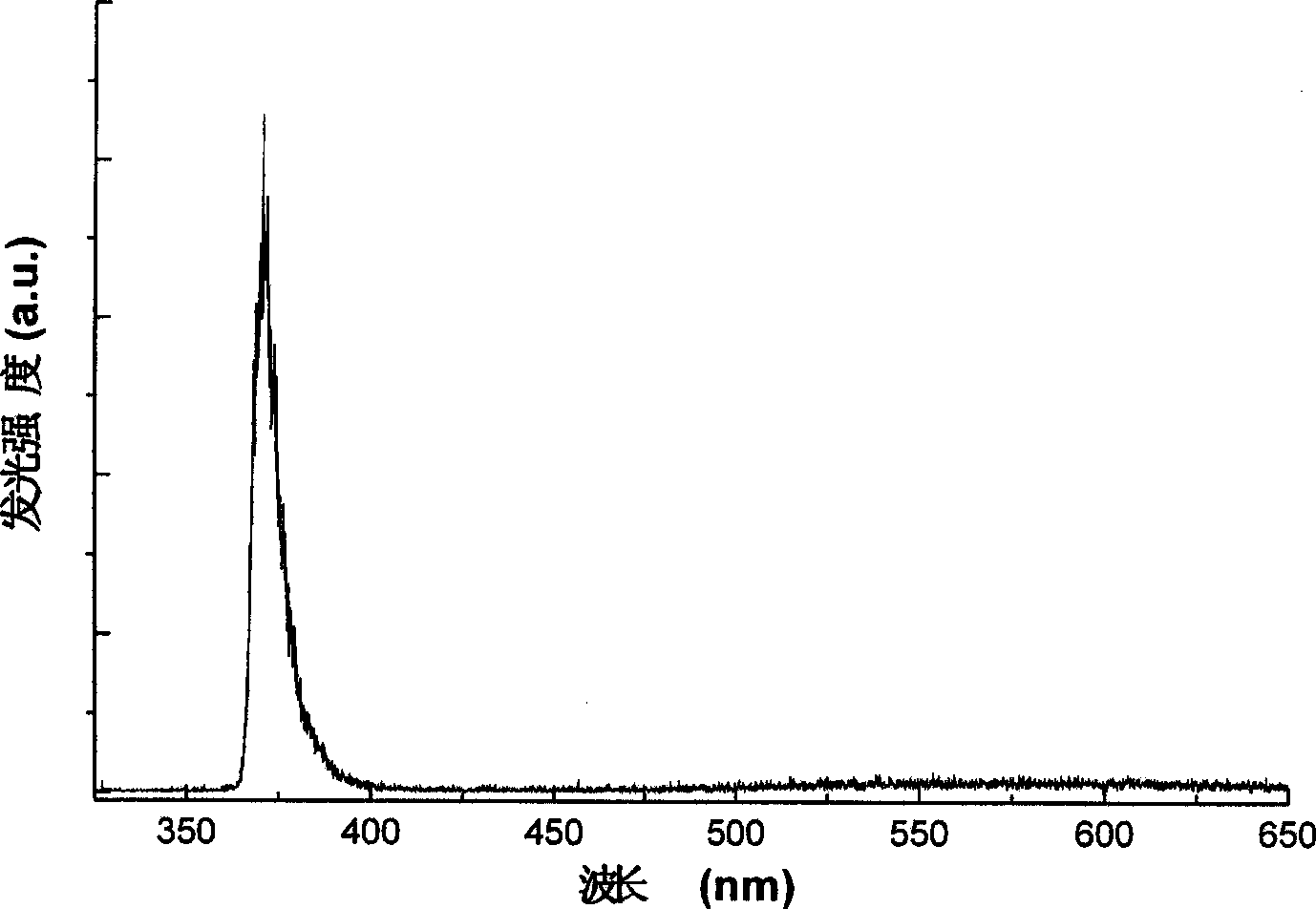

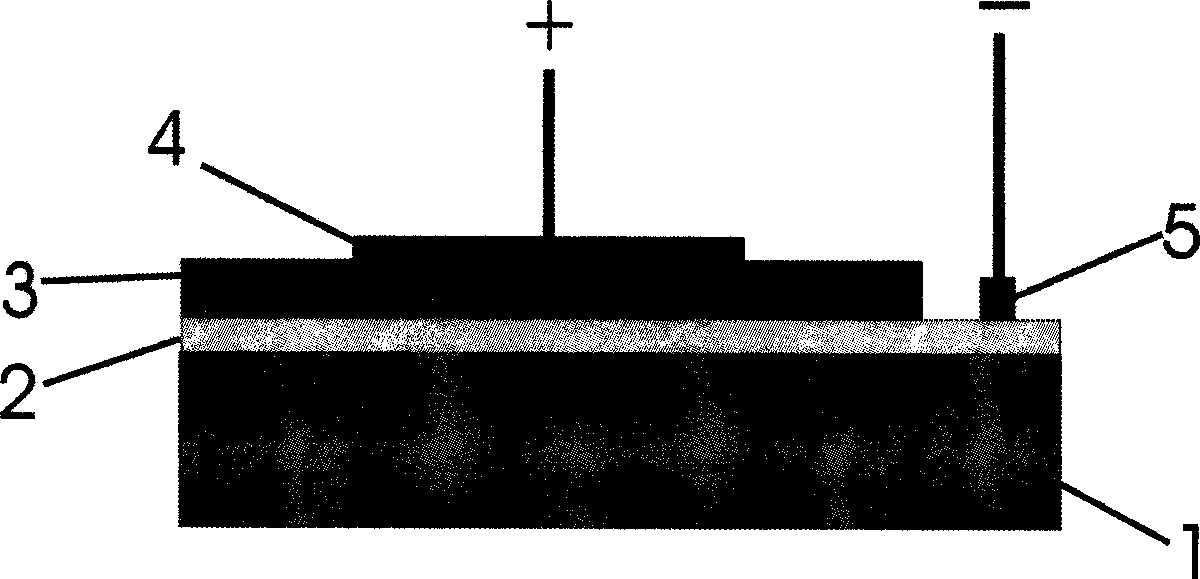

ActiveCN101505035AGood electro-ultraviolet lasing luminescence propertiesImprove performanceLaser detailsLaser active region structureIndiumRadio frequency magnetron sputtering

The invention discloses an n -zinc oxide / p- nickel oxide heterogeneous pn junction ultraviolet laser diode and a preparation method thereof. The heterogeneous pn junction diode at least comprises a pn junction, a substrate and an ohm contacting electrode, wherein the pn junction is the heterogeneous pn junction by plating a p-type nickel oxide film on an n-type zinc oxide film; and the substrate is a sapphire plated with n-type GaN. The preparation method comprises the following steps: firstly preparing the n-type ZnO film layer on the substrate by the radio frequency magnetron sputtering technology; then sputtering a p-type NiO film layer on the n-type ZnO film layer to form the heterogeneity pn junction; finally manufacturing a pn junction electrode by a sputtering method or a thermal evaporation method; sputtering gold electrodes or platinum electrodes or nickel platinum electrodes or ITO electrodes on the NiO surface; plating indium electrodes or aluminum electrodes or gold electrodes on the GaN or the edge of ZnO; and making the electrodes form ohm contact after annealing alloying. The heterogeneous pn junction diode has the advantages of better electro-ultraviolet lasing luminescence characteristic, peak luminous wavelength of about 375 nm, simple preparation process and low cost.

Owner:常熟紫金知识产权服务有限公司

Robust Group III Light Emitting Diode for High Reliability in Standard Packaging Applications

InactiveUS20030201453A2Solid-state devicesSemiconductor/solid-state device manufacturingHigh humidityOhmic contact

Abstract of the Disclosure A physically robust light emitting diode is disclosed that offers high-reliability in standard packaging and that will withstand high temperature and high humidity conditions. The diode comprises a Group III nitride heterojunction diode with a p-type Group III nitride contact layer, an ohmic contact to the p-type contact layer, and a sputter-deposited silicon nitride composition passivation layer on the ohmic contact. A method of manufacturing a light emitting diode and an LED lamp incorporating the diode are also disclosed.

Owner:CREE INC

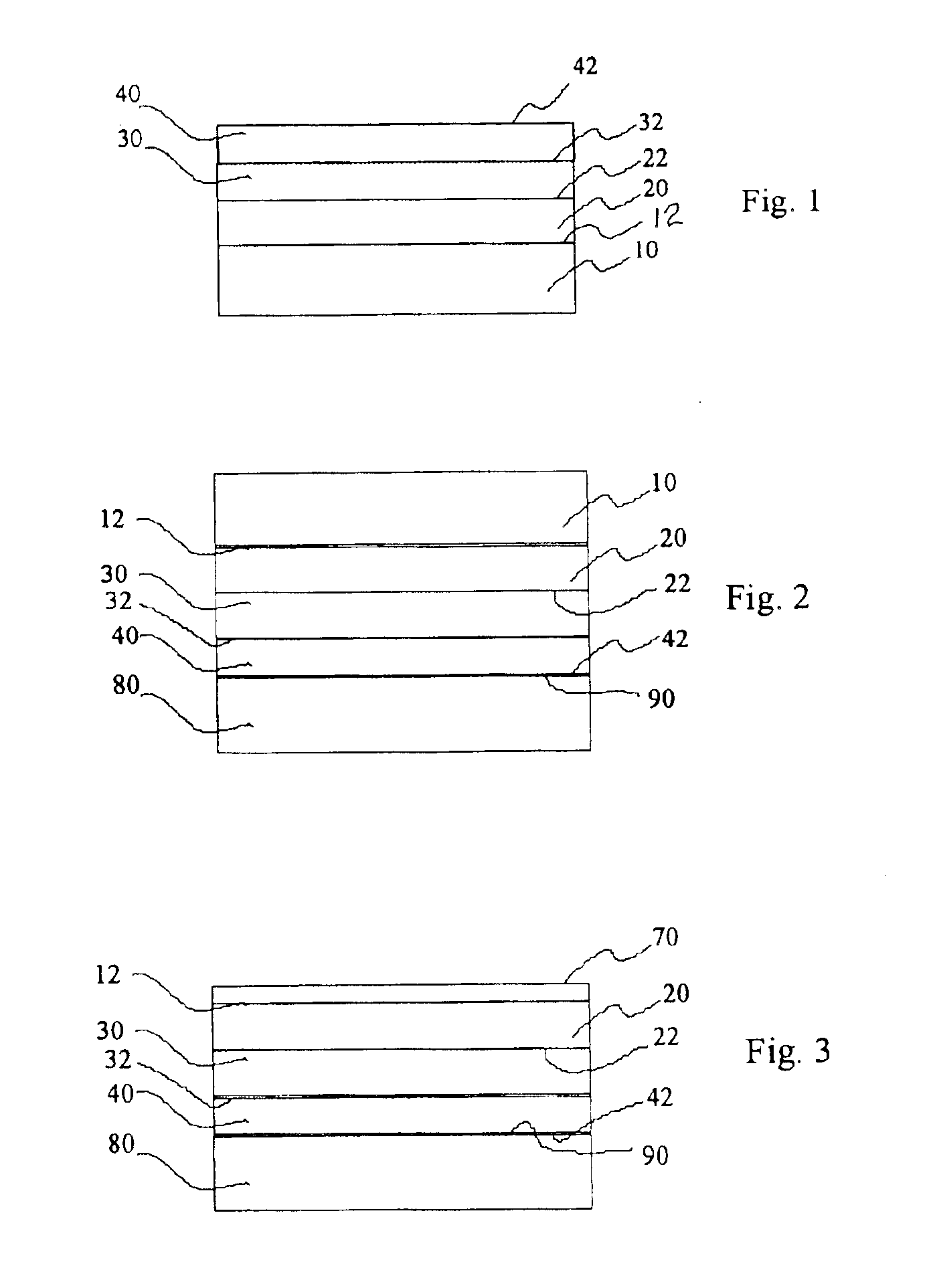

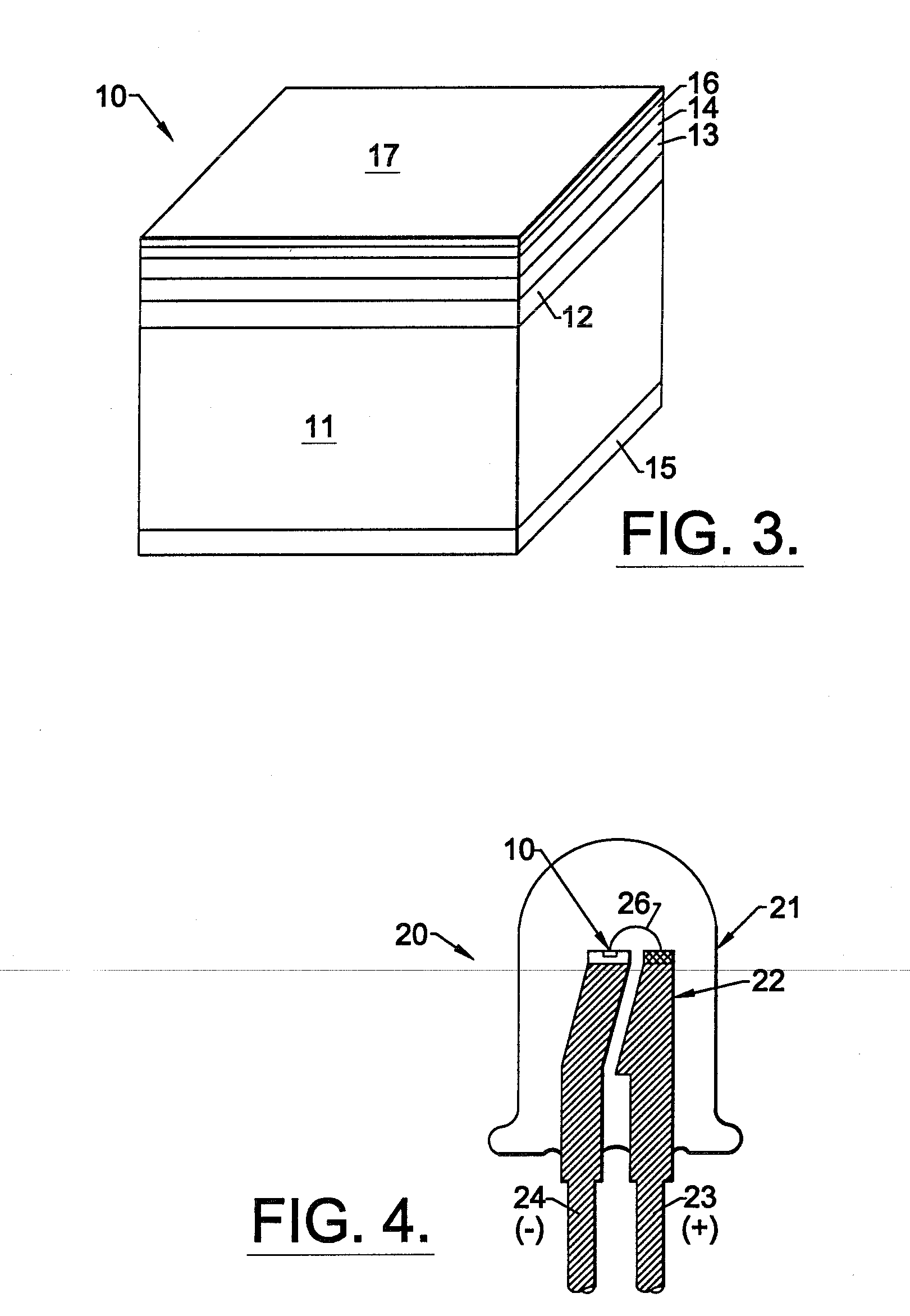

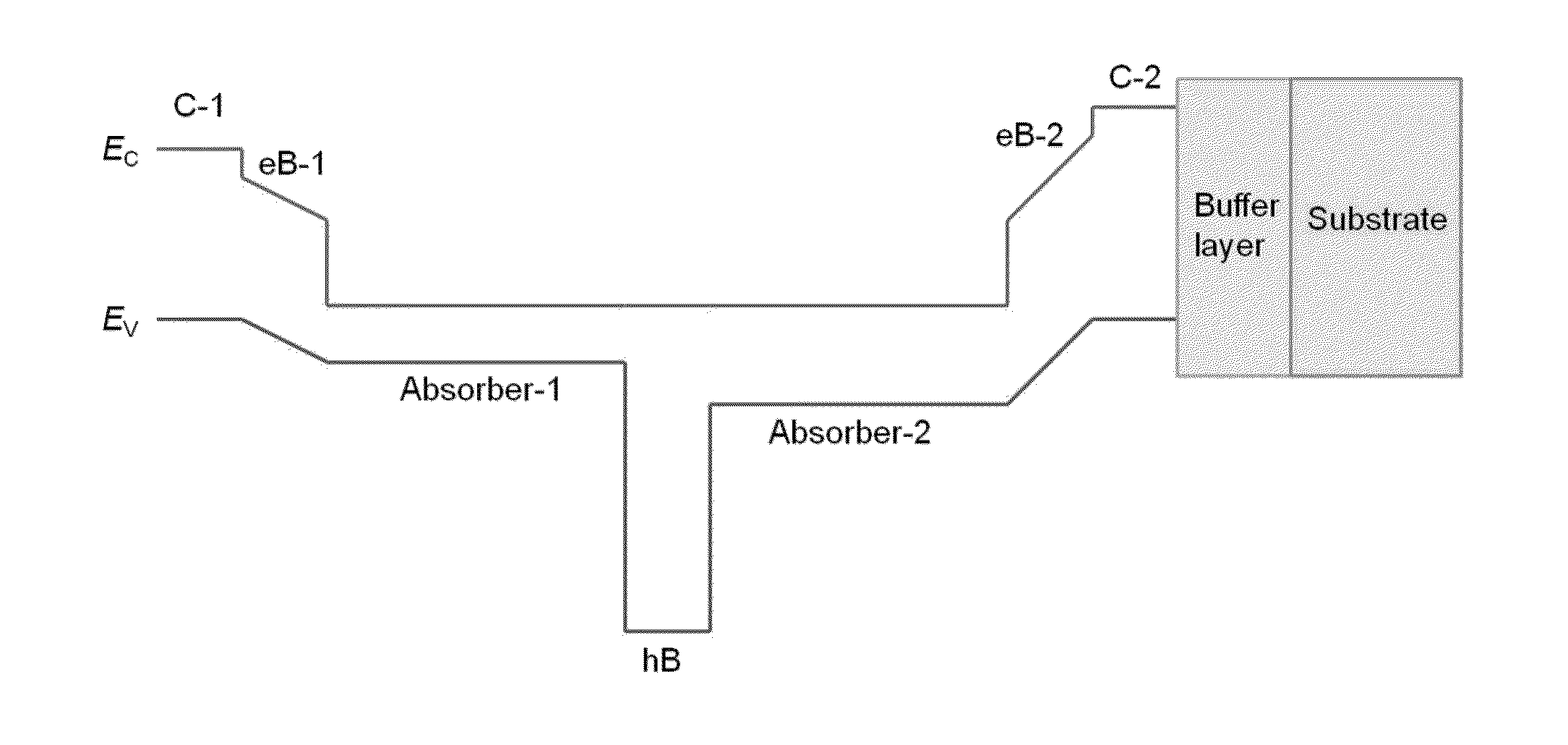

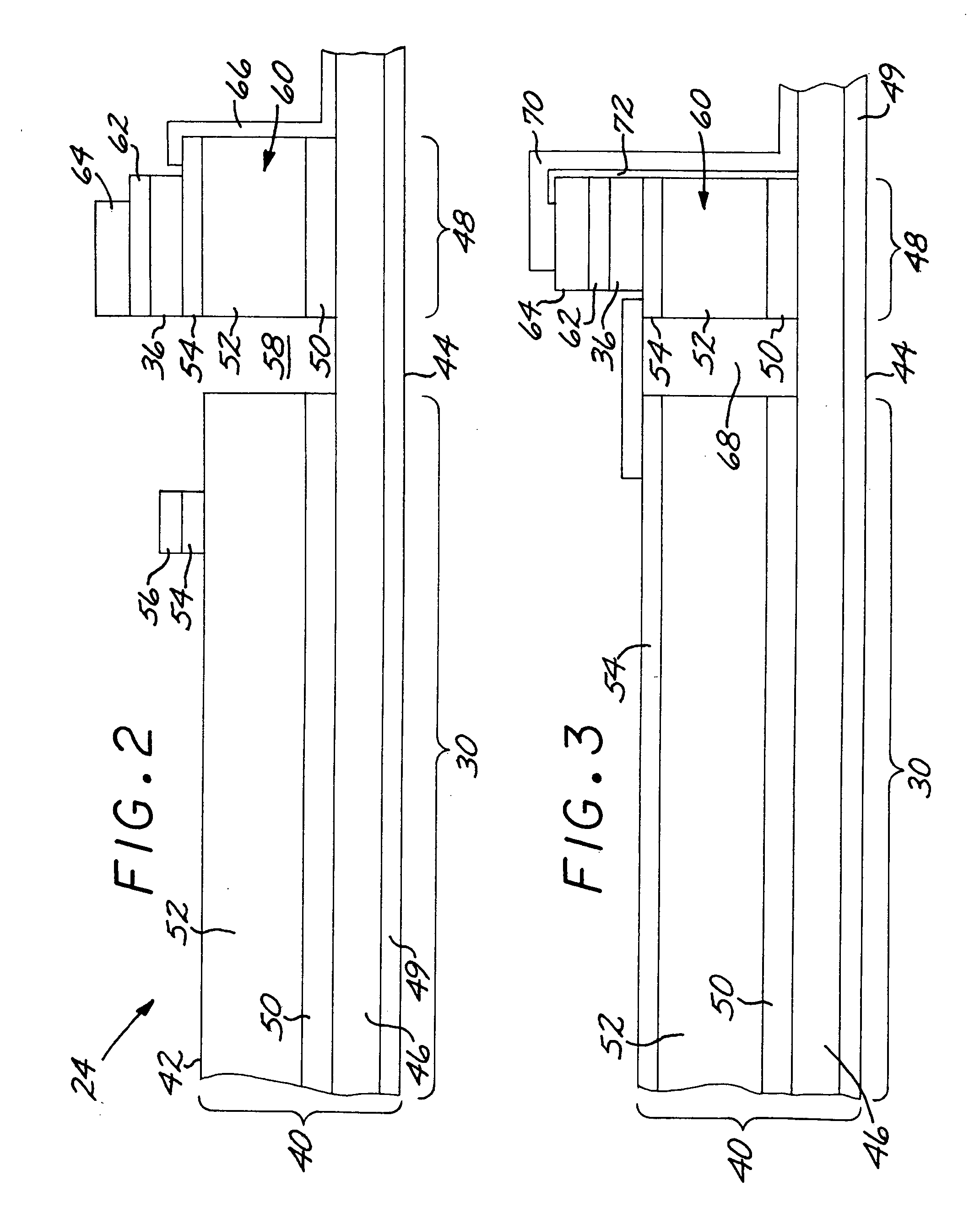

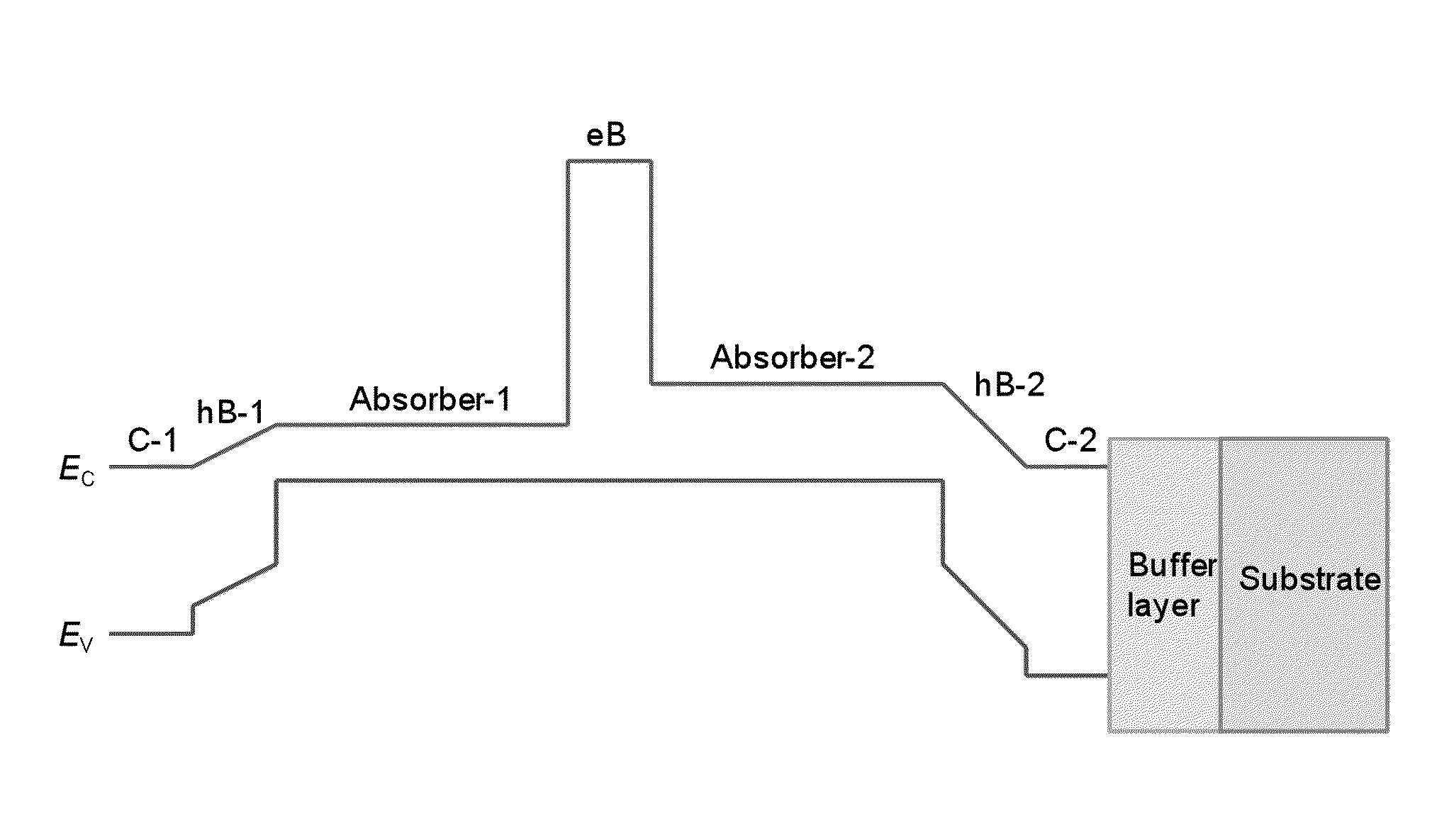

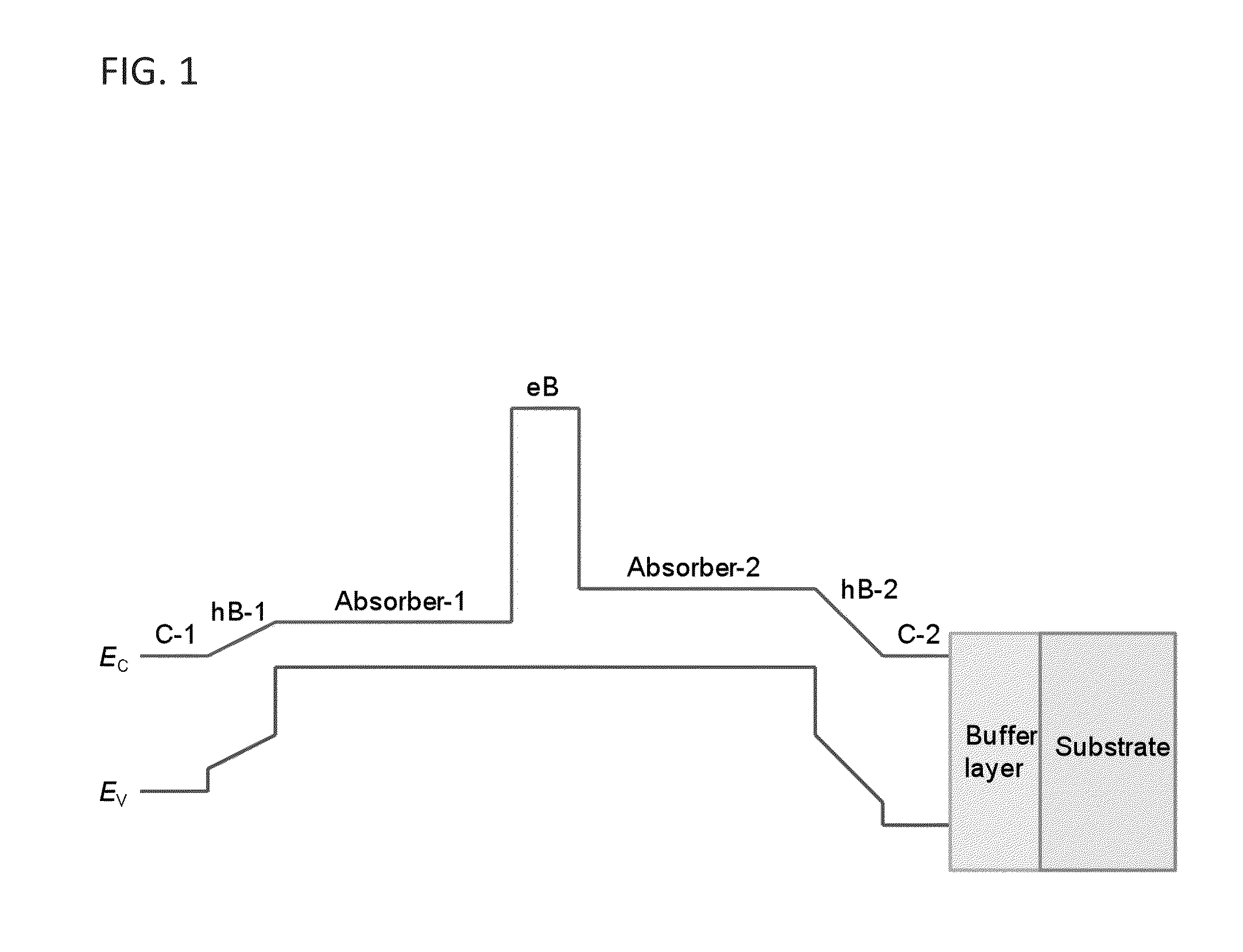

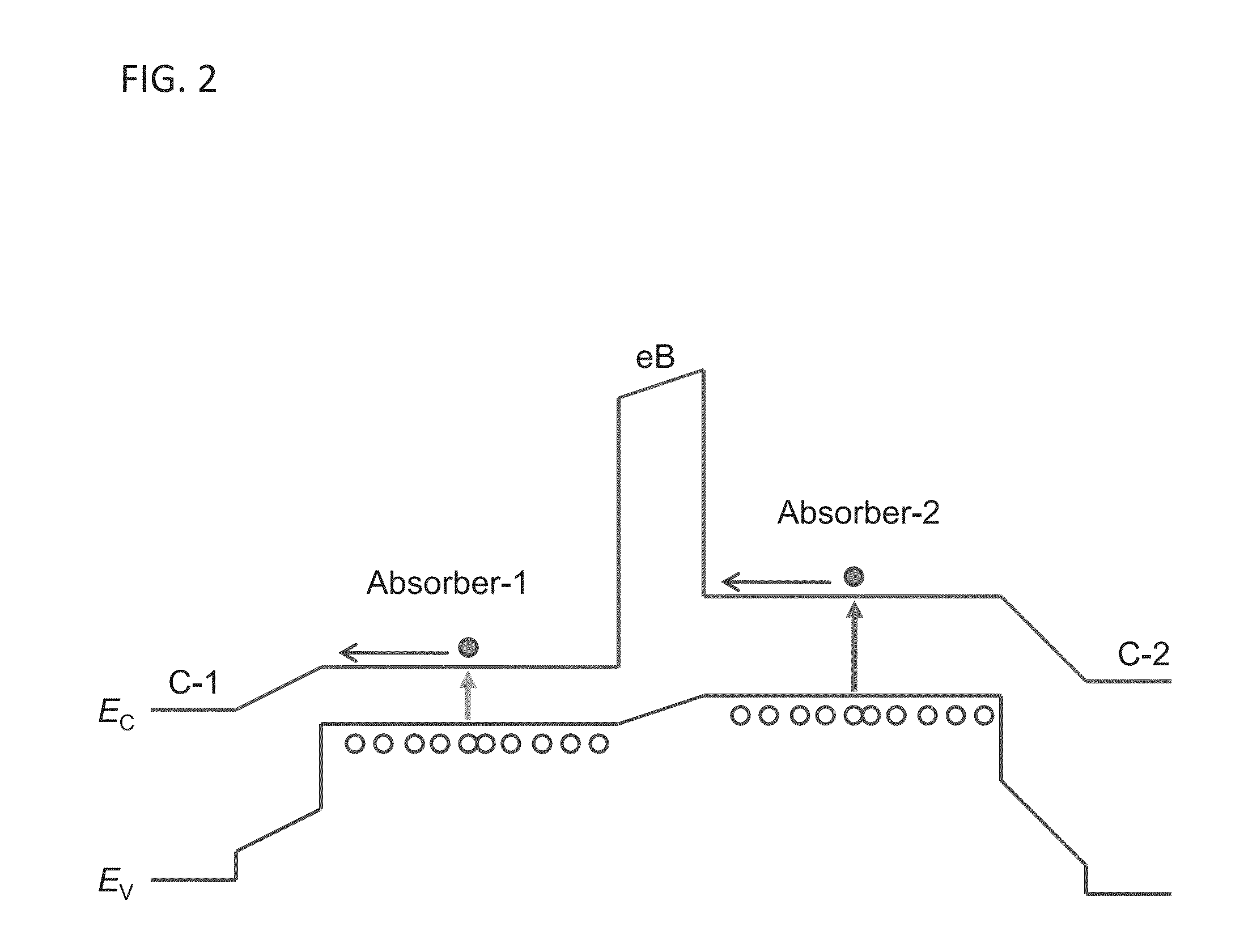

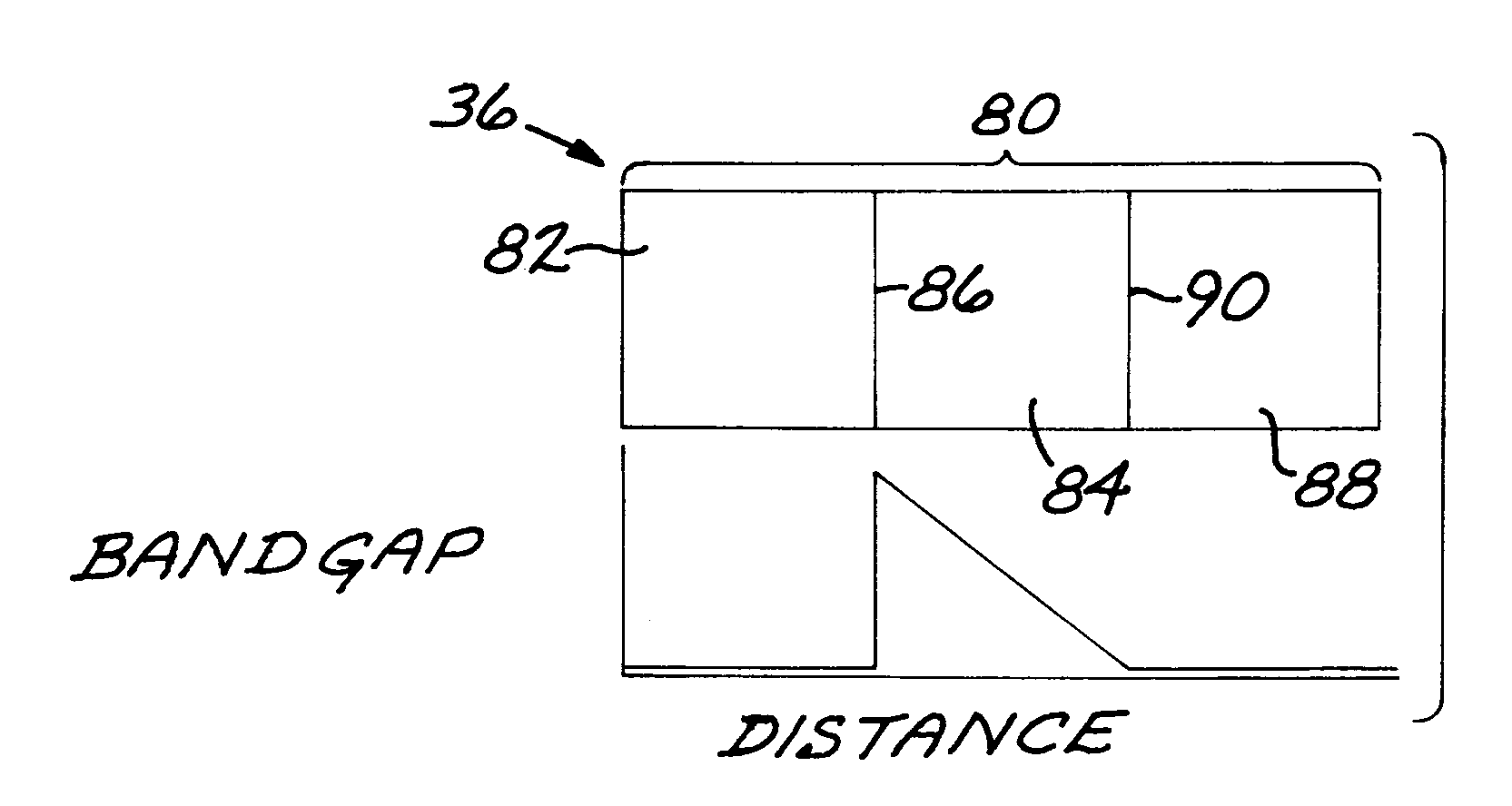

Single-band and dual-band infrared detectors

Bias-switchable dual-band infrared detectors and methods of manufacturing such detectors are provided. The infrared detectors are based on a back-to-back heterojunction diode design, where the detector structure consists of, sequentially, a top contact layer, a unipolar hole barrier layer, an absorber layer, a unipolar electron barrier, a second absorber, a second unipolar hole barrier, and a bottom contact layer. In addition, by substantially reducing the width of one of the absorber layers, a single-band infrared detector can also be formed.

Owner:CALIFORNIA INST OF TECH

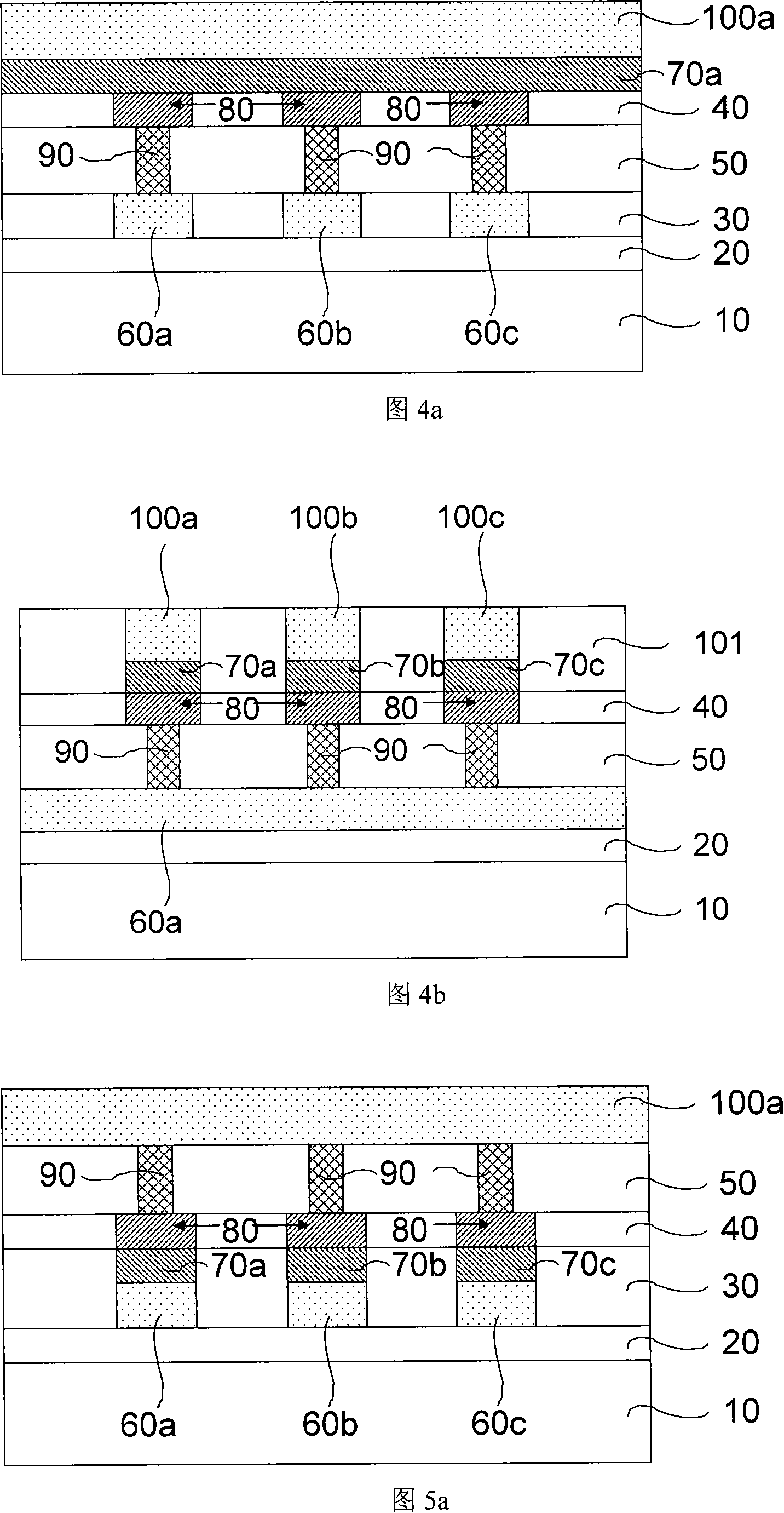

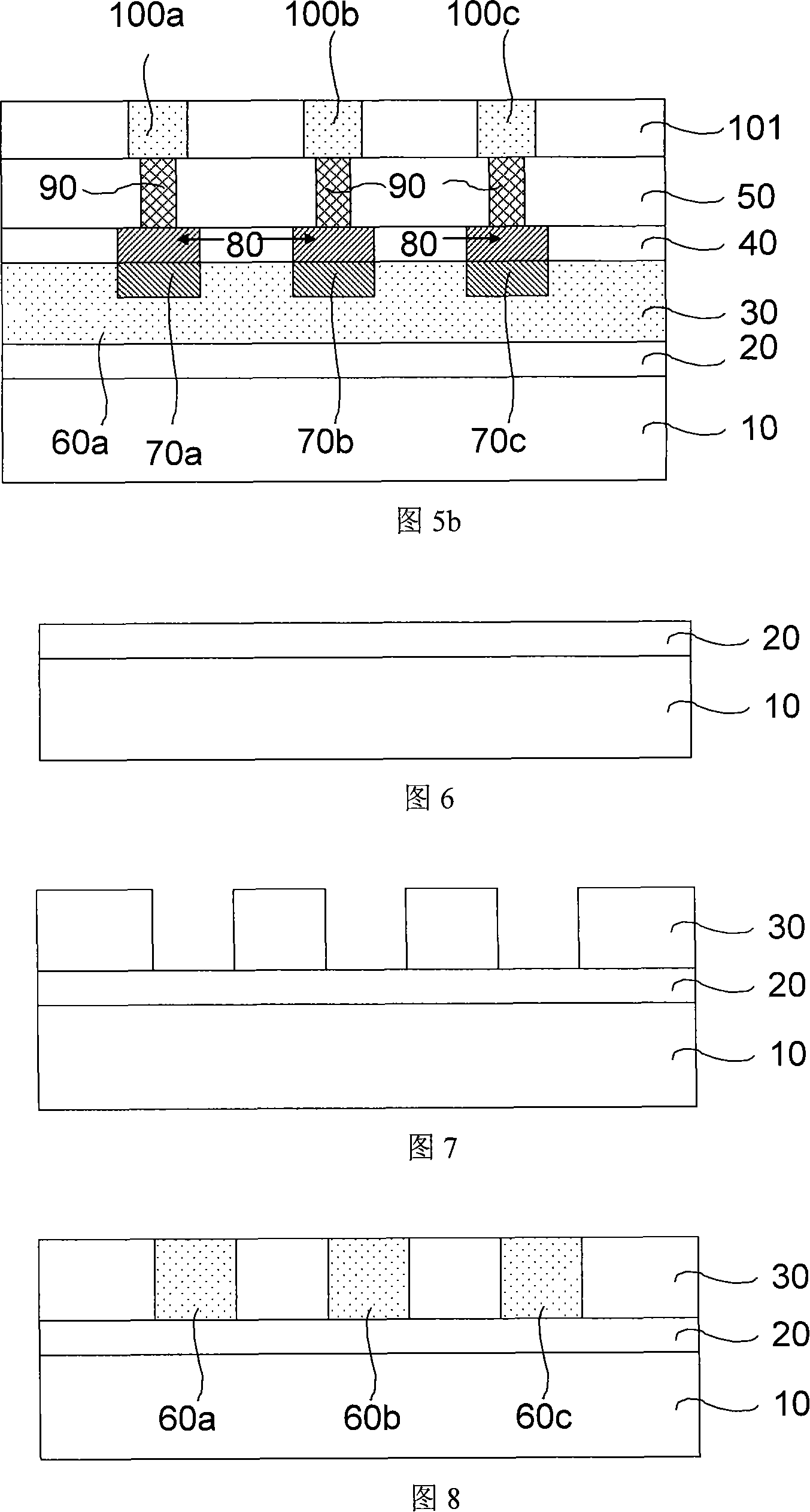

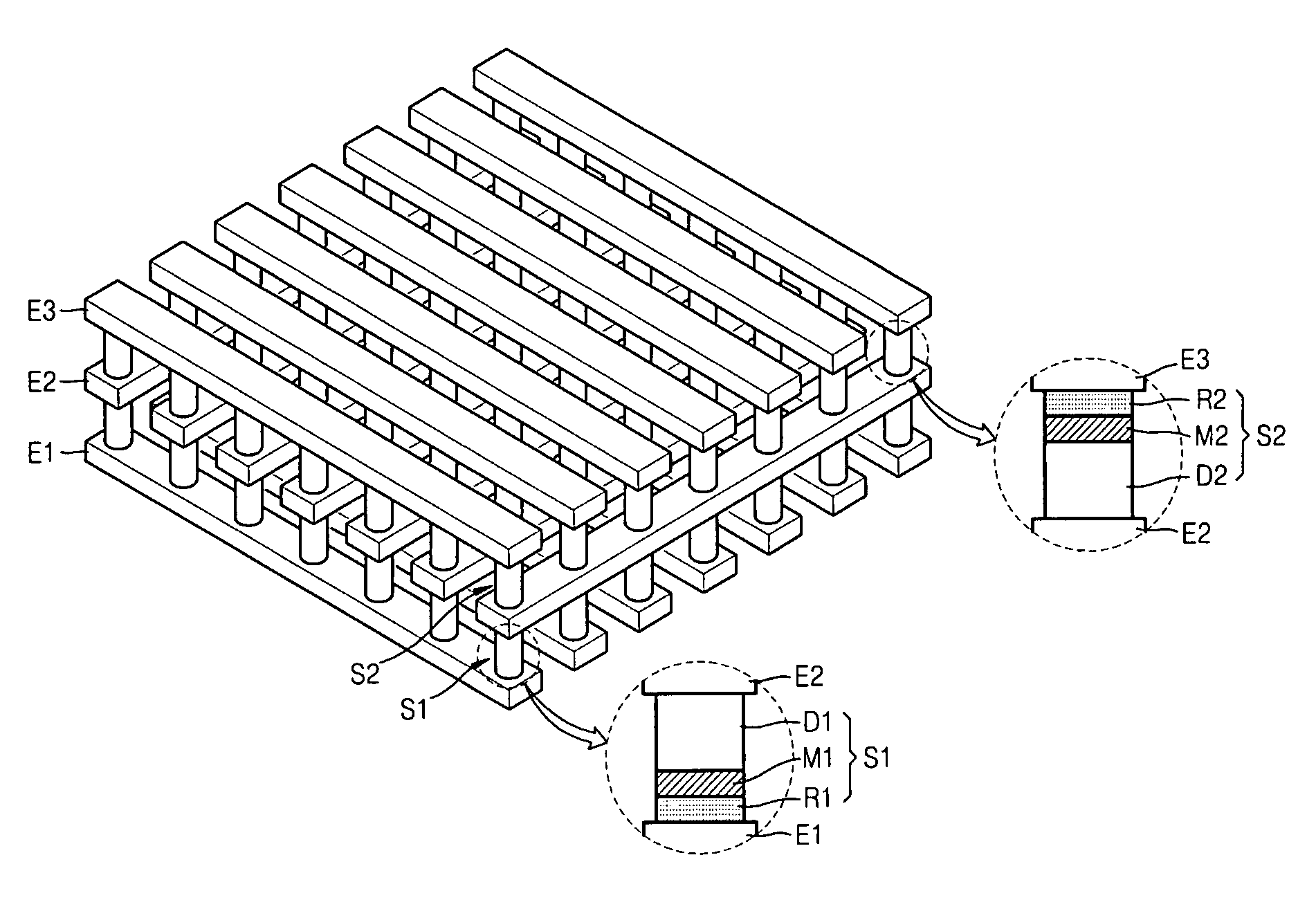

Phase change memory with diode unit selective connection and its making method

InactiveCN101106151AImprove storage densitySemiconductor/solid-state device detailsSolid-state devicesPhase-change memoryMetal electrodes

The invention pertains to the field of microelectronic technology, specifically to a phase-change memory based on diode unit gating and the fabrication method thereof. The phase-change memory comprises word lines with the properties of semiconductor thin film, one or more metal electrodes, phase-change materials with the properties of semiconductor thin film, and site lines with the properties of semiconductor thin film. Heterojunction diodes formed by the word lines or the site lines and the phase-change thin-film materials, or Schottky diodes formed by the word lines or the site lines and the metal electrodes serve as gating units of the memory in a structure of 1D / 1R. The phase-change memory in the invention is simple in structure management and fabrication method, and independent of the silicon substrate. The array stacking of a plurality of phase-change memories can be realized, and thereby the memory density is greatly increased.

Owner:FUDAN UNIV +1

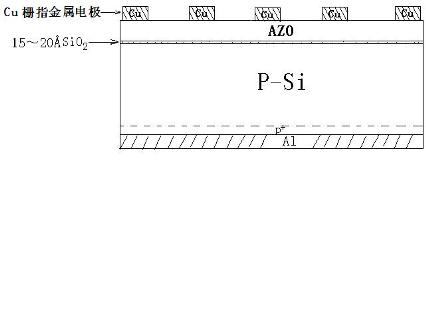

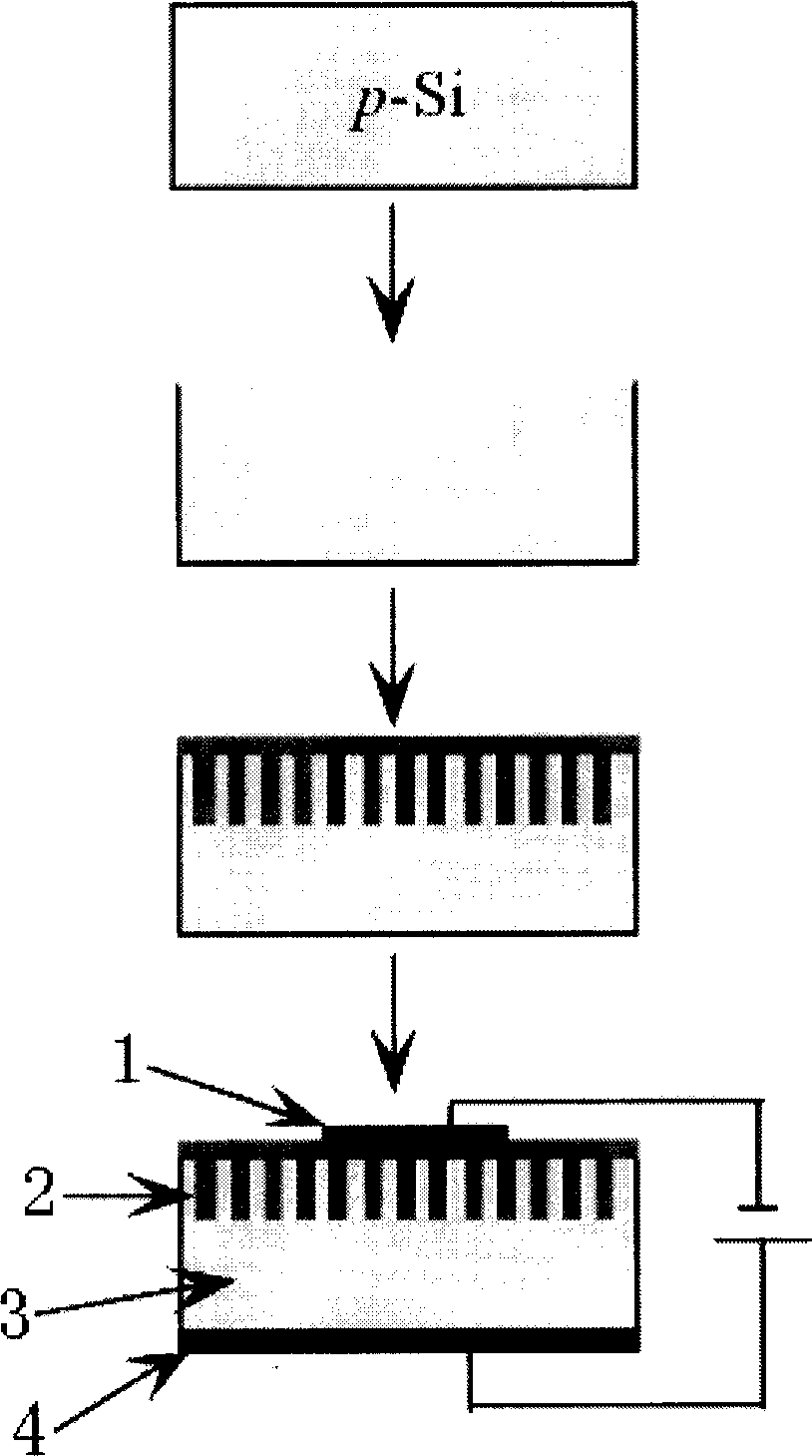

Method for preparing silicon-based SIS heterojunction photoelectric device

InactiveCN102034902AIncrease the open circuit voltageImprove conversion efficiencyFinal product manufactureSemiconductor devicesVisible near infraredPhotovoltaic effect

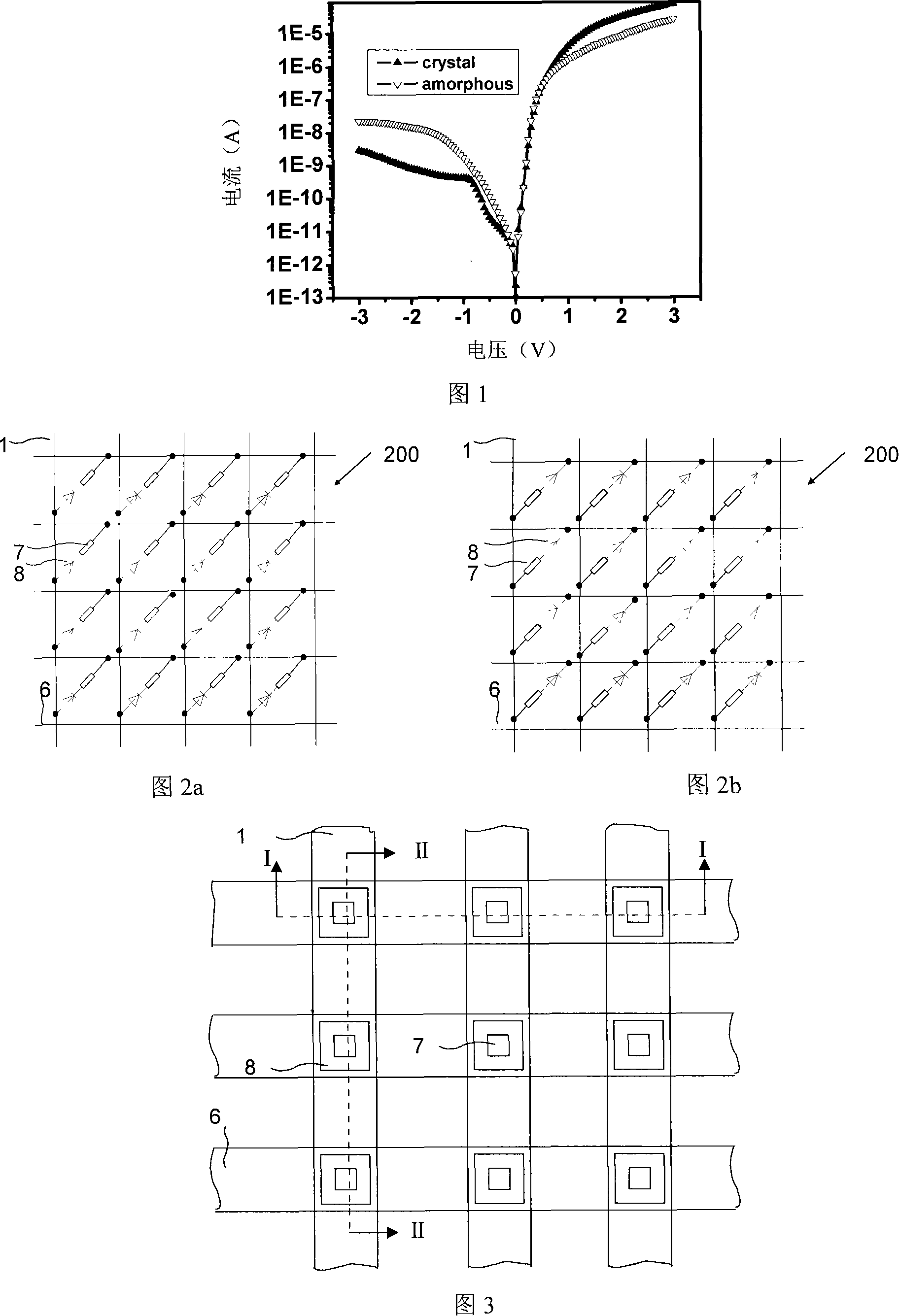

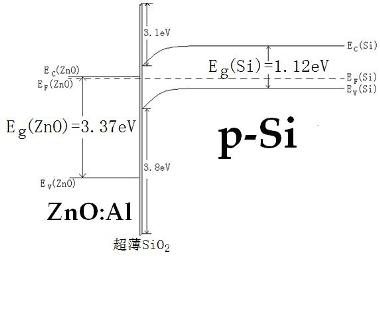

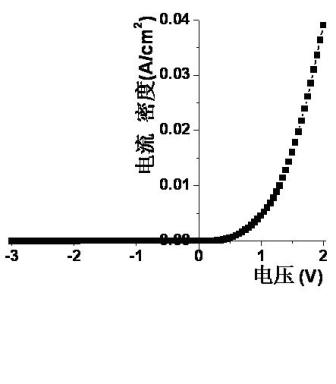

The invention relates to a method for preparing a direct current (DC) magnetron sputtering AZO / SiO2 / p-SiSIS heterojunction photoelectric device, and belongs to the technical field of methods for preparing silicon-based heterojunction photoelectric devices. By growth of an ultrathin SiO2 layer through low-temperature thermal oxidation, DC magnetron sputtering of an AZO emitter, antireflection and collection of an electrode film, a novel AZO / SiO2 / p-SiSIS ultraviolet-visible-near-infrared broad-spectrum heterojunction photoelectric device is successfully prepared. An I / V curve of the prepared AZO / SiO2 / p-SiSIS heterojunction has good rectification characterisitic and very low reverse dark current, so a good heterojunction diode is formed between AZO and p-Si. Under the condition of AM 1.5 illumination, the open-circuit voltage VOC is 230mV, the photoelectric conversion efficiency eta is 0.025 percent, and the photovoltaic effect is obvious. By combining different characteristics of a wide band gap of the AZO and a relatively narrow band gap of a Si material for mutual complementation, the SIS heterojunction can be developed into a low-cost solar cell, and also can become an excellent-performance ultraviolet-visible-near-infrared enhanced broad-spectrum photoelectric detector.

Owner:SHANGHAI UNIV

Heterojunction diode with reduced leakage current

ActiveUS7138668B2Improve pressure resistanceImprove leakage currentSemiconductor/solid-state device manufacturingDiodeSemiconductorSemiconductor device

An aspect of the present invention provides a semiconductor device that includes a first semiconductor region of a first conductivity type and a second semiconductor region of a second conductivity type, having a different band gap from the first semiconductor region and forming a heterojunction with the first semiconductor region.

Owner:NISSAN MOTOR CO LTD

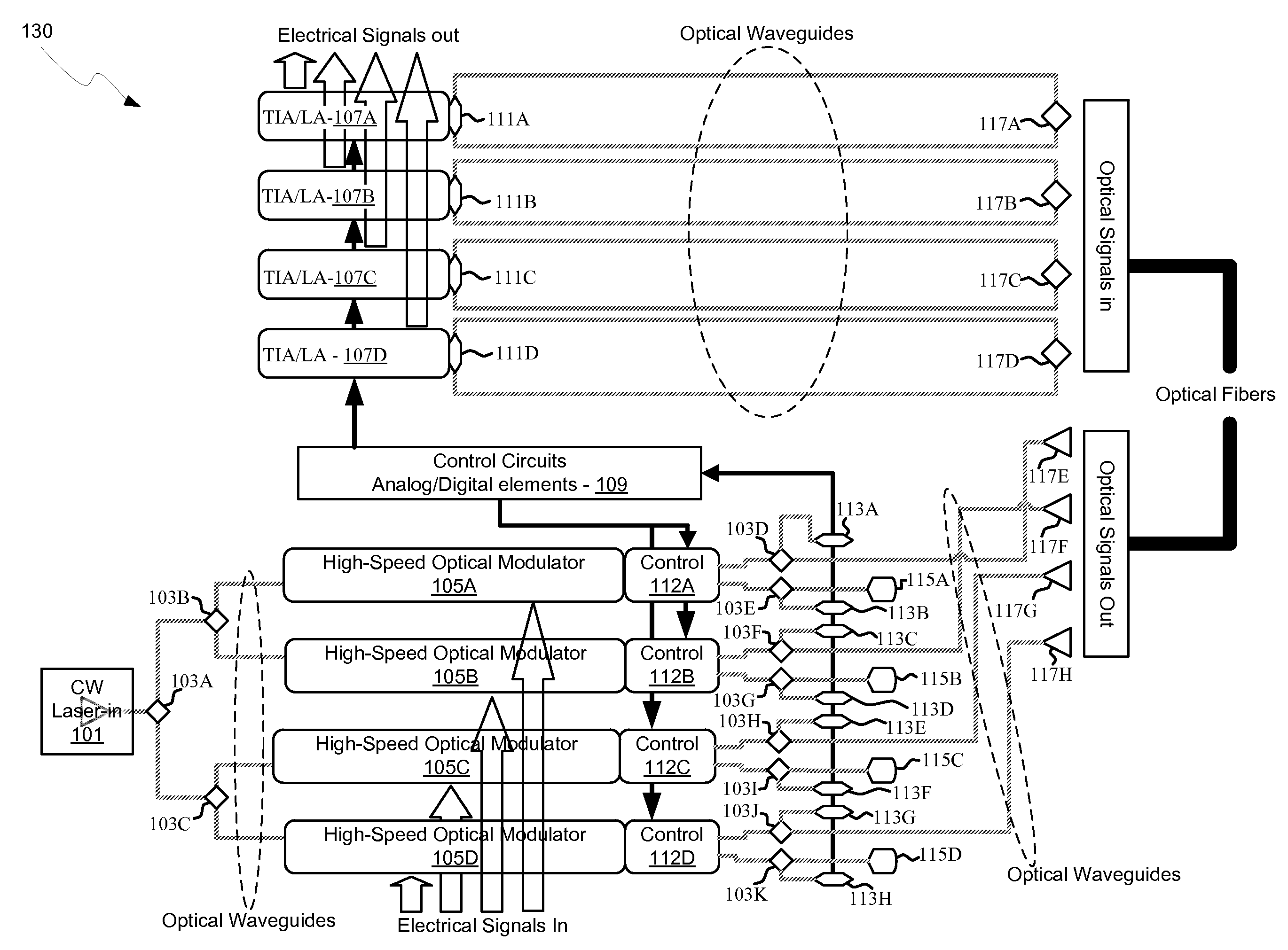

Method and system for optoelectronics transceivers integrated on a CMOS chip

Methods and systems for optoelectronics transceivers integrated on a CMOS chip are disclosed and may include receiving optical signals from optical fibers via grating couplers on a top surface of a CMOS chip, which may include a guard ring. Photodetectors may be integrated in the CMOS chip. A CW optical signal may be received from a laser source via grating couplers, and may be modulated using optical modulators, which may be Mach-Zehnder and / or ring modulators. Circuitry in the CMOS chip may drive the optical modulators. The modulated optical signal may be communicated out of the top surface of the CMOS chip into optical fibers via grating couplers. The received optical signals may be communicated between devices via waveguides. The photodetectors may include germanium waveguide photodiodes, avalanche photodiodes, and / or heterojunction diodes. The CW optical signal may be generated using an edge-emitting and / or a vertical-cavity surface emitting semiconductor laser.

Owner:LUXTERA

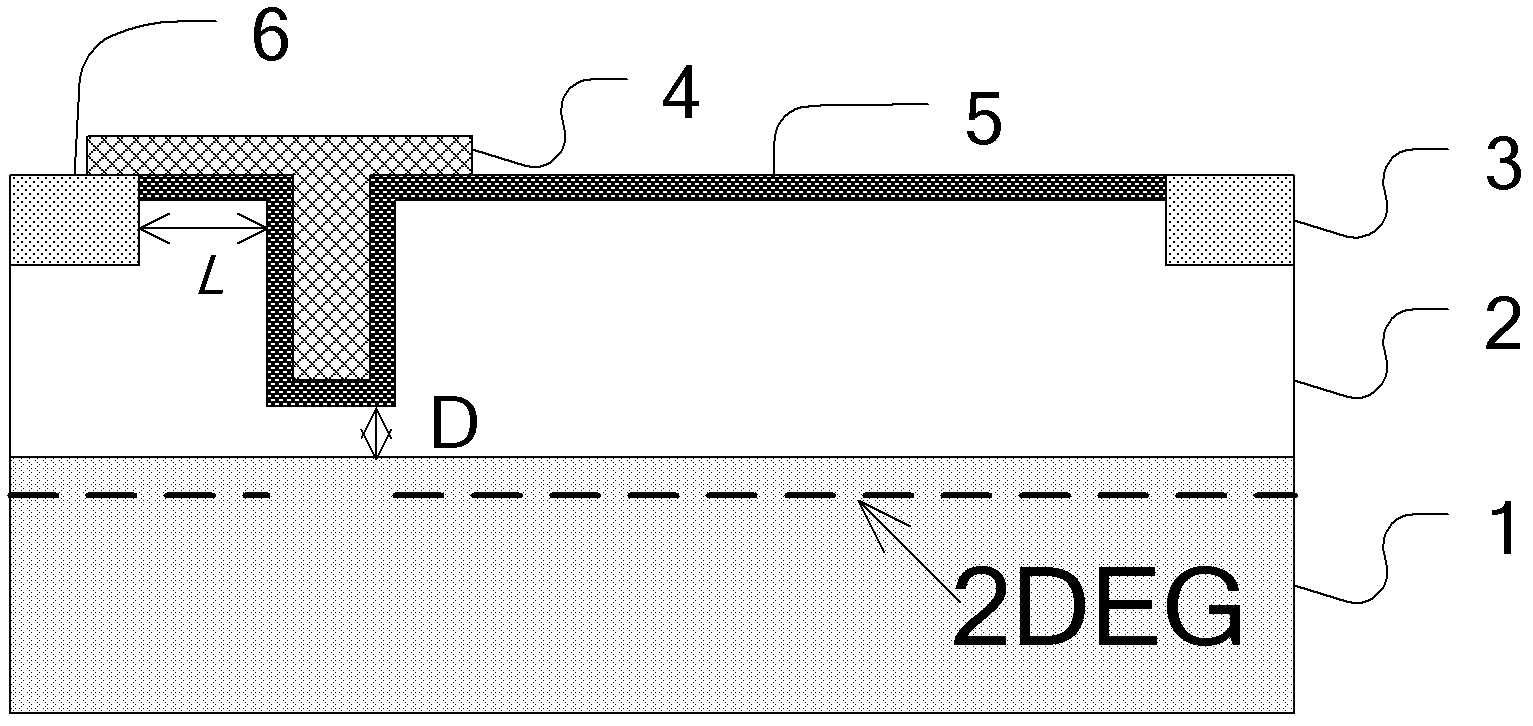

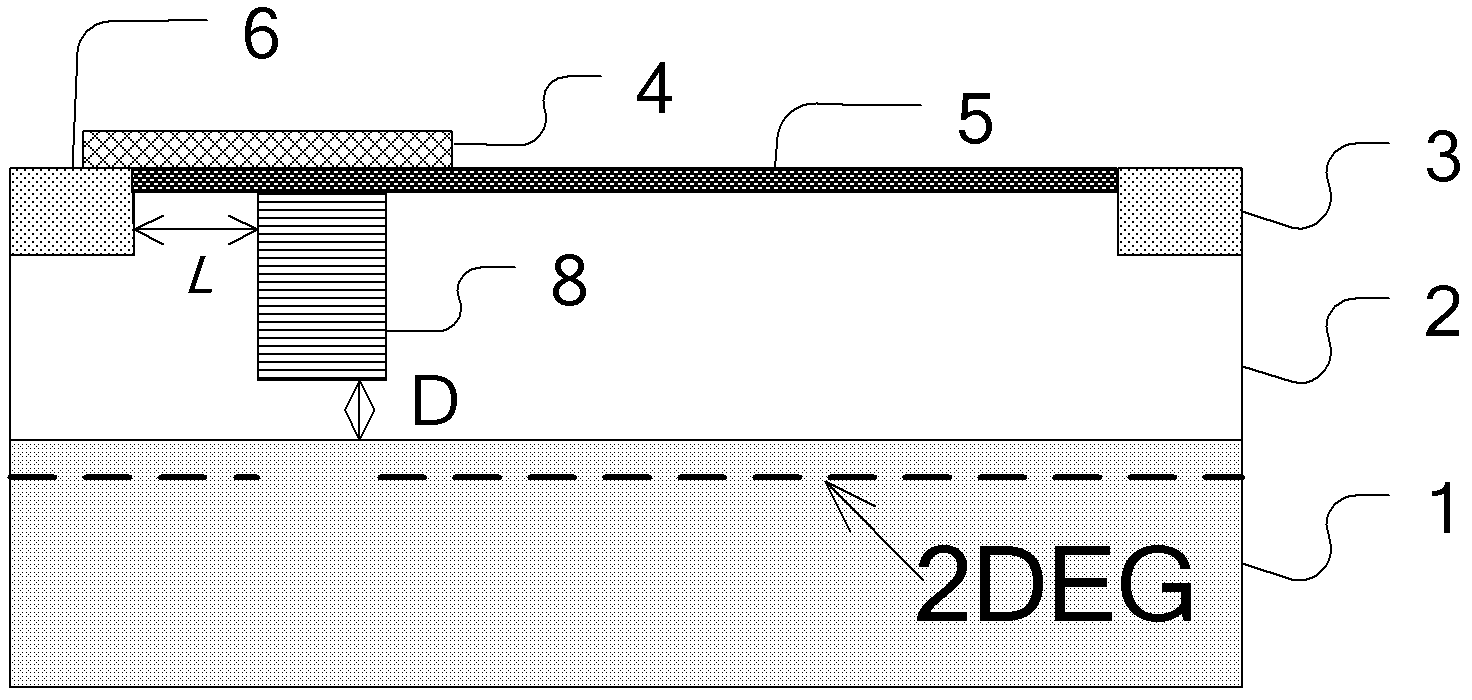

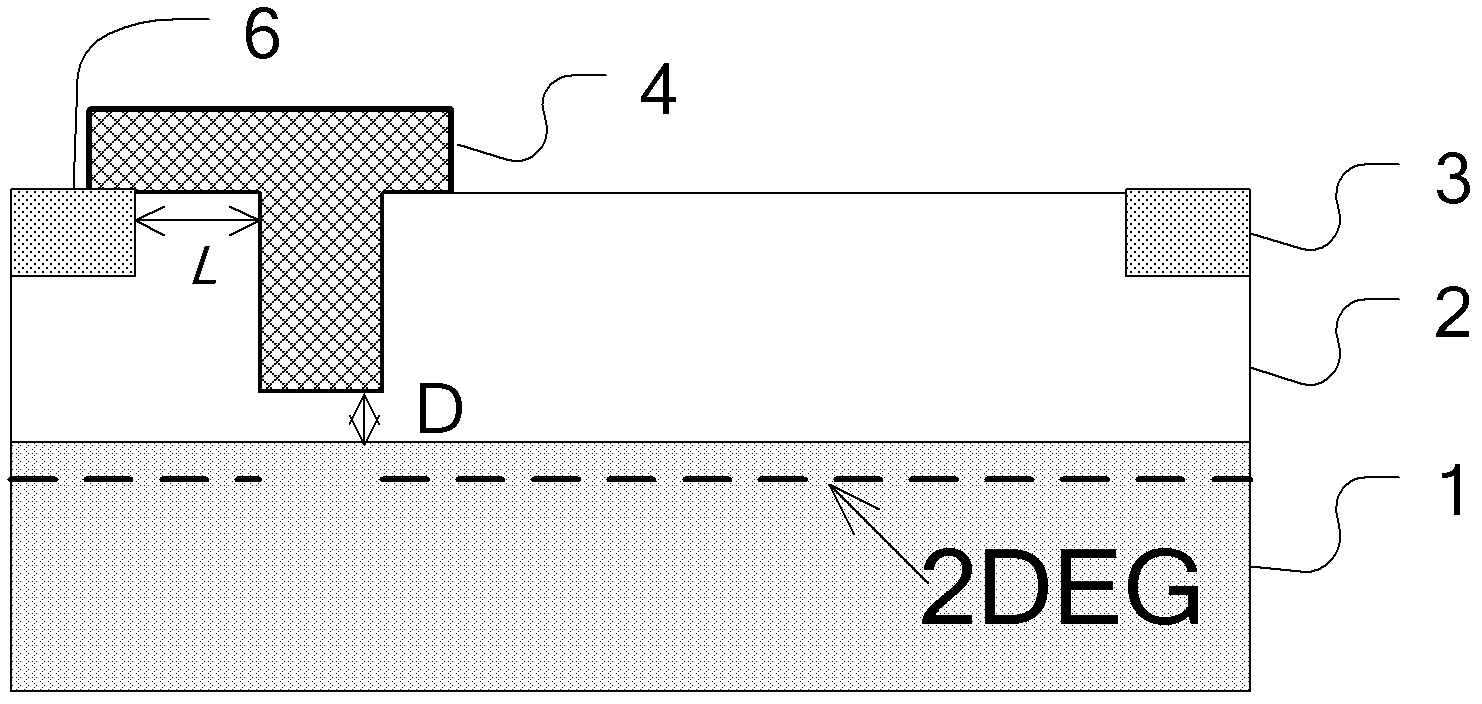

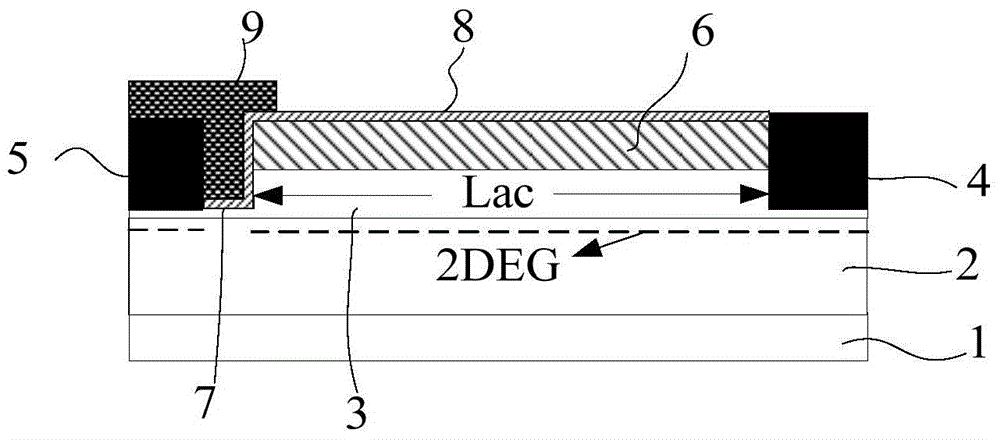

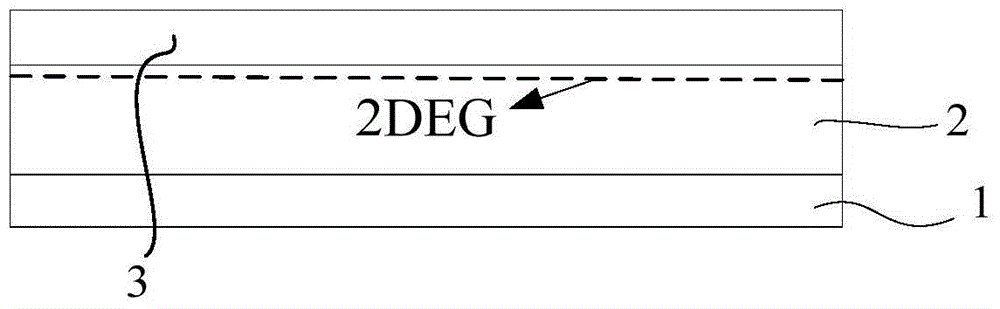

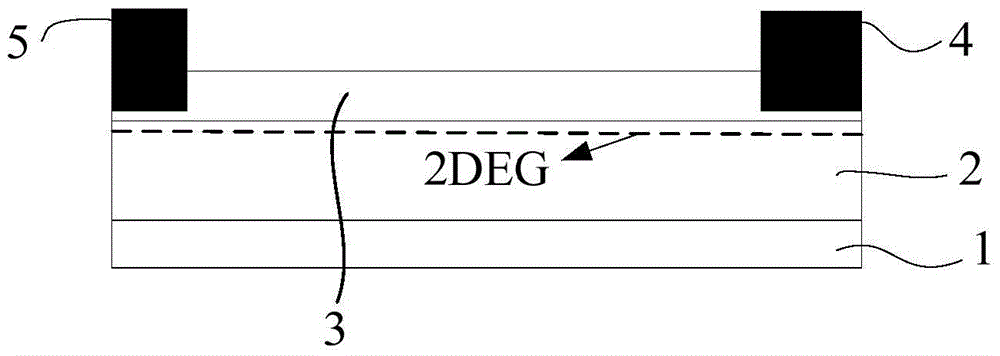

Gallium nitride heterojunction MIS grid-control power diode and manufacturing method thereof

The invention relates to the technical field of semiconductor devices, in particular to a gallium nitride heterojunction MIS grid-control power diode and a manufacturing method thereof. The gallium nitride heterojunction MIS grid-control power diode is characterized in that the two-dimensional electron gas below Schottky metal is exhausted by etching the barrier layer below the anode Schottky metal, insulating media and Schottky metal are precipitated in the etched groove to form a Schottky metal / insulting medium / semiconductor (MIS) grid-control structure, the MIS grid-control structure can control the on and off of a device and can effectively reduce the reverse leakage of the device and increase the reverse voltage resistance of the device; an Ohm / Schottky metal short-circuit mixed anode is formed at the anode of the diode, and low positive turning-on voltage of the device can be achieved. The gallium nitride heterojunction MIS grid-control power diode has the advantages of high reverse voltage resistance, high breakover currents, low turning-on voltage, low breakover resistance, low power consumption and the like. The manufacturing method is especially applicable to the gallium nitride heterojunction diode.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

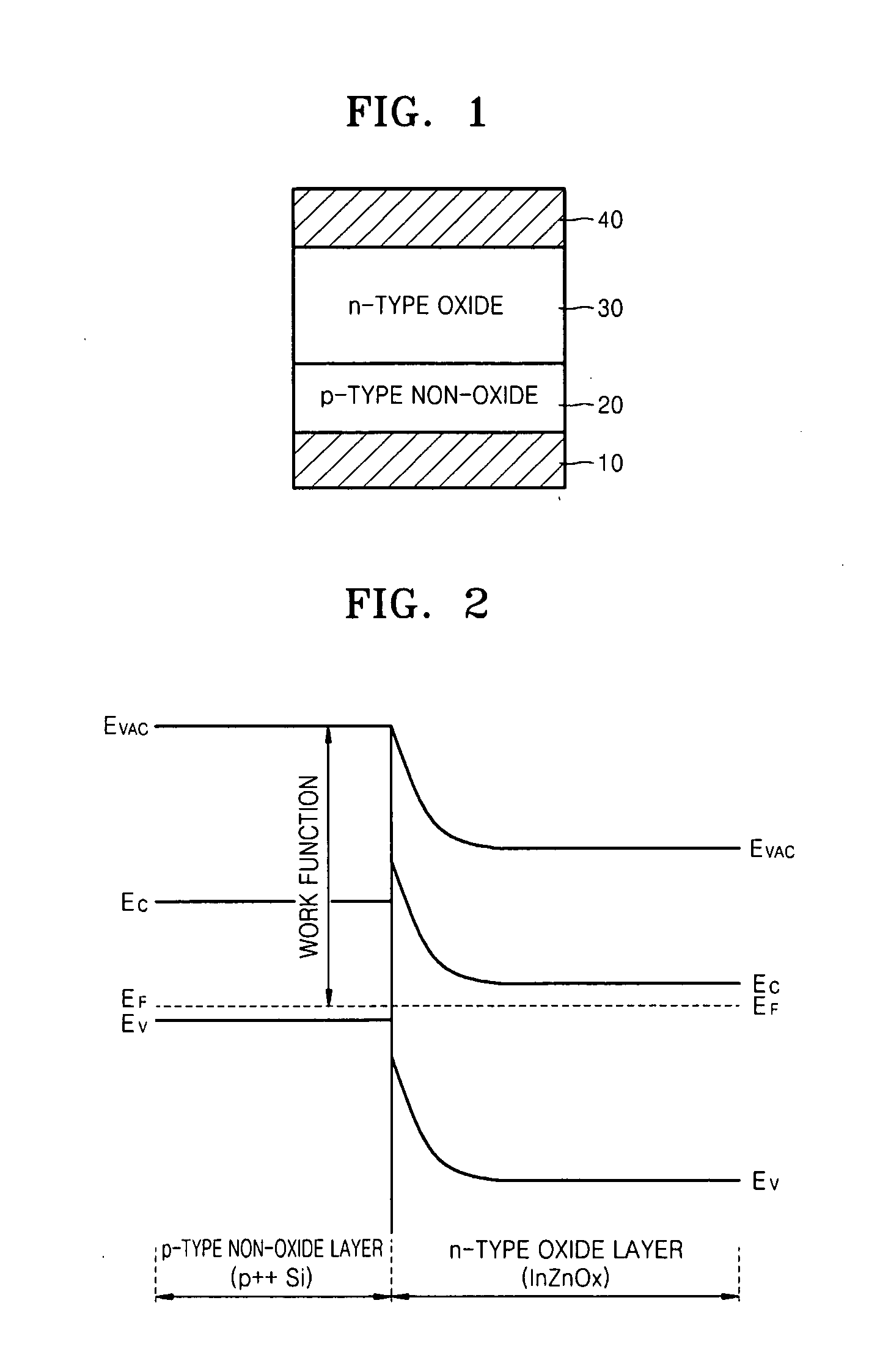

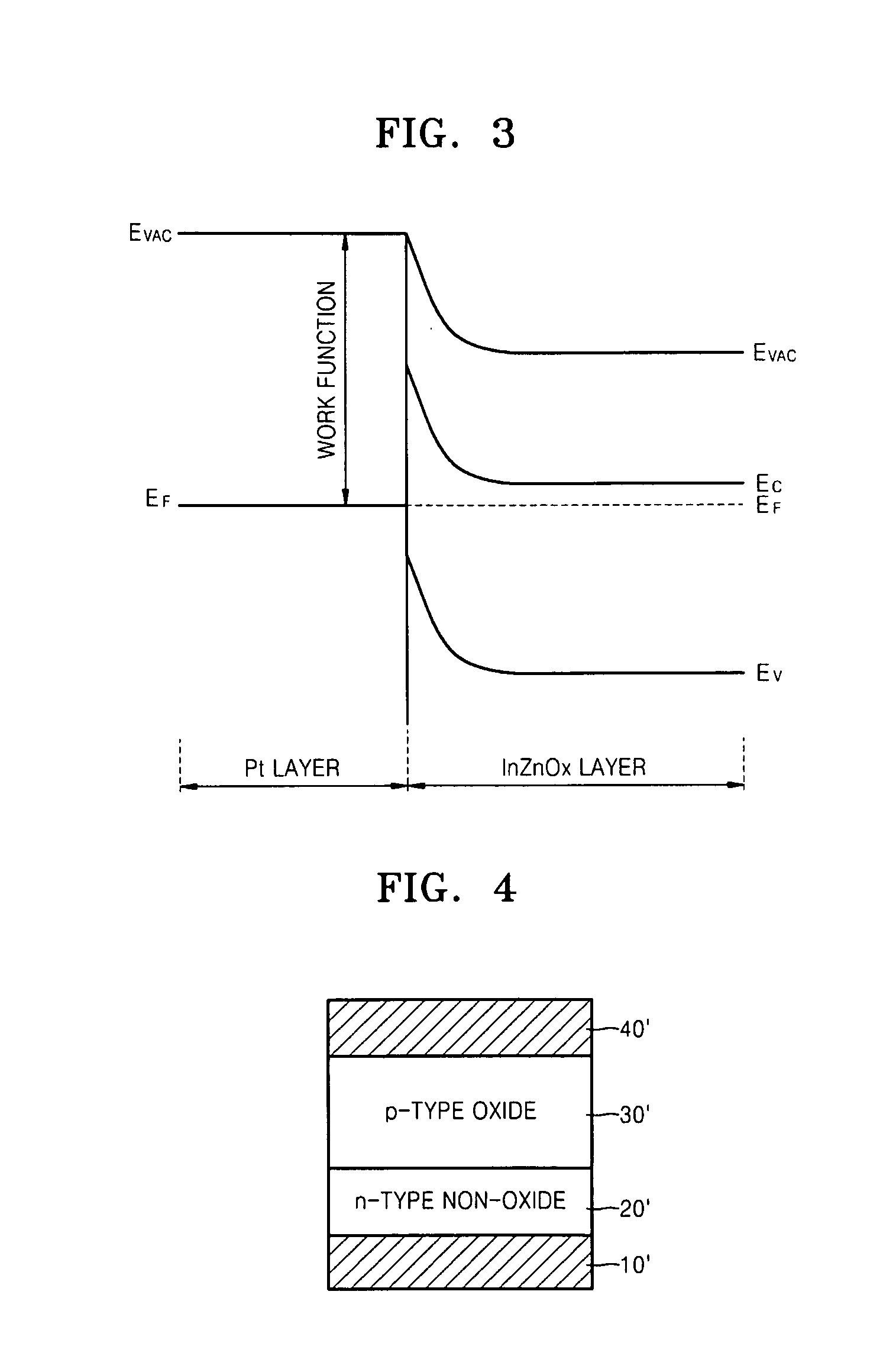

Heterojunction diode, method of manufacturing the same, and electronic device including the heterojunction diode

ActiveUS20100308297A1Solid-state devicesSemiconductor/solid-state device manufacturingWork functionForward voltage

Example embodiments relate to a heterojunction diode, a method of manufacturing the heterojunction diode, and an electronic device including the heterojunction diode. The heterojunction diode may include a first conductive type non-oxide layer and a second conductive type oxide layer bonded to the non-oxide layer. The non-oxide layer may be a Si layer. The Si layer may be a p++ Si layer or an n++ Si layer. A difference in work functions of the non-oxide layer and the oxide layer may be about 0.8-1.2 eV. Accordingly, when a forward voltage is applied to the heterojunction diode, rectification may occur. The heterojunction diode may be applied to an electronic device, e.g., a memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

Robust group III light emitting diode for high reliability in standard packaging applications

InactiveUS20050095737A1Solid-state devicesSemiconductor/solid-state device manufacturingHigh humidityOhmic contact

A physically robust light emitting diode is disclosed that offers high-reliability in standard packaging and that will withstand high temperature and high humidity conditions. The diode comprises a Group III nitride heterojunction diode with a p-type Group III nitride contact layer, an ohmic contact to the p-type contact layer, and a sputter-deposited silicon nitride composition passivation layer on the ohmic contact. A method of manufacturing a light emitting diode and an LED lamp incorporating the diode are also disclosed.

Owner:CREE INC

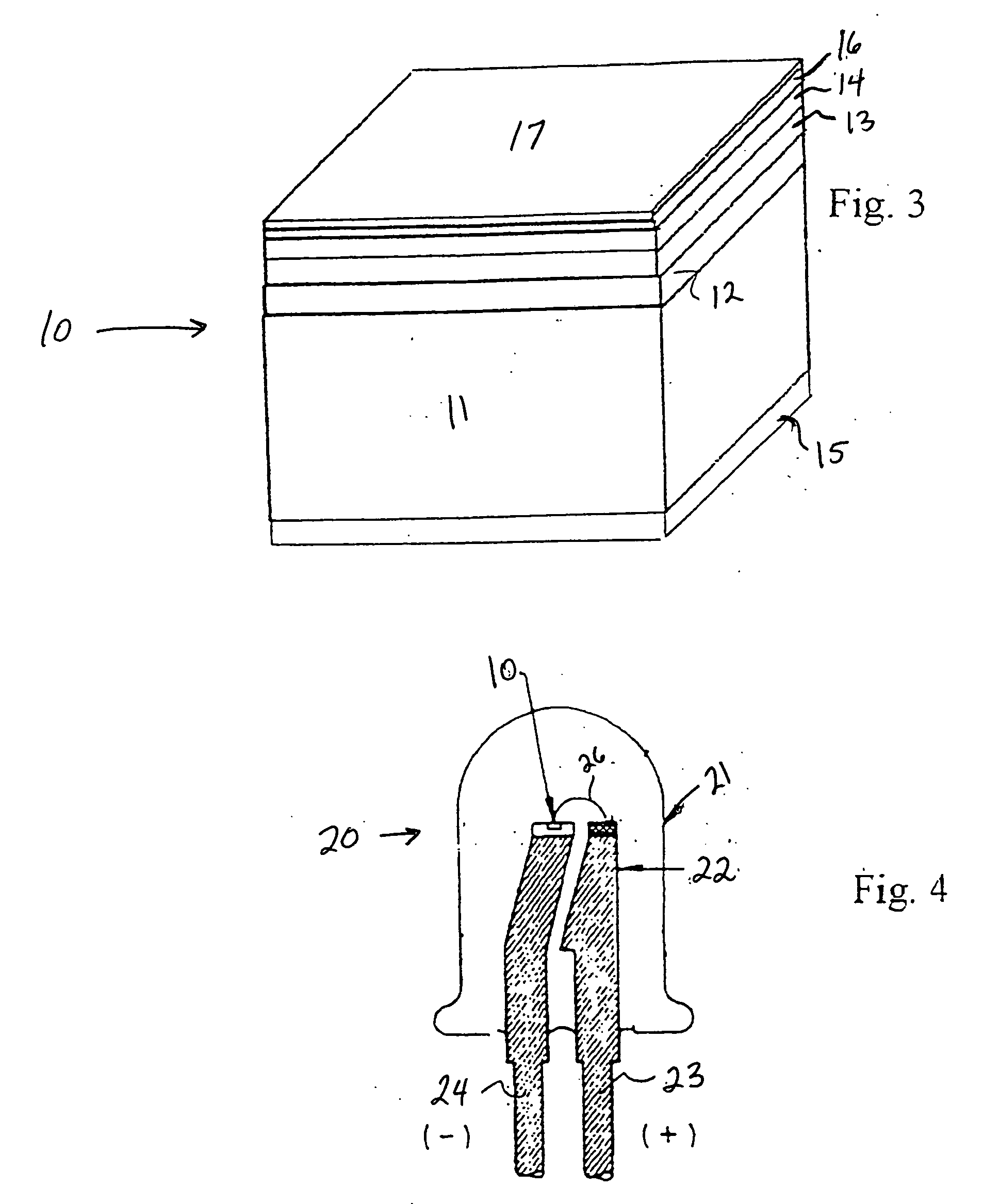

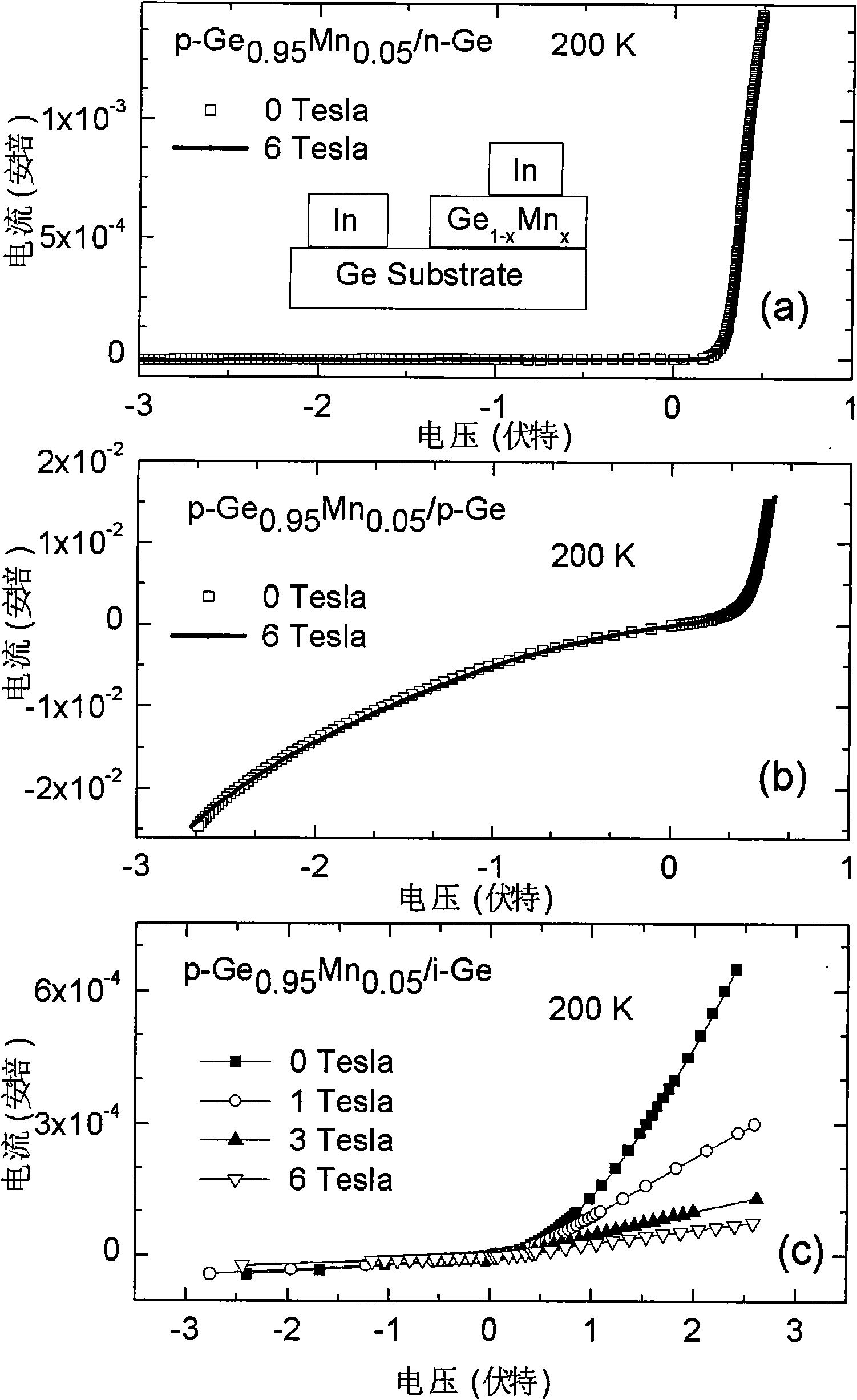

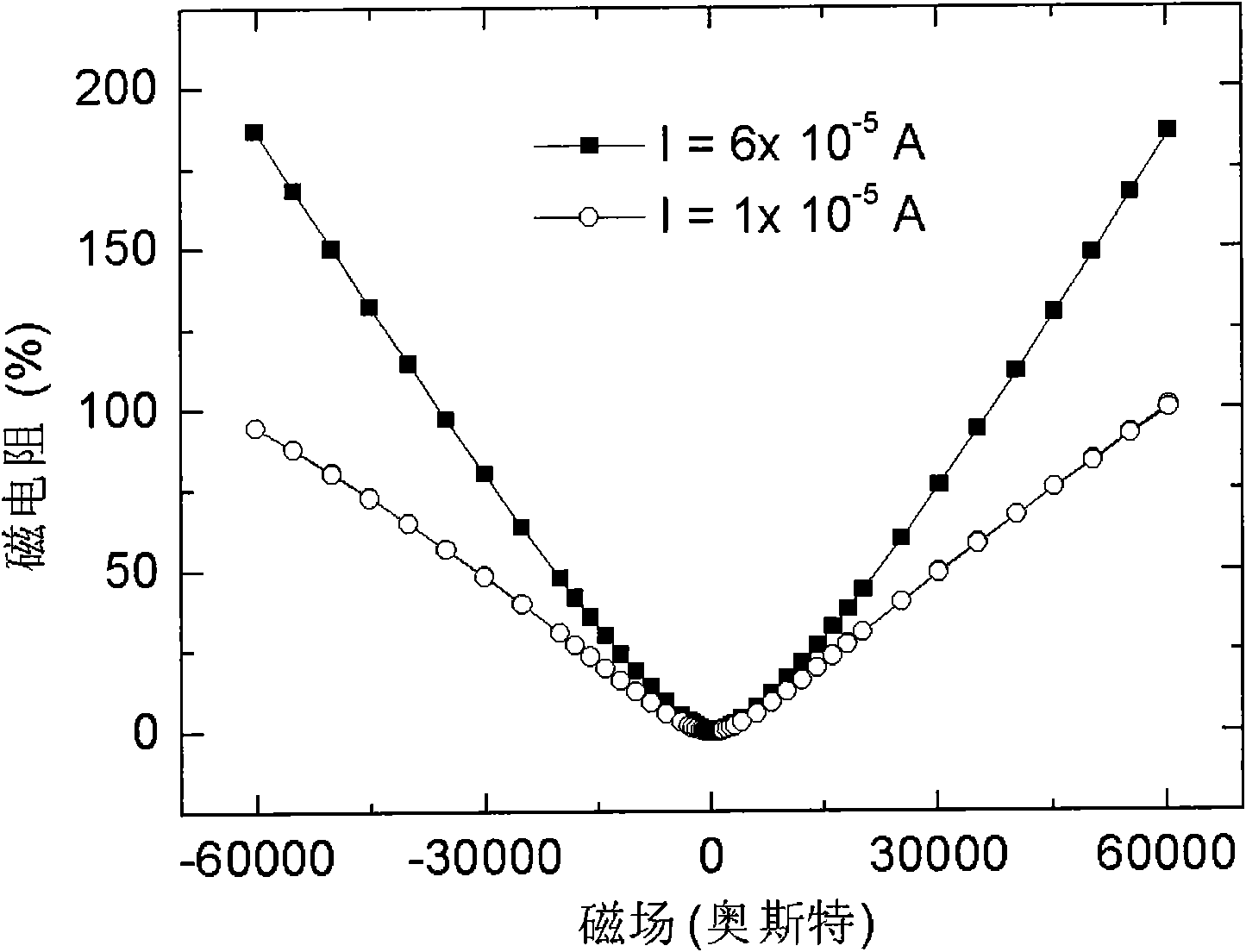

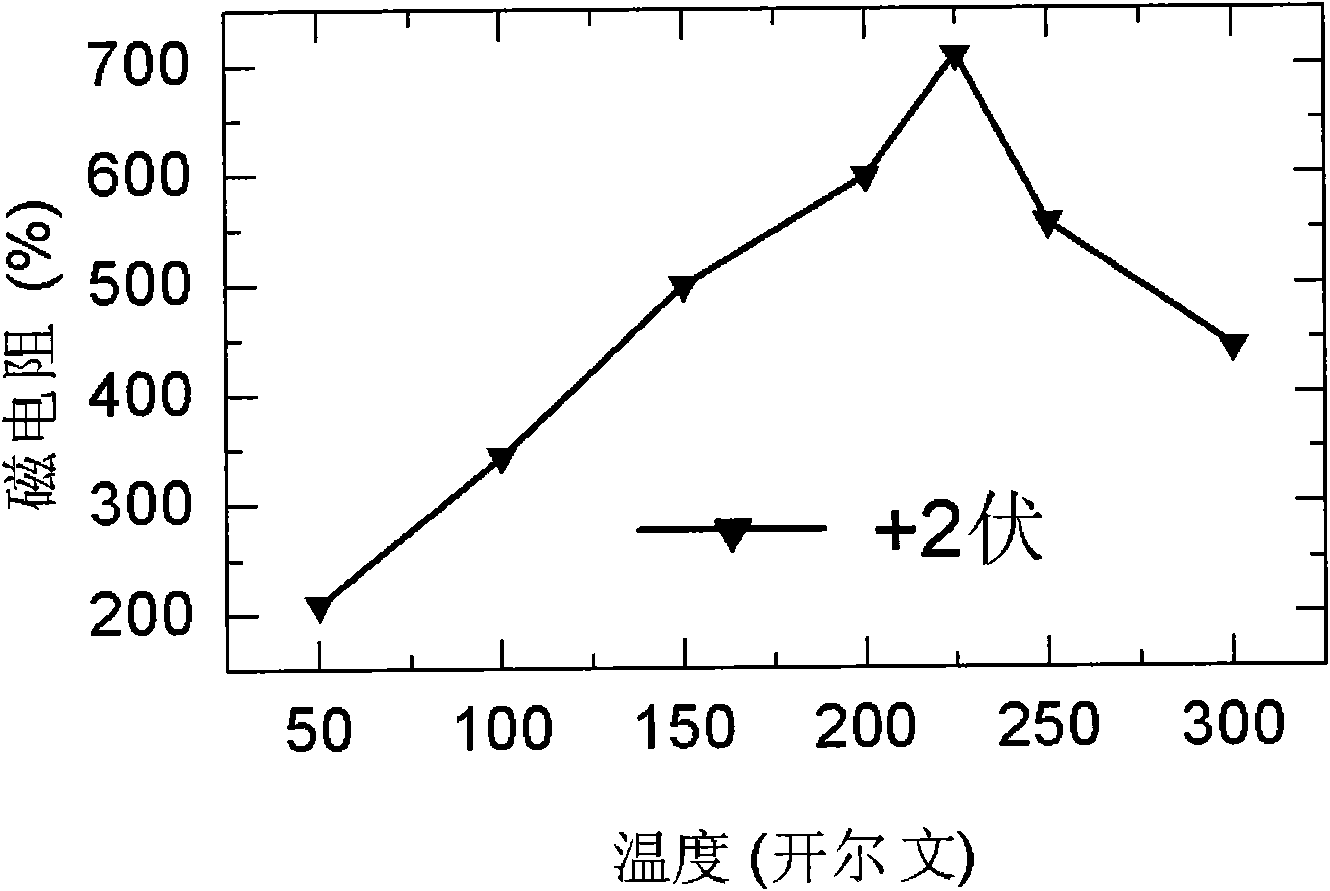

Single crystal germanium manganese magnetic semiconductor/germanium magnetic heterodiode and preparation method thereof

InactiveCN101615634AElectrical transport properties can be tunedSemiconductor/solid-state device manufacturingSemiconductor devicesManganeseSingle crystal

The invention relates to a single crystal germanium manganese magnetic semiconductor / germanium magnetic heterodiode and a preparation method thereof, which belong to the technical field of spinning electronic devices of an information technology. A p-type layer of the heterodiode is a single Ge1-xMnx ferromagnetic semiconductor, the mol percentage content x of manganese is more than 0 and is less than 15 percent; a Ge layer is a commercial intrinsic single crystal semiconductor Ge or an n-type single crystal semiconductor Ge doped with trace Sb, rectification characteristic under room temperature is adjusted and controlled by using a magnetic field, a magnetic resistor has an extreme value near Curie temperature of the Ge1-xMnx, and the preparation process is matched with the preparation process of a silicon semiconductor. The single crystal germanium manganese magnetic semiconductor / germanium magnetic heterodiode is prepared in such a way that molecular-beam epitaxy epitaxially grows a germanium manganese magnetic semiconductor on a single germanium substrate. Meanwhile, the single crystal germanium manganese magnetic semiconductor / germanium magnetic heterodiode prepared by the method can be better matched with the process of the modern silicon semiconductor, thereby having better application prospect on the aspect of the spinning electronic devices.

Owner:SHANDONG UNIV

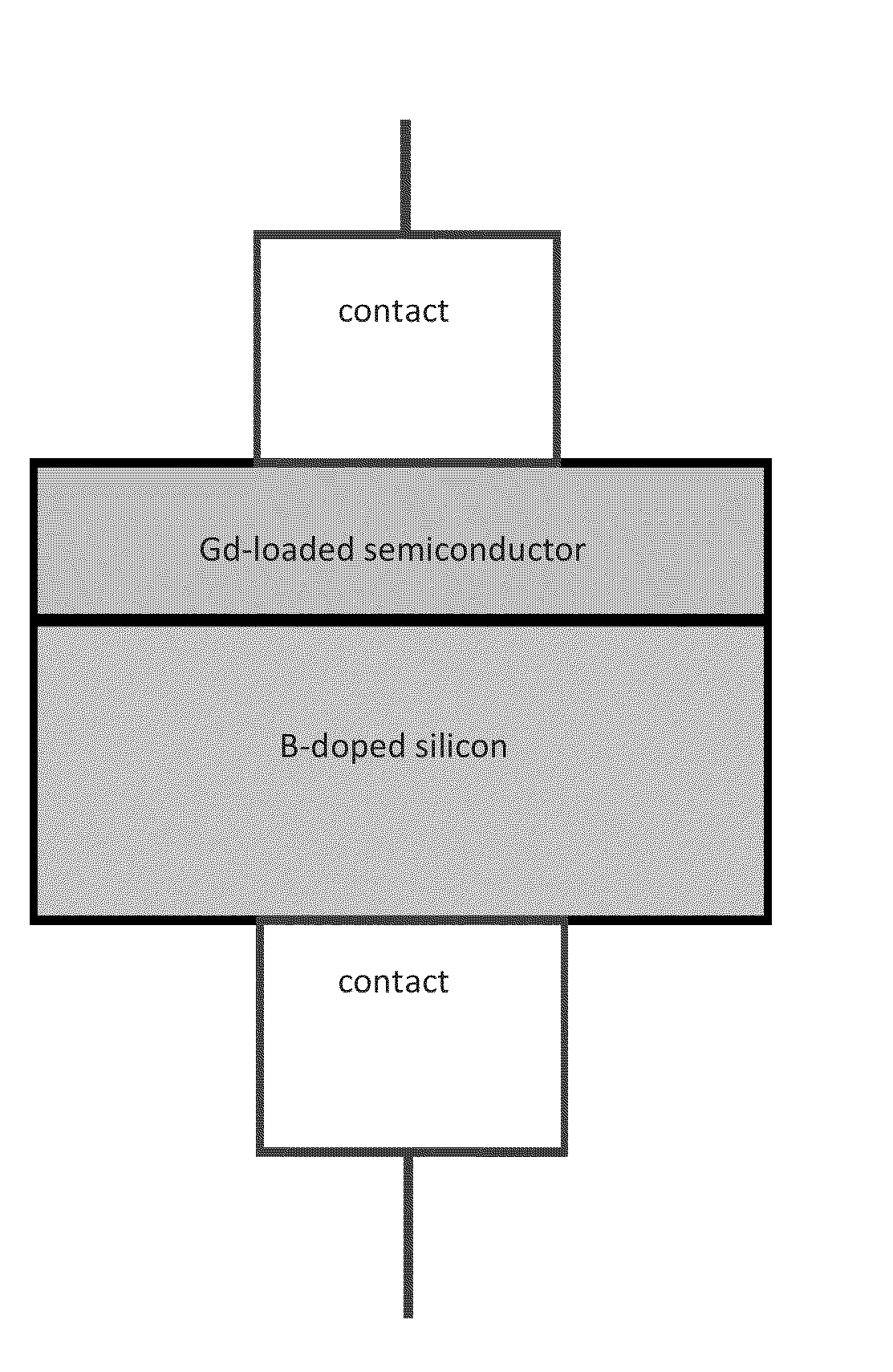

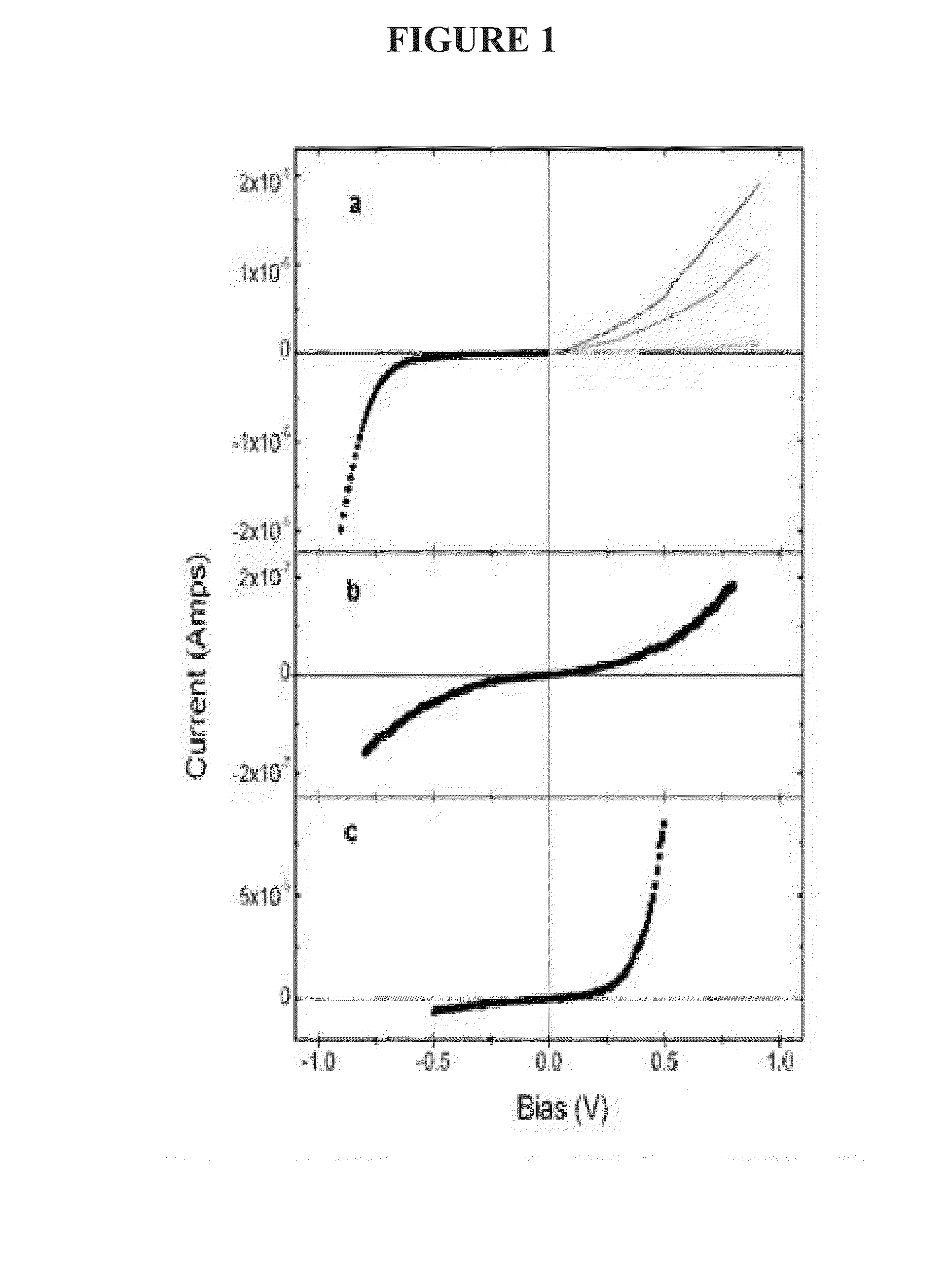

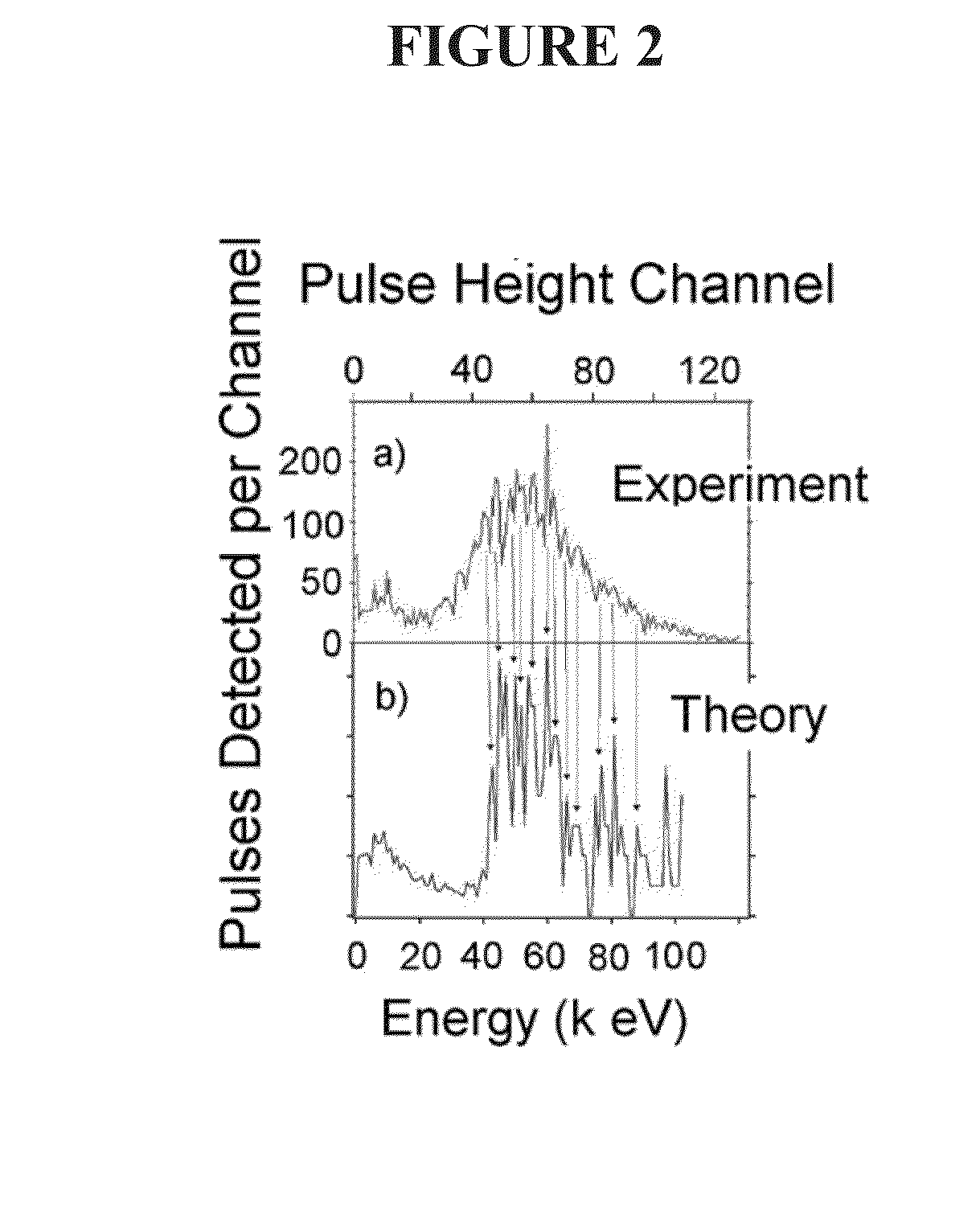

Neutron detection using gd-loaded oxide and nitride heterojunction diodes

InactiveUS20130009262A1High neutron capture cross-sectionHigh sensitivitySolid-state devicesSemiconductor devicesSemiconductor materialsGadolinium

Solid state neutron detection utilizing gadolinium as a neutron absorber is described. The new class of narrow-gap neutron-absorbing semiconducting materials, including Gd-doped HfO2, Gd-doped EuO, Gd-doped GaN, Gd2O3 and GdN are included in three types of device structures: (1) a p-n heterostructure diode with a ˜30 μm Gd-loaded semiconductor grown on a conventional semiconductor (Si or B-doped Si); (2) a p-n junction or a p-i-n trilayer diode with a Gd-loaded semiconductoron one side and single-crystal semiconducting Li2B4O7 layer on the other side of the heterojunction; and (3) a p-n junction or a p-i-n trilayer diode with a Gd-loaded semiconductoron on one side and a boron nitride (BN) semiconductor layer on the other side of the heterojunction.

Owner:QUANTUM DEVICES

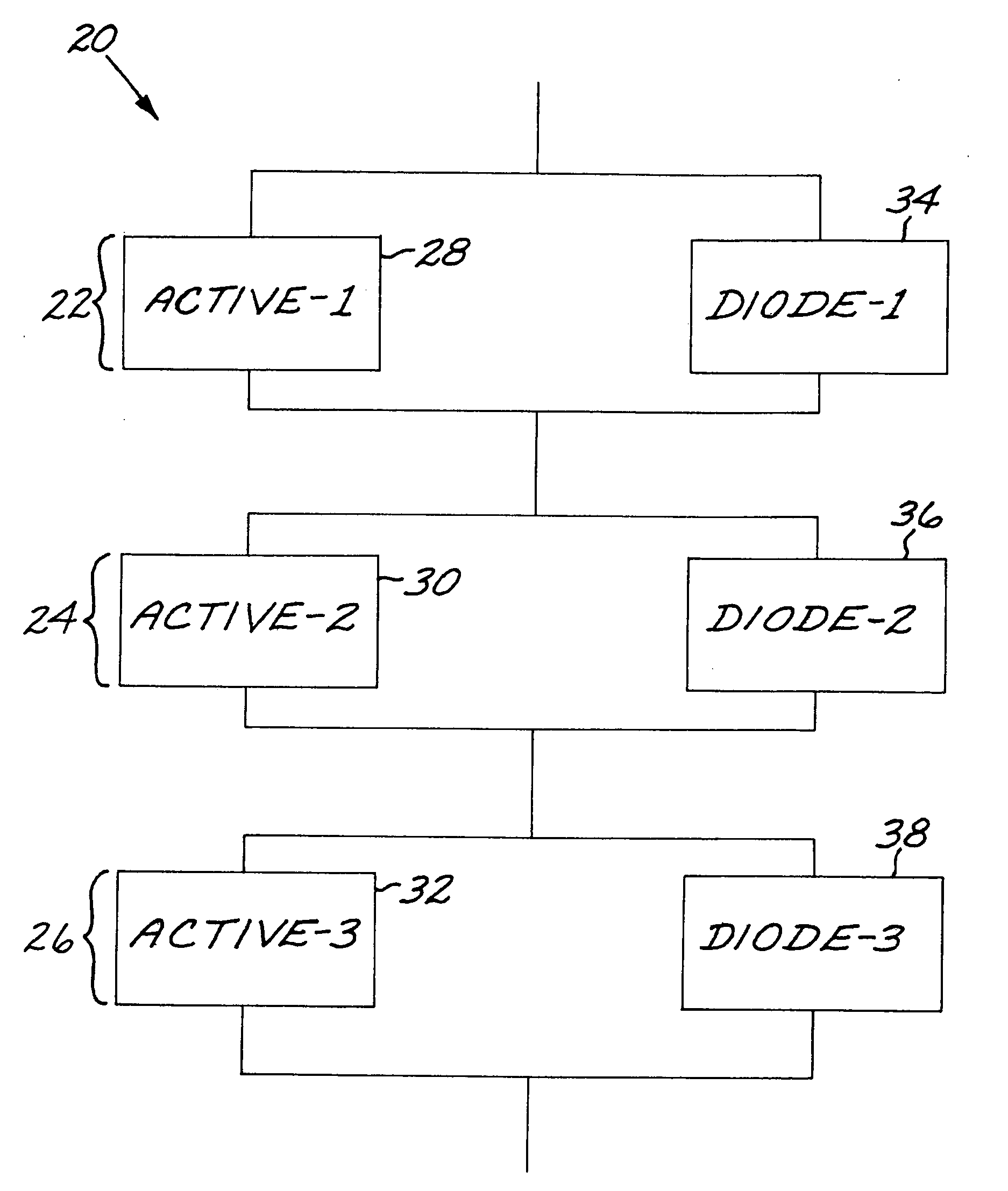

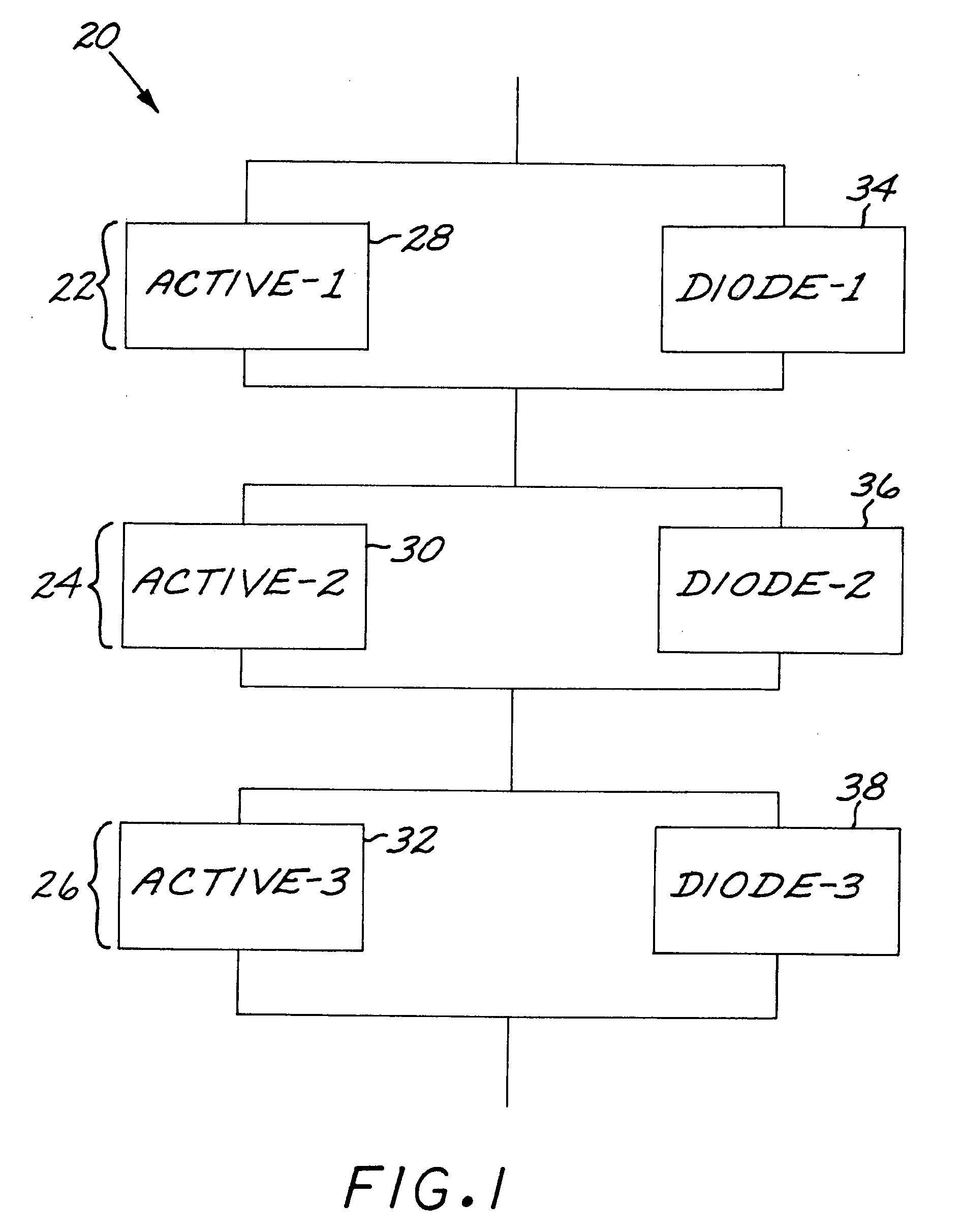

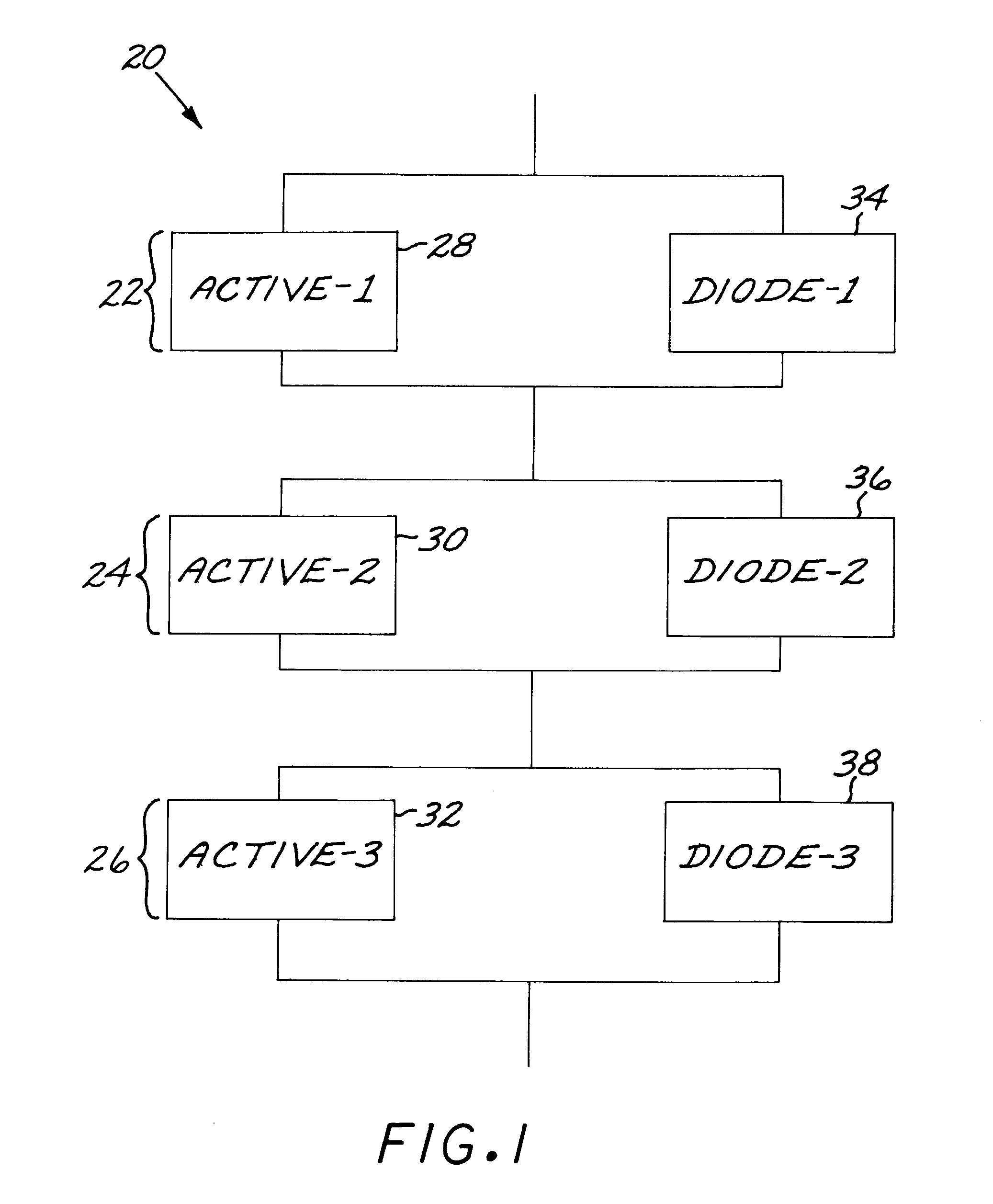

Solar cell array with isotype-heterojunction diode

InactiveUS20060249194A1Minimizes forward voltage dropMinimize power consumptionPV power plantsSolid-state devicesSolar cellEuhedral and anhedral

A solar cell array has at least one solar cell including a photovoltaic structure having a sun-facing front face and a back face, and having an active region, and an isotype heterojunction diode connected in electrical parallel with the active region of the photovoltaic structure.

Owner:THE BOEING CO

Heterojunction pn diode based on silicon nanoline and producing method thereof

InactiveCN1889275AIncrease chance of compoundingImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionP type silicon

The present invention relates to a heterogenous pn junction diode based on silicon nano wire and preparation method. Said diode features that it is p- silicon nano wire / n- wide bandgap oxide heterogenous pn junction formed by depositing n-type wide bandgap oxide in vertical orientation grown p - type silicon nano wire array. Said diode preparation method is: using non - electrode metal electrochemical deposition method to etch forming p type silicon nano wire on p type silicon wafer, then using formed vertical arrangement p type silicon nano array as templet depositing n-type wide bandgap oxide, finally respectively sputtering metal electrode on p type silicon back and n-type zinc oxide surface, forming ohmic contact electrode through annealing alloying. Said method prepared p - Si / n wide bandgap oxide heterogenous pn junction diode fully utilizes nano structure possessed large specific surface area, increasing carrier recombination probability and having lower positive direction cut-in voltage and large forward current density.

Owner:WUHAN UNIV

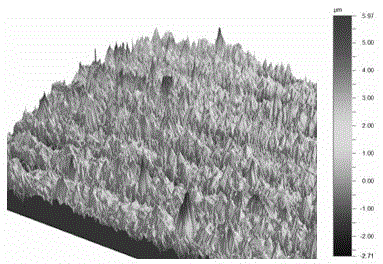

Preparation method of pointed-cone-shaped zinc oxide/nickel oxide heterojunction diodes

The invention relates to the preparation technology of heterojunction ultraviolet laser diodes, in particular to a method for preparing pointed-cone-shaped p-NiO (nickel oxide) / n-ZnO (zinc oxide) heterojunctions by combining the film coating technology and the femtosecond laser technology. According to the method, firstly, heat oxidation is utilized to form a NiO layer on a nickel sheet, then, an atomic layer deposition method is utilized for preparing a ZnO layer, next, an ITO (indium tin oxide) transparent upper electrode is formed outside the n-type ZnO layer by a sputtering method, finally, a pointed-cone-shaped array is formed on the nickel sheet covered with an NiO / ZnO / ITO layer by the femtosecond laser processing technology, pointed-cone-shaped p-NiO / n-ZnO heterojunctions are formed, voltage is applied to the ITO and the bottom of the nickel sheet, and the electroluminescence can be realized.

Owner:南通东湖国际商务服务有限公司

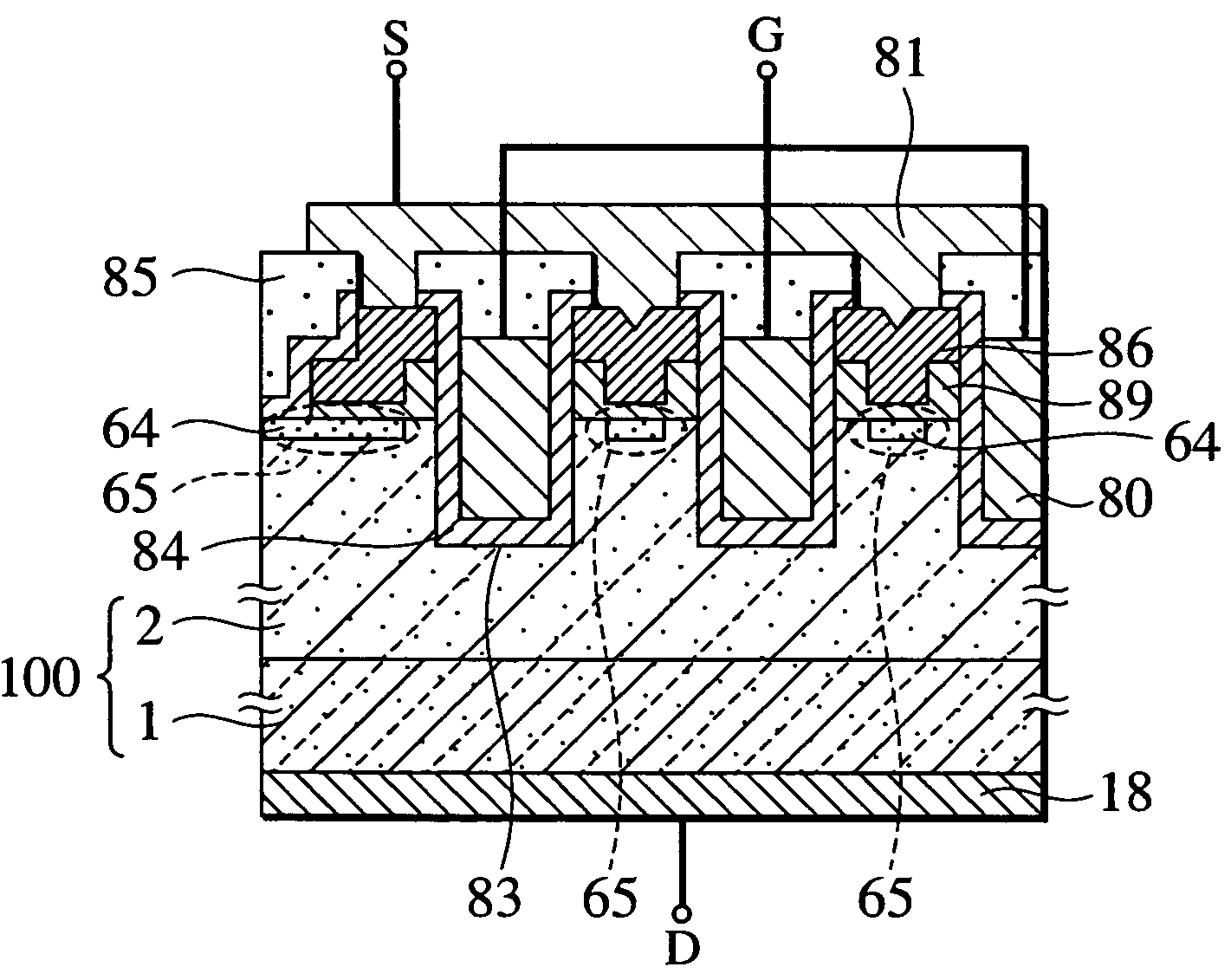

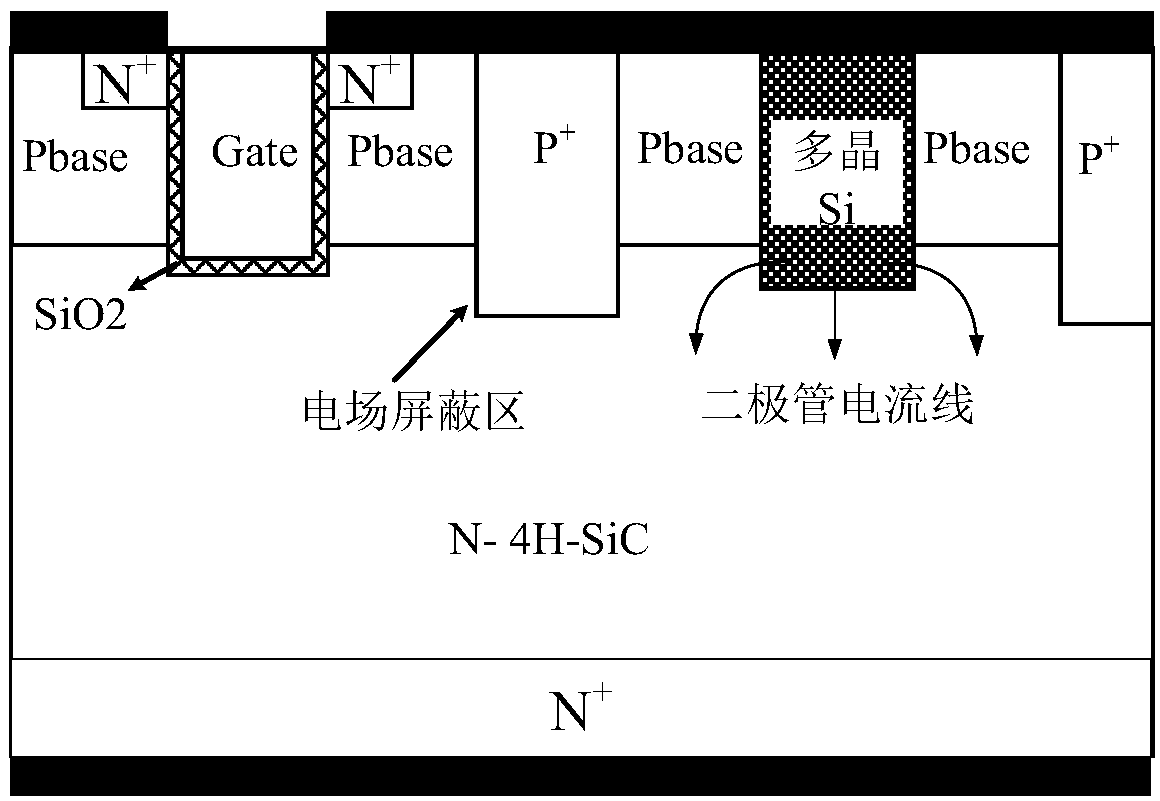

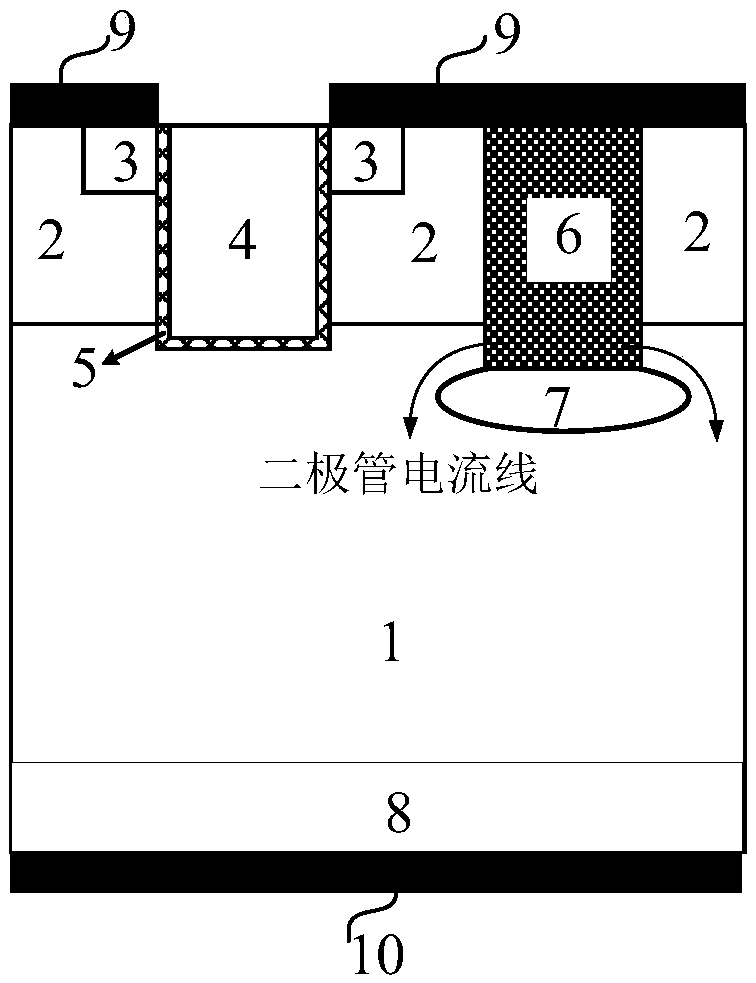

A heterojunction freewheel diode integrated silicon carbide groove gate MOSFET

ActiveCN109103186AAchieve protectionHighly integratedSolid-state devicesSemiconductor devicesMOSFETFreewheel

The invention relates to the field of power semiconductors, and provides a heterojunction freewheel diode integrated silicon carbide groove gate MOSFET, which is used for overcoming the disadvantagesof large cell area and low integration degree of the existing silicon carbide groove gate MOSFET with an integrated freewheel diode. A P + type electric field shield region is arranged directly underthe anode region of the heterojunction diode in the cell structure of the silicon carbide trench gate MOSFET provided by the invention, the electric field shielding effect required by the heterojunction diode is realized while the heterojunction diode is integrated; in the anode region of the heterojunction diode, polysilicon with different doping types and concentrations can be used to adjust theon-voltage drop of heterojunction diodes. The invention not only integrates the freewheeling diode on the silicon carbide trench gate MOSFET, but also has the advantages of low conduction loss and low switching loss, high integration level and low area cost.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Single-band and dual-band infrared detectors

Bias-switchable dual-band infrared detectors and methods of manufacturing such detectors are provided. The infrared detectors are based on a back-to-back heterojunction diode design, where the detector structure consists of, sequentially, a top contact layer, a unipolar hole barrier layer, an absorber layer, a unipolar electron barrier, a second absorber, a second unipolar hole barrier, and a bottom contact layer. In addition, by substantially reducing the width of one of the absorber layers, a single-band infrared detector can also be formed.

Owner:CALIFORNIA INST OF TECH

Solar cell array with isotype-heterojunction diode

InactiveUS7659474B2Less sensitiveTime stablePV power plantsSolid-state devicesSolar cellHeterojunction diode

A solar cell array has at least one solar cell including a photovoltaic structure having a sun-facing front face and a back face, and having an active region, and an isotype heterojunction diode connected in electrical parallel with the active region of the photovoltaic structure.

Owner:THE BOEING CO

Method and system for optoelectronics transceivers integrated on a CMOS chip

Methods and systems for optoelectronics transceivers integrated on a CMOS chip are disclosed and may include receiving optical signals from optical fibers via grating couplers on a top surface of a CMOS chip, which may include a guard ring. Photodetectors may be integrated in the CMOS chip. A CW optical signal may be received from a laser source via grating couplers, and may be modulated using optical modulators, which may be Mach-Zehnder and / or ring modulators. Circuitry in the CMOS chip may drive the optical modulators. The modulated optical signal may be communicated out of the top surface of the CMOS chip into optical fibers via grating couplers. The received optical signals may be communicated between devices via waveguides. The photodetectors may include germanium waveguide photodiodes, avalanche photodiodes, and / or heterojunction diodes. The CW optical signal may be generated using an edge-emitting and / or a vertical-cavity surface emitting semiconductor laser.

Owner:CISCO TECH INC

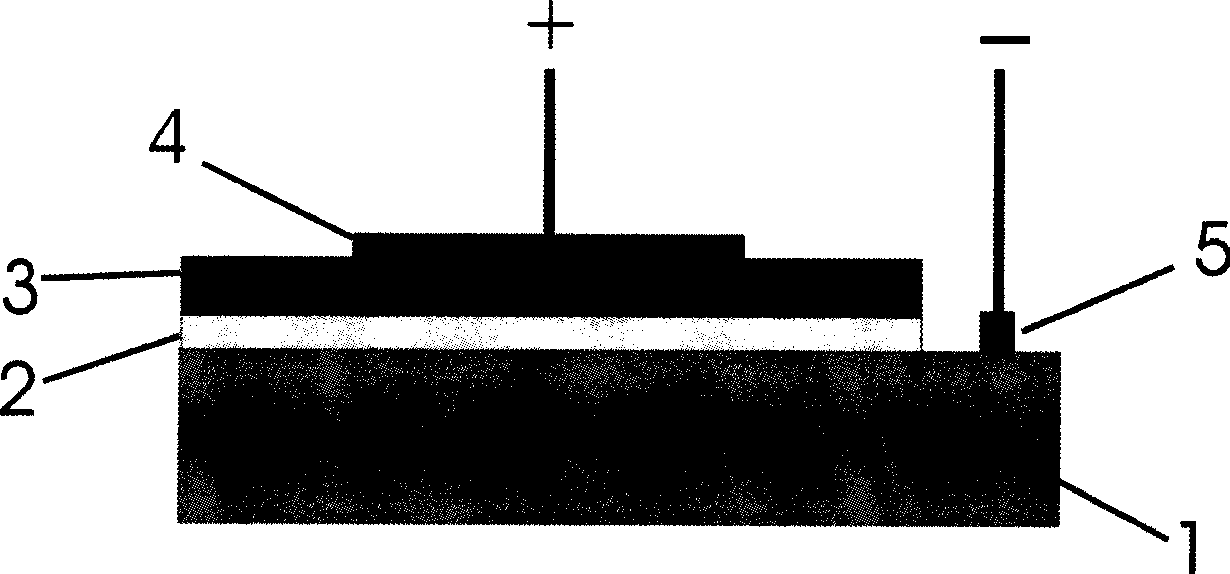

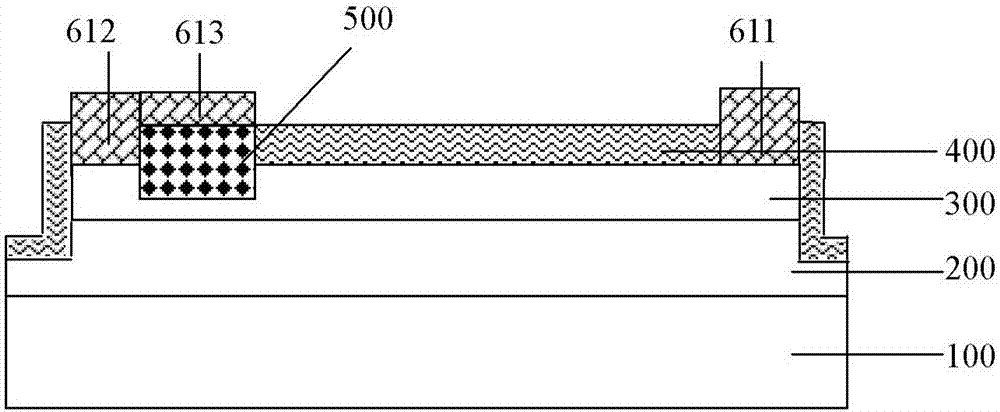

GaN-based heterojunction diode and preparation method thereof

ActiveCN107978642AAdjust the forward turn-on voltageImprove breakdown voltageSemiconductor/solid-state device manufacturingDiodeProtection layerReverse leakage current

The invention discloses a GaN-based heterojunction diode and a preparation method thereof. The GaN-based heterojunction diode comprises a GaN intrinsic layer and a barrier layer which sequentially grow on a substrate; one part of groove area is formed in one part of barrier layer; a high-hole concentration structure layer covers the upper surface of a groove; a cathode electrode is located in onepart of area, which is not covered with the high-hole concentration structure layer, on the upper surface of the barrier layer; a first part of an anode electrode is located in the other part of area,which is not covered with the high-hole concentration structure layer, on the upper surface of the barrier layer and the position of the first part is next to the high-hole concentration structure layer; a second part of the anode electrode covers the upper surface of the high-hole concentration structure layer; and a passivation protection layer covers an area, which is not covered with the cathode electrode and the anode electrode, on the upper surface of the barrier layer. The GaN-based heterojunction diode is high in reliability and good in repeatability, adjustment of threshold voltage of the diode can be achieved, and the GaN-based heterojunction diode with low threshold voltage and low reverse leakage current is obtained.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI +1

Preparation method of tapered zinc oxide/nickel oxide heterojunction diode

ActiveCN103280498BAchieve electroluminescenceSemiconductor devicesUltravioletAtomic layer deposition

The invention relates to the preparation technology of heterojunction ultraviolet laser diodes, in particular to a method for preparing pointed-cone-shaped p-NiO (nickel oxide) / n-ZnO (zinc oxide) heterojunctions by combining the film coating technology and the femtosecond laser technology. According to the method, firstly, heat oxidation is utilized to form a NiO layer on a nickel sheet, then, an atomic layer deposition method is utilized for preparing a ZnO layer, next, an ITO (indium tin oxide) transparent upper electrode is formed outside the n-type ZnO layer by a sputtering method, finally, a pointed-cone-shaped array is formed on the nickel sheet covered with an NiO / ZnO / ITO layer by the femtosecond laser processing technology, pointed-cone-shaped p-NiO / n-ZnO heterojunctions are formed, voltage is applied to the ITO and the bottom of the nickel sheet, and the electroluminescence can be realized.

Owner:南通东湖国际商务服务有限公司

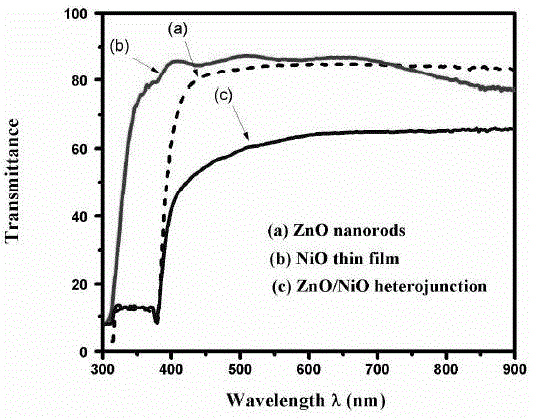

NiO/ZnO nano-rod based heterojunction diode and preparation method thereof

InactiveCN106784156AImprove performanceSimple methodFinal product manufactureSemiconductor devicesNano structuringHYDROSOL

The invention aims to provide a preparation method of a NiO / ZnO nano-rod based heterojunction diode. According to the preparation method, FTO (fluorine-doped tin oxide) conductive glass is used as a substrate, and a method for sol-gel spin coating is adopted to obtain a ZnO nano-rod heterojunction diode with a NiO nano structure for surface modification. The preparation method is simple and feasible, can achieve film forming at a low temperature, has good film-forming property and good device performance, and has broad application prospects in the field of photoelectric devices.

Owner:上海芯石微电子有限公司